Patents

Literature

104results about How to "Reduce parasitism" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Micromachined Capacitive Microphone

InactiveUS20060280319A1Wide and flat frequency responseHigh sensitivitySemiconductor electrostatic transducersDeaf-aid setsElectrical conductorEngineering

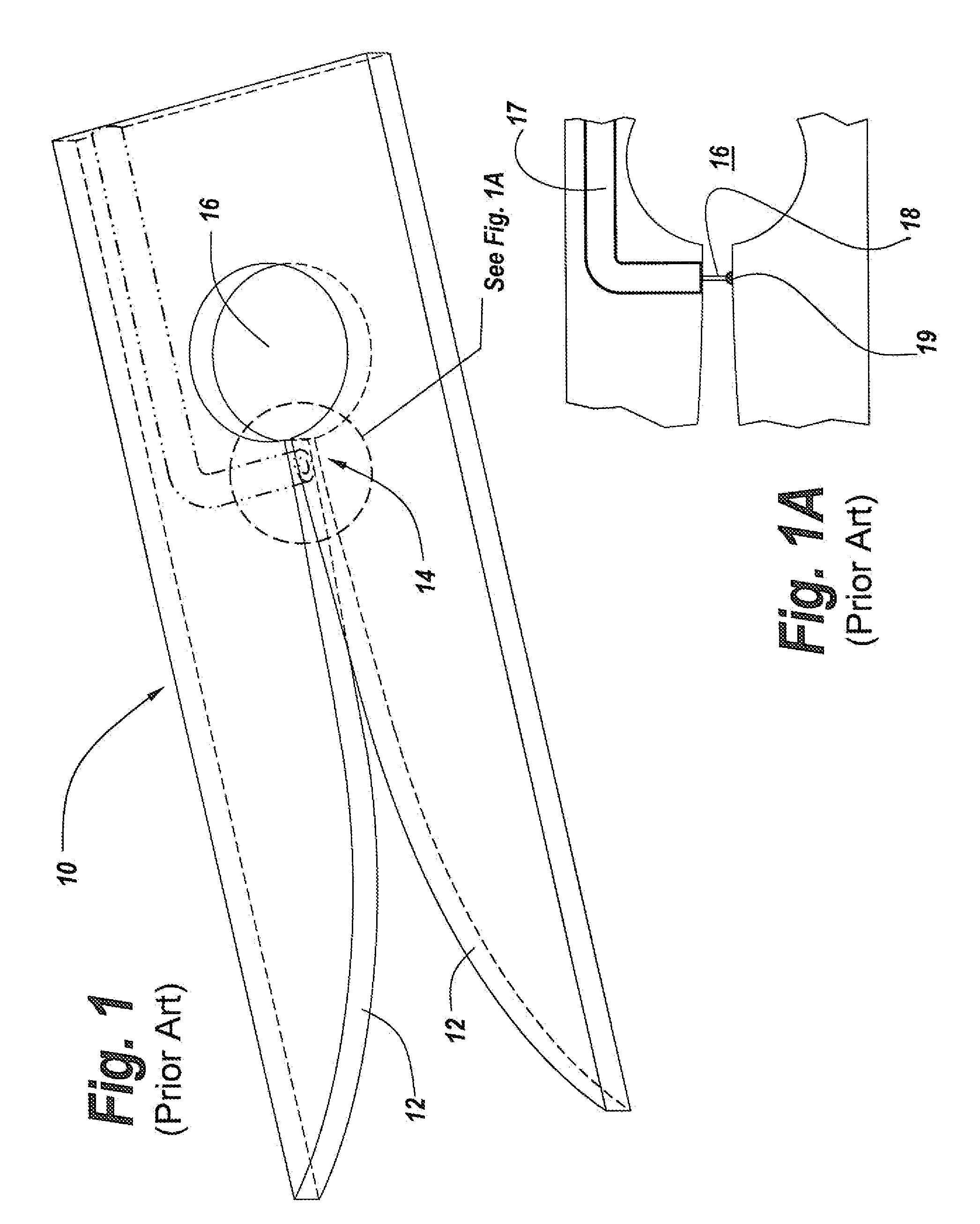

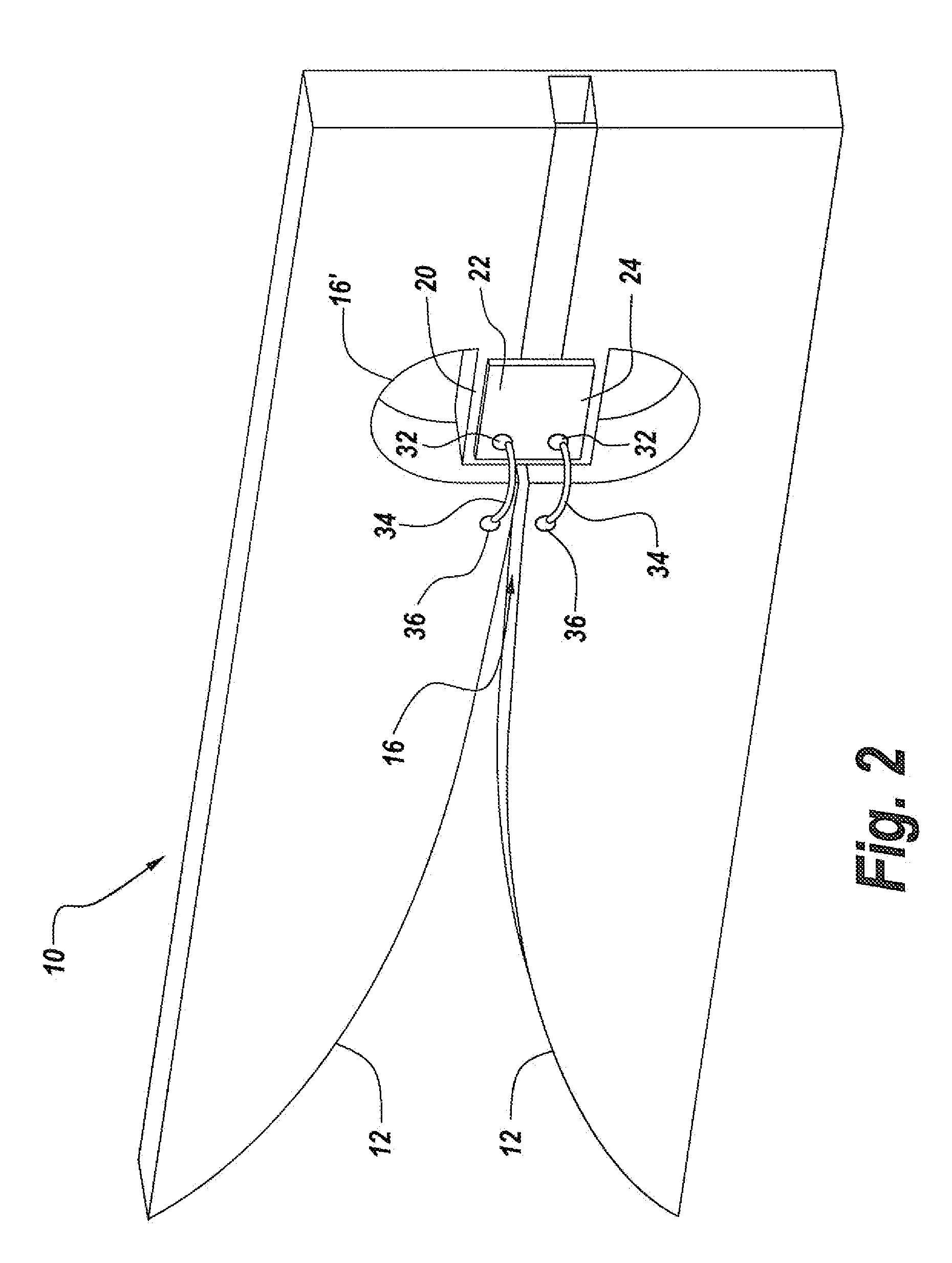

This invention relates to a micromachined capacitive microphone having a shallowly corrugated diaphragm that is anchored at one or more locations on the support has a plurality of dimples to support itself and rest freely on the perforated backplate. The diaphragm whose ends are not anchored is bounded by the taps of edge rail. Also disclosed includes: a fixed perforated backplate having one or more regions; an adjustable cantilever formed by the diaphragm, the support and the backplate; a plurality of dimples maintaining vertical separation between diaphragm and backplate; and the patterning of conductor electrodes carried by diaphragm and backplate.

Owner:GENERAL MEMS CORP

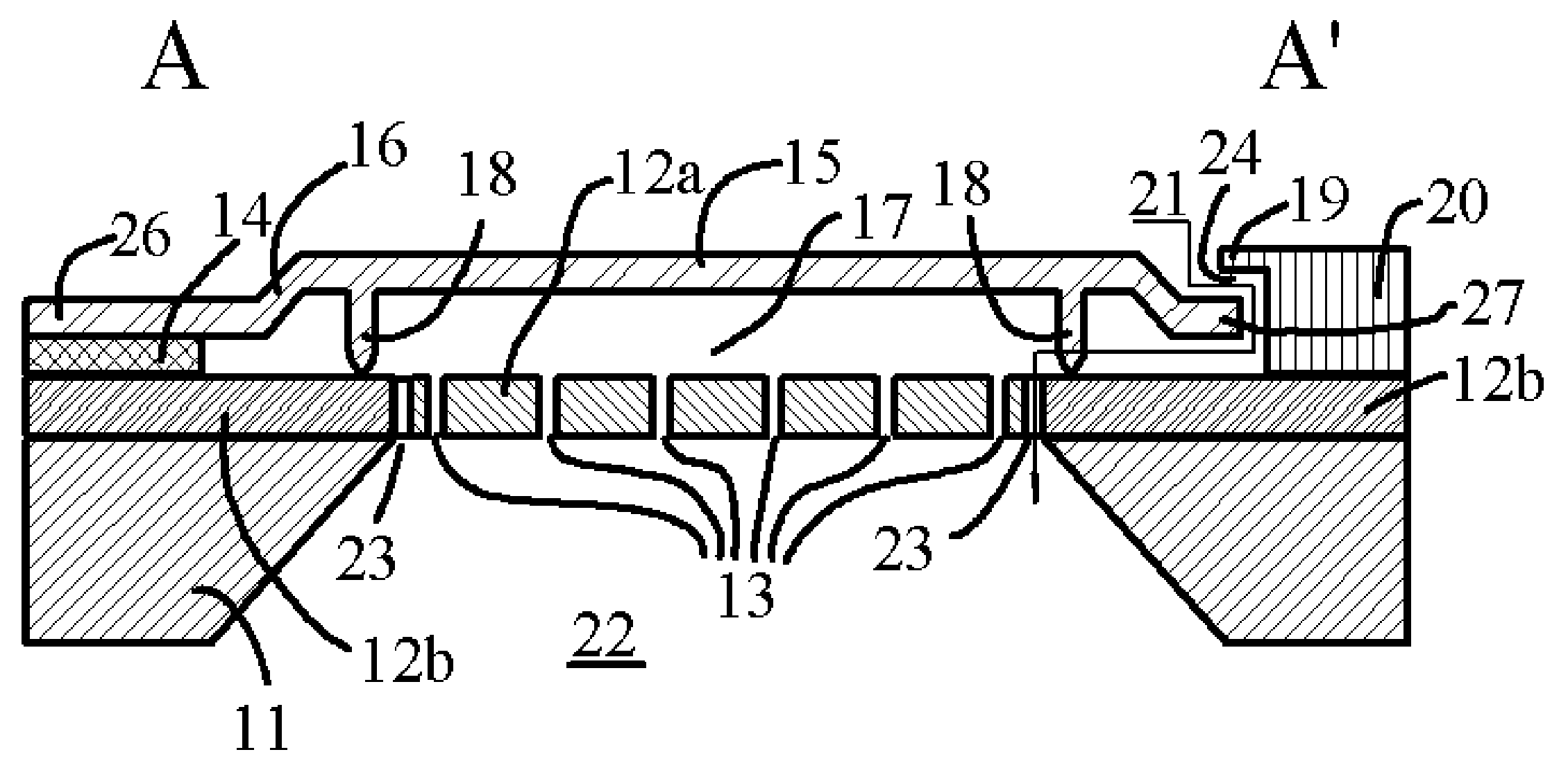

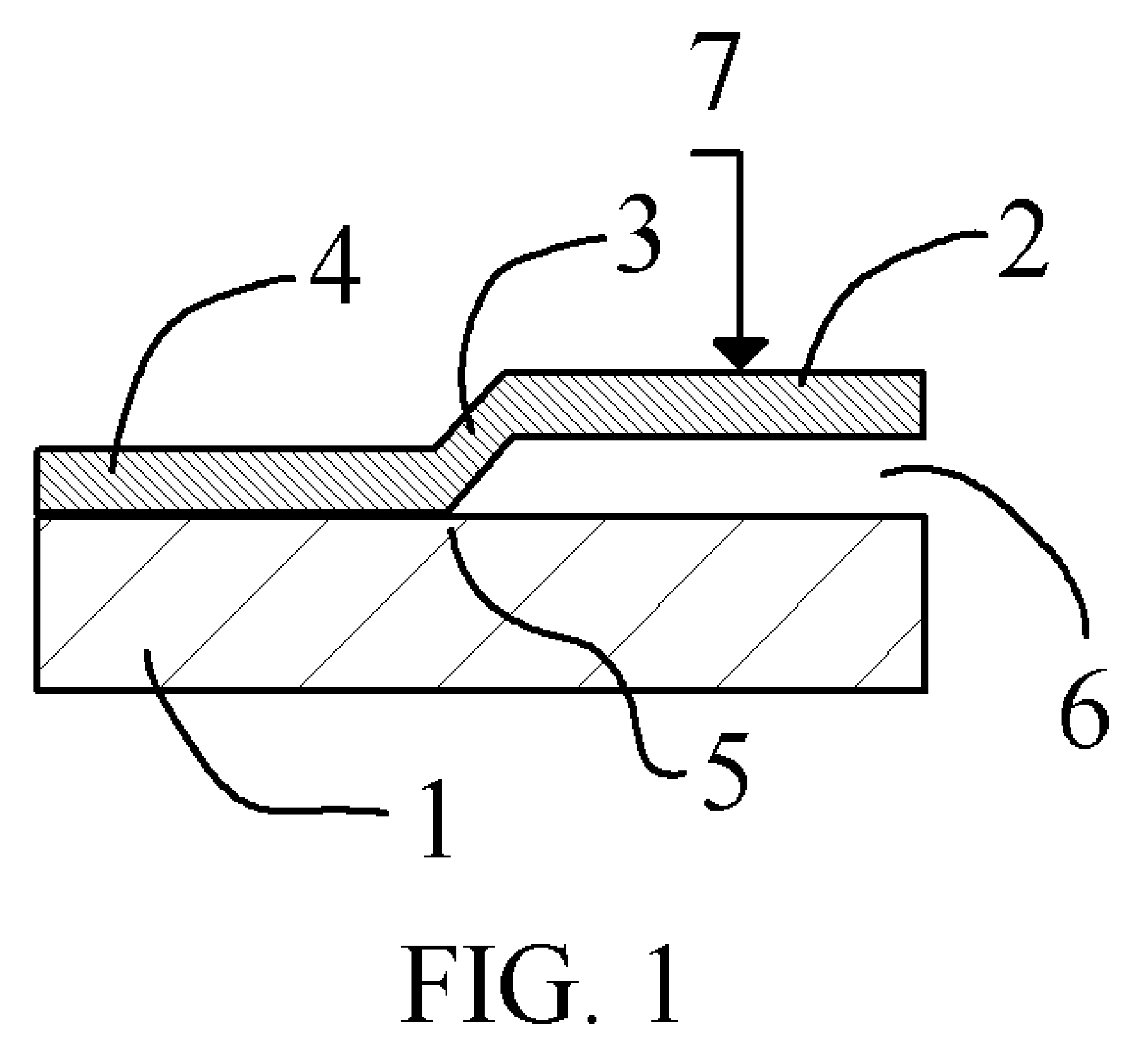

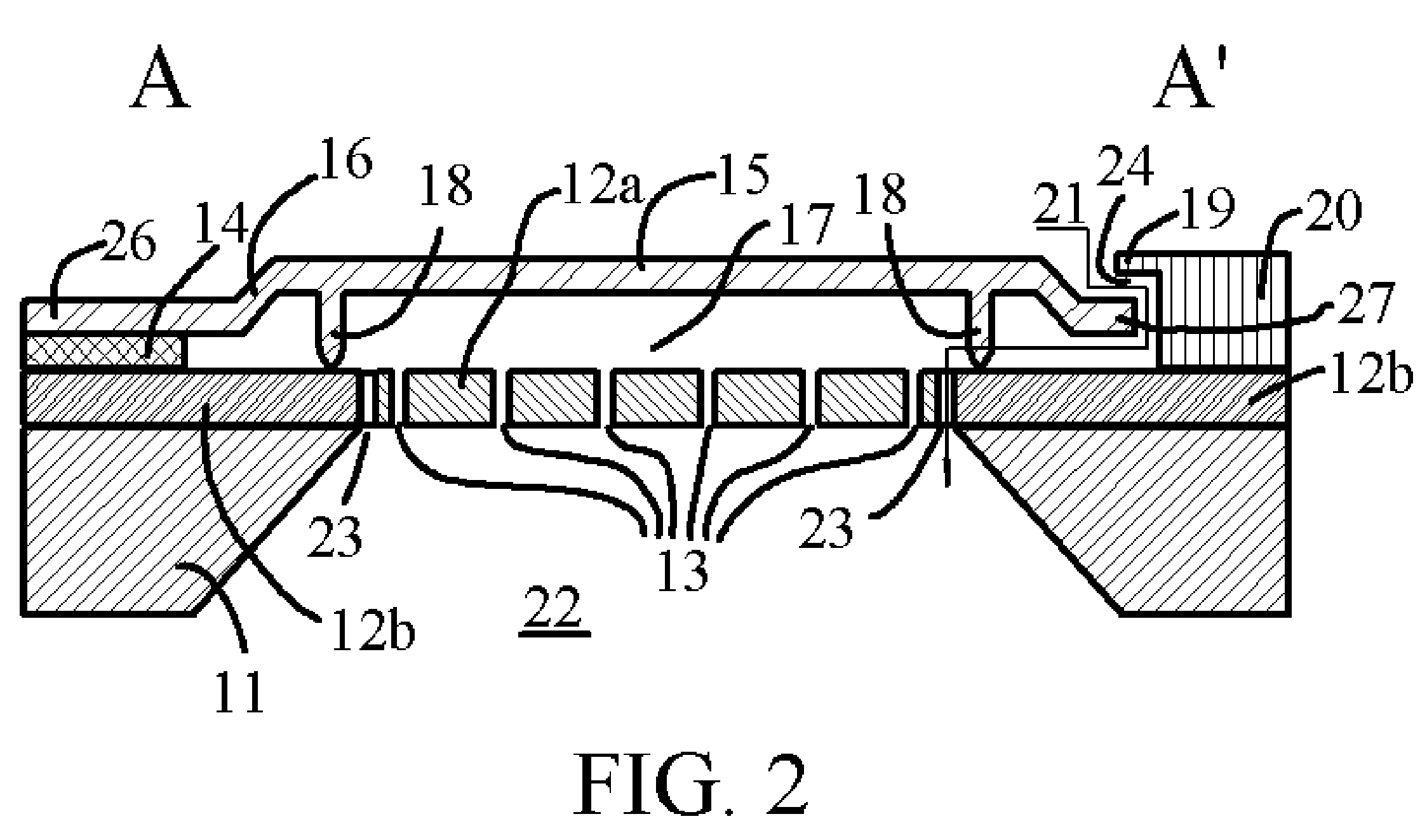

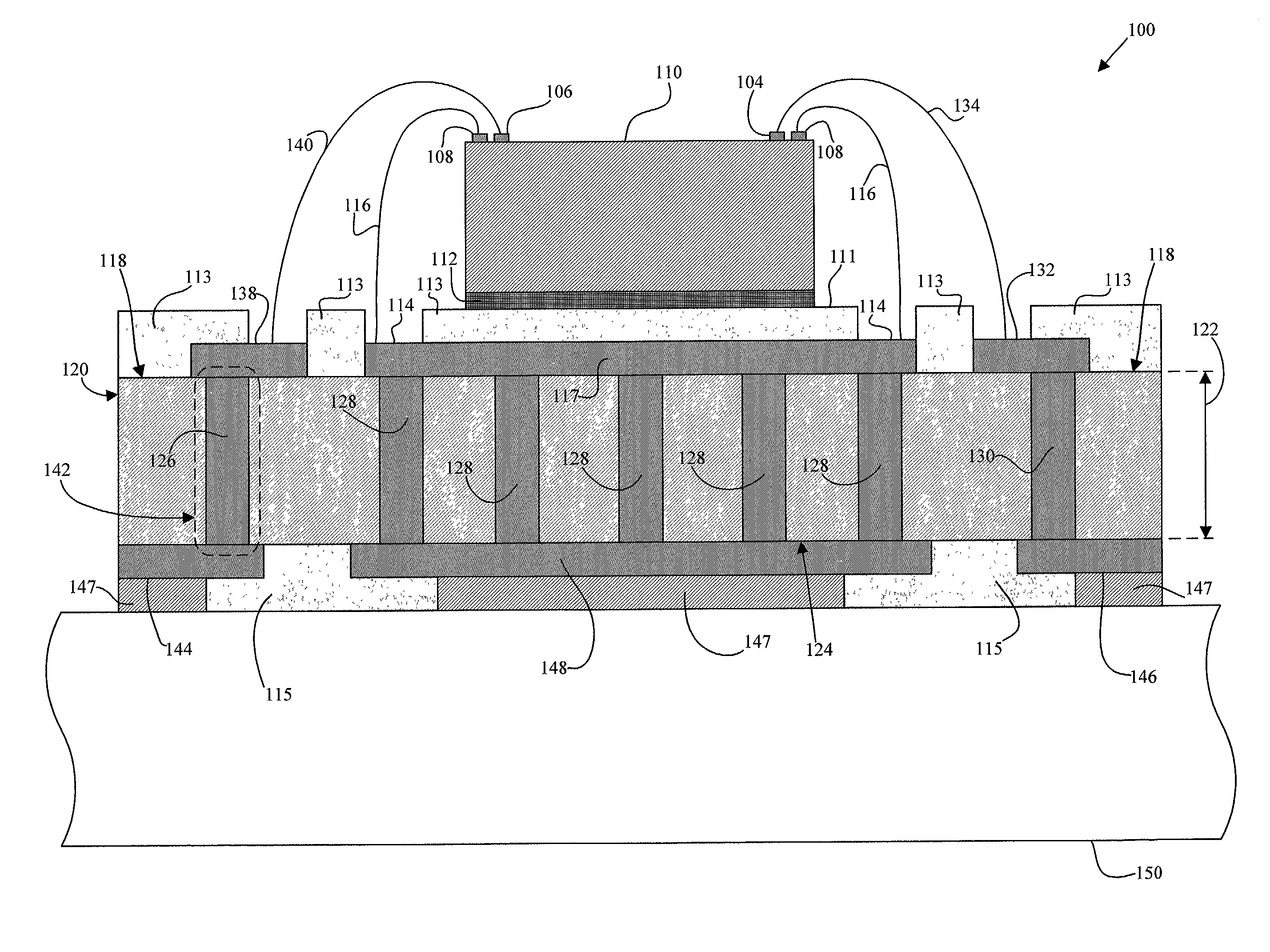

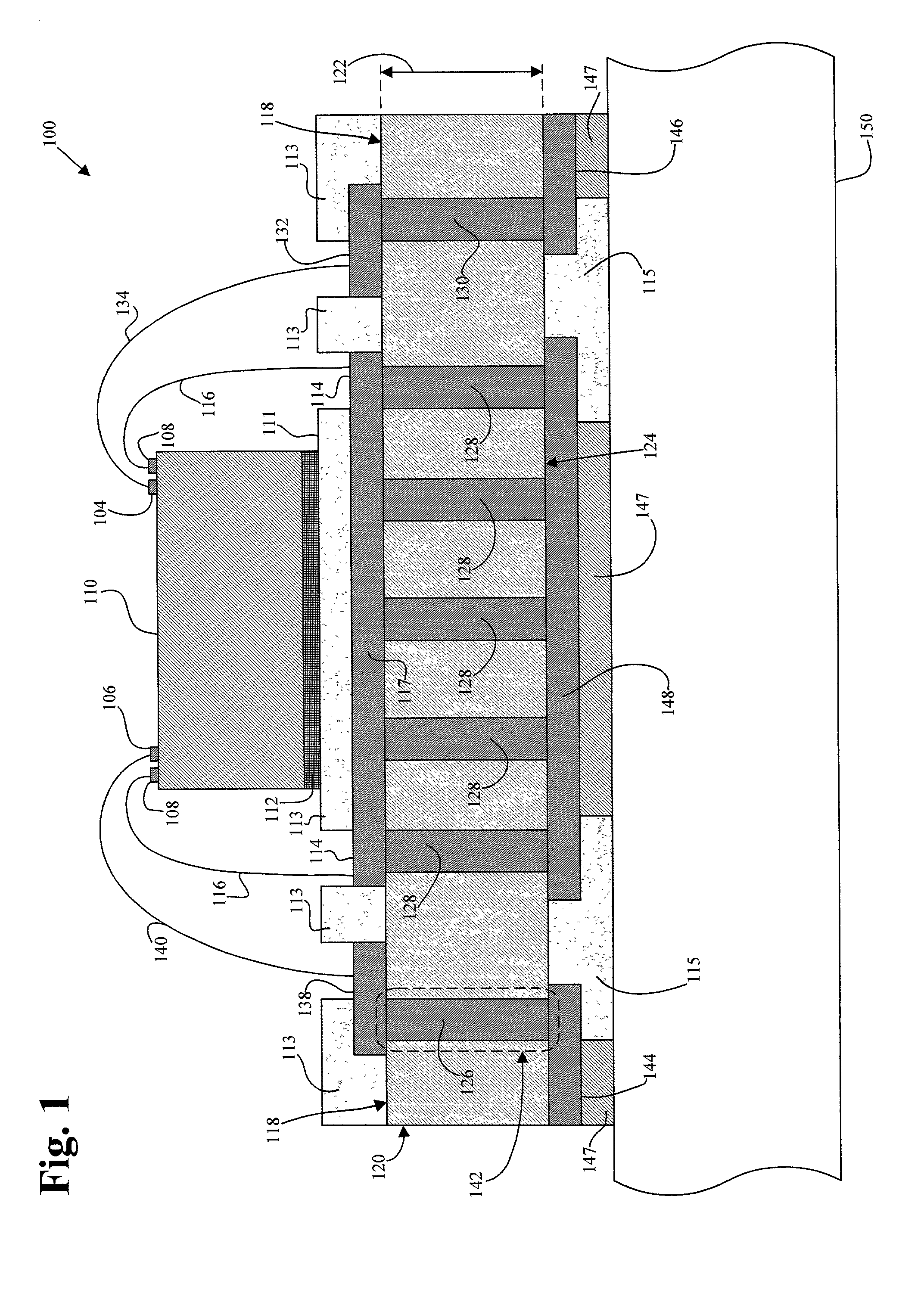

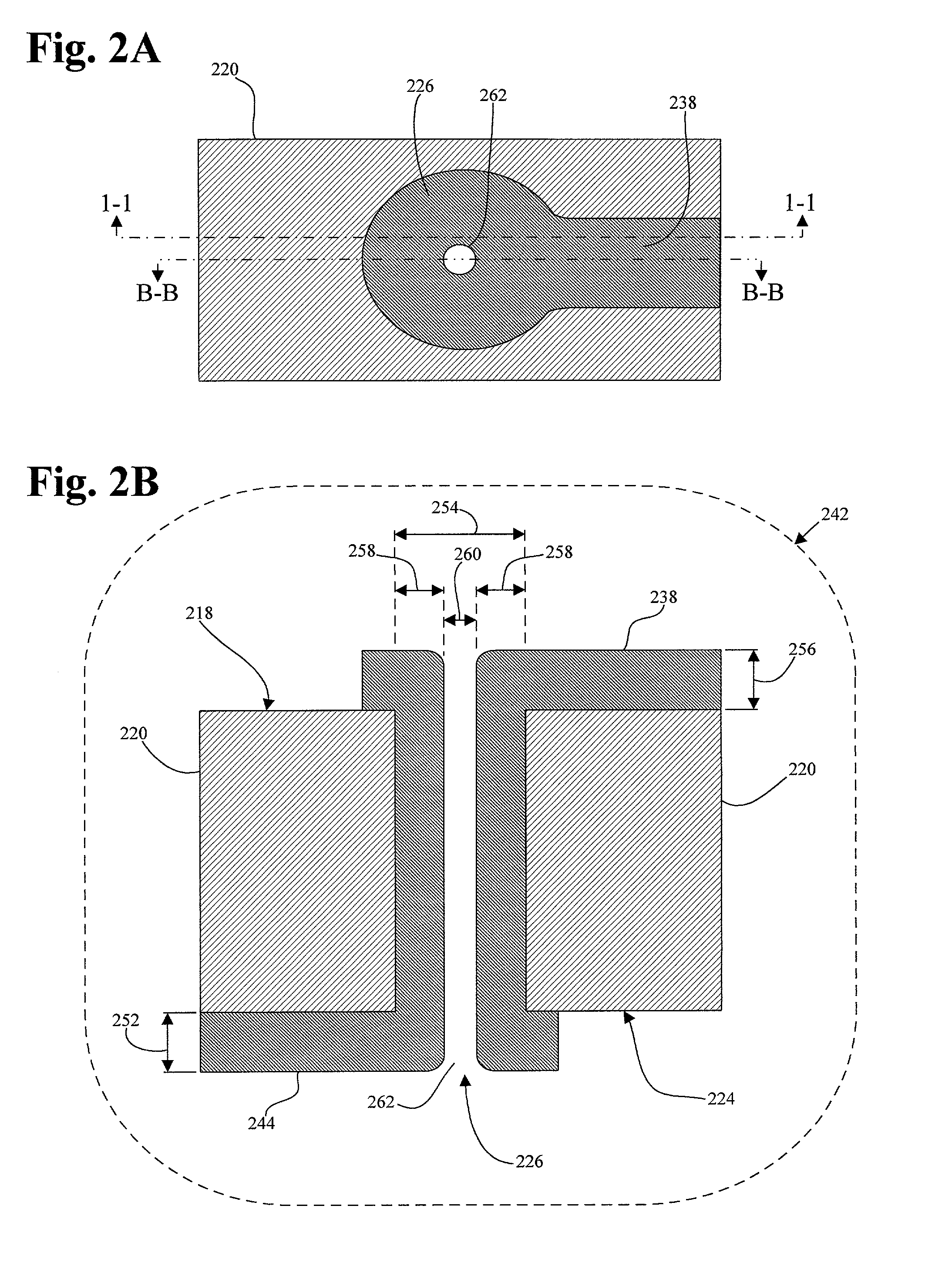

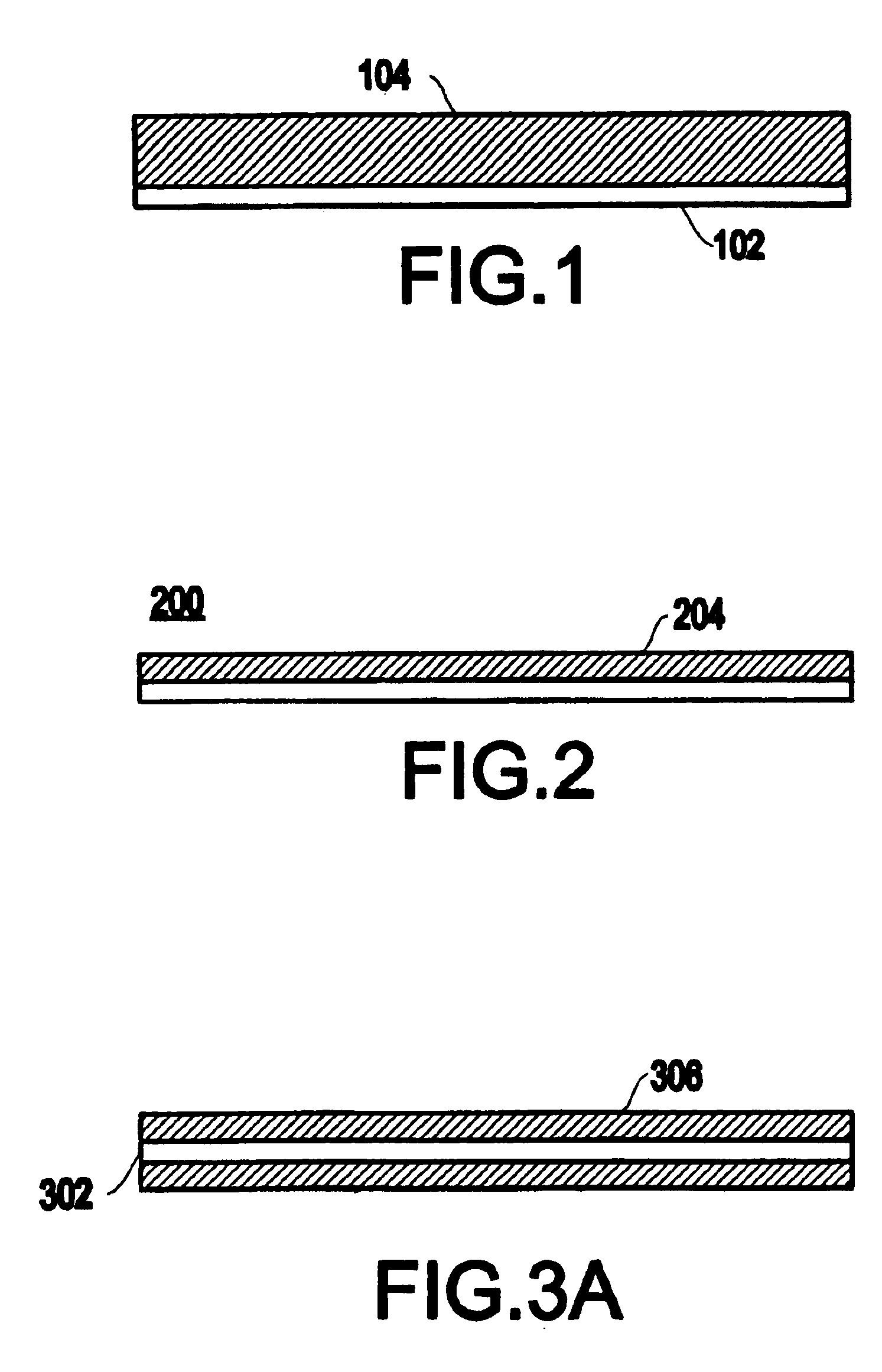

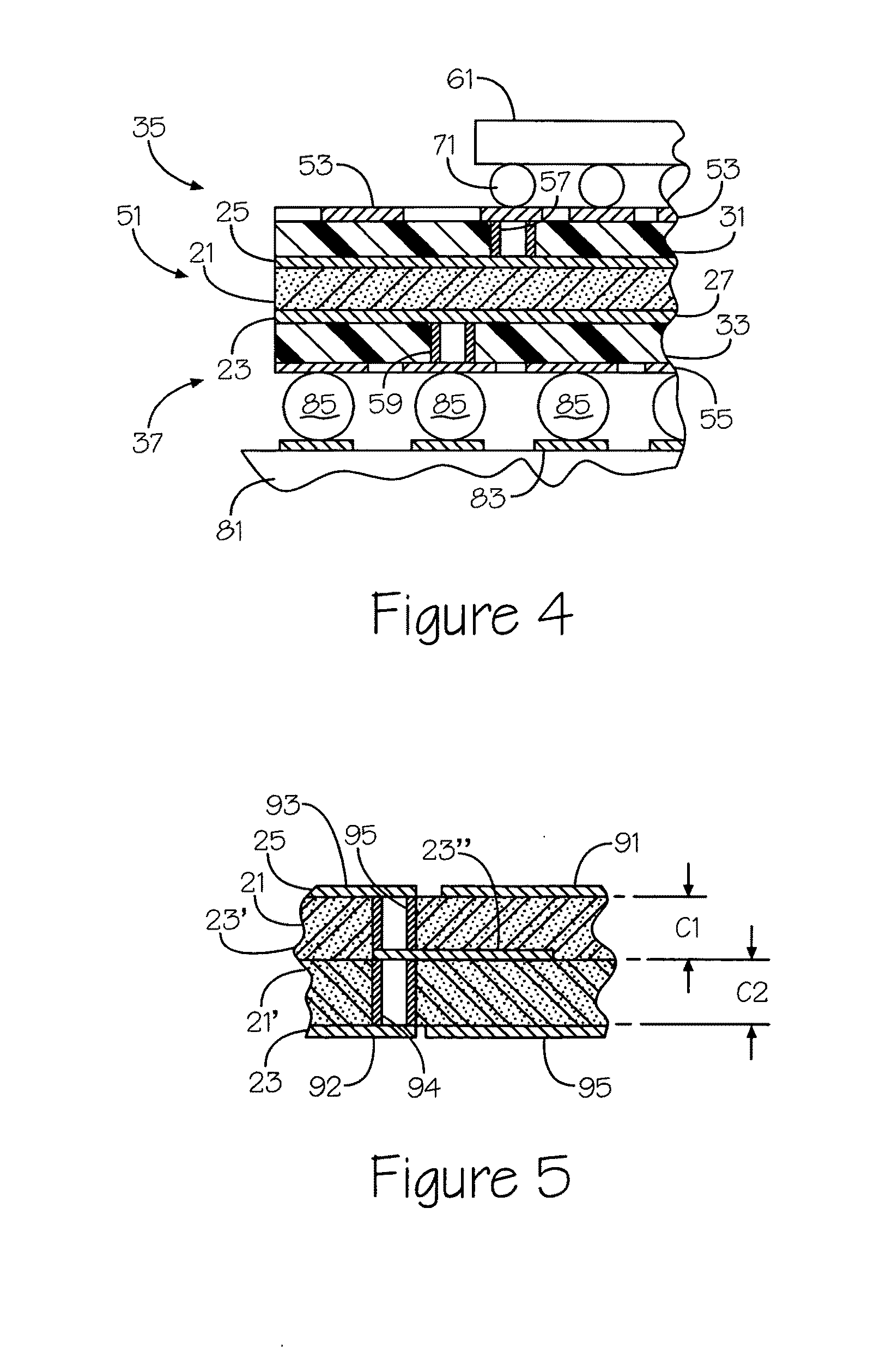

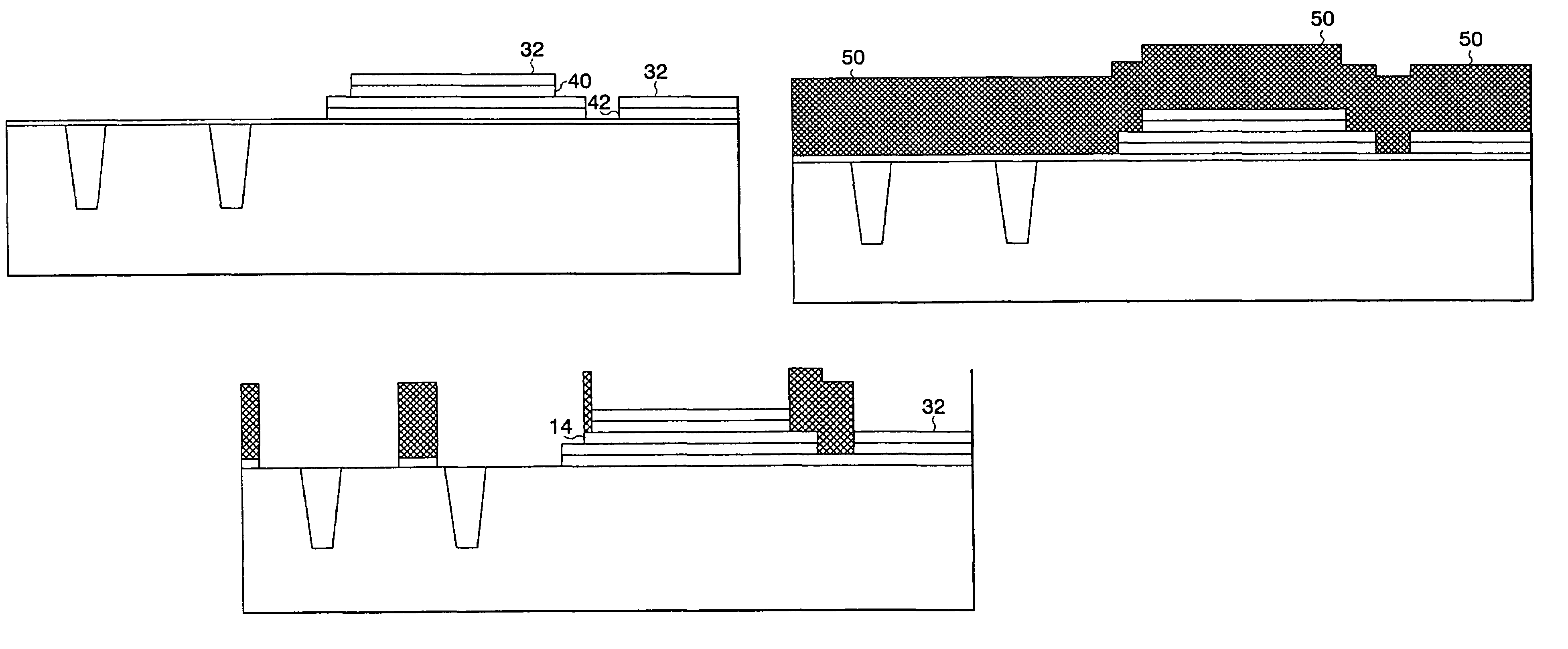

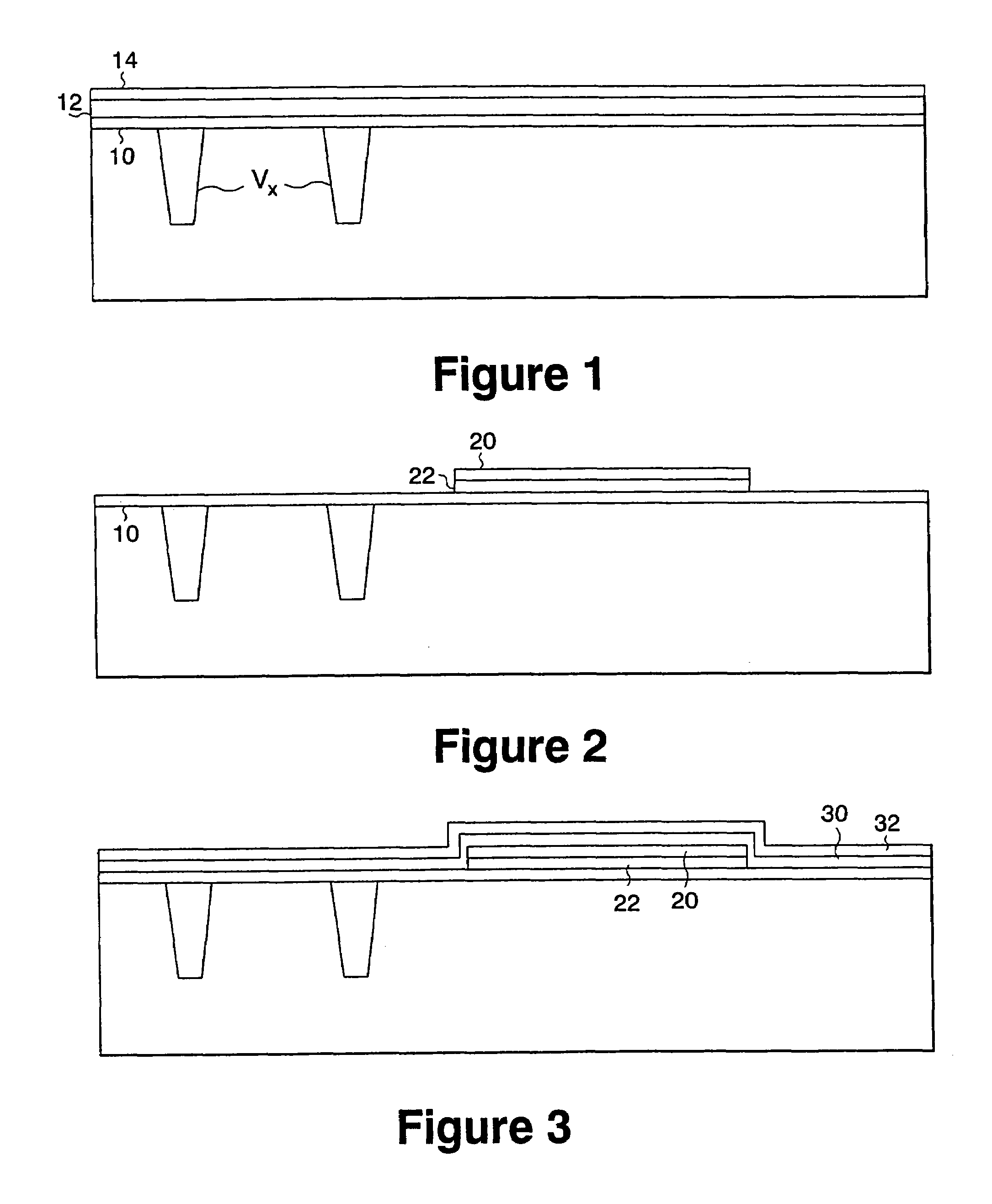

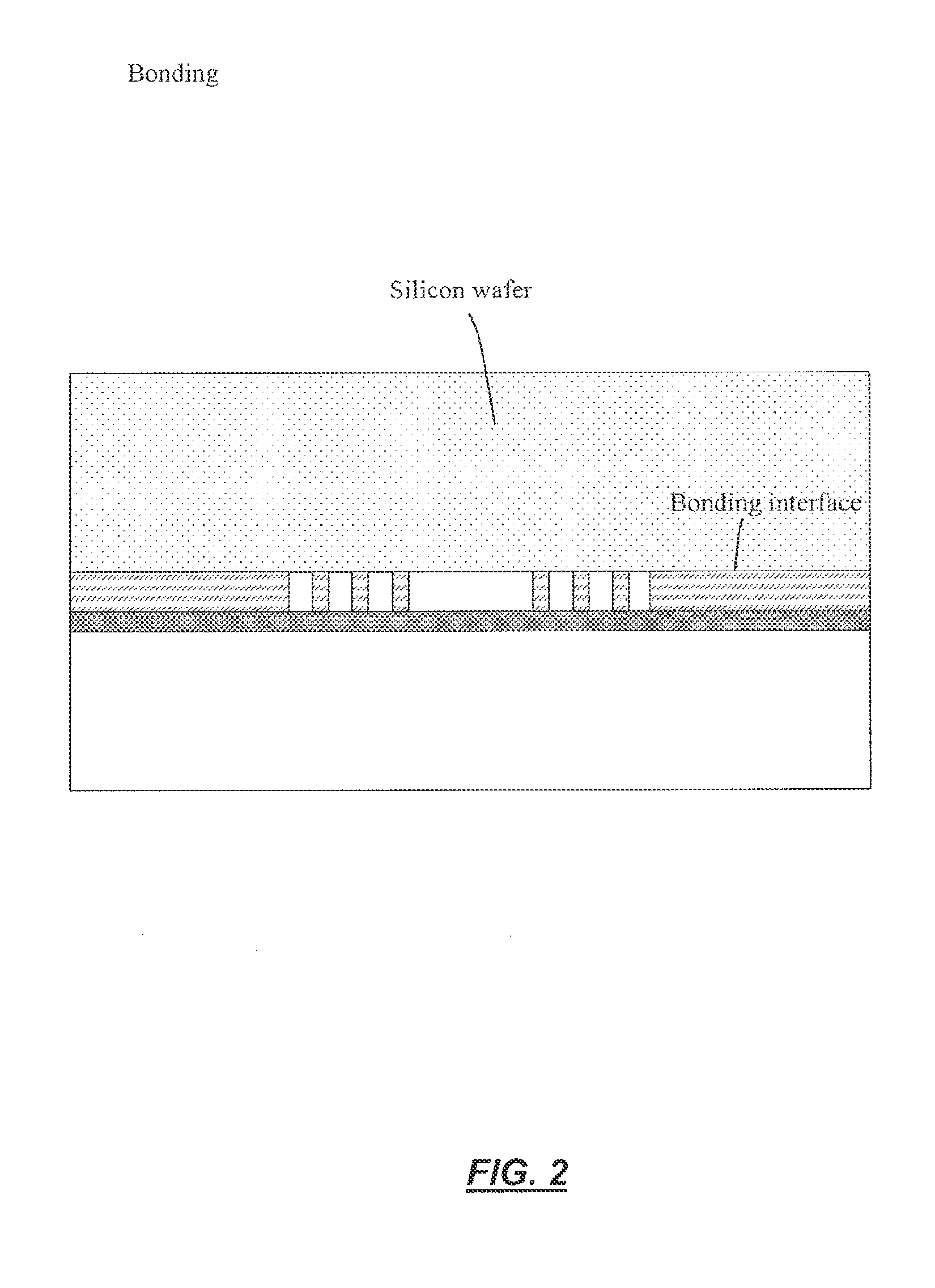

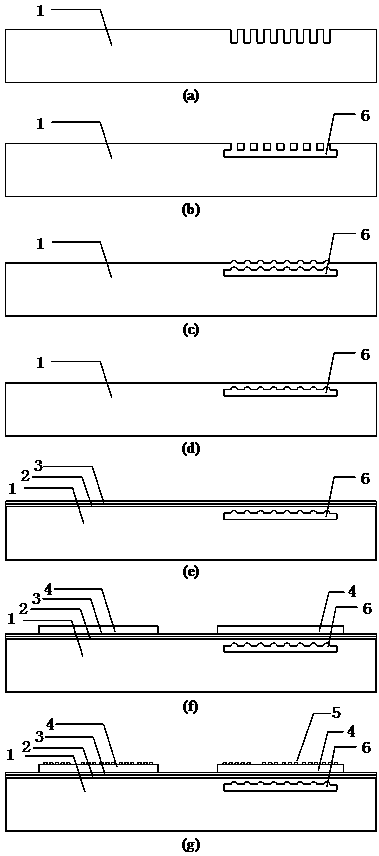

Microelectromechanical systems using thermocompression bonding

InactiveUS6853067B1Reduce parasitic capacitanceReduce parasitismDecorative surface effectsSemiconductor/solid-state device detailsReduced sizeEngineering

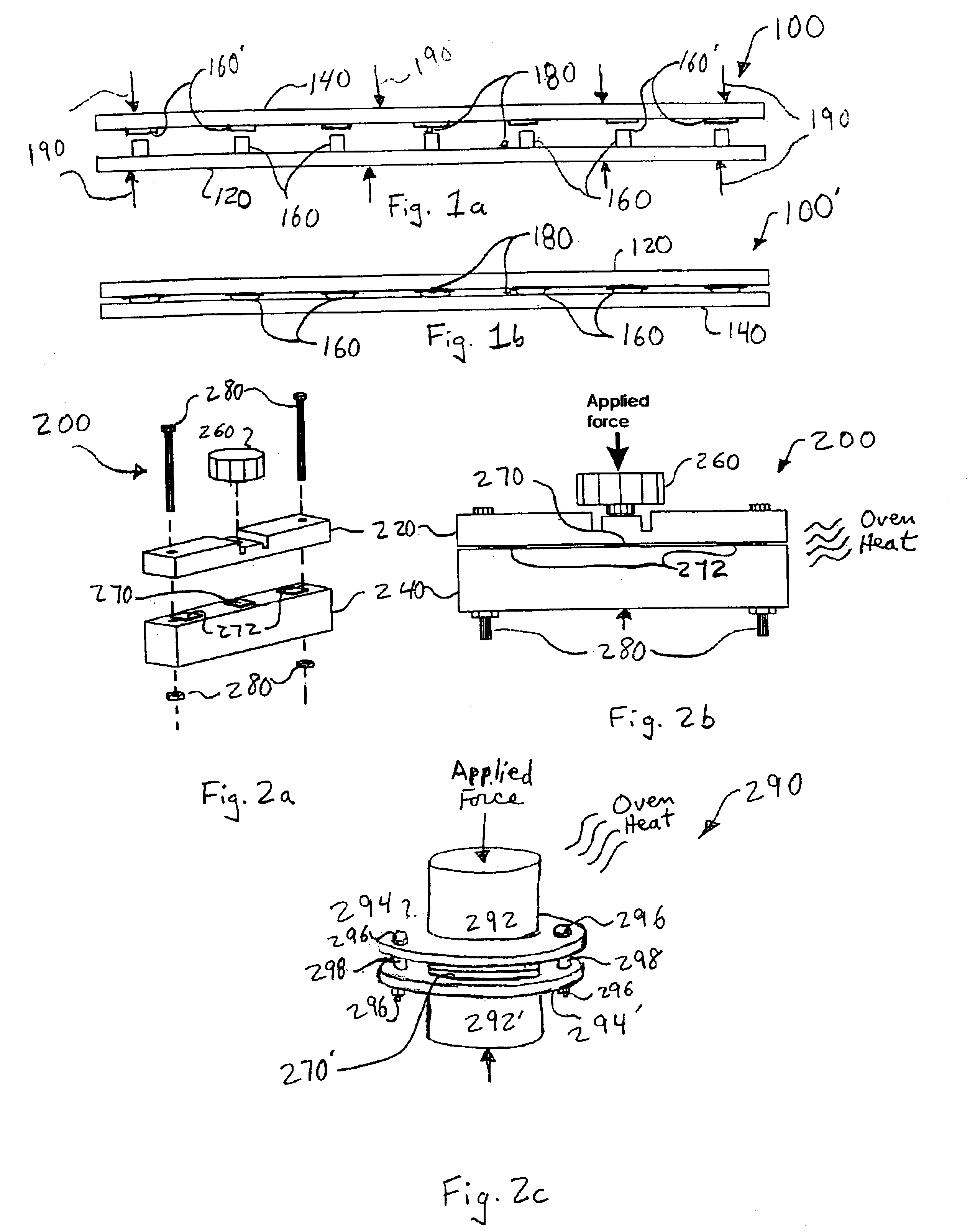

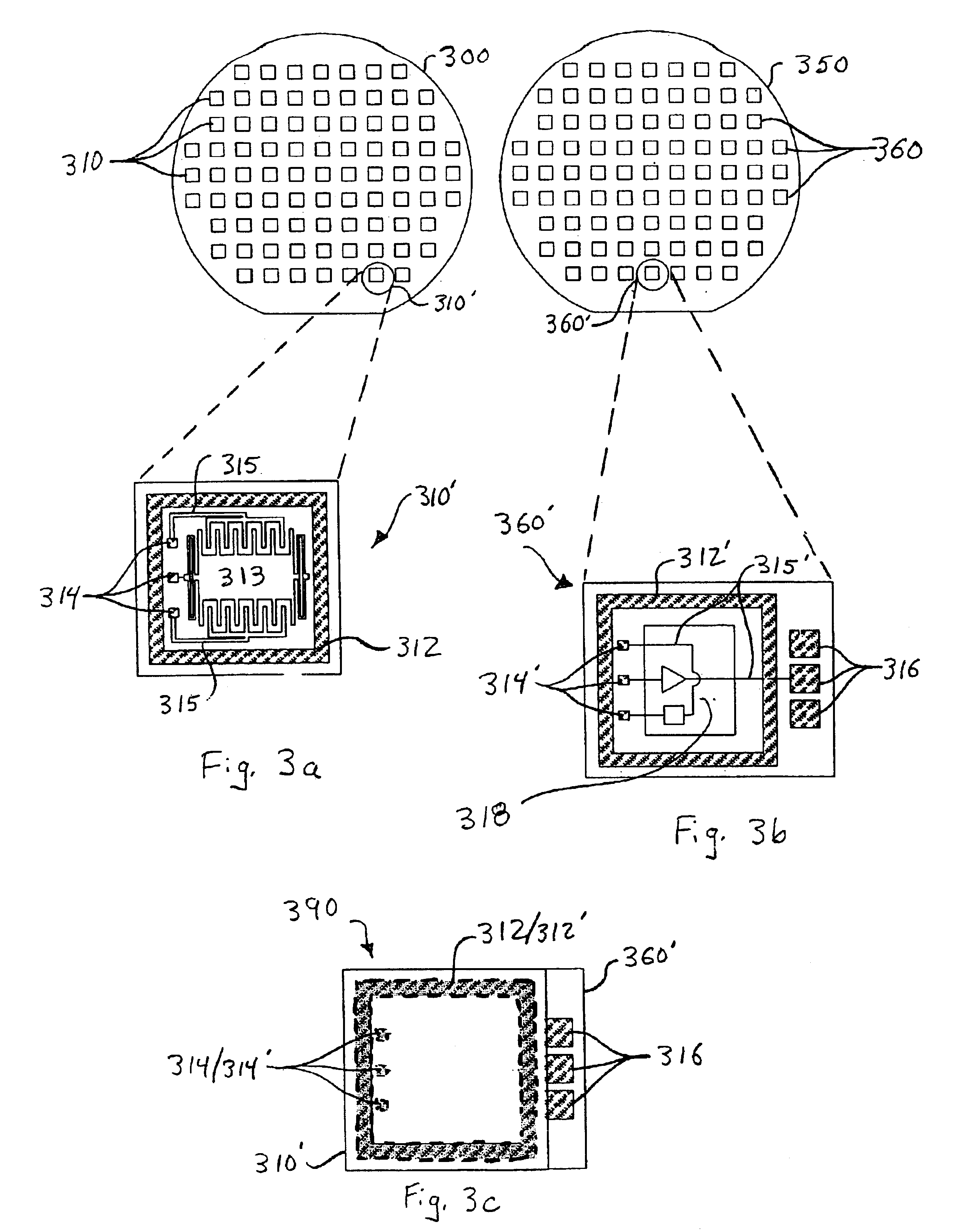

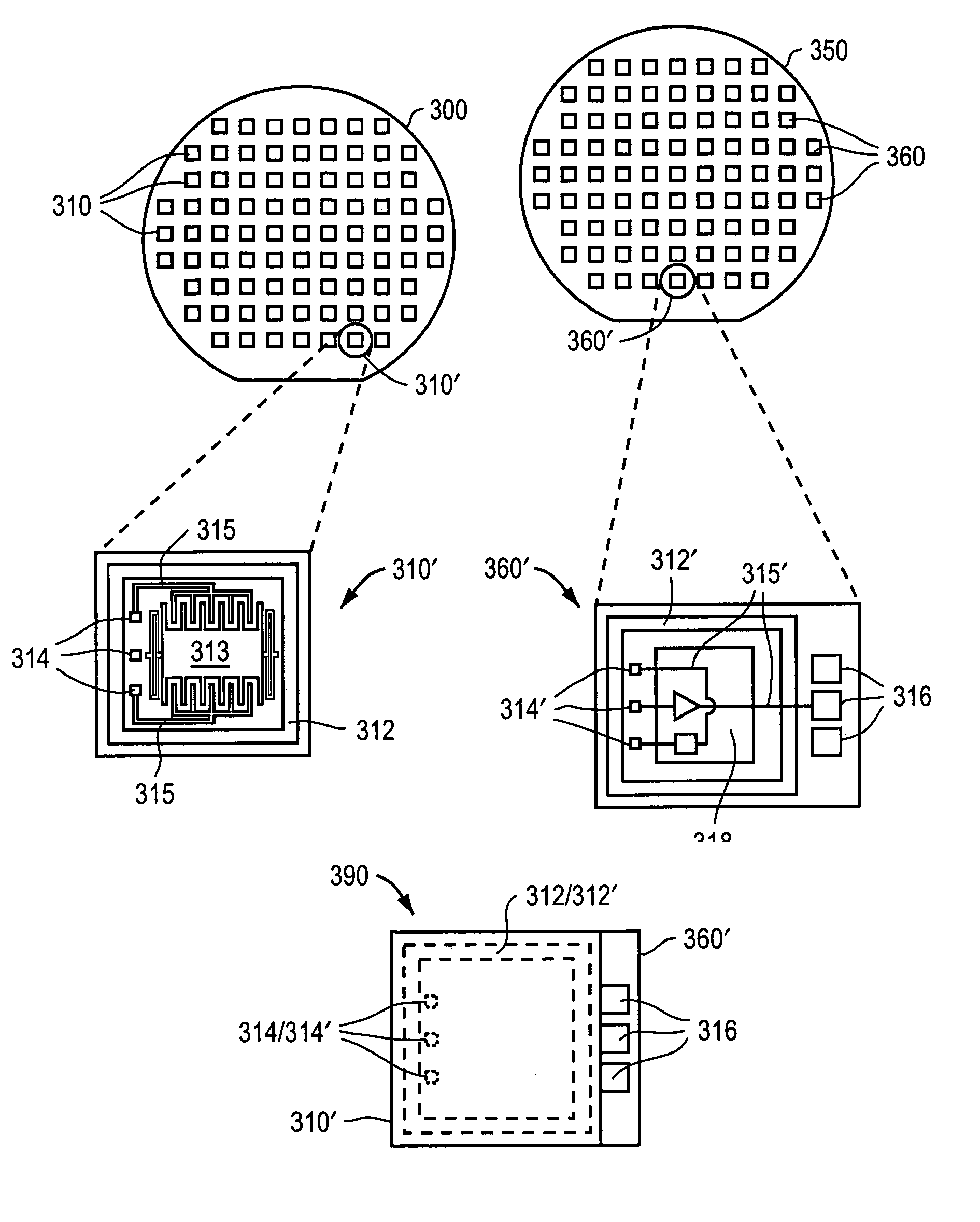

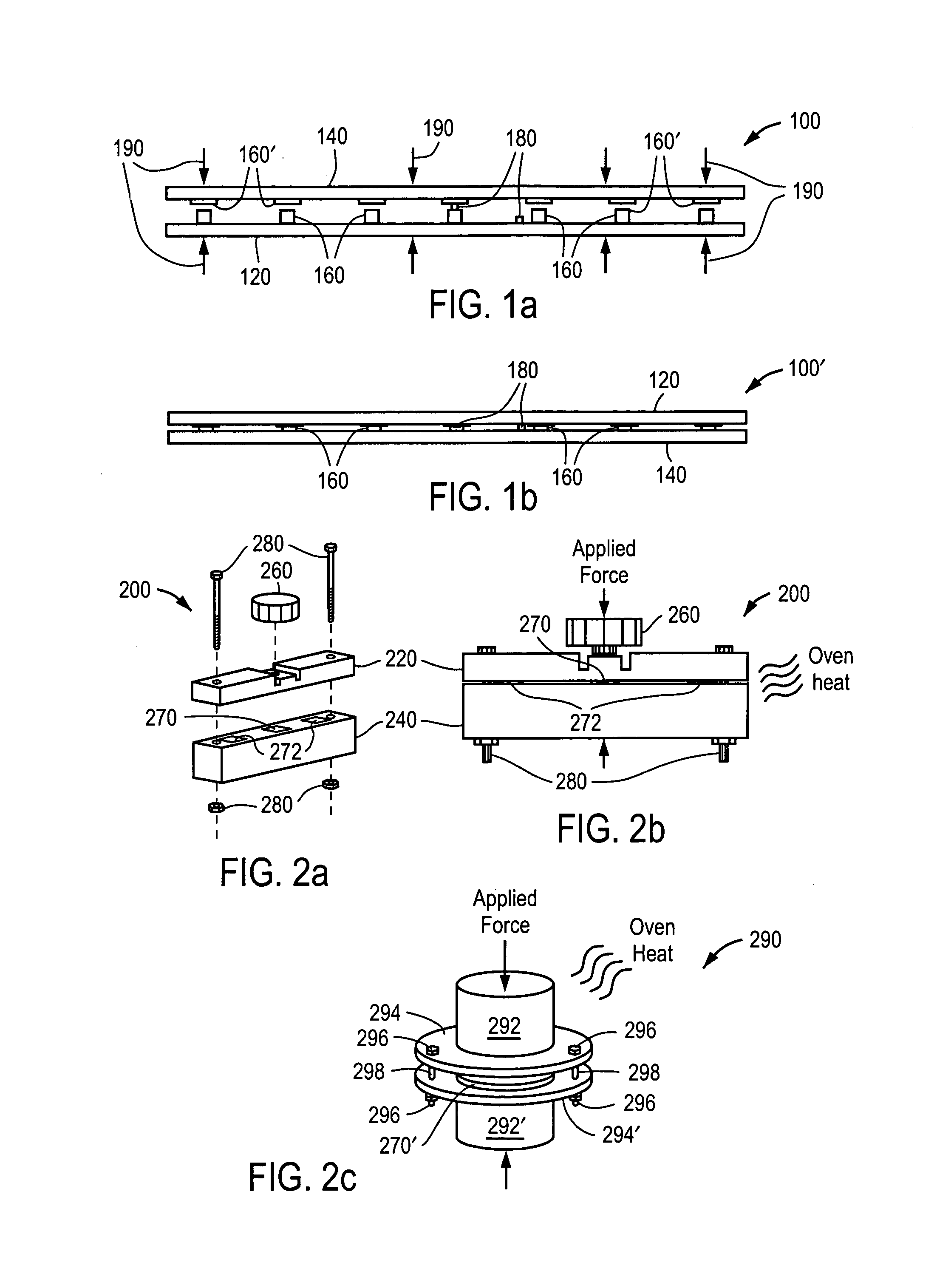

Improved microelectromechanical systems (MEMS), processes and apparatus using thermocompression bonding are disclosed. For example, process embodiments are disclosed in which wafer-scale as well as die-scale thermocompression bonding is utilized to encapsulate MEMS and / or to provide electrical interconnections with MEMS. Apparatus embodiments include apparatus for performing thermocompression bonding and bonded hybrid structures manufactured in accordance with the process embodiments. Devices having various substrate bonding and / or sealing configurations variously offer the advantage of reduced size, higher manufacturing yields, reduced costs, improved reliability, improved compatibility with existing semiconductor manufacturing process and / or greater versatility of applications.

Owner:MICROASSEMBLY TECH

Microelectromechanical systems using thermocompression bonding

InactiveUS7276789B1Electrical interconnections formedReduce parasitic capacitanceDecorative surface effectsSemiconductor/solid-state device detailsReduced sizeEngineering

Improved microelectromechanical systems (MEMS), processes and apparatus using thermocompression bonding are disclosed. For example, process embodiments are disclosed in which wafer-scale as well as die-scale thermocompression bonding is utilized to encapsulate MEMS and / or to provide electrical interconnections with MEMS. Apparatus embodiments include apparatus for performing thermocompression bonding and bonded hybrid structures manufactured in accordance with the process embodiments. Devices having various substrate bonding and / or sealing configurations variously offer the advantage of reduced size, higher manufacturing yields, reduced costs, improved reliability, improved compatibility with existing semiconductor manufacturing process and / or greater versatility of applications.

Owner:MICROASSEMBLY TECH

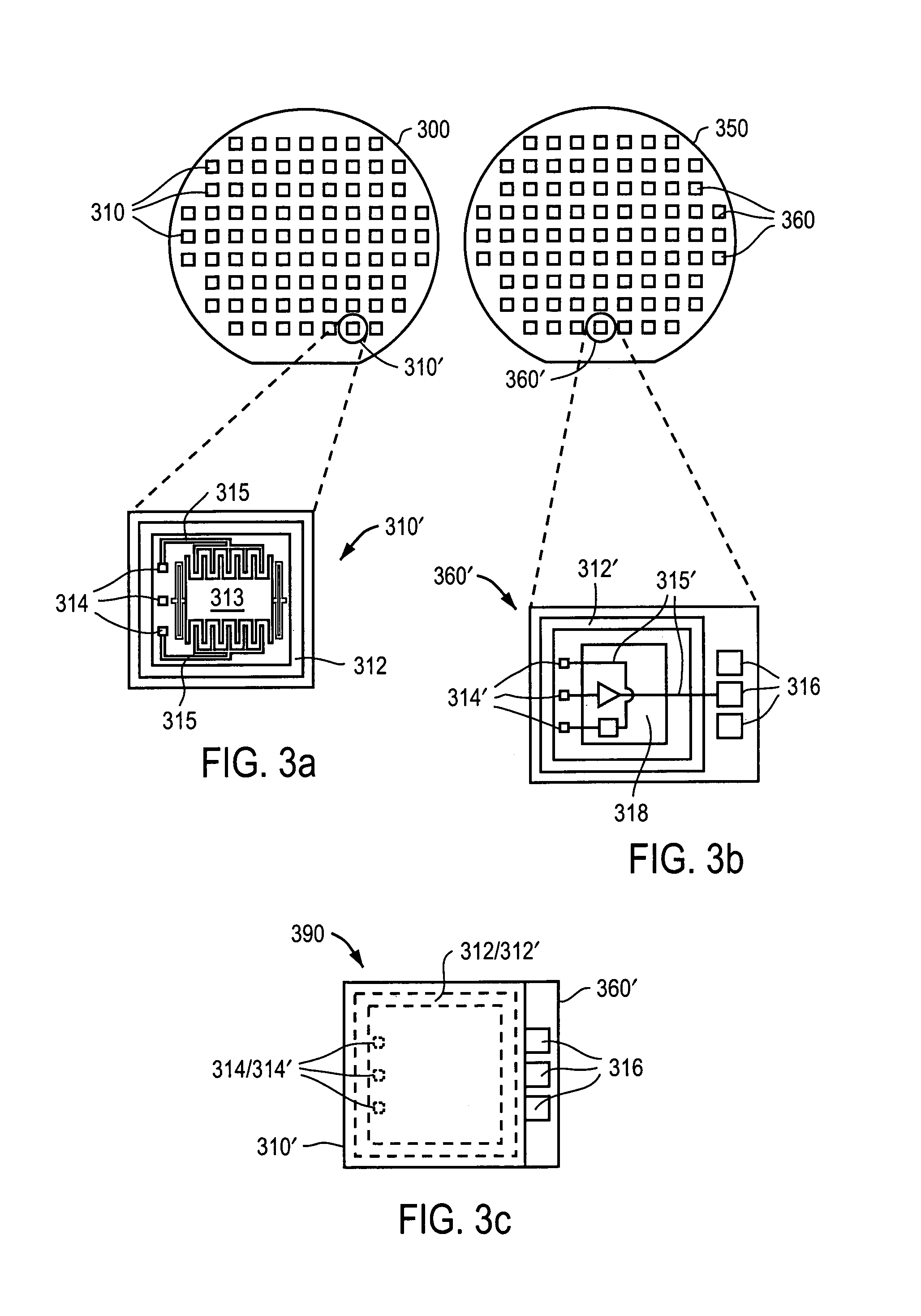

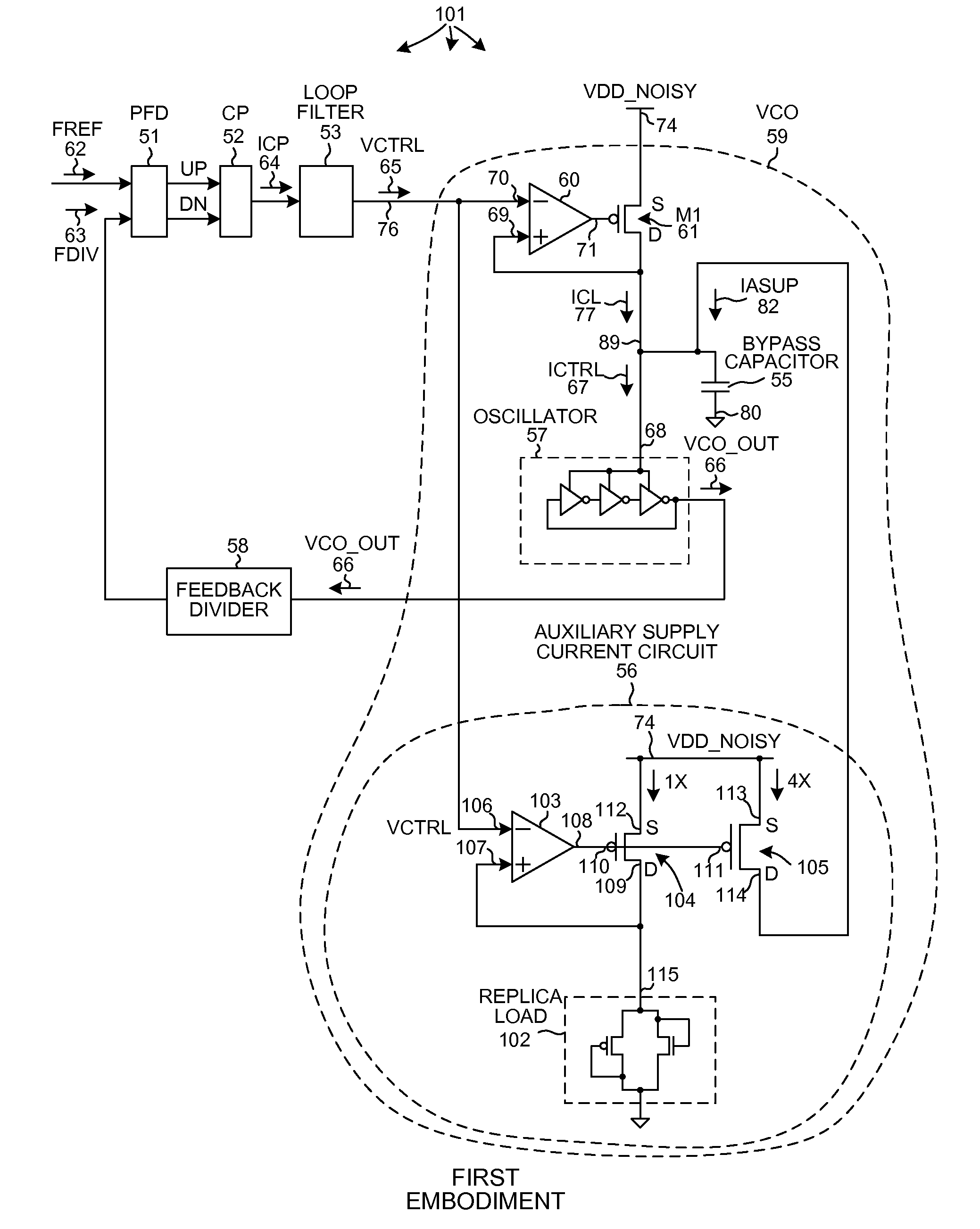

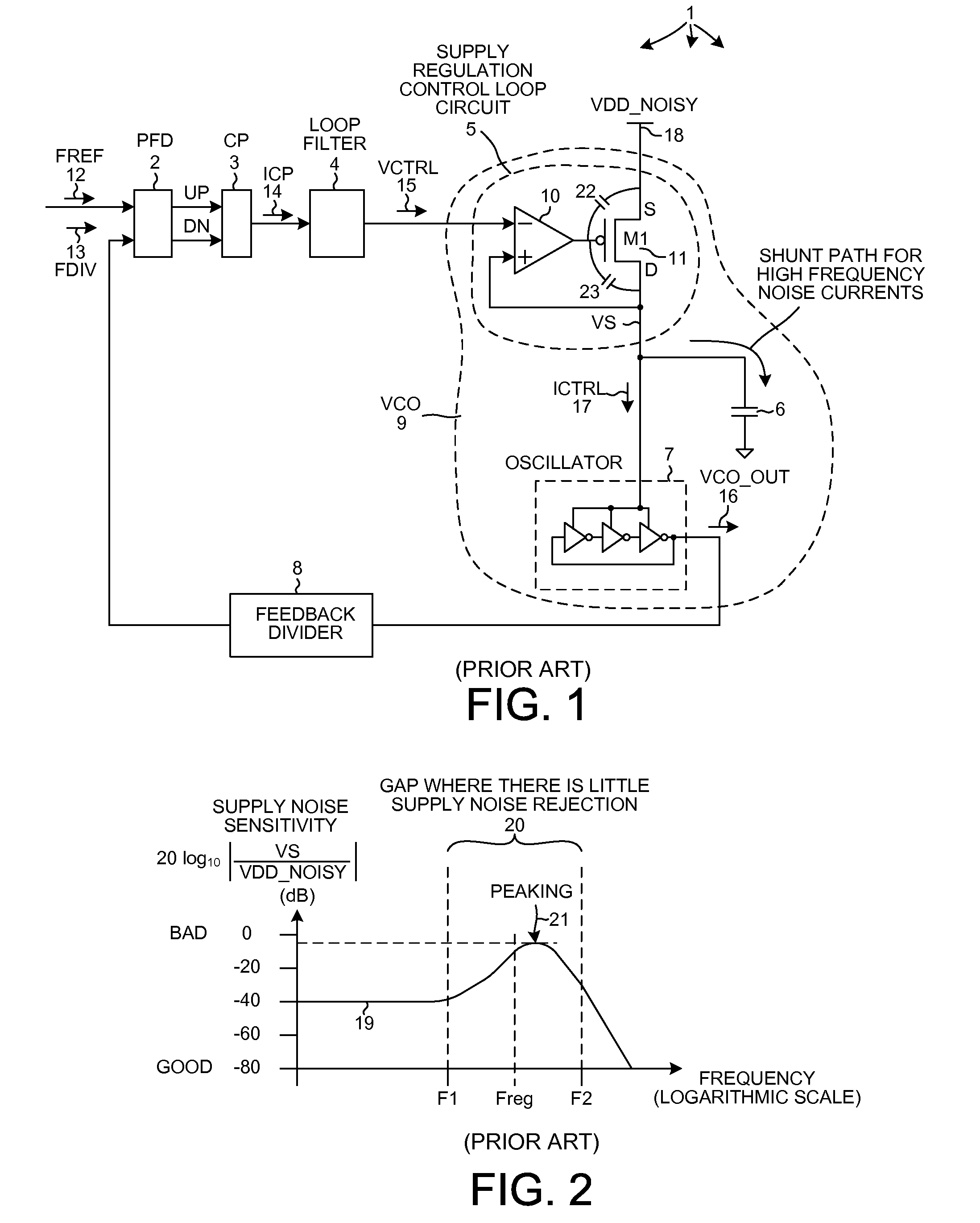

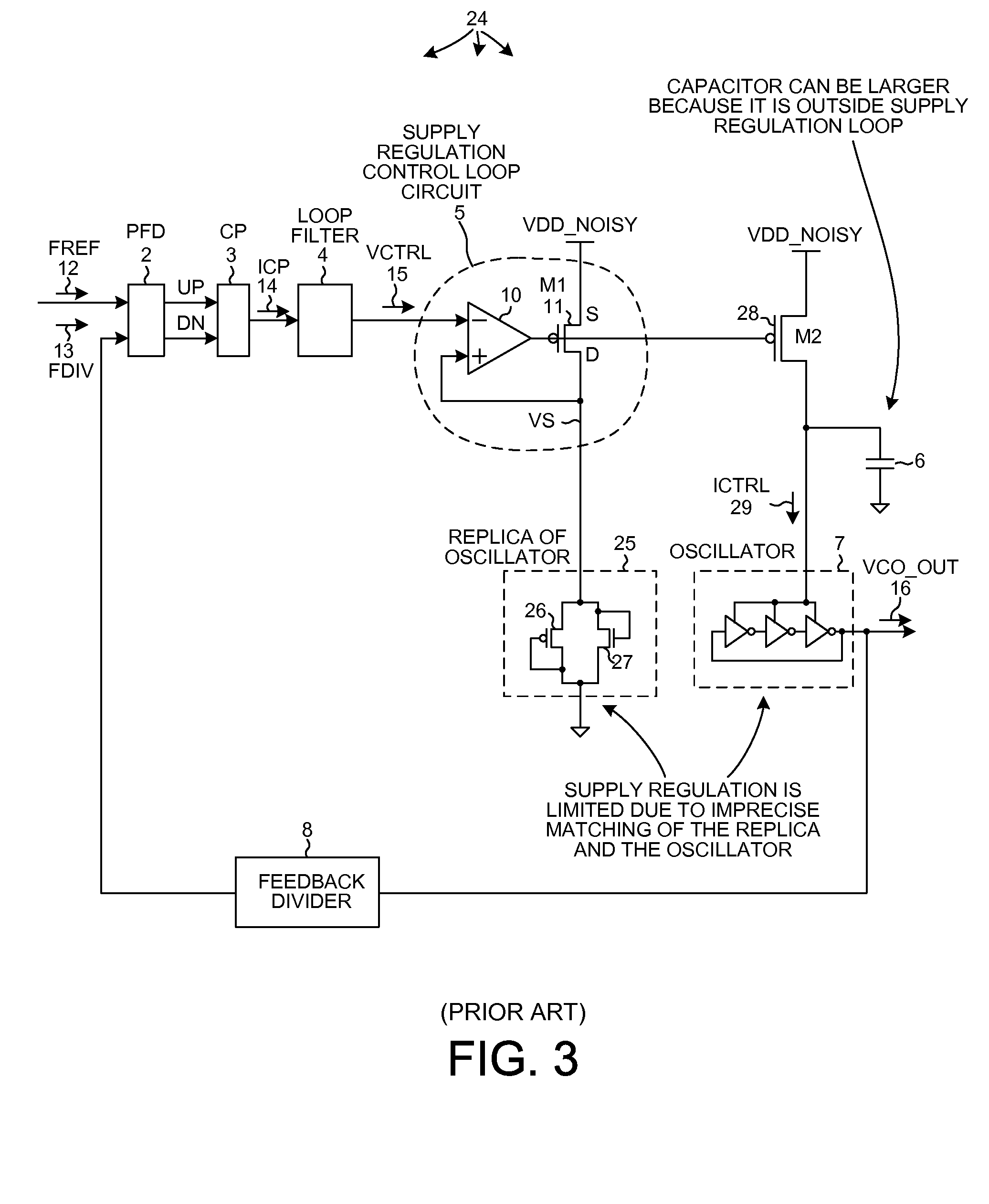

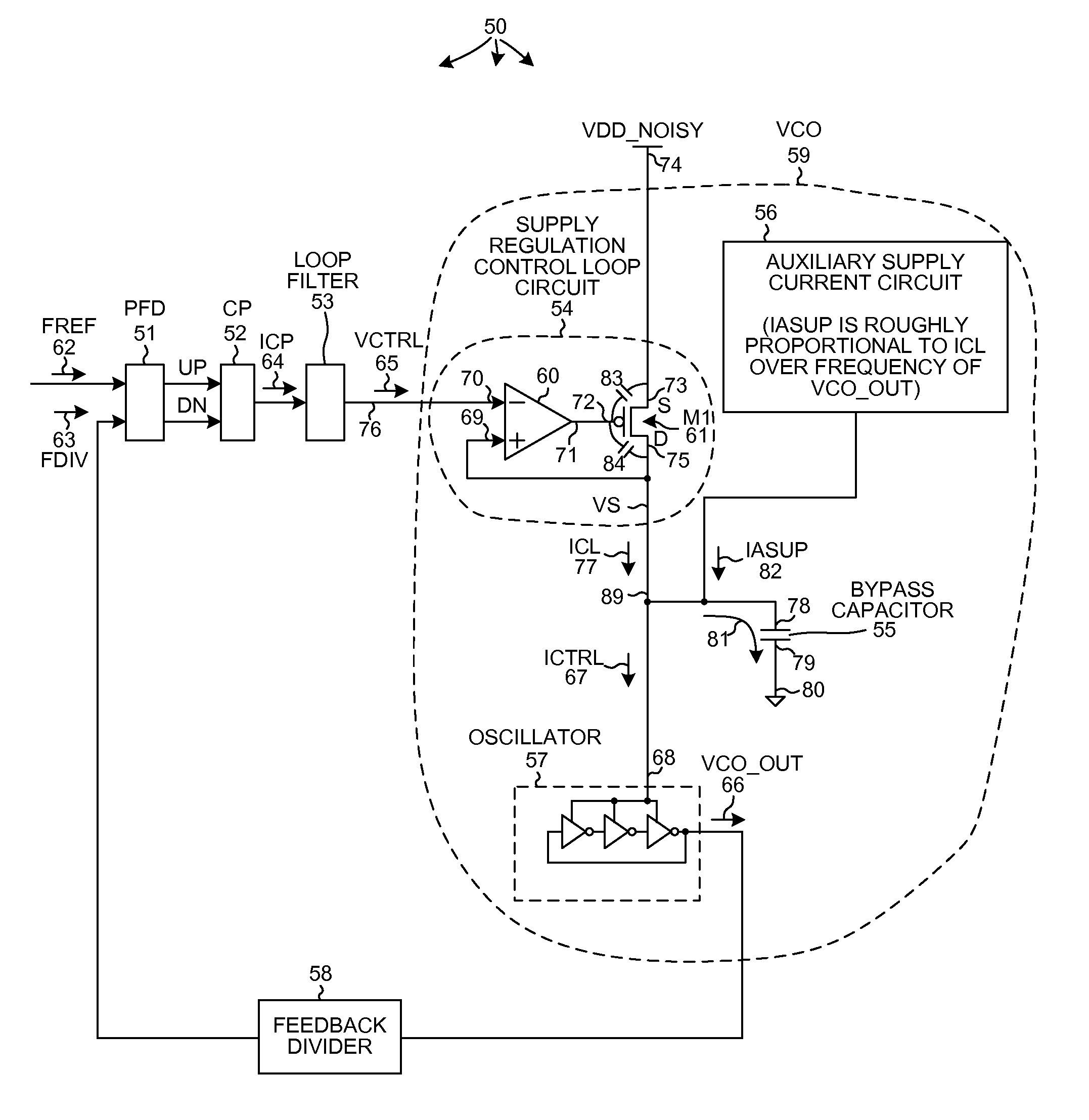

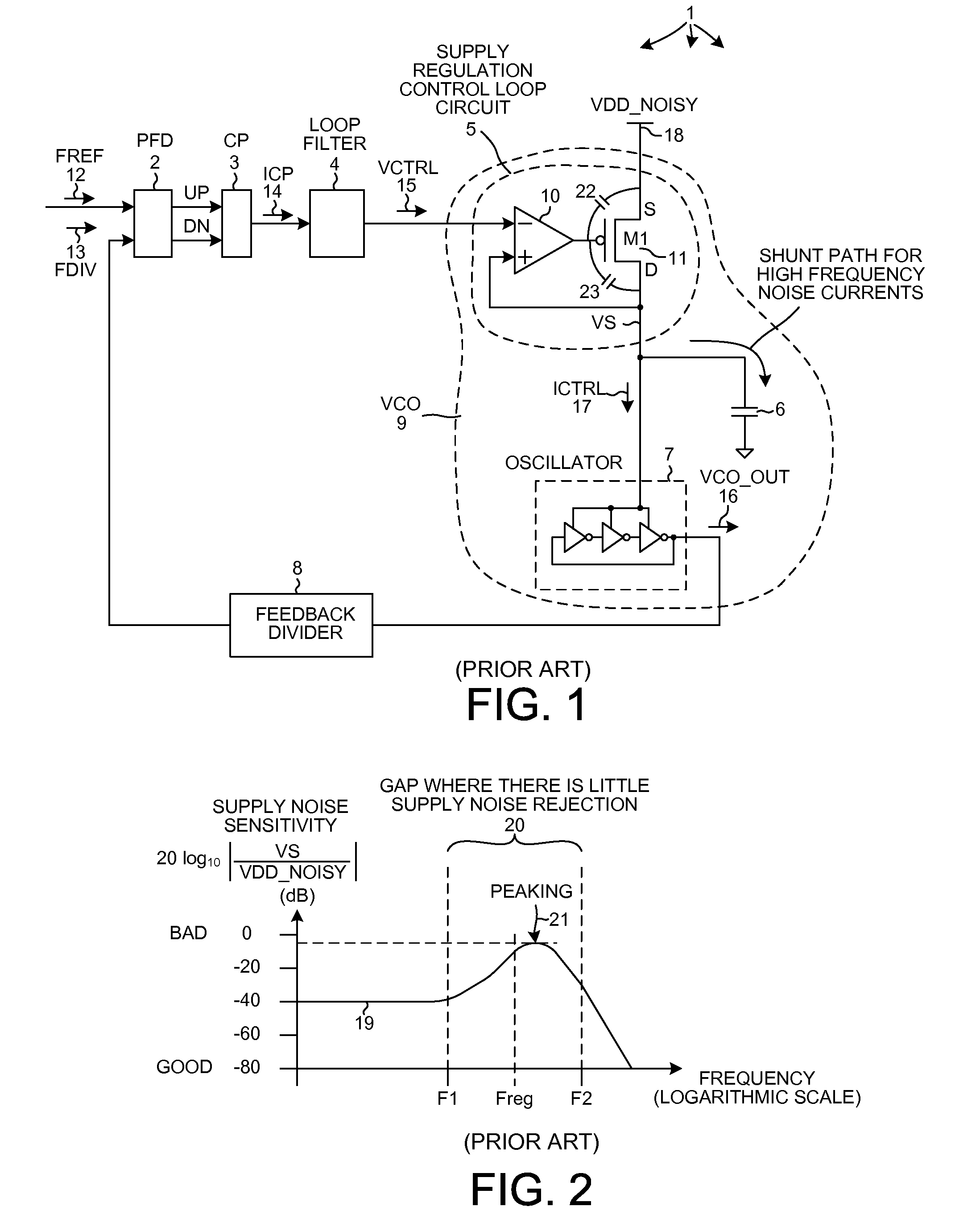

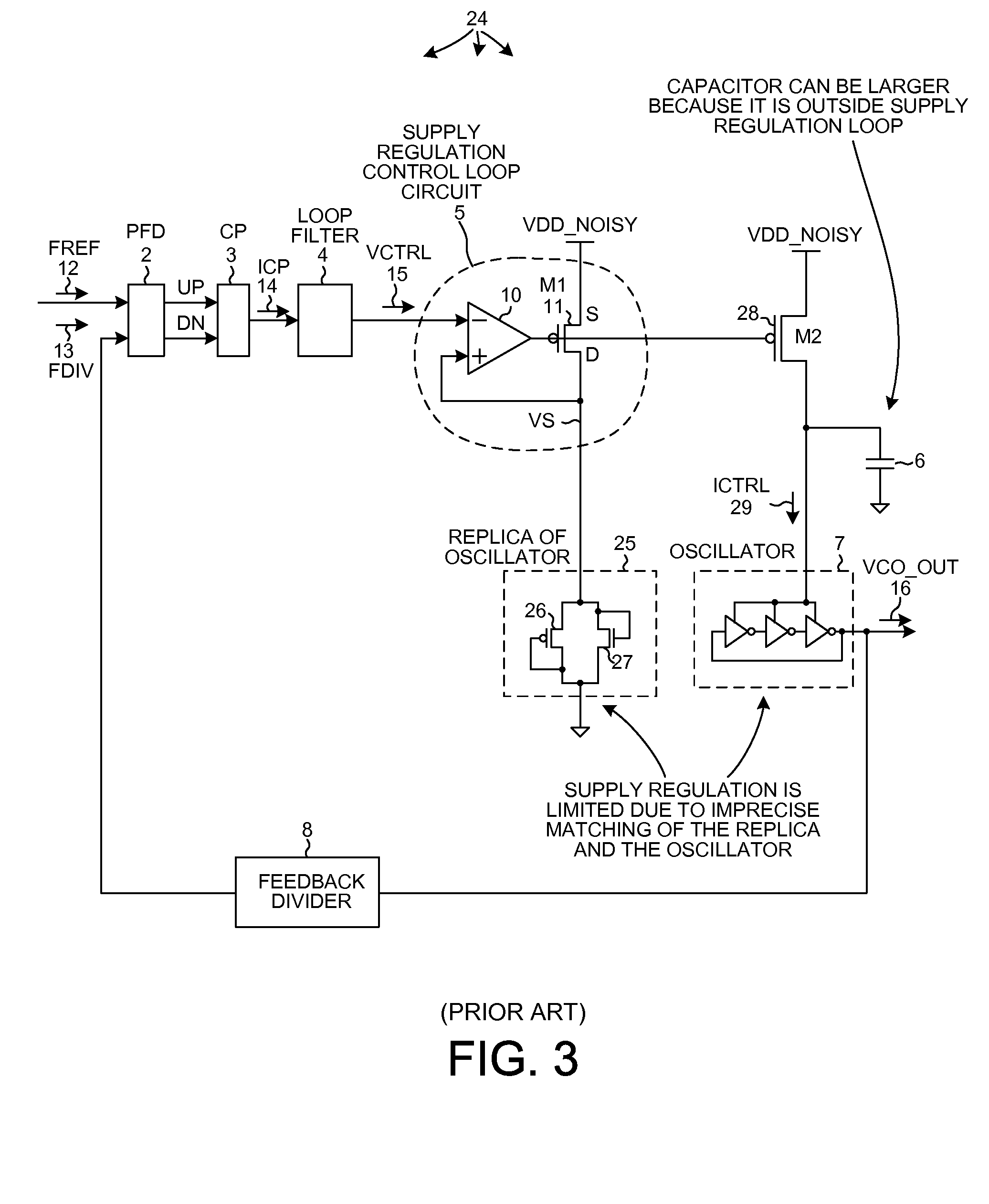

Supply-regulated vco architecture

ActiveUS20120256693A1Increase capacitanceReduce amountPulse automatic controlCapacitanceInjection locked

A supply-regulated VCO exhibits reduced or no supply sensitivity peaking. The VCO includes an oscillator whose supply current is regulated to control the oscillating frequency of the oscillator. A VCO input signal controls the supply current so that there is a relationship between the input signal and the oscillator output frequency. Power supply noise that might otherwise affect oscillator operation is shunted from a supply current input lead of the oscillator to ground by a bypass capacitor. In one example, an auxiliary circuit supplies an auxiliary supply current to the oscillator, thereby reducing the amount of supply current a supply regulation control loop circuit must supply. In another example, a supply regulation control loop circuit supplies a control current to a main oscillator, but the bypass capacitor is not coupled to this oscillator but rather is coupled to a slave oscillator that is injection locked to the main oscillator.

Owner:QUALCOMM INC

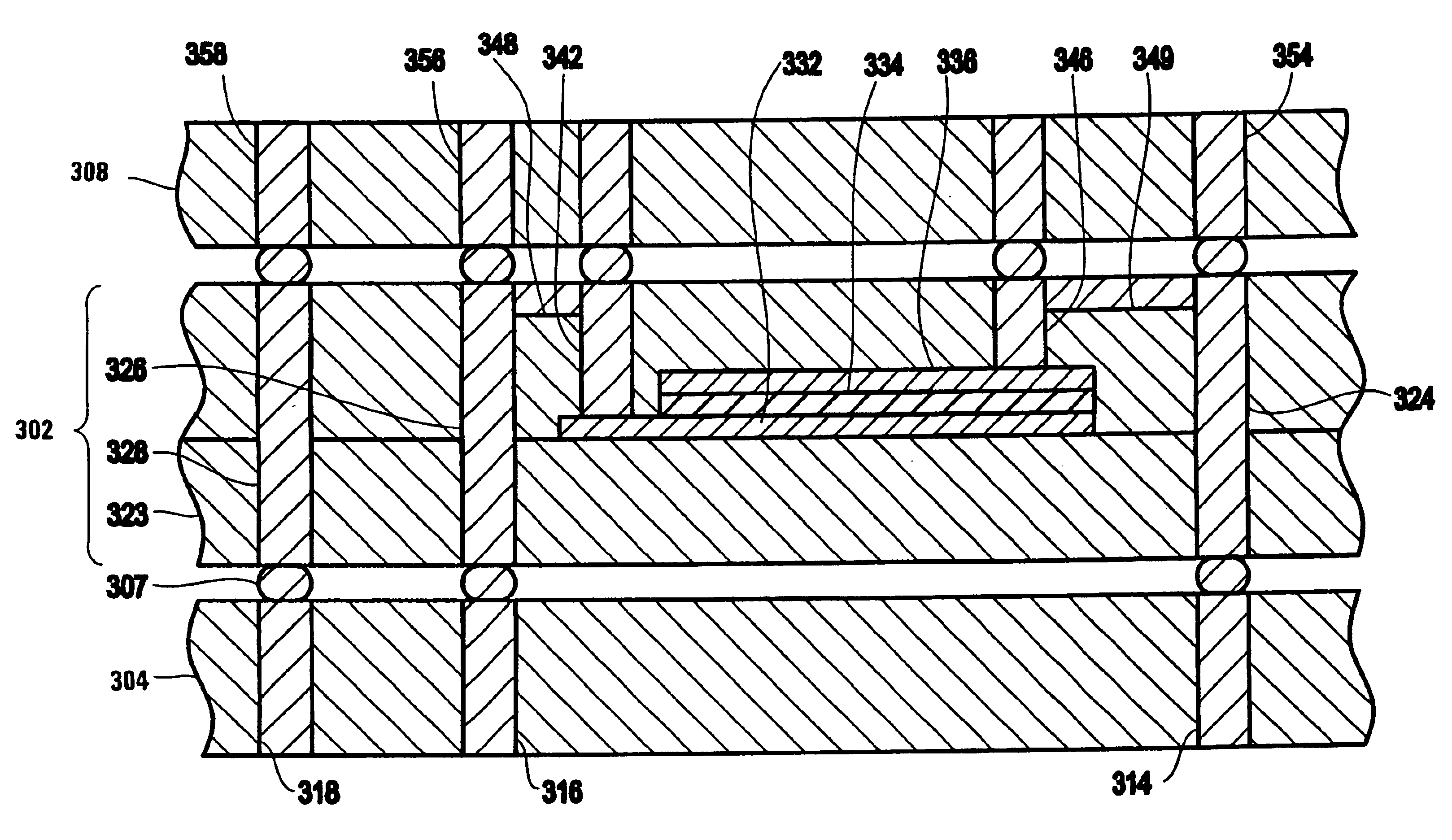

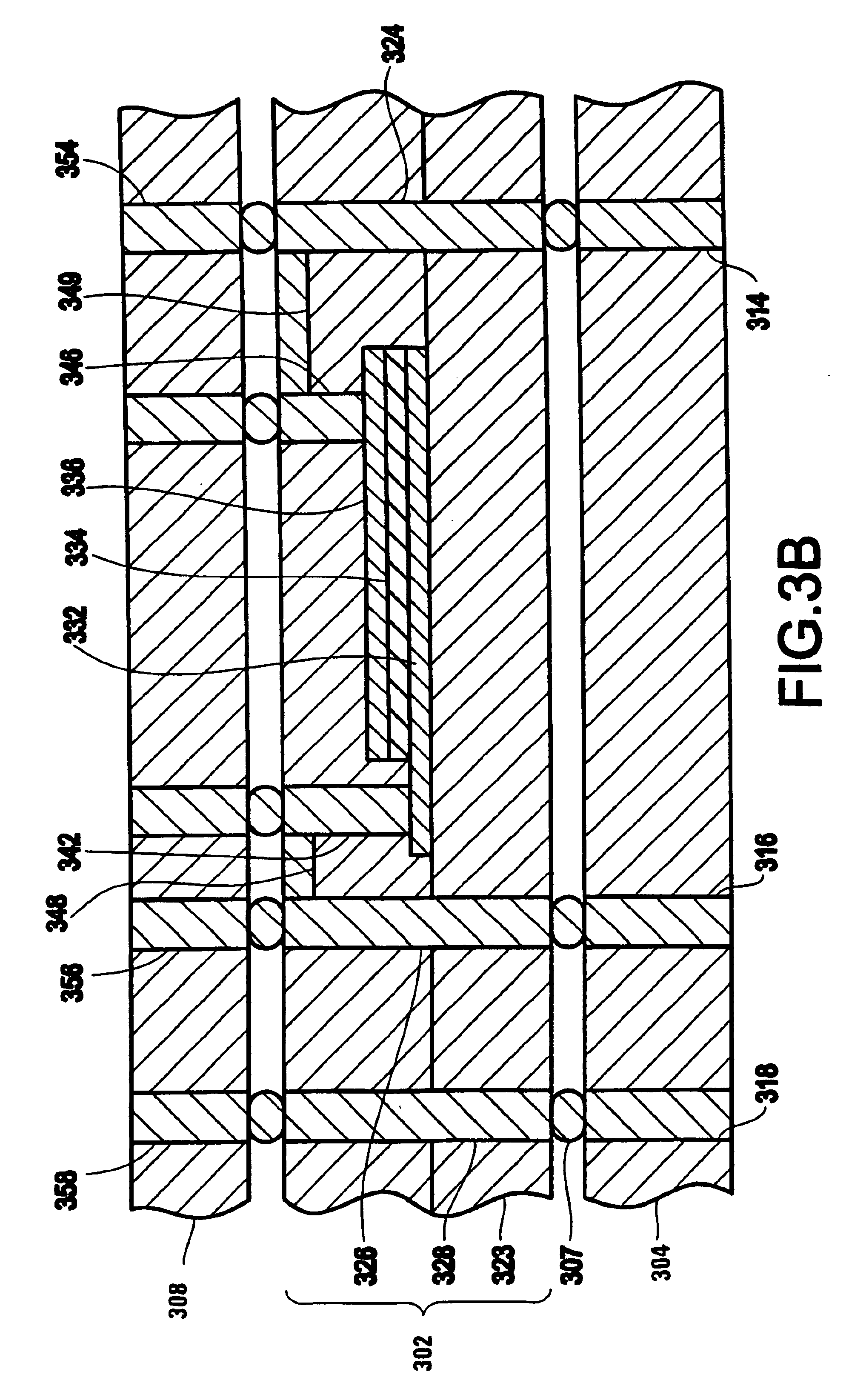

Structure and method for fabrication of a leadless chip carrier

InactiveUS6960824B1Effective coolingReduce parasitismSemiconductor/solid-state device detailsSolid-state devicesElectrical connectionEngineering

Structure and method for fabrication of a leadless chip carrier have been disclosed. A disclosed embodiment comprises a substrate having a top surface for receiving a semiconductor die. The disclosed embodiment also comprises a printed circuit board attached to a bottom surface of the substrate. The disclosed embodiment further comprises at least one via in the substrate, which provides an electrical connection between a signal bond pad of the semiconductor die and the printed circuit board. The at least one via also electrically connects a substrate bond pad and the printed circuit board. The substrate bond pad is further connected to the signal bond pad of the semiconductor die by a signal bonding wire. The at least one via further provides an electrical connection between the signal bond pad of the semiconductor die and a land that is electrically connected to the printed circuit board.

Owner:SKYWORKS SOLUTIONS INC

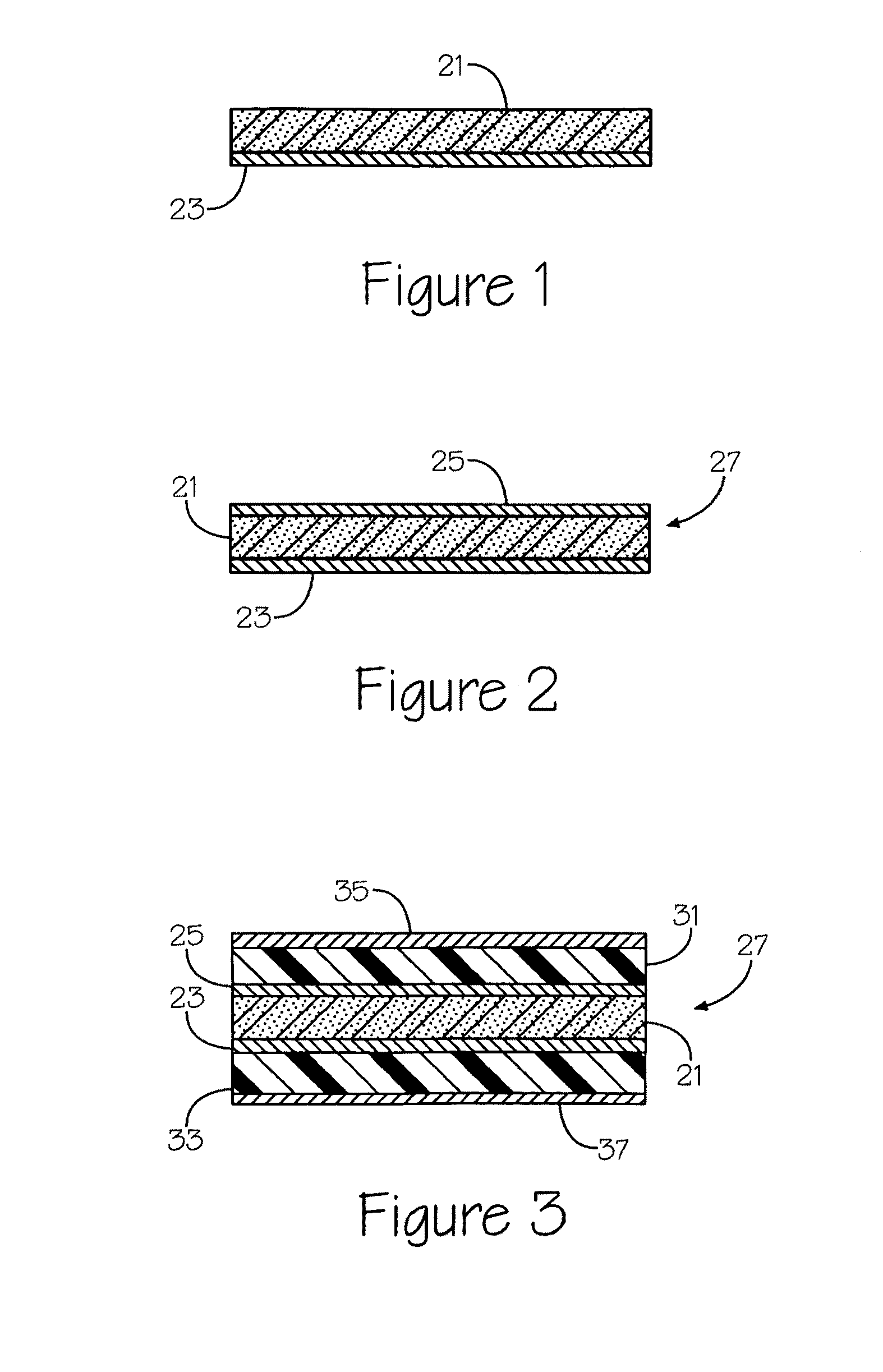

Interposer capacitor built on silicon wafer and joined to a ceramic substrate

InactiveUS6791133B2Improve performanceHigh yieldTransistorSemiconductor/solid-state device detailsLead zirconate titanateBarium strontium titanate

An interposer, located between an integrated circuit having power, ground and signal connections and a ceramic substrate having power, ground and signal connections, that includes an oxide layer formed on a polished surface of a silicon substrate, a thin film dielectric capacitor formed on the oxide layer, a plurality of metallized that electrically connect to either of the electrodes of the thin film dielectric capacitor, and vias than conduct power, ground and signals between a the ceramic substrate and the integrated circuit. The interposer connects the metallized vias to the integrated circuit by solder connections and also connects the vias conducting power, ground and signals from the ceramic substrate to the interposer by solder connections. The dielectric of the thin film dielectric capacitor may be selected from the group of high-K titanates, such as, barium zirconate titanate, barium strontium titanate, pure barium titanate, barium titanate modified with Pb, Nb, W, Ca, Mg, and Zn, lead titanate, lead zirconate titanate, and polycrystalline lanthanum-modified lead zirconate titanate, or other high-K dielectrics, such as, lead niobate and its derivatives, and lead tungstate and its derivatives.

Owner:GLOBALFOUNDRIES US INC

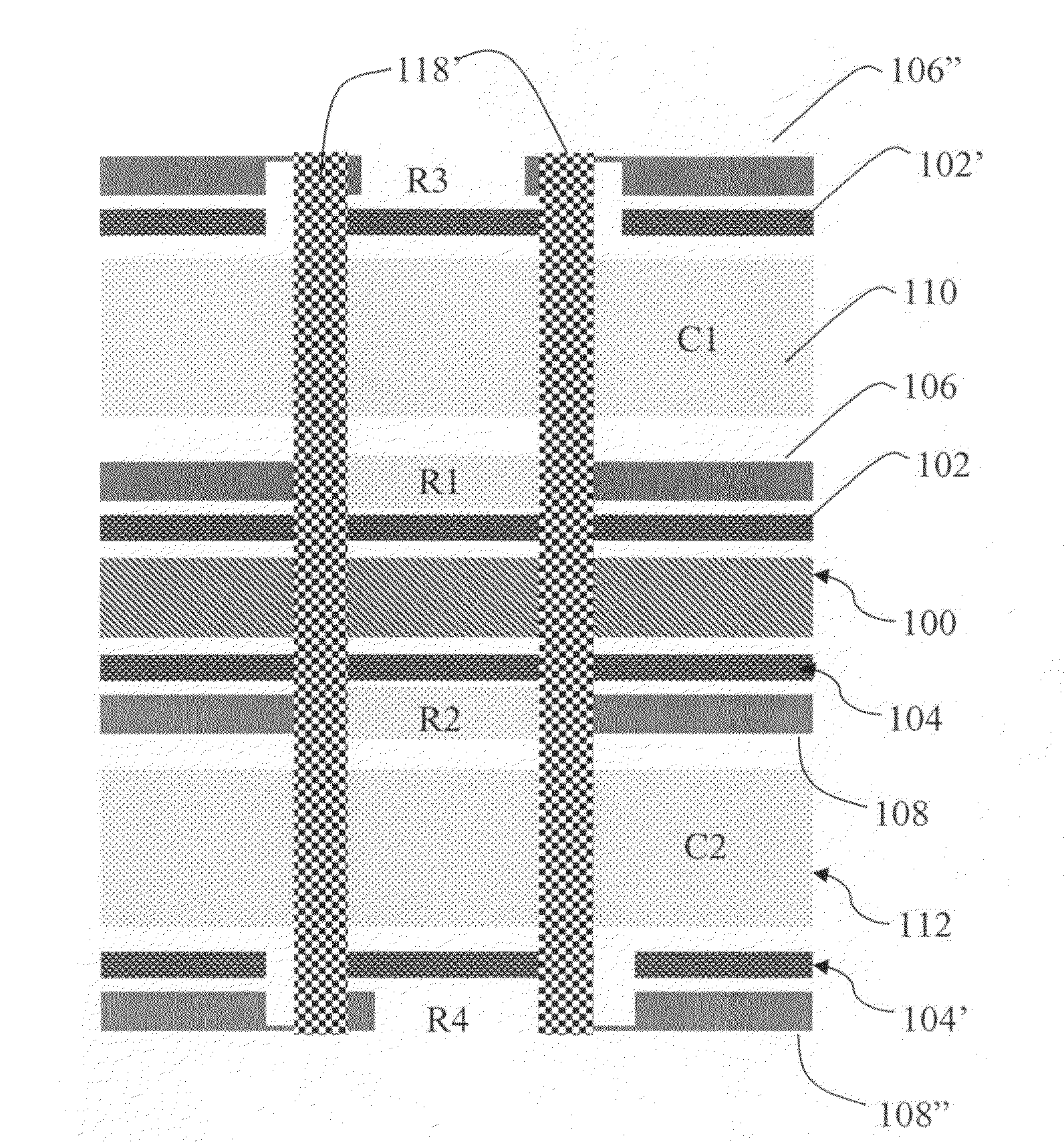

Mulit-layer embedded capacitance and resistance substrate core

InactiveUS20100060381A1Reduce inductanceReduce parasitismMultiple-port networksSolid-state devicesCapacitanceDielectric

A multi-layer imbedded capacitance and resistance substrate core. At least one layer of resistance material is provided. The layer of resistance material has a layer of electrically conductive material embedded therein. At least one layer of capacitance material of high dielectric constant is disposed on the layer of resistance material. Thru-holes are formed by laser.

Owner:TTM TECH NORTH AMERICA LLC

Supply-regulated VCO architecture

ActiveUS8362848B2Reduce amountReduce peakPulse automatic controlGenerator stabilizationCapacitanceInjection locked

A supply-regulated VCO exhibits reduced or no supply sensitivity peaking. The VCO includes an oscillator whose supply current is regulated to control the oscillating frequency of the oscillator. A VCO input signal controls the supply current so that there is a relationship between the input signal and the oscillator output frequency. Power supply noise that might otherwise affect oscillator operation is shunted from a supply current input lead of the oscillator to ground by a bypass capacitor. In one example, an auxiliary circuit supplies an auxiliary supply current to the oscillator, thereby reducing the amount of supply current a supply regulation control loop circuit must supply. In another example, a supply regulation control loop circuit supplies a control current to a main oscillator, but the bypass capacitor is not coupled to this oscillator but rather is coupled to a slave oscillator that is injection locked to the main oscillator.

Owner:QUALCOMM INC

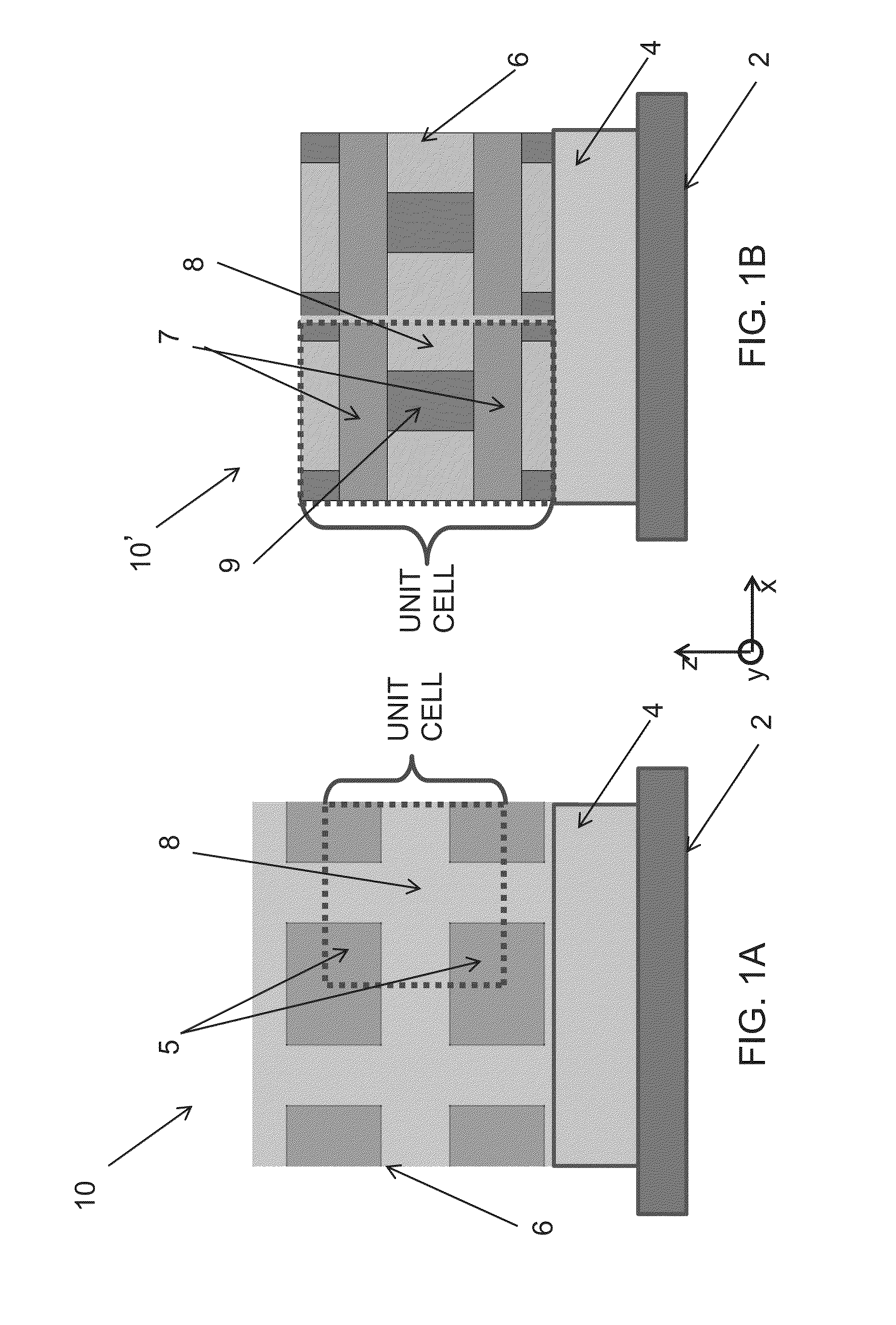

Acoustic bandgap structures for integration of MEMS resonators

ActiveUS20150237423A1Reduce constraintsReduce parasitismMicrophonesTransducer detailsResonant cavityAcoustics

Example acoustic bandgap devices provided that can be fabricated in a semiconductor fabrication tool based on design check rules. An example device includes a substrate lying in an x-y plane and defining an x-direction and a y-direction, an acoustic resonant cavity over the substrate, and a phononic crystal disposed over the acoustic resonant cavity by generating the phononic crystal as a plurality of unit cells disposed in a periodic arrangement. Each unit cell include: (a) at least one higher acoustic impedance structure having a longitudinal axis oriented in the y-direction and a thickness in the x-direction greater than or about equal to a minimal feature thickness of the semiconductor fabrication tool, and (b) at least one lower acoustic impedance material bordering at least a portion of the at least one higher acoustic impedance structure and forming at least a portion of a remainder of the respective unit cell.

Owner:MASSACHUSETTS INST OF TECH

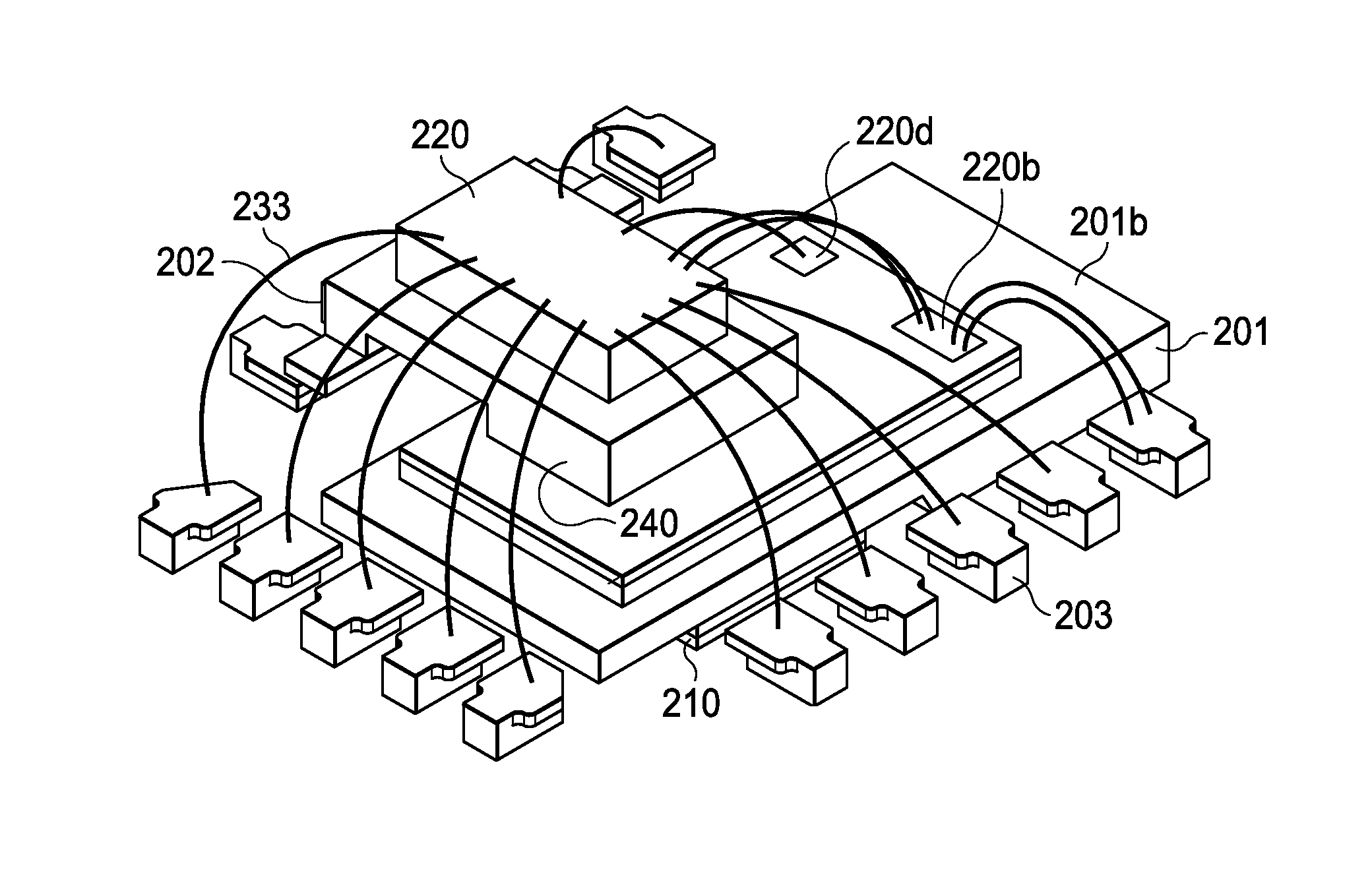

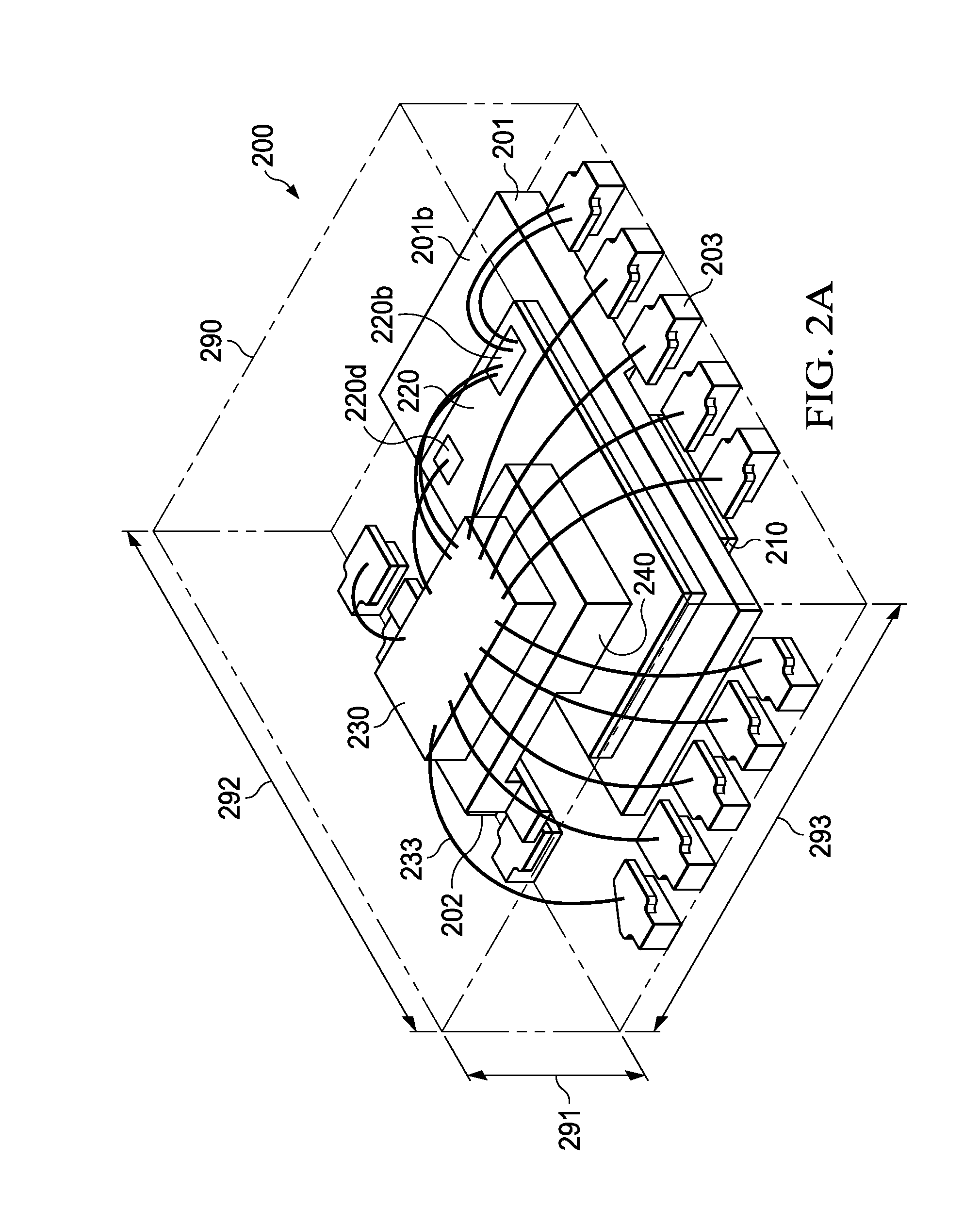

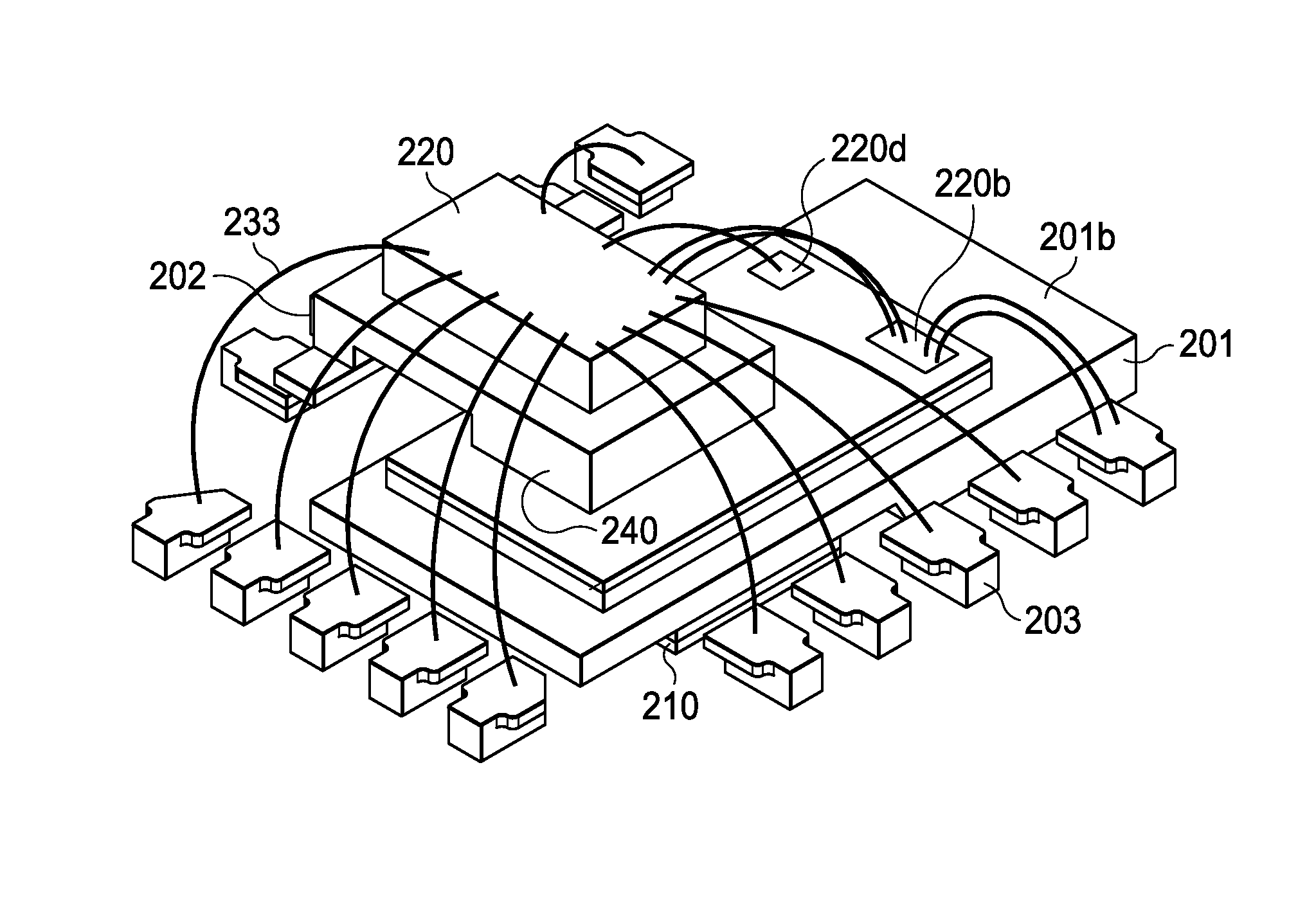

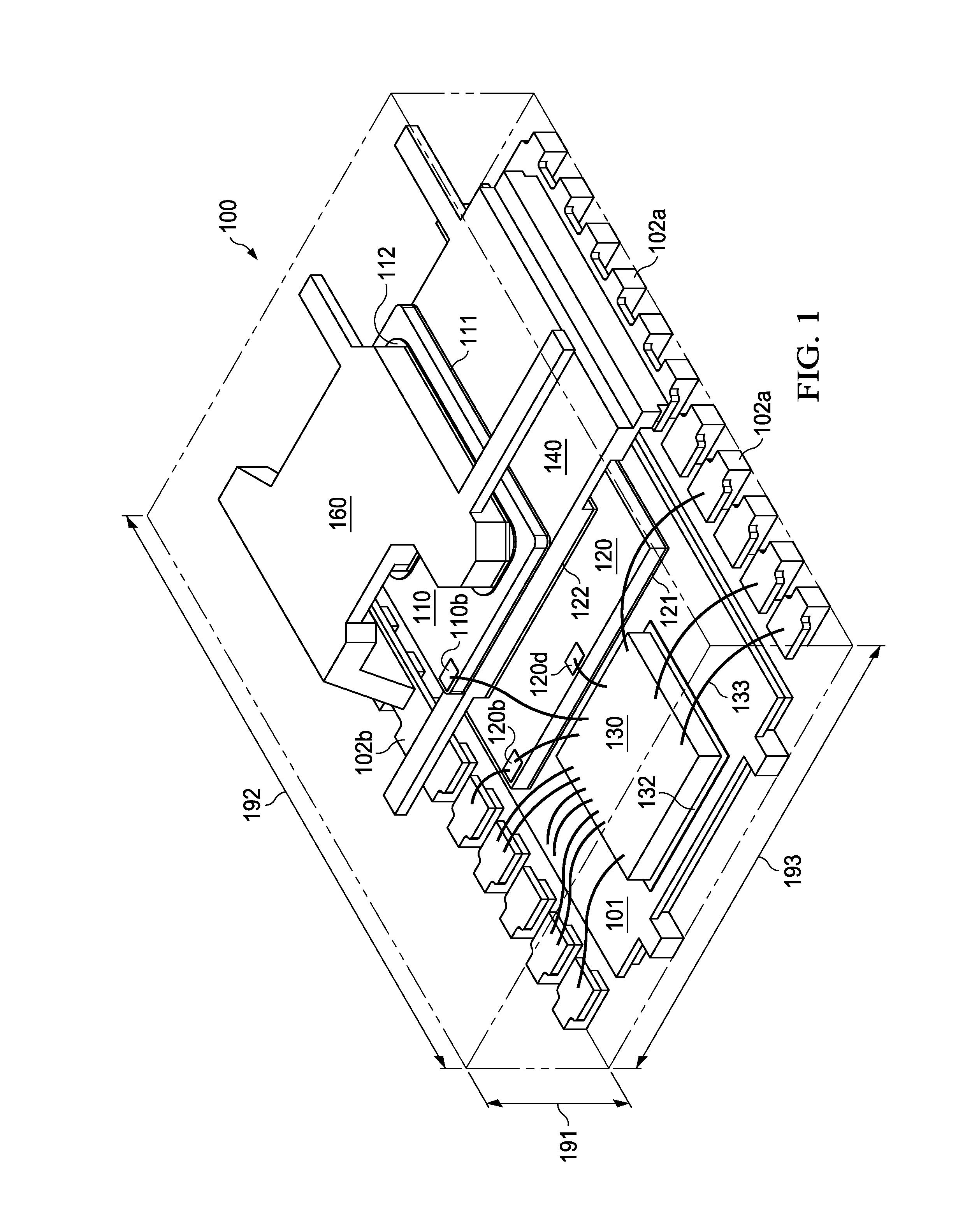

Stacked Synchronous Buck Converter Having Chip Embedded in Outside Recess of Leadframe

ActiveUS20150221584A1Reduce the overall heightLow powerSemiconductor/solid-state device detailsSolid-state devicesBuck converterSemiconductor chip

A power supply system (200) has a QFN leadframe with leads and a pad (201, switch node terminal); a pad surface having a portion recessed with a depth (270) and an outline suitable for attaching a semiconductor chip. A first FET chip (220) is vertically stacked to the opposite pad surface. A clip (240) is vertically stacked on the first FET chip and tied to a lead (202, grounded output terminal). A second FET chip (210) has its source terminal attached to the recessed portion and its drain (210a, input terminal) and gate (210b) terminals co-planar with the un-recessed portion. A driver-and-controller chip (230) is attached to the clip. Packaging compound (290) encapsulates the parts but leaves a pad surface and the drain and gate terminals of the second FET chip un-encapsulated.

Owner:TEXAS INSTR INC

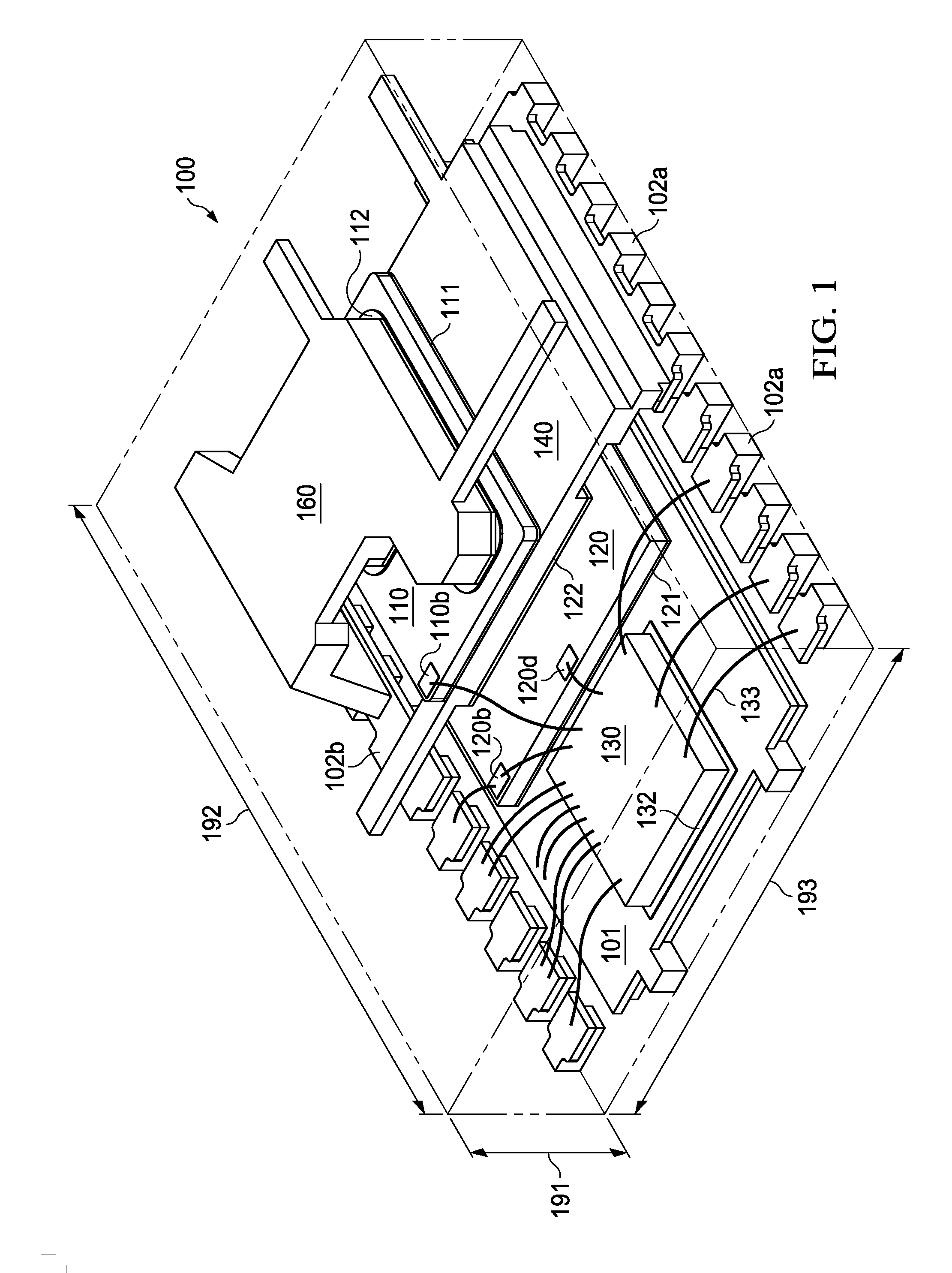

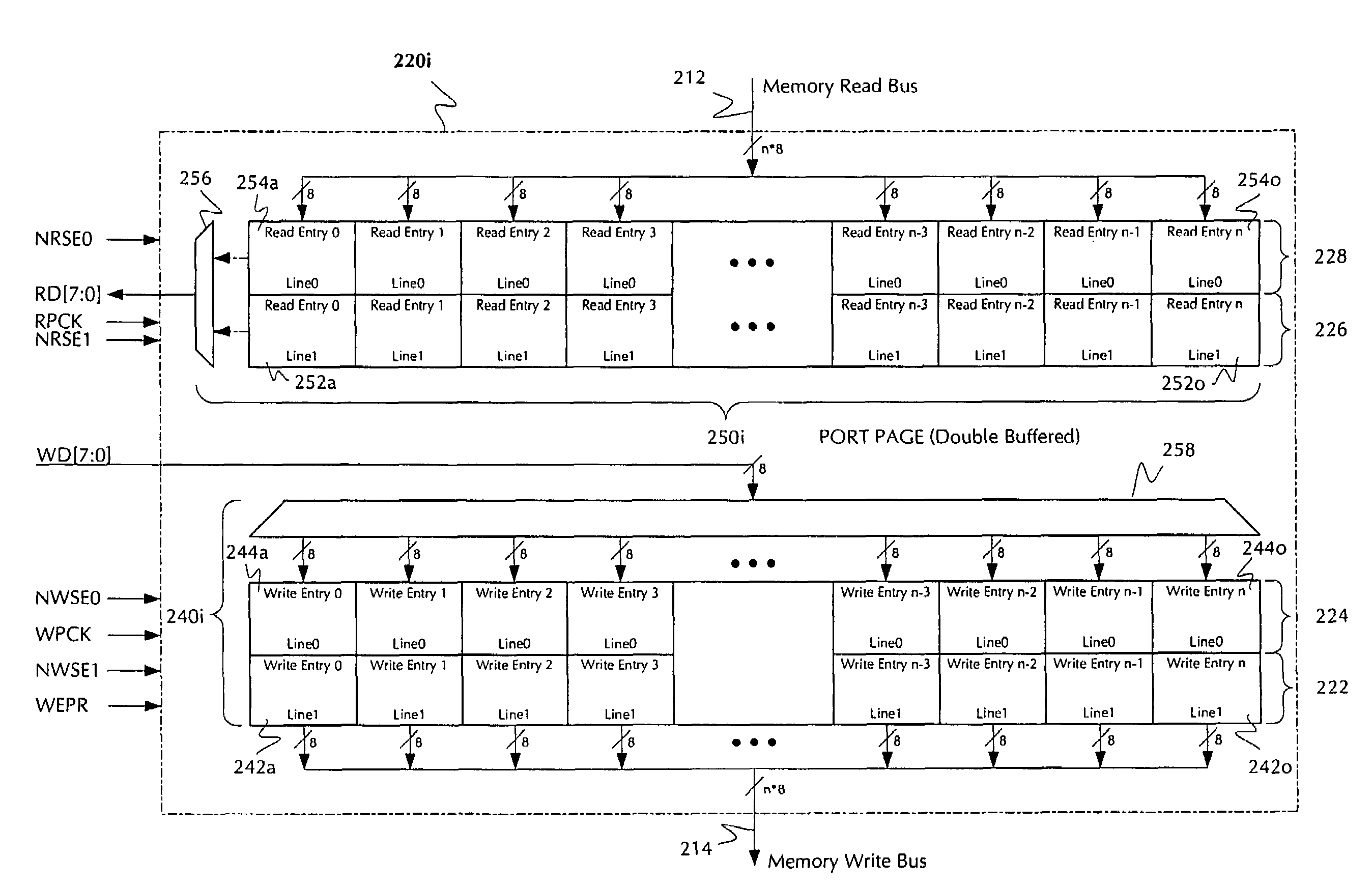

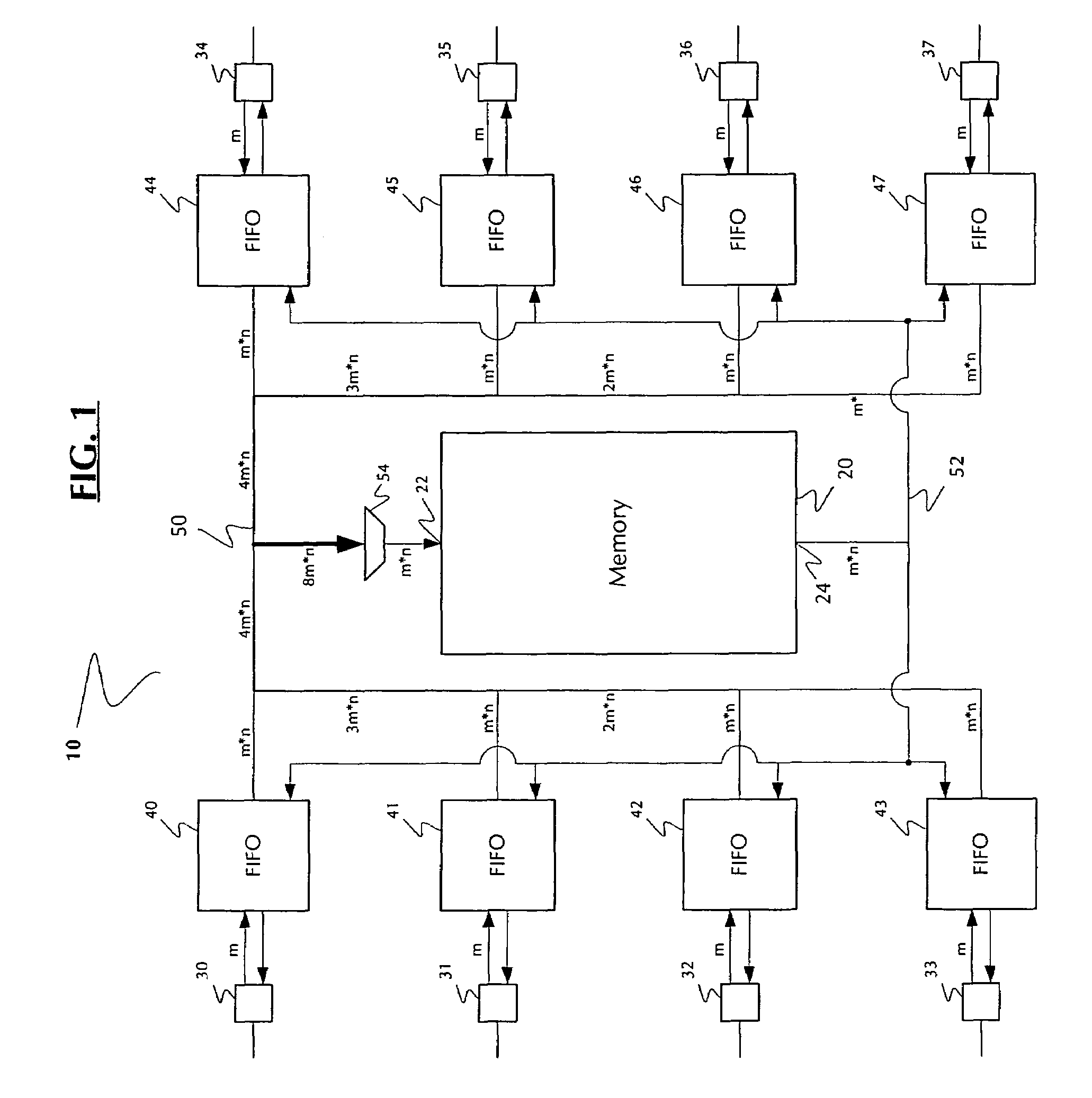

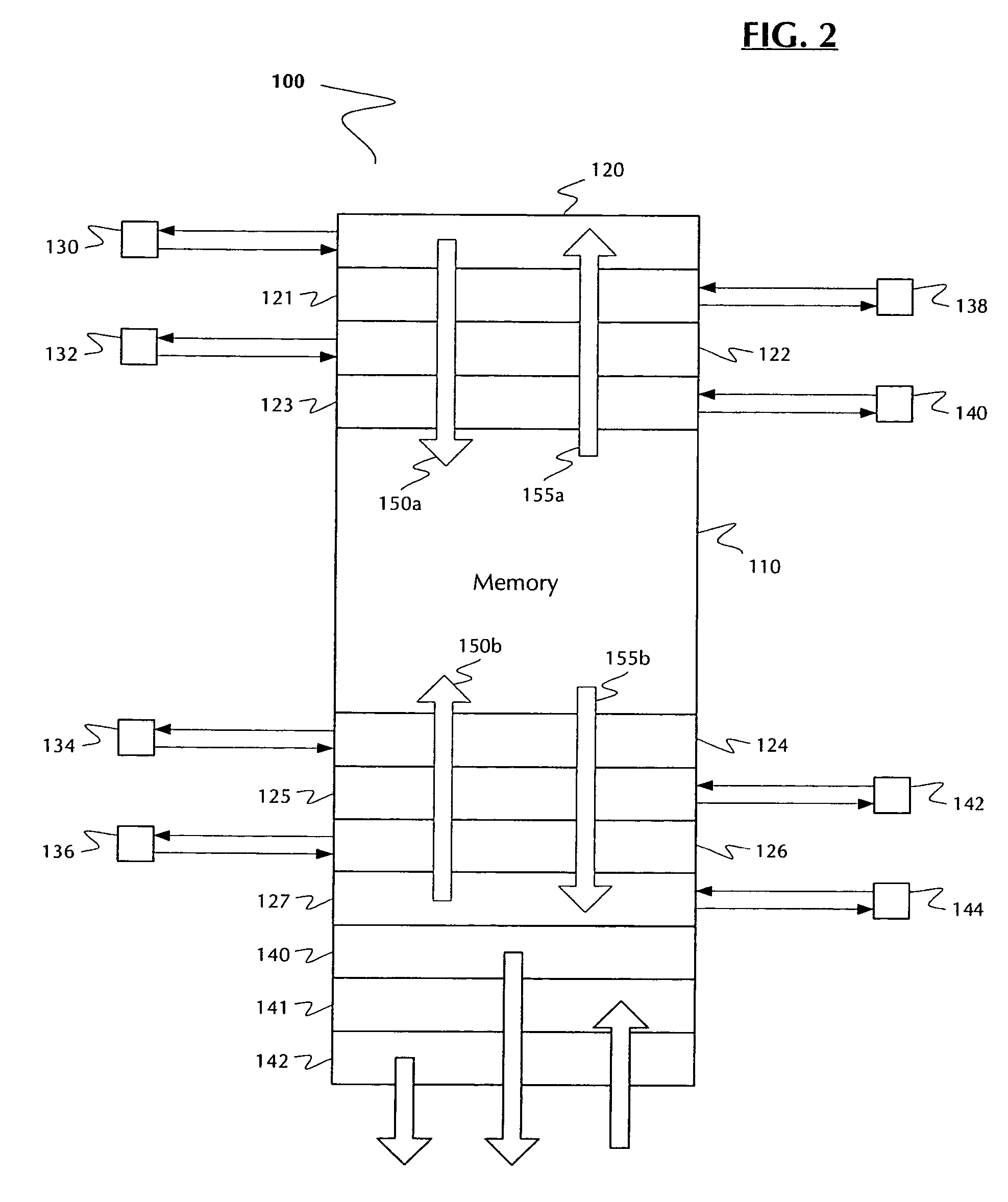

Multiport memory architecture, devices and systems including the same, and methods of using the same

A multiport memory architecture, systems including the same and methods for using the same. The architecture generally includes (a) a memory array; (b) a plurality of ports configured to receive and / or transmit data; and (c) a plurality of port buffers, each of which is configured to transmit the data to and / or receive the data from one or more of the ports, and all of which are configured to (i) transmit the data to the memory array on a first common bus and (ii) receive the data from the memory array on a second common bus. The systems generally include those that embody one or more of the inventive concepts disclosed herein. The methods generally relate to writing blocks of data to, reading blocks of data from, and / or transferring blocks of data across a memory. The present invention advantageously reduces latency in data communications, particularly in network switches, by tightly coupling port buffers to the main memory and advantageously using point-to-point communications over long segments of the memory read and write paths, thereby reducing routing congestion and enabling the elimination of a FIFO. The invention advantageously shrinks chip size and provides increased data transmission rates and throughput, and in preferred embodiments, reduced resistance and / or capacitance in the memory read and write busses.

Owner:MARVELL ASIA PTE LTD

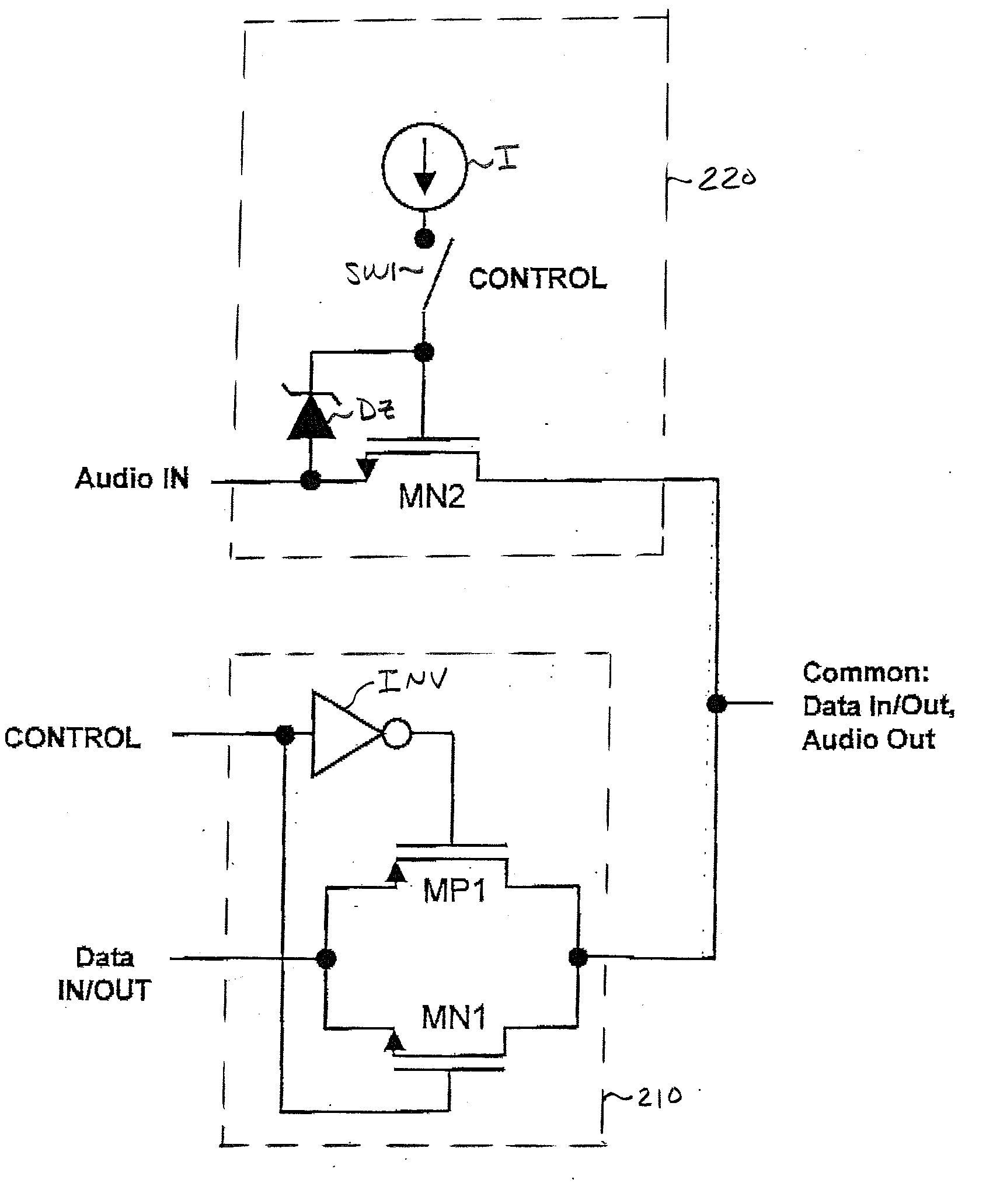

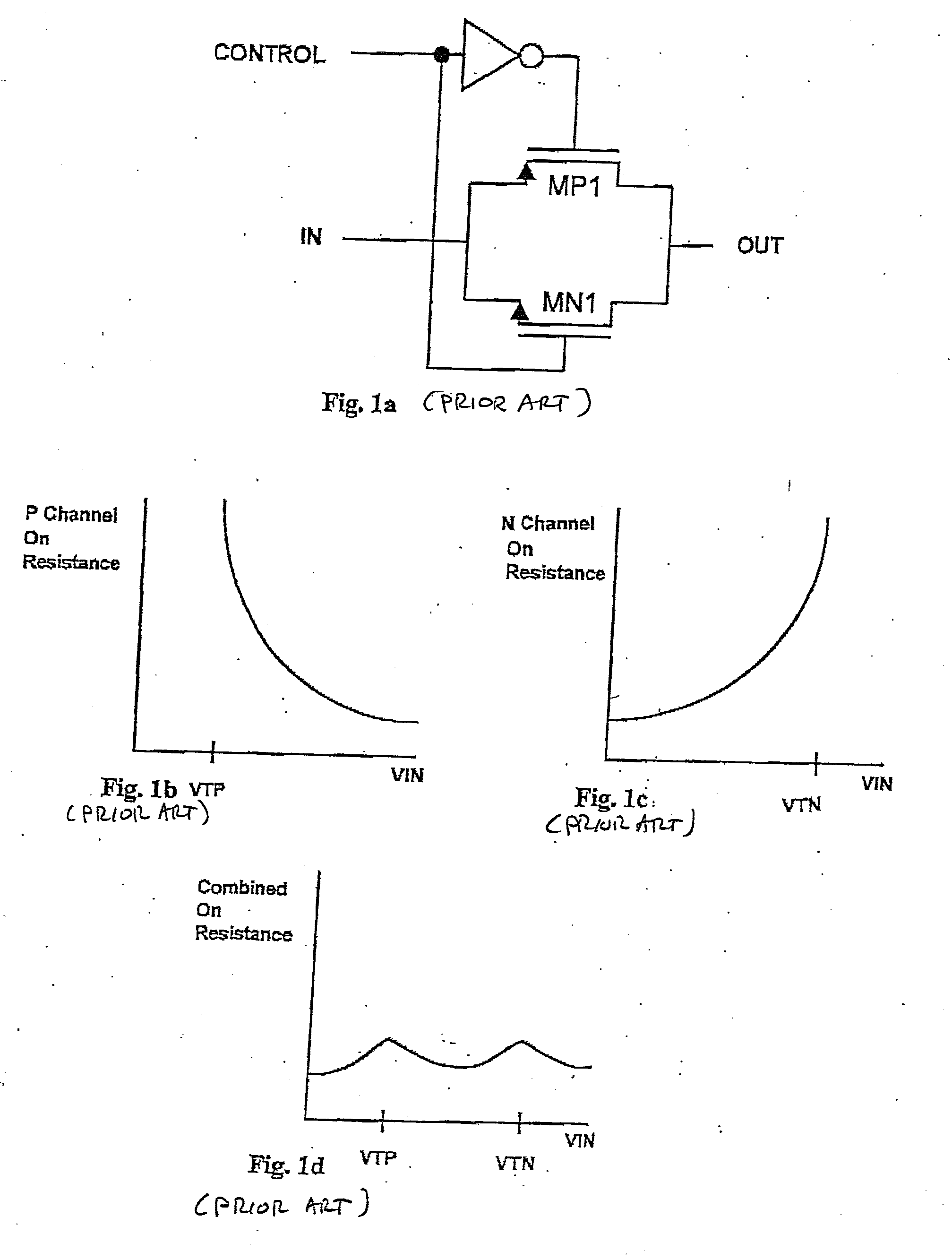

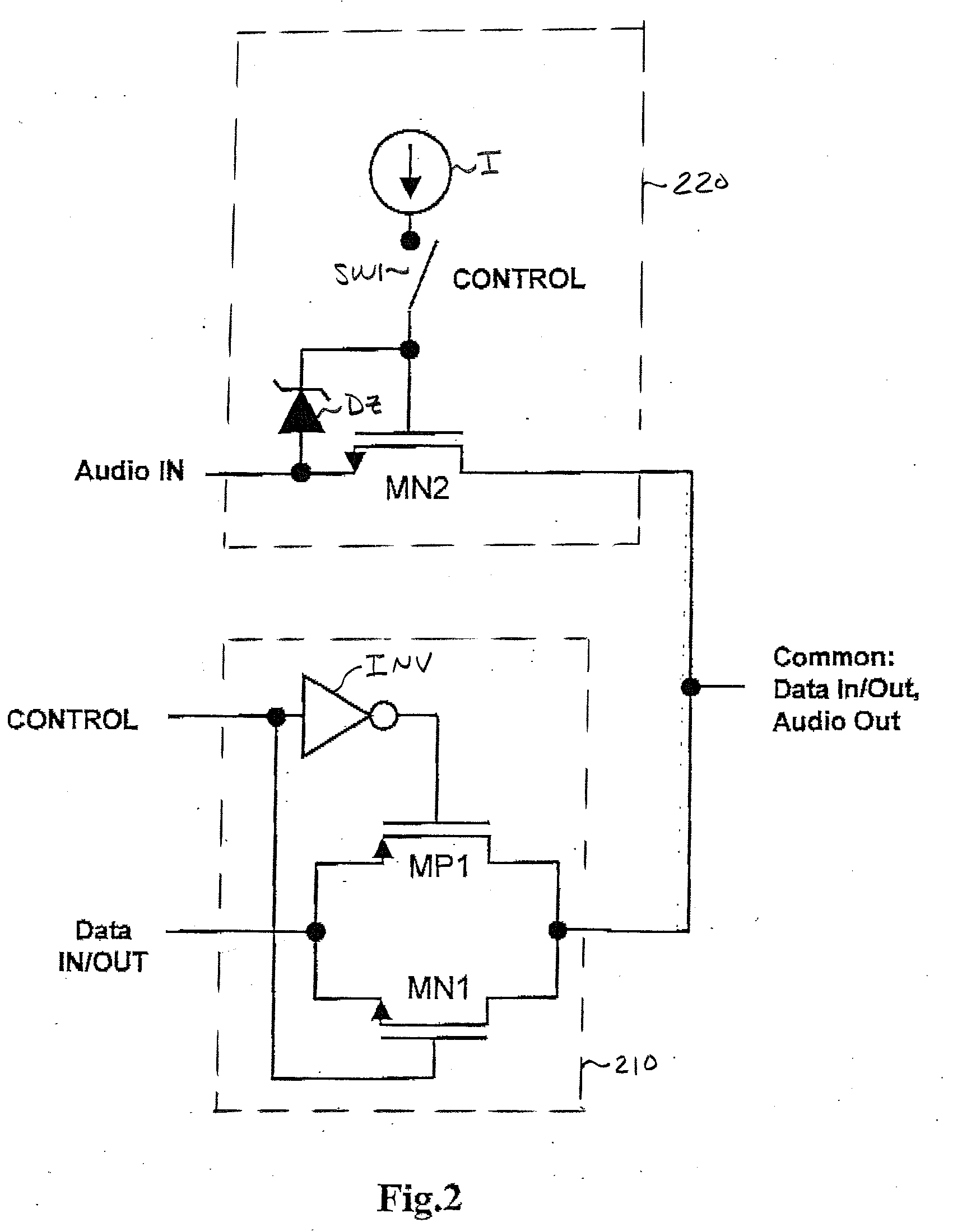

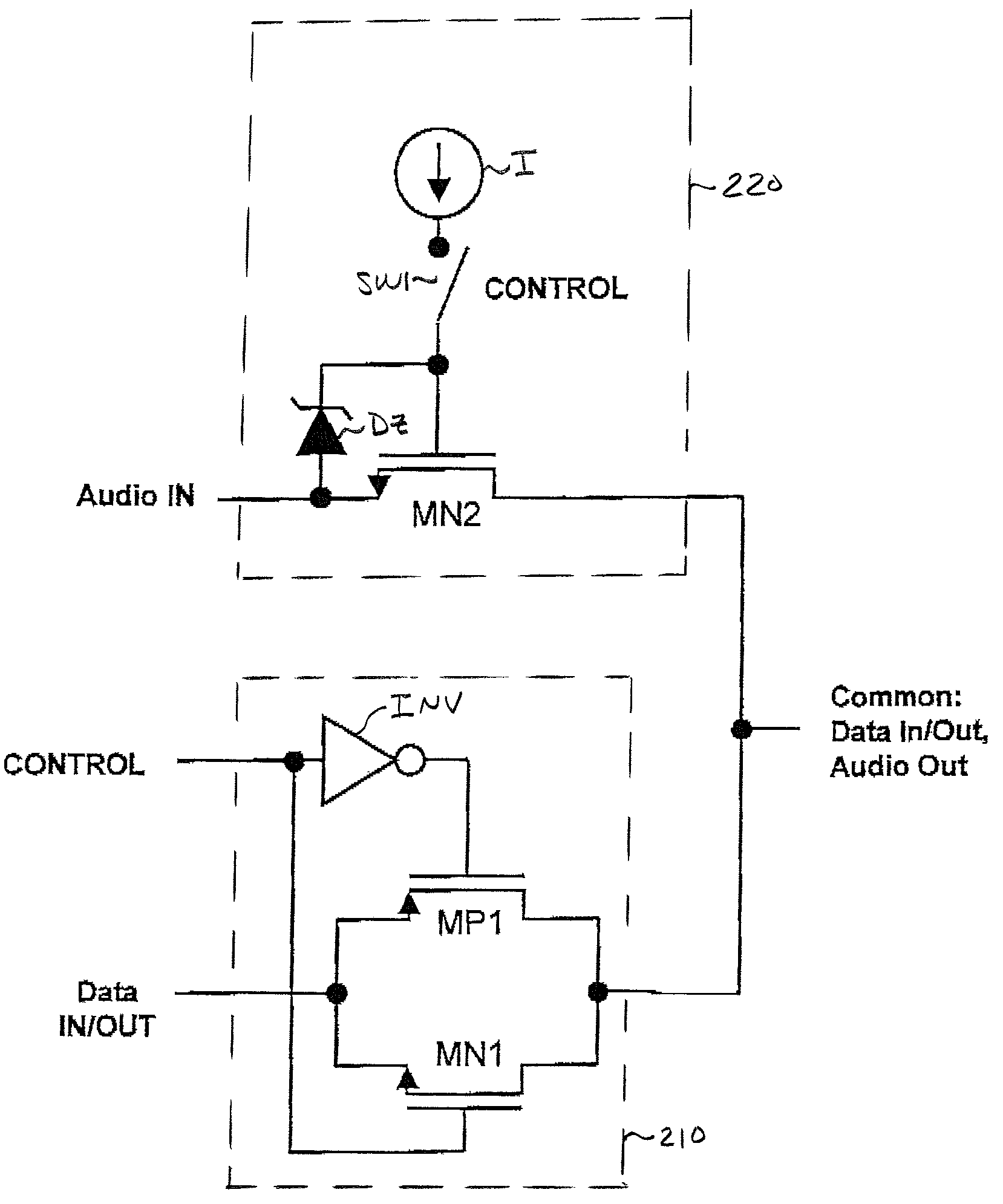

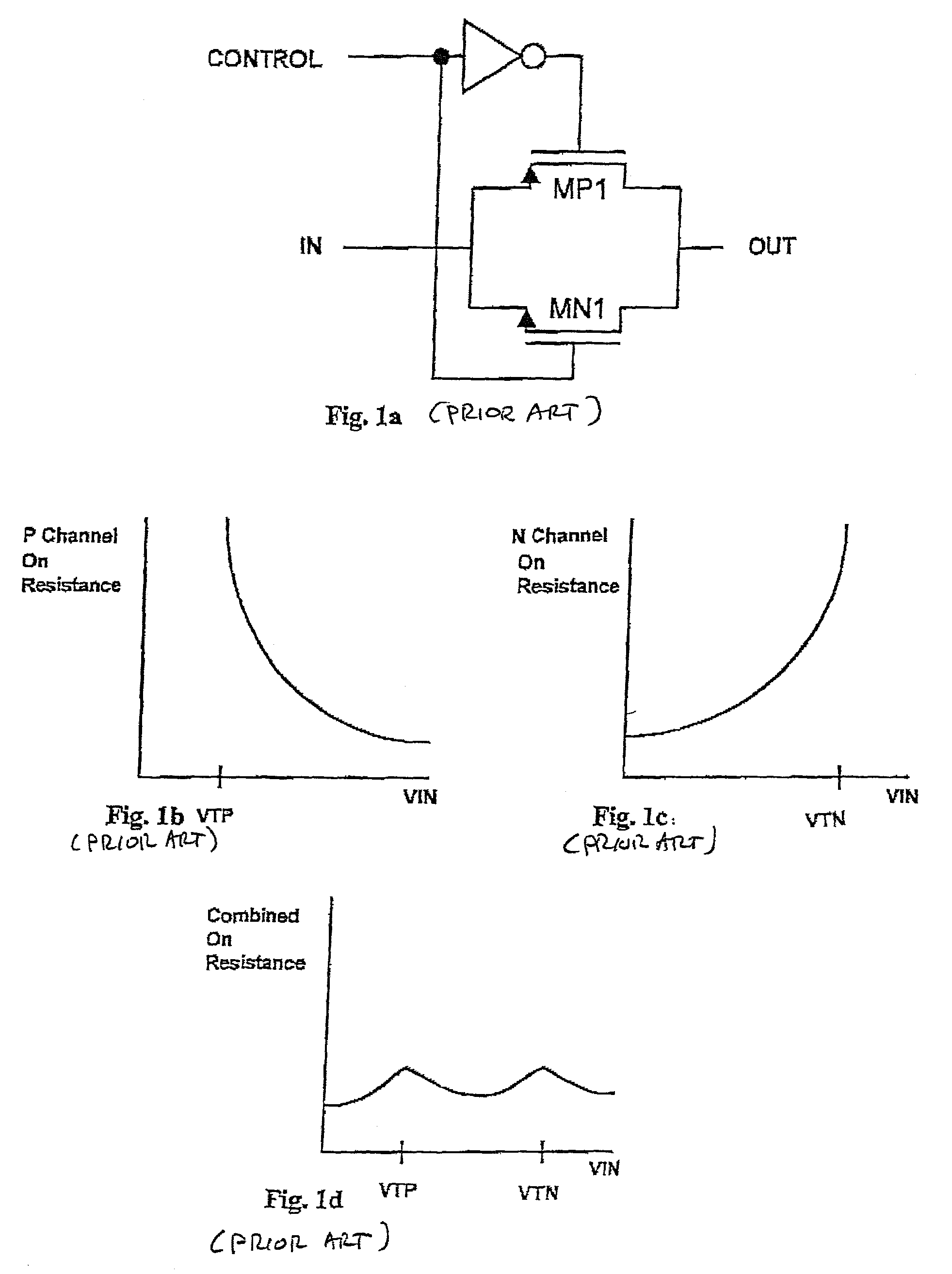

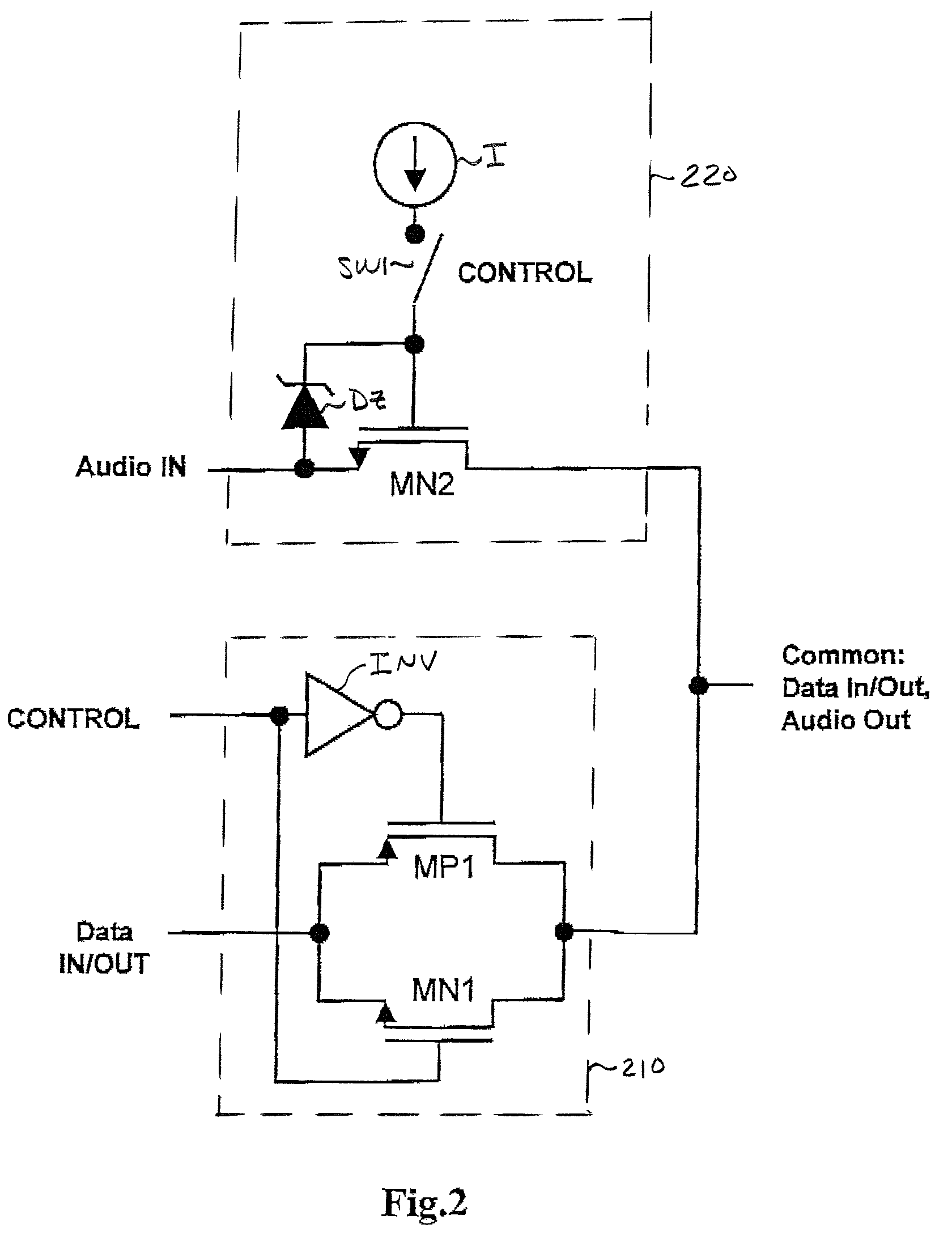

Method And Apparatus For Switching Audio And Data Signals Through A Single Terminal

ActiveUS20070132501A1Minimal distortionIncrease the areaTransistorElectronic switchingDigital dataMOSFET

A MOSFET-based, multi signal-switching circuit controllably passes analog / audio signals and digital signals through a common terminal to a single connector. Analog / audio signals are coupled through a single N-channel MOSFET analog signal switch which, when turned-ON, minimizes distortion of the analog / audio signal and capacitive loading to an adjacent, MOS-based or CMOS-based digital data signal switch. A respective turn-OFF circuit maintains its associated switch MOSFET turned OFF.

Owner:INTERSIL INC

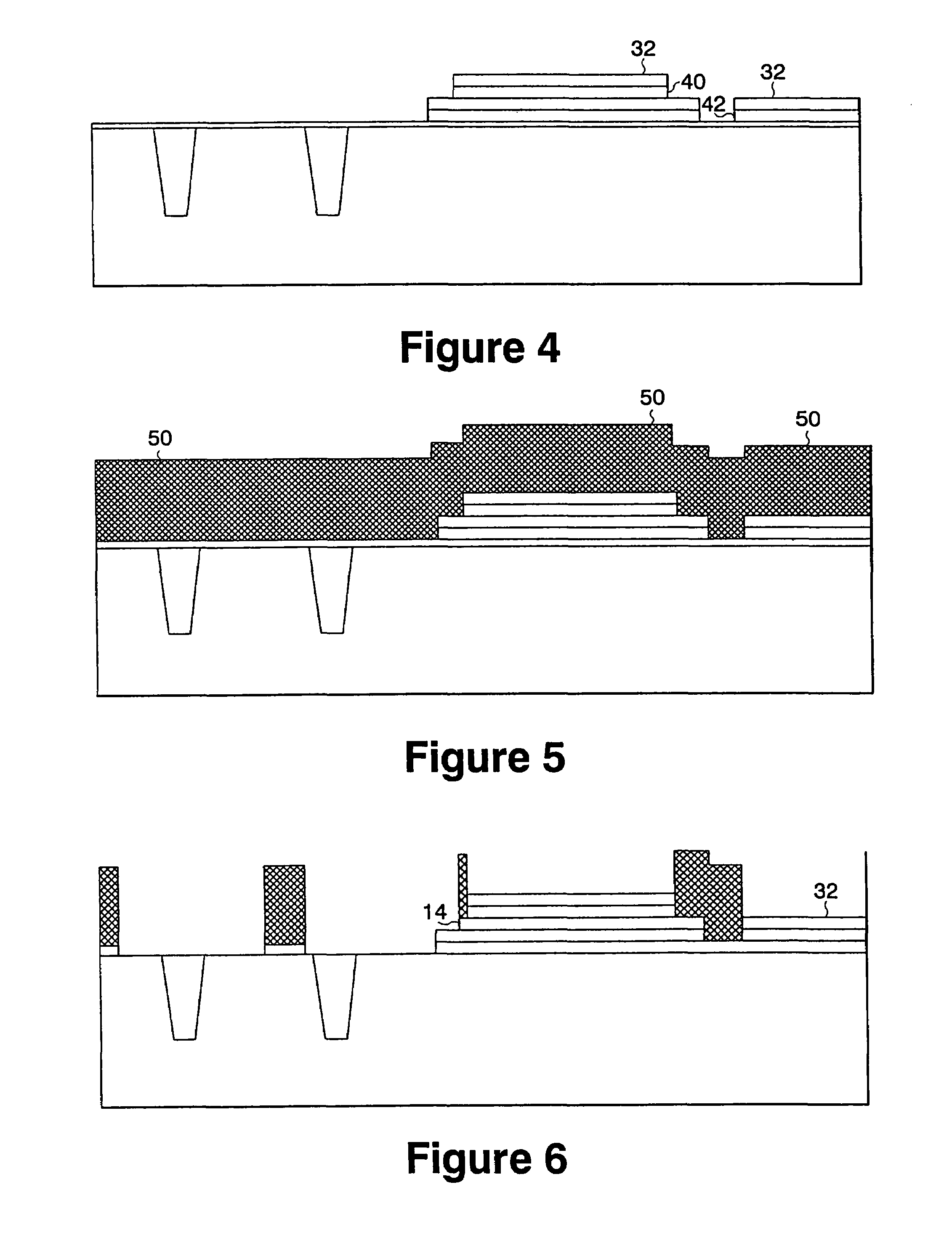

Method of fabrication of MIMCAP and resistor at same level

InactiveUS7022246B2Reduce parasitismEasy to useElectrolytic capacitorsDecorative surface effectsFront end of lineCapacitor

A method is disclosed of fabricating a MIMCAP (a capacitor (CAP) formed by successive layers of metal, insulator, metal (MIM)) and a thin film resistor at the same level. A method is also disclosed of fabricating a MIMCAP and a thin film resistor at the same level, and a novel integration scheme for BEOL (back-end-of-line processing) thin film resistors which positions them closer to FEOL (front-end-of-line processing) devices.

Owner:GLOBALFOUNDRIES US INC

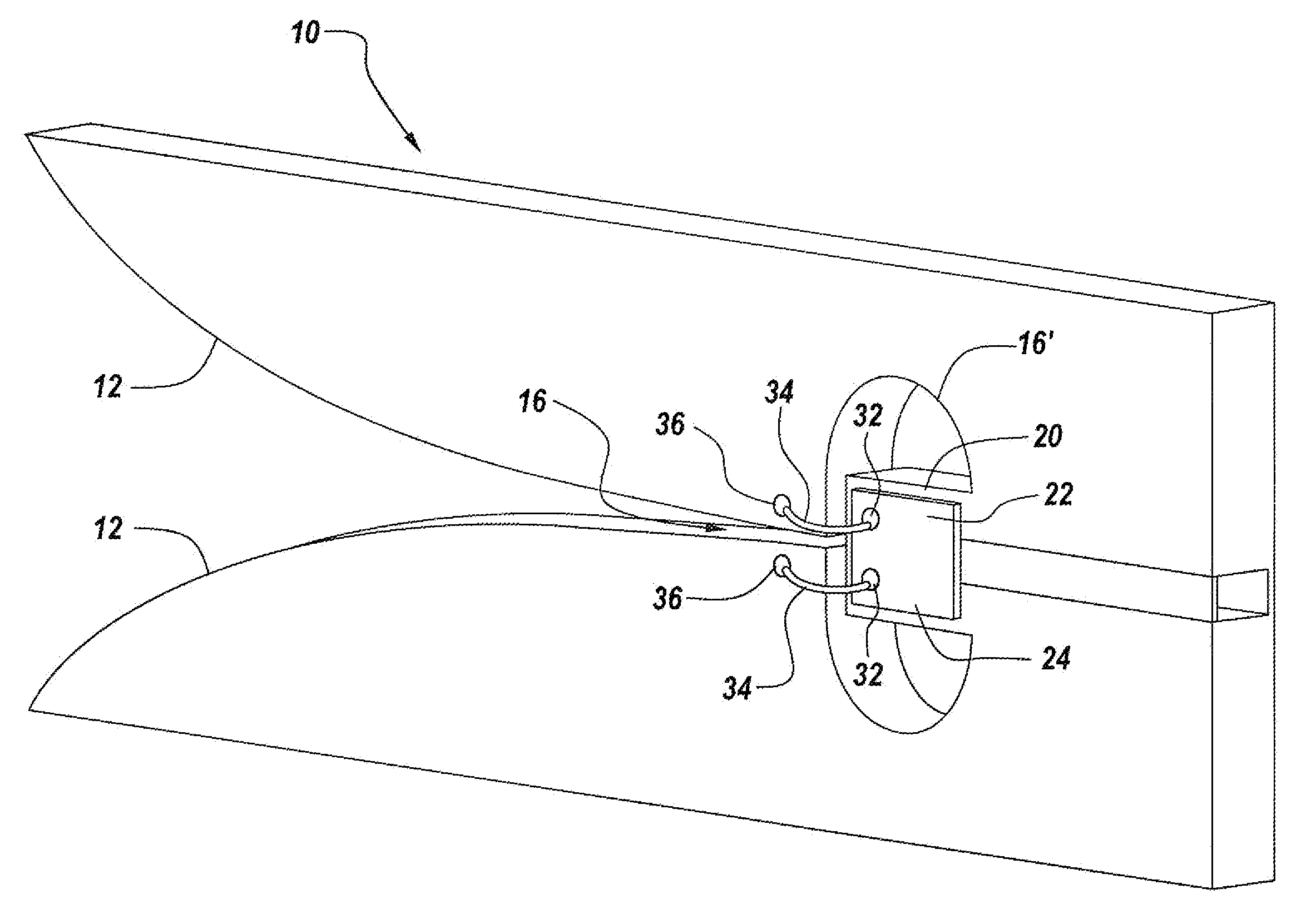

Method for direct connection of mmic amplifiers to balanced antenna aperture

ActiveUS20110001679A1Broaden VSWR bandwidthReduce rippleWaveguide hornsSemiconductor/solid-state device detailsAudio power amplifierMmic amplifiers

A MMIC amplifier is directly connected to the balanced feed points at the aperture of an antenna to eliminate the distance between electronics coupled to the antenna and the antenna itself, such that interfaces, components and connection lines which introduce losses and parasitic effects that degrade system performance are eliminated due the direct connection. Expanding the aperture of the antenna to accommodate the direct connection of a MMIC amplifier to balanced feed points of an antenna has been found to have no deleterious effects on antenna performance. Moreover, when coupling the MMIC amplifier to an unbalanced coaxial line, any associated ripple is minimized due to the direct connection.

Owner:BAE SYST INFORMATION & ELECTRONICS SYST INTERGRATION INC

Gradually-appoximant analog-digital converter

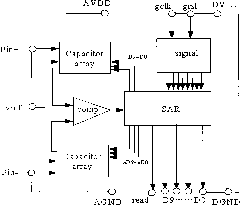

InactiveCN101800551AReduce the numberReduce areaAnalogue/digital conversionElectric signal transmission systemsCapacitanceThree stage

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

Duck cultivation method using rice field

InactiveCN105284732AAccelerate ecological balanceMaintain production environmentPlant cultivationCultivating equipmentsPesticide pollutionAgriculture

The present invention discloses a duck cultivation method using rice fields. The method comprises the following steps: selecting small and medium-sized ducks with exuberant vitality, wide adaptability and crude feed tolerance; carrying out centralized brooding of ducklings under good breeding management condition; feeding the ducklings with feed until the duck weight reaches 75 g or more; timely dispersing the ducklings to a rice field in an appropriate density in conjunction with rice growth time; and feeding the ducklings with reasonable feed at a specified time point. The duck cultivation method disclosed by the present invention can effectively control the damage of pests in the rice field, promotes ecological balance, controls pesticide pollution, ensures good agricultural environment, promotes rice yield increase, reduces agricultural cost and increases framer income, so that pollution-free and safe rice and duck meat are simultaneously produced in limited space of the rice field.

Owner:六安市裕青生态养殖有限责任公司

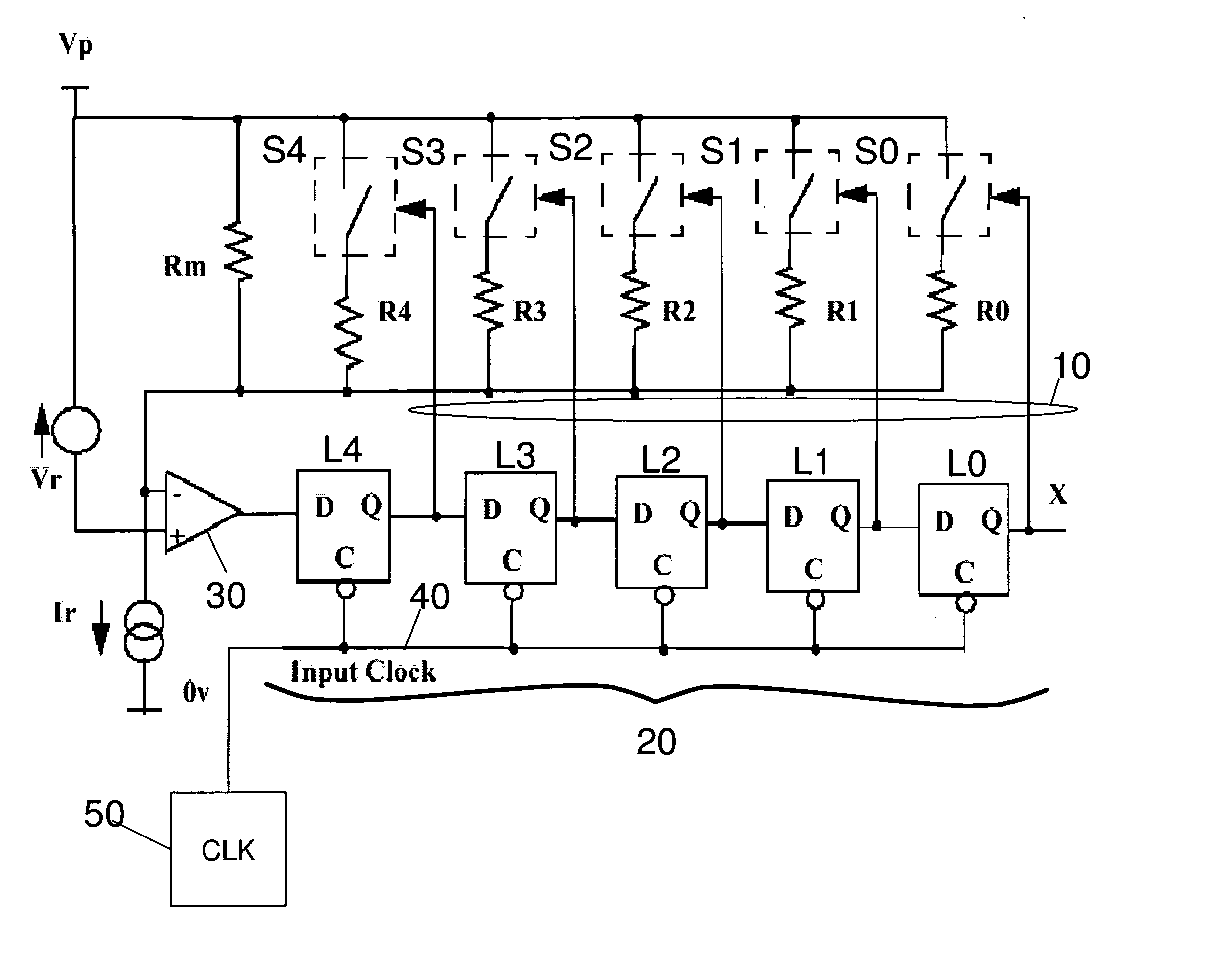

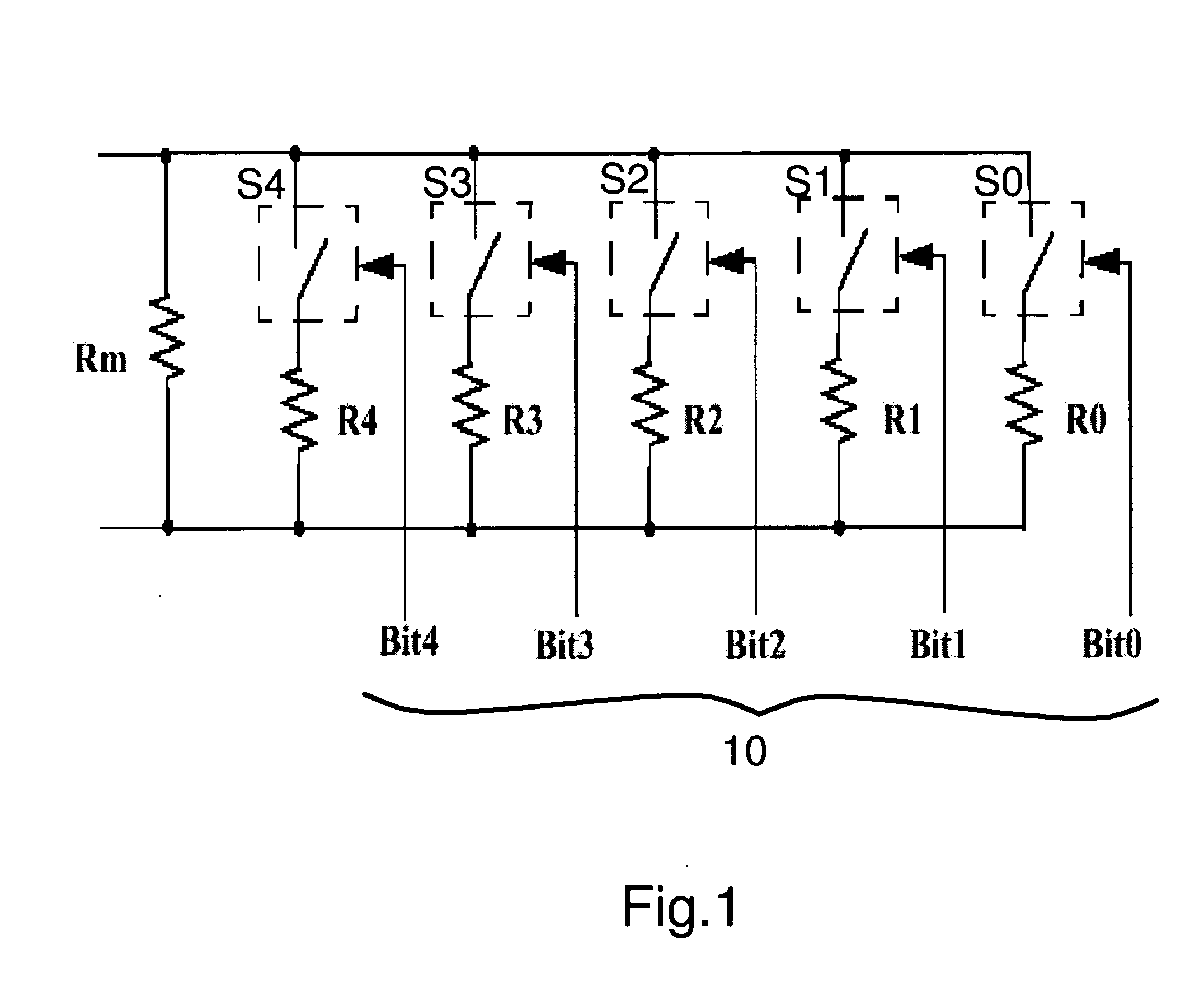

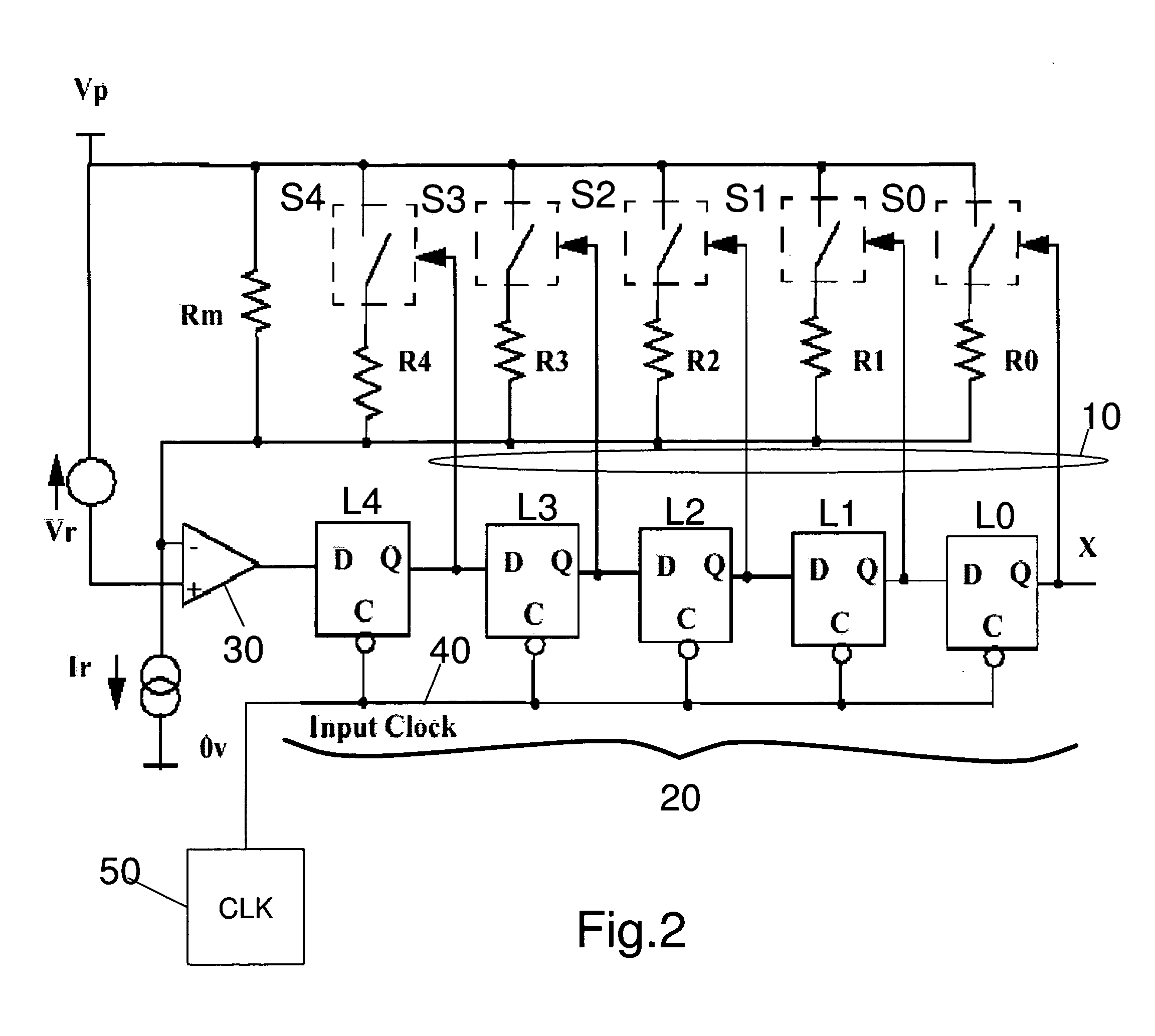

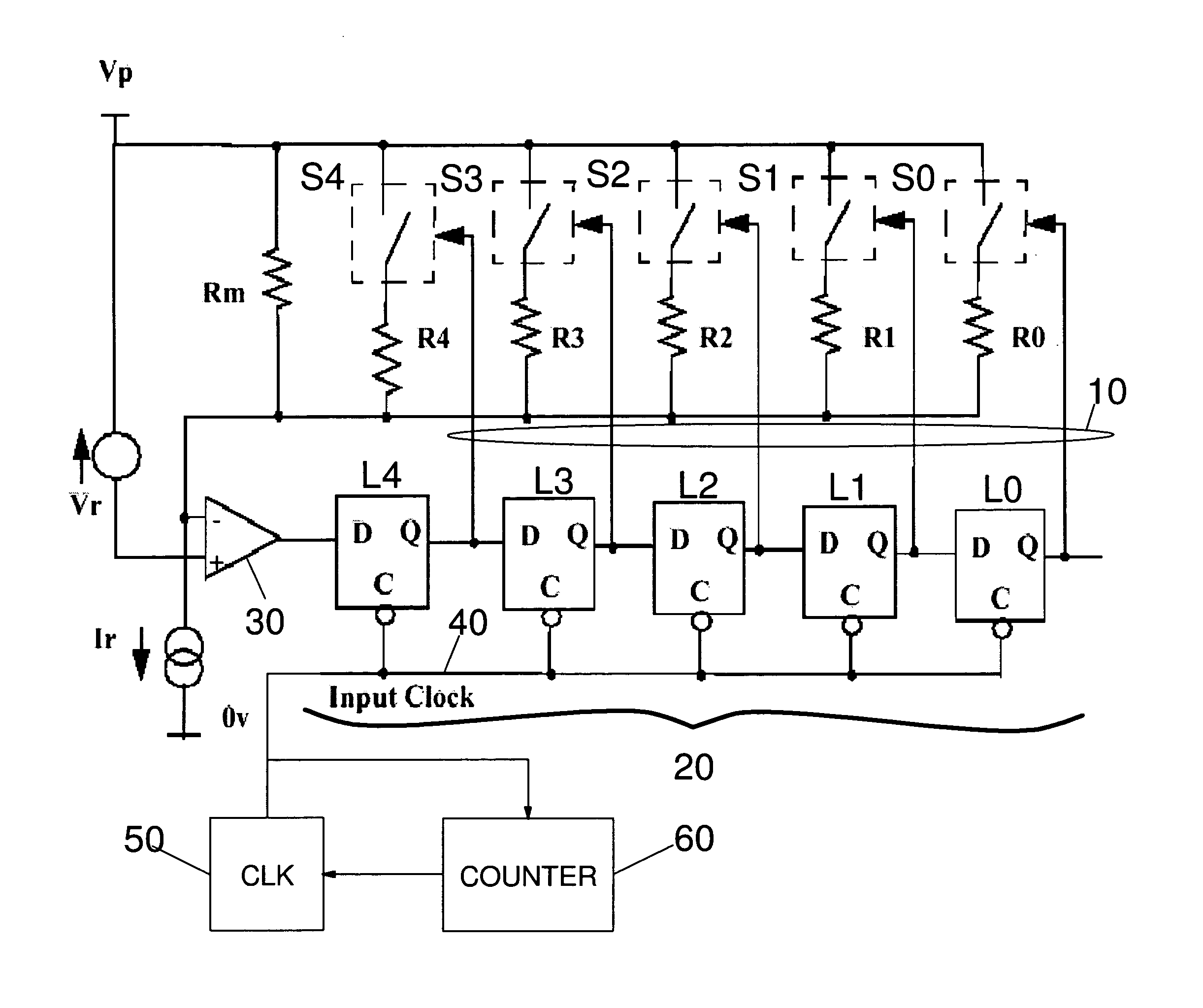

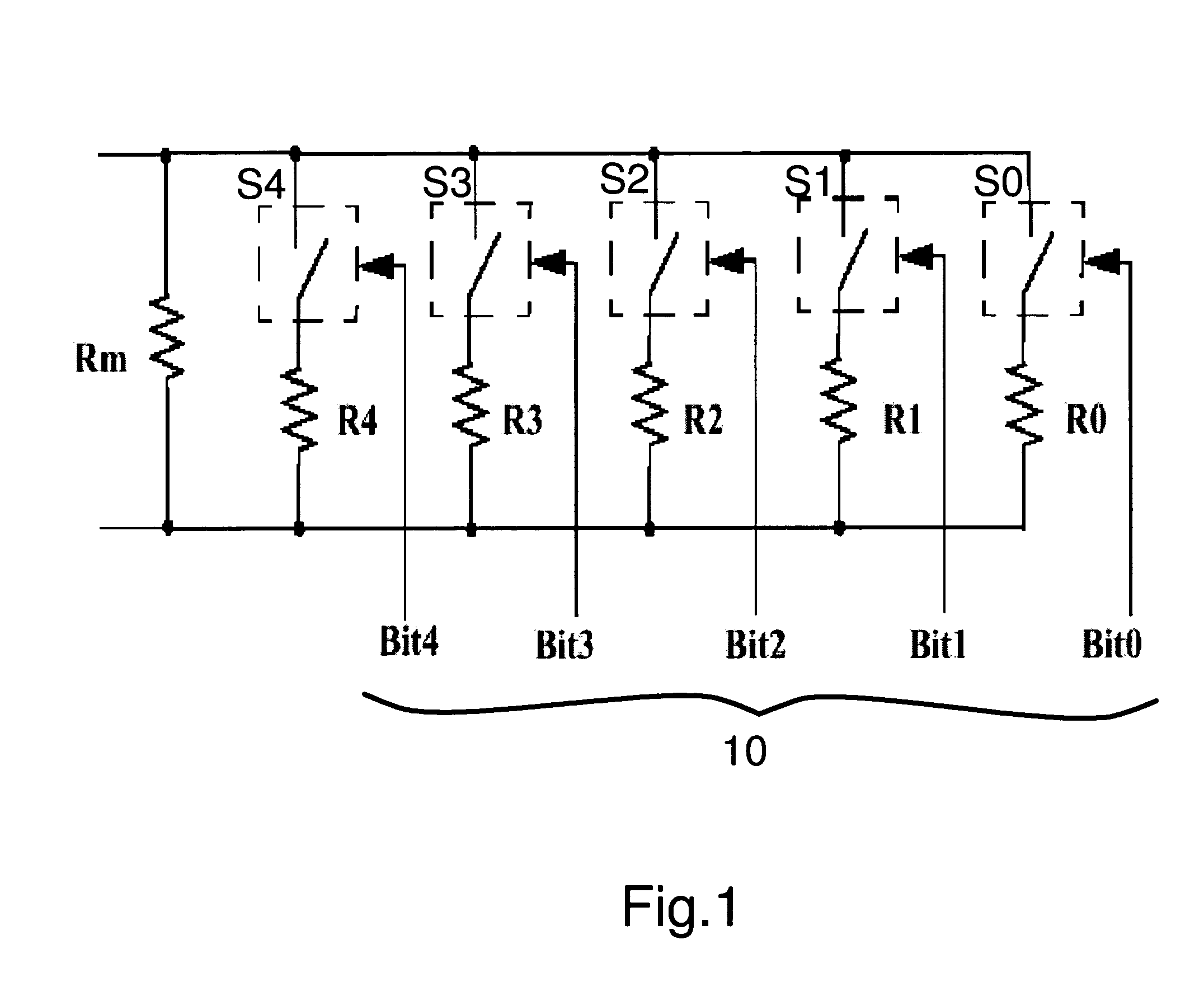

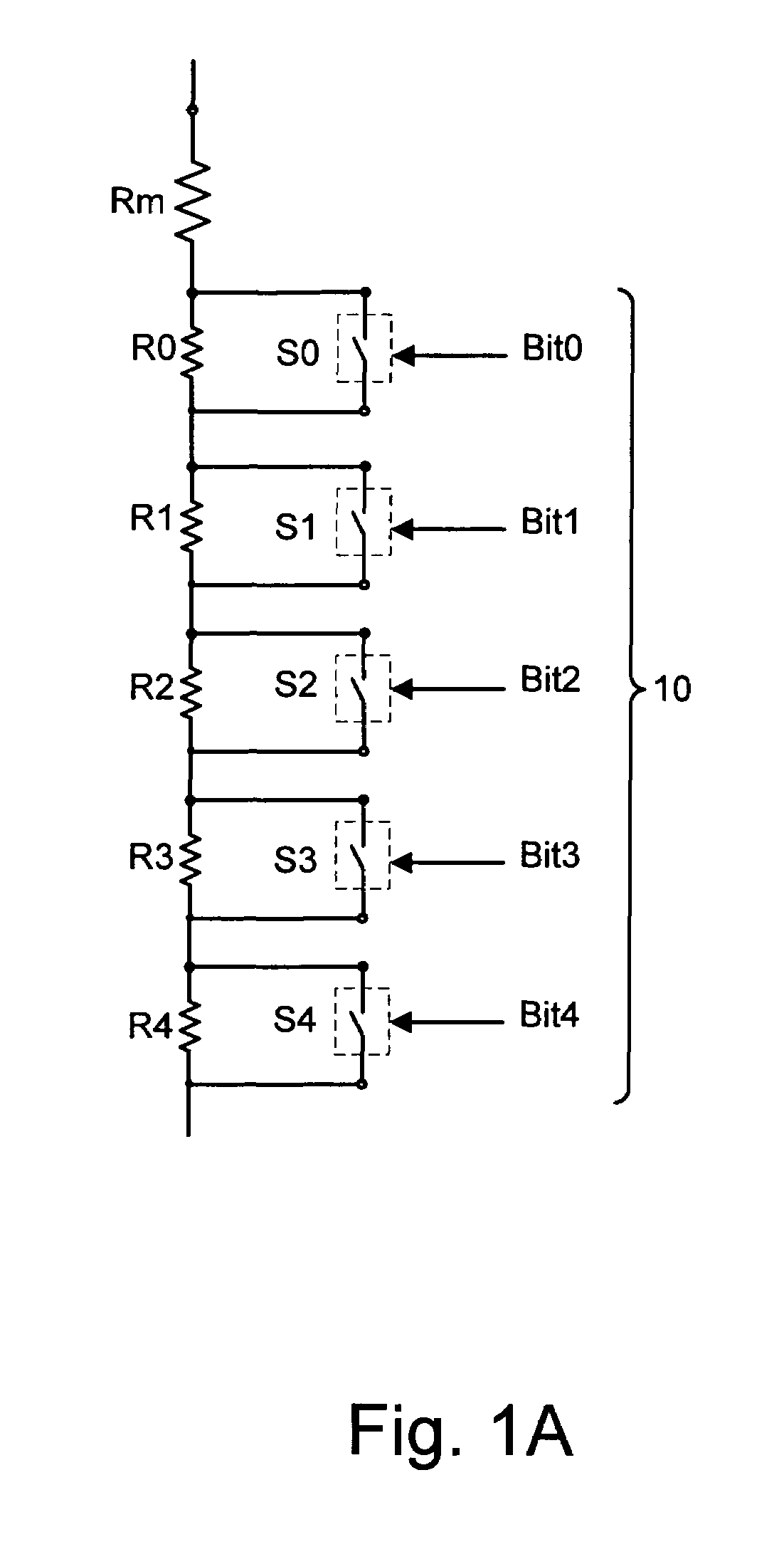

Electronic component value trimming systems

InactiveUS20050127978A1Coupling noiseCancel noiseReliability increasing modificationsElectric signal transmission systemsShift registerControl vector

Described is a system for trimming the value of an electronic component. The system comprises: at least one trimming component, each trimming component having an associated switch for selectively connecting that trimming component to the electronic component in response to a corresponding bit in a control vector. A comparator is included for generating an output bit having a first value if a net value of the electronic component and any connected trimming components differs from a desired value. A controller connected to the switches and the comparator generates the control vector in dependence on the output of comparator, the controller comprising a shift register for sequentially receiving successive output bits from the comparator; wherein the control vector comprises the contents of the shift register and wherein a bit of said first value in control vector effects switching of the corresponding switch.

Owner:IBM CORP

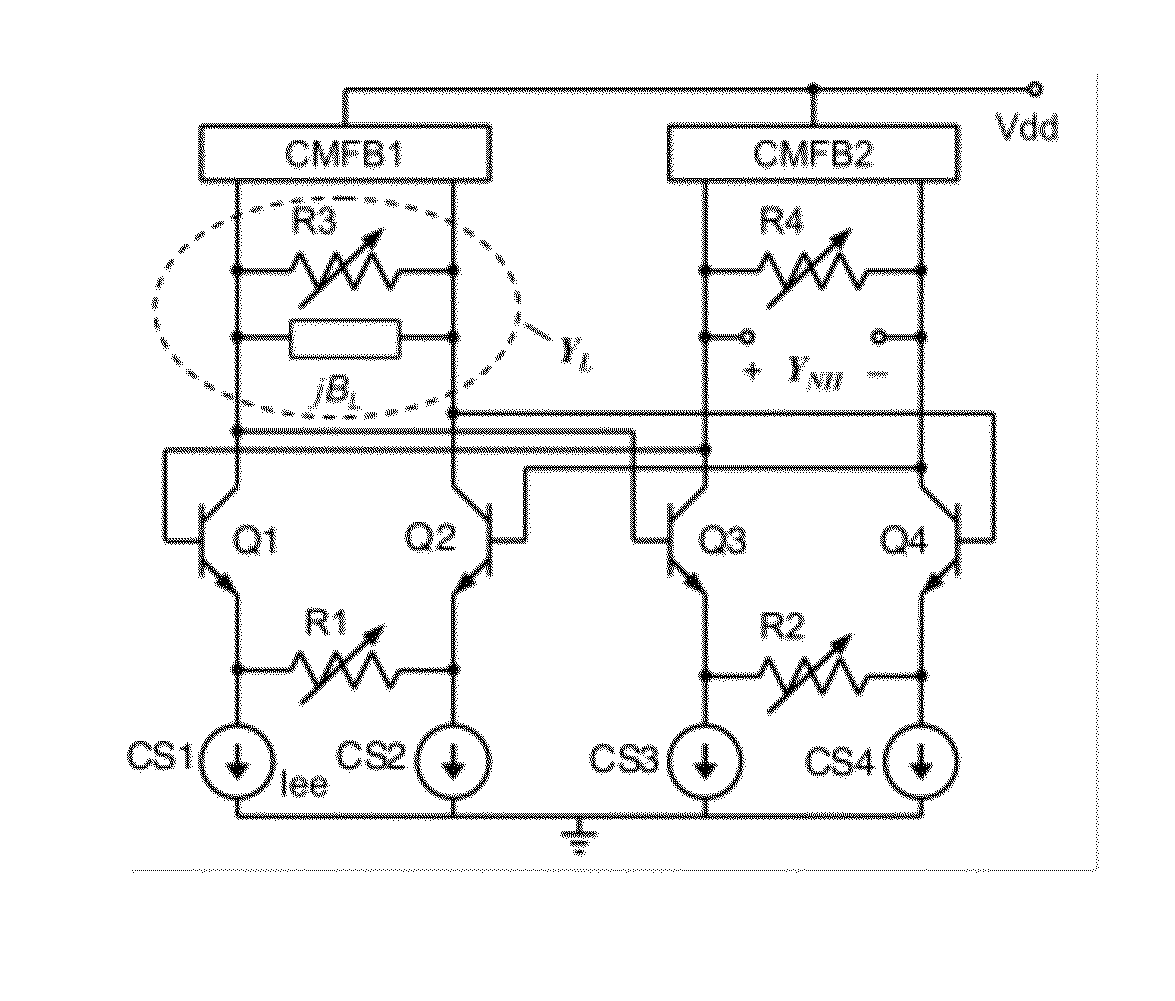

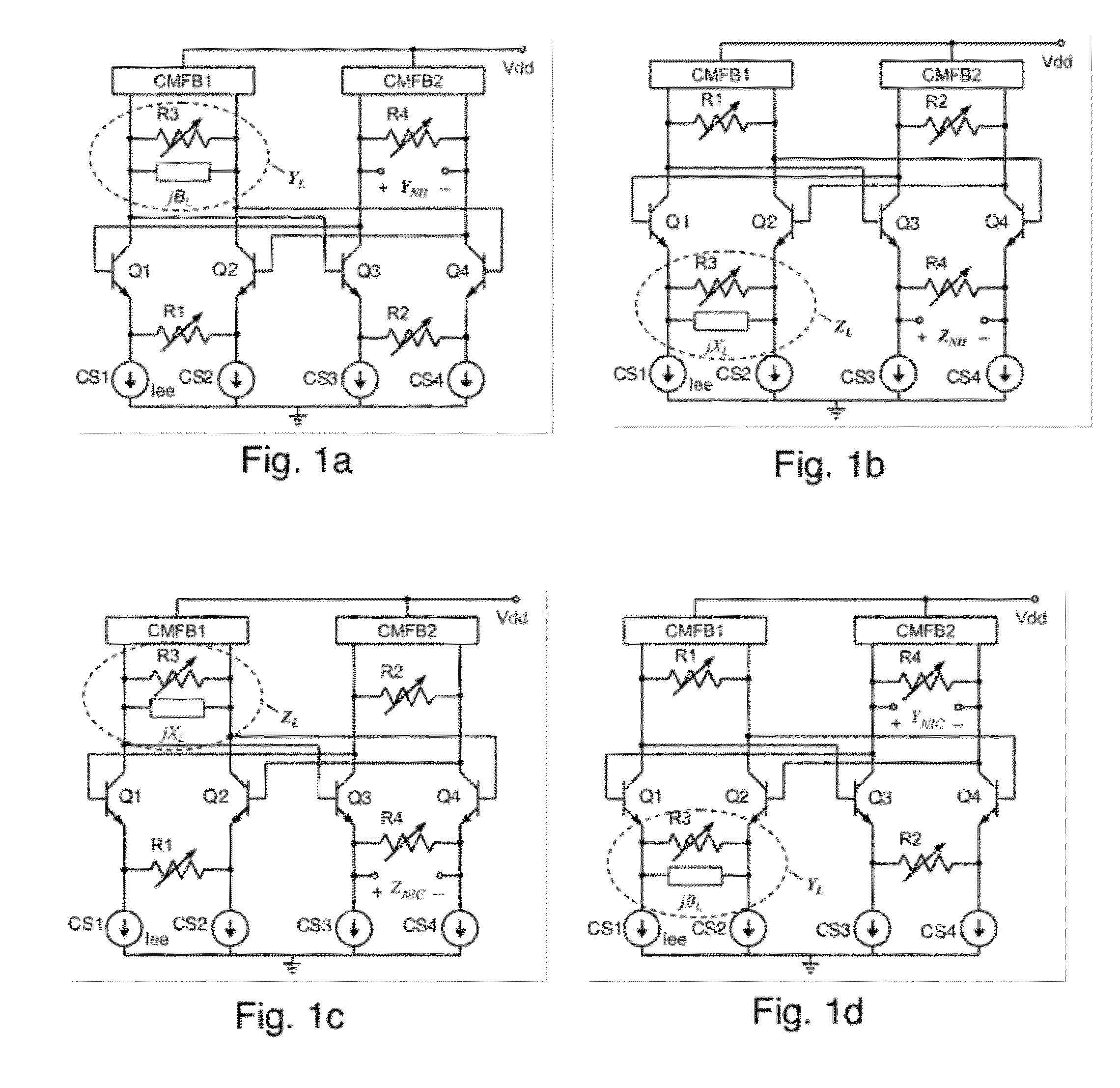

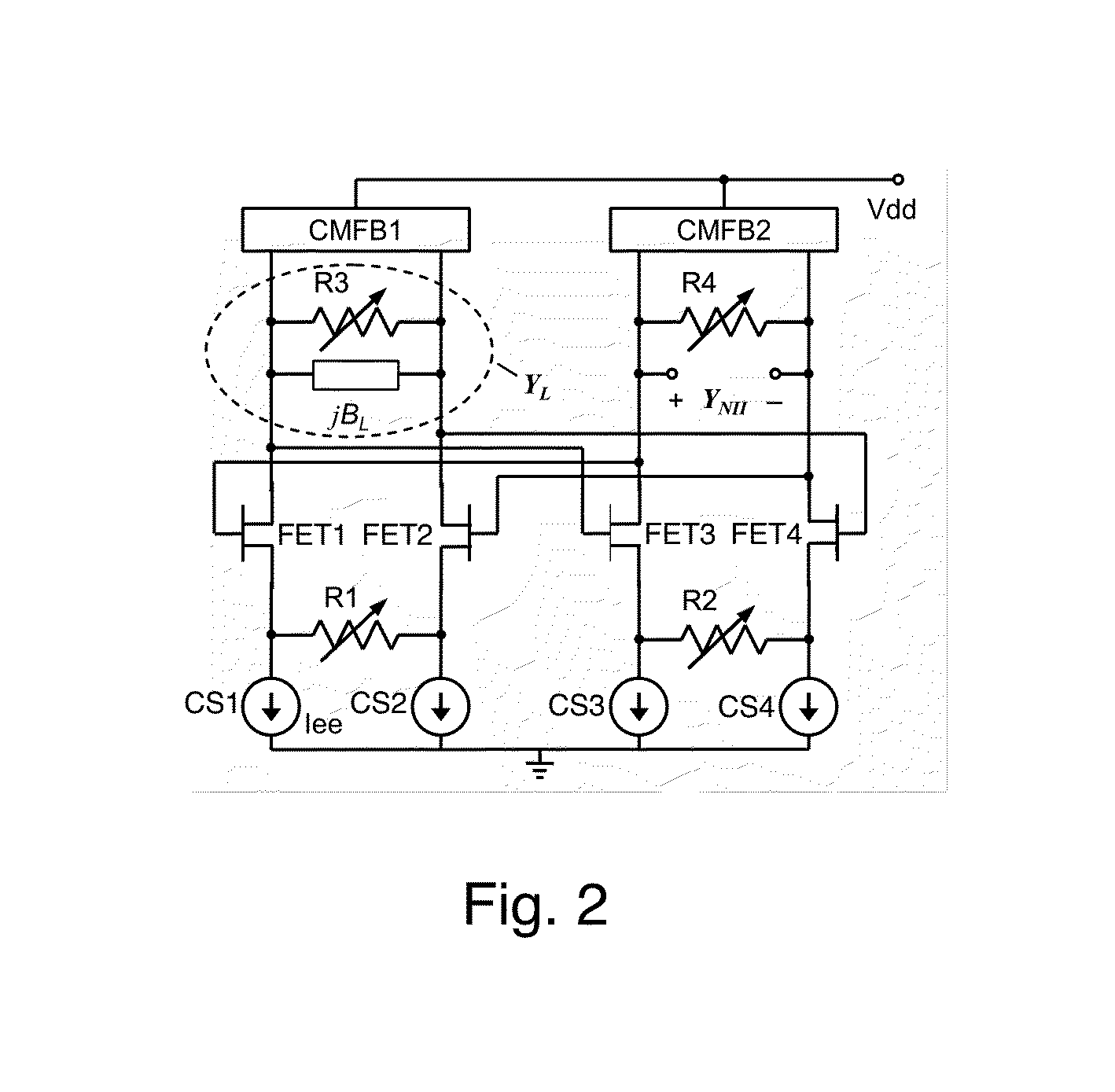

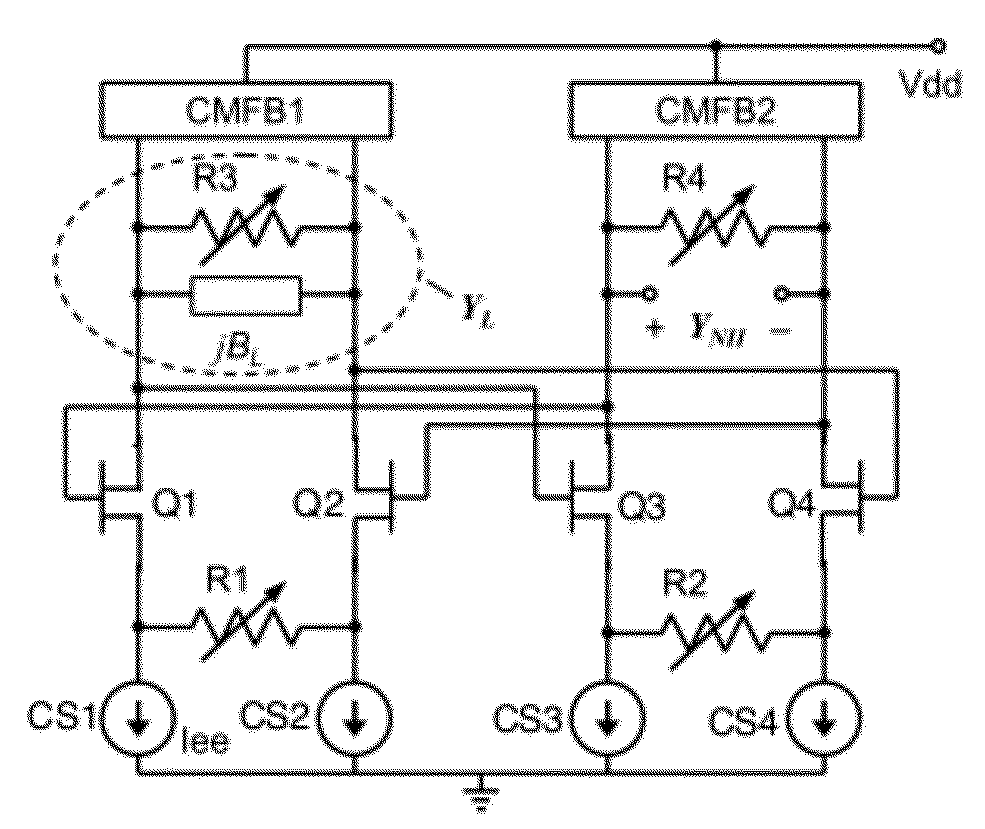

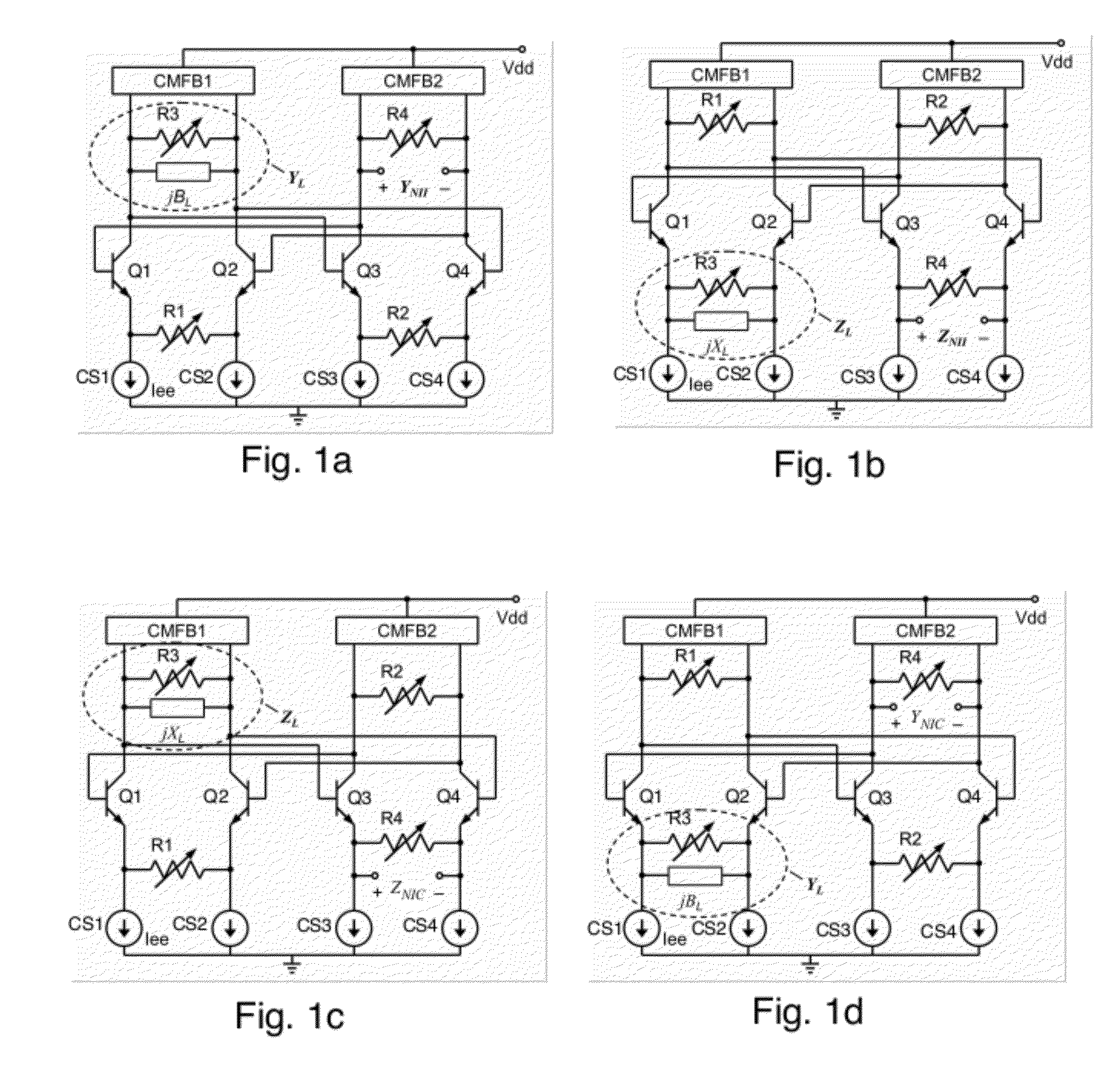

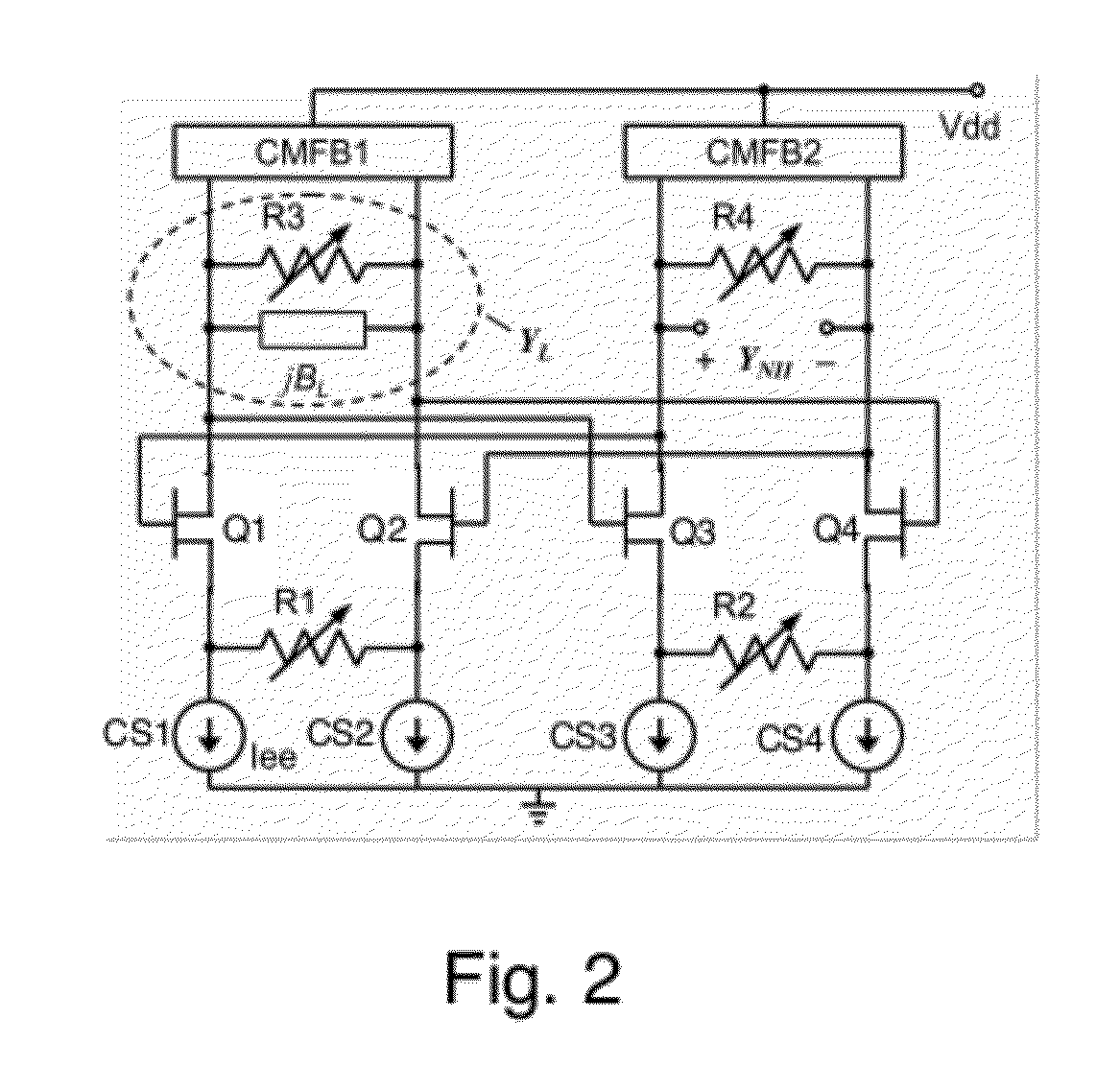

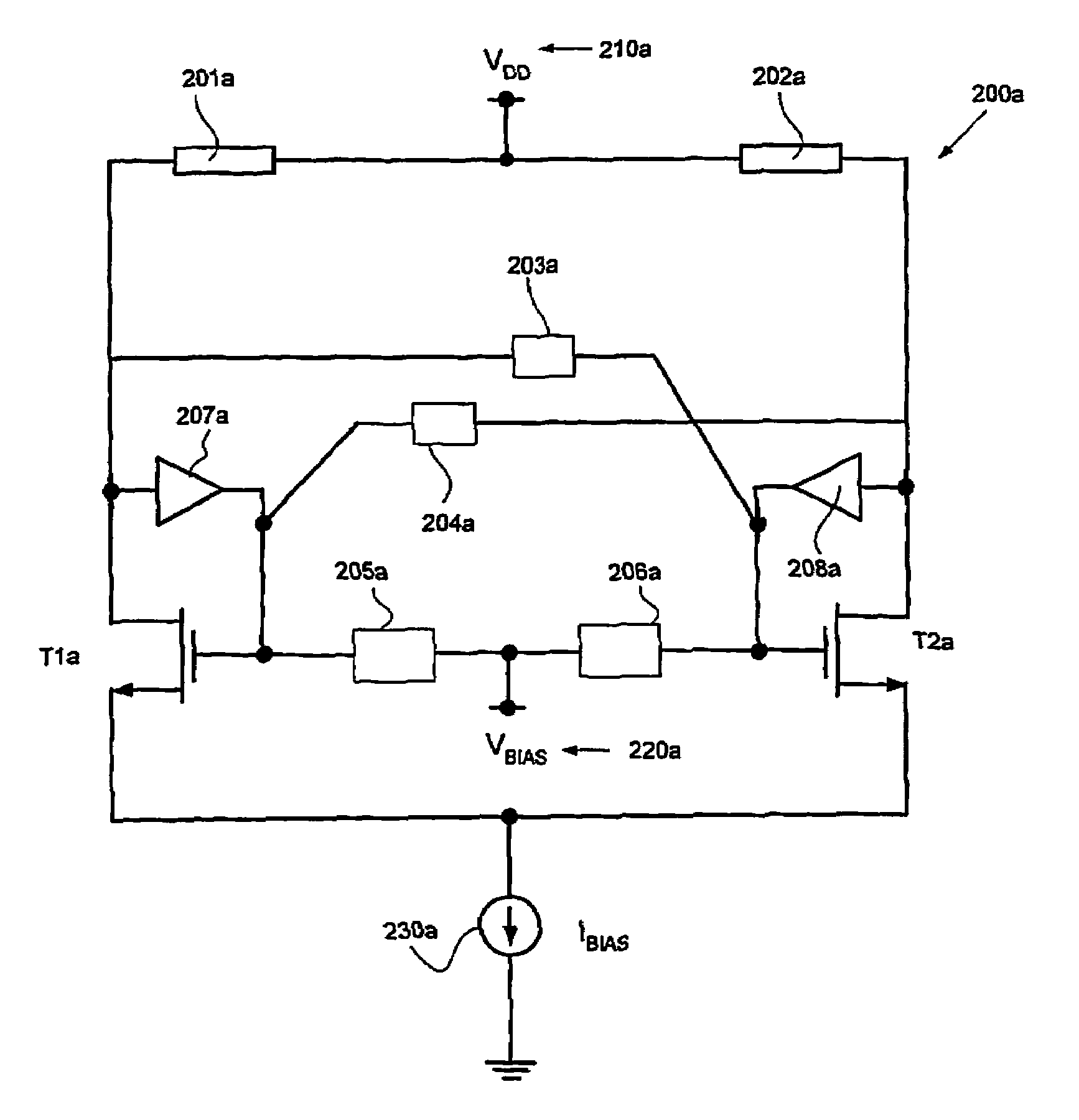

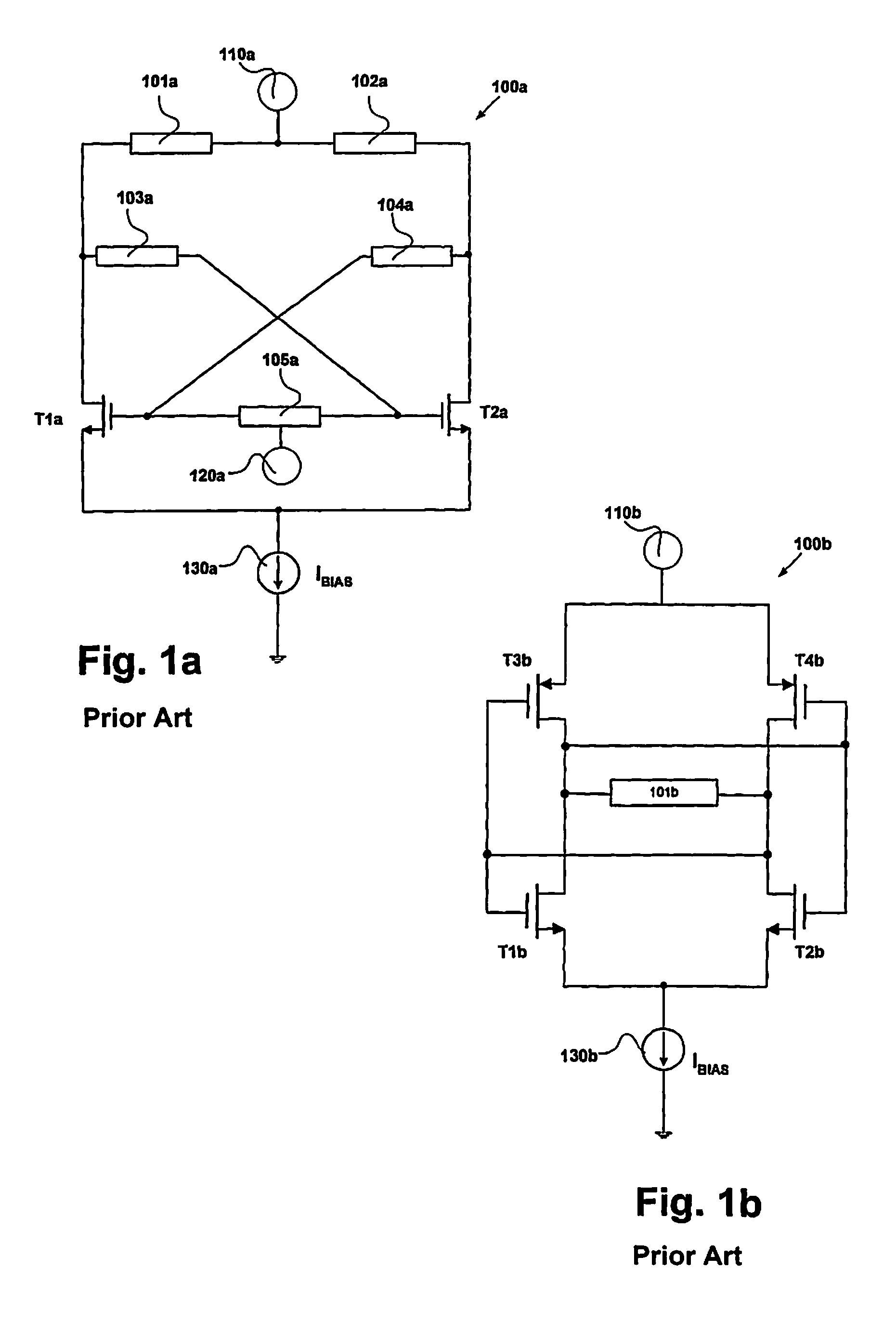

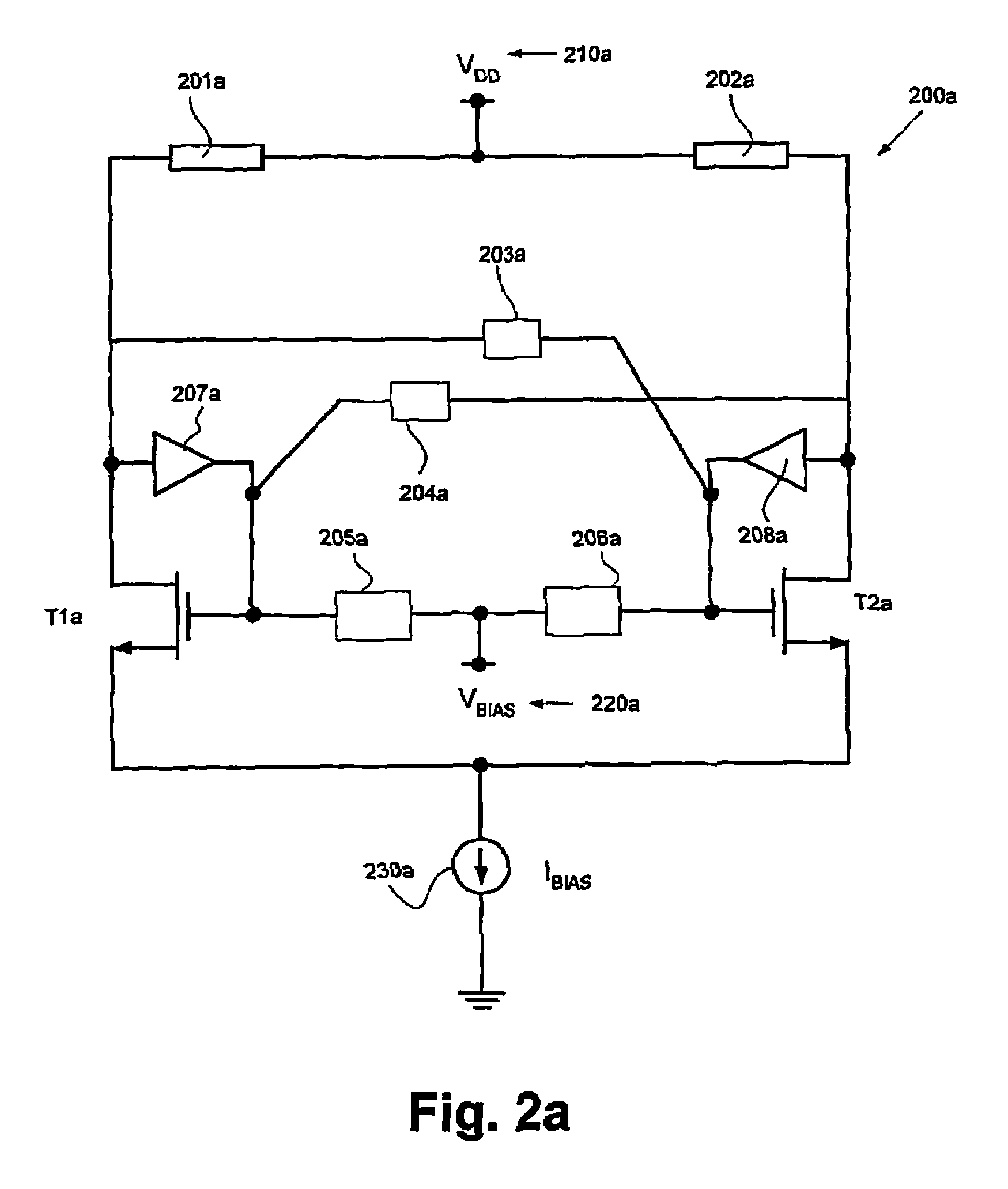

Differential negative impedance converters and inverters with variable or tunable conversion ratios

ActiveUS8988173B2Reduce parasitismImprove matchImpedence convertorsNetwork simulating reactancesCapacitanceEngineering

A differential circuit topology that produces a tunable floating negative inductance, negative capacitance, negative resistance / conductance, or a combination of the three. These circuits are commonly referred to as “non-Foster circuits.” The disclosed embodiments of the circuits comprises two differential pairs of transistors that are cross-coupled, a load immittance, multiple current sources, two Common-Mode FeedBack (CMFB) networks, at least one tunable (variable) resistance, and two terminals across which the desired immittance is present. The disclosed embodiments of the circuits may be configured as either a Negative Impedance Inverter (NII) or a Negative Impedance Converter (NIC) and as either Open-Circuit-Stable (OCS) and Short-Circuit-Stable (SCS).

Owner:HRL LAB

Electronic component value trimming systems

InactiveUS7081842B2Simple controllerEasy to implementReliability increasing modificationsElectric signal transmission systemsShift registerControl vector

Described is a system for trimming the value of an electronic component. The system comprises: at least one trimming component, each trimming component having an associated switch for selectively connecting that trimming component to the electronic component in response to a corresponding bit in a control vector. A comparator is included for generating an output bit having a first value if a net value of the electronic component and any connected trimming components differs from a desired value. A controller connected to the switches and the comparator generates the control vector in dependence on the output of comparator, the controller comprising a shift register for sequentially receiving successive output bits from the comparator; wherein the control vector comprises the contents of the shift register and wherein a bit of said first value in control vector effects switching of the corresponding switch.

Owner:IBM CORP

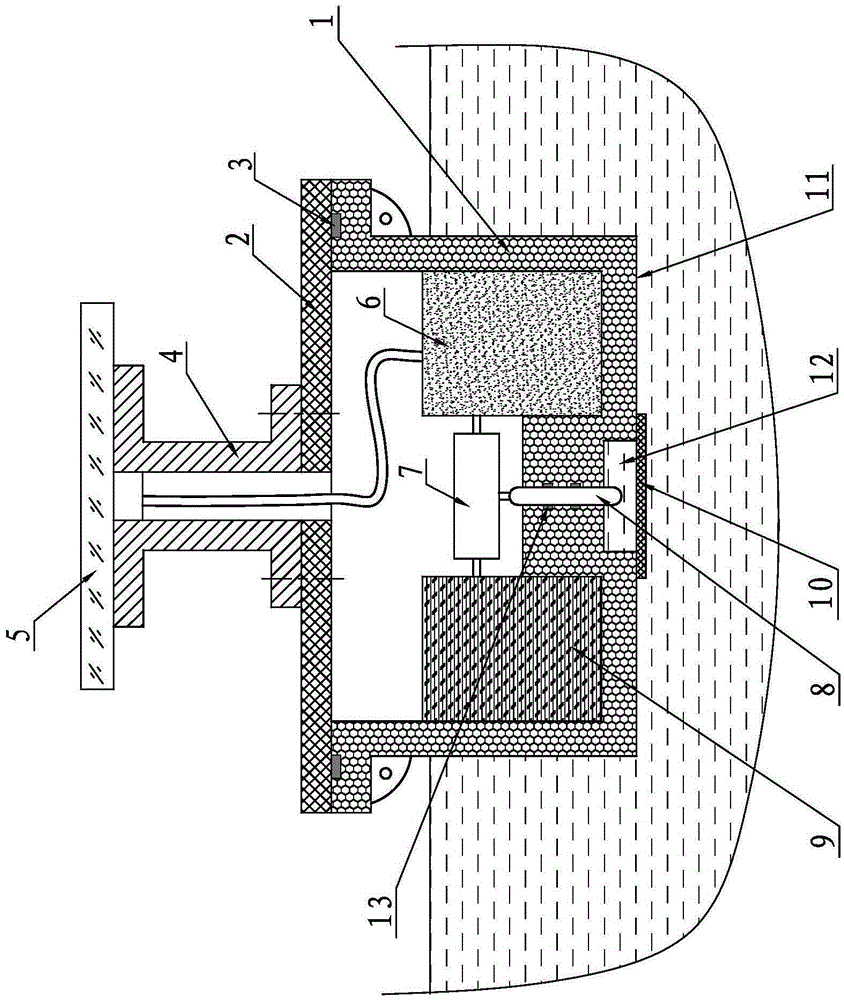

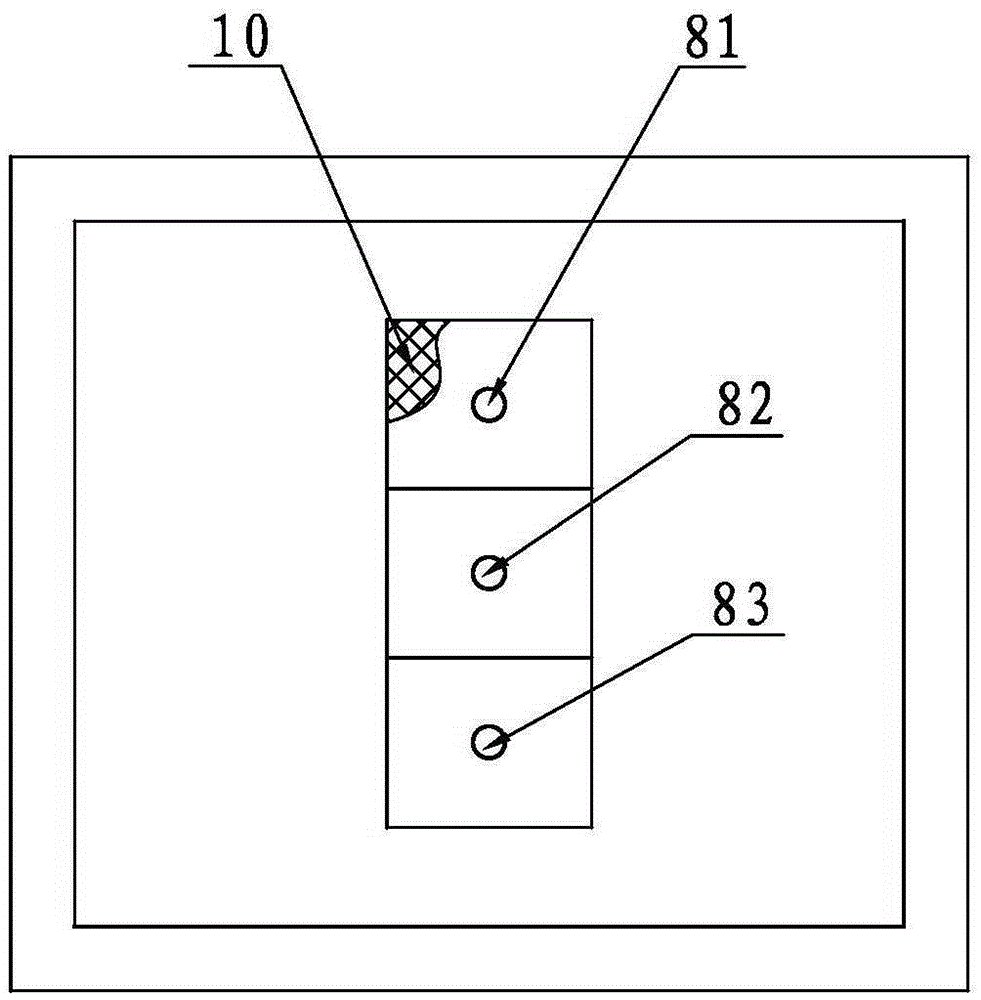

Floating type water quality detection device in aquaculture Internet of Things online monitoring system

PendingCN105403677AAvoid damageEliminate electricity safety accidentsTesting waterWater qualityIntegrated circuit layout

The invention provides a floating type water quality detection device in an aquaculture Internet of Things online monitoring system. The floating type water quality detection device comprises a floating shell, a sealing cover, a port sealing piece, a supporting seat, a solar power generation plate, a storage battery, an integrated circuit board, a detection sensor group and a signal transmitter, wherein the storage battery, the integrated circuit board and the signal transmitter are arranged in the floating shell; the detection sensor group for detecting temperatures, dissolved oxygen and pH (Potential of Hydrogen) values are hermetically mounted at the bottom of the floating shell; the sealing cover is hermetically mounted at the upper port of the floating shell; the lower end face of the supporting seat is fixedly arranged on the sealing cover and the solar power generation plate is mounted on the upper end face of the supporting seat; the solar power generation plate is electrically connected with the storage battery; the storage battery supplies power to the integrated circuit board, the detection sensor group and the signal transmitter. The floating type water quality detection device can be used for carrying out real-time synchronous detection on the water temperatures, the dissolved oxygen and the pH values of a pond; an external electric supply is not needed and an electric wire does not need to be erected in the pond; the floating type water quality detection device is one of key equipment in the aquaculture Internet of Things online monitoring system.

Owner:常州市金坛区水产技术指导站

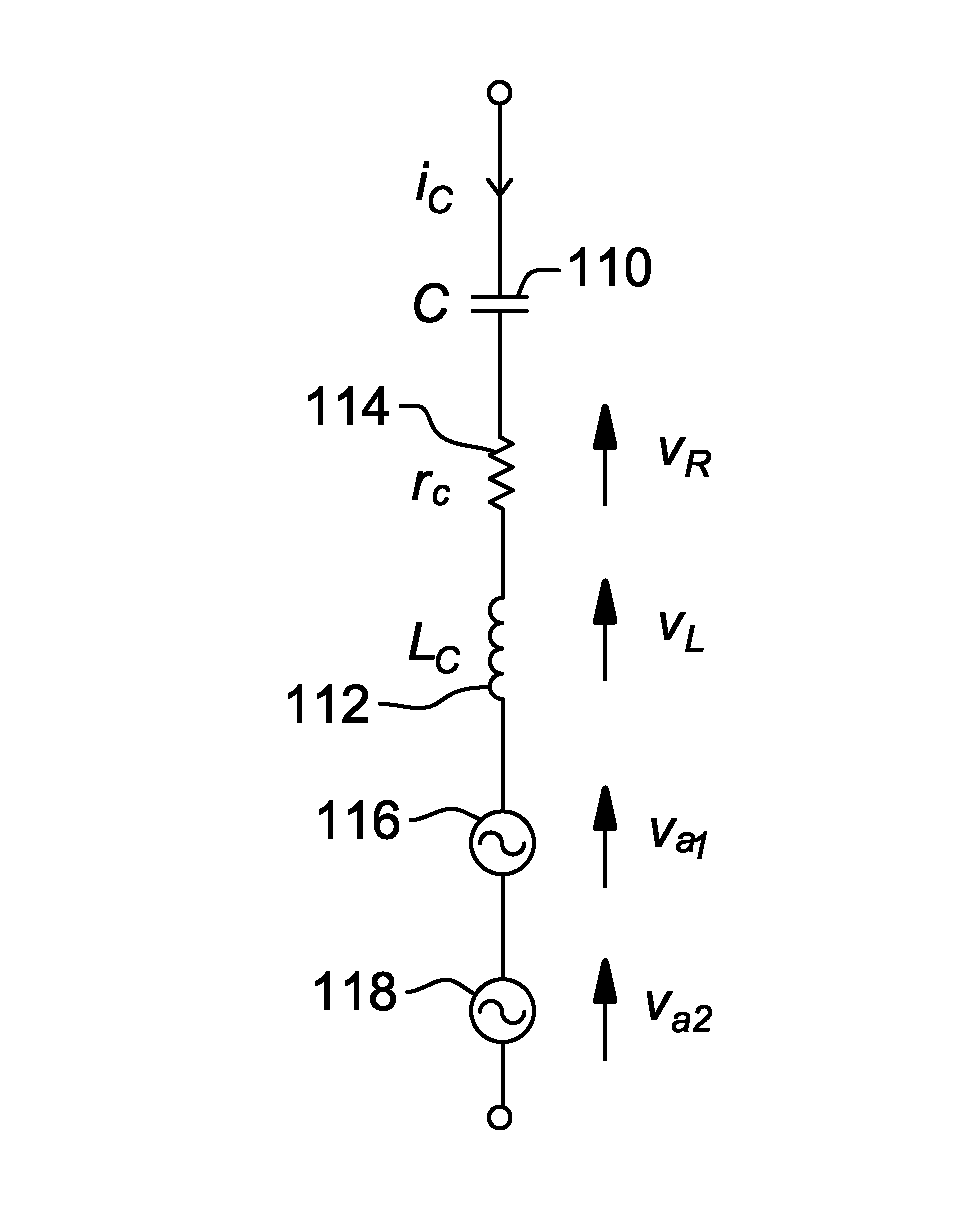

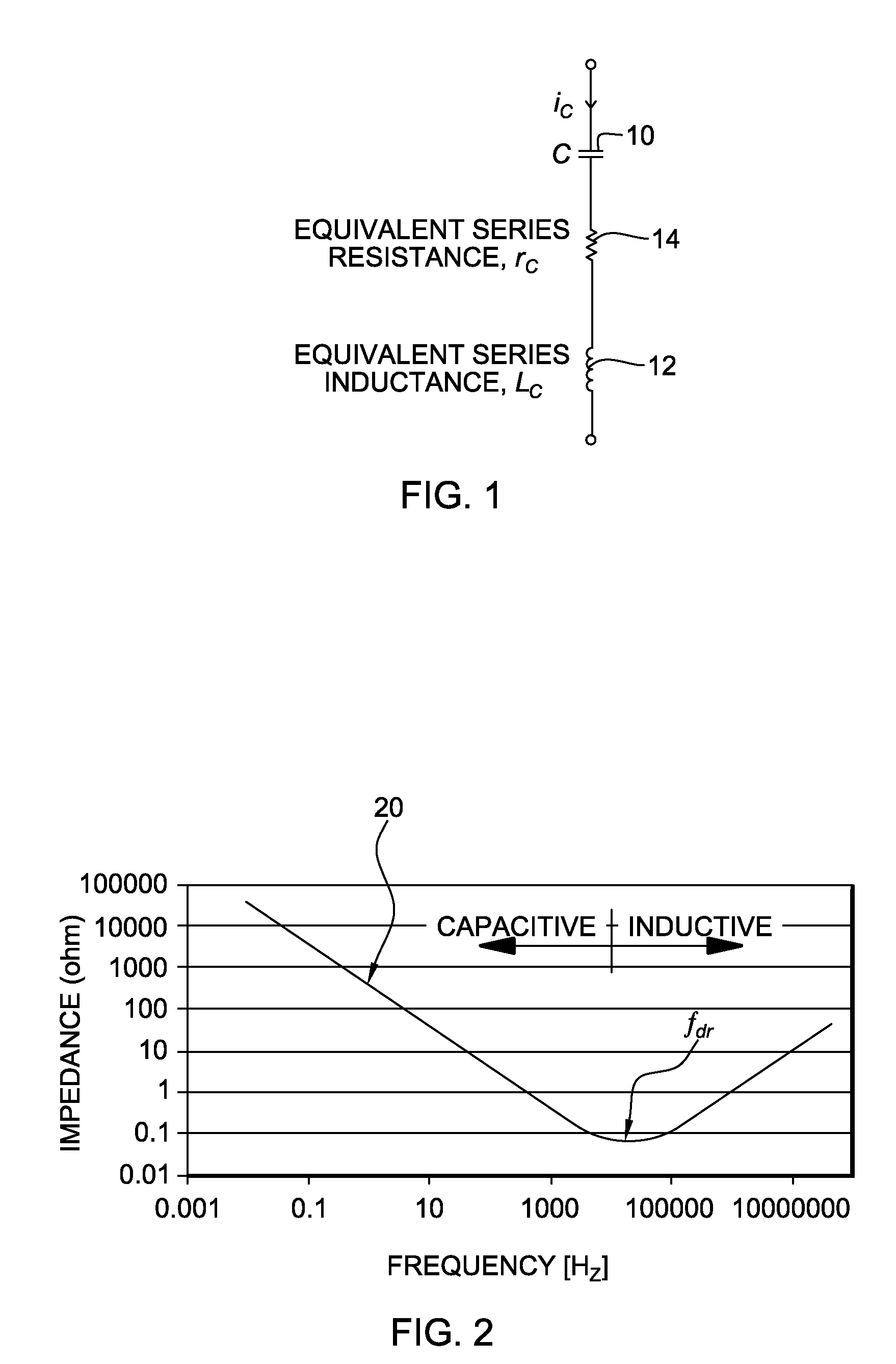

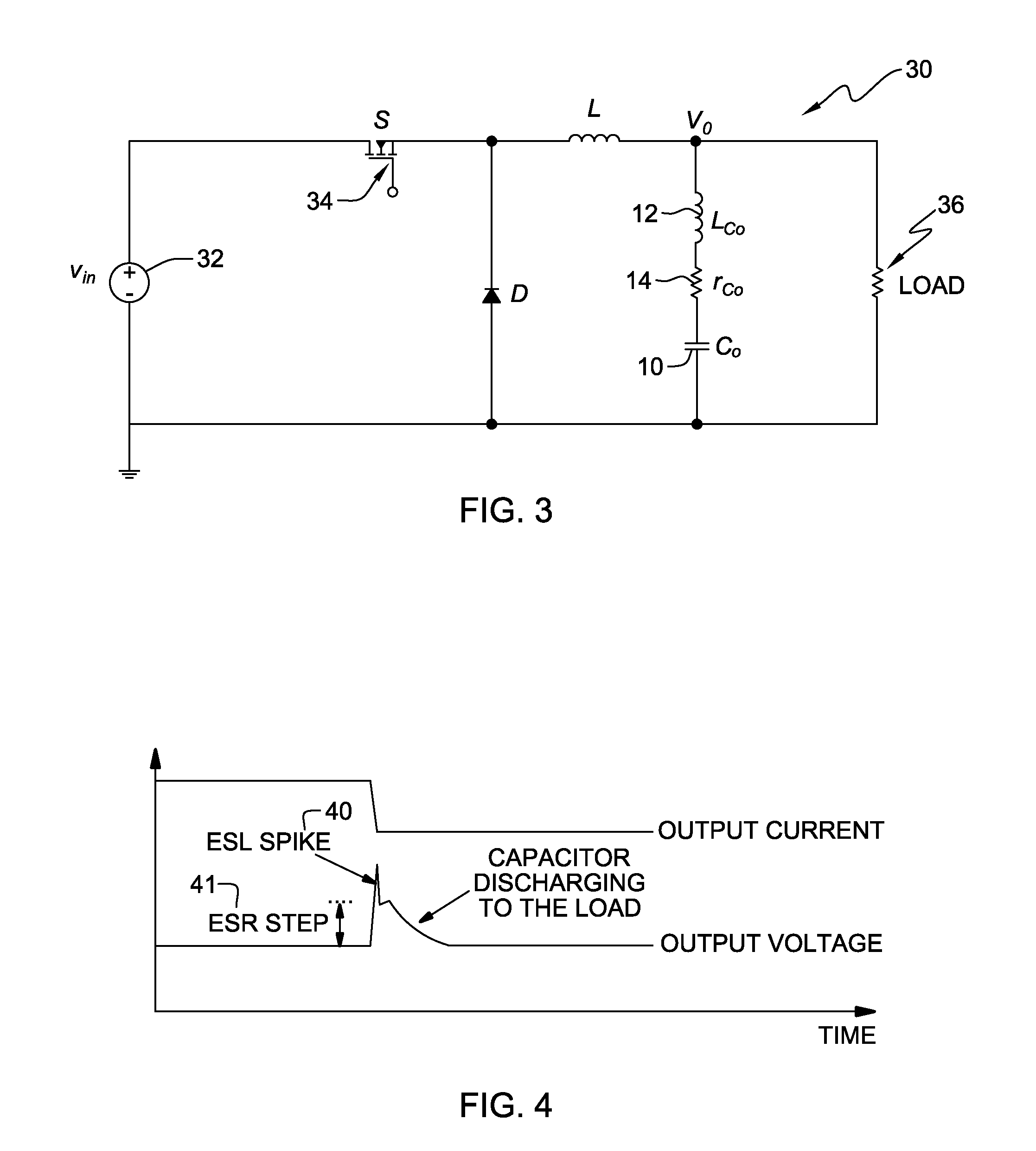

Method and apparatus for suppressing noise caused by parasitic inductance and/or resistance in an electronic circuit or system

ActiveUS20100283437A1Reduce parasitic effectsReduce parasitismDc-dc conversionElectronic switchingElectronic circuitEngineering

Reducing, suppressing or canceling series parasitic inductance and / or resistive effects that affect the frequency response of components, elements and / or circuits in an electronic circuit or system that exhibit capacitance is disclosed. Noise generated by series parasitic inductance and / or parasitic resistance of the components, the physical orientation of the components, and / or the layout of components, devices and / or conductive tracks (board traces) on printed circuit boards within an electronic circuit or system is reduced, suppressed or canceled. The reduction, suppression or cancellation is achieved by adding a voltage source in series with a part or component of the electronic circuit or system that exhibits capacitance, the current source being adapted to deliver a compensating voltage of roughly equal magnitude and roughly opposite phase to parasitic voltage associated with the part or component.

Owner:CITY UNIVERSITY OF HONG KONG

Interposer capacitor built on silicon wafer and joined to a ceramic substrate

InactiveUS20040014313A1Improve performanceHigh yieldTransistorSemiconductor/solid-state device detailsLead zirconate titanateBarium strontium titanate

An interposer, located between an integrated circuit having power, ground and signal connections and a ceramic substrate having power, ground and signal connections, that includes an oxide layer formed on a polished surface of a silicon substrate, a thin film dielectric capacitor formed on the oxide layer, a plurality of metallized that electrically connect to either of the electrodes of the thin film dielectric capacitor, and vias than conduct power, ground and signals between a the ceramic substrate and the integrated circuit. The interposer connects the metallized vias to the integrated circuit by solder connections and also connects the vias conducting power, ground and signals from the ceramic substrate to the interposer by solder connections. The dielectric of the thin film dielectric capacitor may be selected from the group of high-K titanates, such as, barium zirconate titanate, barium strontium titanate, pure barium titanate, barium titanate modified with Pb, Nb, W, Ca, Mg, and Zn, lead titanate, lead zirconate titanate, and polycrystalline lanthanum-modified lead zirconate titanate, or other high-K dielectrics, such as, lead niobate and its derivatives, and lead tungstate and its derivatives.

Owner:GLOBALFOUNDRIES US INC

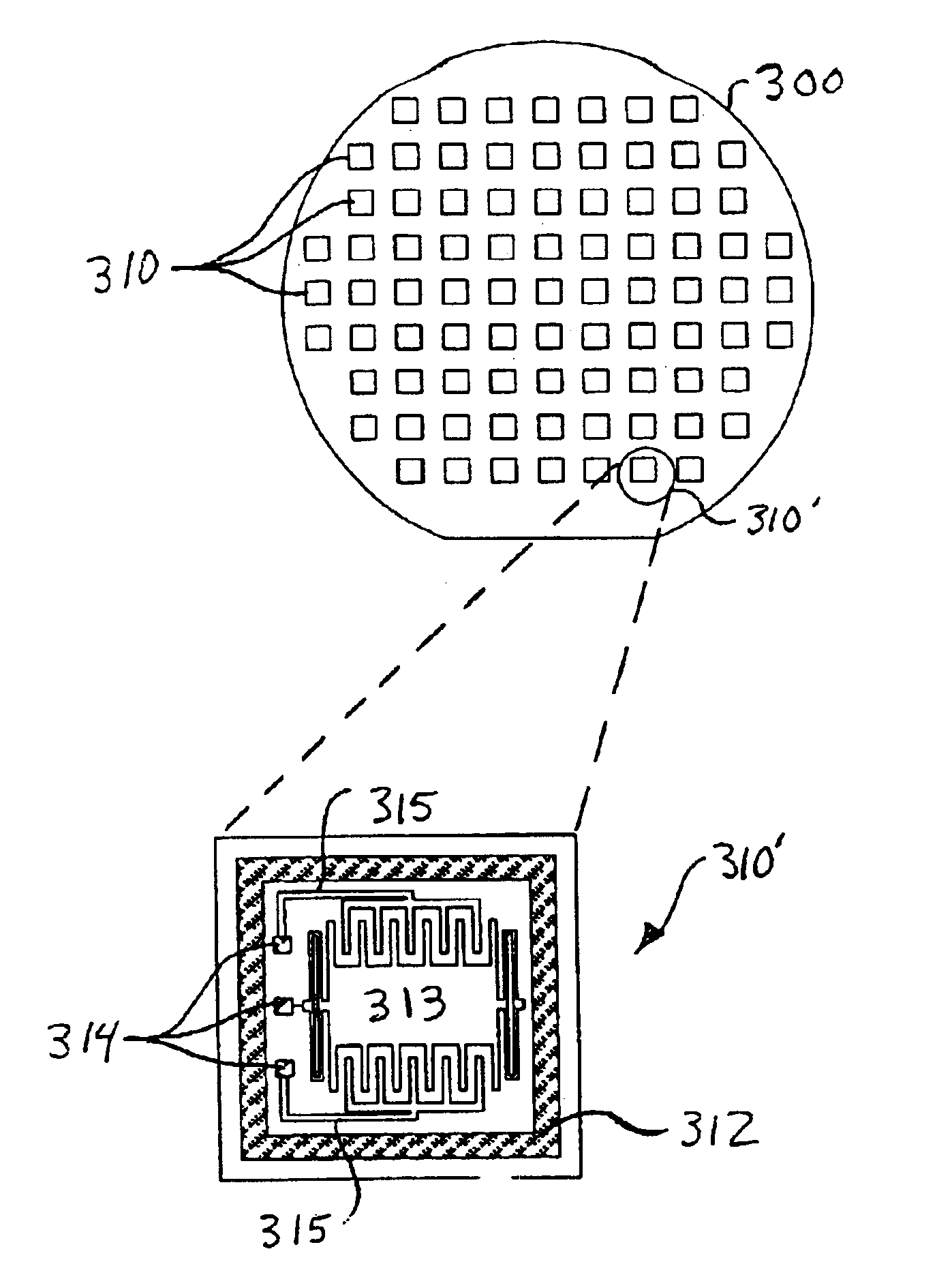

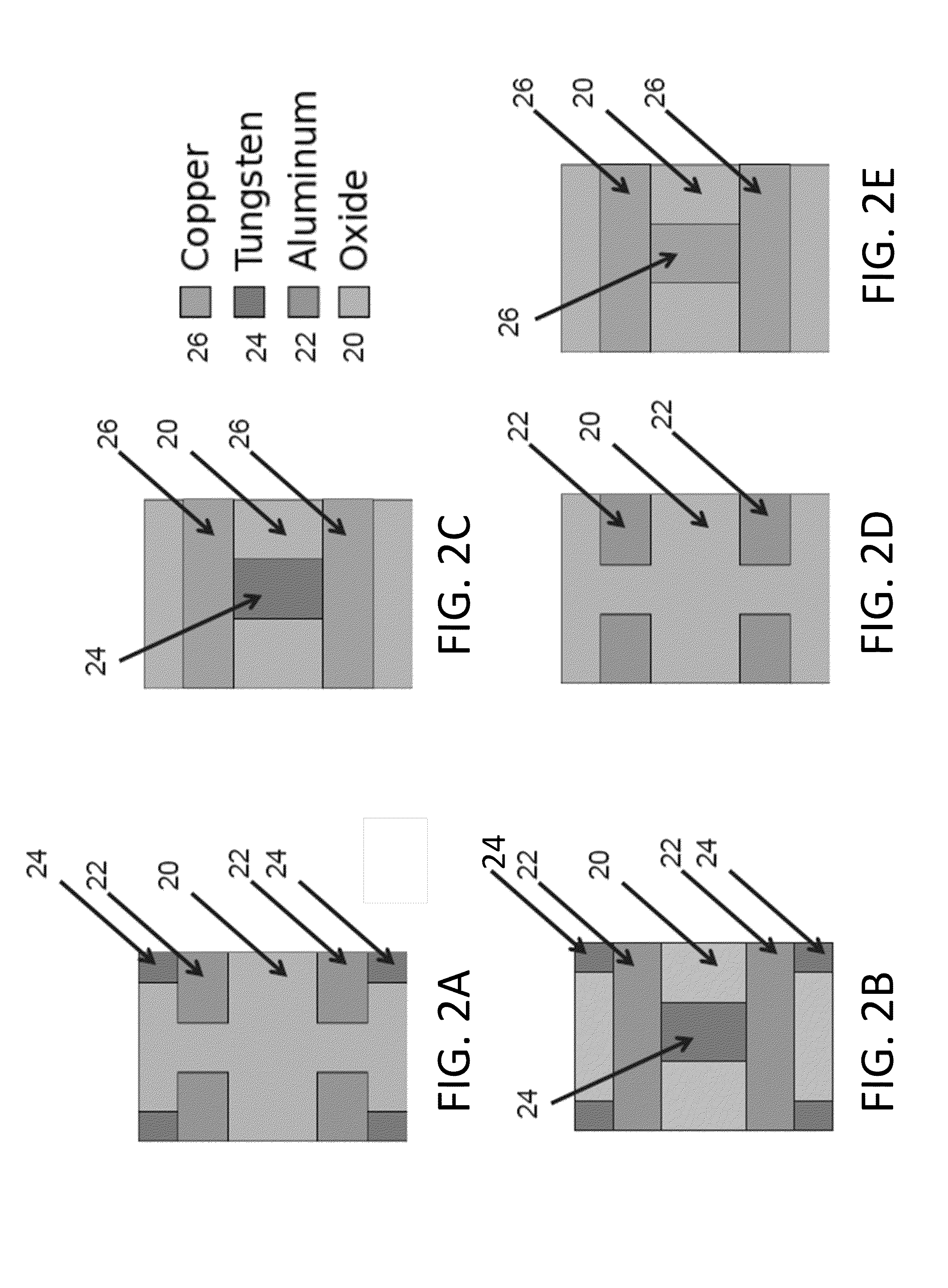

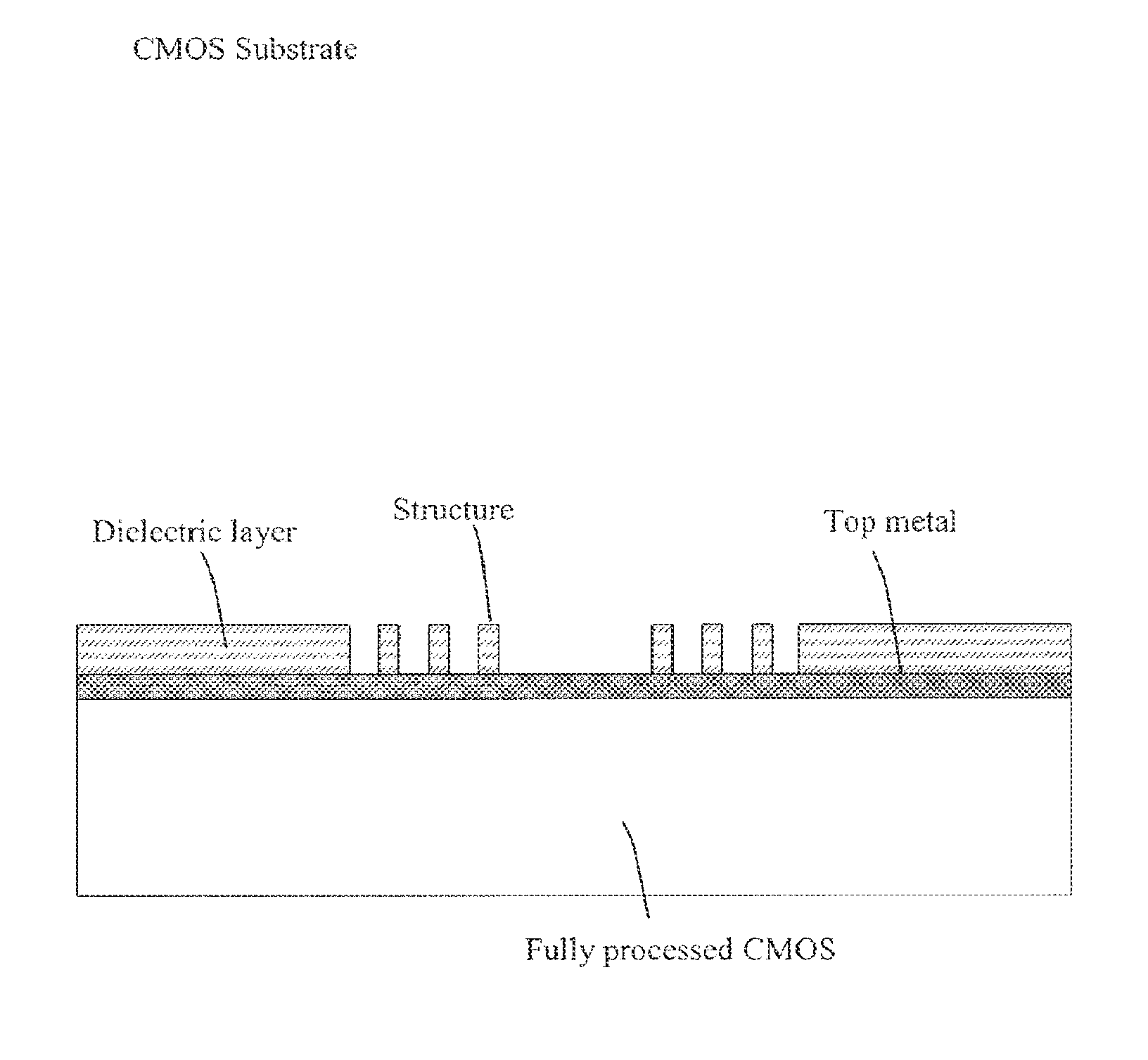

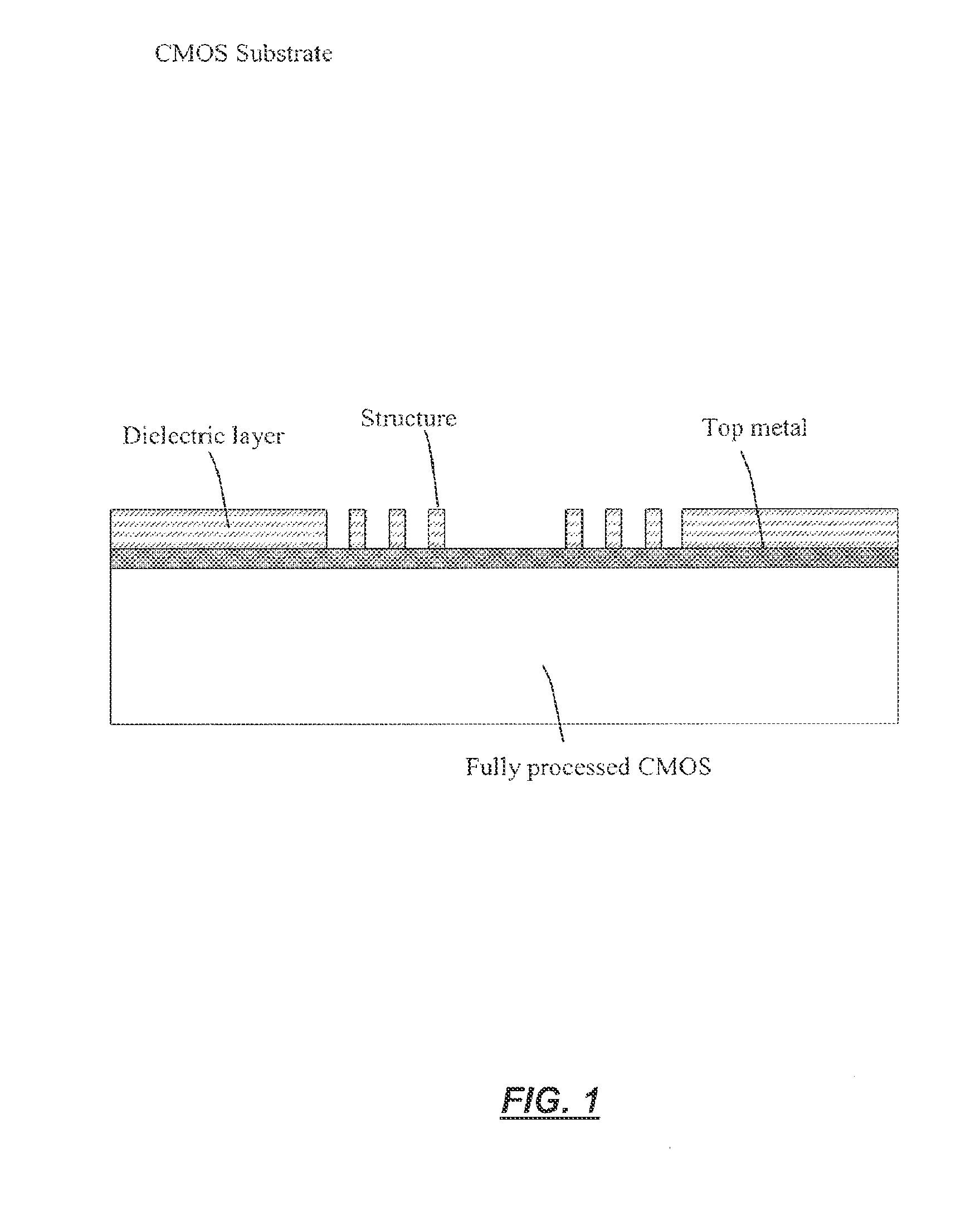

Method and structure of monolithetically integrated inertial sensor using IC foundry-compatible processes

ActiveUS20120248506A1Small sizeReduce parasitismSemiconductor/solid-state device testing/measurementSolid-state devicesFoundryCMOS

The present invention relates to integrating an inertial mechanical device on top of a CMOS substrate monolithically using IC-foundry compatible processes. The CMOS substrate is completed first using standard IC processes. A thick silicon layer is added on top of the CMOS. A subsequent patterning step defines a mechanical structure for inertial sensing. Finally, the mechanical device is encapsulated by a thick insulating layer at the wafer level.Comparing to the incumbent bulk or surface micromachined MEMS inertial sensors, the vertically monolithically integrated inertial sensors have smaller chip size, lower parasitics, higher sensitivity, lower power, and lower cost.

Owner:MOVELLA INC

Differential negative impedance converters and inverters with variable or tunable conversion ratios

ActiveUS20120256709A1Reduce parasitismGood device matchingImpedence convertorsNetwork simulating reactancesCapacitanceEngineering

A differential circuit topology that produces a tunable floating negative inductance, negative capacitance, negative resistance / conductance, or a combination of the three. These circuits are commonly referred to as “non-Foster circuits.” The disclosed embodiments of the circuits comprises two differential pairs of transistors that are cross-coupled, a load immittance, multiple current sources, two Common-Mode FeedBack (CMFB) networks, at least one tunable (variable) resistance, and two terminals across which the desired immittance is present. The disclosed embodiments of the circuits may be configured as either a Negative Impedance Inverter (NII) or a Negative Impedance Converter (NIC) and as either Open-Circuit-Stable (OCS) and Short-Circuit-Stable (SCS).

Owner:HRL LAB

Oscillator circuit

ActiveUS7679465B2Quick switchHigh frequencyElectric pulse generatorOscillations generatorsElectrical and Electronics engineeringEngineering

The present invention relates to an oscillator circuit having a resonant element, an active element, a feedback loop, and an additional loop comprising a phase shifting element.

Owner:TELEFON AB LM ERICSSON (PUBL)

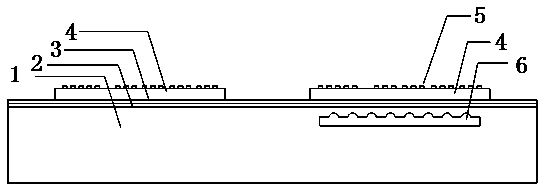

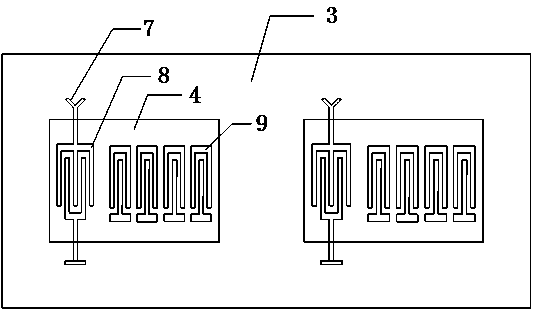

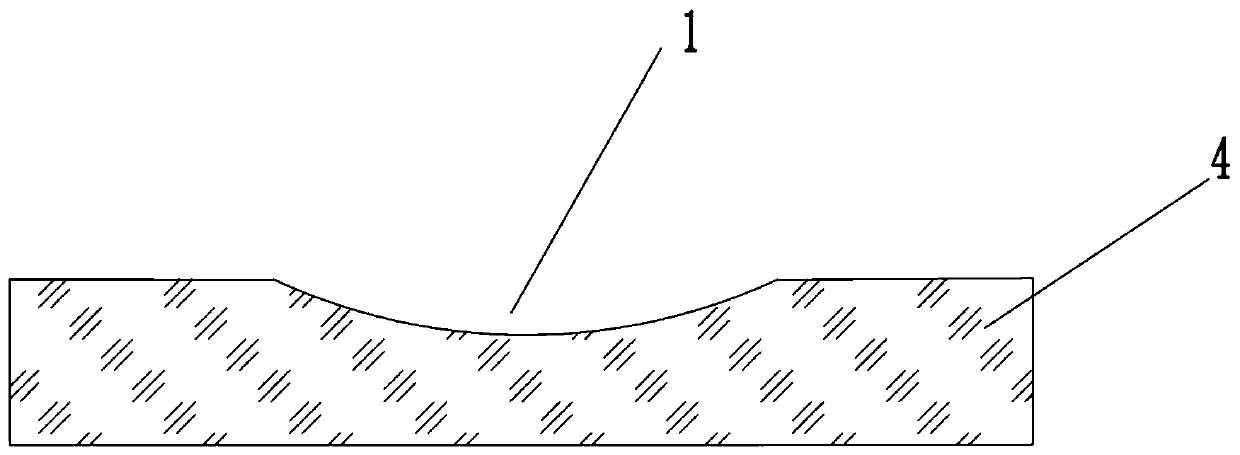

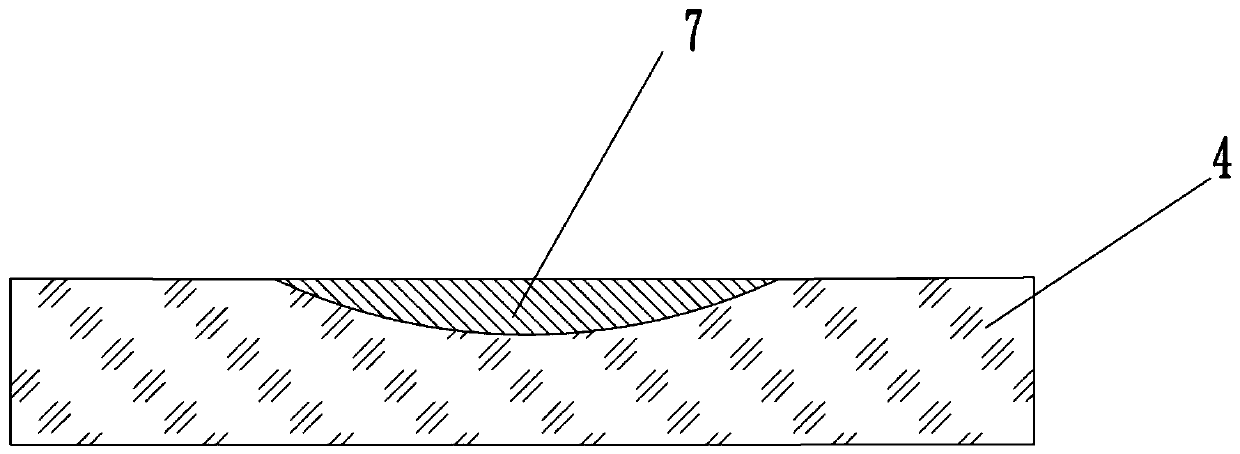

Temperature and pressure integrated sensor and preparation method thereof

InactiveCN110006490AWireless passiveAchieve monolithic integrationFluid pressure measurementThermometers using physical/chemical changesElectricityHigh pressure

The invention discloses a temperature and pressure integrated sensor and a preparation method thereof, belongs to the technical field of sensors, and aims to solve the technical problem that signals acquired by the sensor through wire transmission are affected and even cannot work in some extremely severe environments. A temperature and pressure integrated sensor comprises a substrate and a piezoelectric material arranged on the surface of the substrate, a resonator is arranged on the piezoelectric material, and a sealing cavity is formed in the substrate. The temperature is measured by utilizing the effect that the resonant frequency of the delay line SAW resonator deposited on the piezoelectric material can be changed along with the external temperature; the pressure is measured by utilizing the effect that the resonant frequency of the delay line SAW resonator growing on the cavity can be changed along with the external pressure. The temperature and pressure integrated sensor does not need to be driven by an internal energy source and does not need a wire to transmit signals, so that the sensor has the characteristics of being wireless, passive and capable of working in extremely severe environments such as high temperature, high pressure and sealed space.

Owner:HOHAI UNIV CHANGZHOU

Semi-suspension graphene field effect transistor preparation method

ActiveCN105047562AAvoid damageAvoid contaminationSemiconductor/solid-state device manufacturingSemiconductor devicesGrapheneChemical vapor deposition

The invention discloses a semi-suspension graphene field effect transistor preparation method, and relates to the technical field of transistors. The semi-suspension graphene field effect transistor preparation method comprises the following steps that photoresist is coated on a substrate so that a photoresist pattern is formed; the photoresist pattern acts as a mask film to form a substrate structure with grooves; metal-based graphene is prepared via a chemical vapor deposition method; a metal layer is deposited on the upper surface of metal-based graphene; the metal base below metal-based graphene is corroded so that a graphene assembly is formed; the graphene assembly is transferred to the substrate structure with the grooves; a second photoresist pattern is formed on the upper surface of the metal layer; the second photoresist pattern acts as the mask film to form a drain electrode and a source electrode; and the second photoresist pattern acts as the mask film, and gate metal is deposited on an insulating medium. Damage and contamination of graphene can be avoided by the method. Interface scattering of the substrate is reduced by separation of graphene and the substrate so that high mobility of carriers in graphene is realized and high-frequency performance of a graphene transistor is enhanced.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

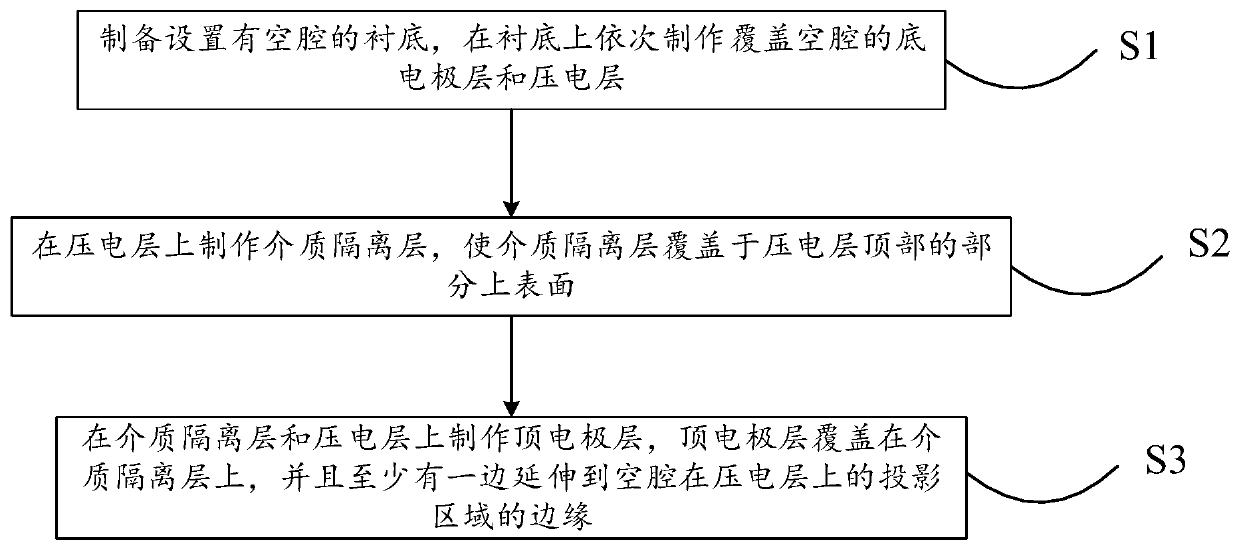

Top electrode structure of bulk acoustic wave resonator and manufacturing process

PendingCN111211757AGuaranteed stabilityIncrease stressImpedence networksMechanical reliabilityIsolation layer

The invention discloses a top electrode structure of a bulk acoustic wave resonator and a manufacturing process, and the manufacturing process comprises the steps: preparing a substrate with a cavity,and sequentially manufacturing a bottom electrode layer and a piezoelectric layer, which cover the cavity, on the substrate; manufacturing a dielectric isolation layer on the piezoelectric layer, sothat the dielectric isolation layer covers part of the upper surface of the top of the piezoelectric layer; and manufacturing a top electrode layer on the dielectric isolation layer and the piezoelectric layer, the dielectric isolation layer being covered with the top electrode layer, and at least one side of the top electrode layer extending to the edge of the projection area of the cavity on thepiezoelectric layer. The dielectric isolation layer enhances the mechanical reliability and used for buffering when the stress change of the device layer is increased, and parasitic and reflected transverse waves of radio-frequency signals can be reduced. The mass load layer can form abrupt change of acoustic impedance at the edge of the top electrode layer, increase impedance of the parallel resonator, greatly weaken parasitic resonance, reduce pseudo-resonance and achieve the purpose of improving Q value.

Owner:HANGZHOU JWL TECH INC

Method and apparatus for switching audio and data signals through a single terminal

ActiveUS7482853B2Minimal distortionIncrease the areaTransistorPulse automatic controlCapacitanceDigital data

A MOSFET-based, multi signal-switching circuit controllably passes analog / audio signals and digital signals through a common terminal to a single connector. Analog / audio signals are coupled through a single N-channel MOSFET analog signal switch which, when turned-ON, minimizes distortion of the analog / audio signal and capacitive loading to an adjacent, MOS-based or CMOS-based digital data signal switch. A respective turn-OFF circuit maintains its associated switch MOSFET turned OFF.

Owner:INTERSIL INC

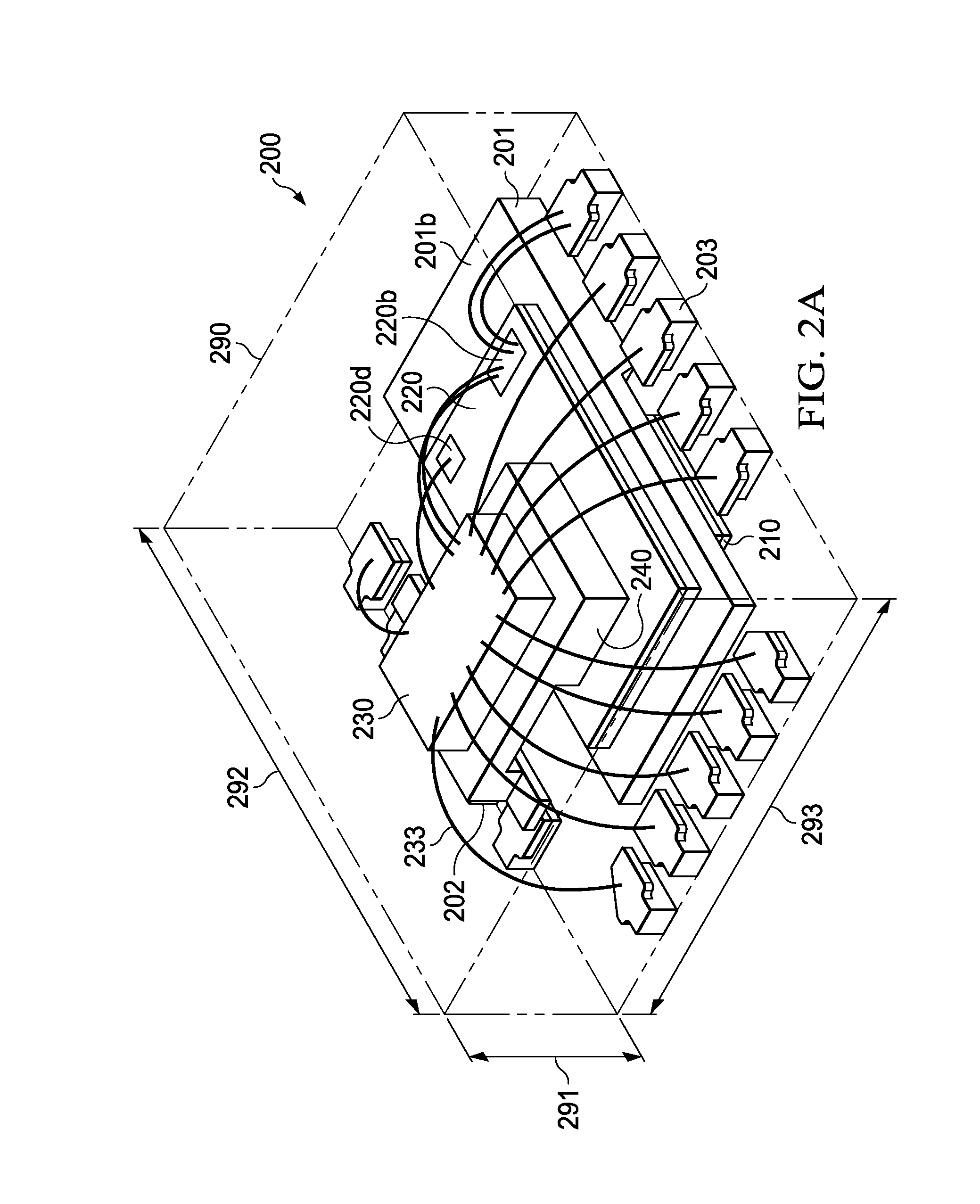

Stacked synchronous buck converter having chip embedded in outside recess of leadframe

ActiveUS9184121B2Reduce the overall heightLow powerSemiconductor/solid-state device detailsSolid-state devicesBuck converterSemiconductor chip

A power supply system (200) has a QFN leadframe with leads and a pad (201, switch node terminal); a pad surface having a portion recessed with a depth (270) and an outline suitable for attaching a semiconductor chip. A first FET chip (220) is vertically stacked to the opposite pad surface. A clip (240) is vertically stacked on the first FET chip and tied to a lead (202, grounded output terminal). A second FET chip (210) has its source terminal attached to the recessed portion and its drain (210a, input terminal) and gate (210b) terminals co-planar with the un-recessed portion. A driver-and-controller chip (230) is attached to the clip. Packaging compound (290) encapsulates the parts but leaves a pad surface and the drain and gate terminals of the second FET chip un-encapsulated.

Owner:TEXAS INSTR INC