Patents

Literature

100results about How to "Achieve monolithic integration" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

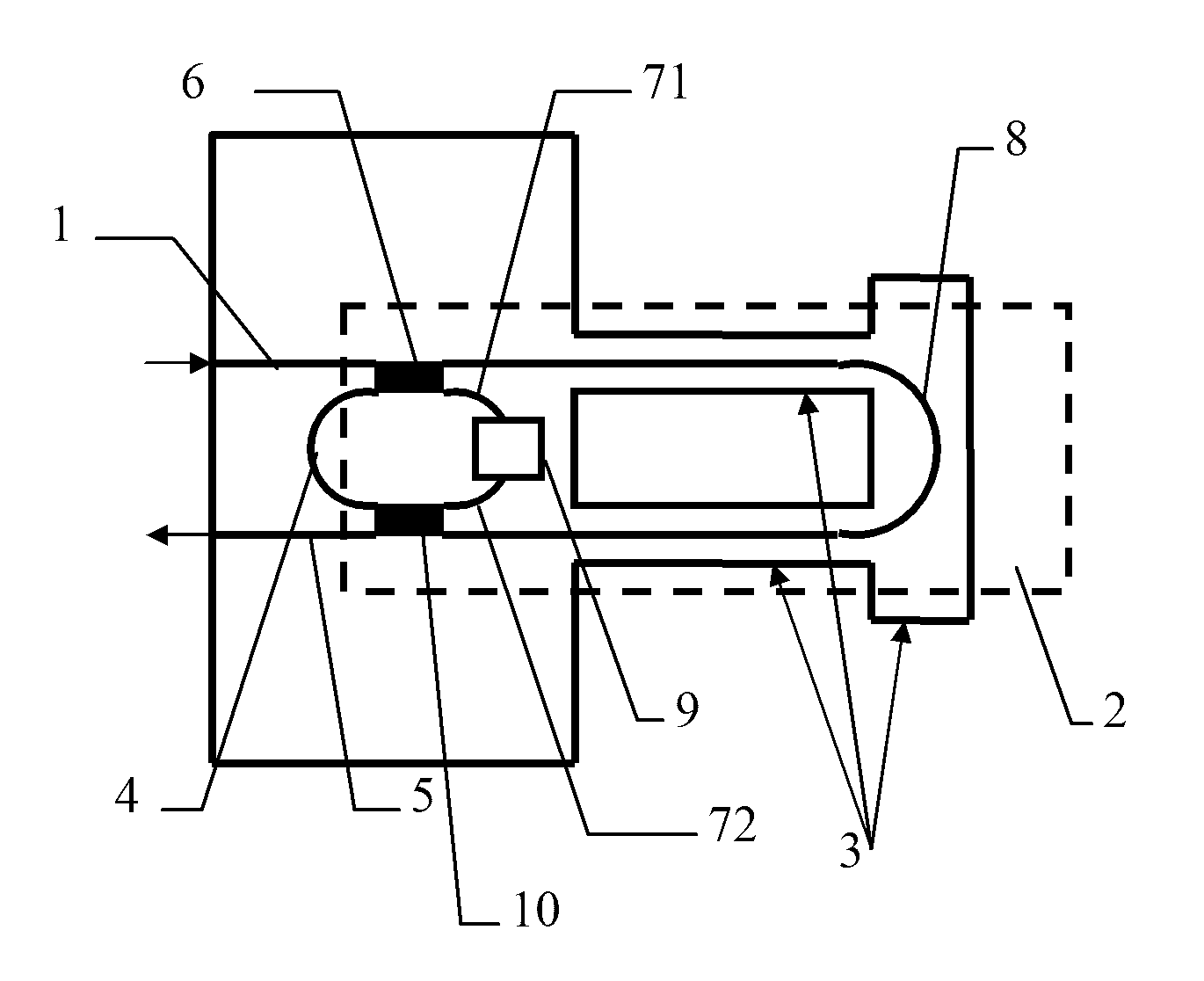

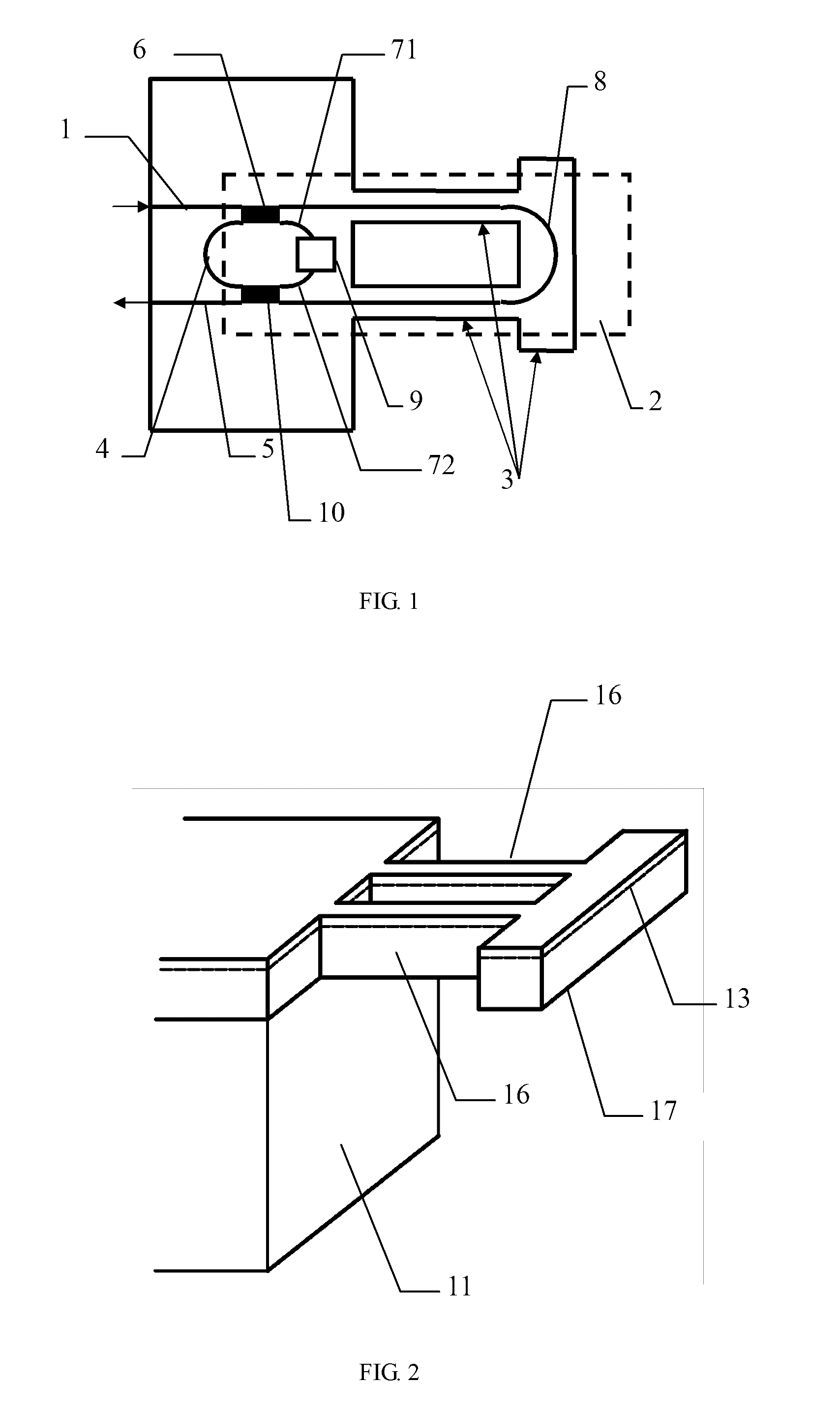

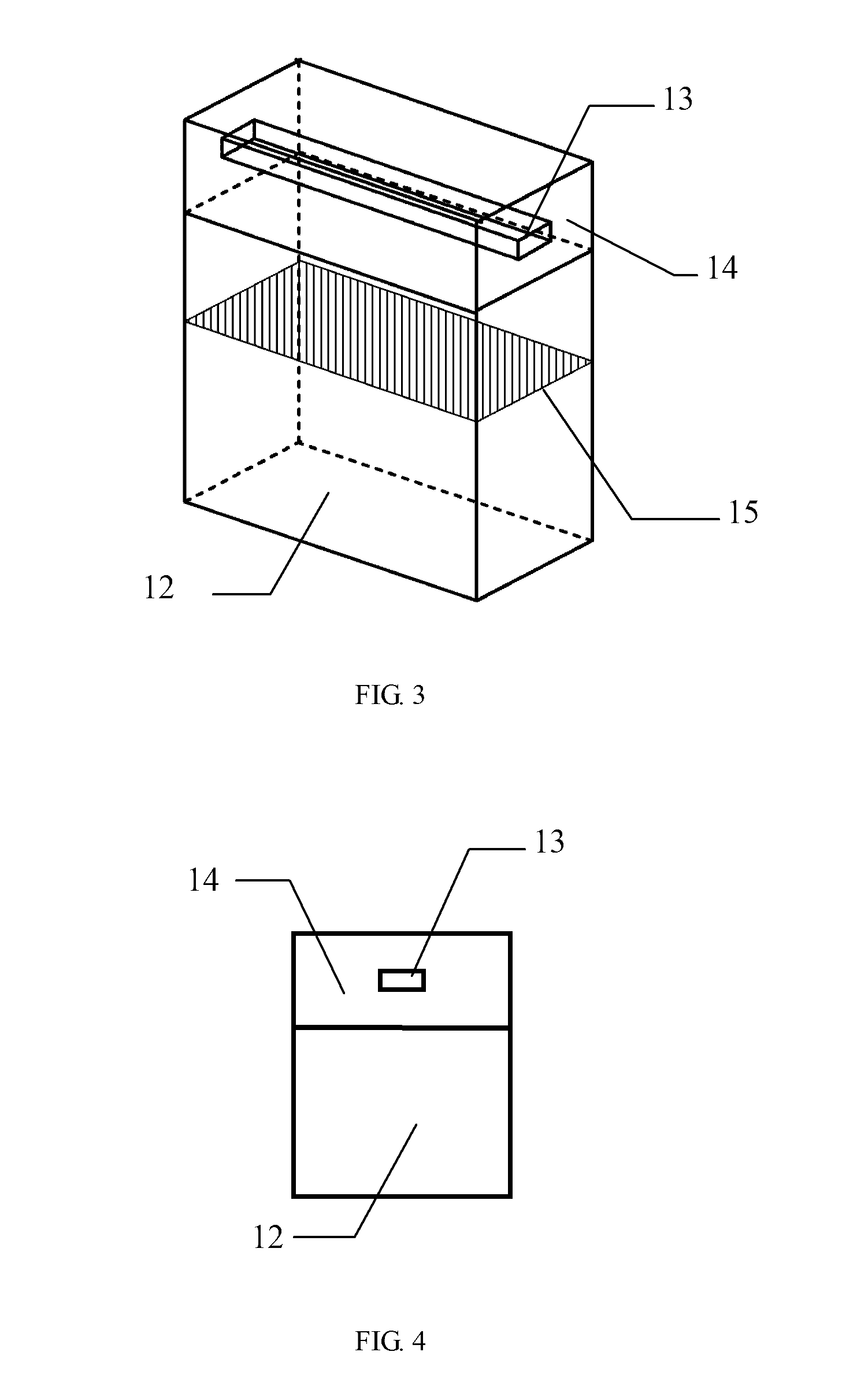

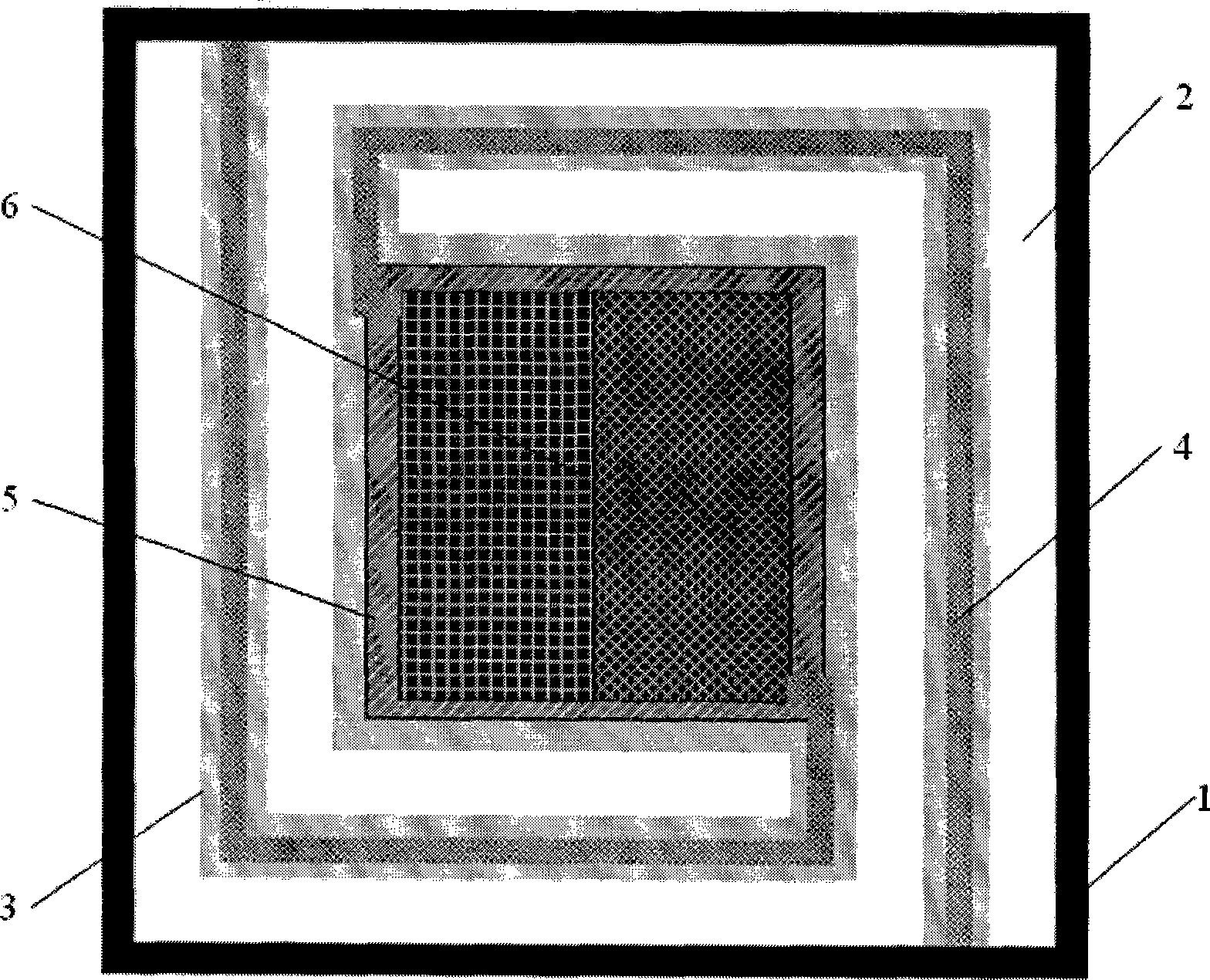

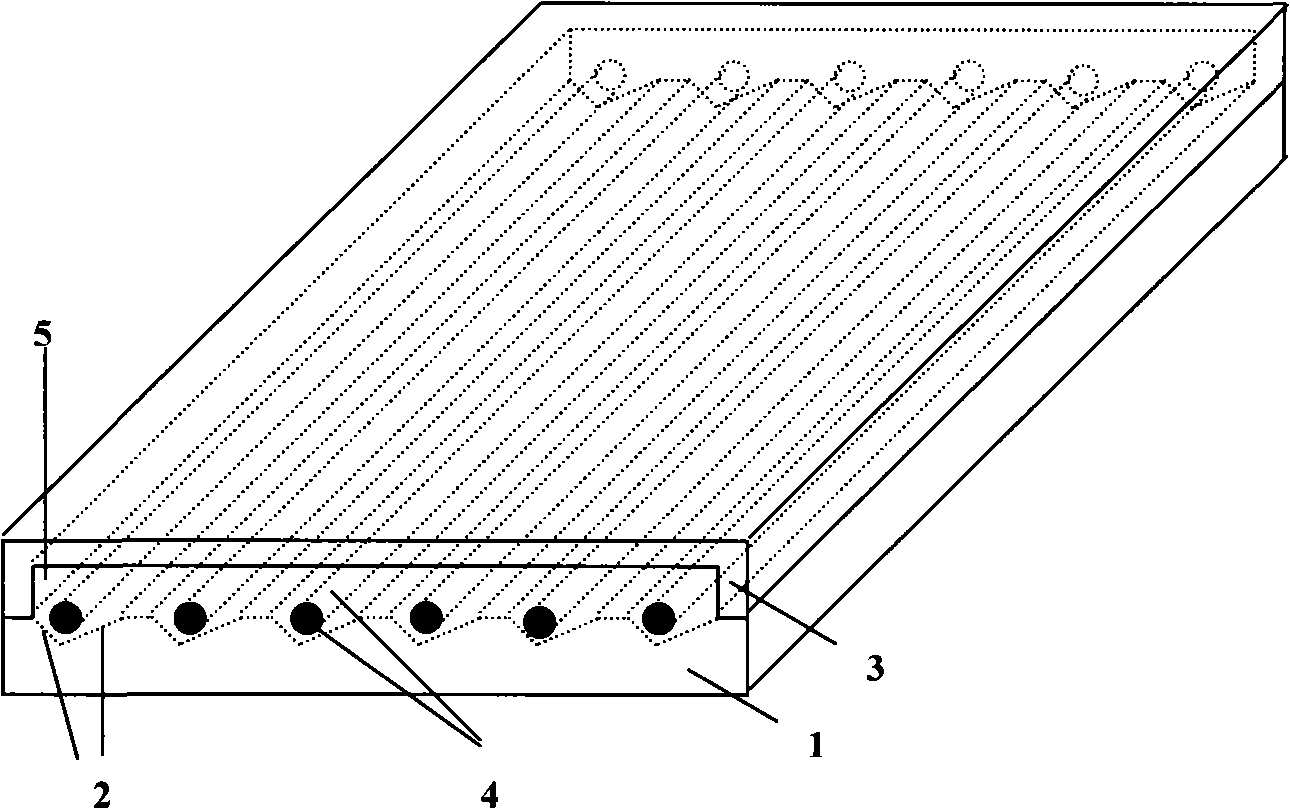

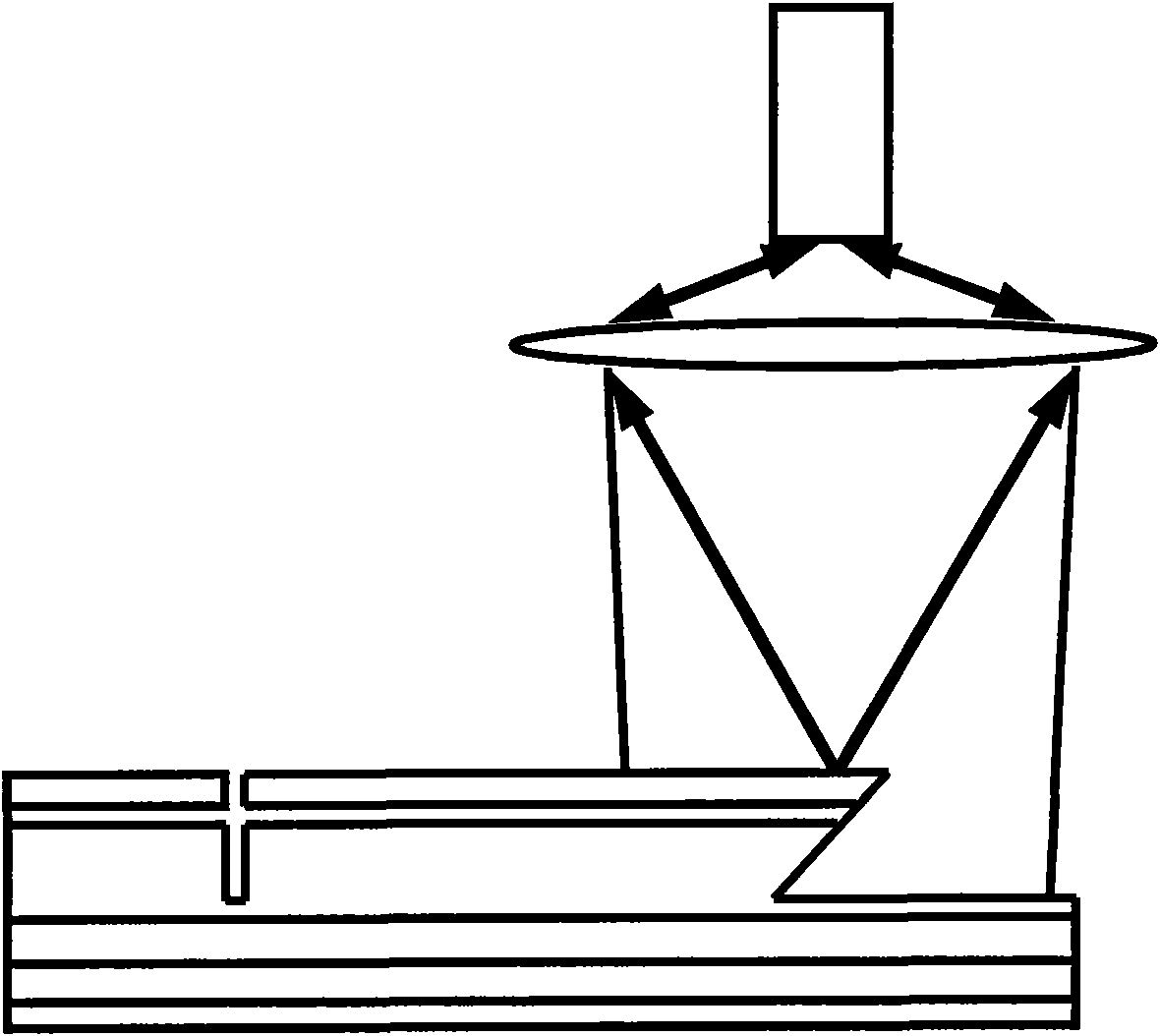

Cantilever beam structural resonant-type integrated optical waveguide accelerometer

ActiveUS20110303008A1Small sizeEasy to produceAcceleration measurement using interia forcesOptical light guidesAccelerometerPhase difference

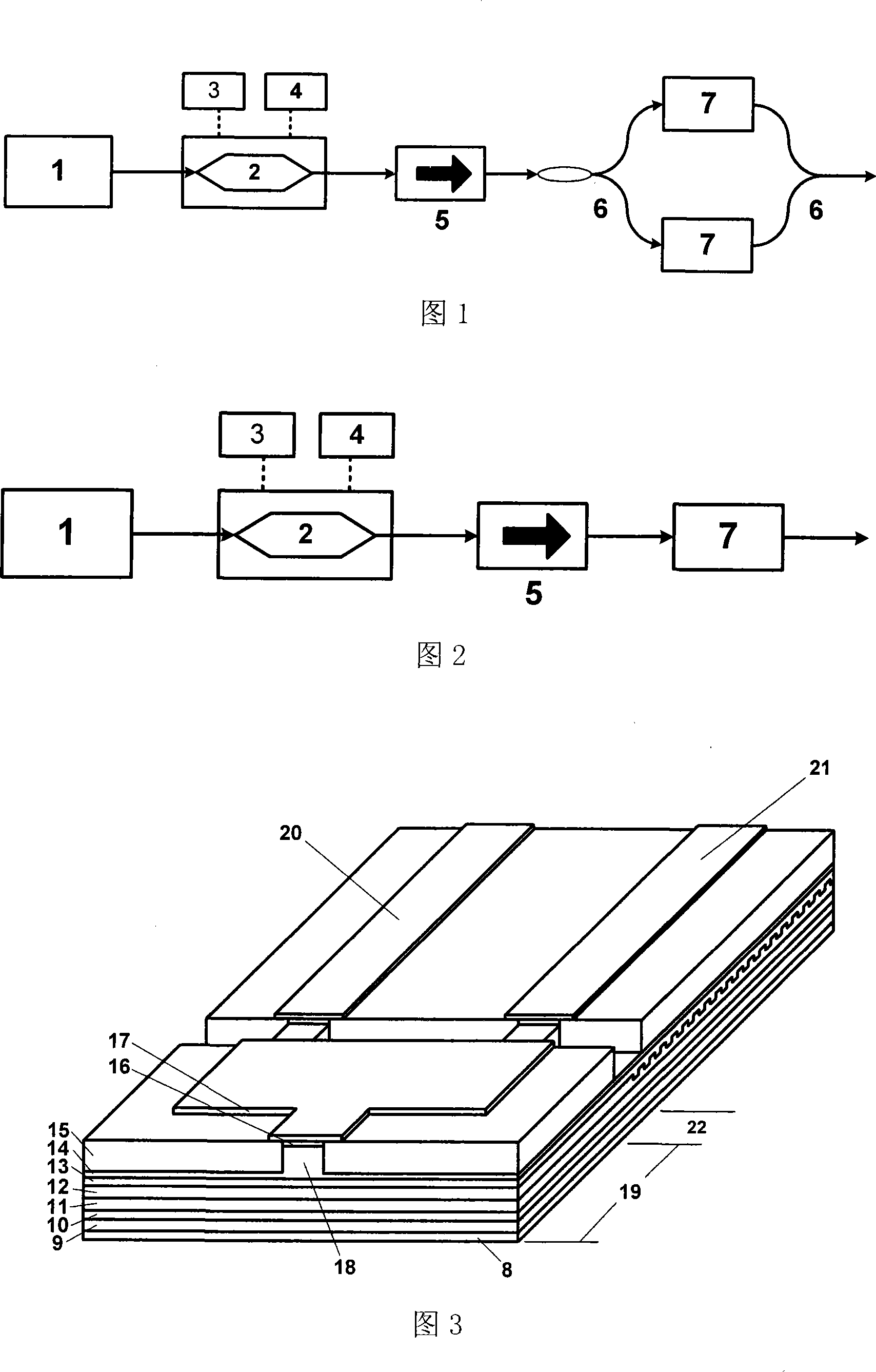

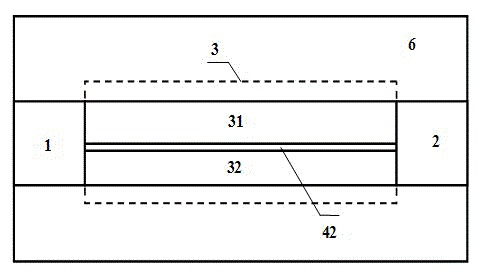

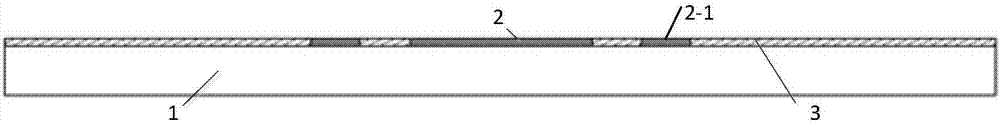

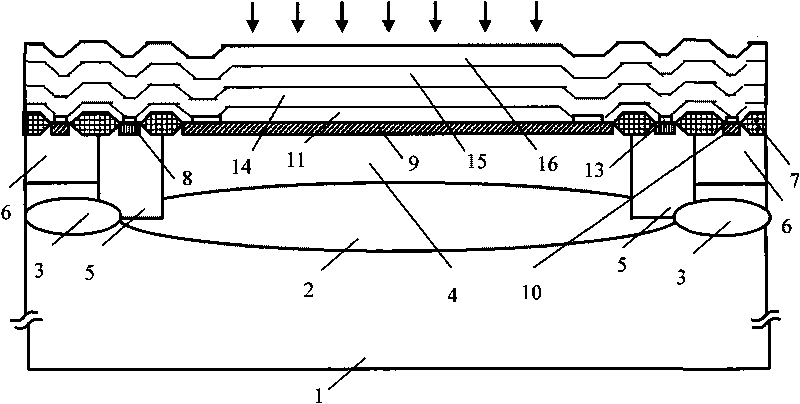

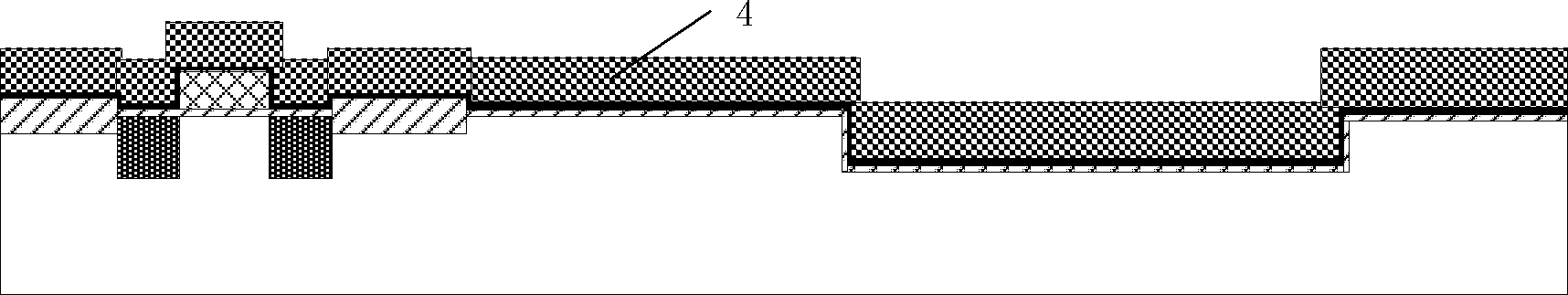

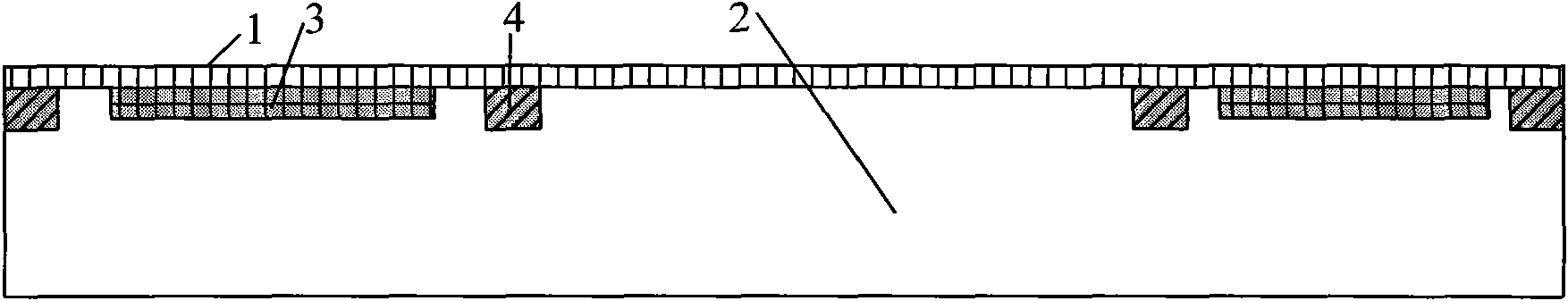

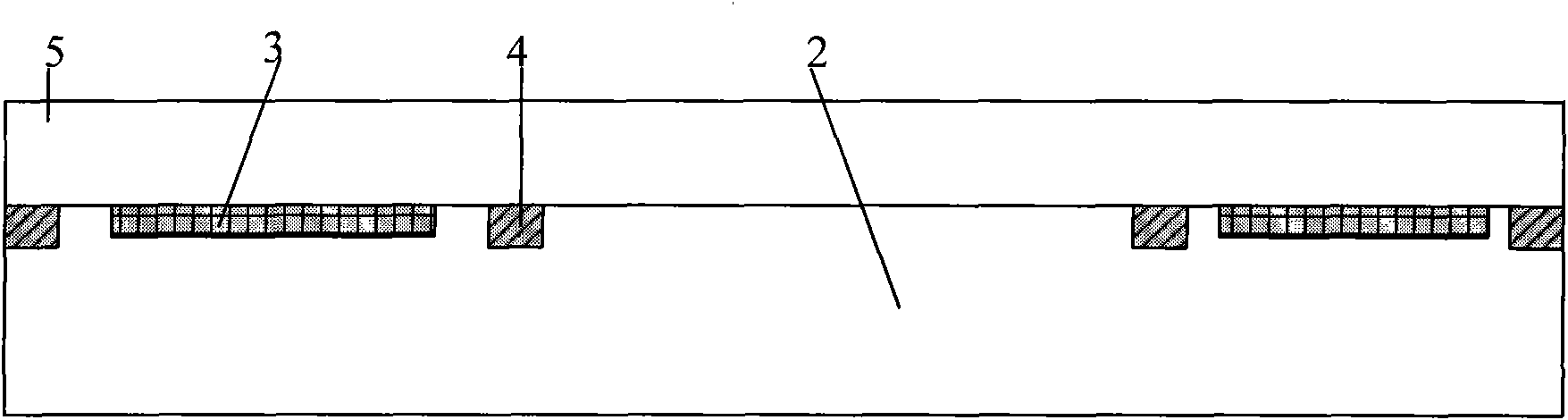

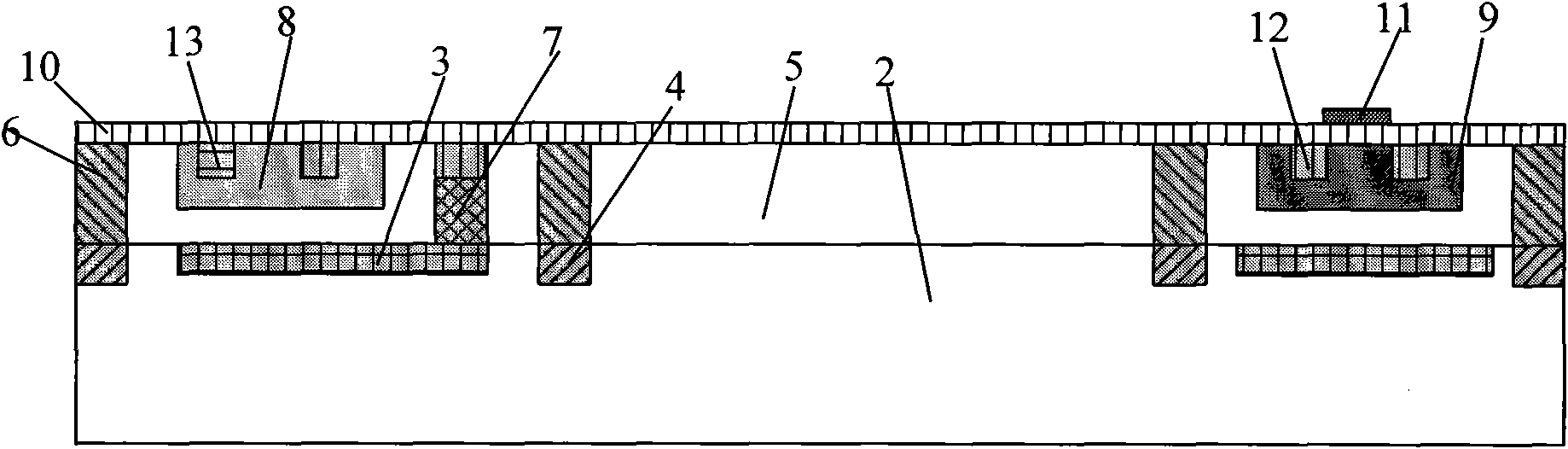

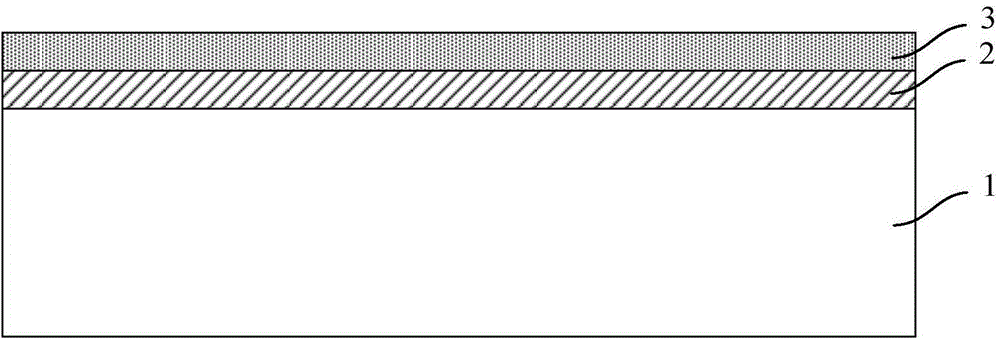

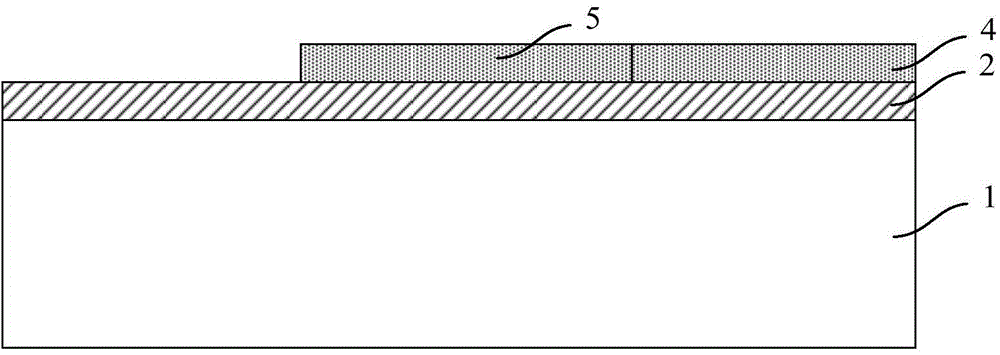

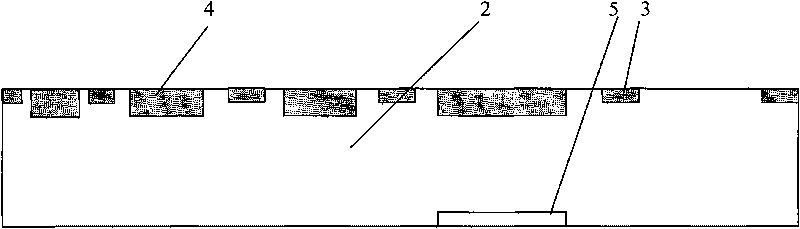

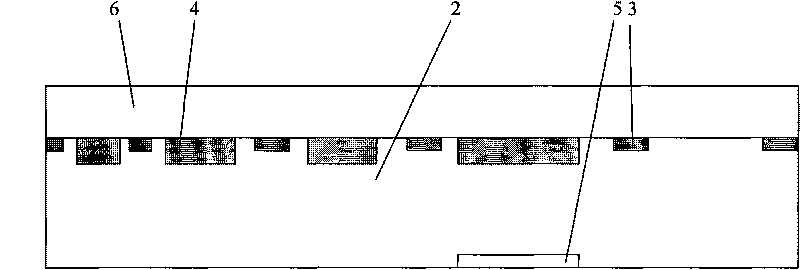

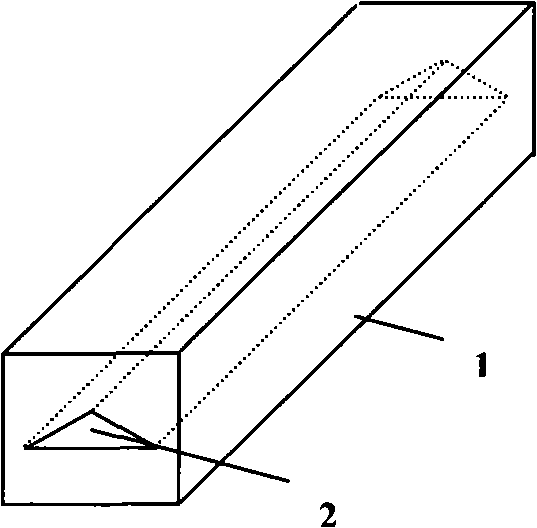

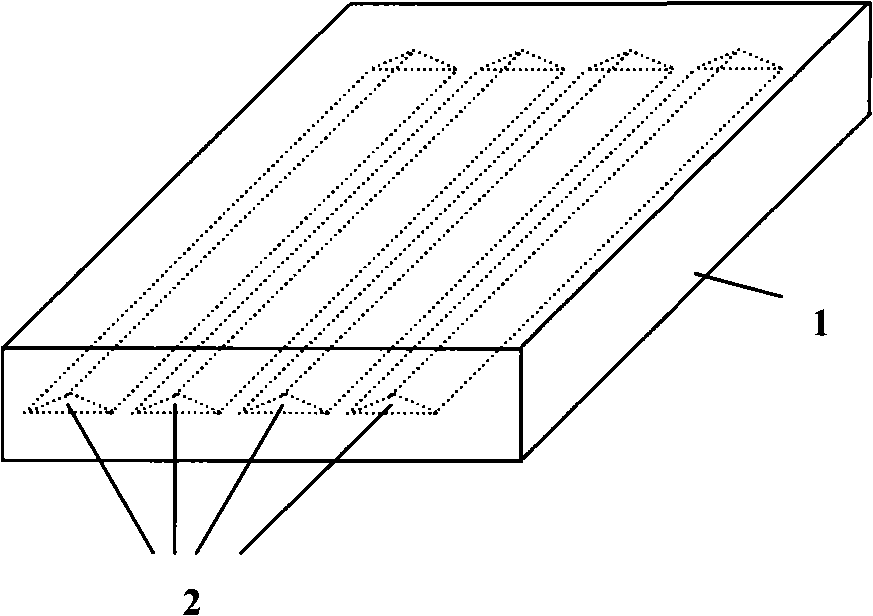

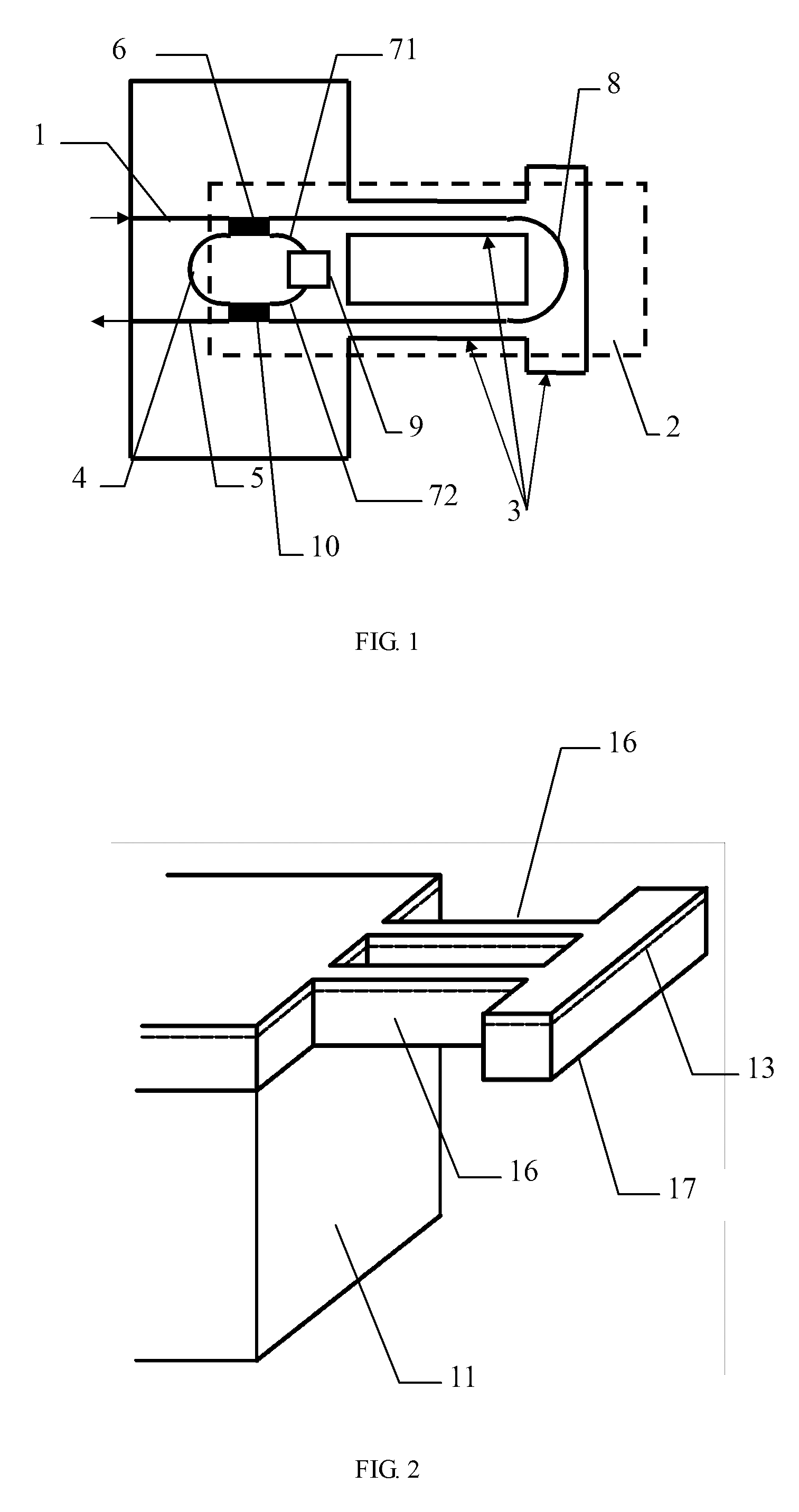

A cantilever beam structural resonant-type integrated optical waveguide accelerometer, includes an input waveguide (1), a dissymmetrical structural Mach-Zehnder interferometer (2), a micro-mechanical vibration cantilever beam (3), a short curved waveguide (4) and an output waveguide (5); all the waveguide structures and the cantilever beam use the integrated optical micromachining technique, and the device single-scale integration can be realized by using the temperature-insensitive organic polymer optical waveguide structure and the organic polymer substrate, the key technique indexes such as detection sensitivity, dynamic range are extensively adjusted. The phase difference of the optical signal can be measured by detecting the optical intensity of the resonant frequency of the optical circuit so as to achieve high sensitive acceleration detection, and to be free from the effect of the ambient temperature disturbance and waveguide birefringence.

Owner:SOUTHEAST UNIV

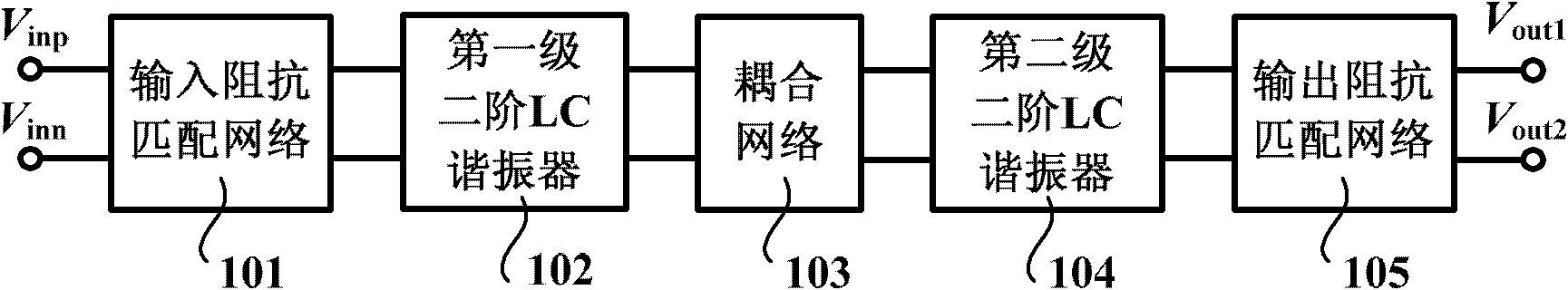

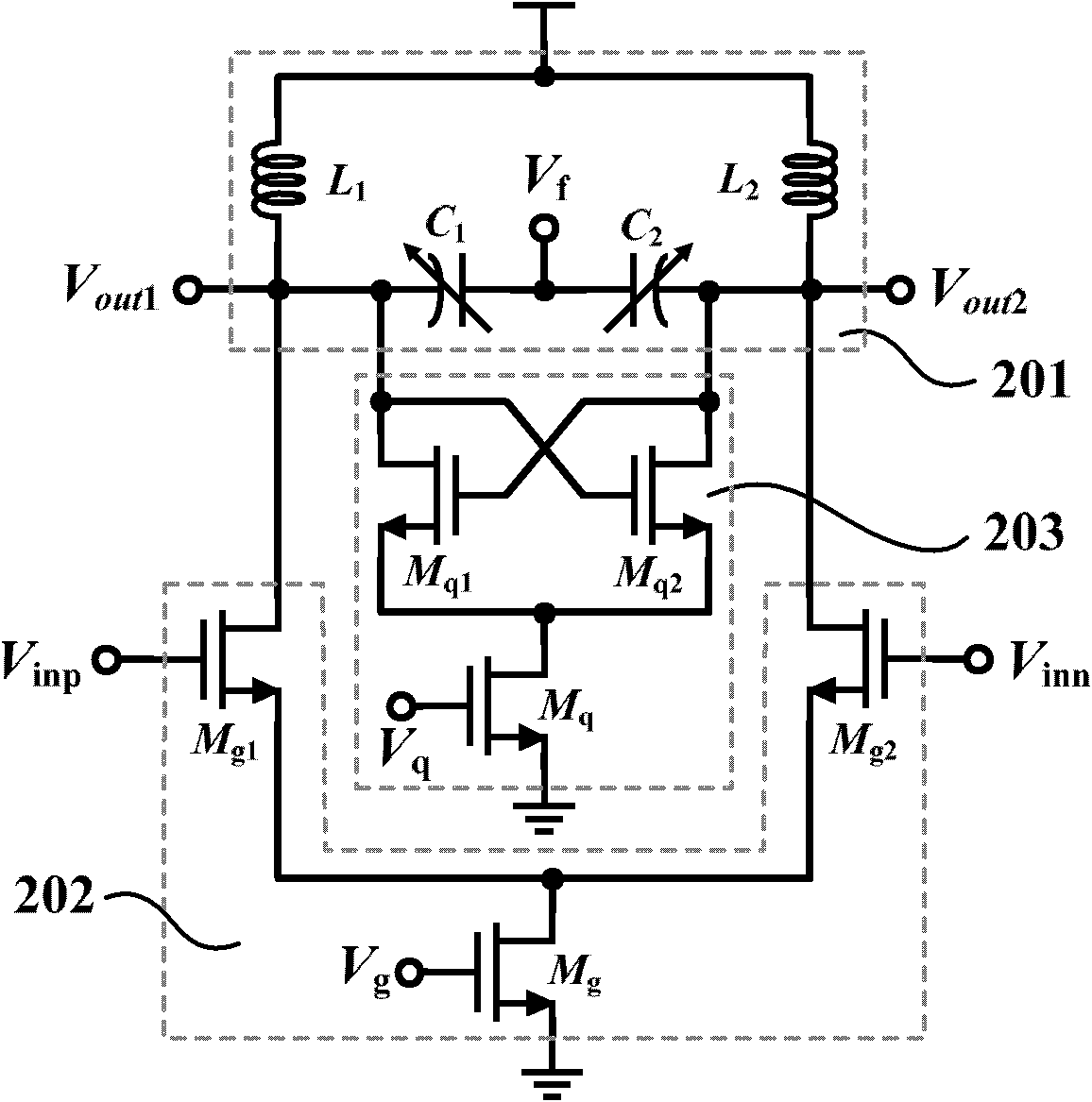

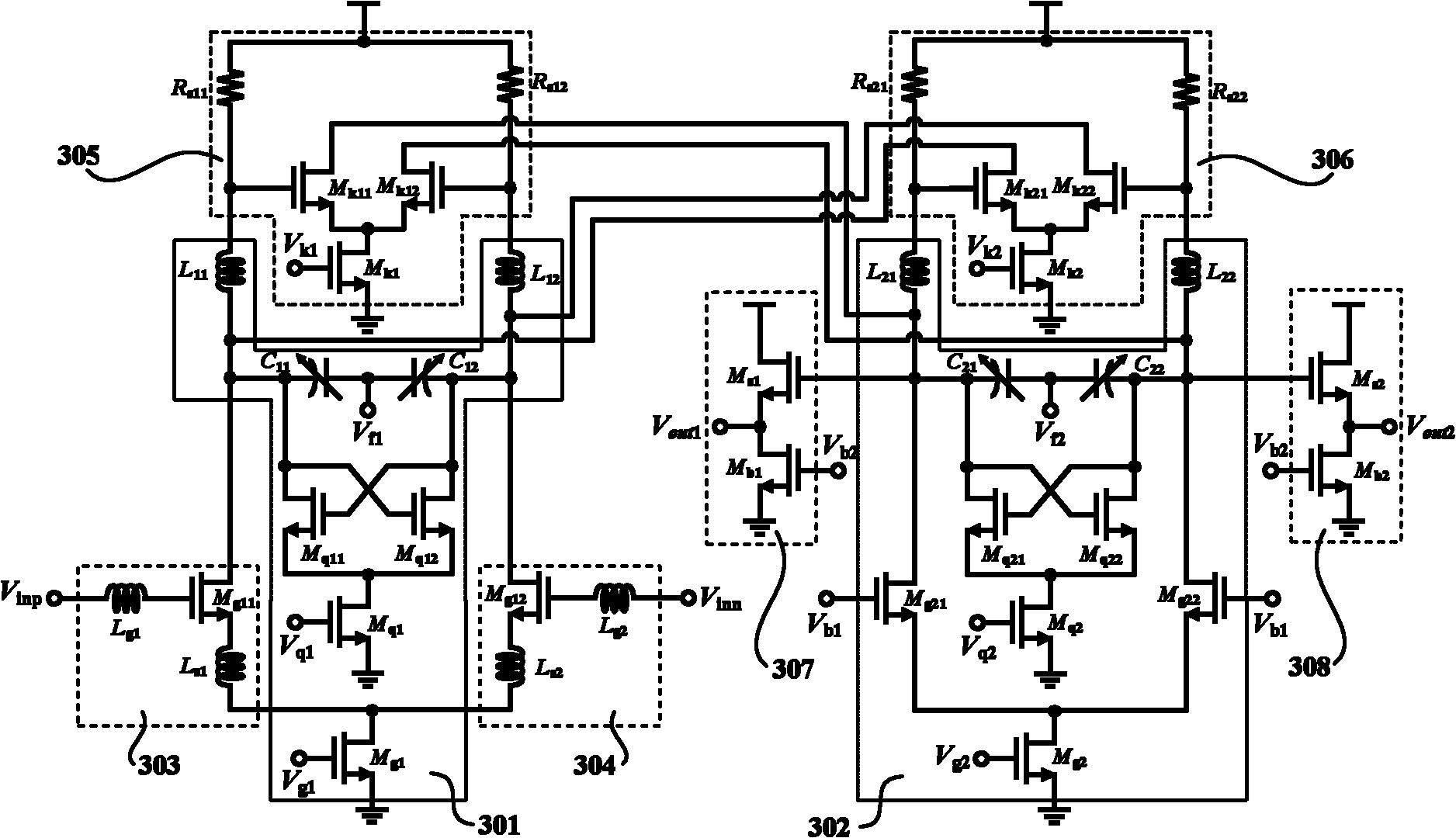

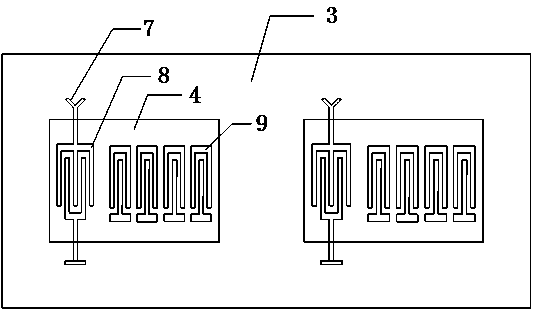

Fourth-order active LC radio frequency band pass filter

ActiveCN102340294ASolve the problem of poor in-band flatnessIssues with poor in-band flatness achievedFrequency selective two-port networksLc resonatorLc resonant circuit

The invention, which belongs to the integrated circuit design technology field, relates to a fourth-order active LC radio frequency band pass filter. Based on a CMOS technology, forms of current detection resistor and transconductance are used to simulate inductive coupling and to couple a two-level second-order LC resonator into the fourth-order LC band pass filter. The band pass filter comprises: the two-level second-order LC resonance circuits with a same connection mode and symmetrical structures, two input impedance matching circuits, two interstage coupling circuits and two output impedance matching circuits. In-band flatness of the second-order active LC band pass filter is bad. By using the radio frequency band pass filter of the invention, the above problem can be solved. The CMOS technology can be used to perform integration on a sheet so that an integration level can be substantially raised, which provides a feasible scheme for realizing monolithic integration on a radio-frequency front end of a wireless receiver.

Owner:SOI MICRO CO LTD

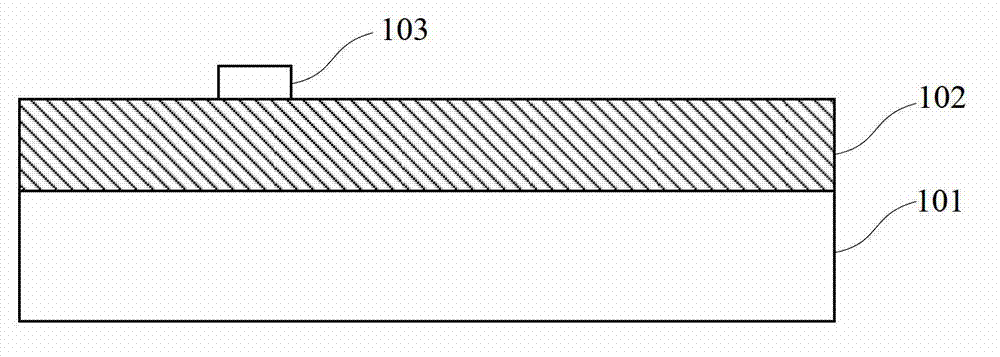

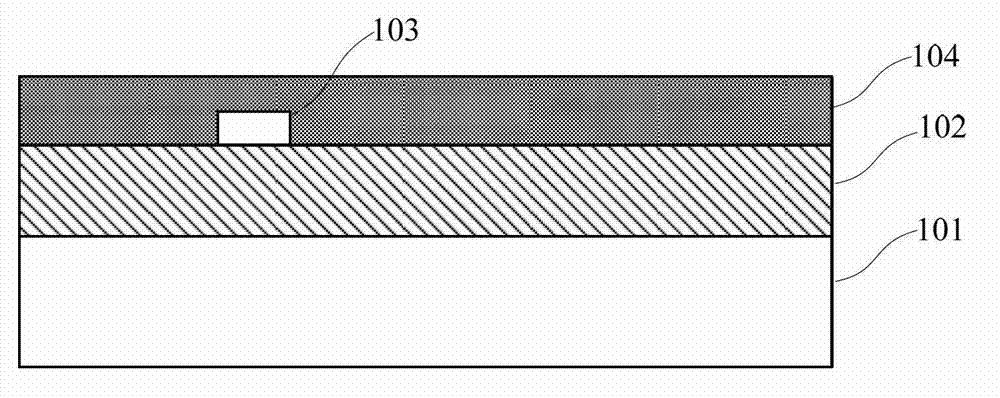

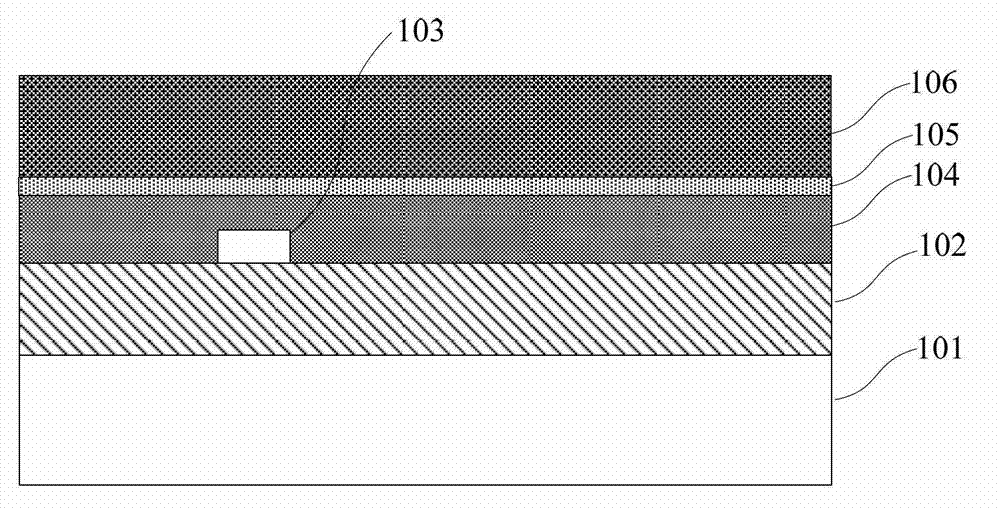

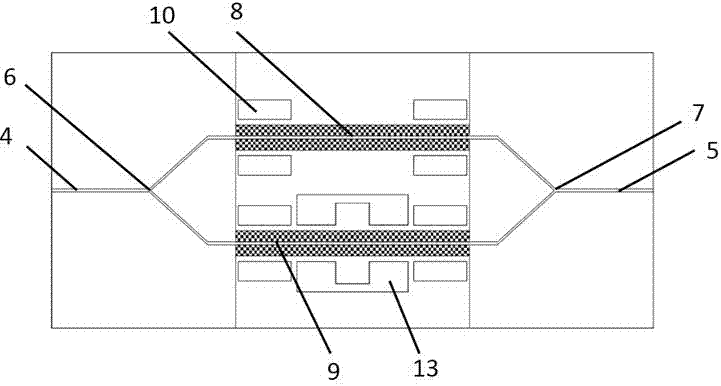

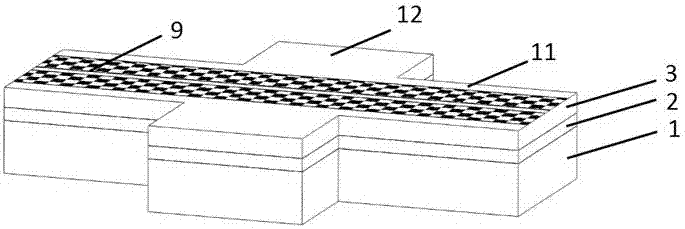

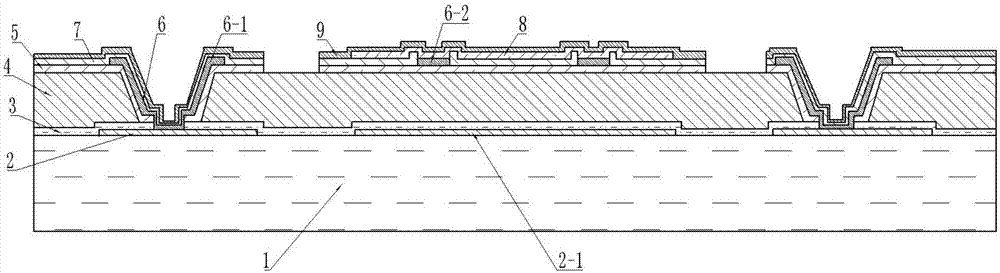

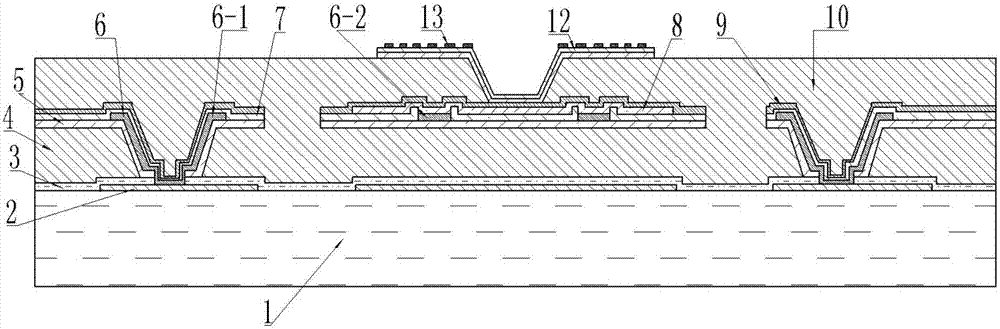

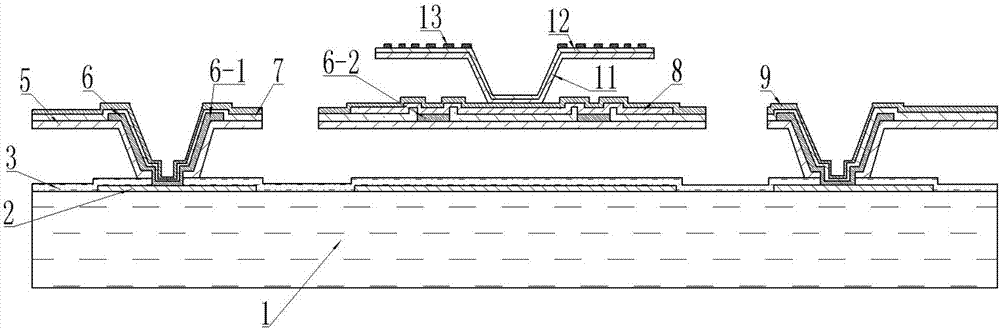

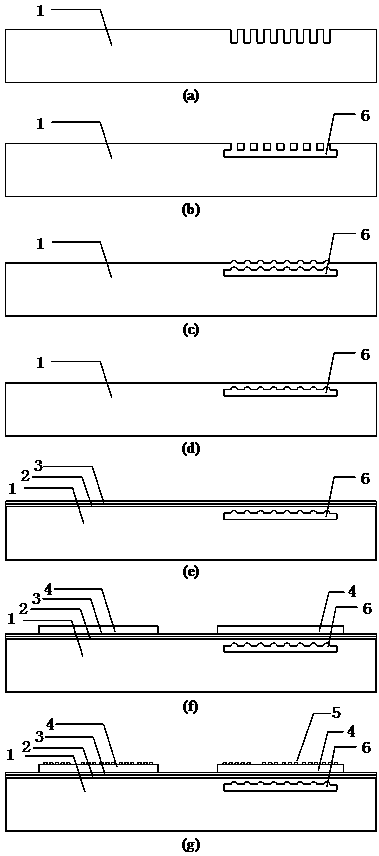

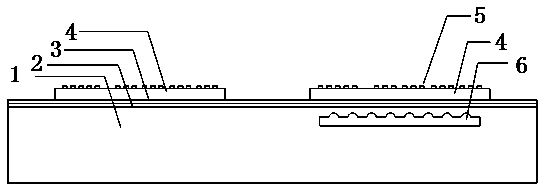

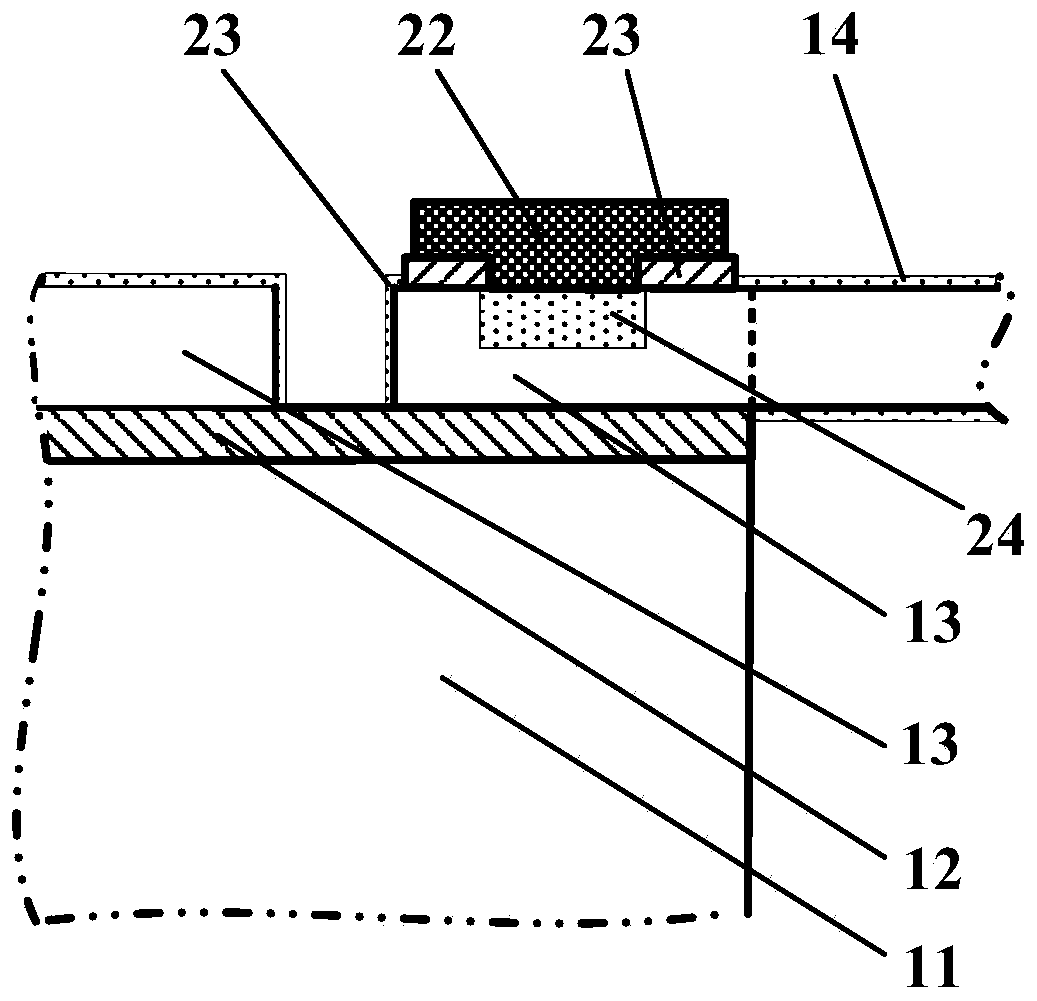

Hybrid integrated laser based on BCB (benzocyclobutene) bonding process and manufacturing method thereof

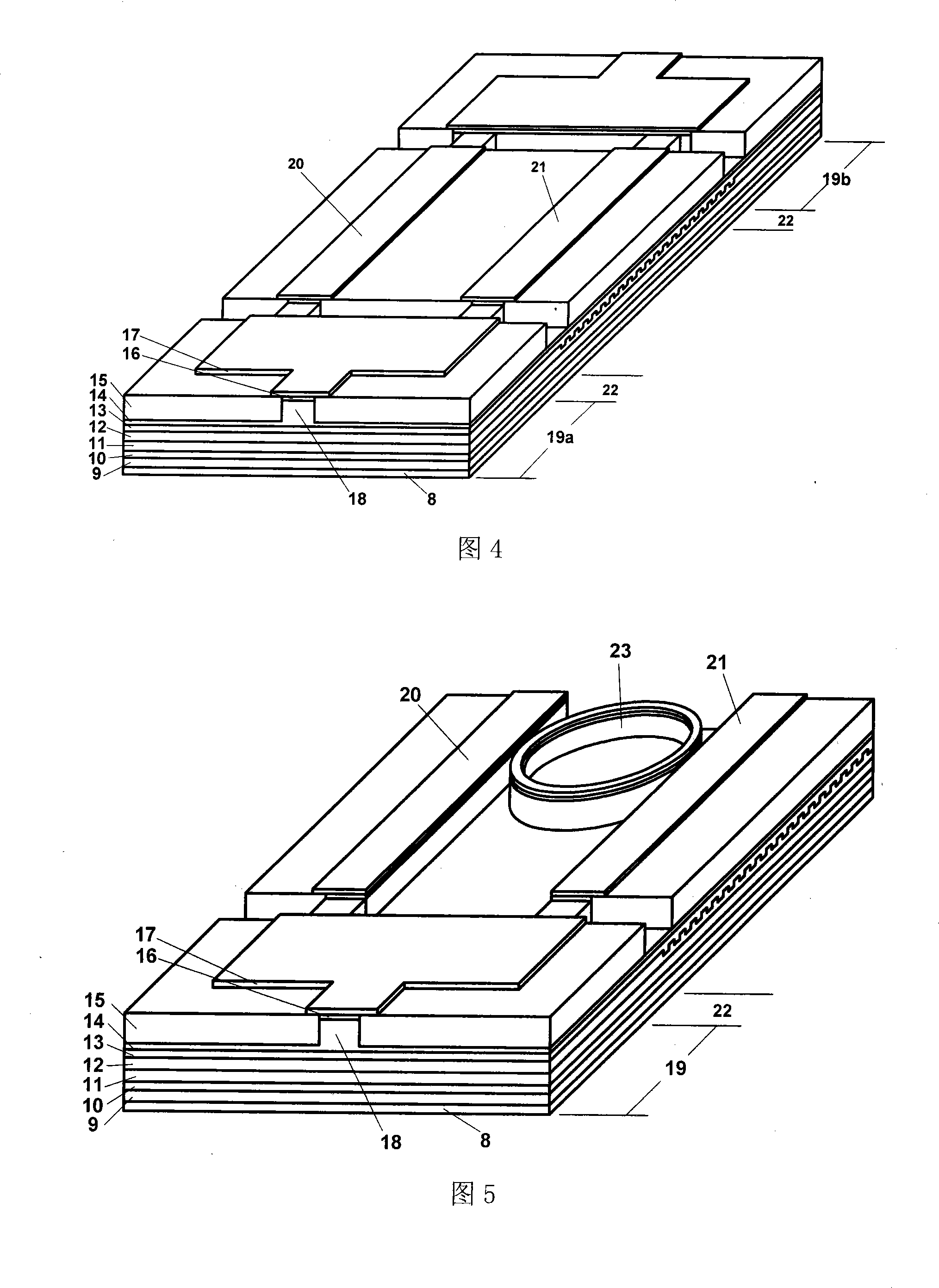

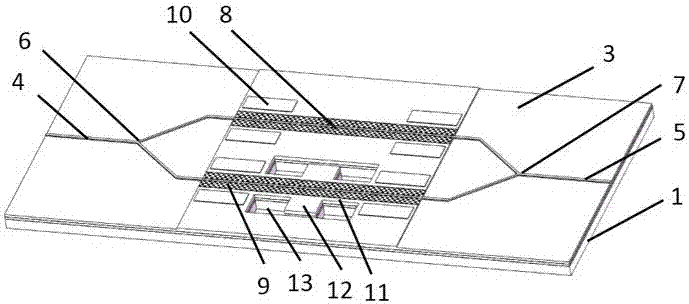

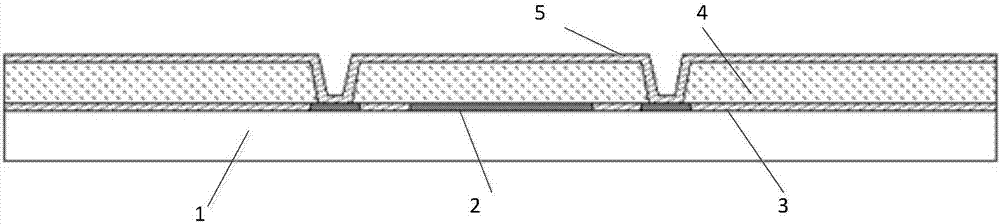

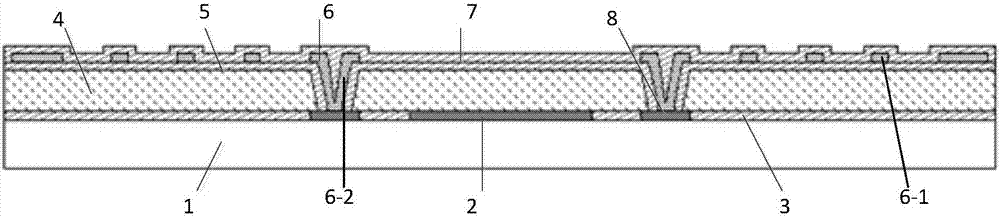

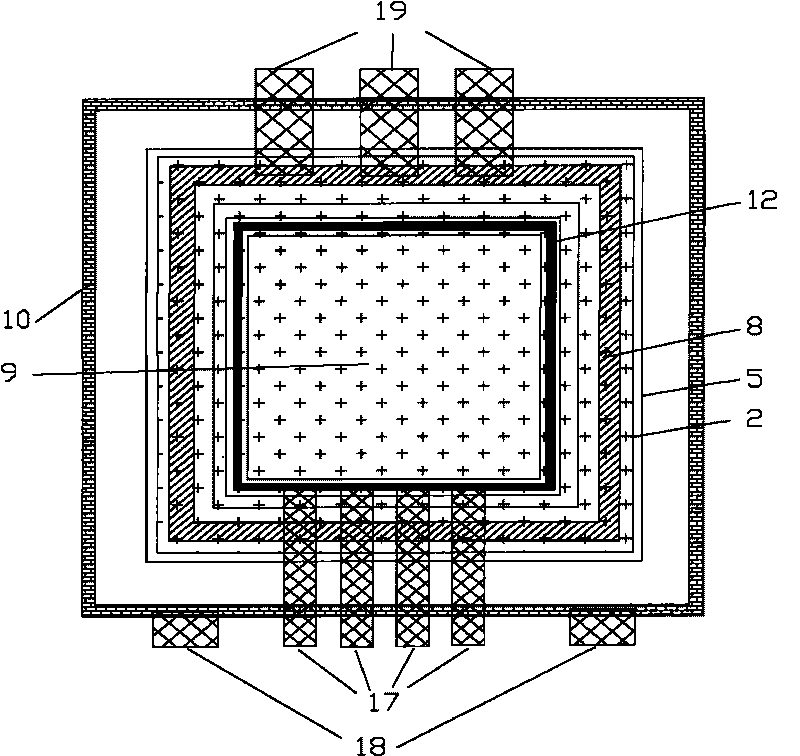

ActiveCN102904159AAchieve monolithic integrationSmall sizeOptical wave guidanceLaser detailsBonding processContact layer

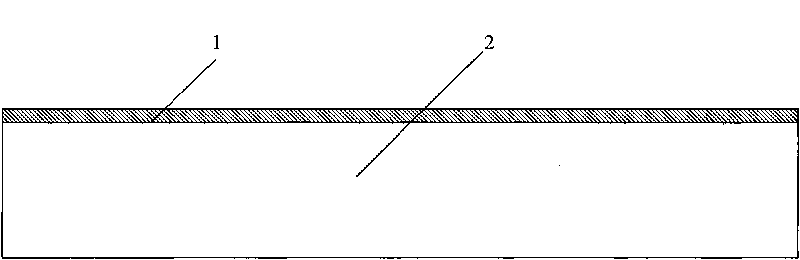

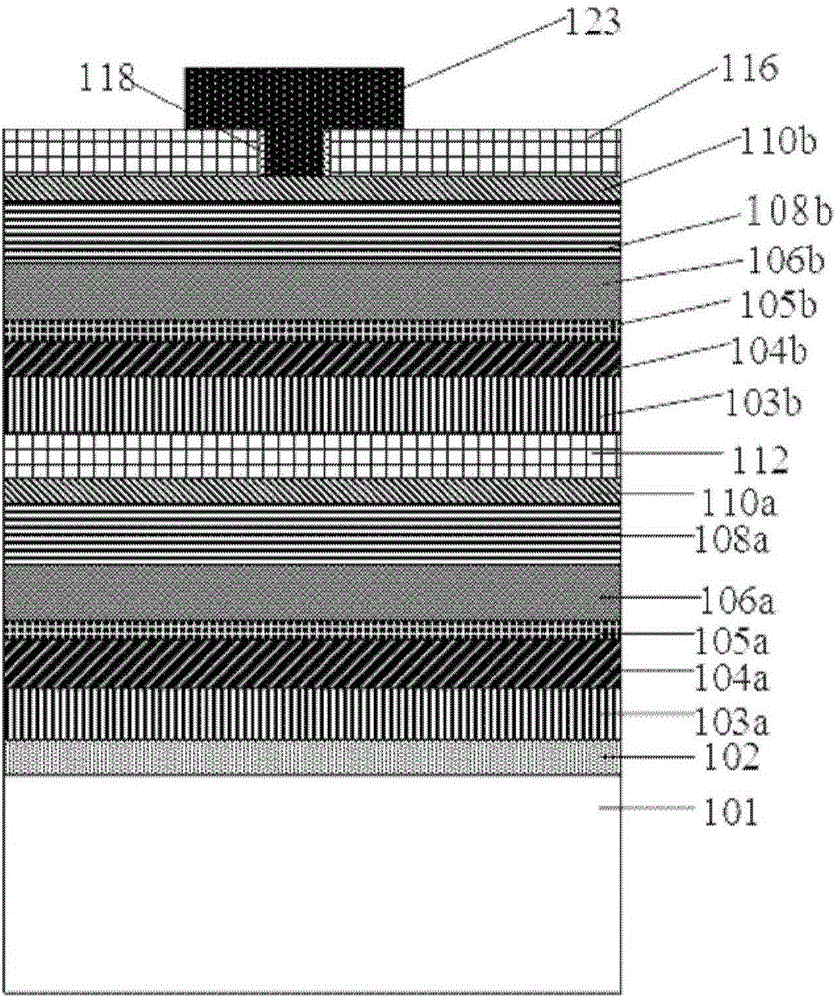

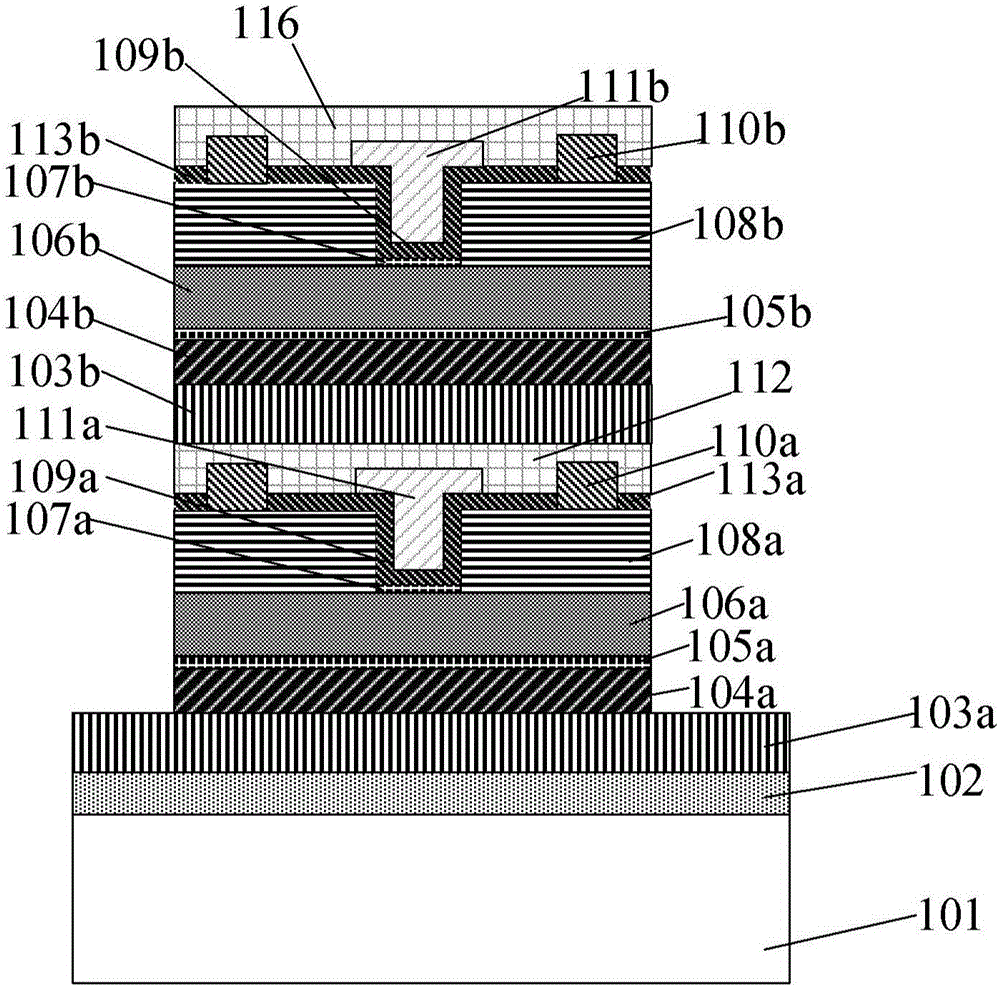

The invention provides a hybrid integrated laser based on BCB (benzocyclobutene) bonding process and a manufacturing method thereof. The hybrid integrated laser comprises an SOI-based optical waveguide chip including a silicon substrate, a buried oxide layer and a silicon waveguide structure, a BCB coating layer, a III-V group laser epitaxial layer, a heat sink through hole and a polycrystalline silicon heat sink filled in the heat sink through hole, wherein the III-V group laser epitaxial layer is provided with a bottom contact layer, an active layer, a tunnel junction and a top contact layer; the heat sink through hole runs through the III-V group laser epitaxial layer, the BCB coating layer and the buried oxide layer, as well as a silicon nitride isolation layer combined with the he surface of the III-V group laser epitaxial layer and provided with electrode through holes and an electrode structure. The hybrid integrated laser based on BCB bonding process and the manufacturing method thereof realize the monolithic integration of the SOI-based optical waveguide chip and the III-V group laser epitaxial layer by adopting the BCB bonding process, and improve the performance of the laser by introducing the polycrystalline silicon heat sink structure. The hybrid integrated laser based on BCB bonding process can be used as a silicon substrate light source device and provides an on-chip light source for a silicon substrate light integrated chip.

Owner:南通新微研究院 +1

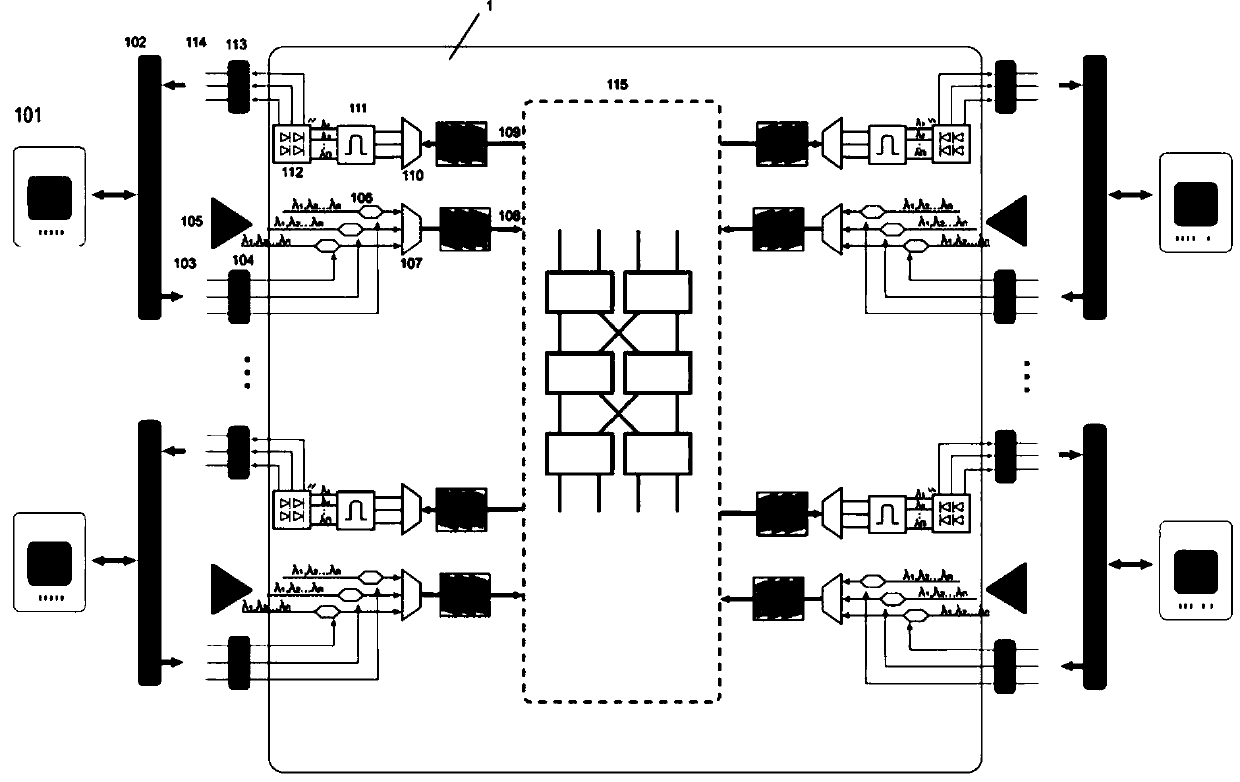

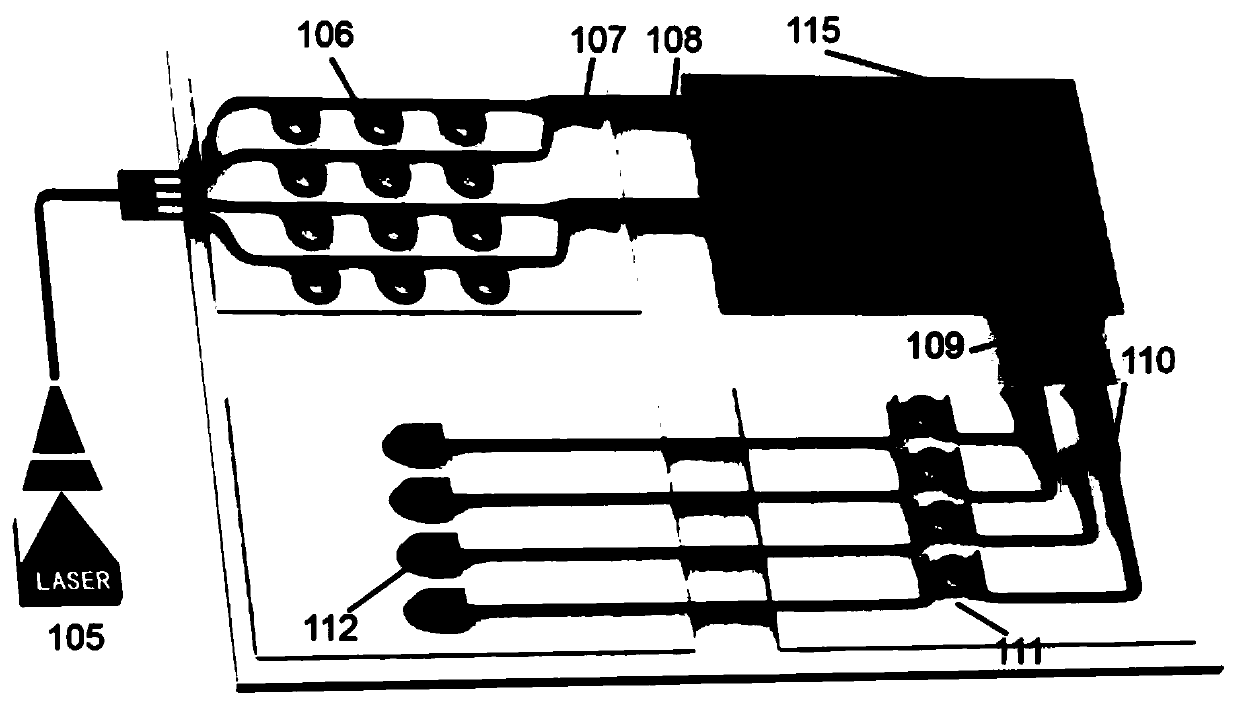

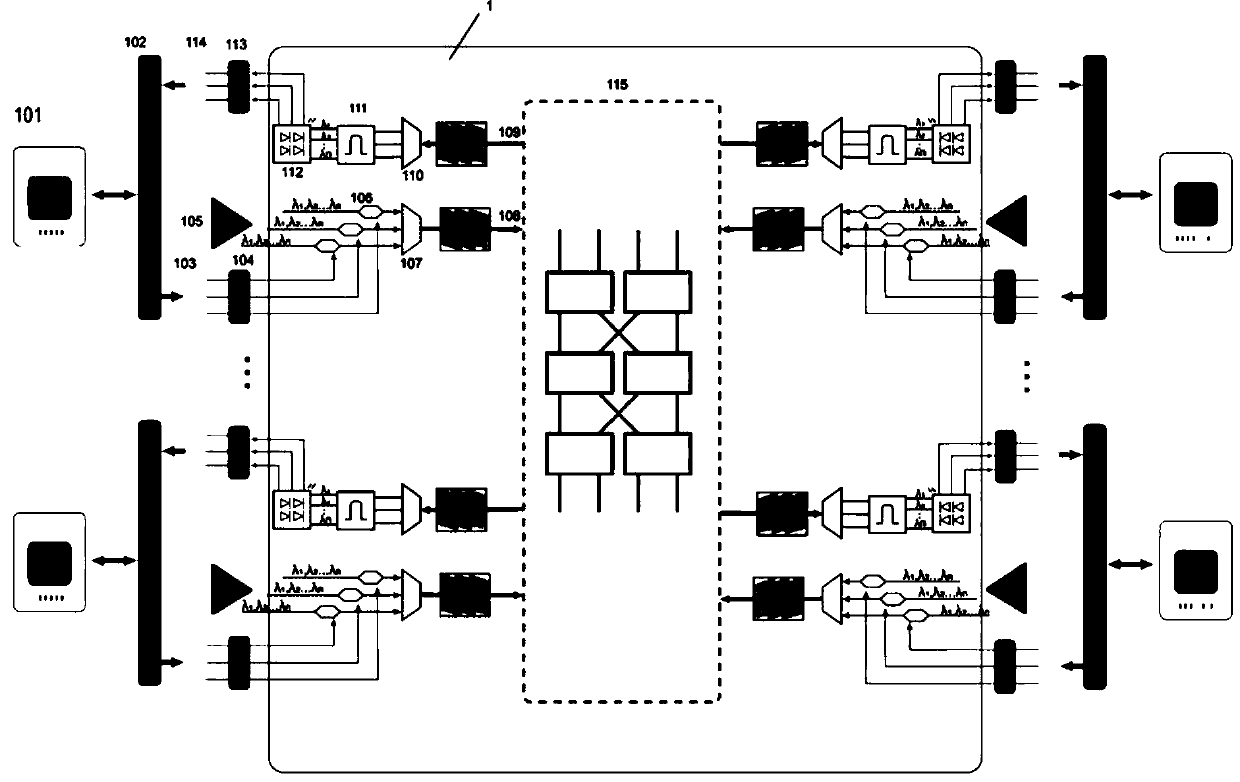

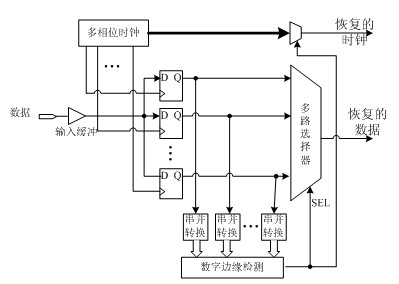

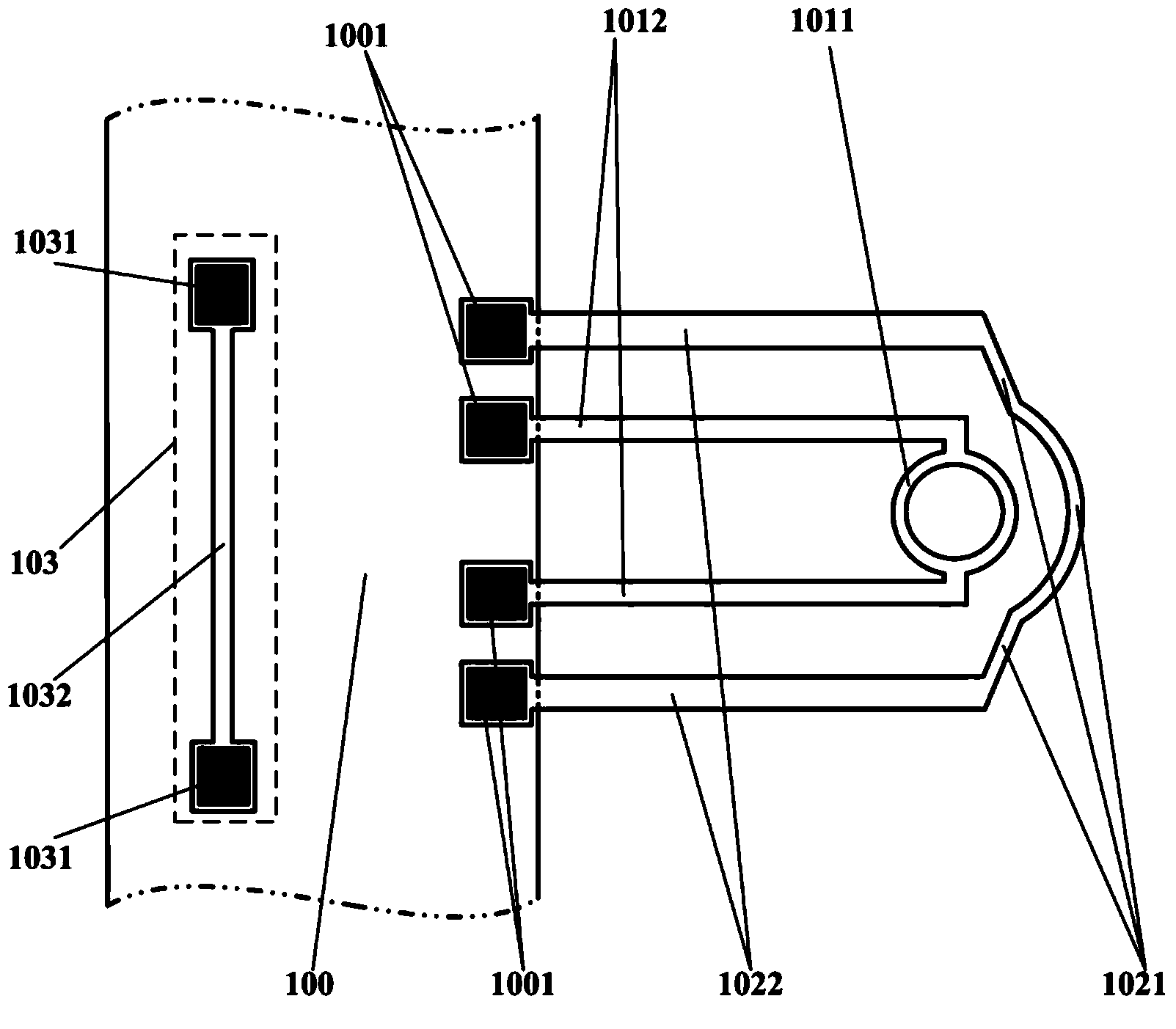

Silicon-based integrated on-chip multimode optical switching system compatible with wavelength division multiplexing signals

ActiveCN110012368AReduce power consumptionLower latencyMultiplex system selection arrangementsOptical light guidesCarrier signalEngineering

A silicon-based integrated on-chip multimode optical switching system compatible with wavelength division multiplexing signals comprises a multimode optical switching array, N groups of wavelength division-mode division multiplexing optical signal transmitting and receiving systems, and a peripheral driving circuit system, an electrical serial-parallel conversion and parallel-serial conversion system and a high-speed data input and output electrical bus which are used for supporting the system on the chip. According to the system, high-speed serial electric signals generated by data processing nodes are converted into parallel multi-channel electric signals to be input; the optical signal is converted into an optical signal through a modulator array and is loaded on an optical carrier wave of which the wavelength and the mode are multiplexed together; the optical signals enter the multi-mode optical switching array through the multi-mode waveguide input port, are demultiplexed into optical signals of multiple channels after reaching the target port, are converted into parallel electric signals through the photoelectric detector, and are finally reduced into high-speed serial signals to be provided for a data node of the target port for use. The system has the characteristics of low energy consumption, high bandwidth and low delay. The data input interface and the data output interface are both electric domains and are compatible with data interfaces of various existing processors.

Owner:LANZHOU UNIVERSITY

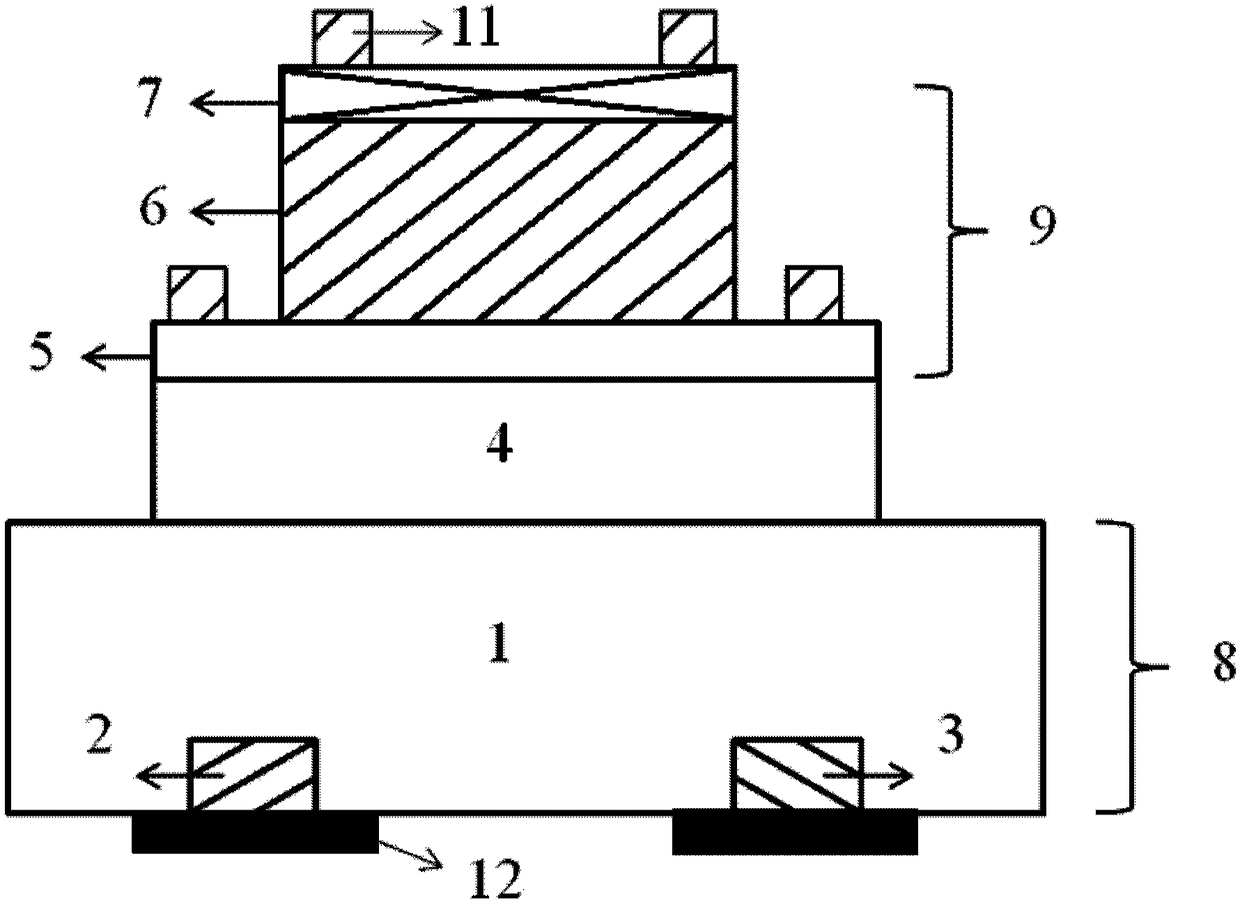

Integrated opto-electronic device for generating high-frequency microwave by light heterodyne method

InactiveCN101222118AAchieve monolithic integrationSemiconductor laser arrangementsLaser output parameters controlSidebandOpto electronic

The invention belongs to the photoelectronic device preparation technical range in the microwave photonics field, in particular relates to an integrated photoelectronic device which utilizes an optical heterodyne method to generate high-frequency microwaves. A main laser and a slave laser of the integrated photoelectronic device are parallelly arranged on a substrate on which a lower optical guiding layer, an MQW active layer, a grating layer, an upper optical guiding layer, an upper cladding and an ohmic contact layer are orderly extended outwards and integrated together; one end of the main laser and one end of the slave laser realize coupling of modulation sidebands through a multimode interferometer or an annulet structure, and injection locking is performed; then coupling out is performed by the multimode interferometer, heterodyne is performed, the high-frequency microwaves can be obtained. Therefore, differences of laser radiated wavelengths are realized by means of controlling working temperature and injection current of a DFB laser, thereby achieving the effect of injection locking of sidebands. The invention has a novel structure and simple production process, and has broad application prospect in the future high-speed communication field.

Owner:TSINGHUA UNIV

Non-refrigeration infrared detector array based on polysilicon PN junction and preparing method thereof

InactiveCN101435722ACompatible with the production processEase of monolithic integrationPyrometry using electric radation detectorsPhysicsDetector array

The invention relates to a non-refrigerated infrared detector array based on temperature characteristics of a polycrystalline silicon PN junction and a preparation method thereof. The preparation method for the array comprises the following steps: step A, etching, filling and flatting a deep groove in order to divide an infrared detection unit transversely; step B, depositing an embedded oxygen layer and a top silicon layer on the front side of a bottom silicon layer; step C, forming an insulated isolation groove on the front side of the top silicon layer in each infrared detection unit and manufacturing a polycrystalline silicon conducting wire on an insulated cantilever beam; step D, setting a plurality of tandem polycrystalline silicon PN junctions on the top silicon layer in each infrared detection unit; step E, forming a double-layer metal wiring; and step F, manufacturing a suspended insulated cantilever beam in the each infrared detection unit, and etching the bottom silicon layer to form a cavity. The preparation method uses favorable temperature characteristics of the polycrystalline silicon PN junction to obtain detection result of infrared radiation strength through measuring changes of voltage at two ends of the polycrystalline silicon PN junction.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

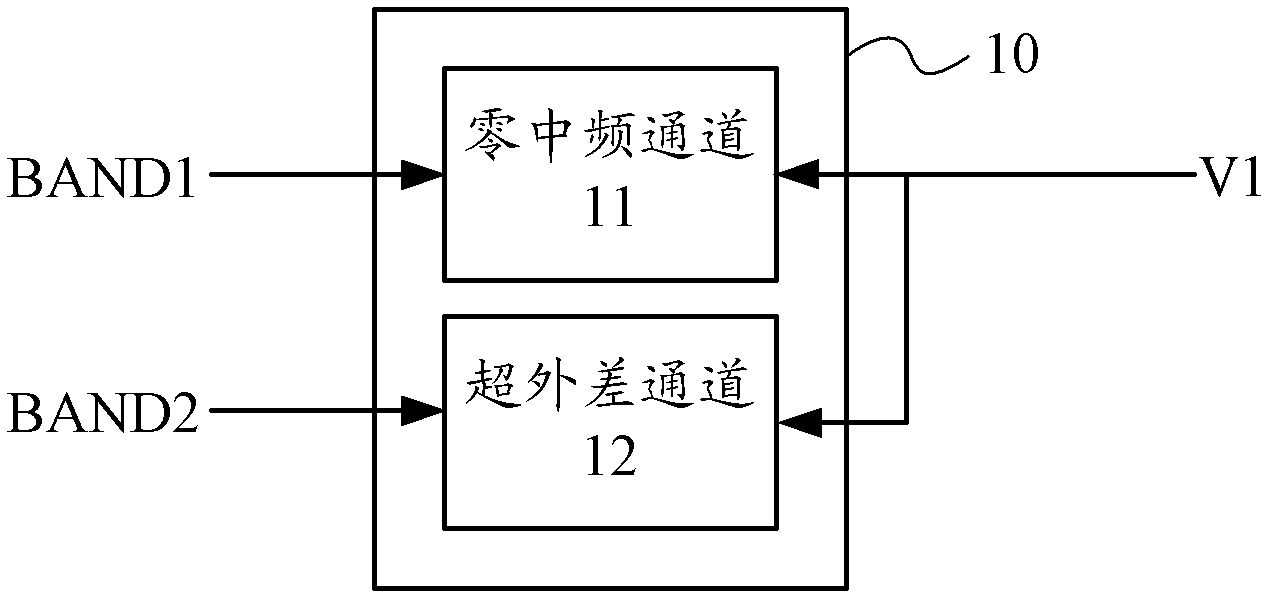

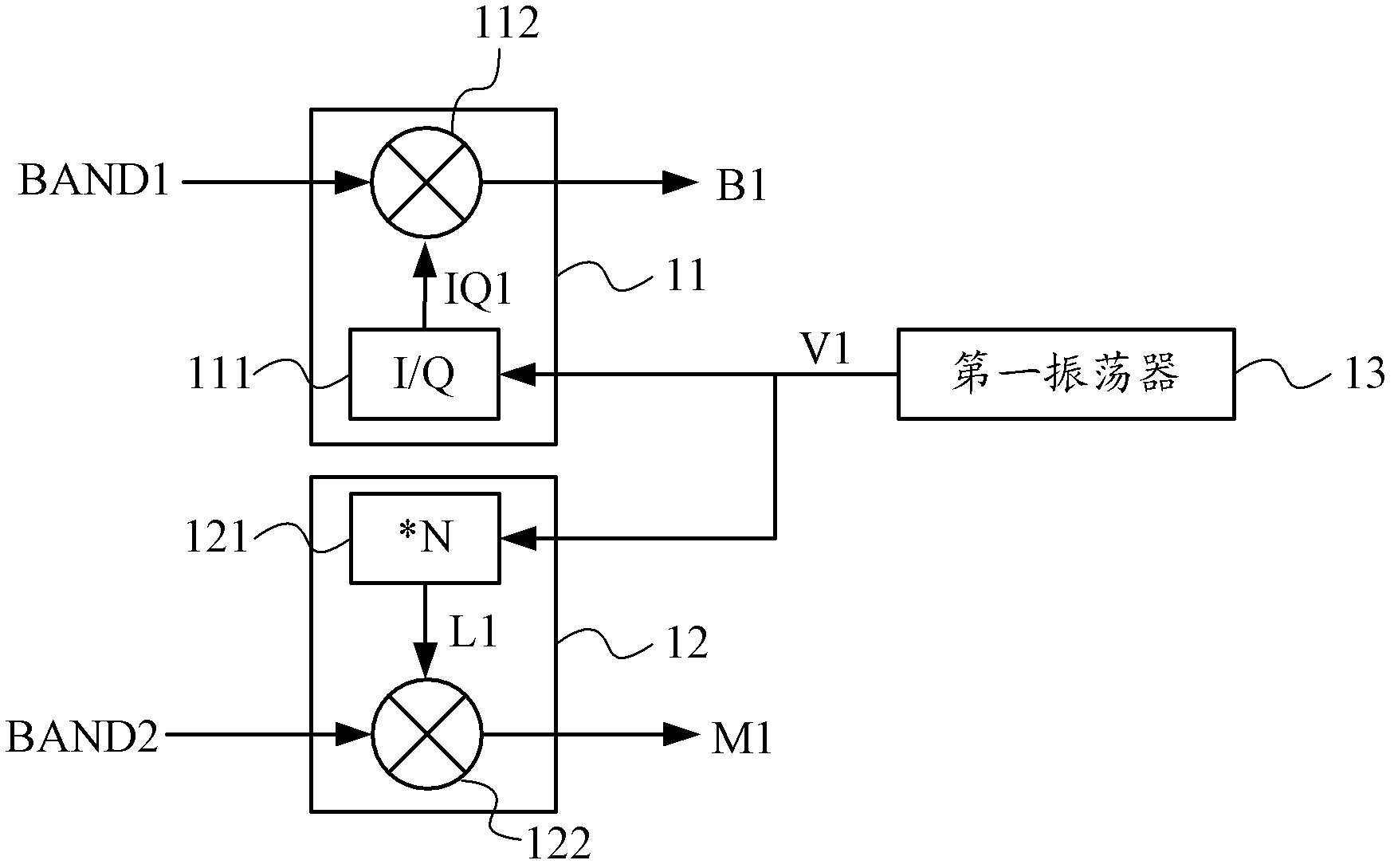

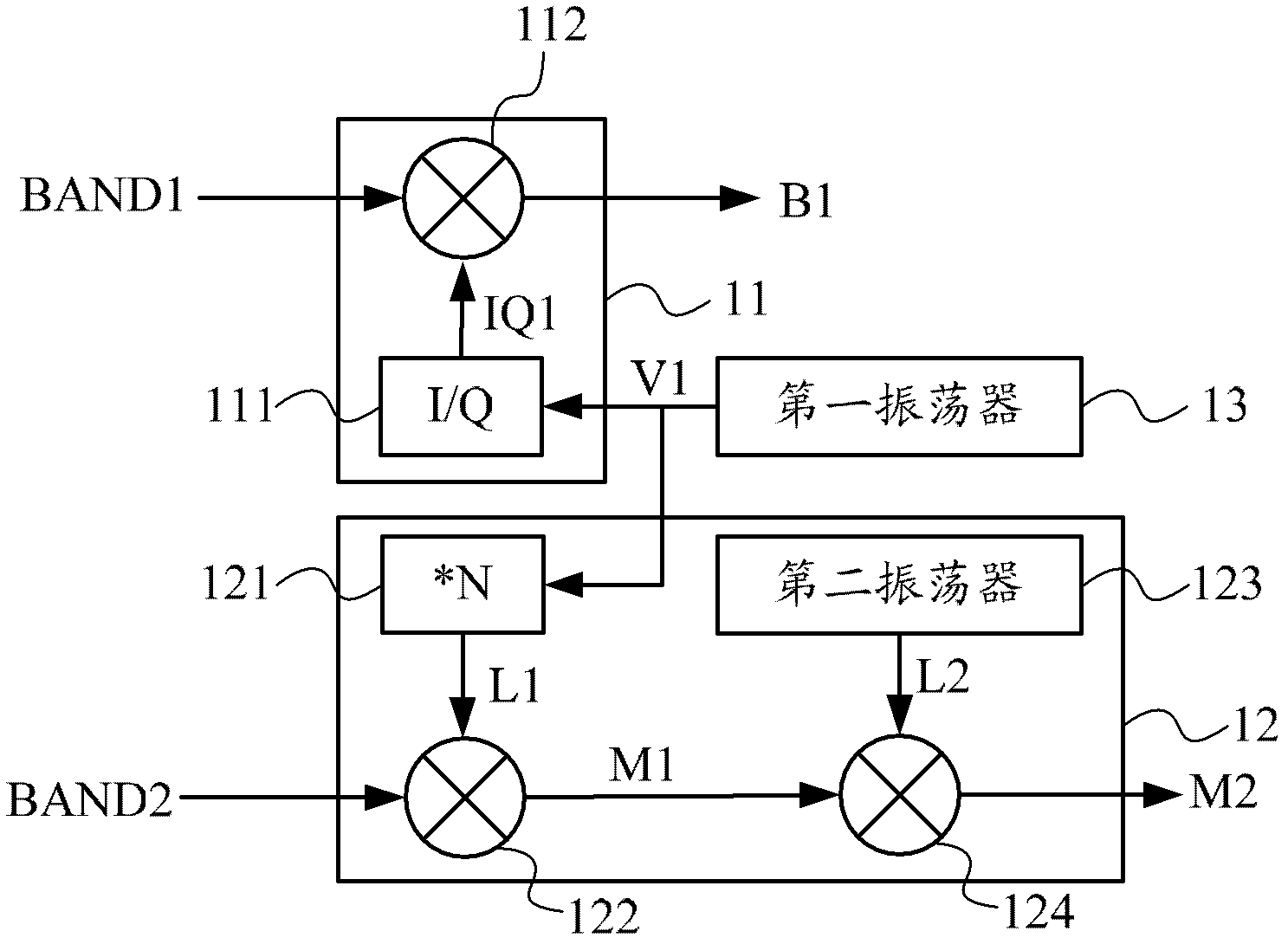

Receiver and receiving method

ActiveCN102308484AAchieve monolithic integrationOvercoming the problem of mutual influence of oscillating signalsNetwork topologiesTransmissionIntermediate frequencyRadio frequency signal

The invention provides a receiver and a receiving method, which can achieve a monolithic integration of a plurality of receiving channels. The receiver comprises a zero intermediate frequency channel which conducts an IQ down conversion on the radio-frequency signal of a first frequency channel by means of a frequency division signal or a frequency doubling signal of a first oscillation frequency, and a superhet channel which conducts a down conversion on the radio-frequency signal of a second frequency channel by means of the frequency division signal or the frequency doubling signal of the first oscillation frequency, wherein the first frequency channel is different from the second frequency channel. The zero intermediate frequency channel and the superhet channel use the same oscillation signal or the frequency division signal or the frequency doubling signal of the oscillation signal, and thereby the problem that the oscillation signals influence each other due to the simple integration of two channels is overcome, and the monolithic integration of a plurality of receiving channels can be realized.

Owner:HUAWEI TECH CO LTD

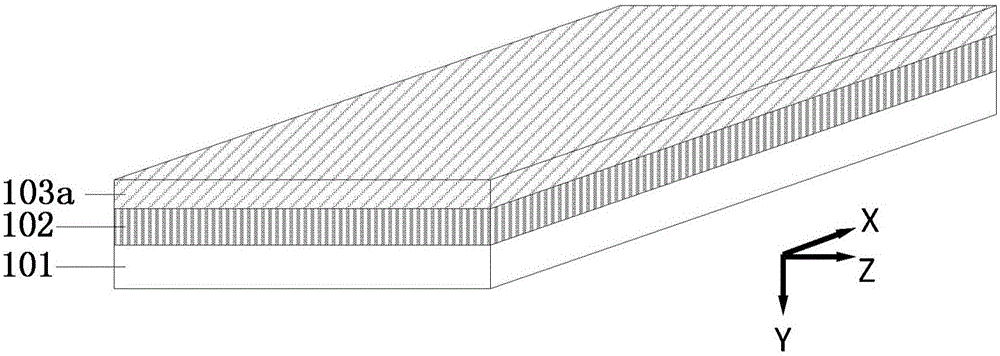

Integrated polarization converter based on silicon-based L-shaped waveguide structure

The invention discloses an integrated polarization converter based on a silicon-based L-shaped waveguide structure. The integrated polarization converter comprises an input waveguide used for inputting optical signals, an output waveguide used for outputting optical signals, a silicon-based L-shaped waveguide used for polarization rotation and a wrapping layer. The input waveguide and the output waveguide are respectively in direct end face coupling with the silicon-based L-shaped waveguide, a transverse slot is formed in a longitudinal arm of the silicon-based L-shaped waveguide, a longitudinal slot is formed in a transverse arm of the silicon-based L-shaped waveguide, and the wrapping layer wasps the outer side of the input waveguide, the outer side of the output waveguide and the outer side of the silicon-based L-shaped waveguide. The integrated polarization converter has the advantages of being easy to implement, high in converting efficiency, compact in structure, little in loss, large in fabrication tolerance and the like.

Owner:SOUTHEAST UNIV

Elasto-optical type photonic crystal waveguide accelerometer

InactiveCN107478861AReduce device sizeRaise the limit of detectionAcceleration measurement using interia forcesPhysicsOptical path

The invention discloses an elasto-optical type photonic crystal waveguide accelerometer comprising an input waveguide, an output waveguide, a Mach-Zehnder Interferometer and a micro over beam structure; the micro over beam structure is employed so as to sense the external acceleration changes; the slow light enhancement photonic crystal waveguide technology can enhance the material refractive index changes under stress and electric field effects, thus improving the detection accuracy; the electric light crystal material and the piezoelectric material are employed so as to realize modulation-demodulation optical path and sensing optical path single chip integration; the accelerometer is high in integration level, high in detection precision, low in modulation half-wave voltage, and high in limit sensitivity.

Owner:ZHEJIANG UNIV

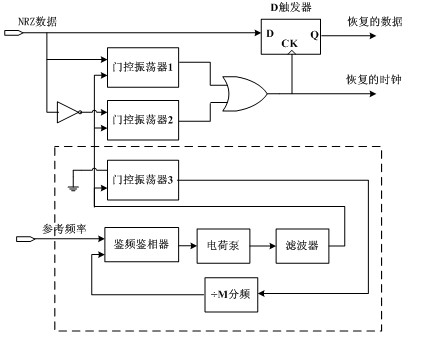

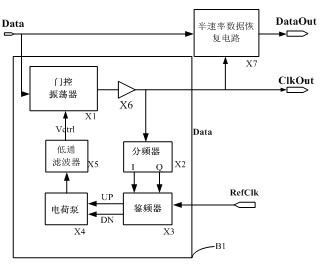

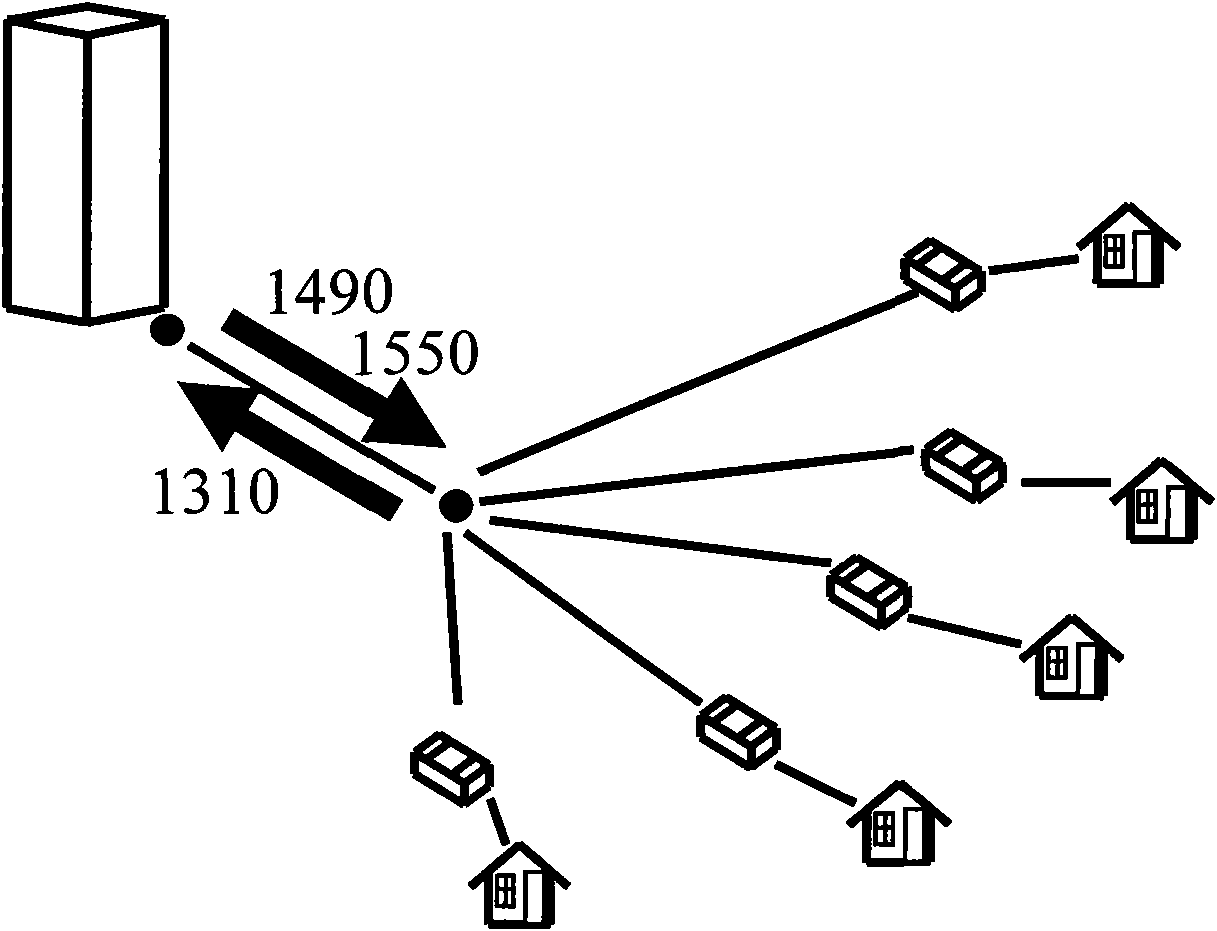

Ultrahigh-speed burst mode clock restoring circuit based on gate-control oscillator

InactiveCN102611440AAchieve monolithic integrationLow costPulse automatic controlLow-pass filterControl signal

The invention provides an ultrahigh-speed burst mode clock restoring circuit based on a gate-control oscillator, comprising the gate-control oscillator, four frequency dividers, a frequency-discrimination device, a charge pump, a low-pass filter, an interior clock buffer and a semi-velocity data restoring circuit. The ultrahigh-speed burst mode clock restoring circuit is characterized in that an output clock of the gate-control oscillator can restore a clock signal from input data of any phases within a plurality of bit times when data turn over under traction action of the input data, wherein the phase of the clock signal is aligned with the phase of the input data; the four frequency dividers, the frequency-discrimination device, the charge pump, the low-pass filter and the interior clock buffer are used for analyzing relation of output lock signal frequency and reference frequency and providing a control signal for the gate-control oscillator, and the semi-velocity data restoring circuit resets the data according to the restored clock signal to generate a restored data signal. The ultrahigh-speed burst mode clock restoring circuit disclosed by the invention is suitable for an optical fiber communication system, and in particular relates to a burst mode optical communication system taking a ten-gigabit Ethernet passive optical network technology as representation.

Owner:SOUTHEAST UNIV

Polarization sensitive type non-freezing infrared detector and manufacturing method thereof

ActiveCN107150995AAchieve monolithic integrationReduce difficultyTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesScarificationMetal grating

The invention relates to a polarization sensitive type non-freezing infrared detector which comprises a first-layer suspension structure, wherein the first-layer suspension structure is a non-freezing infrared detector; a second-layer suspension structure is arranged on the first-layer suspension structure; the second-layer suspension structure comprises a grating support layer and a metal grating structure arranged on the grating support layer. An optical system is simplified, and the reality and the effectiveness of images are improved. The invention further relates to a manufacturing method of the polarization sensitive type non-freezing infrared detector. The manufacturing method comprises the following steps: 1, manufacturing a second scarification layer and a grating support layer on a conventional non-freezing infrared detector without structure release; 2, manufacturing the metal grating structure; 3, performing structure release, thereby forming the polarization sensitive type non-freezing infrared detector.

Owner:YANTAI RAYTRON TECH

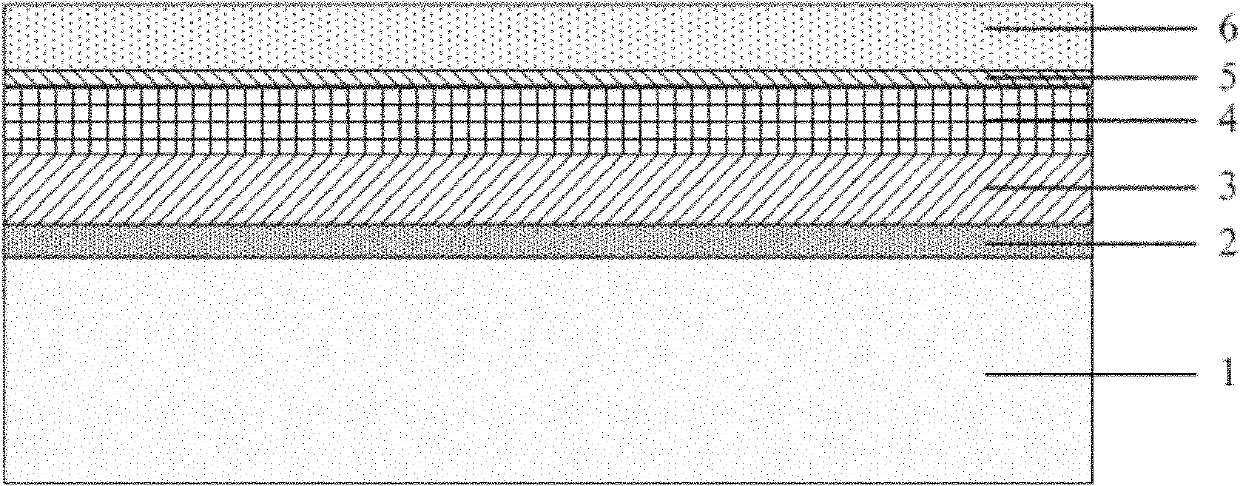

Dual-layer polarization uncooled infrared detector structure and preparation method thereof

ActiveCN107117579AImprove fill factor and infrared absorption efficiencyHigh fill factorTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesPolarization sensitiveResonant cavity

The invention relates to a dual-layer polarization uncooled infrared detector structure. The uncooled infrared detector structure comprises a semiconductor base and a detector body, wherein the detector body comprises an insulating medium layer, a metal reflecting layer, a first support layer, a metal electrode layer, a first protective layer, a second support layer, an electrode metal layer, a thermosensitive layer and a second protective layer; a first resonant cavity is formed between the first support layer and the insulating medium layer; a second resonant cavity is formed between the first protective layer and the second support layer; the thermosensitive layer is arranged on the electrode metal layer, and the dual-layer structure improves the infrared absorption efficiency of the pixel; a polarization structure is arranged on the second protective layer so as to realize the monolithic integration of a polarization sensitive type infrared detector, thereby greatly lowering the difficulty of the optical design; the invention further relates to a preparation method of the detector structure. The preparation method comprises a step of preparing the dual-layer uncooled infrared detector, and further comprises the step of preparing the polarization structure on the dual-layer uncooled infrared detector.

Owner:YANTAI RAYTRON TECH

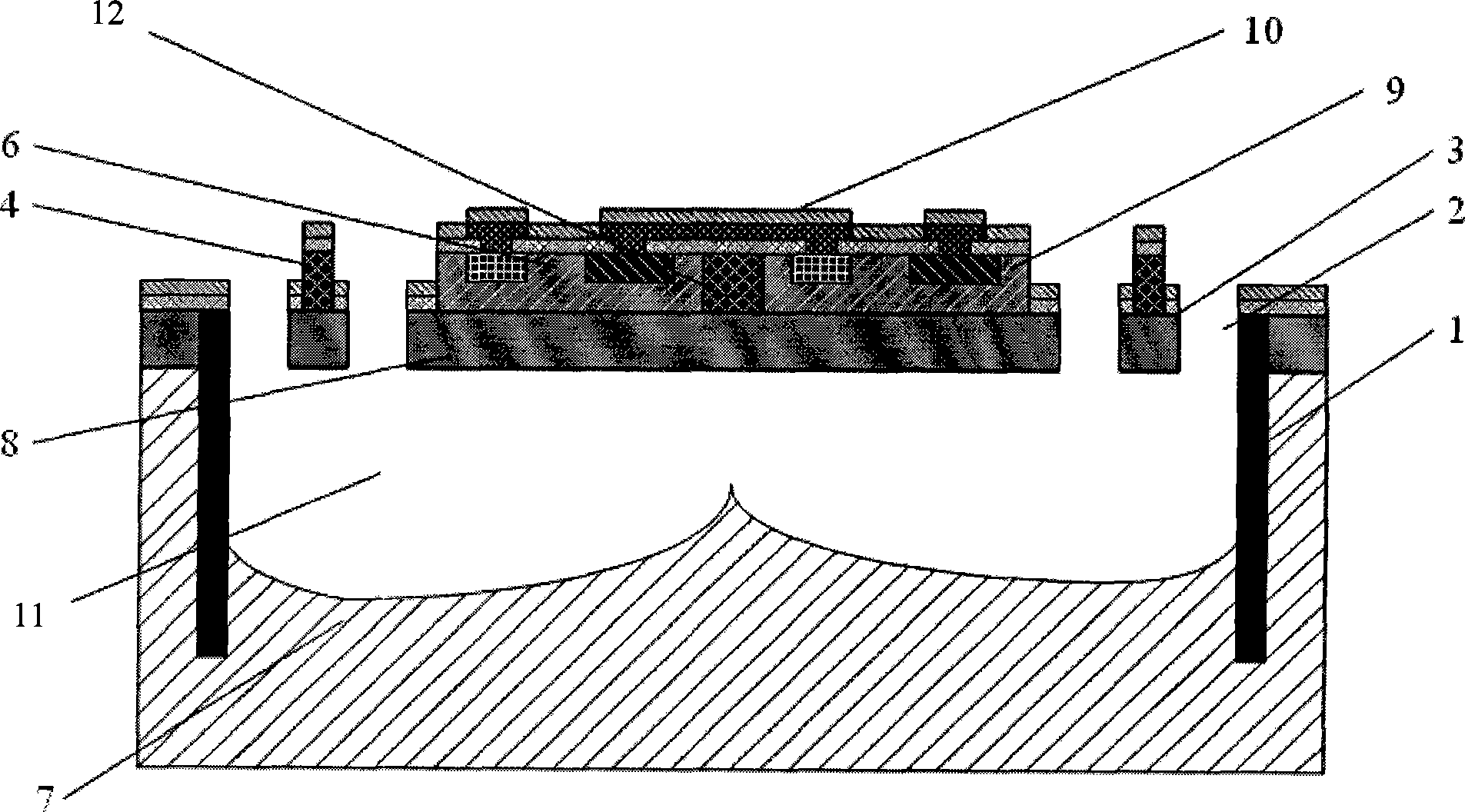

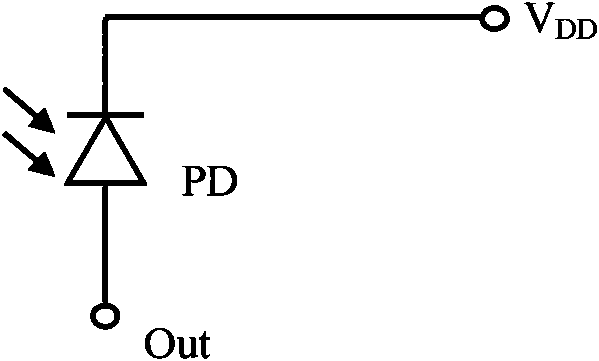

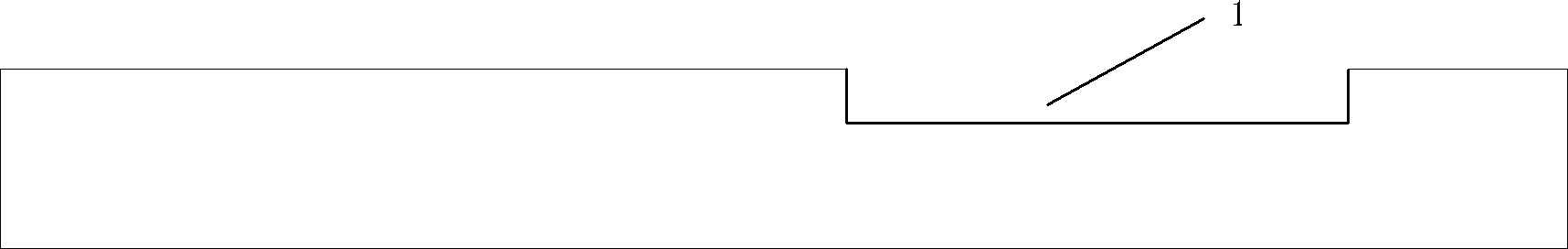

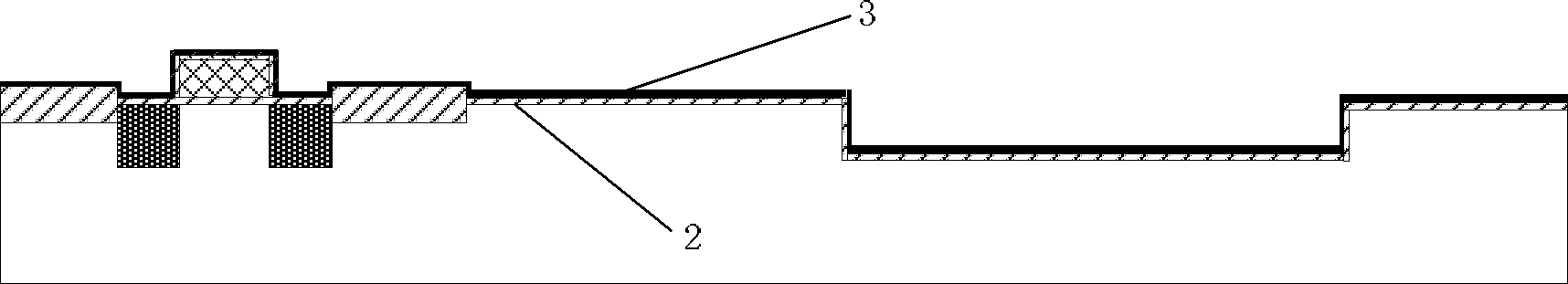

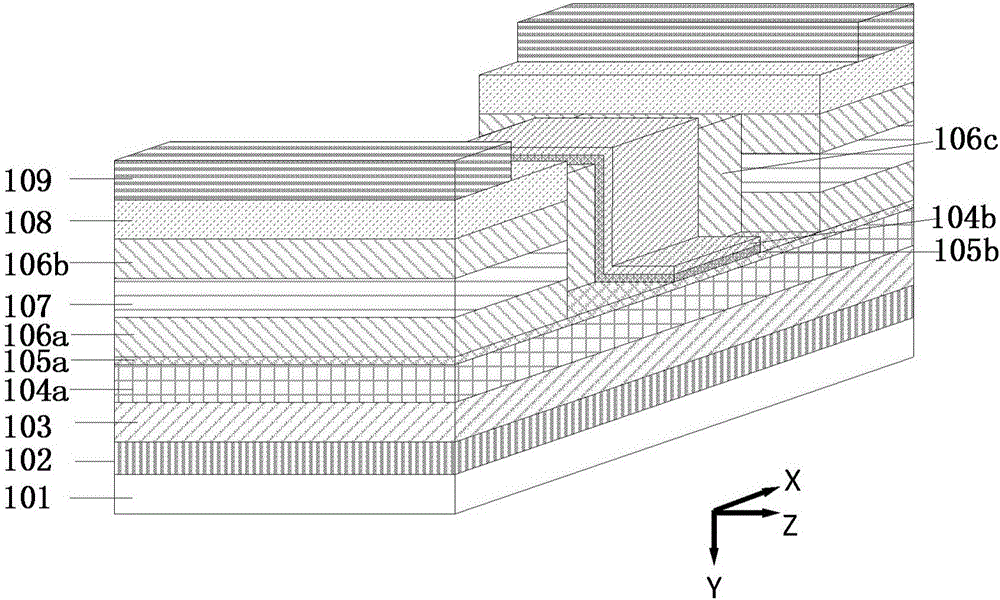

Silicon-based photoelectric detector for photoelectric monolithic integration and preparation method thereof

ActiveCN101719504AOvercome the disadvantage of low frequency responseOvercome the shortcoming of poor shortwave responseFinal product manufactureSemiconductor/solid-state device manufacturingMetallic aluminumSilicon oxide

The invention discloses a silicon-based photoelectric detector for photoelectric monolithic integration and a preparation method thereof, which relates to a silicon-based photoelectric monolithic integrated circuit. The invention provides the silicon-based photoelectric detector which is completely compatible with the commercial BCD standard technology and is used for photoelectric monolithic integration, and provides the preparation method thereof. The silicon-based photoelectric detector is provided with a P type silicon substrate, a BN+ epitaxial layer, a BP+ epitaxial layer, an N-EPI epitaxial layer, an N-well layer, a P-well layer, a P+ layer, an N+ layer, an Al layer, a field oxide layer, SiO2 insulating medium layers and a Si3N4 surface passivation layer, wherein the P type silicon substrate, the BN+ epitaxial layer, the BP+ epitaxial layer, the N-EPI epitaxial layer, the N-well layer, the P-well layer, the P+ layer and the N+ layer are arranged on the same silicon wafer; the field oxide layer is a silicon oxide layer generated on the surface of the silicon wafer; a metallic aluminum layer is deposited on the surface of the silicon wafer; three SiO2 insulating medium layers are attached to the silicon substrate from bottom to top according to the preparation sequence through the deposition technology; and the Si3N4 surface passivation layer is attached to the SiO2 insulating medium layers through the deposition technology.

Owner:XIAMEN UNIV

MEMS integration method

InactiveCN102515089AReduce parasitic capacitance and distributed capacitanceHigh precisionDecorative surface effectsChemical vapor deposition coatingPhotoresistCMOS

The invention discloses an MEMS integration method. The method comprises steps of: first etching an MEMS area groove, manufacturing a CMOS circuit in an area outside the groove and completing all IC technologies except metal interconnection; then precipitating an IC protective layer and manufacturing an MEMS structure in the groove by employing an MEMS surface sacrificial layer technology; then etching to form lead wire apertures of the IC area, precipitating and imaging the metal to form metal interconnection; finally using photoresist to protect the area outside the groove, removing a sacrificial layer and releasing an MEMS movable structure to obtain a monolithic integration chip. The invention employs MEMS-IC-MEMS intersect manufacturing technology to complete MEMS and IC monolithic integration, reduces height difference between the MEMS structure and the IC through the groove, and reduces pressure of the integration technology on photolithography; meanwhile, technology adjustment avoids metal shedding and improves technology quality and yield.

Owner:PEKING UNIV

Method for manufacturing monolithic polysilicon cantilever structure

InactiveCN102086019ASolve stickingAchieve monolithic integrationDecorative surface effectsChemical vapor deposition coatingGyroscopeSignal processing circuits

The invention relates to a method for manufacturing a monolithic polysilicon cantilever structure. In the invention, a processing step of the polysilicon cantilever structure is inserted in a conventional BiCMOS (Bipolar Complementary Metal Oxide Semiconductor) technical process, the deposition and the annealing of polysilicon are finished and an MEMS (Micro-Electro-Mechanical Systems) high-temperature process is prevented from influencing on the metalation process before the metalation process. In the release process of the polysilicon cantilever structure, a special etching solution is adopted, and a negative photoresist is used as a post of the polysilicon cantilever structure so as to effectively avoid the problem of substrate adhesion in the cantilever structure release process by using a wet method. The method provided by the invention solves the technical problems of compatibility between a manufacture process of the polysilicon cantilever structure and a processing process of a BiCMOS circuit, realizes the monolithic integration of the polysilicon cantilever structure and a BiCMOS signal processing circuit, and can be widely applied to the monolithic integration manufacture field of MEMS sensors, such as capacitive accelerometers, gyroscopes, and the like.

Owner:NO 24 RES INST OF CETC

Coupler structure based on BCB bonding technology and production method thereof

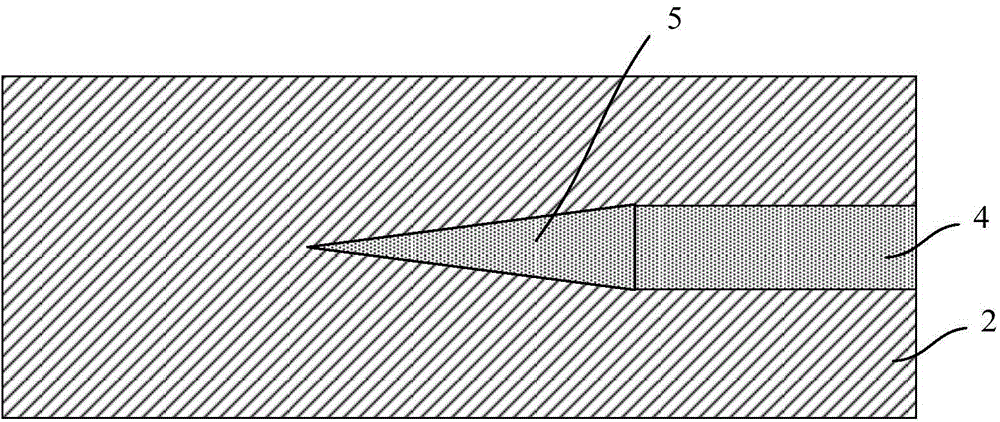

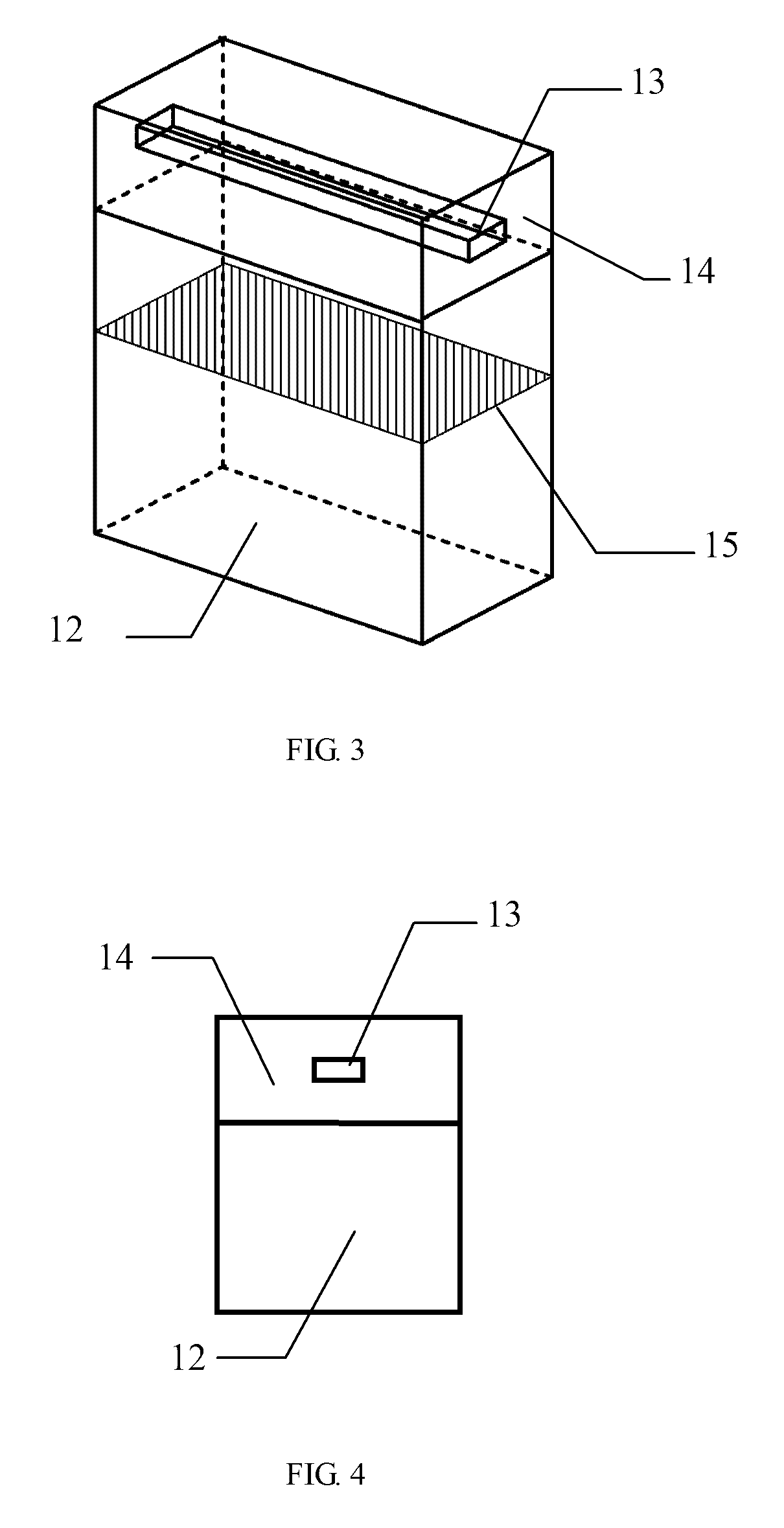

The invention provides a coupler structure based on BCB bonding technology and a production method thereof. The coupler structure is characterized in that a silicon substrate and a buried oxide layer disposed on the silicon substrate are provided; a silicon waveguide is disposed on the buried oxide layer, and a first cone-shaped coupling structure is connected with one end of the silicon waveguide; a BCB cladding is disposed on the surface of the buried oxide layer, and is used to cover the silicon waveguide and the first cone-shaped coupling structure; an III-V group optical gain structure is disposed on the surface of the BCB cladding, and a second cone-shaped coupling structure is connected with one end of the III-V group optical gain structure; the first cone-shaped coupling structure and the second cone-shaped coupling structure are in a reverse arrangement, and the projected parts on the horizontal plane are superposed with each other. The mixed integration of the III-V group optical gain structure and the silicon waveguide can be realized, and the mode conversion zone can be formed by adopting the reserve arrangement of the first cone-shaped coupling structure and the second cone-shaped coupling structure, and therefore the length of the coupling structure can be greatly shortened, and the coupling efficiency is high; when the thickness of the BCB cladding is changed, the change amplitude is small, and the coupling efficiency is more stable.

Owner:南通新微研究院 +1

Manufacturing method of monolithic integrated pressure sensor

InactiveCN101719482ACompatible processing technologySolve the technical problems of processing technology compatibilitySemiconductor/solid-state device manufacturingForce measurement using piezo-resistive materialsIntegrated circuitCorrosion

The invention discloses a manufacturing method of a monolithic integrated pressure sensor. Te In the invention, overcomes the problem of processing technology compatibility of a resistance type pressure sensor and an amplification processing circuit is solved, combines the processing technology of the resistance type pressure sensor and the processing technology of the amplification processing circuit are combined, and utilizes a special clamp for protecting an integrated circuit and a piezoresistor on the front surface are utilized, meanwhile, a deep slot is formed below the piezoresistor through corrosion, so that the piezoresistor is successfully manufactured on a movable silicon film, . The invention solvessolving the technical difficult problem of processing technology compatibility of the pressure sensor and the circuit, and realizing realizes the monolithic integration of the pressure sensor and the circuit. The method is suitable for the processing field of miniaturized high-reliability pressure sensors.

Owner:NO 24 RES INST OF CETC

SOG structure micro heat pipe and its manufacture method

InactiveCN101266112AExpand the scope of useReduce shear forceIndirect heat exchangersWorking fluidVisibility

The invention provides a SOG(Silicon on Glass)micro heat pipe and the production method. Wherein, the structure uses a silicon chip as substrate, uses synthetic glass as cover film, and the two are sealed together to form enclosed construction through electrostatic bonding, then the liquid-filled is carried out through a pinhole set aside on the silicon chip, and the liquid-filled hole is vacuum-sealed to form a micro flat structure heat pipe whose cavity is filled with certain working fluid. Due to a glass silk, which not only can reduce radius of the meniskus at the gas-solution interface, but also can increase the number of cusp district in a groove, thus improves capillary force for the circumfluence of working fluid. The cover film uses glass sheet, thus enhances visibility so as to carry out real-time observation and monitoring for the functional mode of micro heat pipe. The invention also uses a rectangular cavity etched on the glass as the circulation space of saturated vapor. The connected vapor circulation space can reduce shear friction caused by the high-speed reverse movement of vapor flow and liquid flow at the steam-liquid interface, thus improves the entrainment limit of heat pipe, which ultimately increases the maximum heat output.

Owner:HARBIN INST OF TECH

Temperature and pressure integrated sensor and preparation method thereof

InactiveCN110006490AWireless passiveAchieve monolithic integrationFluid pressure measurementThermometers using physical/chemical changesElectricityHigh pressure

The invention discloses a temperature and pressure integrated sensor and a preparation method thereof, belongs to the technical field of sensors, and aims to solve the technical problem that signals acquired by the sensor through wire transmission are affected and even cannot work in some extremely severe environments. A temperature and pressure integrated sensor comprises a substrate and a piezoelectric material arranged on the surface of the substrate, a resonator is arranged on the piezoelectric material, and a sealing cavity is formed in the substrate. The temperature is measured by utilizing the effect that the resonant frequency of the delay line SAW resonator deposited on the piezoelectric material can be changed along with the external temperature; the pressure is measured by utilizing the effect that the resonant frequency of the delay line SAW resonator growing on the cavity can be changed along with the external pressure. The temperature and pressure integrated sensor does not need to be driven by an internal energy source and does not need a wire to transmit signals, so that the sensor has the characteristics of being wireless, passive and capable of working in extremely severe environments such as high temperature, high pressure and sealed space.

Owner:HOHAI UNIV CHANGZHOU

Methane sensor based on single heating element, preparation method and application

InactiveCN104316574AReduce power consumptionImprove consistencyMaterial resistanceAnti jammingPhysics

The invention discloses a methane sensor based on a single heating element, a preparation method and application. The methane sensor is suitable for industrial and mining enterprises and comprises a heating element, a measuring element, and an environment temperature measuring element, wherein a heater of the heating element of the methane sensor and a measuring component of the measuring element are suspended in air through supporting arms; the heating element independently heats to the high-temperature working state; the measuring element is independently used for detecting gas concentration; the temperature on a detecting sheet of the environment temperature measuring element detects is used for temperature compensation. The processing technology of the methane sensor is compatible with the CMOS (Complementary Metal Oxide Semiconductor) technology. The sensor has the advantages that the sensor is simple in structure, low in power dissipation, high in sensitivity, good in anti-jamming performance, and low in cost.

Owner:CHINA UNIV OF MINING & TECH

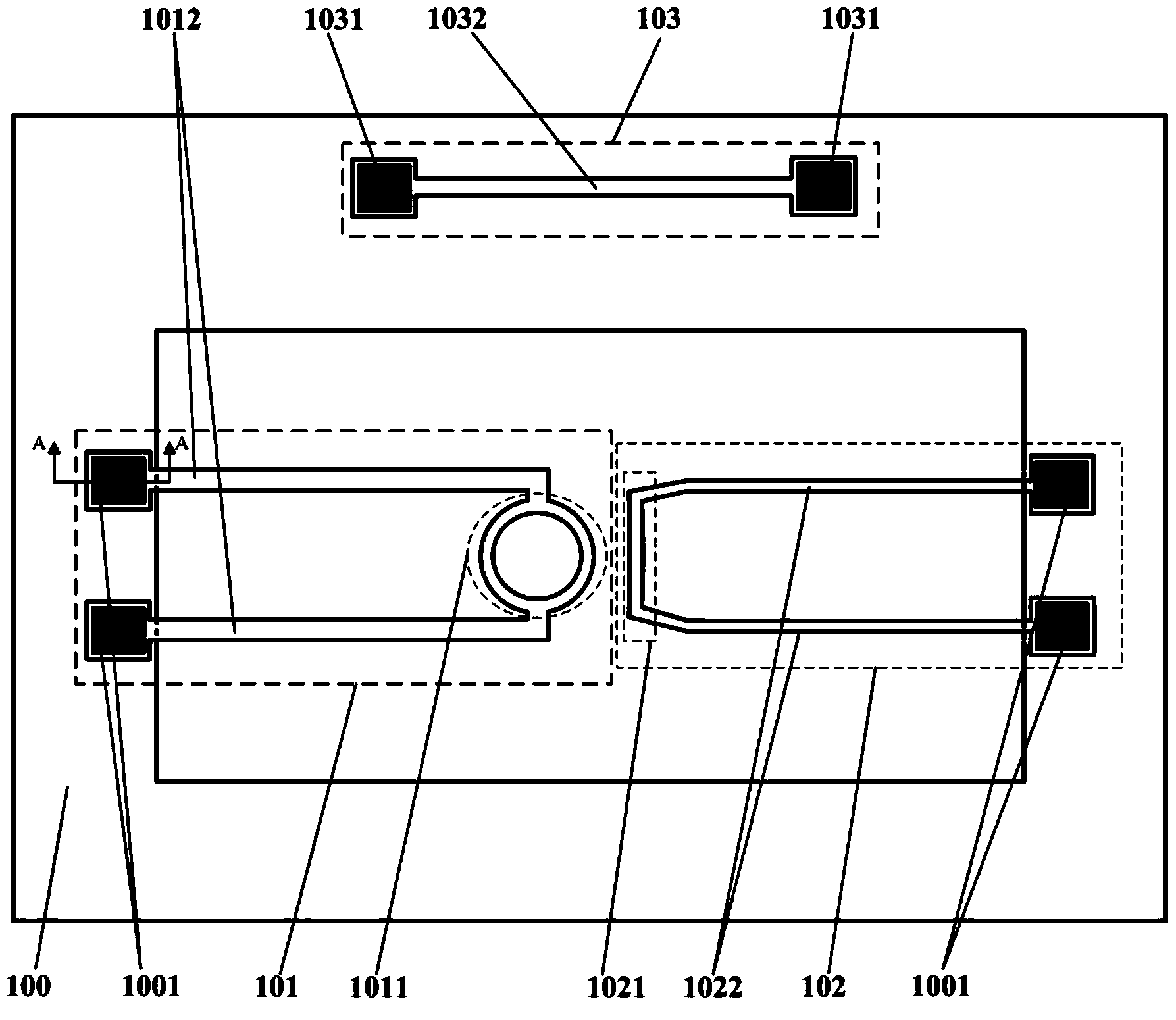

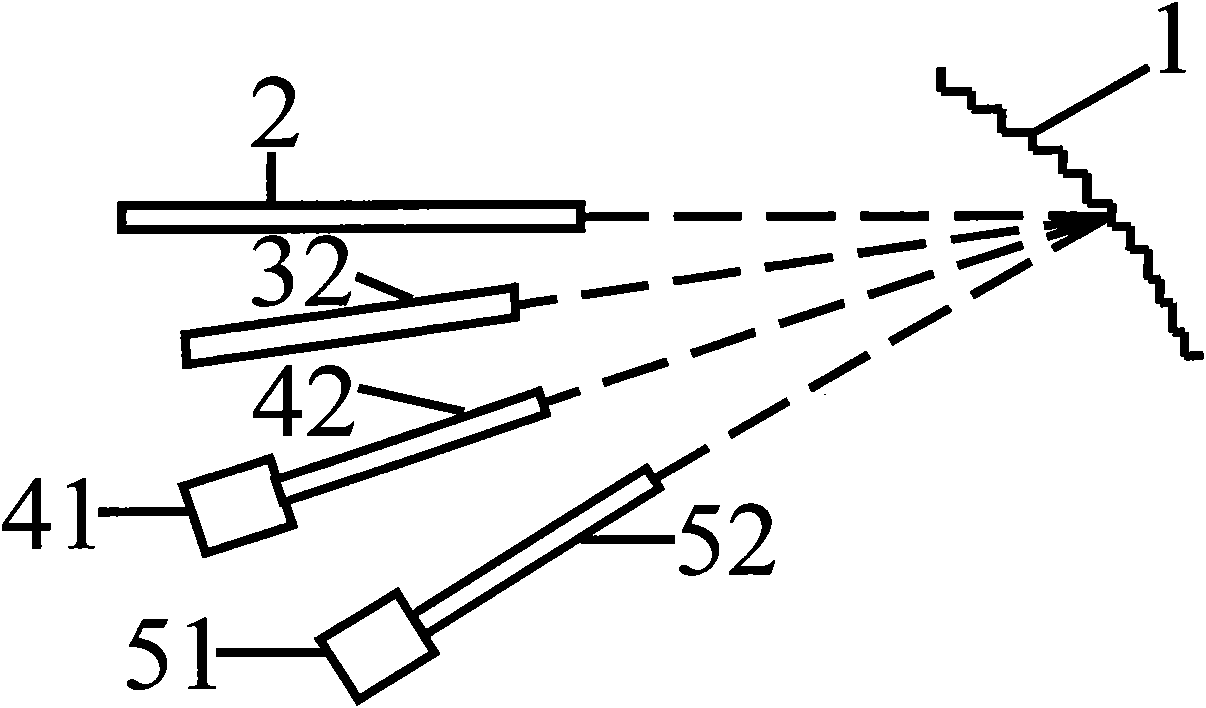

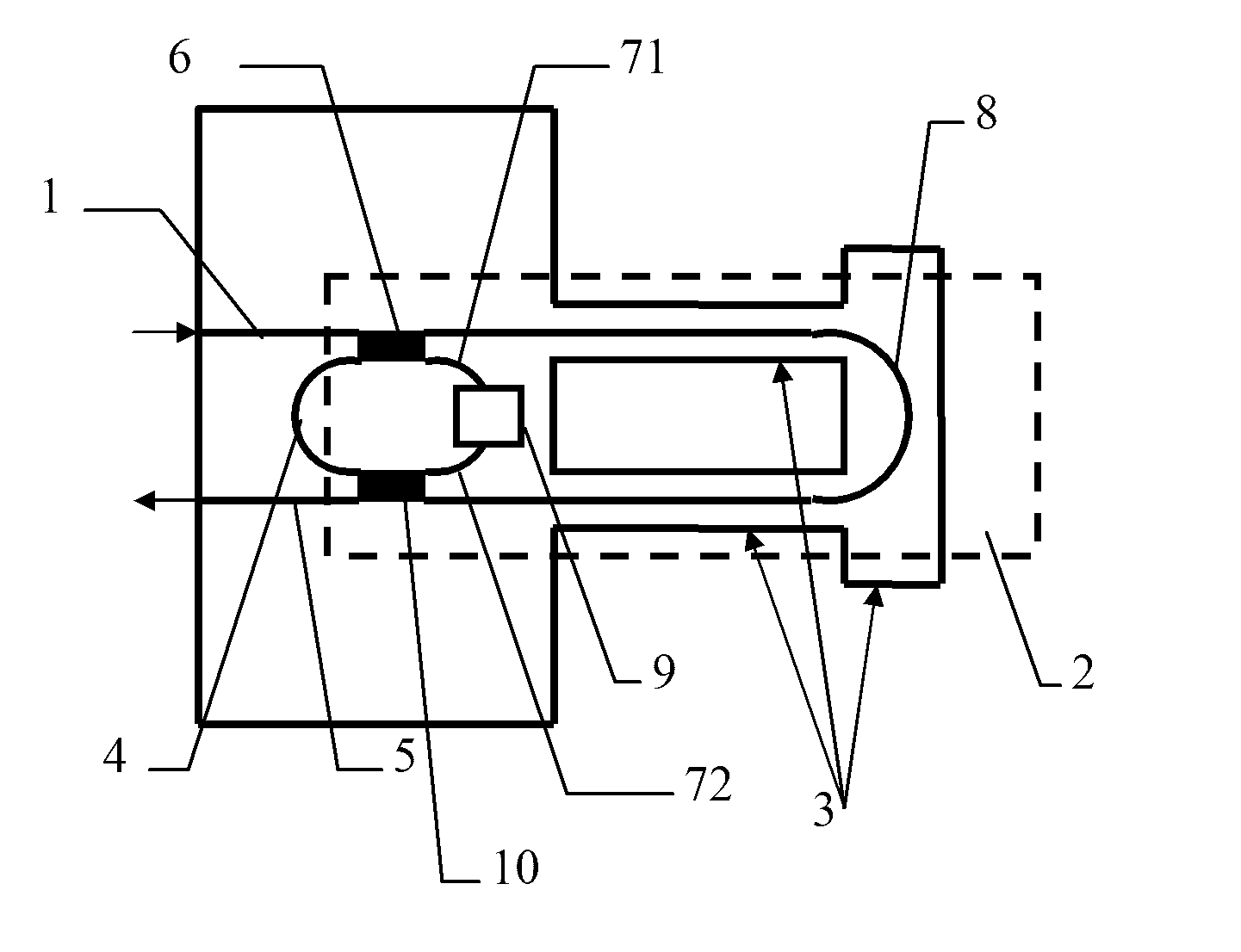

Monolithically integrated multiplexer transceiver based on etched diffraction grating

InactiveCN101666893AAchieve monolithic integrationReduce coupling timesCoupling light guidesHigh volume manufacturingTransceiver

The invention discloses a monolithically integrated multiplexer transceiver based on an etched diffraction grating, which mainly consists of an etched diffraction grating, an input and output waveguide, a gain waveguide and two multimode waveguide detectors. A downlink optical signal entering through the input and output waveguide is coupled to the two multimode waveguide detectors through the etched diffraction grating. The etched diffraction grating reflects one part of light emitted from the front head face of the gain waveguide back to the gain waveguide through a certain order of diffraction, and forms a resonant laser cavity for generating an uplink optical signal with the rear reflection head face of the gain waveguide. The etched diffraction grating reflects the other part of lightto the input and output waveguide through another order of diffraction at the same time to be further coupled in the optical fiber as the uplink optical signal for transmission. The invention truly realizes the monolithic integration, decreases the coupled times with the optical fiber, reduces the size, improves the integration and is applicable to the mass production.

Owner:ZHEJIANG UNIV

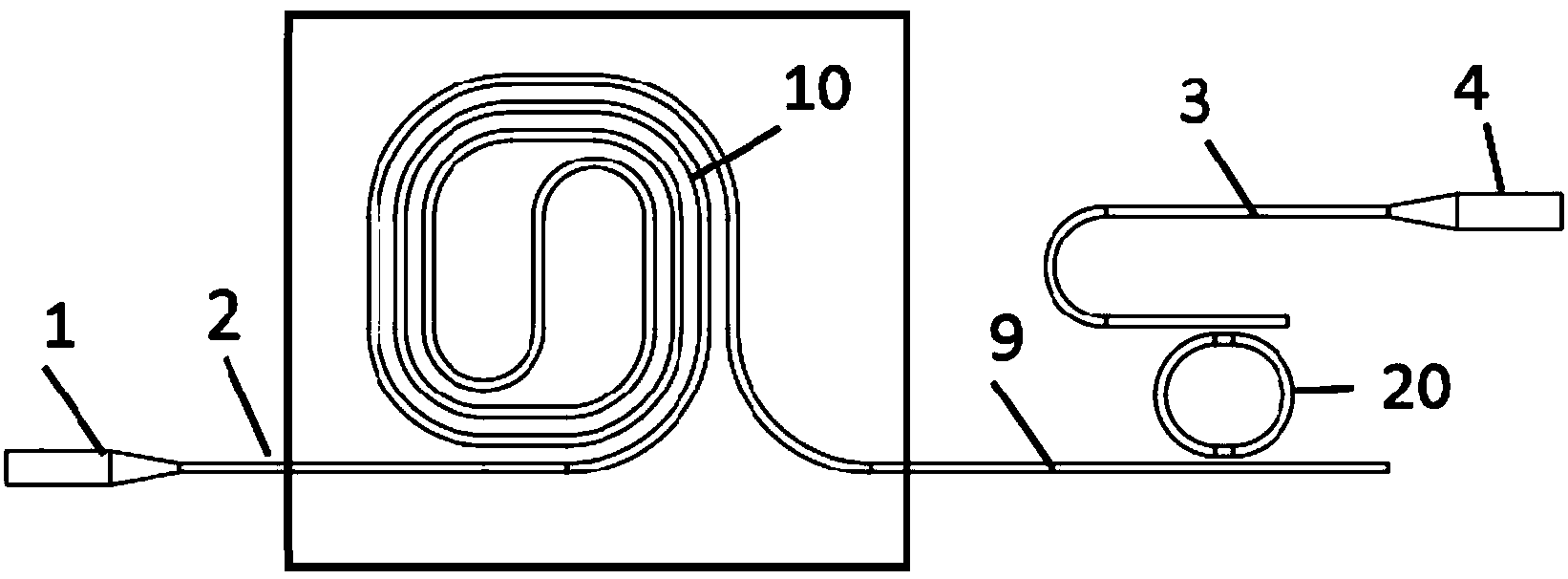

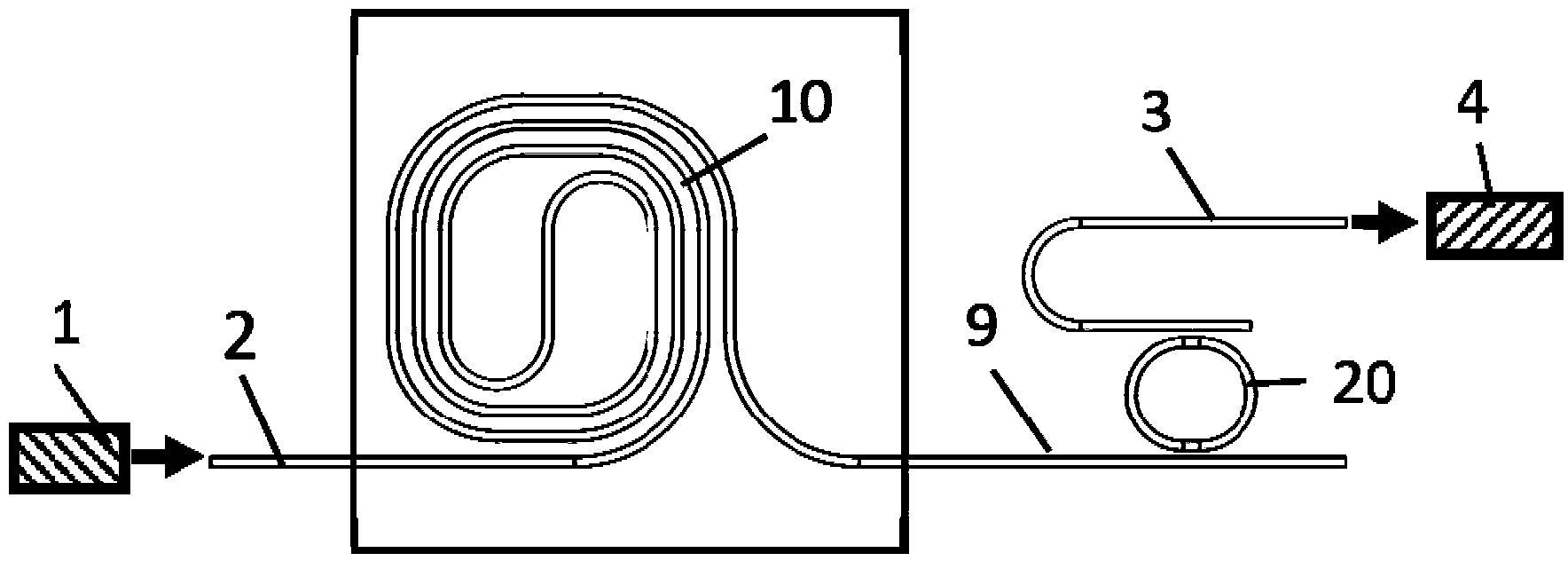

Raman spectrum based optical waveguide sensor

The invention discloses a Raman spectrum based optical waveguide sensor. The Raman spectrum based optical waveguide sensor comprises an input waveguide, a spiral sensing waveguide, a filter, a connecting waveguide and an output waveguide, wherein a detection window is formed in an upper cladding layer of the spiral sensing waveguide, the input end of the spiral sensing waveguide is connected with a wavelength tunable laser by the input waveguide, the output end of the spiral sensing waveguide is connected with one side of the filter by the connecting waveguide, and the other side of the filter is connected with an optical power meter by the output waveguide. The Raman spectrum based optical waveguide sensor can qualitatively analyze a single sample or a gas-liquid mixed sample, utilizes the planar optical waveguide as a Raman spectrum excitation and collection medium, and is integrated with the filter to obtain a small, low-cost and untagged sensor.

Owner:ZHEJIANG UNIV

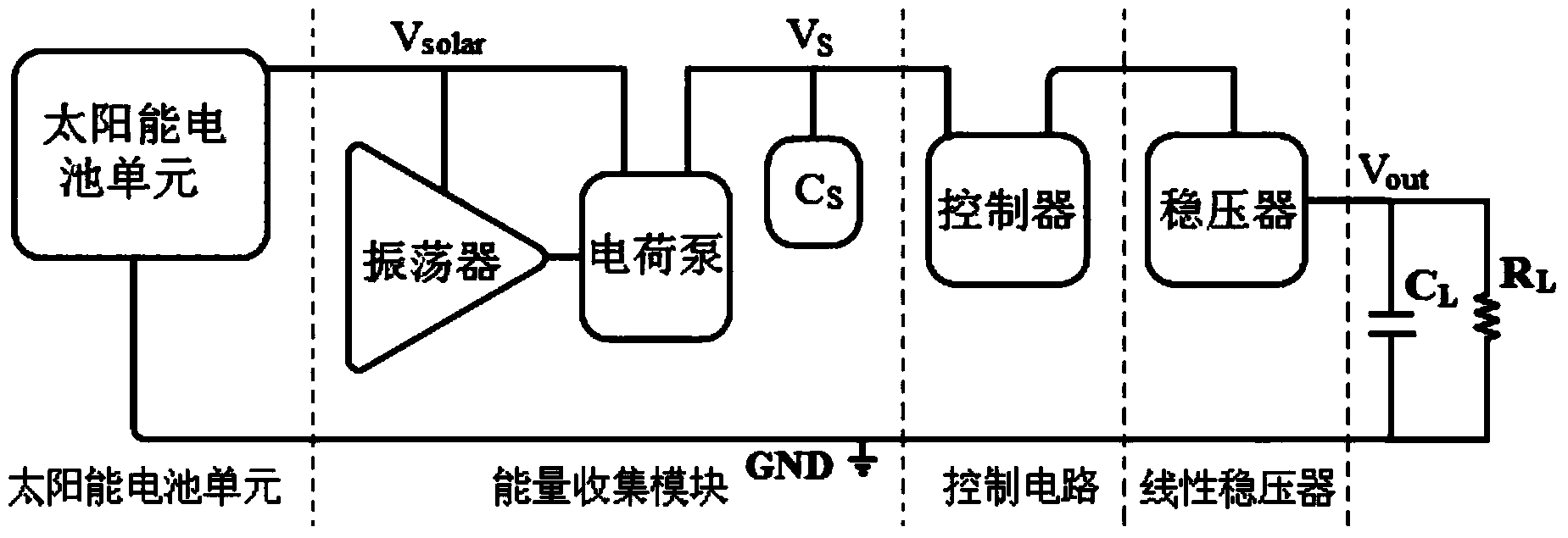

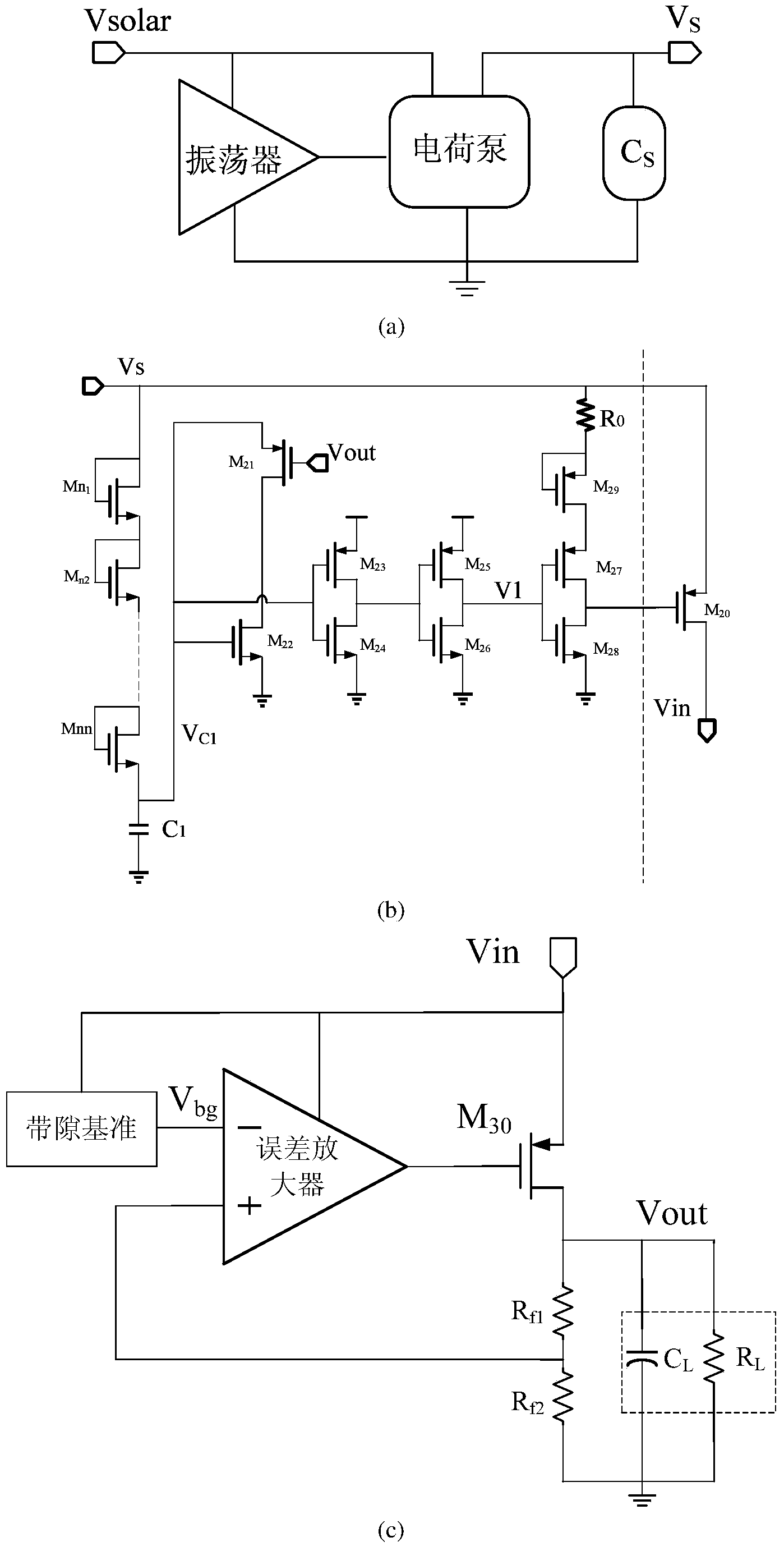

Integrated on-chip solar cell power supply system

InactiveCN103762708AReduce overall power consumptionThe overall structure is simpleBatteries circuit arrangementsPhotovoltaicsRadio frequencyEnergy harvesting

The invention belongs to the technical field of solar energy and provides an integrated on-chip solar cell power supply system. The purposes are to improve the overall efficiency of an on-chip power supply system, and provide lasting and stable energy supplies for micro power consumption systems such as radio frequency identification and wireless sensor network nodes. According to the technical scheme, the integrated on-chip solar cell power supply system comprises a set of solar cell units, an energy collecting module, a control circuit and a linear stabilizer, wherein the solar cell units are connected in parallel by the adoption of a metal interconnection technology, the energy collecting module comprises a ring oscillator, charge pumps connected in series in a multi-stage mode and an energy storage capacitor, and the linear stabilizer comprises a starting circuit, a band-gap reference and an operational amplifier and is used for providing stable working voltage VDD for a load circuit. The integrated on-chip solar cell power supply system is mainly applied to designing and manufacturing solar cells.

Owner:TIANJIN UNIV

Ring gate field effect transistor and preparation method thereof

ActiveCN106711194AReduce scatterImprove mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricElectrical conductor

The invention relates to a ring gate field effect transistor and a preparation method thereof. The preparation method includes the following steps that: a first gate dielectric layer, a channel layer, a second interface control layer, a source-drain layer and a semiconductor material layer are formed on a substrate; the semiconductor material layer is removed through etching, a structure shaped like a Chinese character ''tu' is formed in a channel region along a longitudinal direction through etching, the etching of the protruding part of the structure shaped like a Chinese character ''tu' is performed until arriving at the second interface control layer, and the etching of two sides of the structure shaped like a Chinese character ''tu' is performed until arriving at the first gate dielectric layer; third interface control layers grow on two side walls of the protruding part of the channel region, and a second gate dielectric layer and a second gate metal layer are formed on the upper surface of the protruding part from bottom to top, wherein the upper surface of the protruding part is separated from a source region and a drain region by a certain distance, and the second gate dielectric layer and the second gate metal layer extend to the side walls of the third interface control layers and the upper surfaces of flat stages at two sides of the protruding part; and a source-drain metal layer is formed at a portion at the upper surface of the source-drain layer in the source region and the drain region, wherein the portion is adjacent to the outer side of the upper surface of the source-drain layer. According to the transistor provided by the invention, channel scattering can be decreased, channel carrier mobility, gate control ability and current driving ability can be improved, and a short channel effect and a DIBL effect can be effectively suppressed.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

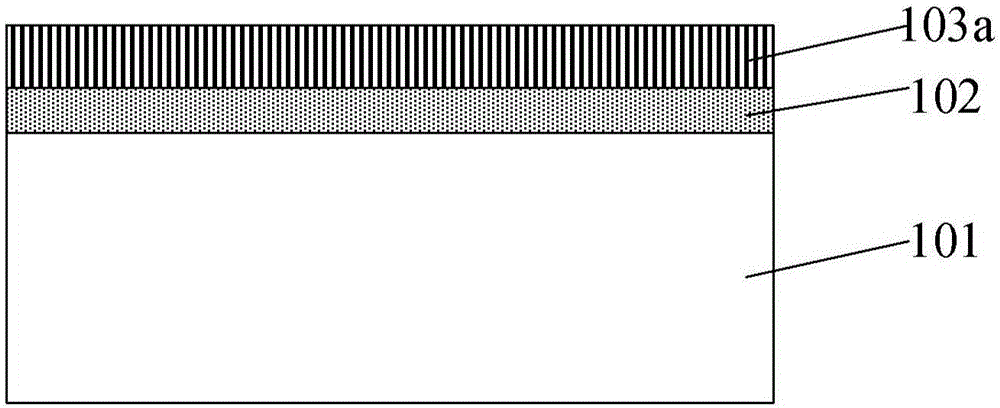

Substrate structure with high mobility and preparation method thereof

ActiveCN102569364AAchieve monolithic integrationImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesOxide semiconductorCMOS

The invention discloses a substrate structure with high mobility and the preparation method thereof, and belongs to the technical filed of semi-conductor integration. The substrate structure includes a single crystal silicon substrate, a buffer layer, a potential barrier layer, an indium-gallium-arsenic monocrystal layer, a blocking layer and a germanium monocrystal layer, wherein the buffer layer is placed on the single crystal silicon substrate; the potential barrier layer is placed on the buffer layer; the indium-gallium-arsenic monocrystal layer is placed on the potential barrier layer; the blocking layer is placed on the indium-gallium-arsenic monocrystal layer; and the germanium monocrystal layer is placed on the blocking layer. Through adopting the substrate structure and the preparation method thereof, a CMOS (complementary metal oxide semiconductor) device with high mobility and the combination of indium, gallium, arsenic and germanium can be realized on the silica-based substrate, or other semi-conductor devices with high mobility can be prepared on the indium-gallium-arsenic monocrystal layer and the germanium monocrystal layer, the substrate structure can be used for preparing the silica-based device, and the photoelectric device can be prepared through adopting the potential barrier layer, the monolithic integration of multiple unit semi-conductor devices can be facilitated, the performance can be improved, and the power consumption can be reduced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

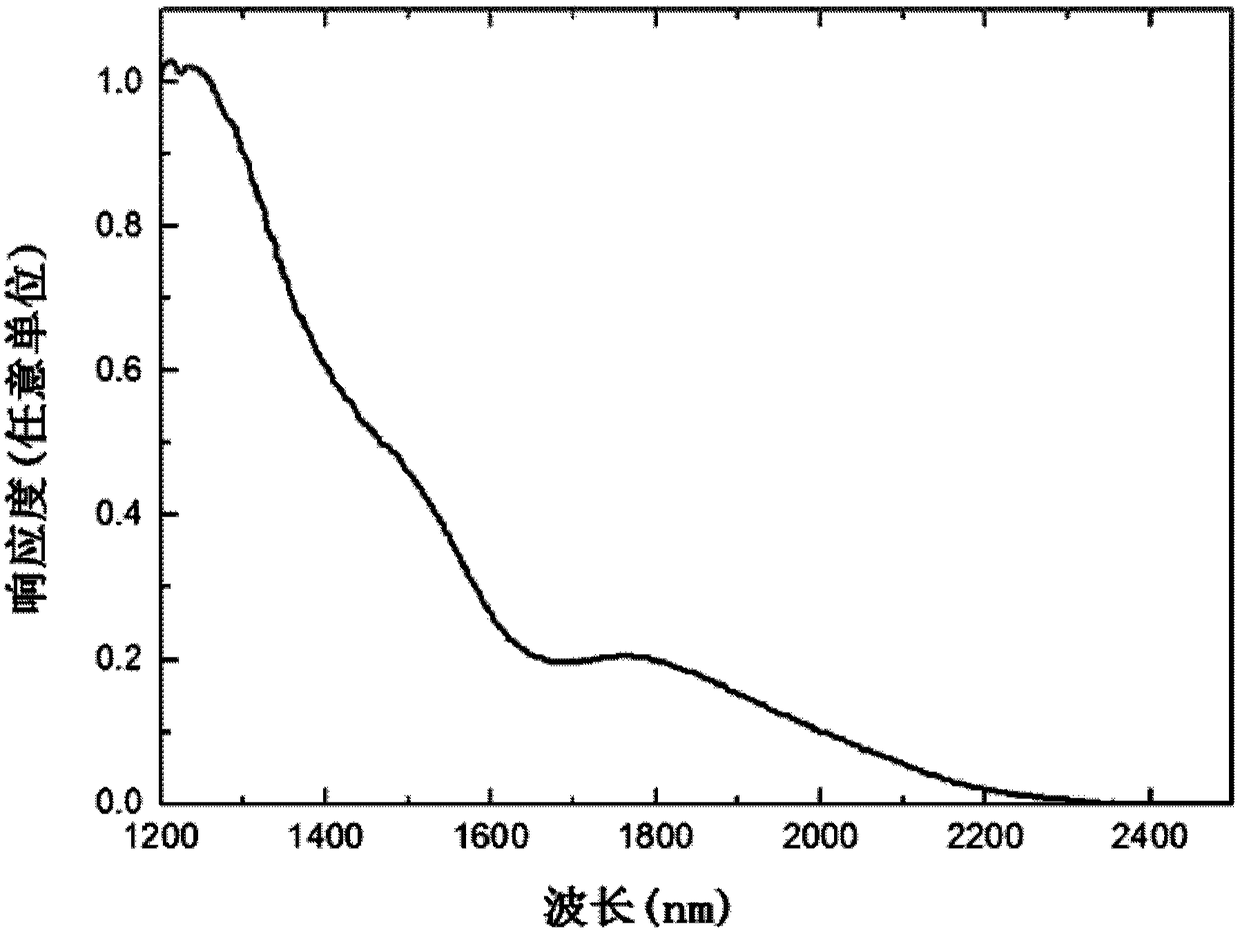

Visible-short wave infrared detector and preparation method thereof

ActiveCN108346713AAchieve monolithic integrationImplement detectionFinal product manufactureSemiconductor devicesPhotovoltaic detectorsP type doping

The invention relates to a visible-short wave infrared detector and a preparation method thereof. The preparation method comprises the steps of forming a P-type doping region and an N-type doping region of a silicon visible light detector on the back of a silicon substrate; forming a protective layer on the P-type doping region and the N-type doping region; epitaxially growing a germanium-tin light absorption layer of a germanium-tin infrared light detector on the front of the silicon substrate; removing the protective layer on the P-type doping region and the N-type doping region so as to complete the fabrication of the silicon visible light detector and the germanium-tin infrared light detector. The preparation method not only can utilize the advantages of low cost, high reliability andthe like of the traditional Si CMOS process, but also can realize monolithic integration of a photoelectric detector in a real sense.

Owner:江苏联格科技有限公司

Cantilever beam structural resonant-type integrated optical waveguide accelerometer

ActiveUS8640542B2Small sizeLight weightAcceleration measurement using interia forcesOptical light guidesAccelerometerPhase difference

A cantilever beam structural resonant-type integrated optical waveguide accelerometer, includes an input waveguide (1), a dissymmetrical structural Mach-Zehnder interferometer (2), a micro-mechanical vibration cantilever beam (3), a short curved waveguide (4) and an output waveguide (5); all the waveguide structures and the cantilever beam use the integrated optical micromachining technique, and the device single-scale integration can be realized by using the temperature-insensitive organic polymer optical waveguide structure and the organic polymer substrate, the key technique indexes such as detection sensitivity, dynamic range are extensively adjusted. The phase difference of the optical signal can be measured by detecting the optical intensity of the resonant frequency of the optical circuit so as to achieve high sensitive acceleration detection, and to be free from the effect of the ambient temperature disturbance and waveguide birefringence.

Owner:SOUTHEAST UNIV

Vertically-integrated double-gate MOSFET structure and preparation method therefor

ActiveCN106298886AImprove mobilityImprove gate control abilitySolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsEngineering

The invention discloses a vertically-integrated double-gate MOSFET structure and a preparation method therefor. Compared with a conventional planar MOSFET structure, the vertically-integrated double-gate MOSFET structure adopts an III-V group semiconductor material with high electron mobility / hole mobility as a channel material; due to the adopted double-gate structure, the gate control capability of an MOSFET device is effectively improved, and influence from a short channel effect and the like is reduced; an NMOS and a PMOS are integrated in a vertical direction, so that the integration degree of devices on a unit wafer area is improved; and vertical through holes are adopted to realize interconnection of the devices in the vertical direction, so that the length of an interconnecting lead is effectively shortened while the operation speed of the devices is improved. The vertically-integrated double-gate MOSFET structure provided by the invention has an important application value in a post-Moore era CMOS integration technology and a high-performance III-V group semiconductor device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

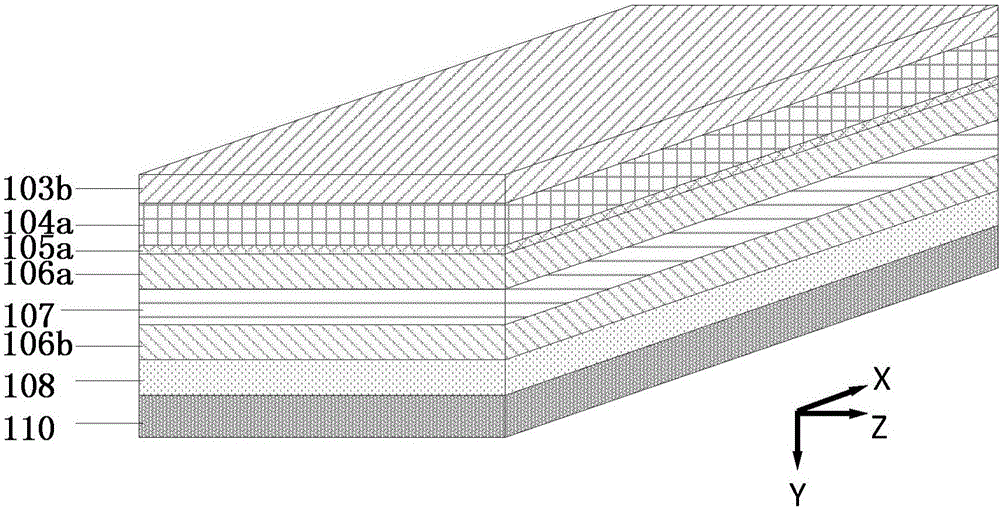

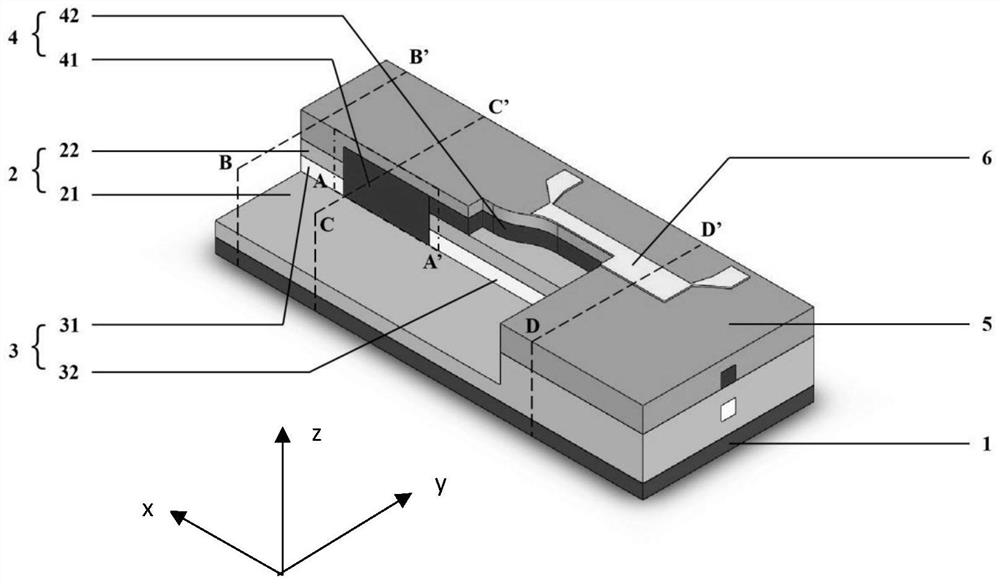

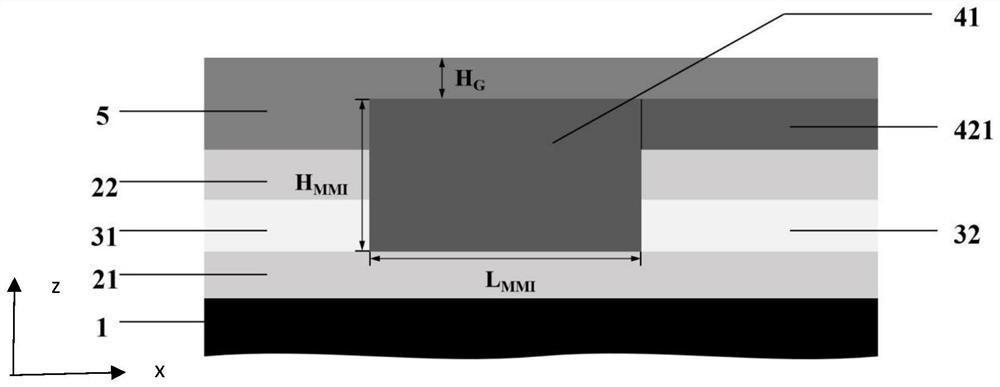

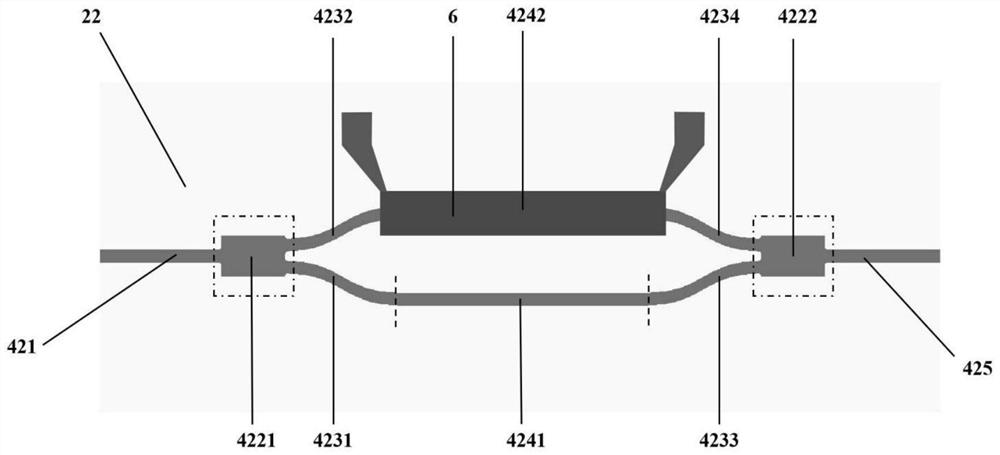

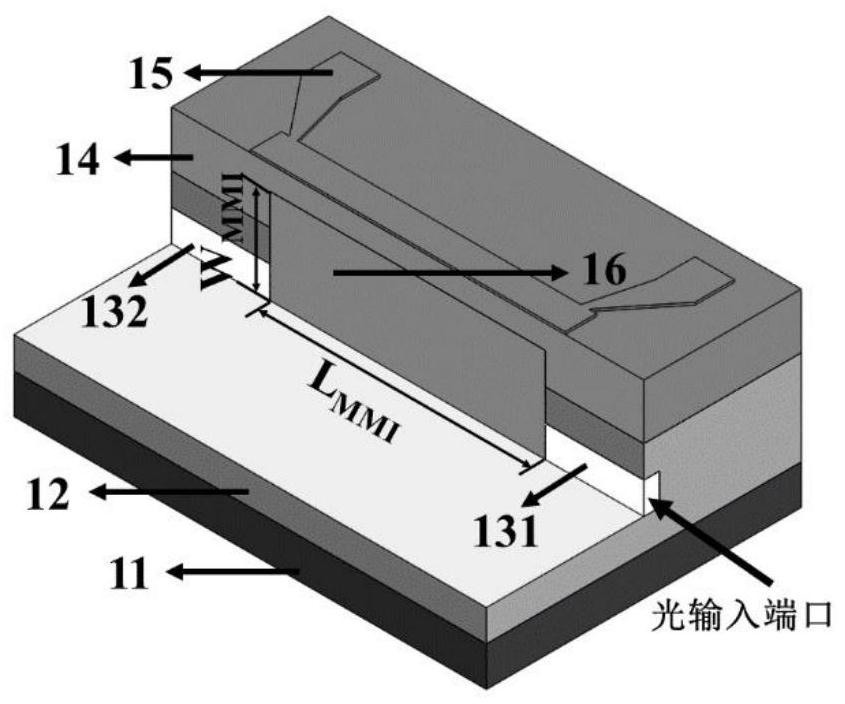

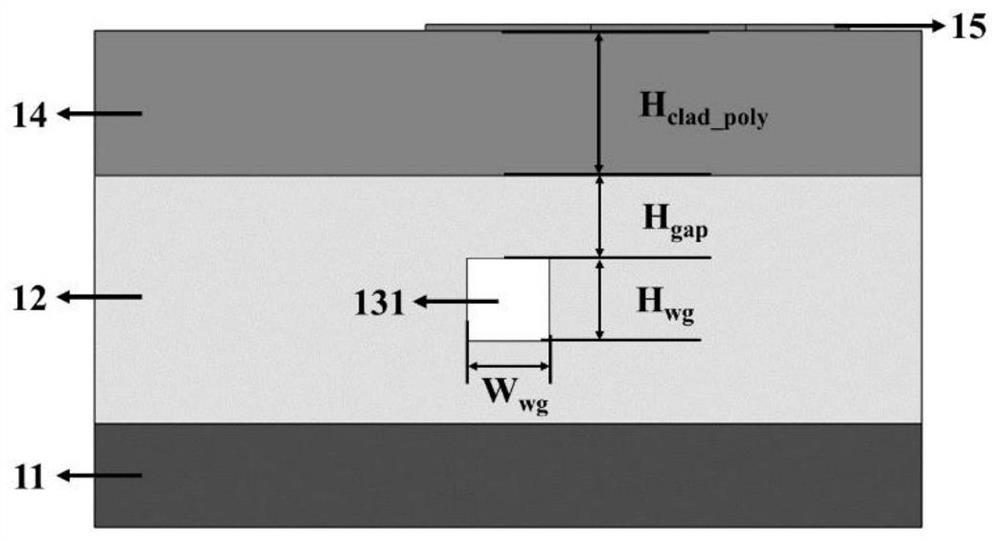

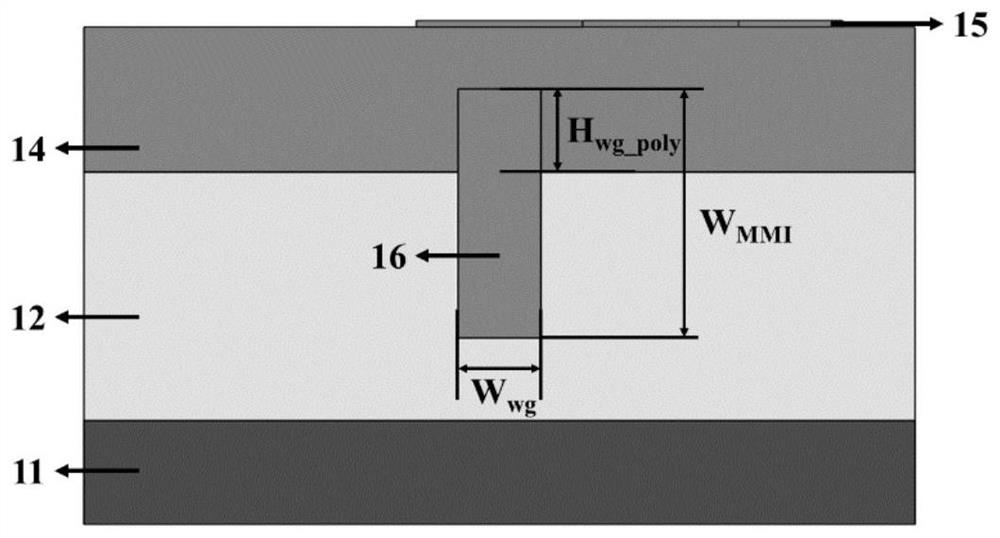

Organic-inorganic hybrid integrated variable optical attenuator and preparation method thereof

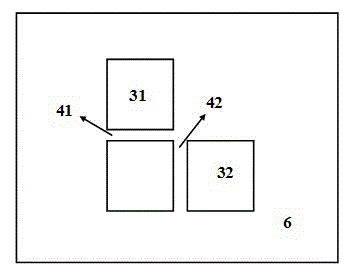

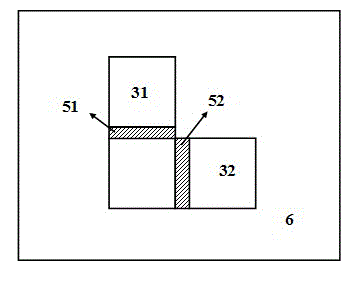

PendingCN114089474ACompact structureReduce power consumptionCoupling light guidesOptical waveguide light guideConvertersRefractive index

The invention discloses an organic-inorganic hybrid integrated variable optical attenuator and a preparation method thereof, and belongs to the technical field of planar optical waveguide devices and preparation thereof. The organic-inorganic hybrid integrated variable optical attenuator is composed of a silicon substrate, a silicon dioxide lower cladding layer, a germanium-doped silicon dioxide input waveguide and a germanium-doped silicon dioxide output waveguide which are of strip-shaped structures, an interlayer converter based on a vertical MMI structure, a boron and phosphorus-doped silicon dioxide upper cladding layer, a 1 * 1 Mach-Zehnder thermo-optical switch, a polymer upper cladding layer and a heating electrode, wherein the refractive indexes of the input waveguide and the output waveguide are larger than the refractive index of the silicon dioxide upper cladding. The vertical MMI is compact in structure, a VOA device of a traditional inorganic PLC is replaced with a polymer thermo-optical switch type VOA device, and transmission of light from a lower-layer inorganic waveguide to an upper-layer polymer waveguide is achieved; the light transmission power is efficiently adjusted, device power consumption is low, and monolithic integration of organic and inorganic photonic devices is achieved; and the organic-inorganic hybrid integrated variable optical attenuator is compatible with an existing silicon dioxide PLC technology, is easy for large-scale production and low in cost.

Owner:JILIN UNIV

Organic-inorganic hybrid integrated polymer variable optical attenuator and preparation method thereof

ActiveCN113296292AAchieve monolithic integrationLow costNon-linear opticsPolymer optical waveguideOptical communication

The invention discloses an organic-inorganic hybrid integrated polymer variable optical attenuator with a vertical multimode interference device structure and a preparation method thereof, and belongs to the technical field of polymer optical waveguide variable optical attenuators. The silicon dioxide lower cladding layer is prepared on the substrate; the silicon dioxide input waveguide unit, the polymer core layer waveguide unit and the silicon dioxide output waveguide unit are prepared on the silicon dioxide lower cladding layer along the light propagation direction; and the silicon dioxide lower cladding is arranged on the silicon dioxide input waveguide unit, the silicon dioxide upper cladding is arranged on the silicon dioxide lower cladding and wraps the silicon dioxide input waveguide unit and the silicon dioxide output waveguide unit, the polymer cladding is arranged on the silicon dioxide upper cladding and the polymer core layer waveguide unit, and the metal modulation electrode is arranged on the polymer cladding. The variable optical attenuator has the advantages of compact structure, low power consumption, high response speed, large extinction ratio and the like, can be used in a WDM (Wavelength Division Multiplexing) system in optical communication, and plays a role in balancing power.

Owner:JILIN UNIV