Patents

Literature

480 results about "Clock buffer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

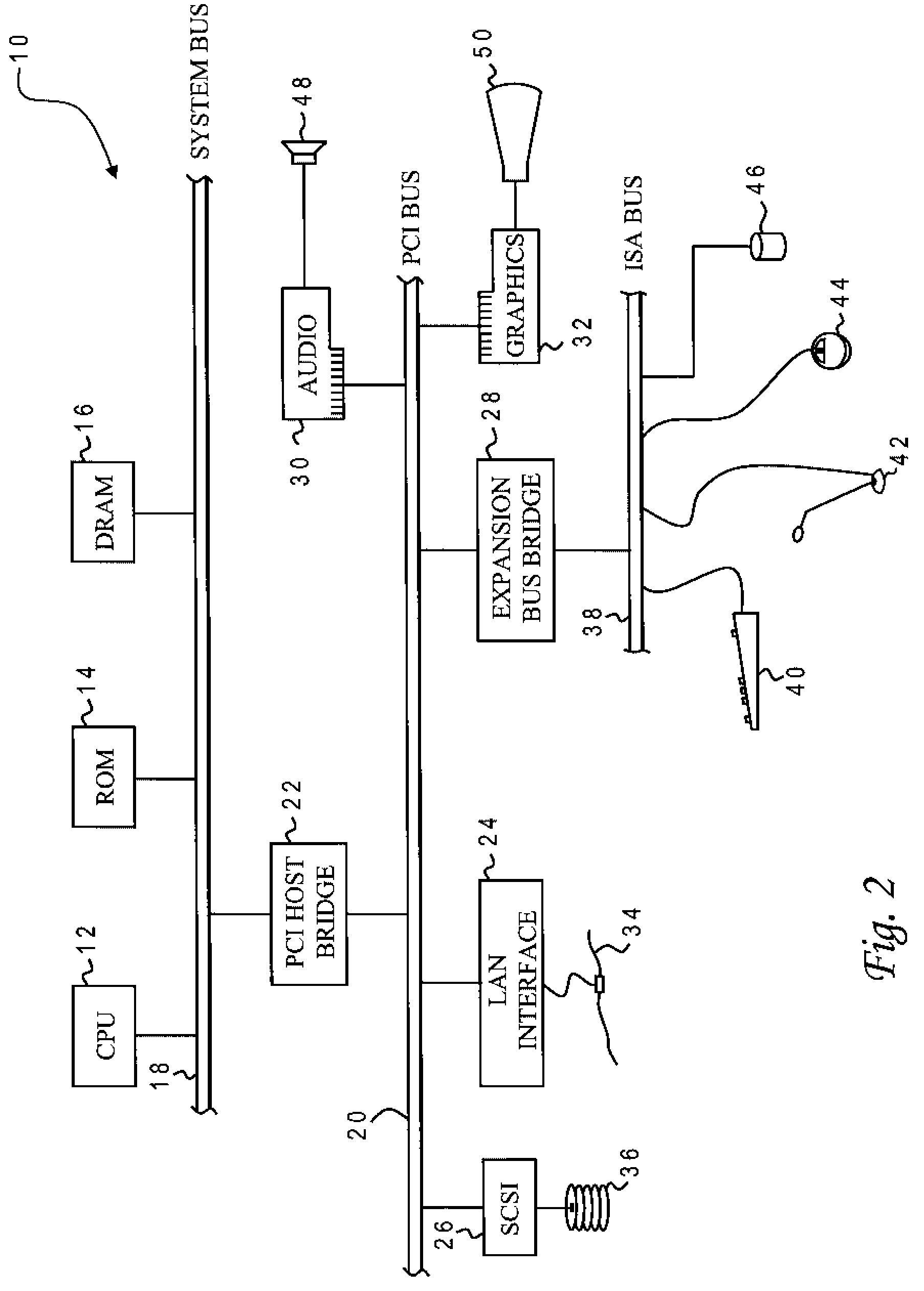

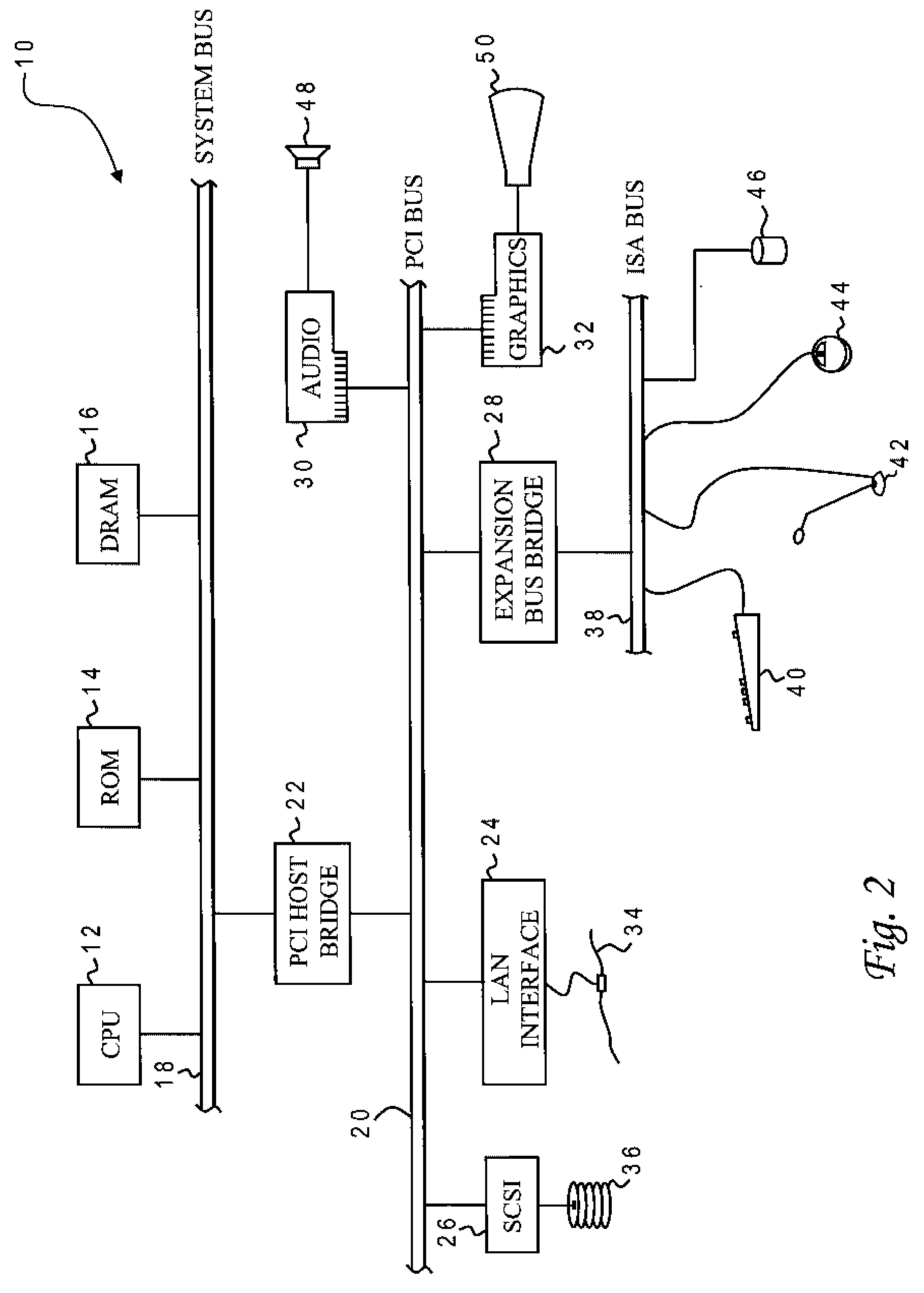

Unified digital architecture

InactiveUS20060029177A1Pulse automatic controlModulated-carrier systemsFinite impulse responseComputer science

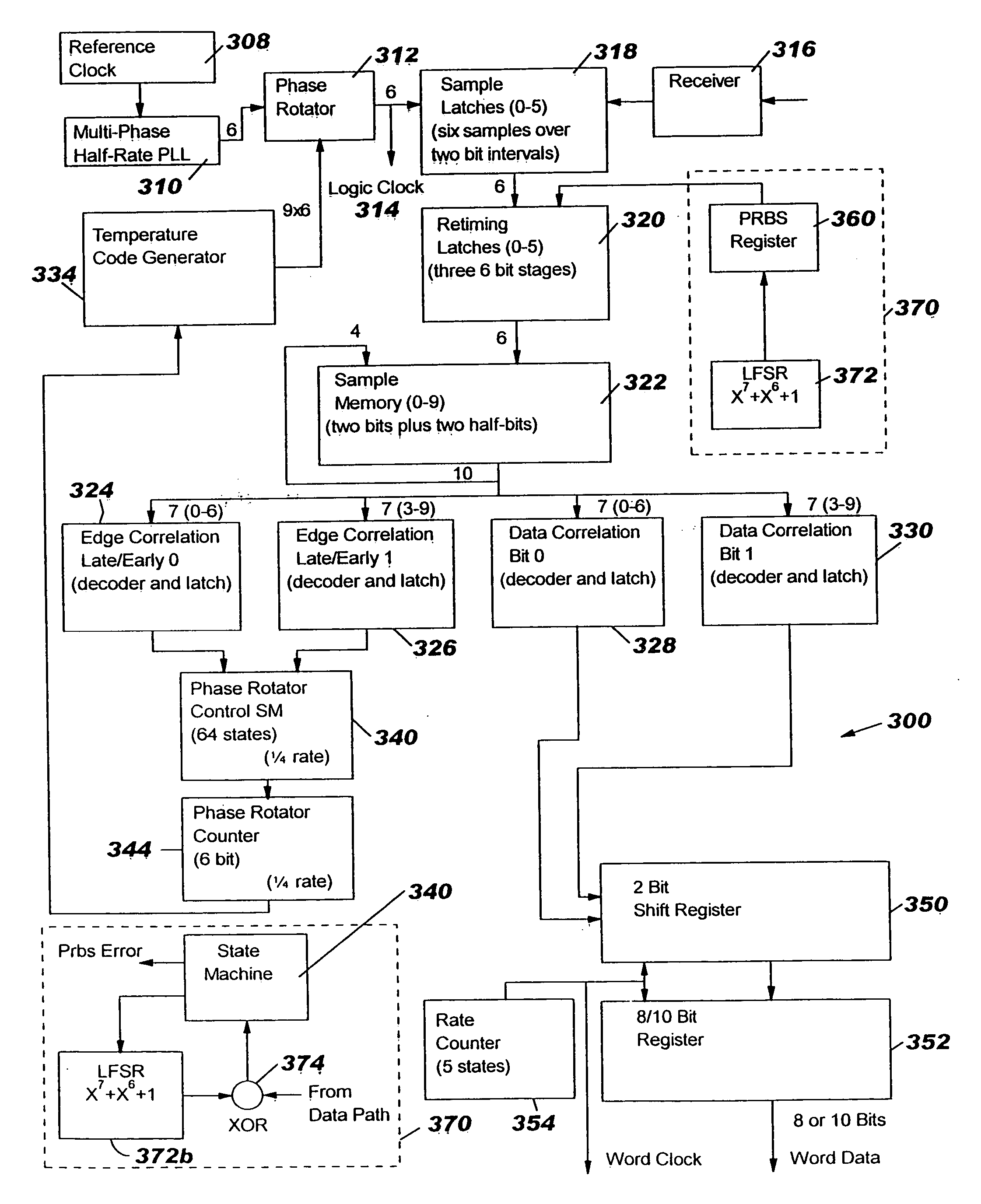

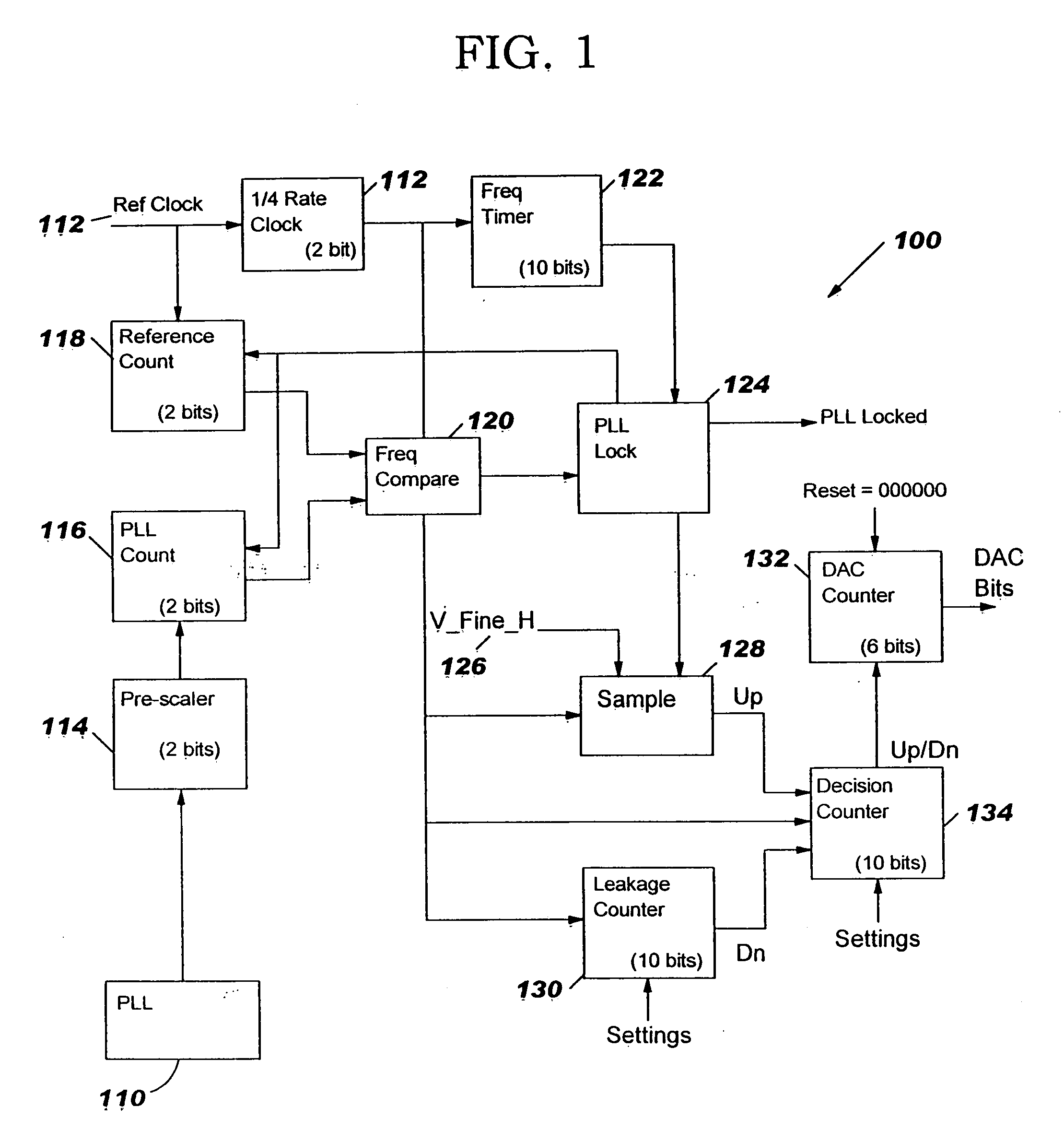

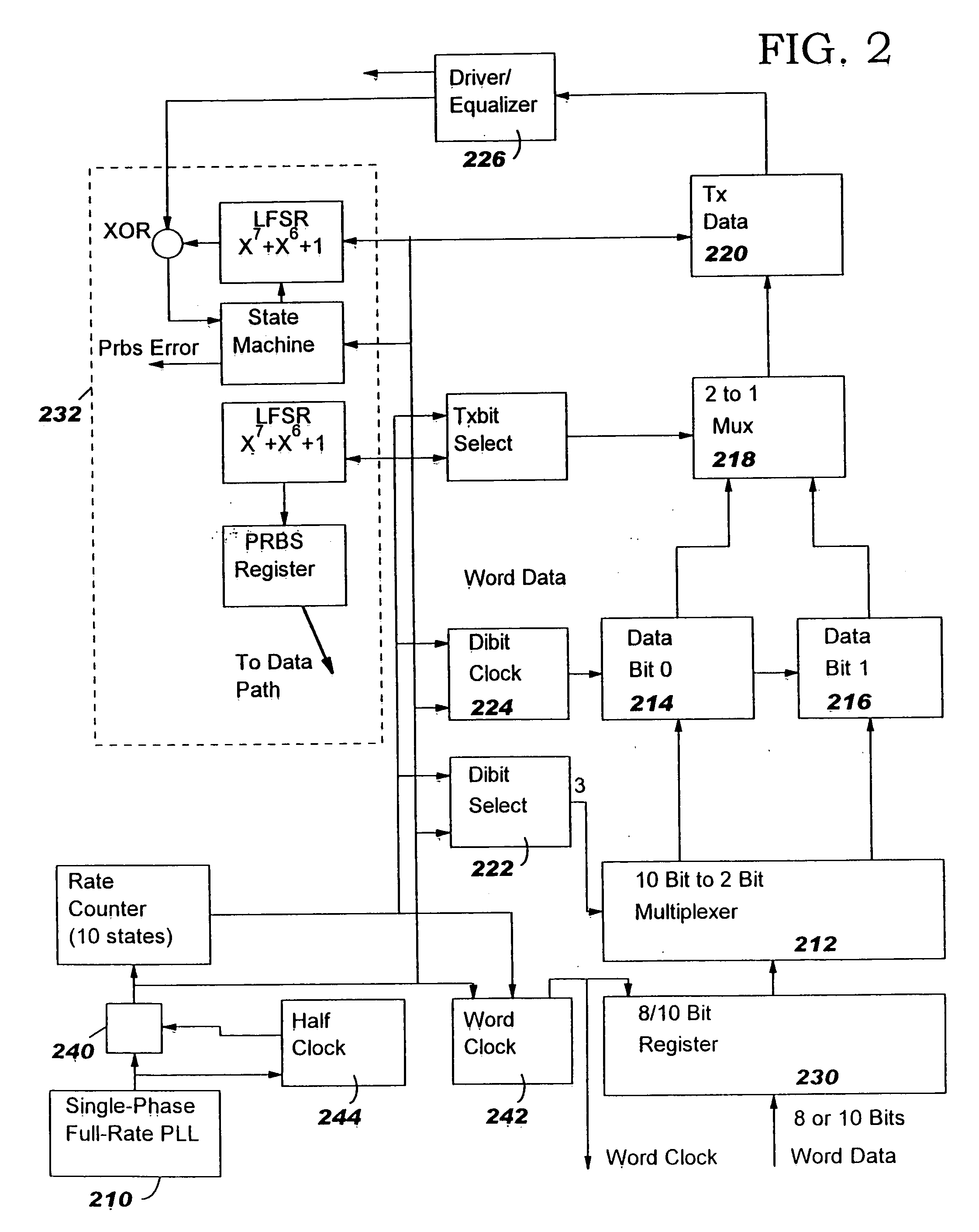

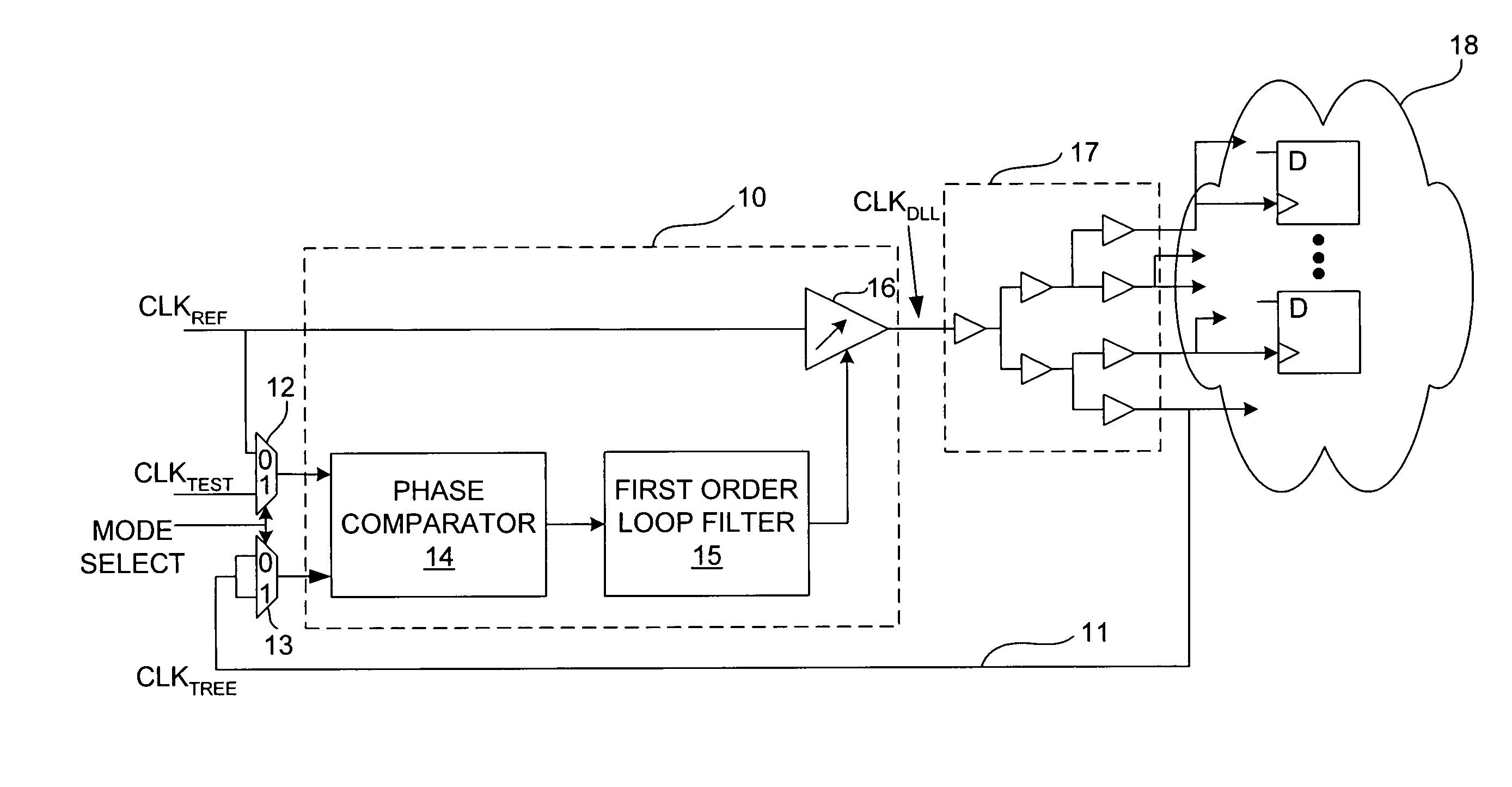

A unified, unidirectional serial link is described for providing data across wired media, such as a chip-to chip or a card-to-card interconnect. It consists of a transmit section and a receive section that are operated as pairs to allow the serial data communication. The serial link is implemented as part of a VLSI ASIC module and derives its power, data and clocking requirements from the host modules. The logic transmitter portion contains a phase locked loop (PLL), a dibit data register, a finite impulse response (FIR) filter and a transmit data register. The phase locked loop comprises both a digital coarse loop and an analog fine loop. The digital receiver portion contains a PLL, an FIR phase rotator, a phase rotator control state machine, and a clock buffer. The transmitter and the receiver each preferably utilize a pseudo-random bit stream (PRBS) generator and checker.

Owner:IBM CORP

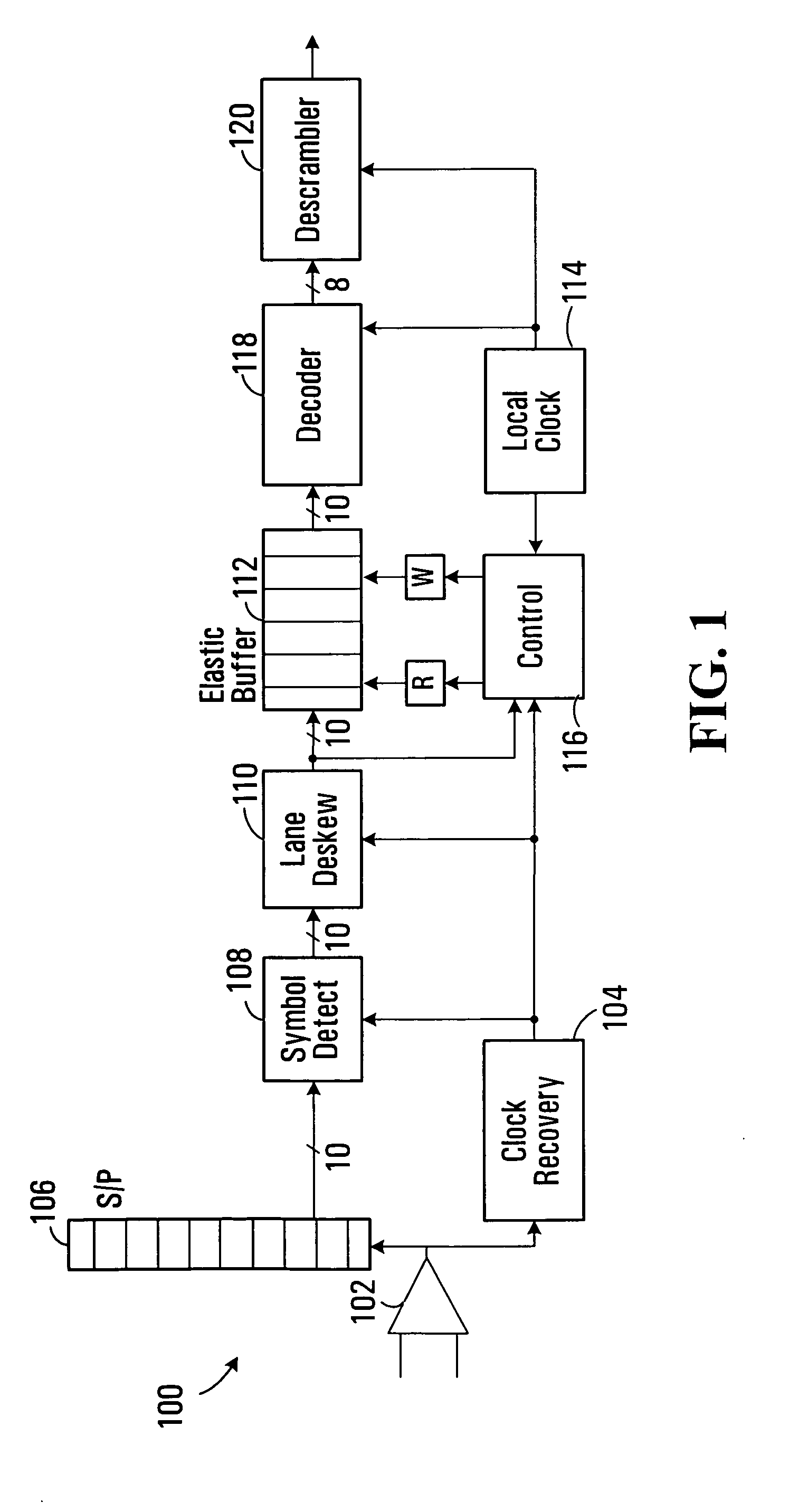

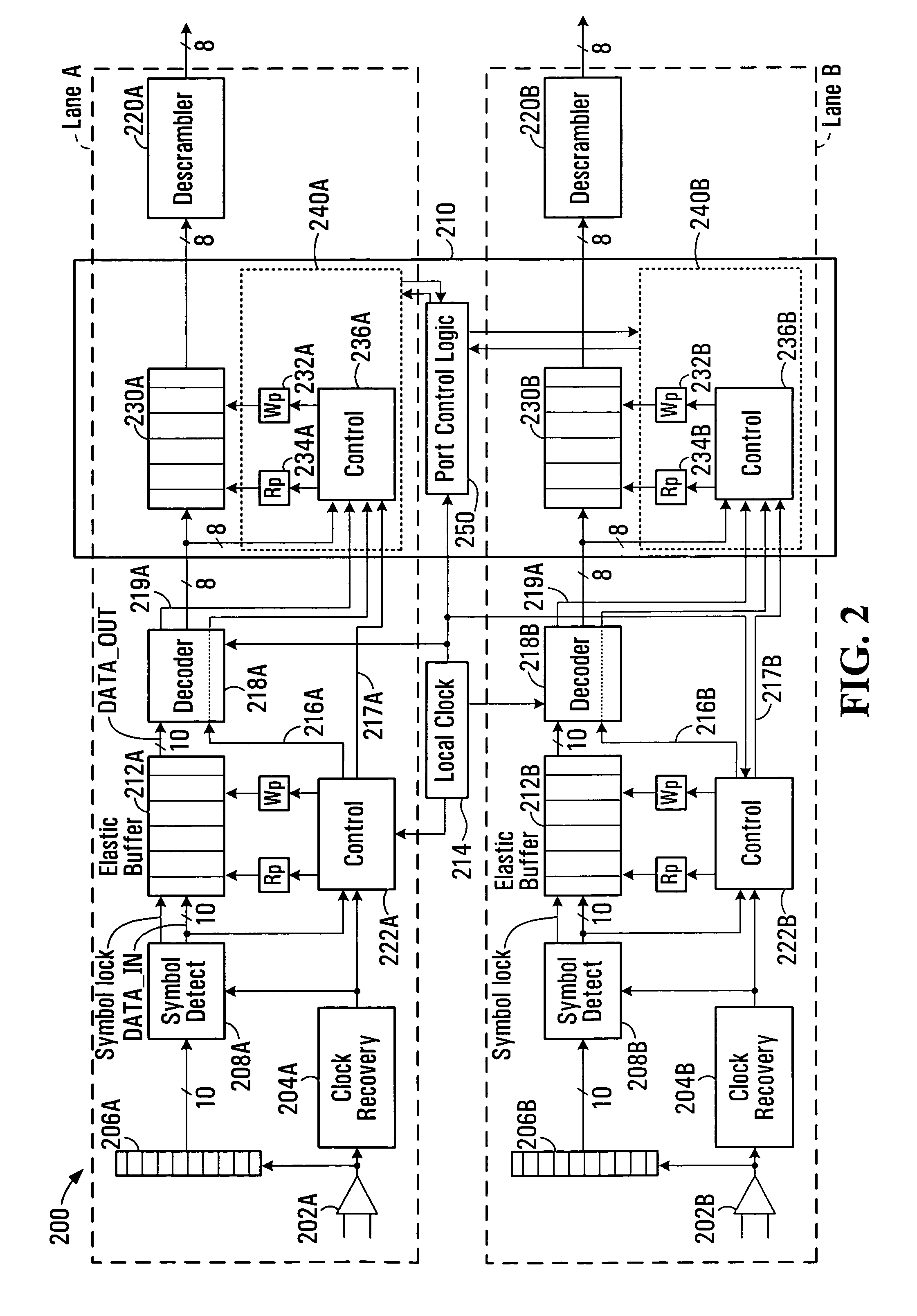

Receiver and method for synchronizing and aligning serial streams

ActiveUS20070177701A1Avoid the needAvoid storage problemsTime-division multiplexSynchronising arrangementClock ratePCI Express

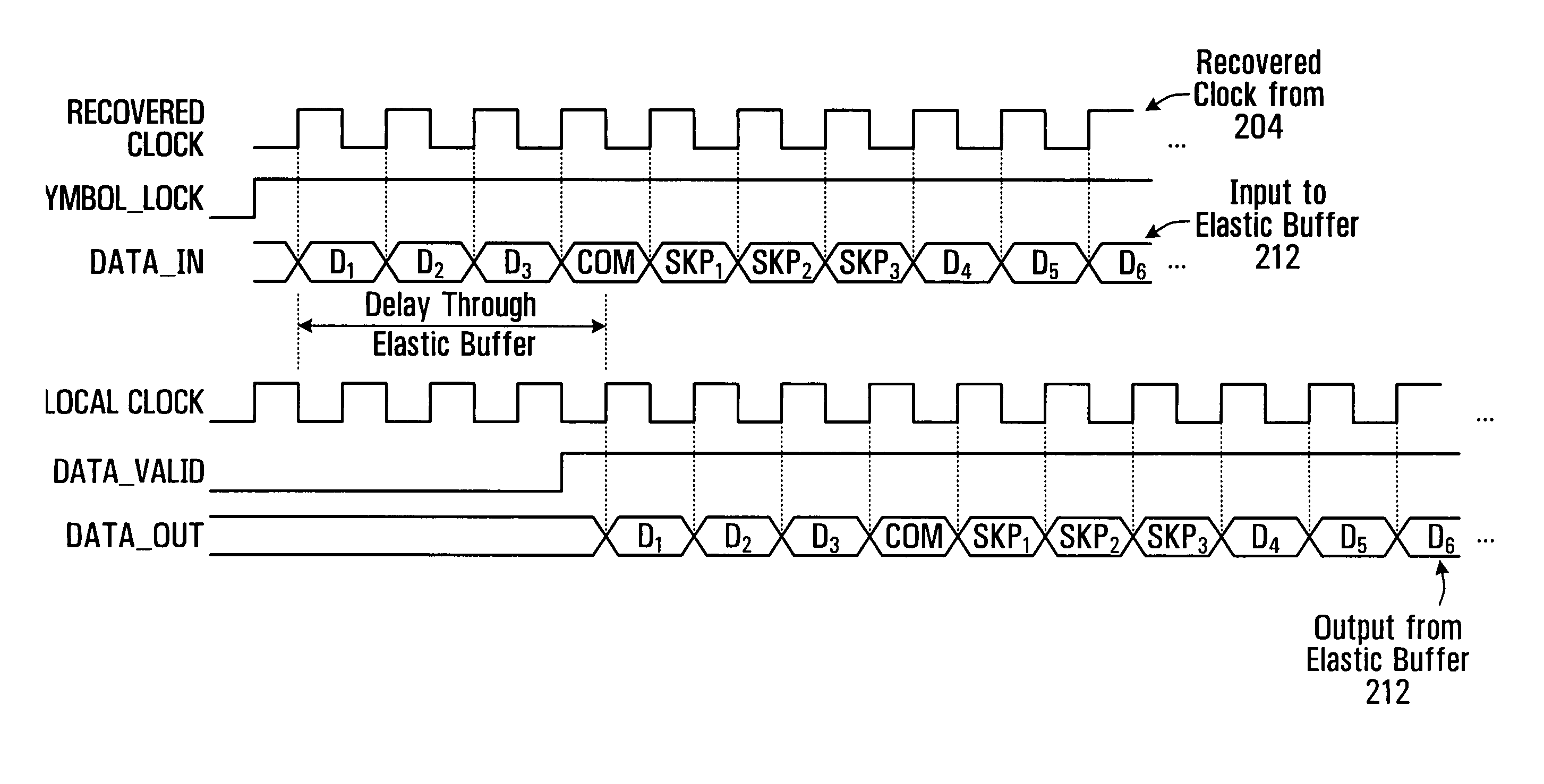

A receiver for receiving a stream of symbols clocked at a first rate, and providing the symbols at a second clock rate uses two buffers. Incoming symbols are written to a first dual clock buffer at the first rate, and read from the first and second buffer, at the second rate. Underflow of the first buffer is signaled to the second buffer, thereby avoiding the need to insert defined clock compensation symbols at the second rate. Symbols received at the second buffer while underflow is signaled may be ignored. Conveniently, the second buffer may also be used to align symbol data across multiple symbol streams using periodic alignment symbols. An exemplary embodiment conforms to the PCI Express standard.

Owner:ATI TECH INC

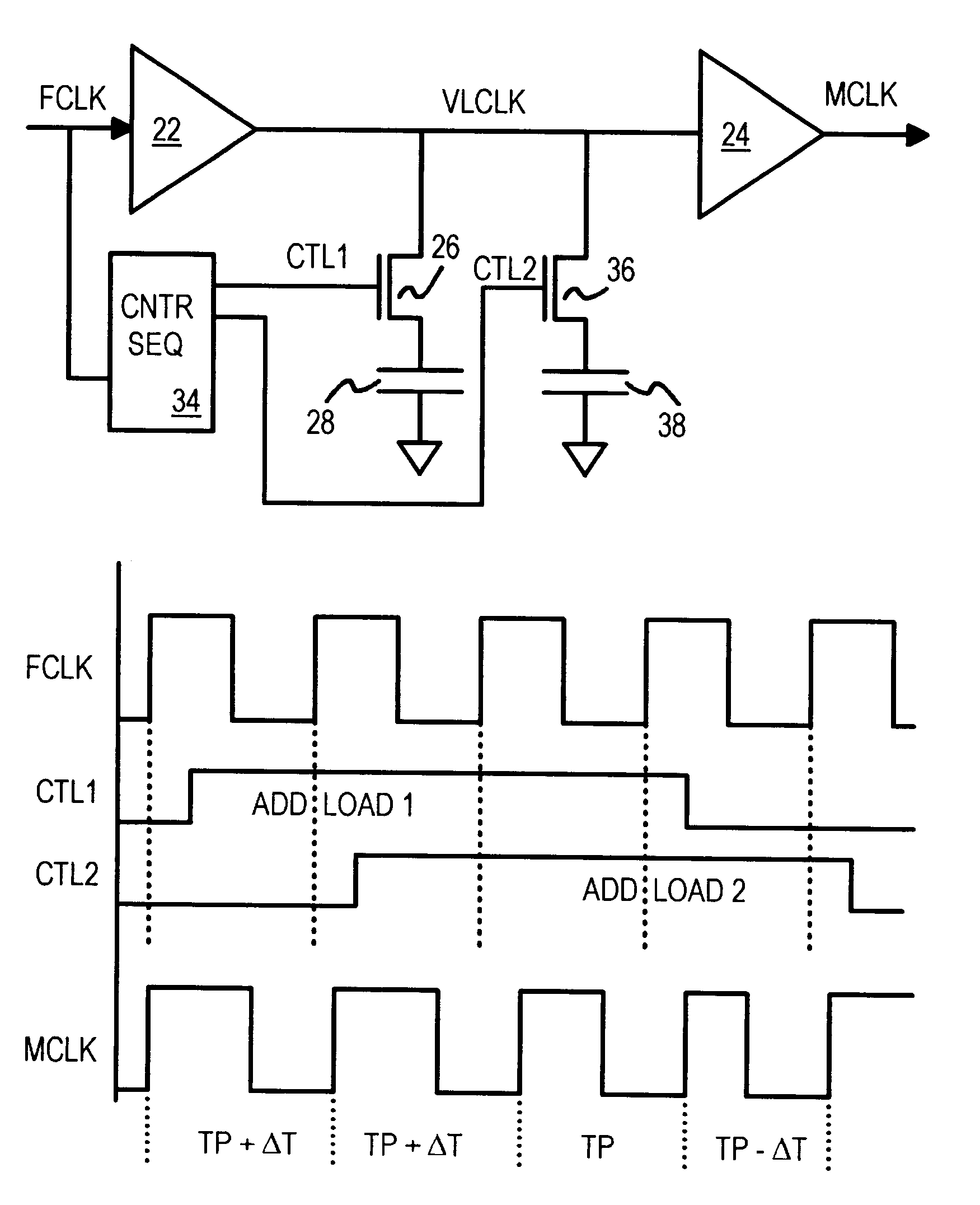

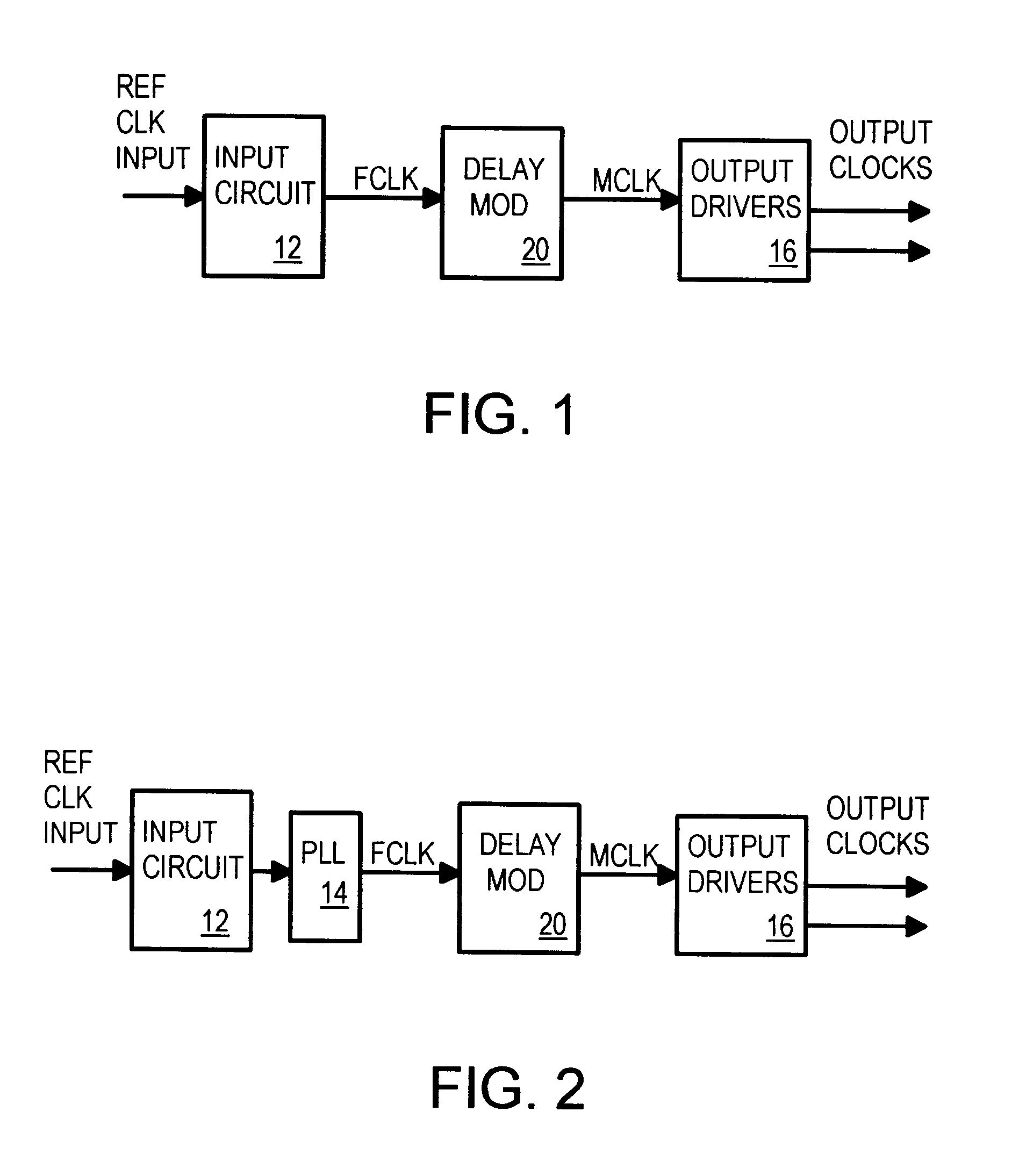

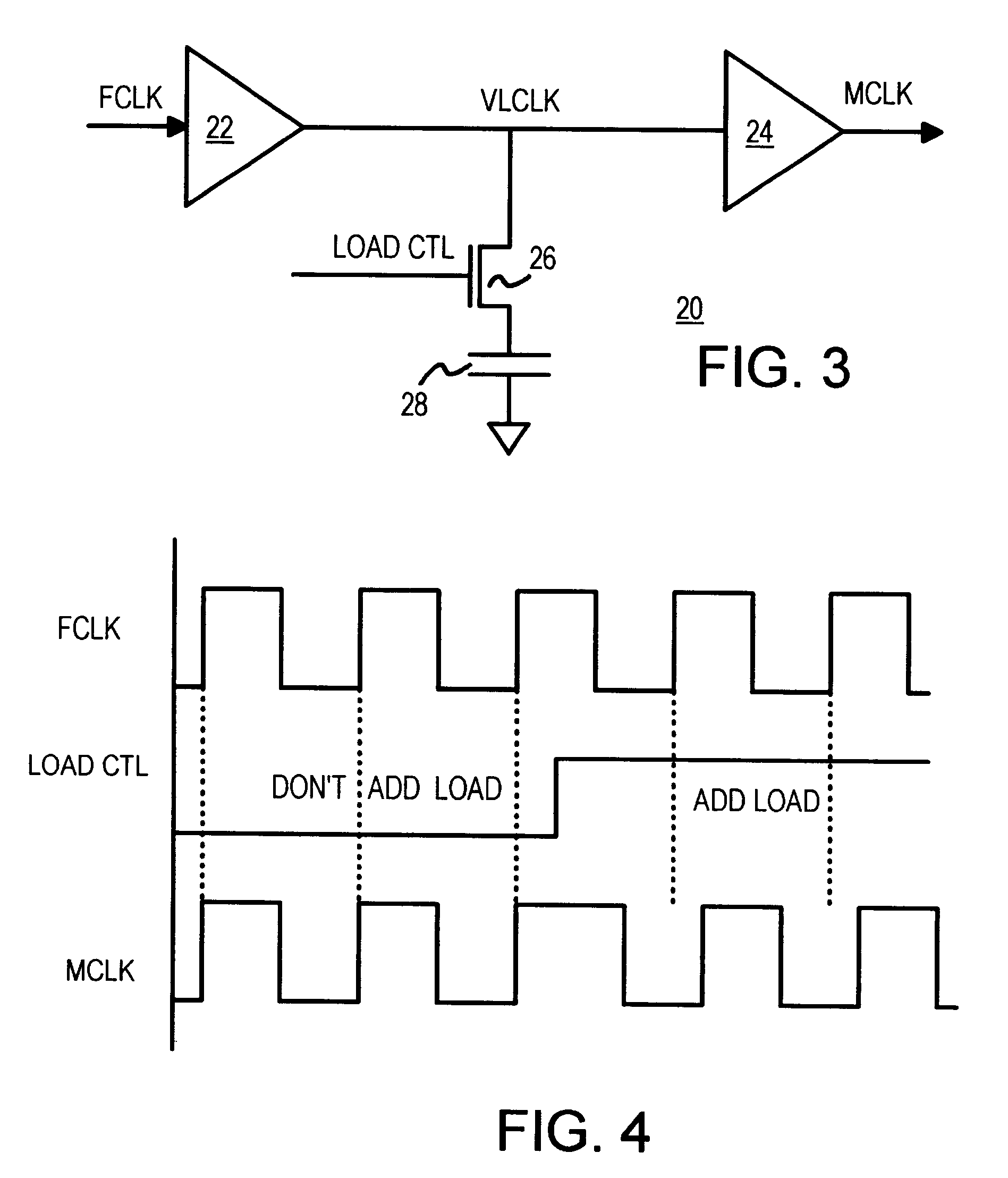

Spread-spectrum clock buffer/driver that modulates clock period by switching loads

A clock modulator spreads the frequency spectrum of an input clock to generate an output clock. A capacitor is connected to an intermediate clock node by a load-switching transistor. When the transistor is turned on, the capacitor increases the loading on the intermediate clock node, increasing delay. When the transistor is turned off, the delay is reduced. Output clock cycle periods are extended when delay is added, and reduced when the transistor turns off. A counter or sequencer is clocked by the input clock and drives the load-switching transistor. The transistor is turned on and off for alternate cycles when the counter is a toggle flip-flop, spreading the frequency over two frequencies every two clock cycles. Two capacitors of different sizes, connected to the intermediate clock node by two transistors, can be switched by a 2-bit sequencer, spreading the output clock over 7 frequencies every 7 clock cycles.

Owner:DIODES INC

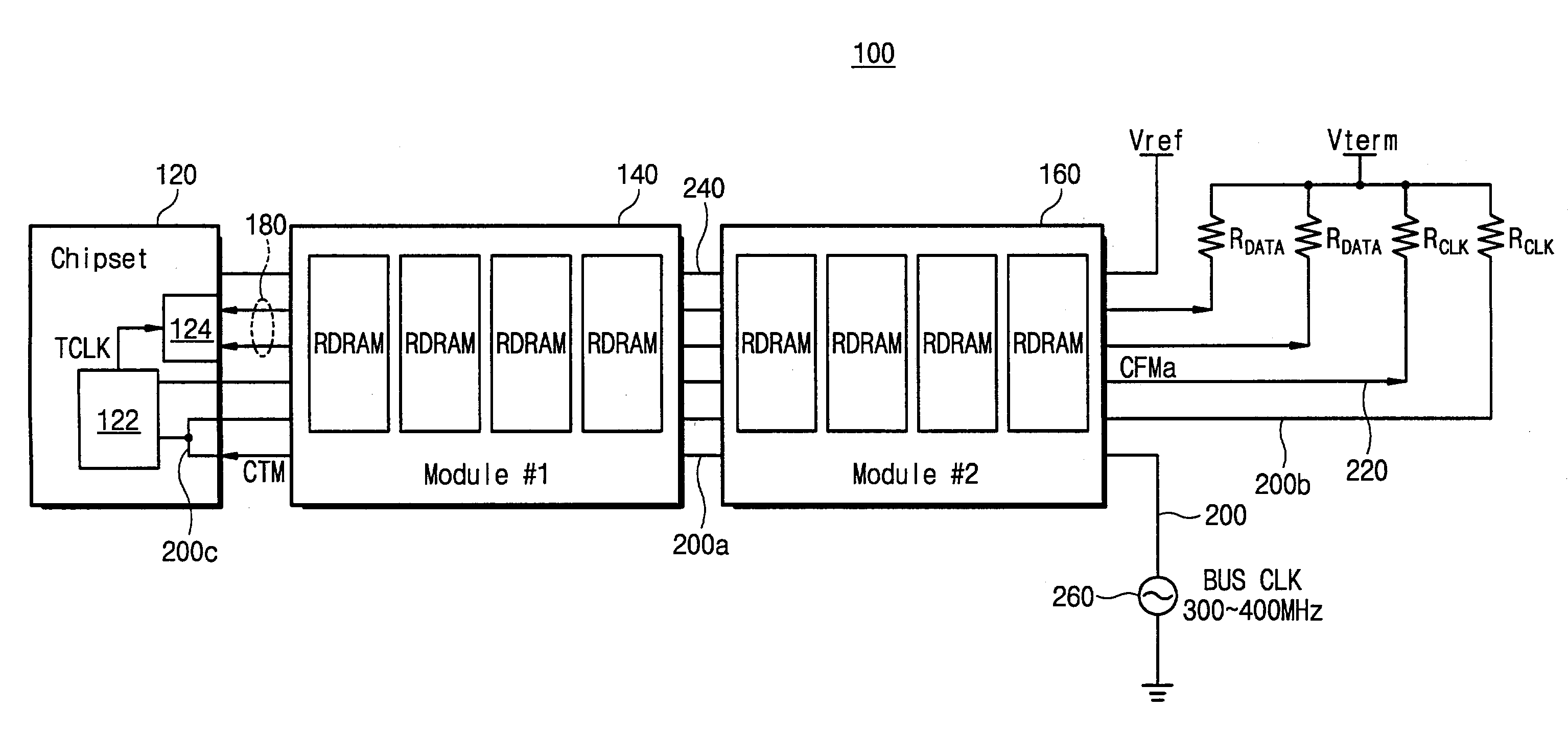

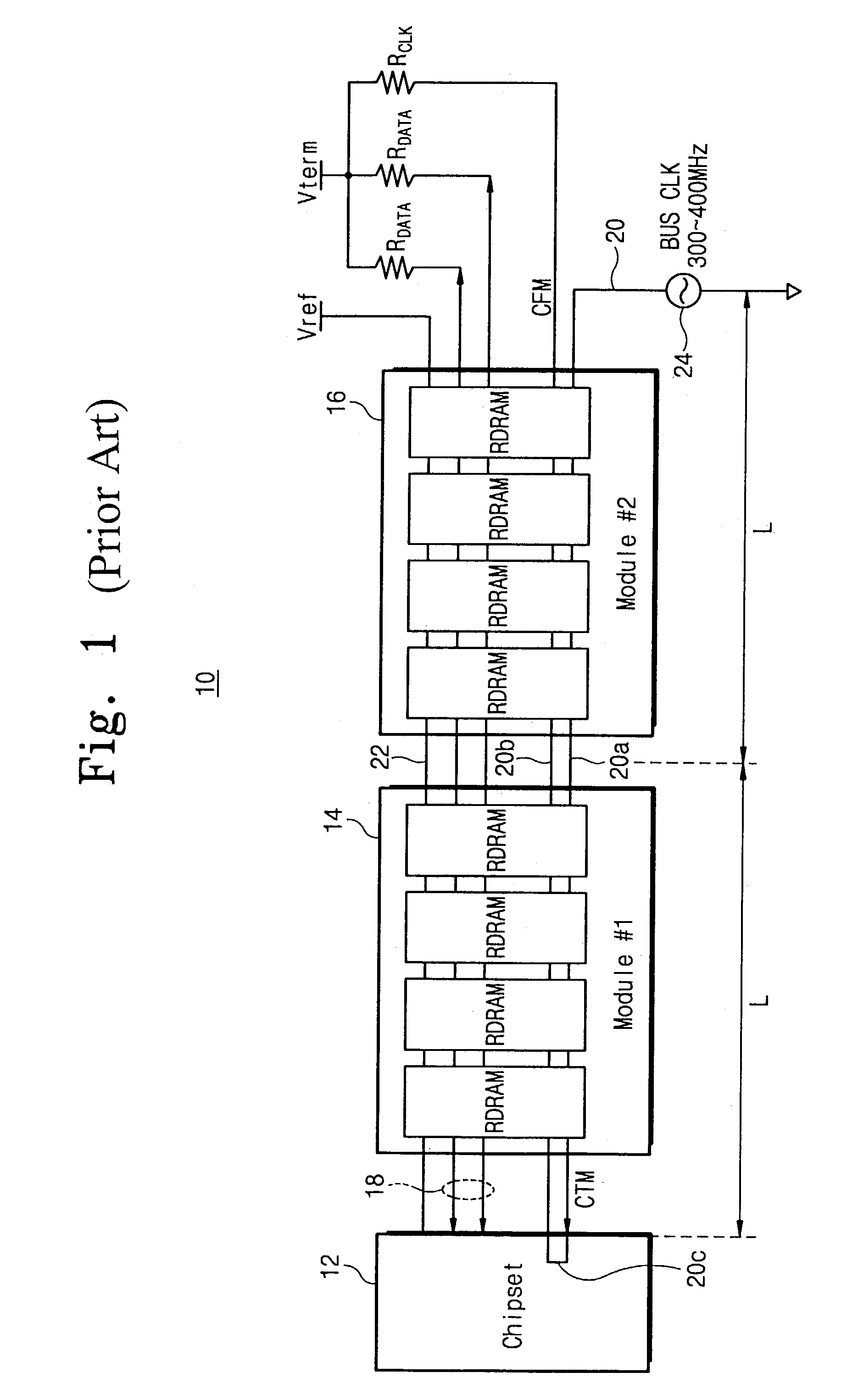

Information processing system has clock lines which are electrically isolated from another clock line electrically connected to clock buffer and termination voltage

ActiveUS7103792B2Prevents undesirable discrepancy of operational timingReduce deteriorationError detection/correctionData resettingInformation processingElectricity

A system includes modules, a clock generator that generates a first clock signal that is applied to the modules, and a chipset that controls the modules, the chipset having a clock buffer that generates a second clock signal. The system includes a first clock line that transfer the first clock signal to the clock buffer, the first clock line connected between the clock generator and a first termination circuit. The system includes a second clock line that transfer the second clock signal to the modules, the second clock line electrically isolated from the first clock line, the second clock line connected between the clock buffer and a second termination circuit.

Owner:SAMSUNG ELECTRONICS CO LTD

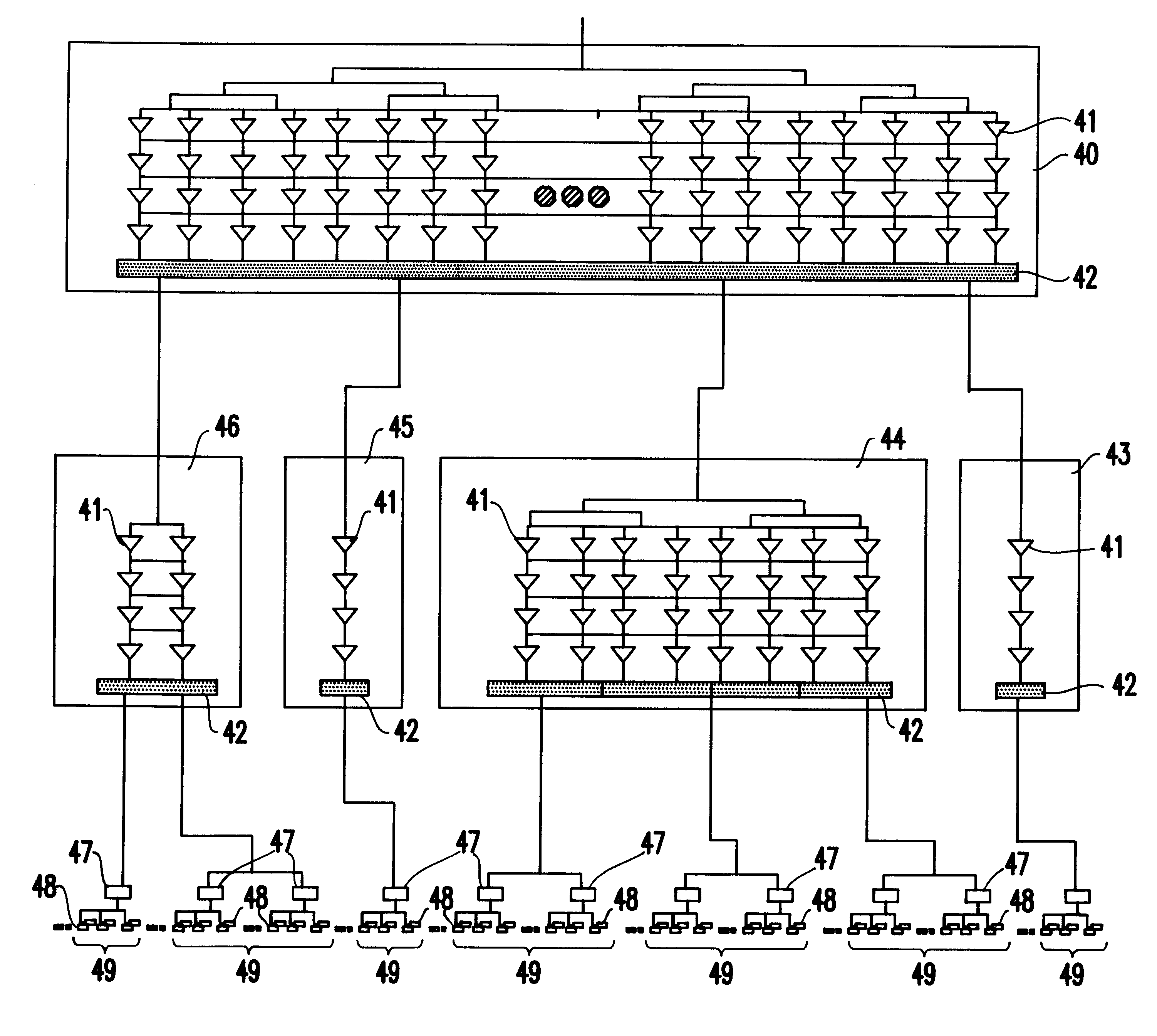

Method and apparatus for routing low-skew clock networks

An integrated circuit chip comprises a plurality of clock distribution sub-networks each including a clock input for receiving a clock signal, each of the clock distribution sub-networks having a capacitance, as seen from the clock input, substantially equivalent to others of the clock distribution sub-networks; and a structured clock buffer having a size based on a load of the clock distribution sub-networks, and providing the clock signal to the clock distribution sub-networks.

Owner:IBM CORP

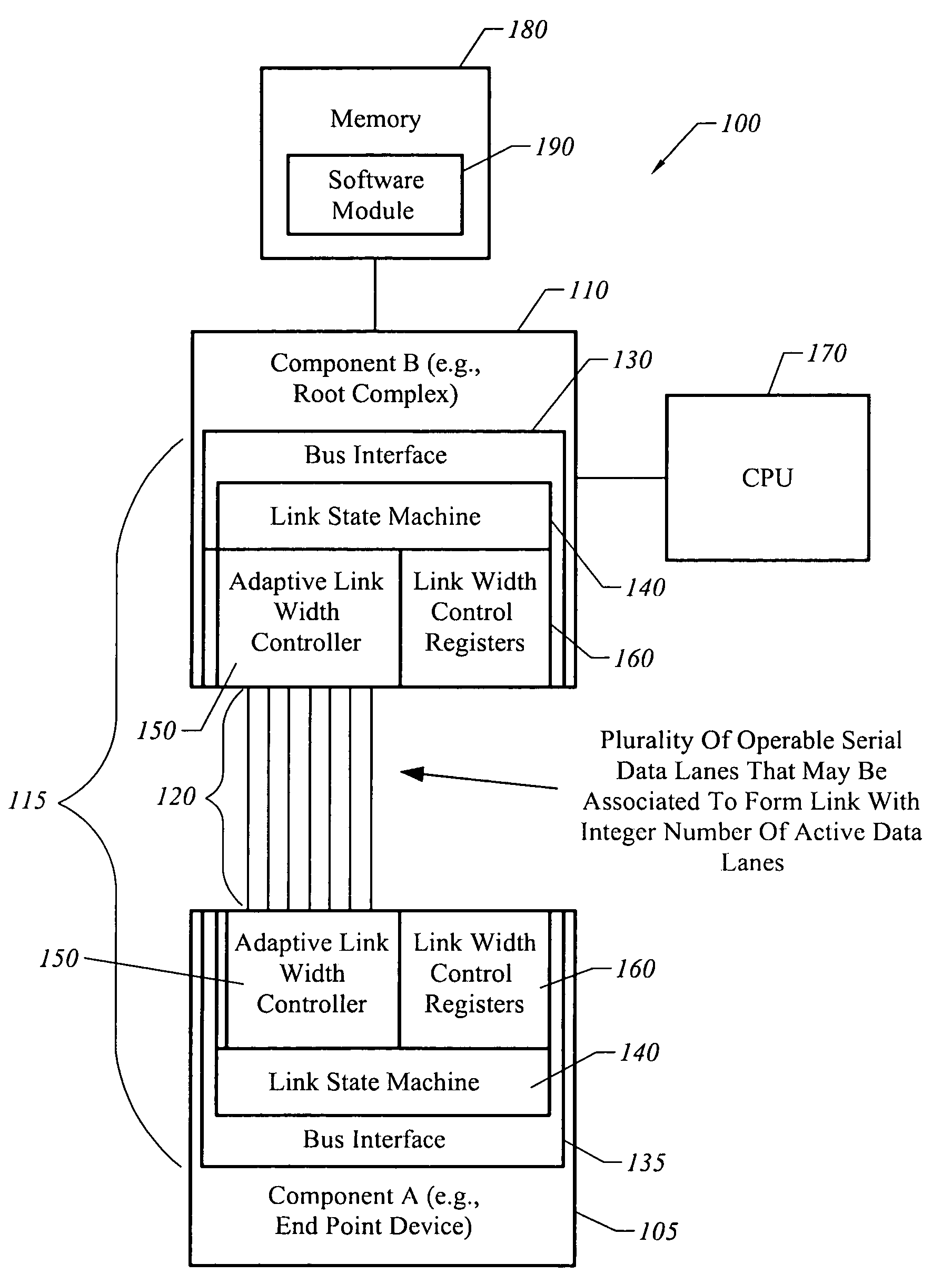

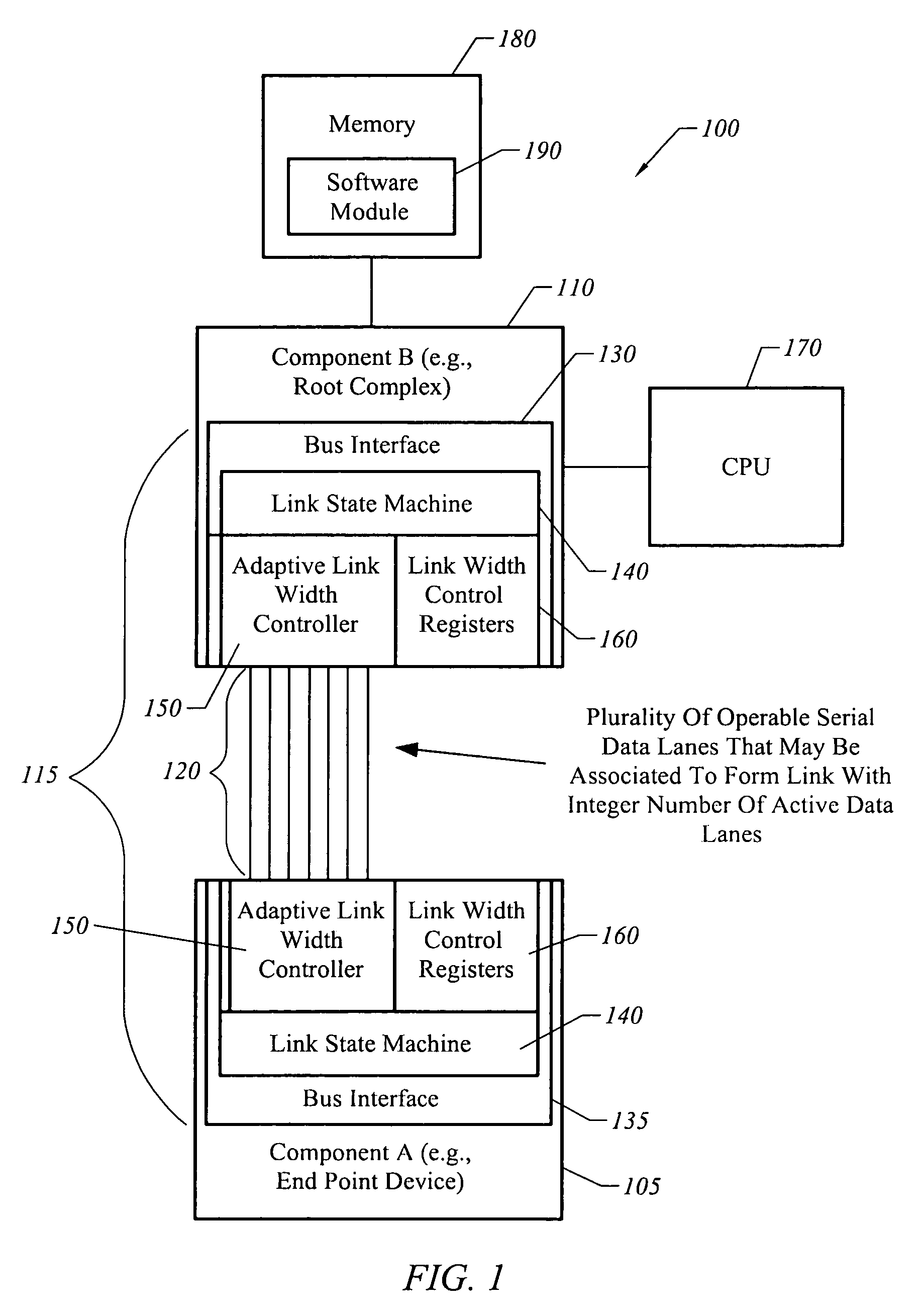

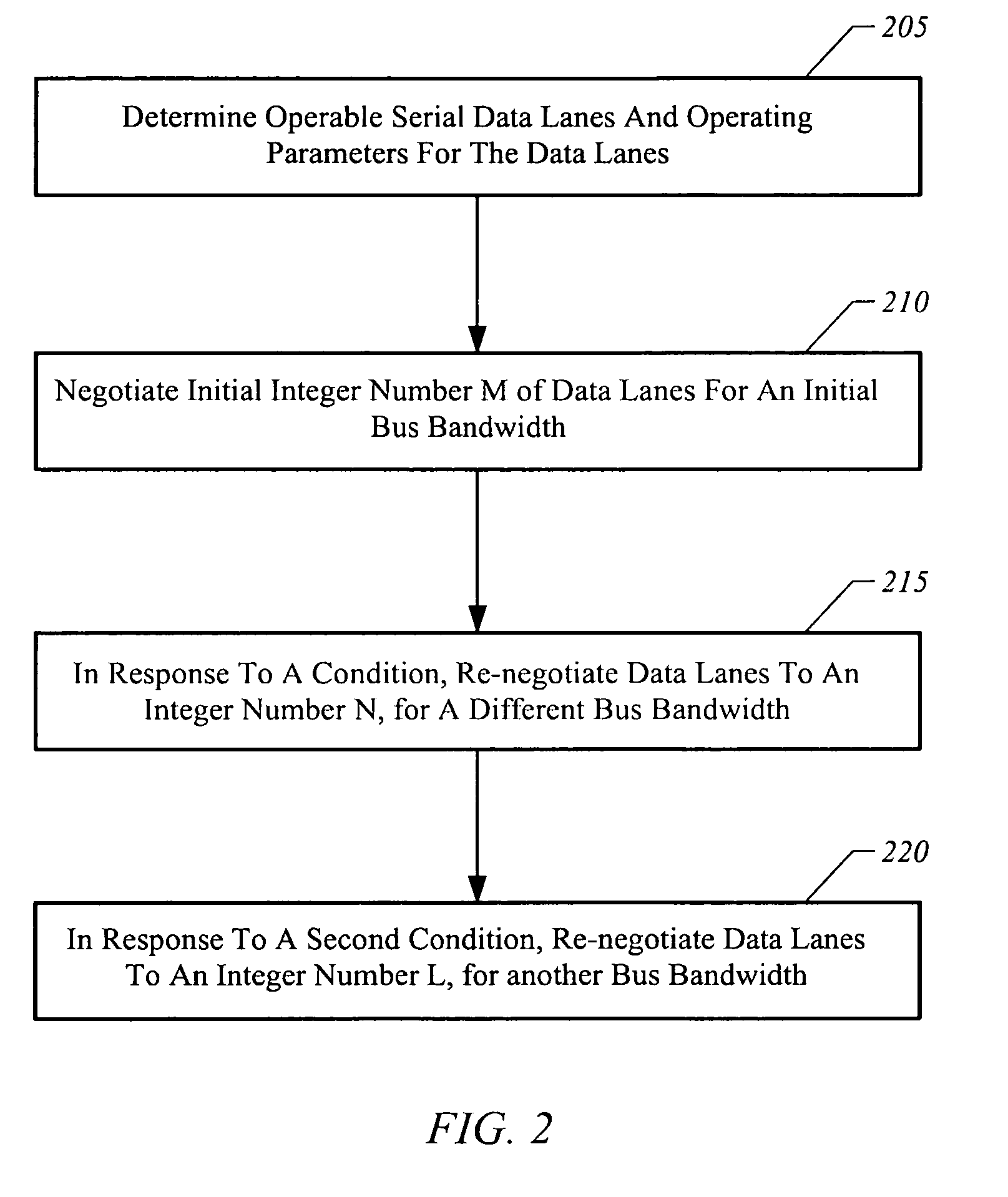

Logical-to-physical lane assignment to reduce clock power dissipation in a bus having a variable link width

InactiveUS7370132B1Reducing bus powerEnergy efficient ICTStatic indicating devicesBandwidth requirementEmbedded system

Owner:NVIDIA CORP

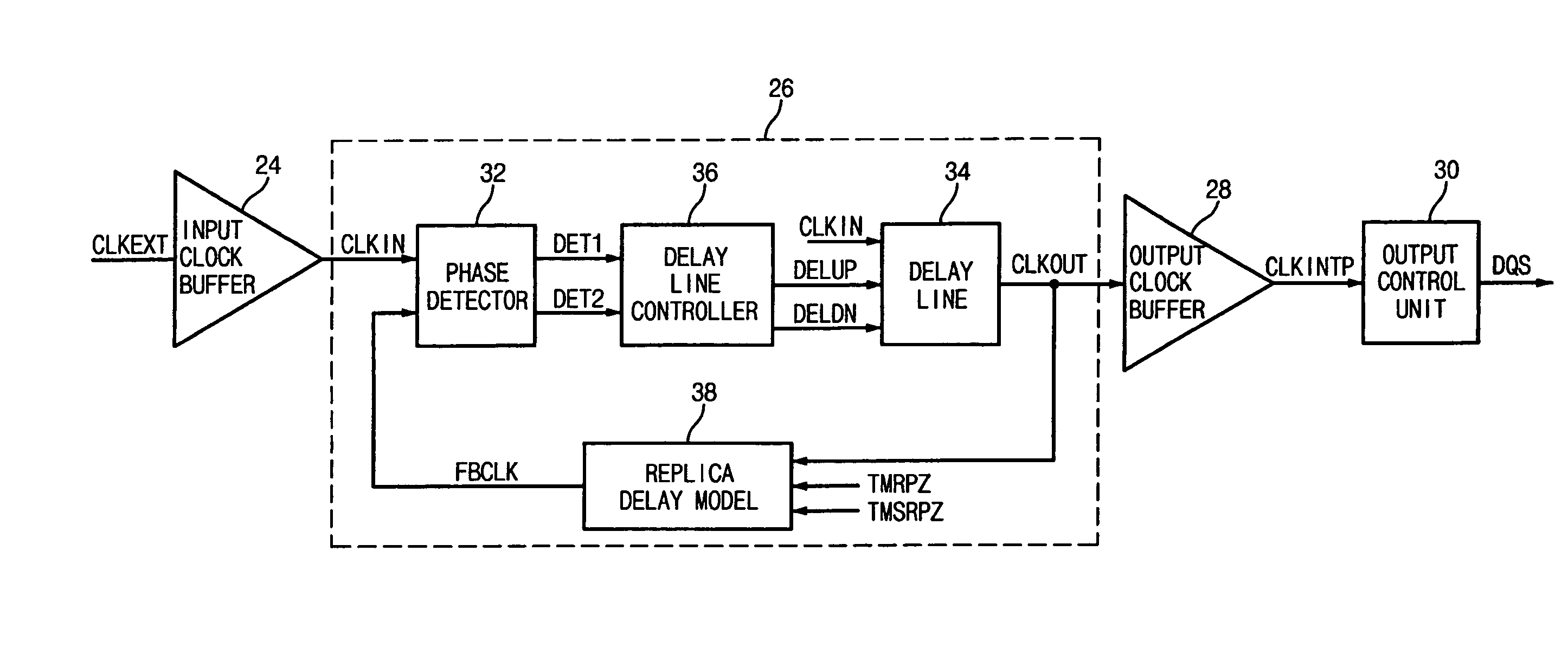

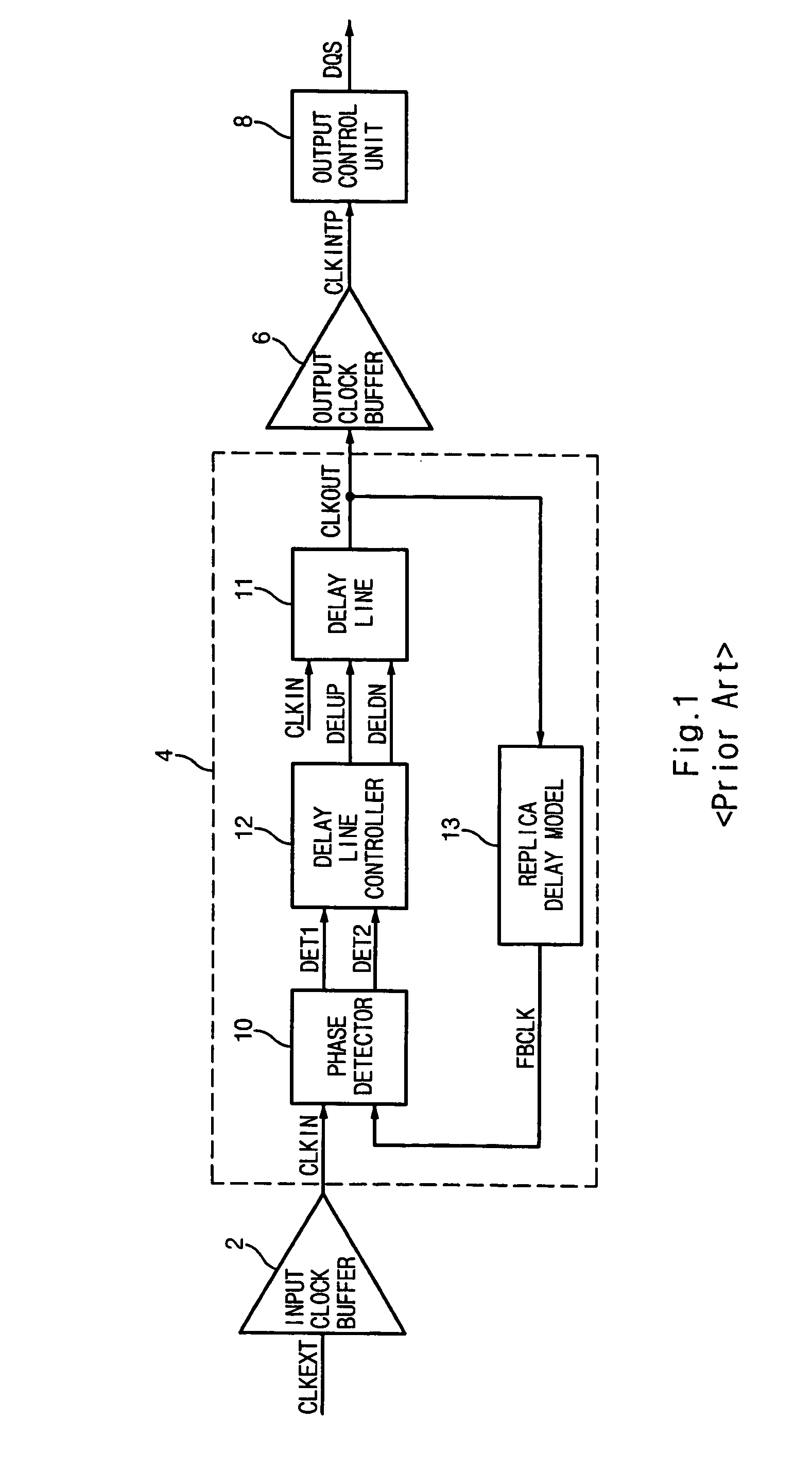

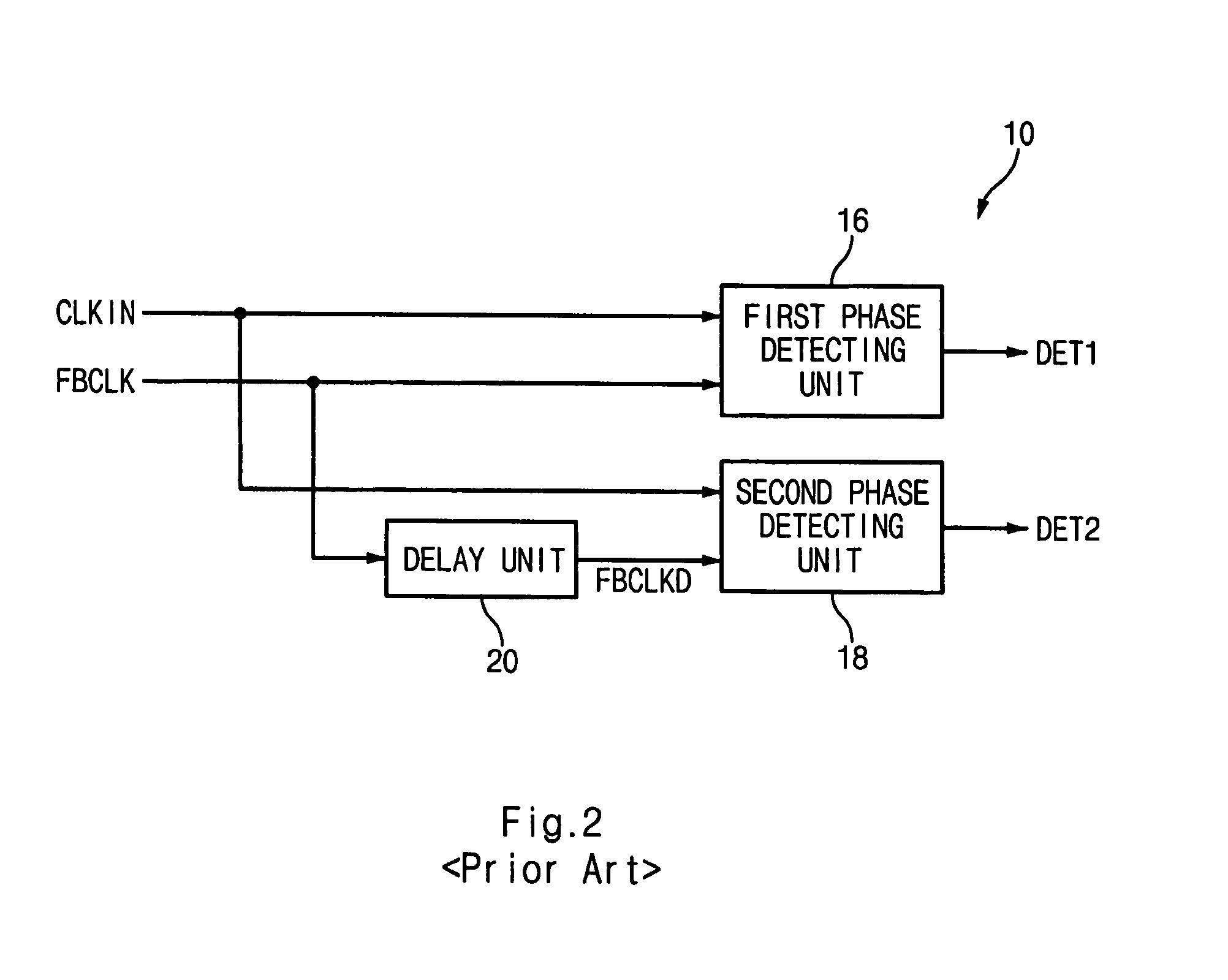

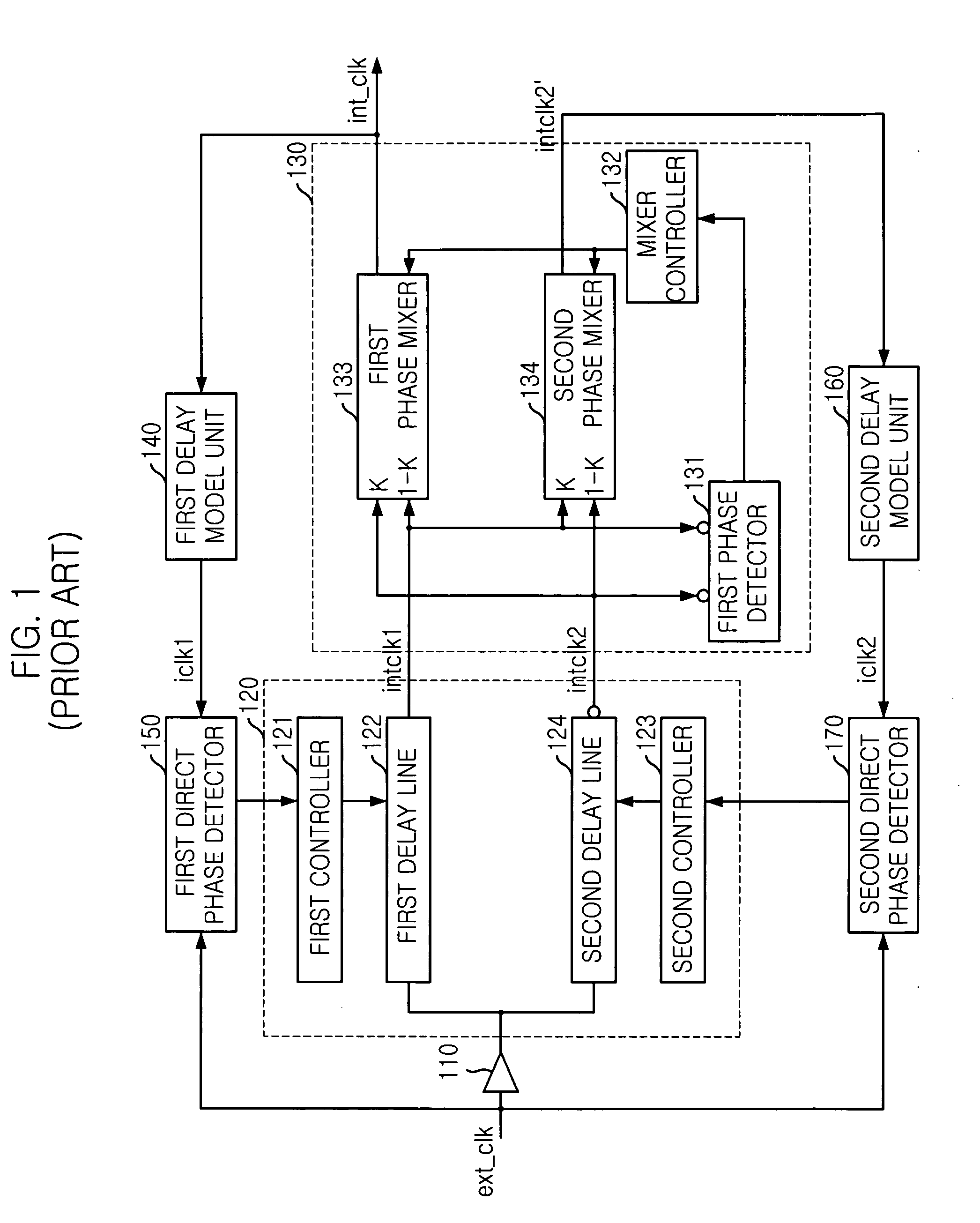

Memory device having delay locked loop

ActiveUS6985401B2Minimize skewPulse automatic controlServometer circuitsControl signalDelay-locked loop

A memory device minimizes the skew between an external clock and a DQS (or DQ) after the locking state by regulating a delay ratio of a replica delay model to compensate errors of process, temperature or voltage change. The memory device comprises: an input clock buffer for buffering an externally inputted external clock to generate an internal clock; a DLL for delaying the internal clock to synchronize a phase of the external clock with that of a DQS; an output clock buffer for buffering an output clock outputted from the DLL; and an output control unit for generating the DQS using a clock outputted from the output clock buffer. Here, the DLL comprises a replica delay model for modeling delay factors of the input clock buffer and other delay factors until the output clock outputted from the delay line is outputted to the outside of a chip, and for regulating a delay ratio in response to a plurality of control signals inputted externally in a test mode.

Owner:SK HYNIX INC

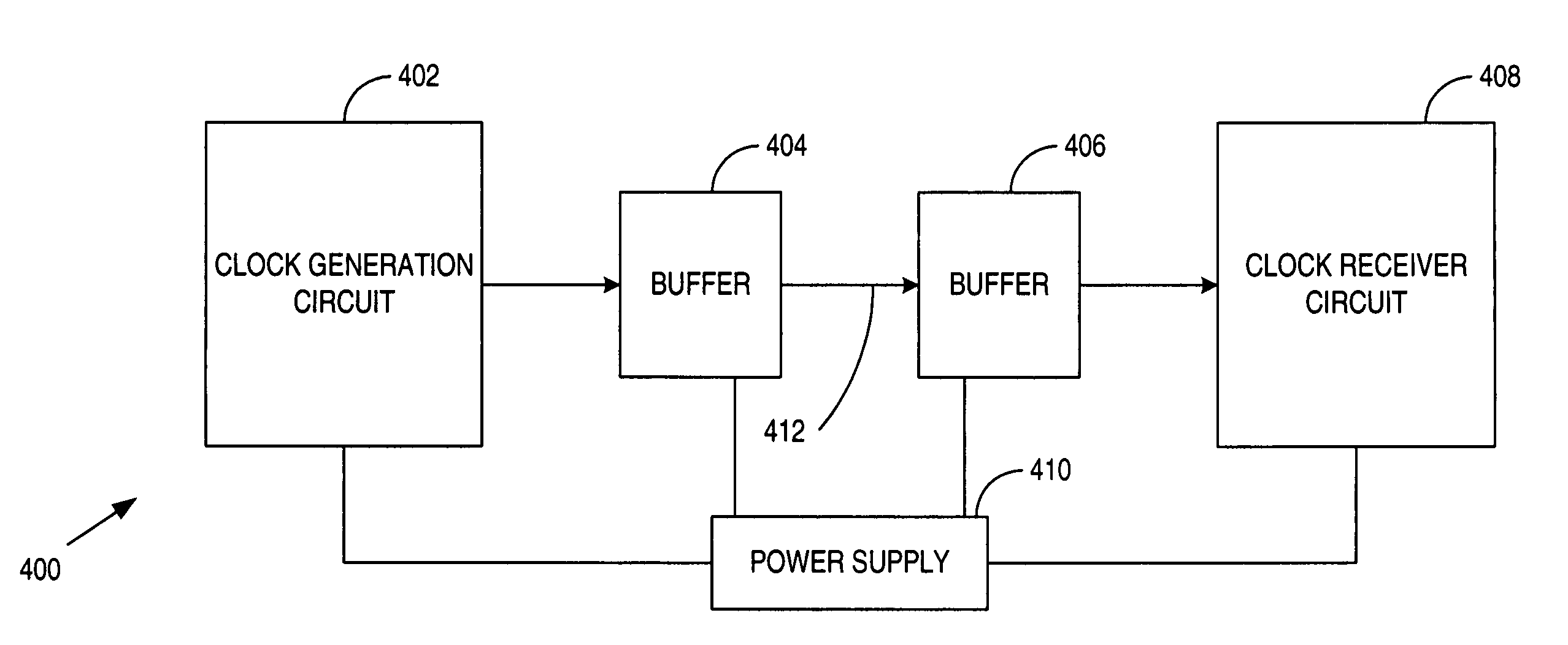

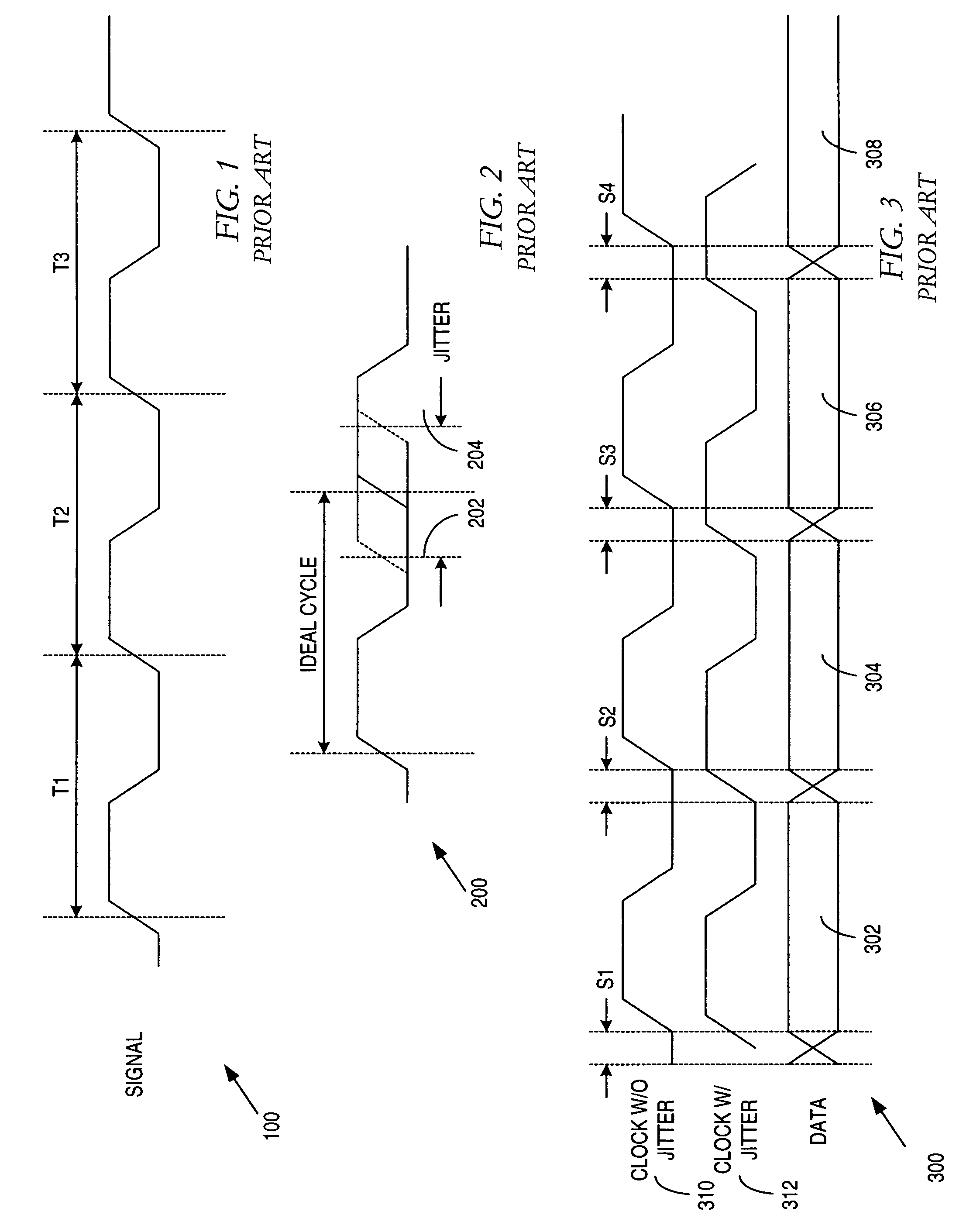

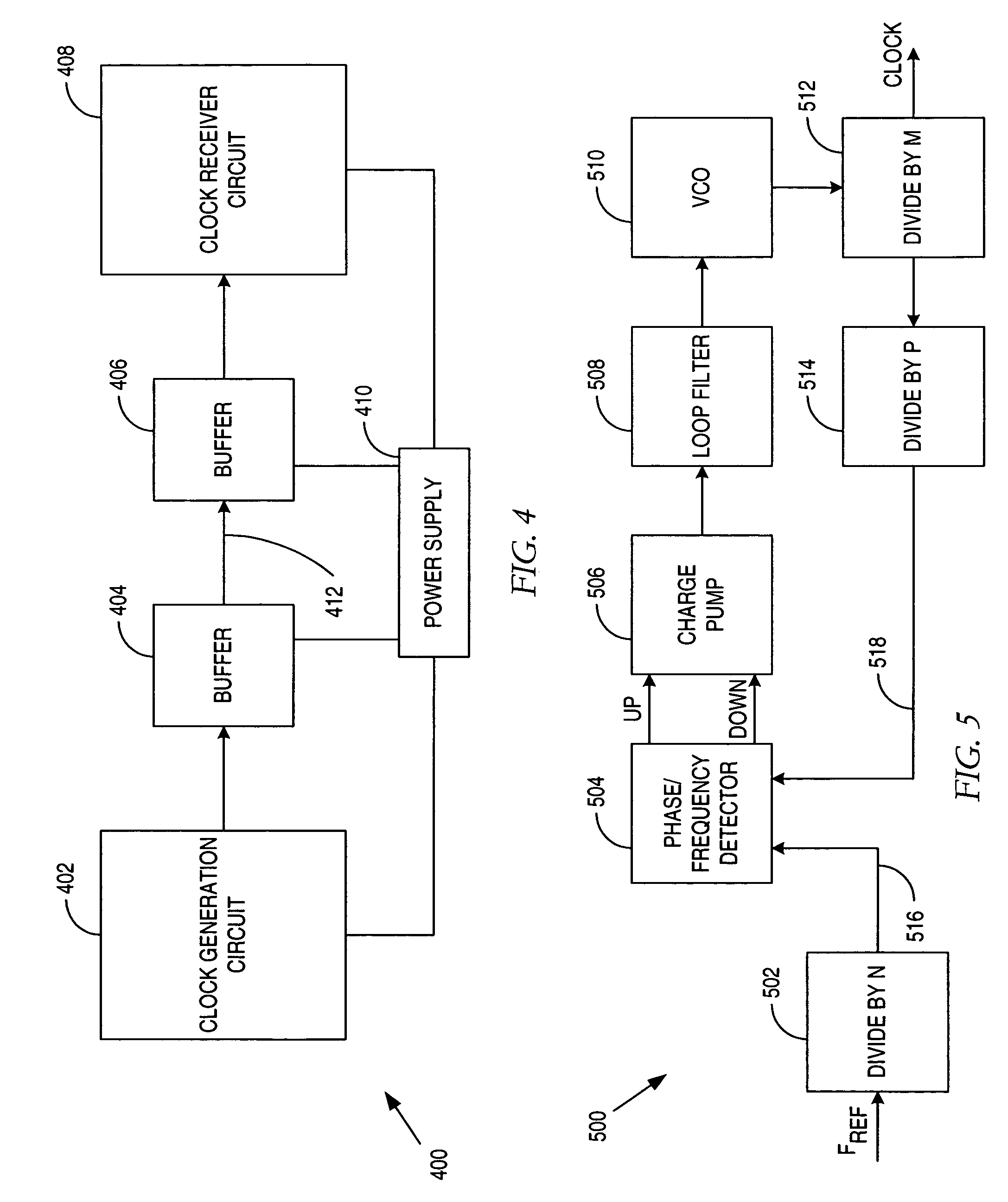

Method and apparatus for a reference clock buffer system

ActiveUS7142005B1Reduces power-supplyReduces noise-induced jitterPulse automatic controlElectronic switchingData bufferCross coupled

Owner:XILINX INC

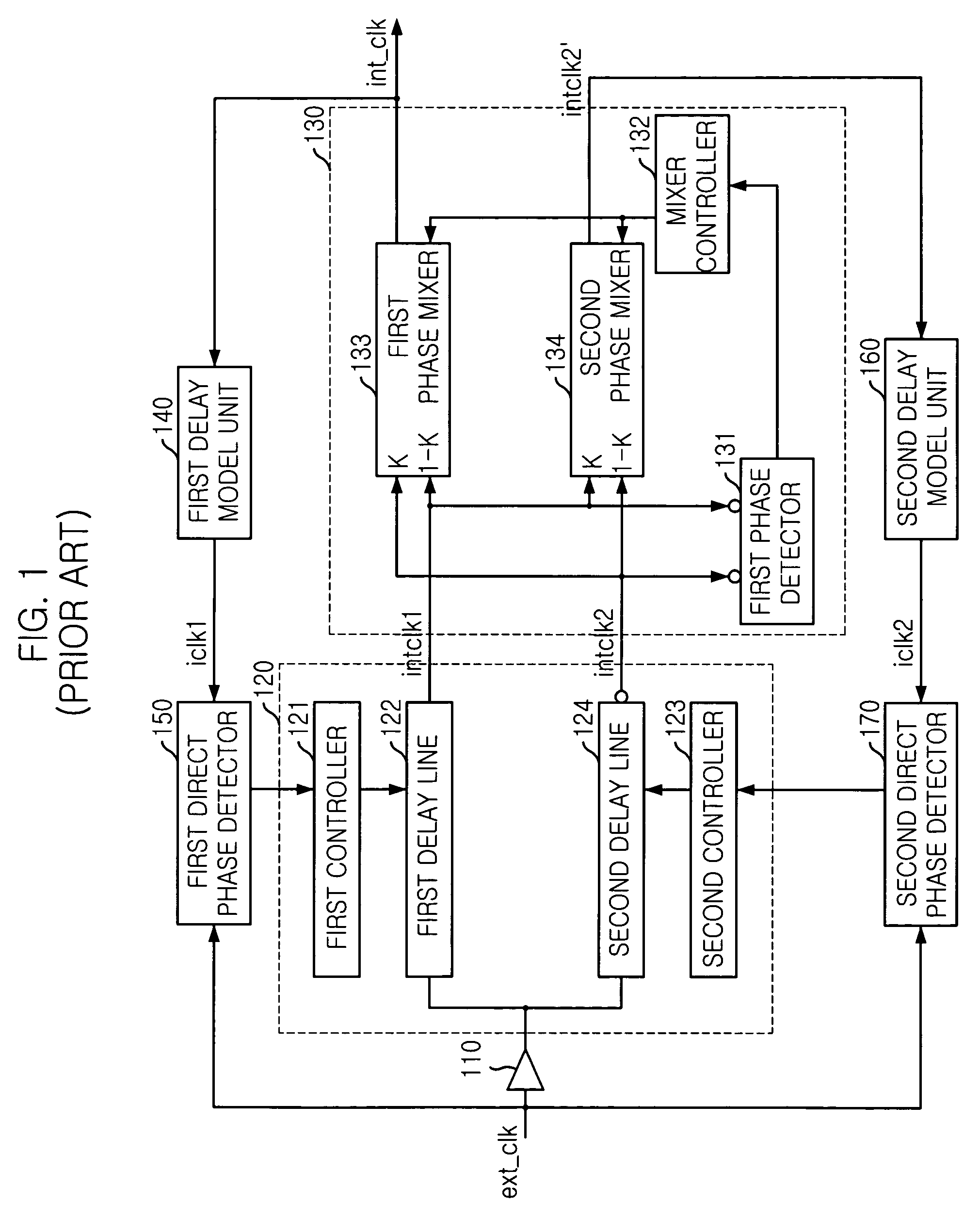

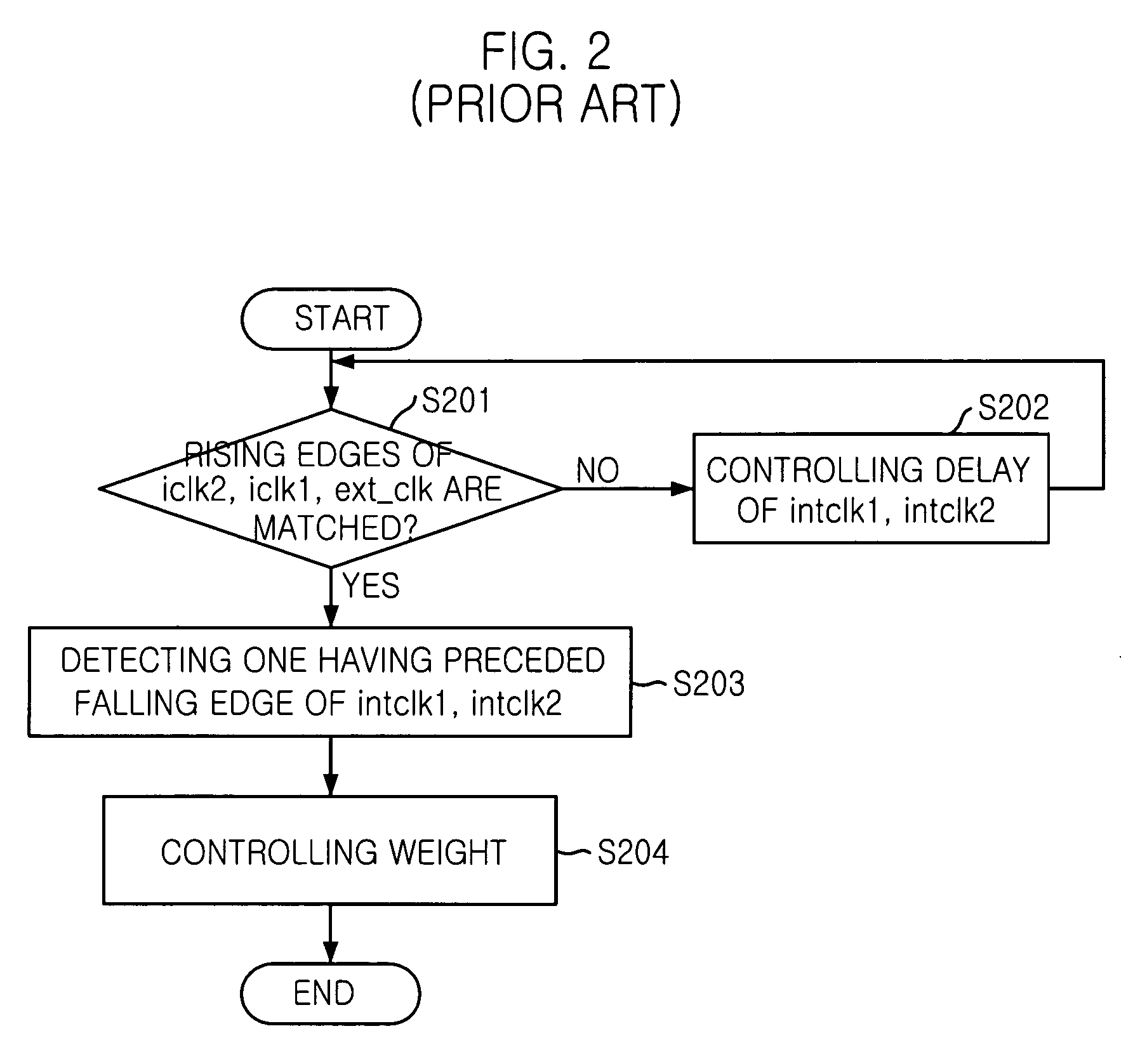

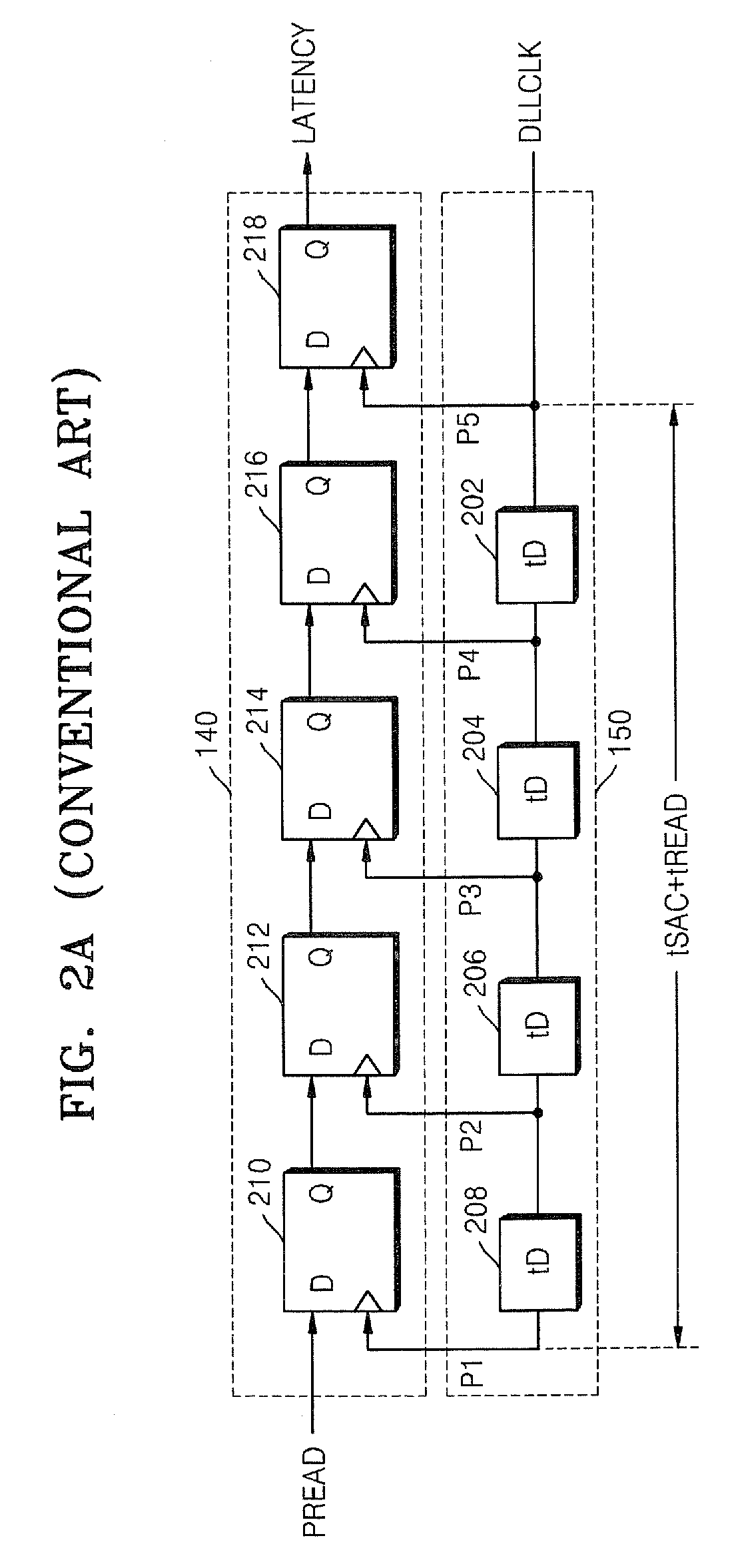

Delay locked loop and its control method

InactiveUS7046059B2Small sizeLow powerPulse automatic controlDigital storageDelay-locked loopEngineering

A delay locked loop (DLL) capable of correcting a duty ratio of a clock signal including: a clock buffer which receives an external clock signal for outputting a rising edge clock signal; a delay unit for delaying the rising edge clock signal based on a first comparison signal in order to generate a first internal clock signal, a second internal clock signal, a first delay locking signal and a second delay locking signal; a duty correction unit for receiving the first and the second internal clock signals and the first and the second delay locking signals and generating a delay locked clock signal by correcting a duty cycle of the external clock signal; and a clock feed-back unit for receiving the delay locked clock signal and the external clock signal in order to generate the first comparison signal.

Owner:SK HYNIX INC

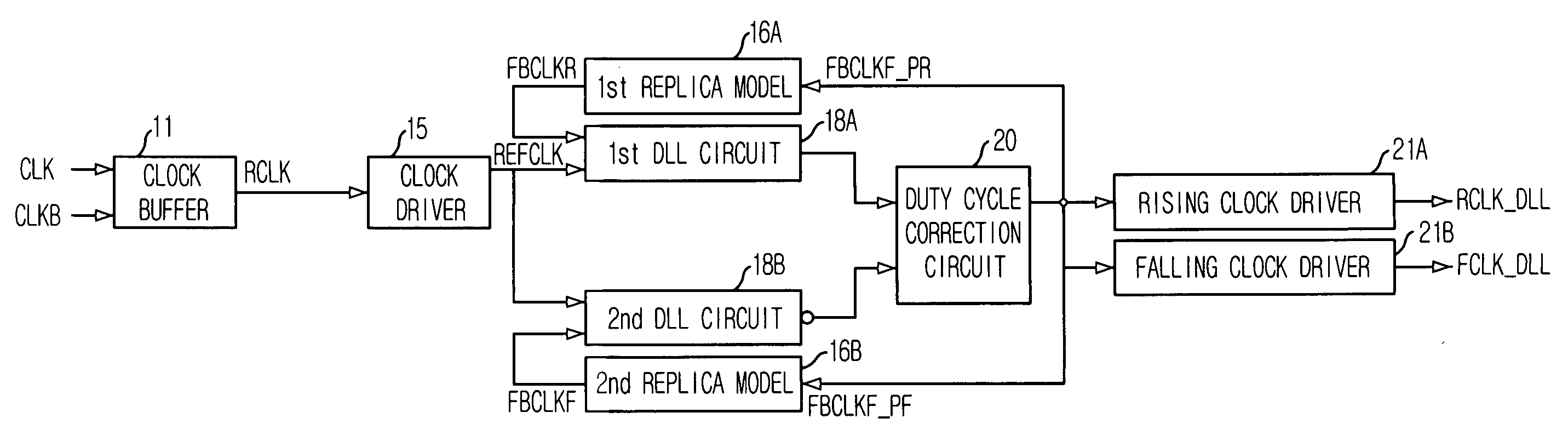

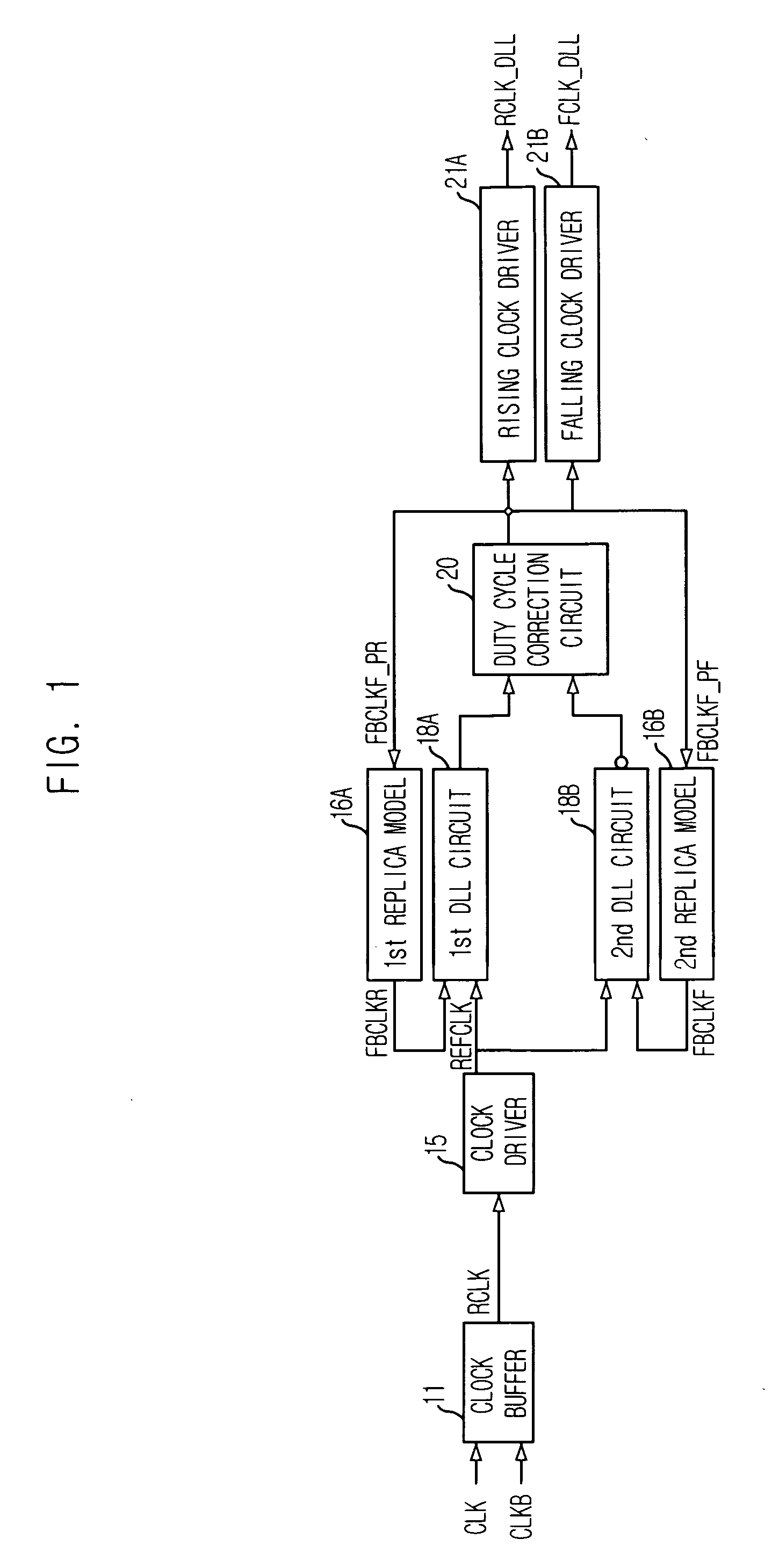

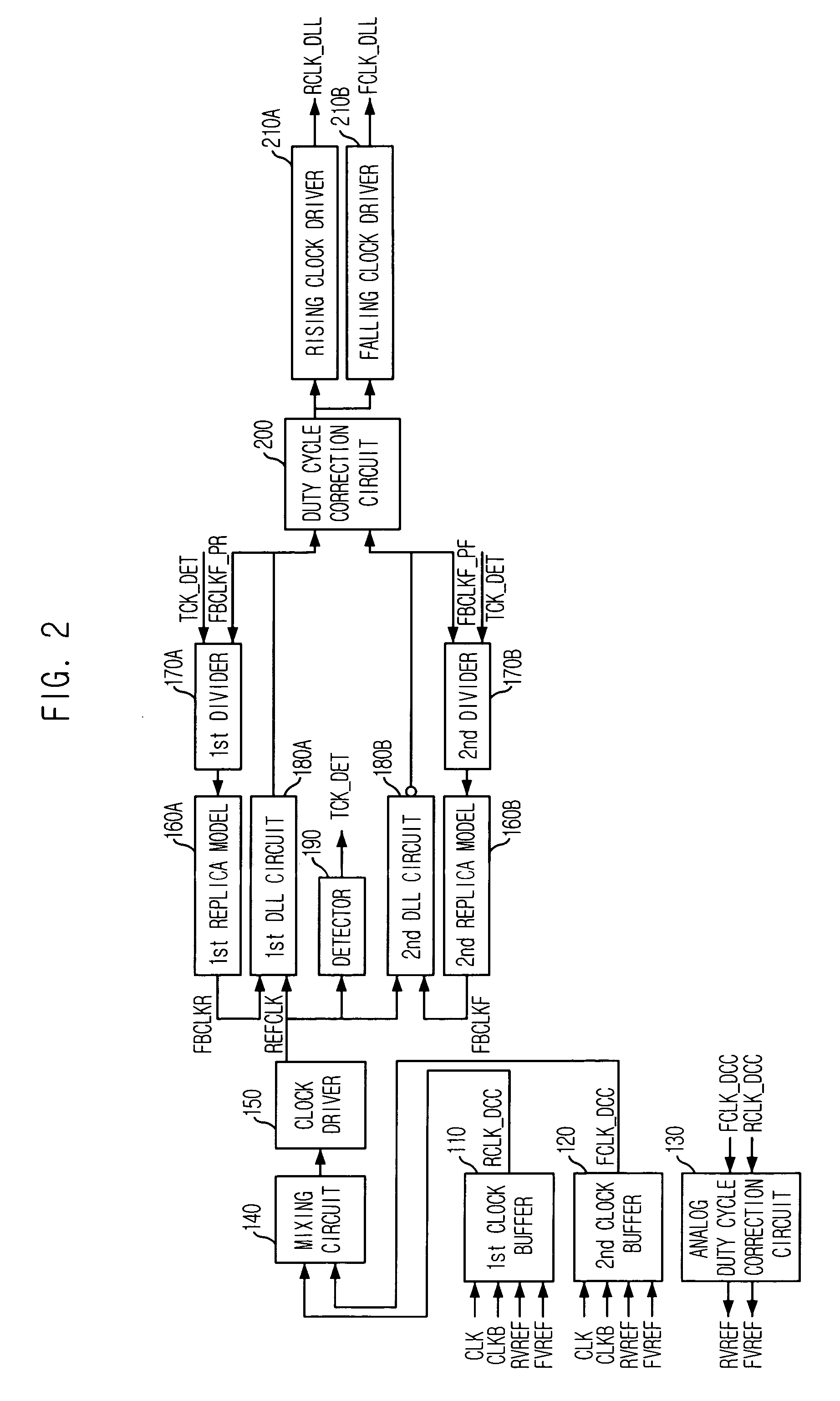

Semiconductor memory device capable of easily performing delay locking operation under high frequency system clock

A semiconductor memory device includes a first clock buffer for outputting a first internal clock signal in response to an inverted signal of the system clock signal and for correcting a duty cycle ratio of the first internal clock signal in response to a control signal; a second clock buffer for outputting a second internal clock signal in response to the system clock signal and for correcting a duty cycle ratio of the second internal clock signal in response to the control signal; an analog duty cycle correction circuit for outputting the control signal corresponding to the duty cycle ratio of the first and second internal clock signals; a mixing circuit for mixing the first and second internal clock signals and for outputting a third internal clock signal whose duty cycle is corrected; and a DLL circuit for outputting a delay-locked clock signal by using the third internal clock signal.

Owner:SK HYNIX INC

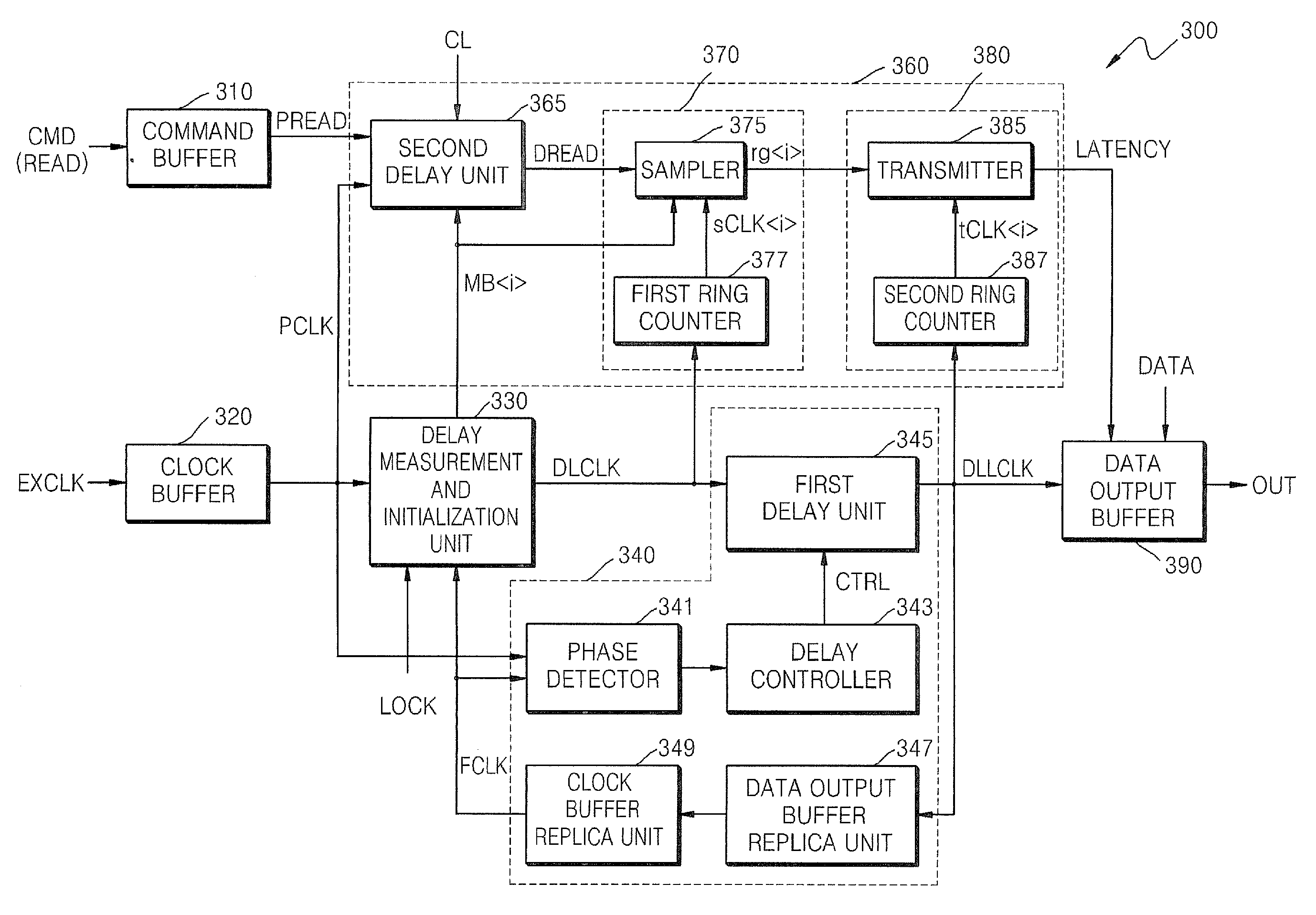

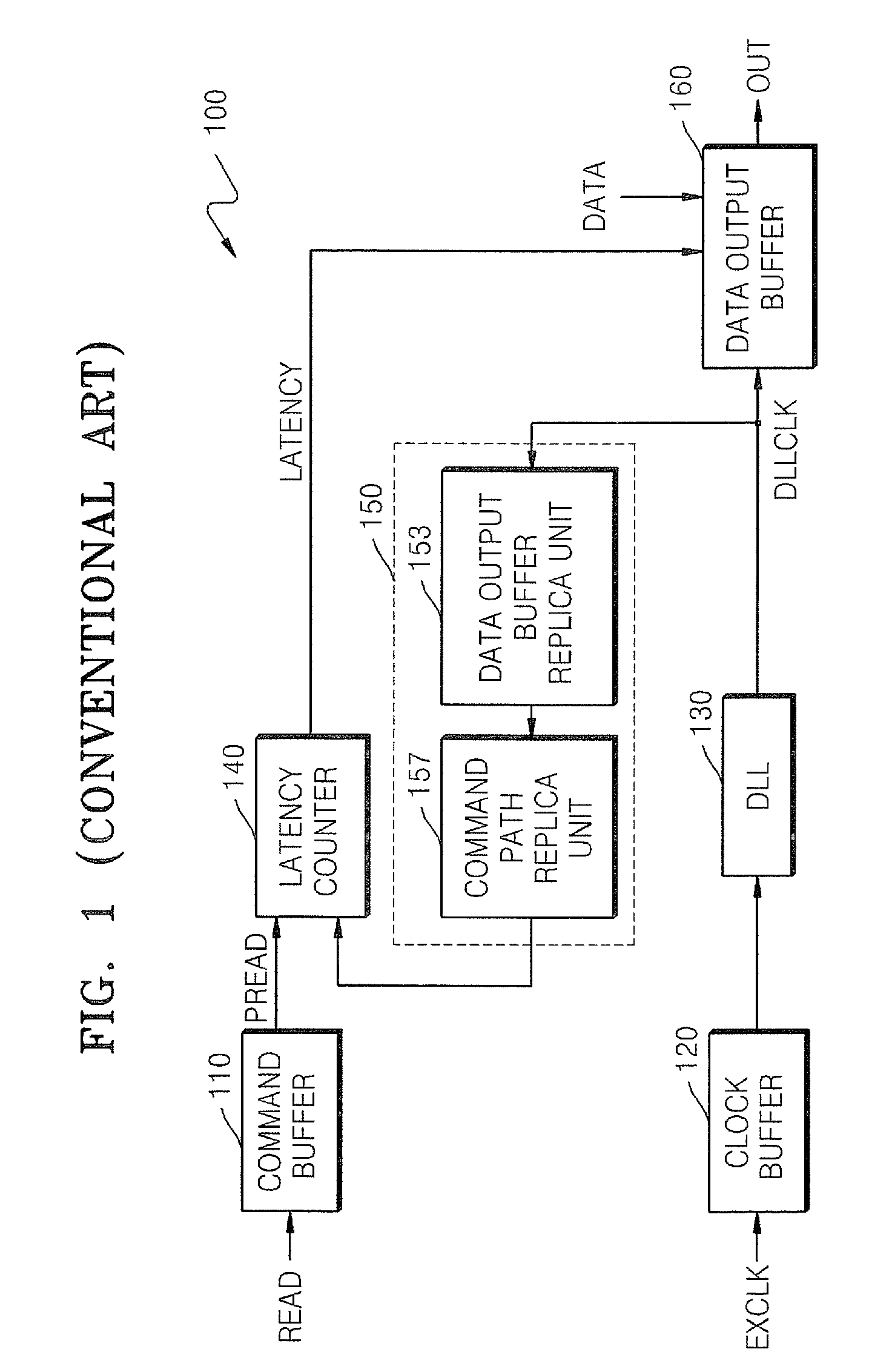

Semiconductor memory devices for controlling latency

A semiconductor memory device includes a command buffer that receives an external command and outputs a first command signal, a clock buffer that receives an external clock signal and outputs a first internal clock signal, a delay measurement and initialization unit that receives the first internal clock signal and a fourth internal clock signal and responsively outputs a second internal clock signal and a plurality of delayed signals corresponding to a delay time between when the external clock signal is input and data is output, a delay locked loop that receives the second internal clock signal and outputs a third internal clock signal and the fourth internal clock signal, a latency signal generation unit that delays the first command signal by a delay time between when the second internal clock signal is input to the delay locked loop and when the third internal clock signal is output from the delay locked loop, and then outputs the delayed first command signal as a latency signal, in response to the second and third internal clock signals and the delayed signals, and a data output buffer that outputs the data in response to the latency signal and the third internal clock signal.

Owner:SAMSUNG ELECTRONICS CO LTD

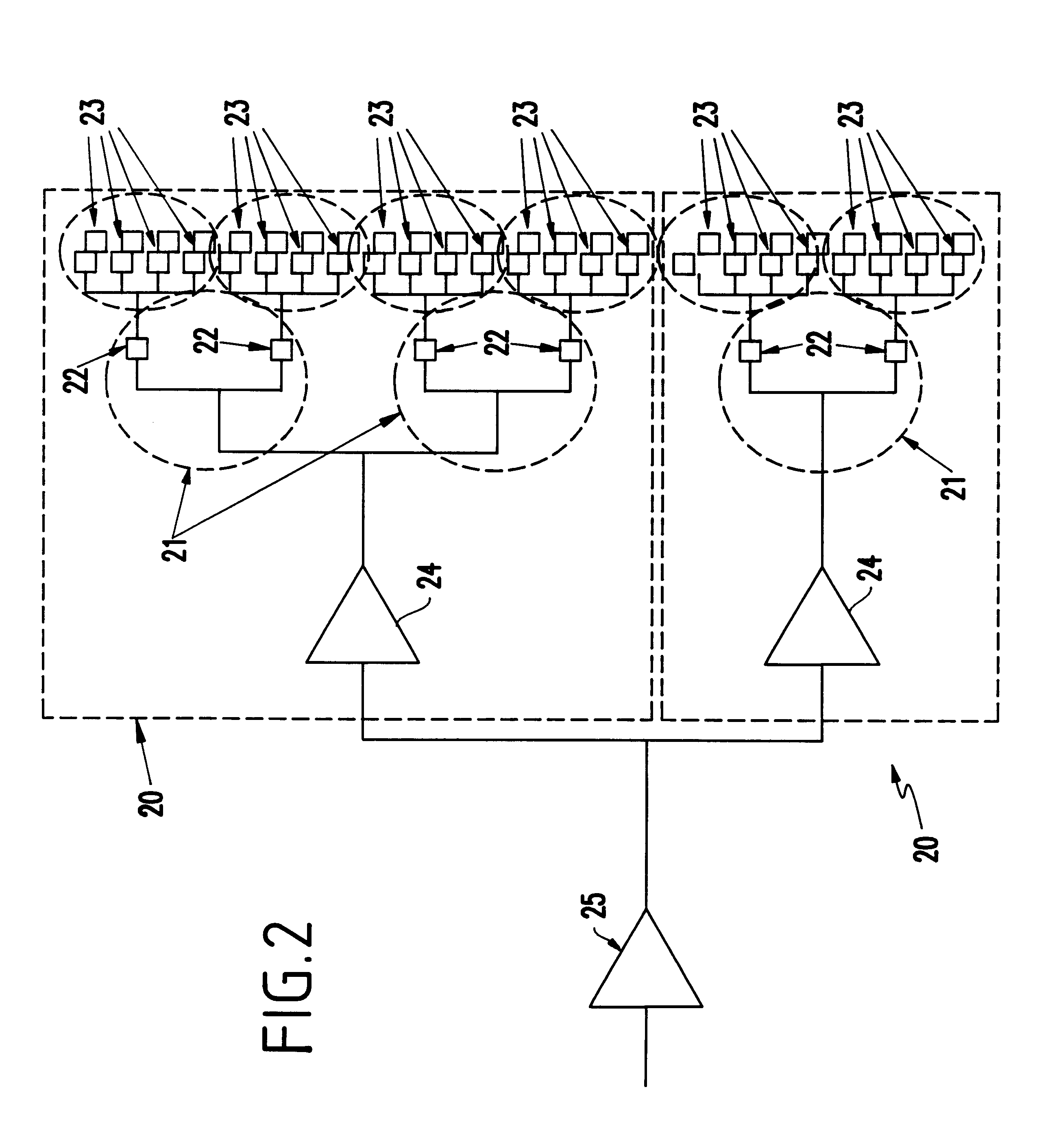

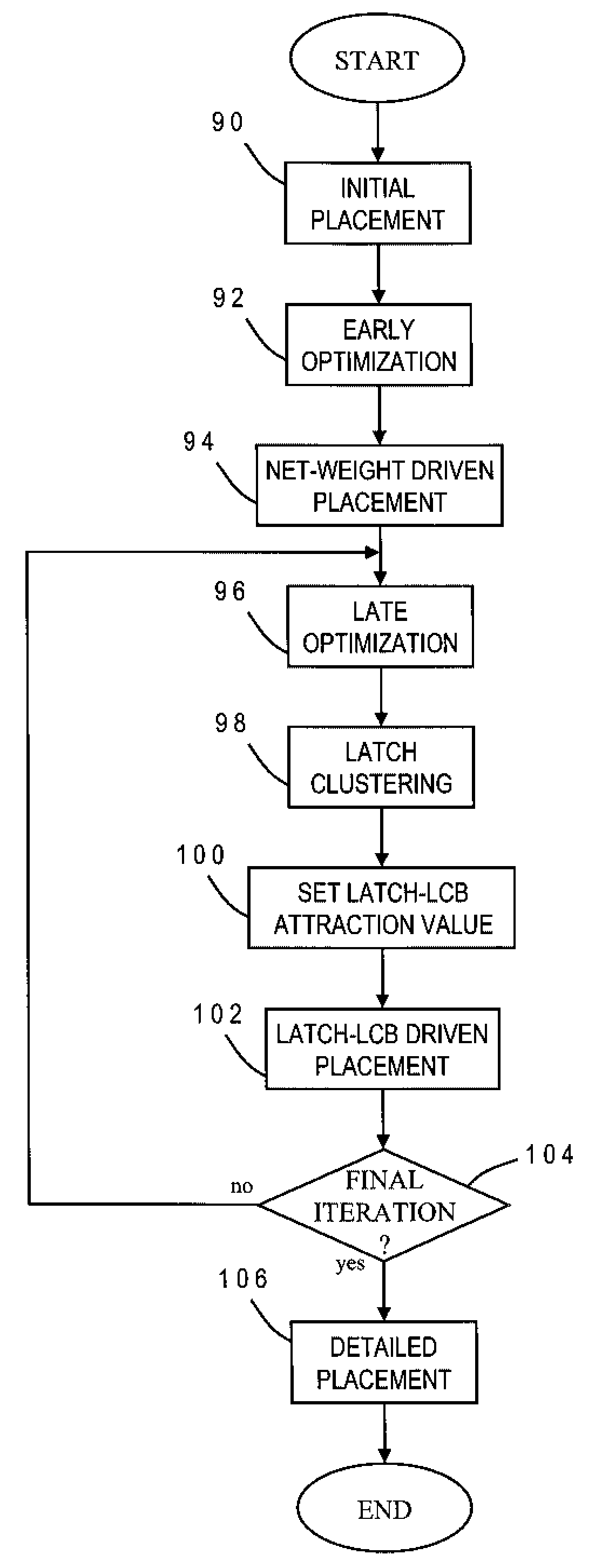

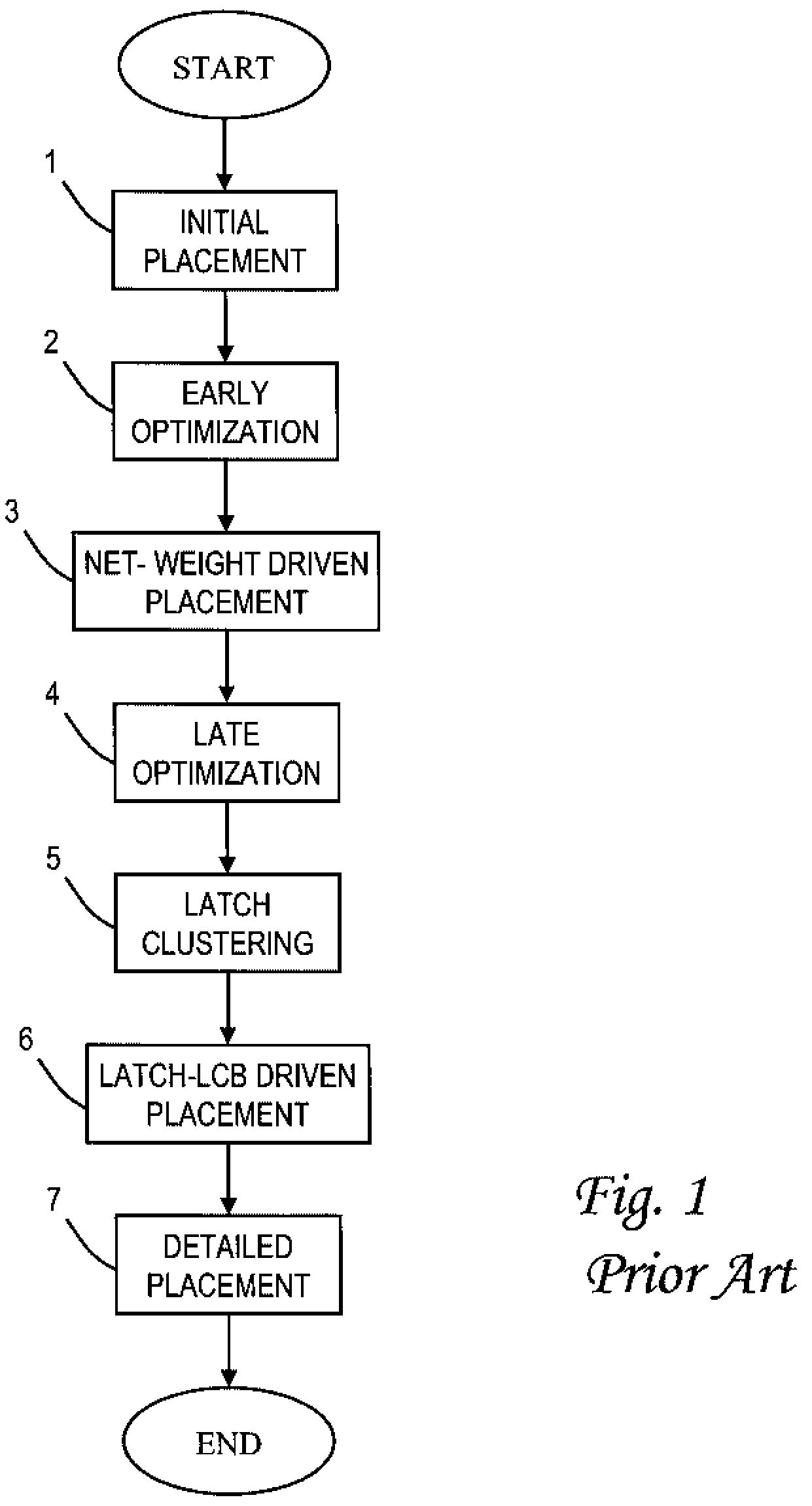

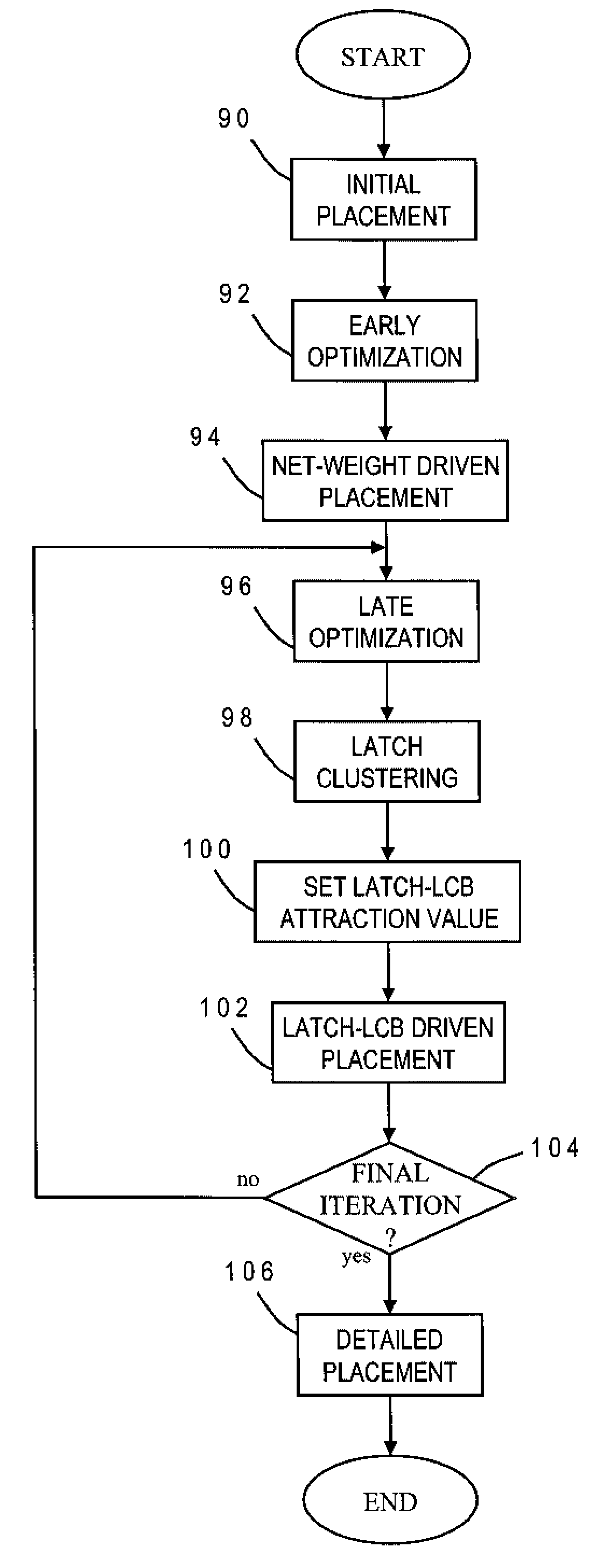

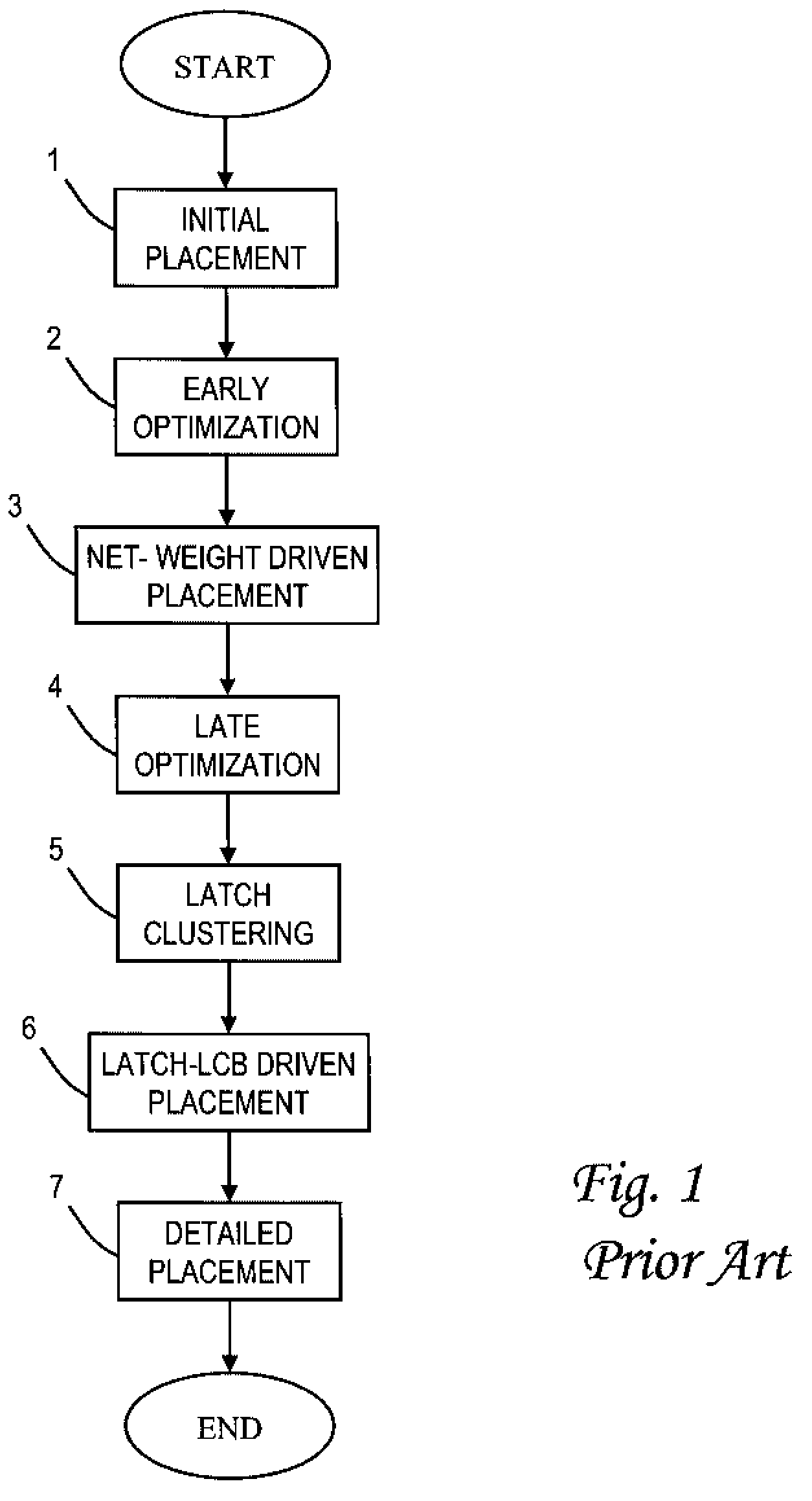

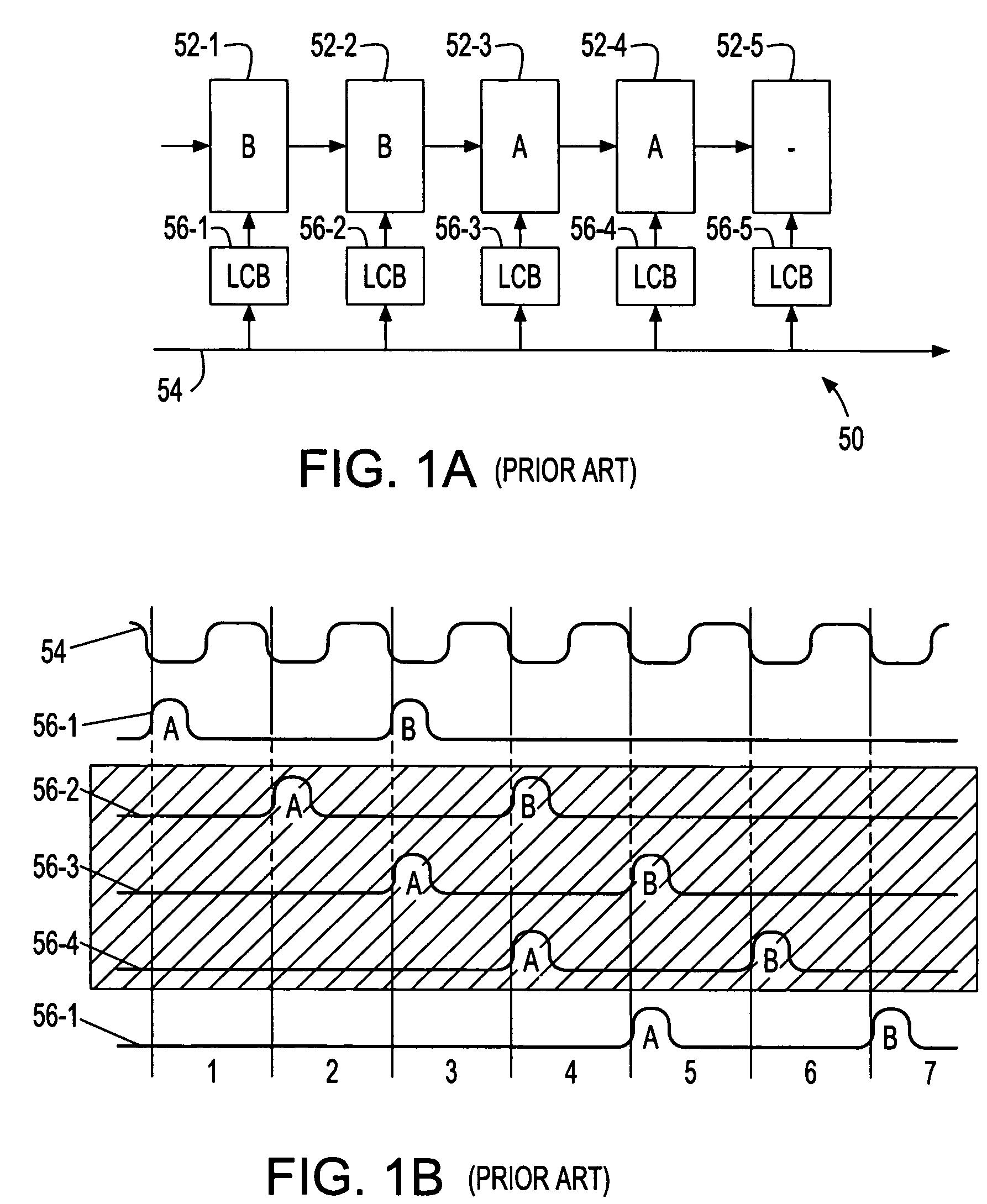

Latch placement for high performance and low power circuits

ActiveUS7549137B2Sacrificing timing requirementSimple methodComputer aided designSoftware simulation/interpretation/emulationPower circuitsClock buffer

A novel iterative latch placement scheme wherein the latches are gradually pulled by increasing attraction force until they are eventually placed next to a clock distribution structure such as a local clock buffer (LCB). During the iterations, timing optimizations such as gate sizing and re-buffering are invoked in order to keep the timing estimation accurate. By applying the iterative clock net weighting adjustment, the present invention allows tighter interaction between logic placement and clock placement which leads to higher quality timing and significant power savings.

Owner:GLOBALFOUNDRIES U S INC

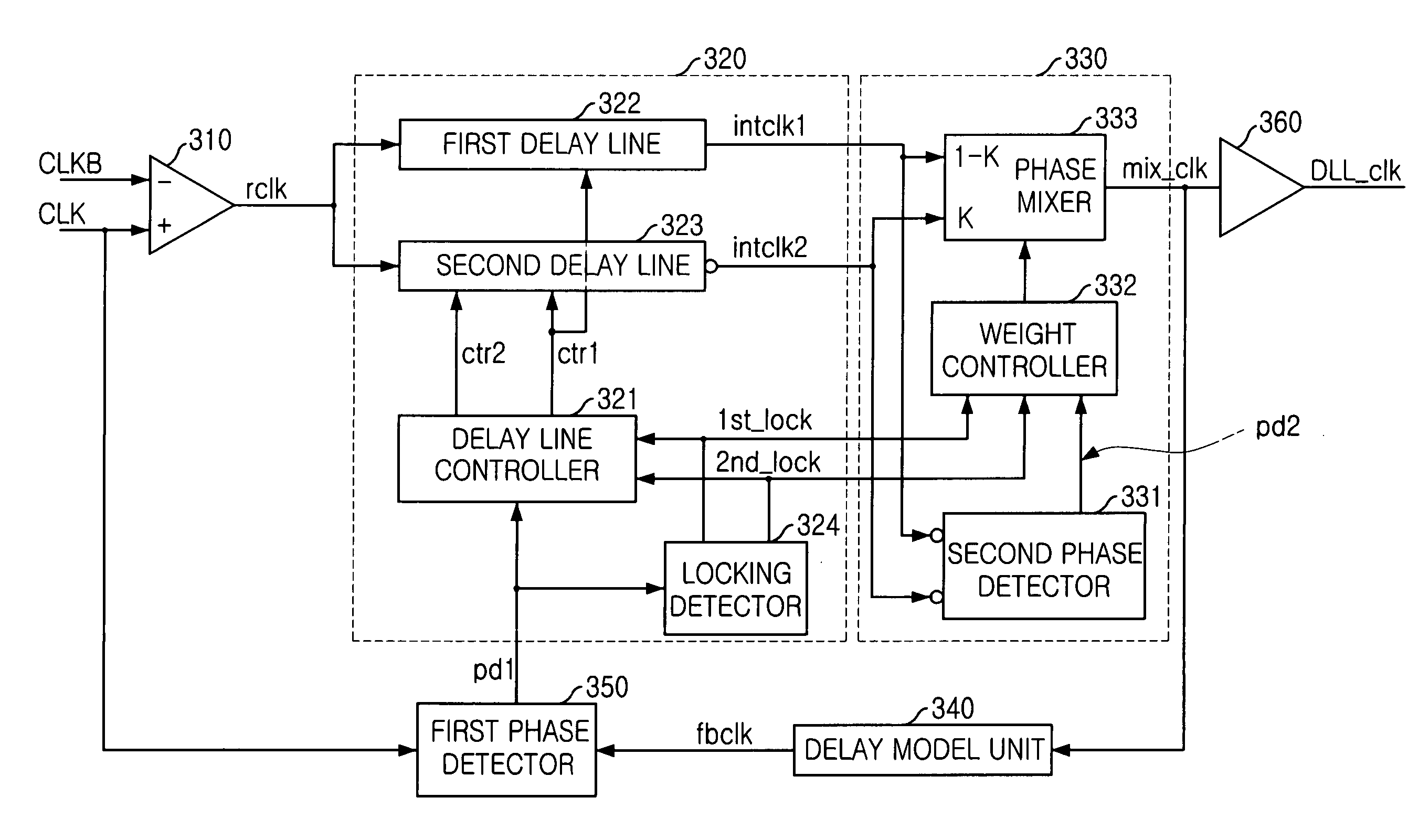

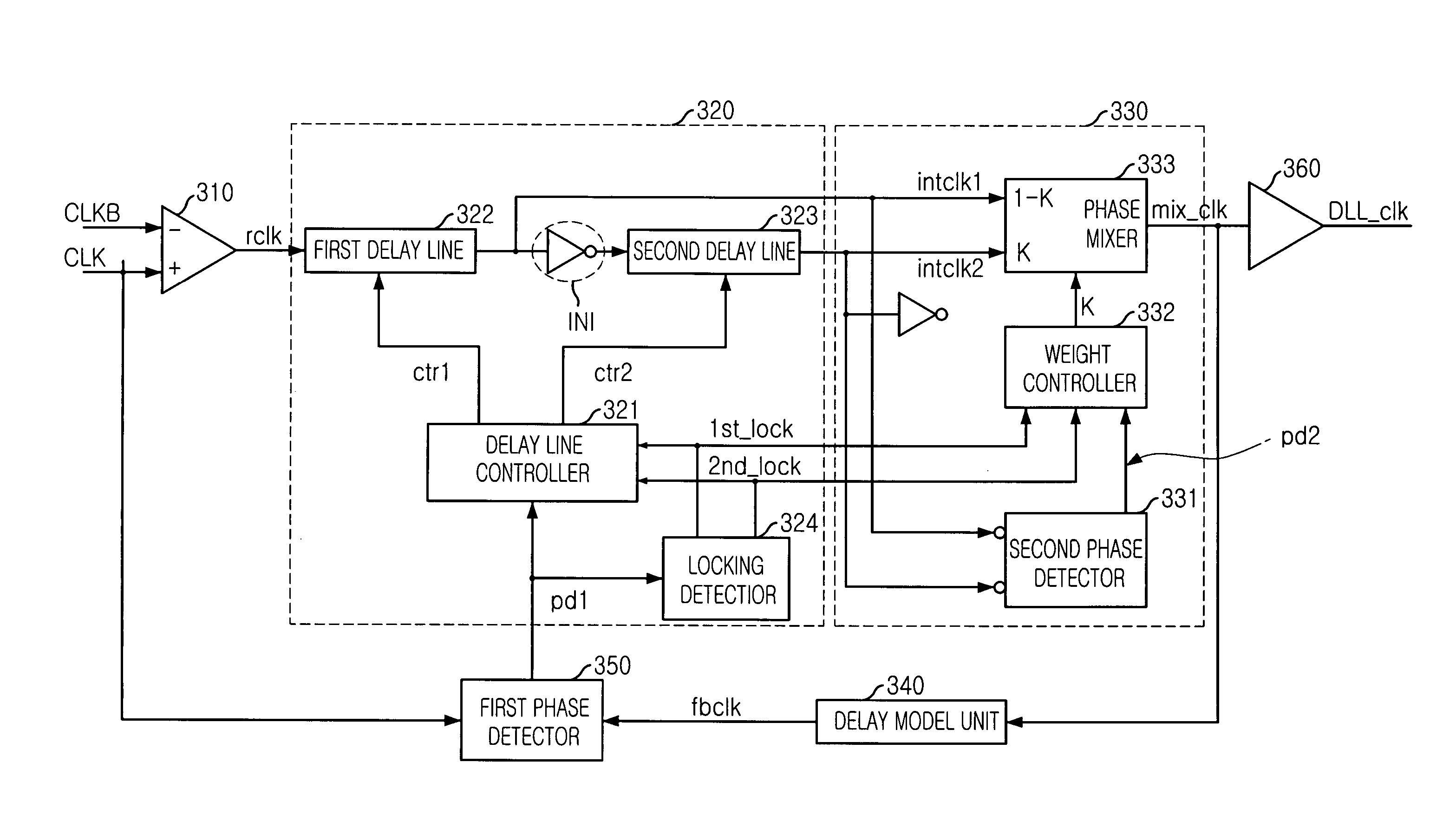

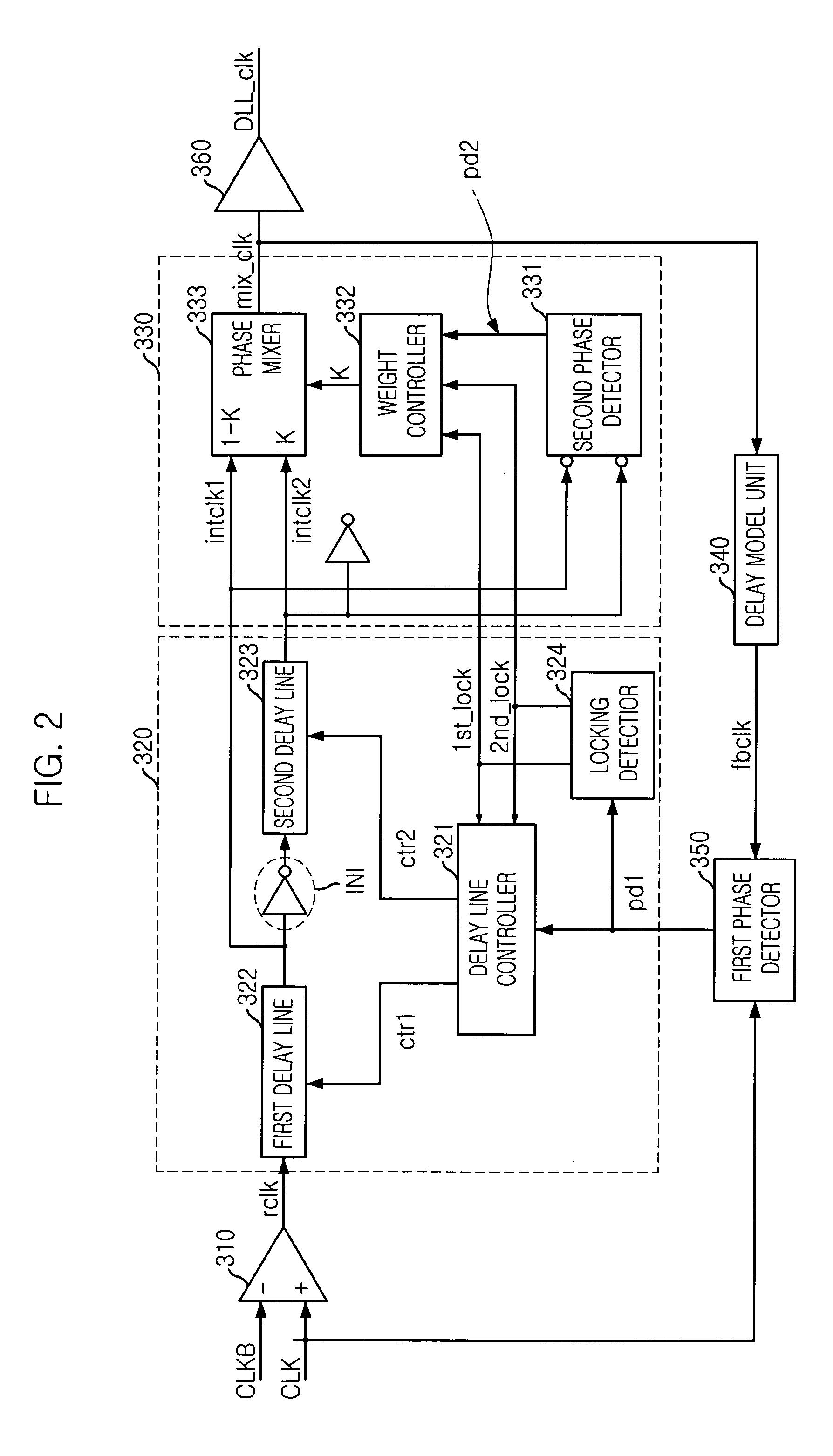

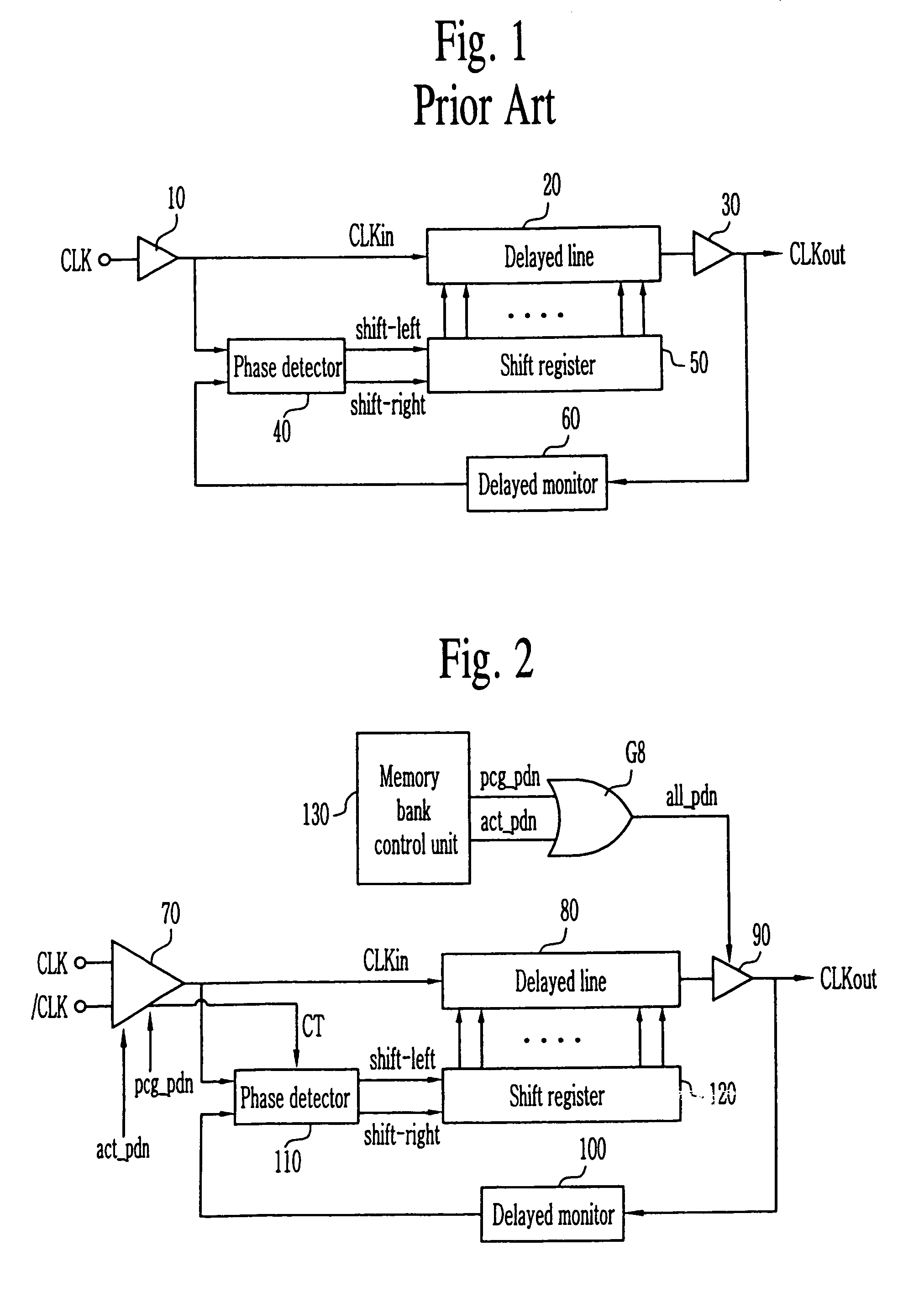

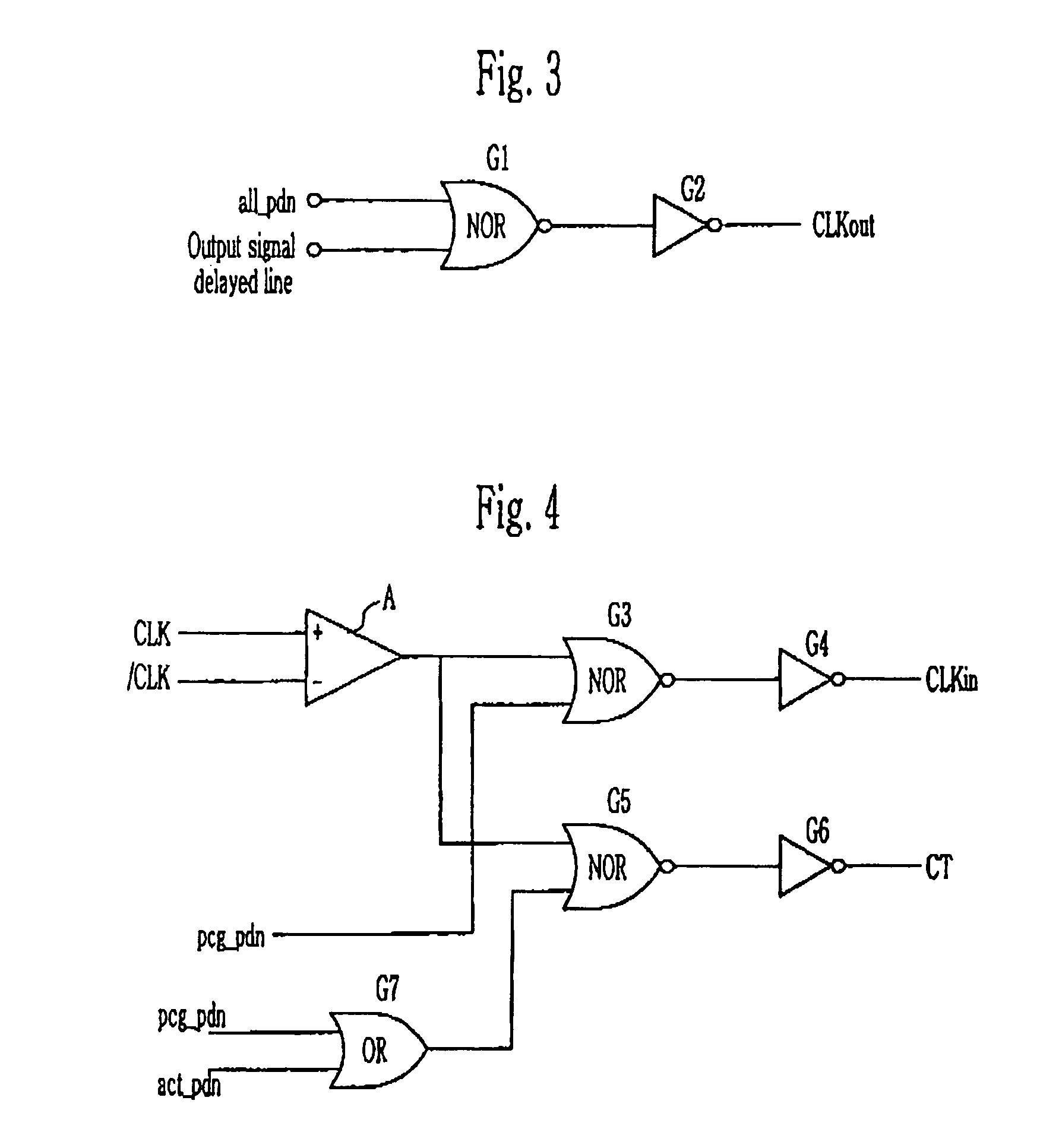

Delay locked loop and its control method for correcting a duty ratio of a clock signal

ActiveUS7142026B2Small sizeReduce power consumptionPulse automatic controlContinuous to patterned pulse manipulationPhase detectorDelay-locked loop

A delay locked loop (DLL) capable of correcting a duty ratio including: a clock buffer for receiving an external clock signal and an inverted external clock signal to generate a rising edge clock signal; a delay unit for delaying the rising edge clock signal based on a first comparison signal in order to generate a first internal clock signal, a second internal clock signal, a first delay locking signal and a second delay locking signal; a duty correction unit for receiving the first and the second internal clock signals and the first and the second delay locking signals to generate a mixed clock signal; a delay model unit for delaying the mixed clock signal to generate a feed-backed clock signal; and a first phase detector for receiving the external clock signal and the feed-backed clock signal to generate the first comparison signal.

Owner:SK HYNIX INC

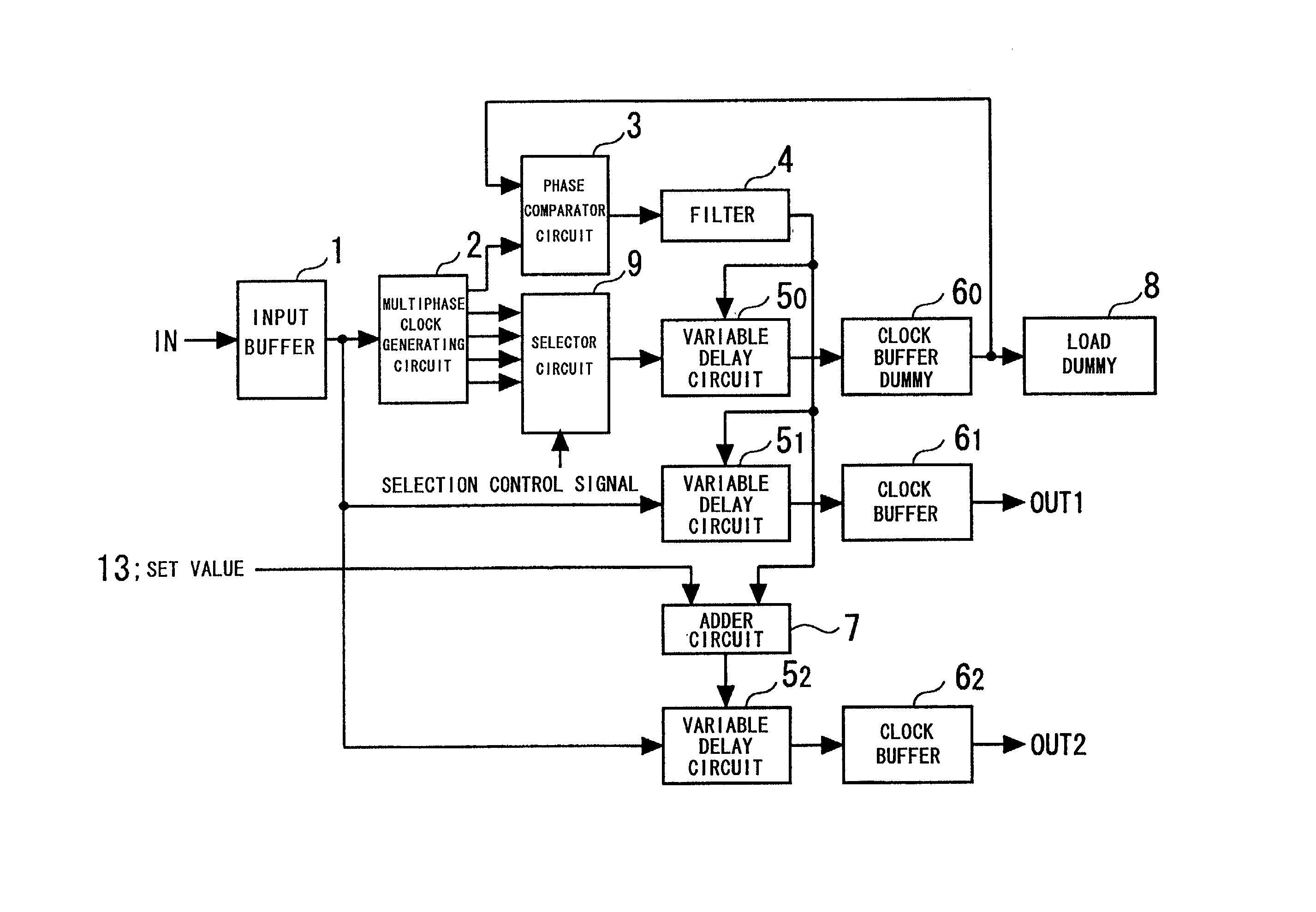

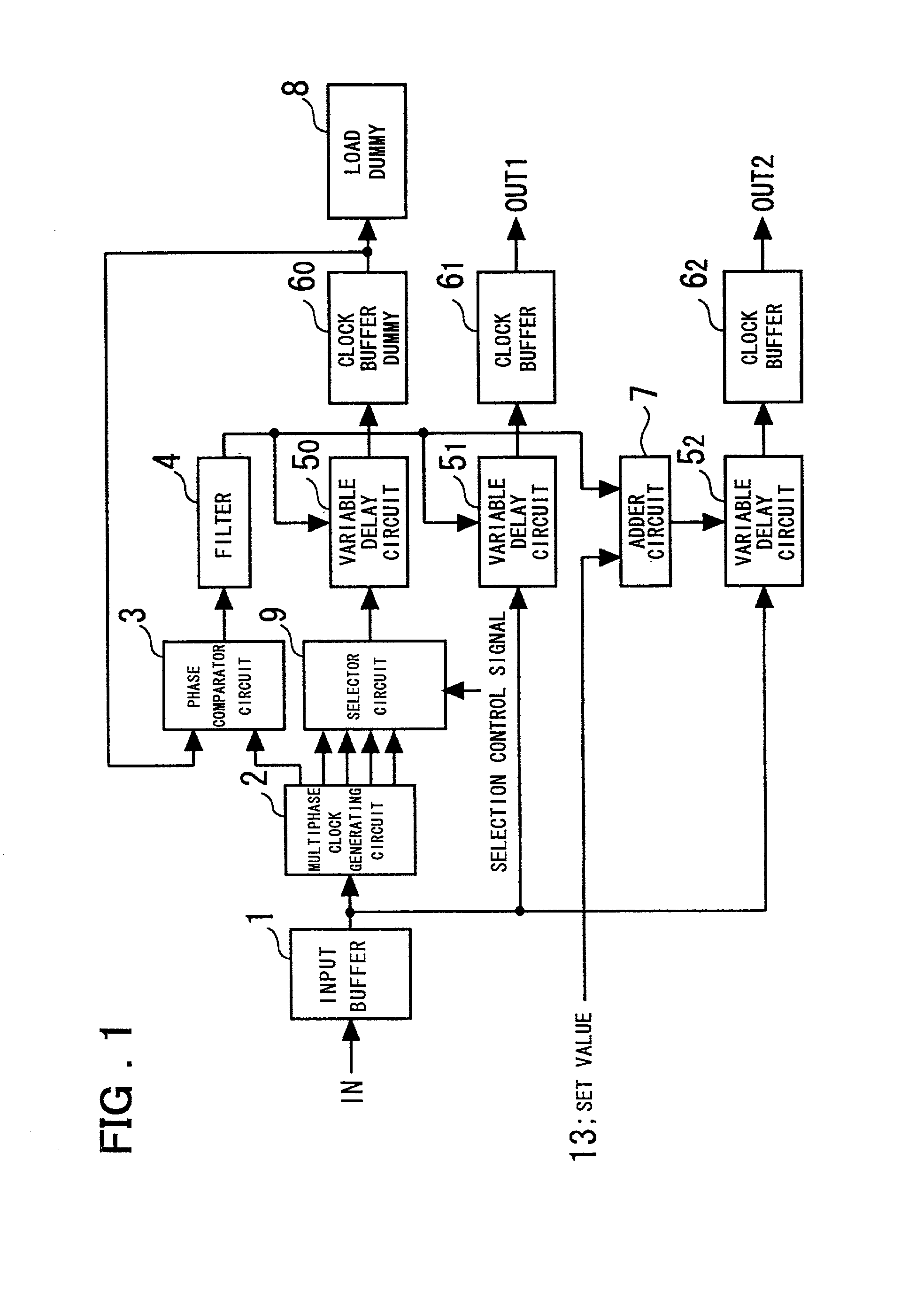

Clock control circuit and method

InactiveUS20020070783A1Generate accuratelyPulse automatic controlSingle output arrangementsPhase differenceComparators circuits

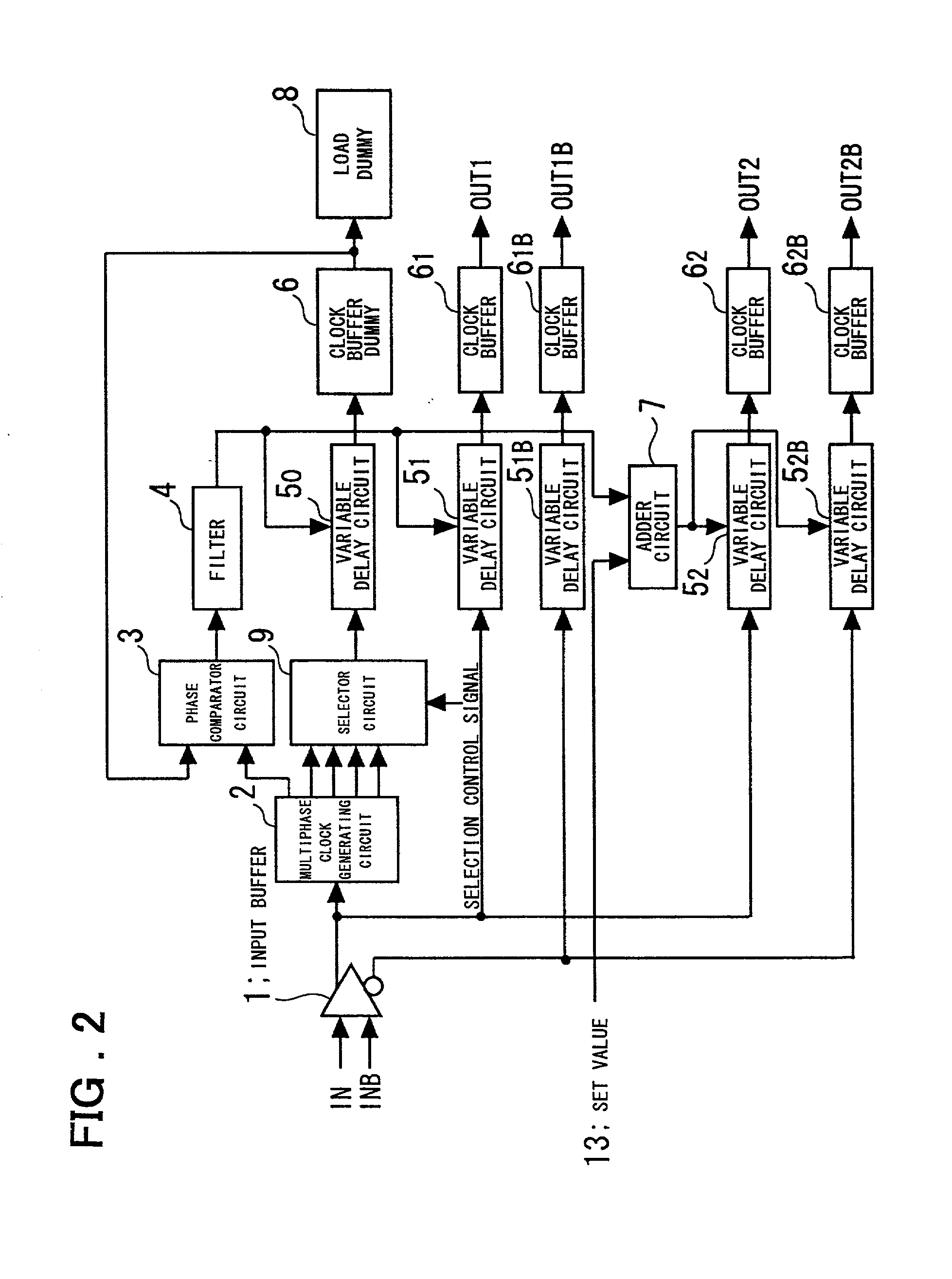

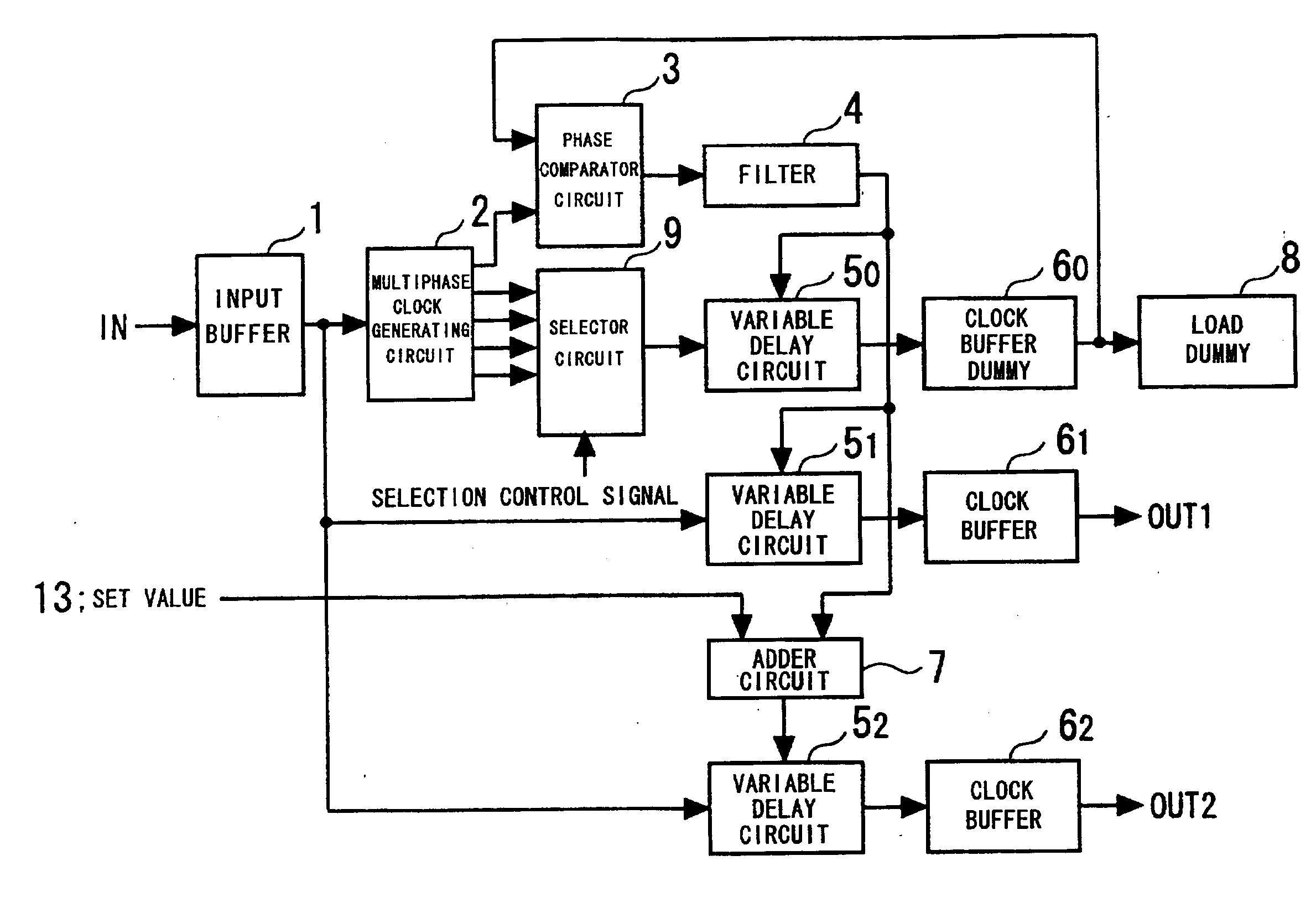

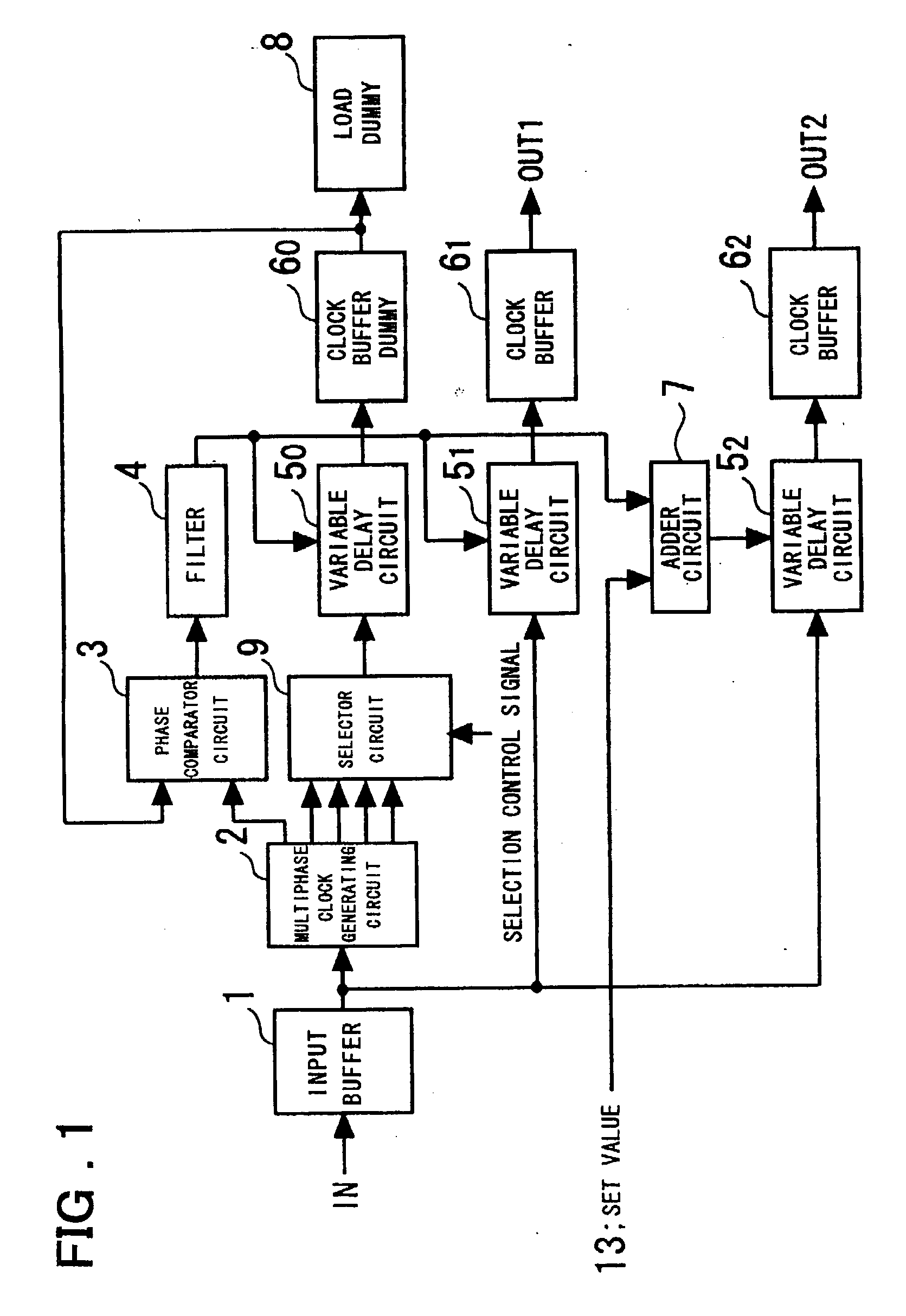

A clock control circuit includes a multiphase clock generating circuit receiving an output signal of a input buffer for generating multiphase clocks; a selector circuit receiving multiphase clocks output from the multiphase clock generating circuit for selecting one of the multiphase clocks; a first variable delay circuit for delaying the output of the selector circuit; a clock buffer dummy receiving the output signal of the variable delay circuit ; a phase comparator circuit for detecting a phase difference between an output from the multiphase clock generating circuit and an output of the clock buffer dummy; and a filter for smoothing the output of the phase comparator circuit. The first variable delay circuit has its delay time varied by the output of the filter. The clock control circuit further includes a second variable delay circuit, receiving the output signal of the input buffer, having its delay time varied by the output of the filter; an adder circuit for adding the filter output and an input set value; a third variable delay circuit, receiving the output signal of the input buffer, having its delay time varied by the output of the adder circuit; and clock buffers receiving output signals of respective ones of the second and third variable delay circuits.

Owner:RENESAS ELECTRONICS CORP

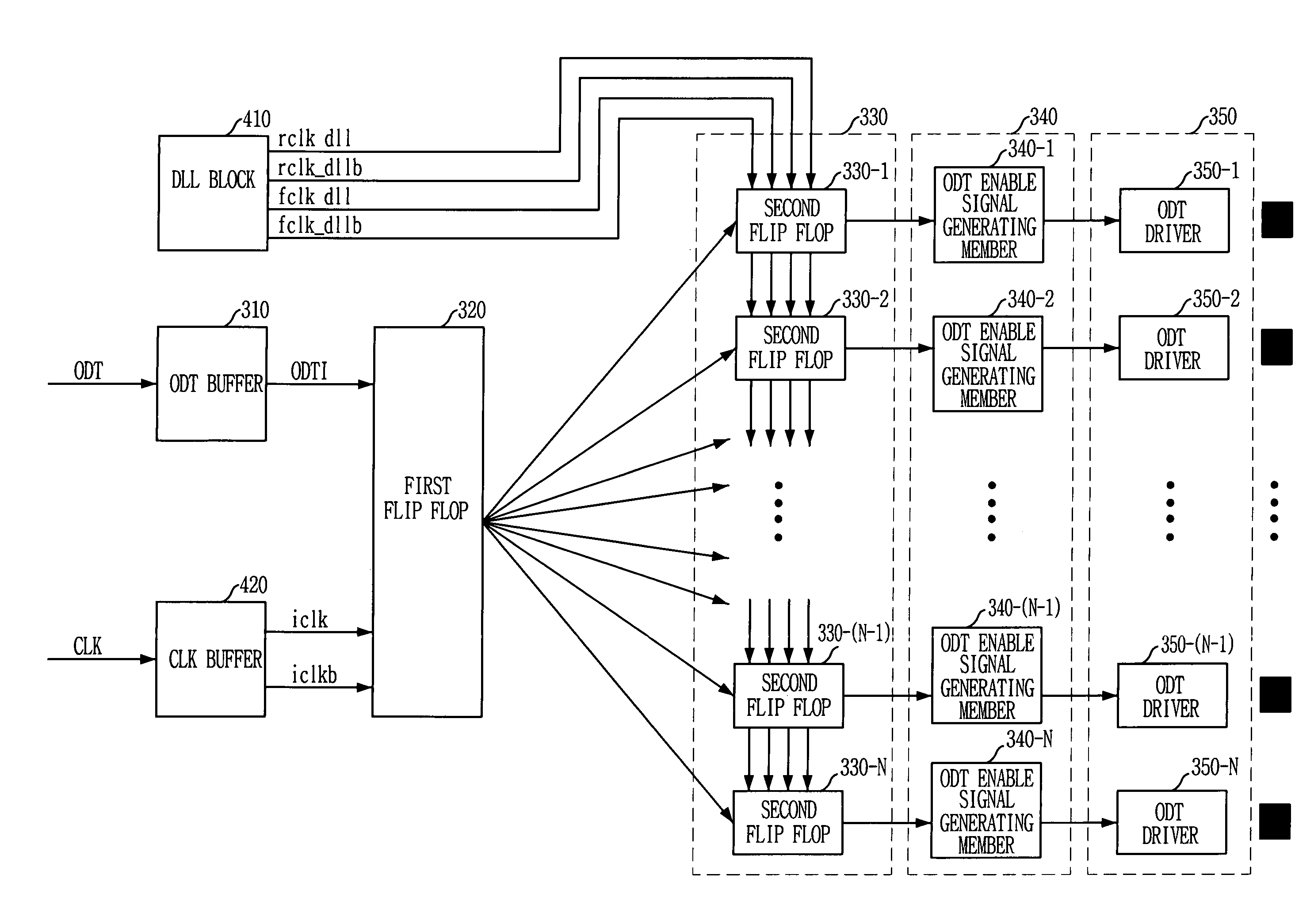

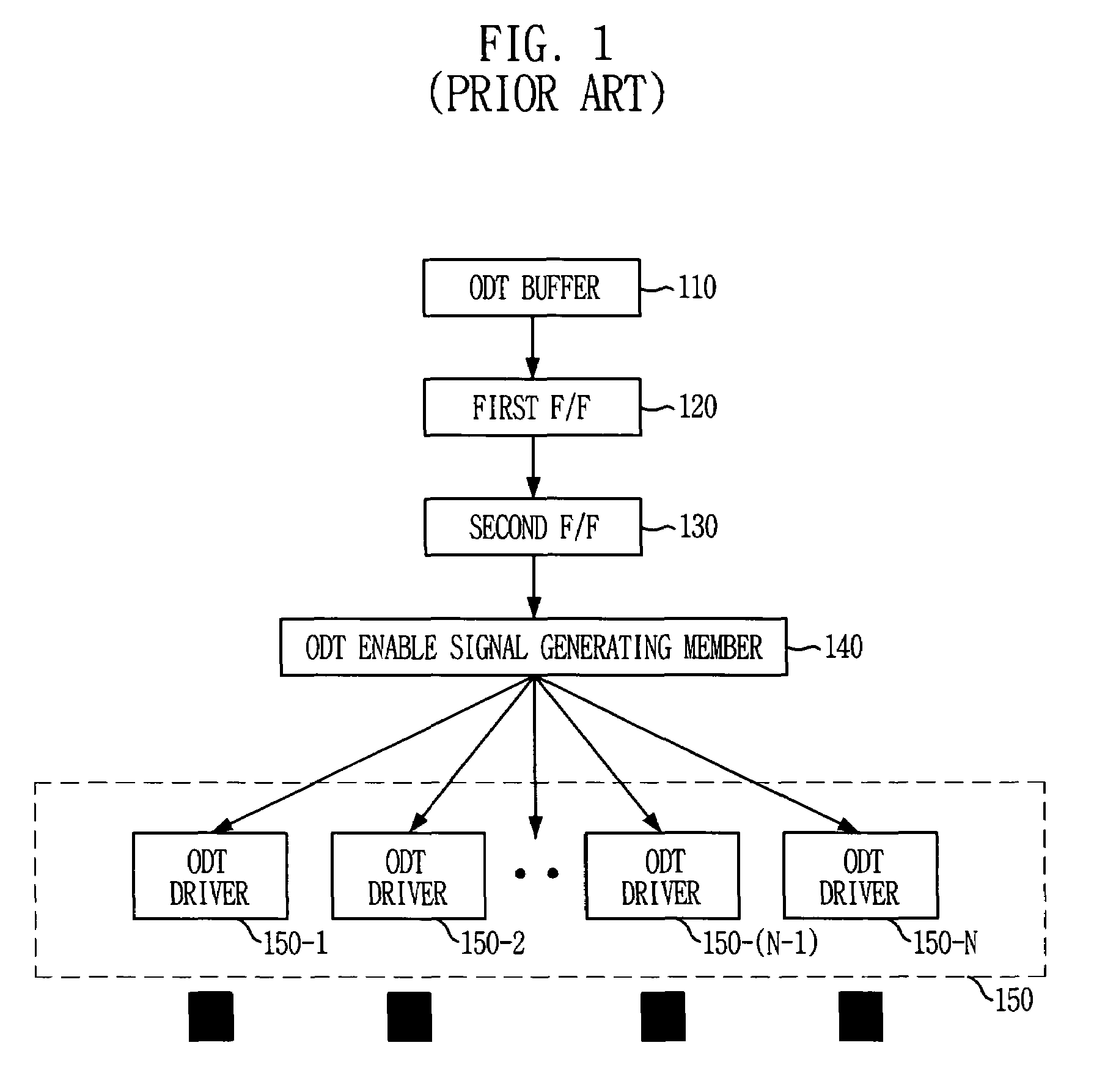

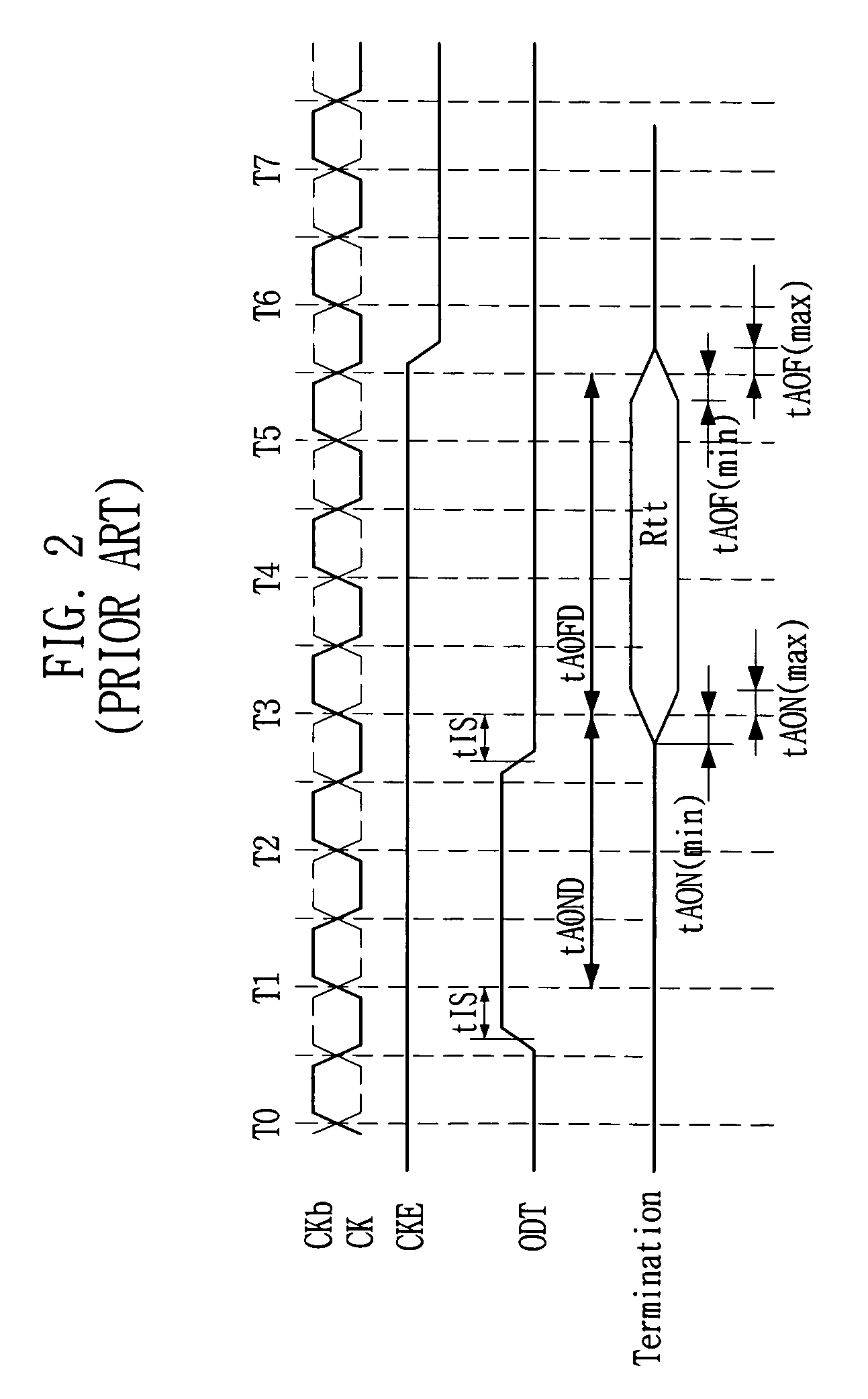

Circuit for performing on-die termination operation in semiconductor memory device and its method

InactiveUS7019555B2Minimizes effect of delayEasy to driveReliability increasing modificationsBaseband system detailsDelay-locked loopVoltage reference

A circuit for performing an on-die termination operation includes a clock buffer for outputting first and second buffered clocks using an external clock and an external inverting clock applied thereto externally; an on-die termination buffer for comparing each other an ODT signal and a reference voltage, which are applied thereto from an external chip set, to generate an on-die termination comparison signal; a first flip-flop member for transferring the on-die termination comparison signal as a plurality of parallel output signals based on the first and second buffered clocks outputted from the clock buffer; and a plurality of second flip-flop members, which corresponds to each of the parallel output signals outputted from the first flip-flop member, for transferring the parallel output signals outputted from the first flip-flop member based on delayed lock loop clocks outputted from a delayed lock loop.

Owner:SK HYNIX INC

Latch Placement for High Performance and Low Power Circuits

ActiveUS20080148203A1Sacrificing timing requirementSimple methodComputer aided designSoftware simulation/interpretation/emulationEngineeringPower circuits

A novel iterative latch placement scheme wherein the latches are gradually pulled by increasing attraction force until they are eventually placed next to a clock distribution structure such as a local clock buffer (LCB). During the iterations, timing optimizations such as gate sizing and re-buffering are invoked in order to keep the timing estimation accurate. By applying the iterative clock net weighting adjustment, the present invention allows tighter interaction between logic placement and clock placement which leads to higher quality timing and significant power savings.

Owner:GLOBALFOUNDRIES US INC

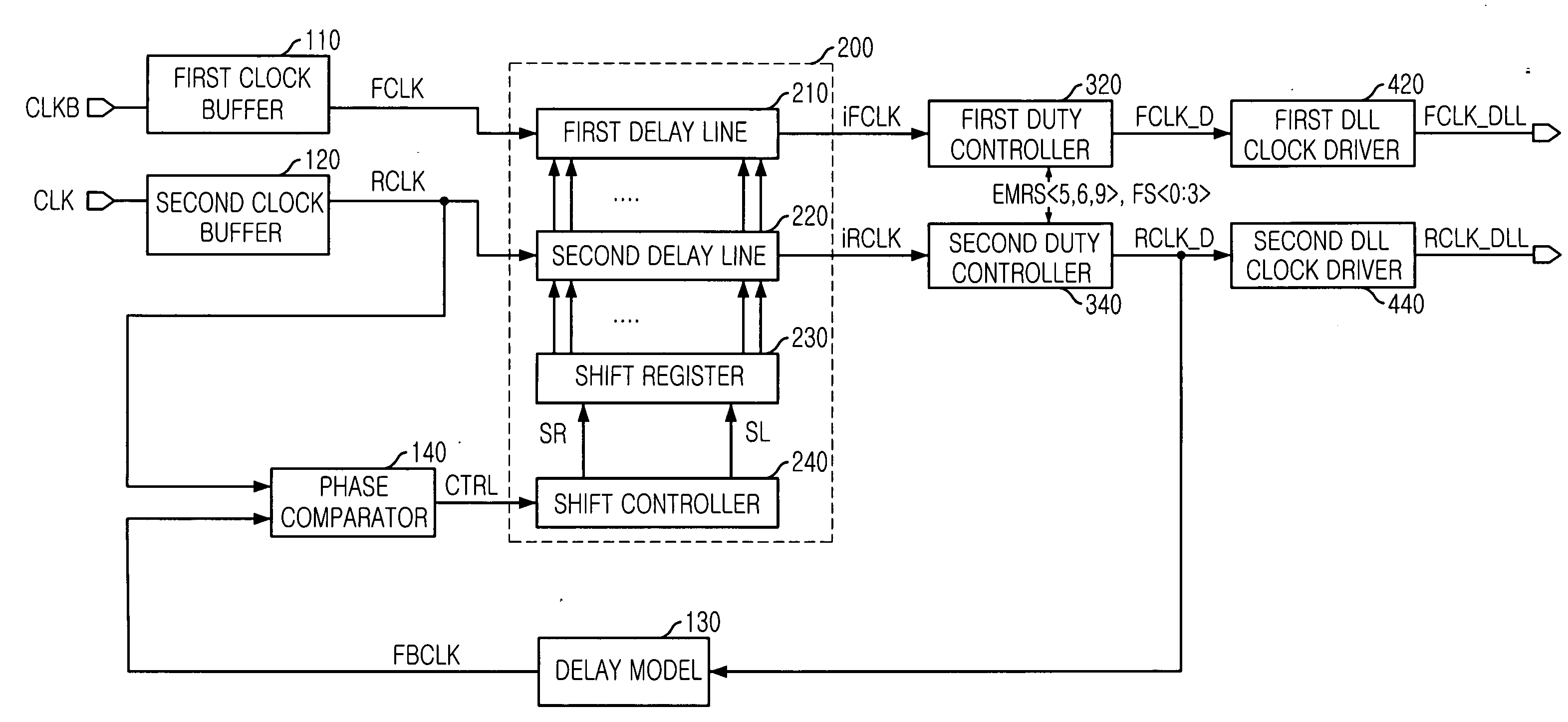

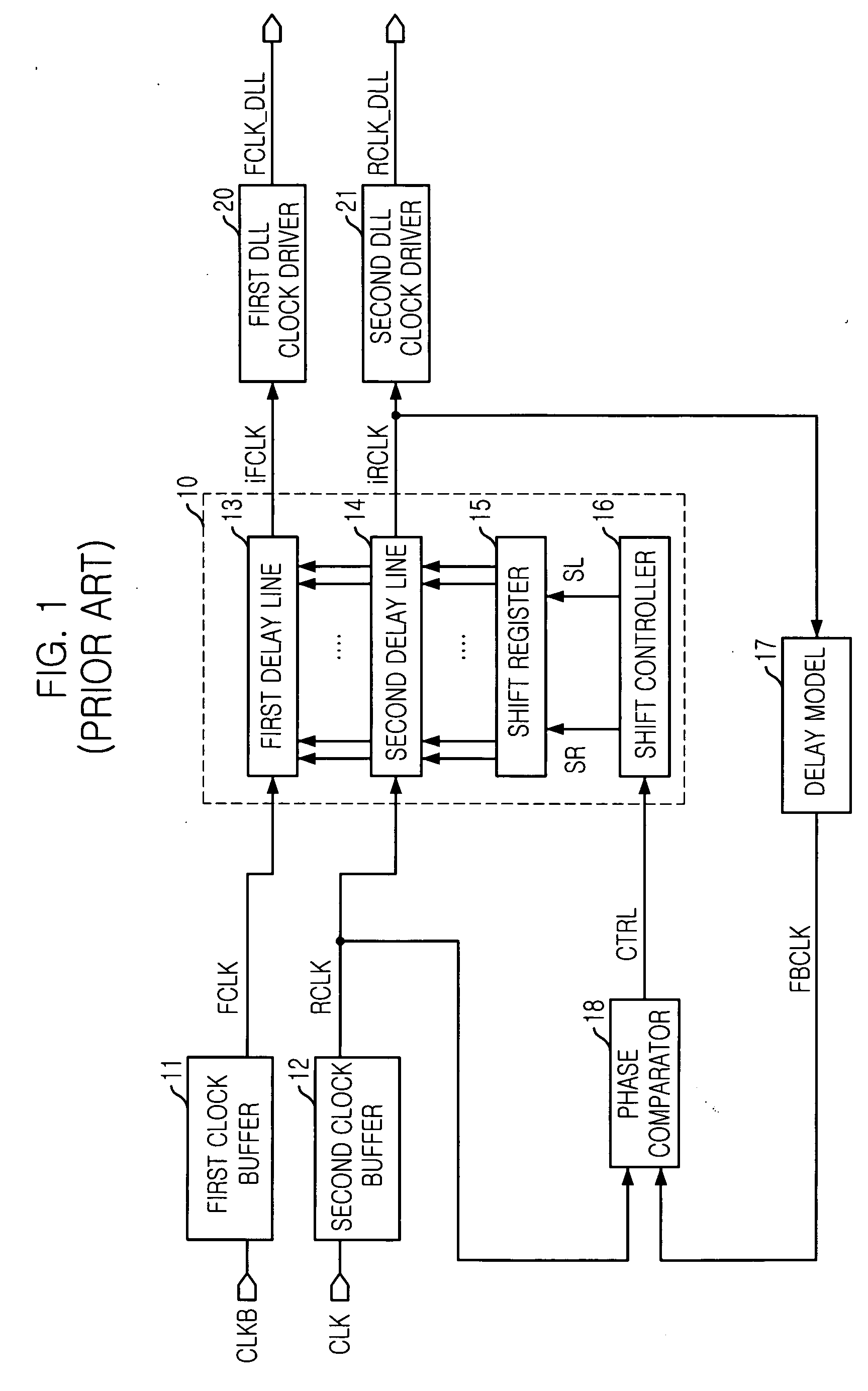

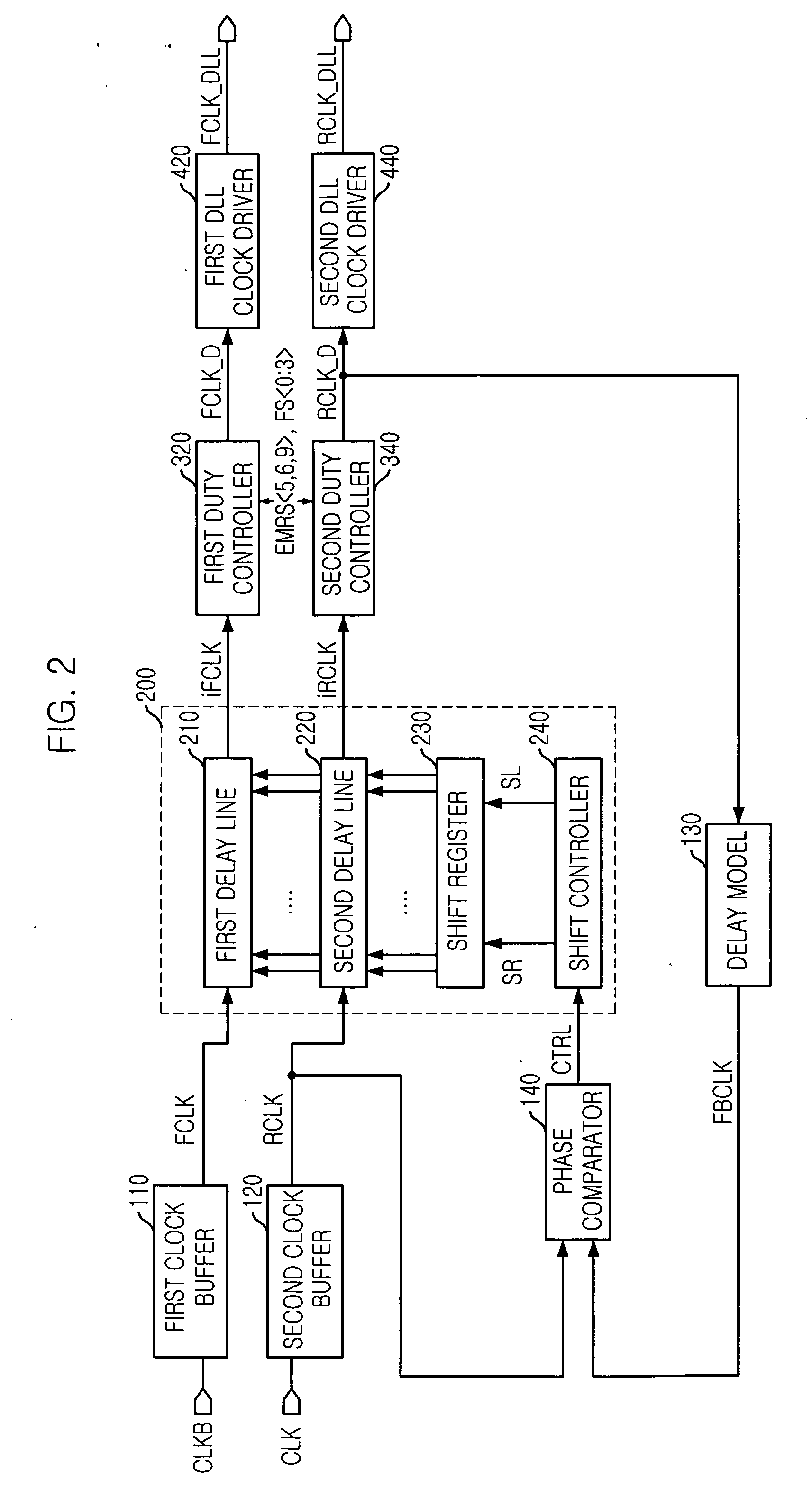

Delay locked loop for controlling duty rate of clock

ActiveUS20060197565A1Safety devices for lifting equipmentsPulse automatic controlShift registerDelay-locked loop

There is provided a DLL capable of controlling a duty rate of a clock by a fuse option or an EMRS input. The DLL includes a first clock buffer, a second clock buffer, a first delay line, a second delay line, a shift register, a first duty control unit, a second duty control unit, a first DLL driver, a second DLL driver, a delay model, a phase comparator, and a shift control unit. In the DLL, a first duty control unit and a second duty control unit control each duty rate of the output clocks of a first and a second delay lines respectively through the EMRS input or the fuse option. Therefore, it is possible to control the duty rate of DLL clocks through the EMRS input or the fuse option.

Owner:SK HYNIX INC

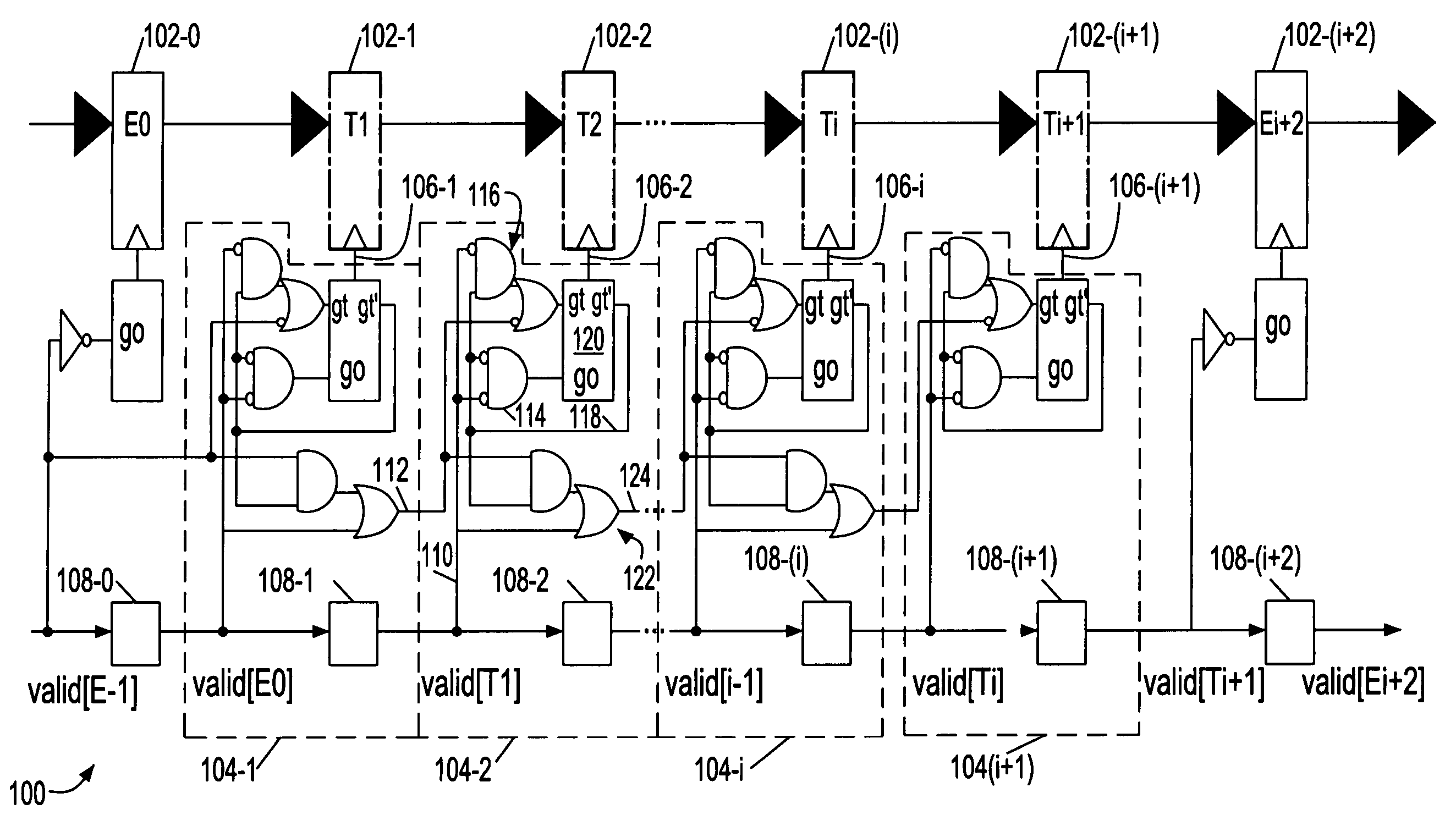

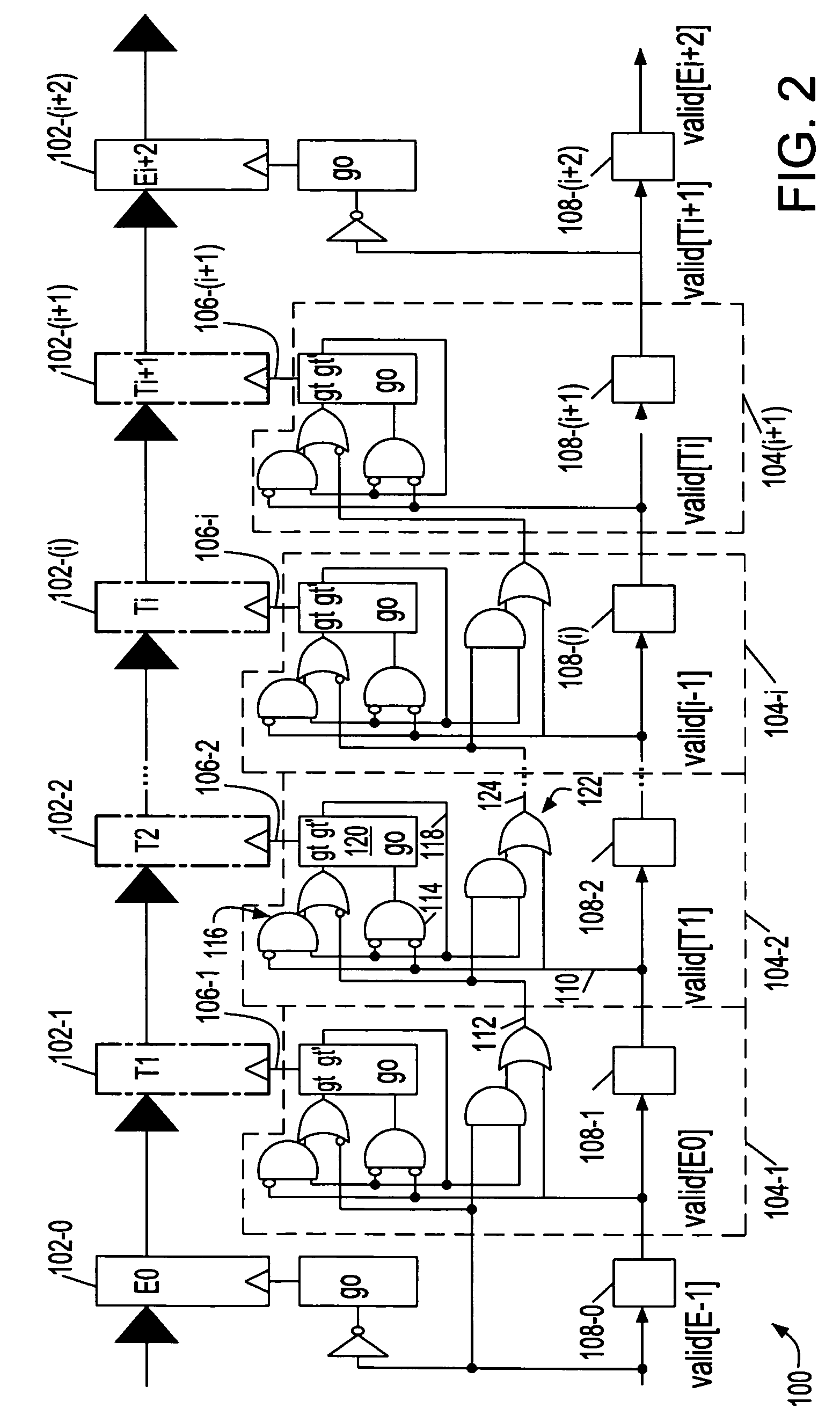

Synchronous pipeline with normally transparent pipeline stages

ActiveUS7076682B2Increase flexibilityReducing pipeline operating frequencyVolume/mass flow measurementDigital computer detailsEngineeringIntermediate stage

A synchronous pipeline segment and an integrated circuit (IC) including the segment. The segment includes an input stage, an output stage and at least one intermediate stage. A place holder latch associated with each stage indicates whether valid stage data is in the stage. A local clock buffer provides a local clock gating a corresponding stage. The input and output stages are normally opaque and intermediate stages are normally transparent. Data items pass locally asynchronously between the input and output stages and are separated by opaque gated intermediate stages.

Owner:IBM CORP

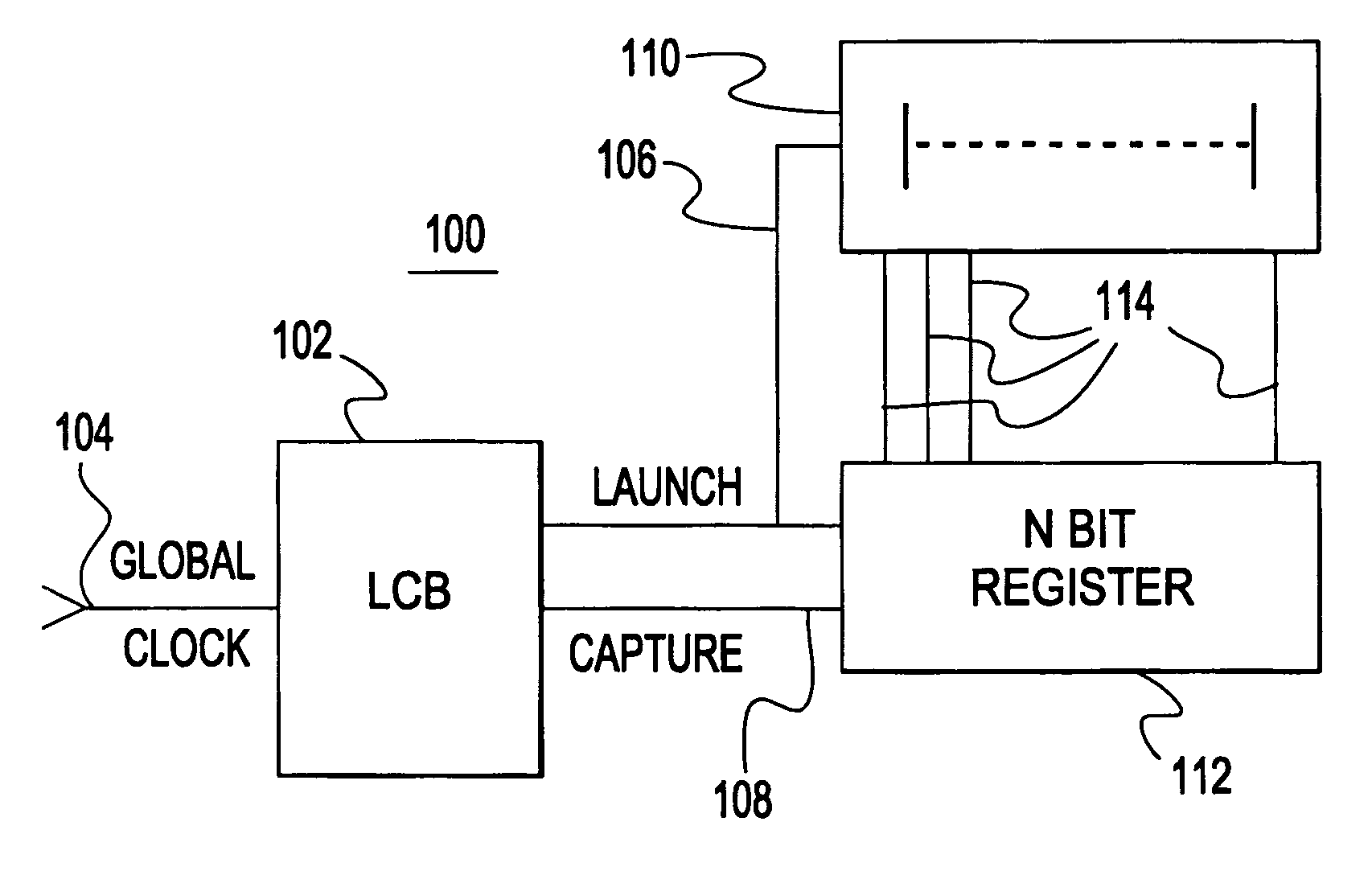

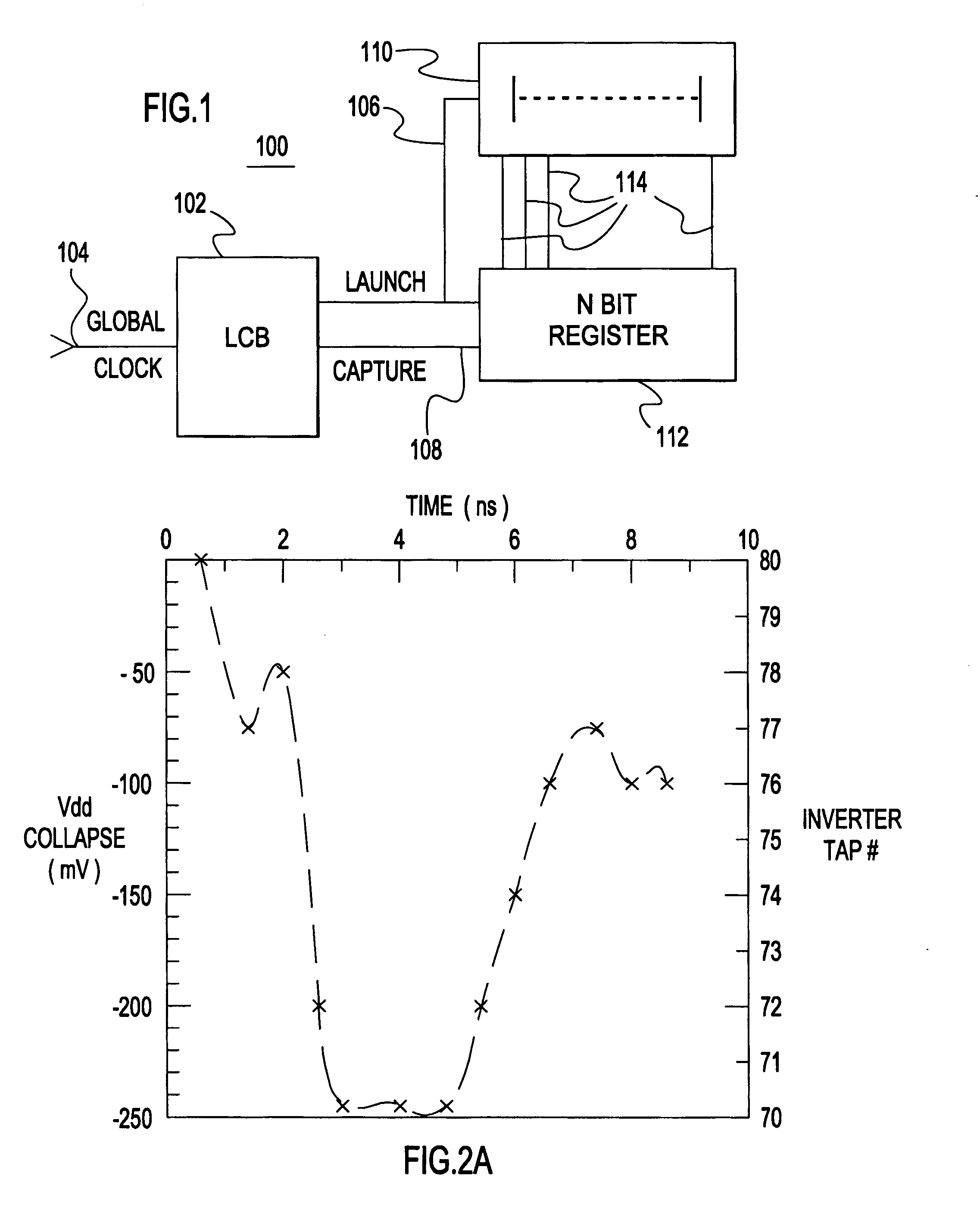

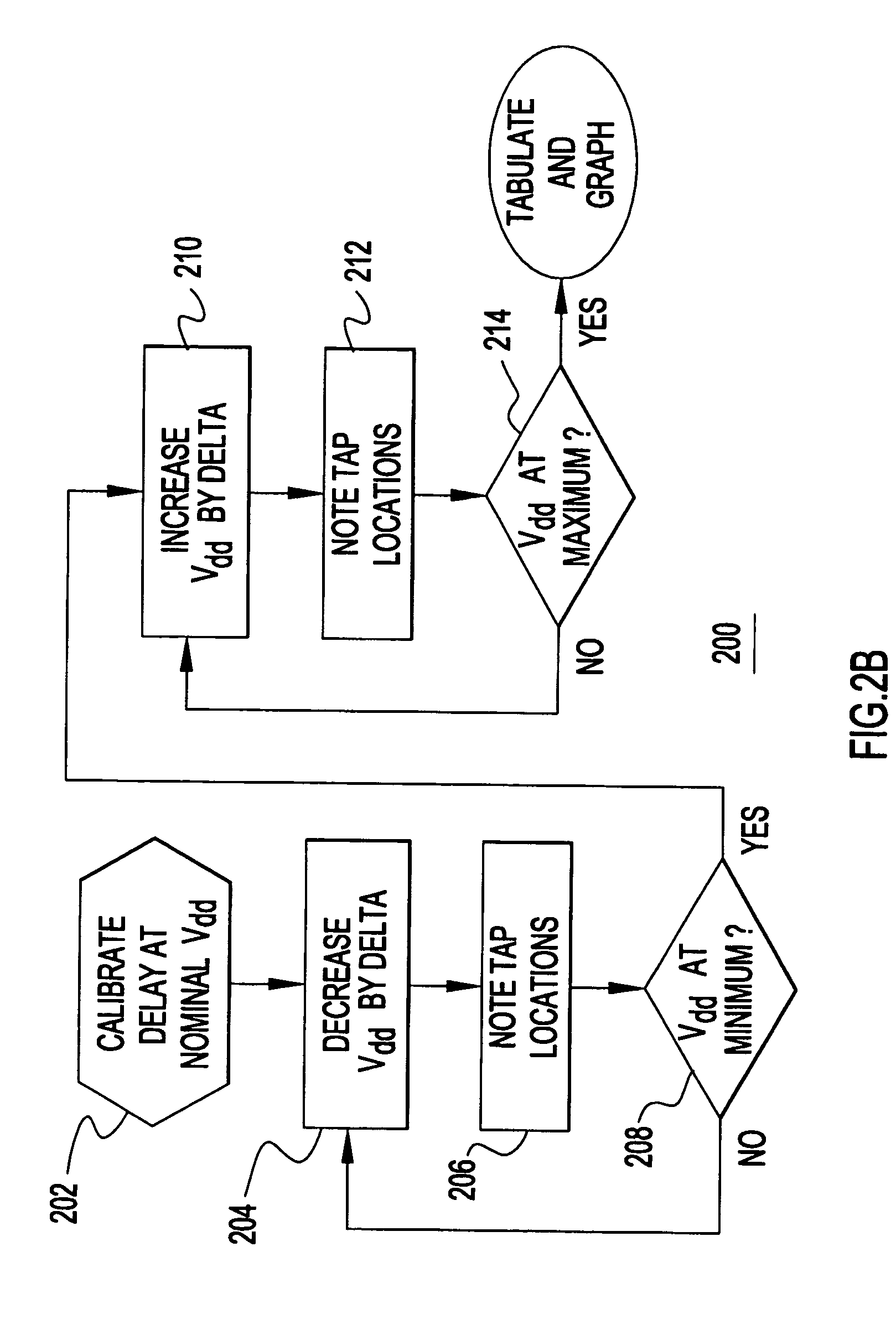

Built in self test circuit for measuring total timing uncertainty in a digital data path

InactiveUS20050107970A1Accurately determineAccurate recoveryDigital circuit testingElectromechanical unknown time interval measurementDigital dataCoupling

A circuit for measuring timing uncertainty in a clocked digital path and in particular, the number of logic stages completed in any clock cycle. A local clock buffer receives a global clock and provides a complementary pair of local clocks. A first local (launch) clock is an input to a delay line, e.g., 3 clock cycles worth of series connected inverters. Delay line taps (inverter outputs) are inputs to a register that is clocked by the complementary clock pair to capture progression of the launch clock through the delay line and identify any variation (e.g., from jitter, VDD noise) in that progression. Global clock skew and across chip gate length variation can be measured by cross coupling launch clocks from a pair of such clock buffers and selectively passing the local and remote launch clocks to the respective delay lines.

Owner:GLOBALFOUNDRIES INC

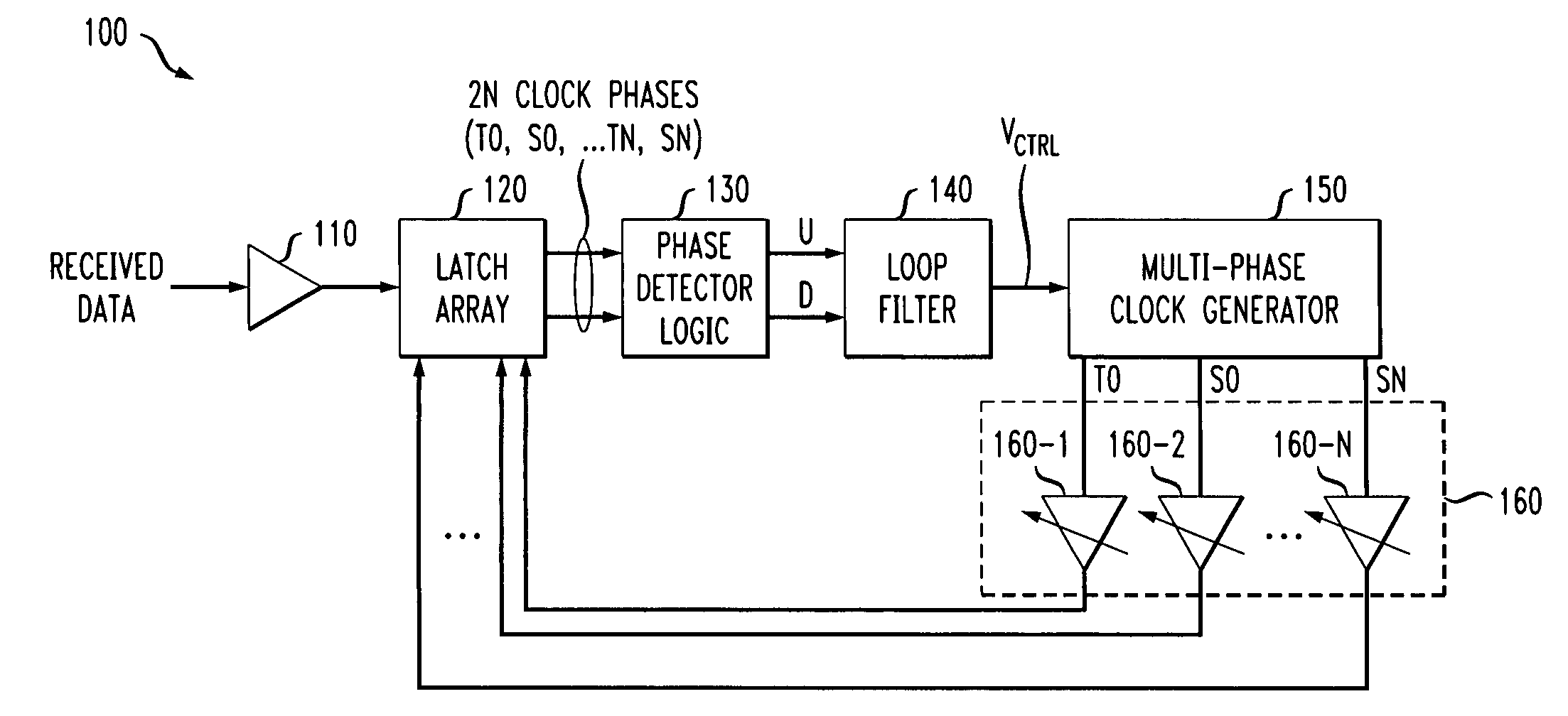

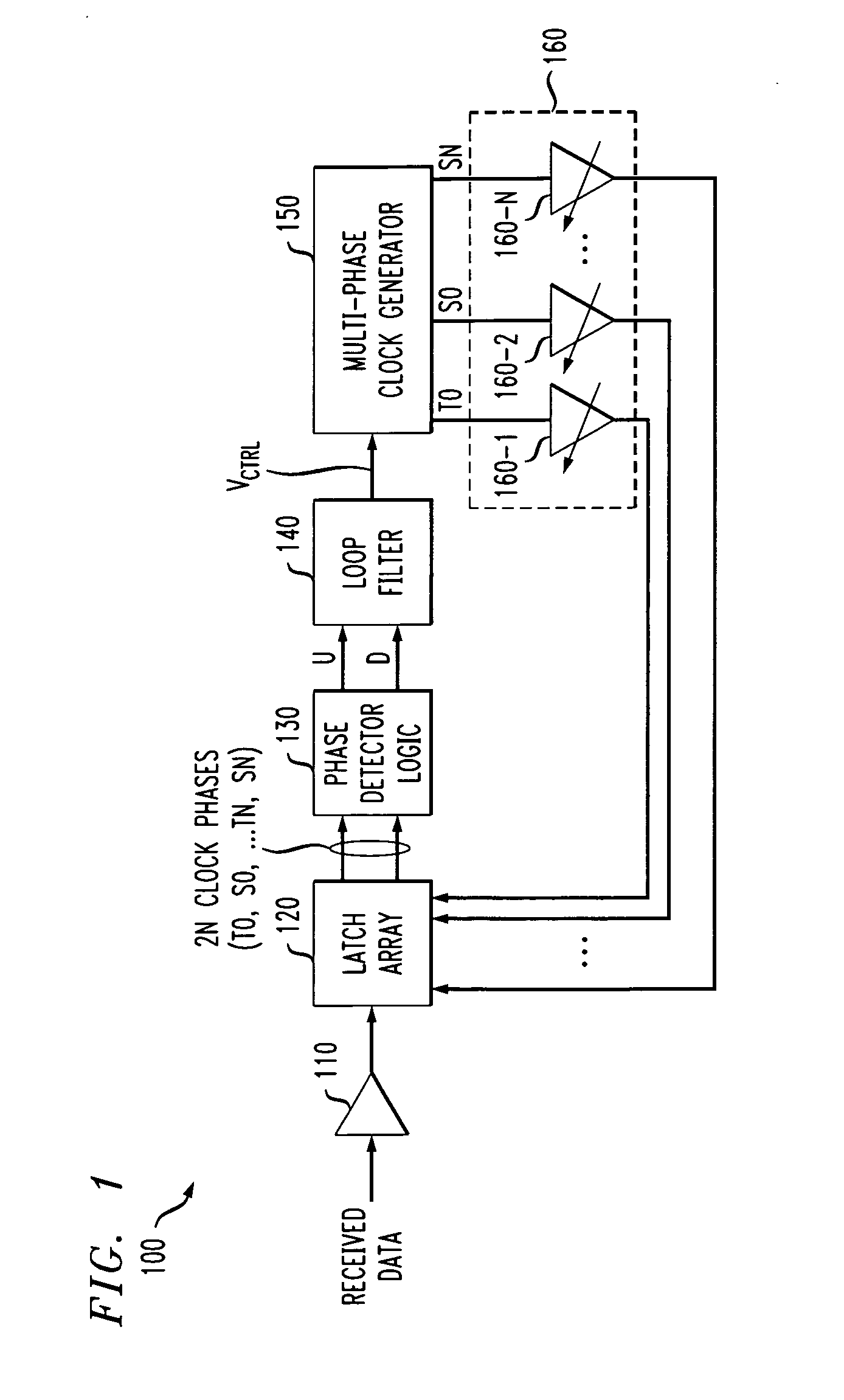

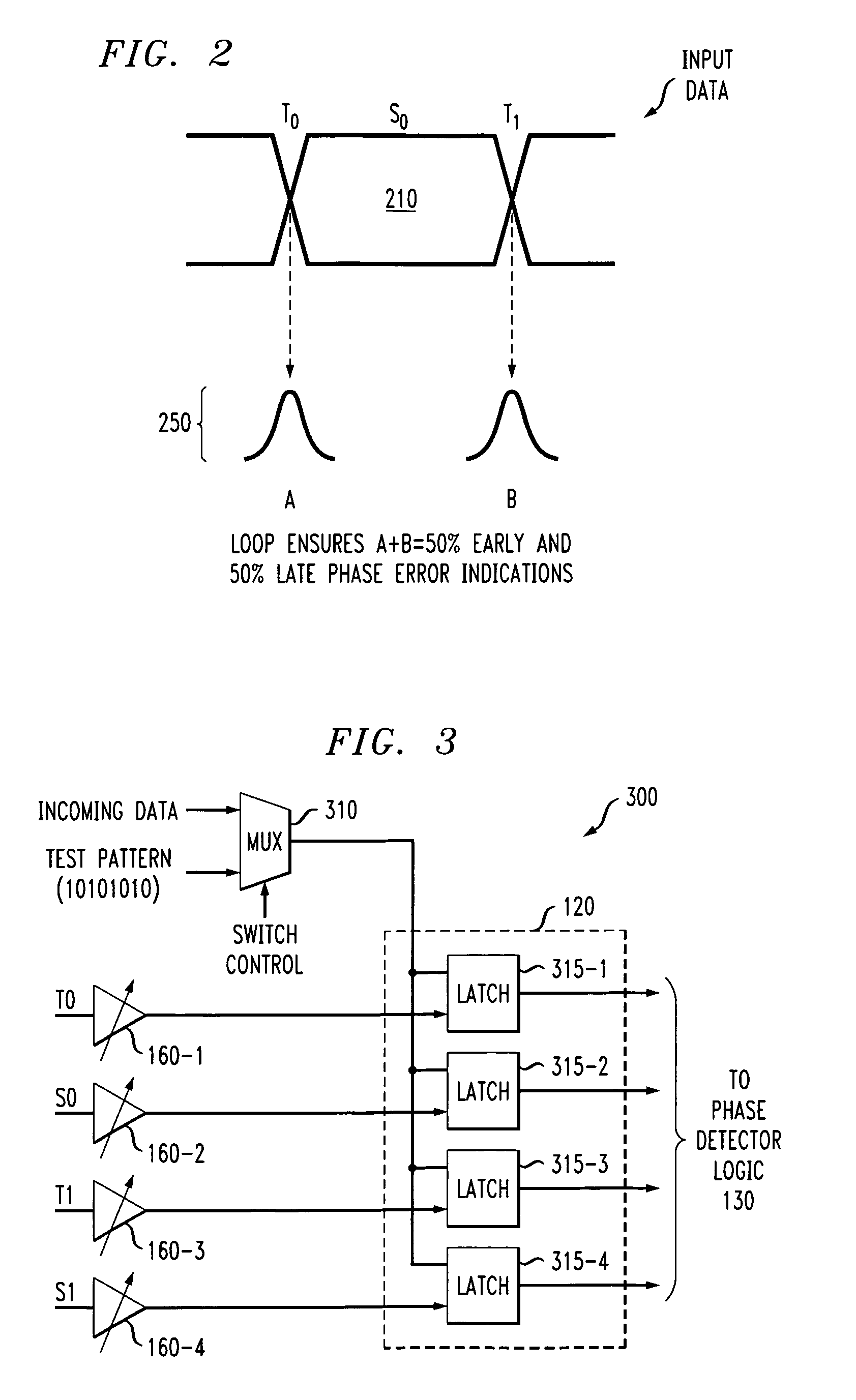

Method and apparatus for clock skew calibration in a clock and data recovery system using multiphase sampling

InactiveUS20080080649A1Pulse automatic controlSynchronisation signal speed/phase controlBang bang phase detectorComputer science

Methods and apparatus are provided for clock skew calibration in a clock and data recovery system. One aspect of the invention compensates for skew among a plurality of clocks in a clock and data recovery system. The clocks are applied to a plurality of latches to sample an incoming signal. A reference signal, such as a Nyquist signal, is applied to a data input of each of the latches. Statistics of “early” and “late” corrections applied to at least one of the clocks by a bang-bang phase detector in the clock and data recovery system are evaluated and a delay of a clock buffer associated with the at least one clock is adjusted to obtain approximately a 50% early-to-late ratio for the at least one clock. The clock and data recovery system ensures that the early-to-late ratio for the sum of the plurality of clocks is approximately 50%.

Owner:AVAGO TECH INT SALES PTE LTD

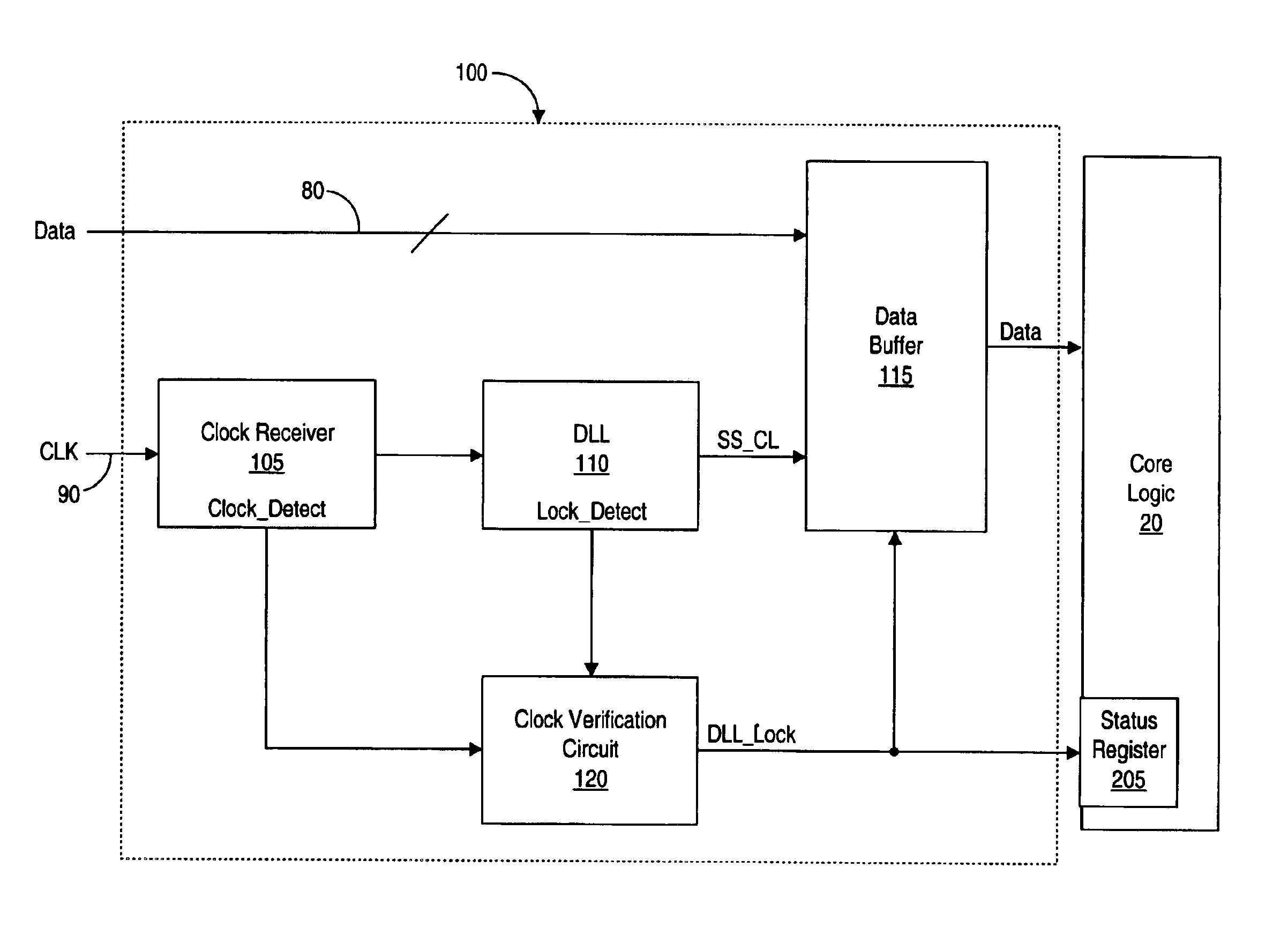

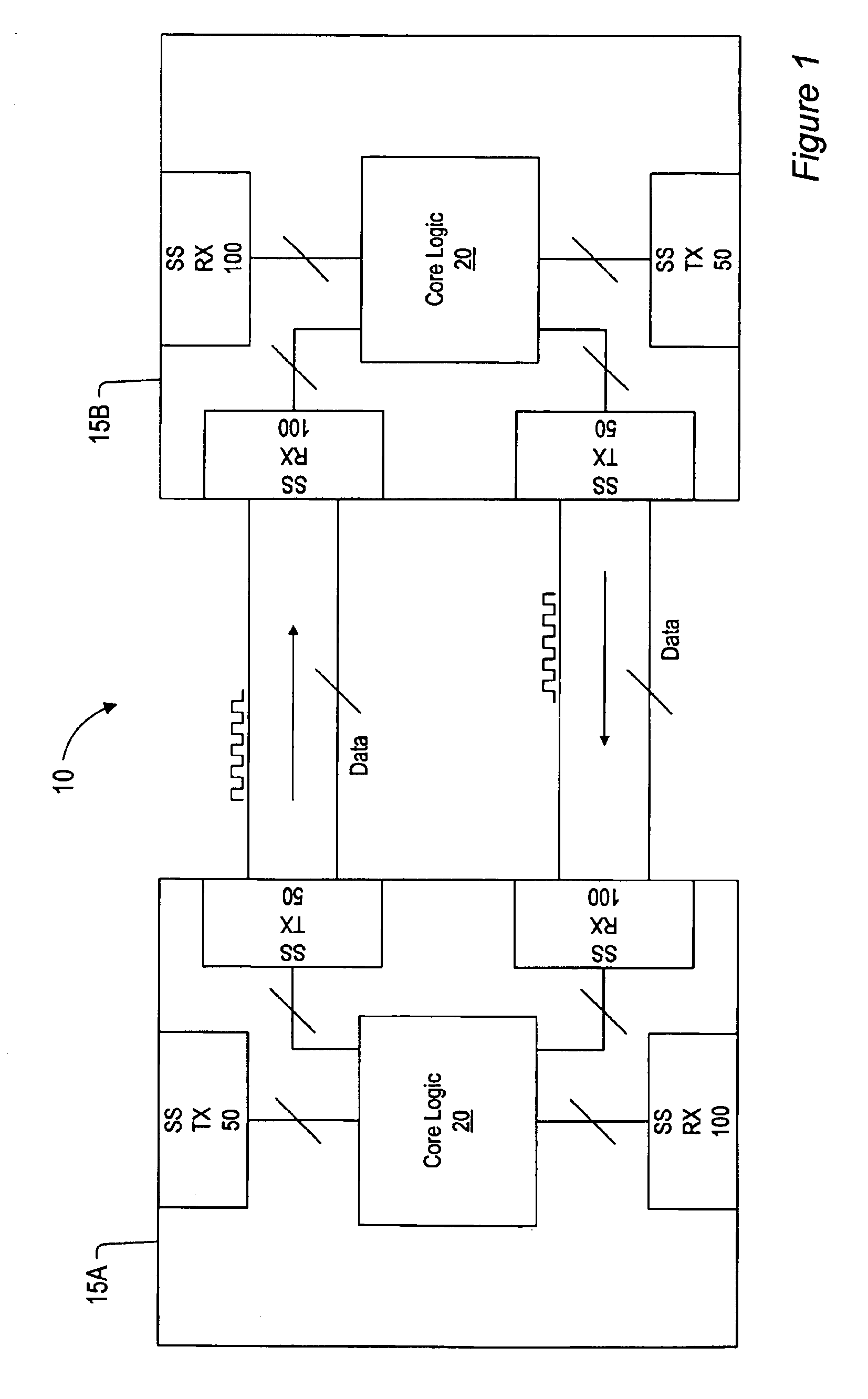

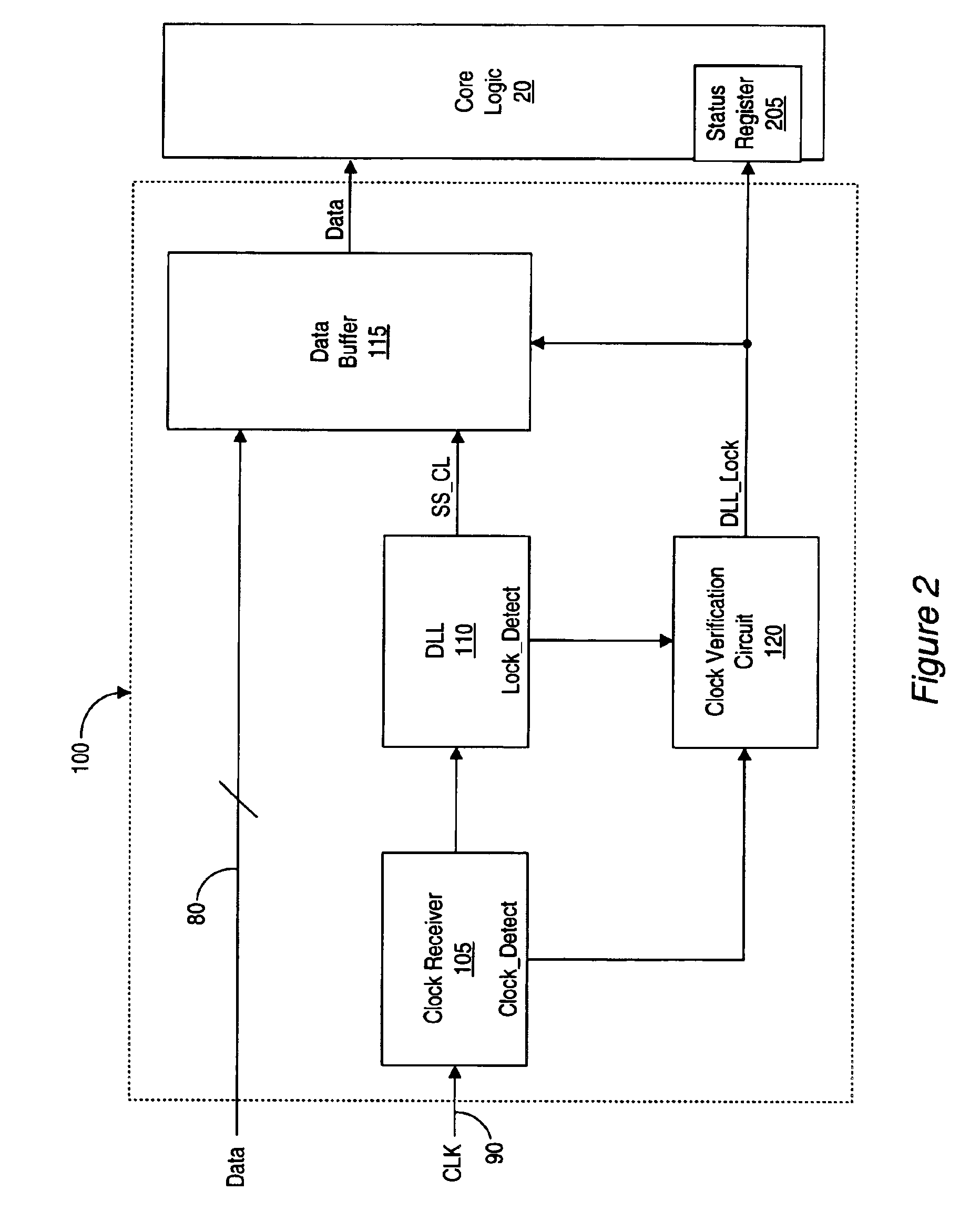

Source synchronous receiver link initialization and input floating control by clock detection and DLL lock detection

InactiveUS6937680B2Guaranteed uptimeSynchronisation information channelsPulse automatic controlClock validationSource-synchronous

A method and apparatus for operating a source synchronous receiver. In one embodiment, a source synchronous receiver may include a clock receiver comprising a clock detector and a clock signal buffer. The clock detector may be configured to detect a first clock signal and assert a clock detect signal responsive to detecting the first clock signal. The clock buffer may receive the first clock signal and produce a second clock signal, which may be driven to a digital locked loop (DLL) circuit, where the second clock signal is regenerated and driven to a data buffer of the source synchronous receiver. The clock detect signal may be received by a clock verification circuit. The clock verification circuit may be configured to initiate a reset of the source synchronous receiver upon a failure to receive the clock detect signal. The resetting of the source synchronous receiver may be performed locally, and does not reset the core logic of the device in which it is implemented, nor any other source synchronous port on the device. Thus, other source synchronous ports on the device, as well as the core logic, may be able to continue operations as normal. The method and apparatus may include a source synchronous receiver that is hot-swappable.

Owner:ORACLE INT CORP

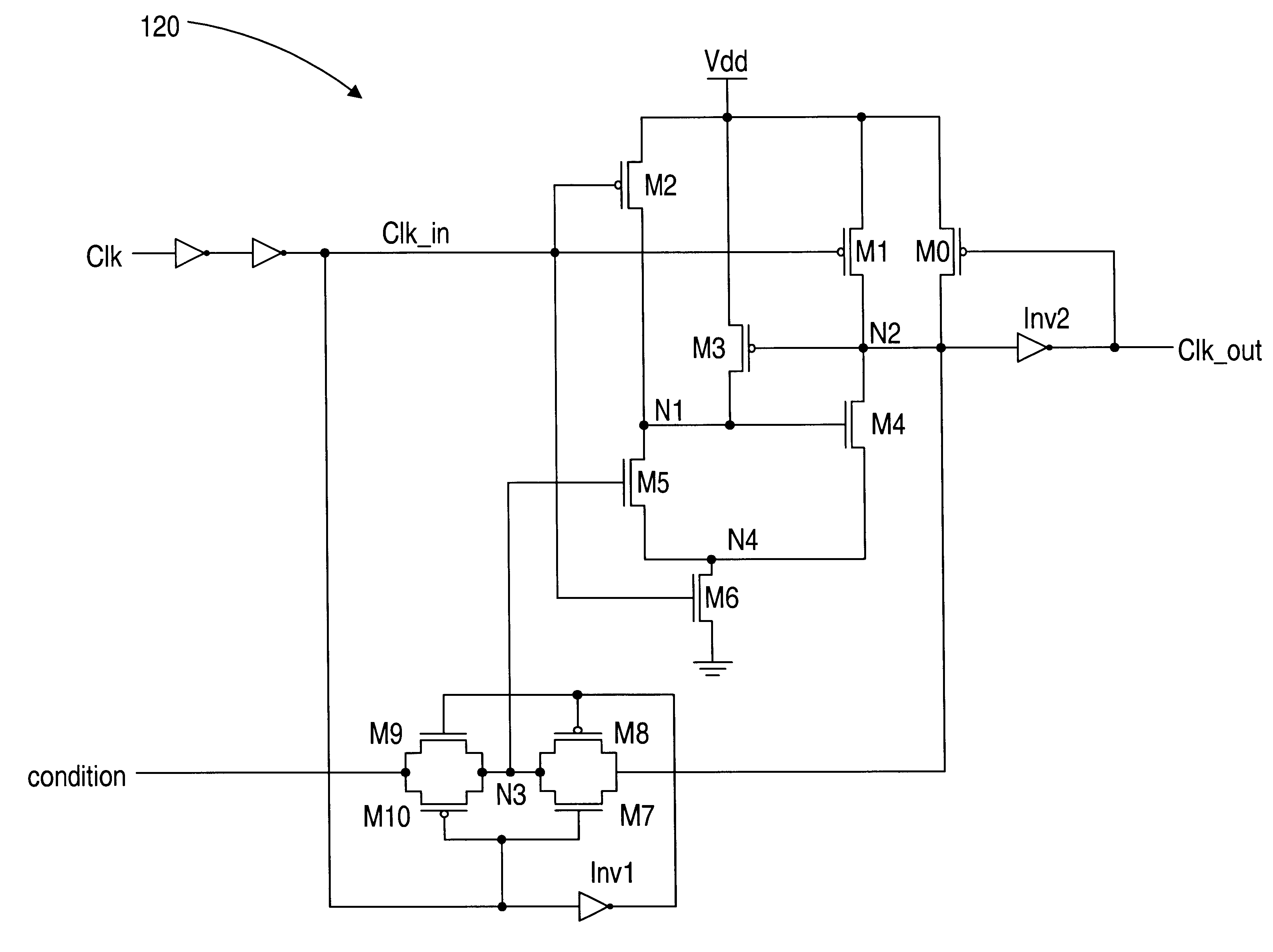

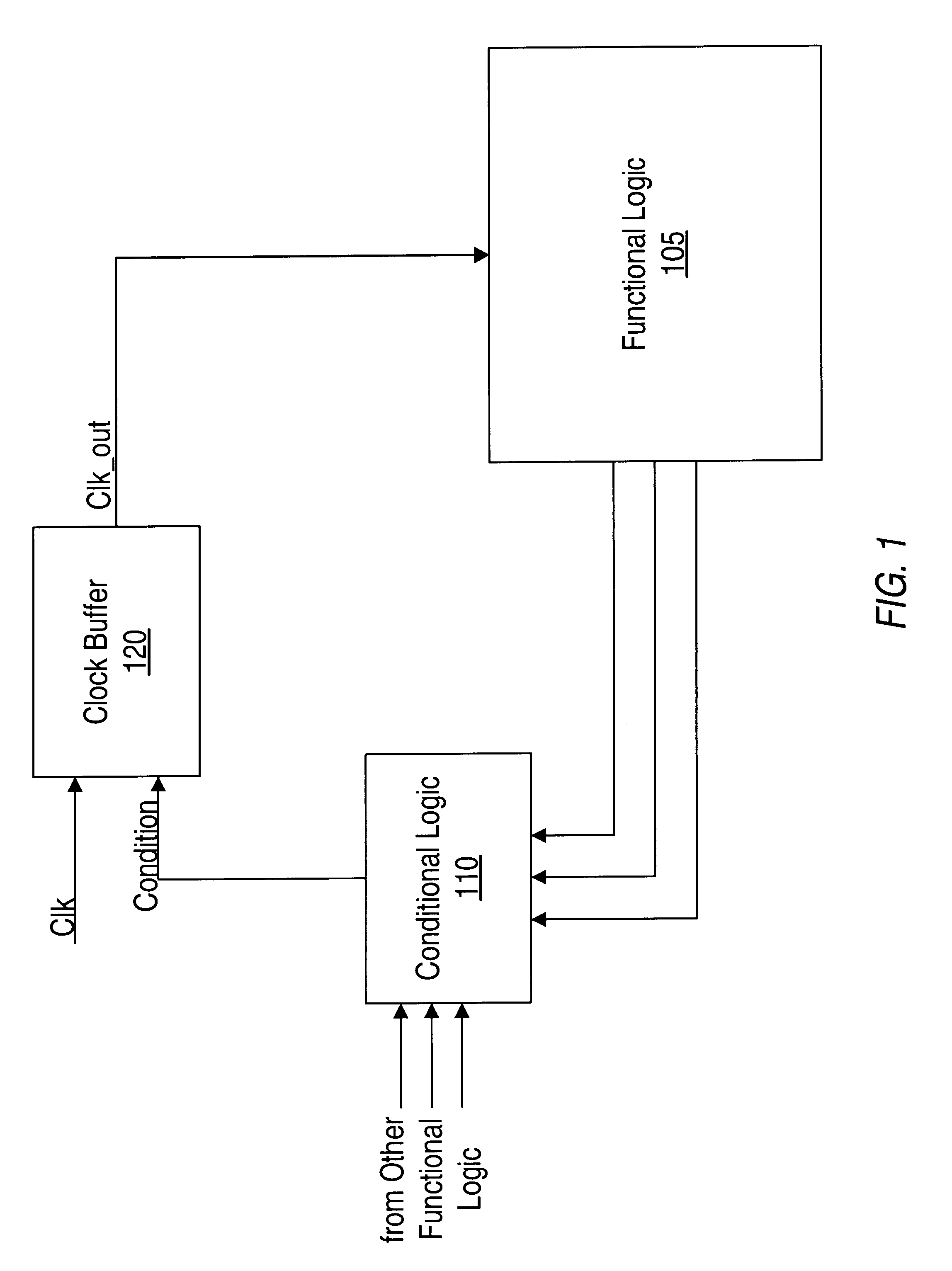

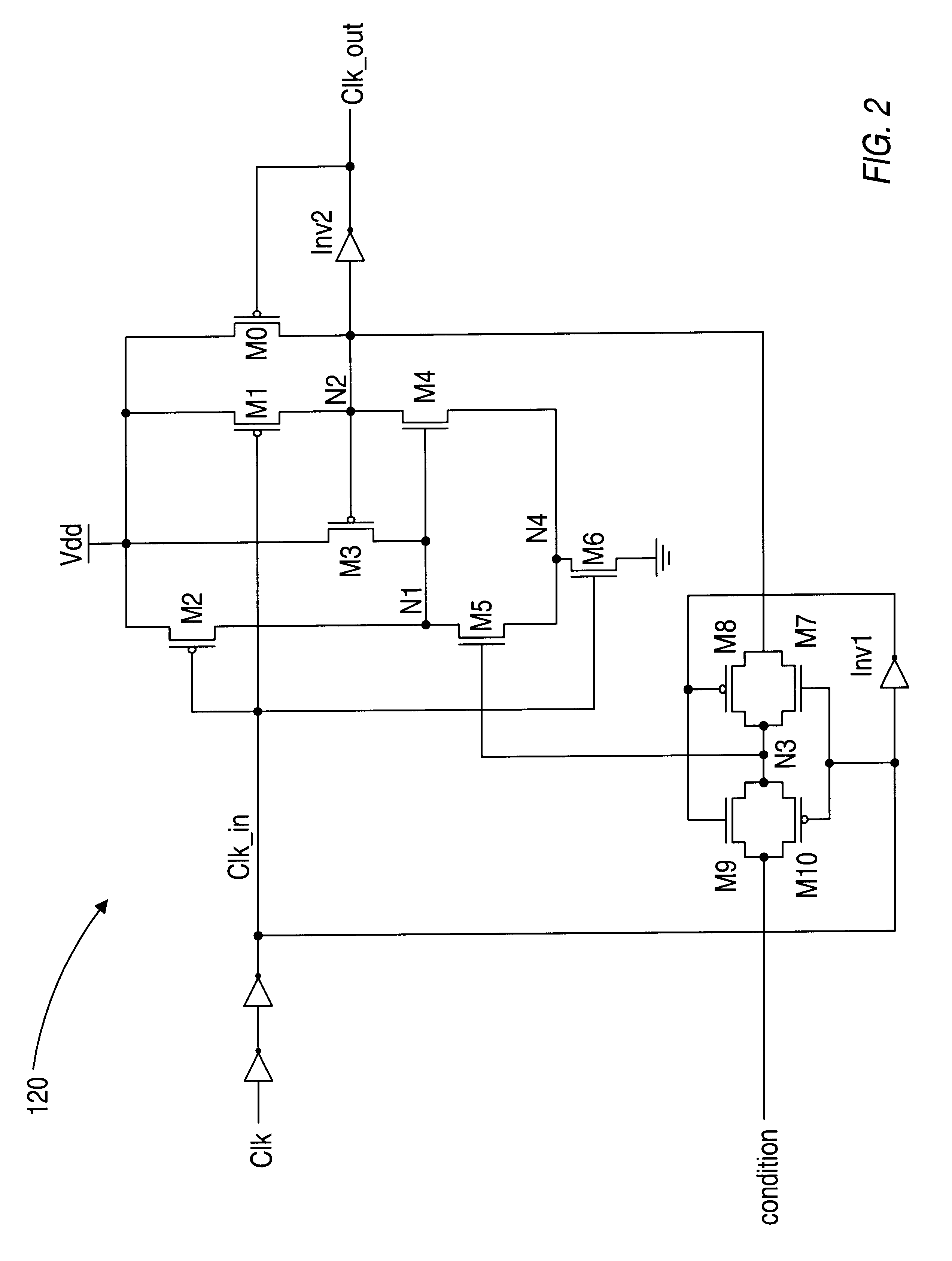

Conditional clock buffer circuit

InactiveUS6411152B1Power reduction by control/clock signalElectric pulse generatorTransistorClock buffer

A conditional clock buffer circuit is disclosed. In one embodiment, a conditional clock buffer circuit includes a precharge circuit, a first transistor and a second transistor coupled to the precharge circuit via the first node and the second node, a third transistor coupled to the first transistor and the second transistor. The first transistor may be activated responsive to a condition external to the clock buffer circuit. When the first transistor is activated, an output clock signal driven by the clock buffer circuit may be inhibited.

Owner:QUALCOMM INC

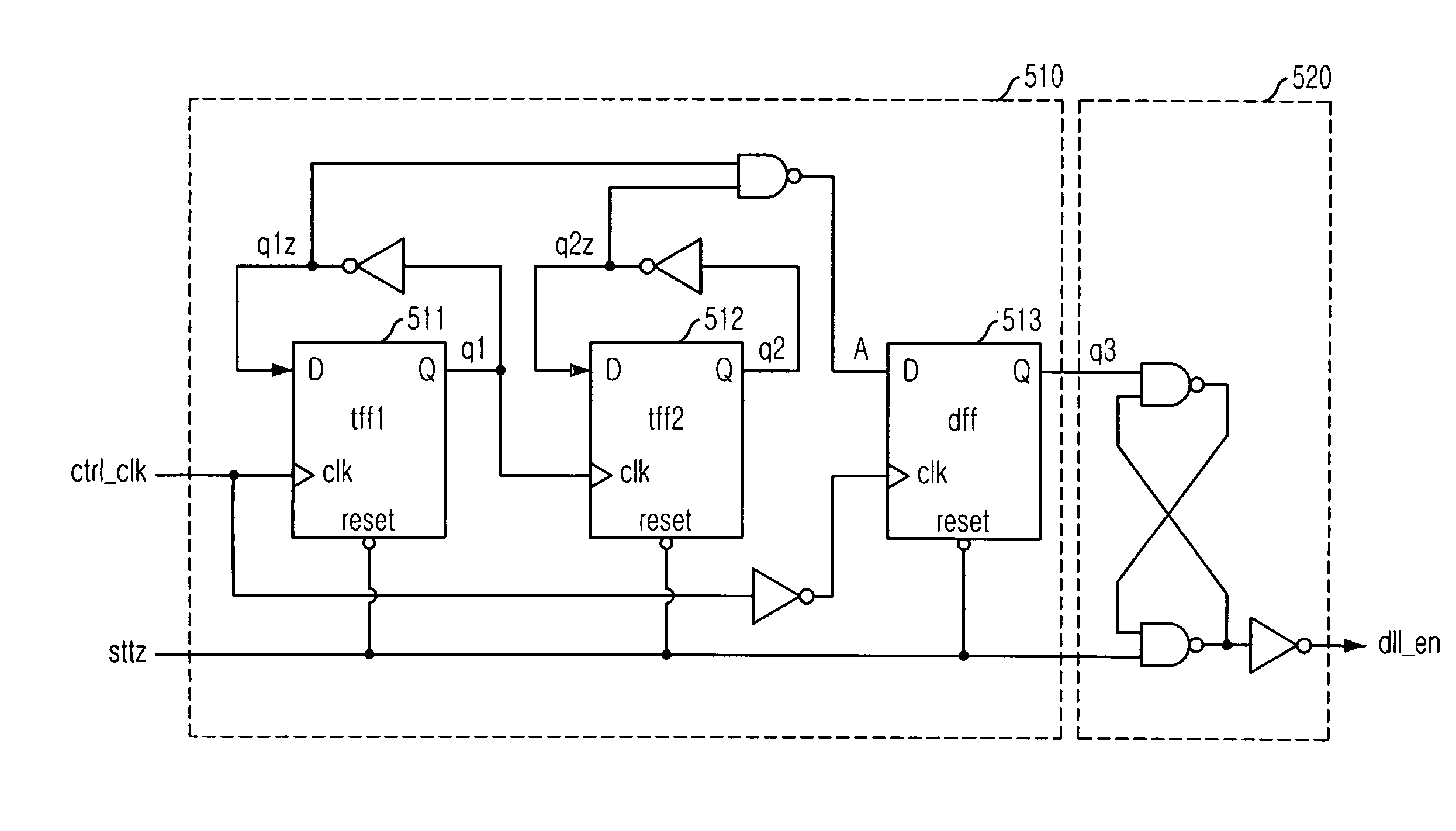

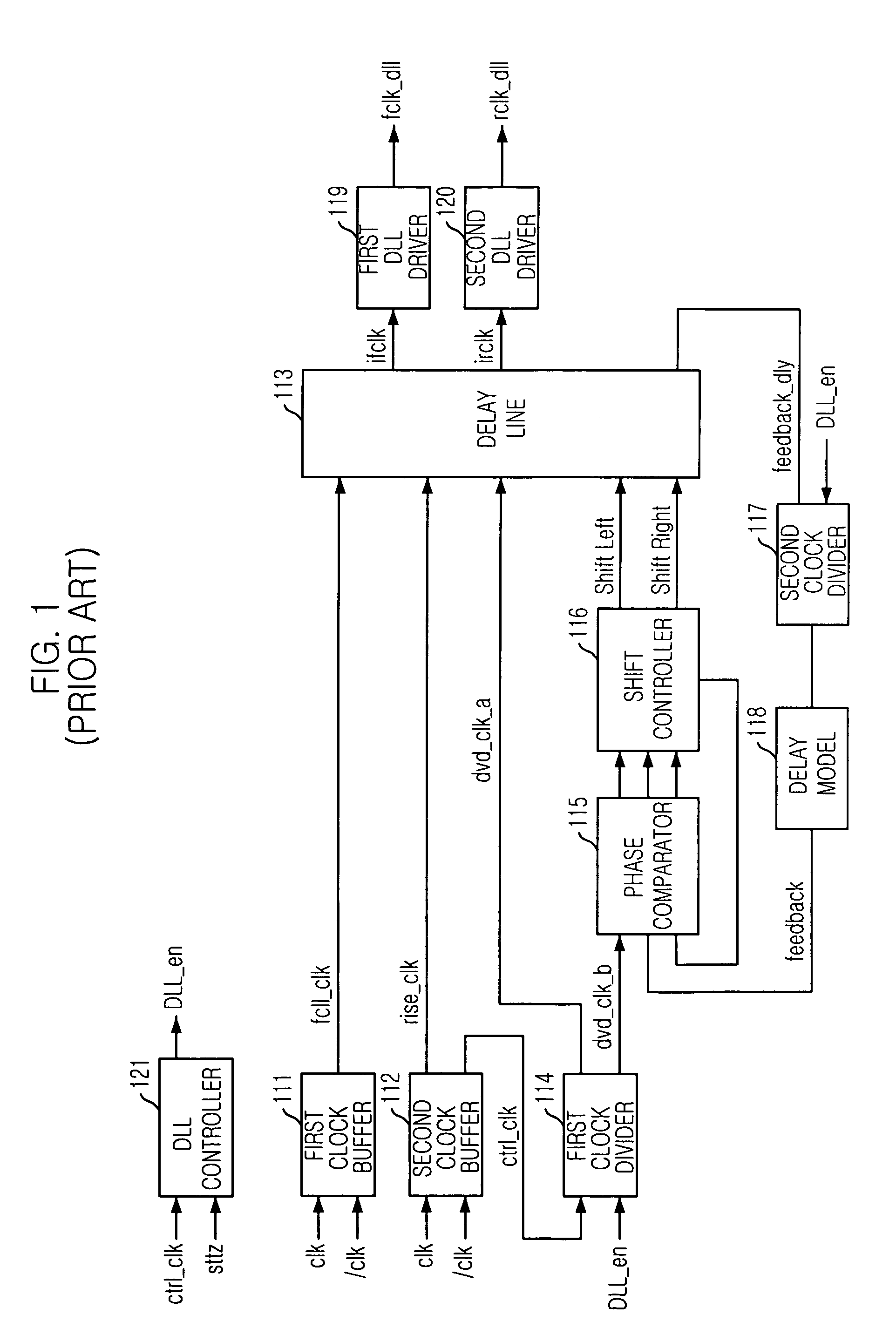

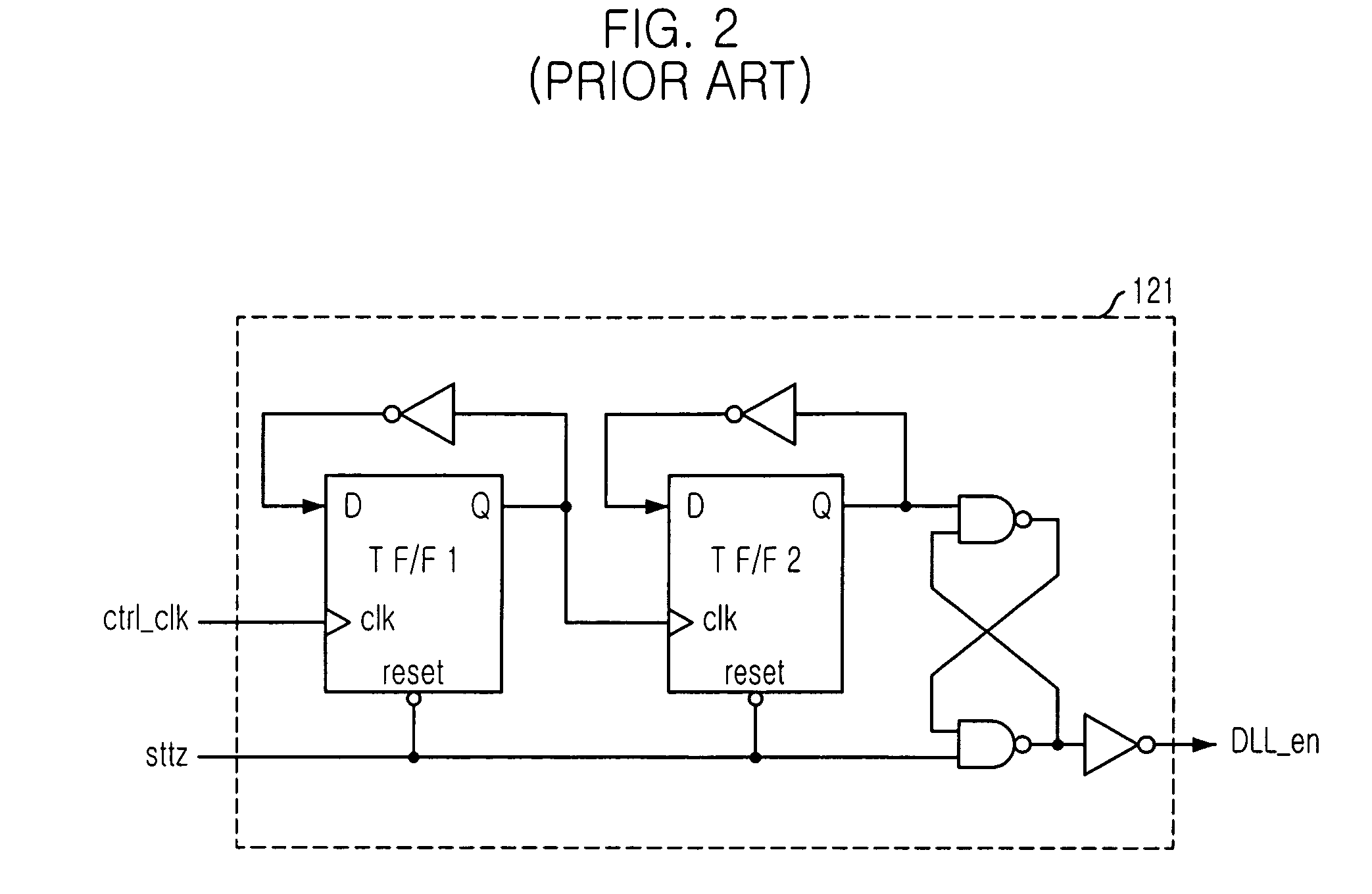

Delay locked loop in semiconductor memory device and locking method thereof

Provided is a delay locked loop (DLL) adapted for high-speed operation of a semiconductor memory device. The delay locked loop (DLL) includes: a clock buffer; a plurality of clock dividers; and a controller for activating an enable signal at a falling edge of a control clock by using a reset bar signal and a control clock outputted from the clock buffer.

Owner:SK HYNIX INC

Synchronizing circuit

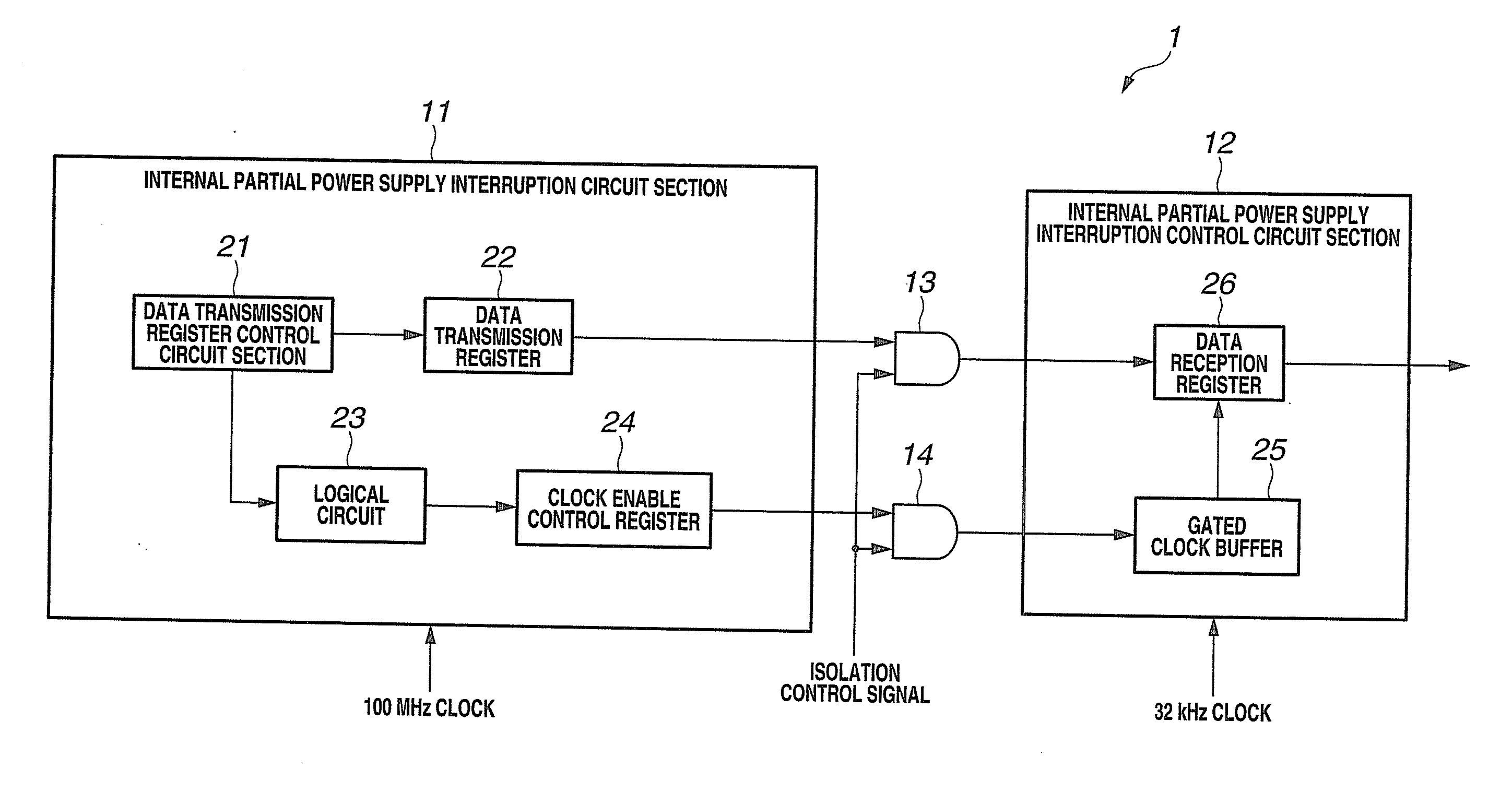

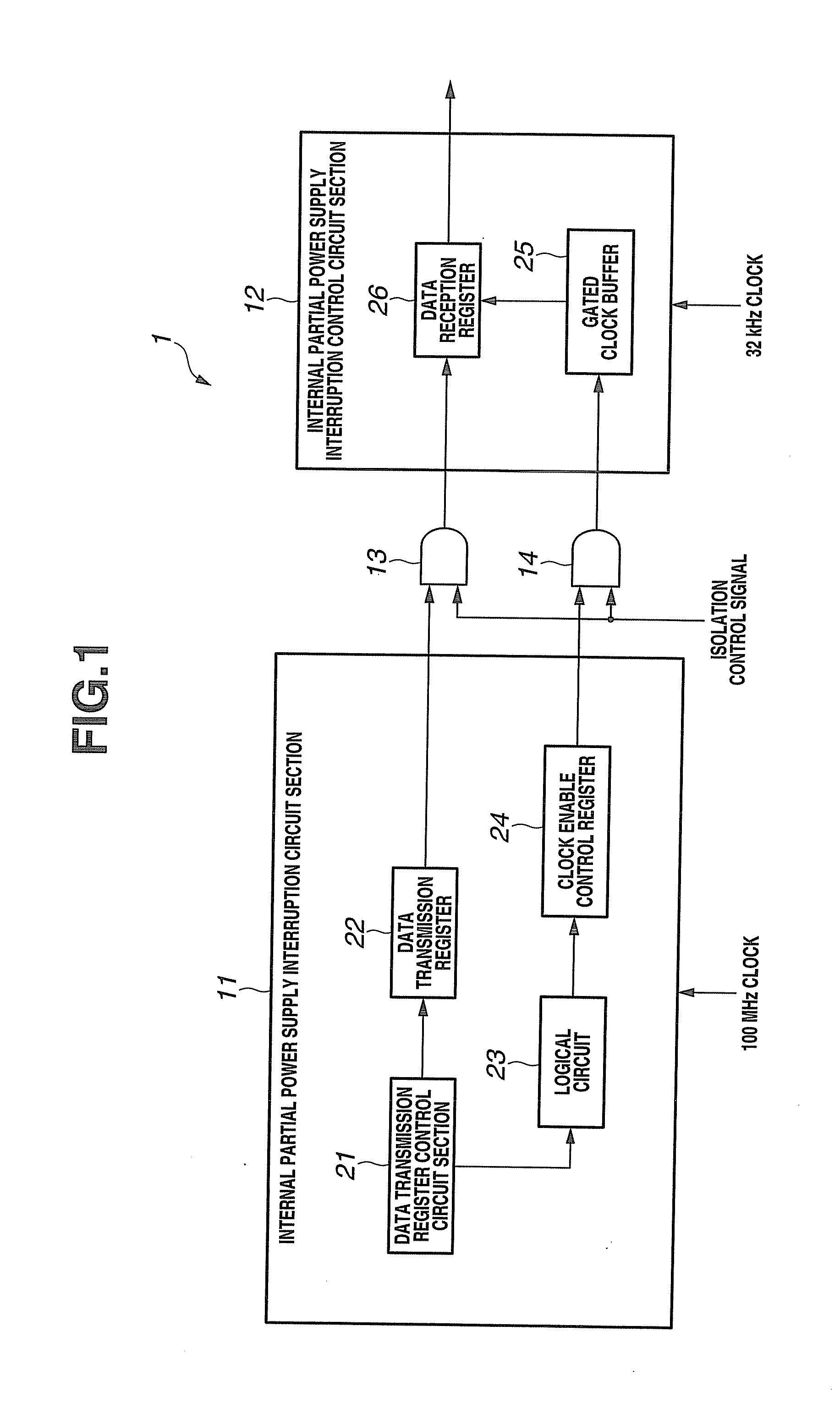

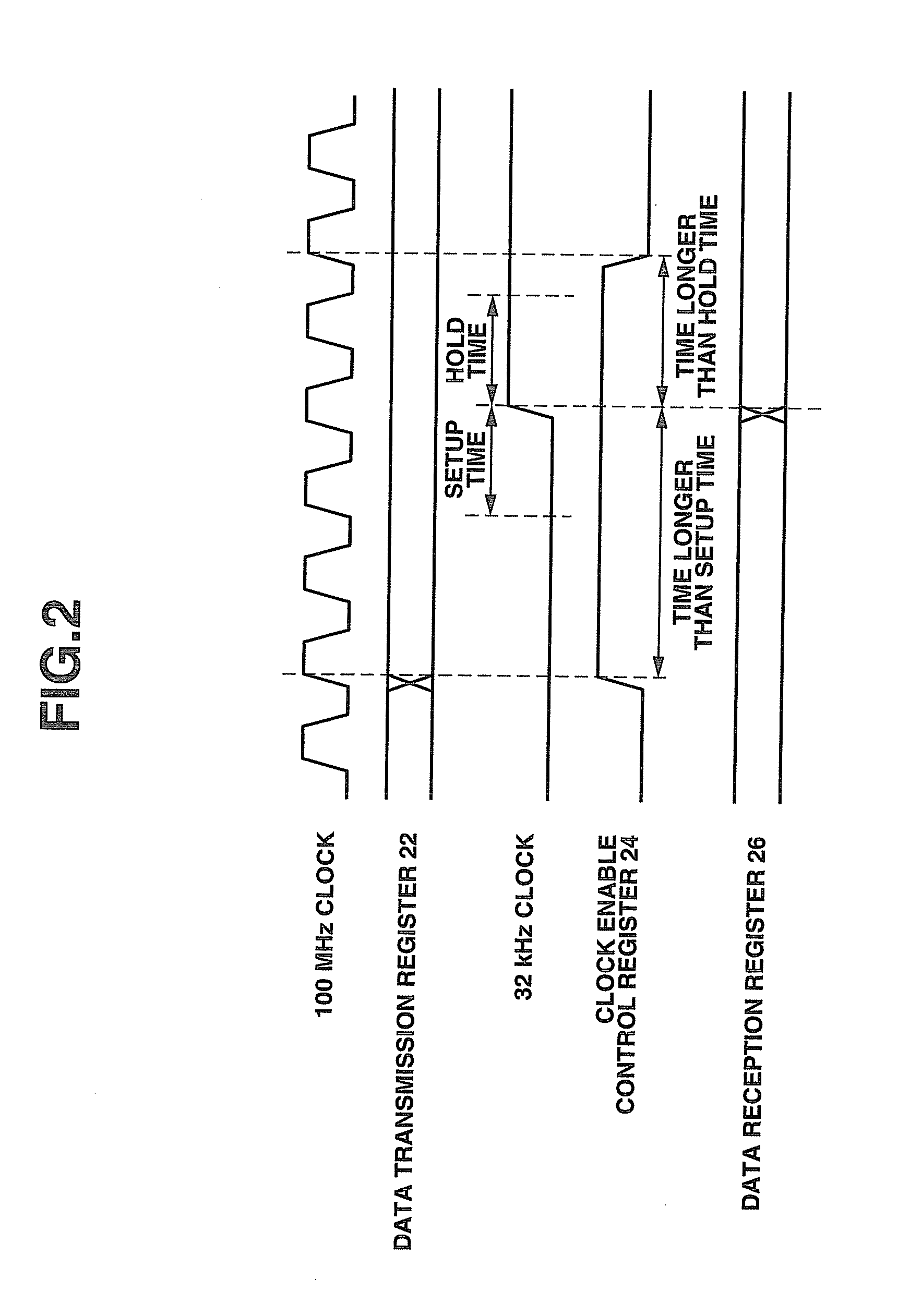

InactiveUS20100169675A1Power supply for data processingGenerating/distributing signalsProcessor registerControl signal

A synchronizing circuit includes an internal partial power supply interruption circuit section which can be subjected to a power supply interruption and includes a data transmission register configured to output data for controlling a power supply interruption and a clock enable control register configured to output an enable signal; an internal partial power supply interruption control circuit section configured to control a power supply interruption and includes a gated clock buffer configured to control a clock signal based on the enable signal, and a data reception register configured to take in data based on the controlled clock signal; and an isolation cell configured to output an output from the internal partial power supply interruption circuit section as a fixed value when the internal partial power supply interruption circuit section has been subjected to a power supply interruption.

Owner:KK TOSHIBA

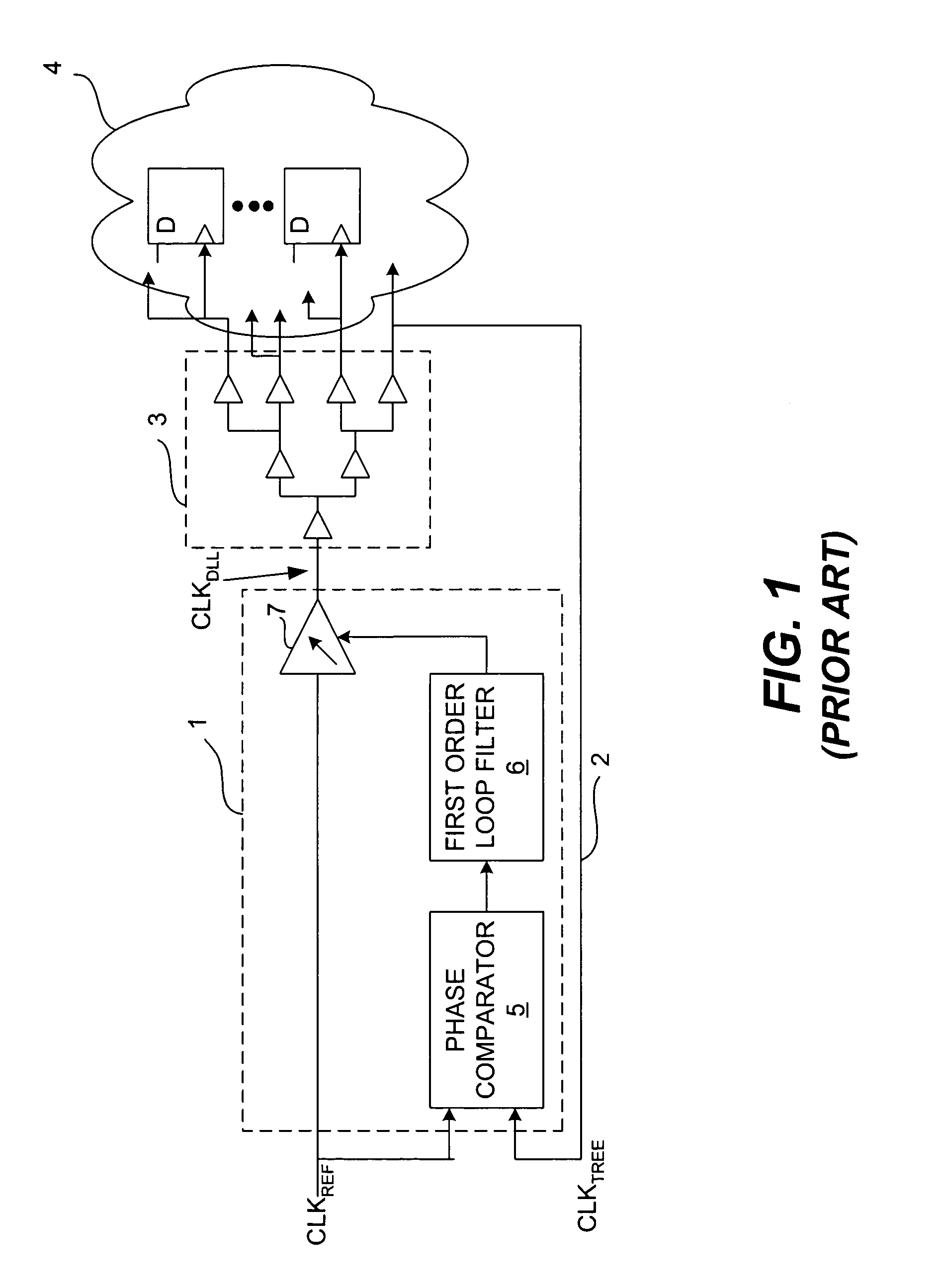

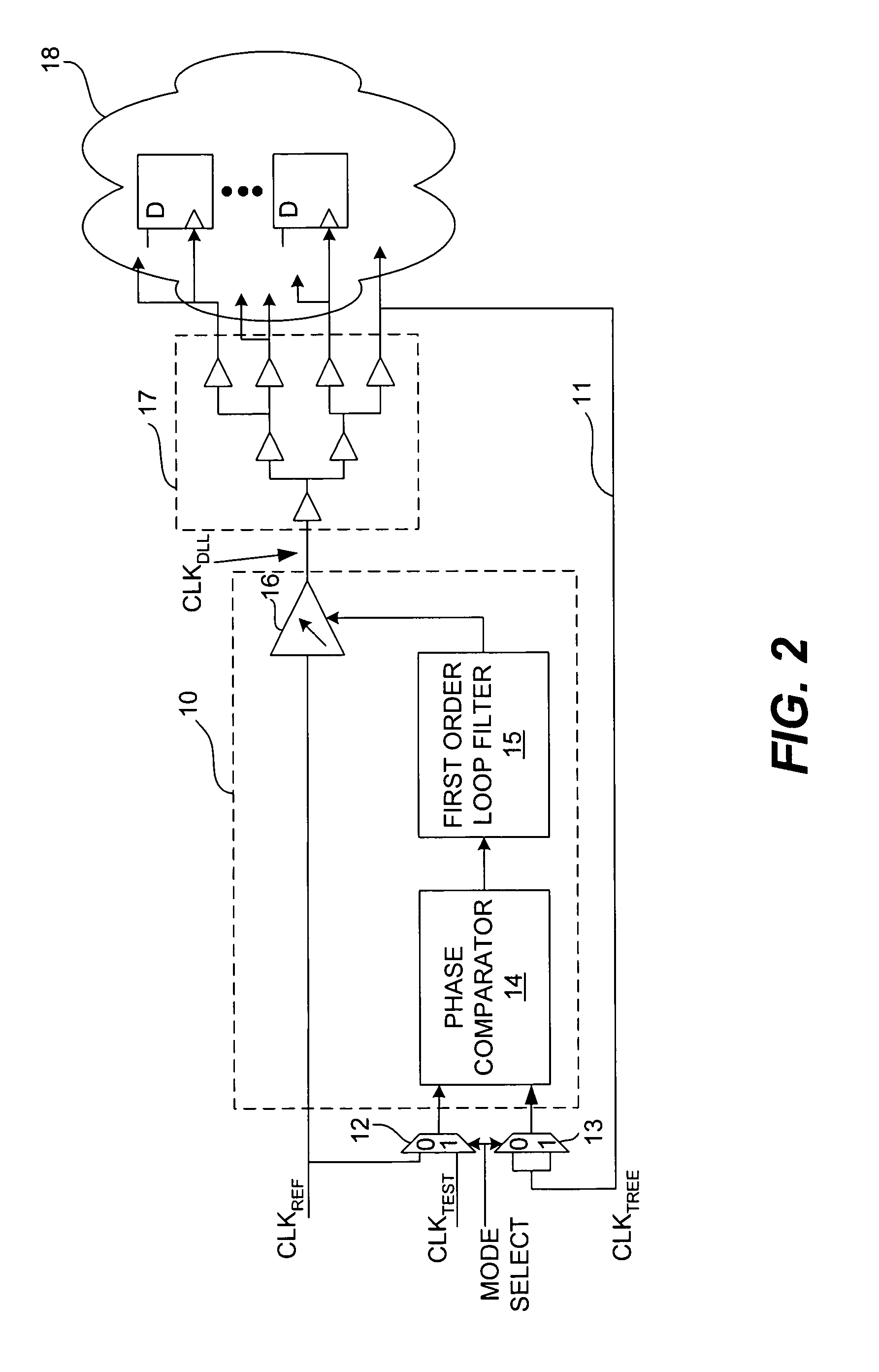

Delay-locked loop and a method of testing a delay-locked loop

ActiveUS6995554B2Offset errorPulse automatic controlElectronic circuit testingPhase differenceDelay-locked loop

A delay-locked loop (DLL) of an integrated circuit (IC) with testing circuitry and a method for testing a DLL. During test mode, a phase comparator of the DLL receives a test clock in place of the reference clock and determines the phase difference between the test clock and the dock fed back to the DLL from a clock buffer tree. A variable delay element of the DLL then shifts the reference clock in time by an amount that depends on that phase difference. The variable delay element can be exercised by varying the phase of the test clock with respect to the reference clock by a known phase offset to cause the variable delay element to produce a range of delays. Whether the variable delay element is functioning properly can be determined by checking whether the phase of the test clock is aligned with the phase of the feedback clock.

Owner:AVAGO TECH INT SALES PTE LTD

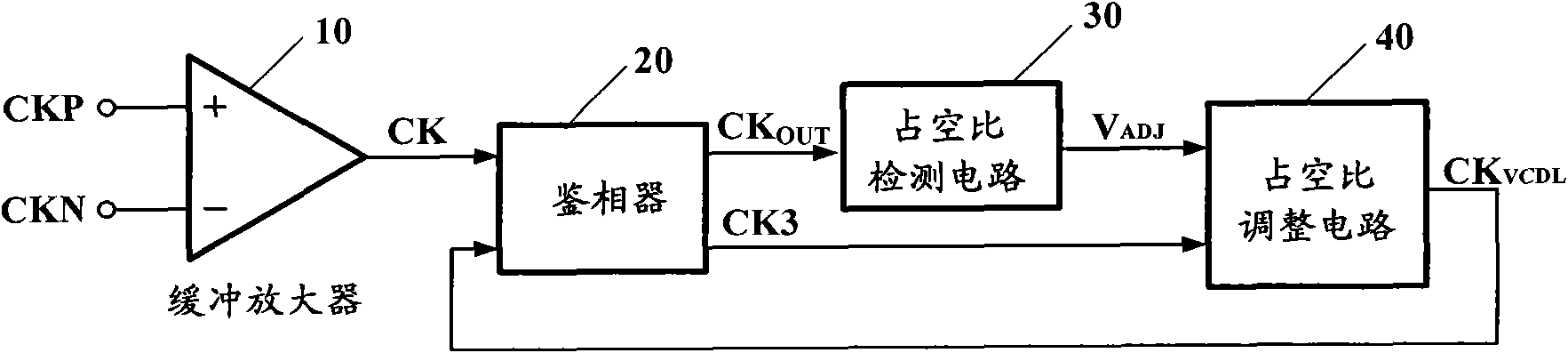

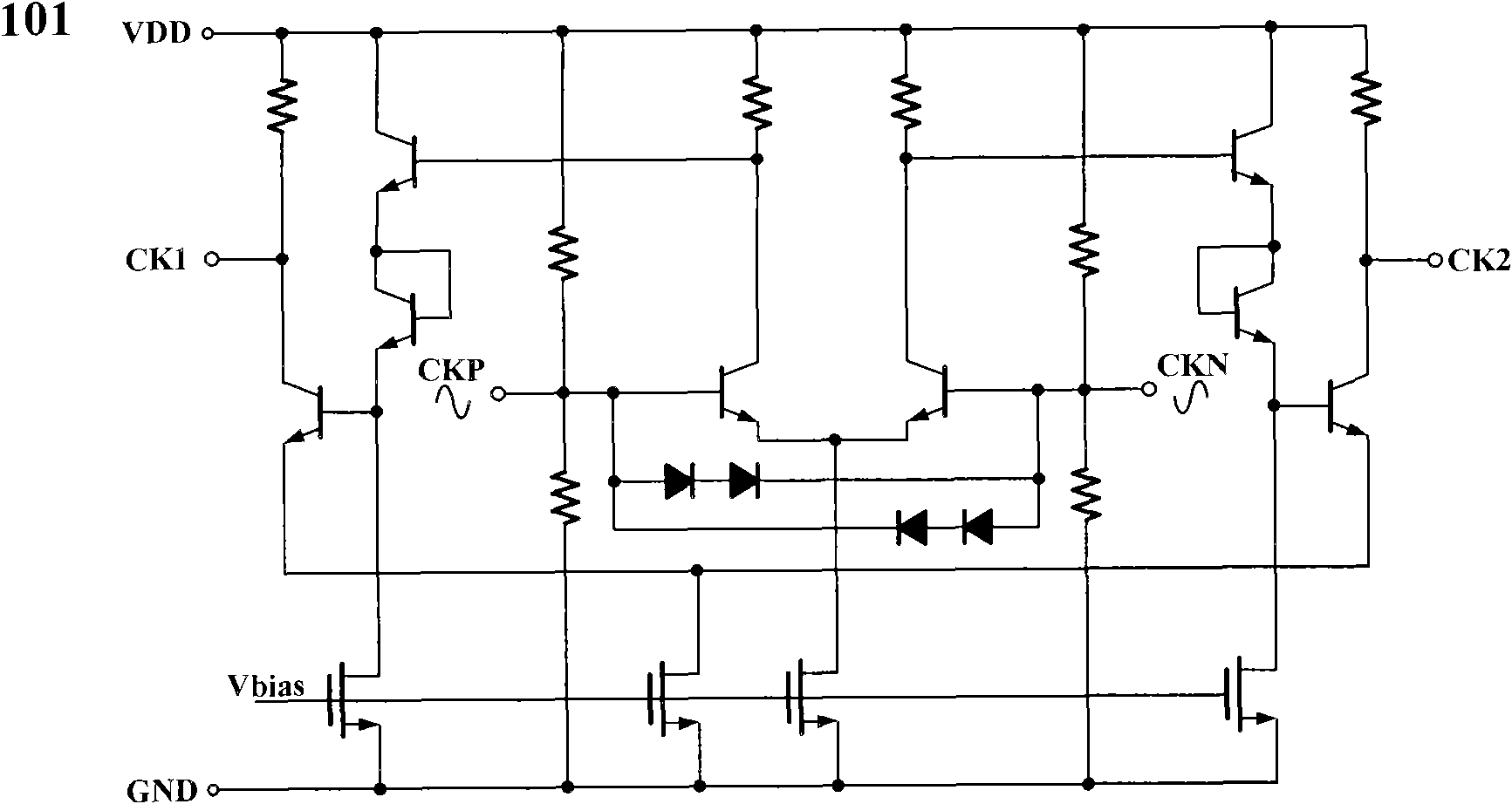

Clock adjustment circuit and adjustment method for clock circuit

InactiveCN102075167AReduce complexityFast adjustmentPulse train pattern monitoringDiscriminatorAudio power amplifier

The invention provides a clock adjustment circuit and an adjustment method for a clock circuit. The clock adjustment circuit comprises a clock buffer amplifier, a phase discriminator and a duty cycle adjustment circuit, wherein the clock buffer amplifier is used for receiving an external differential clock signal, shaping the differential clock signal into a single-end square wave clock signal and outputting the single-end square wave clock signal; the phase discriminator is used for receiving the single-end square wave clock signal from the clock buffer amplifier and a feedback signal from the duty cycle adjustment circuit, comparing the phase of the single-end square wave clock signal with the phase of the feedback signal to acquire a phase difference, and outputting the phase difference; and the duty cycle adjustment circuit is used for adjusting the duty cycle of the feedback signal by using the phase difference to acquire an adjusted feedback signal. The differential signal is shaped into the single-end square wave clock signal, the single-end square wave clock signal is compared with the feedback signal to acquire the phase difference, and the duty cycle is adjusted according to the phase difference, so that the complexity of duty cycle adjustment and hardware implementation can be effectively reduced, phase errors and the ripple waves of control voltage can be reduced, and adjustment accuracy is improved.

Owner:XIDIAN UNIV

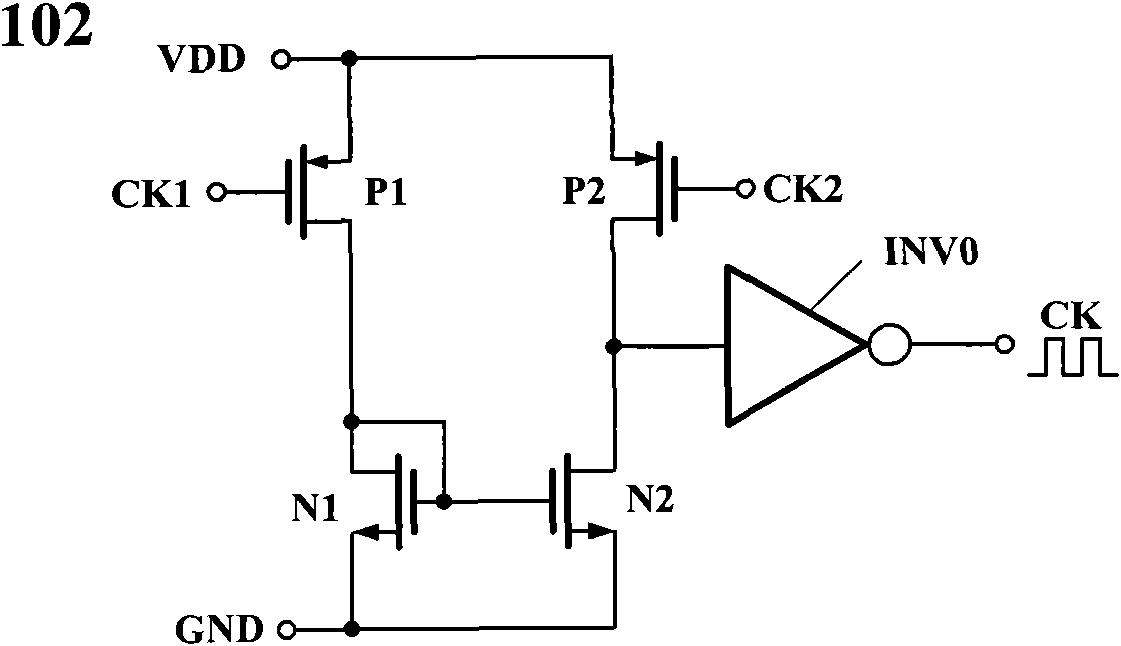

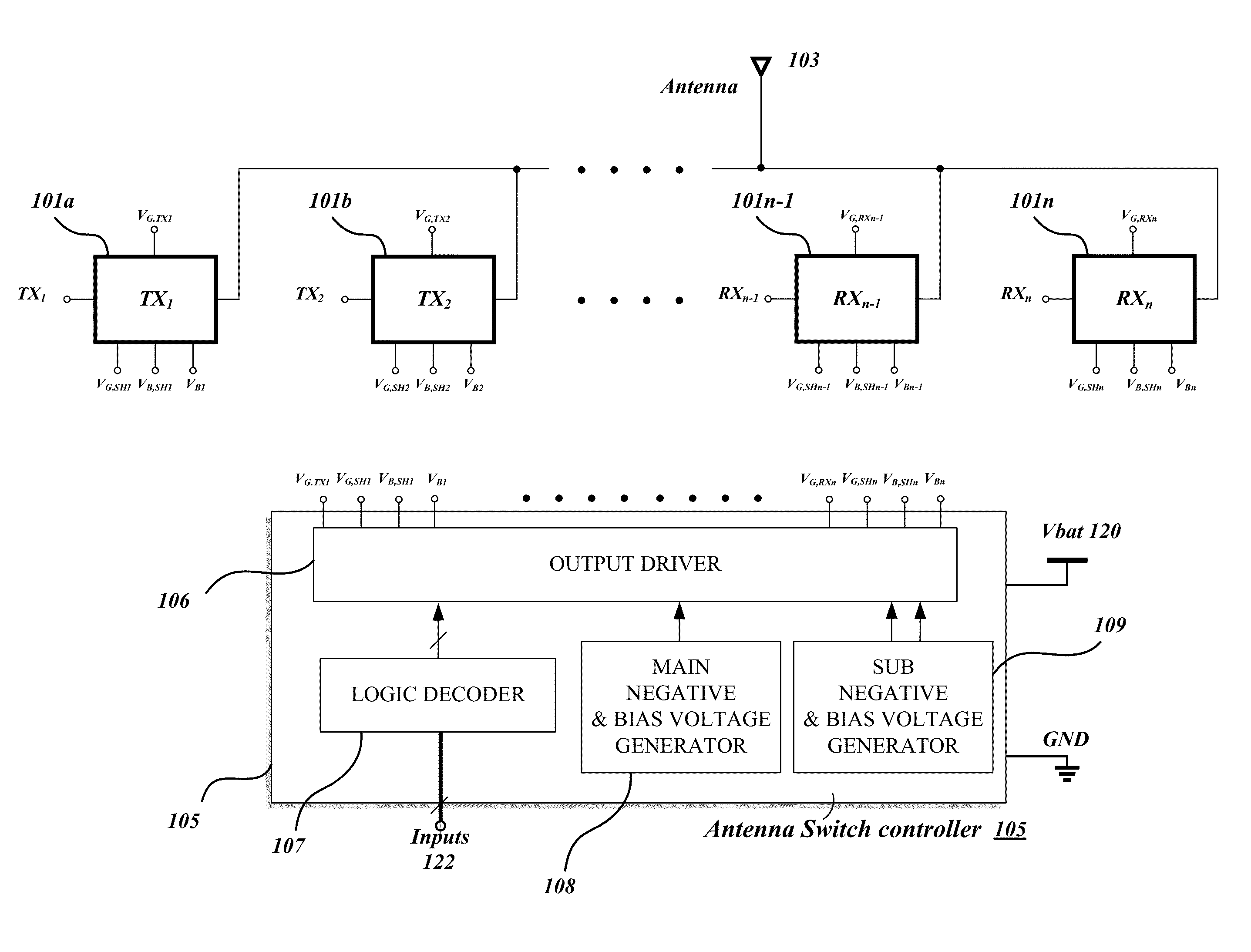

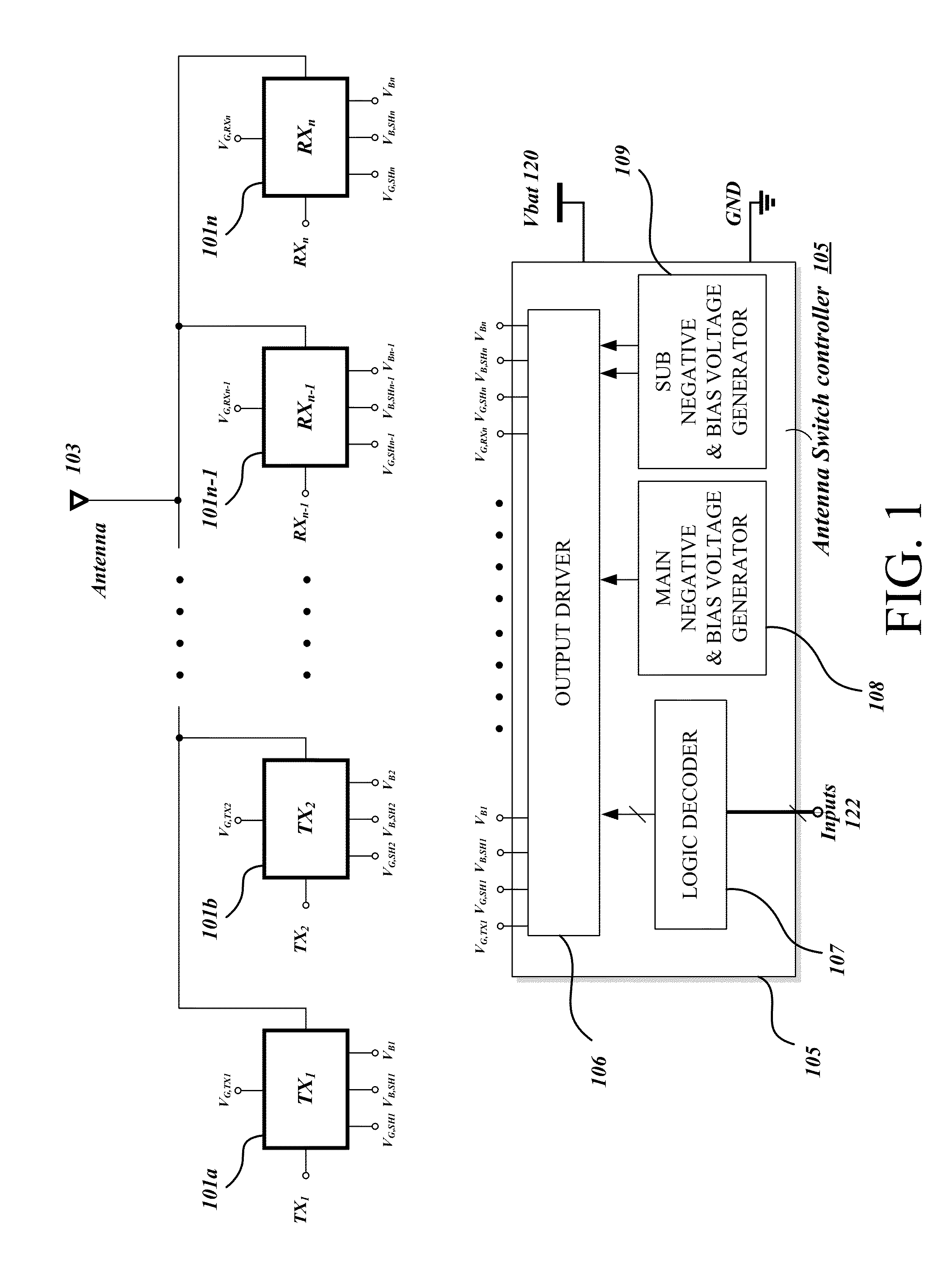

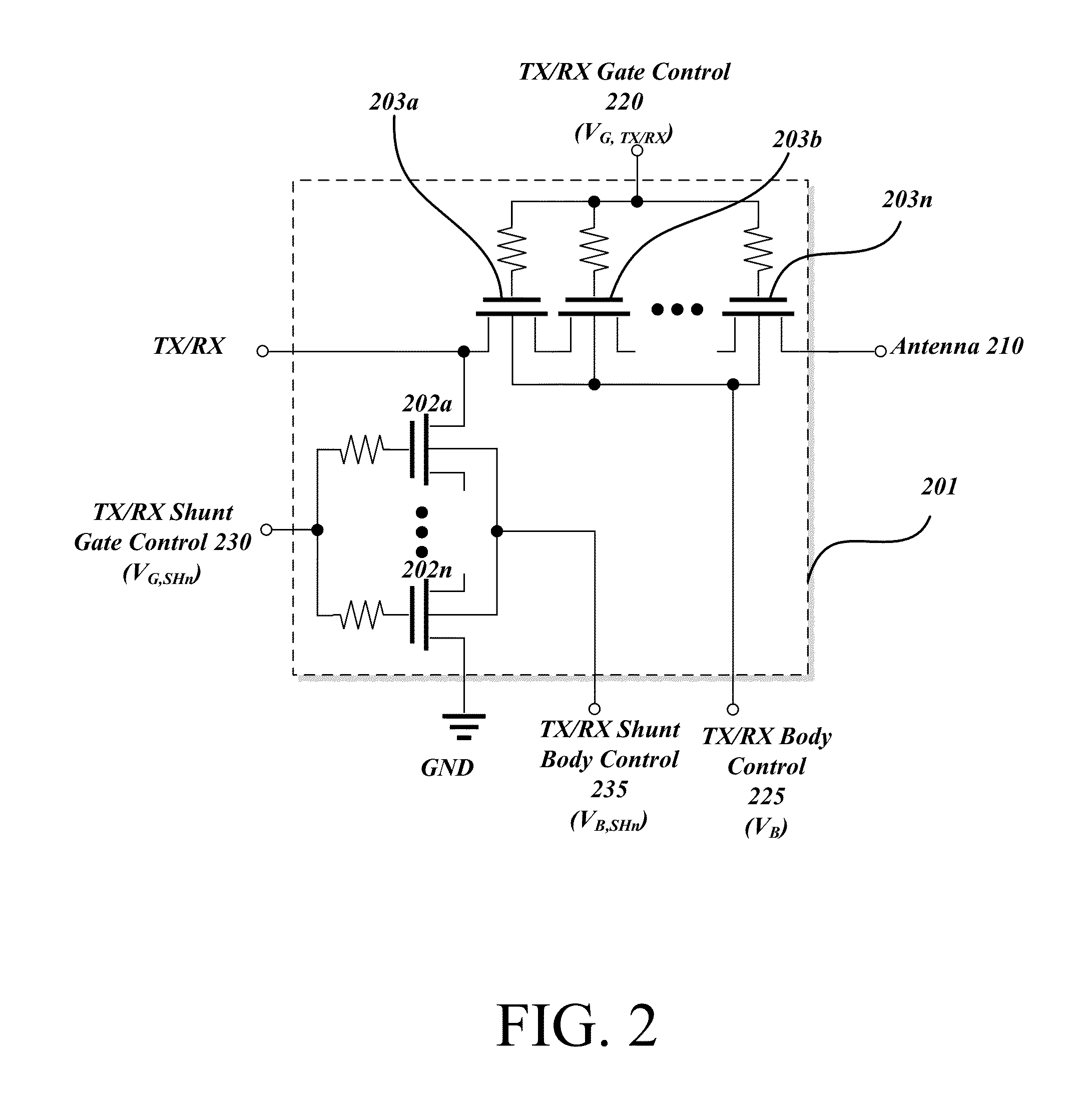

Systems, Methods, and Apparatuses for Negative-Charge-Pump-Based Antenna Switch Controllers Utilizing Battery Supplies

Systems, methods, and apparatuses may provide for antenna switch controllers. An example antenna switch controller may include: a plurality of antenna switches commonly connected to one or more antennas, where each of the plurality of antenna switches includes a plurality of stacked transistors, where one of the plurality of antenna switches is enabled when transmitting or receiving one or more radio frequency (RF) signals via the one or more antennas; a voltage generator that receives an external supply voltage from a battery, where the voltage generator generates an internal supply voltage, where the internal supply voltage remains constant despite fluctuations in the external supply voltage from the battery; a clock buffer that generates clock signals from the constant internal supply voltage; and a charge pump that receives the clock signals and generates a constant negative voltage, where the constant negative voltage is for biasing of one or more of the plurality of antenna switches that are disabled.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Clock control circuit and method

InactiveUS20030200518A1Generate accuratelyPulse automatic controlSingle output arrangementsPhase differenceComparators circuits

Owner:RENESAS ELECTRONICS CORP

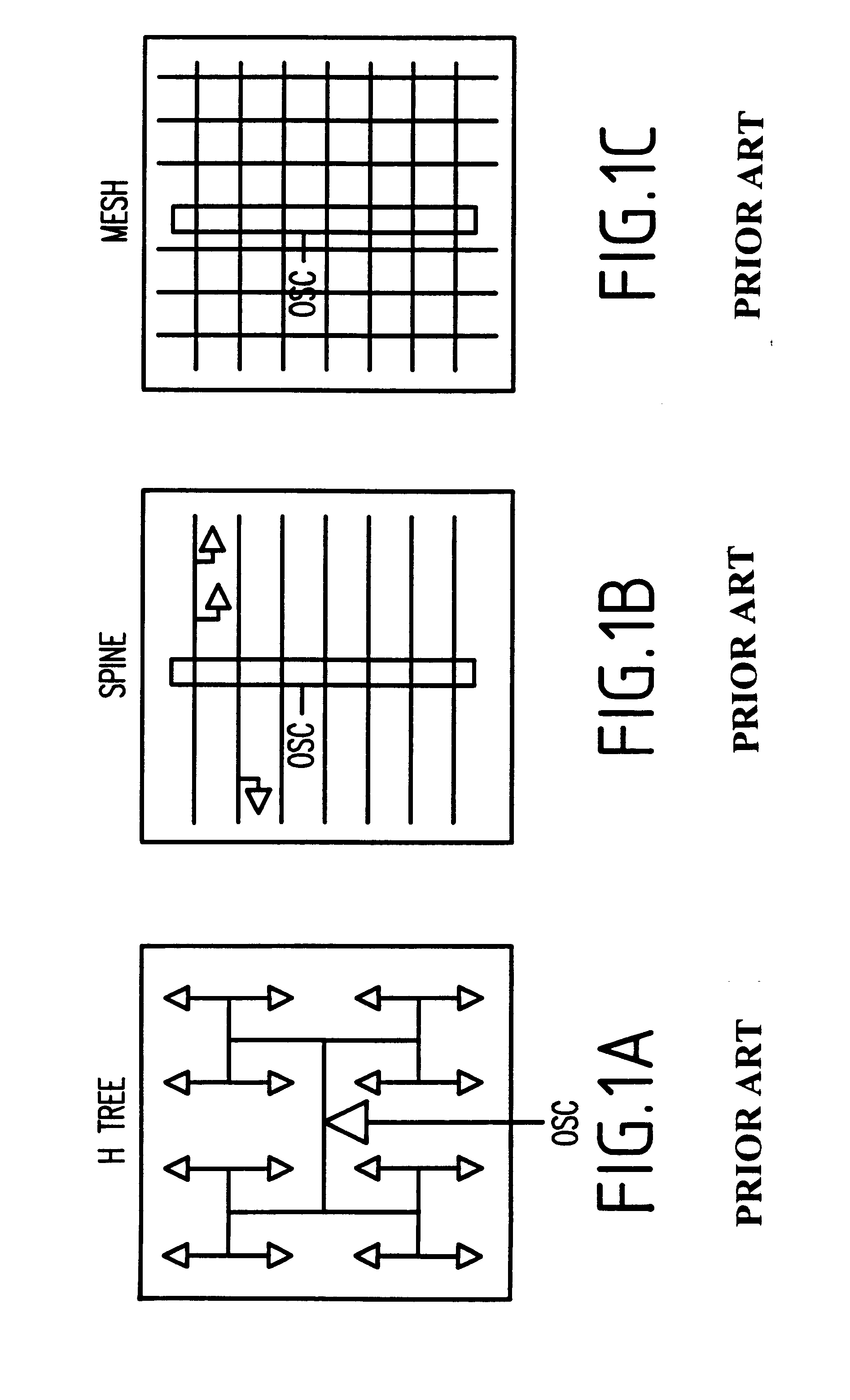

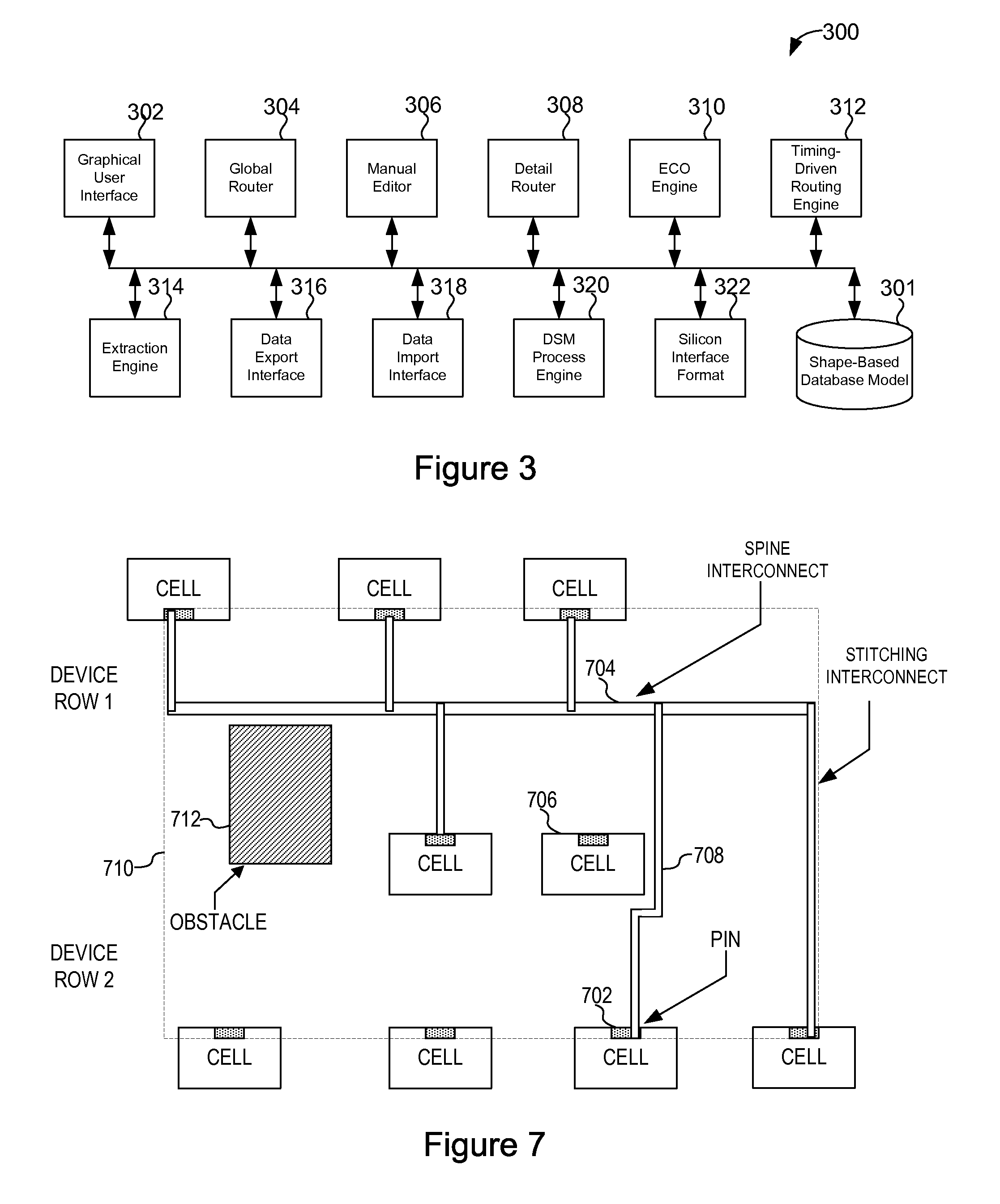

Clock tree generation and routing

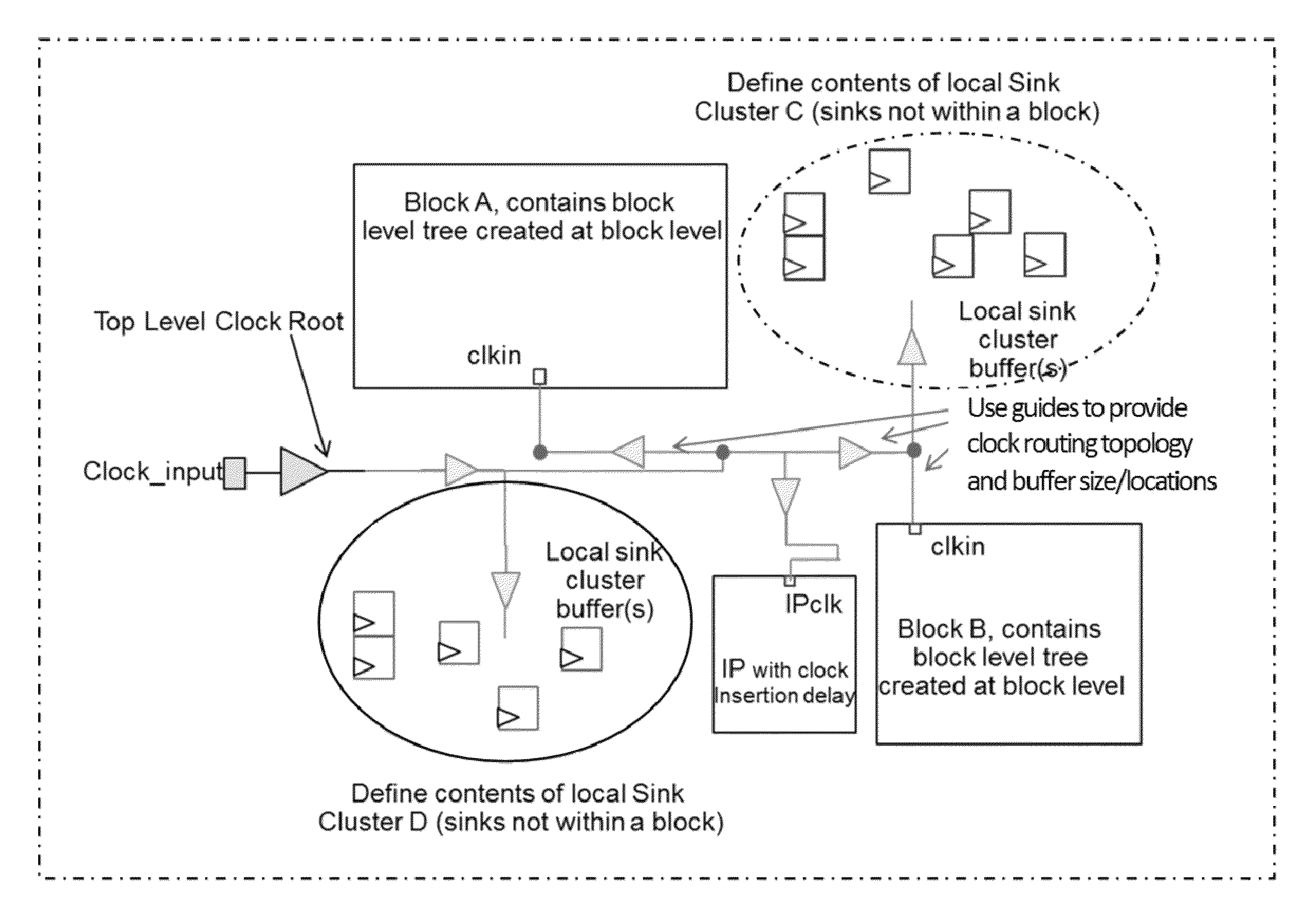

ActiveUS8966425B1Ample structureAmple controlComputer aided designSpecial data processing applicationsClock treeMajorization minimization

A technique generates small scale clock trees using a spine-based architecture (using spine routing) while also using clustered placement. Techniques are used to control clock sink cluster contents in order to minimize clock skew, minimize clock buffer count, and minimize use of routing resources. This approach also provides the user with ample structure and control to customize small efficient clock trees, and can also reduce clock power consumption.

Owner:PULSIC

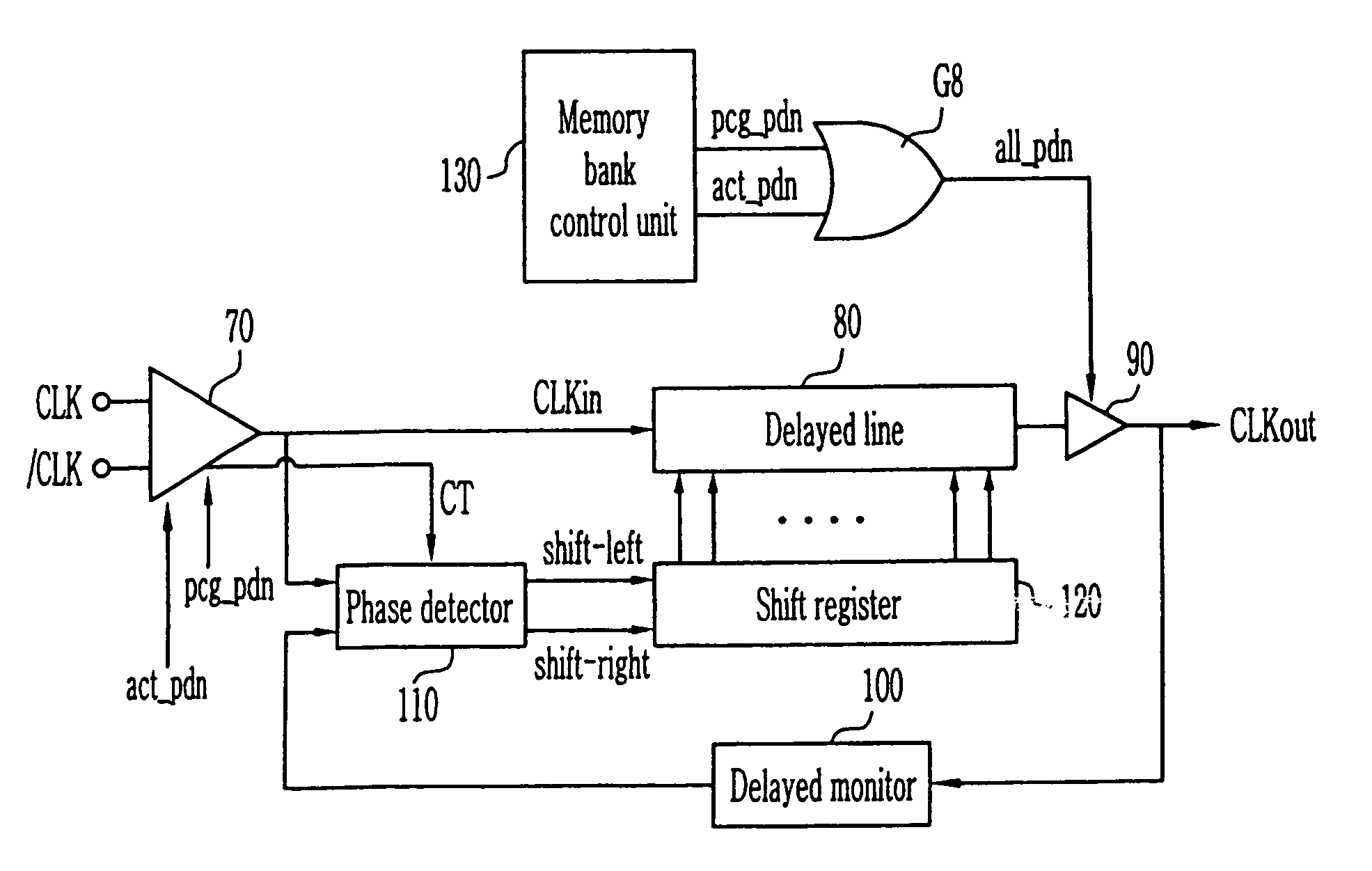

Delayed locked loops and methods of driving the same

InactiveUS7046061B2Reduce power consumptionPulse automatic controlDigital storagePhase detectorShift register

Disclosed are a delay locked loop (DLL) and a method of driving the same. The delay locked loop includes a clock buffer for buffering an inputted external clock to generate an internal clock, the clock buffer generating a control signal for disabling the internal clock depending on whether the power is down, a delayed line for delaying the internal clock, a clock driver for buffering the output of the delayed line to generate a clock signal, the clock driver disabling the clock signal depending on whether the power is down, a delay monitor for delaying the external clock, a phase detector for detecting the difference in a phase between the internal clock and the output of the delayed monitor to generate a detected signal, the phase detector being disabled according to the control signal, and a shift register for controlling the delayed line according to the detected signal from the phase detector. Therefore, it is possible to sufficiently satisfy power down excitation time while reducing current consumption of the entire semiconductor device during the power down state.

Owner:SK HYNIX INC