Patents

Literature

432results about How to "Accurate recovery" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

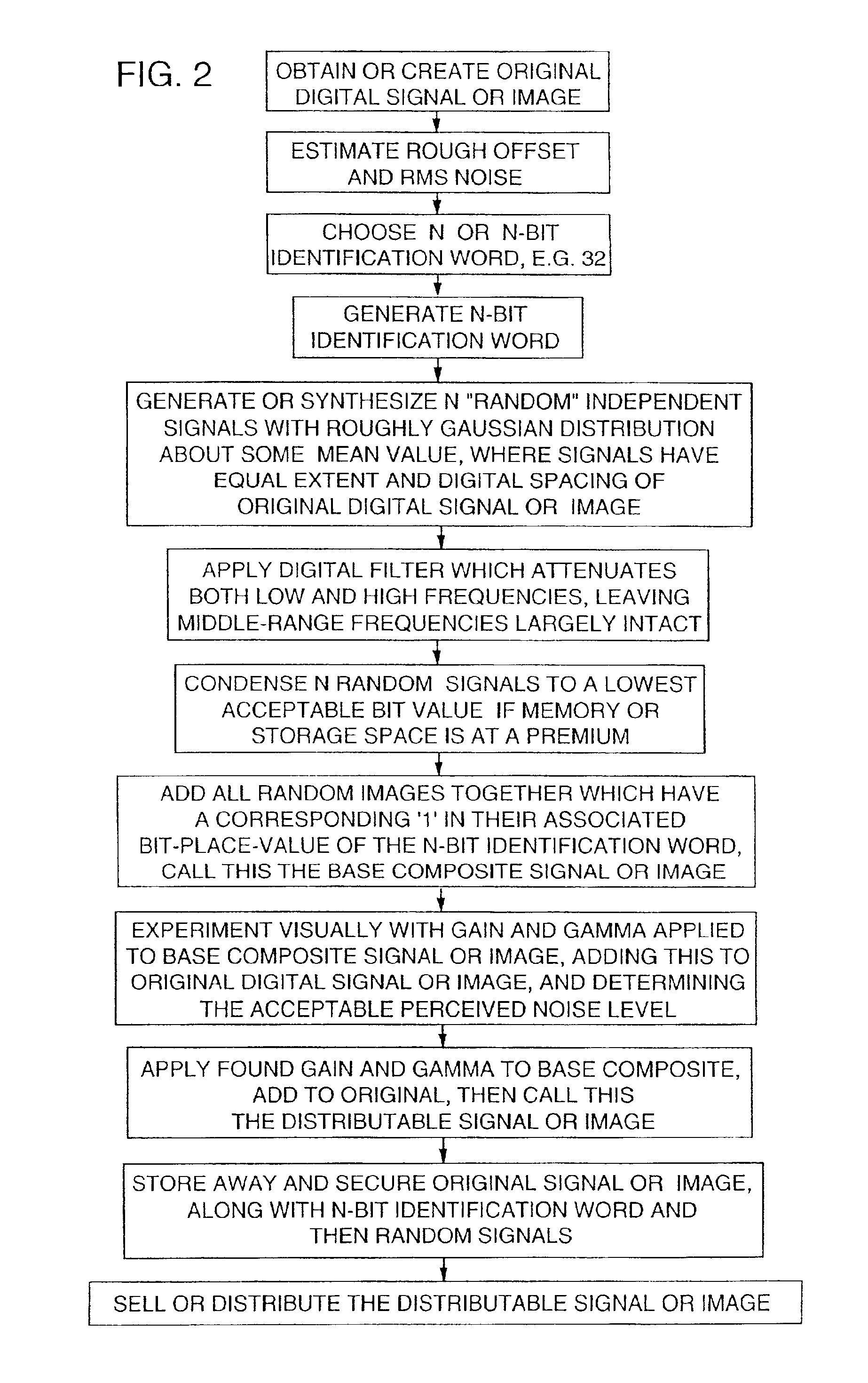

Steganographic encoding and decoding of auxiliary codes in media signals

InactiveUS20060062386A1Accurate recoveryTelevision system detailsPaper-money testing devicesVIT signalsAudio signal

Owner:DIGIMARC CORP

Steganographic encoding and decoding of auxiliary codes in media signals

InactiveUS6944298B1Accurate recoveryTelevision system detailsData representation error detection/correctionAudio frequencyAudio signal

One aspect of the invention is a method of decoding an auxiliary code embedded in an audio signal. The method performs a statistical decoding of a multibit auxiliary code embedded in an audio signal. The auxiliary code has been repetitively embedded in the audio signal. The method decodes code values of the auxiliary code from two or more different portions of the audio signal, each having the multibit auxiliary code. It then uses the code values decoded from two or more different portions to determine statistically the code values of the auxiliary code. Another aspect of the invention is another method of decoding an auxiliary code embedded in an audio signal. The method receives an audio signal suspected of being embedded with an auxiliary code. It evaluates a statistical feature of a portion of the audio signal to decode code values of the auxiliary code from the audio signal. It then determines a code value in the auxiliary code based on the statistical feature. The statistical feature may comprise, for example, the power of the audio signal. The statistical feature may be analyzed over different portions of the audio signal to decode two or more values of the auxiliary code.

Owner:DIGIMARC CORP

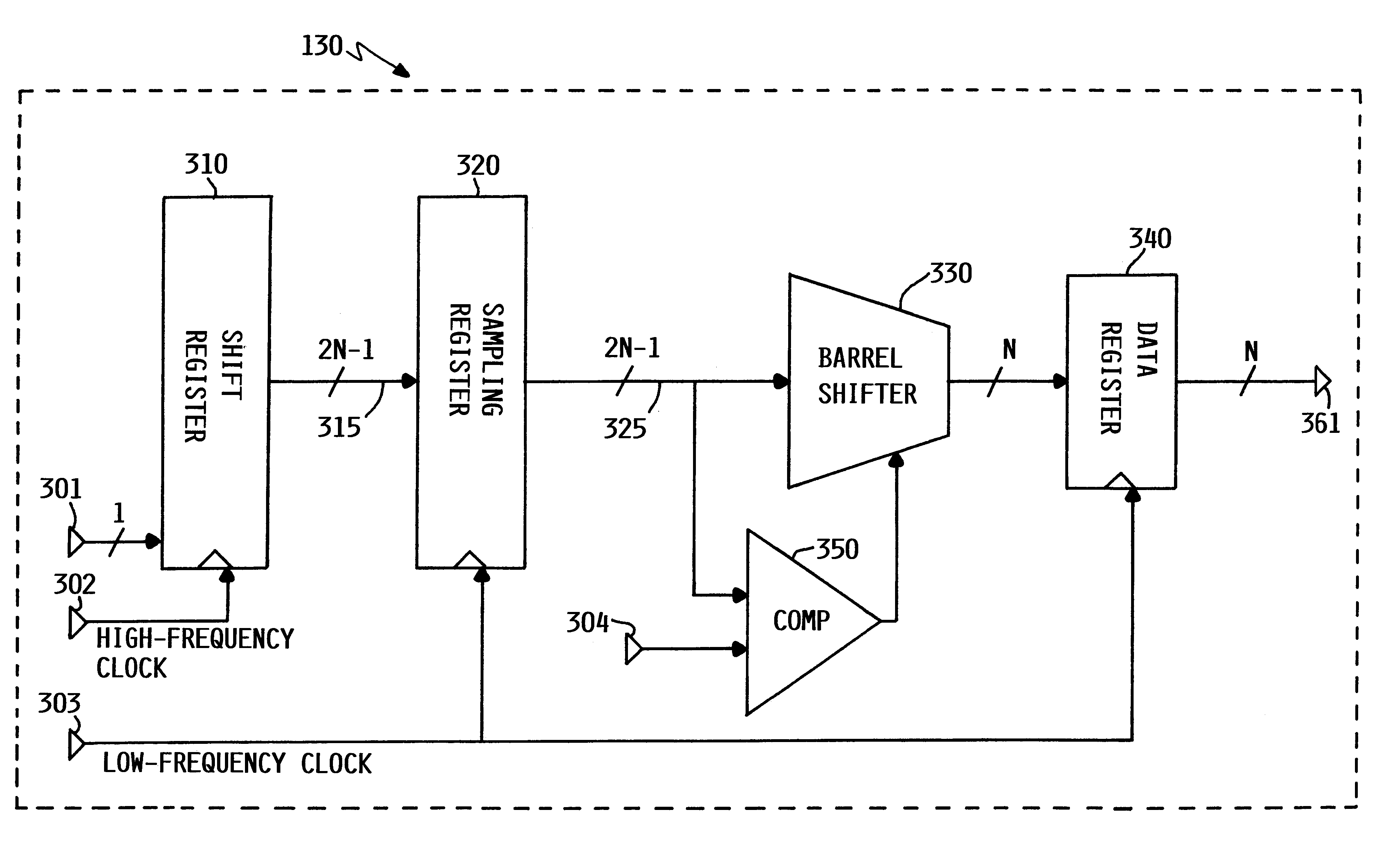

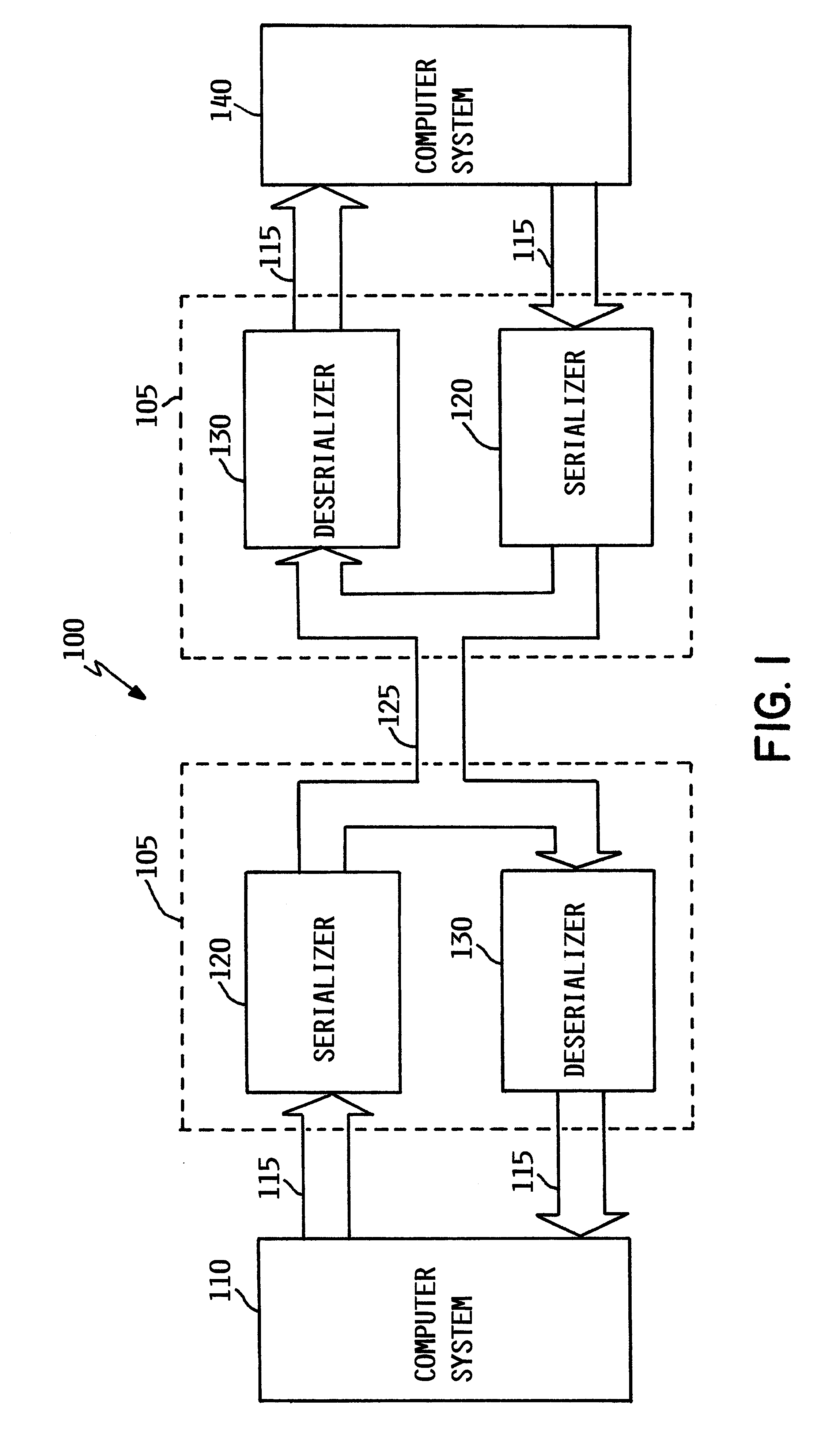

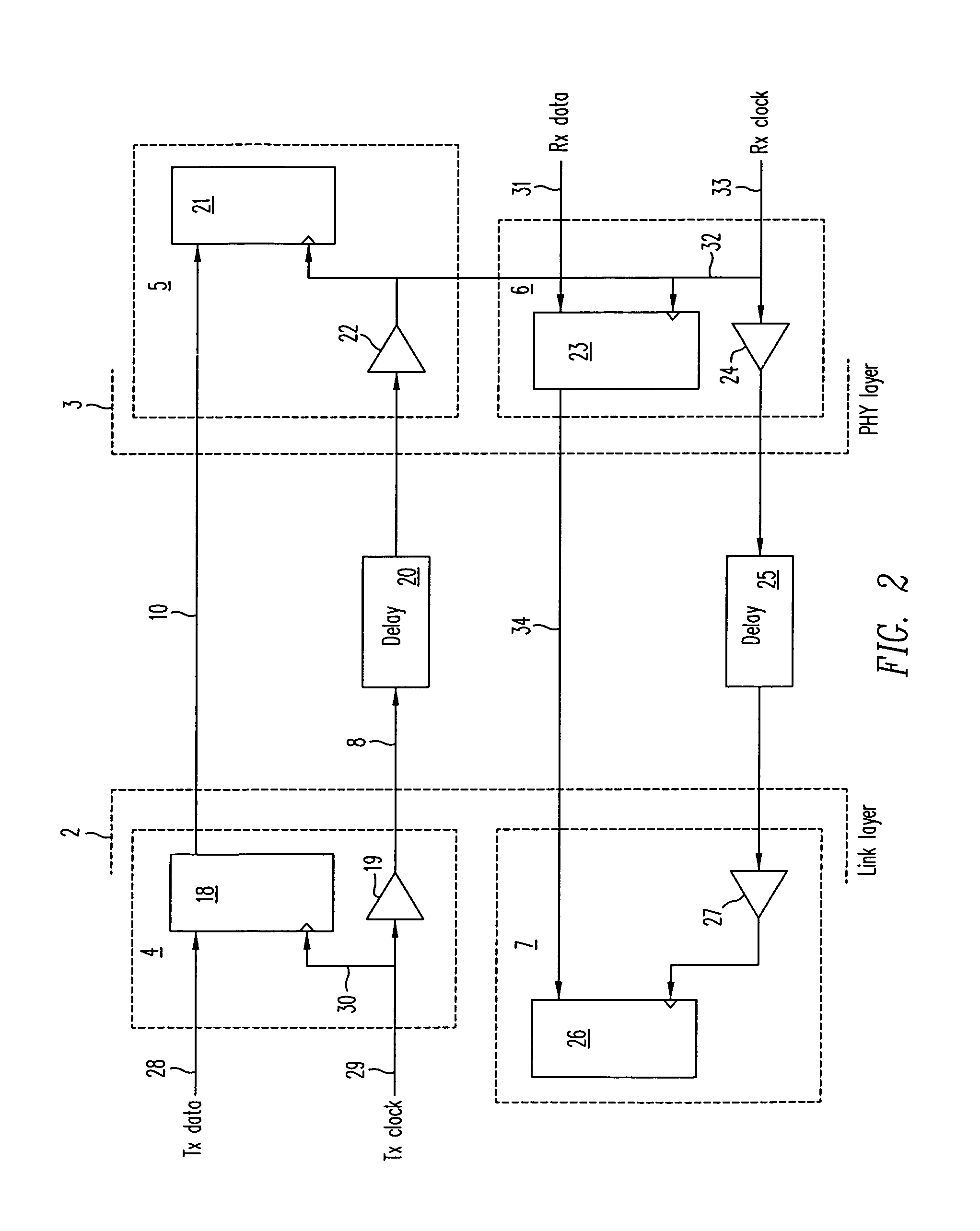

Apparatus and method for optimized self-synchronizing serializer/deserializer/framer

InactiveUS6459393B1Negatively impact design timeNegatively integrated circuit clock loadingParallel/series conversionViruses/bacteriophagesSerial transferTelecommunications link

An apparatus and method for improving the communication capabilities of computer systems is disclosed. The most preferred embodiments of the present invention use a series of data buffers and data registers to process an incoming high speed data signal. By using the buffers and registers, the incoming signal can be reformatted and manipulated at a much lower frequency than the original transmission frequency. The deserializer of the present invention also samples a greater portion of the incoming data signal than usual to further increase reliability. These various features of the invention provide for a more stable and reliable communication link and will also provide a less expensive solution for serialization / deserialization. The present invention includes a serializer that receives parallel data input from a computer and serializes the data for transmission over a high-speed serial communication link. On the receiving end, the present invention provides a deserializer that can quickly and efficiently transform the serial data back into parallel form for use within the computer system on the receiving end. By utilizing two related clock signals, one clock signal being an integer multiple of the other, a self-synchronizing serializer / deserializer can be created. In addition, by increasing the size of the data sample on the receiving end, the comparisons necessary to retrieve a parallel signal from a serial transmission can occur at a much lower frequency than the frequency of the serial transmission. In the most preferred embodiment, the invention is provided as a integrated solution manufactured on a Peripheral Component Interconnect (PCI) card, thereby allowing the present invention to be easy installed into existing computer systems.

Owner:MEDIATEK INC

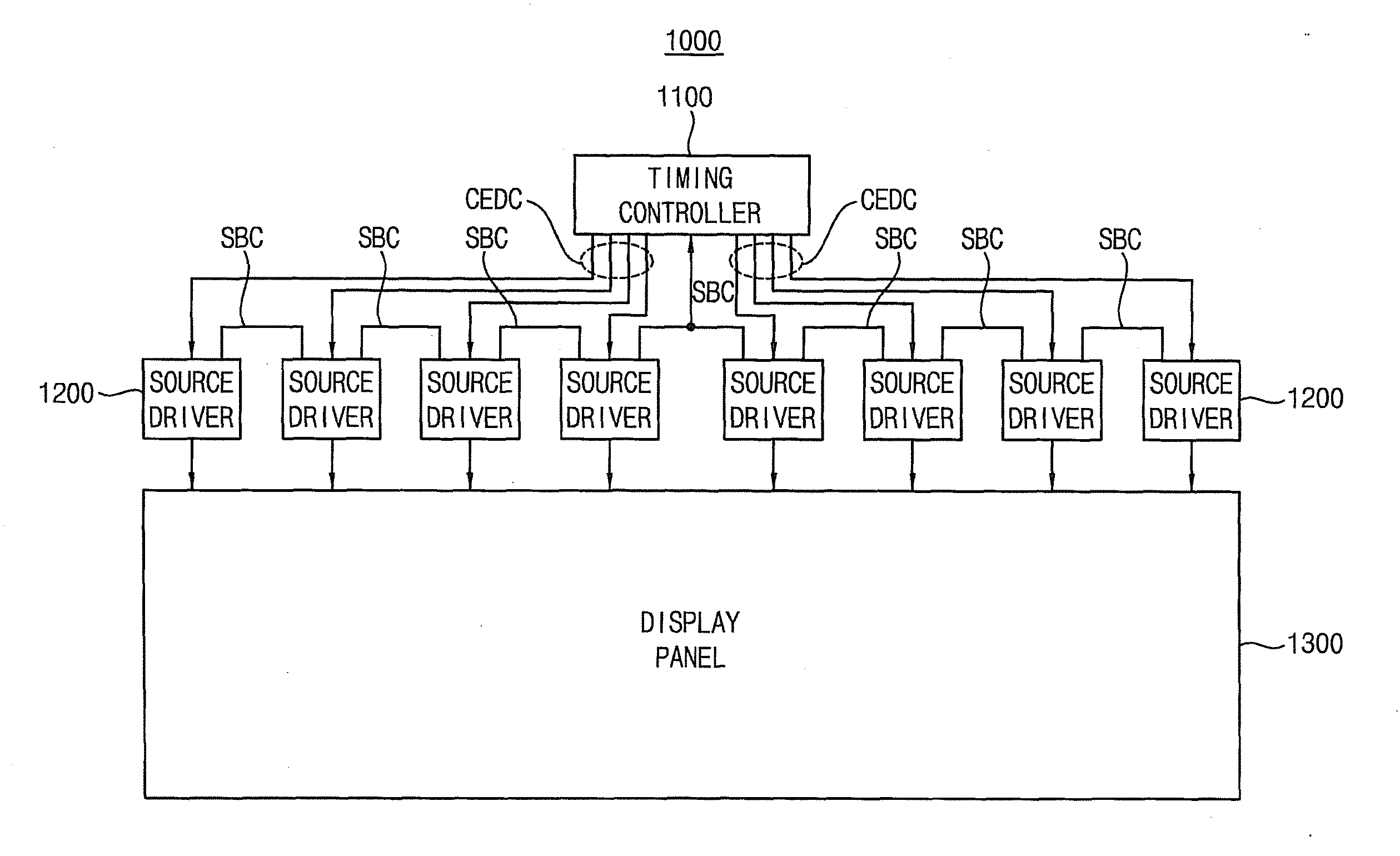

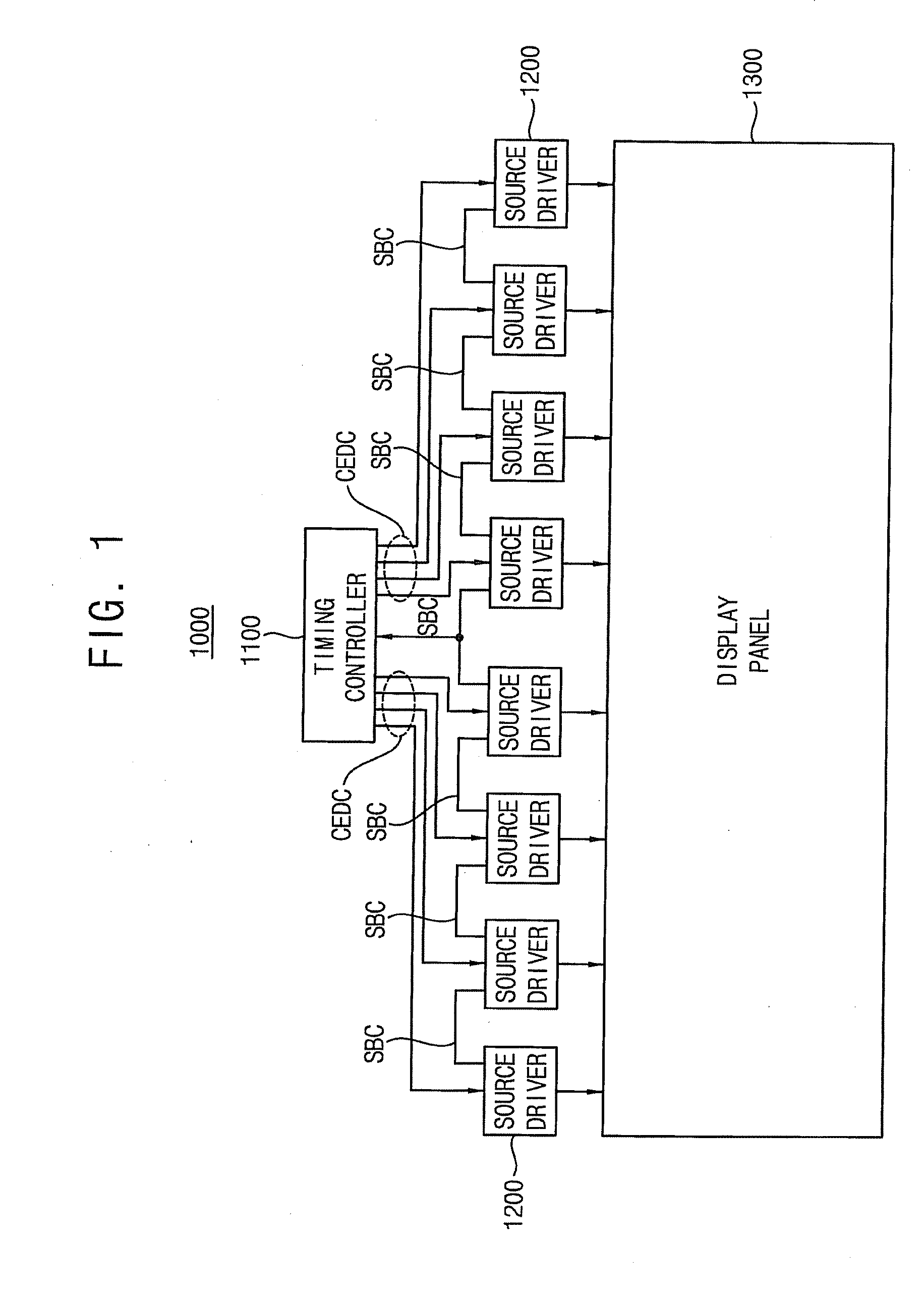

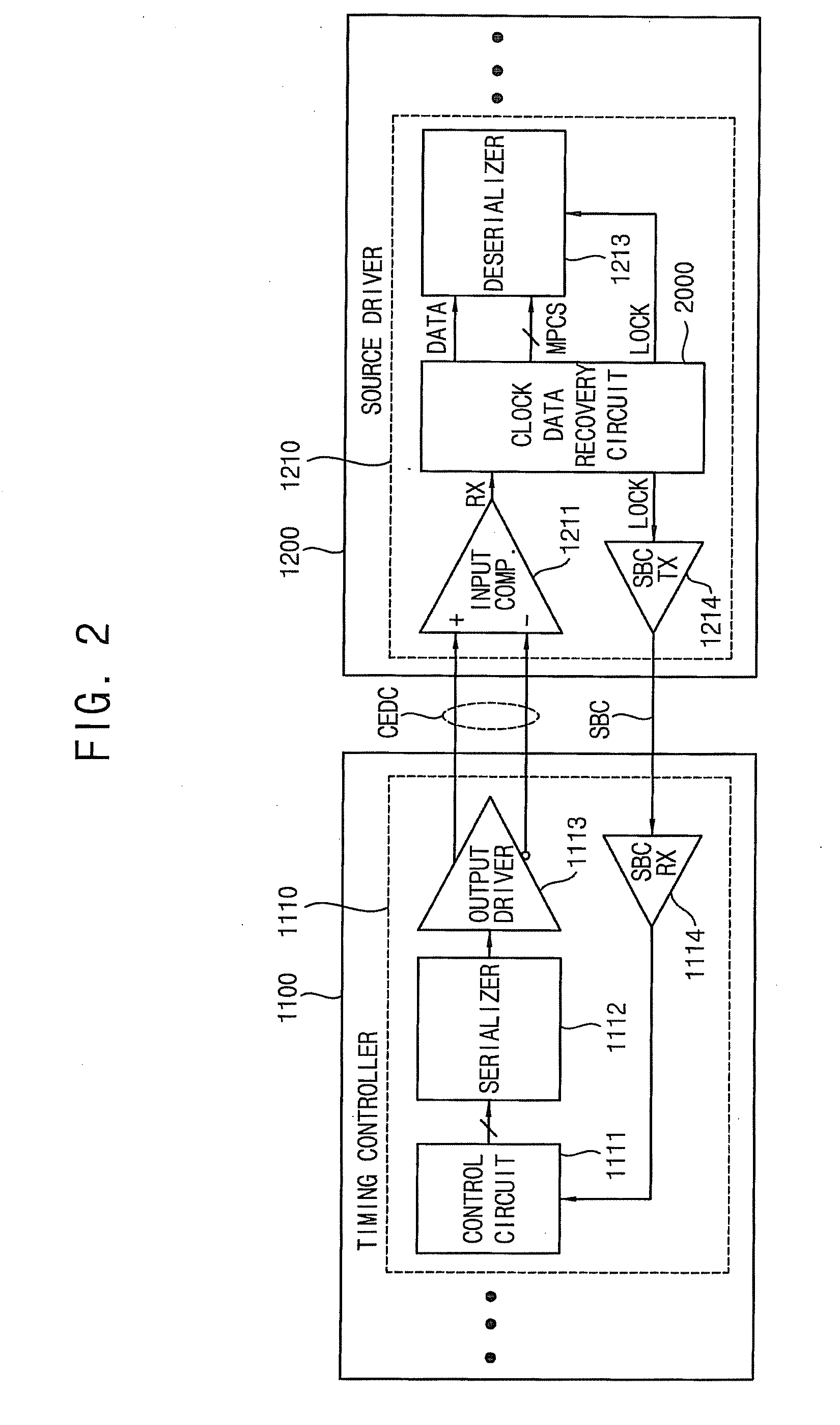

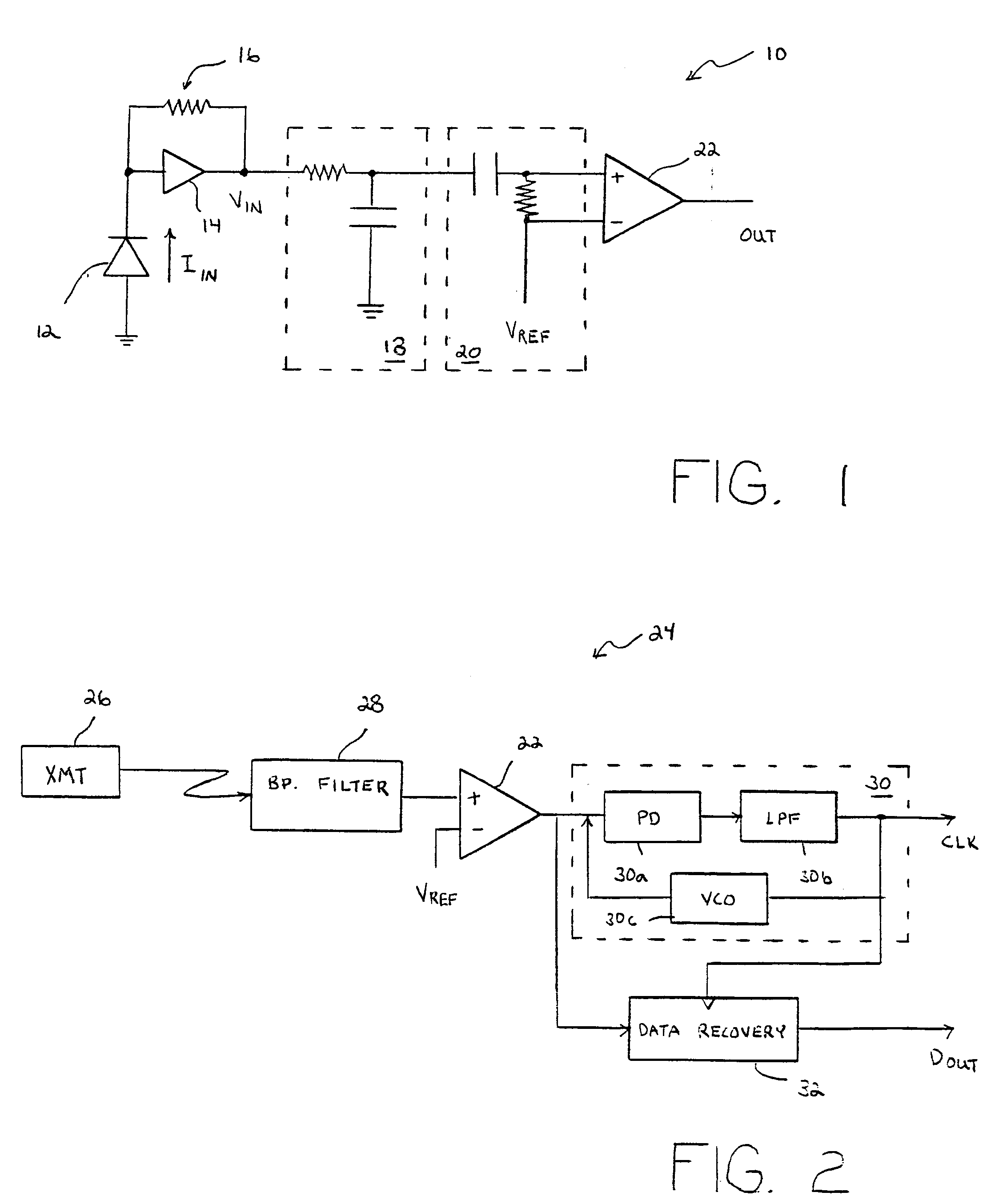

Clock and data recovery circuit of a source driver and a display device

ActiveUS20110037758A1Accurate recoveryReceiver initialisationPulse automatic controlClock recoveryVIT signals

A clock and data recovery (CDR) circuit of a source driver includes a clock recovery unit and a delay locked loop unit. The clock recovery unit receives data bits and a clock code periodically inserted into the data bits through a clock embedded data channel in a display data mode, and is configured to generate a clock signal by detecting an edge of the clock code. The delay locked loop unit is configured to generate a multi-phase clock signal based on the clock signal in the display data mode.

Owner:SAMSUNG ELECTRONICS CO LTD

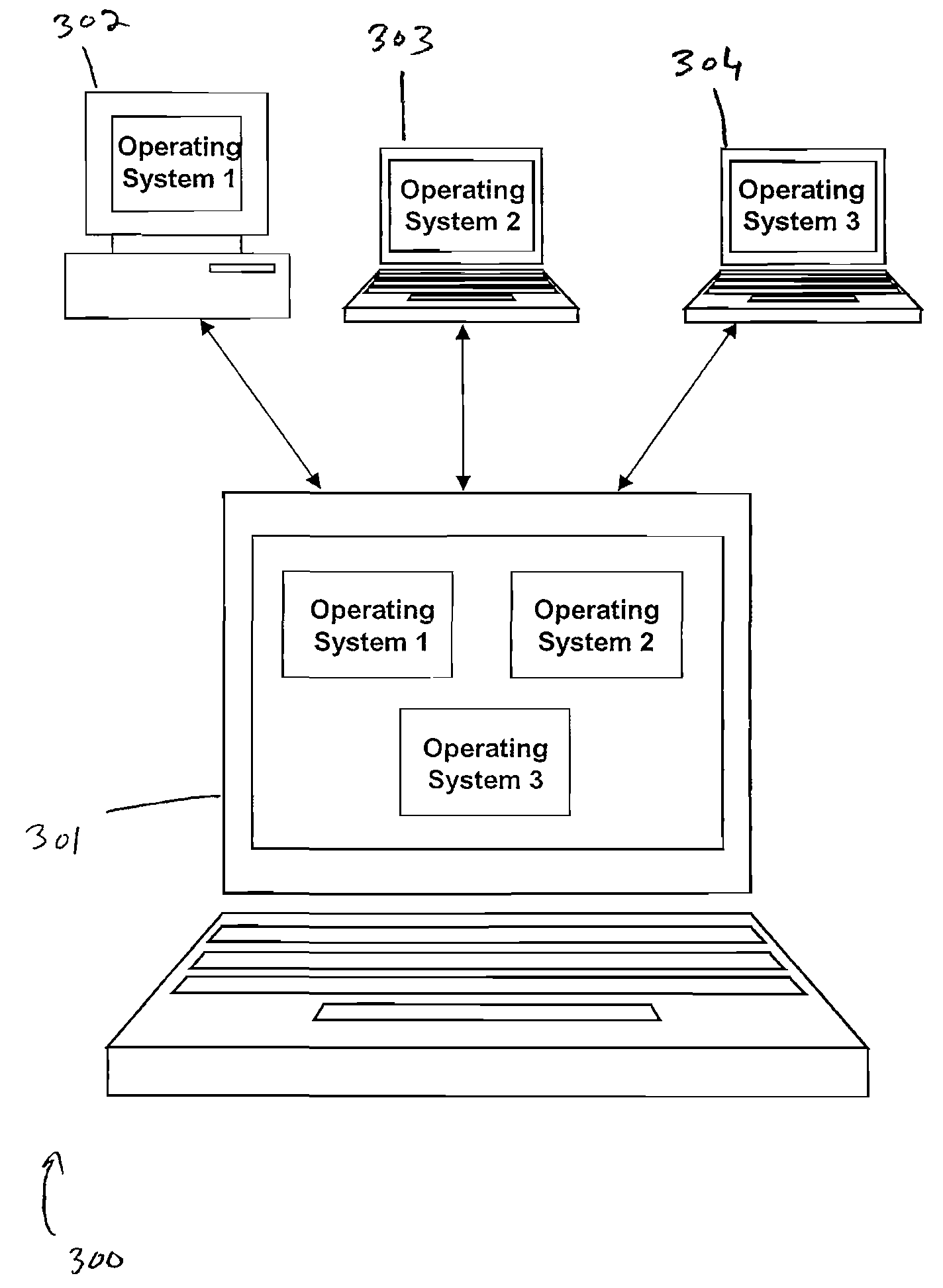

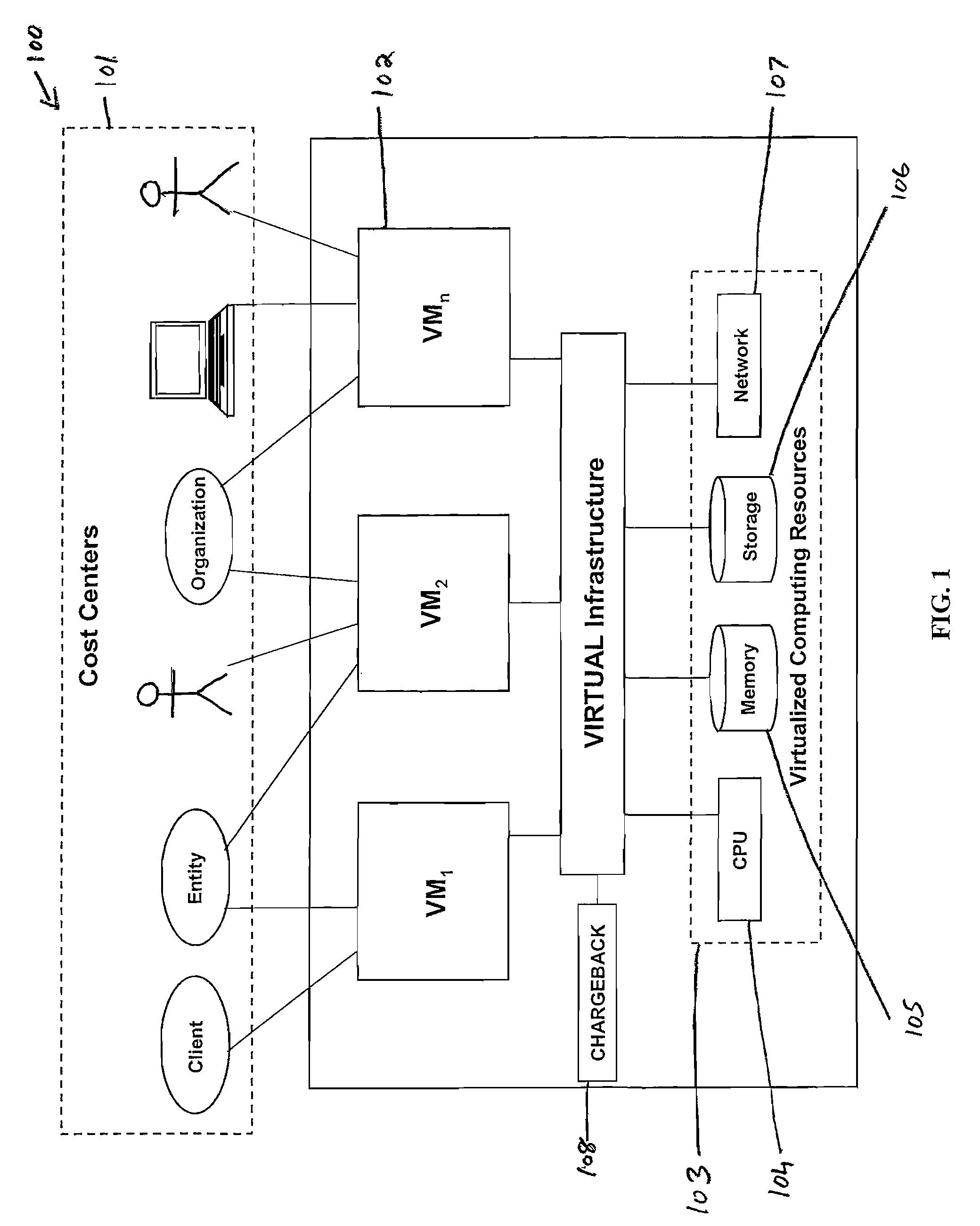

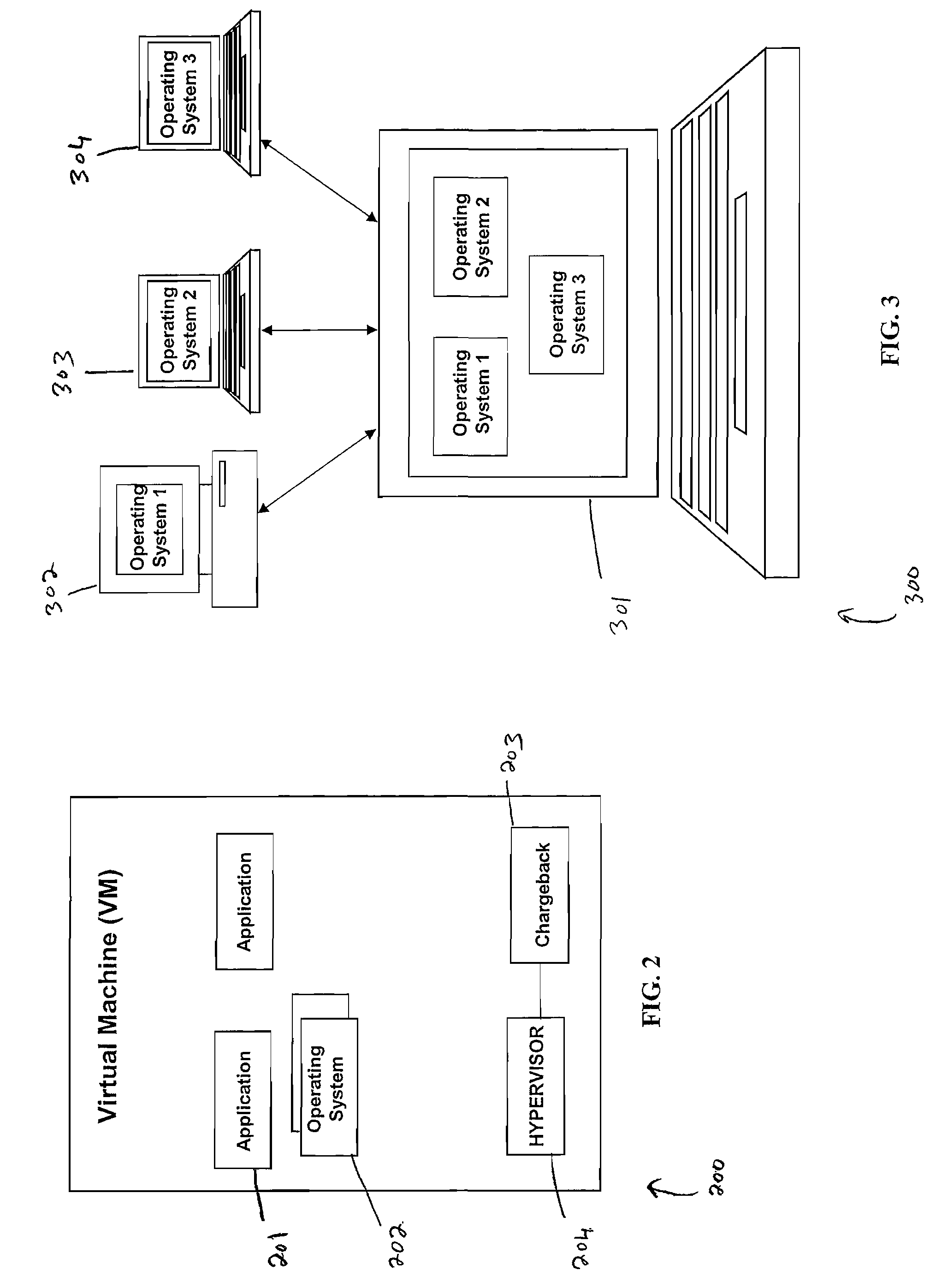

Method, system and apparatus for calculating chargeback for virtualized computing resources

InactiveUS20090164356A1Accurate calculationAccurately reportComplete banking machinesTelephonic communicationVirtualizationCost recovery

Method, system and apparatus for calculating chargeback for virtualized computing resources in a virtualized environment allowing efficient use of computing resources, improving costs recovery including fixed and over-usage cost of utilizing computing resources.

Owner:QUEST SOFTWARE INC

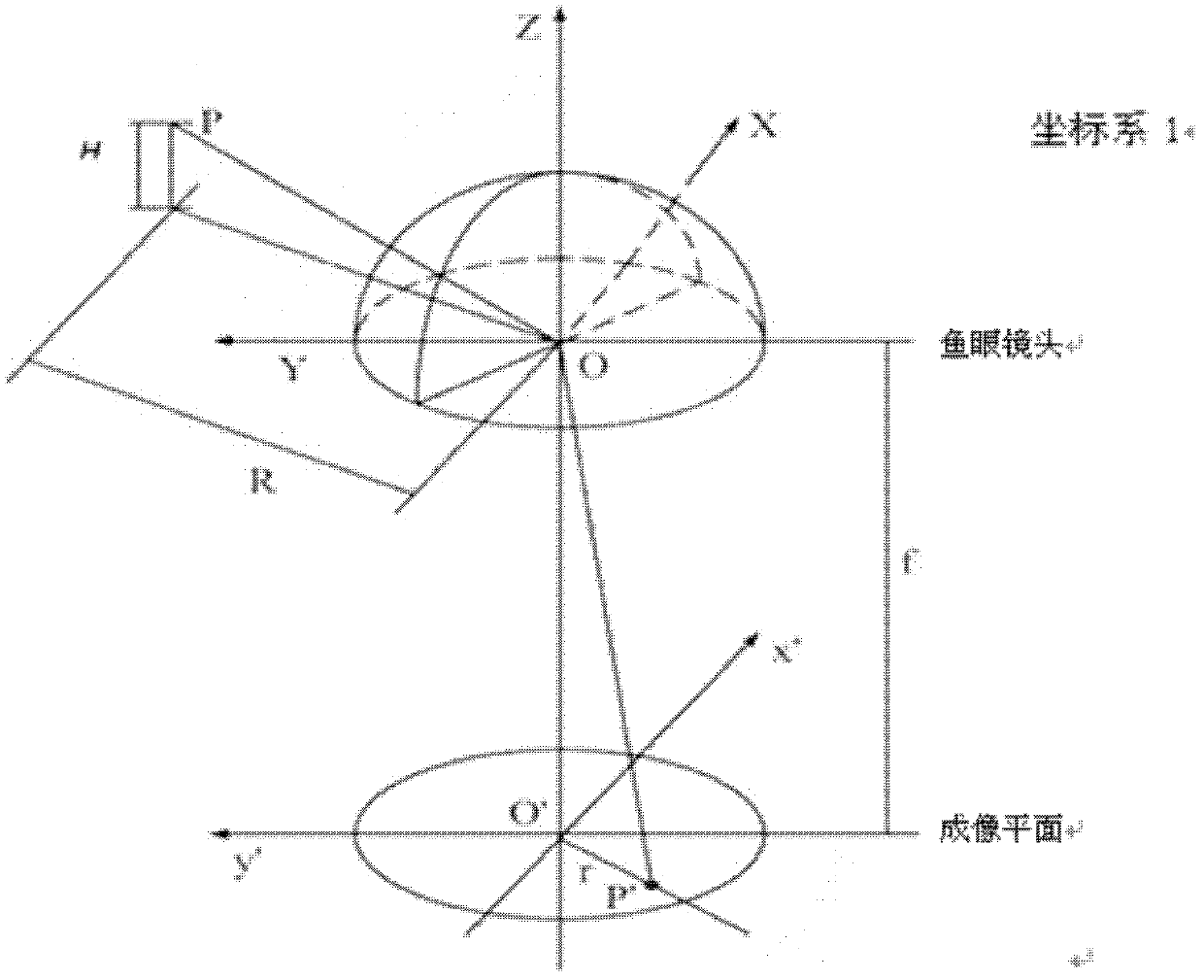

Fish eye lens calibration and fish eye image distortion correction method

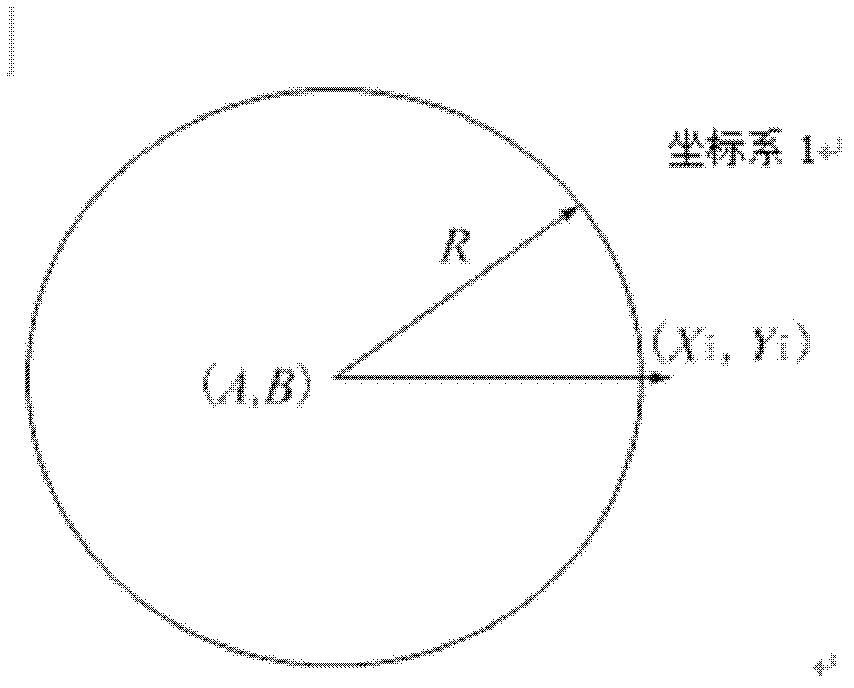

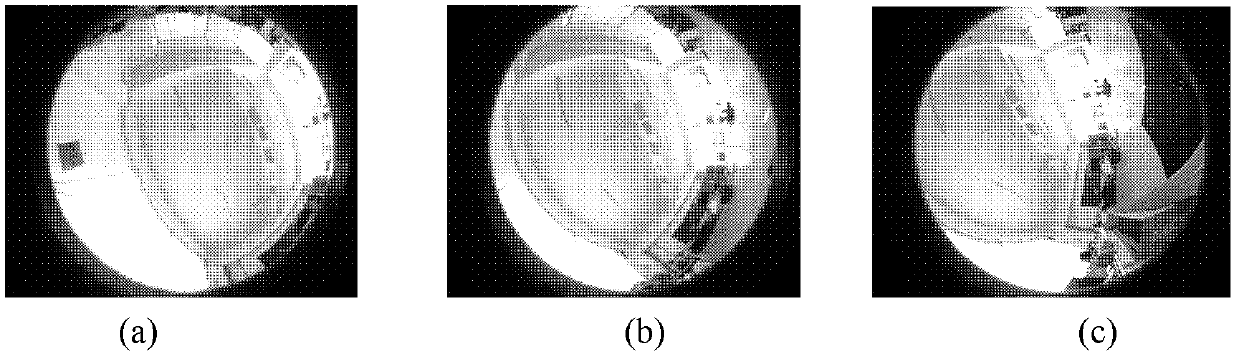

InactiveCN102663734AQuick correctionPromote recoveryImage enhancementImage analysisDigital signal processingVertical projection

The invention relates to a fish eye lens calibration and fish eye image distortion correction method which belongs to the field of digital image processing and is very suitable for occasions of vision navigation, mobile monitoring and so on. Since imaging using a large wide angle will cause serious distortion, generally, imaging correction is needed to facilitate human eye observation. The method provided by the invention is mainly technically characterized by establishing a space coordinate system 1 and employing a least square curve-fitting method to calibrate a fish eye image to determine the center andthe radius of a fish eye lens, establishing a cylindrical projection model in a space coordinate system UV, and setting one-to-one relationships among an image point q2 of the fish eye image, a point q1 on object sphere and a point q projected on a cylinder, wherein q1 is in vertical projection relation with a bottom plane on which q2 is located and line q1q parallels to line oq2, thus achieving the purpose of fish eye image correction.

Owner:TIANJIN UNIVERSITY OF TECHNOLOGY

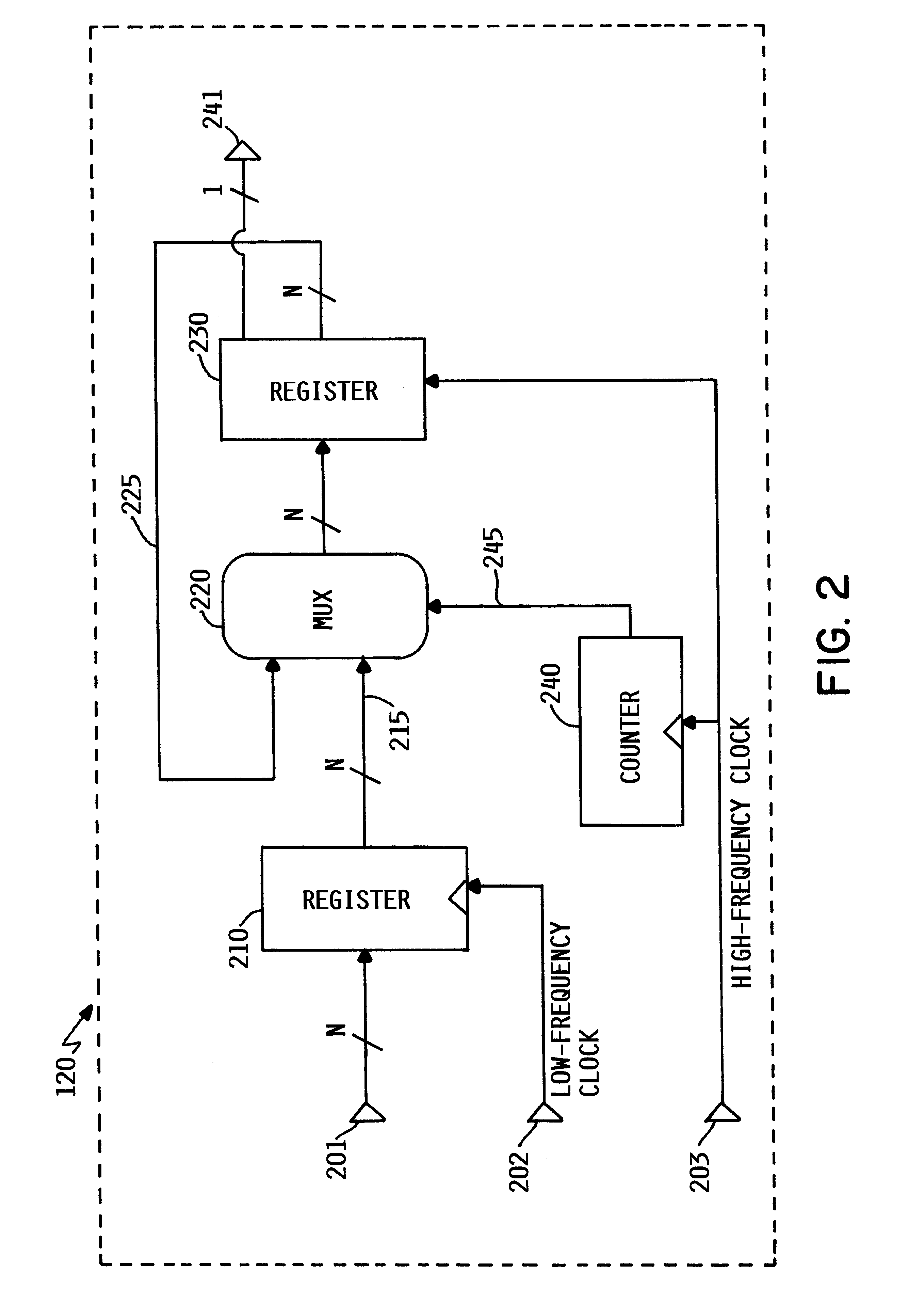

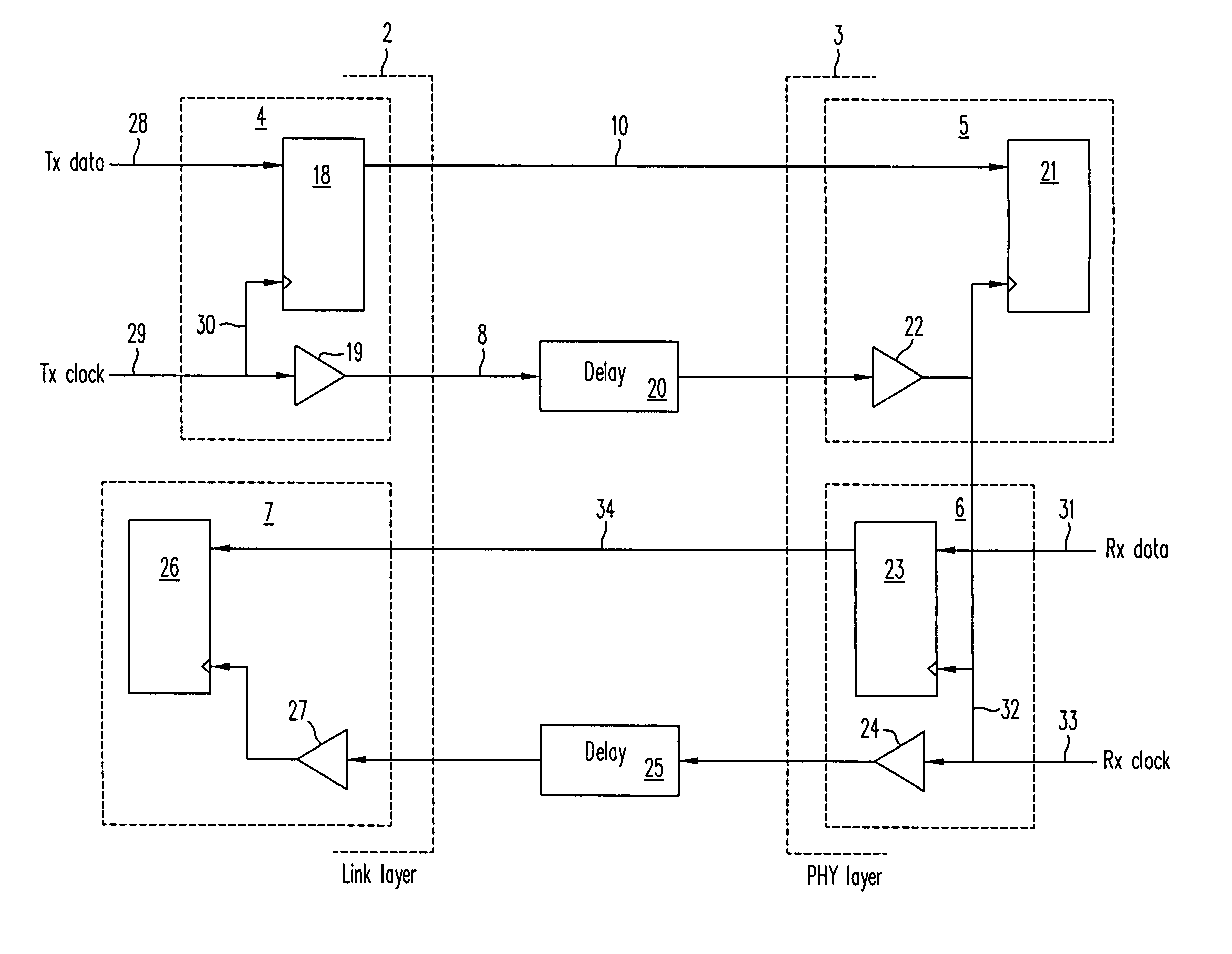

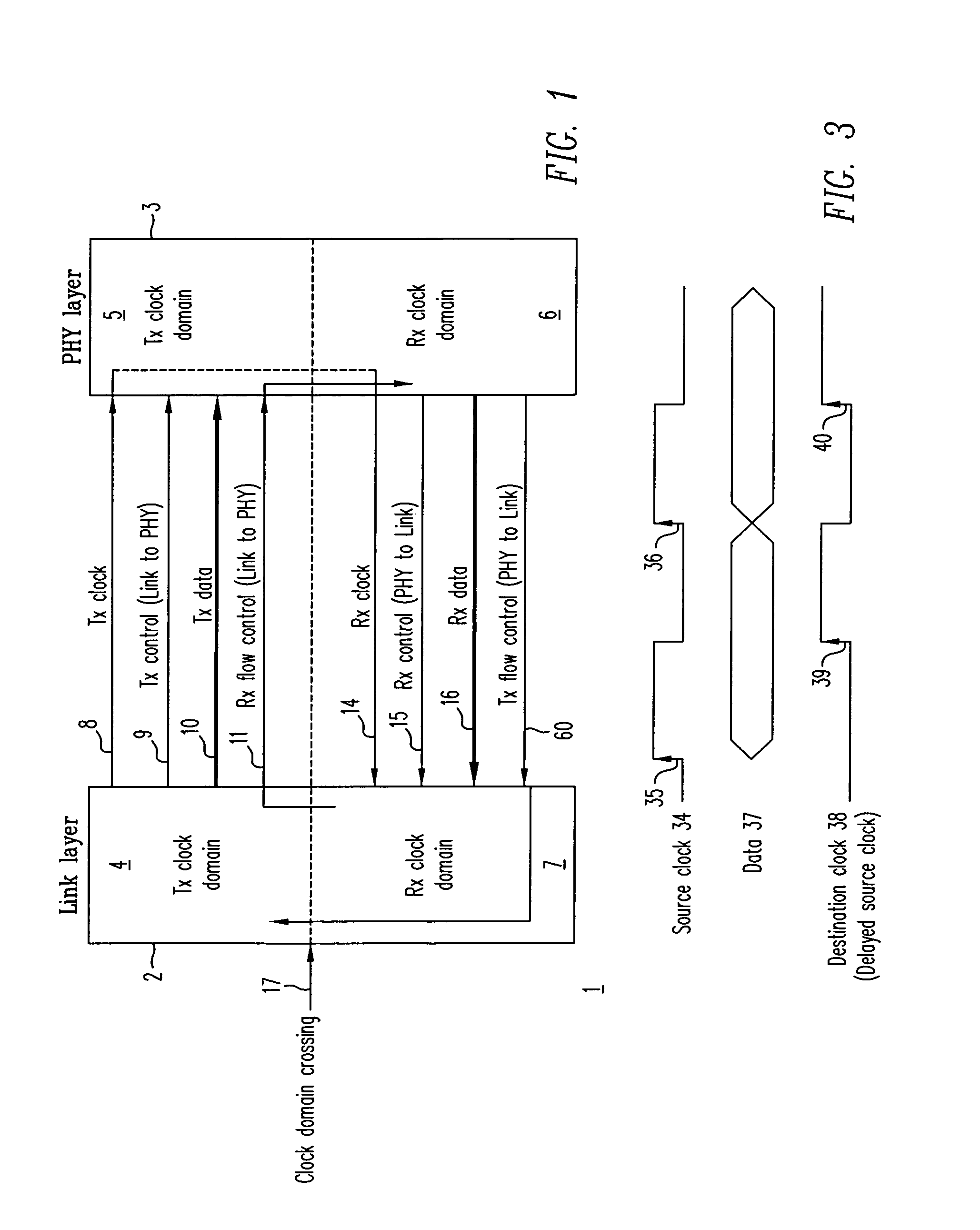

Method and system for source synchronous clocking

InactiveUS7110423B1Accurate recoveryEliminate needSynchronisation information channelsTime-division multiplexProcessor registerData signal

A source synchronous clocking synchronizes data and clock signals transmitted between an ATM layer and a link layer. The source synchronous clocking includes a source clock domain in a first layer which includes a register having a first input for receiving a data signal, a second input for receiving a clock signal, and an output; and a buffer having an input for receiving the clock signal and an output, the buffer generating a delay that is substantially equivalent to a delay through the register. The source synchronous clocking further includes a destination clock domain in a second layer which includes a register having a first input and a second input, the first input of the register of the destination clock domain being coupled to the output of the register in the source clock domain.

Owner:CISCO TECH INC +1

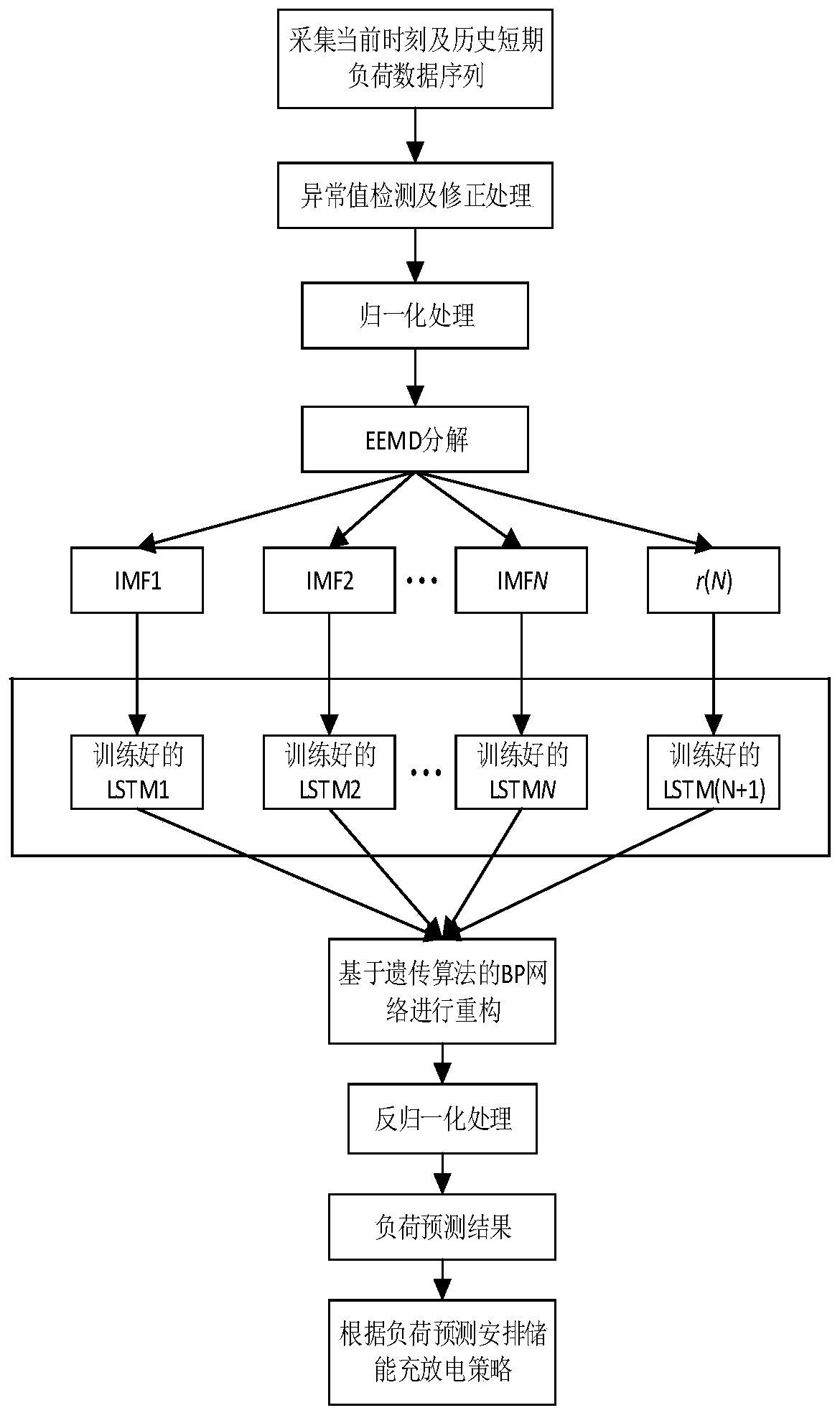

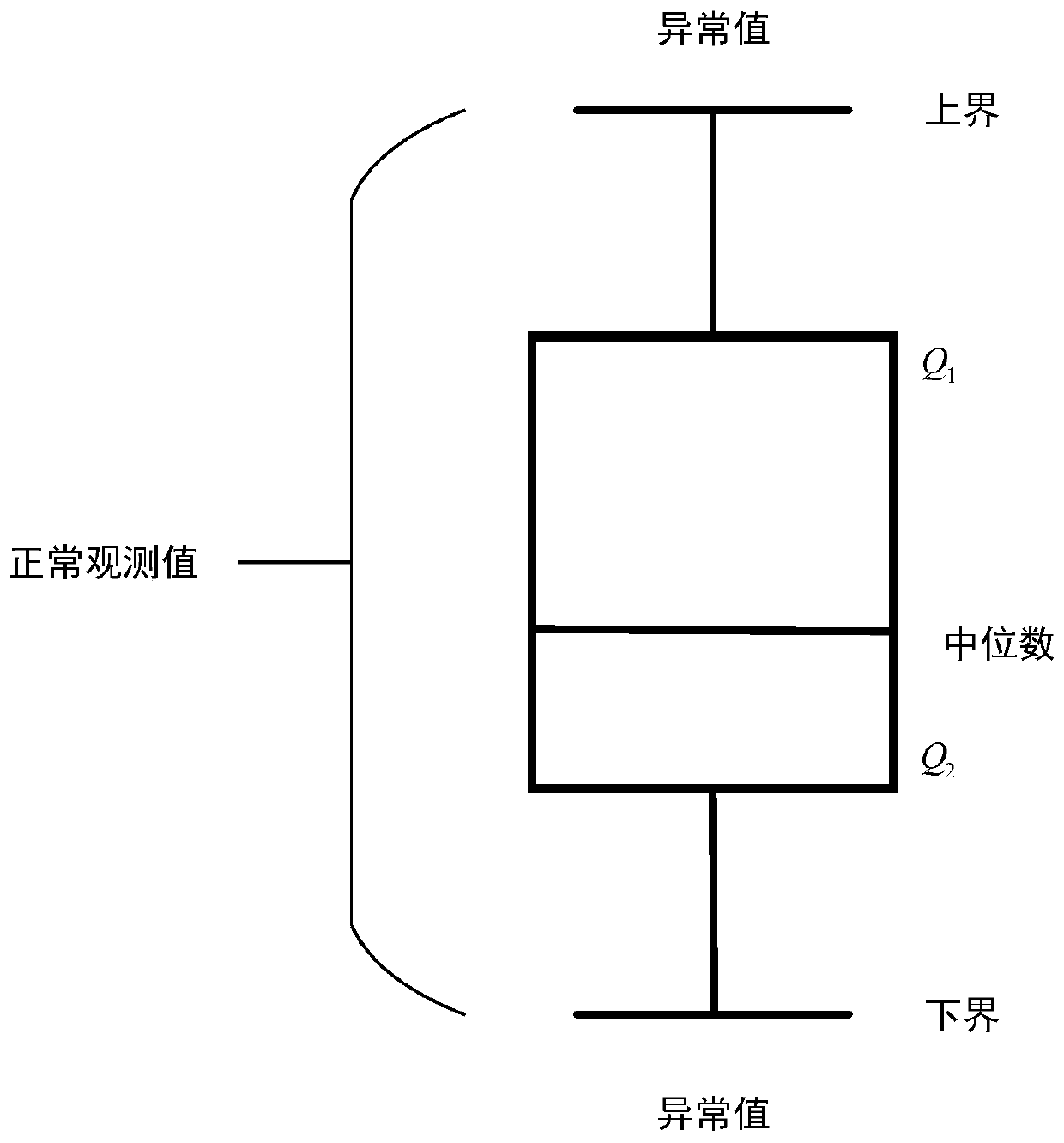

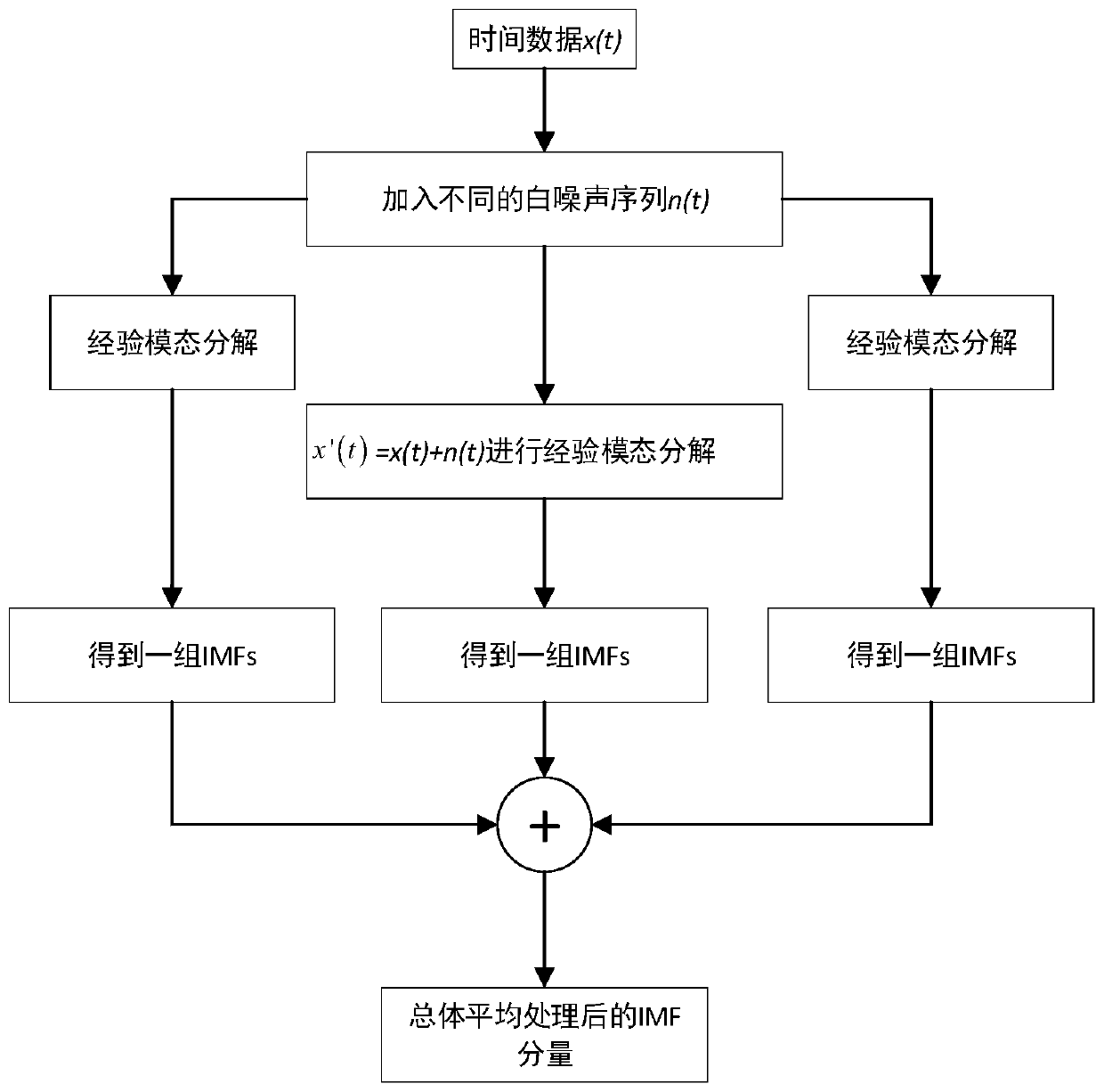

Energy storage device control method based on ensemble empirical mode decomposition and LSTM

ActiveCN110059844AOvercome Mode Aliasing PhenomenonImprove accuracyForecastingNeural architecturesDecompositionCharge discharge

The invention relates to an energy storage device control method based on ensemble empirical mode decomposition and LSTM. The method comprises the following steps: firstly, performing normalization processing and ensemble empirical mode decomposition on historical short-term load data in first n + 2 time periods in continuous n + 2 time periods to obtain a subsequence or a residual component as aninput item; training an LSTM model by taking a subsequence or a residual component corresponding to historical short-term load data in a later time period as a theoretical output item; preprocessingthe data of the current time period and the historical short-term loads of n time periods closest to the current time period, and inputting the preprocessed data into the trained LSTM model; and afterthe trained LSTM model is utilized to output predicted values, all the predicted values are reconstructed and subjected to reverse normalization processing to obtain a prediction result, and finally,the energy storage device is controlled to charge and discharge according to the prediction result. The method has the advantages of high prediction precision and reasonable charge-discharge operation of the energy storage device.

Owner:DONGHUA UNIV

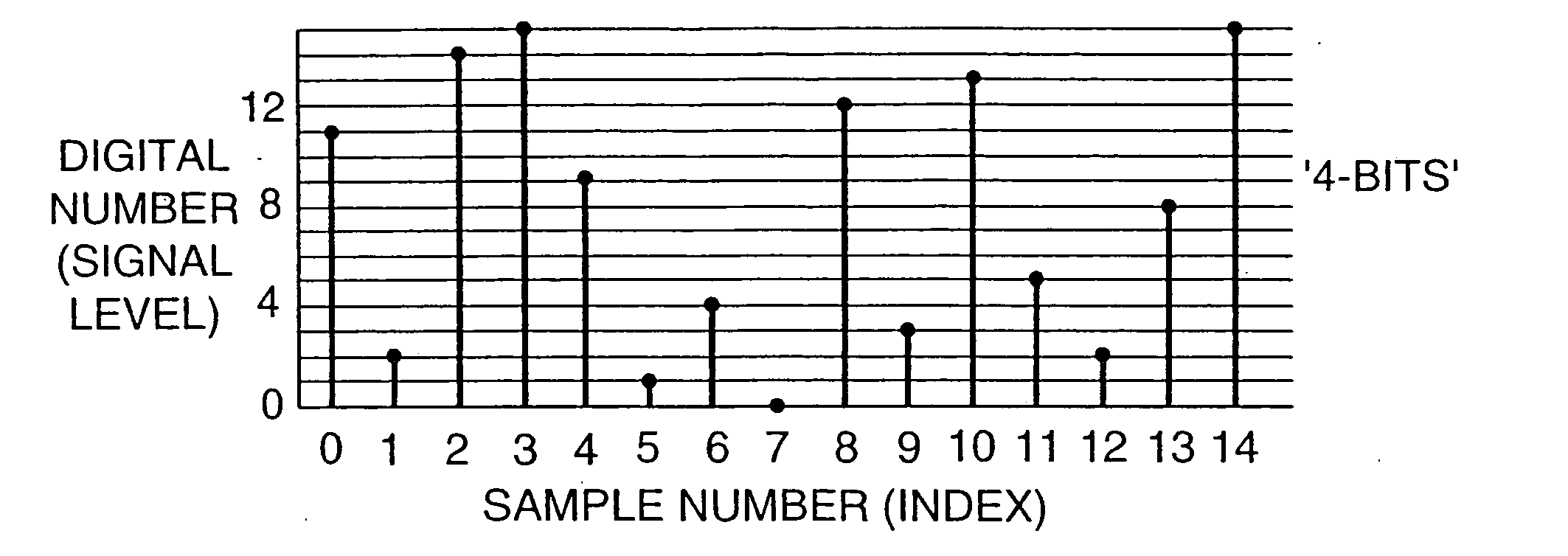

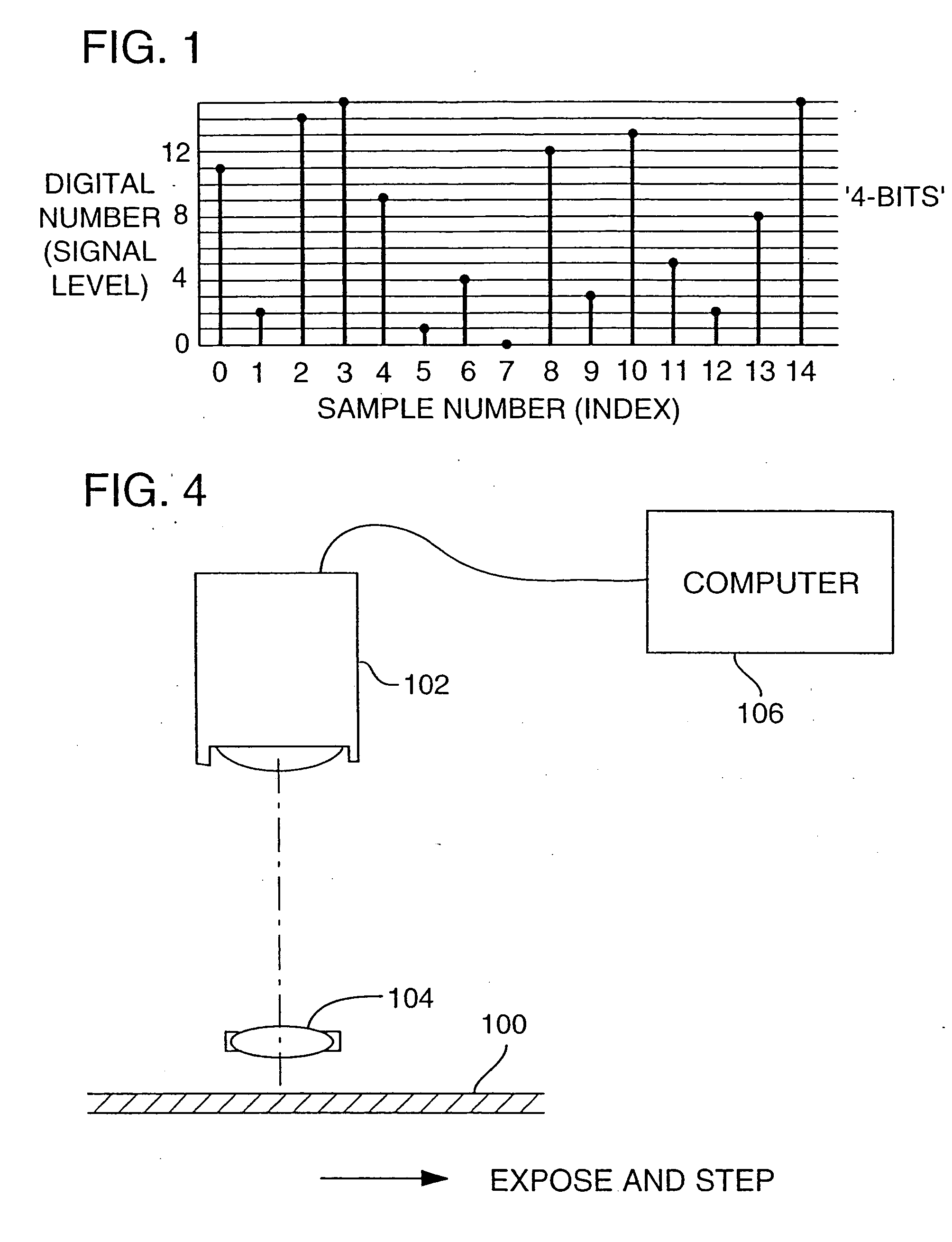

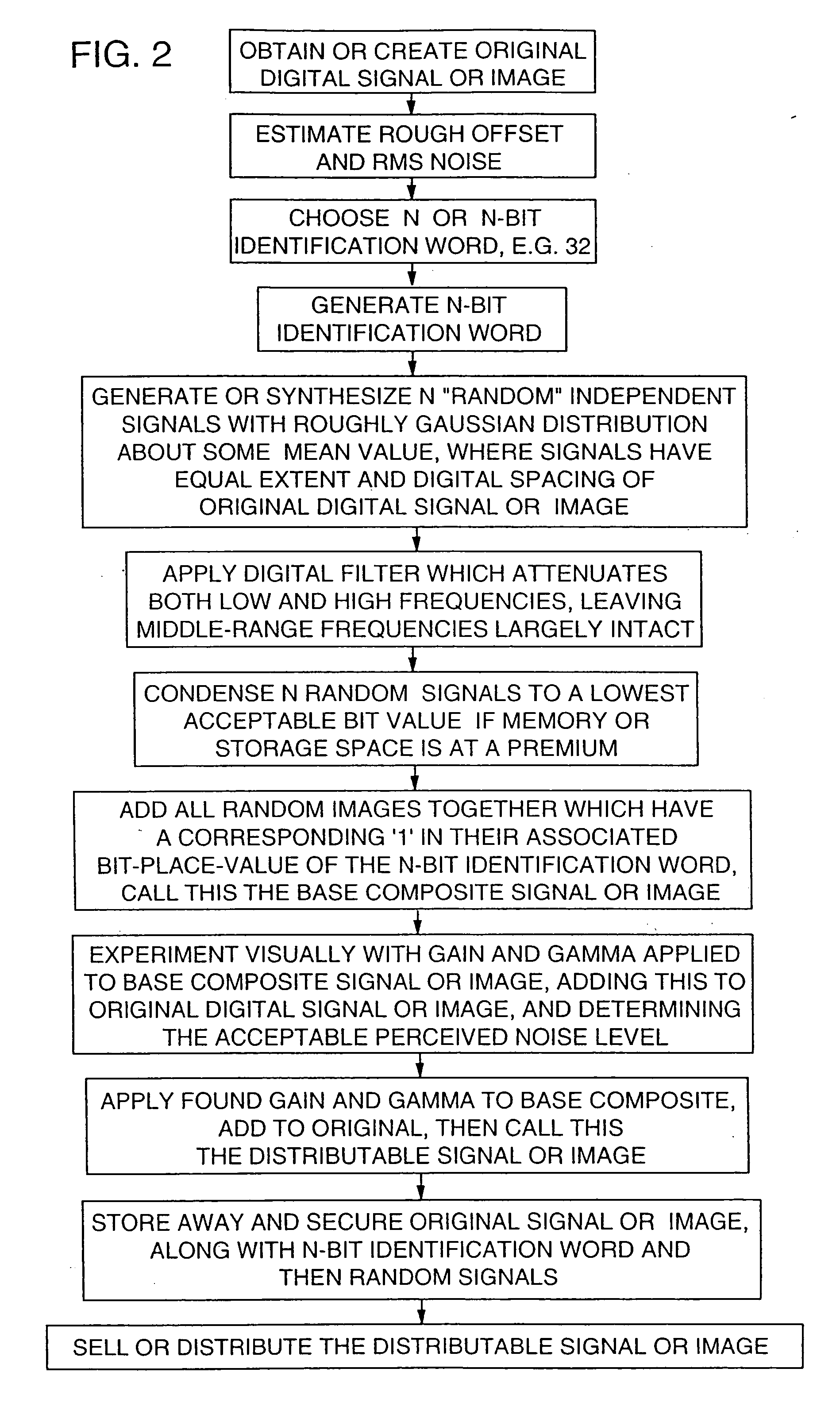

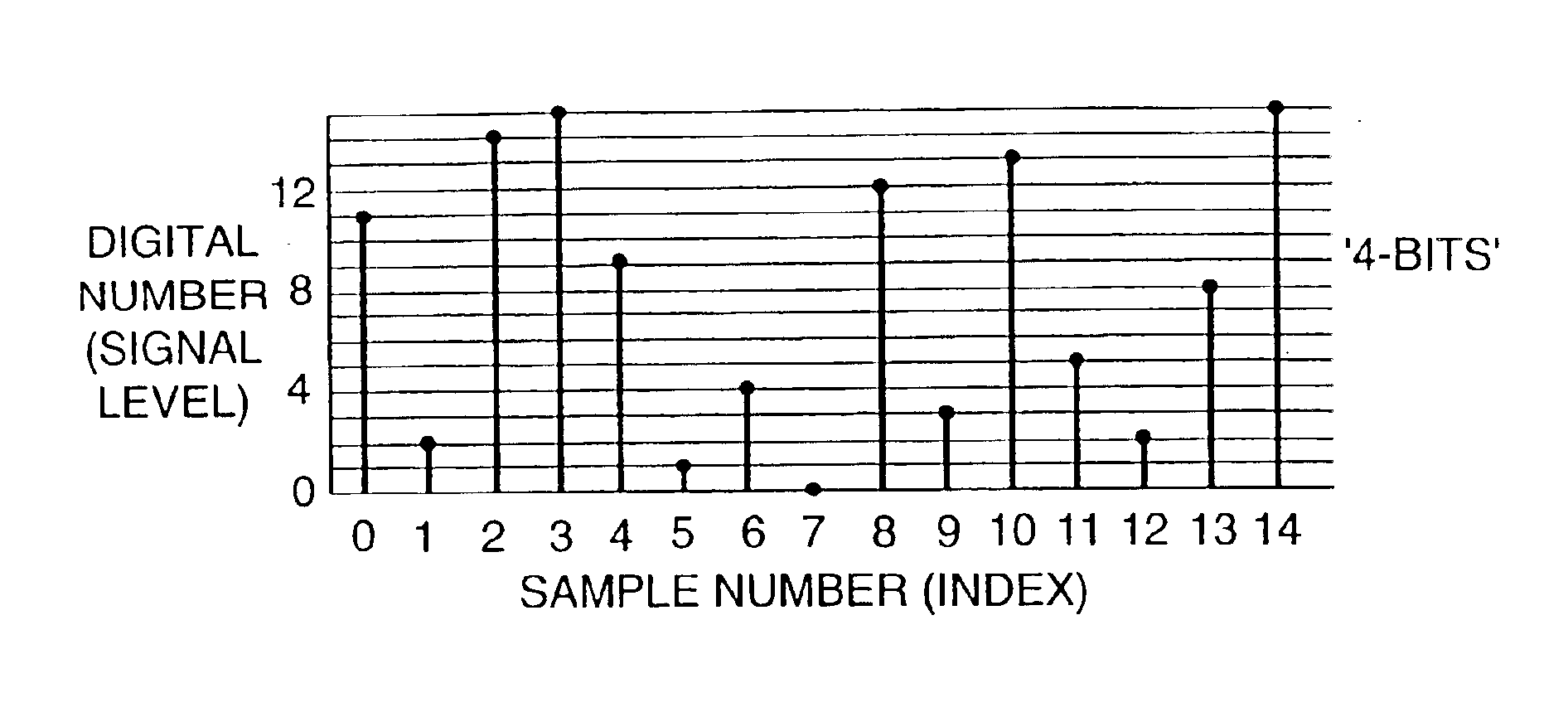

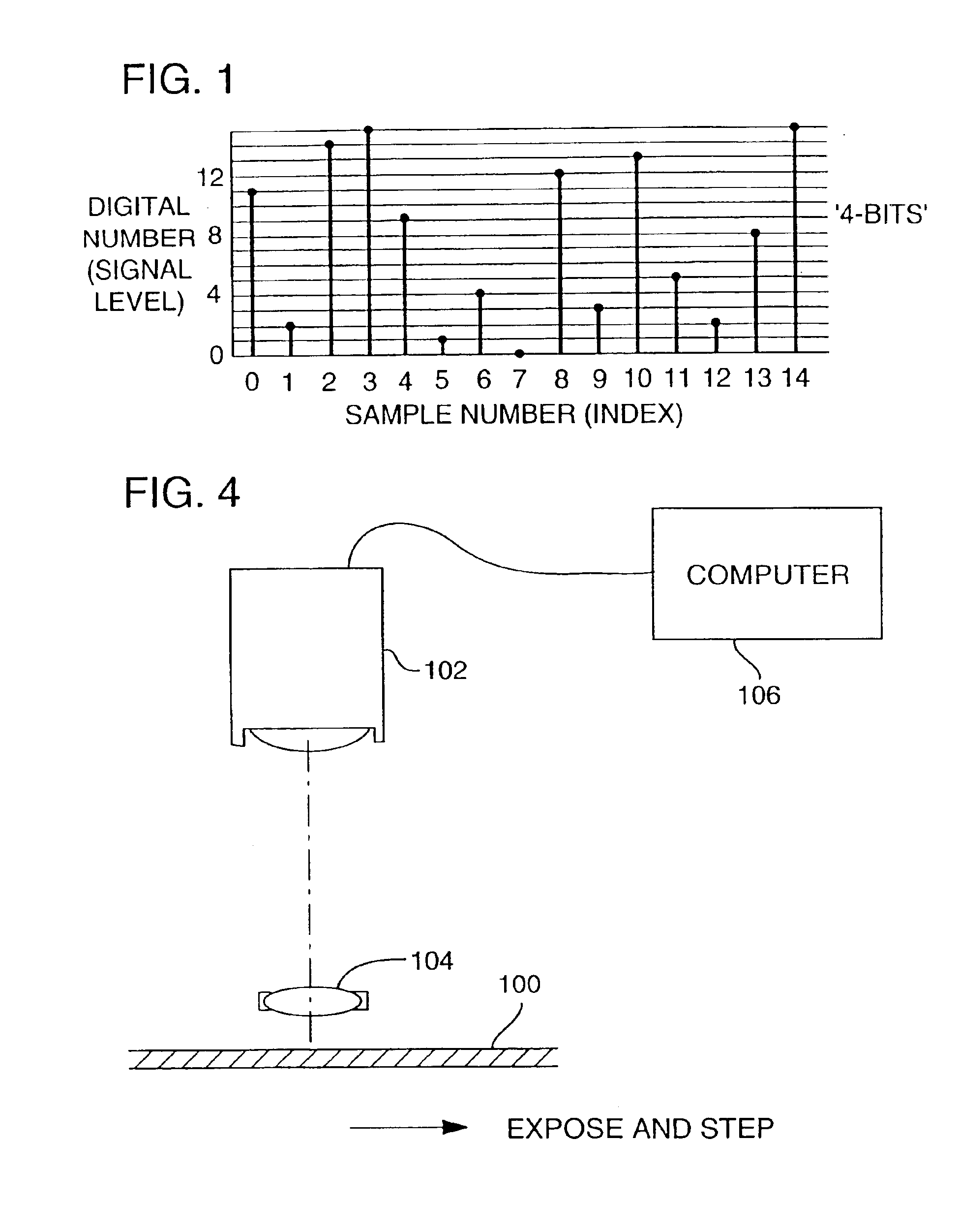

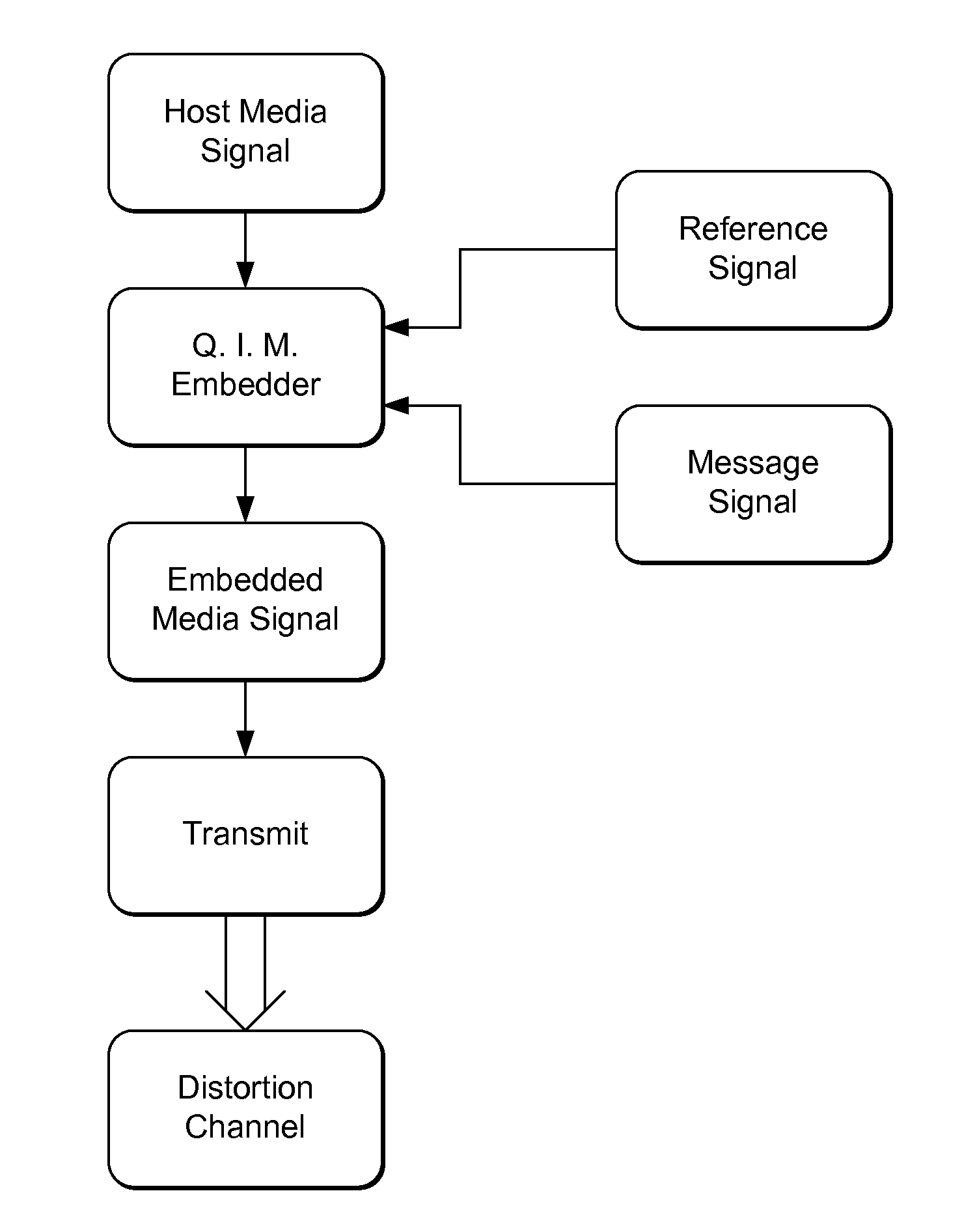

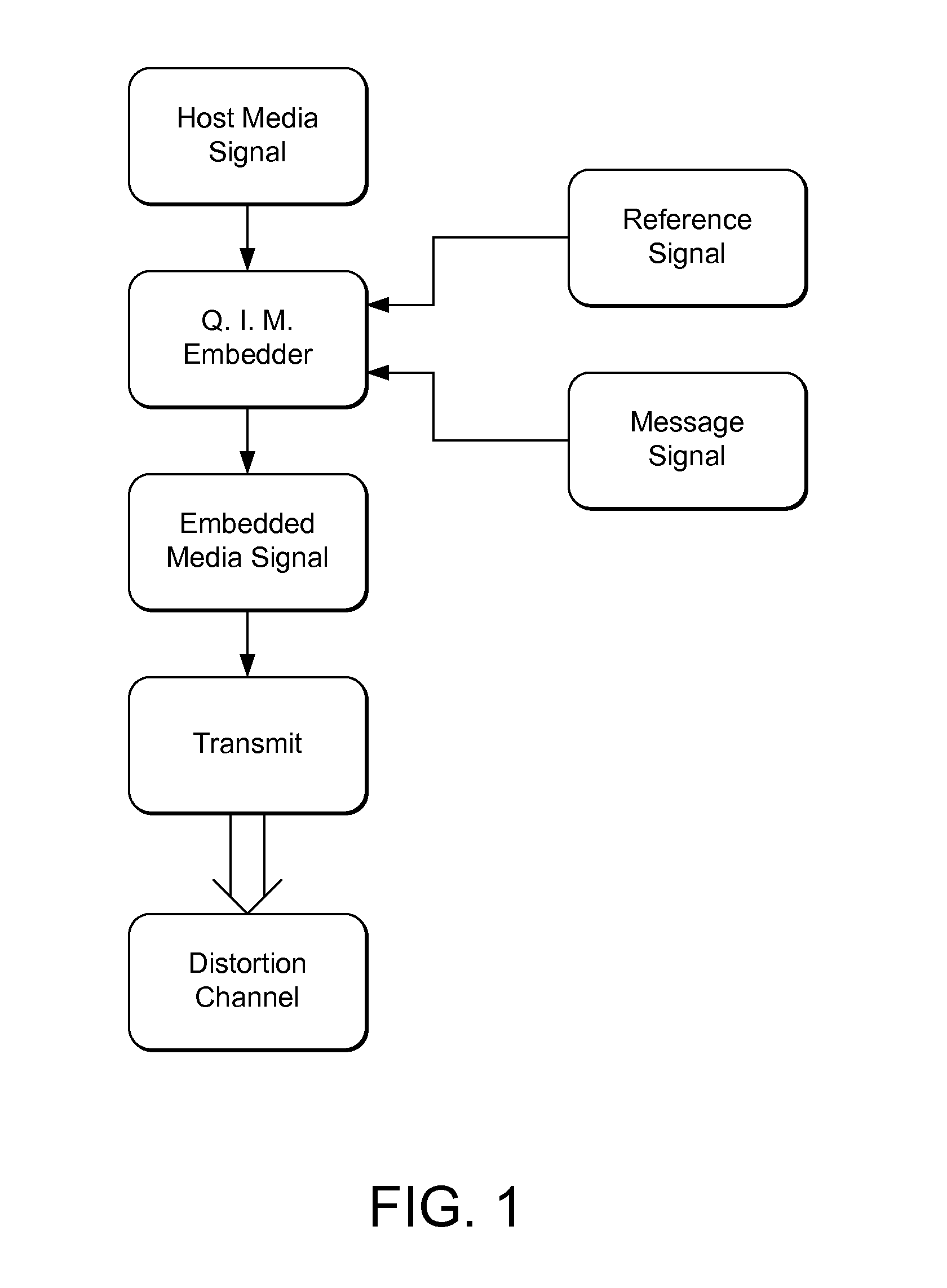

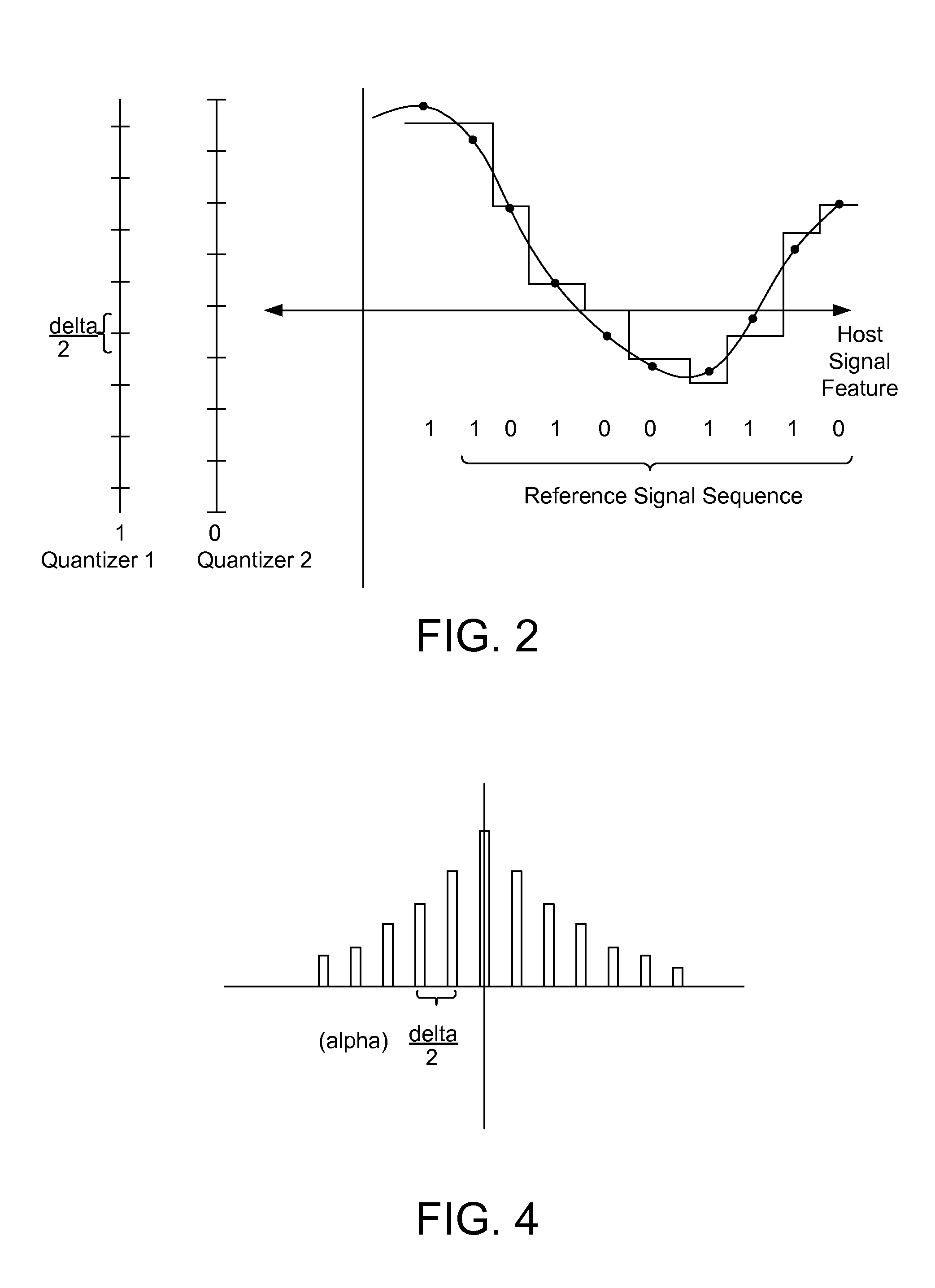

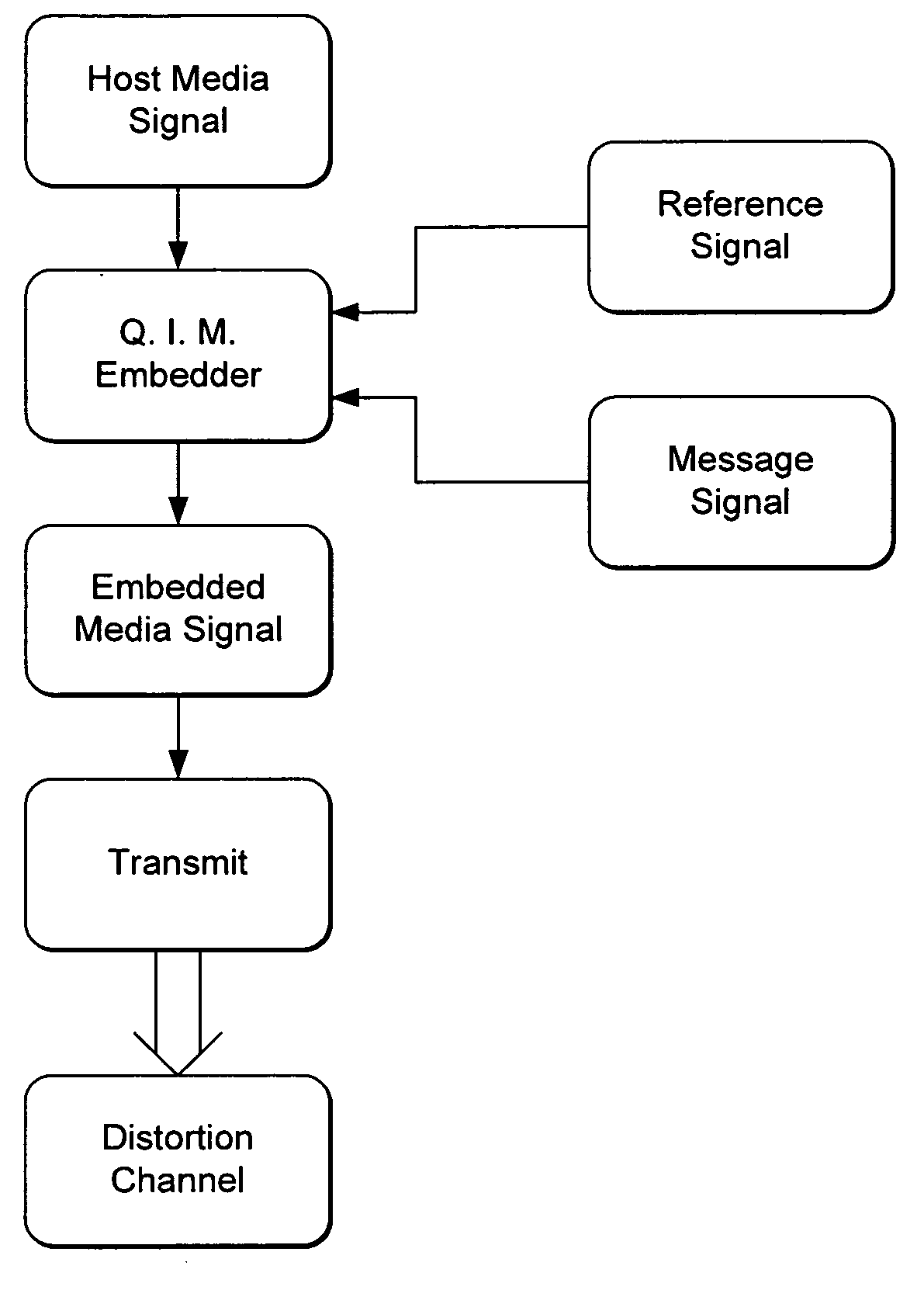

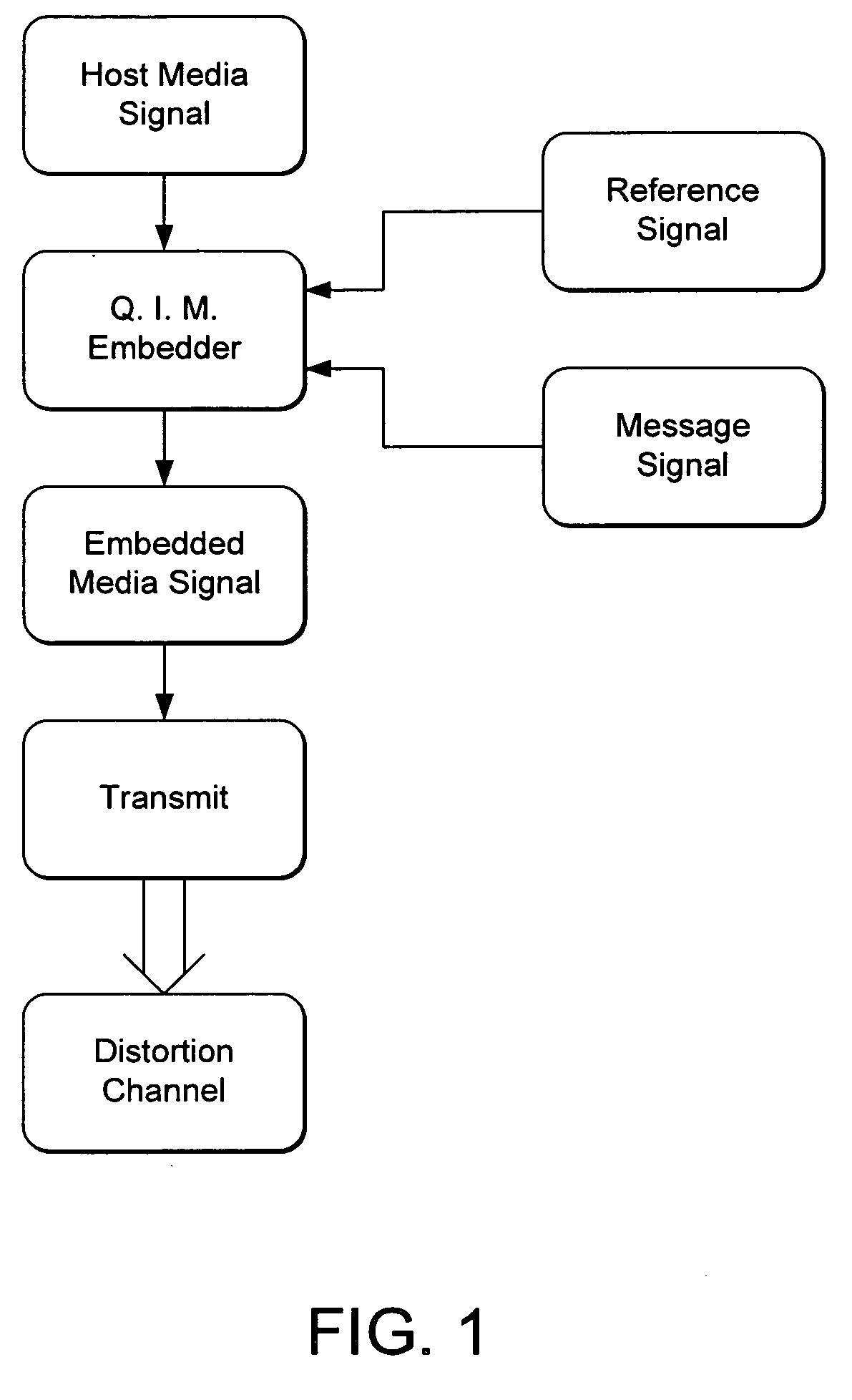

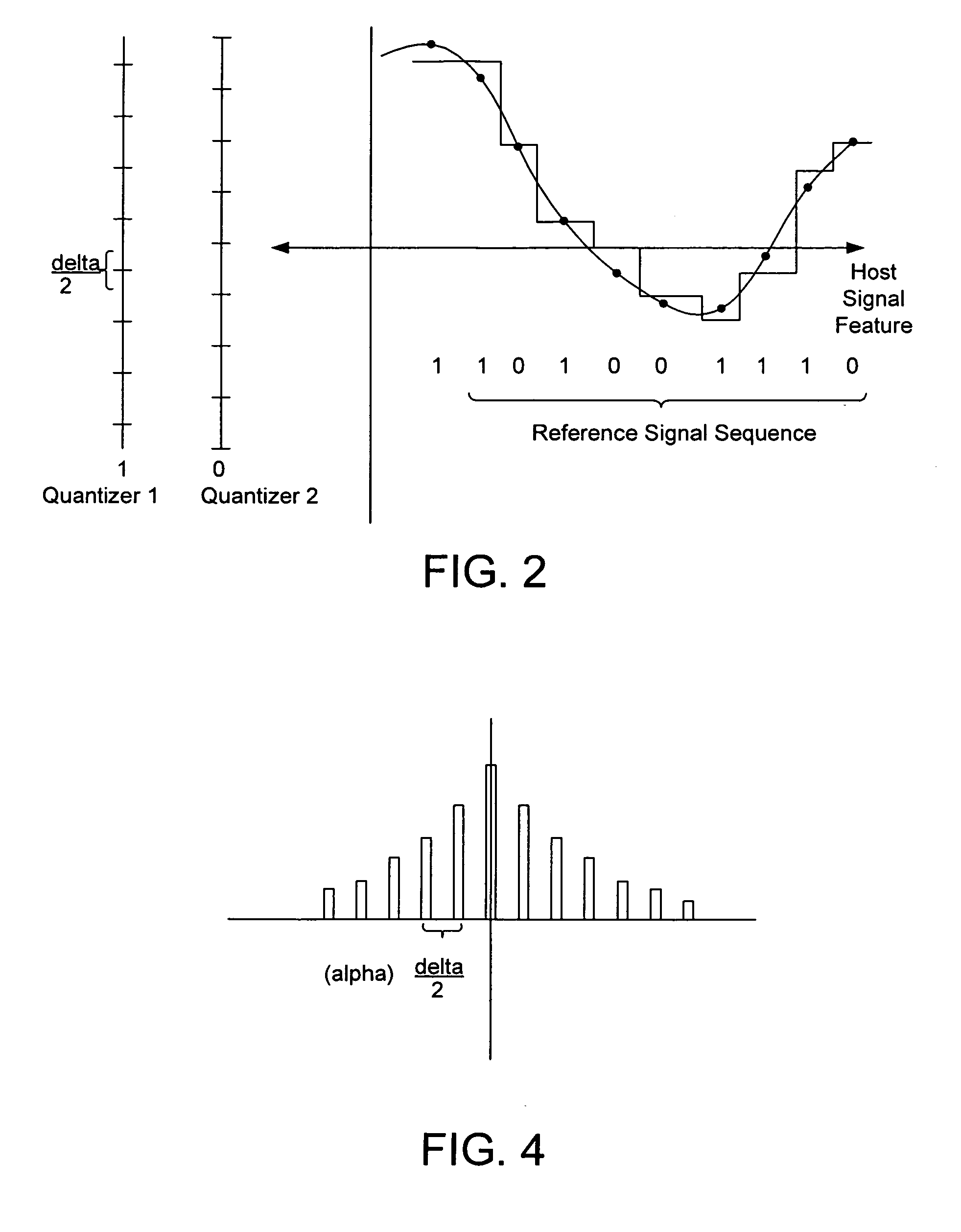

Quantization-Based Data Embedding in Mapped Data

InactiveUS20110044494A1Reduce errorsReduce the impactSpeech analysisCharacter and pattern recognitionAlgorithmDistortion

Novel methods and systems for quantization based data embedding and reading in host signals, such as image, audio and video signals. To embed auxiliary data in a host signal, an embedder maps the host signal from a first domain into a mapped signal in a second domain. The embedder performs quantization based embedding of auxiliary data into the host signal using quantizers. The quantizers are adapted such that the relationship between corresponding quantizers in the first and second domains satisfies a predetermined constraint. The mapping improves the robustness of the data embedding method by increasing the chances that the embedded data can be recovered by an auxiliary data reader after modifications. A related embedding method projects the mapped signal unto a vector, and specifically, a pseudorandom vector. It performs quantization based embedding on the projected signal. The use of this projection provides added robustness of the embedded data to noise and other forms of distortion.

Owner:DIGIMARC CORP

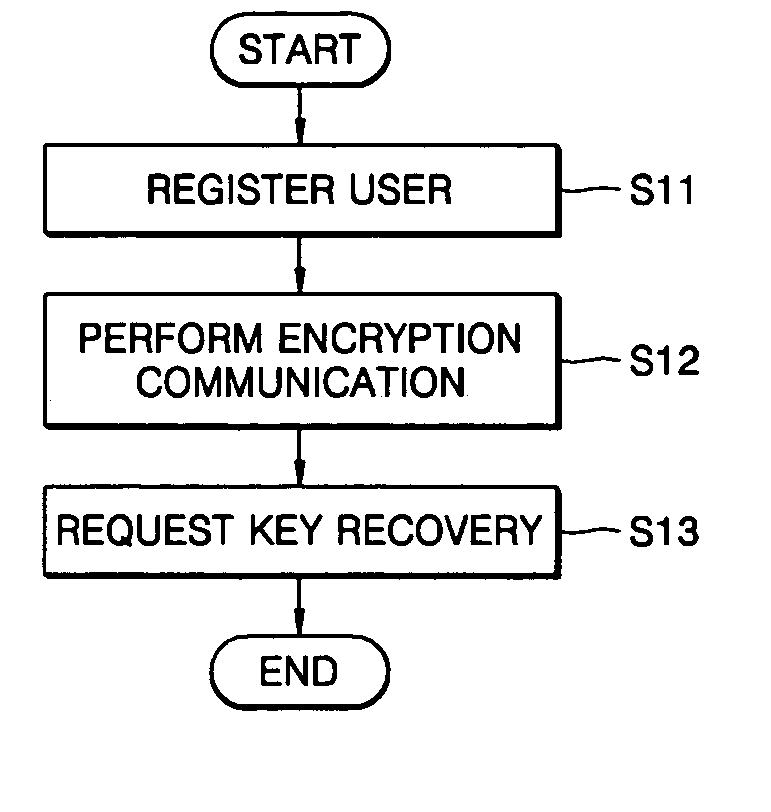

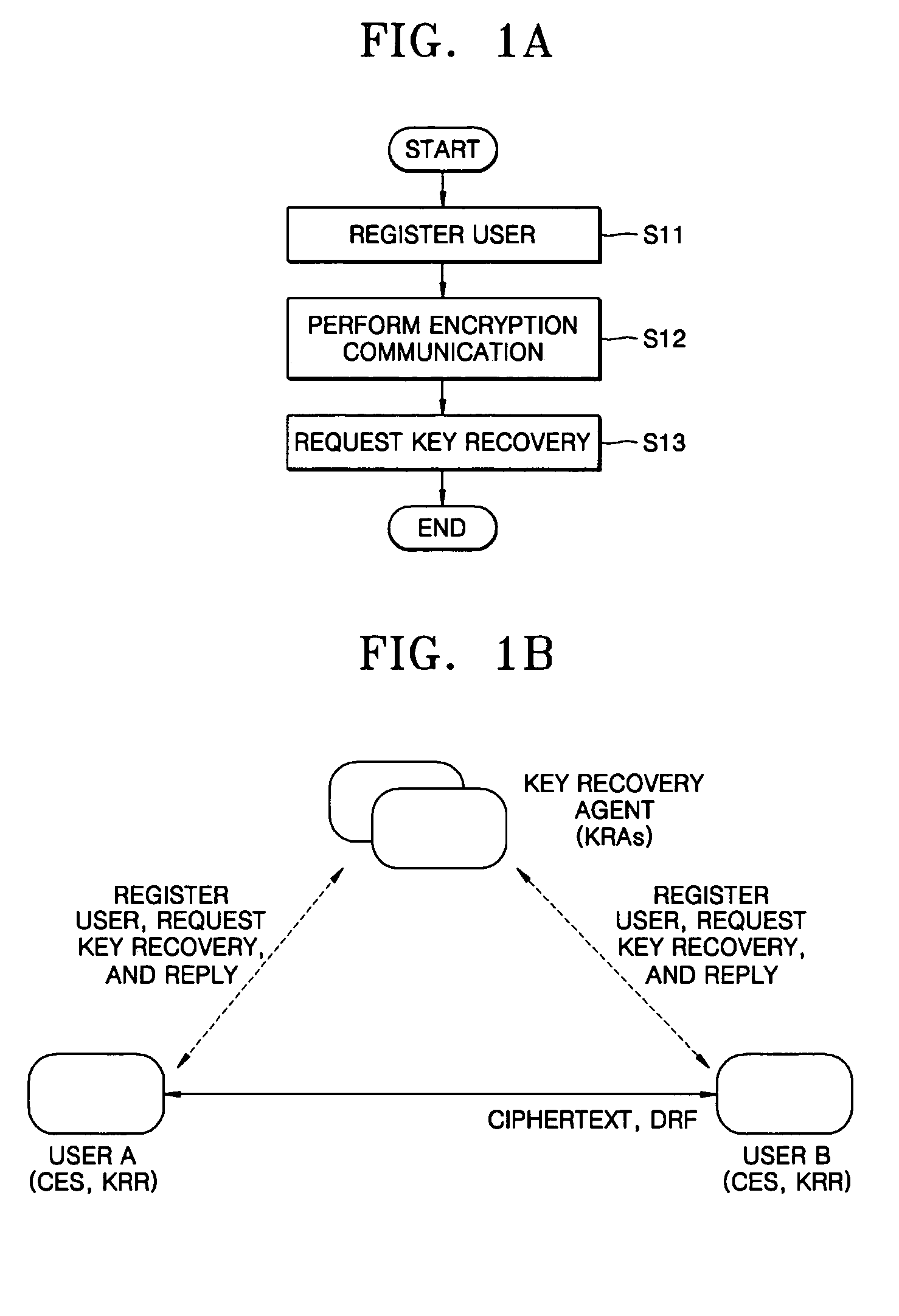

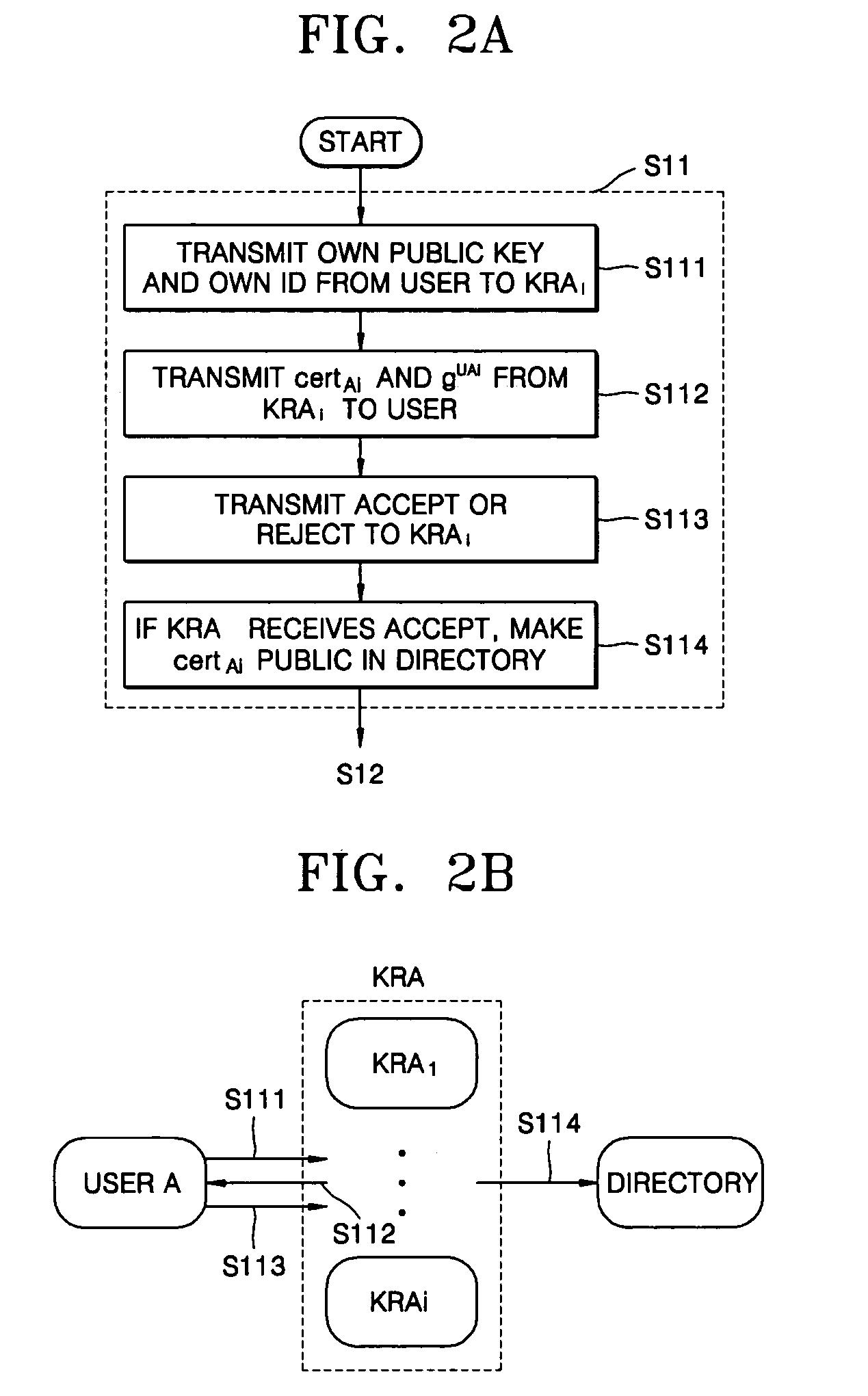

Method of transmitting and receiving message using encryption/decryption key

InactiveUS20050141718A1Accurate recoveryKey distribution for secure communicationPublic key for secure communicationEncryption decryptionSession key

Provided is a method of transmitting and receiving a message using an encryption / decryption key, by which each of a sender and a recipient can generate an encryption / decryption key and recover a key used for encryption / decryption while transmitting and receiving the message using an electronic device. The method includes: (a) a user generating his / her own private key and a public key, registering the public key with a key recovery agent (KRA), and setting shared secret information; and (b) a sender transmitting the recovery information necessary for decryption of the transmission message to a recipient, and the recipient generating a key necessary for the decryption from the recovery information and decrypting the transmission message. The method may further include the recipient requesting recovery of the session key to the KRA.

Owner:ELECTRONICS & TELECOMM RES INST

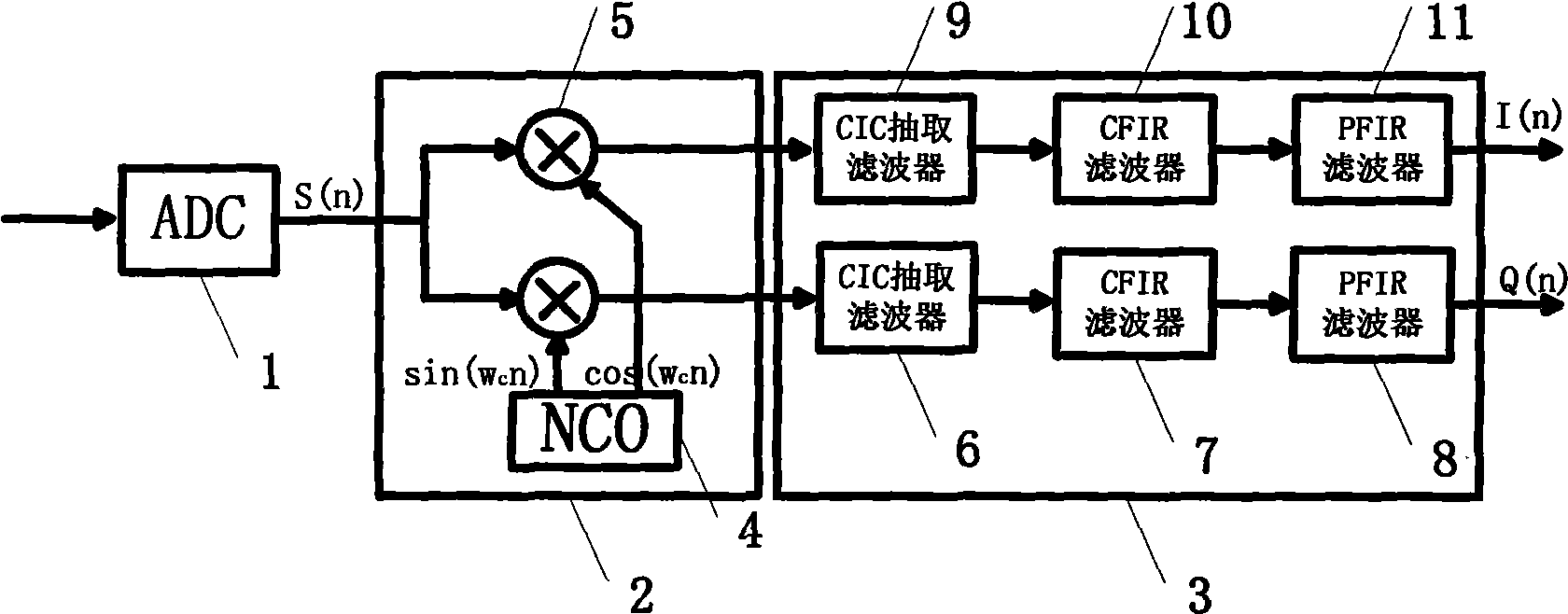

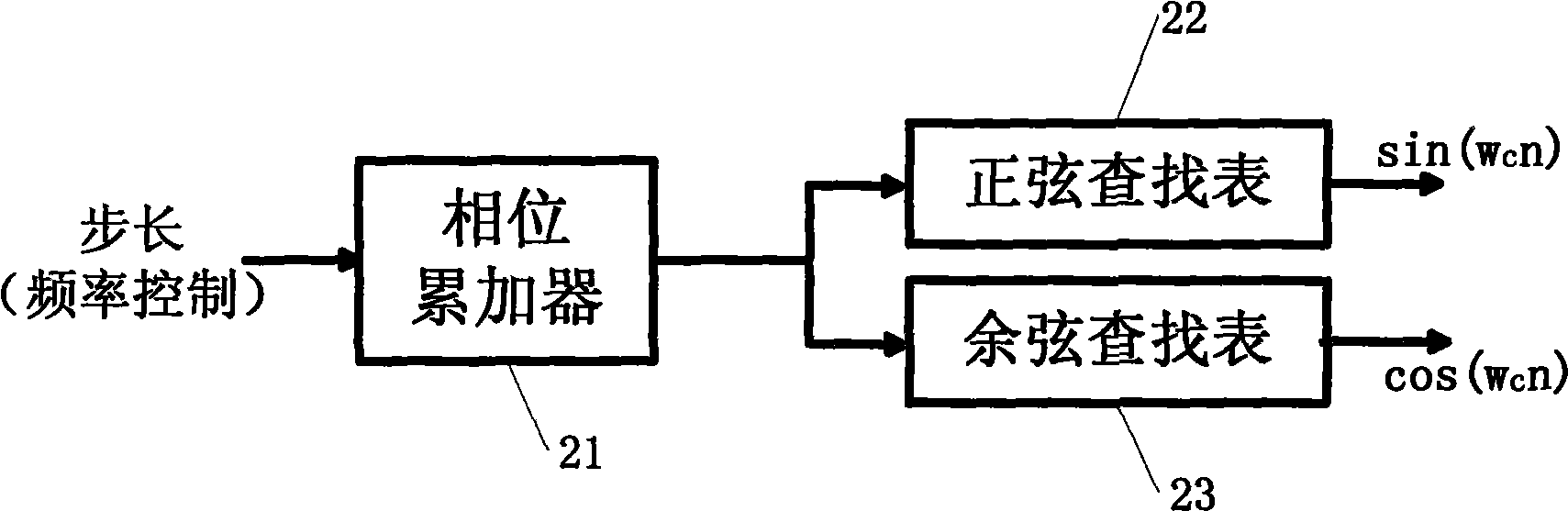

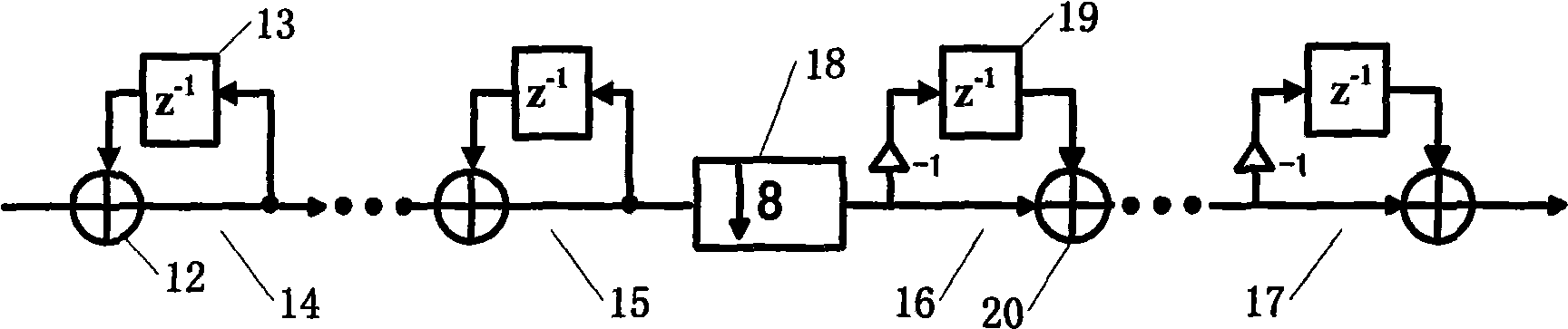

Digital signal down variable frequency processing system based on MIMO real time test platform

InactiveCN101510756AEasy to implementProcessing speedDigital technique networkTransmitter/receiver shaping networksDigital signal processingNumerically controlled oscillator

The invention discloses a digital signal down-conversion processing system based on an MIMO real-time testing platform, pertaining to the technical field of digital signal processing. The system comprises four DDC modules and each DDC module consists of four independent digital signal down-conversion processing channels. Each channel consists of an analog-to-digital converter, a digital quarter mixer and a digital decimation filter set. The digital quarter mixer consists of a digital controlled oscillator and two paths of multipliers, and the digital controlled oscillator is respectively connected with the two multipliers; the digital decimation filter set consists of two groups of filters with complete same parameters and each filter group respectively comprises a CIC decimation filter, a CFIR compensation filter and a PFIR matched filter which are connected in sequence. The system has good expansibility and modularization and can meet the requirements of real-time and high-speed performance.

Owner:SHANDONG UNIV

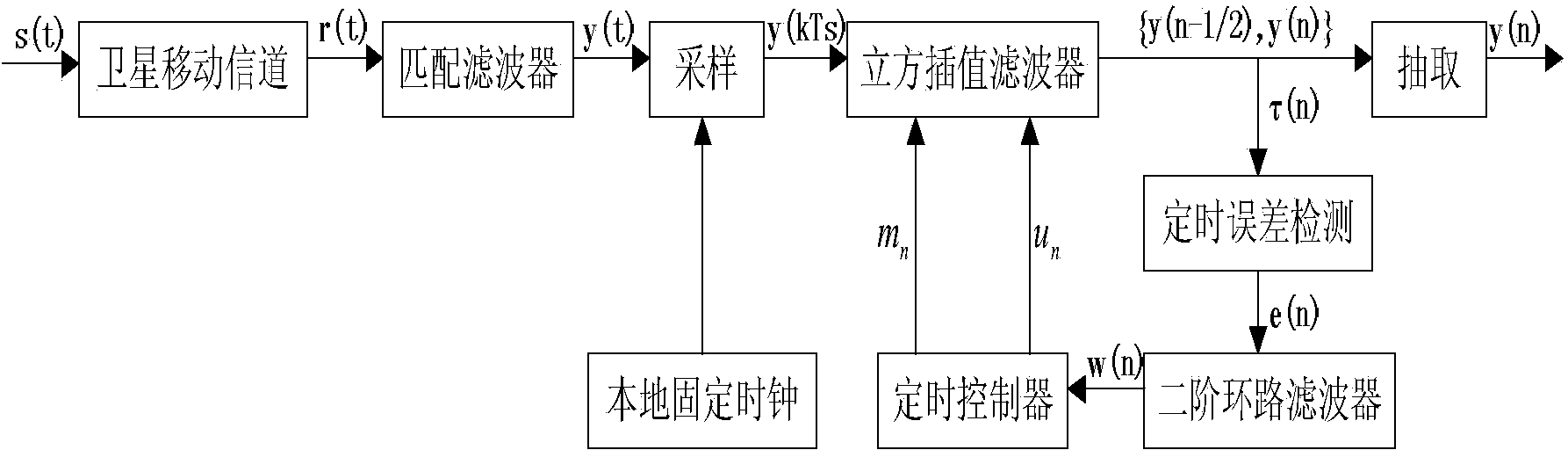

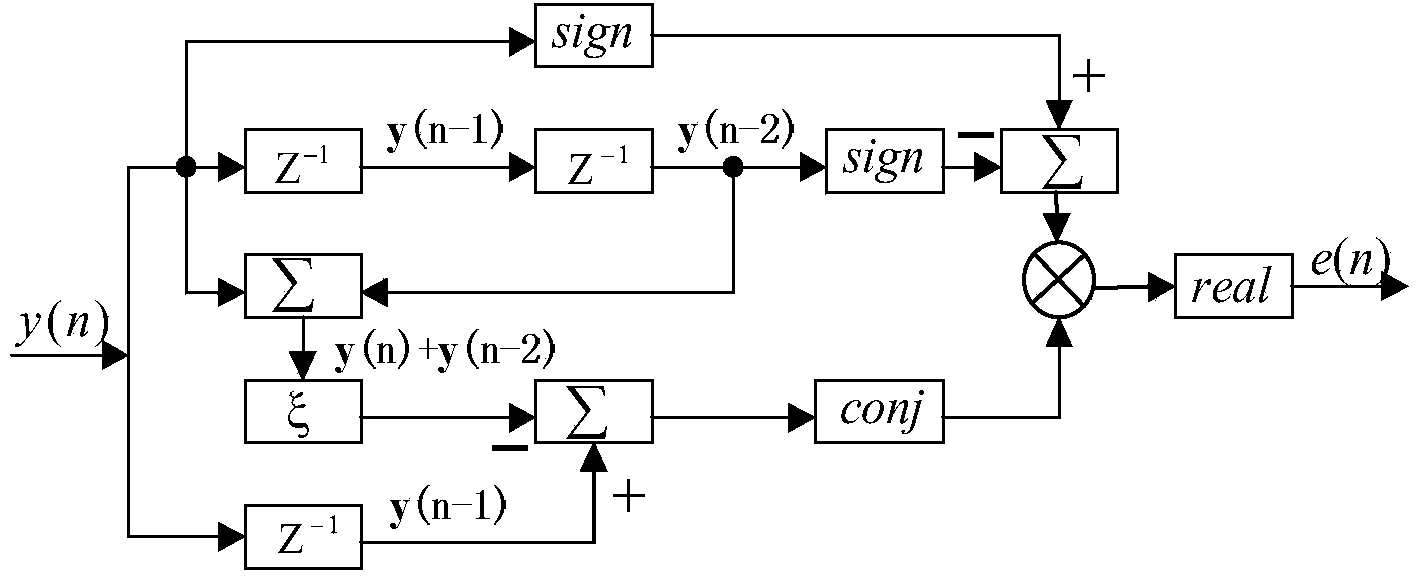

Satellite communication timing synchronization error detection method based on full-digital receiving

ActiveCN103457680AEliminate timing error skewEasy to lockReceivers monitoringSynchronising arrangementTime informationCoded element

Disclosed is a satellite communication timing synchronization error detection method based on full-digital receiving. In view of wide application of a Gardner algorithm in a timing synchronization loop and the limitation of the Gardner algorithm to band-limited signals, when polarity jump happens to two adjacent symbols, after two adjacent code elements are utilized for cosine roll-off forming filtering, the relation between samples of two best sampling points and the sample of a middle point of the two best sampling points is utilized, the effect of different adjacent symbols to the middle value is firstly taken into consideration and the effect value is calculated according to the minimum mean-square error criterion, and is then eliminated; when polarity jump does not happen to the adjacent symbols, how to reduce self noise generated by the situation that timing information can not be acquired is taken into consideration. A sign function sign (.) in an E-Gardner algorithm is utilized to solve the problem. Under the satellite channel environment, the enhancing algorithm is simple in structure, under the condition of a small roll-off coefficient, the performance of QPSK modulating signal clock capturing and error detection is improved, and the satellite communication timing synchronization error detection method based on full-digital receiving can effectively eliminate self-noise and reduce system resource consumption.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

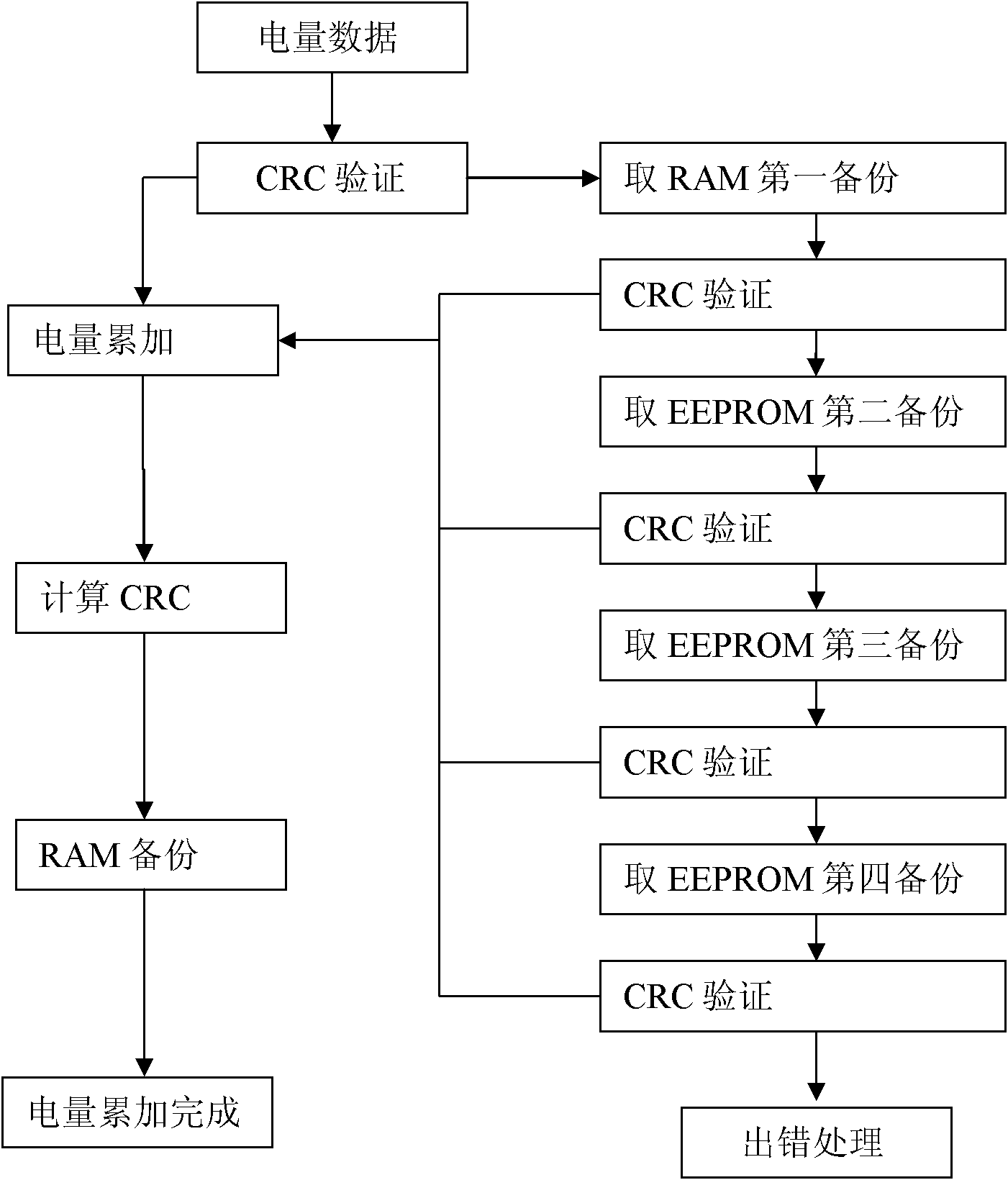

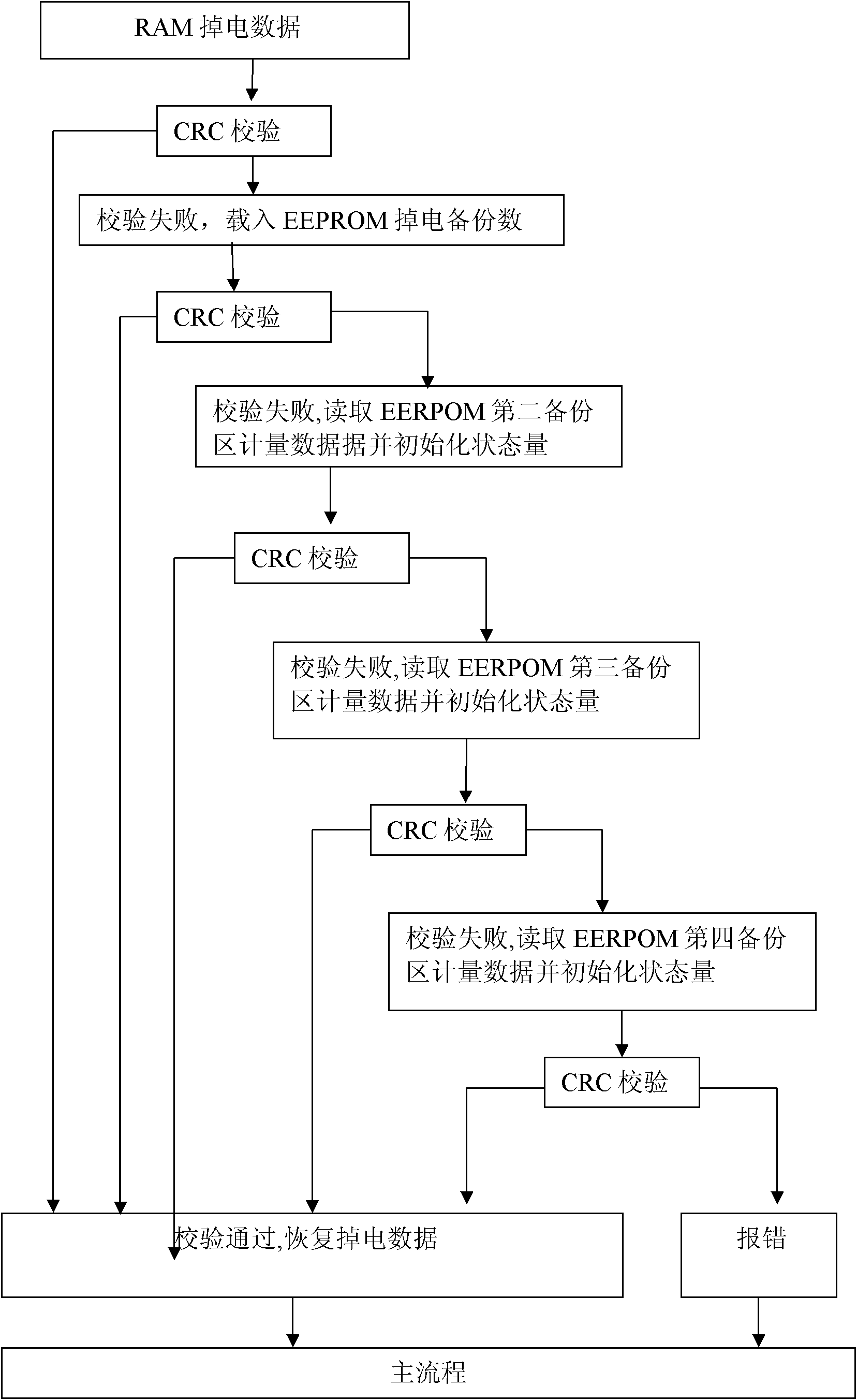

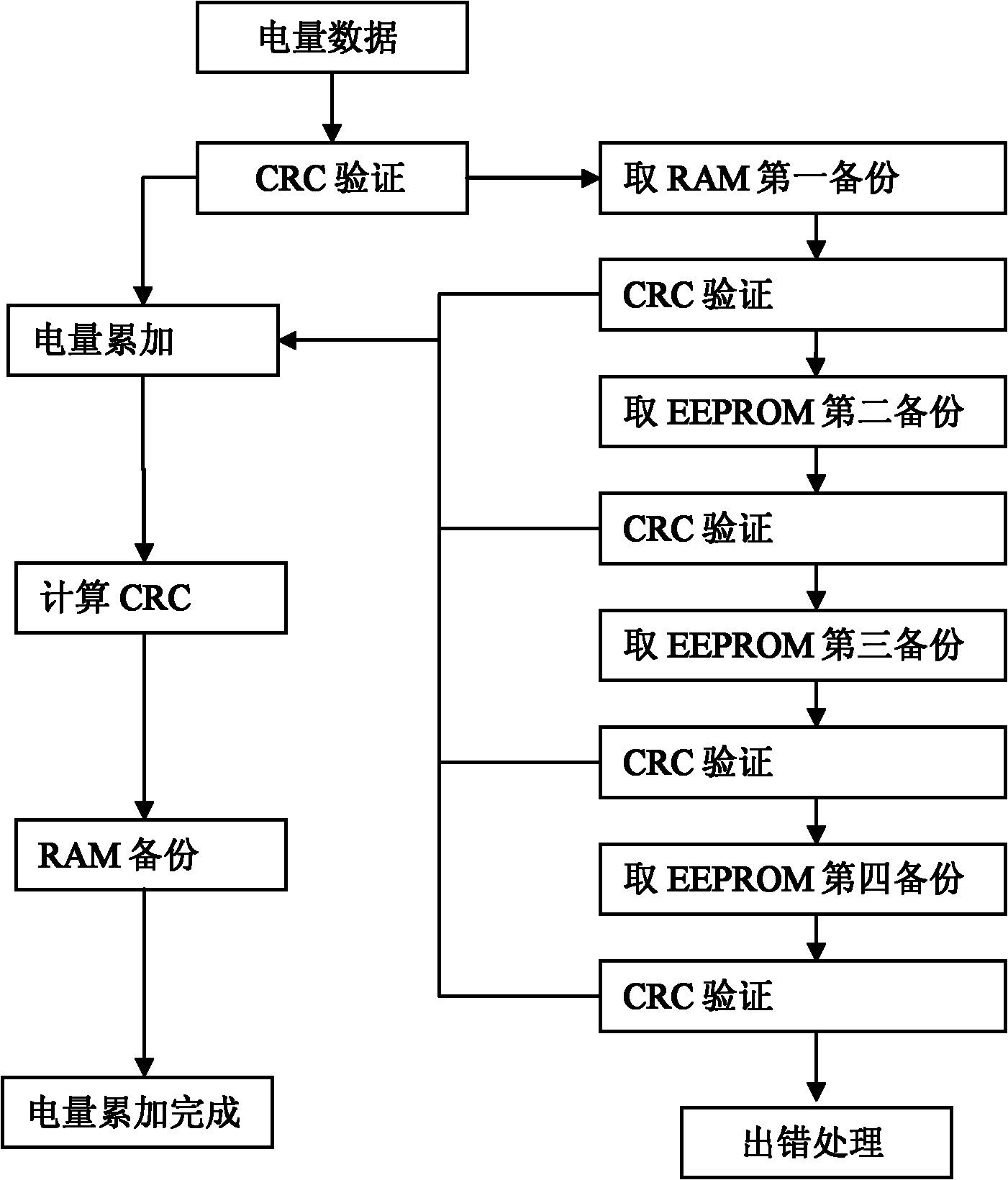

Method for managing high reliability of electric energy measurement data

InactiveCN101923112AReliable preservationAccurate recoveryElectrical measurementsElectric energyData reliability

The invention discloses a method for managing the high reliability of electric energy measurement data, mainly comprising the steps of preserving and dividing backup regions, preserving the measurement data and recovering the current measurement data. The invention ensures that the data can be preserved more accurately by setting a plurality of data backup regions, provides full preparation for recovering the data, ensures that the data can be recovered or updated more accurately through various judgments and verifications and effectively ensures the reliability of the measurement data. Besides, the position of an indicator is judged before a random storage receives the data and the length of a buffer zone is reasonably set, thereby the measurement data can not be damaged by other modules.

Owner:ZHUHAI ZHONGHUI MICROELECTRONICS

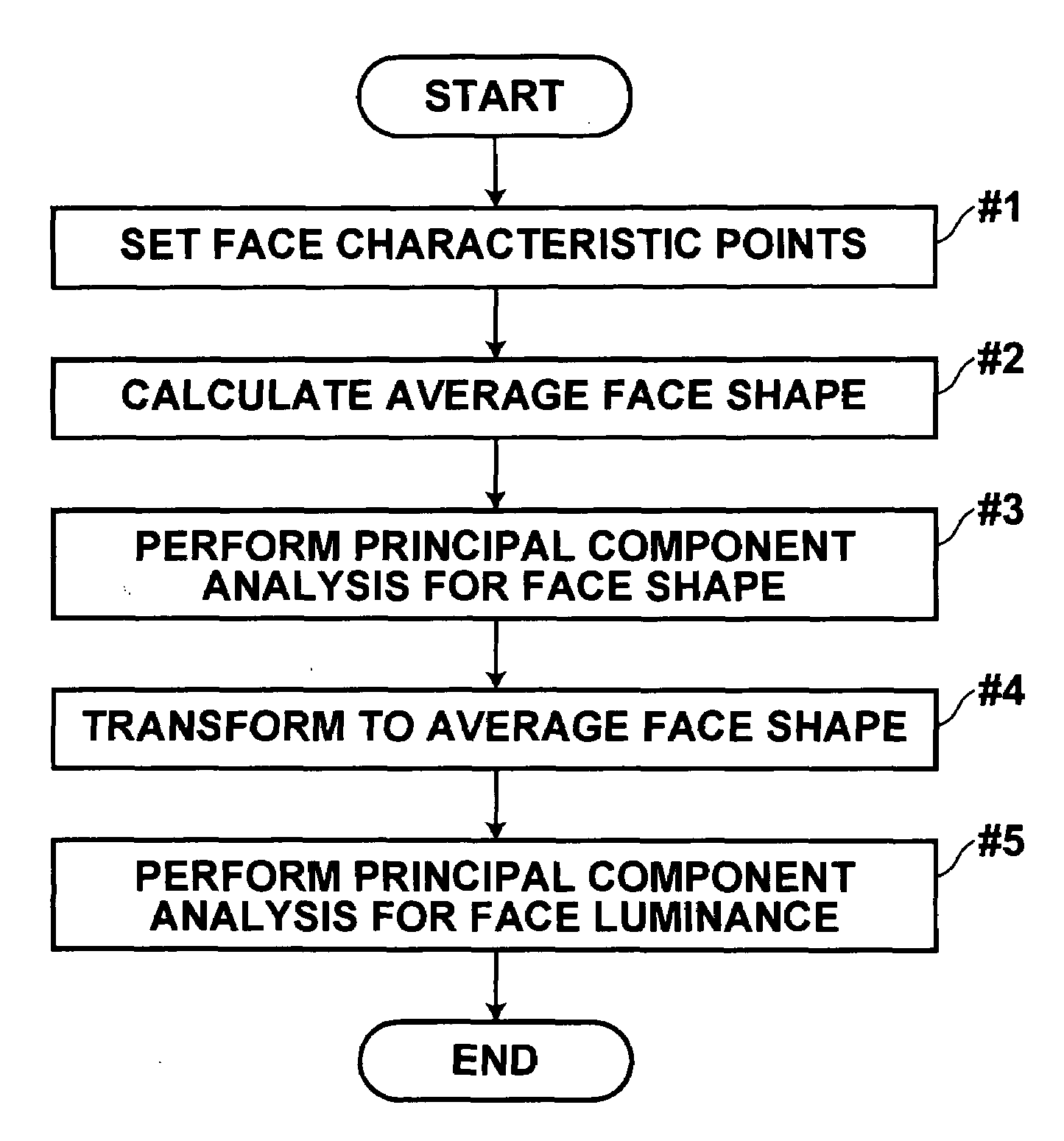

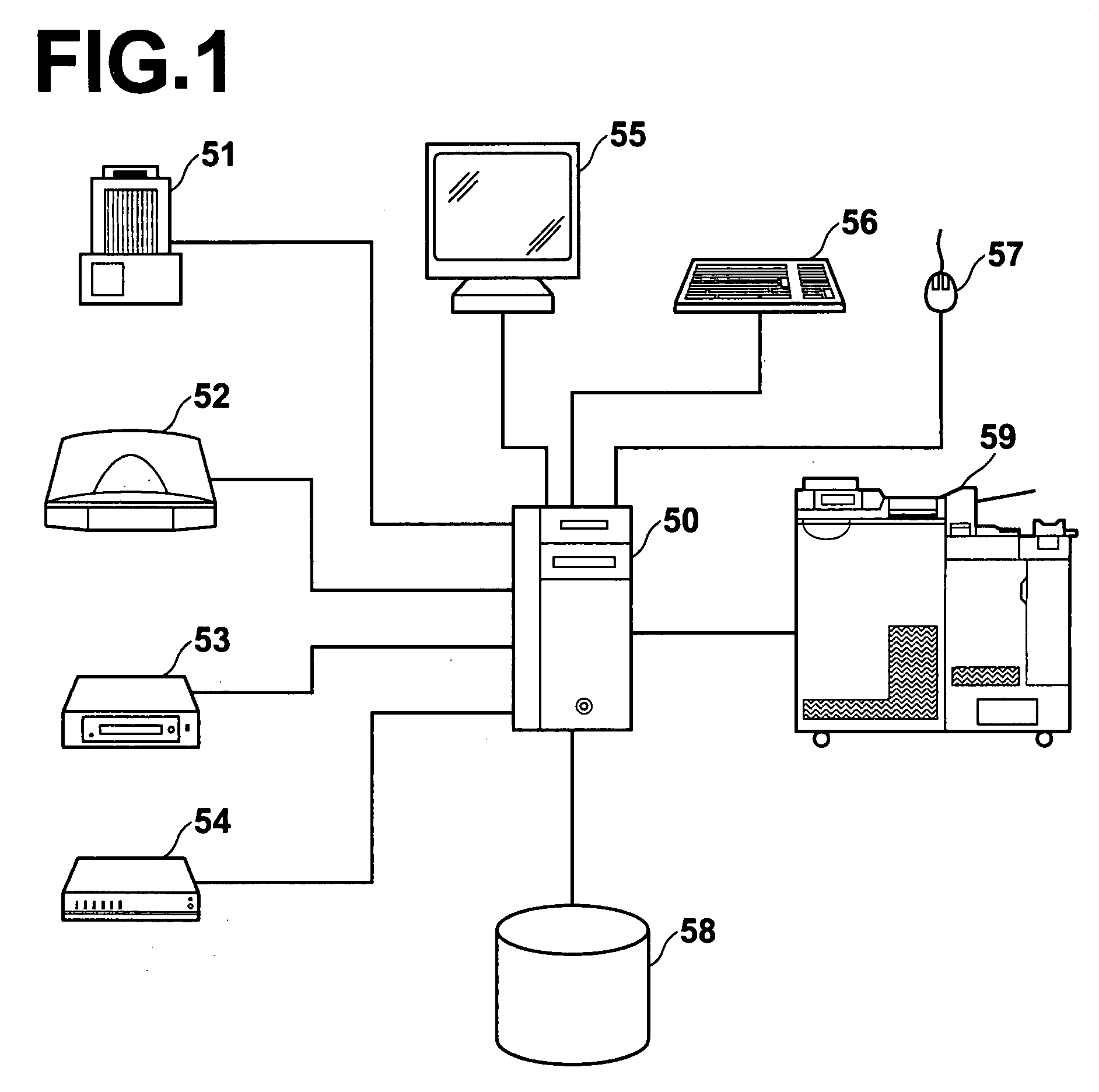

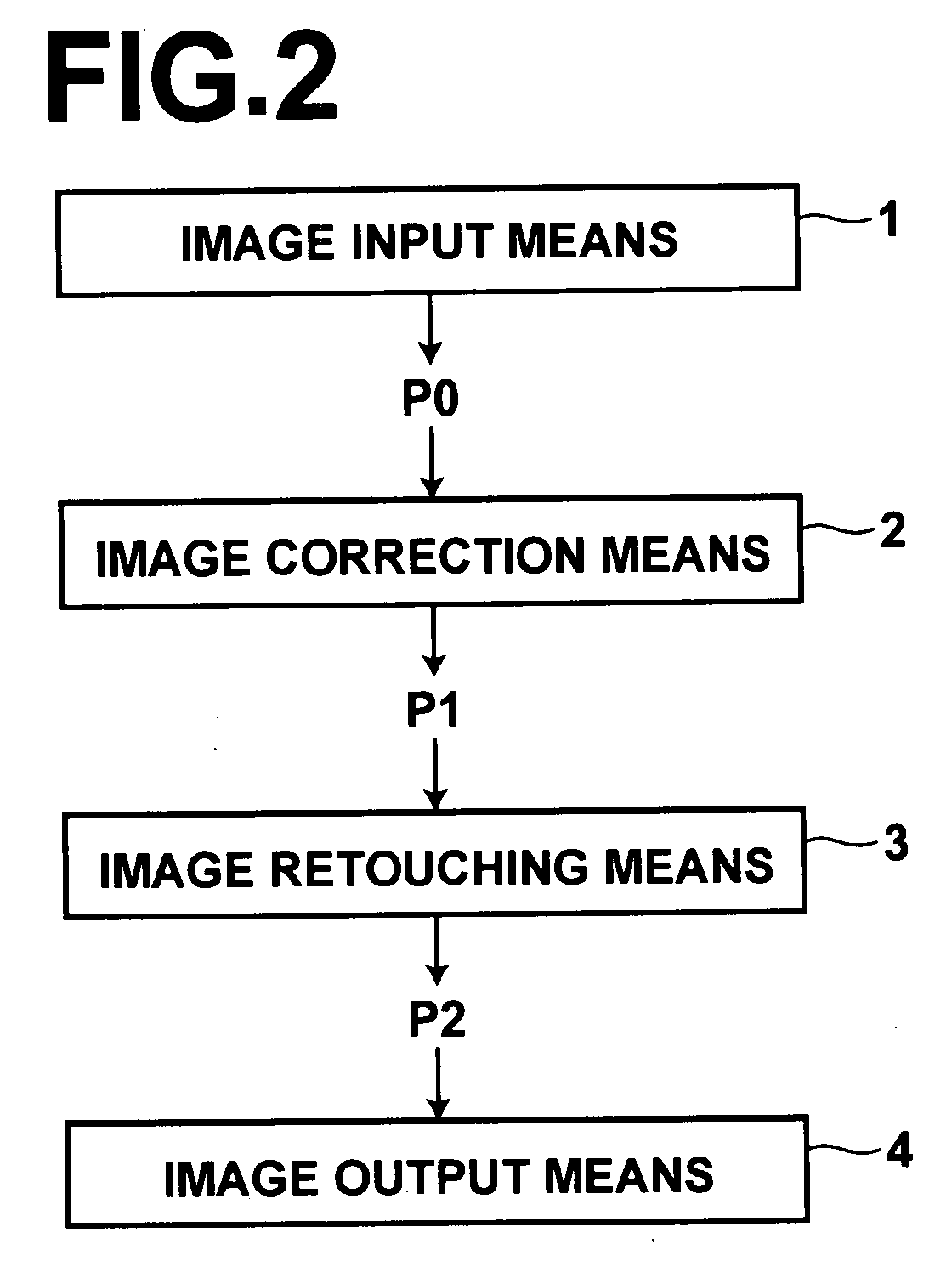

Image processing method, apparatus, and computer readable recording medium including program therefor

ActiveUS20070201750A1Recovered accurately and easilyHigh quality imagingSubcutaneous biometric featuresBlood vessel patternsImaging processingMathematical model

A face portion of an input image, an example of a predetermined structure, is applied to a mathematical model by the image recovery / addition section to recover a missing element of the face portion in the input image. The mathematical model is generated by a predetermined statistical method, such as the AAM scheme or the like, based on a plurality of sample images representing the face portion including the recovery target element. Thereafter, the face portion is reconstructed to include the missing element based on the parameter corresponding to the face portion obtained by applying the face portion to the model, and the face portion of the input image is replaced by the reconstructed face portion to produce a restored image by the image reconstruction section.

Owner:FUJIFILM CORP

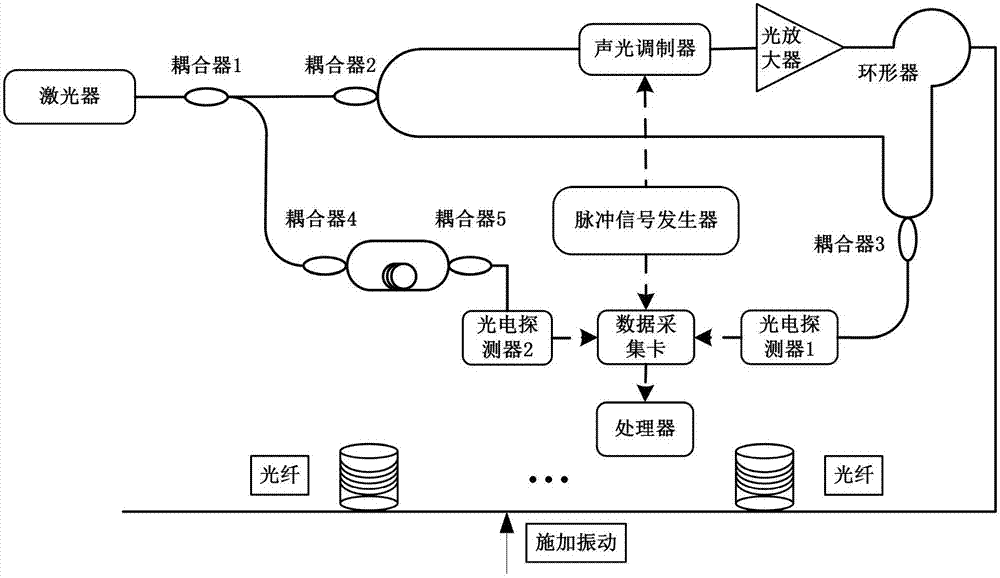

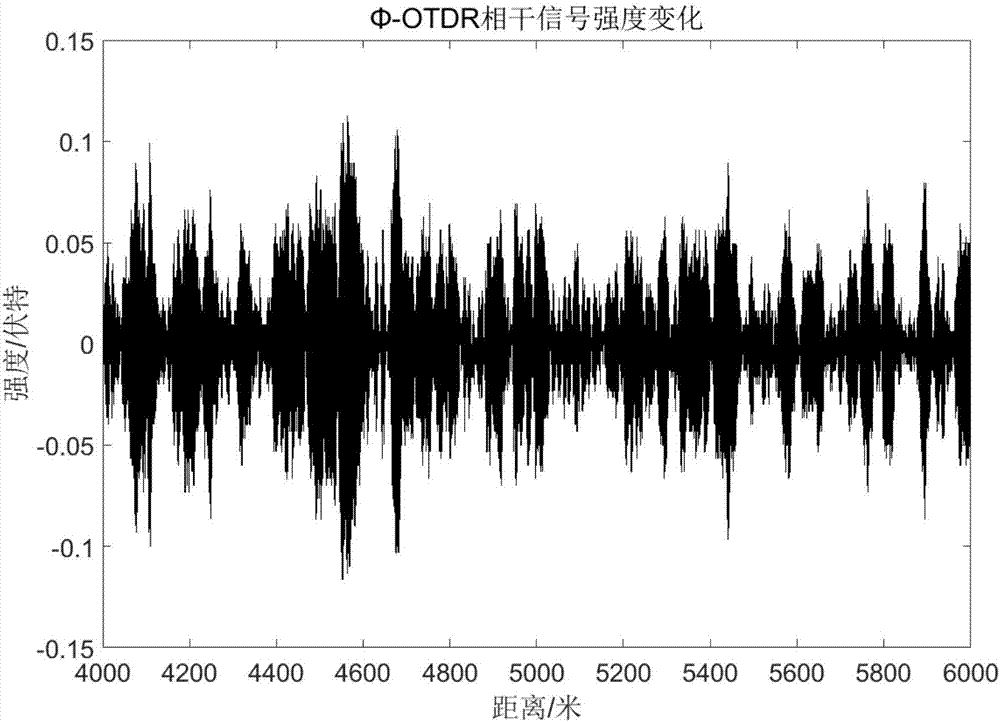

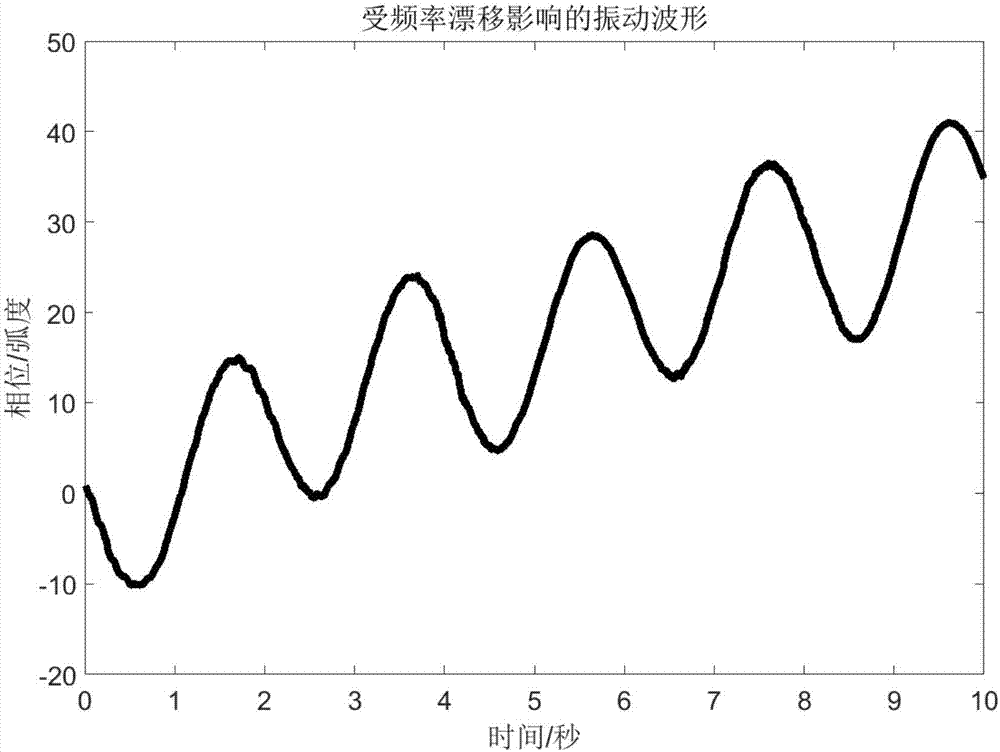

Frequency drift compensation-based phase sensitive optical time domain reflectometer and measuring method thereof

ActiveCN107957276AEliminate the effects of frequency driftAccurate recoverySubsonic/sonic/ultrasonic wave measurementUsing wave/particle radiation meansTime delaysMach–Zehnder interferometer

The invention discloses a frequency drift compensation-based phase sensitive optical time domain reflectometer and a measuring method thereof. According to the system, a Mach-Zehnder interferometer (MZI) with fixed arm length difference is formed and a laser frequency drift detection module is formed by introducing time delay optical fiber and connecting optical fiber with specific optical path difference on the basis of the traditional phi-OTDR. The frequency drift of the layer is obtained according to the signal intensity of the MZI in the system and the phase position of a phi-OTDR sensingsystem is compensated through a phase compensation algorithm, so that the influence on the sensing property of the phi-OTDR by the frequency drift of the laser is eliminated. The influence on the sensing property by the frequency drift of the laser is eliminated by constructing a novel phi-OTDR system, the influence of noise can be reduced by processing methods such as phase compensation, and theaccuracy of quantitatively measuring a vibration event by the system is improved.

Owner:NANJING UNIV

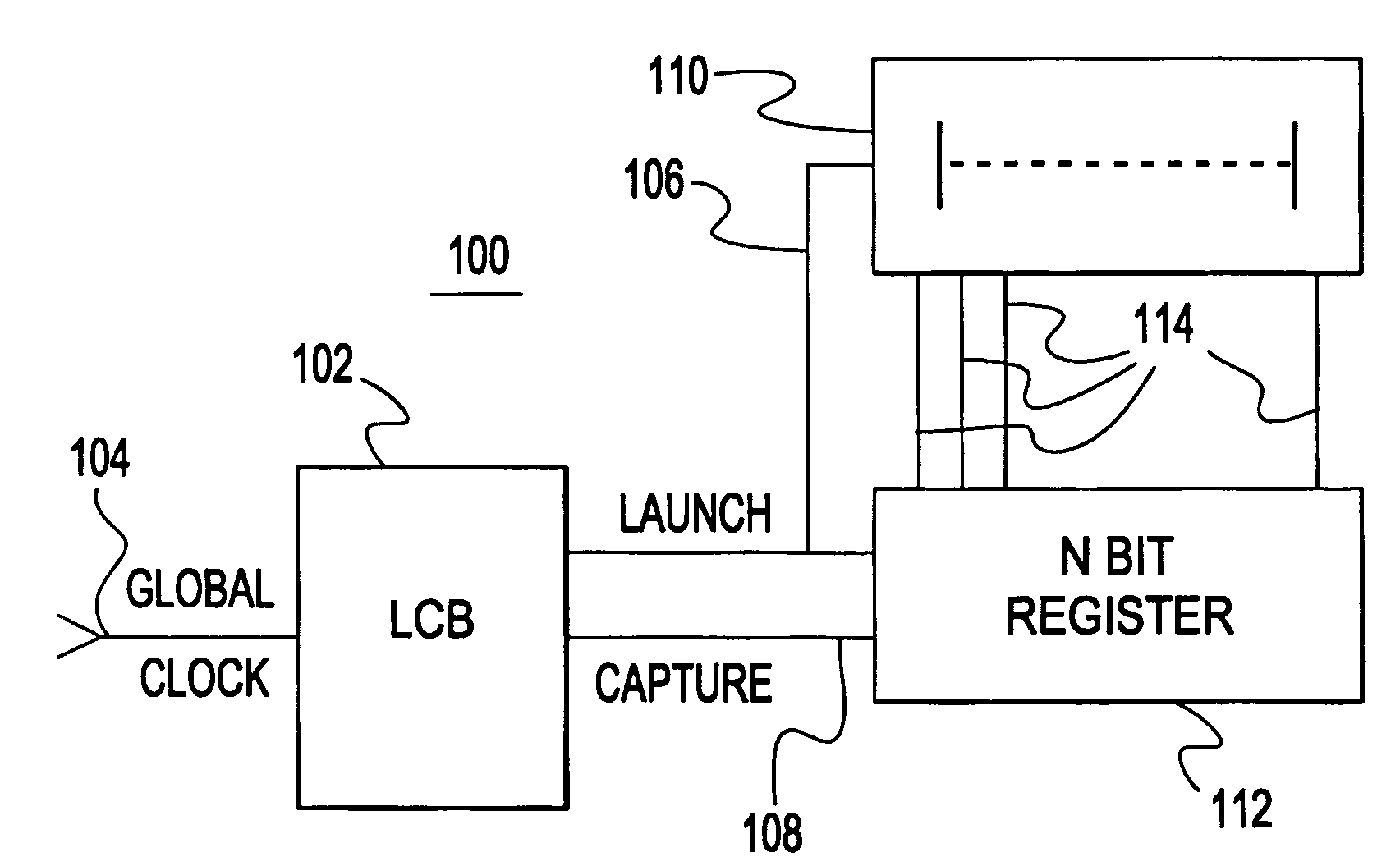

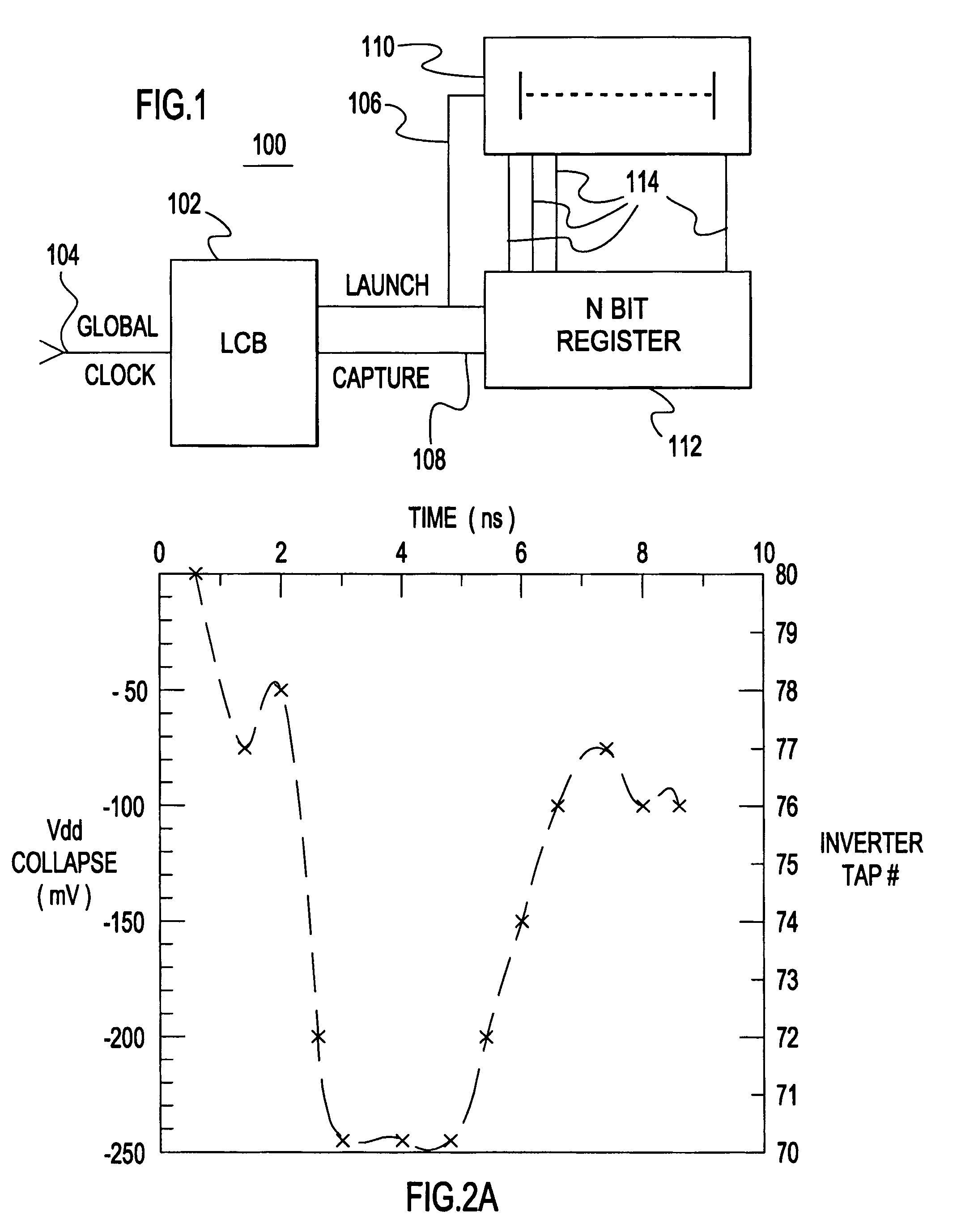

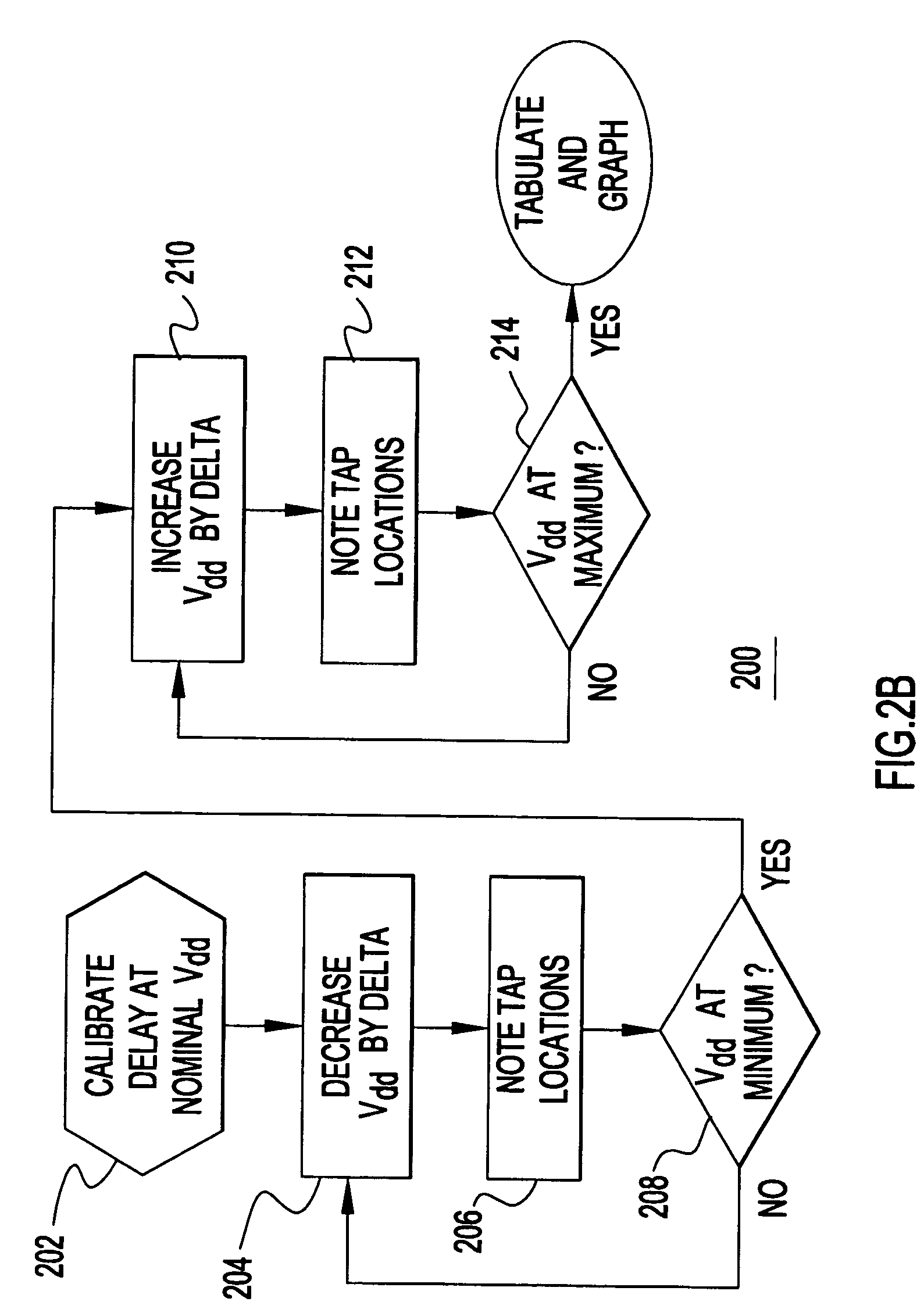

Built in self test circuit for measuring total timing uncertainty in a digital data path

InactiveUS7400555B2Accurately determineAccurate recoveryDigital circuit testingElectromechanical unknown time interval measurementDigital dataProcessor register

A circuit for measuring timing uncertainty in a clocked digital path and in particular, the number of logic stages completed in any clock cycle. A local clock buffer receives a global clock and provides a complementary pair of local clocks. A first local (launch) clock is an input to a delay line, e.g., 3 clock cycles worth of series connected inverters. Delay line taps (inverter outputs) are inputs to a register that is clocked by the complementary clock pair to capture progression of the launch clock through the delay line and identify any variation (e.g., from jitter, VDD noise) in that progression. Global clock skew and across chip gate length variation can be measured by cross coupling launch clocks from a pair of such clock buffers and selectively passing the local and remote launch clocks to the respective delay lines.

Owner:GLOBALFOUNDRIES INC

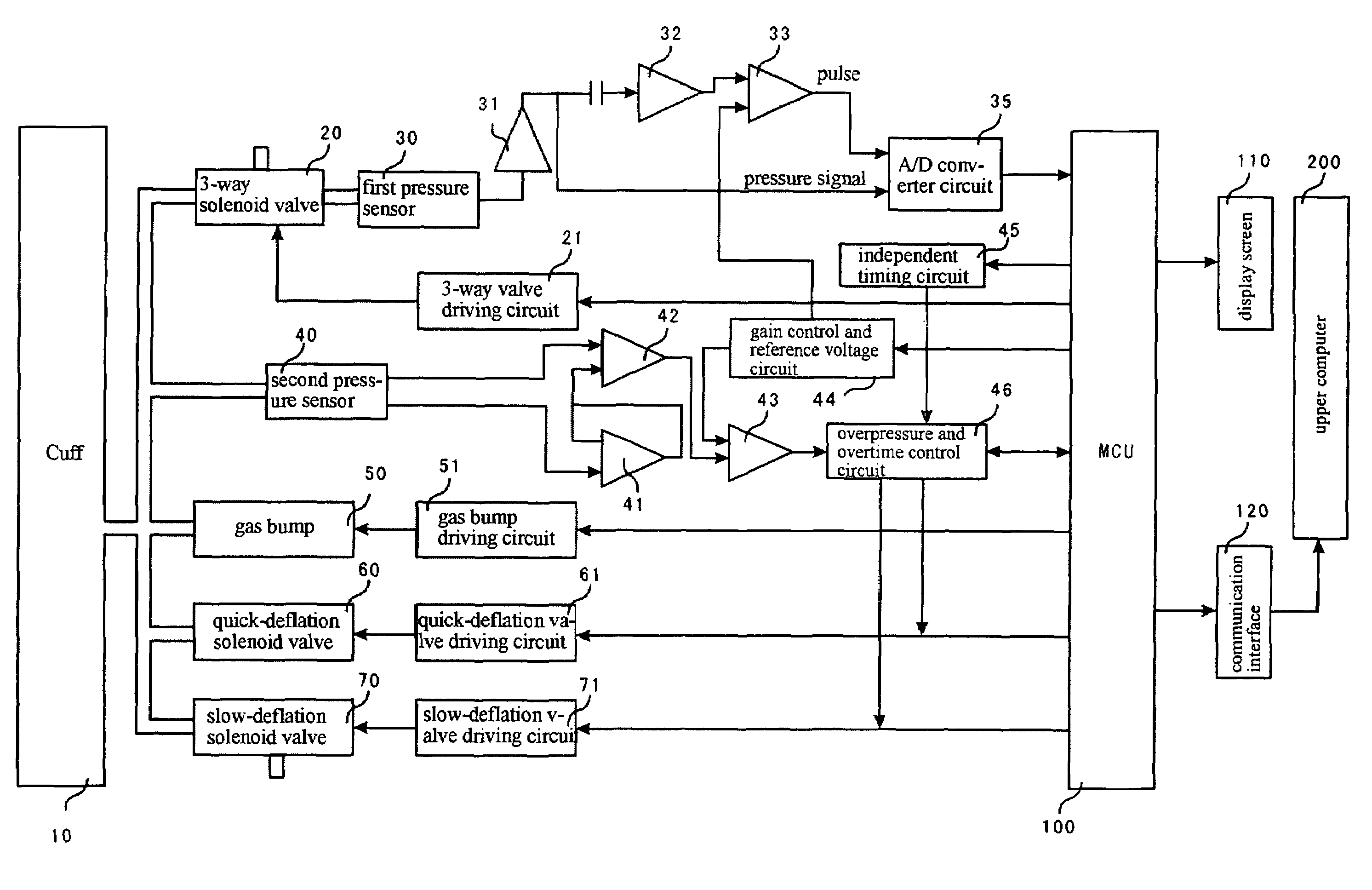

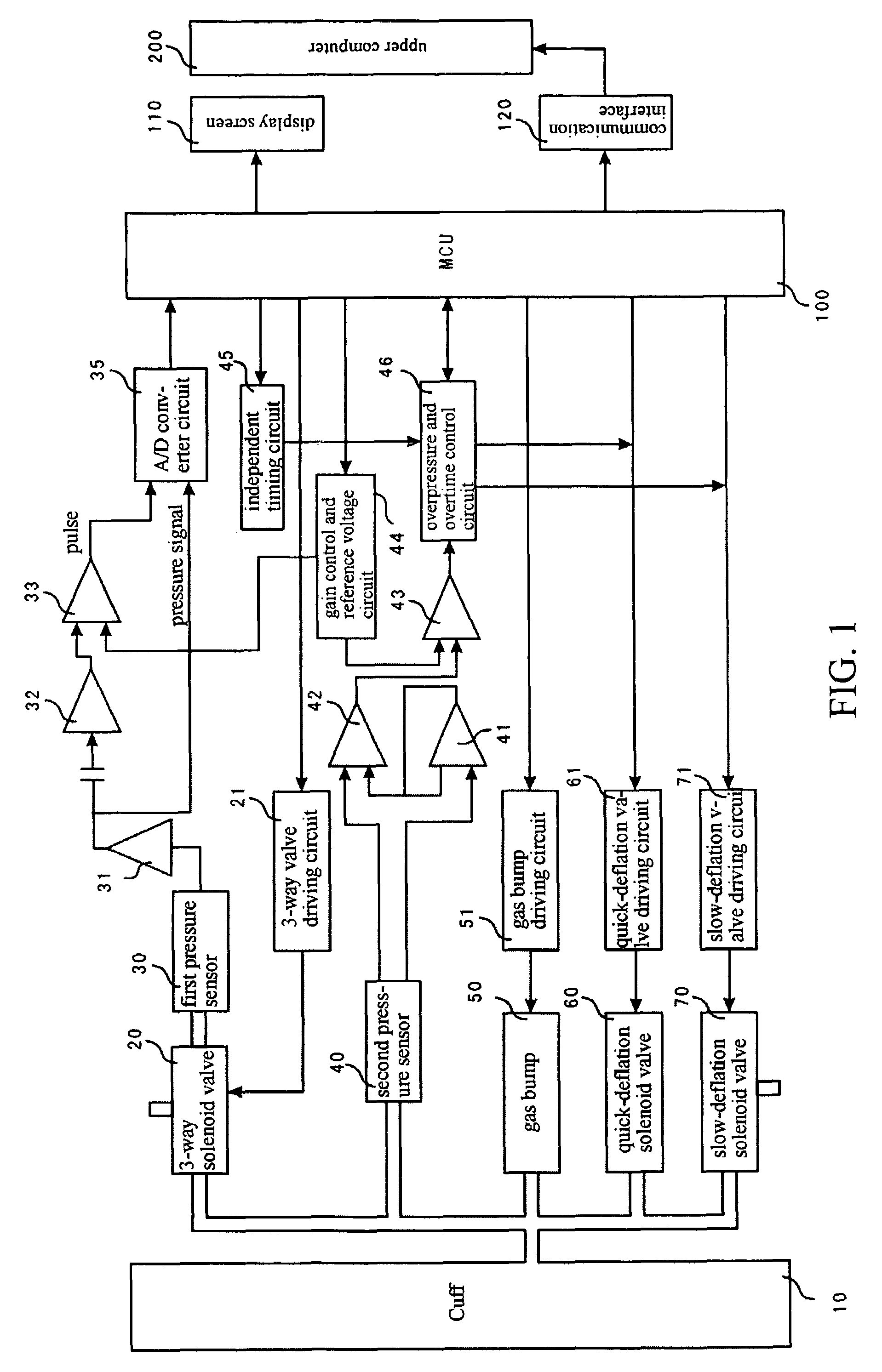

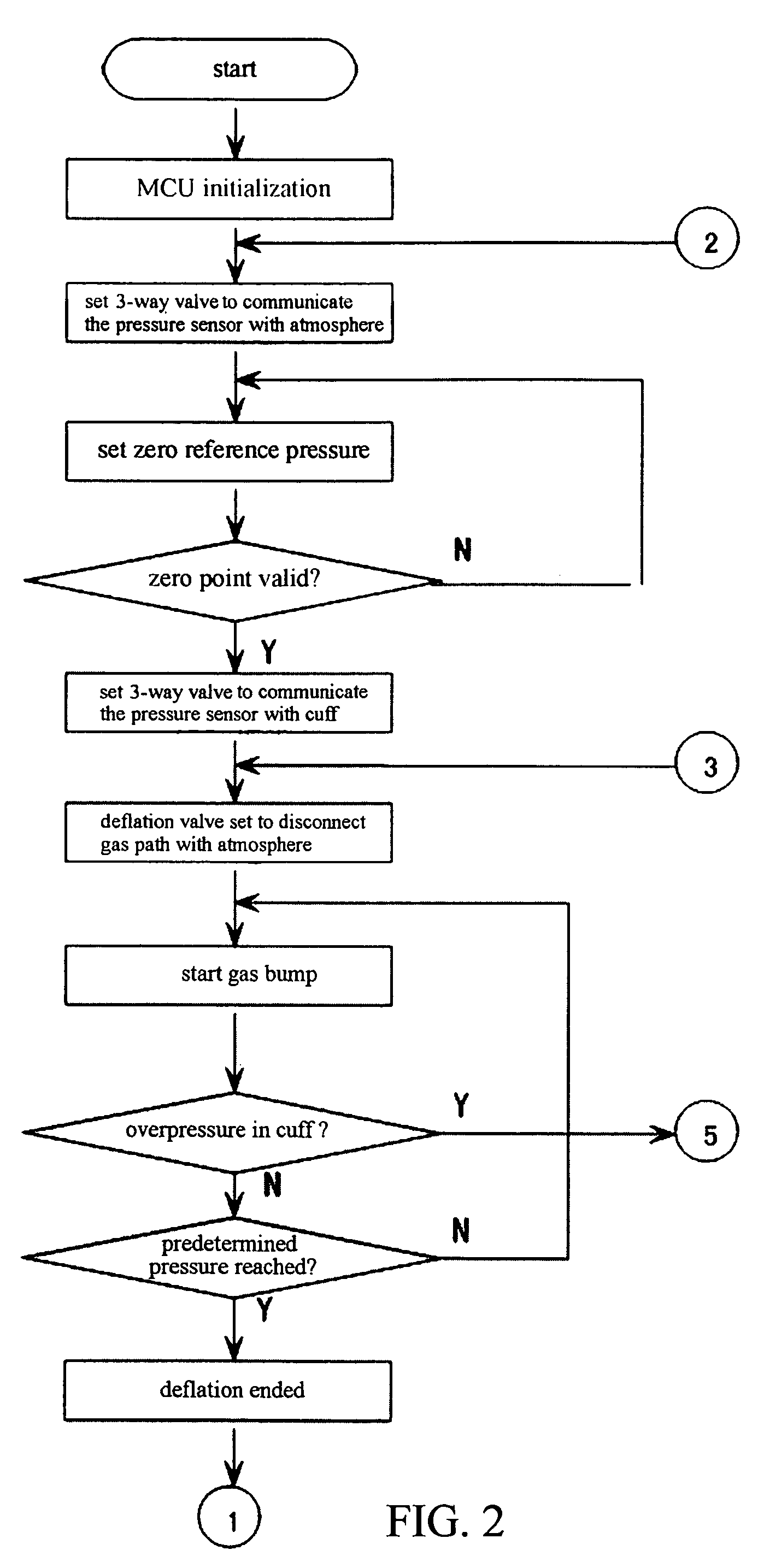

Non-invasive electronic method and apparatus for measuring blood pressure

ActiveUS7468038B2High measurement accuracyAccurate recoveryCatheterDiagnostic recording/measuringAir atmosphereSolenoid valve

Provided is a non-invasive electronic method and apparatus for measuring blood pressure, in which the data is processed with an algorithm of non-linear fitting for recovering trend envelope of an oscillating PW by a firmware, so that the trend envelope of PW amplitude can be recovered accurately, and the obtained average pressure shows higher degree of agreement with the real situation in clinic. In this apparatus, a 3-way solenoid valve (20) is arranged between a cuff (10) and a first pressure sensor (30), wherein the common port of the 3-way solenoid valve (20) is connected with the first pressure sensor (30), the normally open port thereof connected with the cuff (10), and the normally closed port thereof connected with the air atmosphere during zeroing process. Moreover, an independent timing circuit (45) is provided additionally. In the measurement method of the present invention, the zeroing is performed with the help of the 3-way solenoid valve (20). Once a state of overtime or overpressure occurs, an air bump (50) is immediately closed, and a quick-deflation solenoid valve (60) is opened so that the pressure in the cuff (10) is released to ensure safe application.

Owner:SHENZHEN MINDRAY BIO MEDICAL ELECTRONICS CO LTD

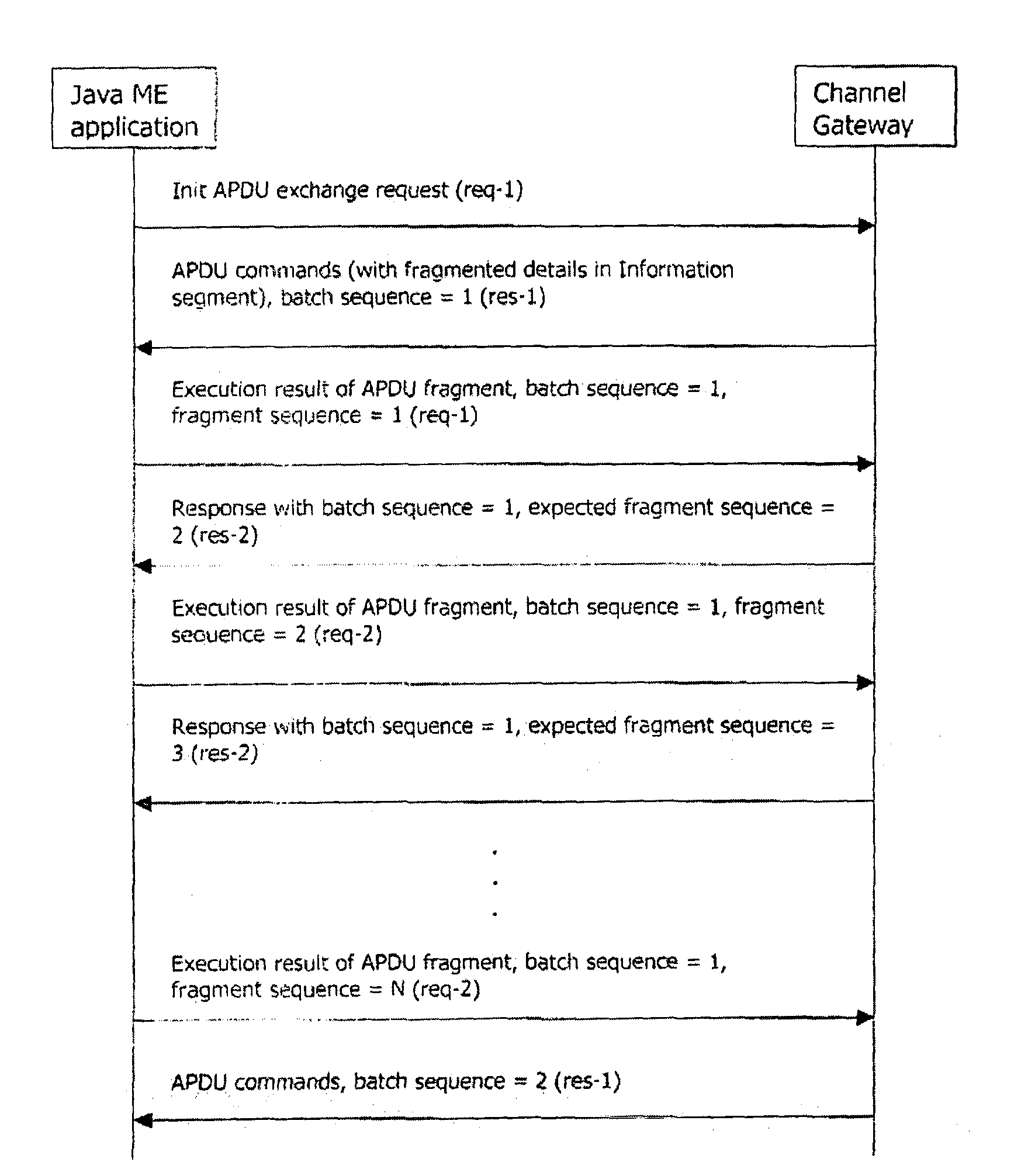

Process for communication between a device running JAVA me and a server over the air, as well as related system

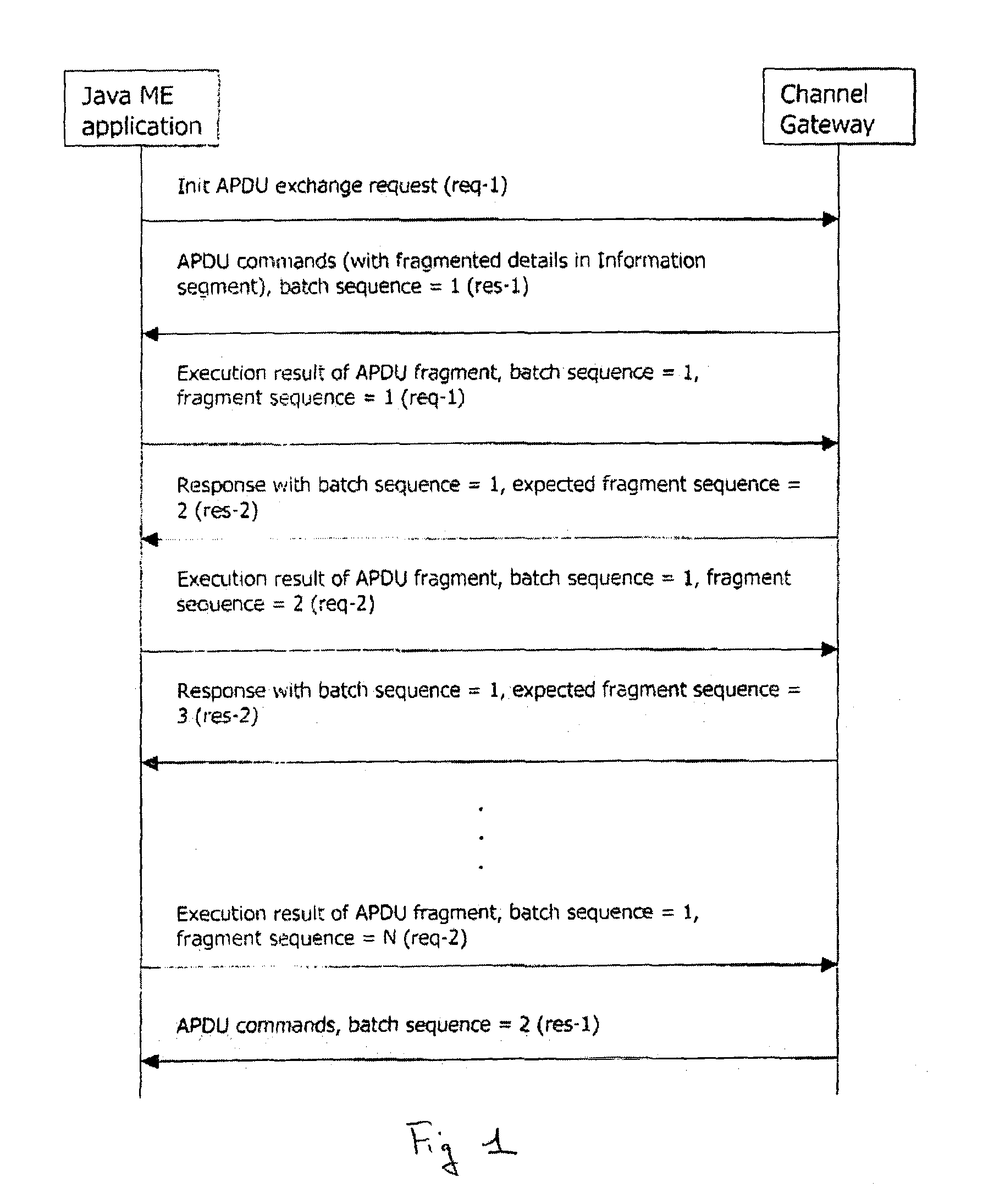

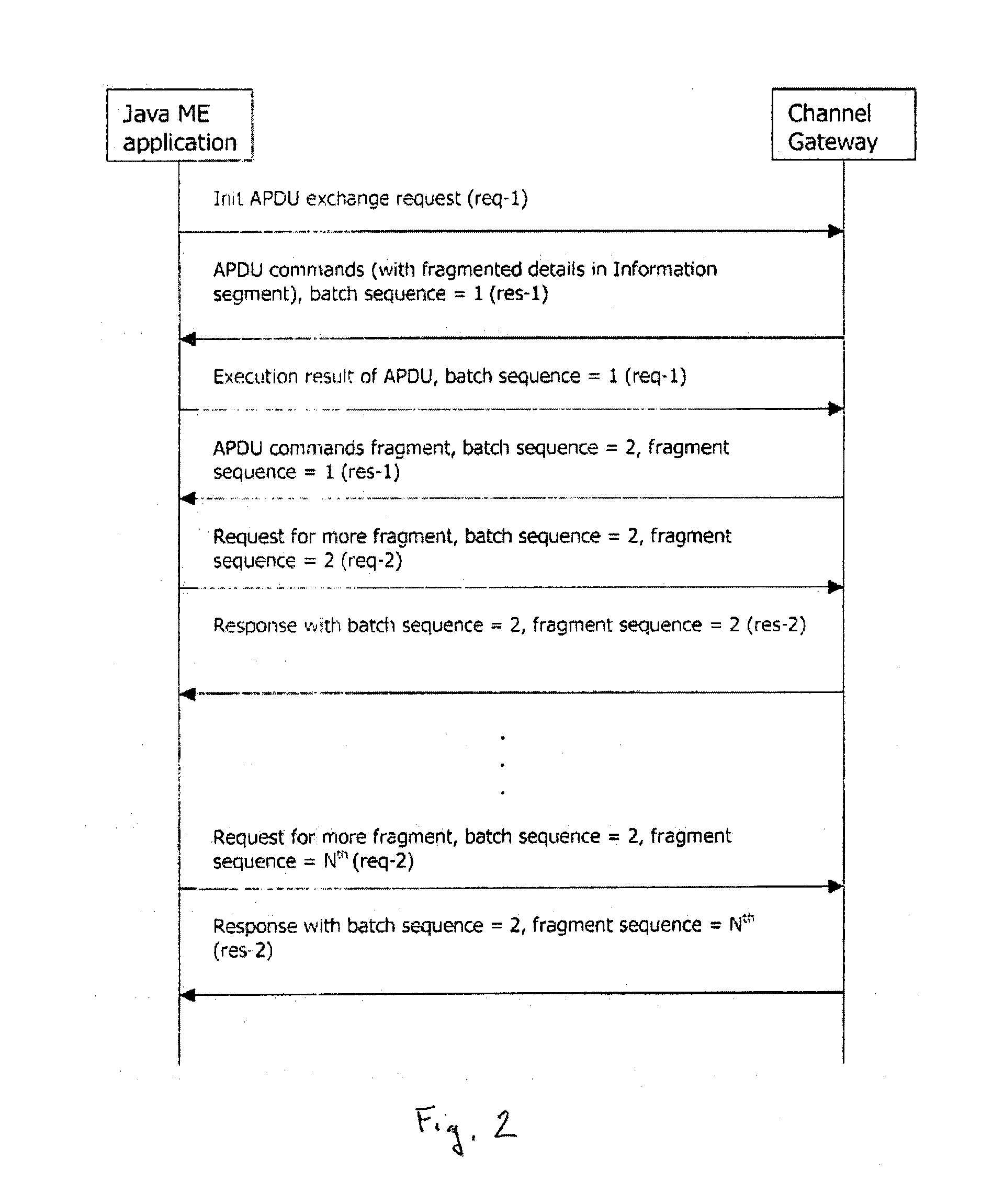

InactiveUS20100070649A1Accurate recoveryMultiple digital computer combinationsTransmissionBinary responseHypertext Transfer Protocol over Secure Socket Layer

Process of communication via HTTP or HTTPS between a device running Java ME® and a server over the air, said server receiving and transmitting SOAP (Simple Object Access Protocol) messages from / to an operator on a host over a network and being capable of exchanging SOAP messages under Application Protocol Data Unit (APDU) data form / with the device, characterized in that the SOAP messages are translated from / to binary messages according to a protocol in the server, said binary messages being exchanged with the device, the binary messages being binary request messages or binary response messages.

Owner:CASSIS INTION

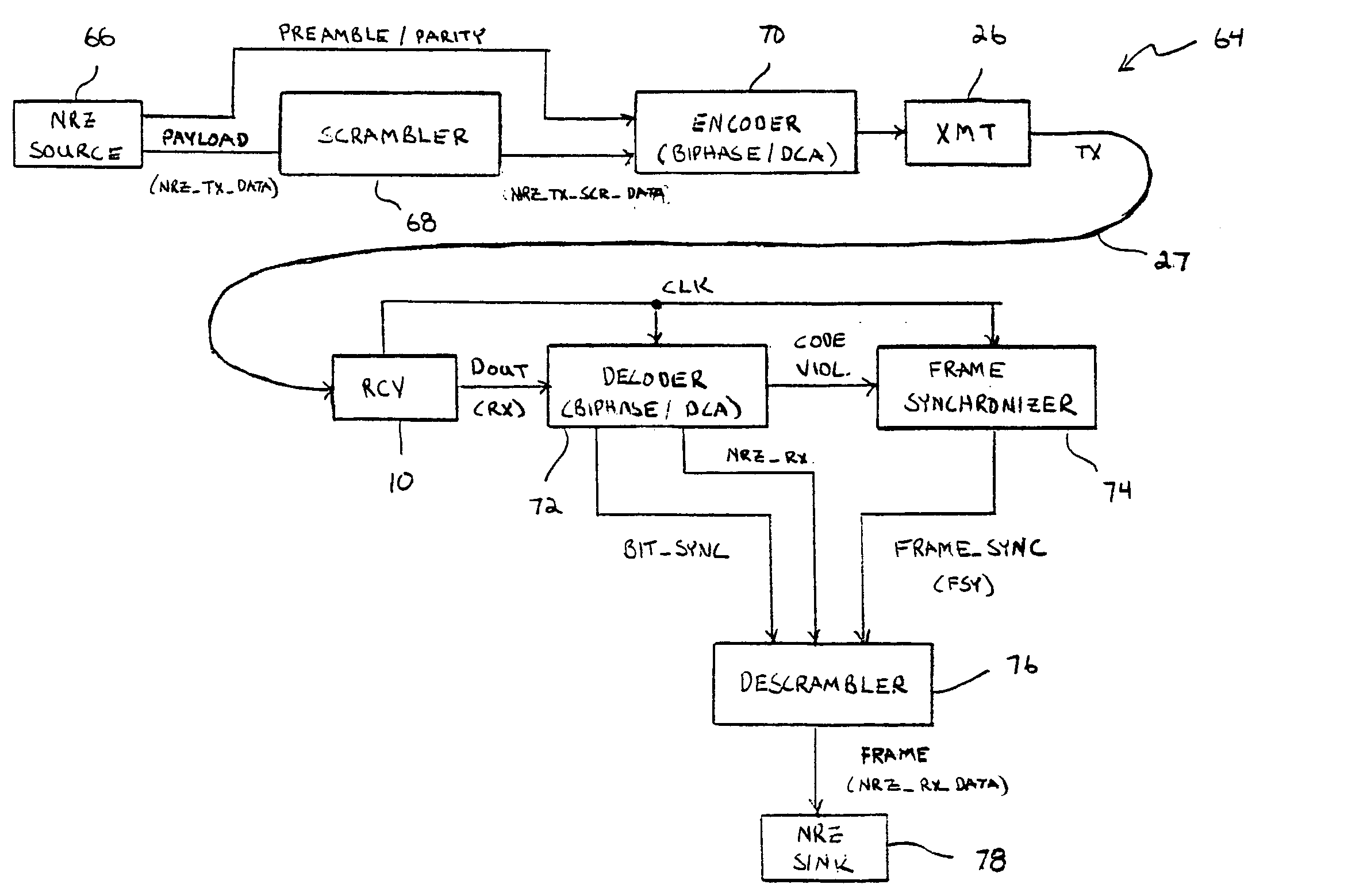

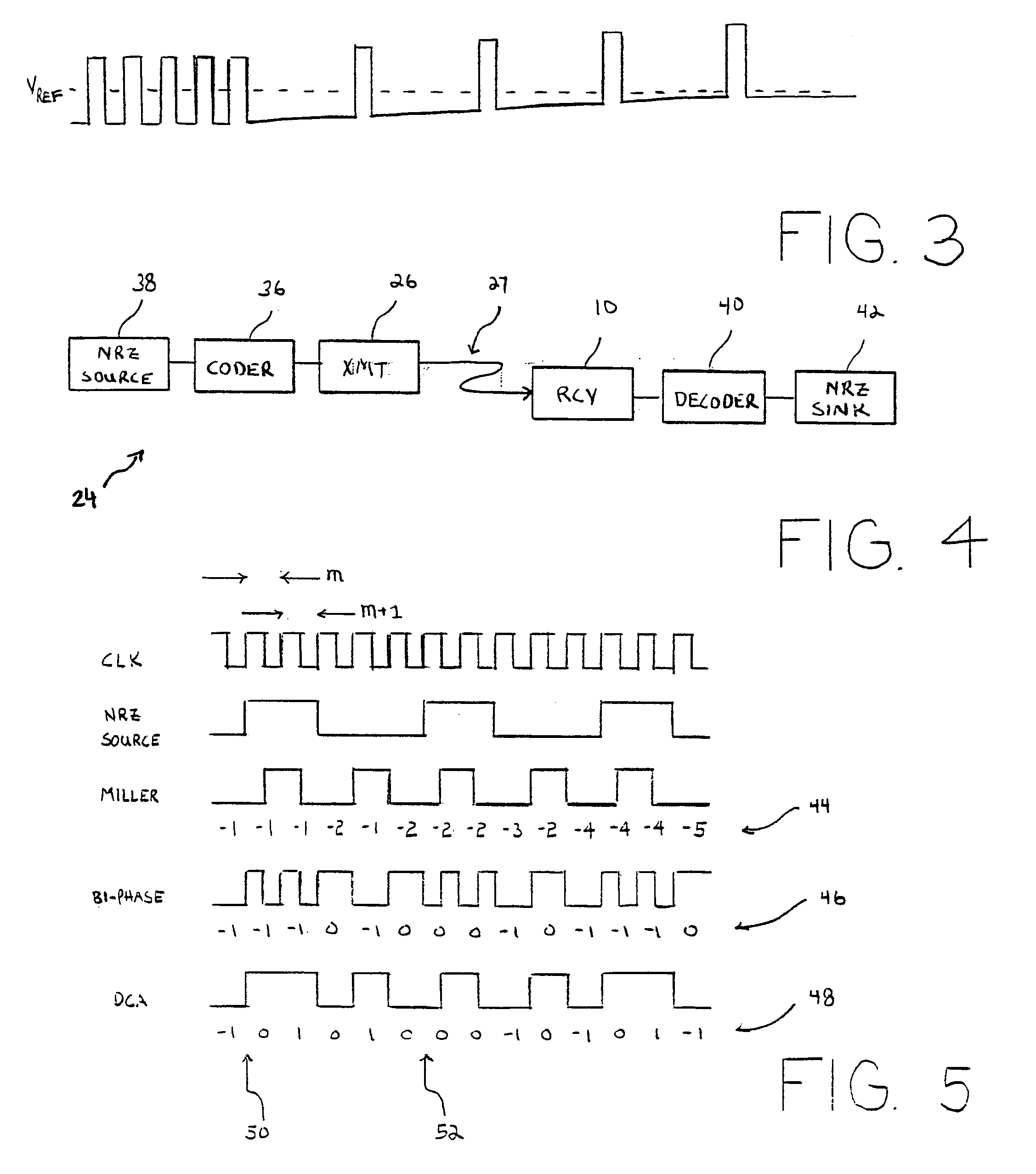

Selective scrambler for use in a communication system and method to minimize bit error at the receiver

ActiveUS20060083328A1Shorten the overall cycleEliminate accumulationError prevention/detection by using return channelPulse automatic controlShift registerCommunications system

A communication system for transmitting and receiving a sequence of bits, and the methodology for transferring that sequence of bits are provided. The communication system includes a transmitting circuit and a receiving circuit. Within the transmitting circuit is a scrambler that comprises a shift register, an enable circuit, and an output circuit. The shift register temporarily stores n bits within the sequence of bits, and the enable circuit enables the shift register to store bits that arise only within the payload section of a frame. The output circuit includes a feedback, and several taps within the n stages to scramble logic values within the sequence of n bits output from the shift registers thus effectively preventing in most instances the sequence of bits from exceeding n number of the same logic value. Within the receiving circuit is a descrambler also having a shift register, an enable circuit, and an output circuit. The descrambler recompiles the scrambled data back to its original form. The scrambler is preferably placed before an encoder in the transmission path to minimize data dependent, low frequency jitter. The encoder is used to place a coding violation into the frame to signal the beginning of each frame, and to encode the parity with an offset against any DC accumulation of the coding violation and the scrambled payload to eliminate all DC accumulation (baseline wander) within each frame.

Owner:MICROCHIP TECH INC

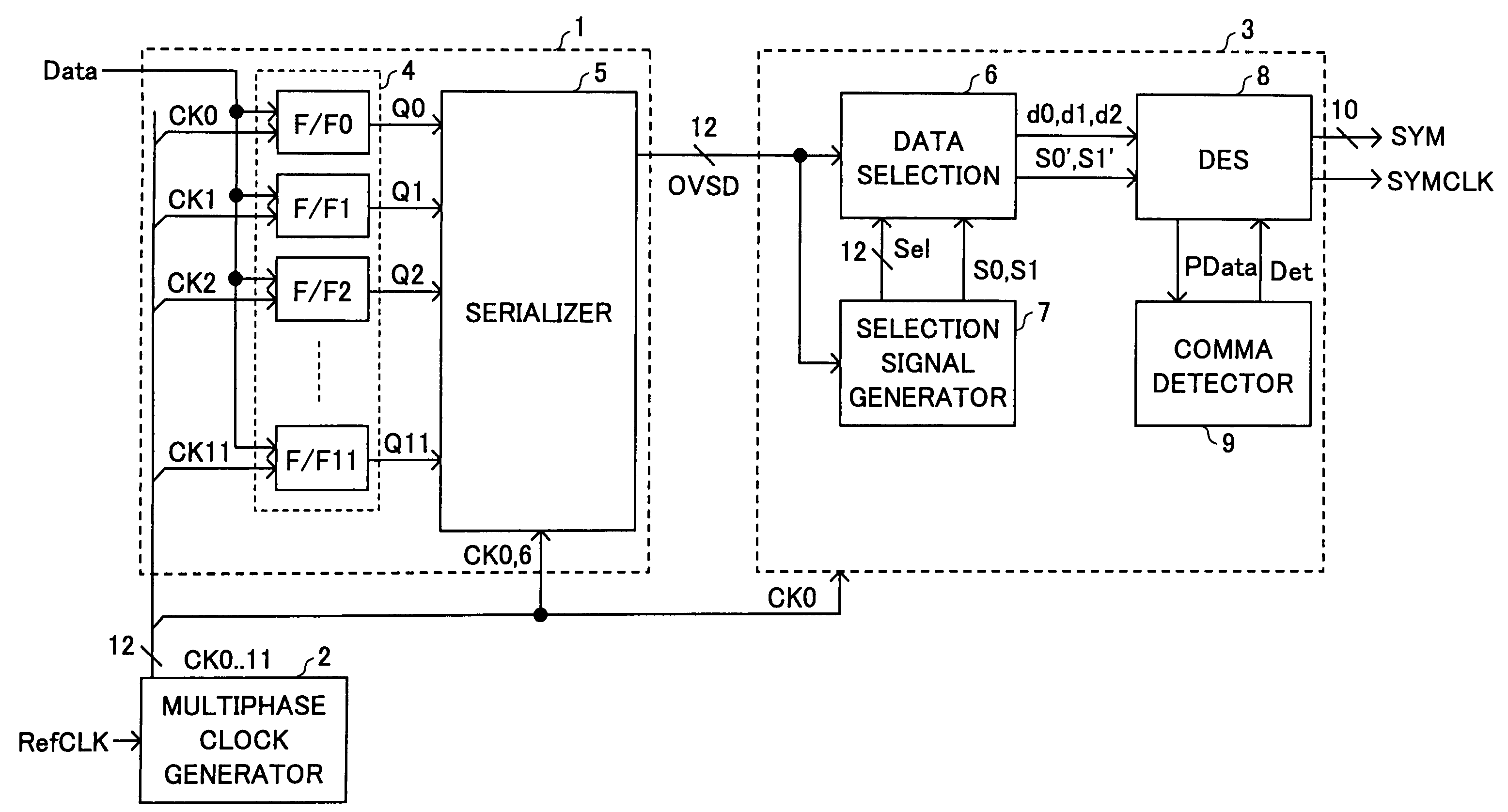

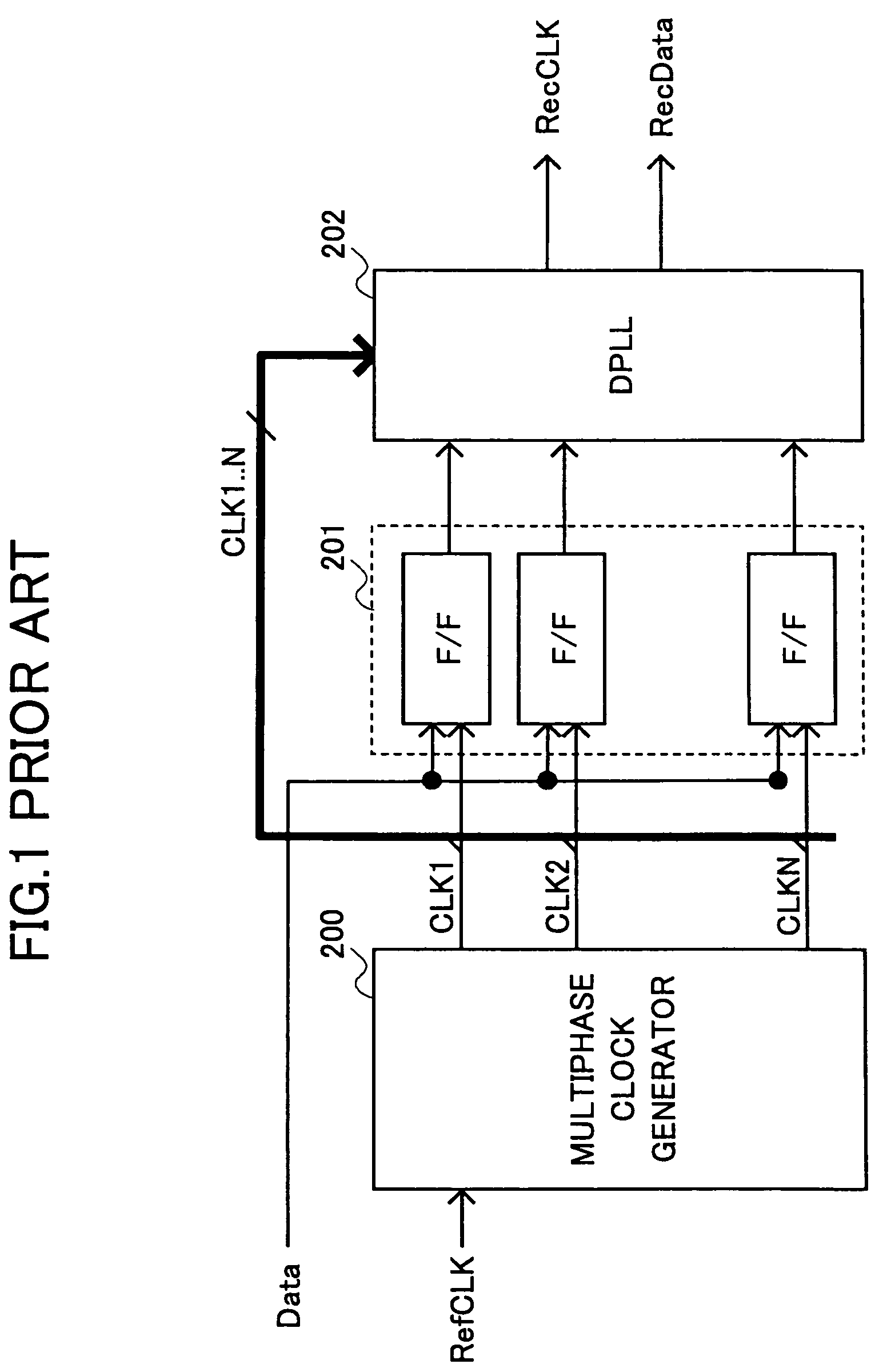

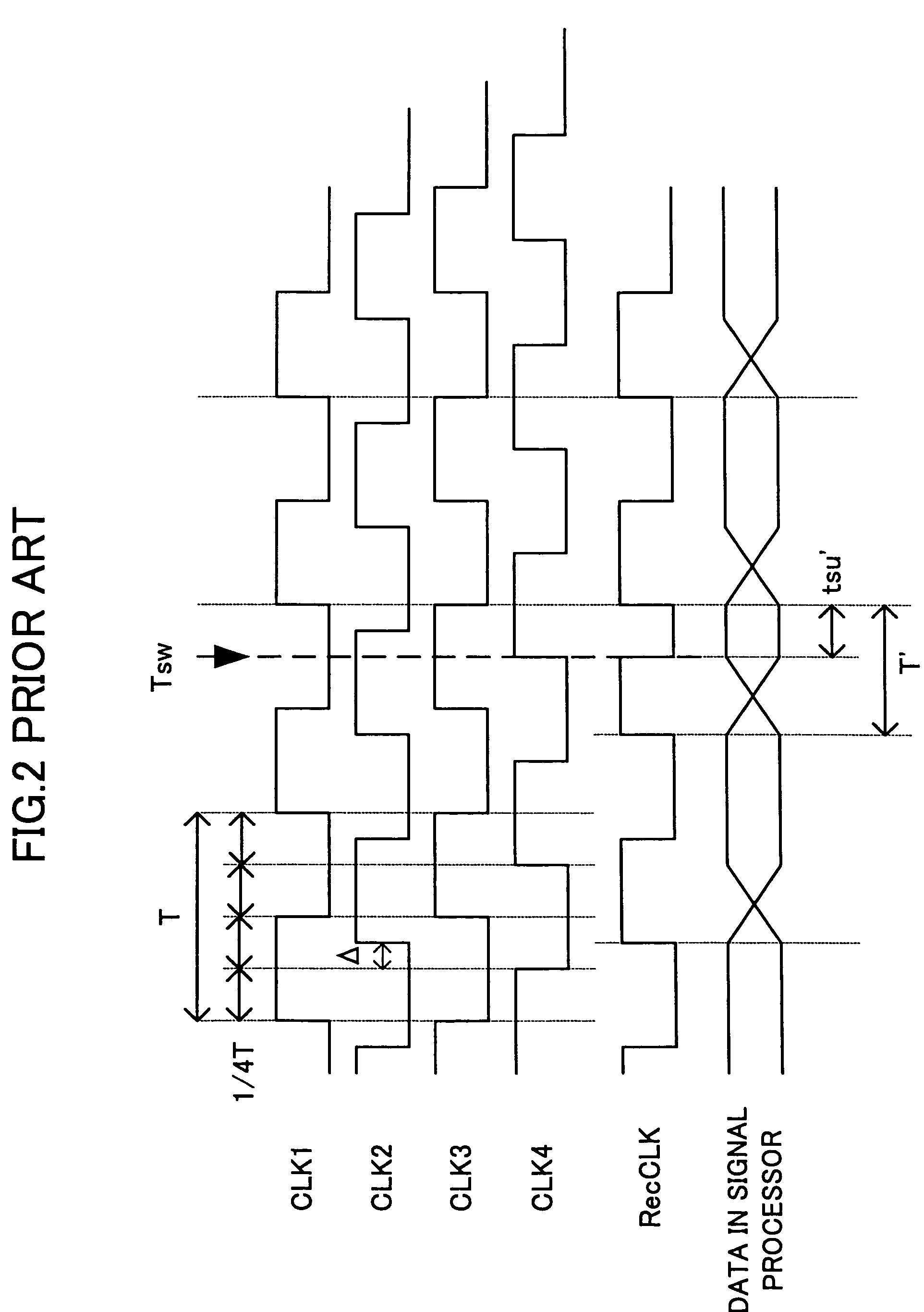

Data recovery method and data recovery circuit

ActiveUS7684531B2Restore accuratelyLess influenceLine-faulsts/interference reductionSynchronising arrangementComputer scienceData recovery circuit

A data recovery method includes the steps of:(a) oversampling data that have been transmitted serially in sync with a first clock of frequency f1, using a multiphase clock generated by shifting a phase of a second clock of frequency f2 at a prescribed interval, the second frequency f2 of the multiphase clock being at or below the first frequency f1; (b) extracting f1 / f2 bits on average from the oversampled data; and(c) recovering the extracted bits to restore the received data.

Owner:RICOH KK

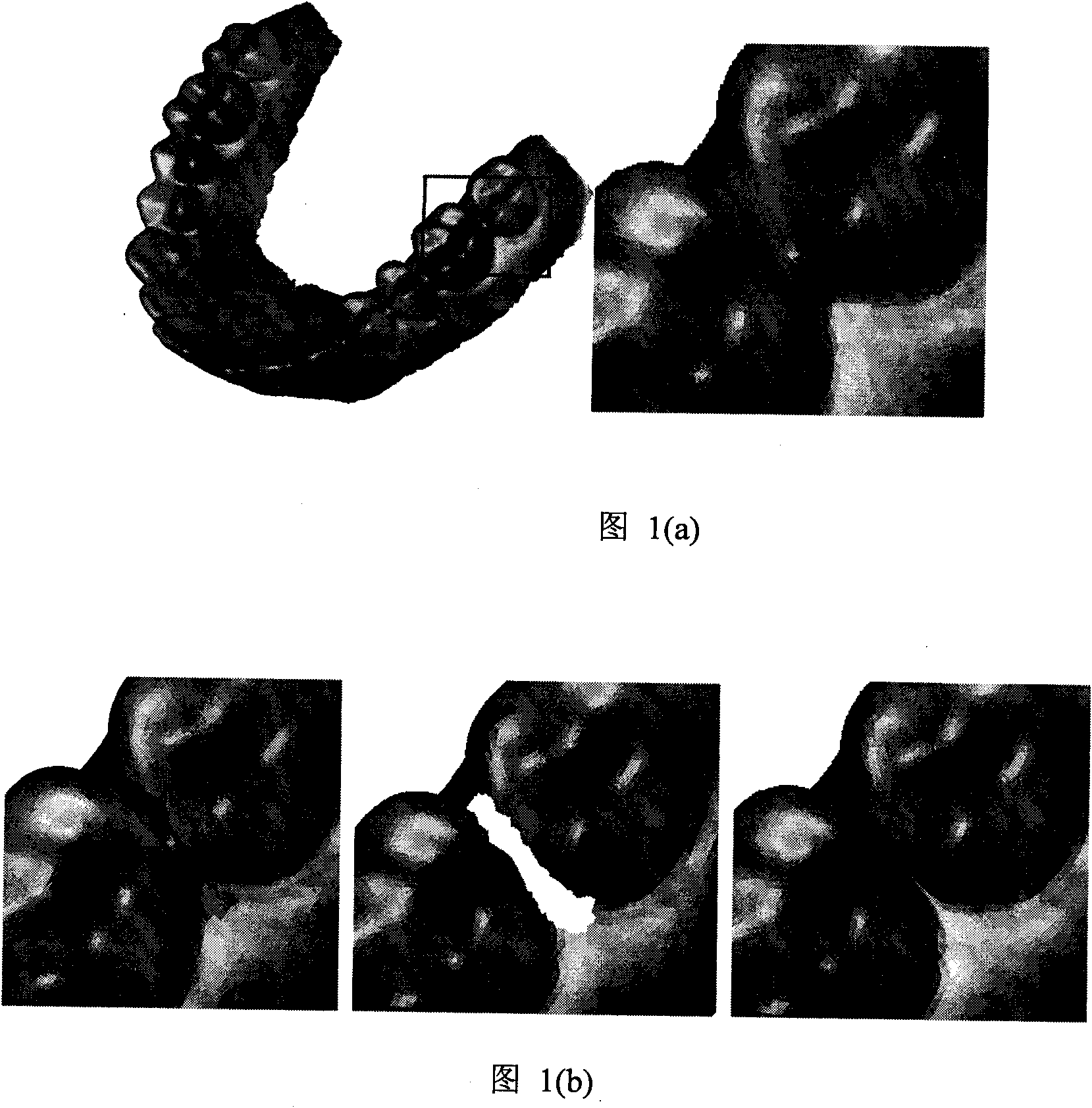

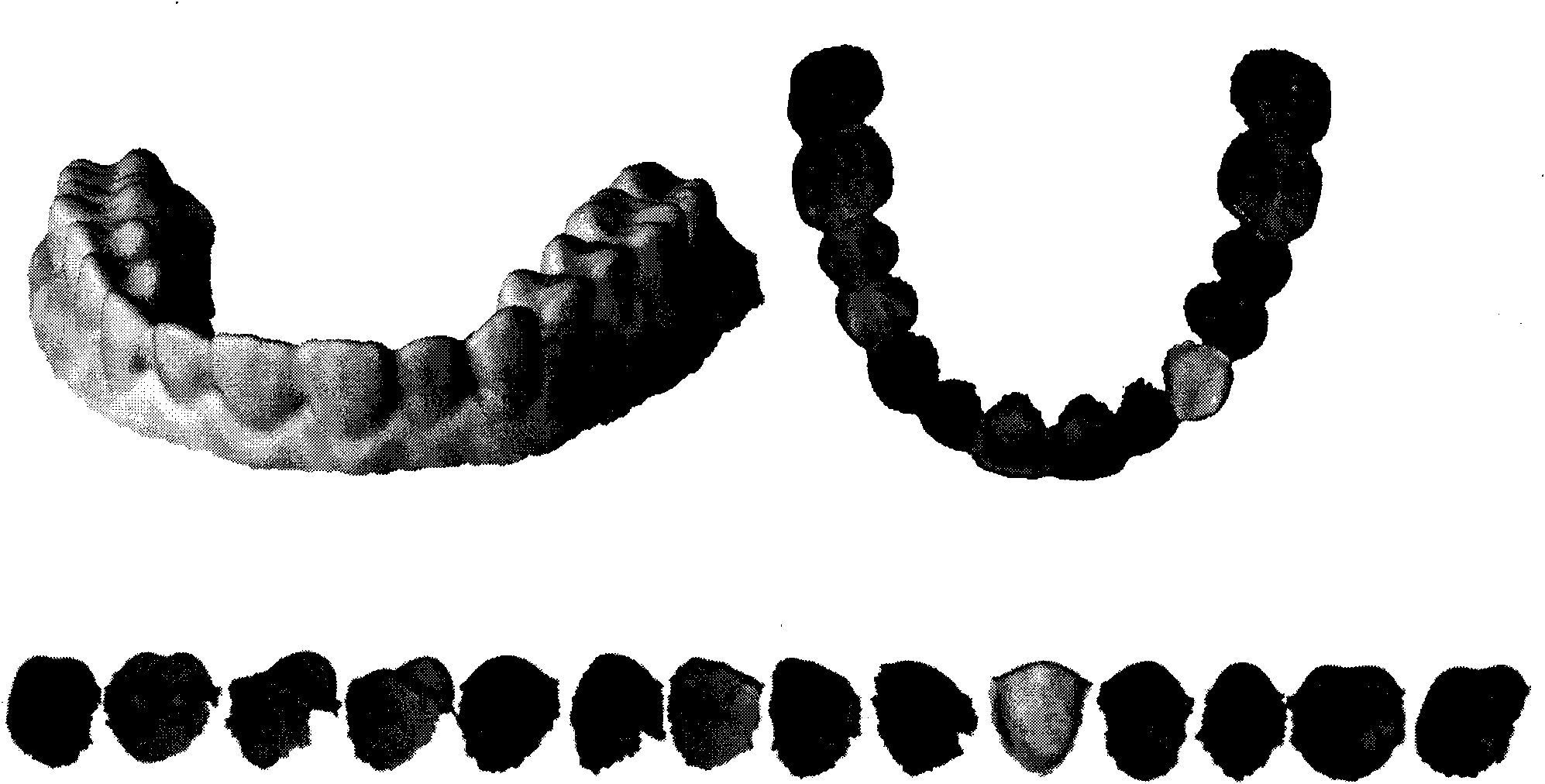

Method for accurately recovering single tooth form on three-dimensional tooth-mandible model

InactiveCN101604354APromote recoveryAutomatic recoverySpecial data processing applicationsComputer-aidedComputer aid

The invention discloses a method for accurately recovering a single tooth form on a three-dimensional tooth-mandible model, and belongs to the field of computer-aided biomedical engineering. The method mainly comprises the following steps: (1) identifying and deleting a fusion part between teeth; and (2) according to hole boundary information generated after deleting the fusion part, constructing a curved surface sheet which accords with a practical spatial position relation between the teeth and can synchronously reflect local characteristics of corresponding tooth parts. The method of the invention only comprises simple human-computer interaction operation, has high automation degree, mainly carries out linear computation, can quickly, stably and accurately recover the form of a deletion part of the single tooth on the three-dimensional tooth-mandible model, and has important application value in the field of computer-aided oral orthodontics.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS +1

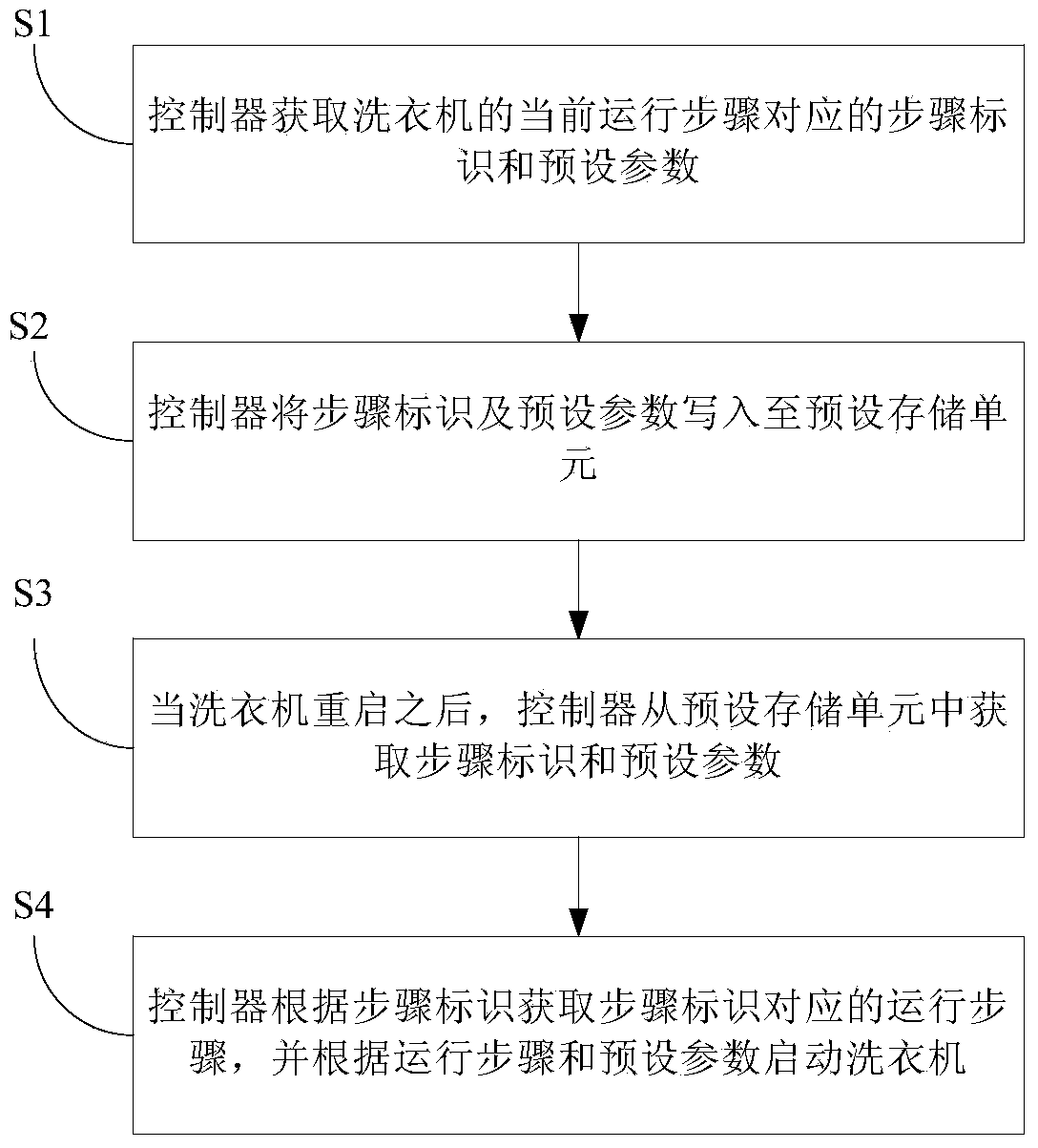

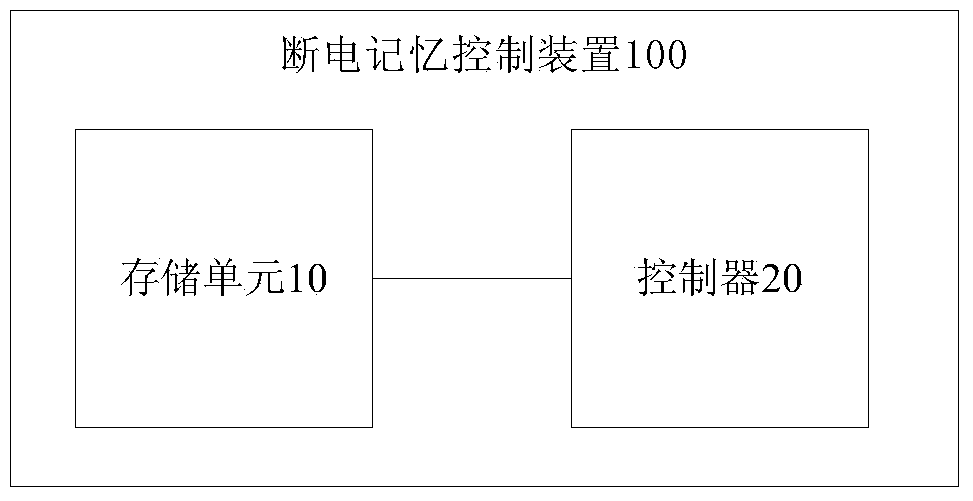

Washing machine, power failure memory control method thereof and power failure memory control device of washing machine

ActiveCN104233701ARealize the function of power-off memorySimple control methodControl devices for washing apparatusTextiles and paperRelevant informationMemory functions

The invention provides a washing machine, a power failure memory control method thereof and a power failure memory control device of the washing machine. The power failure memory control method comprises the following steps of (S1) acquiring step marks corresponding to current running steps of the washing machine and preset parameters by using a controller; (S2) writing the step marks and the preset parameters into a preset storage unit by using the controller; (S3) acquiring the step marks and the preset parameters in the preset storage unit by using the controller after the washing machine is restarted; and (S4) acquiring running steps corresponding to the step marks according to the step marks and starting the washing machine according to the running steps and the preset parameters. By a step-by-step memorizing method, relevant information of the current running steps of the washing machine is stored in real time, the working state of the washing machine can be accurately recovered to a working state before power failure when the washing machine is restarted, and a power failure memory function is fulfilled; and circuits are simple in structure, the cost of the circuits is reduced, and the power failure memory control method is easy to implement.

Owner:WUXI LITTLE SWAN ELECTRIC CO LTD

Quantization-Based Data Embedding in Mapped Data

InactiveUS20090022360A1Reduce errorsReduce impactSpeech analysisCharacter and pattern recognitionAlgorithmDistortion

Novel methods and systems for quantization based data embedding and reading in host signals, such as image, audio and video signals. To embed auxiliary data in a host signal, an embedder maps the host signal from a first domain into a mapped signal in a second domain. The embedder performs quantization based embedding of auxiliary data into the host signal using quantizers. The quantizers are adapted such that the relationship between corresponding quantizers in the first and second domains satisfies a predetermined constraint. The mapping improves the robustness of the data embedding method by increasing the chances that the embedded data can be recovered by an auxiliary data reader after modifications. A related embedding method projects the mapped signal unto a vector, and specifically, a pseudorandom vector. It performs quantization based embedding on the projected signal. The use of this projection provides added robustness of the embedded data to noise and other forms of distortion.

Owner:DIGIMARC CORP

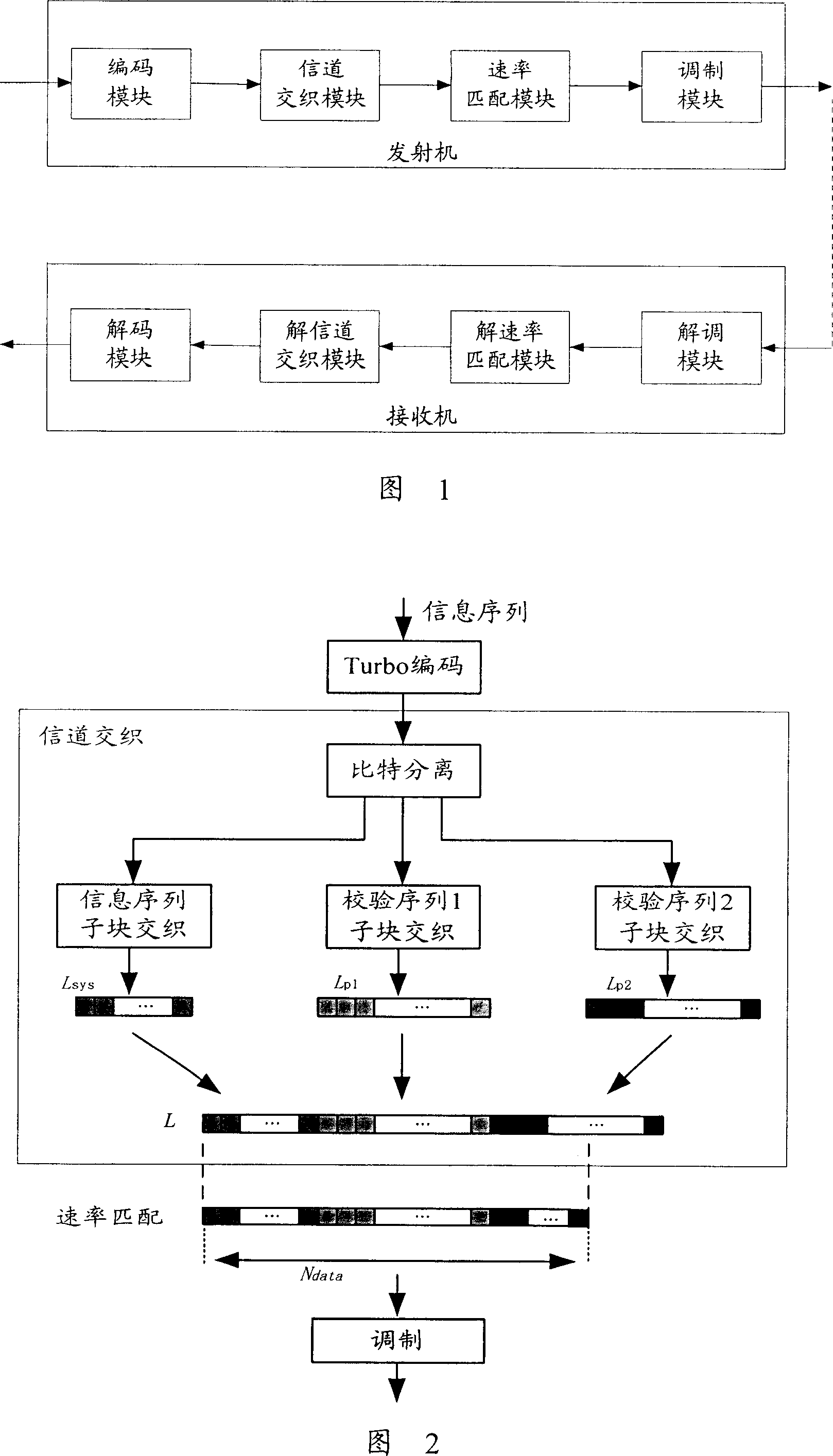

Method and system for transmitting information

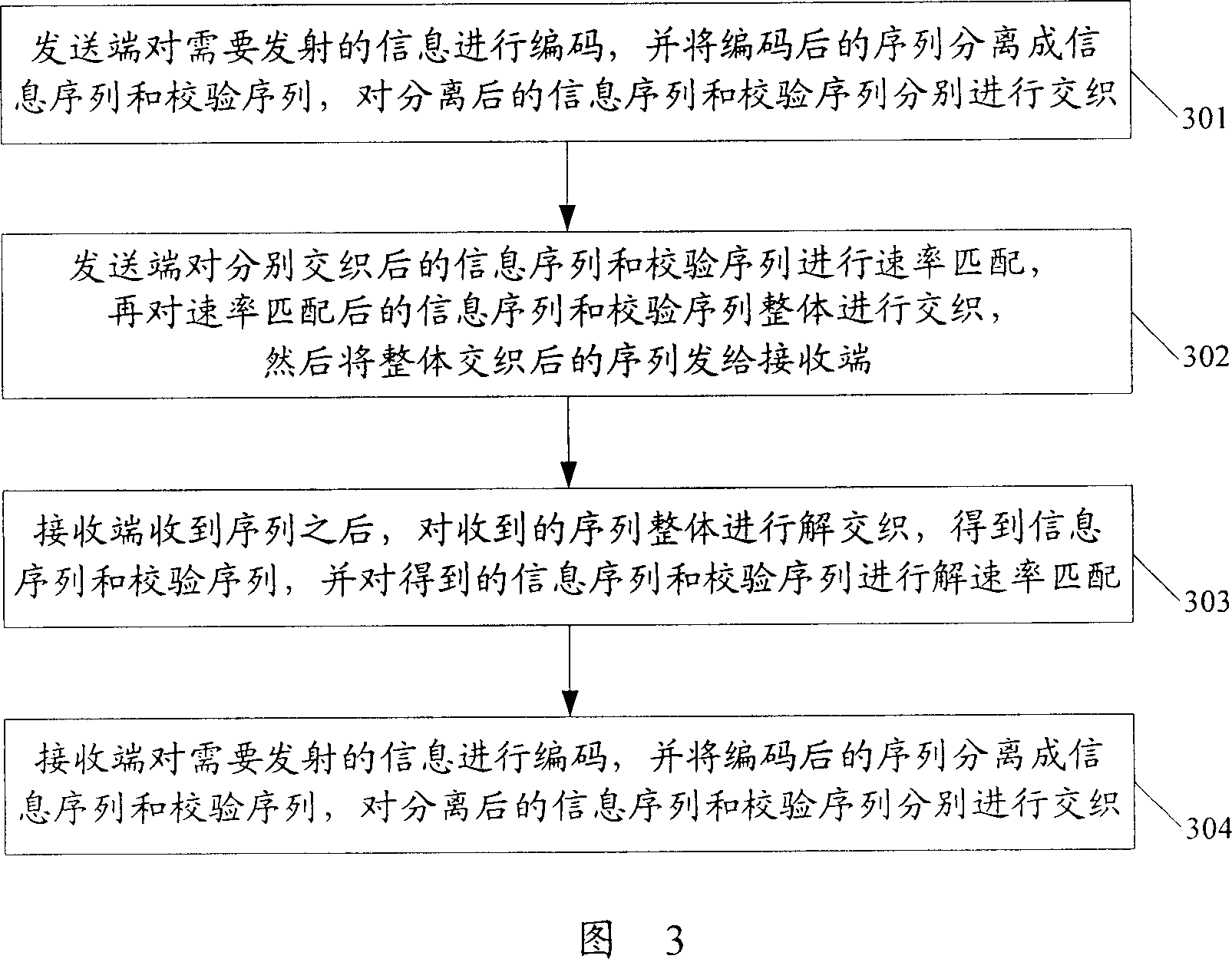

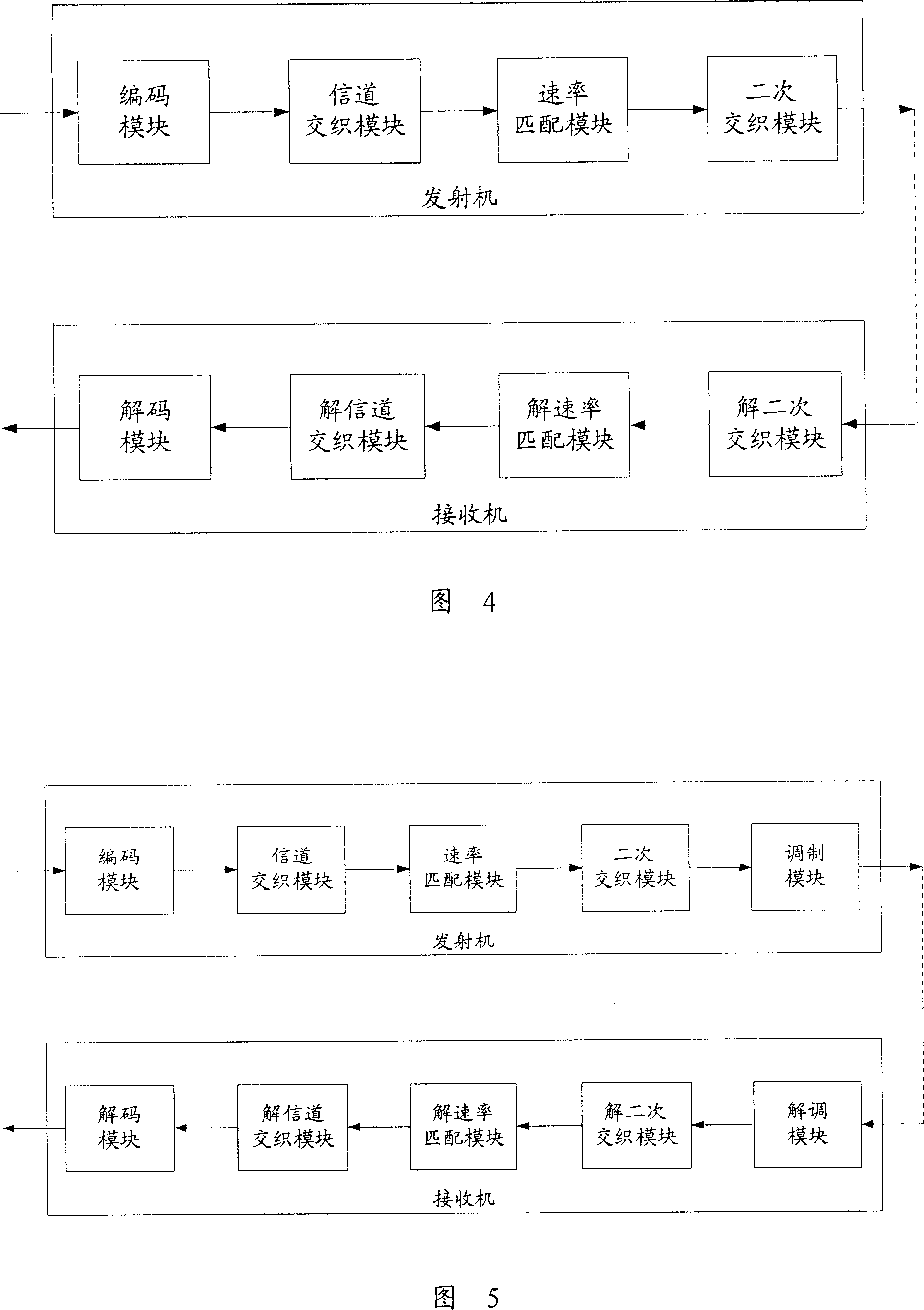

InactiveCN101090293AGood choiceReduce performance lossAmplitude-modulated carrier systemsRadio transmission for post communicationCode moduleTransmitter

This invention discloses a method for transmitting information including: the transmitting end codes information to be emitted, interlaces channels and matches rate, then interlaces the matched information sequence and check sequence integratedly and transmits them to the receiving end, which de-interlaces the integer of the sequence and then caries out de-rate match, de-channel interlace and decoding to resume the information sequence. This invention also provides a system for transmitting information including a transmitter and a receiver, in which, the transmitter includes a coding module, a channel interlacing module and a decoding module.

Owner:HUAWEI TECH CO LTD

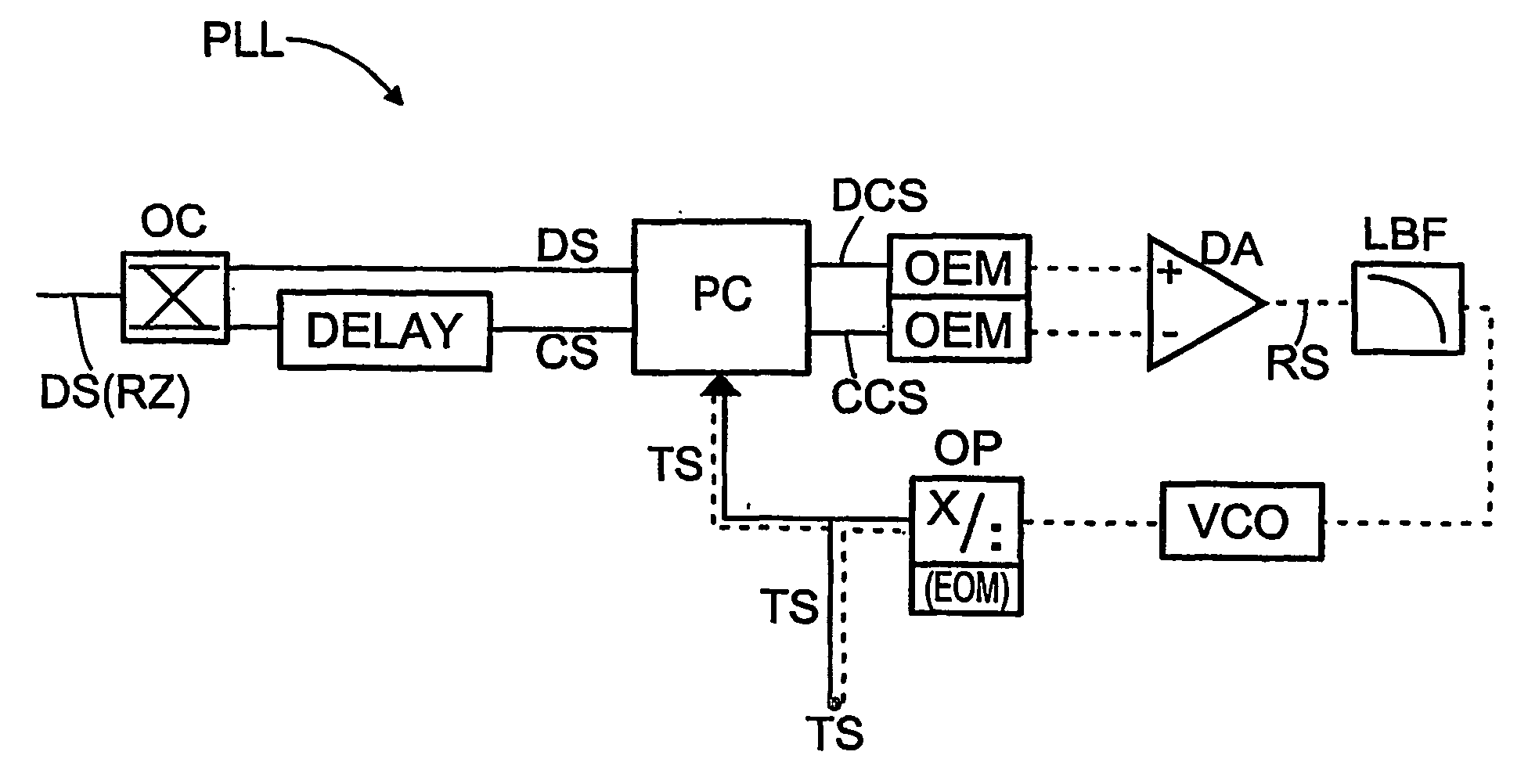

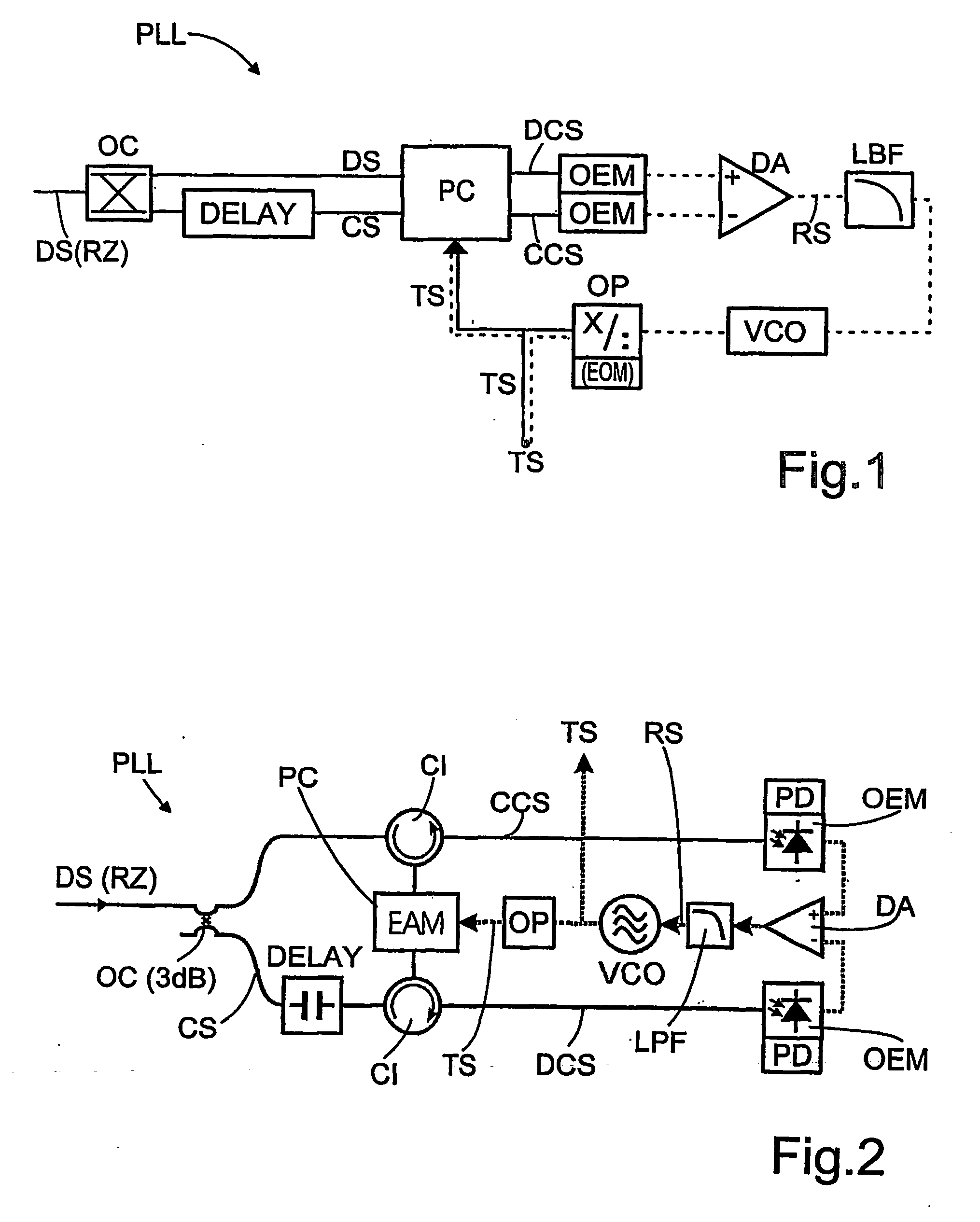

Opto-electric phase-locked loop for recovering the clock signal in a digital optical transmission system

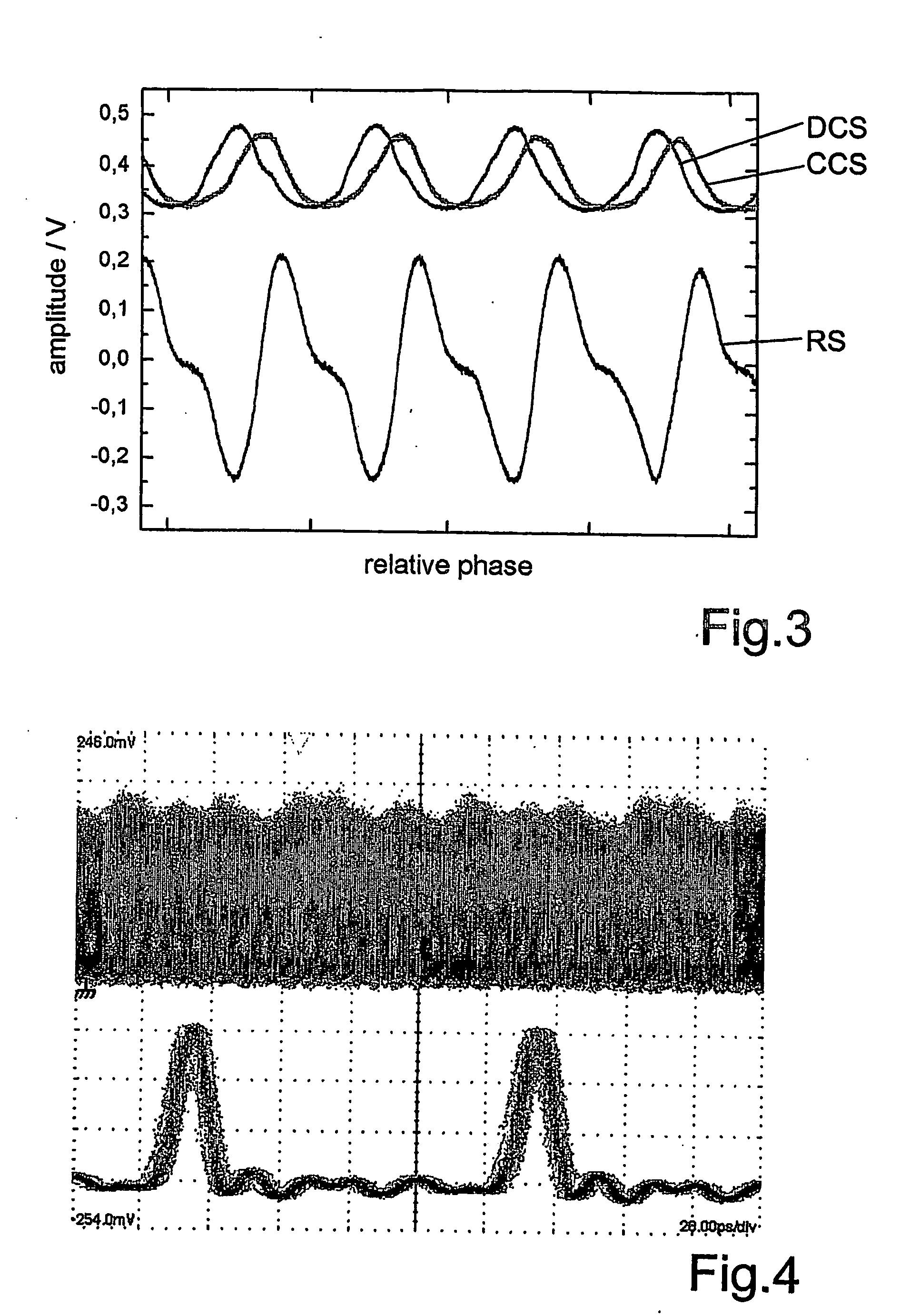

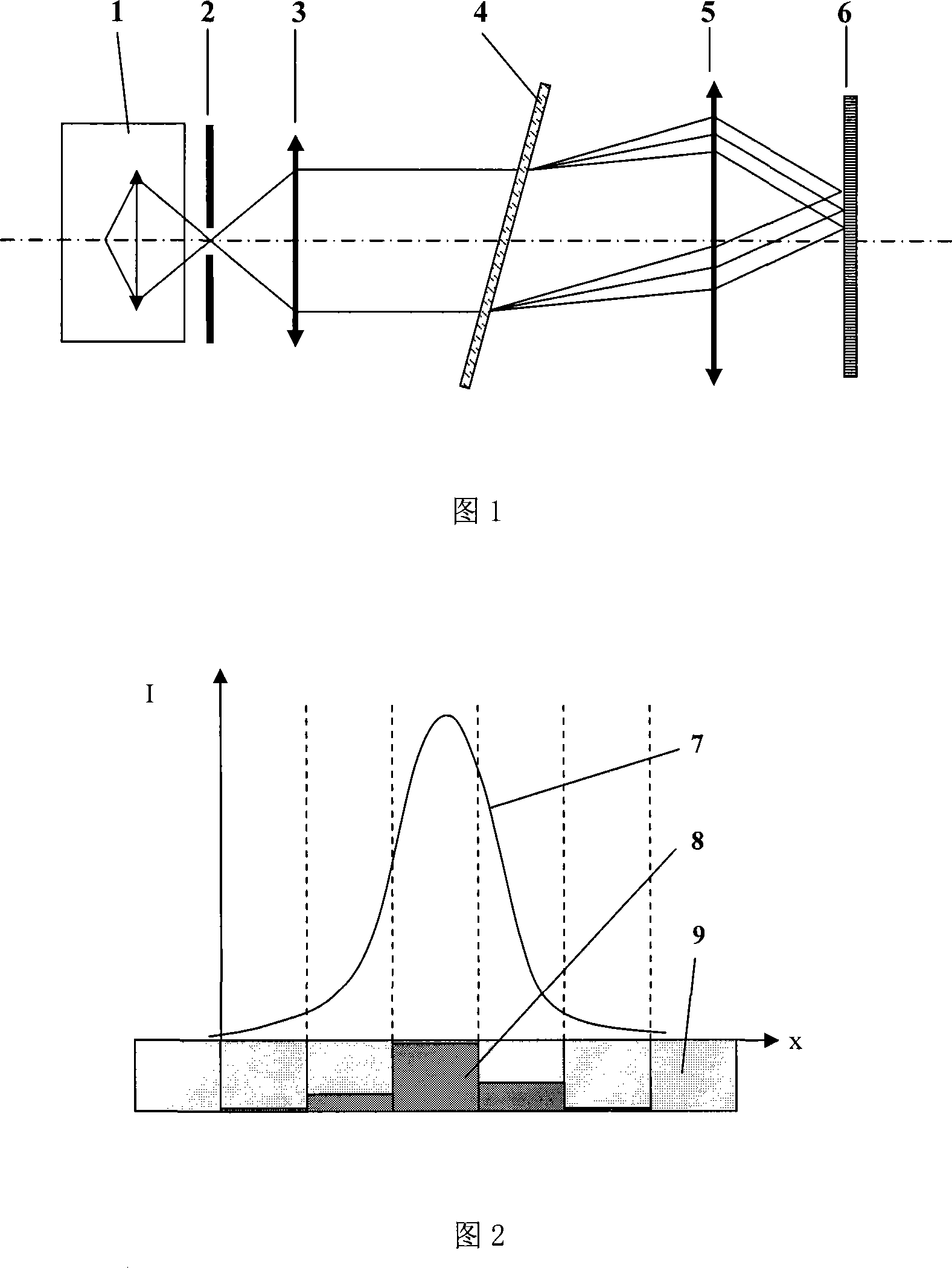

InactiveUS20070166047A1Optimal stabilityCost efficientSynchronisation by photonic/optical meansElectromagnetic receiversPhase shiftedSignal-to-noise ratio (imaging)

A phase-locked loop for a differential recovery of the clock signal wherein an extracted data signal (DS) is conveyed via a phase delay element and thence to a phase comparator. In the phase comparator comparison signals, whose phase shifts can be set relative to one another, differential phase evaluation is carried out. This results in a control signal (RS) whose operating point, independent of the power of the transmit channel, always lies in the center of the control range. In the inventive differential timing recovery, the dependencies on power fluctuations, signal-to-noise ratio, the pulse shape and on transmitted bit patterns are eliminated to the greatest possible extent.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV

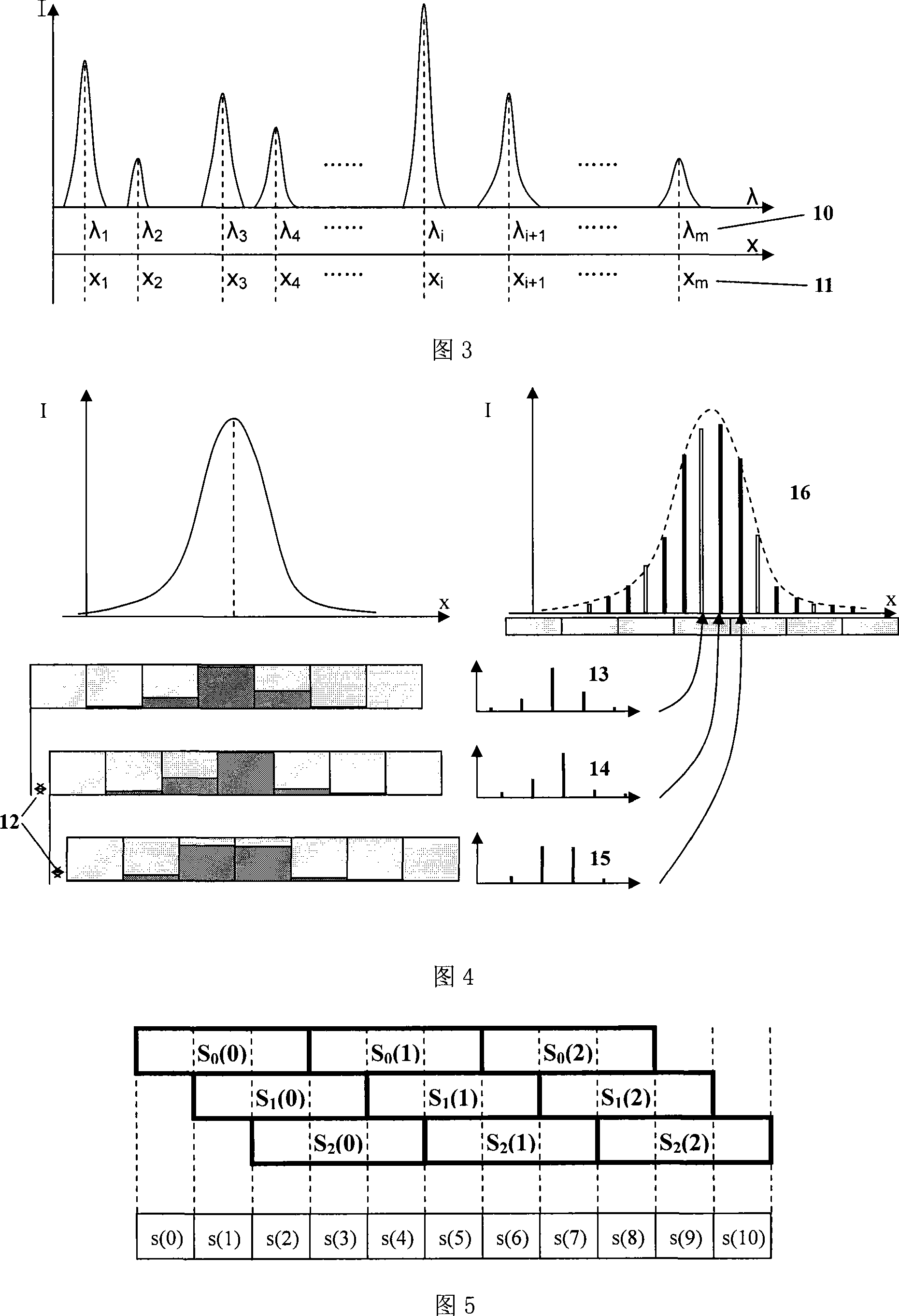

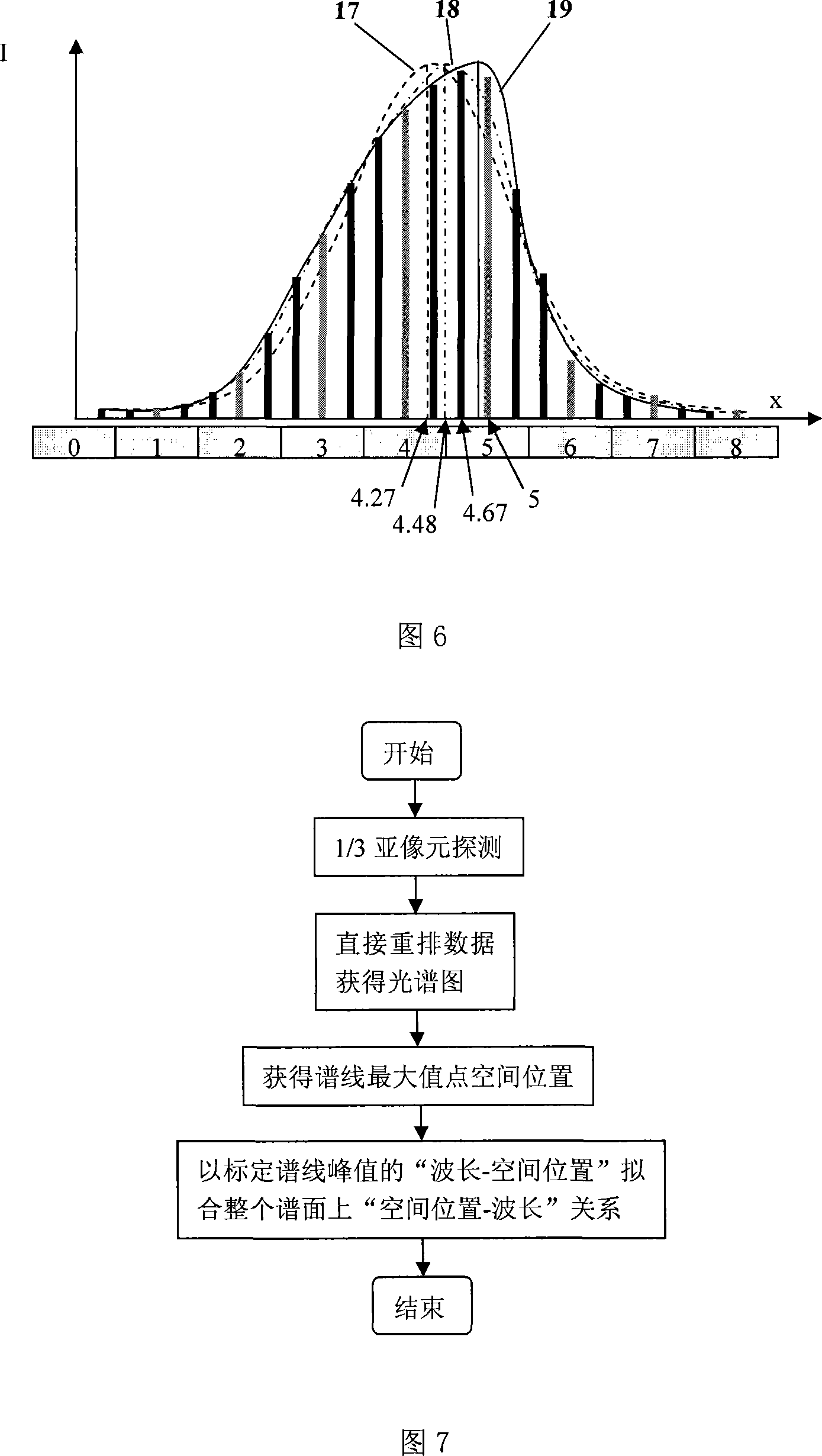

Wavelength calibration method of optical spectrum instruments

InactiveCN101158599AIncrease sampling rateHigh-resolutionRadiation pyrometrySpectrum investigationSpectral patternImage resolution

A wavelength calibration method of spectral instrumentation mainly relating to wave length calibration method adopting spectral instrumentation of array detector pertains to the filed of wave length calibration technology of spectral instrumentation. The spectral instrumentation of the method adopts array detectors and lighting source of linear spectra, spatial locations of every spectrum peak of the lighting source are acquired from the spectrogram output from the instrumentation, and the 'spatial location - wave-length relationship' on the power spectrum is fitted by according these spectrum peak wavelength and the corresponding spatial locations thereof, thus corresponding wavelength of every pixel of the detector is confirmed, the spatial locations of every spectrum peak of the lighting source is acquired through processes as following: sub-pixel detecting; sub-pixel reestablishing; spectrum peak spatial locations acquiring. The sub-pixel detecting of the invention increases sampling ratio of spectrogram, spectrogram with improved resolution in acquired; the comprehensive applications of sub-pixel detecting, sub-pixel reestablishing and spectrum contour fitting further increases the wavelength accuracy of spectral instrumentation with array detectors step by step. The invention has prominent effect.

Owner:TSINGHUA UNIV

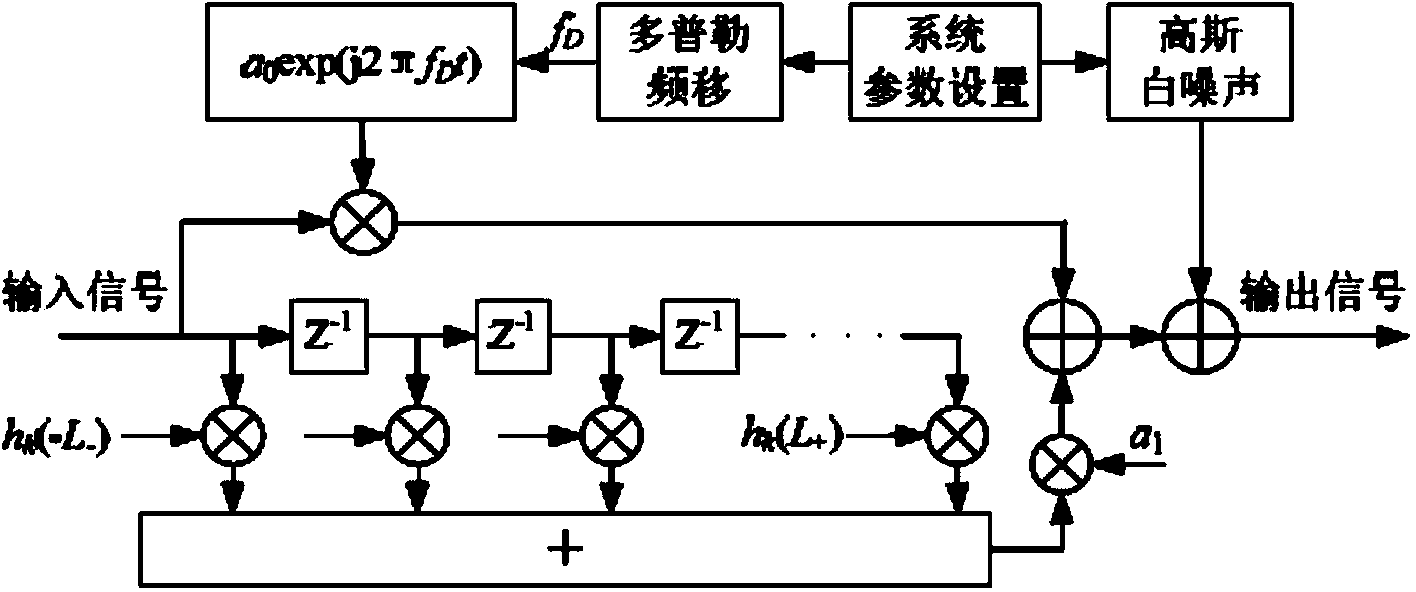

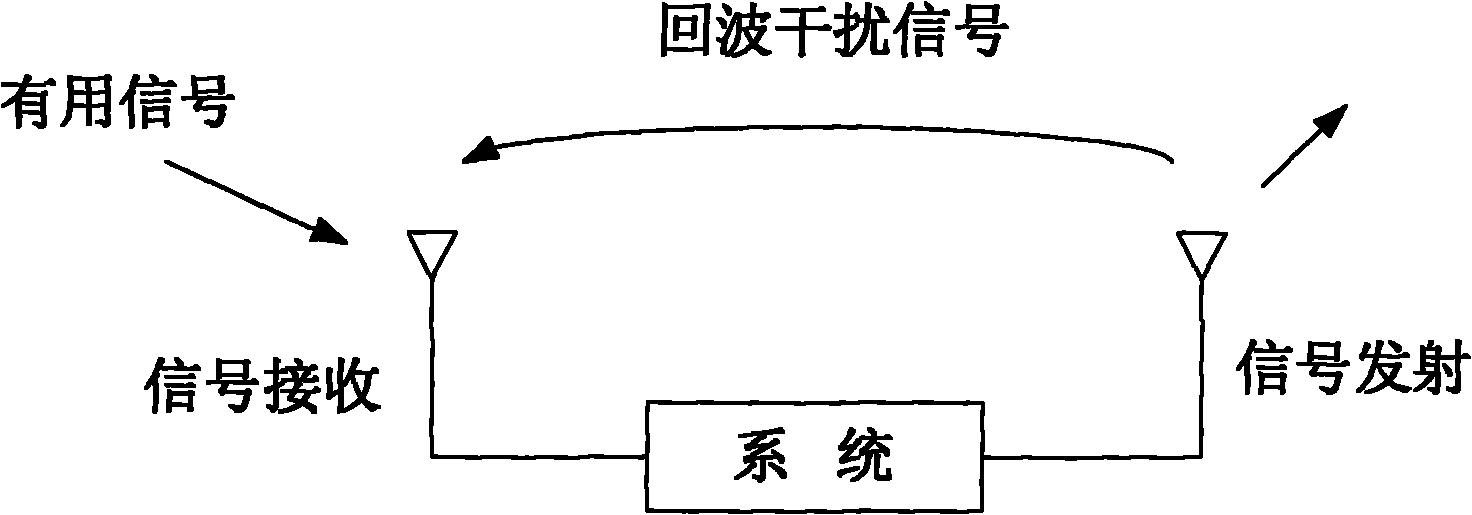

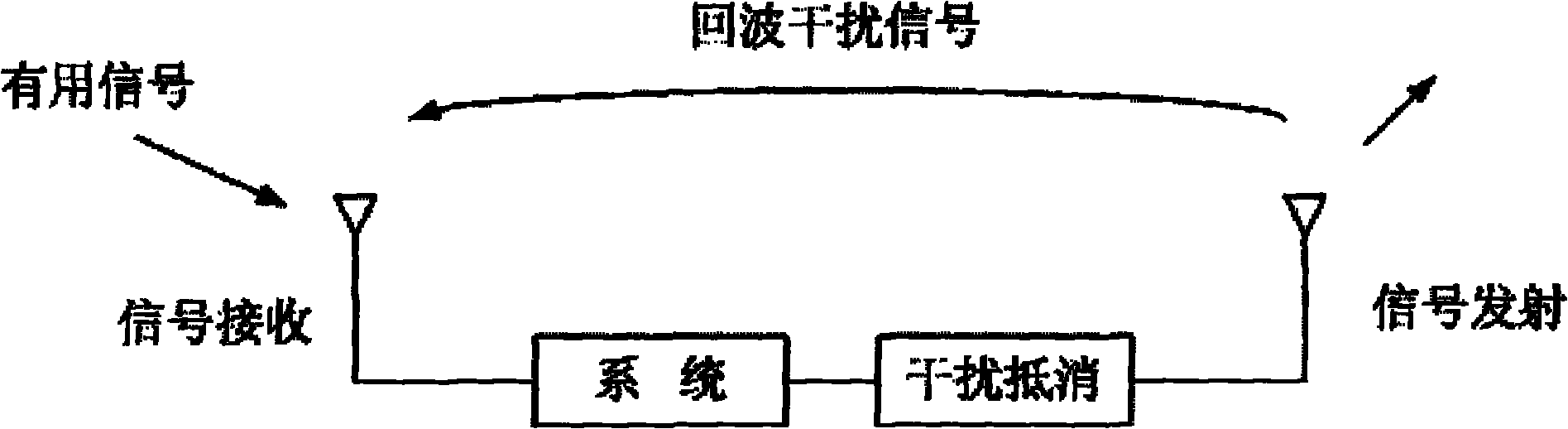

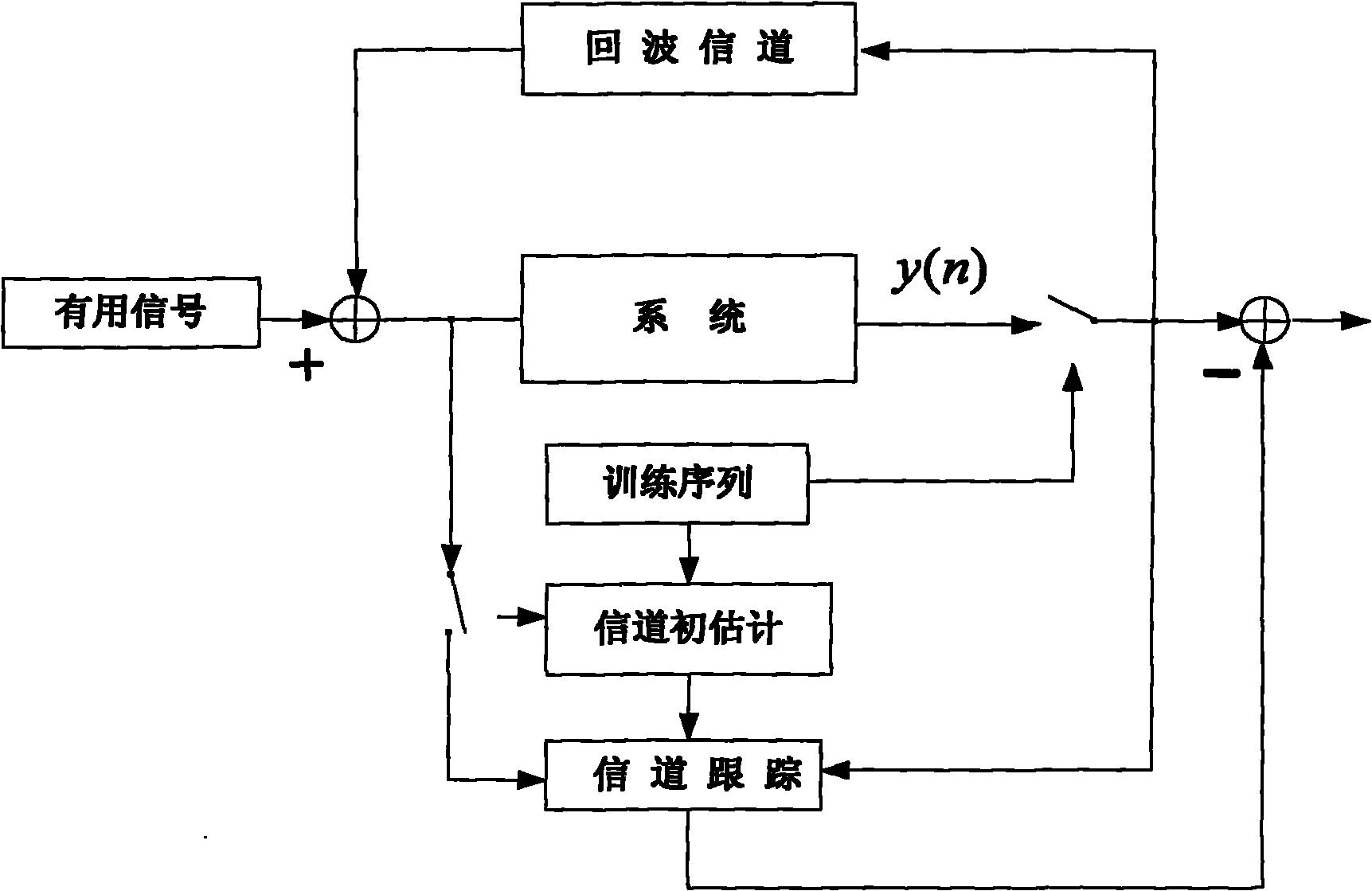

Variable-step self-adaptive echo interference cancellation method based on preliminary channel estimation

ActiveCN101924717AFast convergenceSmall steady state errorBaseband system detailsEngineeringSelf adaptive

The invention discloses a variable-step self-adaptive echo interference cancellation method based on preliminary channel estimation, which comprises a preliminary channel estimation process based on correlation detection, a channel tracking process based on a variable-step self-adaptive algorithm and an echo cancellation process, wherein the initial characteristic parameters of the echo channel are acquired in the preliminary channel estimation process; the precise channel tracking process is completed according to the channel characteristic parameters acquired by the channel preliminary estimation process; and the extraction of useful signals is completed in the echo cancellation process. The invention is suitable for processing the problems of channel estimation, channel identification,channel tracking and echo interference cancellation in time-invariant channels and time-variant channels. The method can quickly capture the characteristics of the echo channel, track the variation process of the channel in real time, and accurately restore the signals submerged in echo interference noise in real time.

Owner:SUNWAVE COMM +1

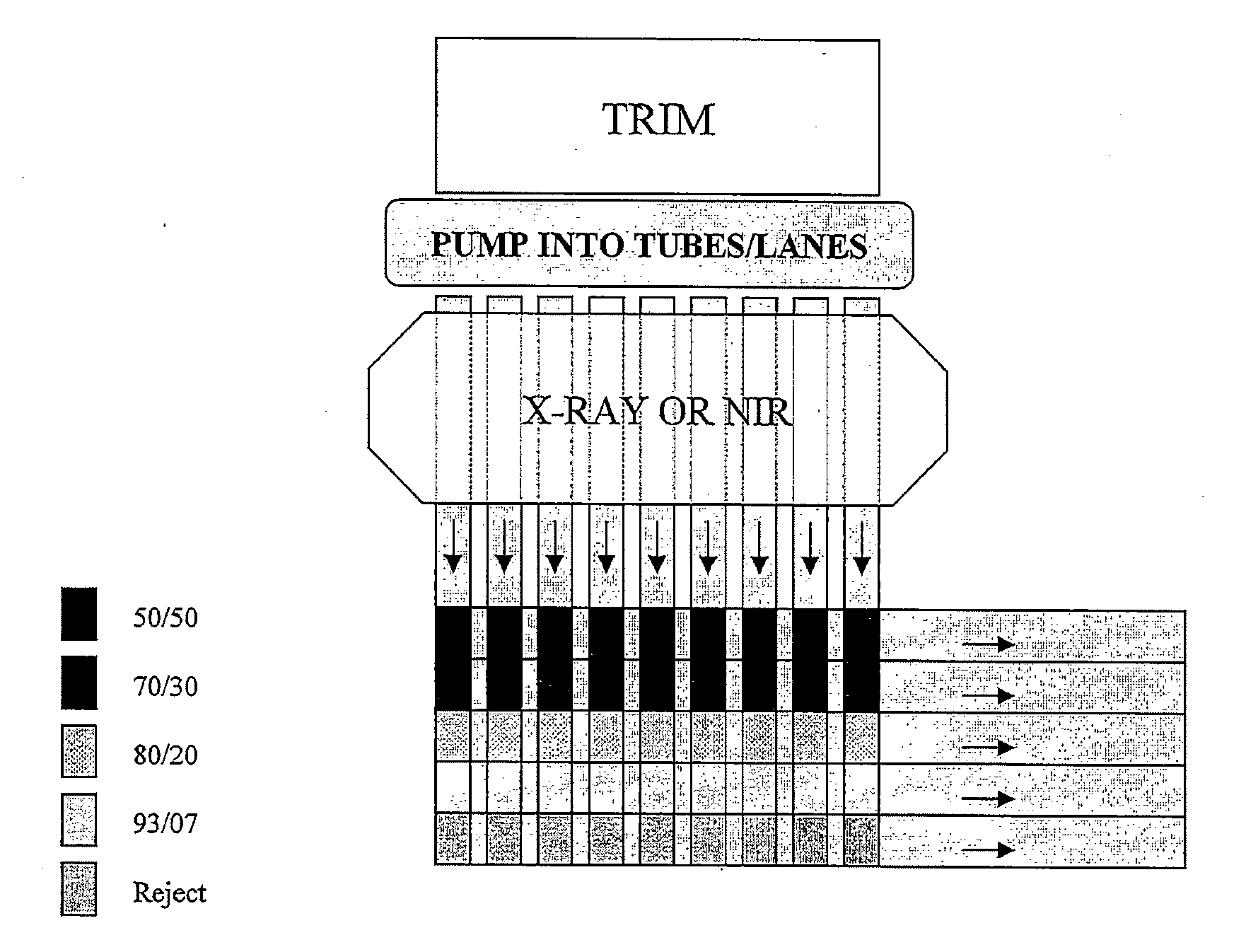

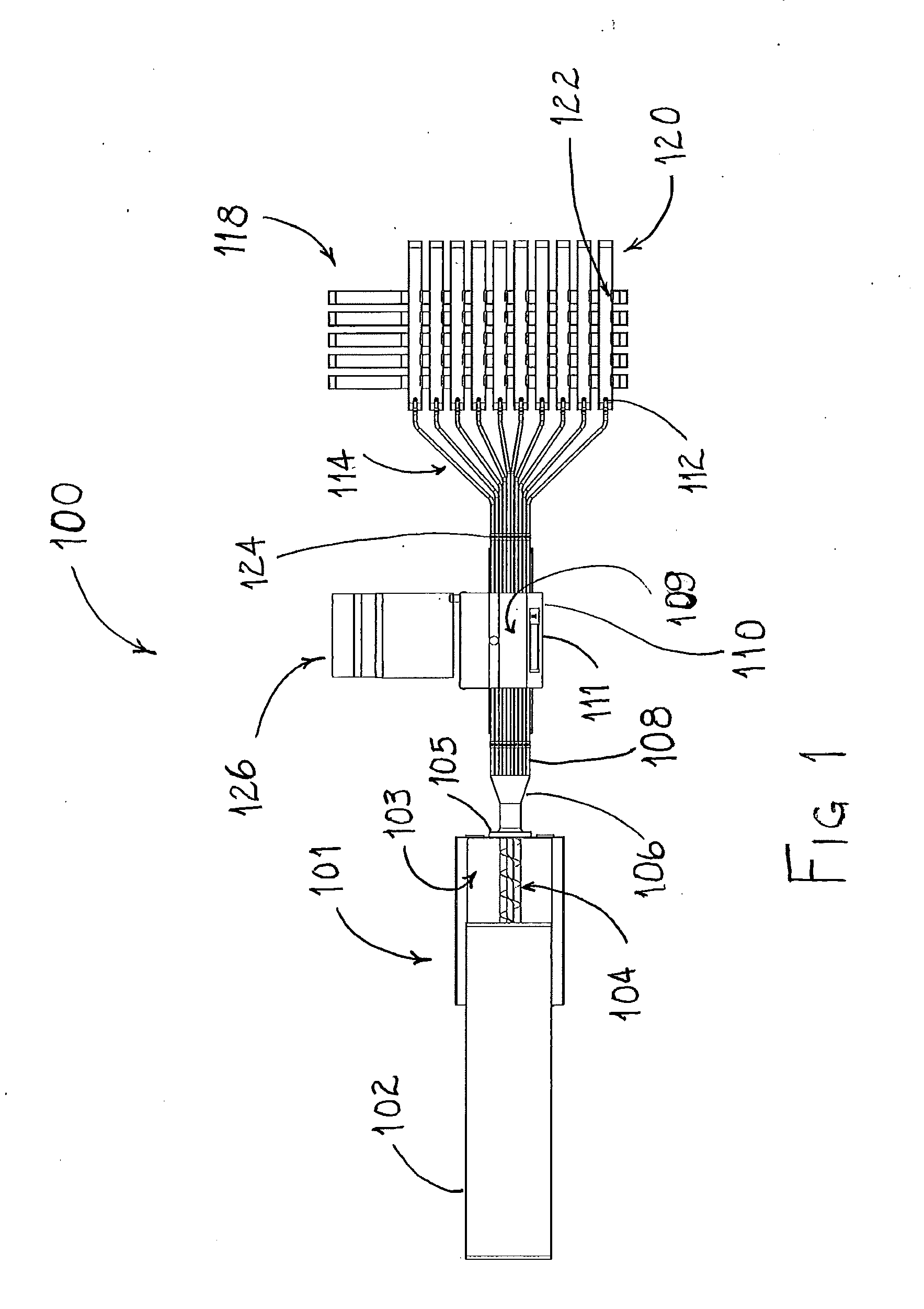

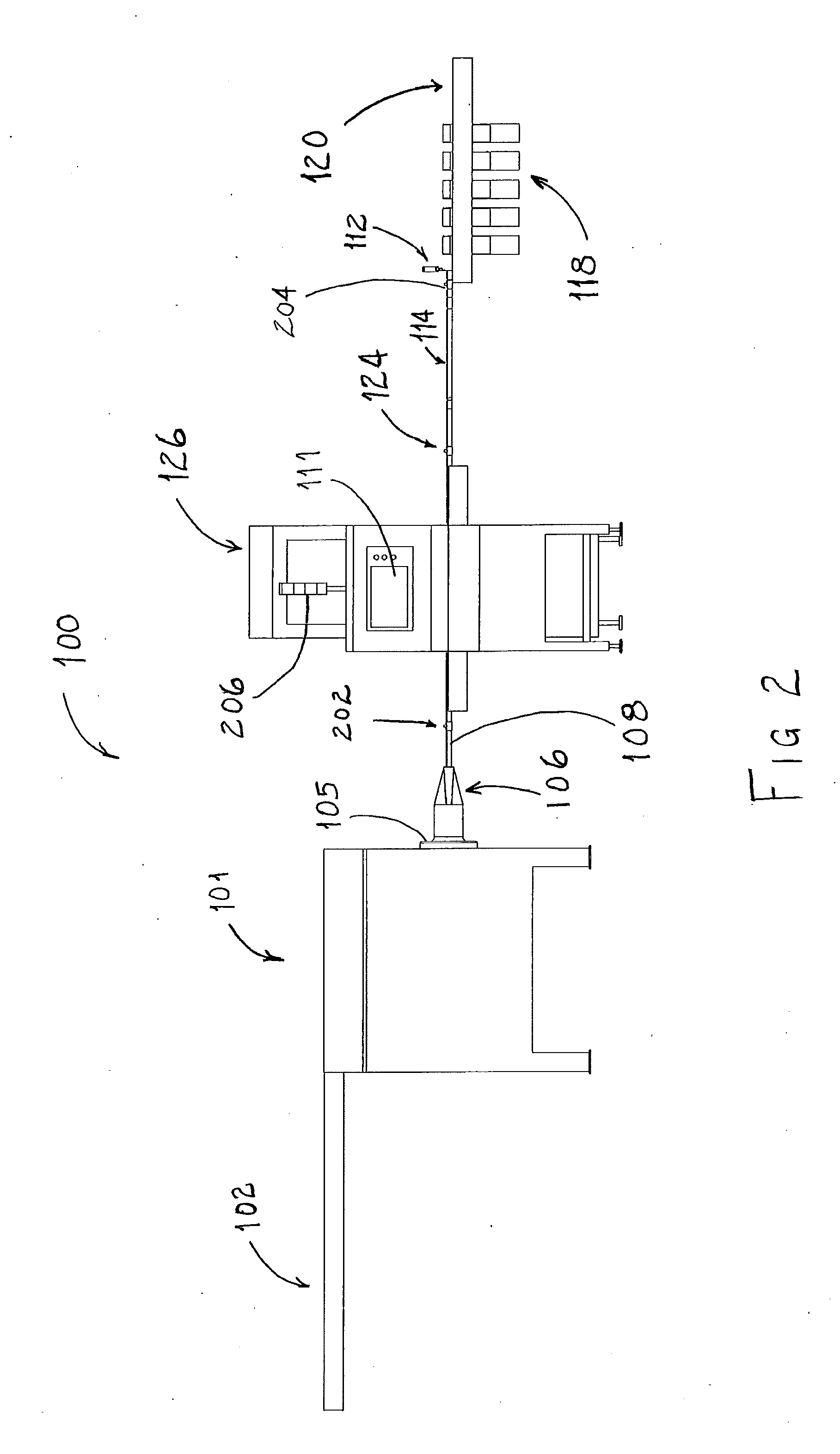

System and method for lean recovery using non invasive sensors

InactiveUS20120128838A1Accurate recoveryRind cutting-off apparatusCharacter and pattern recognitionNon invasiveFat content

An apparatus and method for non-invasive lean recovery from a sparse lean product, where the method can include conveying ground sparse lean product through a conveyance channel where the conveyance channel extends along a path that extends through a scanning position adjacent a scanner. The process includes scanning along a predetermined length with the scanner the ground sparse lean product traveling through the conveyance channel and further analyzing the scan and determining the percent fat content for each ground sparse lean product segment which is defined by the predetermined length of the ground sparse lean product within the volume of the conveyance channel and the cross section areas of the conveyance channel. The process can further include directing each ground sparse lean product segment down one of a plurality of processing paths corresponding to the one defined fat content range in which the corresponding percent fat content falls.

Owner:TYSON FOODS

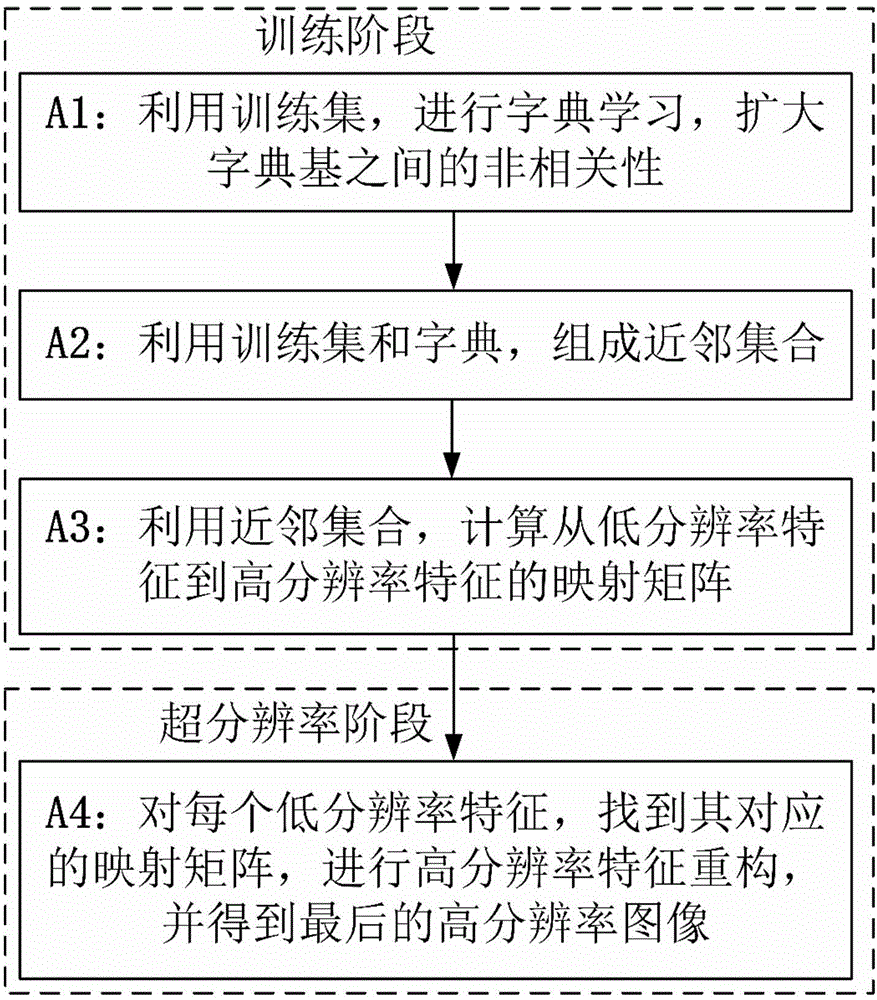

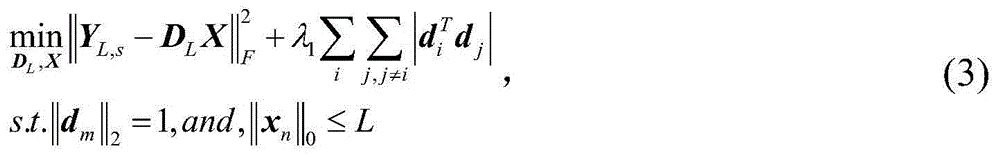

Image super-resolution method

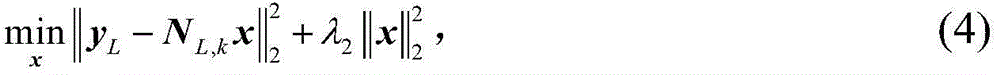

ActiveCN104899830AEnhance non-correlationQuality improvementGeometric image transformationFeature setImage resolution

The present invention discloses an image super-resolution method. The method comprises: training a low-resolution dictionary DL; calculating high and low resolution neighbor sets {NH} and {NL}; calculating a mapping matrix set {Fi} from low resolution features to high resolution features; extracting a low-resolution image block set {PL} and a low-resolution feature set {yL} for input low-resolution image IL; selecting the most approximate dictionary-based dk from the low-resolution dictionary DL for each low-resolution feature yL, and utilizing a corresponding mapping matrix set Fk to recover matching high resolution features yH; adding all reconstructed high resolution features {yH} to the matching low-resolution image blocks {PL} to obtain the corresponding high-resolution image blocks {PH}, and fusing all the high-resolution image blocks into one high-resolution image IH. According to the method provided by the invention, the processing speed is high, and high-resolution images of high quality can be obtained.

Owner:SHENZHEN GRADUATE SCHOOL TSINGHUA UNIV

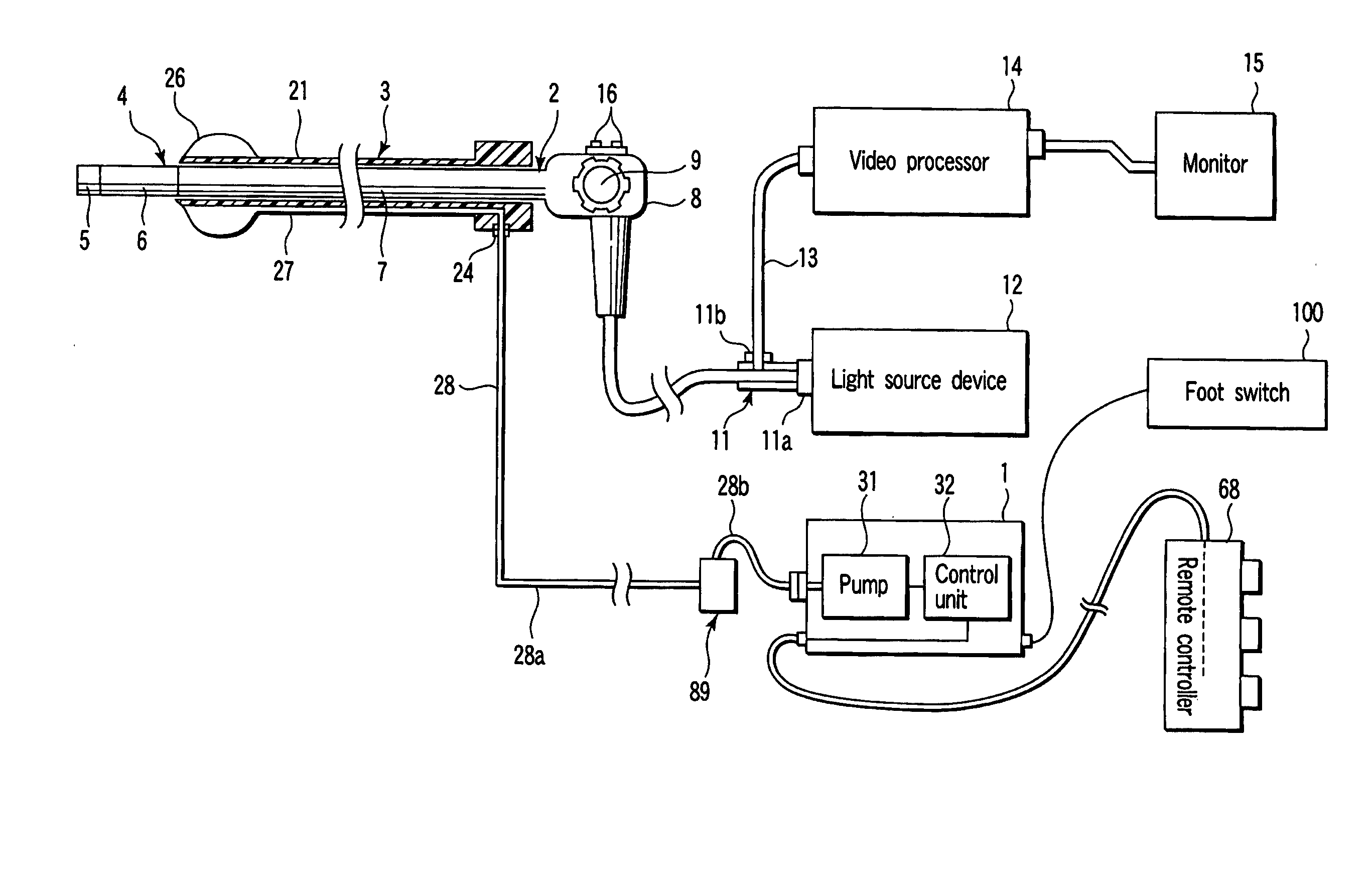

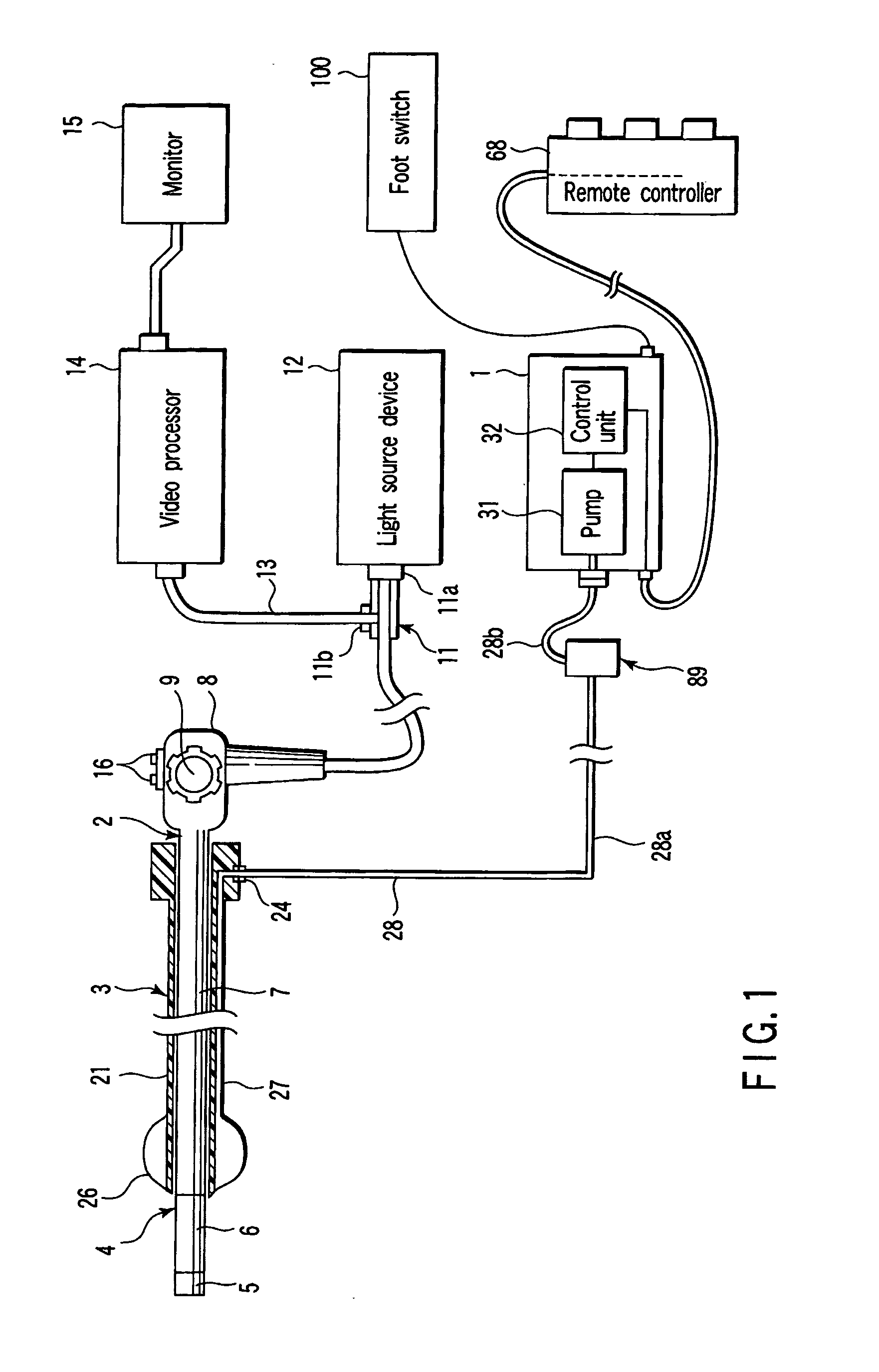

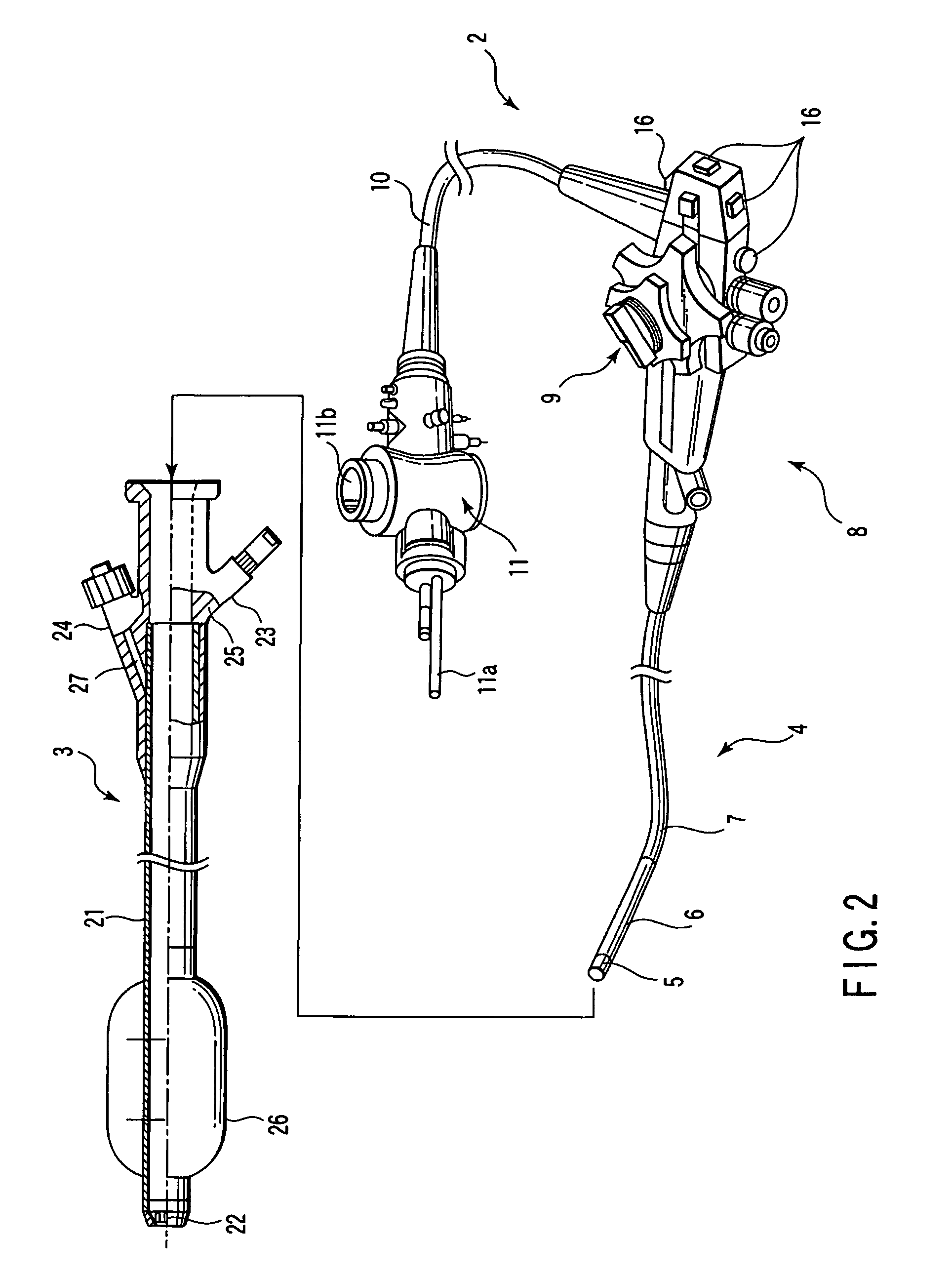

Medical apparatus

In a case where a balloon is broken and a body fluid reversely flows into a feed / discharge tube during a suction operation of a balloon control apparatus, a pump is stopped by operation-canceling section after passing of a preset predetermined time, and the suction operation of sucking the fluid into a bottle is canceled. Thereby, the amount of recovered liquid in the bottle is limited within a predetermined capacity. Thus, even in the case where the body fluid reversely flows into the feed / discharge tube, the body fluid does not overflow from the bottle, and the body liquid can properly recovered in the bottle.

Owner:OLYMPUS MEDICAL SYST CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com