Patents

Literature

236results about How to "Reduce circuit complexity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

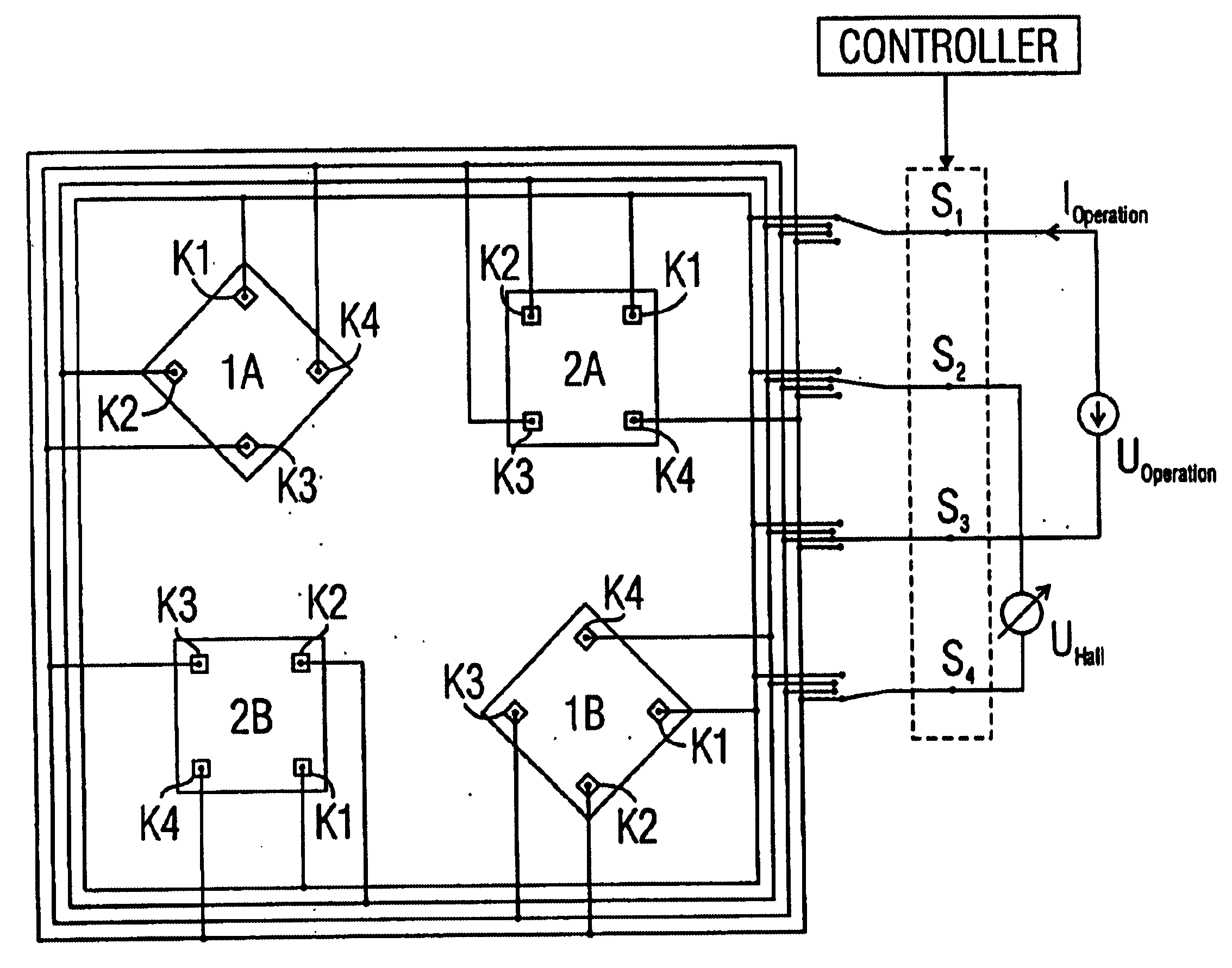

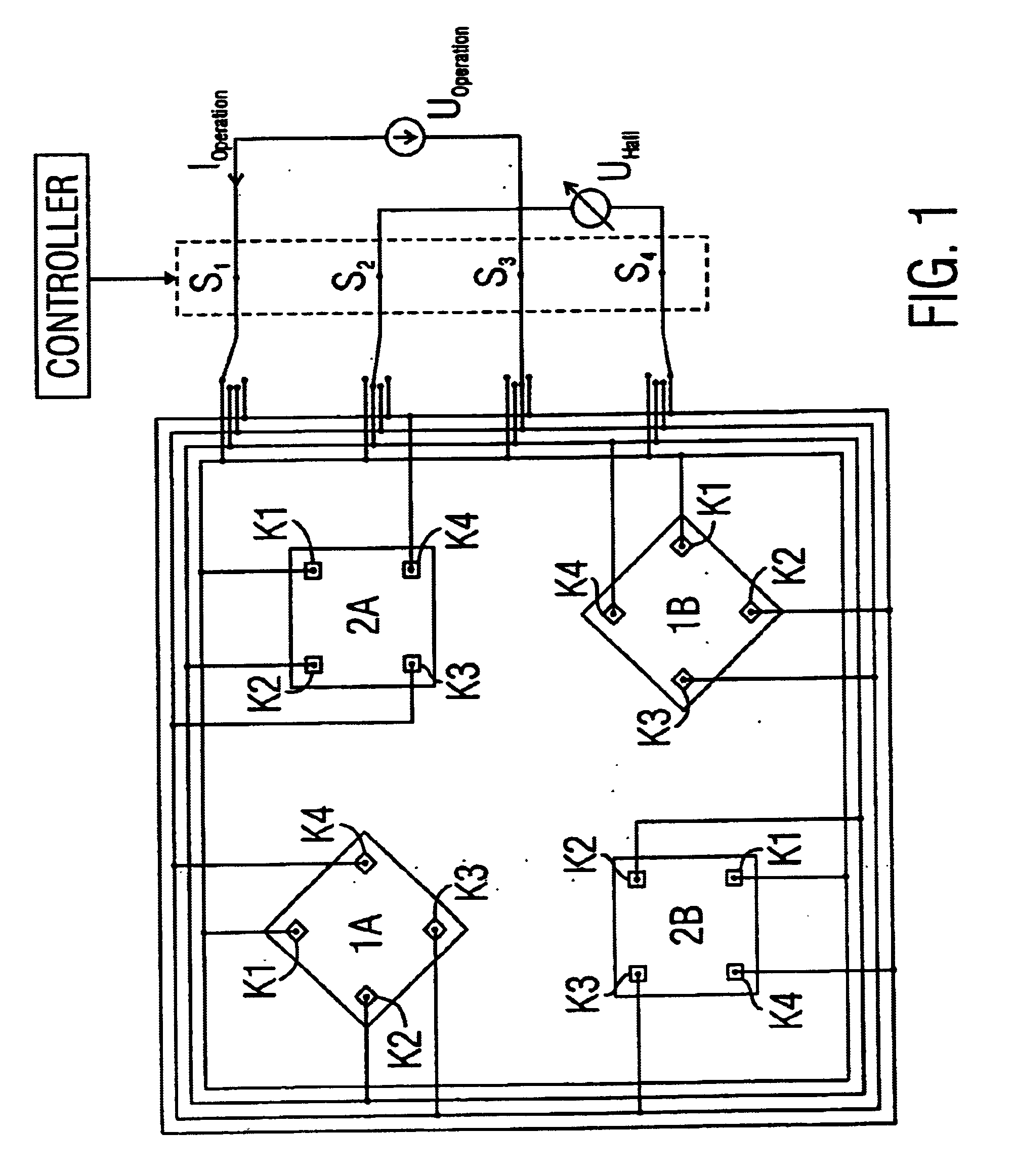

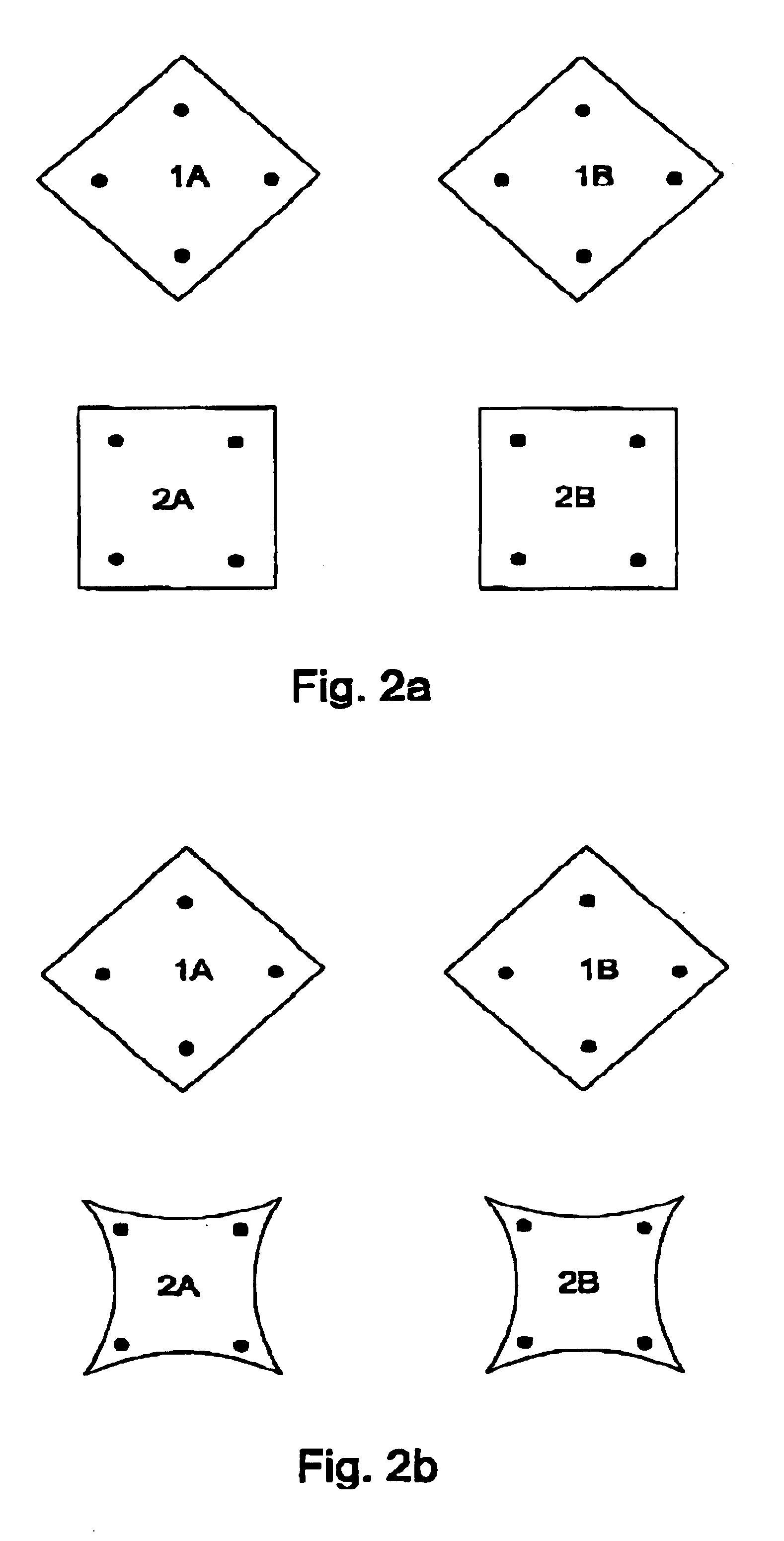

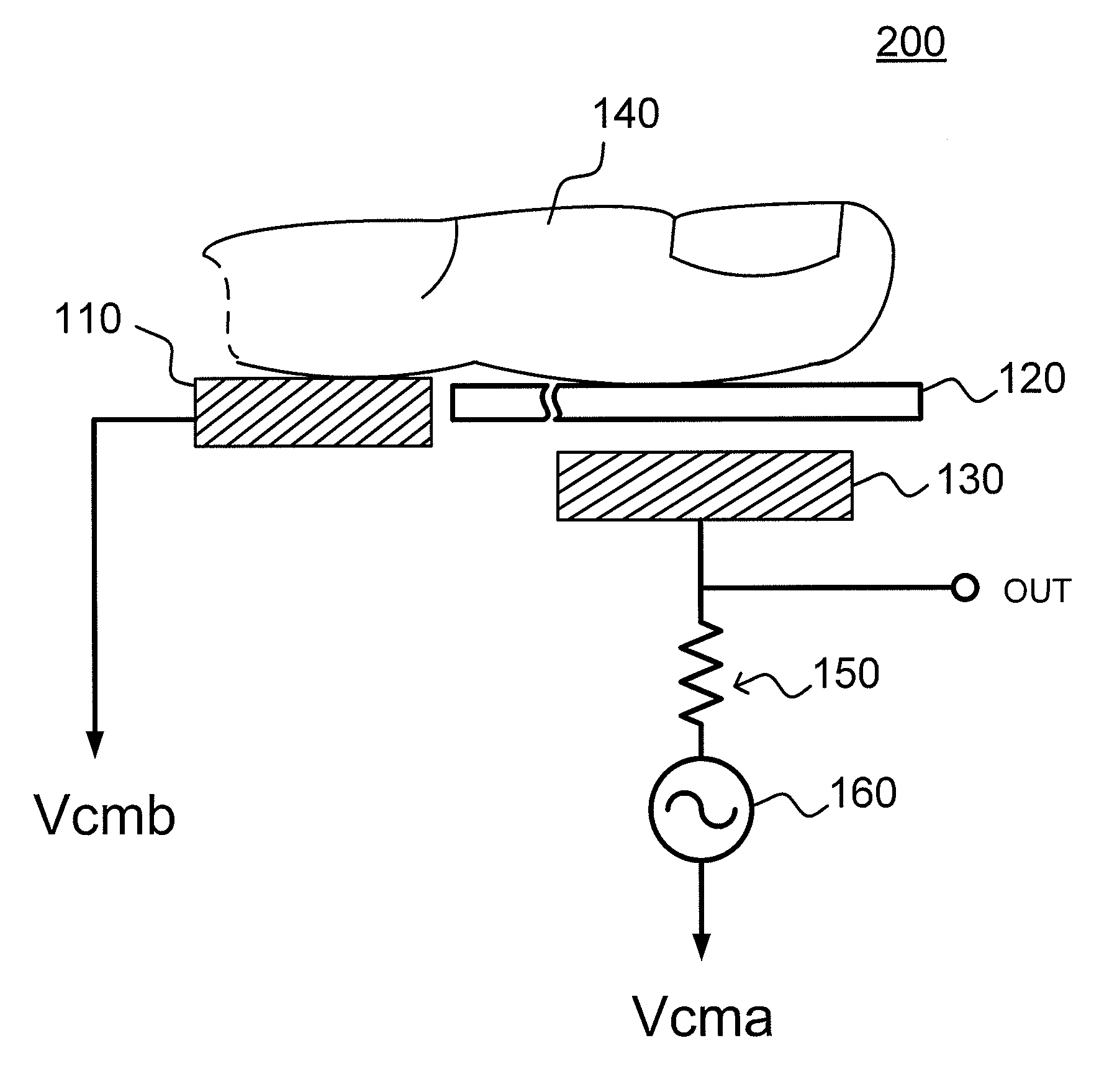

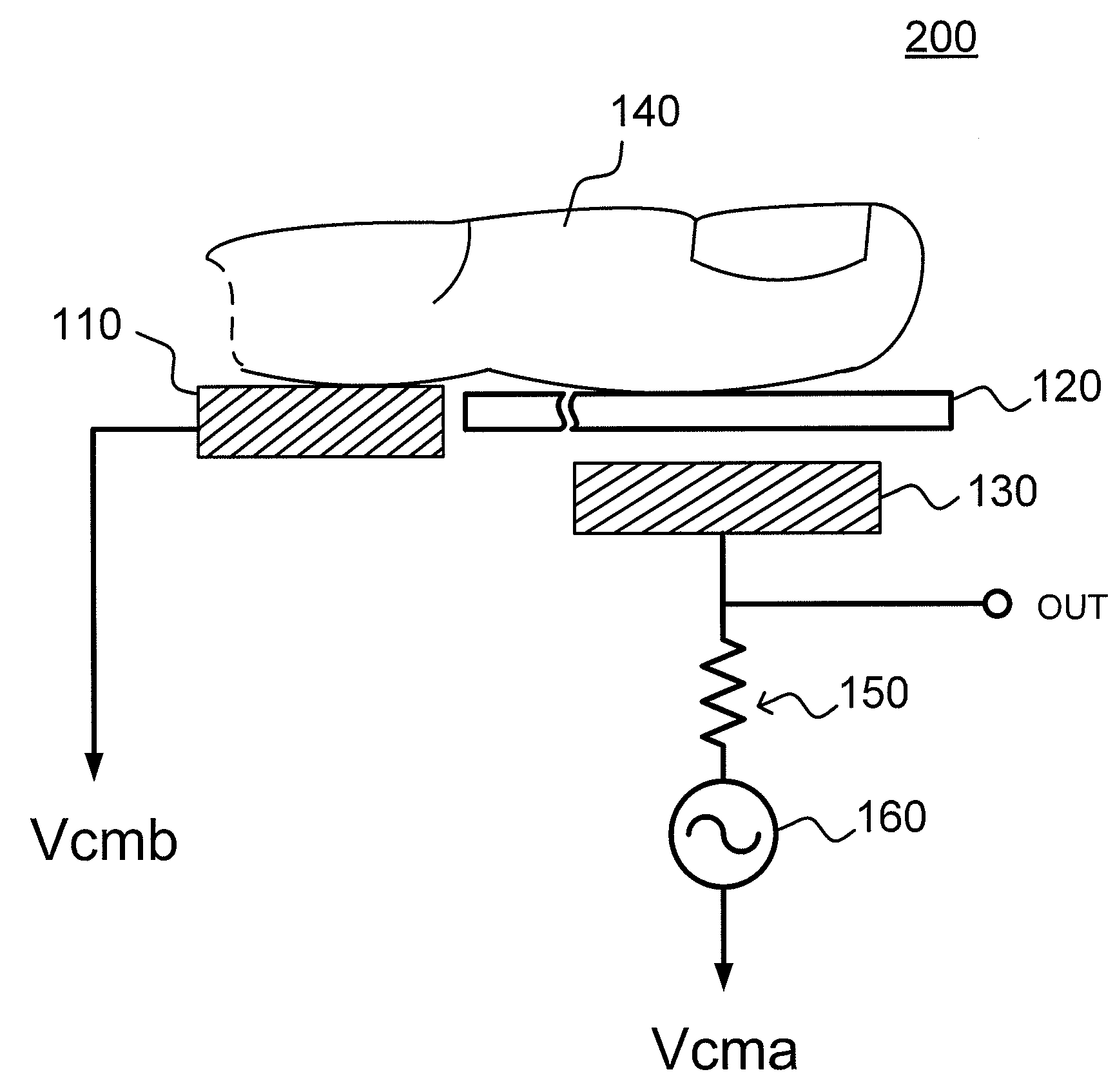

Hall sensor array for measuring a magnetic field with offset compensation

InactiveUS6768301B1Less complicated to manufactureReduce signalingSolid-state devicesMagnetic field measurement using galvano-magnetic devicesSensor arrayVoltage source

A Hall sensor array for offset-compensated magnetic field measurement comprises a first and at least one additional pair of Hall sensor elements. Each Hall sensor element has four terminals, of which two act as power supply terminals for supplying an operating current and two act as measurement terminals for measuring a Hall voltage. Respective first supply terminals of each Hall sensor element are connected together and to a first terminal of a common voltage source and respective second supply terminals of each Hall sensor element are connected together and to a second terminal of the common voltage source so that the common voltage source supplies an operating current for the Hall sensor elements. The Hall sensor elements are operated in the spinning current mode so that the offset voltages of the Hall sensor elements approximately cancel one another out in a revolution so that the Hall signal contributions which actually depend on the magnetic field remain.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV

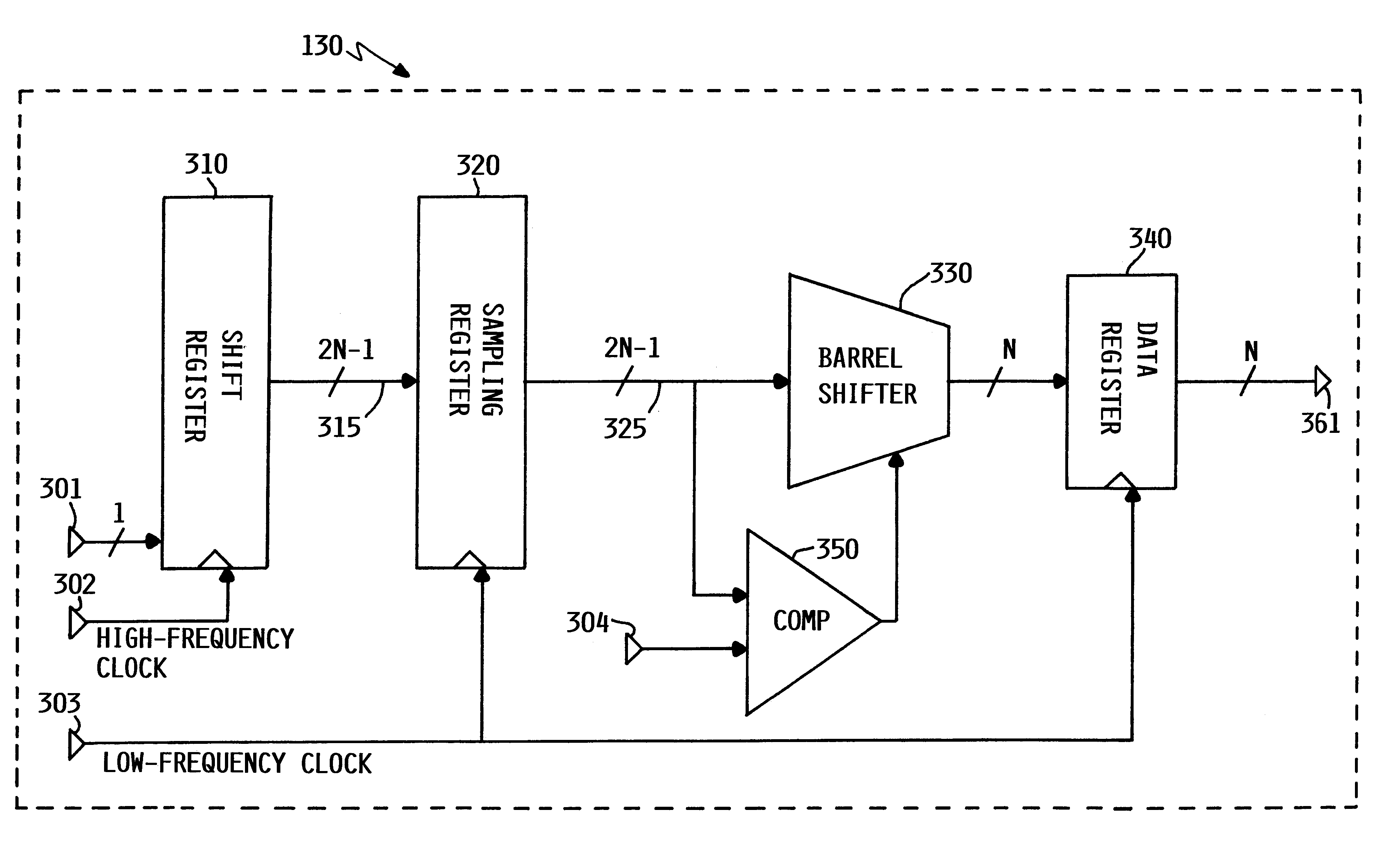

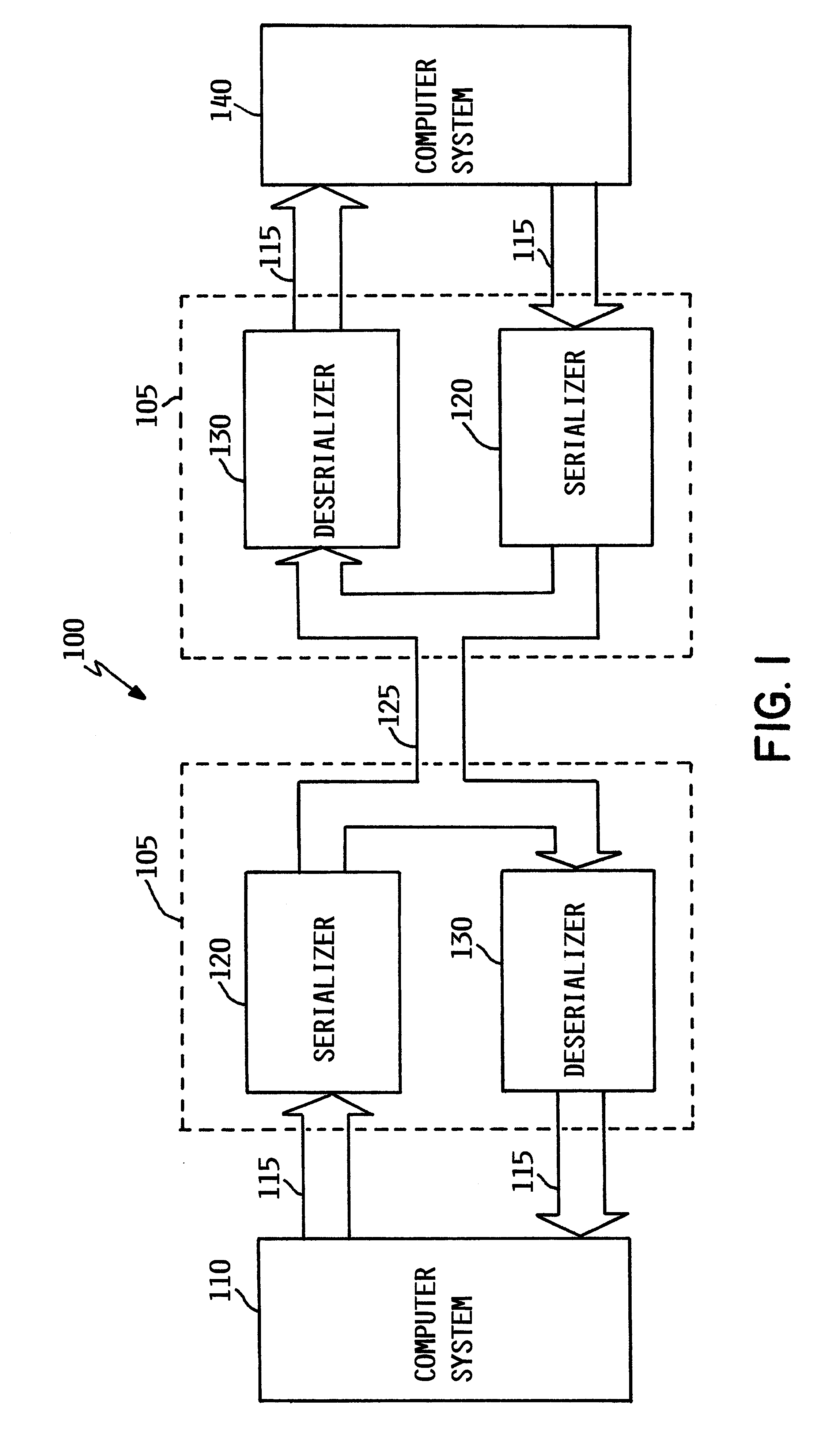

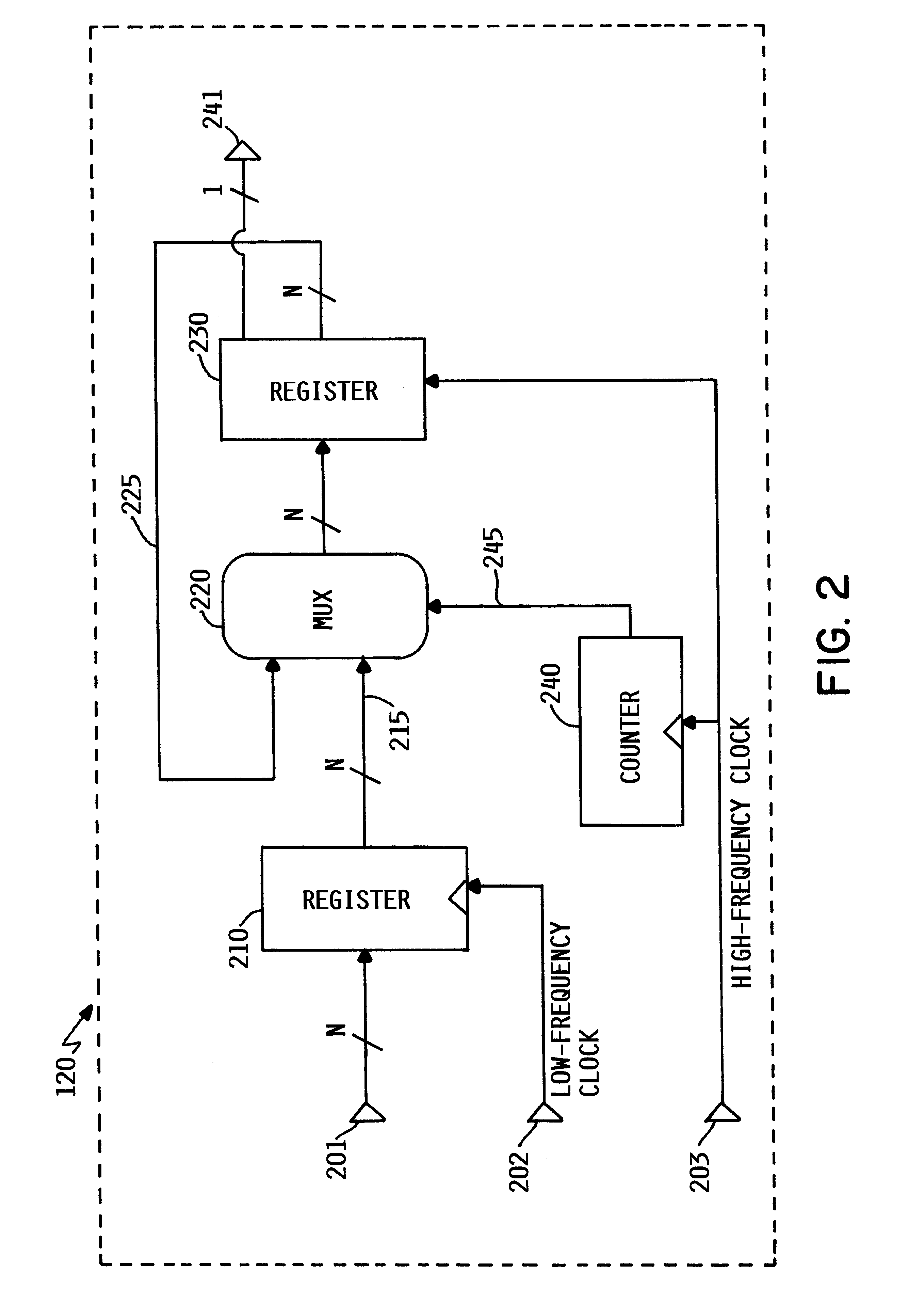

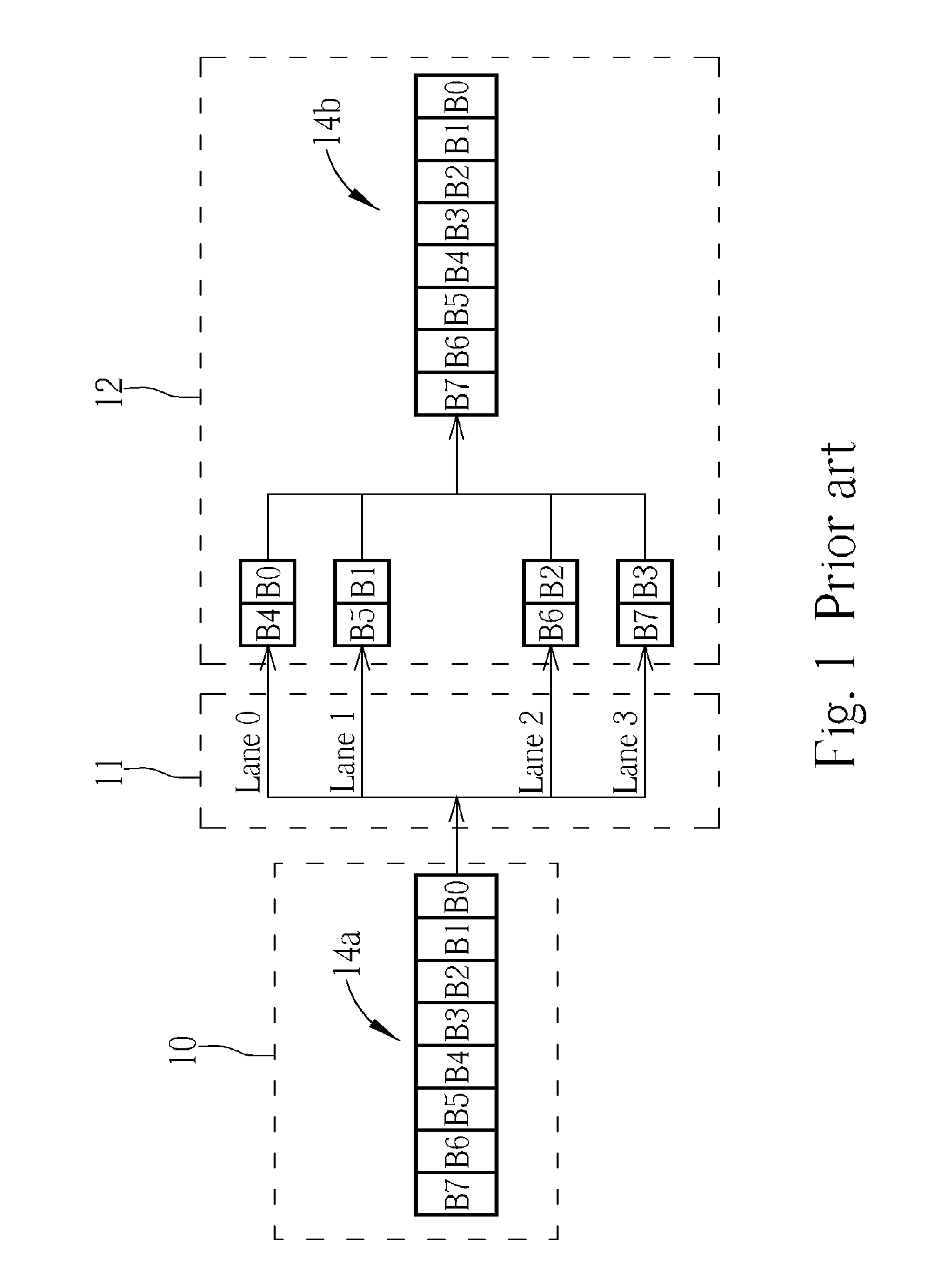

Apparatus and method for optimized self-synchronizing serializer/deserializer/framer

InactiveUS6459393B1Negatively impact design timeNegatively integrated circuit clock loadingParallel/series conversionViruses/bacteriophagesSerial transferTelecommunications link

An apparatus and method for improving the communication capabilities of computer systems is disclosed. The most preferred embodiments of the present invention use a series of data buffers and data registers to process an incoming high speed data signal. By using the buffers and registers, the incoming signal can be reformatted and manipulated at a much lower frequency than the original transmission frequency. The deserializer of the present invention also samples a greater portion of the incoming data signal than usual to further increase reliability. These various features of the invention provide for a more stable and reliable communication link and will also provide a less expensive solution for serialization / deserialization. The present invention includes a serializer that receives parallel data input from a computer and serializes the data for transmission over a high-speed serial communication link. On the receiving end, the present invention provides a deserializer that can quickly and efficiently transform the serial data back into parallel form for use within the computer system on the receiving end. By utilizing two related clock signals, one clock signal being an integer multiple of the other, a self-synchronizing serializer / deserializer can be created. In addition, by increasing the size of the data sample on the receiving end, the comparisons necessary to retrieve a parallel signal from a serial transmission can occur at a much lower frequency than the frequency of the serial transmission. In the most preferred embodiment, the invention is provided as a integrated solution manufactured on a Peripheral Component Interconnect (PCI) card, thereby allowing the present invention to be easy installed into existing computer systems.

Owner:MEDIATEK INC

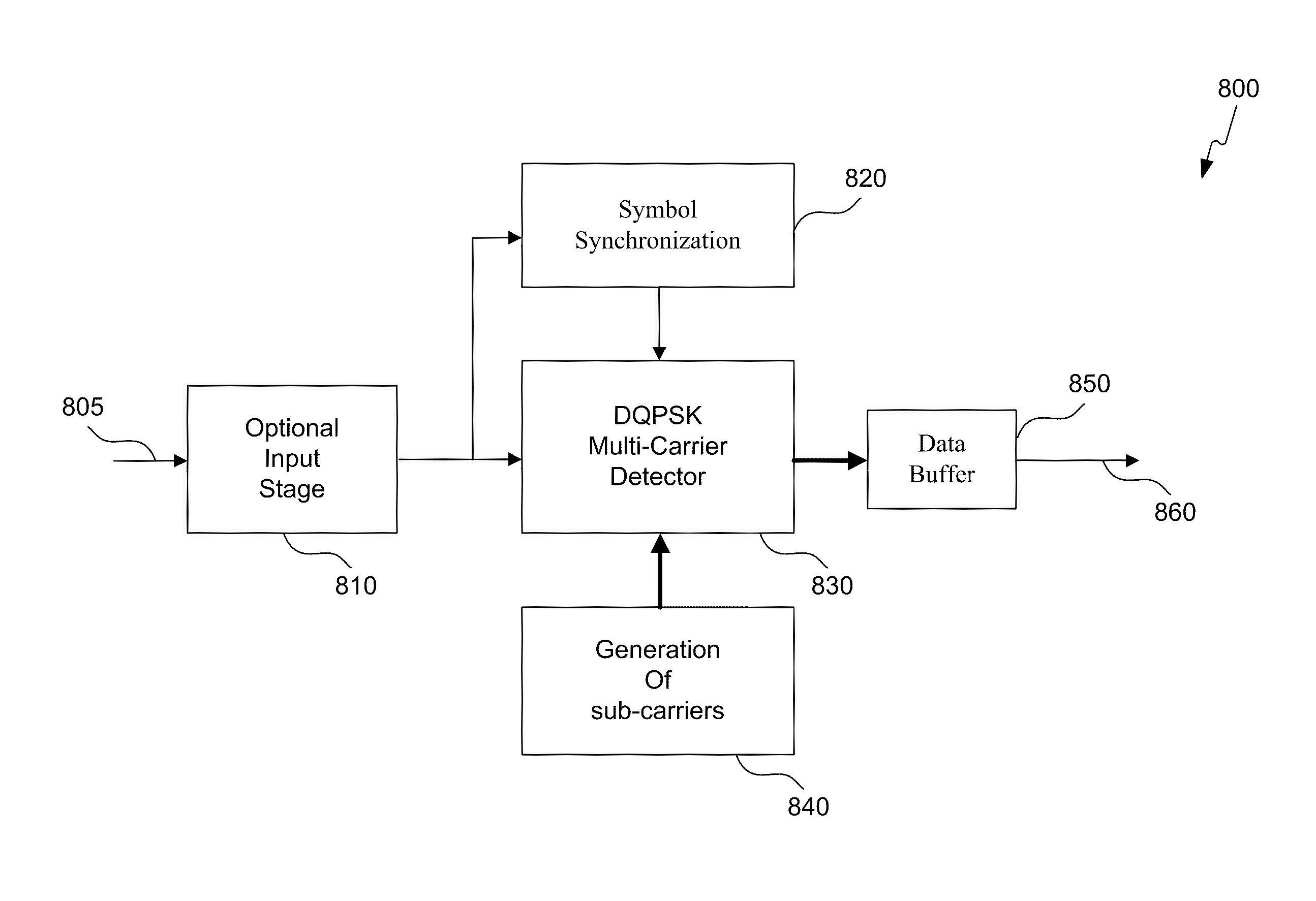

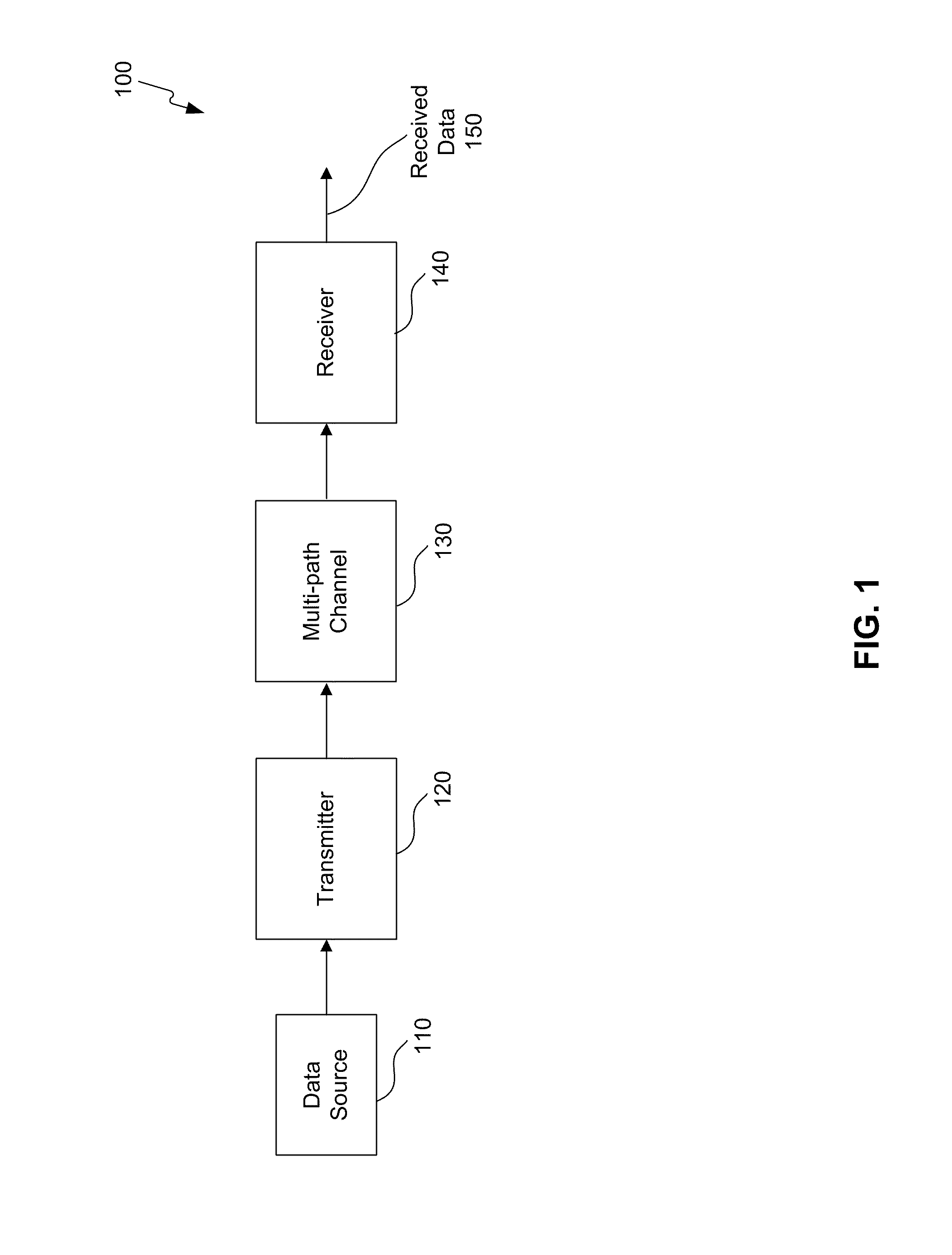

Data transmission via multi-path channels using orthogonal multi-frequency signals with differential phase shift keying modulation

ActiveUS9197470B2Reduce circuit complexityReduce computational processingSecret communicationPhase-modulated carrier systemsDifferential quadrature phase shift keyingEngineering

Owner:INNURVATION

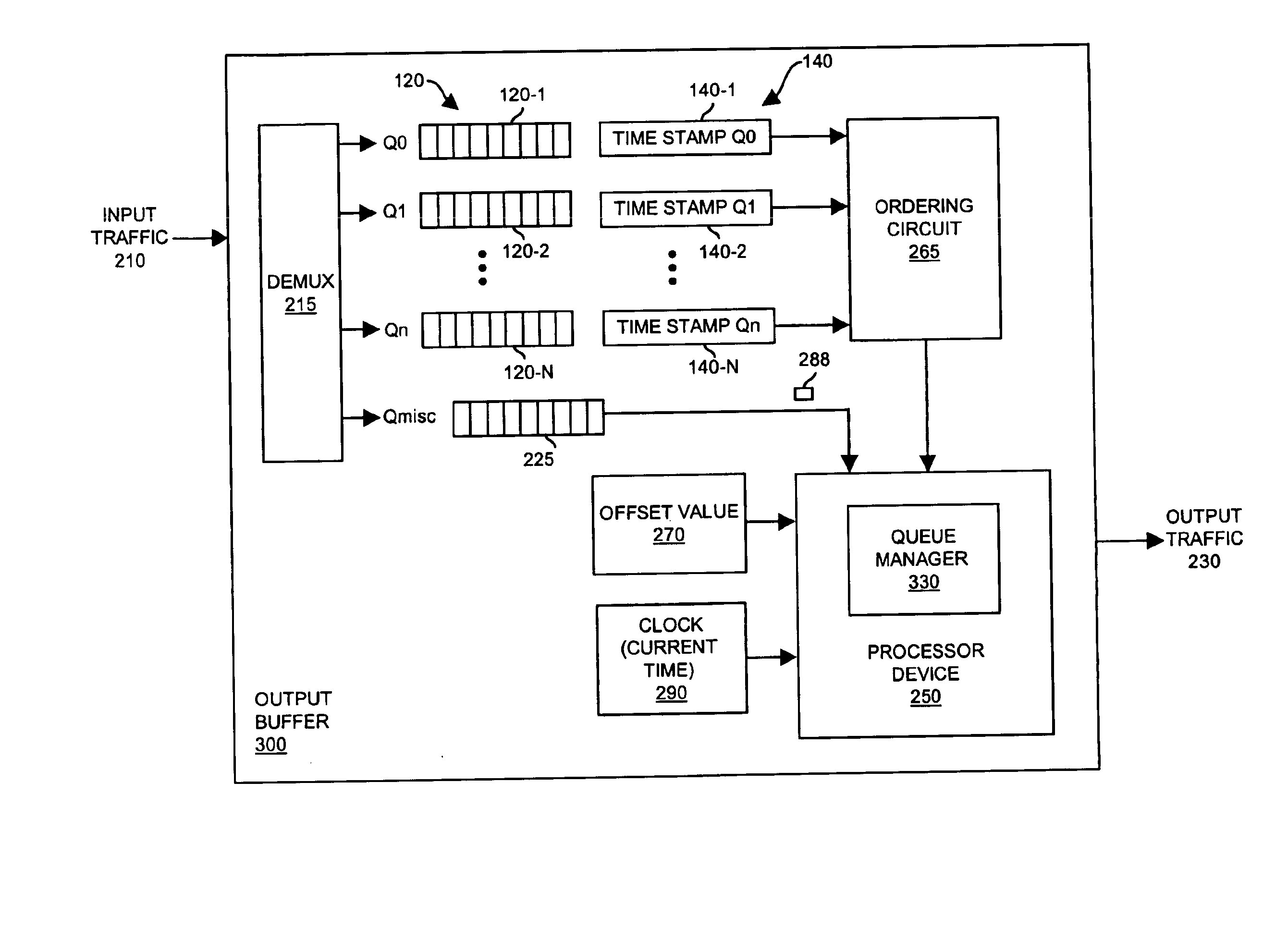

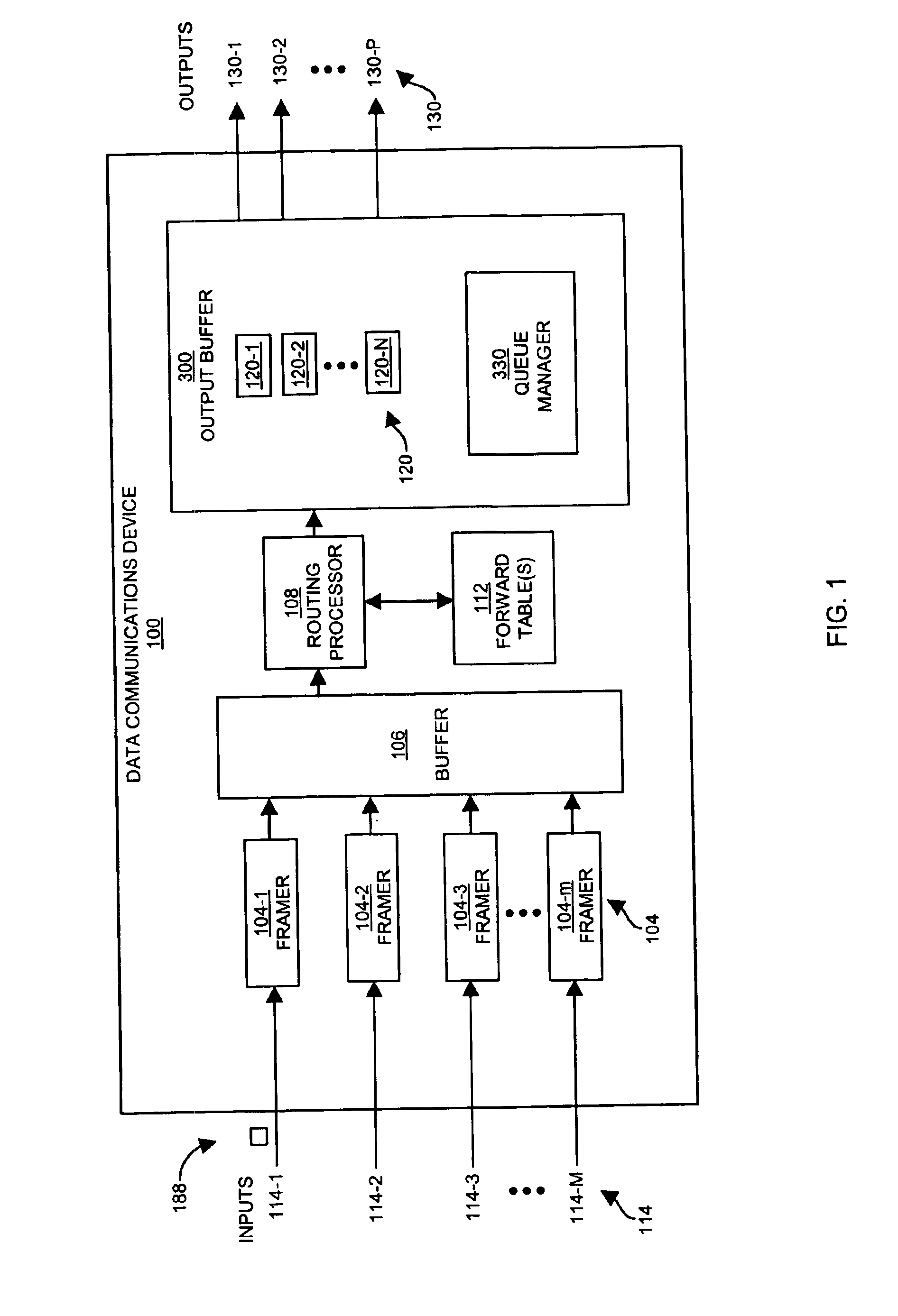

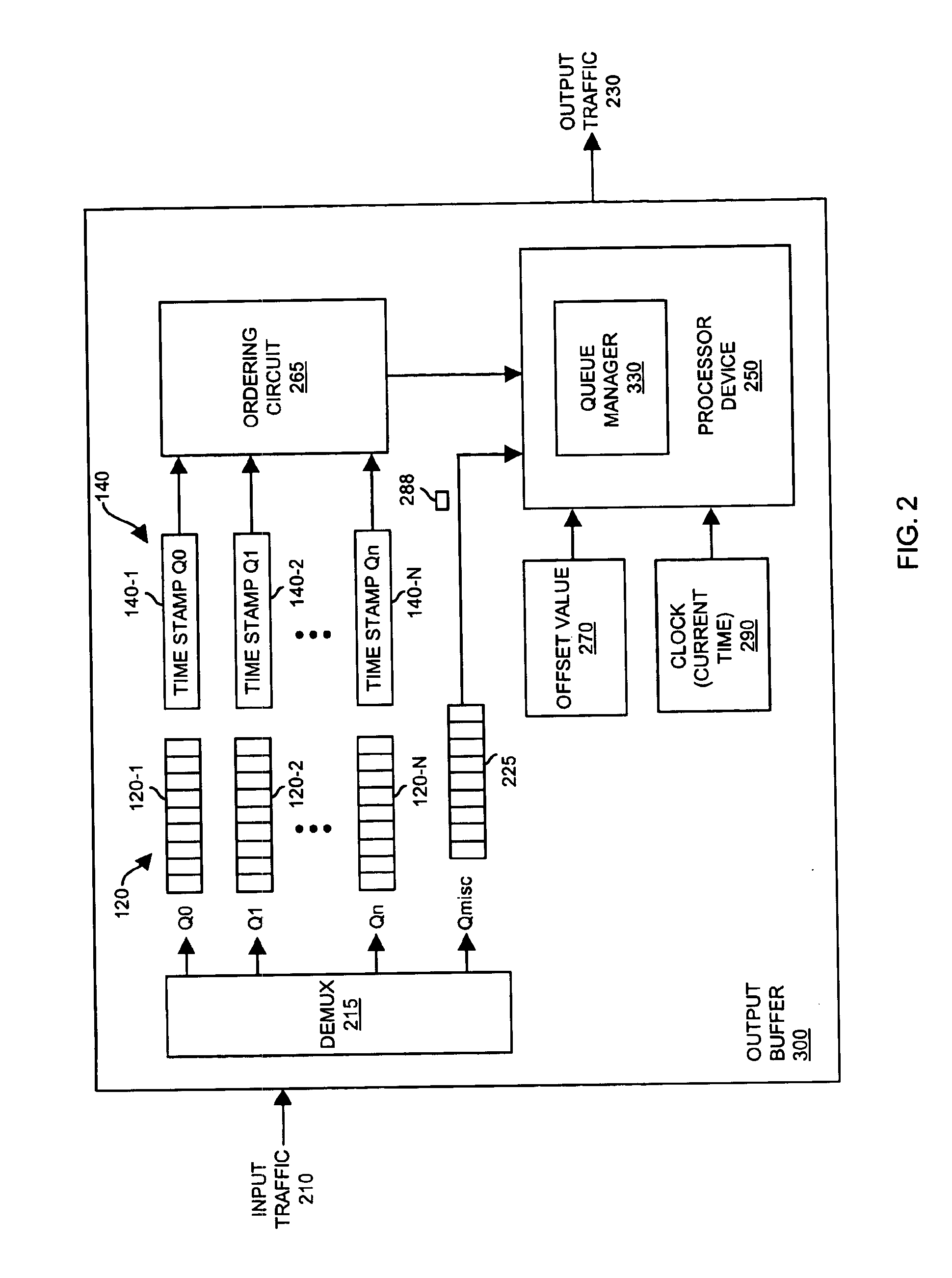

Methods and apparatus for maintaining queues

InactiveUS6876952B1Reduce circuit complexityTime indicationError preventionReal-time clockData stream

One or more queues store data information such as packets or data flows for later transmission to downstream communication devices. A real-time clock tracks current time and an advancement of a moving time reference, which is displaced with respect to the current time of the clock by an offset value. Thus, as current time advances, the moving time reference also advances in time. Upon servicing a queue, a time stamp associated with the serviced queue is also advanced in time. To monitor a rate of outputting data from the one or more queues, a processor device at least occasionally adjusts the offset value so that the moving time reference and values of the time stamps advance in relation to each other. Consequently, by tracking a relative time difference between current time of the real-time clock and a relative advancement of time stamps, a rate of outputting data information from the queue is monitored over time.

Owner:CISCO TECH INC

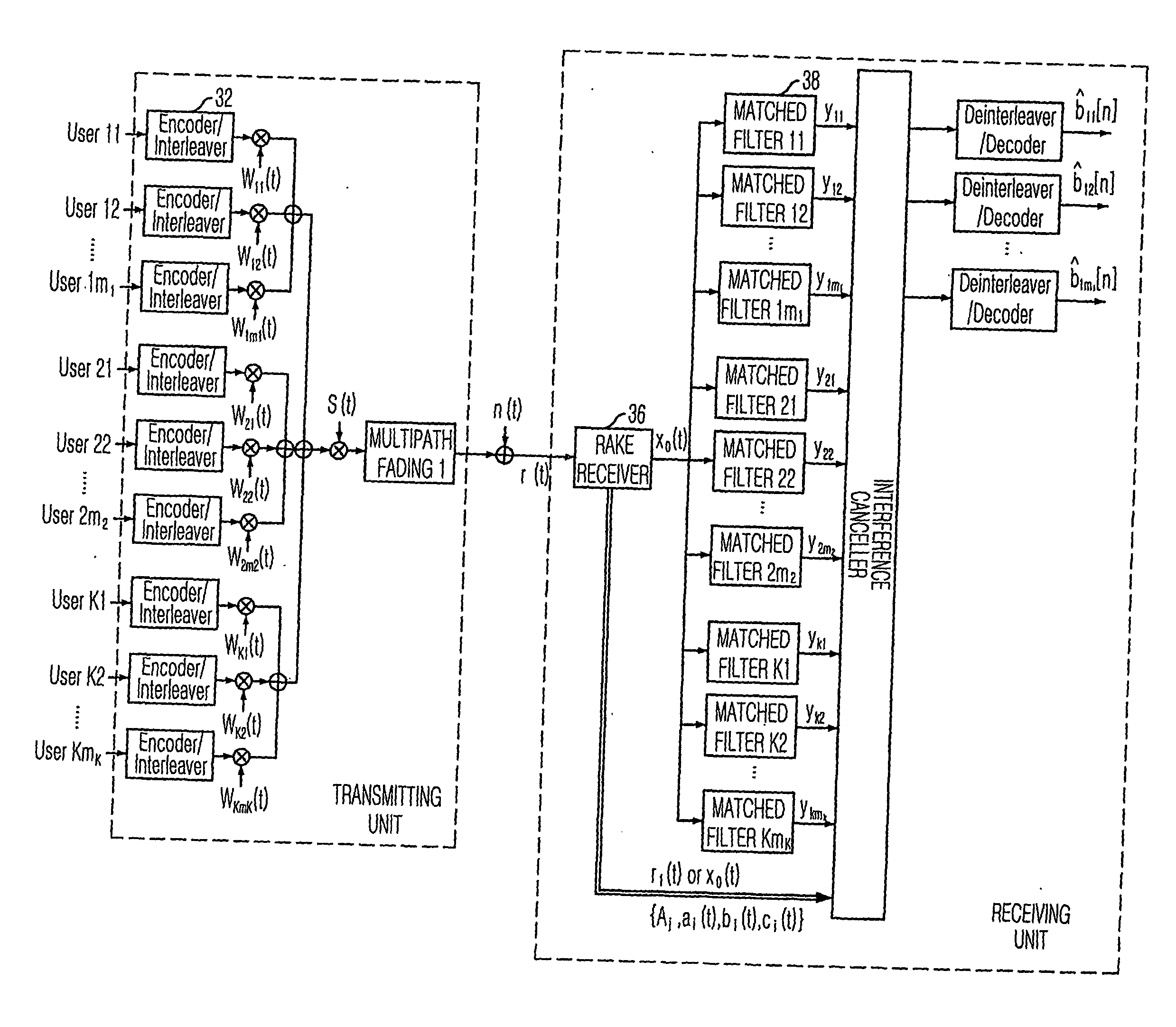

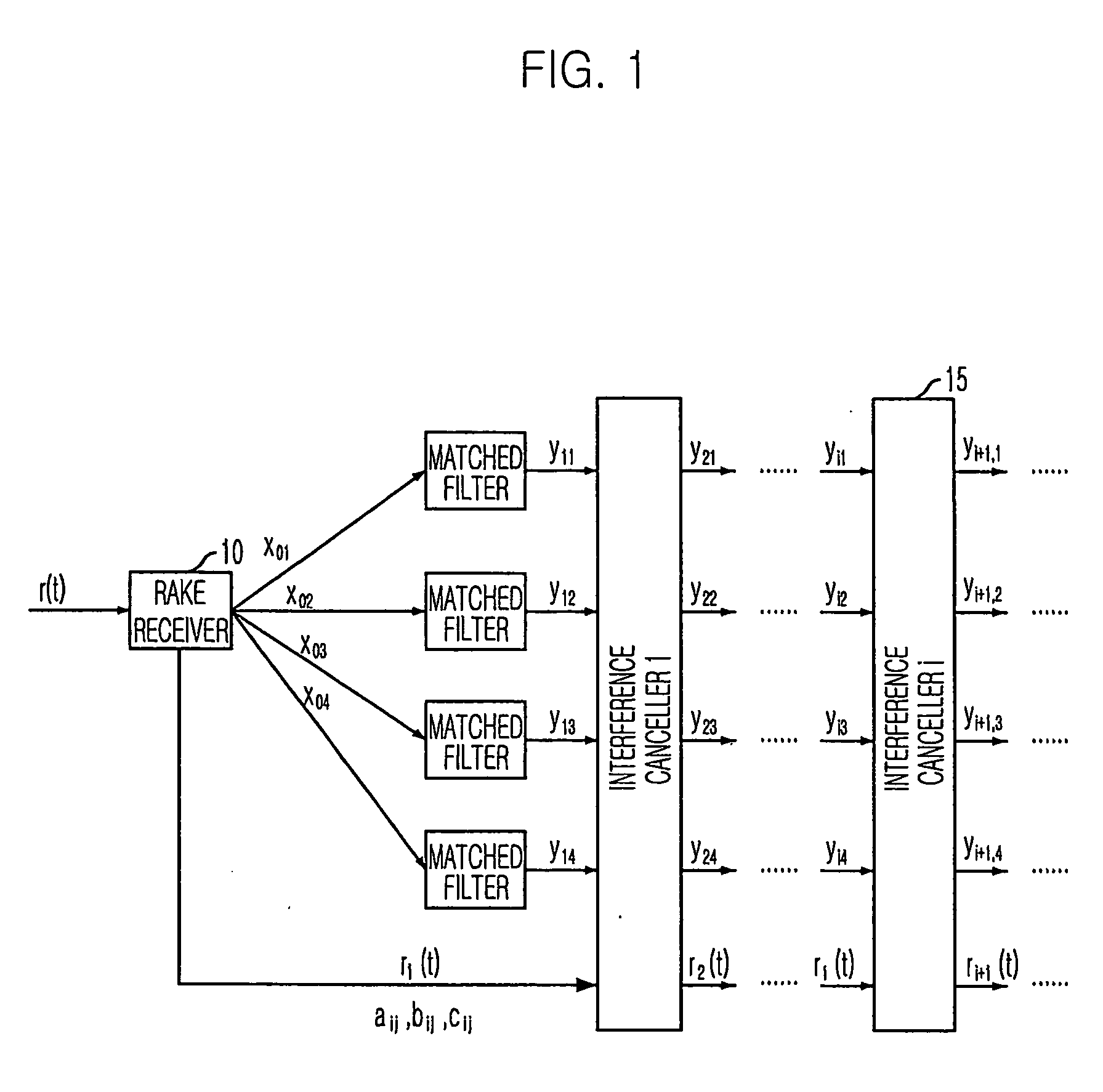

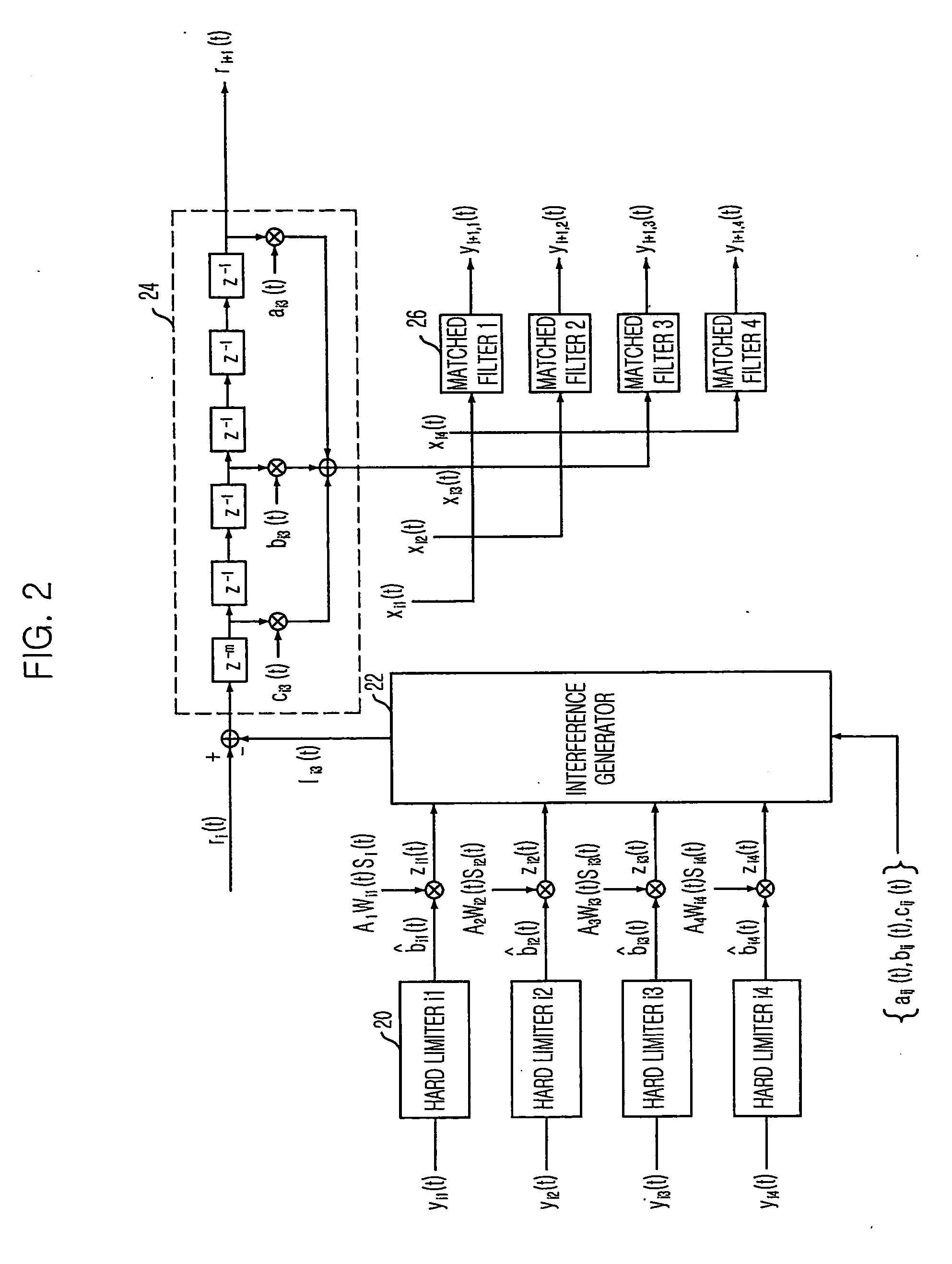

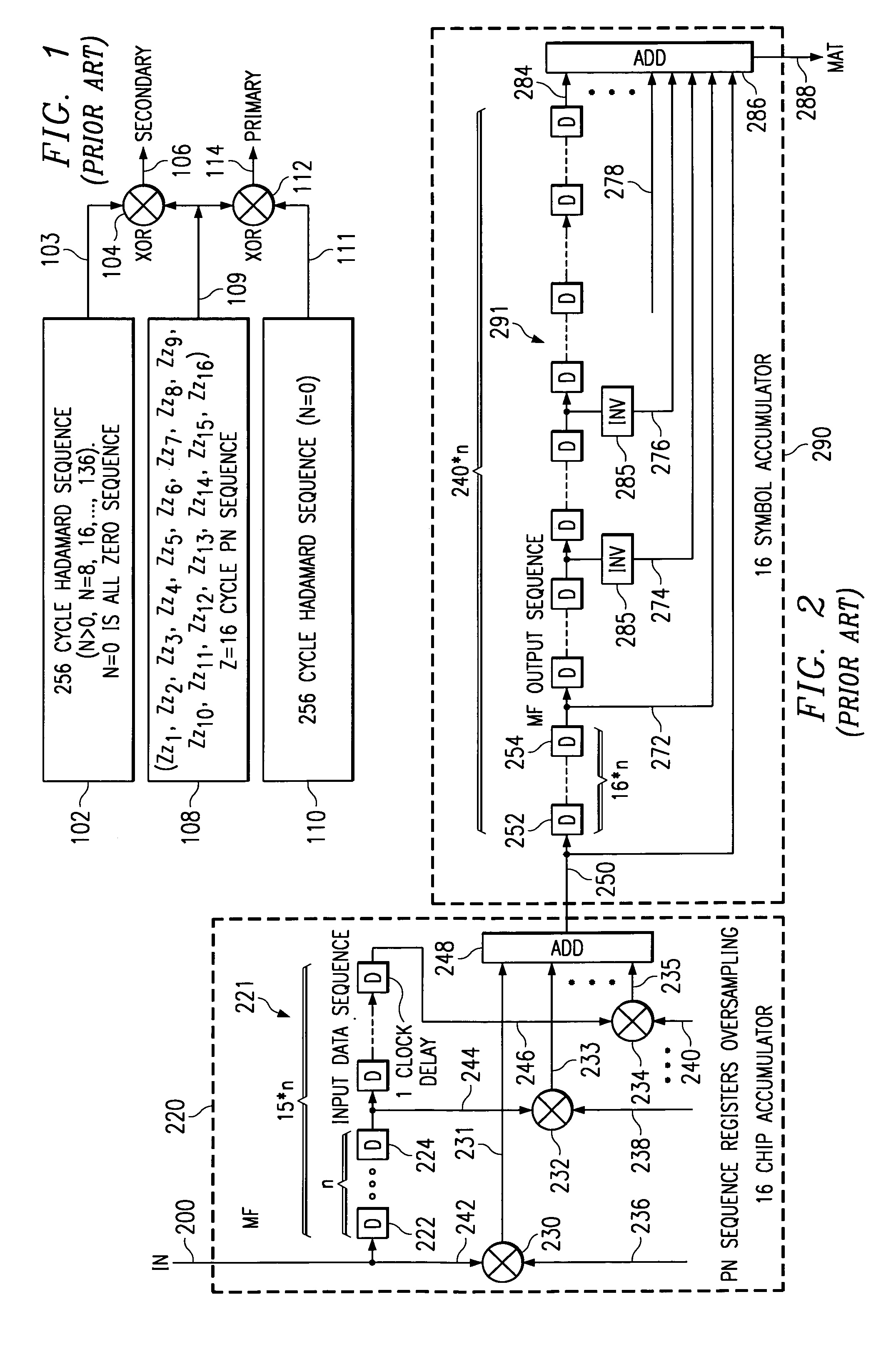

Multistage adaptive parallel interference canceller

InactiveUS20060013289A1Minimizing degradation of orthogonalityReduce circuit complexityCode division multiplexTransmissionInterference cancellerInterference elimination

A multistage adaptive parallel interference canceller is disclosed. The multistage adaptive parallel interference canceller for a downlink receiver includes: a plurality of stages of interference cancellation units. Each of interference cancellation units includes: a matched filter for matching a signal from a rake receiver each channel signal and generating a matched signal; a soft decision unit of which a slope is monotonically increased, for performing soft decision of the matched signal and generating a soft-decided signal; a weight controller for controlling the slope of the soft decision unit; a respreader for respreading the soft-decided signal based on a walsh code and a scrambling code and generating a respread signal; an interference calculator for calculating interference signals due to another user signal and multipath signals; and an interference canceller for canceling the interference signals from an input signal received in the rake receiver.

Owner:HWANG IN KWAN

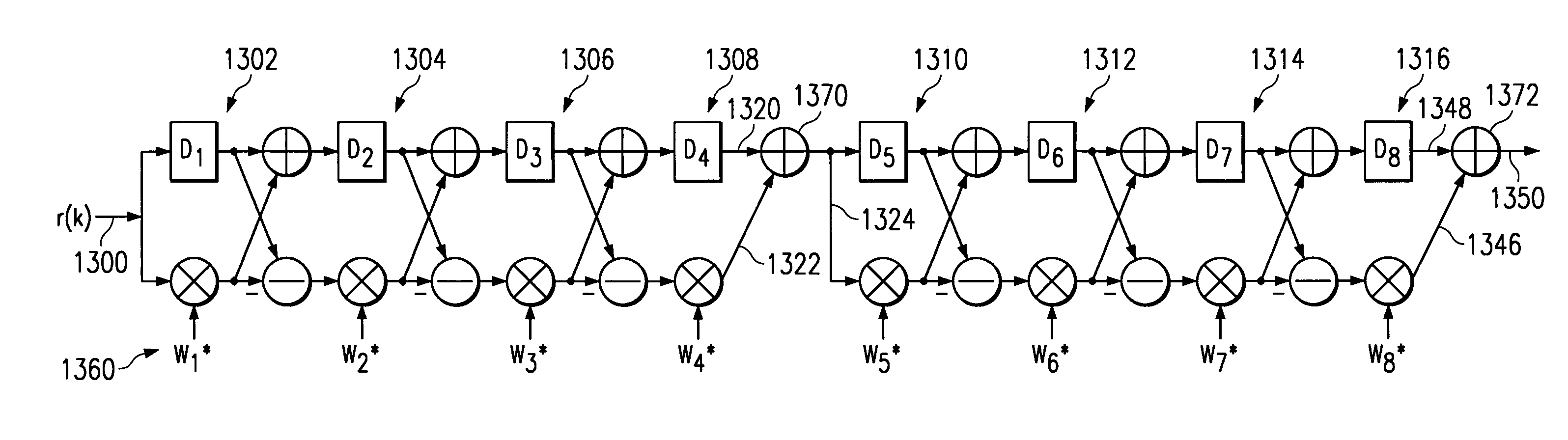

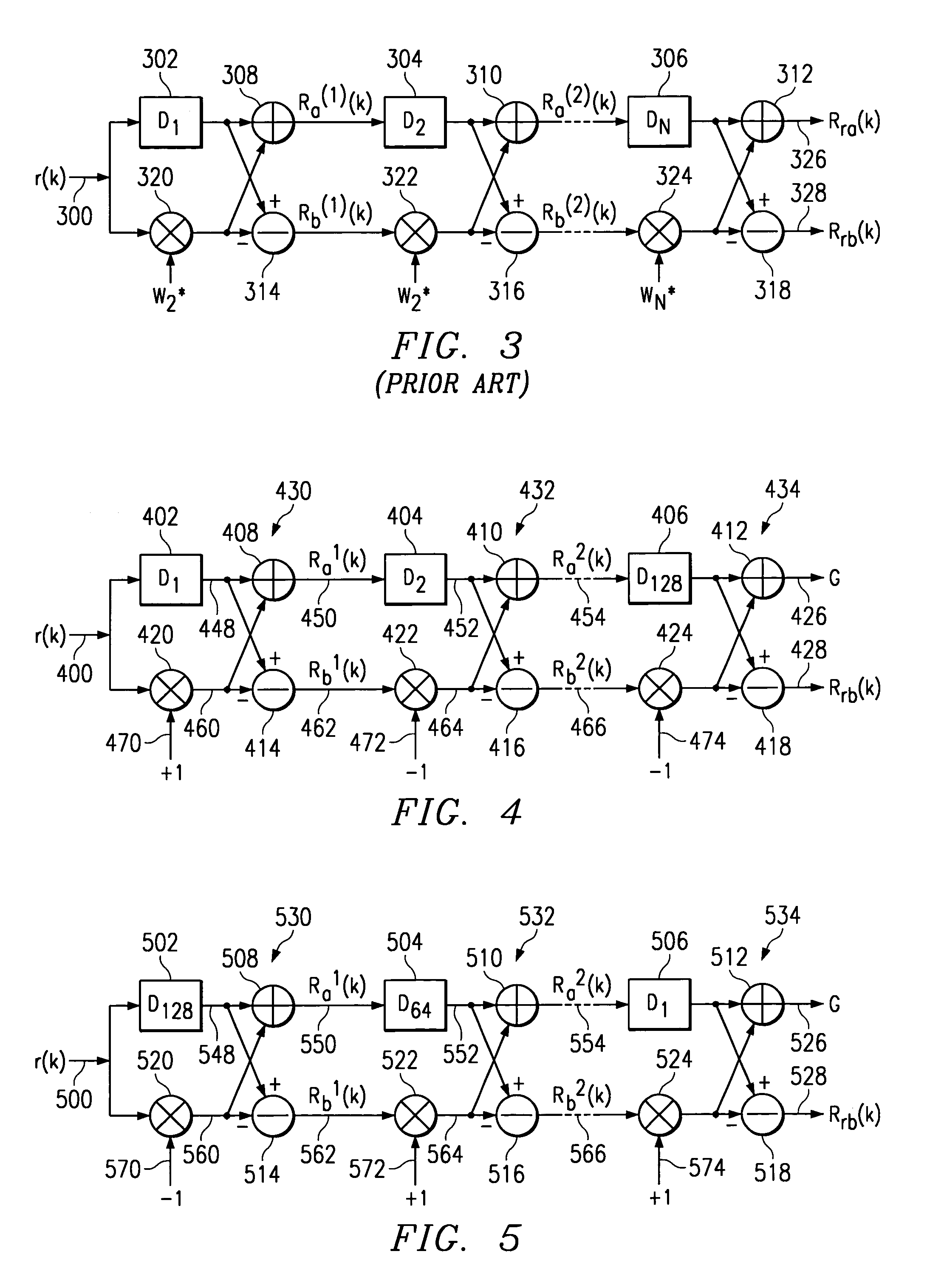

Reduced complexity primary and secondary synchronization codes with good correlation properties for WCDMA

InactiveUS7039036B1Reduce circuit complexityReduce areaTime-division multiplexMultiplex code generationMaximum latencyComputer science

A circuit for processing binary sequences is designed with a plurality of stages (530–534) coupled to provide plural signal paths (526,528). Each stage includes respective signal paths (550,562) for a first Ra1(k) and a second Rb1(k) data sequence. Each stage further includes a respective delay circuit (502) having a different delay from said respective delay circuit of each other stage (504,506) of the plurality of stages. A stage having a greatest delay (502) precedes other stages (504,506) in the plurality of stages of at least one of the plural signal paths.

Owner:TEXAS INSTR INC

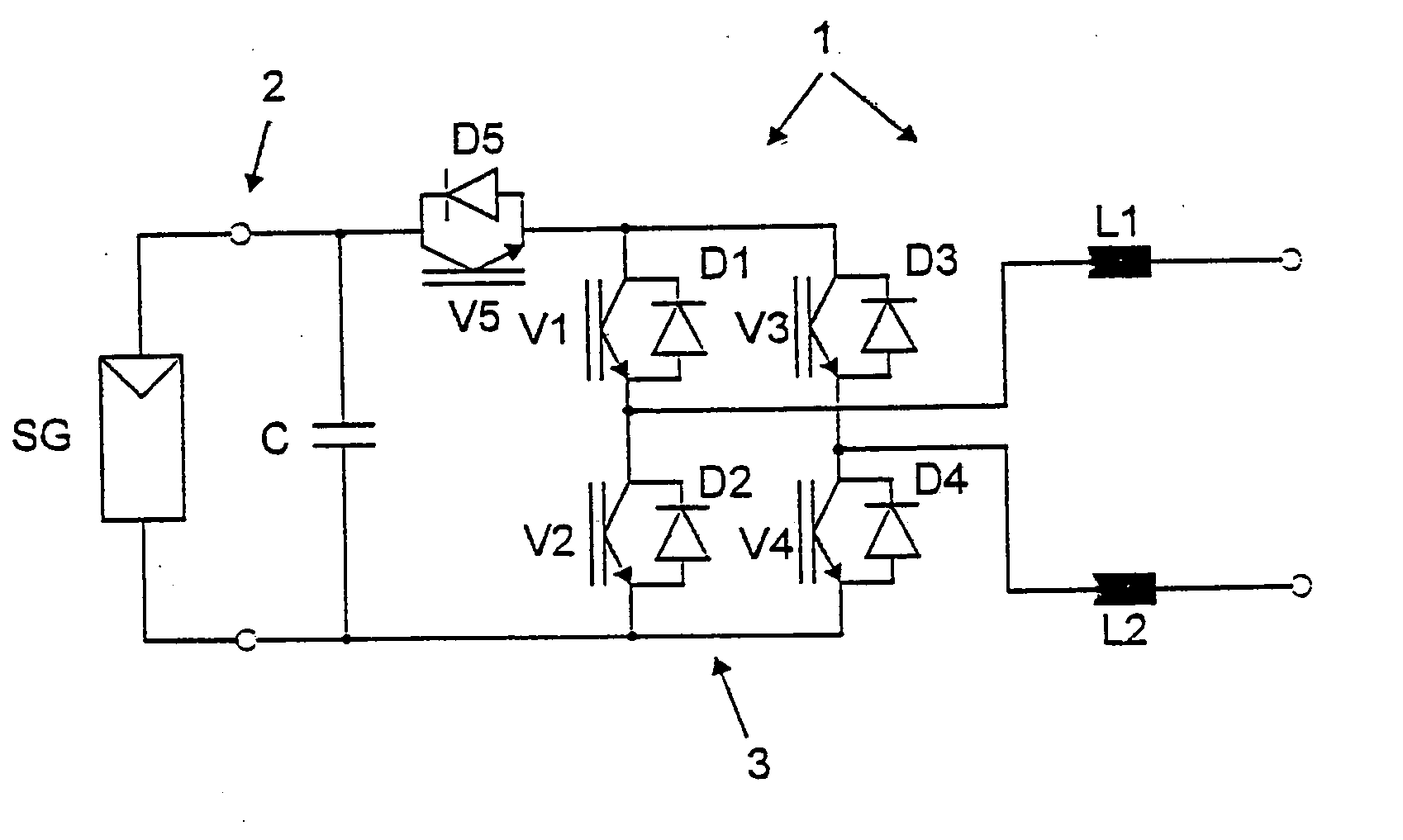

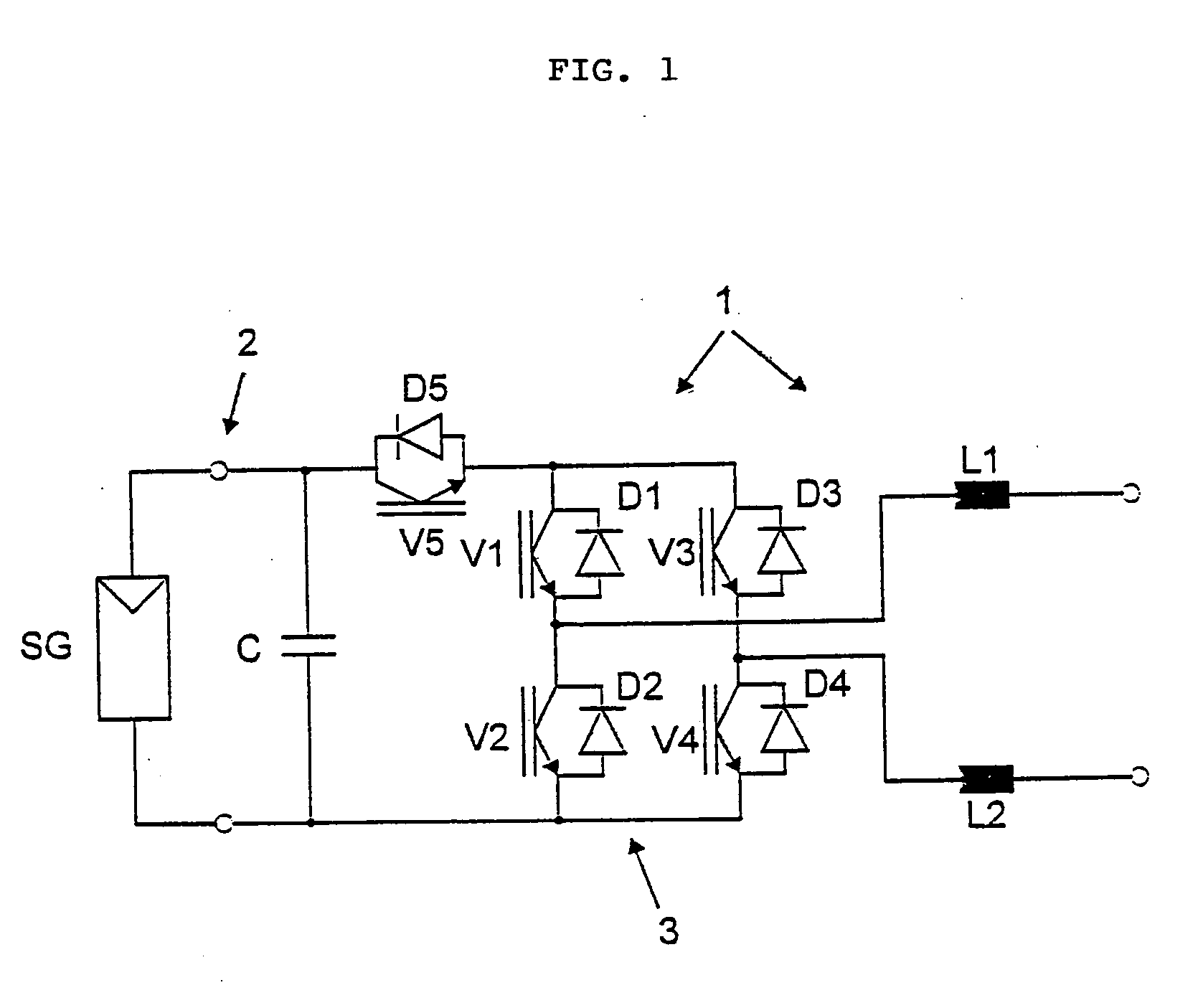

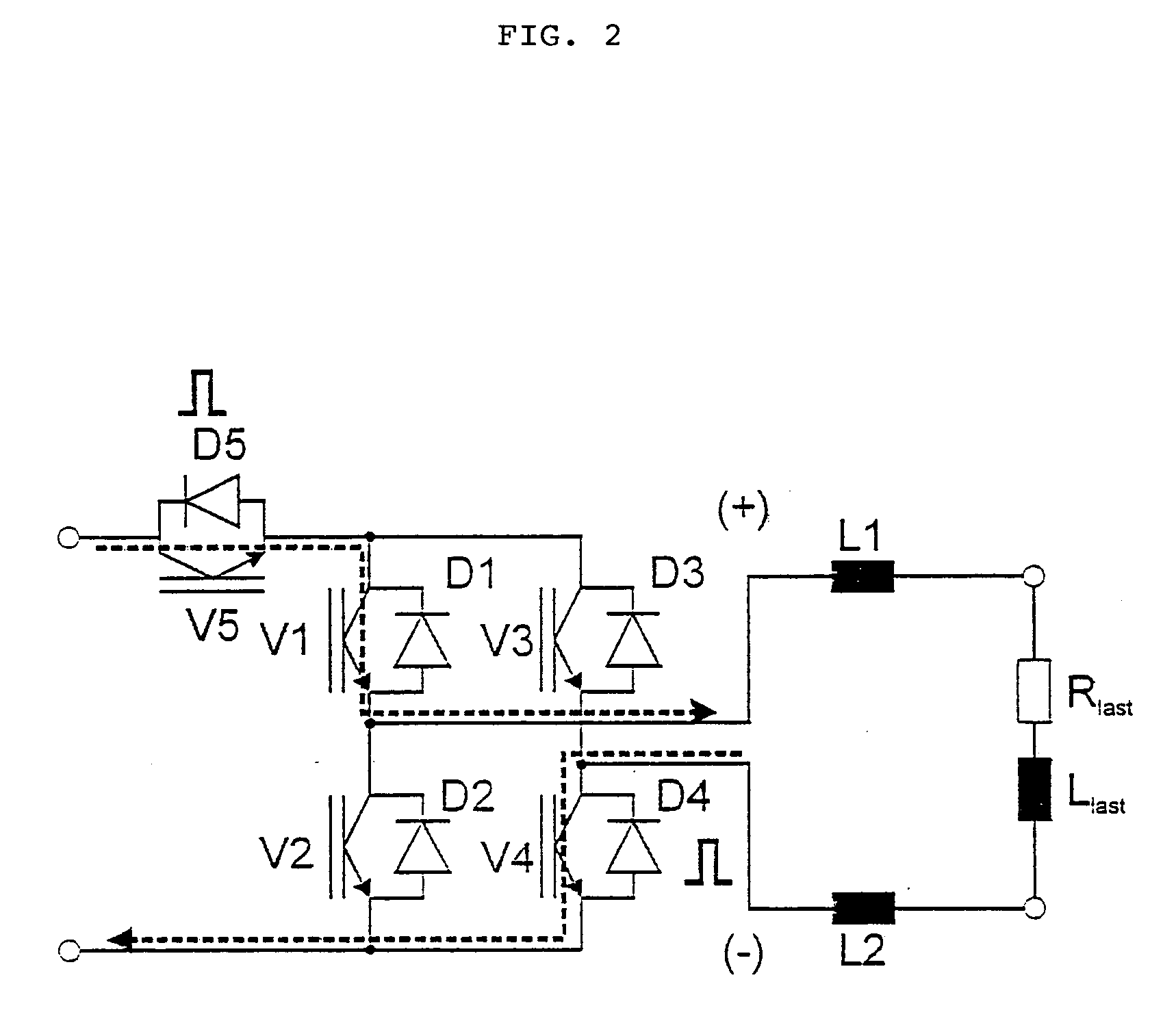

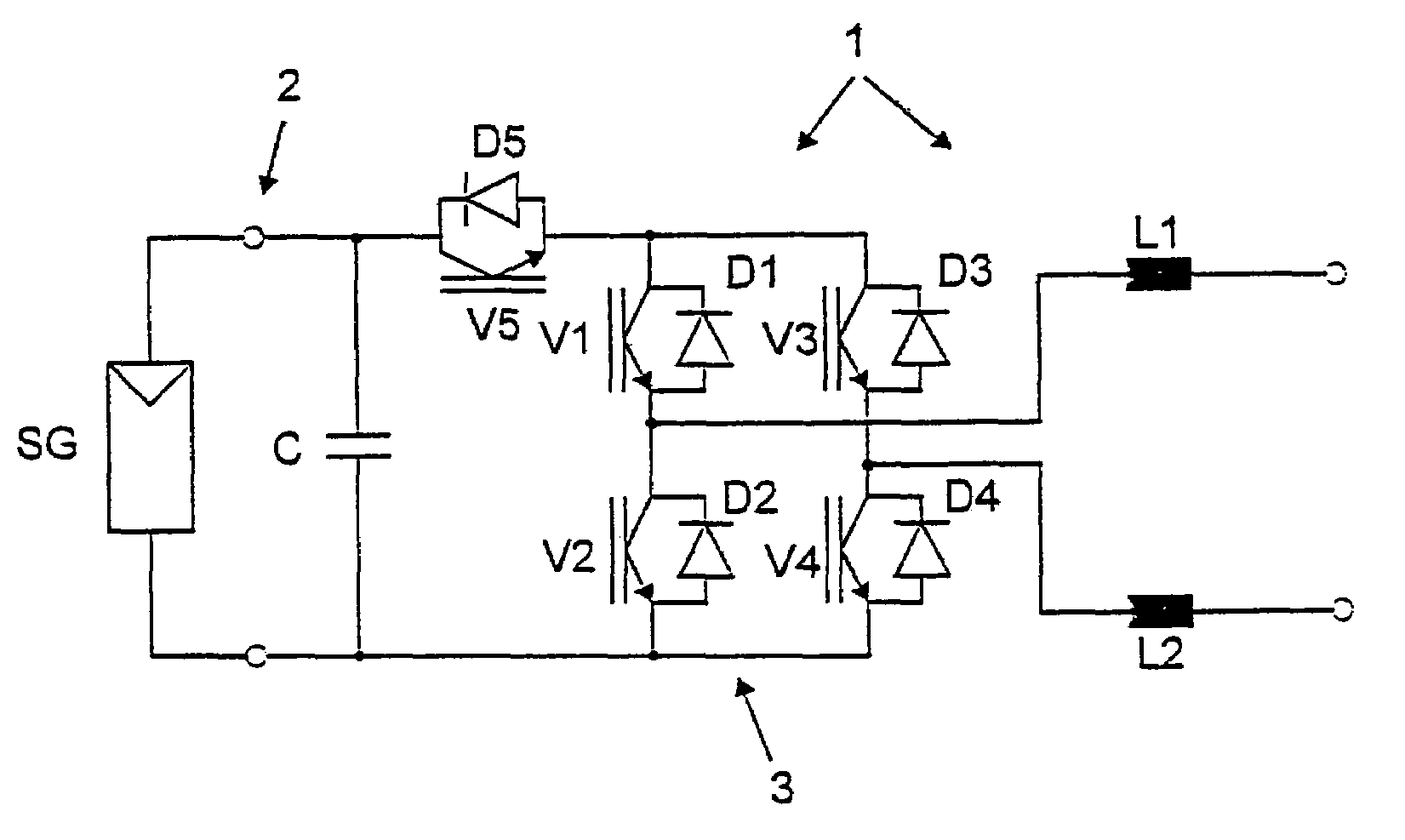

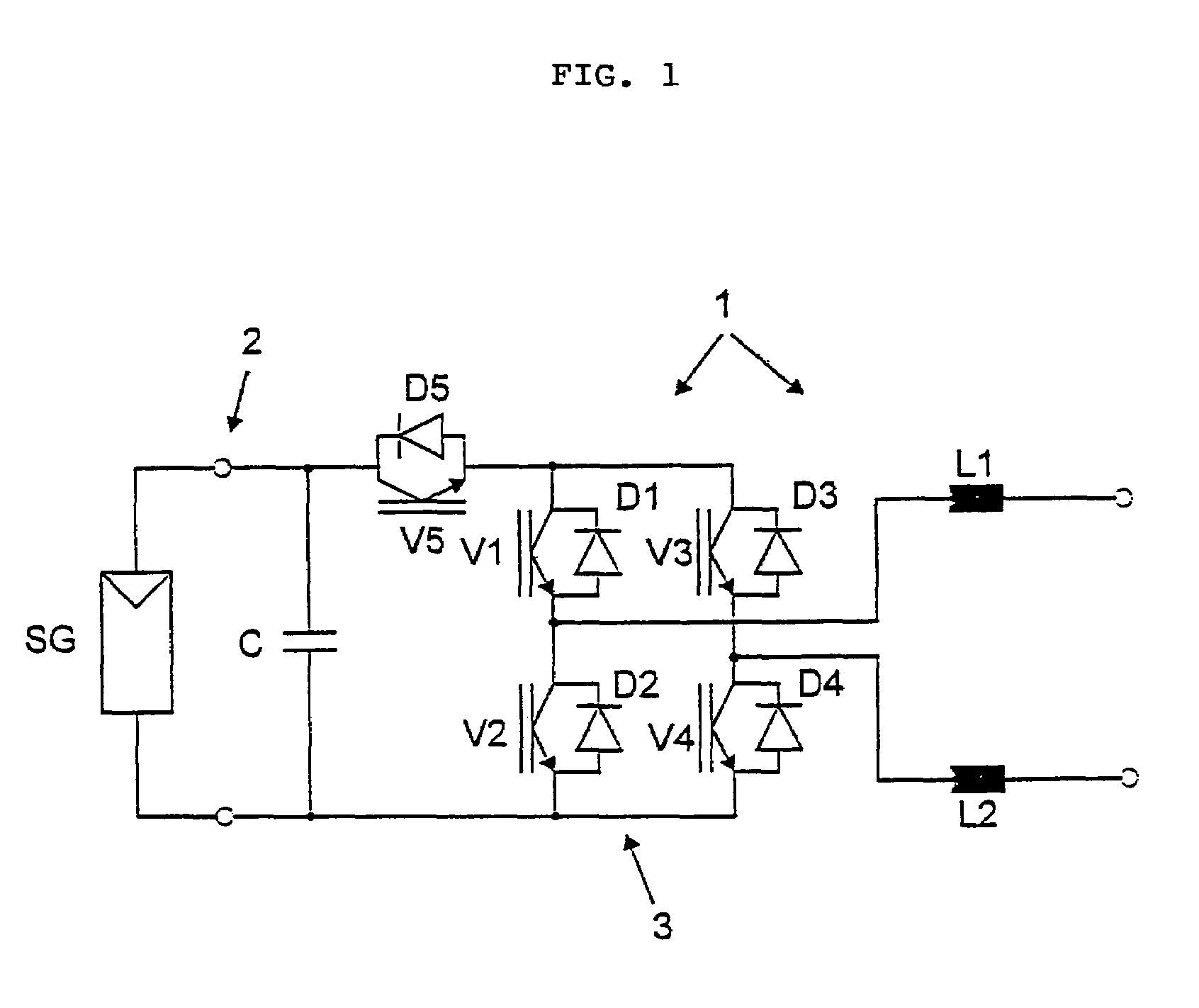

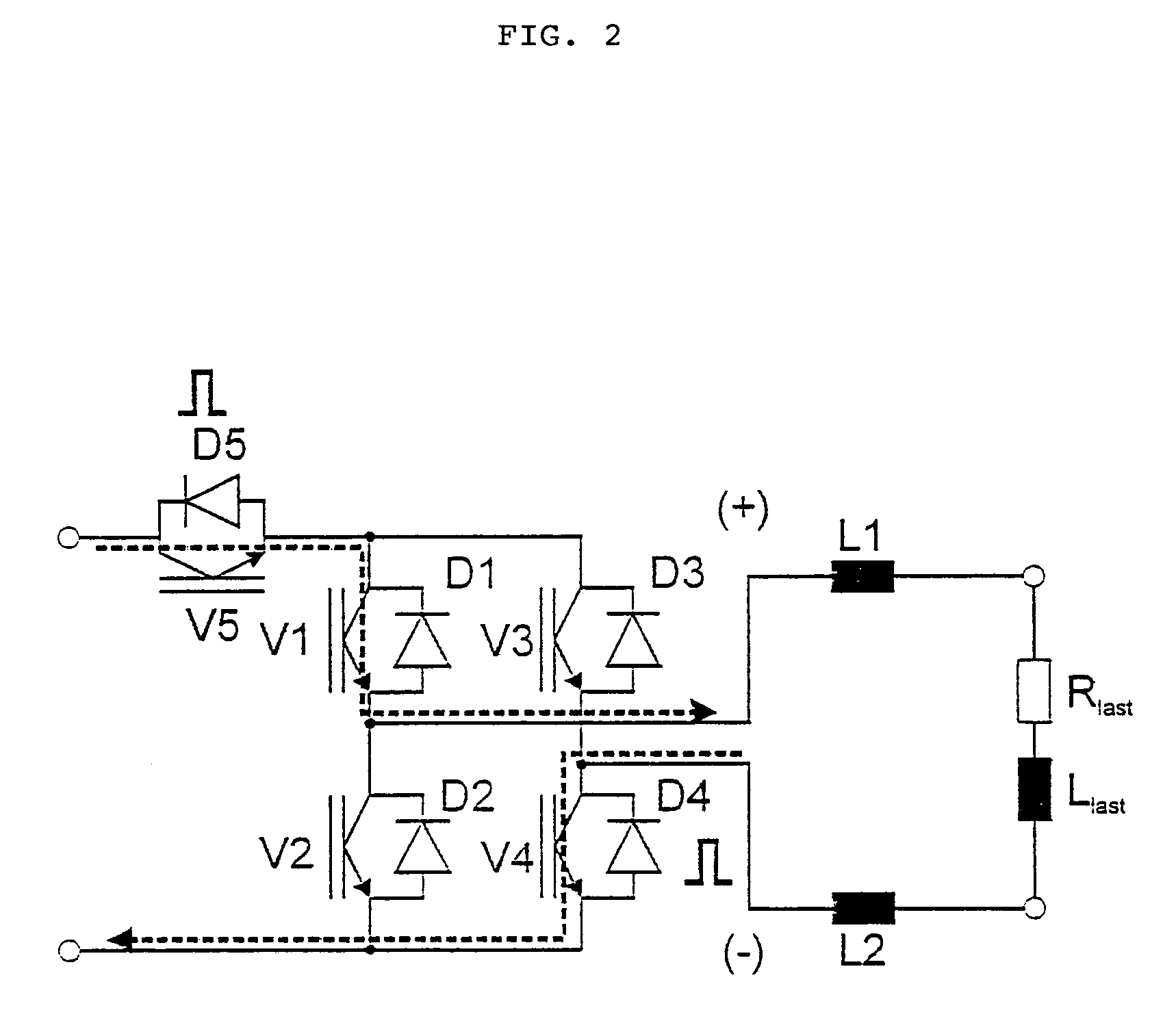

Method of converting a direct current voltage from a source of direct current voltage, more specifically from a photovoltaic couse of direct current voltage, into a alternating current voltage

ActiveUS20050286281A1Simple low-loss circuitryReduce material costsPhotovoltaic energy generationDc-ac conversion without reversalClock rateAlternating current

An inverter is devised to avoid high-frequency voltages at input terminals and to allow good efficiency thanks to its simple and cost-optimized circuit layout. This is achieved by a method of converting a direct current voltage, more specifically from a photovoltaic source of direct current voltage, into an alternating current voltage at a frequency through a bridge circuit comprising switching elements (V1-V4) and free-wheeling elements (D1-D4), said switching elements (V1-V4) being on the one side gated at the frequency and on the other side clocked at a high clock rate, a direct current voltage circuit, an alternating current voltage circuit and a plurality of free-wheeling phases being provided. It is provided that, during the free-wheeling phases, the alternating current voltage circuit is decoupled from the direct current voltage circuit by means of a switching element disposed in the direct current voltage circuit, a free-wheeling current flowing through one of the free-wheeling elements (D1) in the bridge circuit when in the decoupled state.

Owner:SMA SOLAR TECH AG

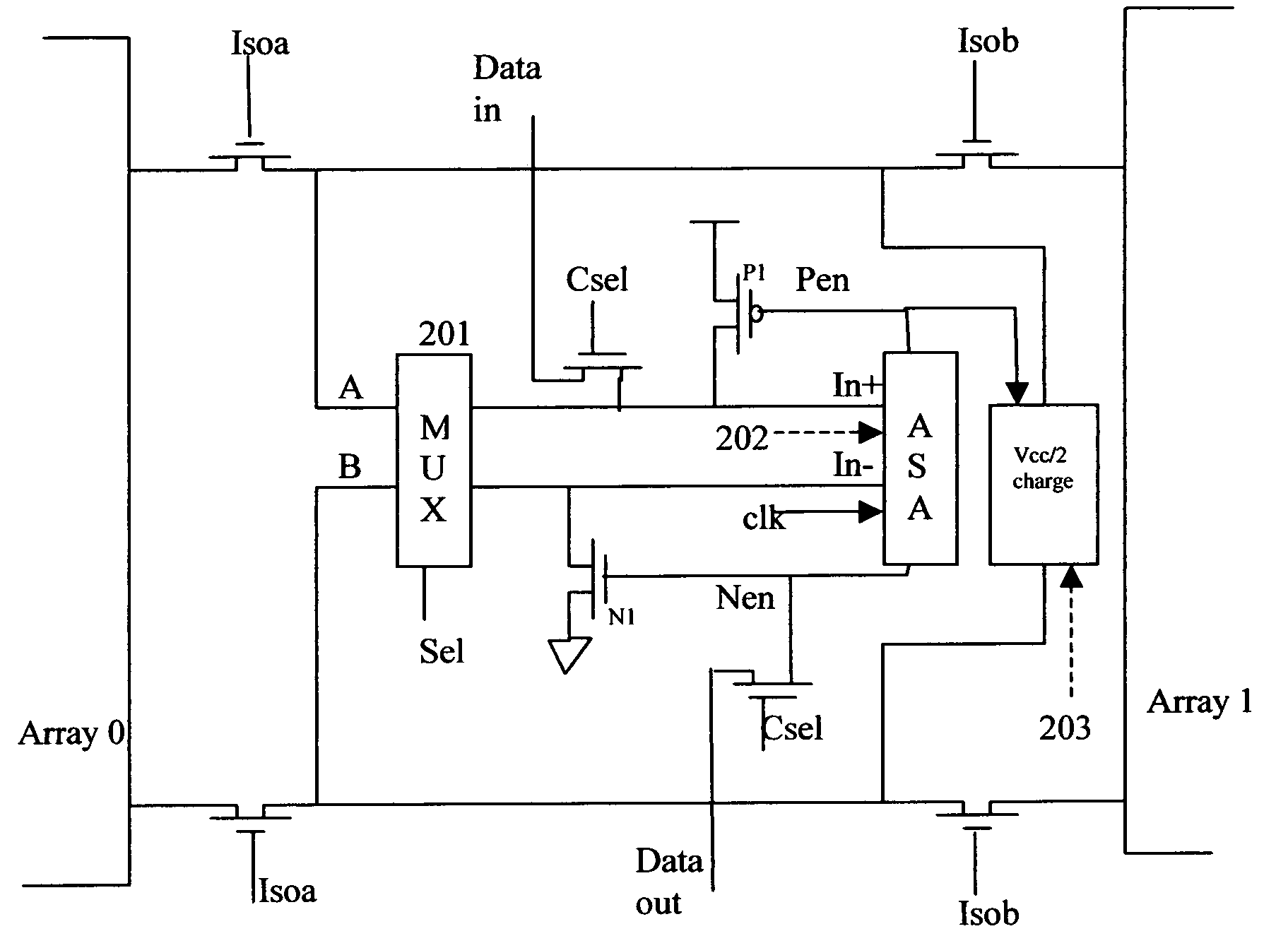

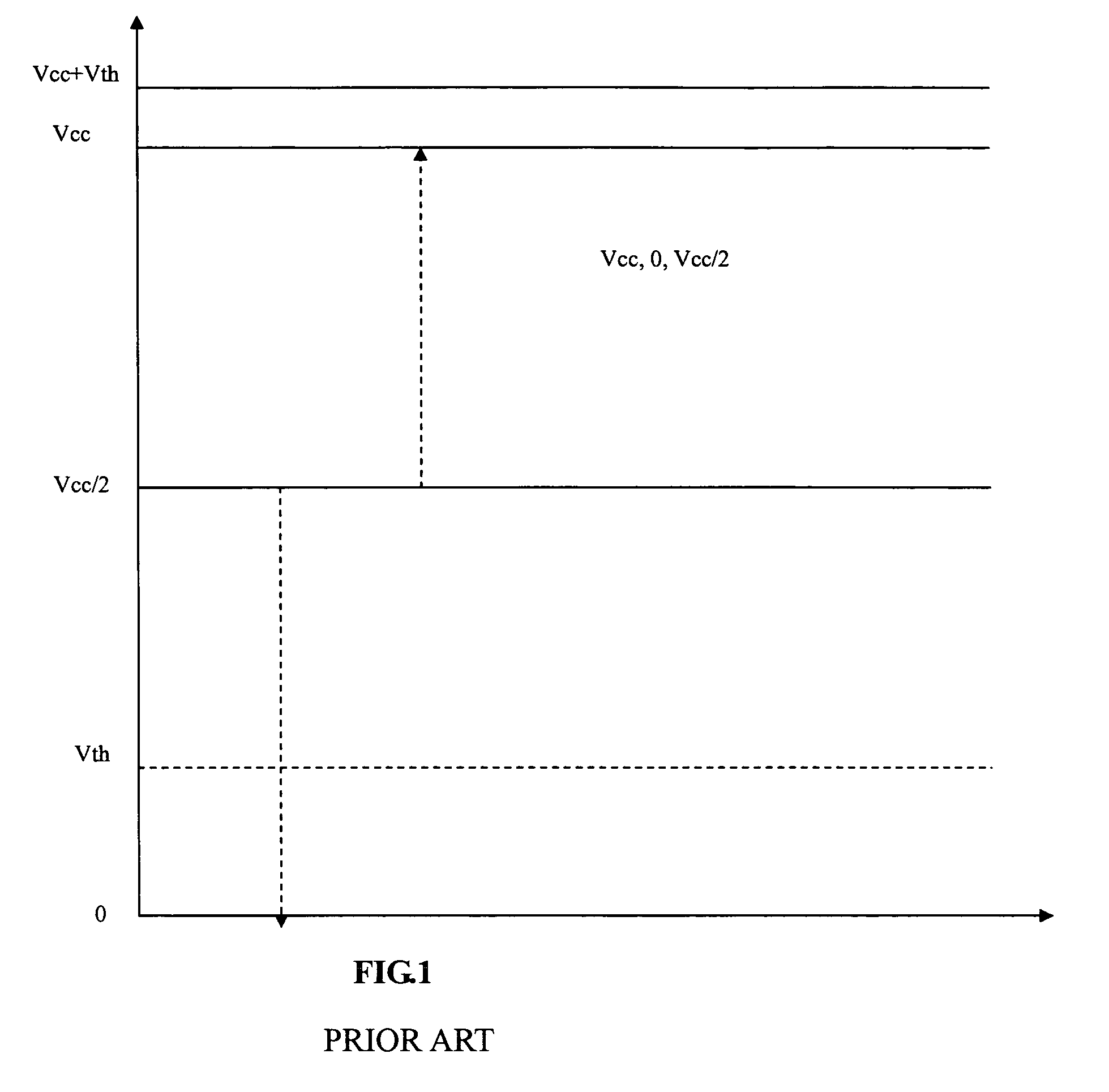

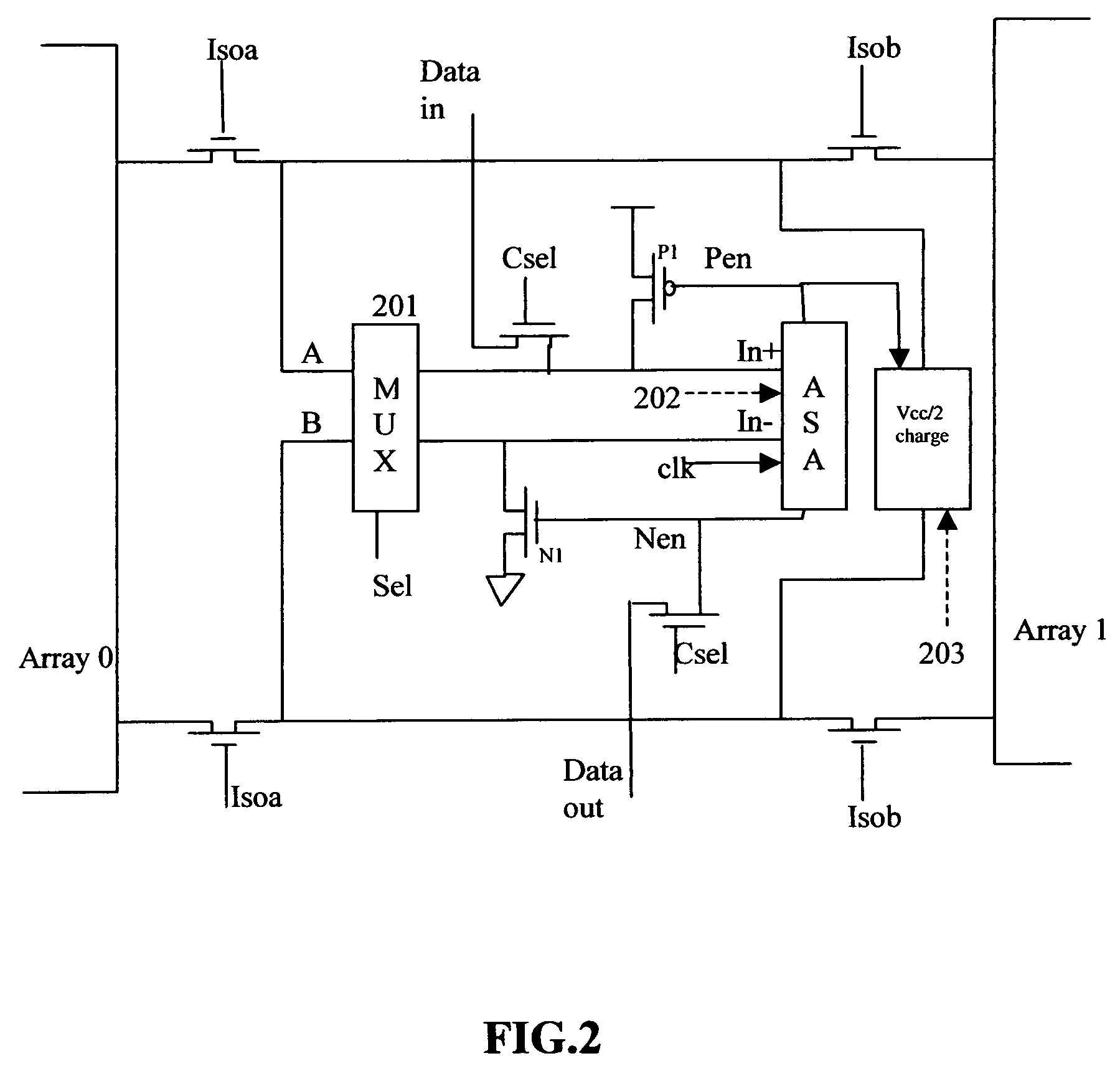

Low power, high speed read method for a multi-level cell DRAM

A method of storing, sensing and restoring three voltage levels (1.5 bit per cell) of a plurality of memory cells in Dynamic random access memory is disclosed. An asymmetrical sense amplifier, ASA, together with a 2 to 2 multiplex, will be used to detect the voltage difference on the bit lines and transfer the voltage difference to digital data. ASA is designed to have one input stronger than the other input. The multiplex is controlled by a signal so that the connection between bit line pair and two inputs of ASA is switched at different time and logical address. Other transistors and circuits are also used to store and restore the voltage levels into memory cells. Coding algorithms are used to get fast read speed of this multi-level cell DRAM.

Owner:LIU BO

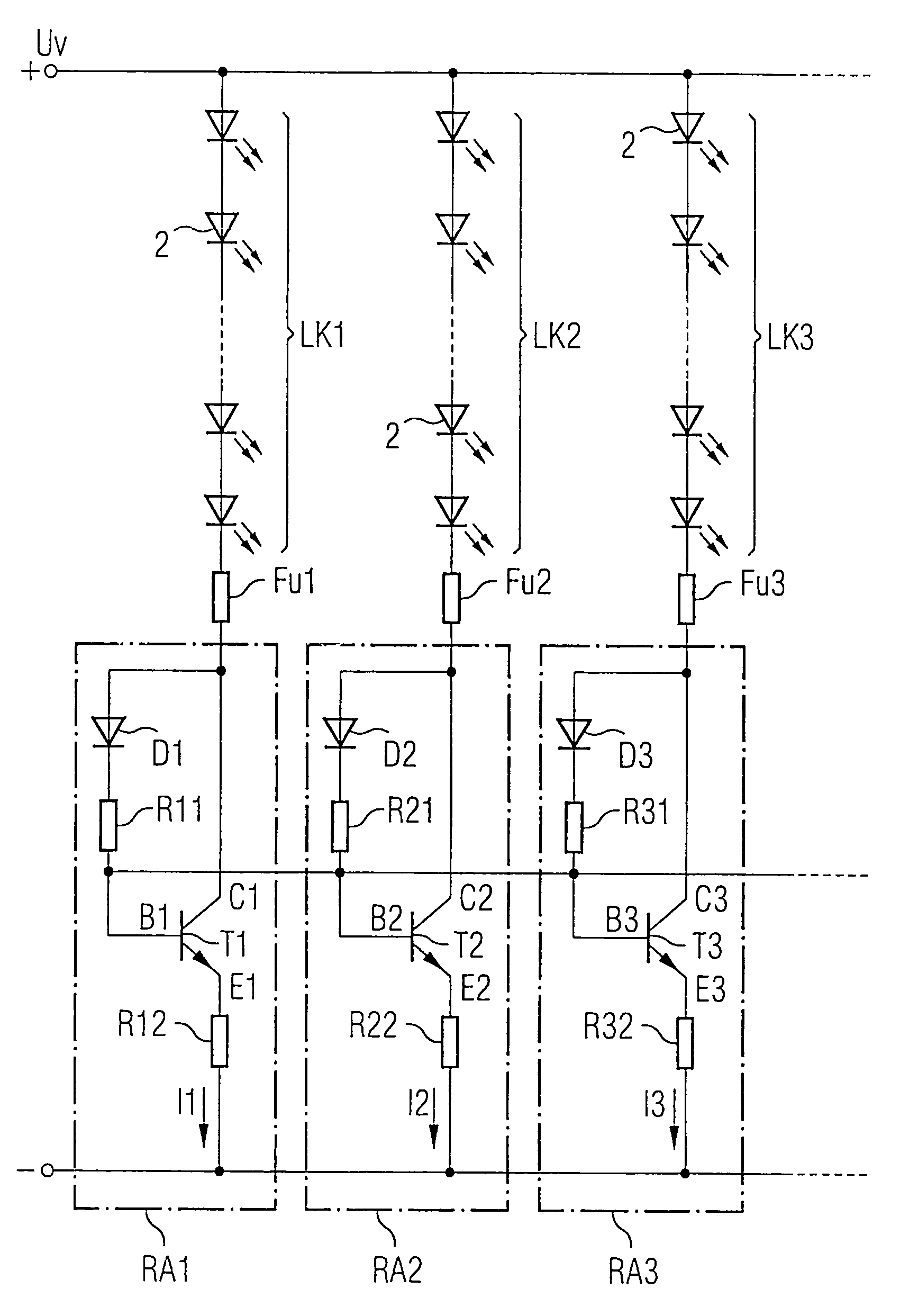

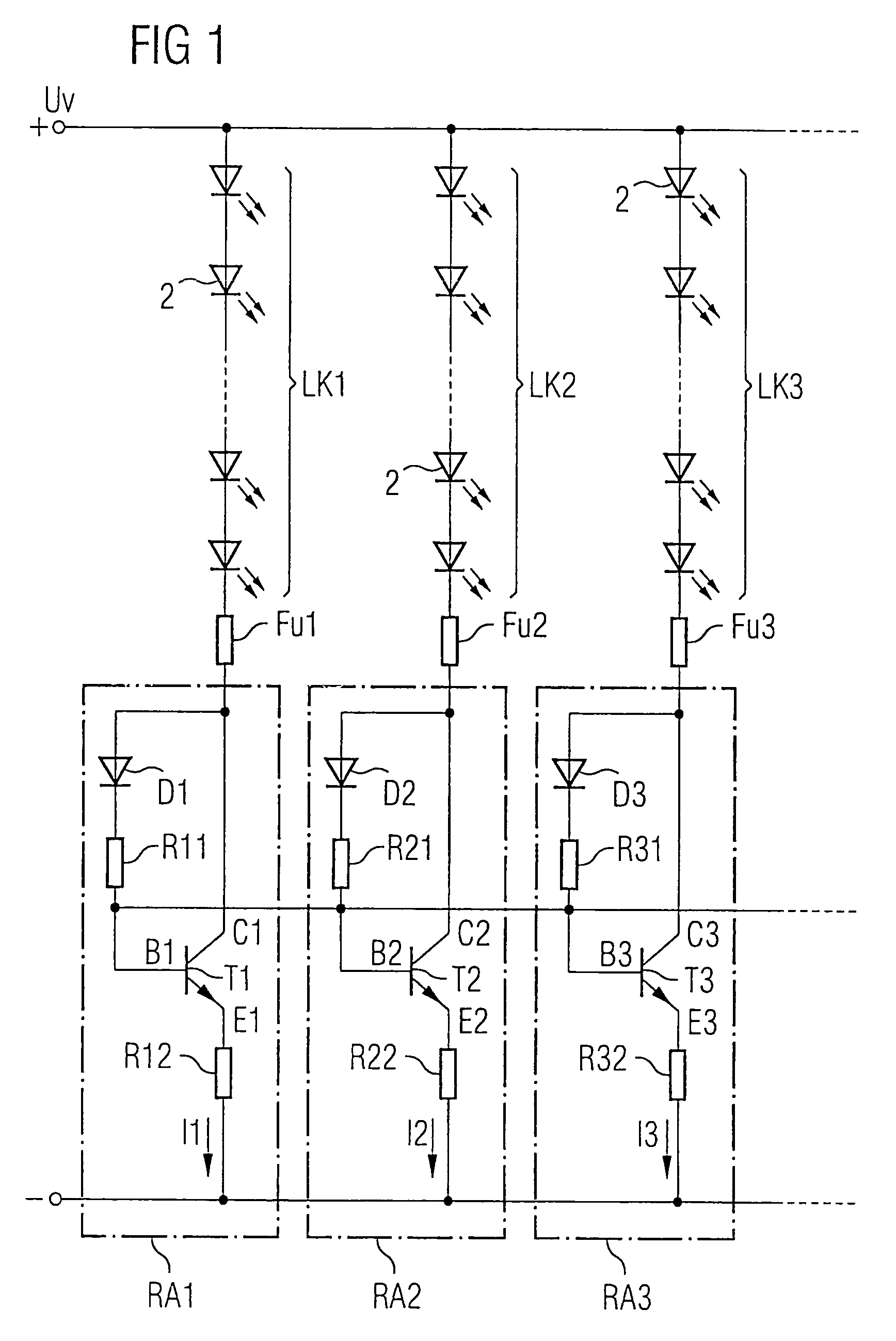

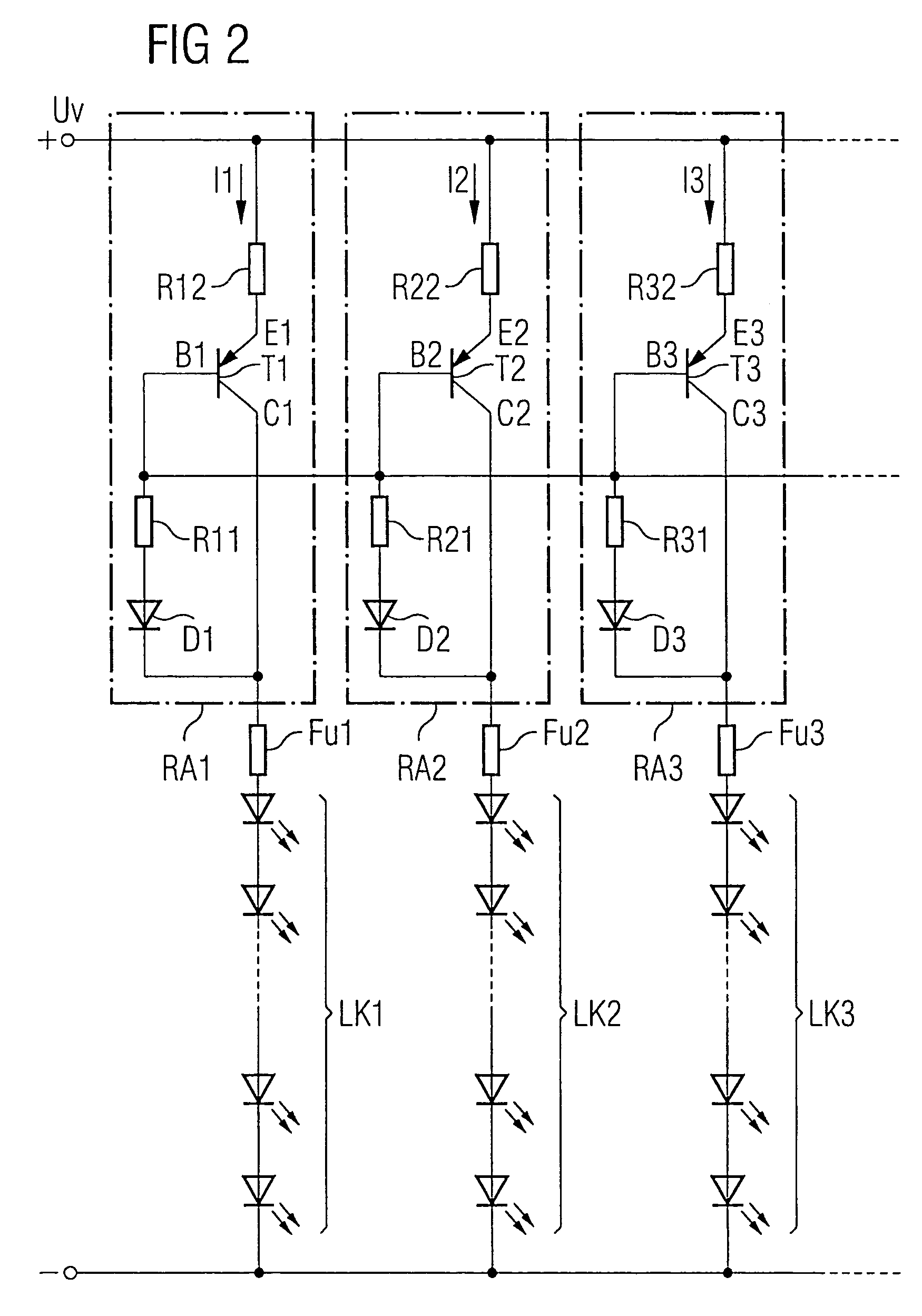

Circuit for an LED array

InactiveUS7317287B2Small currentMaintain distributionElectroluminescent light sourcesElectric light circuit arrangementVoltageCathode

Owner:OSRAM OPTO SEMICON GMBH & CO OHG

Method of converting a direct current voltage from a source of direct current voltage, more specifically from a photovoltaic source of direct current voltage, into a alternating current voltage

ActiveUS7411802B2Simple circuitImprove efficiencyPhotovoltaic energy generationDc-ac conversion without reversalClock rateEngineering

An inverter is devised to avoid high-frequency voltages at input terminals and to allow good efficiency thanks to its simple and cost-optimized circuit layout. This is achieved by a method of converting a direct current voltage, more specifically from a photovoltaic source of direct current voltage, into an alternating current voltage at a frequency through a bridge circuit comprising switching elements (V1-V 4) and free-wheeling elements (D1-D4), said switching elements (V1-V4) being on the one side gated at the frequency and on the other side clocked at a high clock rate, a direct current voltage circuit, an alternating current voltage circuit and a plurality of free-wheeling phases being provided. It is provided that, during the free-wheeling phases, the alternating current voltage circuit is decoupled from the direct current voltage circuit by means of a switching element disposed in the direct current voltage circuit, a free-wheeling current flowing through one of the free-wheeling elements (D1) in the bridge circuit when in the decoupled state.

Owner:SMA SOLAR TECH AG

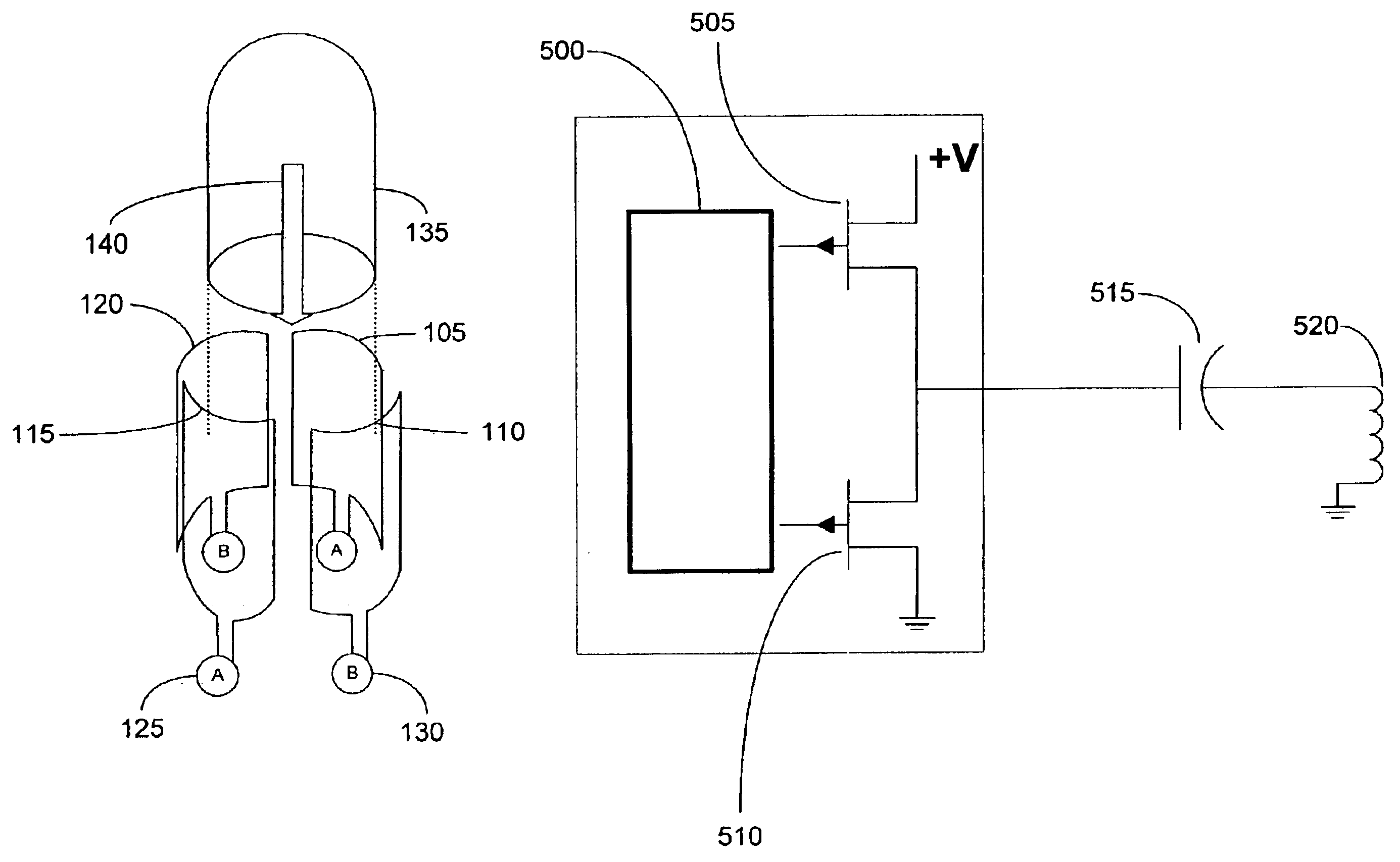

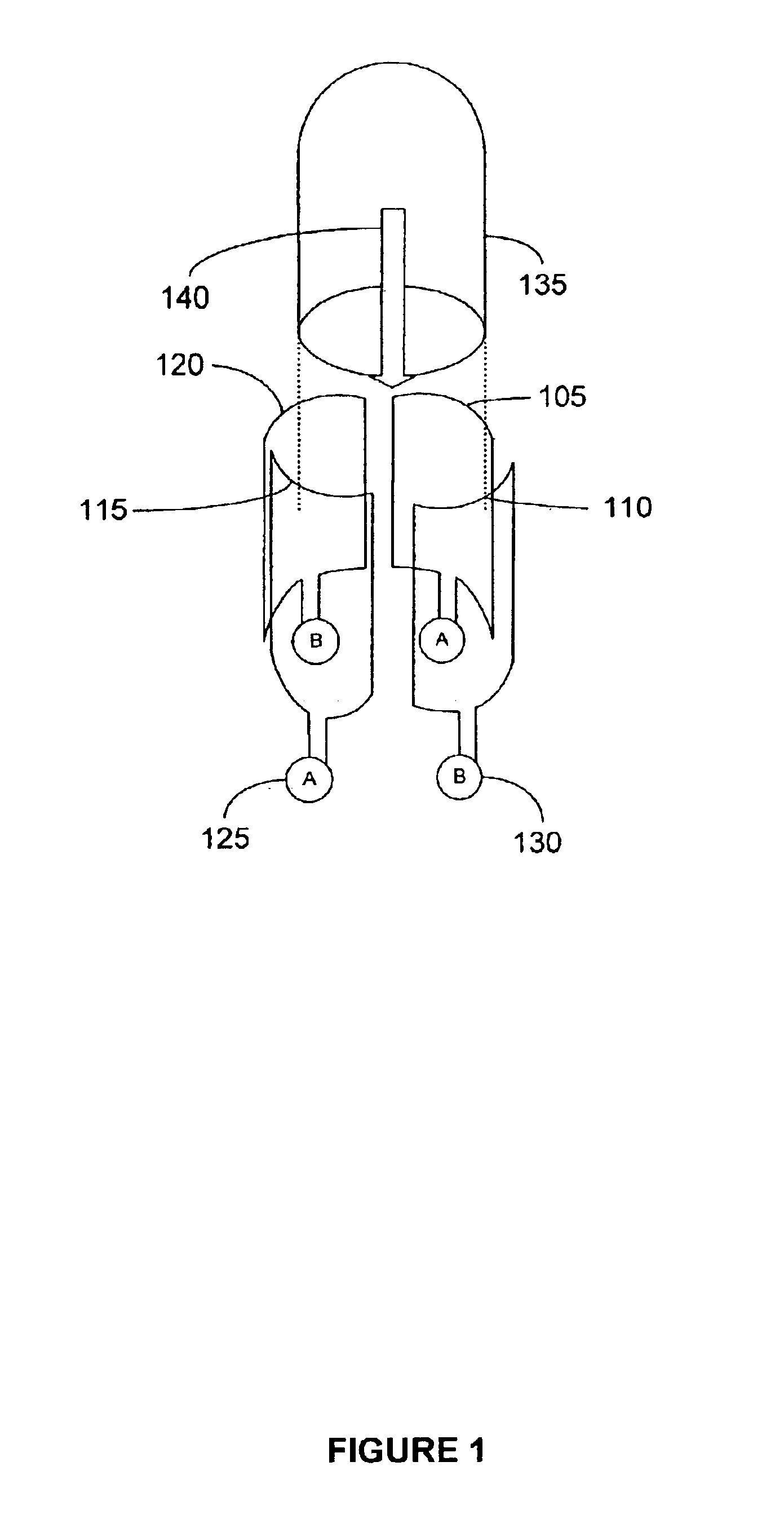

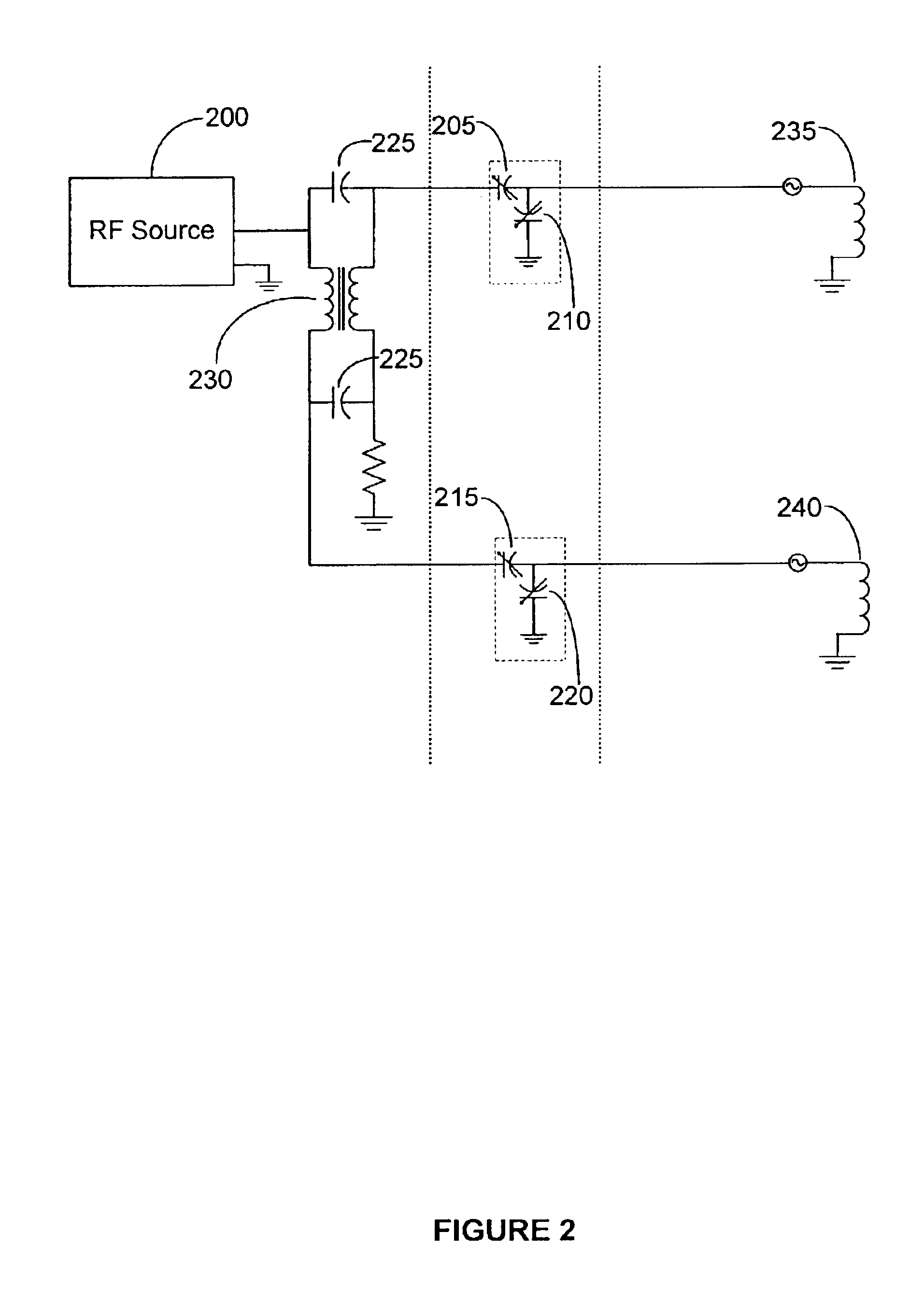

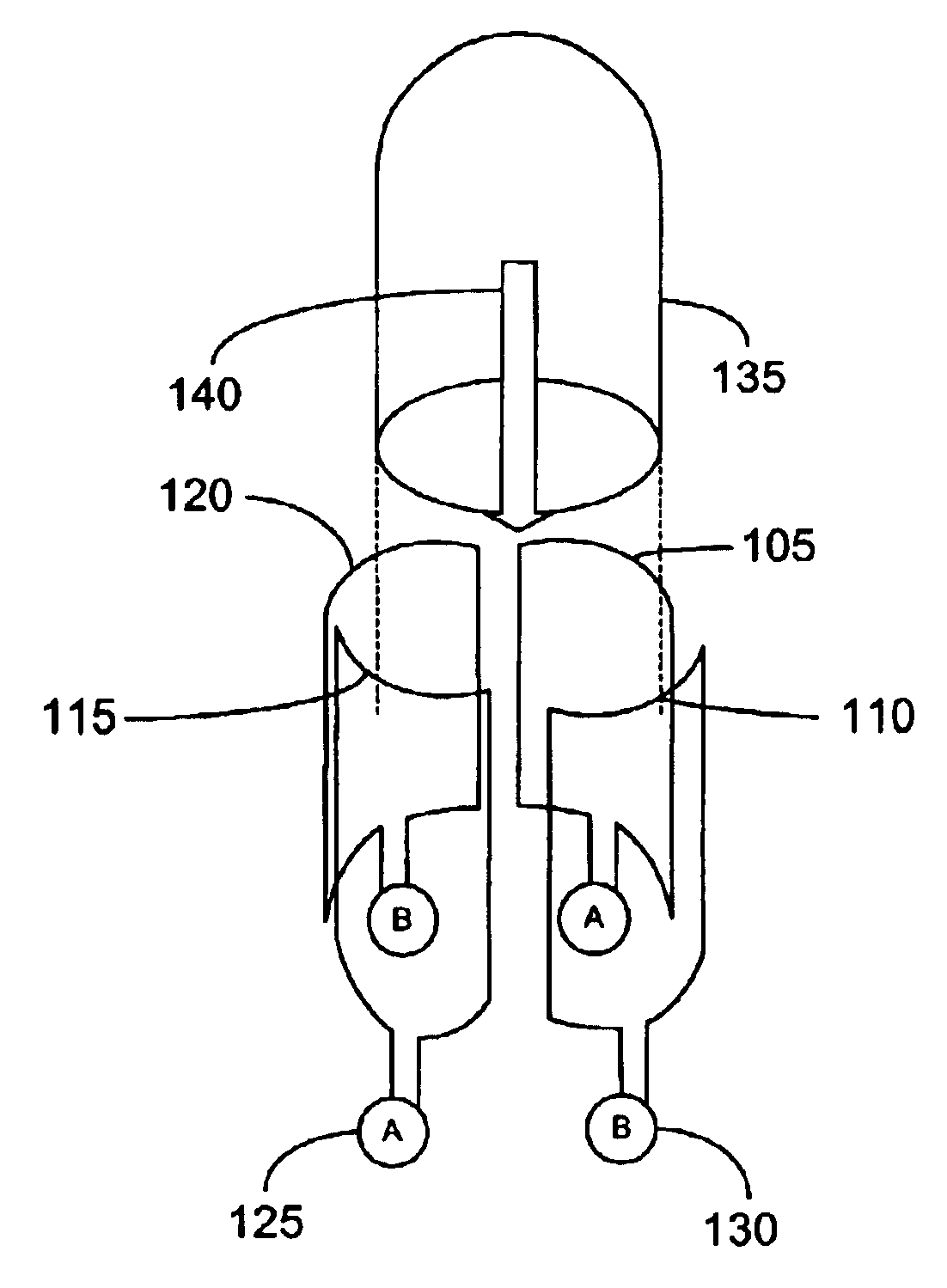

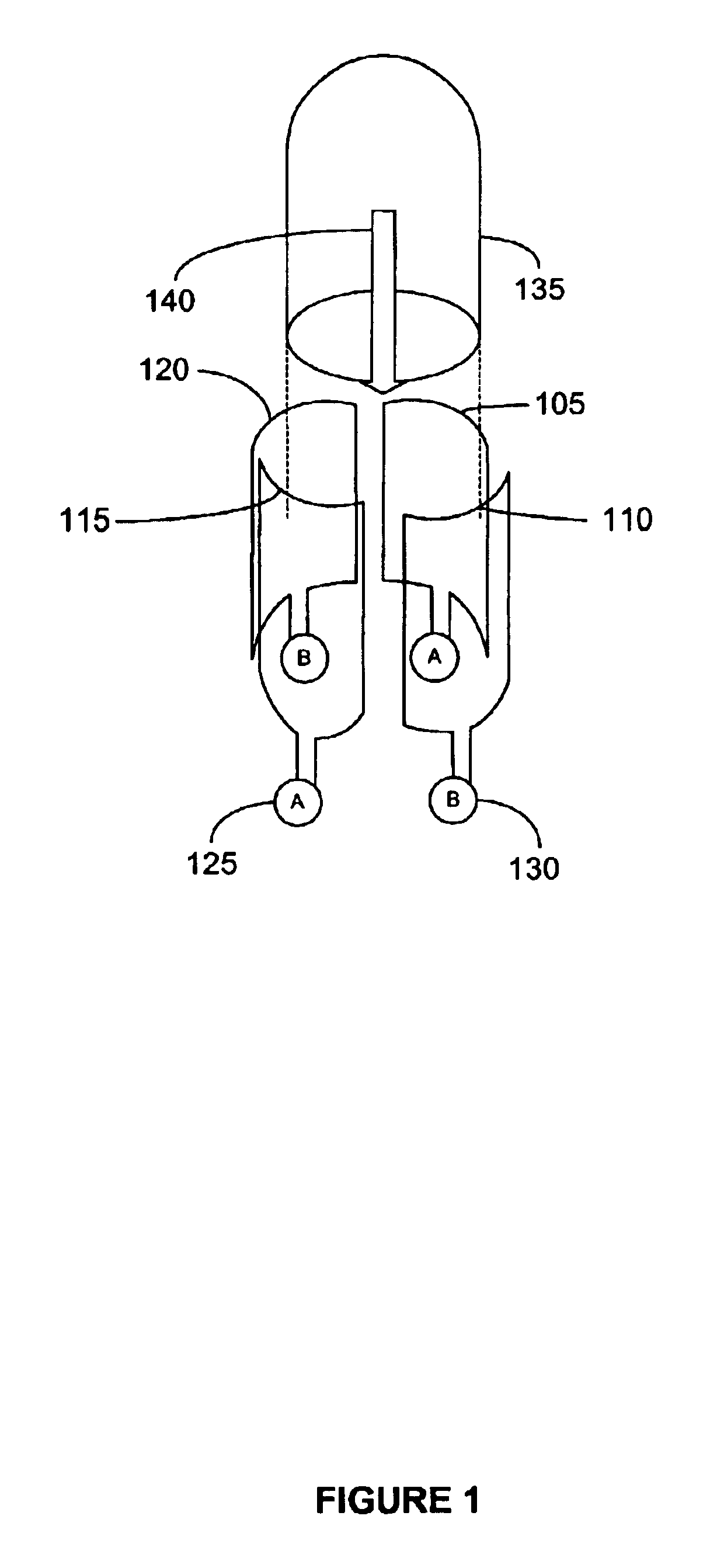

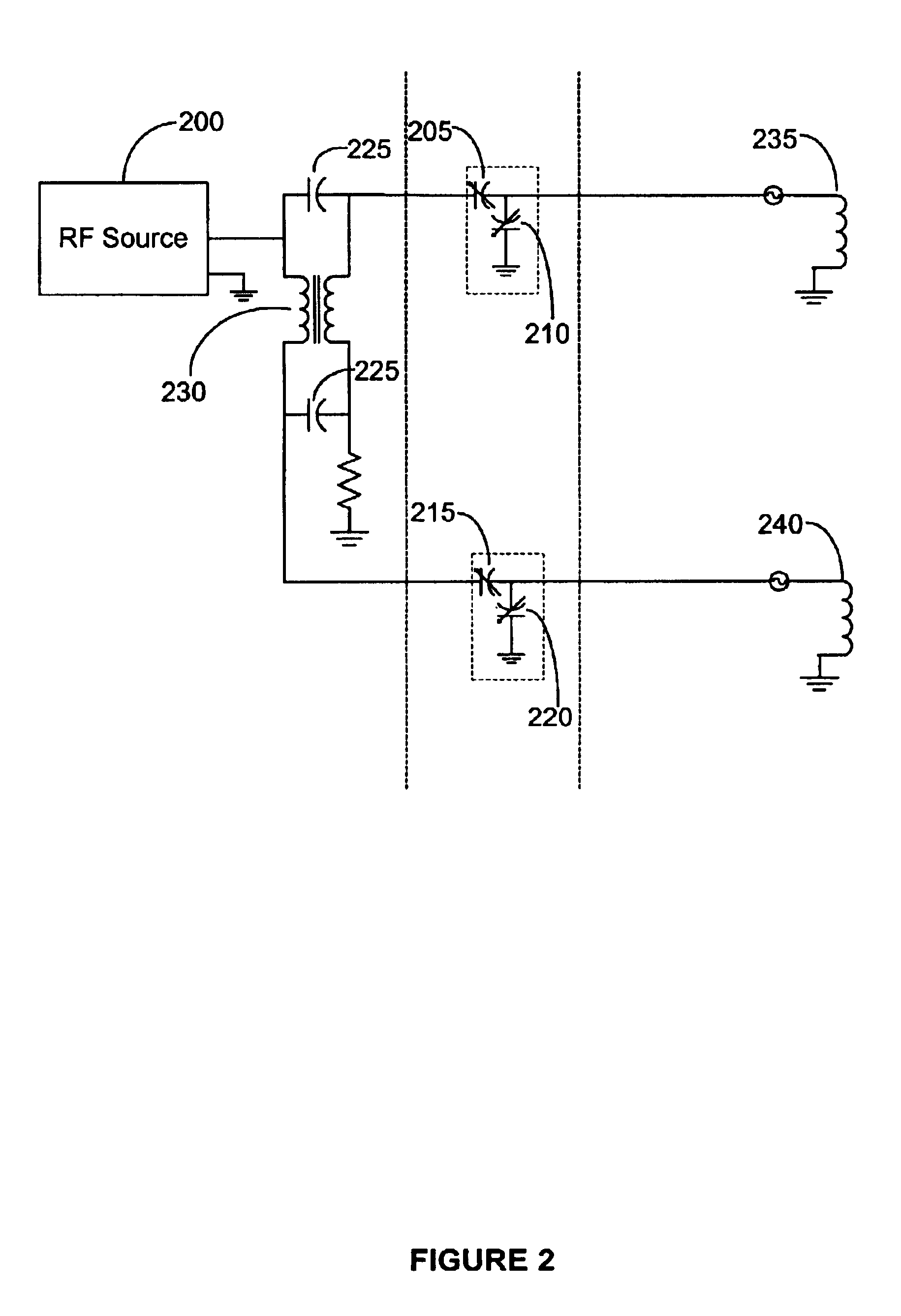

Plasma production device and method and RF driver circuit with adjustable duty cycle

InactiveUS7084832B2Efficient couplingLow output impedanceMultiple-port networksResonant long antennasCapacitanceDriver circuit

An RF driver circuit and an orthogonal antenna assembly / configuration, are disclosed as part of a method and system for generating high density plasma. The antenna assembly is an orthogonal antenna system that may be driven by any RF generator / circuitry with suitable impedance matching to present a low impedance. The disclosed RF driver circuit uses switching type amplifier elements and presents a low output impedance. The disclosed low-output impedance RF driver circuits eliminate the need for a matching circuit for interfacing with the inherent impedance variations associated with plasmas. Also disclosed is the choice for capacitance or an inductance value to provide tuning for the RF plasma source. There is also provided a method for rapidly switching the plasma between two or more power levels at a frequencies of about tens of Hz to as high as hundreds of KHz.

Owner:PLASMA CONTROL SYST LLC +1

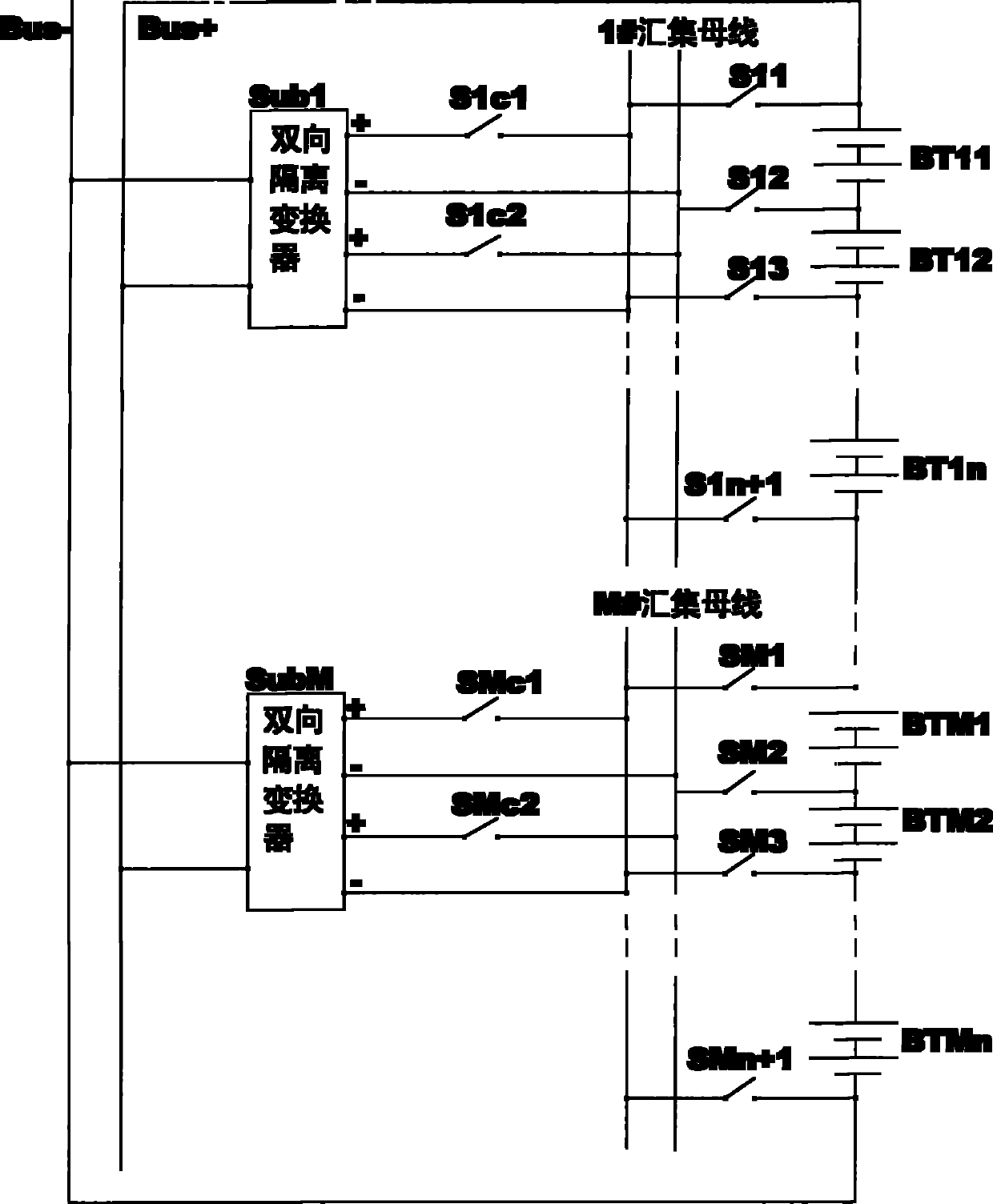

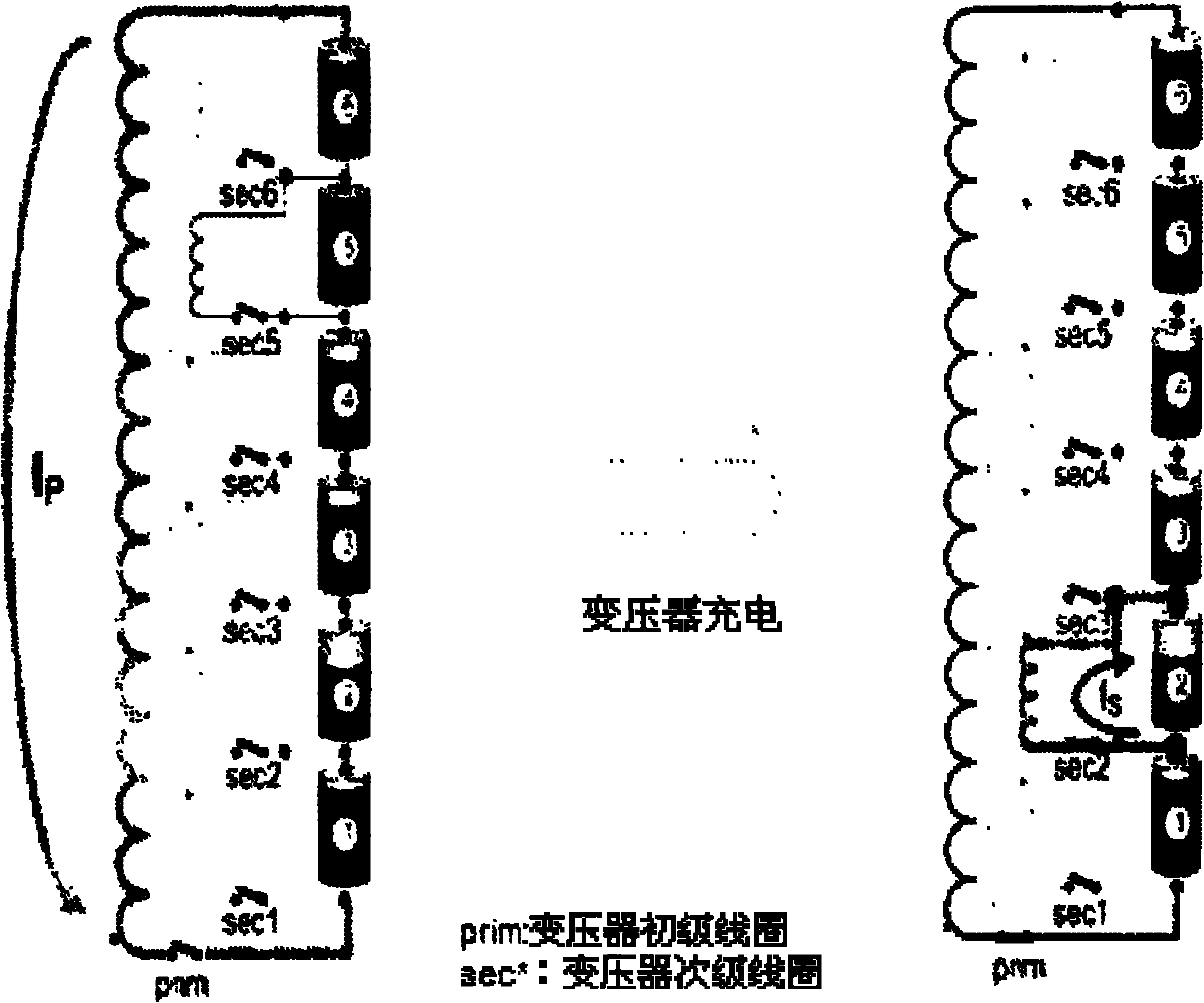

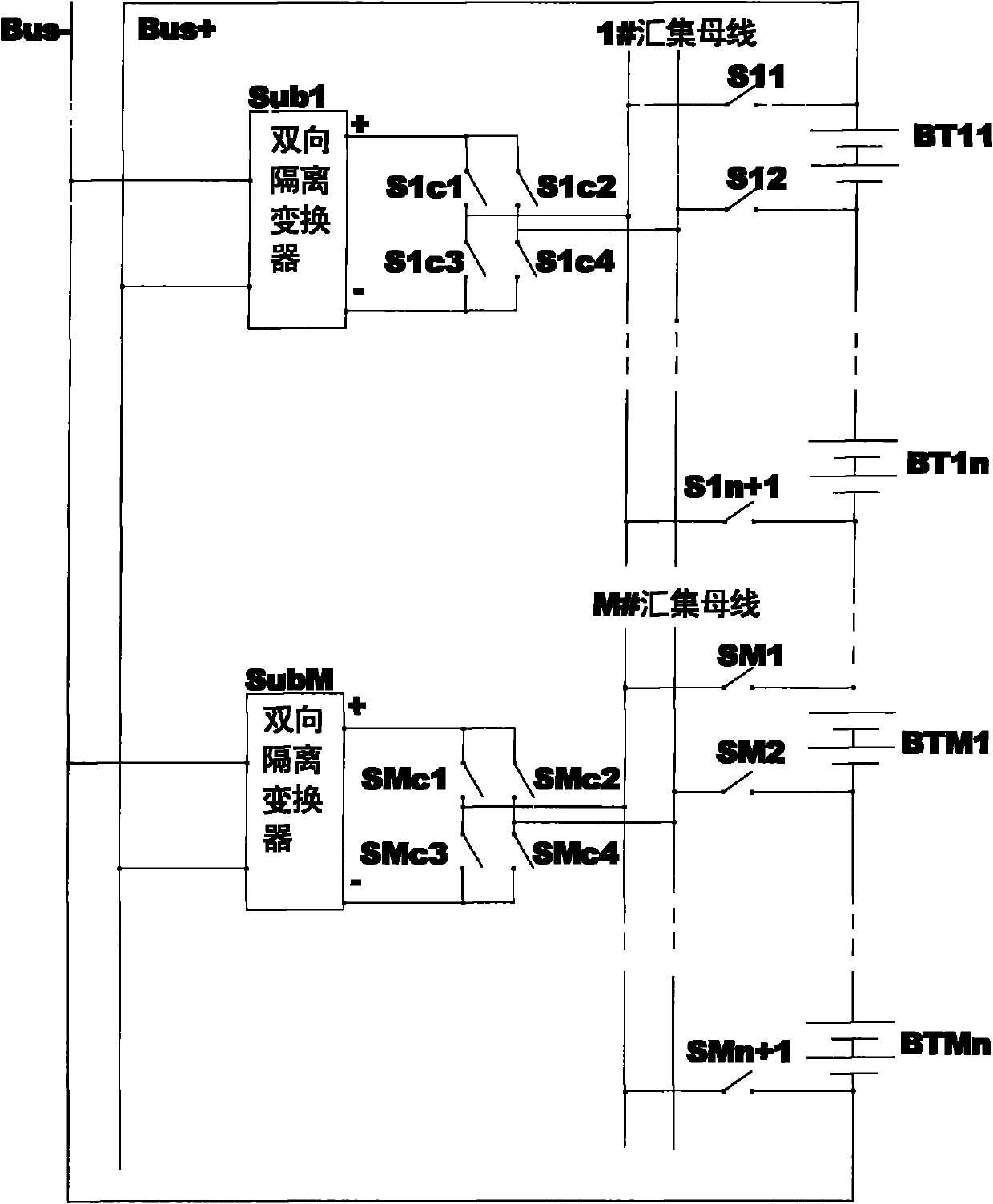

Method and circuit for dynamically equalizing battery management system

ActiveCN101917047AReduce in quantityReduce circuit complexityBatteries circuit arrangementsElectric powerCircuit complexityEnergy transfer

The invention relates to a method and a circuit for dynamically equalizing a battery management system. The method comprises the following steps of: 1) detecting the voltage of each single battery in each group of battery packs sequentially connected in series by using embedded control software; 2) judging the location number of the single battery which needs to be charged or discharged separately and has excessively low or high voltage by using a central processing unit (CPU); 3) giving a control command out by using the CPU, controllably gating a corresponding polarity selecting switch block to perform polarity inversion on a collection bus, controllably gating a corresponding battery selecting switch block to perform polarity matching at the same time, controlling the working direction of a bidirectional isolation transformer and connecting the single battery which needs to be charged or discharged separately and has the excessively low or high voltage to the connection bus for charging or discharging so as to realize energy transfer; and 4) repeating the steps 1) to 3) until the voltage of each single battery in each group of battery packs sequentially connected in series is in a set allowable error range so as to realize dynamic equilibrium. The number of charging and discharging devices and circuit complexity of the battery management system can be reduced remarkably.

Owner:SHENZHEN KELIE TECH

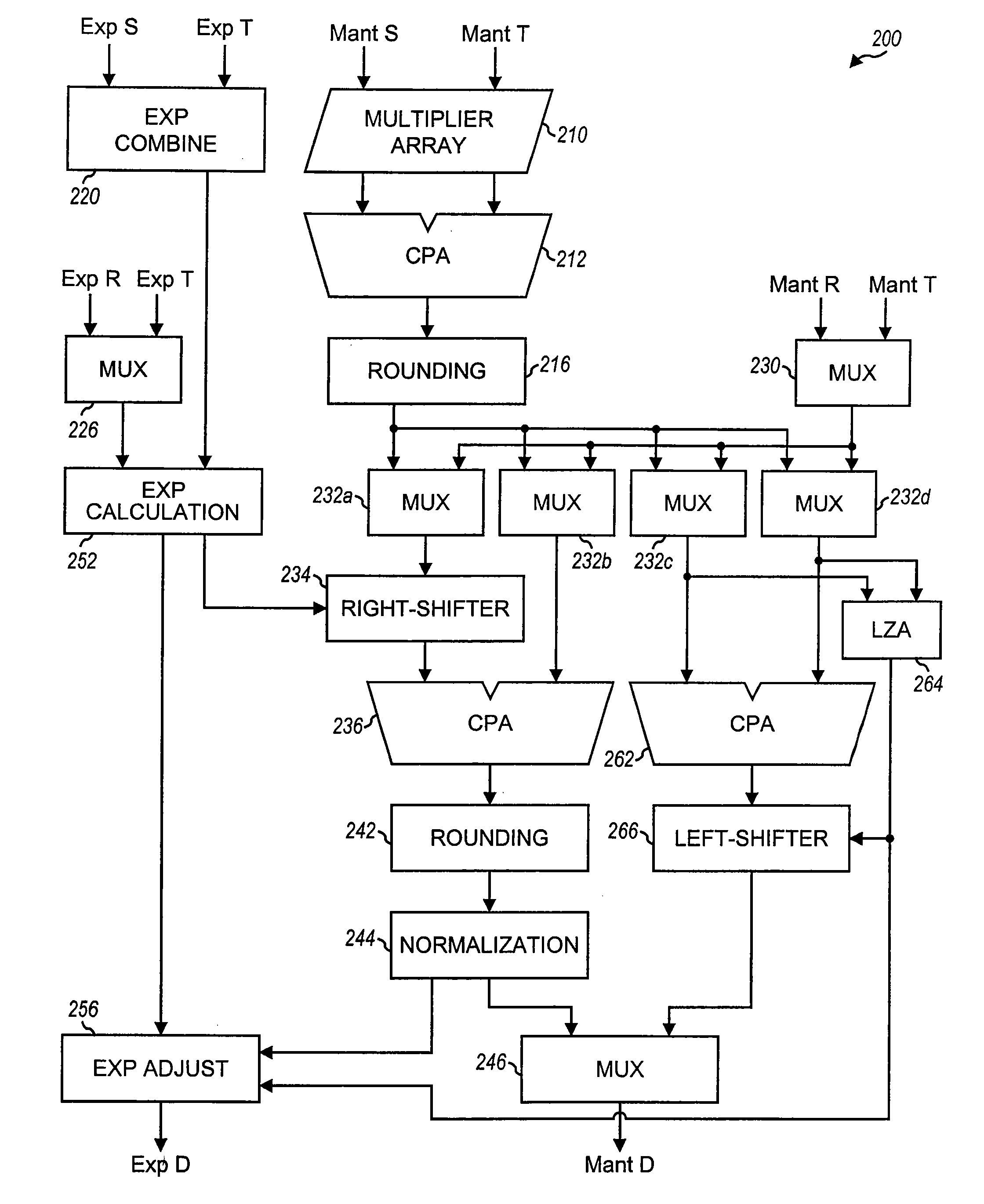

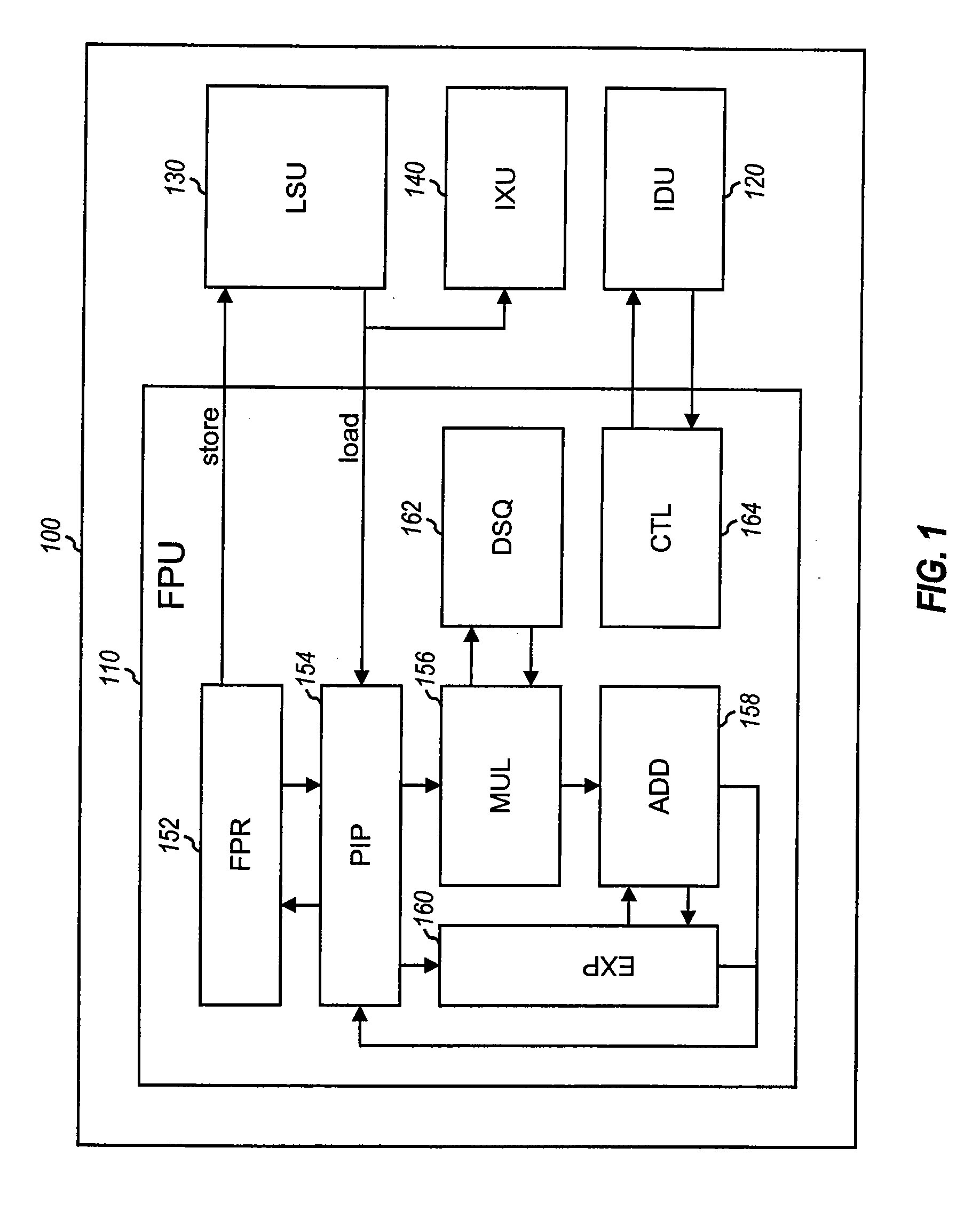

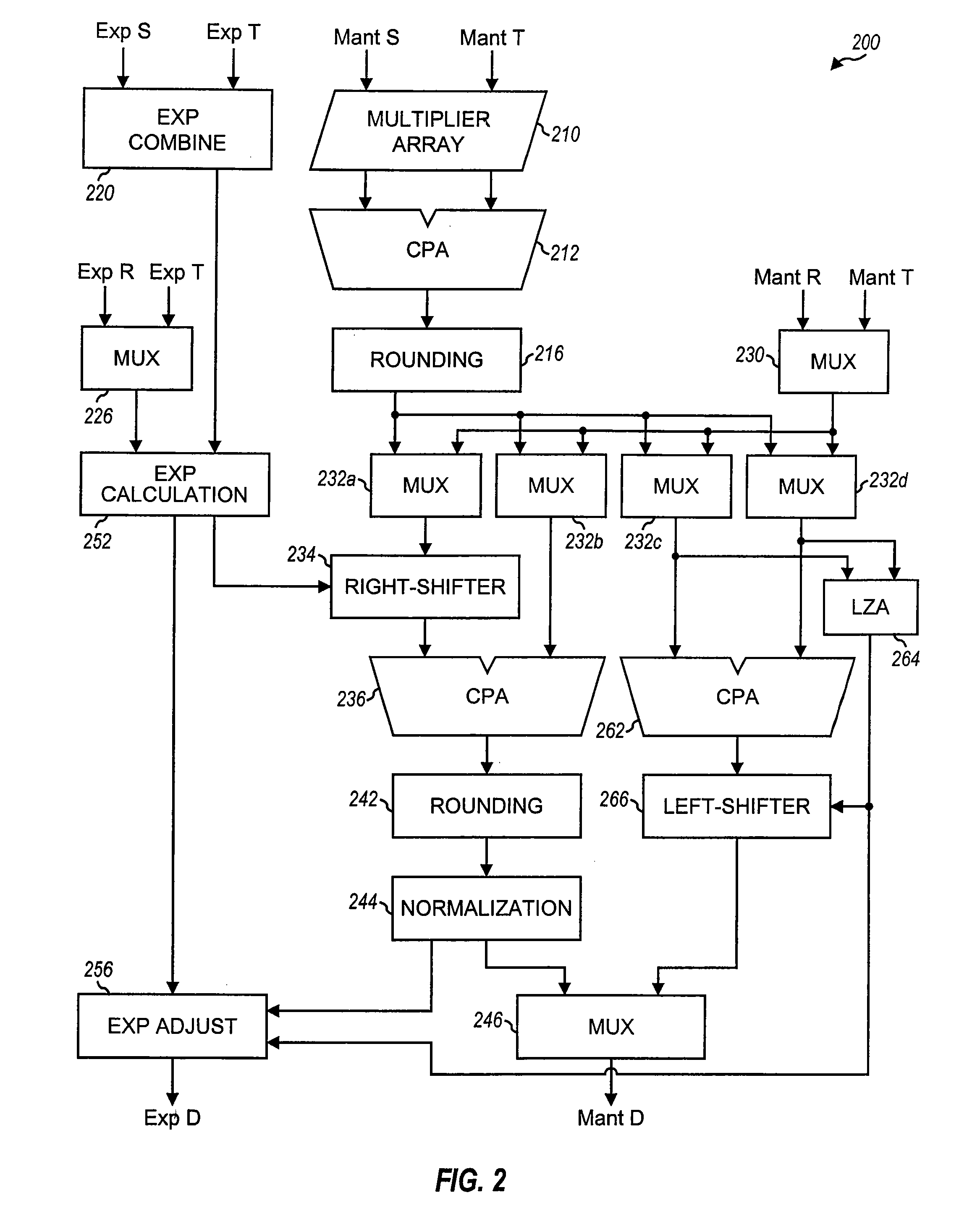

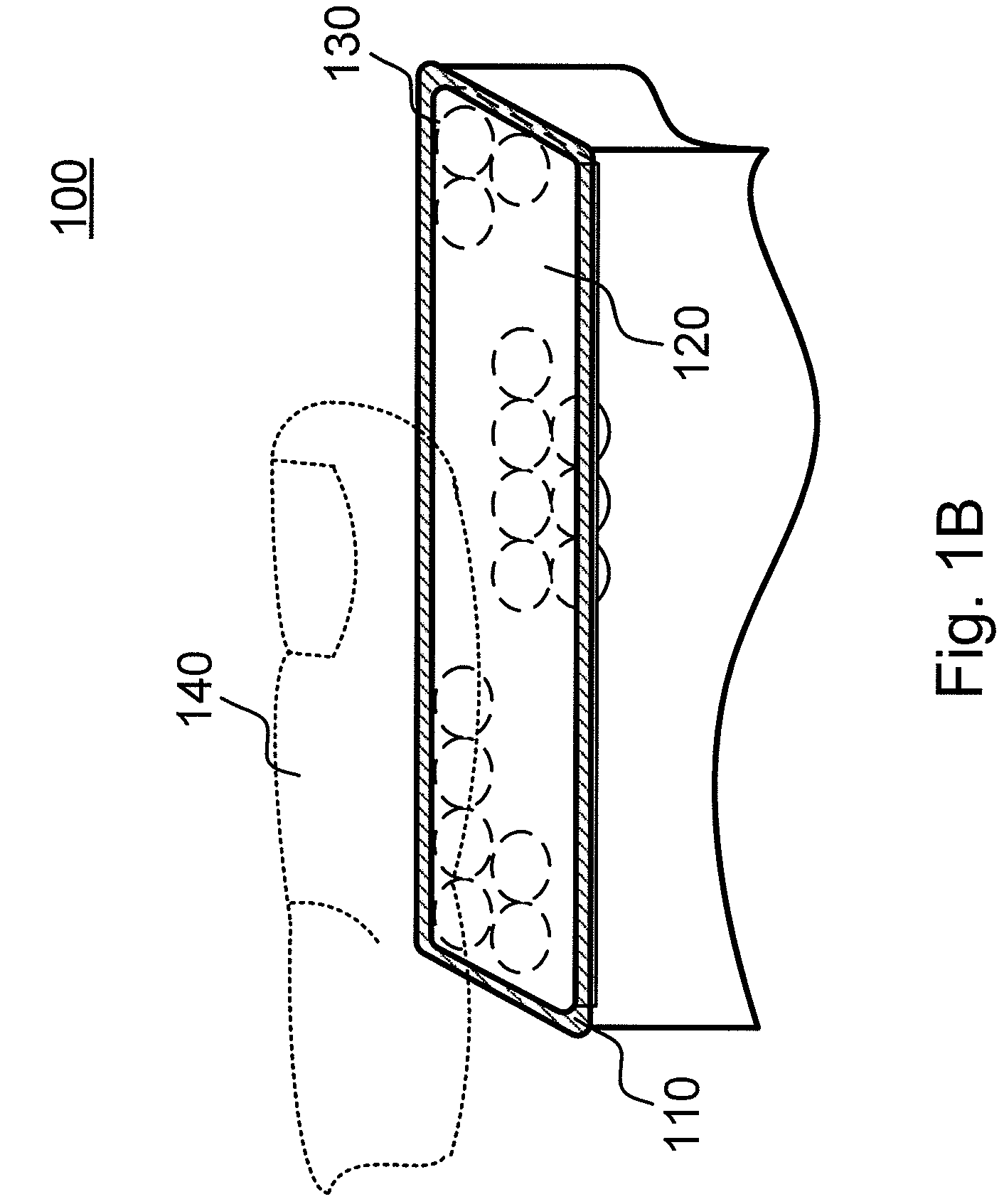

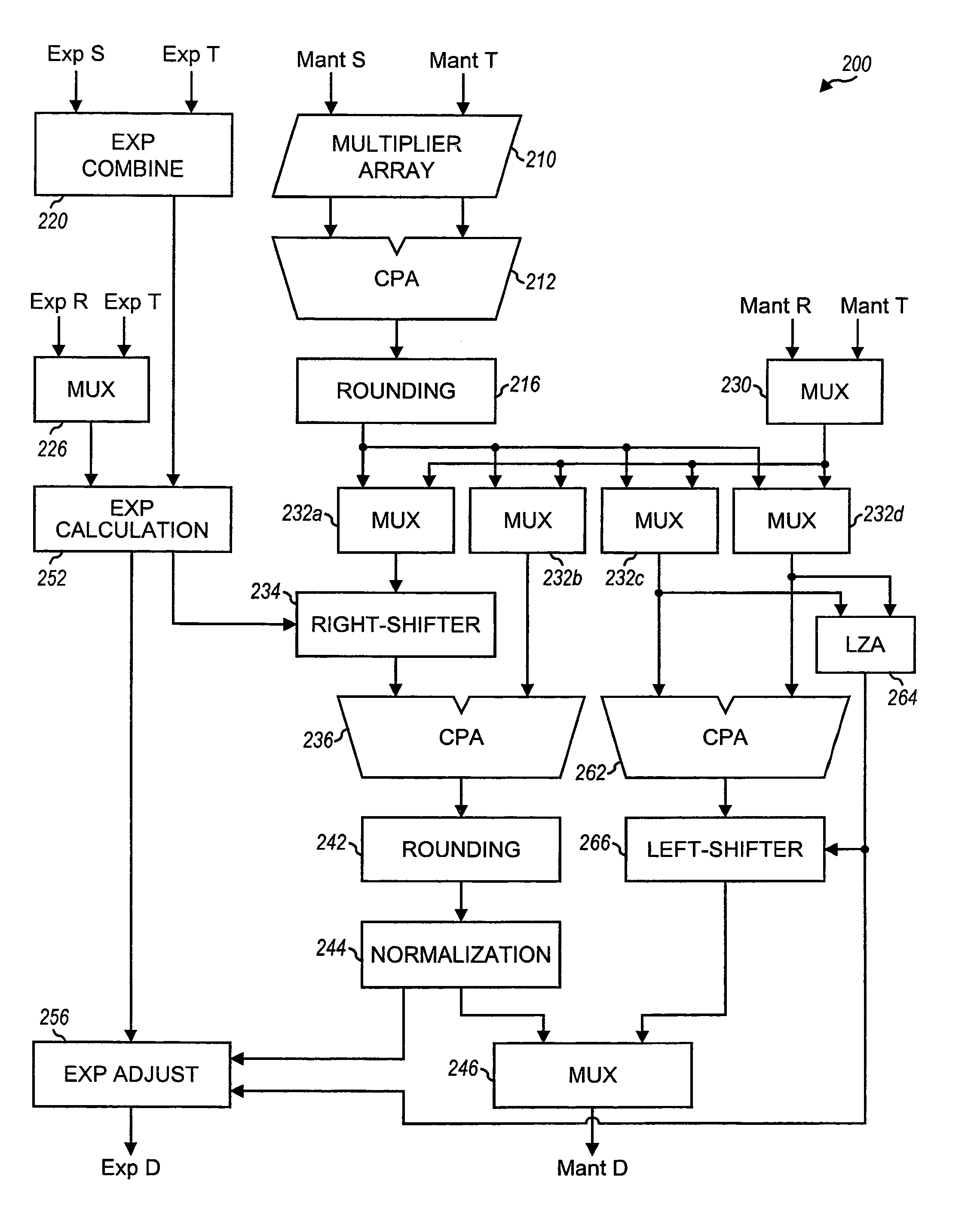

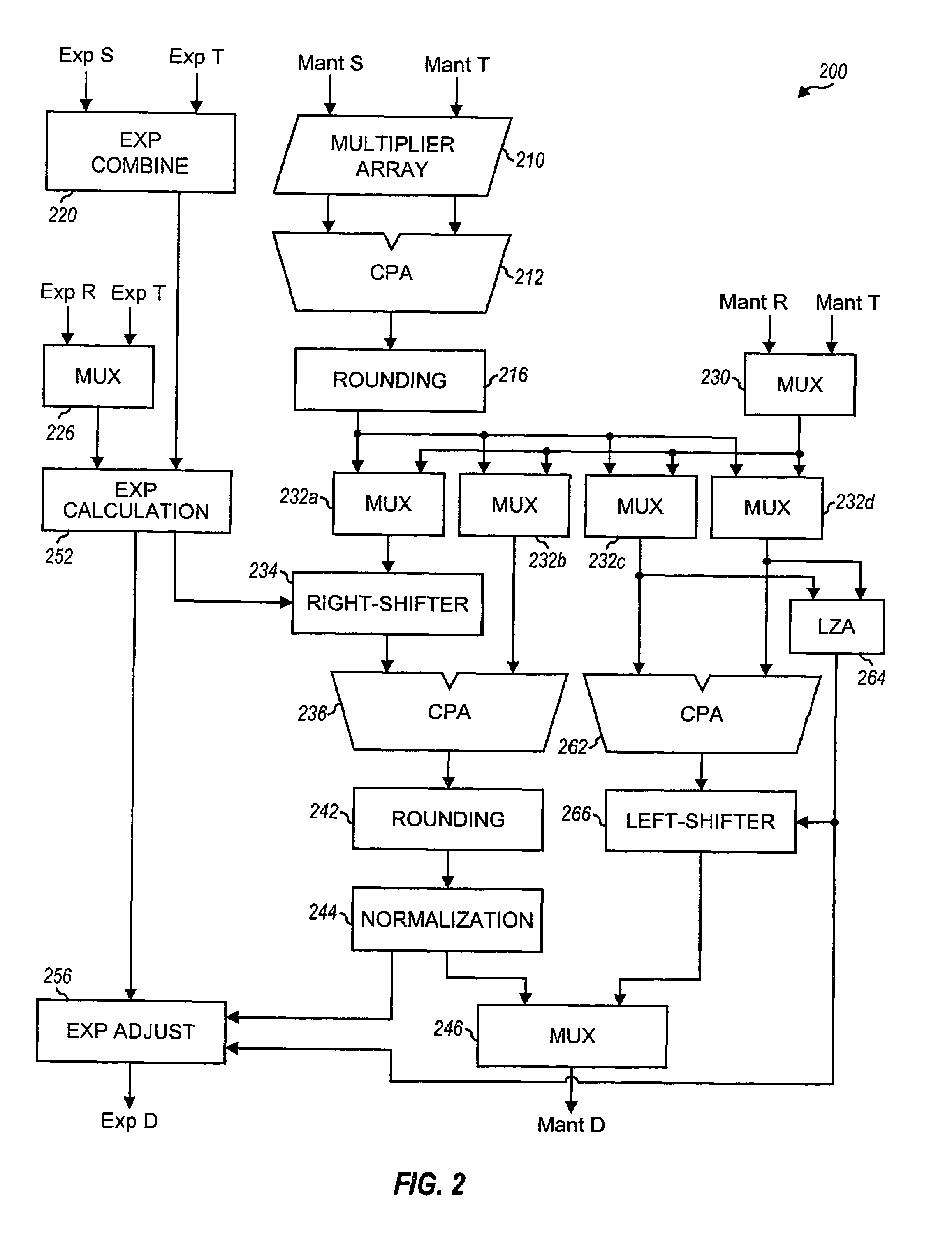

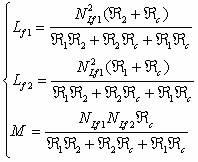

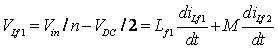

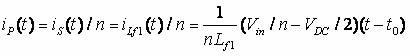

Processor With Improved Accuracy For Multiply-Add Operations

InactiveUS20080183791A1Improve accuracyReduce circuit complexityComplex mathematical operationsData conversionCircuit complexityBinary multiplier

Floating-point processors capable of performing multiply-add (Madd) operations and incorporating improved intermediate result handling capability. The floating-point processor includes a multiplier unit coupled to an adder unit. In a specific operating mode, the intermediate result from the multiplier unit is processed (i.e., rounded but not normalized or denormalized) into representations that are more accurate and easily managed in the adder unit. By processing the intermediate result in such manner, accuracy is improved, circuit complexity is reduced, operating speed may be increased.

Owner:ARM FINANCE OVERSEAS LTD

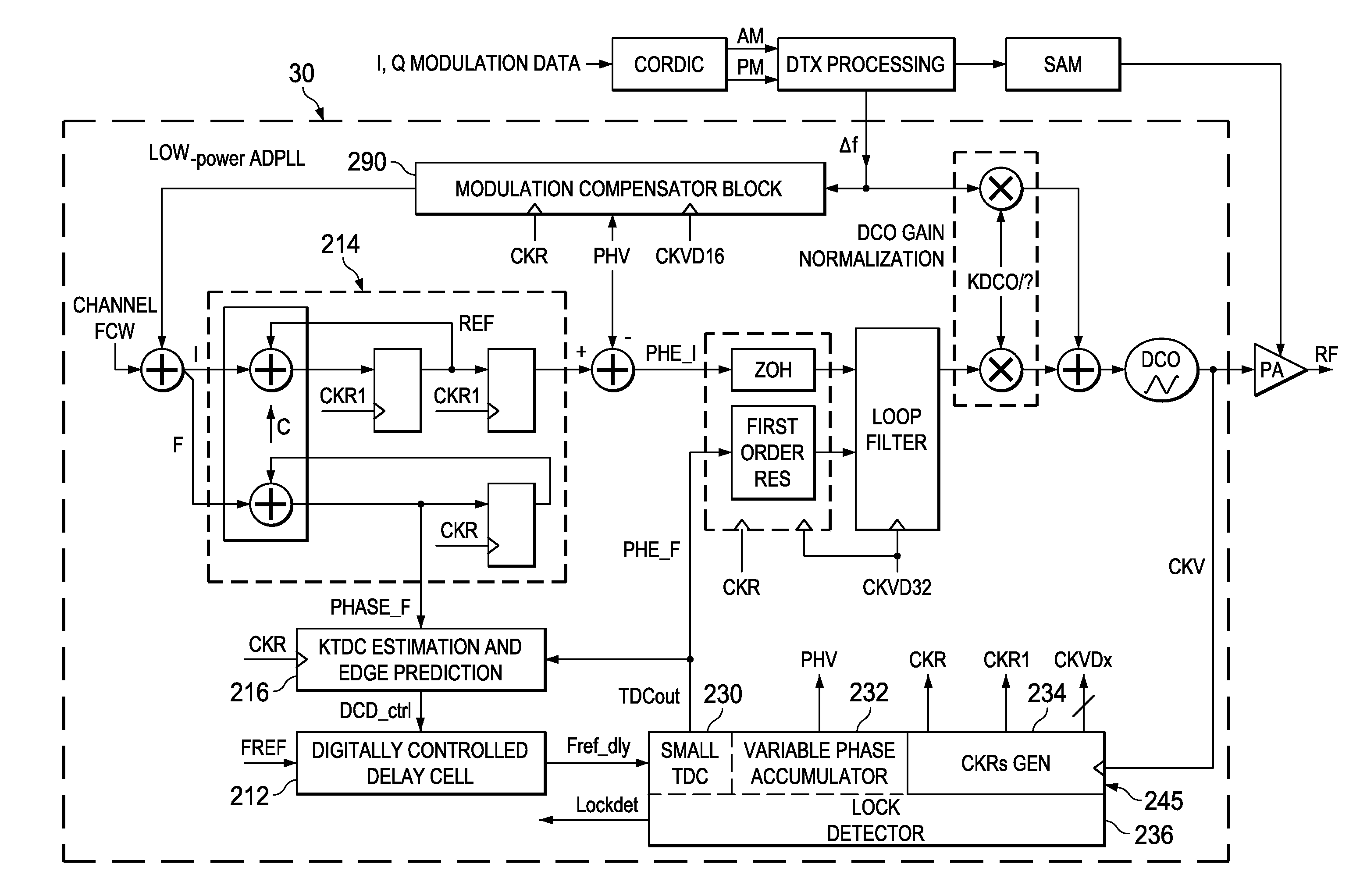

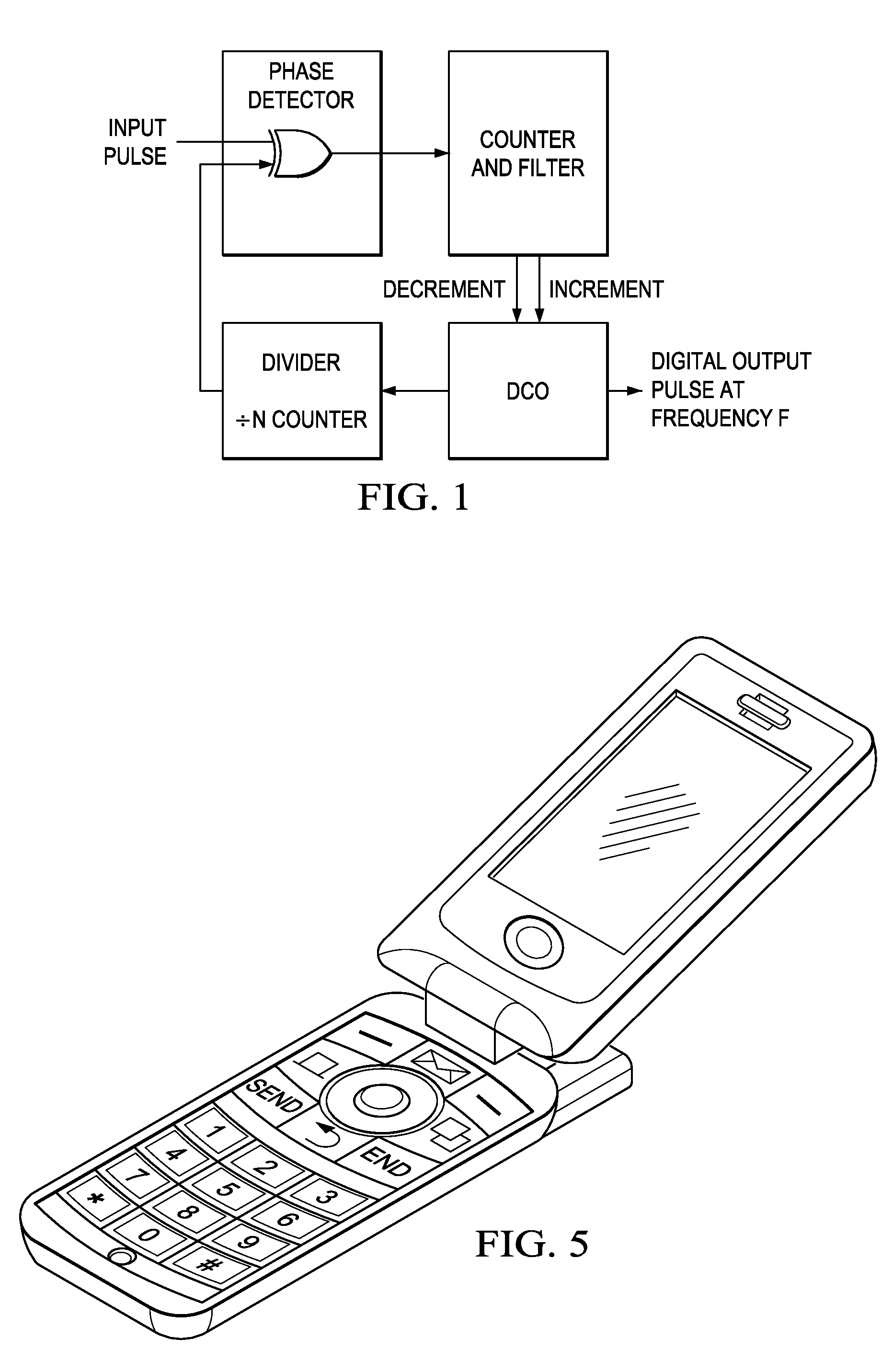

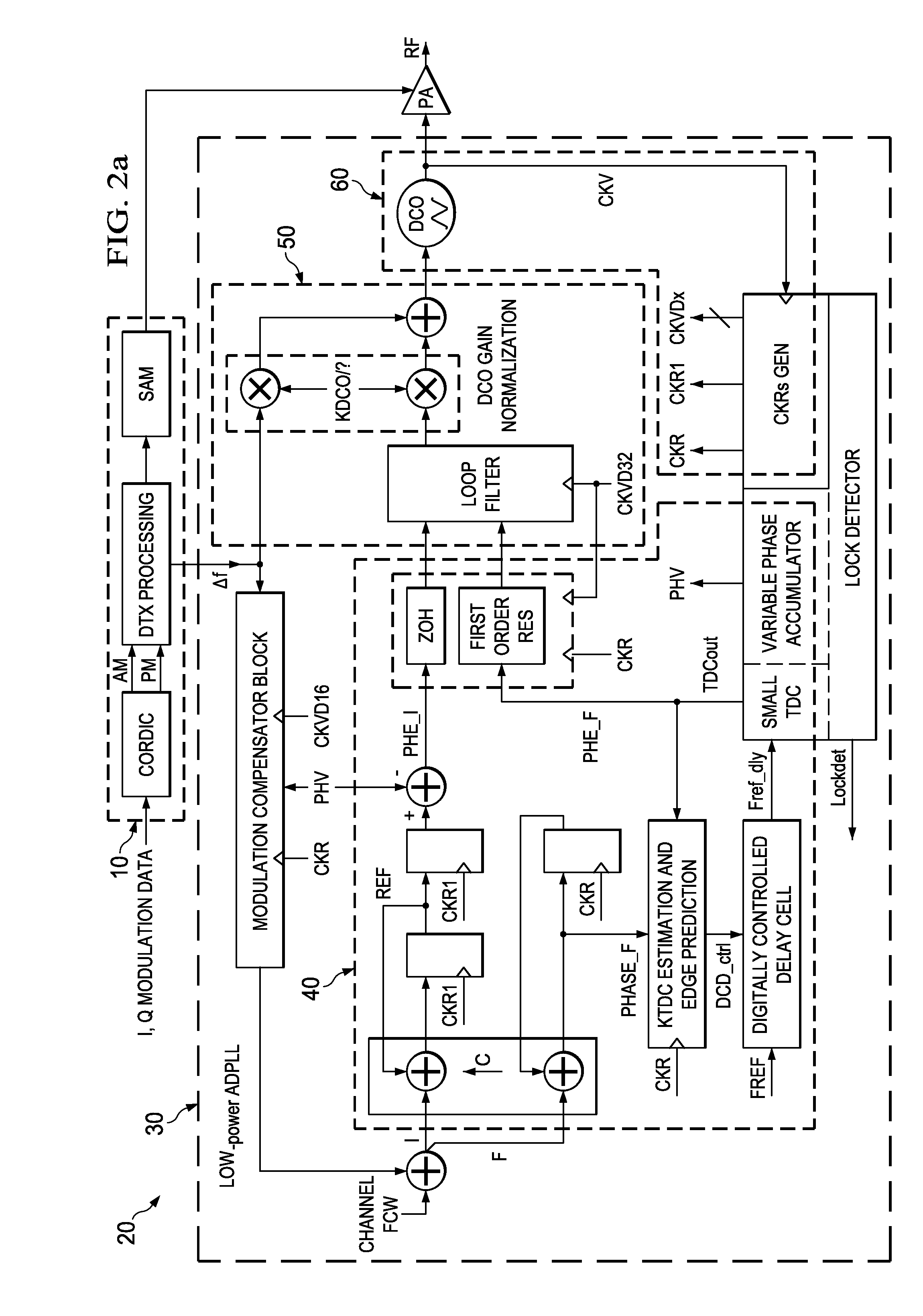

Low Power All Digital PLL Architecture

ActiveUS20080315959A1Reduce circuit complexityReduce noiseSimultaneous amplitude and angle modulationPulse automatic controlEngineeringLow frequency

A new all digital PLL (ADPLL) circuit and architecture and the corresponding method of implementation are provided. The ADPLL processes an integer and a fractional part of the phase signal separately, and achieves power reduction by disabling circuitry along the integer processing path of the circuit when the ADPLL loop is in a locked state. The integer processing path is automatically enabled when the loop is not in lock. Additional power savings is achieved by running the ADPLL on the lower-frequency master system clock, which also has the effect of reducing spur levels on the signals.

Owner:TEXAS INSTR INC

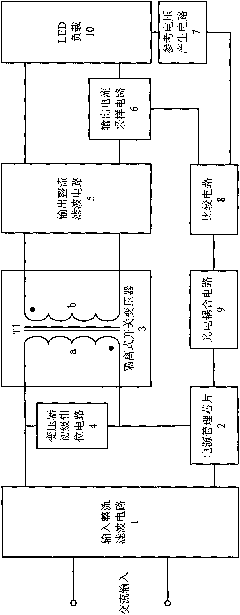

High-efficiency LED constant current driving circuit

InactiveCN101801136AReduce circuit complexitySmall circuit sizeElectric light circuit arrangementEnergy saving control techniquesSampling circuitsVoltage reference

The invention relates to a high-efficiency LED constant current driving circuit. The circuit comprises an input rectification filter circuit, a switch power supply management chip, an isolation switch transformer, a primary clamping circuit of the transformer, an output rectification filter circuit, an output current sampling circuit, a reference voltage generation circuit, a comparison circuit and a photoelectrical coupling circuit, wherein the input end of the input rectification filter circuit is connected with commercial AC electricity, while the output end is connected with a primary winding of the isolation switch transformer through the switch power supply management chip; the primary clamping circuit of the transformer is connected in parallel with the primary winding of the isolation switch transformer; the input end of the output rectification filter circuit is connected with the primary winding of the isolation switch transformer, while the output end is connected with LED load; an output current sampling circuit is connected in series with the LED load; the input end of the reference voltage generation circuit is connected with the LED load; and the input end of the comparison circuit is connected with the output current sampling circuit and the reference voltage generation circuit, while the output end is connected with the switch power supply management chip through the photoelectrical coupling circuit. The circuit improves the circuit integration degree, the reliability, the constant current precision and the circuit conversion efficiency.

Owner:SHANGHAI UNIV

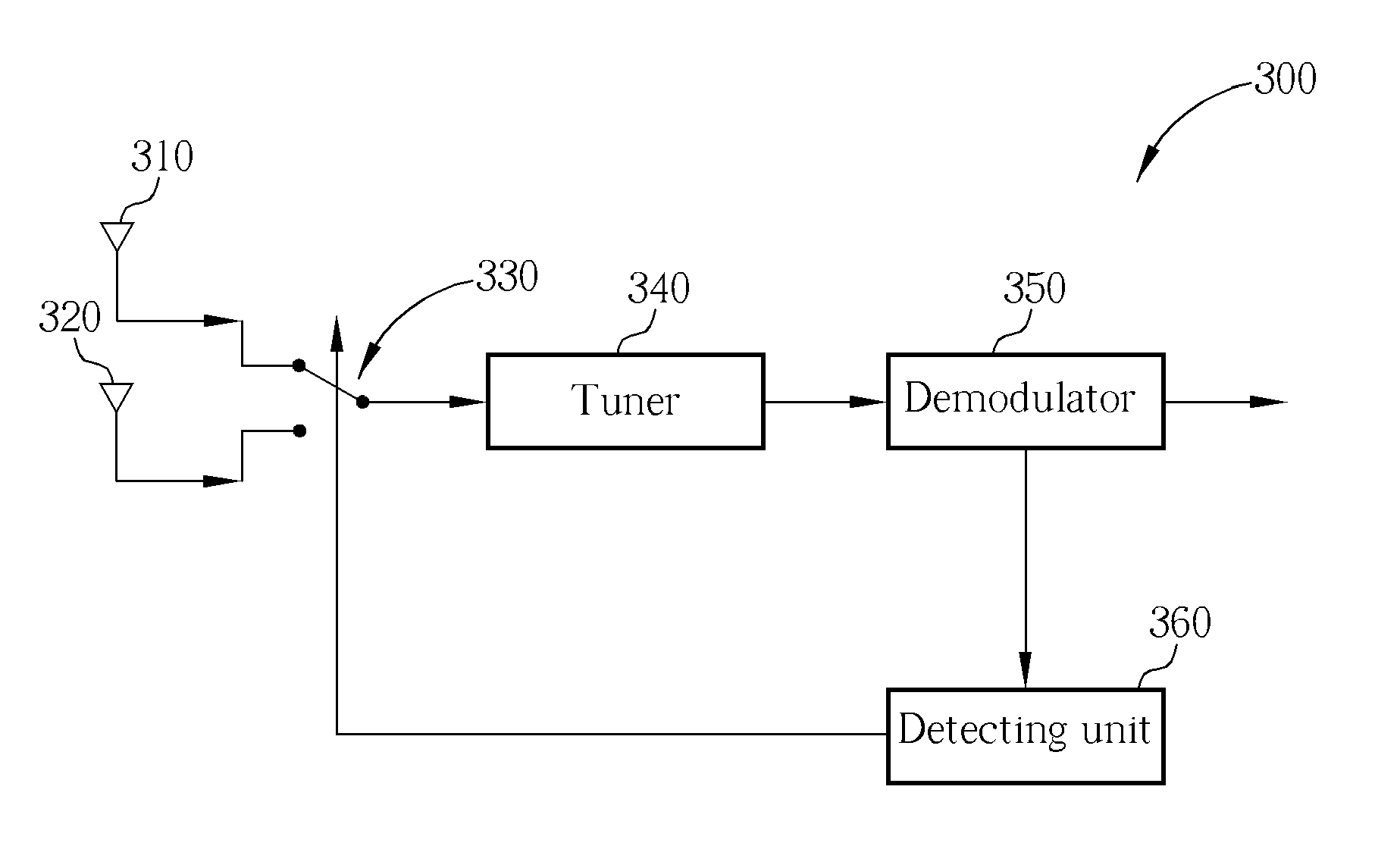

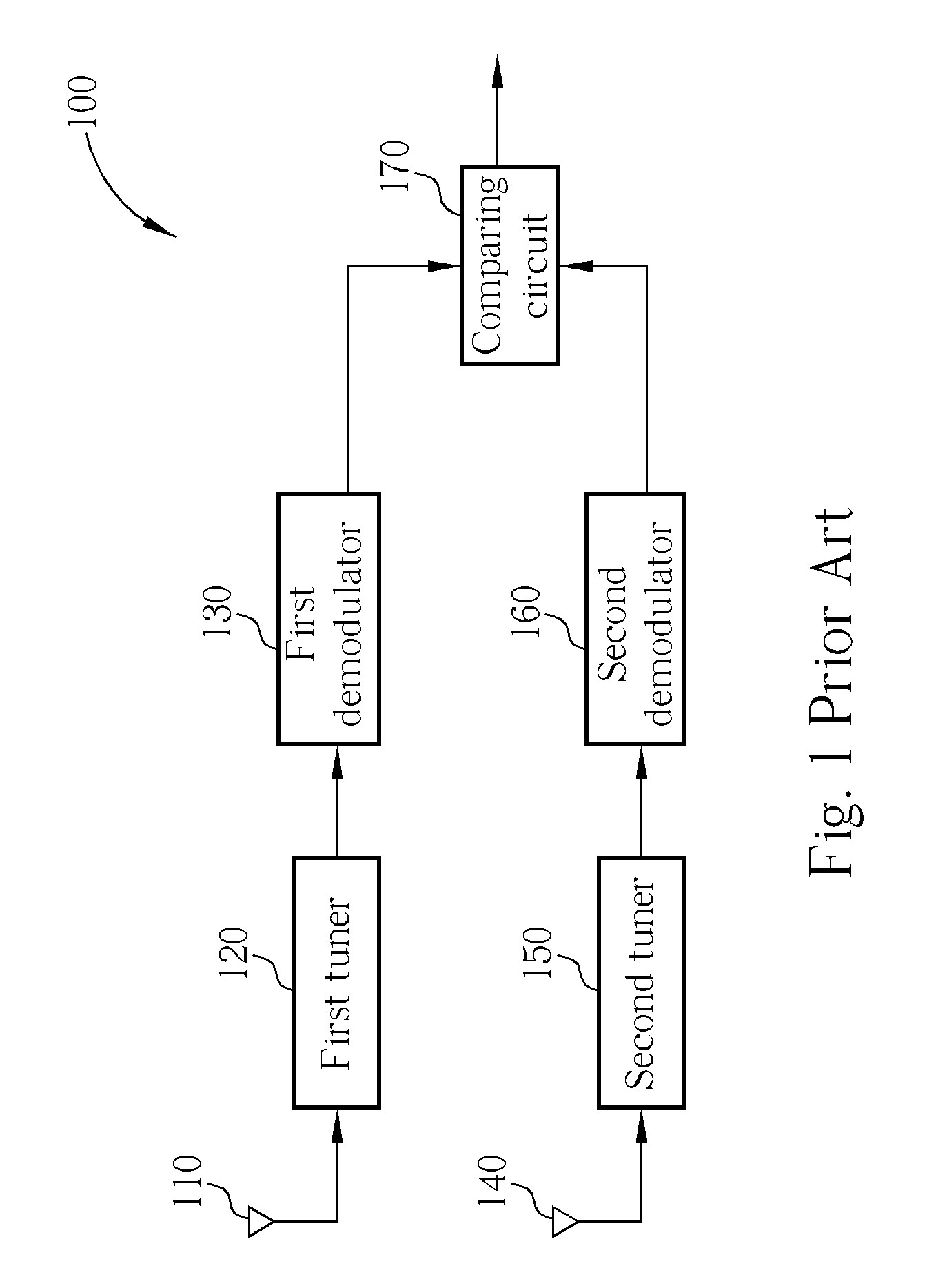

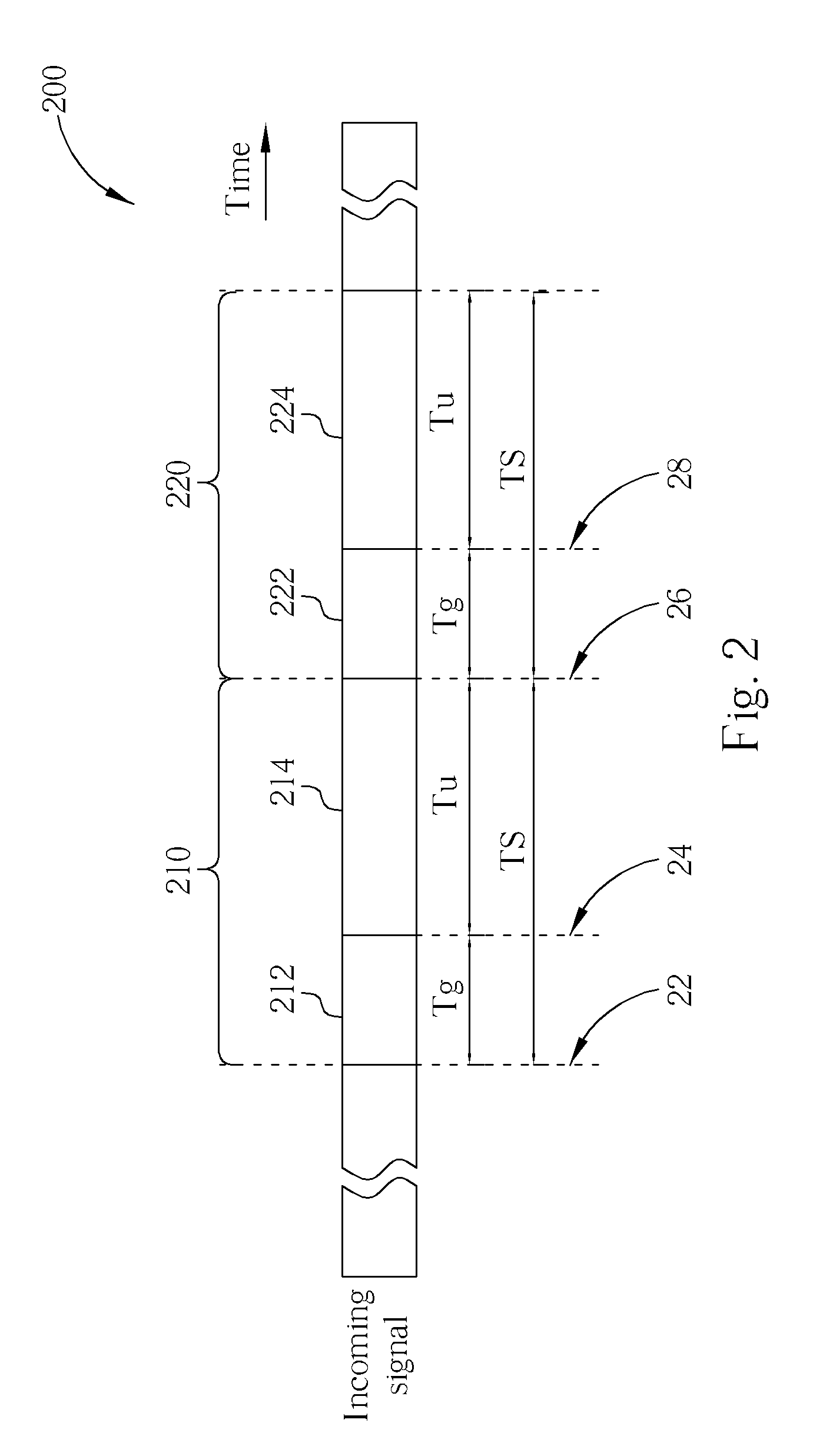

Method and apparatus for antenna diversity

InactiveUS20050254608A1Reduce circuit complexityLow costSpatial transmit diversityPolarisation/directional diversityGuard intervalEngineering

A method for antenna diversity includes: determining a first strength of the first antenna according to a received signal received by the first antenna; receiving the guard interval of a first symbol or a second symbol or both using the second antenna and determining a second strength of the second antenna; and determining which one of the first and the second antennas to receive the useful duration of the second symbol according to the first and the second strengths.

Owner:REALTEK SEMICON CORP

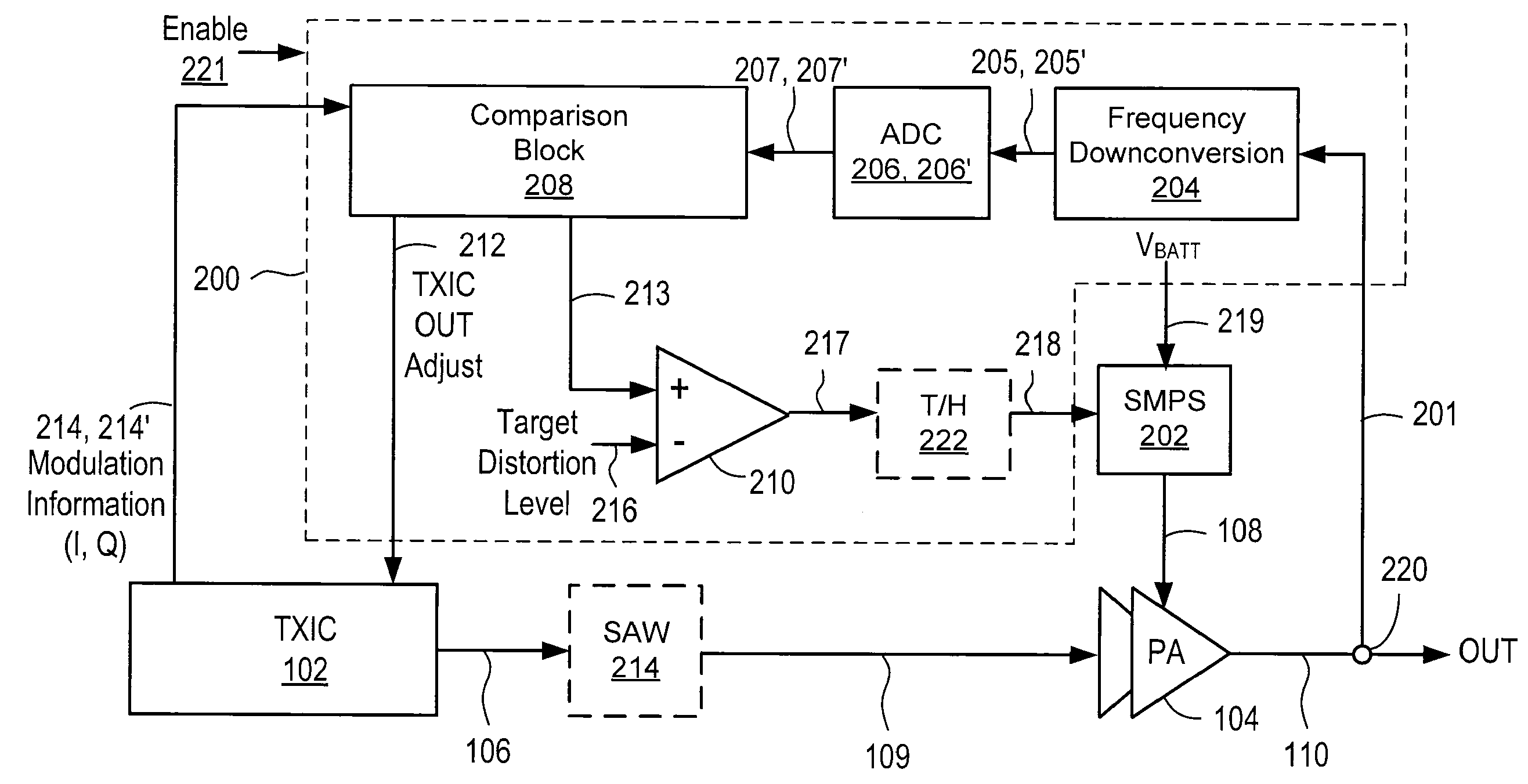

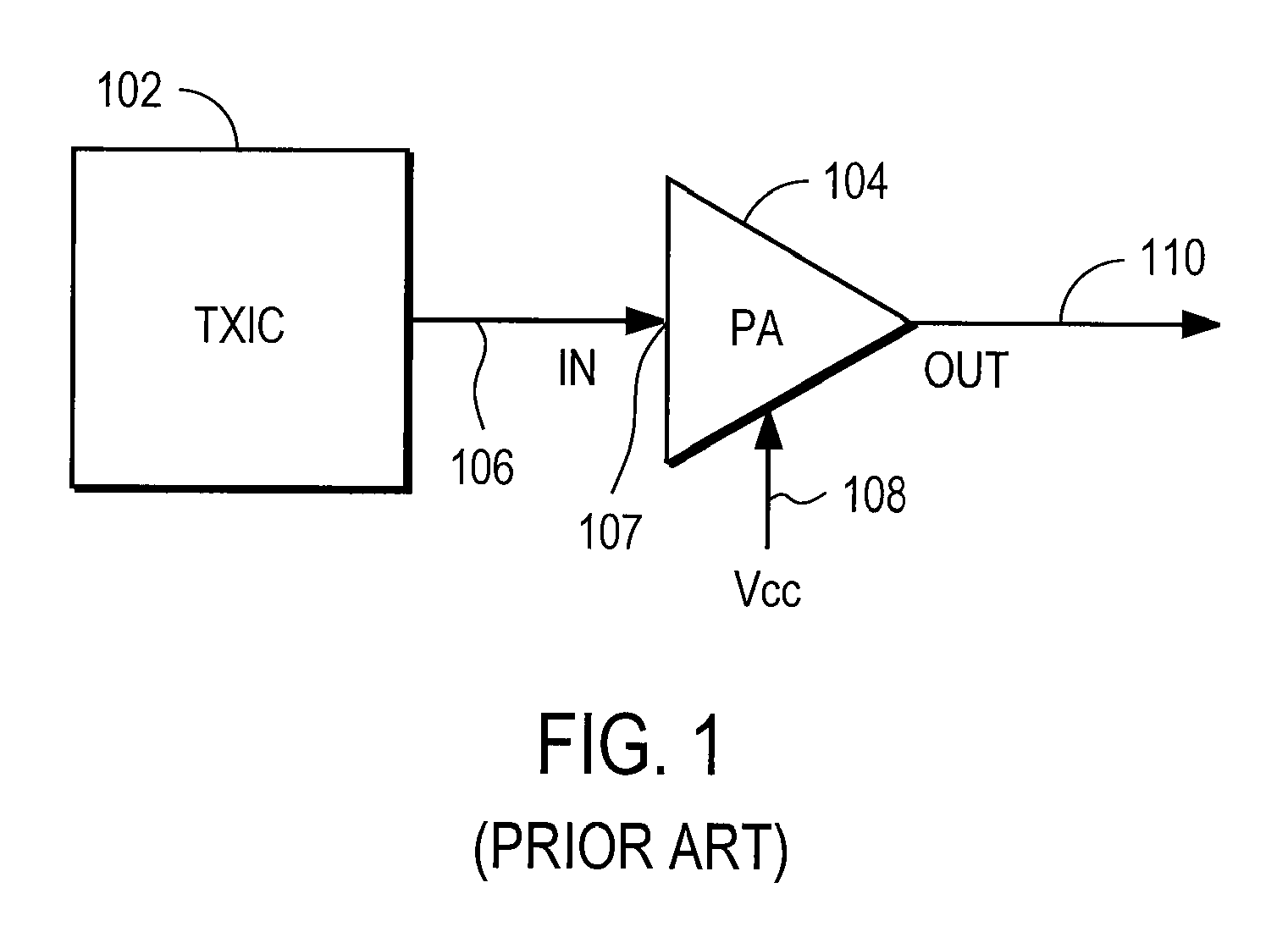

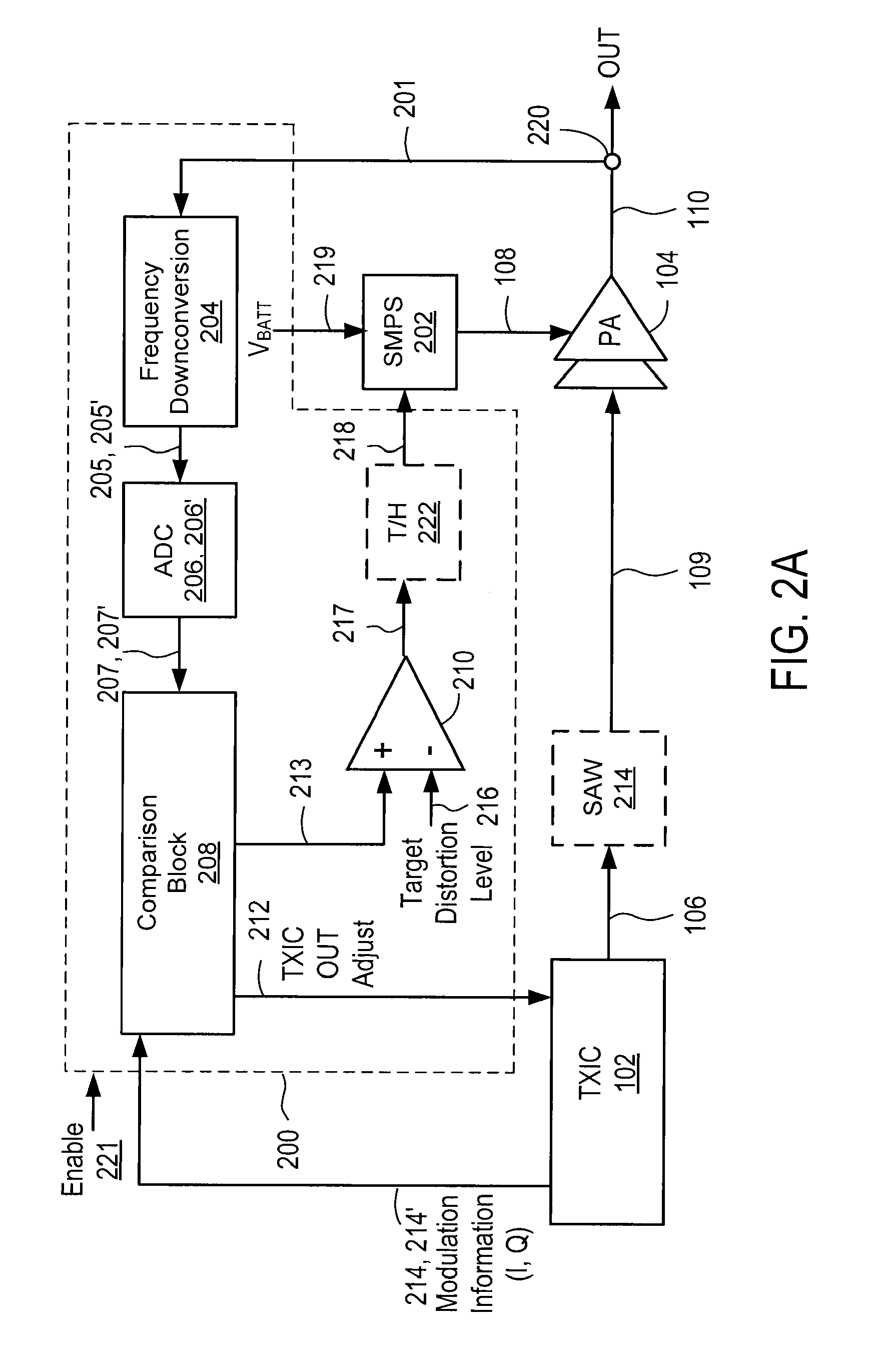

RF power amplifier controlled by estimated distortion level of output signal of power amplifier

ActiveUS20090117865A1Fast in response timeReduce circuit complexityResonant long antennasPhase feedback adaptive predistortionRadio frequencyDistortion

A radio frequency (RF) power amplifier system is provided, in which a distortion of the RF output signal from the power amplifier is estimated by comparing the RF output signal with reference modulation information. The supply voltage to the power amplifier is adjusted so that the estimated distortion of the RF output signal corresponds to a predetermined distortion level. The predetermined distortion level is set to represent an acceptable distortion level at the RF output signal.

Owner:QUANTANCE

Fingerprint sensing circuit

InactiveUS8041083B2Reduce power consumptionReduce circuit complexityResistance/reactance/impedencePrint image acquisitionEngineeringSignal source

Owner:XUESHAN TECH INC

Processor with improved accuracy for multiply-add operations

InactiveUS7346643B1Improve accuracyReduce circuit complexityComputation using non-contact making devicesComplex mathematical operationsOperating speedOperation mode

Floating-point processors capable of performing multiply-add (Madd) operations and incorporating improved intermediate result handling capability. The floating-point processor includes a multiplier unit coupled to an adder unit. In a specific operating mode, the intermediate result from the multiplier unit is processed (i.e., rounded but not normalized or denormalized) into representations that are more accurate and easily managed in the adder unit. By processing the intermediate result in such manner, accuracy is improved, circuit complexity is reduced, operating speed may be increased.

Owner:ARM FINANCE OVERSEAS LTD

Modular photovoltaic power electronic converter based on coupling inductance

InactiveCN102570830AReduced duty cycle lossReduce circuit complexityBatteries circuit arrangementsAc-dc conversionPhase shiftedCoupling inductor

The invention relates to a modular photovoltaic power electronic converter based on coupling inductance, which comprises a solar-cell panel, a maximum power point tracking circuit, a photovoltaic converter, load and a storage battery. The photovoltaic converter is formed by a direct current / direct current (DC / DC) phase shifted full bridge and a direct current / alternating current (DC / AC) inversion bridge. The coupling inductance is introduced to the voltage-multiplying rectification side of a DC / DC phase shifted full bridge circuit. The coupling inductance can not only quickly reduce primary side circulation current through the coupling effect to reduce duty ratio loss accordingly but also ensure the filtering effect of power frequency half-sinusoid voltage modulated by sinusoidal pulse width modulation (SPWM) and output by the voltage-multiplying rectification side of the DC / DC phase shifted full bridge circuit and can achieve a leading arm zero voltage switch of a phase shifted full bridge circuit. Alternating current electricity is output at the DC / AC grade through the power frequency inversion bridge. The converter is simple in structure, low in cost, high in efficiency, easy to achieve and capable of being used in not only a photovoltaic system but also other new energy systems.

Owner:SHANGHAI DIANJI UNIV

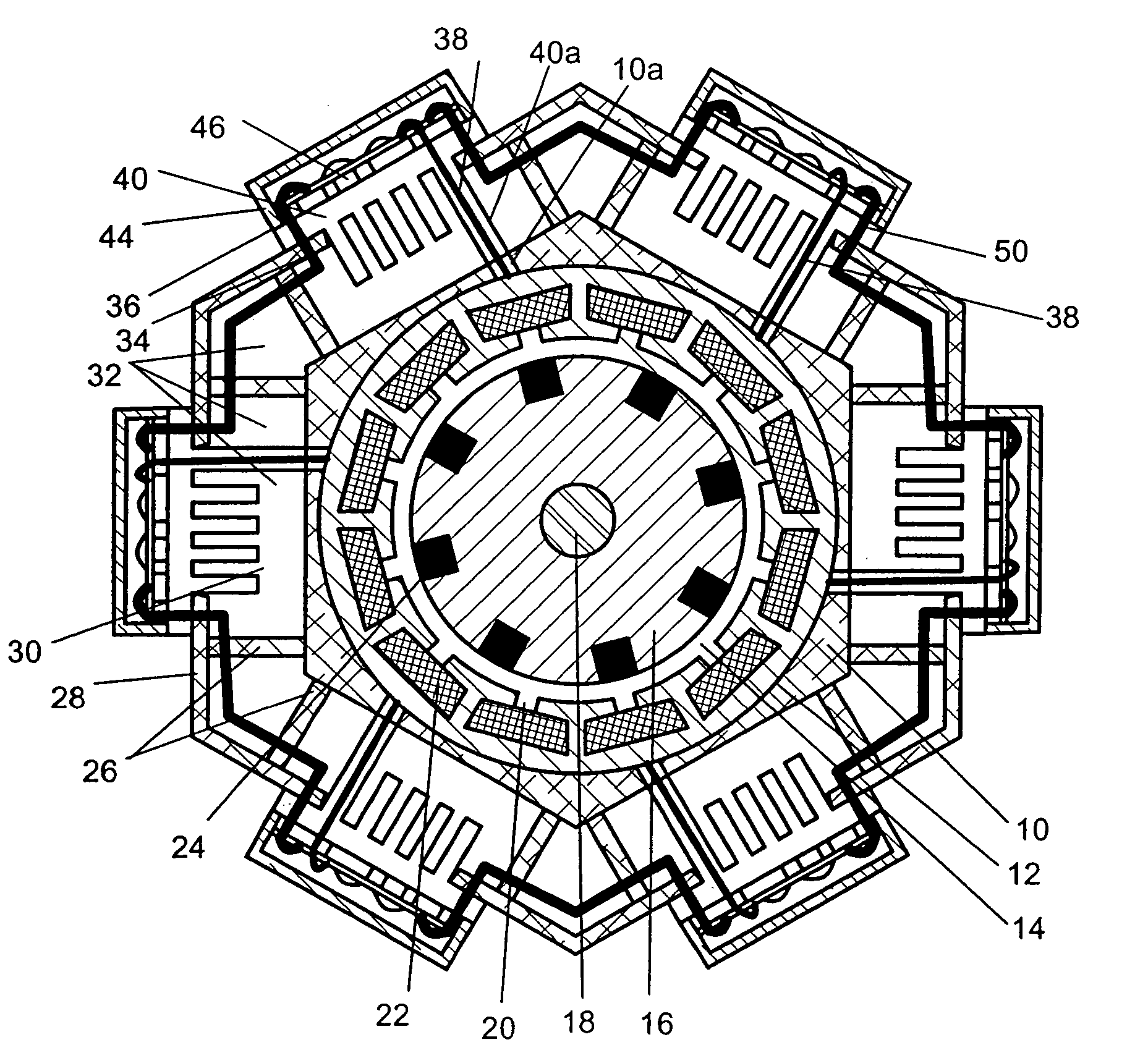

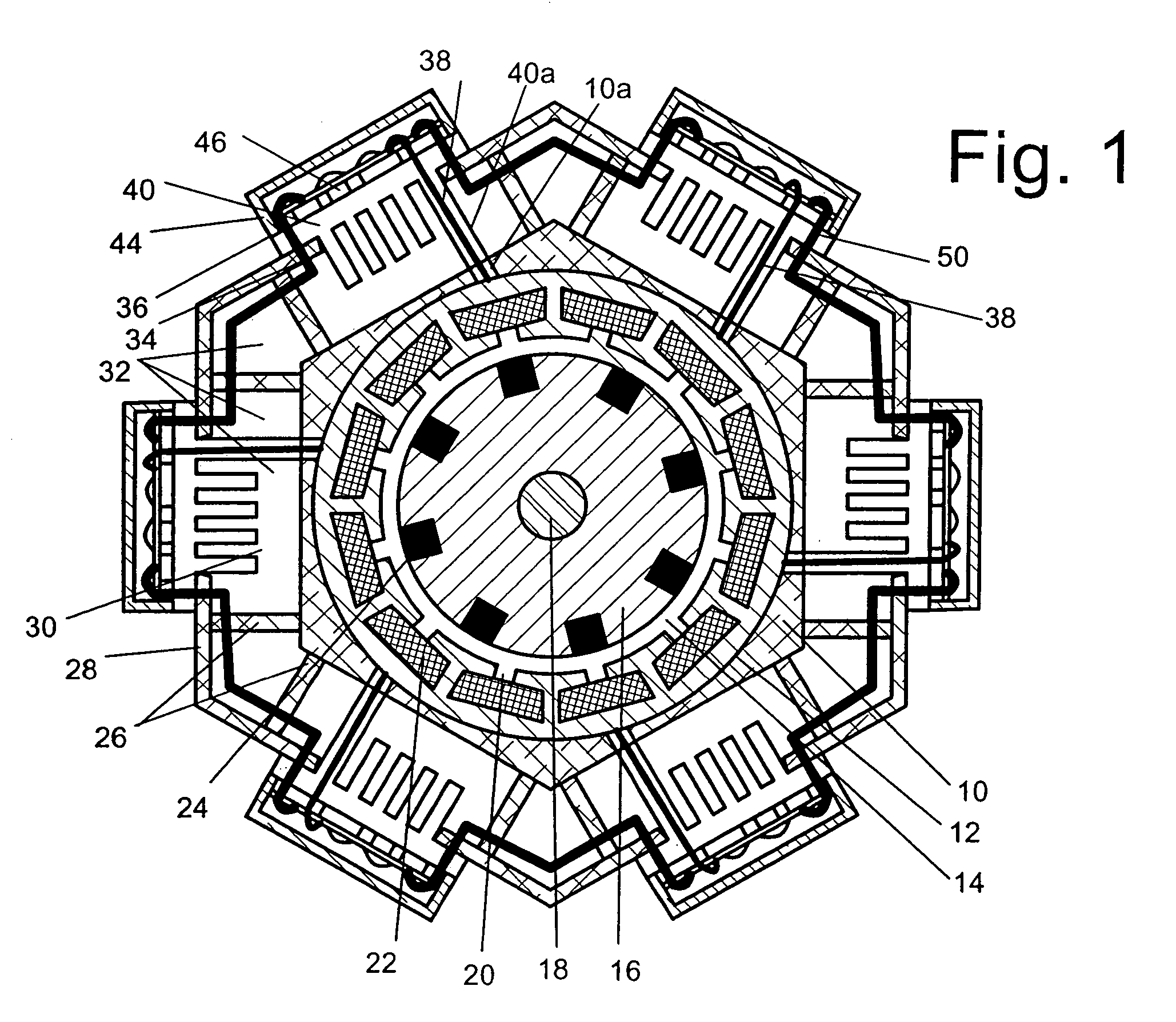

Fluid cooled electric machine

InactiveUS7049716B2Produce economicallyReliable in operationAssociation with control/drive circuitsCooling/ventillation arrangementPower controlElectricity

Owner:COMPACT DYNAMICS

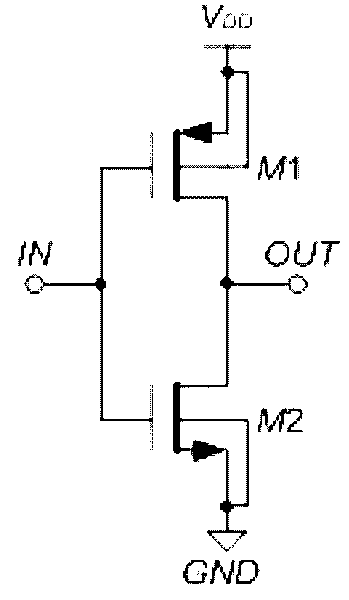

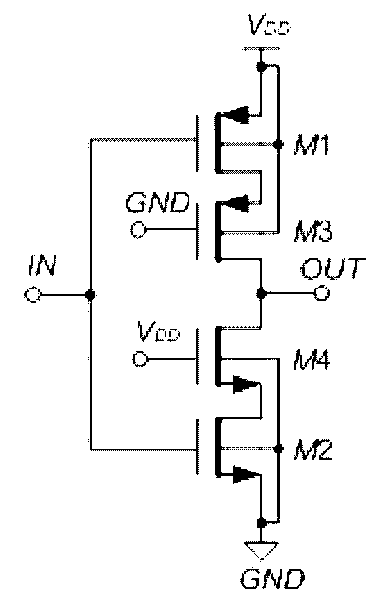

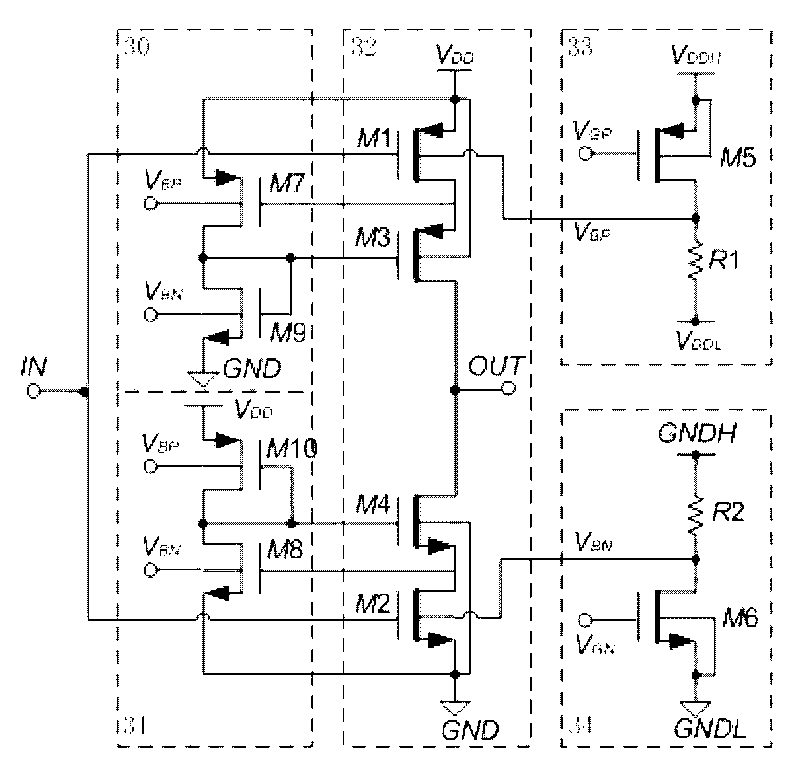

Gain bootstrap type C class reverser and application circuit thereof

InactiveCN101692603AChip footprint is smallReduce circuit complexityElectric pulse generator detailsAnalog to digital conversionSetting time

The invention discloses a gain bootstrap type C class reverser and an application circuit thereof. Based on a C class reverser 32 in the prior art, the gain bootstrap type C class reverser is additionally provided with micropower gain bootstrap modules 30 and 31 and bulk potential modulation modules 33 and 34, wherein the gain bootstrap modules 30 and 31 greatly improve the steady-state gain of the C class reverser under the condition of not losing the output swing or increasing the circuit power consumption significantly so as to improve the integral precision of a gain bootstrap type C class reverser-based pseudo-differential structure switched capacitor integrator and the analog-to-digital conversion precision of an analog-to-digital converter, and broaden the application range of the C class reverser; and the bulk potential modulation modules 33 and 34 make the steady-state characteristics (gain, bandwidth, static power consumption and the like) and the dynamic characteristics (slew rate, setting time, dynamic power consumption and the like) of the whole reverser consistent under the condition of different corners, and greatly improve the stability and the robustness of the application circuit of the gain bootstrap type C class reverser under the condition of not increasing the power consumption significantly.

Owner:ZHEJIANG UNIV

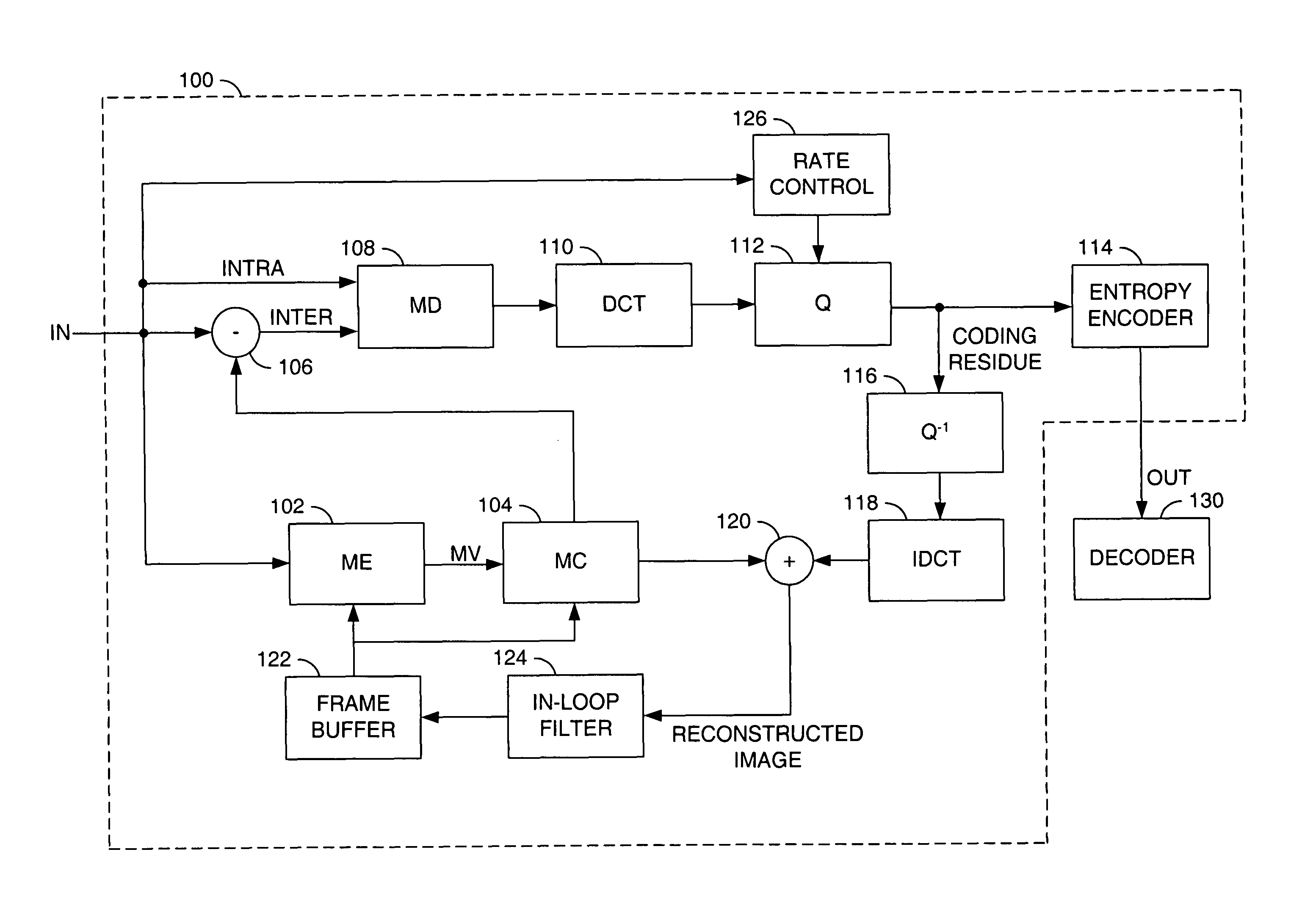

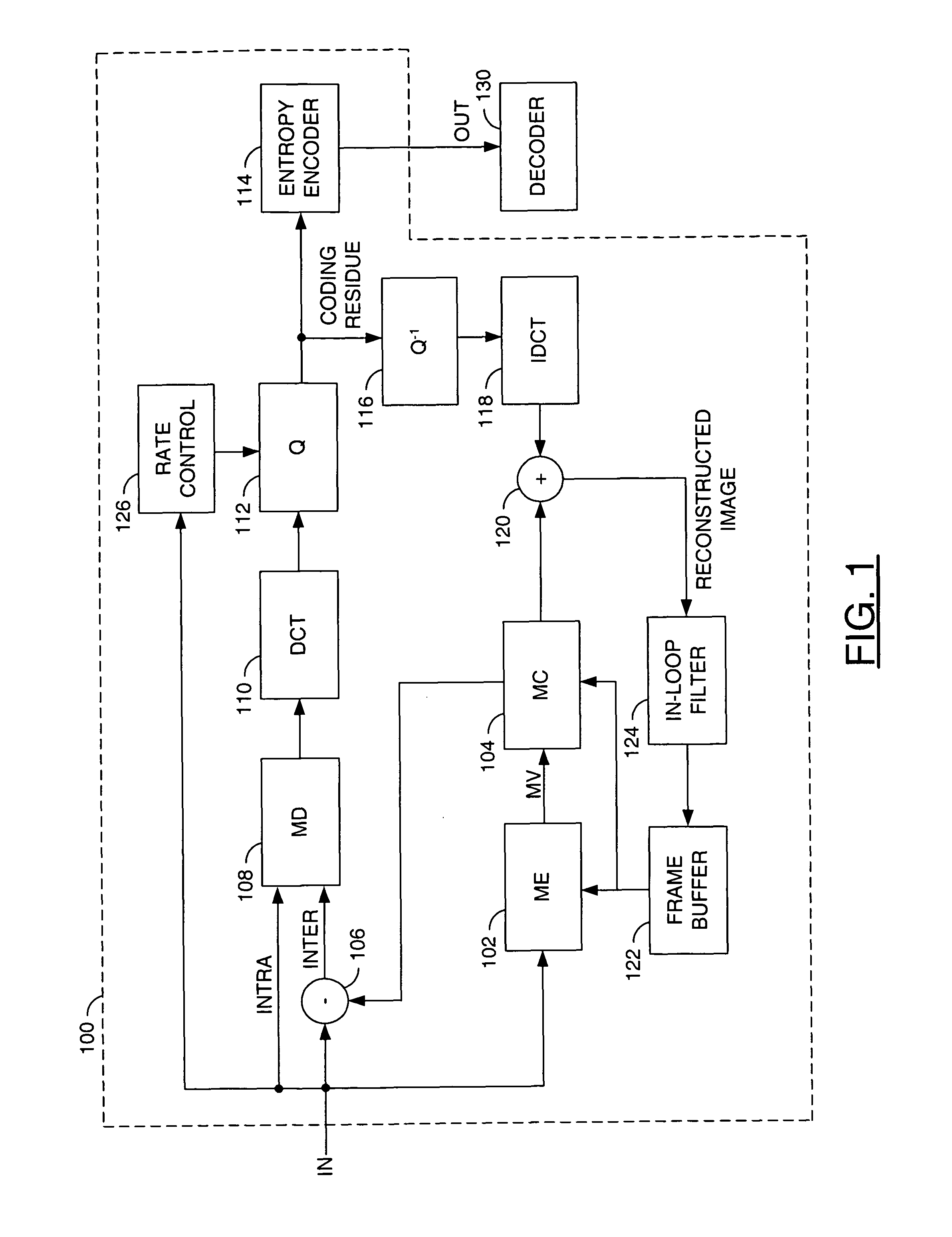

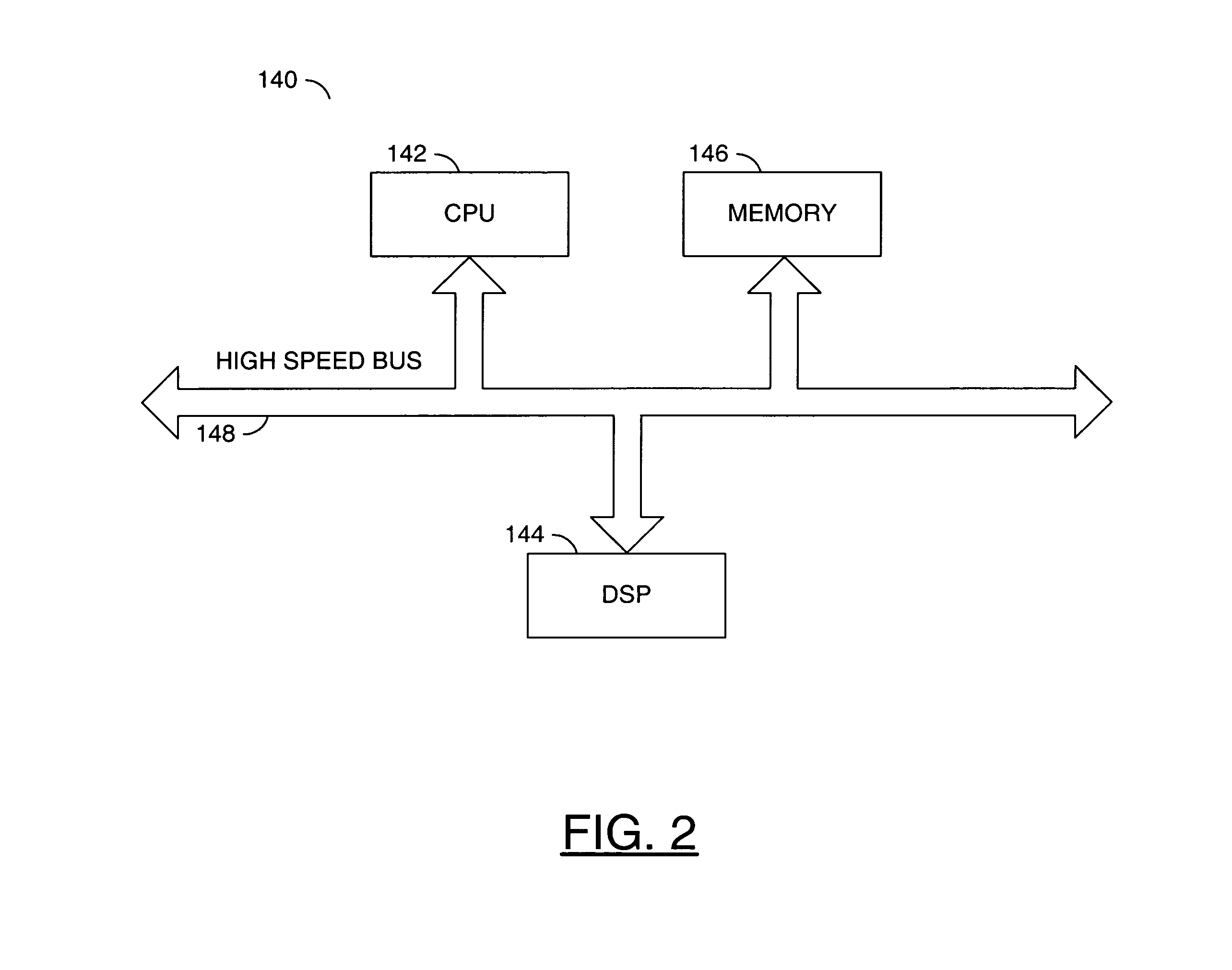

Mode decision using approximate 1/2 pel interpolation

ActiveUS8265151B1Reduce switching powerMinimize error propagation problemColor television with pulse code modulationColor television with bandwidth reductionVideo encodingComputer science

A method for video encoding is disclosed. The method generally includes the steps of (A) generating first sub-pel data for at least one of (i) a motion estimation and (ii) a mode decision by first filtering reference data and (B) generating second sub-pel data for a motion compensation by second filtering the reference data. Wherein a first performance of the first filtering may be different than a second performance of the second filtering.

Owner:AMBARELLA TAIWAN +1

Plasma production device and method and RF driver circuit

InactiveUS7132996B2Efficient couplingImproved antenna designResonant long antennasElectric discharge tubesCapacitanceDriver circuit

An RF driver circuit and an orthogonal antenna assembly / configuration, are disclosed as part of a method and system for generating high density plasma. The antenna assembly is an orthogonal antenna system that may be driven by any RF generator / circuitry with suitable impedance matching to present a low impedance. The disclosed RF driver circuit uses switching type amplifier elements and presents a low output impedance. The disclosed low-output impedance RF driver circuits eliminate the need for a matching circuit for interfacing with the inherent impedance variations associated with plasma. Also disclosed is the choice for capacitance or an inductance value to provide tuning for the RF plasma source.

Owner:LAM RES CORP +1

Fingerprint Sensing Circuit

ActiveUS20080317300A1Prevent inaccurate sensing resultsEasy to implementResistance/reactance/impedencePrint image acquisitionSignal sourceFingerprint

Owner:XUESHAN TECH INC

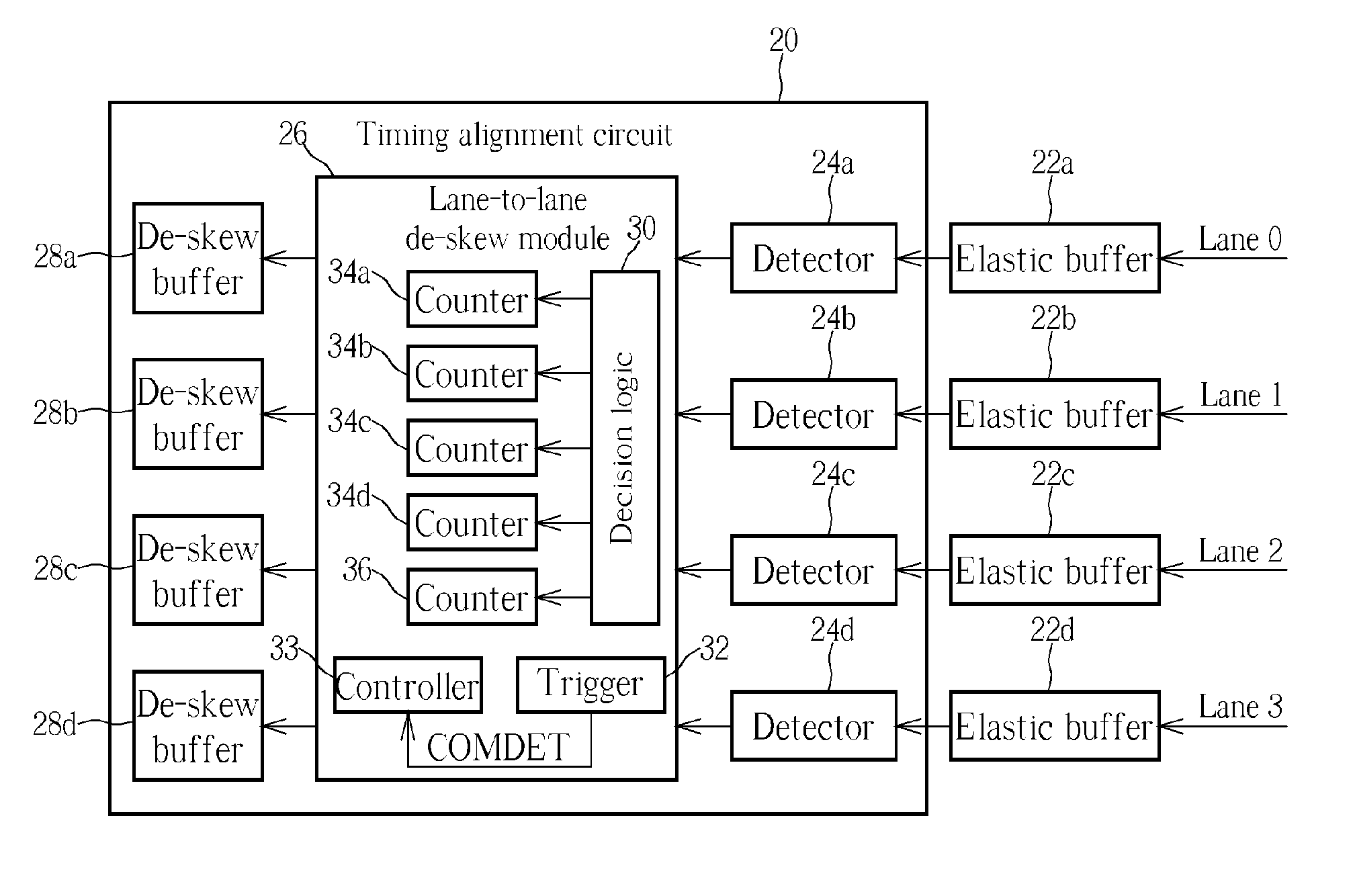

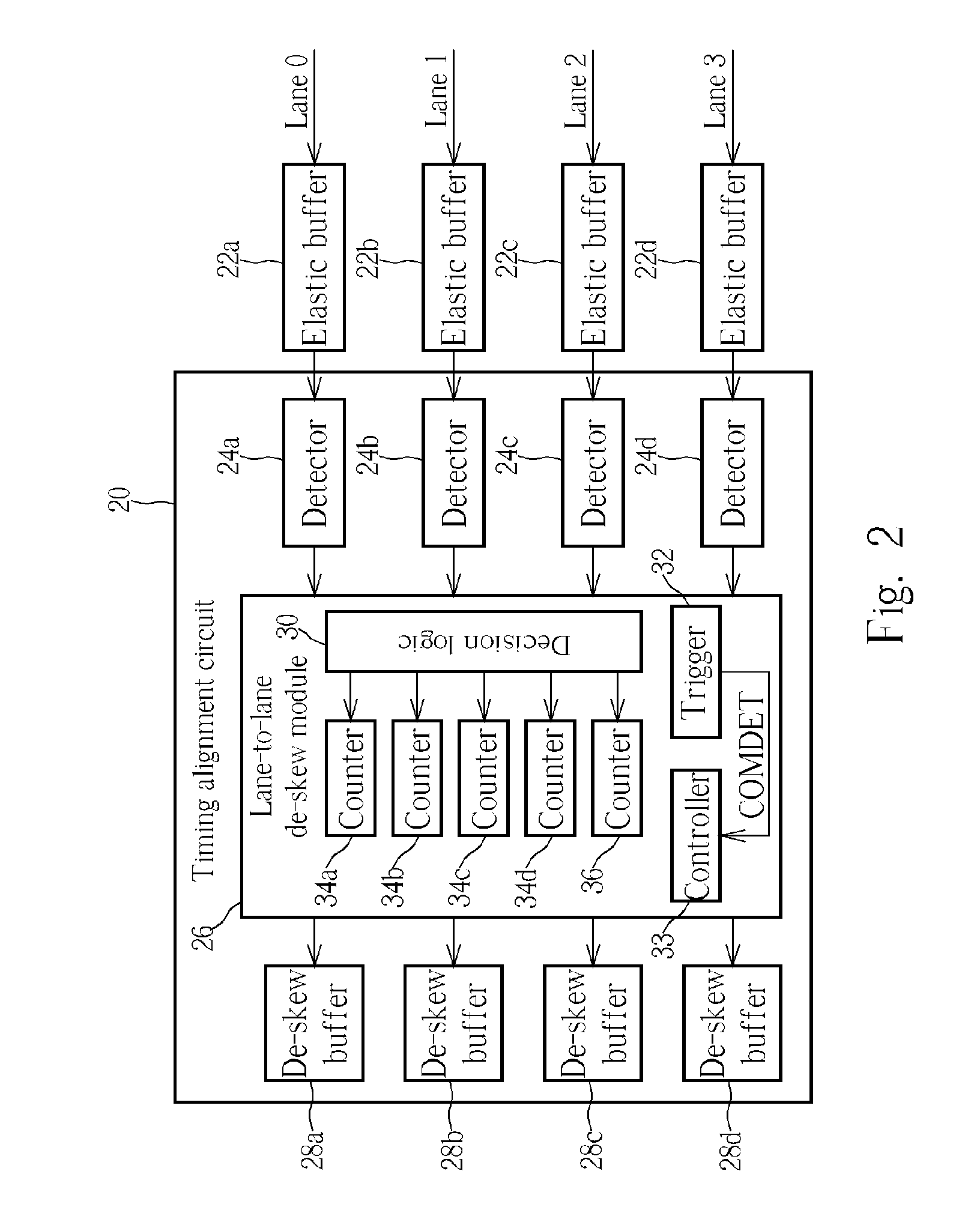

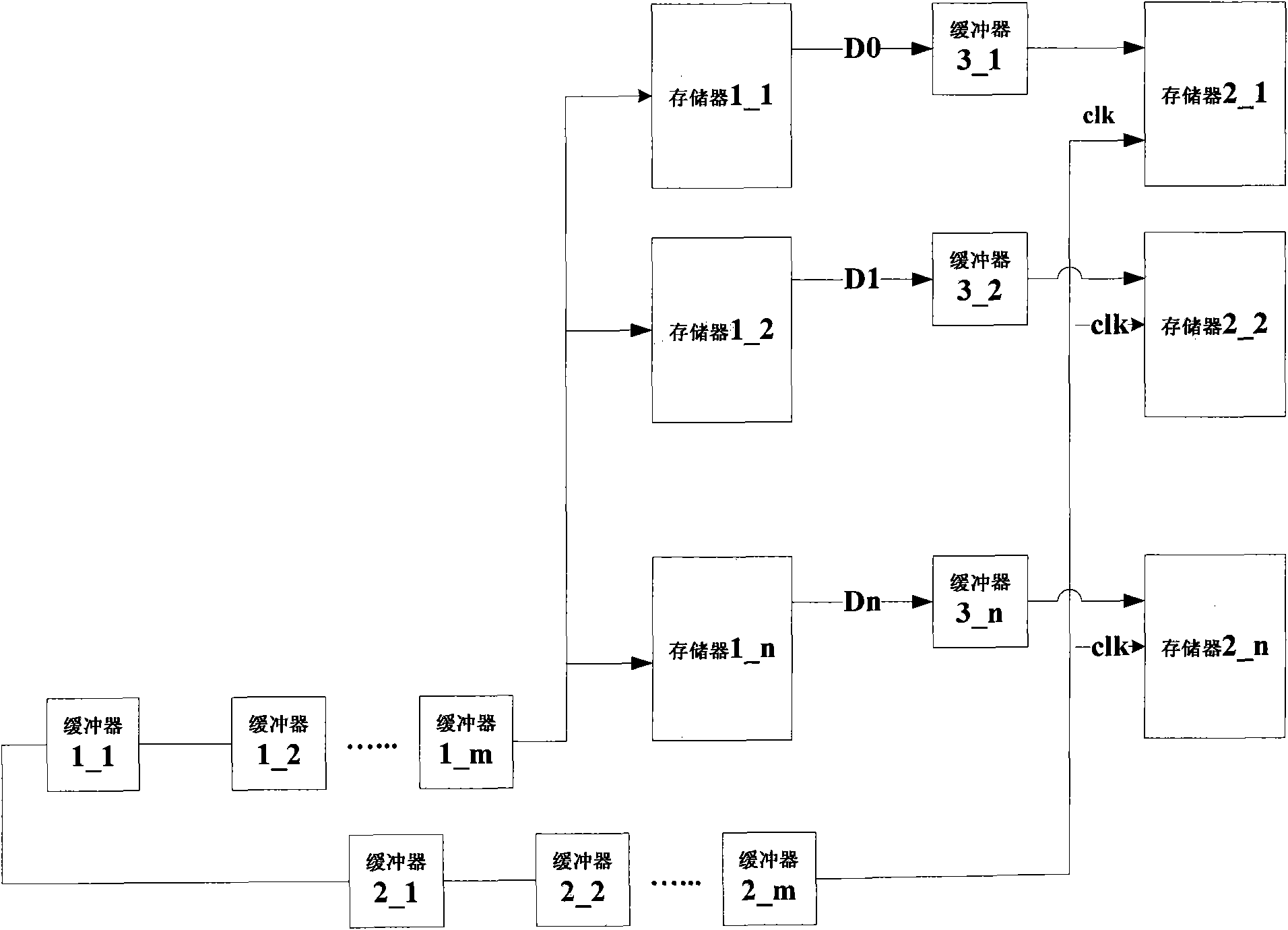

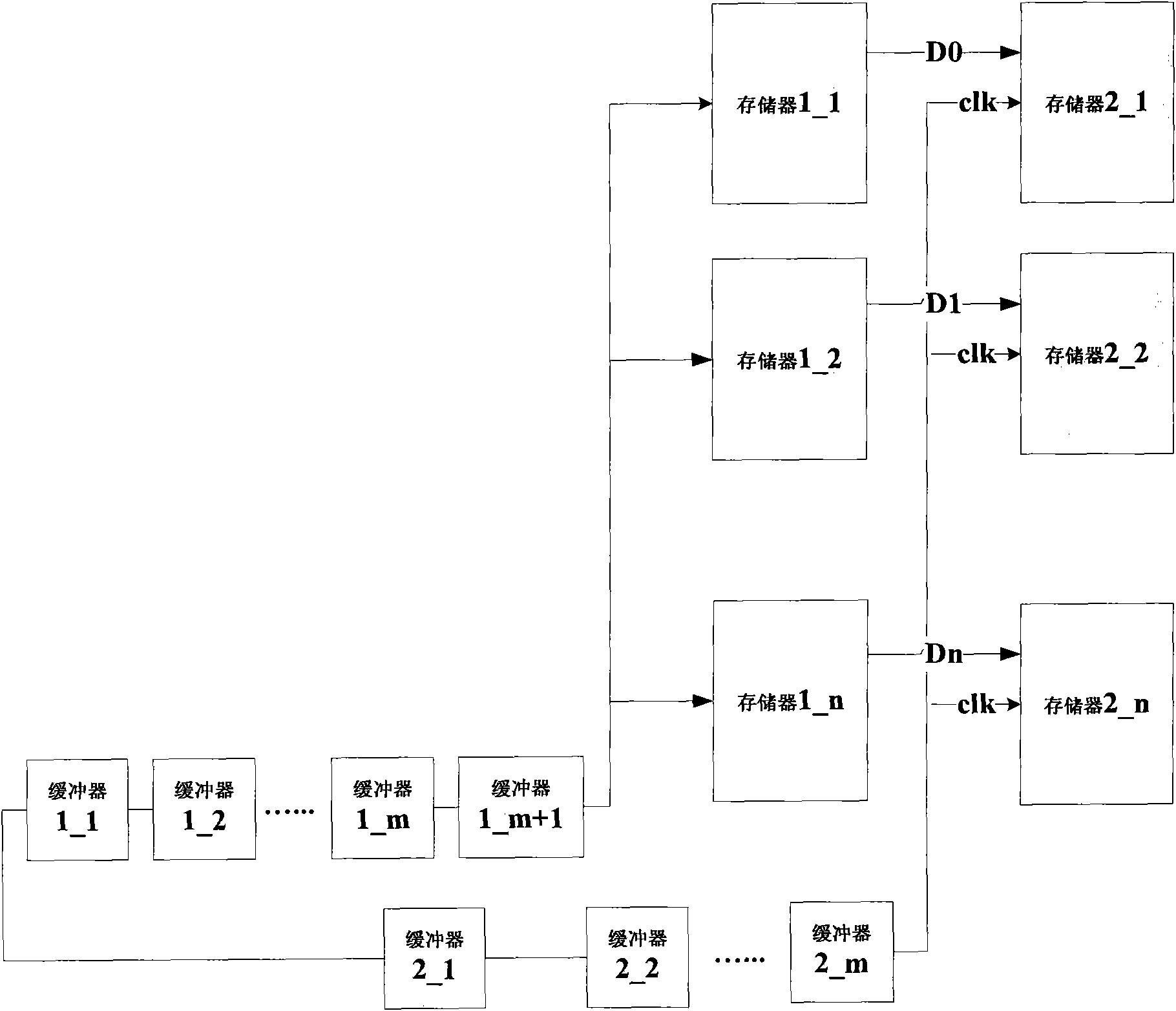

Circuit and method for aligning data transmitting timing of a plurality of lanes

ActiveUS20070124623A1Improve performanceReduce circuit complexityError detection/correctionData resettingData transmissionComputer science

Owner:VIA TECH INC

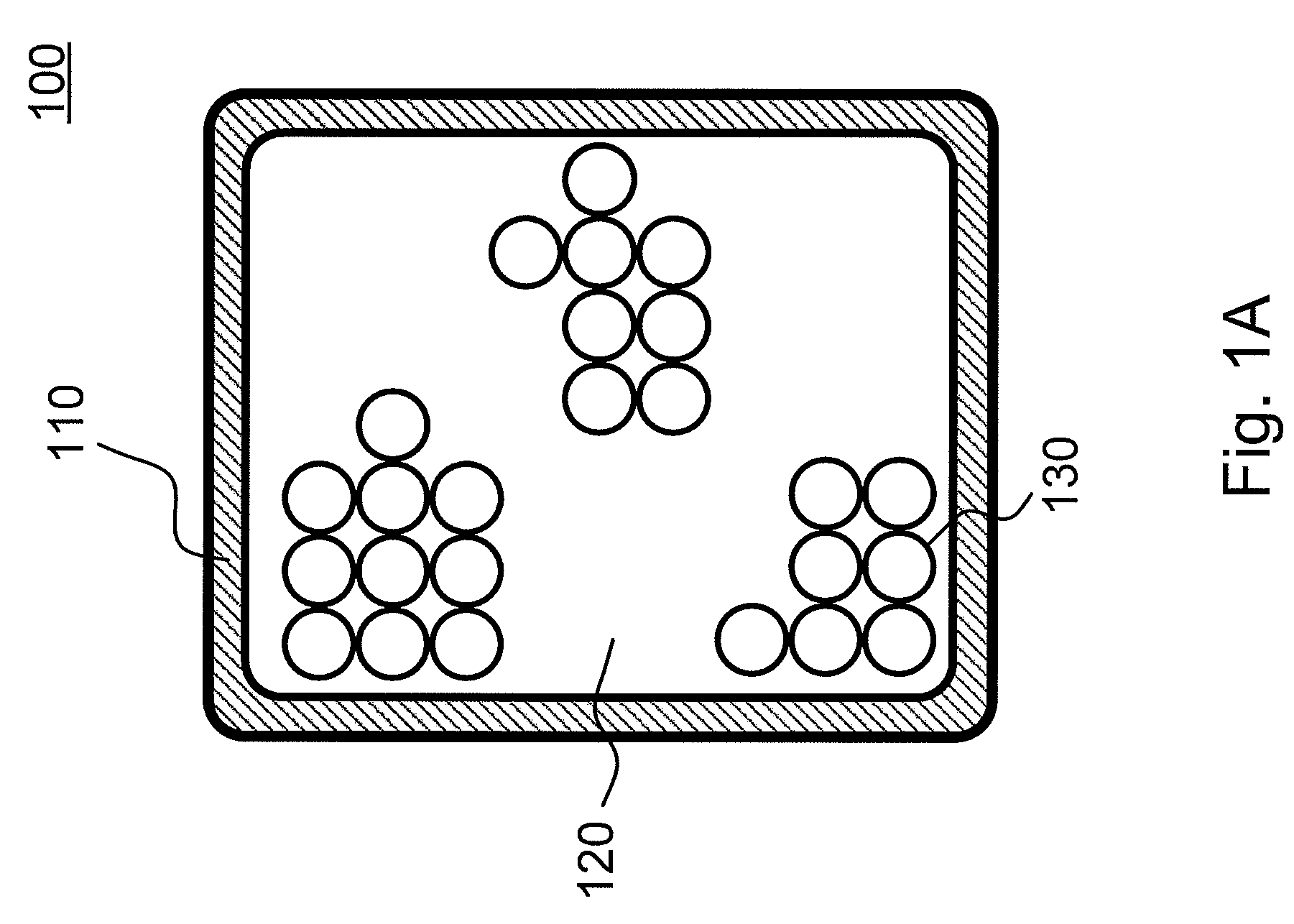

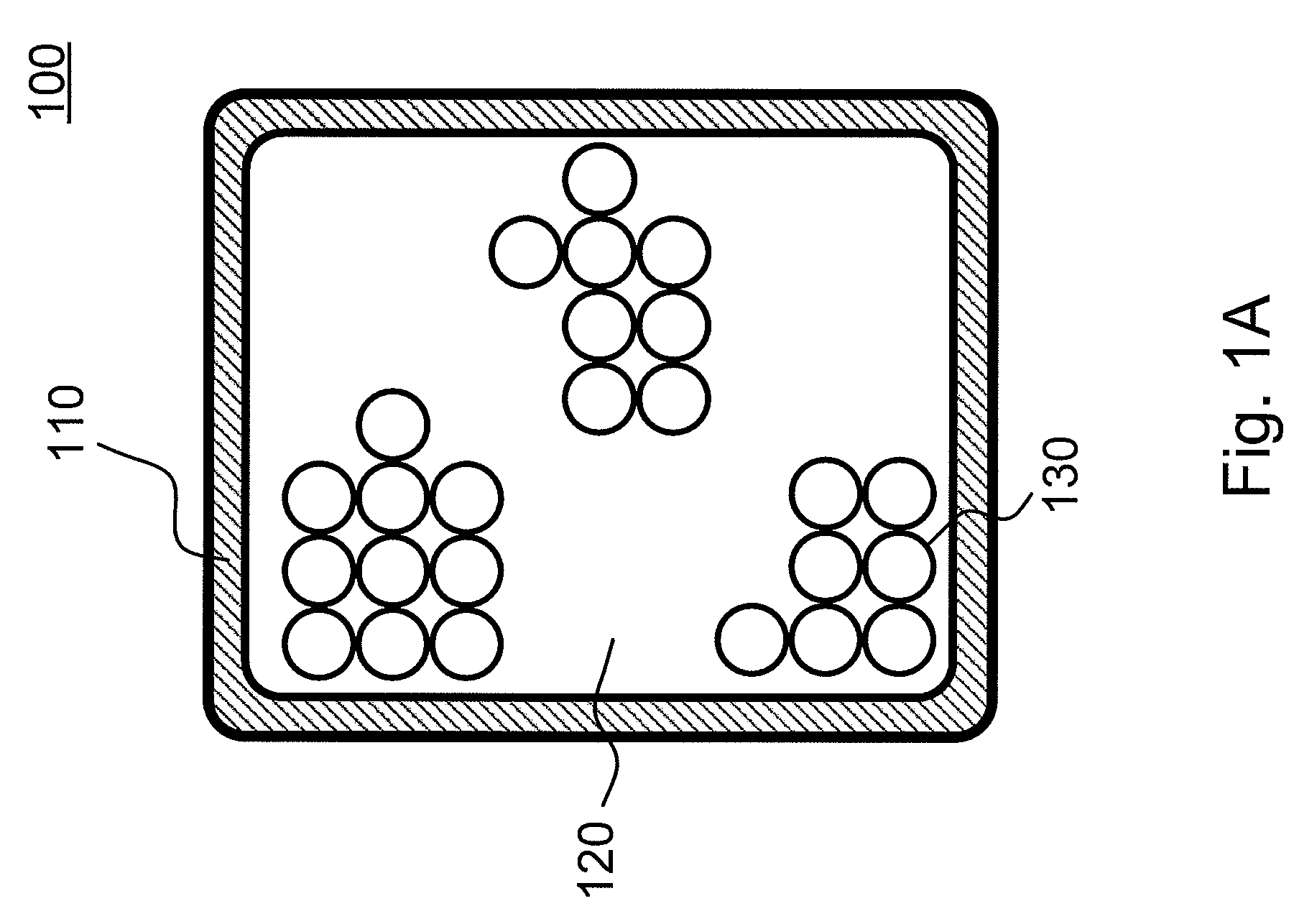

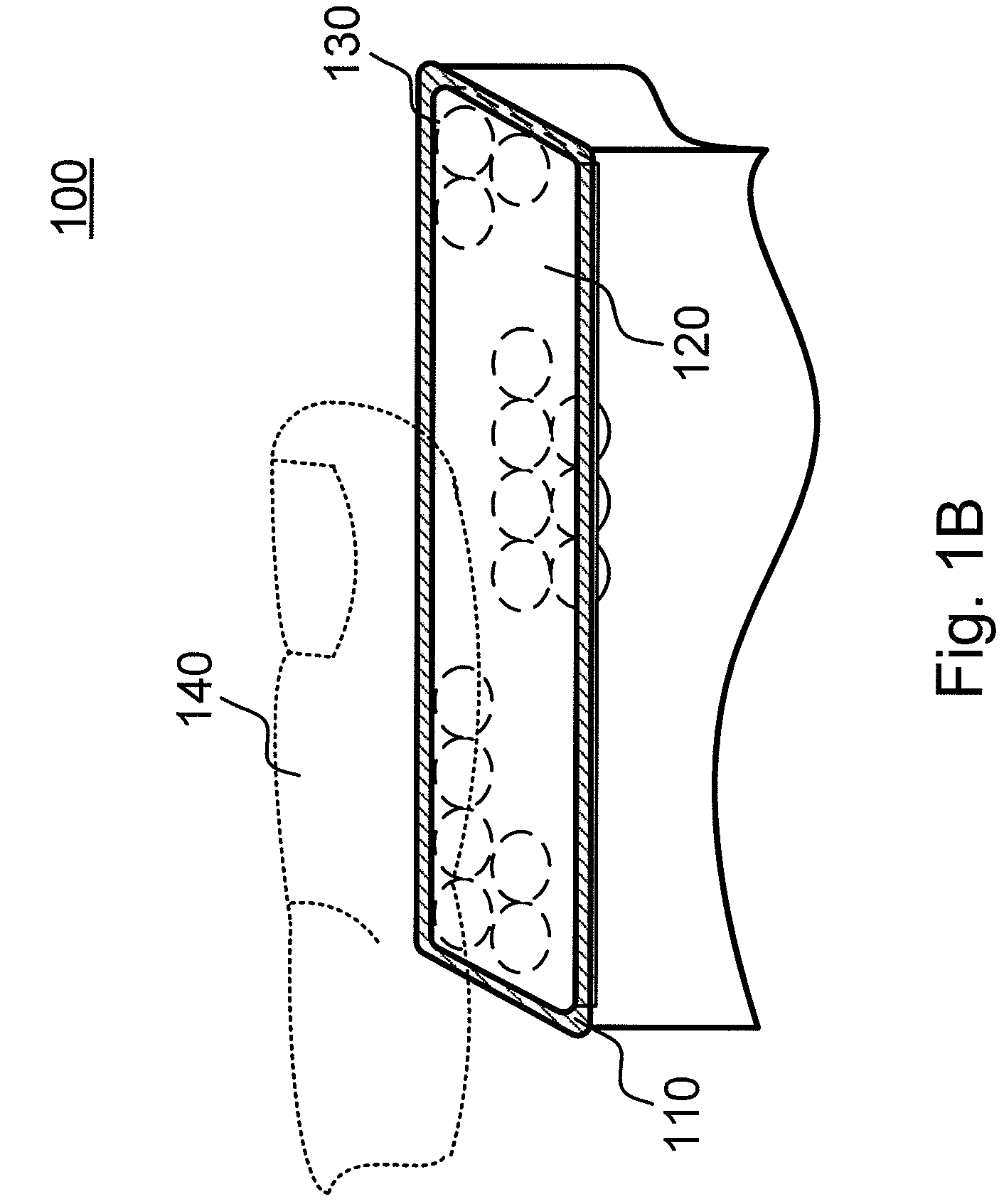

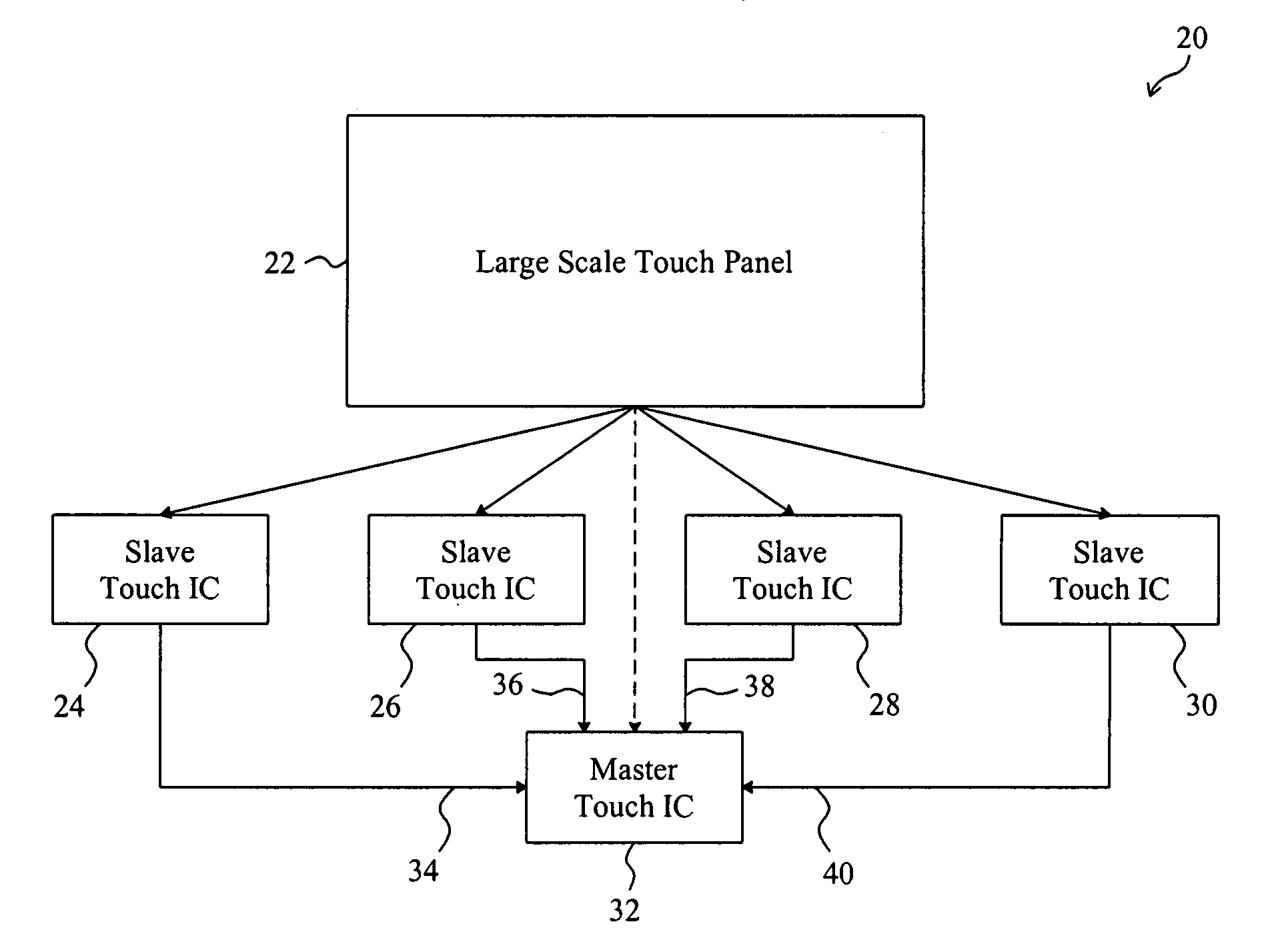

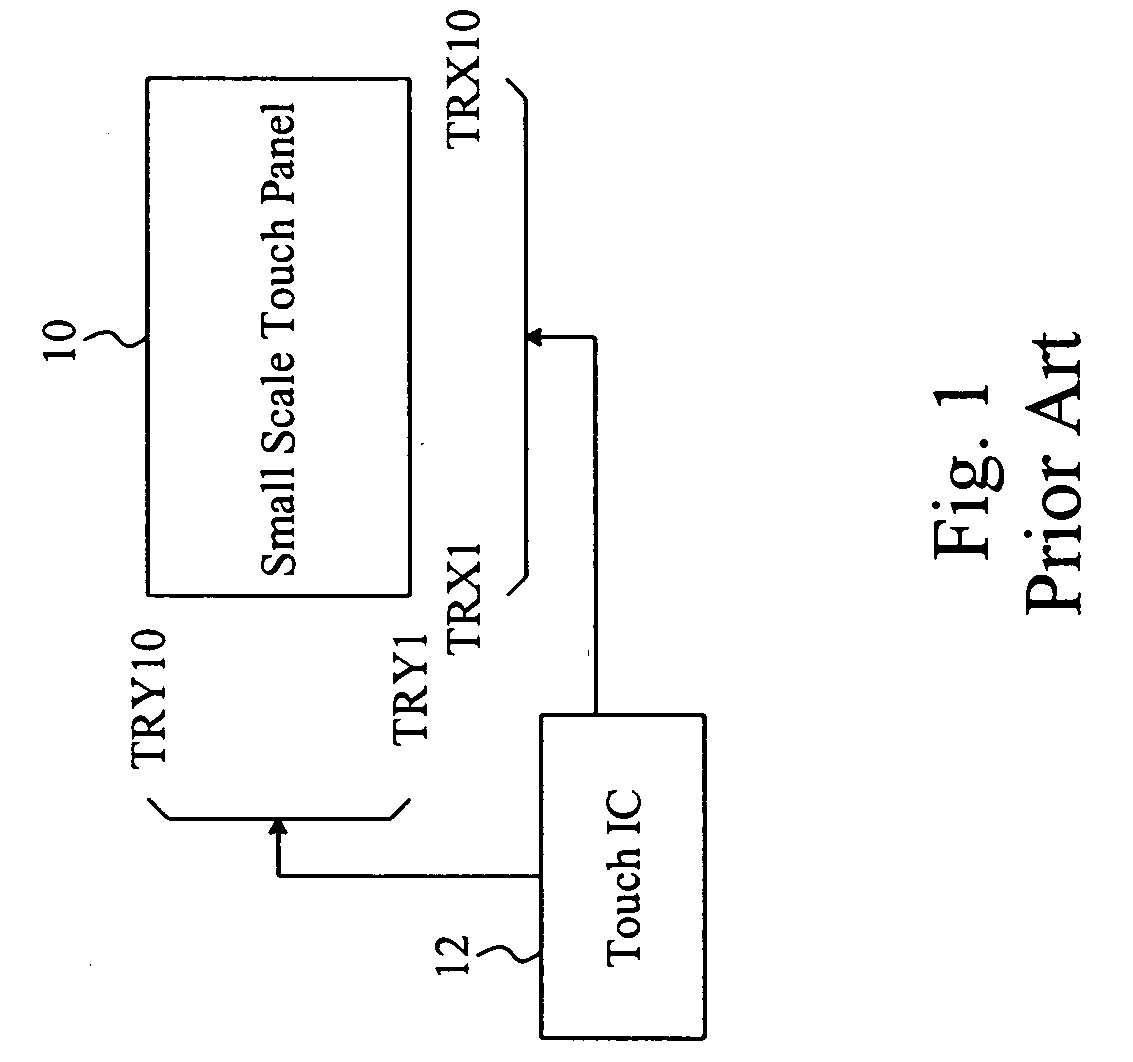

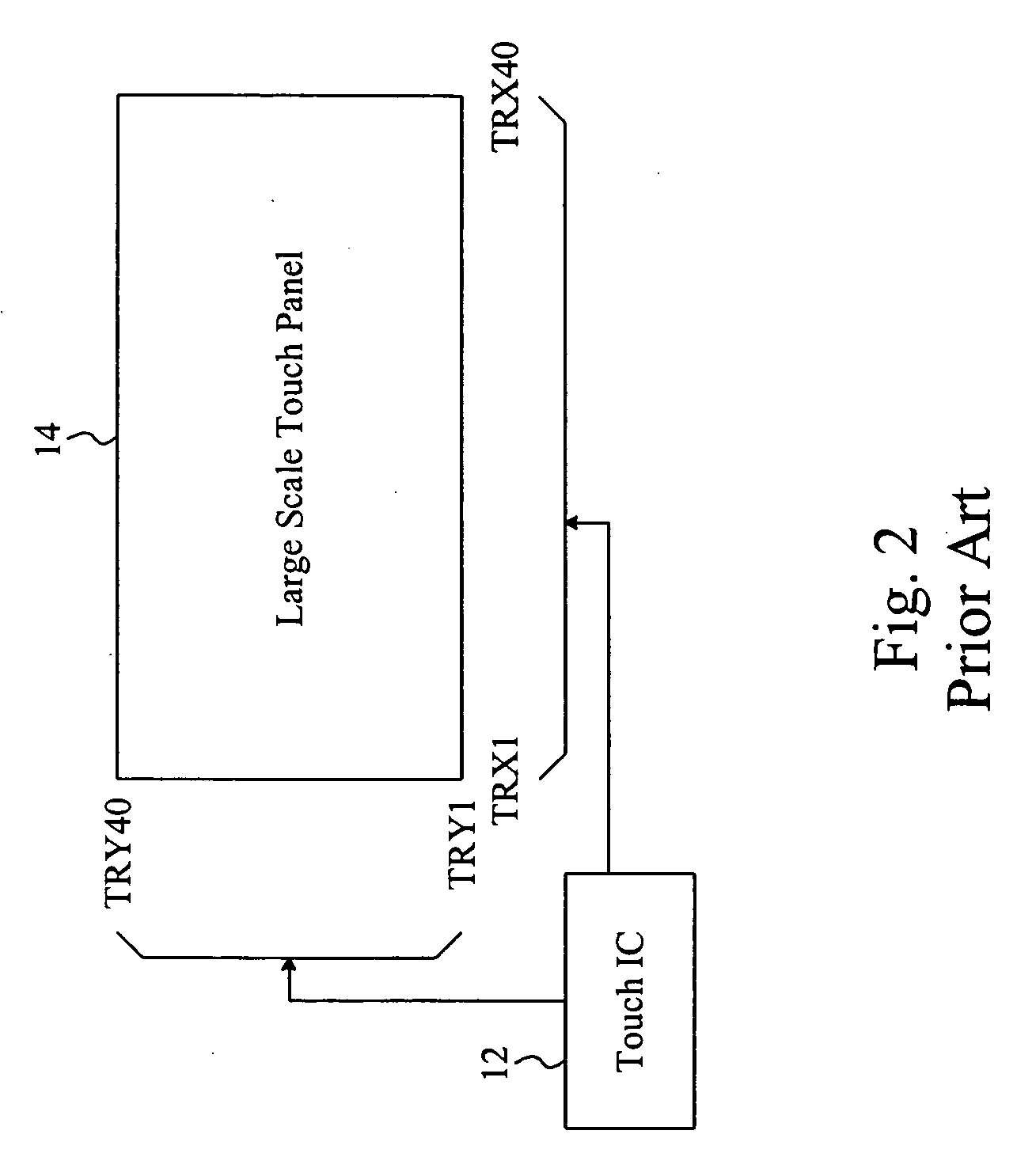

Circuit complexity reduction of a capacitive touch system

InactiveUS20090251430A1Increase ratingsReduce complexityInput/output processes for data processingSensing dataCircuit complexity

A capacitive touch system uses at least two first integrated circuits to simultaneously scan a touch panel, each of the first integrated circuits only for scanning a portion of the touch panel. Therefore, the capacitive touch system can maintain a good frame rate, even the touch panel is a large scale touch panel. Each of the first integrated circuits transmits its sensed data to a second integrated circuit where a calculation with the received sensed data is executed. The second integrated circuit has at least a common pin connected to each of the first integrated circuits, and therefore the number of pins of the second integrated circuit is reduced.

Owner:ELAN MICROELECTRONICS CORPORATION

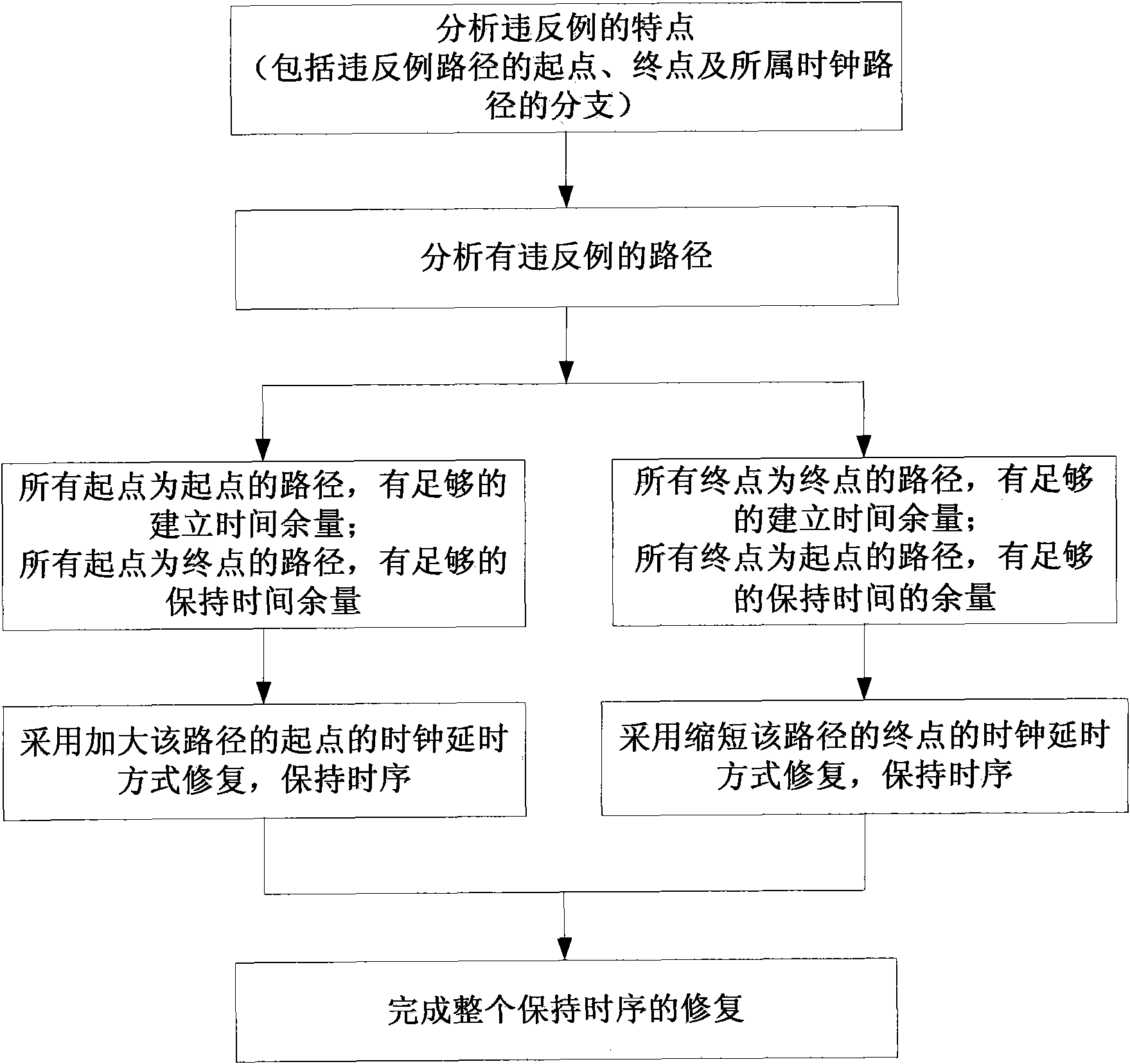

Time sequence repairing method

InactiveCN102339338AReduce circuit complexitySmall design areaSpecial data processing applicationsData channelTiming margin

The invention discloses a time sequence repairing method, which is used for solving the problem of increase in chip design area caused by repair of a time sequence circuit during integrated circuit application by intervening with a clock channel and transferring a part of design problems of a data channel onto the clock channel. The method comprises the following steps of: analyzing the characteristic of a time sequence violating example; analyzing routes in which violating examples exists; when all routes of which start points of the violating examples serve as start points are provided with sufficient build-up time margins and all routes of which start points of the violating examples serve as end points are provided with sufficient build-up time margins, repairing and keeping a time sequence by increasing the clock delays of the start points of the routes; and when all routes of which end points of the violating examples serve as end points are provided with sufficient build-up time margins and all routes of which end points of violating examples serve as start points are provided with sufficient build-up time margins, repairing and keeping a time sequence by decreasing the clock delays of the end points of the routes. In the method disclosed by the invention, different clock delay design modes are selected, so that the circuit complexity of the integrated circuit chip design can be lowered effectively, and the chip design area is reduced.

Owner:SHANGHAI HUAHONG INTEGRATED CIRCUIT

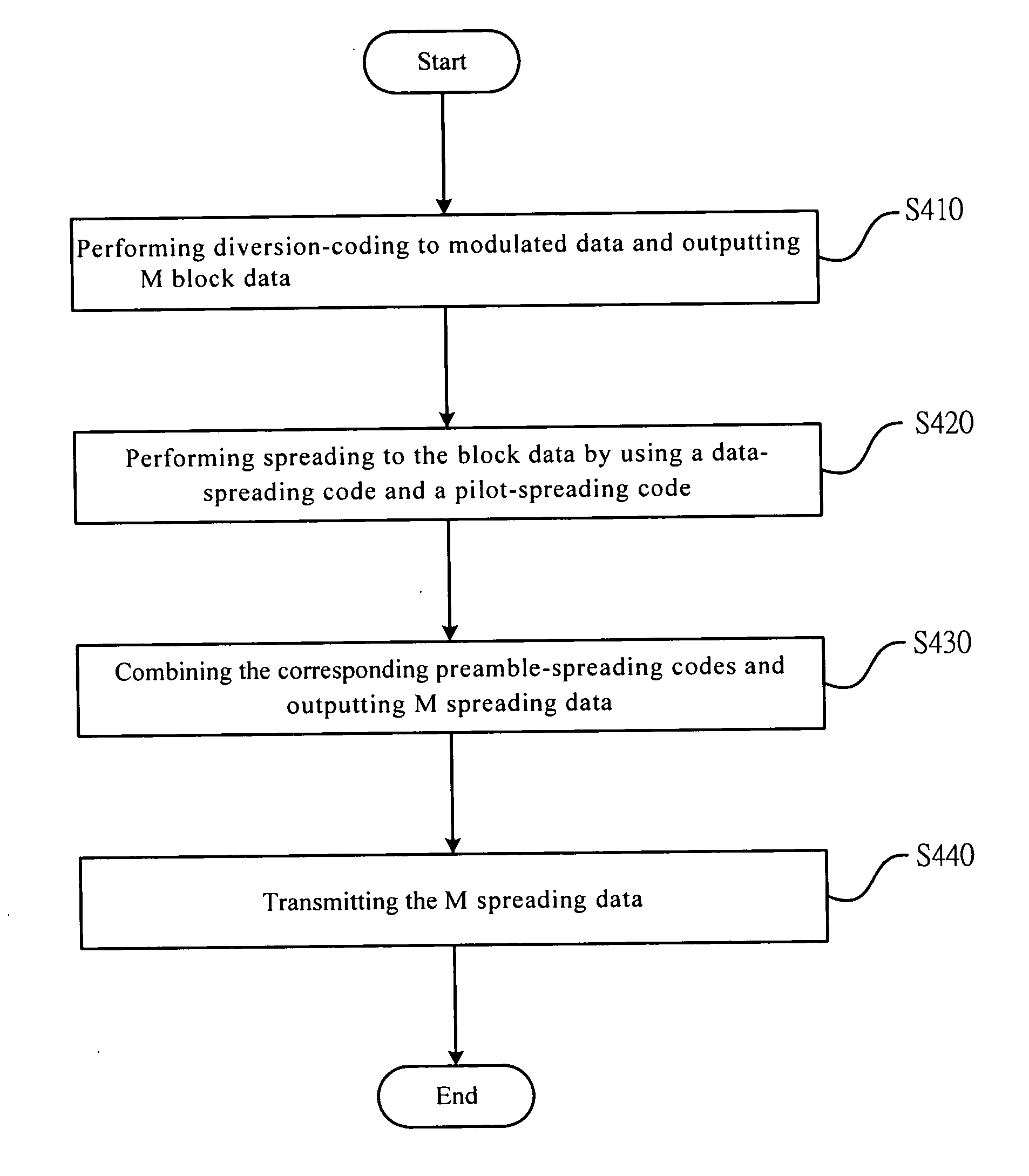

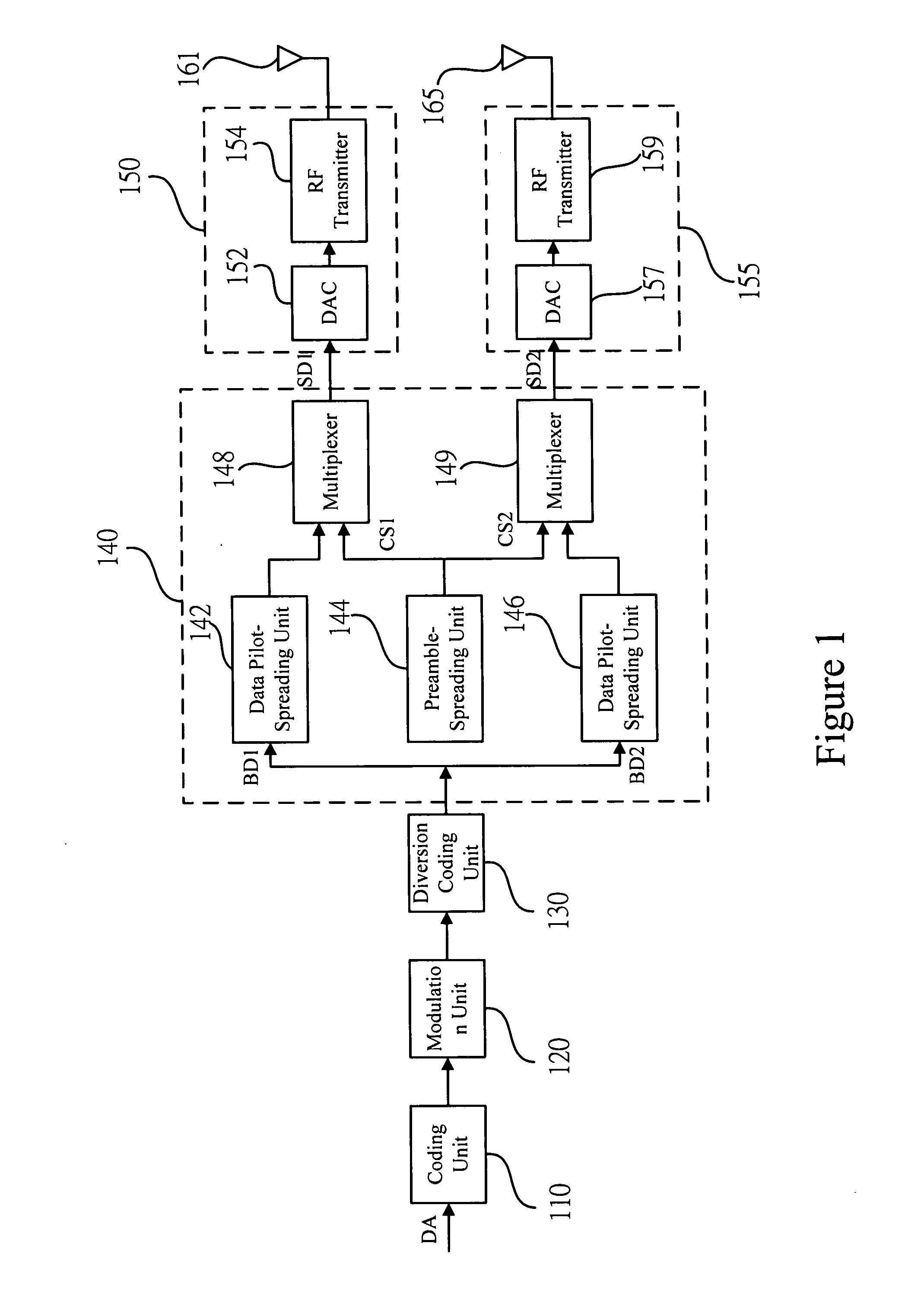

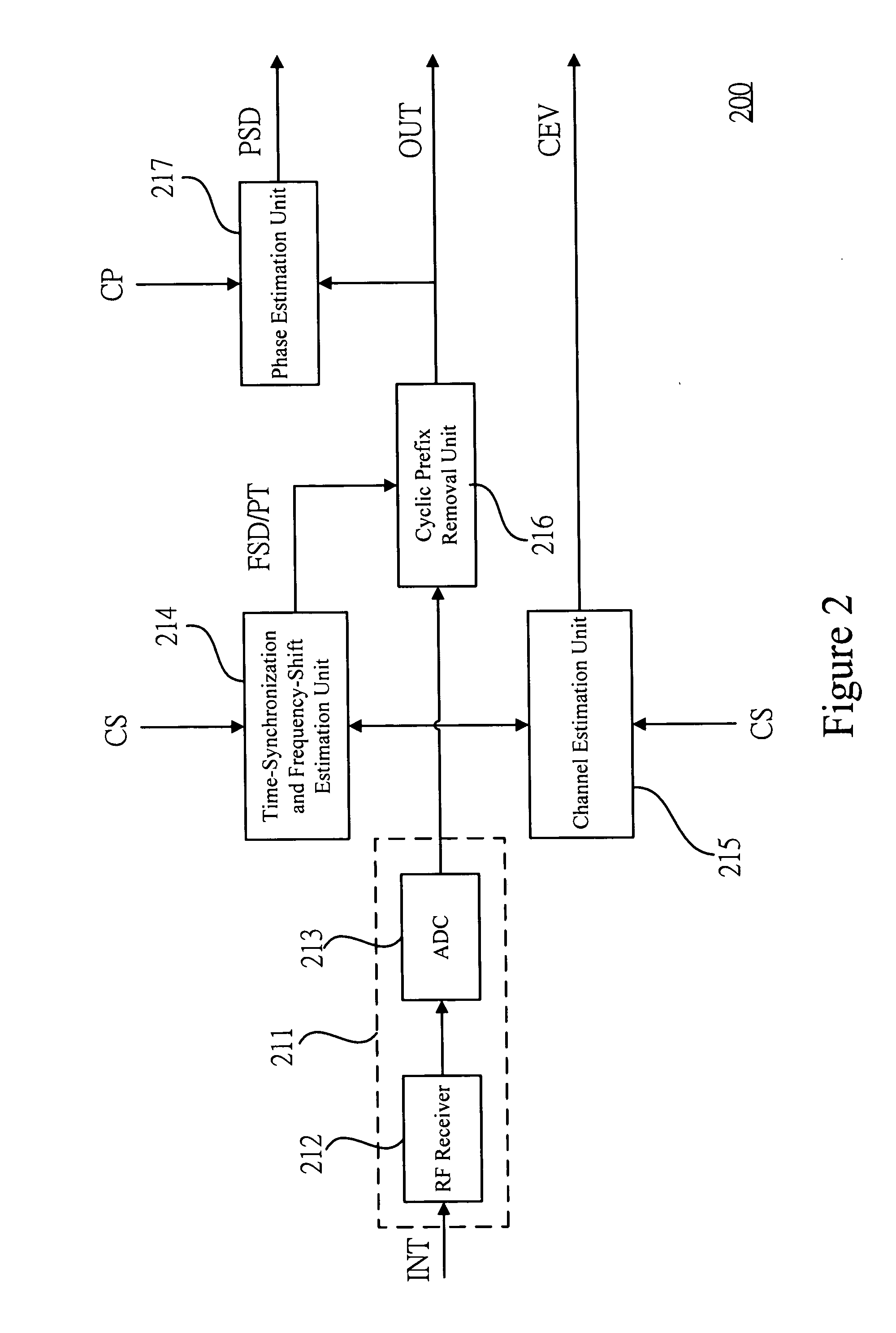

MIMO-CDMA apparatus and the coding/decoding method thereof

InactiveUS20070133659A1Reduce output signalEnhanced signalMultiplex communicationDiversity/multi-antenna systemsDecoding methodsCode division multiple access

A Multiple-Output Multiple-Input Code-Division Multiple Access (MIMO-CDMA) apparatus and the coding method thereof. The apparatus includes a transmitter side and receiver side. Both of the transmitter side and the receiver side have a plurality of antennas for achieving the effect of multi-path transmission and receiving. In addition, at the receiver side, use preamble-spreading codes and space-time block coding technology to eliminate multi-path signal interference as well as to modify carrier frequency shift of the received signal.

Owner:NAT CHUNG SHAN INST SCI & TECH

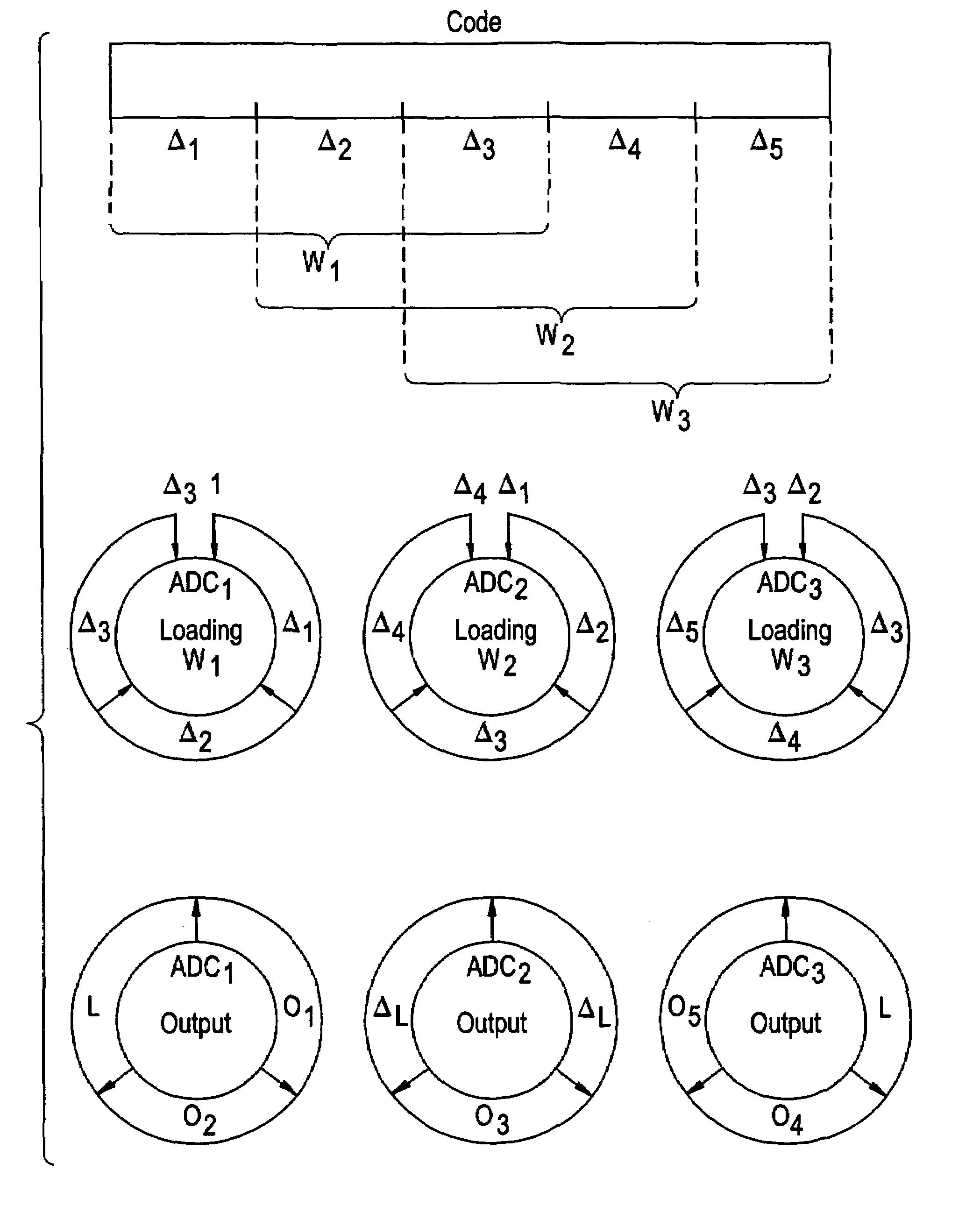

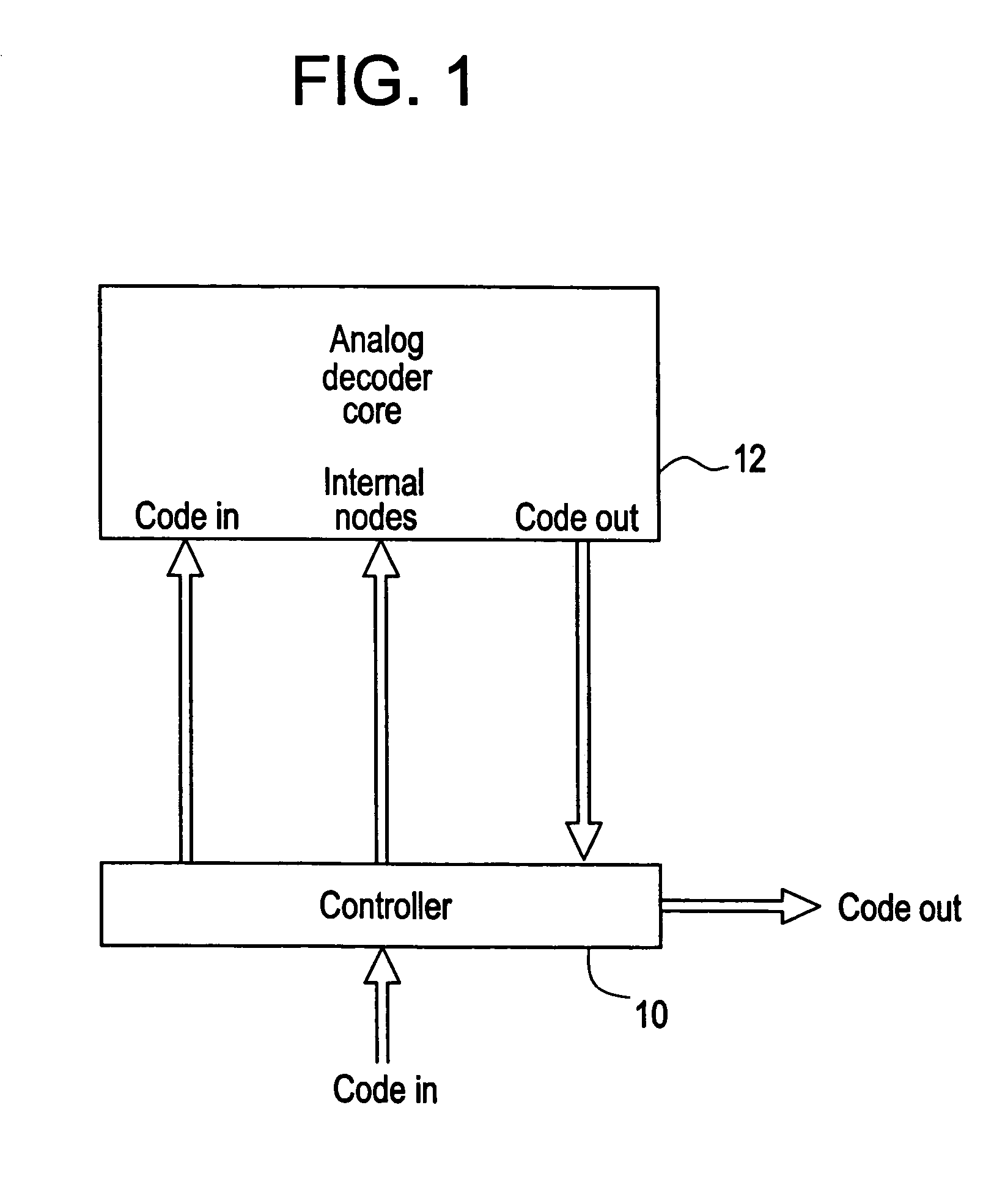

Analog decoding method and decoder

ActiveUS7071846B2Reduce circuit complexityAnalogue/digital conversionElectric signal transmission systemsDecoding methodsComputer hardware

Owner:PIECE FUTURE PTE LTD