Patents

Literature

627 results about "Serializer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Serializer.net was a webcomic subscription service and artist collective published by Joey Manley and edited by Tom Hart and Eric Millikin that existed from 2002 to 2013. Designed to showcase artistic alternative webcomics using the unique nature of the medium, the works on Serializer.net were described by critics as "high art" and "avant-garde". The project became mostly inactive in 2007 and closed alongside Manley's other websites in 2013.

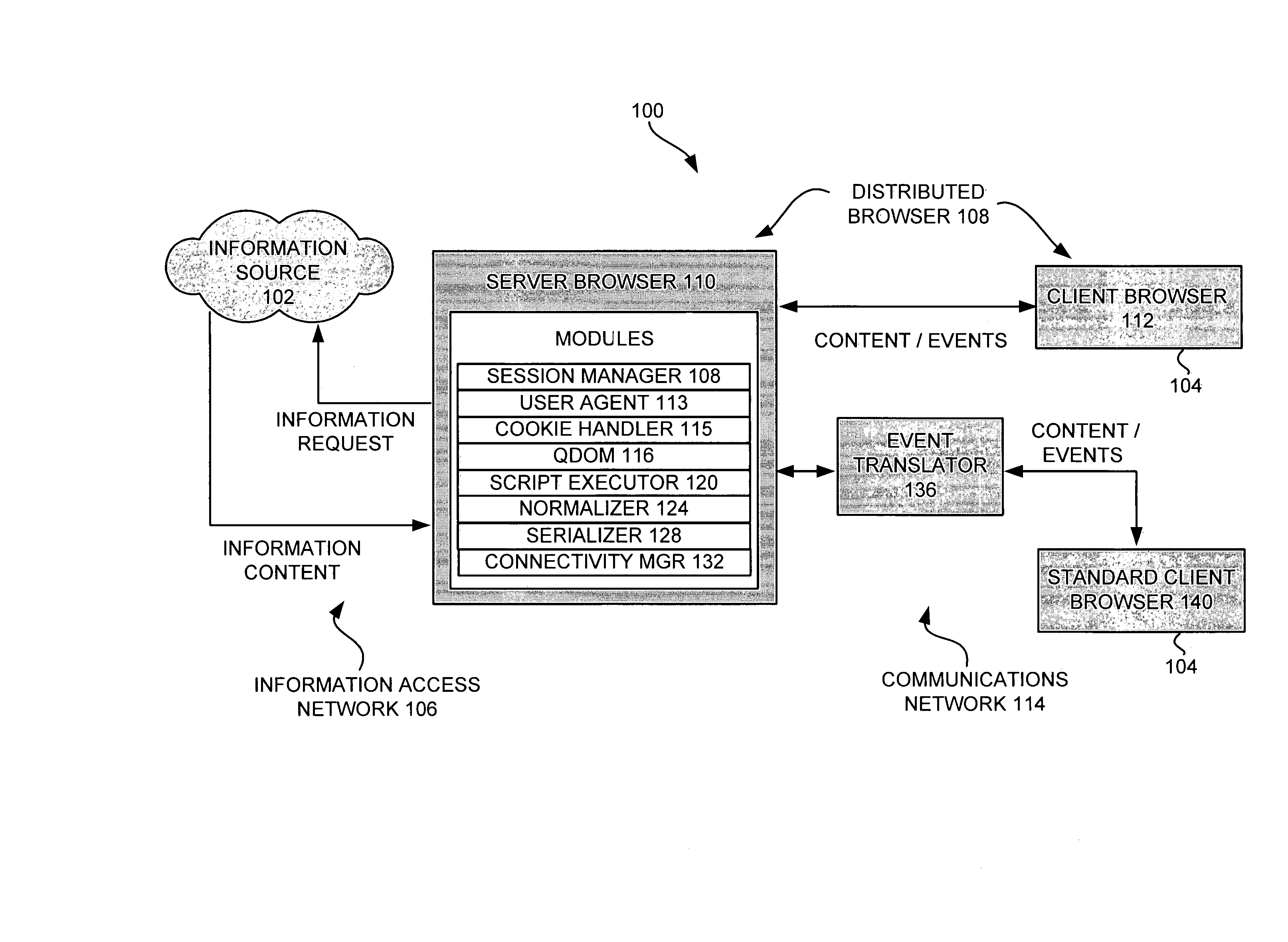

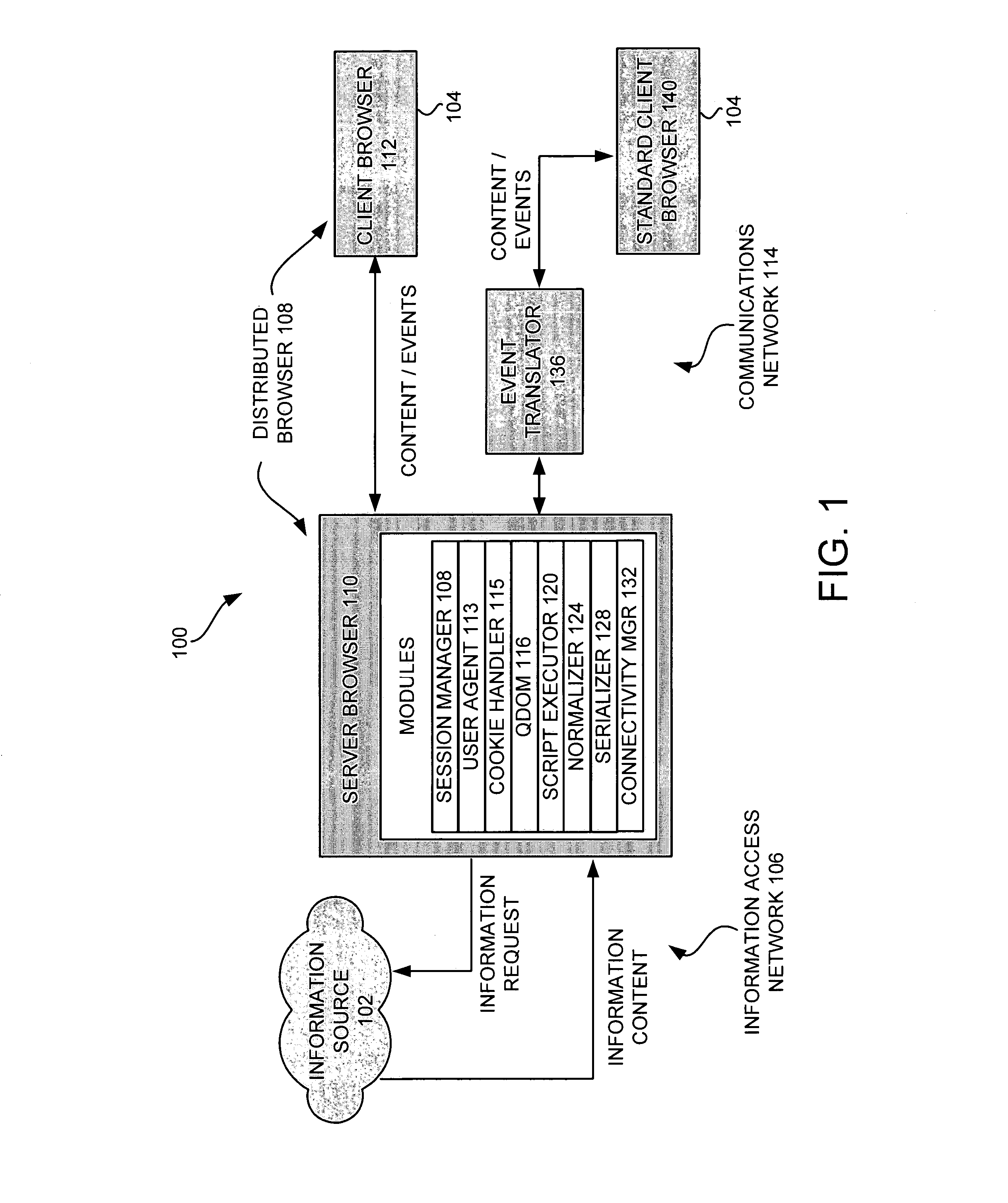

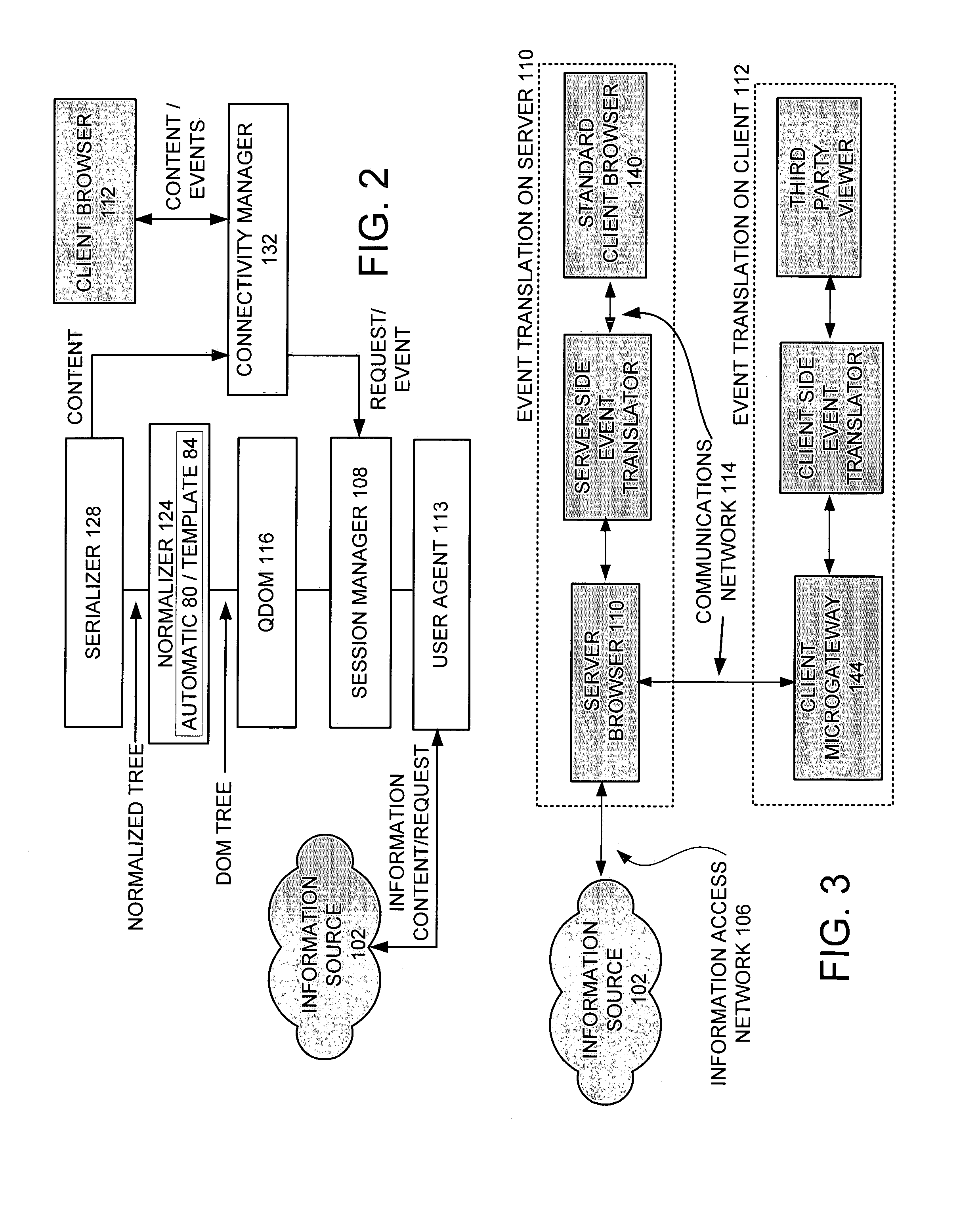

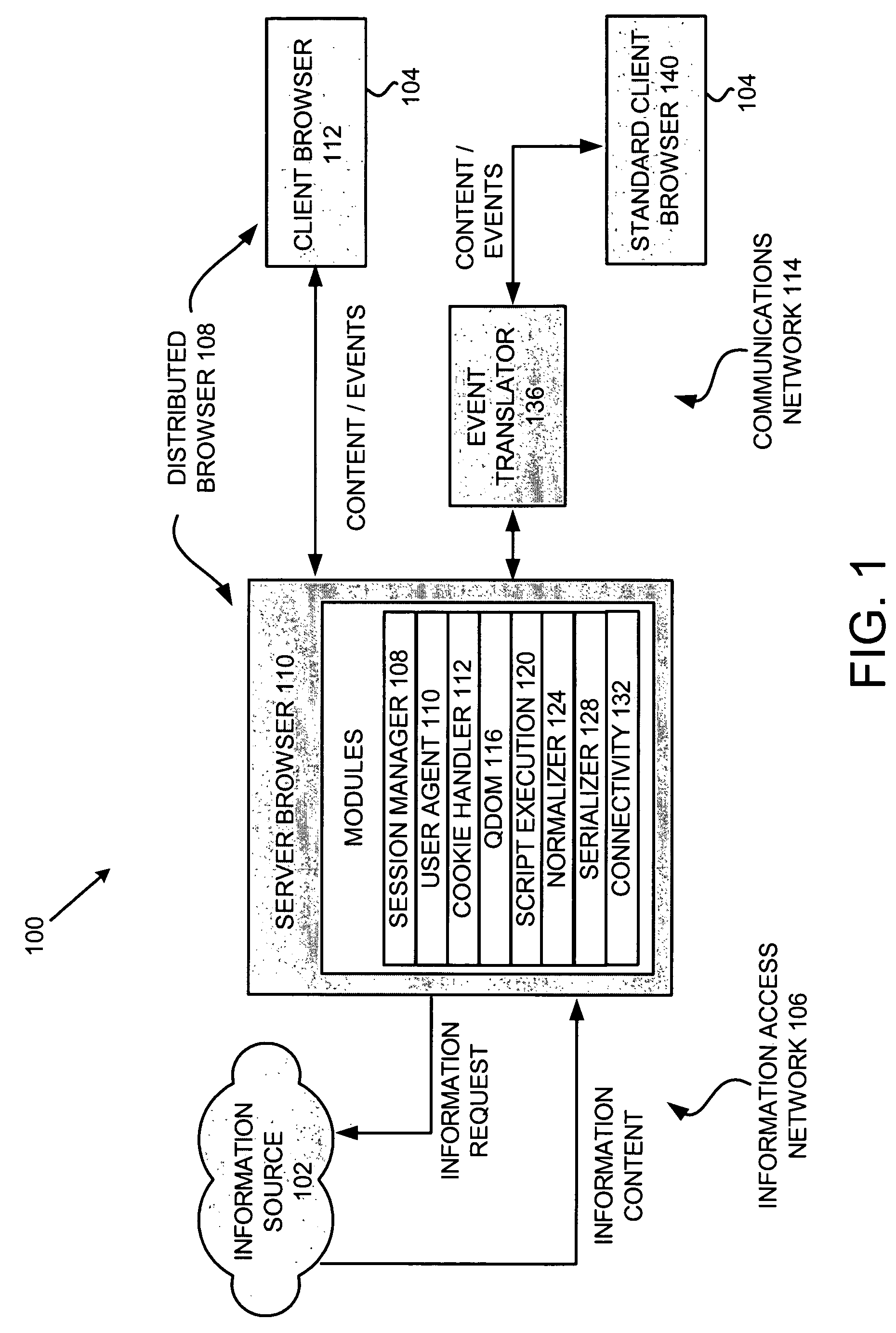

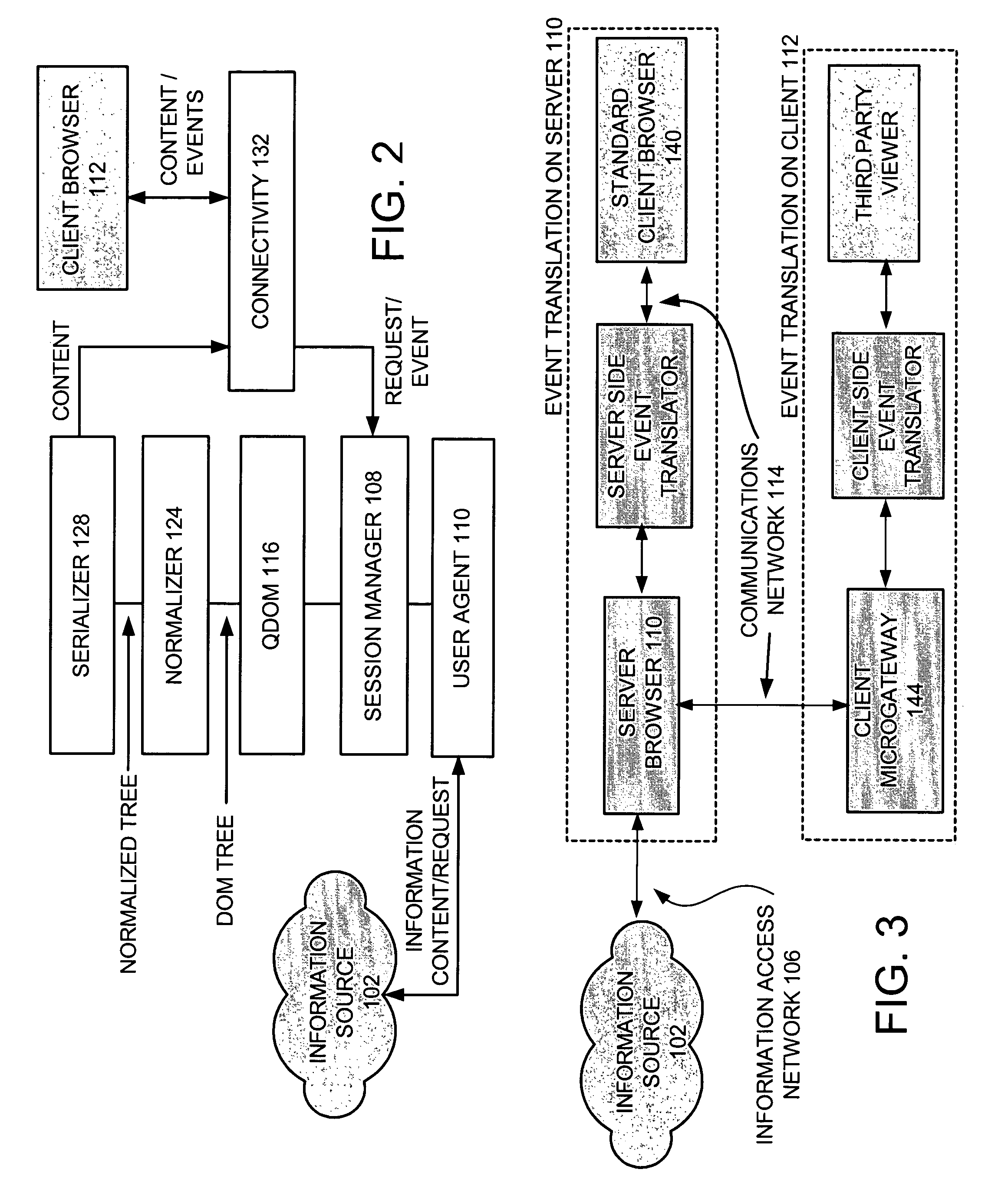

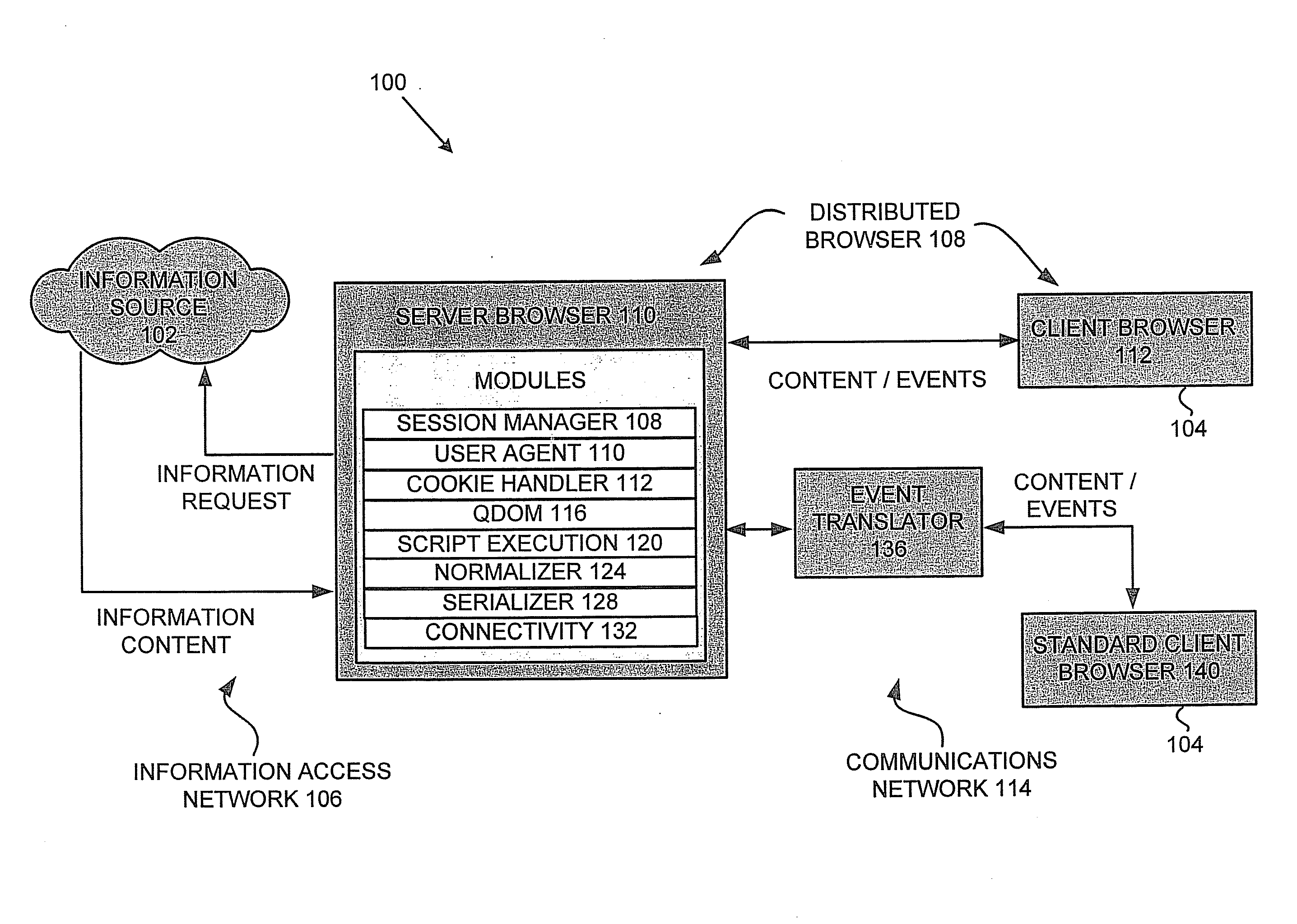

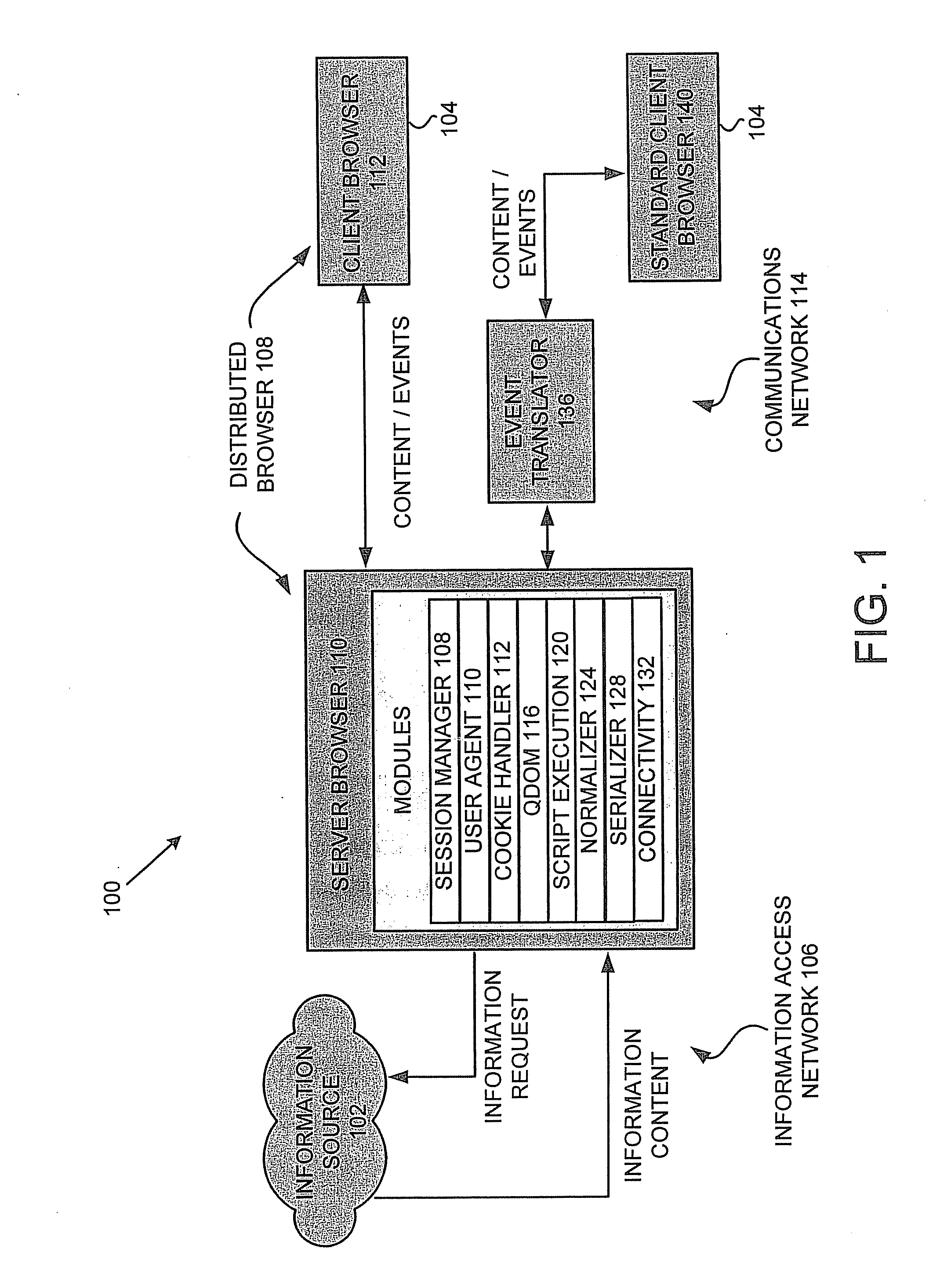

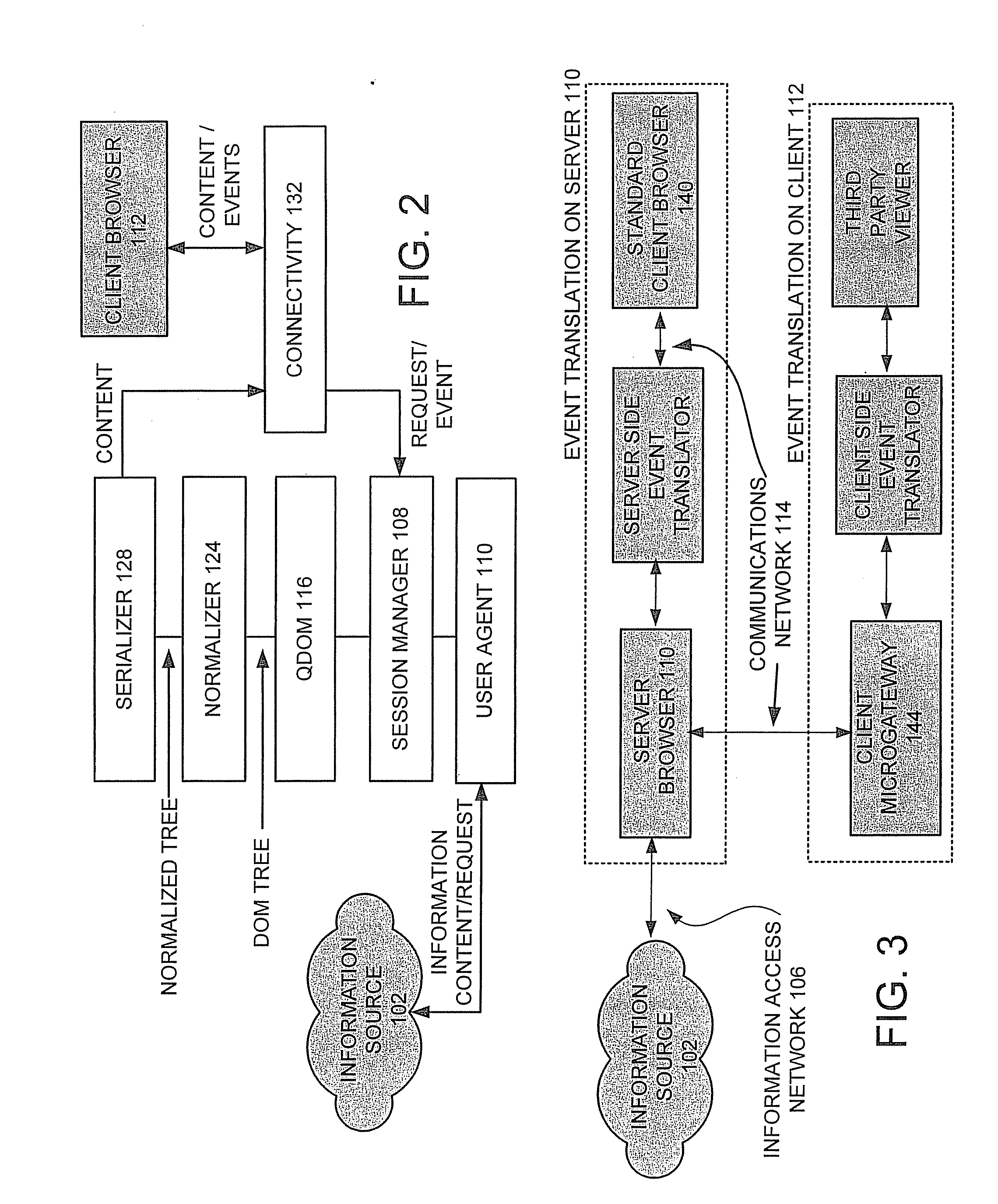

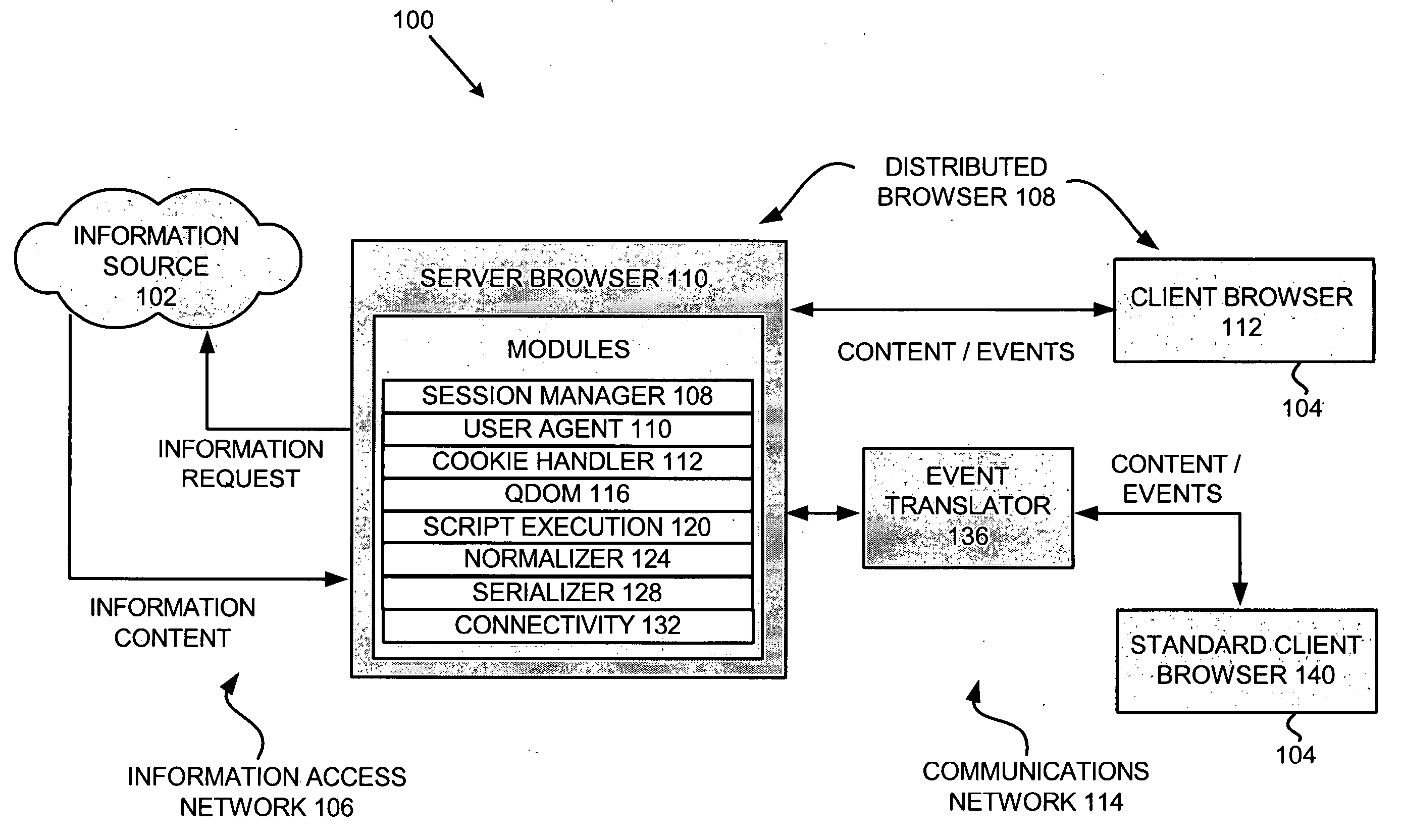

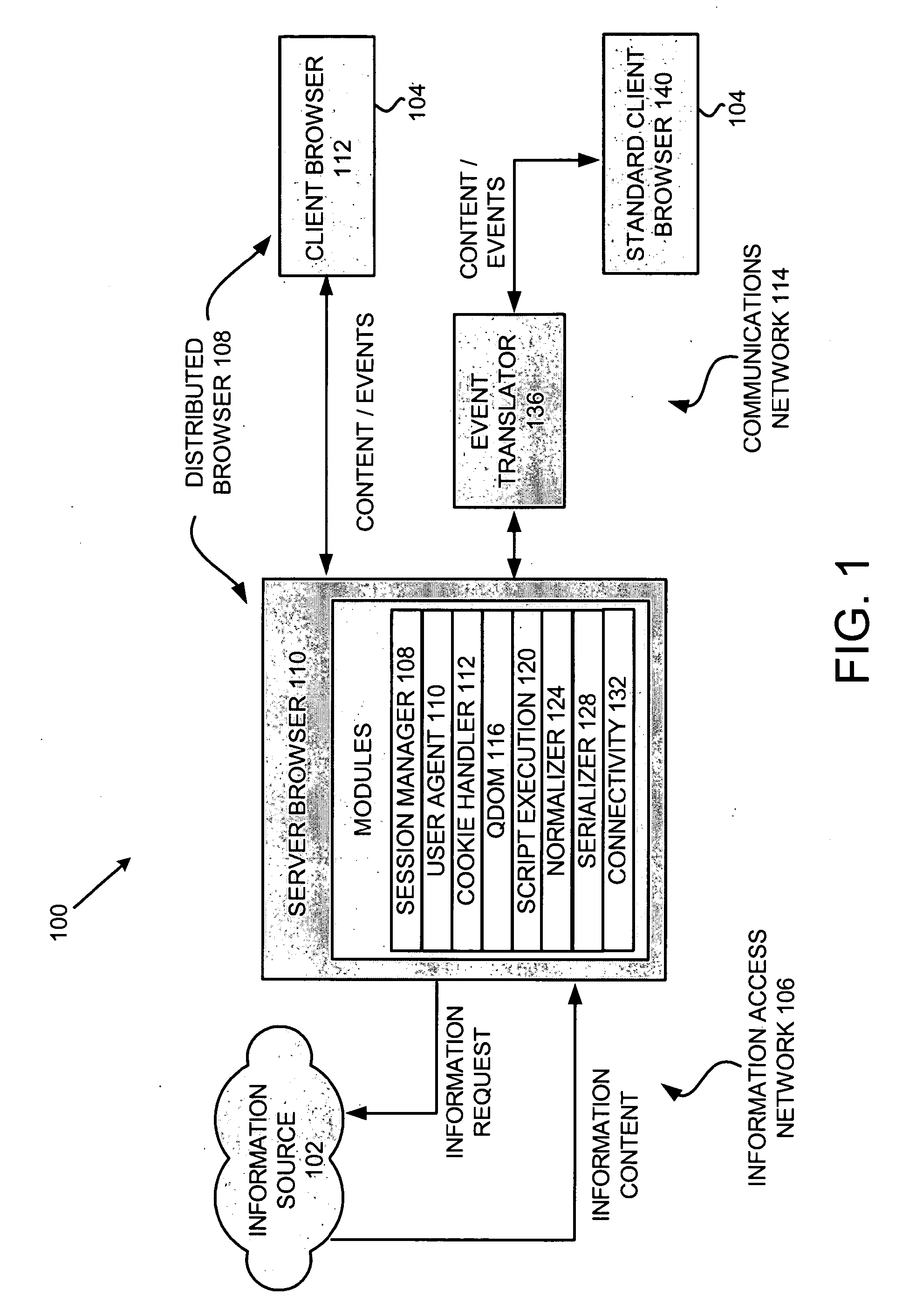

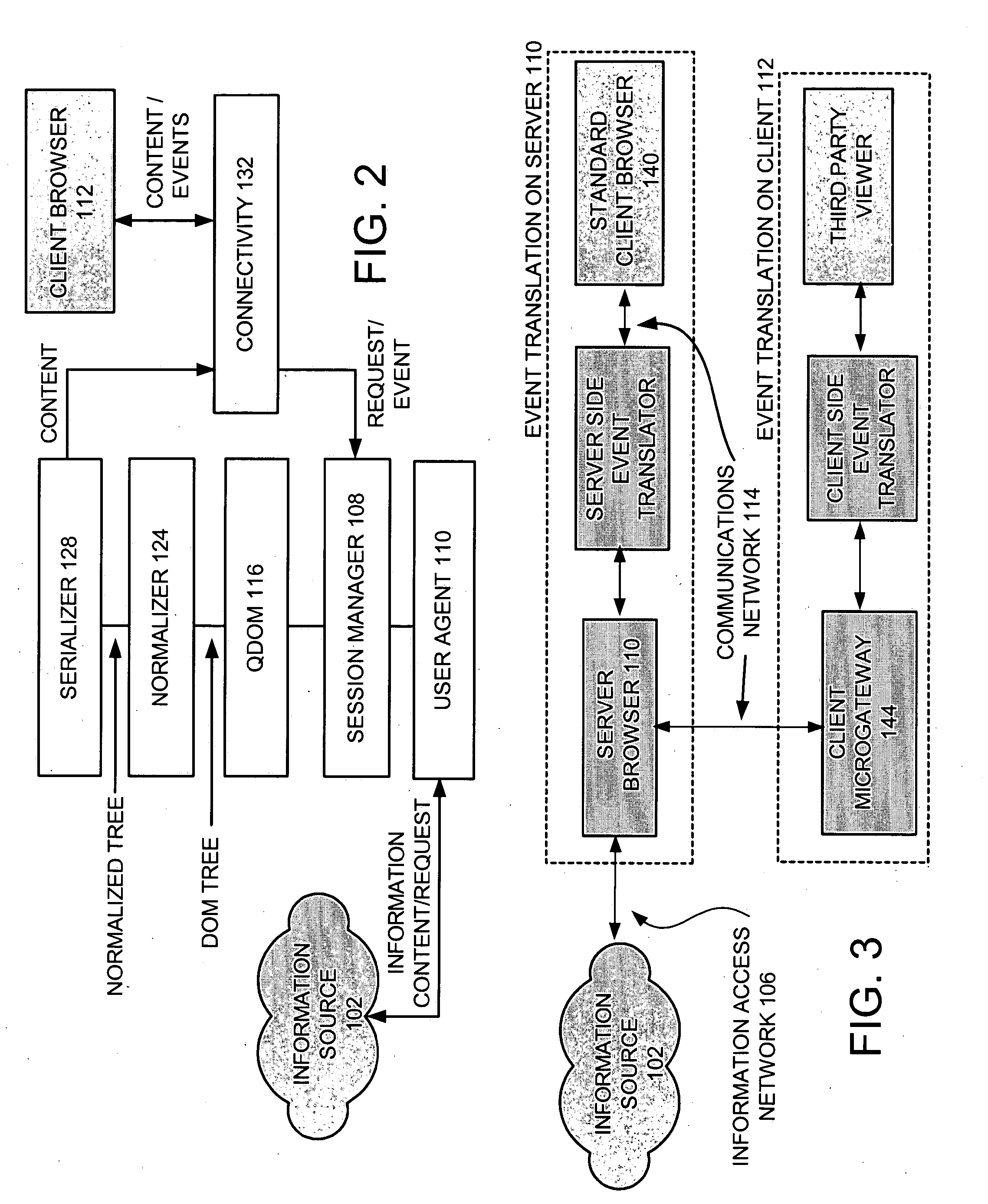

System and method for accessing customized information over the internet using a browser for a plurality of electronic devices

InactiveUS7072984B1High CPU powerLarge displayDigital data information retrievalMultiple digital computer combinationsComputer compatibilityClient-side

A system and method is provided for enabling an electronic device to efficiently access information content. A server browser accesses the information content over a network. The accessed information content is retrieved and adapted for presentation for the electronic device. A serializer dynamically formats the adapted information content according to a client browser. The client browser receives and presents the information content on the electronic device. An event translator is included to provide additional compatibility with commercially available client browsers.

Owner:RPX CORP

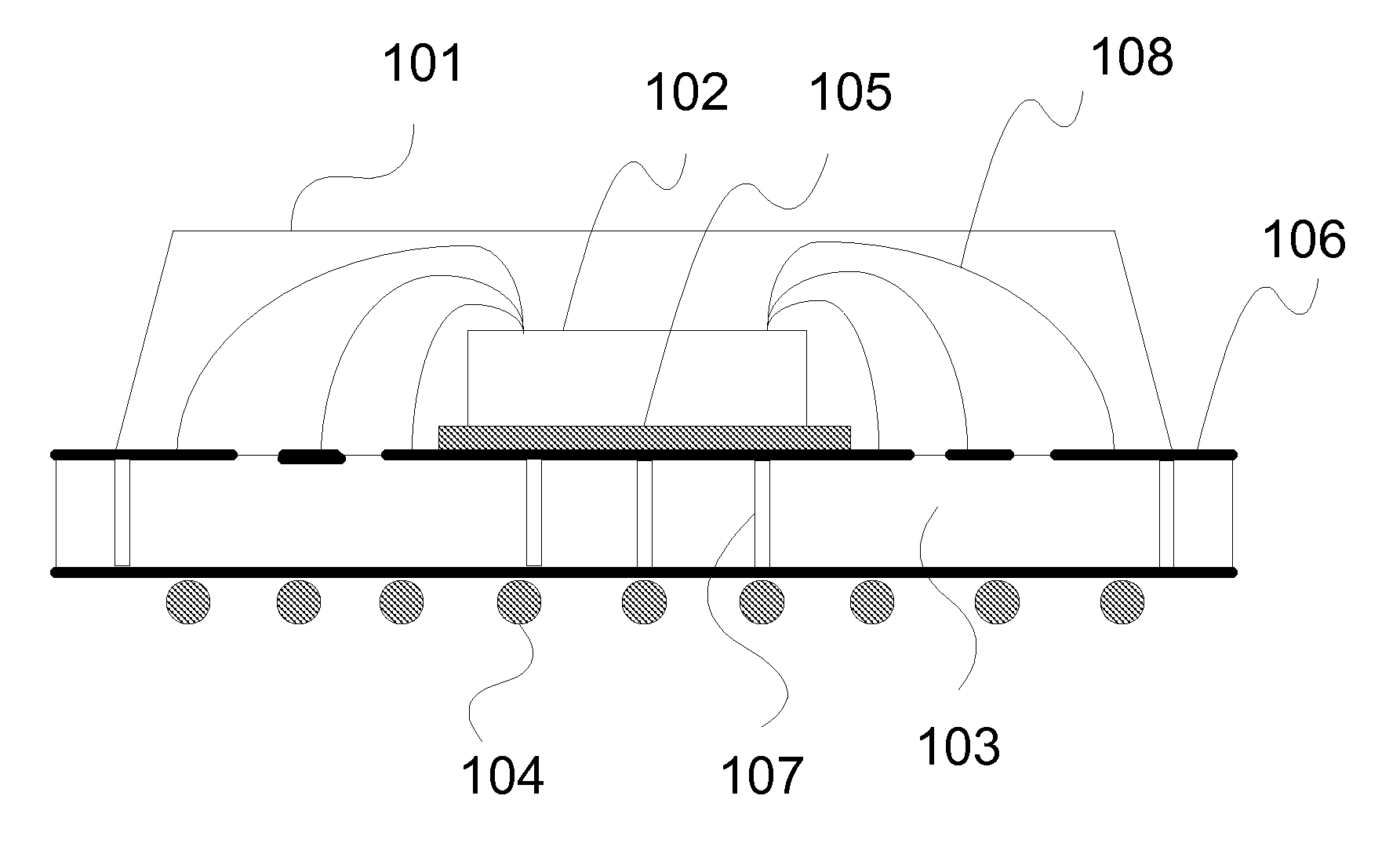

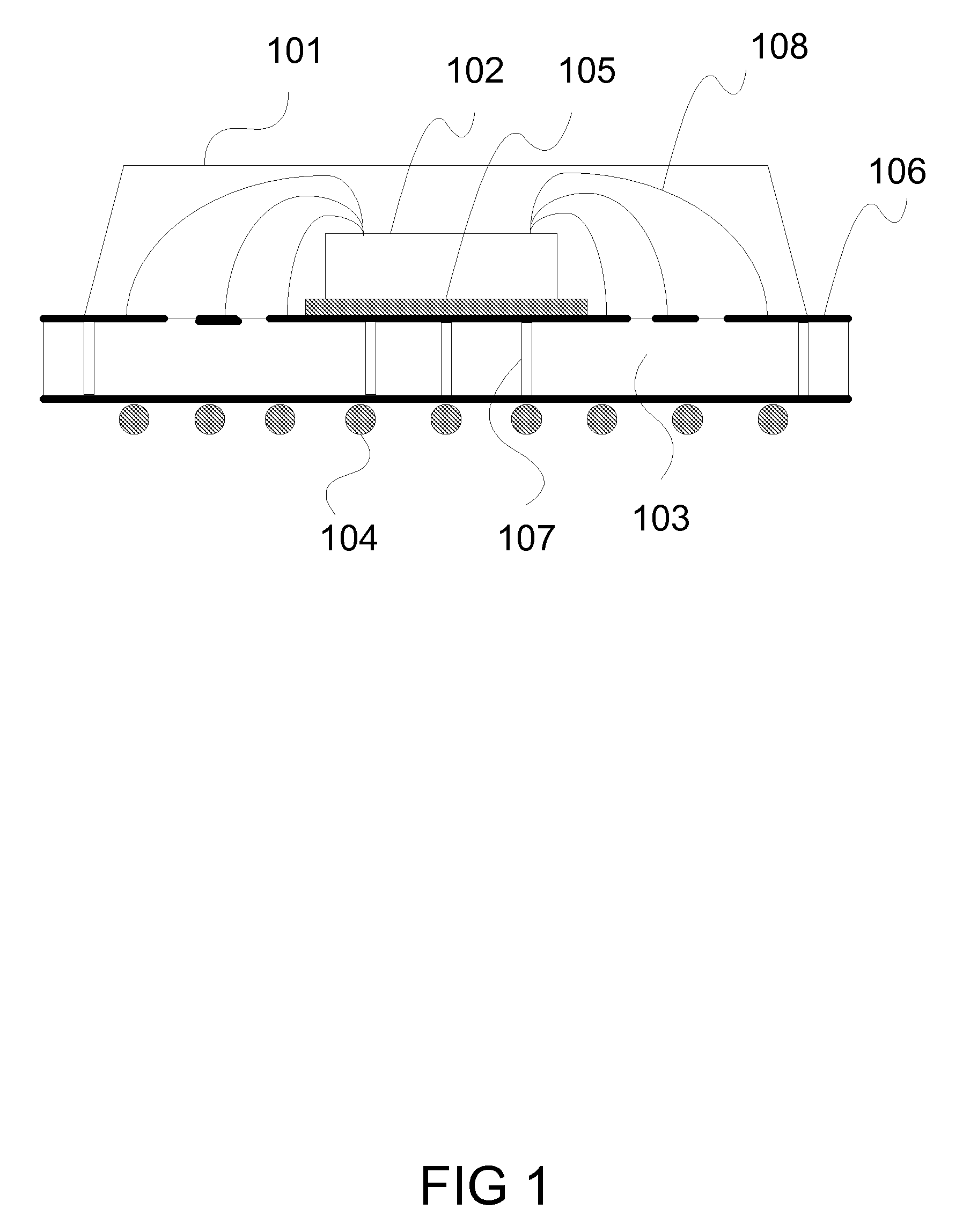

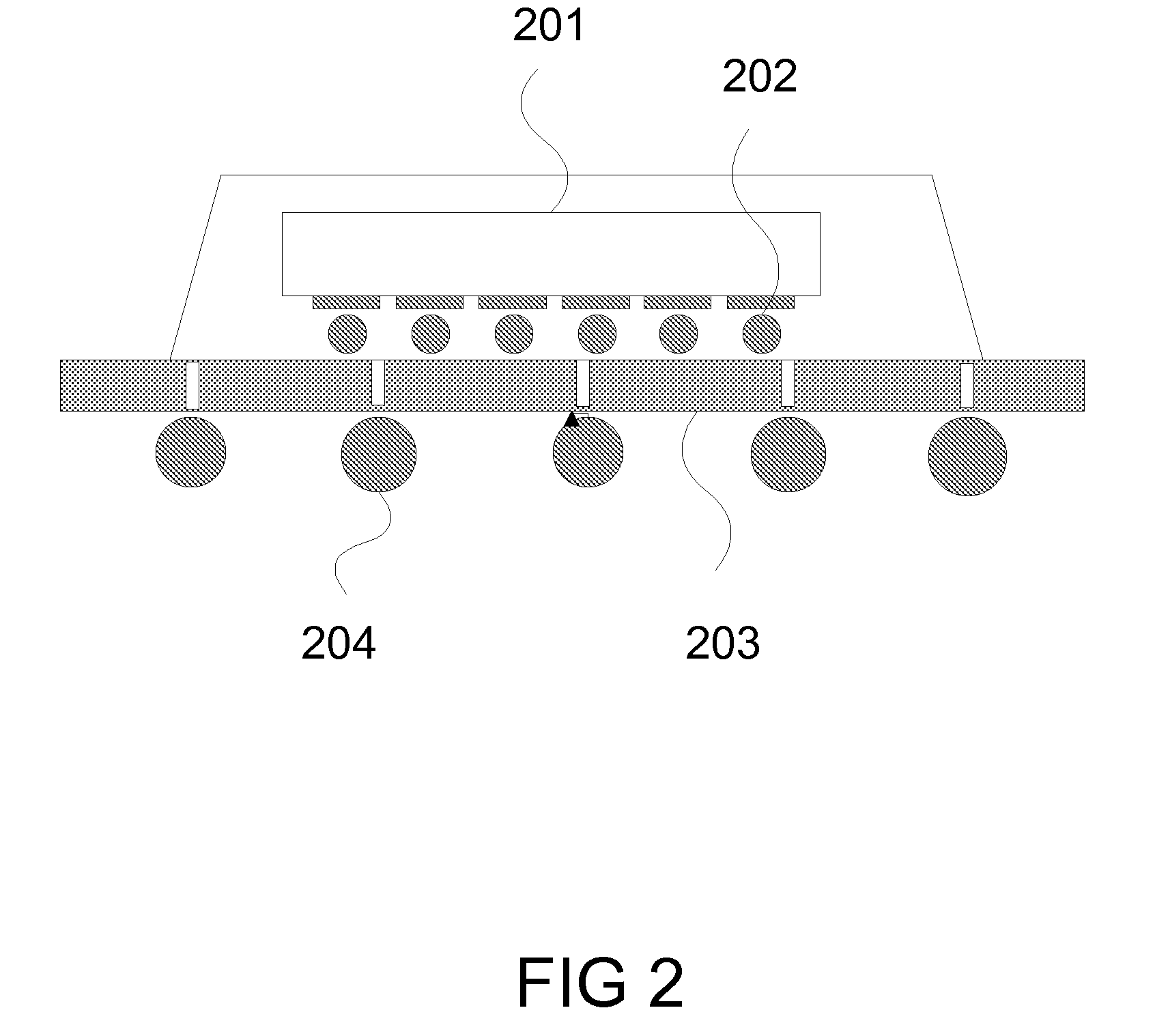

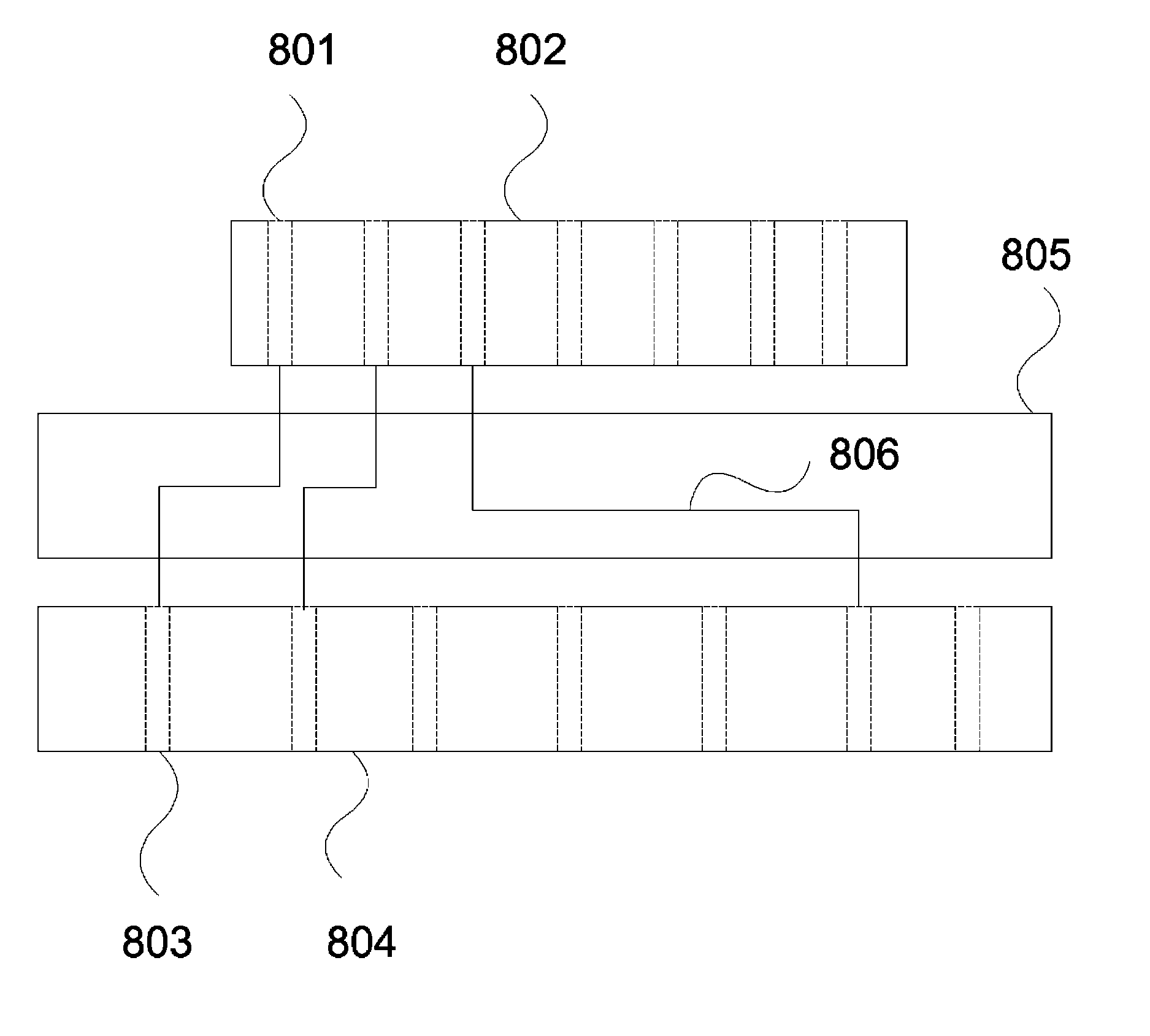

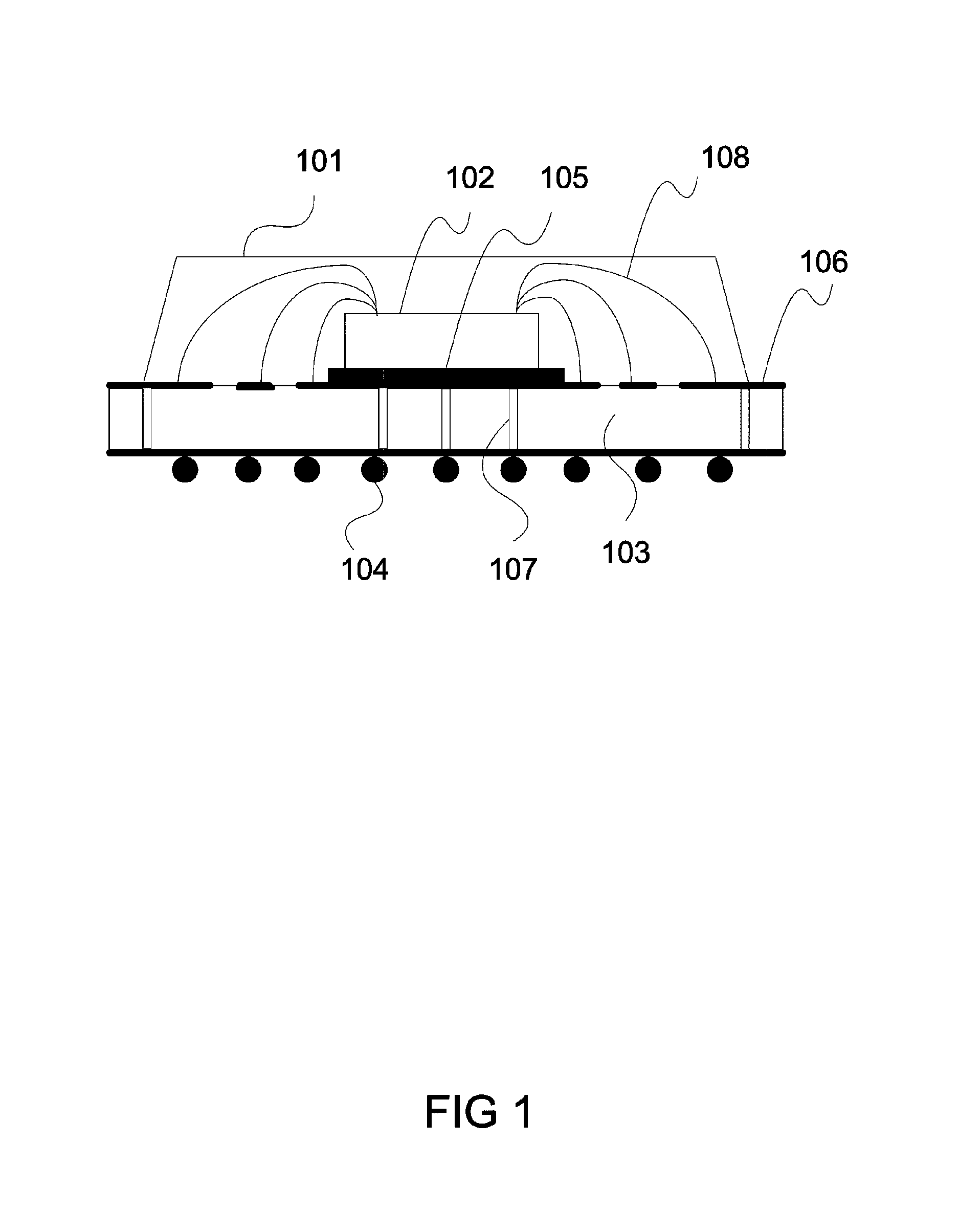

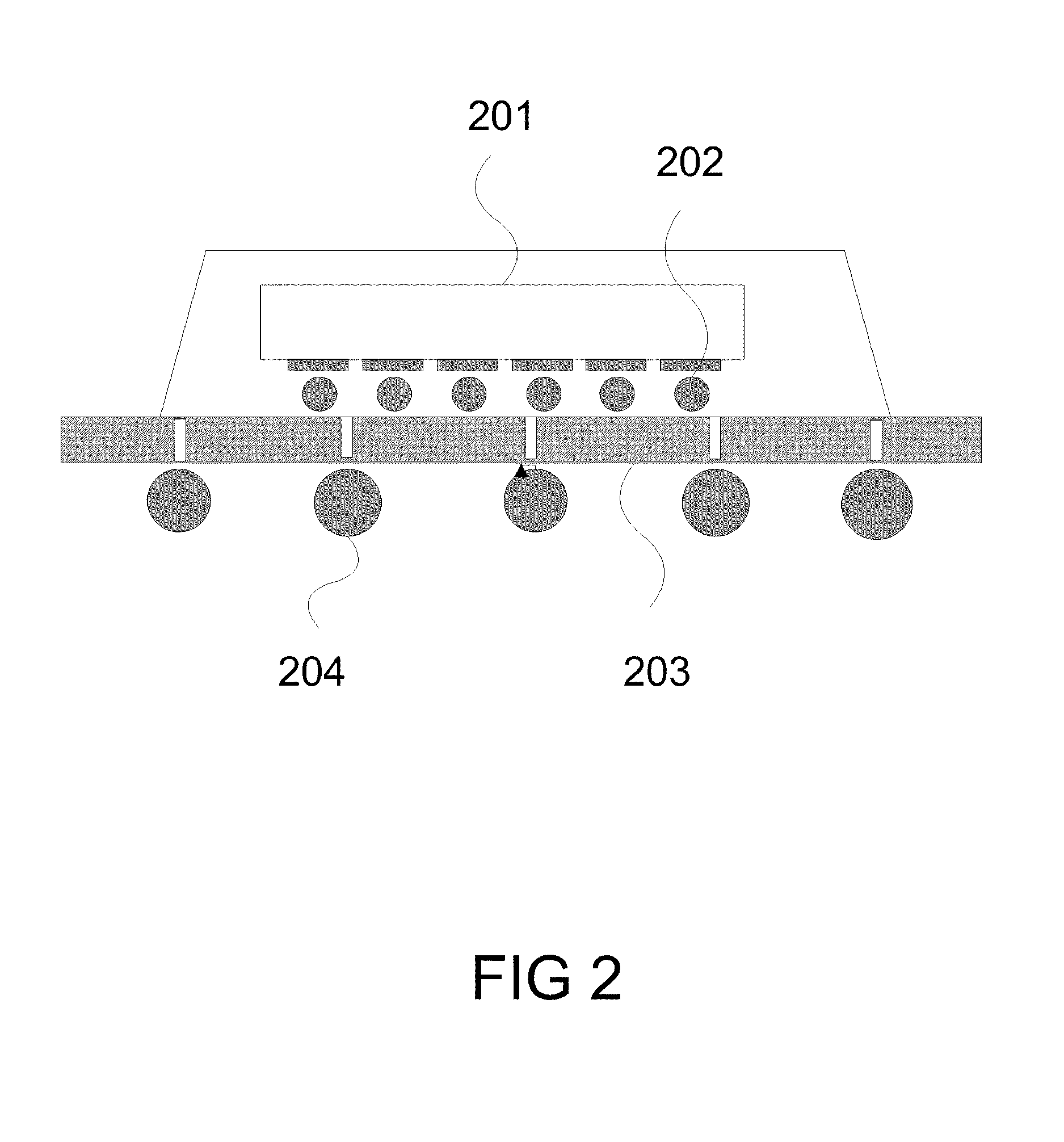

Stacking Integrated Circuits containing Serializer and Deserializer Blocks using Through Silicon Via

ActiveUS20100058580A1Reduce and eliminate inductanceReduce and eliminate and capacitancePrinted circuit assemblingSemiconductor/solid-state device detailsThrough-silicon viaIntegrated circuit

Methods and systems for stacking multiple chips with high speed serialiser / deserialiser blocks are presented. These methods make use of Through Silicon Via (TSV) to connect the dice to each other, and to the external pads. The methods enable efficient multilayer stacking that simplifies design and manufacturing, and at the same time, ensure high speed operation of serialiser / deserialiser blocks, using the TSVs.

Owner:BROADPAK CORP

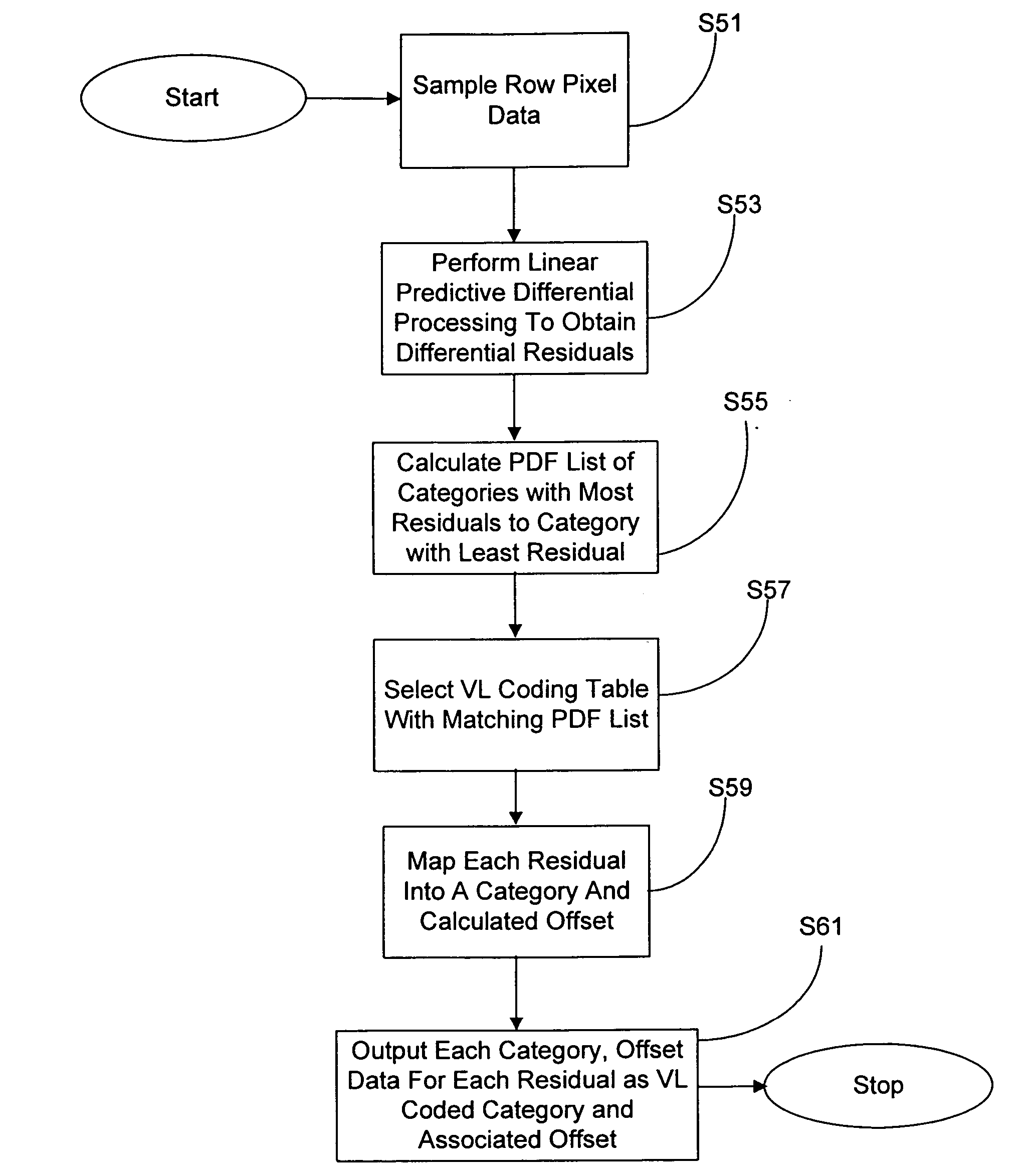

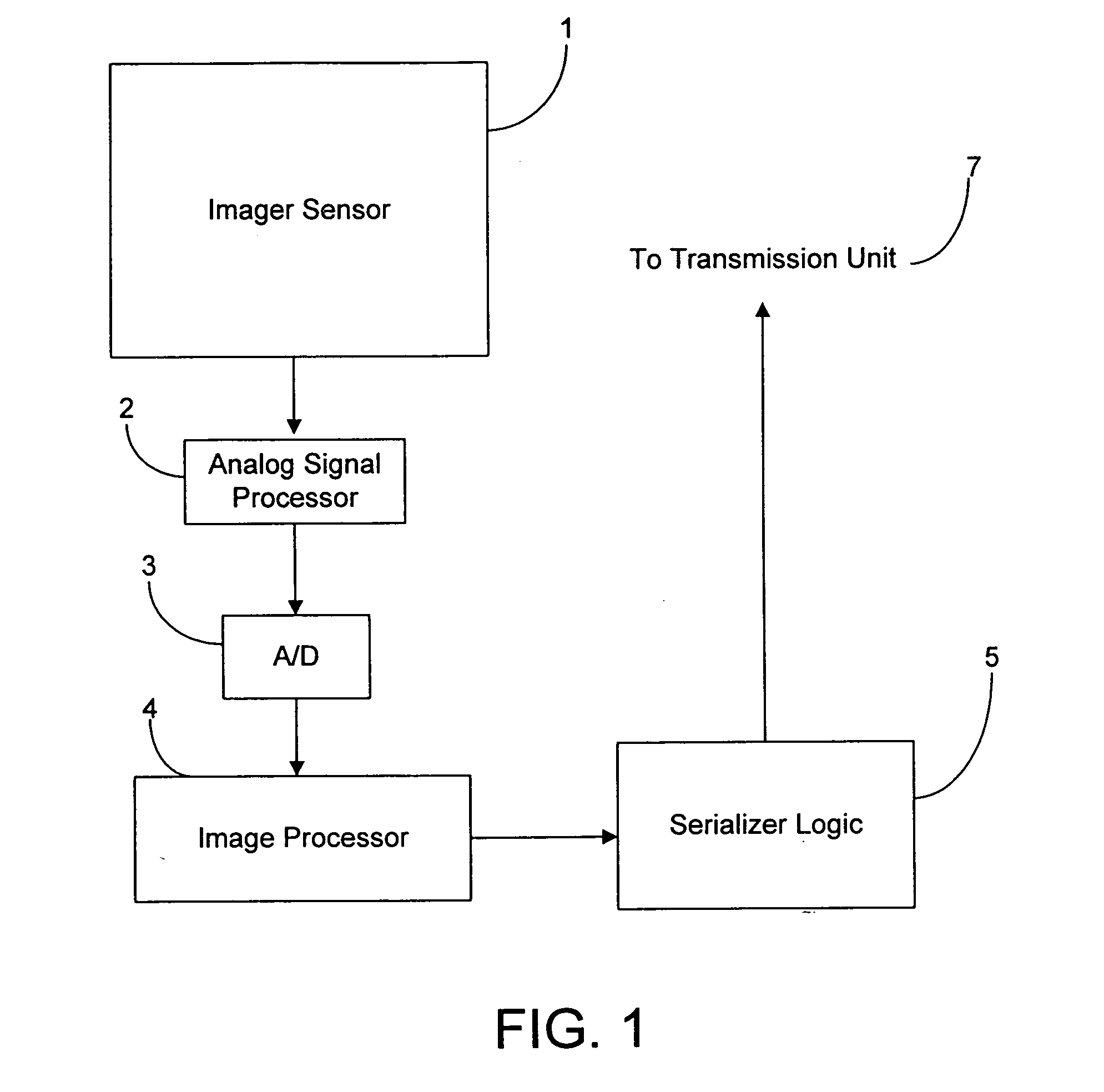

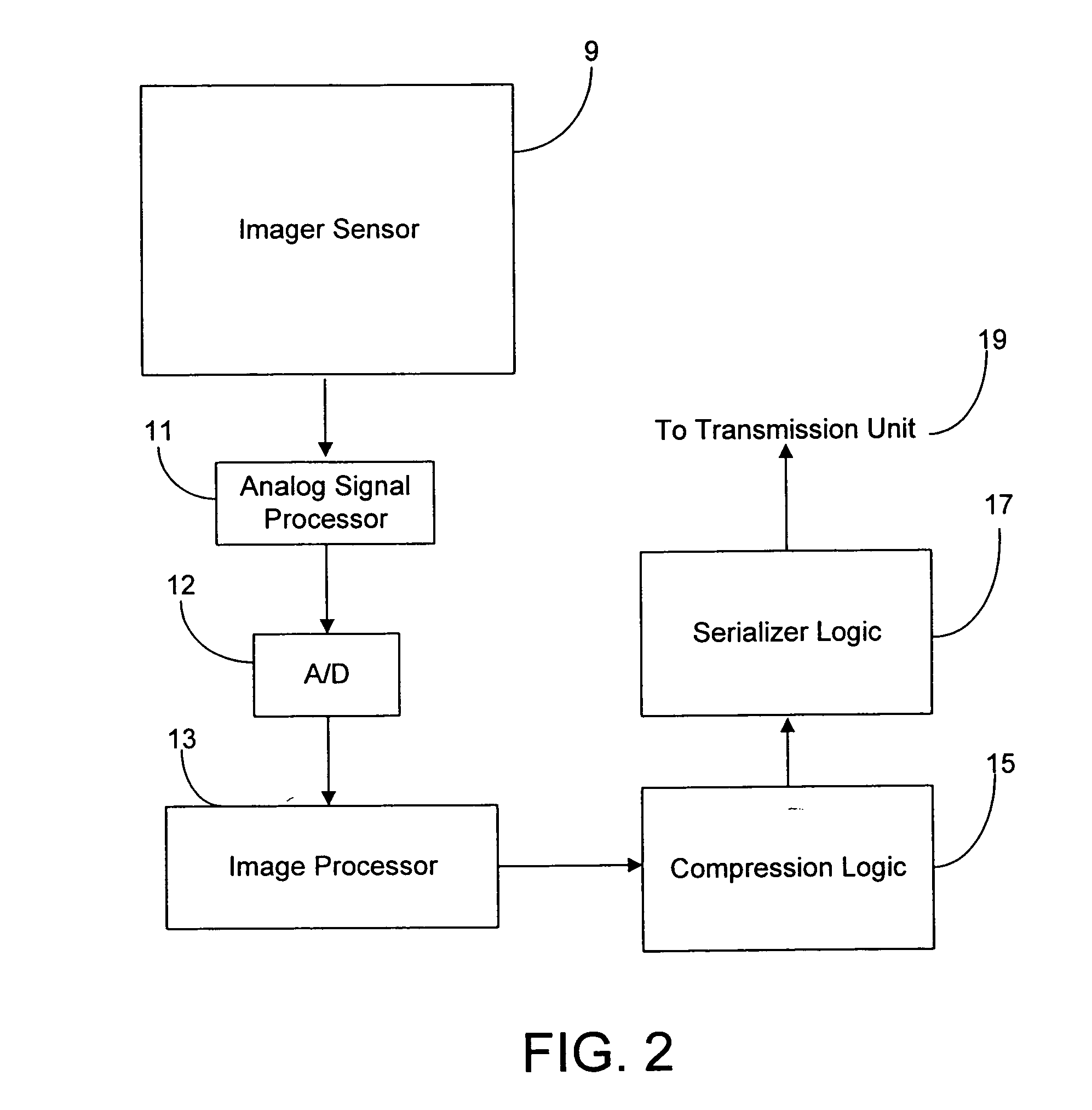

Compression system for integrated sensor devices

ActiveUS20070127831A1Image compression can be improvedReduce variationCharacter and pattern recognitionTelevision systemsAdaptive compressionVariable length

An imaging system incorporating adaptive compression which includes determining linear predictive differential residuals from an imager array pixel row. The differential residuals are classified into categories, each category having a range of differential residuals associated with it. The categories are analyzed to produce an ordered list having categories with most to least frequent residuals falling within a respective residual range associated with a respective category. The ordered list is then used to select a variable length encoding table with a matching ordered list. Variable length encoded category and range position offset data is output to a serializer unit, where the range position offset refers to a position in a range associated with a particular category.

Owner:MICRON TECH INC

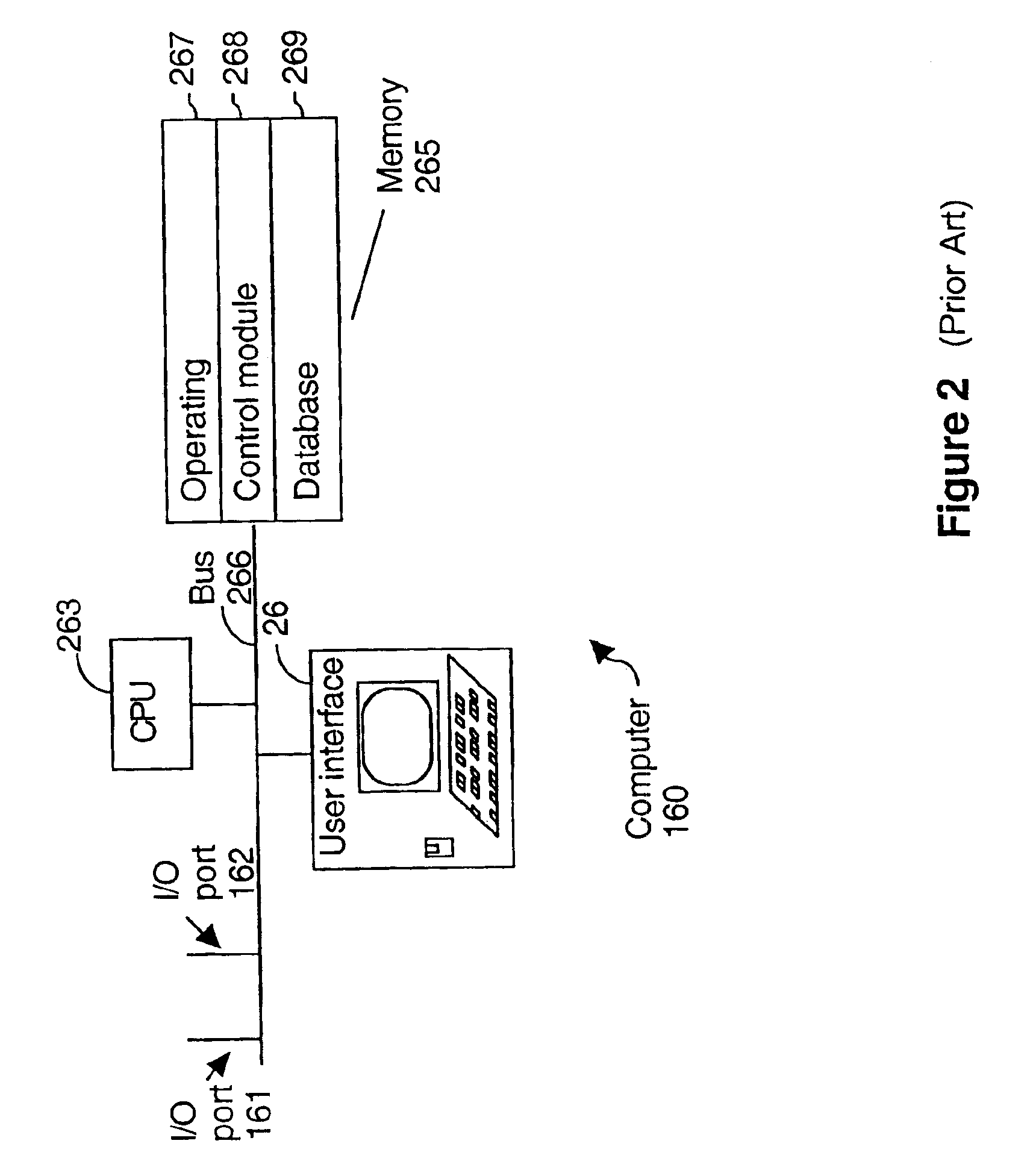

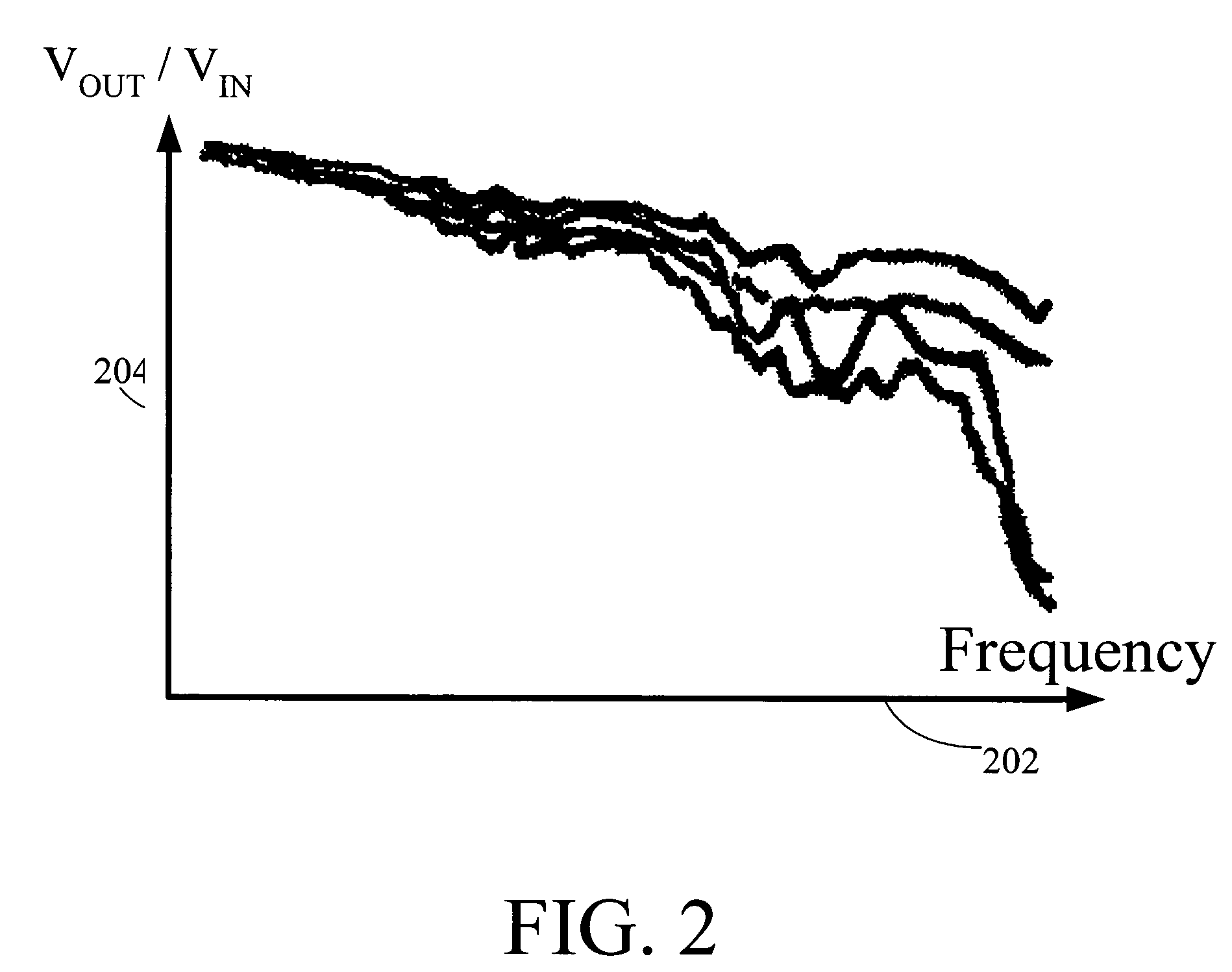

Statistically-Adapted Receiver and Transmitter Equalization

InactiveUS20100329325A1High error rateReduce error rateMultiple-port networksDelay line applicationsTraining periodData integrity

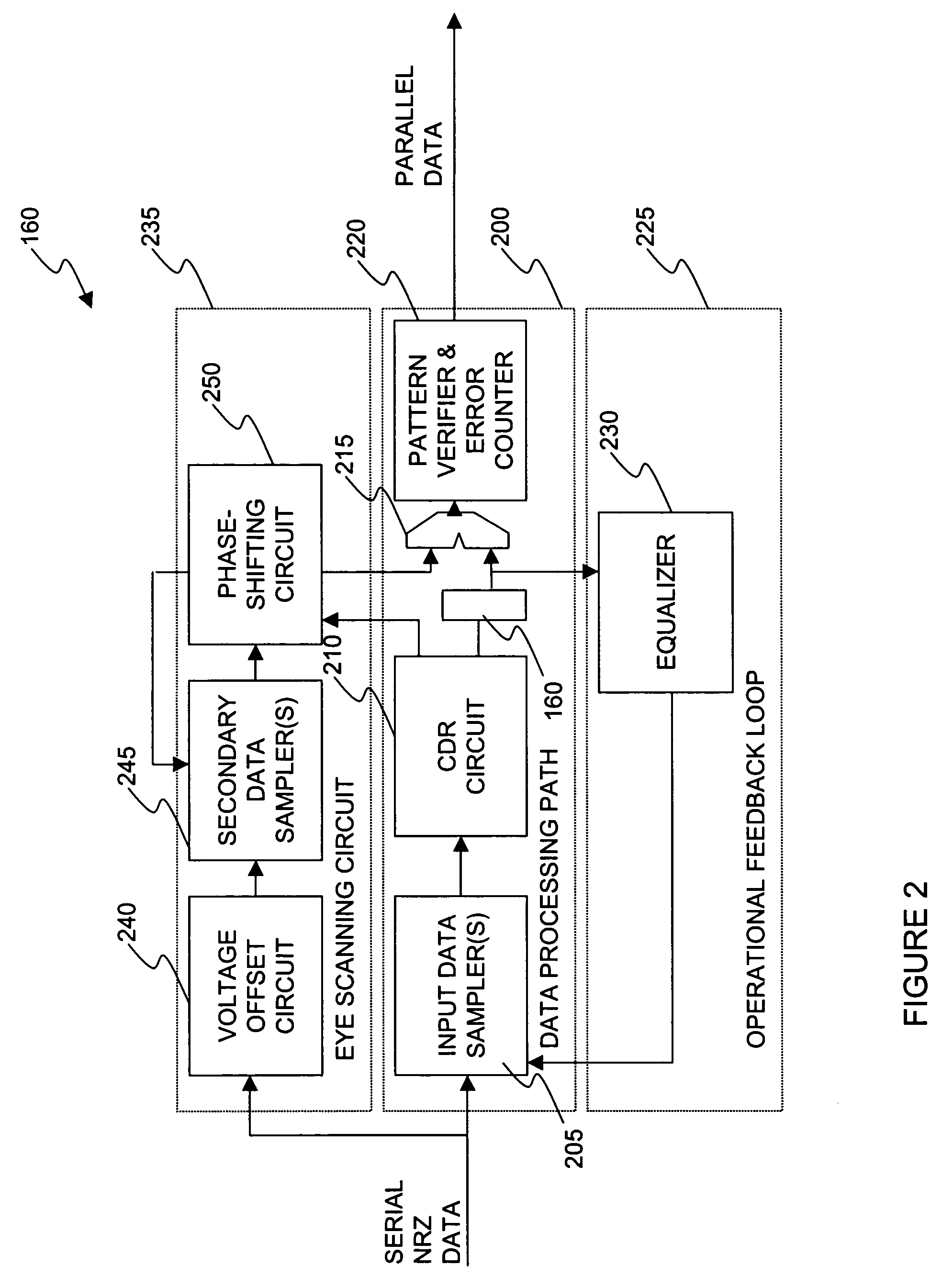

In described embodiments, adaptive equalization of a signal in, for example, Serializer / De-serializer transceivers by a) monitoring a data eye in a data path with an eye detector for signal amplitude and / or transition; b) setting the equalizer response of at least one equalizer in the signal path while the signal is present for statistical calibration of the data eye; c) monitoring the data eye and setting the equalizer during periods in which received data is allowed to contain errors (such as link initiation and training periods) and periods in which receive data integrity is to be maintained (such as normal data communication).

Owner:LSI CORPORATION

Stacking integrated circuits containing serializer and deserializer blocks using through silicon via

ActiveUS8014166B2Efficiently routedReduce and eliminate and capacitanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringThrough-silicon via

Methods and systems for stacking multiple chips with high speed serialiser / deserialiser blocks are presented. These methods make use of Through Silicon Via (TSV) to connect the dice to each other, and to the external pads. The methods enable efficient multilayer stacking that simplifies design and manufacturing, and at the same time, ensure high speed operation of serialiser / deserialiser blocks, using the TSVs.

Owner:BROADPAK CORP

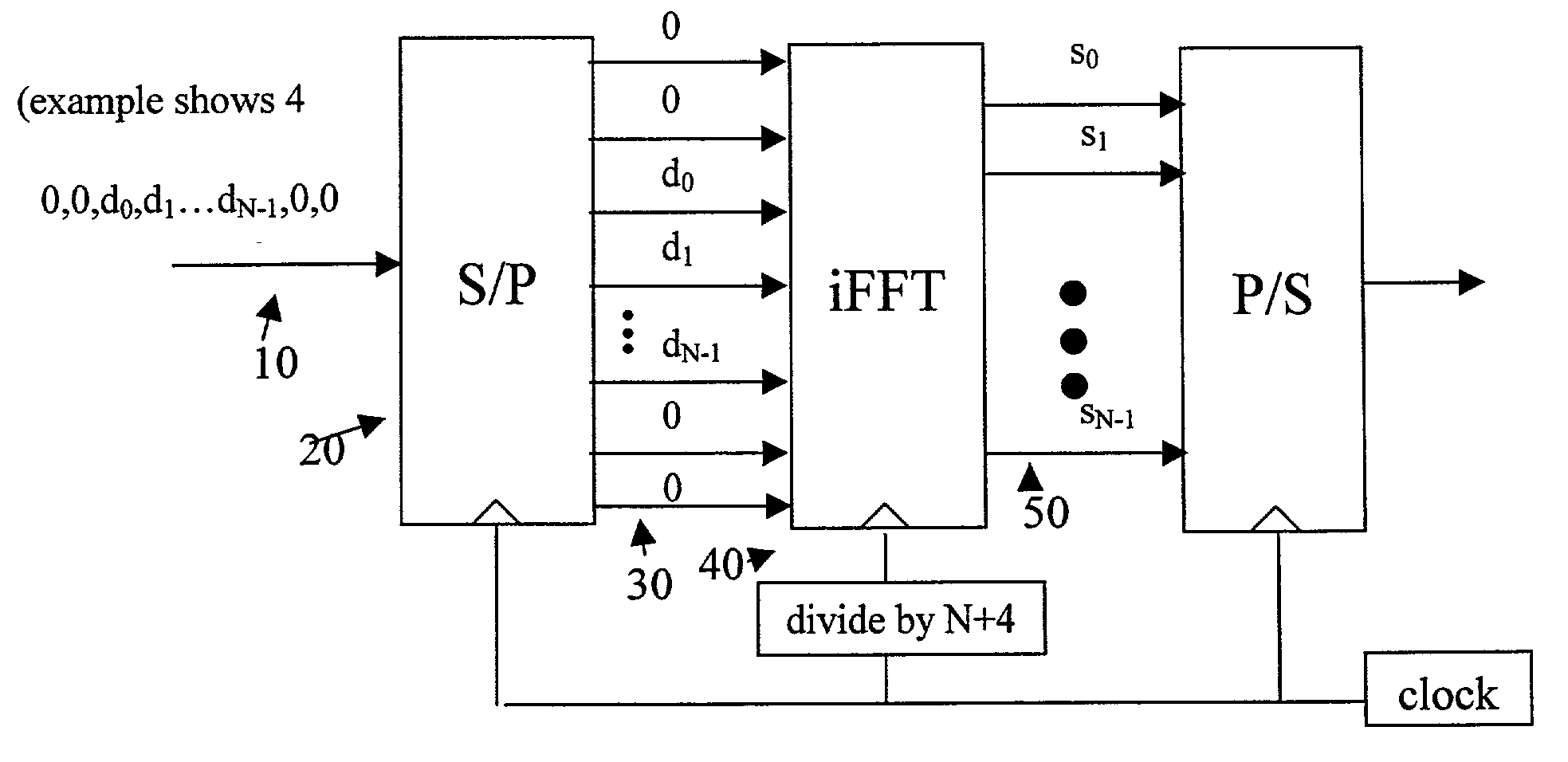

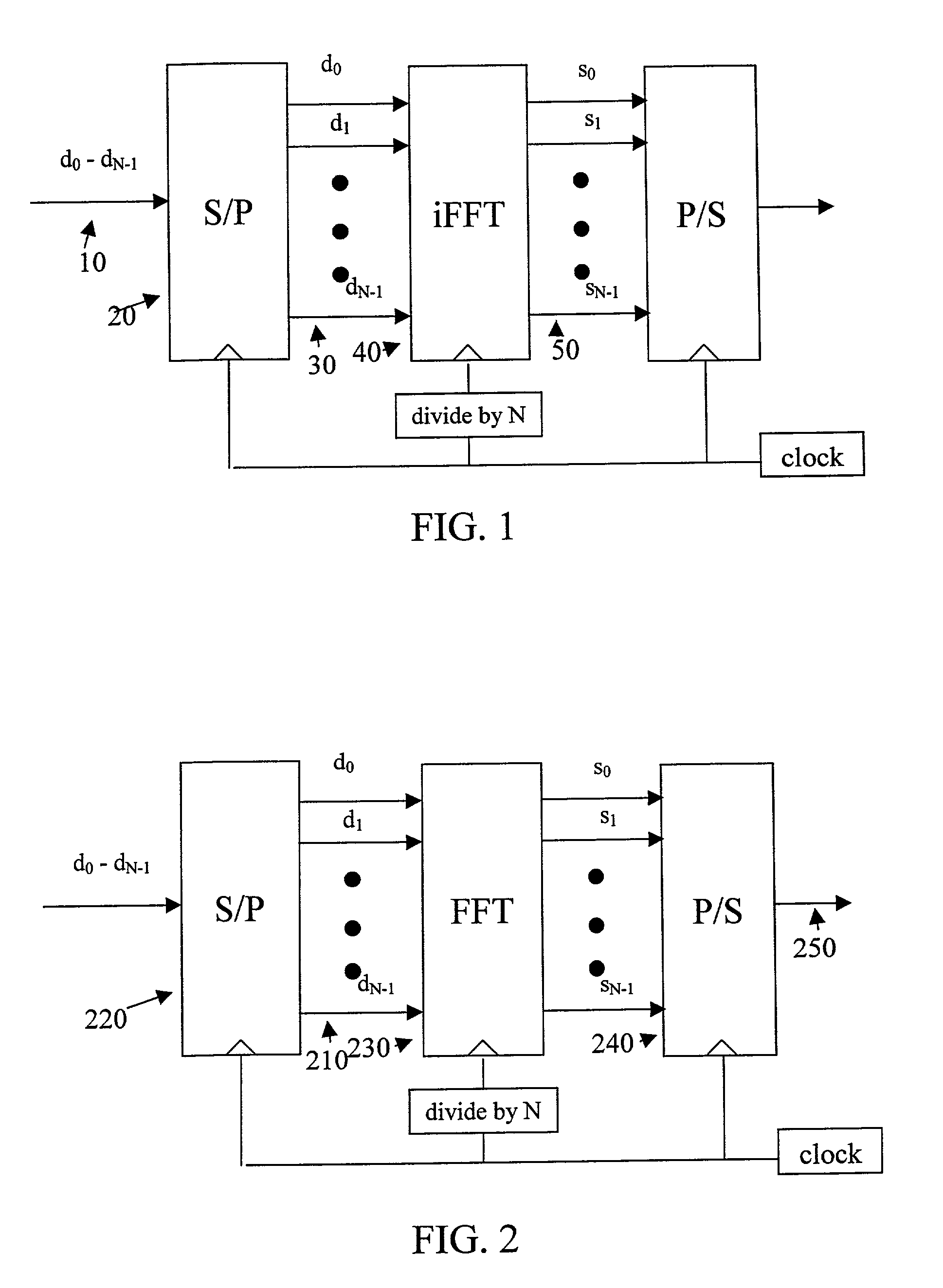

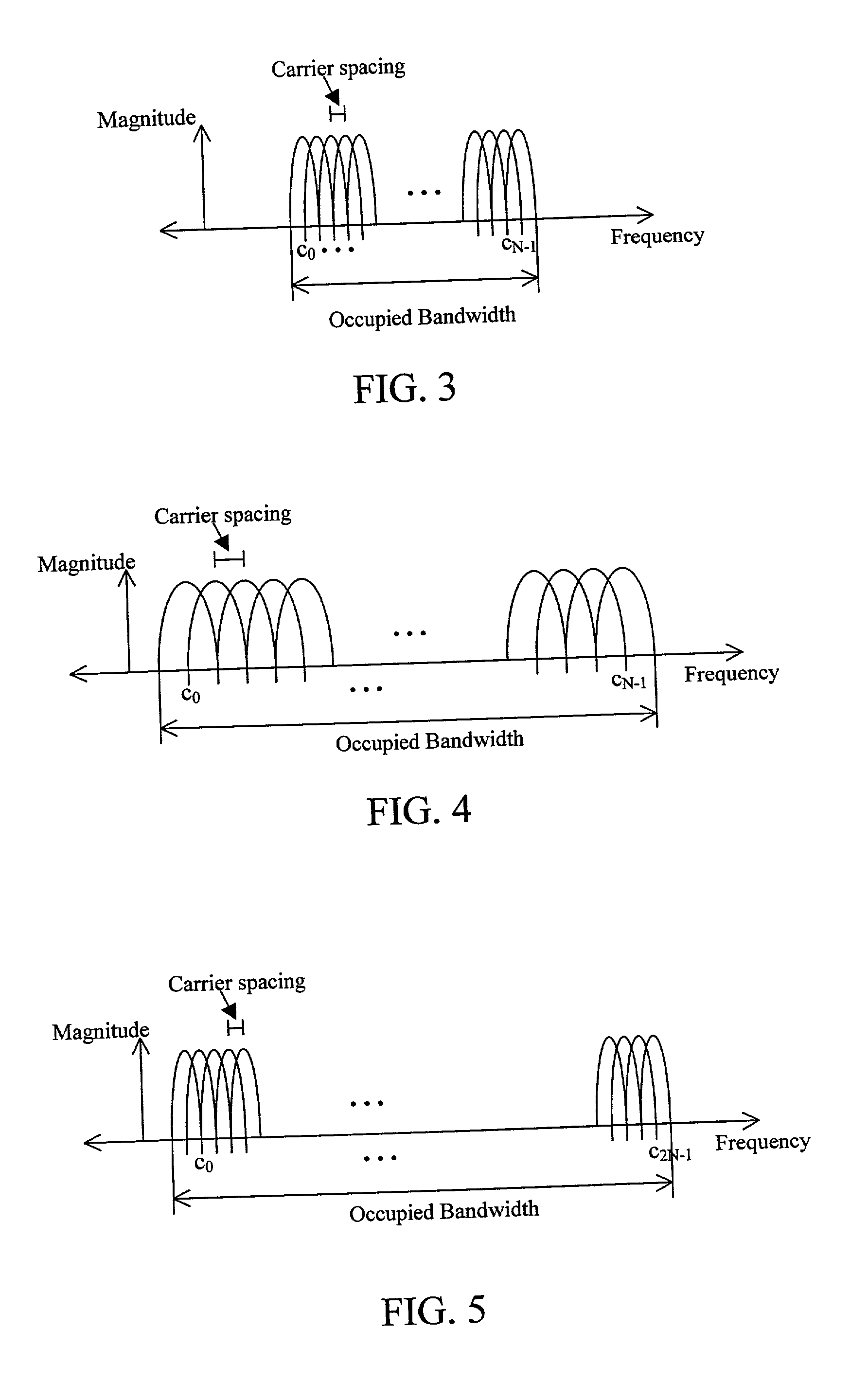

Multi-carrier communication systems employing variable symbol rates and number of carriers

ActiveUS20020006167A1Error detection/prevention using signal quality detectorTransmission path divisionCommunications systemClock rate

A multi-carrier communication system such as an OFDM or DMT system has nodes which are allowed to dynamically change their receive and transmit symbol rates, and the number of carriers within their signals. Changing of the symbol rate is done by changing the clocking frequency of the nodes' iFFT and FFT processors, as well as their serializers and deserializers. The nodes have several ways of dynamically changing the number of carriers used. The selection of symbol rate and number of carriers can be optimized for a given channel based on explicit channel measurements, a priori knowledge of the channel, or past experience. Provision is made for accommodating legacy nodes that may have constraints in symbol rate or the number of carriers they can support. The receiver can determine the correct symbol rate and number of carriers through a priori knowledge, a first exchange of packets in a base mode that all nodes can understand, or an indication in the header of the data packet which is transmitted in a base mode of operation that all nodes can understand.

Owner:THE CONNECTIVITY PATENT TRUST

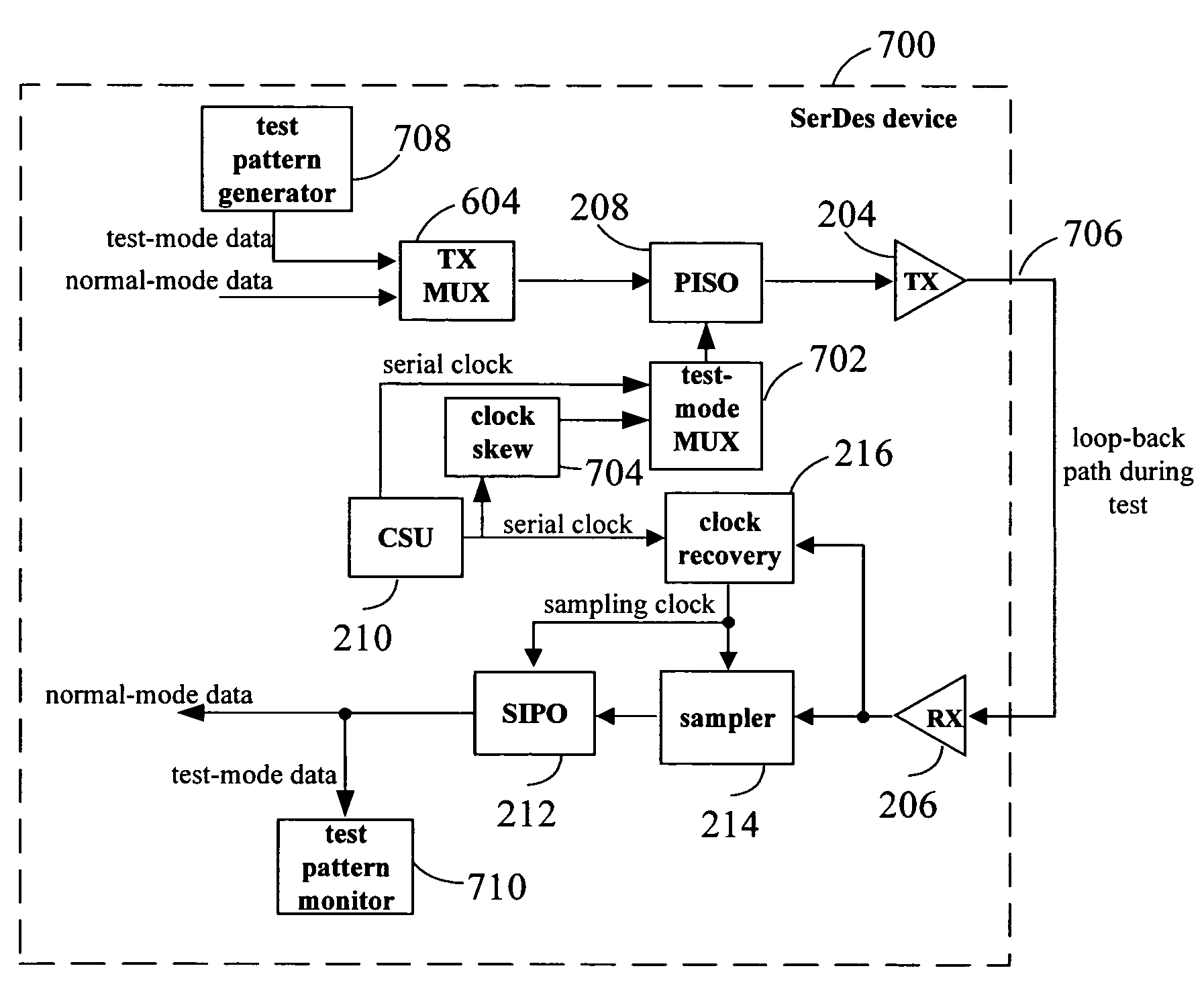

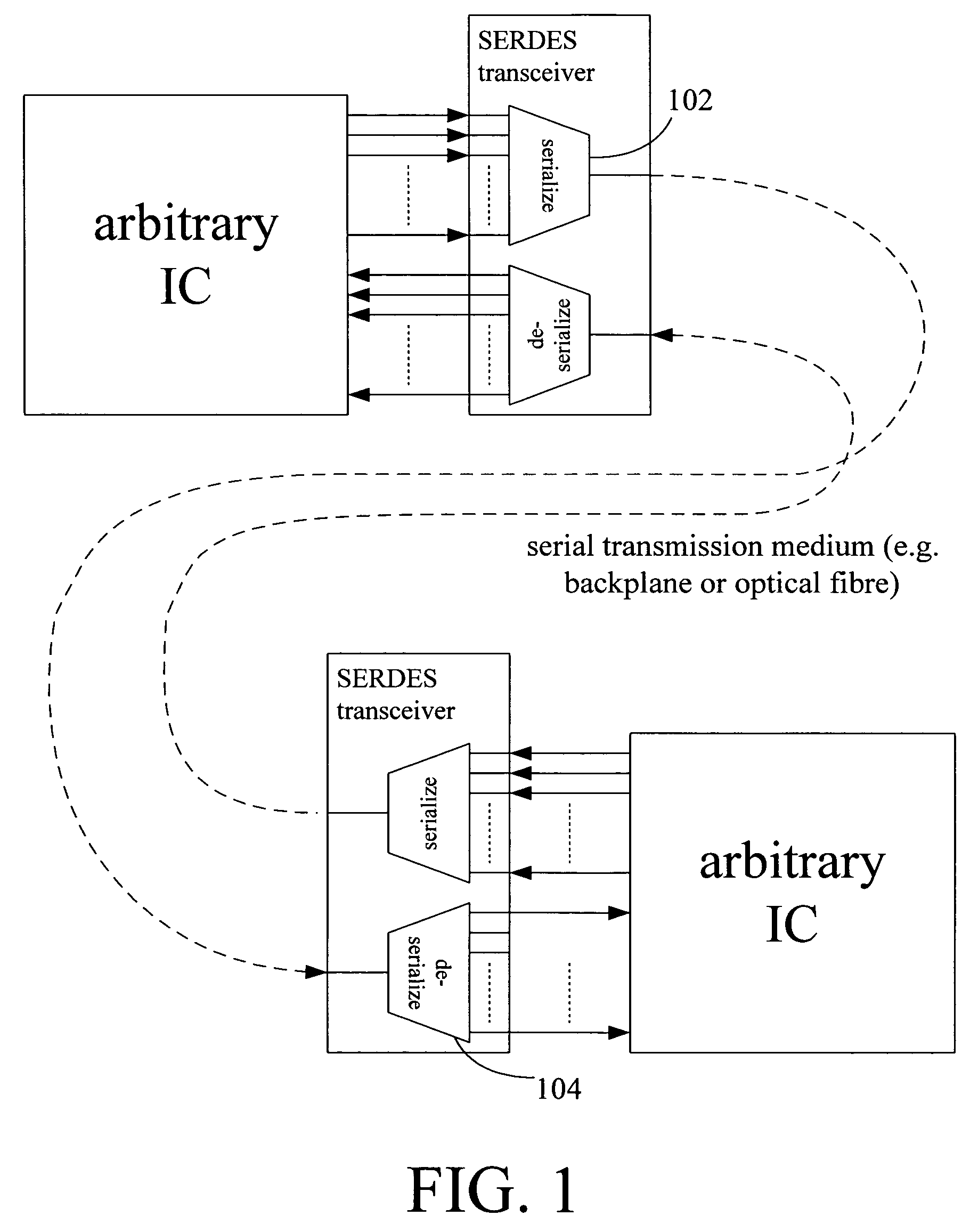

Systems and methods for a built in test circuit for asynchronous testing of high-speed transceivers

ActiveUS7363563B1Maintain performanceCost prohibitiveError preventionPulse automatic controlBuilt-in self-testSerializer

Methods and apparatus provide a transceiver, such as a serializer / deserializer device (SerDes), with enhanced built-in self test (BIST). A built-in self test circuit is provided that decouples a clock signal used for receiving data from a clock signal used in transmitting data. This permits data tracking circuitry of a receiver to be efficiently tested with a relatively simple loop back test.

Owner:MICROSEMI STORAGE SOLUTIONS

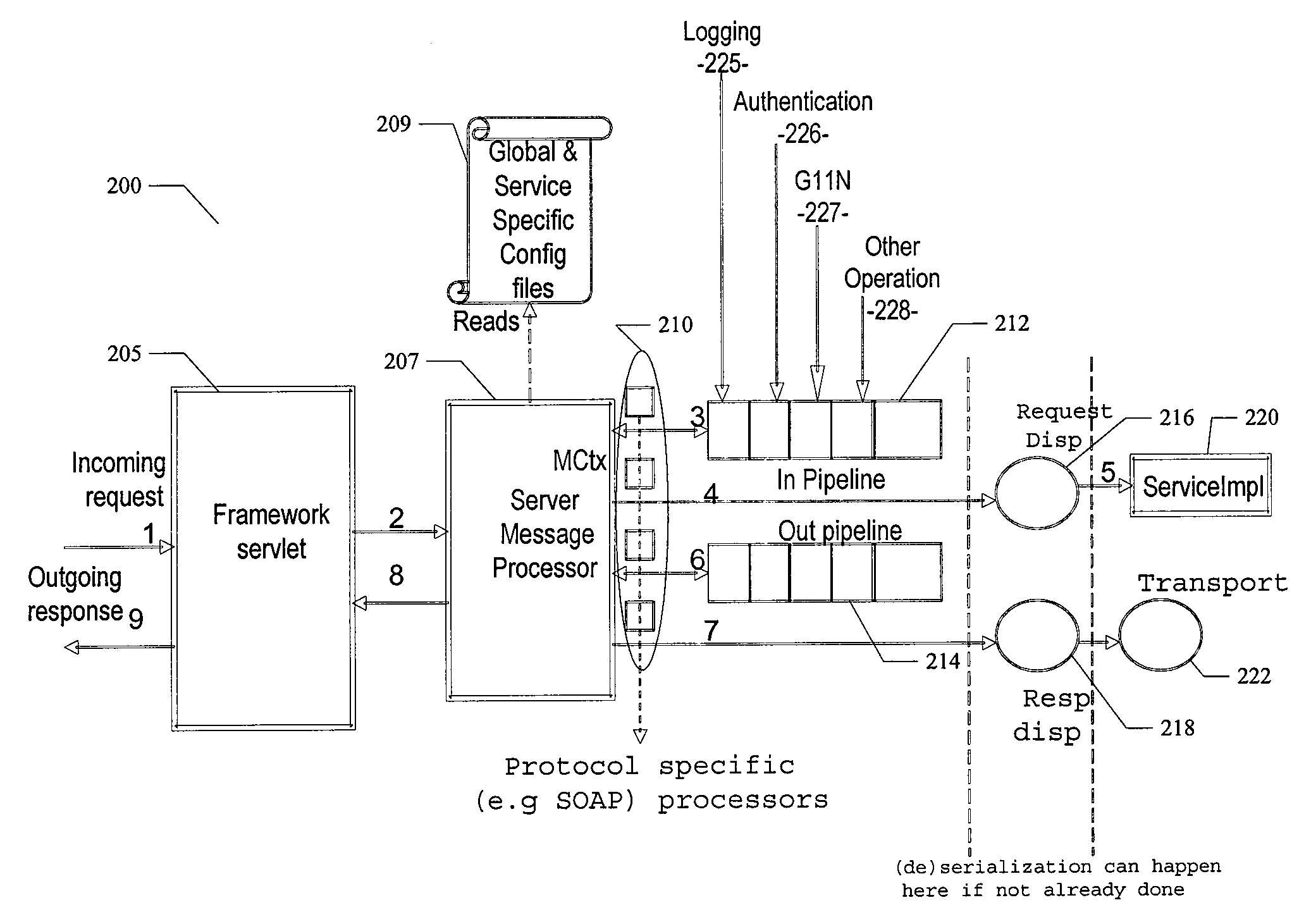

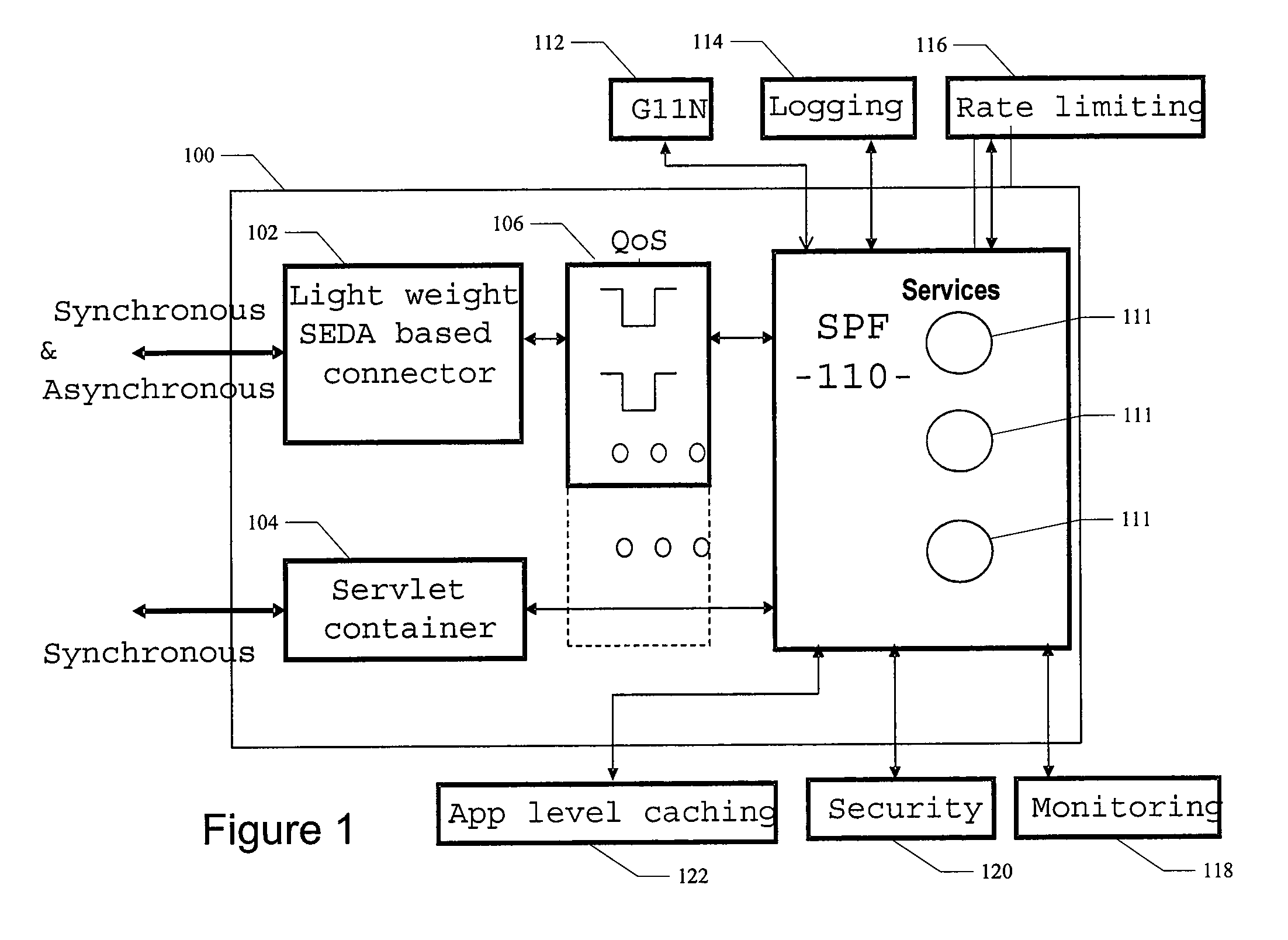

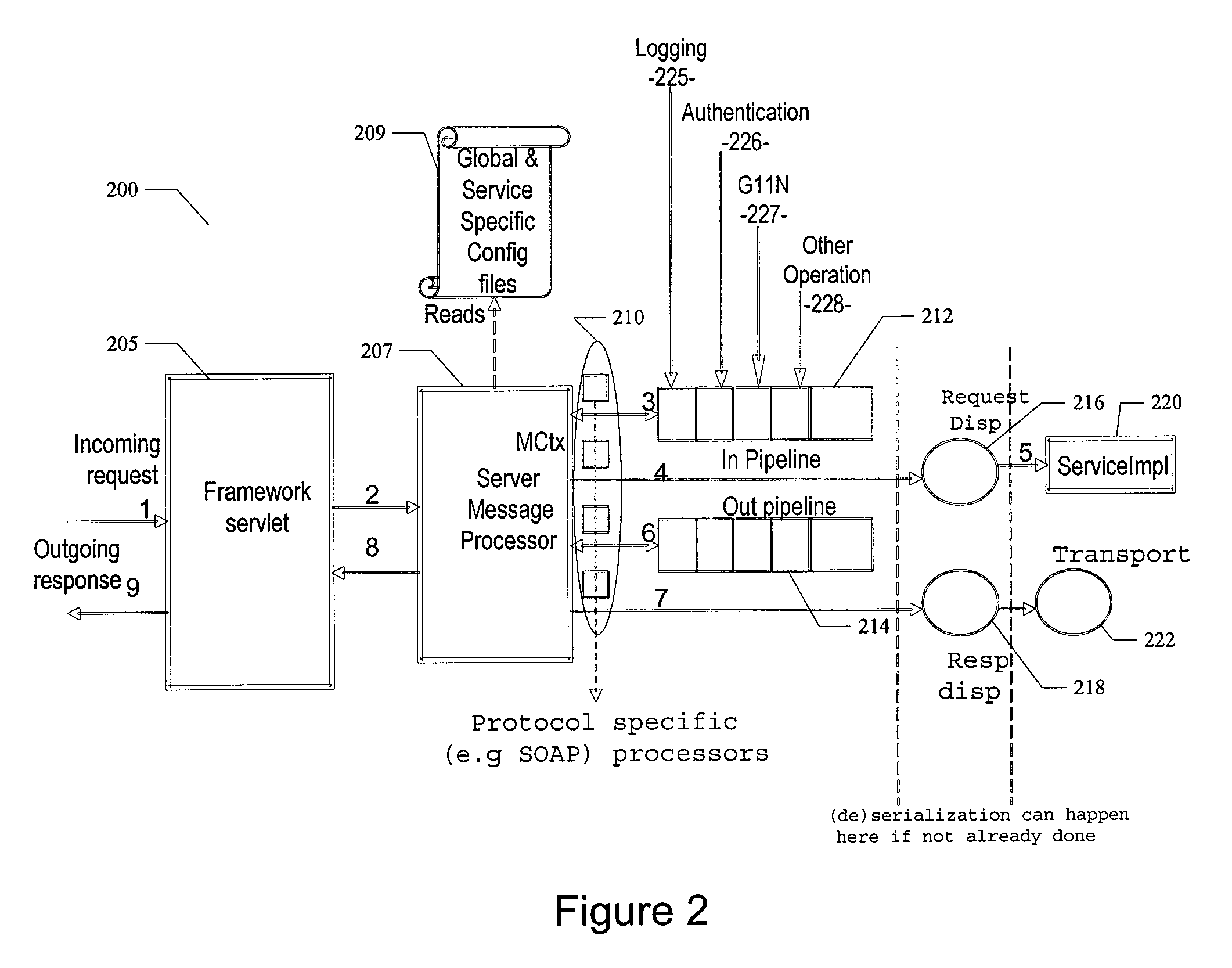

System and method for processing messages using a common interface platform supporting multiple pluggable data formats in a service-oriented pipeline architecture

InactiveUS20100083281A1TransmissionSpecific program execution arrangementsPublic interfaceSerialization

A computer-implemented system and method for processing messages using a common interface platform supporting multiple pluggable data formats in a service-oriented pipeline architecture is disclosed. The method in an example embodiment includes deserializing or serializing a request / response message using a pluggable serializer / deserializer mechanism and a corresponding pluggable data format parser. An example embodiment uses a common model for serialization / deserialization regardless of the data format, resulting in a consistent and efficient mechanism.

Owner:PAYPAL INC

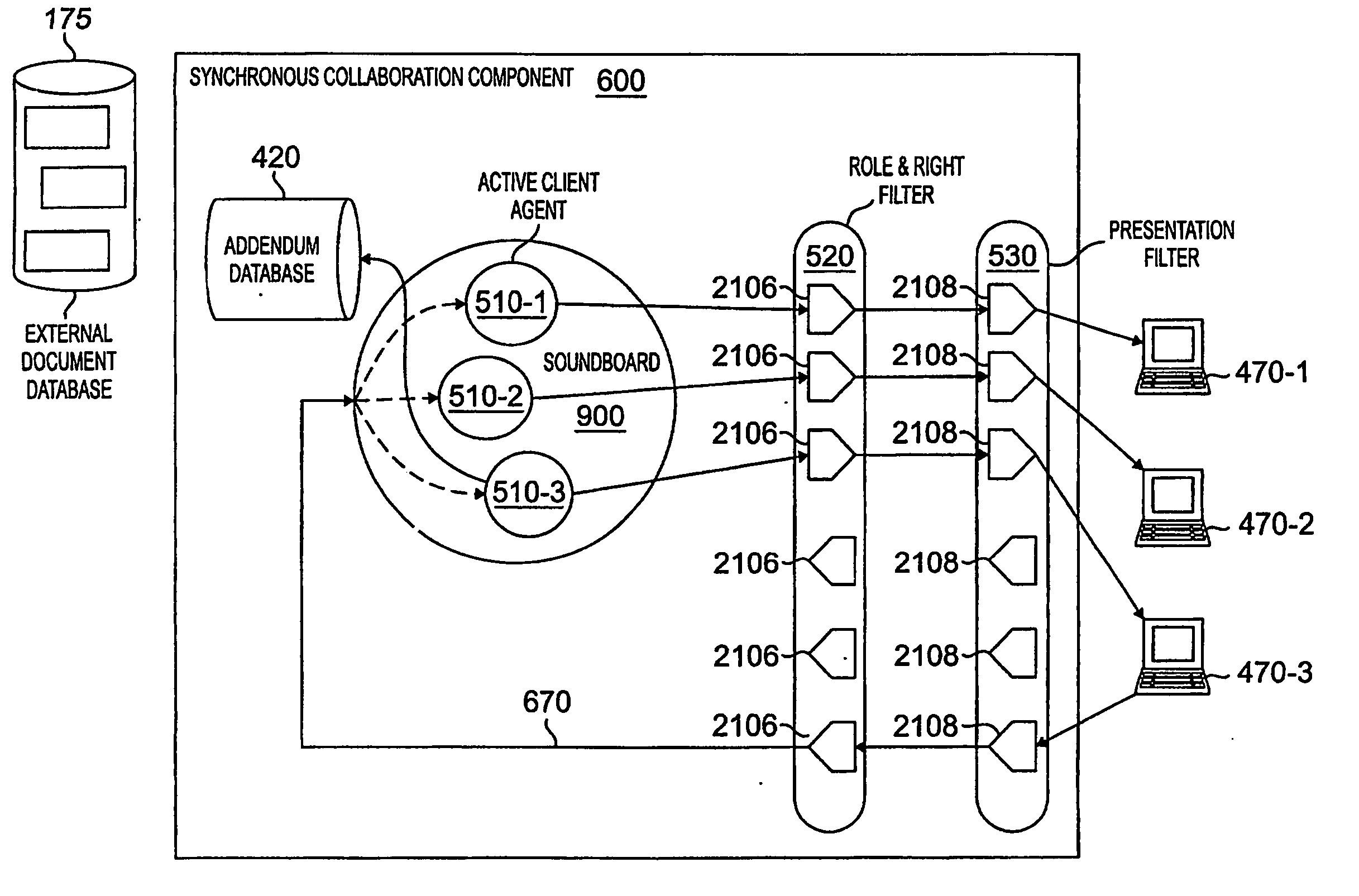

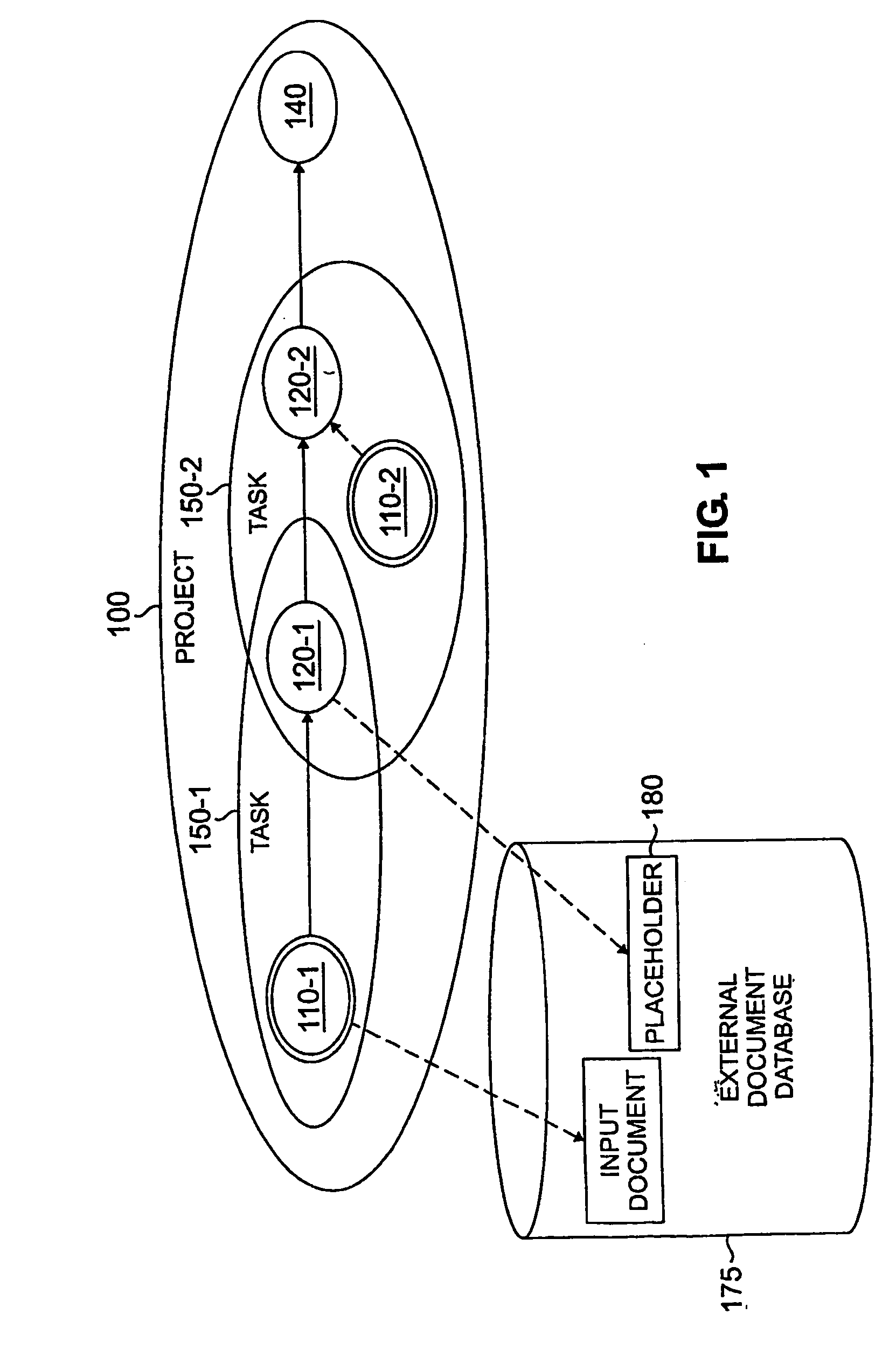

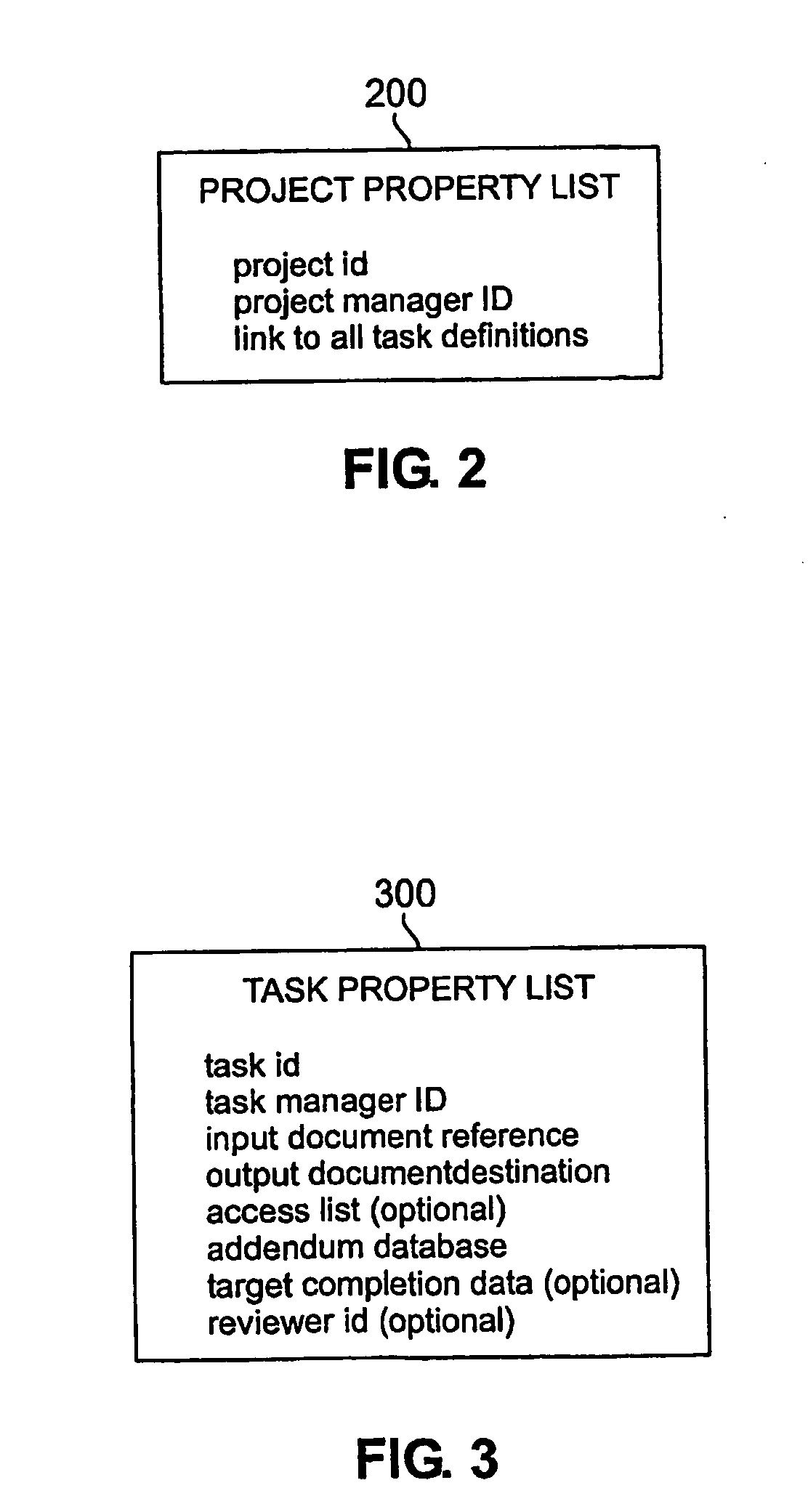

Method and apparatus for synchronous project collaboration

InactiveUS20060136441A1Easy transitionOffice automationSpecial data processing applicationsBroadcastingDocumentation

A disclosed project management system allows one or more team members to share documents in asynchronous and synchronous collaboration modes. A synchronous collaboration system is provided as an incremental addition that extends a conventional asynchronous collaboration system. One or more users can transition between asynchronous and synchronous collaboration modes. A plurality of users can interact in a synchronous collaboration mode to create and modify documents and perform other project tasks without requiring a token. A serializer initially receives each of the change requests and serializes them. The serialized requests are then sent to a broadcaster that broadcasts the requests to all users. Each user implements the broadcast change requests to the document as they are received so that shared documents are presented to each user in the same way at any given time.

Owner:JUBA HISASHI

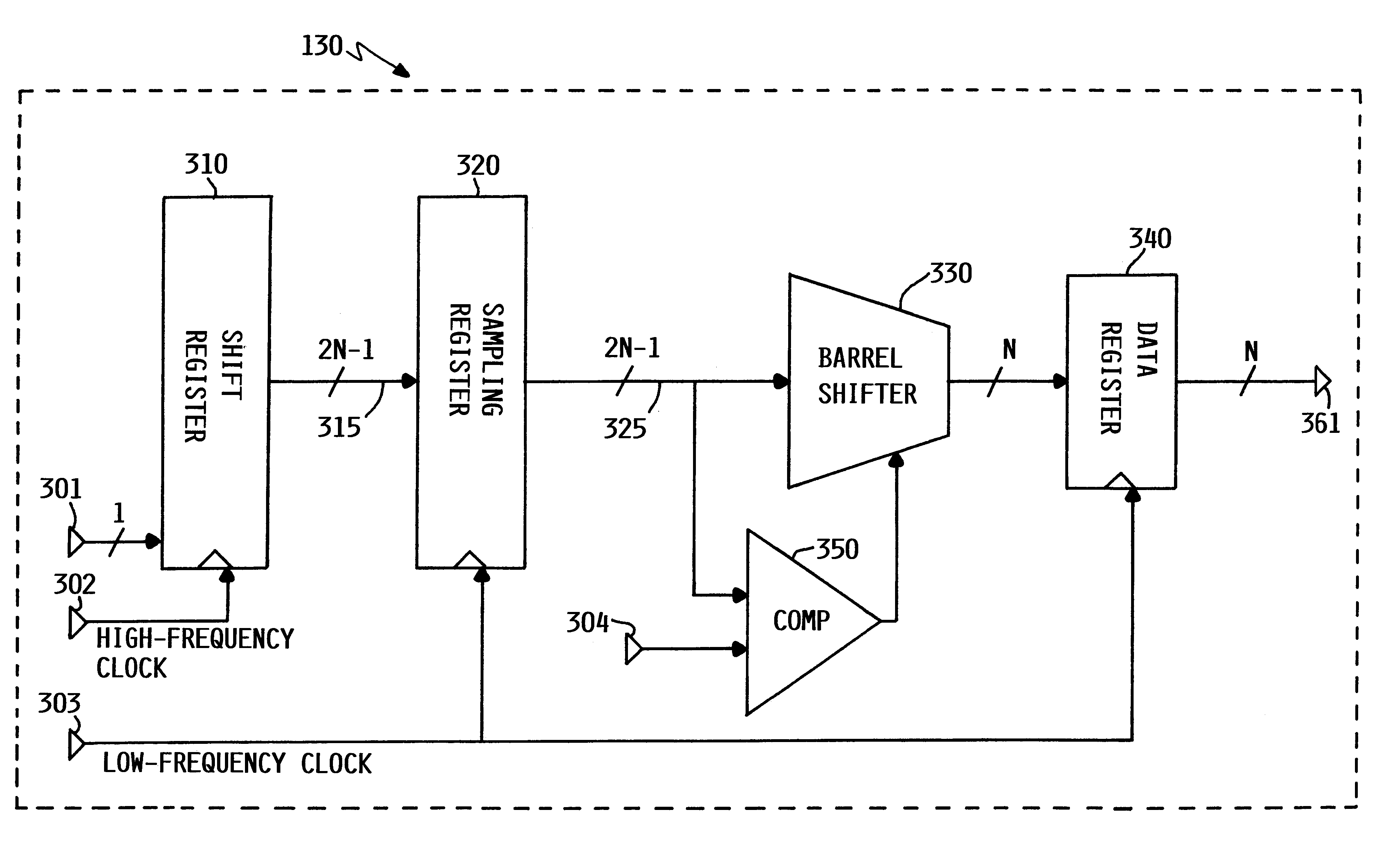

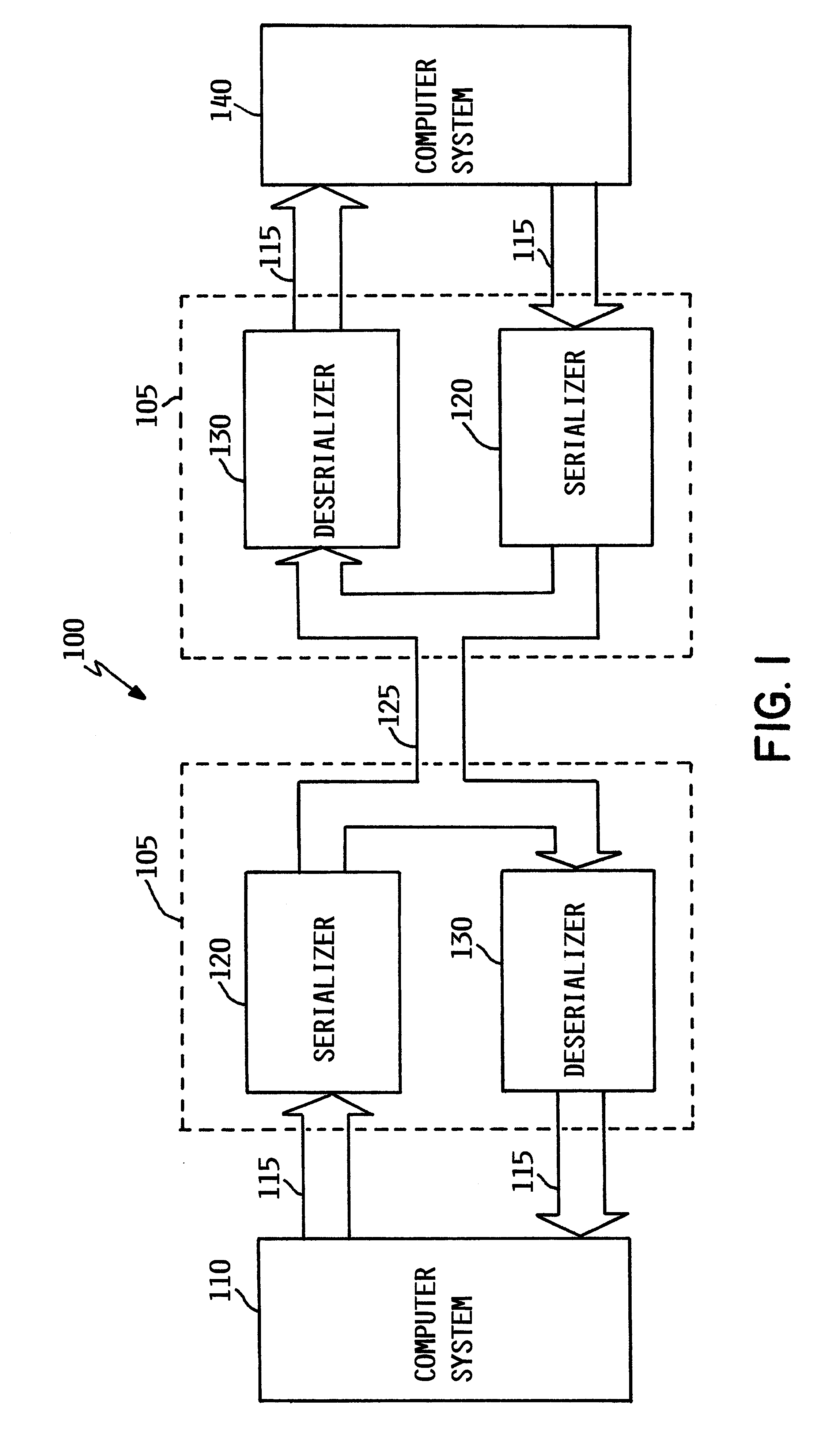

Apparatus and method for optimized self-synchronizing serializer/deserializer/framer

InactiveUS6459393B1Negatively impact design timeNegatively integrated circuit clock loadingParallel/series conversionViruses/bacteriophagesSerial transferTelecommunications link

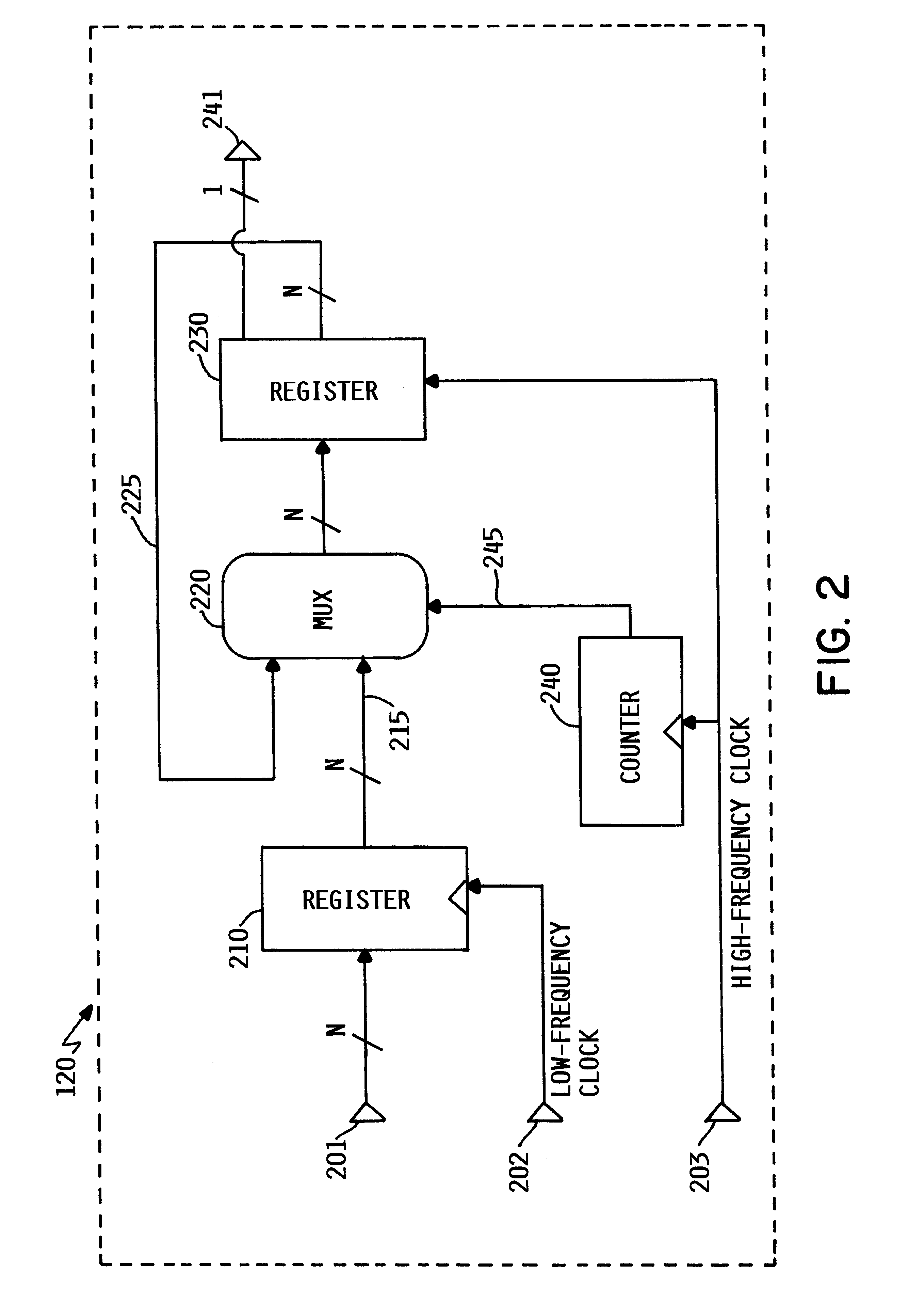

An apparatus and method for improving the communication capabilities of computer systems is disclosed. The most preferred embodiments of the present invention use a series of data buffers and data registers to process an incoming high speed data signal. By using the buffers and registers, the incoming signal can be reformatted and manipulated at a much lower frequency than the original transmission frequency. The deserializer of the present invention also samples a greater portion of the incoming data signal than usual to further increase reliability. These various features of the invention provide for a more stable and reliable communication link and will also provide a less expensive solution for serialization / deserialization. The present invention includes a serializer that receives parallel data input from a computer and serializes the data for transmission over a high-speed serial communication link. On the receiving end, the present invention provides a deserializer that can quickly and efficiently transform the serial data back into parallel form for use within the computer system on the receiving end. By utilizing two related clock signals, one clock signal being an integer multiple of the other, a self-synchronizing serializer / deserializer can be created. In addition, by increasing the size of the data sample on the receiving end, the comparisons necessary to retrieve a parallel signal from a serial transmission can occur at a much lower frequency than the frequency of the serial transmission. In the most preferred embodiment, the invention is provided as a integrated solution manufactured on a Peripheral Component Interconnect (PCI) card, thereby allowing the present invention to be easy installed into existing computer systems.

Owner:MEDIATEK INC

Universal serializer/deserializer

InactiveUS7010612B1Parallel/series conversionTime-division multiplexNetwork Communication ProtocolsComputer module

A universal serializer / deserializer (“ser / des”) is disclosed that provides hardware implemented modules of those functions determined to be most applicable to a communications protocol. Functionality that is determined to be more unique for a given protocol is implemented in software. Accordingly, a universal ser / des is provided that is able to be used for a plurality of different protocols now known, and configured to communicate with protocols that may be developed in the future.

Owner:MAYFIELD XI +8

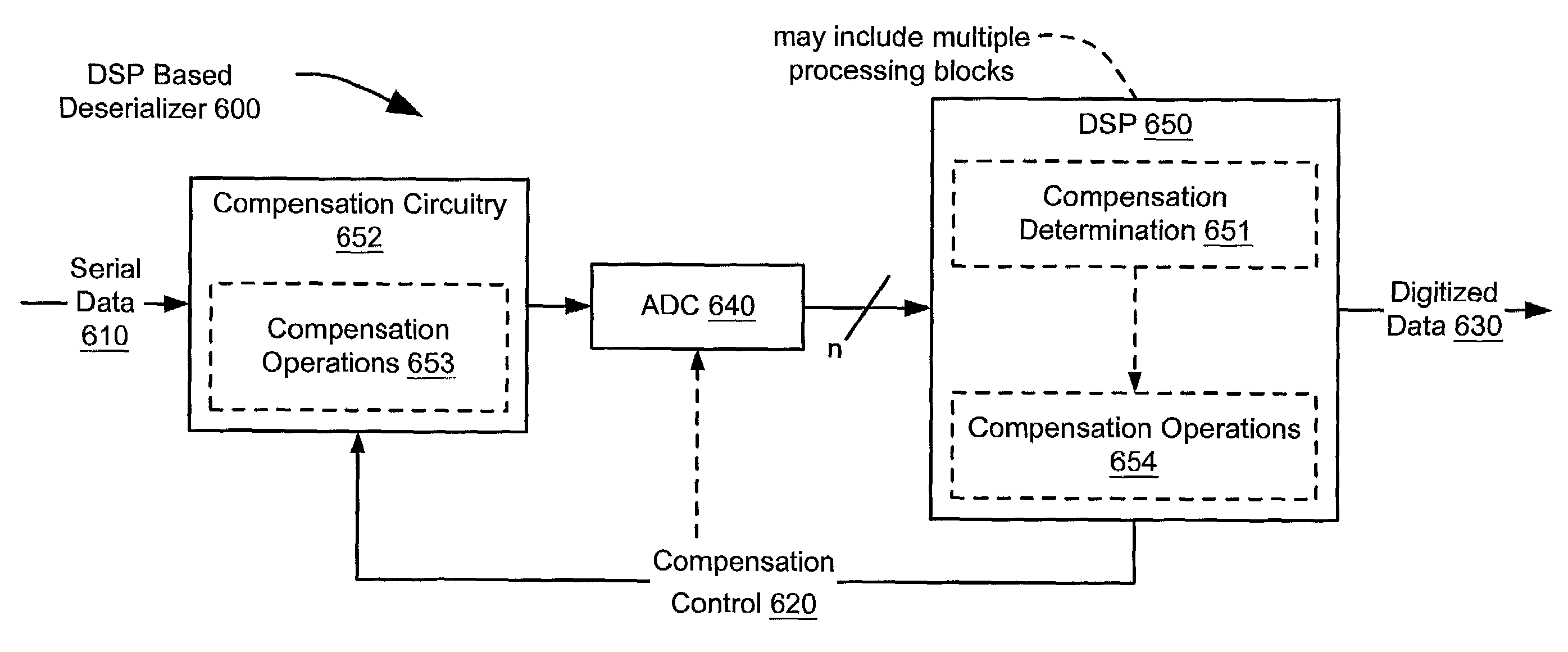

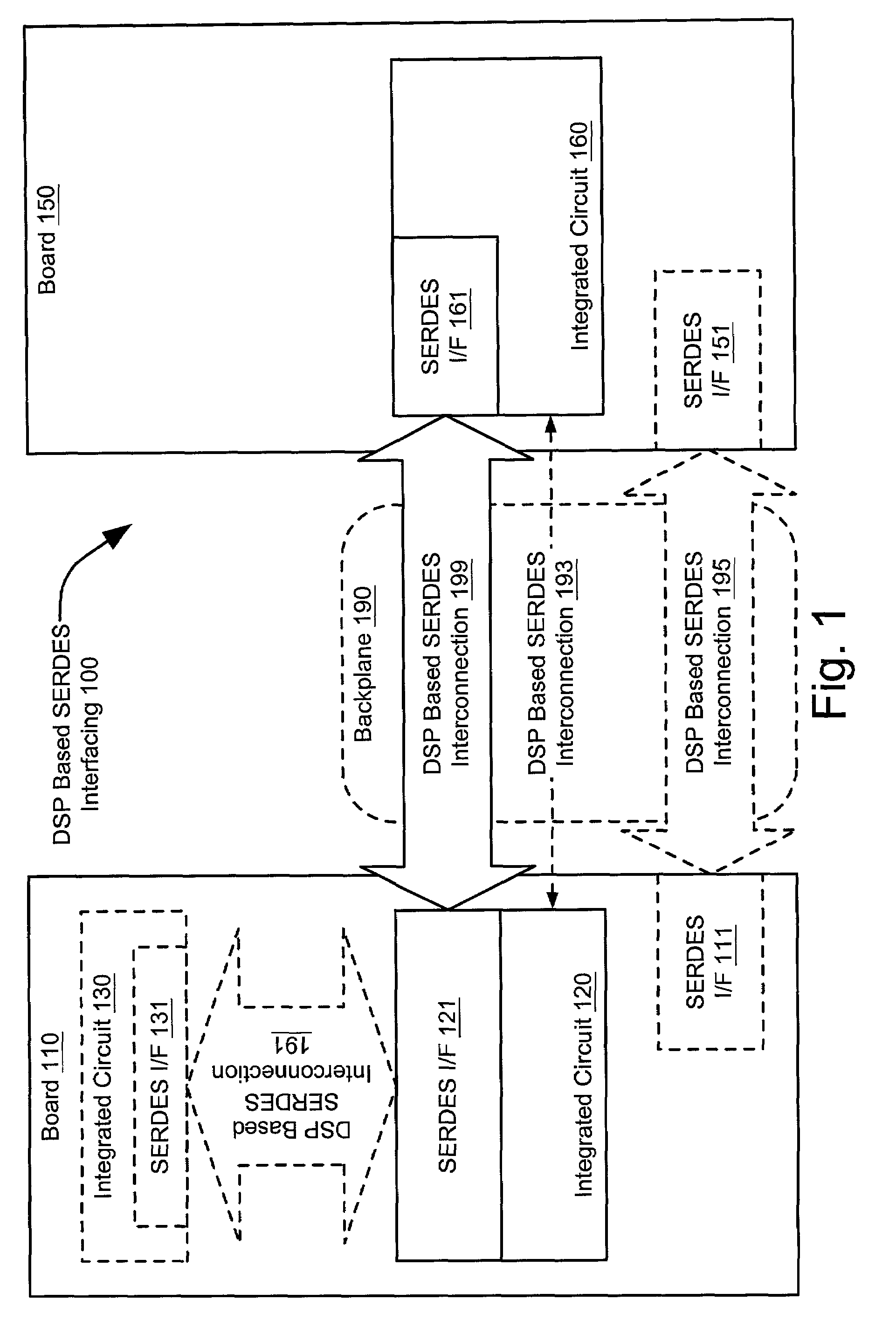

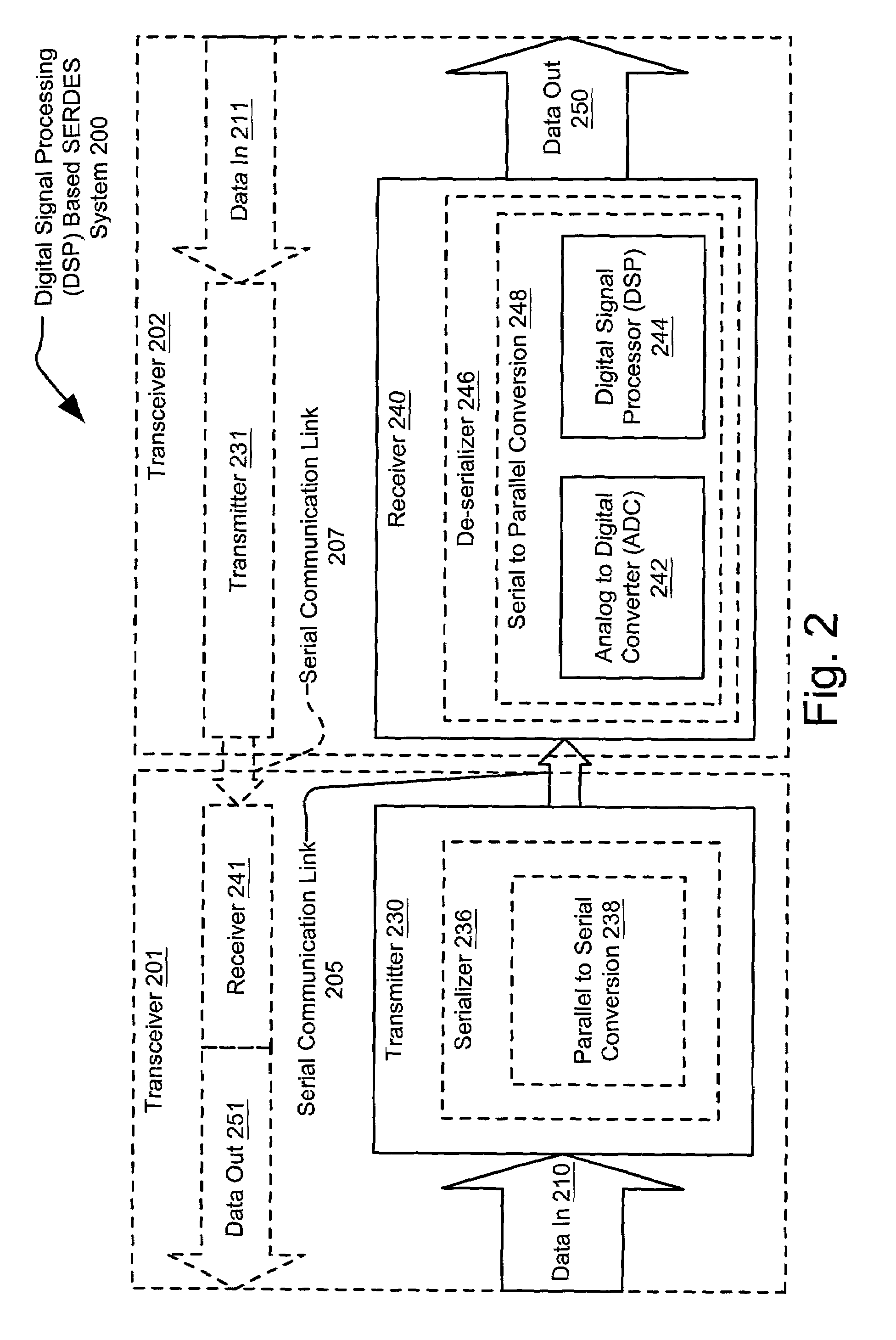

Digital signal processing based de-serializer

ActiveUS7336729B2Lower performance requirementsSolve problemsElectric signal transmission systemsAmplitude-modulated carrier systemsDigital signal processingSerialization

A DSP based SERDES performs compensation operations to support high speed de-serialization. A receiver section of the DSP based SERDES includes one or more ADCs and DSPs. The ADC operates to sample (modulated) analog serial data and to produce digitized serial data (digital representation of the modulated analog serial data). The DSP communicatively couples to the ADC and receives the digitized serial data. Based upon the known characteristics of the digitized serial data and the digitized serial data itself, the DSP determines compensation operations to be performed upon the serial data to compensate for inadequacies of the receiver and / or channel response. These compensation operations may be (1) performed on the analog serial data before digitization by the ADC; (2) applied to the ADC to modify the operation of the ADC; and / or (3) performed on the digitized serial data by the DSP or another device.

Owner:AVAGO TECH INT SALES PTE LTD

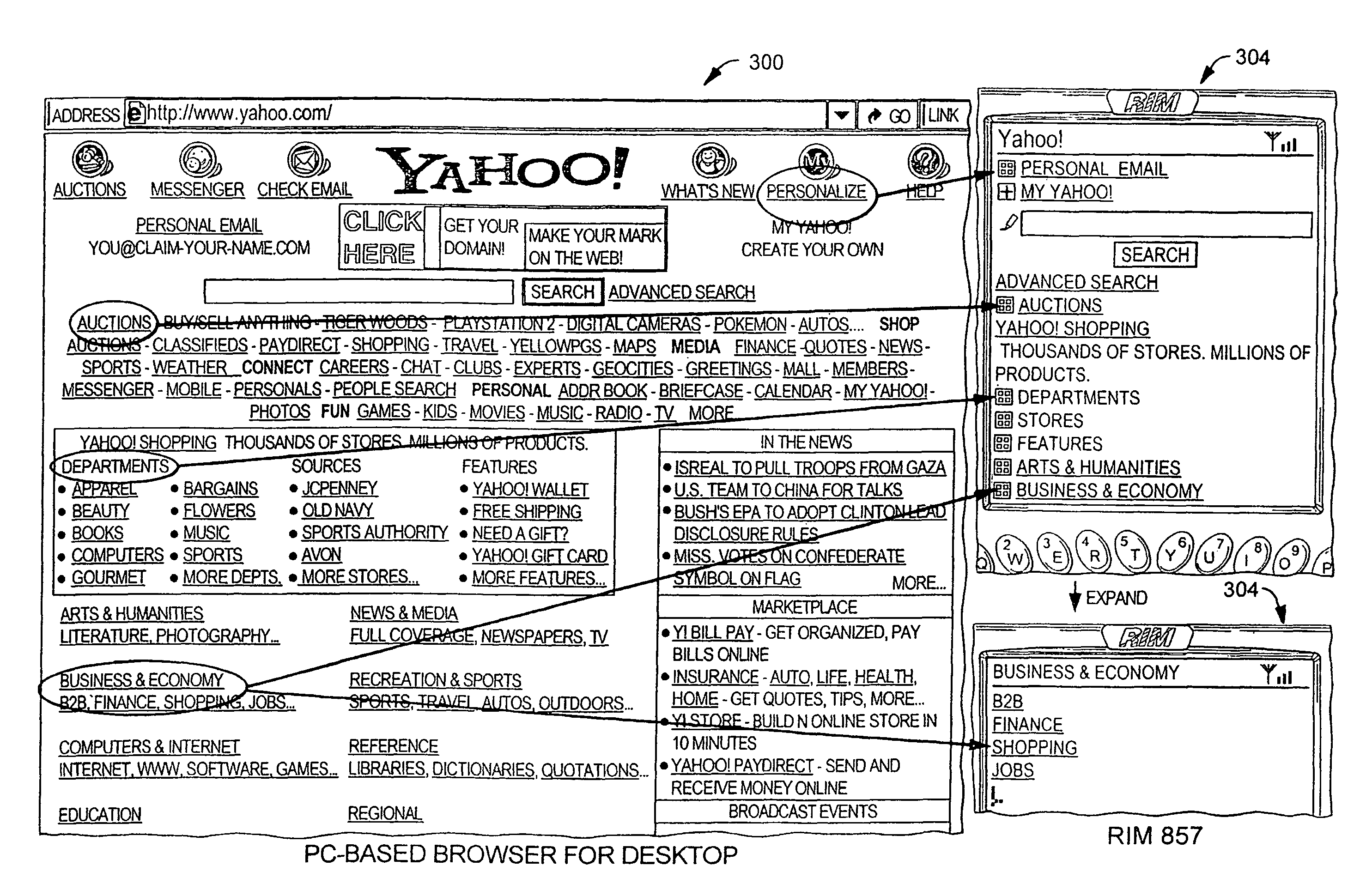

System and method for providing and displaying information content

InactiveUS7747782B2Large displayLarge facilityDigital data information retrievalMultiple digital computer combinationsScrollingClient-side

A system and method is provided for enabling an electronic device to efficiently access information content. A server browser accesses the information content over a network. The accessed information content is retrieved and adapted for presentation for the electronic device. A serializer dynamically formats the adapted information content according to a client browser. The client browser receives and presents the information content on the electronic device. An event translator is included to provide additional compatibility with commercially available client browsers. The information content is formatted to selectively minimize the horizontal scrolling required to view the content. The need for horizontal scrolling is selectively removed where not necessary to preserve the context. Each component or sub-component of the original area, such as a frame, table row, table cell or nested table, is considered separately and may be preserved, resized, or replaced. Where the context requires that the content be wider than the viewable area of the screen, horizontal scrolling is preserved.

Owner:RPX CORP

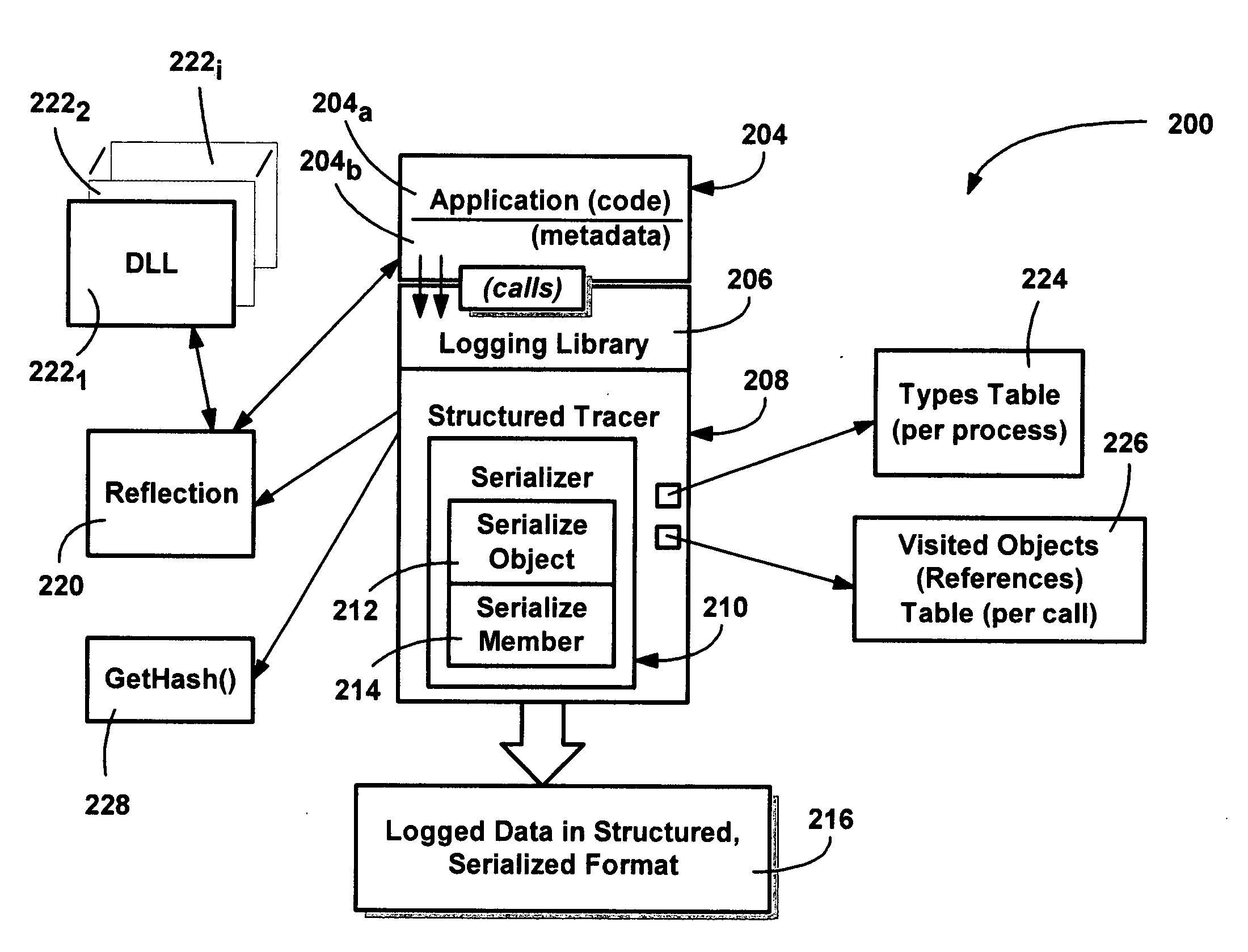

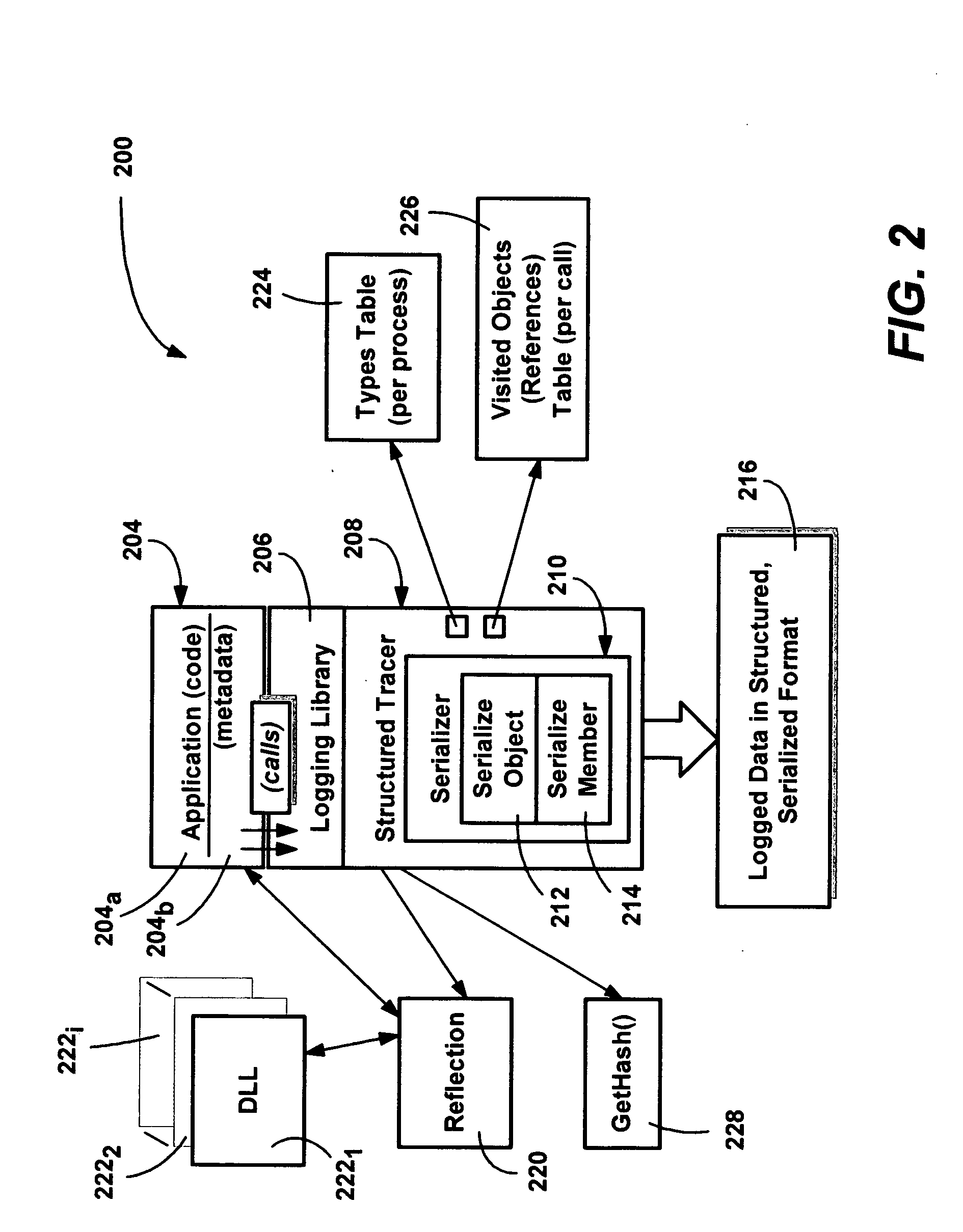

Serialization for structured tracing in managed code

InactiveUS20050097110A1Highly readableBroaden applicationDigital data information retrievalDigital data processing detailsComplex typeManaged code

A system and method, useful in tracing program execution, for serializing data, such as an object data, into consistent, structured (e.g., XML) output. A serializer processes an object's data, and for each set of data, records the object's data in a structured (e.g., XML) format that reflects the object's current state. Nodes corresponding to fields and properties of the object are nested in the structure. Simple types define nodes with the current data value associated with the tag. More complex types including arrays, collections, dictionaries and exceptions are stored as individual members of a type, with any complex members further broken down into sub-nodes. Object data including custom collections, dictionaries, non-public fields and properties and properties with only get-accessor are serialized. The resulting output, such as in an XML formatted structure, is easy to read by humans, and is easily processed, such as for automated analysis purposes.

Owner:MICROSOFT TECH LICENSING LLC

System and Method for Displaying Information Content with Selective Horizontal Scrolling

InactiveUS20100268773A1High CPU powerLarge displayDigital data information retrievalMultiple digital computer combinationsScrollingClient-side

A system and method is provided for enabling an electronic device to efficiently access information content. A server browser accesses the information content over a network. The accessed information content is retrieved and adapted for presentation for the electronic device. A serializer dynamically formats the adapted information content according to a client browser. The client browser receives and presents the information content on the electronic device. An event translator is included to provide additional compatibility with commercially available client browsers. The information content is formatted to selectively minimize the horizontal scrolling required to view the content. The need for horizontal scrolling is selectively removed where not necessary to preserve the context. Each component or sub-component of the original area, such as a frame, table row, table cell or nested table, is considered separately and may be preserved, resized, or replaced. Where the context requires that the content be wider than the viewable area of the screen, horizontal scrolling is preserved.

Owner:NOKIA CORP

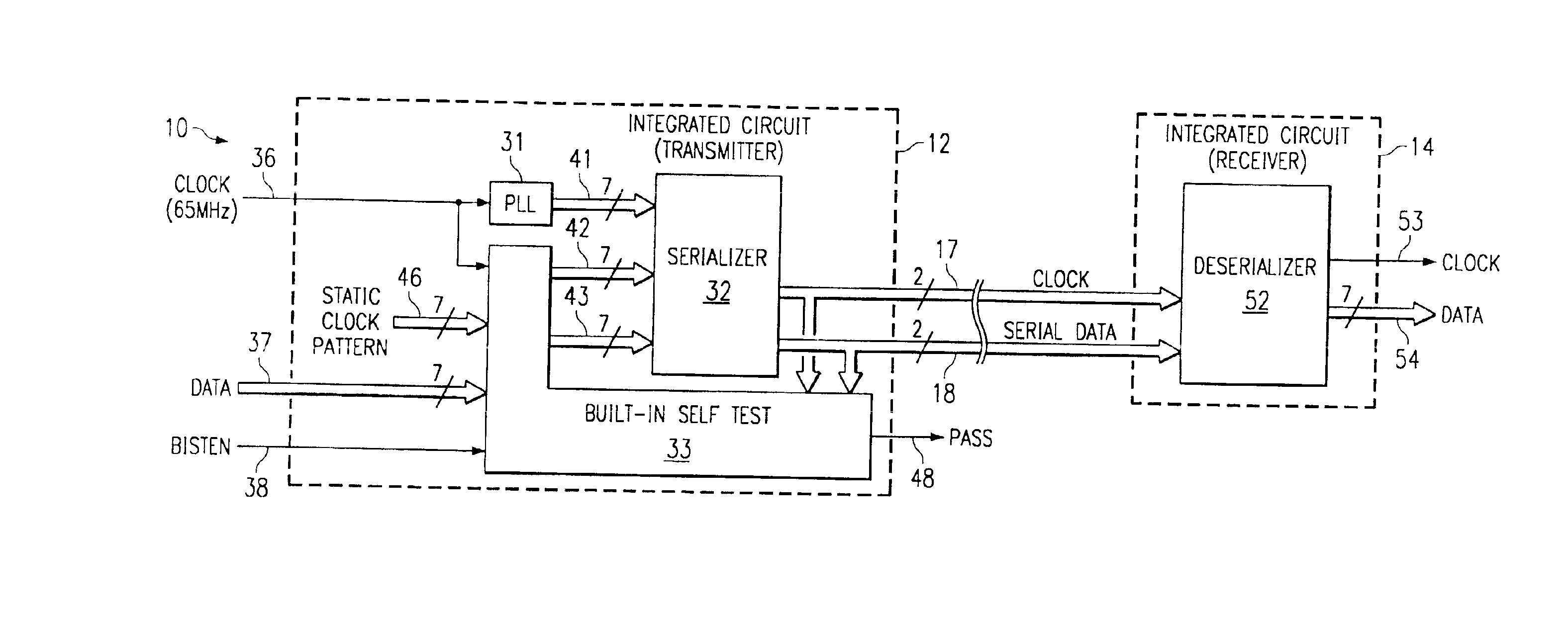

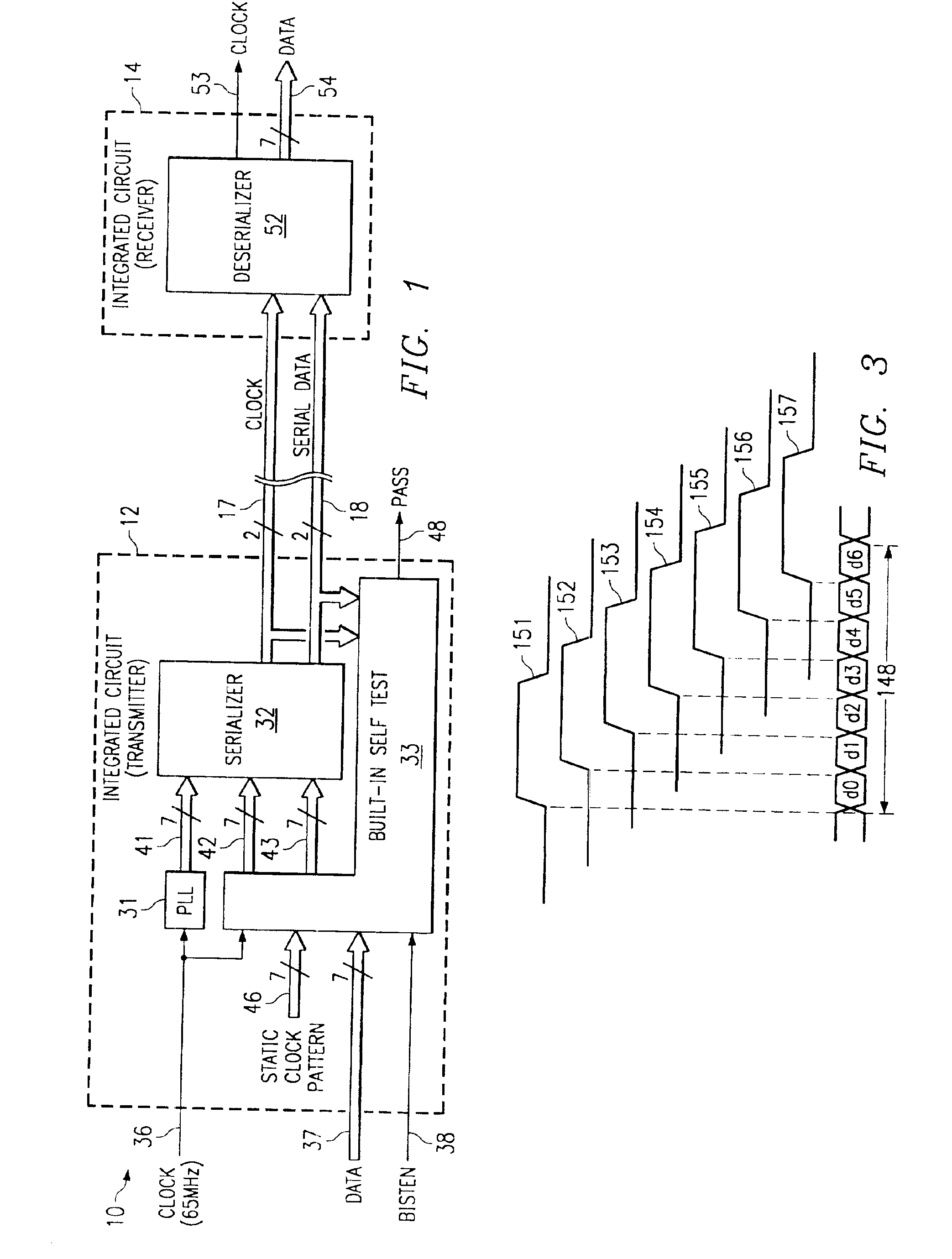

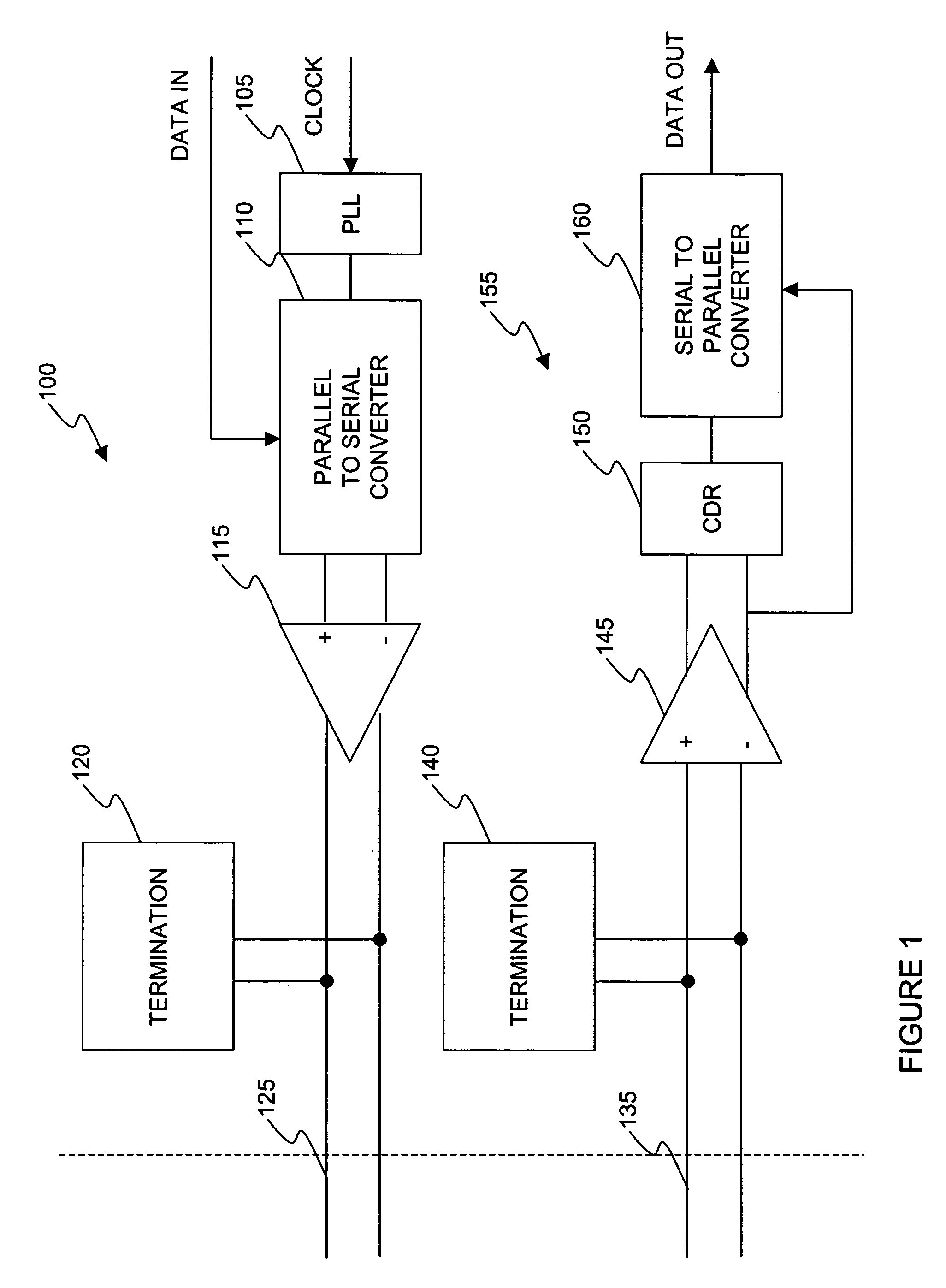

Method and apparatus for testing a serial transmitter circuit

InactiveUS6865222B1Easy to testNeed can be addressedCorrect operation testingAmplitude-modulated carrier systemsComputer scienceBuilt-in self-test

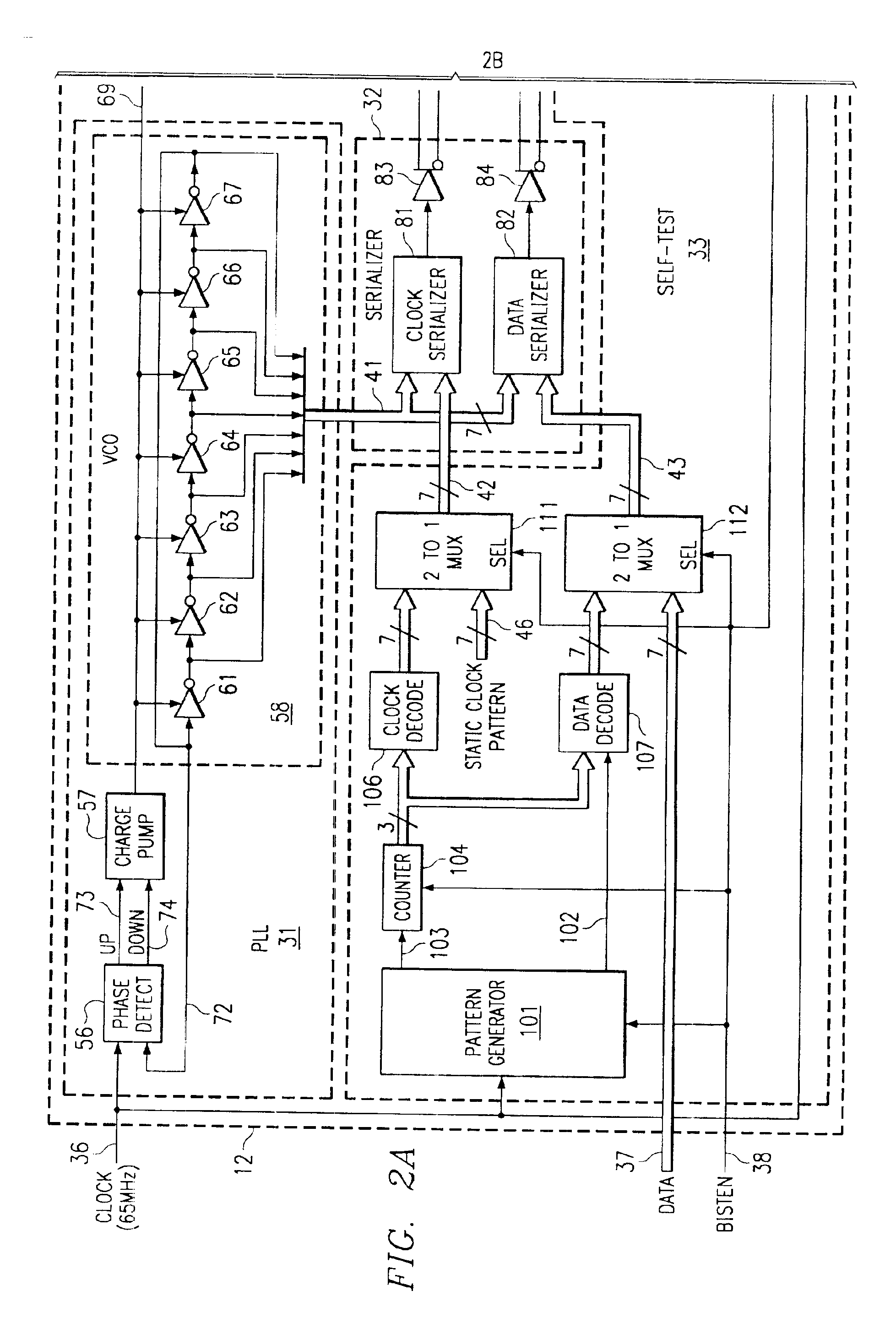

An integrated circuit (12) contains a serializing transmitter, including a phase locked loop (31) that supplies seven clocks (41) with different phases to a serializer circuit (32). The serializer circuit accepts 7-bit words at a parallel input (42), and outputs these words serially in an end-to-end manner on a twisted pair (17), as a clock signal. The serializer circuit also accepts 7-bit words on a further parallel input (43), and transmits them serially in an end-to-end manner on a twisted pair (18), as serialized data. The integrated circuit also includes a built-in self-test circuit (33), which can supply test information to the two parallel inputs of the serializer circuit, and which can monitor the two twisted pairs while the serializer circuit operates at high data rates typical of normal operation, in order to detect any errors introduced by the serializer circuit. The self-test circuit produces a single digital output (48) to indicate whether an error has been detected.

Owner:TEXAS INSTR INC

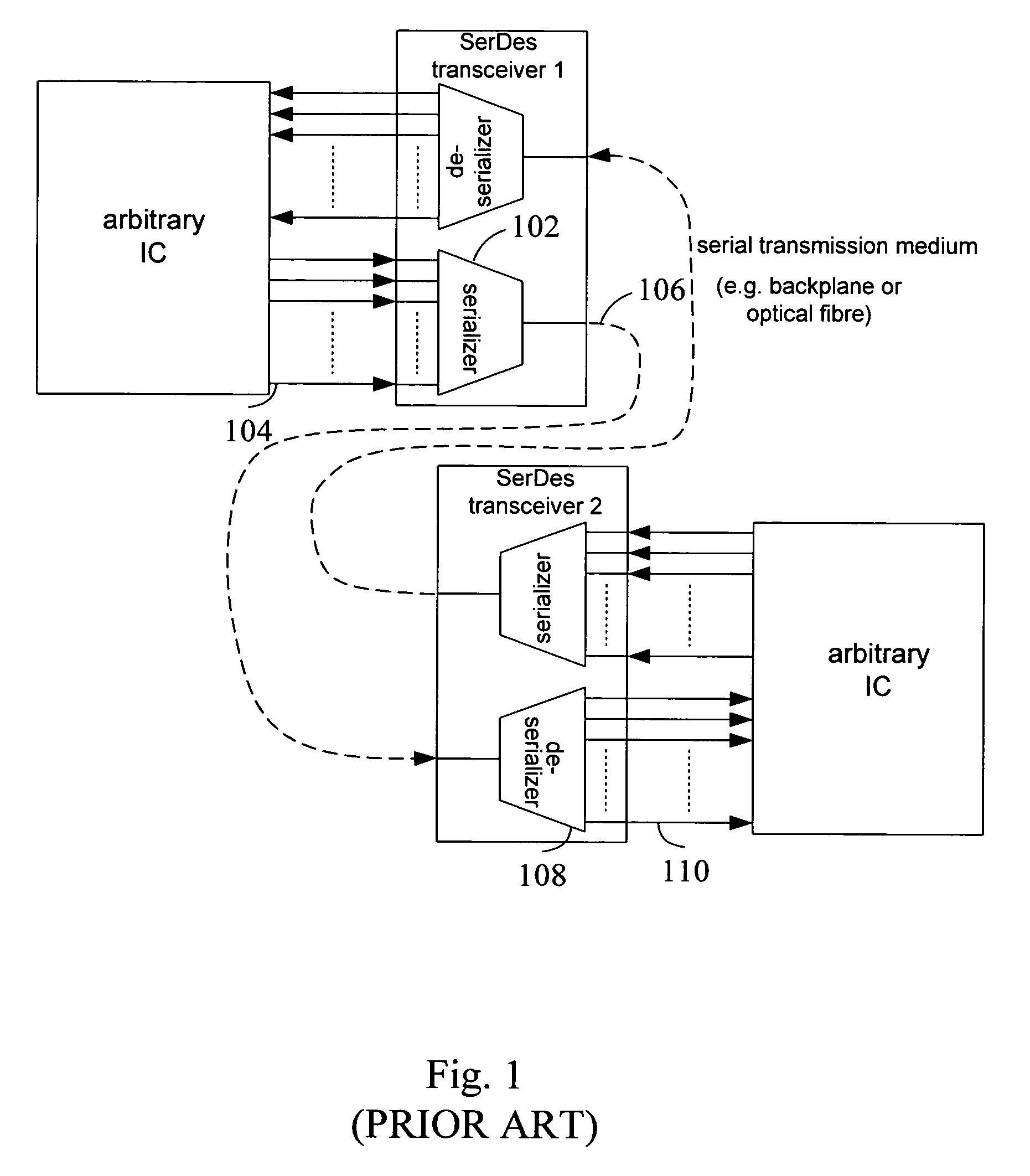

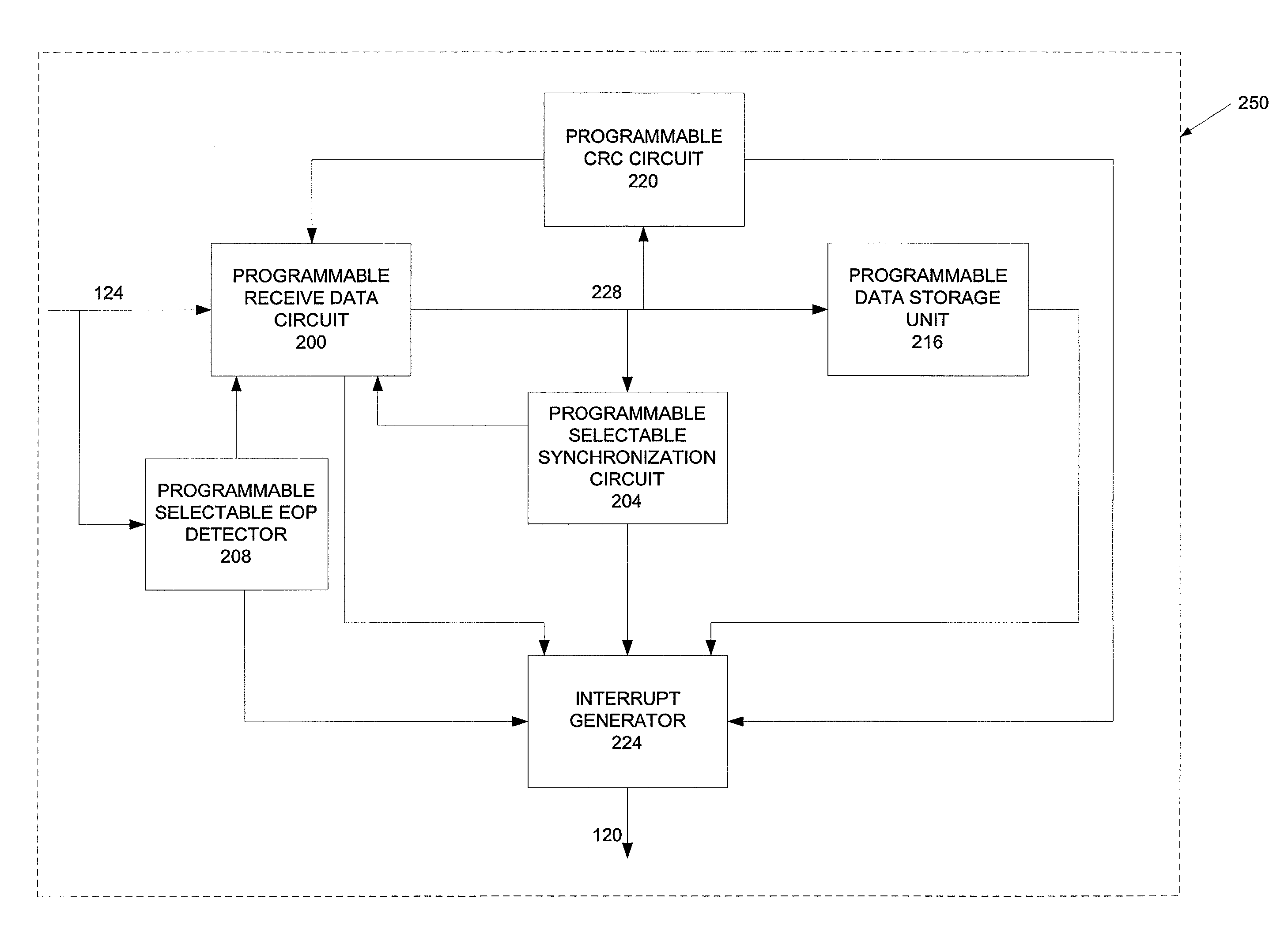

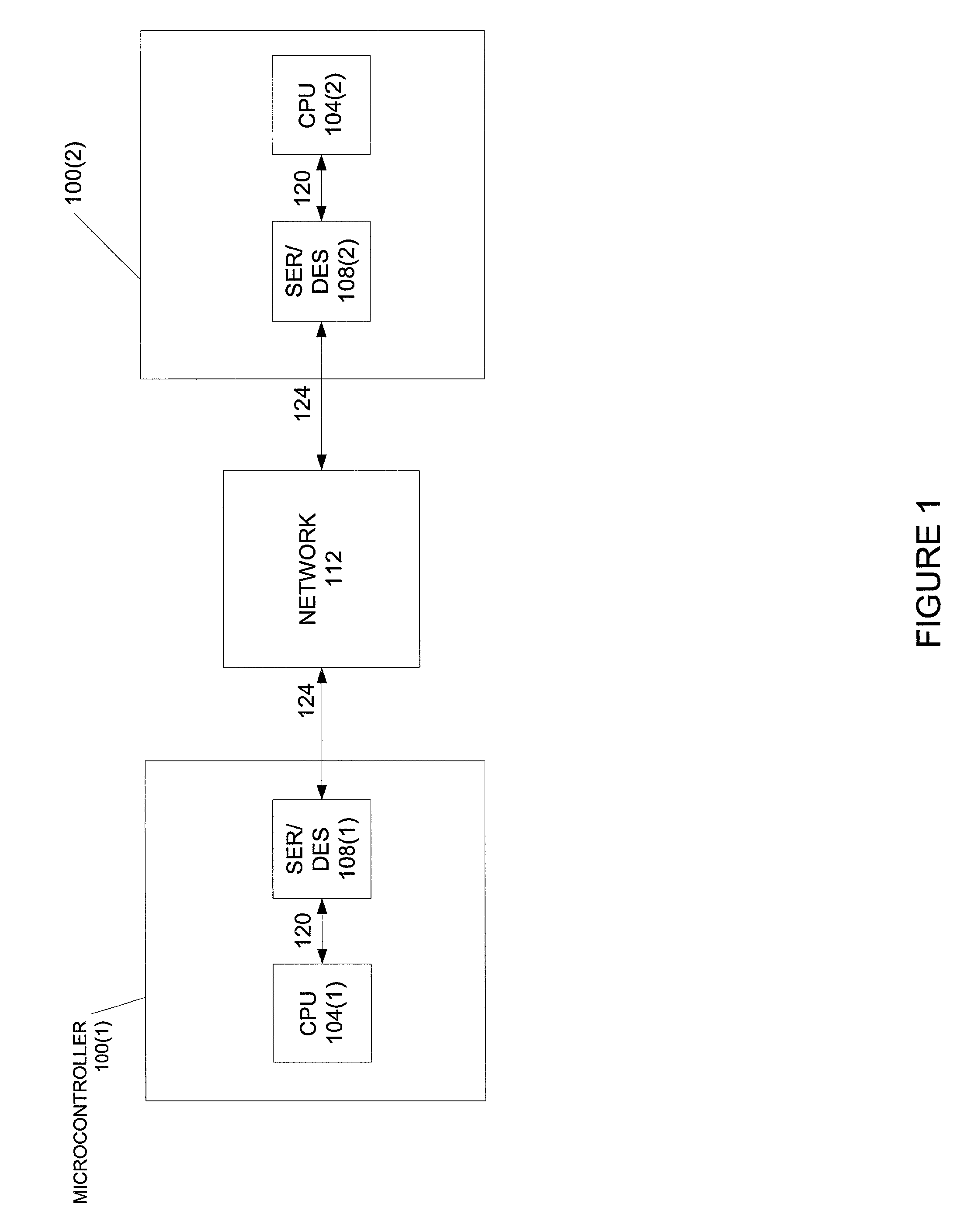

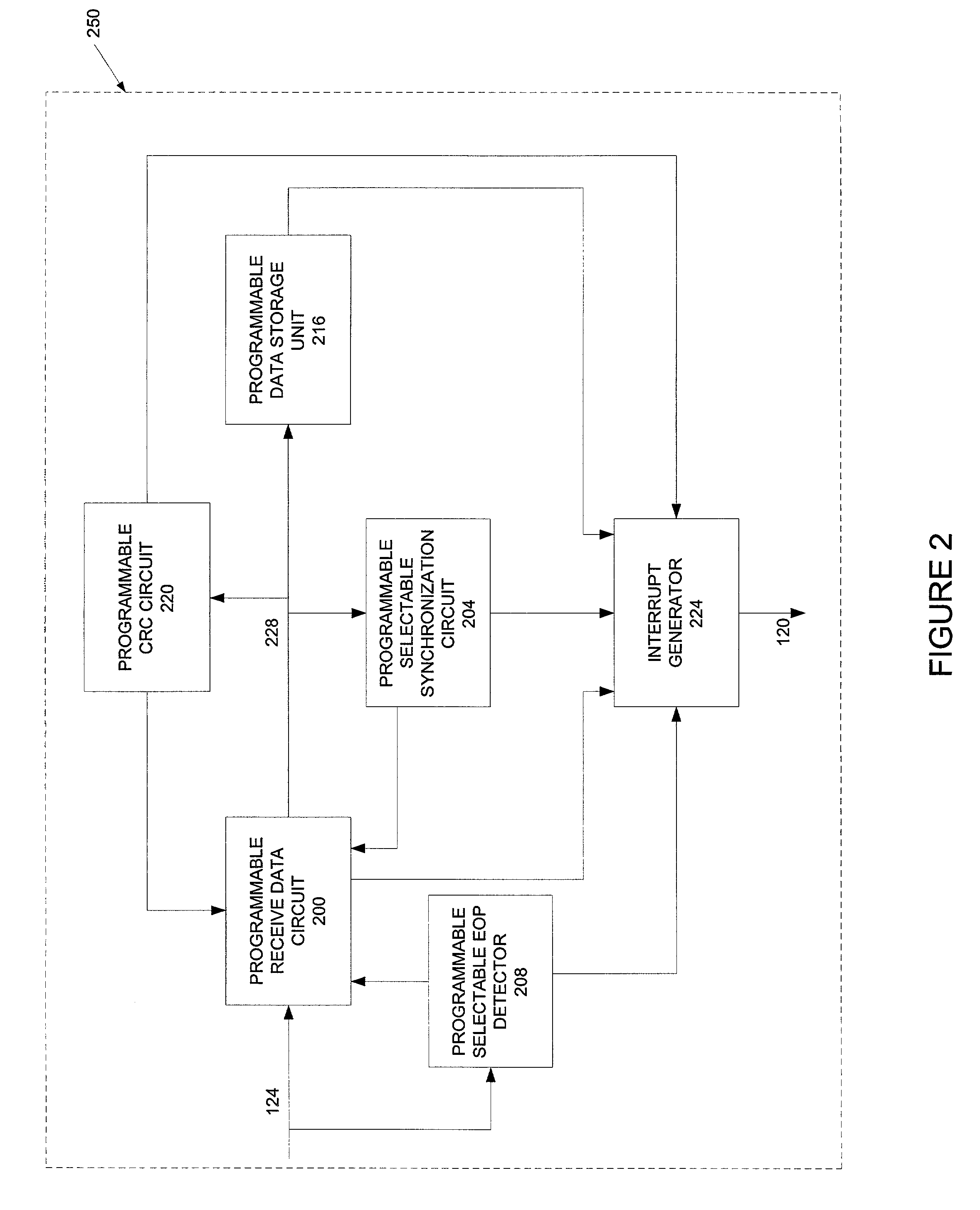

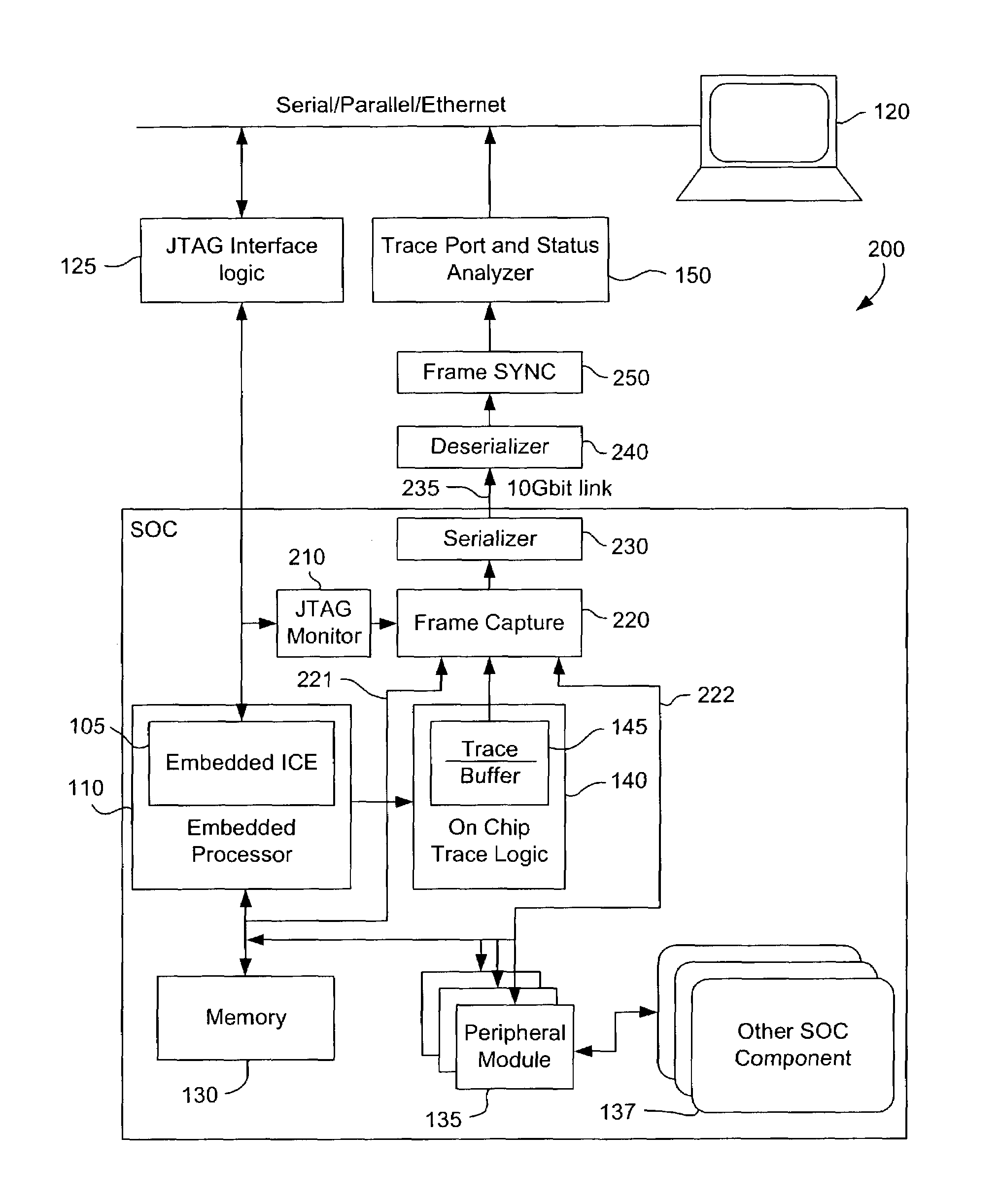

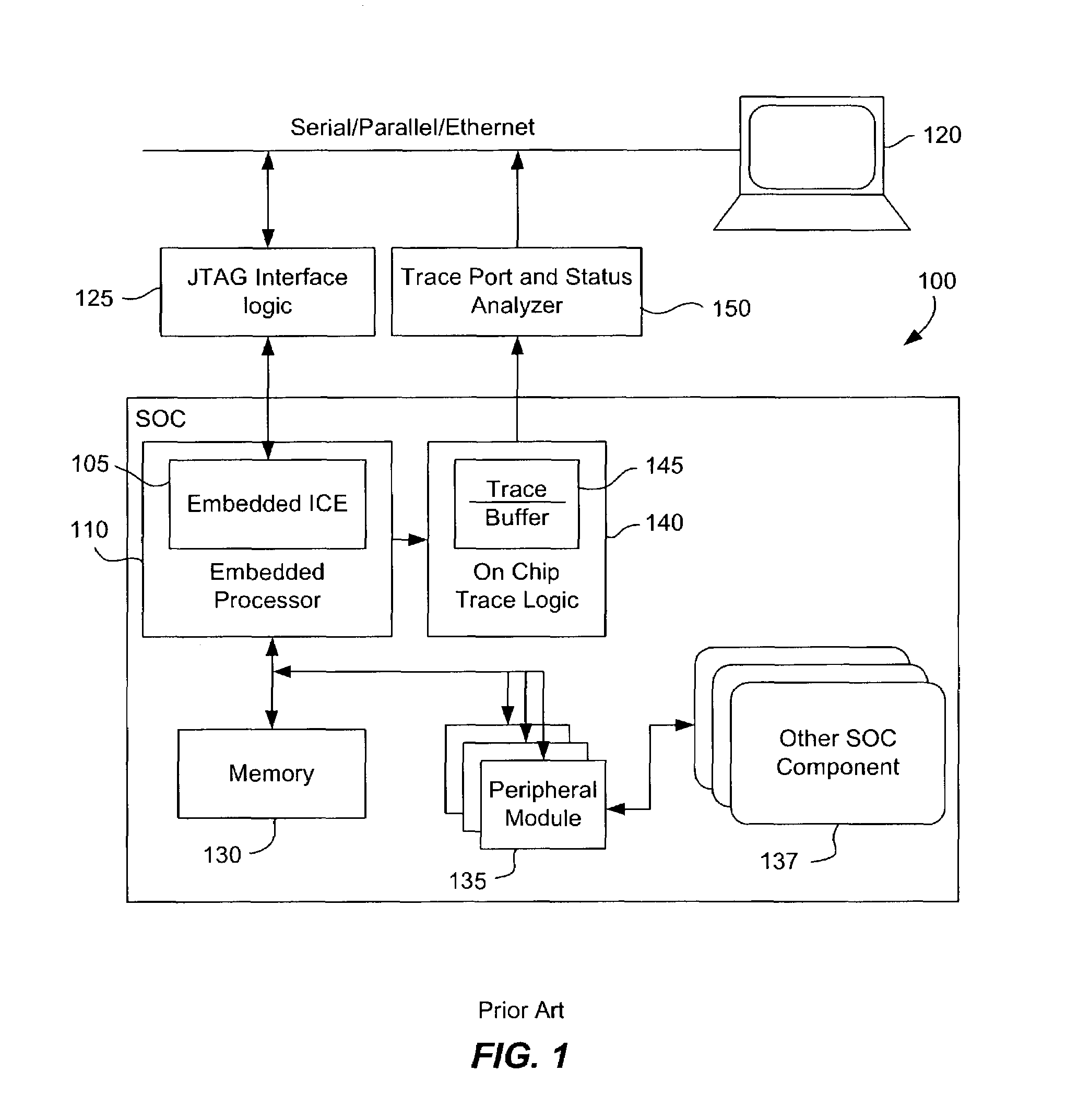

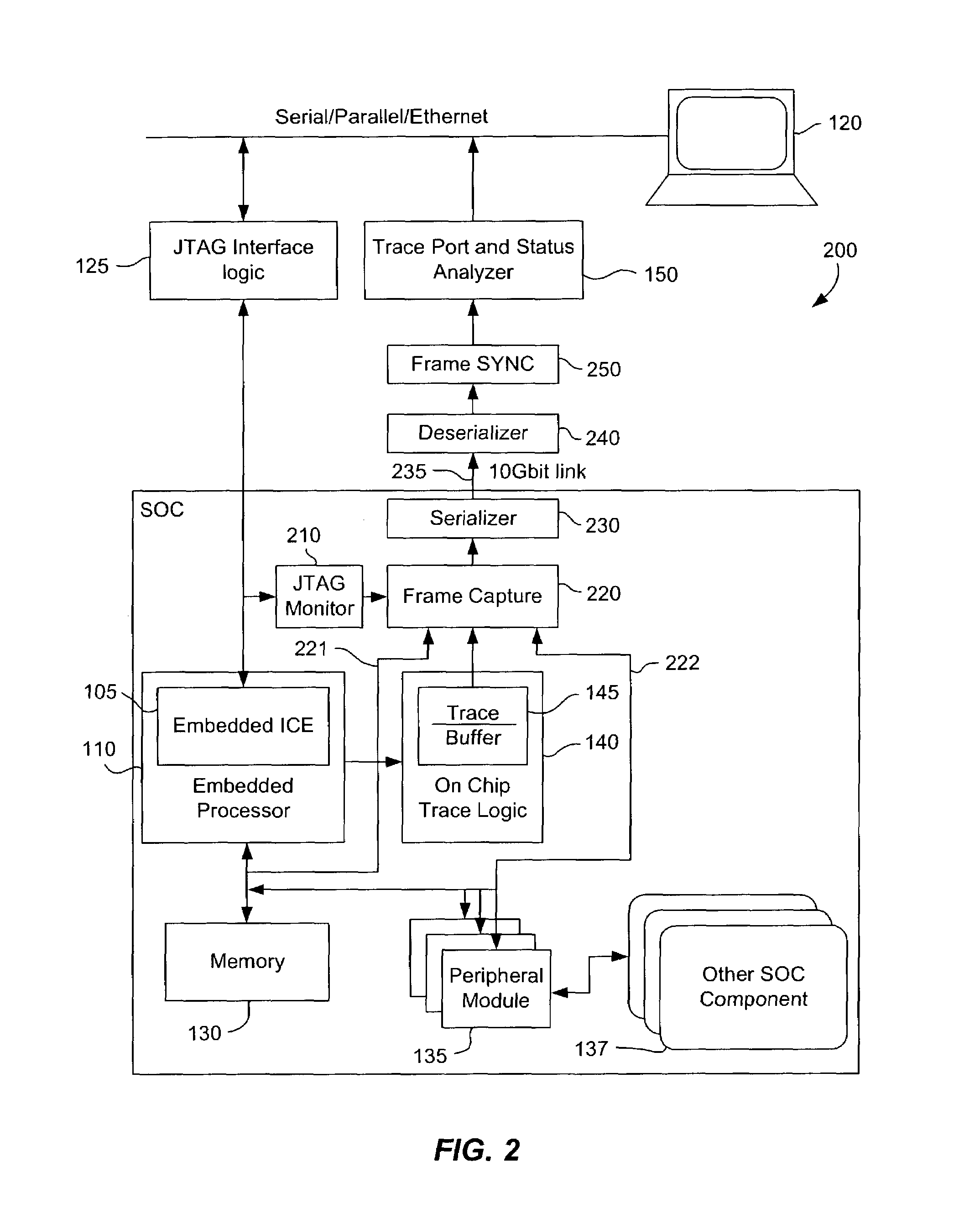

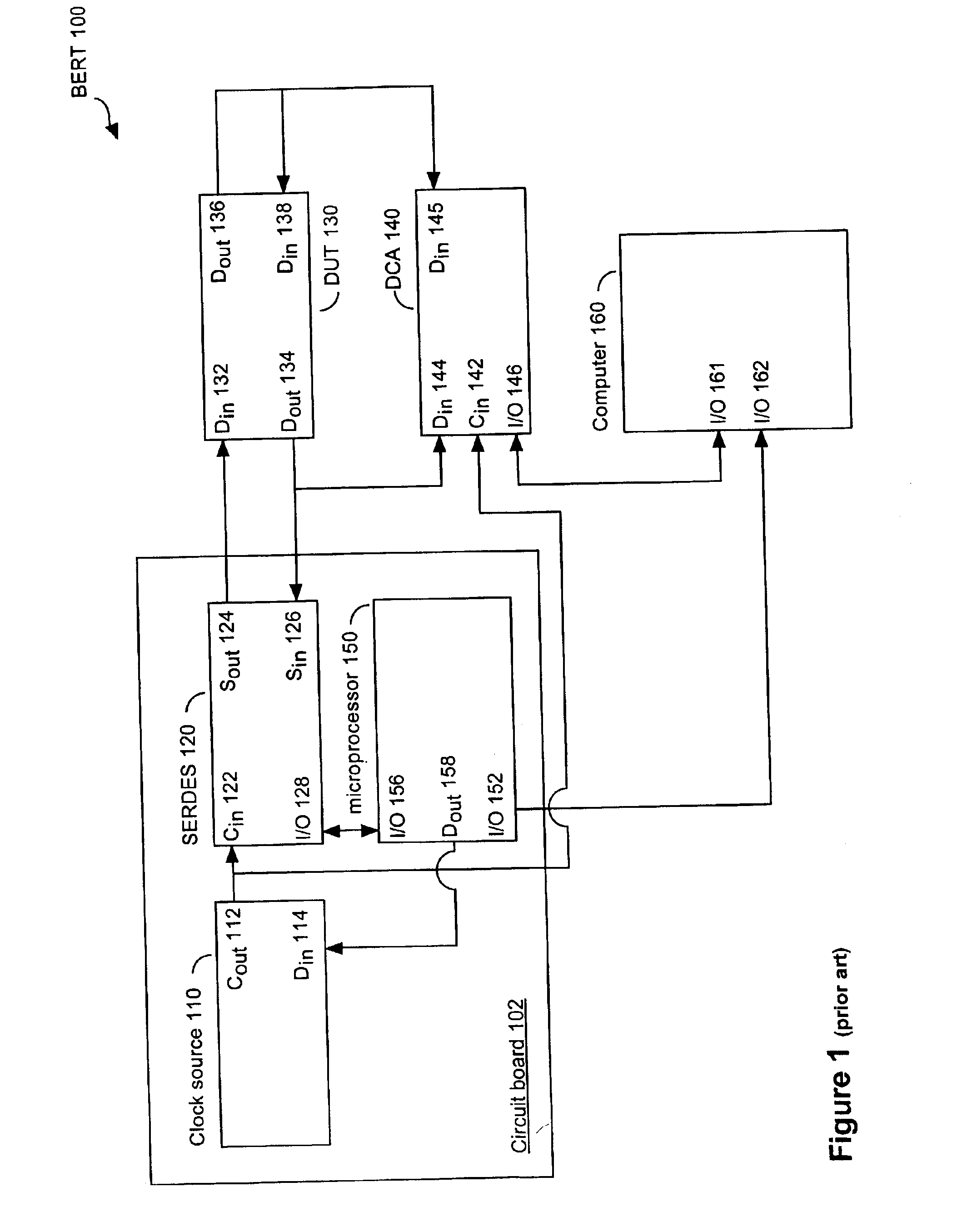

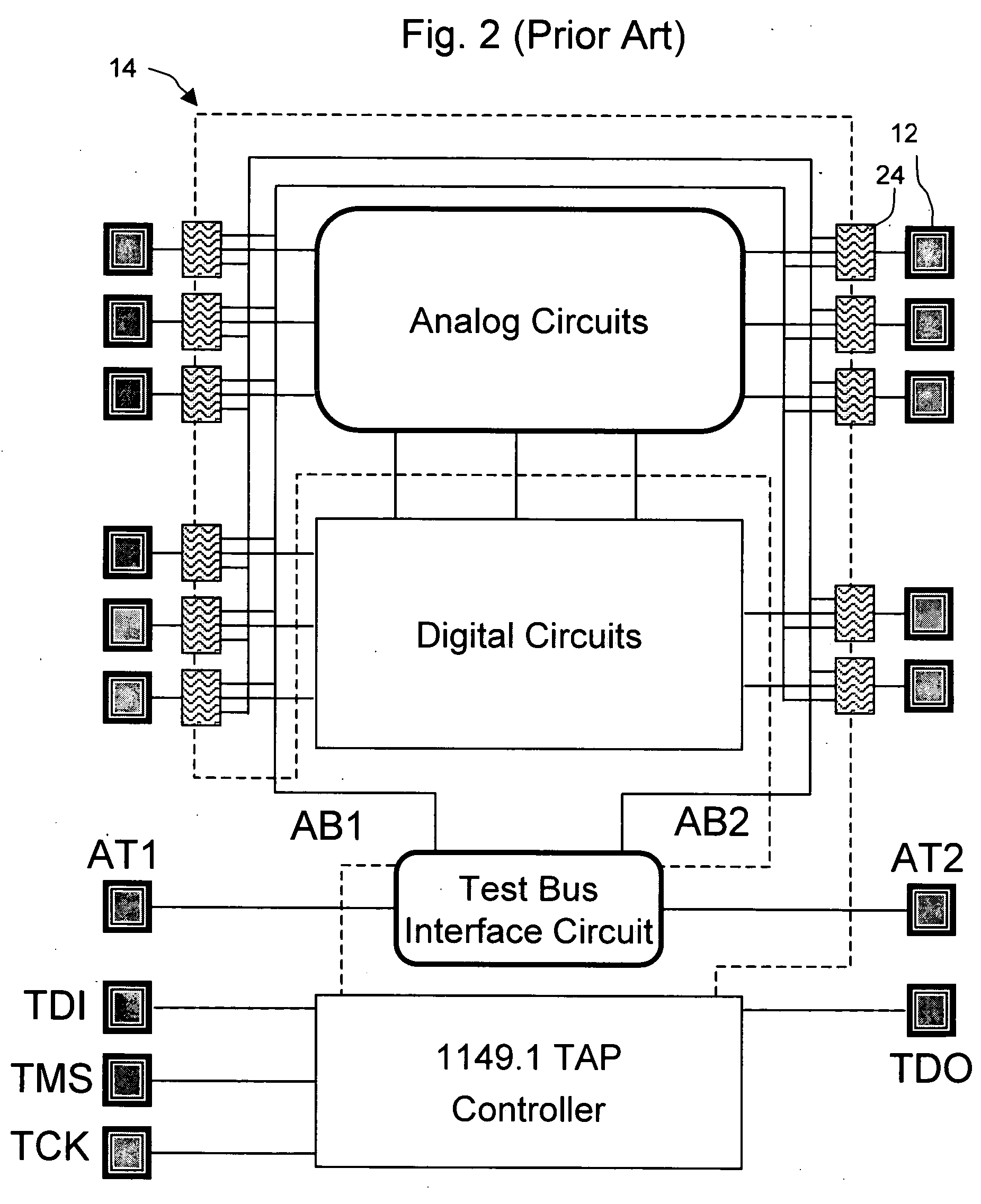

Apparatus and method for testing and debugging an integrated circuit

An integrated circuit which utilizes a serial trace output interface instead of the known parallel trace output interface for transferring test data from the integrated circuit, thereby reducing the number of pins needed for outputting test data. Specifically, a preferred embodiment of the present invention uses a serializer / deserializer (SERDES) interface which captures output testing data in frames, serializes the framed data, and outputs the serialized data on at least one pin. The output serialized data is deserialized, and the deserialized data is synchronized in order to find the frame boundaries. The synchronized frames are then unpacked to retrieve the original testing data. Another preferred embodiment of the present invention uses a bi-directional SERDES both for inputting testing and debugging instructions and data from the analysis software and for outputting testing and debugging results and data to the analysis software.

Owner:MARVELL ASIA PTE LTD

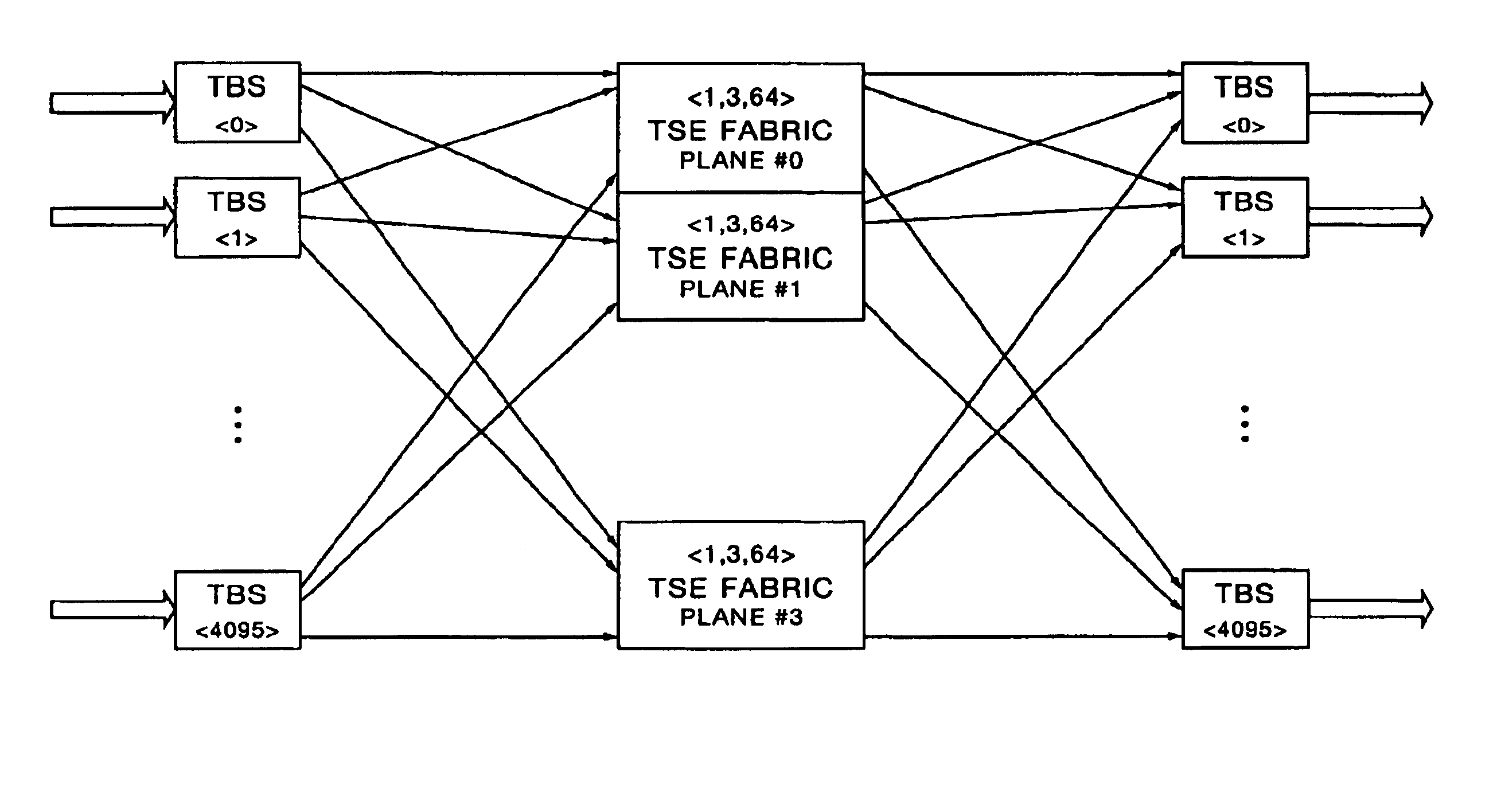

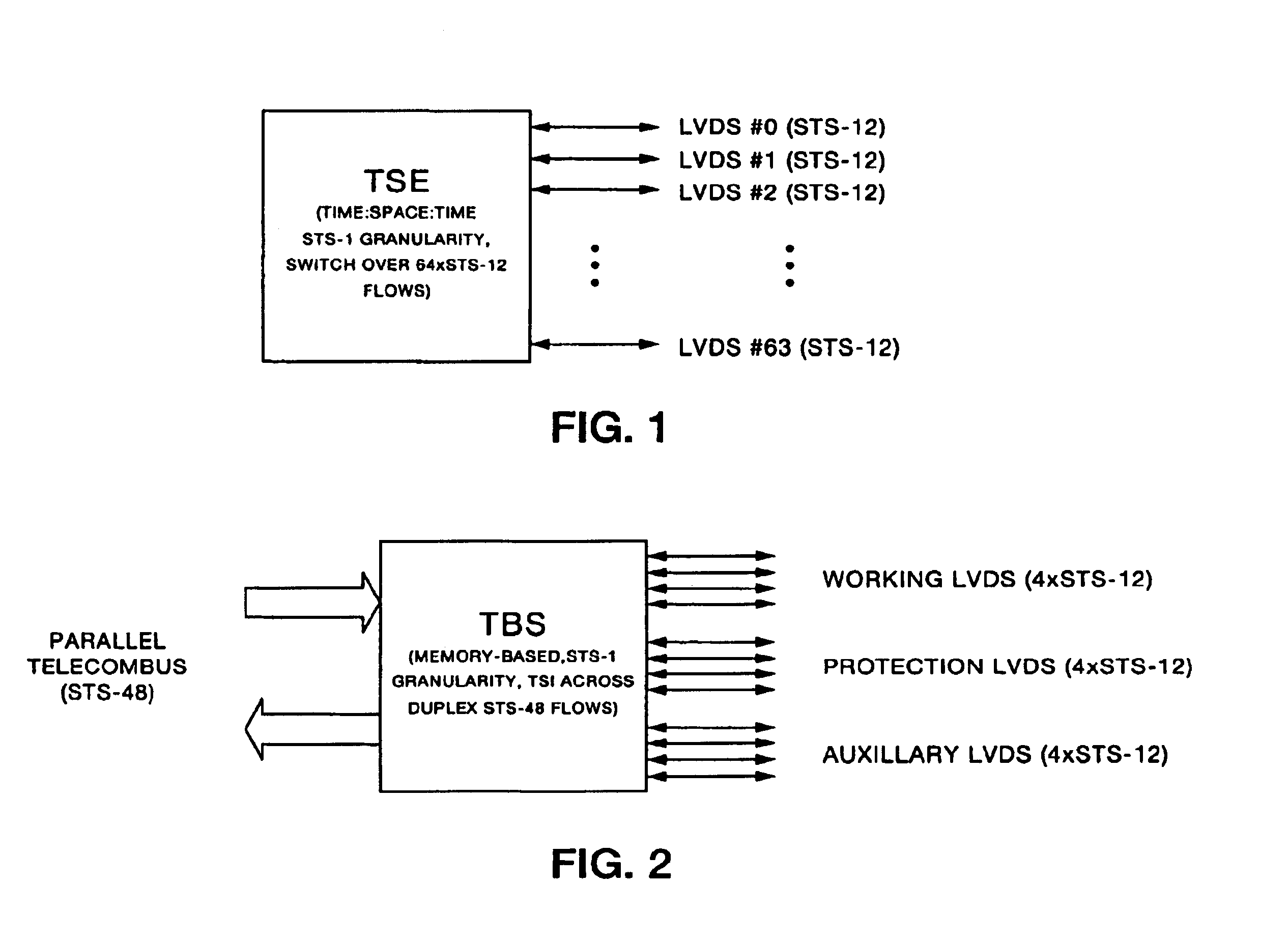

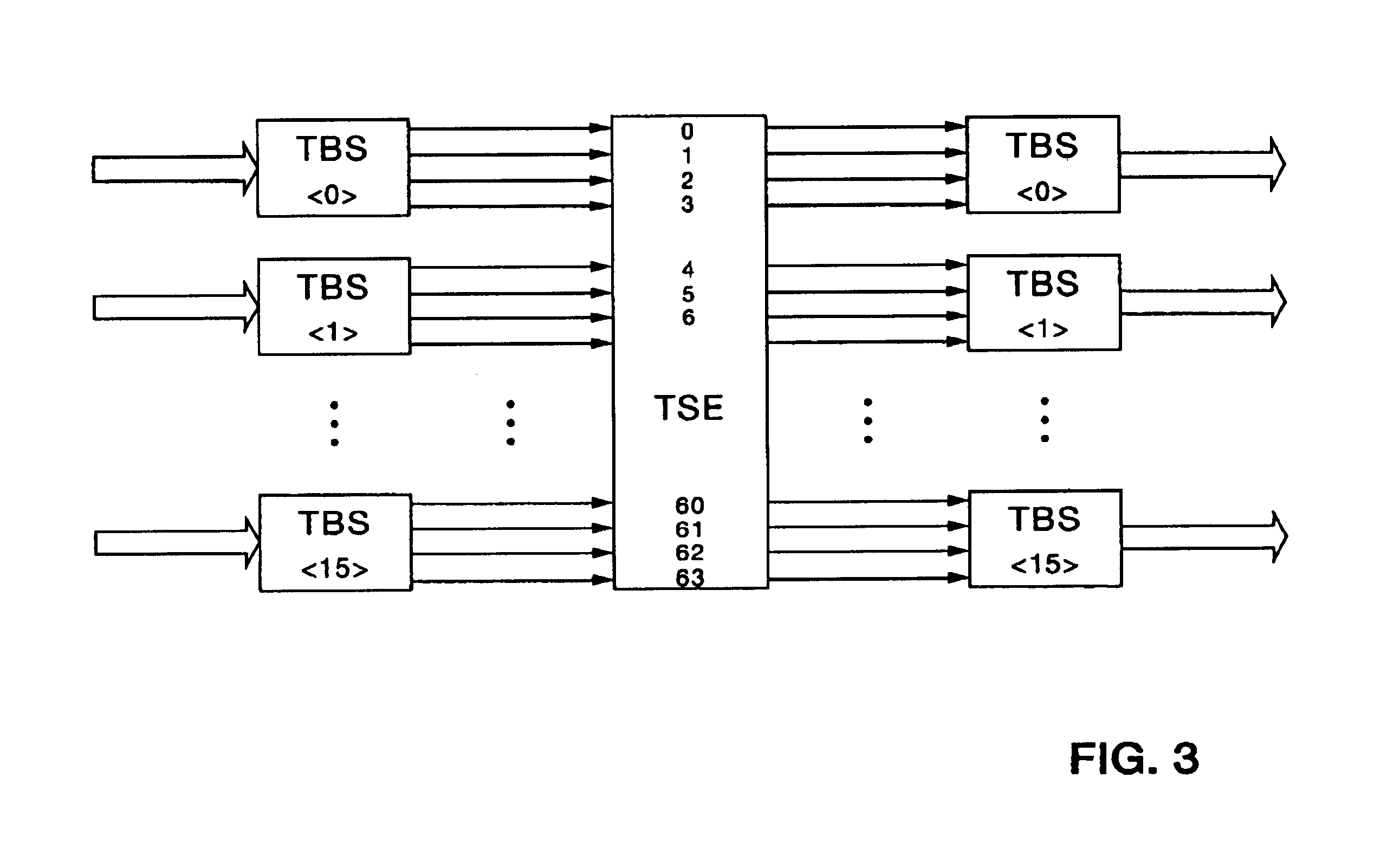

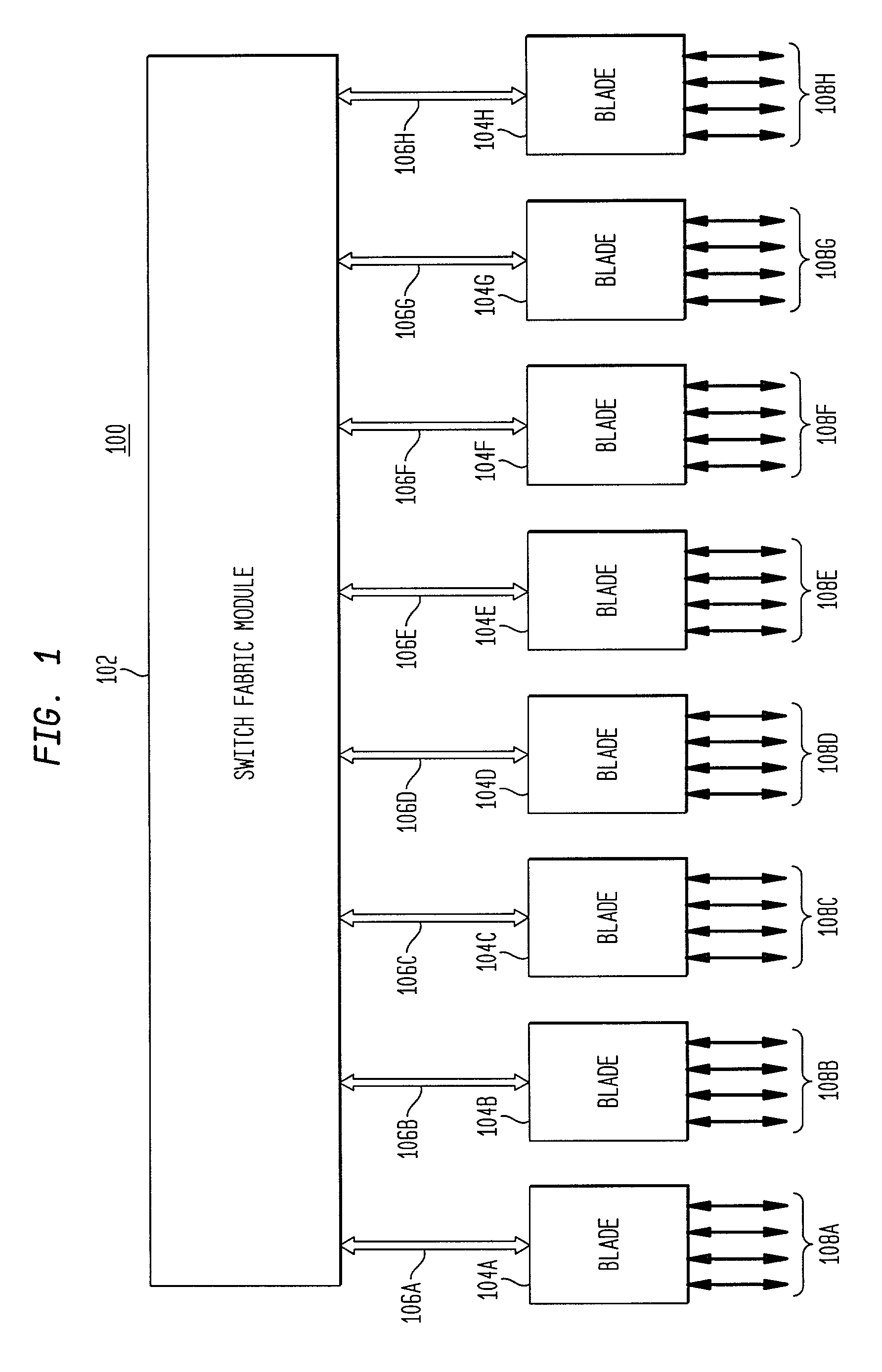

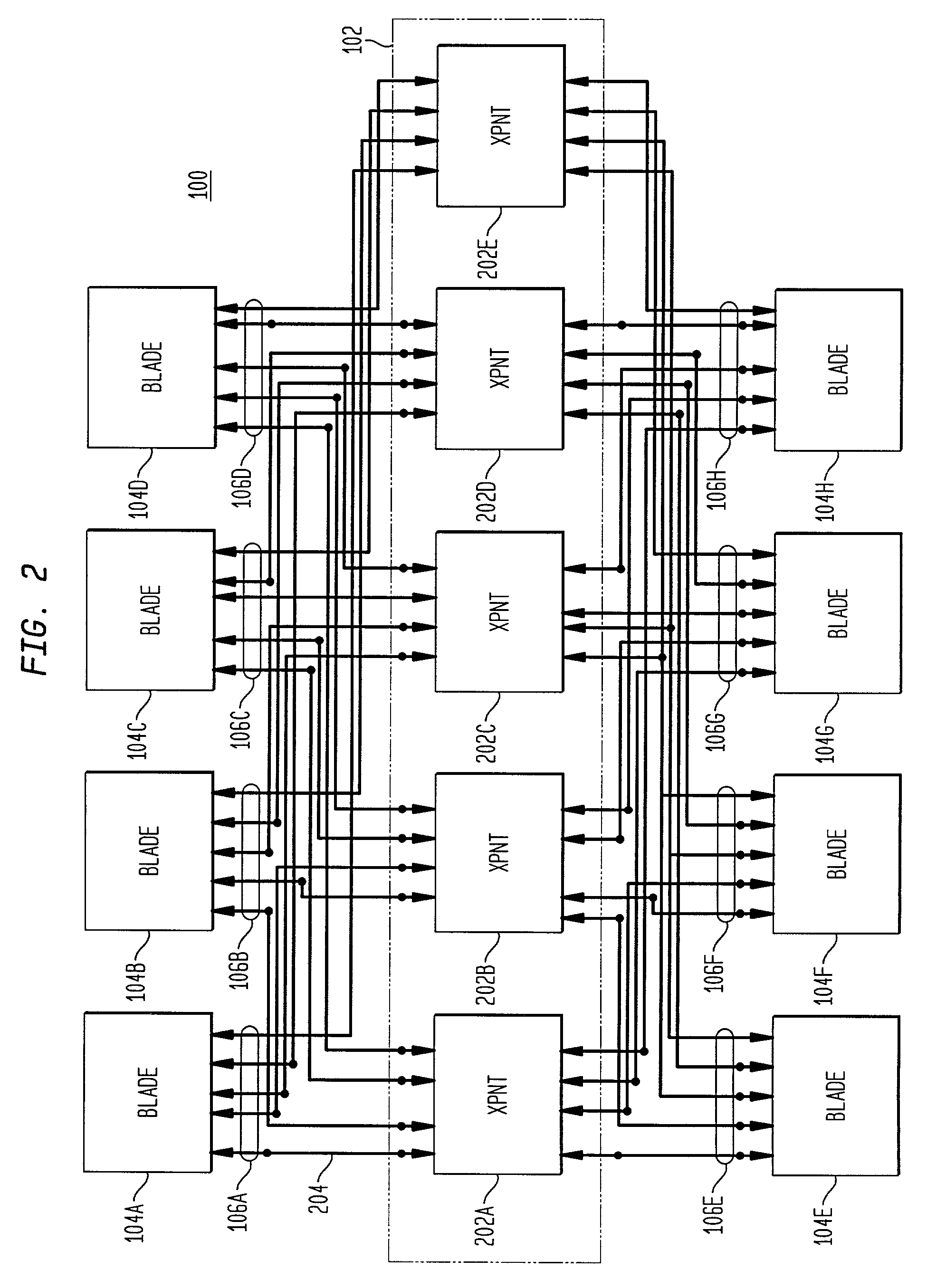

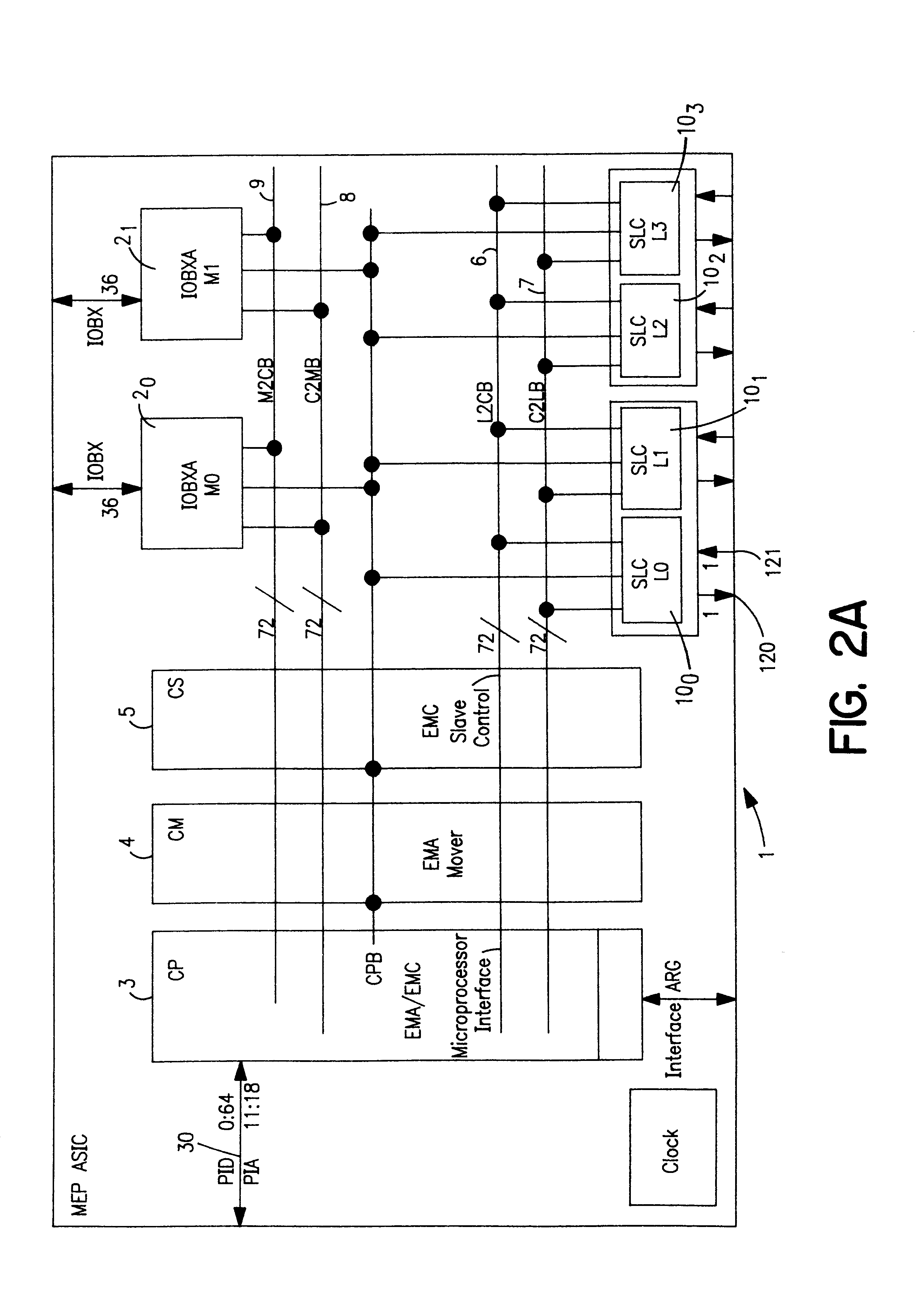

Flexible, self-aligning time and space switch fabrics

A time:space:time switch fabric incorporating an odd integer number of spatially distributed data switches and a plurality of spatially distributed data serializers. Each data switch has a first plurality of ingress ports, an equal plurality of egress ports, and a space switch for selectably interconnecting any one of the ingress ports to any one of the egress ports. Each data serializer has an input bus for receiving signals to be routed through the switch fabric, an output bus for outputting signals routed through the switch fabric, a plurality of egress ports selectably connectible to any one of the data switch ingress ports, and an equal plurality of ingress ports selectably connectible to any one of the data switch egress ports. The ingress / egress ports are characterized by:(A) p planes, where p is a power-of-two integer less than or equal to the number of data serializer ingress and egress ports;(B) s stages, where s is an odd integer number; and,(C) a depth d, where d is a power-of-two integer less than or equal to the number of data switch ingress and egress ports.

Owner:PMC-SIERRA

System and Method for Providing and Displaying Information Content

InactiveUS20100228880A1Large displayLarge facilityDigital data information retrievalMultiple digital computer combinationsScrollingClient-side

A system and method is provided for enabling an electronic device to efficiently access information content. A server browser accesses the information content over a network. The accessed information content is retrieved and adapted for presentation for the electronic device. A serializer dynamically formats the adapted information content according to a client browser. The client browser receives and presents the information content on the electronic device. An event translator is included to provide additional compatibility with commercially available client browsers. The information content is formatted to selectively minimize the horizontal scrolling required to view the content. The need for horizontal scrolling is selectively removed where not necessary to preserve the context. Each component or sub-component of the original area, such as a frame, table row, table cell or nested table, is considered separately and may be preserved, resized, or replaced. Where the context requires that the content be wider than the viewable area of the screen, horizontal scrolling is preserved.

Owner:NOKIA CORP

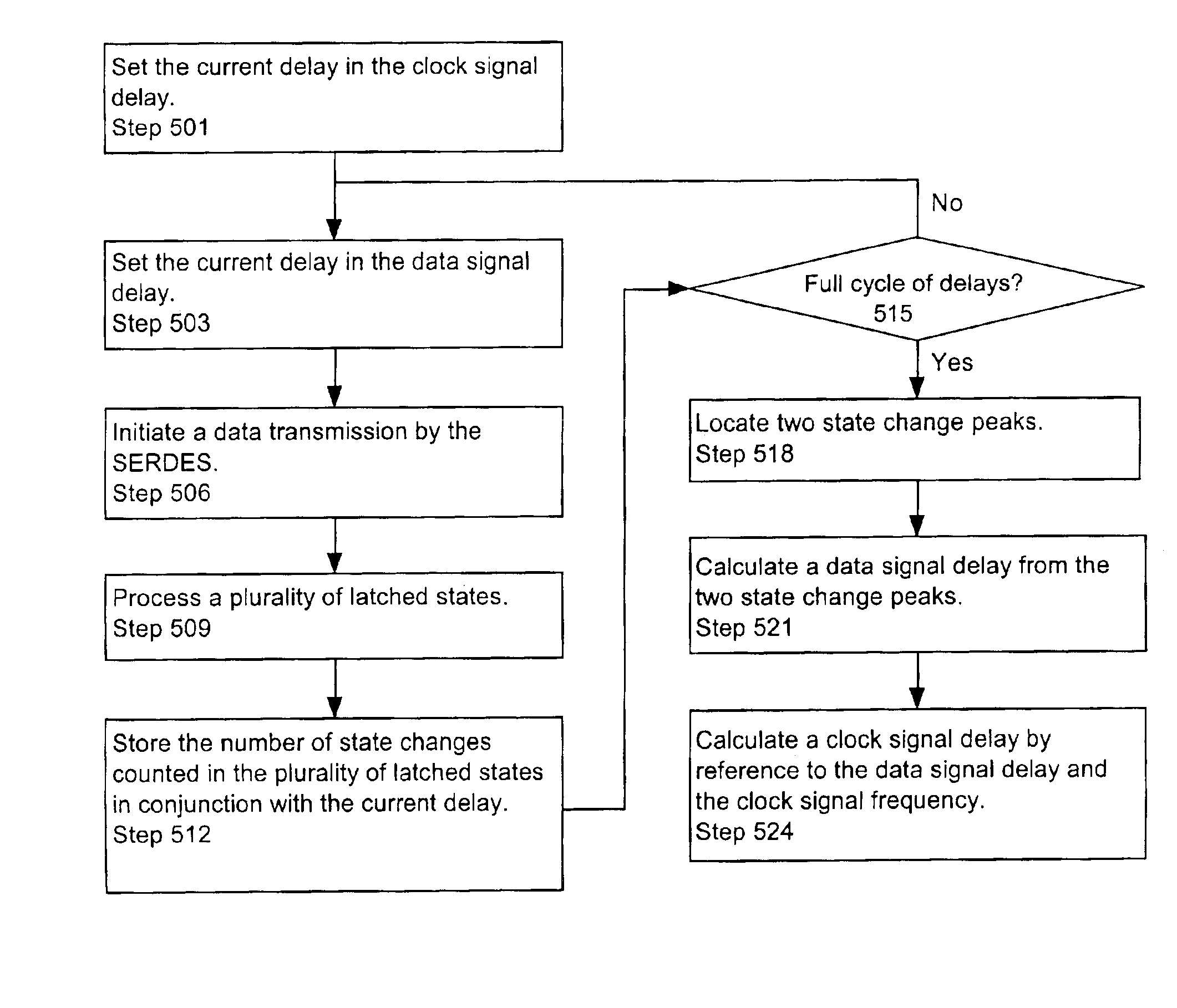

System and method of processing a data signal

InactiveUS6937949B1Reducing and eliminating jitterDigital circuit testingNoise figure or signal-to-noise ratio measurementData signalSerializer

Systems and methods for testing bit processing capacities of electronic devices and for reducing or eliminating jitter that compromises the ability of electronic devices to perform this task. Embodiments include circuitry and a methodology for locating and employing a data signal delay—in conjunction with a latch—to reduce or eliminate jitter from serial encoded data generated by a serializer / deserializer. The data signal delay ensures that the latch latches a state of the serial encoded data at a position within a data signal cycle of minimum jitter.

Owner:II VI DELAWARE INC

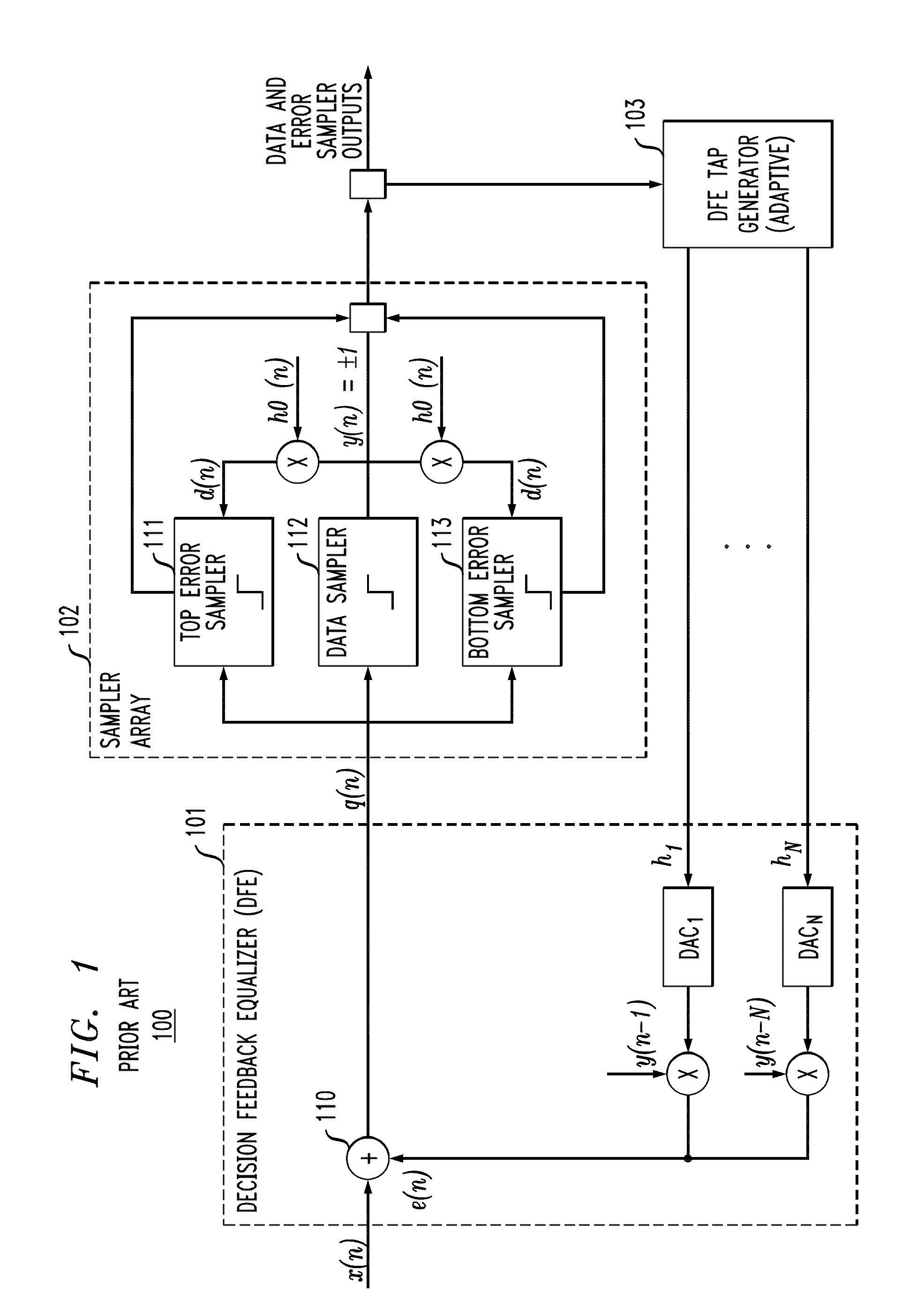

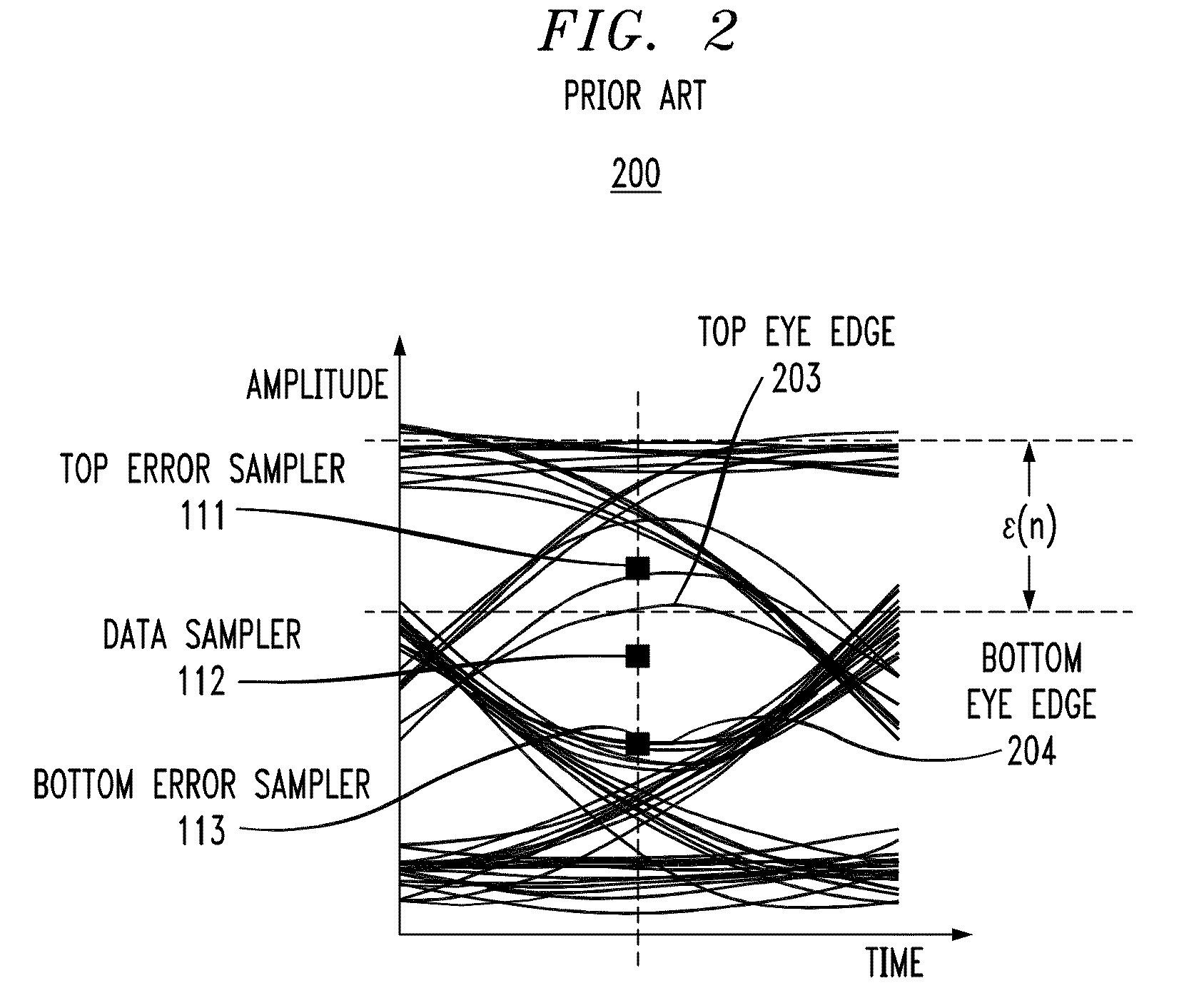

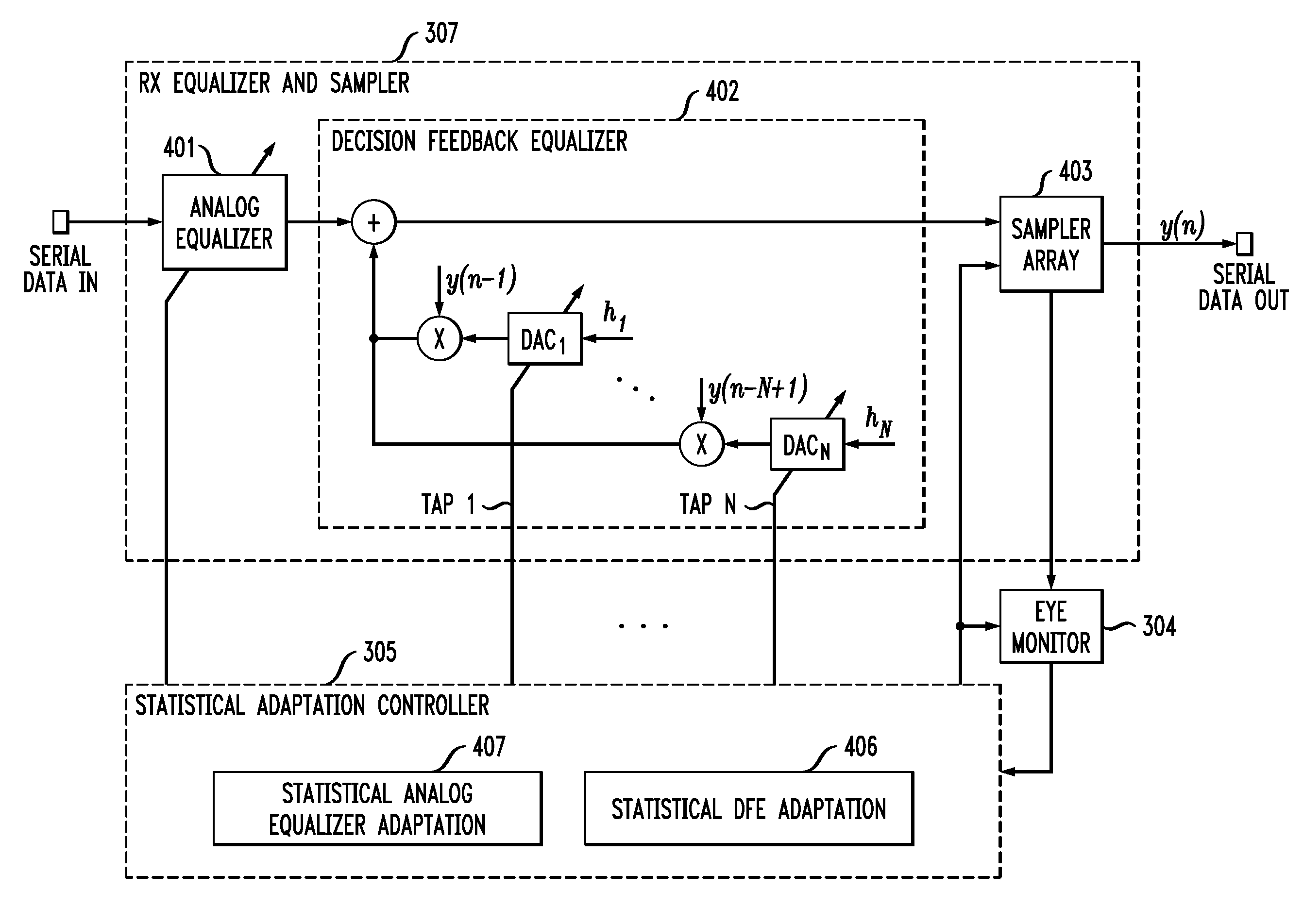

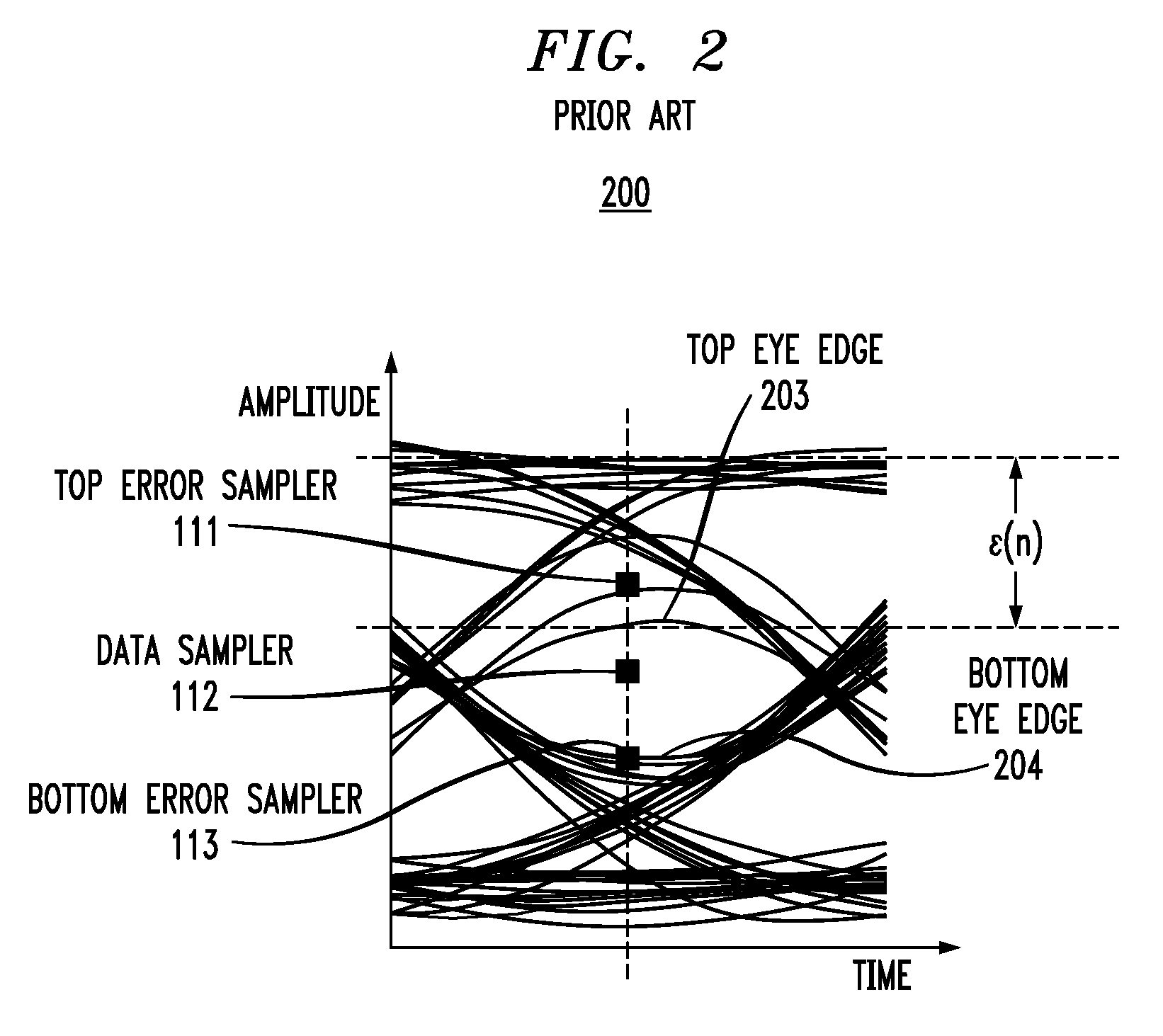

Real-Time Eye Monitor for Statistical Filter Parameter Calibration

In described embodiments, filter parameters for a filter applied to a signal in, for example, a Serializer / De-serializer (SerDes) receiver and / or transmitter are generated based on real-time monitoring of a data eye. The real-time eye monitor monitors data eye characteristics of the signal present in a data path, the data path applying the filter to the signal. The eye monitor generates eye statistics from the monitored data eye characteristics and an adaptive controller generates a set of parameters for the filter of the data path for statistical calibration of the data eye, wherein the eye monitor continuously monitors the data eye and the adaptive controller continuously generates the set of parameters based on the eye statistics.

Owner:LSI CORPORATION

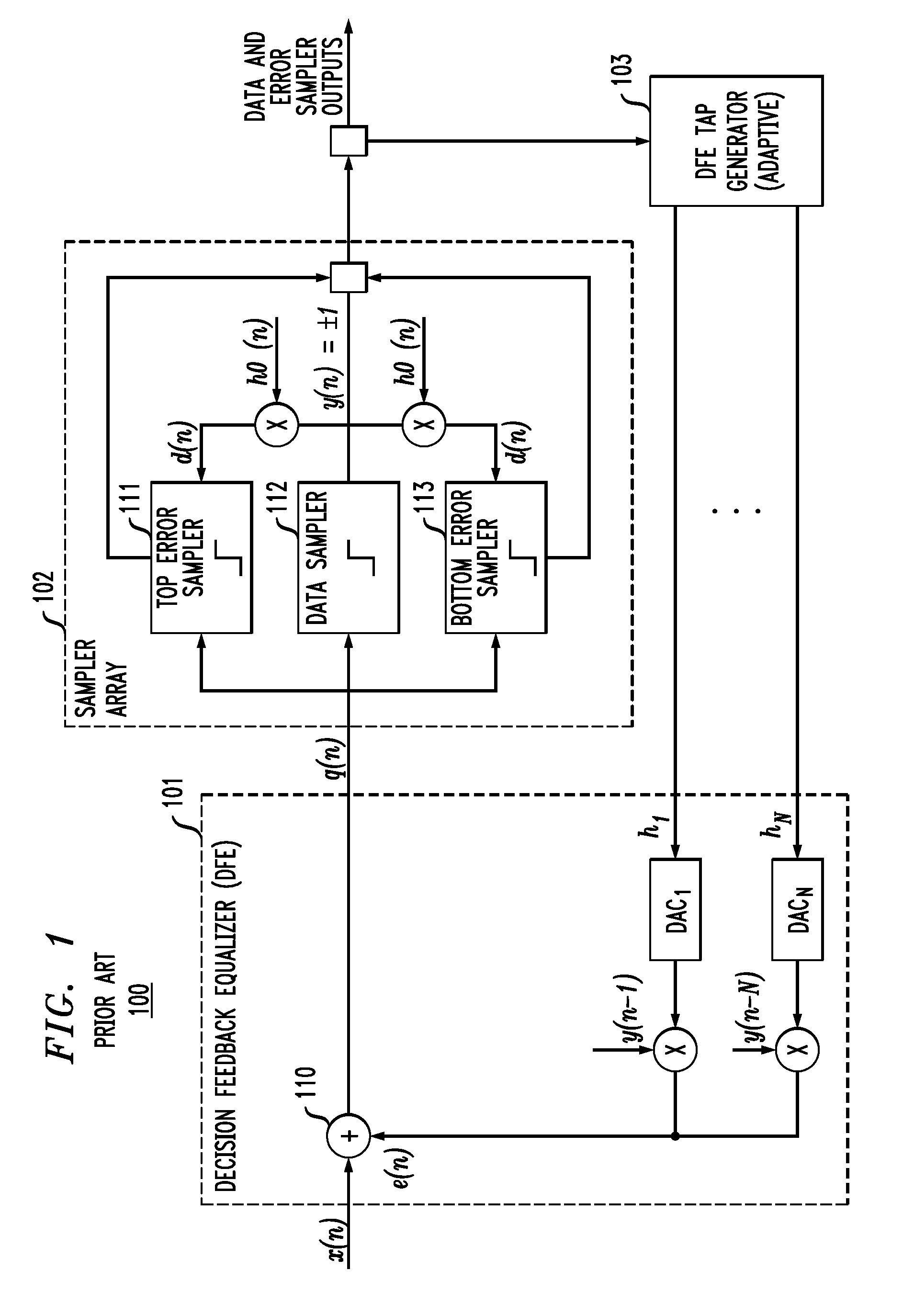

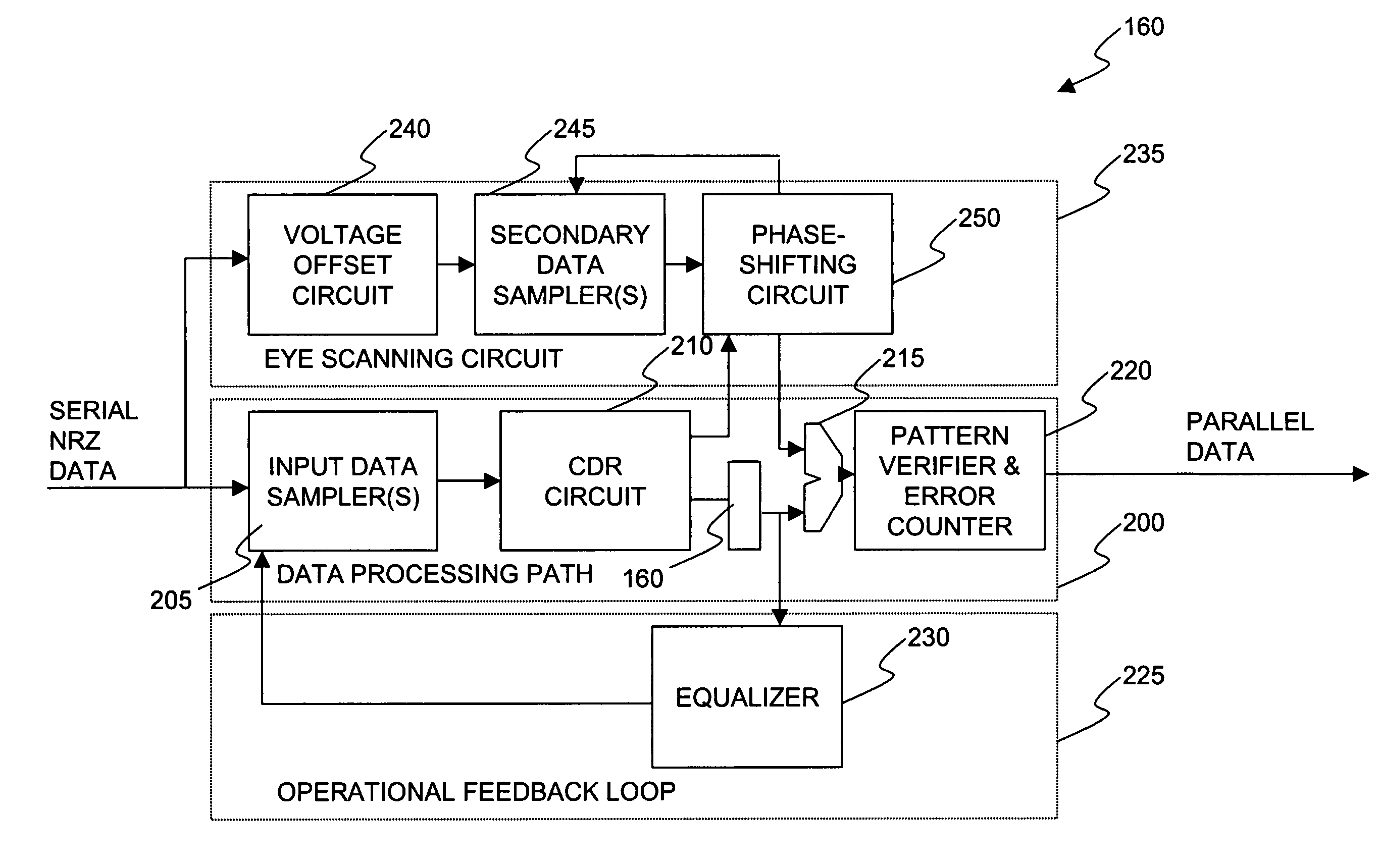

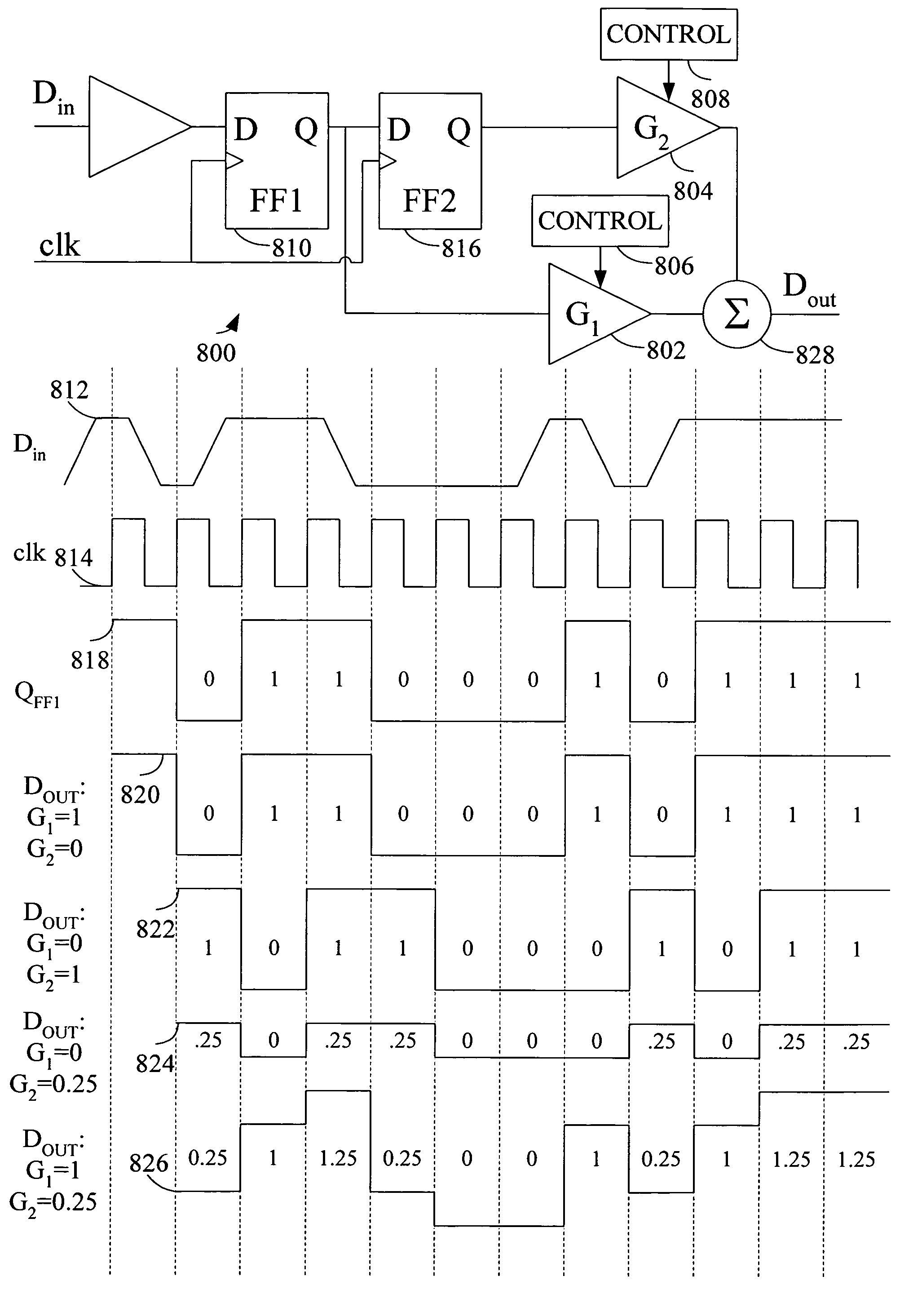

Circuit and method for evaluating the performance of an adaptive decision feedback equalizer-based serializer deserializer and serdes incorporating the same

A circuit and method for evaluating serializer deserializer (SERDES) performance that is particularly advantageous when the SERDES has a decision feedback equalizer (DFE). In one embodiment, the circuit has a data processing path and an operational feedback loop coupled to said data processing path and containing an equalizer, perhaps a DFE. In that embodiment, the circuit includes an eye scanning circuit coupled to said data processing path but separate from said equalizer and configured to measure at least one dimension of an eye relative to which said equalizer is configured for operation without substantially affecting said operation.

Owner:TEXAS INSTR INC

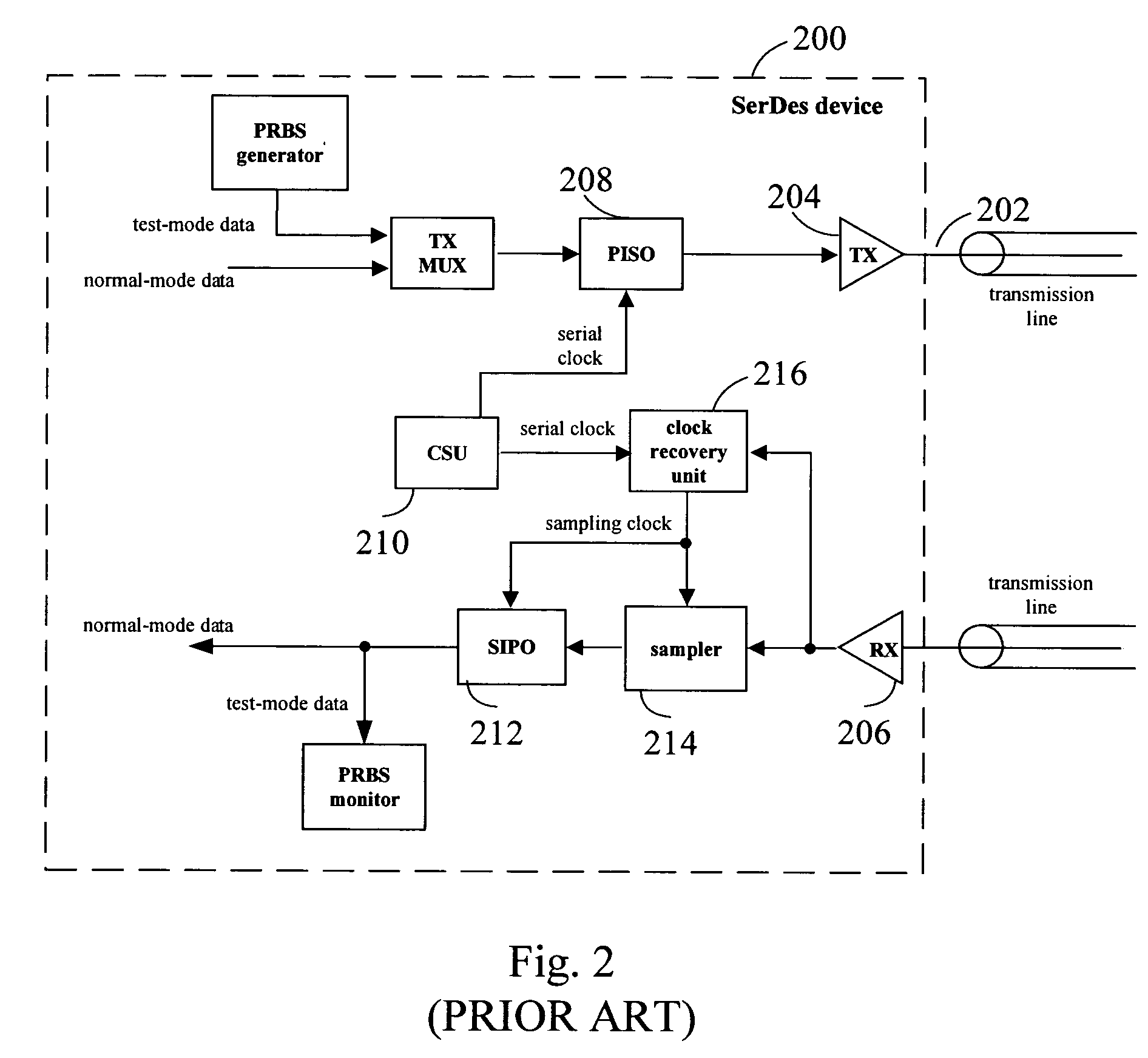

Built in self test (BIST) for high-speed serial transceivers

InactiveUS7756197B1Advantageously highly scaleableIncrease data rateCorrect operation testingTransmission monitoringFinite impulse responseTransceiver

A relatively high-speed serial data transmitter incorporates built in self test (BIST). The BIST circuit advantageously provides tests modes to obviate the need to build expensive test equipment for high-speed serial data devices, such as a serializer / deserializer (SerDes) or other transceivers. Multiple data paths in a finite impulse response (FIR) filter of transmitter of the SerDes or a transceiver can be independently tested. The transmitter output can also be selectively degraded to test a receiver of a transceiver. An attenuated output signal can be provided to test receiver sensitivity. A low-pass filter can be invoked to emulate a backplane, while a loopback circuit can provide the emulated backplane attenuation to the receiver to permit testing of the equalization circuitry of a receiver without requiring the presence of an actual backplane for testing.

Owner:MICROSEMI STORAGE SOLUTIONS

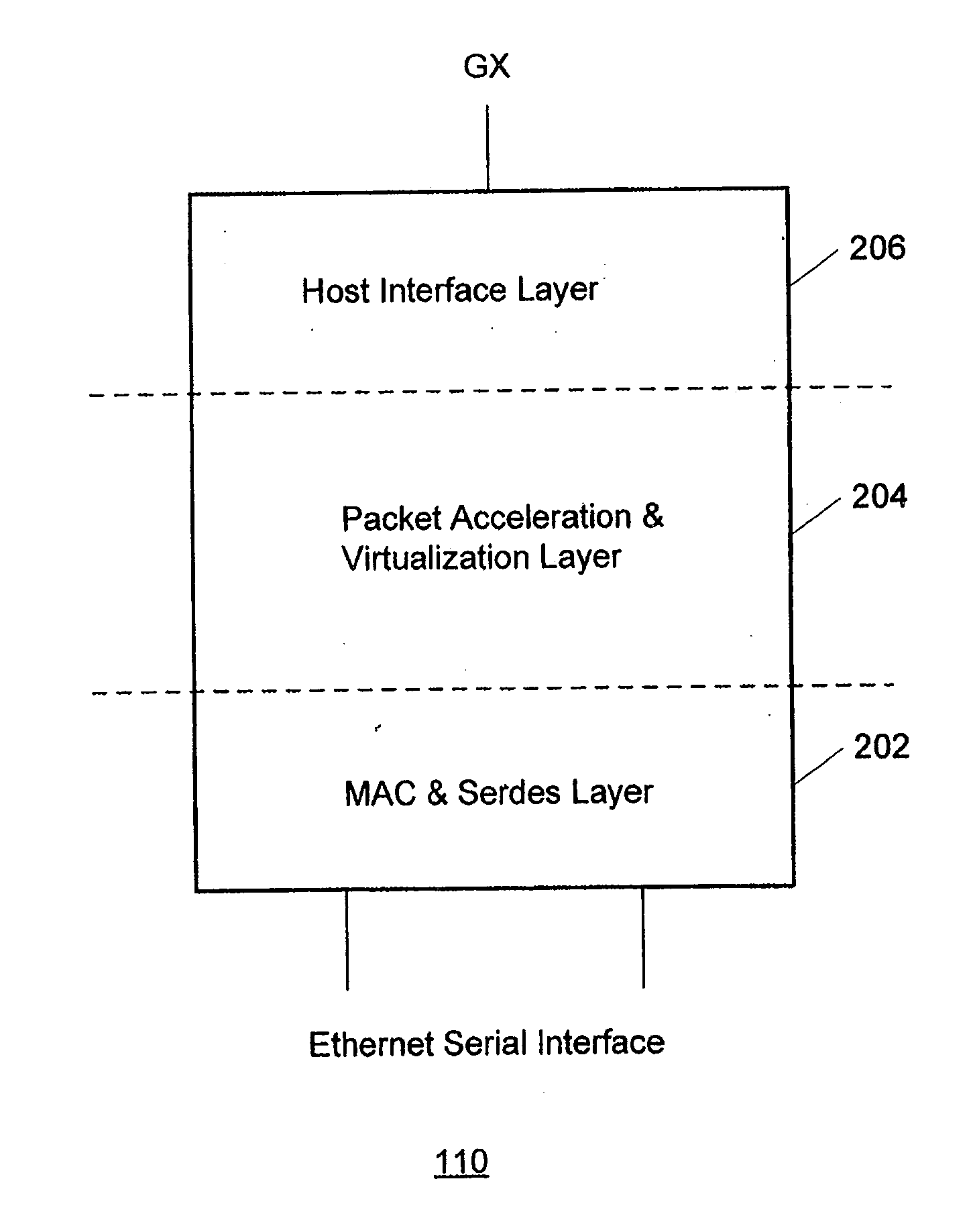

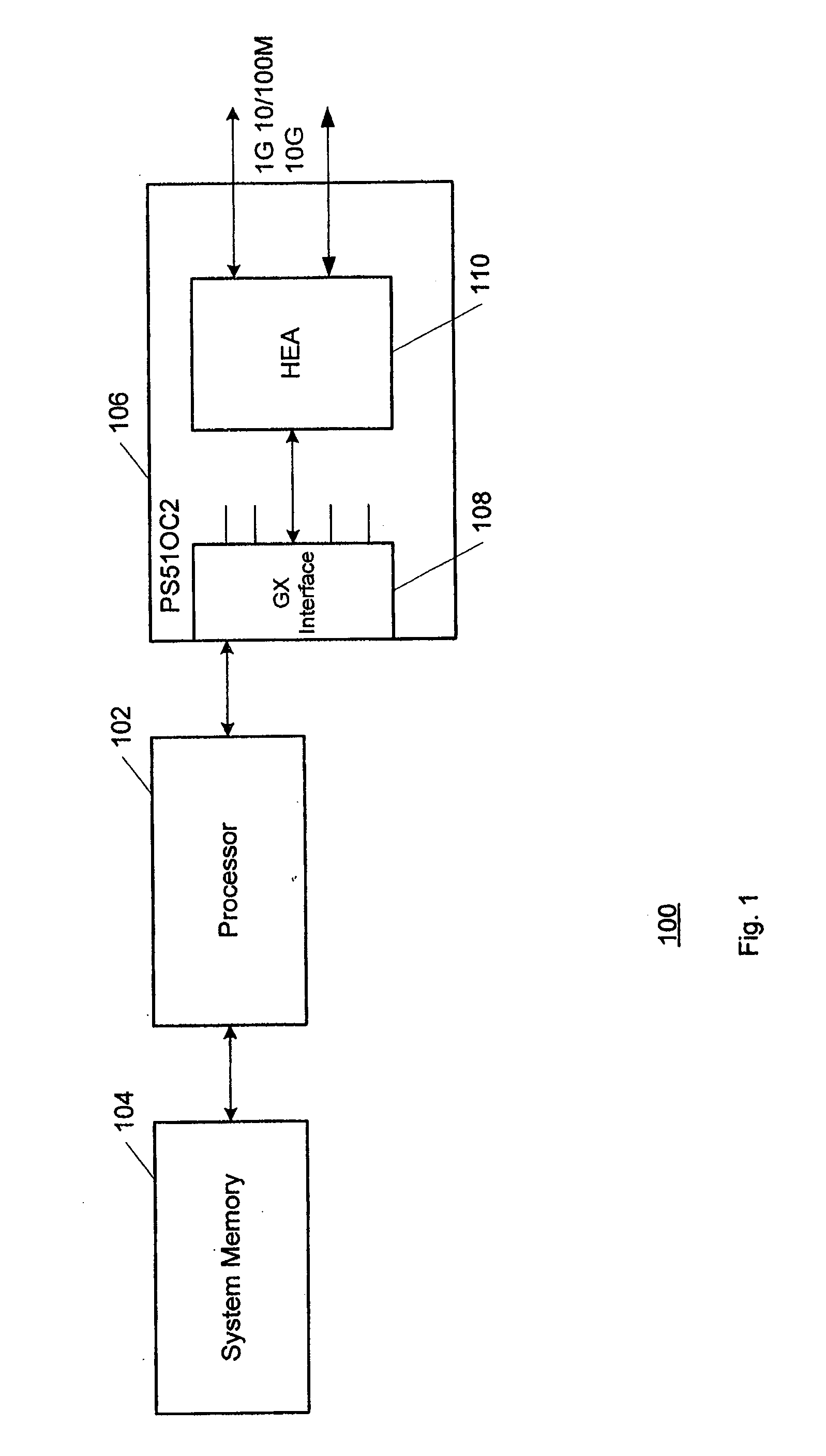

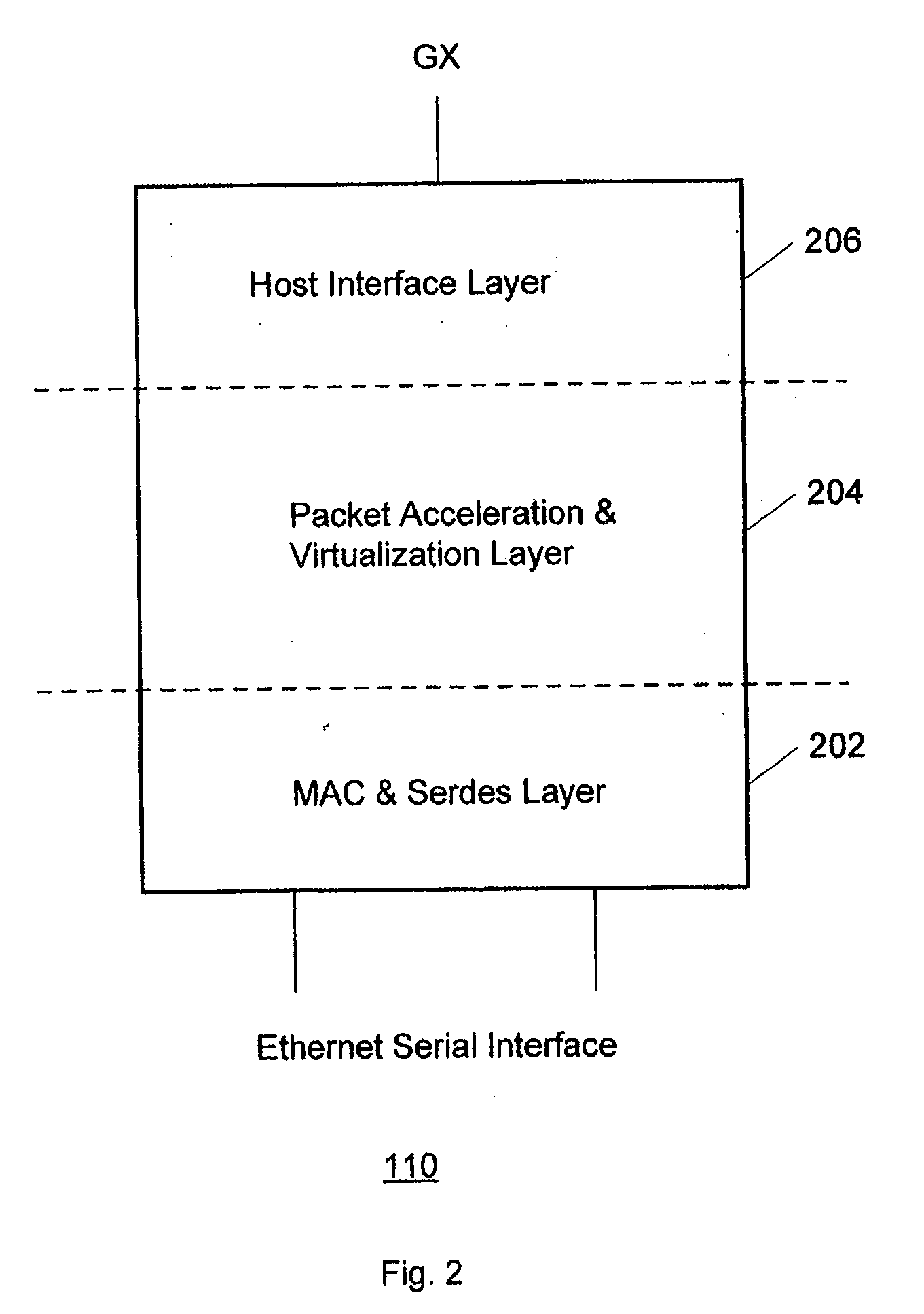

Configurable ports for a host ethernet adapter

A system and method in accordance with the present invention allows for an adapter to be utilized in a server environment that can accommodate both a 10 G and a 1 G source utilizing the same pins. This is accomplished through the use of a high speed serializer / deserializer (high speed serdes) which can accommodate both data sources. The high speed serdes allows for the use of a relatively low reference clock speed on the NIC to provide the proper clocking of the data sources and also allows for different modes to be set to accommodate the different data sources. Finally the system allows for the adapter to use the same pins for multiple data sources.

Owner:INT BUSINESS MASCH CORP

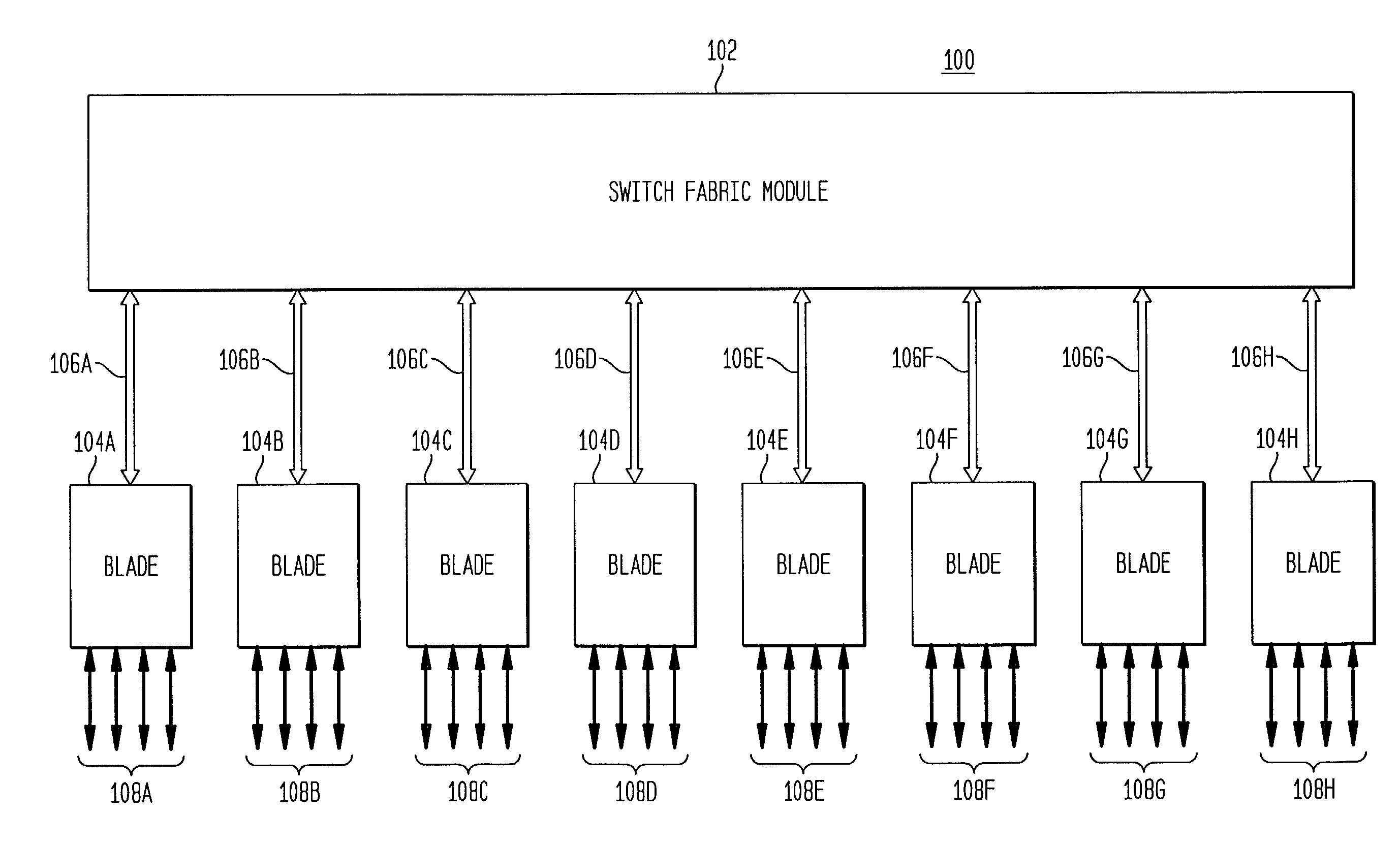

Backplane interface adapter

InactiveUS7236490B2Multiplex communicationData switching by path configurationNetwork switchHigh performance network

A backplane interface adapter for a high-performance network switch. The backplane interface adapter receives narrow input cells carrying packets of data and outputs wide striped cells to a switching fabric. One traffic processing path through the backplane interface adapter includes deserializer receivers, a traffic sorter, wide cell generators, stripe send queues, a backplane transmit arbitrator, and serializer transmitters. Another traffic processing path through the backplane interface adapter includes deserialize receivers, a stripe interface, stripe receive synchronization queues, a controller, wide / narrow cell translator, destination queues, and serializer transmitters. An encoding scheme for packets of data carried in wide striped cells is provided.

Owner:AVAGO TECH INT SALES PTE LTD

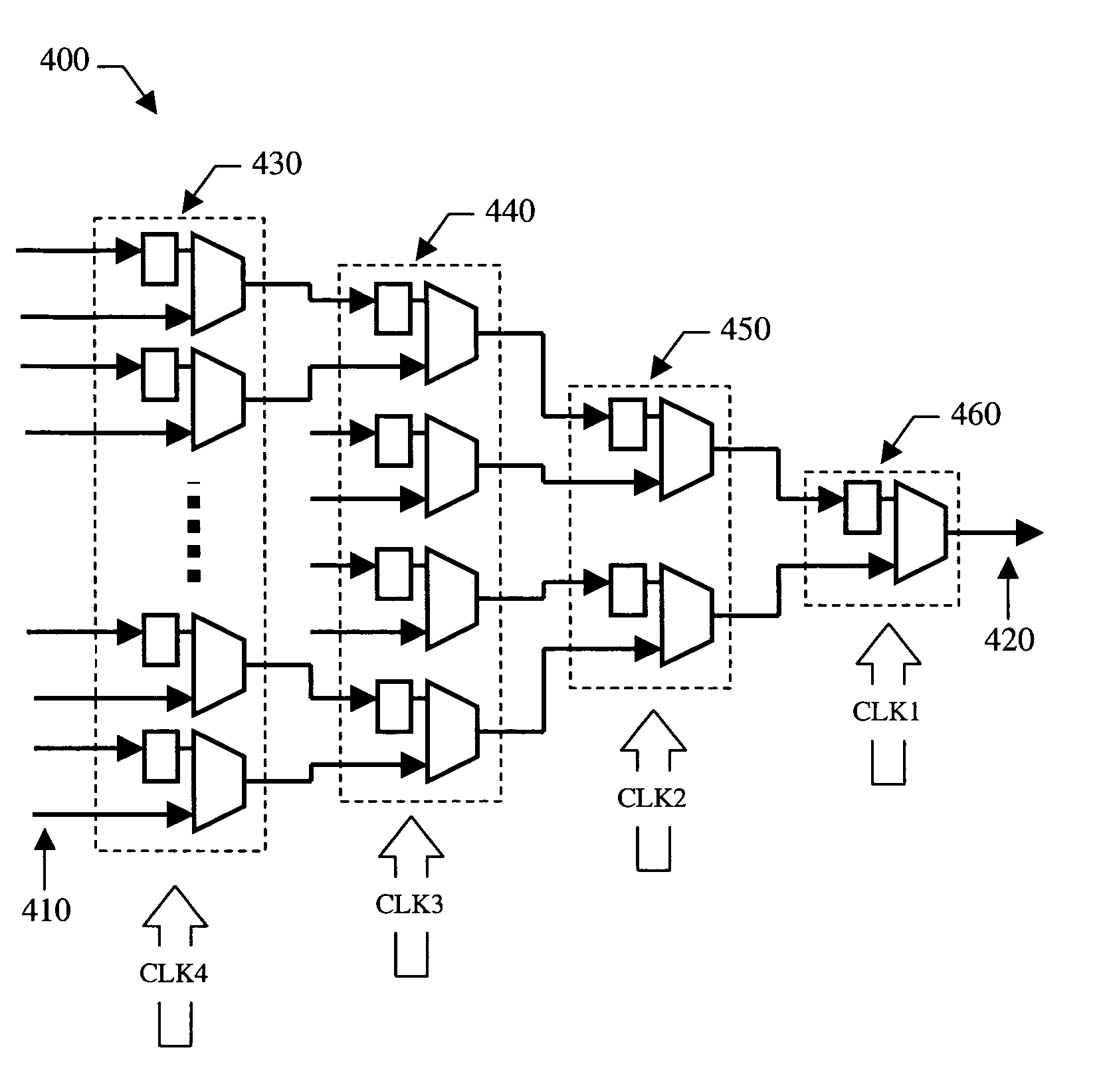

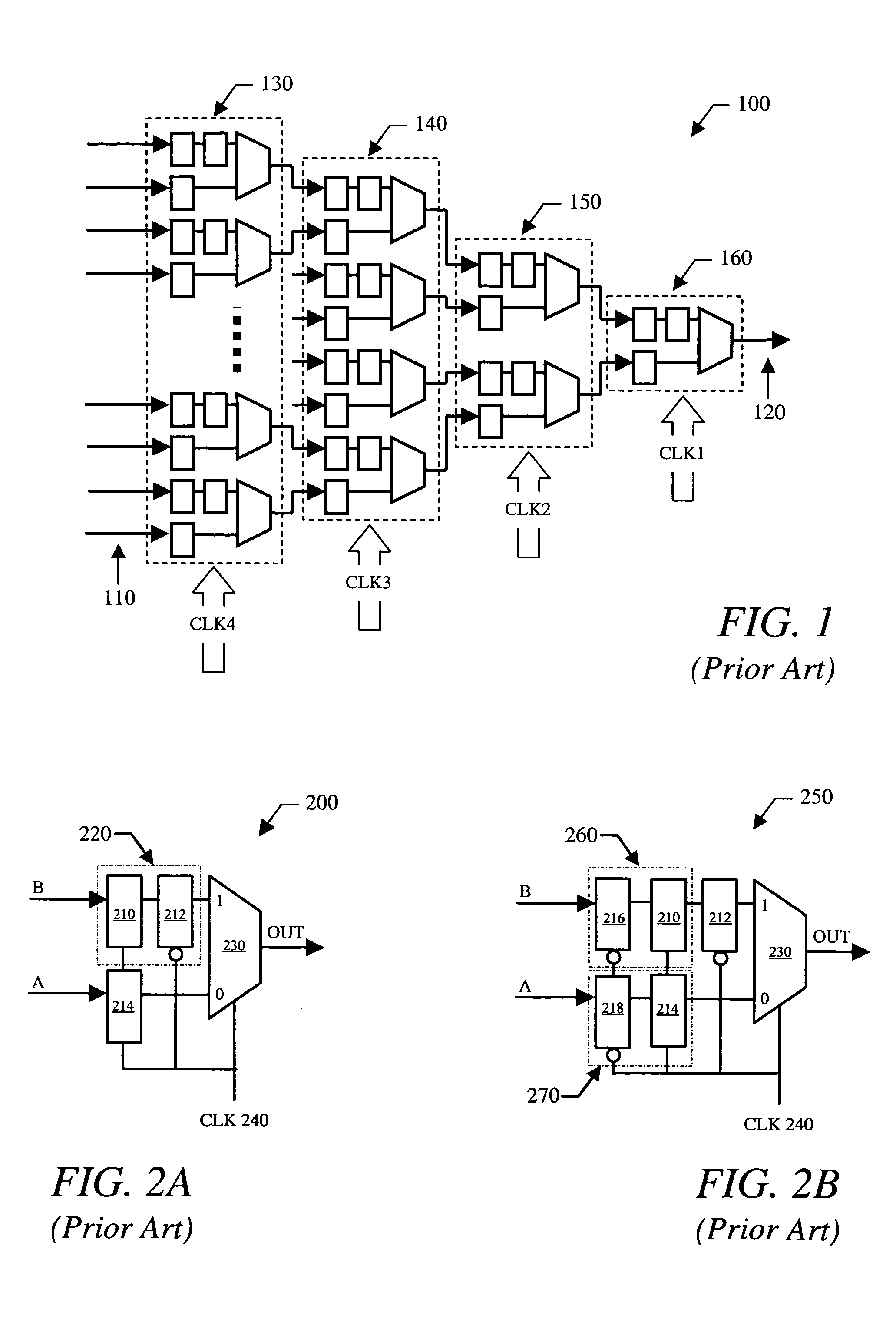

Low power serializer circuit and method

InactiveUS7006021B1Avoid operation failureReduce power consumptionParallel/series conversionComputations using pulse rate multipliers/dividersMultiplexingTransceiver

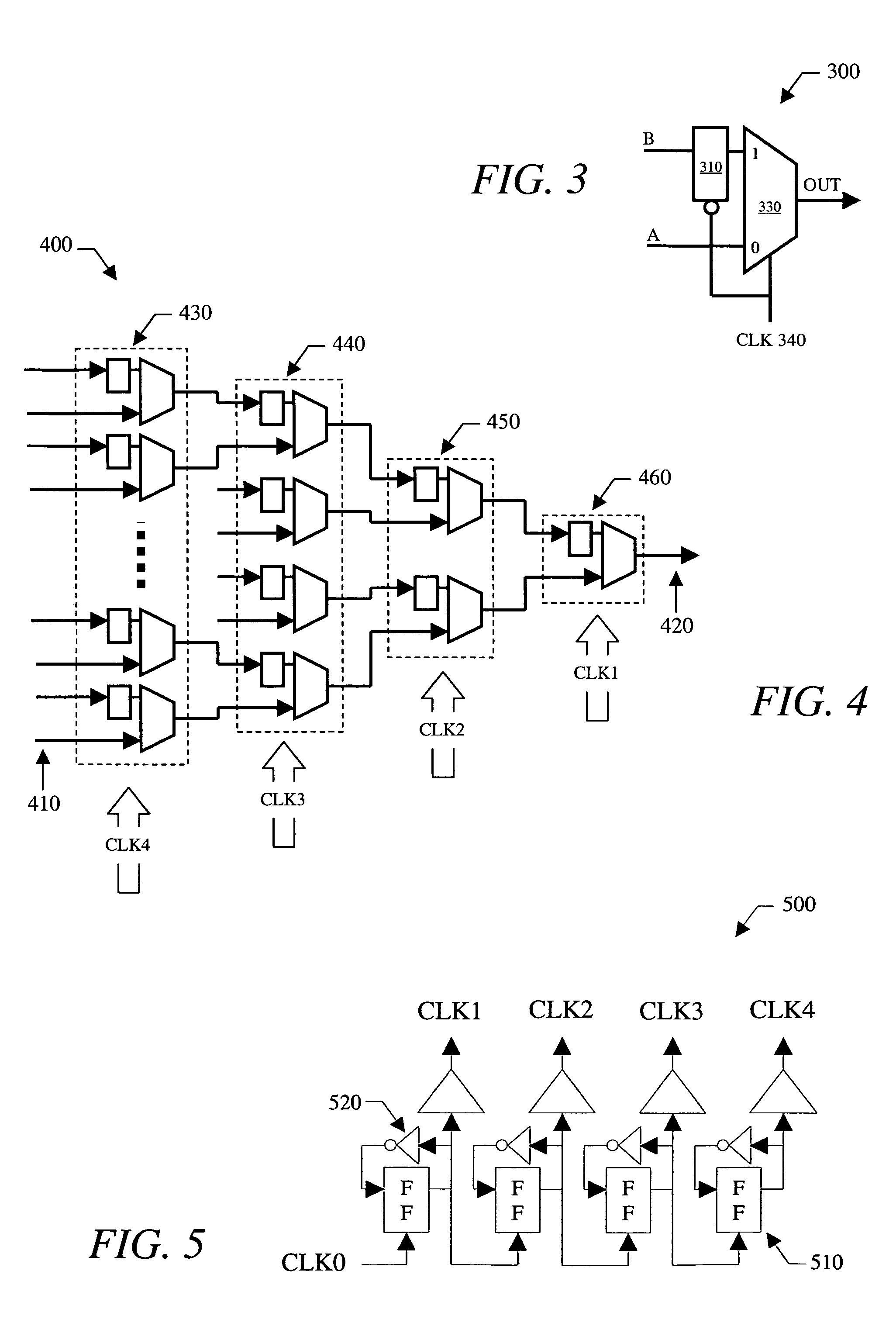

A serializer within, for example, a transceiver is provided having multiple stages of pipelined multiplexing cells. Each multiplexing cell may be substantially the same and each comprises no more than one latch. In some embodiments, each multiplexing cell includes a multiplexer comprising a pair of inputs and a single latch, which is coupled to one input of the multiplexer. No latches are coupled to the other input of the multiplexer. The serializer generally includes a plurality of stages. Each successive stage includes one-half the number of multiplexing cells included in the previous stage, and each successive stage is clocked by a clocking signal that transitions at twice the frequency of the previous stage clock signal.

Owner:RPX CORP

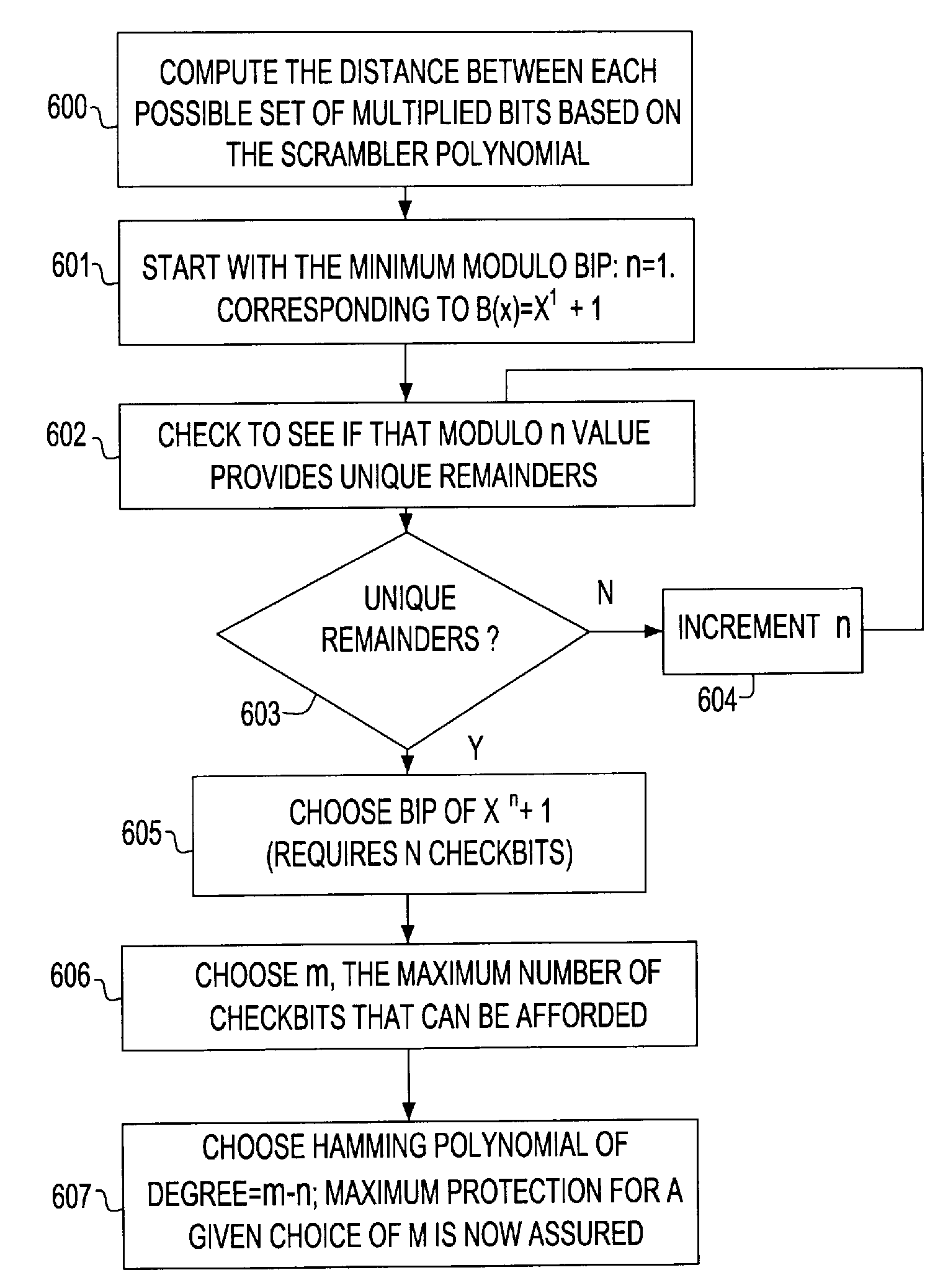

Forward error correction encoding for multiple link transmission capatible with 64b/66b scrambling

InactiveUS20080109707A1Reduce overheadCorrection errorError detection/correctionCode conversionHamming codeHigh bandwidth

Owner:IBM CORP

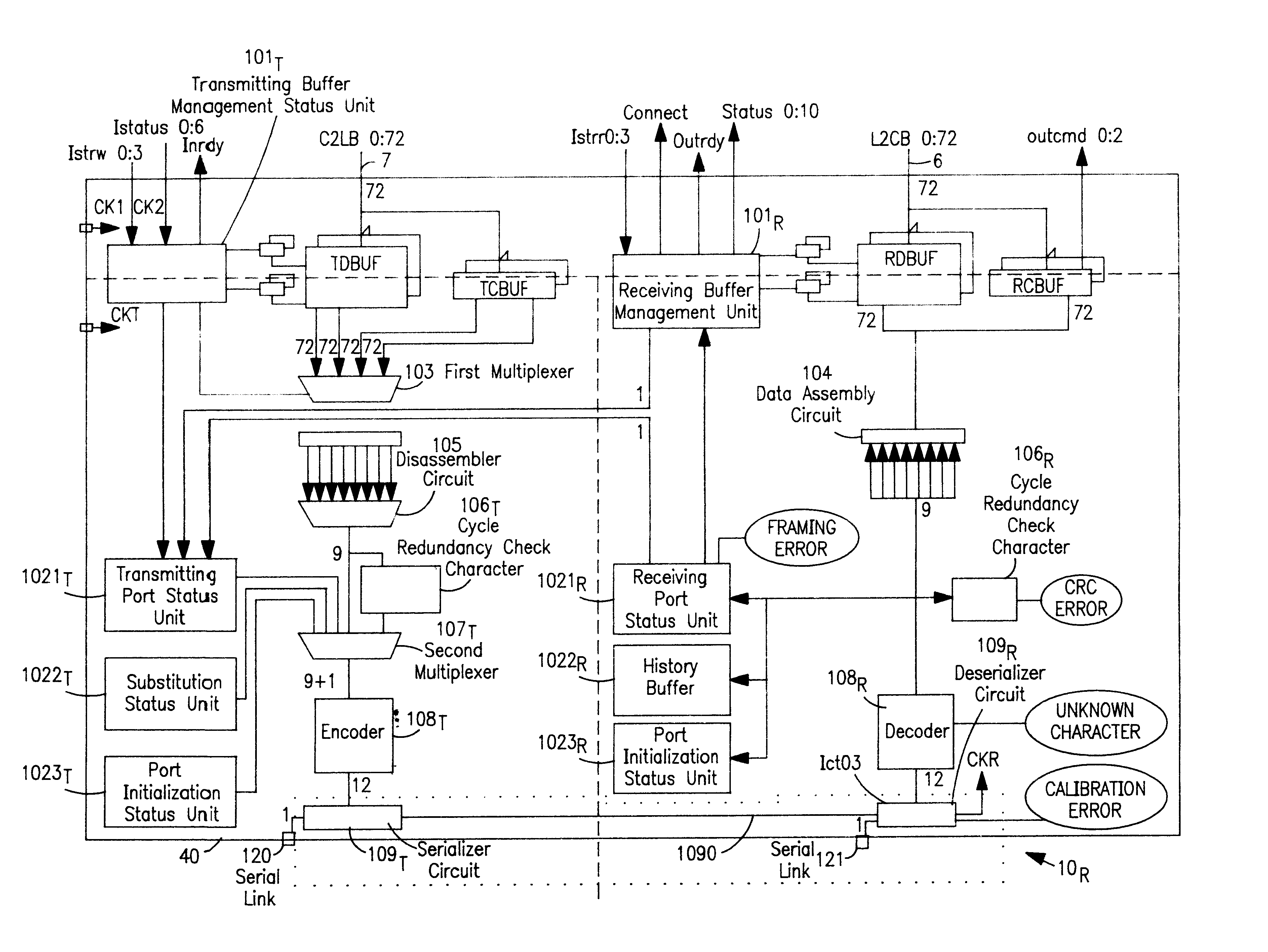

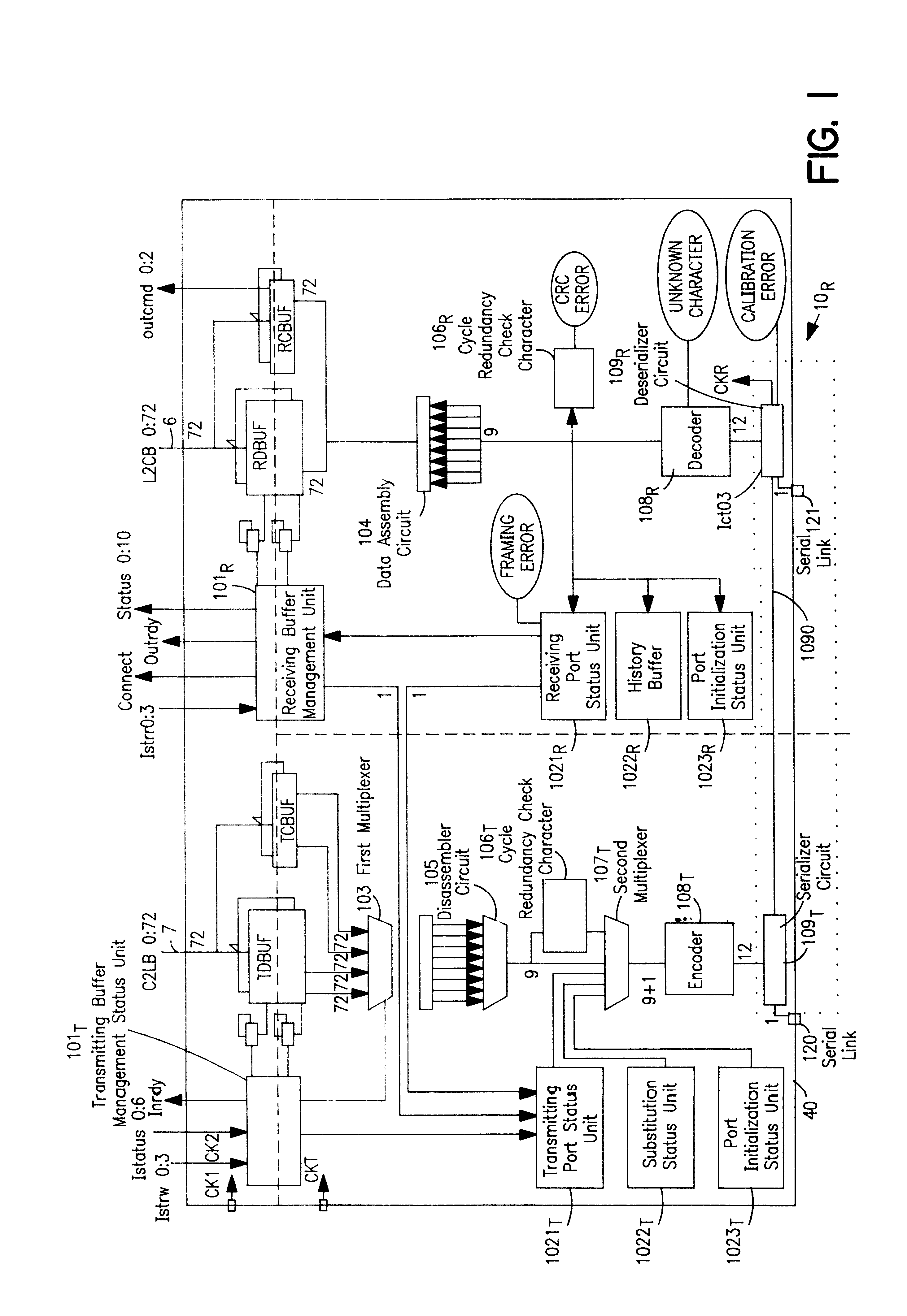

Device and process for detecting errors in an integrated circuit comprising a parallel-serial port

InactiveUS6173423B1Detecting errorAccurate operationFunctional testingRedundant data error correctionExclusive orEngineering

A device for detecting errors with an integrated self-check, on an integrated circuit comprising a serial link control function for constituting an input-output port (109) between a parallel bus (L2CB, C2LB) and a serial link. The integrated circuit comprises a serializer circuit (109T) on output and a deserializer circuit (109R) on input. An insertion buffer I-sb has each of its outputs connected to one input of an exclusive OR operation with two inputs. The second input of the exclusive OR operation receives a piece of information (o-s) to be transmitted in order to constitute, with the insertion information issuing from the insertion buffer, a piece of substitute information. An additional buffer (I-tb) makes it possible to compare the sequence supplied as output from the exclusive OR with a sequence stored in the additional buffer (I-tb) in order to validate the transmission of the substitute sequence. A history buffer (HIB) stores characters received from the deserializer and makes it possible to diagnose the error.

Owner:BULL SA

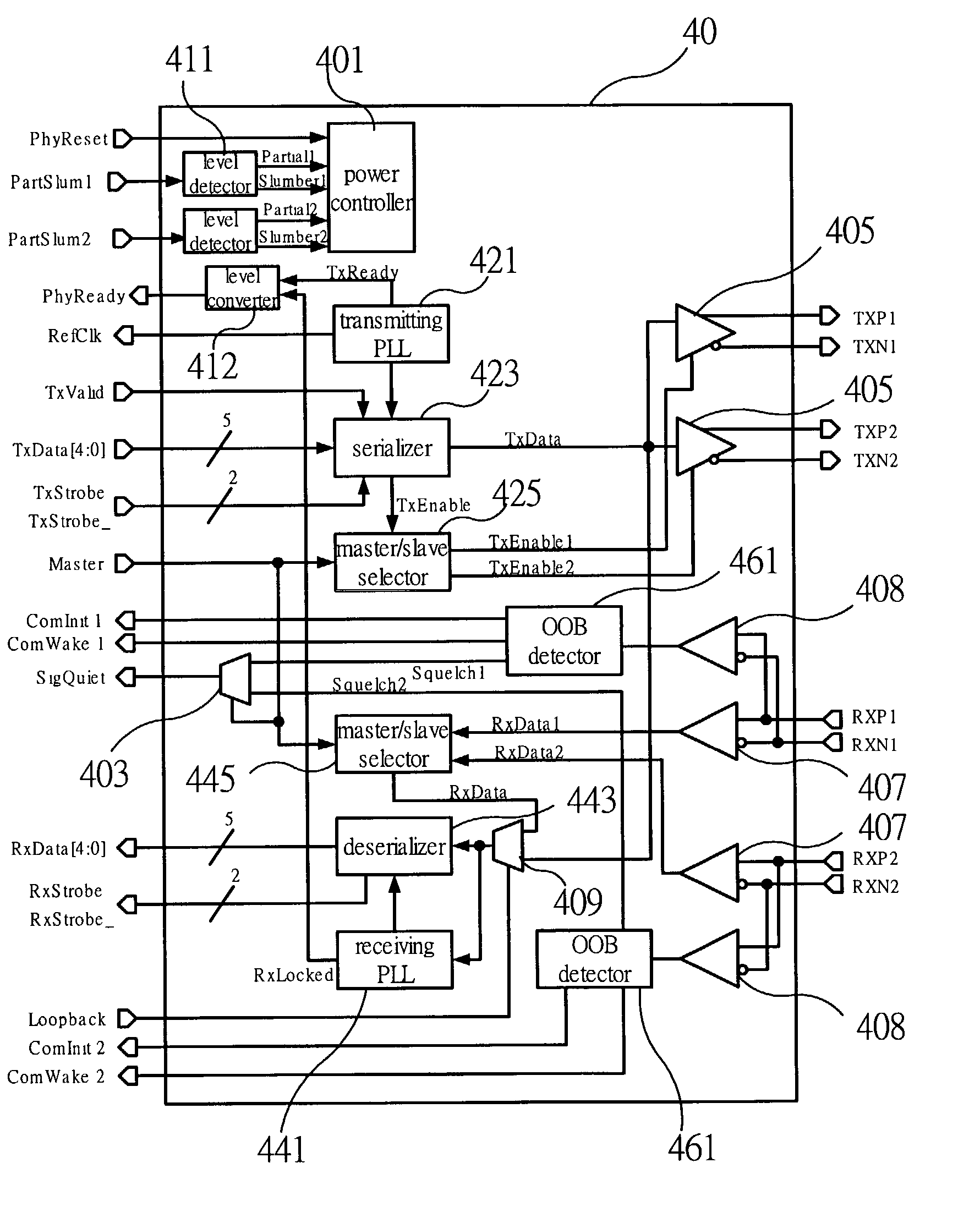

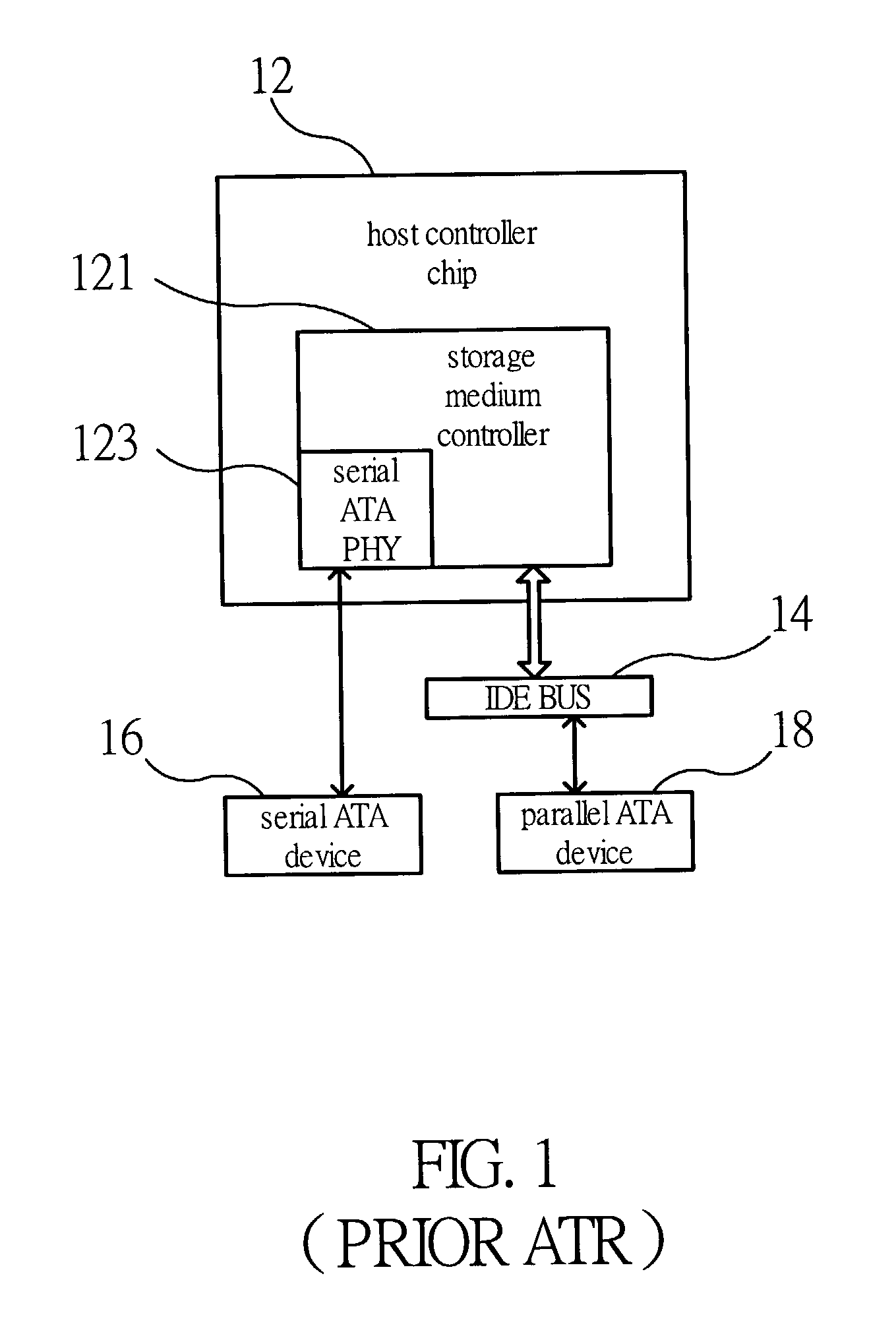

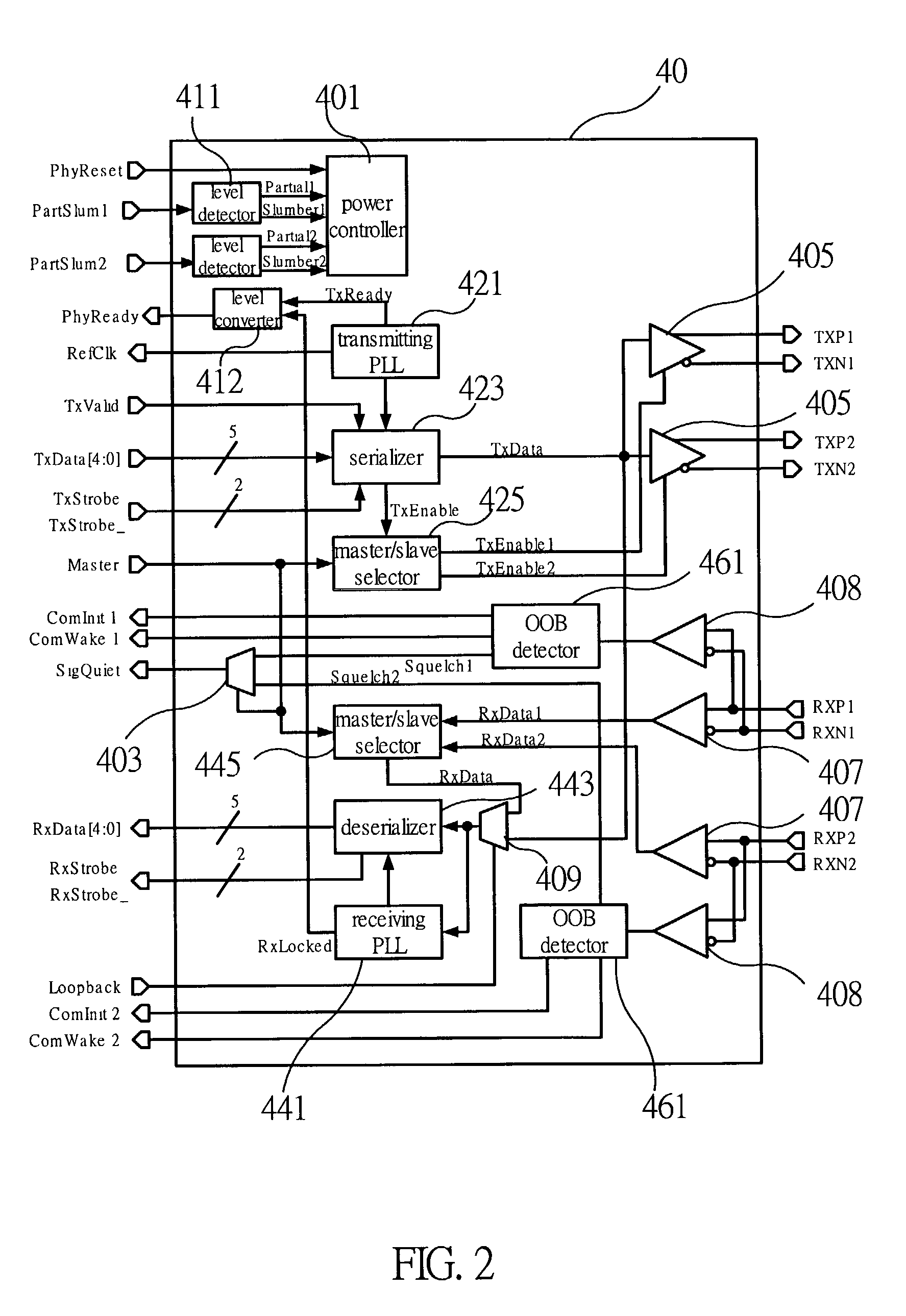

Circuit and signal encoding method for reducing the number of serial ATA external PHY signals

InactiveUS7020834B2Reduce in quantityMinimize the numberError preventionTransmission systemsControl signalData signal

A Circuit for reducing the number of serial ATA external PHY signals includes: a serializer / deserializer, connected to a storage medium controller through a set of parallel signal transmitting lines and a set of parallel signal receiving lines, so as to convert signals between parallel and serial specifications; a phase locked loop, connected to the serializer / deserializer so as to generate a clock signal required for data signal transmission; at least one pair of transmitter and receiver, each connected to the serializer / deserializer, each transmitter able to transmit the serial data signal from the serializer through a set of serial signal transmitting lines to a serial ATA device, and each receiver able to receive the serial data from the serial ATA device through a set of serial signal receiving lines to the deserializer; and at least one OOB signal detector, each connected to the corresponding receiving lines, so as to detect the out of band signals from the serial ATA device. The Circuit also employs in certain applications a signal encoding approach for reducing the number of serial ATA external PHY signals, wherein an encoder and a decoder are employed to encode control signals and status signals into special data codes transmitted between a serial ATA external PHY and a storage medium controller, so as to minimize the number of interface signals.

Owner:VIA TECH INC

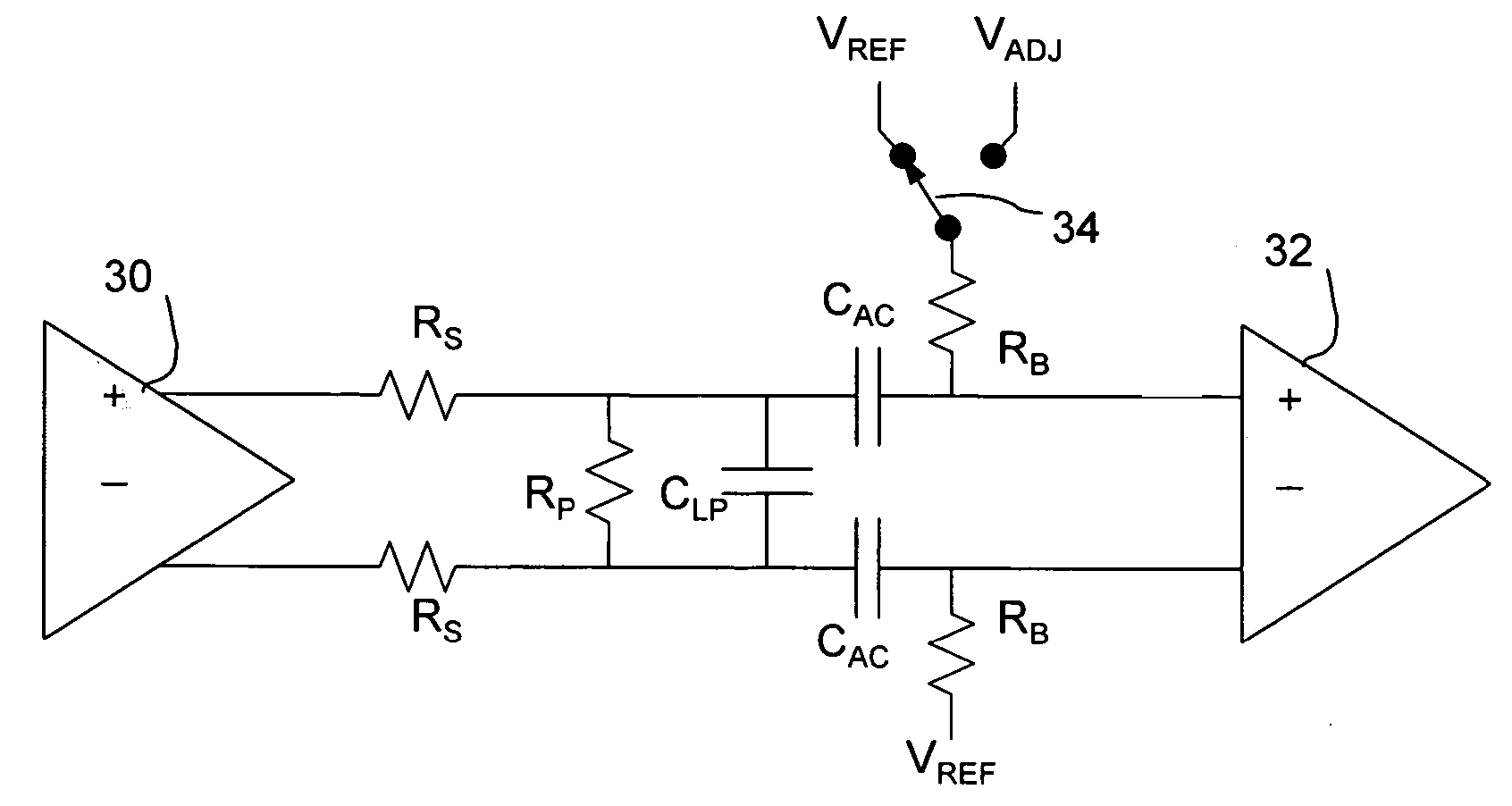

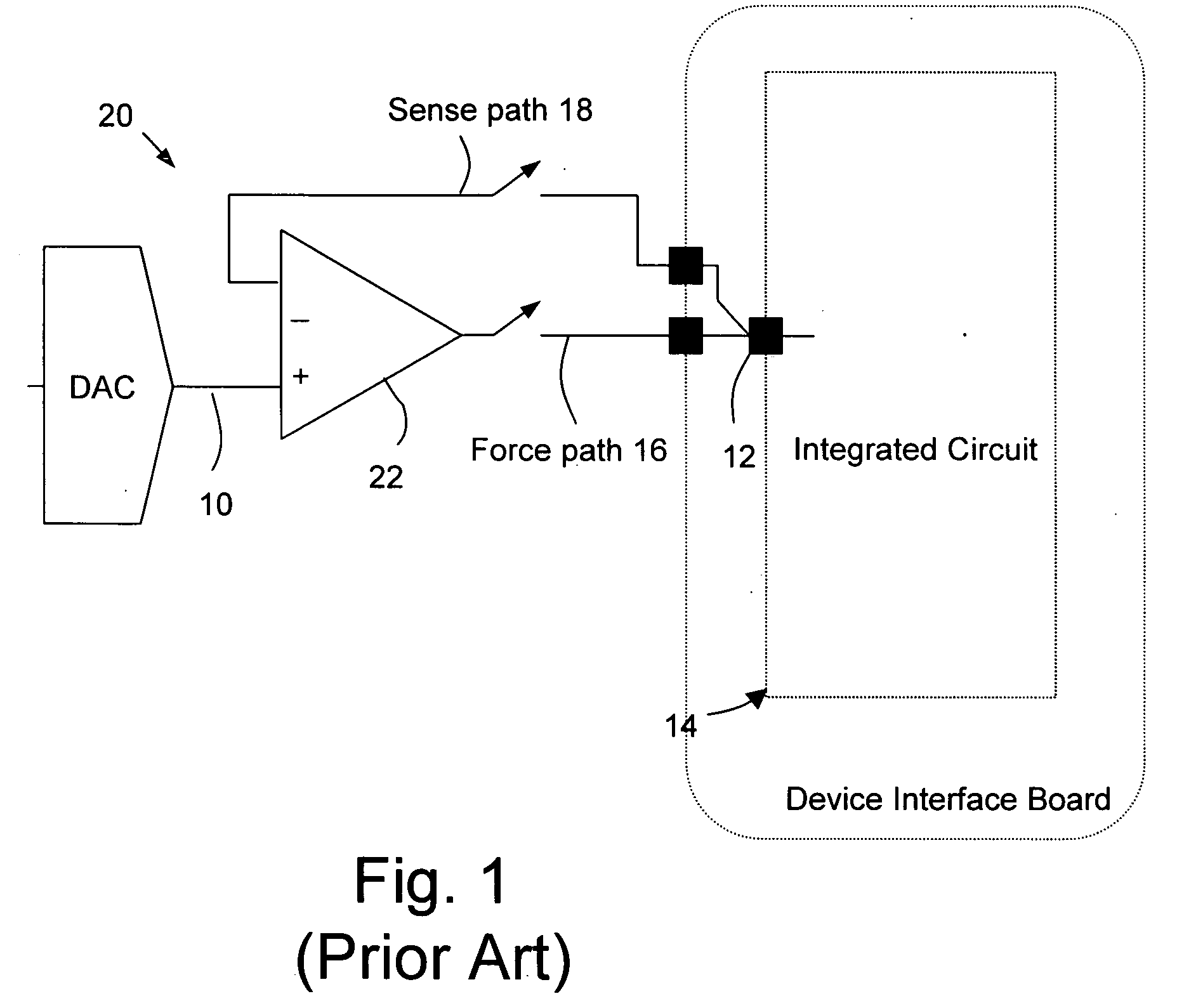

Circuit and method for testing high speed data circuits

InactiveUS20040123197A1Digital circuit testingError detection/correctionCapacitanceDigital transition

A circuit and method are described in which a DC voltage or current is connected to a high frequency, AC-coupled signal path between a transmitter and a receiver, and the bit error rate of the data transmission is tested while applying an altered bias voltage to the received signal. The bias voltage can be connected via a resistor, inductor or transistors. The transmitted signal is attenuated resistively, and a load capacitance is applied whose value causes digital transition times to exceed one unit interval. An intended application is testing of an integrated circuit, serializer / deserializer (serdes) operating above 1 GHz.

Owner:MENTOR GRAPHICS CORP