Patents

Literature

510 results about "Serial transfer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Serial transfer Transmission of information as sequential units. For example, if two computers connected by a single wire wish to communicate an 8-bit unit of information, the sending computer would transmit each of the eight bits in sequence over the wire, while the receiving computer would reassemble the sequential bits into...

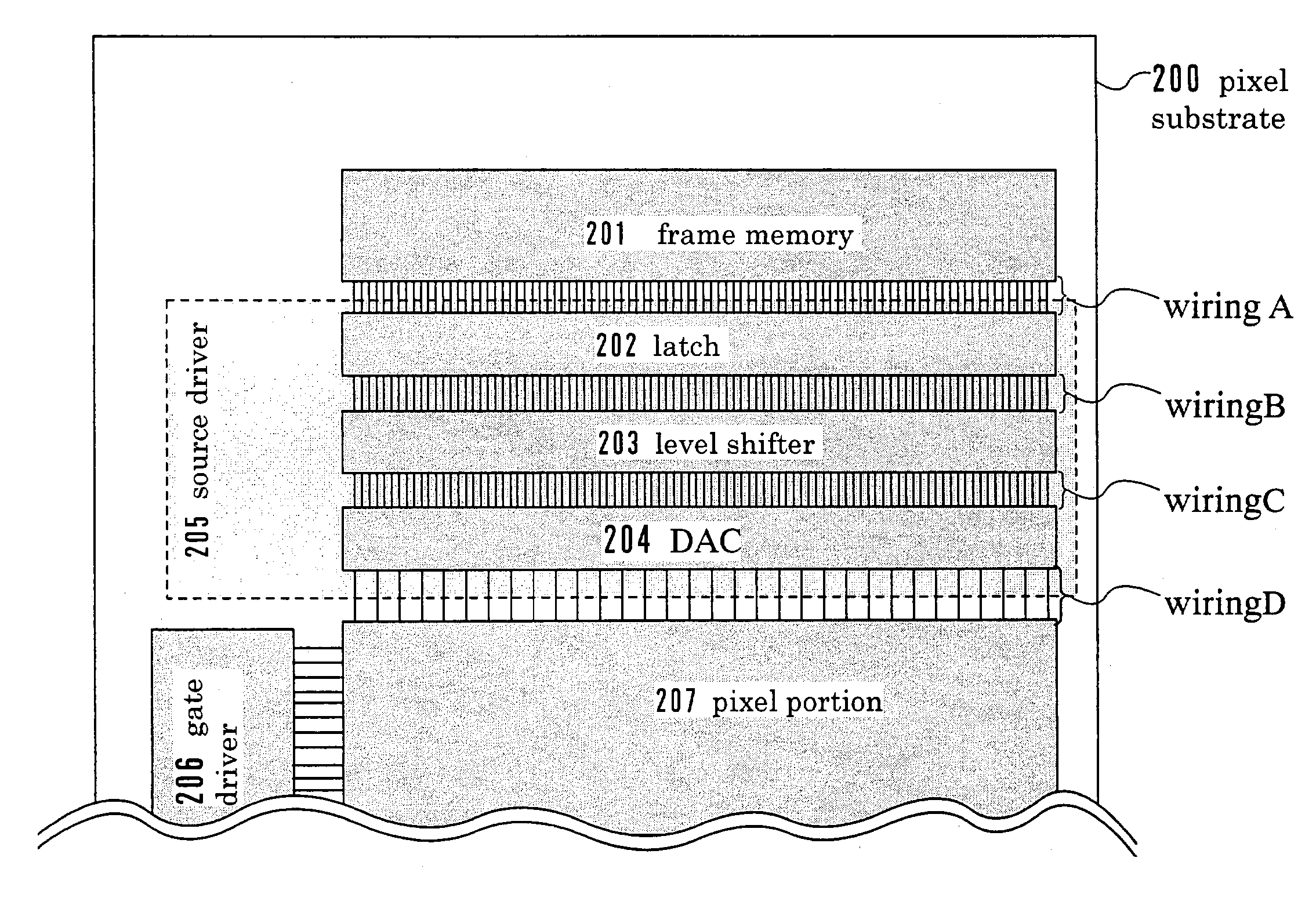

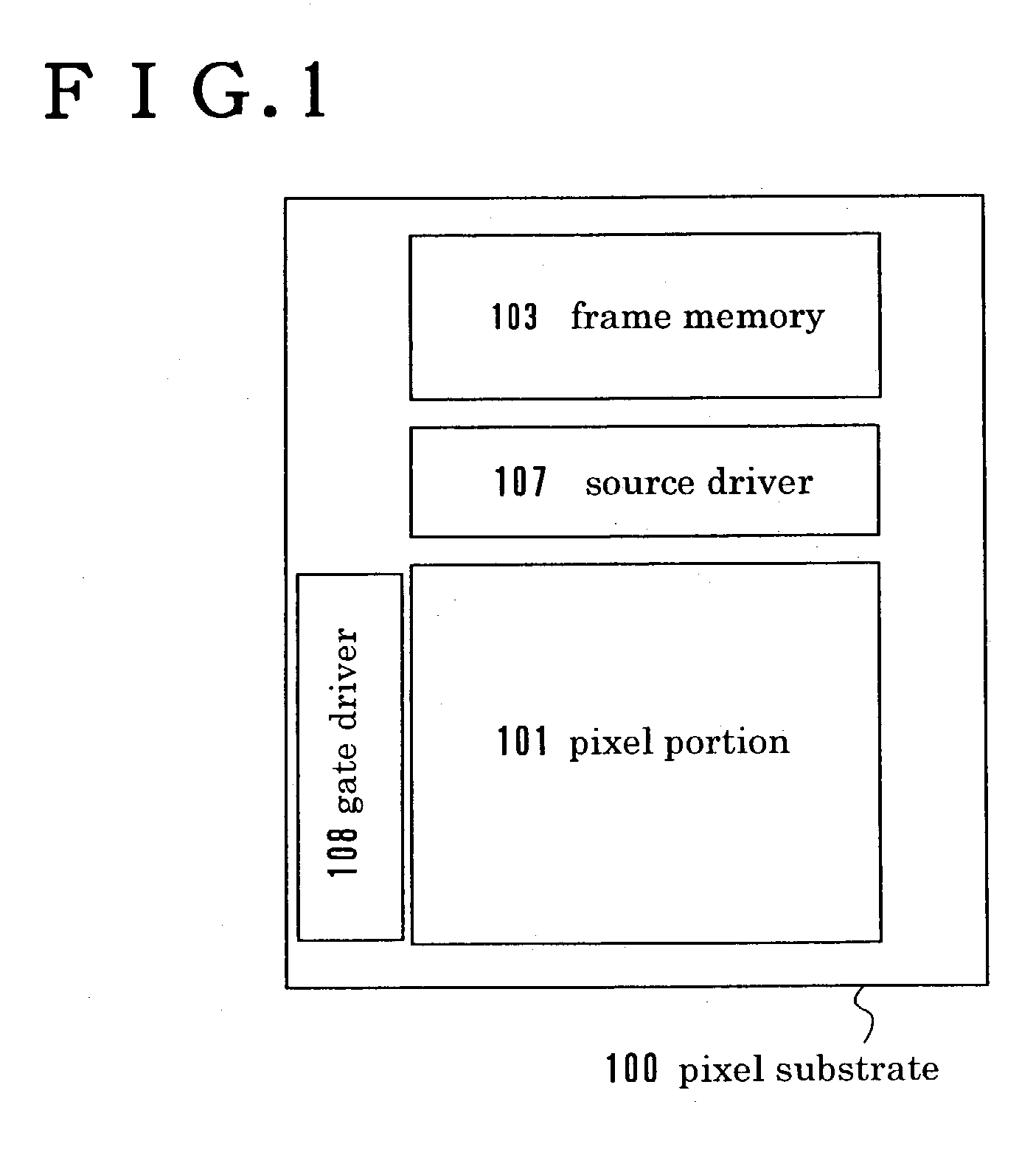

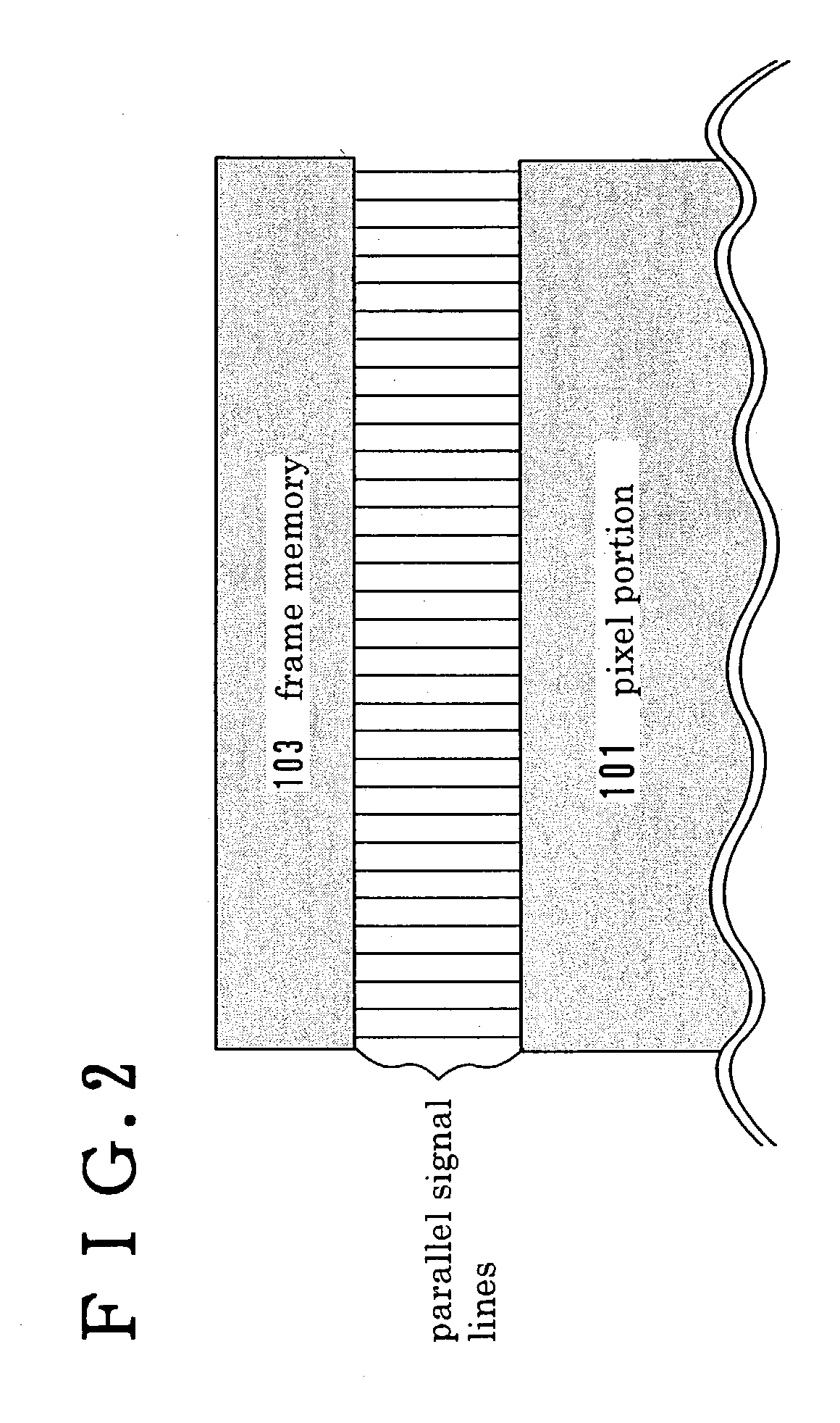

Display device and method for driving the same

According to a display device of the present invention, a frame memory is integrally formed on a substrate (pixel substrate) on which a pixel portion is formed. With this construction, one row of data can be simultaneously read from the frame memory and can be input to a drive circuit for pixels in parallel. As a result, a need for transferring image data in serial is eliminated. Then, a parallel / serial converting circuit and a serial output circuit, and a serial / parallel converting circuit and a parallel input circuit are not necessary. Therefore, a display device having a frame memory and a pixel portion can be constructed in a simpler construction and with an easier circuit. As a result, the noise can be reduced, and the low power consumption can be achieved.

Owner:SEMICON ENERGY LAB CO LTD

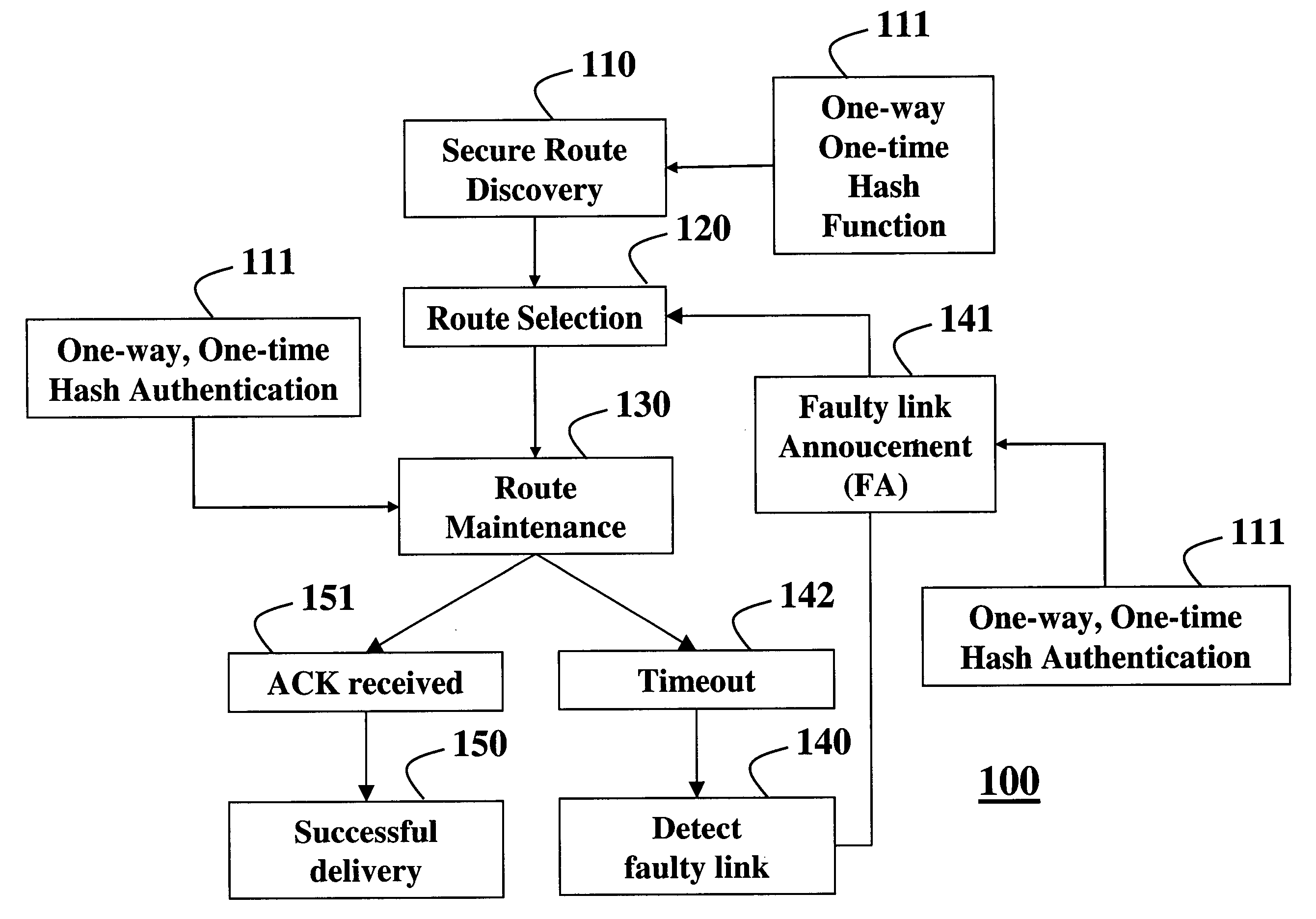

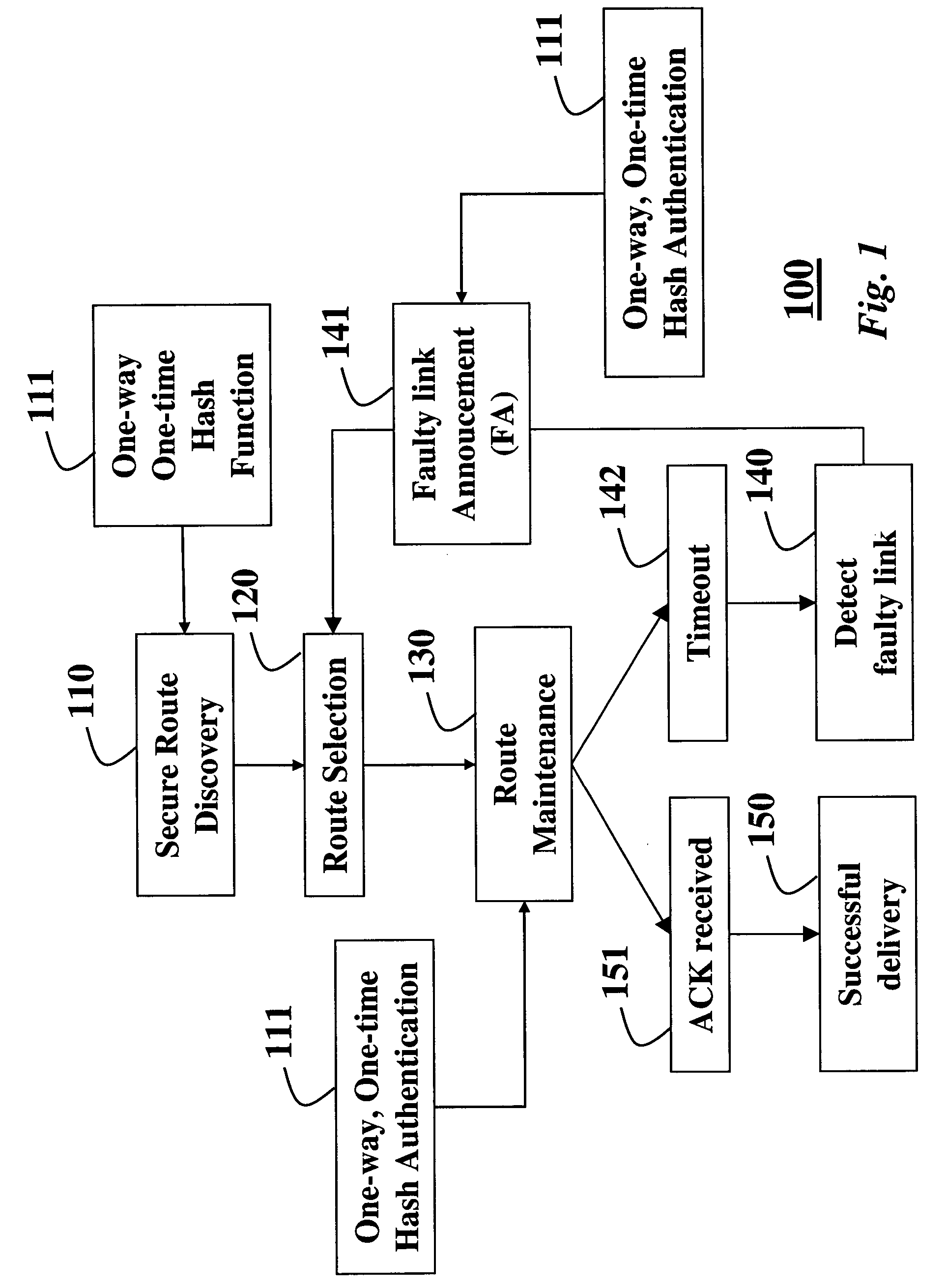

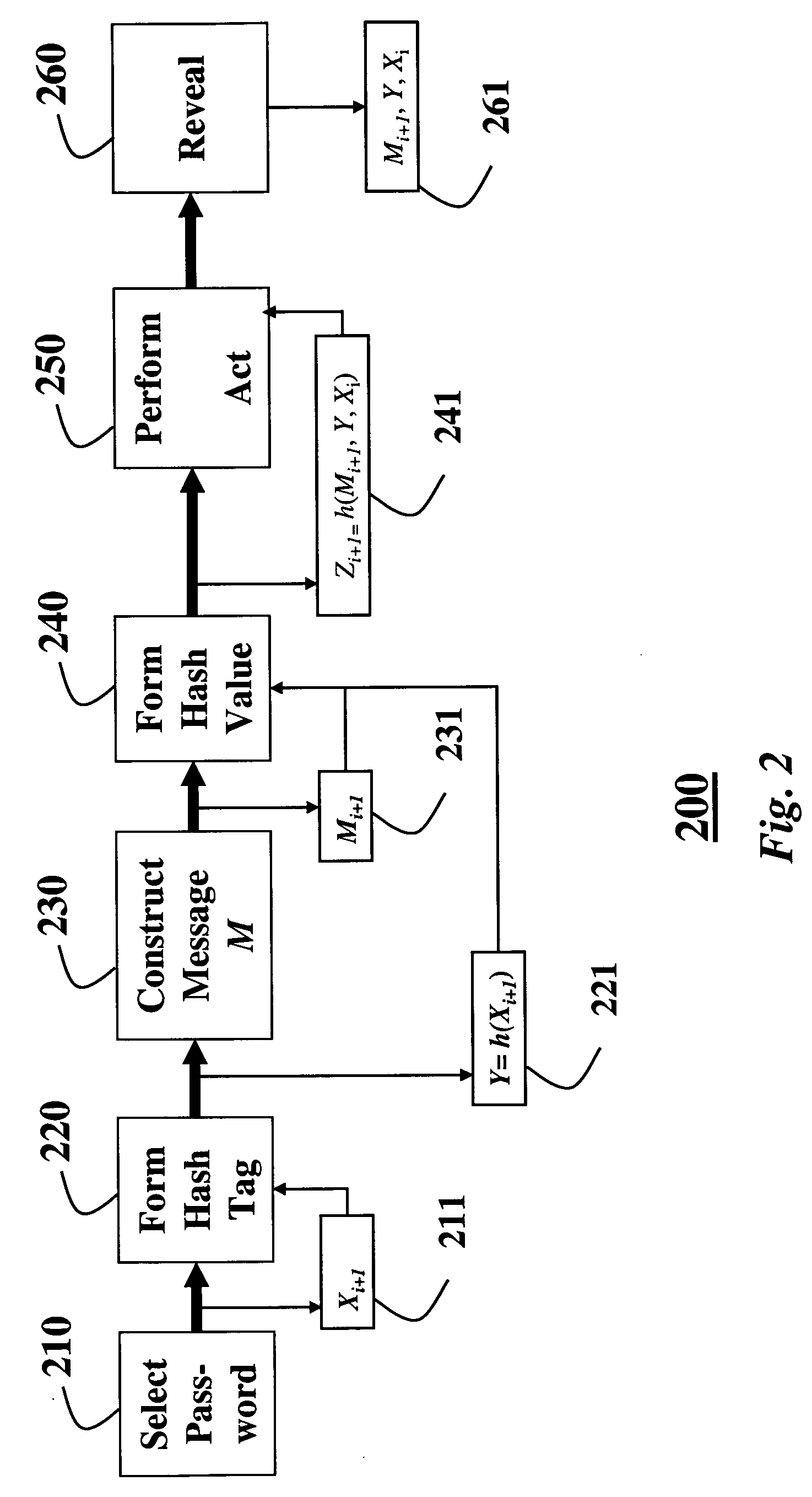

Secure routing protocol for an ad hoc network using one-way/one-time hash functions

InactiveUS20050036616A1User identity/authority verificationDigital data authenticationData packSerial transfer

A method authenticates packets that are transmitted serially in a network. A current password is selected for a current packet to be transmitted. The current packet includes current data. A one-way / one-time hash function is applied to the current password to form a current tag. A next password is selected for a next packet that includes next data, and the one-way / one-time hash function is applied to the next password to form a next tag. The one-way / one-time hash function is then applied to the next data, the next tag, and the current password to obtain a hashed value. The current packet is then transmitted to include the hash value, the current data, the current tag, and a previous password of a previous transmitted packet to authenticate the current data.

Owner:MITSUBISHI ELECTRIC INFORMATION TECH CENT AMERICA ITA

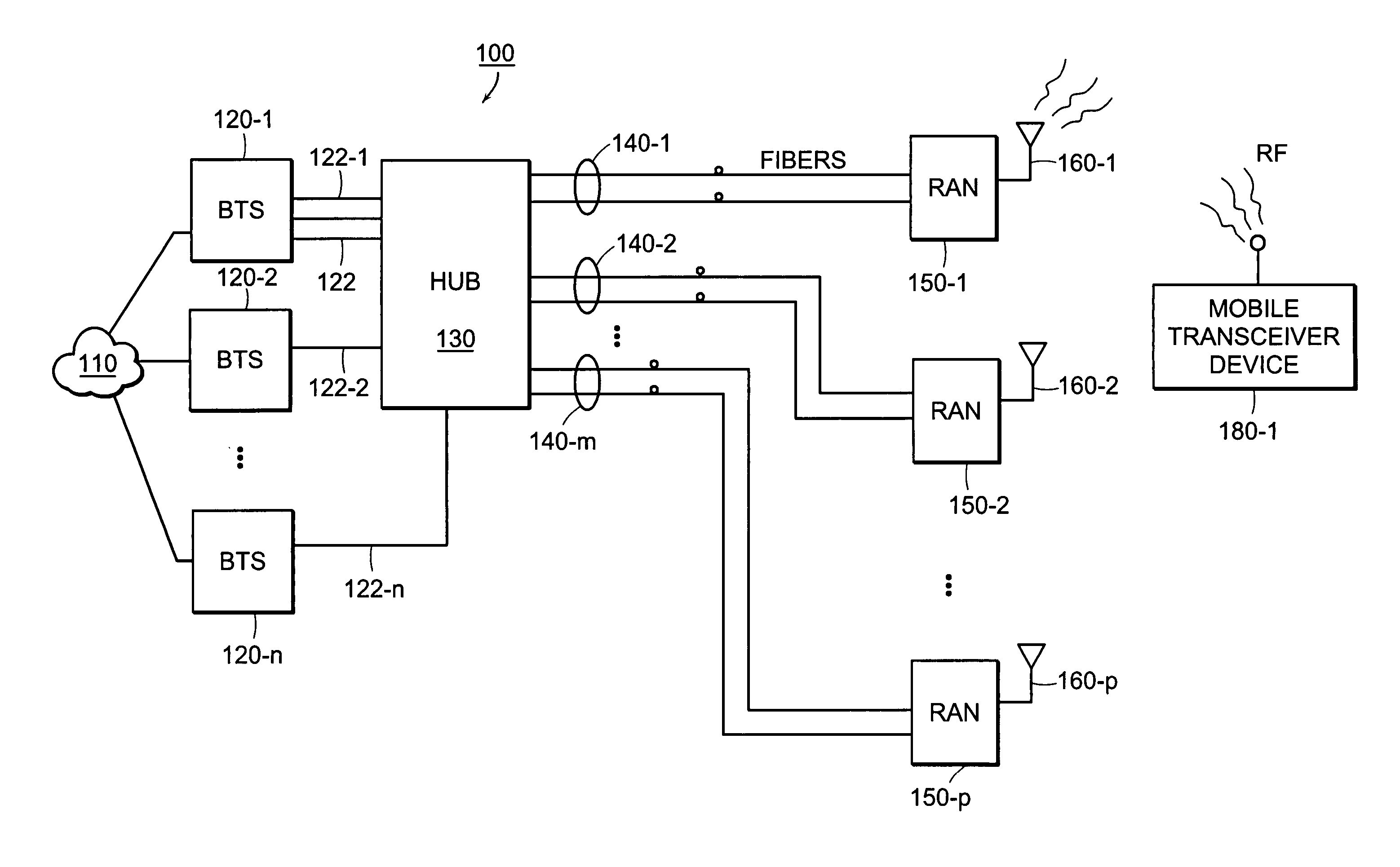

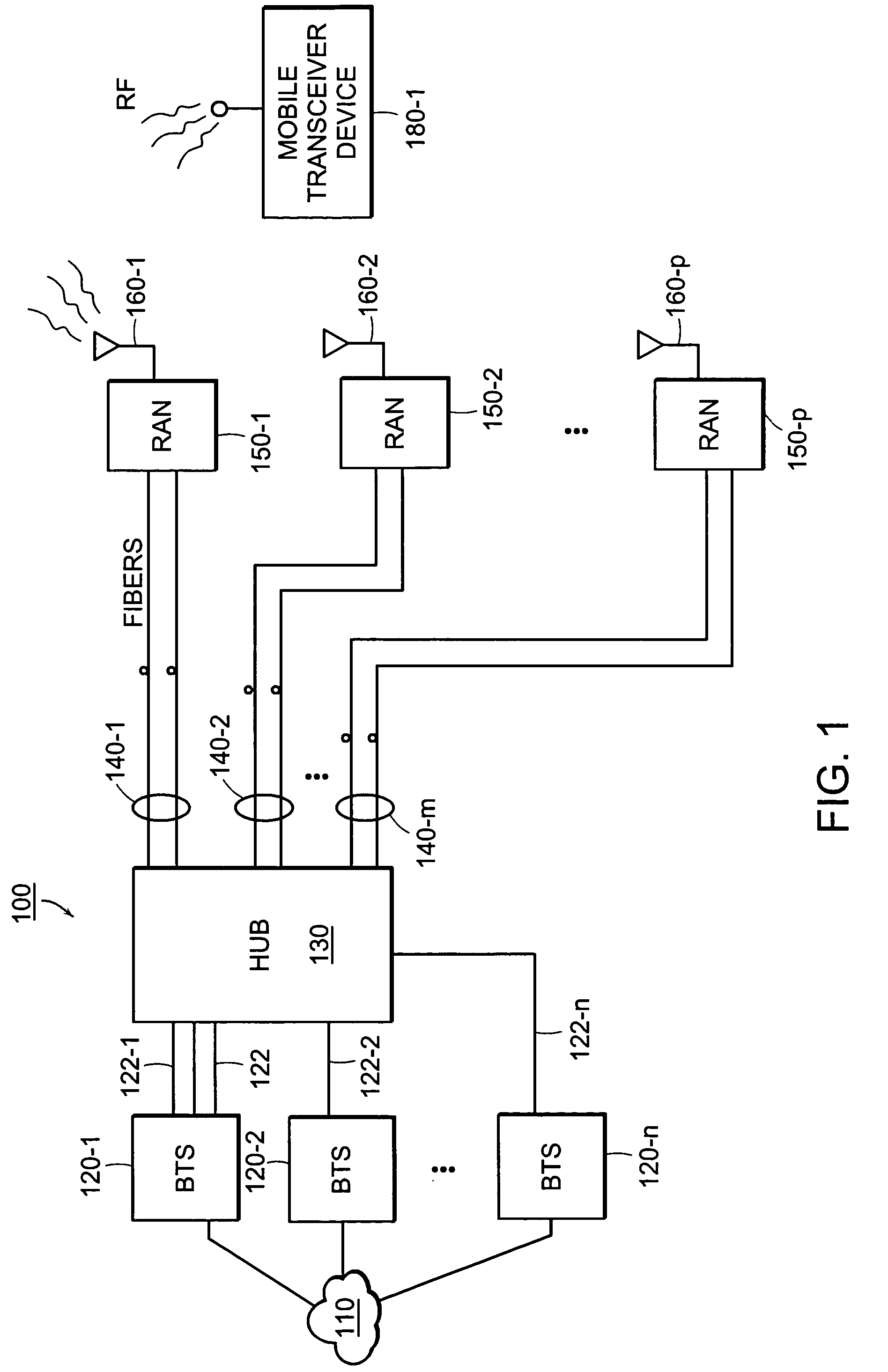

System and method for retransmission of data

InactiveUS7215651B2Guaranteed normal transmissionError prevention/detection by using return channelFrequency-division multiplex detailsSerial transferTelecommunications link

Owner:COMMSCOPE TECH LLC

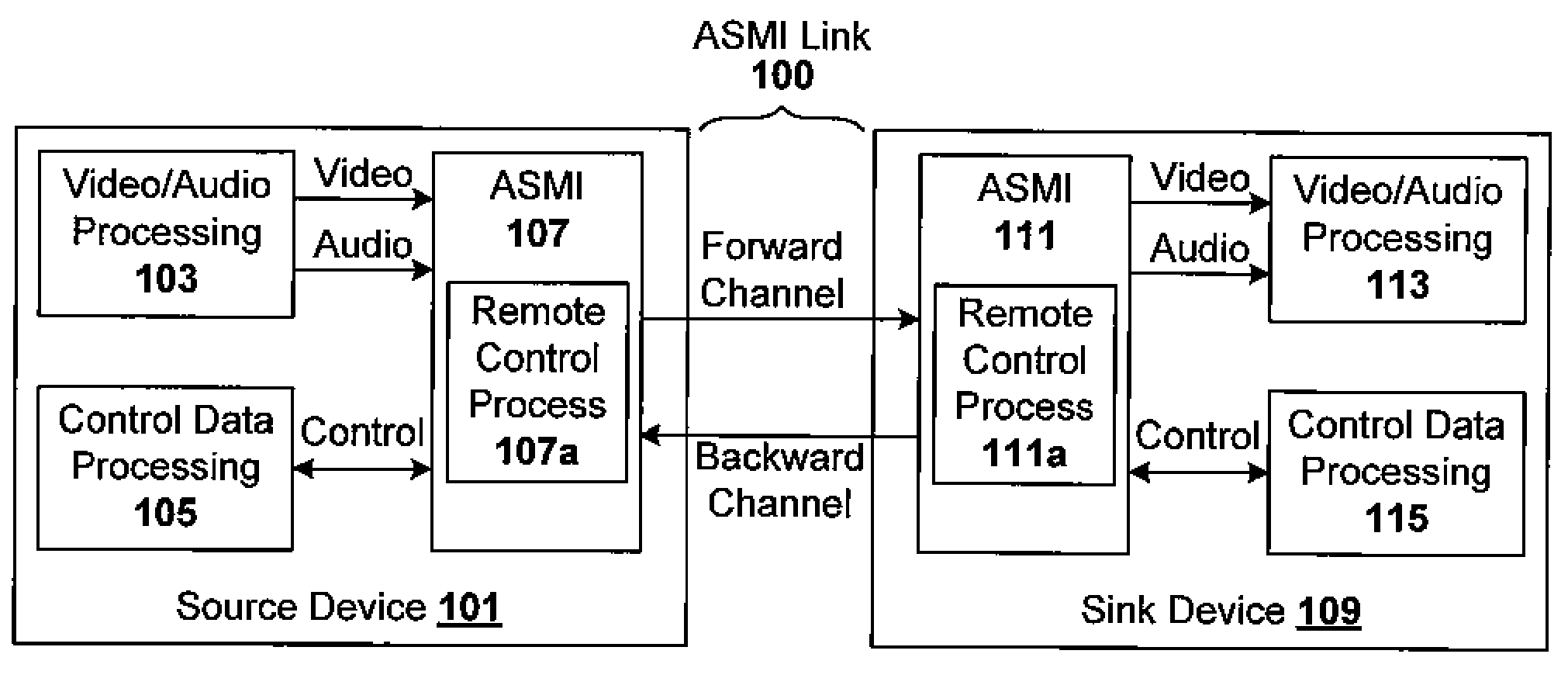

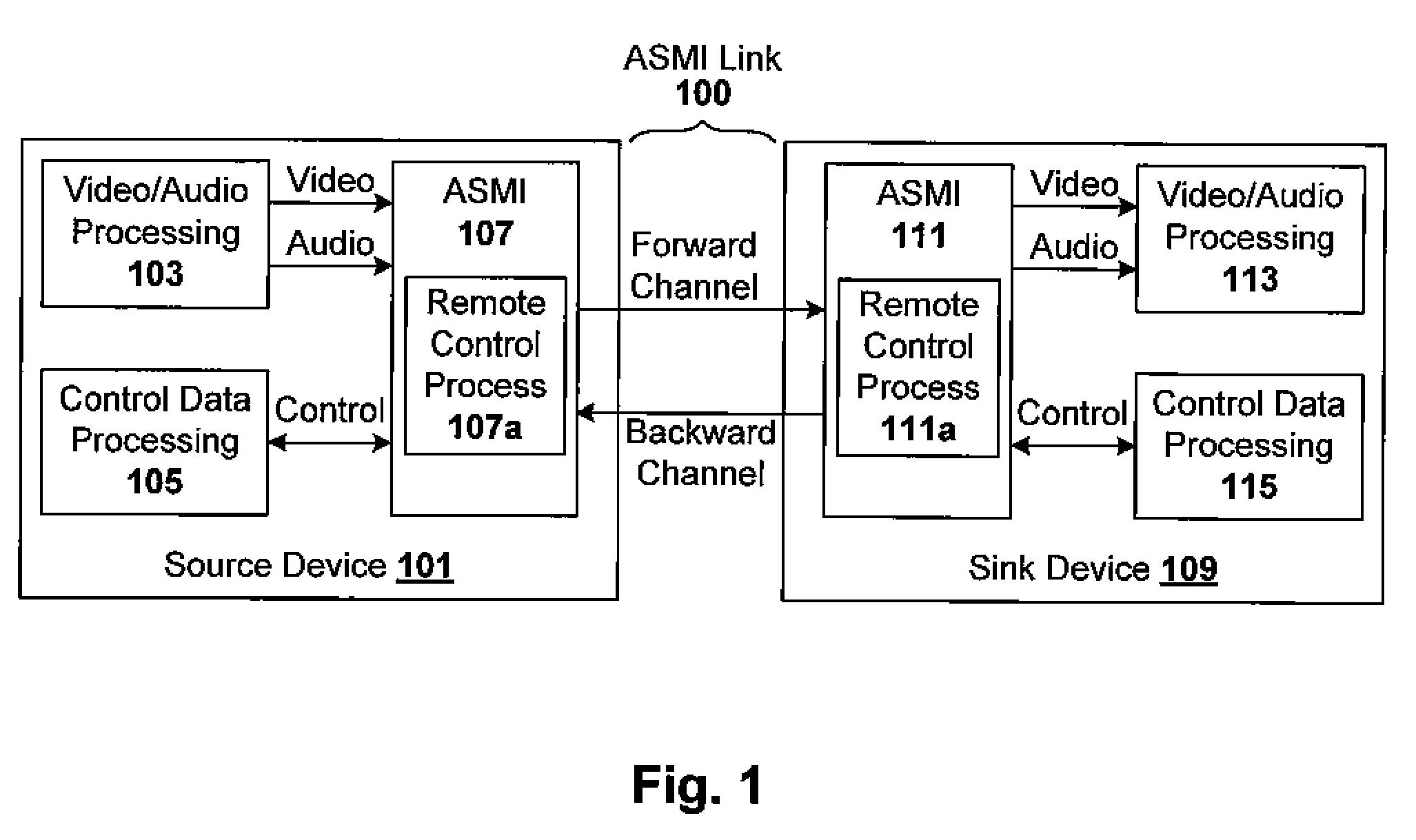

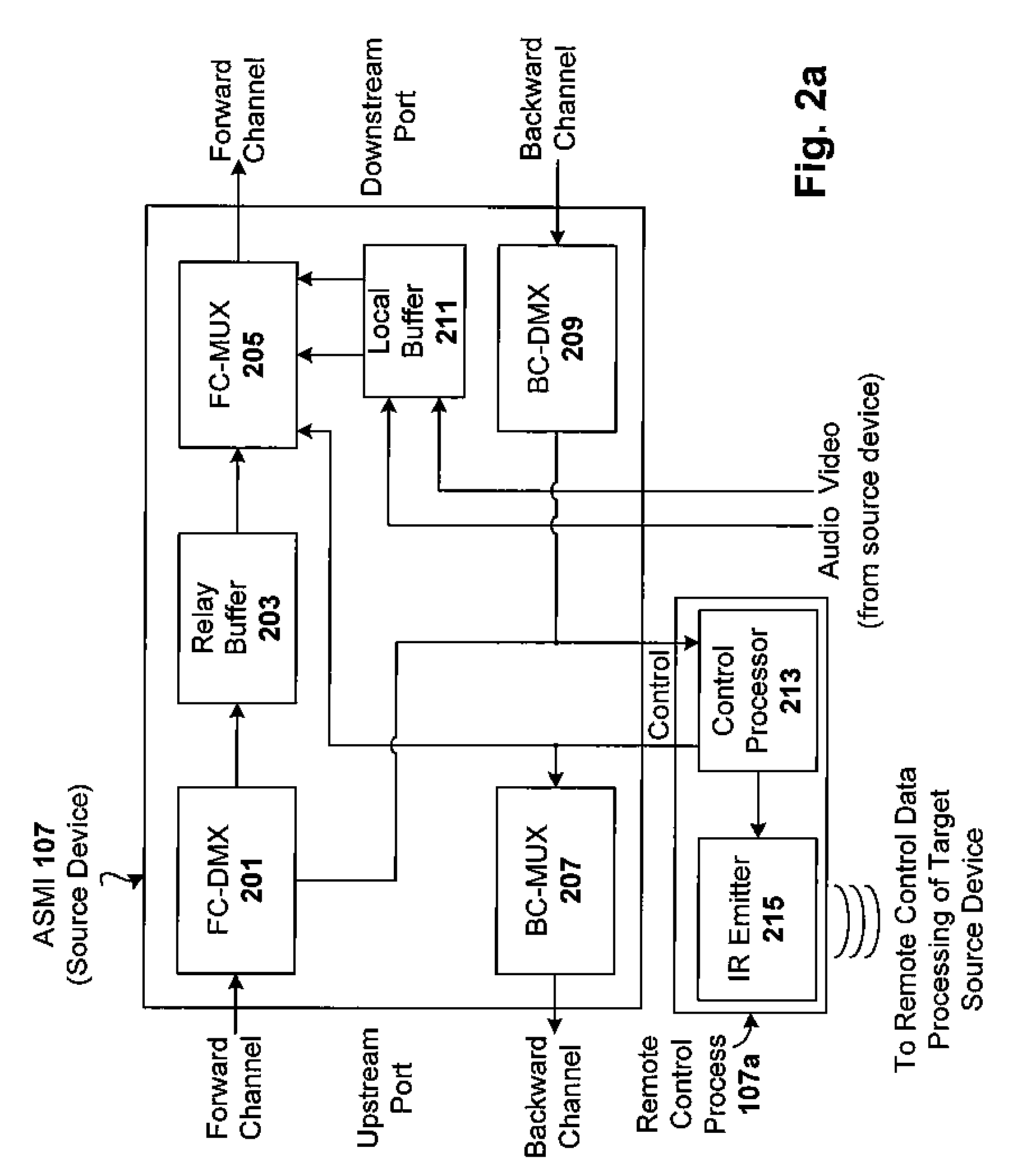

Integrated remote control signaling

InactiveUS20070292135A1Electric signal transmission systemsElectromagnetic transmissionTransmission protocolSerial transfer

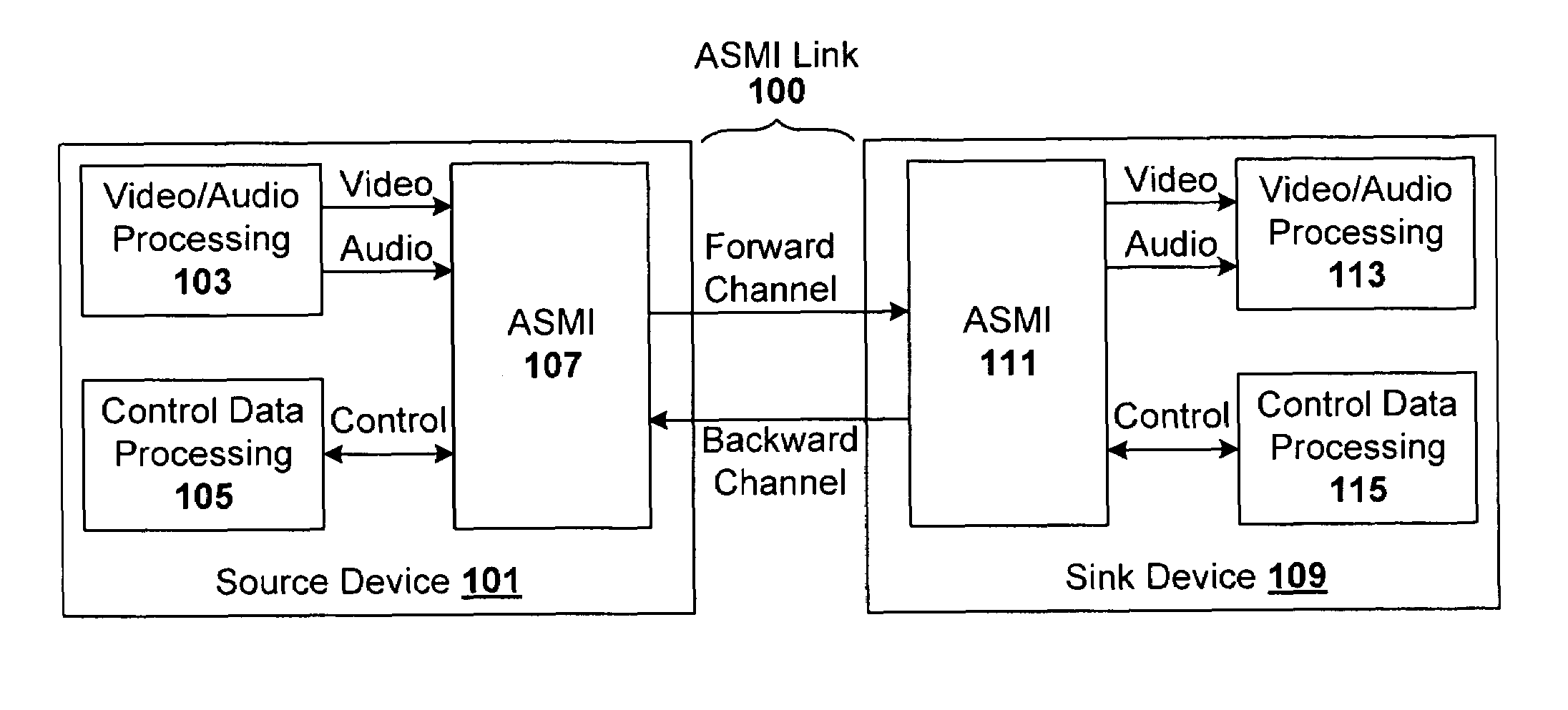

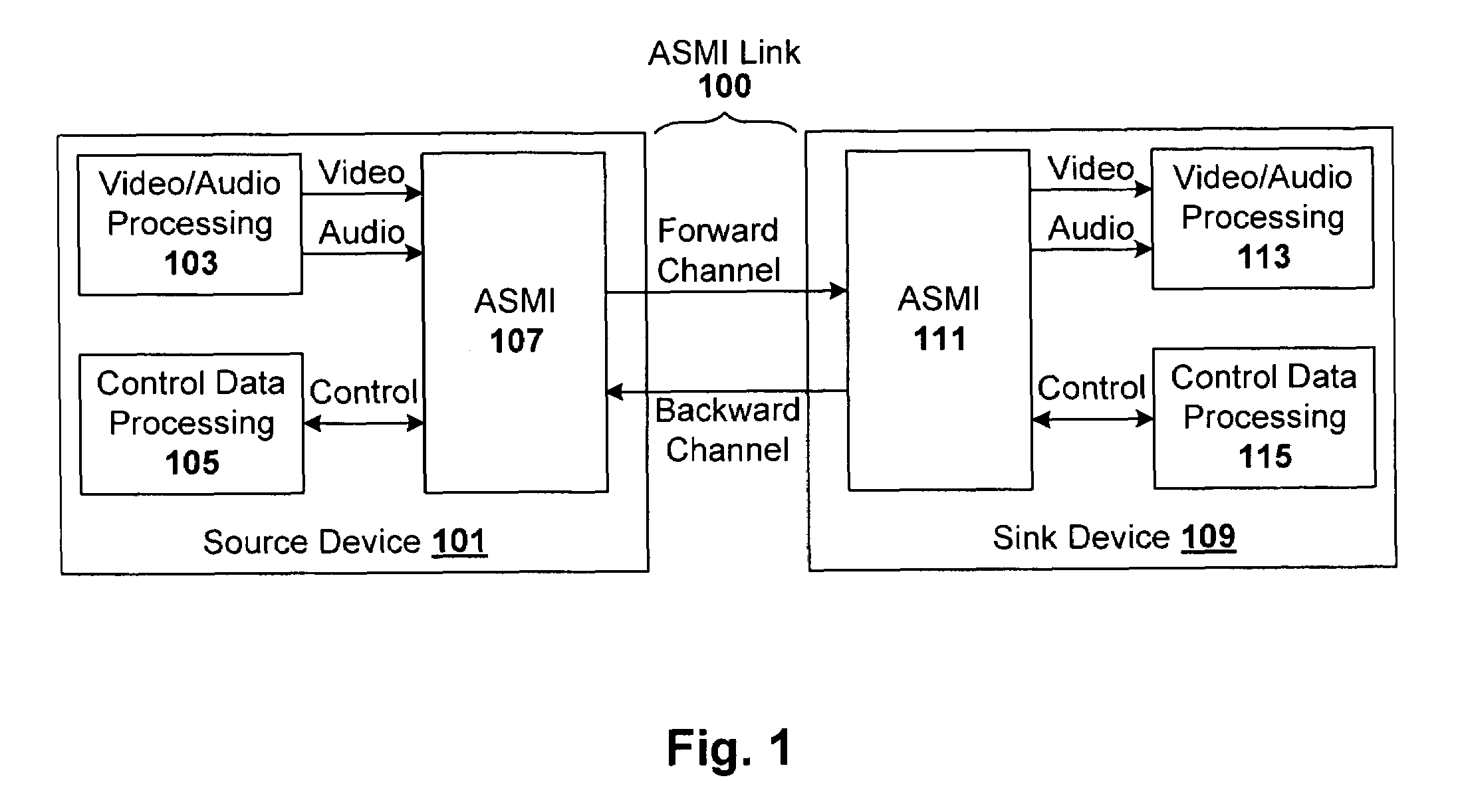

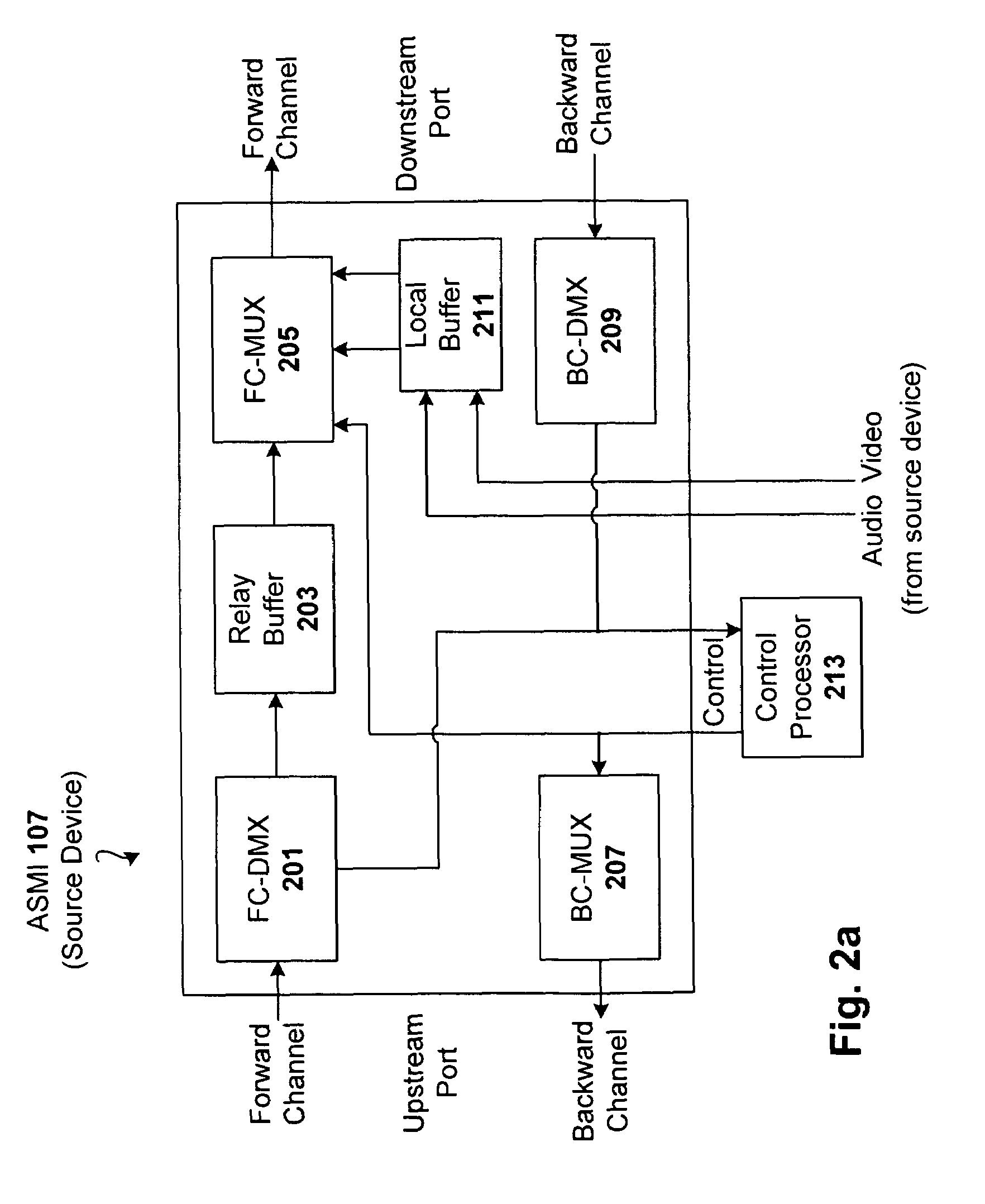

A serial transmission protocol and architecture are provided that can be used to forward remote control data between sink (e.g., DTV) and source (e.g., DVD player) devices, in addition to other data such as video and / or audio or other payload. The target device need not be in the line of sight of the remote control beam. Daisy-chained devices will pass the remote control signal to the appropriate target device, so that the user can point any remote control at the DTV or other conveniently located device in the system, and still control the actual target device. The communication channel that carries payload, processing control, and remote control data can be implemented with wired or wireless of technology (or a combination thereof). In one particular embodiment, the communication channel is implemented with a single fiber. A number of presentation and entertainment system applications that employ remote control technology (e.g., home theater, audio, and computer implemented systems) can benefit from embodiments of the present invention.

Owner:OWLINK TECH

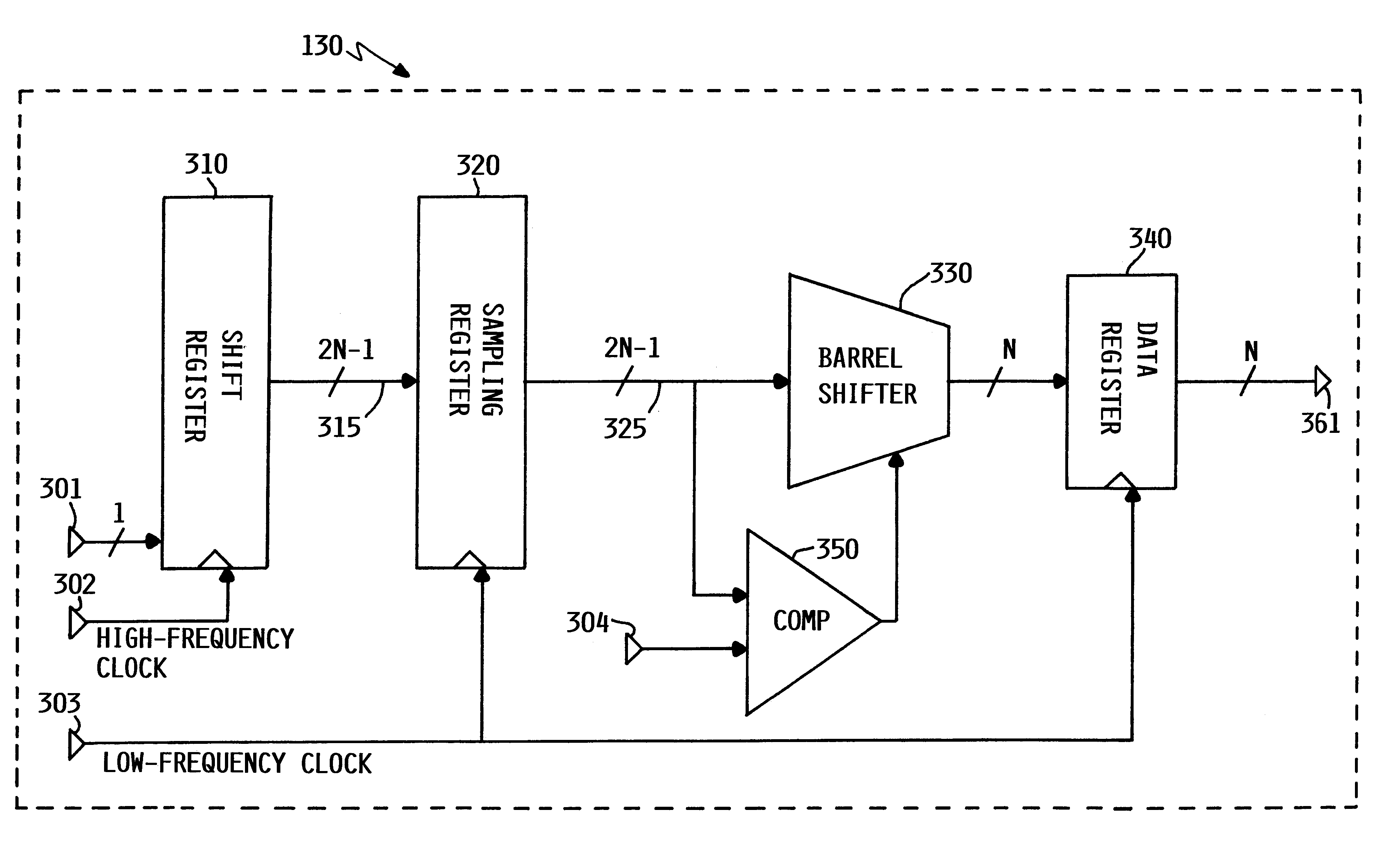

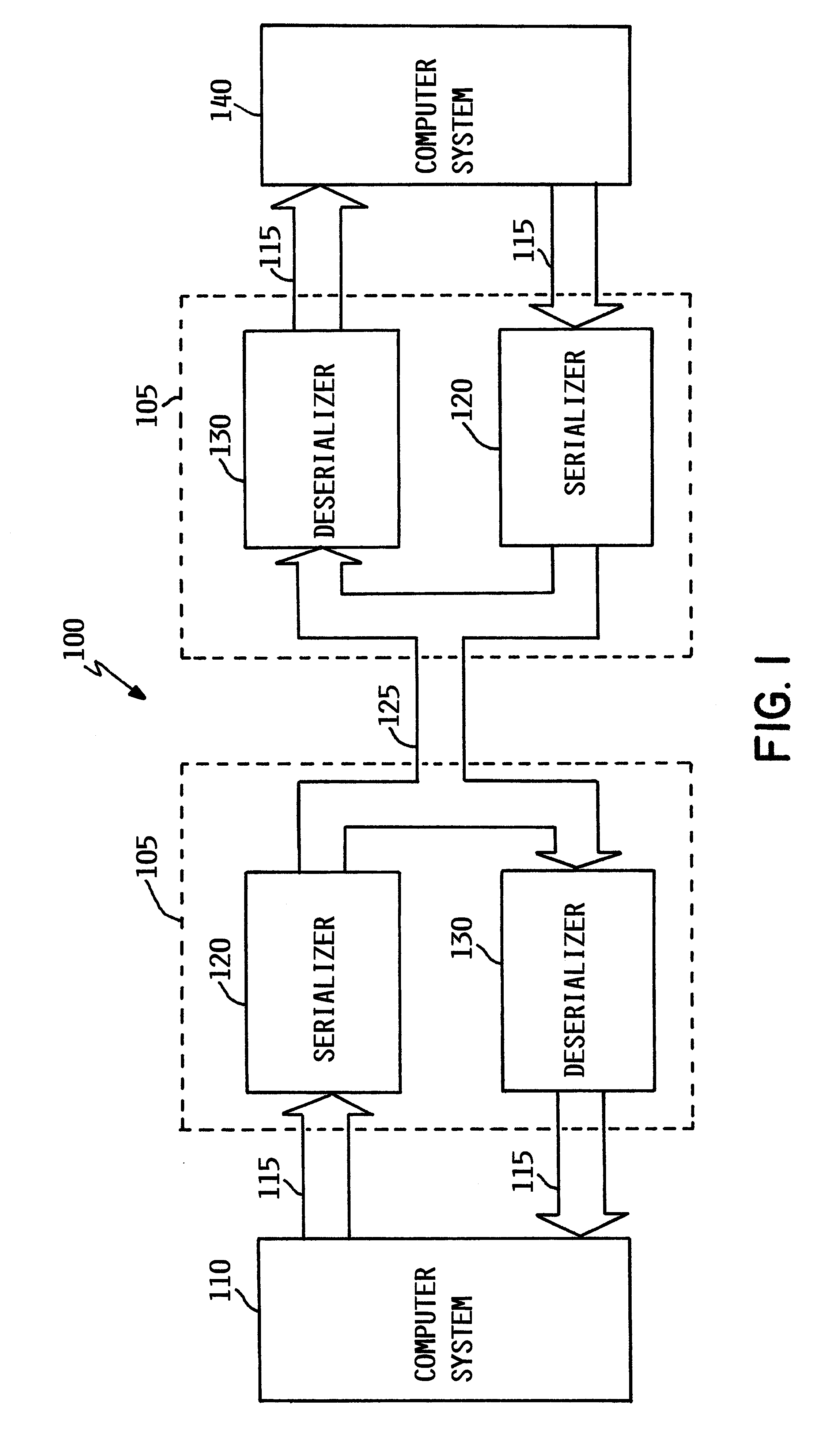

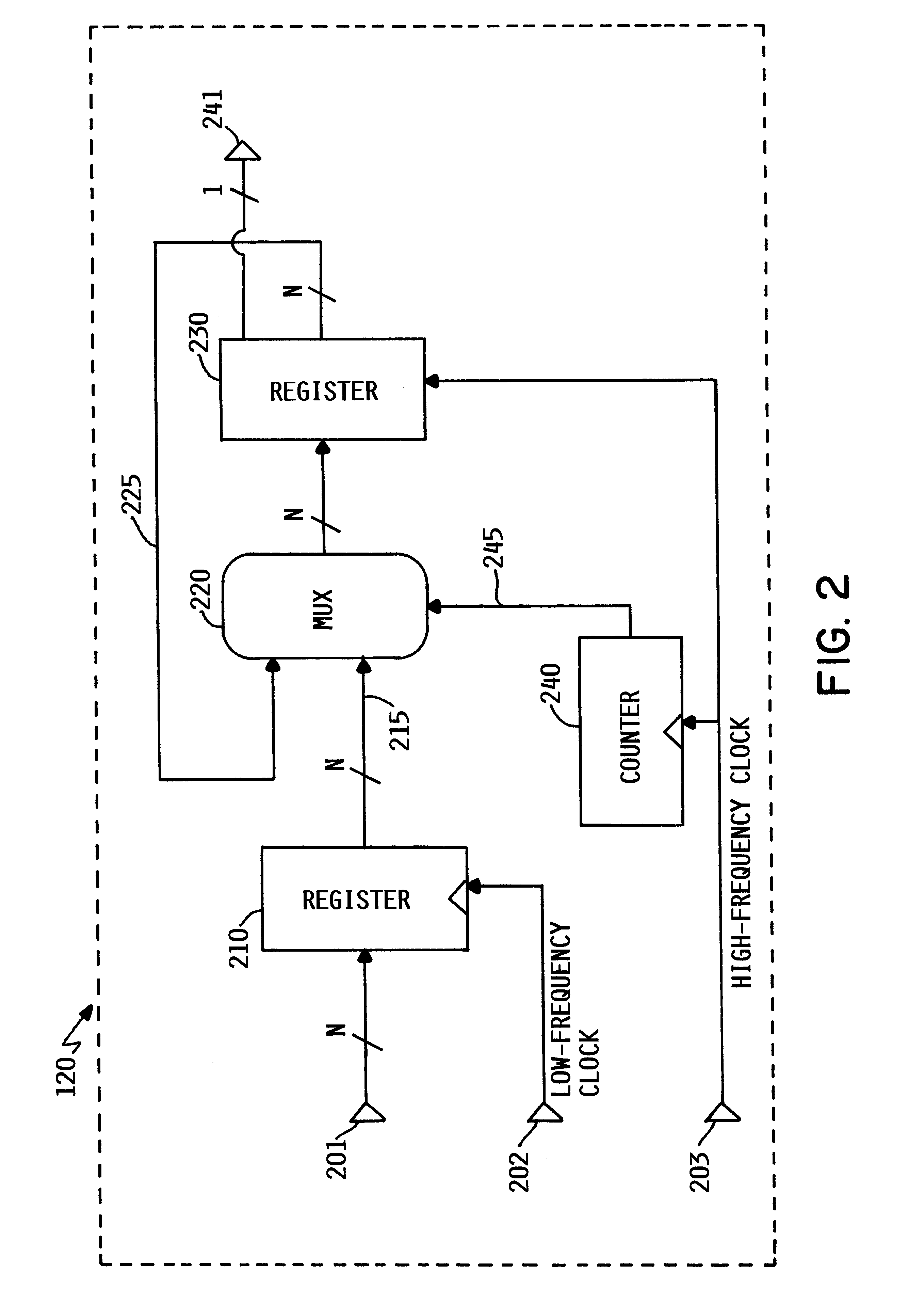

Apparatus and method for optimized self-synchronizing serializer/deserializer/framer

InactiveUS6459393B1Negatively impact design timeNegatively integrated circuit clock loadingParallel/series conversionViruses/bacteriophagesSerial transferTelecommunications link

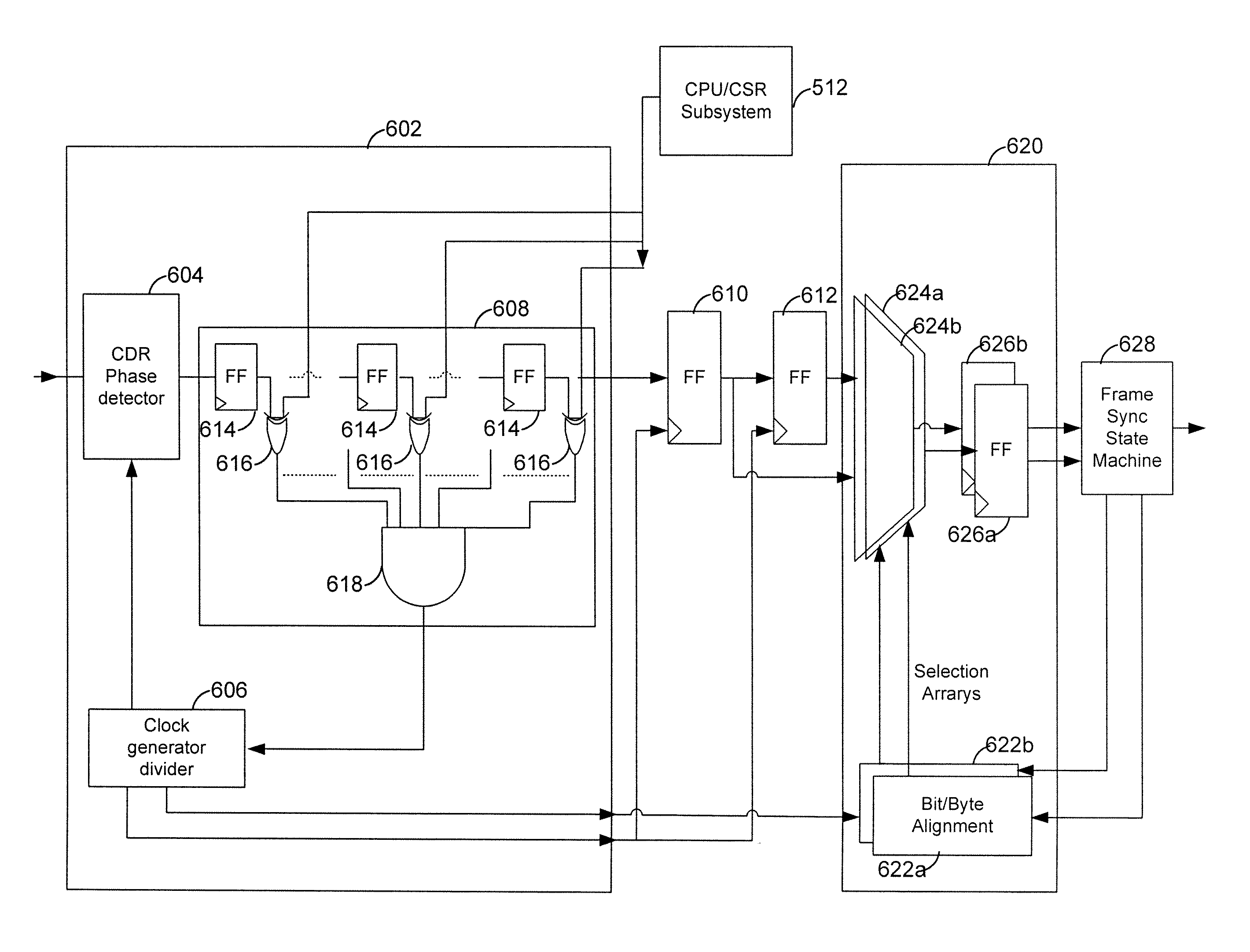

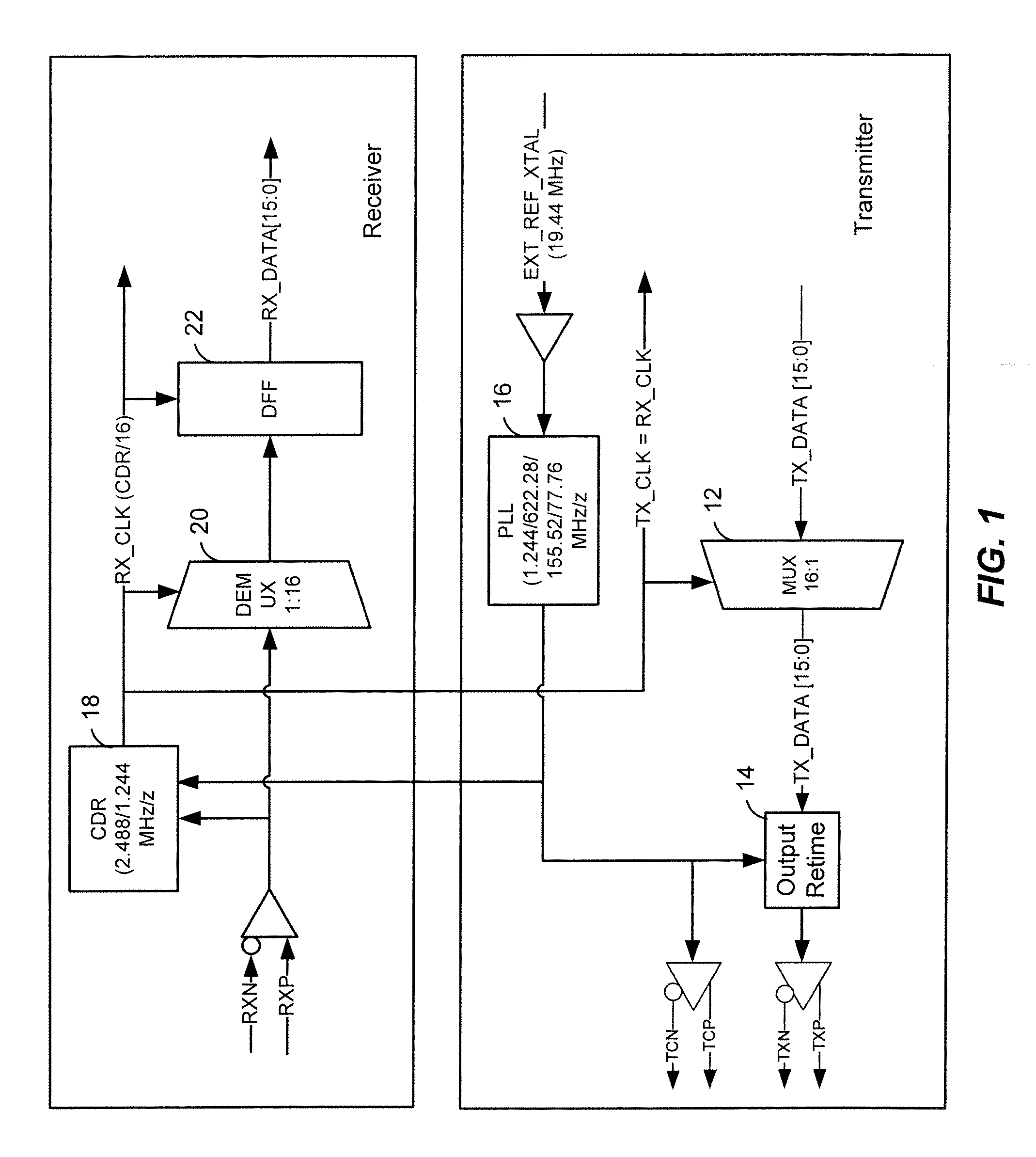

An apparatus and method for improving the communication capabilities of computer systems is disclosed. The most preferred embodiments of the present invention use a series of data buffers and data registers to process an incoming high speed data signal. By using the buffers and registers, the incoming signal can be reformatted and manipulated at a much lower frequency than the original transmission frequency. The deserializer of the present invention also samples a greater portion of the incoming data signal than usual to further increase reliability. These various features of the invention provide for a more stable and reliable communication link and will also provide a less expensive solution for serialization / deserialization. The present invention includes a serializer that receives parallel data input from a computer and serializes the data for transmission over a high-speed serial communication link. On the receiving end, the present invention provides a deserializer that can quickly and efficiently transform the serial data back into parallel form for use within the computer system on the receiving end. By utilizing two related clock signals, one clock signal being an integer multiple of the other, a self-synchronizing serializer / deserializer can be created. In addition, by increasing the size of the data sample on the receiving end, the comparisons necessary to retrieve a parallel signal from a serial transmission can occur at a much lower frequency than the frequency of the serial transmission. In the most preferred embodiment, the invention is provided as a integrated solution manufactured on a Peripheral Component Interconnect (PCI) card, thereby allowing the present invention to be easy installed into existing computer systems.

Owner:MEDIATEK INC

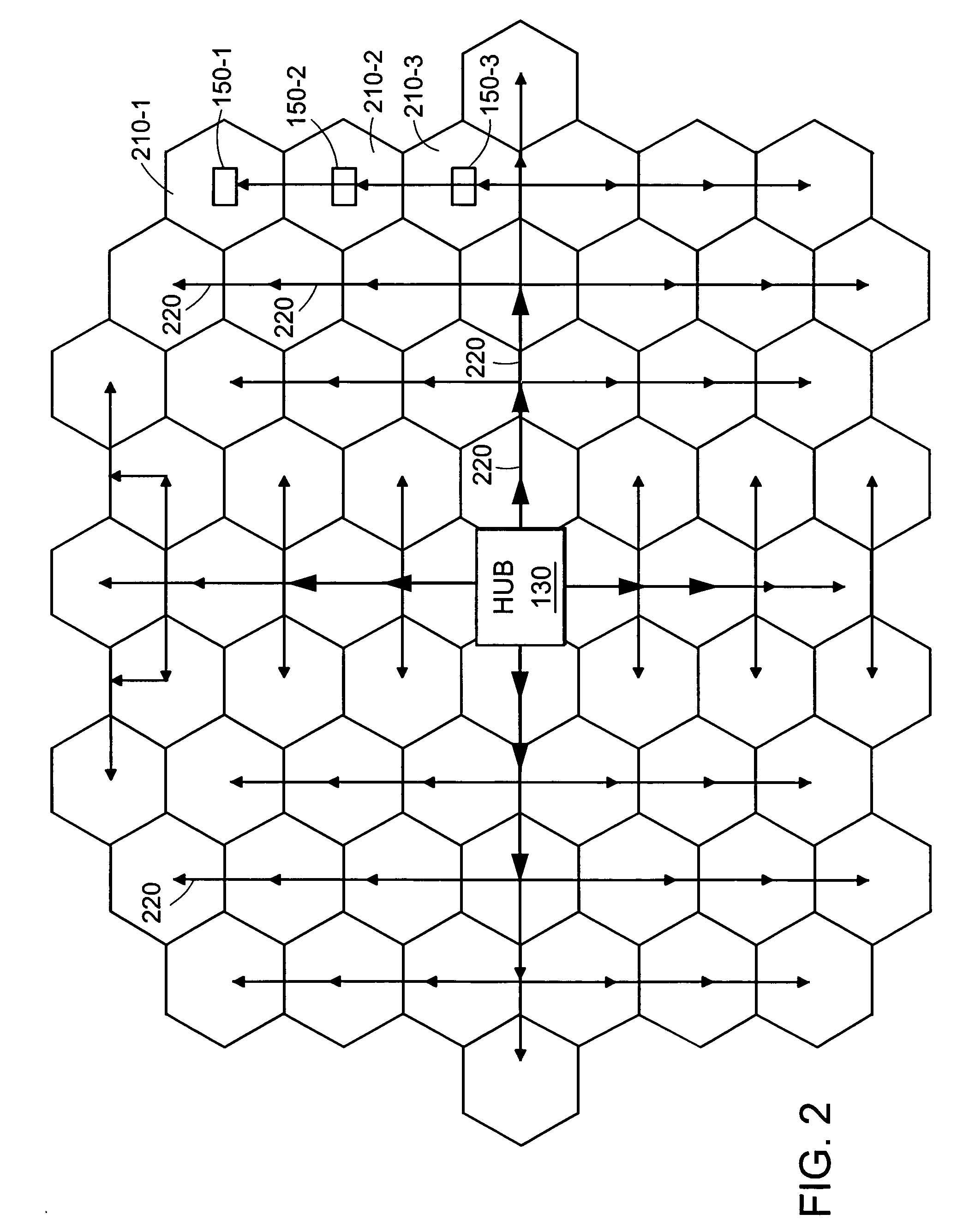

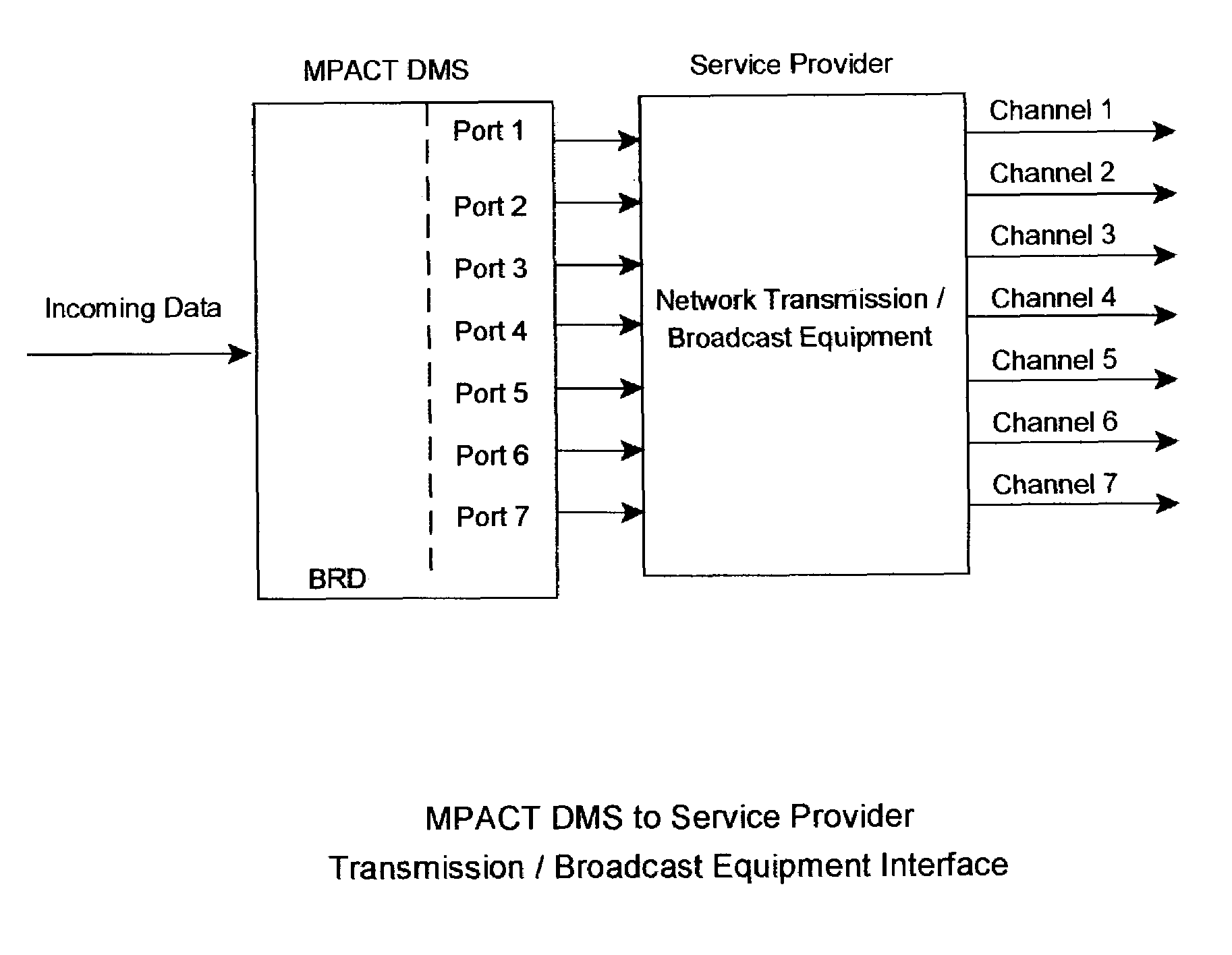

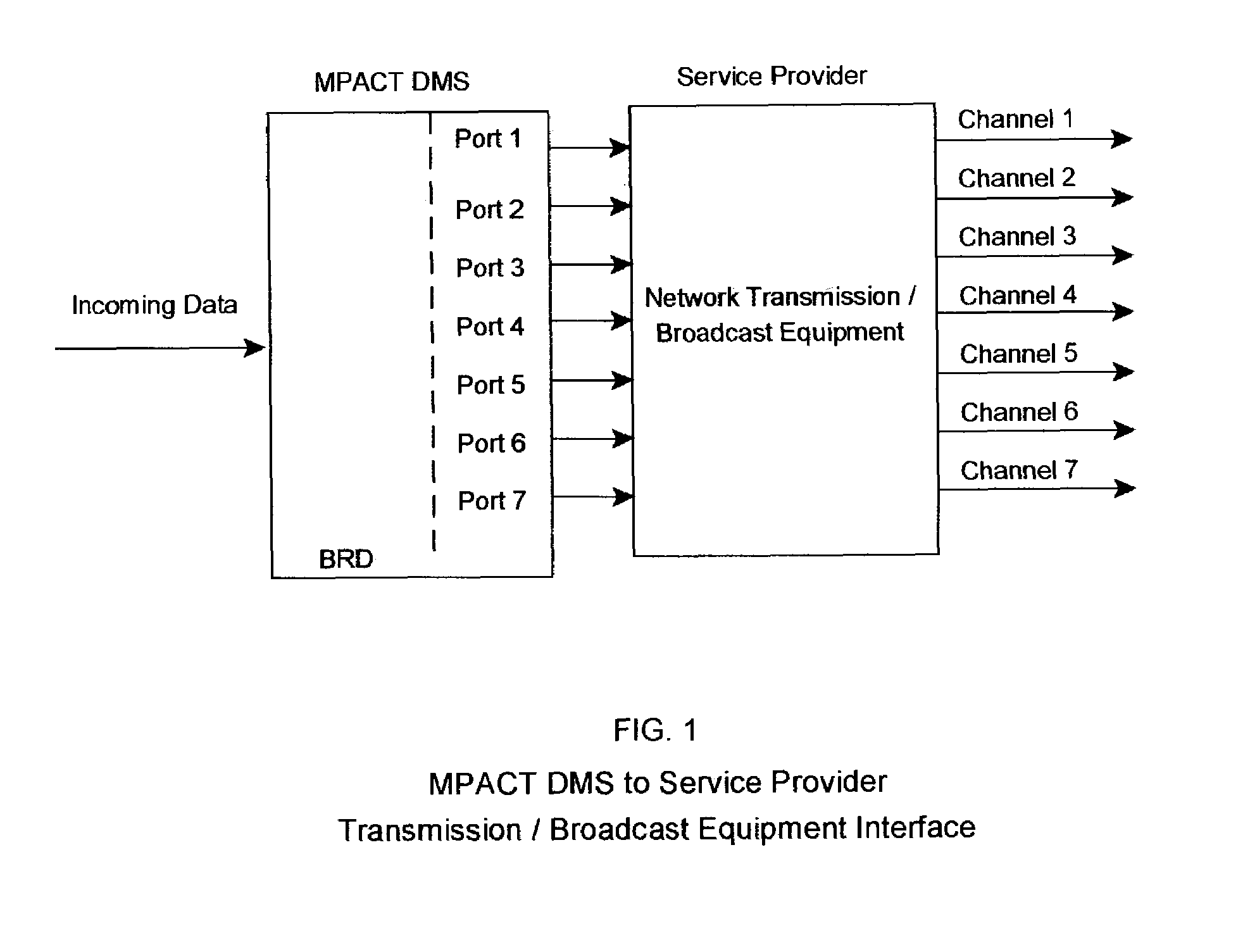

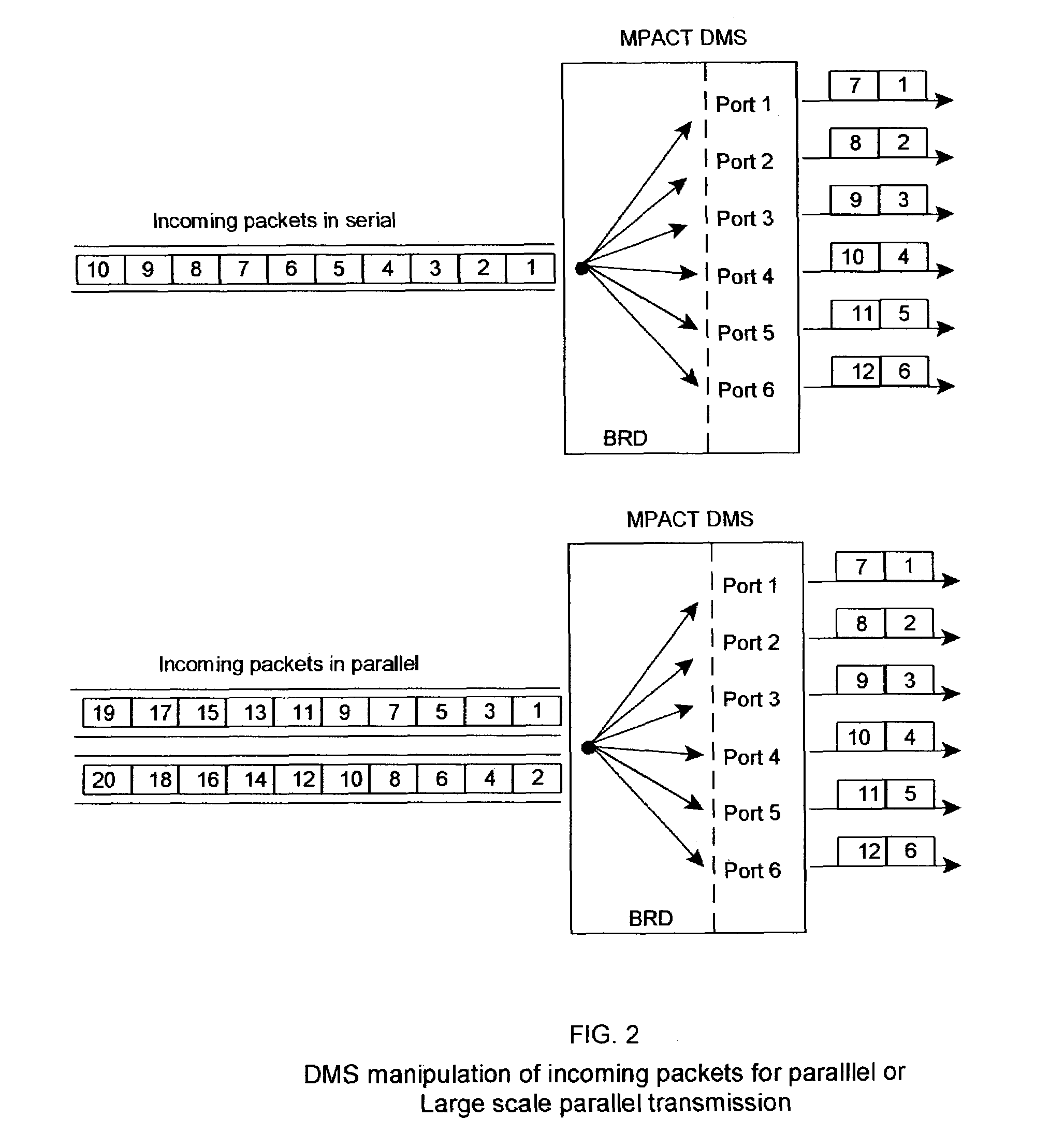

Massively parallel computer network-utilizing MPACT and multipoint parallel server (MPAS) technologies

InactiveUS7552192B2High bandwidthSmall sizeBroadband local area networksMultiple digital computer combinationsSerial transferOn demand

A Process and apparatus for high speed data transfer for communications networks, computers, computer networks and network interfaces, via software, and apparatus mimicking the human brain and nervous system, by utilization of highly distributed storage of data and massively parallel data transfer and reception over multiple channels / pathways resulting in greater bandwidth than that of serial transmissions. The primary purpose of which is to provide highspeed data transfer for data-on-demand networks such as Video-on-Demand. Therefore, the processes, architectures and topologies described herein may be interfaced with satellite systems, CATV systems, Virtual Networks, wireless services; utilized by Internet Service Providers, and any broadcaster / service provider capable of multiple channel / frequency broadcasts and reception via satellite, cable, terrestrial, or other mediums.

Owner:CARMICHAEL RONNIE GEROME

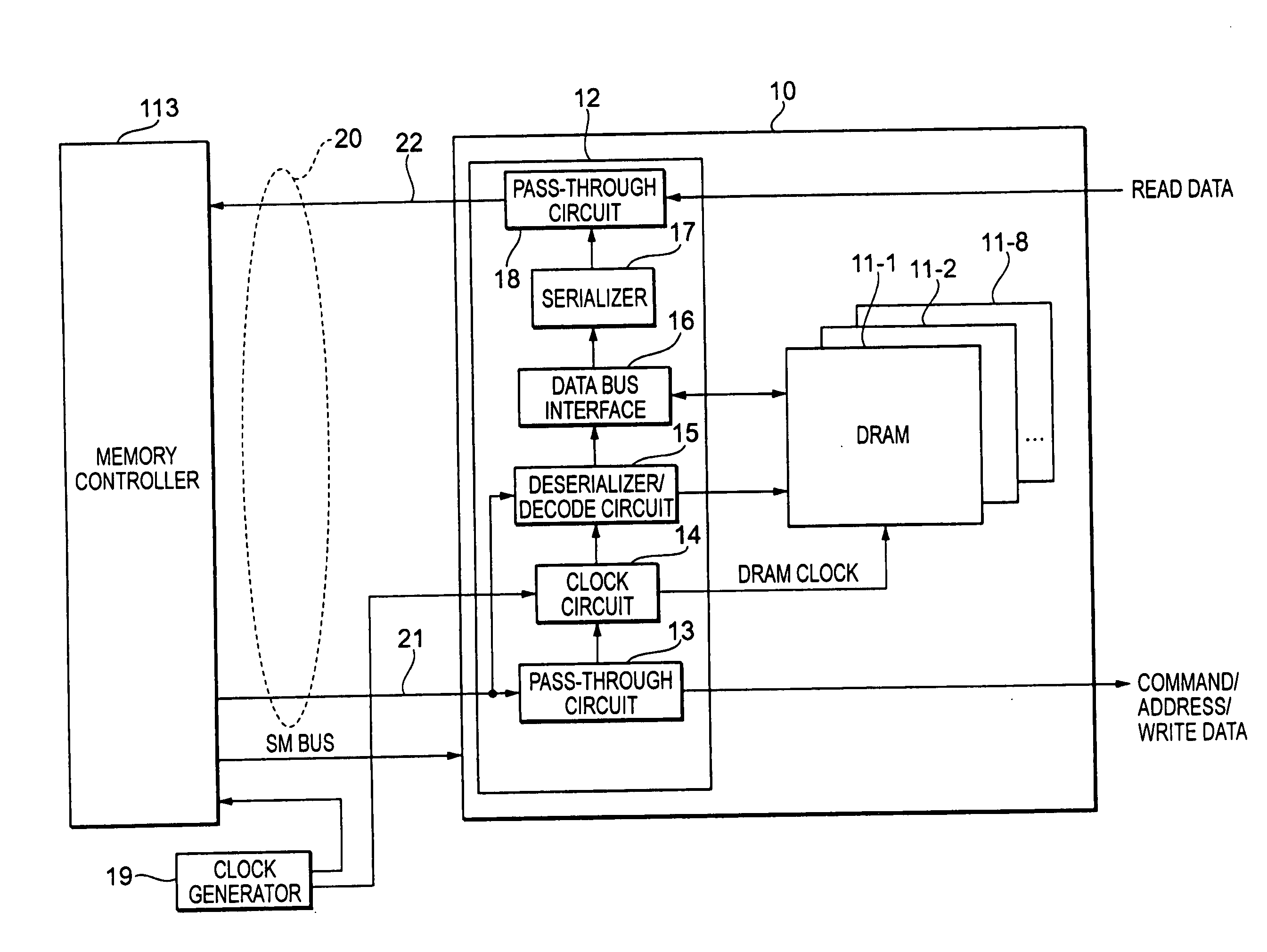

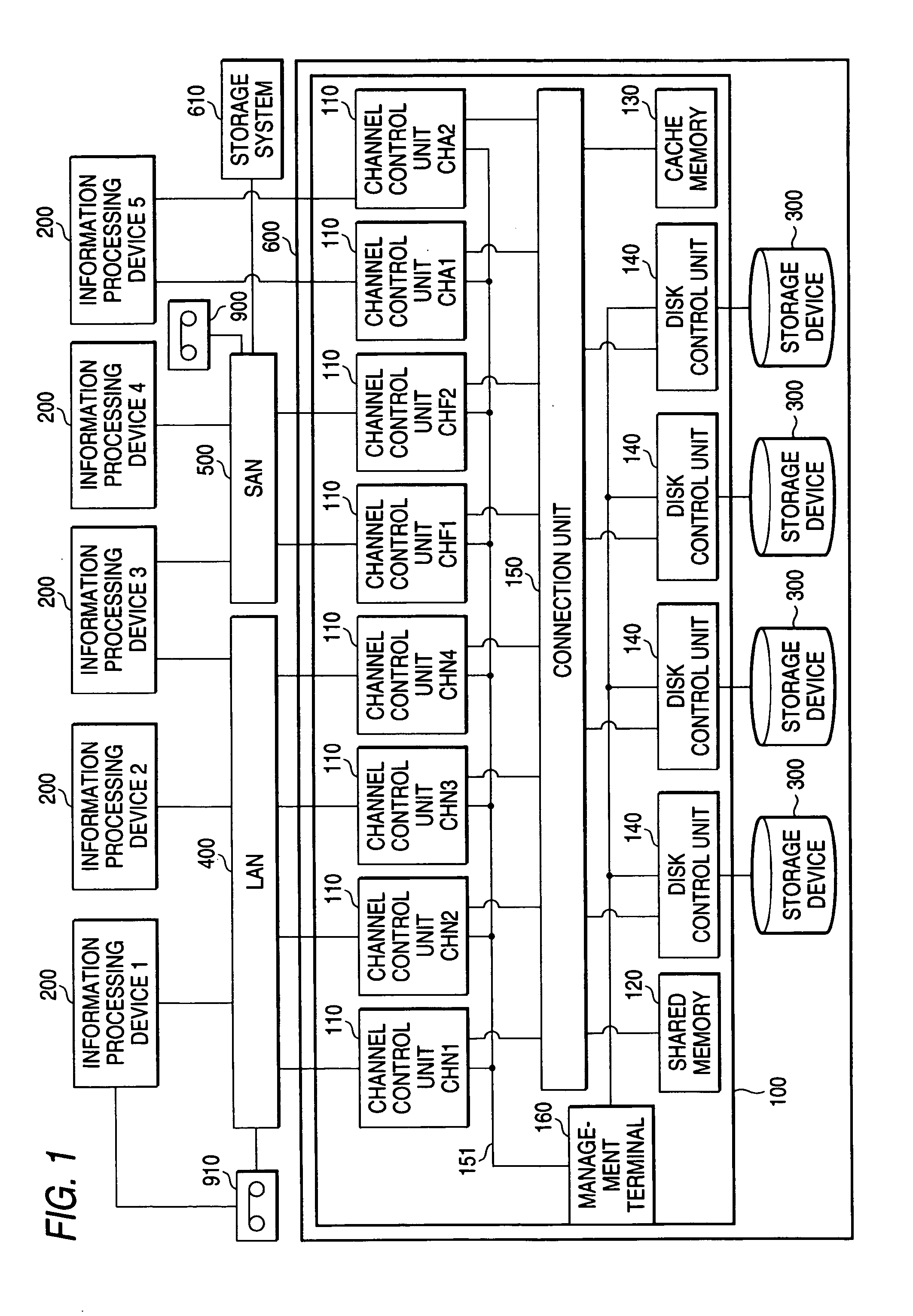

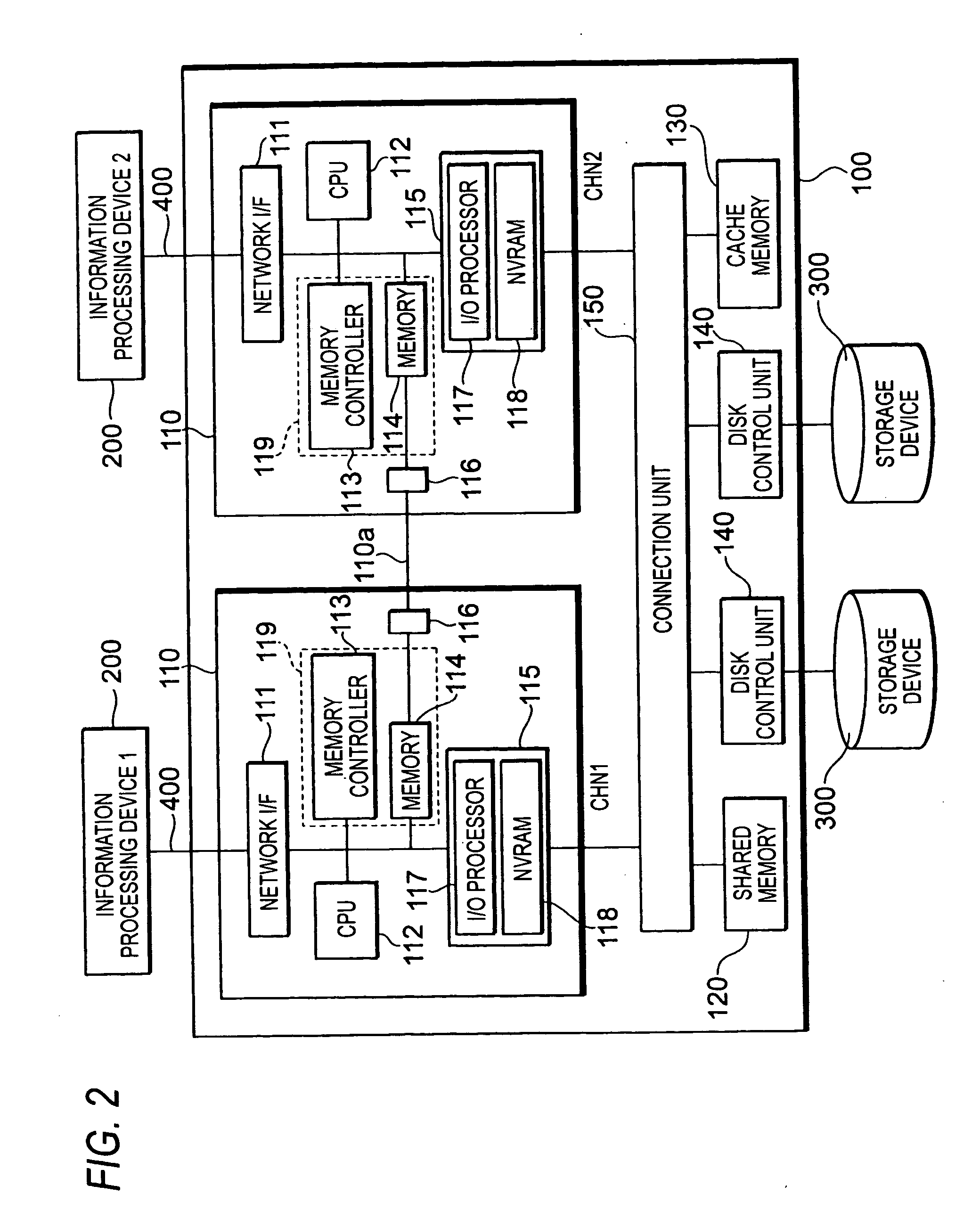

Storage device control apparatus

InactiveUS20060047899A1Improve reliabilitySufficient reliabilityError detection/correctionMemory systemsSerial transferControl memory

A storage device control apparatus includes a channel control unit for outputting an I / O request for a storage device, having a CPU for receiving a data input / output request in a file unit, an I / O processor for outputting the I / O request corresponding to the data input / output request in the file unit in response to an instruction from the CPU, and a memory system for temporarily storing information required for a file access process of the CPU. The memory system includes a plurality of memory modules and a memory controller for controlling memory access to the plurality of memory modules, a command, an address and data being serially transmitted from the memory controller to each of the memory modules. Each of the memory modules has a plurality of memory elements and a plurality of buffer units. The memory controller and the memory system are connected by duplicated serial interfaces.

Owner:HITACHI LTD

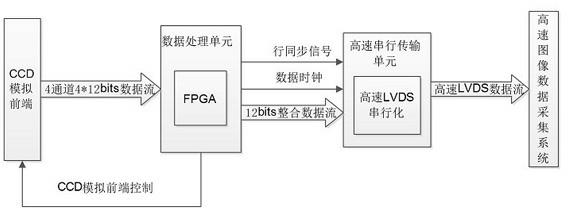

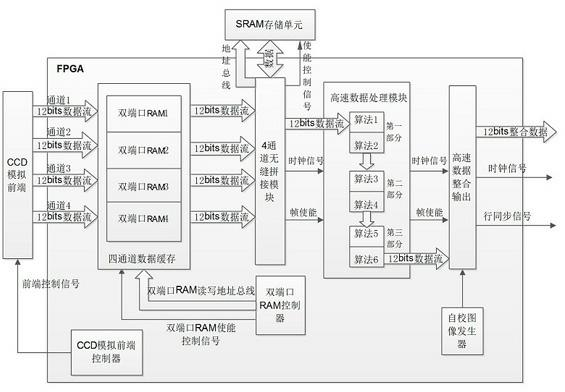

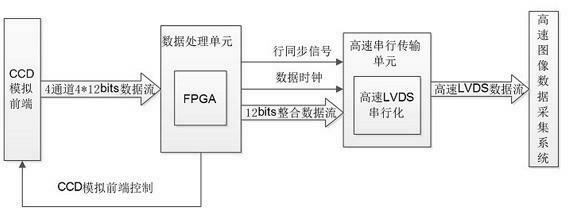

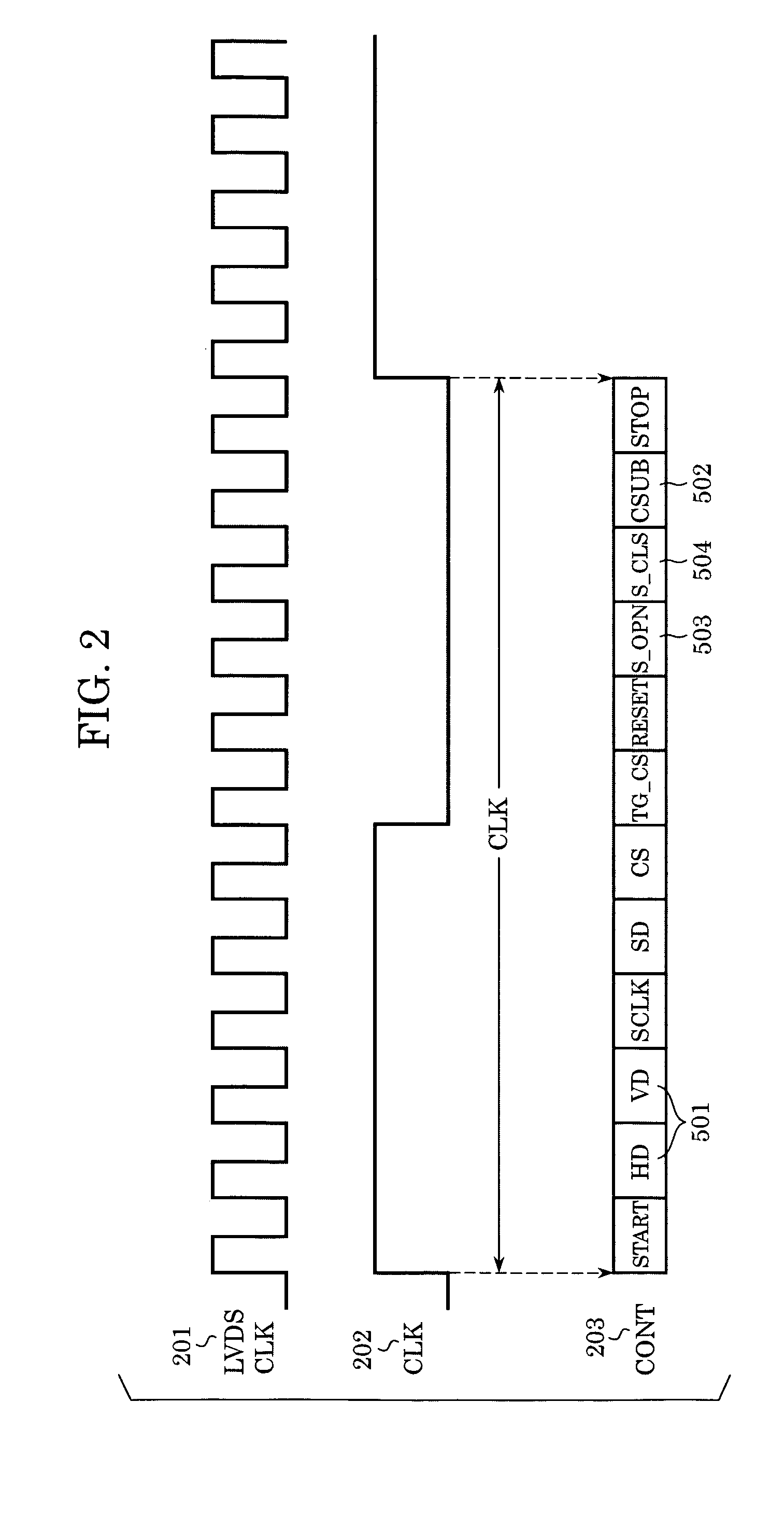

Data processing and transmitting system of high-speed multichannel CCD (charge-coupled device)

InactiveCN102638661AReal-time processingReduce in quantityTelevision system detailsPulse modulation television signal transmissionSerial transferData stream

The invention discloses a data processing and transmitting system of high-speed multichannel CCD (charge-coupled device), which comprises a CCD analog front end, a data processing unit, a high-speed serial transmission unit and a high-speed image data collection system which are sequentially connected. The CCD analog front end is used for converting an analog signal output by a CCD detector and subjected to sampling and pulse control into n channels of digital image data via n A / D (analog / digital) converters, transmitting the digital image data to the data processing unit, and acquiring data of each channel at the same time. The data processing unit is used for transmitting single-channel high-speed data streams, a data transmitter clock and a horizontal synchronizing signal acquired from integration of the digital image data to the high-speed serial transmission unit. The high-speed serial transmission unit is used for converting single-channel high-speed data streams via LVDS (low-voltage differential signaling) serial chips into high-speed LVDS data streams for transmitting. The high-speed image data collection system is used for collecting the high-speed serial LVDS data streams and realizing real-time storing and displaying of the image data.

Owner:NANJING UNIV OF SCI & TECH

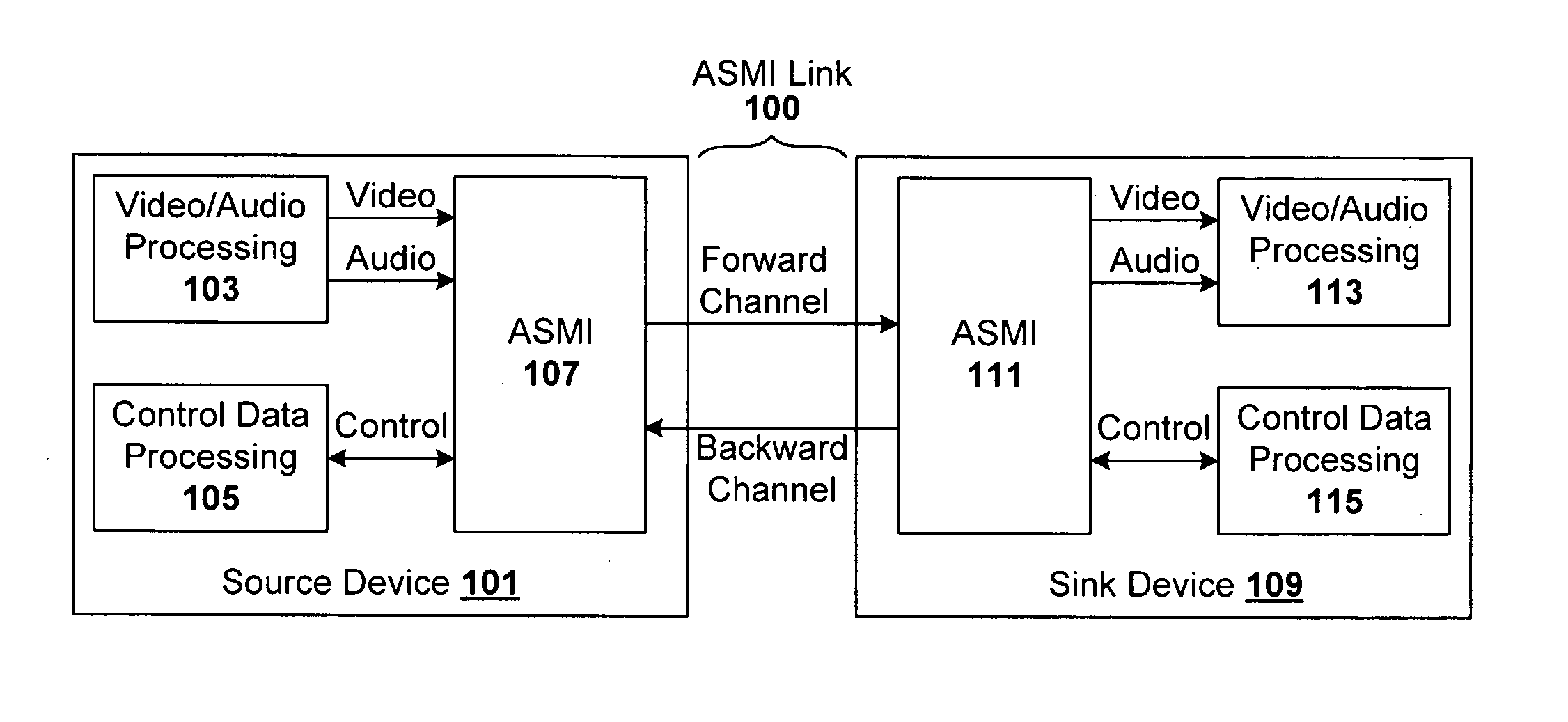

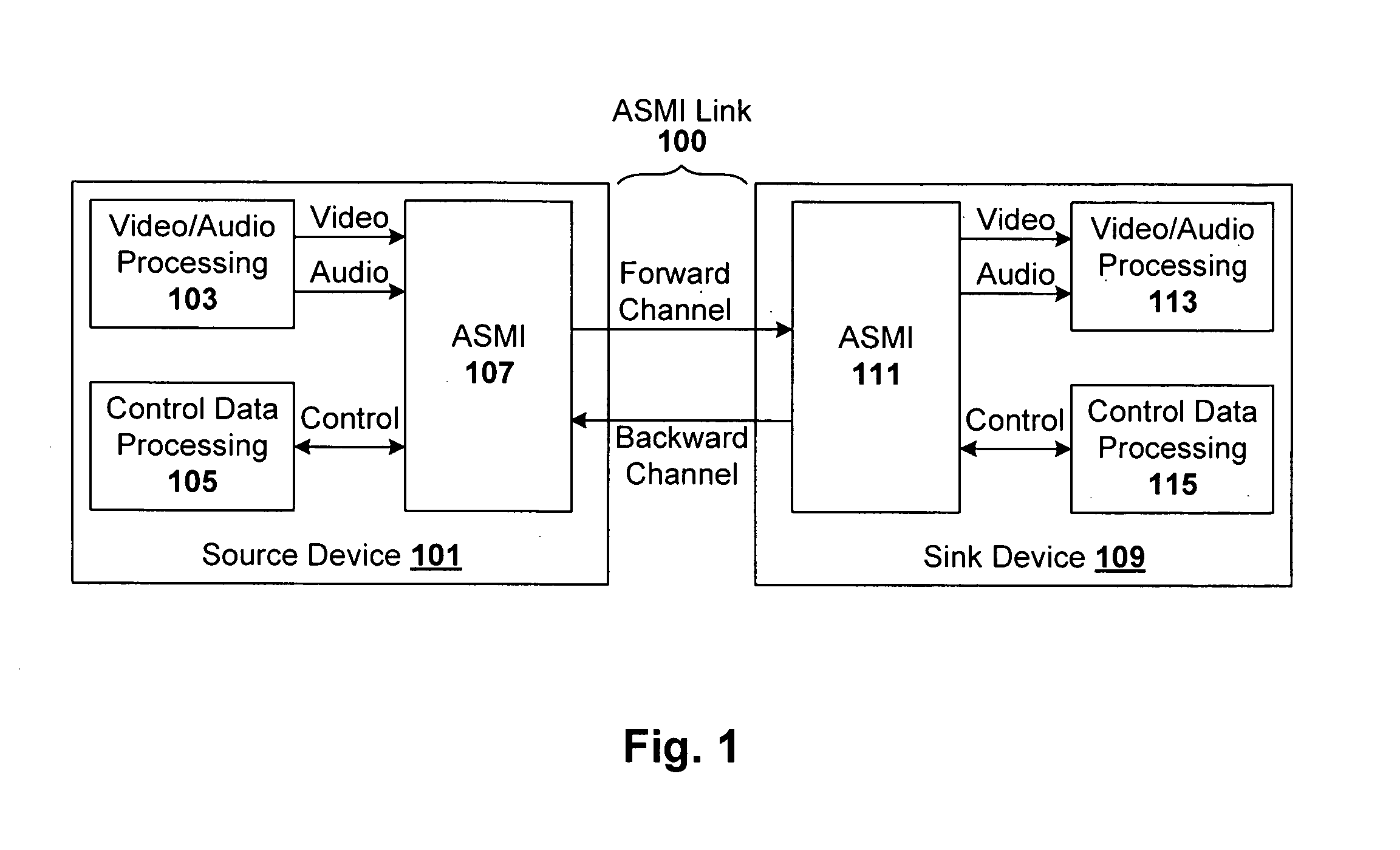

Protocol for uncompressed multimedia data transmission

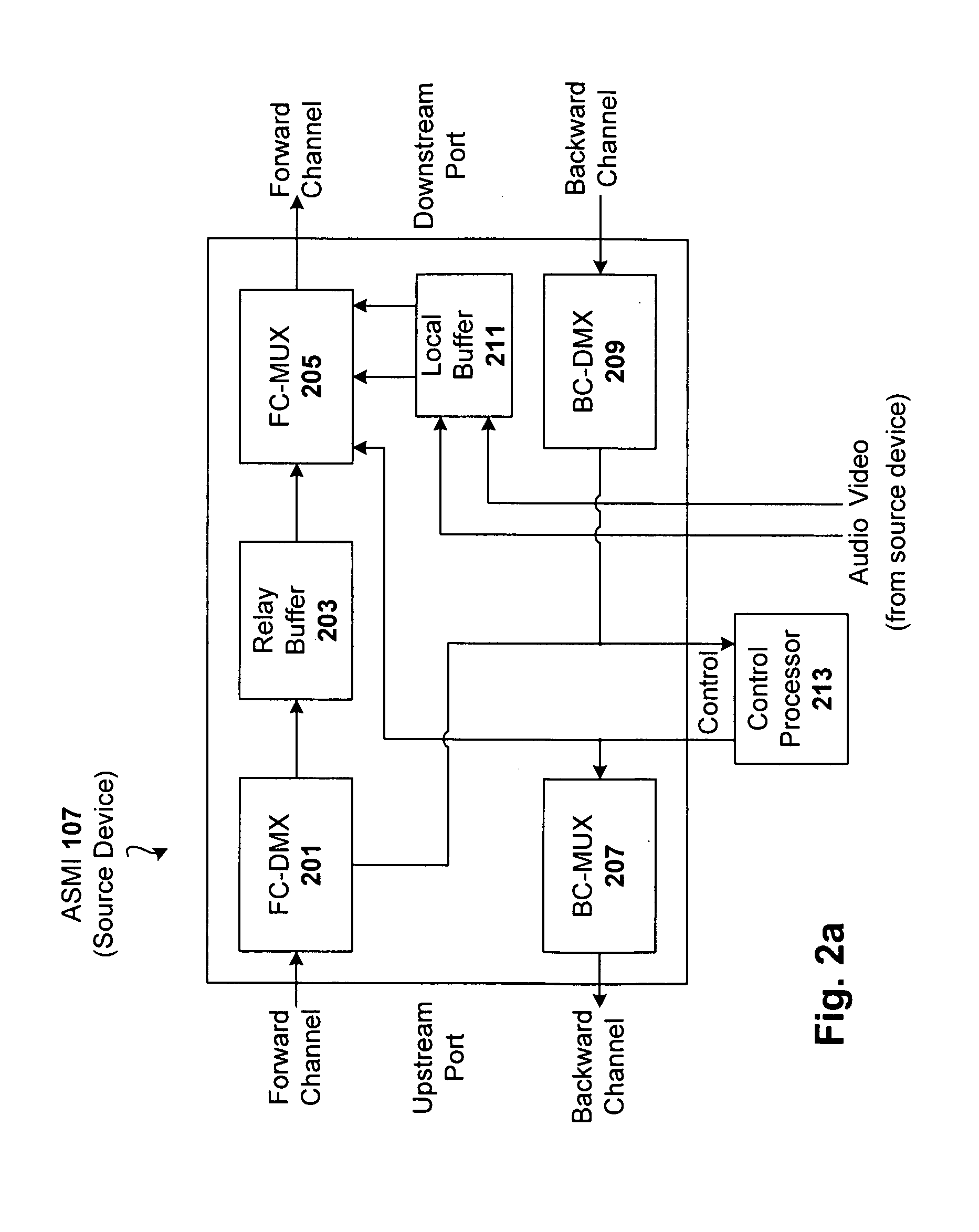

ActiveUS7386641B2Static indicating devicesMultiple digital computer combinationsSerial transferTransmission protocol

A serial transmission protocol and architecture are provided that can be used to transmit uncompressed multimedia (e.g., video / audio / control data) over a high speed serial forward communication channel. A backward channel is also provided, for communicating control data. The protocol is implemented with a flexible packet format that supports all different modes of video data, and also supports 24 bit and 30 bit video data (or higher). An example application where the architecture and protocol can be used is a home entertainment multimedia system. A mechanism to implement EDID pass-through and protocols such as HDCP is also provided.

Owner:OWLINK TECH

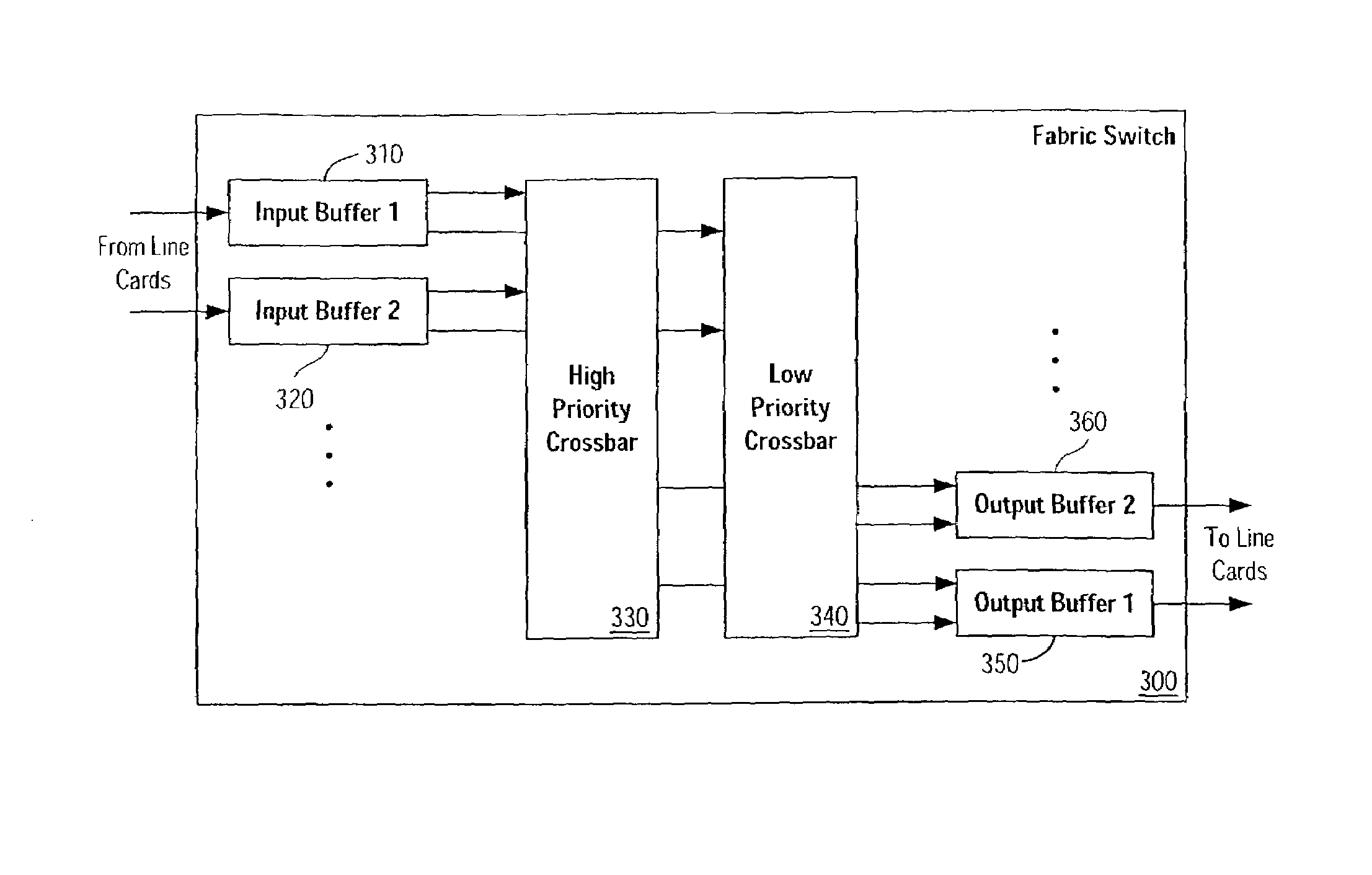

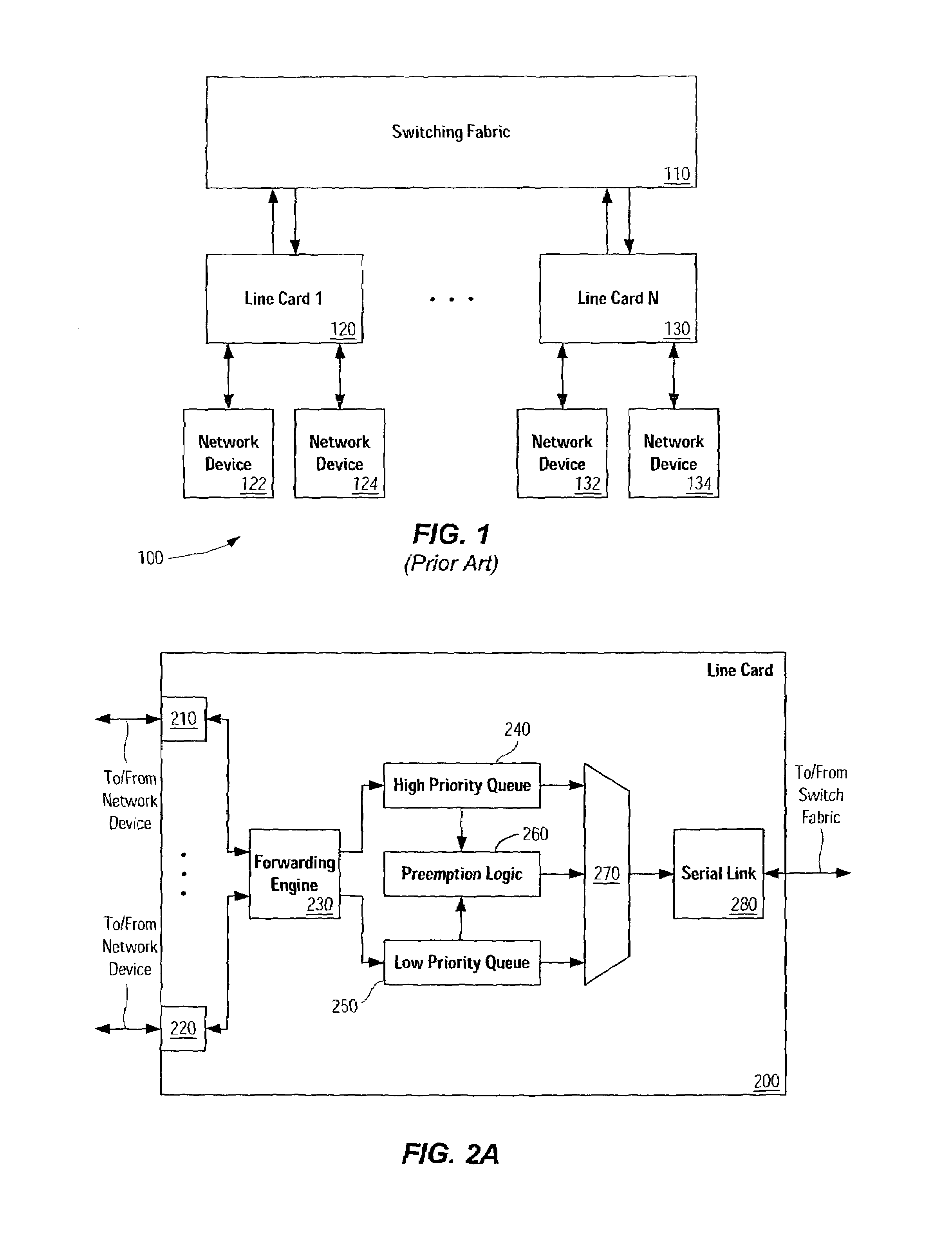

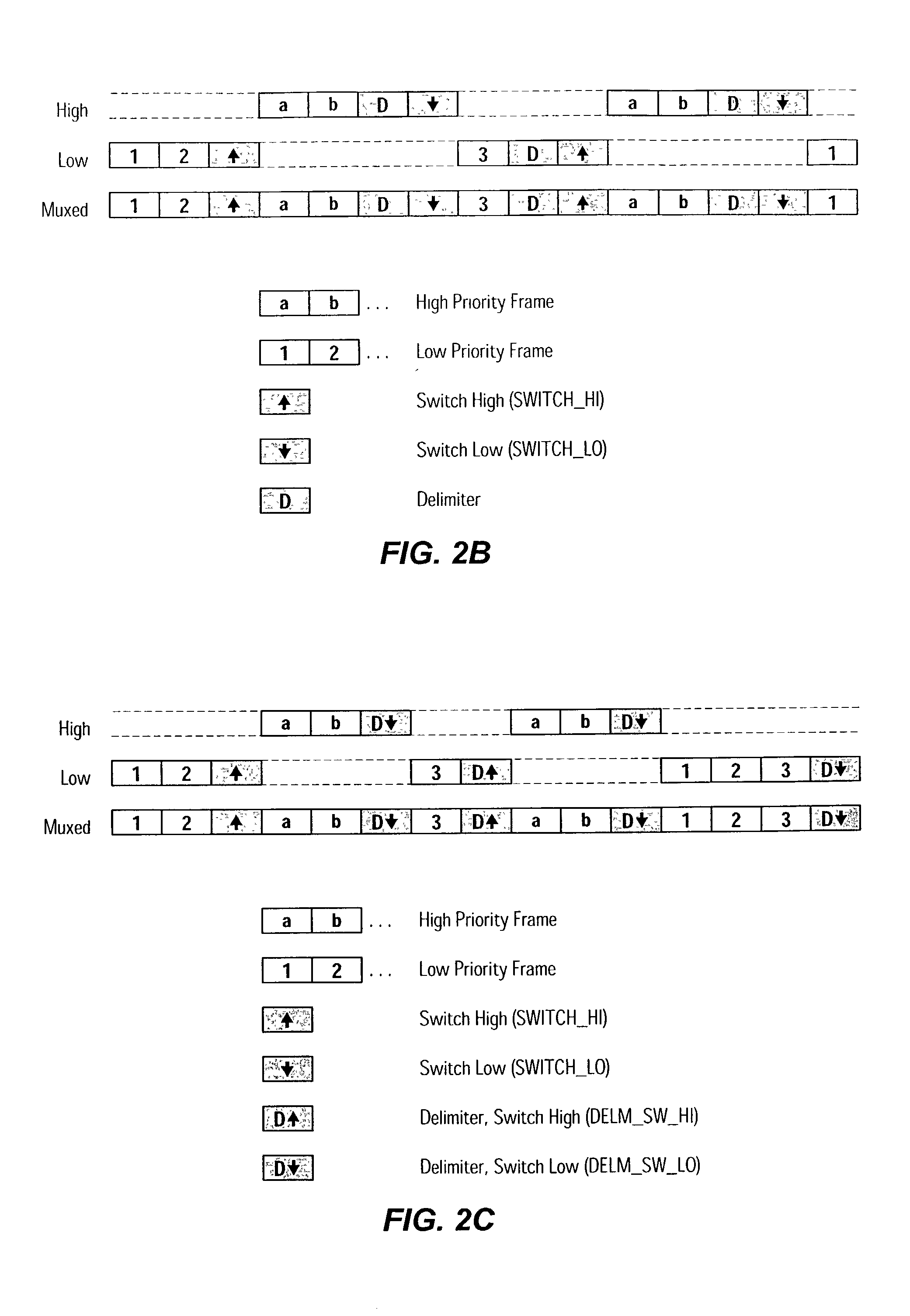

Prioritization and preemption of data frames over a switching fabric

InactiveUS7464180B1Digital computer detailsData switching by path configurationSerial transferData stream

Network switching and / or routing devices can use multiple priority data streams and queues to support prioritized serial transmission of data from line cards (or the like) through a fabric switch to other line cards (or the like). Preemption logic is used to insert within a data stream commands indicating a switch from one priority level data to another. Delimiter commands and combination switch / delimiter commands can also be used. Multiple crossbars are implemented in the fabric switch to support the various data stream priority levels.

Owner:CISCO TECH INC

Protocol for uncompressed multimedia data transmission

ActiveUS20080005310A1Static indicating devicesMultiple digital computer combinationsSerial transferTransmission protocol

A serial transmission protocol and architecture are provided that can be used to transmit uncompressed multimedia (e.g., video / audio / control data) over a high speed serial forward communication channel. A backward channel is also provided, for communicating control data. The protocol is implemented with a flexible packet format that supports all different modes of video data, and also supports 24 bit and 30 bit video data (or higher). An example application where the architecture and protocol can be used is a home entertainment multimedia system. A mechanism to implement EDID pass-through and protocols such as HDCP is also provided.

Owner:OWLINK TECH

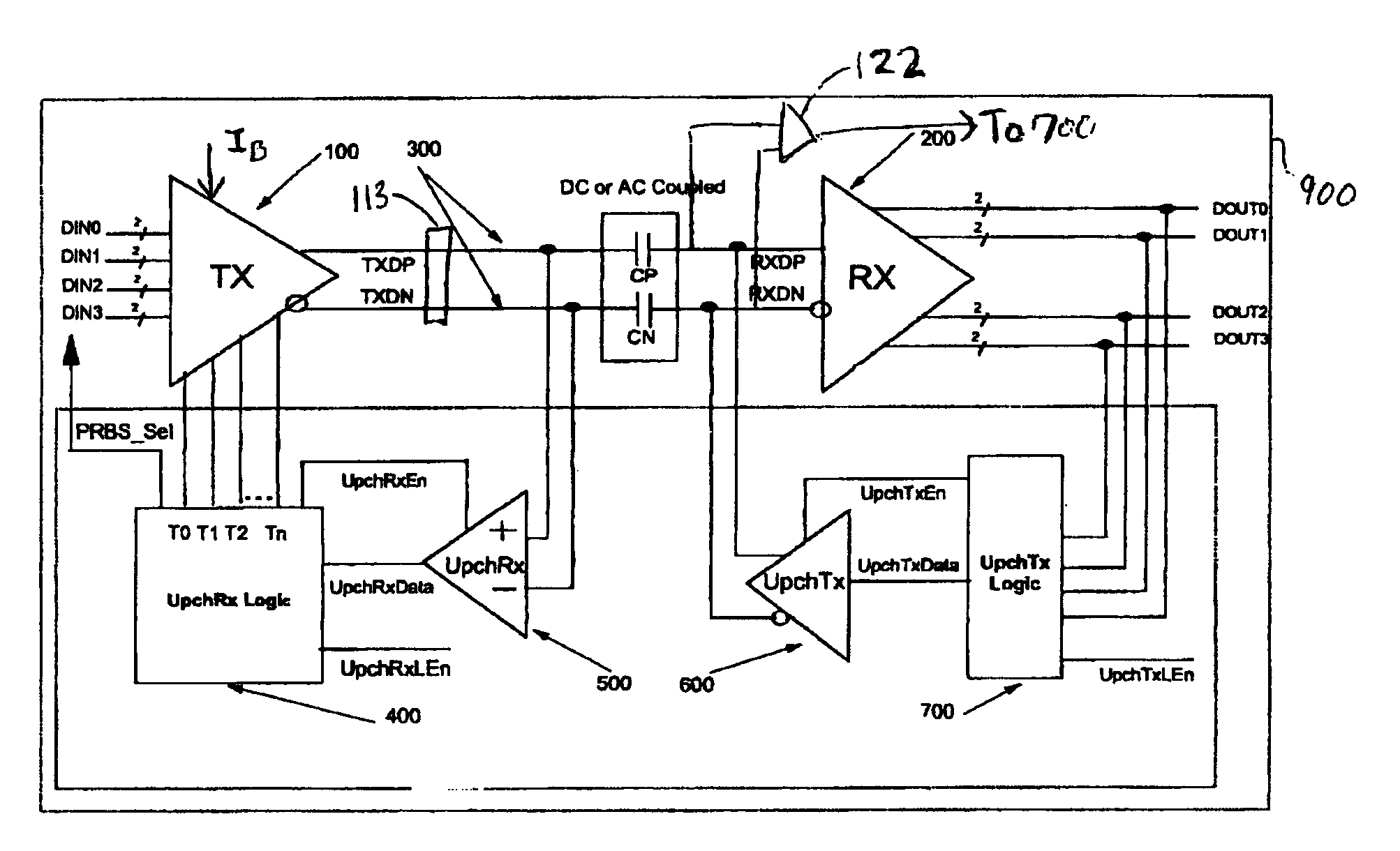

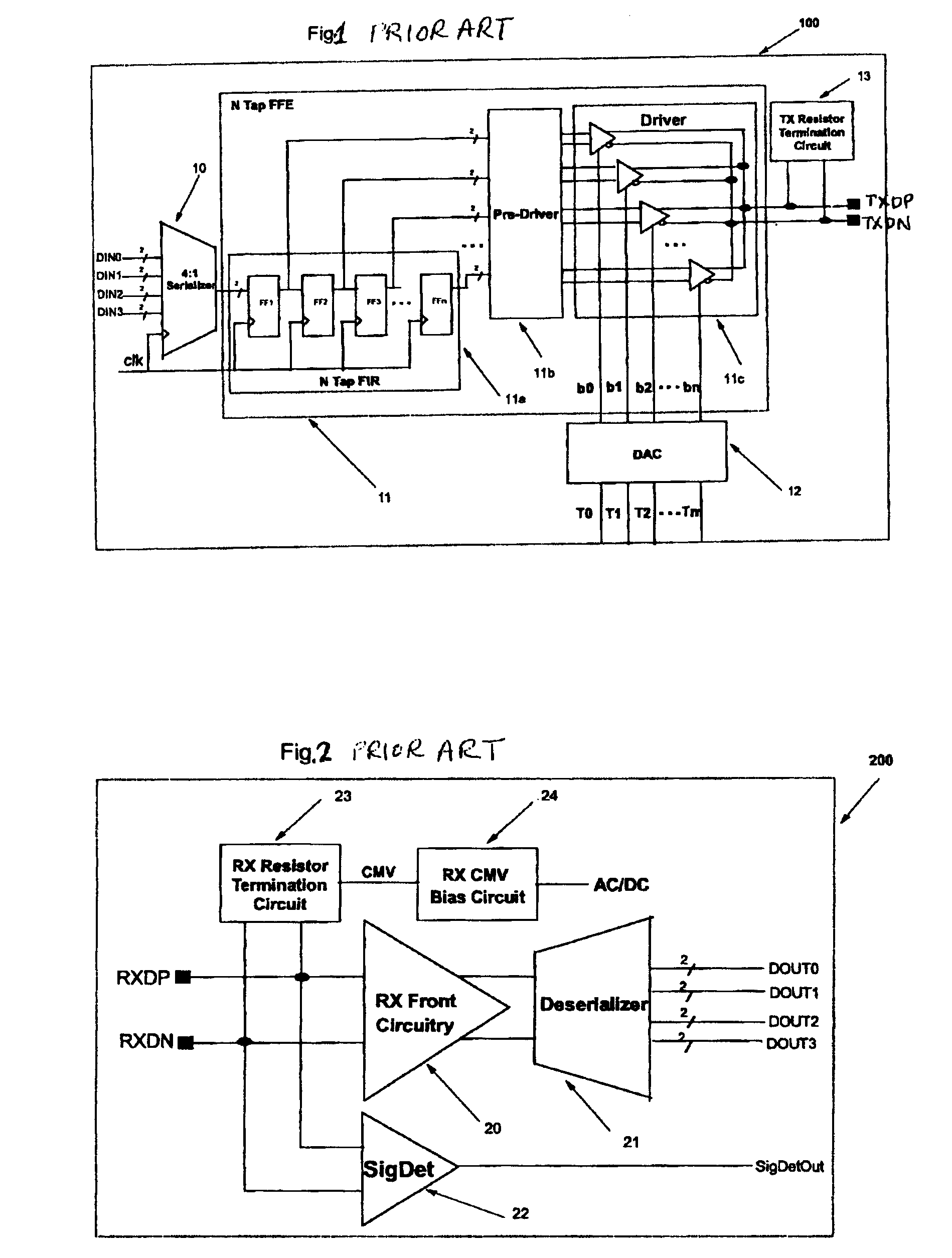

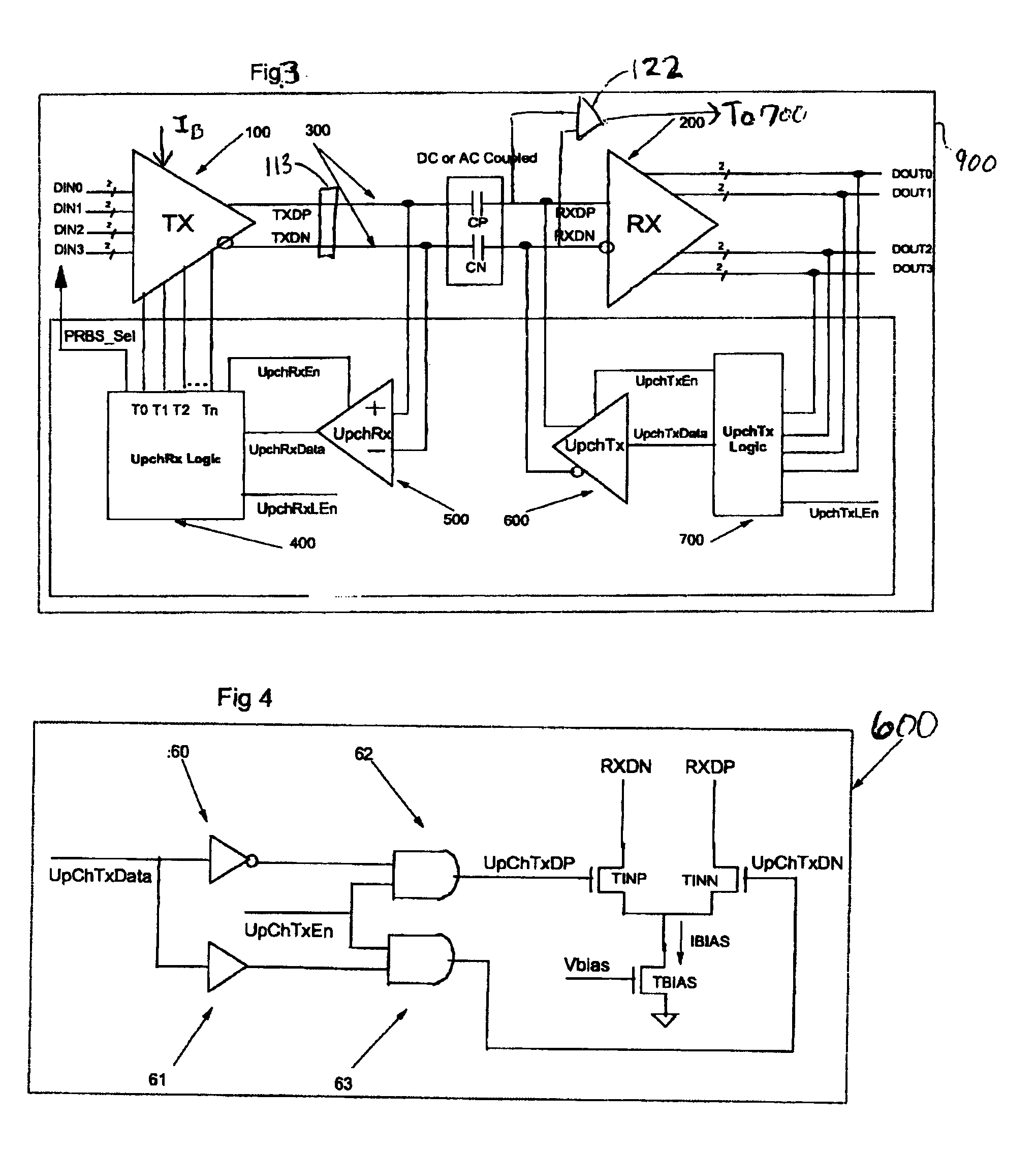

Automatic adaptive equalization method and system for high-speed serial transmission link

InactiveUS20050281343A1Reduce areaAdditional parasitic loadSecret communicationTransmitter/receiver shaping networksSelf adaptiveSerial transfer

A data communication system includes a transmitter unit and a receiver unit. The transmission unit has a transmission characteristic that is adjustable in accordance with equalization information. The transmission unit is operable to transmit a predetermined signal and the receiver unit is operable to receive the predetermined signal. The receiver unit is further operable to generate the equalization information by examining the eye opening of the received signal, and to transmit the equalization information to the transmitter unit.

Owner:IBM CORP

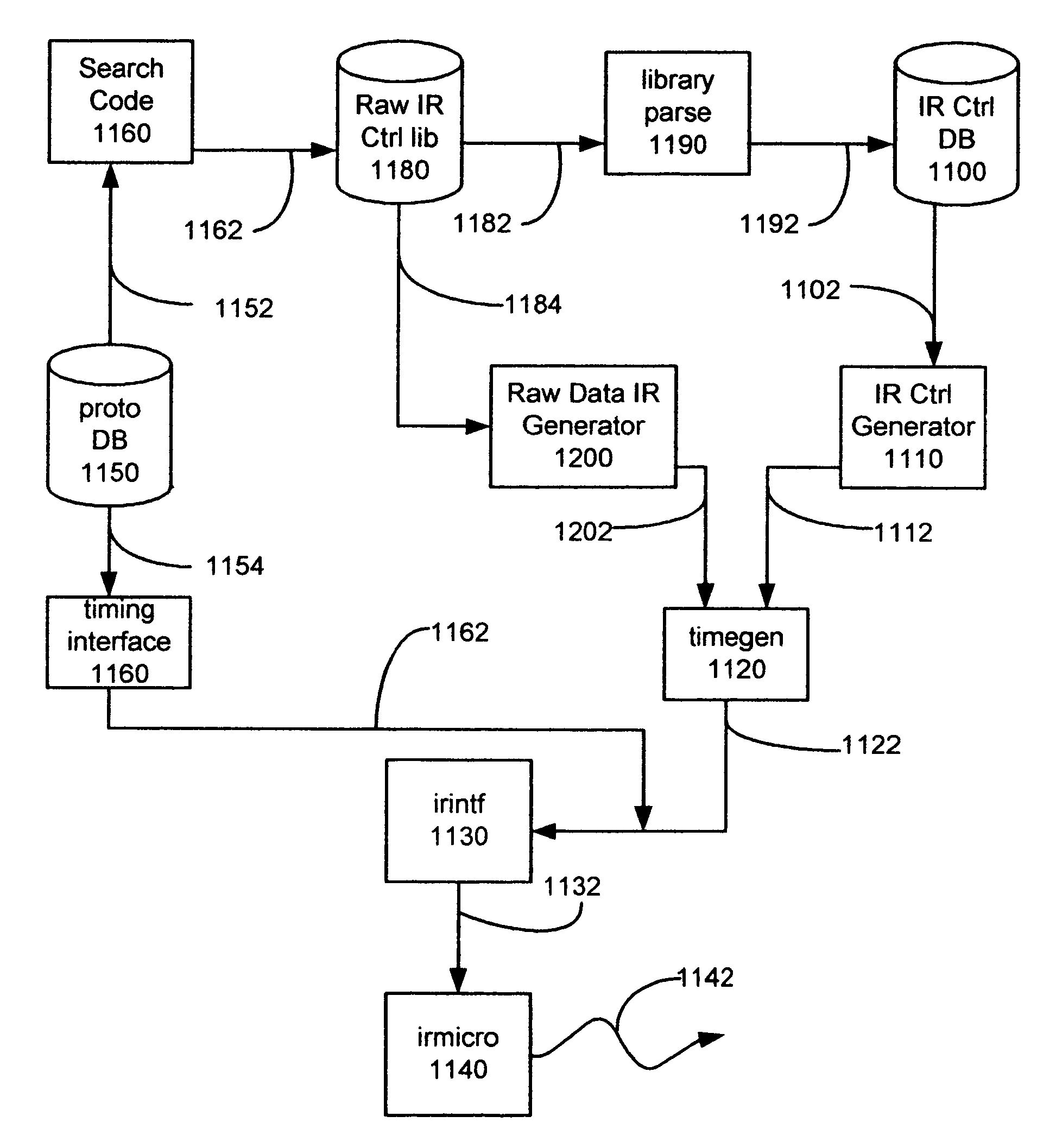

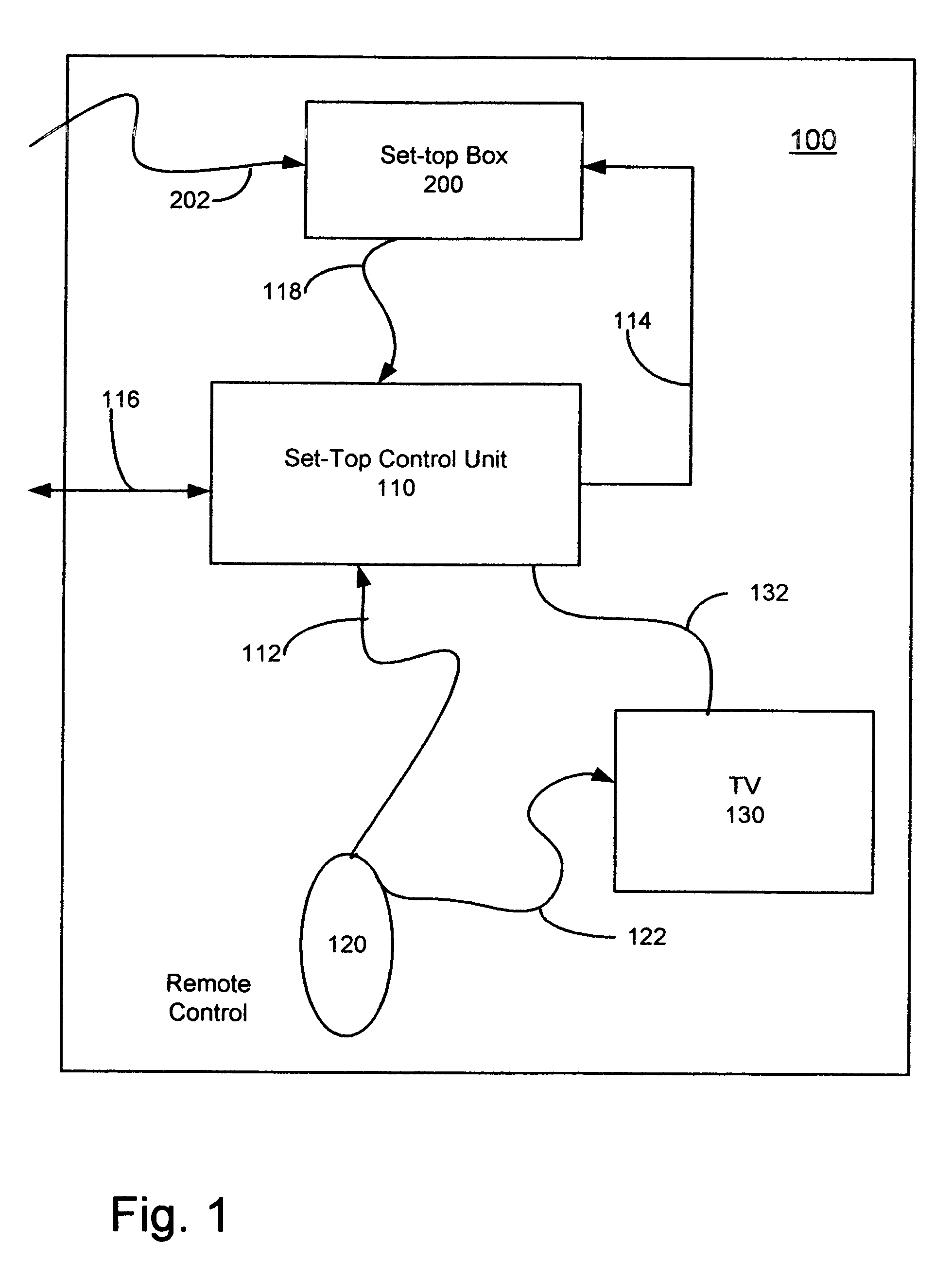

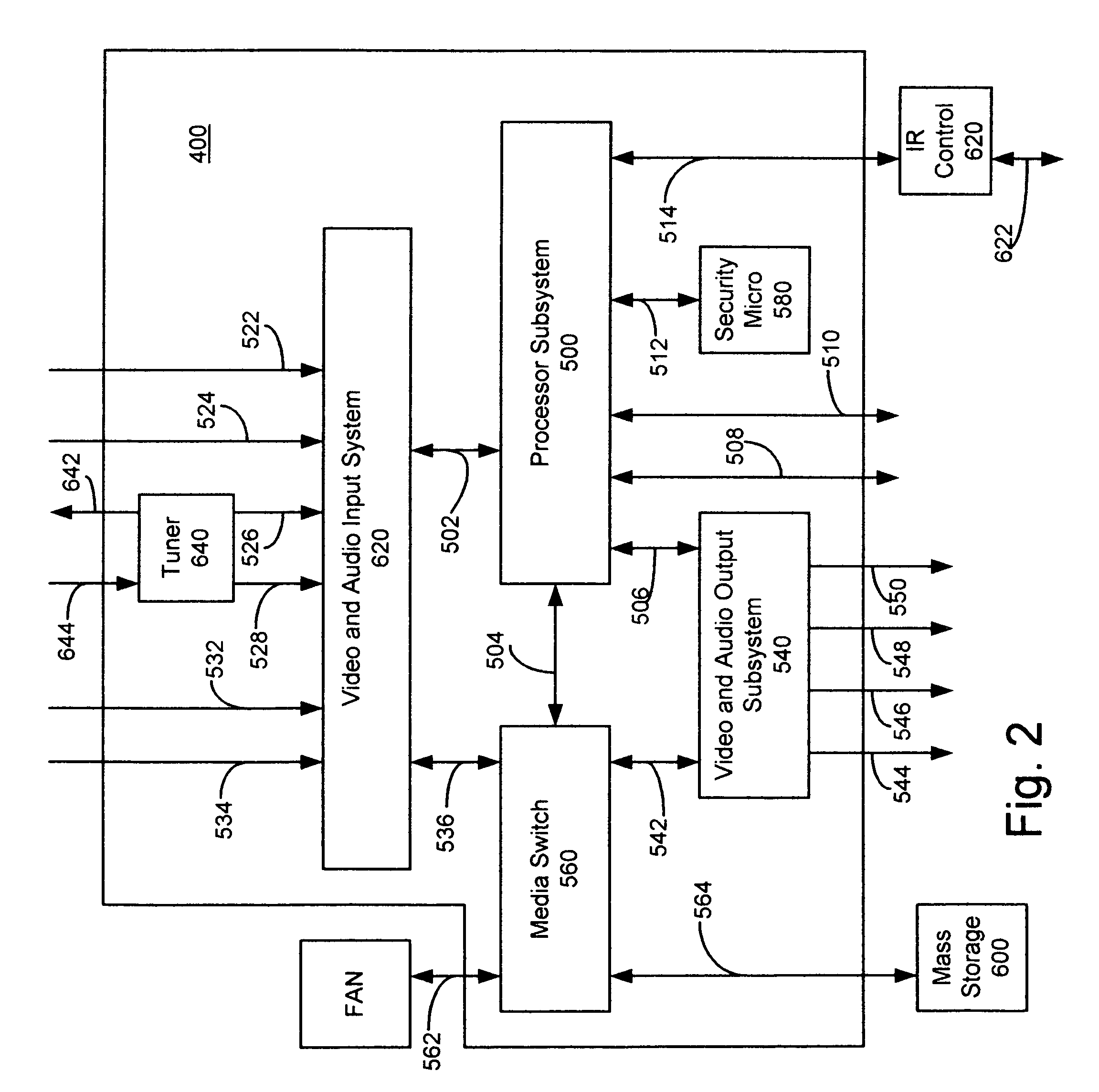

Method and apparatus for controlling at least one set-top box

InactiveUS7484234B1Provide goodSimple interfaceTelevision system detailsAnalogue secracy/subscription systemsSerial transferEmbedded system

A method and apparatus for providing control of a set-top box through IR blasting control by a system containing at least one computer is discussed. The system is coupled to a mass storage system. The system includes an IR control database that resides on the mass storage system. The IR control database contains at least one IR control entry and an IR control packet. The IR control packet is generated from a first IR control entry of the IR control database. The system controls a set-top box by serial transmission of the IR control packet.

Owner:TIVO SOLUTIONS INC

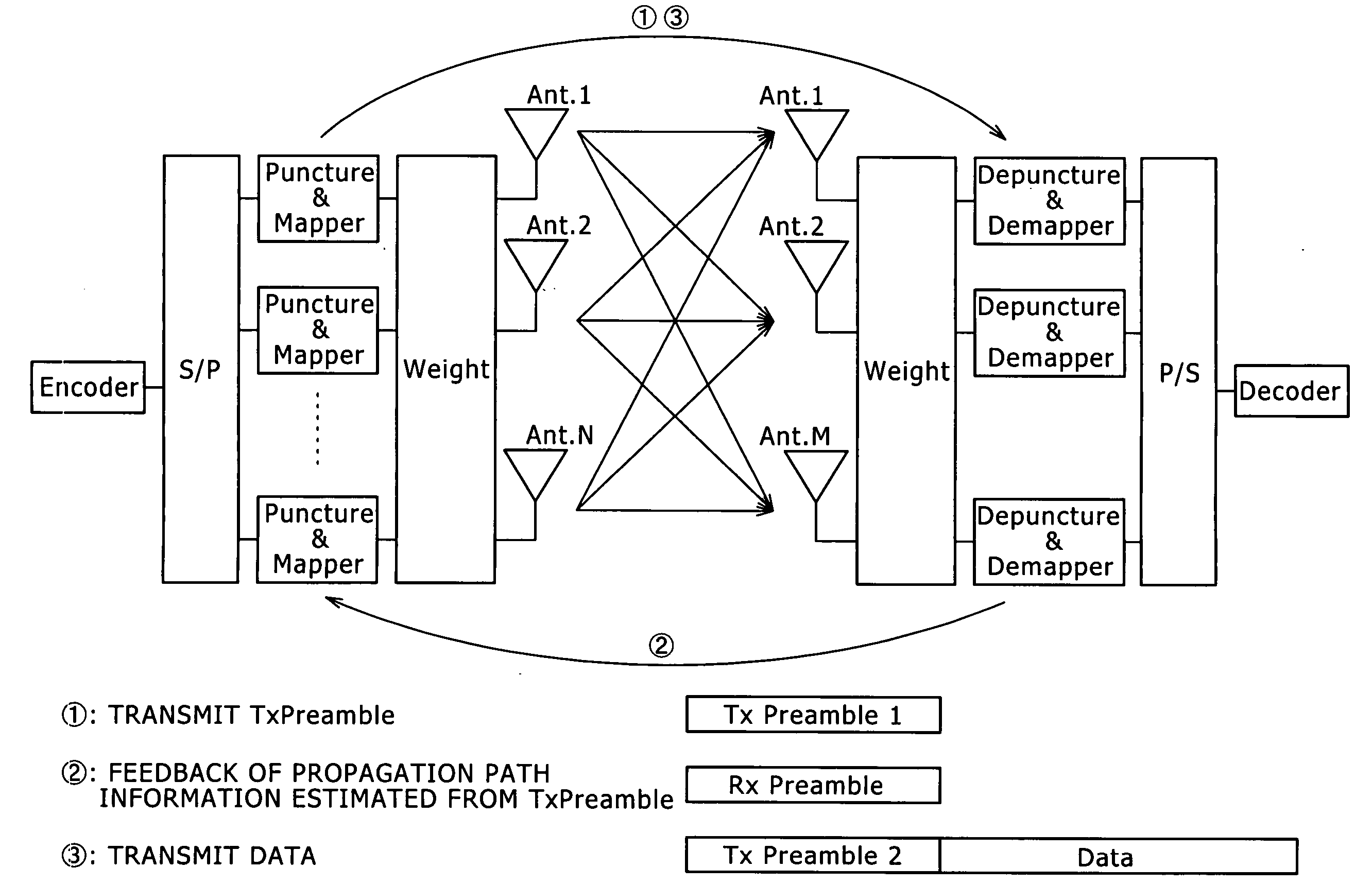

Wireless communication system

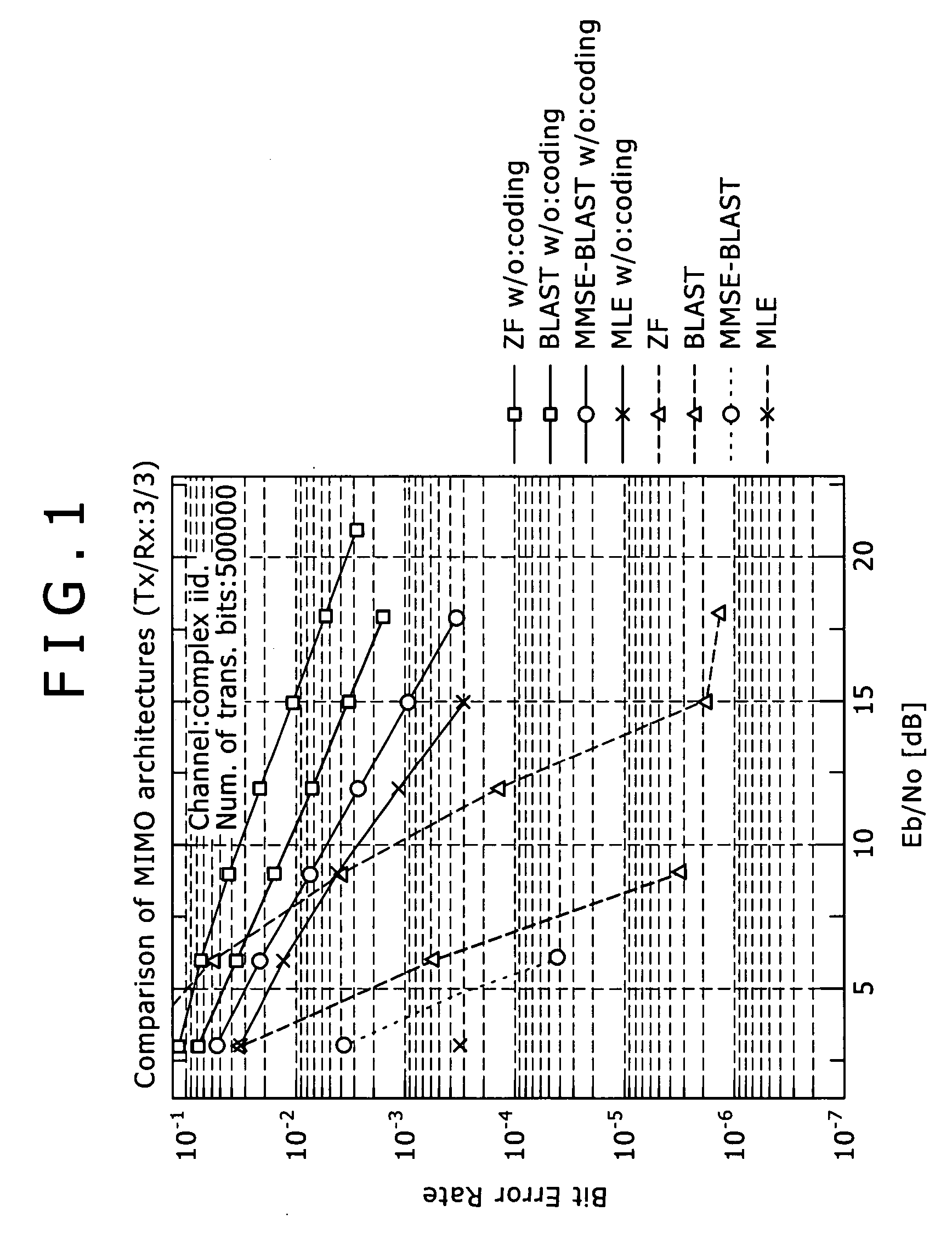

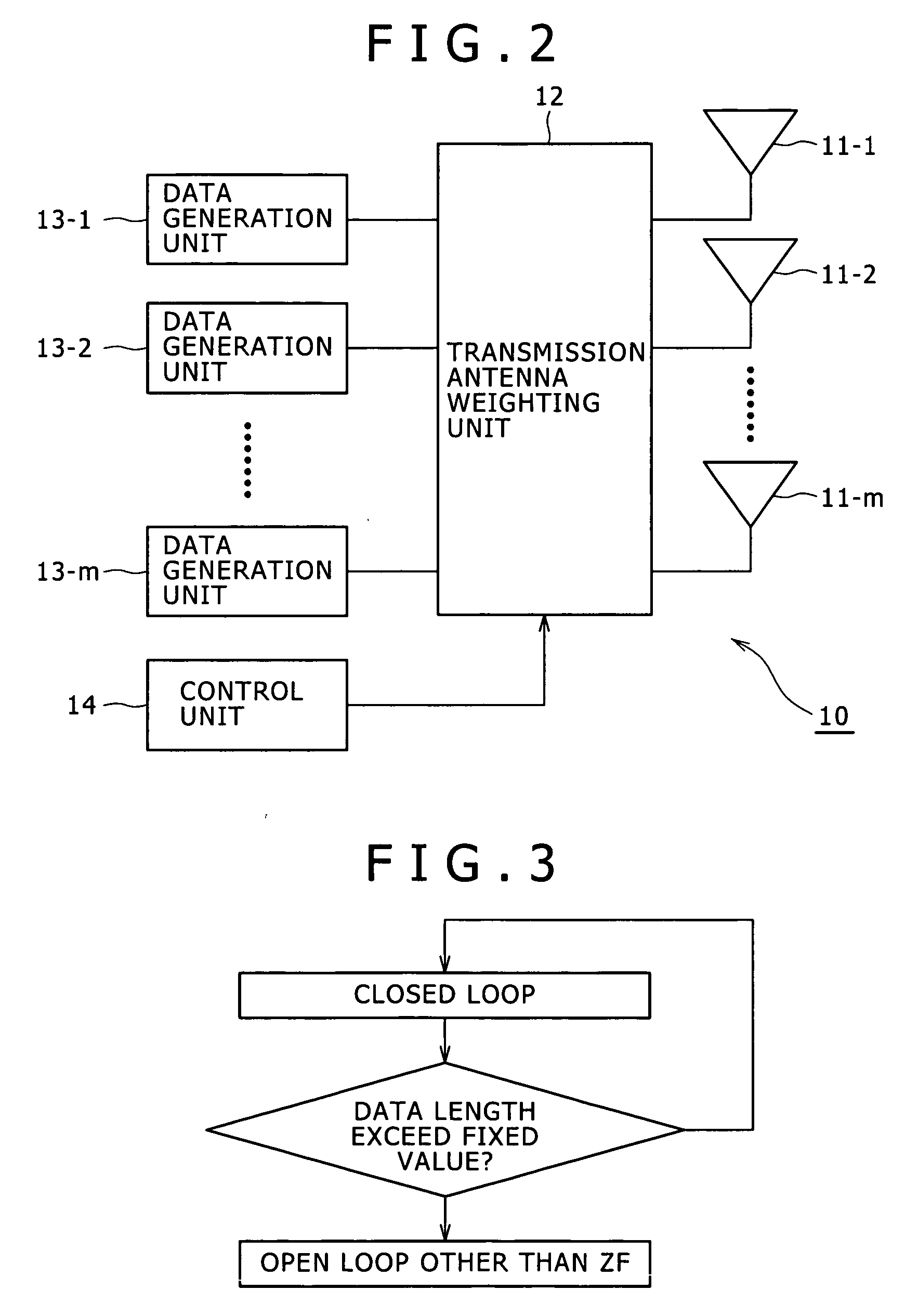

ActiveUS20050243942A1Improve transmission performanceInhibit deteriorationSpatial transmit diversityMultiplex communicationSerial transferTemporal change

In order to transmit a large amount of data in series at a time with a MIMO communication scheme while avoiding deterioration of decoding characteristics due to change over time by a channel matrix, a wireless communication system uses an open-loop type and a closed-loop type of MIMO communication modes in combination and switches to the open-loop MIMO communication mode in response to the information that the amount of data to be transmitted at a time has exceeded a predetermined amount of bits or a predetermined transmission time during data transmission under the closed-loop MIMO communication mode. By discontinuing useless closed-loop MIMO communication and switching to the open-loop MIMO communication mode that is better than Zero-forcing, the decoding characteristics are prevented from simply becoming deteriorated.

Owner:SONY CORP

Method and apparatus for data frame synchronization

InactiveUS7983308B1Multiplex system selection arrangementsTime-division multiplexSerial transferData synchronization

A circuit to synchronize with a data transmission includes a comparator to read a set of data within a serialized data transmission, compare the set of data to a predetermined data pattern and output a comparison result. For a serialized data transmission, the comparator receives the serialized transmission and a shift register serially coupled to the comparator to hold the data pattern. A synchronization detector receives a comparison hit vector based on the comparison result from the comparator and aligns a boundary of a data frame according to the comparison hit vector if the comparison hit vector indicates a match between the data pattern in the set of data and the predetermined data pattern. For a deserialized data transmission, each stage of a multistage shift register read a set of data from the deserialized data transmission and selectively outputs the set of data to a comparator which compares each set to a predetermined data pattern and output a comparison result. A synchronization detector receives the comparison result from the comparator and aligns a boundary of a data frame according to the comparison result if the comparison result indicates a match between a data pattern sub-set within a combined data pattern and the predetermined data pattern, where the sets of deserialized data comprise the combined data pattern.

Owner:MARVELL INT LTD

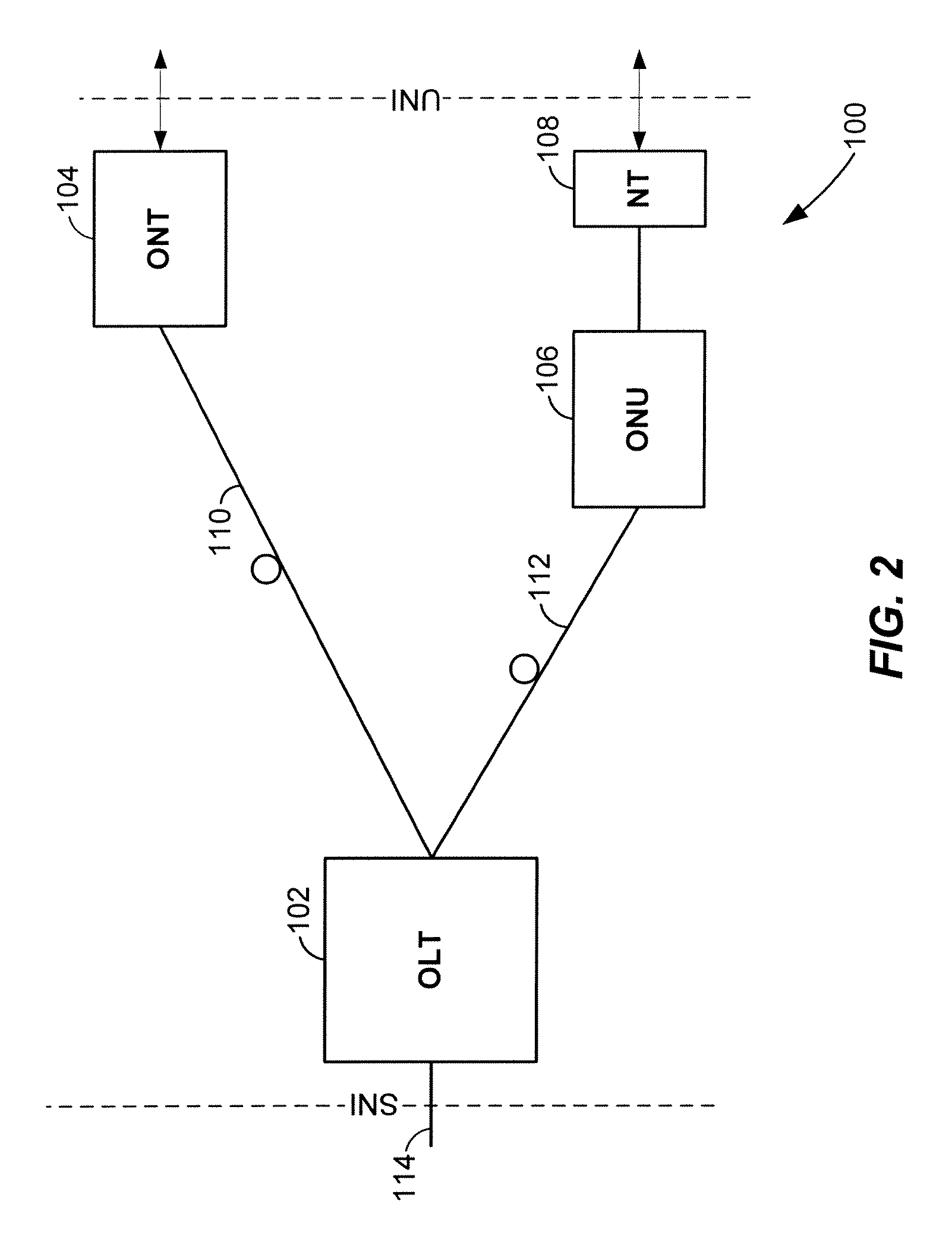

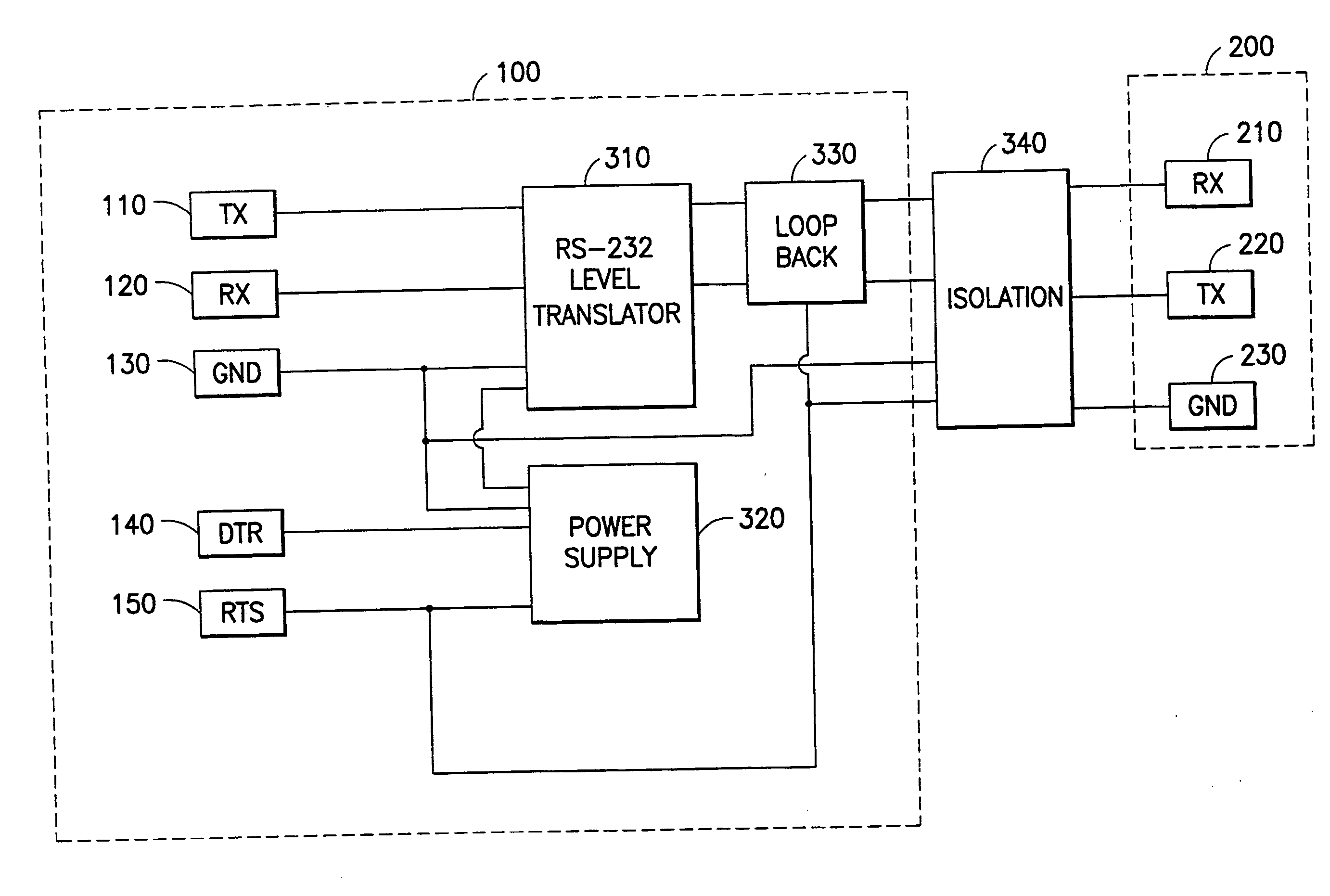

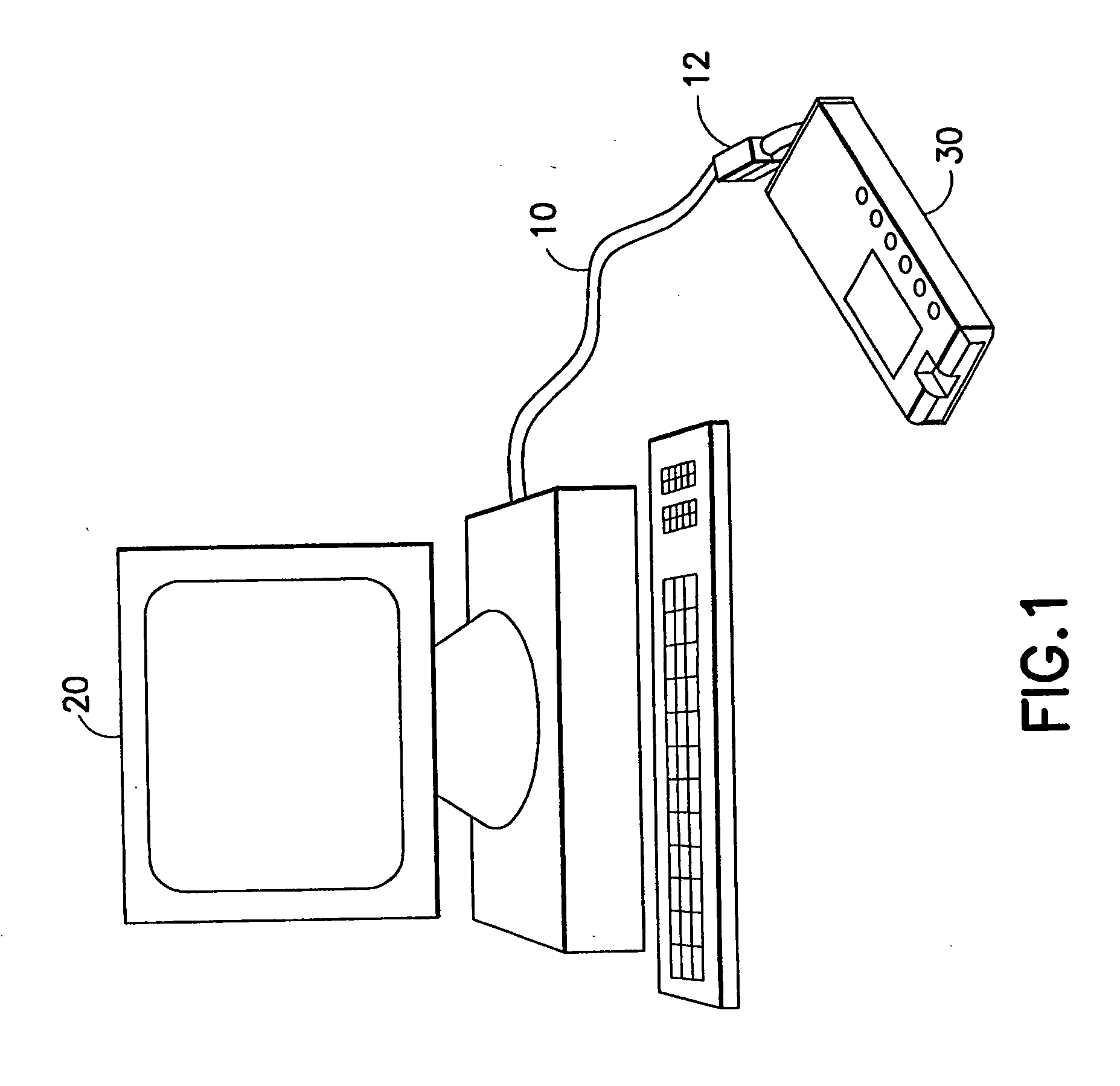

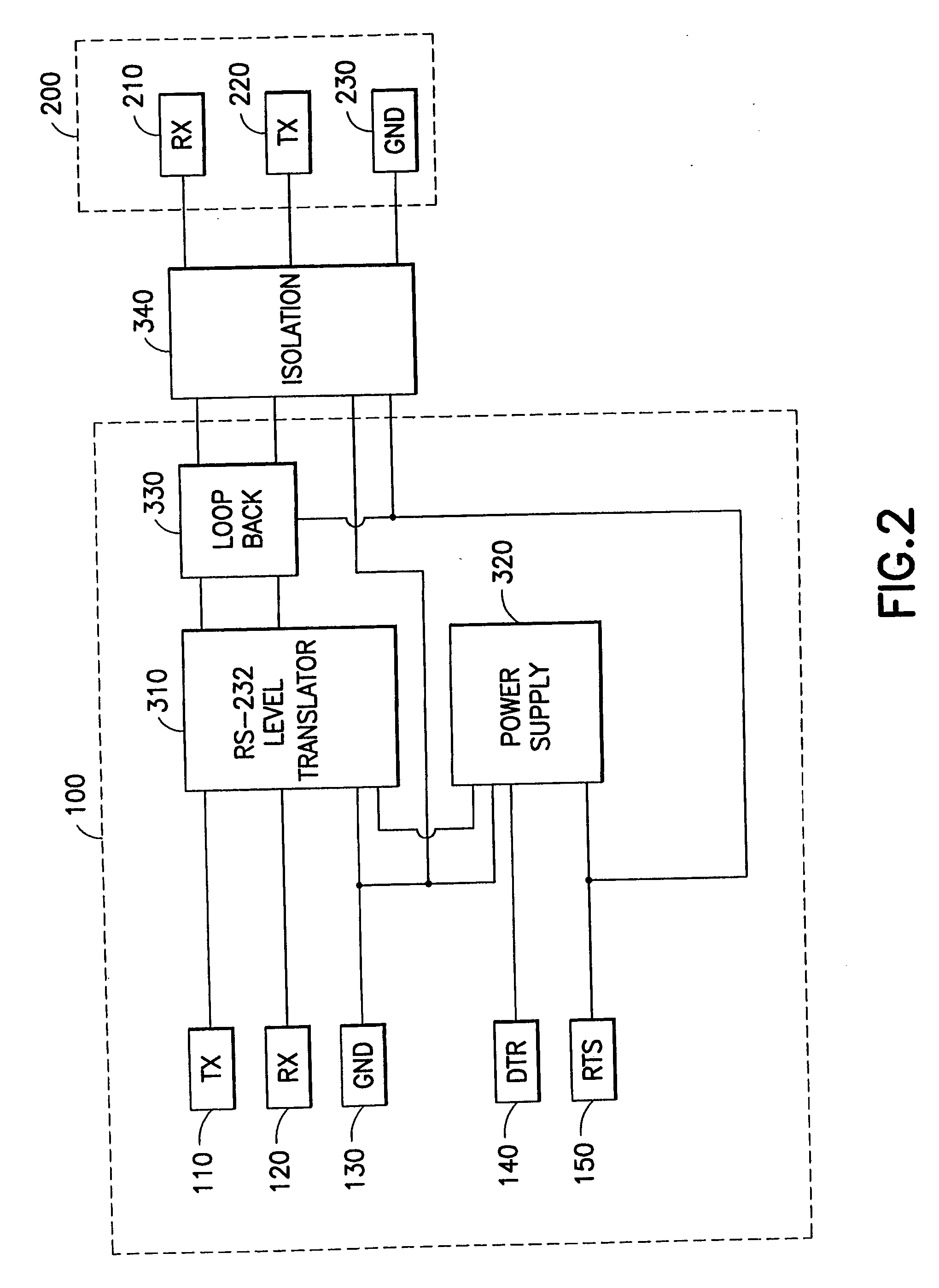

Self powered serial-to-serial or USB-to-serial cable with loopback and isolation

ActiveUS20050001179A1Simple interfaceOvercome disadvantagesDigital data processing detailsMaterial analysis by optical meansSerial transferGraphics

The cable for a medical device is an optically isolated serial transmission cable, used to connect a base device with a serial port, or the like, to a medical device. In an alternate embodiment of the invention, the invention enables auto detection of the cable. The base device is used to power the cable electronics. In another embodiment of the present invention, the interface cable is also supported by graphical and text message display that assists users in connecting the cable to both the medical device and a base device.

Owner:EMBECTA CORP

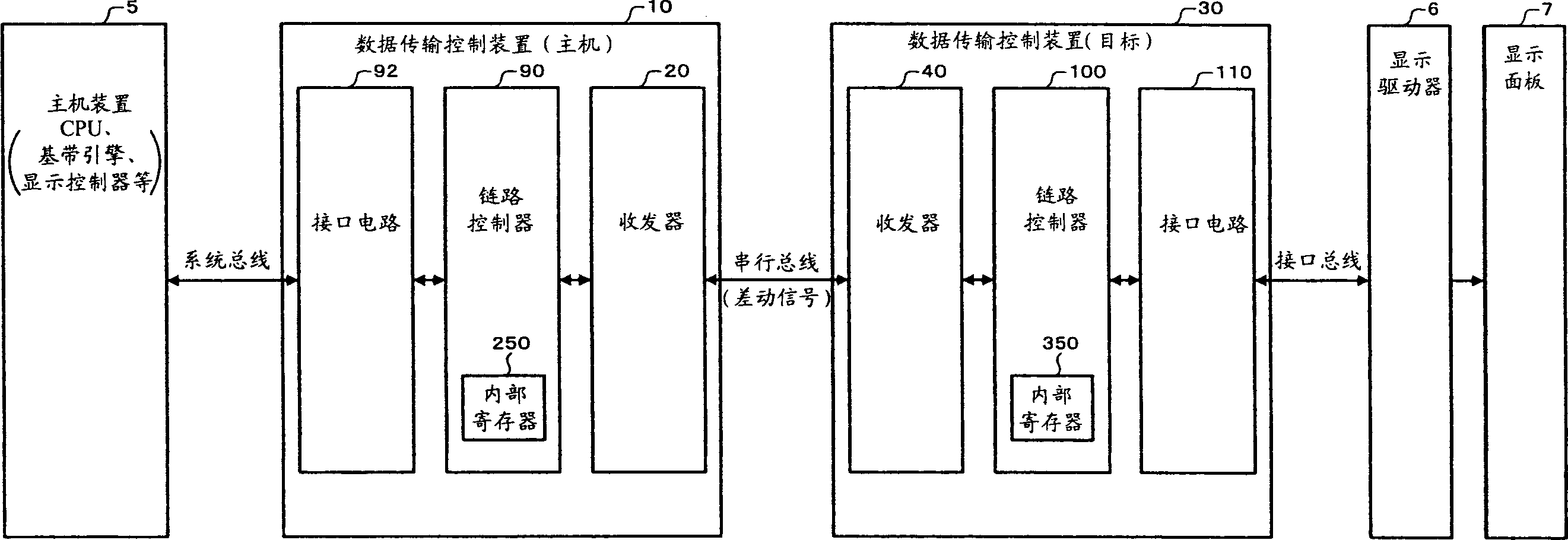

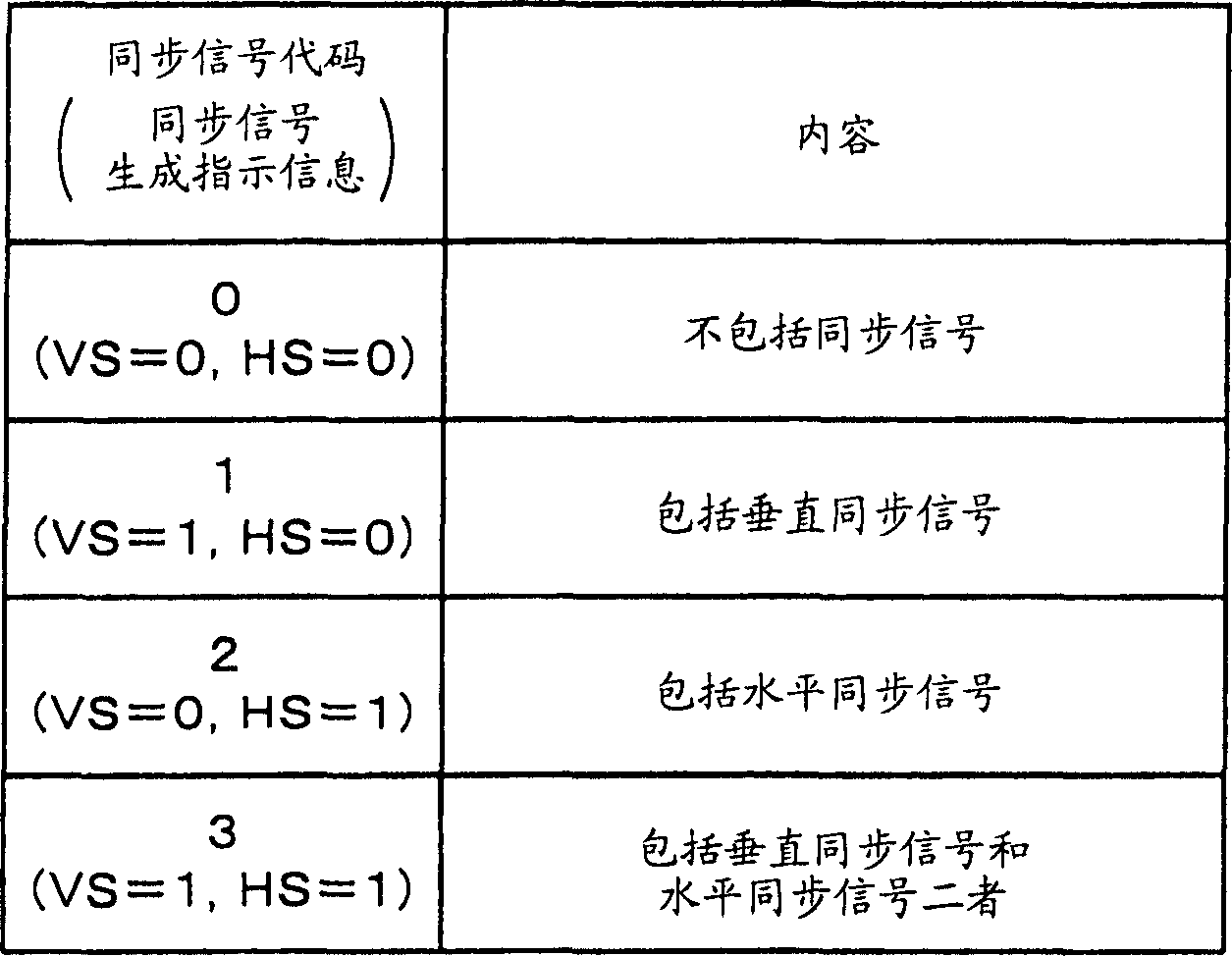

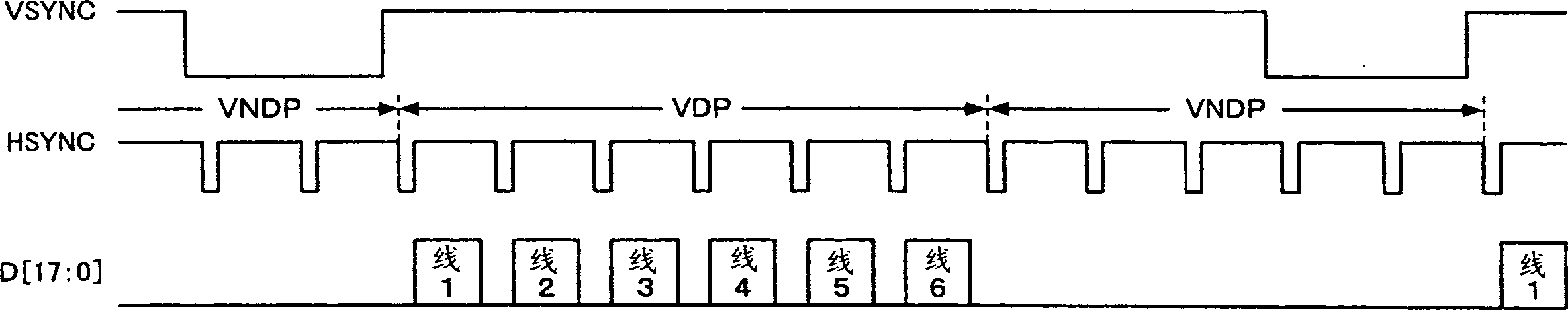

Data transfer control device and electronic instrument

InactiveCN1838102ACathode-ray tube indicatorsSynchronising arrangementSerial transferElectronic instrument

A data transfer control device includes: a link controller which analyzes a packet received through a serial bus; an interface circuit which generates interface signals and outputs the interface signals to an interface bus; and a reset signal output circuit which outputs a reset signal to the interface circuit. The link controller analyzes a packet to determine whether or not the received packet includes synchronization signal generation direction information (synchronization signal code). The reset signal output circuit outputs the reset signal to the interface circuit when the link controller has determined that the received packet includes the synchronization signal generation direction information.

Owner:SEIKO EPSON CORP

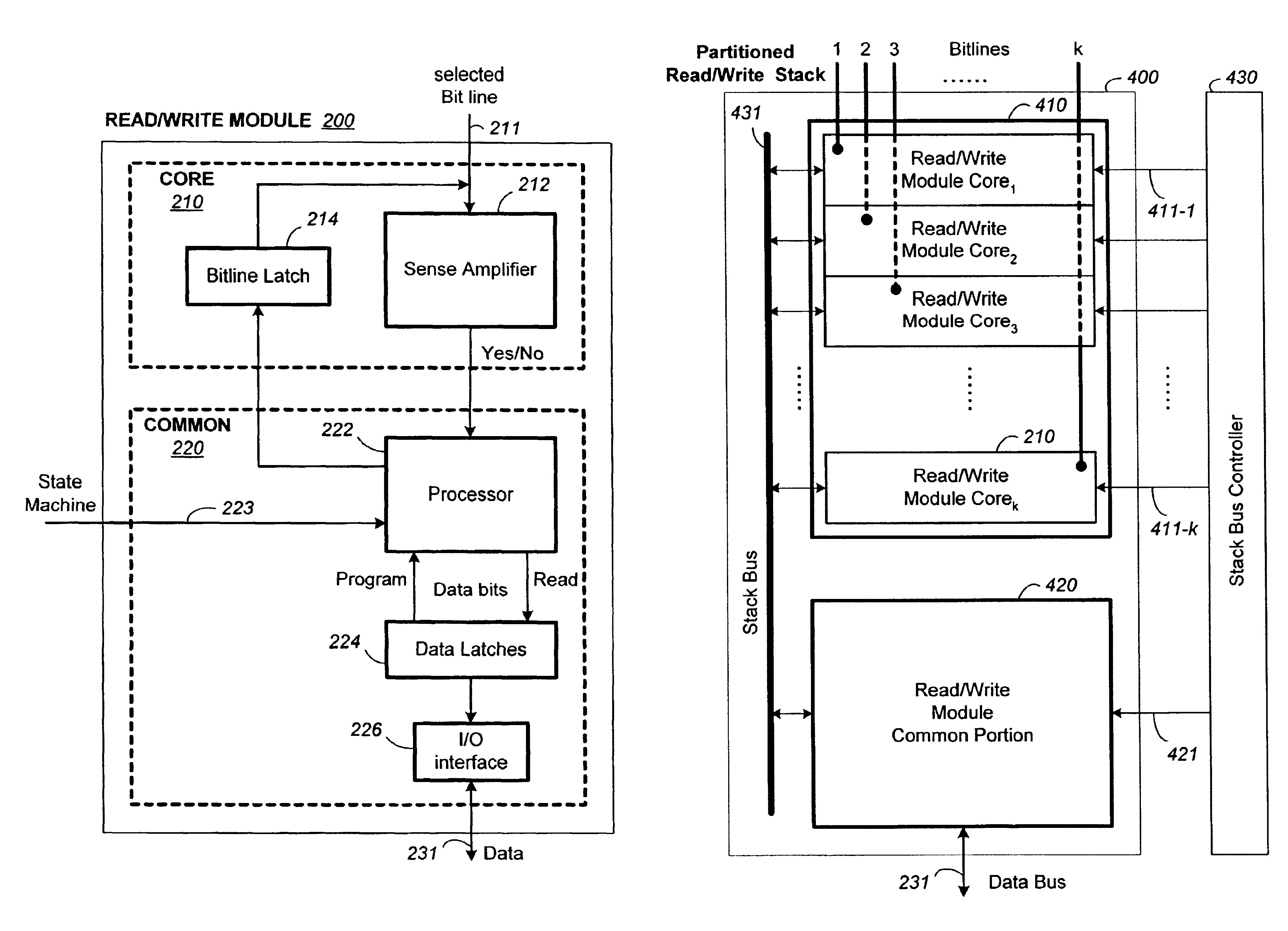

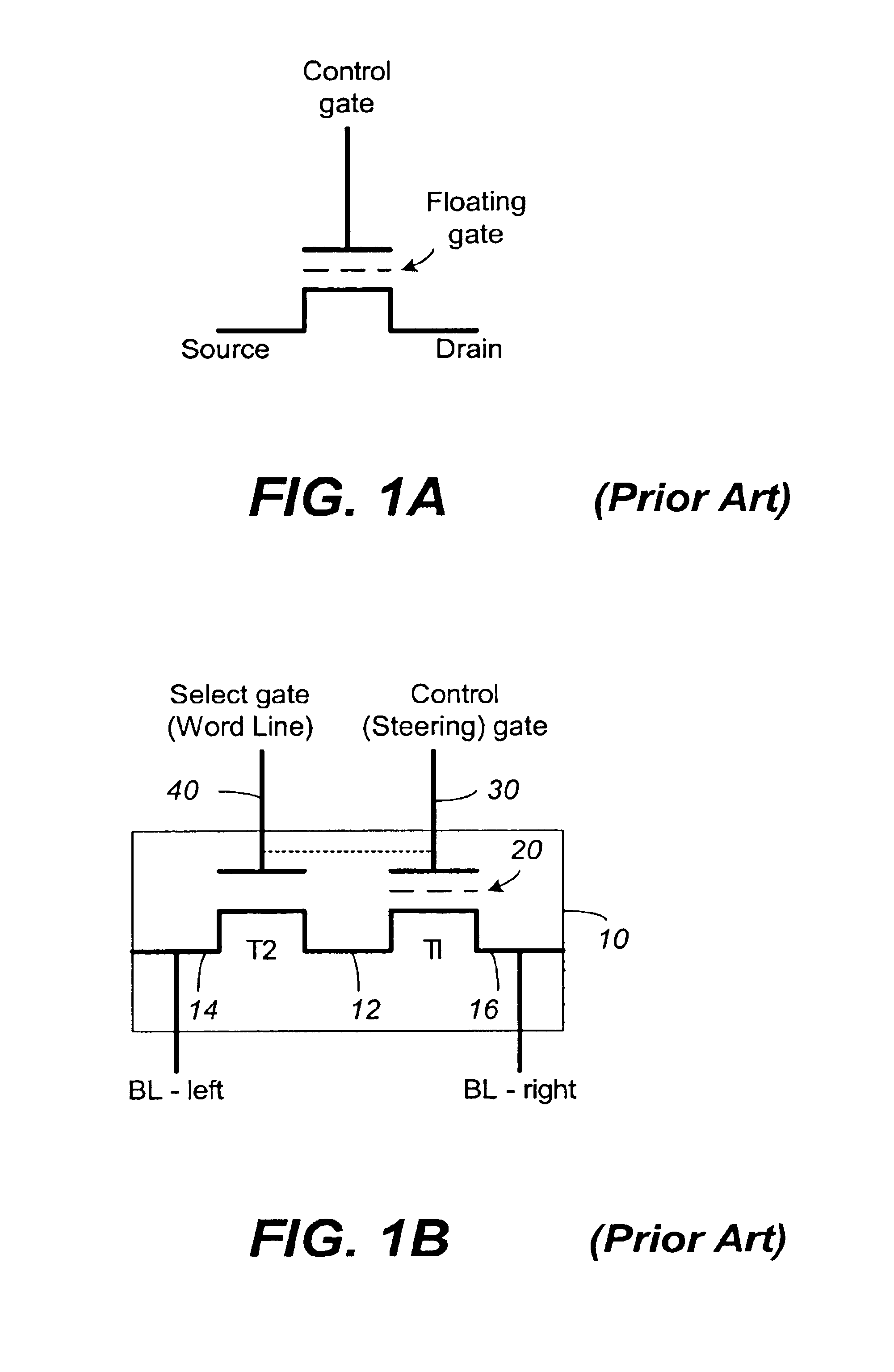

Highly compact non-volatile memory and method therefor with space-efficient data registers

InactiveUS6940753B2Improve performanceReduce redundancyRead-only memoriesDigital storagePower inverterSerial transfer

A non-volatile memory device capable of reading and writing a large number of memory cells in parallel has an architecture that reduces redundancy in the multiple read / write circuits to a minimum. In one aspect, data latches associated with the multiple read / write circuits are I / O enabled and coupled in a compact manner for storage and serial transfer. They are implemented by one or more chain of link modules, which can selectively behave as inverters or latches. A method enables the use of a minimum number of link modules by cycling data between a set of master link modules and a substantially smaller set of slave link modules.

Owner:SANDISK TECH LLC

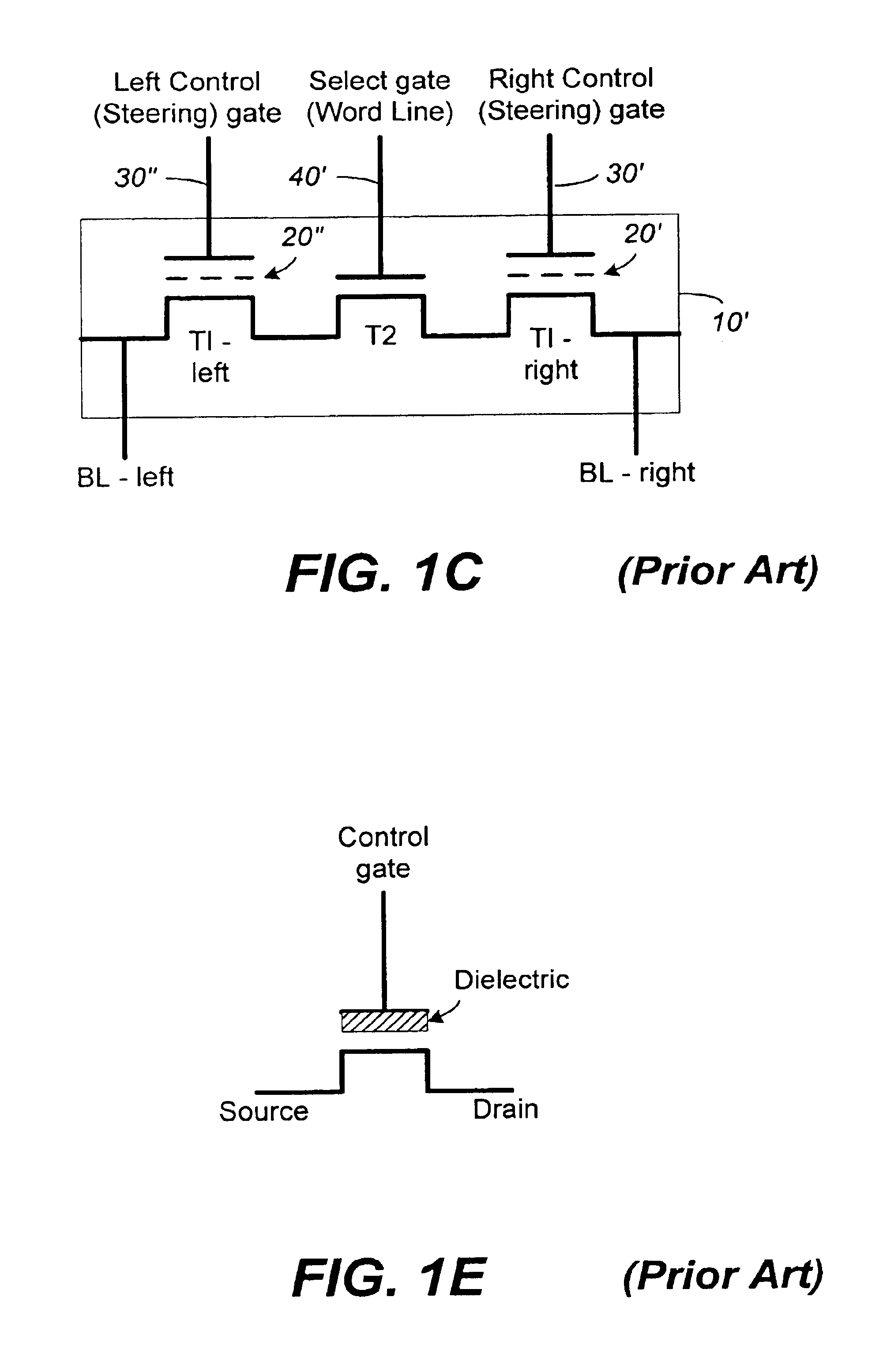

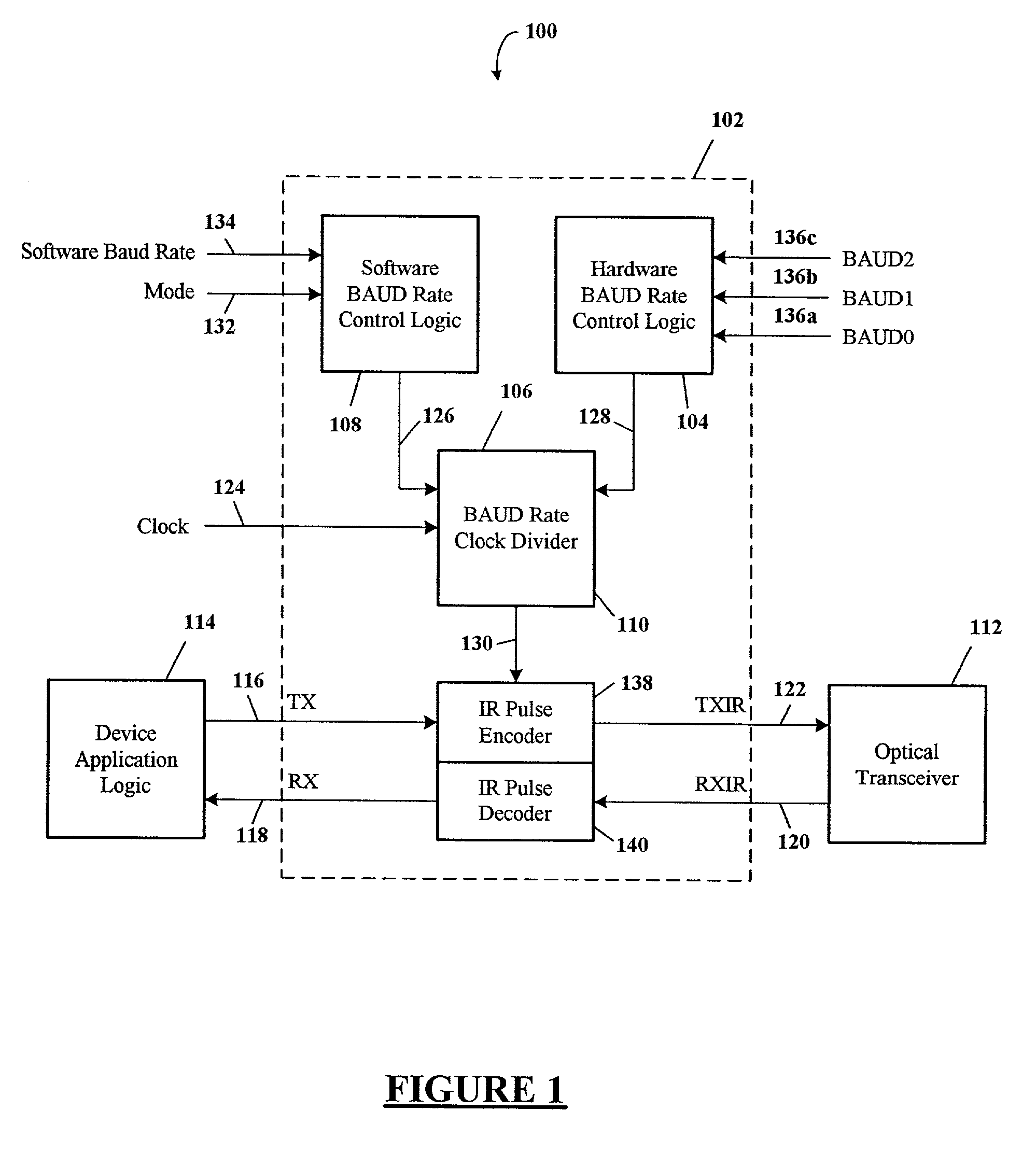

Infrared encoder/decoder having hardware and software data rate selection

InactiveUS20020176138A1Reduce system resourceClose-range type systemsElectromagnetic transmittersInfraredSerial transfer

An infrared encoder / decoder selects the data rate of a serial transmission of data by changing an input clock speed, setting the operating characteristics of a clock divider circuit by hardware inputs or selecting a clock speed by software commands that program the operating characteristics of a clock divider circuit. Having three alternate ways, two hardware and one software, of selecting the data rate of the serial transmission allows greater flexibility in the application and interfacing of a single integrated circuit package infrared encoder / decoder with all types of digital logic circuits and systems. An encoder / decoder having standard pulse width output and input compatibility with infrared industry standards, e.g., IrDA, and infrared transceivers is achieved in a flexible and cost effective low power integrated circuit package.

Owner:MICROCHIP TECH INC

System and method for master-slave data transmission based on a flexible serial bus for use in hearing devices

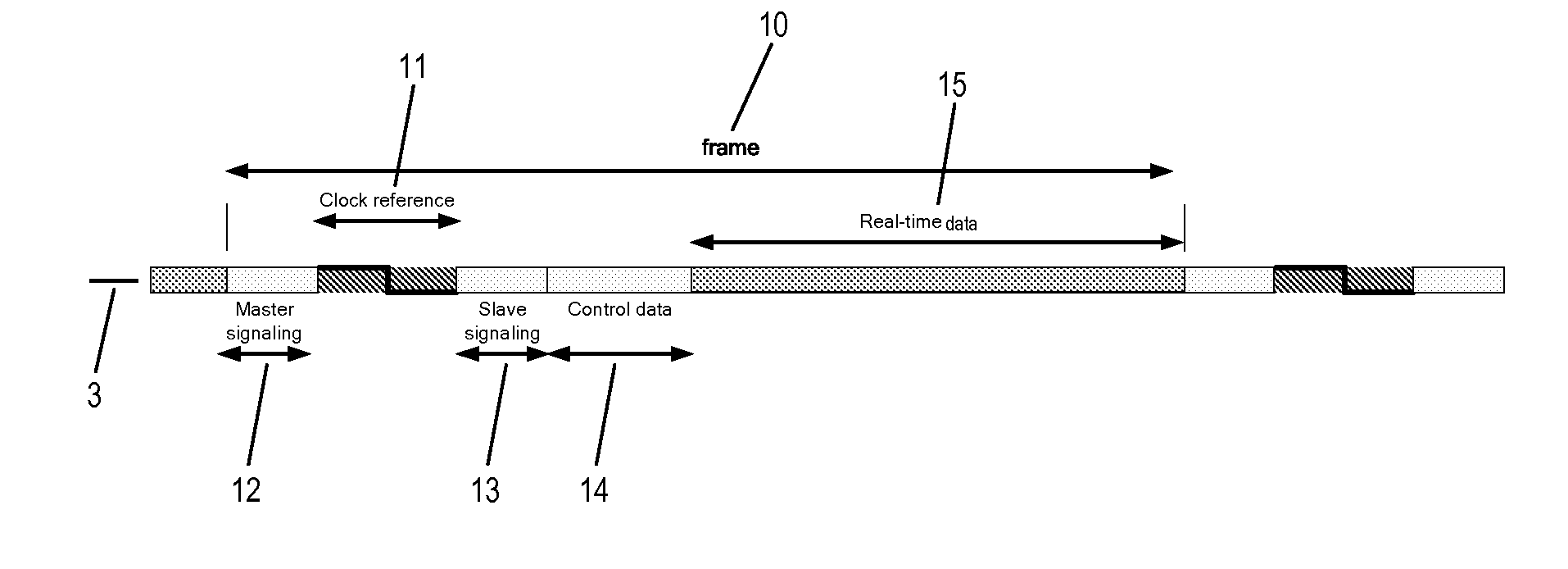

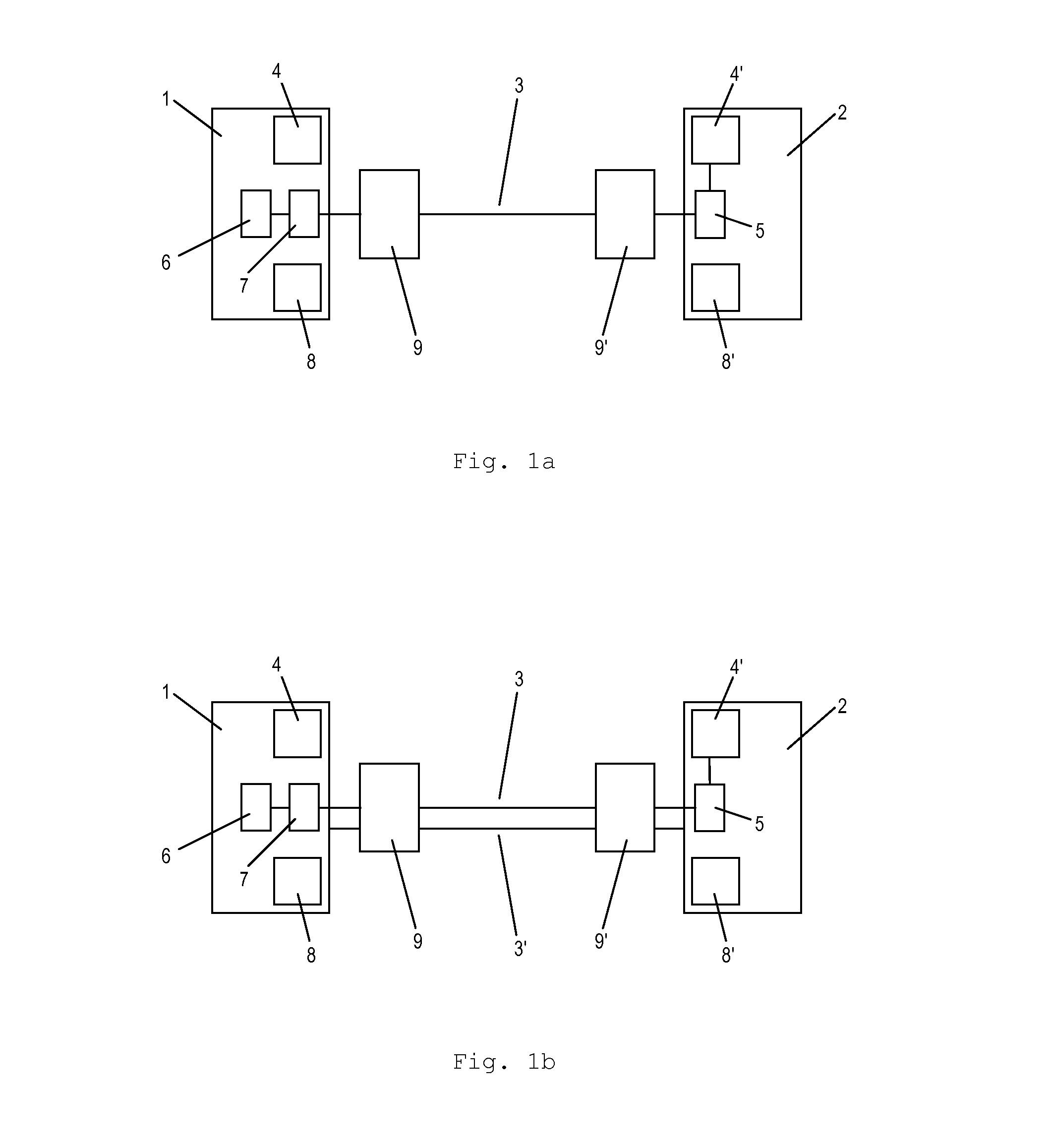

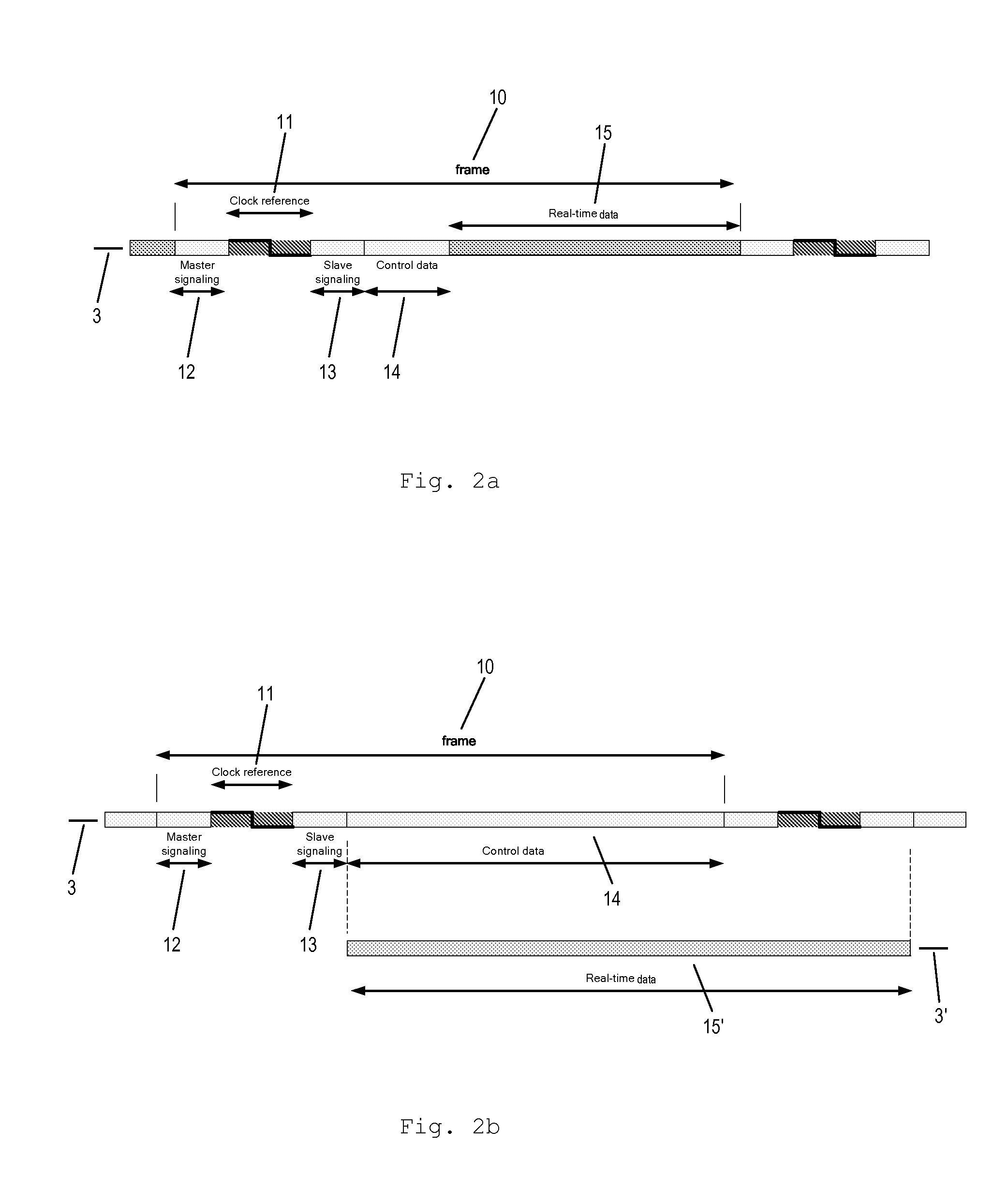

ActiveUS20150339257A1Minimize the numberMinimum use of spaceSynchronisation signal speed/phase controlGenerating/distributing signalsSerial transferNetwork Communication Protocols

A data transmission system for use in hearing devices includes a master unit with a first local bit clock and a slave unit with a second local bit clock. The master unit and the slave unit are connected to each other via a bus line, and are configured to communicate over the bus line according to a communication protocol based on a frame-wise serial transmission of bits. Each frame includes a clock reference, a master signalling interval, a slave signalling interval and a data payload. The slave unit further includes a clock recovery device for synchronising the second local bit clock with the first local bit clock based on the clock reference transmitted once per frame by the master unit. A corresponding method for data transmission is also provided. Moreover, hearing devices including such a data transmission system as well as uses of such a method for data transmission are proposed.

Owner:SONOVA AG

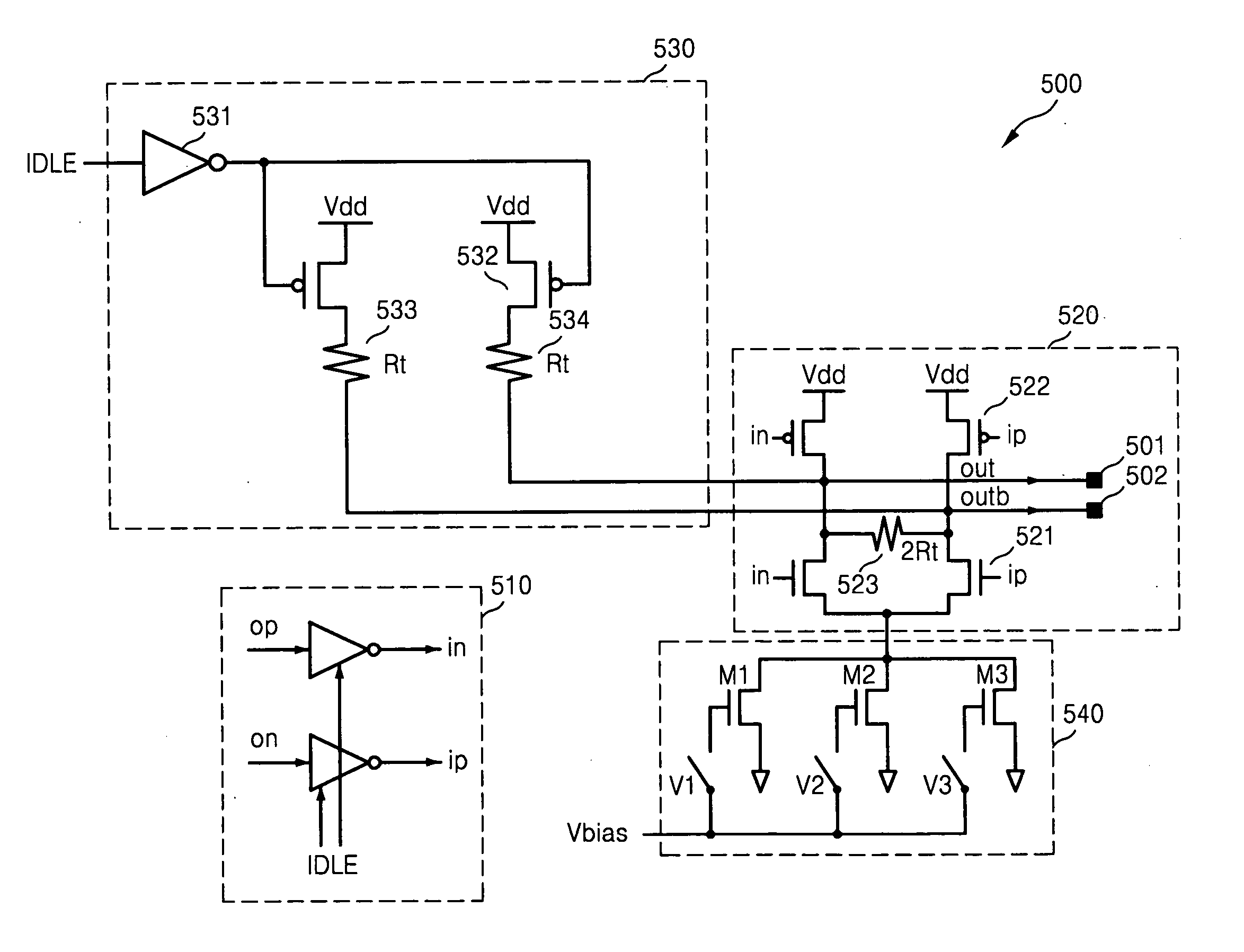

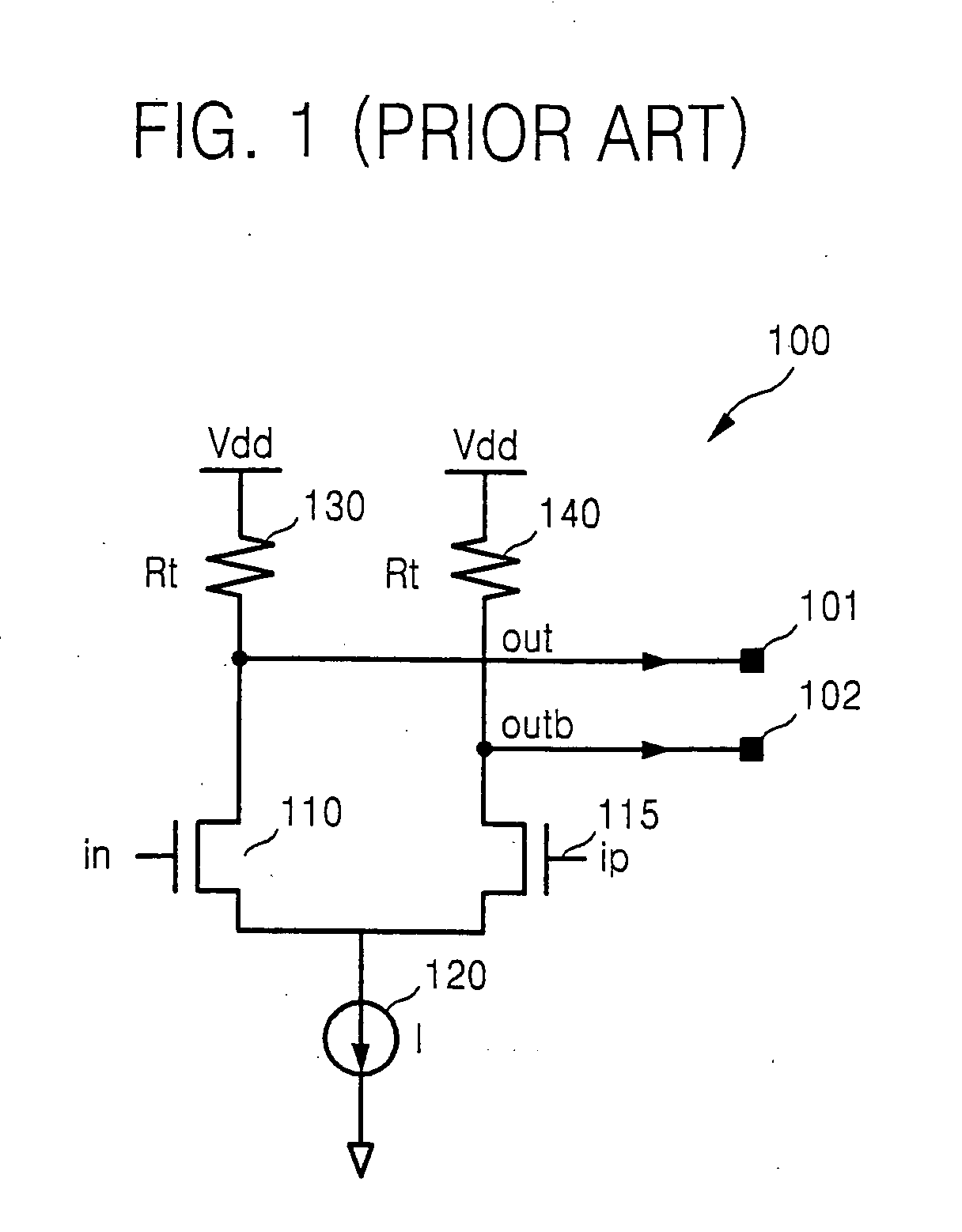

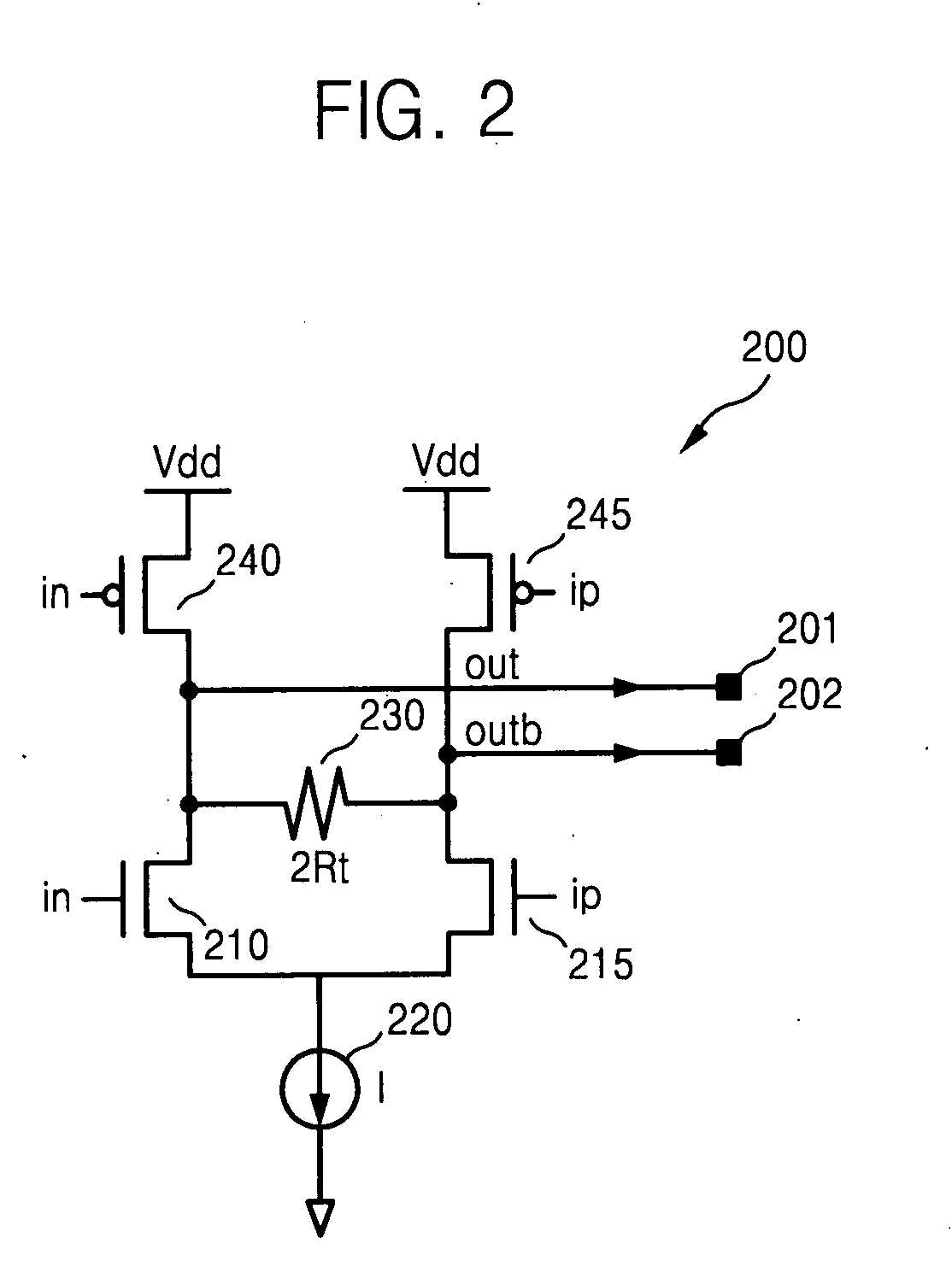

Transmission line drivers and serial interface data transmission devices including the same

InactiveUS20080024178A1Reduce power consumptionReliability increasing modificationsPower reduction by control/clock signalSerial transferData signal

A transmission line driver and a serial interface data transmission device including the same are provided. The transmission line driver includes a pre-driver configured to generate and output differential input data signals based on a serial transmission data signal, a differential amplifier configured to receive the differential input data signals and to output differential output data signals, and a common mode controller configured to drive the differential output data signals to a predetermined common mode voltage in an idle mode. Accordingly, power consumption can be reduced and a common mode specification can be supported.

Owner:SAMSUNG ELECTRONICS CO LTD

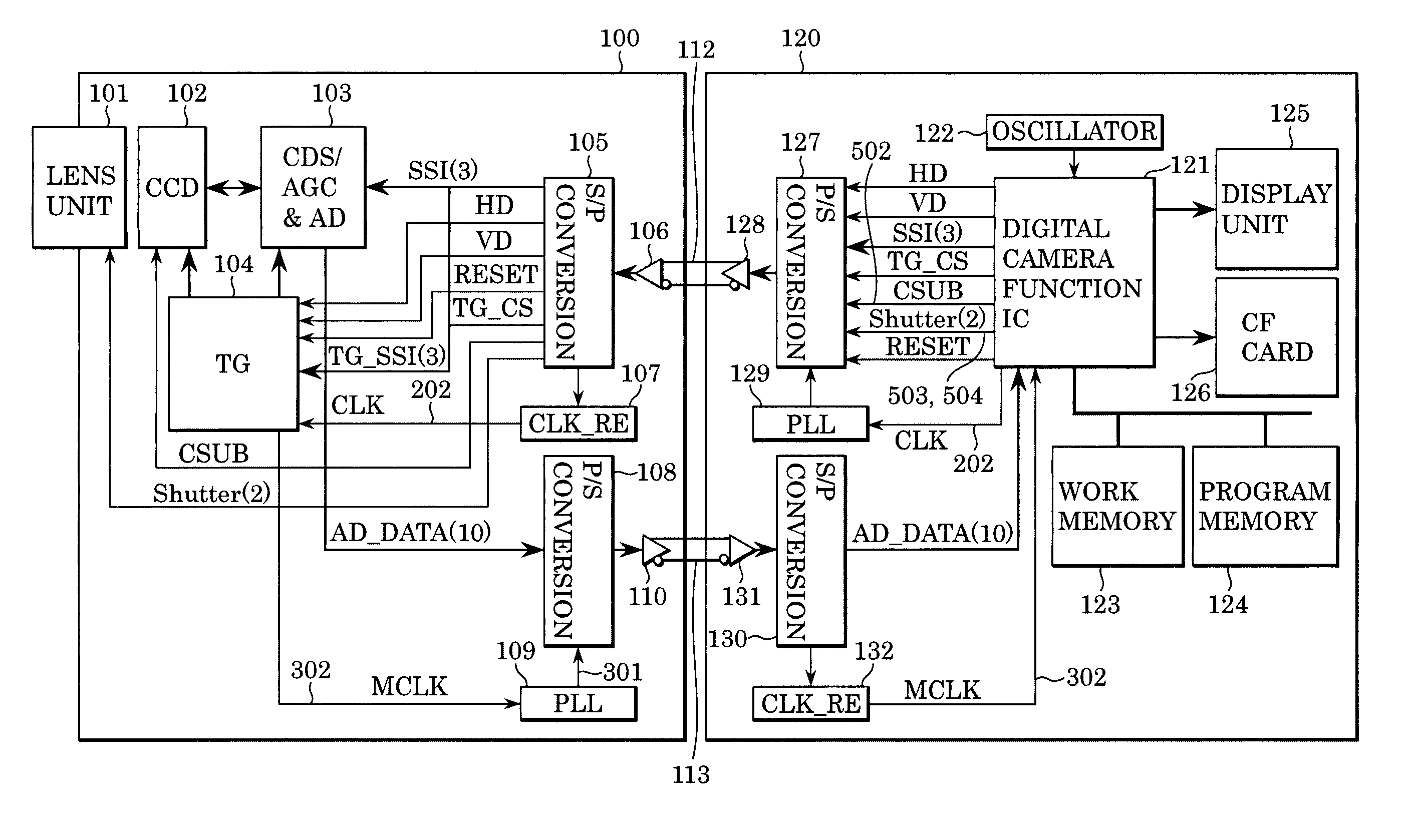

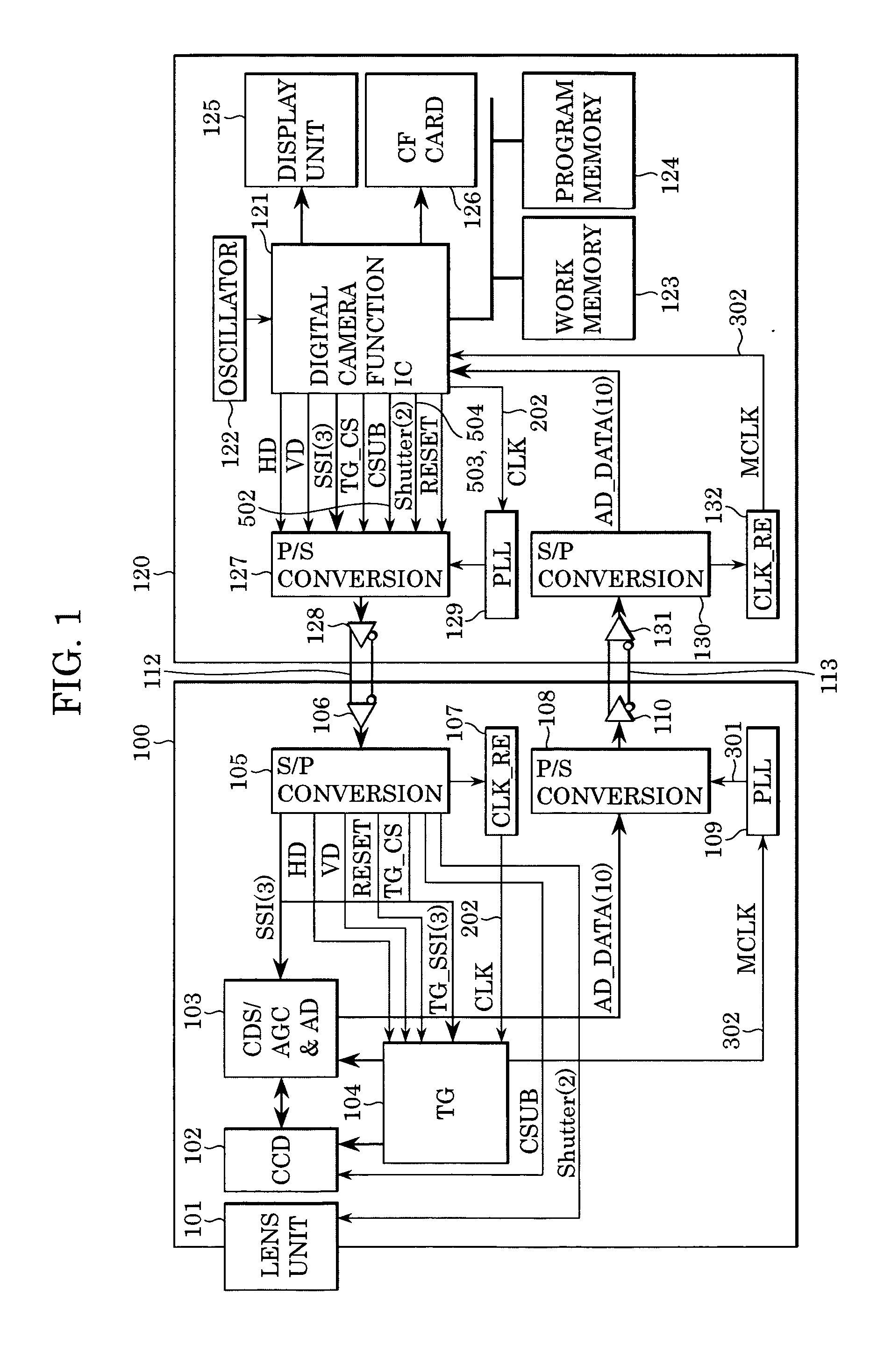

Image capturing system and control method of the same

InactiveUS20050179782A1Improve image qualitySynchronization is simpleTelevision system detailsPicture signal generatorsSerial transferData translation

An image capturing system includes an image-capturing unit and a main unit, capable of serial communication therebetween. The main unit generates a first clock signal, converts data to be transmitted to the image-capturing unit into serial data using the first clock signal, and transmits the serial data to the image-capturing unit. The image-capturing unit detects a serial transfer frequency from the received serial signal, reproduces the first clock signal, generates a second clock signal from the reproduced first clock signal, converts a taken image into serial data using the second clock signal, and transmits this data to the main unit. The main unit then reproduces the second clock signal from the serial data transmitted from the image-capturing unit, and utilizes the second clock signal to generate the first clock signal, thereby synchronizing the image-capturing unit and the main unit.

Owner:CANON KK

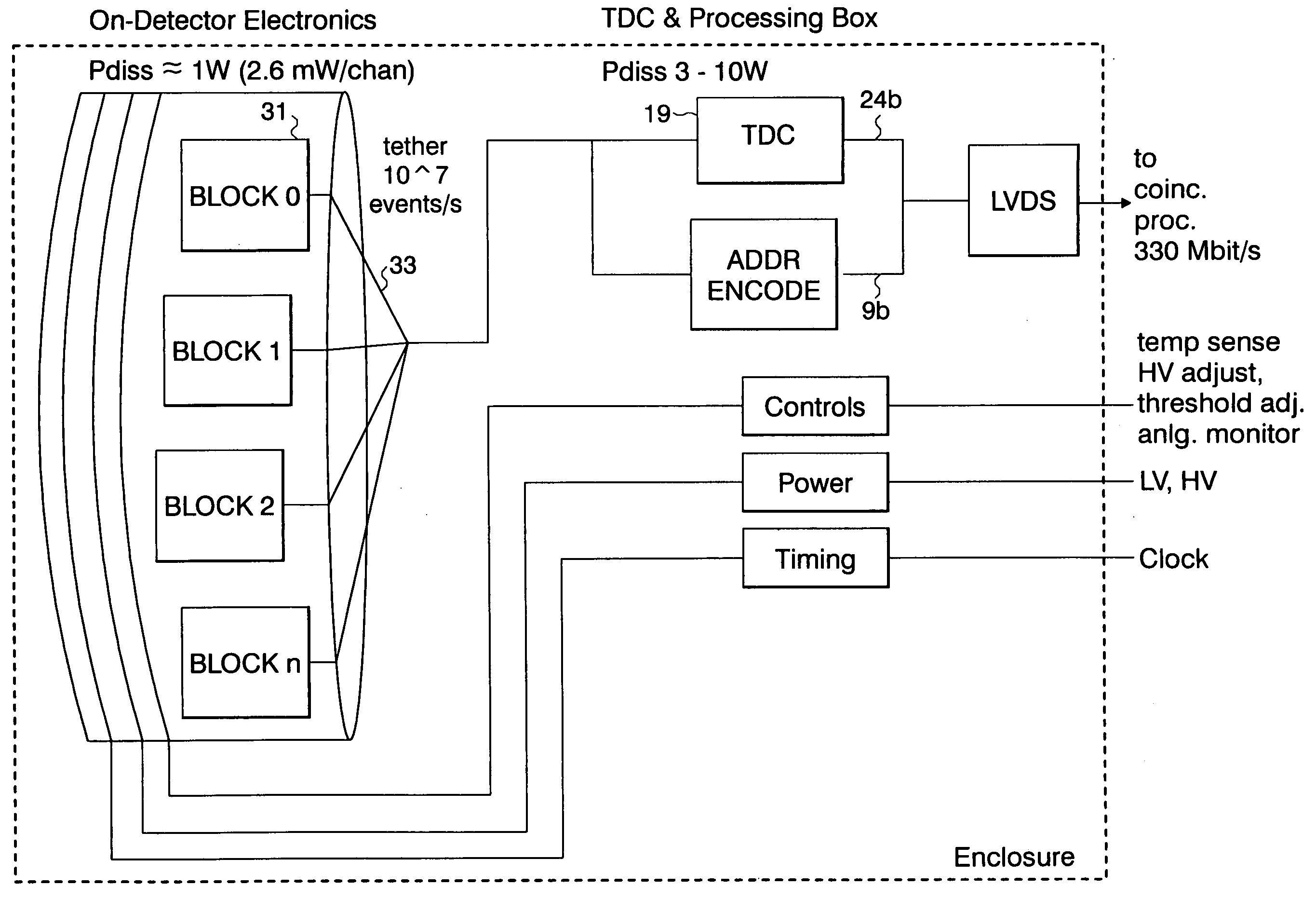

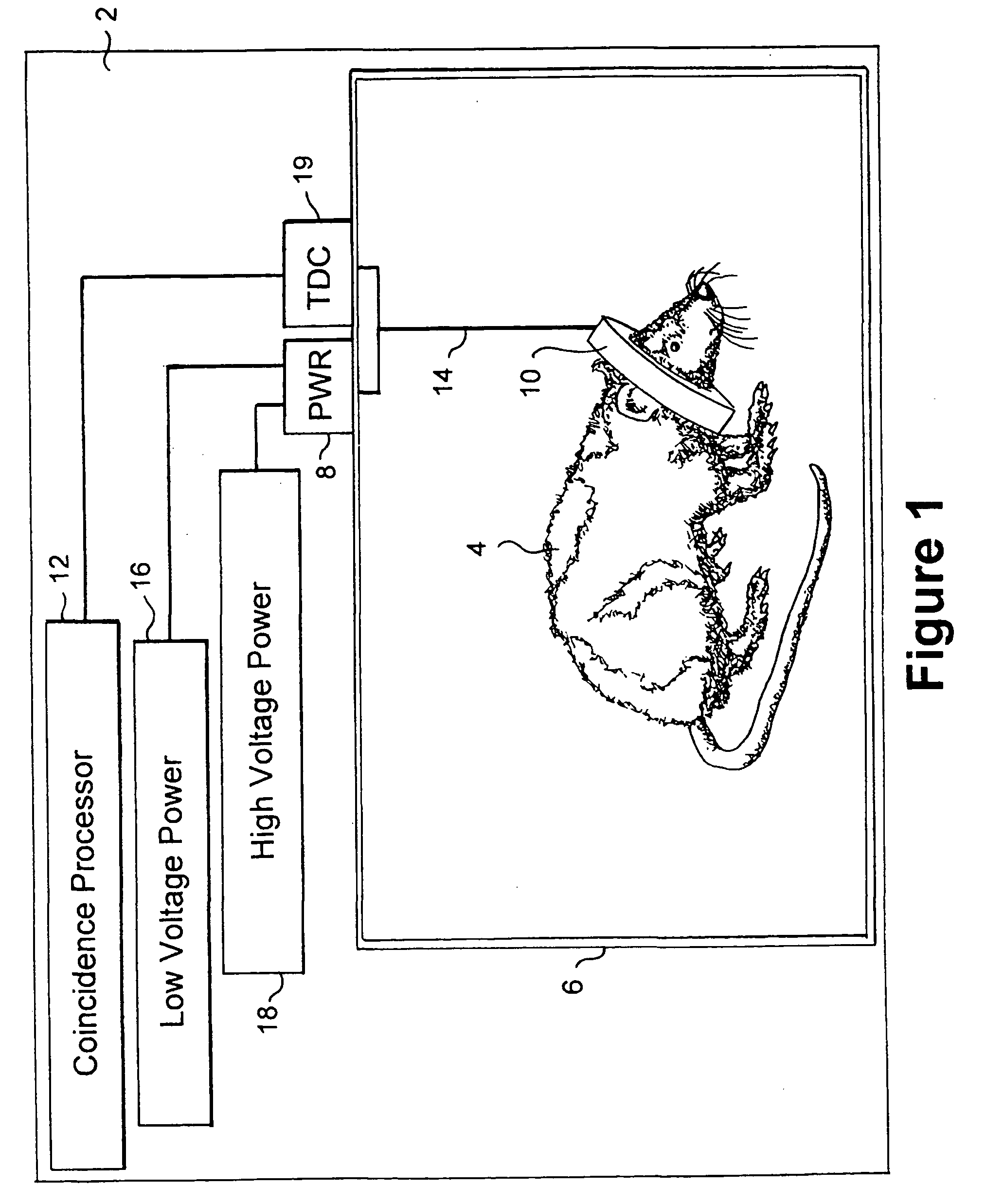

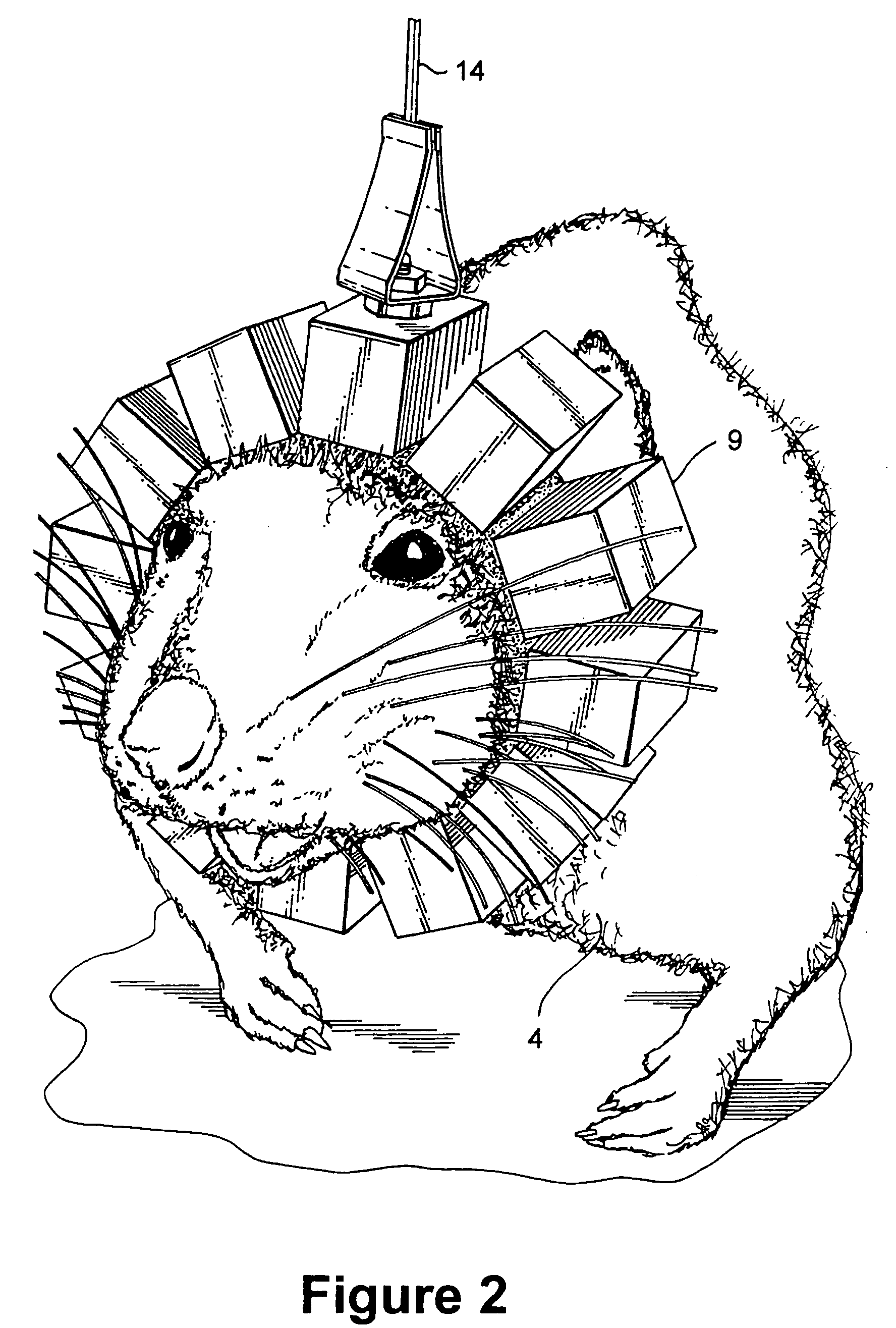

Compact conscious animal positron emission tomography scanner

ActiveUS20050082486A1Reduce power consumptionMagnetic measurementsHandling using diaphragms/collimetersSerial transferEngineering

A method of serially transferring annihilation information in a compact positron emission tomography (PET) scanner includes generating a time signal for an event, generating an address signal representing a detecting channel, generating a detector channel signal including the time and address signals, and generating a composite signal including the channel signal and similarly generated signals. The composite signal includes events from detectors in a block and is serially output. An apparatus that serially transfers annihilation information from a block includes time signal generators for detectors in a block and an address and channel signal generator. The PET scanner includes a ring tomograph that mounts onto a portion of an animal, which includes opposing block pairs. Each of the blocks in a block pair includes a scintillator layer, detection array, front-end array, and a serial encoder. The serial encoder includes time signal generators and an address signal and channel signal generator.

Owner:BROOKHAVEN SCI ASSOCS

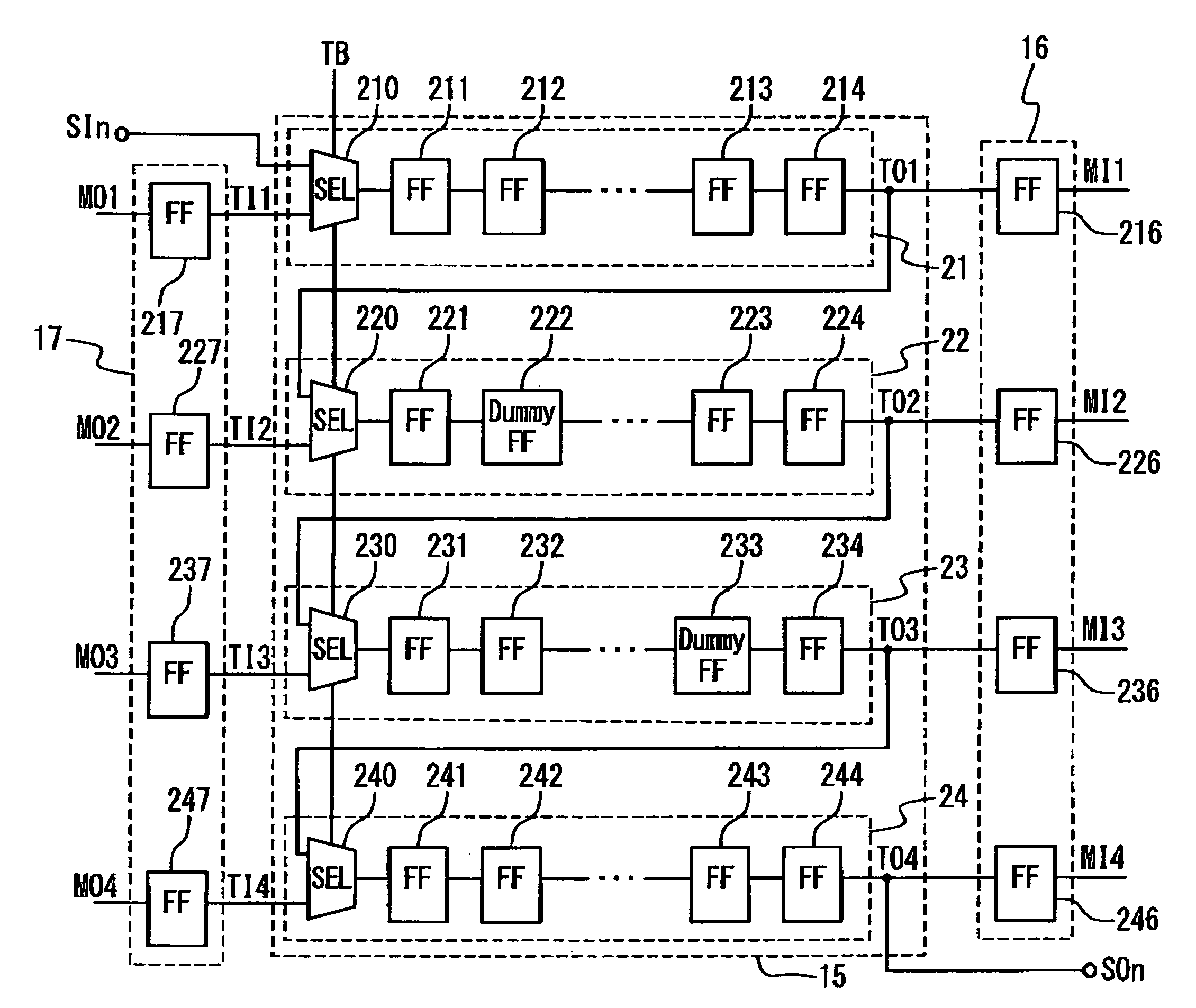

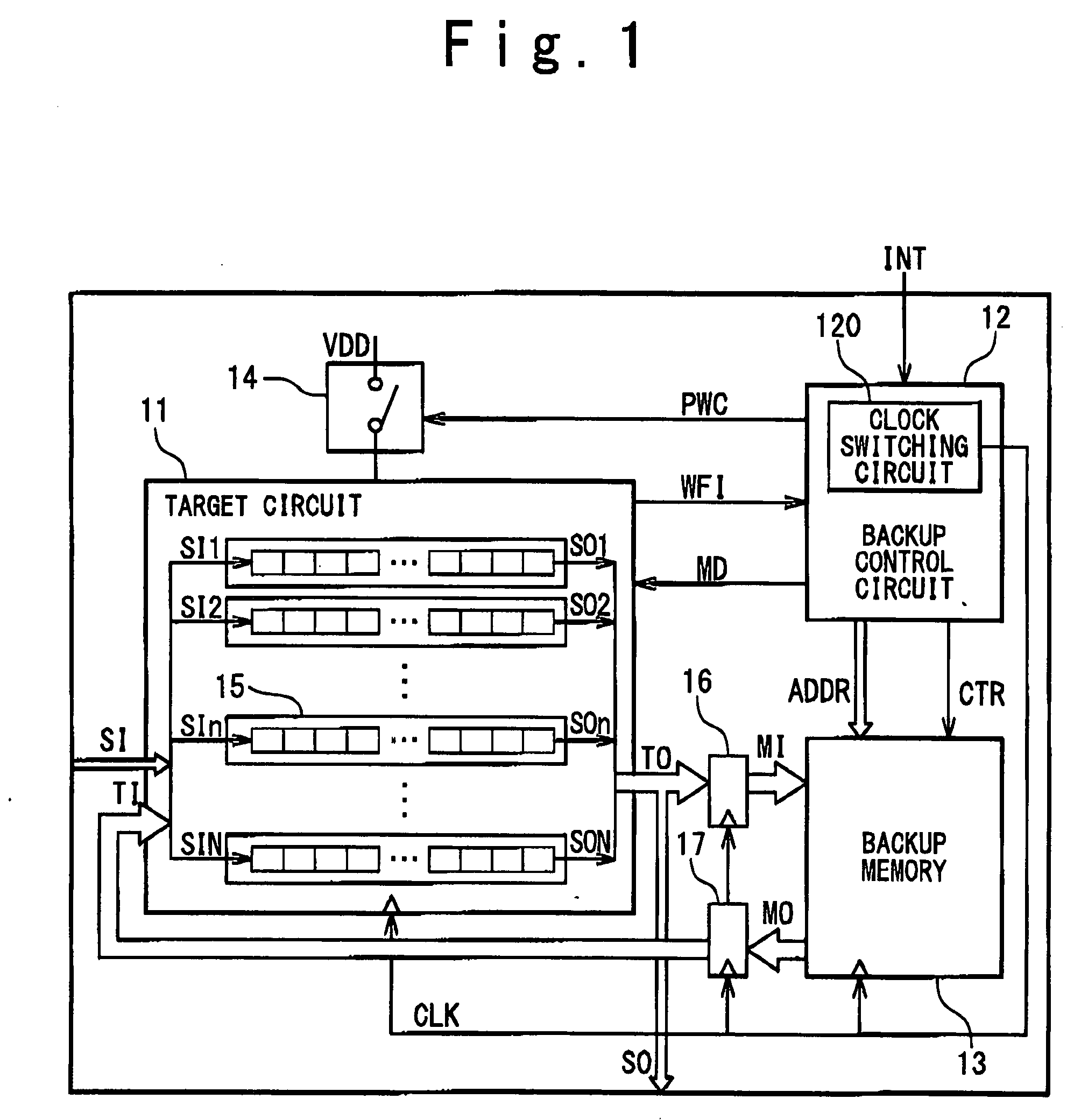

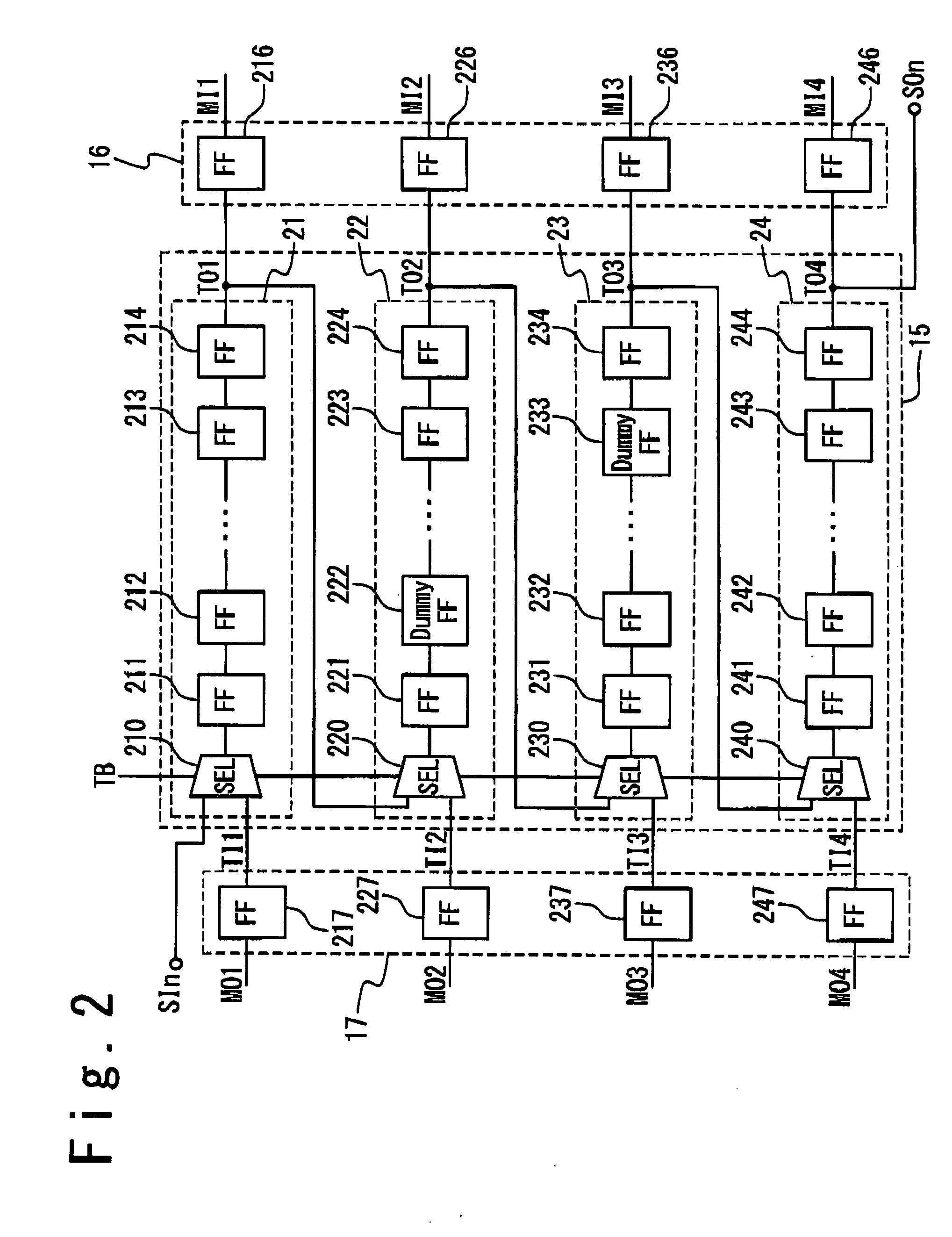

Semiconductor integrated circuit and control method thereof

A semiconductor integrated circuit includes a target circuit configured to operate in a normal mode, to form a scan chain to serially transfer a test data through the scan chain, in a scan path test mode, and to form a plurality of sub scan chains to save an internal node data in a memory in a save mode; and a backup control circuit configured to supply to the target circuit, a system clock signal in the normal mode, a test clock signal in the scan path test mode, and a save / recover clock signal in the save mode, and to control the target circuit and the memory such operations in the normal mode, the scan path test mode, and the save mode are performed. The test clock signal is slower than the system clock signal, and the save / recover clock signal is slower than the system clock signal and faster than the test clock signal.

Owner:RENESAS ELECTRONICS CORP

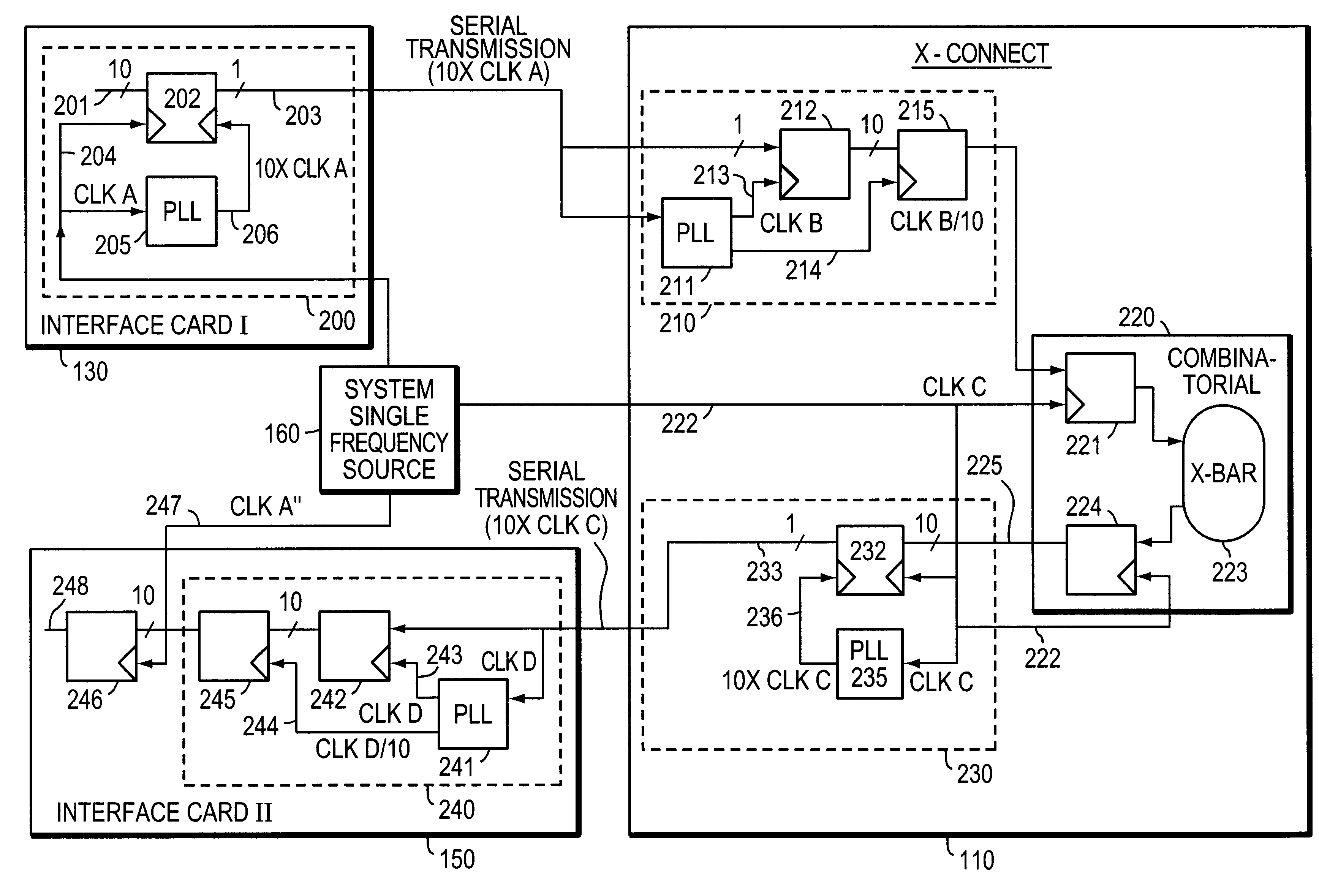

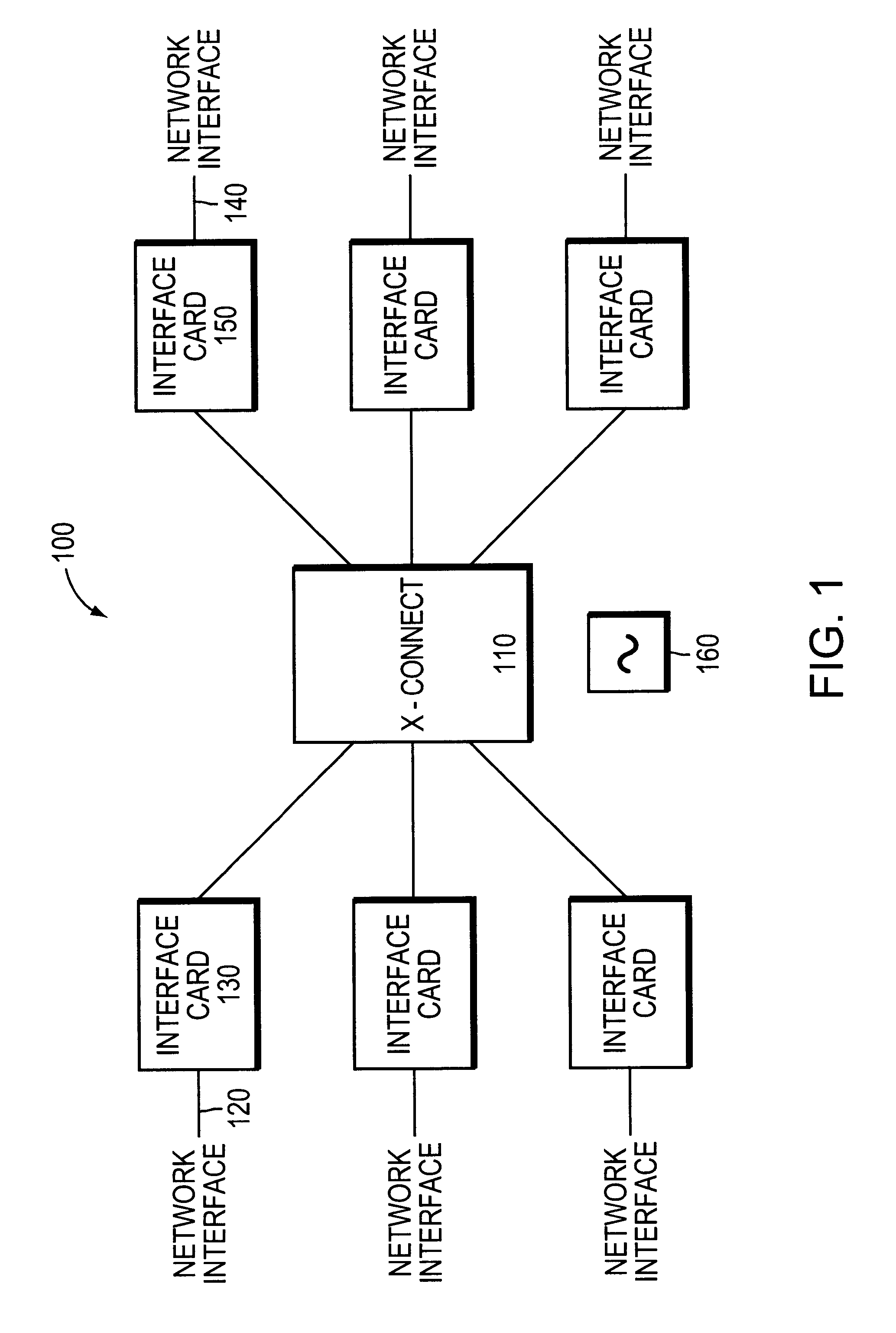

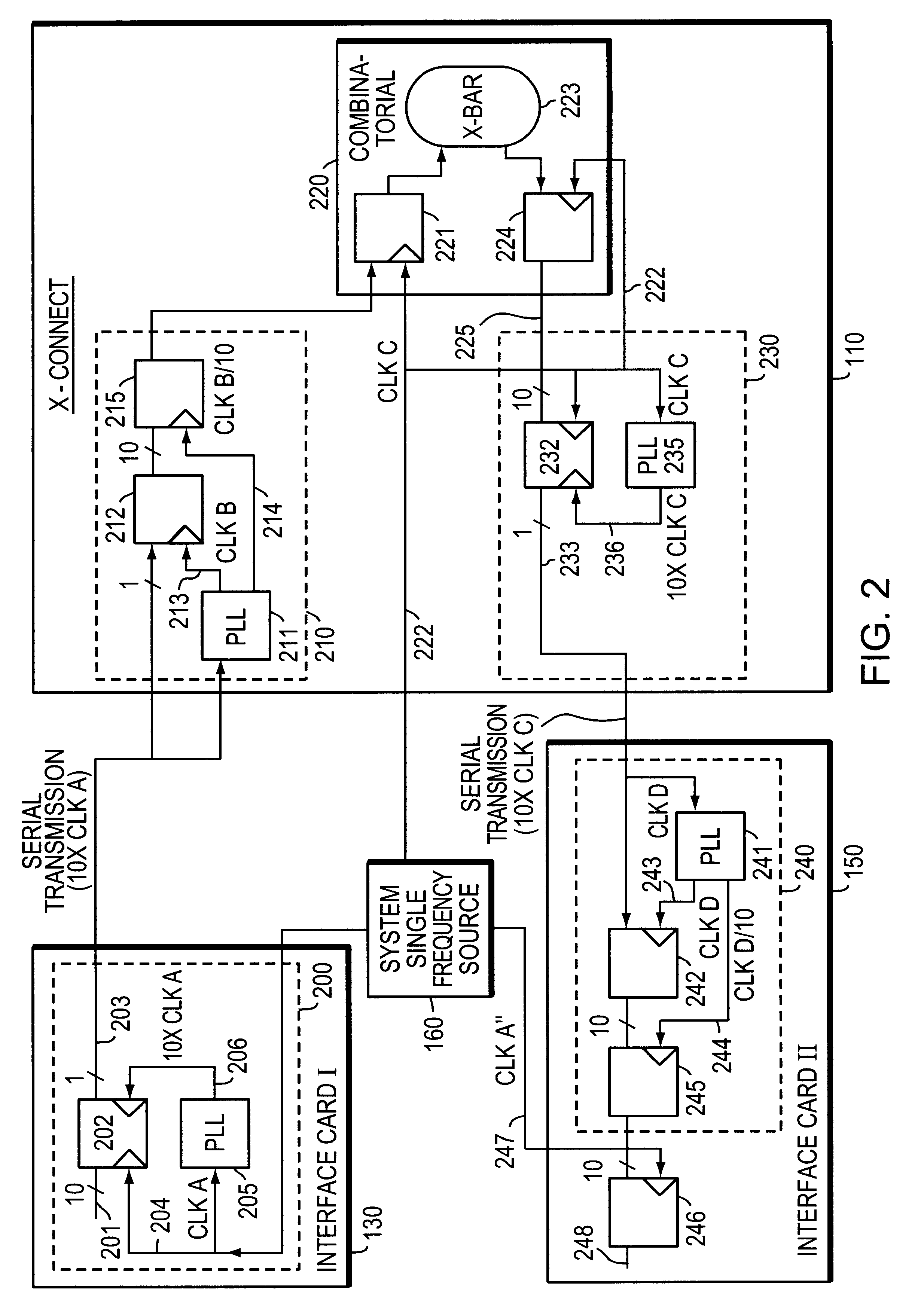

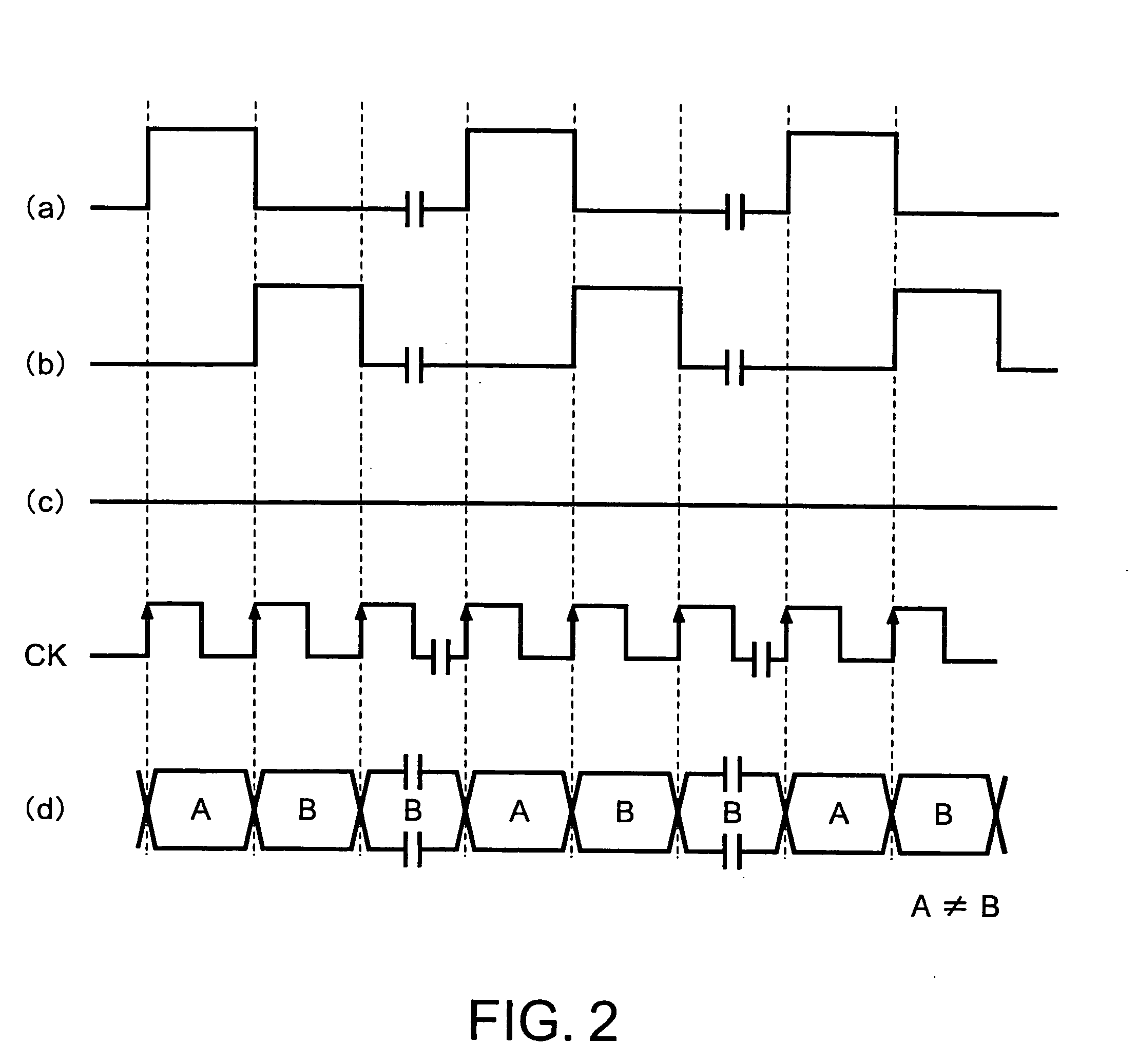

Synchronous pipelined switch using serial transmission

InactiveUS6424649B1Multiplex system selection arrangementsTime-division multiplexSerial transferComputer science

The invention provides a method and system for operating a switch, in which incoming data cells are converted from parallel to serial for synchronous input to a switch interconnect, converted from serial to parallel for parallel switching, converted from parallel to serial for synchronous output from the switch interconnect, and converted from serial to parallel for output. The switch interconnect and its input and output interfaces are controlled by a single frequency source, so that all serial data communication paths into and out of the switch interconnect are phase synchronized to within one clock cycle. A single frequency source for the switch system is coupled to the input interfaces, to output interfaces, and to the switch interconnect. The input interfaces each include a PLL which synchronizes to the single frequency source once for all serial communication to the switch interconnect. The switch interconnect includes one PLL for each input interface which synchronizes to the serial input from that input interface, and one PLL for each output interface which synchronizes to the single frequency source once for all serial communication to the output interface. Similarly, the output interfaces each include a PLL which synchronizes to the serial output from the switch interconnect. The switch interconnect is coupled to the single frequency source and operates in phase therewith.

Owner:CISCO TECH INC

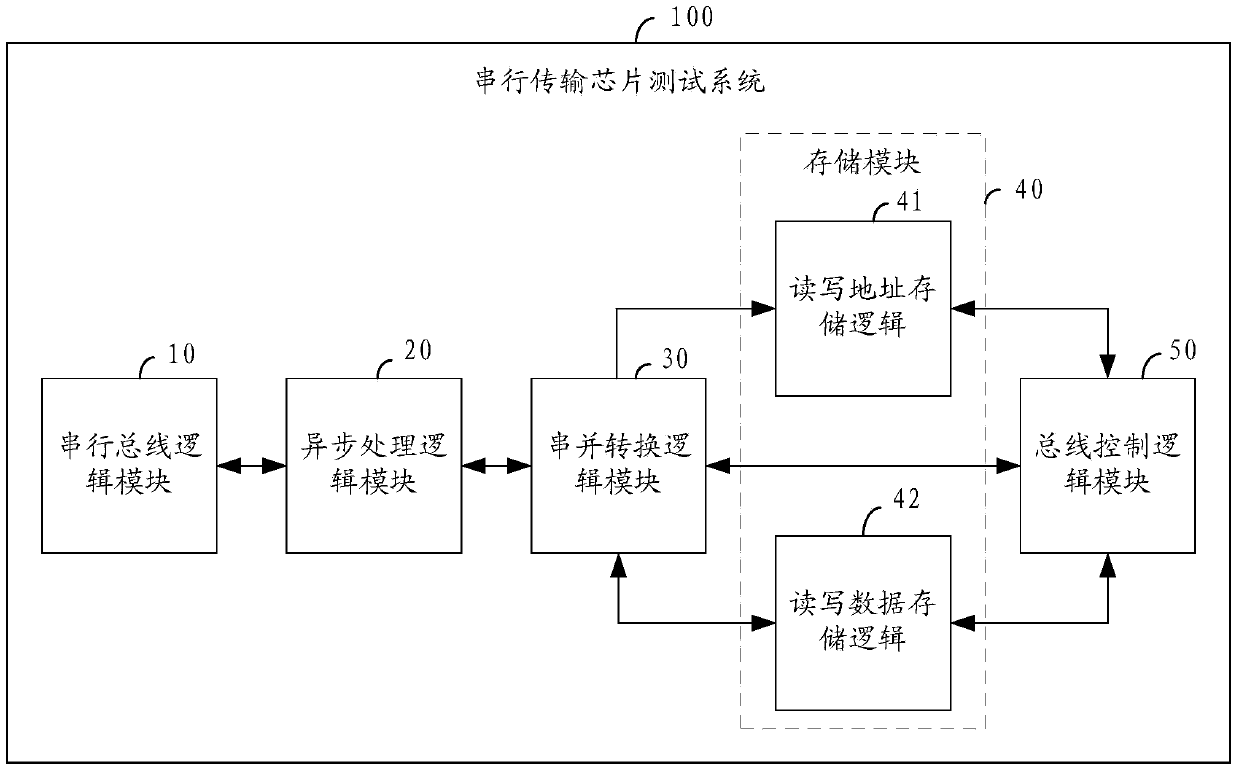

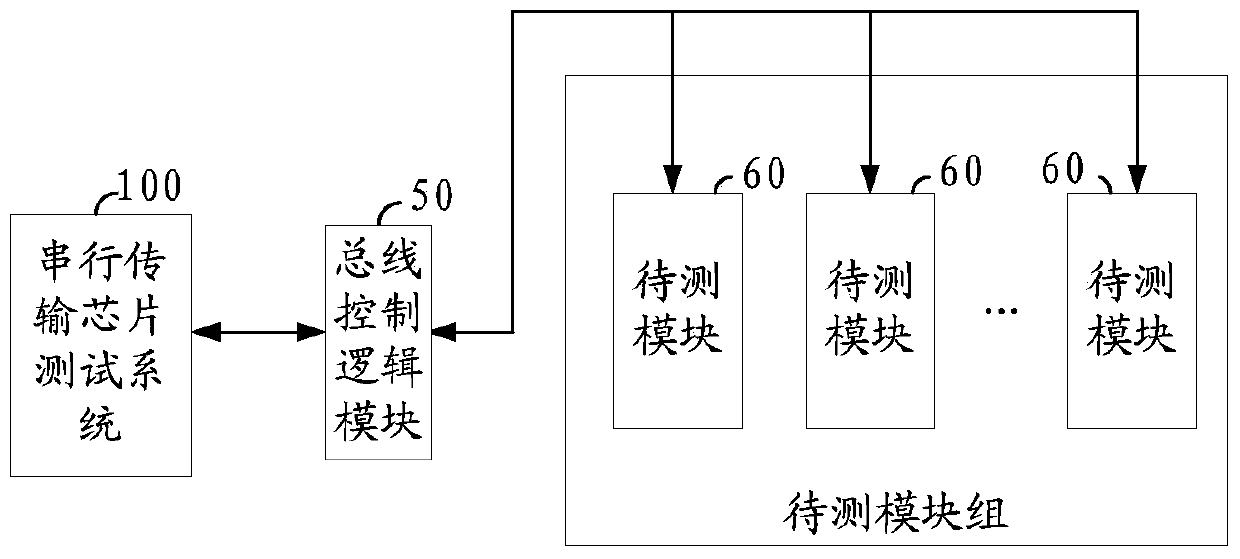

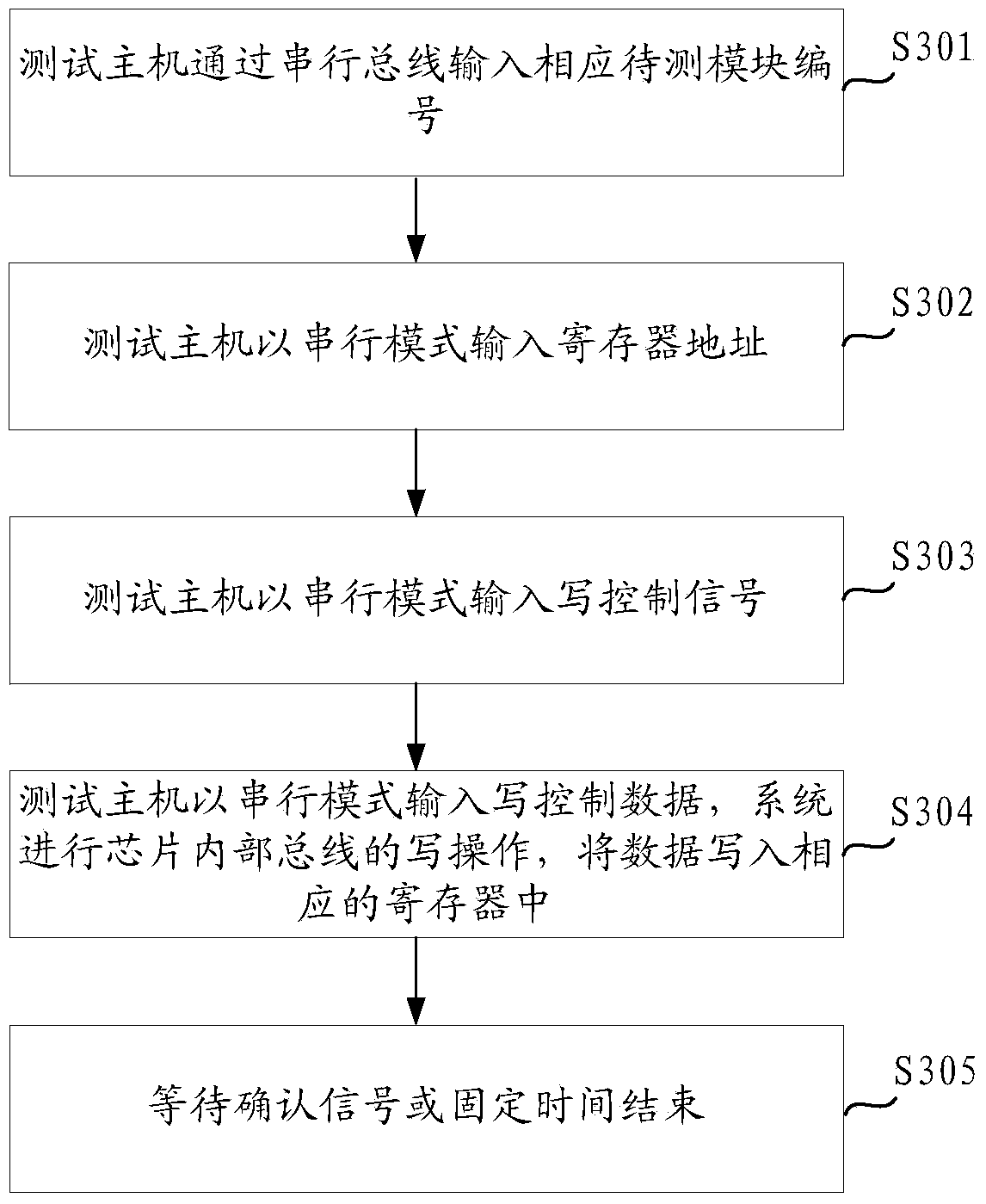

Serial transmission chip test method, serial transmission chip test system and integrated chip

ActiveCN103744009AReduce testing costsShorten test timeElectronic circuit testingSerial transferProcessor register

The invention is applicable to the field of chip test and provides a serial transmission chip test method. The method comprises the following steps: receiving test information sent by a test host through a serial bus, wherein the test information includes the number of a to-be-tested module, the address of a to-be-tested module register, reading and writing control commands and control data; carrying out asynchronous processing and serial-parallel conversion on the received test information and storing the converted test information; and writing the control data into the to-be-tested module register through a bus inside a chip according to the writing control command and the address of the to-be-tested module register, or reading data from the to-be-tested module register through the bus inside the chip according to the reading control command and the address of the to-be-tested module register and sending the read data to the test host through a serial mode after test information receiving is completed. Therefore, multiple logical units can be tested at the same time, the number of chip I / Os is reduced, and the test time is saved.

Owner:RAMAXEL TECH SHENZHEN

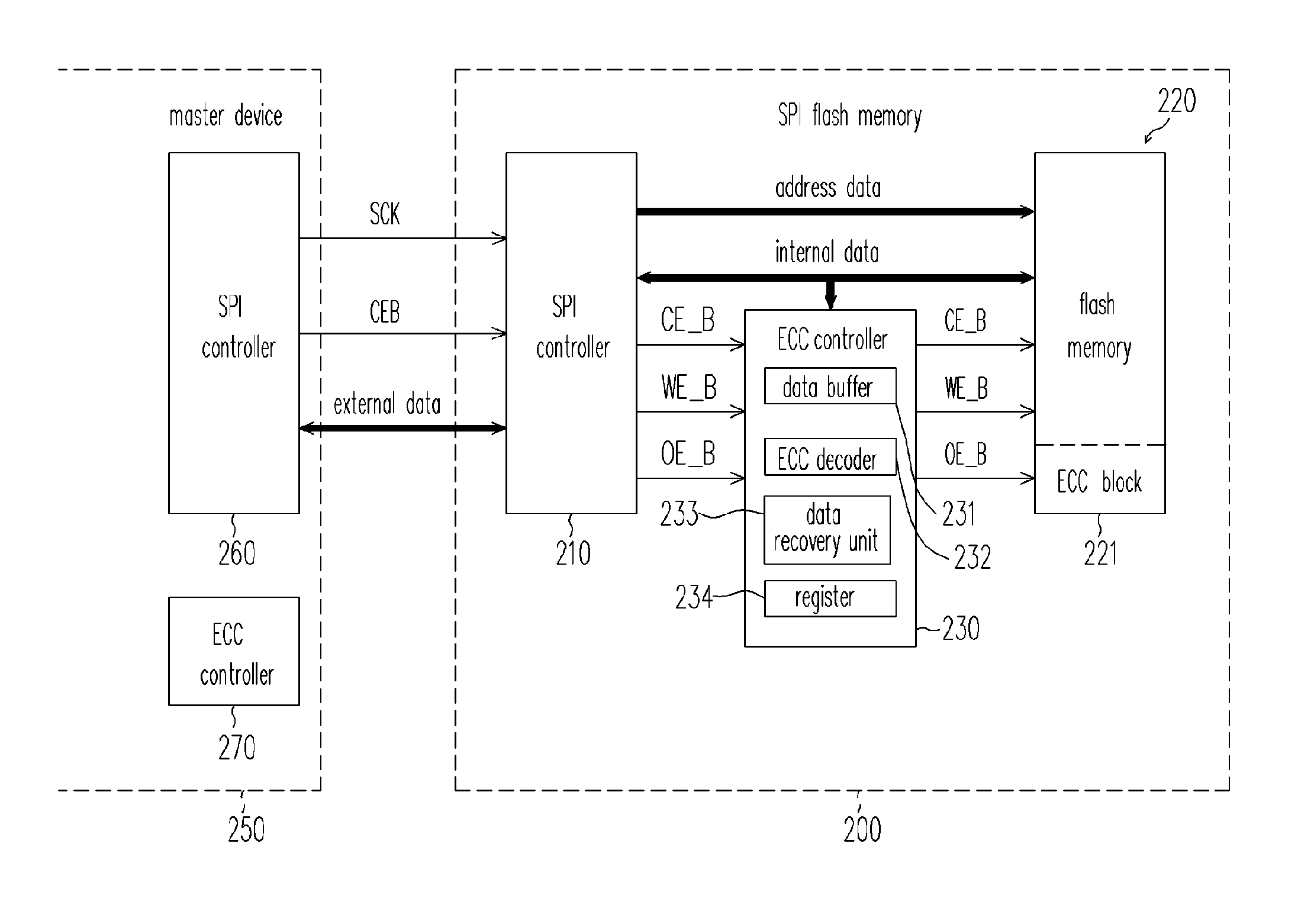

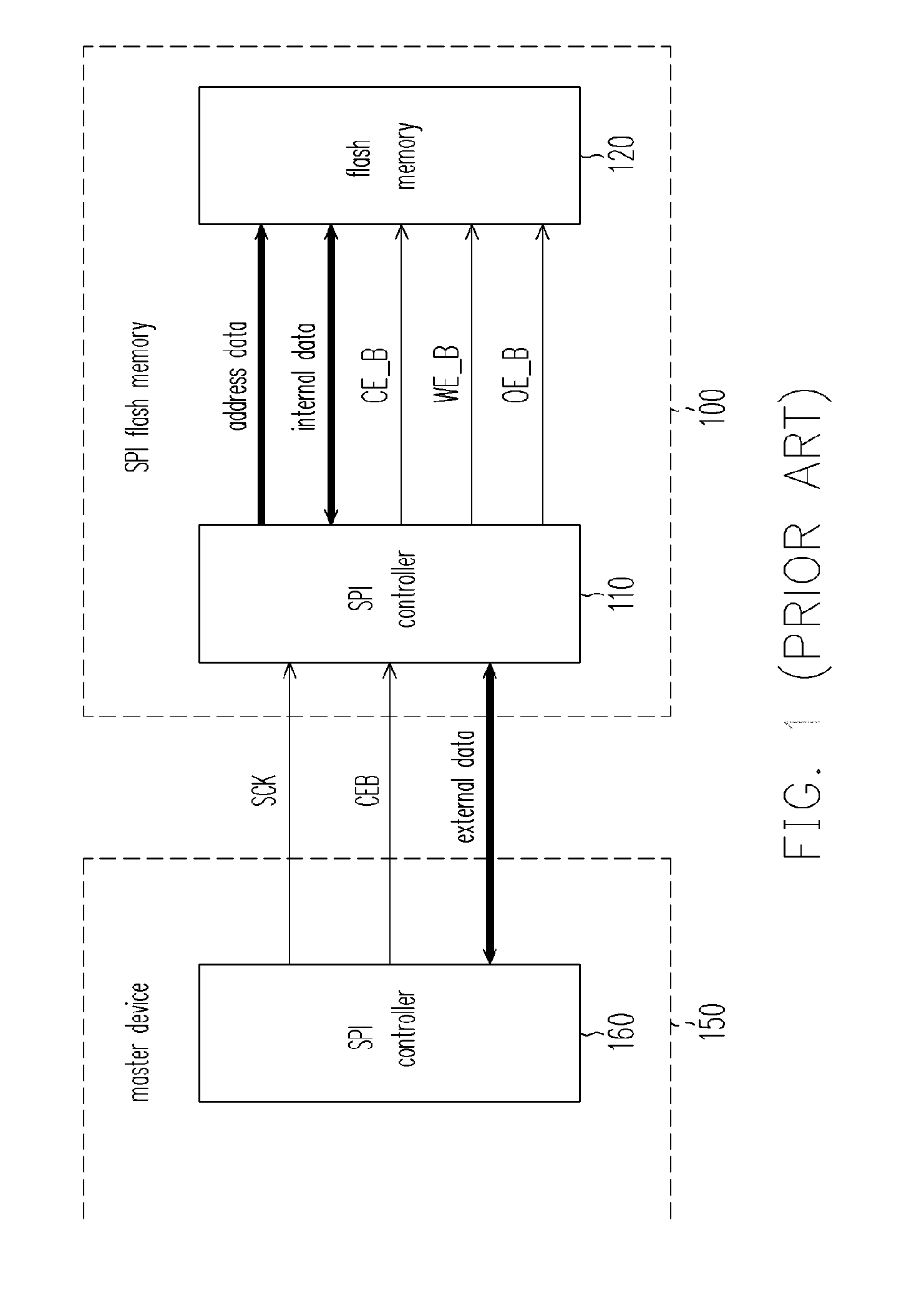

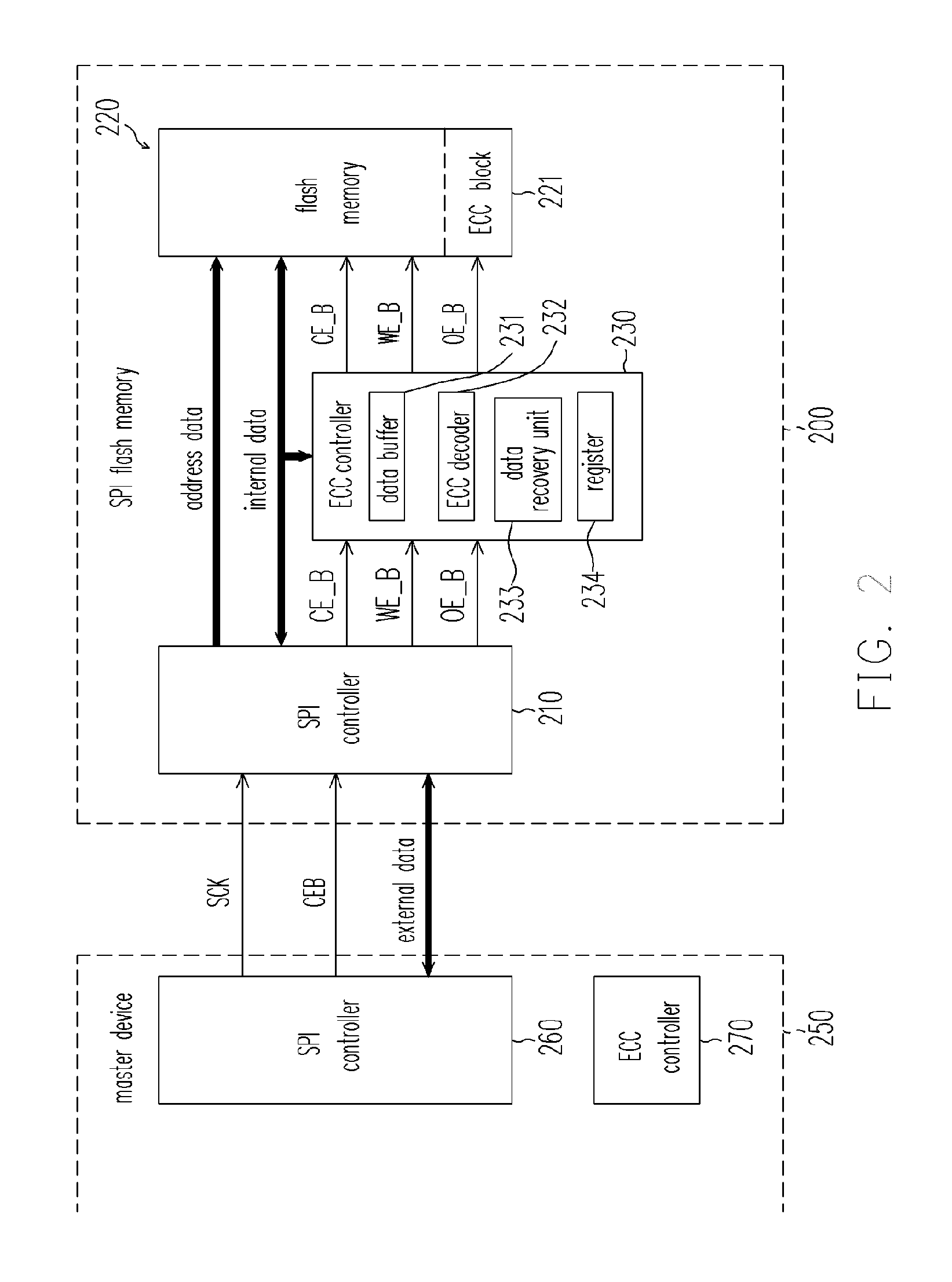

Memory device with serial transmission interface and error correction mehtod for serial transmission interface

InactiveUS20060236204A1Error data is eliminatedReduce loadError detection/correctionDigital storageSerial transferData transmission

The present invention provides a memory device with the serial transmission interface and an error correction method for the serial transmission interface. The memory device comprises an error correction mechanism to detect or automatically correct the error earlier to make sure the correctness of the data transmission while the serial transmission interface accesses the memory. Further, the action of error corrections and data re-transmissions performed by the master device can be reduced.

Owner:SUNPLUS TECH CO LTD

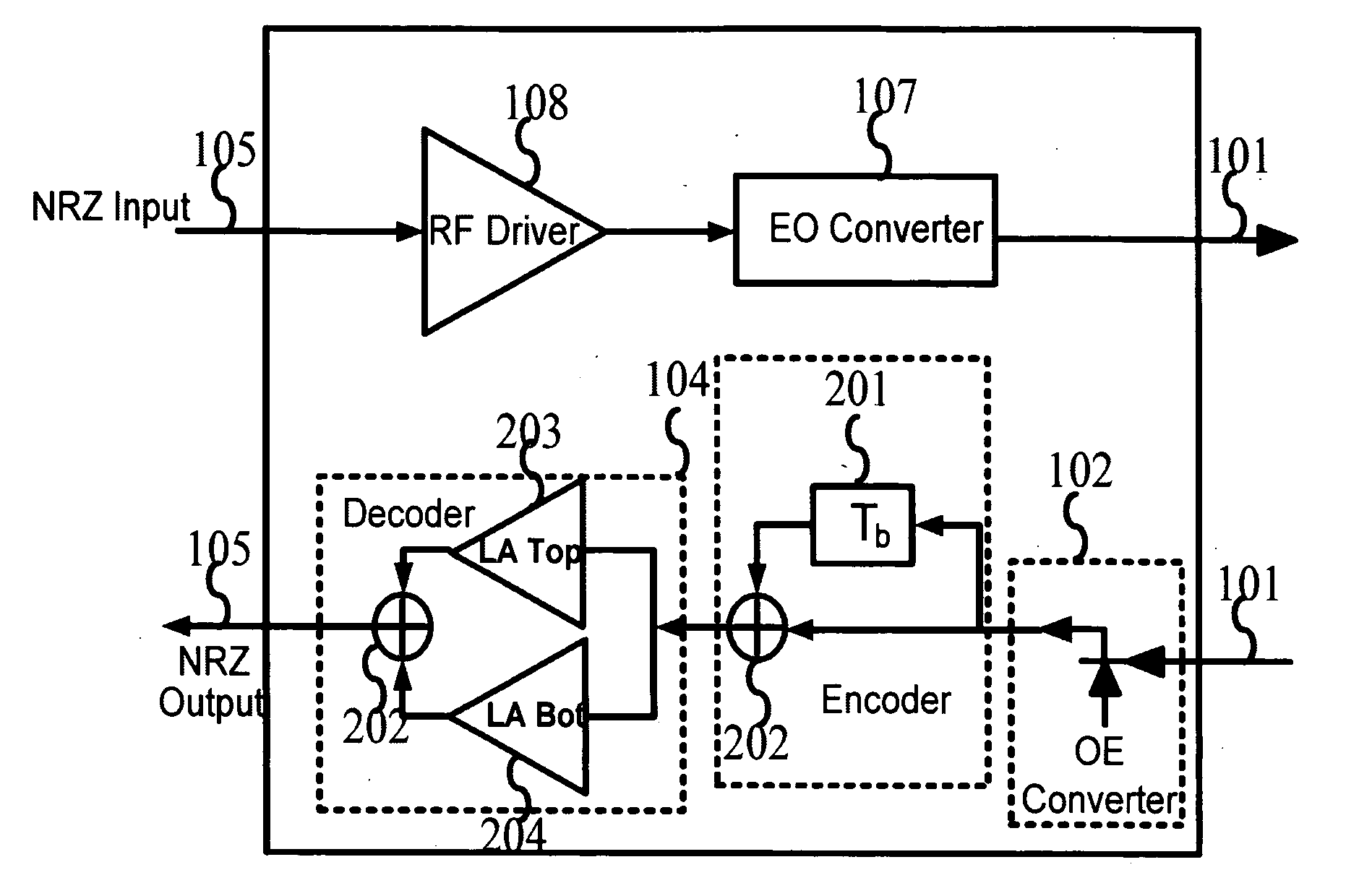

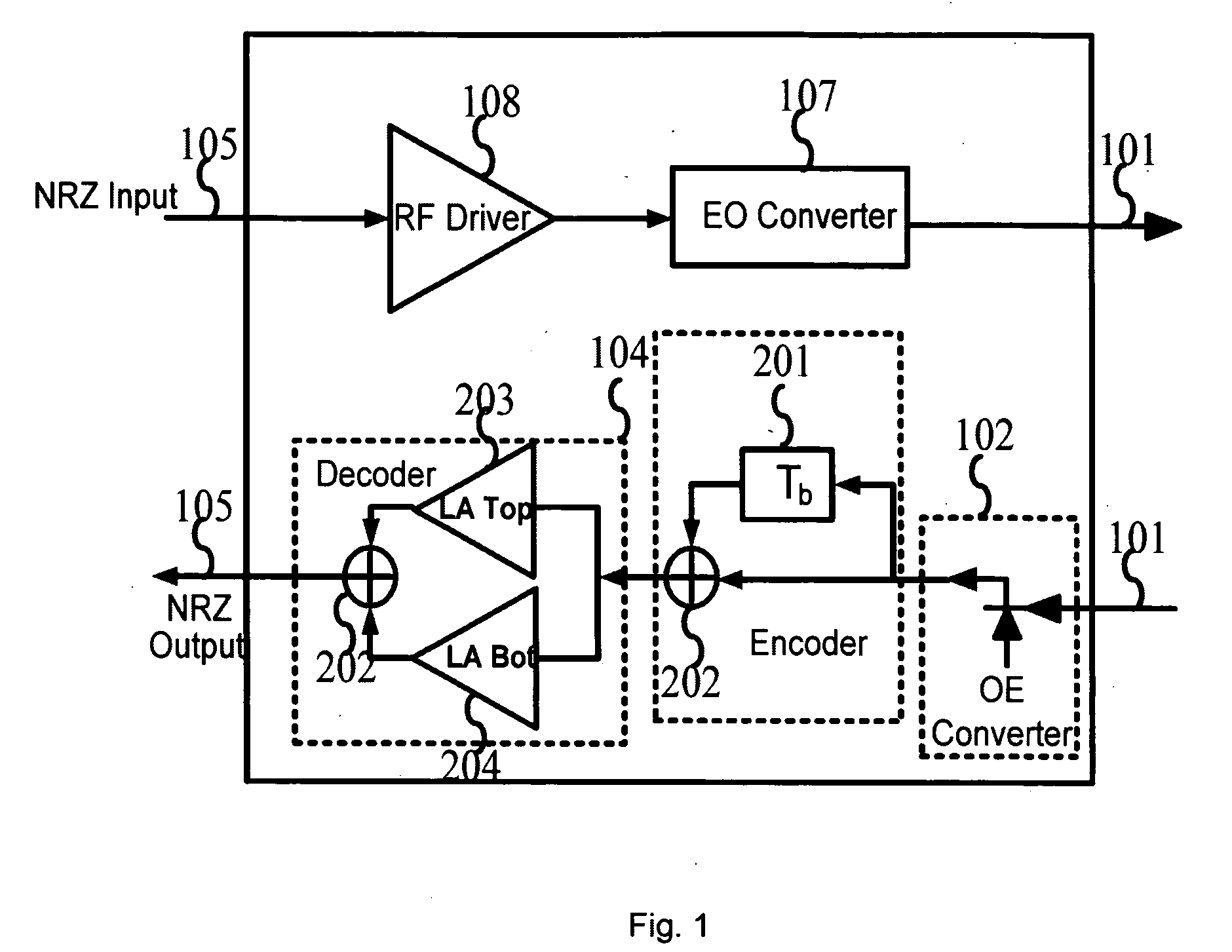

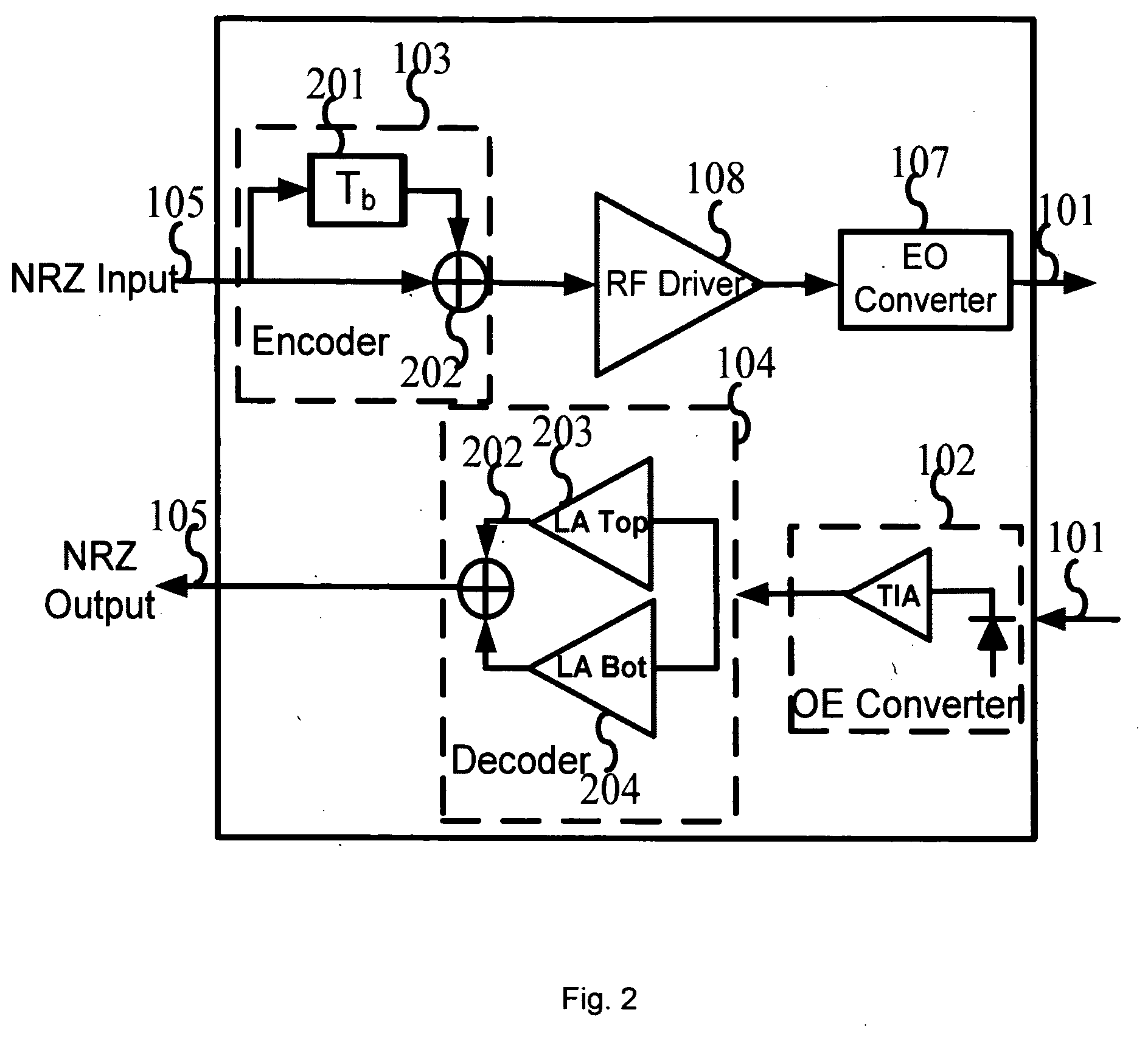

Multiple Electrical Level Dispersion Tolerant Optical Apparatus

InactiveUS20090047025A1Component is readilyGood optical transmission performanceElectromagnetic transceiversSerial transferFiber

An optical apparatus consisting of a transmitter, receiver, or transceiver, utilizing a multiple level special electrical layer modulation and / or demodulation scheme to significantly lower the bandwidth required for high speed communication and / or parallel interconnect systems. It can be used either to enhance the transmission performance of the transceiver, or to eliminate the need for bulky and / or expensive optical components to lower the cost. It can be used in the design of transponders, transceivers, and active cabling systems, for 10 Gb / s, 40 Gb / s, 100 Gb / s and other high bit rate transmission systems that utilize single mode or multi-mode fibers for serial or parallel transmission of high speed optical signals.

Owner:HONG JIN +1

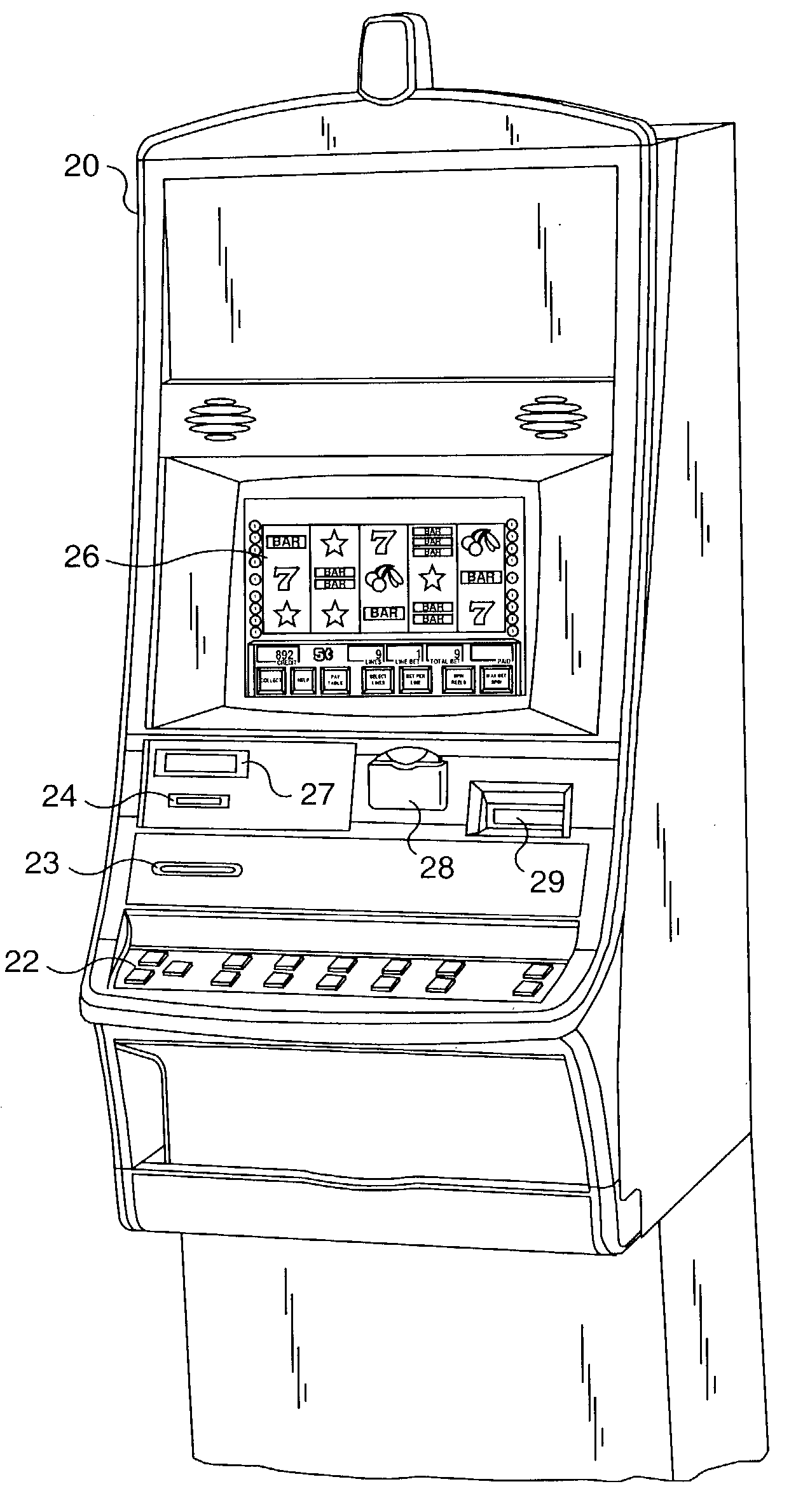

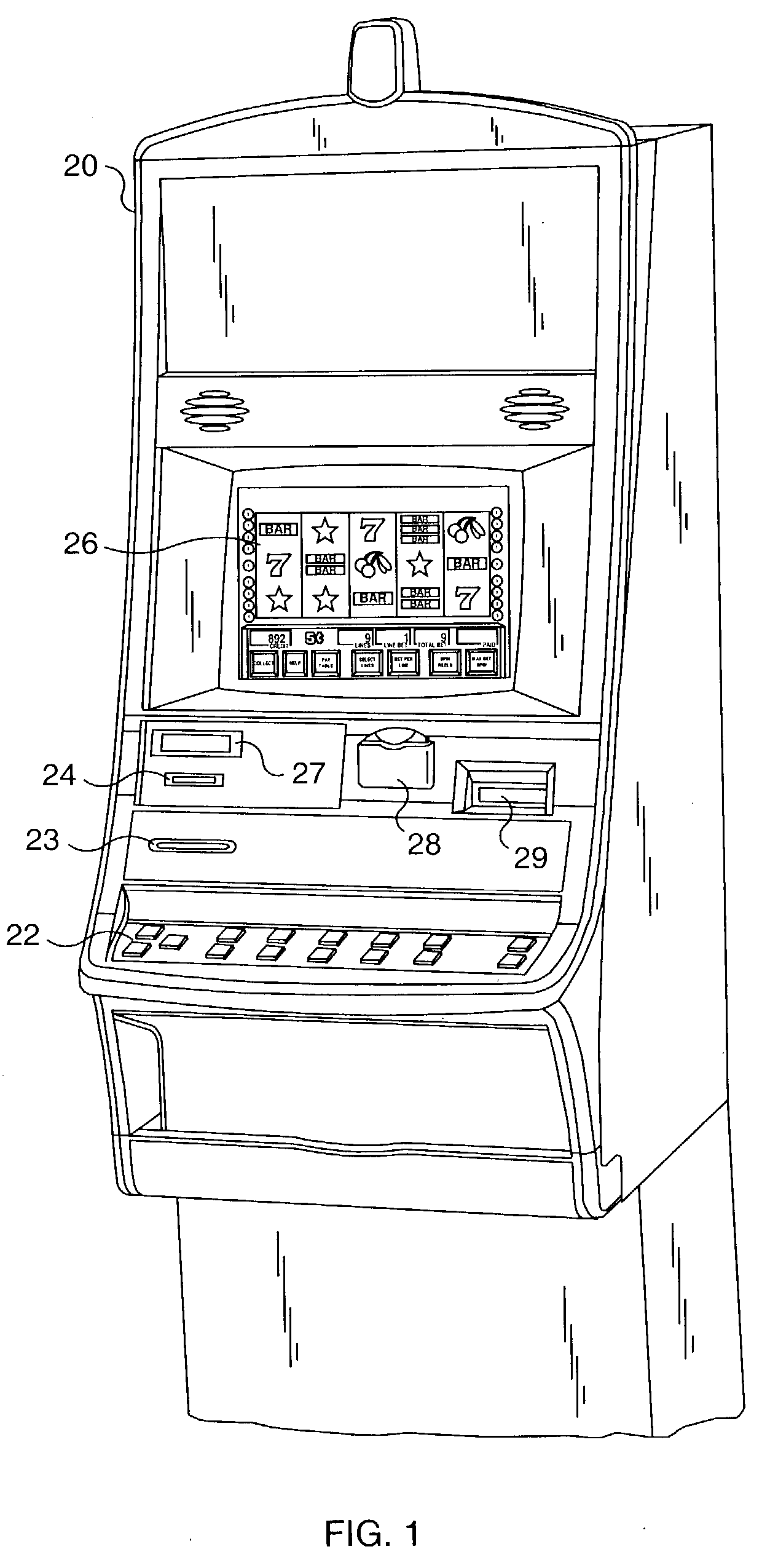

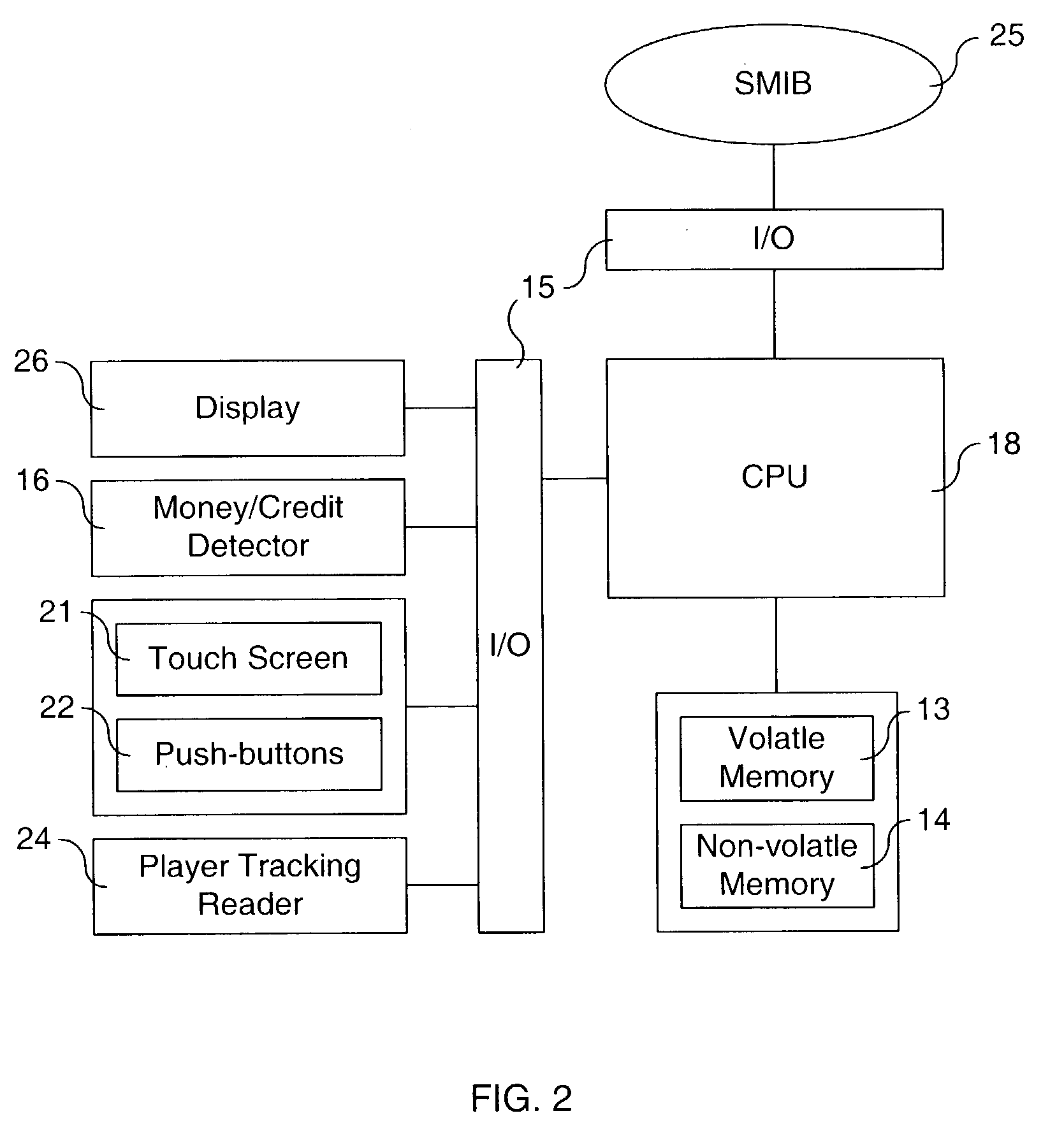

Gaming terminal data monitoring network

InactiveUS8197344B2Reliable and secure audit trailSimplify their oversightCard gamesApparatus for meter-controlled dispensingCommunication interfaceNetwork Communication Protocols

A method of storing data serially transmitted between a gaming terminal and a computer on one or more servers in a network. The gaming terminal and computer are typically linked in gaming establishments by a serial communication link utilizing serial communication protocols. Although this data is stored on the gaming establishment's computers, it is also highly desirable to make this data accessible on a secure server. Data is monitored and captured directly at the gaming terminal with a communication interface. The communication interface converts the captured data from a serial communication protocol into a network communication protocol for storage on a server in a network.

Owner:BALLY GAMING INC

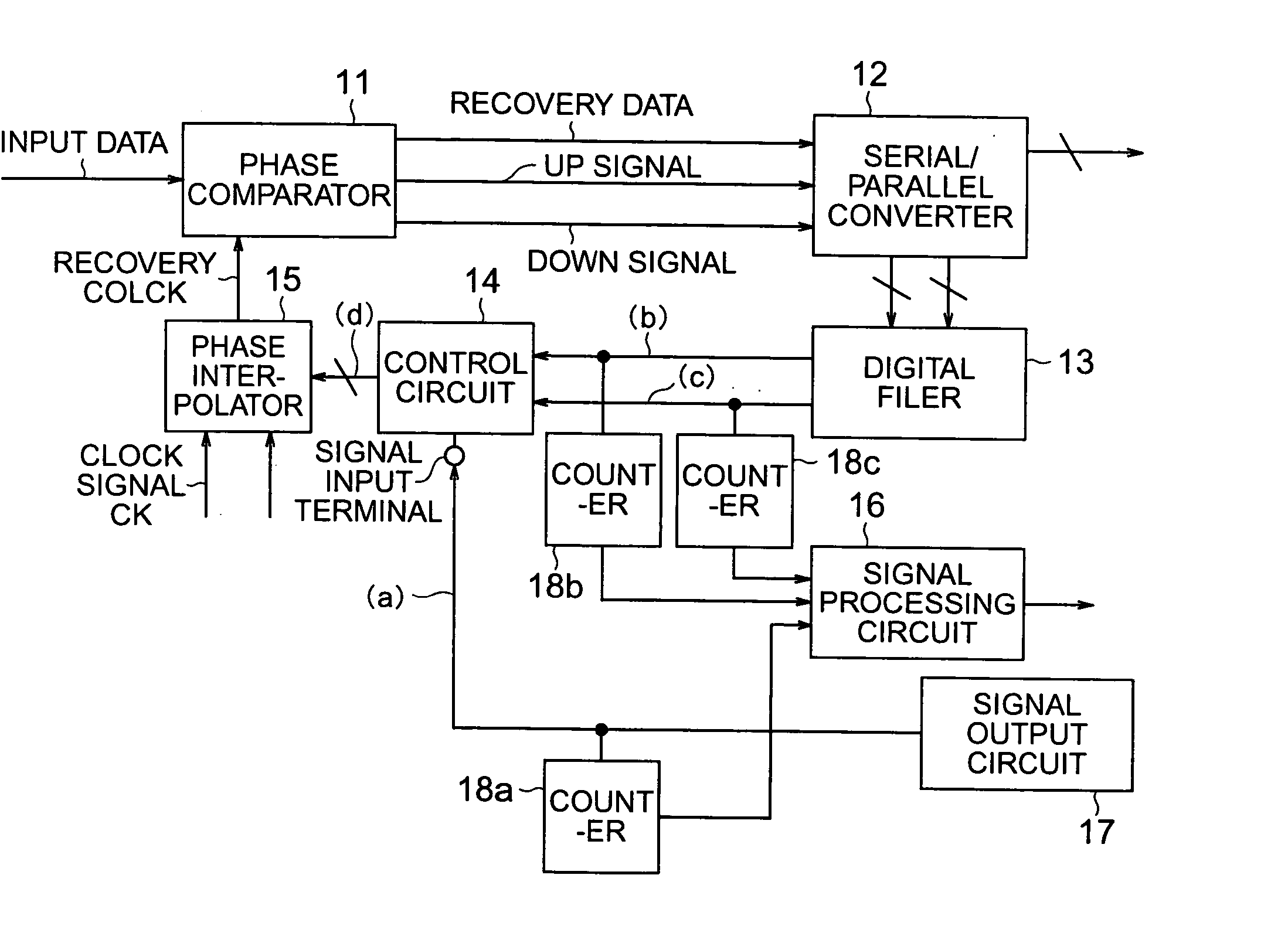

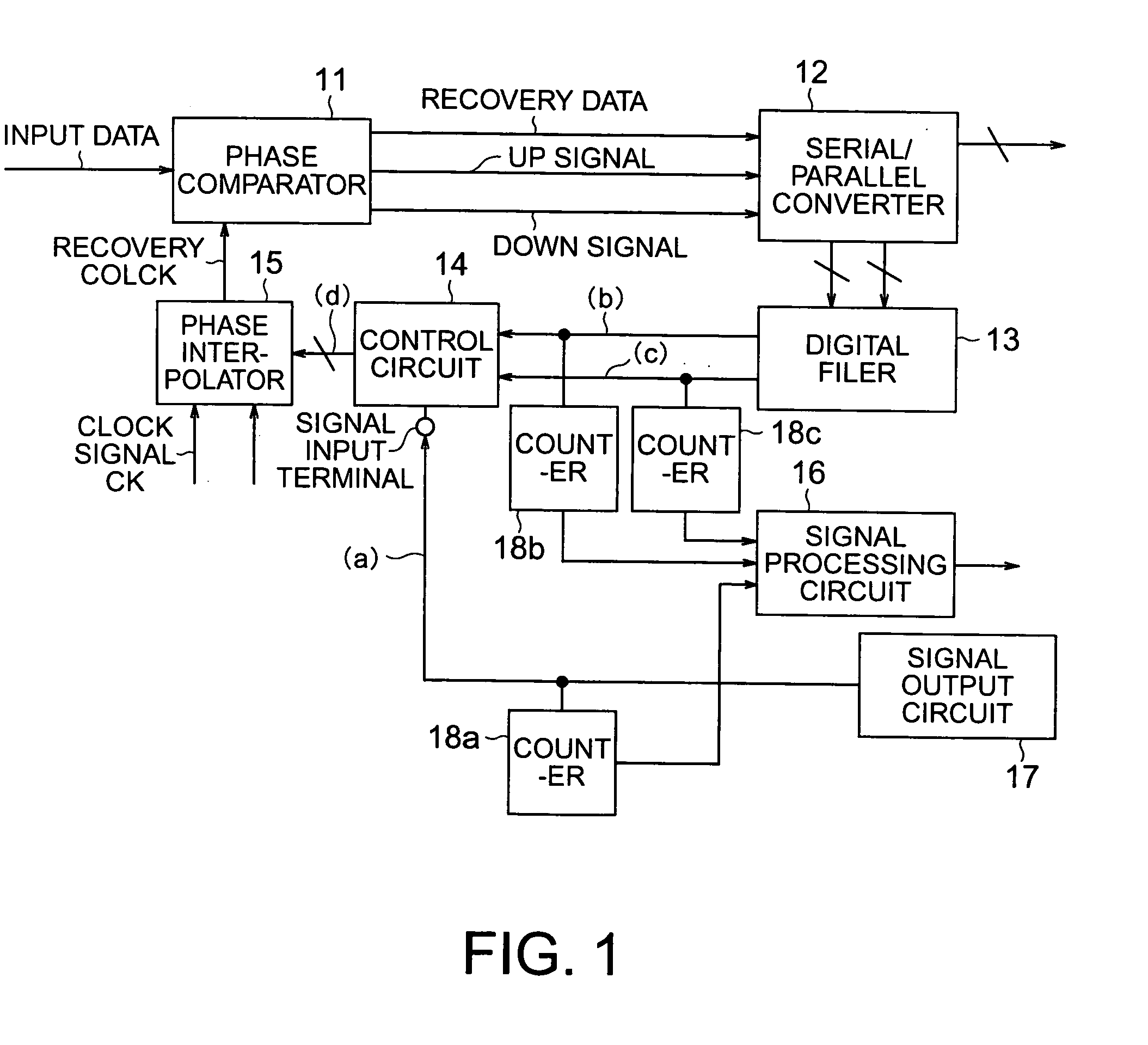

Semiconductor integrated circuit and method for testing the same

InactiveUS20050201500A1Digital circuit testingModulated-carrier systemsSerial transferSignal processing circuits

According to the present invention, there is provided a semiconductor integrated circuit having a receiver which receives reception data and executes reception processing on the basis of a clock signal supplied from a PLL and a transmitter which receives parallel transmission data and executes serial transmission processing on the basis of the clock signal, and having a loop back function of supplying data output from the transmitter to the receiver for test, the receiver, as a CDR circuit, executing control so as to make the phase of the input data coincide with that of the recovery clock by a negative feedback loop having a phase comparator which receives input data and a recovery clock, compares a phase of the input data with that of the recovery clock, and outputs recovery data and a phase comparison result in a serial form, a serial / parallel conversion circuit which receives the phase comparison result, or the phase comparison result and the recovery data from the phase comparator, executes serial / parallel conversion, and outputs the phase comparison result in a parallel form, a digital filer which receives the phase comparison result from the serial / parallel conversion circuit, executes averaging processing for the phase comparison result in a predetermined period, and outputs the phase comparison result, a control circuit which receives the phase comparison result from the digital filer and outputs a control signal to control the phase of the recovery clock, and a phase interpolator which receives the clock signal and generates the recovery clock on the basis of the control signal, and the CDR circuit including a signal output circuit which inputs, to one of the control circuit and the digital filer, a signal to forcibly shift the phase of the recovery data in the negative feedback loop by a predetermined amount, a first counter which counts the number of pulses of the signal output from the signal output circuit in a predetermined period and outputs a first count value, a second counter which counts the number of pulses of the phase comparison result, which has undergone the averaging processing and is output from the digital filer, and outputs a second count value, and a signal processing circuit which receives the first count value and the second count value and compares the first count value with the second count value to determine presence / absence of a capability for absorbing the phase shift generated by the signal.

Owner:KK TOSHIBA