Patents

Literature

320results about How to "Synchronization is simple" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

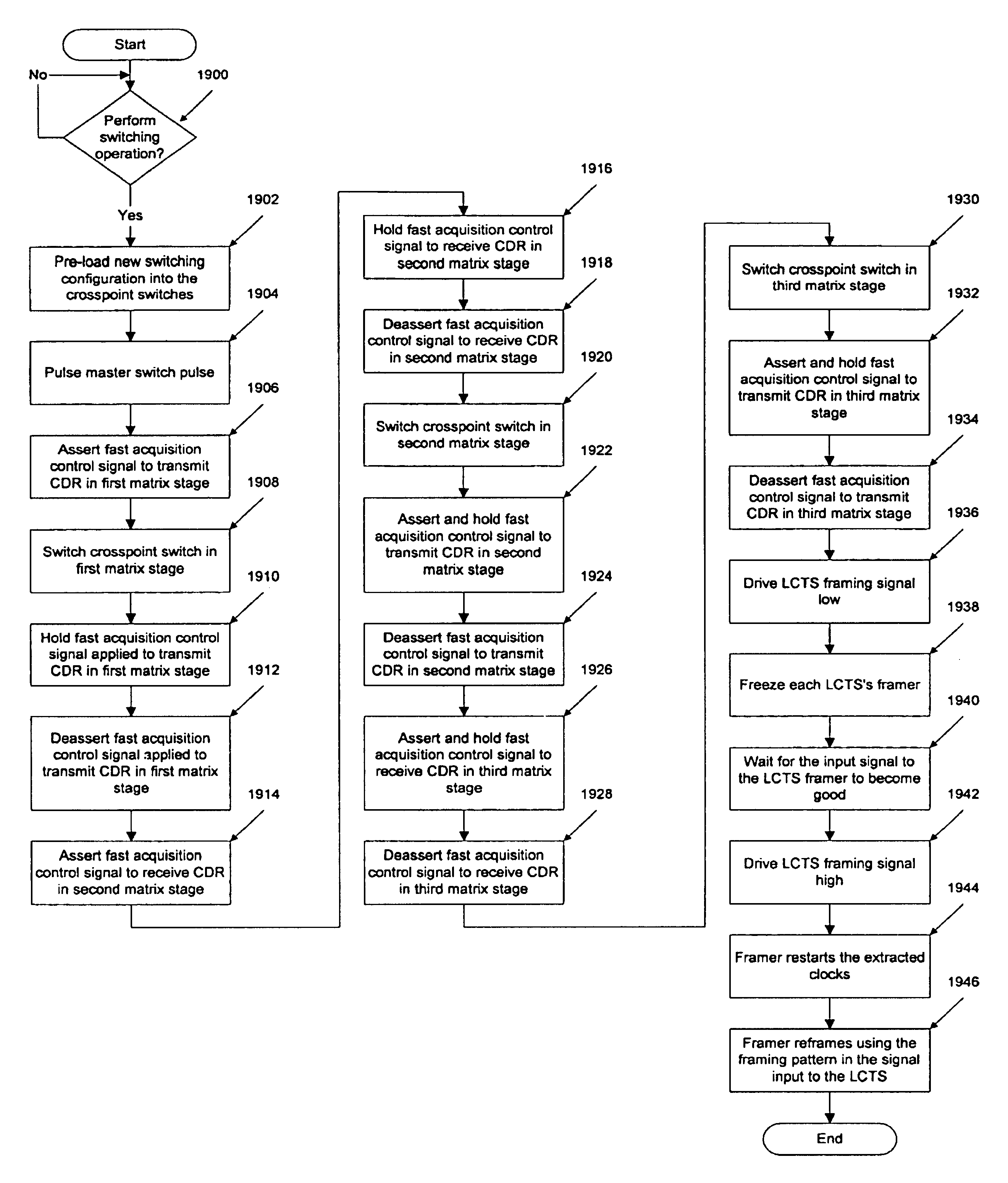

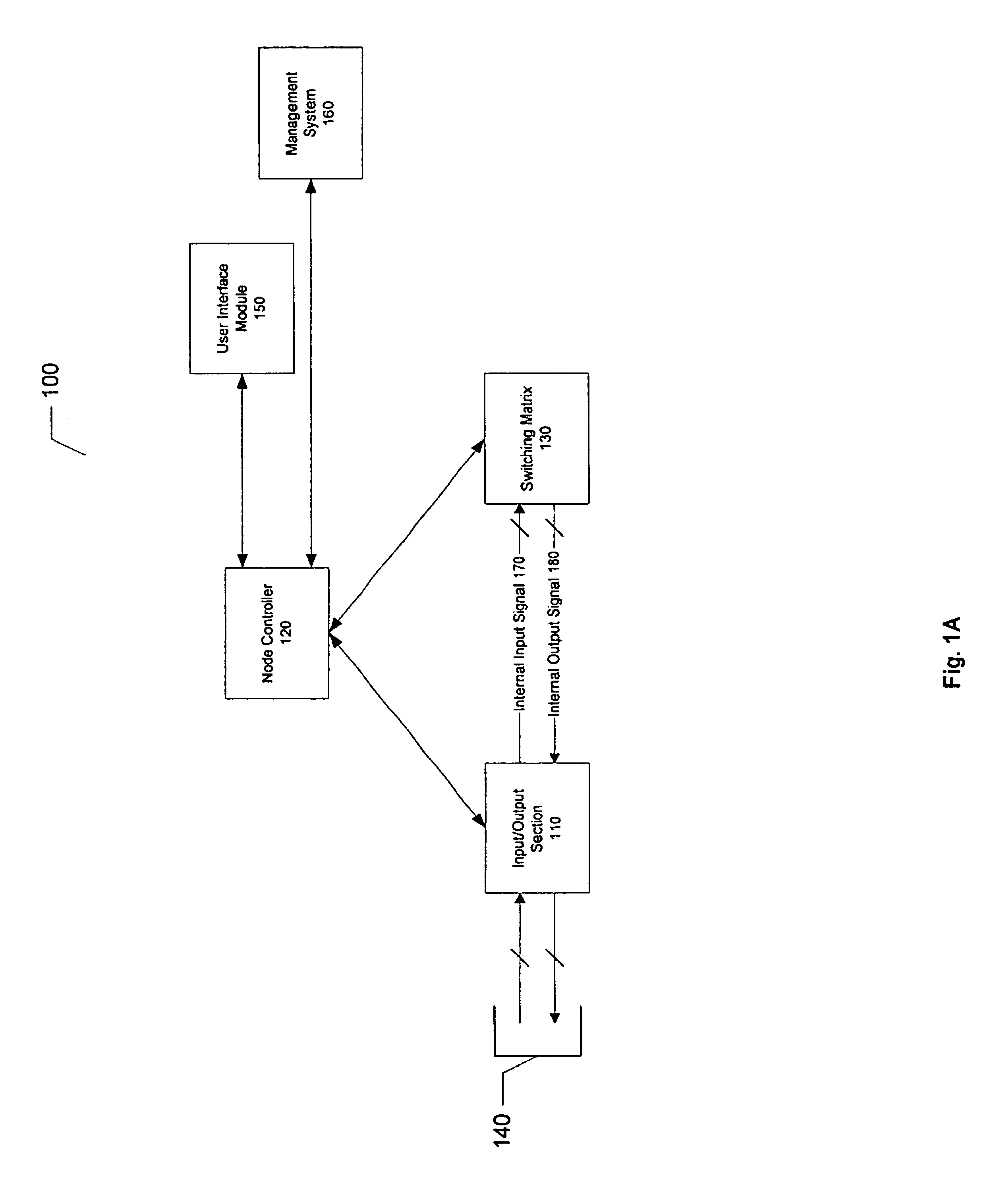

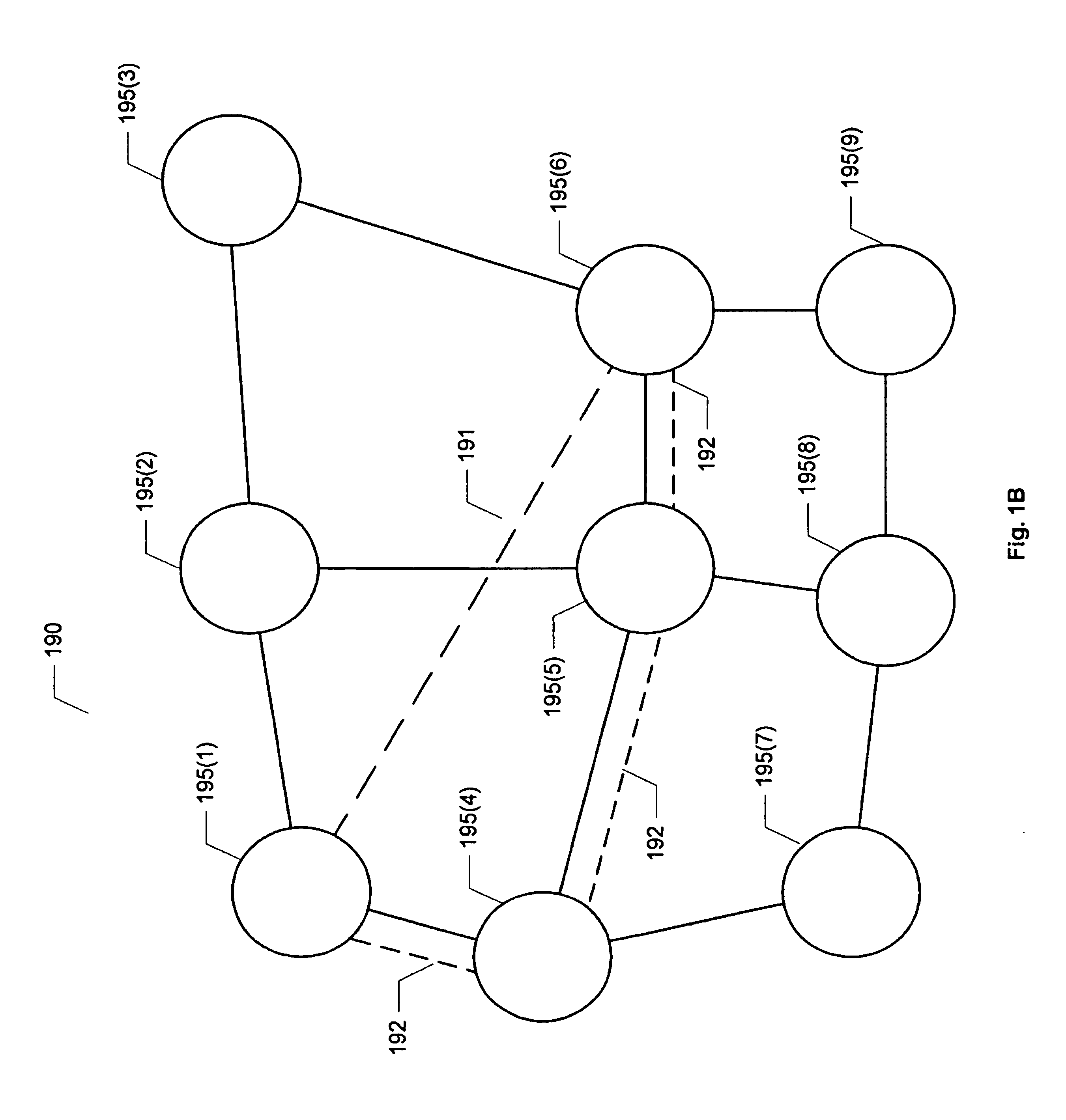

Method and apparatus for a rearrangeably non-blocking switching matrix

InactiveUS6982974B1Simple and inexpensiveAvoid disturbanceMultiplex system selection arrangementsElectronic switchingOptical backplaneEngineering

A switching apparatus is disclosed that employs a relatively simple and inexpensive switching matrix, but which avoids interruption of existing connections when connections are added or removed. The switching matrix switches errorlessly by controlling the point in time at which switching occurs. Using such a technique, switching can be performed without disturbing the connections already configured in the switching matrix, and so is referred to herein as being non-blocking. Optionally, the incoming data can be rearranged to provide a larger window of time in which the switching matrix can be switched. In the case of a switch using an optical backplane, this also allows more time for various components of the system (e.g., clock / data recovery units) to re-acquire lock. The switching apparatus includes a switching matrix and control circuitry. The switching matrix has a matrix input, a control input and a number of matrix outputs, and is configured to receive an information stream at the matrix input. The information stream includes a number of portions, while the control circuitry has a control output coupled to the control input. The control circuitry is configured to initially configure the switching matrix to output the information stream at a one of the matrix outputs and to subsequently configure the switching matrix to output the information stream at another of the matrix outputs during a period of time during which the one of the portions is transiting the switching matrix.

Owner:CISCO TECH INC

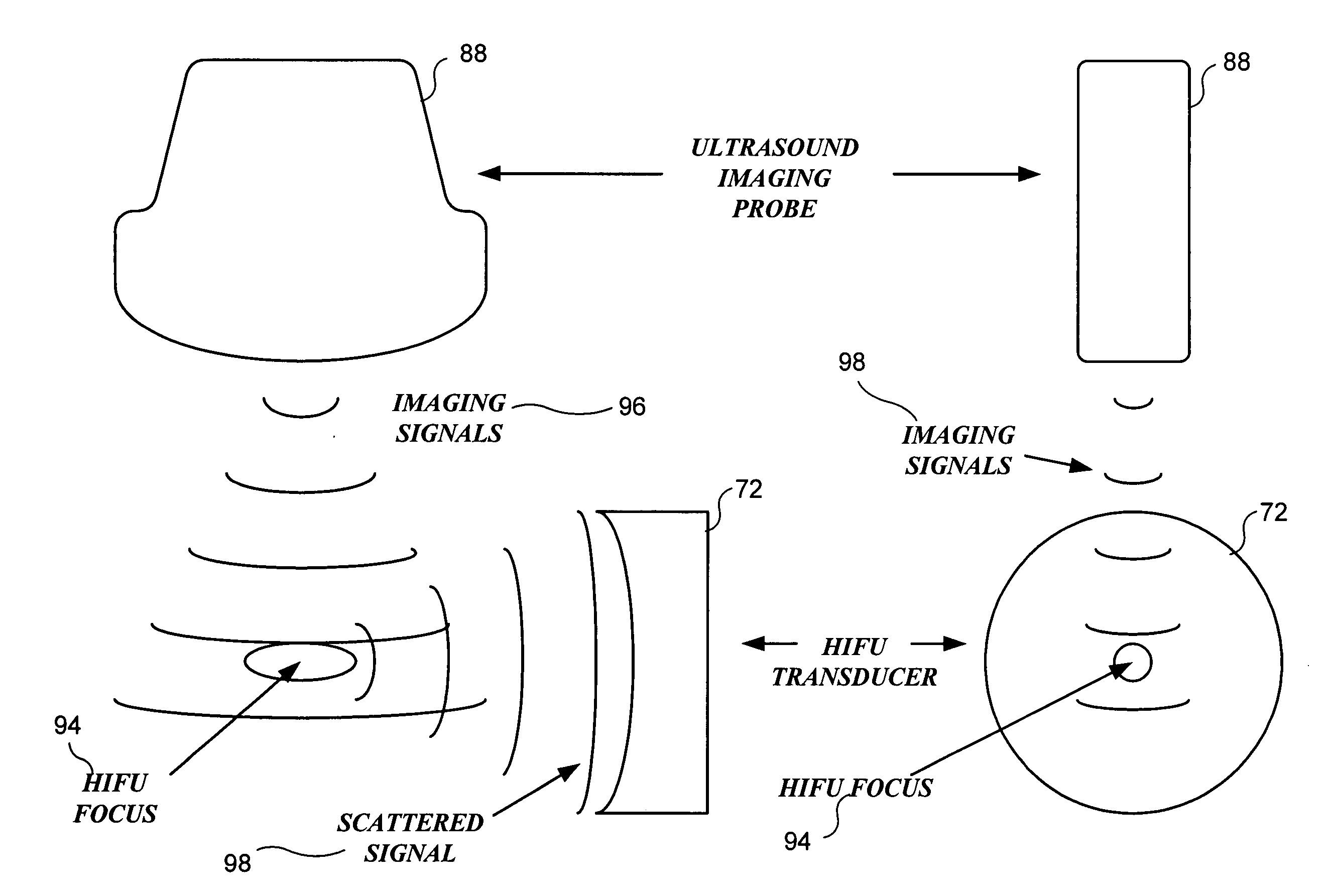

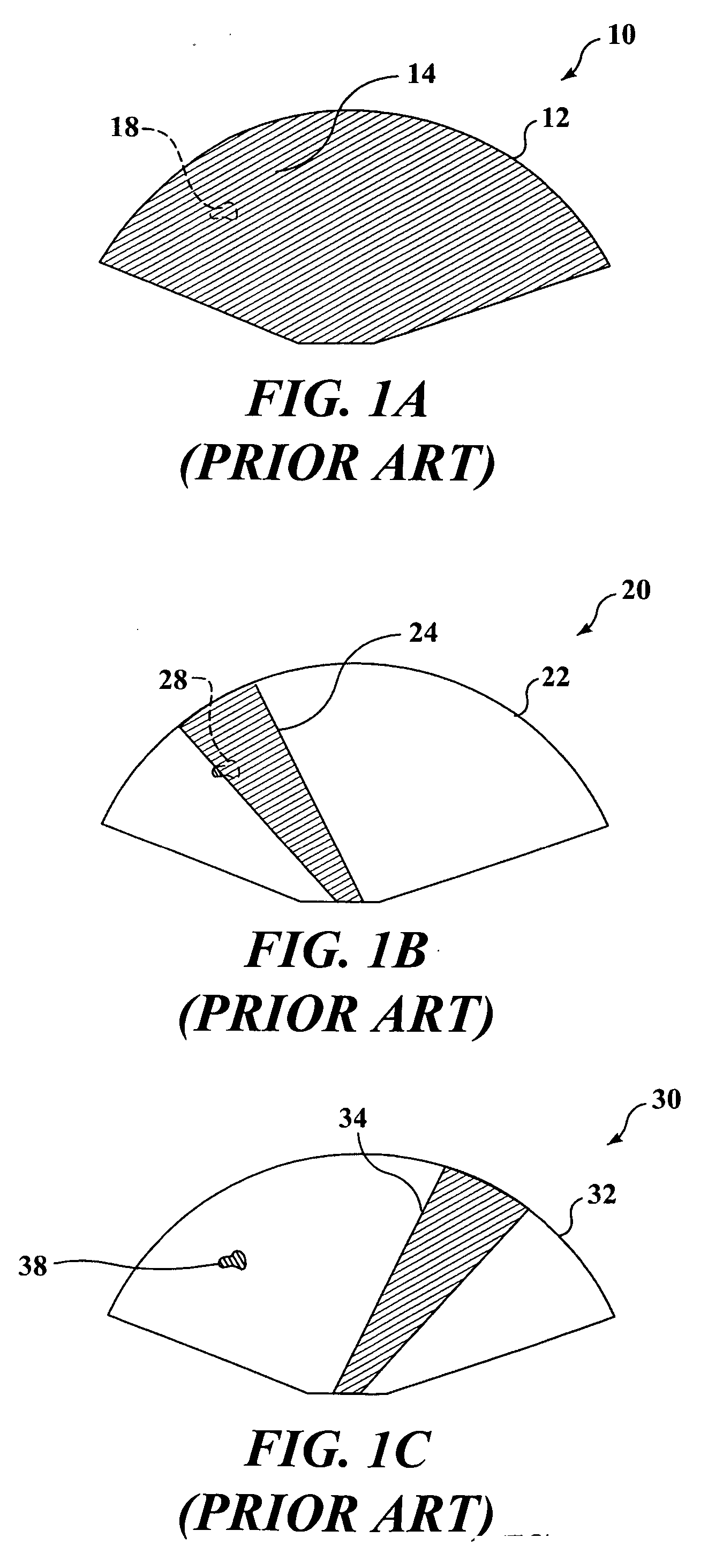

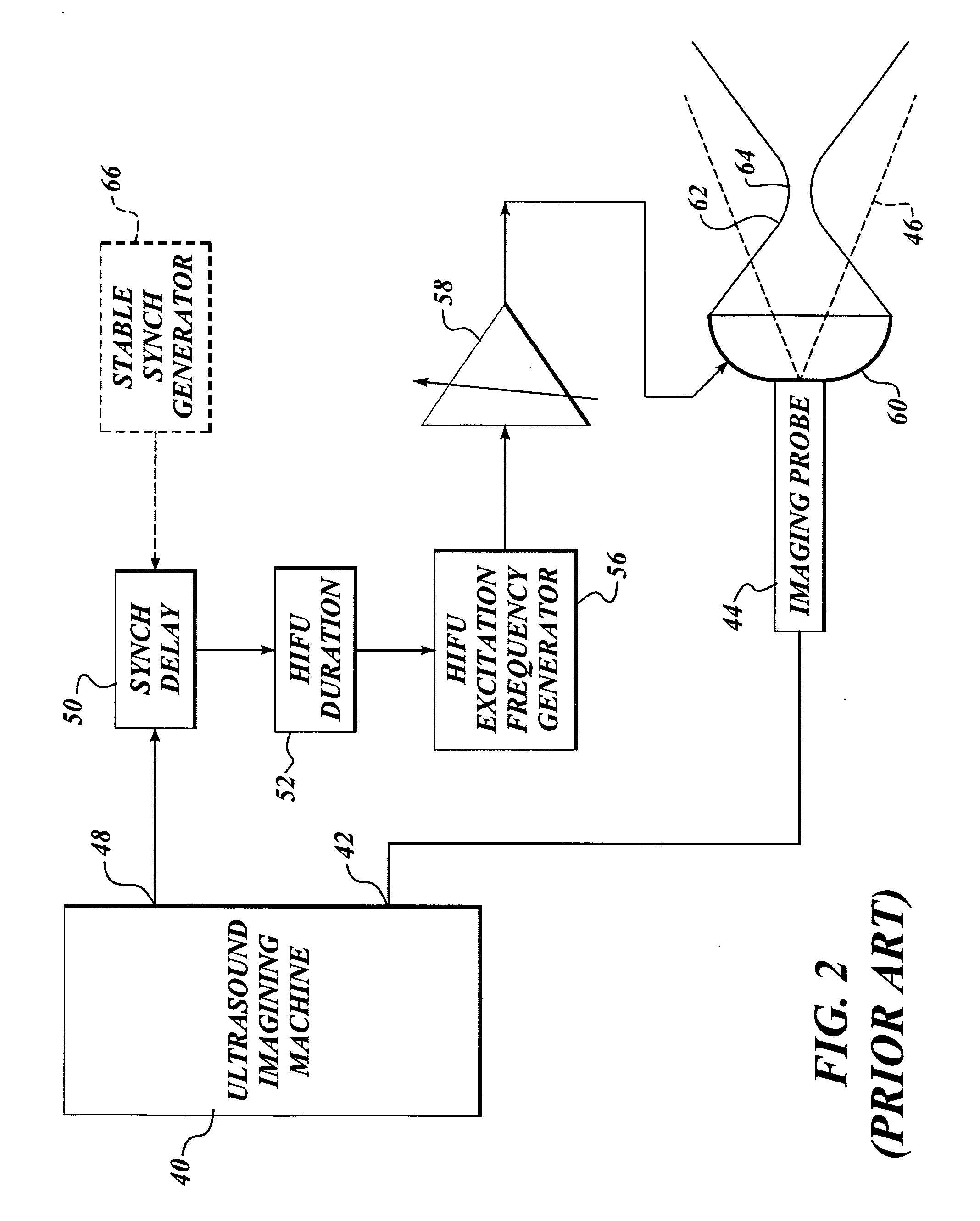

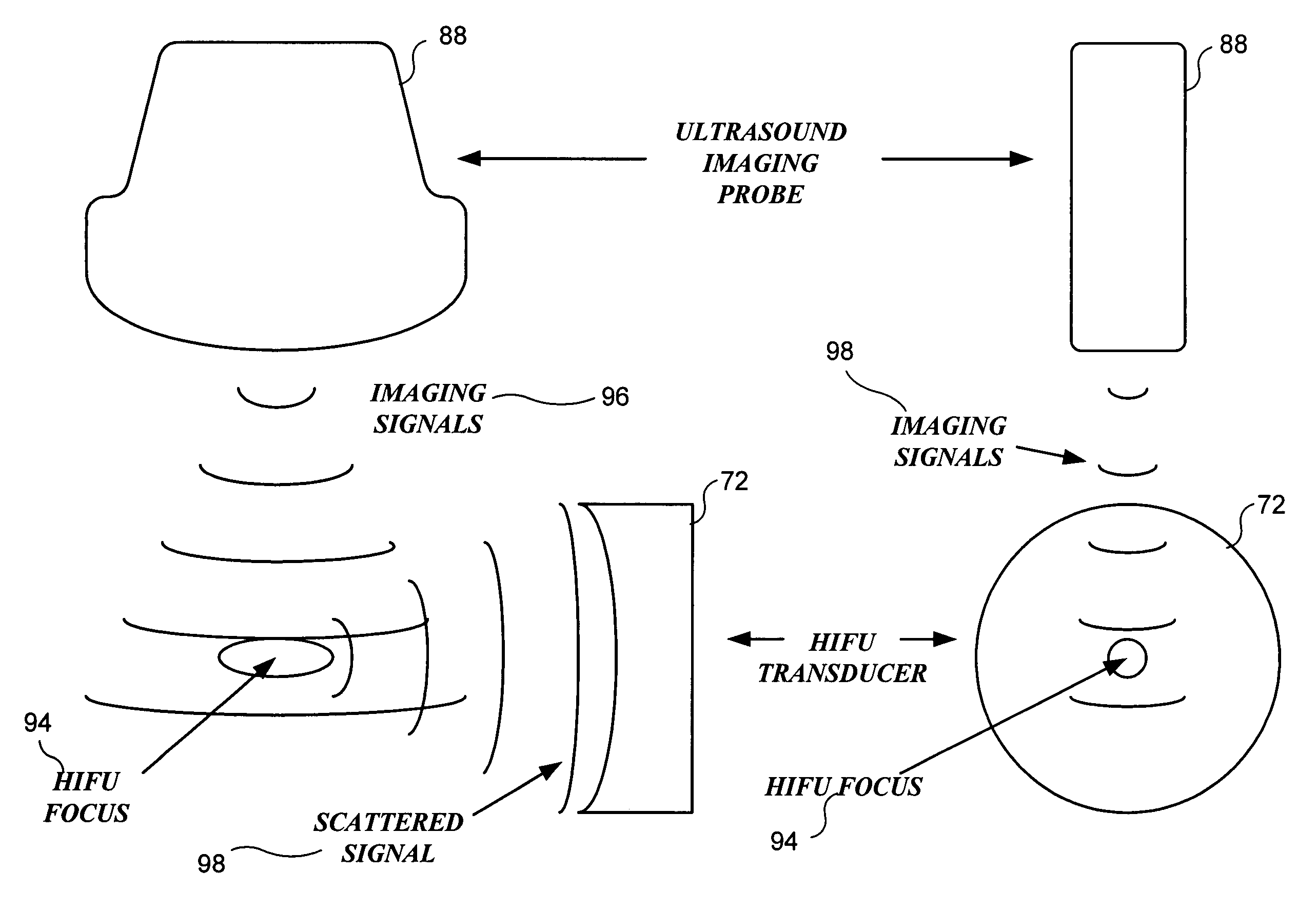

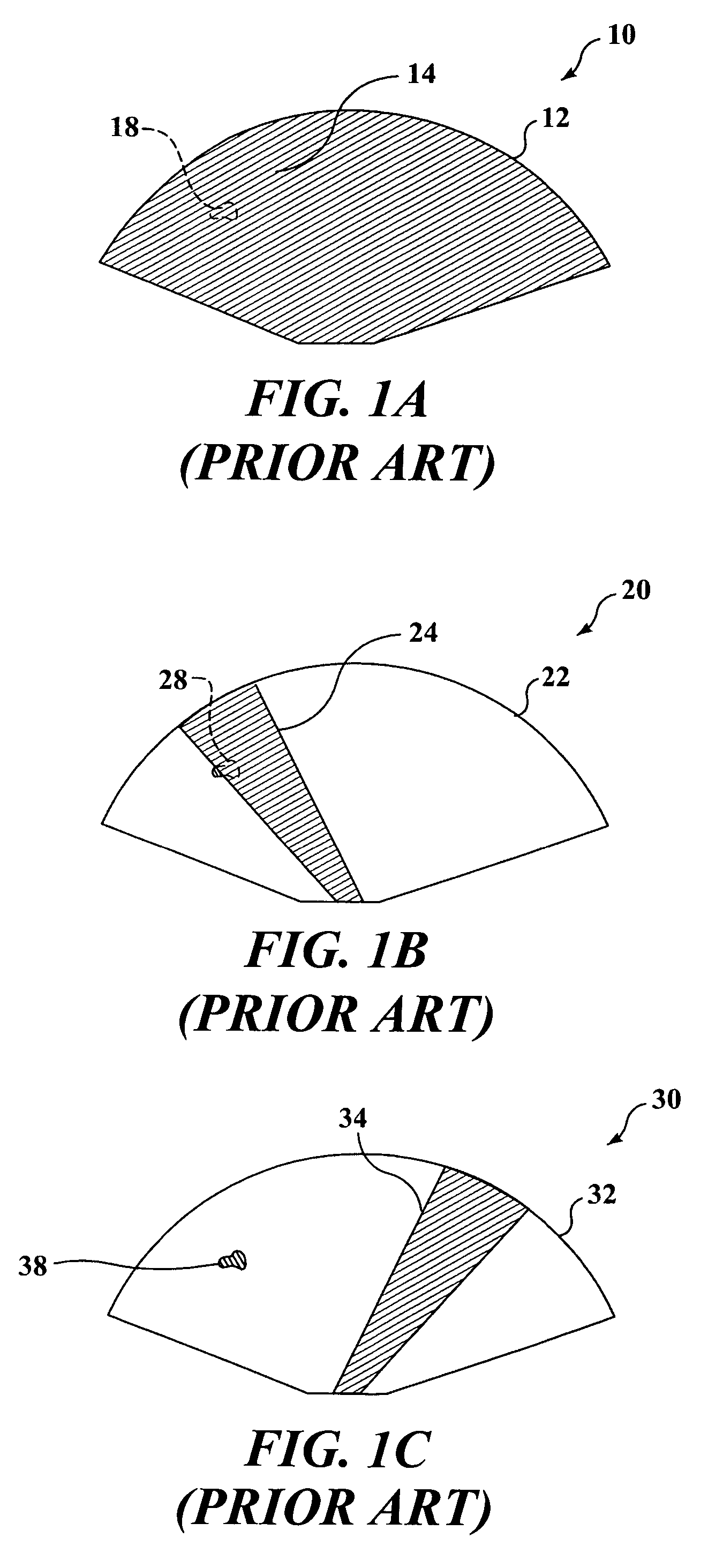

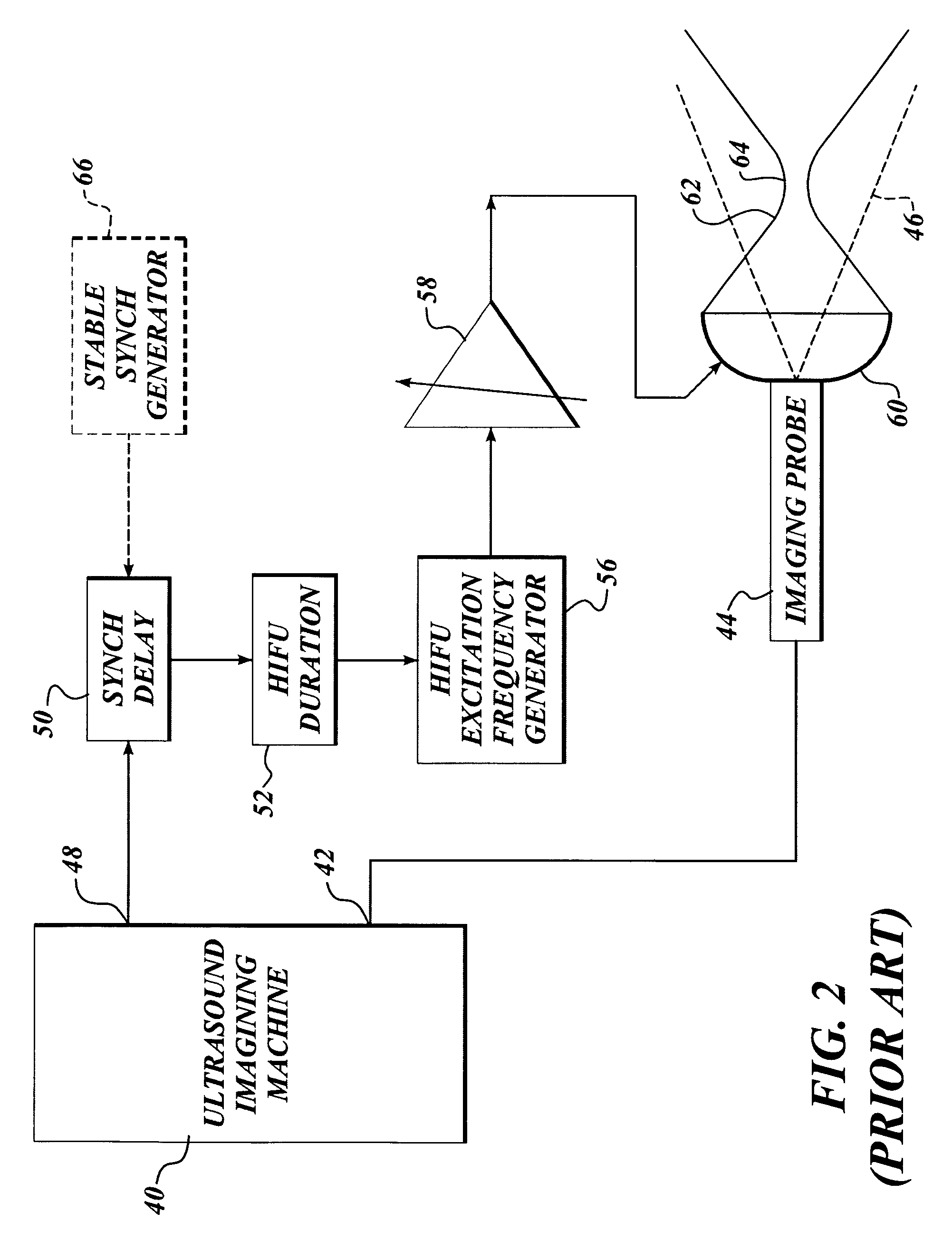

Method and system to synchronize acoustic therapy with ultrasound imaging

ActiveUS20070055155A1Synchronization is simpleGood synchronizationUltrasonic/sonic/infrasonic diagnosticsUltrasound therapyUltrasound imagingSonification

Interference in ultrasound imaging when used in connection with high intensity focused ultrasound (HIFU) is avoided by employing a synchronization signal to control the HIFU signal. Unless the timing of the HIFU transducer is controlled, its output will substantially overwhelm the signal produced by ultrasound imaging system and obscure the image it produces. The synchronization signal employed to control the HIFU transducer is obtained without requiring modification of the ultrasound imaging system. Signals corresponding to scattered ultrasound imaging waves are collected using either the HIFU transducer or a dedicated receiver. A synchronization processor manipulates the scattered ultrasound imaging signals to achieve the synchronization signal, which is then used to control the HIFU bursts so as to substantially reduce or eliminate HIFU interference in the ultrasound image. The synchronization processor can alternatively be implemented using a computing device or an application-specific circuit.

Owner:UNIV OF WASHINGTON

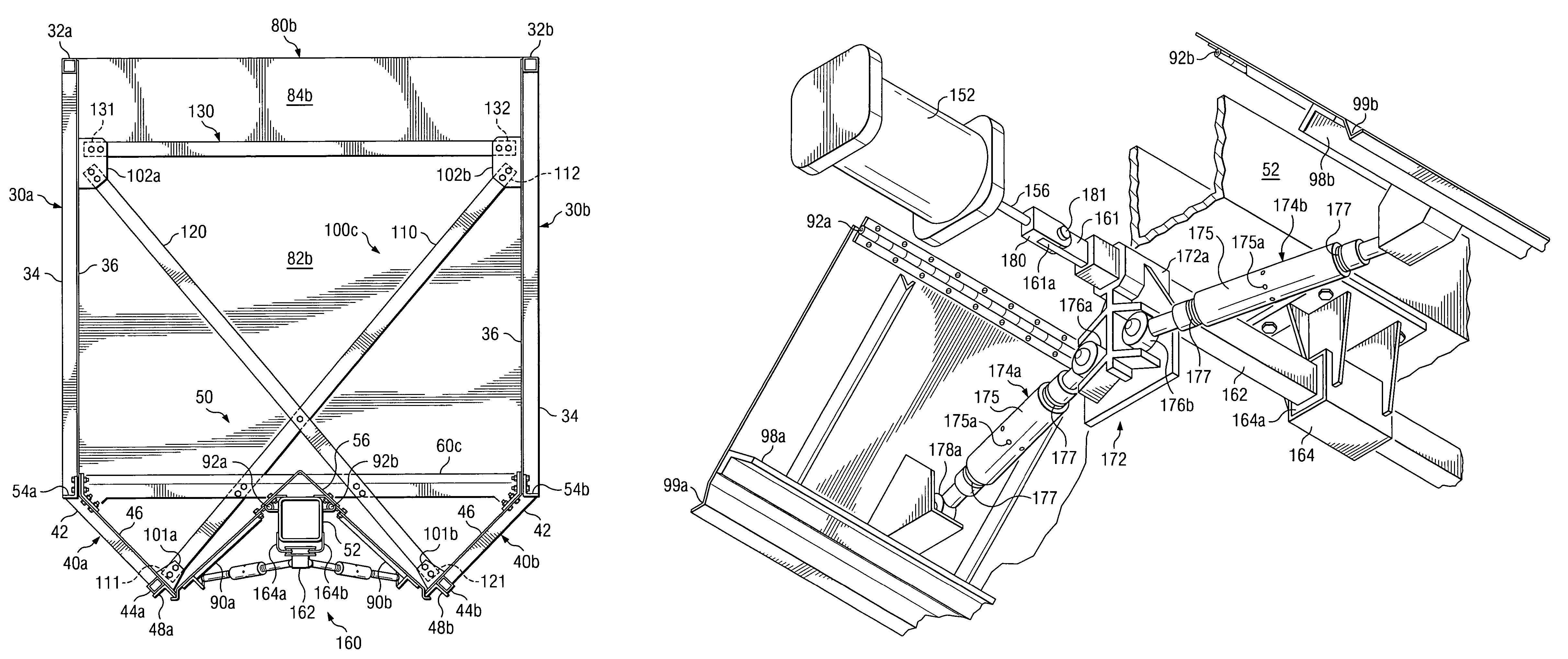

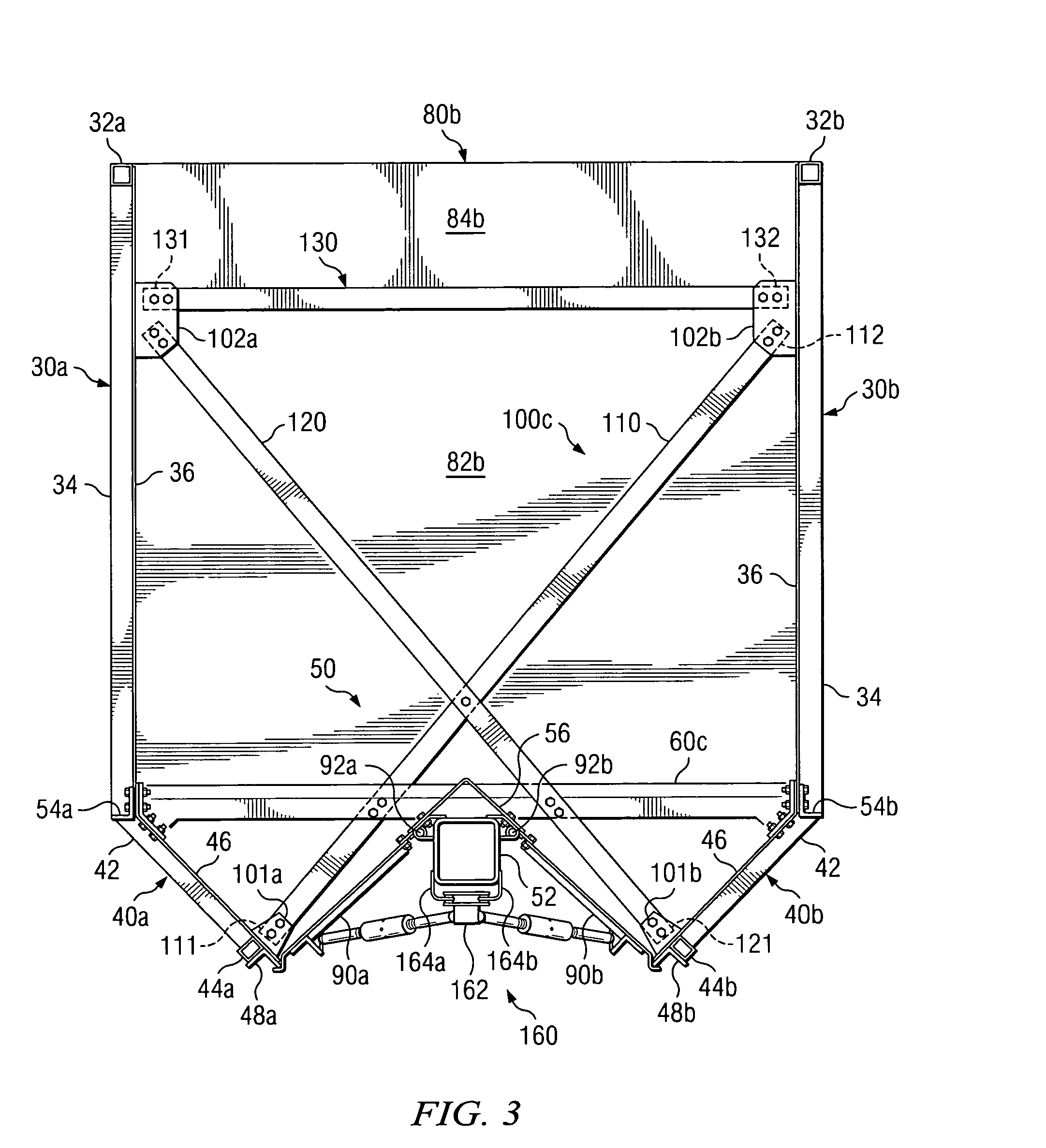

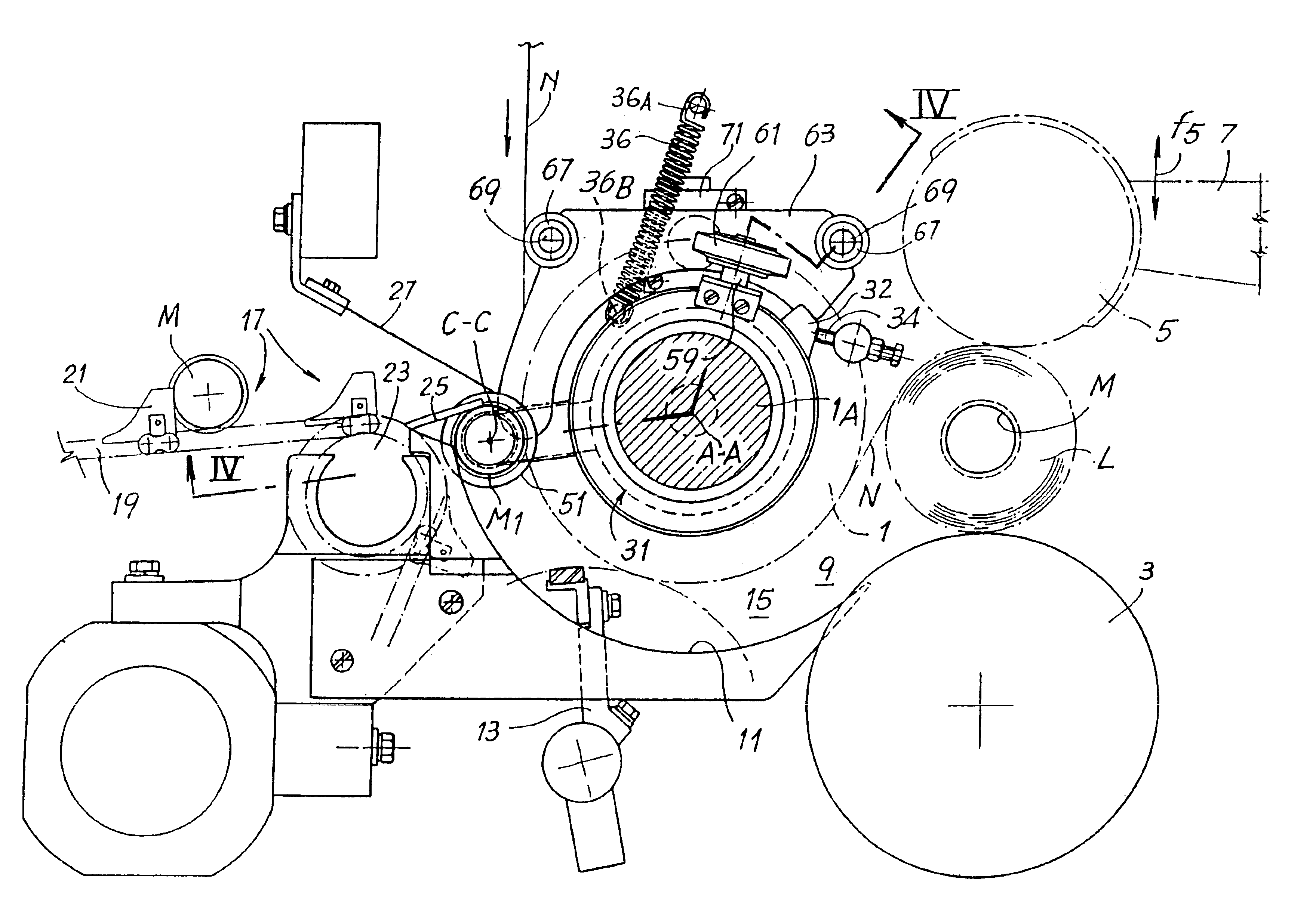

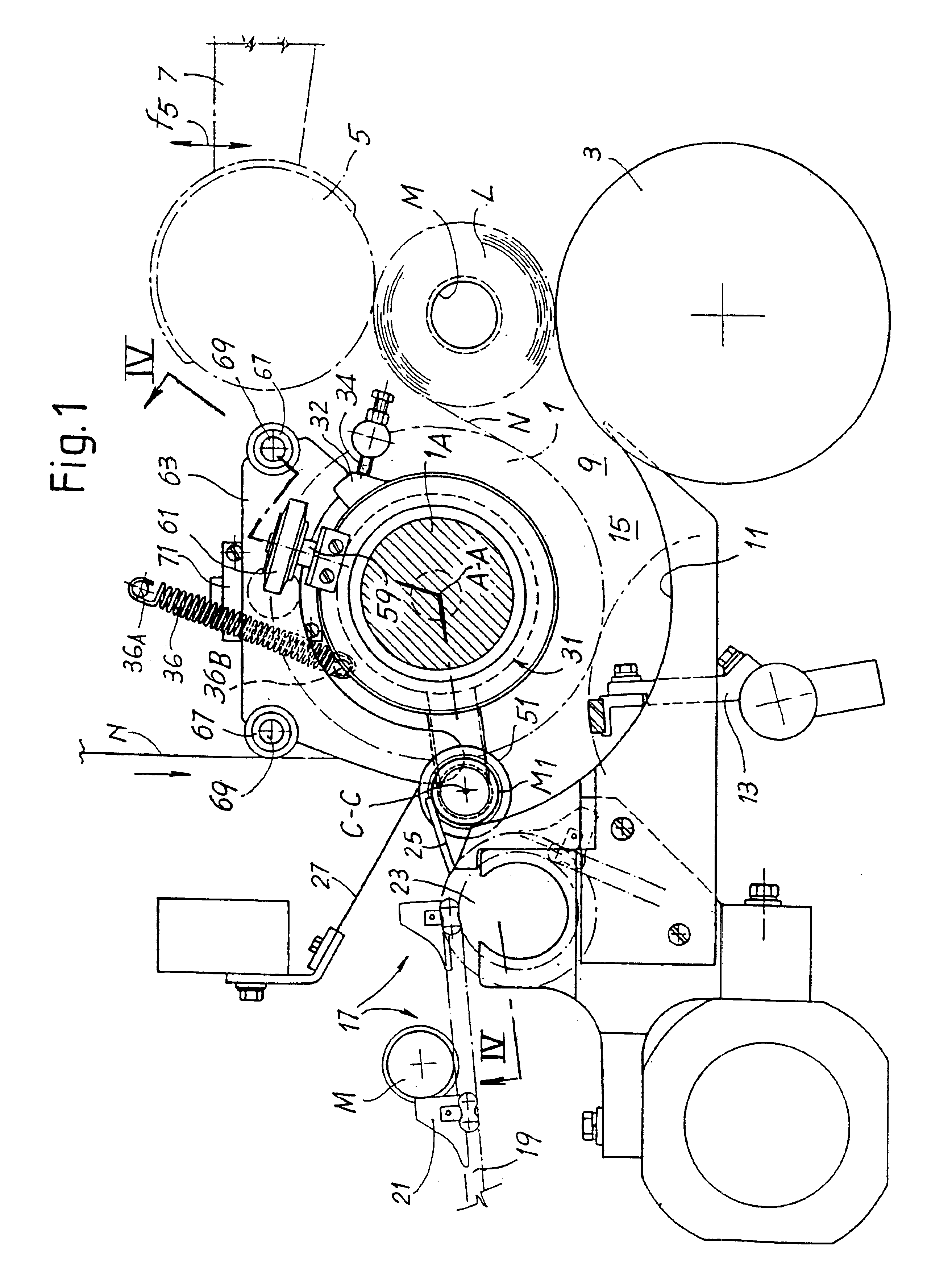

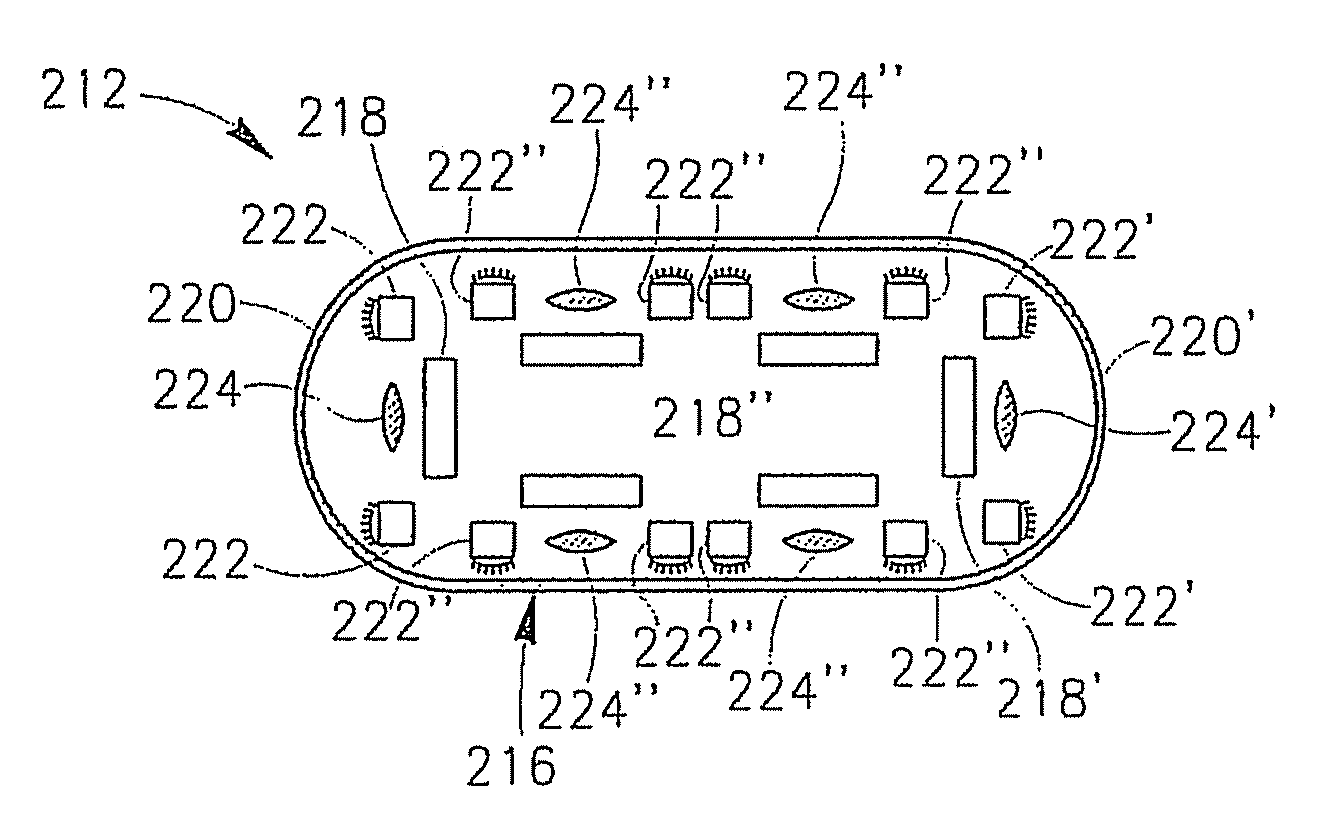

Railcar with discharge control system

ActiveUS7051661B2Improve carrying capacityReduce weightHopper carsWagons/vansControl systemOpen form

A railcar with discharge control system is disclosed. In one embodiment, a railway car includes an underframe and at least one hopper for transporting lading. The railway car further including the underframe including a center sill which defines in part a longitudinal axis of the railway car. A discharge opening formed proximate to a lower portion of the hopper. A respective door assembly pivotally mounted adjacent to the discharge opening to control the flow of lading from the hopper. The door assembly operable for movement between a first, closed position and a second, open position relative to the discharge opening. A discharge control system operable to move the door assembly between the first position and the second position. The discharge control system operably moves generally longitudinally along the axis of the railway car to move the door assemblies between the first, closed position and the second, open position.

Owner:TRINITY IND INC

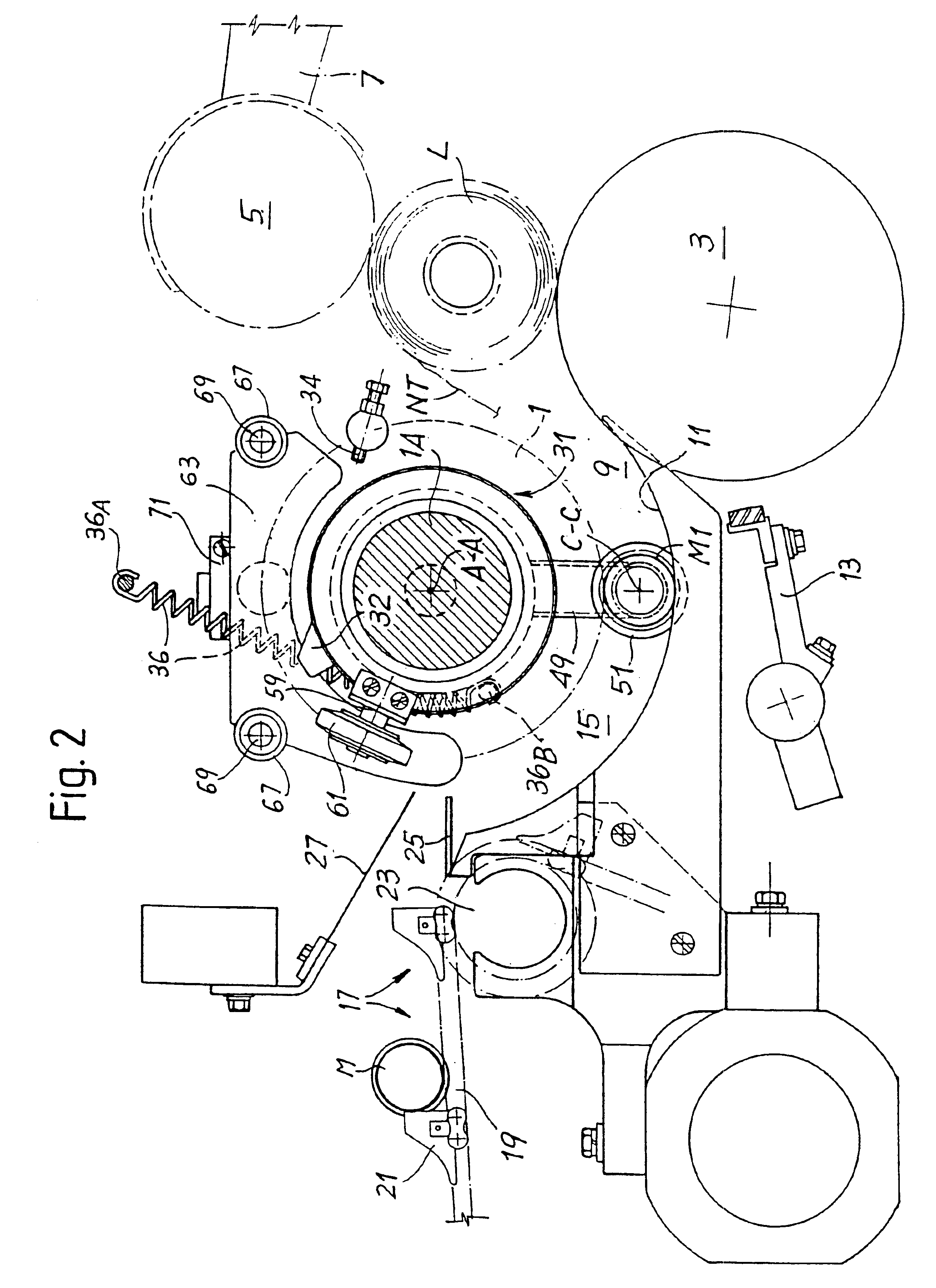

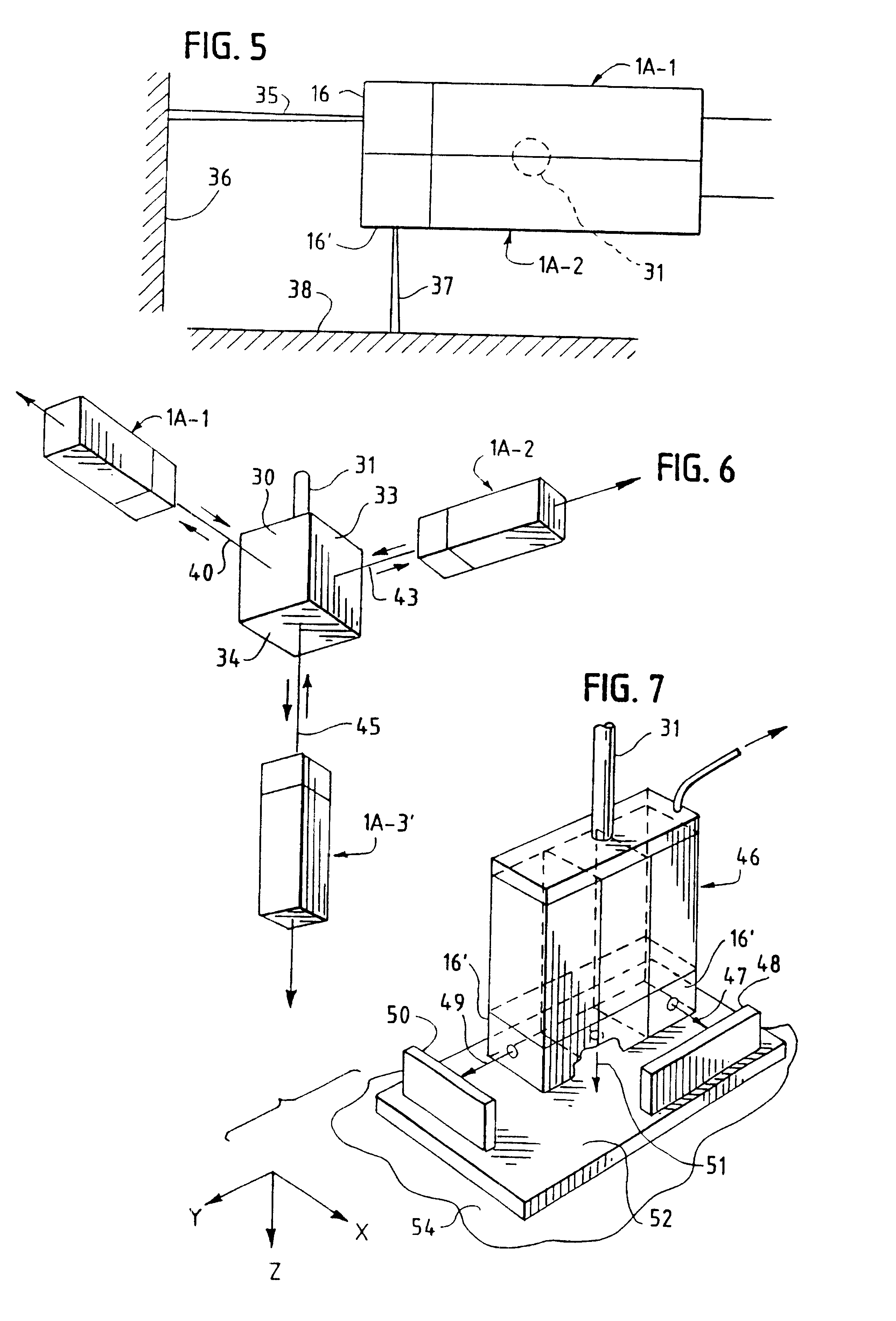

Method and device for the production of rolls of web material without a winding core

InactiveUS6595458B1Suitable for high production speedEfficient and fast and reliableFilament handlingWebs handlingEngineeringInsertion device

A surface rewinding machine for the production of rolls of wound web material is described. The machine comprises: a winding cradle (1, 3, 5) for winding the web material and sequentially forming rolls (R) of wound web material; an insertion device (25) for inserting sequentially, into said winding cradle, winding spindles (M1; M) on which the rolls are formed; an insertion path for the spindles inside the winding cradle. A suction system (51) which follows the spindles along at least one portion of the insertion path so as to produce a vacuum inside the spindles is also envisaged.

Owner:FABIO PERINI SPA

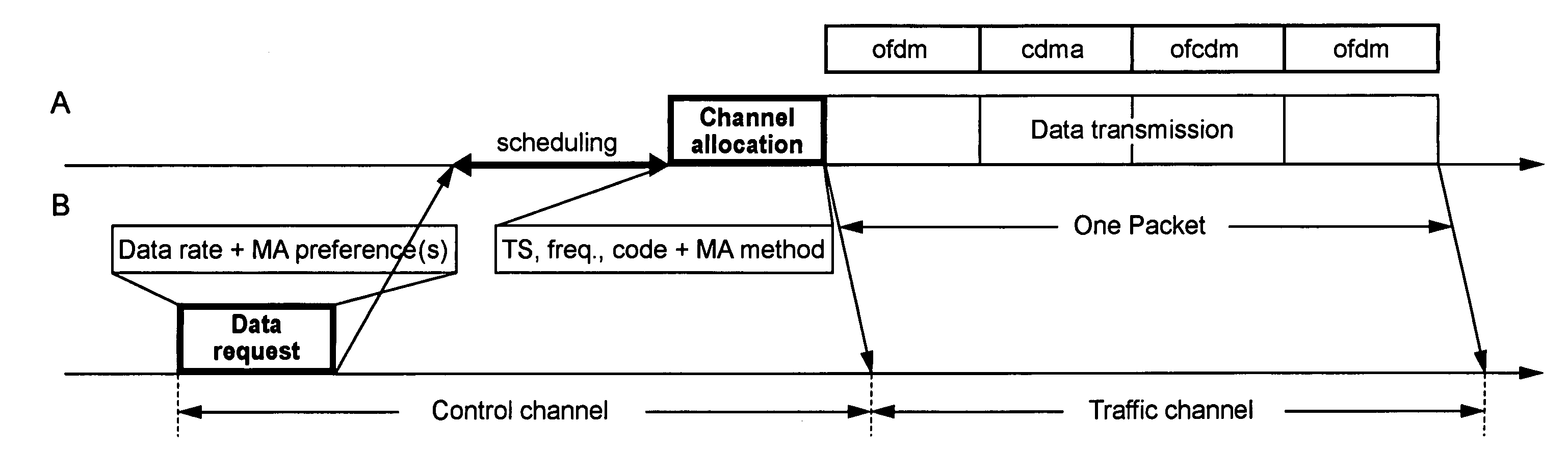

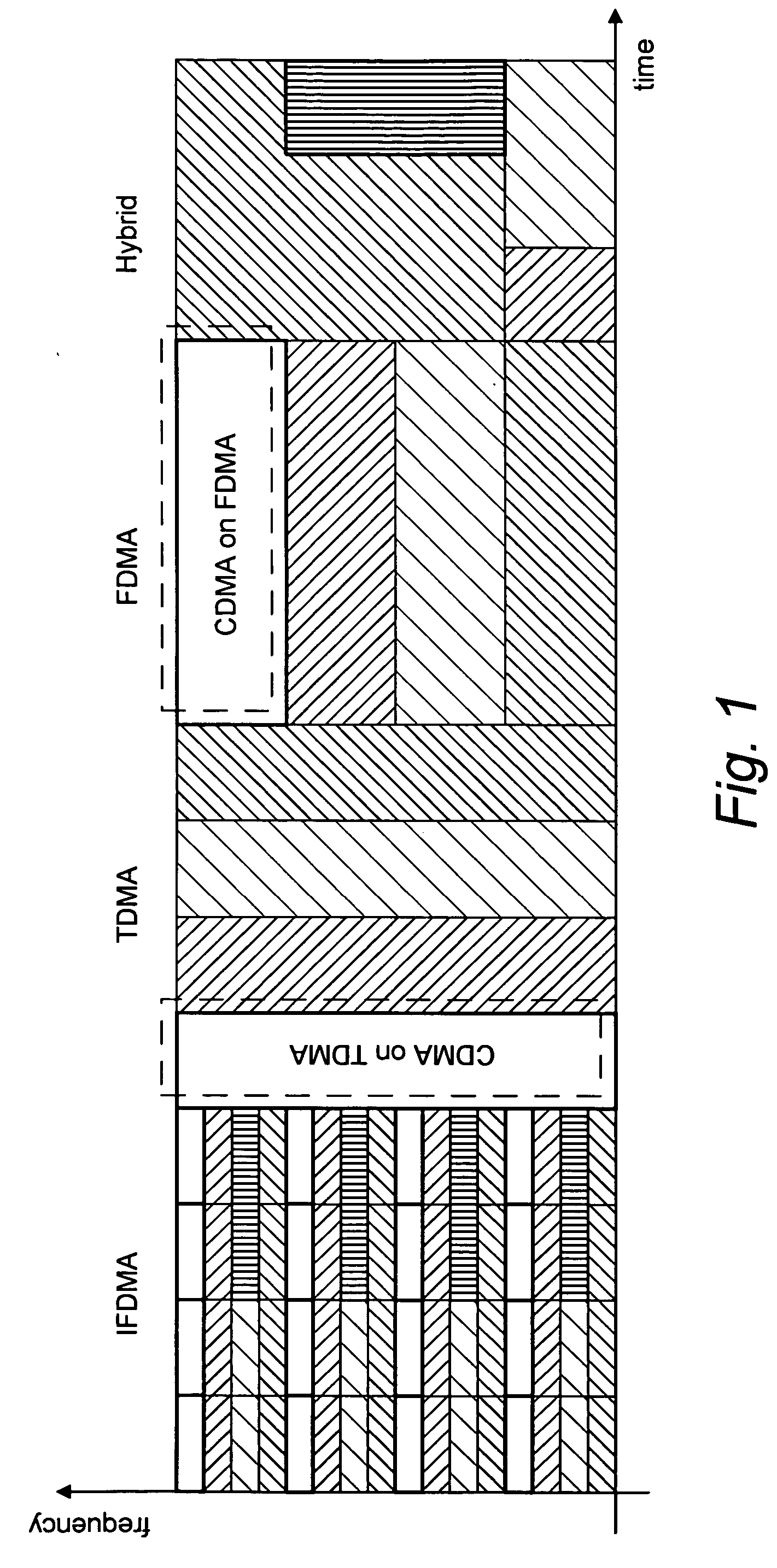

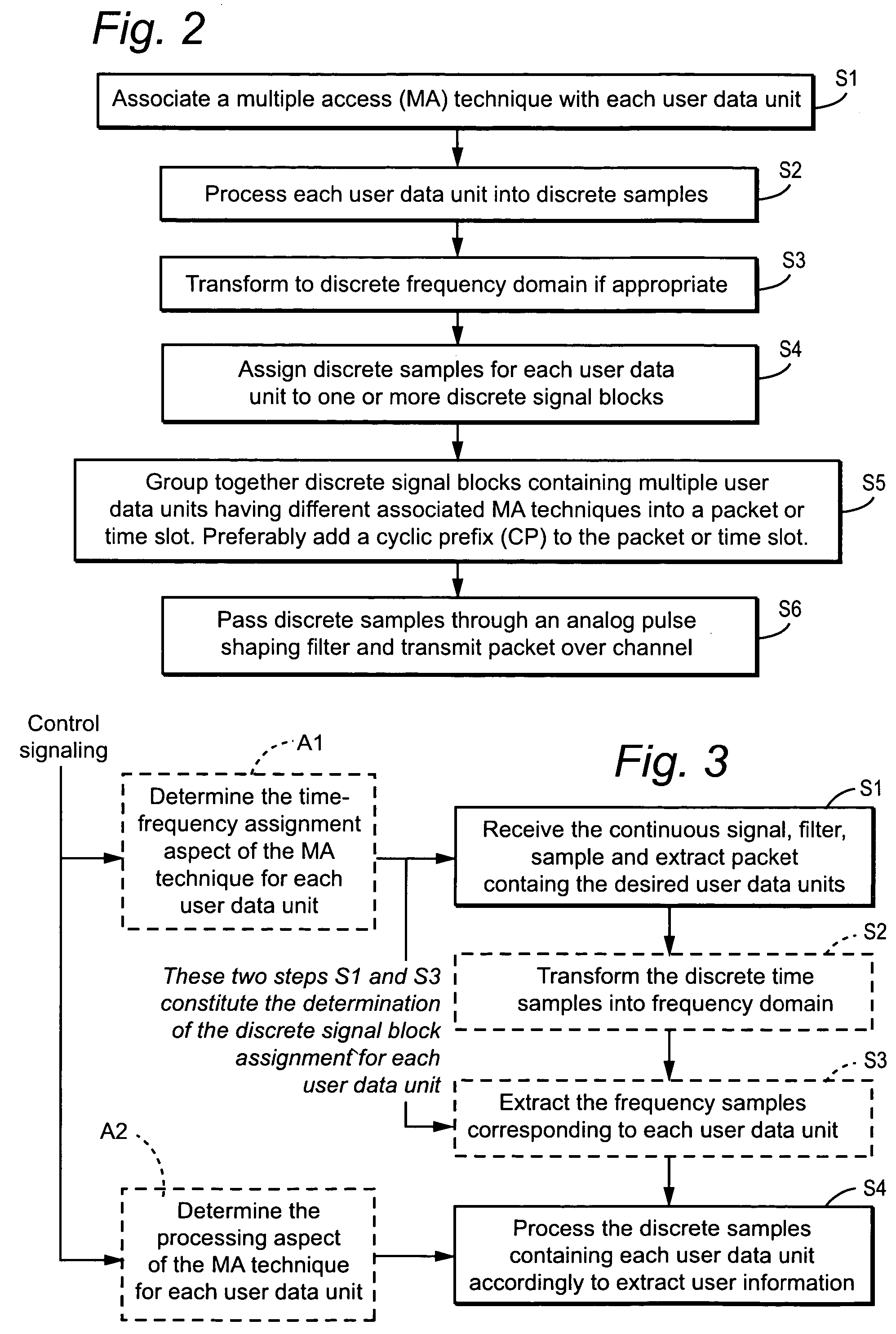

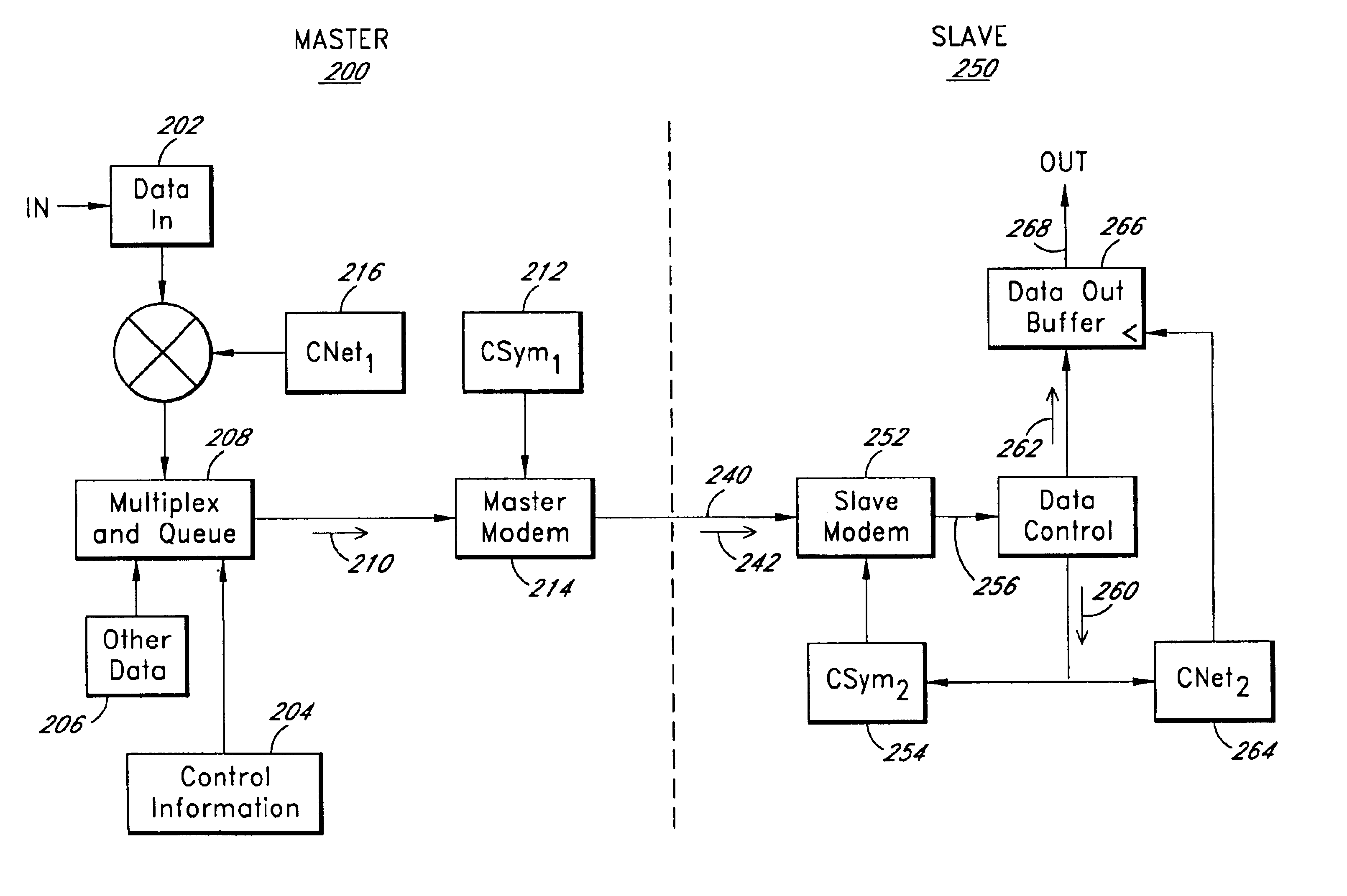

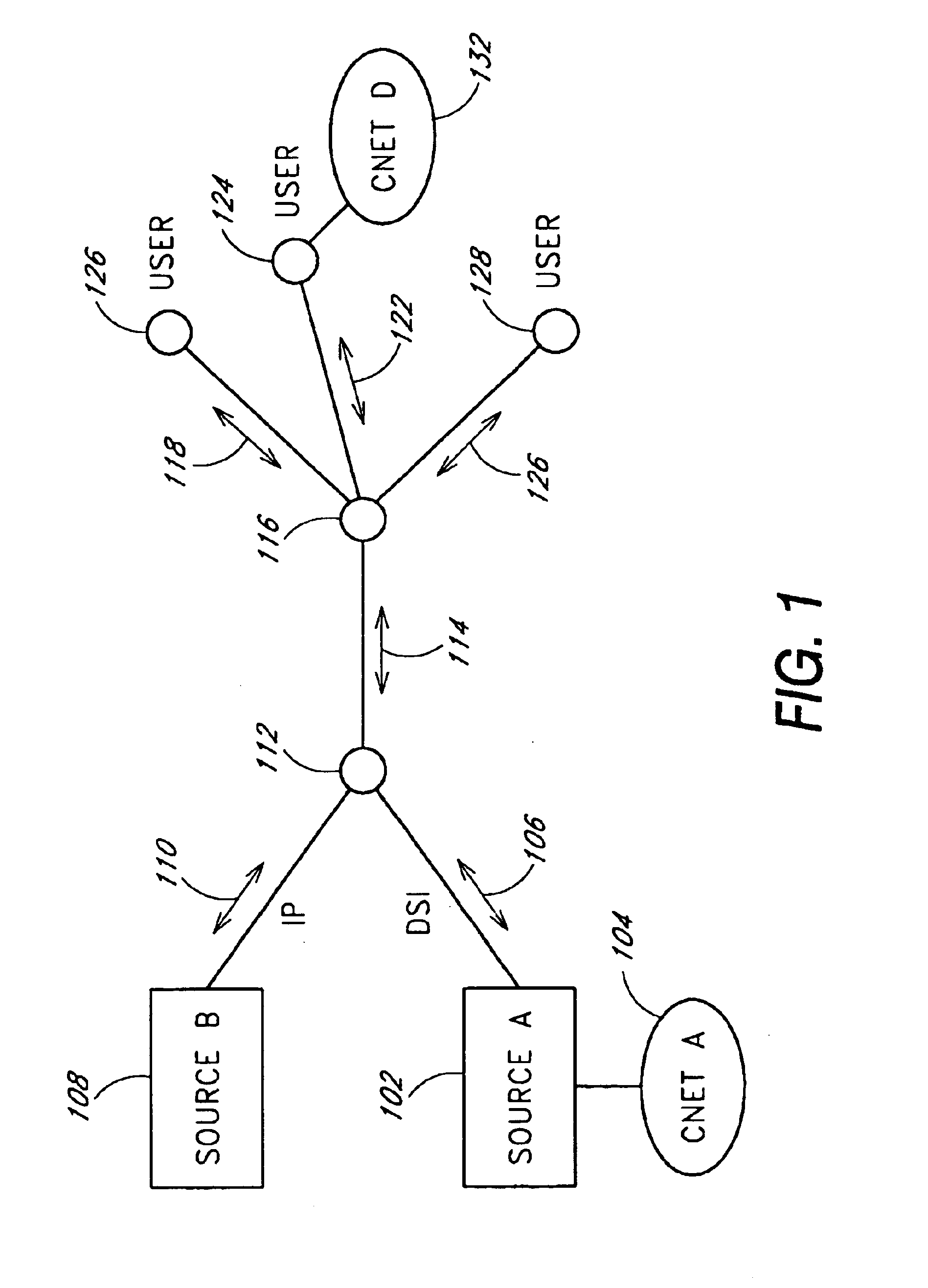

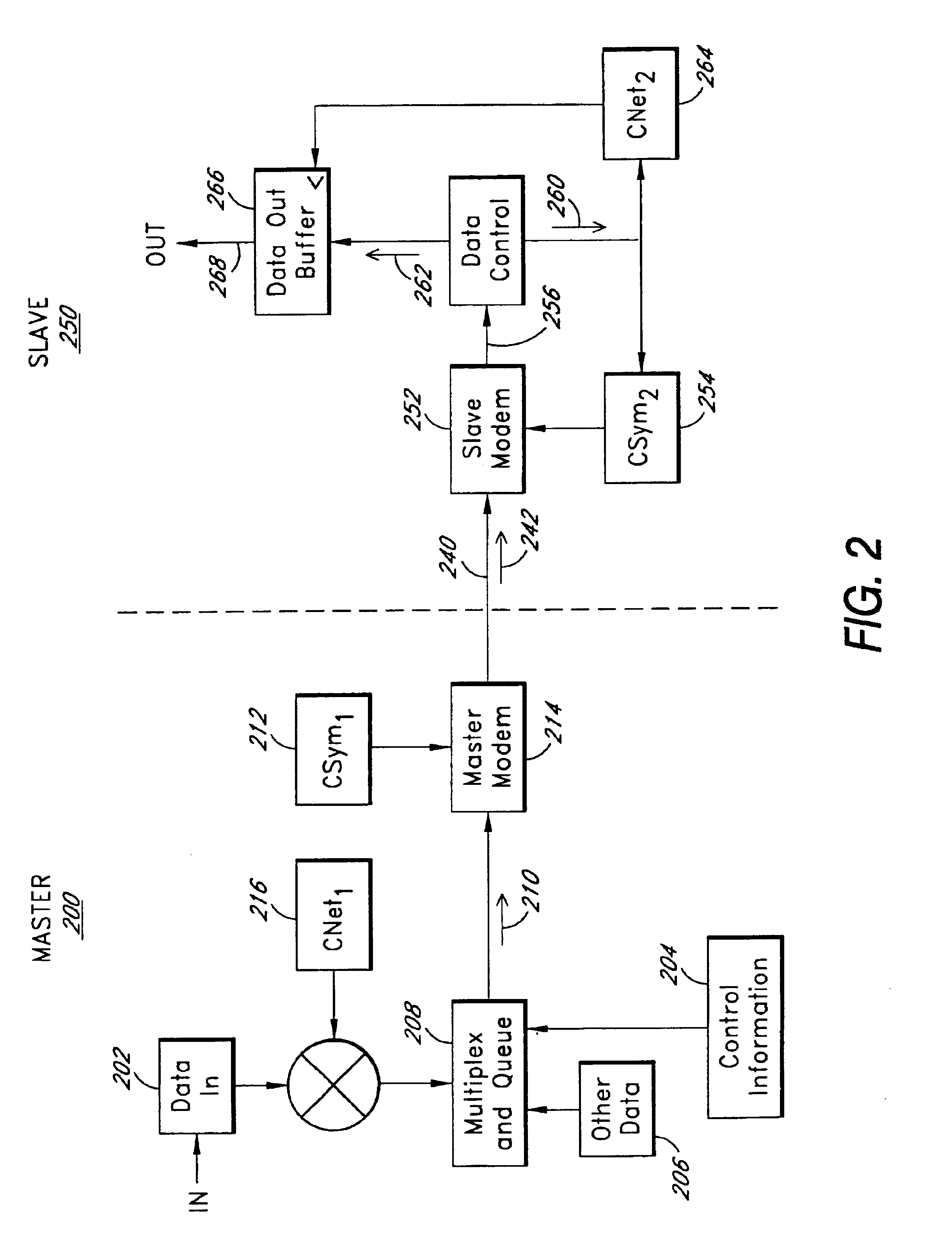

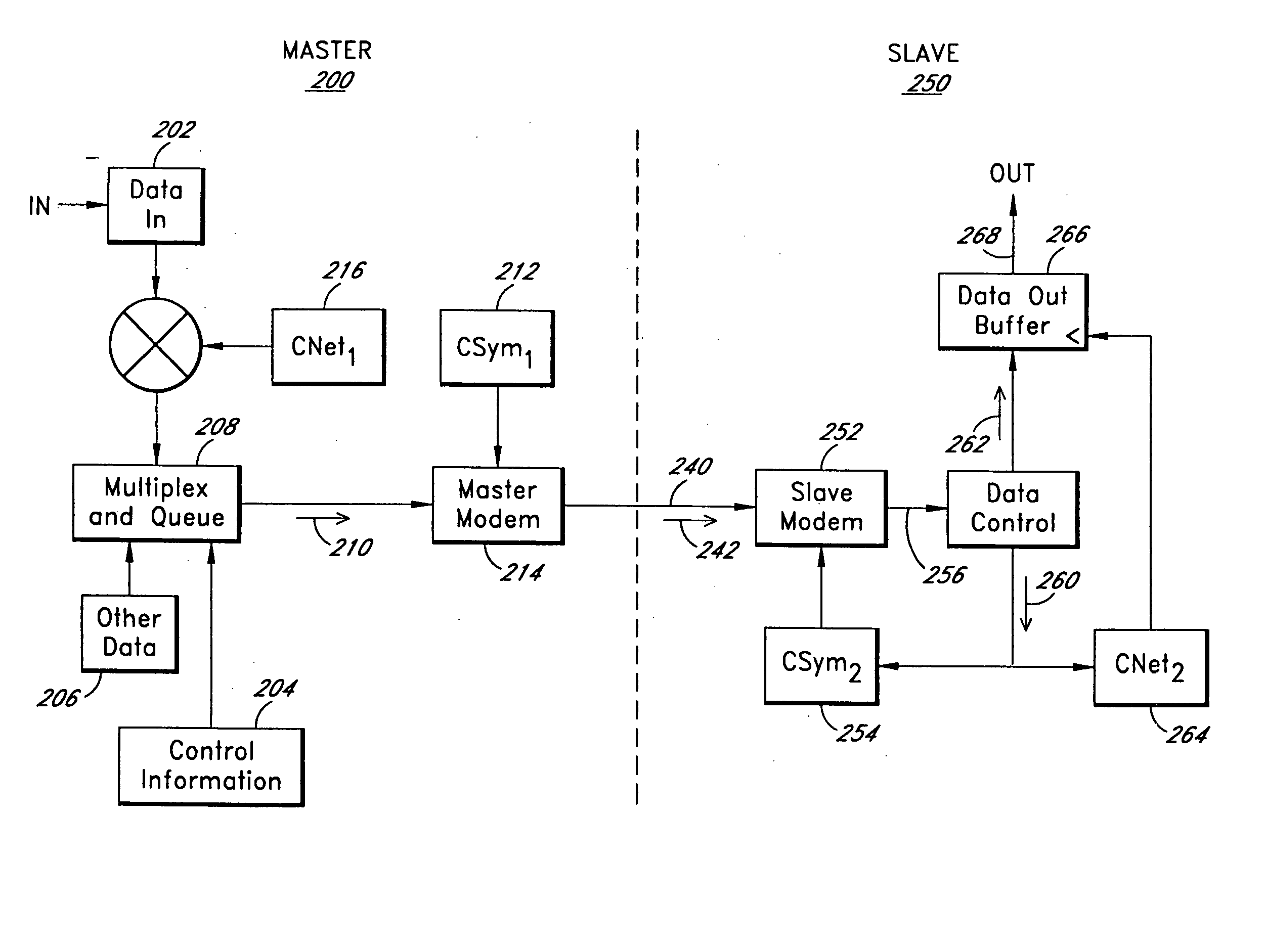

Method, apparatus, and communications interface for sending and receiving data blocks associated with different multiple access techniques

ActiveUS20060050664A1Convenient to accommodateSynchronization is simpleMultiple modulation transmitter/receiver arrangementsTime-division multiplexCommunication interfaceRadio interface

A unified and flexible signaling method and radio interface accommodate different multiple access schemes, e.g, FDMA, TDMA, CDMA, OFCDM, and IFDMA. Each user data unit is associated with one of several different multiple access techniques that defines how multiple users access communication resources. Each user data unit is processed into discrete samples, where the discrete samples for each user data unit are assigned to one or more respective discrete signal blocks. Discrete samples associated with different multiple access techniques are processed and grouped together into a time slot or packet for transmission over a communication channel.

Owner:OT PATENT ESCROW LLC

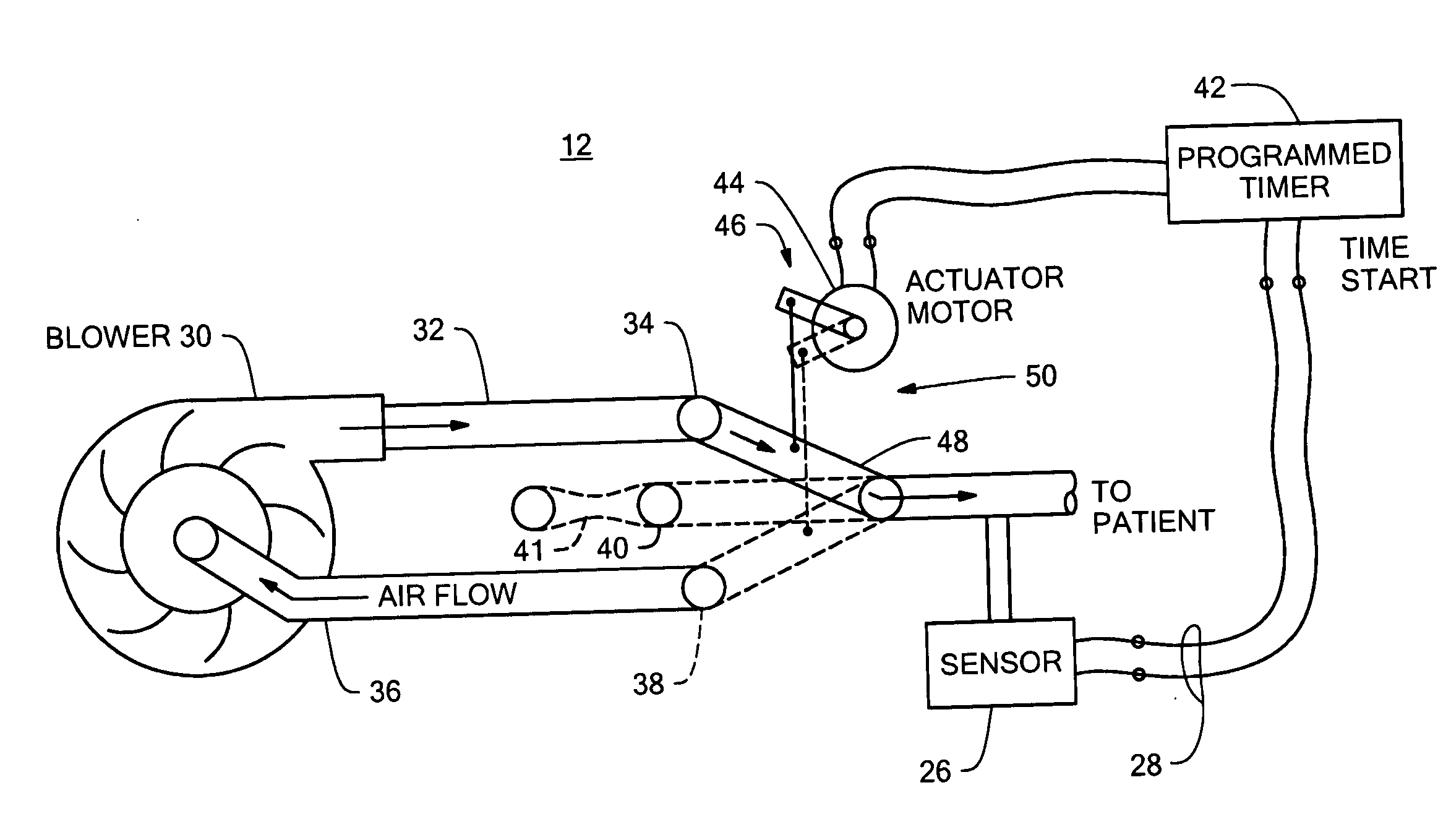

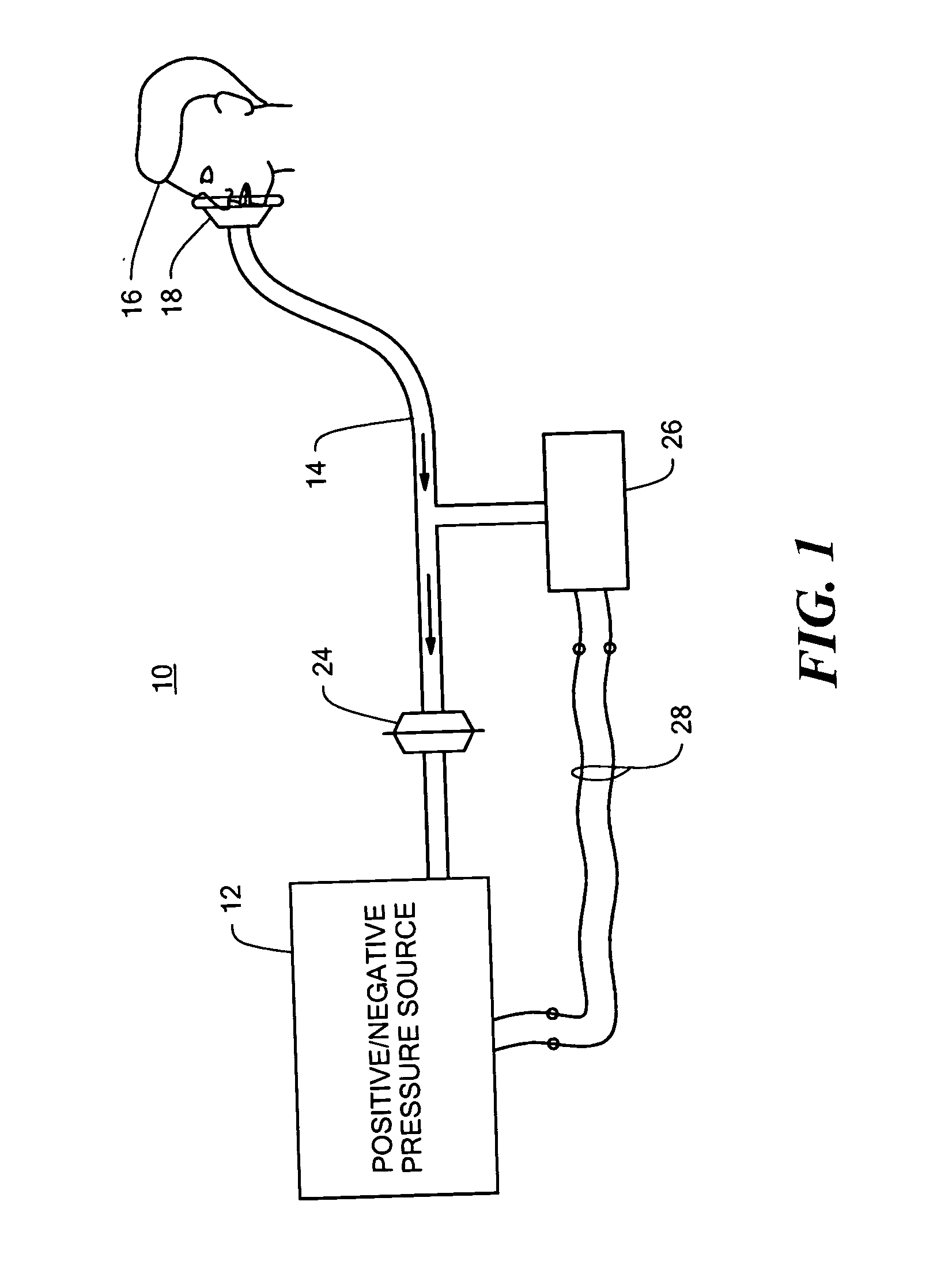

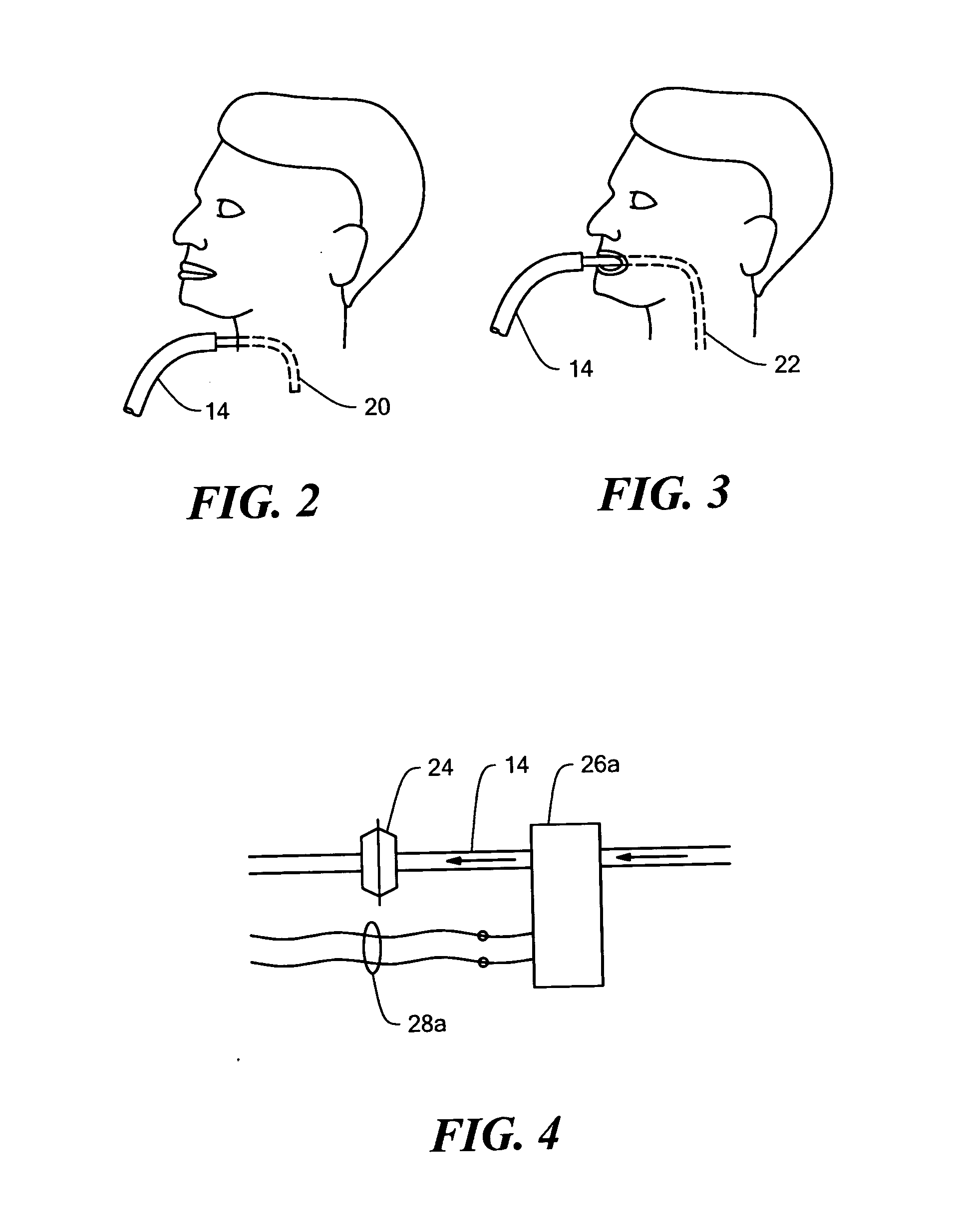

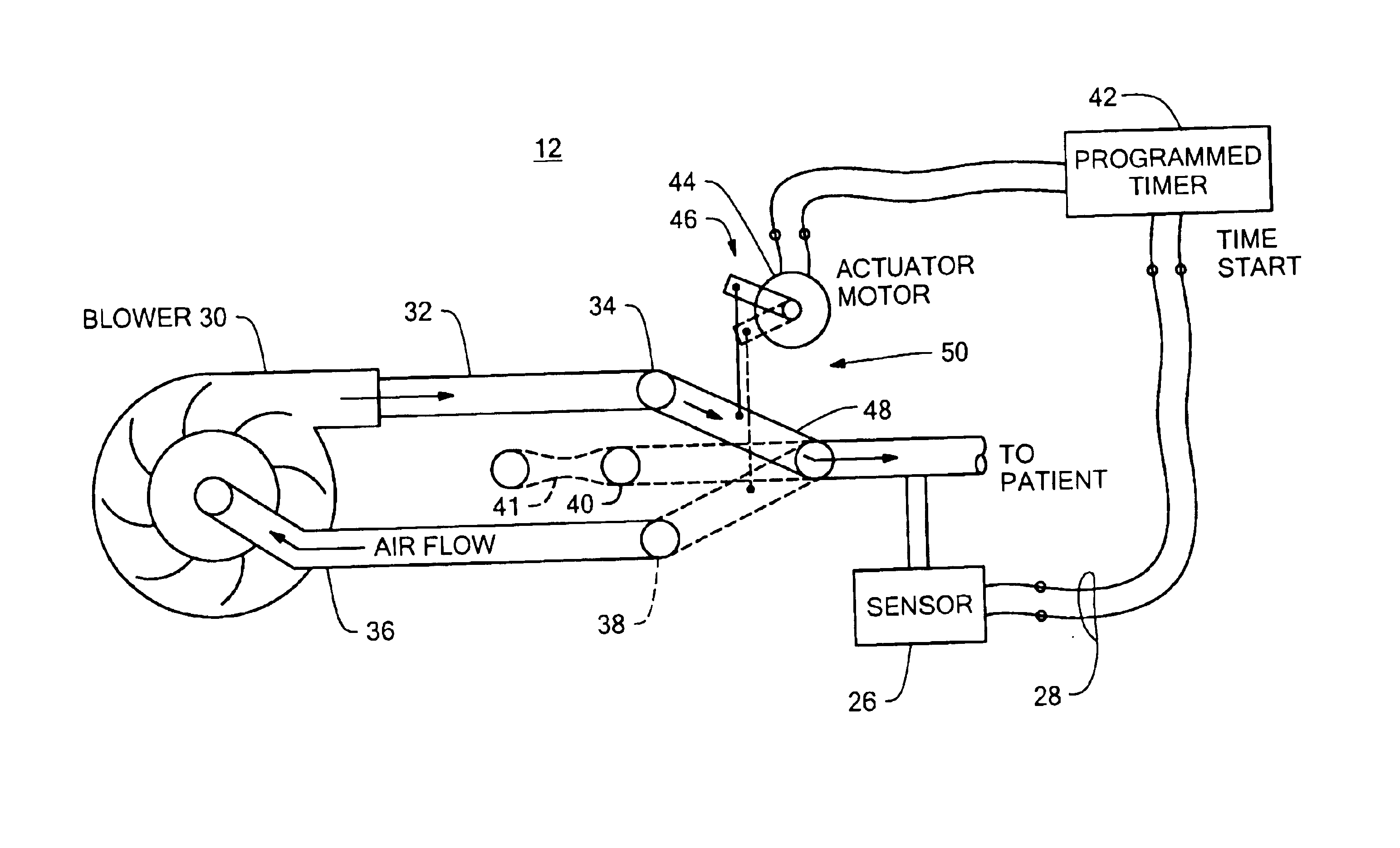

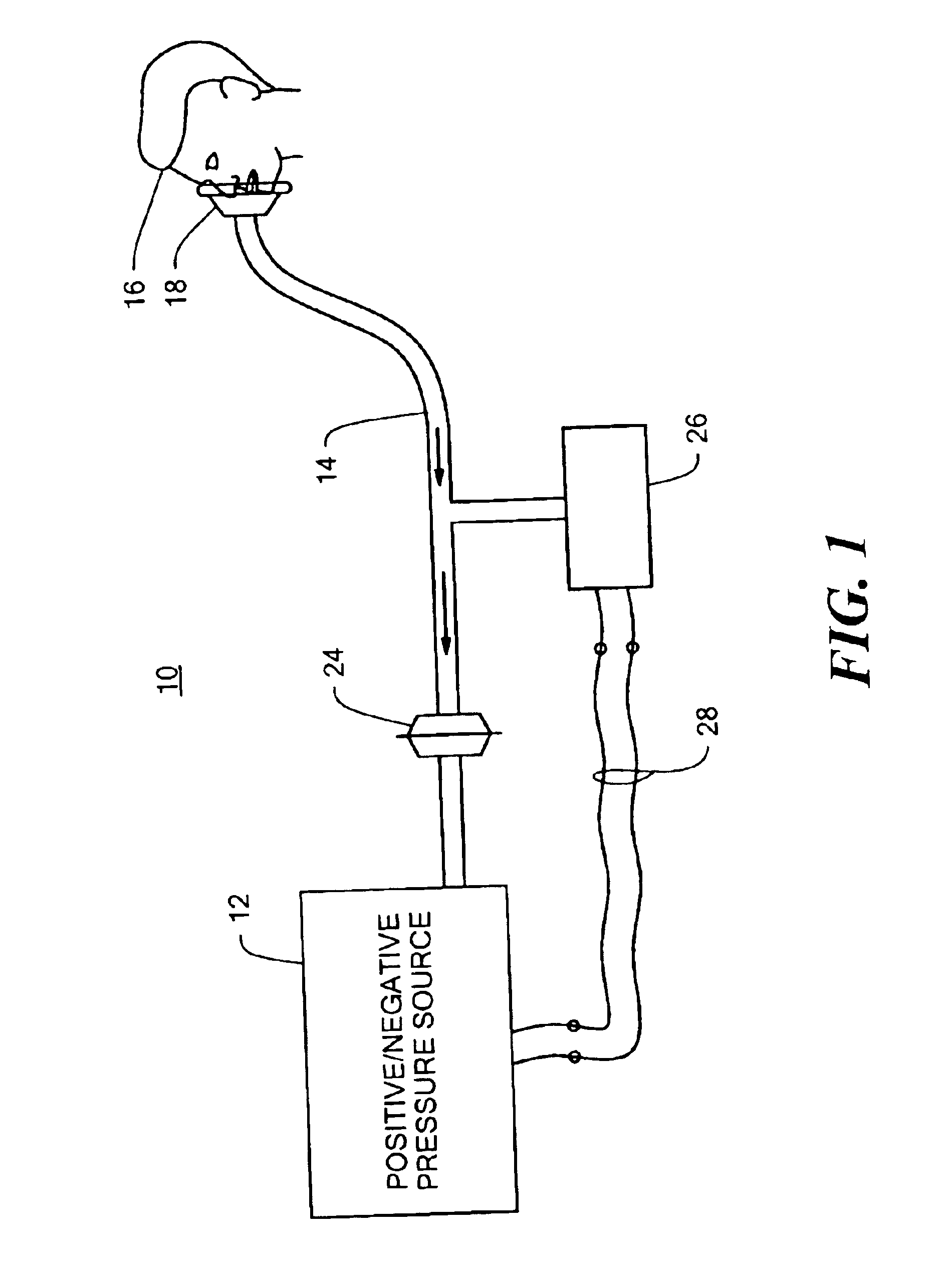

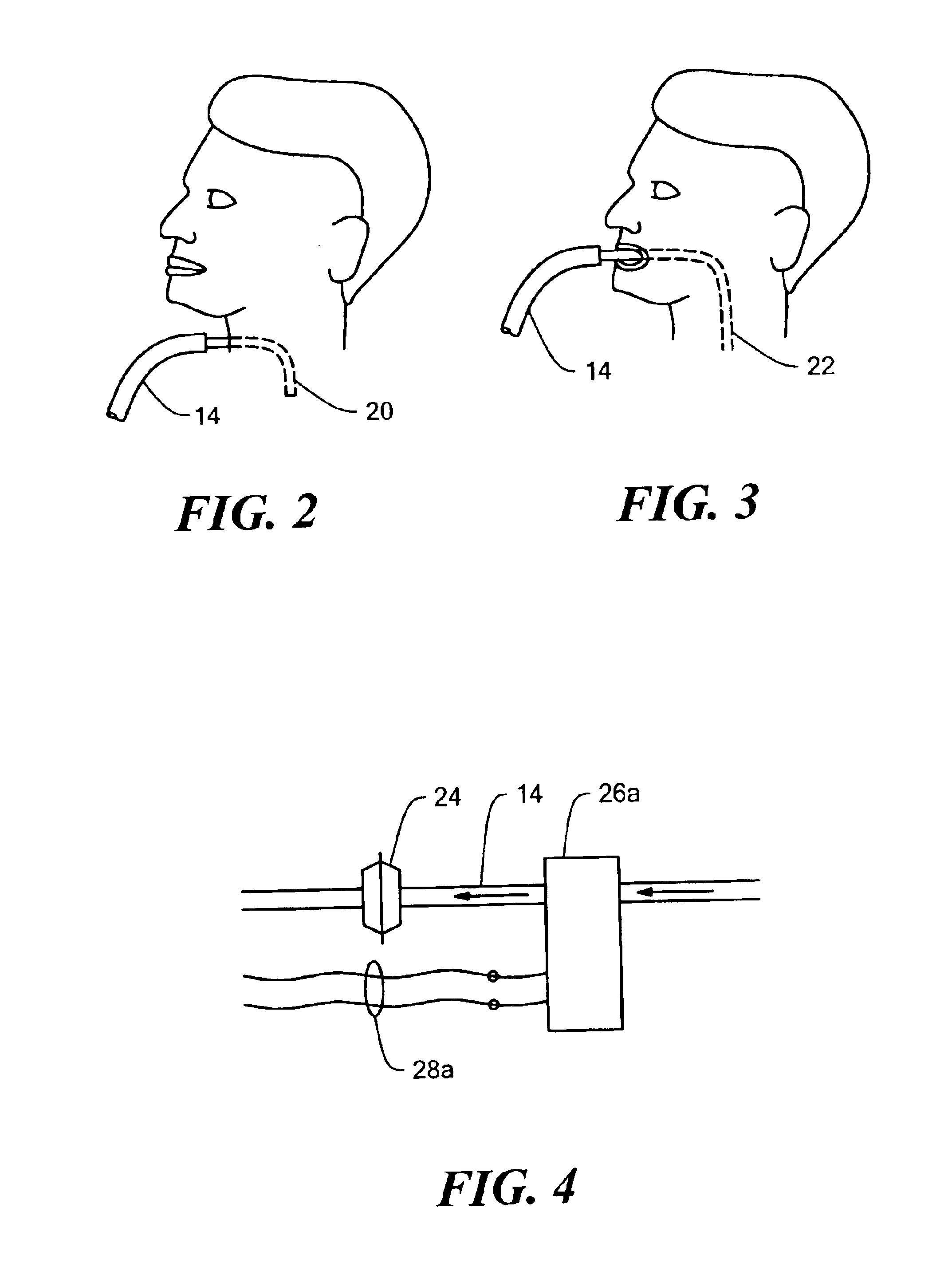

Insufflation-exsufflation system for removal of broncho-pulmonary secretions with automatic triggering of inhalation phase

ActiveUS20050039749A1Synchronization is simpleIncrease inhalationRespiratorsOperating means/releasing devices for valvesBroncho-pulmonaryPositive pressure

An improved insufflation-exsufflation system for removal of broncho-pulmonary secretions with automatic triggering of inhalation phase includes a conduit for connection to a patient's airway; a pressure source with a positive pressure port and a negative pressure port; a switching device selectively connecting the conduit to the positive pressure port, the negative pressure port and the dwell port; the sensor system for sensing an inhalation by the patient; and a controller system for driving the switching device to connect the conduits sequentially to the positive port, the negative port and the dwell port and to return again to the positive port in response to the sensor system sensing an inhalation by the patient while the conduit is connected to the dwell port.

Owner:RIC INVESTMENTS LLC

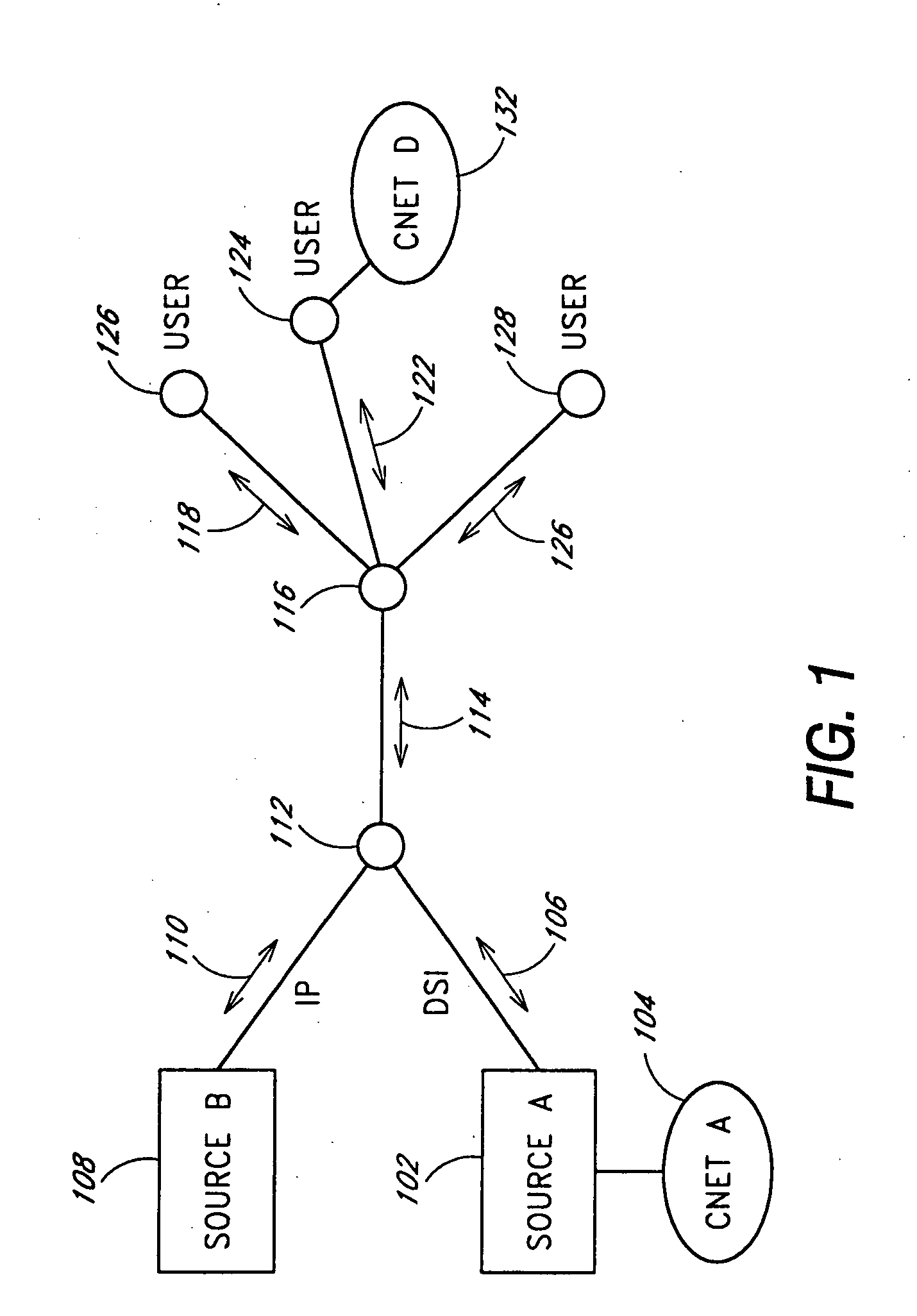

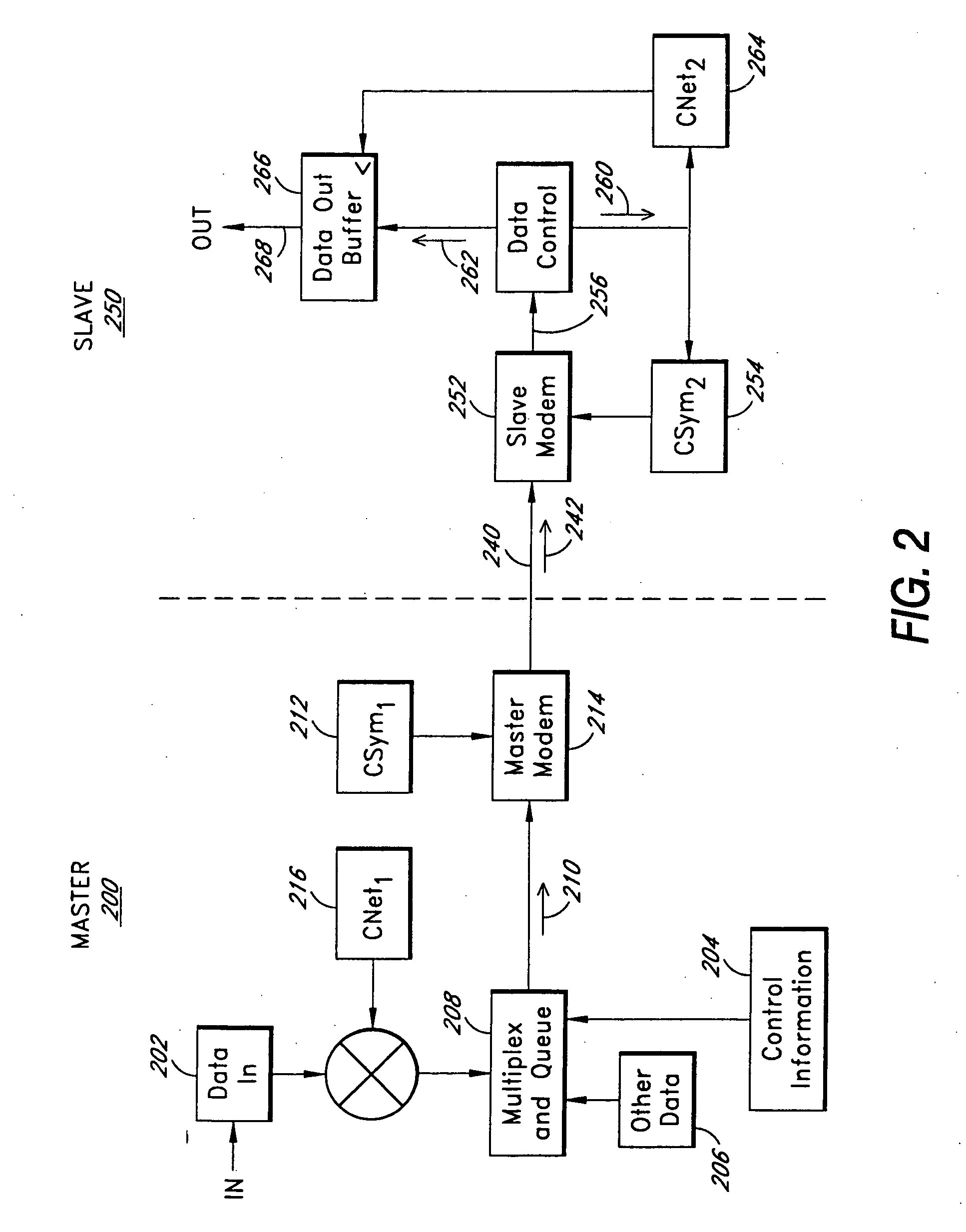

Synchronizing clocks across a communication link

InactiveUS6944188B2Accurate and fast data transferSynchronization is simpleSynchronisation arrangementNetwork traffic/resource managementTelecommunications linkImage resolution

Apparatus, system and method for synchronizing one or more clocks across a communication link. A slave clock may be synchronized to a master clock by means of a synchronization signal sent from the master to the slave clock side of the link. The synchronization signal may be an expected signal pattern sent at intervals expected by the slave side. The slave clock may correlate received signals with a representation of the expected synchronization signal to produce a correlation sample sequence at a first sample rate which is related as n times the slave clock rate. The synchronization signal receipt time indicated by the correlation sample sequence may be refined by interpolating the correlation sample sequence around a best correlation sample to locate a best interpolation at an interpolation resolution smaller than the sample resolution. The best interpolation may in turn be further refined by estimating between interpolator outputs adjacent to the best interpolation output. The synchronization signal receipt time thus determined is compared to the expected time based upon the slave clock, which is adjusted until the times match. After initialization, all slave clock errors are preferably accumulated to prevent long-term slip between the slave and master clocks. Formerly independent master and slave clocks synchronized across the communication link constitute a noncommon clock which may be compared on each side of the link to secondary independent clocks, and the secondary independent clocks may then be separately synchronized by adjusting one to have the same difference from its local noncommon clock as the secondary clock on the other side of the link has from its local noncommon clock.

Owner:WI LAN INC

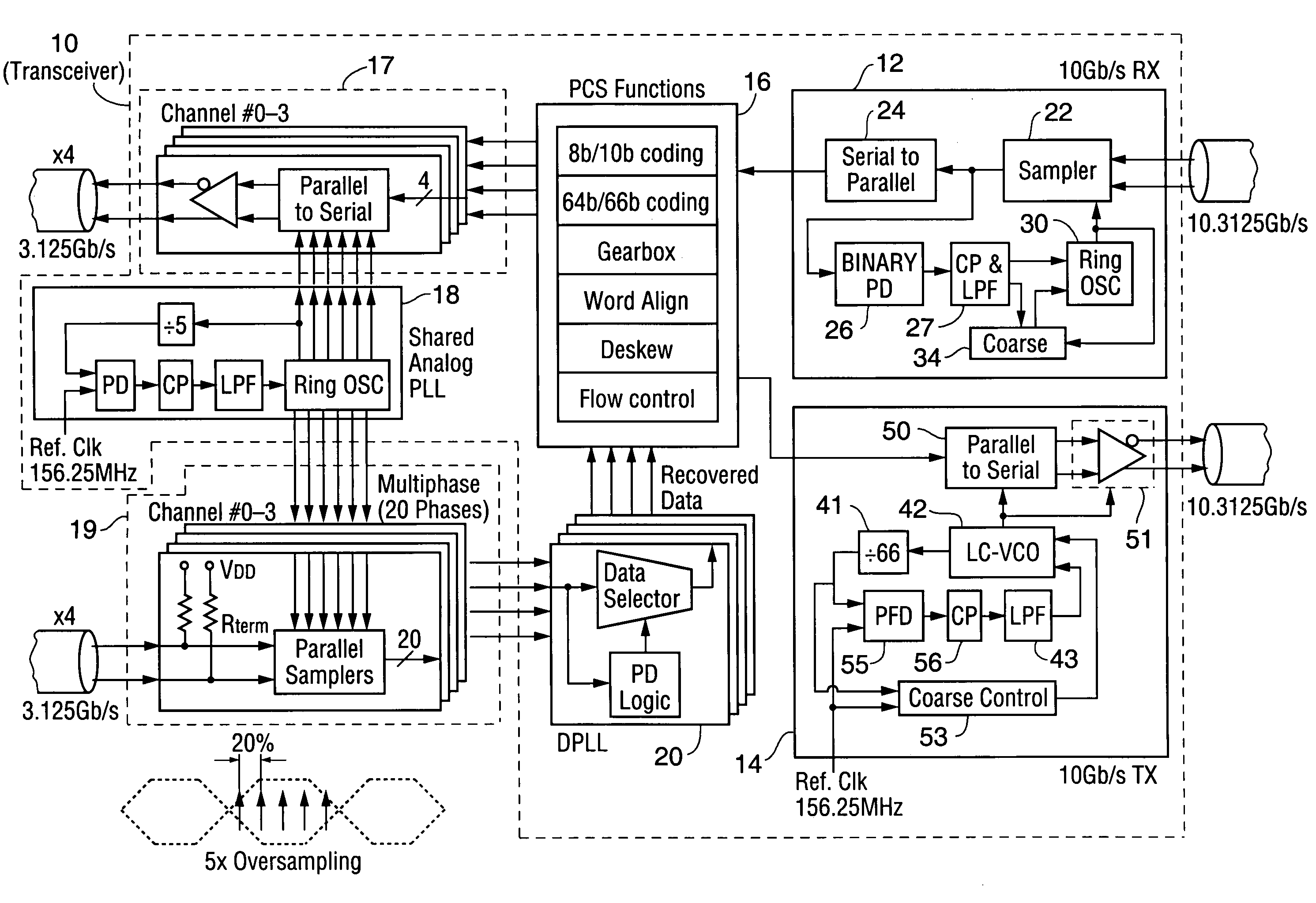

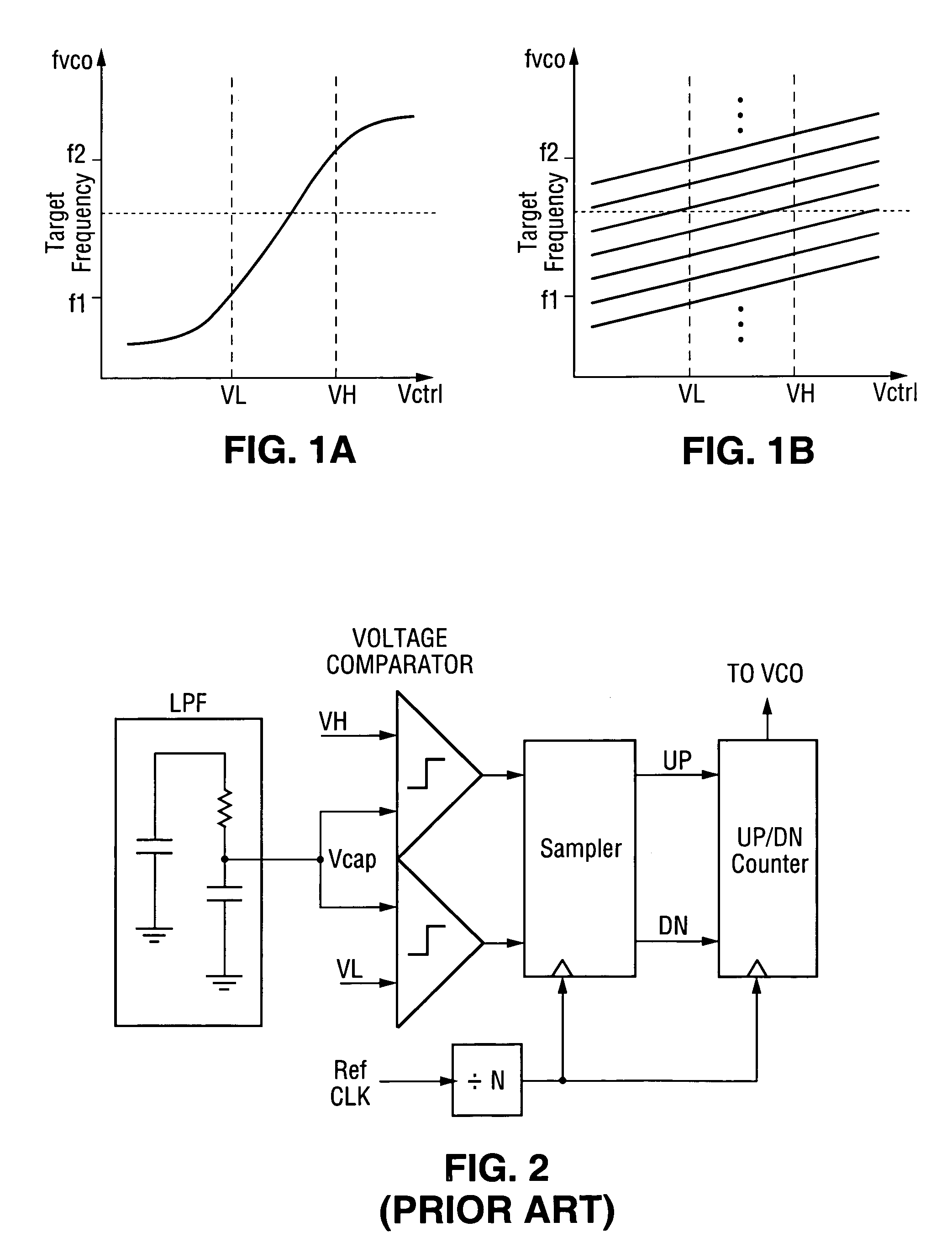

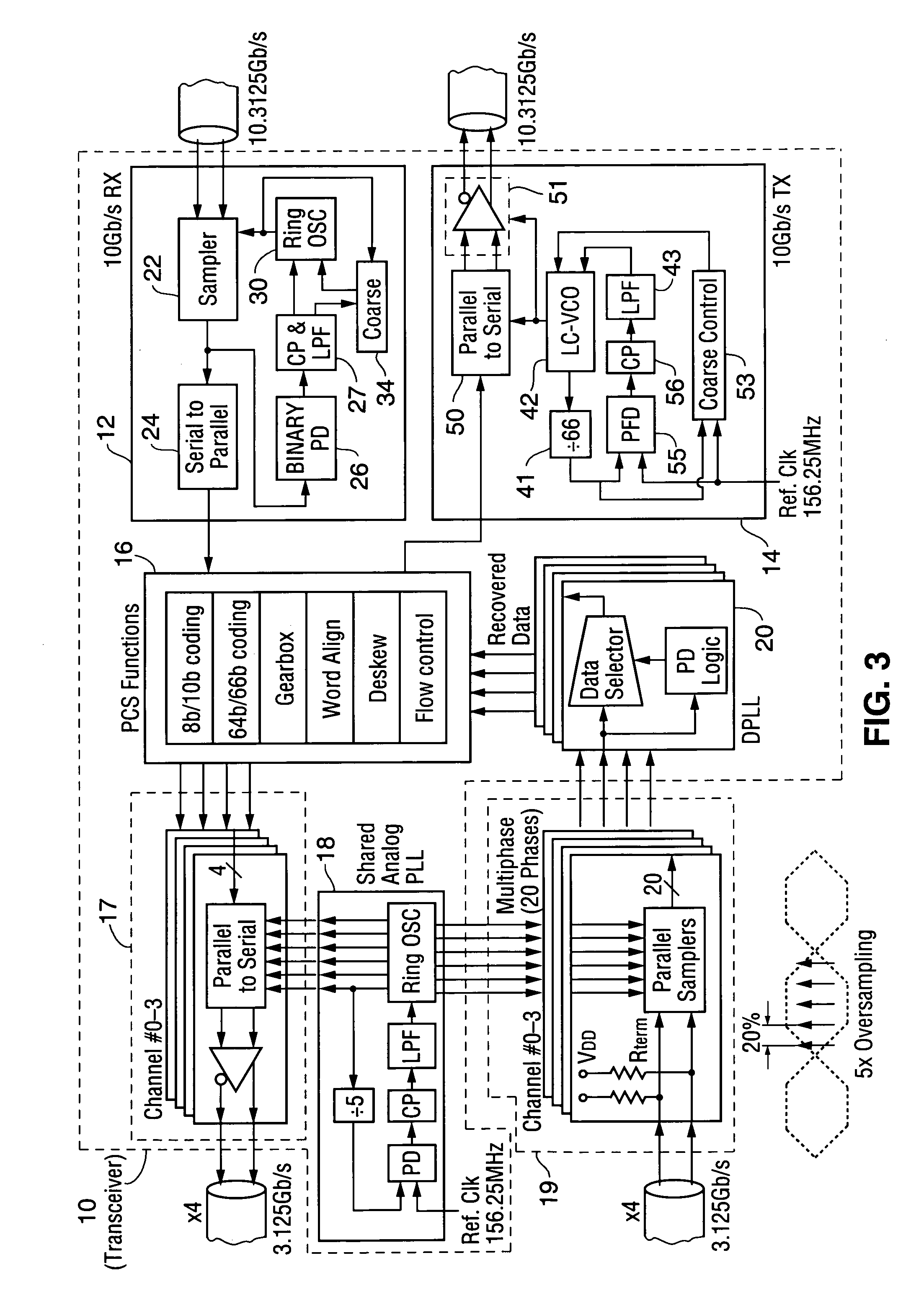

Phase lock loop with coarse control loop having frequency lock detector and device including same

ActiveUS7102446B1Improve portabilitySynchronization is simplePulse automatic controlCounting chain pulse countersTransceiverPhase locked loop circuit

A phase lock loop (PLL) for controlling a sampling clock or other clock, and a data sampling circuit, transceiver, or other device including such a PLL. The PLL includes a multi-range VCO, at least one fine control loop for controlling the VCO, and a coarse control loop for controlling the VCO by changing its frequency-voltage characteristic. The coarse control loop includes a frequency lock detector and voltage range monitoring logic. Typically, the frequency lock detector locks operation of the coarse control loop when the difference between the VCO output clock frequency and a reference frequency decreases to within a predetermined threshold, and the unlocked coarse control loop employs the voltage range monitoring logic to change the VCO frequency-voltage characteristic when the VCO's fine control voltage leaves a predetermined range. Other aspects are a transceiver (including at least two receiver interfaces and a transmitter interface) implementing a clocking scheme employing no more than three PLLs for clock generation, and a transceiver having a multi-layered receiver interface including digital circuitry and a single clock-generating PLL (an analog PLL for generating a multiphase clock to be shared by all layers of the receiver interface). Each receiver interface layer performs blind oversampling on a different received signal using the multiphase clock and the digital circuitry includes multilayered digital phase lock loop circuitry which receives the oversampled data.

Owner:LATTICE SEMICON CORP

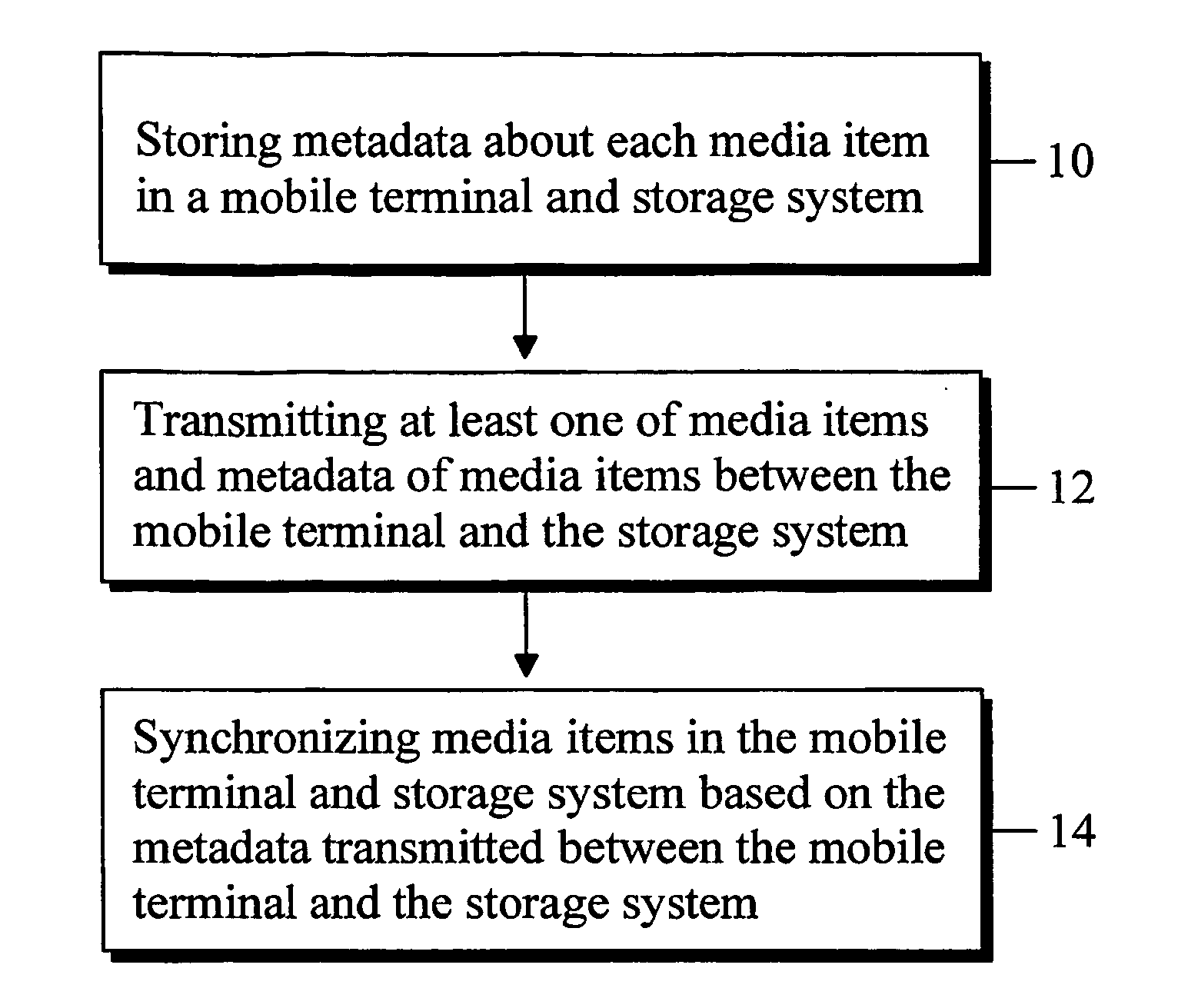

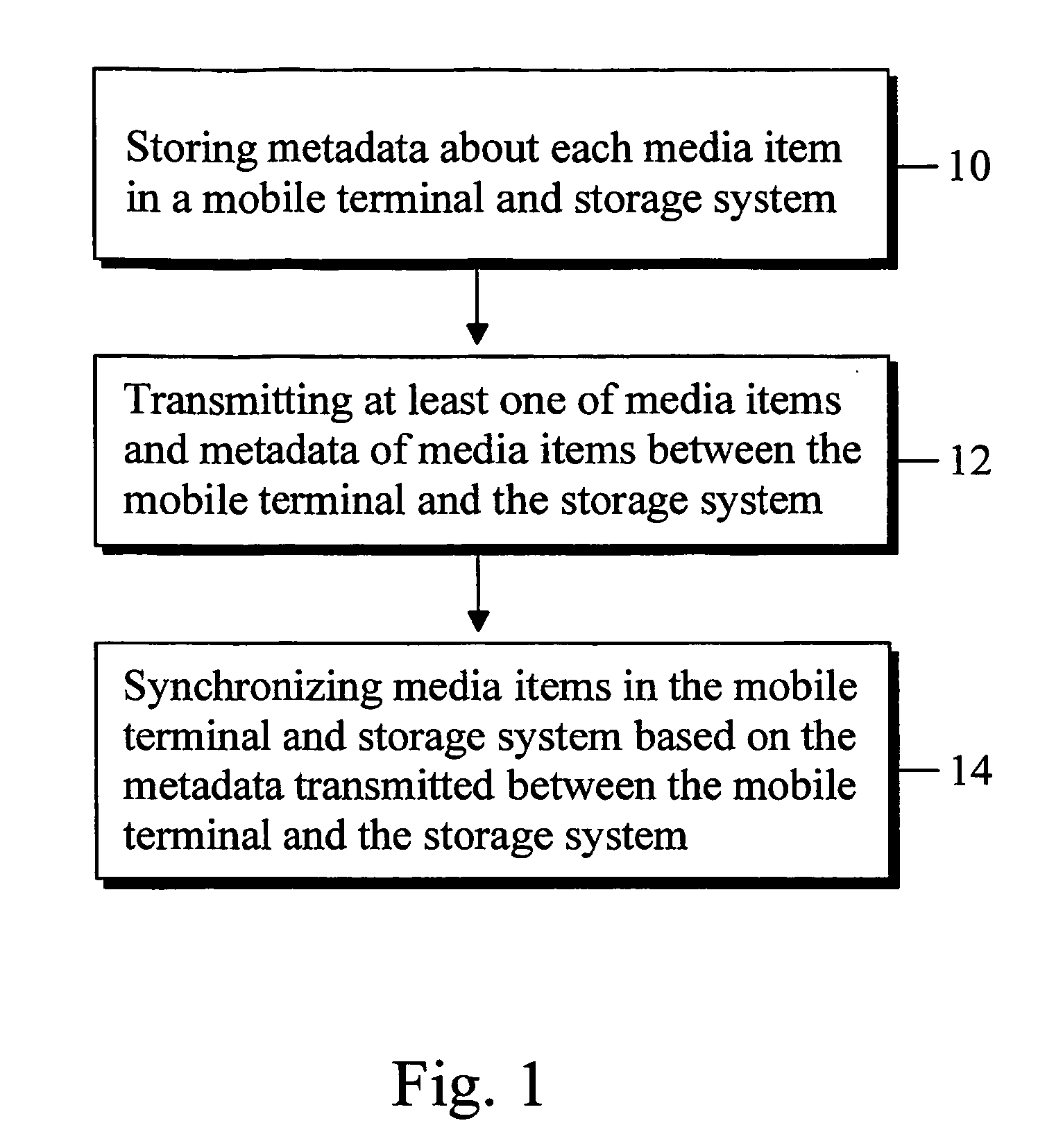

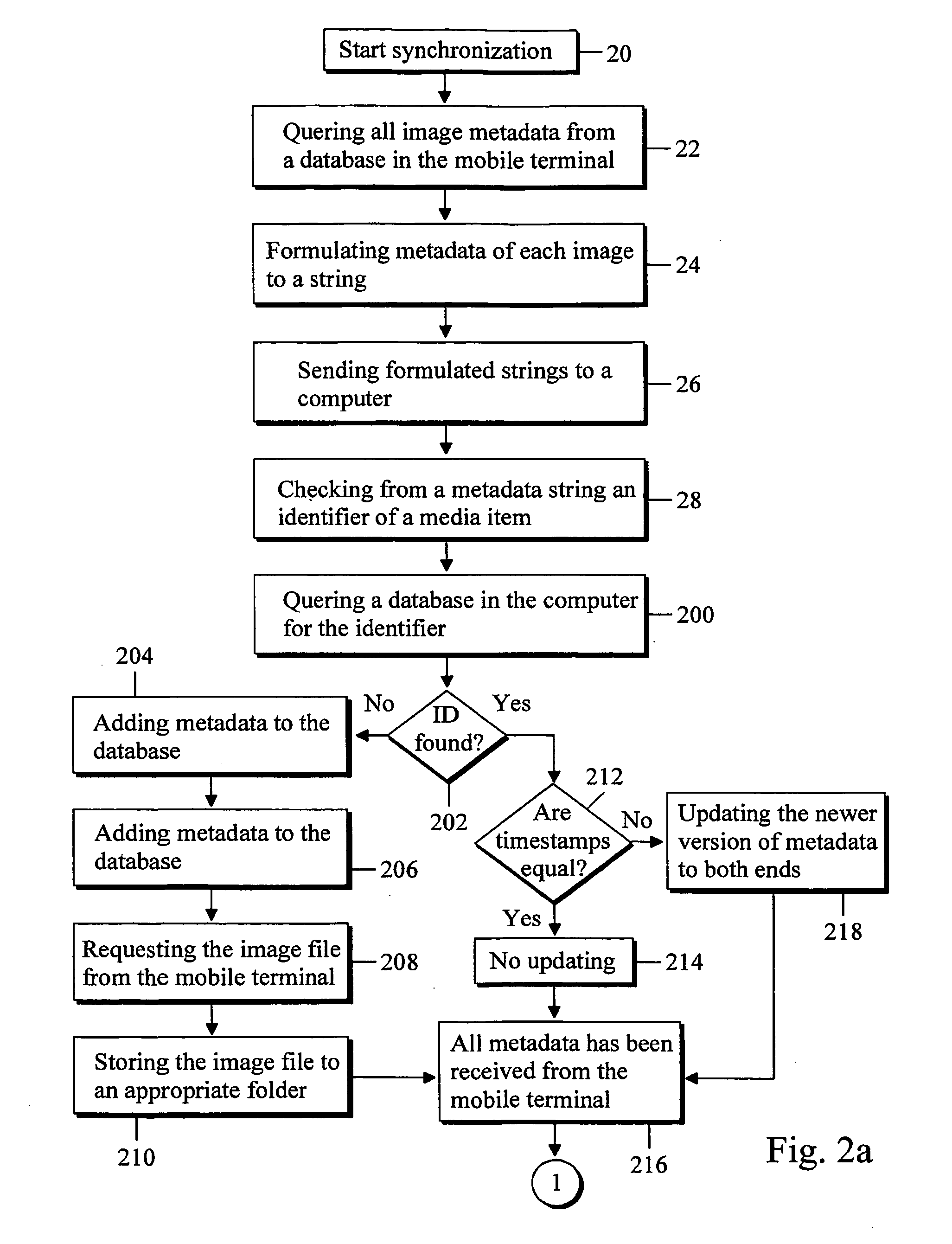

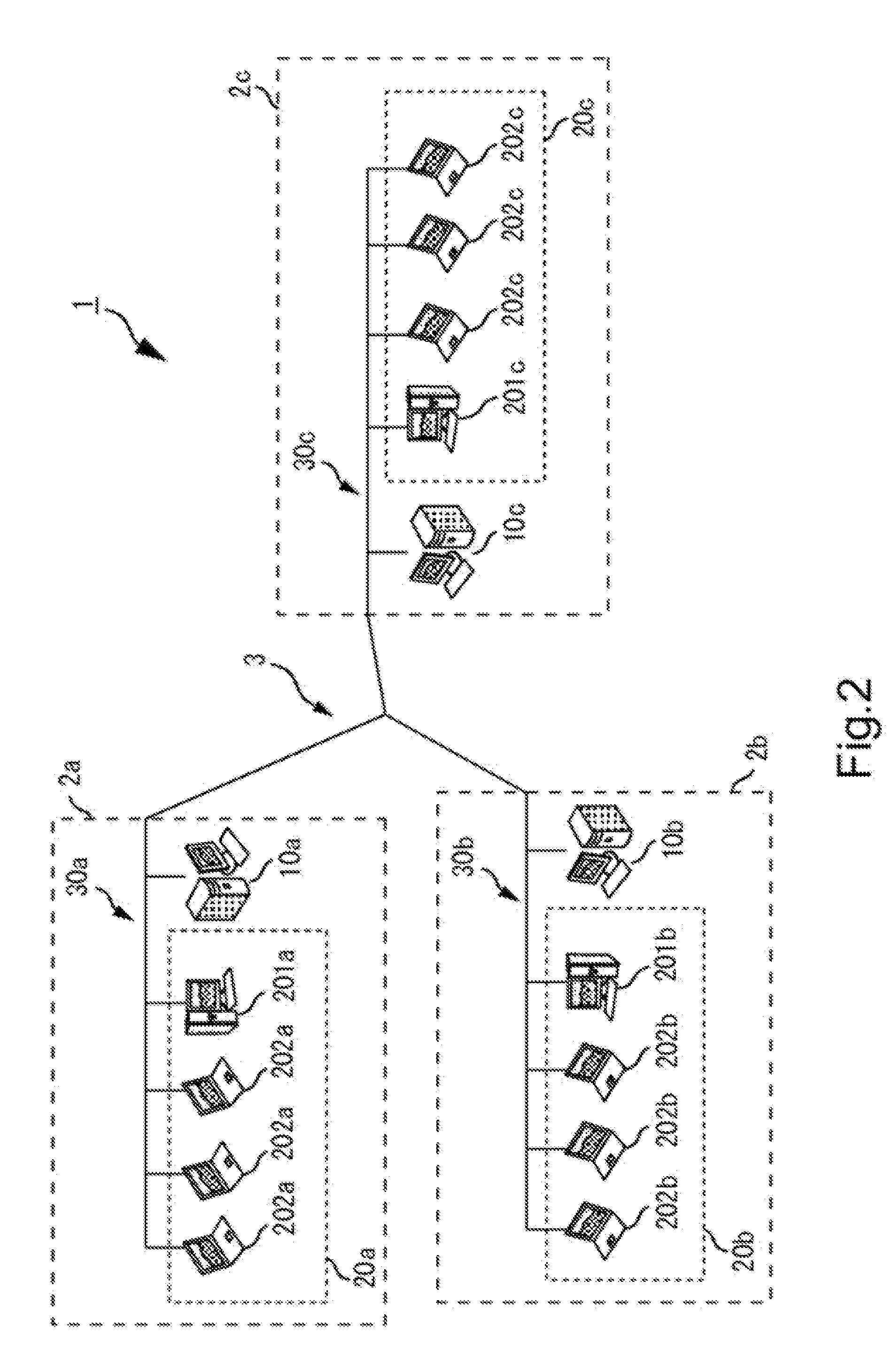

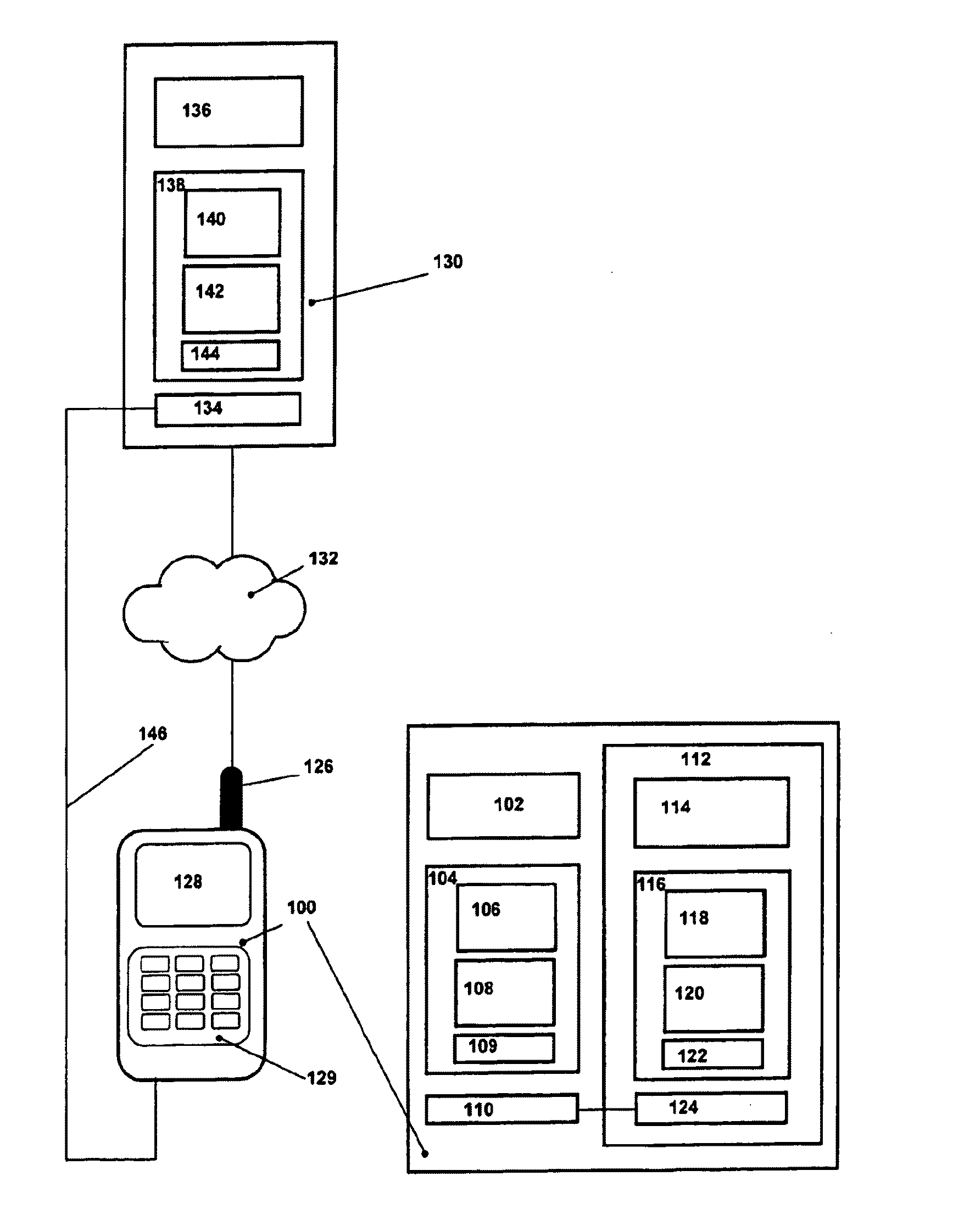

Method, system, computer programs and devices for management of media items

InactiveUS20070198746A1Simple solutionSynchronization is simpleMultimedia data retrievalMultiple digital computer combinationsMetadataDigital pictures

The invention discloses a solution for synchronization of media items between a mobile terminal and another terminal device. The metadata structure (and metadata associations to media items) in the mobile terminal is updated based on the categorization work a user does in the storage system in assigning files to folders. Correspondingly, media items are rearranged in the storage system based on new metadata assignments in the mobile terminal. A media item refers e.g. to a digital picture, a sound clip, a video clip etc.

Owner:NOKIA CORP

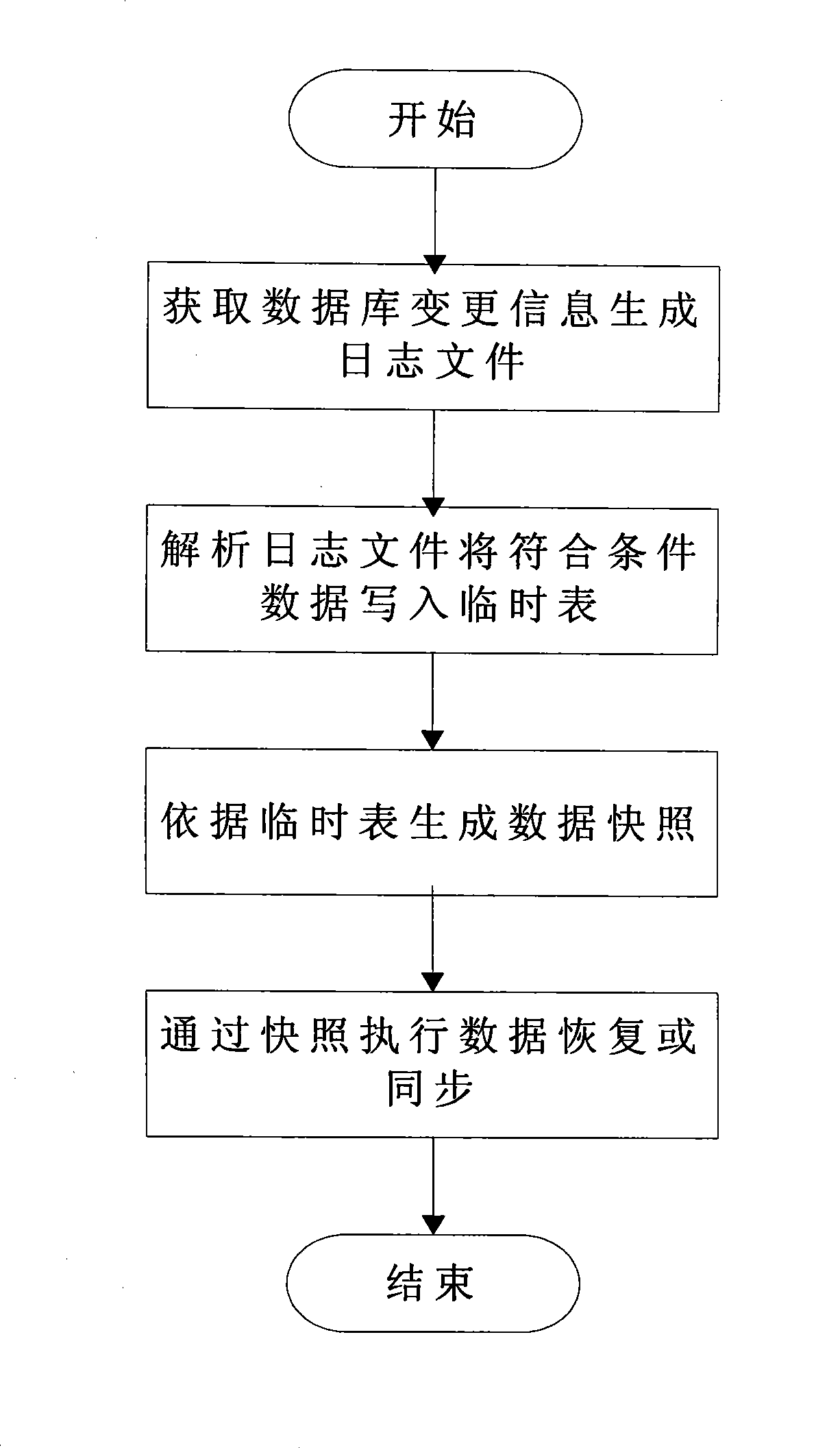

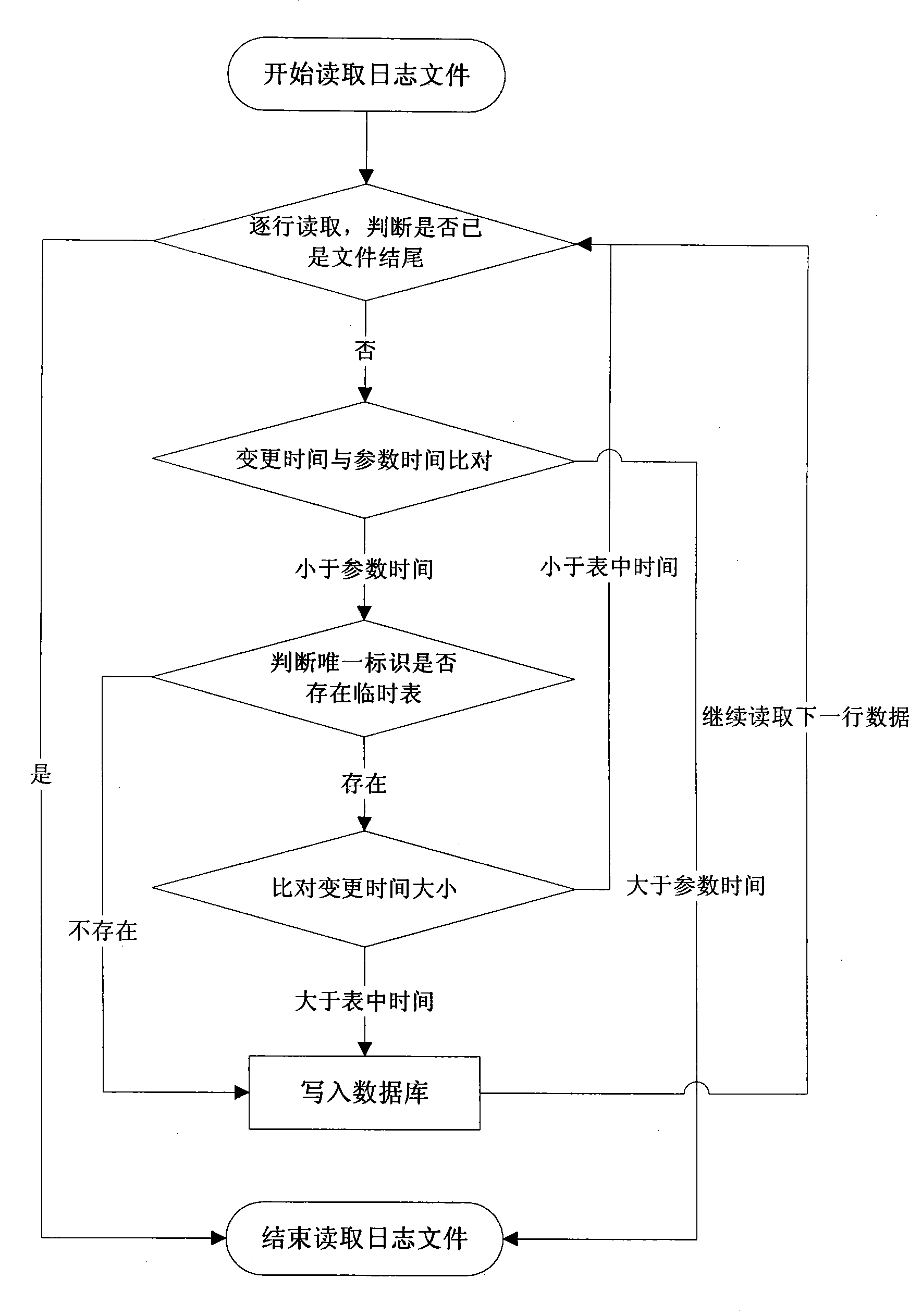

Data restoring and synchronizing method based on log snapshot

InactiveCN101436207AReduce storage overheadReduce system costSpecial data processing applicationsLogfileData memory

The invention relates to the field of occupation of the mass data memory space and backup and recovery of historical data, and in particular provides a data recovery and synchronization method based on log snapshots. The data recovery and synchronization method based on the log snapshots adopts log files with given format to record changed information of data of databases each time; the changed information is formatted, positioned and stored into the log files; an analytic program calls an approximate algorithm to acquire effective data on set time points by means of multithreading; the data is temporarily stored into a temporary table, and abstract data snapshots are generated according to the temporary table; and data recovery and synchronization is realized by utilization of the snapshots. The data recovery and synchronization method based on the log snapshots can greatly reduce the burden of a database system, obviously improve the efficiency of the database system and an application system, save a great deal of memory space, and reduce the operation cost of the systems.

Owner:INSPUR TIANYUAN COMM INFORMATION SYST CO LTD

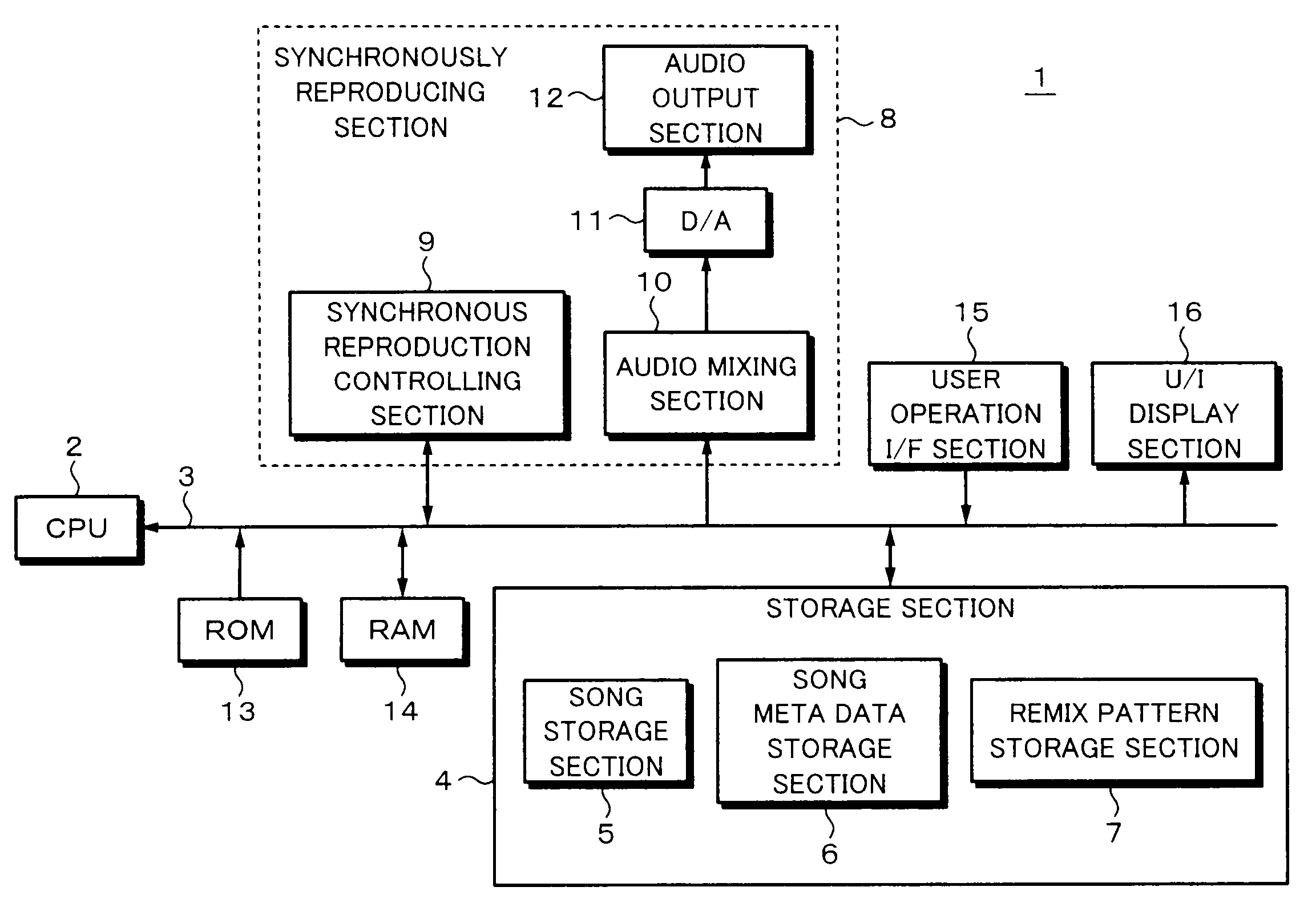

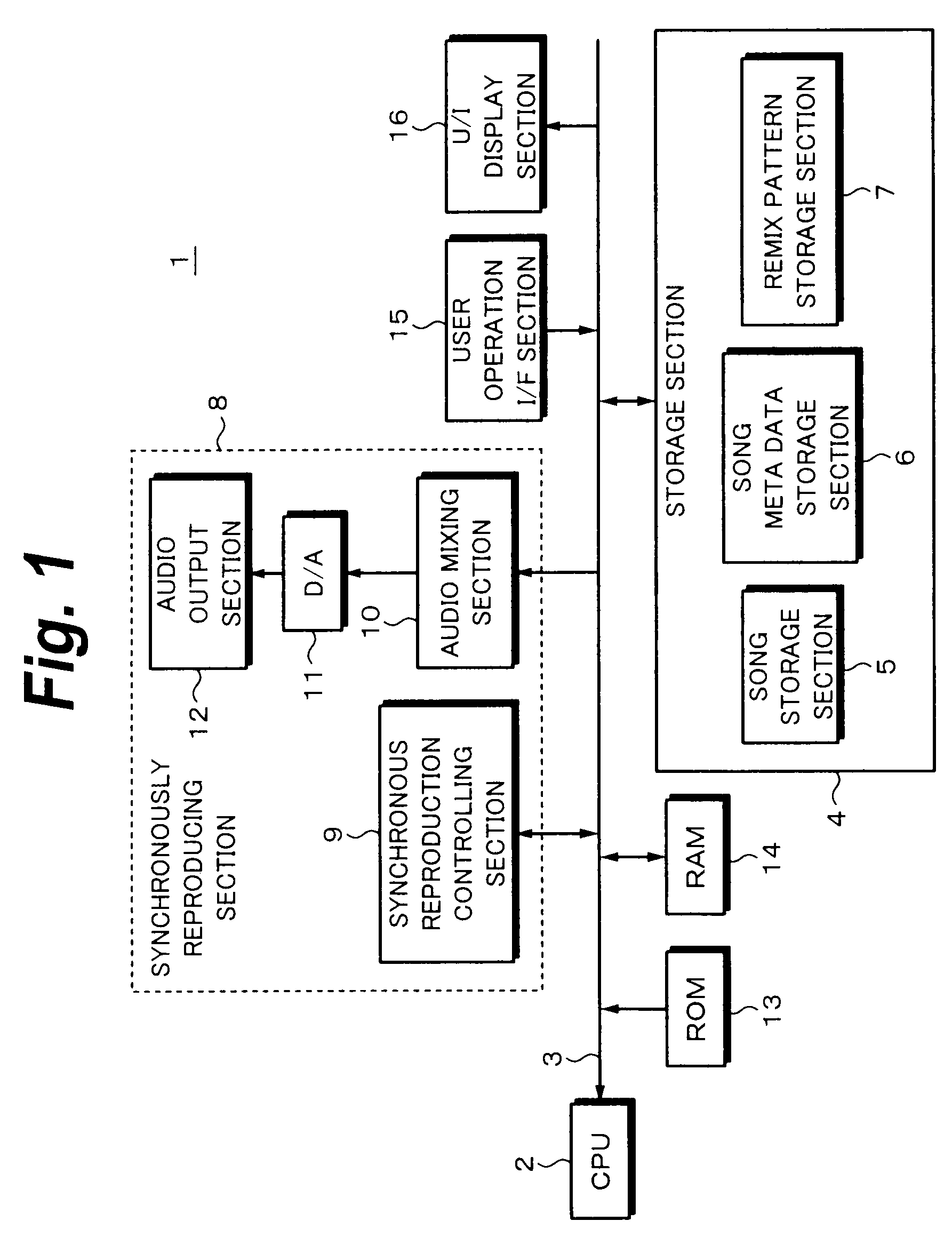

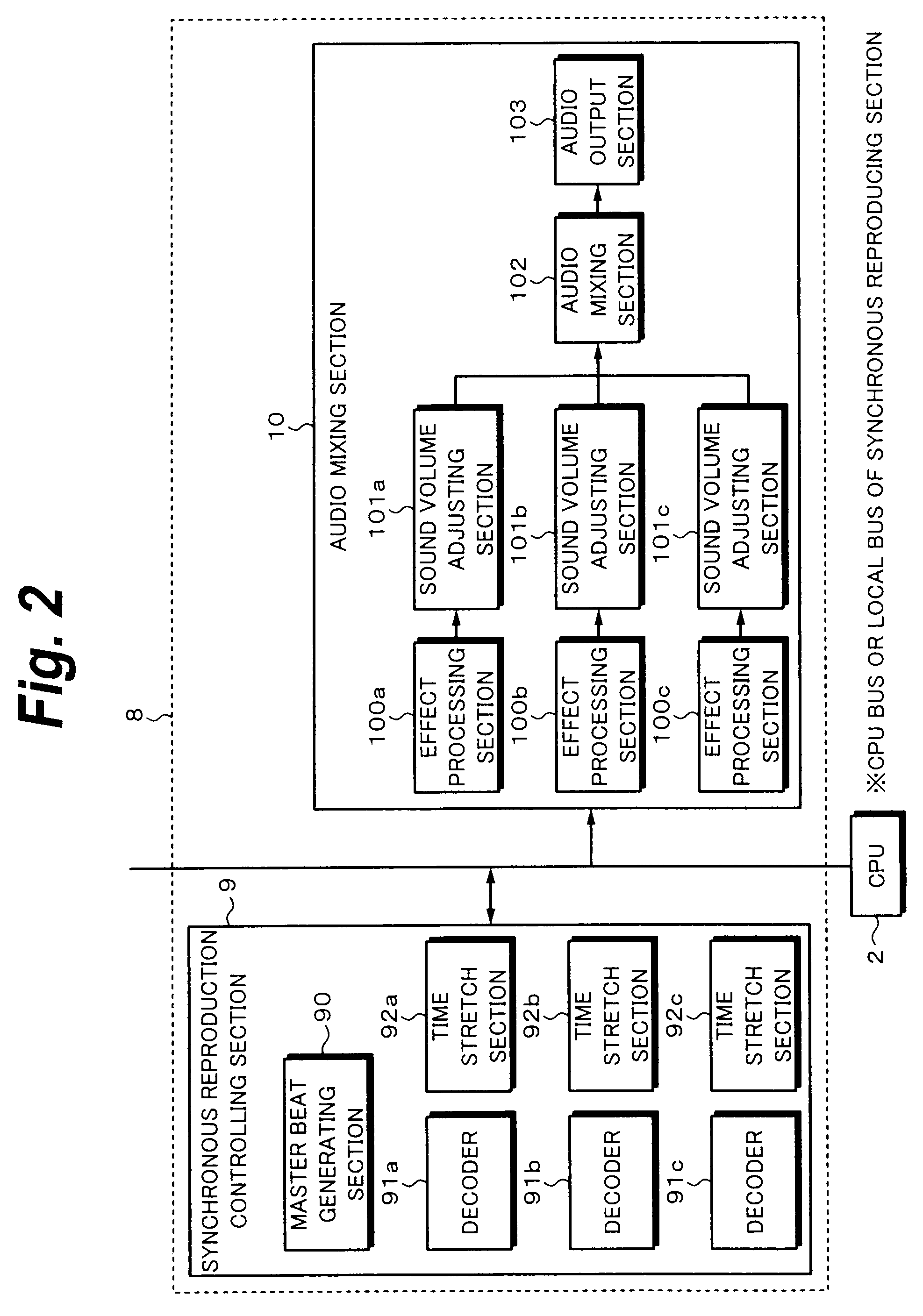

Music edit device and music edit method

InactiveUS20090272253A1ConstantSynchronization is simpleElectrophonic musical instrumentsElectronic editing digitised analogue information signalsLow loadTime line

A music editing apparatus is provided that uses so-called time line meta data that describe a beat and melody structure of a song to automatically accomplishes an automatic DJ remix play with a low load. The apparatus also includes a synchronous reproduction controlling section which sends a master beat to the remix processing section and reproduces a plurality of songs corresponding to a remix process which the remix processing section designates corresponding to a remix pattern and the meta data and a mixing section which mixes the songs reproduced by the synchronous reproduction controlling section. The synchronous reproduction controlling section also includes a phase comparator which compares a phase of a beat synchronous signal generated from the meta data supplied from the remix processing section with that of the master beat signal; an integrating circuit which integrates a phase compared output of the phase comparator; and a correcting section which corrects a tempo based on an integrated output of the integrating circuit.

Owner:SONY CORP

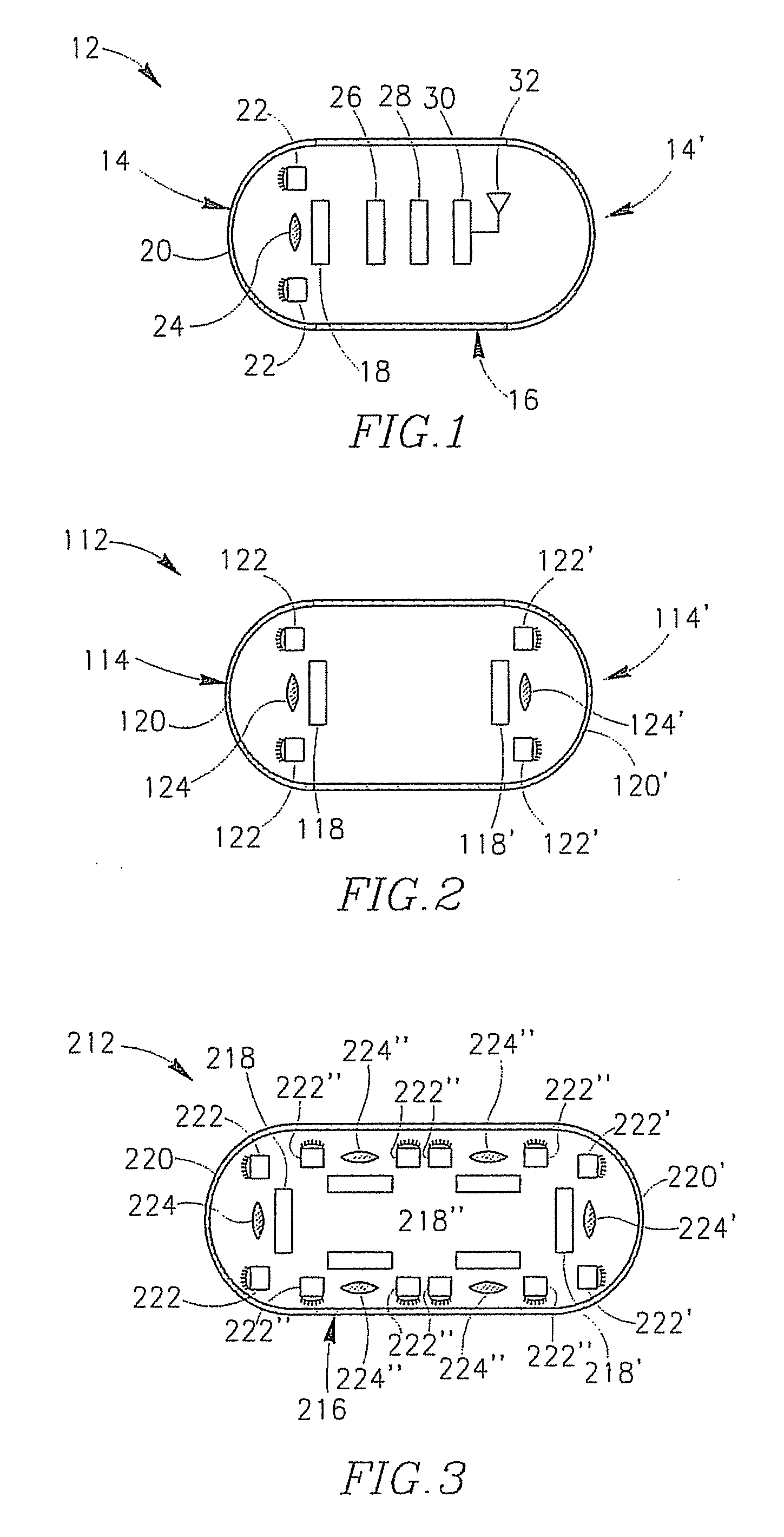

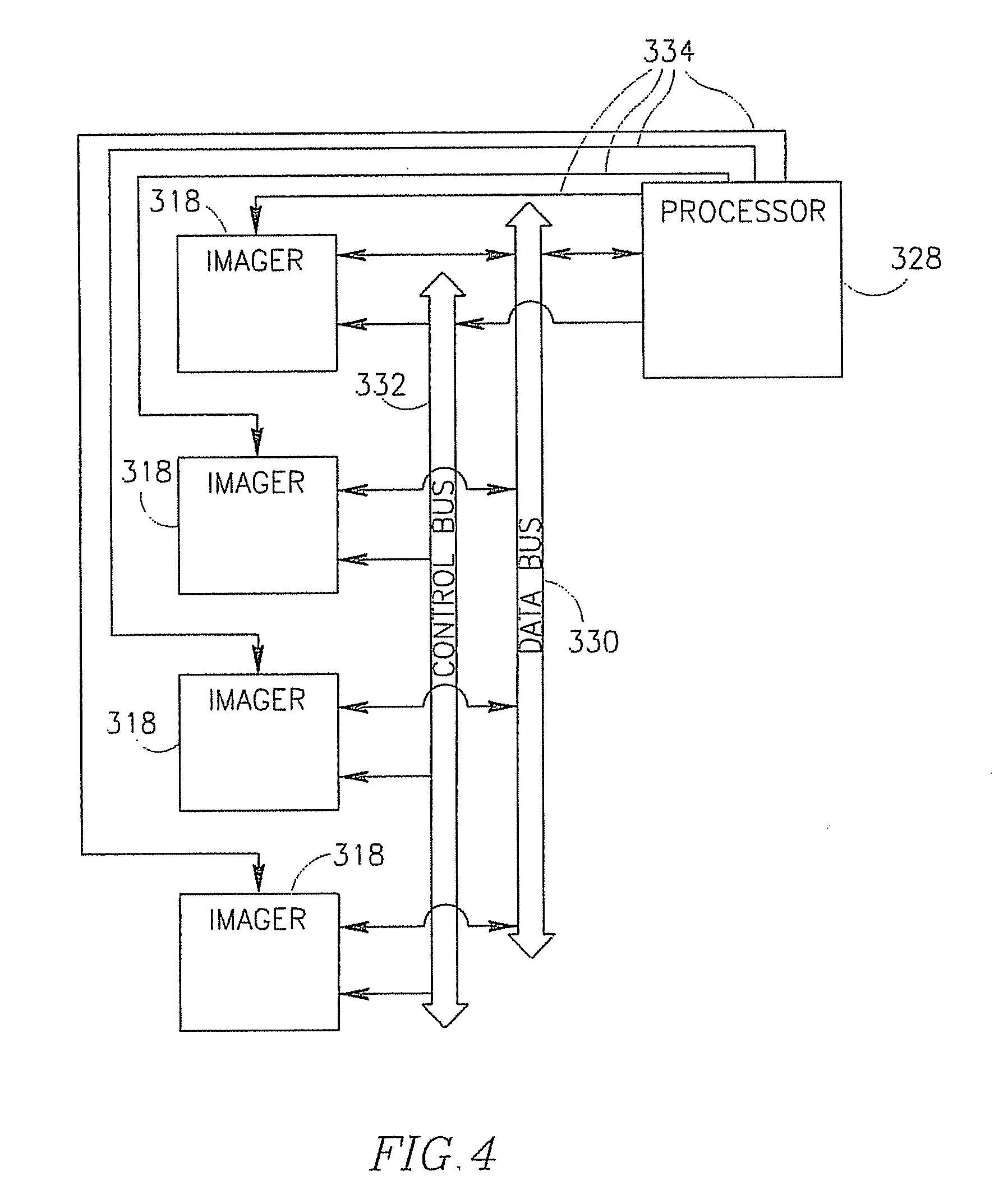

In-vivo sensing device and method for communicating between imagers and processor thereof

InactiveUS20100013914A1Reduce power consumptionLower Level RequirementsEndoscopesColor television detailsIn vivoComputer science

Owner:GIVEN IMAGING LTD

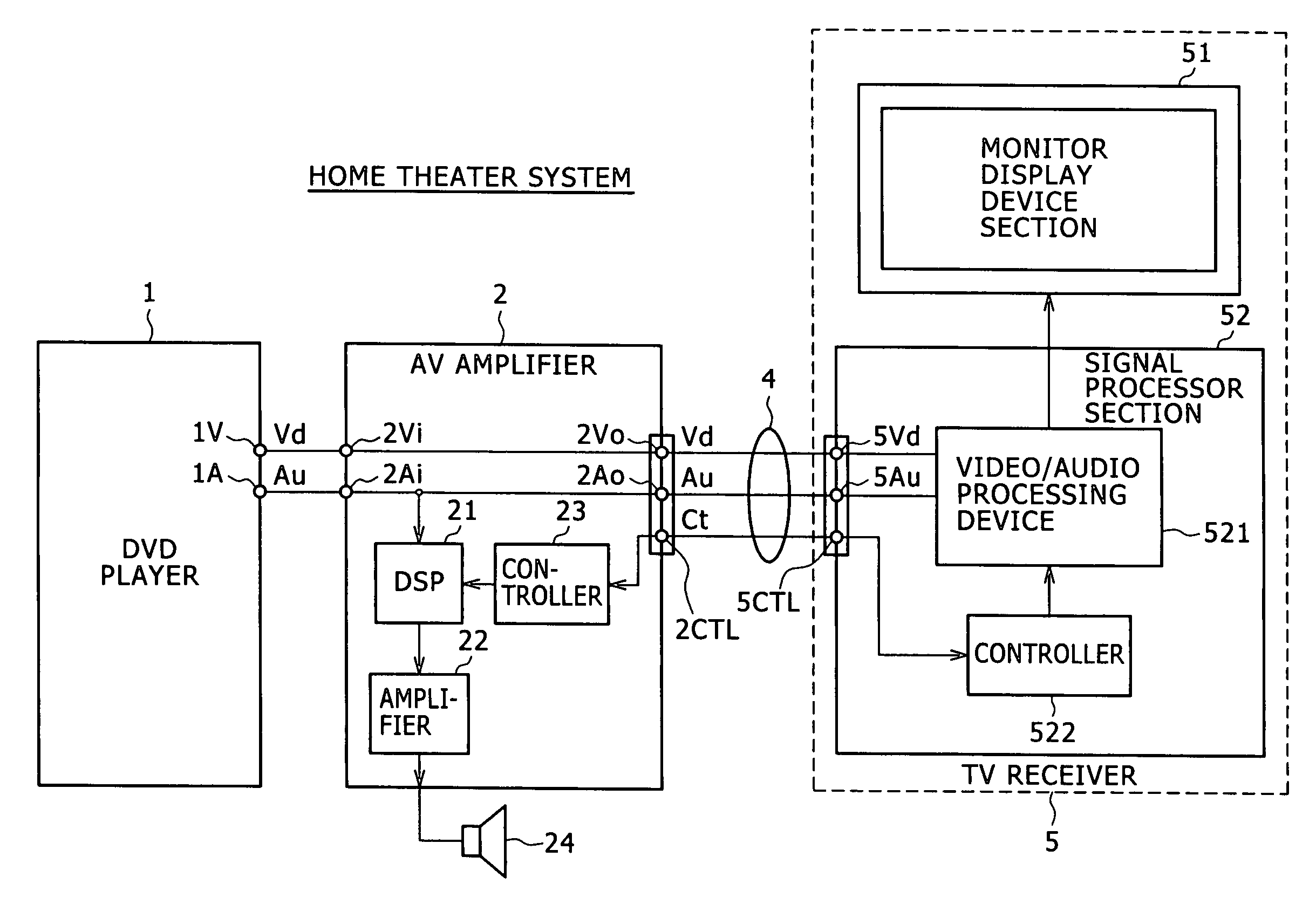

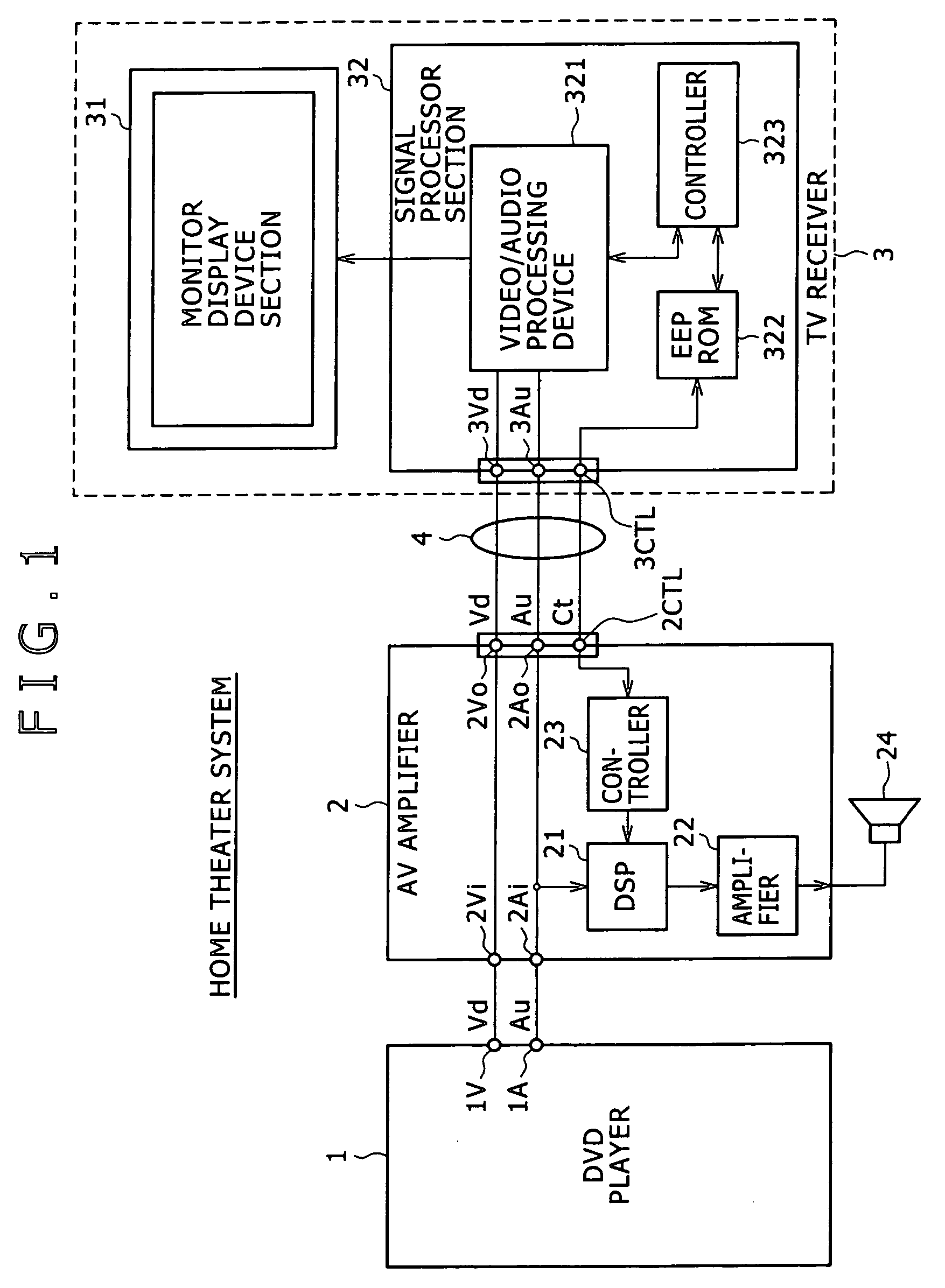

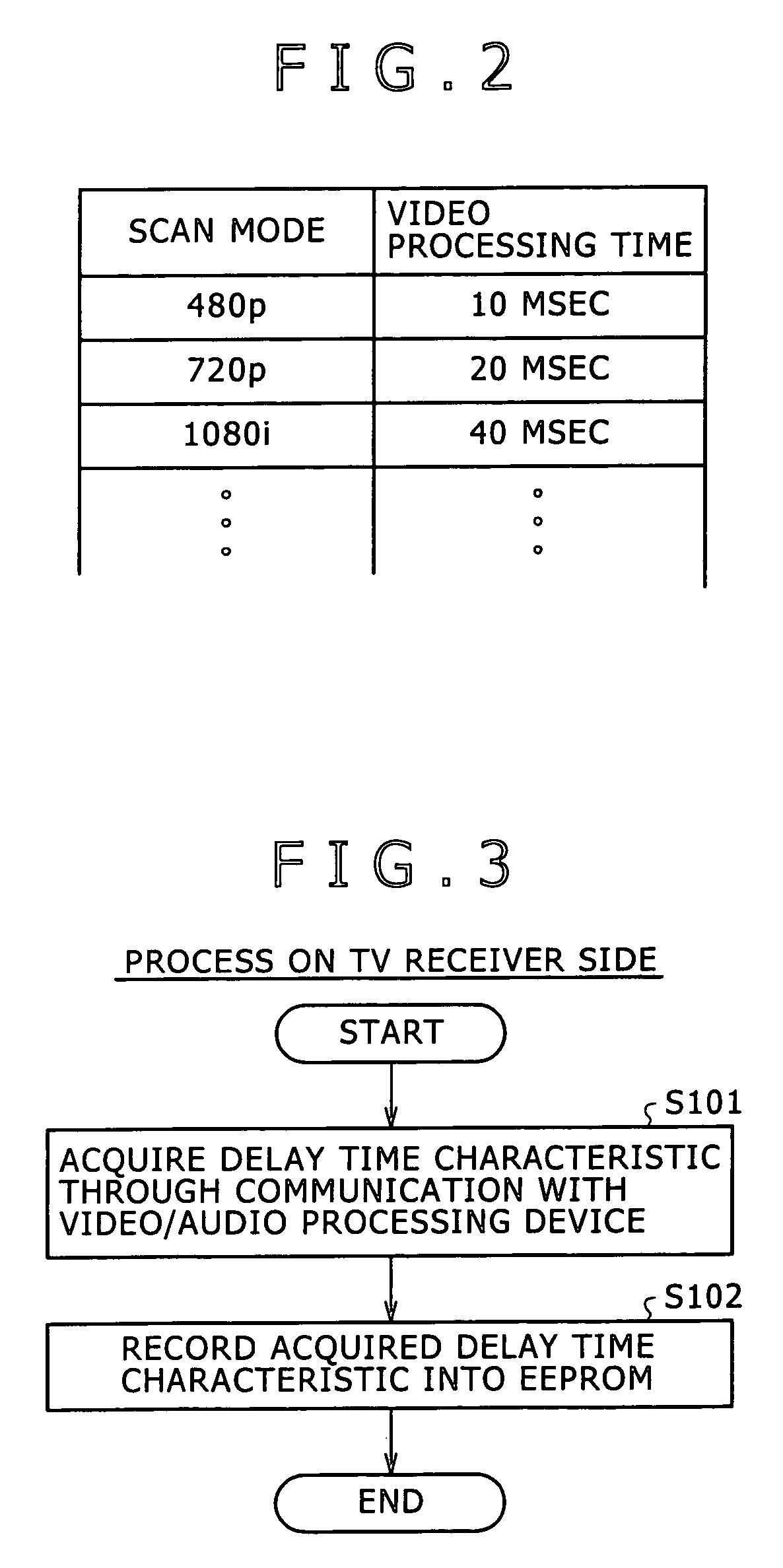

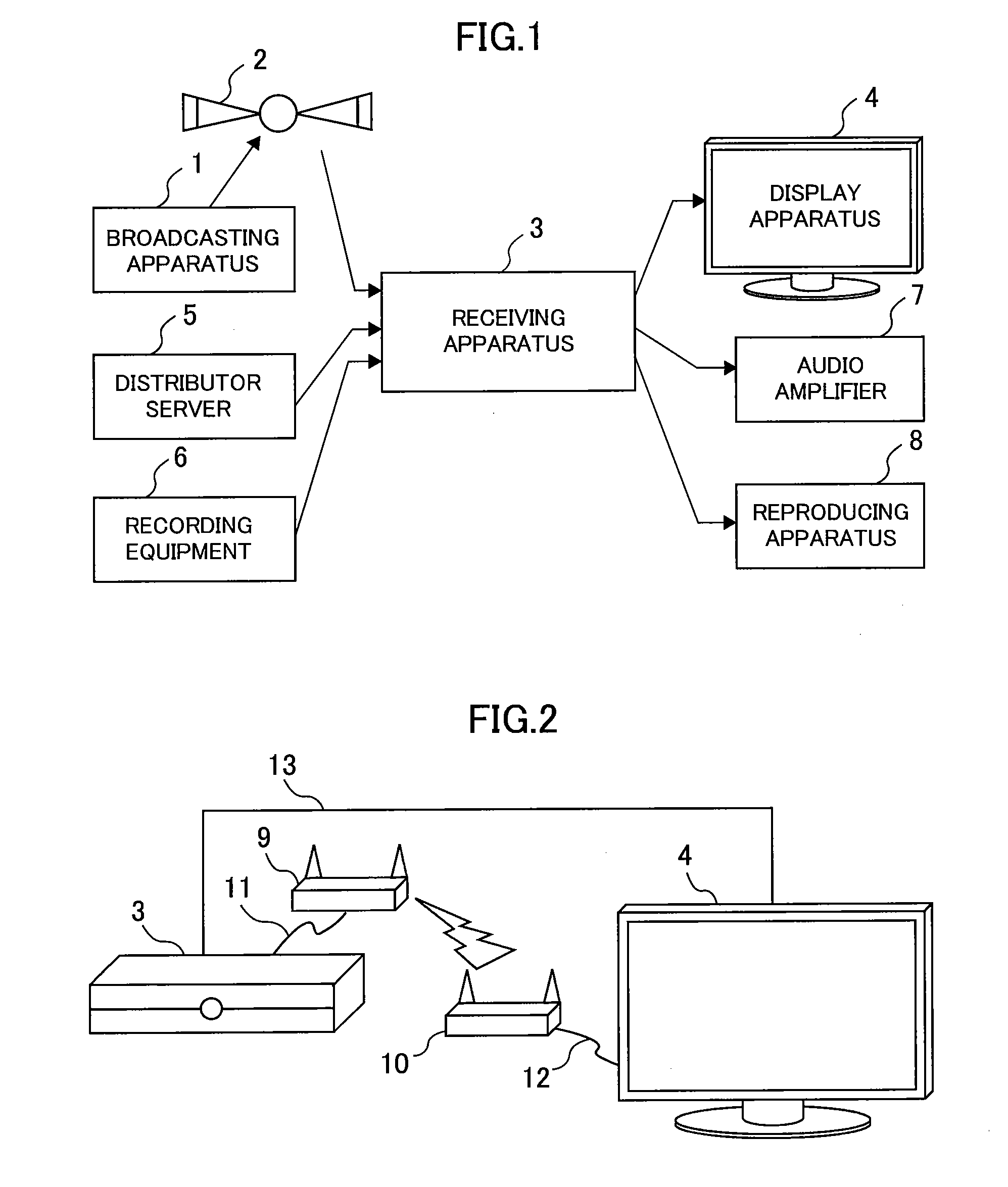

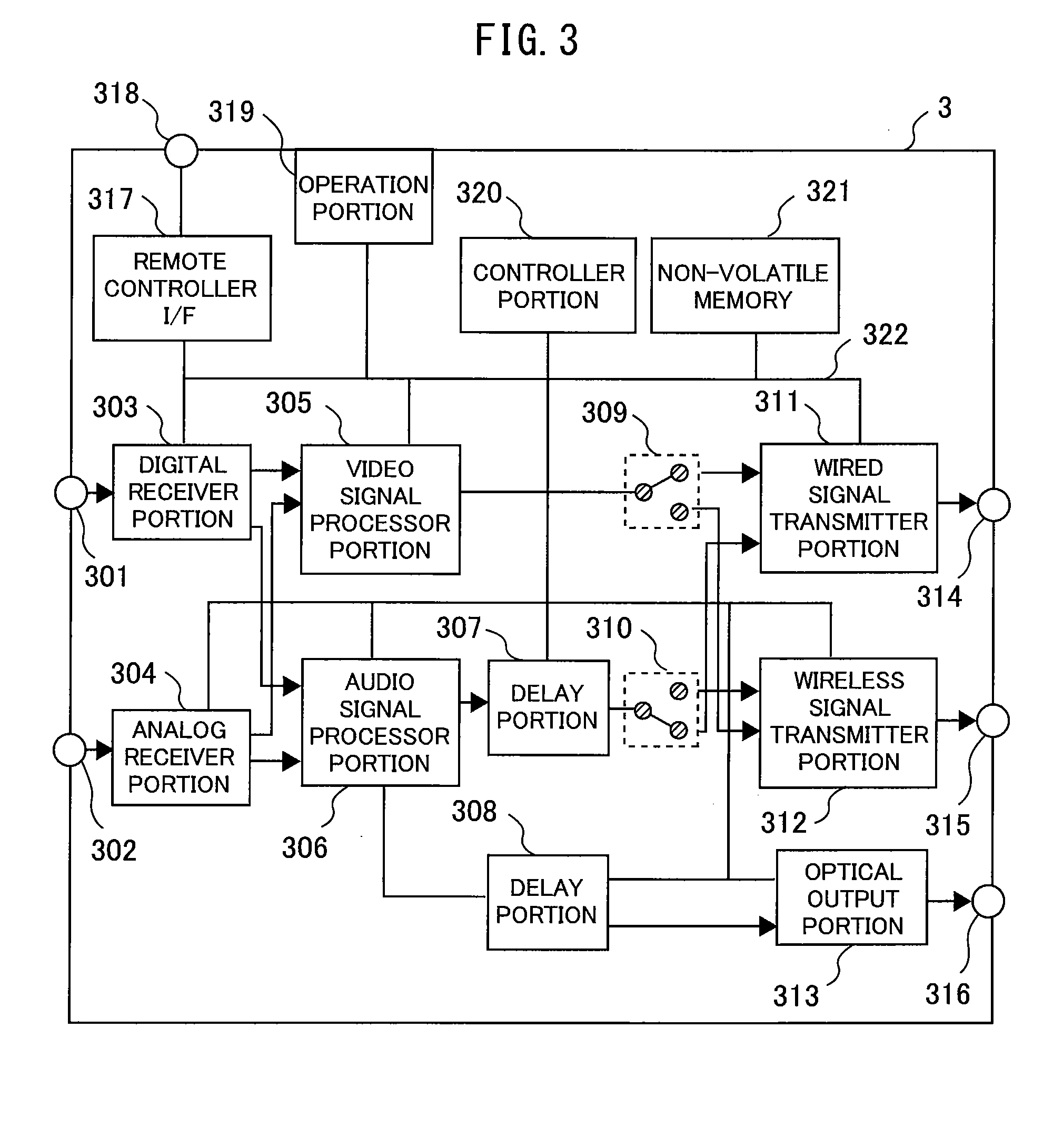

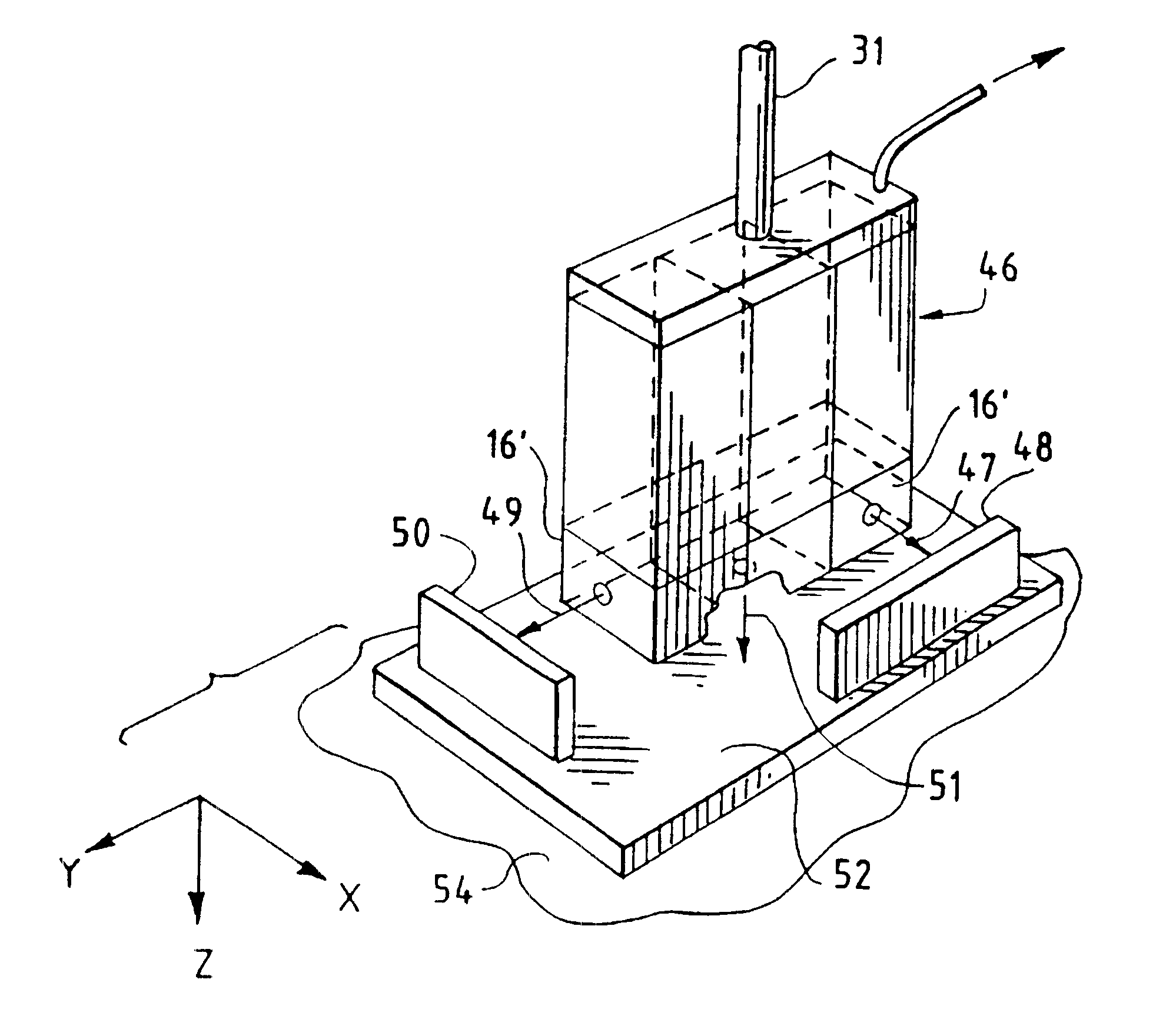

Video/audio processor system, amplifier device, and audio delay processing method

InactiveUS20060012710A1Easily synchronizedAvoid errorsTelevision system detailsCarrier indexing/addressing/timing/synchronisingSignal onLip sync

A system processes an audio signal and a video signal by using different devices, thereby preventing a so-called lip sync error. The processing time (represented by processing-time information) from the start of reception of a supplied video signal in a video processor apparatus to the start of displaying a video corresponding to the video signal on a display screen of a display device is acquired in an amplifier device from the video processor apparatus through a control signal line. In accordance with the acquired processing time, a delay processor delays processing of an audio signal supplied from the delay processor.

Owner:SONY CORP

Insufflation-exsufflation system for removal of broncho-pulmonary secretions with automatic triggering of inhalation phase

InactiveUS6860265B1Synchronization is simpleIncrease volumeRespiratorsOperating means/releasing devices for valvesBroncho-pulmonaryPositive pressure

An improved insufflation-exsufflation system for removal of broncho-pulmonary secretions with automatic triggering of inhalation phase includes a conduit for connection to a patient's airway; a pressure source with a positive pressure port and a negative pressure port; a switching device selectively connecting the conduit to the positive pressure port, the negative pressure port and the dwell port; the sensor system for sensing an inhalation by the patient; and a controller system for driving the switching device to connect the conduits sequentially to the positive port, the negative port and the dwell port and to return again to the positive port in response to the sensor system sensing an inhalation by the patient while the conduit is connected to the dwell port.

Owner:RIC INVESTMENTS LLC

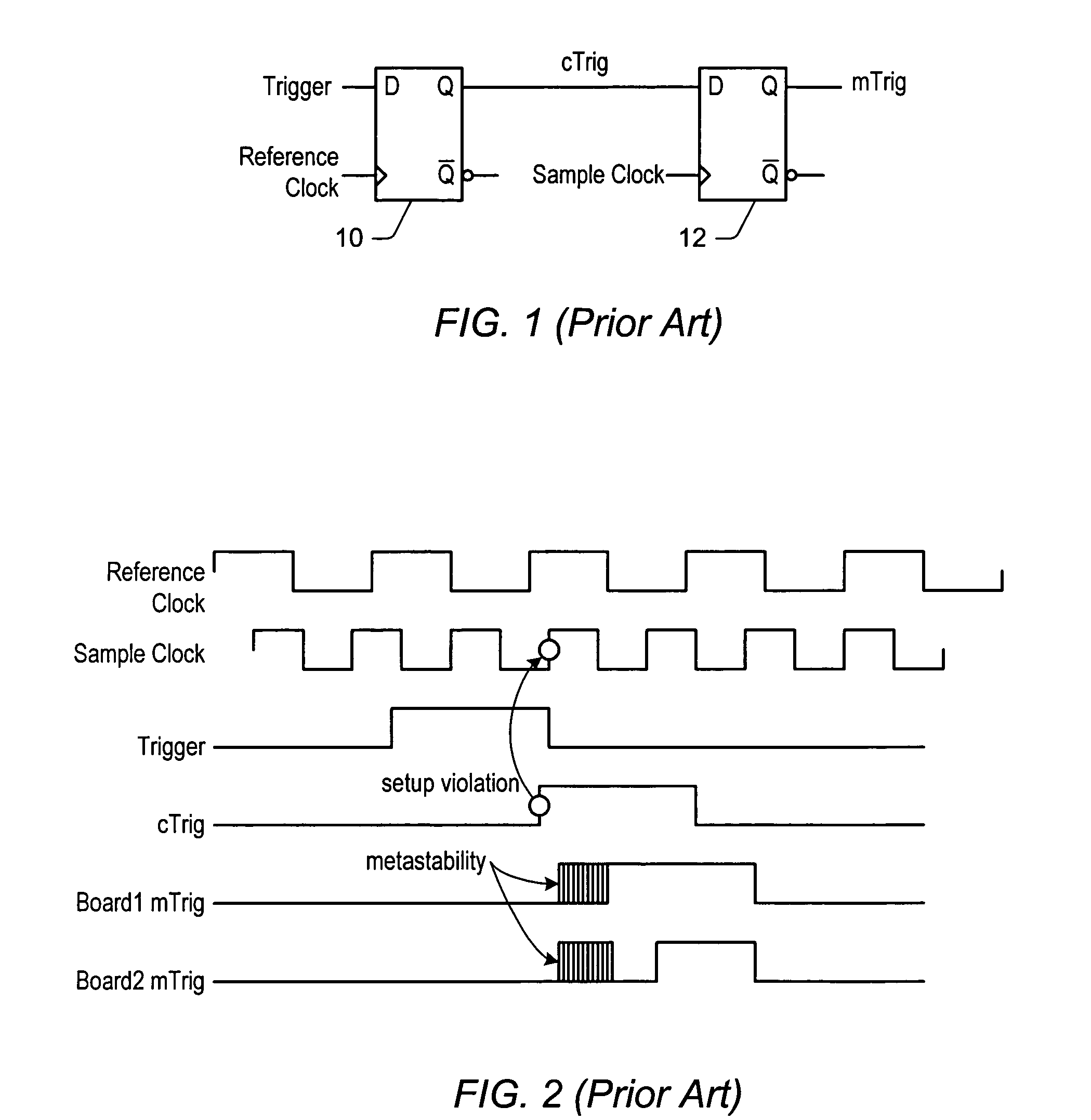

Application programming interface for synchronizing multiple instrumentation devices

ActiveUS7315791B2Reduce in quantitySynchronization is simpleProgramme controlStructural/machines measurementGraphicsApplication programming interface

An application programming interface (API) for synchronizing multiple devices in a system. The API includes a plurality of functions invocable in a program to synchronize multiple devices, where each function is executable to perform a respective functionality related to synchronizing the devices, and at least one of the functions is executable to access a plurality of instrument drivers corresponding respectively to the plurality of devices to synchronize the plurality of devices. In synchronizing the plurality of devices, the functions determine a trigger clock signal for each of the plurality of devices, and synchronize the plurality of devices based on the determined trigger clock signals. The API also includes a plurality of attributes corresponding to respective properties of the system related to synchronization of the devices, including one or more trigger attributes and / or one or more trigger clock attributes for each of the devices. The API representations may be text-based and / or graphical.

Owner:NATIONAL INSTRUMENTS

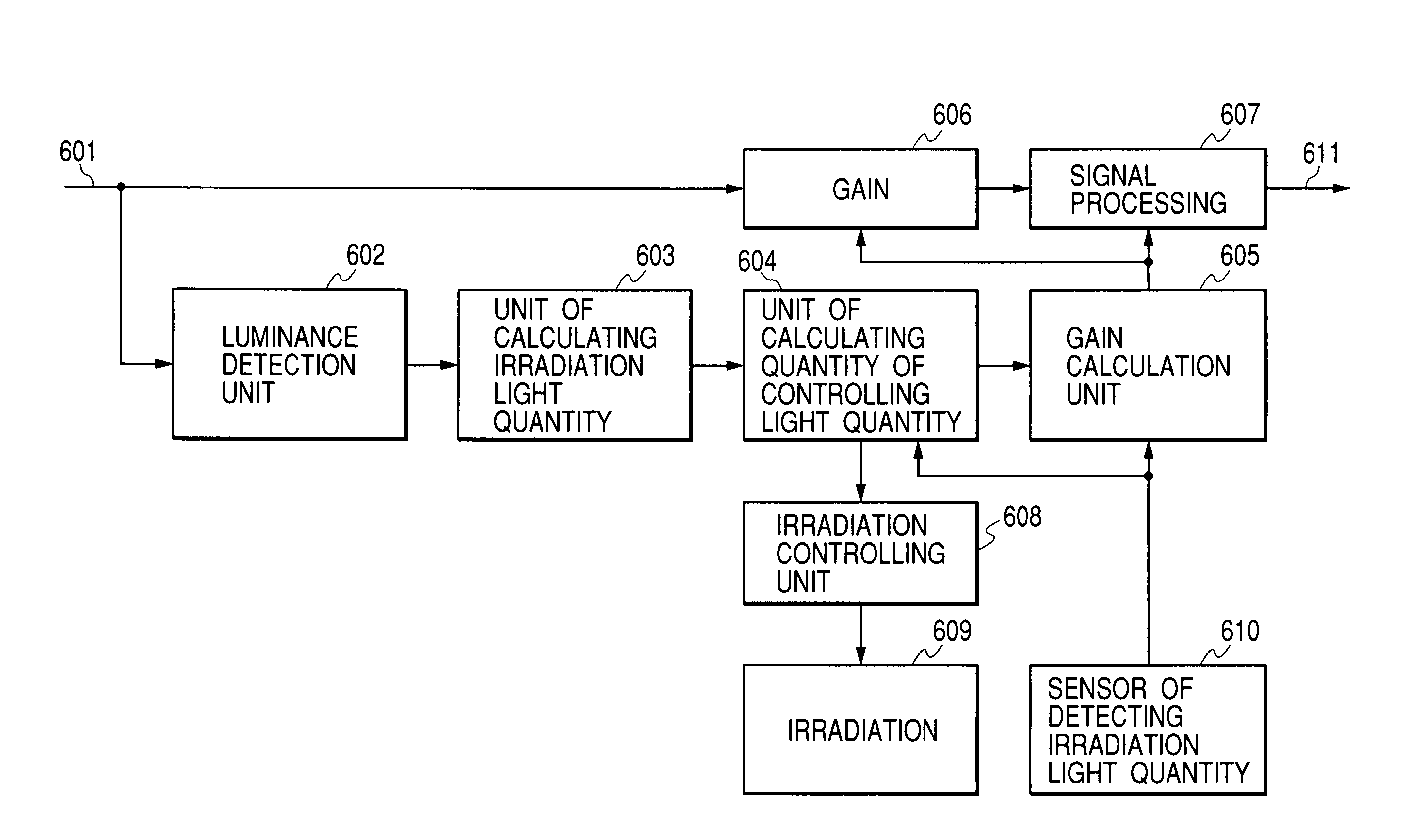

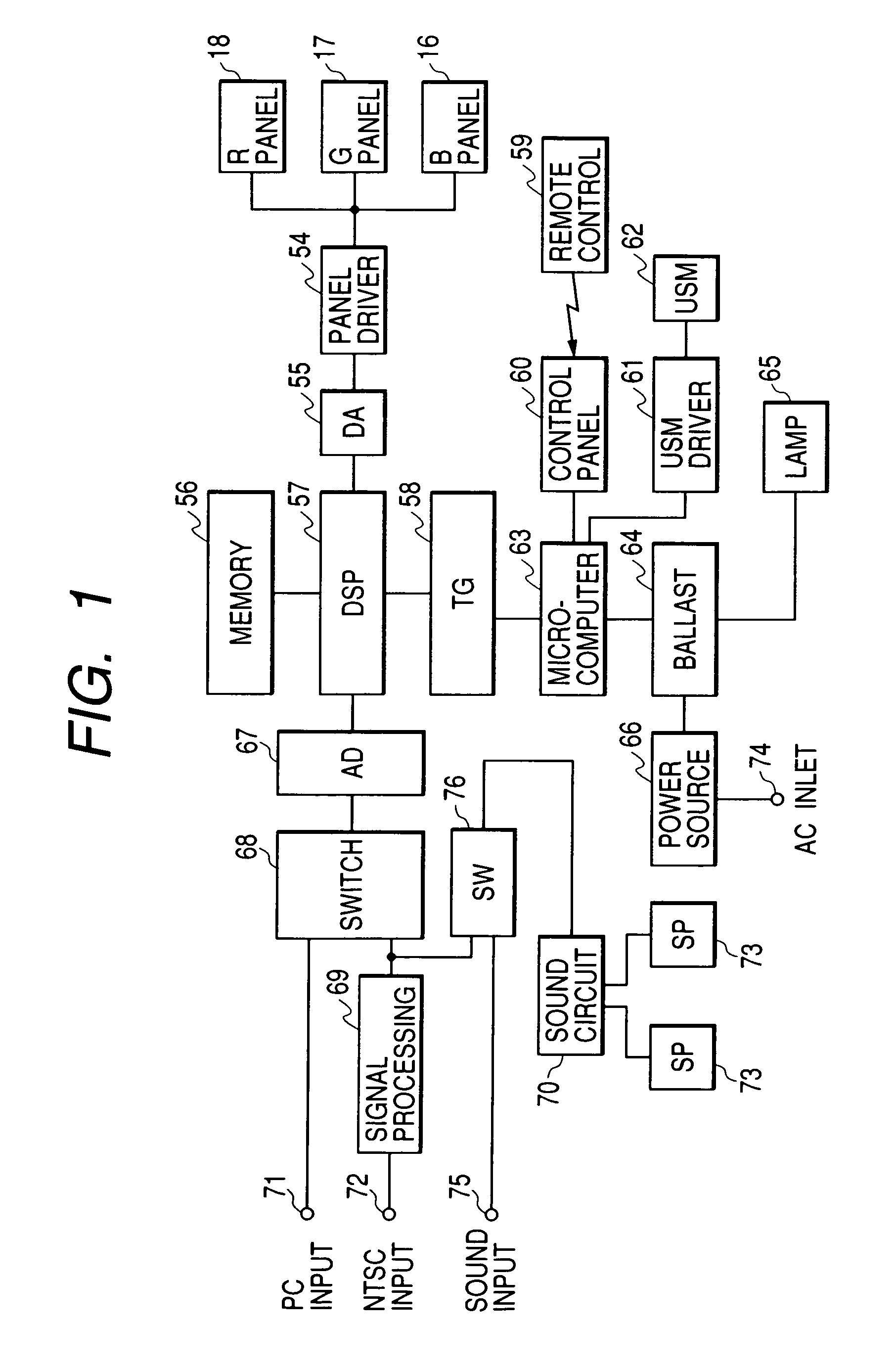

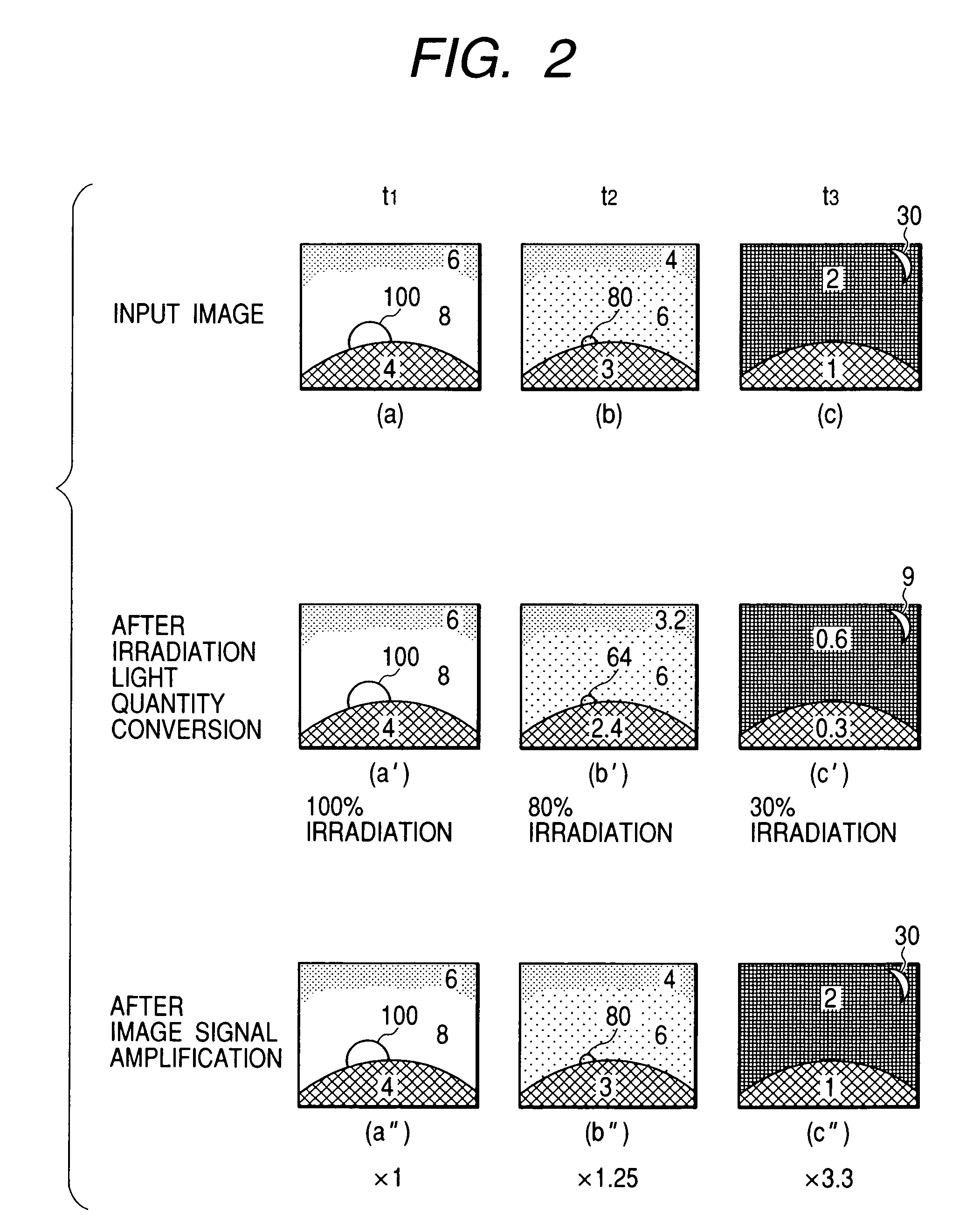

Display apparatus and image signal processing apparatus

InactiveUS7027016B2Improve picture qualityImprove dynamic rangeTelevision system detailsProjectorsHysteresisImaging quality

To attain high image quality such as high resolution and high dynamic range in a display apparatus for irradiating light generated by a light source onto a light modulating element and for forming a display image plane from the light transmitted through or reflected by the light modulating element.The apparatus is configured to control irradiation light quantity, in which the high image quality is provided by an unit for temporarily storing display signal, an unit for adjusting signal under an analog state, a unit for differentiating a rate of change in light quantity at the time of increase and at the time of decrease and a unit for controlling light quantity to resemble hysteresis.

Owner:CANON KK

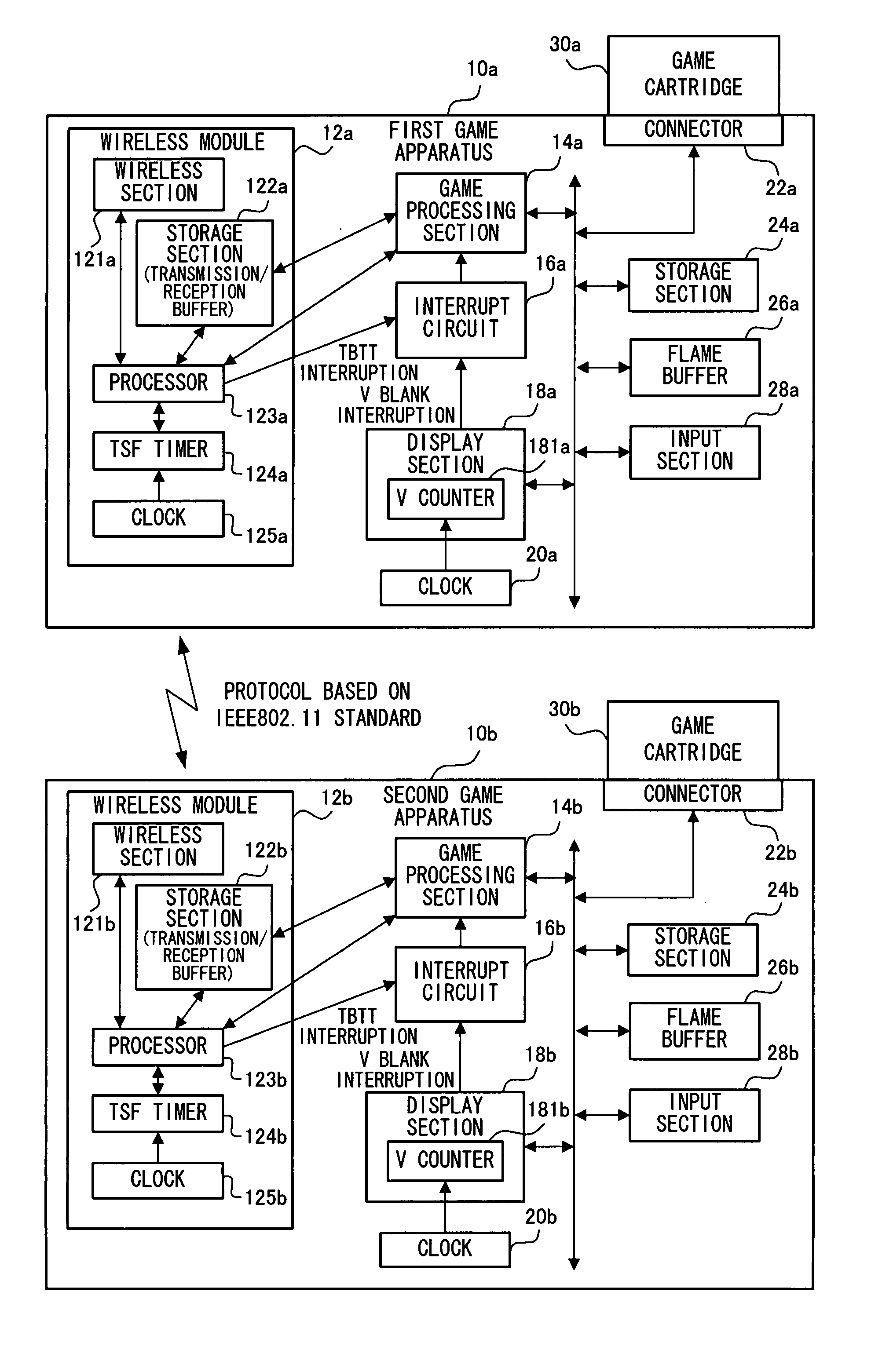

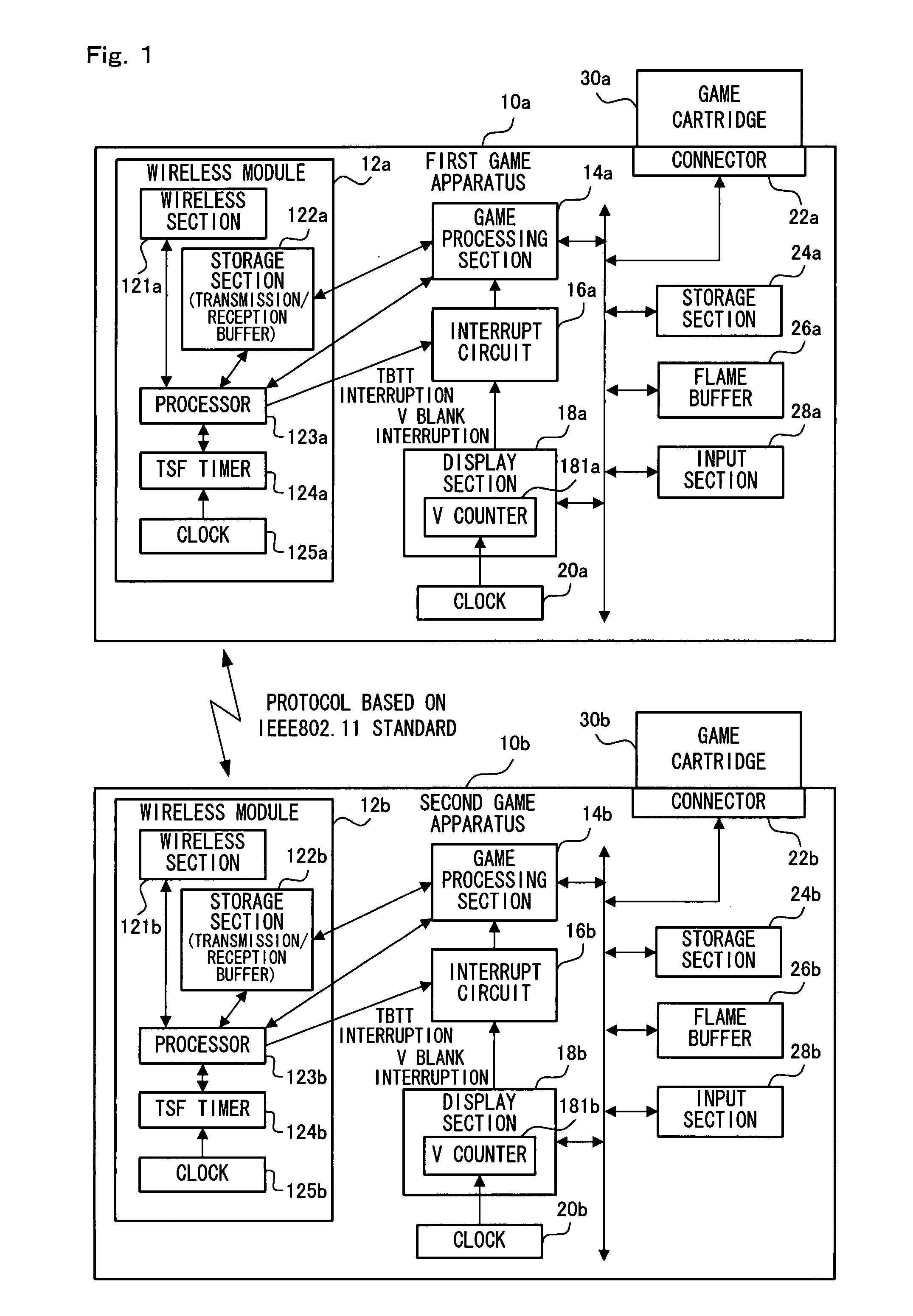

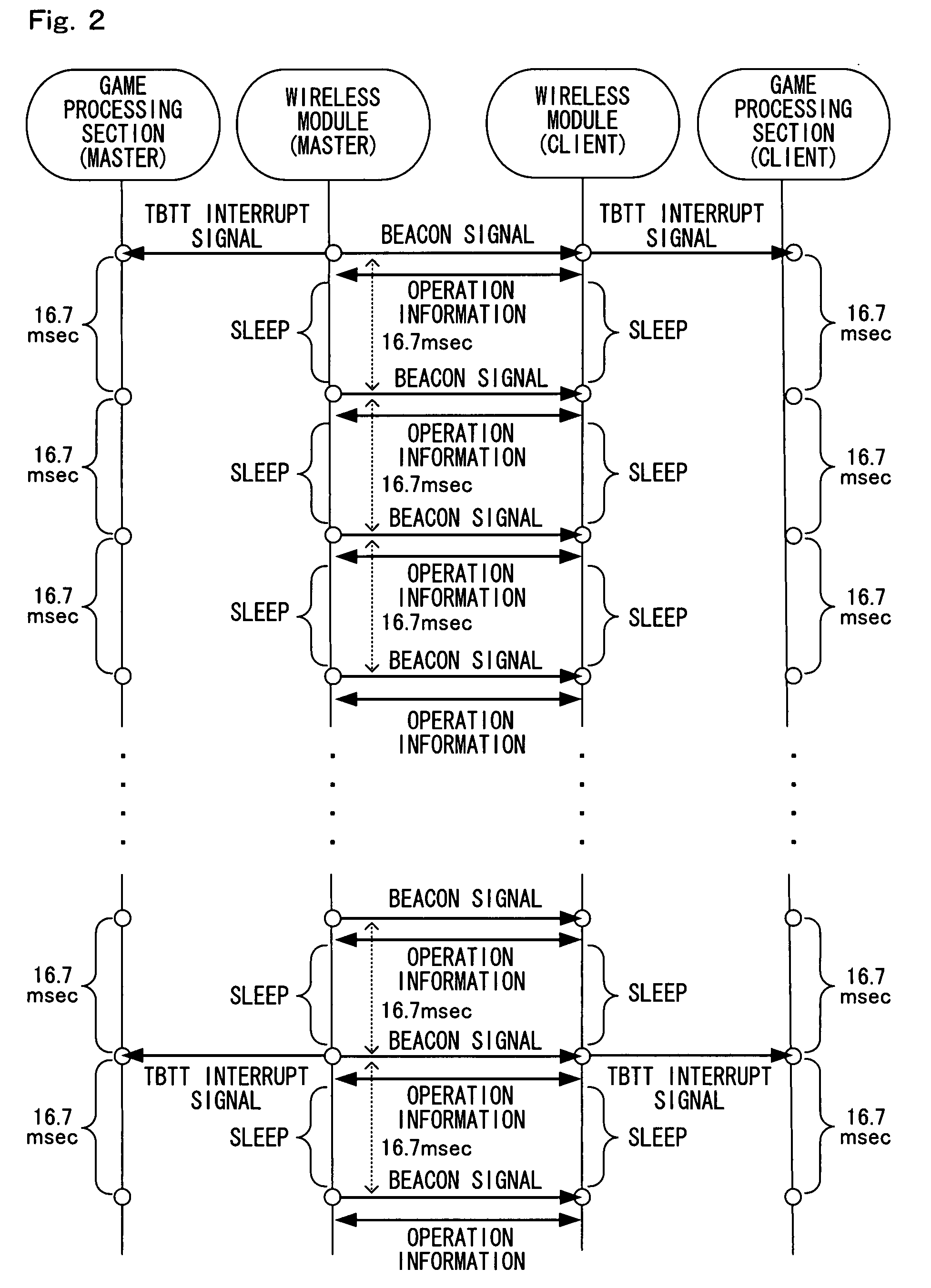

Game apparatus, wireless module and game system

InactiveUS20080096662A1Synchronization is simpleMinimize changesSynchronisation arrangementVideo gamesWirelessTransmission time

A master wireless module transmits a beacon signal to a client wireless module in the same cycle as a game processing cycle. Each of the master wireless module and the client wireless module outputs an interrupt signal when a transmission time of the beacon signal arrives. A game processing section of each of the master wireless module and the client wireless module adjusts a V counter based on the interrupt signal. Therefore, it becomes possible to easily synchronize, when a multiplayer gameplay is performed using a plurality of game apparatuses capable of performing wireless communication with each other, times at which the plurality of game apparatuses execute predetermined processes.

Owner:NINTENDO CO LTD

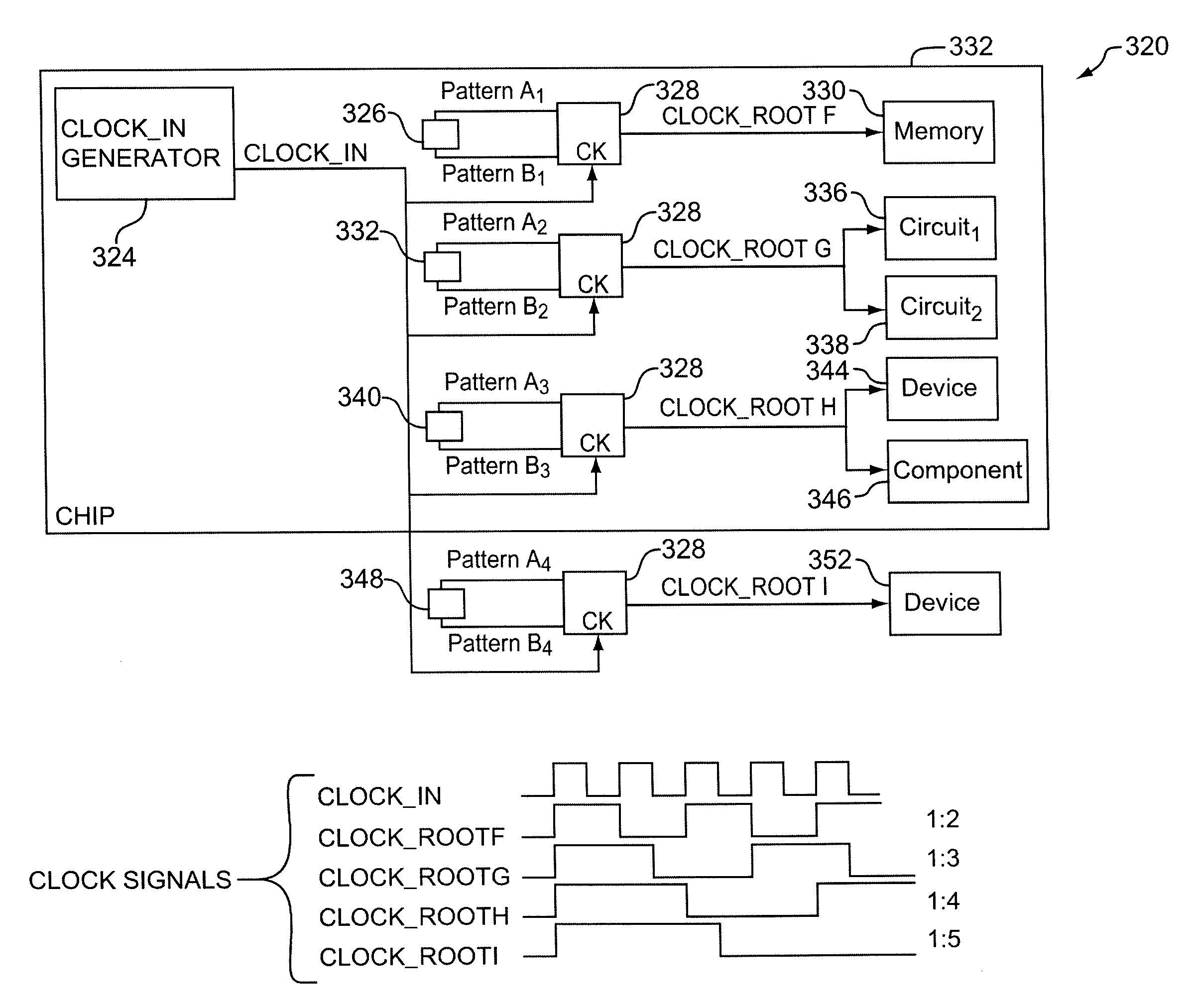

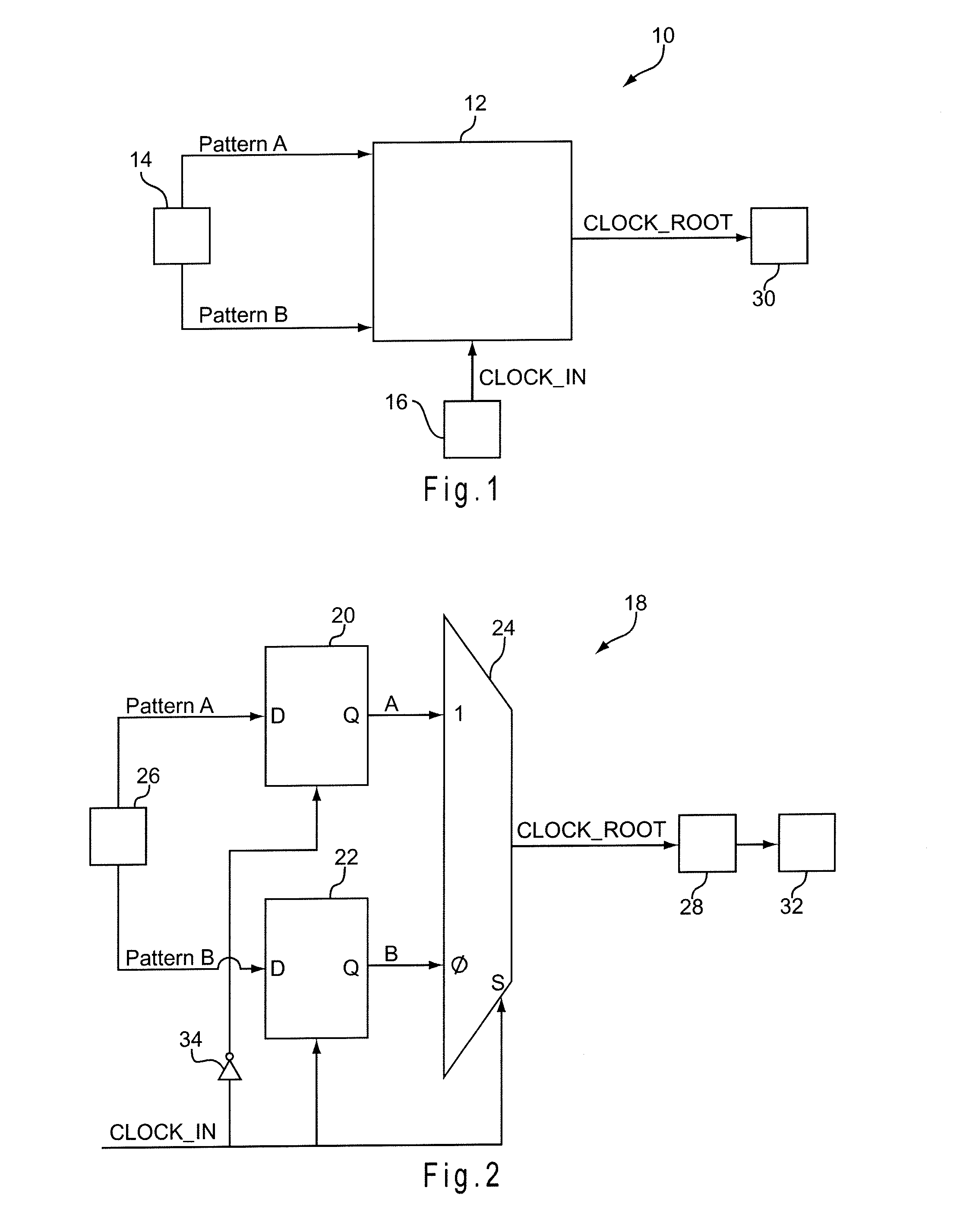

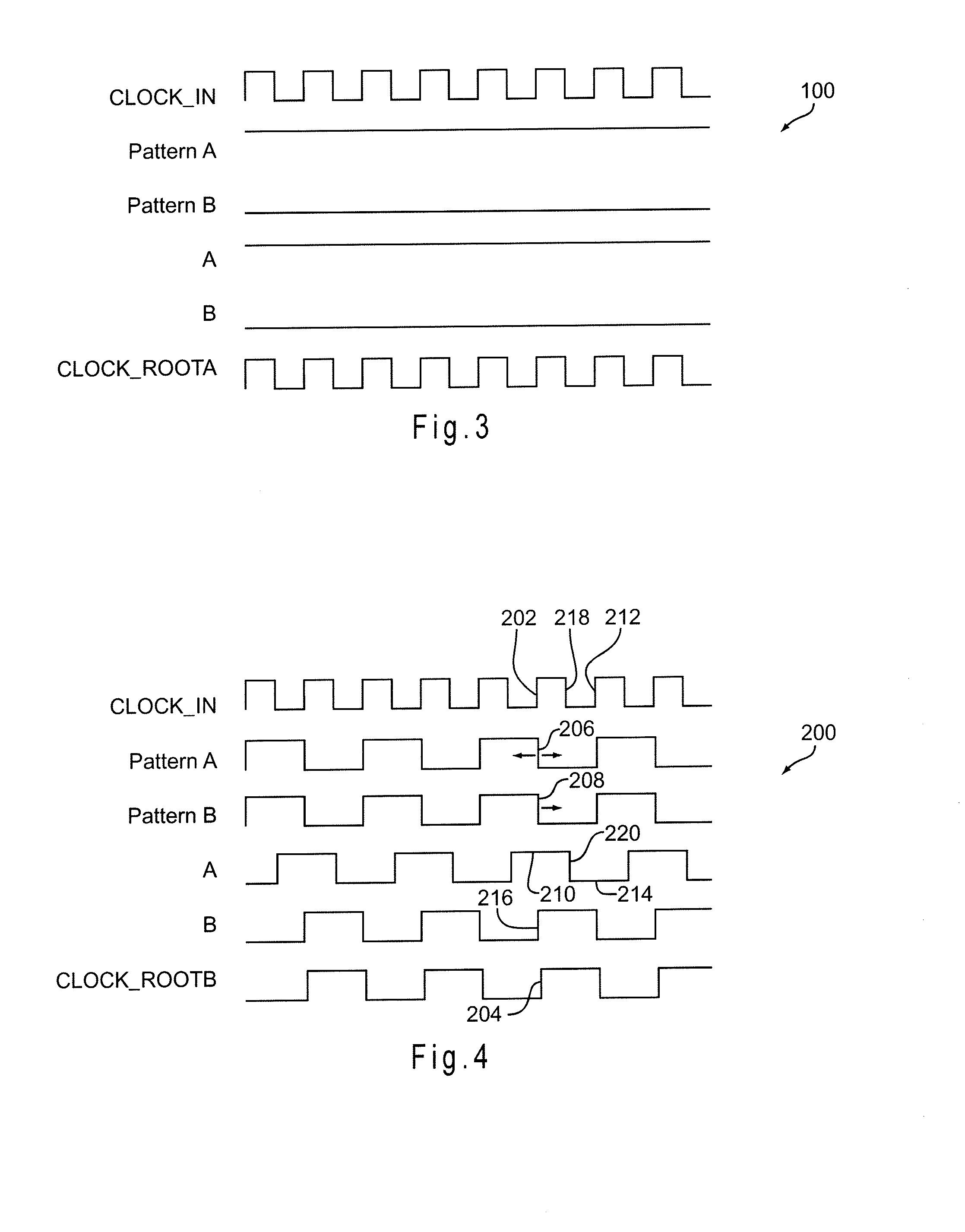

Apparatus and method for generating a clock signal

ActiveUS20080094117A1High strengthSynchronization is simplePulse automatic controlElectronic switchingComputer scienceClock signal

A apparatus and method are disclosed for generating one or more clock signals. A clock signal is generated based on pattern signals and a reference clock signal. When the reference clock signal transitions high, the state of a first pattern signal is output, and when the reference clock signal transitions low, the state of a second pattern signal is output. Successive states of the first and second pattern signals, selected according to the reference clock signal, provide the generated clock signal.

Owner:MARVELL ISRAEL MISL

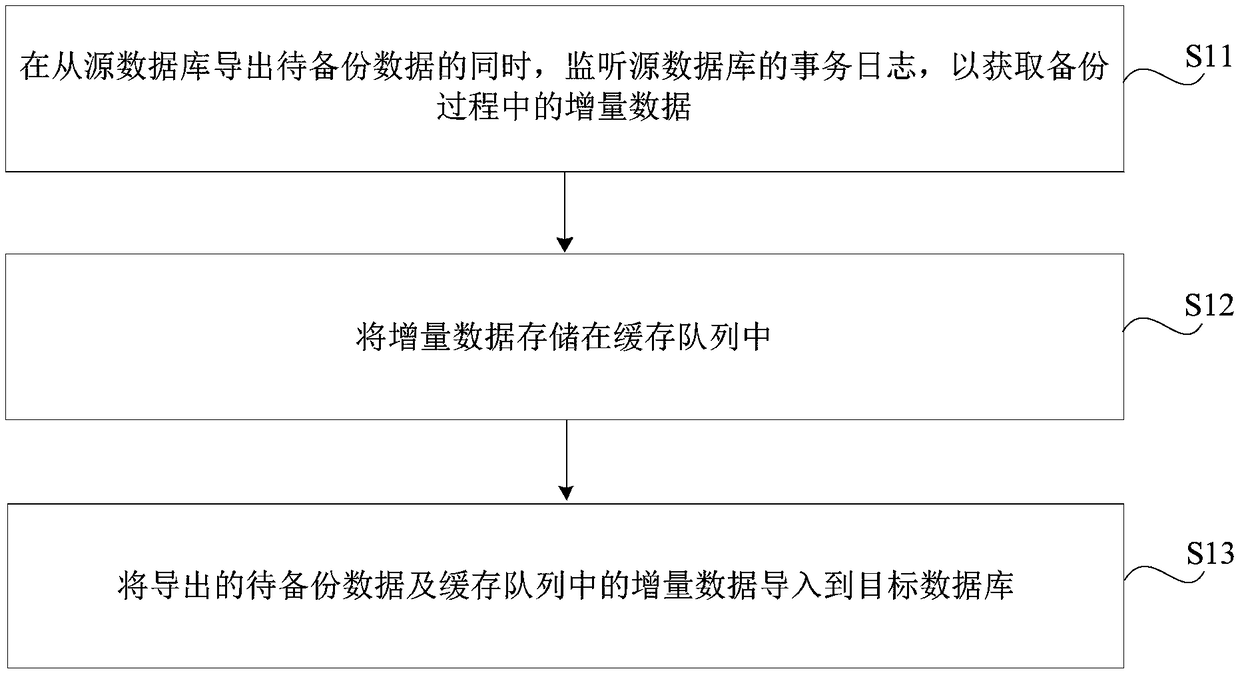

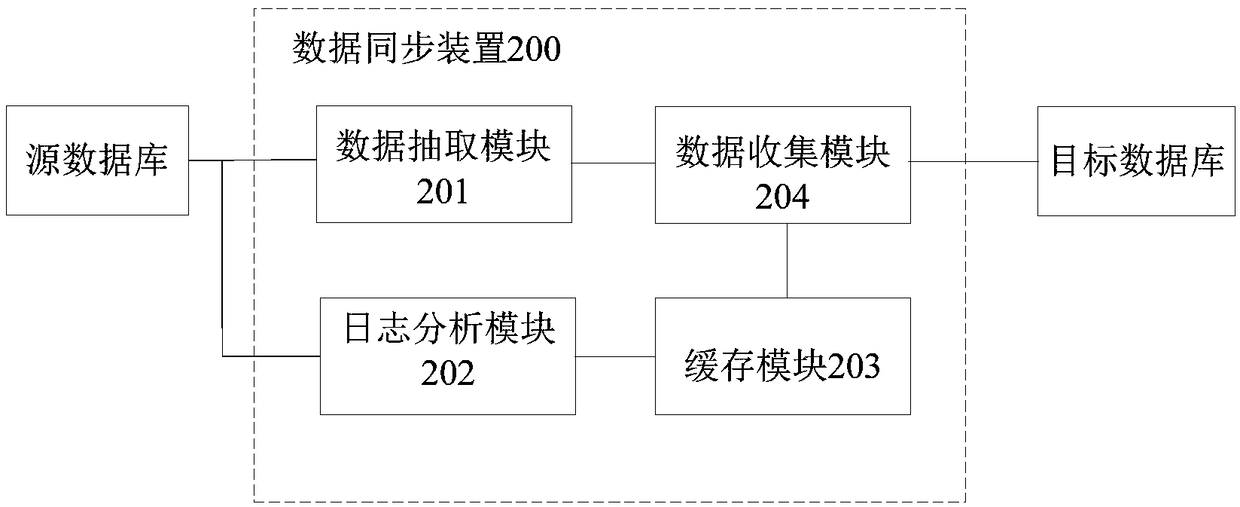

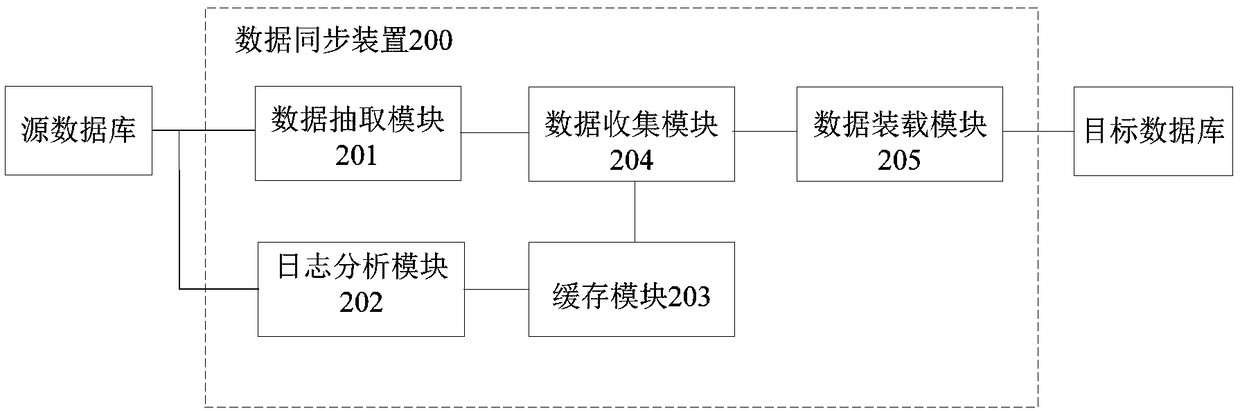

Data synchronization method, apparatus, storage medium, and electronic apparatus

ActiveCN109241175AAvoid lossSimplify the data synchronization processDatabase updatingDatabase distribution/replicationIncremental backupData synchronization

The invention relates to a data synchronization method, a device, a storage medium and an electronic device, which can simultaneously carry out steps of data initialization and incremental synchronization, simplifies the process of the whole database synchronization, and avoids incremental synchronization errors caused by cleaning transaction logs. The method comprises the following steps: while the data to be backed up is derived from the source database, the transaction log of the source database is monitored to obtain incremental data in the backup process; storing the incremental data in acache queue; the exported data to be backed up and the incremental data in the cache queue are imported to the target database.

Owner:NEUSOFT CORP

Video/Audio Reproducing Apparatus

InactiveUS20090180755A1Achieve synchronizationSynchronization is simpleTelevision system detailsPulse modulation television signal transmissionComputer hardwareAudio frequency

A video / audio reproducing apparatus, to be connected via a first apparatus with a second apparatus, comprises: a first receiving portion, which is configured to receive video data, audio data, and first reproduction synchronization information for reproduction synchronization between the video data and the audio data; a second receiving portion, which is configured to receive second reproduction synchronization information for reproduction synchronization between the video data and the audio data from the first apparatus; and a controlling portion, which is configured to reproduce the video data and the audio data received by the first receiving portion, upon basis of the first reproduction synchronization information and the second reproduction synchronization information, which are received by the first receiving portion and the second receiving portion.

Owner:HITACHI LTD

Tool path measurement

InactiveUS6498653B1Small toleranceLarge lateral displacementComputer controlSimulator controlThree-dimensional spaceClassical mechanics

The degree of accuracy a machine tool or the like is moved along a given path is determined by a unique preferably laser beam directing measuring system directing simultaneously or in sequence a laser beam parallel to the orthogonal axes of the two or three dimensional space in which the spindle or other object is to be moved in a path which can diverge appreciably in directions other than the directions of these axes. The beam directing means includes means which provides a measure of the actual positions the object has at various sampling times relative to the axis along which the beam is directed. This actual path position data is compared to the desired path position data used to program the object moving machine to determine the path position error at the sampling times involved.

Owner:OPTODYNE

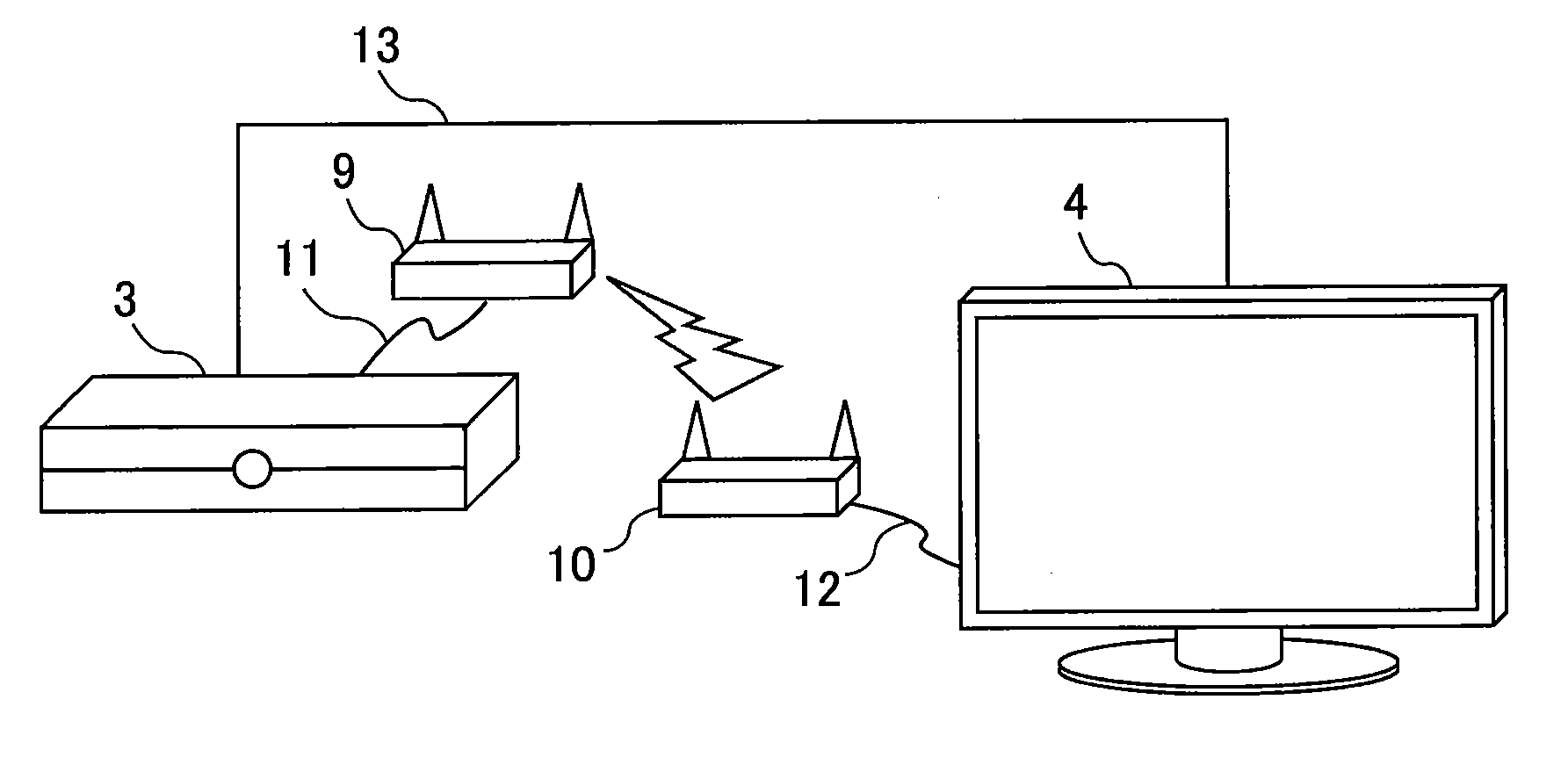

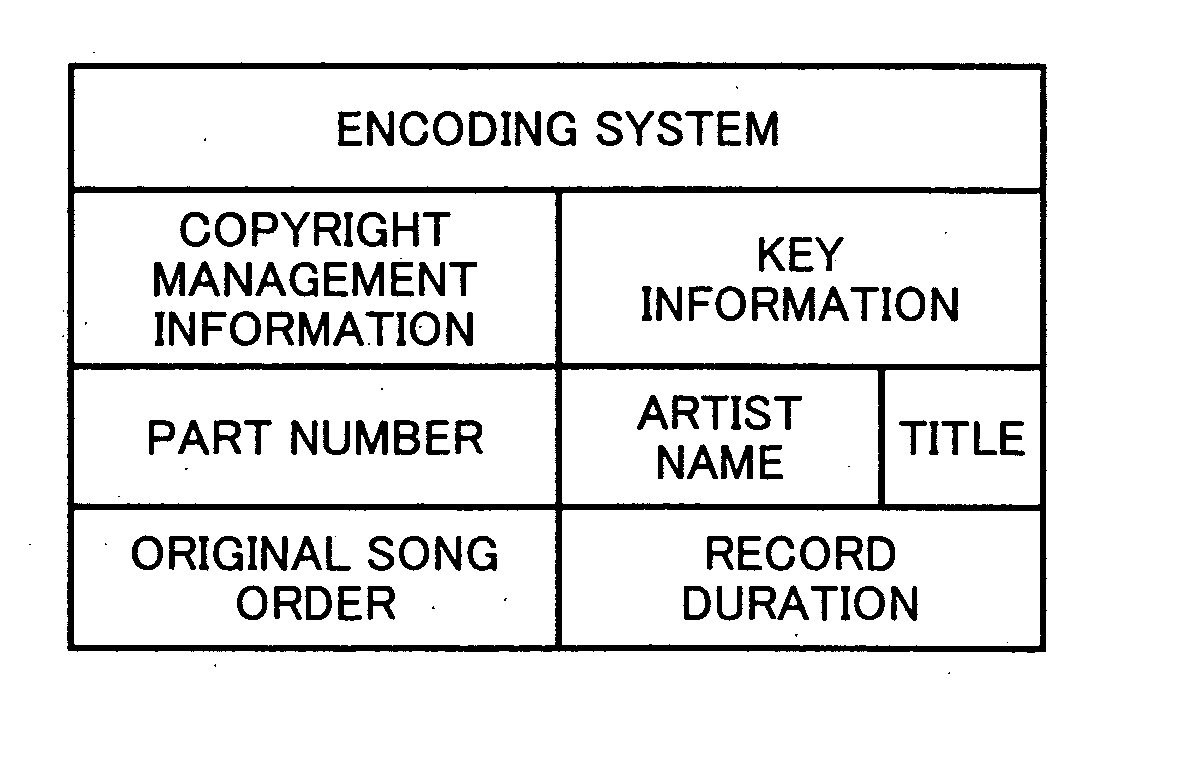

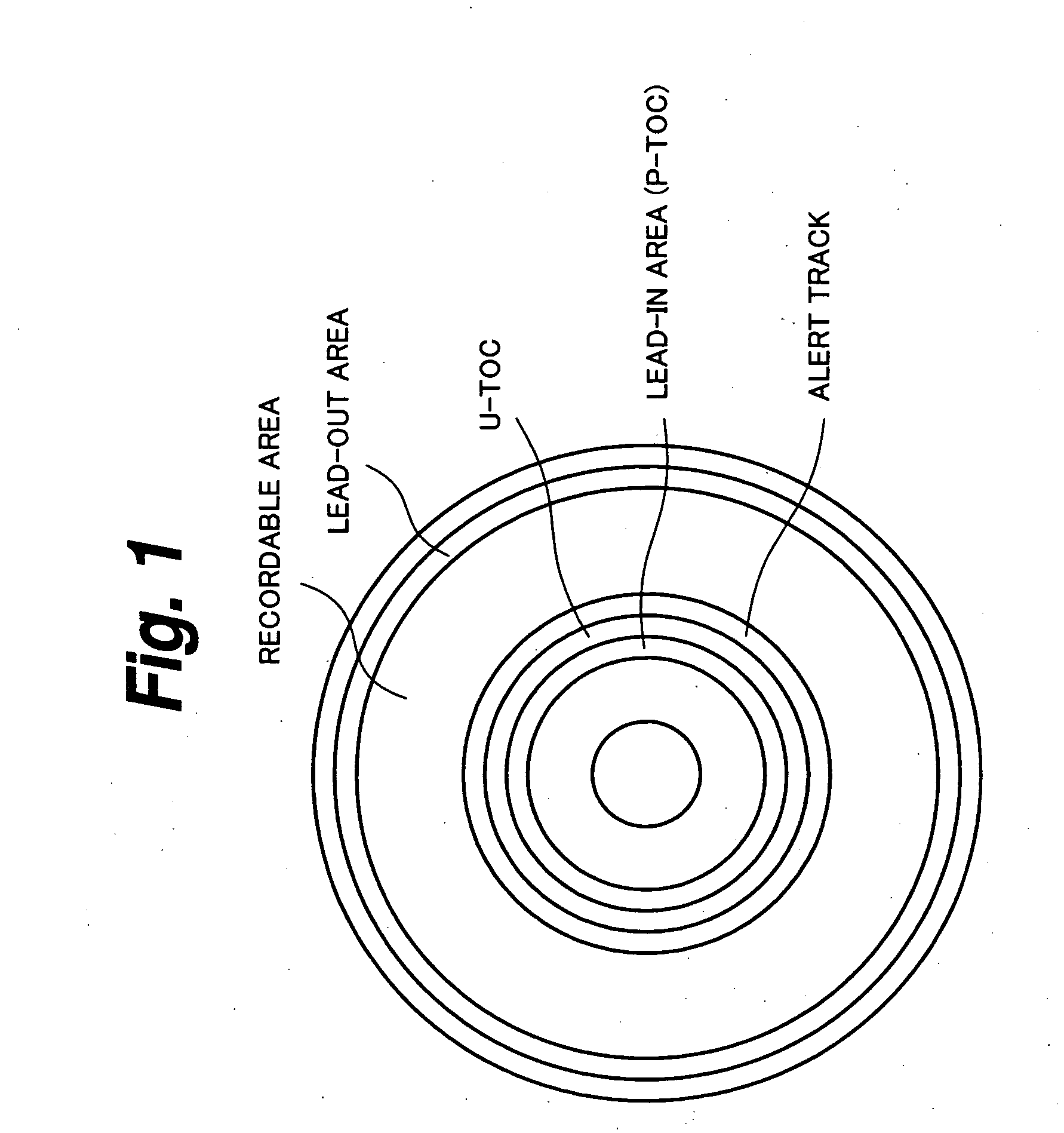

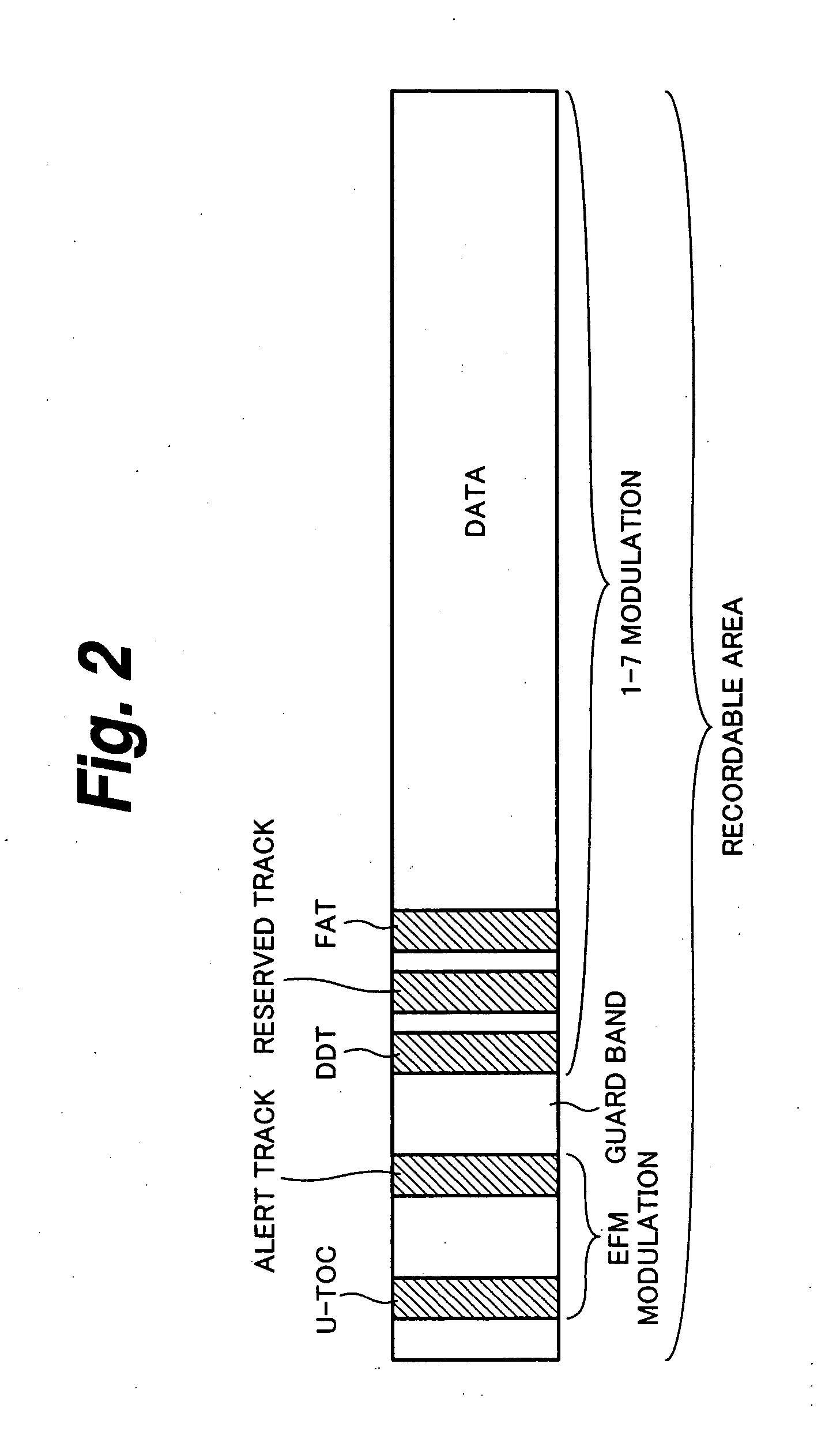

Content data transmission system and content data transmission method

InactiveUS20050273632A1Easy to updateSynchronization is simpleDigital data processing detailsUser identity/authority verificationComputer hardwareCompact disc

A library of a PC is easily synchronized with recorded contents of a disc loaded into a recording and reproducing apparatus (PD). The PC has a dynamic group and a database. Contents of the dynamic group are, dynamically changed. The dynamic group is correlated with the ID of the disc on which the contents of the dynamic group have been recorded. When the CP and the PD are connected, the ID of the disc loaded into the PD is read. The database is referenced for the ID of the disc. When there is a corresponding dynamic group, the dynamic group is compared with the recorded contents of the disc. Contents that exist in the dynamic group and that do not exist on the disc are checked out to the disc. In contrast, contents that exist on the disc and that do not exist in the dynamic group are checked in to the PC. In addition, the reproduction order of contents of the dynamic group is reflected to contents of the disc. The user can synchronize the recorded contents of the disc with the library of the PC only by connecting the PC and the PD.

Owner:SONY CORP

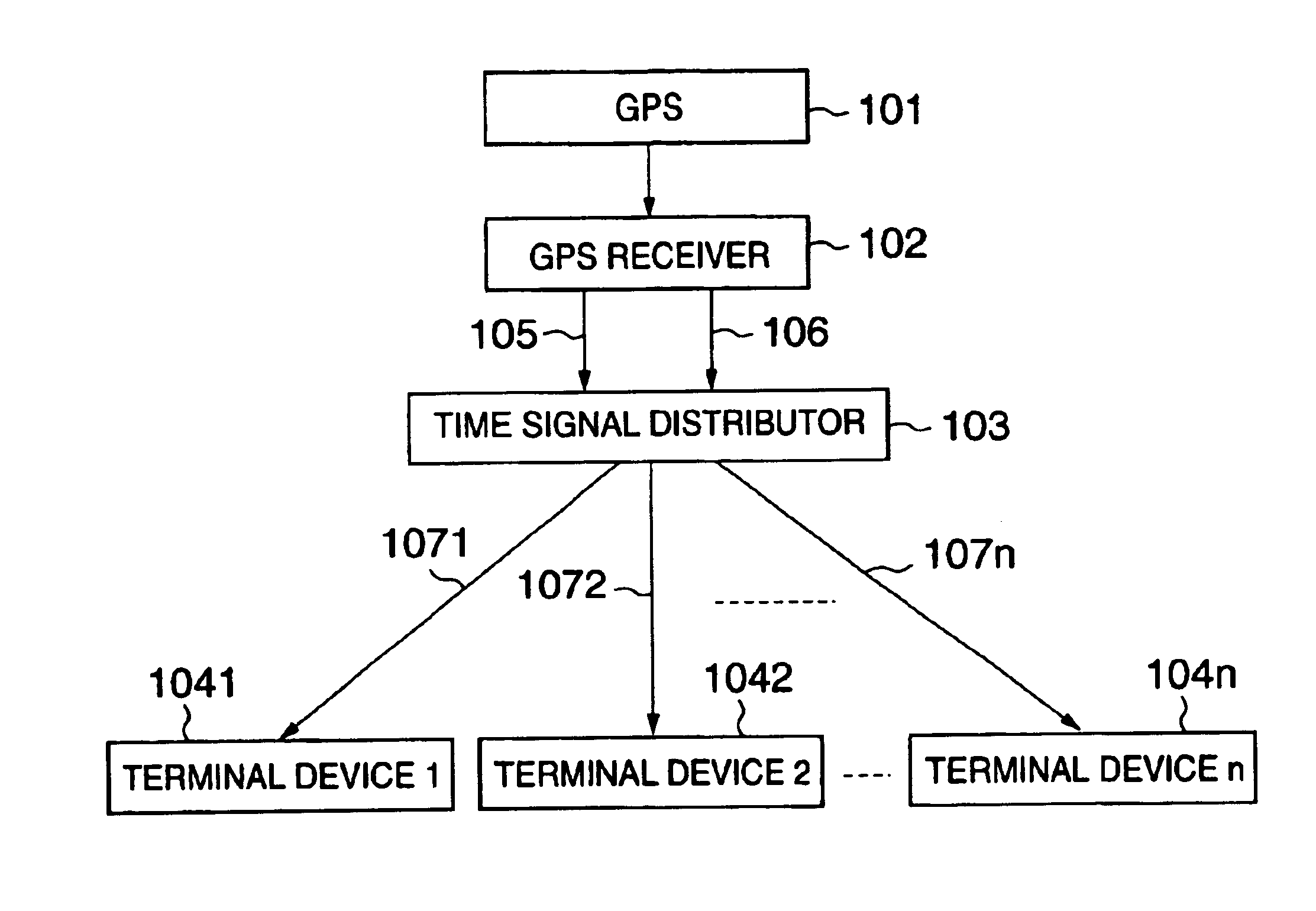

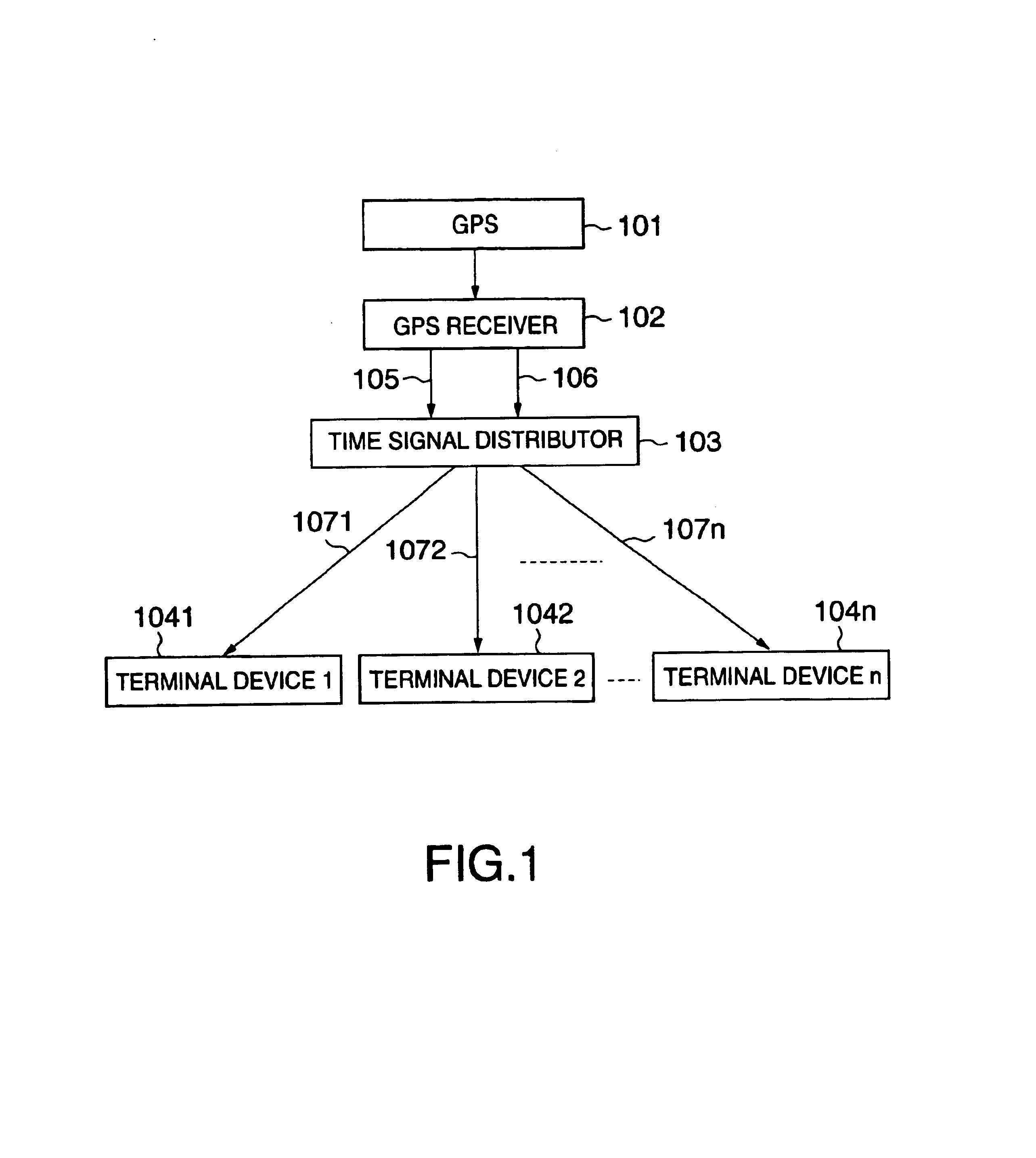

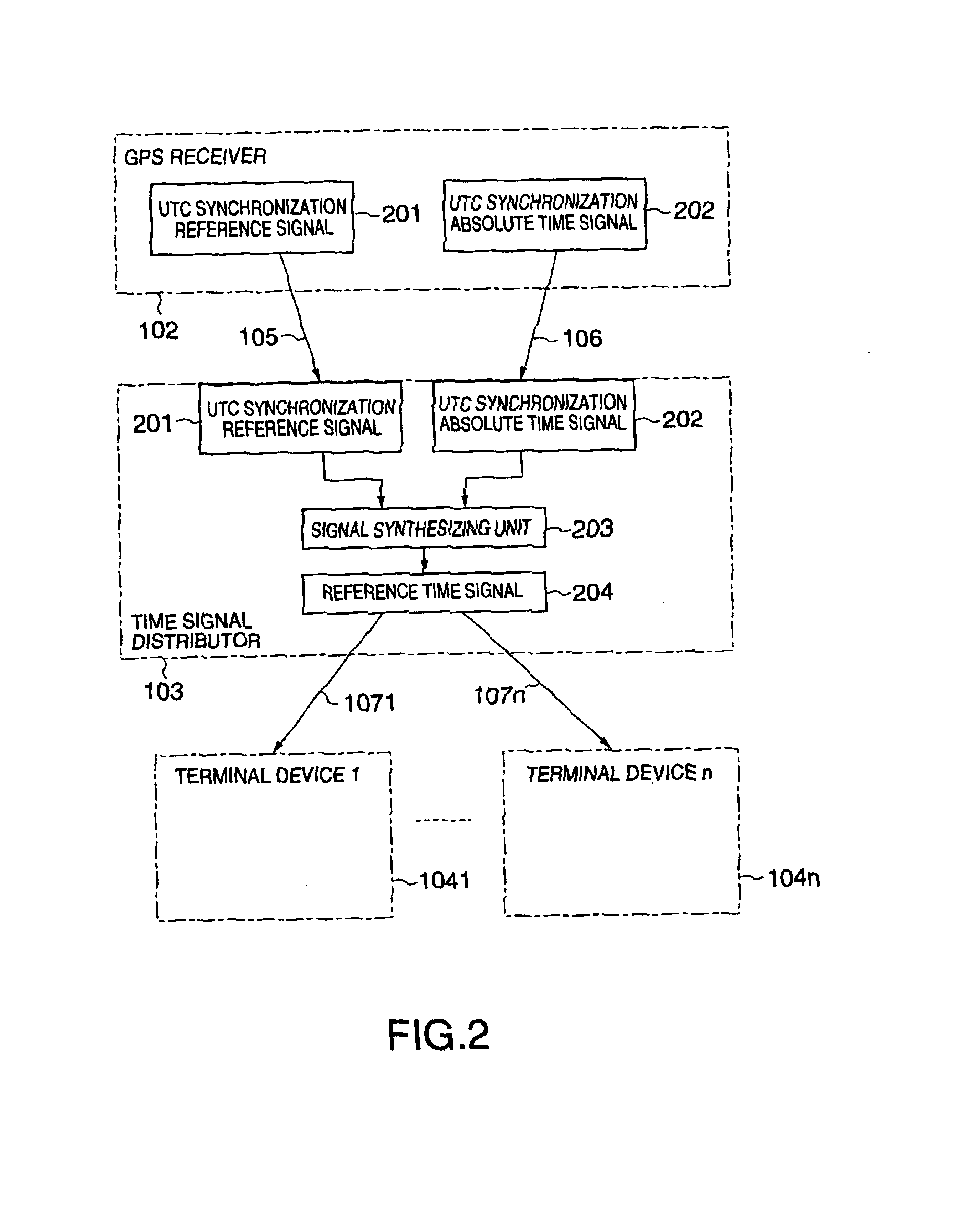

Time synchronizing system

InactiveUS6847691B2Improve accuracyGood economical characteristicSynchronous motors for clocksSetting time indicationControl orientedData synchronization

A time synchronization system comprises a GPS (Global Positioning System) receiver for receiving a time signal from a Global Positioning System (GPS), and outputting a UTC (Universal Time Coordinated) synchronization reference signal synchronizing with UTC and a UTC synchronization absolute time signal, and a time signal distributor for generating a reference time signal synchronizing with UTC from the synchronization reference signal and the absolute time signal, and transmits this reference time signal in distribution to a plurality of distributed control oriented terminal devices. The time synchronization between the plurality of distributed control oriented terminal devices can be thereby taken.

Owner:KK TOSHIBA

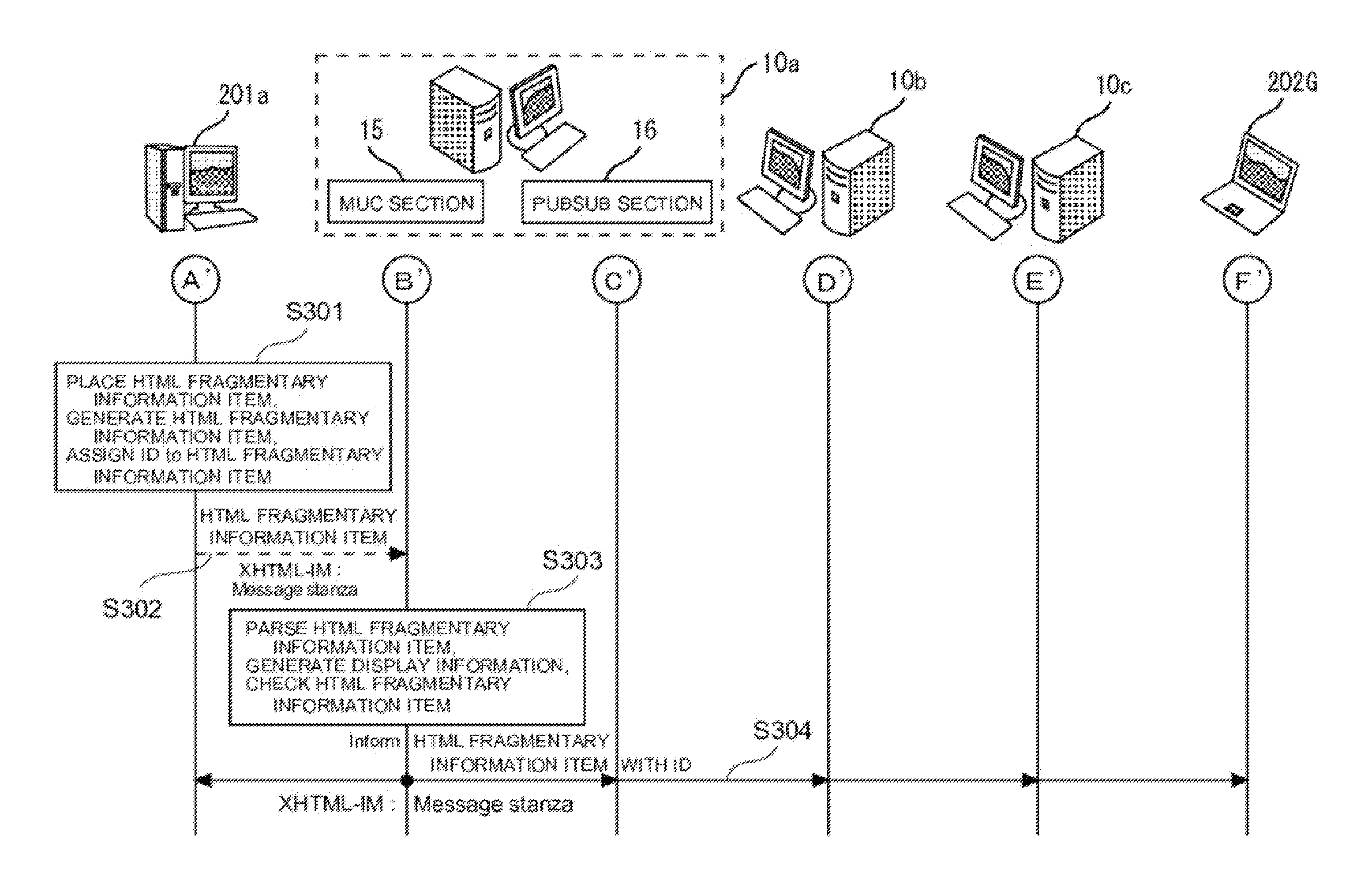

Communication method, master display device, slave display device, and communication system furnished therewith

InactiveUS20110282962A1Synchronization is simpleEasily synchronize structured display informationStatic indicating devicesMultiple digital computer combinationsCommunications systemDisplay device

A master display device and slave display devices share structured display information in which a plurality of html fragmentary information items each including display data are structured through communication via a network and further produce the same display on the basis of the structured display information. The master display device, upon modifying the html fragmentary information item, sends the slave display devices a notice reporting that the html fragmentary information item is modified and an ID (ID information) for identifying the modified html fragmentary information item.

Owner:FUNAI ELECTRIC CO LTD

Method and system to synchronize acoustic therapy with ultrasound imaging

ActiveUS7621873B2Synchronization is simpleGood synchronizationUltrasonic/sonic/infrasonic diagnosticsUltrasound therapyUltrasound imagingSonification

Owner:UNIV OF WASHINGTON

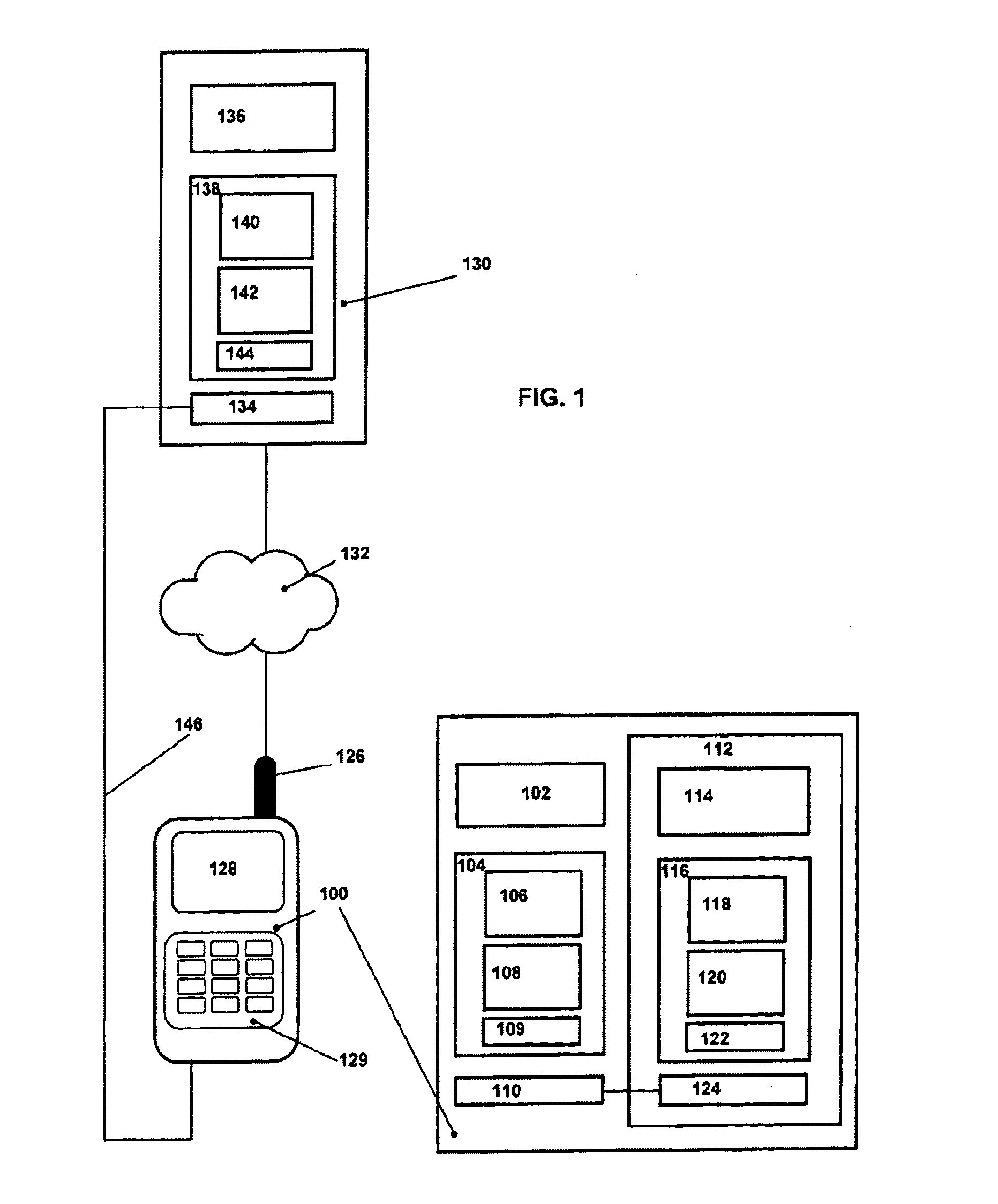

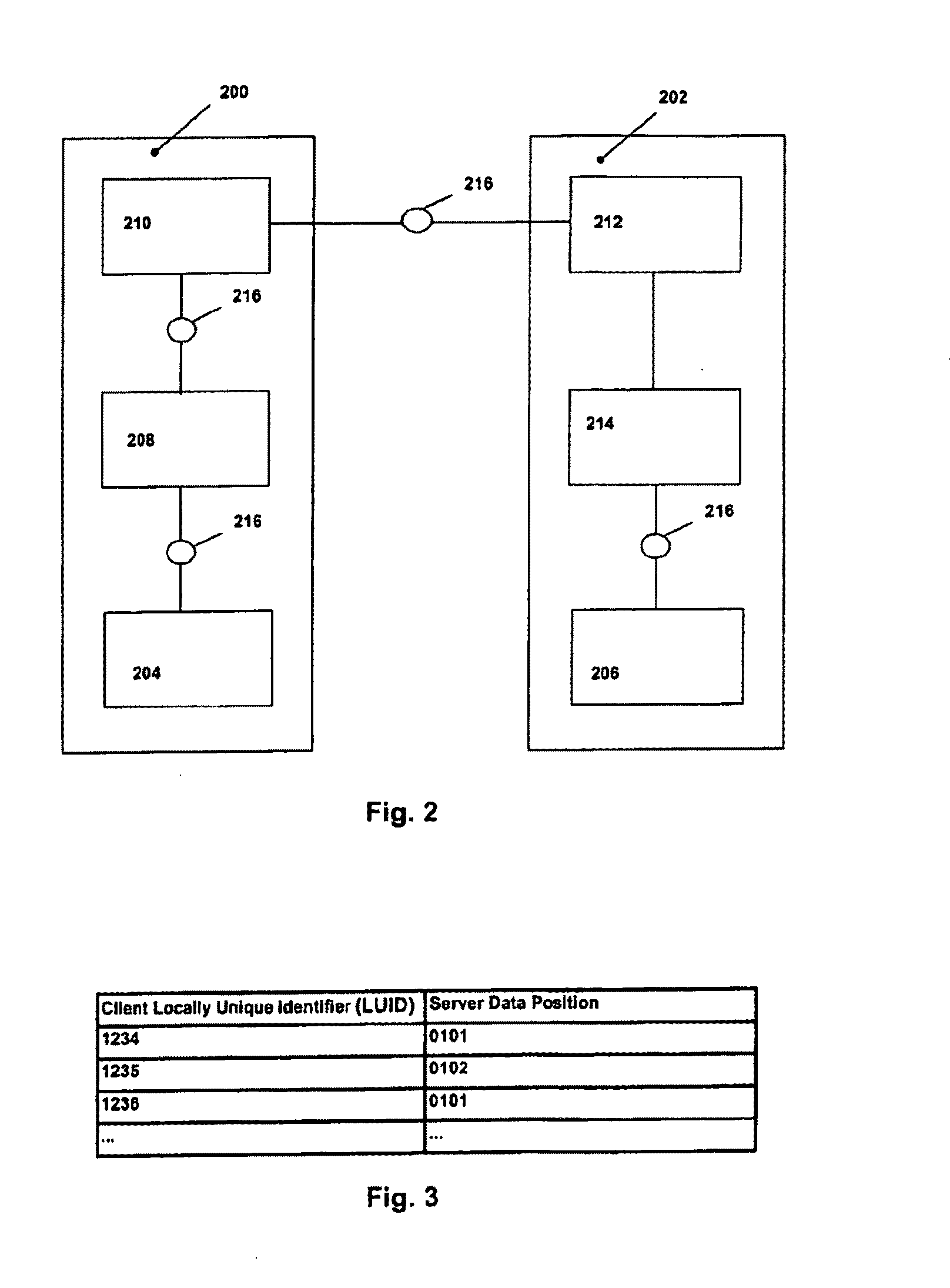

Data Synchronization

InactiveUS20100287307A1Reduced power dissipationReduce amountDigital data processing detailsMultiple digital computer combinationsClient-sideTelecommunications Device

A method for synchronizing a first and a second set of data of a mobile telecommunication device includes: —providing a first processing device, the first processing device including the first set of data, —providing a second processing device, the second processing device including the second set of data, —providing a server, the server being comprised on the first processing device, —providing a client, the client being comprised in the second processing device, —synchronization of the first and the second set of data by way of a communication between the server and the client.

Owner:MORPHO CARDS

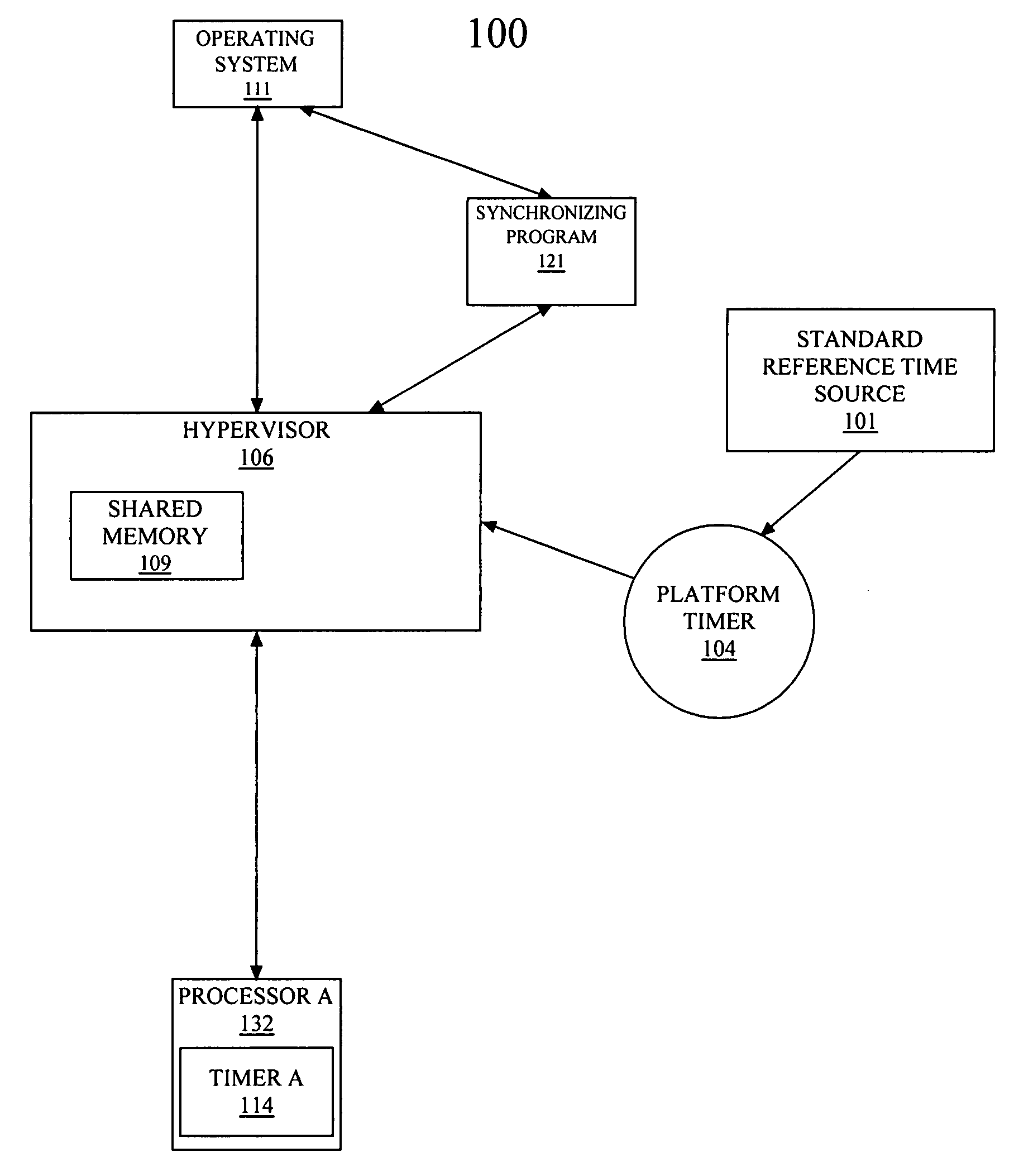

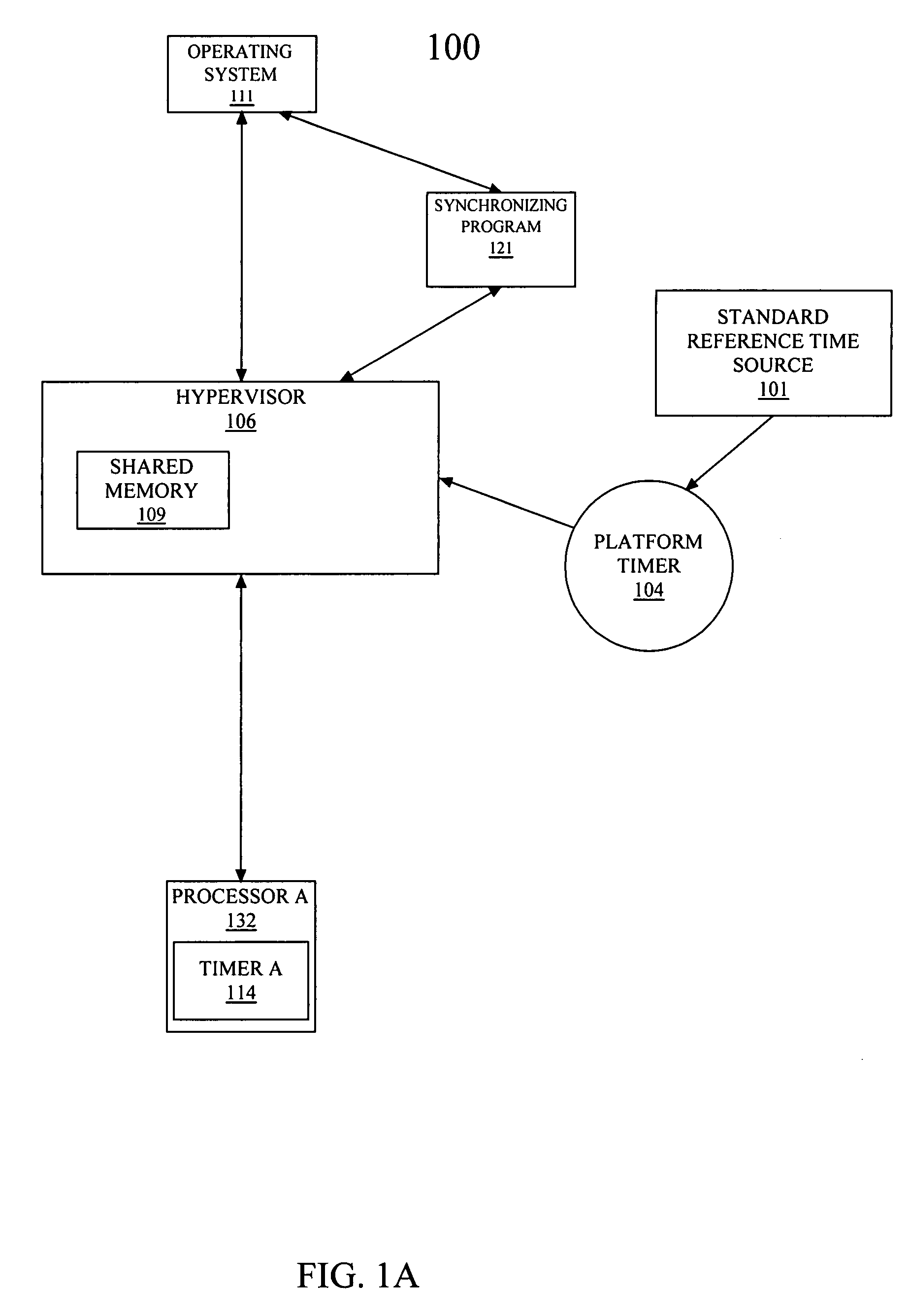

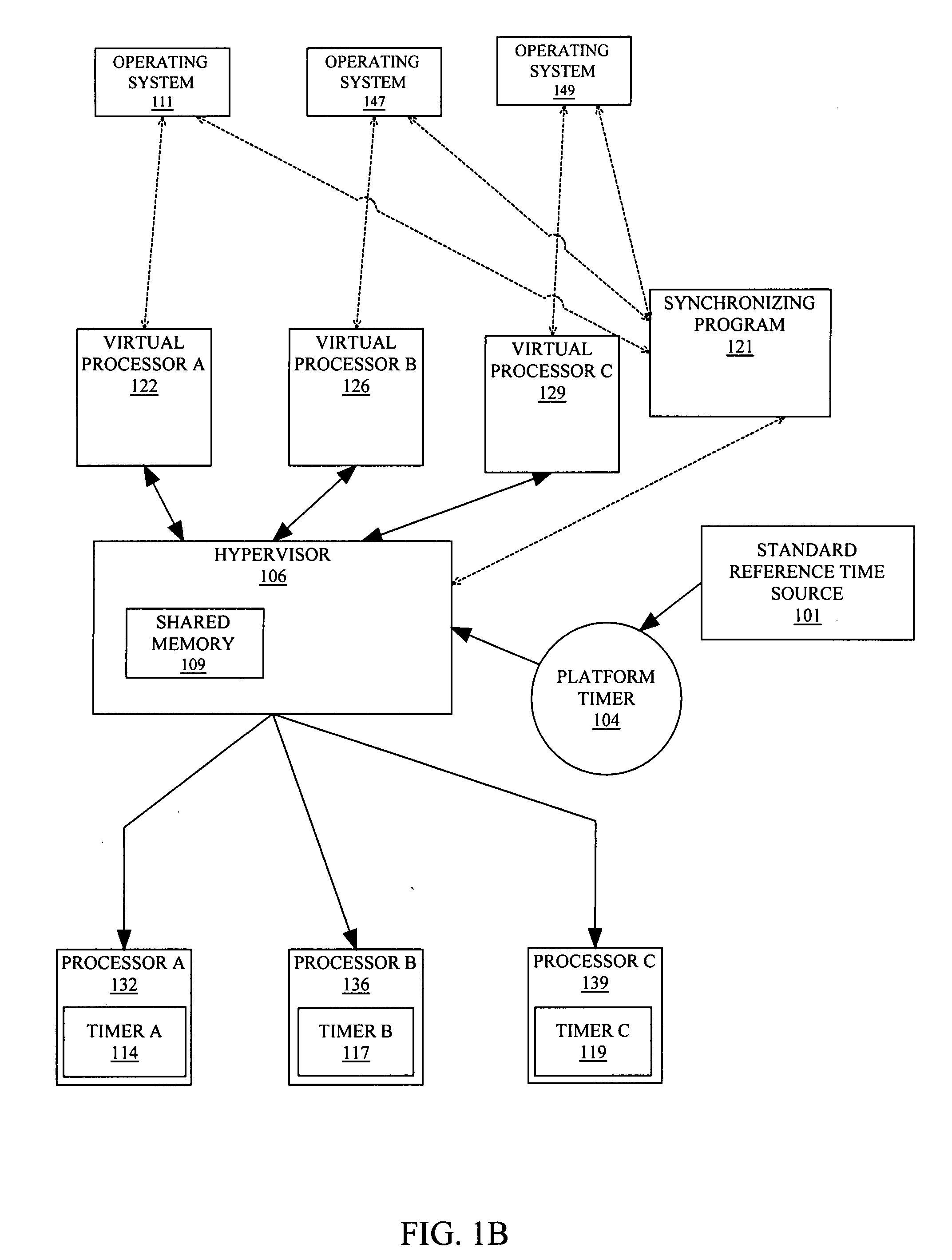

Tracking current time on multiprocessor hosts and virtual machines

ActiveUS20080126820A1Synchronization is simpleAccurate timingMultiple digital computer combinationsGenerating/distributing signalsCurrent timeVirtual machine

An operating system in a virtual environment can obtain the current time of the processor that the OS is utilizing through a method for synchronizing timers on multiple processors with a standard reference time, such as the Coordinated Universal Time (UTC). A hypervisor controlling the processors obtains a number of synchronization values that, together with a local timer counter value, are utilized by the guest operating system to determine the physical processor time.

Owner:CITRIX SYST INC

Synchronizing clocks across a communication link

InactiveUS20070002987A1Synchronization is simpleHigh-precision detectionSynchronisation arrangementNetwork traffic/resource managementTelecommunications linkSlave clock

Apparatus, system and method for synchronizing one or more clocks across a communication link. A slave clock may be synchronized to a master clock by means of a synchronization signal sent from the master to the slave clock side of the link. The synchronization signal may be an expected signal pattern sent at intervals expected by the slave side. The slave clock may correlate received signals with a representation of the expected synchronization signal to produce a correlation sample sequence at a first sample rate which is related as n times the slave clock rate. The synchronization signal receipt time indicated by the correlation sample sequence may be refined by interpolating the correlation sample sequence around a best correlation sample to locate a best interpolation at an interpolation resolution smaller than the sample resolution. The best interpolation may in turn be further refined by estimating between interpolator outputs adjacent to the best interpolation output. The synchronization signal receipt time thus determined is compared to the expected time based upon the slave clock, which is adjusted until the times match. After initialization, all slave clock errors are preferably accumulated to prevent long-term slip between the slave and master clocks. Formerly independent master and slave clocks synchronized across the communication link constitute a noncommon clock which may be compared on each side of the link to secondary independent clocks, and the secondary independent clocks may then be separately synchronized by adjusting one to have the same difference from its local noncommon clock as the secondary clock on the other side of the link has from its local noncommon clock.

Owner:WI LAN INC

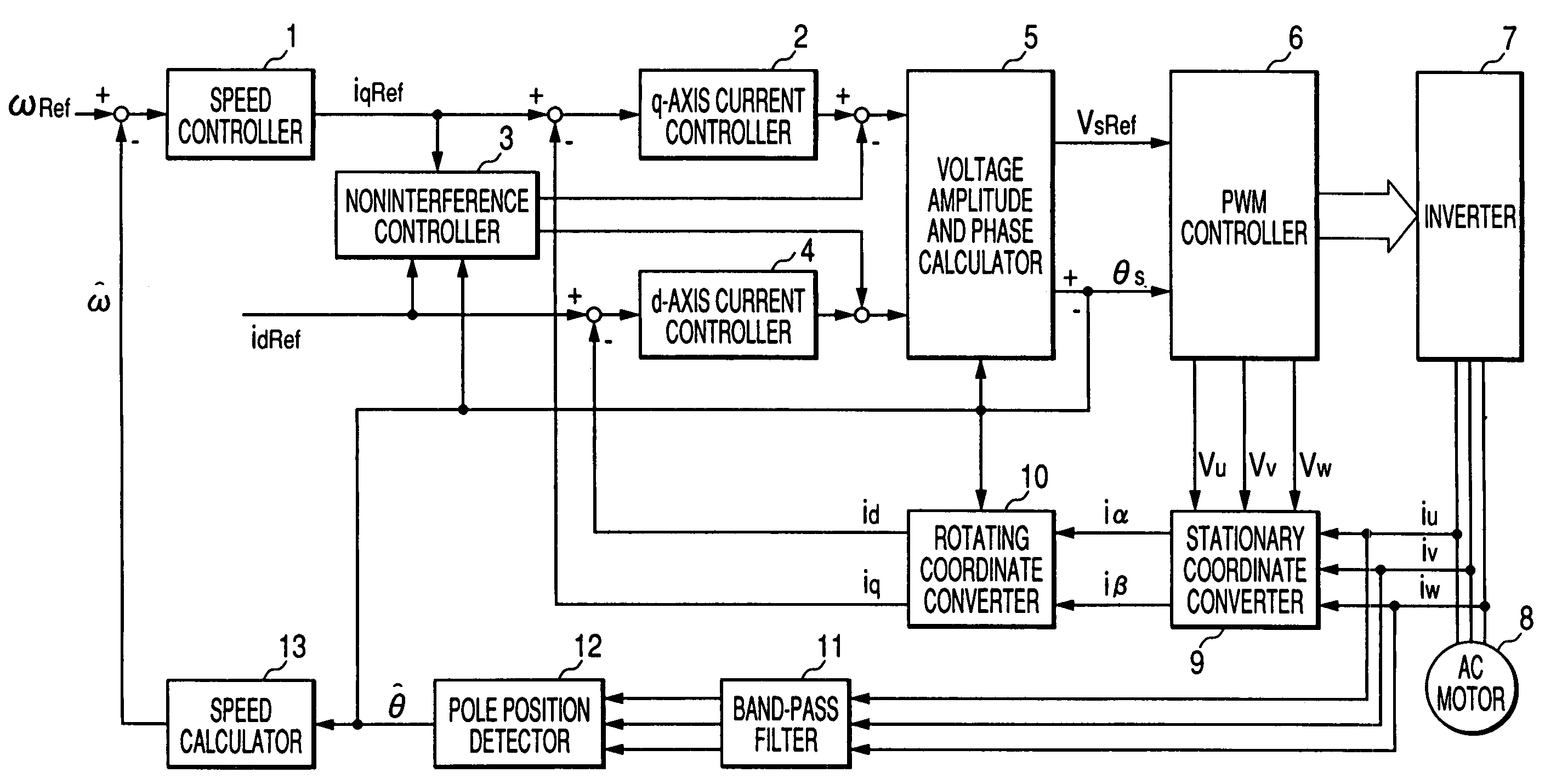

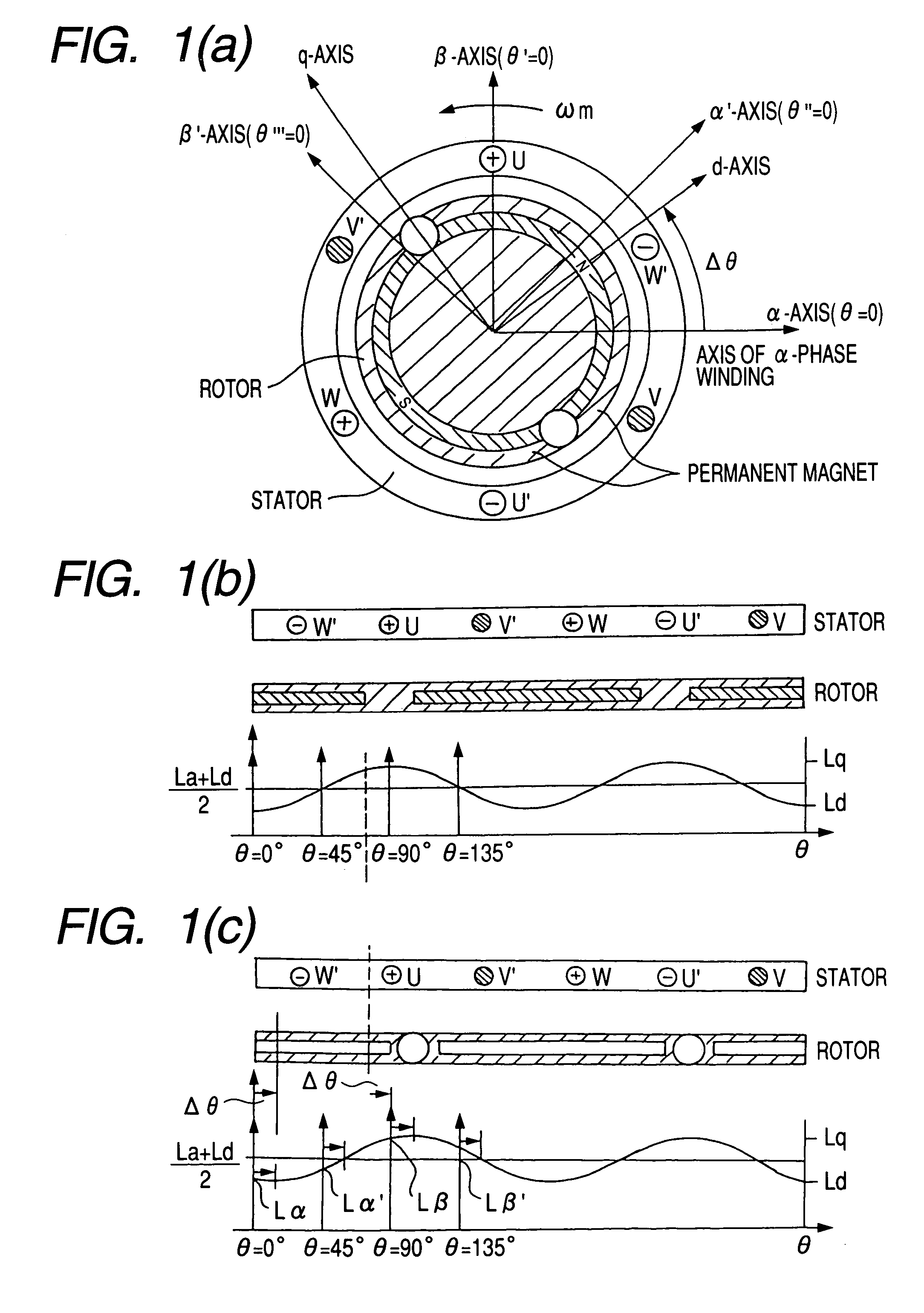

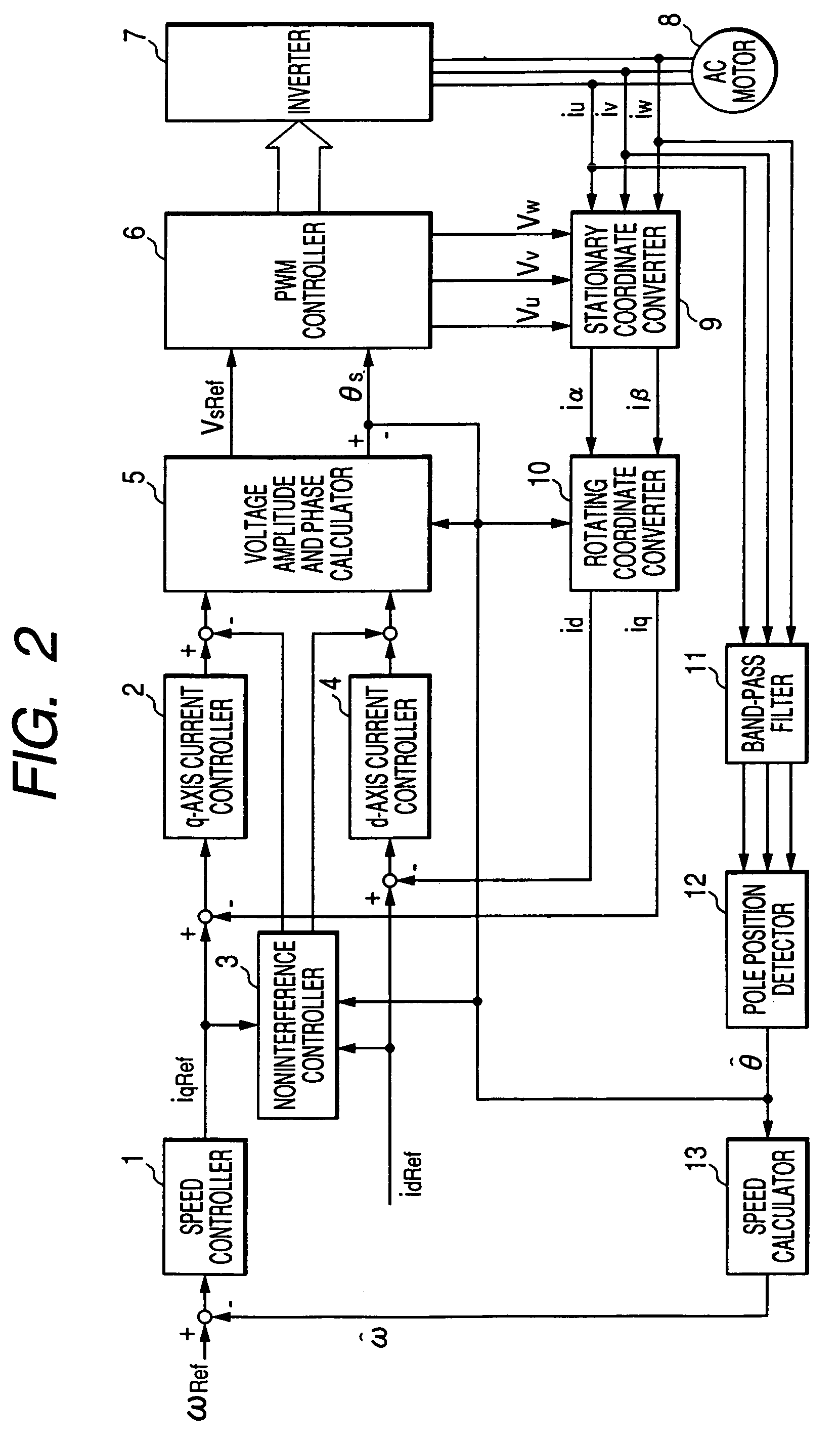

Electric motor pole position sensing method, pole position sensing apparatus, and electric motor control apparatus using the same

InactiveUS7190130B2Easily synchronizeSynchronization is simpleSynchronous motors startersVector control systemsPower inverterEngineering

It is an object of the invention to provide a method which can detect a magnetic pole position easily and surely by using high-frequency currents such as harmonics of an inverter output and carrier frequency components. The invention provides a method of detecting a magnetic pole position of a motor and an apparatus for detecting a magnetic pole position in which, although high-frequency currents of carrier frequency components or the like are used, a special current detecting circuit is not required, and synchronization between the current detection timing and the position calculation can be easily attained, and also to provide an apparatus for controlling a motor using the same.

Owner:YASKAWA DENKI KK

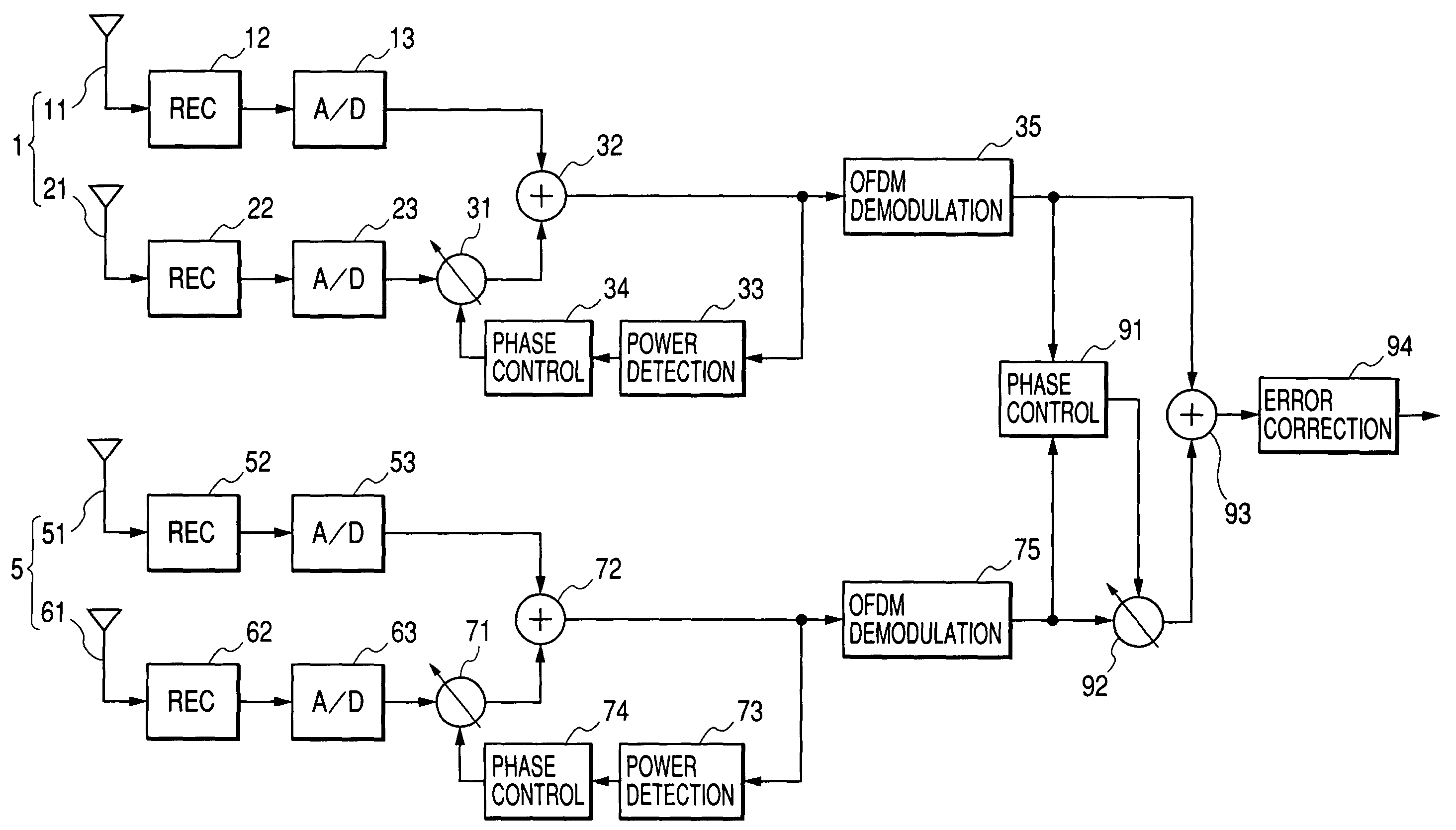

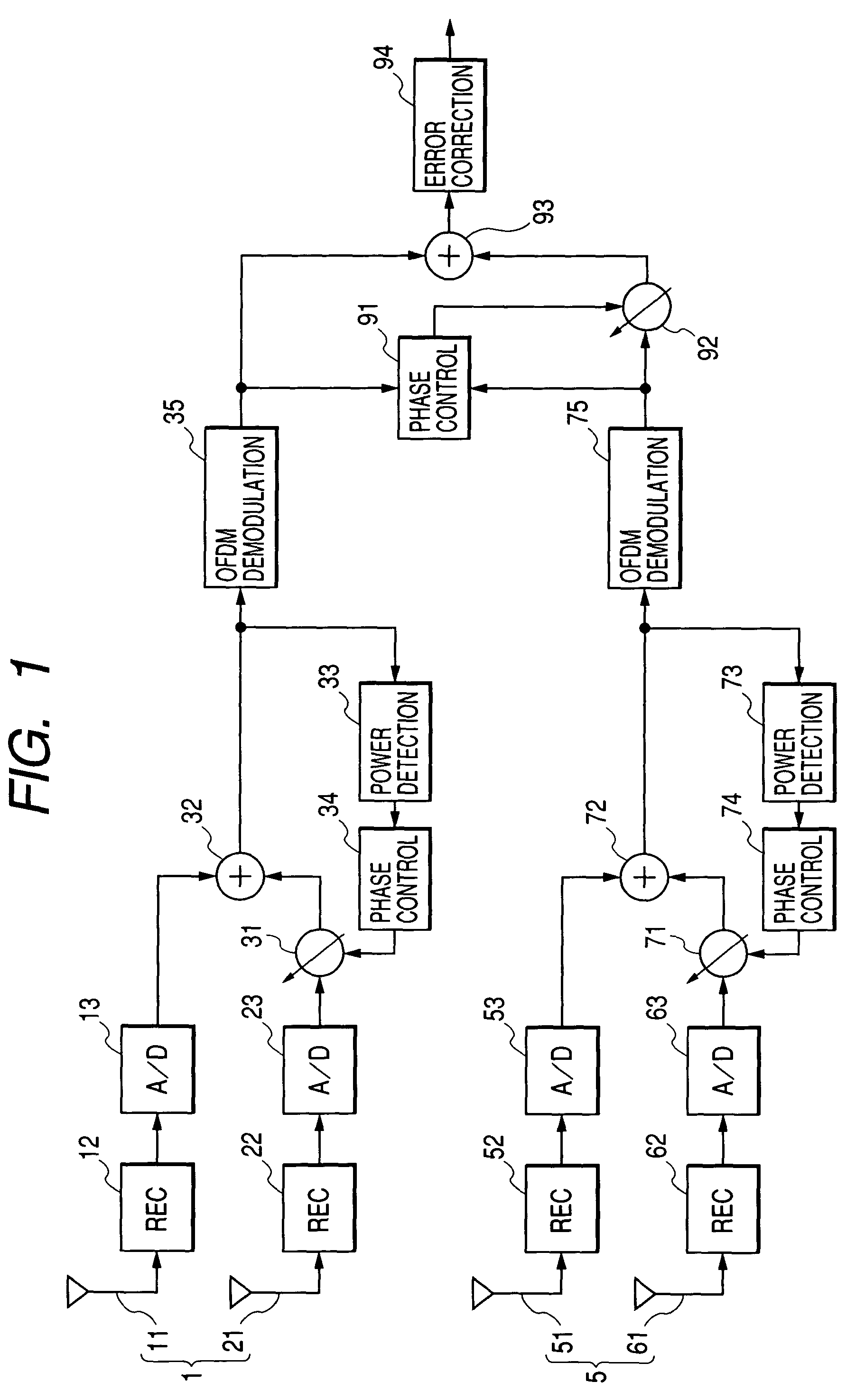

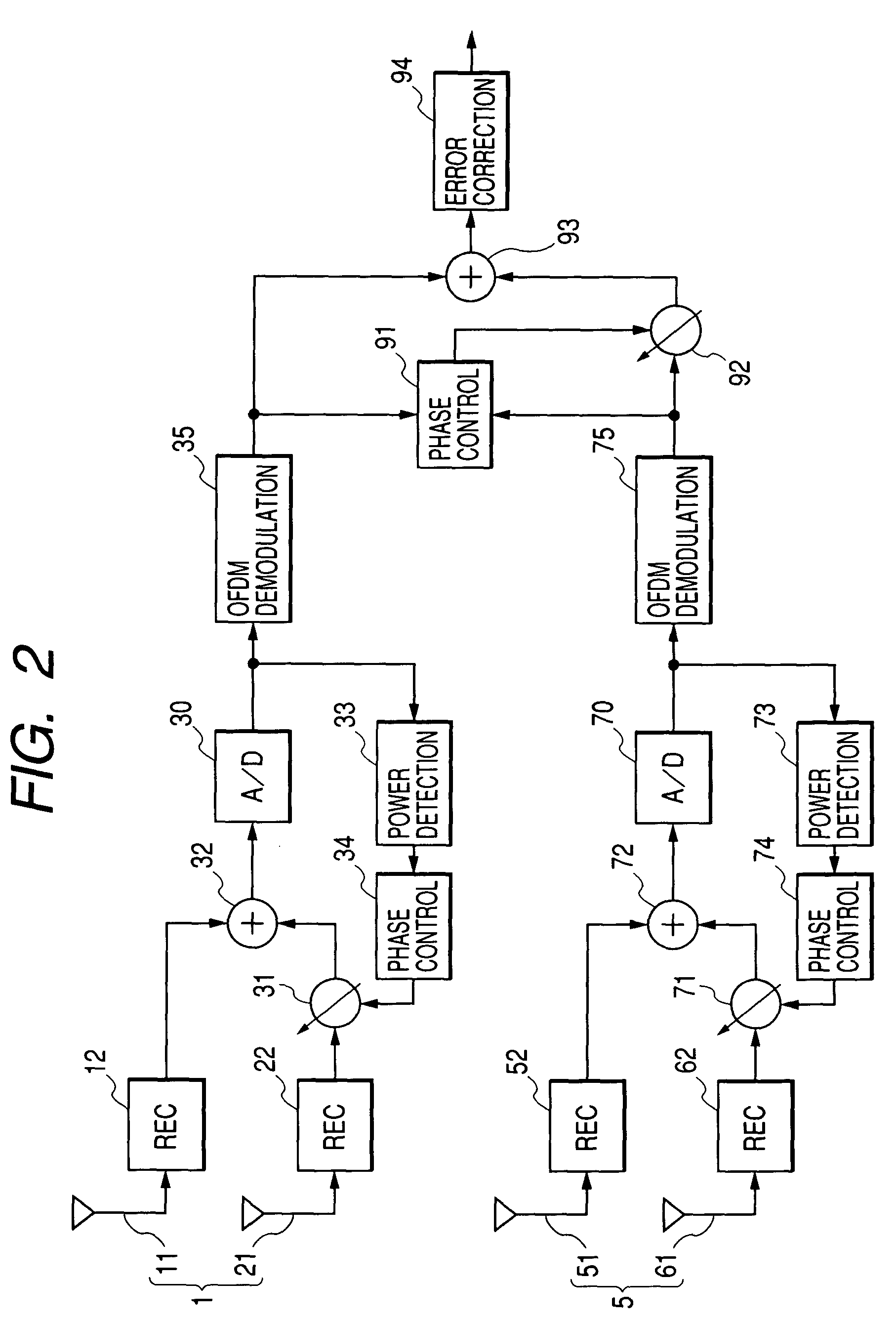

OFDM receiver for easily synchronizing base band signal

InactiveUS7382841B2Synchronization is simpleLow costTelevision system detailsSpatial transmit diversityTime domainBaseband

An OFDM receiver has four antennas or more for receiving an OFDM modulated high frequency signal, and plural OFDM demodulators for inputting a baseband signal of a time domain thereto on the basis of the high frequency signal and outputting the baseband signal of a frequency domain, wherein the OFDM demodulators are arranged every plural antenna groups with two or more of the antennas as one group, and a signal is diversity-synthesized by a first phase shifter until the baseband signal of the time domain is inputted to each of the OFDM demodulators, and the baseband signal of the frequency domain is diversity-synthesized by a second phase shifter.

Owner:ALPS ALPINE CO LTD