Patents

Literature

138 results about "Processor time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

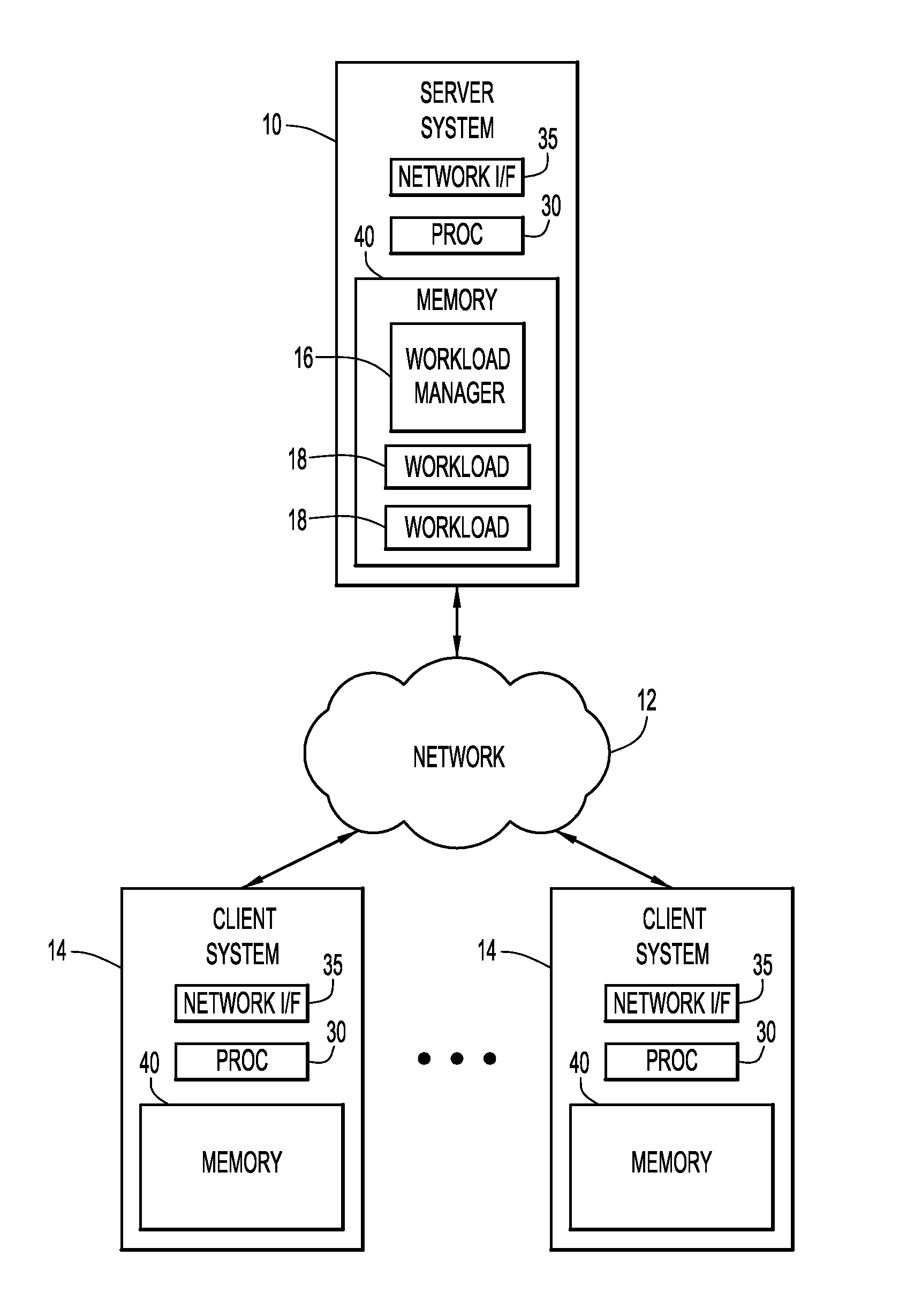

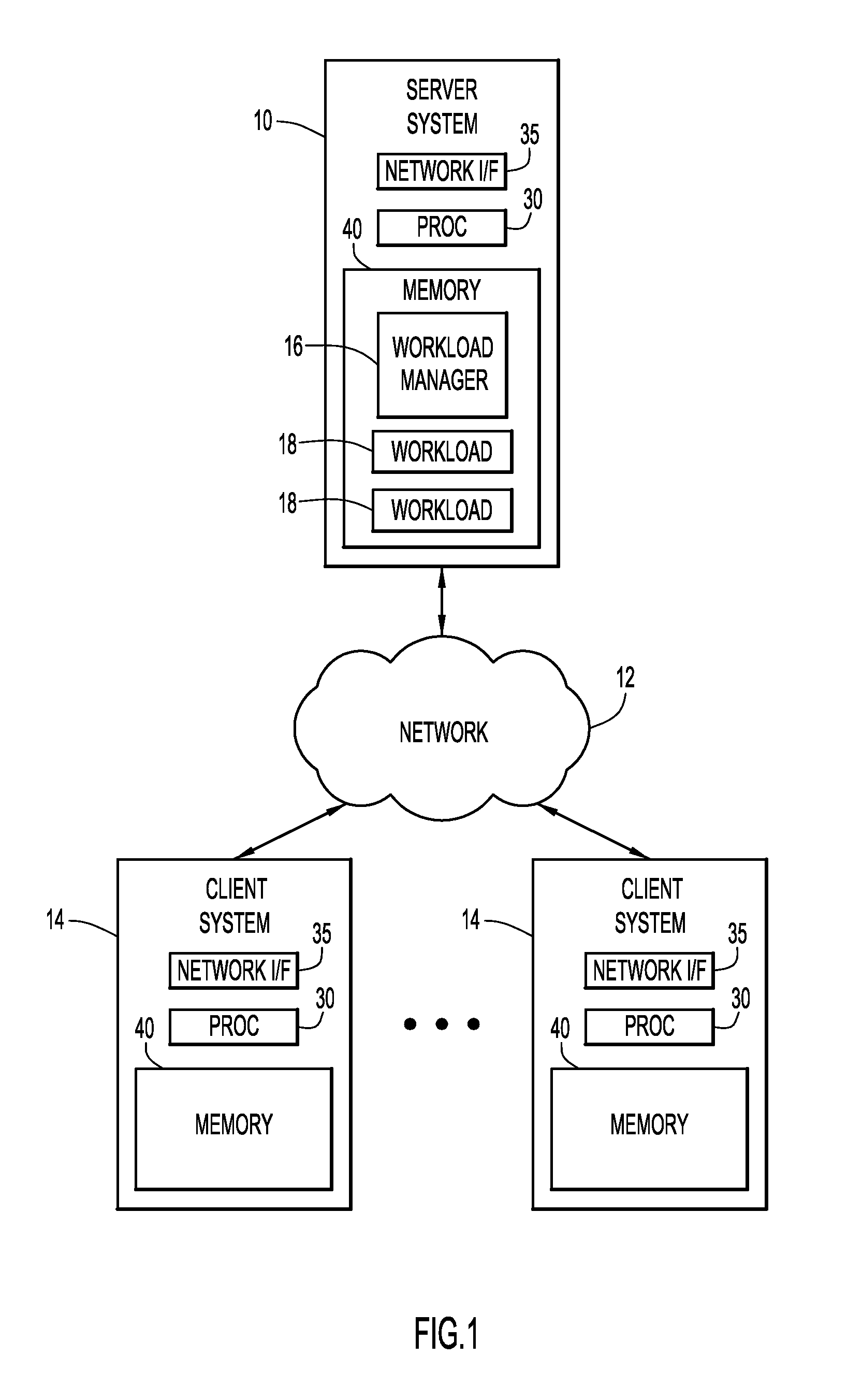

Adaptive resource usage limits for workload management

InactiveUS20140173616A1Resource allocationEnergy efficient computingResource allocationDistributed computing

According to an embodiment of the present invention, a system assigns at least one workload a hard share quantity and at least one other workload a soft share quantity or a hard share quantity. The system allocates a resource to the workloads based on the hard share quantity and the soft share quantity of active workloads in a predefined interval. A hard share quantity indicates a maximum resource allocation and a soft share quantity enables allocation of additional available processor time. Embodiments of the present invention further include a method and computer program product for allocating a resource to workloads in substantially the same manner as described above.

Owner:IBM CORP

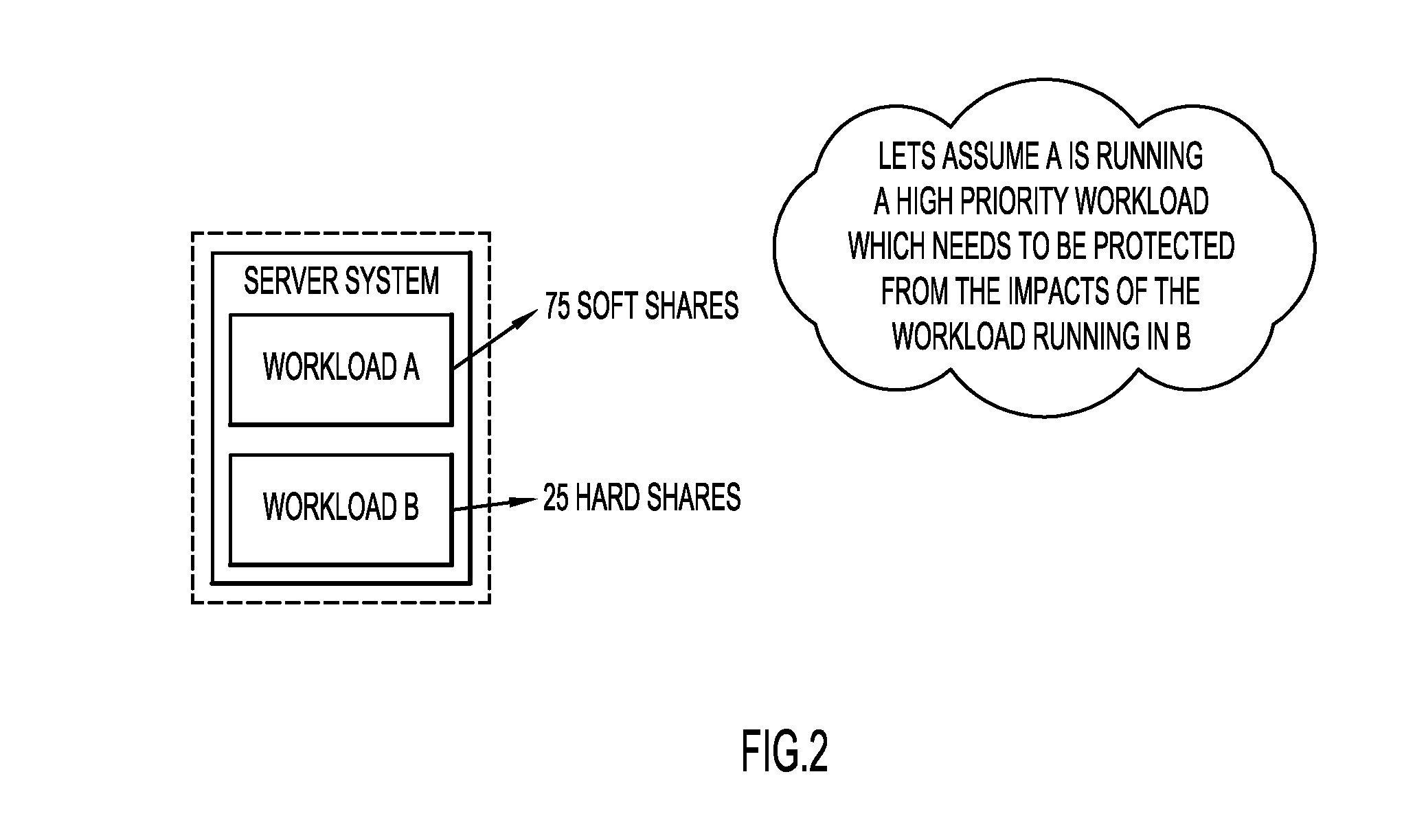

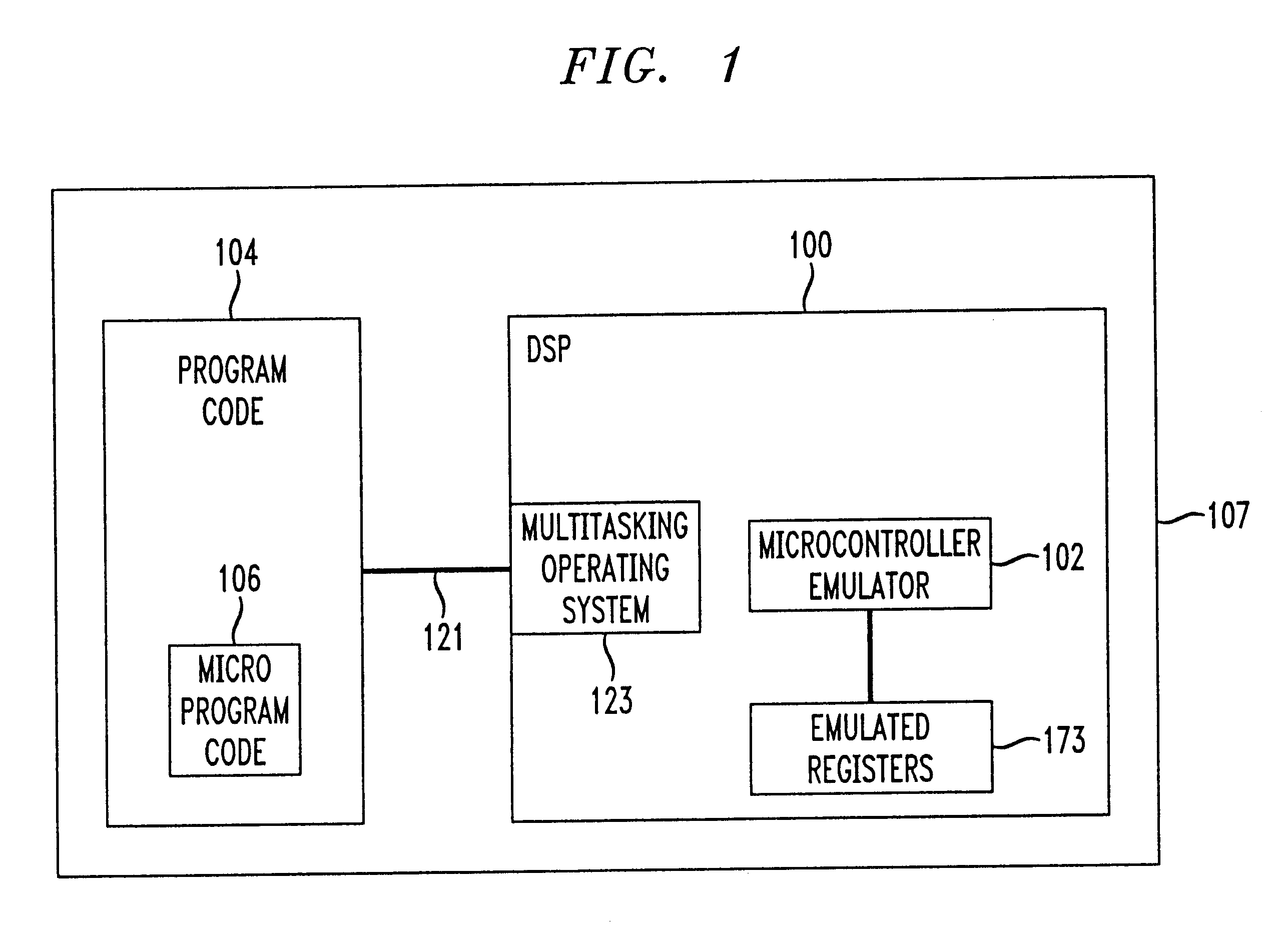

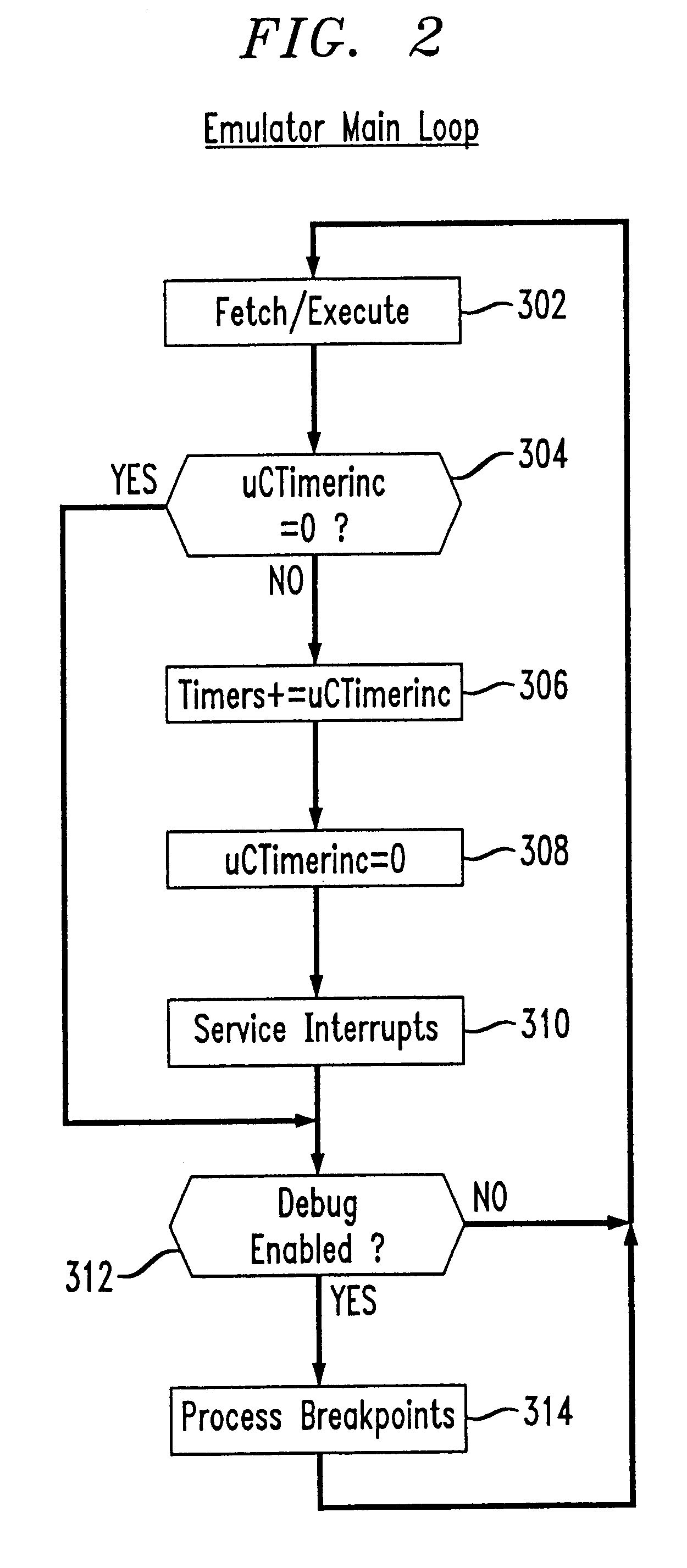

DSP emulating a microcontroller

InactiveUS6564179B1General purpose stored program computerSoftware simulation/interpretation/emulationMicrocontrollerOperational system

The present invention provides a processor device and technique having the capability of providing a two-processor solution with only one processor. In accordance with the principles of the present invention, a host processor is programmed in its native source and machine code language, and an emulated second processor is programmed in a different native source or machine code language particular to that emulated processor, to allow programming specialists in the different processors to develop common code for use on the same host processor. A multitasking operating system is included to allow time sharing operation between instructions from program code relating to the host processor (e.g., a DSP in the disclosed embodiment), and different program code relating to the emulated processor. The program code relating to the host processor (e.g., DSP) is written in program code which is native to the DSP, while the program code relating to the emulated processor (e.g., microcontroller) is written in program code which is native to the microcontroller. The SoftCore emulation module allows both DSP code and control code written for a microcontroller to execute independently on the same processor by multi-tasking resources in the faster, host processor (e.g., in the DSP), giving equal time slots of processor time to each processor (real and emulated).

Owner:LUCENT TECH INC +1

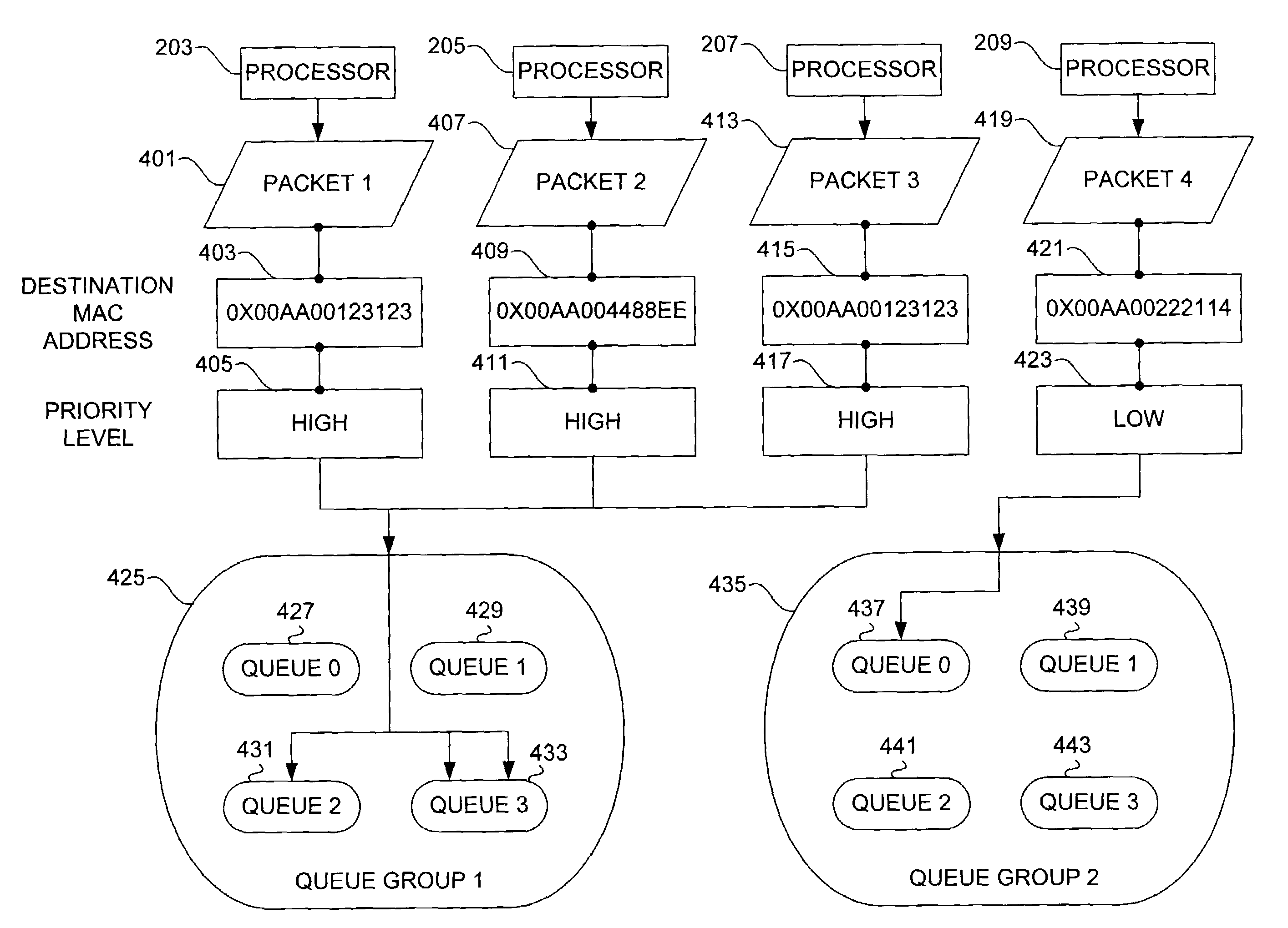

Methods and apparatus for retaining packet order in systems utilizing multiple transmit queues

Methods, apparatus, and articles of manufacture for retaining packet order in multiprocessor systems utilizing multiple transmit queues are disclosed herein. Embodiments of the present invention define multiple transmit queues for a given priority level of packets to enable the multiprocessor system to process and queue packets of equal priority in different transmit queues. Queuing packets of equal priority in different transmit queues minimizes processor time spent attempting to acquire queue-specific resources associated with one particular transmit queue. In addition, embodiments of the present invention provide an assignment mechanism to ensure that packets corresponding to a common flow are queued in the same transmit queue in order to eliminate, to the extent possible, out-or-order packets, which many times results in lost packets and a reduction in realized network throughput.

Owner:INTEL CORP

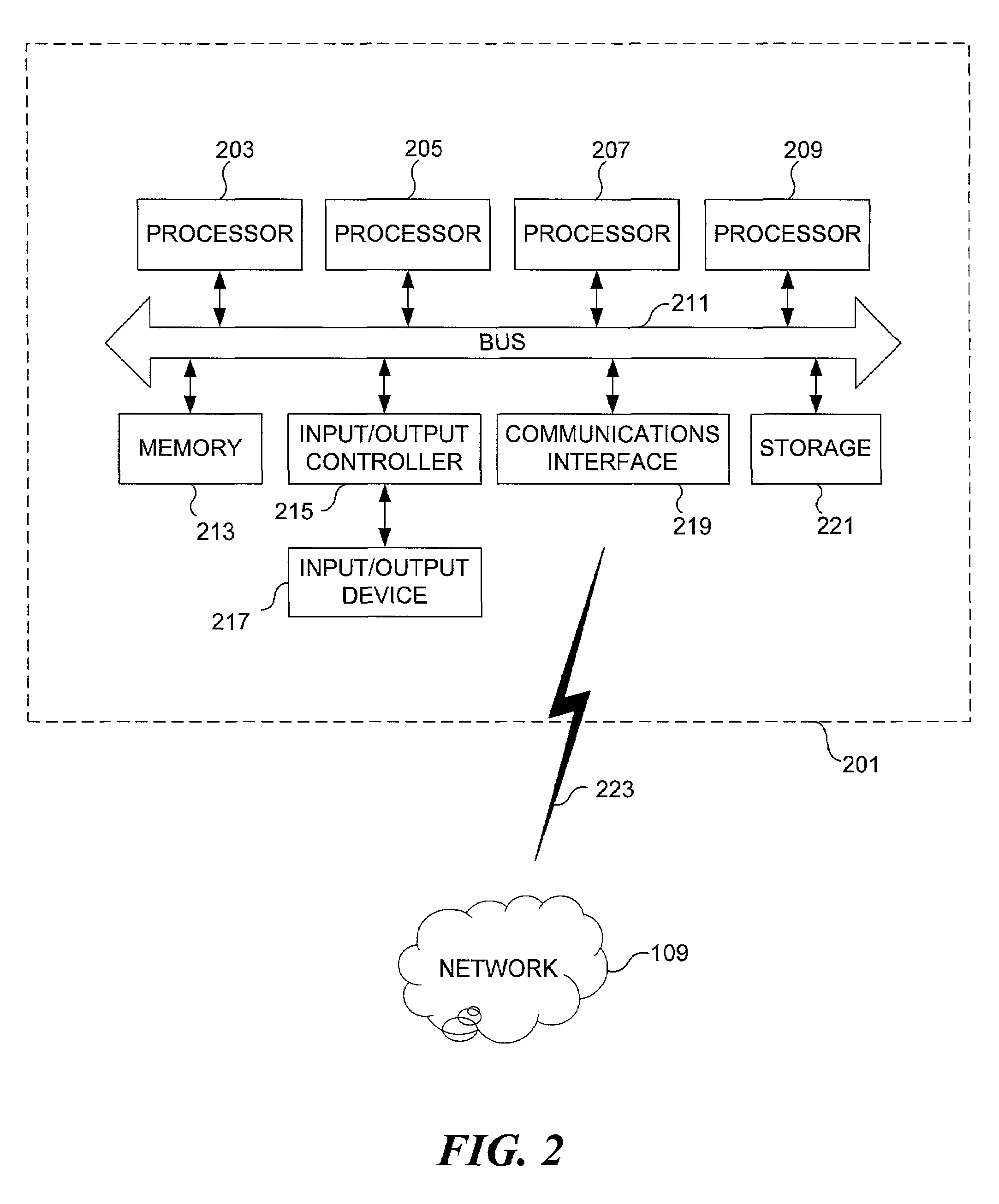

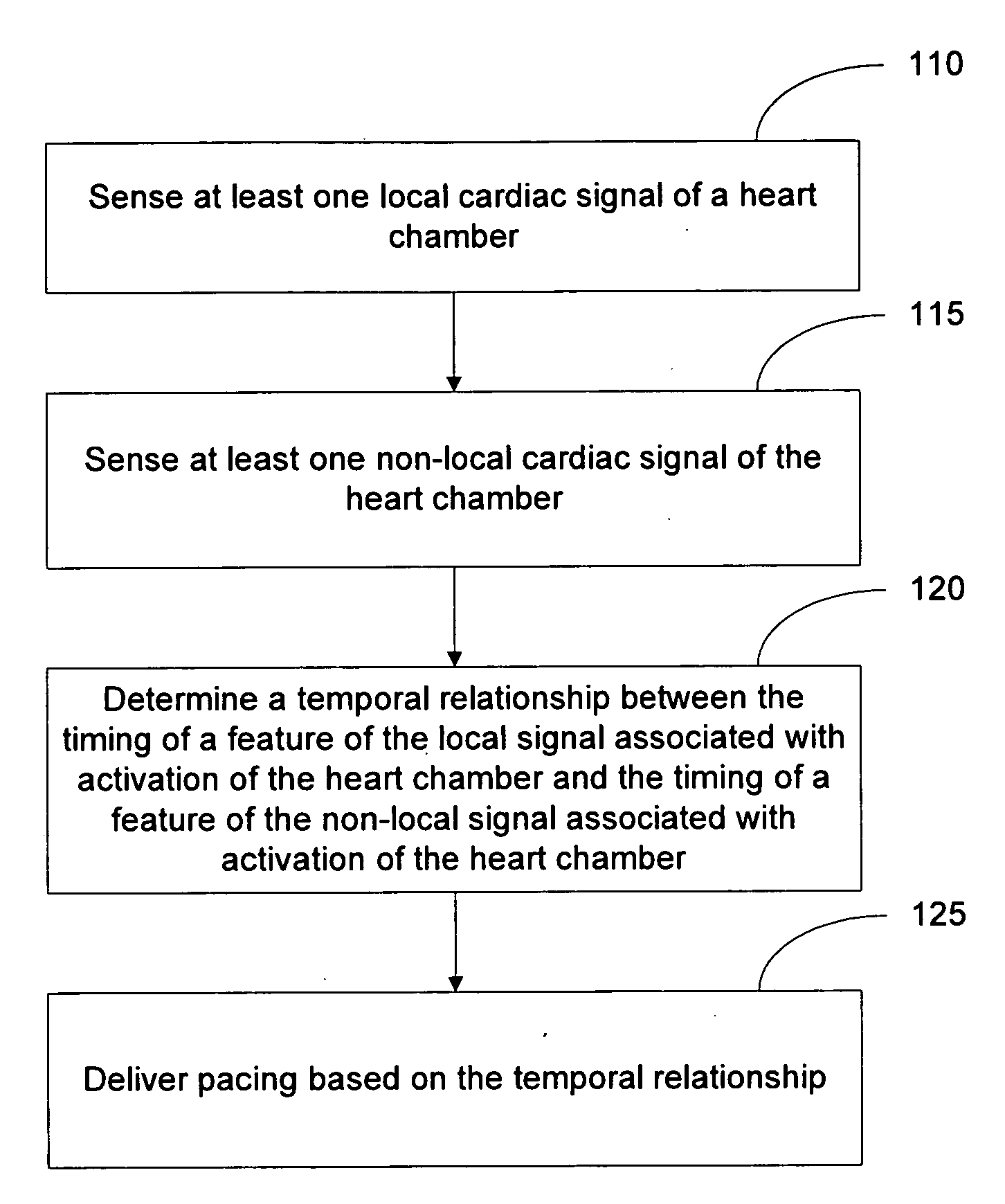

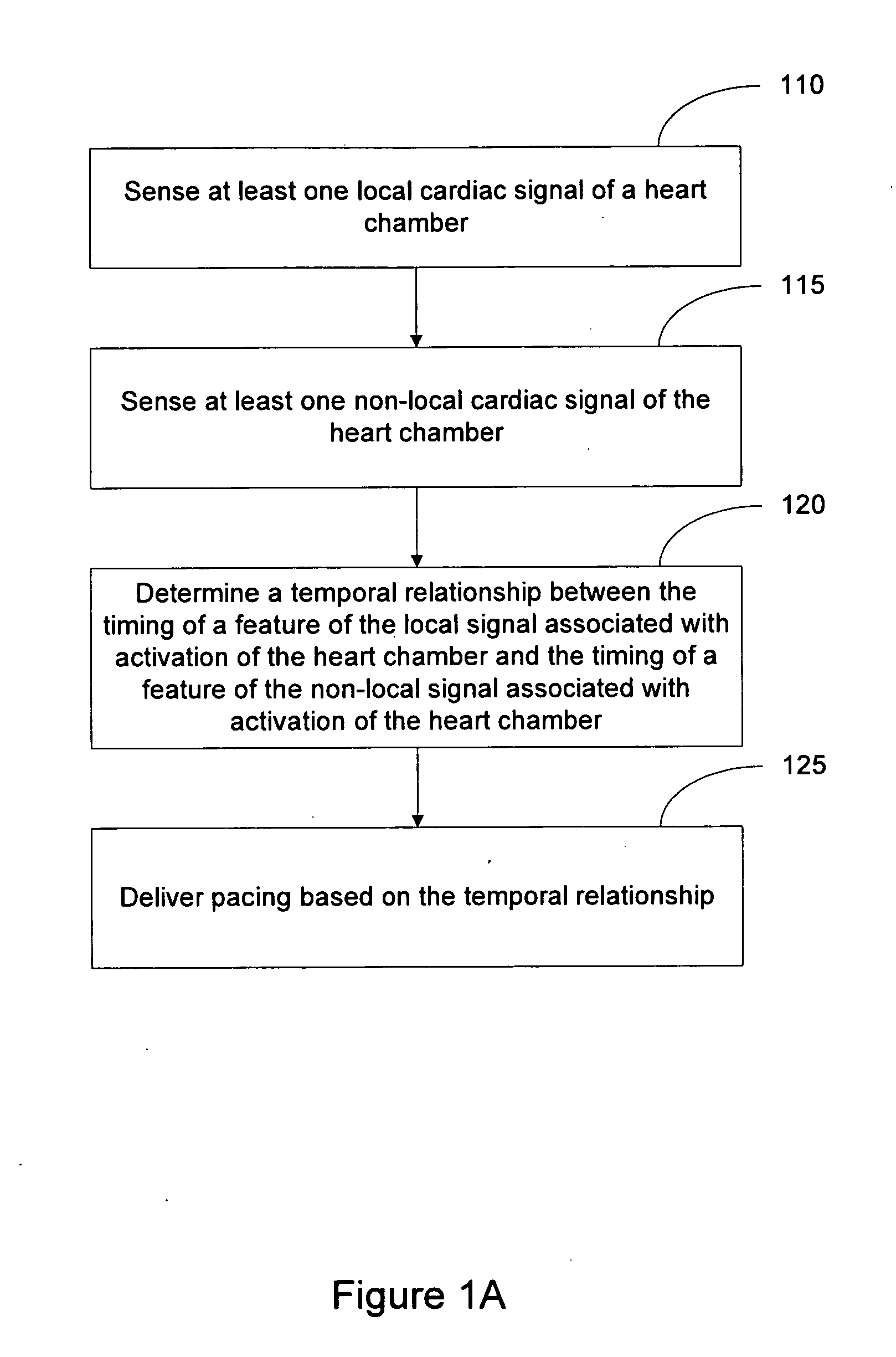

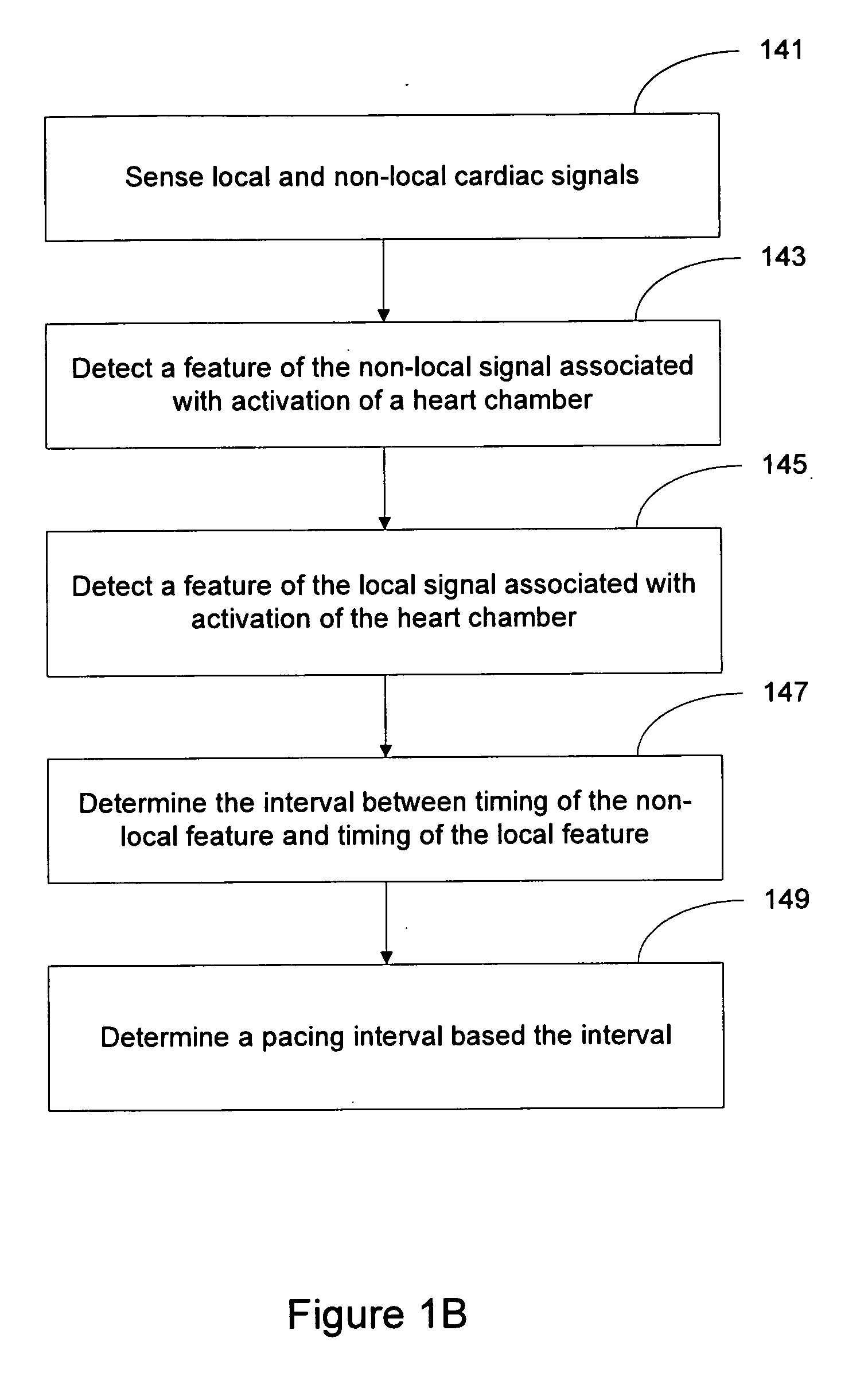

Local and non-local sensing for cardiac pacing

Systems and methods for determining pacing timing intervals based on the temporal relationship between the timing of local and non-local cardiac signal features are described. A device includes a plurality of implantable electrodes electrically coupled to the heart and configured to sense local and non-local cardiac signals. Sense circuitry coupled to first and second electrode pairs senses a local cardiac signal via a first electrode pair and a non-local cardiac signal via a second electrode pair. Detection circuitry is used to detect a feature of the local signal associated with activation of a heart chamber and to detect a feature of the non-local signal associated with activation of the heart chamber. A control processor times delivery of one or more pacing pulses based on a temporal relationship between timing of the local signal feature and timing of the non-local signal feature.

Owner:CARDIAC PACEMAKERS INC

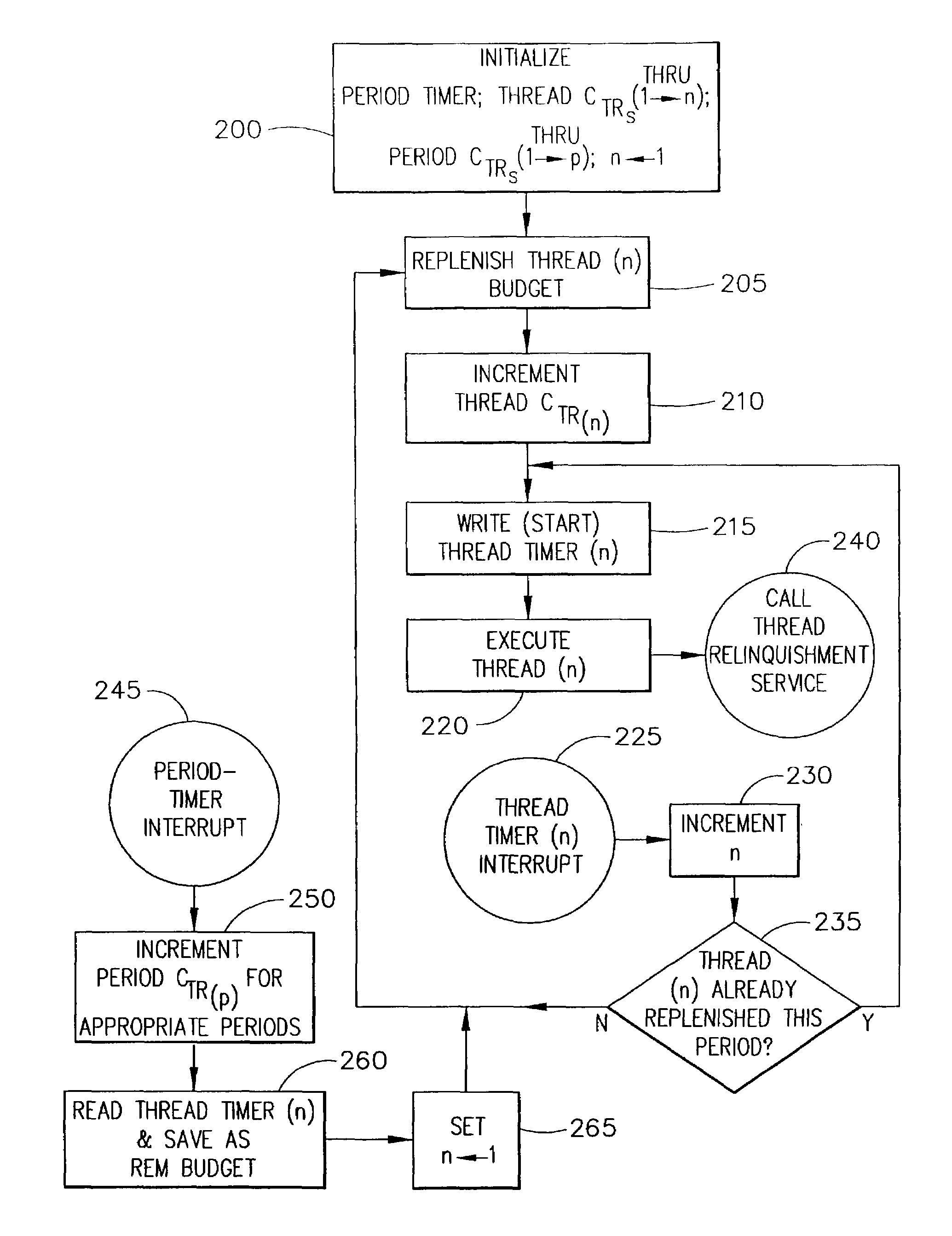

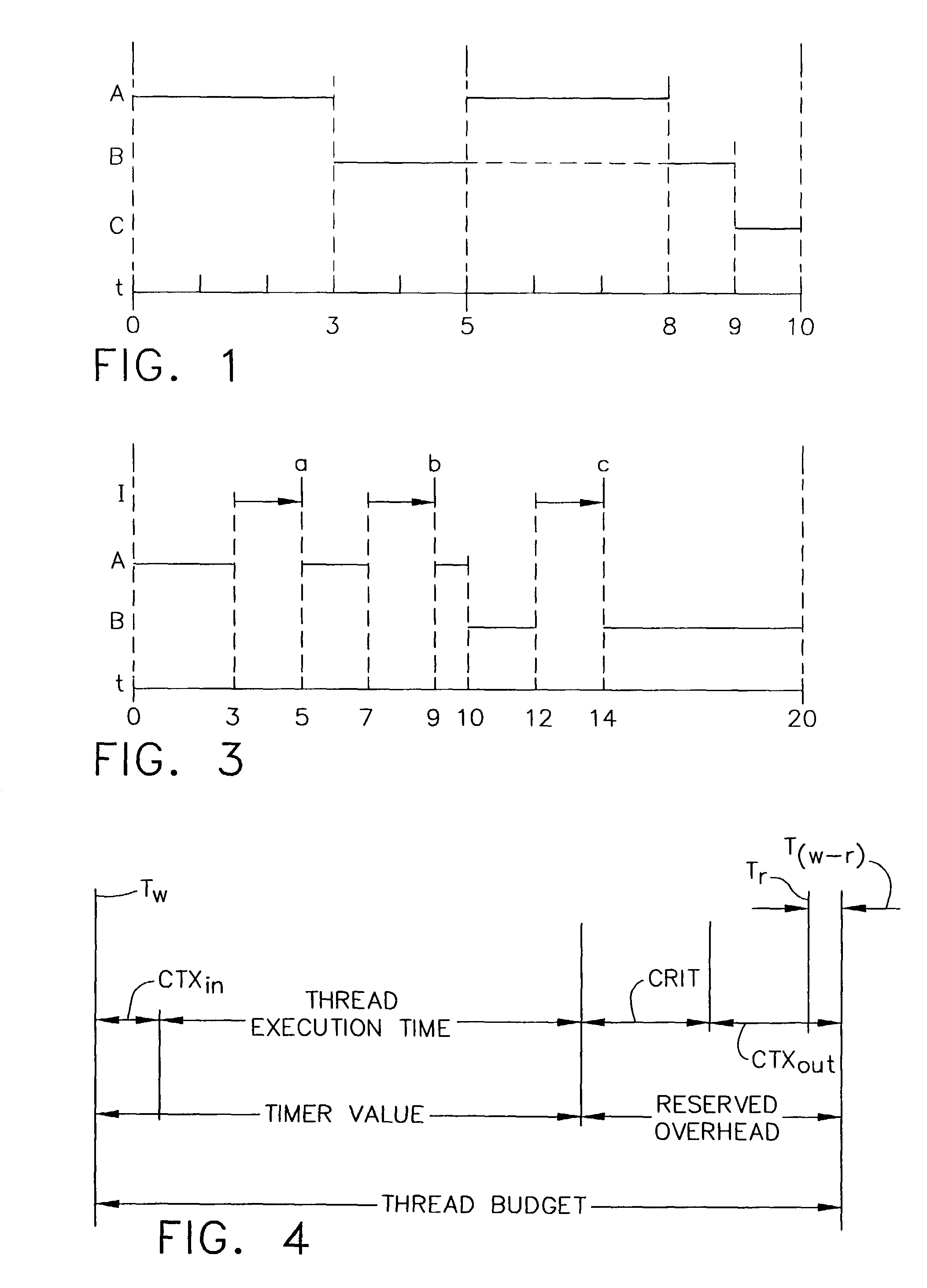

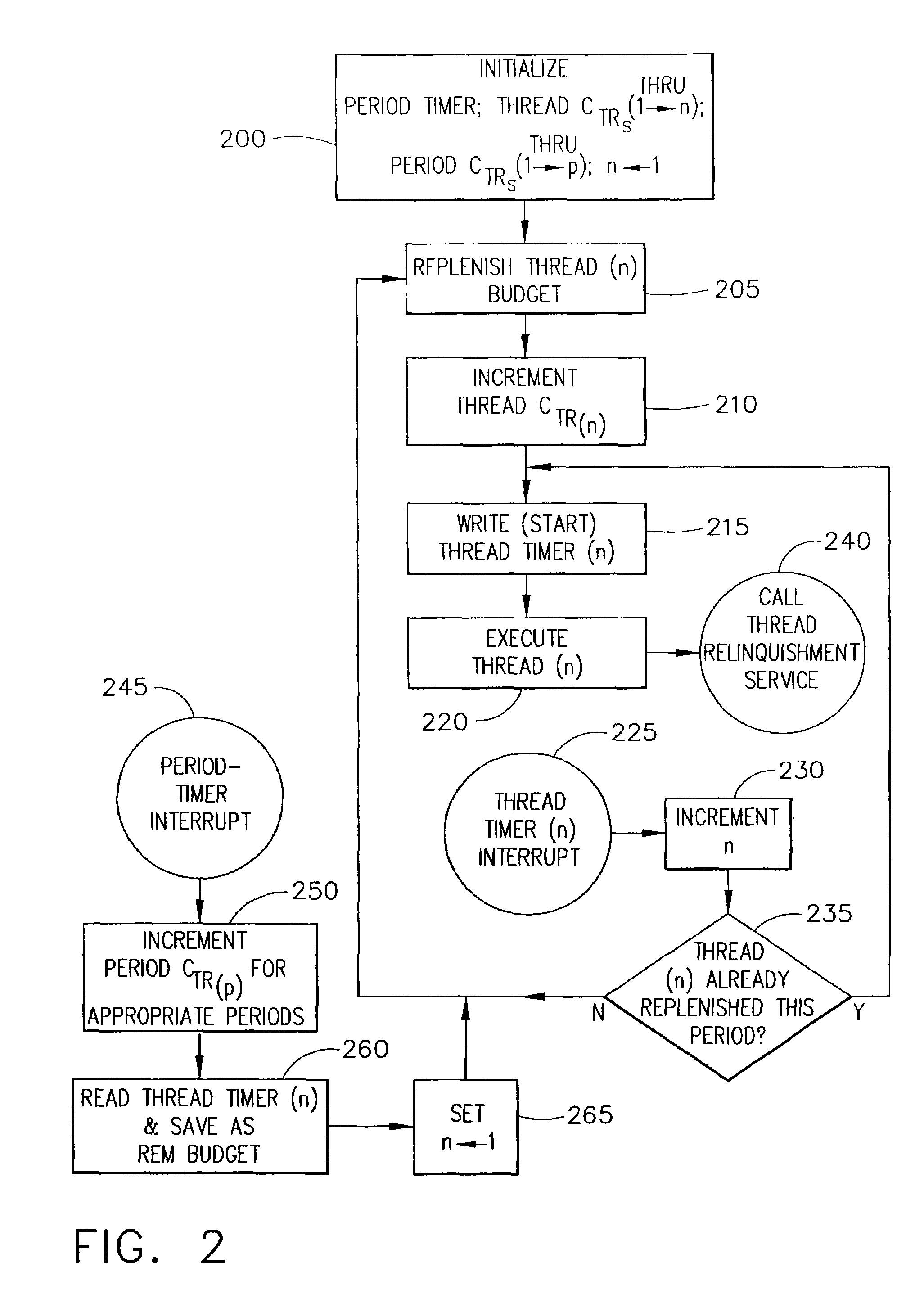

System and method for robust time partitioning of tasks in a real-time computing environment

InactiveUS7207042B2Eliminate needSimplifies enforcementProgram initiation/switchingResource allocationOperational systemApplication software

A time-partitioned system for accounting for processor time consumed by operating system services provided on behalf of an application runs in a real-time environment. The time utilized by the operating system is treated as application processing time, rather than viewing the resultant processor time consumed as an operating system overhead. Each application consists of one or more threads. A time budget is assigned to each thread and to each interrupt. The processor time consumed by the operating system when executing on behalf of a thread or interrupt is charged back to the application or interrupt as part of the application's time budget. Operating system overheads and processor interrupts are thus accounted for accurately enough to determine a schedule for the applications that is enforceable by the operating system at run time.

Owner:HONEYWELL INT INC

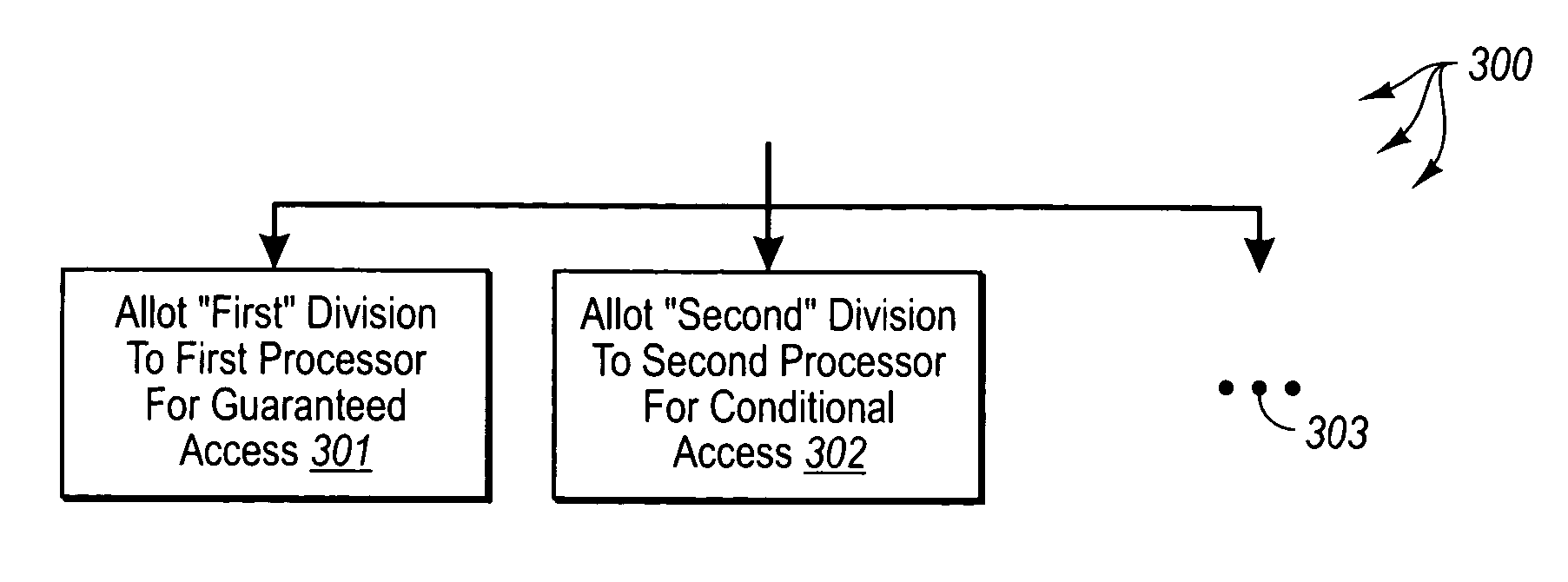

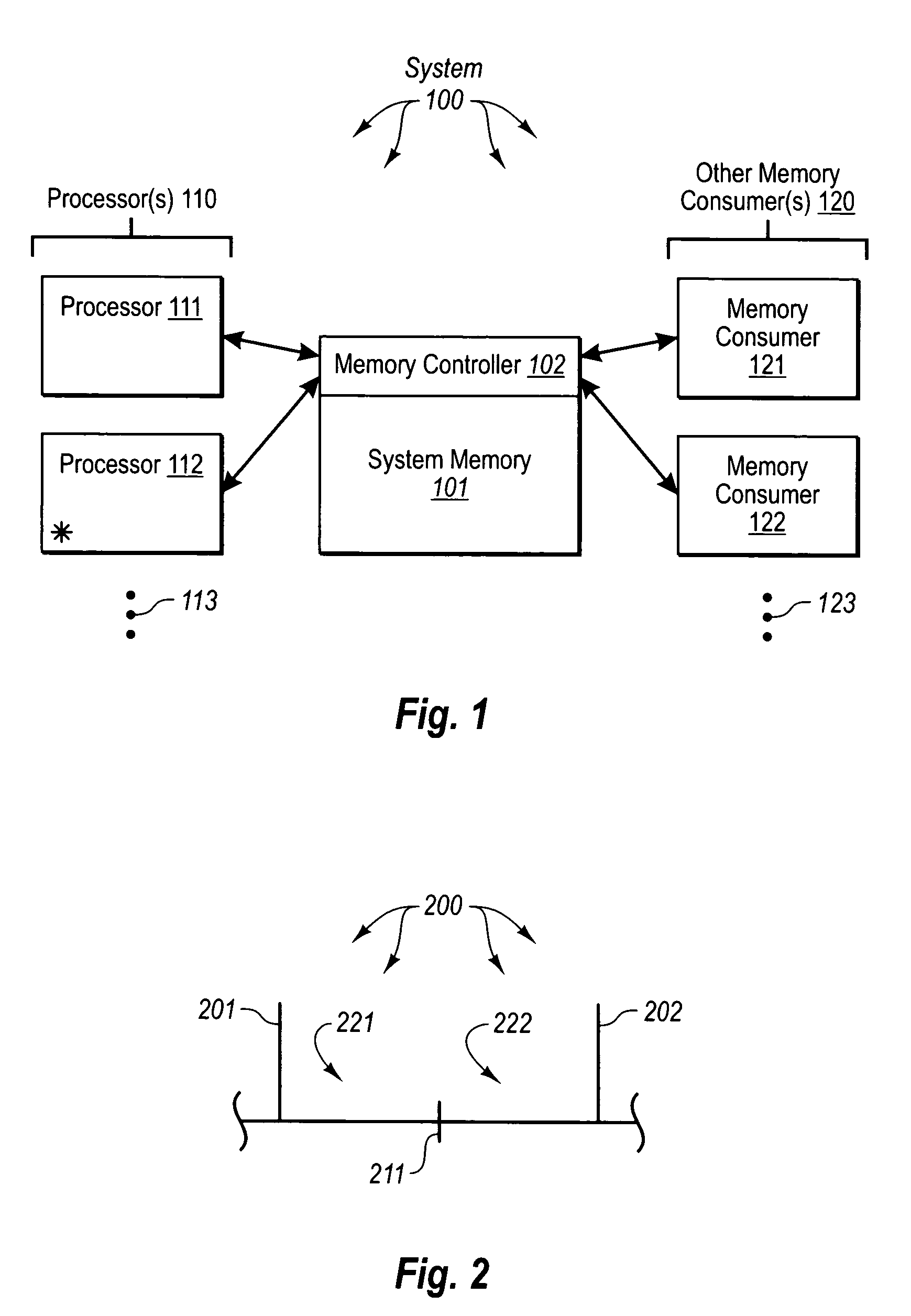

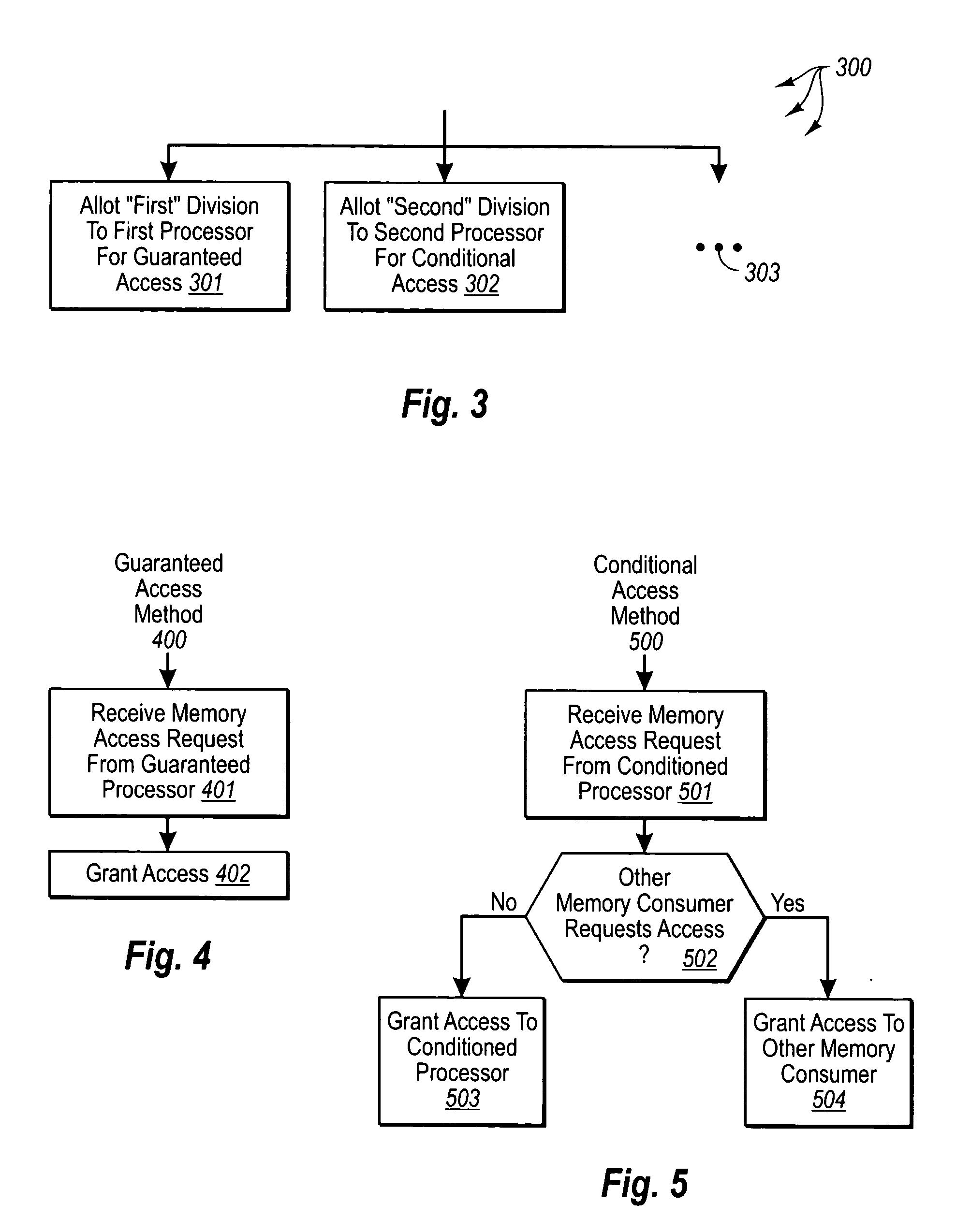

Contingent processor time division multiple access of memory in a multi-processor system to allow supplemental memory consumer access

InactiveUS20050132145A1Efficient managementFewer memory demandsImage memory managementMemory systemsTime division multiple accessMulti processor

Mechanisms in which a memory controller efficiently manages time-division multiple access to system memory for multiple processors and for one or more other memory consumers present in the system. At least one processor is guaranteed access to system memory during its time slot in a memory access cycle, while at least one of the other processors is only conditionally granted access to system memory during its time of the memory access cycle. In particular, these other processors are only granted access if one of more certain other memory consumers has not also requested memory access at the same time. Accordingly, urgent, time-sensitive processes may run on these guaranteed processors, while allowing less time-sensitive processes to run on the other processors. Hence, access to system memory is managed more efficiently.

Owner:II VI DELAWARE INC

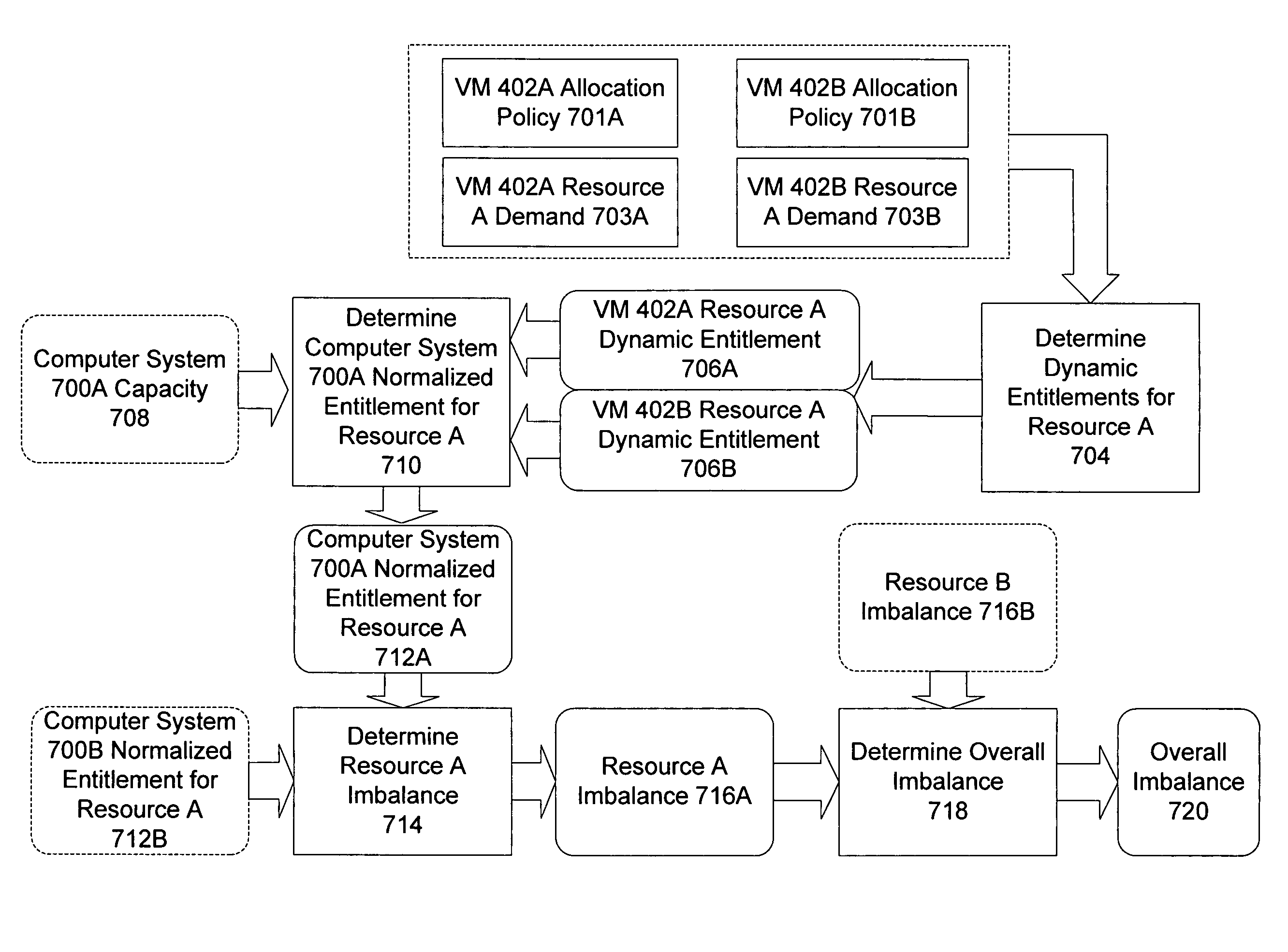

Use of dynamic entitlement and adaptive threshold for cluster process balancing

Processes are balanced among multiple computer systems. The allocation policies and resource demands of multiple processes executing on multiple computer systems are used to determine the resource imbalance of the computer systems. Resource imbalance can be used to determine whether a process should be migrated from one computer system to another. Resource imbalance of multiple resources can be combined to determine overall imbalance of the computer systems. Overall imbalance can be used to determine whether a process should be migrated from one computer system to another. Imbalance of resources can be determined for resources such as processor time, memory, network bandwidth, and storage. Virtual machines can be balanced among multiple computer systems operating in a cluster.

Owner:VMWARE INC

System for reducing the number of programs necessary to render an image

ActiveUS20050231521A1Effective applicationEfficient processingDrawing from basic elementsCathode-ray tube indicatorsGraphicsComputational science

Disclosed is as system for reducing memory and computational requirements of graphics operations. The system provides techniques for combining otherwise individual operations to apply filters to images. The combined filter emerging from the combination spares the processor time and the creation of an entire intermediary image. The system further provides for application of these techniques in many contexts including where the operations are fragment programs in for a programmable GPU.

Owner:APPLE INC

Process scheduler employing ordering function to schedule threads running in multiple adaptive partitions

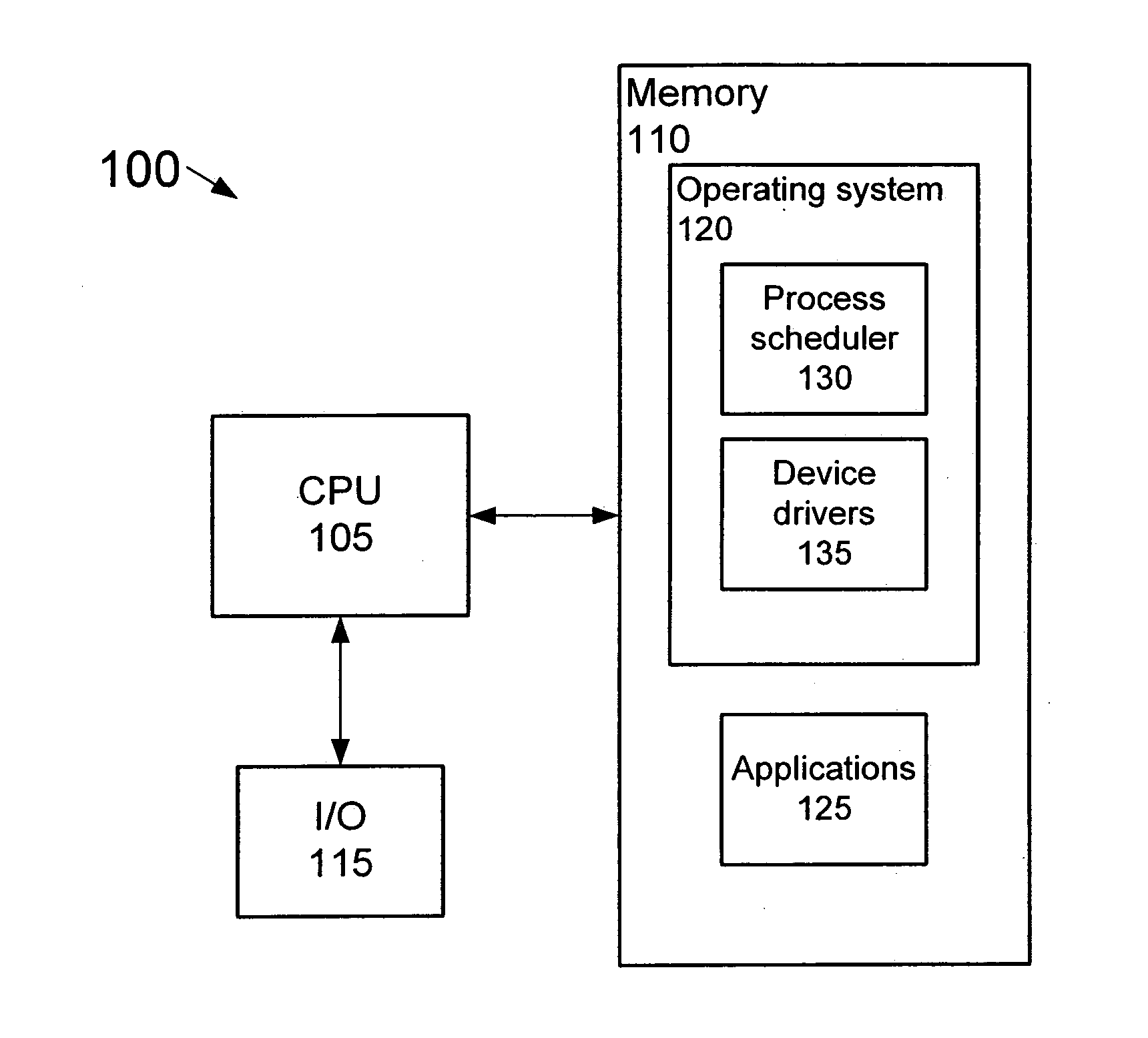

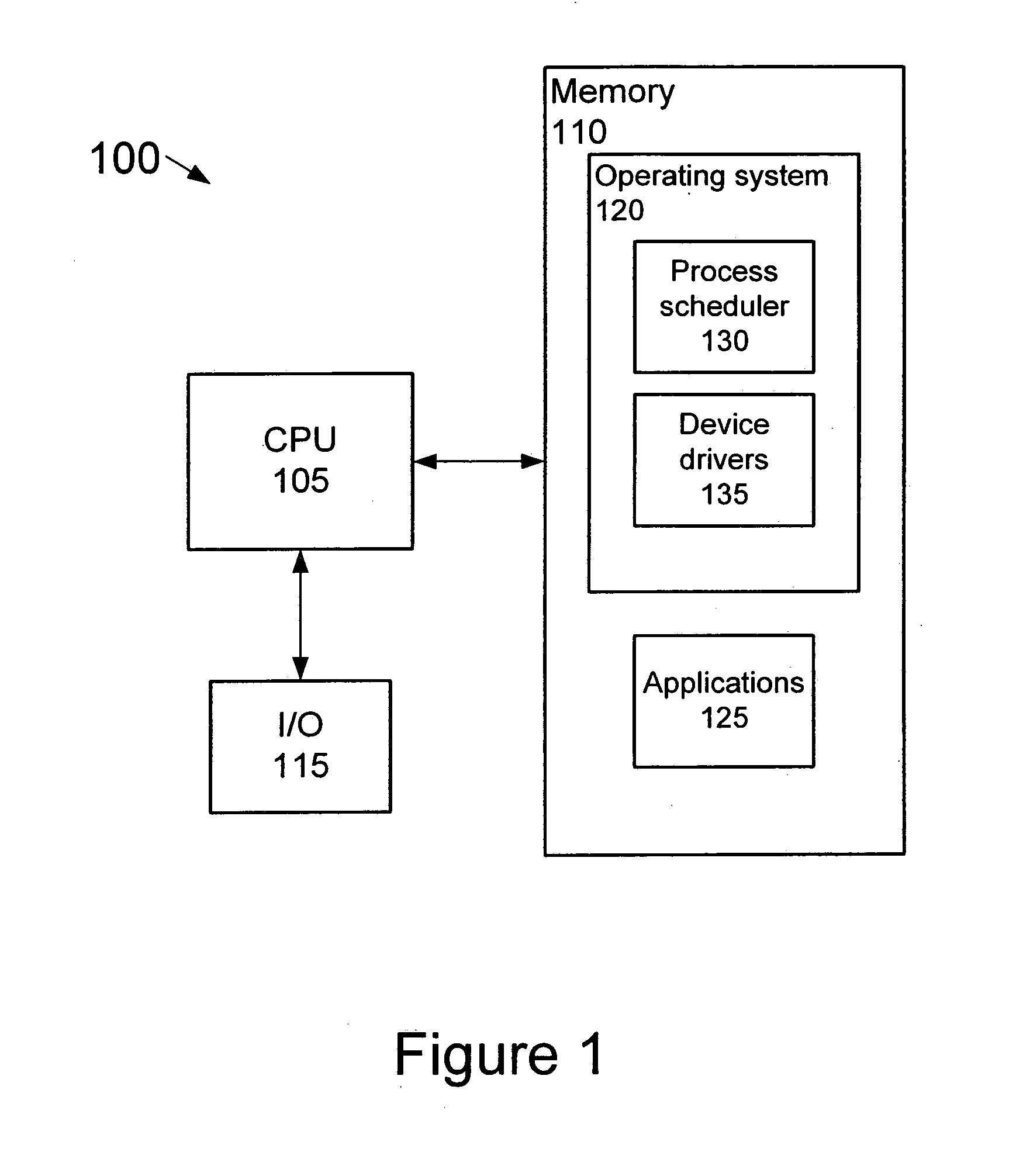

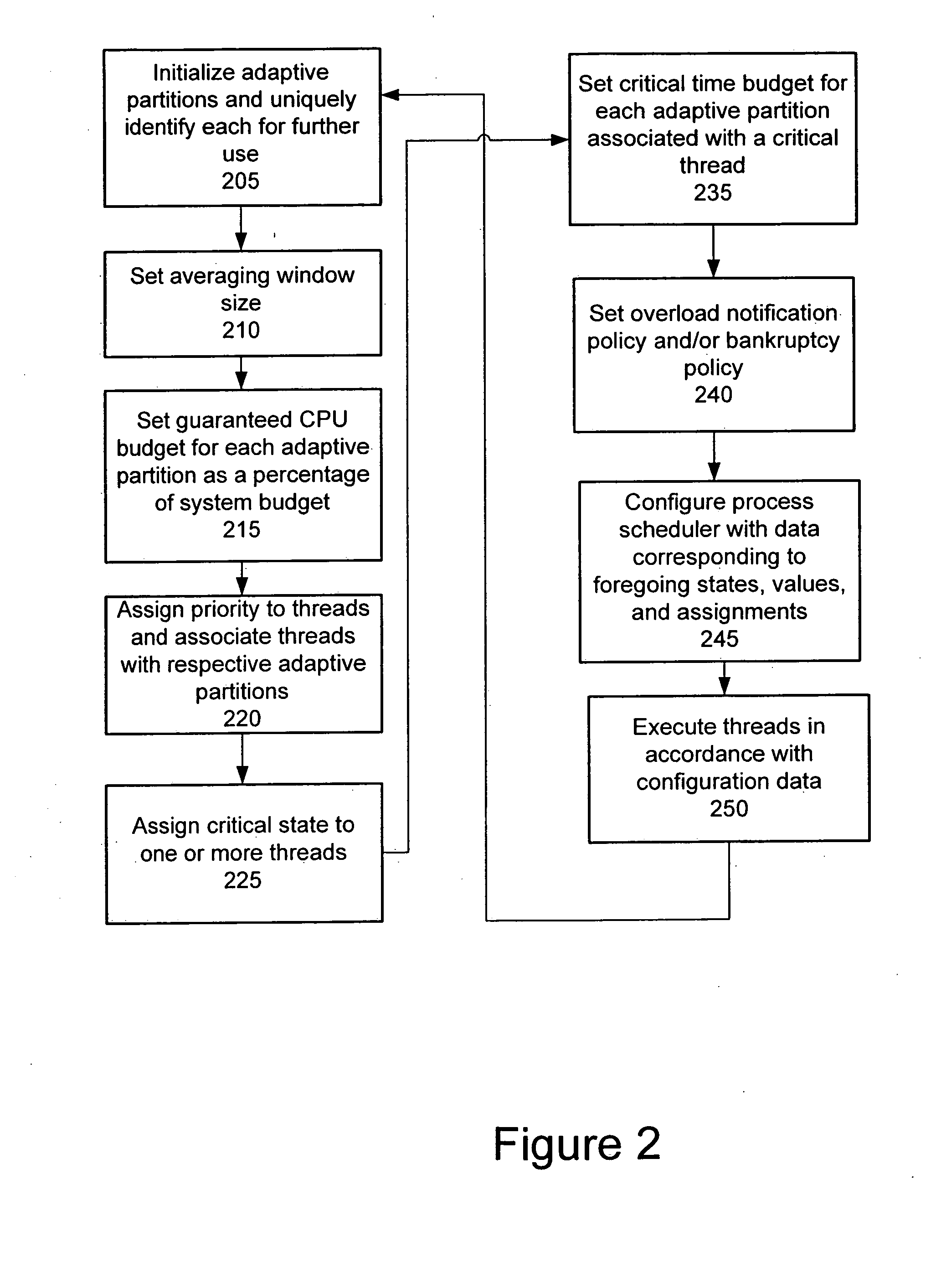

ActiveUS20070061788A1Multiprogramming arrangementsMultiple digital computer combinationsParallel computingStorage cell

A system is set forth that includes a processor, one or more memory storage units, and software code stored in the one or more memory storage units. The software code is executable by the processor to generate a plurality of adaptive partitions that are each associated with one or more process threads. Each of the plurality of adaptive partitions has one or more corresponding scheduling attributes that are assigned to it. The software code further includes a scheduling system that is executable by the processor for selectively allocating the processor to run the process threads based on a comparison between ordering function values for each adaptive partition. The ordering function value for each adaptive partition is calculated using one or more of the scheduling attributes of the corresponding adaptive partition. The scheduling attributes that may be used to calculate the ordering function value include, for example, 1) the process budget, such as a guaranteed time budget, of the adaptive partition, 2) the critical budget, if any, of the adaptive partition, 3) the rate at which the process threads of an adaptive partition consume processor time, or the like. For each adaptive partition that is associated with a critical thread, a critical ordering function value also may be calculated. The scheduling system may compare the ordering function value with the critical ordering function value of the adaptive partition to determine the proper manner of billing the adaptive partition for the processor allocation used to run its associated critical threads. Methods of implementing various aspects of such a system are also set forth.

Owner:MALIKIE INNOVATIONS LTD

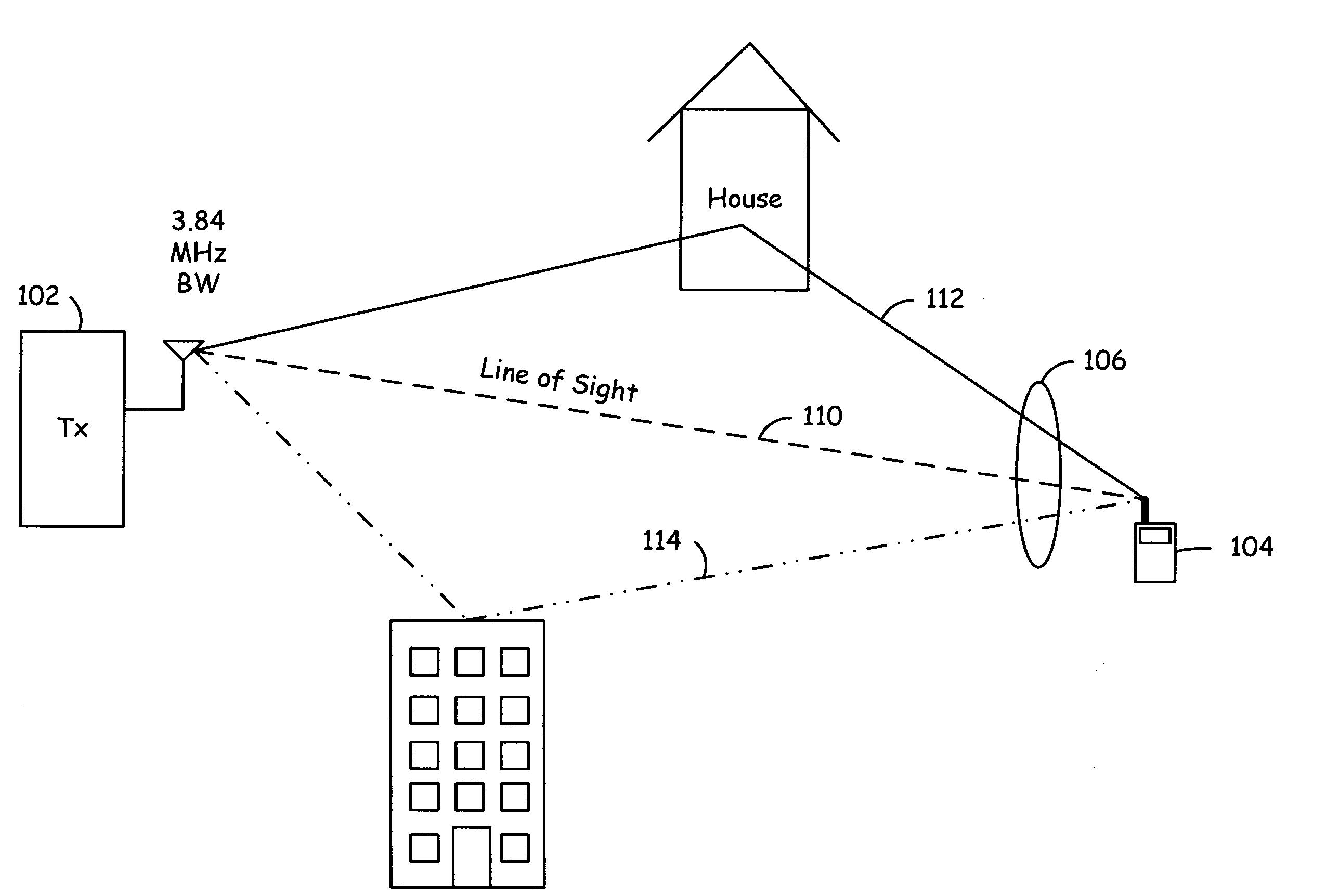

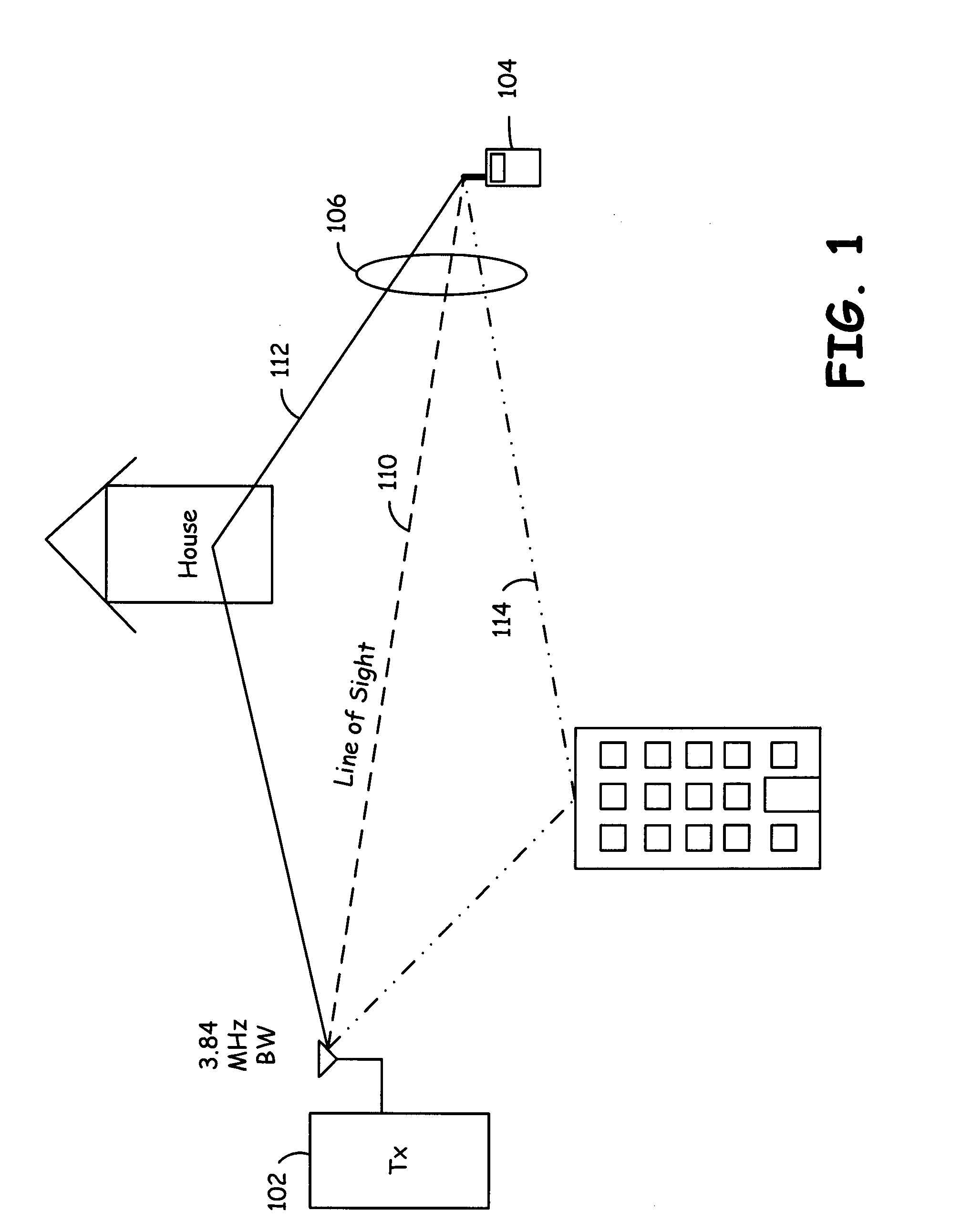

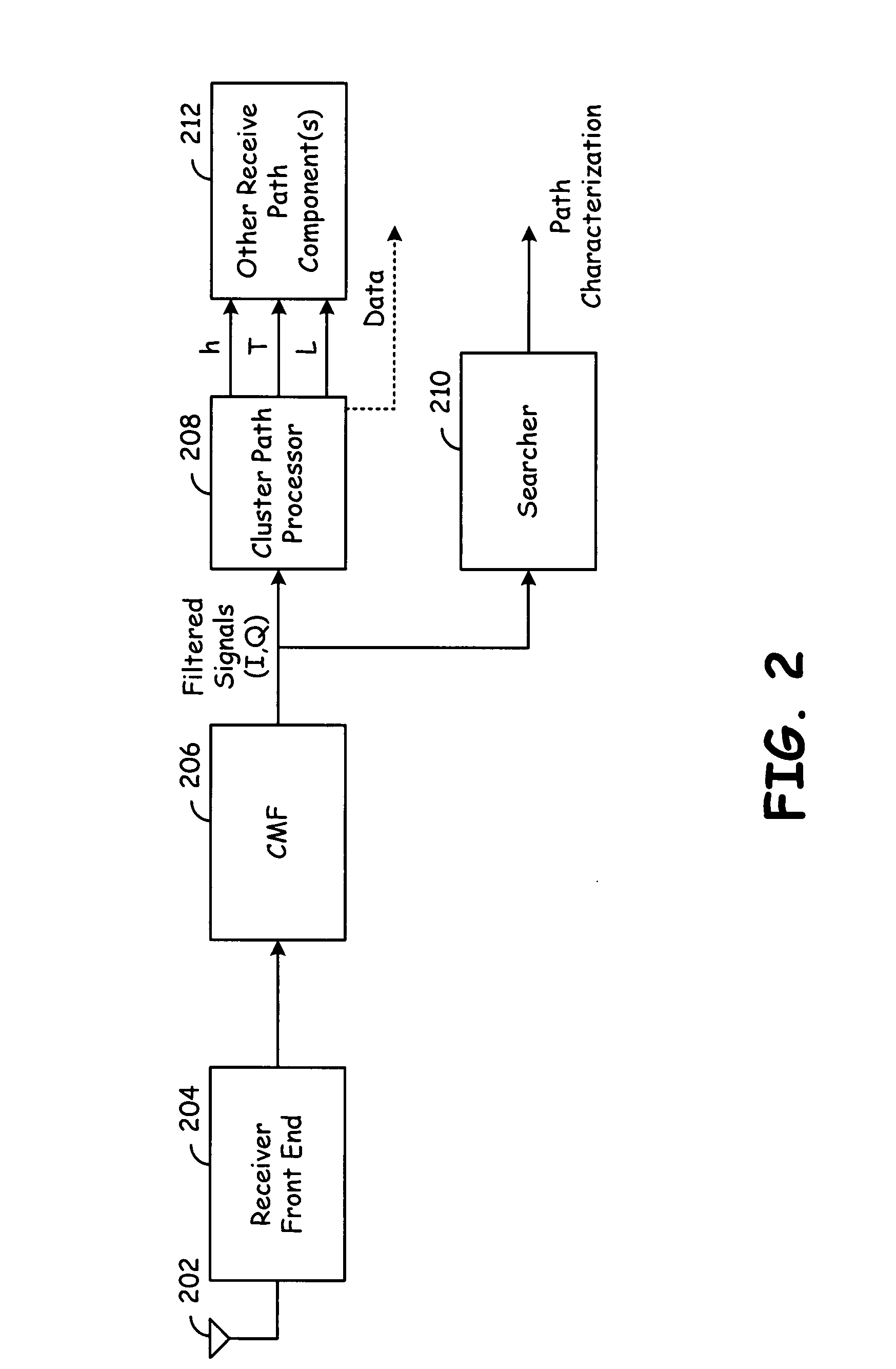

Cluster path processor time alignment for signal suppression/separation in a wireless device

ActiveUS20080075216A1Polarisation/directional diversitySynchronisation error detectionDelay spreadSignal Repression

A system for processing radio frequency (RF) signals includes a searcher and a plurality of Cluster Path Processor (CPPs). The searcher detects a maximum signal energy level and position of at least one of a plurality of individual distinct path signals in a signal cluster of a first information signal, wherein at least a portion of the plurality of individual distinct path signals is received within a duration of a corresponding delay spread. The sampling position is used as a starting sampling location by the plurality of CPPs, including a first information signal CPP and a second information signal CPP. Fine sampling positions of the plurality of CPPs are based upon channel energy estimates for the plurality of individual distinct path signals. CPP outputs are employed to produce channel estimates, which are themselves used in subsequent equalization operations. Sampling positions may change over time in order to satisfy alignment criteria.

Owner:AVAGO TECH INT SALES PTE LTD

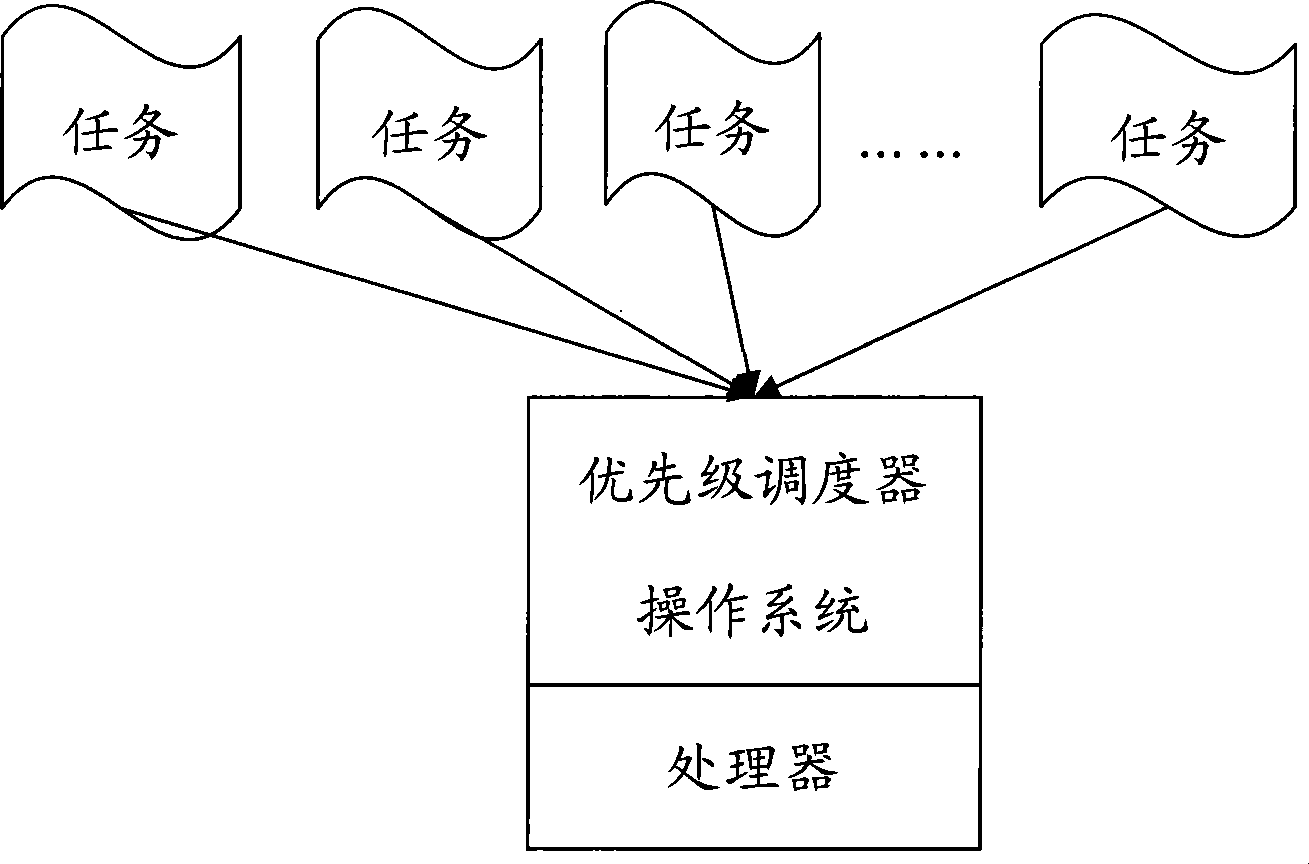

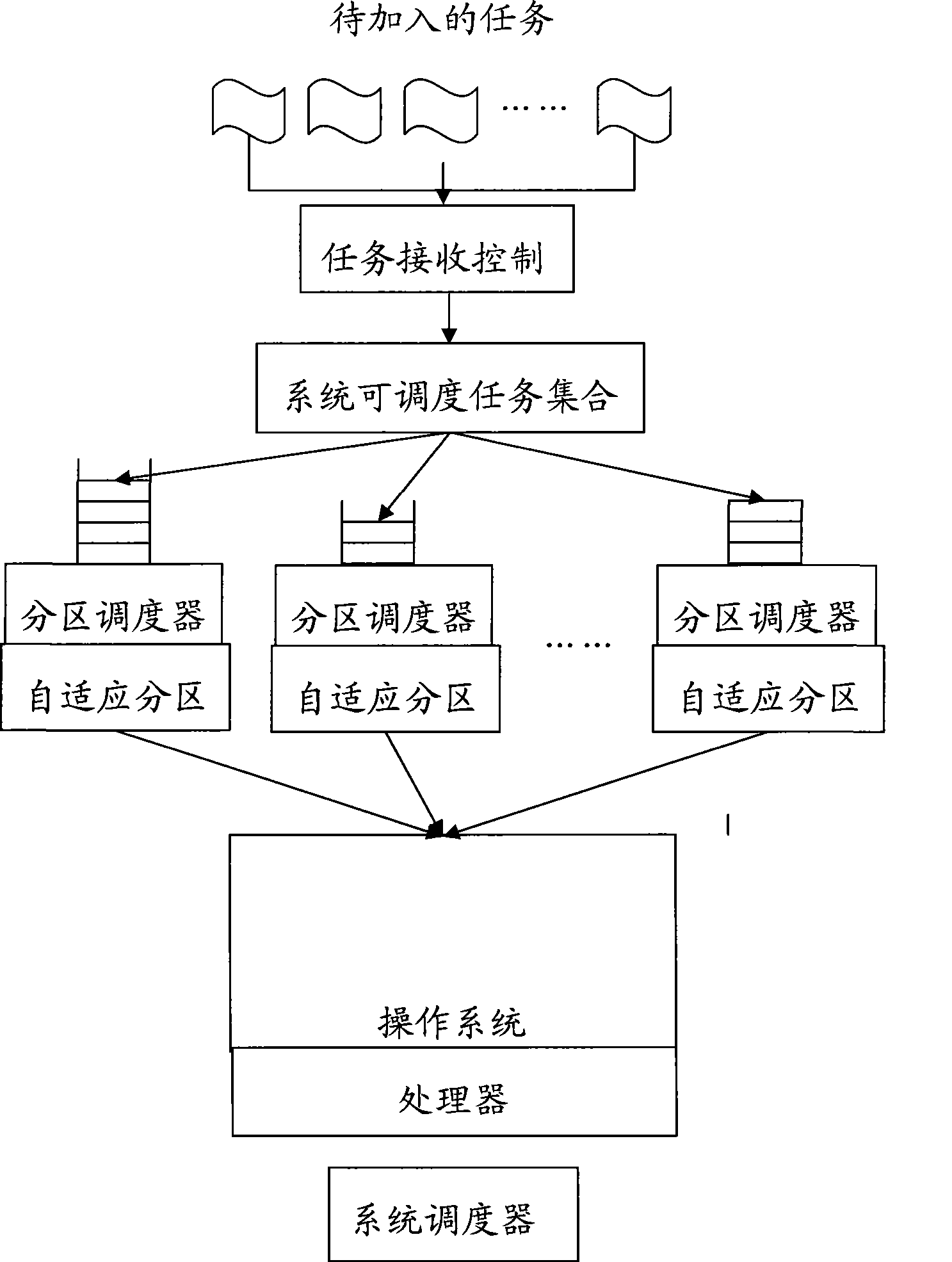

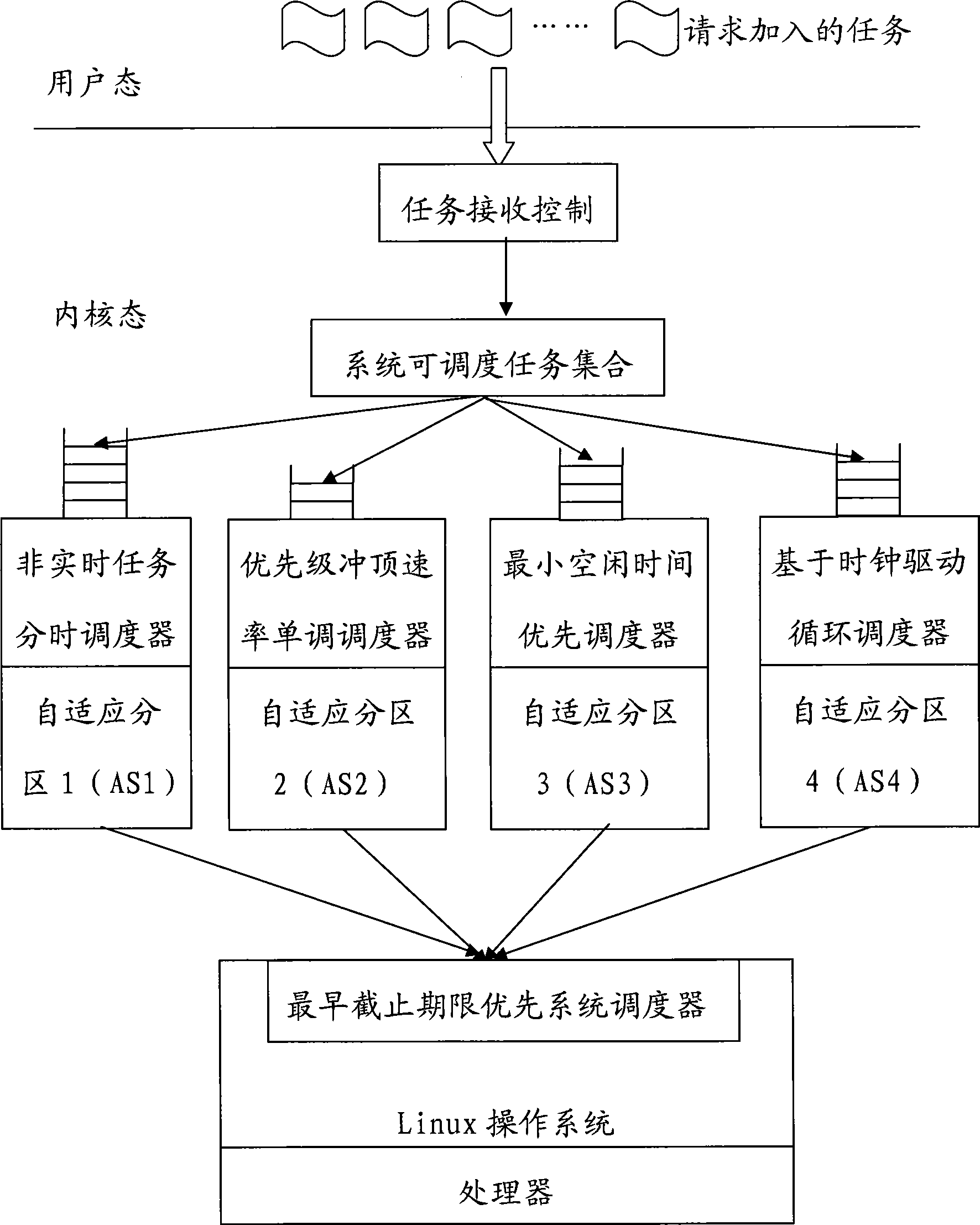

Task scheduling apparatus and method for embedded operating system

ActiveCN101452404ABlock monopolyEfficient schedulingProgram initiation/switchingOperational systemComputer architecture

The present invention relates to a device and a method for dispatching a task of an embedded operation system. The device comprises a processor, a system dispatcher, a system dispatchable task aggregating module and self-adaptive partition modules. The method comprises: firstly, initializing self-adaptive partitions; secondly, according to the proportion of the smallest processor computational capability needed by each self-adaptive partition to the processor computational capability, acquiring processor time distributed for each self-adaptive partition within a system dispatching cycle; and finally, when each self-adaptive partition is dispatched within the system dispatching cycle, distributing processor time for each self-adaptive partition and dispatching the tasks in a task queue within the dispatched processor time by a partition dispatcher of a currently dispatched self-adaptive partition according to a partition dispatching policy. The present invention overcomes the defect that only the static priority tasks of the same type can be subjected to overall dispatch in the dispatching mechanism in the prior embedded operation system.

Owner:成都中兴软件有限责任公司

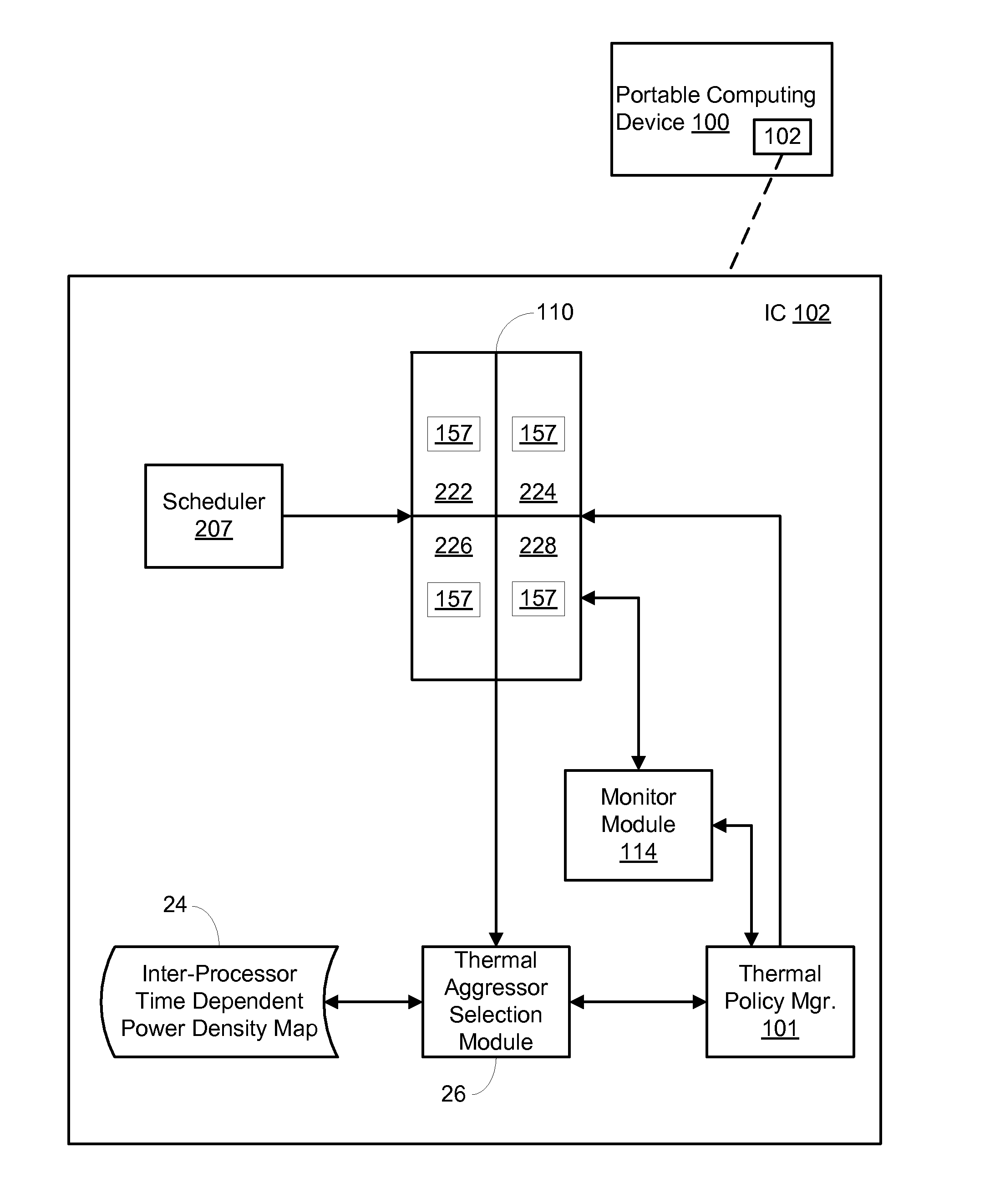

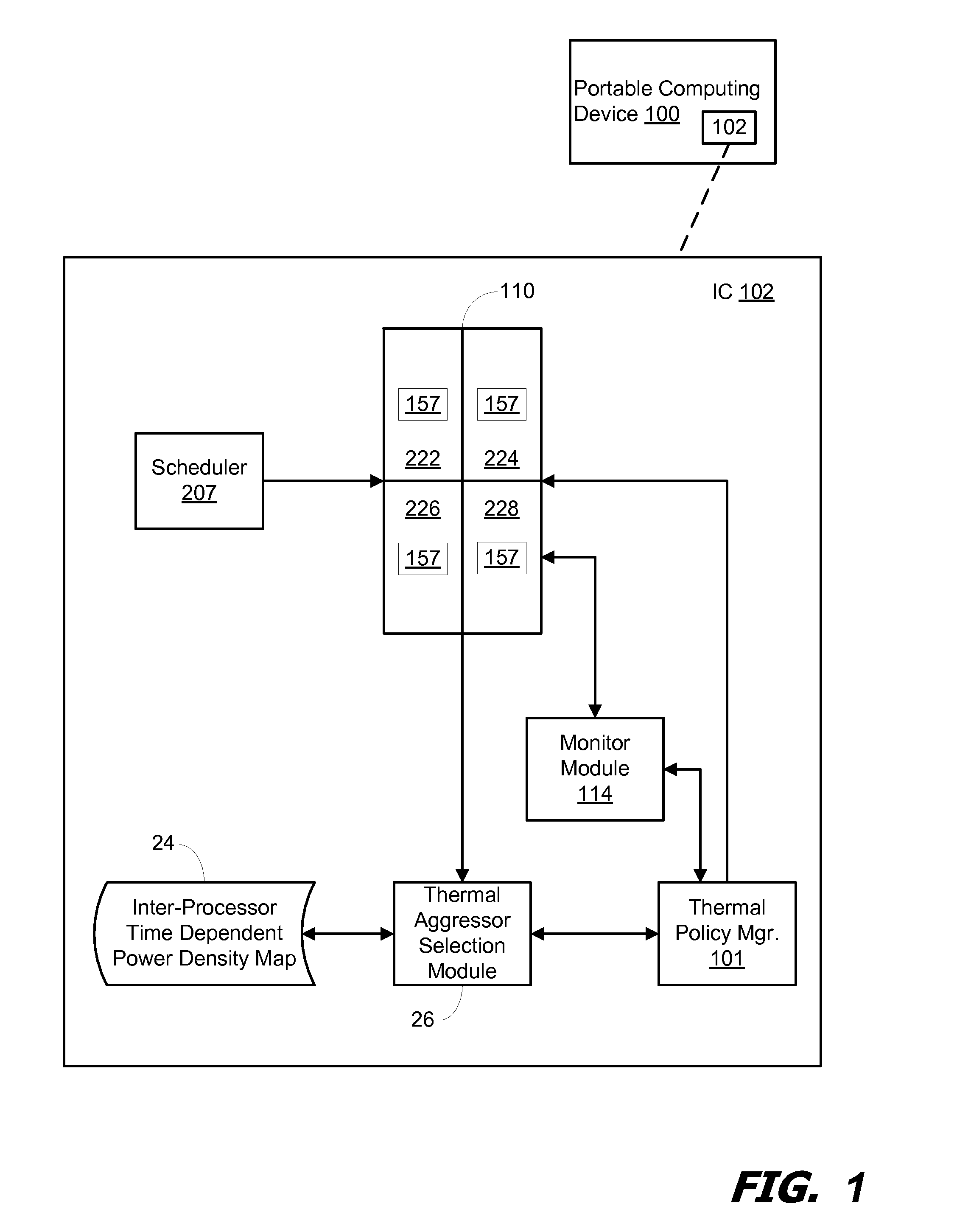

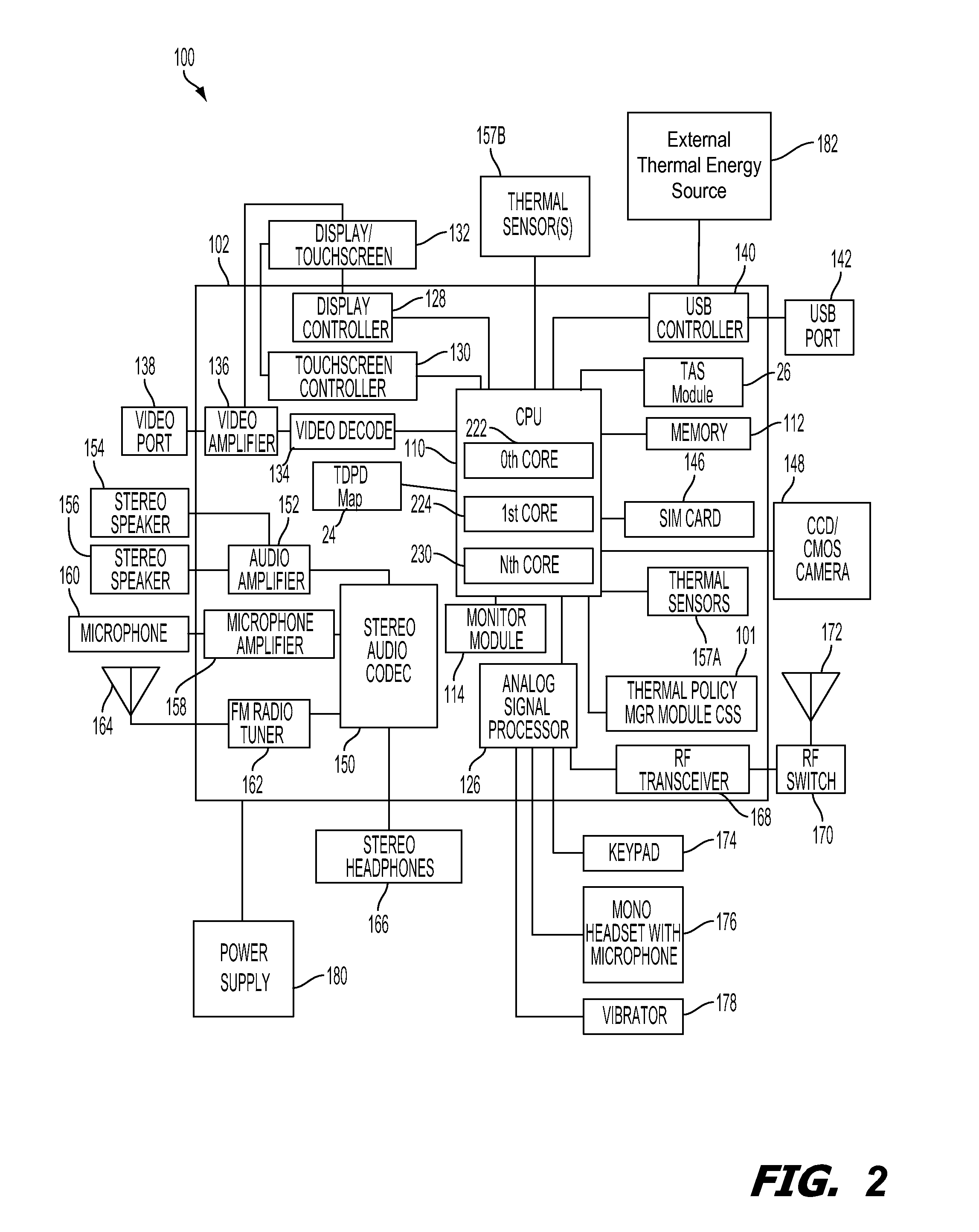

On-chip thermal management techniques using inter-processor time dependent power density data for indentification of thermal aggressors

InactiveUS20130079946A1Reduce the amount of solutionEnergy efficient ICTElectric devicesThermal energyProcessing core

Various embodiments of methods and systems for controlling and / or managing thermal energy generation on a portable computing device are disclosed. Data discarded from one or more processing core registers may be monitored and analyzed to deduce individual workloads that have been processed by each of the cores over a unit of time. From the deduced workloads, the power consumed by each of the cores over the unit of time in order to process the workload can be calculated. Subsequently, a time dependent power density map can be created which reflects a historical and near real time power consumption for each core. Advantageously, because power consumption can be correlated to thermal energy generation, the TDPD map can be leveraged to identify thermal aggressors for targeted, fine grained application of thermal mitigation techniques. In some embodiments, workloads may be reallocated from the identified thermal aggressors to the identified underutilized processing components.

Owner:QUALCOMM INC

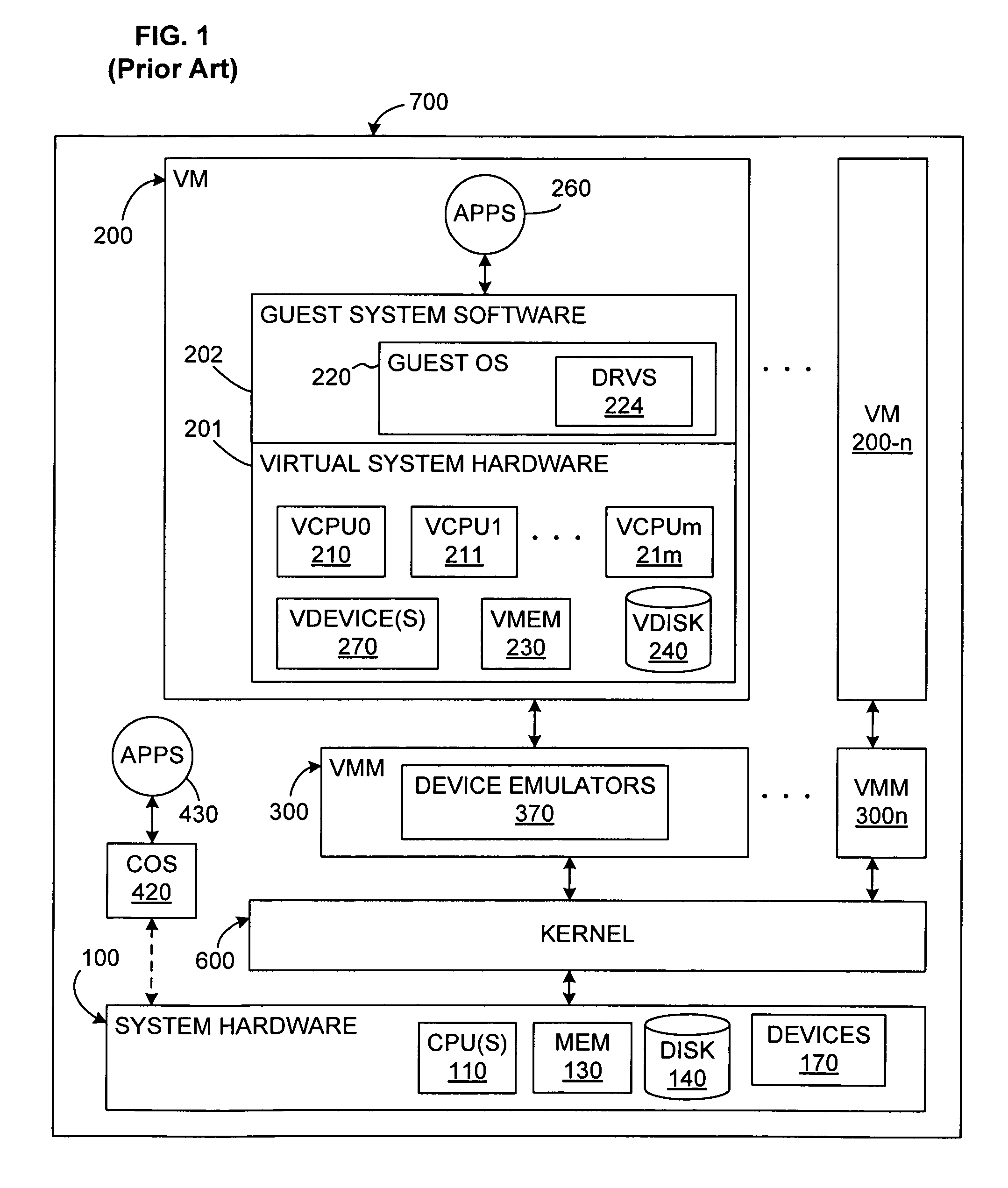

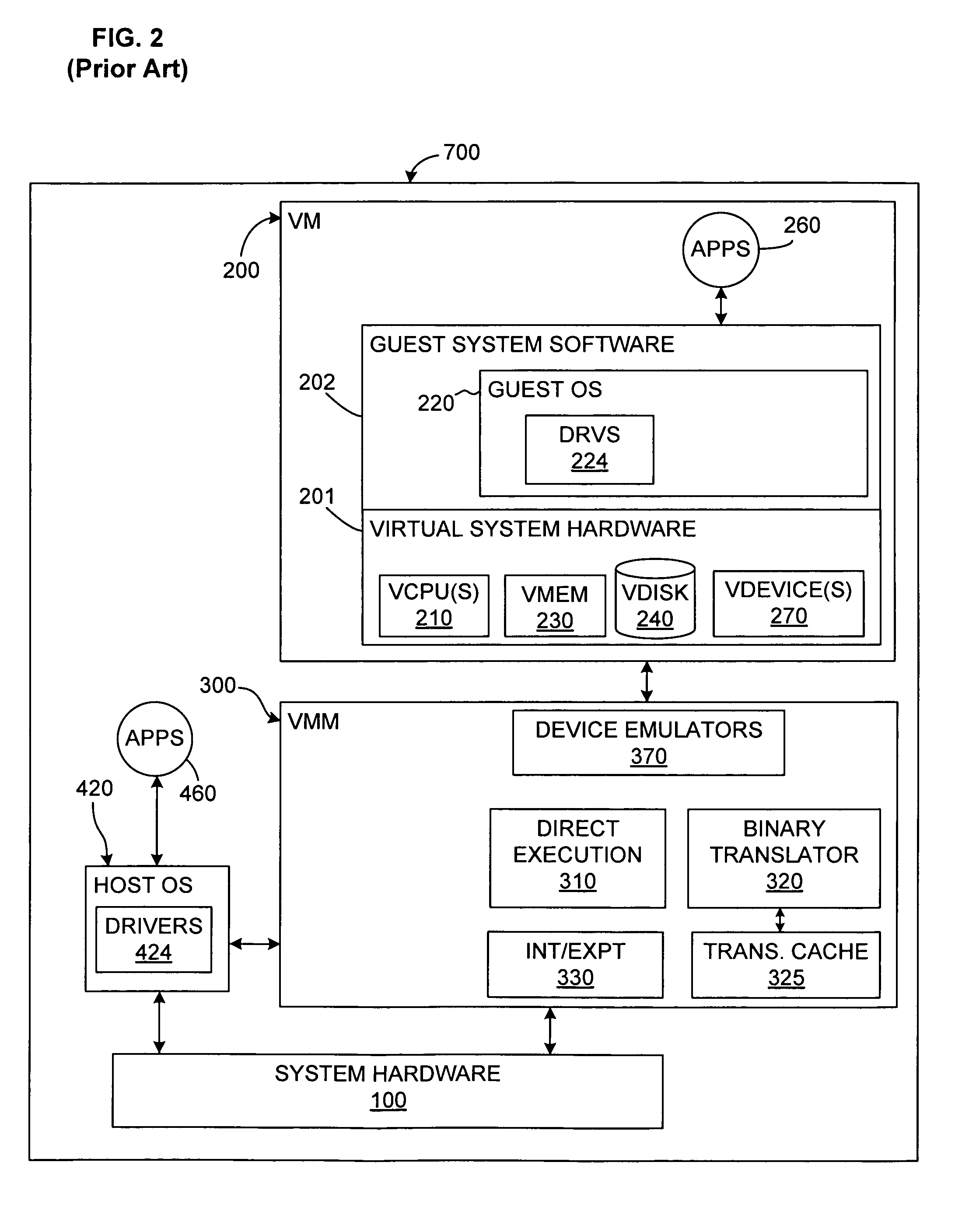

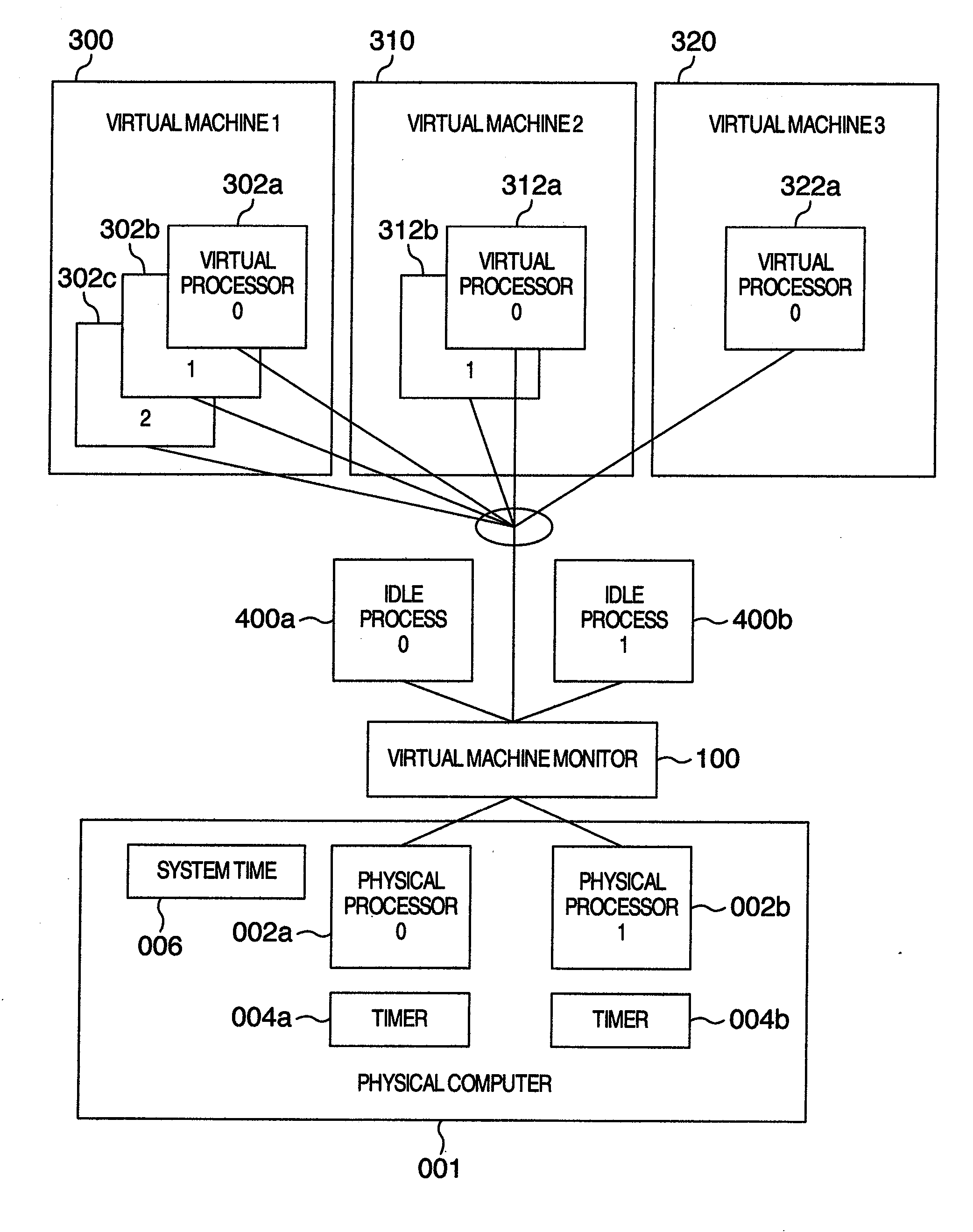

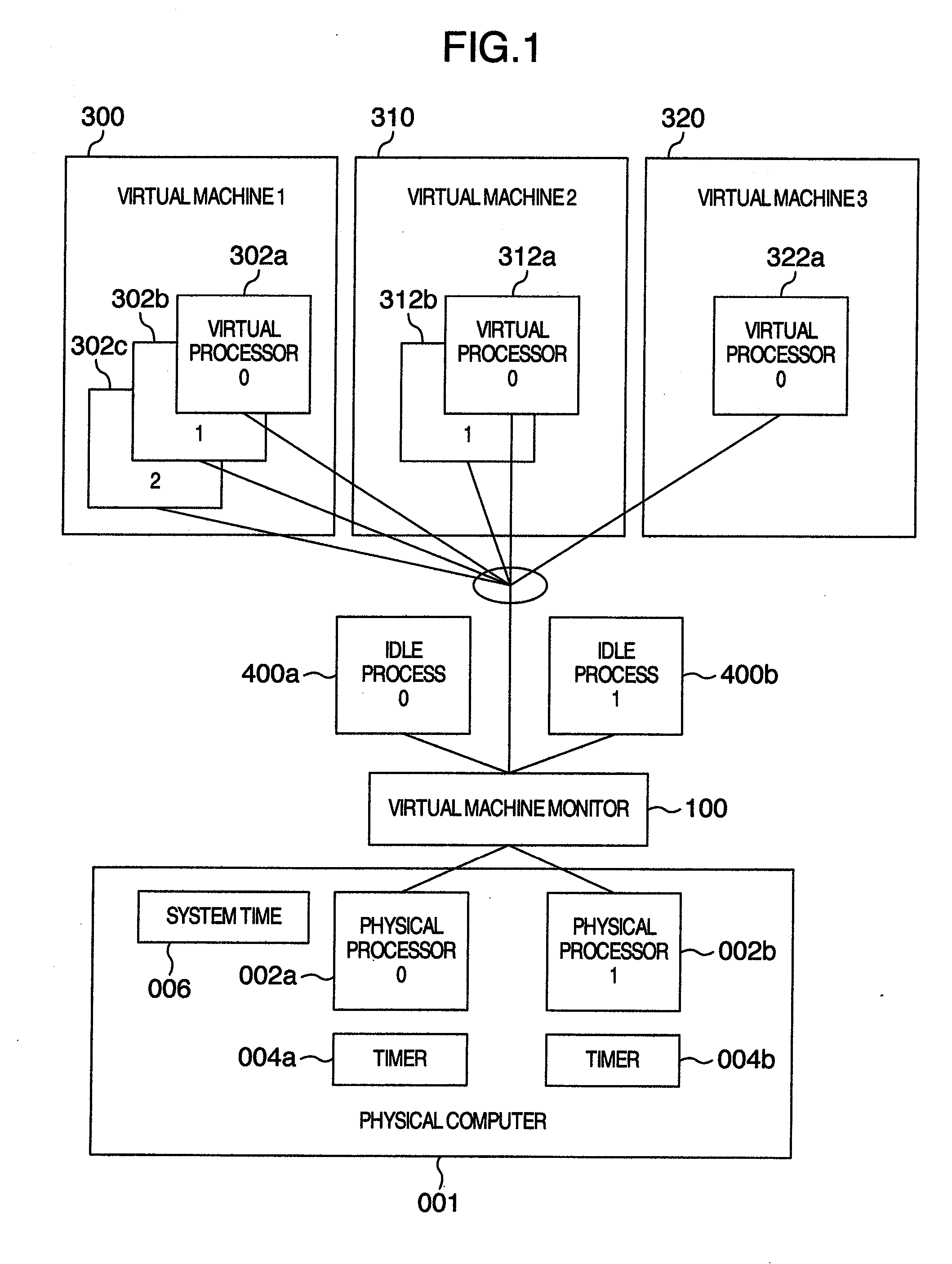

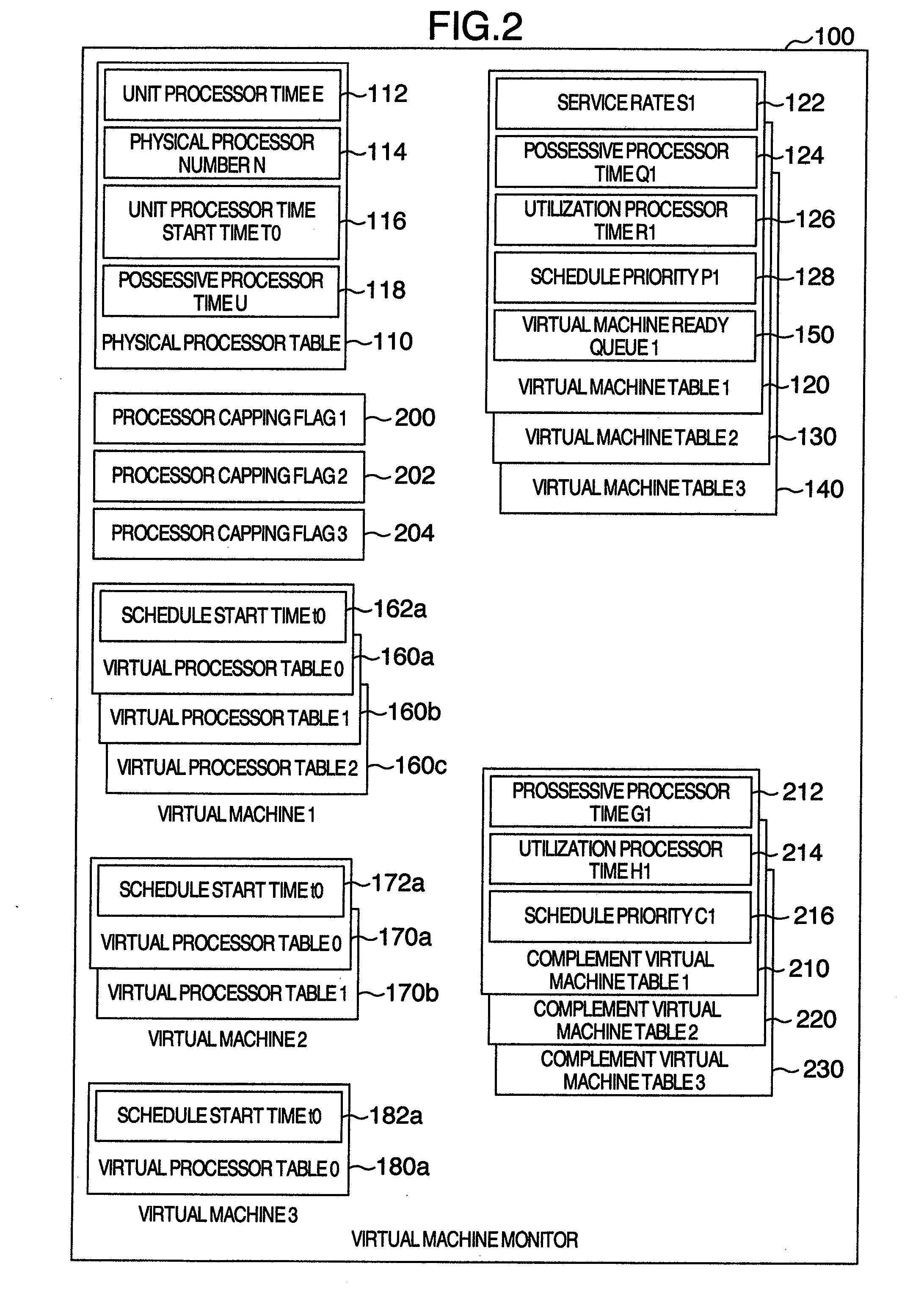

Processor capping method in virtual machine system

InactiveUS20080184227A1Energy efficient ICTEnergy efficient computingVirtual ProcessorProcessor time

In a processor capping method in a virtual machine system, a complement virtual machine is created having a possessive processor time equal to the difference of subtraction of a possessive processor time given to the processor capping enabled virtual machine from a possessive processor time of the whole physical computer; a processor time by which each virtual machine utilizes the physical processor per unit time is determined; schedule priorities of each virtual machine and of the complement virtual machine are determined on the basis of their possessive processor times and the determined utilization processor time as well; and the schedule priority of the processor capping enabled virtual machine is compared with that of the complement virtual machine corresponding to the processor capping enabled computer to decide whether the schedule for the physical processor of the virtual processor the processor capping enabled virtual machine has is permissible or prohibitive.

Owner:HITACHI LTD

Wireless multi-functional computer lock

A wireless multi-functional computer lock comprises at least one meter for measuring at least one of blood pressures, pulses, body temperatures and times of moving steps of a person; a wireless transmitter for transmitting measuring data from the air inlet one meter; a receiver installed on a computer and communicated to the wireless transmitter wirelessly for receiving the data from the wireless transmitter. The wireless transmitter is used to actuate the receiver on the computer so as to enter into a process of inputting passwords, browsing the data and lock the data display on the computer. The wireless transmitter comprises a time switch and a processor, and the time switch serves to select a time period to set the actuate time of the computer.

Owner:KEY MARK TECH

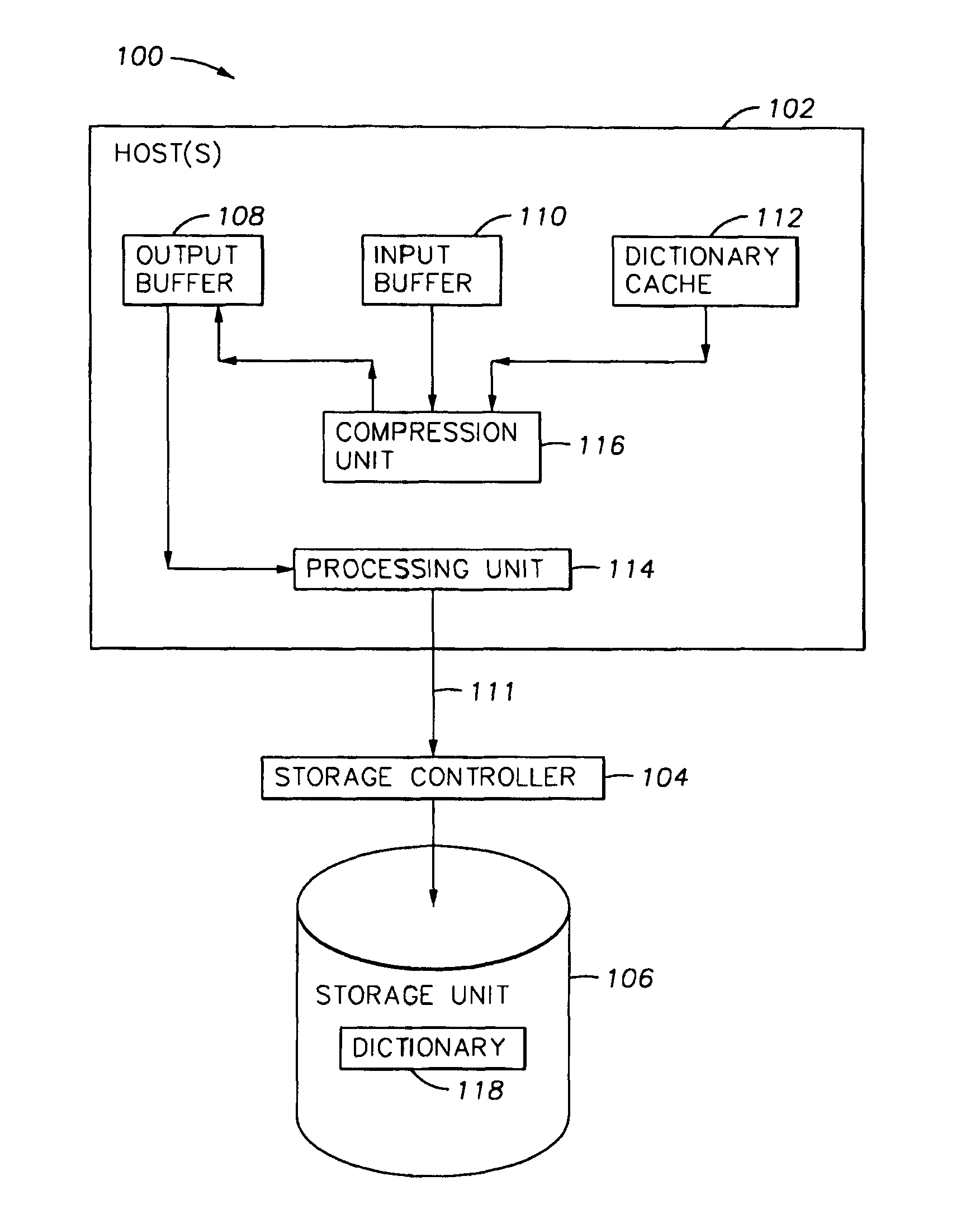

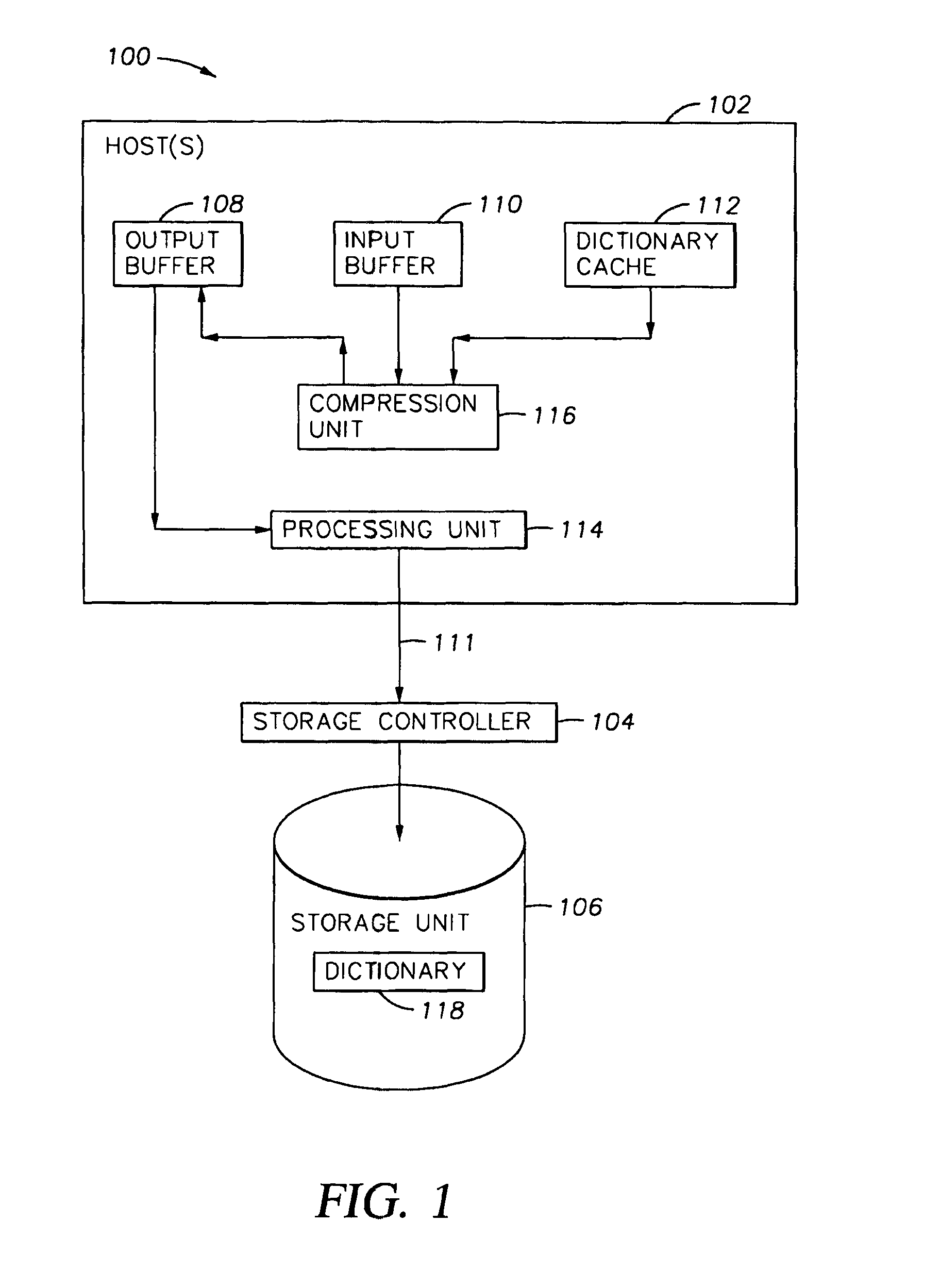

On-line data compression analysis and regulation

InactiveUS7898442B1Conserve valuable processor timeValuable processor timeCode conversionData compressionAnalysis data

Data compression efficacy in a data storage system is analyzed, and data compression modified in accordance with the results of such analysis, thereby saving otherwise wasted processor time when data compression is poor. Multiple input data blocks are received for storage in a data storage subsystem, and a predetermined compression process is applied thereto. Application of the predetermined compression process is evaluated according to a predetermined compression criteria. If the compression fails to satisfy the predetermined compression criteria, application of the predetermined compression process ceases.

Owner:IBM CORP

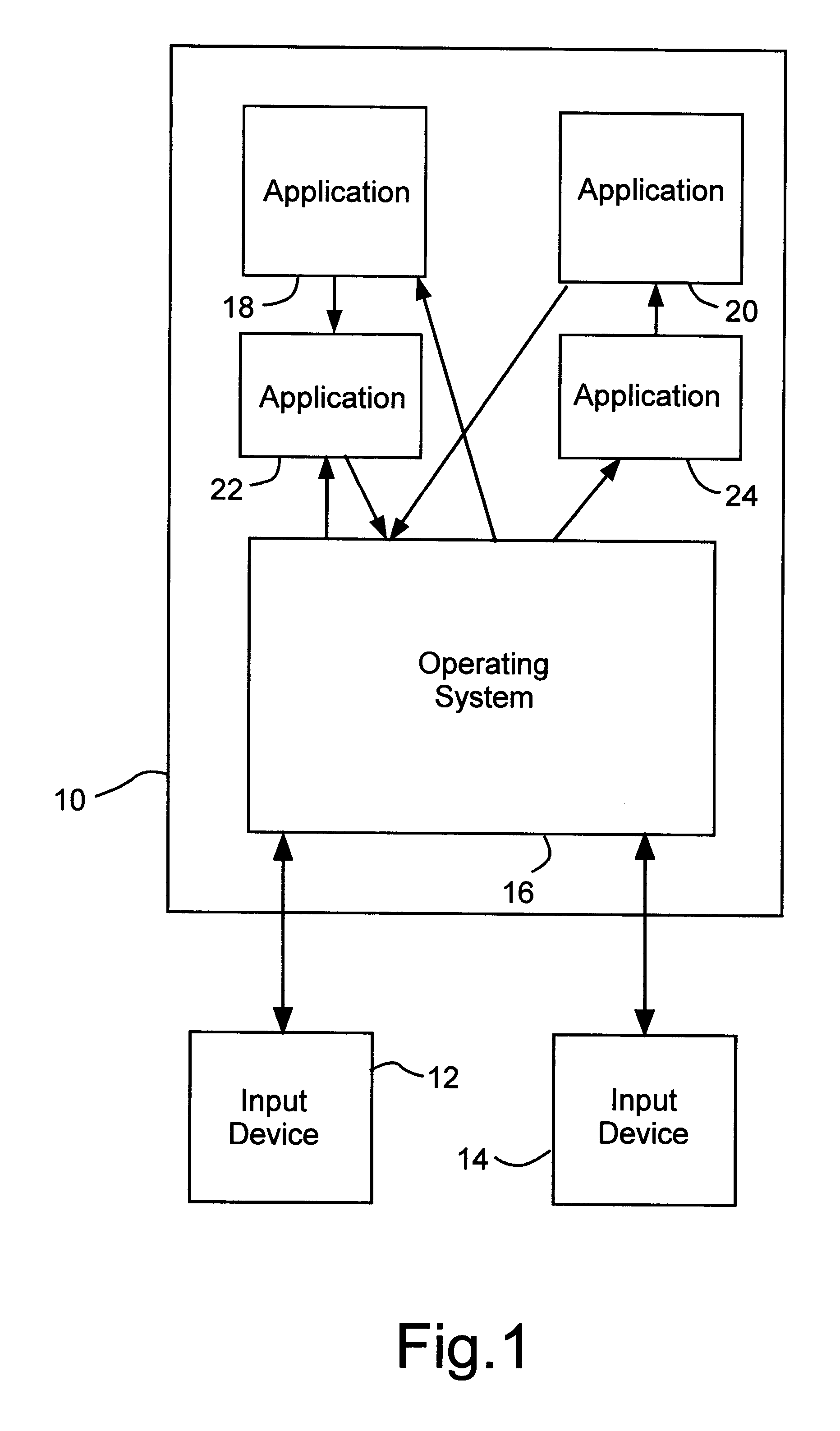

Configurable operating system for control of a mobile I/O device

InactiveUS6996634B1Small and inexpensiveFreeing up spaceProgram loading/initiatingInput/output processes for data processingOperational systemApplication software

An operating system that provides for the capability to accept input from a number of devices, and transfer the data to the appropriate application without using an application to perform routing tasks, thus freeing up more processor time and memory space for the applications. The operating system includes data format translator applications that may be called by the operating system in order to convert the data to the proper format. The decision as to which data format translator application should be called may be made by using information on the input device which the data came from, as well additional information, to determine if a conversion application or other application is required.

Owner:SYMBOL TECH LLC

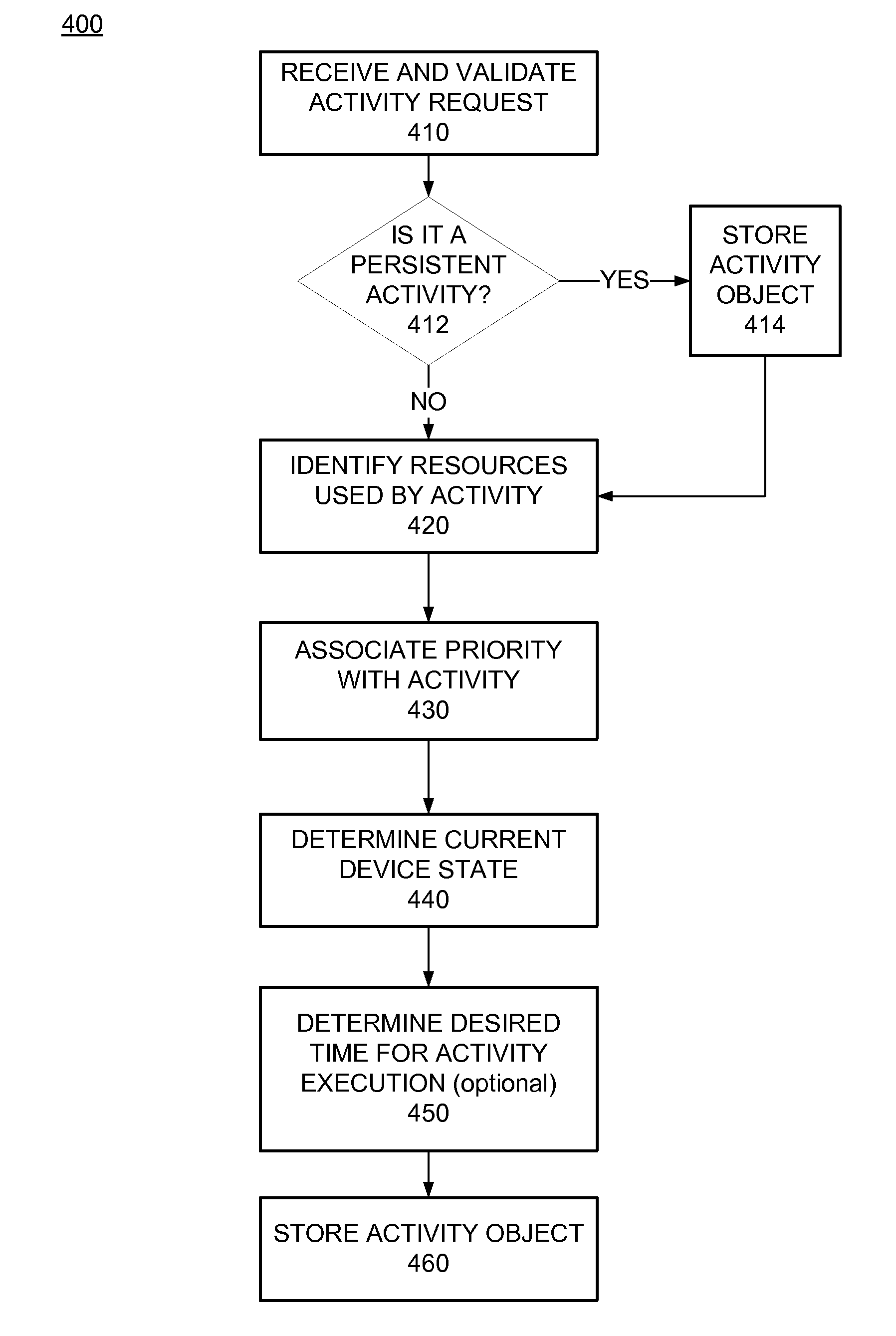

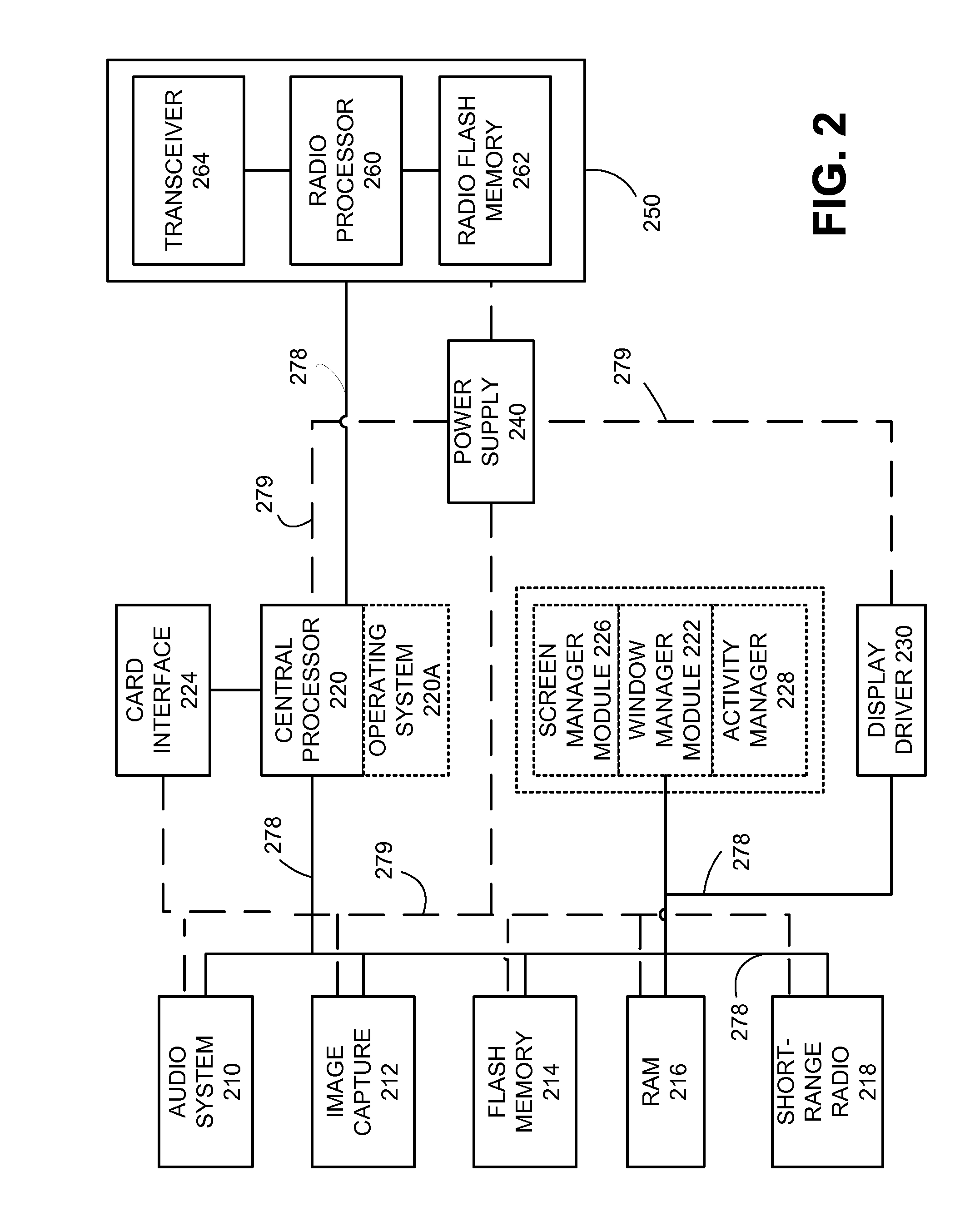

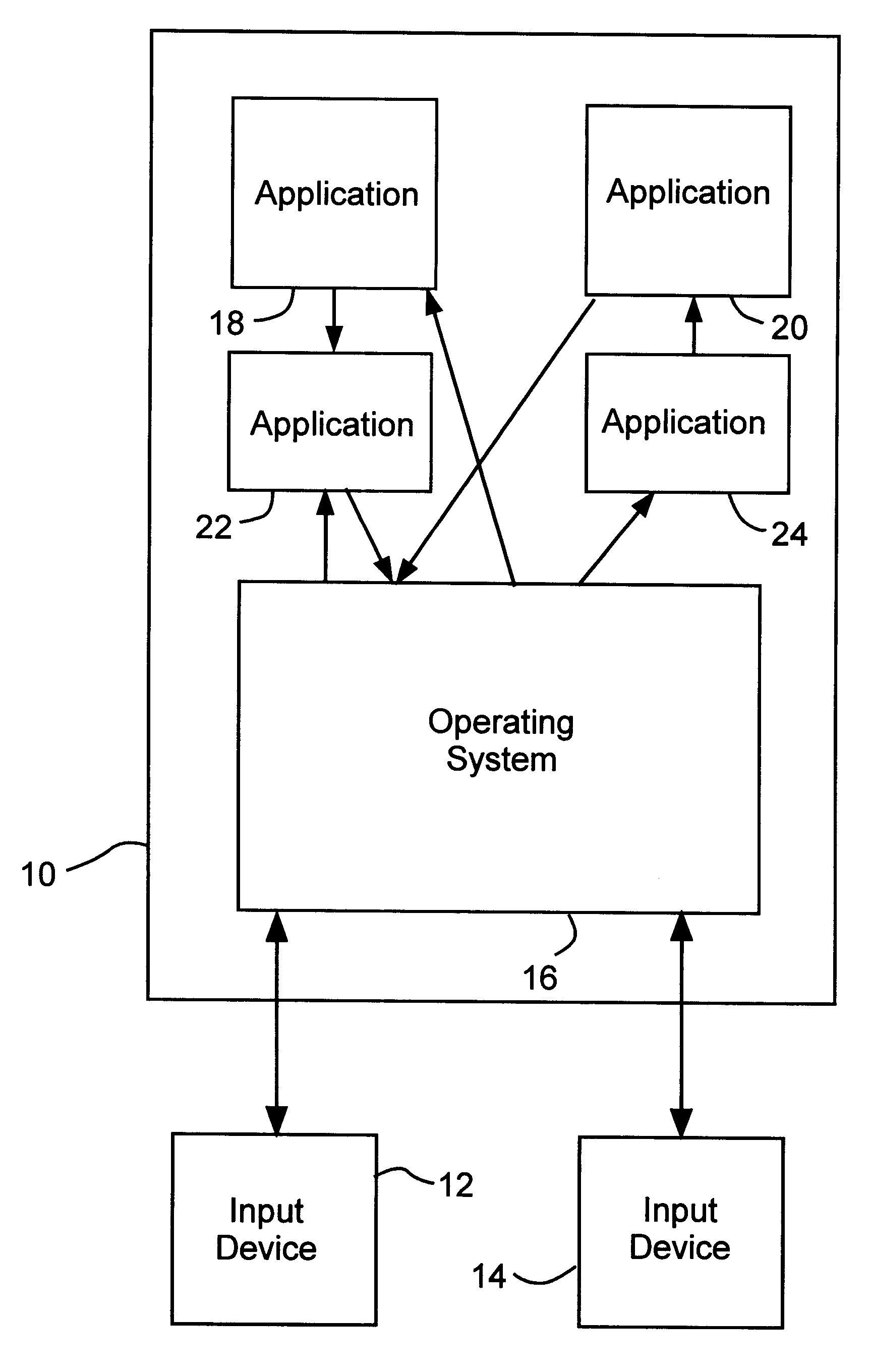

Mobile Computing Device Activity Manager

ActiveUS20120102497A1Improve user interactionImprove performanceResource allocationMemory systemsNetwork connectionApplication software

A system and a method are disclosed for an activity manager providing a centralized component for allocating resources of a mobile computing device among various activities. An activity represents work performed using computing device resources, such as processor time, memory, storage device space or network connections. An application or system service requests generation of an activity by the activity manager, causing the activity manager to associate a priority level with the activity request and identify resources used by the activity. Based on the priority level, resources used and current resource availability of the mobile computing device, the activity manager determines when the activity is allocated mobile computing device resources. Using the priority level allows the activity manager to optimize performance of certain activities, such as activities receiving data from a user.

Owner:QUALCOMM INC

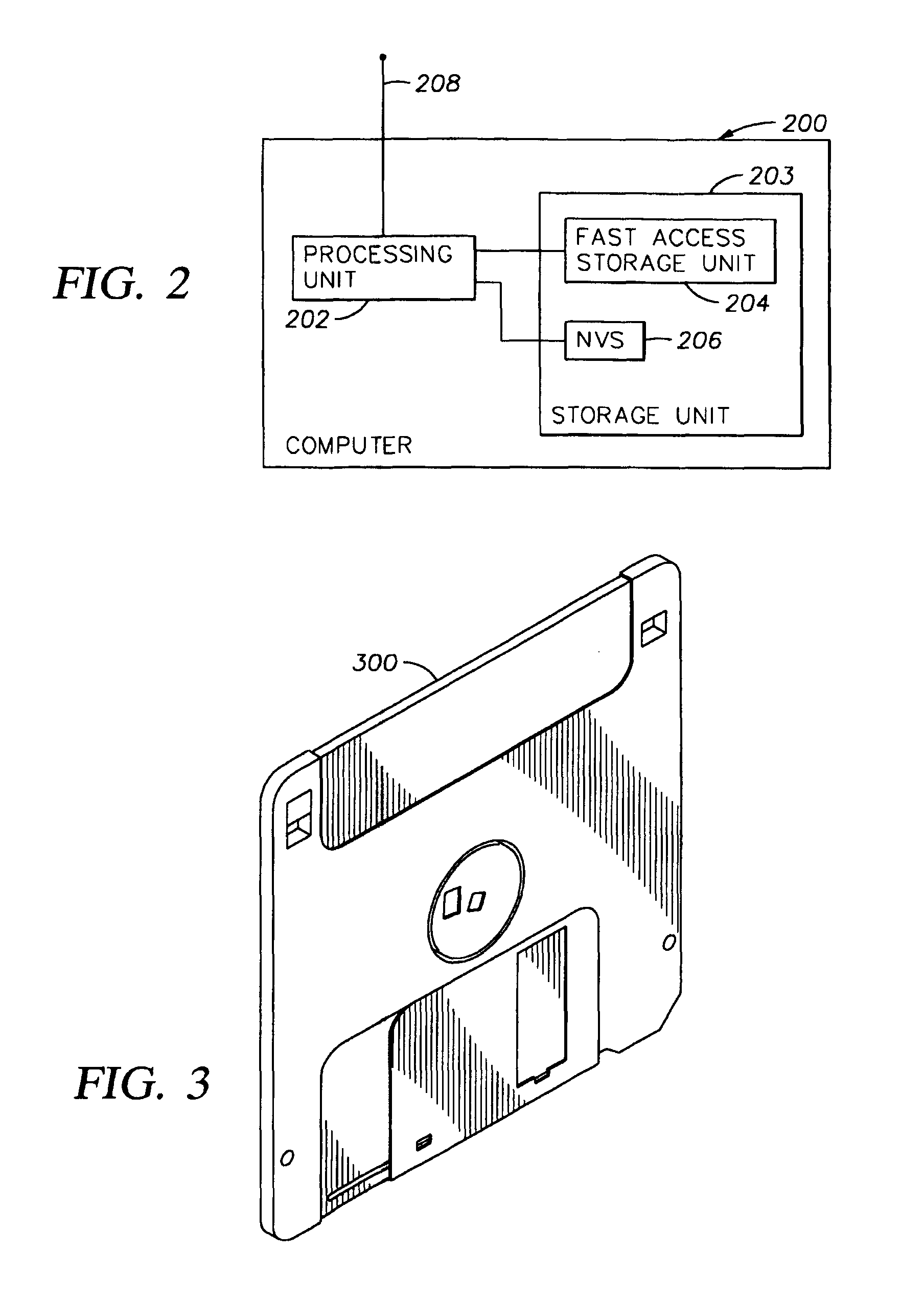

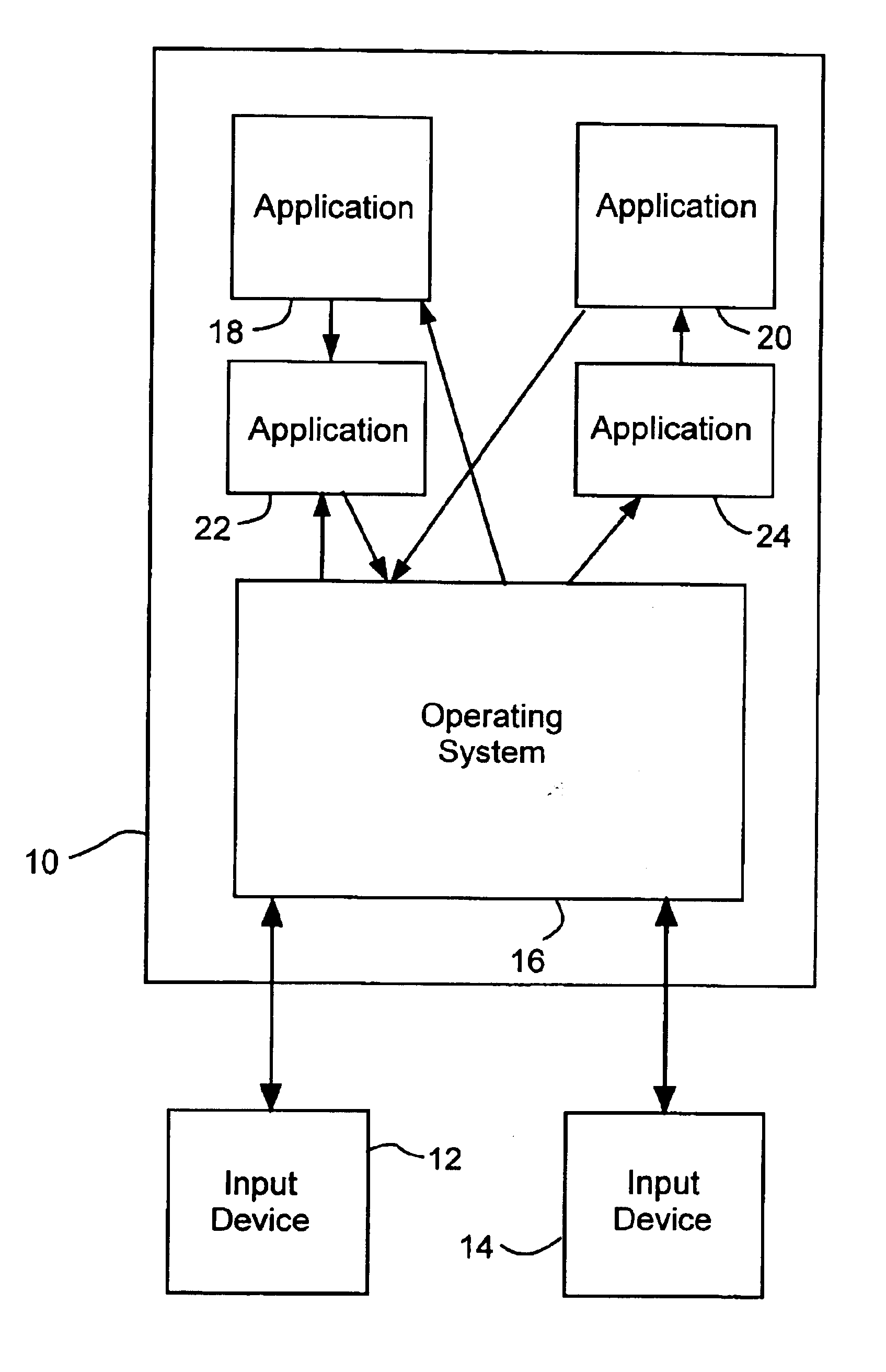

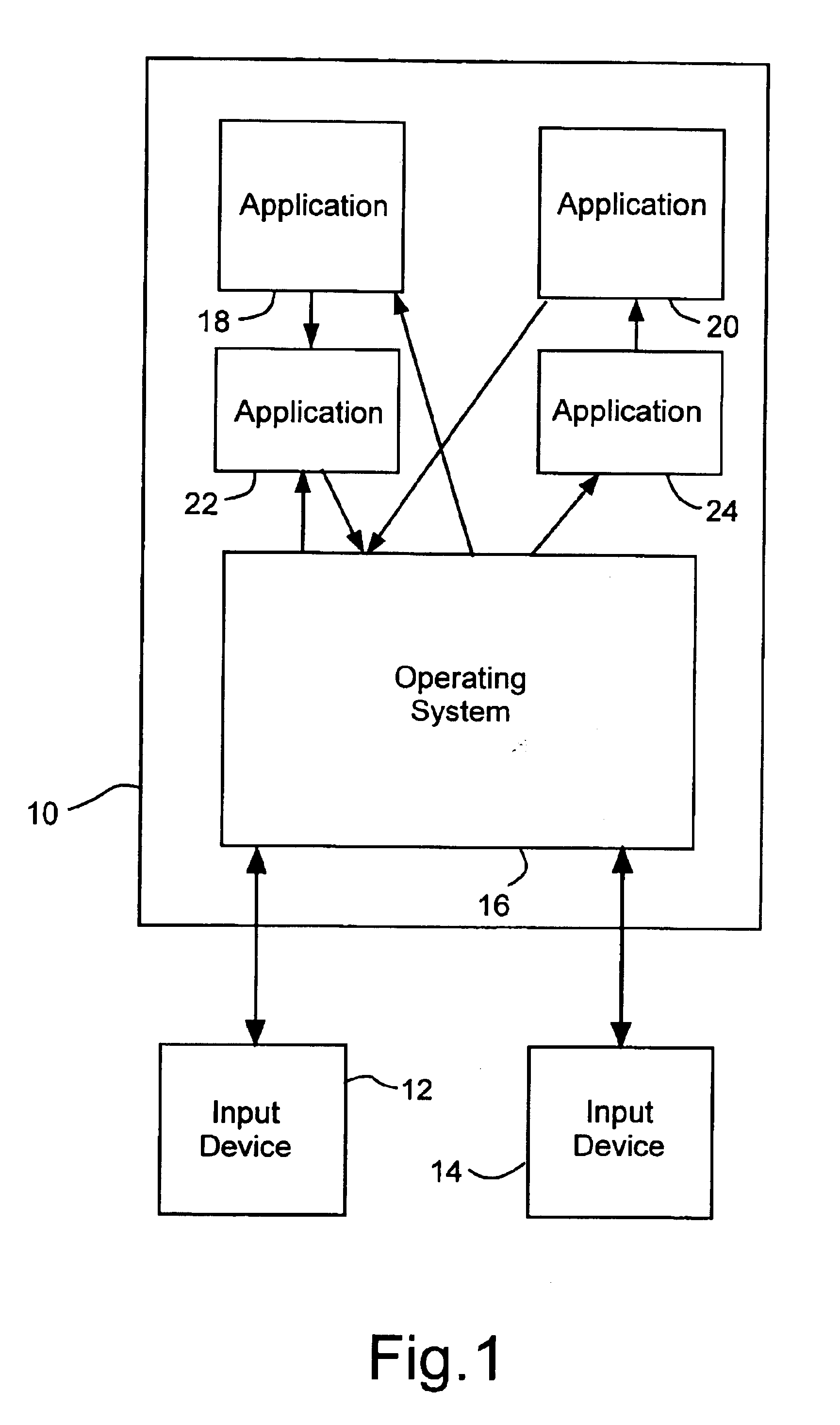

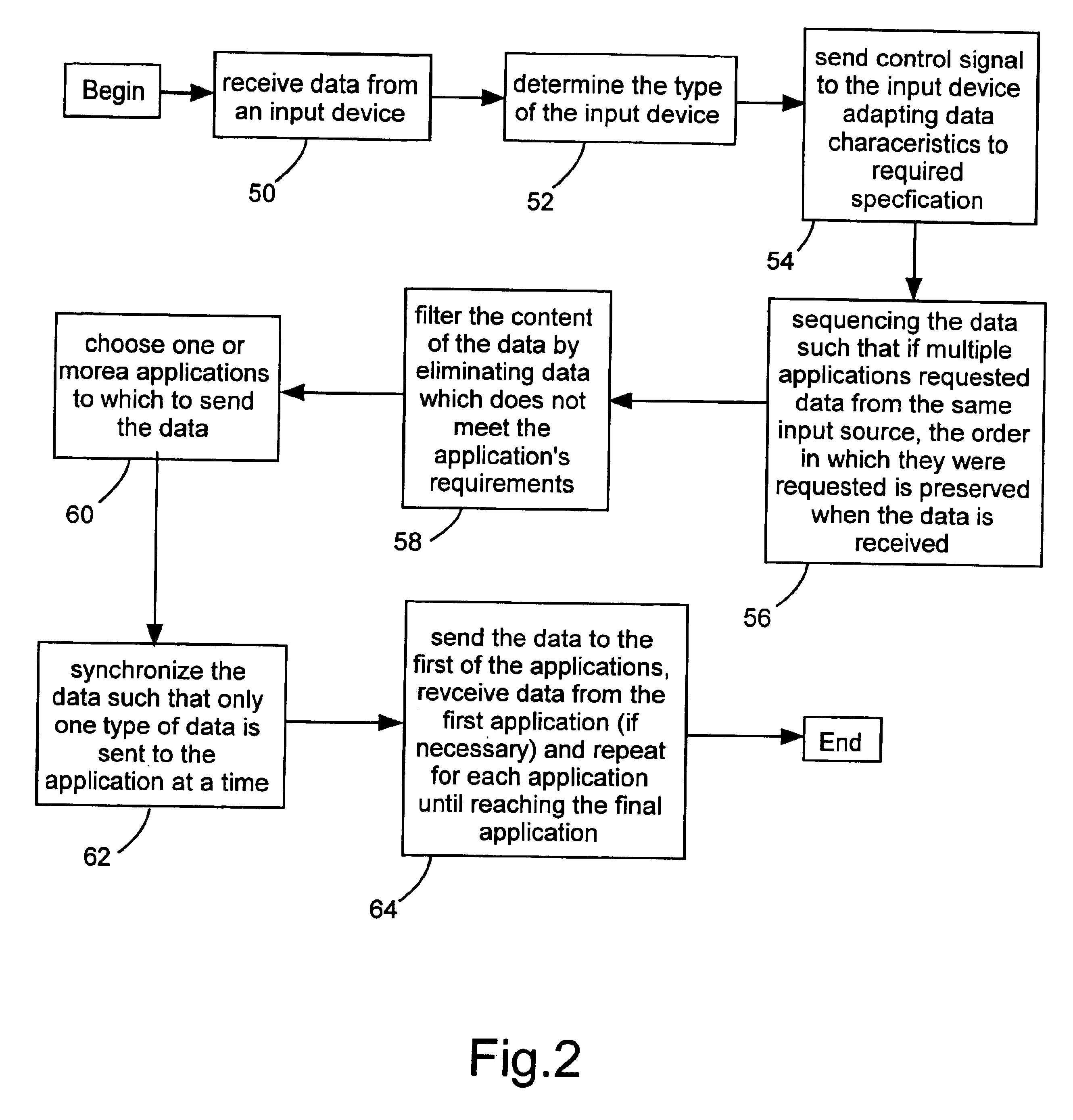

Configurable operating system having multiple data conversion applications for I/O connectivity

InactiveUS6237053B1Reduce in quantityThe process is convenient and fastProgram loading/initiatingOperational systemApplication software

A configurable operating system allows small, inexpensive, and less powerful computers to run a wide variety of applications. The operating system provides for the capability to accept input from a number of input devices, and transfer the data to the appropriate application without using an application to perform the routing tasks, thus freeing up more processor time and memory space for the applications. Data format translator applications may be called by the operating system in order to convert the data to the proper format. The decision as to which application should be called may be made by using information on the input device which the data came from, as well as additional information, to determine if a conversion application or other application is required.A method for using the operating system may include the steps of: receiving data from an input device; determining the type of the input device; choosing one or more applications to send the data through based on the type of the input device; and sending the data to the first of the applications, receiving data from the first of the applications, and repeating for the next of the applications until reaching the last of the applications.

Owner:SYMBOL TECH LLC

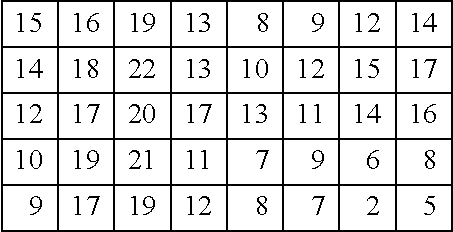

Fast loss less image compression system based on neighborhood comparisons

InactiveUS20040008896A1Reduce varianceEasy to compressCode conversionCharacter and pattern recognitionPixel value differenceImage compression

A fast loss less image compression system based on neighborhood comparisons compares pixel value differences with neighboring pixels and replaces such pixel values with the minimum of the differences. A marker is attached to a block of pixels, such that all the pixels in that block are compared with neighbors of one direction. The marker indicates how all of the pixels in that block are compared. Intermittent Huffman-tree construction is used such that one tree is used for several frames. Huffman coding is used to compress the resulting frame. A single Huffman-tree is constructed once every predetermined number of frames. The frequency of Huffman-tree construction can be performed according to the instantaneous availability of processor time to perform the construction. When more processing time is available, the Huffman-trees are computed more frequently. Such frequency variation can be implemented by using an input video frame buffer. If the buffer is a certain size, then processor time for Huffman-tree construction is available.

Owner:ZAXEL SYST

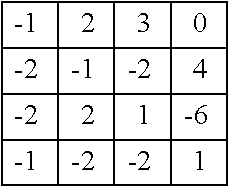

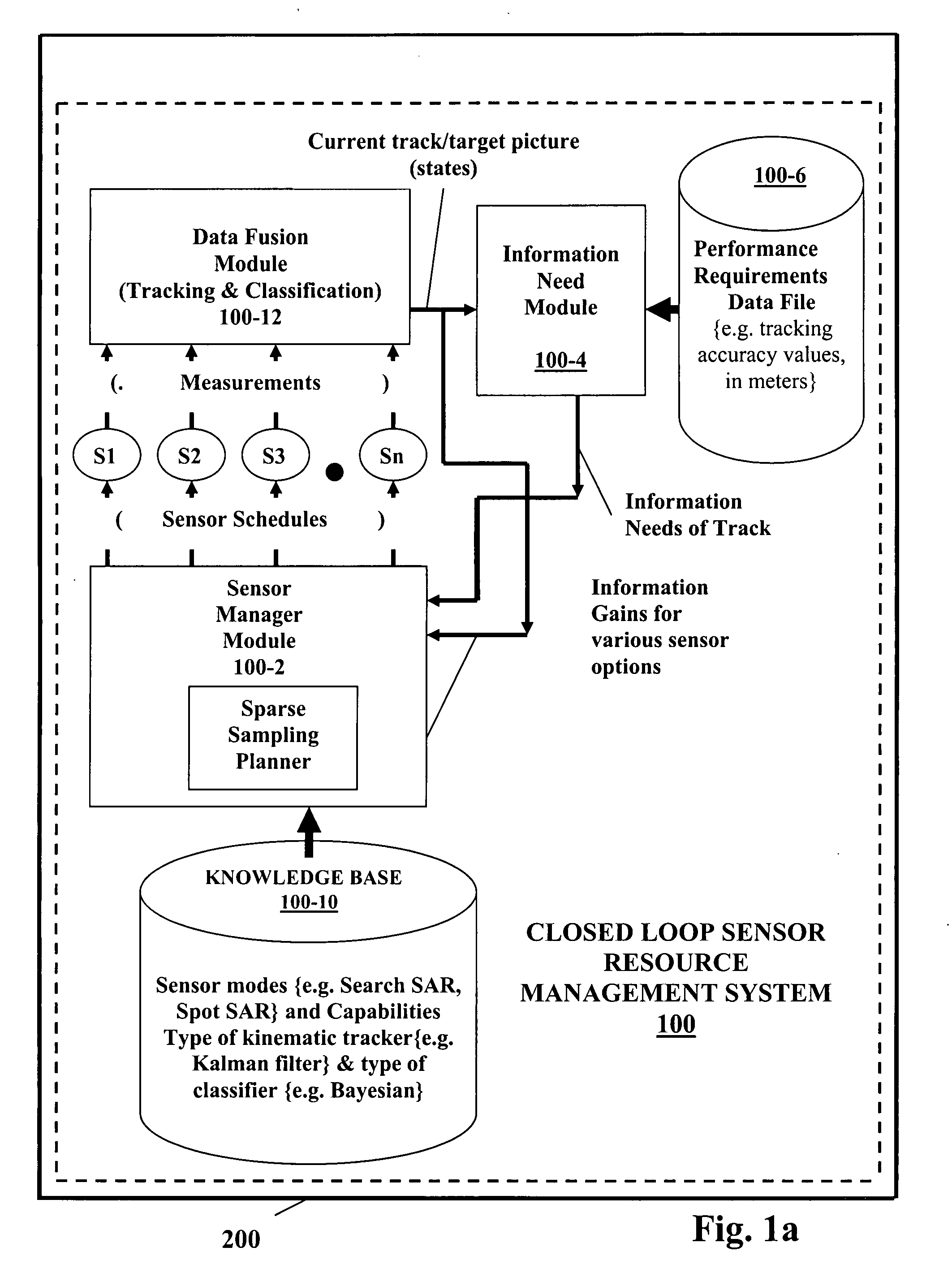

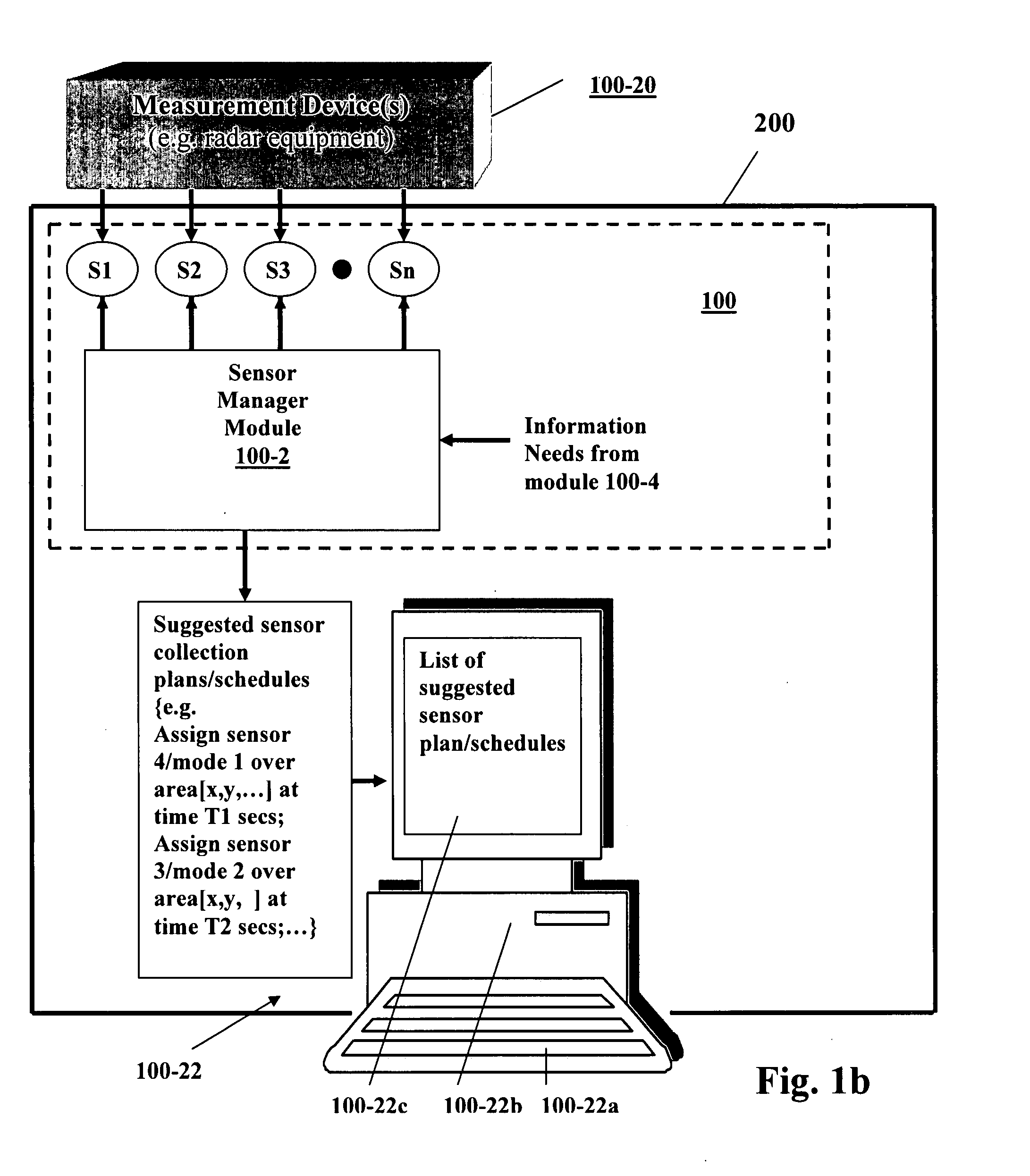

Sparse sampling planner for sensor resource management

ActiveUS20080250875A1Reduce settingsMore top-heavySamplingDigital computer detailsKinematicsHuman resource management

A method and system of a sparse sampling planner uses a finite number of measurements to determine a track's expected intermediate kinematic and classification state for a specific sensor action. It uses the expected track state to compute a reward function. The expected states are further propagated for actions at the next time step to determine the next states and so on. The sampling becomes sparse and the reward function is discounted as one propagates further in time. This produces a state-action tree that is more top-heavy while providing greater accuracy at times closer to the decision point. By doing so, the planner creates a plan comprising a sequence of actions that result in the highest reward. By employing various heuristics to further prune the tree gives highly accurate results with significant savings in computational processor time.

Owner:RAYTHEON CO

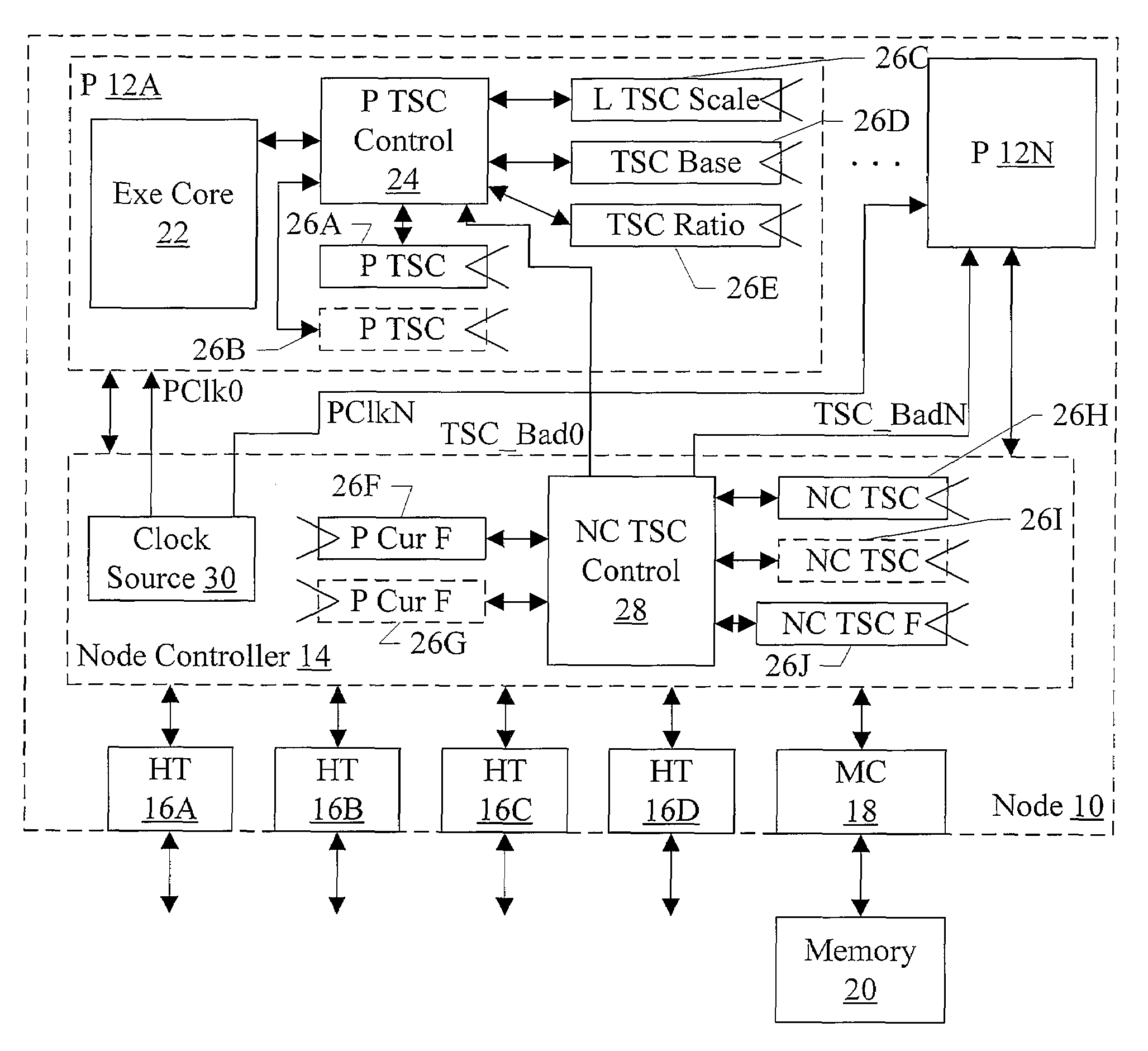

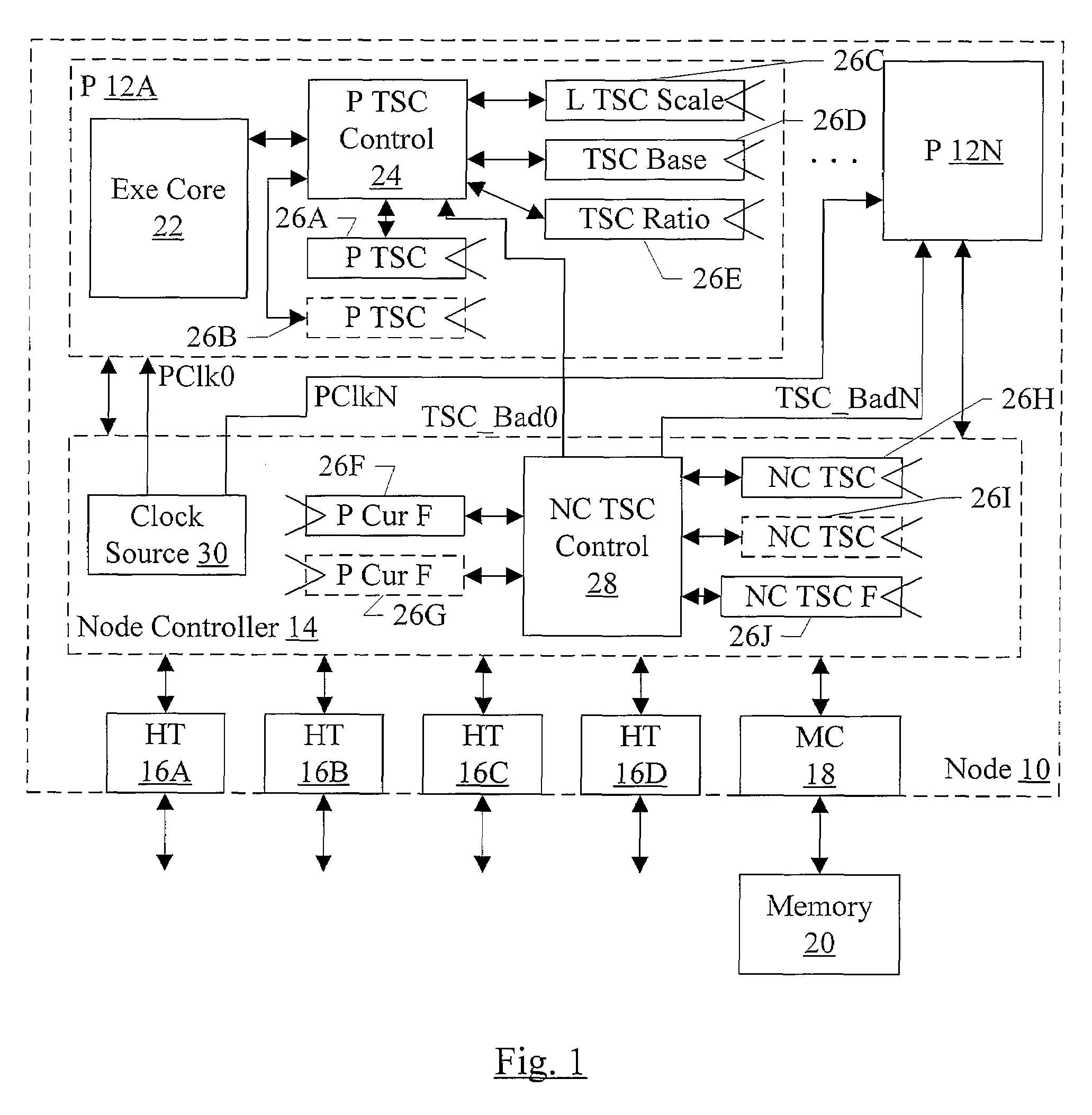

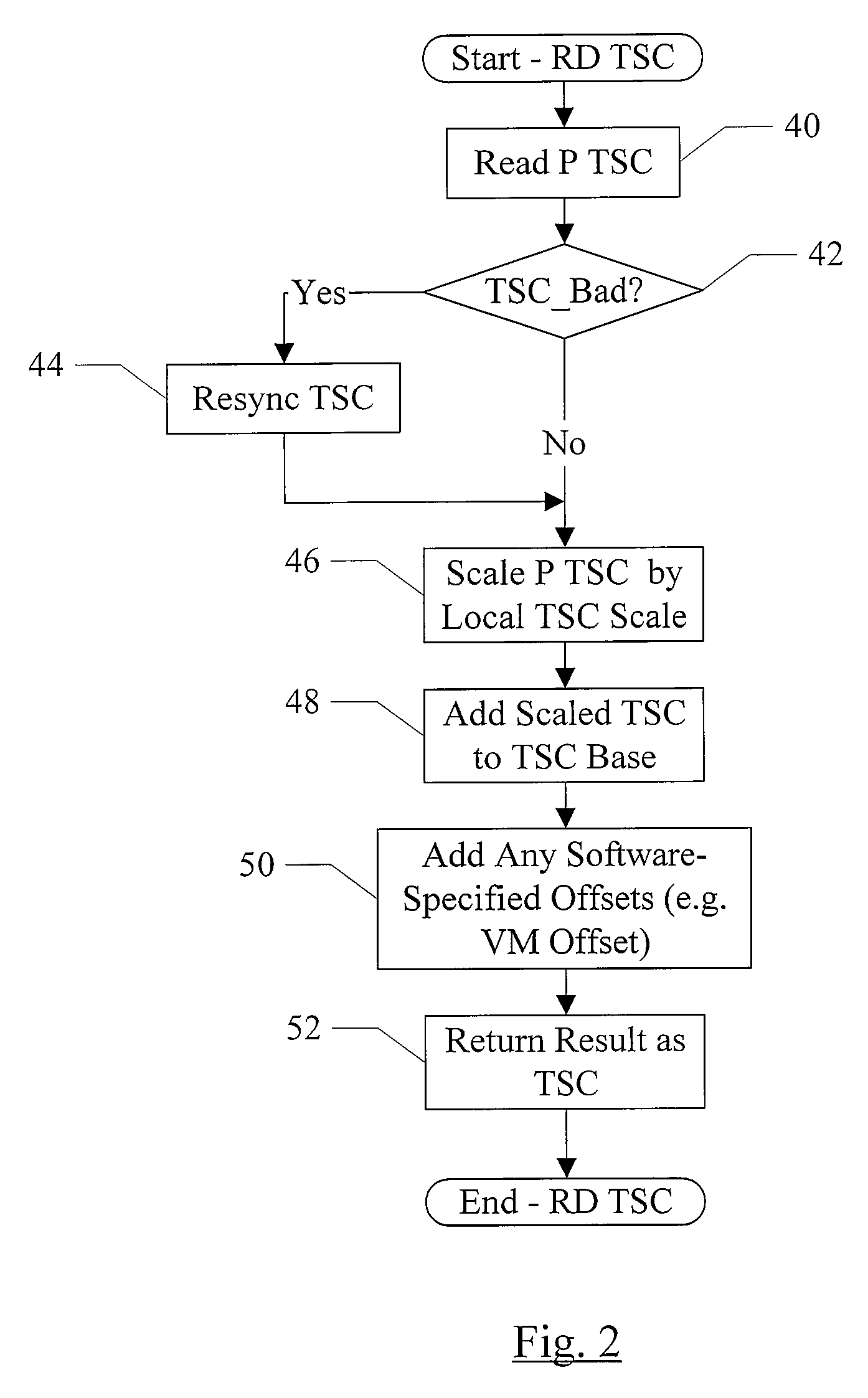

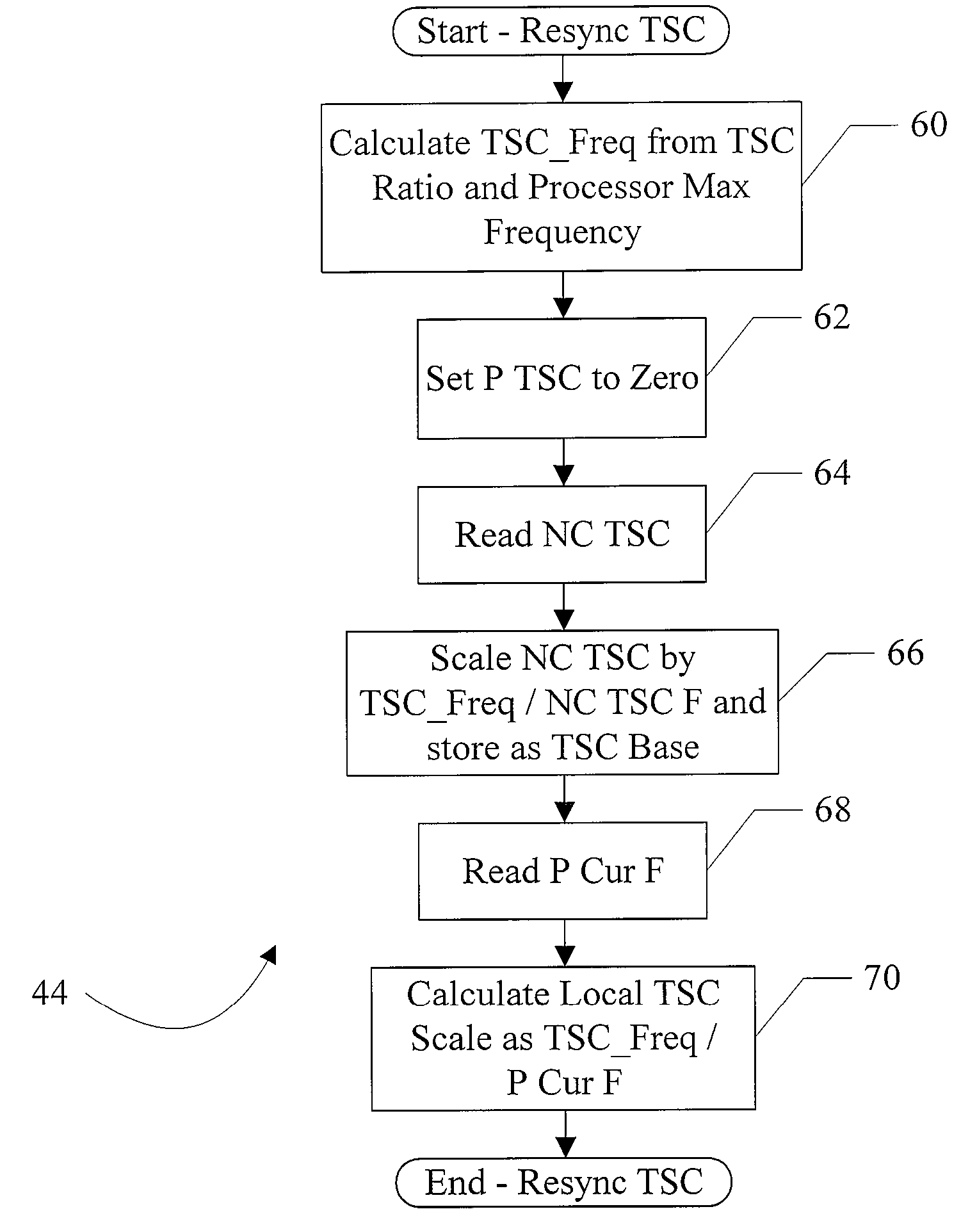

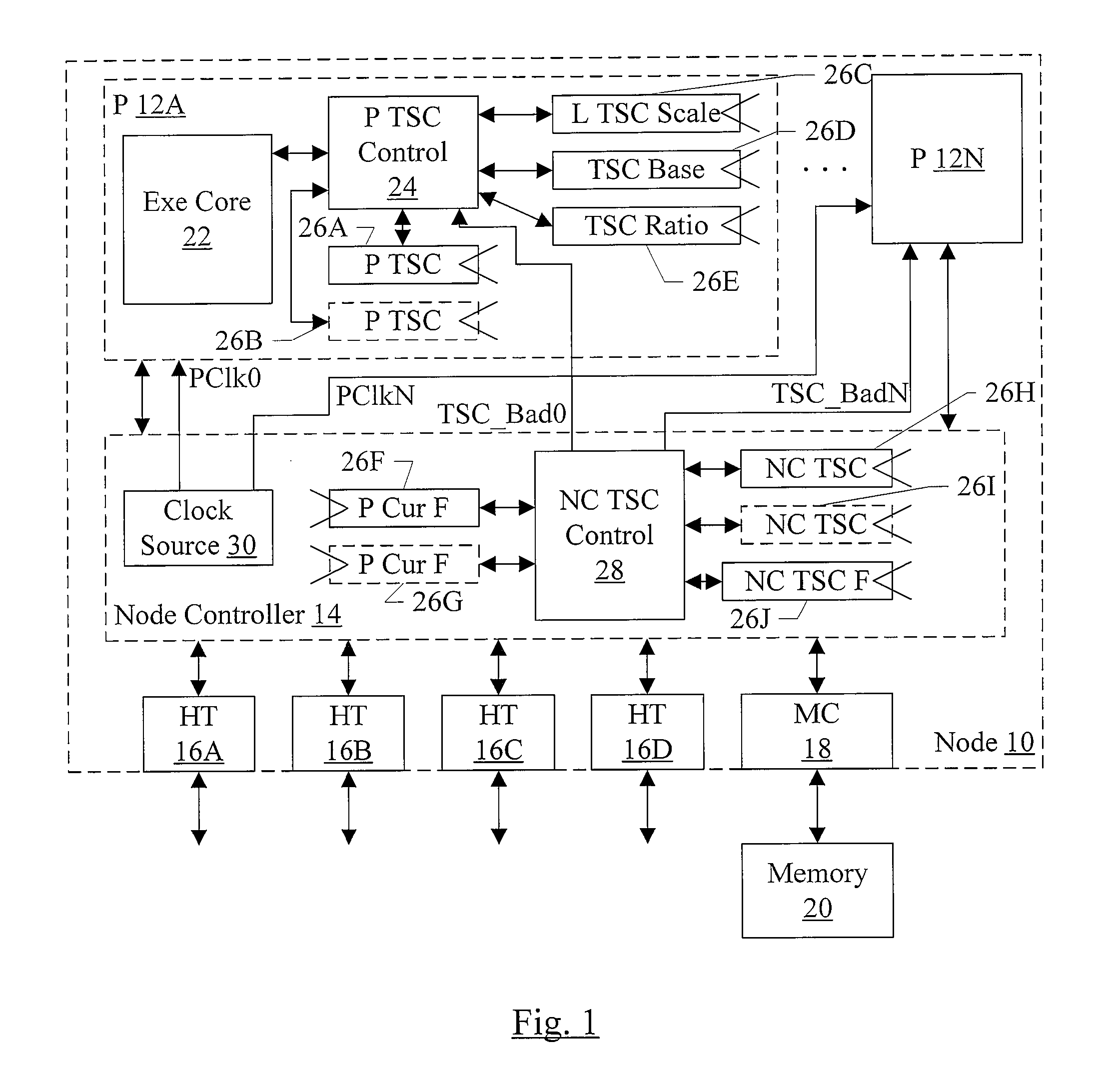

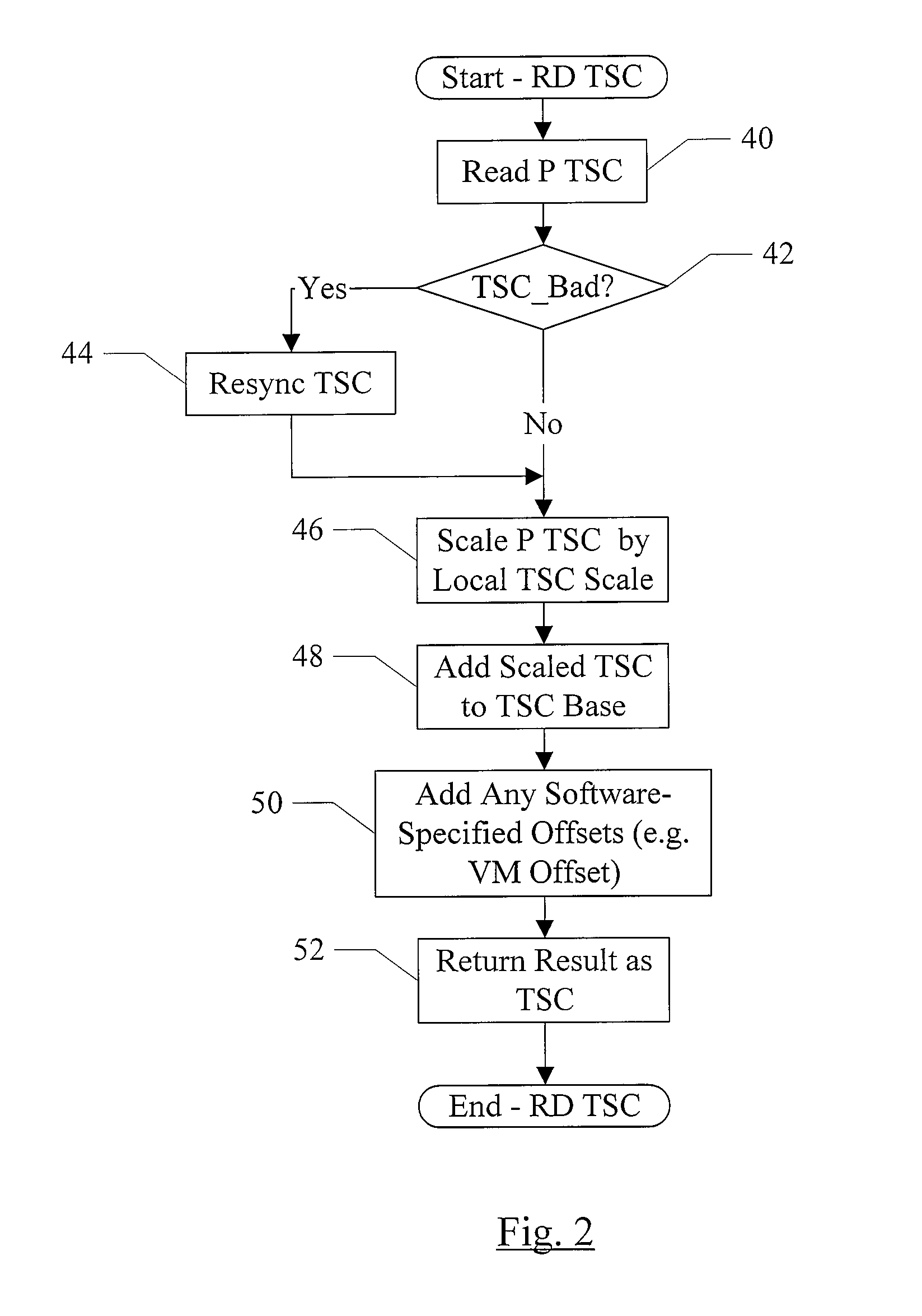

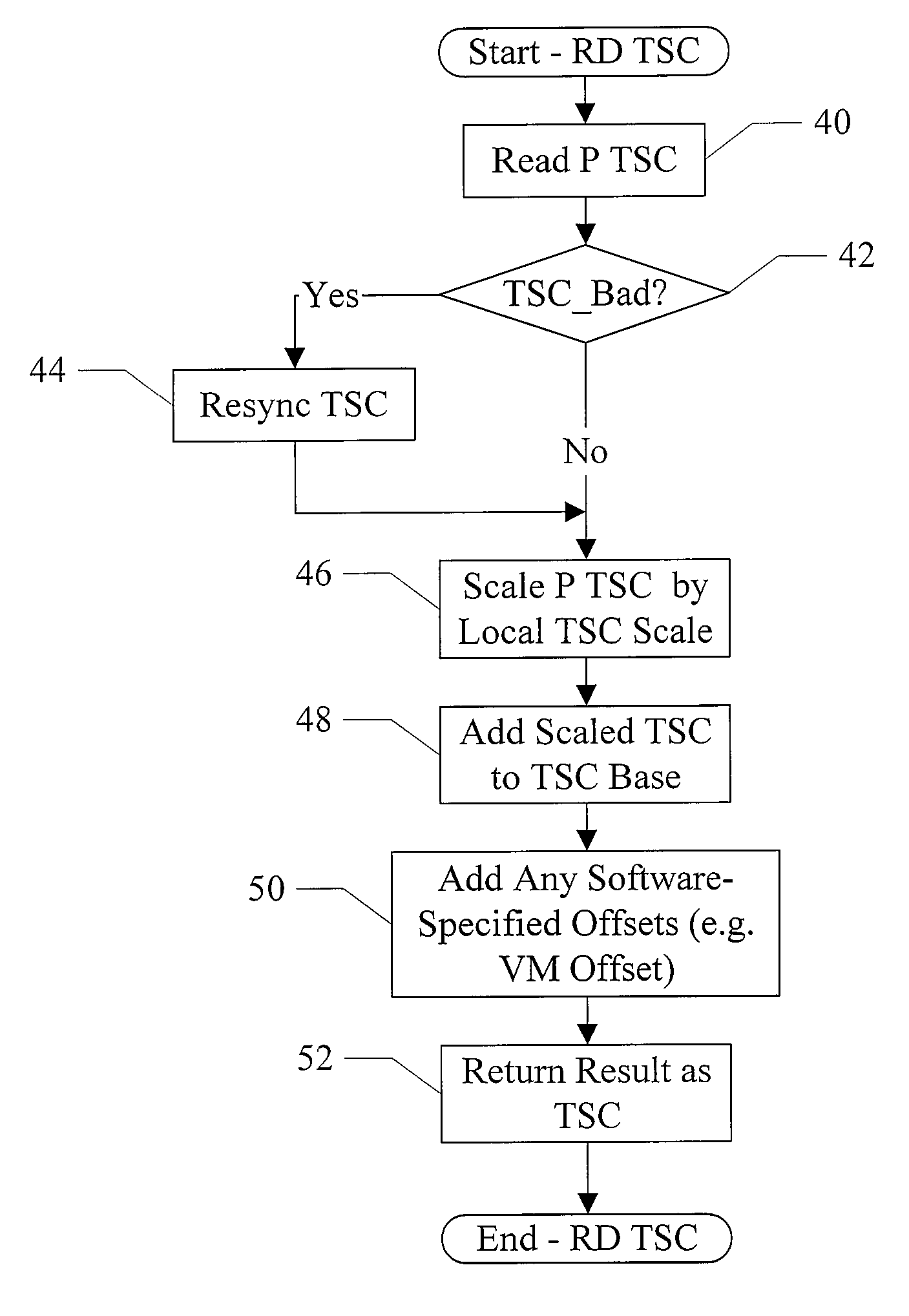

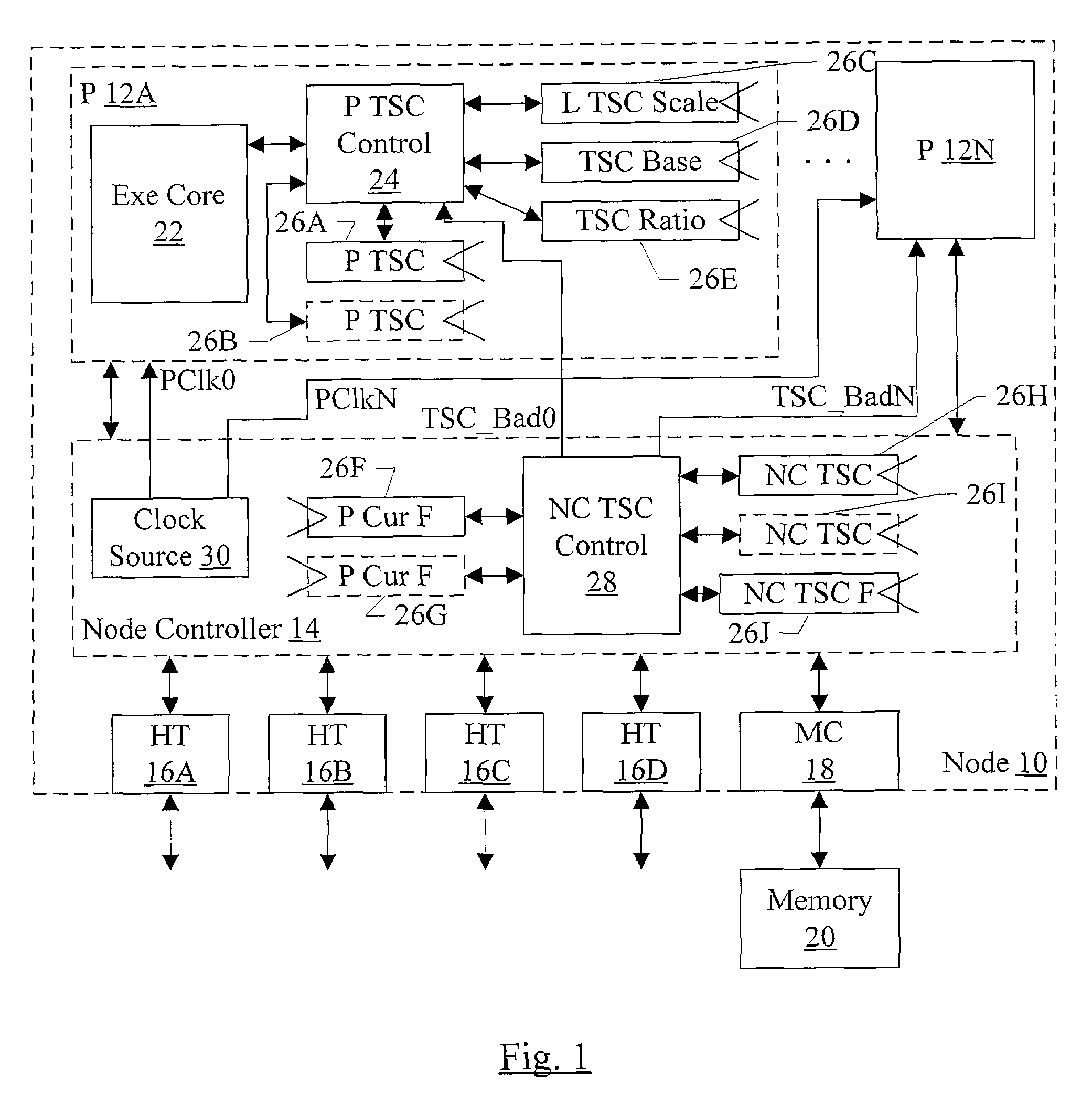

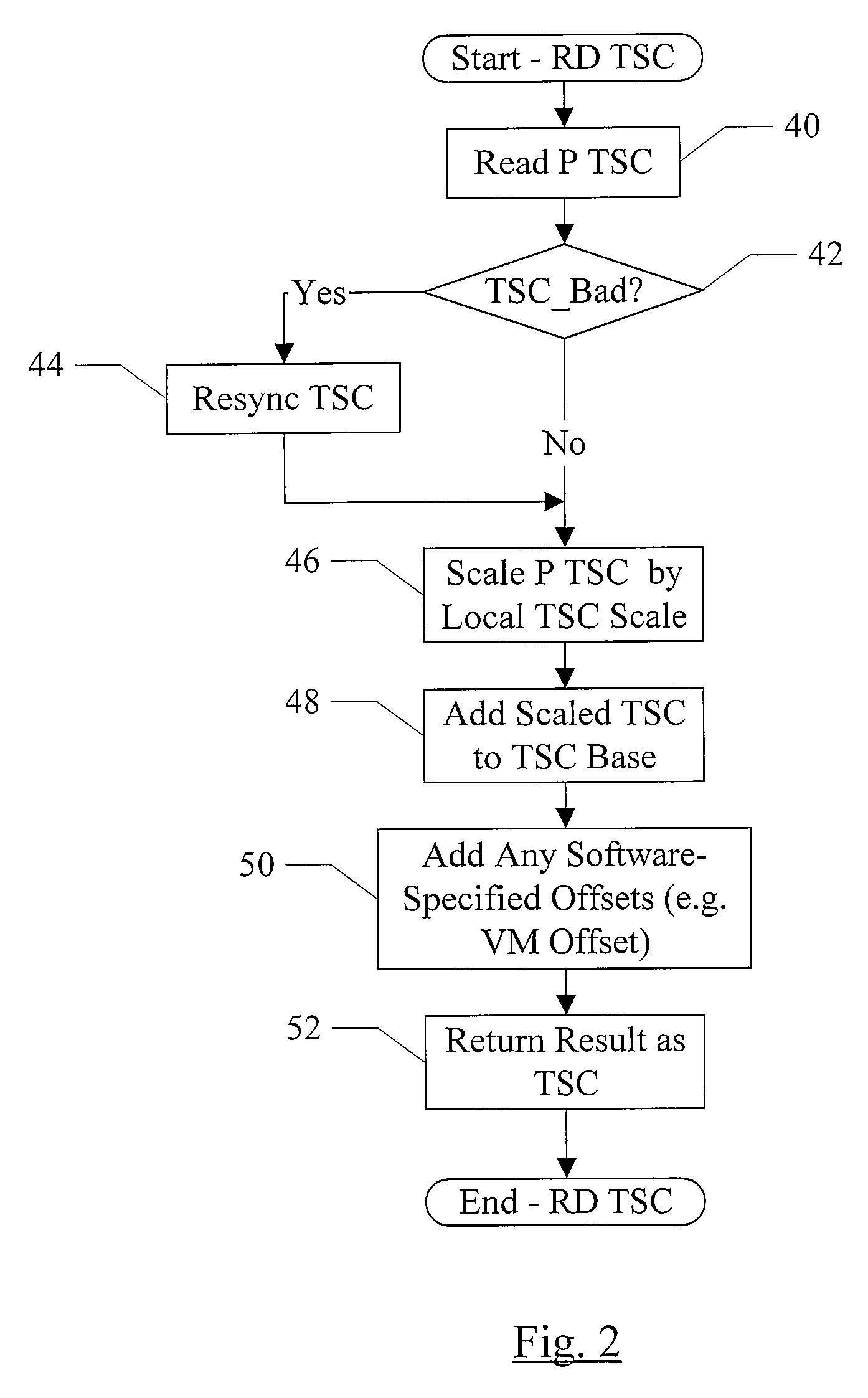

Synchronization of Processor Time Stamp Counters to Master Counter

ActiveUS20090222683A1Multiple digital computer combinationsGenerating/distributing signalsEmbedded systemProcessor time

In one embodiment, an apparatus comprises one or more processors and a controller coupled to the processors. Each processor comprises at least one processor time stamp counter (TSC) and a first control unit configured to maintain the processor TSC. The controller comprises at least one controller TSC and a second control unit configured to maintain the controller TSC. The controller is configured to signal the processor responsive to determining that the processor TSC is out of synchronization with the controller TSC. In response to having been signalled that the processor TSC is out of synchronization, the processor is configured to resynchronize the processor TSC to the controller TSC before generating a result for a read TSC instruction. In response to having not been signalled that the processor TSC is out of synchronization, the processor is configured to generate the result responsive to the processor TSC without resynchronizing.

Owner:ADVANCED MICRO DEVICES INC

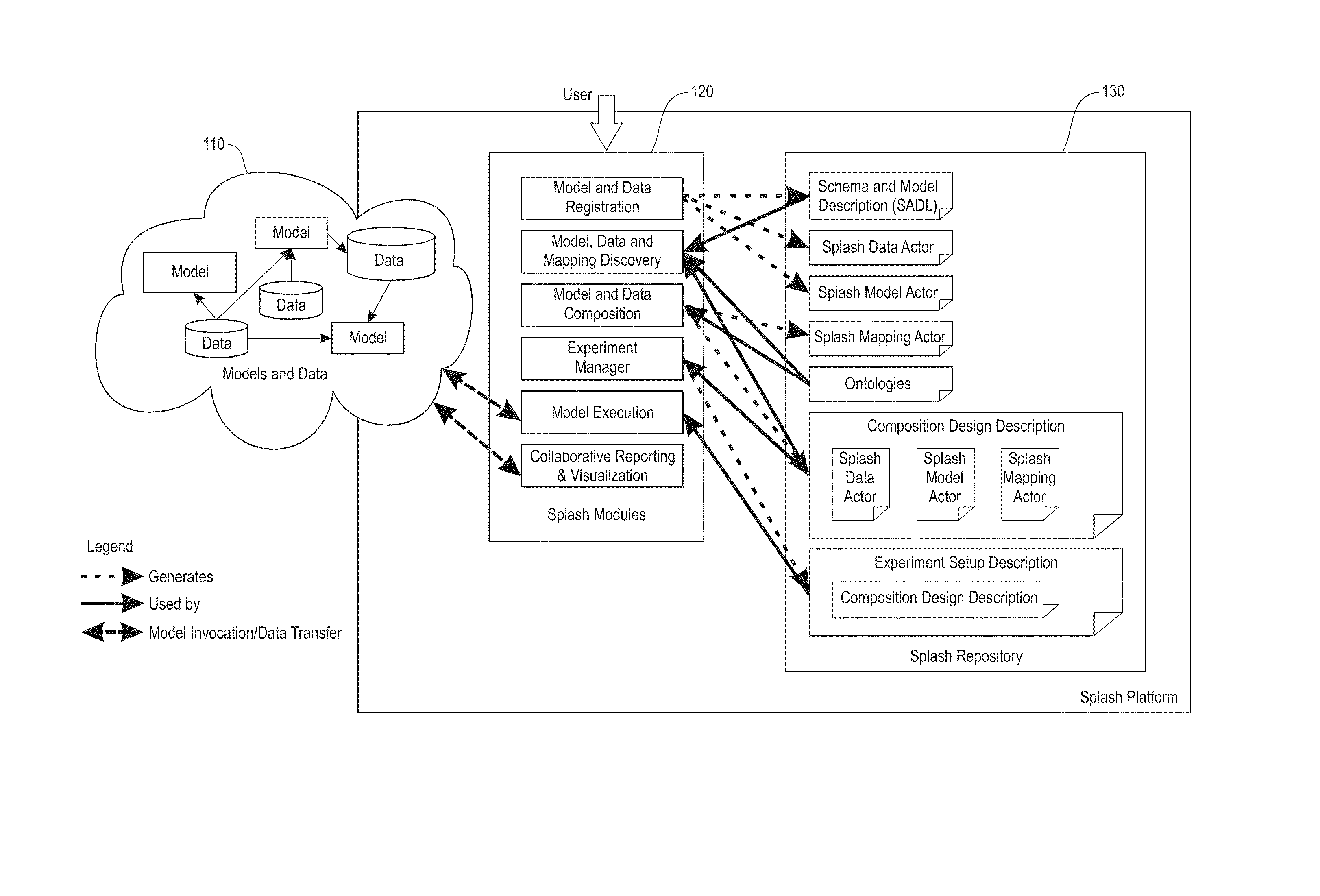

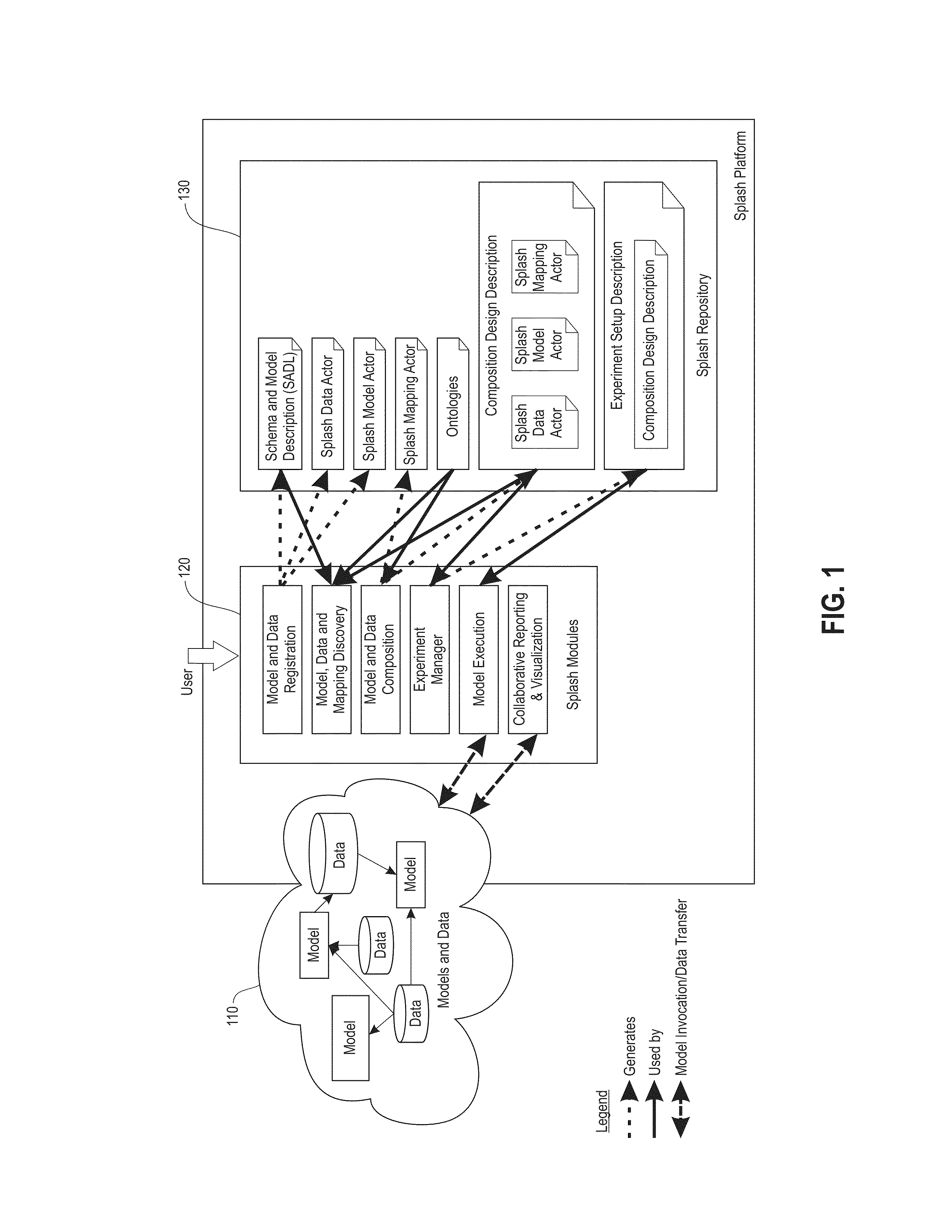

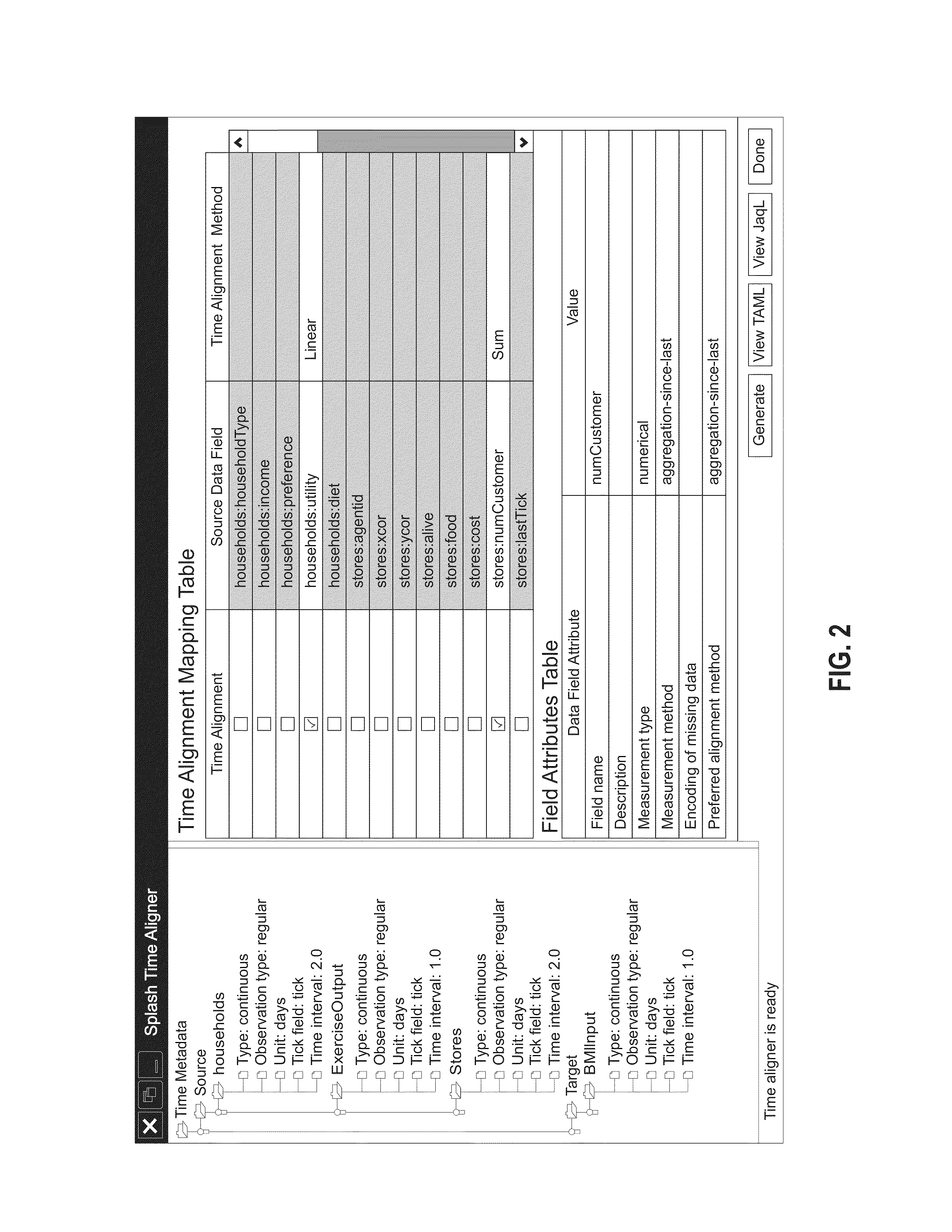

Interpolation techniques used for time alignment of multiple simulation models

InactiveUS9449122B2Design optimisation/simulationSpecial data processing applicationsTime alignmentData mining

A system for performing time conversions that includes a processor configured to generate a set of target time-series data from a set of source time-series data and a memory containing specification information relating to the set of target time-series data and also containing information relating to the set of source time-series data. The source time-series specification and the target time-series specification include time intervals between data values. The system also includes a time alignment algorithm used by the processor for converting the set of source time-series data to the set of target time-series data. The converting includes calculation of a set of cubic-spline interpolation constants and the cubic-spline constants.

Owner:GLOBALFOUNDRIES INC

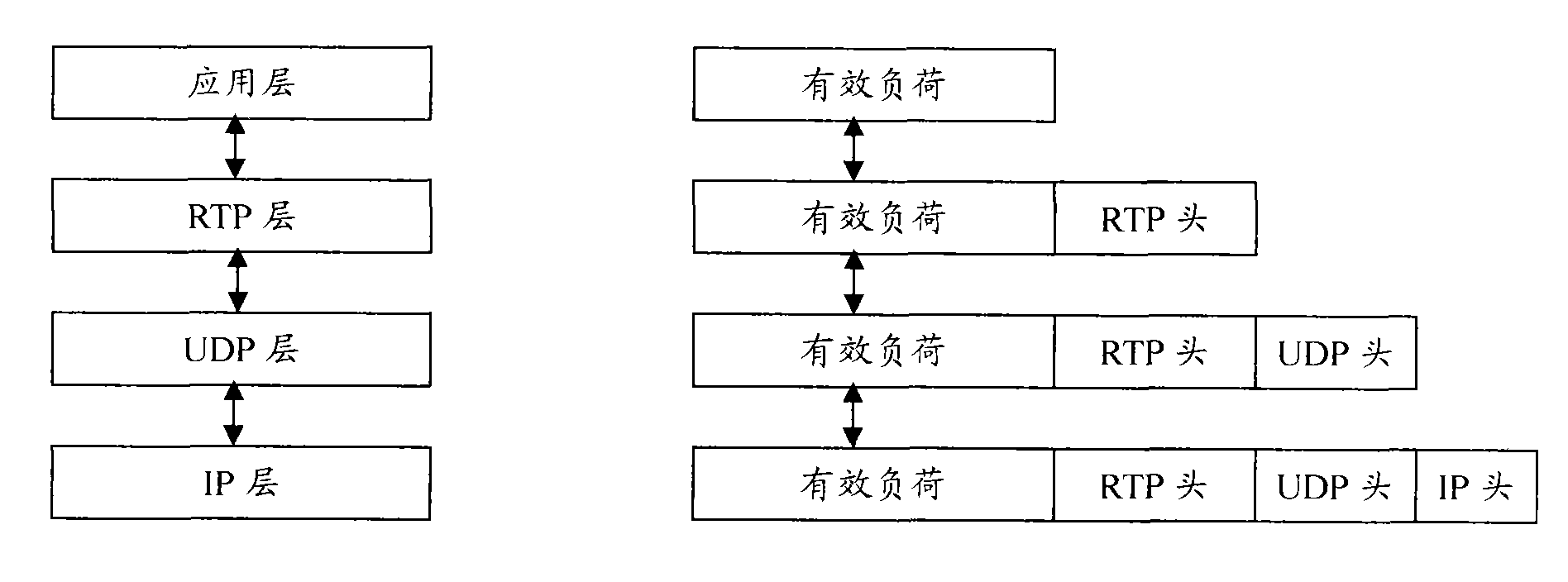

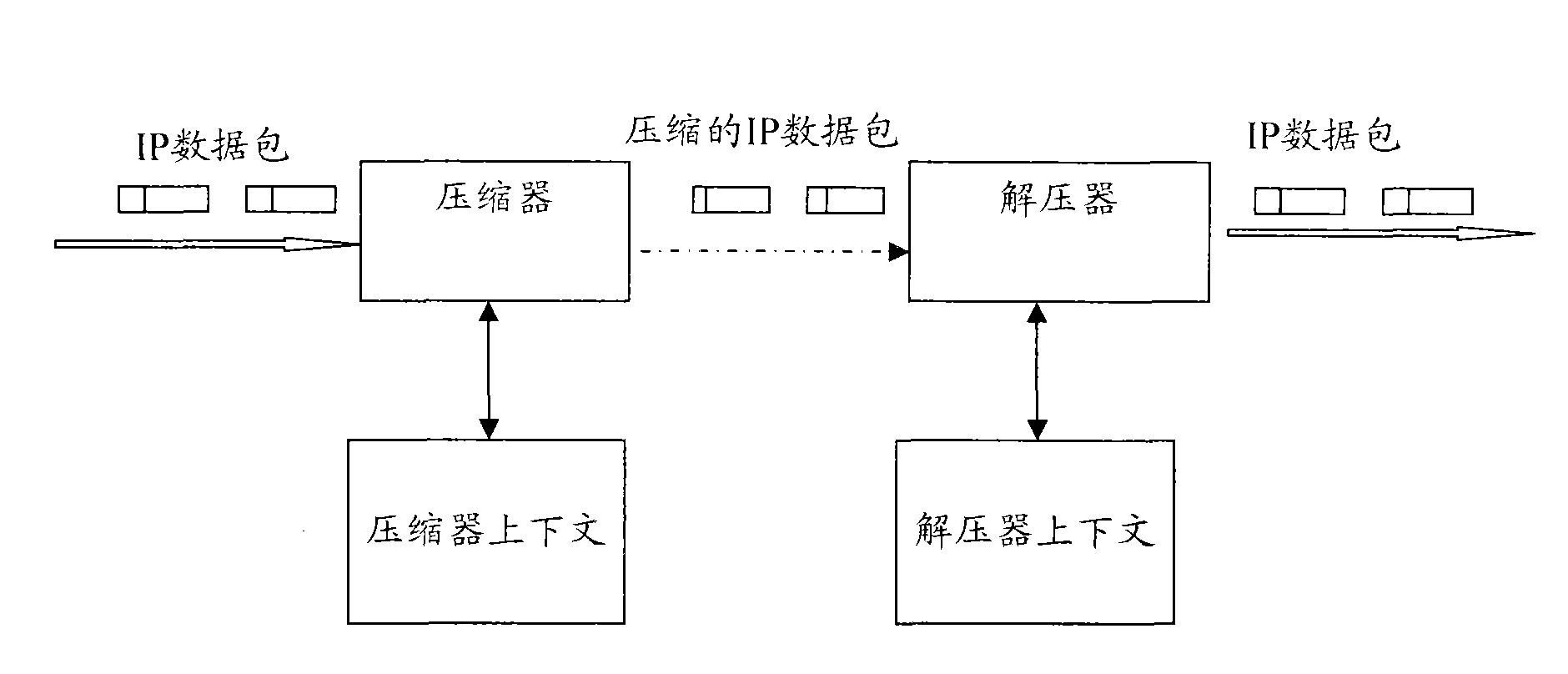

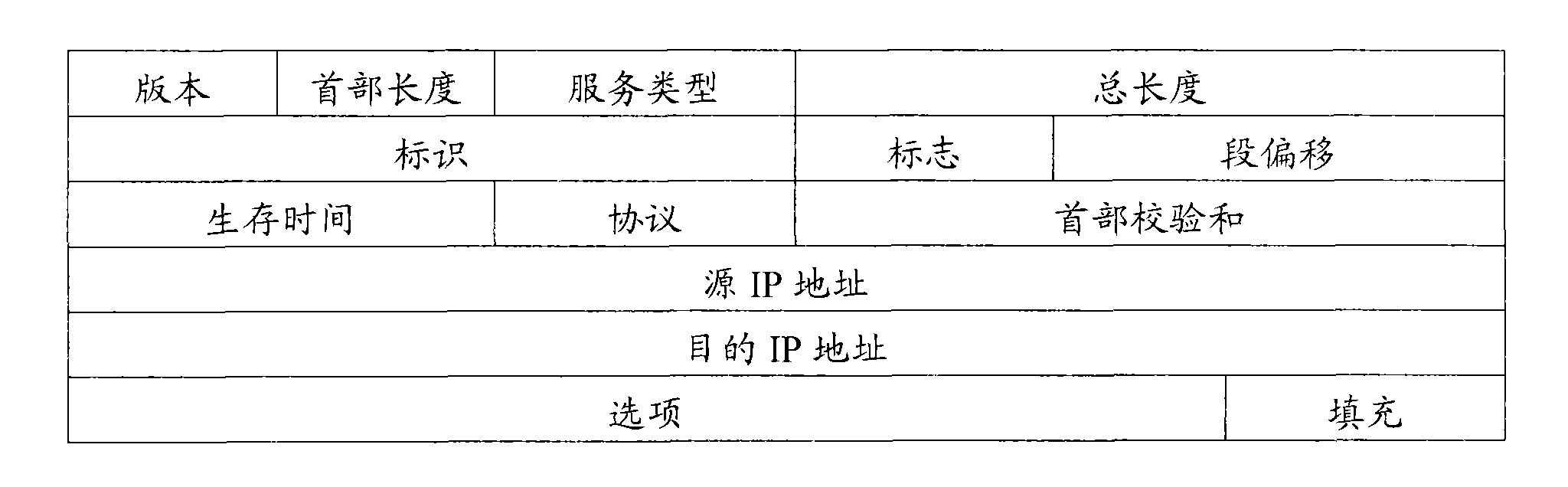

Method for calculating checksums based on data packet IP (Internet Protocol) hearder compression technology

ActiveCN101860904AImprove compression efficiencyReduce consumptionNetwork traffic/resource managementChecksumByte

The invention relates to a method for calculating checksums based on a data packet IP hearder compression technology, wherein in the decompression process, checksums are respectively calculated according to the property of each field of UDP (User Datagram Protocol) and TCP (Transmission Control Protocol) checksums; the checksums are calculated for only one time for invariable fields in the whole stream life cycle; for the basically invariable fields, firstly, the fields are compared with the original IP packet, and if that the fields are not changed is discovered, the checksums do not need to be calculated. By adopting the method for calculating checksums based on the data packet IP hearder compression technology, the consumption of a processor time slice is reduced, the decompression efficiency is improved, the length of the fields which need to be calculated by the compression checksum calculating method is obviously reduced, and for IPv4 / UDP / RTP packets the net load length of which is 20 bytes, the compression checksum calculating method can save calculating amount by 1.7 times, thereby effectively improving the efficiency of IP header compression, reducing the calculating amount of the checksums and saving the system resource expenses; and moreover, the method has fast and convenient processing process, stable and reliable working performance and wider range of application.

Owner:SPREADTRUM COMM (SHANGHAI) CO LTD

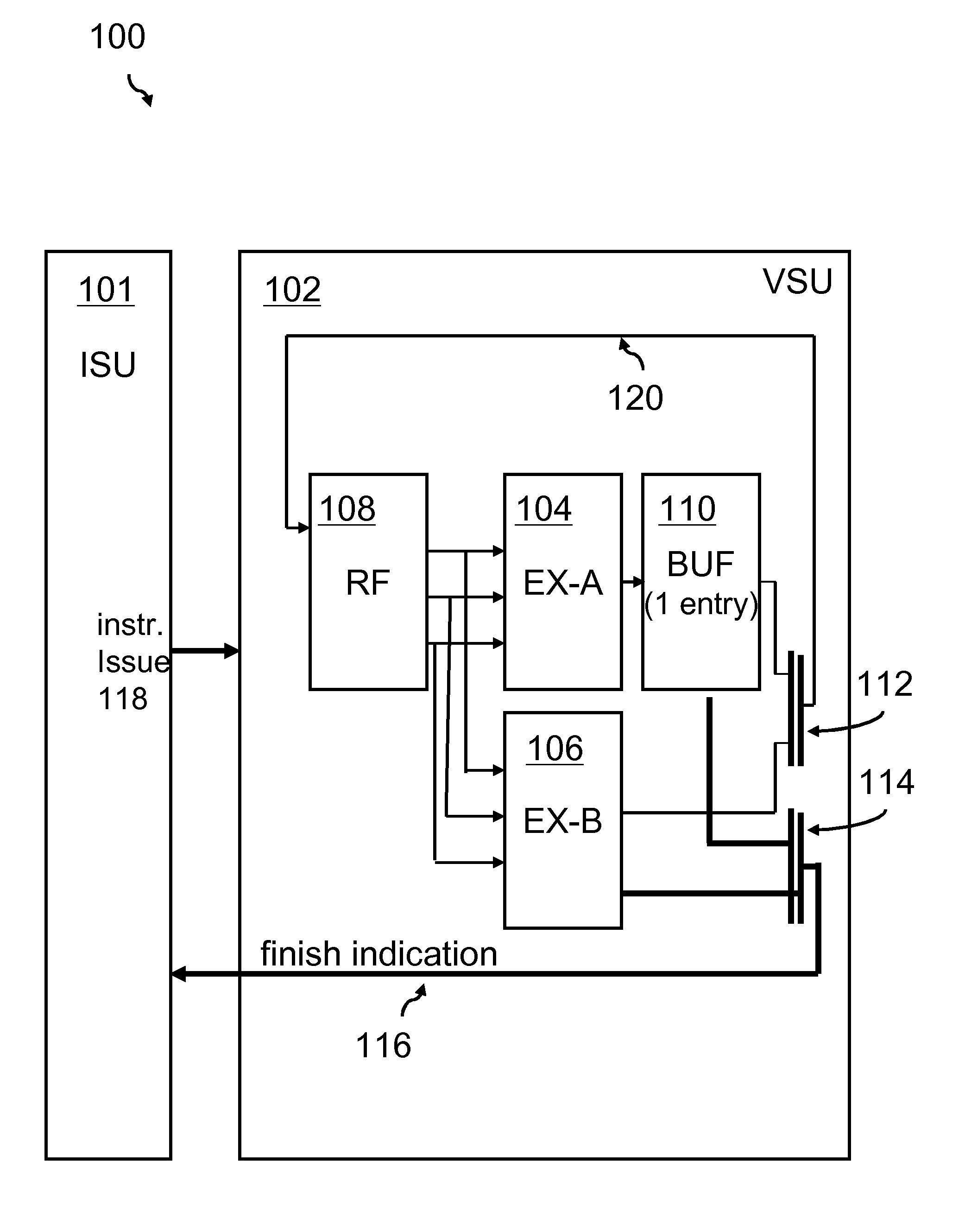

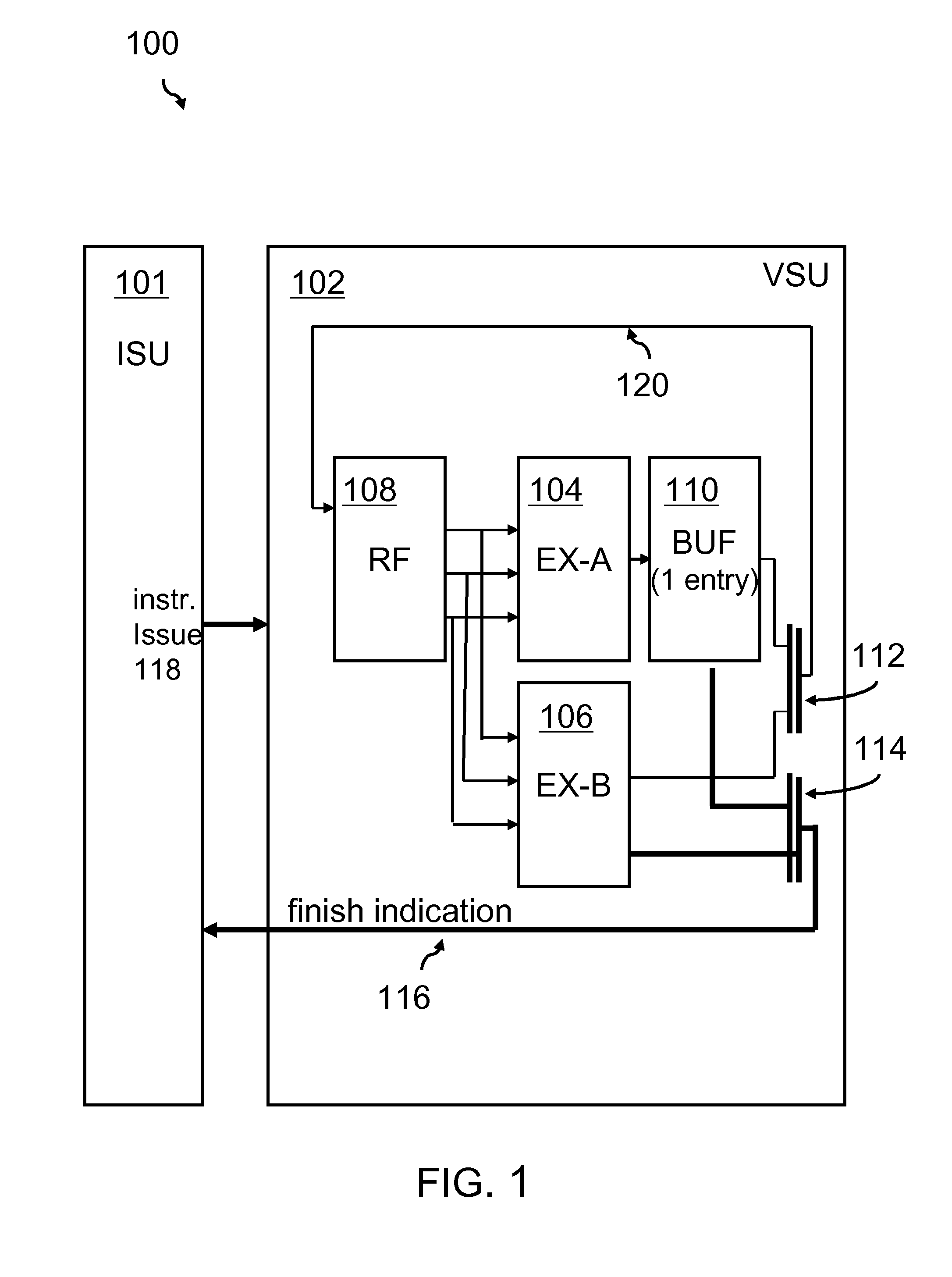

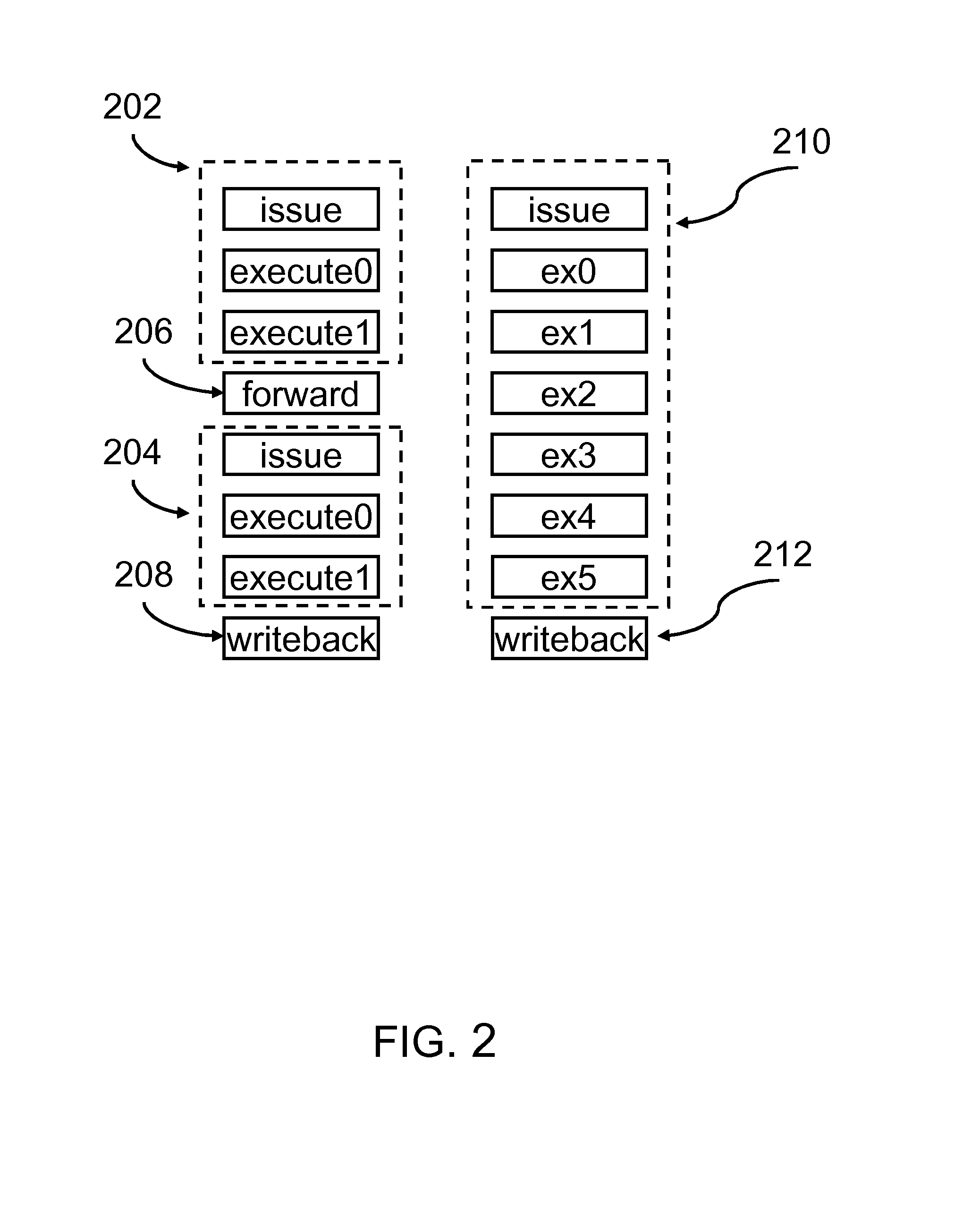

Techniques for increasing instruction issue rate and reducing latency in an out-of-order processor

A technique for operating a processor includes storing a first result to a writeback buffer, in response to a first execution unit of the processor attempting to write the first result of a first completed instruction to a register file of the processor at a same processor time as a second execution unit of the processor is attempting to write a second result of a second completed instruction to the register file. The writeback buffer is positioned in a dataflow between the first execution unit and the register file. A buffer full indicator logic is used to detect that the writeback buffer is unavailable. A buffer unavailable signal is transmitted, from the buffer full indicator logic, in response to detecting the writeback buffer is unavailable. In response to receiving the buffer unavailable signal, a buffer retrieving logic writes the first result from the writeback buffer to the register file.

Owner:GLOBALFOUNDRIES INC

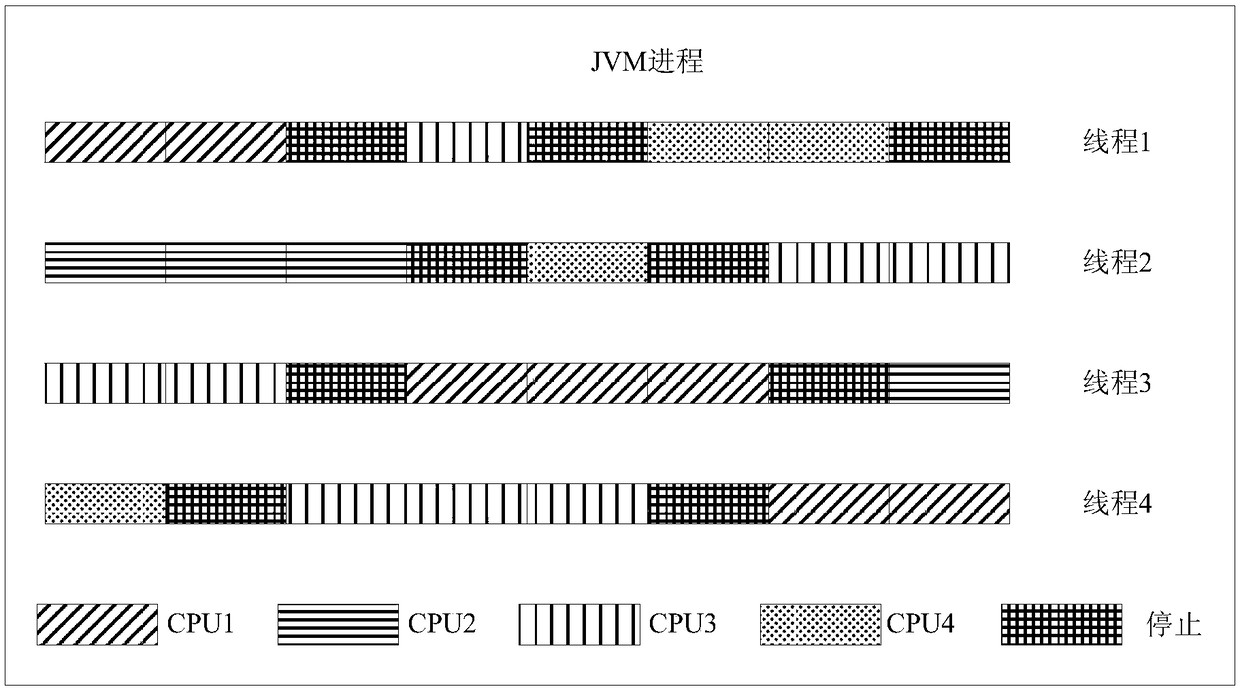

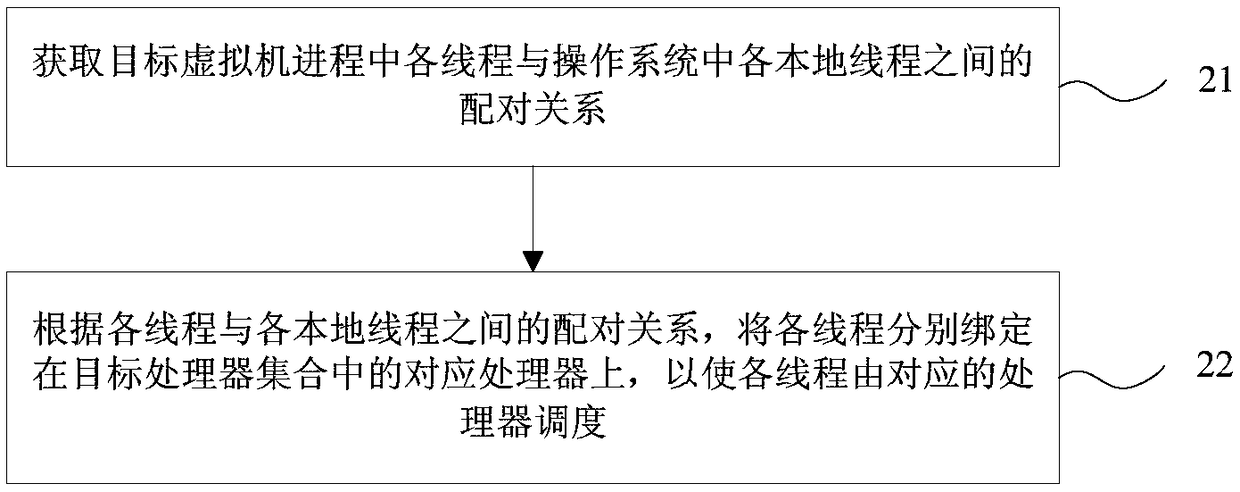

Thread scheduling method and device, electronic equipment and storage medium

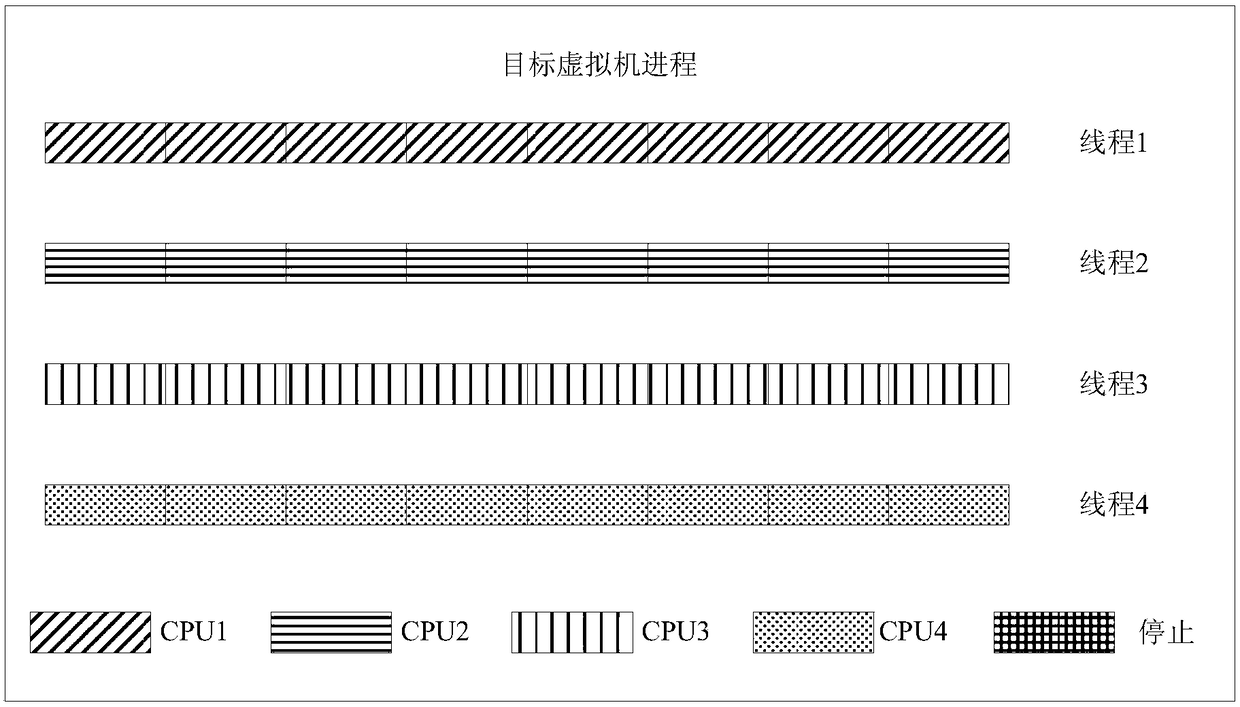

InactiveCN108804211AImprove real-time performanceGuaranteed real-timeProgram initiation/switchingResource allocationOperational systemProcessor scheduling

Embodiments of the invention provide a thread scheduling method and device, electronic equipment and a storage medium. The method comprises the steps of acquiring a pairing relation between each thread in a target virtual machine process and each local thread in an operating system; and according to the pairing relation, binding each thread to a corresponding processor in a target processor set, so that each thread is dispatched by the corresponding processor. According to the technical scheme, the phenomenon that time slices of the same processor are scrambled for when multiple threads are executed is avoided; the problem that multi-thread task queuing is blocked due to excessive service threads of the same processor and overlong service time of real-time threads is solved; the executiontime delay of other threads is shortened; and the real-time performance of thread execution is improved.

Owner:HUAWEI CLOUD COMPUTING TECH CO LTD

Fast, Automatically Scaled Processor Time Stamp Counter

InactiveUS20090222684A1Printing mechanismsMultiple digital computer combinationsClock rateComputer science

In one embodiment, a processor comprises at least one processor time stamp counter (TSC) and a control unit coupled to the processor TSC. The processor TSC corresponds to a TSC that is defined to increment at a TSC clock frequency even though the processor is configurable to operate at one of a plurality of clock frequencies. The control unit is configured to maintain the processor TSC, and is configured to update the processor TSC when the processor is operating at a current clock frequency of the plurality of clock frequencies, wherein the update comprises adding a value to the processor TSC, and wherein the value is based on the ratio of the TSC clock frequency and the current clock frequency.

Owner:GLOBALFOUNDRIES INC

Synchronization of processor time stamp counters to master counter

ActiveUS7941684B2Multiple digital computer combinationsGenerating/distributing signalsEmbedded systemProcessor time

In one embodiment, an apparatus comprises one or more processors and a controller coupled to the processors. Each processor comprises at least one processor time stamp counter (TSC) and a first control unit configured to maintain the processor TSC. The controller comprises at least one controller TSC and a second control unit configured to maintain the controller TSC. The controller is configured to signal the processor responsive to determining that the processor TSC is out of synchronization with the controller TSC. In response to having been signalled that the processor TSC is out of synchronization, the processor is configured to resynchronize the processor TSC to the controller TSC before generating a result for a read TSC instruction. In response to having not been signalled that the processor TSC is out of synchronization, the processor is configured to generate the result responsive to the processor TSC without resynchronizing.

Owner:ADVANCED MICRO DEVICES INC

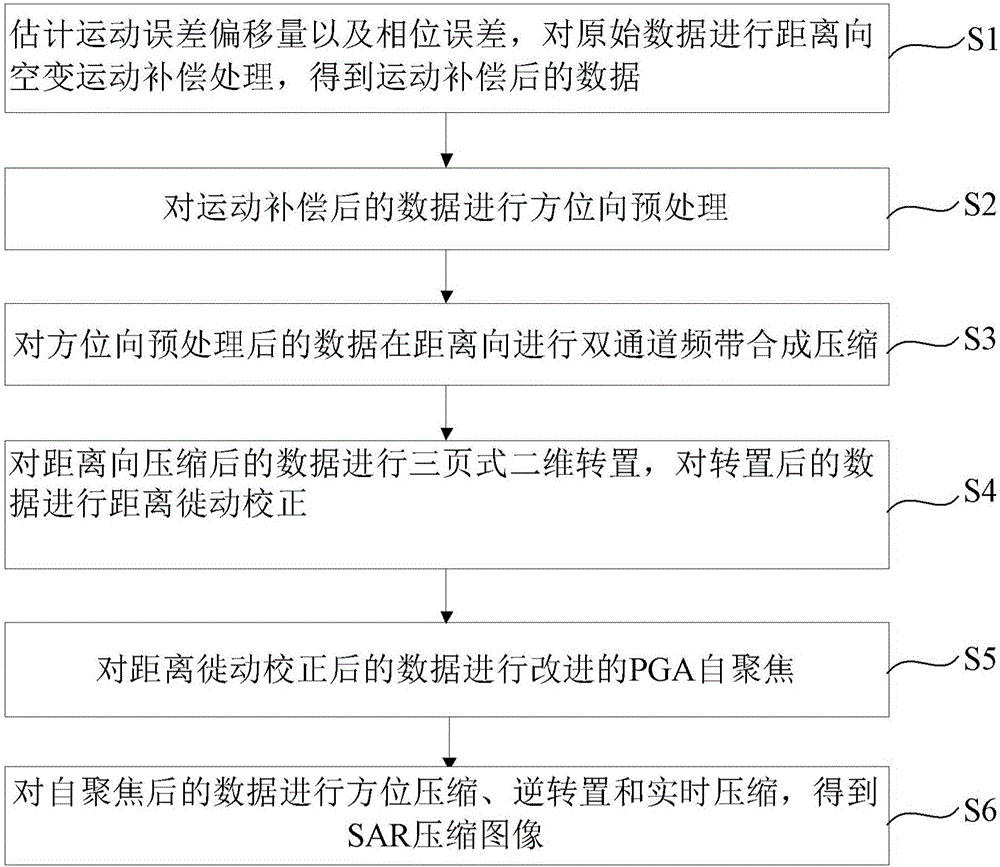

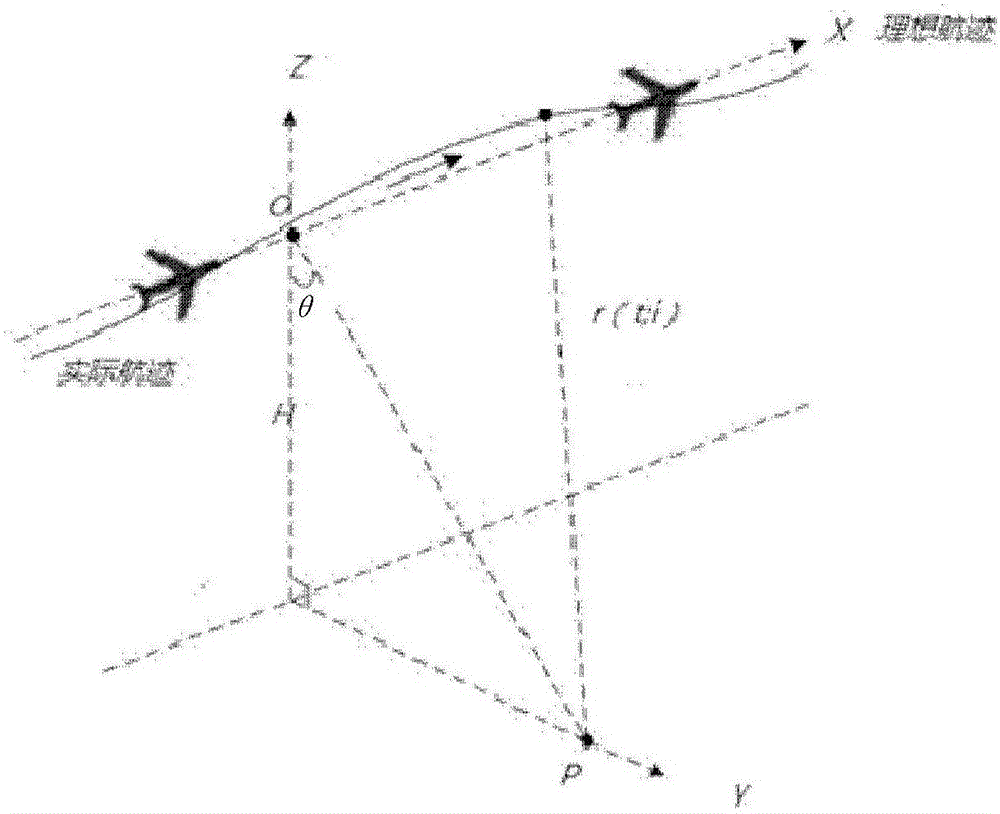

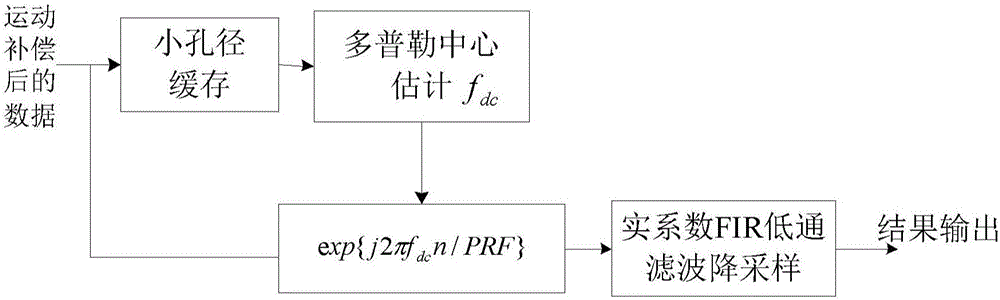

Airborne SAR real-time imaging method

ActiveCN106772374ALower latencyHigh Image Processing QualityRadio wave reradiation/reflectionKinematicsImaging processing

The invention discloses an airborne SAR real-time imaging method. The airborne SAR real-time imaging method comprises the following steps: estimating kinematic error offset and phase error, and executing the range direction space-variant motion compensation processing to the original data so as to obtain the data after the motion compensation; executing the orientation direction pre-processing to the data after the motion compensation; executing the two-channel frequency band synthesis compressing to the data after the orientation direction pre-processing in the range direction; executing the three-page two-dimensional transposition to the data after the range direction compressing, and executing the range migration correction to the data after the transposition; and executing the improved PGA self-focusing to the data after the range migration correction; and executing the orientation compressing, reverse transposition and real-time compressing to the data after the self-focusing, to obtain the SAR compressing image. The method is suitable for an airborne SAR range direction two-channel frequency band synthesized real-time imaging processor, and has the higher image processing quality and lower processor time delay.

Owner:INST OF ELECTRONICS CHINESE ACAD OF SCI

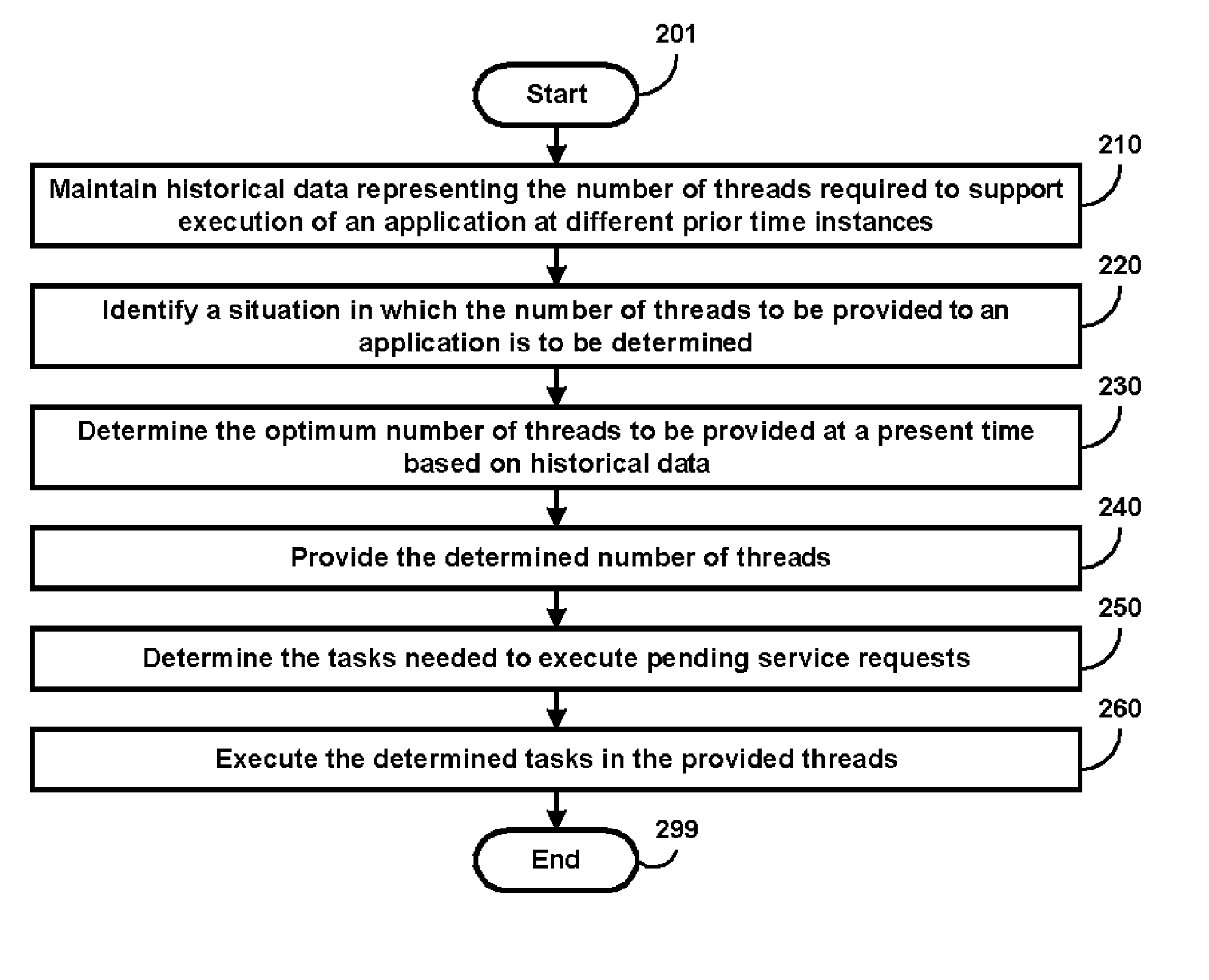

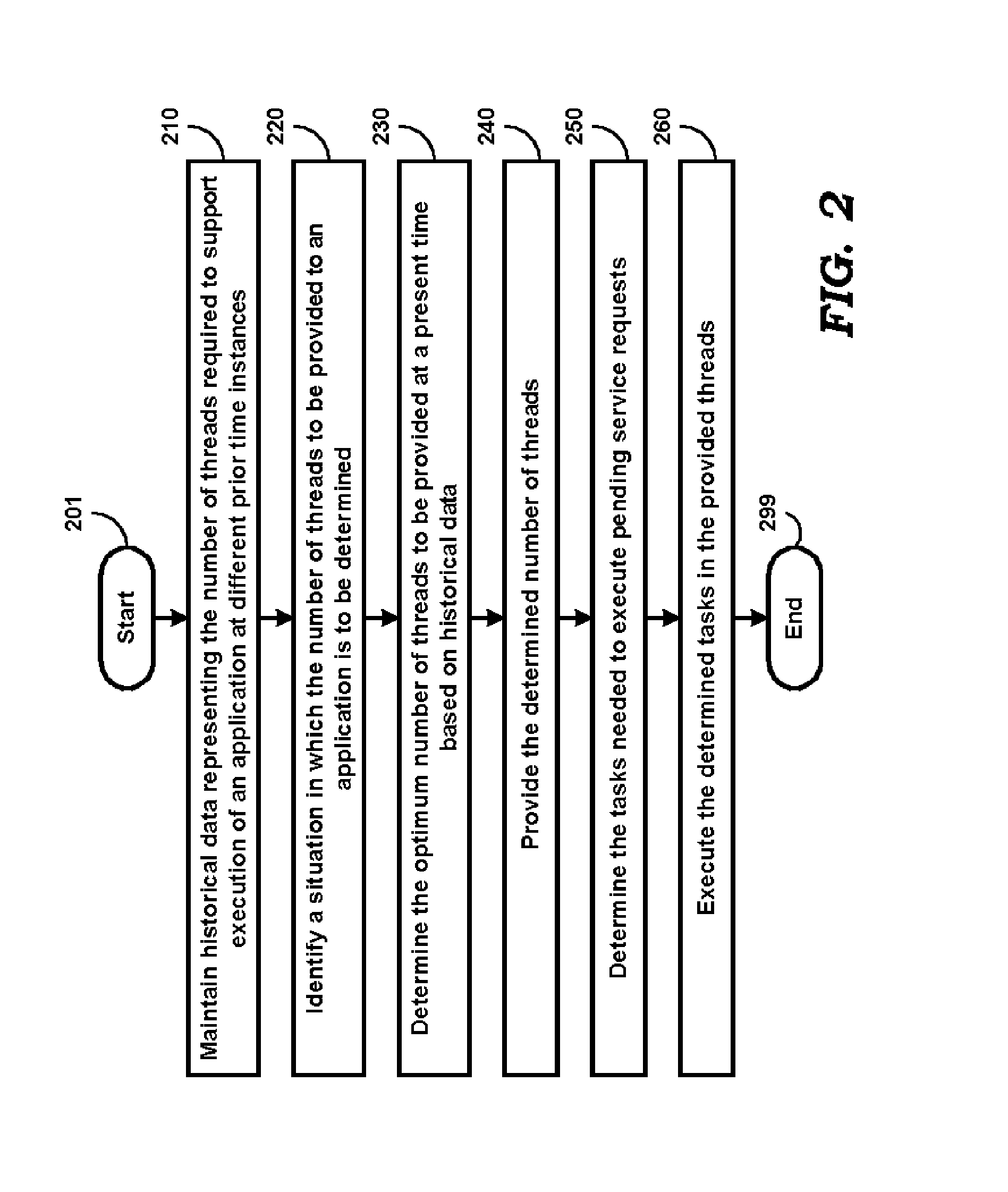

Providing Optimal Number of Threads to Applications Performing Multi-tasking Using Threads

In an environment in which applications perform multi-tasking by using threads, the optimum number of threads to be provided to an application is determined based on historical data. Due to the use of the historical data, optimum number of threads can be accurately determined, leading to better response times for service requests, without creating unneeded overhead on system processing the service requests. In one embodiment, various status information (of potentially several prior weeks) such as number of tasks received and pending, system resources status (e.g. idle processor time and aggreate memory usage in the system), is maintained. In addition, a table may be maintained to indicate the optimum number of threads for a given combination of status information values. Thus, based on the expected status scenario, the optimum number of threads can be determined and provided at various points of time.

Owner:ORACLE INT CORP

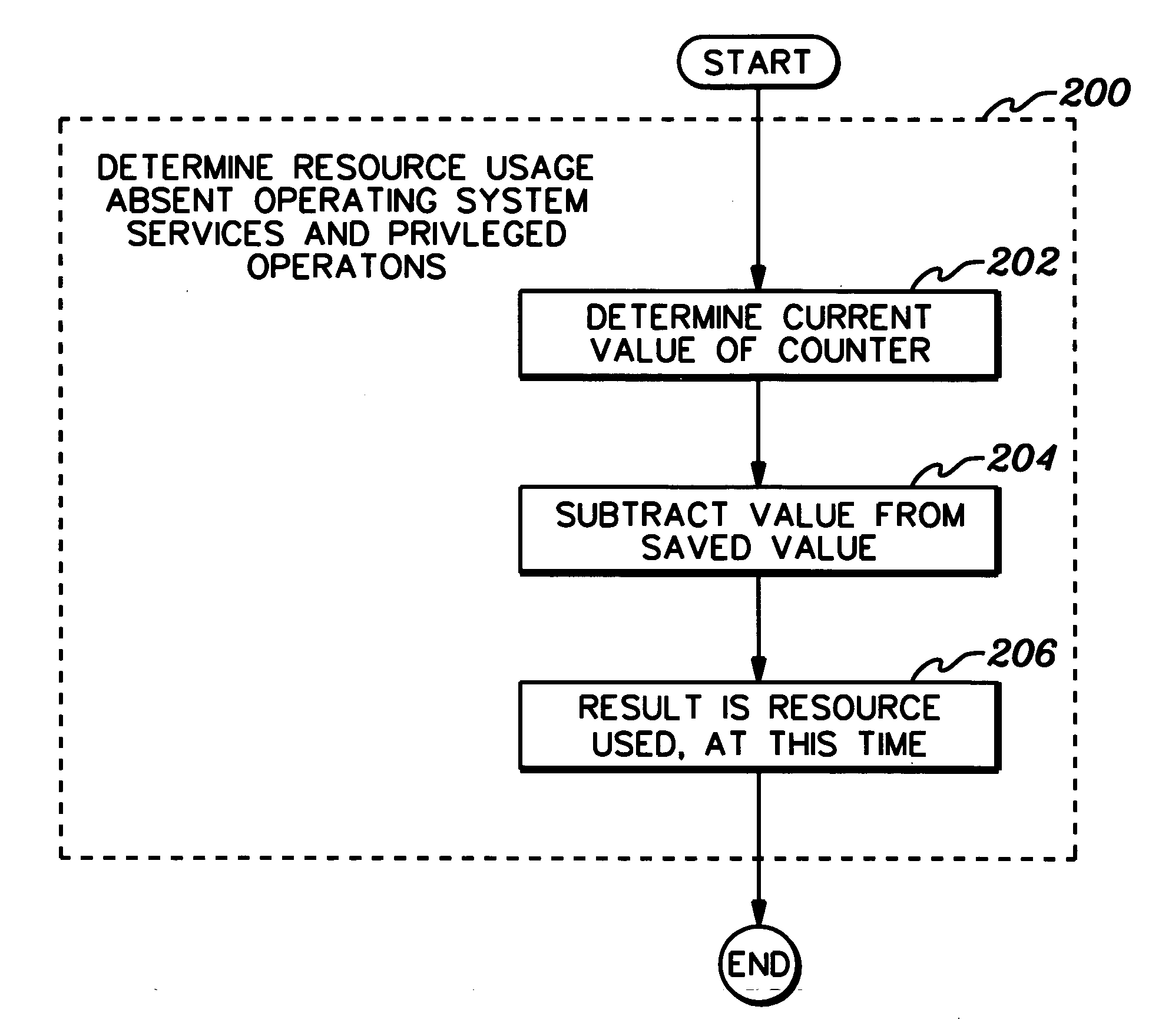

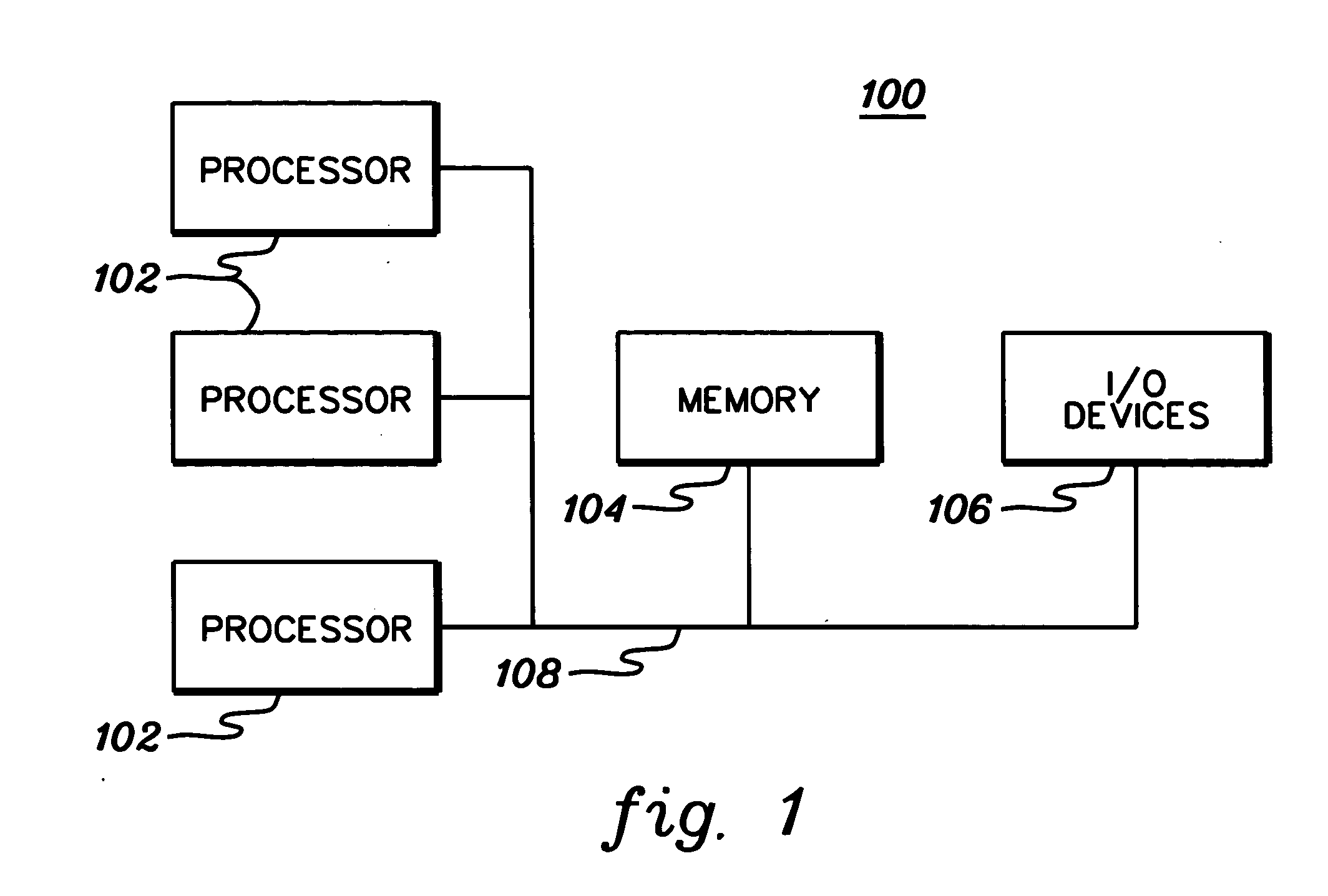

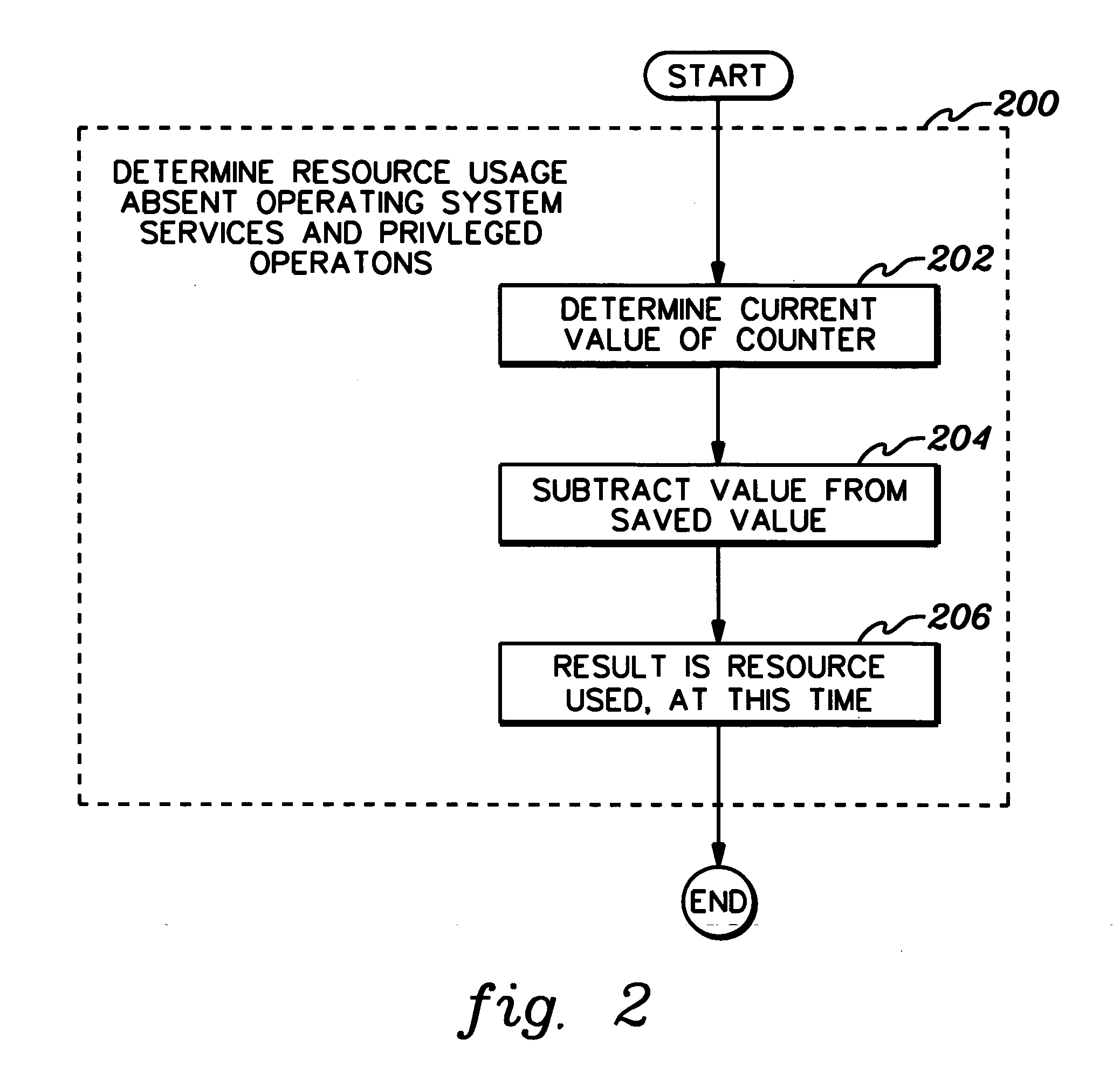

Extract CPU time facility

ActiveUS20070271566A1Error detection/correctionMultiprogramming arrangementsOperational systemApplication software

An efficient facility for determining resource usage, such as a processor time used by tasks. The determination is performed on behalf of user applications that do not require a call to operating system services. The facility includes an instruction that determines elapsed time and reports it to the user as a single unit of operation.

Owner:IBM CORP