Patents

Literature

35147 results about "Storage cell" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Storage Cells. Storage Cells, are one of the core mechanics of storage in Applied Energistics 2, there are two kinds, one for quantities of items, and one for regions of space. Item storage cells can hold up to 63 distinct types of items; the number of items they can store depends in part on how many types they're holding; see also ME Storage Math.

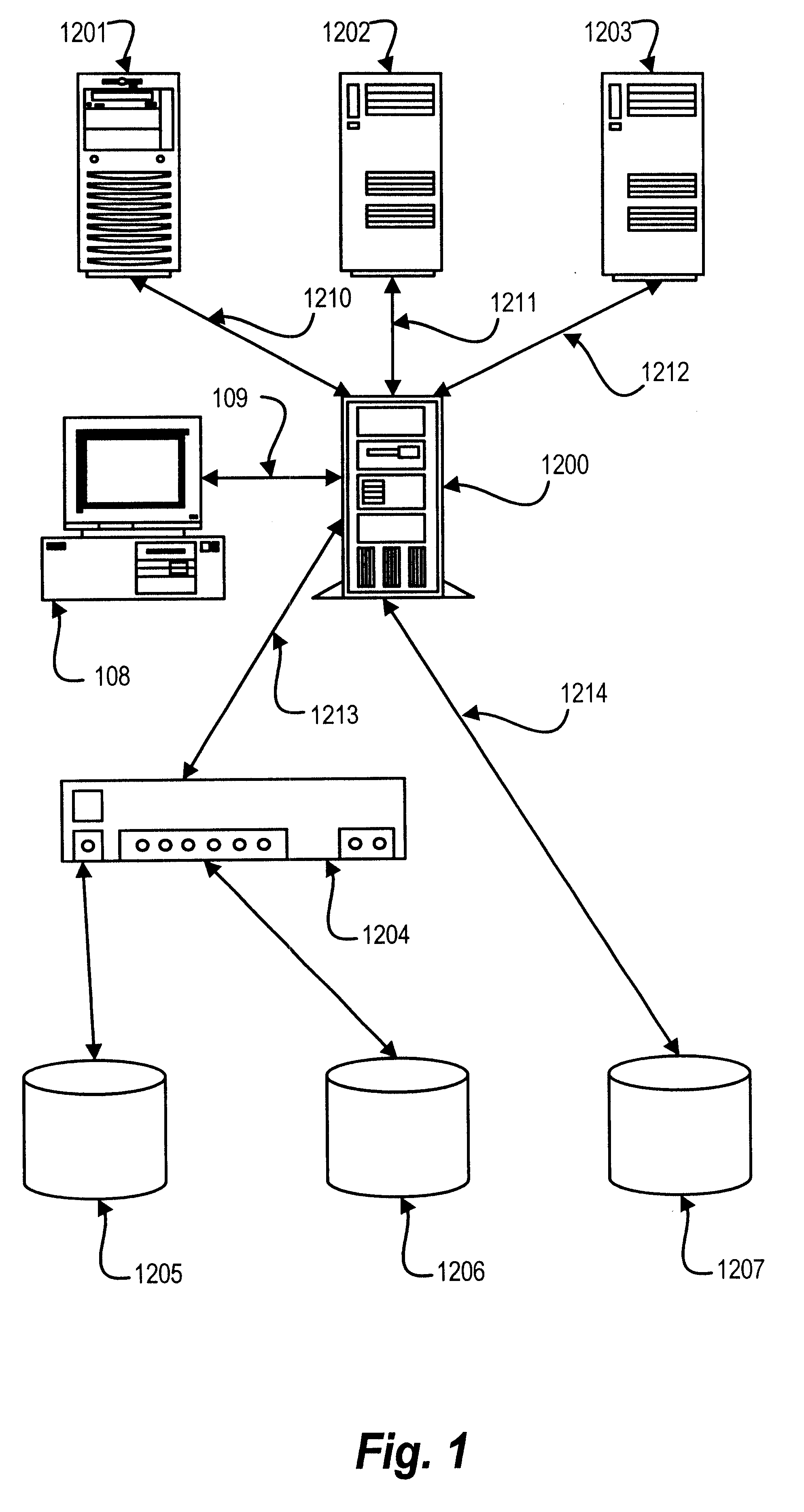

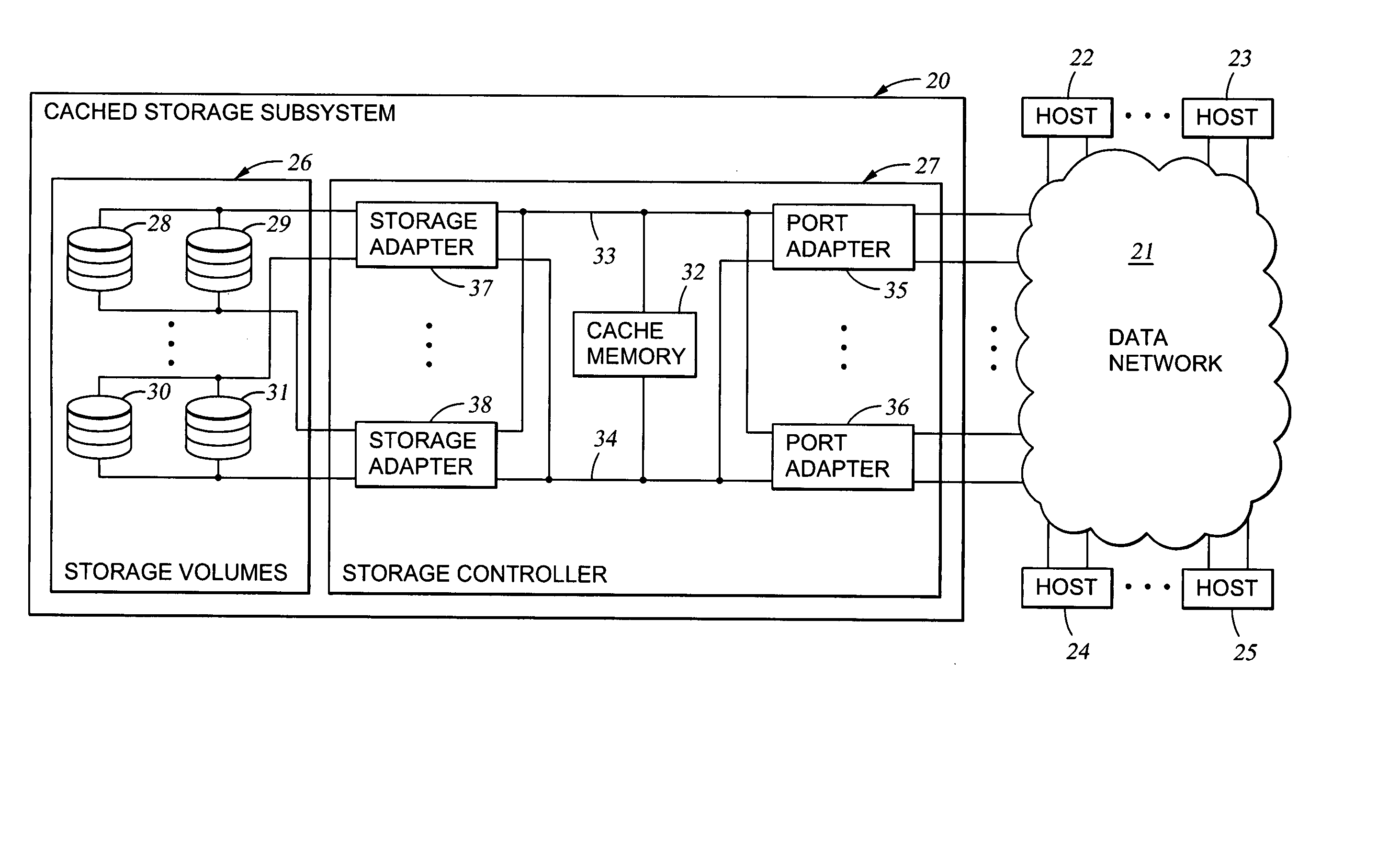

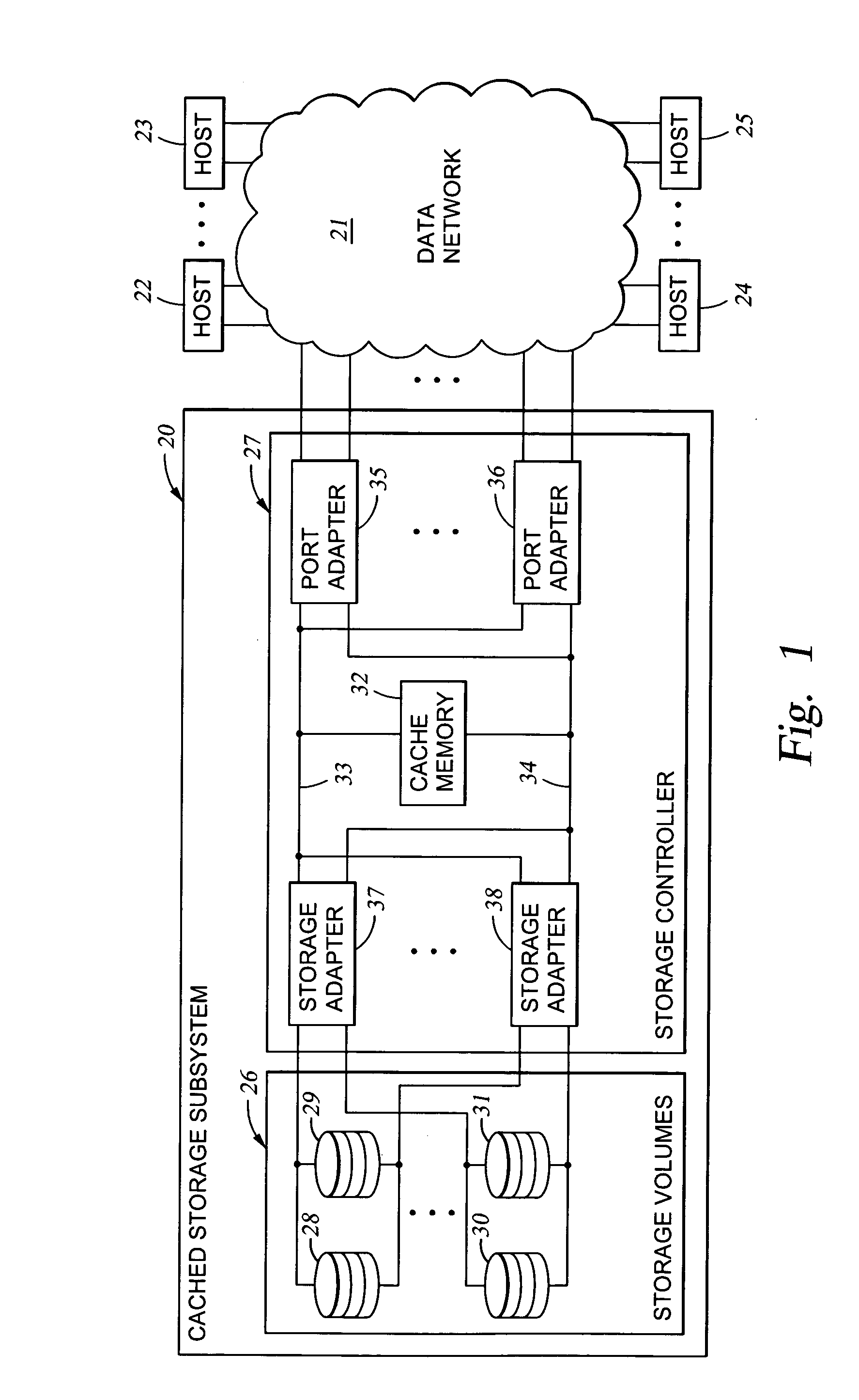

Computer system and process for transferring multiple high bandwidth streams of data between multiple storage units and multiple applications in a scalable and reliable manner

InactiveUS7111115B2Improve reliabilityImprove scalabilityInput/output to record carriersData processing applicationsHigh bandwidthData segment

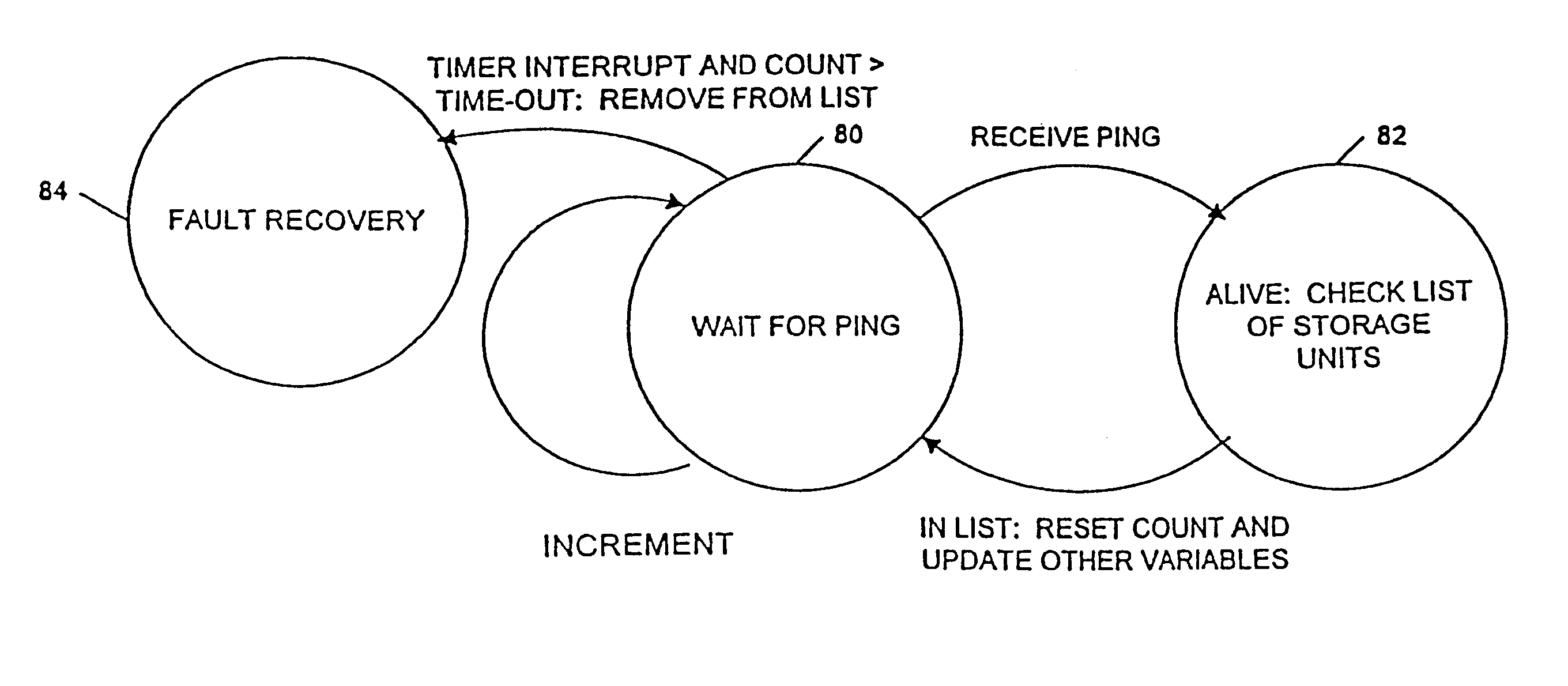

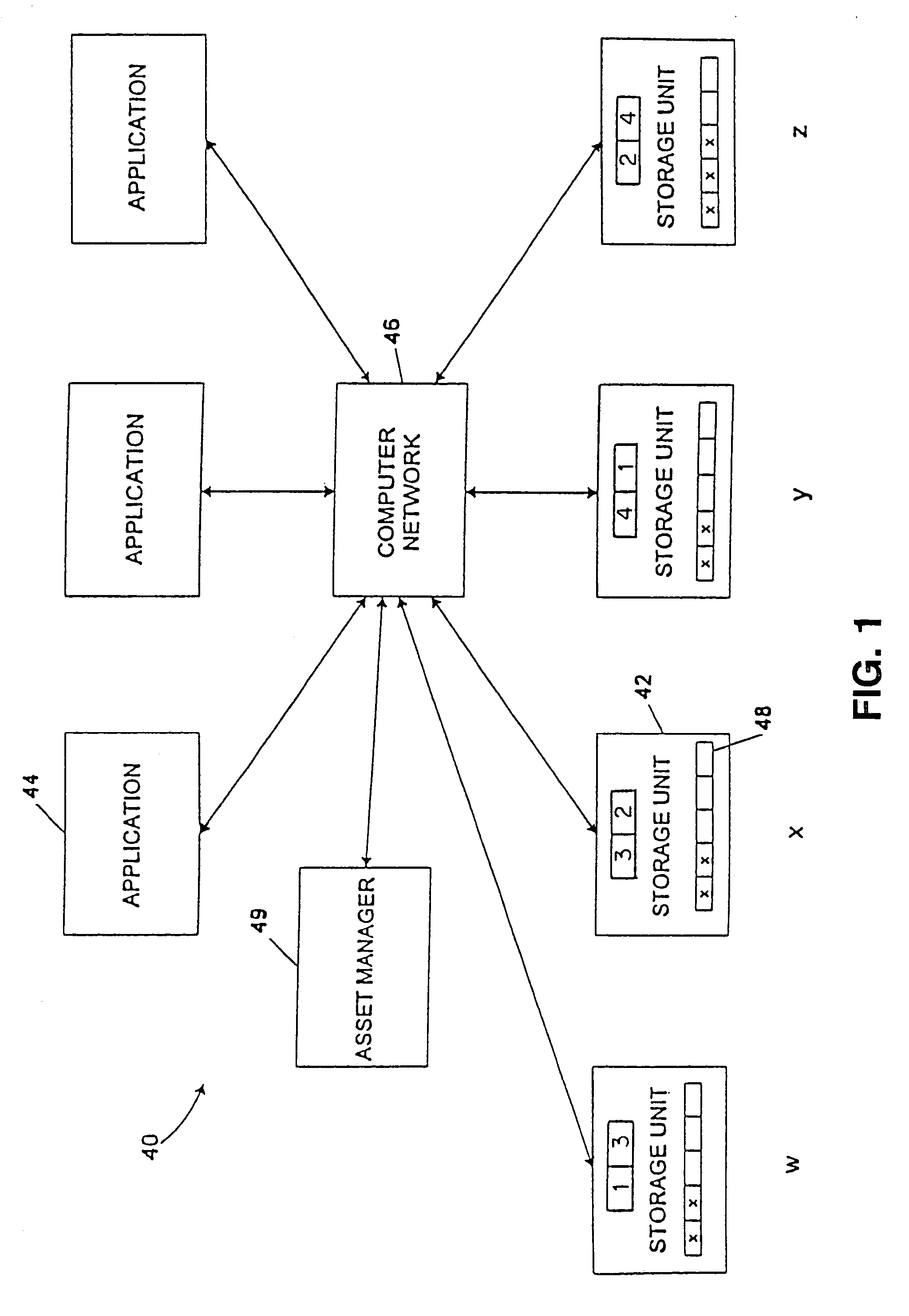

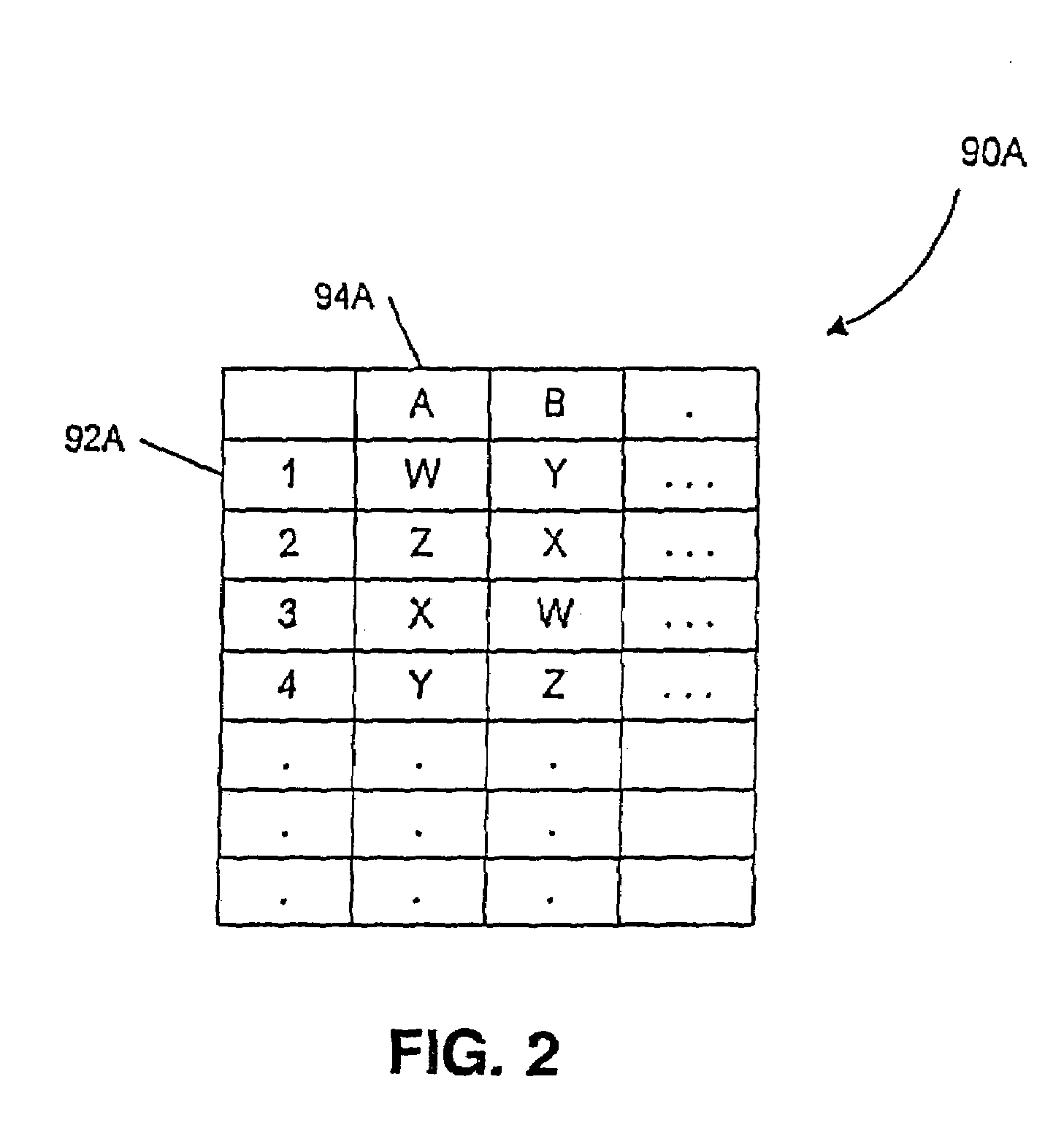

Multiple applications request data from multiple storage units over a computer network. The data is divided into segments and each segment is distributed randomly on one of several storage units, independent of the storage units on which other segments of the media data are stored. At least one additional copy of each segment also is distributed randomly over the storage units, such that each segment is stored on at least two storage units. This random distribution of multiple copies of segments of data improves both scalability and reliability. When an application requests a selected segment of data, the request is processed by the storage unit with the shortest queue of requests. Random fluctuations in the load applied by multiple applications on multiple storage units are balanced nearly equally over all of the storage units. This combination of techniques results in a system which can transfer multiple, independent high-bandwidth streams of data in a scalable manner in both directions between multiple applications and multiple storage units.

Owner:AVID TECHNOLOGY

Method, system, and program for managing data organization

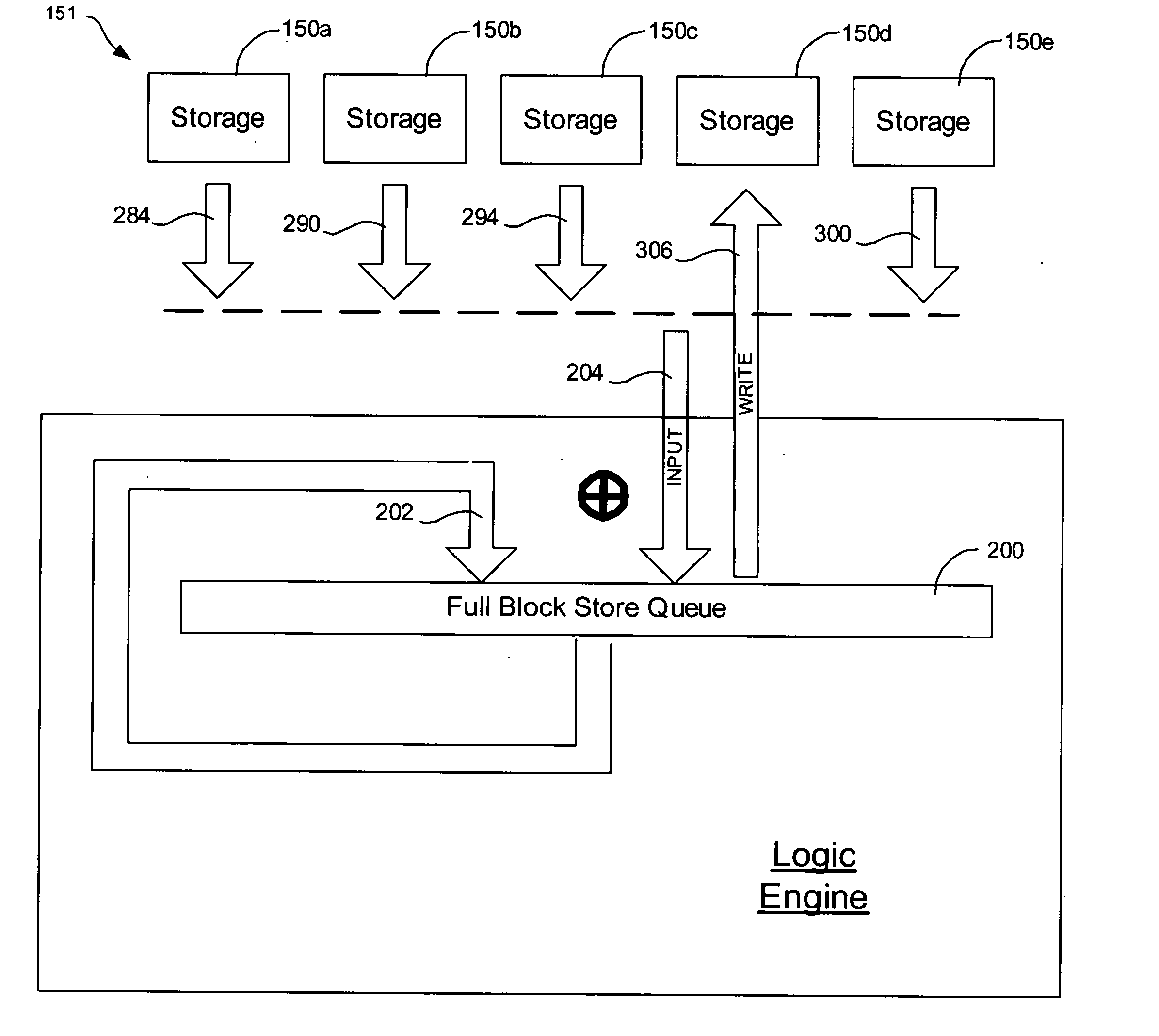

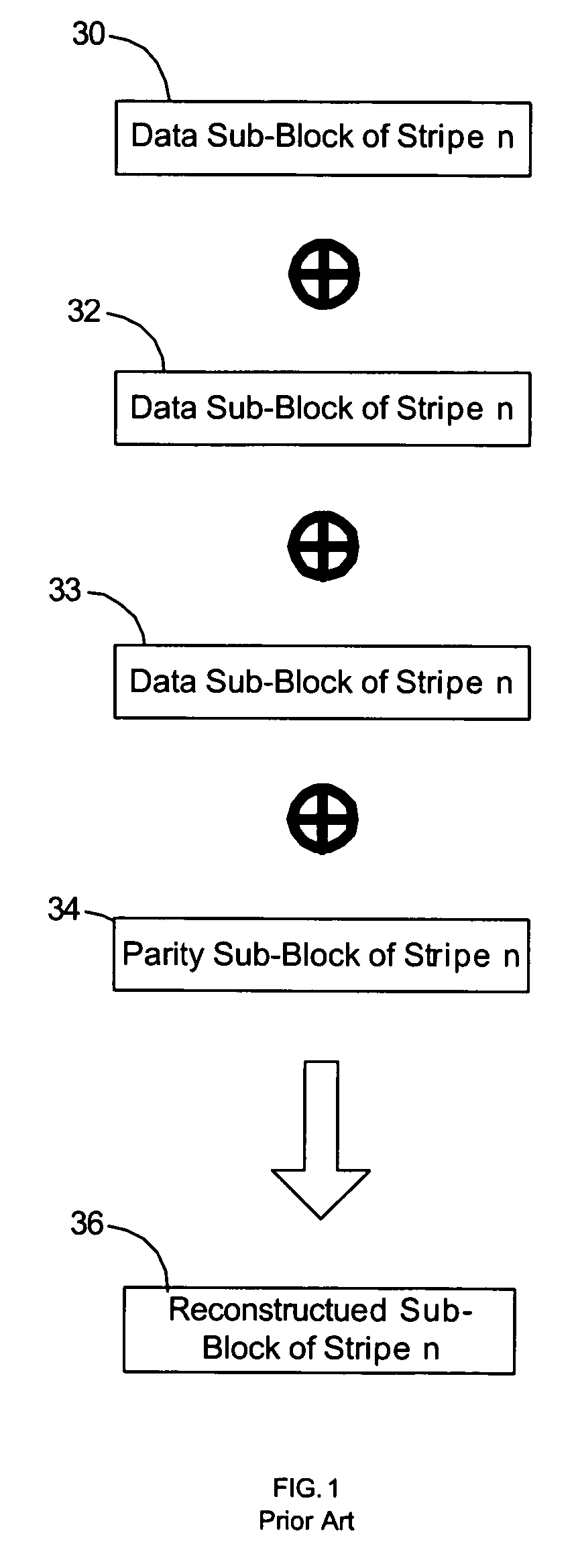

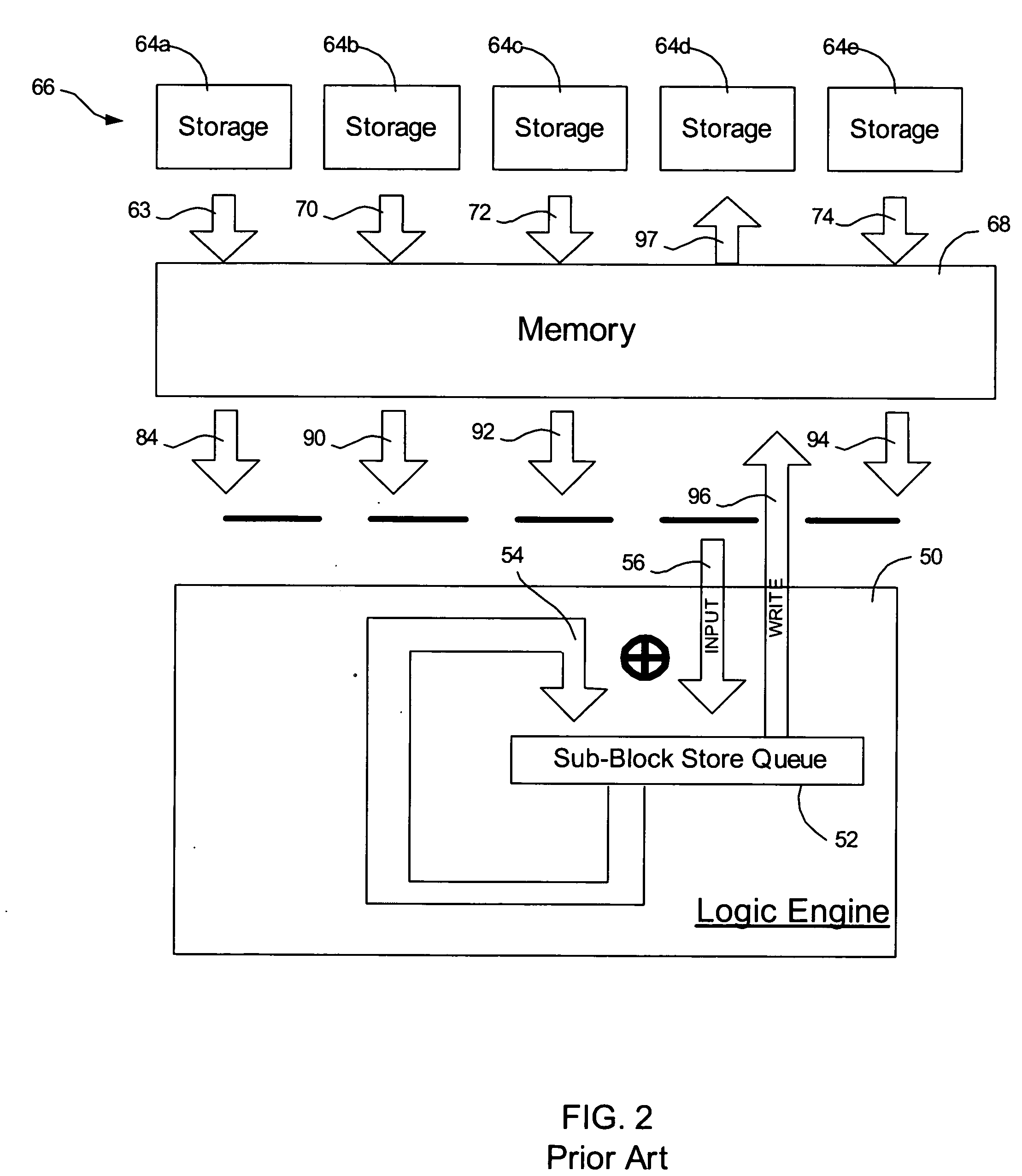

Provided are a method, system, and program for constructing data including reconstructing data organized in a data organization type, such as a Redundant Array of Independent Disks (RAID) organization, for example, which permits data reconstruction In one embodiment, blocks of data are transferred from a stripe of data stored across storage units, such as disk drives in a RAID array, to a logic engine of a storage processor, bypassing the cache memory of the storage processor. A store queue performs a logic function, such as Exclusive-OR, on each block of data as it is transferred from the disk drives, to reconstruct a block of data from the stripe. The constructed block of data may be subsequently transferred to a disk drive of the RAID array to replace a lost block of data in the stripe of data across the RAID array or to replace an old block of parity data.

Owner:INTEL CORP

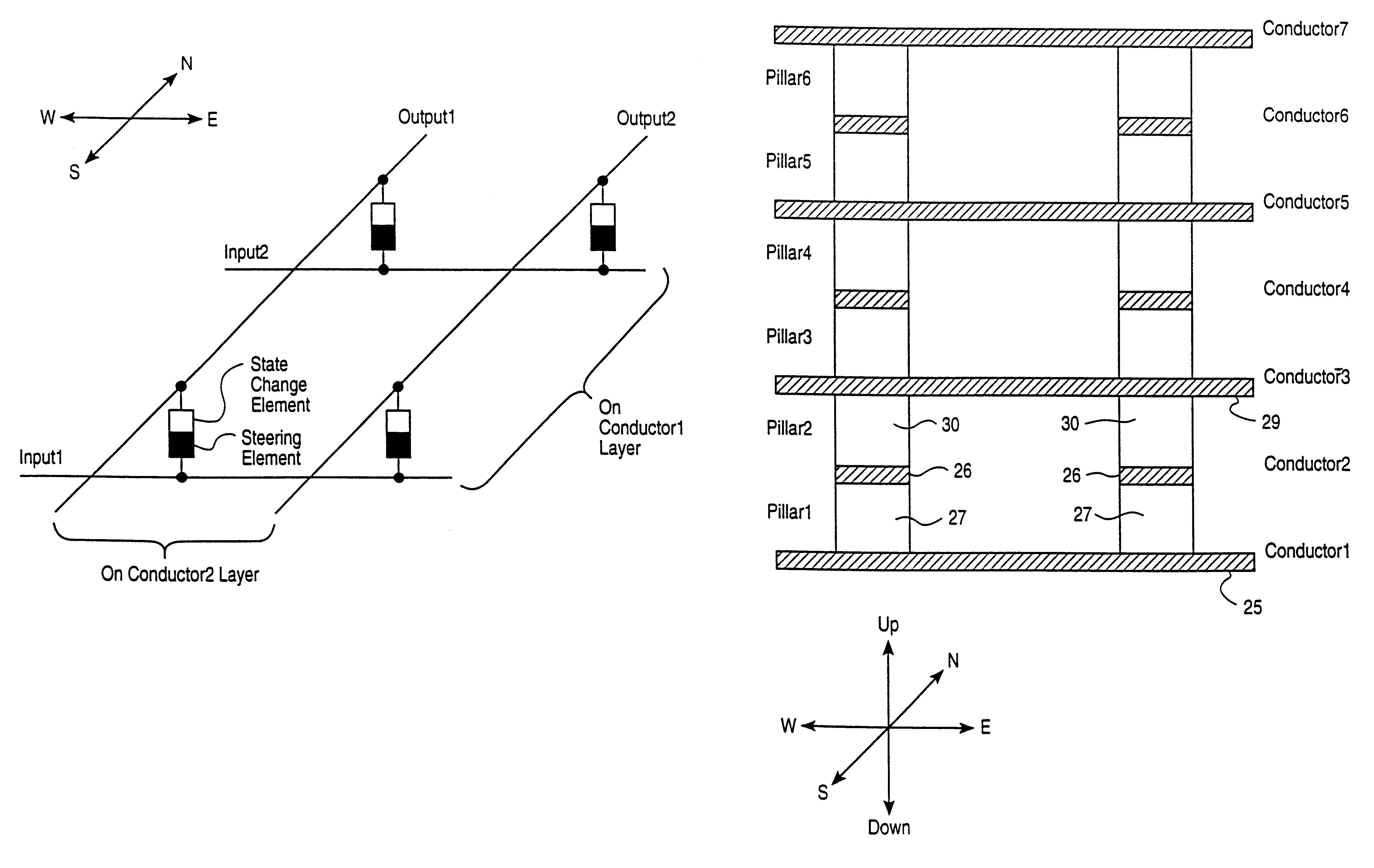

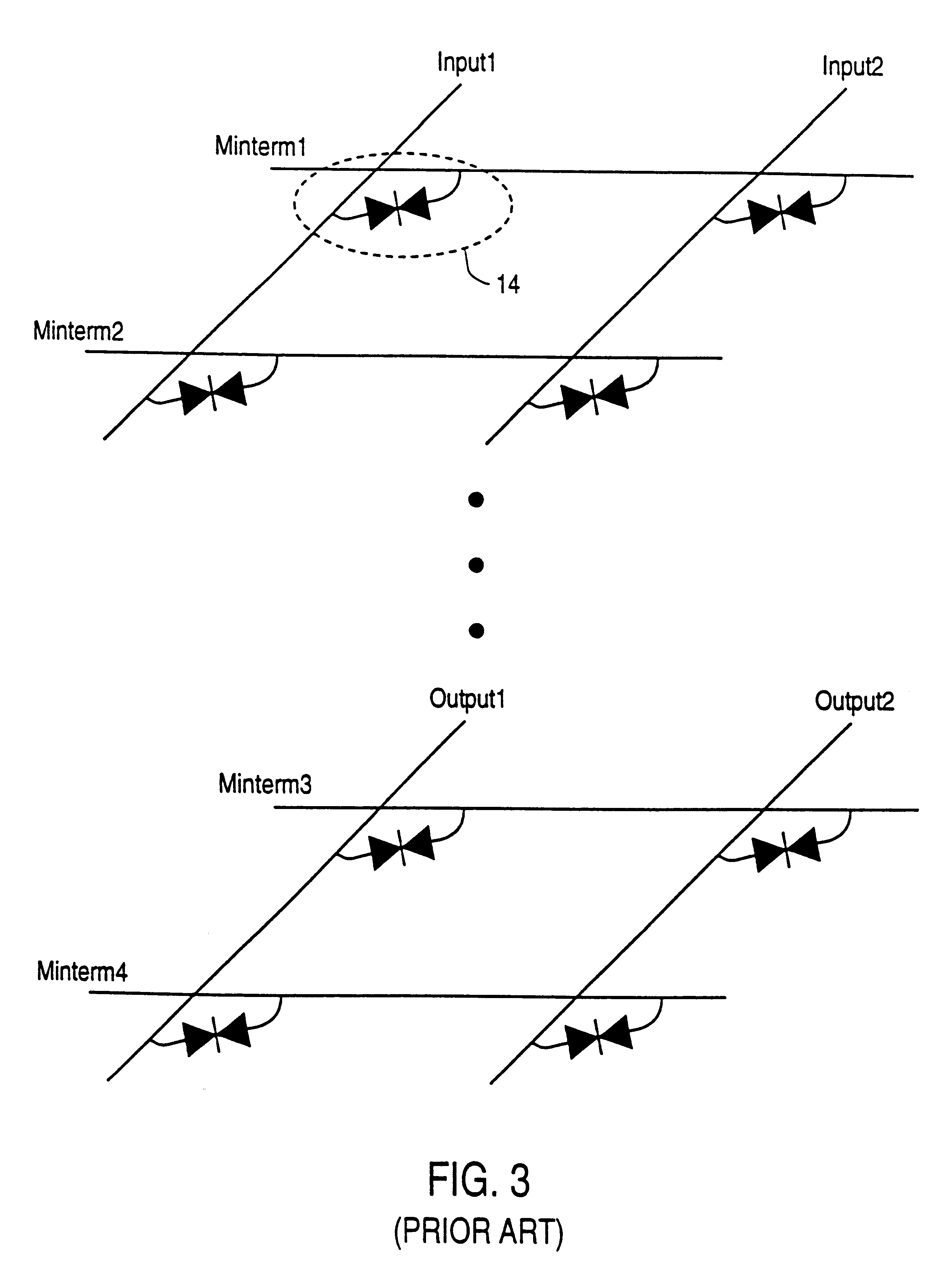

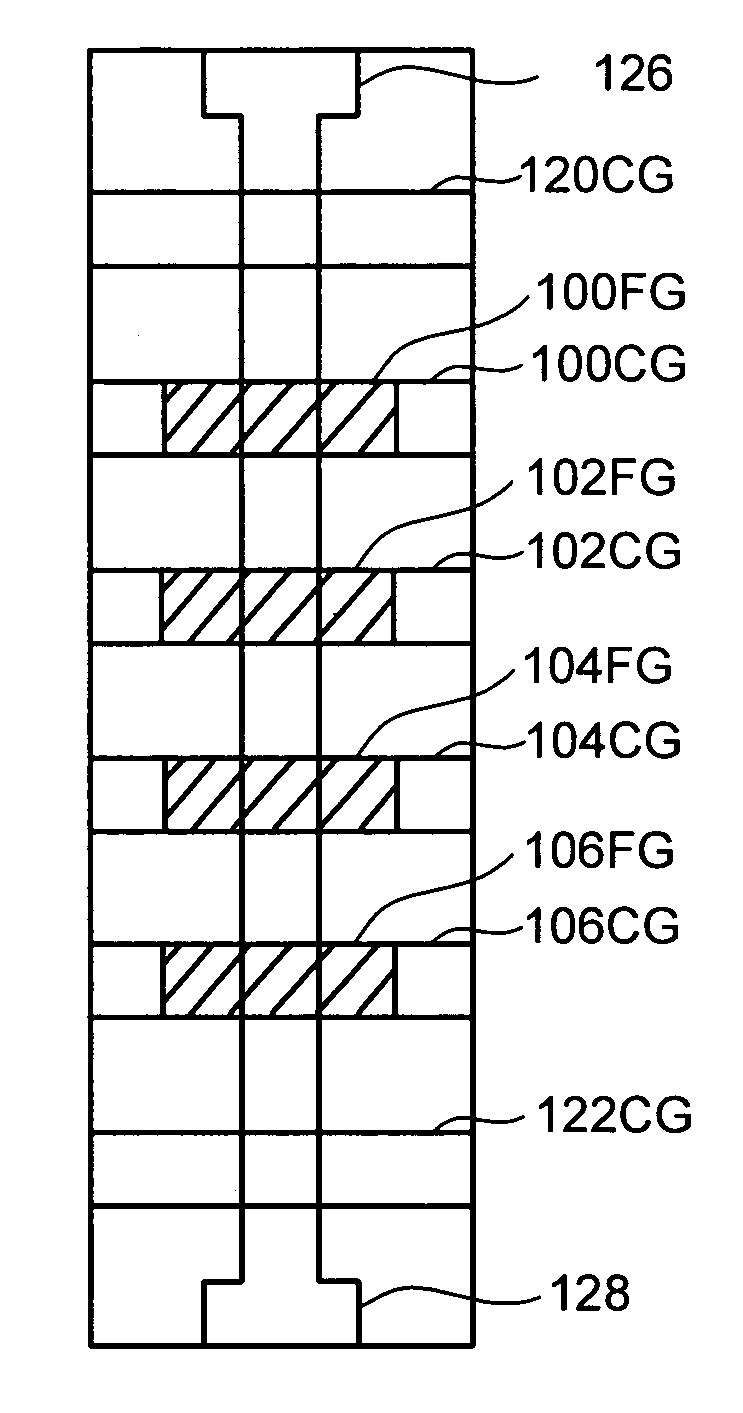

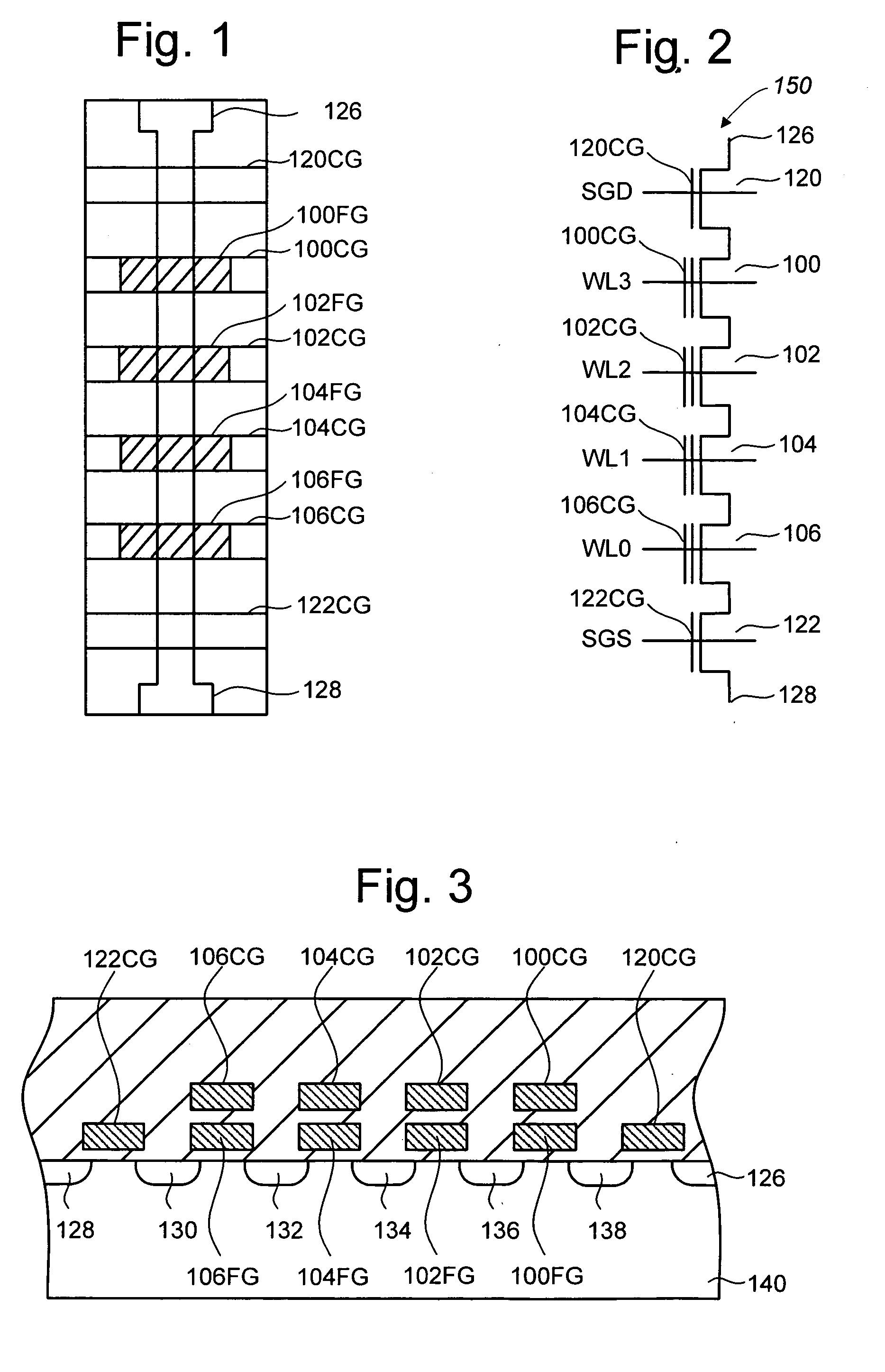

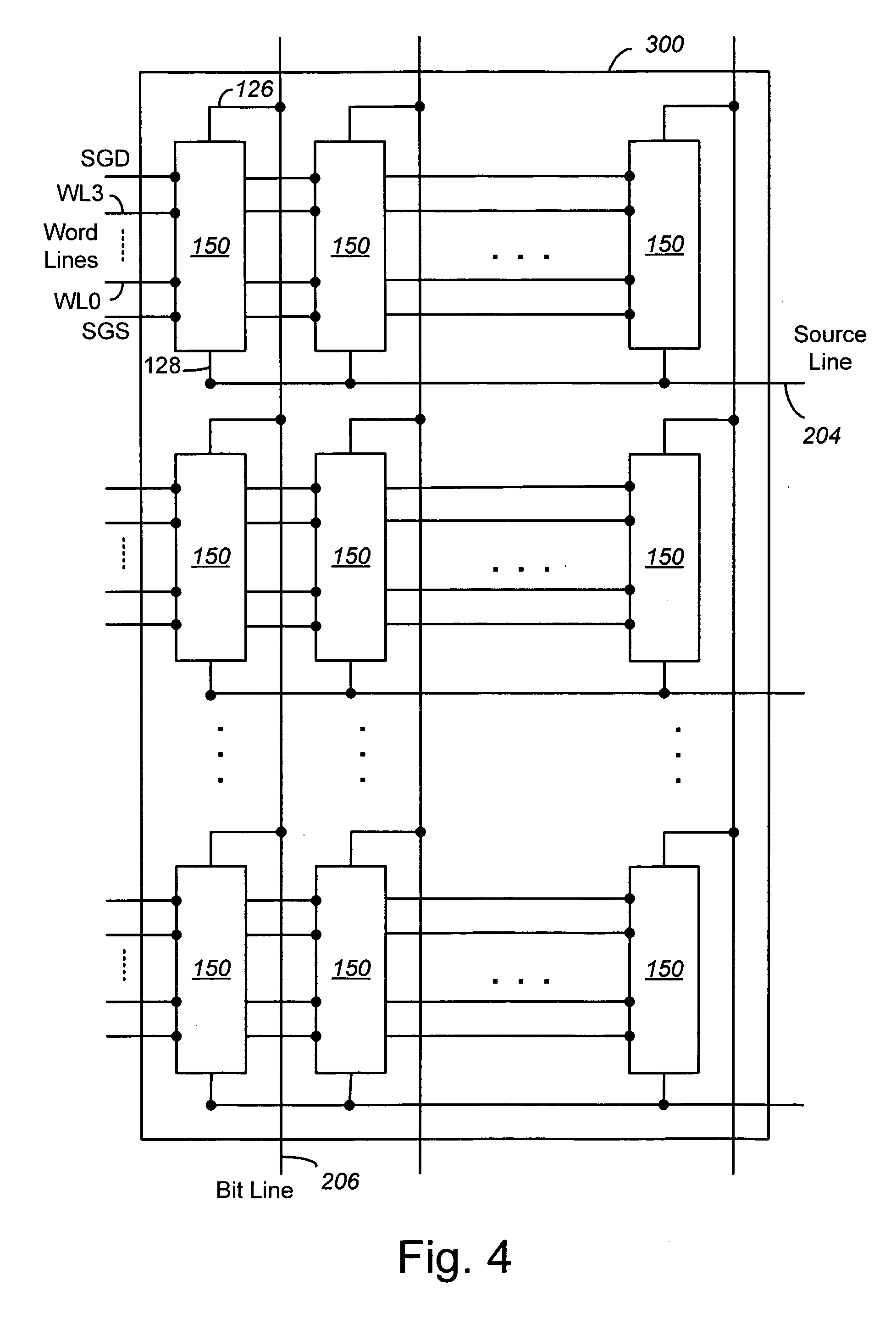

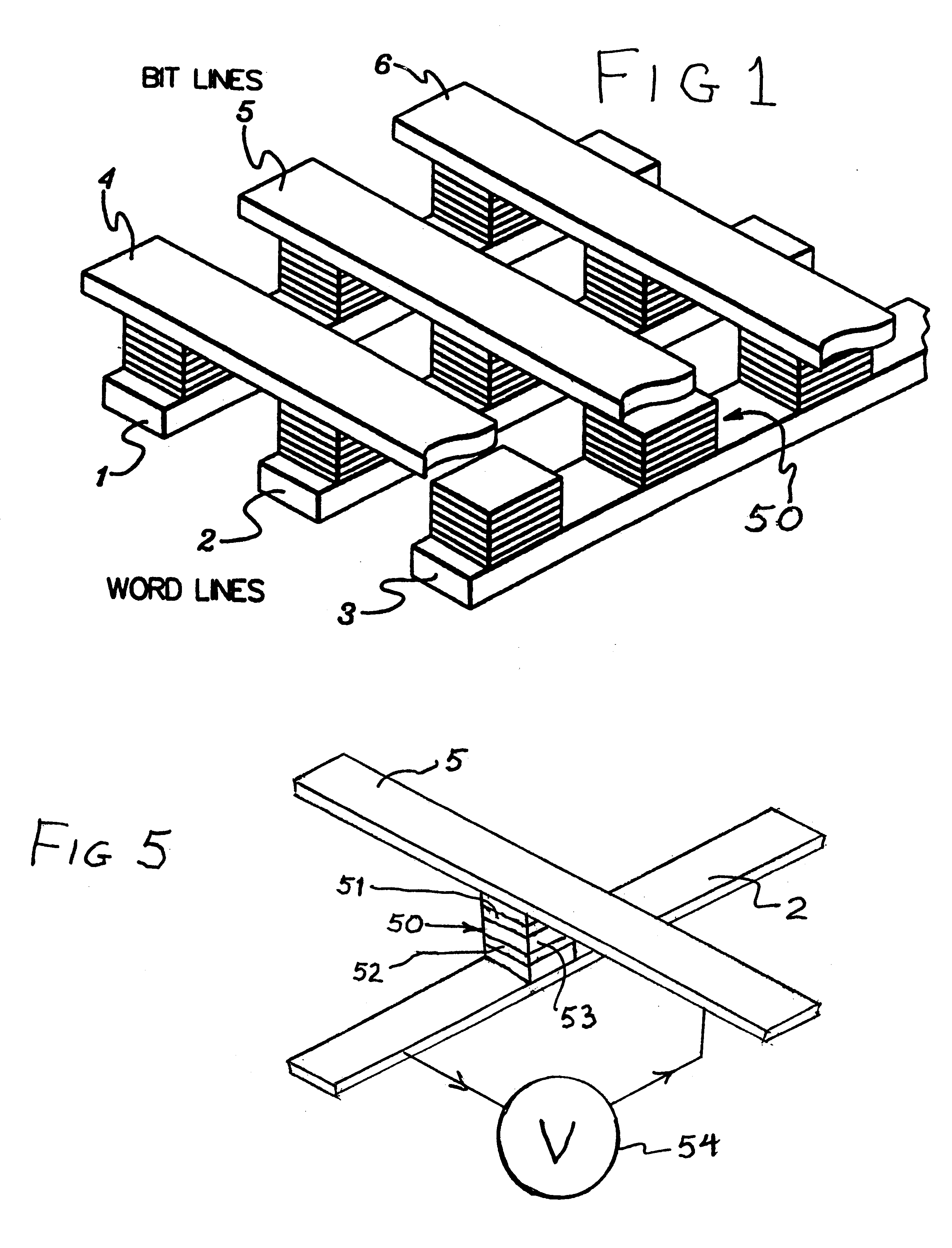

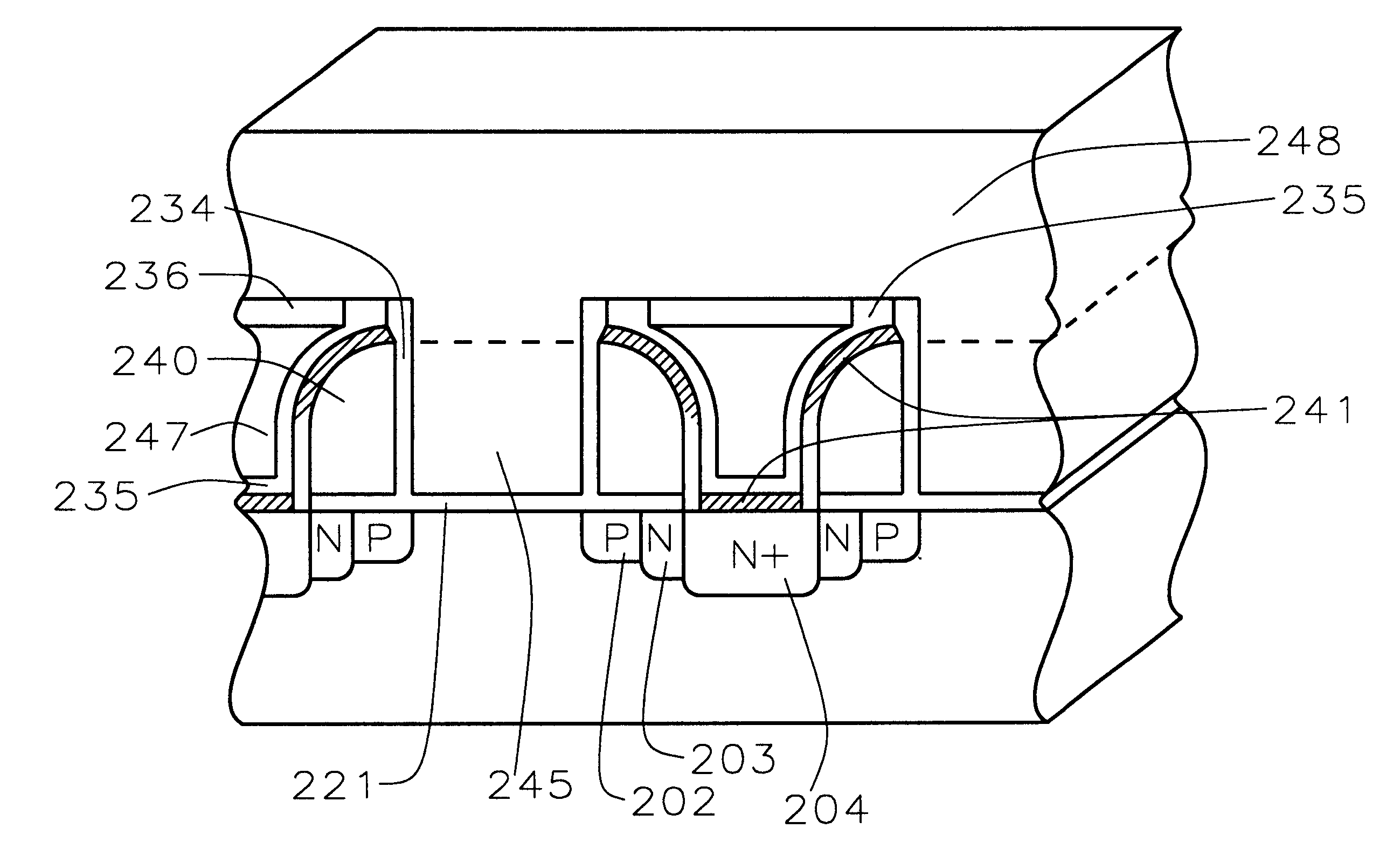

Vertically stacked field programmable nonvolatile memory and method of fabrication

A very high density field programmable memory is disclosed. An array is formed vertically above a substrate using several layers, each layer of which includes vertically fabricated memory cells. The cell in an N level array may be formed with N+1 masking steps plus masking steps needed for contacts. Maximum use of self alignment techniques minimizes photolithographic limitations. In one embodiment the peripheral circuits are formed in a silicon substrate and an N level array is fabricated above the substrate.

Owner:SANDISK TECH LLC

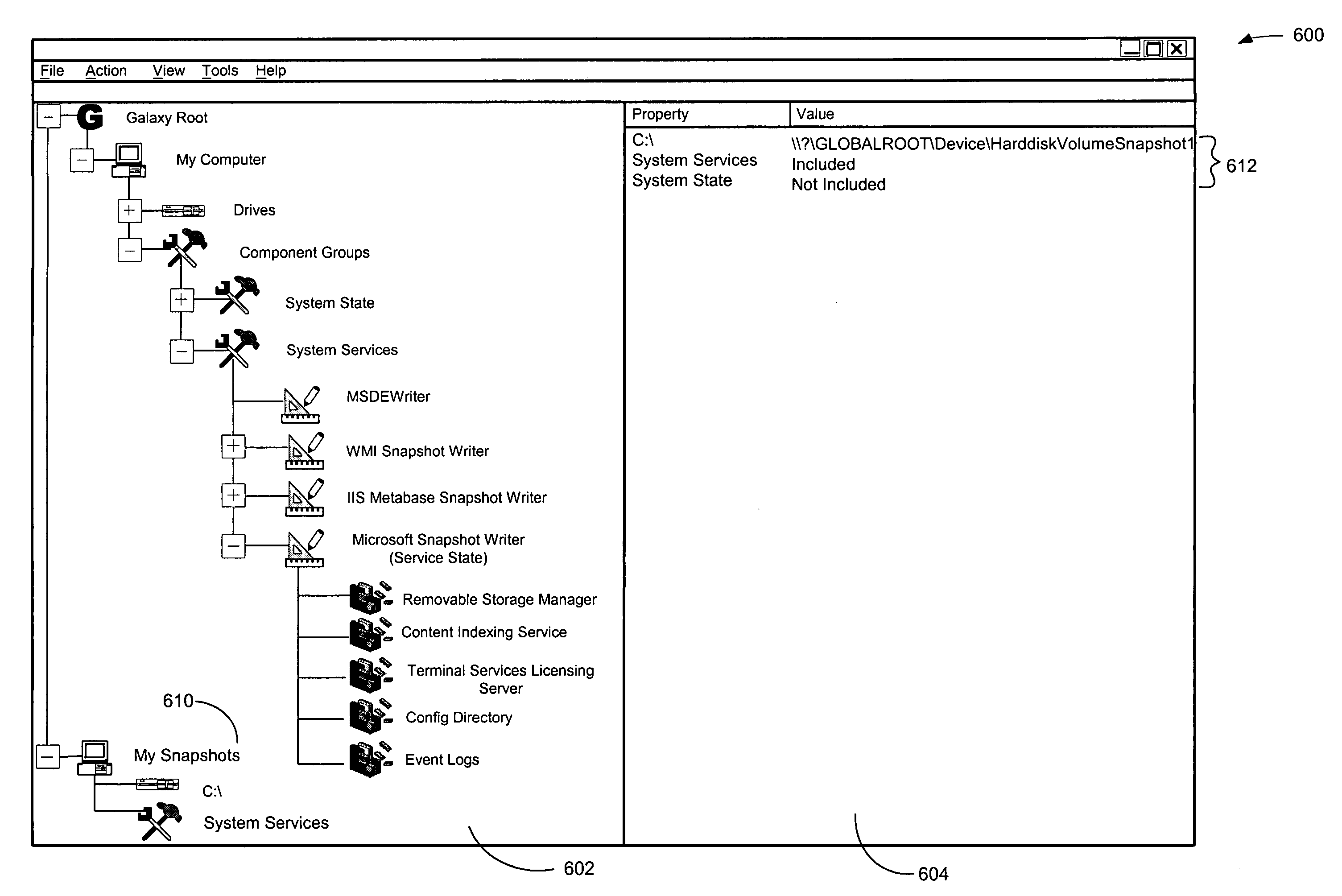

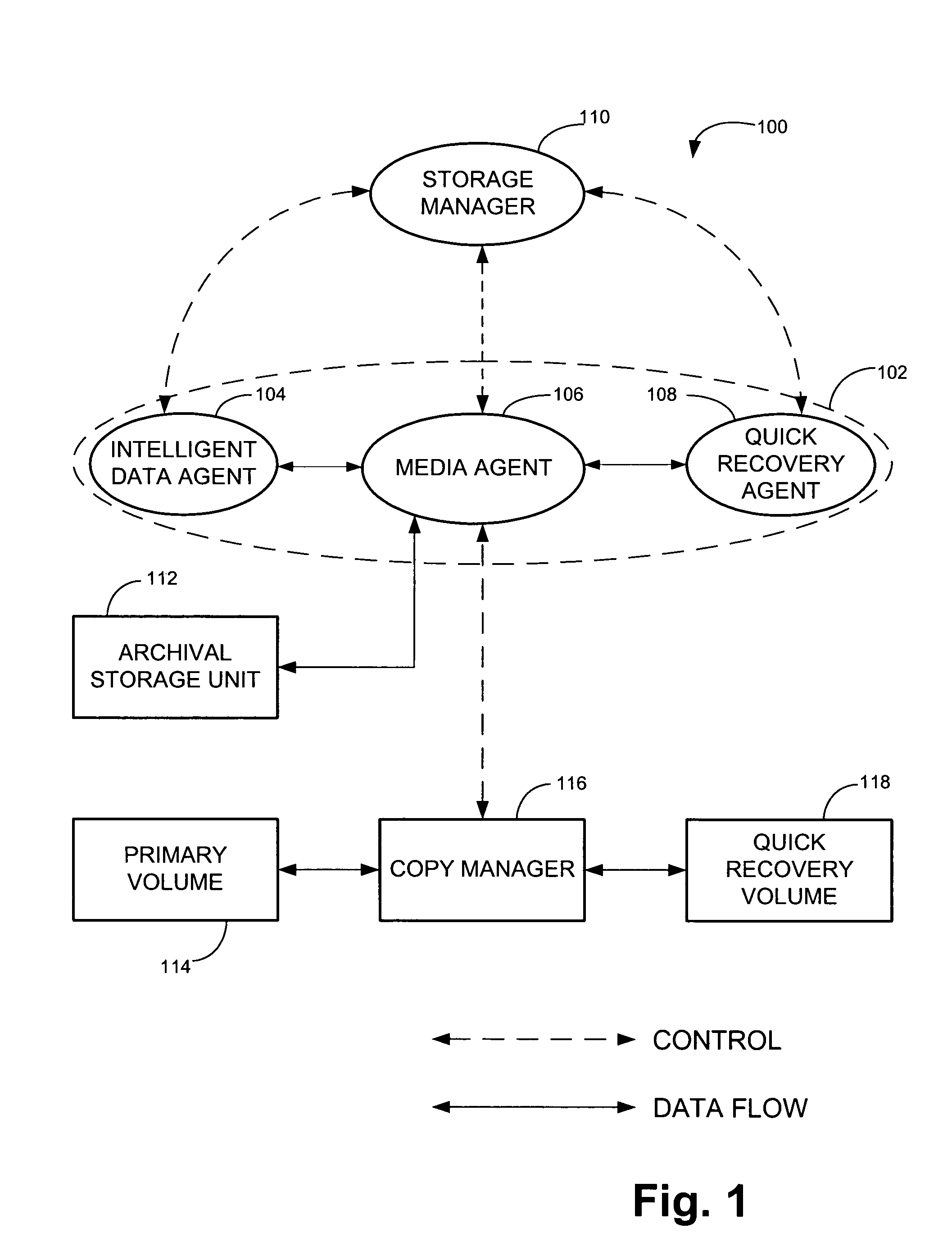

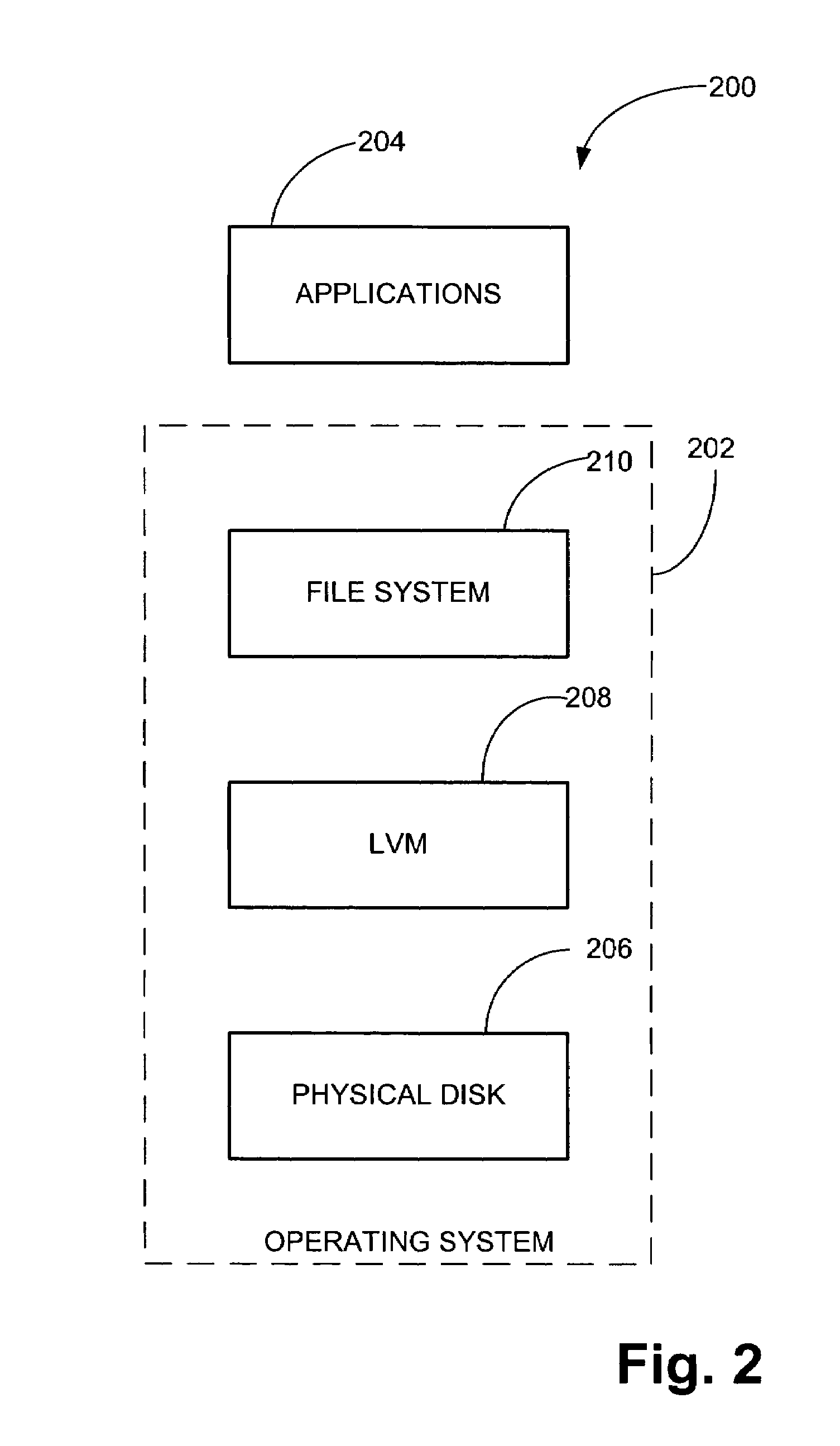

System and method for generating and managing quick recovery volumes

InactiveUS7346623B2Efficient creation and management and recoveryInput/output to record carriersData processing applicationsData setApplication software

The invention relates to computer readable medium storing program code which when executed on a computer causes the computer to perform a method for creating a quick recovery volume of a primary data set used by a first computer in a backup storage system, which includes identifying a snapshot image of the primary data set generated by a snapshot application, creating the quick recovery volume of the primary data set from the snapshot image of the primary data set and controlling transfer of data from the first computer to an archival storage unit. In one embodiment, the invention provides a method for creating a quick recovery volume of a primary data set that includes creating a snapshot image of the primary data set and creating a quick recovery volume of the primary data set from the snapshot image of the primary data set. In another embodiment, the invention provides a user interface screen enabling browser style browsing and recovery of quick recovery volumes and snapshot images.

Owner:COMMVAULT SYST INC

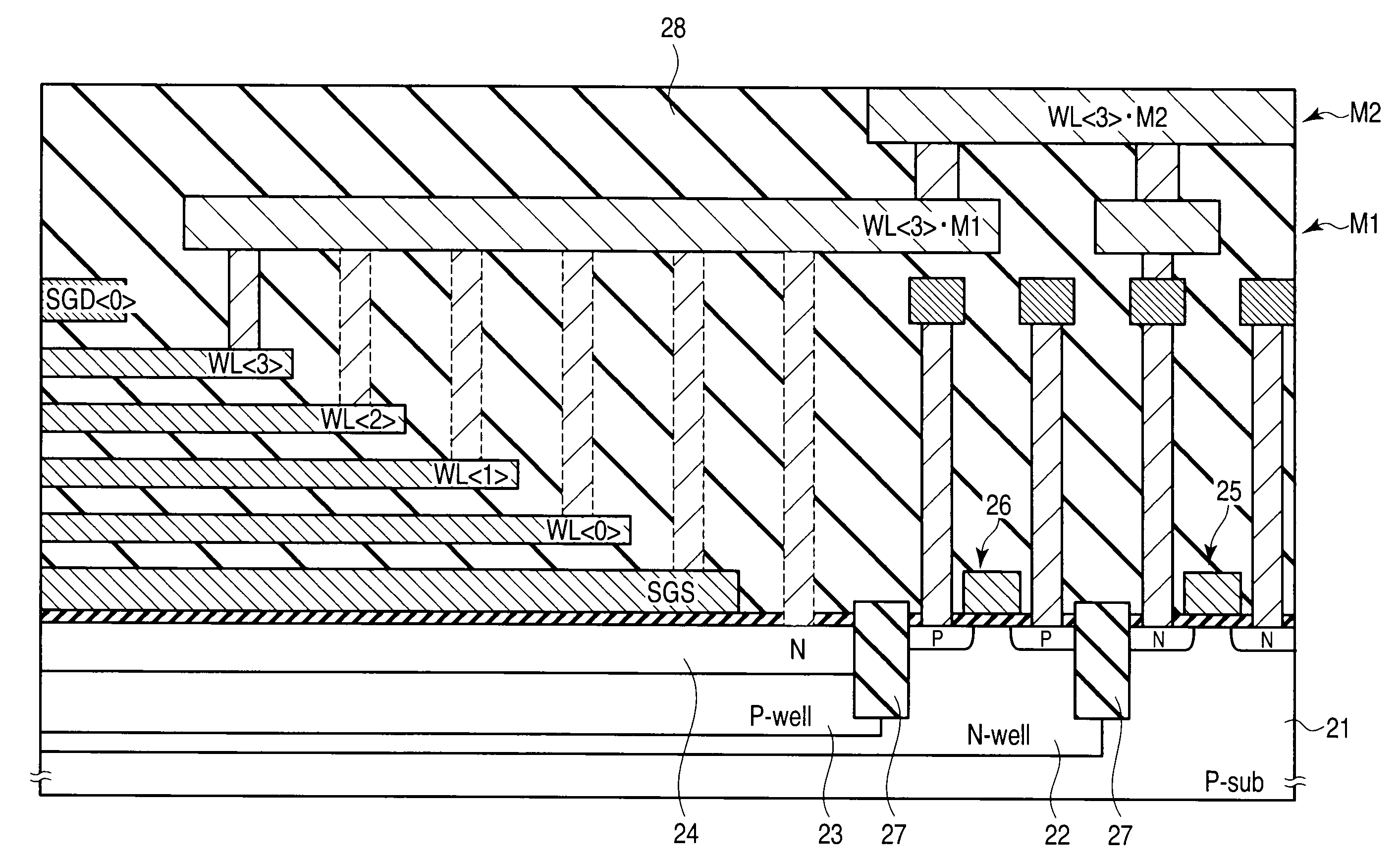

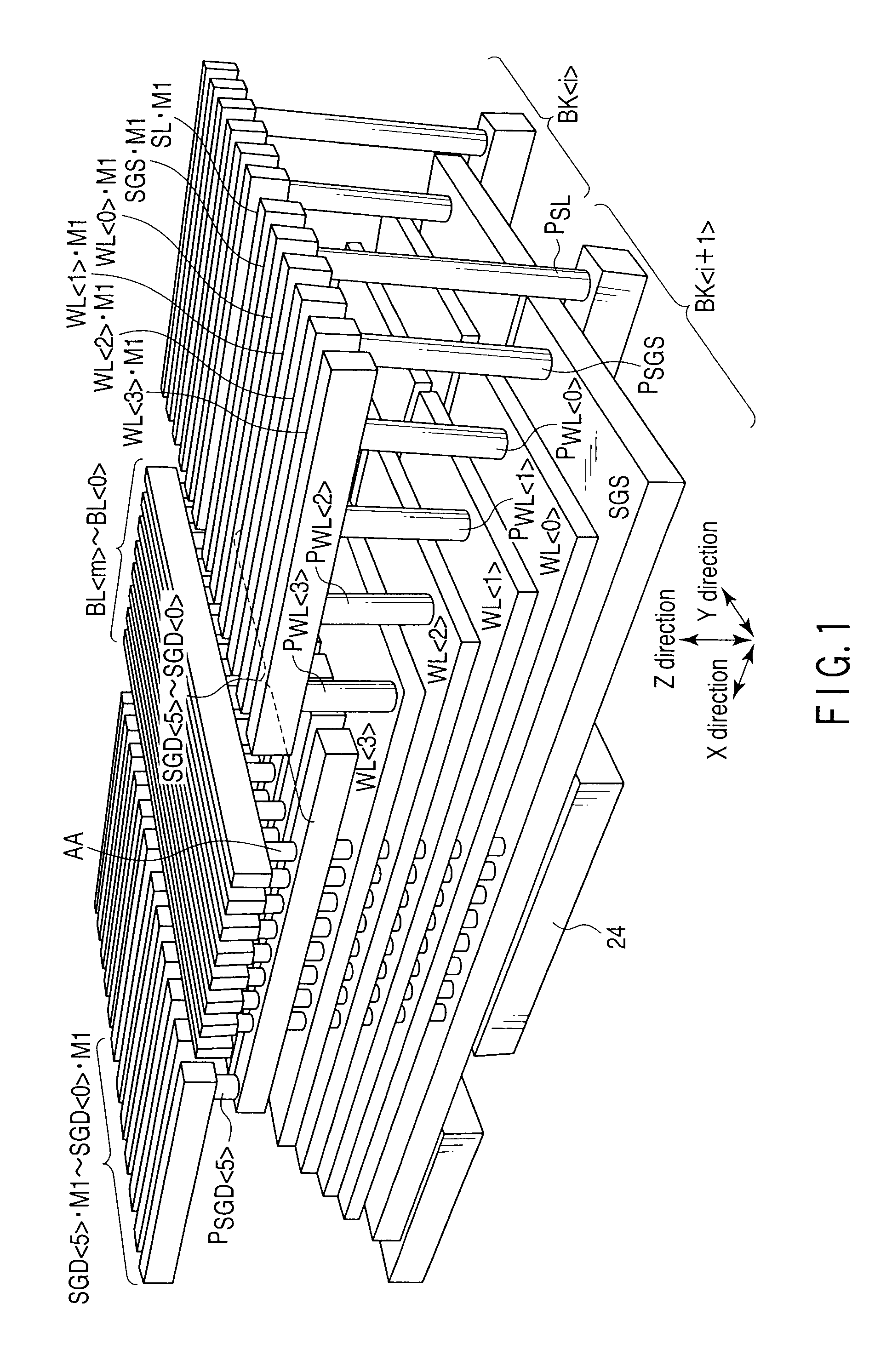

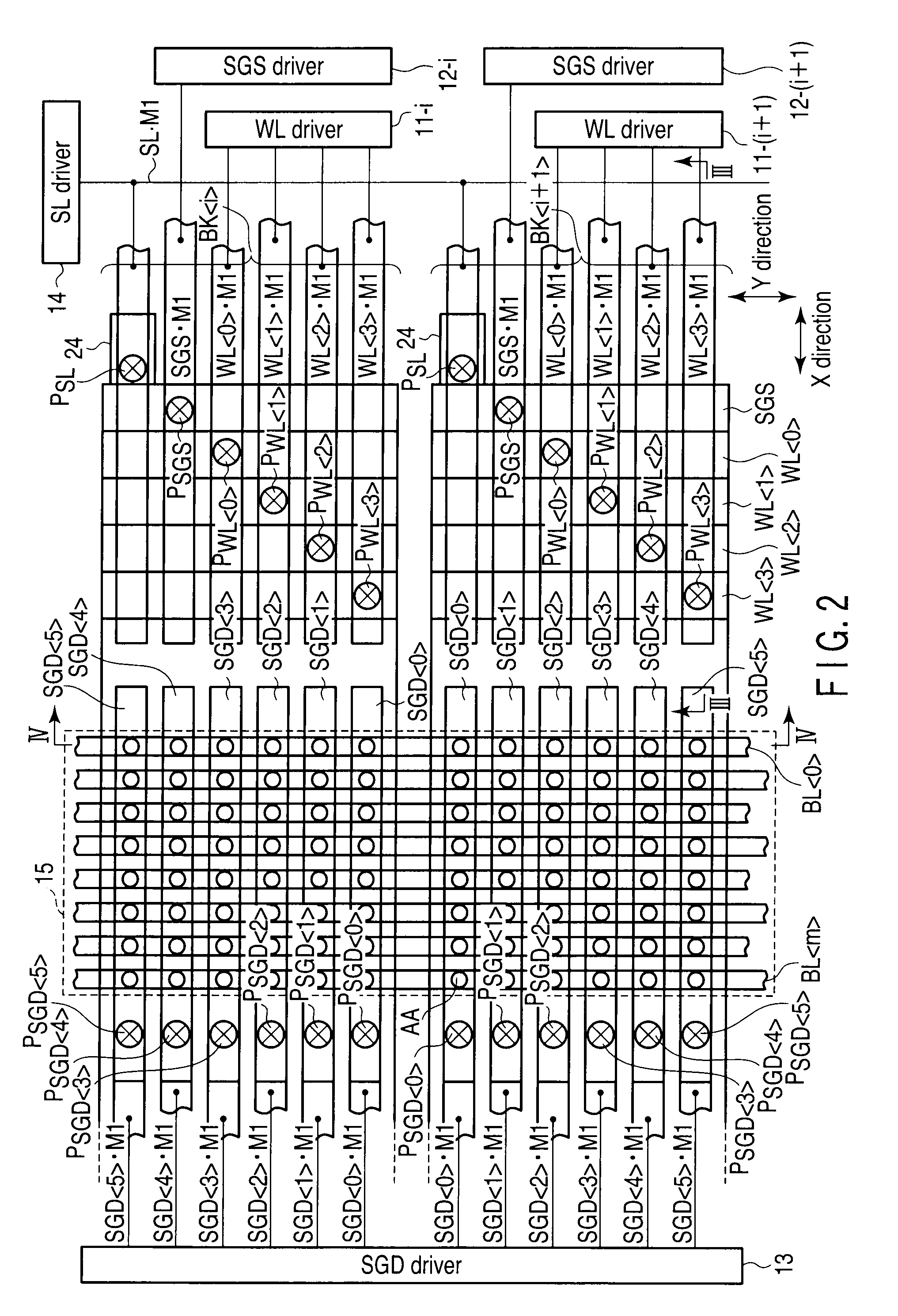

Three dimensional stacked nonvolatile semiconductor memory

A three dimensional stacked nonvolatile semiconductor memory according to an example of the present invention includes a memory cell array comprised of first and second blocks disposed side by side in a first direction, and a driver disposed on one end of the memory cell array in a second direction orthogonal to the first direction. A source diffusion layer, which is common to the first and second blocks, is disposed in a semiconductor substrate, and a contact plug, which has a lower end connected to the source diffusion layer and an upper end connected to a source line disposed above at least three conductive layers, is interposed between the first and second blocks.

Owner:KIOXIA CORP

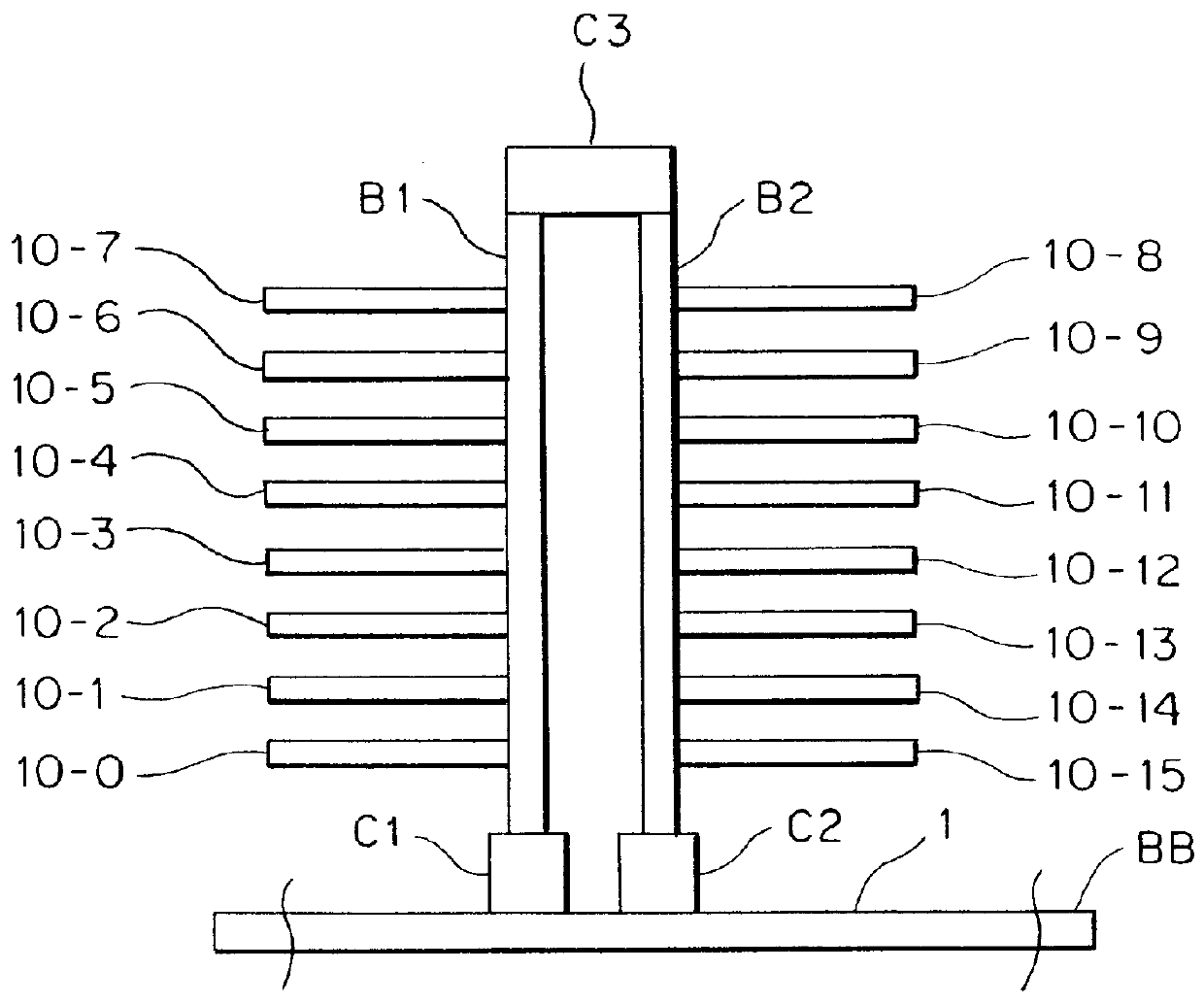

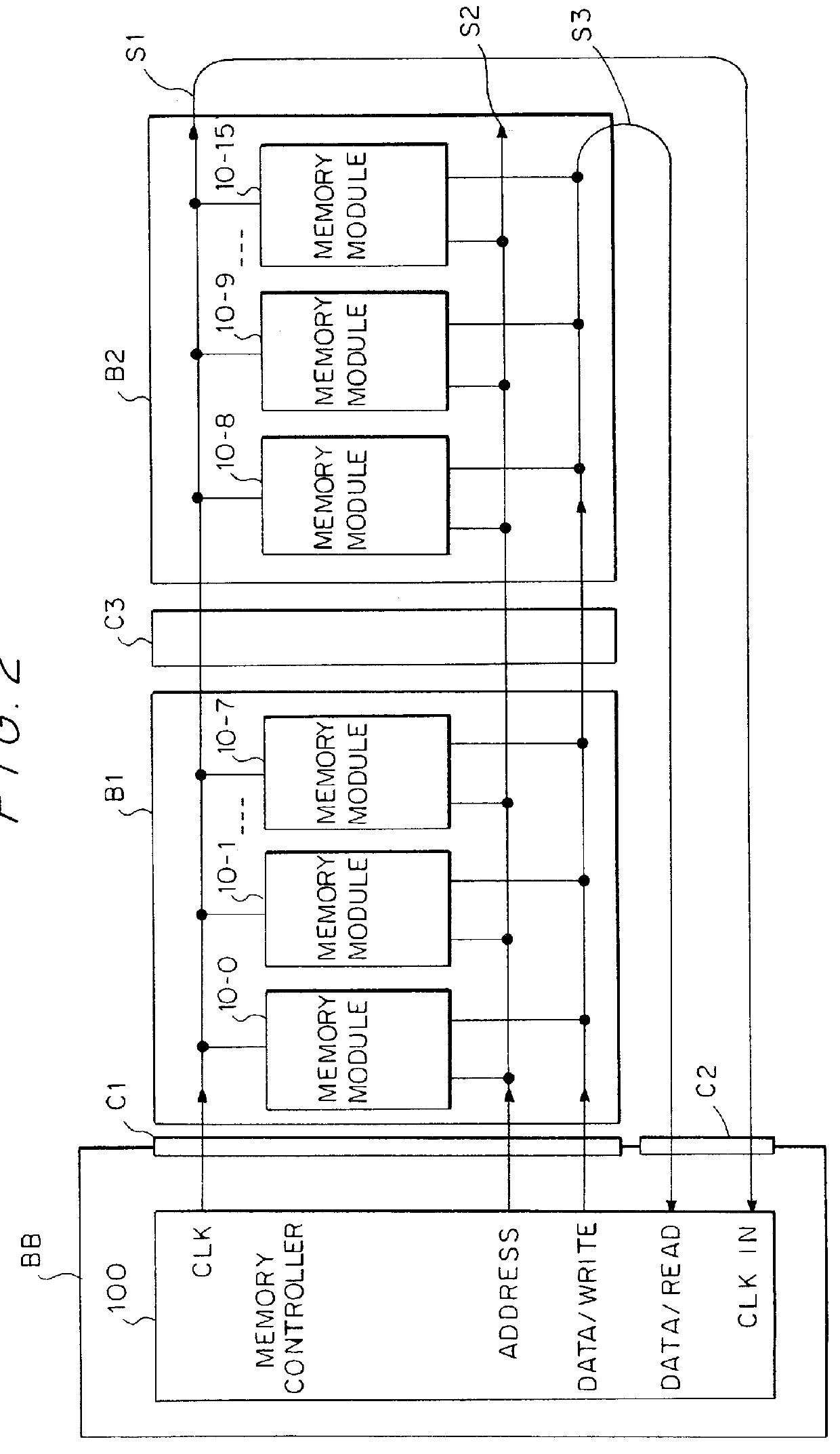

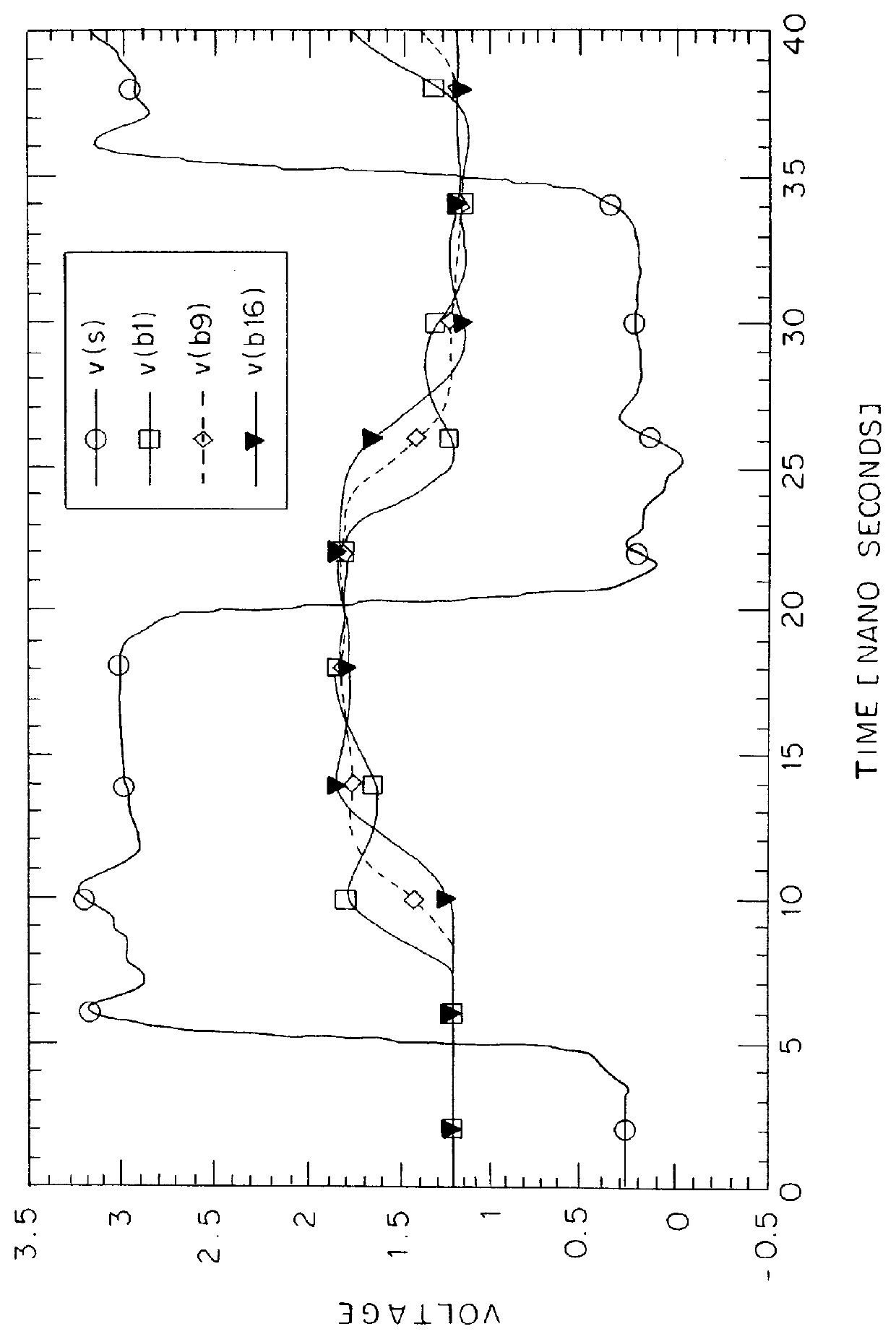

Source-clock-synchronized memory system and memory unit

InactiveUS6034878ALarge data storage capacity per memoryImprove installation densityMemory adressing/allocation/relocationDigital storageMemory bankComputer module

A source-clock-synchronized memory system having a large data storage capacity per memory bank and a high mounting density. The invention includes a memory unit having a first memory riser board B1 mounted on a base board through a first connector C1 and a second memory riser board B2 mounted on the base board BB through a second connector C2. The first memory riser board has a plurality of first memory modules mounted on the front surface thereof and the second memory riser board has a plurality of second memory modules mounted on the front surface thereof. The first and second memory riser boards are arranged in such a way that the back surface of the first memory riser board faces the back surface of the second memory riser board. The invention further includes a board linking connector for connecting signal lines on the first memory riser board to corresponding signal lines on the second memory riser board.

Owner:DELTA KOGYO CO LTD +1

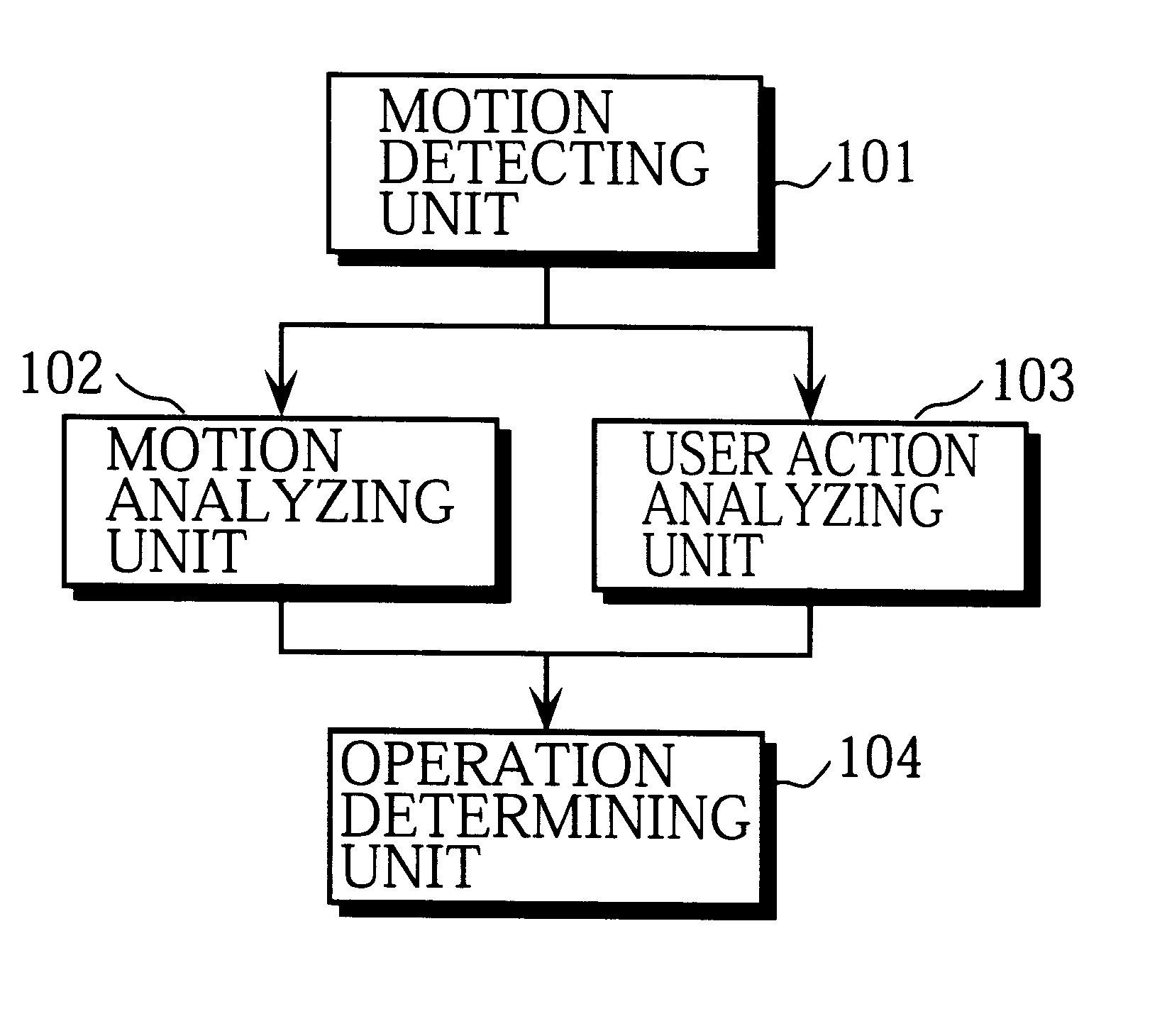

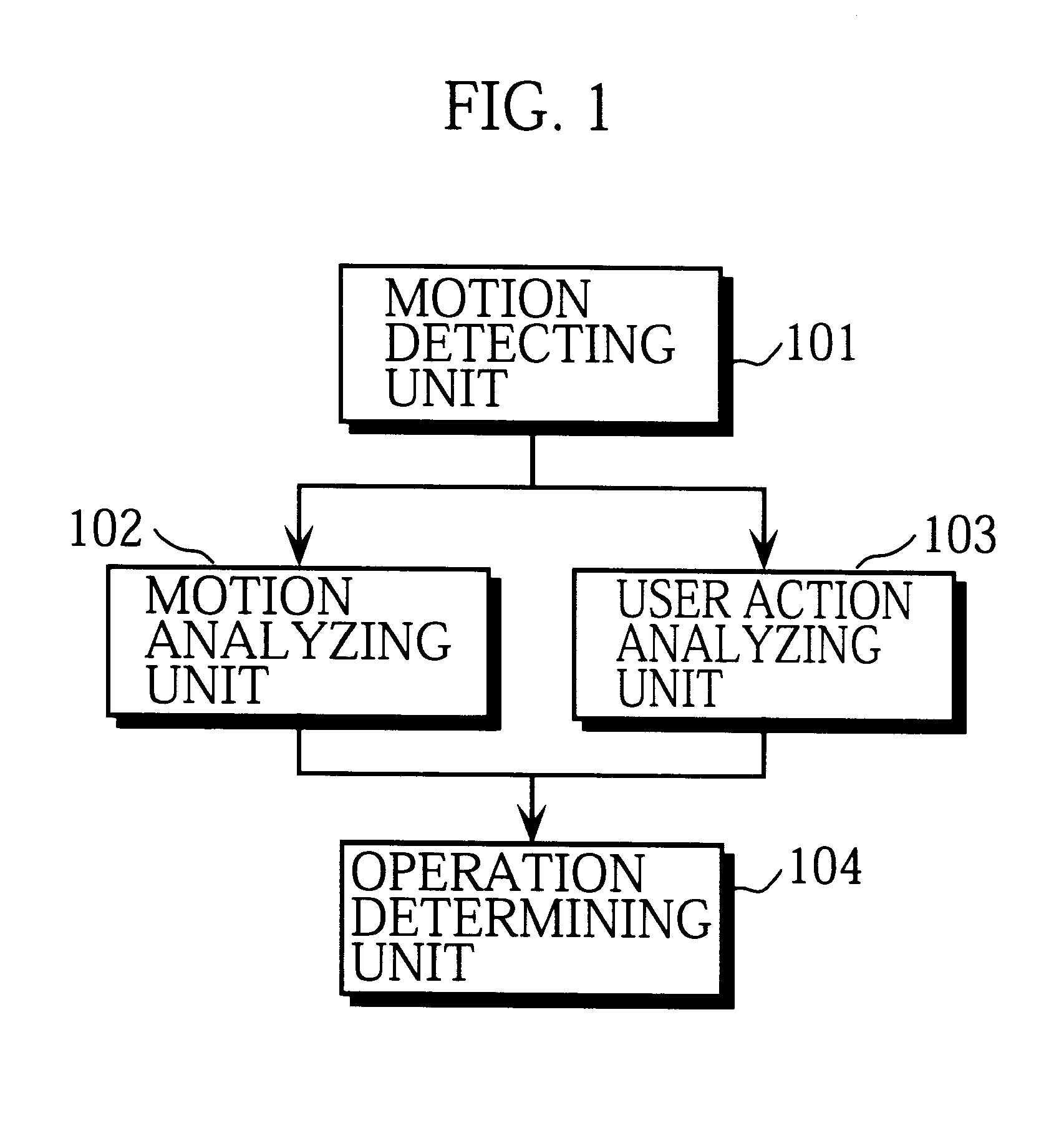

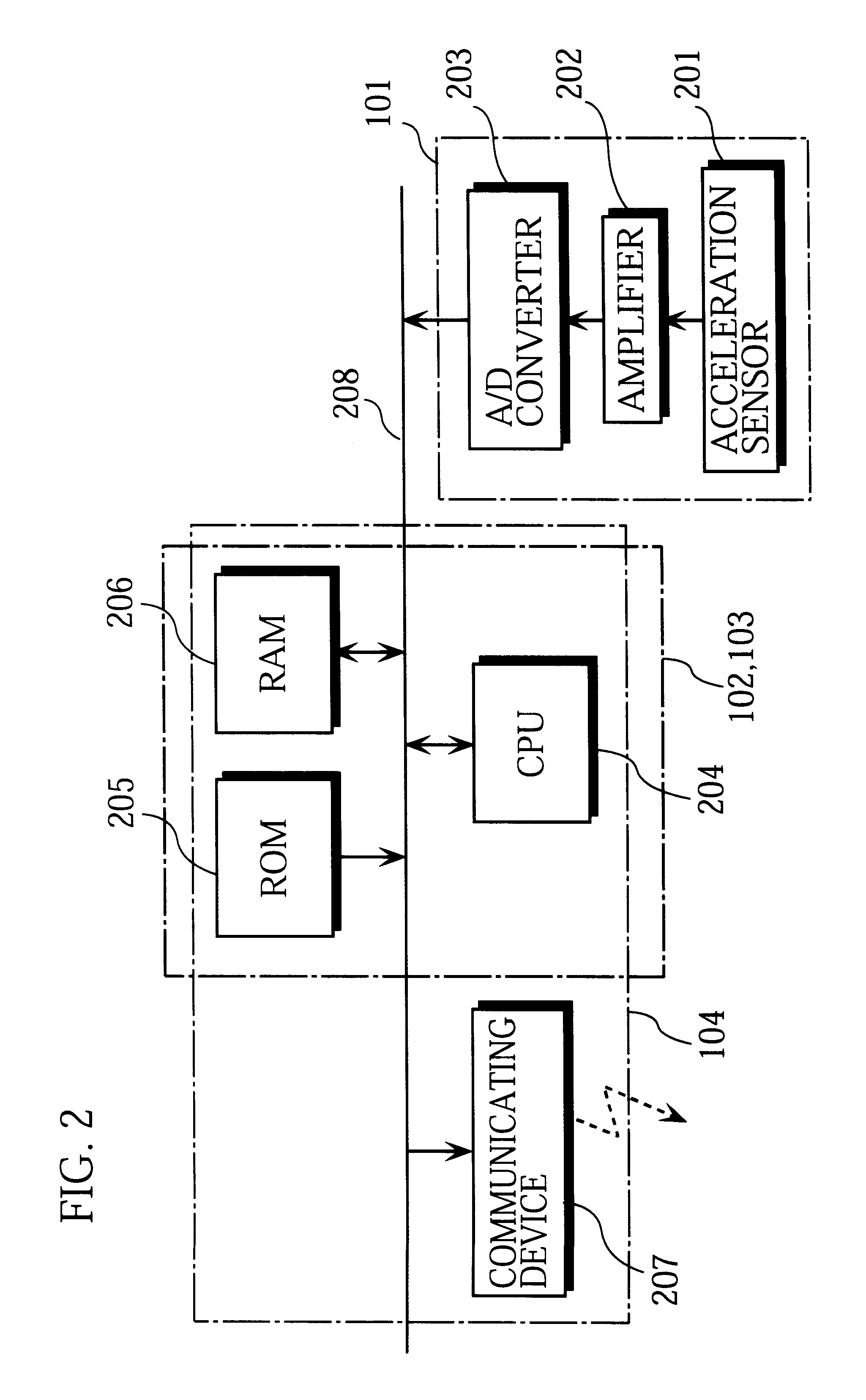

Operation indication outputting device for giving operation indication according to type of user's action

InactiveUS6369794B1Simple procedureLow priceInput/output for user-computer interactionInterconnection arrangementsInformation processingOutput device

A motion detecting unit detects a motion of an operation indication outputting device. A motion analyzing unit analyzes a direction, strength, and number of occurrence of the detected motion. A user action analyzing unit analyzes a type of a user's action by obtaining a frequency distribution from the detected motion. An operation determining unit includes a storing unit which stores operation indications that each correspond to a type of the user's action and a direction and other attributes of a motion of the operation indication outputting device caused by the user's action, and outputs an operation indication corresponding to the analysis results by the motion analyzing unit and user action analyzing unit to an information processing apparatus.

Owner:INTERTRUST TECH CORP

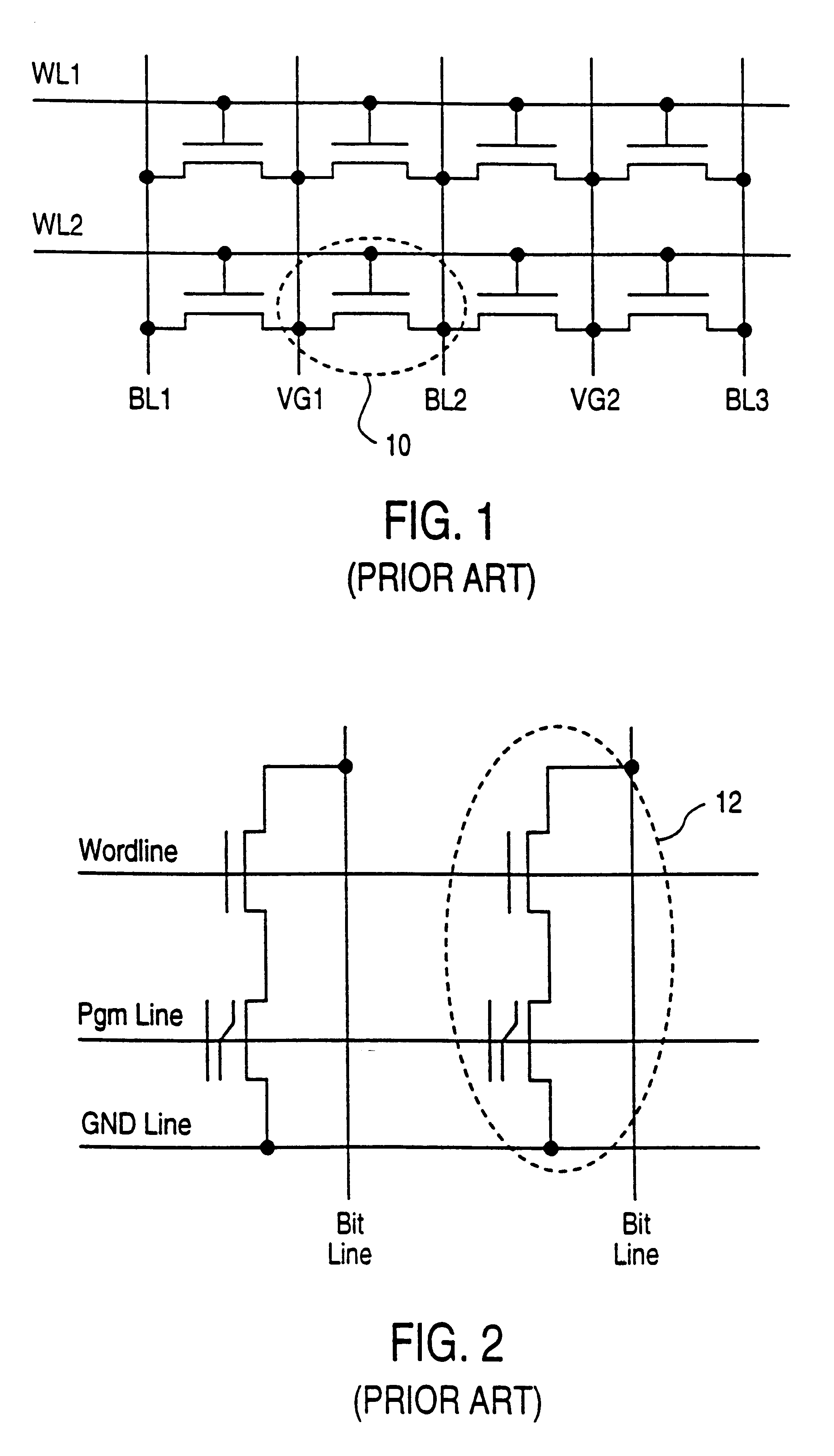

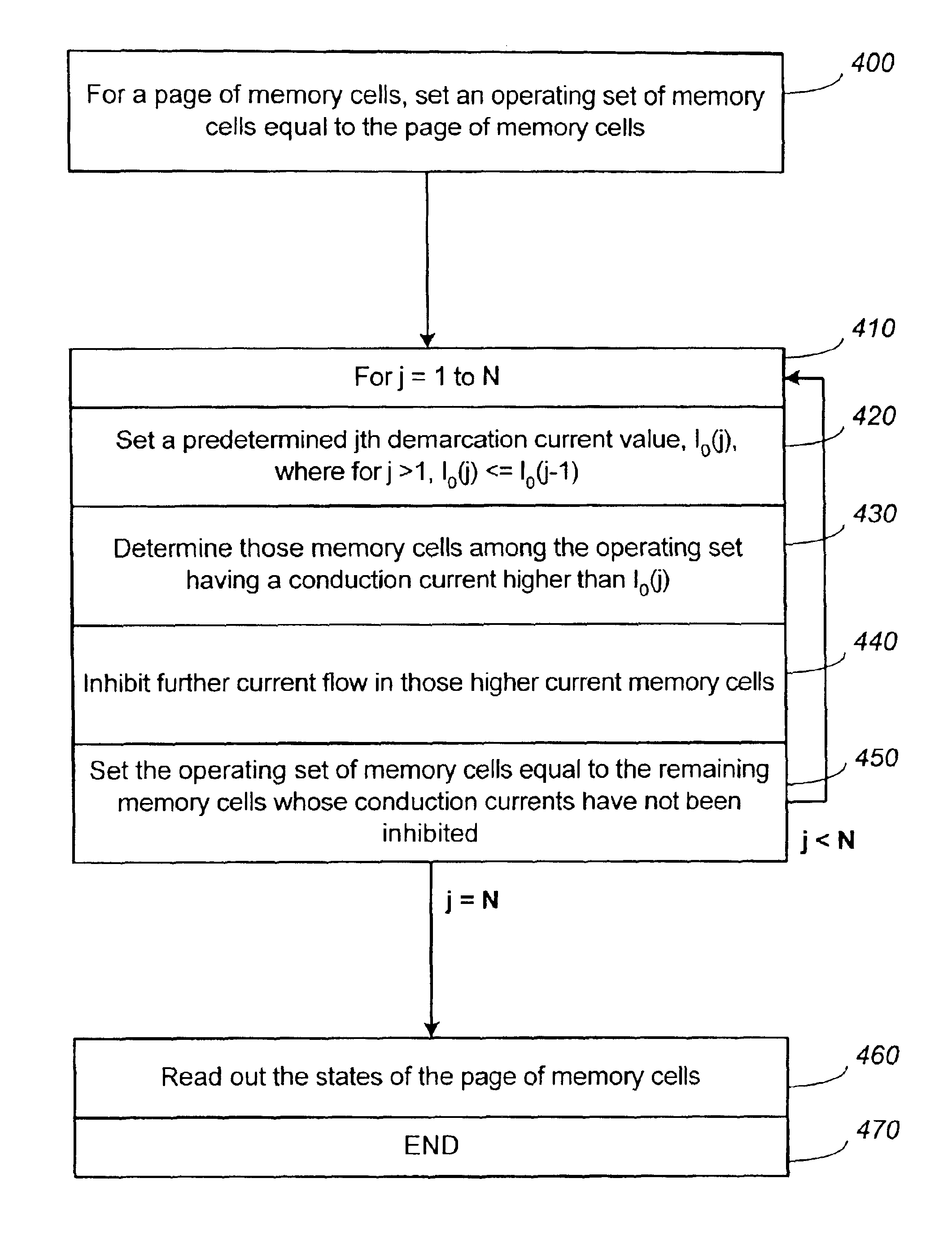

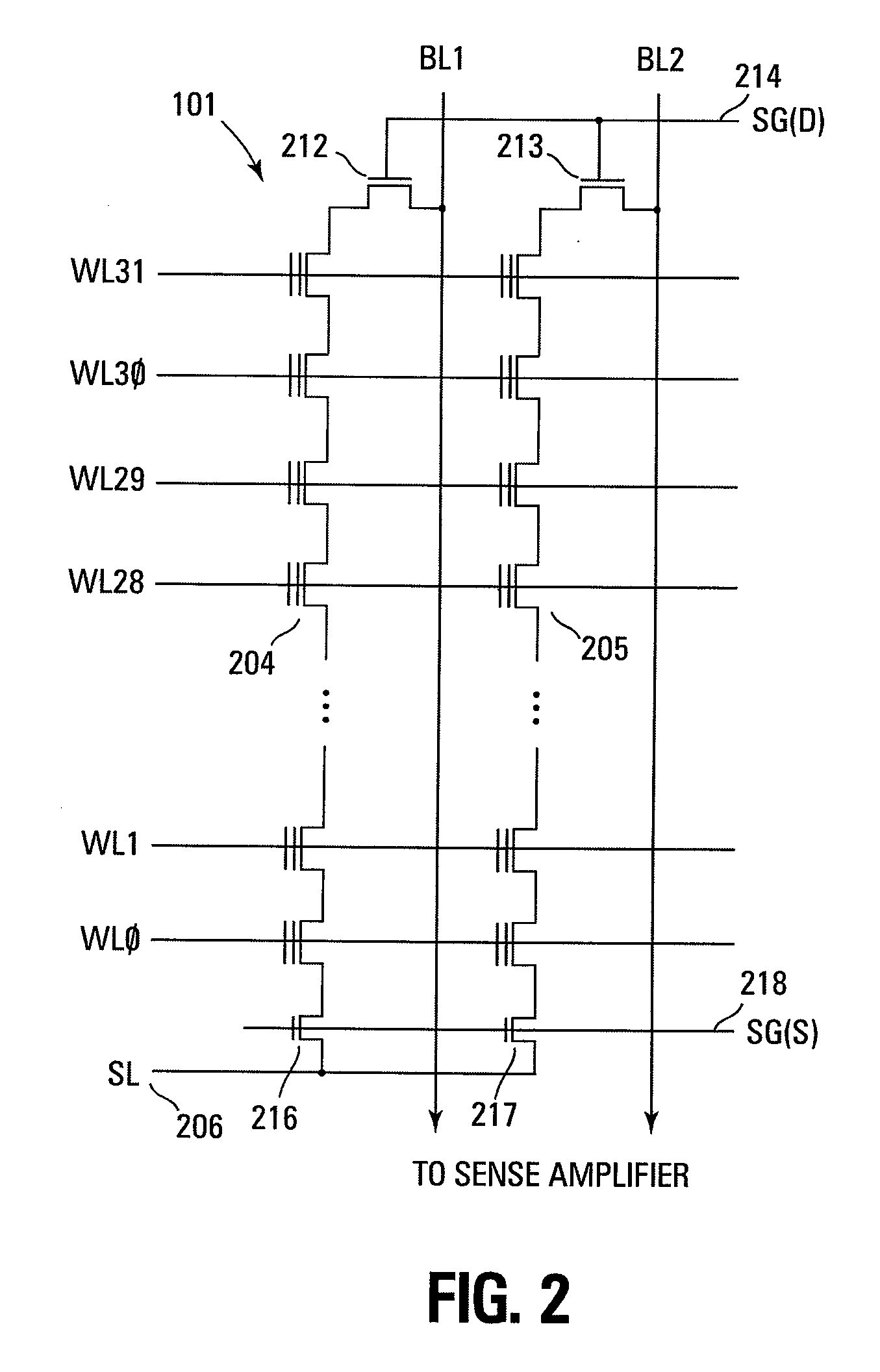

Non-volatile memory and method with reduced neighboring field errors

InactiveUS6987693B2Large capacityImprove performanceRead-only memoriesDigital storageNon-volatile memoryParallel programing

A memory device and a method thereof allow programming and sensing a plurality of memory cells in parallel in order to minimize errors caused by coupling from fields of neighboring cells and to improve performance. The memory device and method have the plurality of memory cells linked by the same word line and a read / write circuit is coupled to each memory cells in a contiguous manner. Thus, a memory cell and its neighbors are programmed together and the field environment for each memory cell relative to its neighbors during programming and subsequent reading is less varying. This improves performance and reduces errors caused by coupling from fields of neighboring cells, as compared to conventional architectures and methods in which cells on even columns are programmed independently of cells in odd columns.

Owner:SANDISK TECH LLC

Compensating for coupling during read operations on non-volatile memory

Shifts in the apparent charge stored on a floating gate (or other charge storing element) of a non-volatile memory cell can occur because of the coupling of an electric field based on the charge stored in adjacent floating gates (or other adjacent charge storing elements). The problem occurs most pronouncedly between sets of adjacent memory cells that have been programmed at different times. To compensate for this coupling, the read process for a given memory cell will take into account the programmed state of an adjacent memory cell.

Owner:SANDISK TECH LLC

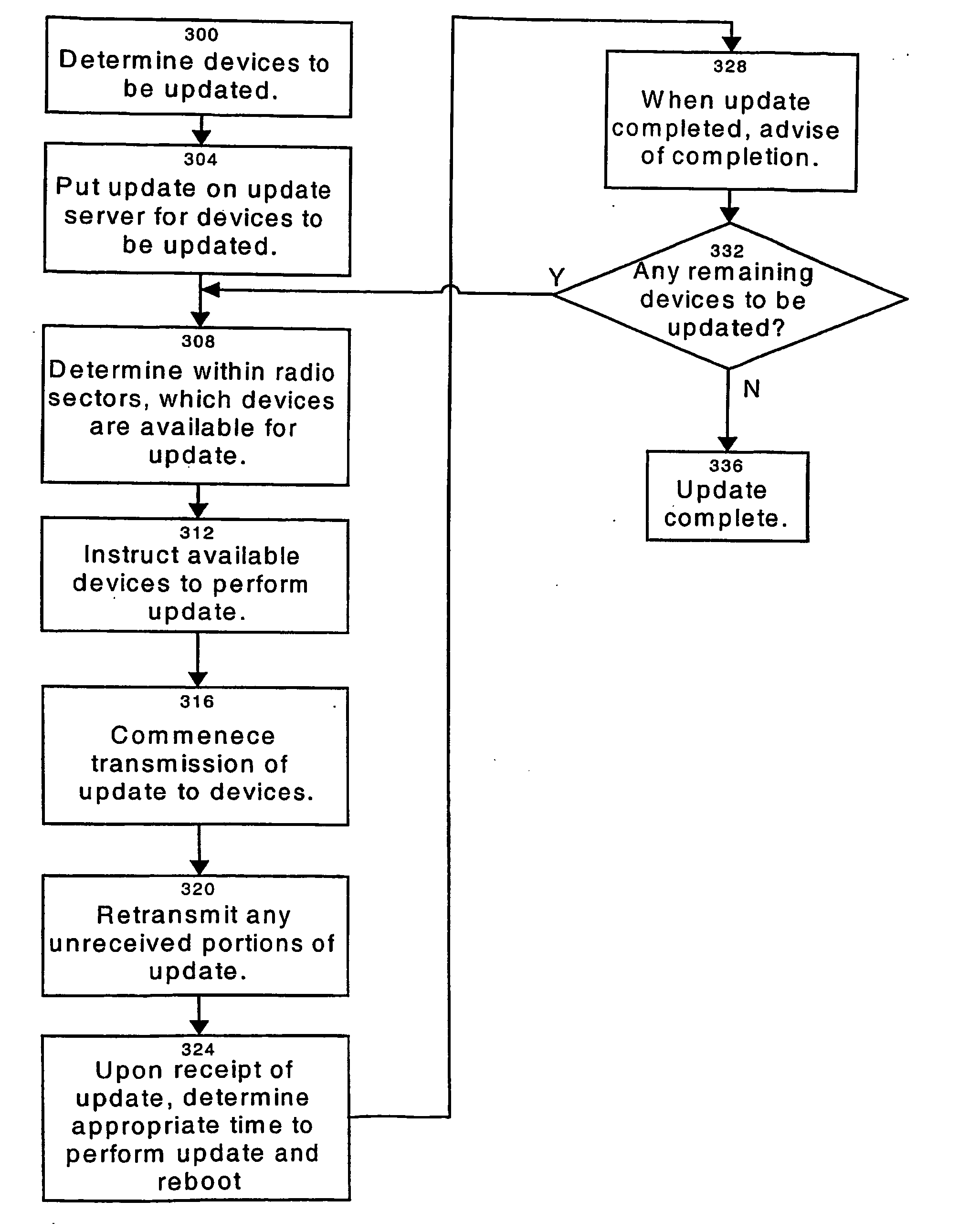

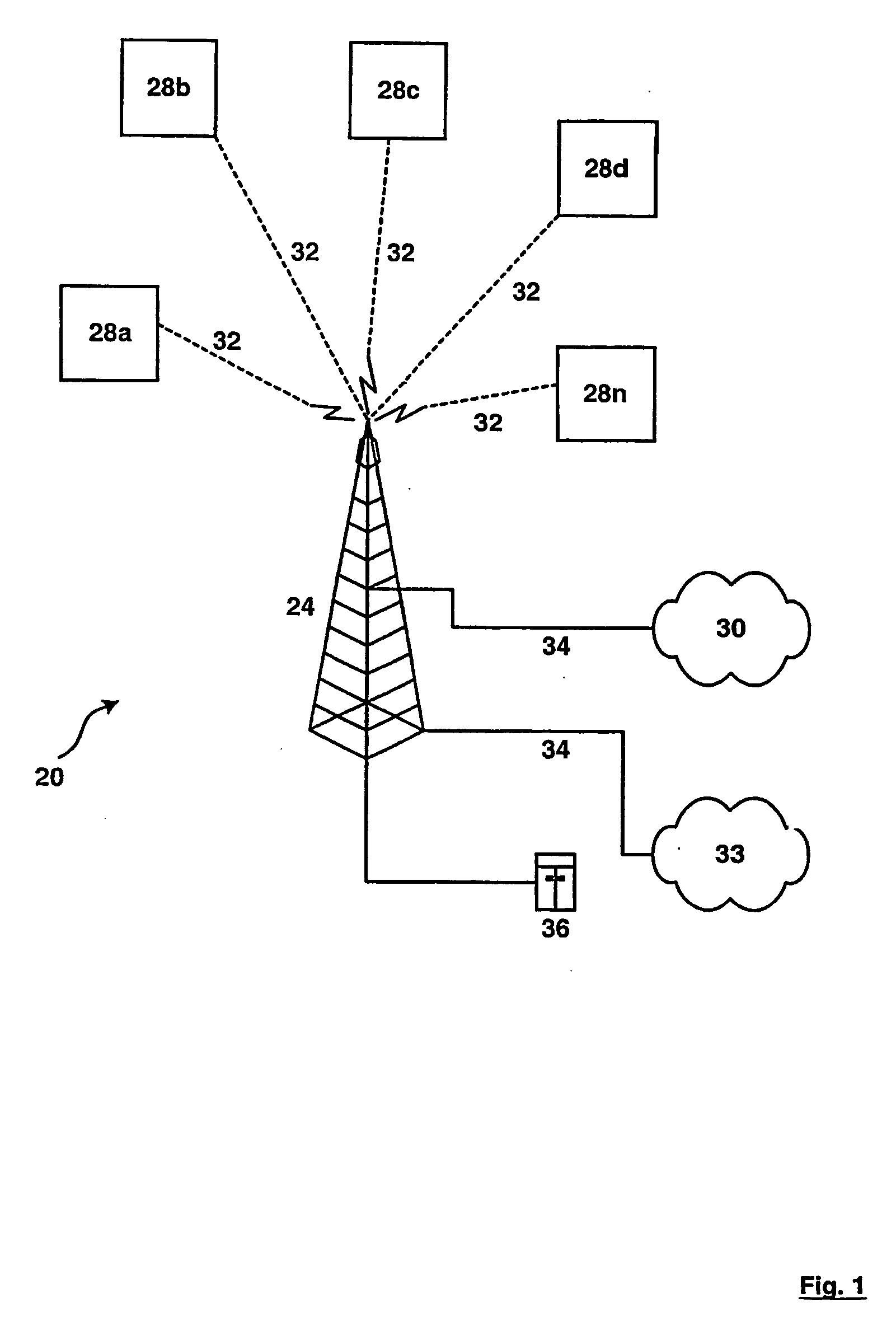

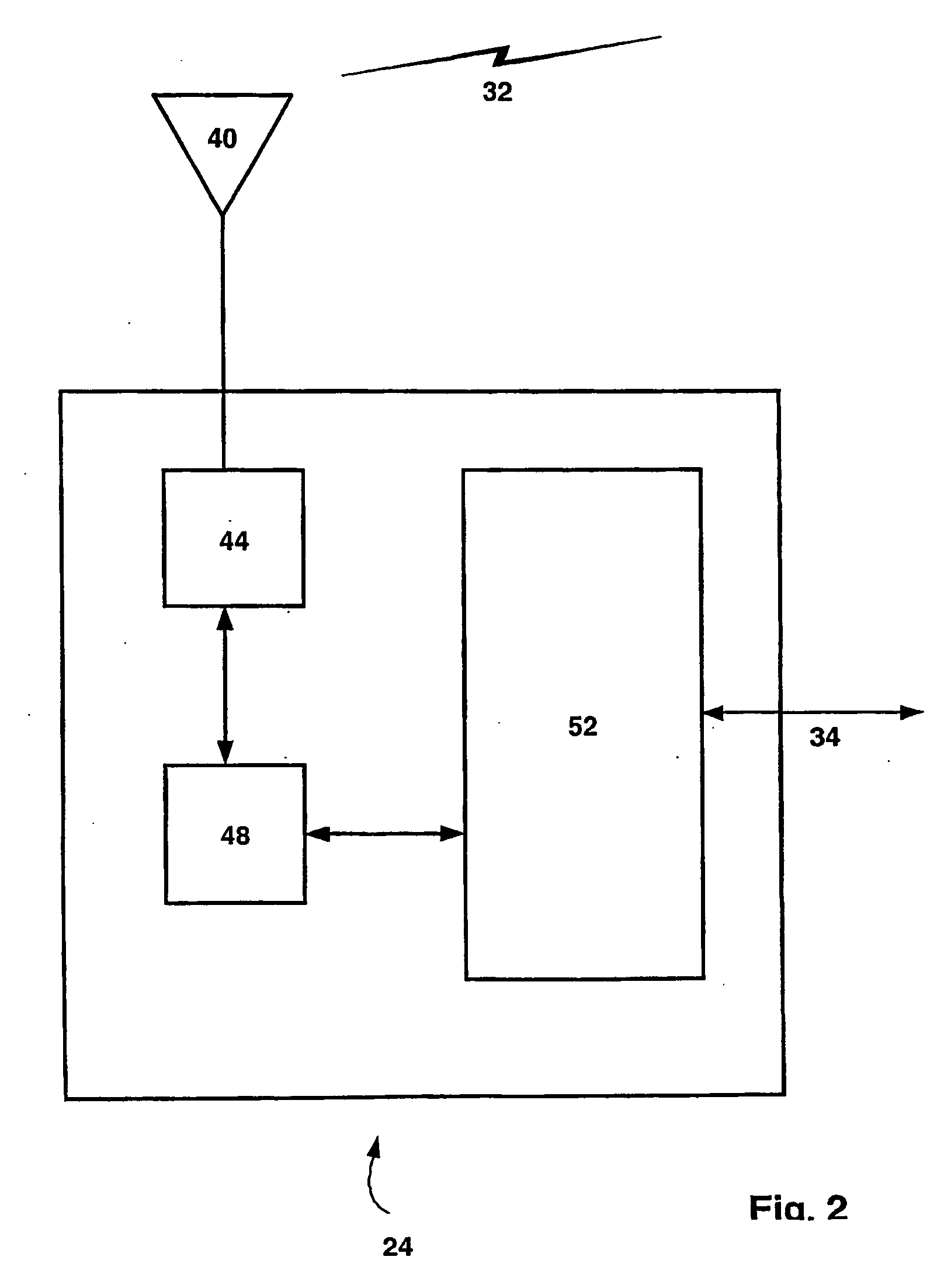

Software update method, apparatus and system

A system for remotely updating software on at least one electronic device connected to a network. The electronic devices have a non-volatile rewritable storage unit divided into at least two partitions, one of which will contain core firmware and the other of which will contain auxiliary software. When an update is received at the device, the updated core firmware is written to overwrite the partition in the rewritable storage unit that contained the auxiliary software. When this is completed and verified, the previous version of the core firmware stored in the storage unit is disabled from execution by the device. Next, the updated auxiliary software is written to overwrite the old version of the core firmware. When this write is complete, the device determines a suitable time for it to be rebooted to execute the updated software. In another embodiment, the present core firmware in the device is copied from the partition it is in to the other partition, overwriting the auxiliary software stored there. The new core firmware received to update the device is overwritten into the first partition, the old copied core firmware being present in case of an upgrade failure, and upon a successful update of the first partition, the auxiliary software is written to the second partition, overwriting the copied old core firmware. In this manner, the position of the core firmware and auxiliary software within the partitions is preserved during normal operation of the device.

Owner:WI LAN INC

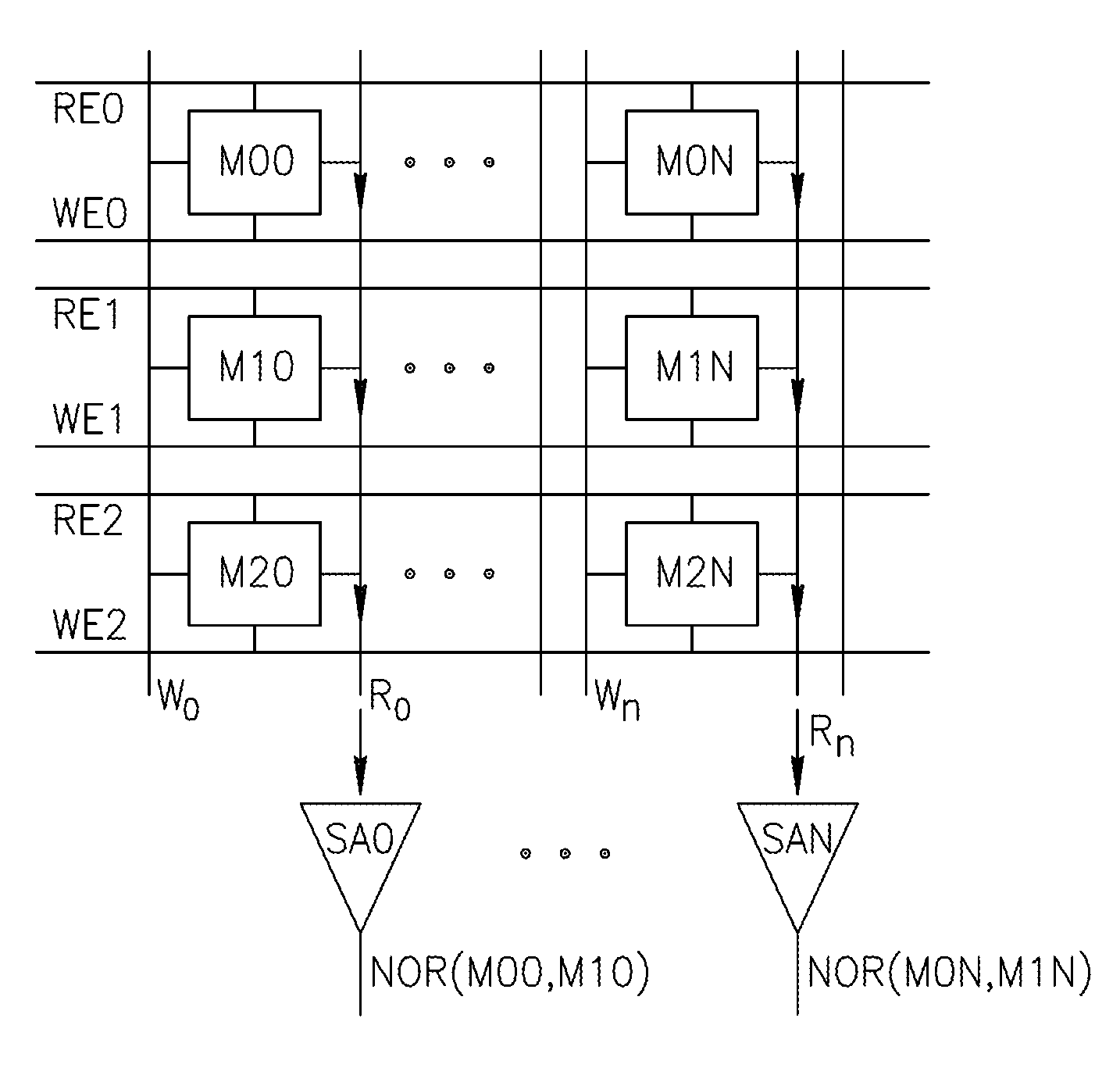

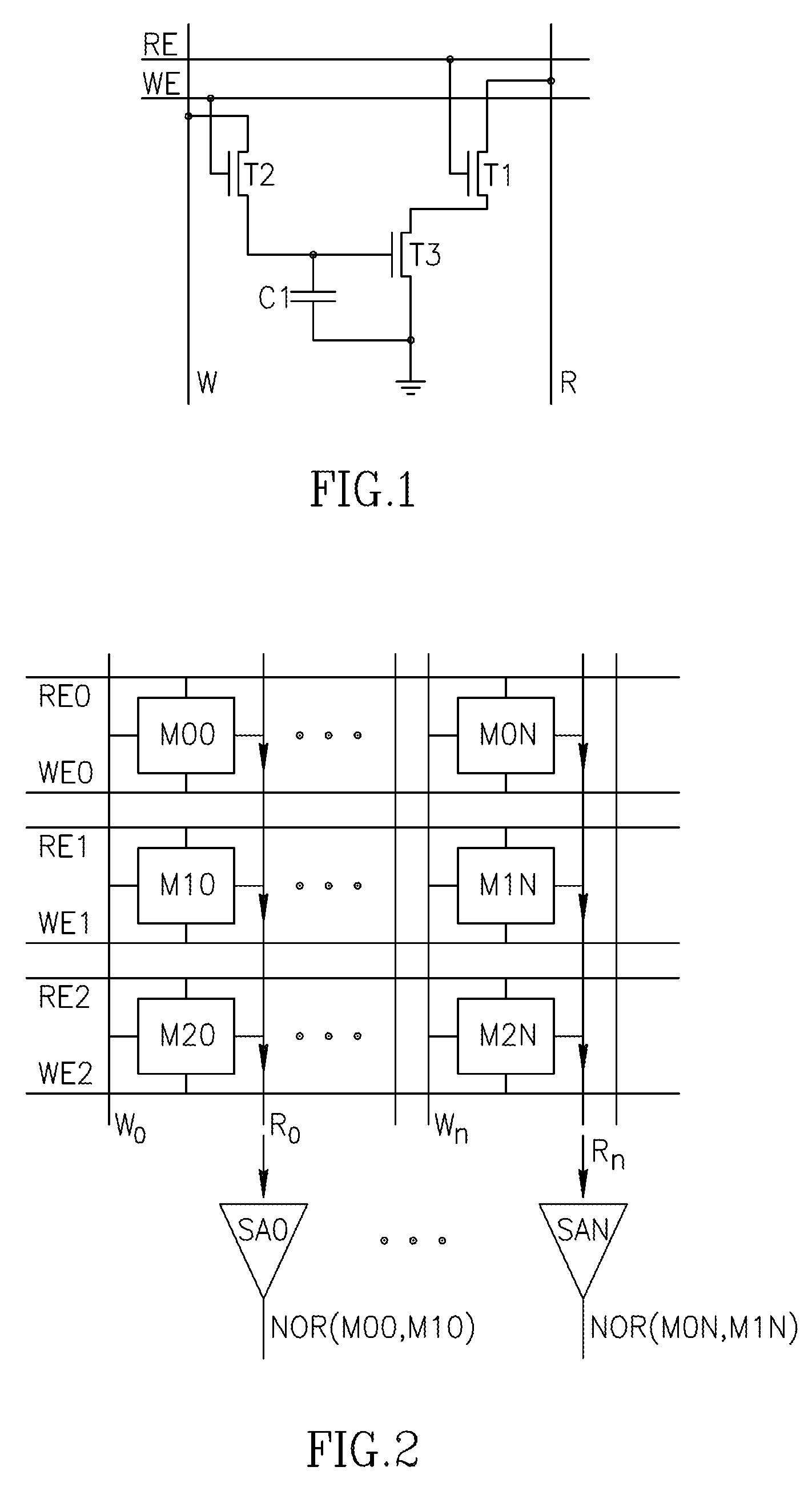

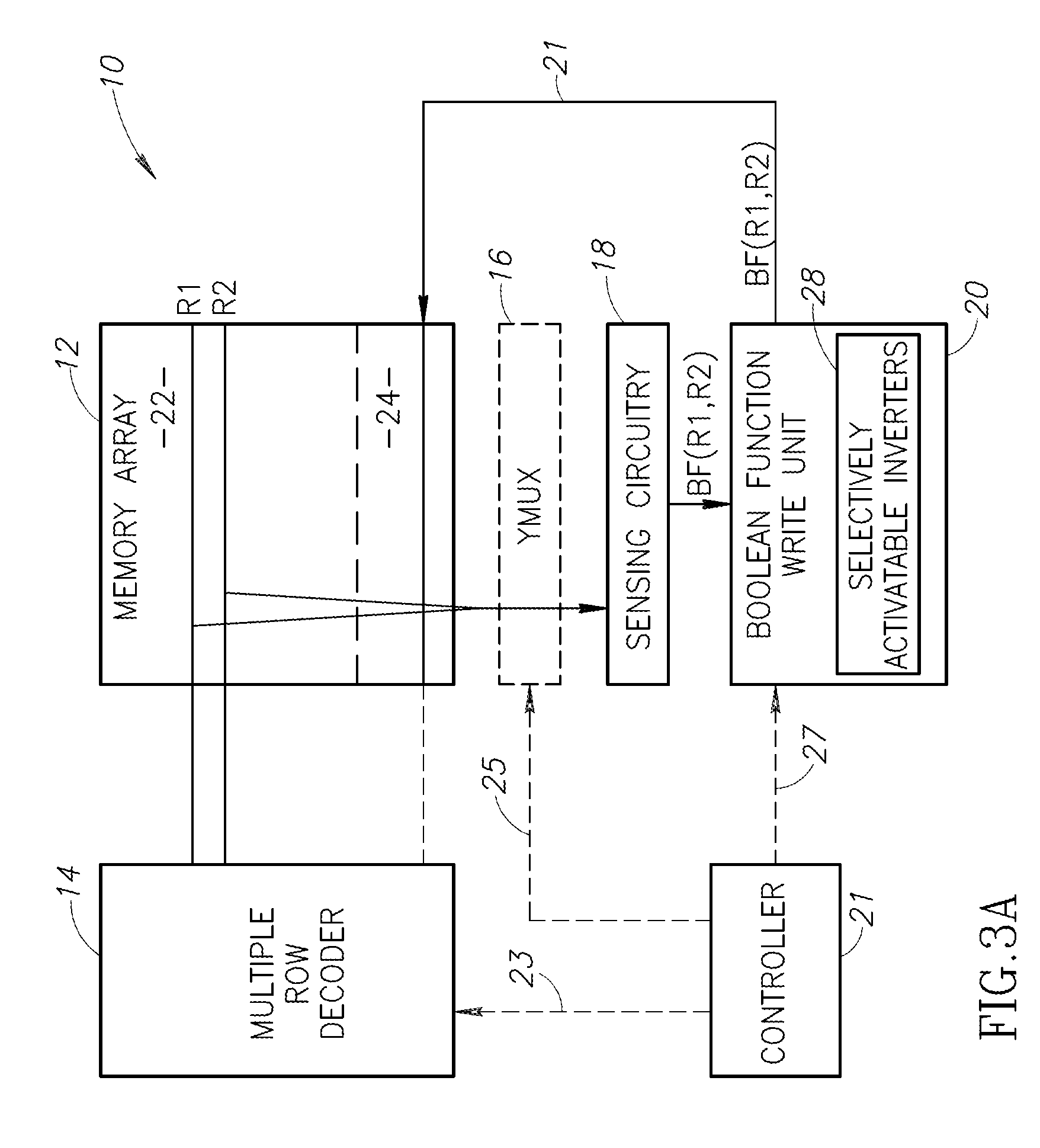

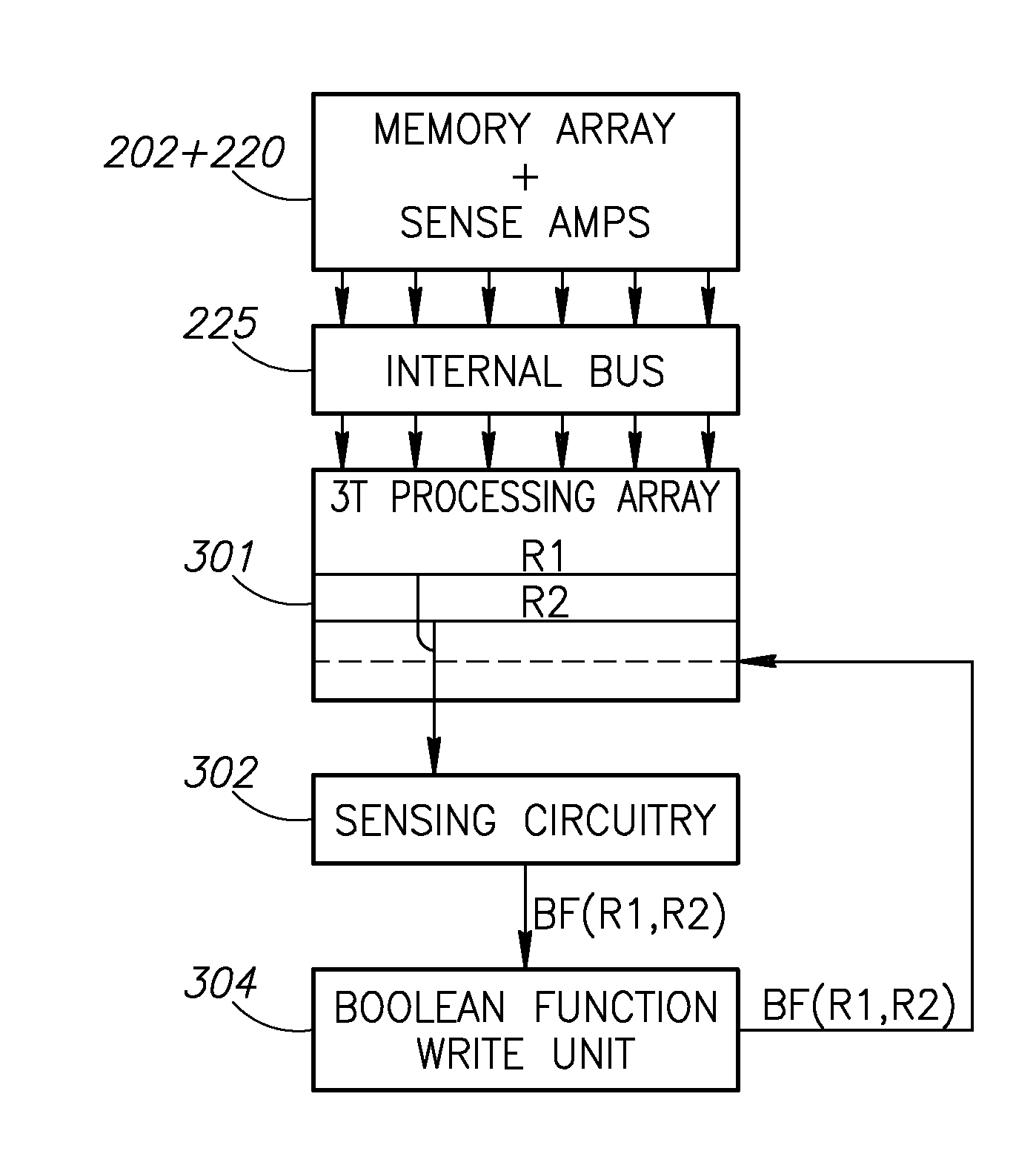

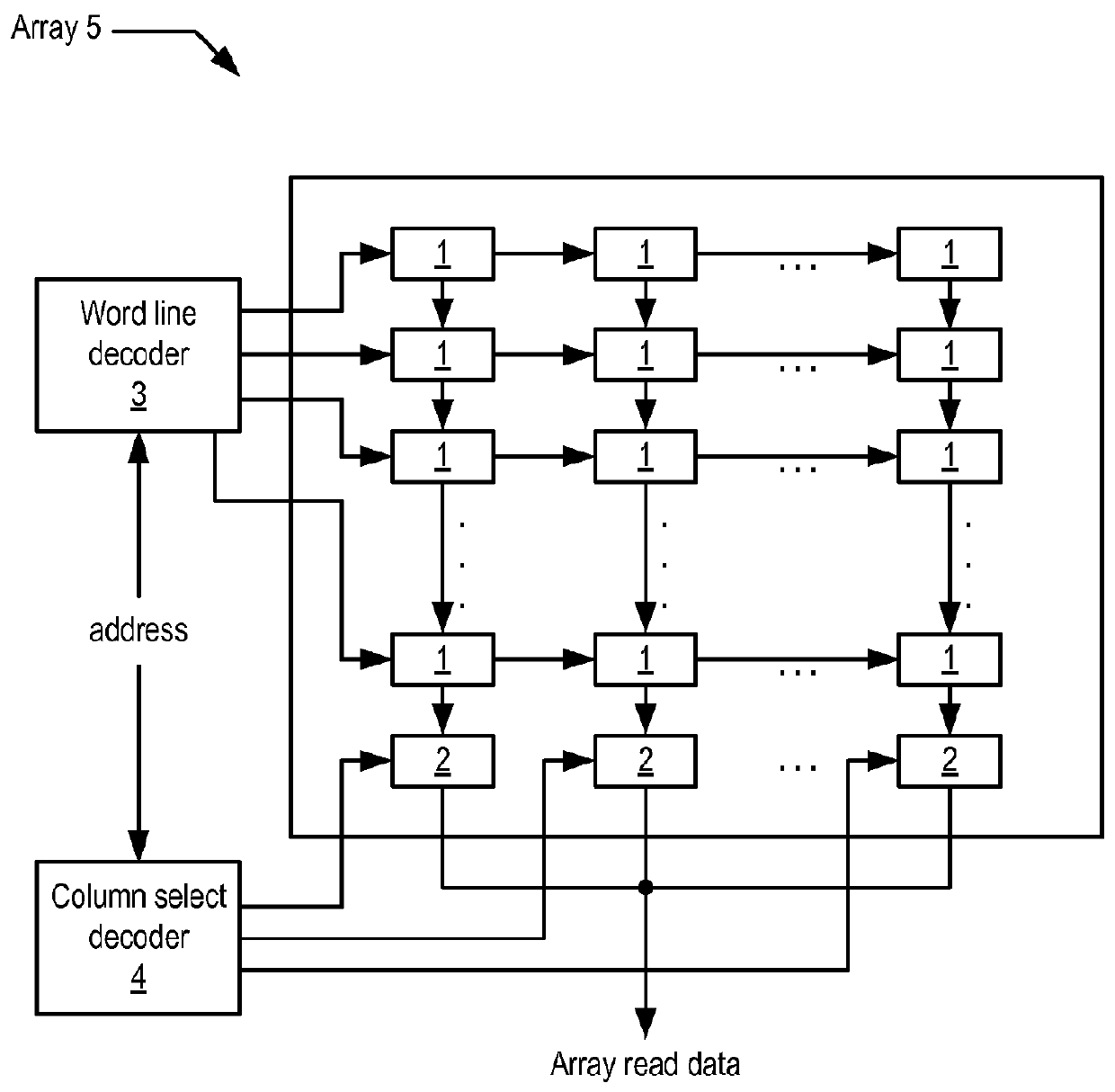

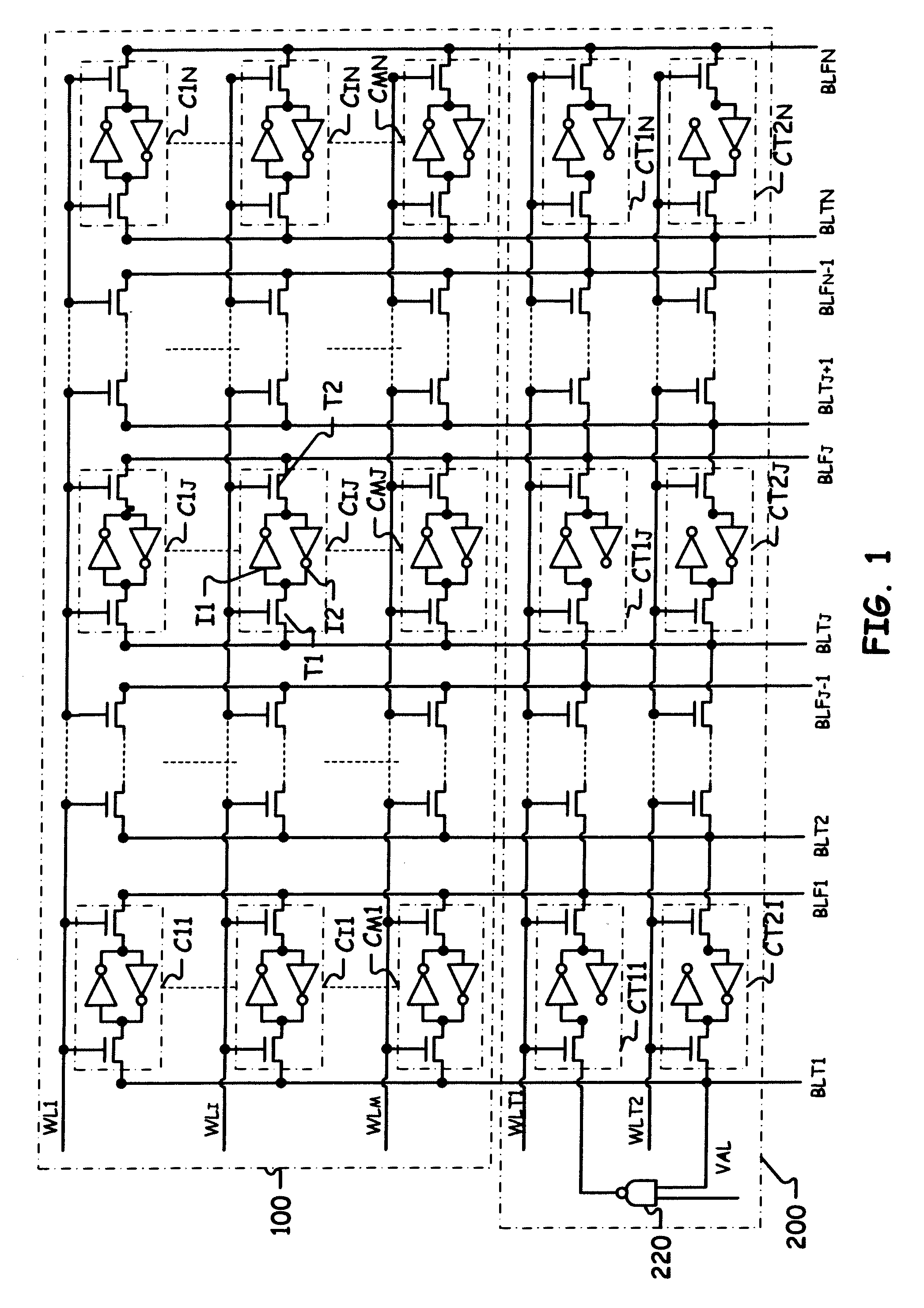

Using storage cells to perform computation

An in-memory processor includes a memory array which stores data and an activation unit to activate at least two cells in a column of the memory array at generally the same time thereby to generate a Boolean function output of the data of the at least two cells. Another embodiment shows a content addressable memory (CAM) unit without any in-cell comparator circuitry.

Owner:GSI TECH

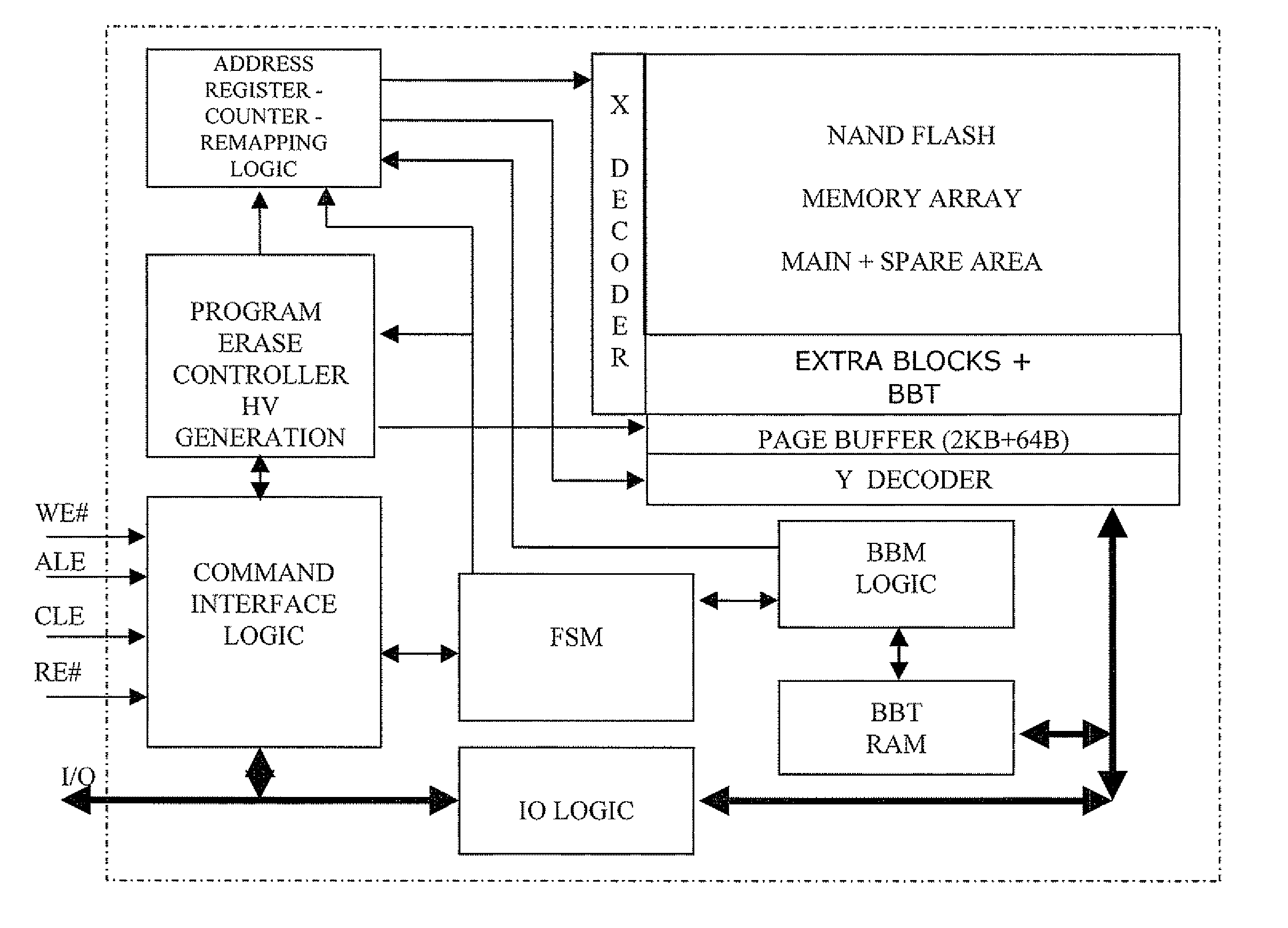

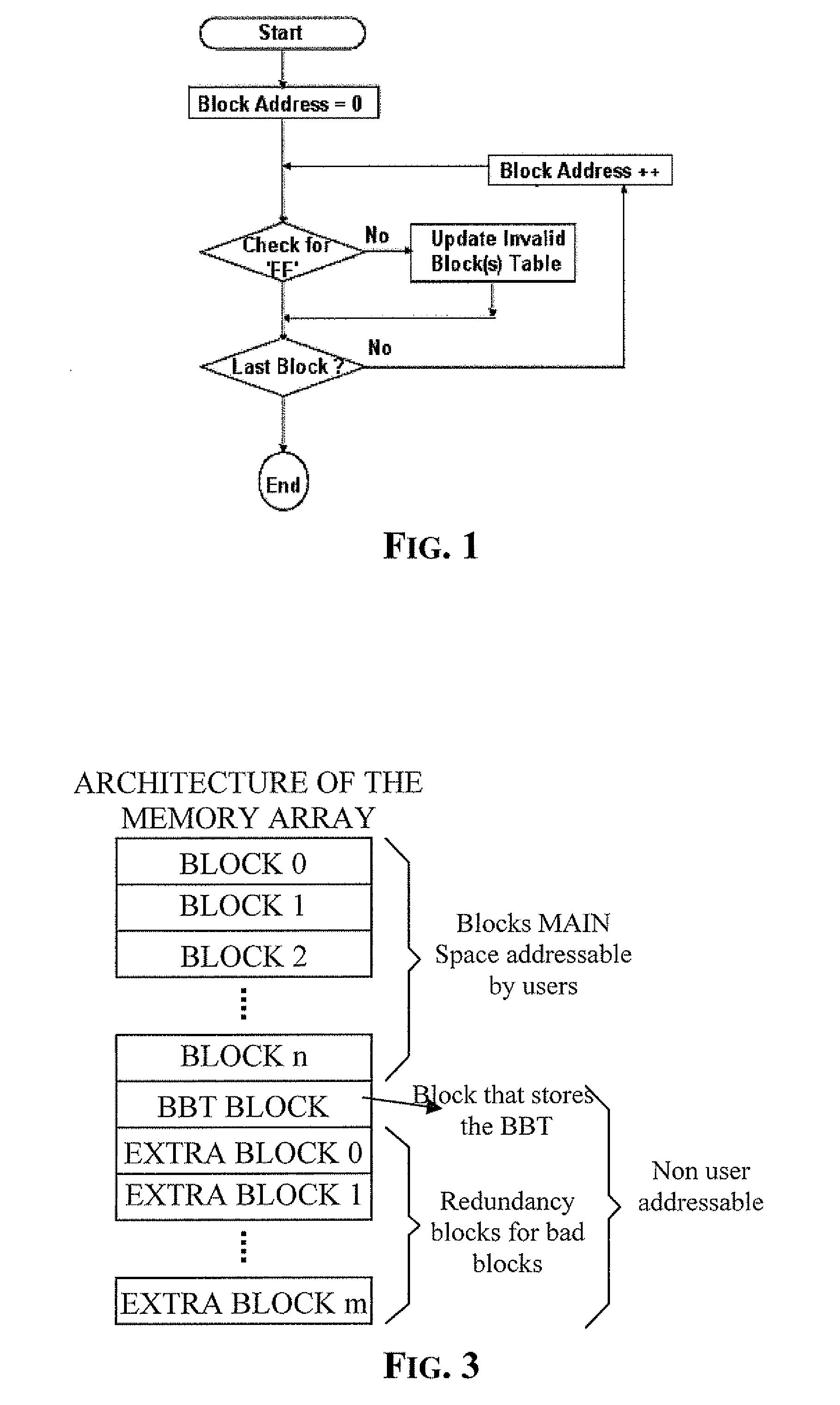

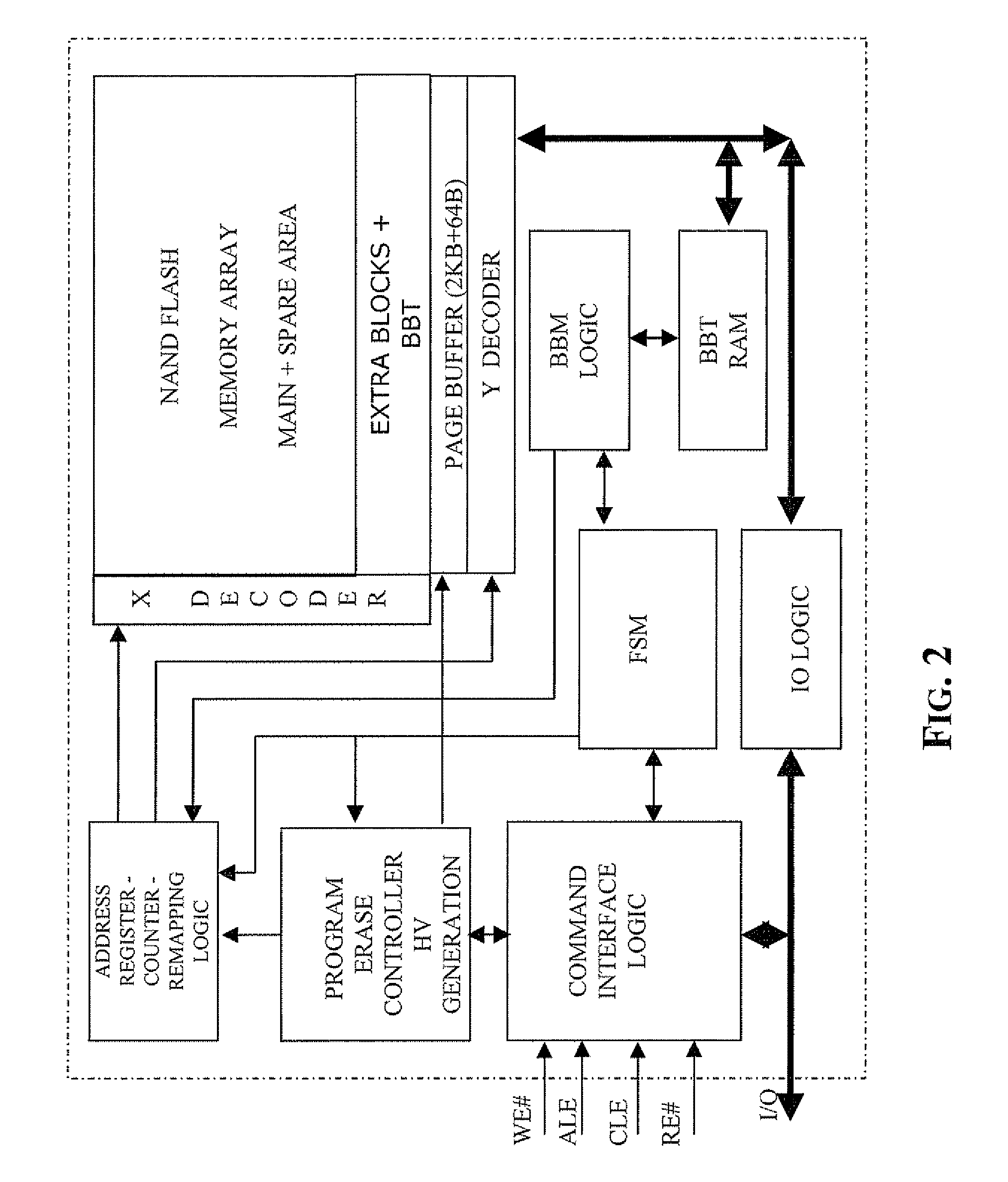

Method of managing fails in a non-volatile memory device and relative memory device

ActiveUS20070109856A1Easy to implementLow costRead-only memoriesDigital storageElectricityWorking life

A method of managing fails in a non-volatile memory device including an array of cells grouped in blocks of data storage cells includes defining in the array a first subset of user addressable blocks of cells, and a second subset of redundancy blocks of cells. Each block including at least one failed cell in the first subset is located during a test on wafer of the non-volatile memory device. Each block is marked as bad, and a bad block address table of respective codes is stored in a non-volatile memory buffer. At power-on, the bad block address table is copied from the non-volatile memory buffer to the random access memory. A block of memory cells of the first subset is verified as bad by looking up the bad block address table, and if a block is bad, then remapping access to a corresponding block of redundancy cells. A third subset of non-user addressable blocks of cells is defined in the array for storing the bad block address table of respective codes in an addressable page of cells of a block of the third subset. Each page of the third subset is associated to a corresponding redundancy block. If during the working life of the memory device a block of cells previously judged good in a test phase becomes failed, each block is marked as bad and the stored table in the random access memory is updated.

Owner:MICRON TECH INC

Method and apparatus for storage unit replacement in non-redundant array

InactiveUS6598174B1Lower performance requirementsMaintaining accessMemory loss protectionReliability/availability analysisRAIDData storing

A method and apparatus used in a storage network facilitates the protection of data in, and replacement of, storage devices about to fail before the failure happens. In a network that includes a set of storage devices organized as a non-redundant (for example RAID 0) array, a storage device about to fail in the non-redundant array can be replaced by another storage device, typically from a pool of spares. The method includes detecting a condition of a first particular storage device in the non-redundant array. Conditions which are detected according to various embodiments indicate that the first particular storage device is suffering events indicating that it is likely to fail, or otherwise suffering from reduced performance. The conditions are detected for example, by the receipt of a signal from the storage device itself, or by the monitoring of statistics concerning the performance of the storage device. The method further provides for selecting a particular spare storage device, which can be used in place of the first particular storage device. In response to detecting the condition, data stored in the first particular storage device is migrated to the second particular storage device, and the second particular storage takes the place of the first particular storage device in the non-redundant array. The first particular storage device can then be gracefully removed from the network without loss of service to the clients computers.

Owner:DELL PROD LP

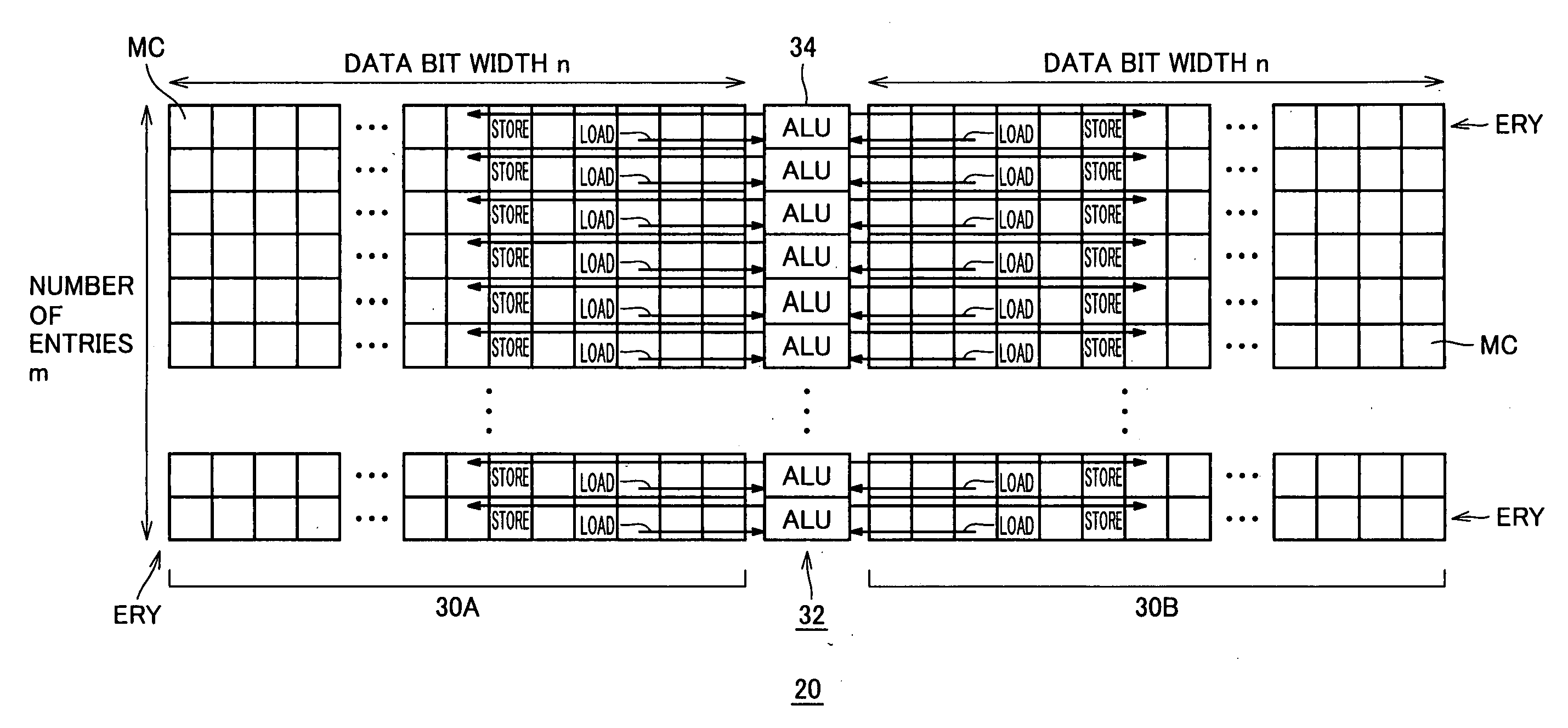

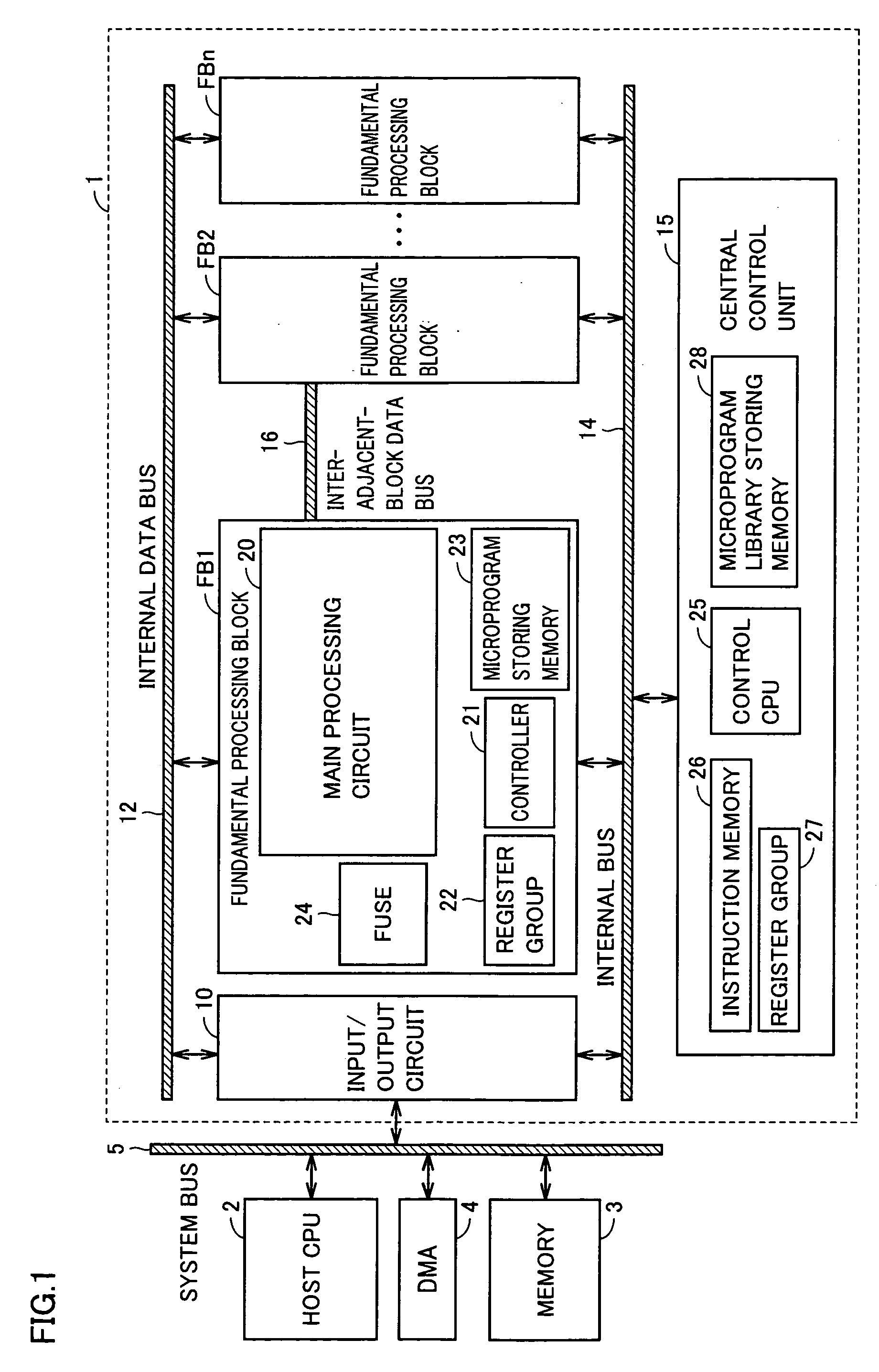

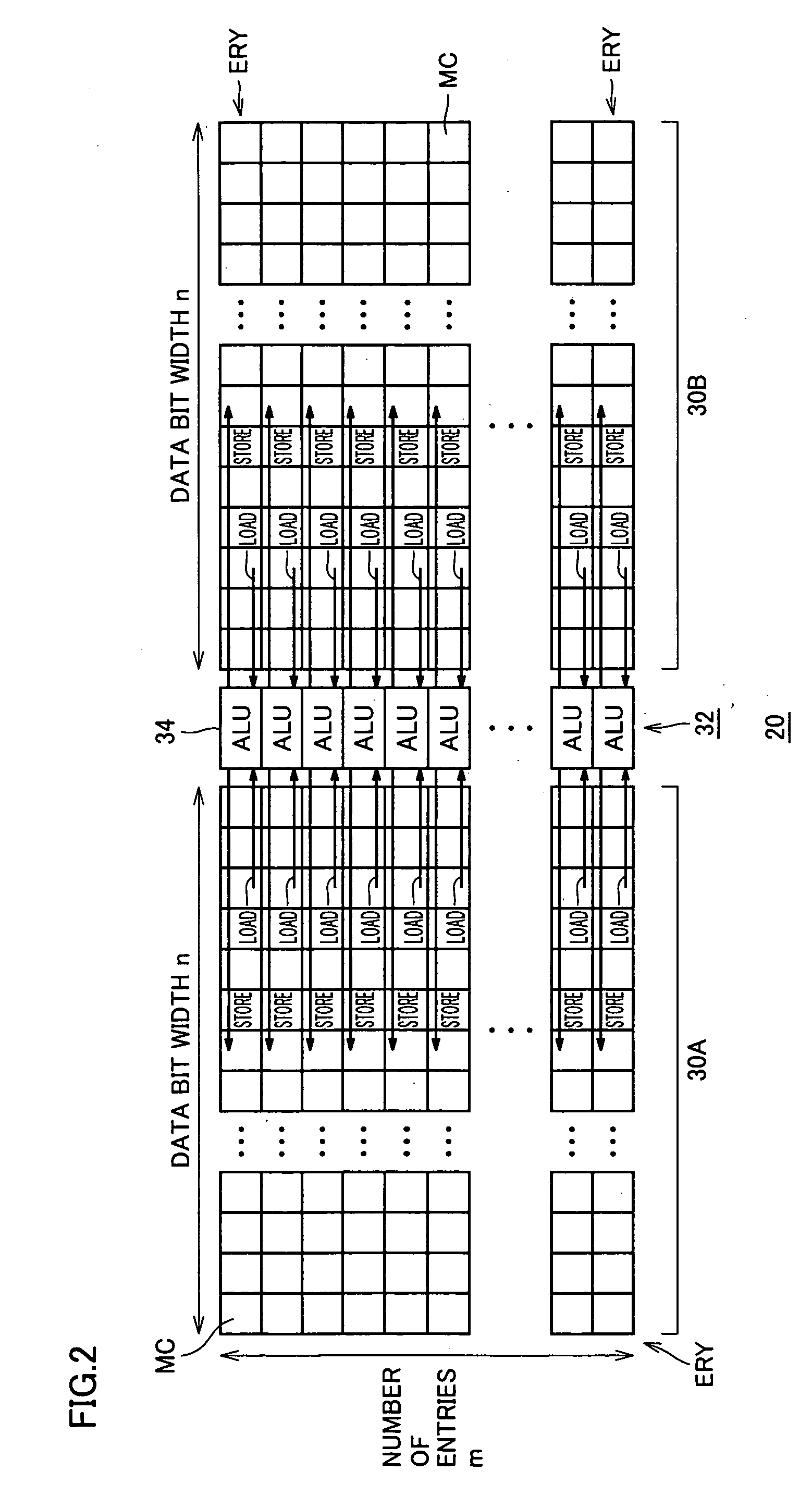

Parallel operational processing device

InactiveUS20070180006A1Easy to operateReduce power consumptionEnergy efficient ICTDigital data processing detailsAudio power amplifierParallel computing

In a parallel operational processing device having an operational processing unit arranged between memory blocks each having a plurality of memory cells arranged in rows and columns, the respective columns of each memory block are alternately connected to the operational processing units on the opposite sides of the memory block. By selecting one word line in one memory block, data can be transferred to two operational processing units. The number of the word lines selected per one operational processing unit is reduced, and power consumption is reduced. The bit operation units and sense amplifiers / write drivers of the operational processing units have arrangement pitch conditions mitigated and are reduced in number, and an isolation region between the memory blocks is not required and the layout area is reduced. Thus, the parallel operational processing device with a layout area and the power consumption reduced, can achieve a fast operation.

Owner:RENESAS ELECTRONICS CORP

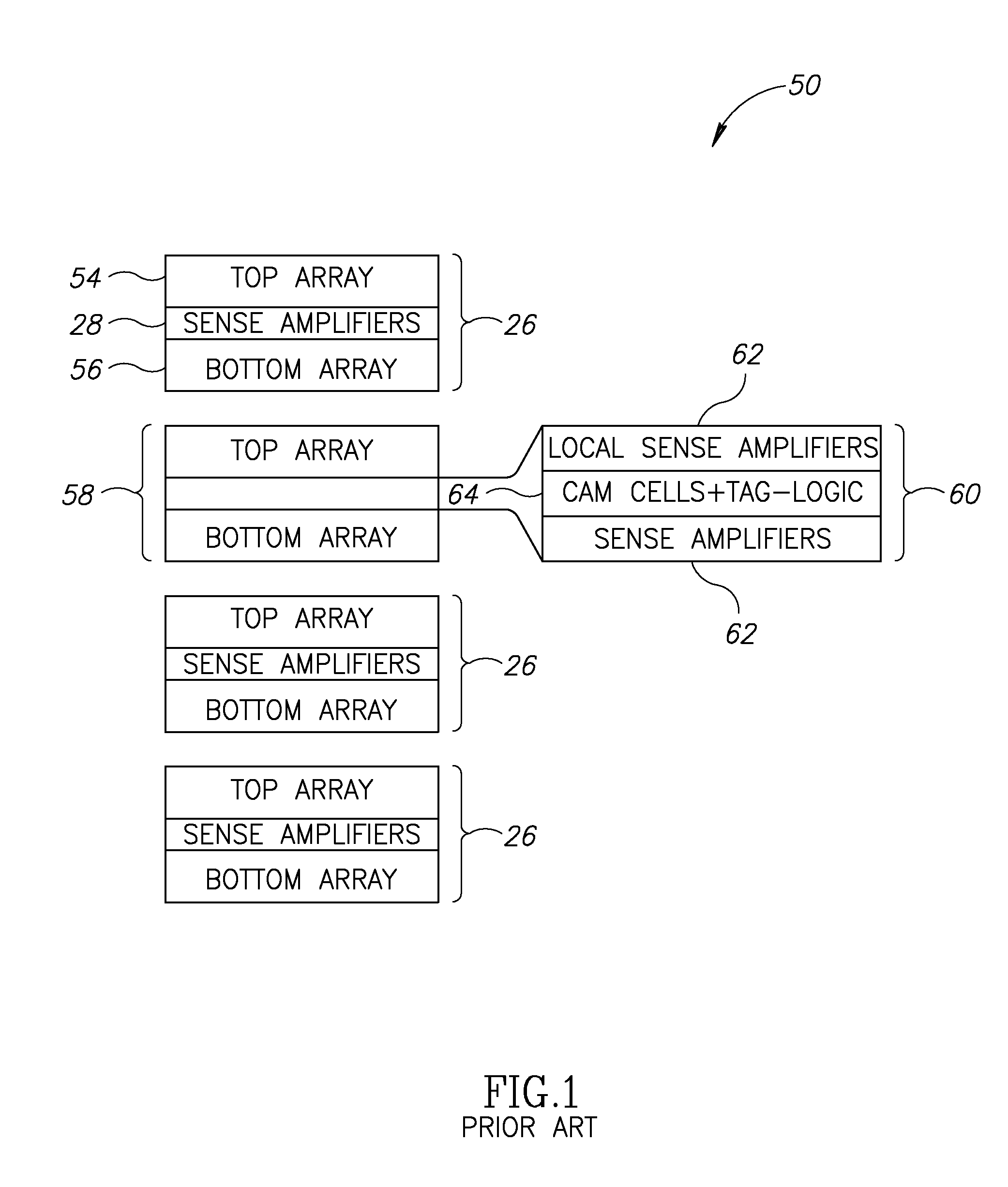

Neighborhood operations for parallel processing

InactiveUS20120246380A1Memory adressing/allocation/relocationDigital storageProcessing elementParallel processing

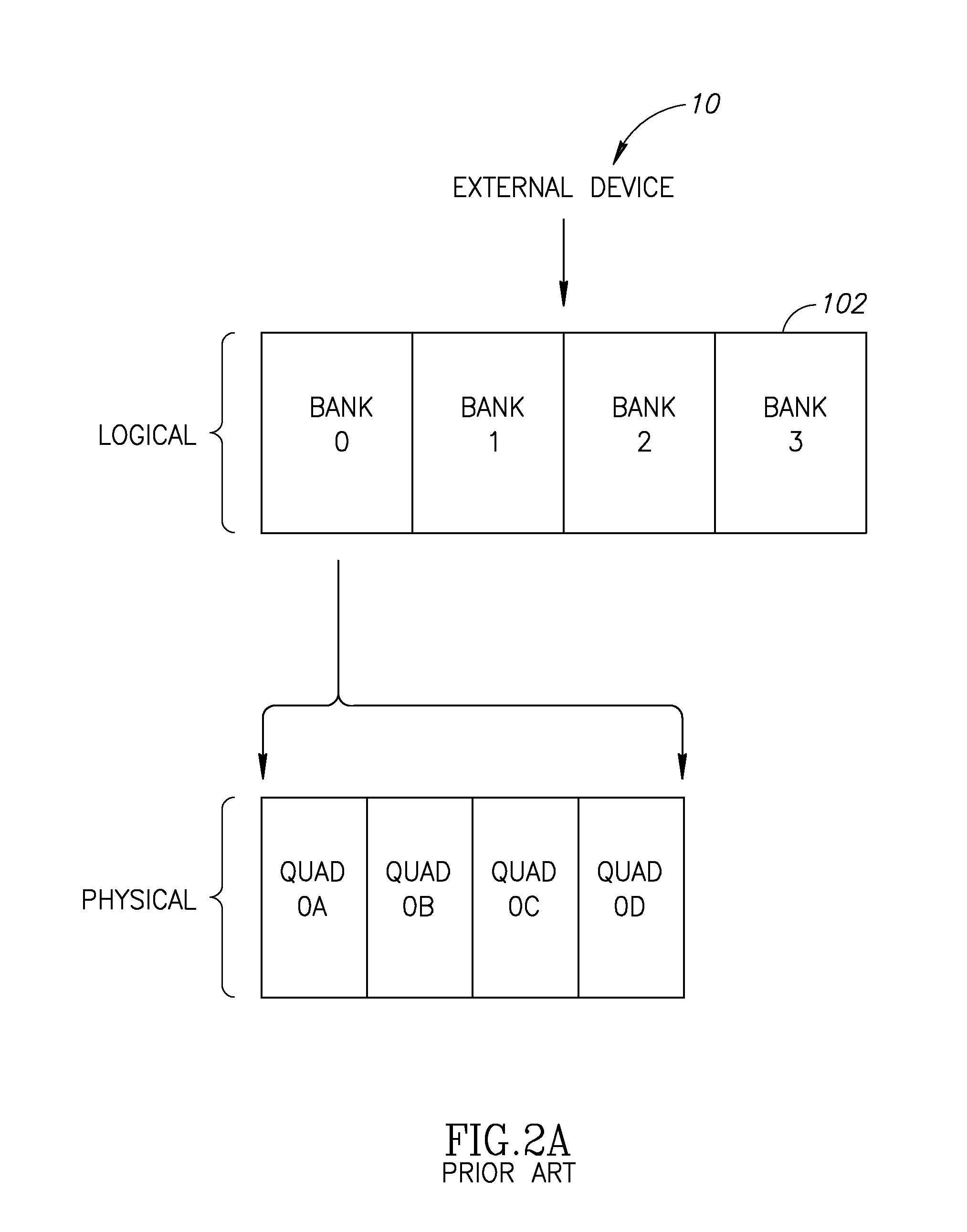

A memory device includes a plurality of storage units in which to store data of a bank, wherein the data has a logical order prior to storage and a physical order different than the logical order within the plurality of storage units and a within-device reordering unit to reorder the data of a bank into the logical order prior to performing on-chip processing. In another embodiment, the memory device includes an external device interface connectable to an external device communicating with the memory device, an internal processing element to process data stored on the device and multiple banks of storage. Each bank includes a plurality of storage units and each storage unit has two ports, an external port connectable to the external device interface and an internal port connected to the internal processing element.

Owner:GSI TECH

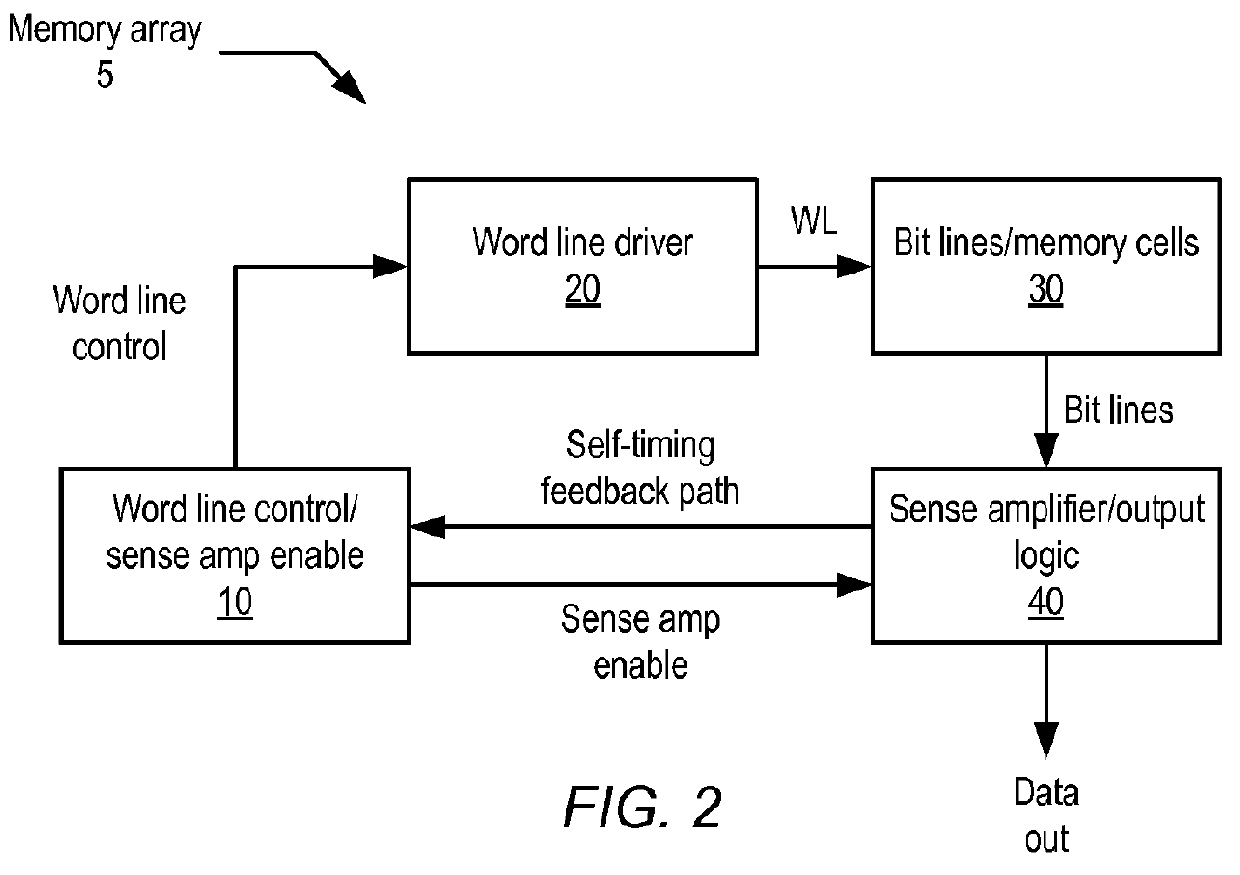

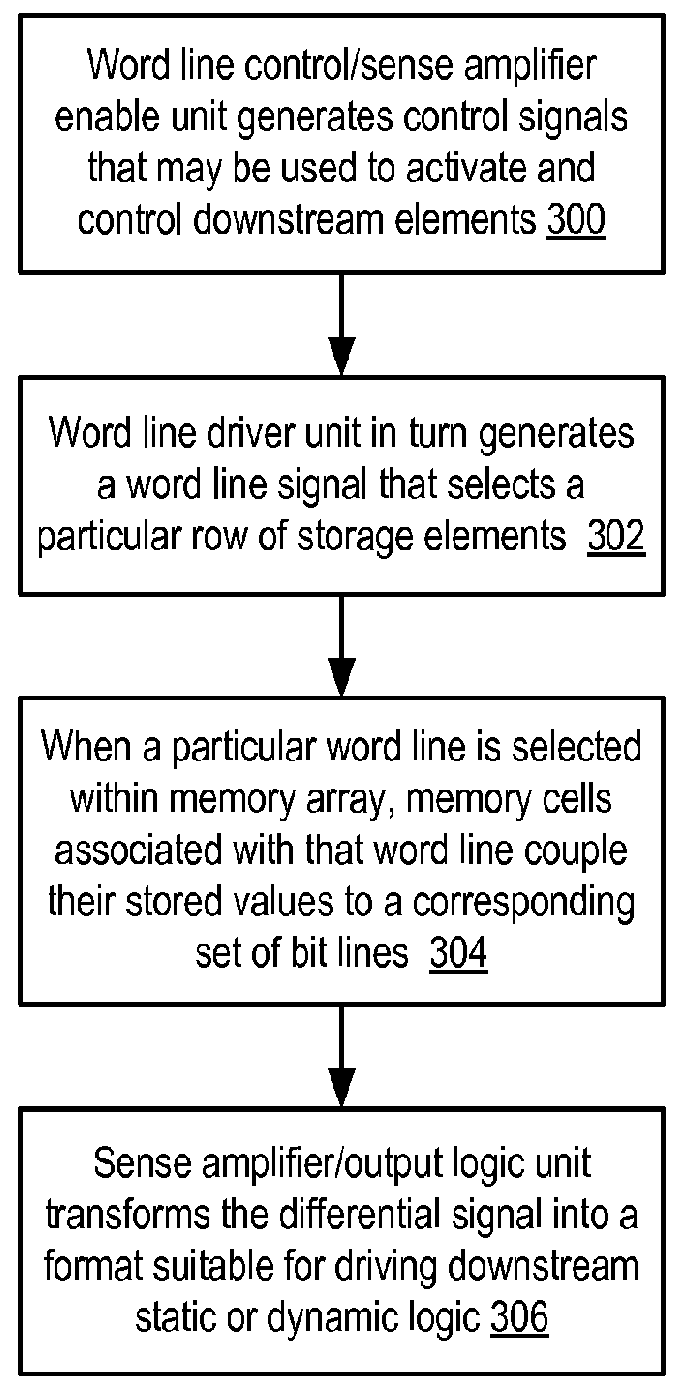

Sense amplifier and sense amplifier latch having common control

A sense amplifier of a memory array may be provided to amplify data presented from storage cells of the memory array. Additionally, a sense amplifier latch may be provided to store data received from the sense amplifier. The sense amplifier may be enabled for operation by a sense amplifier enable signal that is distinct from a clock signal. Moreover, the latch enable signal of the sense amplifier latch may be controlled by the sense amplifier enable signal, such that the sense amplifier latch opens in response to activation of the sense amplifier and closes in response to deactivation of the sense amplifier.

Owner:APPLE INC

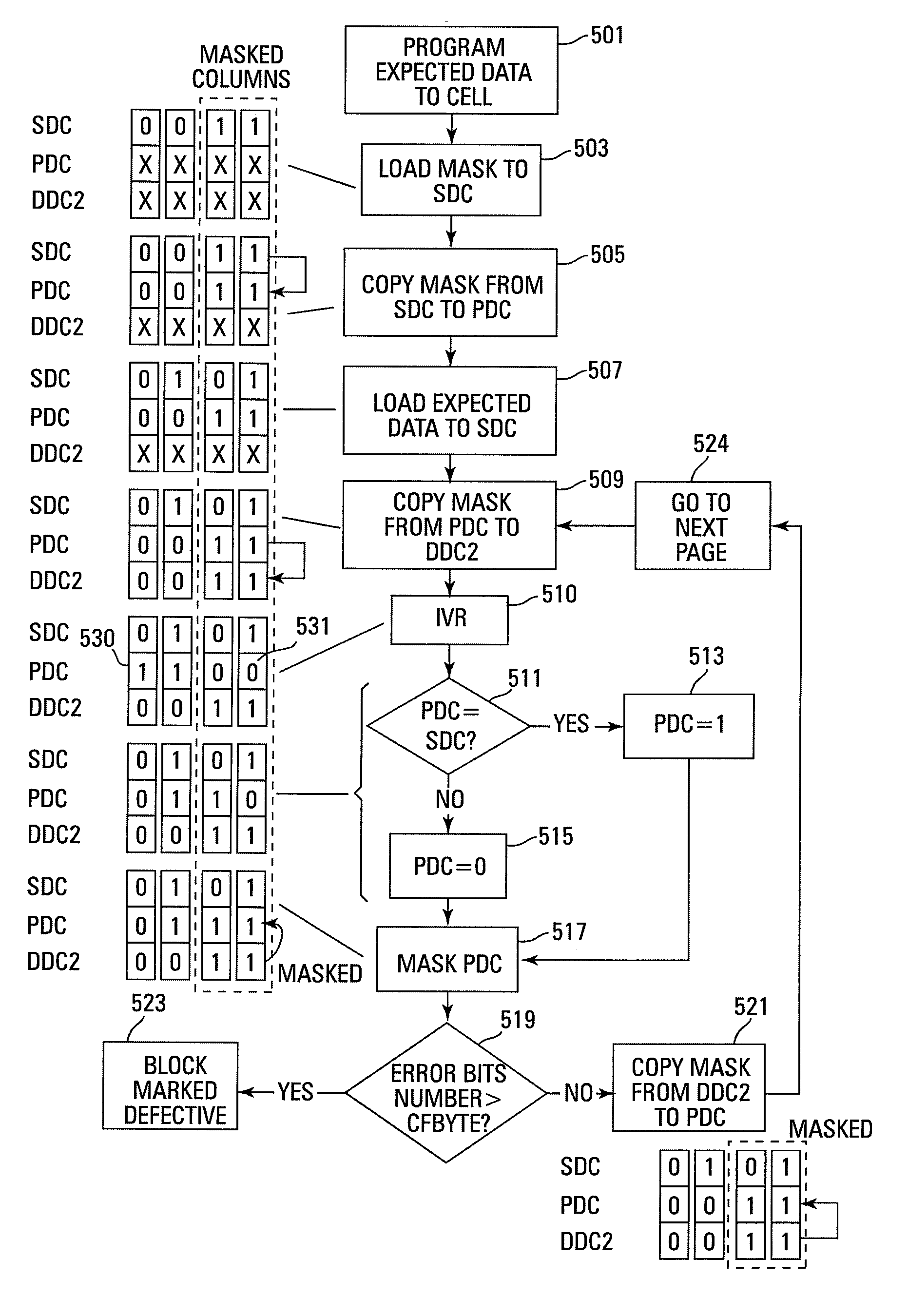

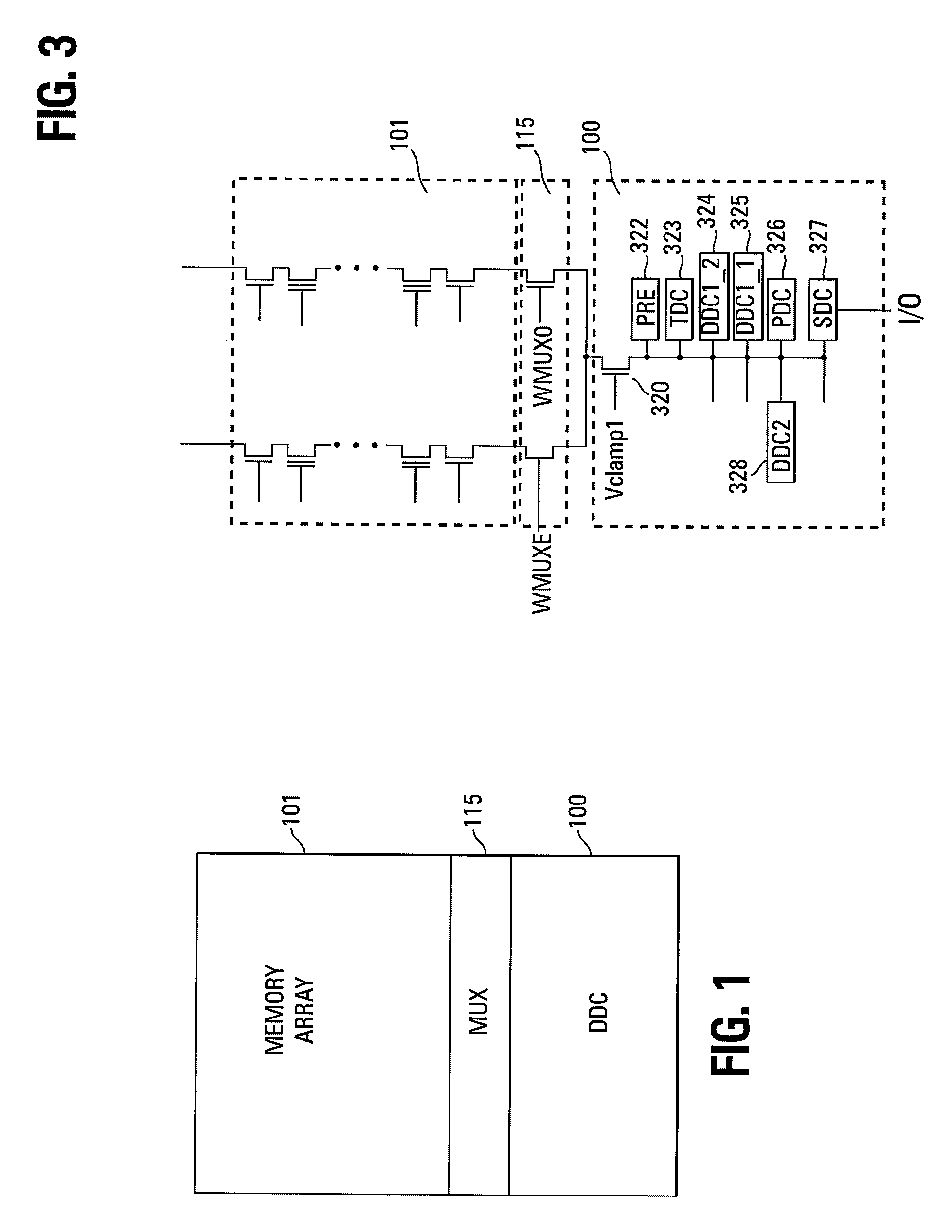

Small unit internal verify read in a memory device

Methods for small unit internal verify read operation and a memory device are disclosed. In one such method, expected data is programmed into a grouping of columns of memory cells (e.g., memory block). Mask data is loaded into a third dynamic data cache of three dynamic data caches. The expected data is loaded into a second data cache. After a read operation of programmed columns of memory cells, the read data is compared to the expected data and error bit indicators are stored in the second data cache in the error bit locations. The second data cache is masked with the mask data so that only those error bits that are unmasked are counted. If the number of unmasked error bit indicators is greater than a threshold, the memory block is marked as unusable.

Owner:MICRON TECH INC

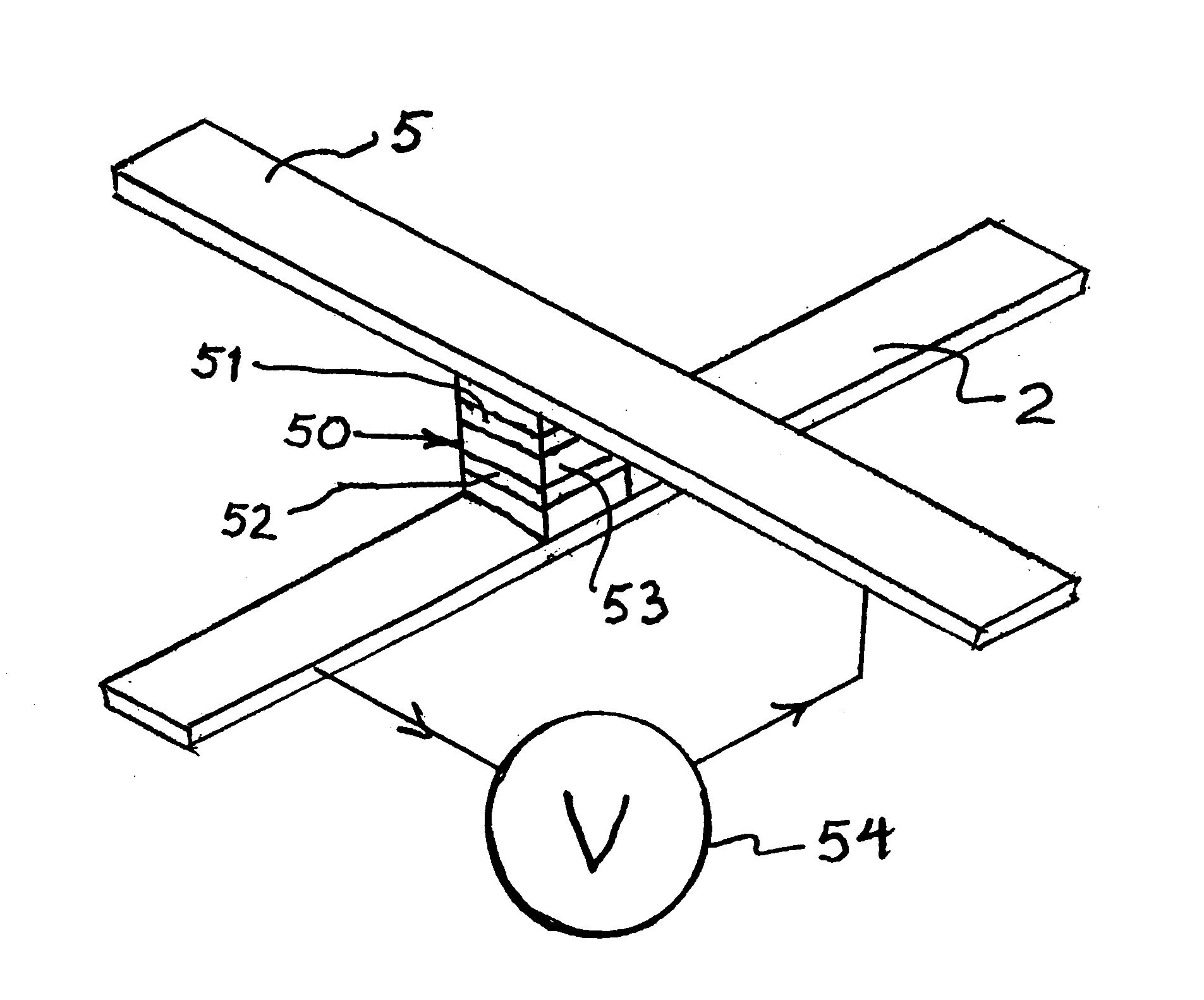

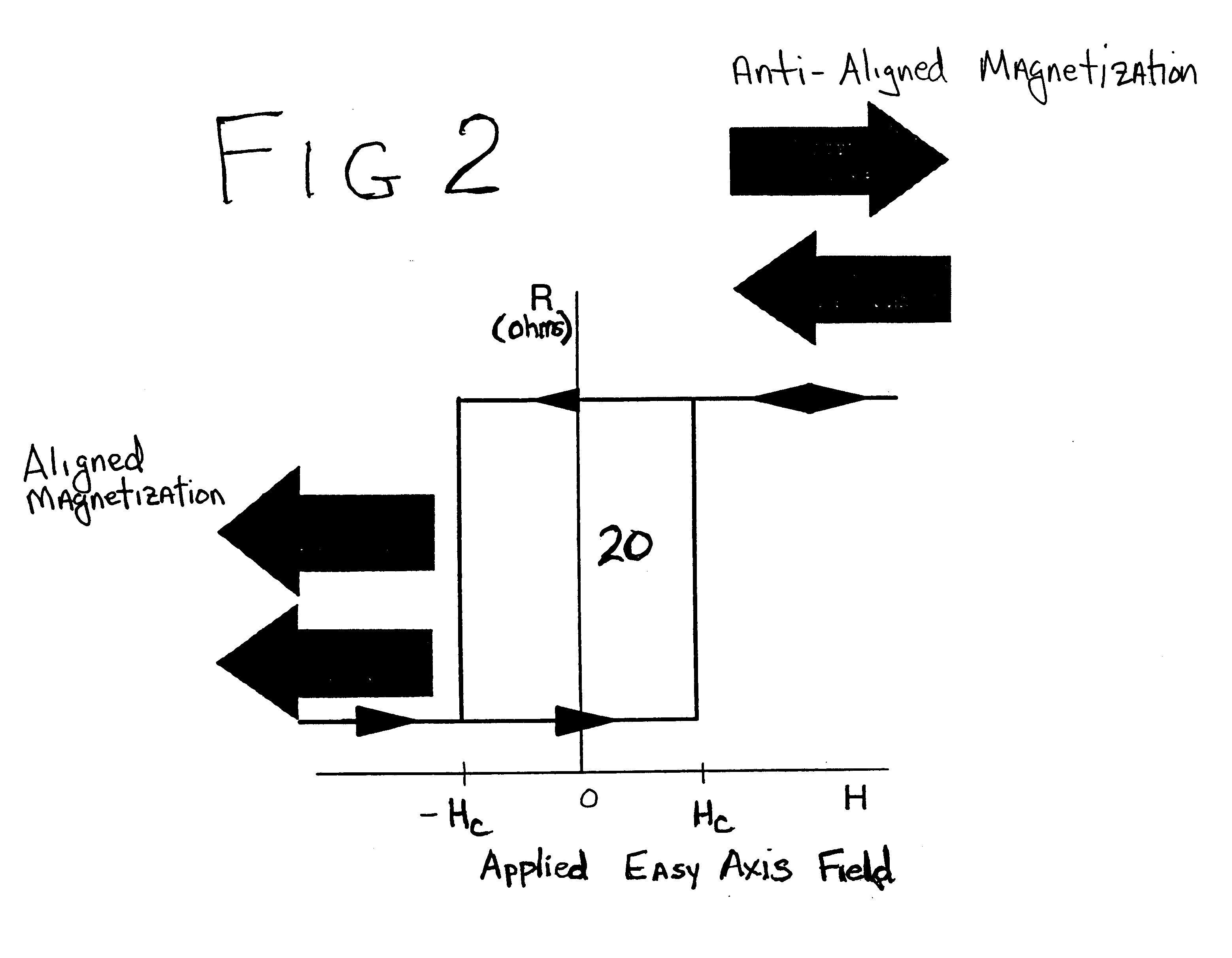

Thermally-assisted magnetic random access memory (MRAM)

It is important to ensure good selectivity of a single magnetic tunnel junction storage cell within a memory array without affecting nearby storage cells. For this purpose, this memory array of storage cells preferably comprises a) an array of electrically conducting bit lines and electrically conducting word lines which form intersections therebetween, b) a storage cell disposed at each of said intersections, each storage cell comprising at least one reversible magnetic region or layer characterized by a magnetization state which can be reversed by applying thereto a selected external magnetic field, said reversible magnetic layer comprising a material whose magnetization state is more easily reversed upon a change in the temperature thereof, and c) a temperature change generator for changing the temperature of said reversible magnetic layer of only a selected one of said array of storage cells at any moment. To select a cell, it is preferable to select a cell by using a brief pulse of tunnelling current between the intersecting bit and word lines at that cell in order to provide sufficient Joule heating to facilitate a change in the magnetization state of its reversible magnetic layer, which preferably comprises a ferrimagnetic material.

Owner:IBM CORP

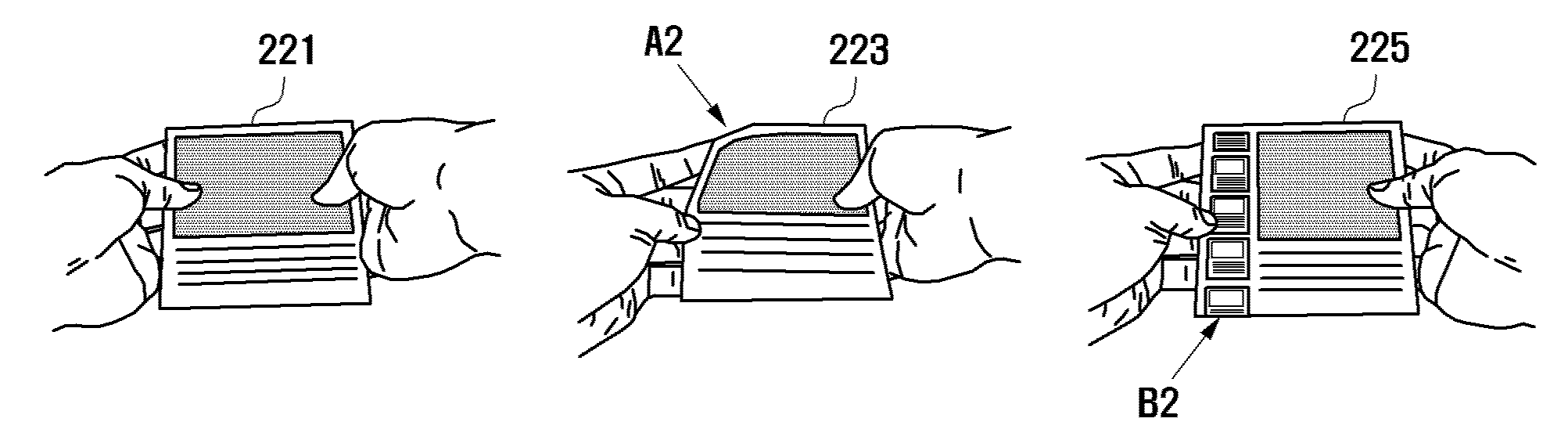

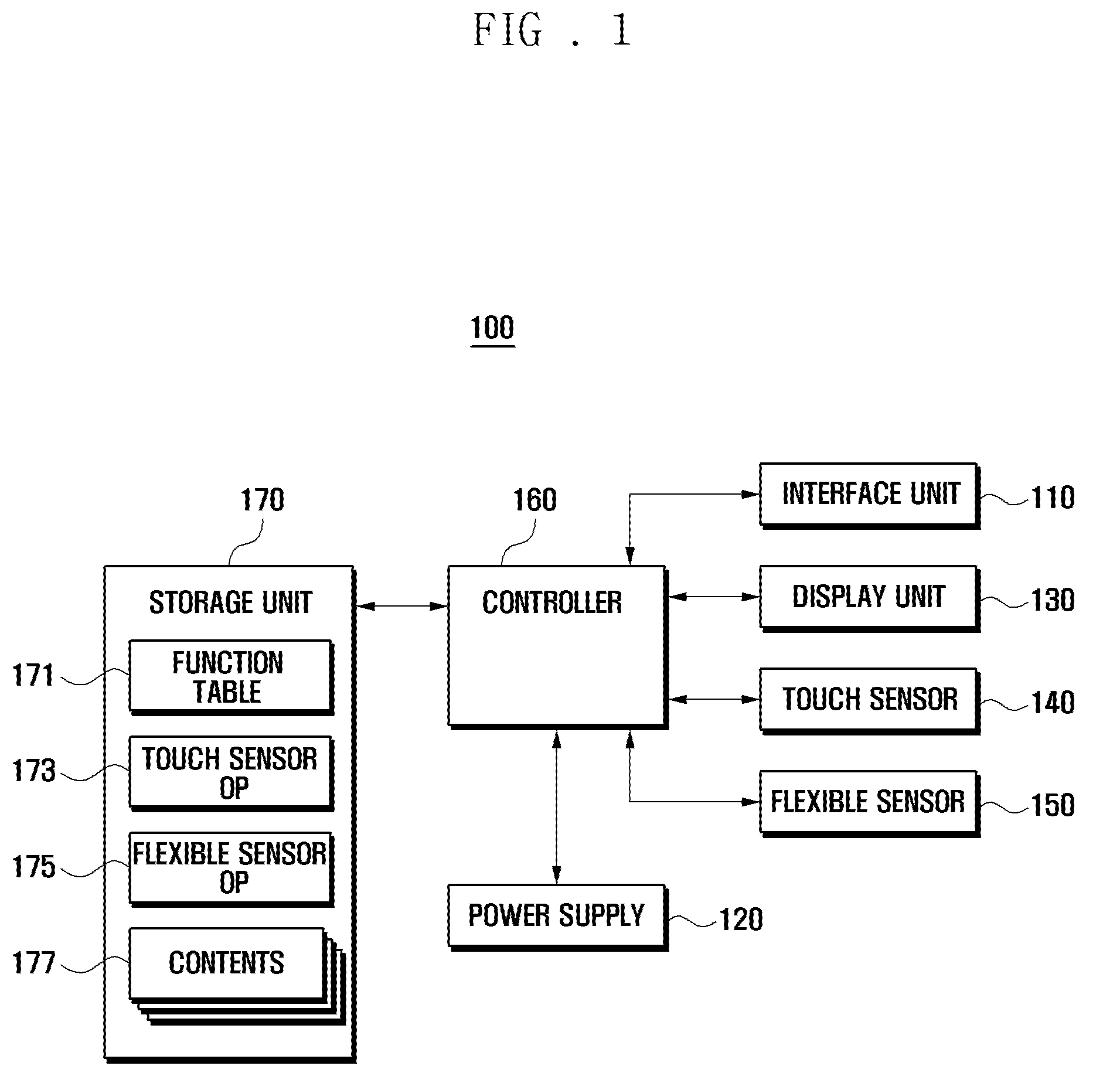

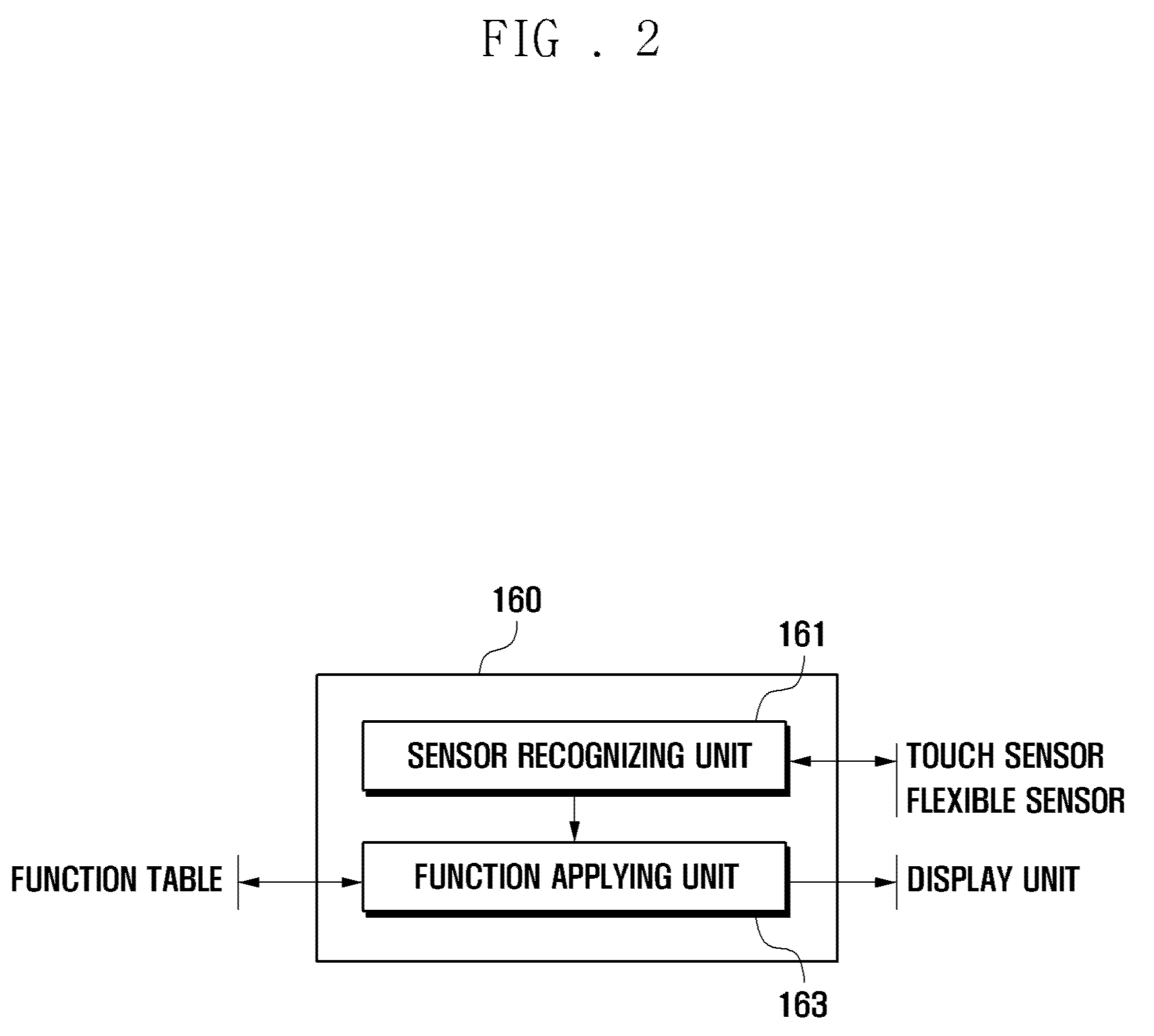

Flexible display device and data displaying method thereof

ActiveUS20100141605A1Digital data processing detailsSubstation equipmentData displayHuman–computer interaction

A flexible display device and a data displaying method thereof are disclosed. The device includes a touch sensor to generate touch events according to touch actions, a flexible sensor to generate a bend signal as one side of the device is bent, a storage unit to store a function table, and a controller to control the components of the device. The function table is configured to define control operations to reproduce currently output contents based on the touch events and the bend events.

Owner:SAMSUNG ELECTRONICS CO LTD

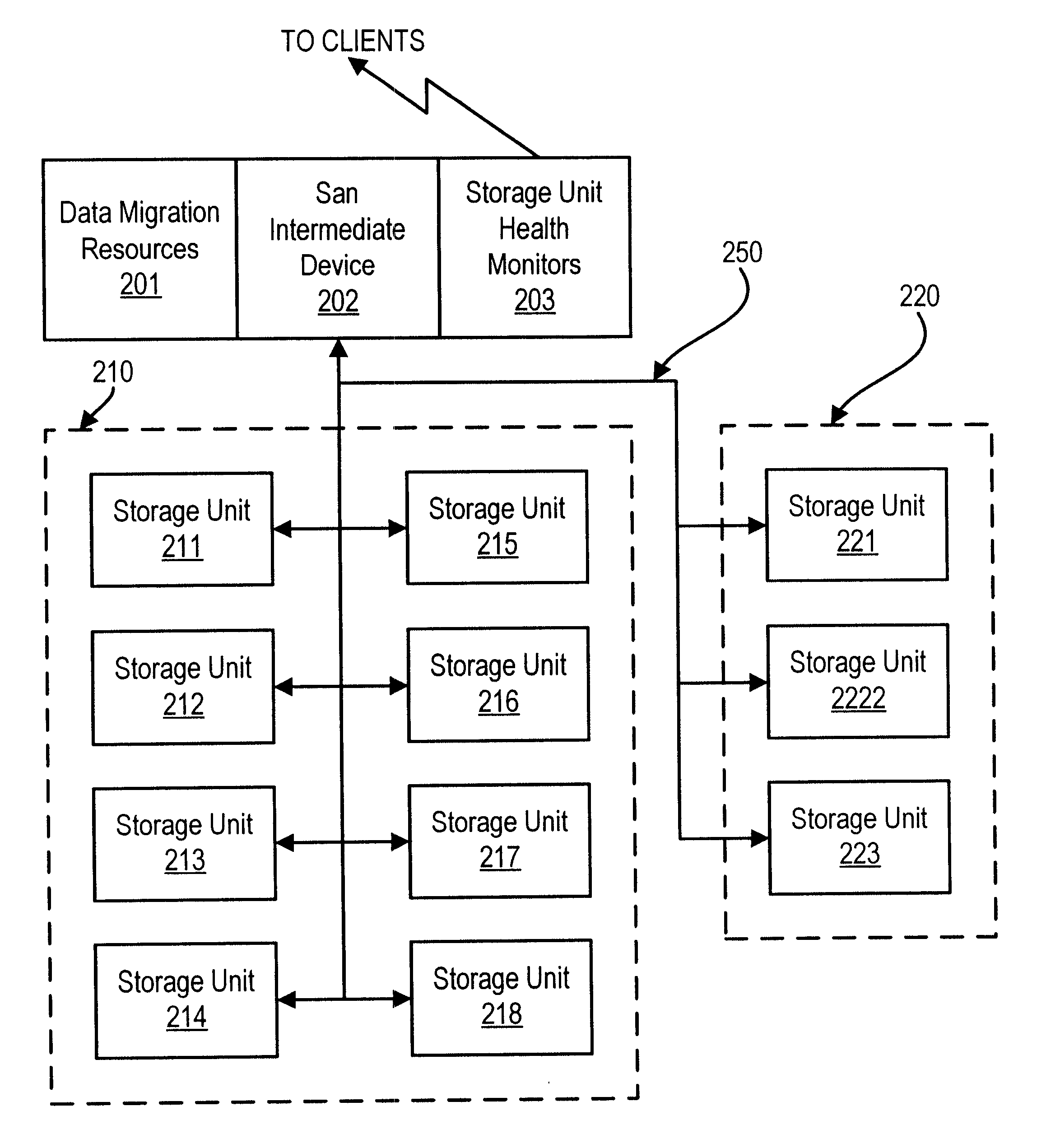

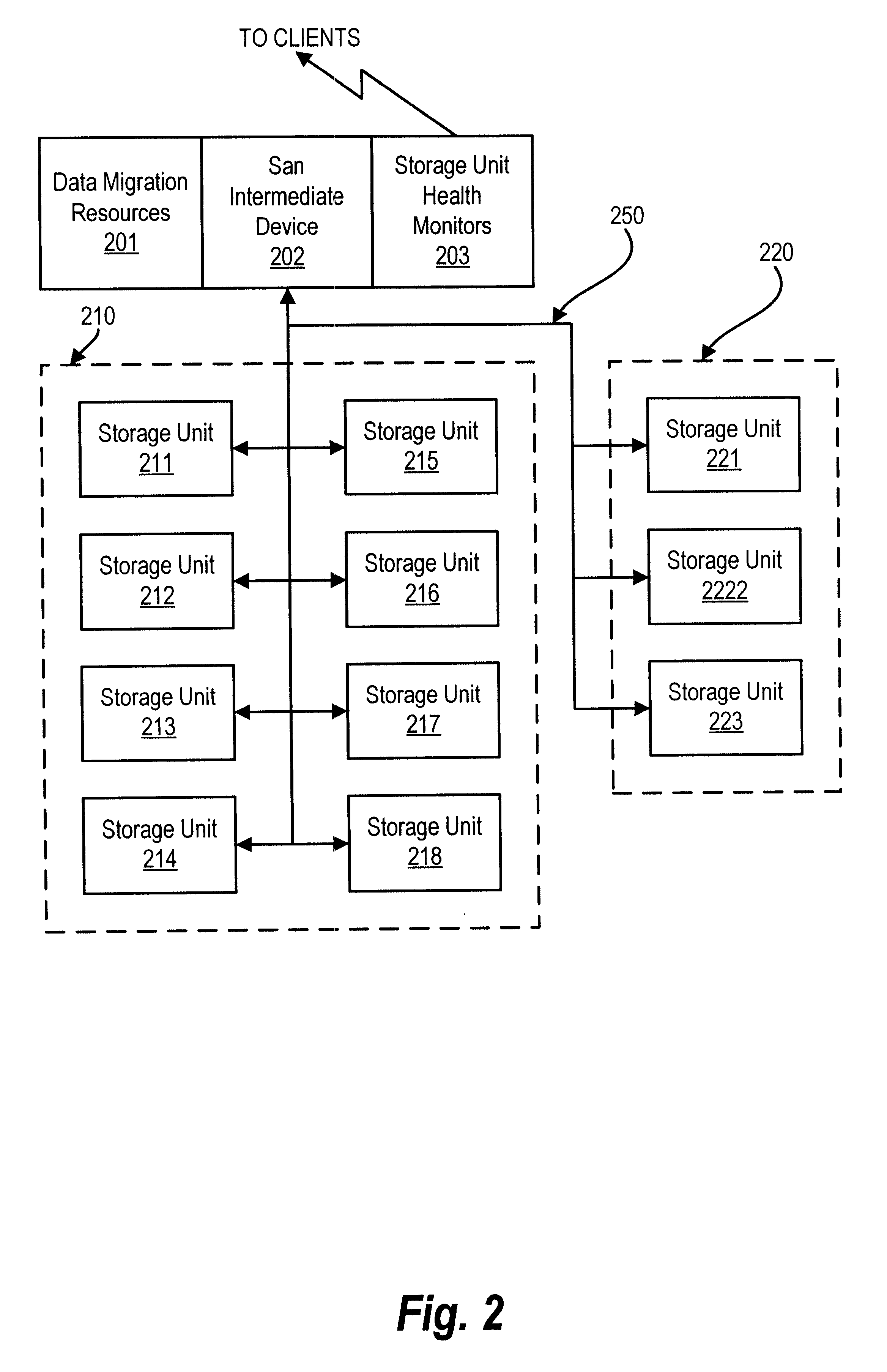

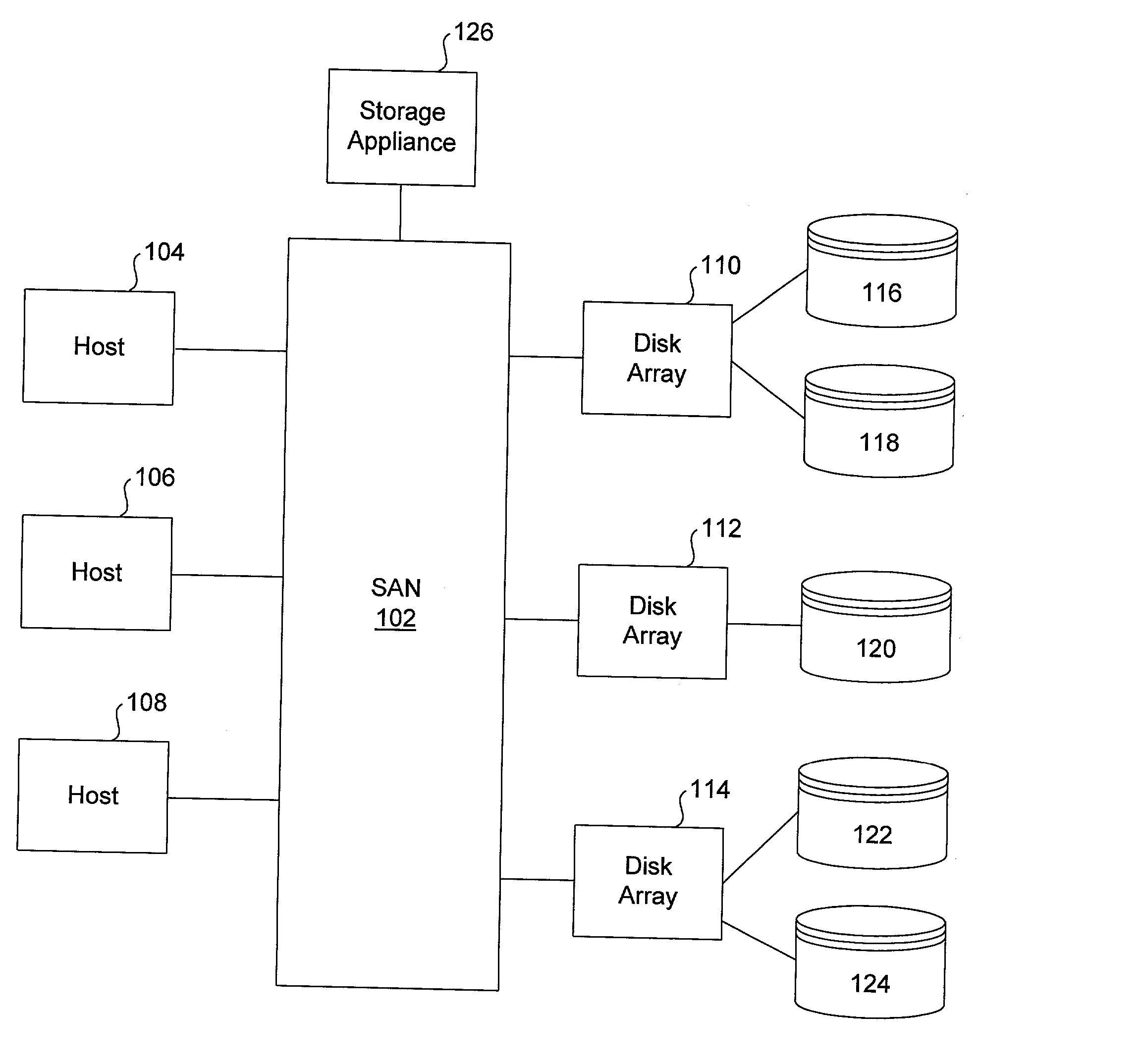

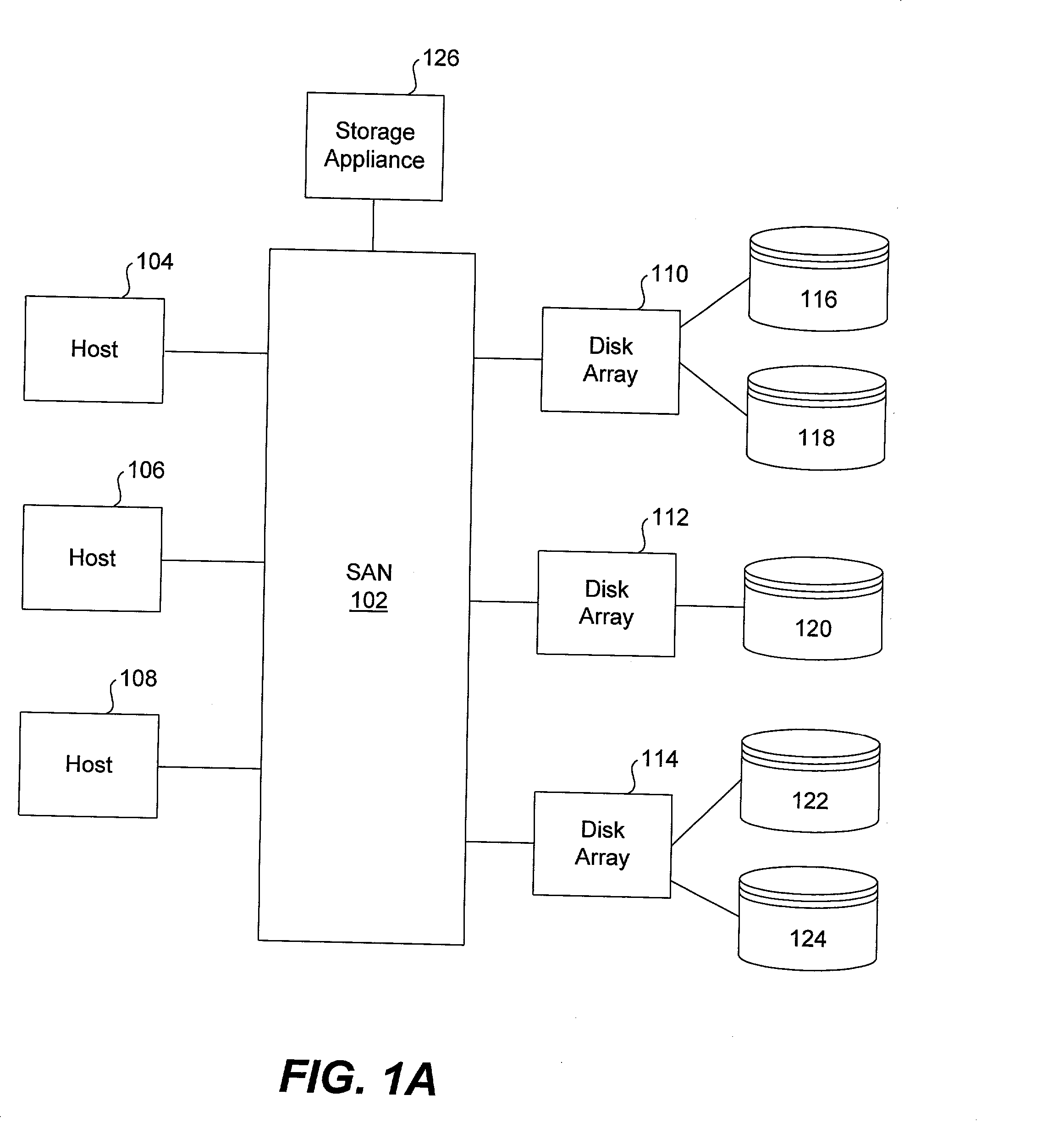

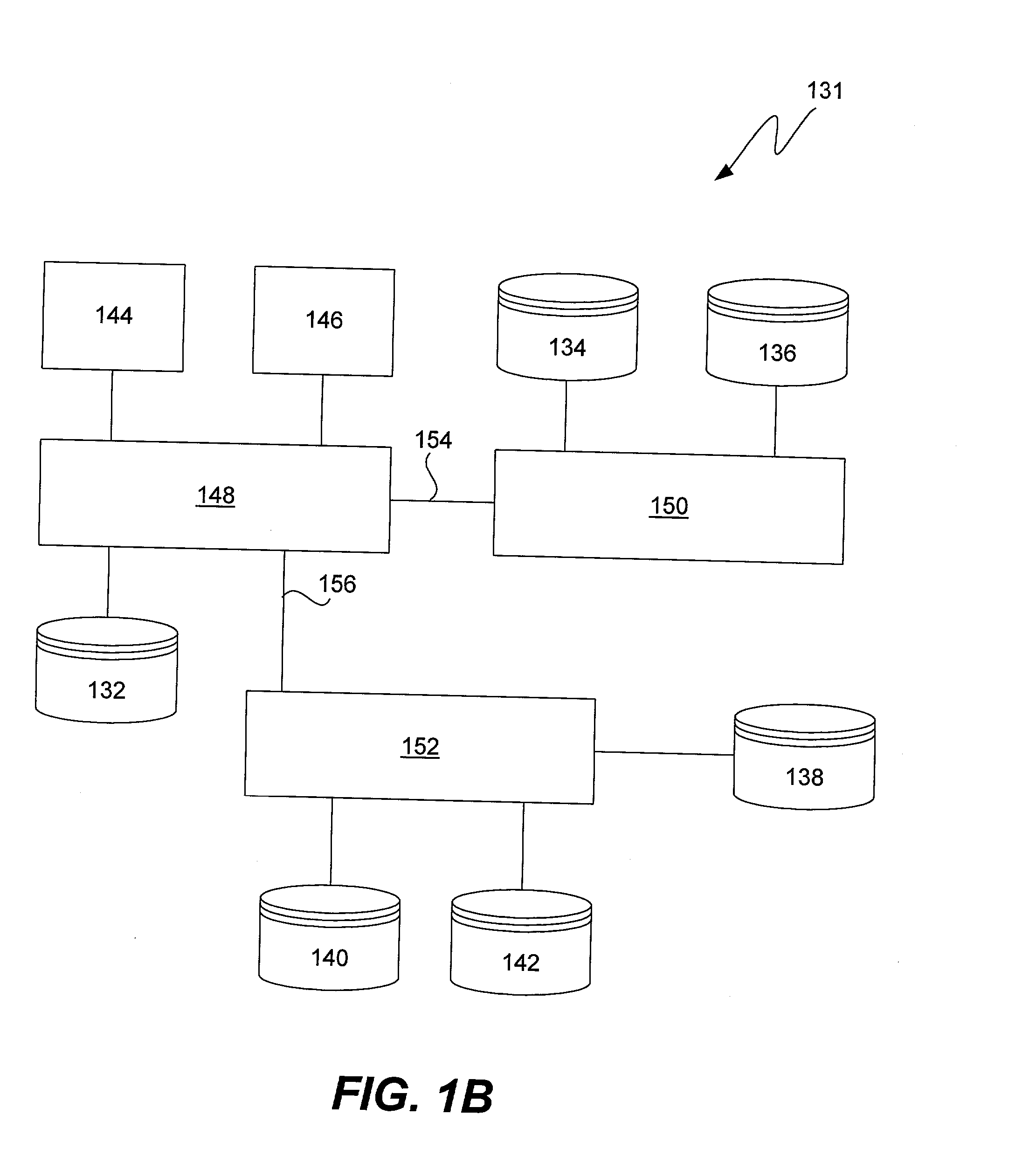

Methods and apparatus for implementing virtualization of storage within a storage area network

ActiveUS20030172149A1Ensure integrityInput/output to record carriersMultiple digital computer combinationsStorage area networkVirtual storage

Methods and apparatus for implementing storage virtualization on a network device of a storage area network are disclosed. A frame or packet is received at a port of the network device. It is then determined that the frame or packet pertains to access of a virtual storage location of a virtual storage unit representing one or more physical storage locations on one or more physical storage units of the storage area network. A virtual-physical mapping between the one or more physical storage locations and the virtual storage location is then obtained. A new or modified frame or packet is then sent to an initiator or a target specified by the virtual-physical mapping.

Owner:CISCO TECH INC

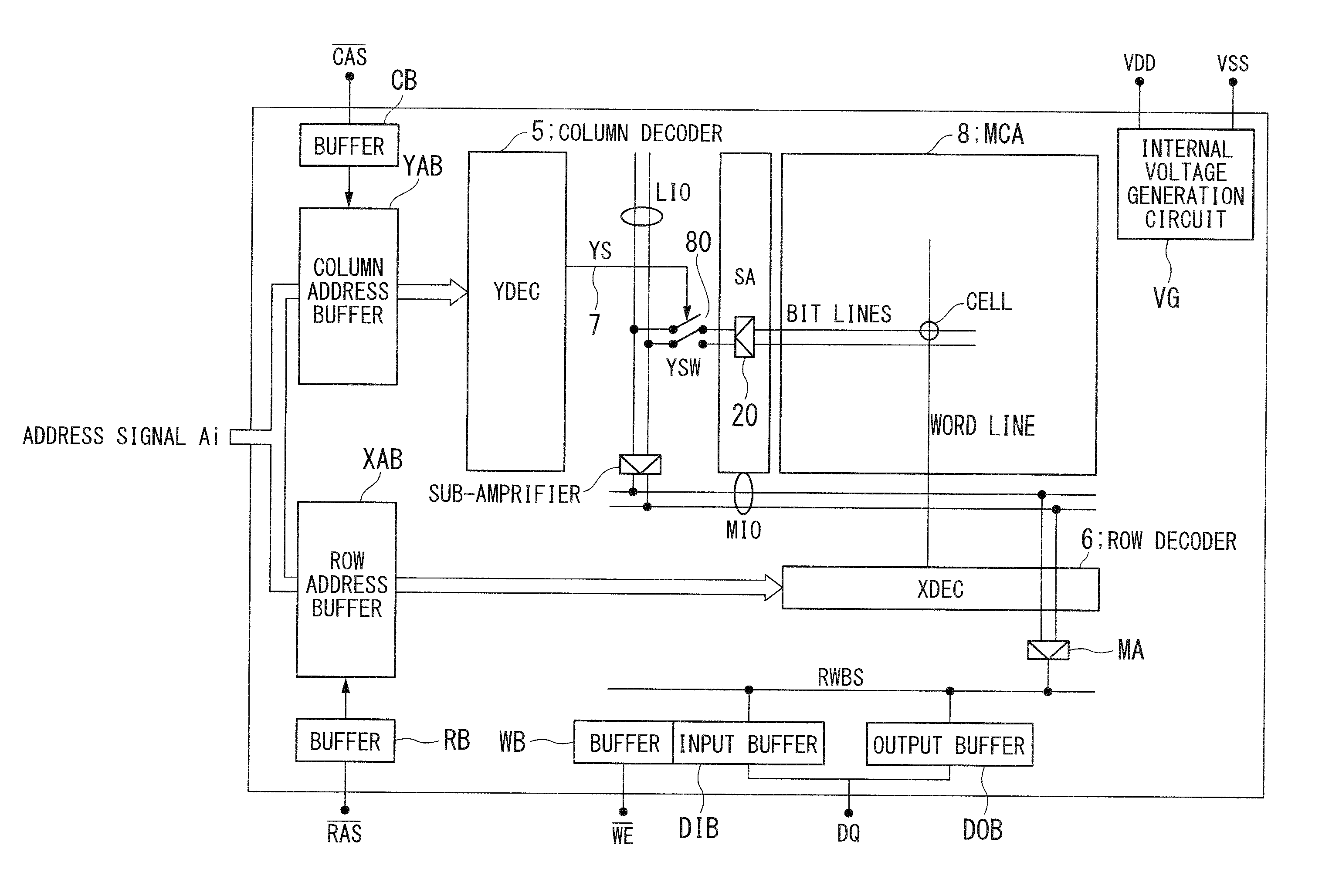

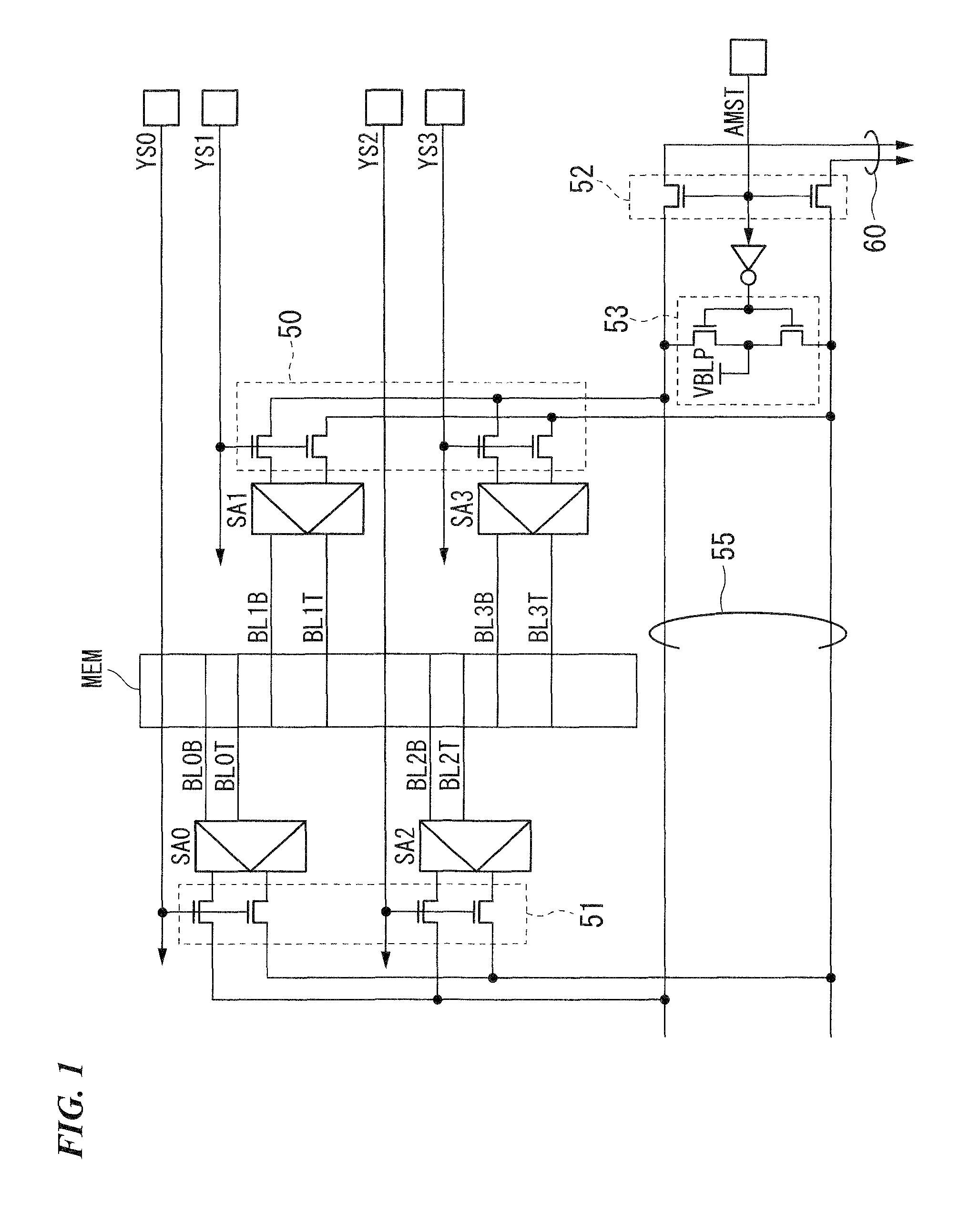

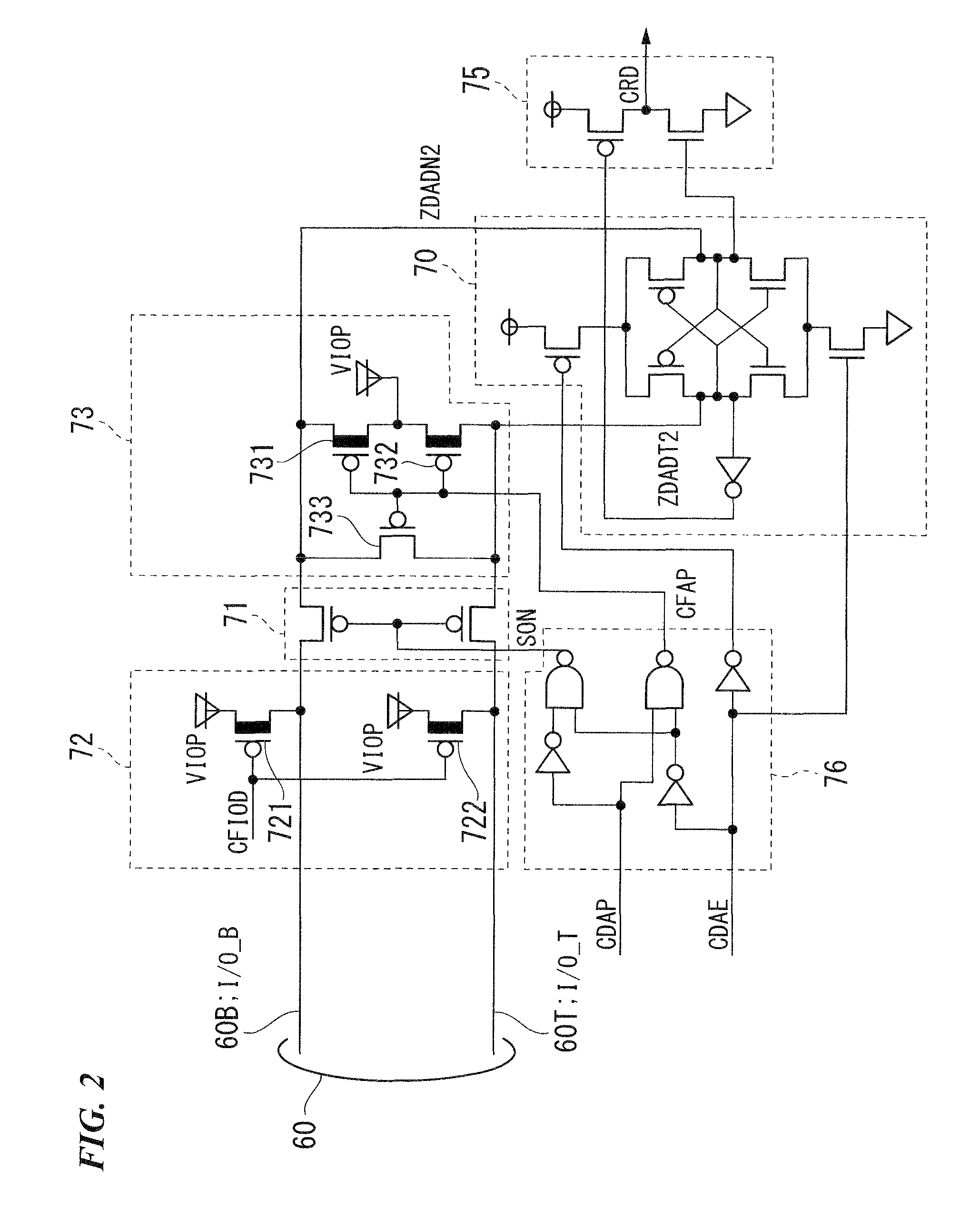

Semiconductor device

A semiconductor device includes a column decoder that generates a column selecting signal that selects any of a plurality of bit line pairs to which memory cells are connected according to a column address that is input; a bit line selecting switch that connects by the column selecting signal any of a plurality of bit line pairs and a data I / O line pair that outputs data that has been read from a memory cell to the outside; a data amplifier that amplifies a voltage differential of a data I / O line pair and outputs data that has been read to an output buffer; a data I / O line switch that is provided in the data I / O lines; an I / O line precharge circuit that precharges a data I / O line pair that is not on the side of the data amplifier; and an amplifier precharge circuit that precharges a data I / O line pair that is on the side of the data amplifier.

Owner:LONGITUDE LICENSING LTD

Memory including a performance test circuit

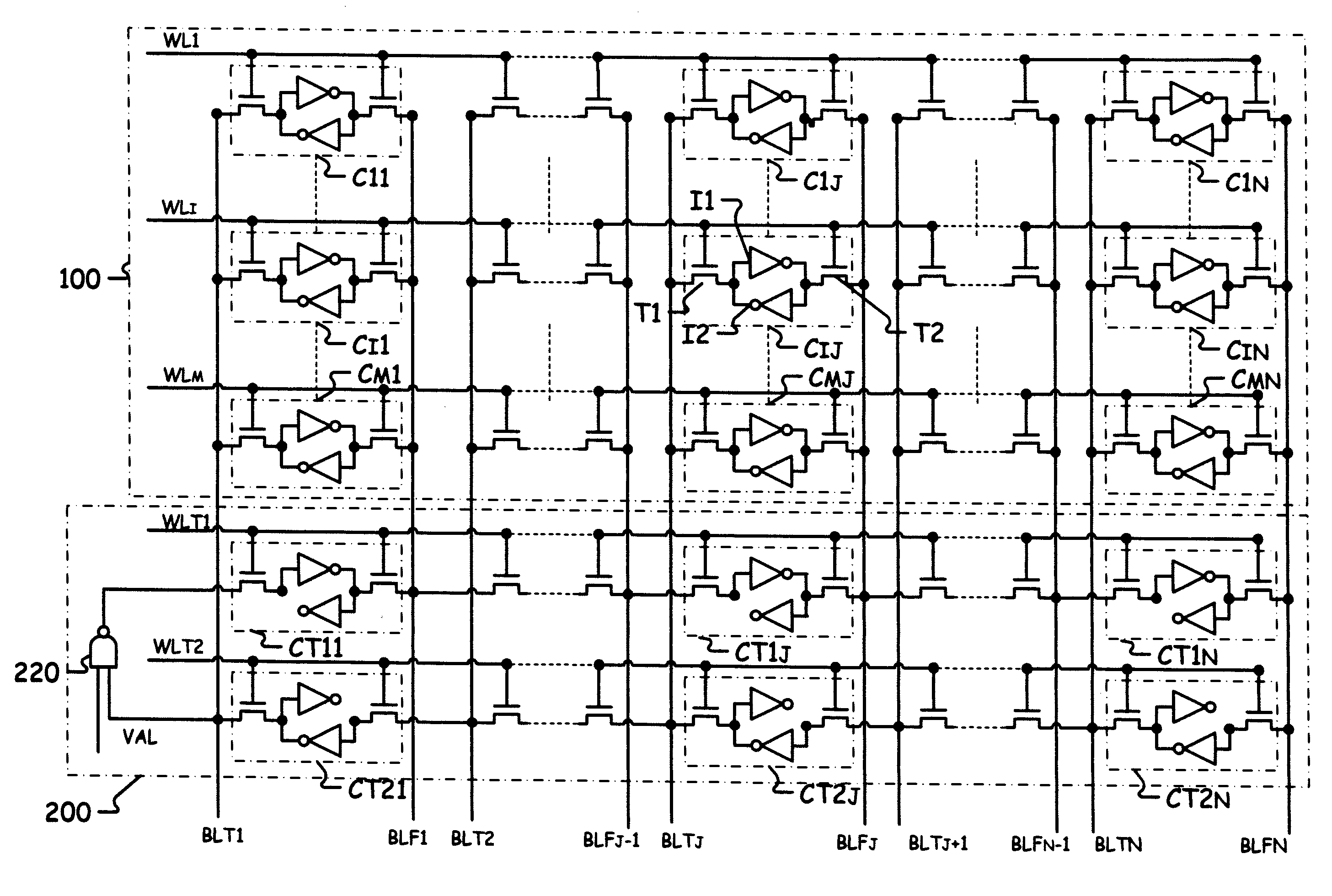

ActiveUS20090154273A1Easy to manufactureLimit memory consumptionElectronic circuit testingError detection/correctionBit lineTerm memory

A memory includes a plurality of memory cells each including a true data input connected to a true bit line and complementary data input connected to a complementary bit line, and two inverters connected head-to-tail firstly to the true data input and secondly to the complementary data input. The memory also includes a test circuit includes a plurality of test cells, each test cell includes a true data input connected to a complementary data input of the preceding test cell and a complementary data input connected to the true data input of the following test cell, the complementary data input of the last test cell being connected to the true data input of the first test cell, each test cell comprising a first inverter connected between the true data input and the complementary data input. The looped chain thus formed propagates a signal whose period is a function of the performance of the storage cells.

Owner:STMICROELECTRONICS SRL

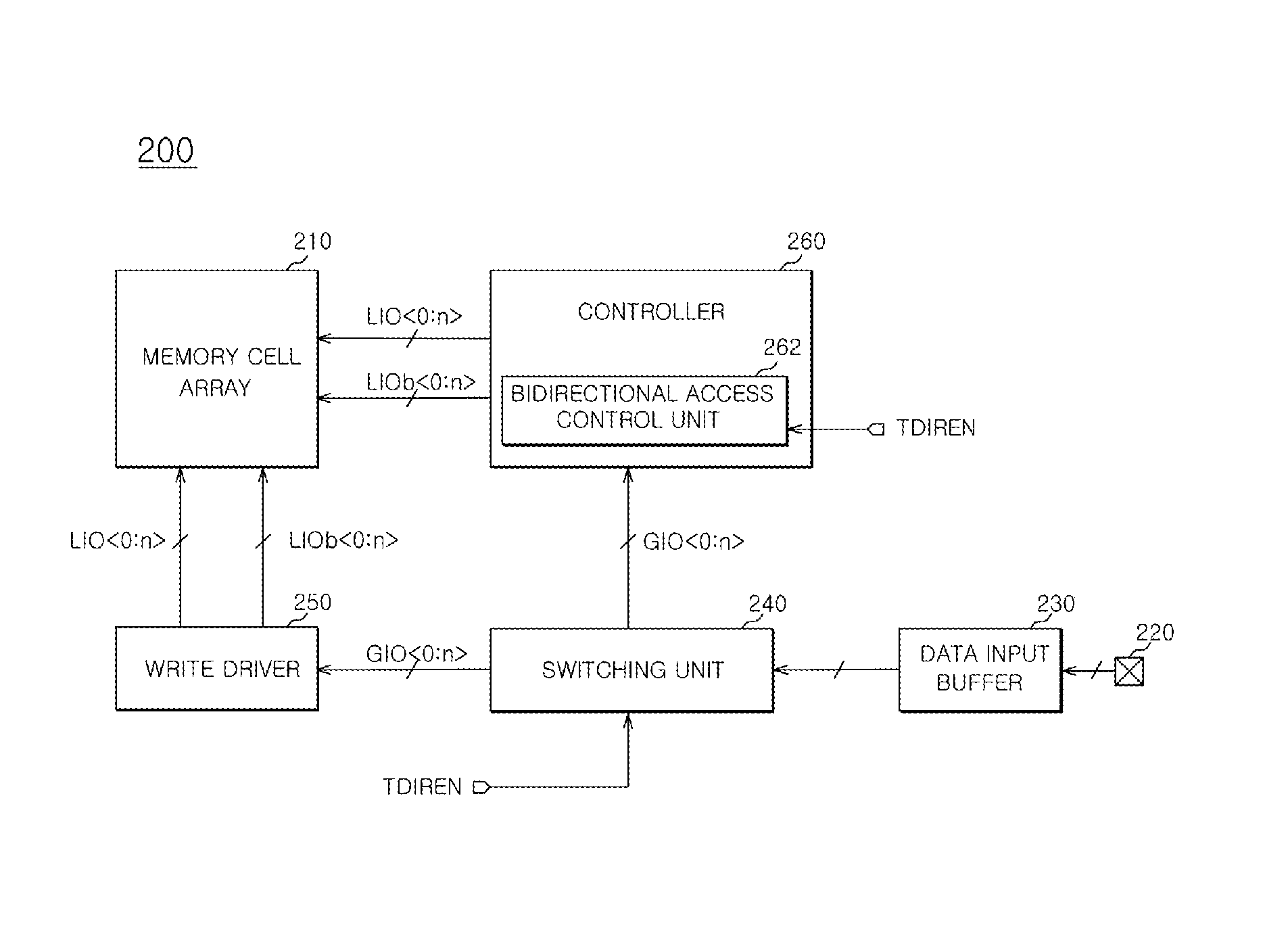

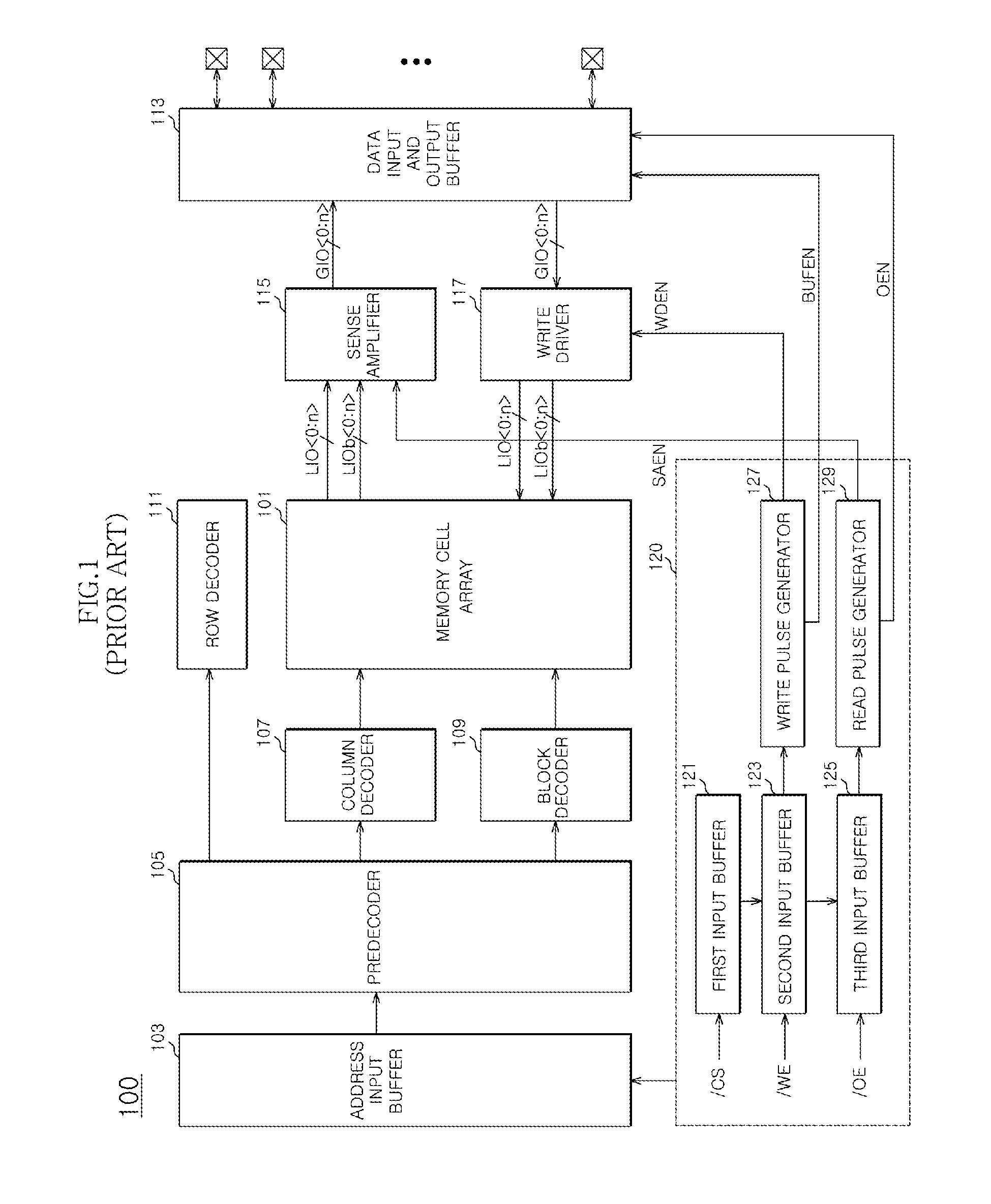

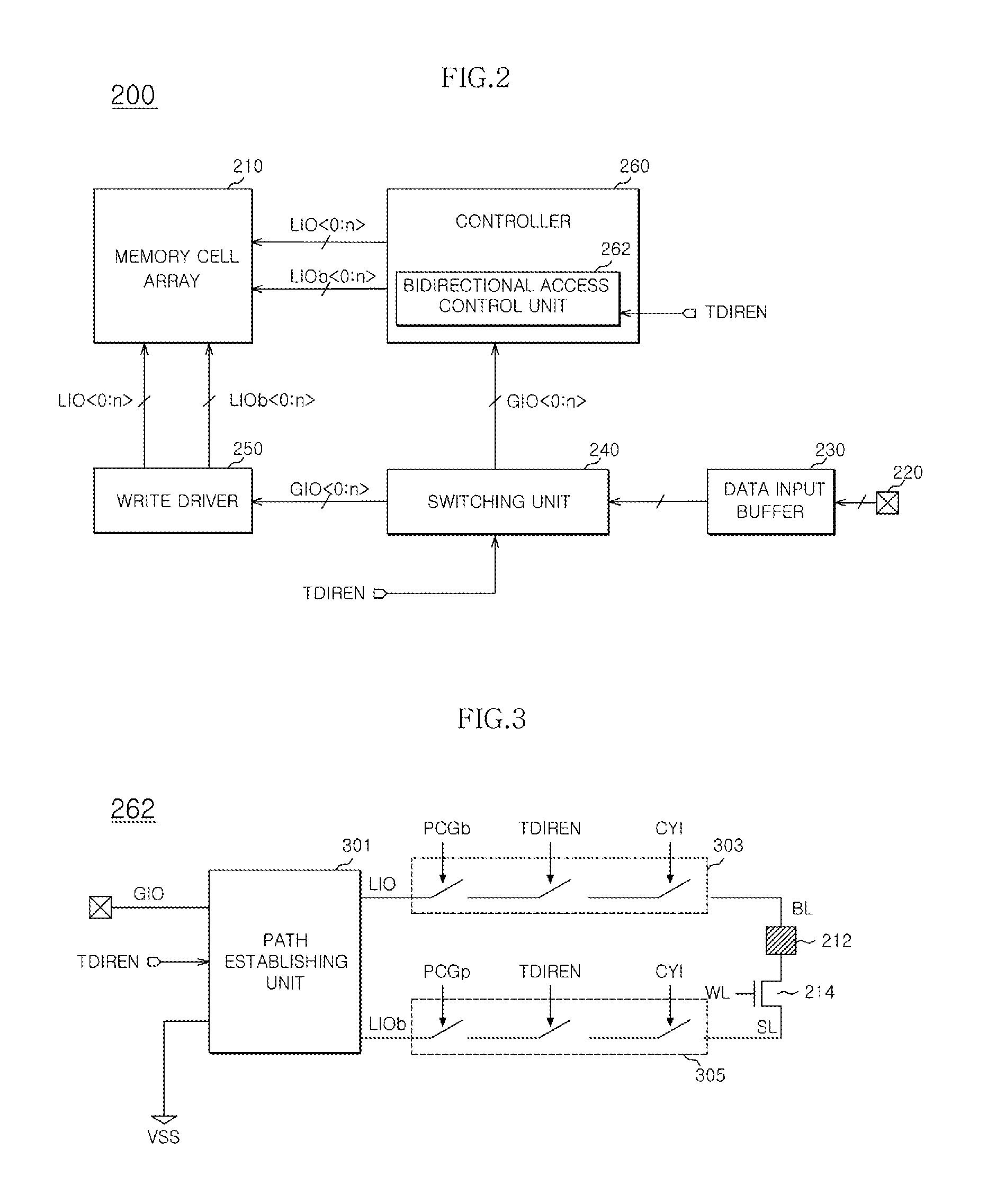

Semiconductor memory apparatus and test circuit therefor

Disclosed is a semiconductor memory apparatus, including: a memory cell array configured to include a plurality of memory cells; a switching unit configured to be coupled to data input and output pads and control a data transfer path of data applied to the data input and output pads in response to a test mode signal; a write driver configured to drive data transferred from the switching unit and write the data in the memory cell array at a normal mode; and a controller configured to transfer the data from the switching unit to the memory cell at a test mode.

Owner:SK HYNIX INC

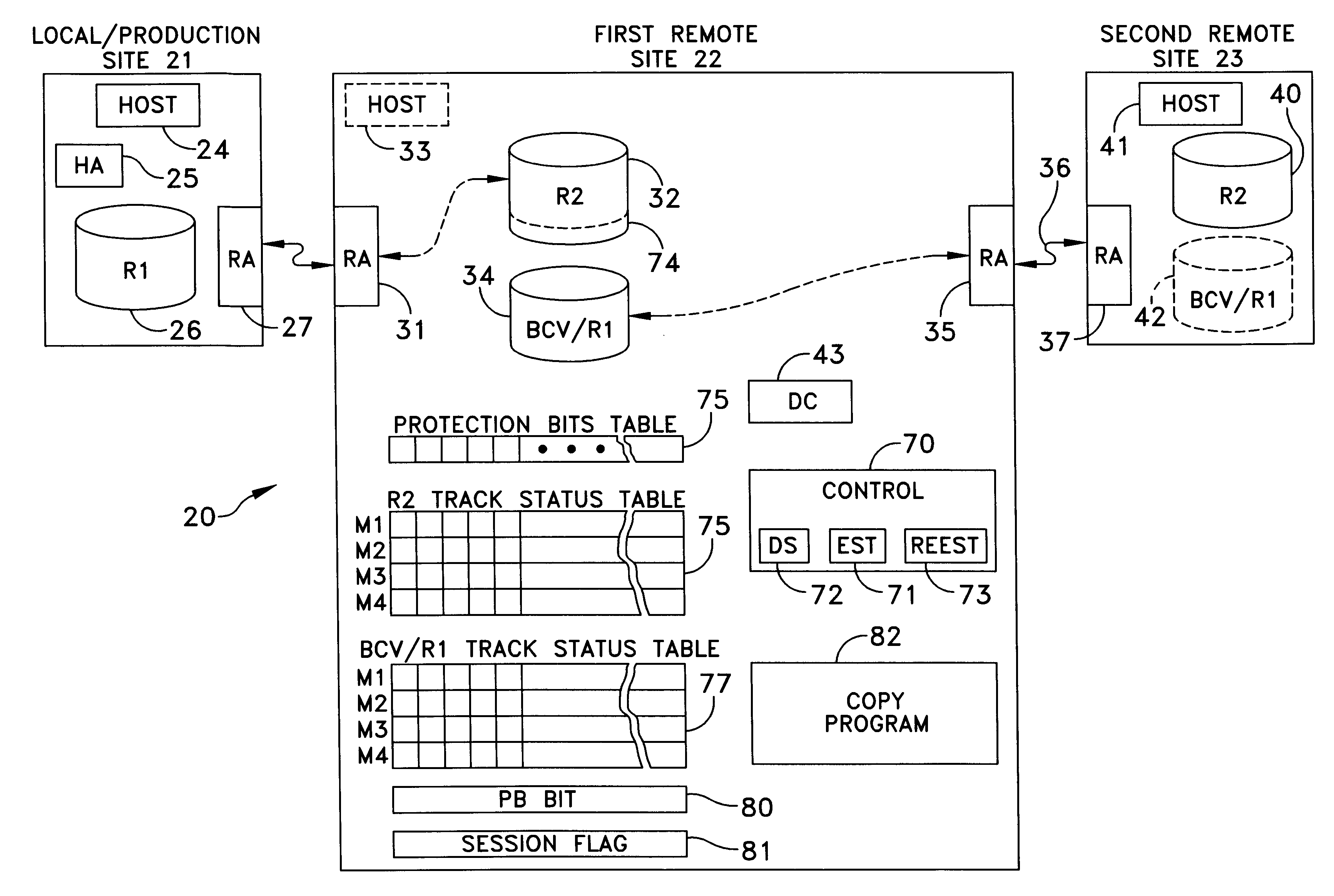

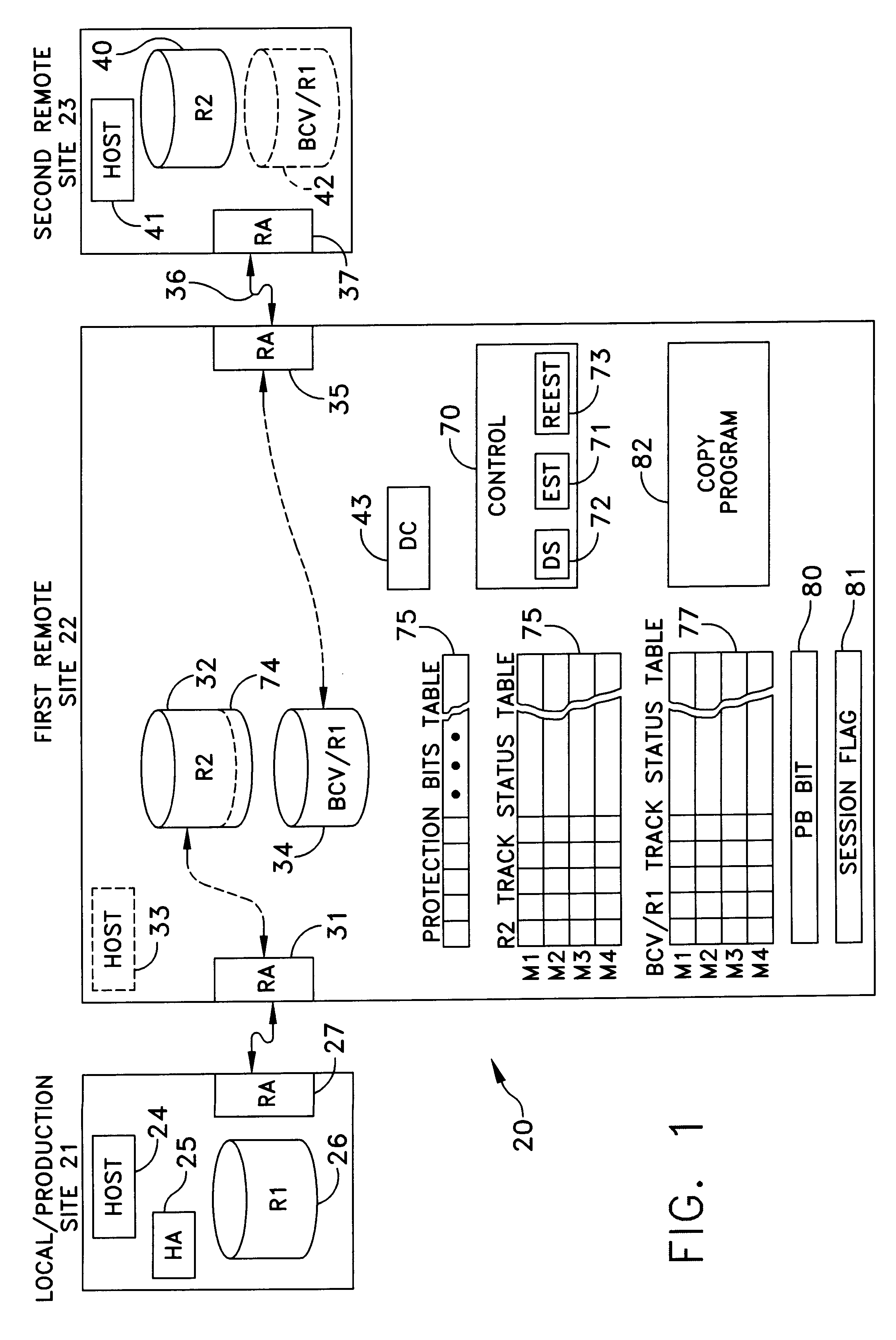

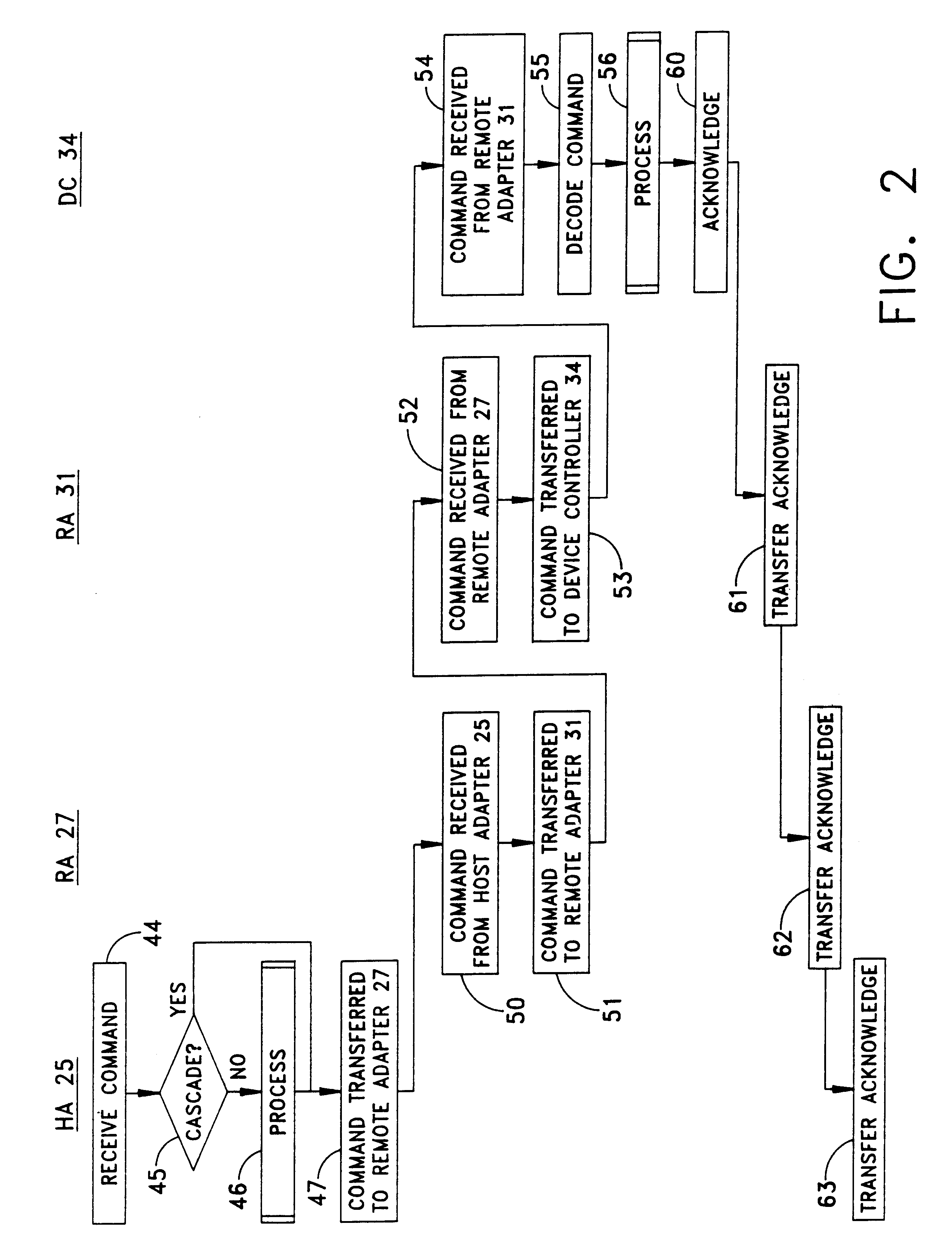

Method and apparatus for cascading data through redundant data storage units

A data storage facility for transferring data from a data altering apparatus, such as a production data processing site to a remote data receiving site. The data storage facility includes a first data store for recording each change in the data generated by the data altering apparatus. A register set records each change on a track-by-track basis. A second data store has first and second operating modes. During a first operating mode the second data store becomes a mirror of the first data store. During a second operating mode the second data store ceases to act as a mirror and becomes a source for a transfer of data to the data receiving site. Only information that has been altered, i.e., specific tracks that have been altered, are transferred during successive operations in the second operating mode. Commands from the local production site initiate the transfers between the first and second operating modes.

Owner:EMC IP HLDG CO LLC

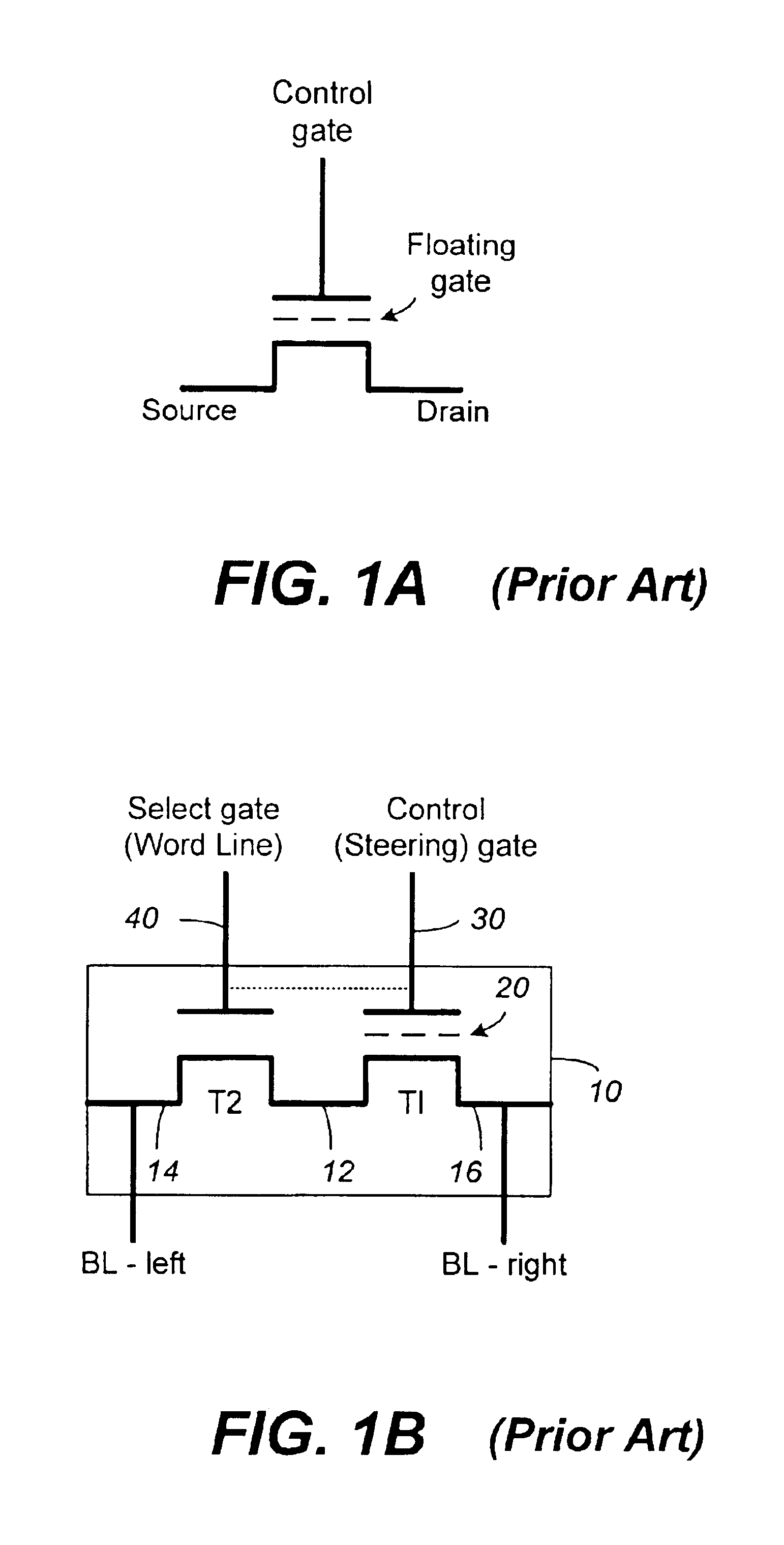

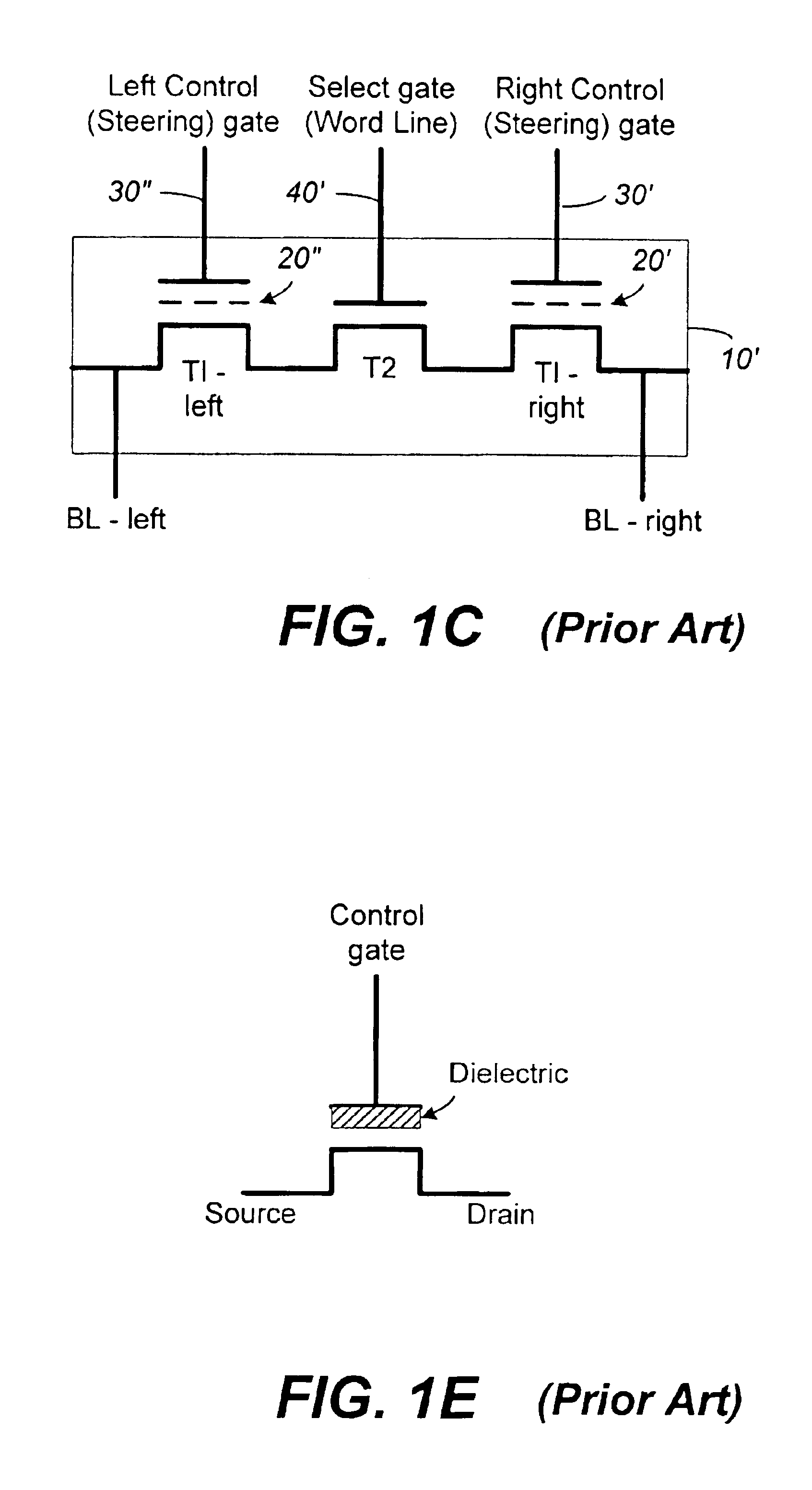

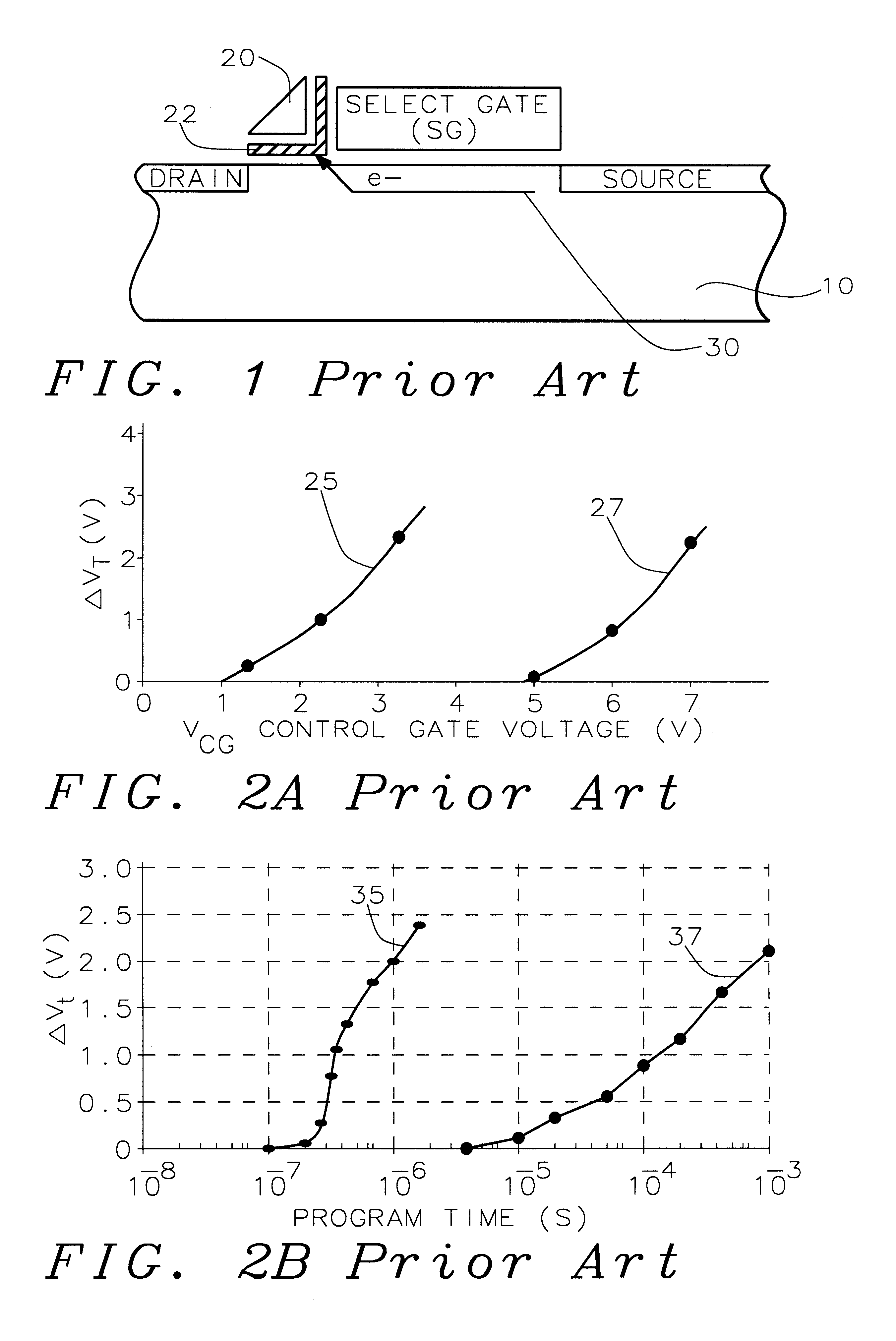

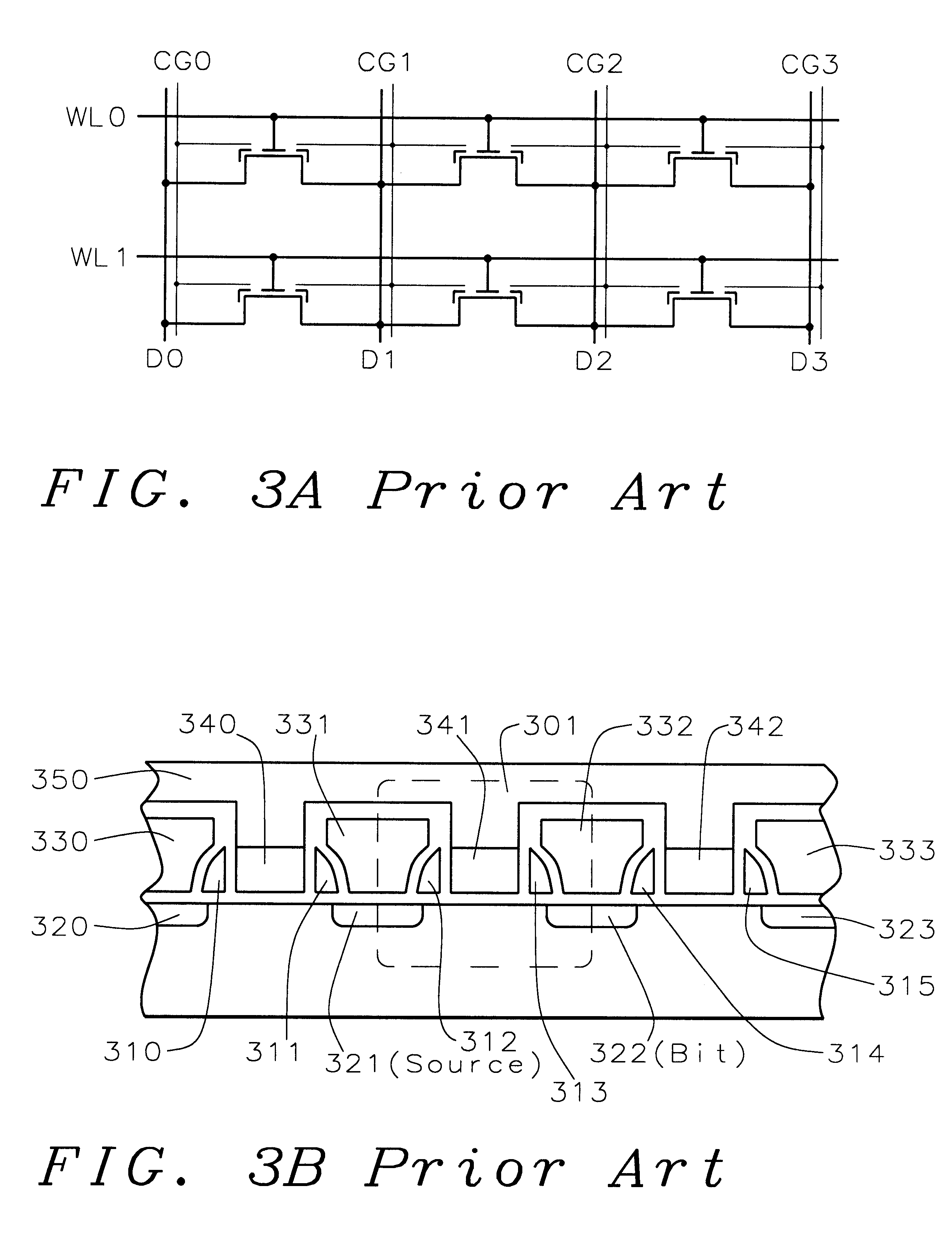

Process for making and programming and operating a dual-bit multi-level ballistic MONOS memory

A fast low voltage ballistic program, ultra-short channel, ultra-high density, dual-bit multi-level flash memory is described with a two or three polysilicon split gate side wall process. The structure and operation of this invention is enabled by a twin MONOS cell structure having an ultra-short control gate channel of less than 40nm, with ballistic injection which provides high electron injection efficiency and very fast program at low program voltages of 3~5V. The cell structure is realized by (i) placing side wall control gates over a composite of Oxide-Nitride-Oxide (ONO) on both sides of the word gate, and (ii) forming the control gates and bit diffusion by self-alignment and sharing the control gates and bit diffusions between memory cells for high density. Key elements used in this process are: 1) Disposable side wall process to fabricate the ultra short channel and the side wall control gate with or without a step structure, and 2) Self-aligned definition of the control gate over the storage nitride and the bit line diffusion, which also runs in the same direction as the control gate. The features of fast program, low voltage, ultra-high density, dual-bit, multi-level MONOS NVRAM of the present invention include: 1) Electron memory storage in nitride regions within an ONO layer underlying the control gates, 2) high density dual-bit cell in which there are two nitride memory storage elements per cell, 3) high density dual-bit cell can store multi-levels in each of the nitride regions, 4) low current program controlled by the word gate and control gate, 5) fast, low voltage program by ballistic injection utilizing the controllable ultra-short channel MONOS, and 6) side wall control poly gates to program and read multi-levels while masking out memory storage state effects of the unselected adjacent nitride regions and memory cells. The ballistic MONOS memory cell is arranged in the following array: each memory cell contains two nitride regions for one word gate, and ½ a source diffusion and ½ a bit diffusion. Control gates can be defined separately or shared together over the same diffusion. Diffusions are shared between cells and run in parallel to the side wall control gates, and perpendicular to the word line.

Owner:HALO LSI INC

Flash memory storage system and method

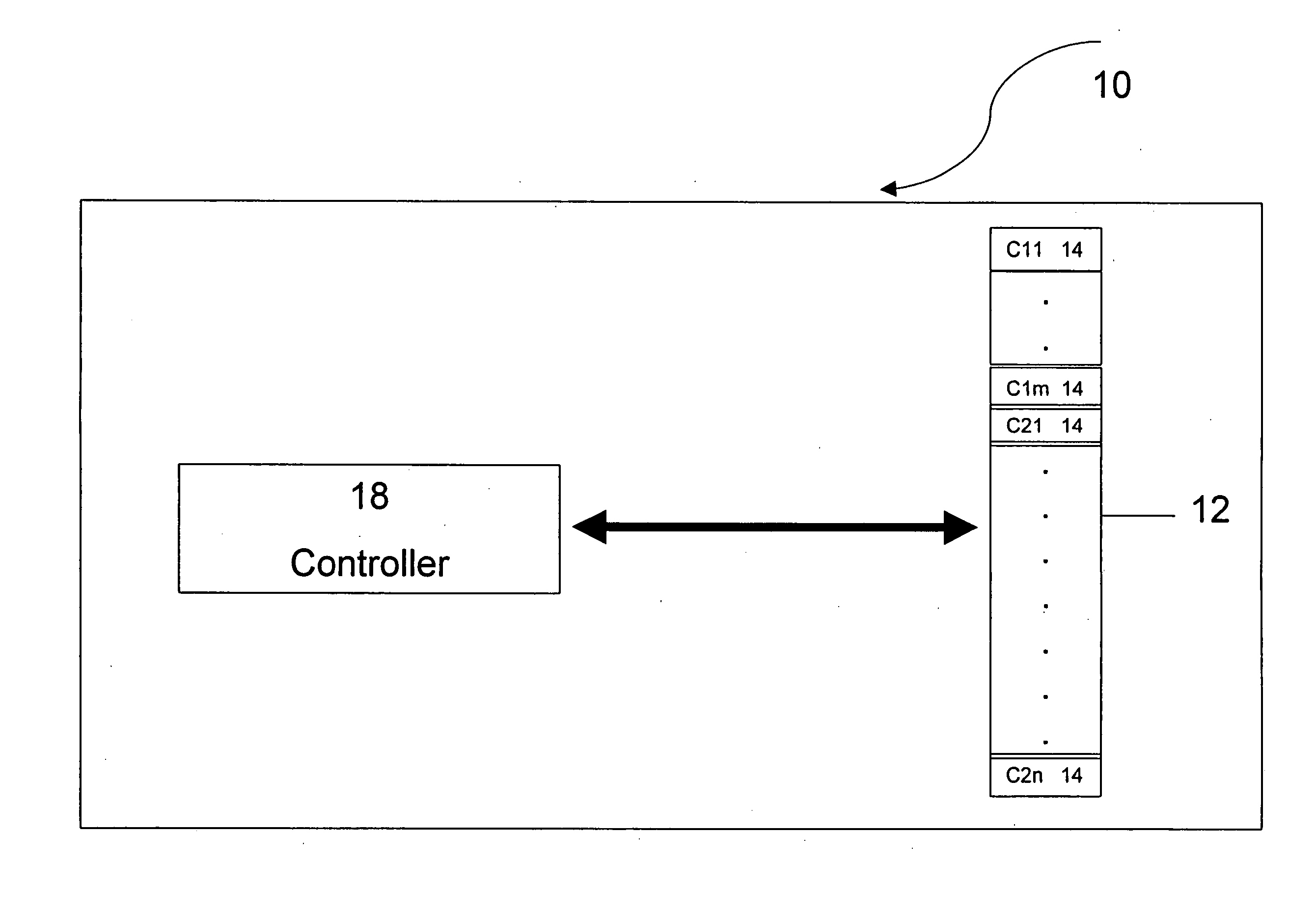

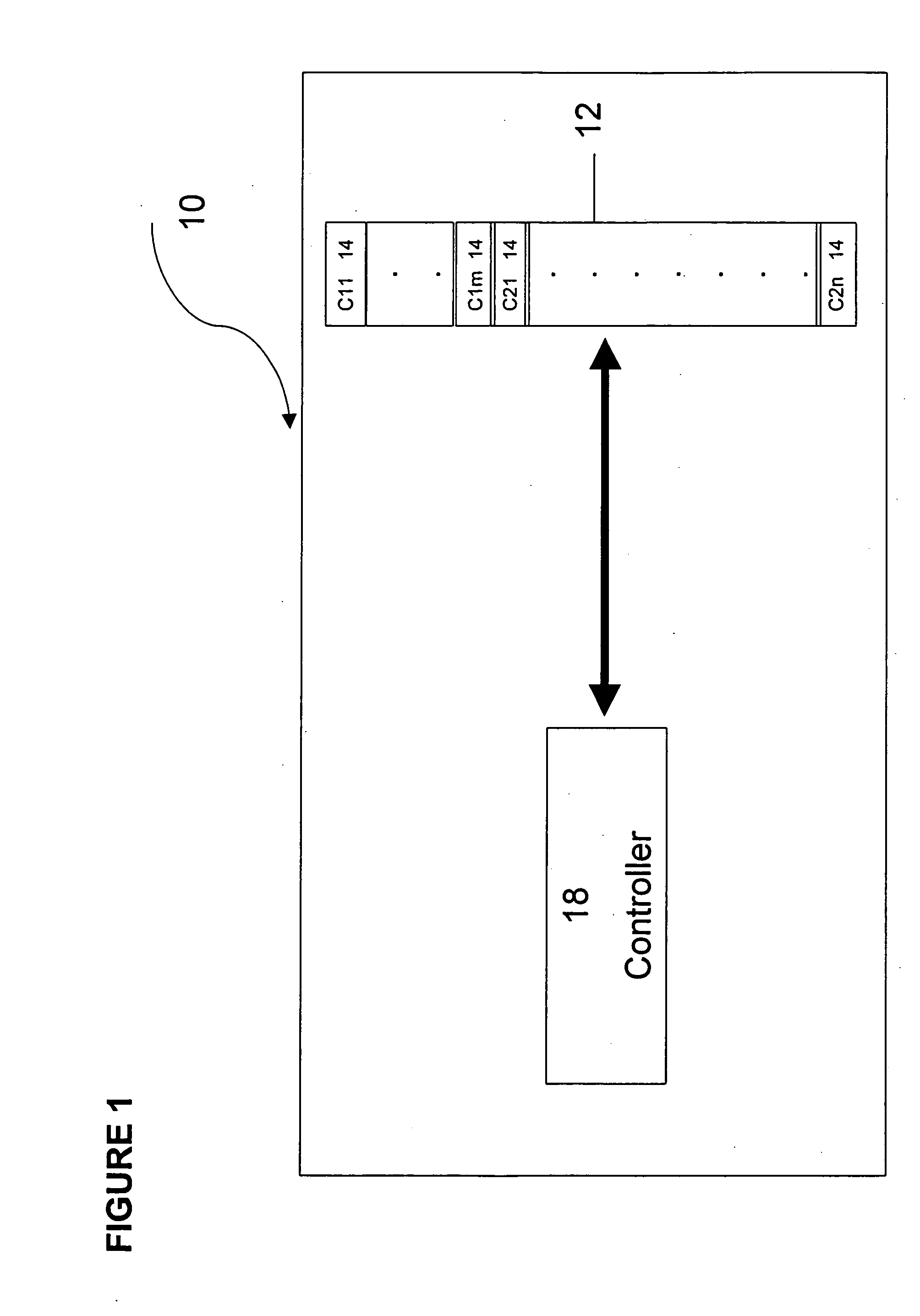

ActiveUS20070061502A1Overcome disadvantagesEqually distributedMemory architecture accessing/allocationRead-only memoriesParallel computingStorage cell

A flash memory storage system includes a memory array containing a plurality of memory cells and a controller for controlling the flash memory array. The controller dedicates a first group of memory cells to operate with a first number of bits per cell and a second, separate group of memory cells to operate with a second number of bits per cell. A mechanism is provided to apply wear leveling techniques separately to the two groups of cells to evenly wear out the memory cells.

Owner:WESTERN DIGITAL ISRAEL LTD

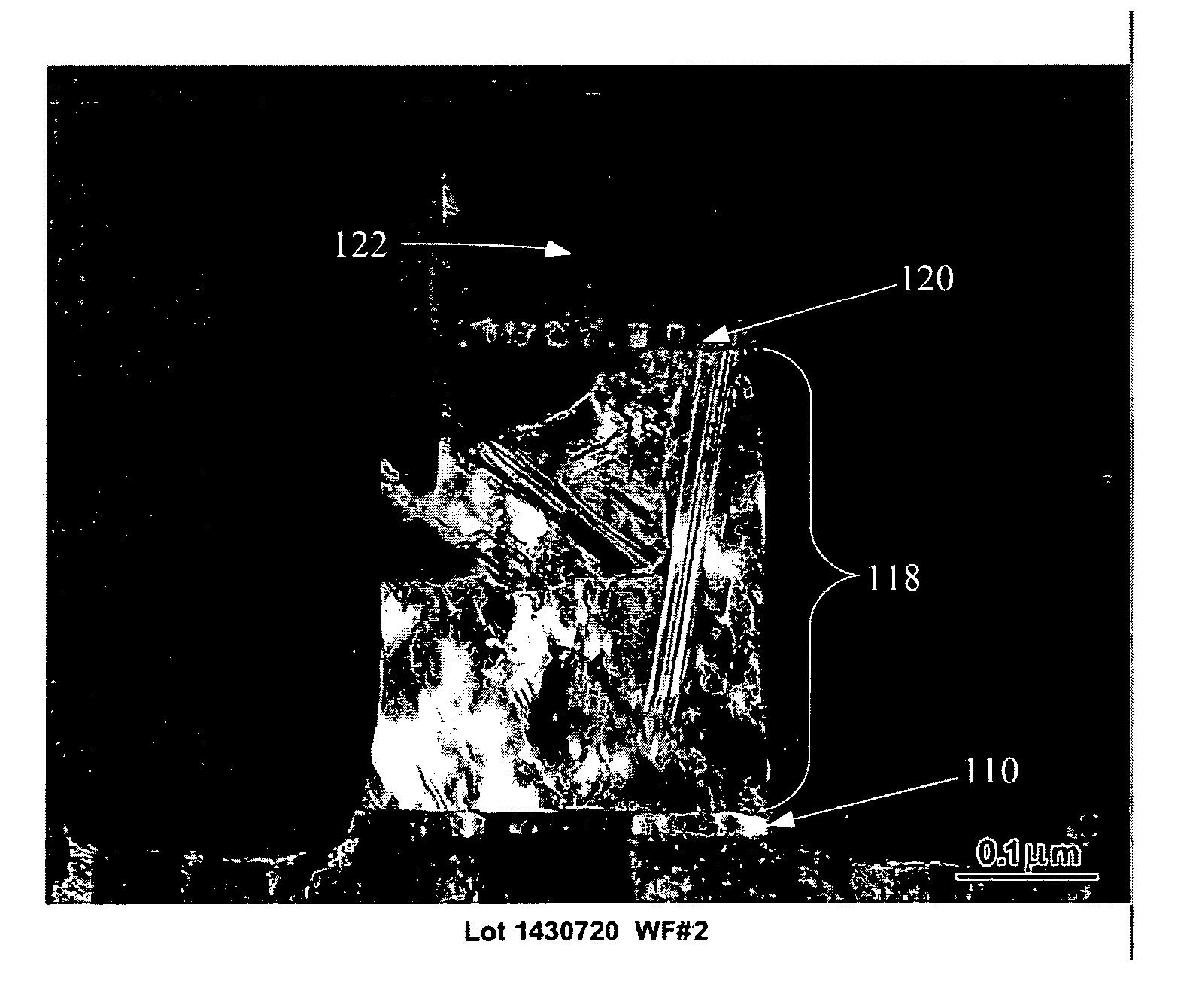

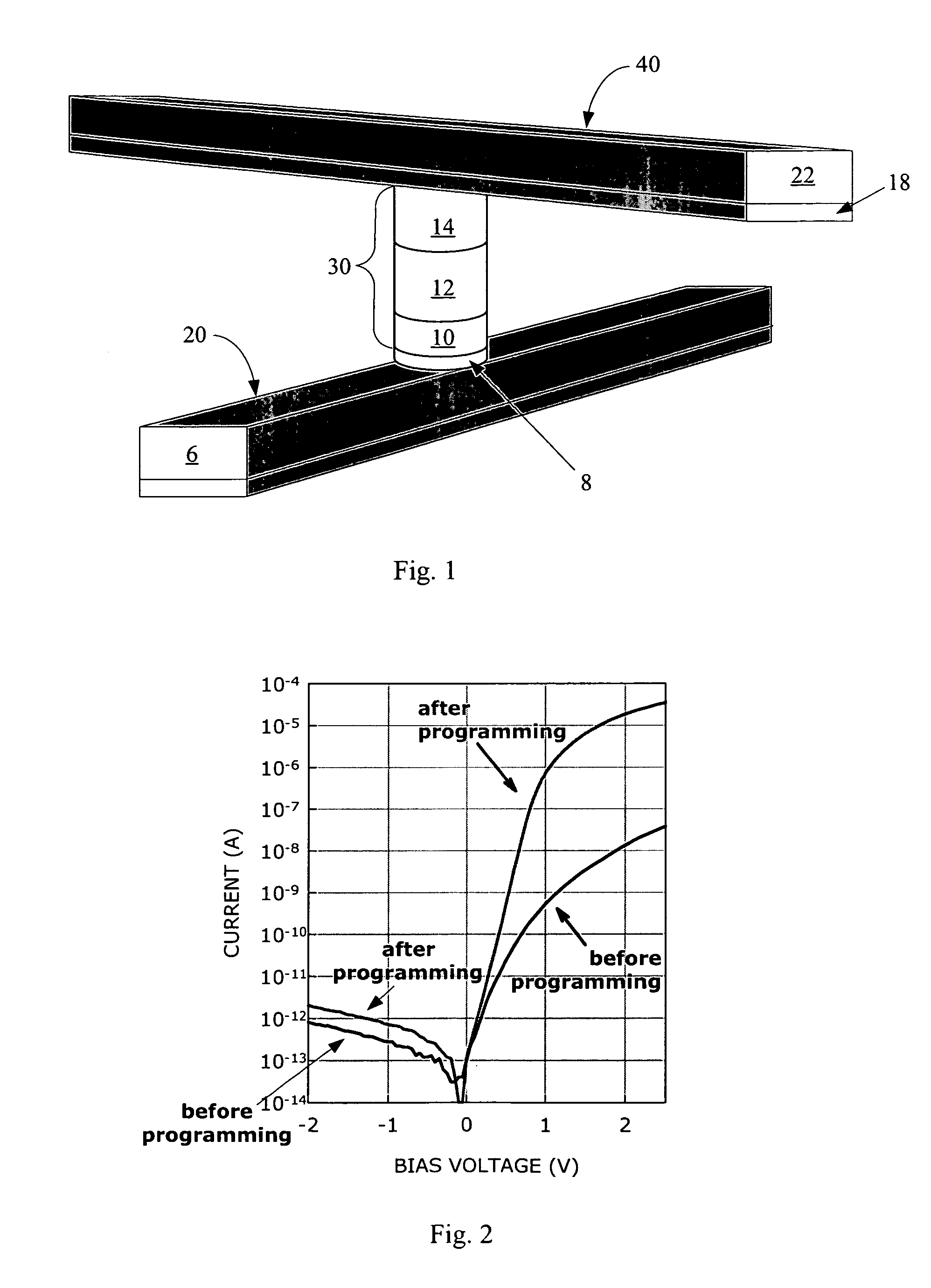

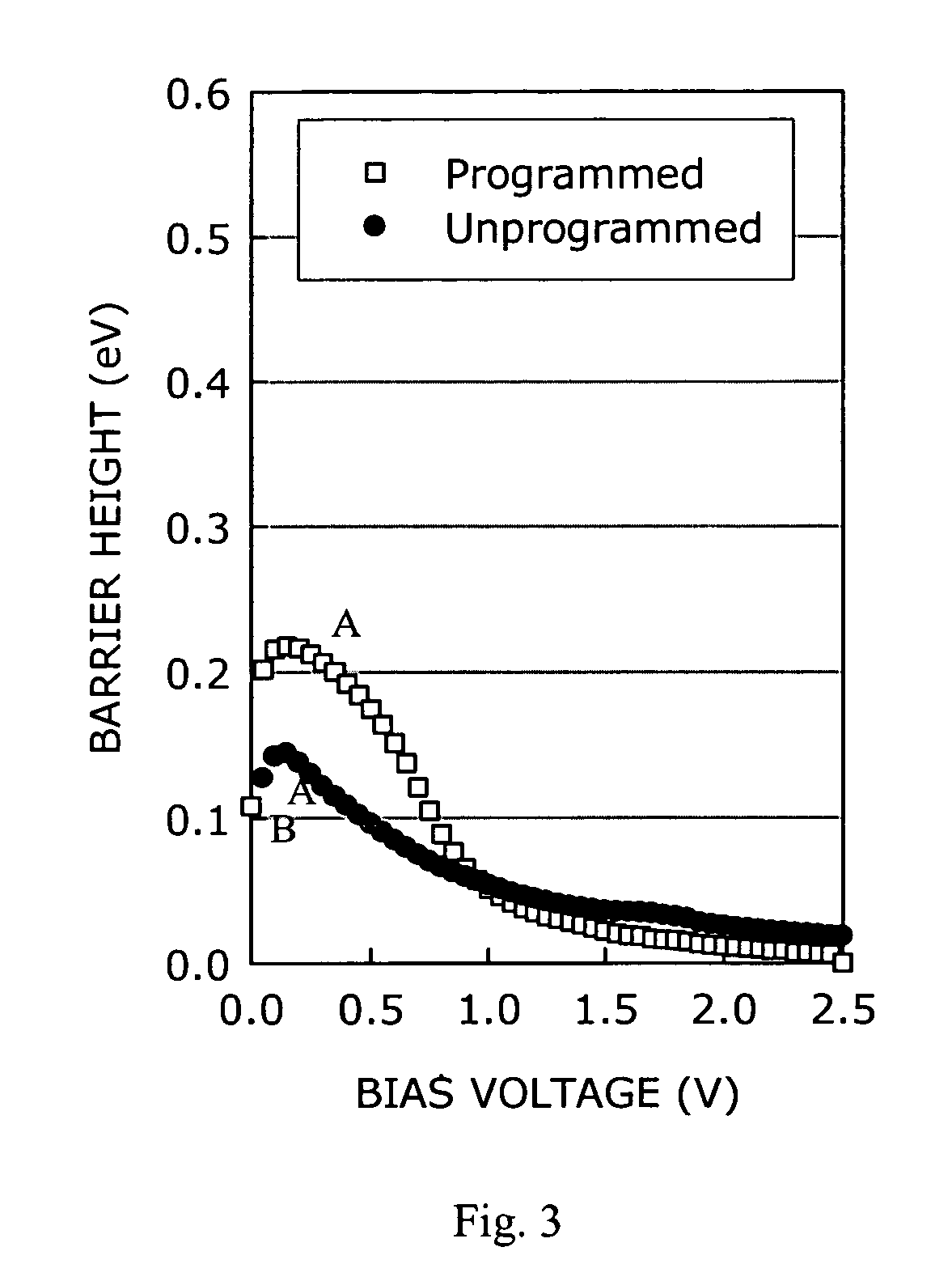

Nonvolatile memory cell operating by increasing order in polycrystalline semiconductor material

A nonvolatile memory cell is described, the memory cell comprising a semiconductor diode. The semiconductor material making up the diode is formed with significant defect density, and allows very low current flow at a typical read voltage. Application of a programming voltage permanently changes the nature of the semiconductor material, resulting in an improved diode. The programmed diode allows much higher current flow, in some embodiments one, two or three orders of magnitude higher, at the same read voltage. The difference in current allows a programmed memory cell to be distinguished from an unprogrammed memory cell. Fabrication techniques to generate an advantageous unprogrammed defect density are described. The memory cell of the present invention can be formed in a monolithic three dimensional memory array, having multiple stacked memory levels formed above a single substrate.

Owner:SANDISK TECH LLC

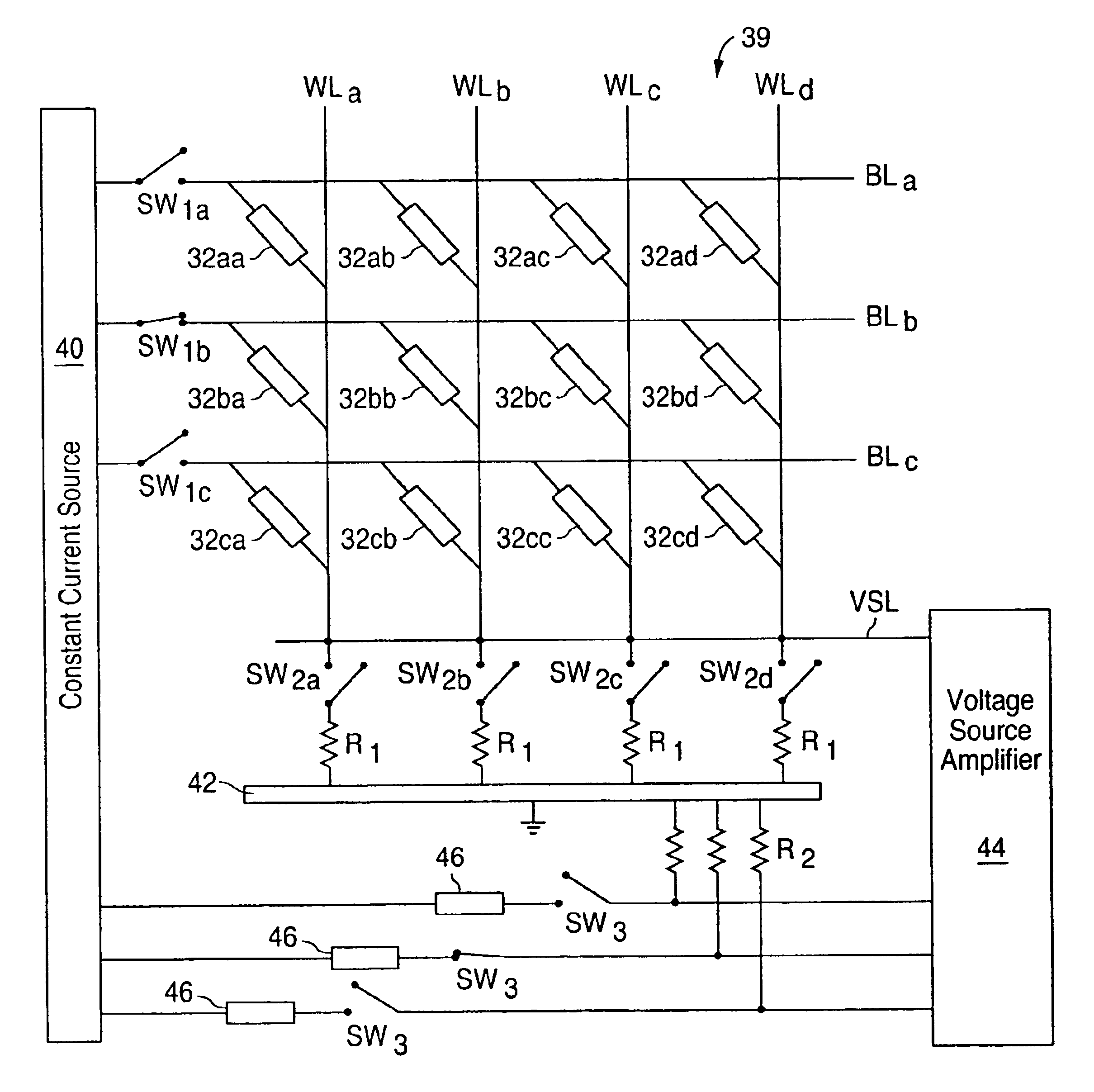

Memory device and method of operating same

An array of phase changing memory cells that includes a current source, a voltage sensor, a plurality of conductive bit lines electrically connected to the current source, a plurality of conductive word lines each electrically connected to a ground plane via a first resistor and to the voltage sensor, and a plurality of memory cells. Each memory cell is connected between one of the bit lines and one of the word lines and includes phase change memory material. One of the memory cells is selected by turning on switches just on the bit line and word line connected thereto, or by turning a switch connected in series between the corresponding bit and word lines, where the read current flows through the selected memory cell and the voltage sensor measures a voltage drop across the selected memory cell.

Owner:SILICON STORAGE TECHNOLOGY

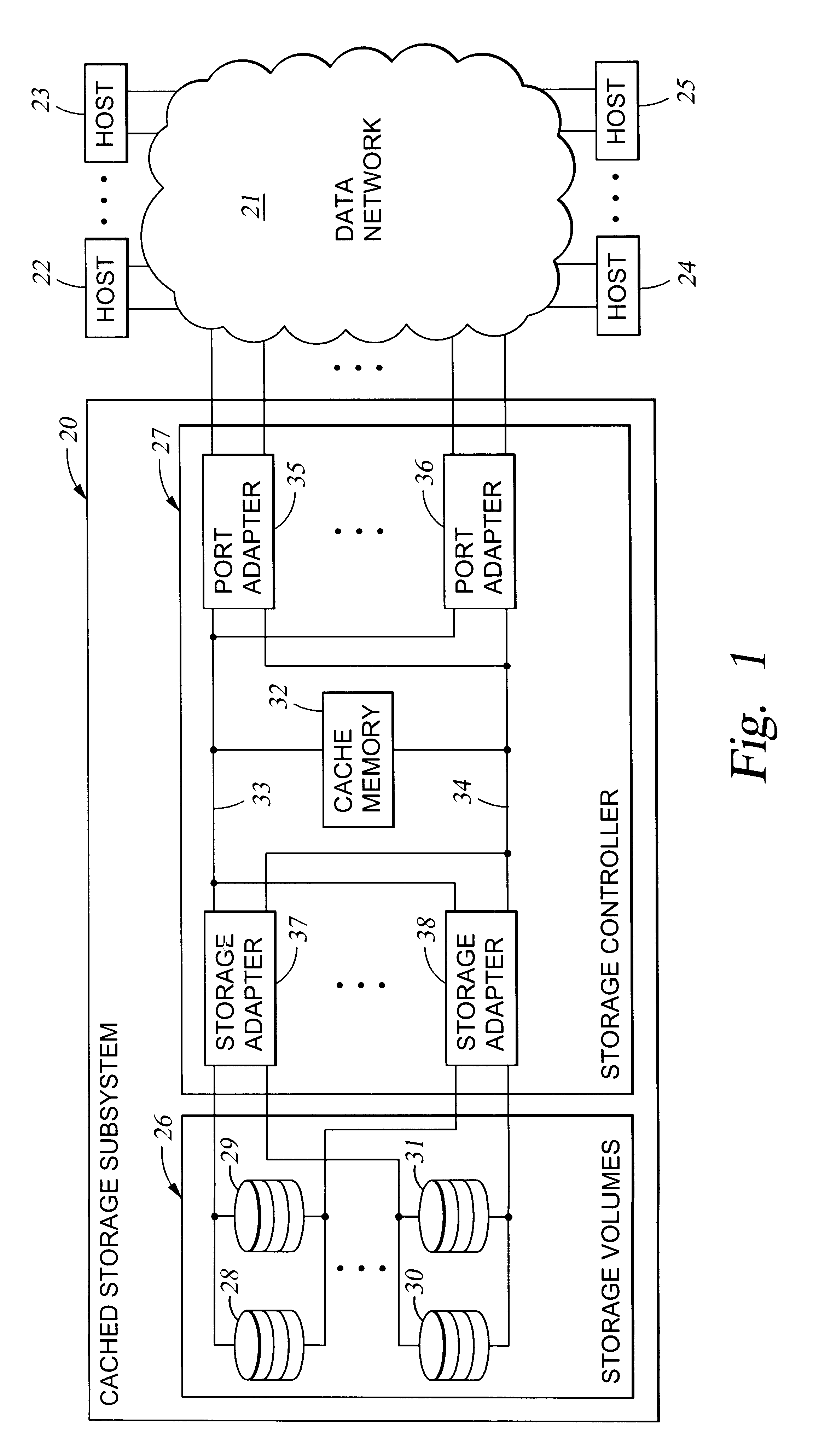

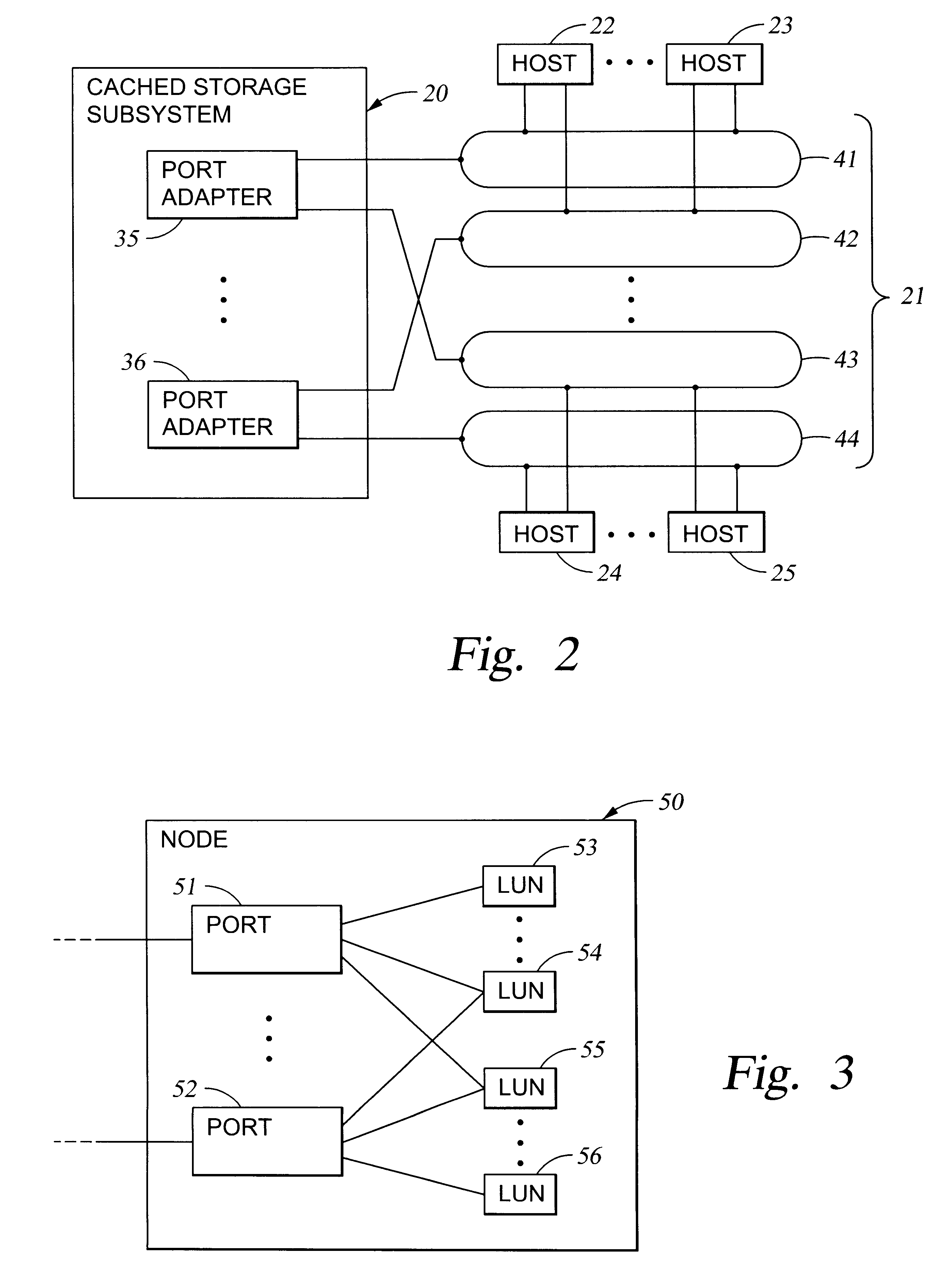

Mapping of hosts to logical storage units and data storage ports in a data processing system

InactiveUS20040054866A1Input/output to record carriersMultiple digital computer combinationsData processing systemData access

An apparatus has host ports for coupling hosts to data storage devices. The data storage devices are configured into logical storage units, and the apparatus is programmed with a mapping of the hosts to respective logical storage units. The apparatus decodes a host identifier and a logical storage unit specification from each data access request received at each host port, and determines whether or not the decoded host identifier and logical storage unit specification are in conformance with the mapping in order to permit or deny data access of the logical storage unit through the host port. For example, the apparatus includes a switch for routing the data storage access requests from the host ports to ports that provide access to the data storage, and a set of logical volumes of storage are accessible from each of the ports that provide access to the data storage.

Owner:EMC IP HLDG CO LLC

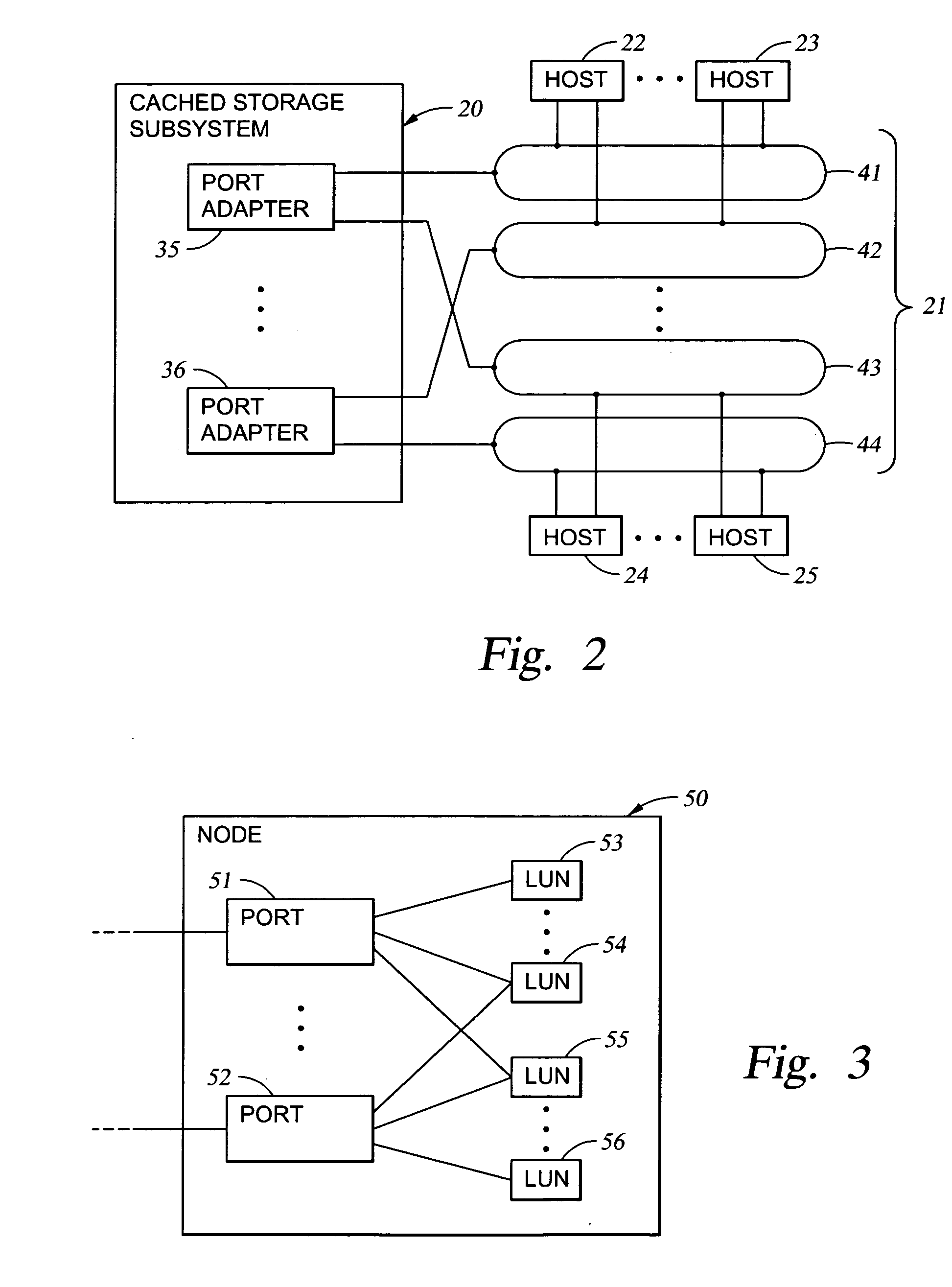

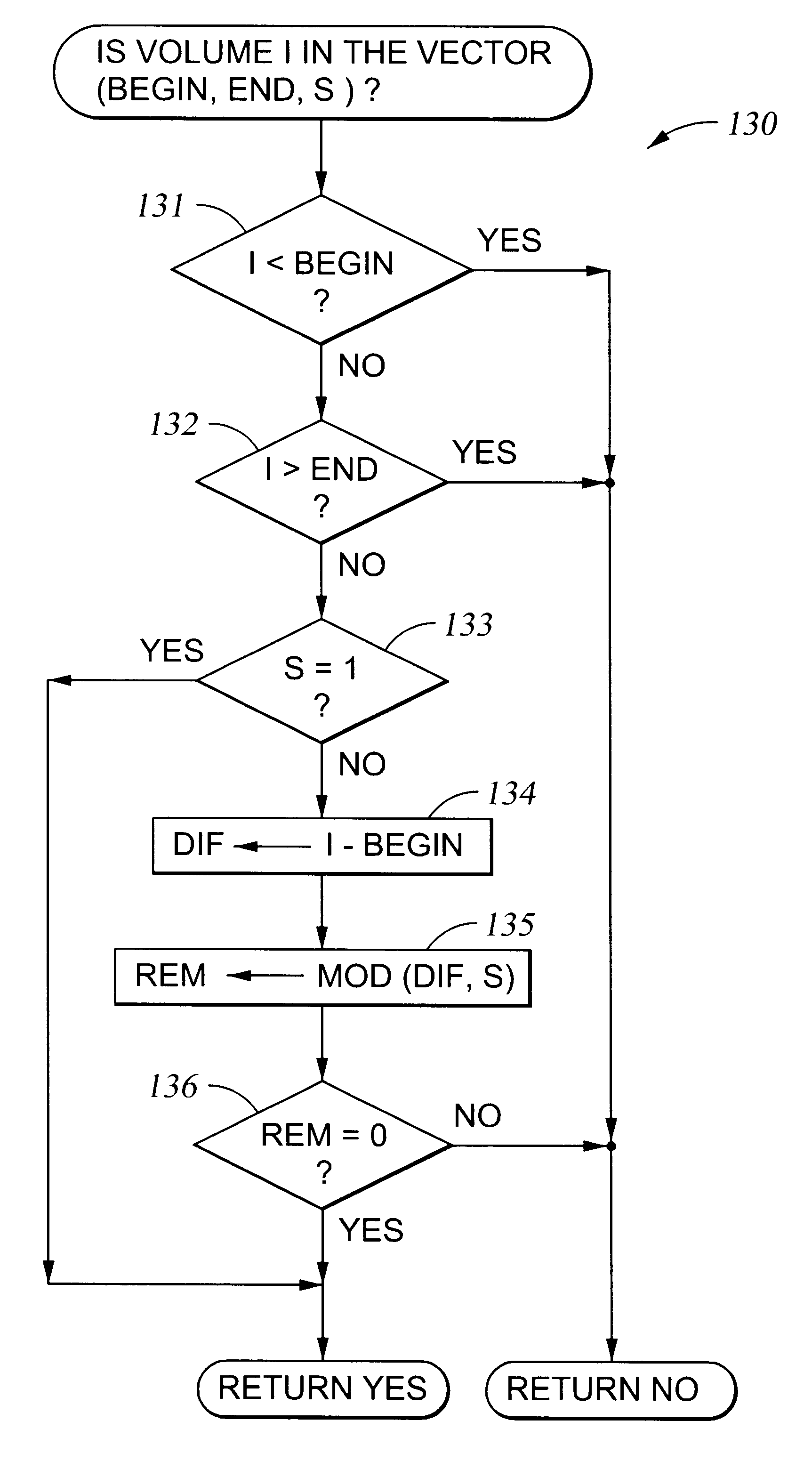

Configuring vectors of logical storage units for data storage partitioning and sharing

InactiveUS6295575B1Input/output to record carriersMemory adressing/allocation/relocationTheoretical computer scienceData store

In a data storage subsystem providing data storage to host processors, a process of configuration defines a subset of the data storage that each host may access. A vector specification is a convenient mechanism for specifying a set of storage volumes that a host may access. For example, for each host processor, there is stored in memory of the data storage subsystem a list of contiguous ranges or vectors of the storage volumes that the host may access. To determine whether or not a specified logical volume number is included in the vector, a modulus of the stride of the vector is computed from the difference between the address of the specified logical volume and the beginning address of the vector, and the modulus is compared to zero. To provide a mapping between logical unit numbers specified by the host and the logical volumes, a contiguous range of logical unit numbers may also be specified for each contiguous range or vector of storage volumes. The logical volume number is computed from a specified logical unit number by computing a difference between the specified logical unit number and the beginning logical unit number, multiplying the difference by the stride of the vector to produce a product, and adding the product to the beginning address of the vector.

Owner:EMC IP HLDG CO LLC