Patents

Literature

139 results about "Physical mapping" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

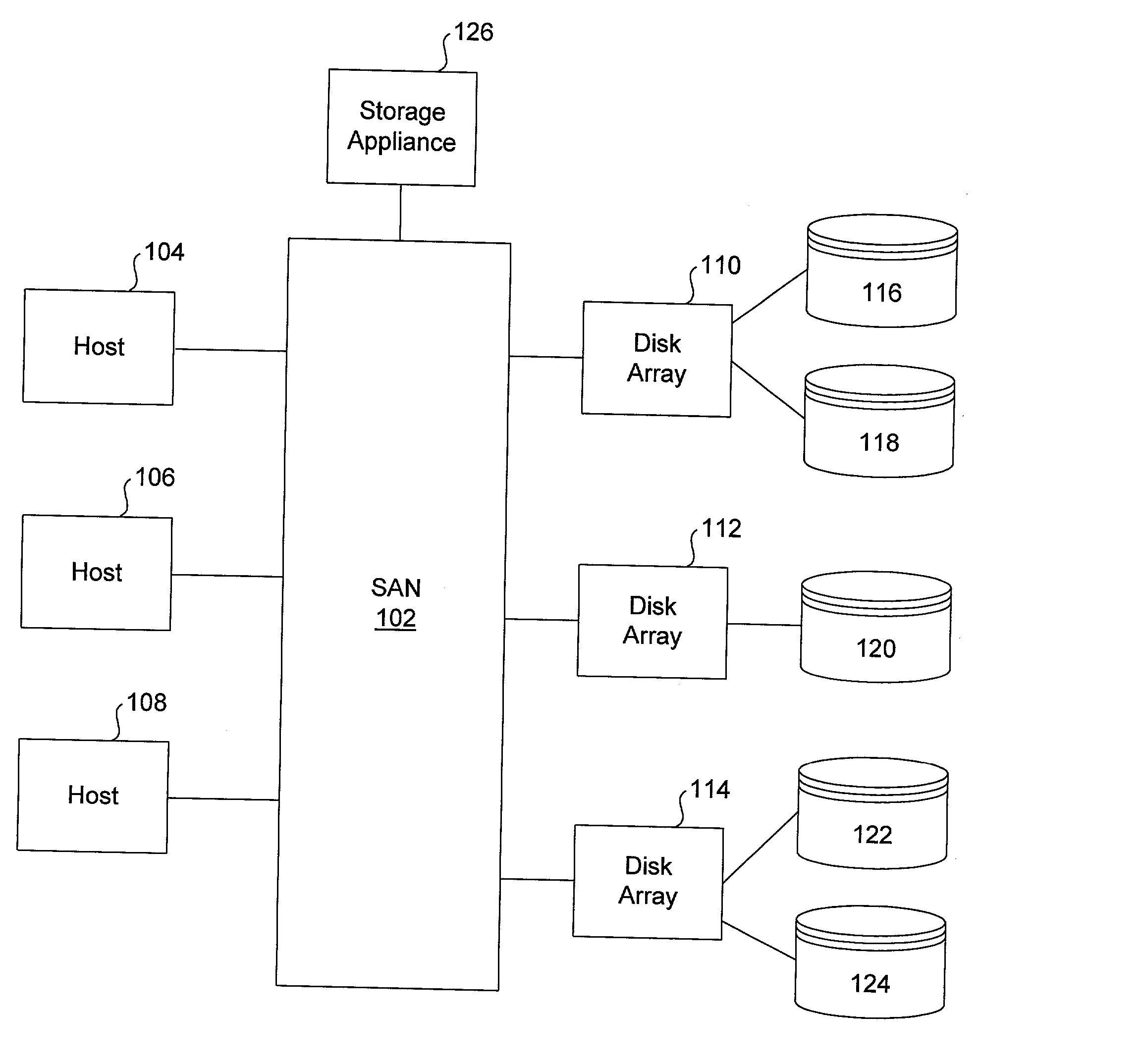

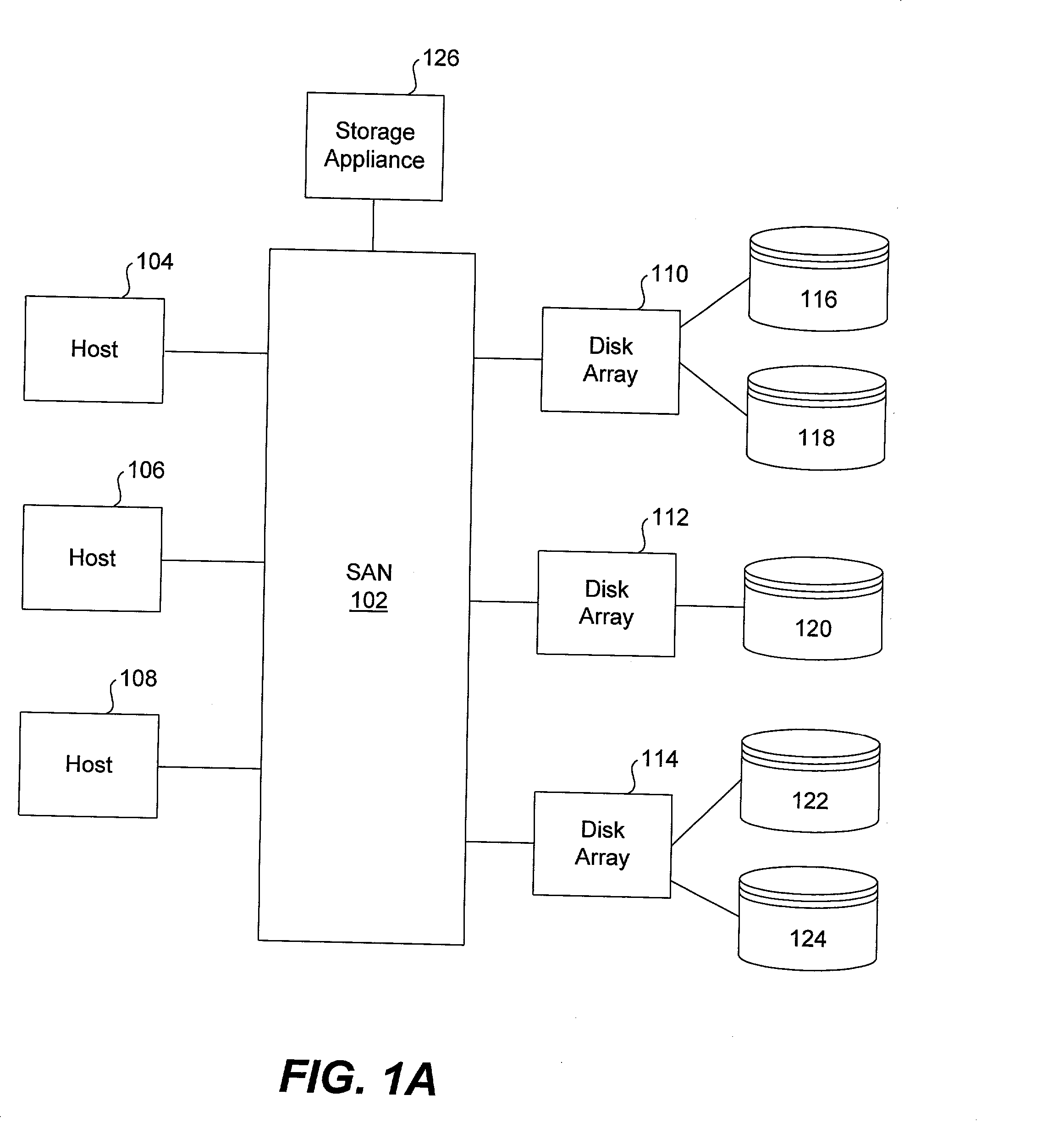

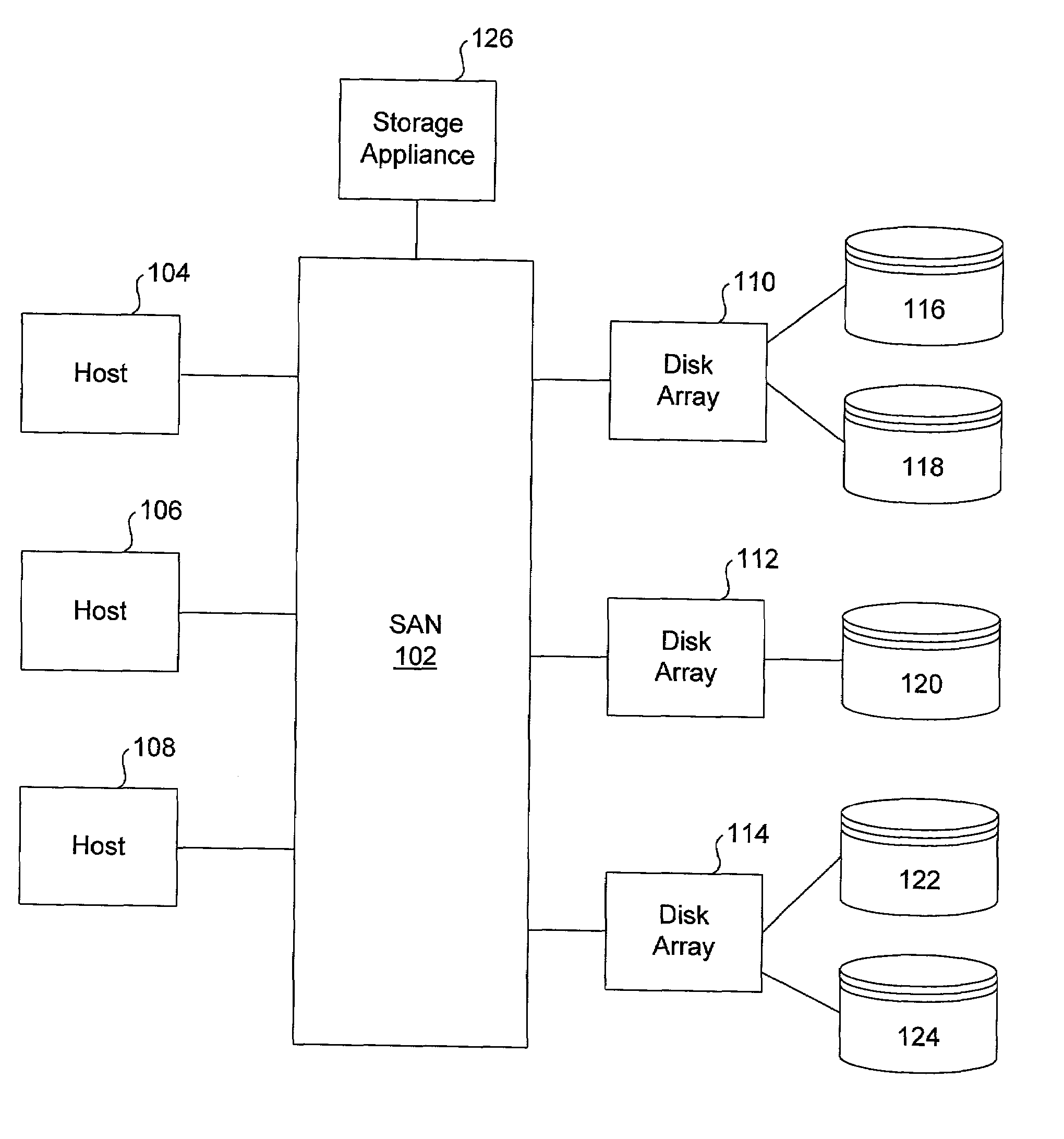

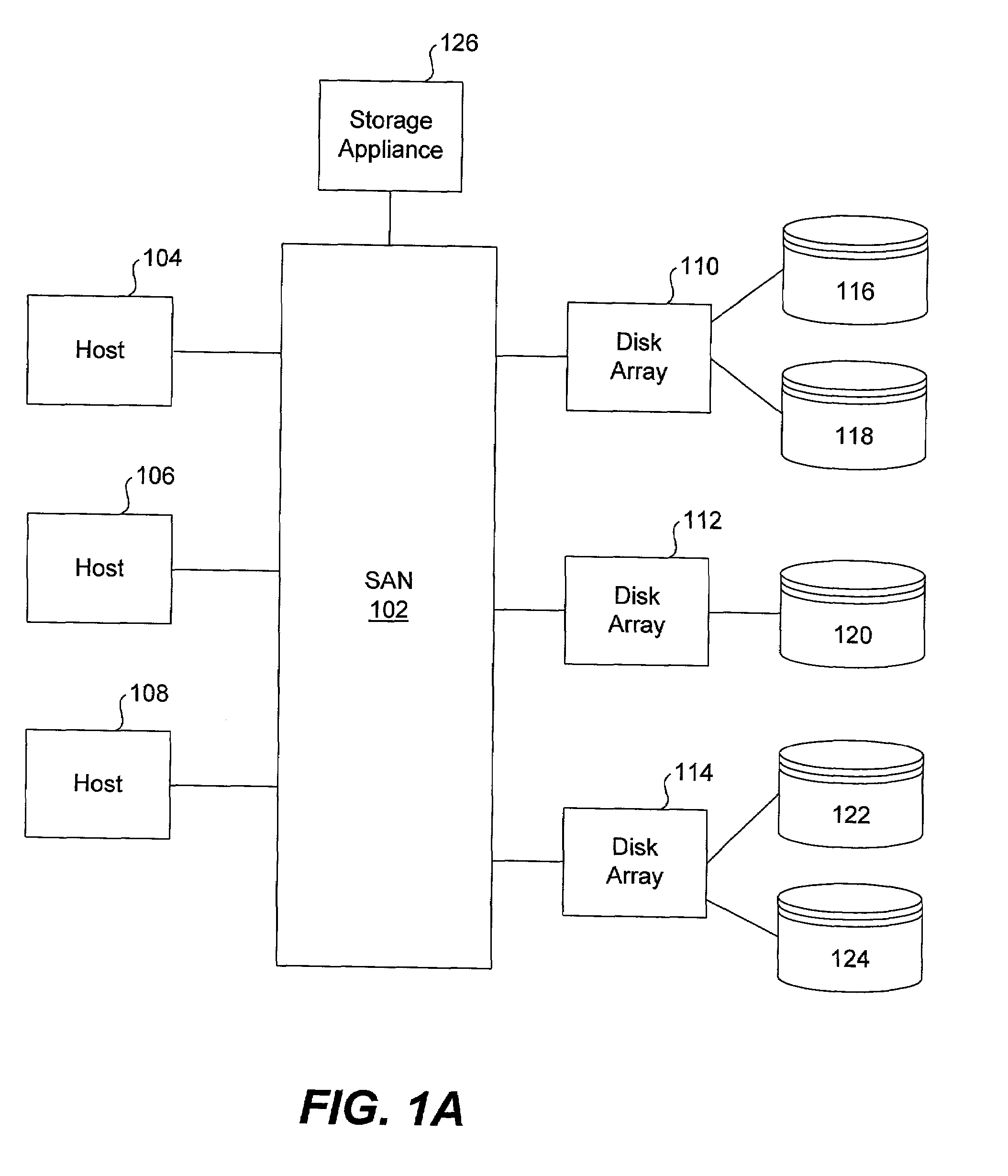

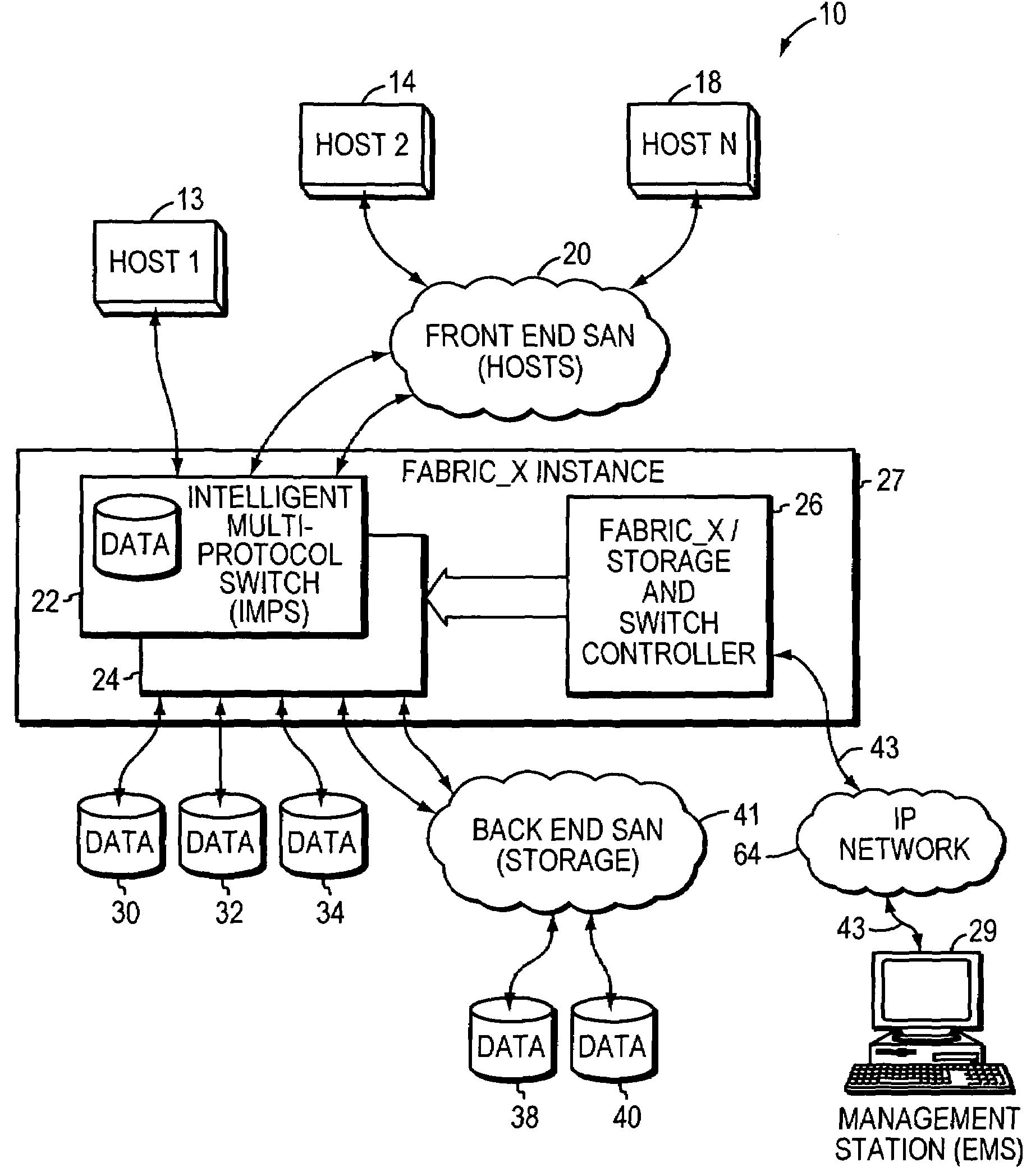

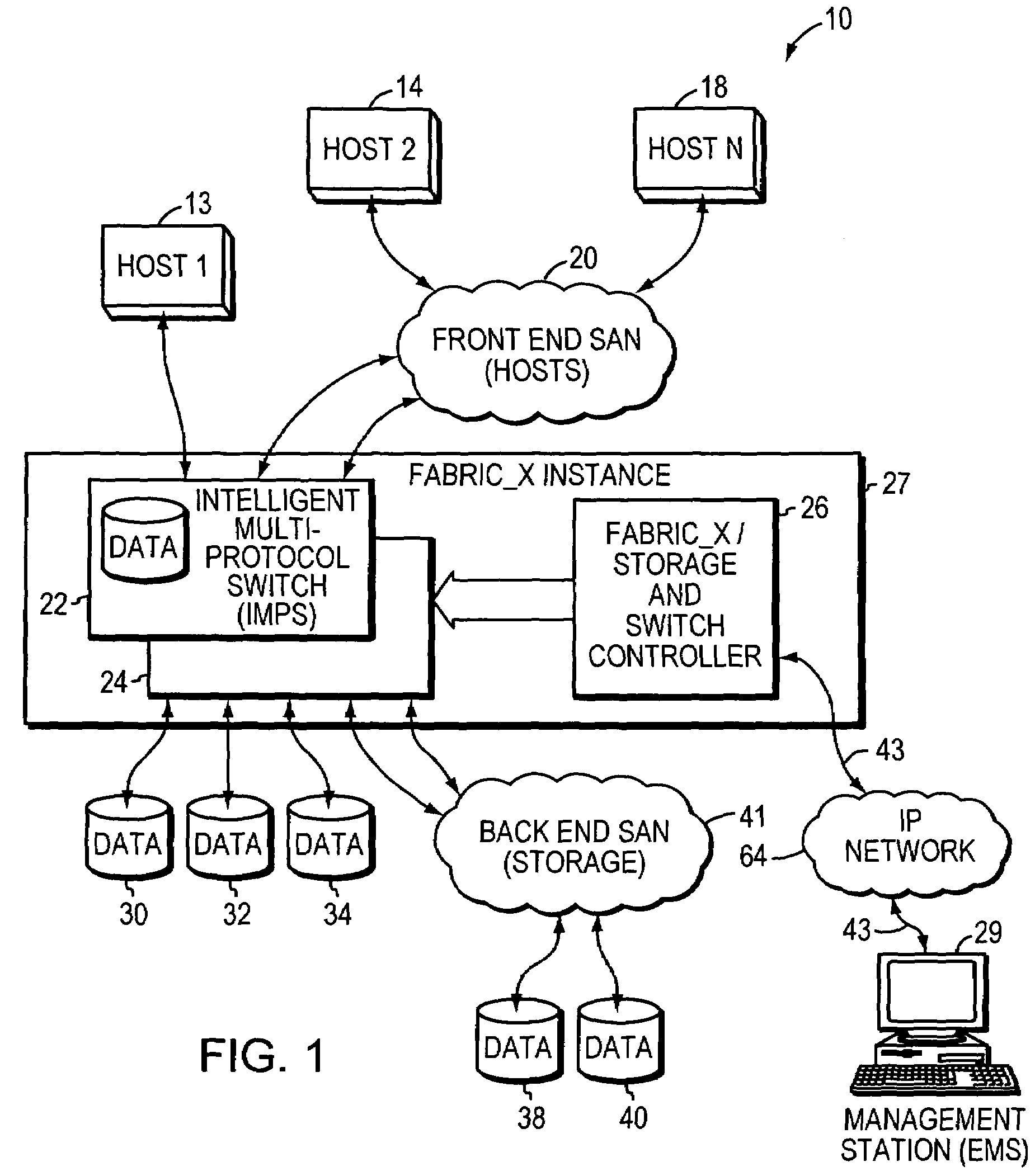

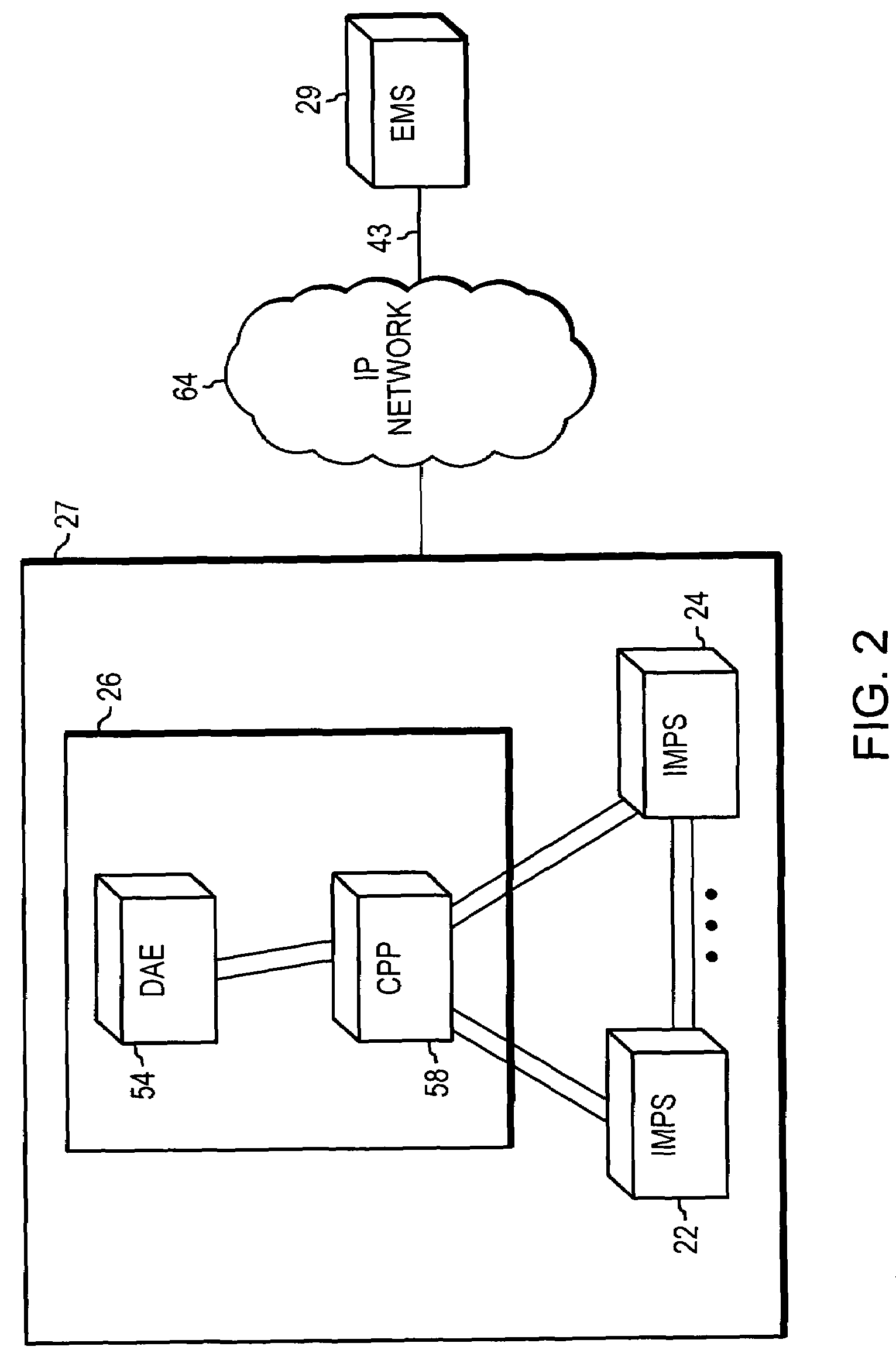

Methods and apparatus for implementing virtualization of storage within a storage area network

ActiveUS20030172149A1Ensure integrityInput/output to record carriersMultiple digital computer combinationsStorage area networkVirtual storage

Methods and apparatus for implementing storage virtualization on a network device of a storage area network are disclosed. A frame or packet is received at a port of the network device. It is then determined that the frame or packet pertains to access of a virtual storage location of a virtual storage unit representing one or more physical storage locations on one or more physical storage units of the storage area network. A virtual-physical mapping between the one or more physical storage locations and the virtual storage location is then obtained. A new or modified frame or packet is then sent to an initiator or a target specified by the virtual-physical mapping.

Owner:CISCO TECH INC

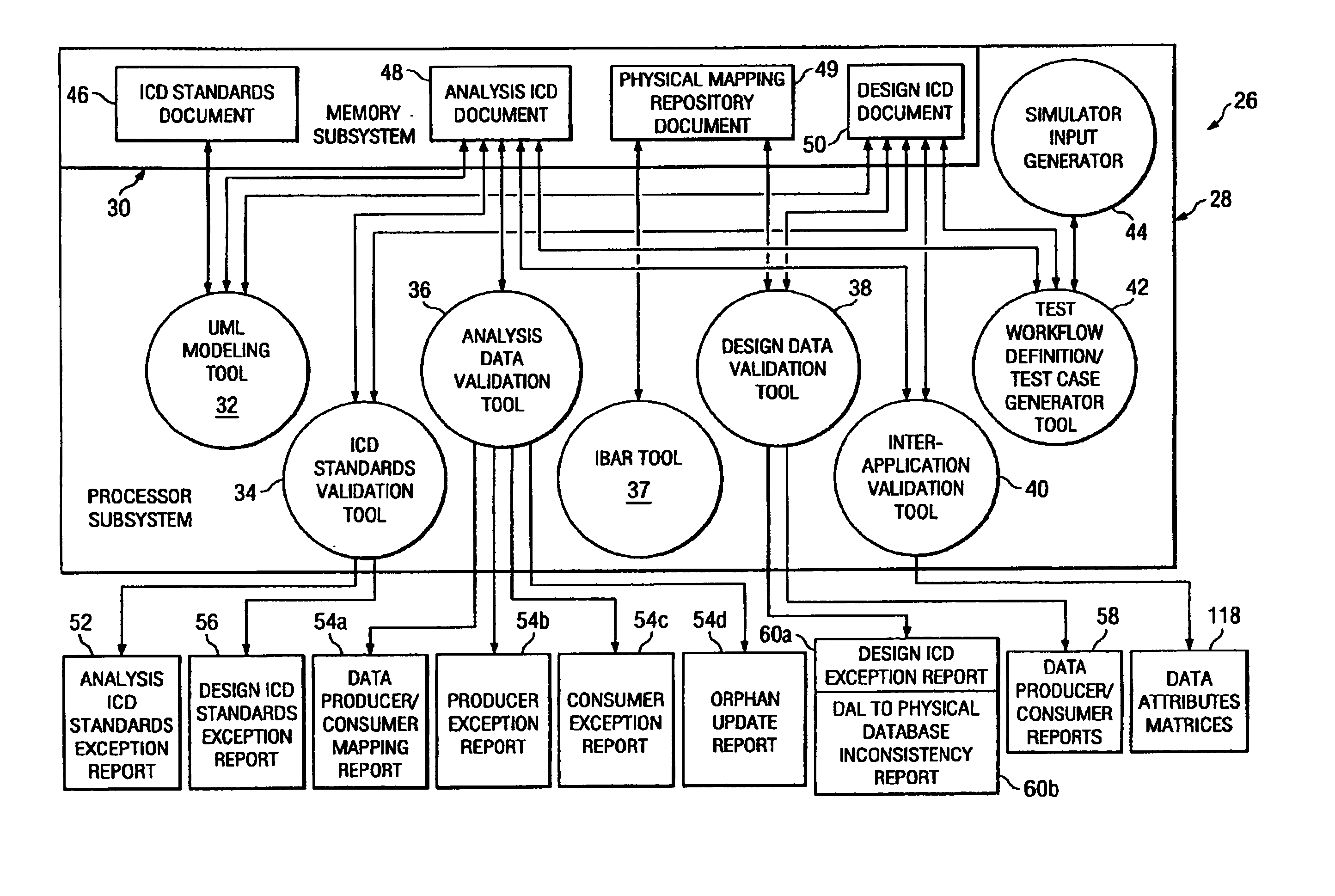

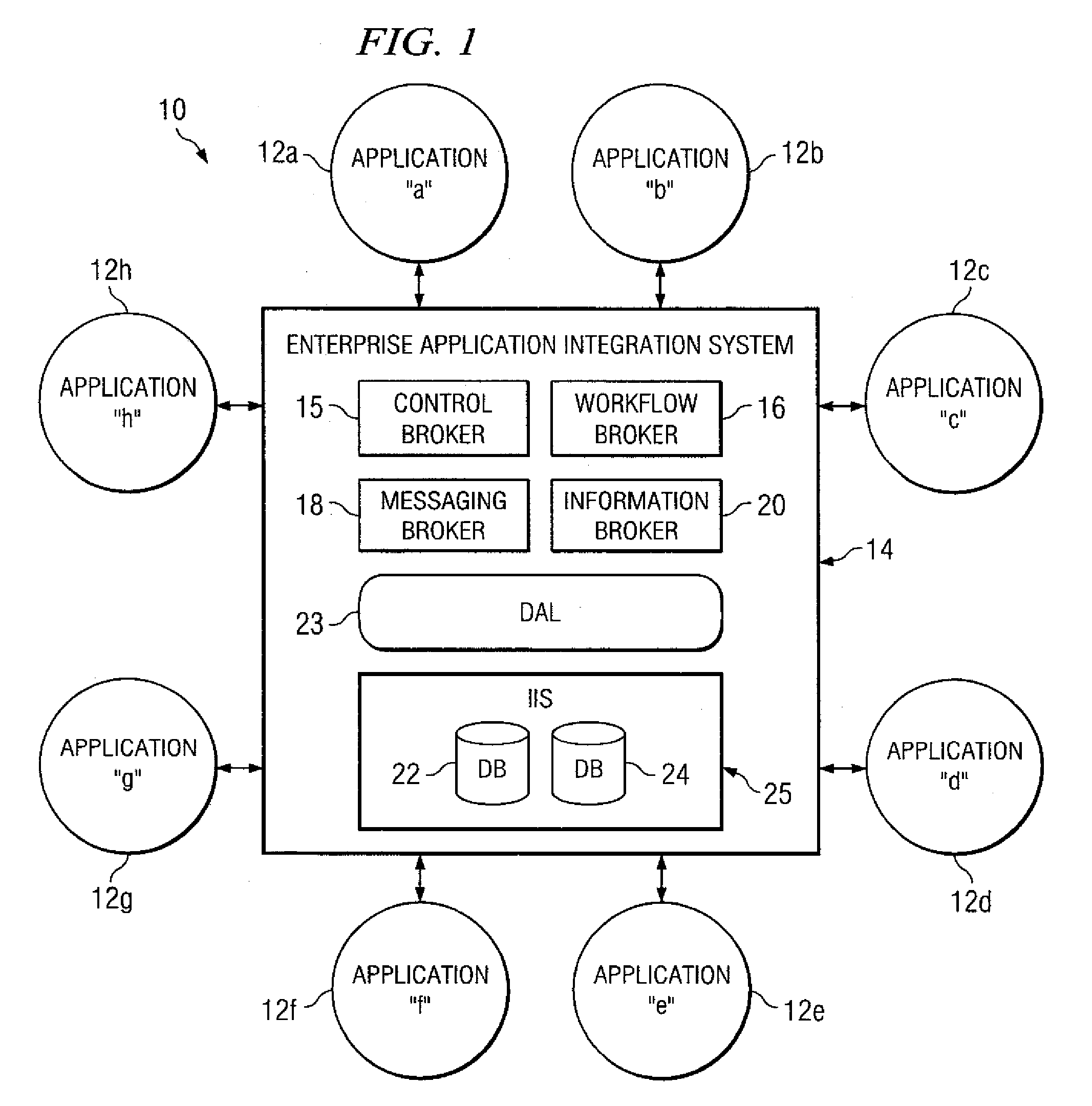

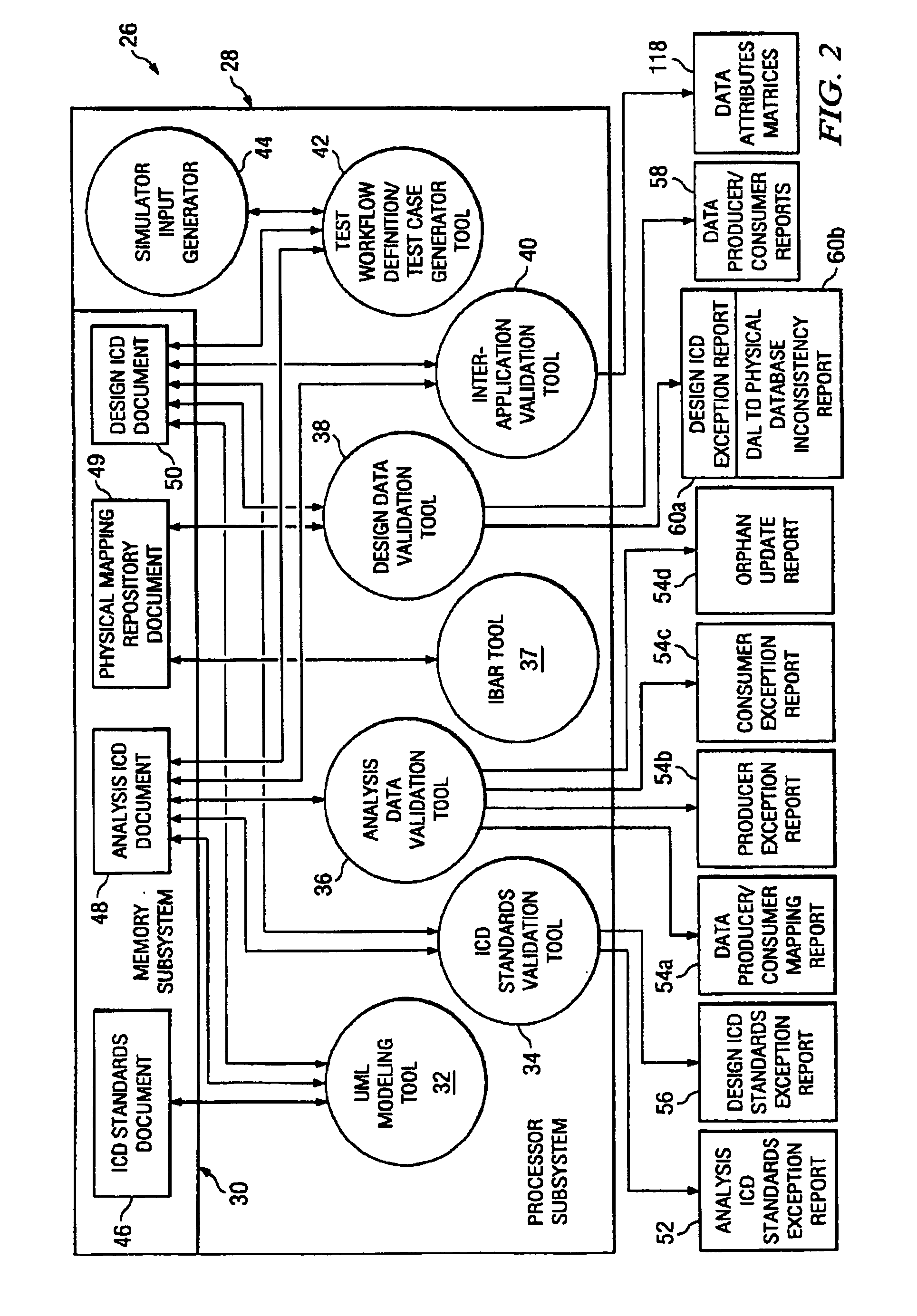

Design data validation tool for use in enterprise architecture modeling

InactiveUS7203929B1Requirement analysisSpecific program execution arrangementsData validationSequence diagram

A selected scenario of a design ICD document for an integrated enterprise is validated by examining each IDL call of each sequence diagram forming part of the selected scenario. A list of data attributes contained in one or more of the IDL calls are generated and each IDL call associated therewith is generated. A physical location to which each such IDL call is mapped is then associated with the IDL call. By analyzing the IDL calls and associated physical locations on a data attribute-by-data attribute basis, inconsistencies in the physical mapping of the data attributes to the databases forming an IIS for the integrated enterprise may be identified and subsequently corrected.

Owner:SPRINT CORPORATION

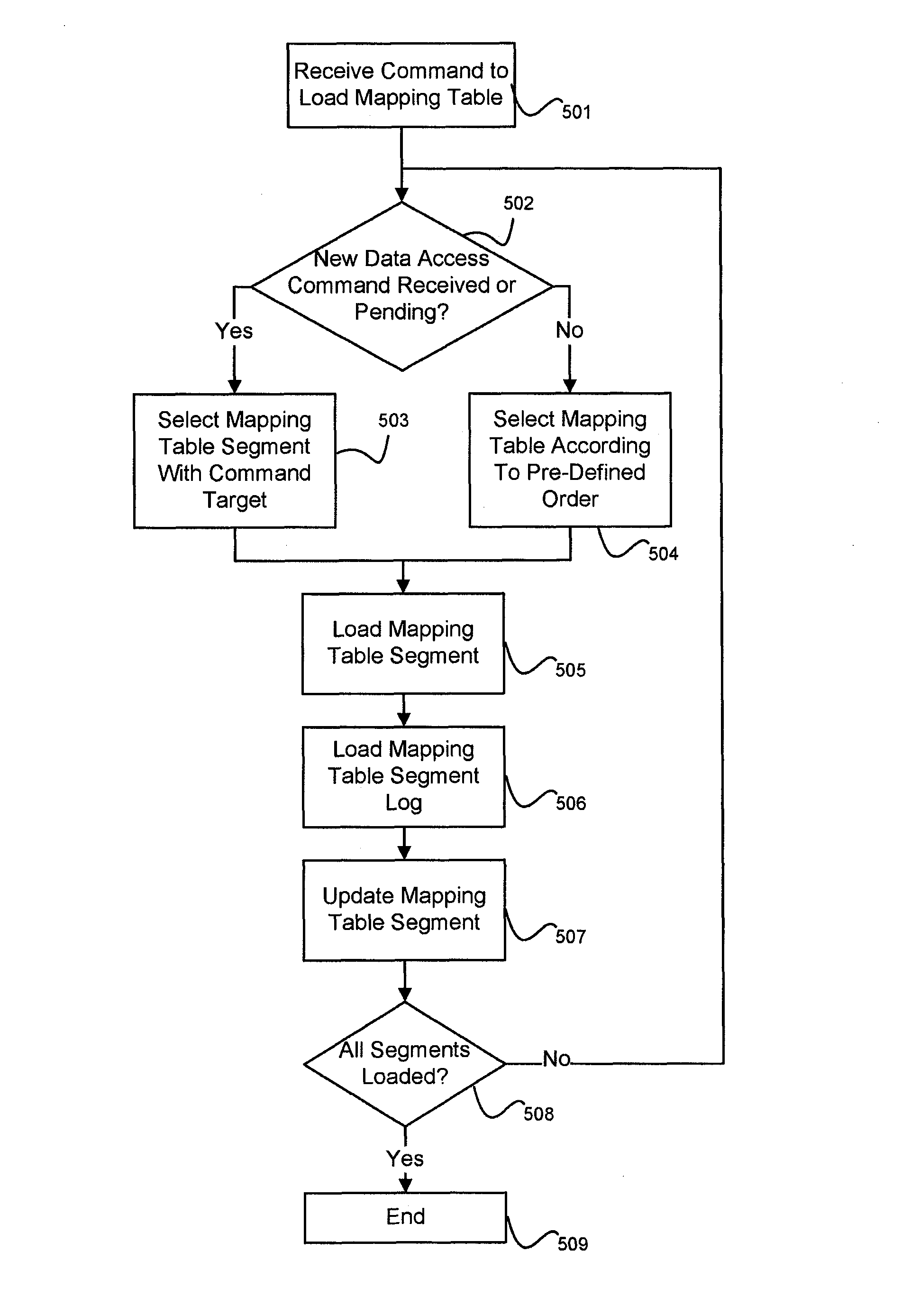

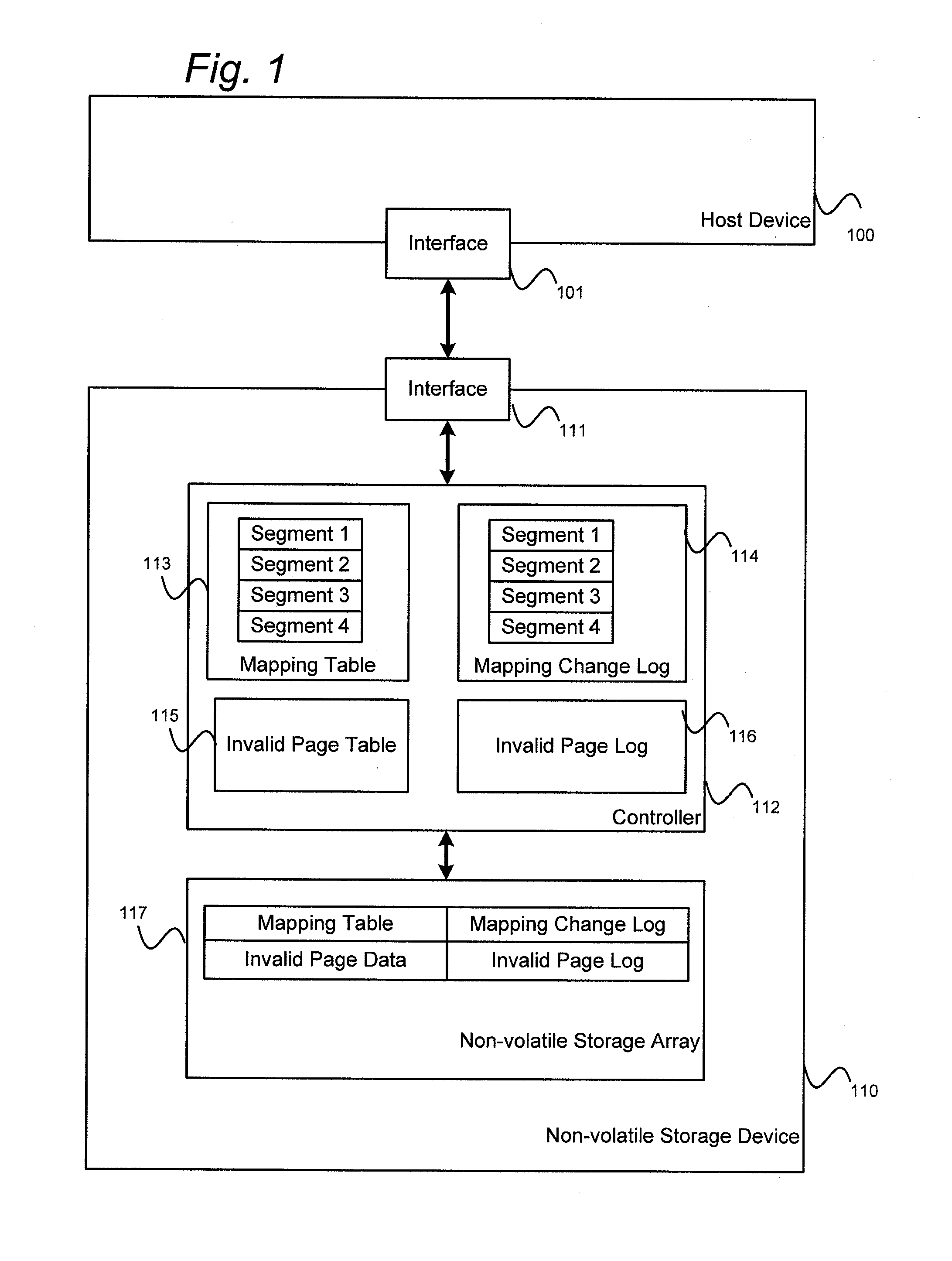

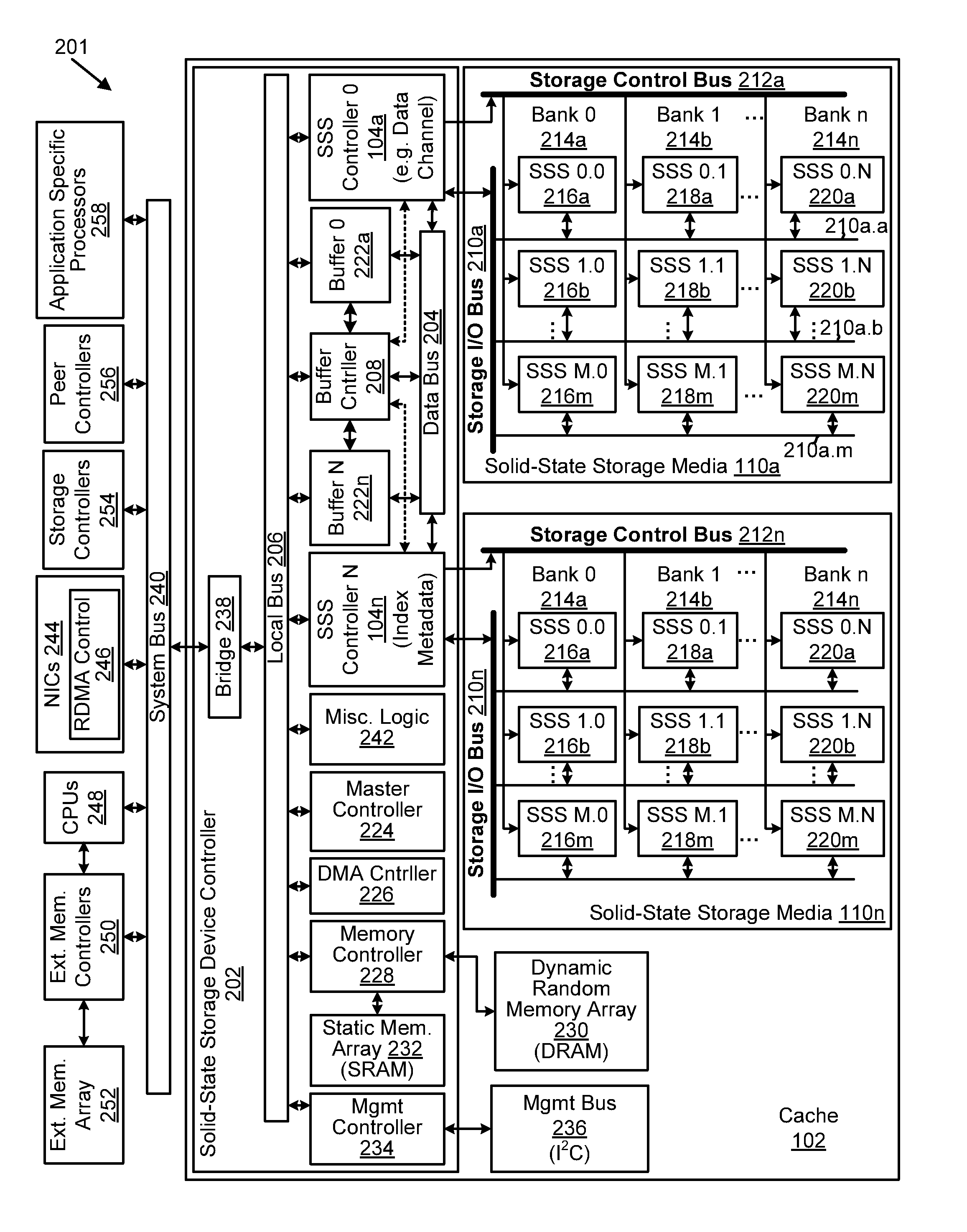

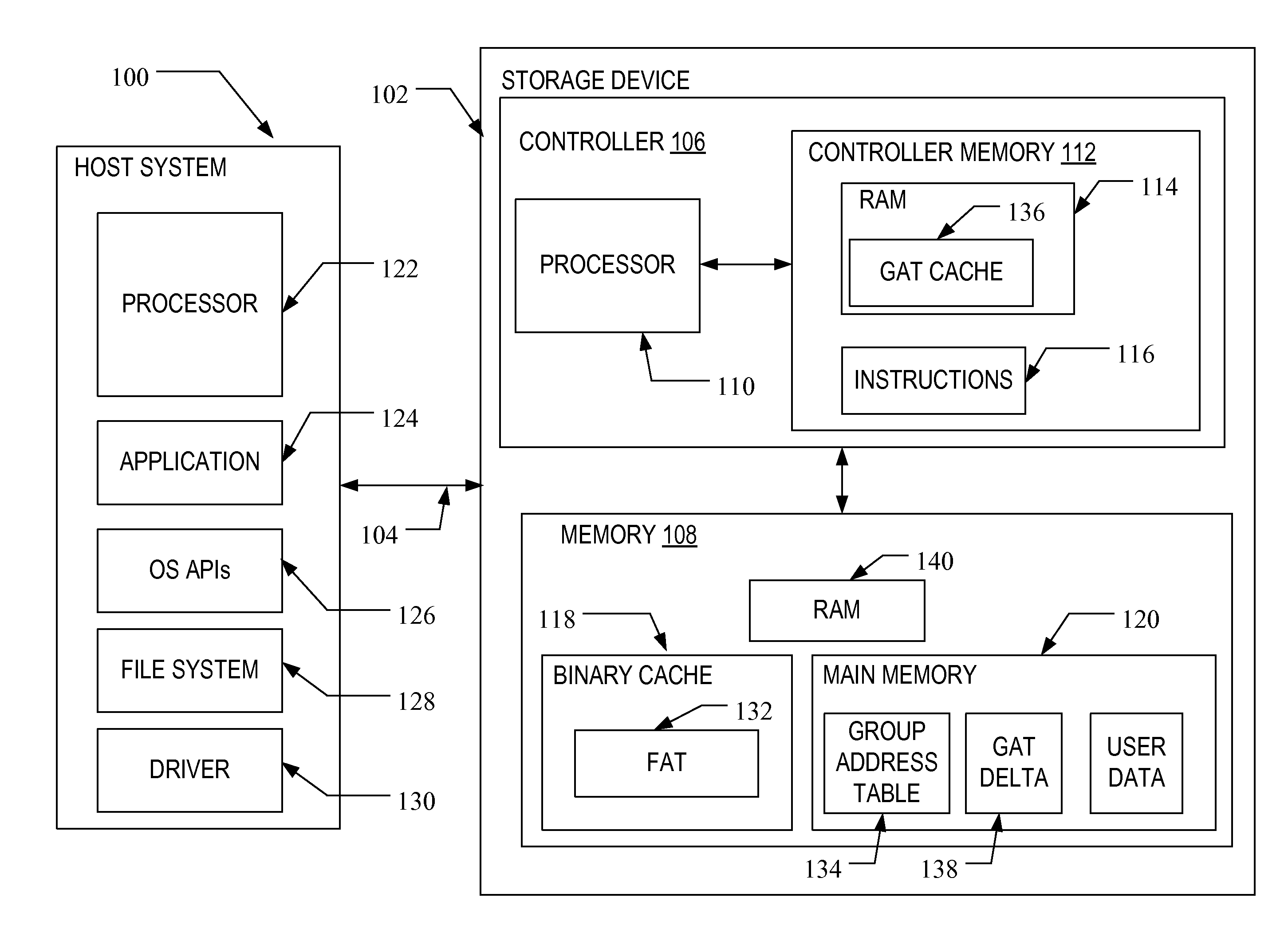

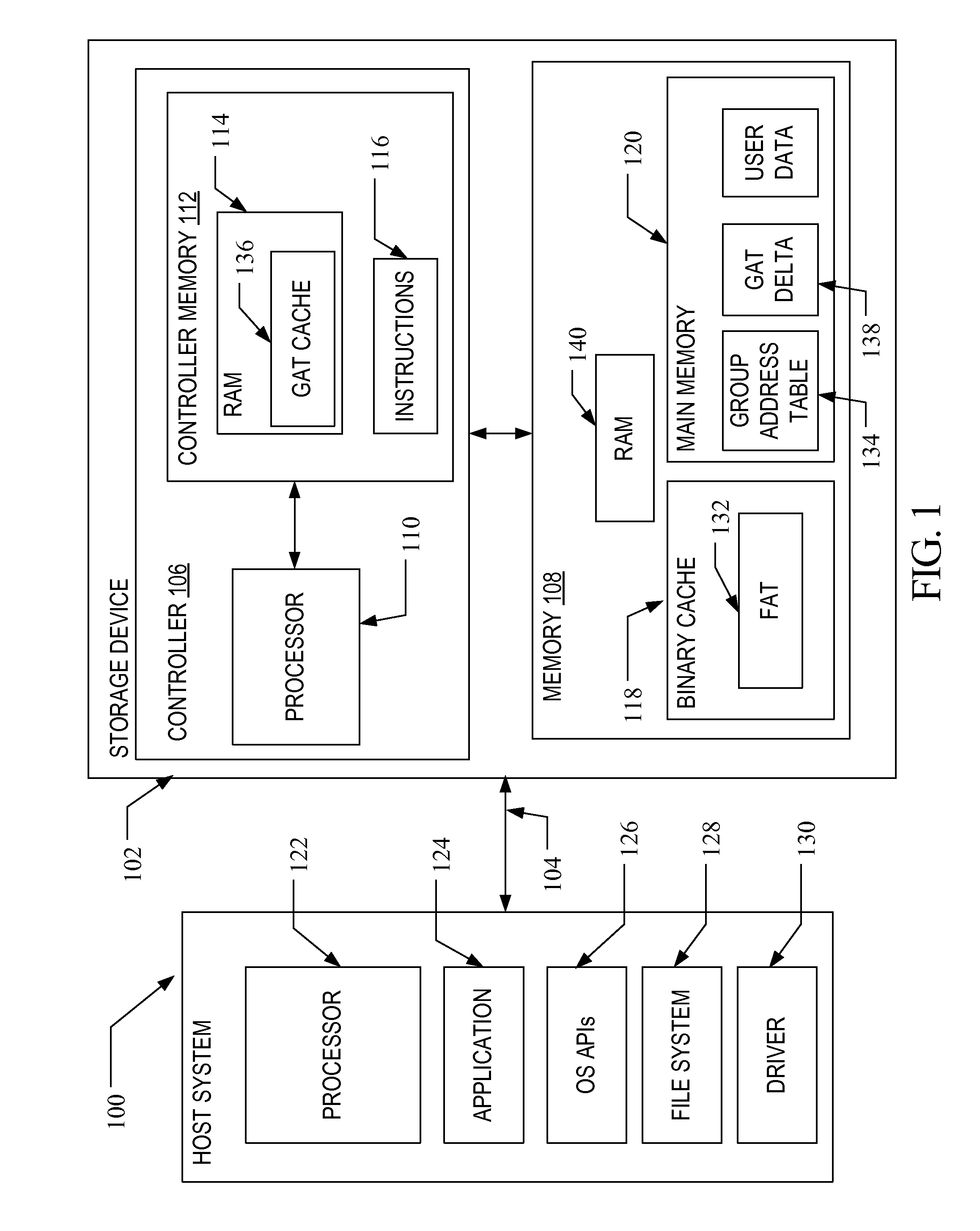

Solid-state drive with reduced power up time

ActiveUS8793429B1Reduce delaysMemory architecture accessing/allocationEnergy efficient ICTSolid-state driveComputer science

A non-volatile storage system is provided with reduced delays associated with loading and updating a logical-to-physical mapping table from non-volatile memory. The mapping table is stored in a plurality of segments, so that each segment can be loaded individually. The segmented mapping table allows memory access to logical addresses associated with the loaded segment when the segment is loaded, rather than delaying accesses until the entire mapping table is loaded. When loading mapping segments, segments can be loaded according to whether there is a pending command or by an order according to various algorithms.

Owner:WESTERN DIGITAL TECH INC

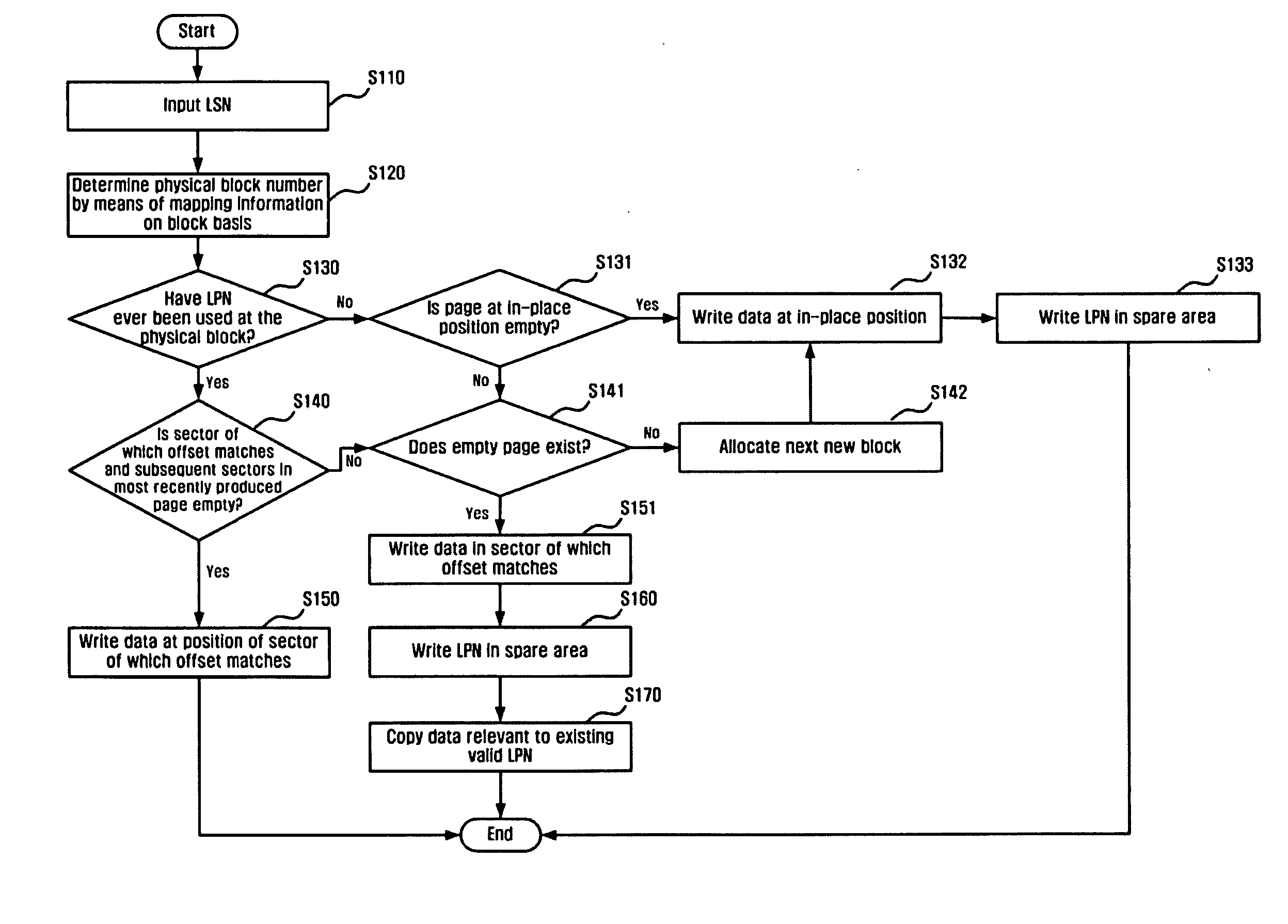

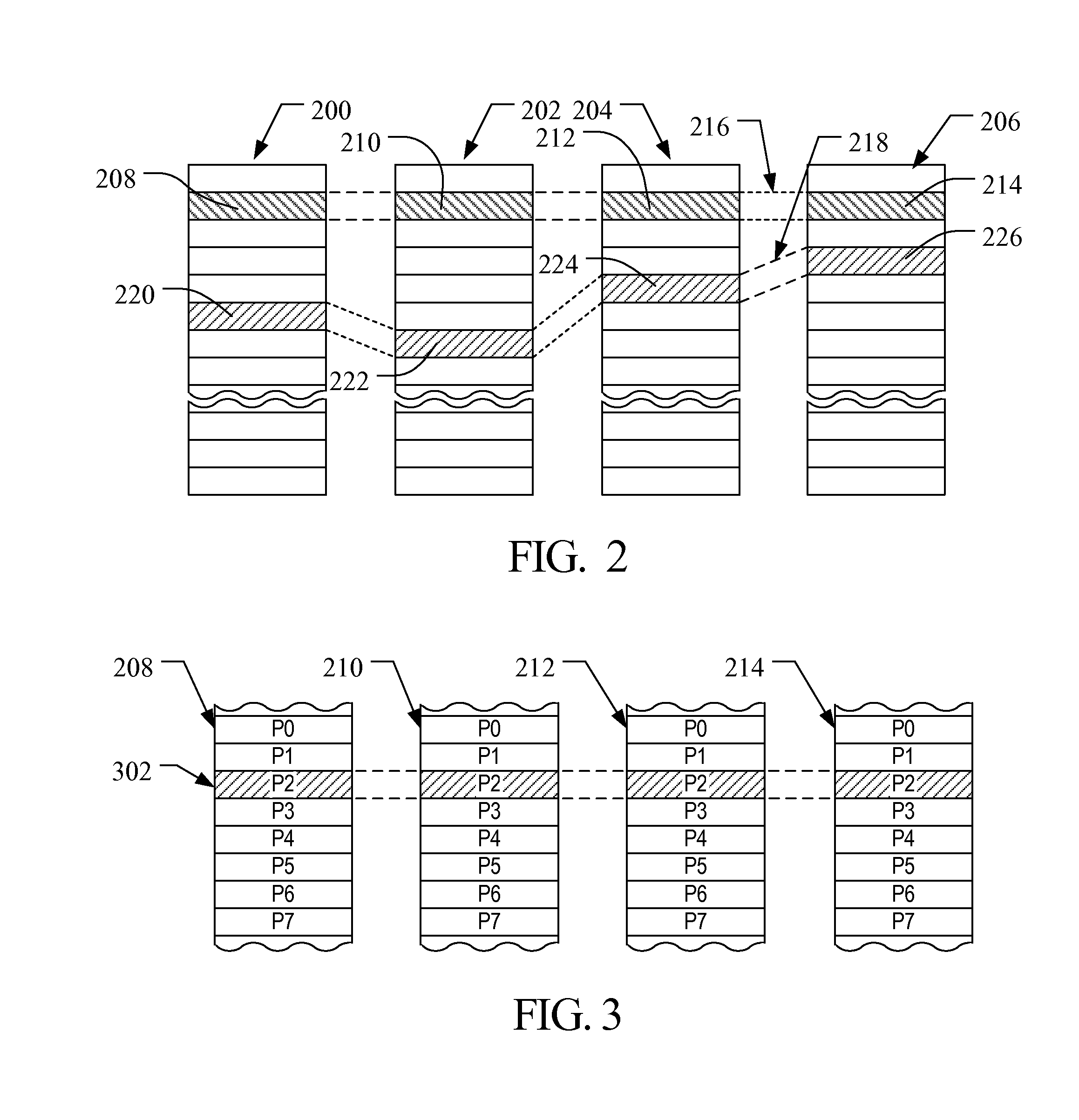

Address mapping method and mapping information managing method for flash memory, and flash memory using the same

ActiveUS20050144368A1Performance maximizationMemory adressing/allocation/relocationSpecial data processing applicationsComputer scienceAddress mapping

A method for minimizing the degradation of performance upon accessing a flash memory using a logical-physical mapping scheme, and a method for efficiently storing and managing information on logical-physical mapping in a flash memory. A method for writing data in a flash memory includes determining whether a sector is empty in a physical page having a most recently written logical page number of data to be written, the offset of the sector matching that of the data to be written; if the sector is empty, writing the data in the sector to the physical page; and if the sector is not empty, selecting an empty physical page to write the data to a sector in the selected empty physical page of which the offset matches that of the data to be written and writing a logical page number for the data to the selected empty physical page.

Owner:SAMSUNG ELECTRONICS CO LTD

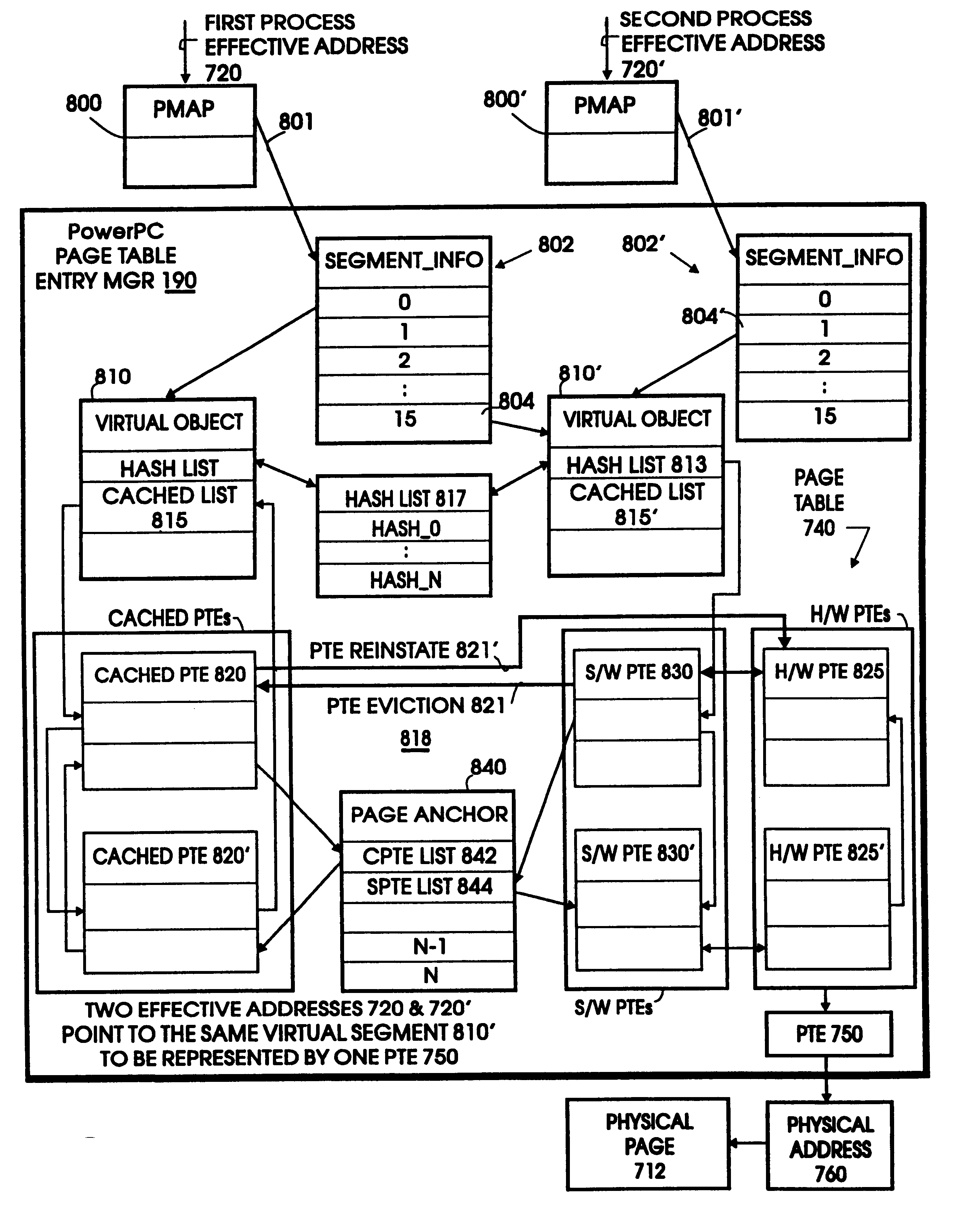

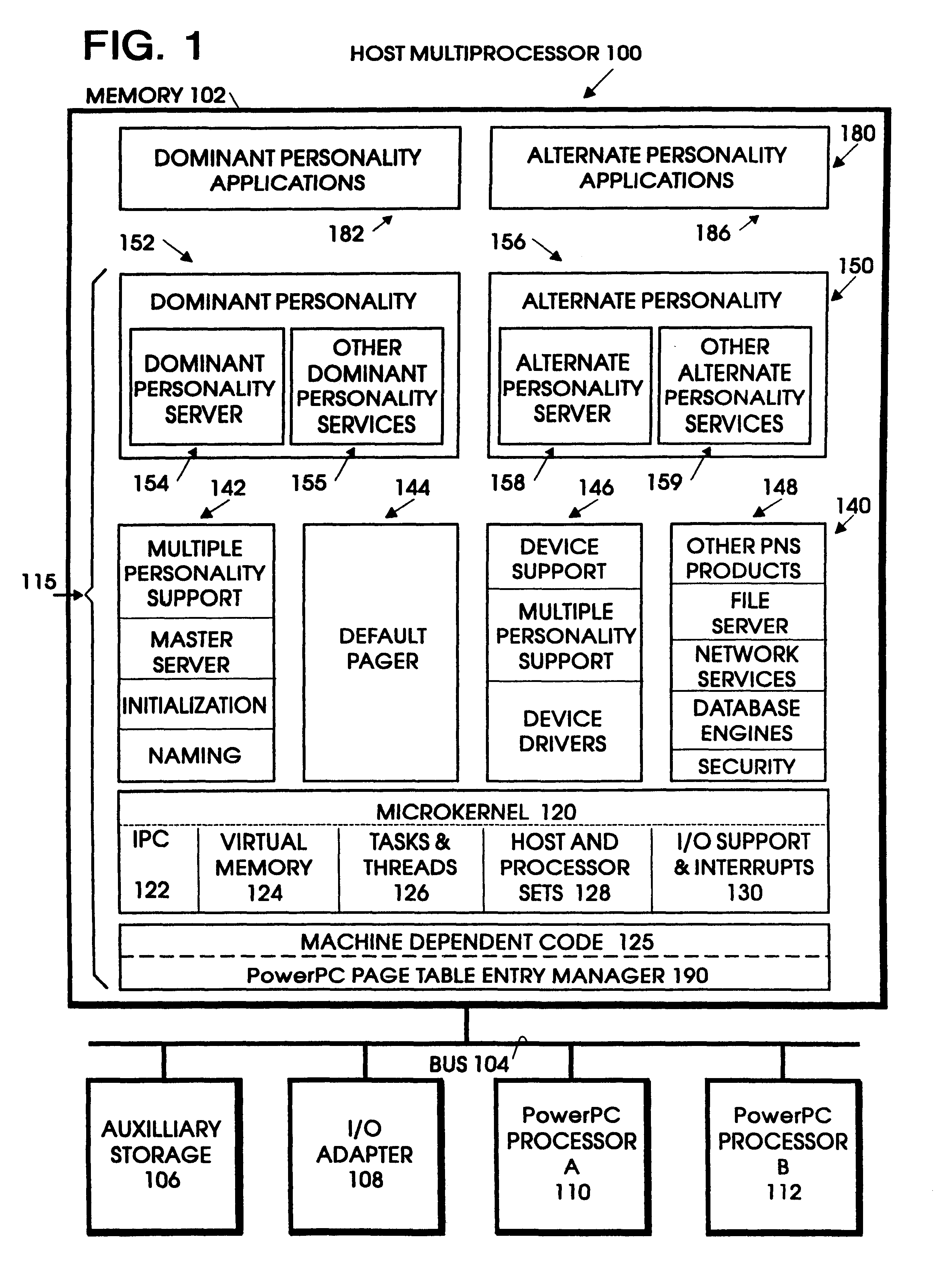

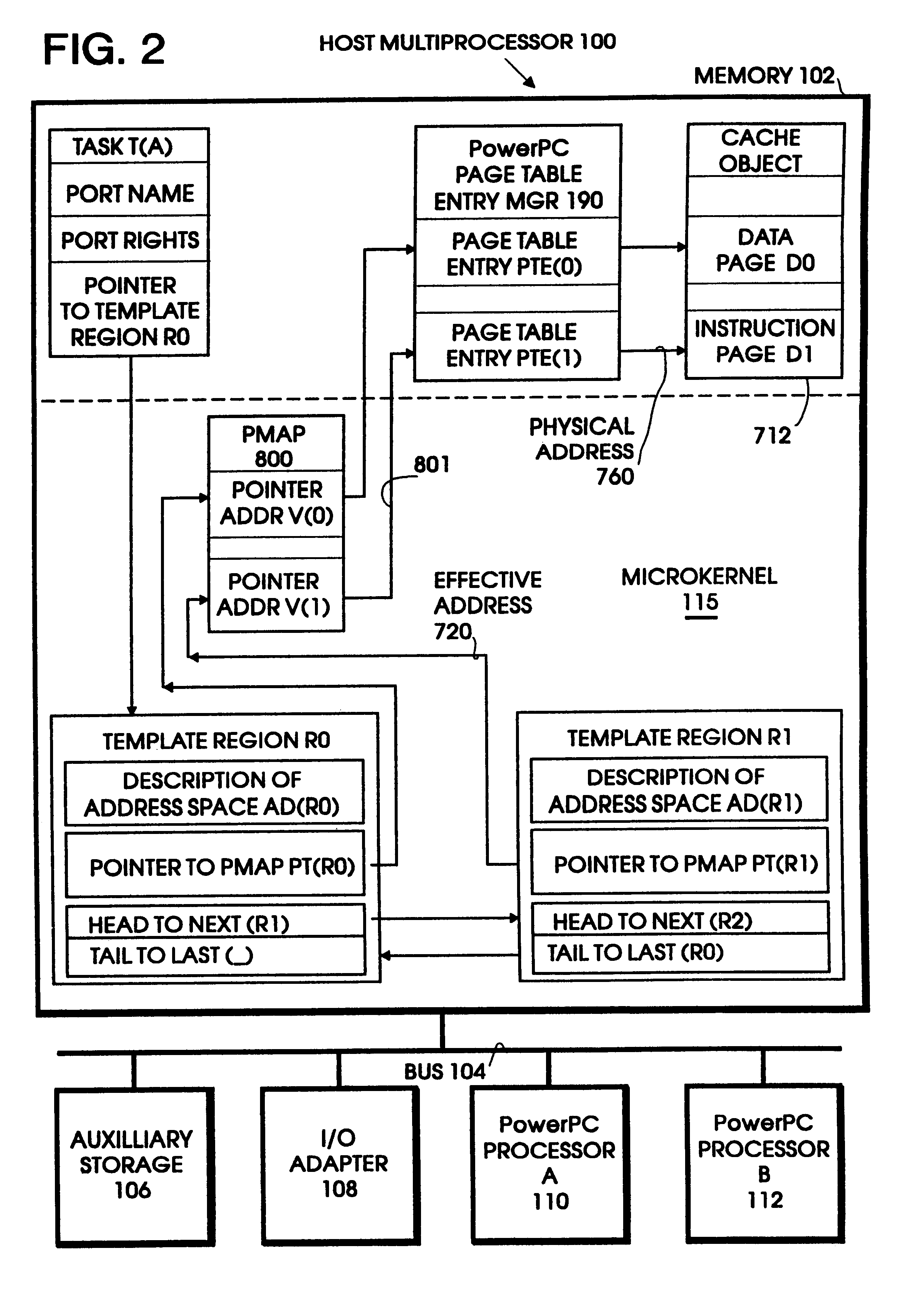

Page table entry management method and apparatus for a microkernel data processing system

InactiveUS6308247B1Maximize system performanceEasy to manageMemory architecture accessing/allocationMemory adressing/allocation/relocationData processing systemManagement unit

A page table entry management method and apparatus provide the Microkernel System with the capability to program the memory management unit on the PowerPC family of processors. The PowerPC processors define a limited set of page table entries (PTEs) to maintain virtual to physical mappings. The page table entry management method and apparatus solves the problem of a limited number of PTEs by segment aliasing when two or more user processes share a segment of memory. The segments are aliased rather than duplicating the PTES. This significantly reduces the number of PTEs. In addition, the method provides for caching existing PTEs when the system actually runs out of PTEs. A cache of recently discarded PTEs provides a fast fault resolution when a recently used page is accessed again.

Owner:IBM CORP

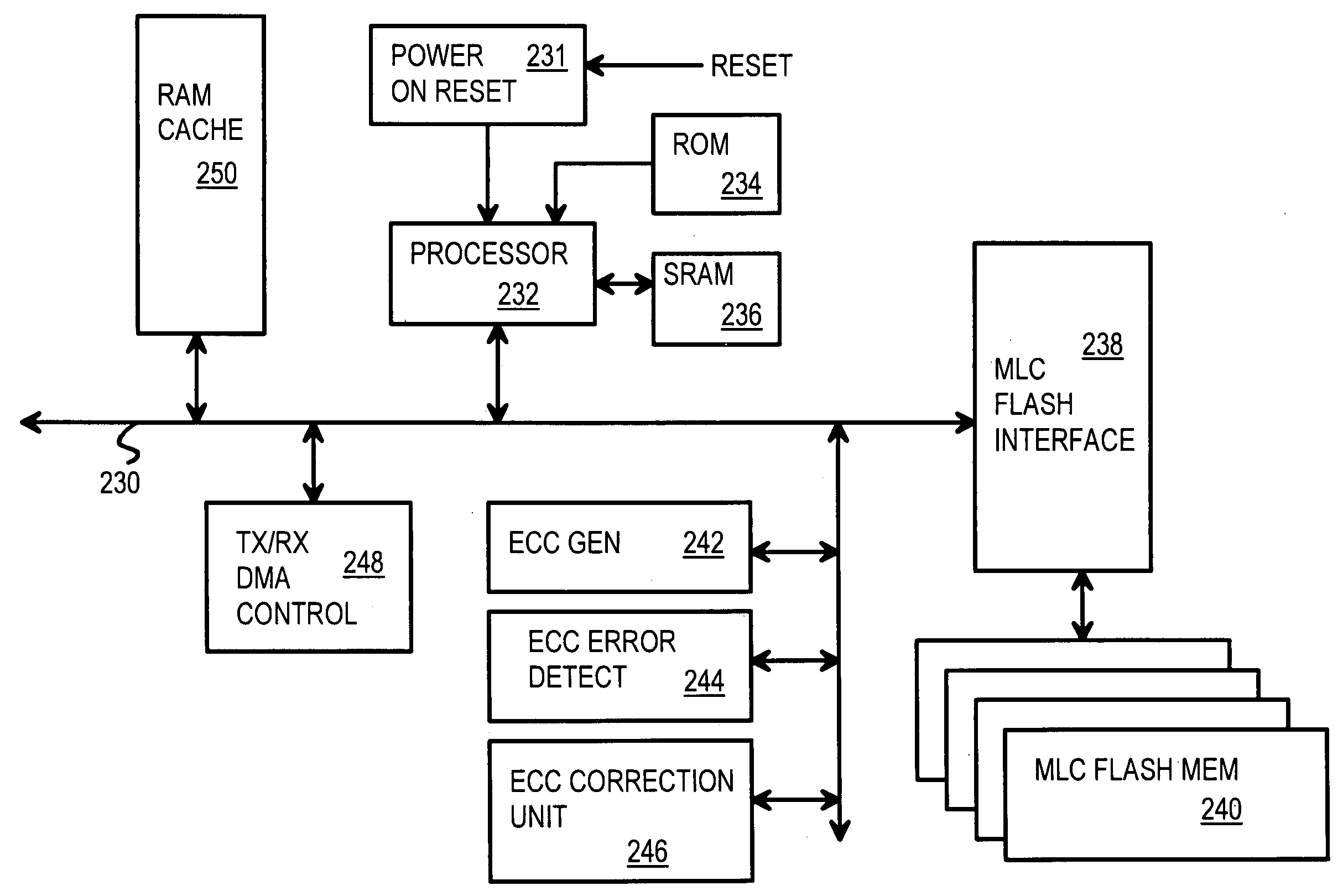

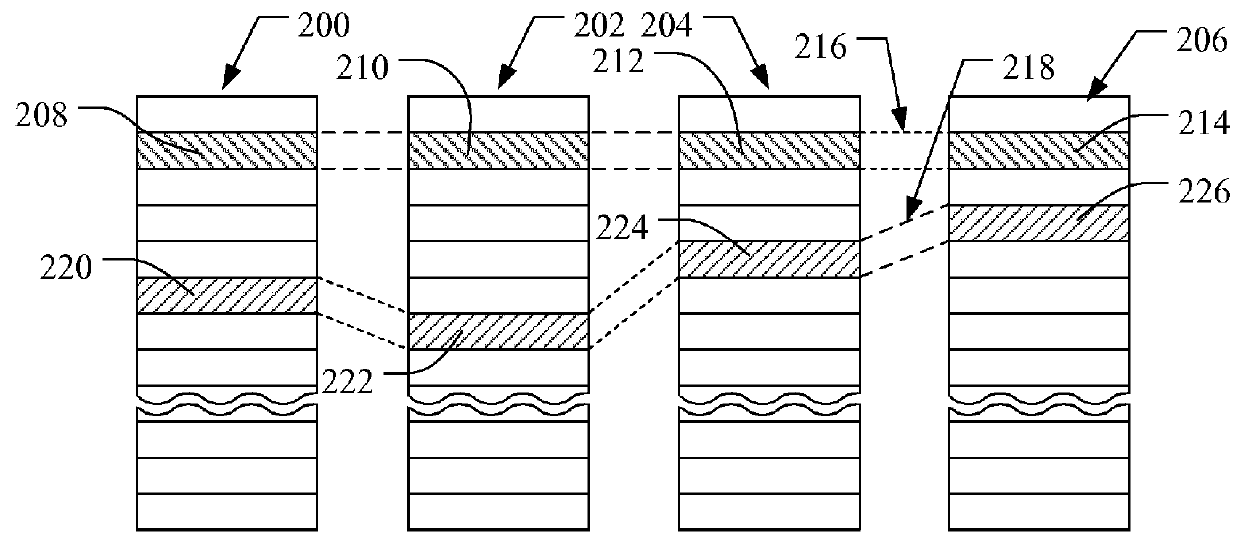

Swappable Sets of Partial-Mapping Tables in a Flash-Memory System With A Command Queue for Combining Flash Writes

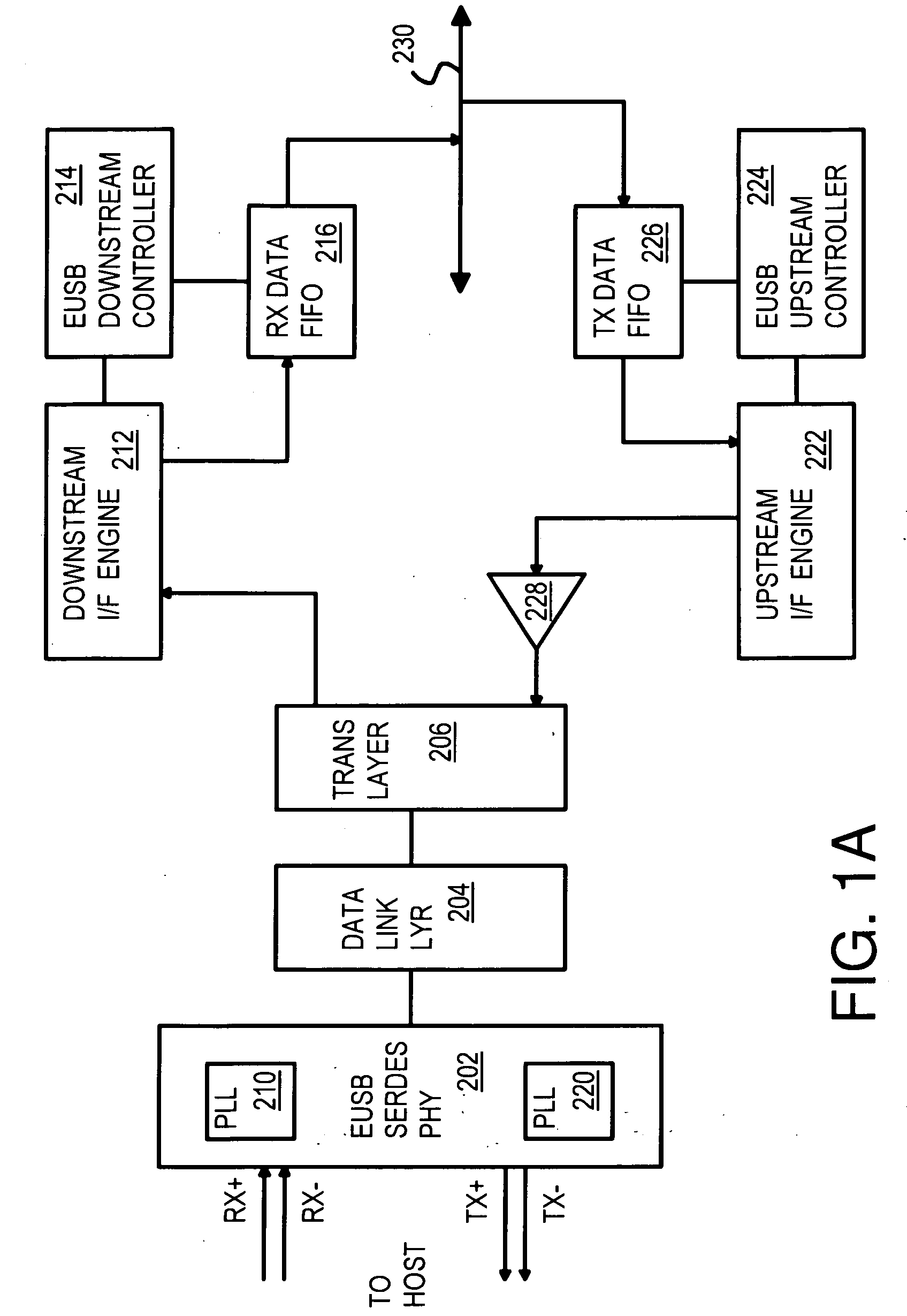

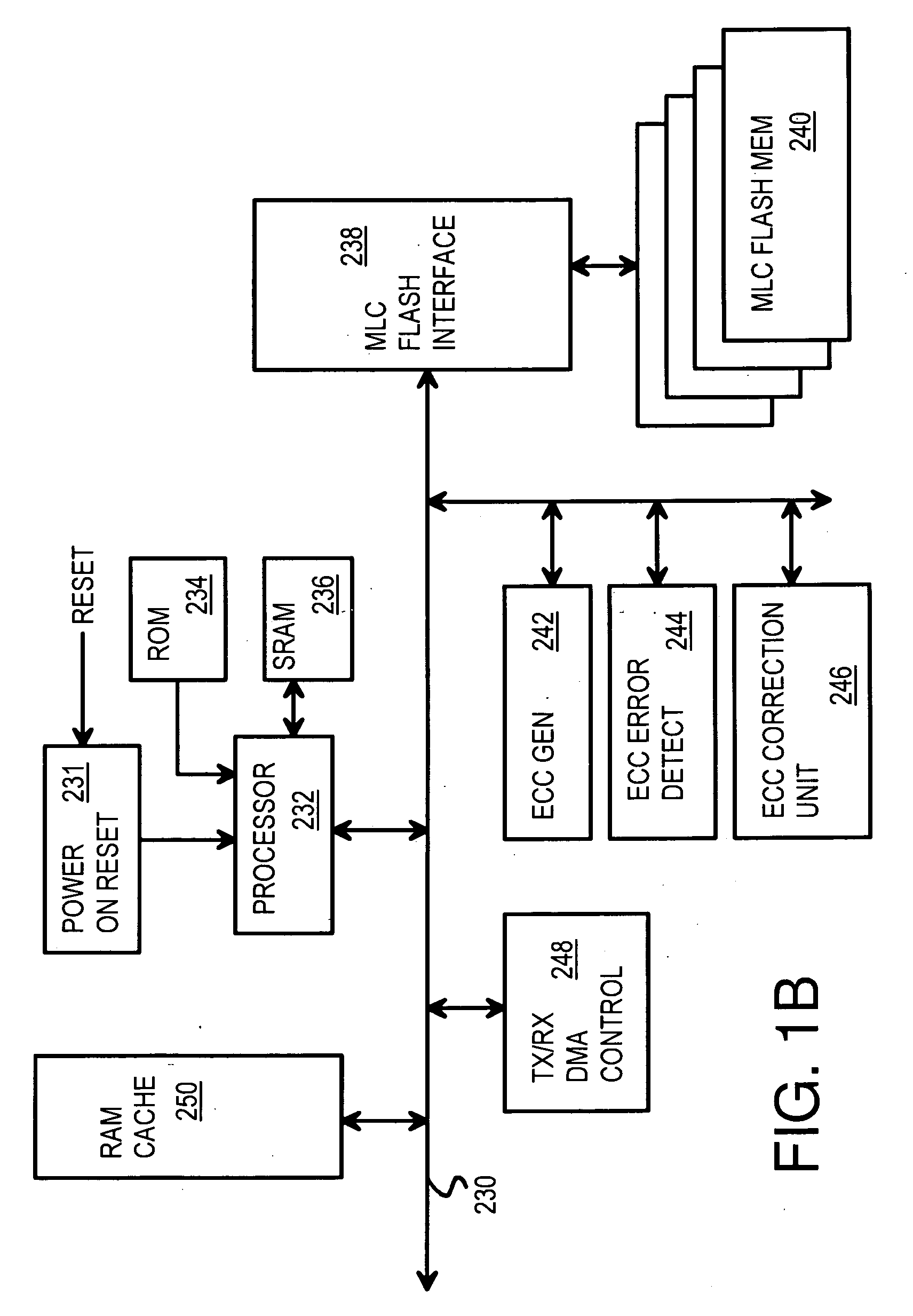

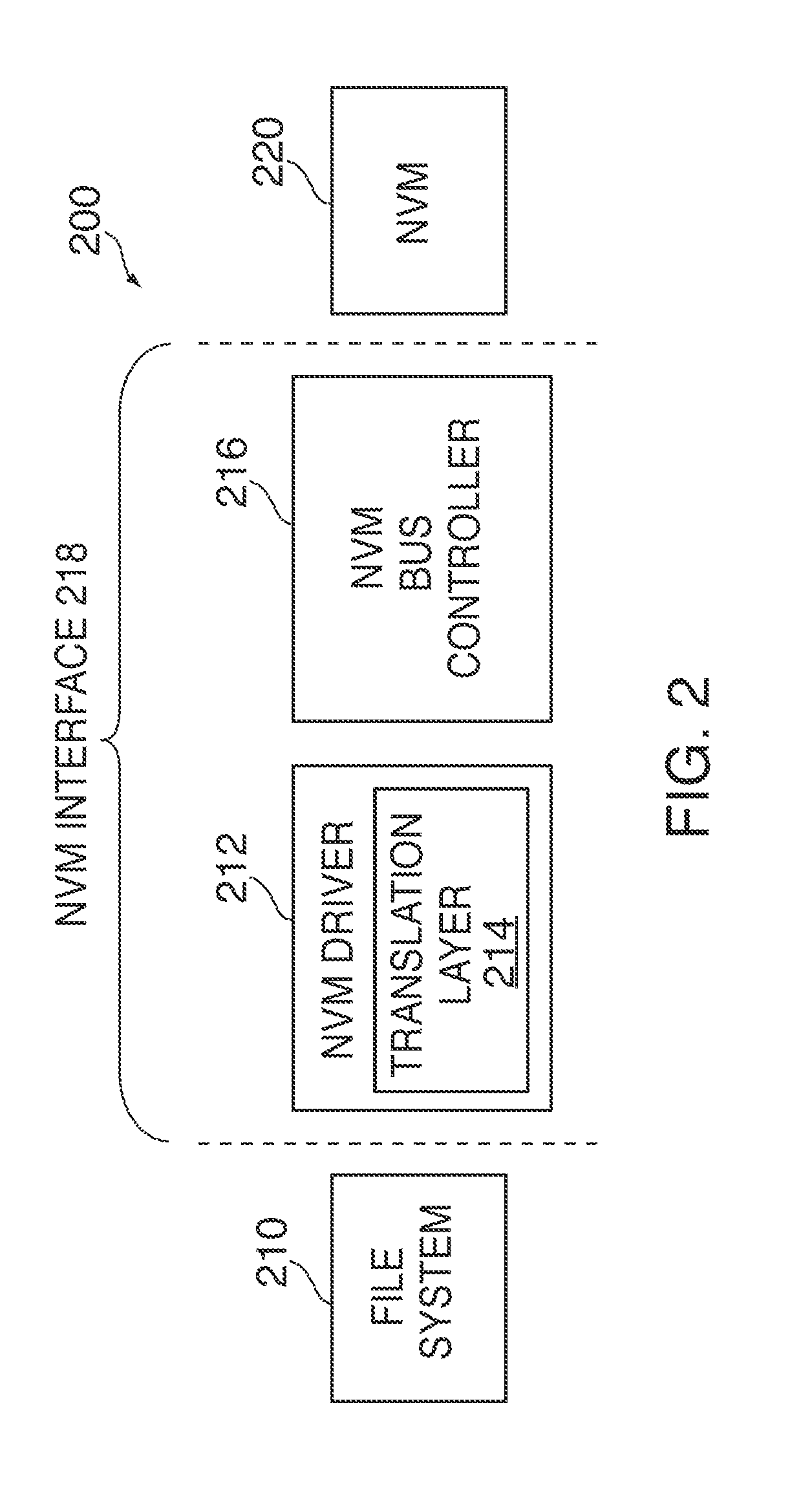

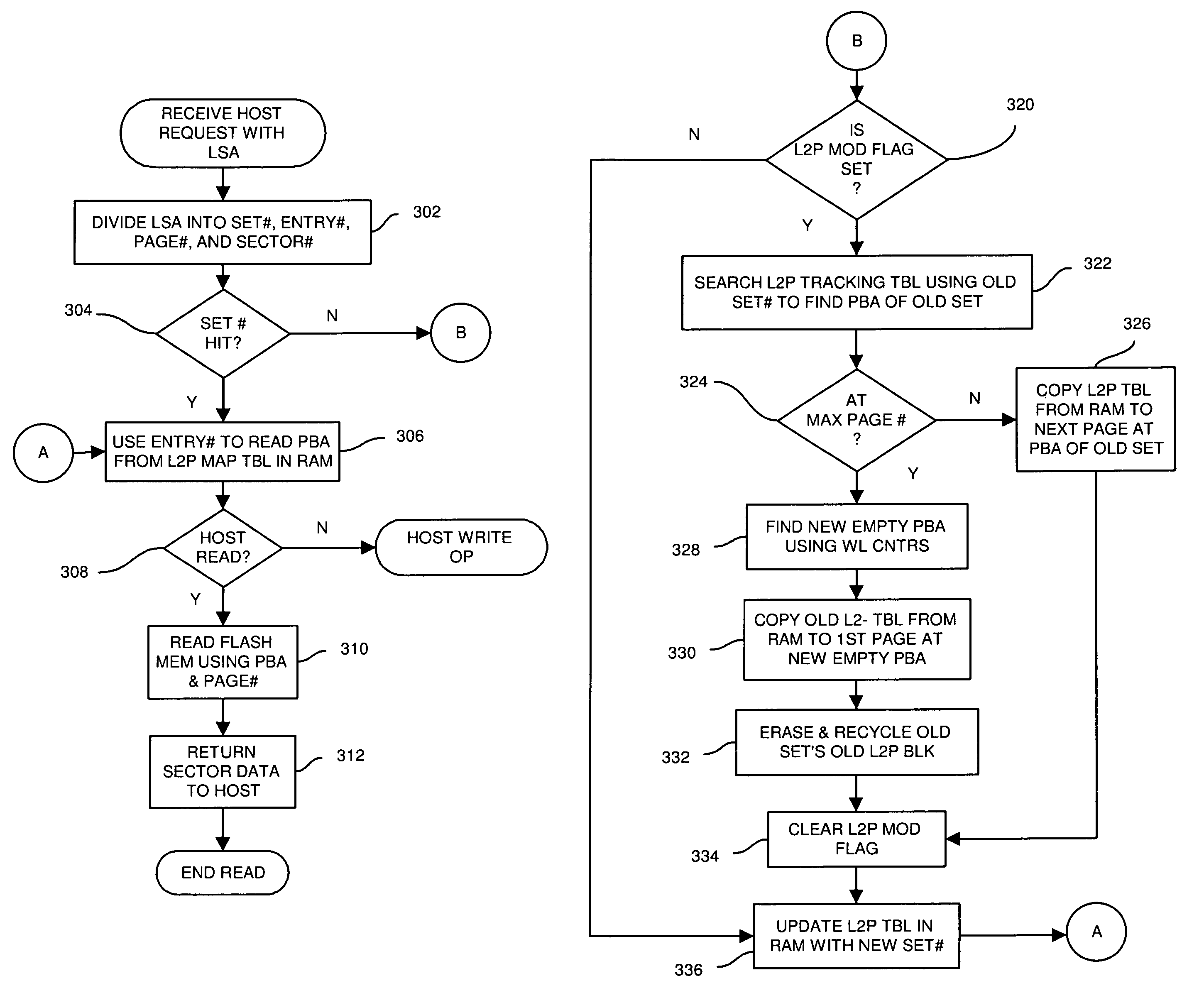

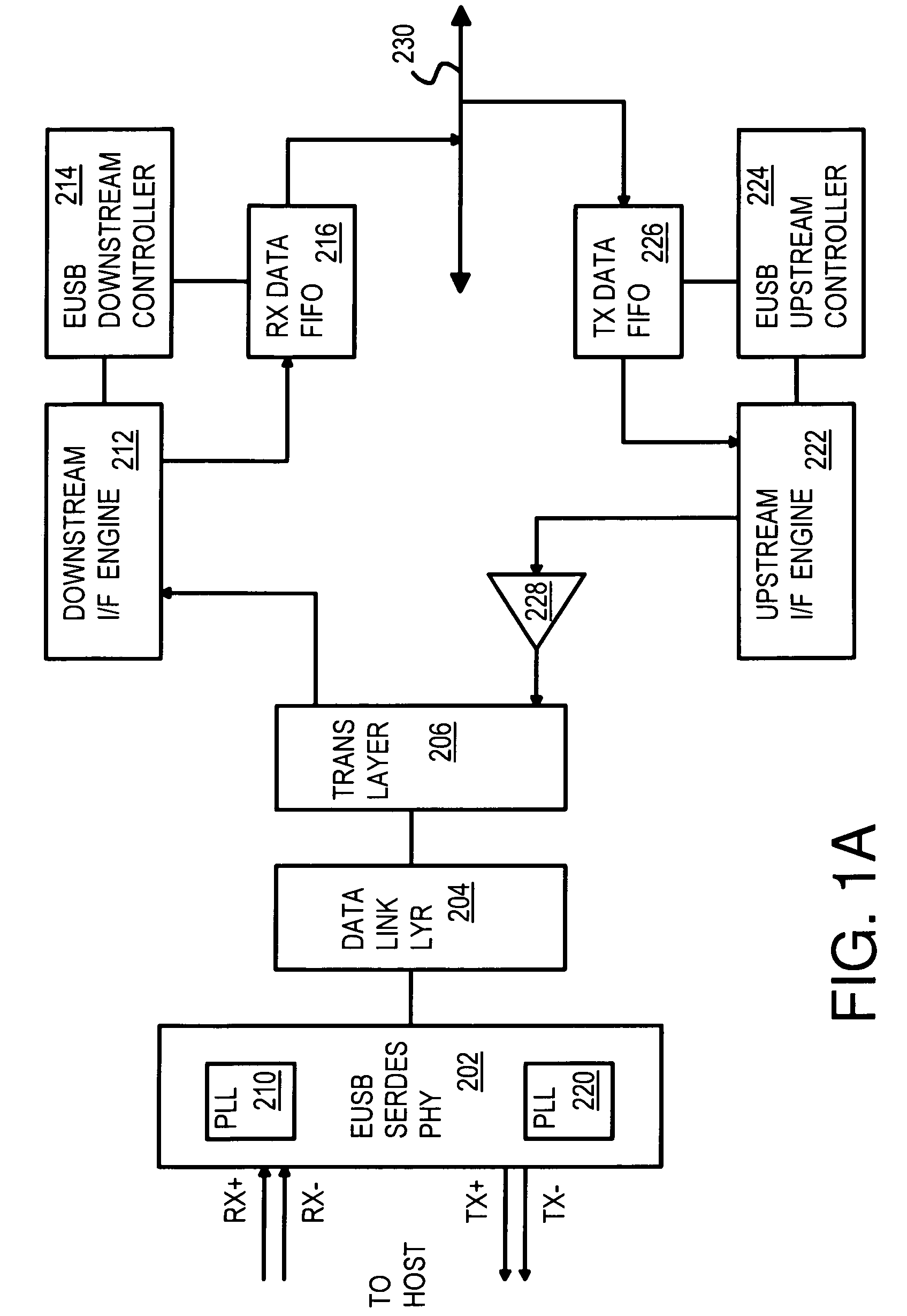

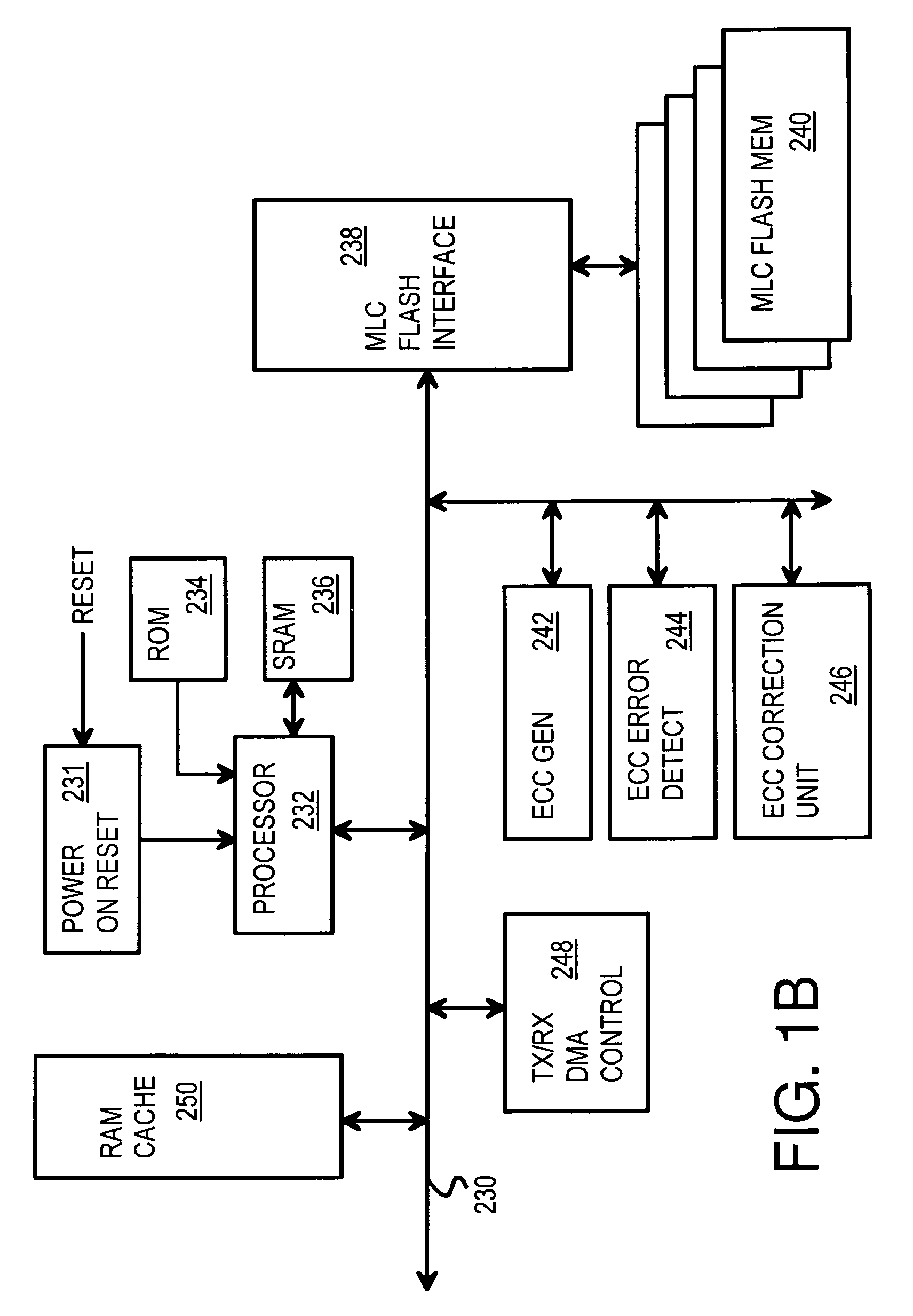

InactiveUS20090113121A1Memory architecture accessing/allocationDistillation regulation/controlFlash memory controllerMulti-level cell

A flash controller has a flash interface accessing physical blocks of multi-level-cell (MLC) flash memory. An Extended Universal-Serial-Bus (EUSB) interface loads host commands into a command queue where writes are re-ordered and combined to reduce flash writes. A partial logical-to-physical L2P mapping table in a RAM has entries for only 1 of N sets of L2P mapping tables. The other N−1 sets are stored in flash memory and fetched into the RAM when a L2P table miss occurs. The RAM required for mapping is greatly reduced. A data buffer stores one page of host write data. Sector writes are merged using the data buffer. The data buffer is flushed to flash when a different page is written, while the partial logical-to-physical mapping table is flushed to flash when a L2P table miss occurs, when the host address is to a different one of the N sets of L2P mapping tables.

Owner:SUPER TALENT TECH CORP

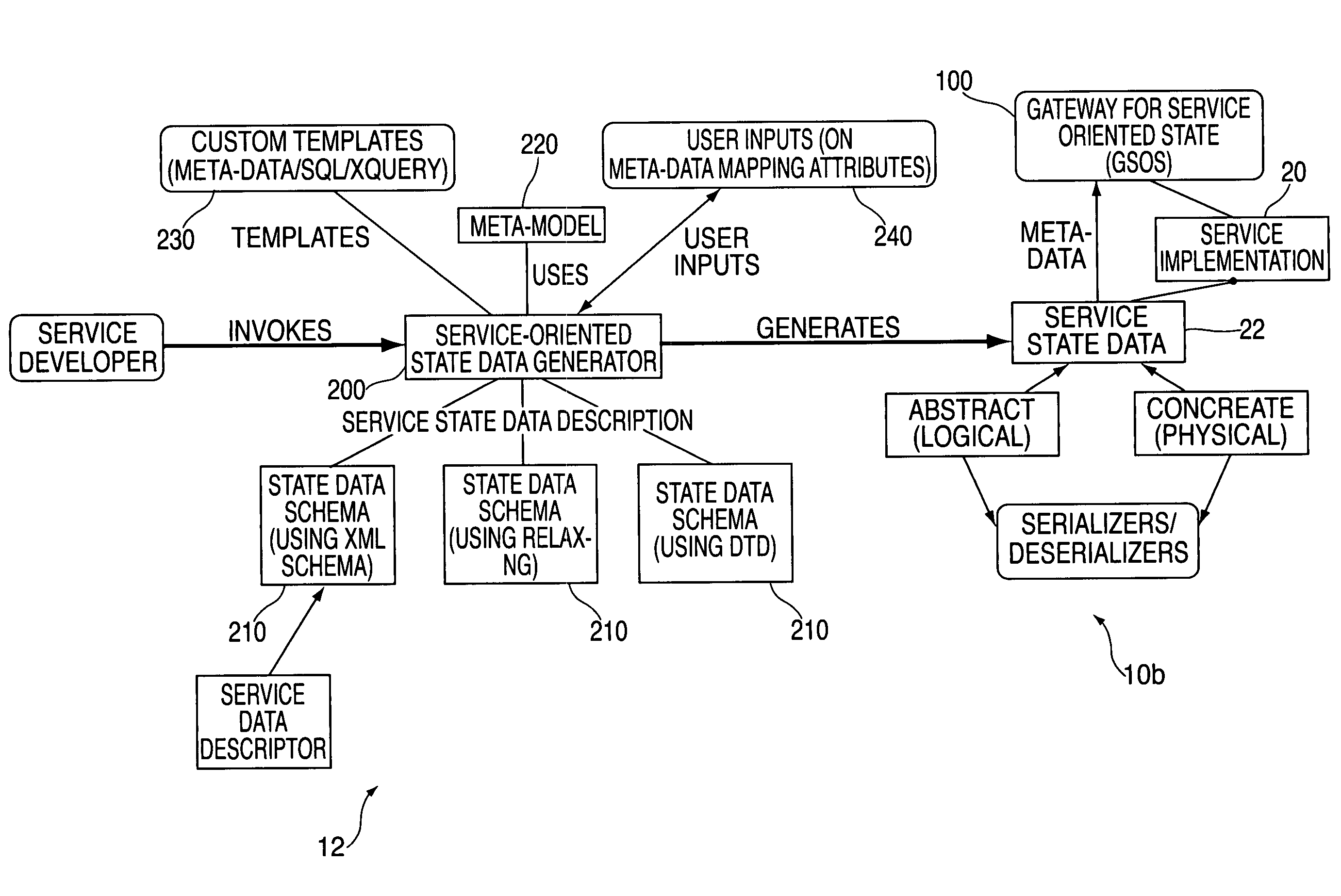

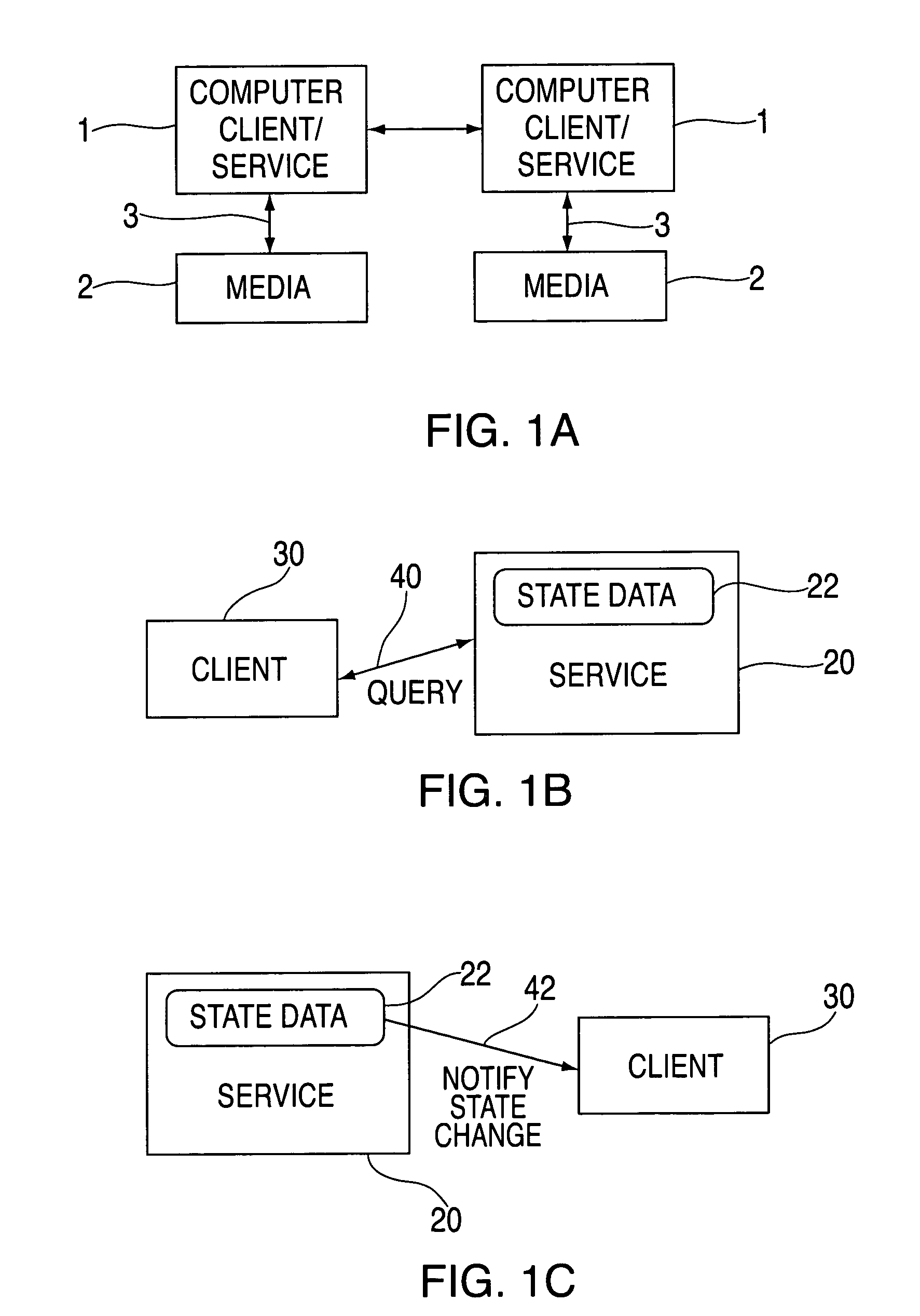

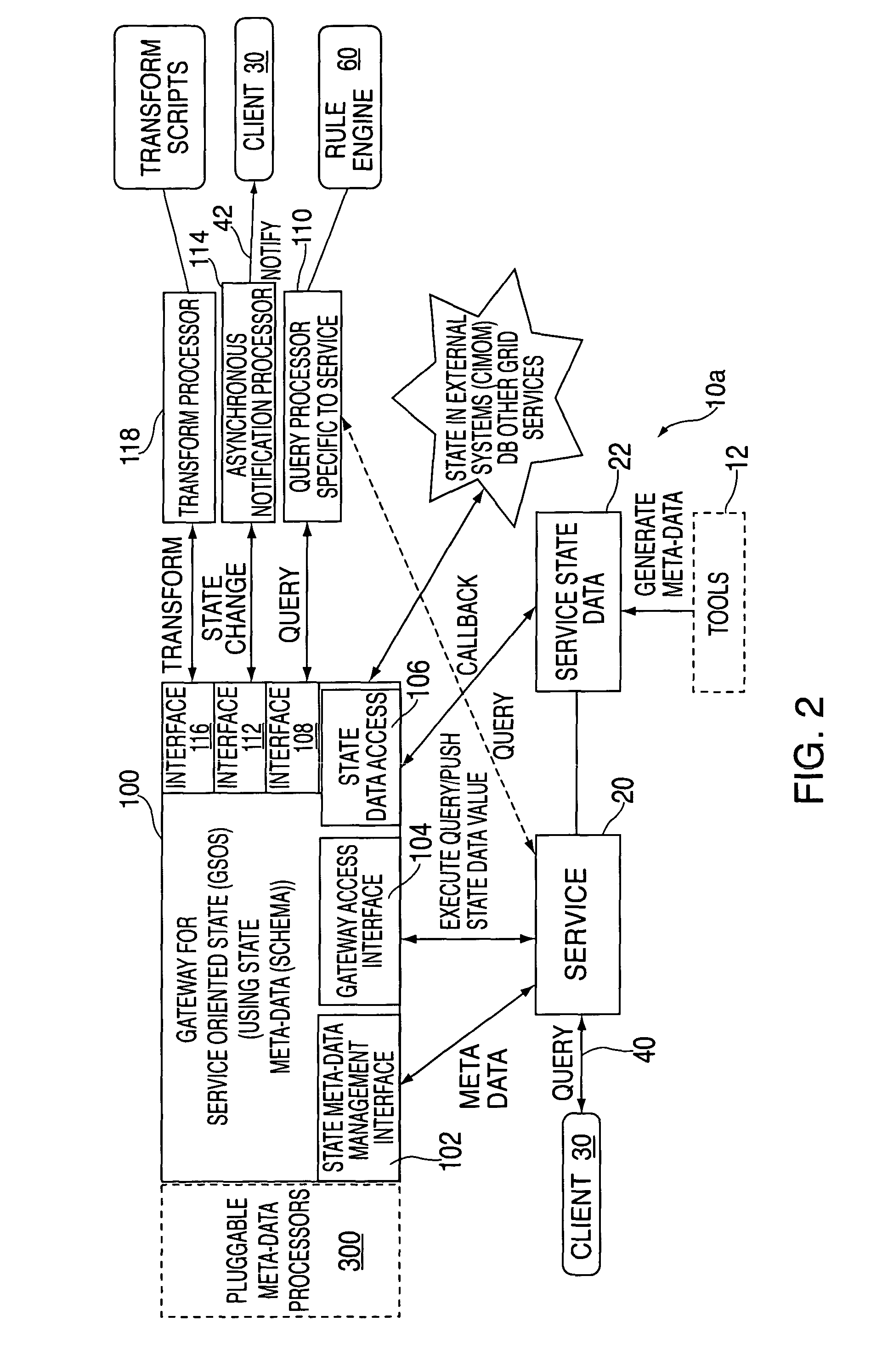

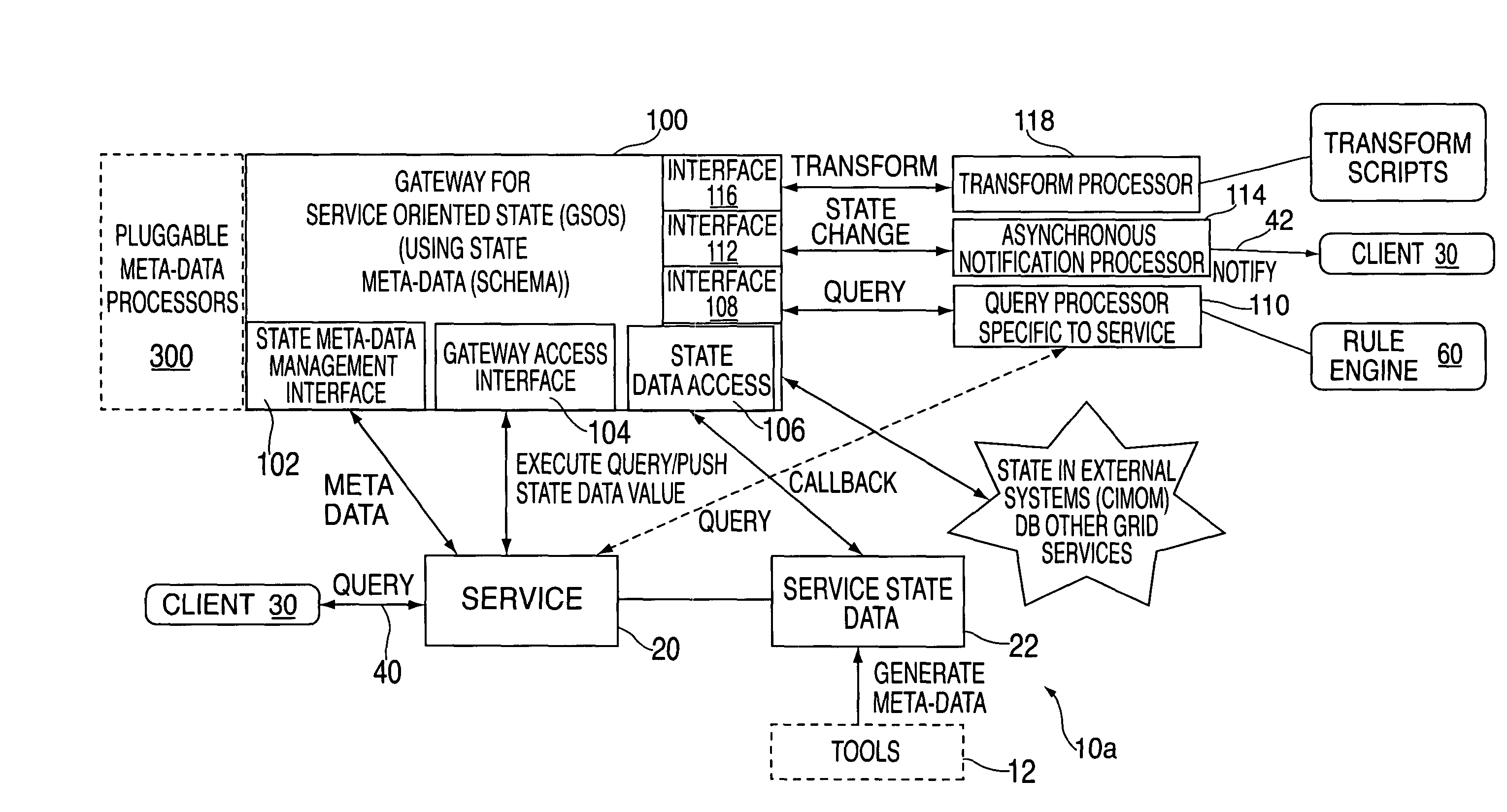

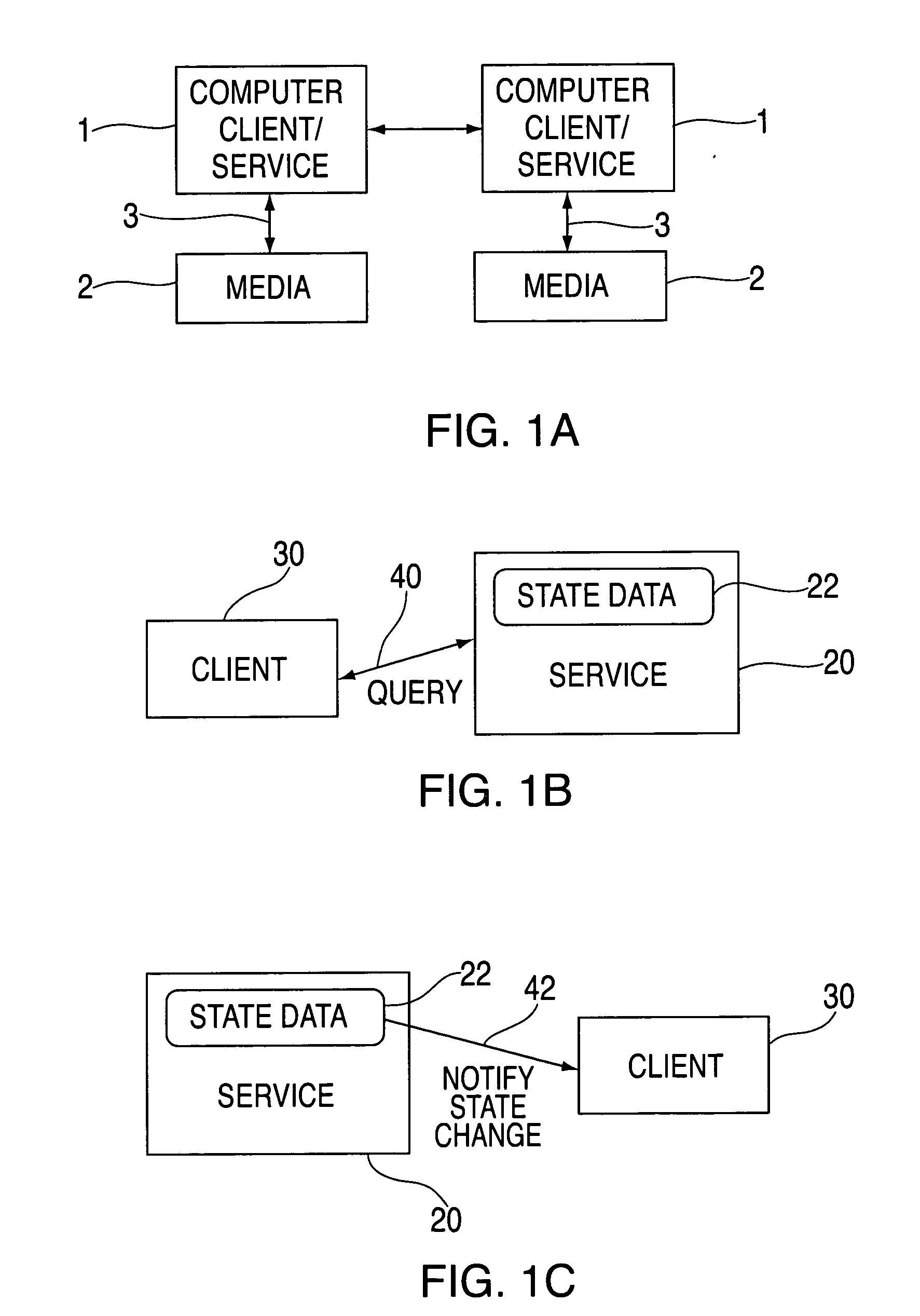

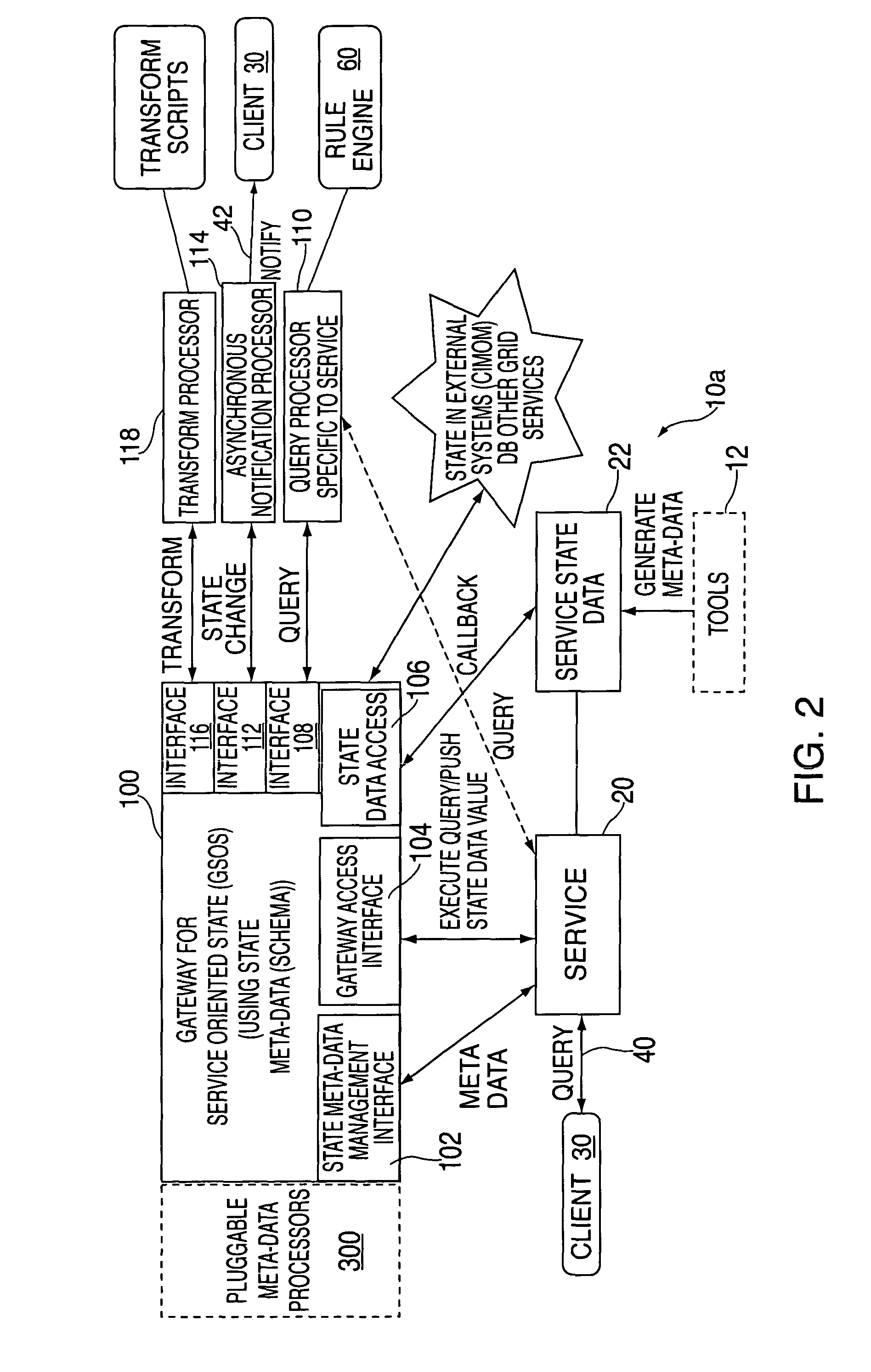

Method and apparatus for generating service oriented state data mapping between extensible meta-data model and state data including logical abstraction

InactiveUS7287037B2Data processing applicationsMultiple digital computer combinationsData descriptionData information

A method and apparatus for generating service state data and extensible meta-data information with a service oriented state data generator (SSDG) comprising: establishing a platform independent, extensible meta-data model for the meta-data information; obtaining state data schema based on a service state data description; defining an extensible set of meta-data attributes and templates corresponding to the meta data based on requirements of a service; and utilizing the meta-data model and based on the state data schema and the attributes, generating service state data based on the service state data schema; and The service state data including at least one of: state data, state data logical mapping, state data physical mapping, meta-data associated with the service state data and meta-data model correlations associated with the meta-data.

Owner:IBM CORP

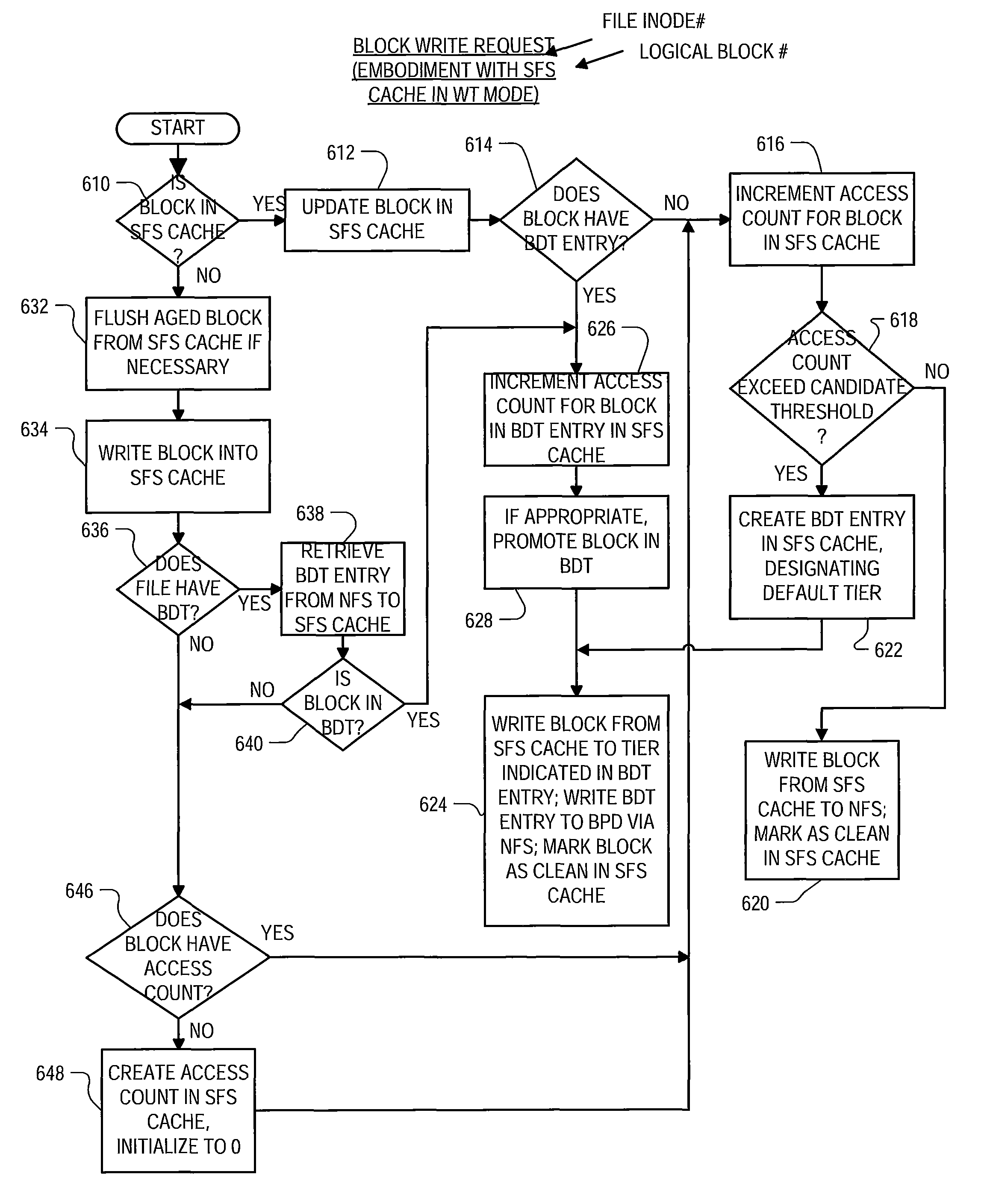

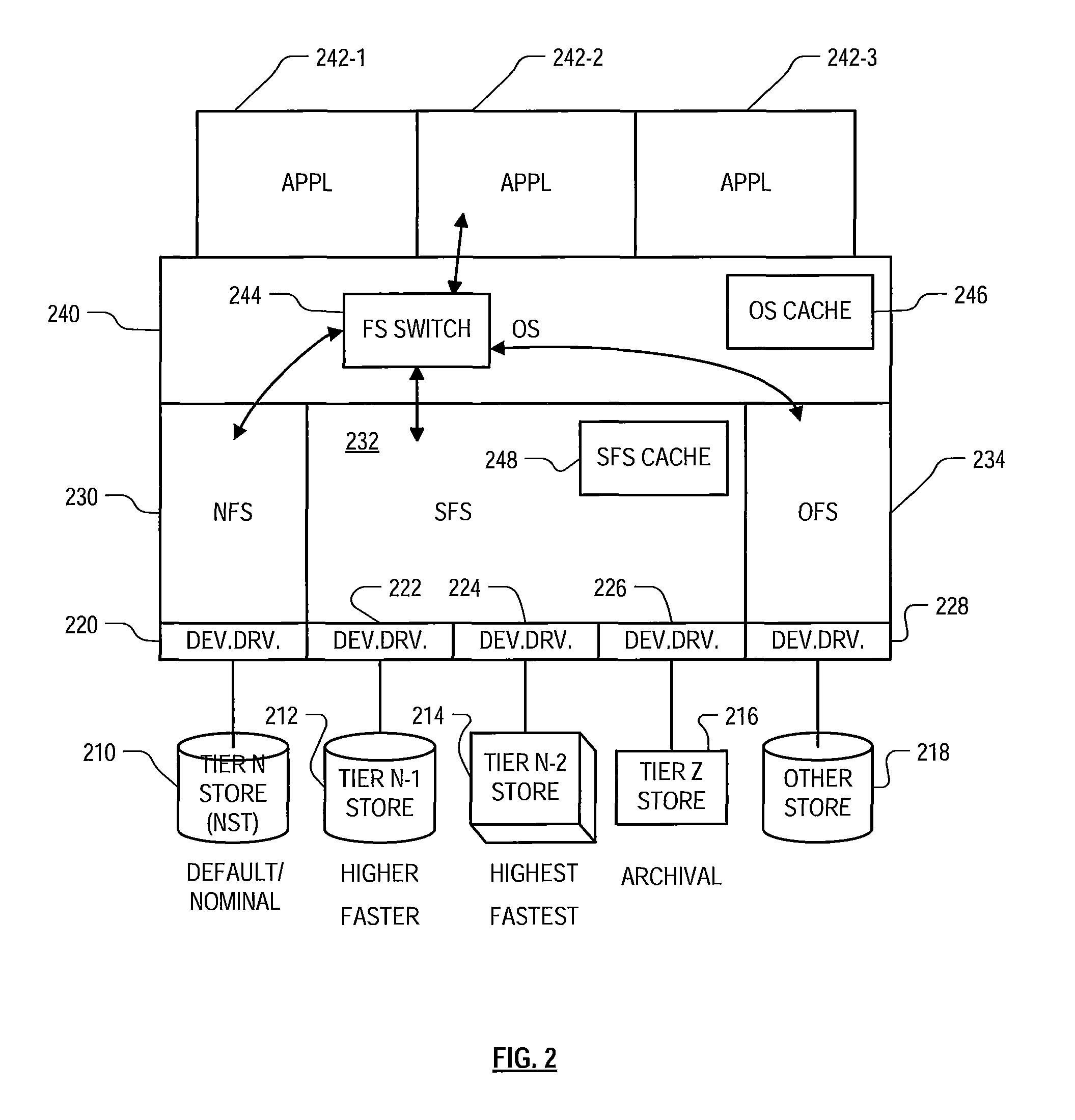

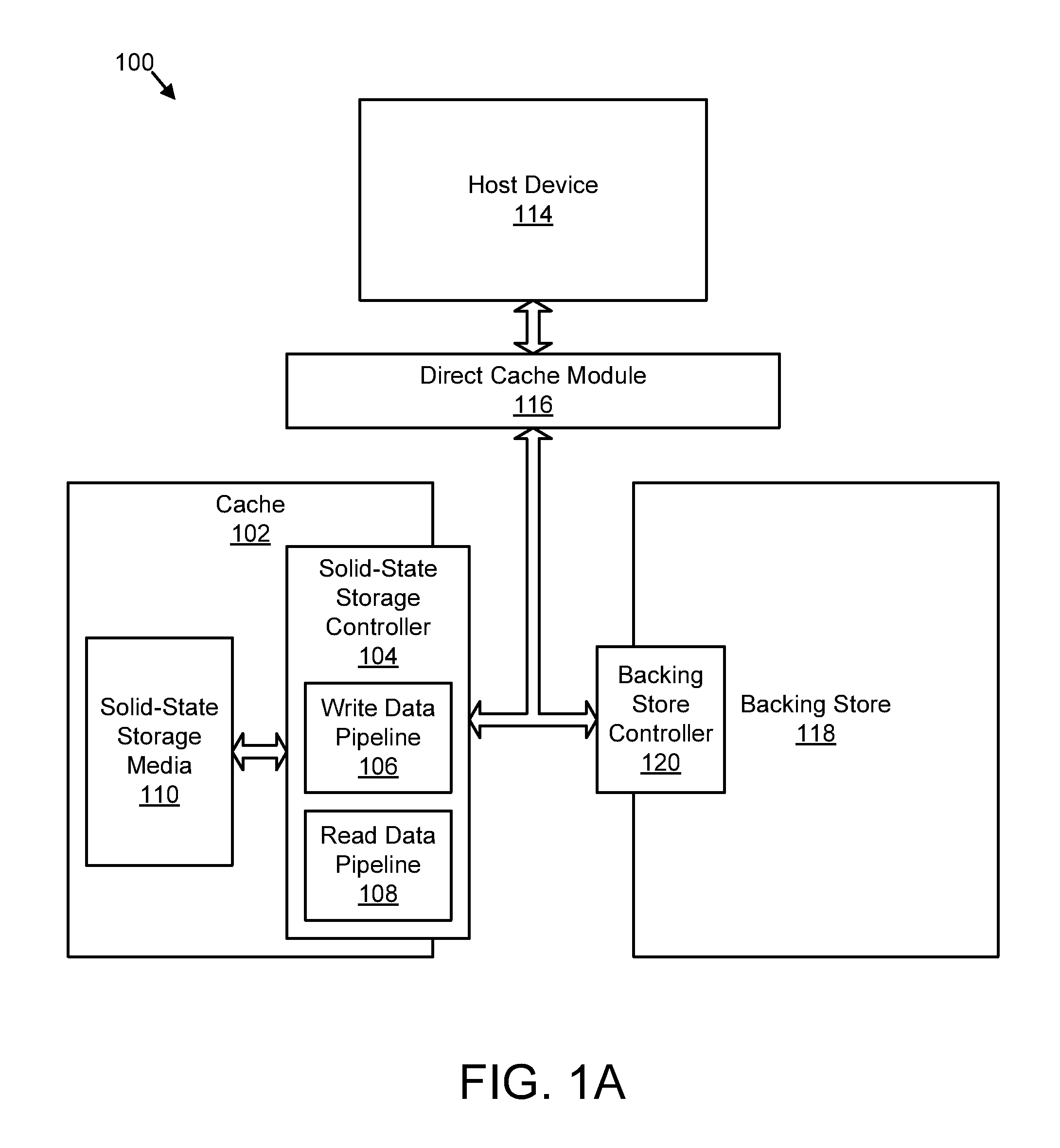

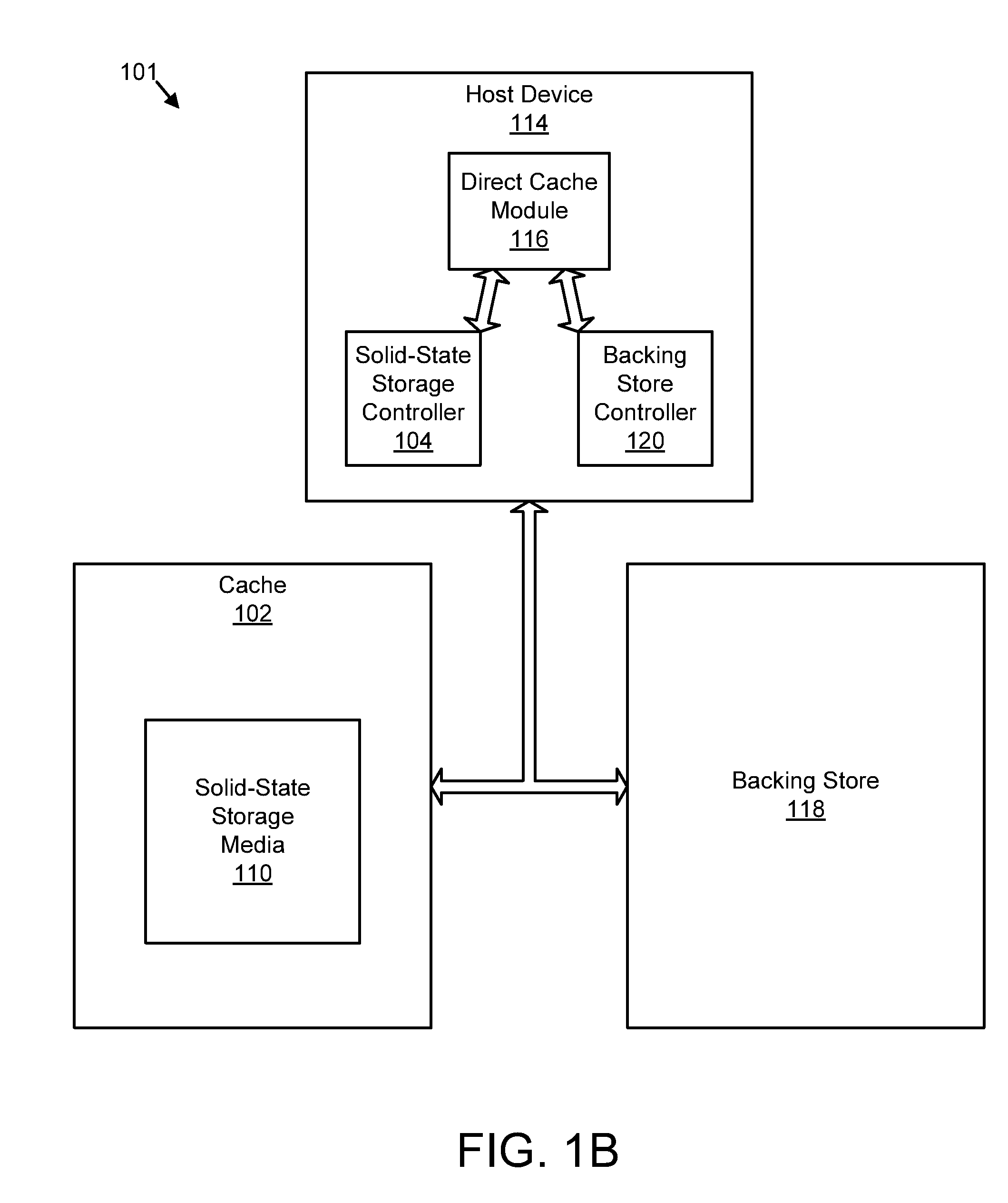

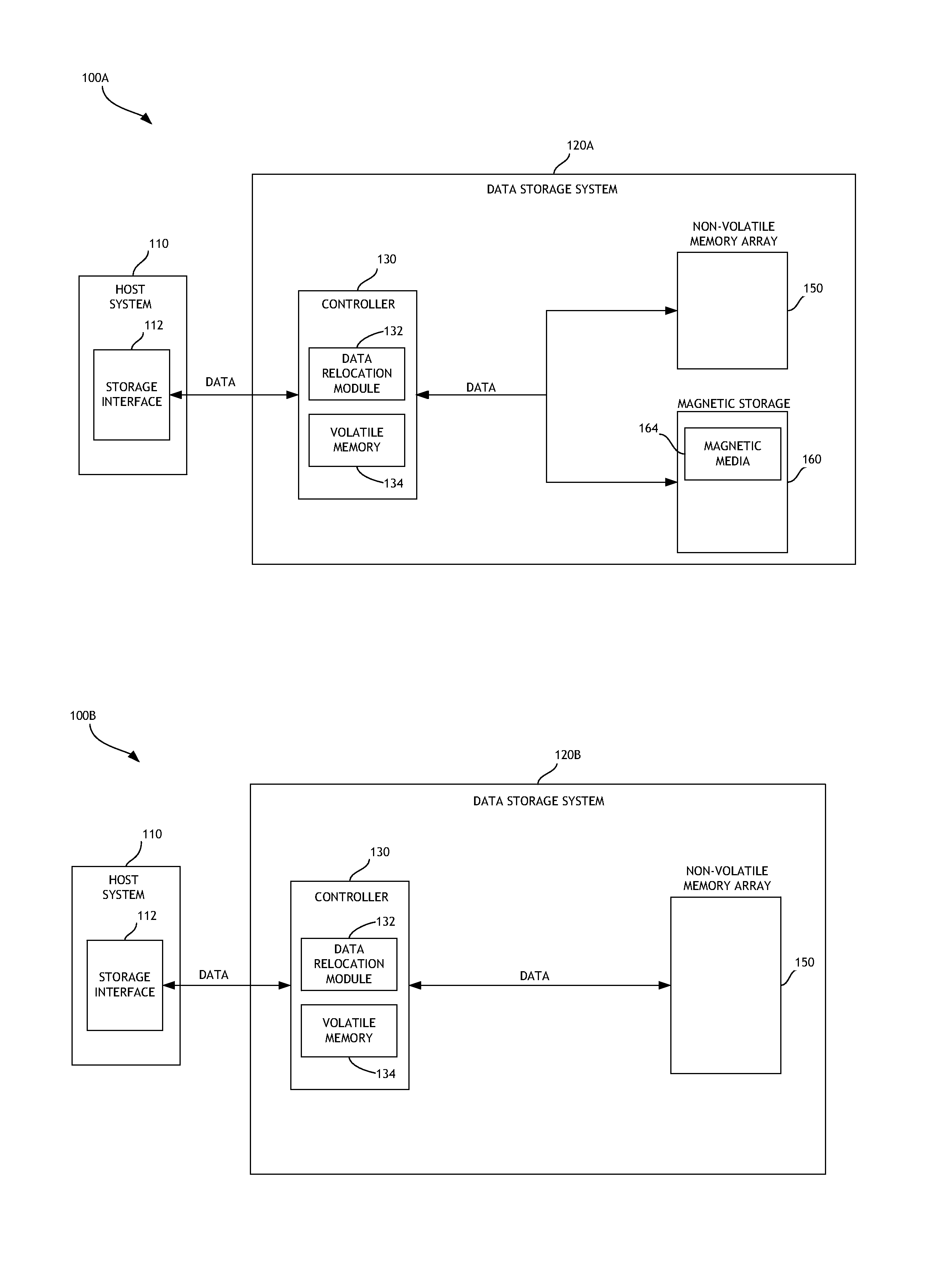

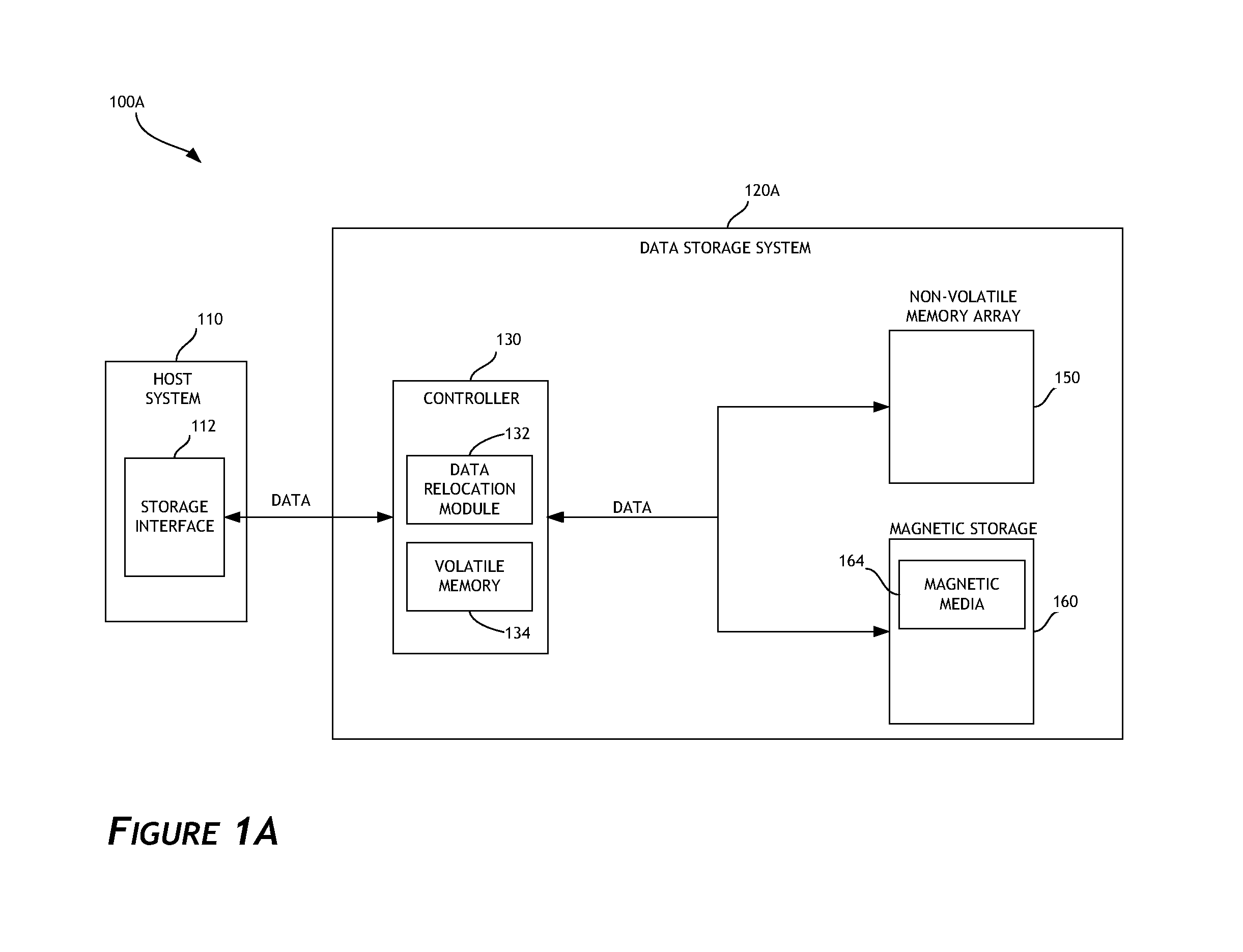

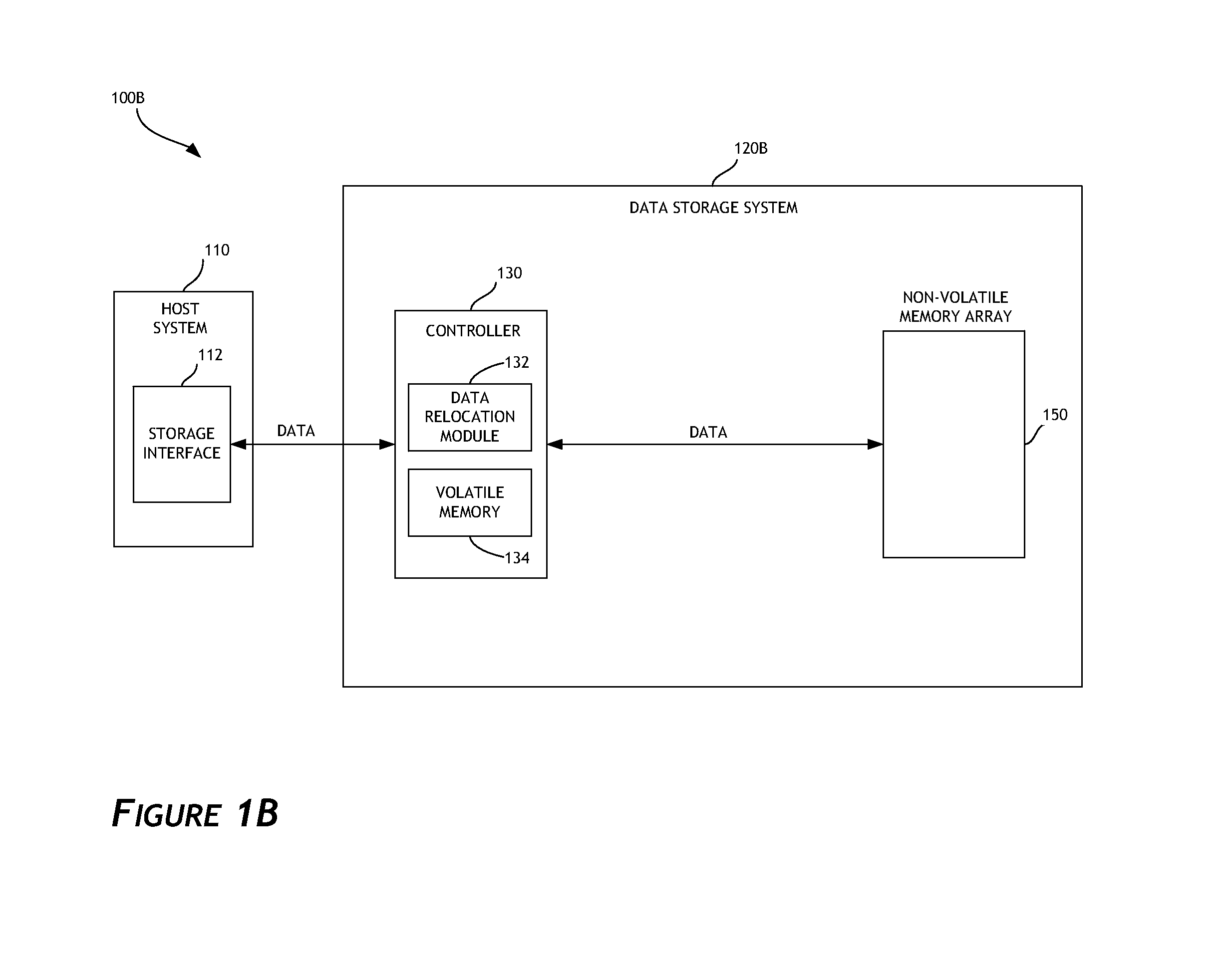

Hybrid storage system

ActiveUS8315995B1Large capacityLow costMemory architecture accessing/allocationDigital data information retrievalGranularityFile system

Roughly described, a tiered storage system has a filesystem that promotes and demotes data among tiers at block granularity. It maintains a logical-to-physical mapping which indicates for each block in a file both the assigned tier and the physical block number within the tier. Methods for performing file- and block-level manipulations are described. In an embodiment, a nominal tier is managed by a native filesystem, and higher tiers are managed by a super filesystem. The super filesystem manages promotion and demotion among the tiers, interfacing with higher tiers directly but interfacing with the nominal tier only through the native filesystem. The native filesystem defines the file namespace in the system, and the logical-to-physical block mapping for blocks in the nominal tier. The super filesystem defines the logical-to-physical mapping for blocks in the higher tiers, but retains the file identification information as defined by the native filesystem.

Owner:PEER FUSION

Methods and apparatus for implementing virtualization of storage within a storage area network

ActiveUS7433948B2Solve insufficient bandwidthGreat bandwidthInput/output to record carriersMultiple digital computer combinationsStorage area networkVirtual storage

Owner:CISCO TECH INC

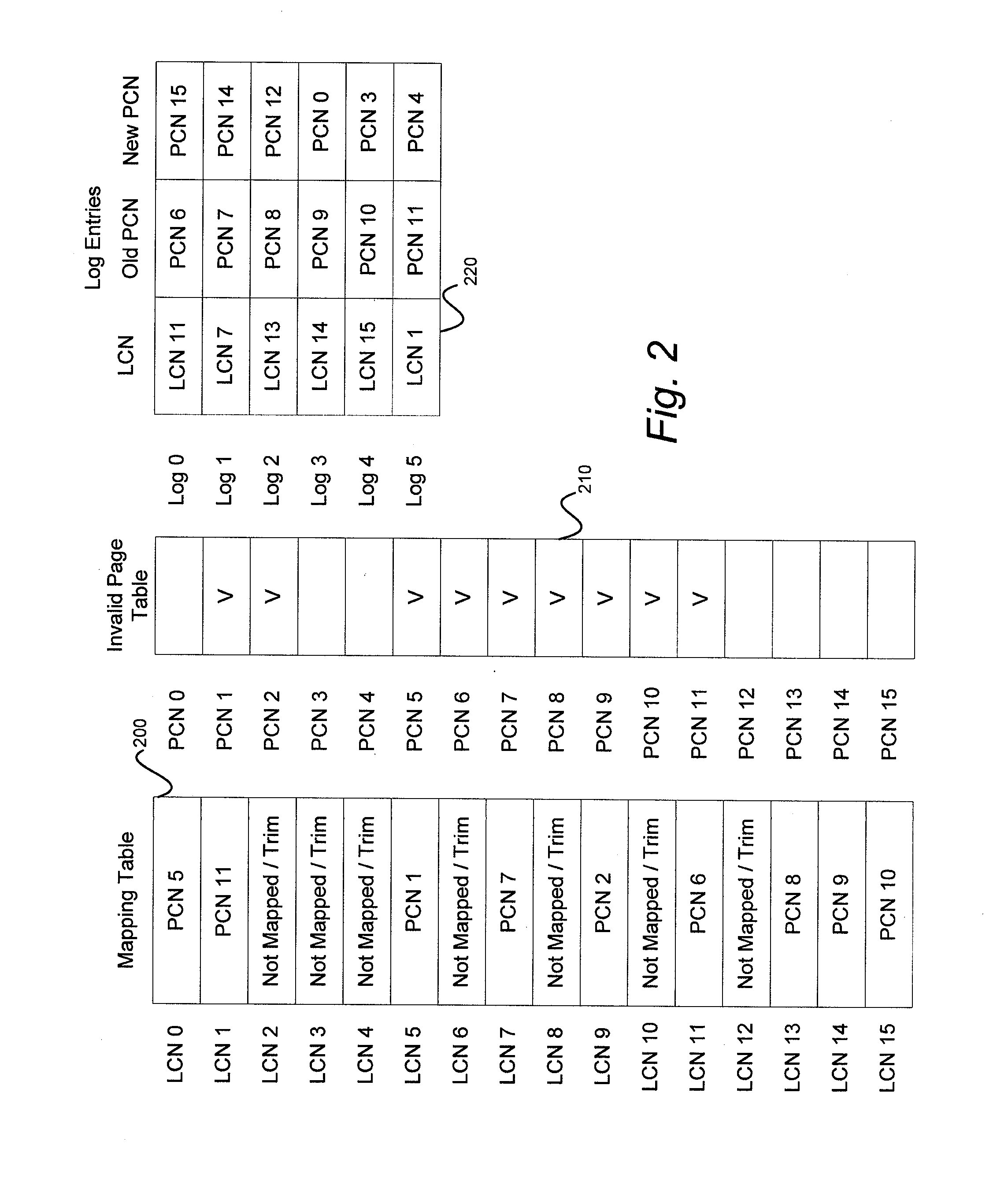

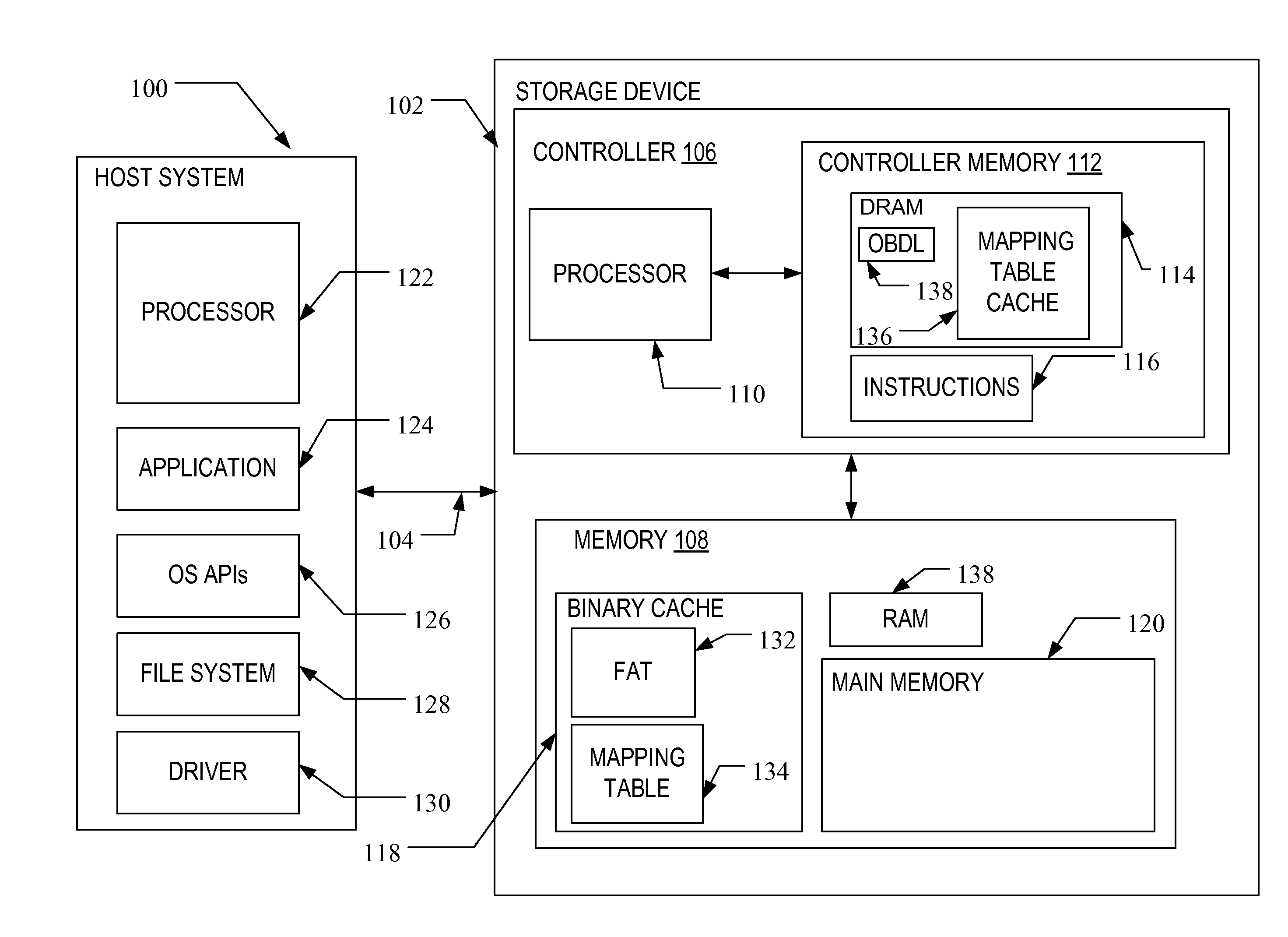

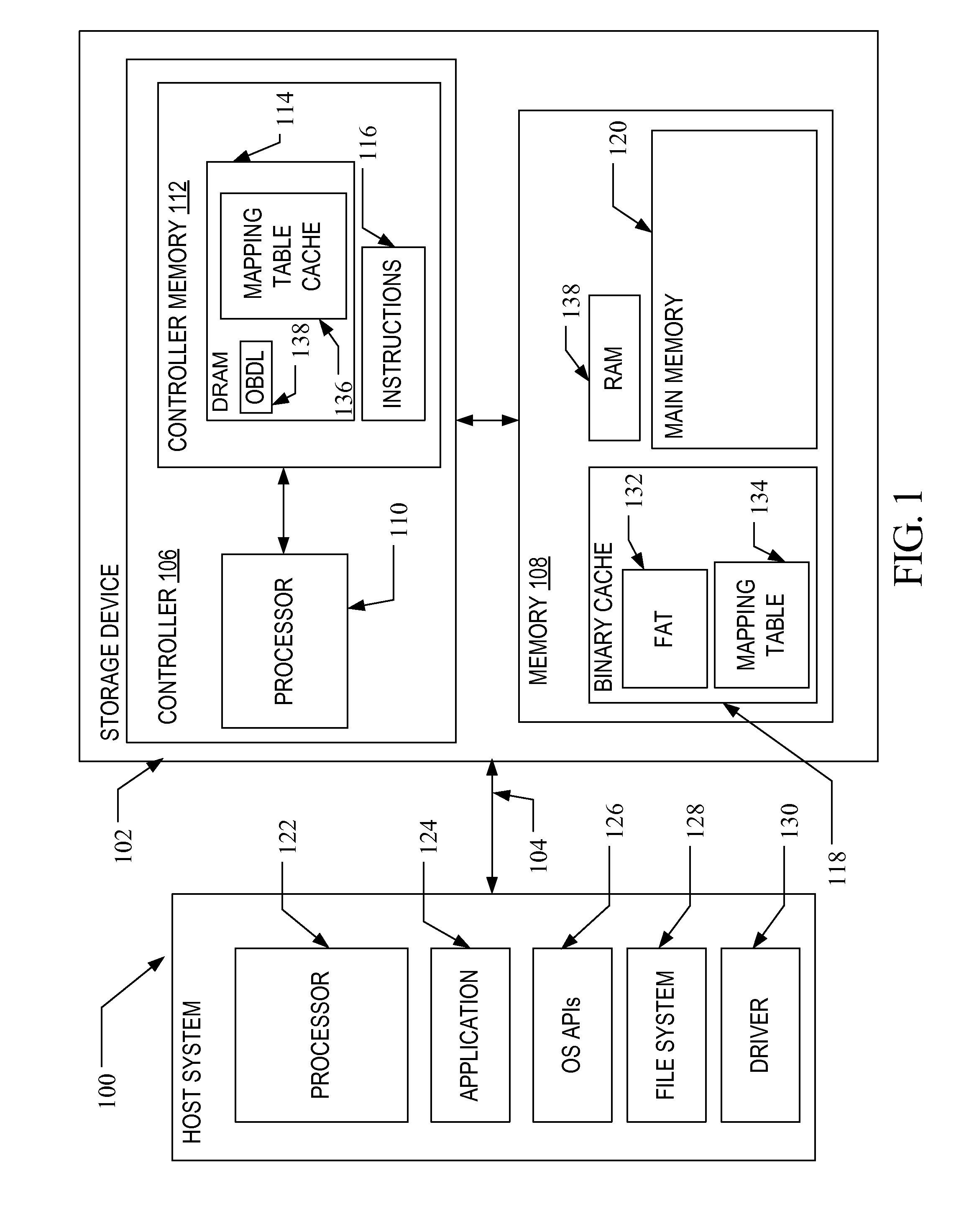

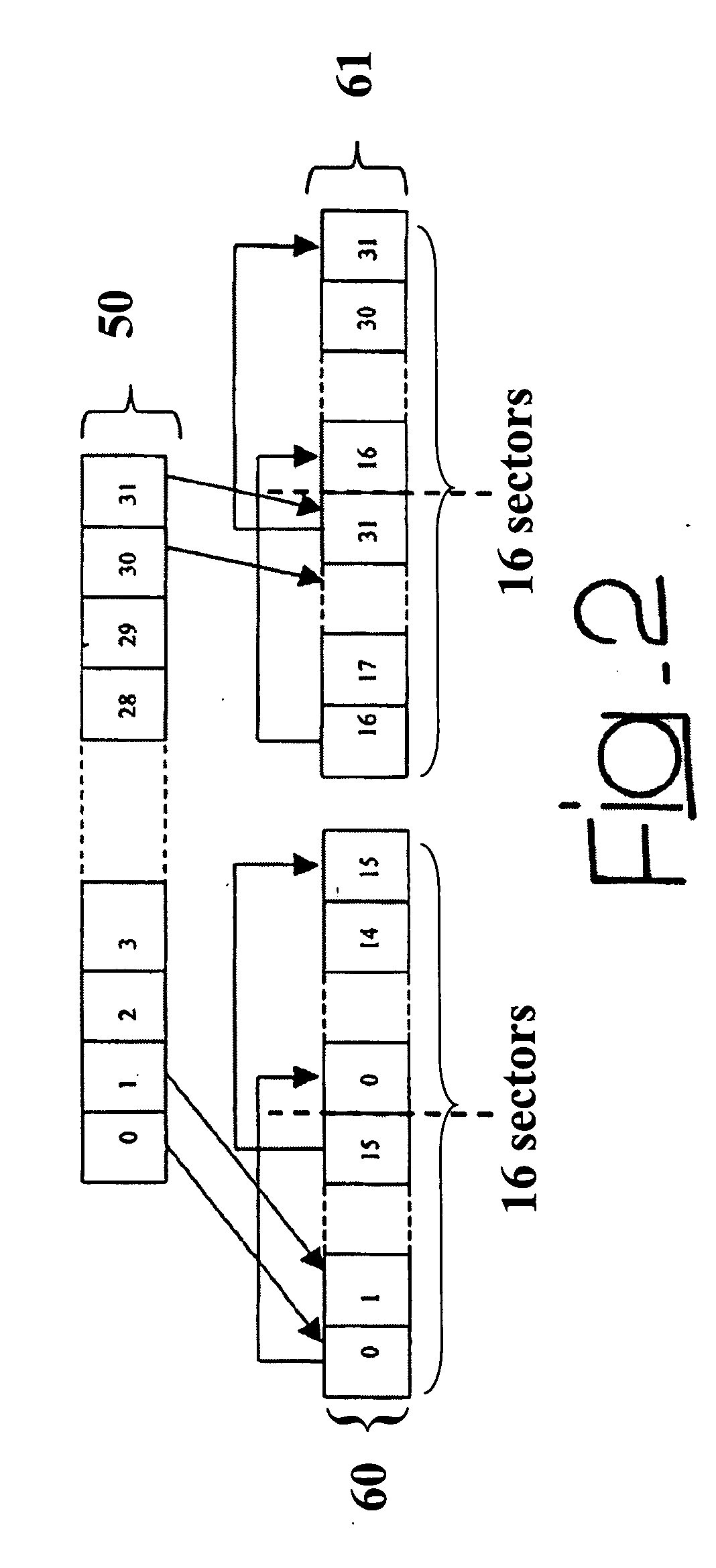

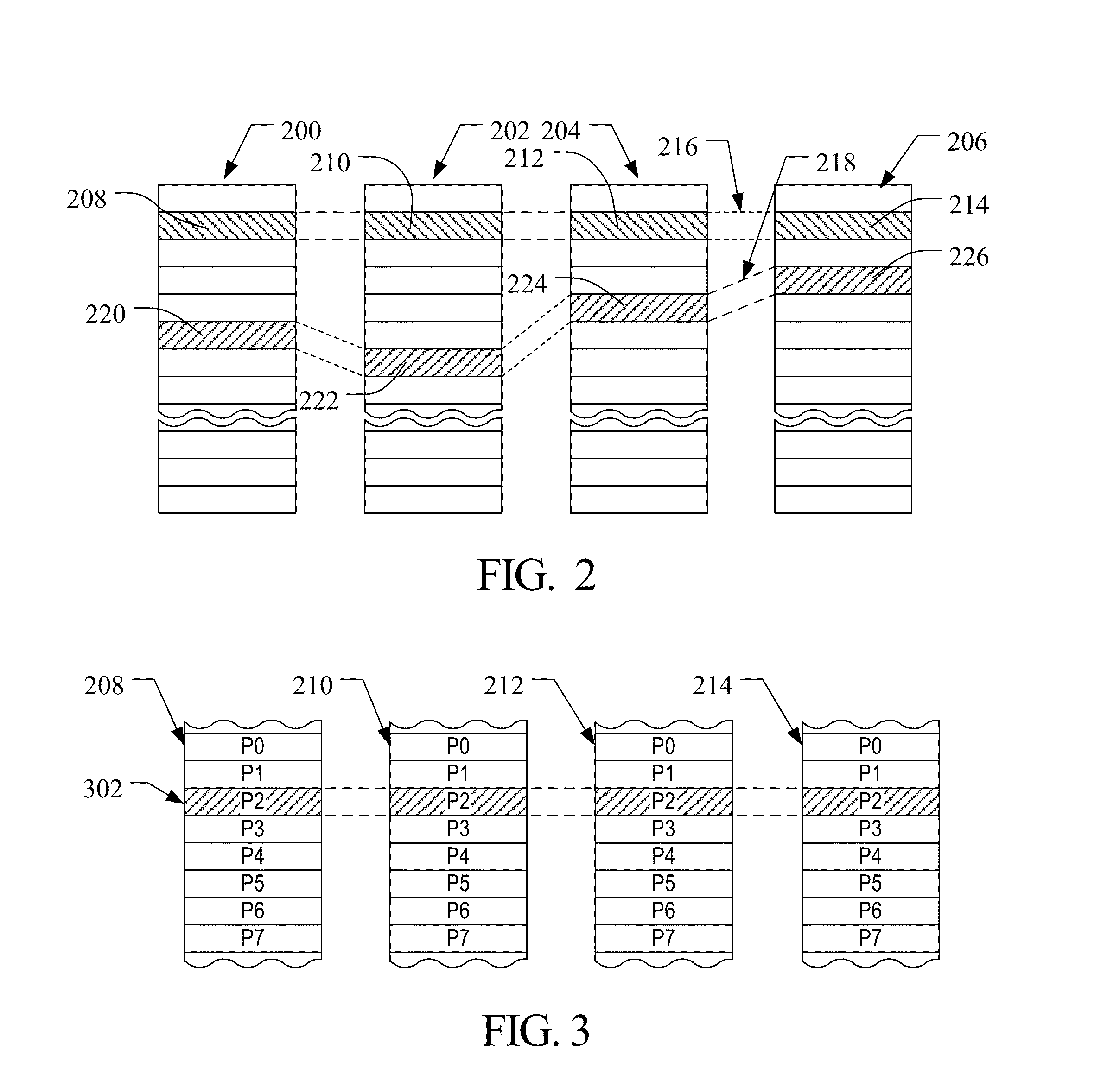

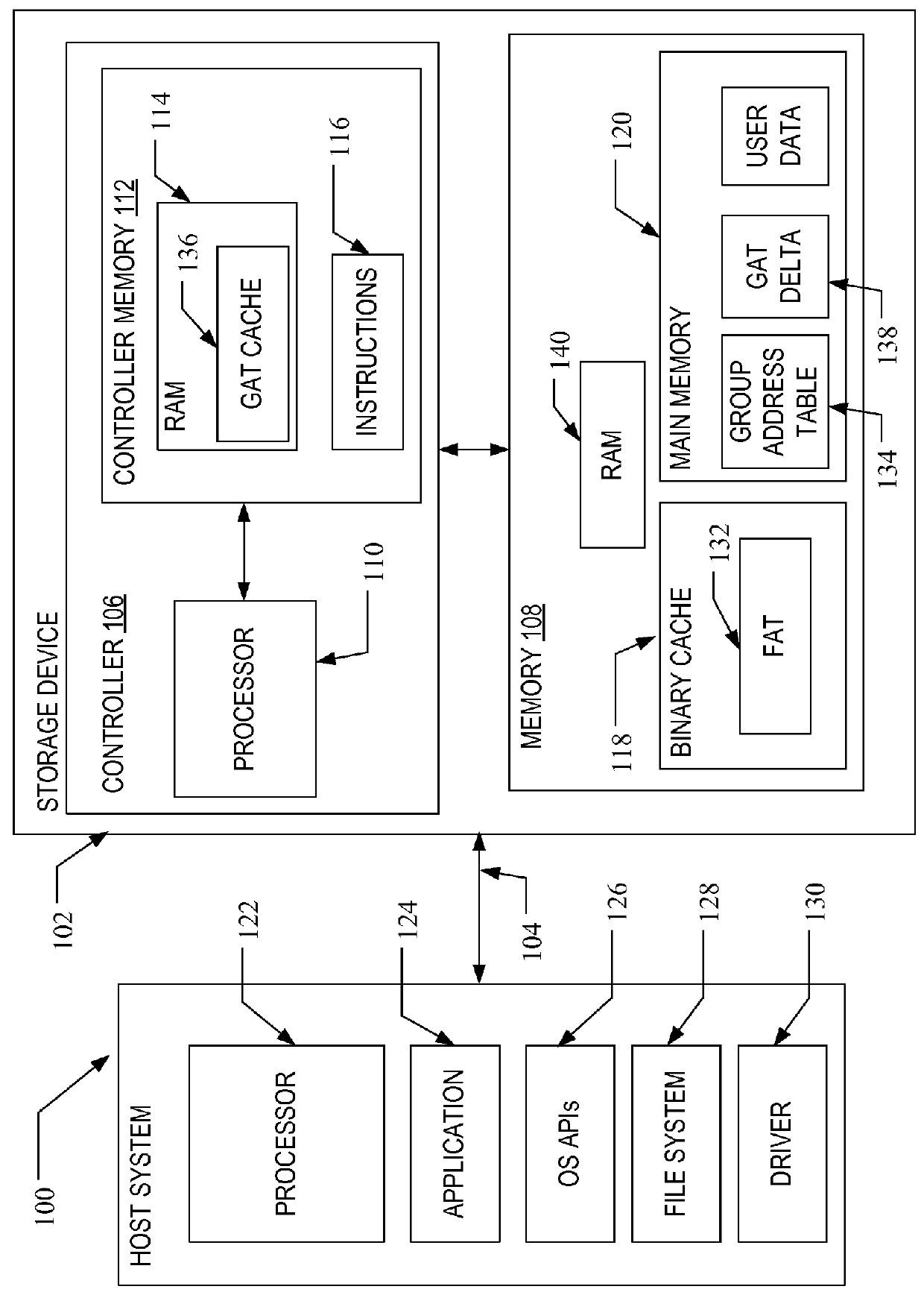

Method and system for interleaving pieces of a mapping table for a storage device

ActiveUS20150347026A1Improve efficiencyImprove read performanceMemory architecture accessing/allocationInput/output to record carriersContiguityVolatile memory

A method and system are disclosed for handling logical-to-physical mapping in a storage device. The method includes the storage device storing in fast access memory, such as DRAM, only a fixed-size subset of the primary mapping table in non-volatile memory, along with contiguity information of physical addresses for logical address not in the subset that are adjacent to the logical addresses in the subset. The system includes a storage device having volatile memory, non-volatile memory and a controller in communication with the volatile and non-volatile memory that is configured to carry out the method noted above.

Owner:SANDISK TECH LLC

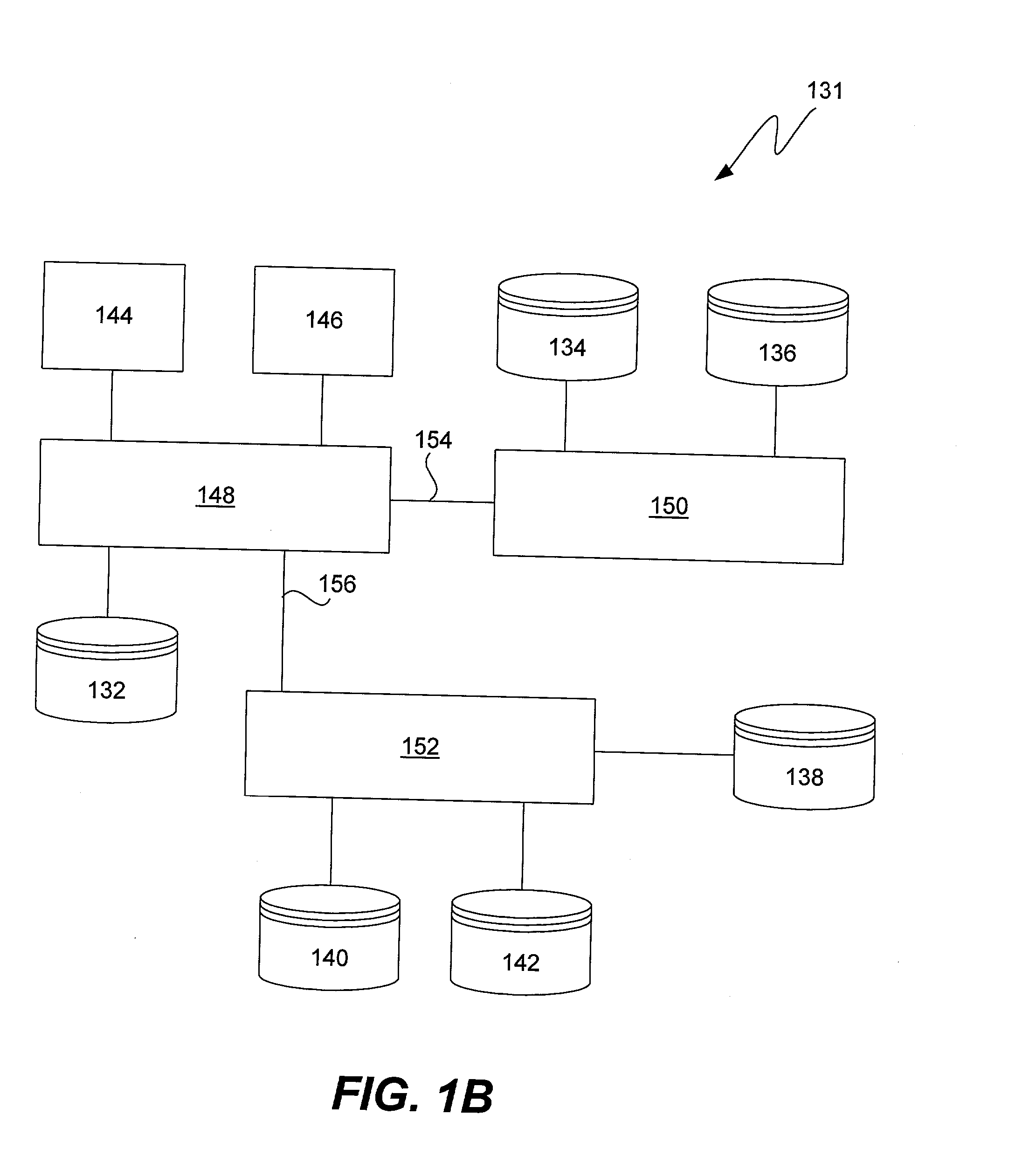

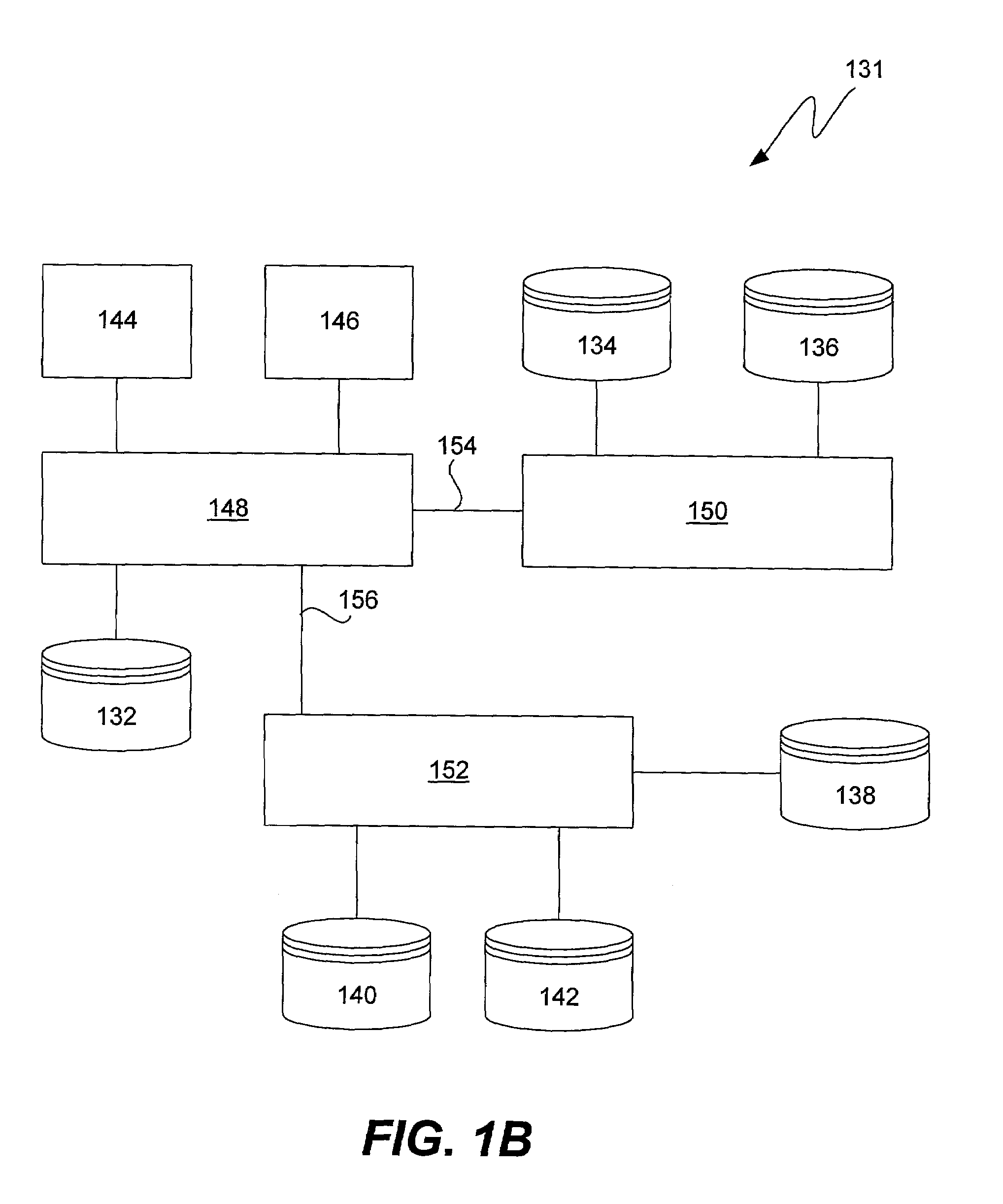

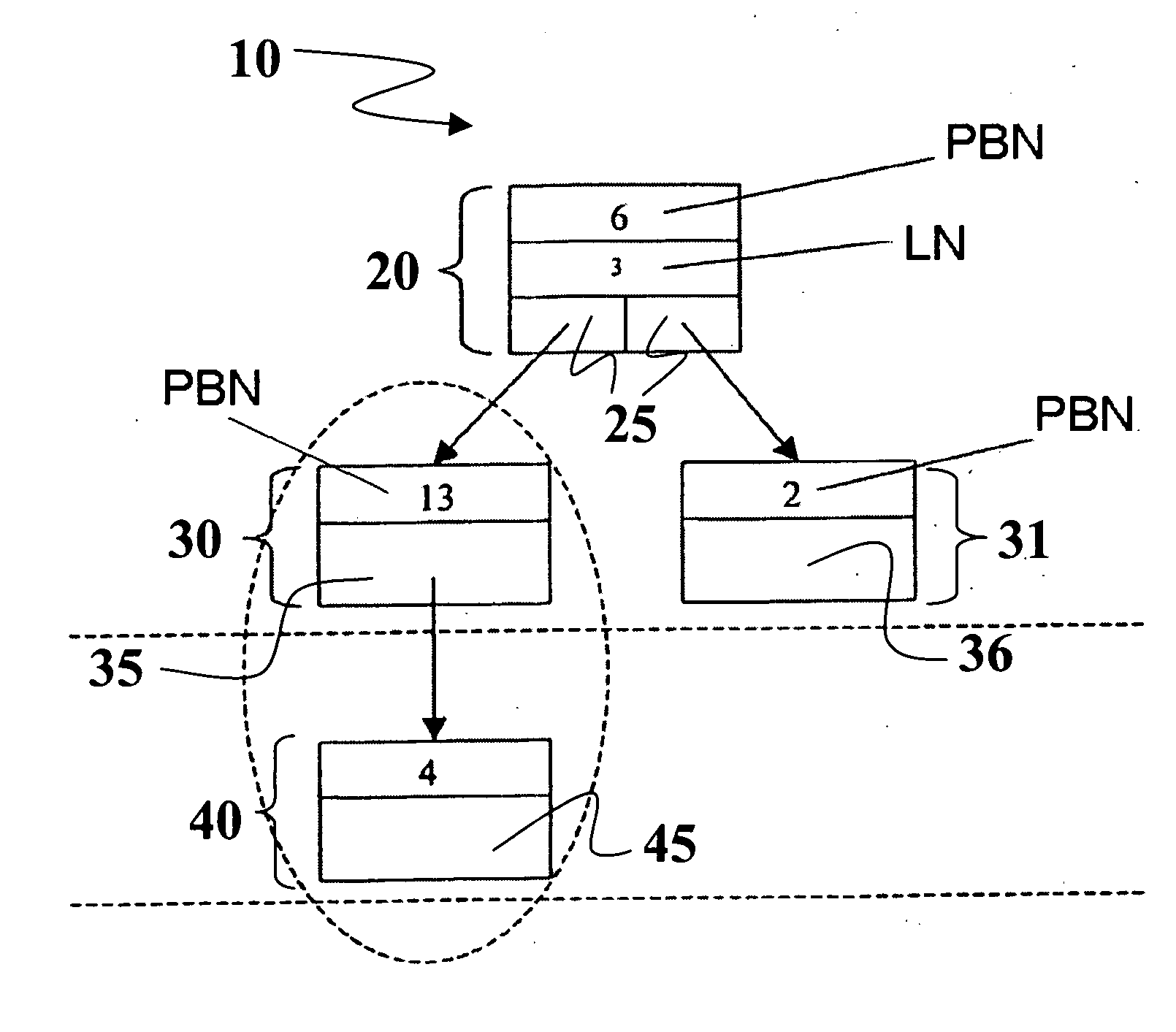

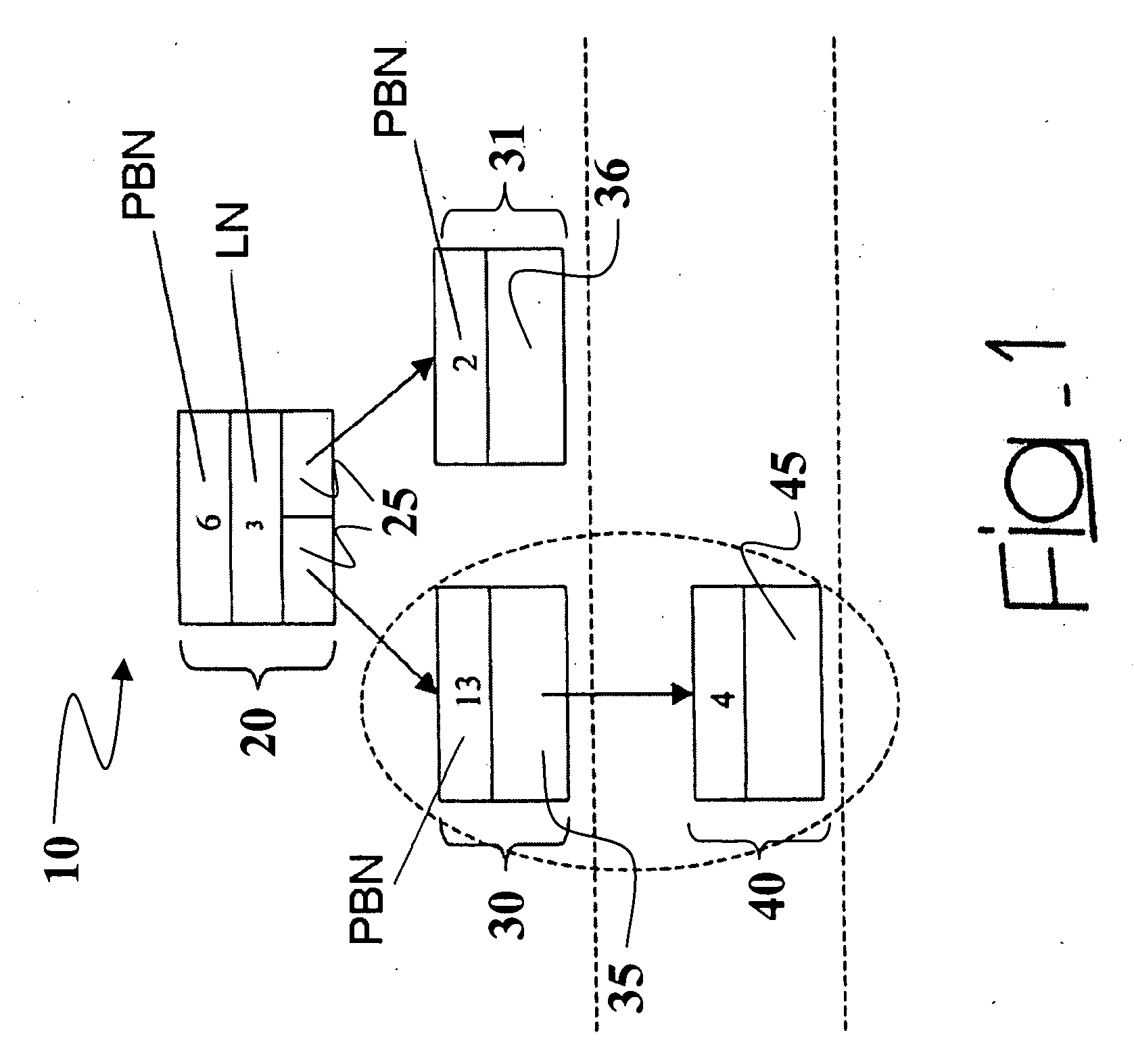

System and method for managing storage networks and providing virtualization of resources in such a network

InactiveUS7206863B1Input/output to record carriersResource allocationStorage area networkResource virtualization

This invention is a system and method for managing one or more data storage networks using a new architecture. A method for handling logical to physical mapping is included in one embodiment with the new architecture. A method for handling errors is included in another embodiment with the new architecture.

Owner:EMC IP HLDG CO LLC

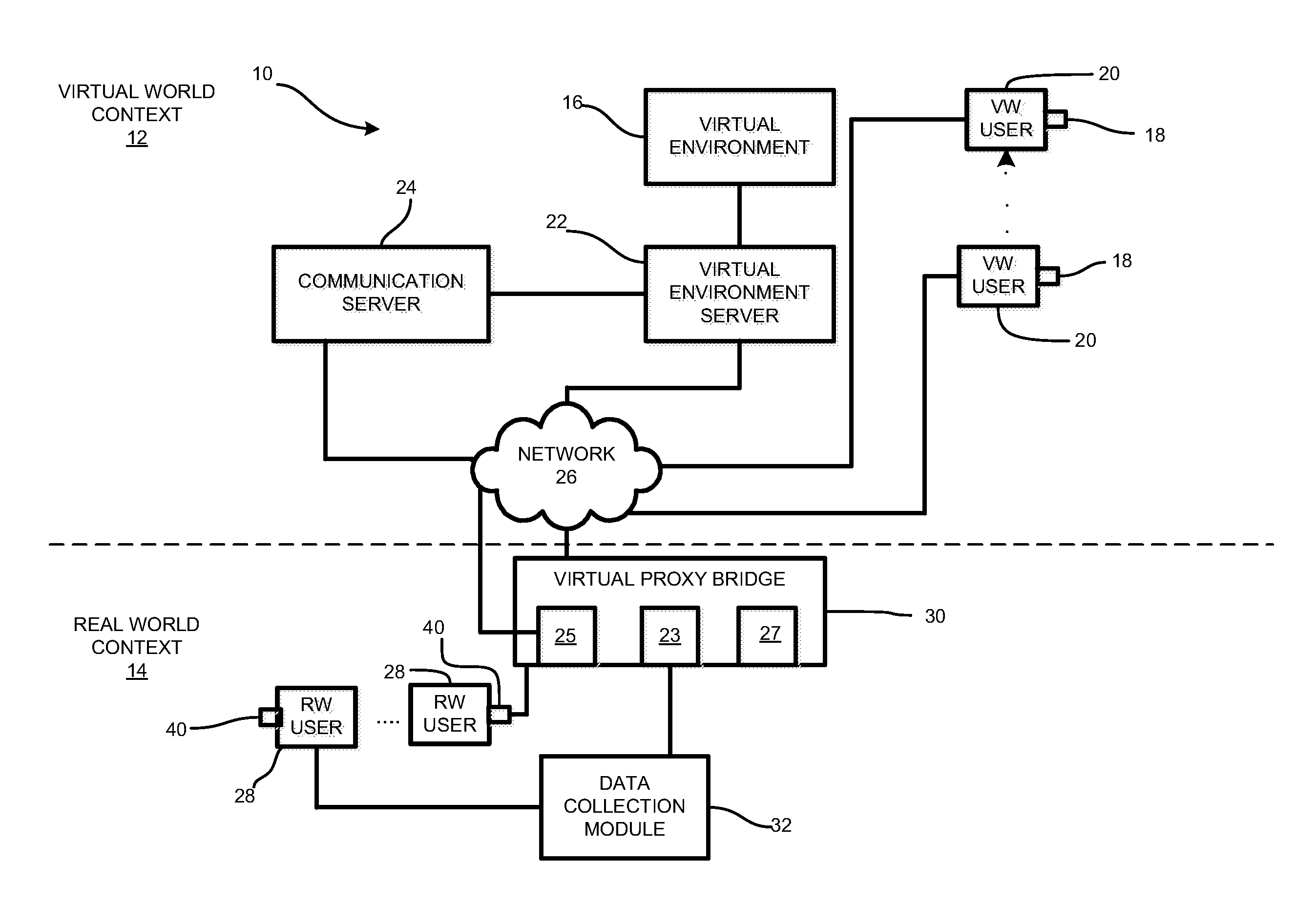

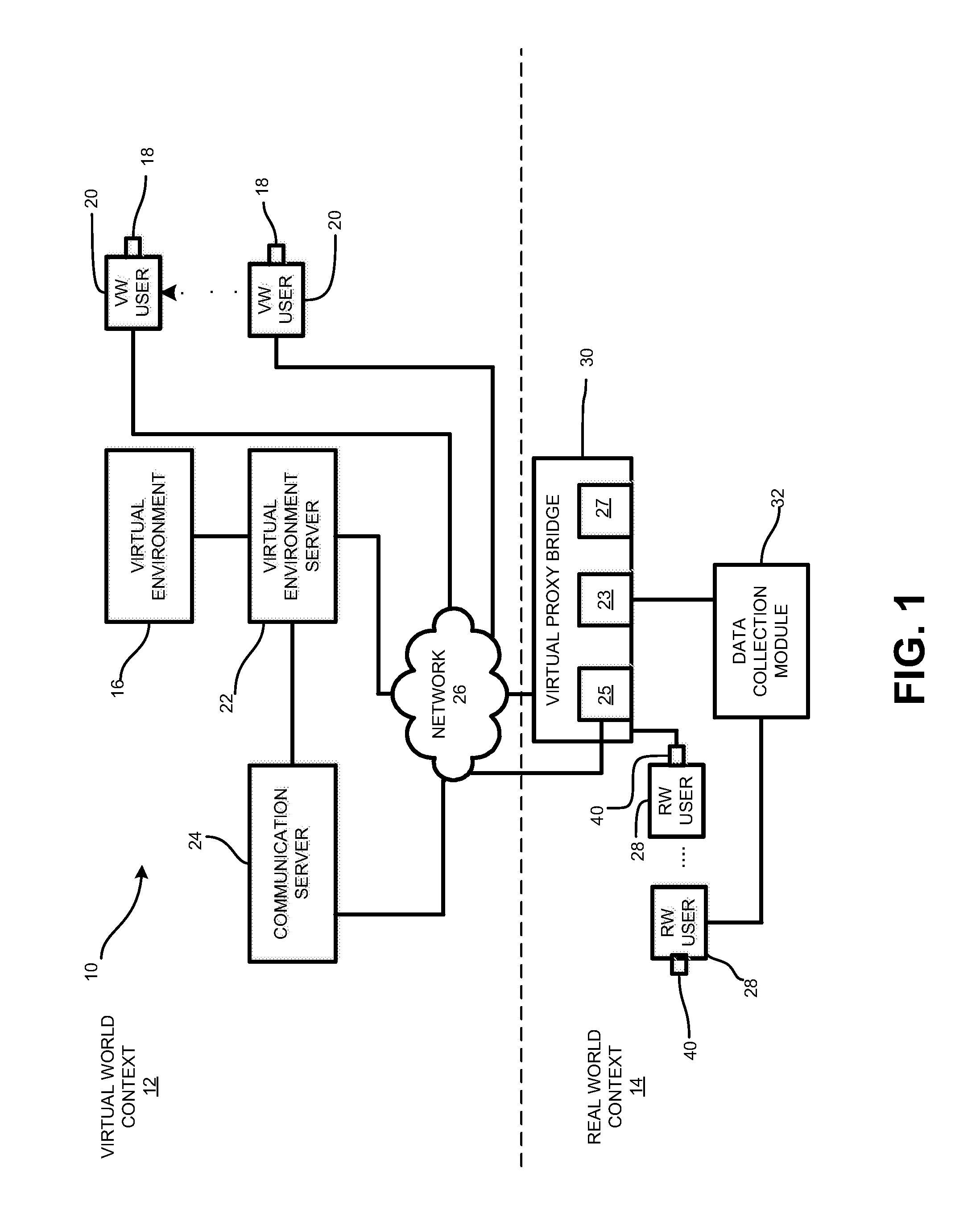

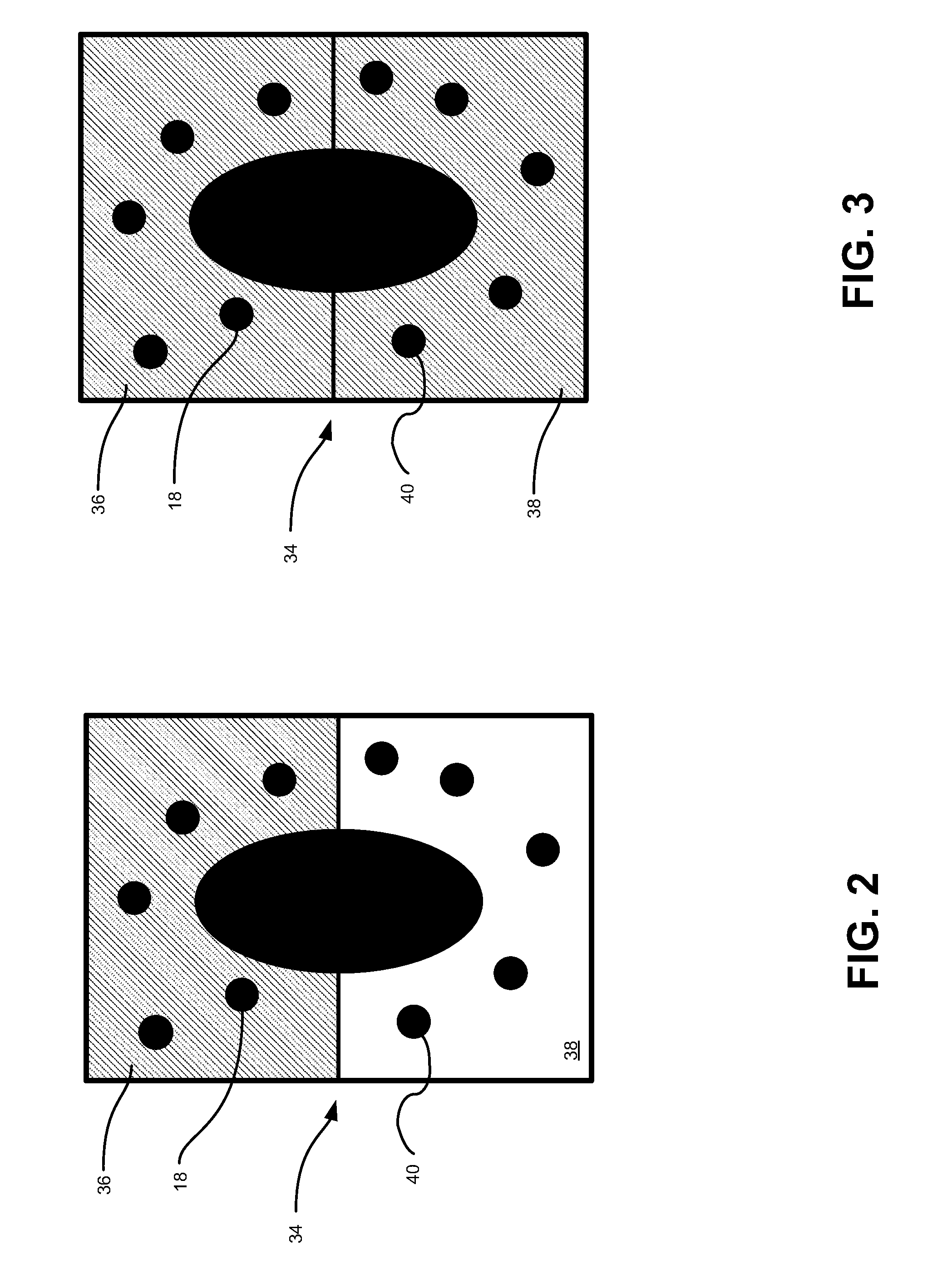

Method and system for physical mapping in a virtual world

A method and system for capturing user actions in the real world and mapping the users, their actions, and their avatars into a three dimensional virtual environment. Data representing real world users are captured, collected and sent to a virtual proxy bridge, which transforms the data into control signal for avatars, which are then mapped to the virtual environment. The real world avatars move around in parallel with the users in the real world via the use of data capture devices such as radio frequency identification (“RFID”) readers, triangulation or global positioning satellite (“GPS”) systems, and cameras. Real world users can therefore be represented as virtual users, thus removing the distinction between real world users and virtual environment users.

Owner:AVAYA INC

Method and apparatus for generating service oriented state data and meta-data using meta information modeling

InactiveUS20050050141A1Data processing applicationsMultiple digital computer combinationsData descriptionData information

A method and apparatus for generating service state data and extensible meta-data information with a service oriented state data generator (SSDG) comprising: establishing a platform independent, extensible meta-data model for the meta-data information; obtaining state data schema based on a service state data description; defining an extensible set of meta-data attributes and templates corresponding to the meta data based on requirements of a service; and utilizing the meta-data model and based on the state data schema and the attributes, generating service state data based on the service state data schema; and The service state data including at least one of: state data, state data logical mapping, state data physical mapping, meta-data associated with the service state data and meta-data model correlations associated with the meta-data.

Owner:IBM CORP

Apparatus, System, and Method for Storing Metadata

InactiveUS20130166831A1Memory architecture accessing/allocationMemory adressing/allocation/relocationComputer scienceDatabase

Apparatuses, systems, and methods are disclosed for storing metadata. A mapping module is configured to maintain a mapping structure for logical addresses of a non-volatile device. A metadata module is configured to store membership metadata for the logical addresses with logical-to-physical mappings for the logical addresses in the mapping structure.

Owner:INTPROP HLDG 2 LLC +1

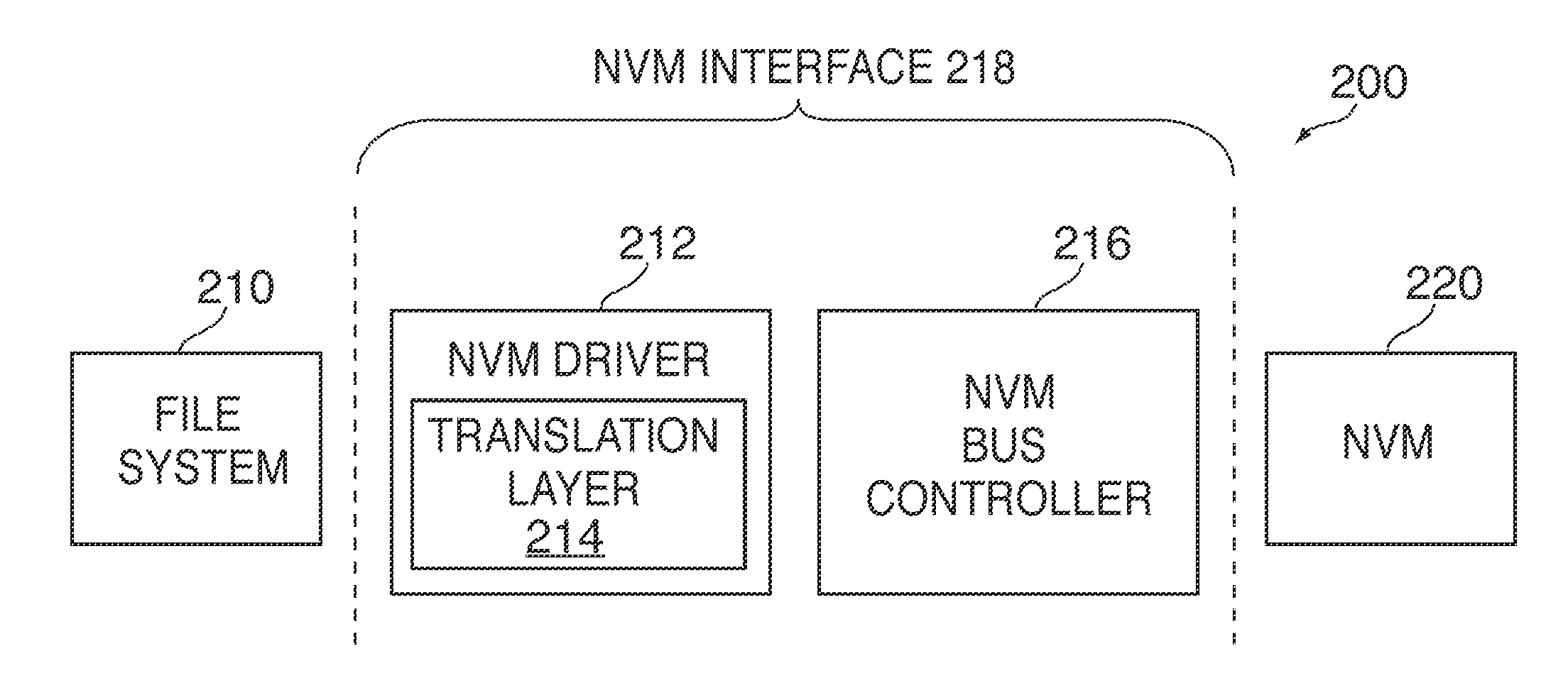

Weave sequence counter for non-volatile memory systems

ActiveUS20130073788A1Memory architecture accessing/allocationMemory adressing/allocation/relocationOperating systemNon-volatile memory

Systems and methods are disclosed for providing a weave sequence counter (“WSC”) for non-volatile memory (“NVM”) systems. The WSC can identify the sequence in which each page of the NVM is programmed. The “weave” aspect can refer to the fact that multiple blocks can be open for programming at once, thus allowing the pages of these blocks to be programmed in a “woven” manner. Systems and methods are also disclosed for providing a host weave sequence counter (“HWSC”). Each time new data is initially programmed to the NVM, this data can be associated with a particular HWSC. The HWSC associated with the data may not change, even when the data is moved to a new page (e.g., for wear leveling purposes and the like). The WSC and HWSC may aid in, for example, performing rollback, building logical-to-physical mappings, determining static-versus-dynamic page statuses, and performing maintenance operations (e.g., wear leveling).

Owner:APPLE INC

Swappable sets of partial-mapping tables in a flash-memory system with a command queue for combining flash writes

InactiveUS8112574B2Memory architecture accessing/allocationDistillation regulation/controlFlash memory controllerMulti-level cell

A flash controller has a flash interface accessing physical blocks of multi-level-cell (MLC) flash memory. An Extended Universal-Serial-Bus (EUSB) interface loads host commands into a command queue where writes are re-ordered and combined to reduce flash writes. A partial logical-to-physical L2P mapping table in a RAM has entries for only 1 of N sets of L2P mapping tables. The other N−1 sets are stored in flash memory and fetched into the RAM when a L2P table miss occurs. The RAM required for mapping is greatly reduced. A data buffer stores one page of host write data. Sector writes are merged using the data buffer. The data buffer is flushed to flash when a different page is written, while the partial logical-to-physical mapping table is flushed to flash when a L2P table miss occurs, when the host address is to a different one of the N sets of L2P mapping tables.

Owner:SUPER TALENT TECH CORP

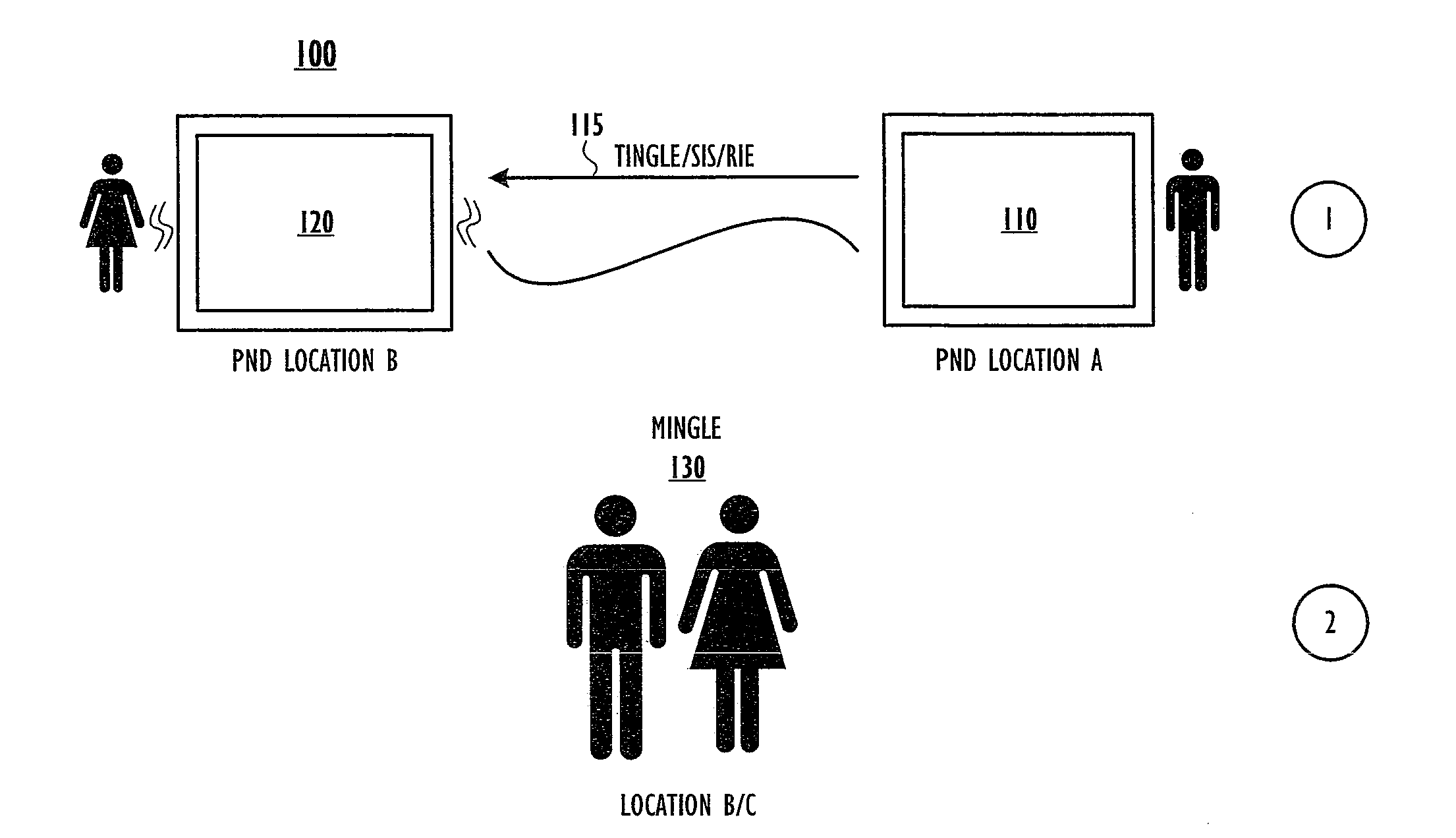

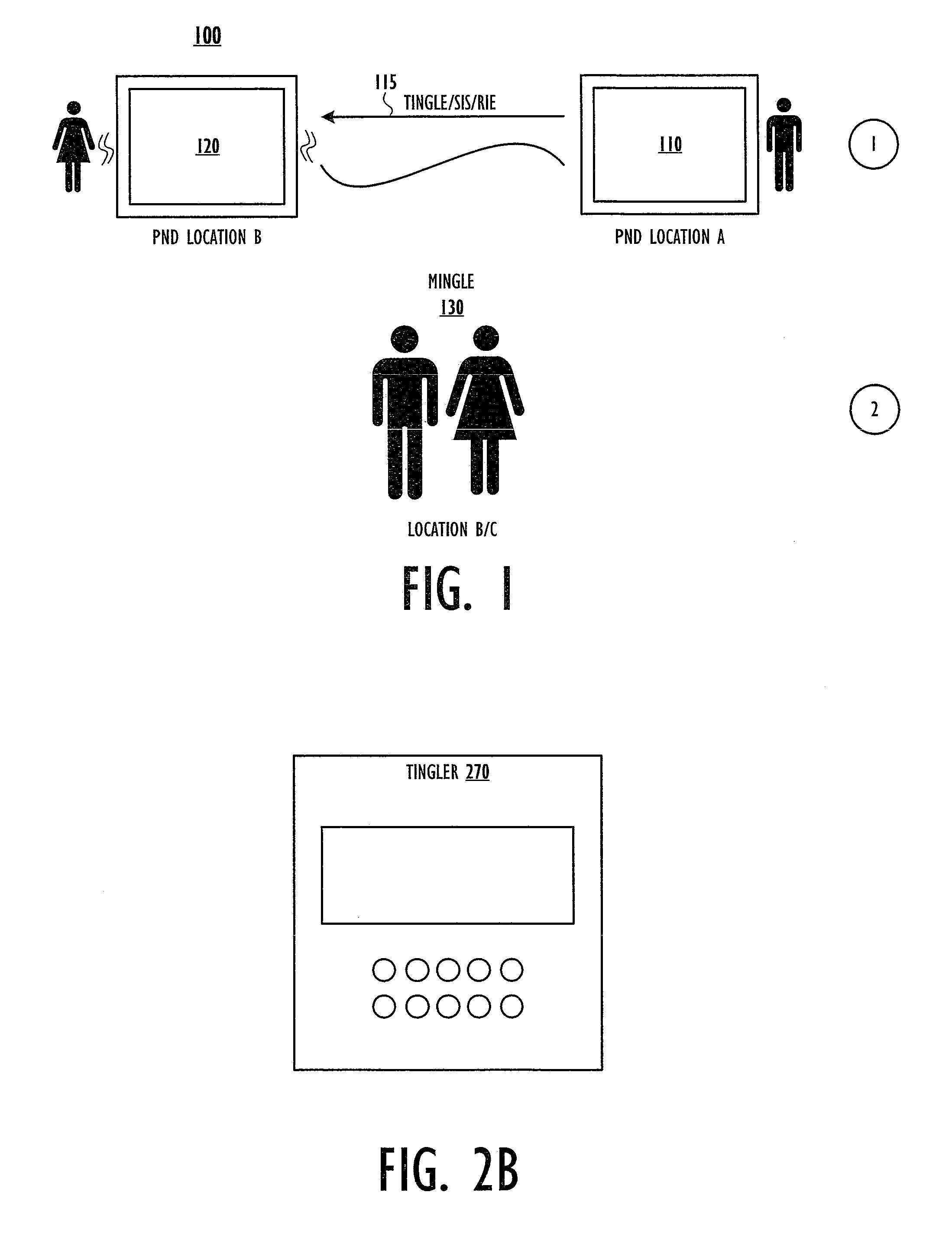

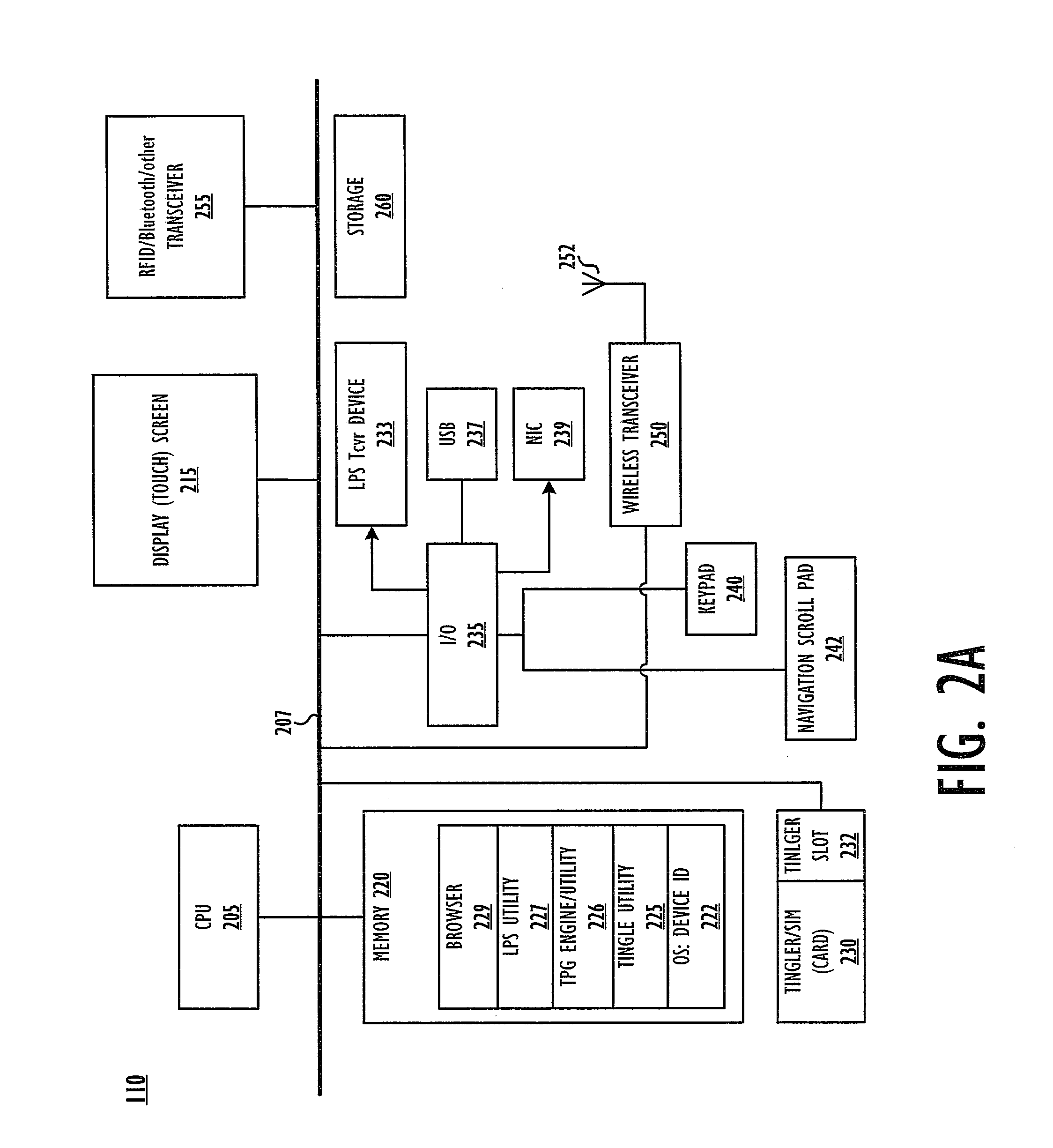

Method, system, and devices for facilitating real-time social and business interractions/networking

ActiveUS20120036181A1Data processing applicationsMultiple digital computer combinationsElectronic communicationCommunication device

A personal networking / communication device (PND) enables real-time social and business interactions / networking within a real environment. A first PND associated with a first person / user in the real environment is within communication range of a second PND. The first PND receives (via electronic communication) and displays a social interaction information signature (SIS) of the second PND. The signature includes a physical mapping / location of the second PND relative to the first PND and provides some information about the second PND's user. Following a selection of the SIS on the first PND, the first PND electronically transmits one or more “request for interaction or information exchange” (RIIE) to the second PND. When the first PND receives a response to the RIIE from the second PND, the user of the first PND receives real-time unequivocal confirmation of whether the second person is interested in interacting / socializing with the user.

Owner:ISIDORE EUSTACE PRINCE

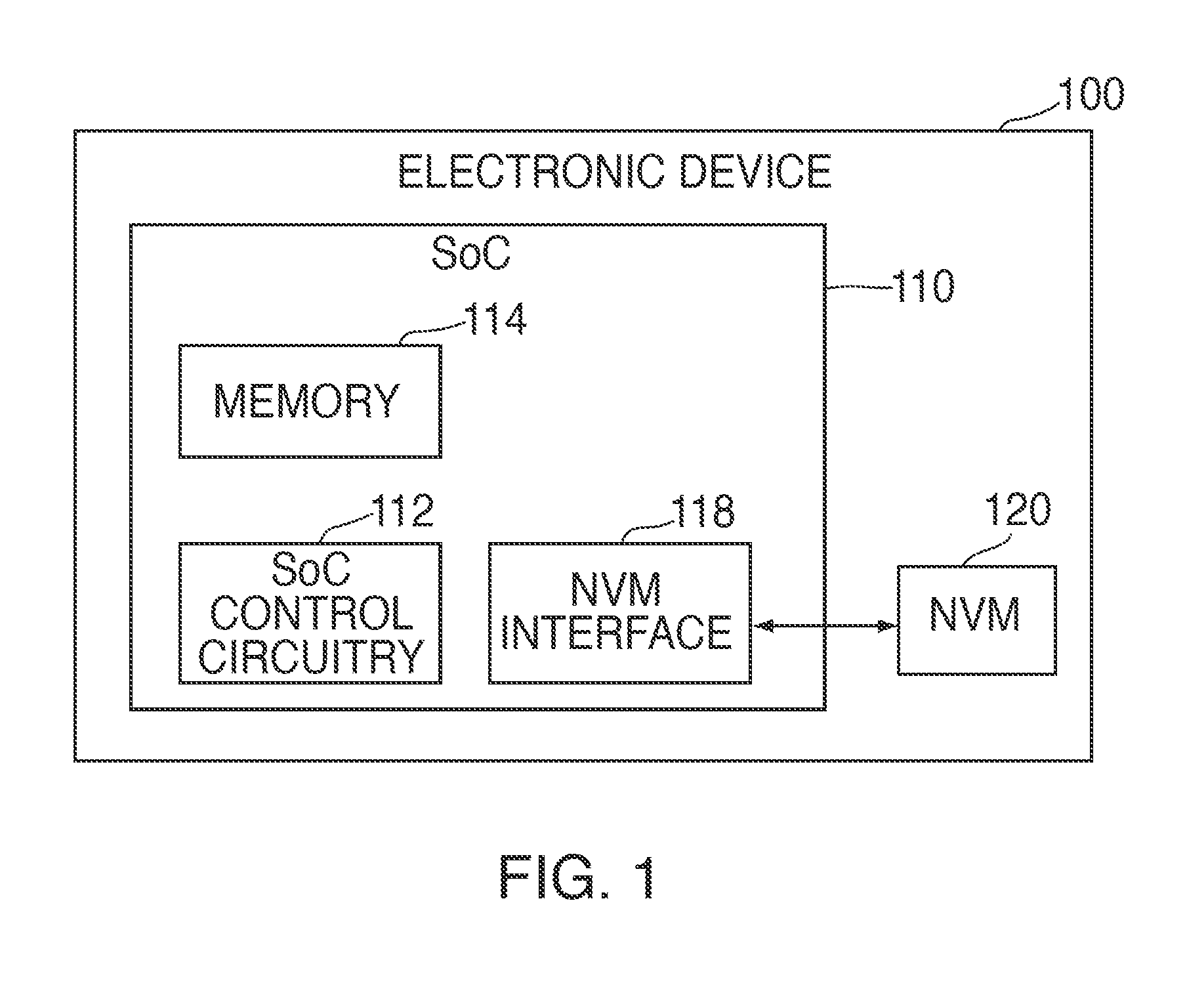

Method and system for dynamic compression of address tables in a memory

ActiveUS20150169465A1Memory architecture accessing/allocationInput/output to record carriersOperating systemVolatile memory

A method and system are disclosed for handling logical-to-physical mapping and increasing the amount of mapping table information that may be stored in a cache in volatile memory. The method includes the storage device storing in fast access memory, such as RAM, a copy of only a portion of the complete mapping information for non-volatile memory of the storage device using a compressed format by compressing the mapping data when a skip pattern of interleaved sequential writes to non-volatile memory are found in the mapping information. The system includes a storage device having volatile memory, non-volatile memory and a controller in communication with the volatile and non-volatile memory that is configured to carry out the method noted above.

Owner:SANDISK TECH LLC

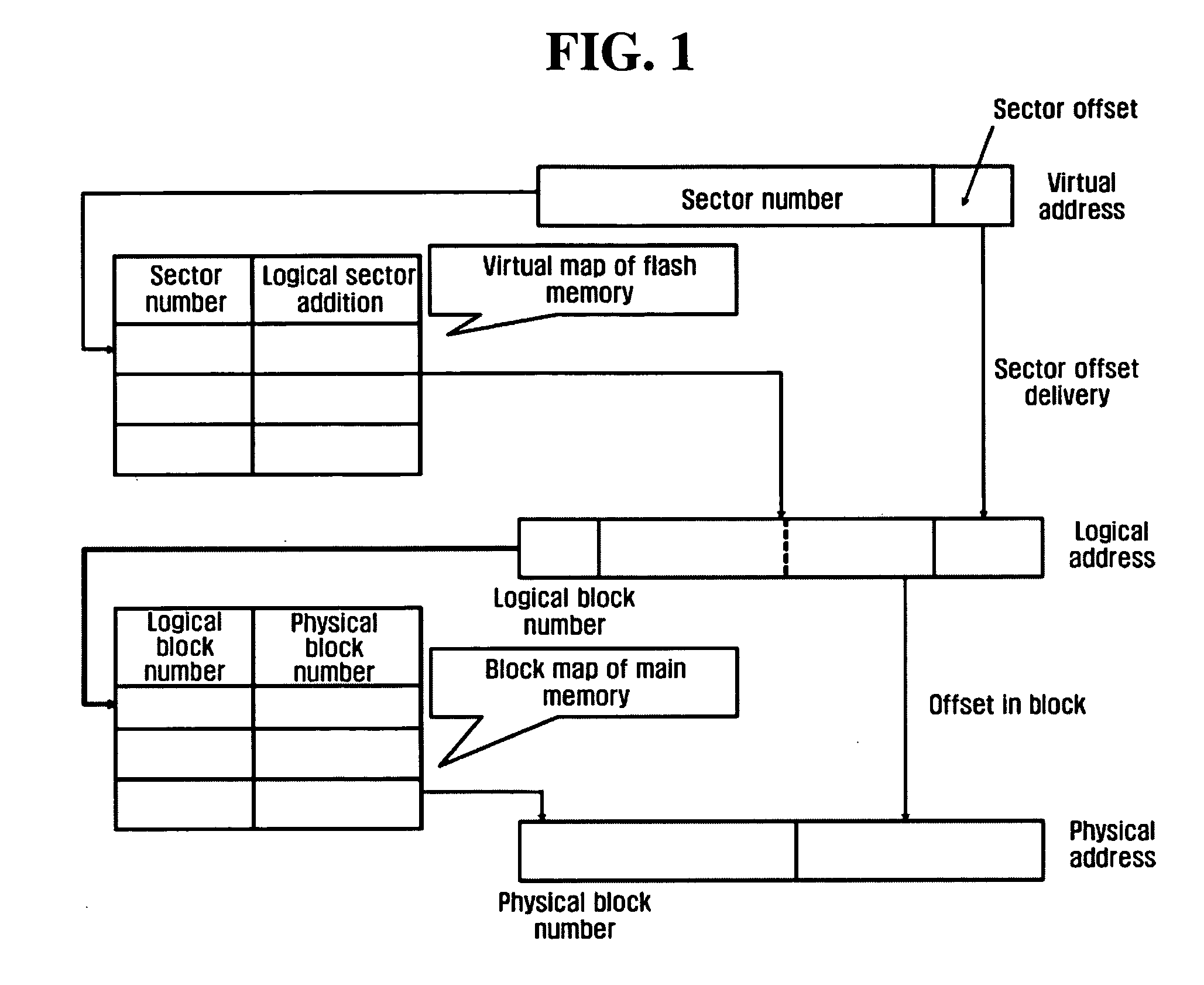

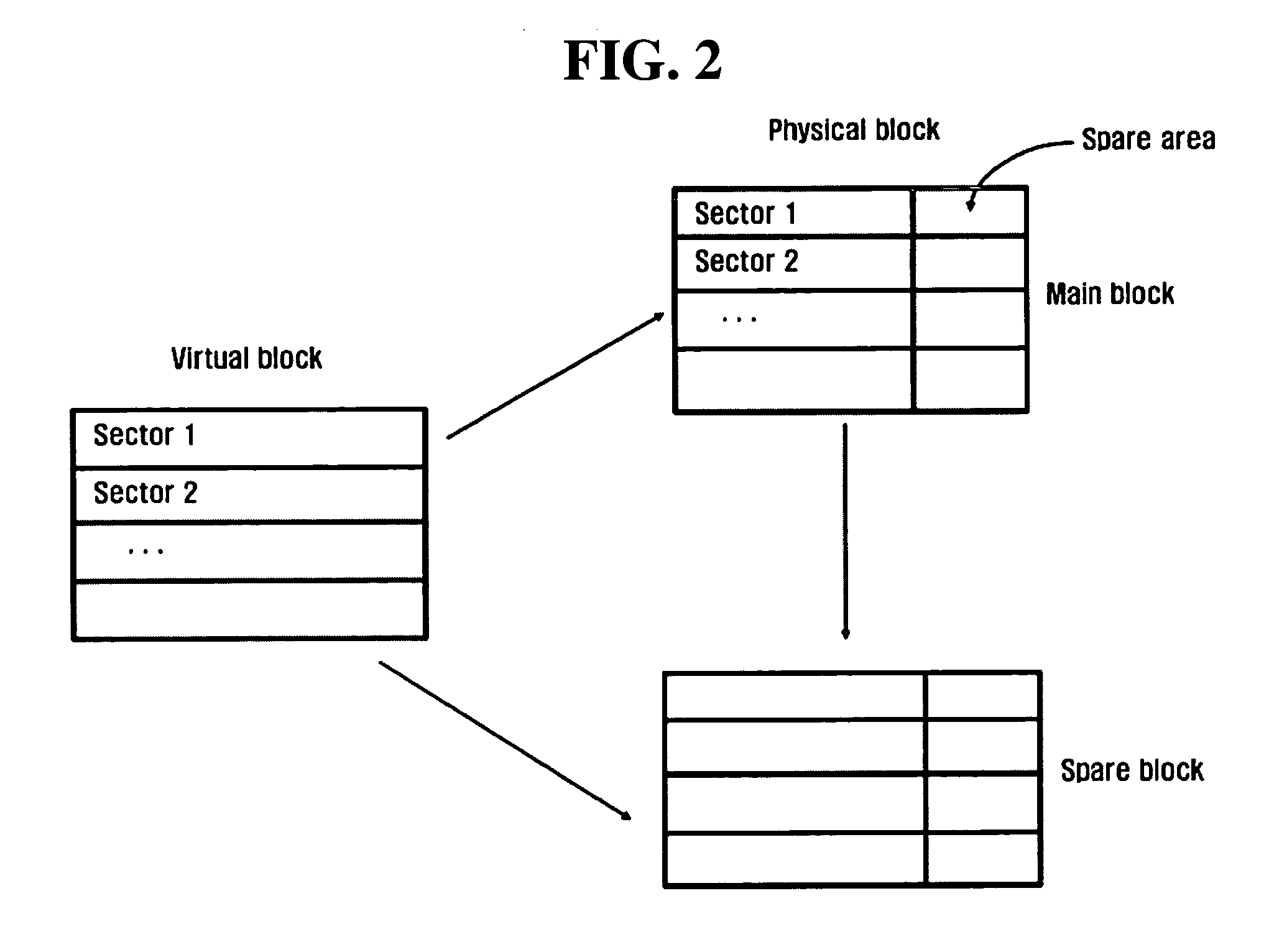

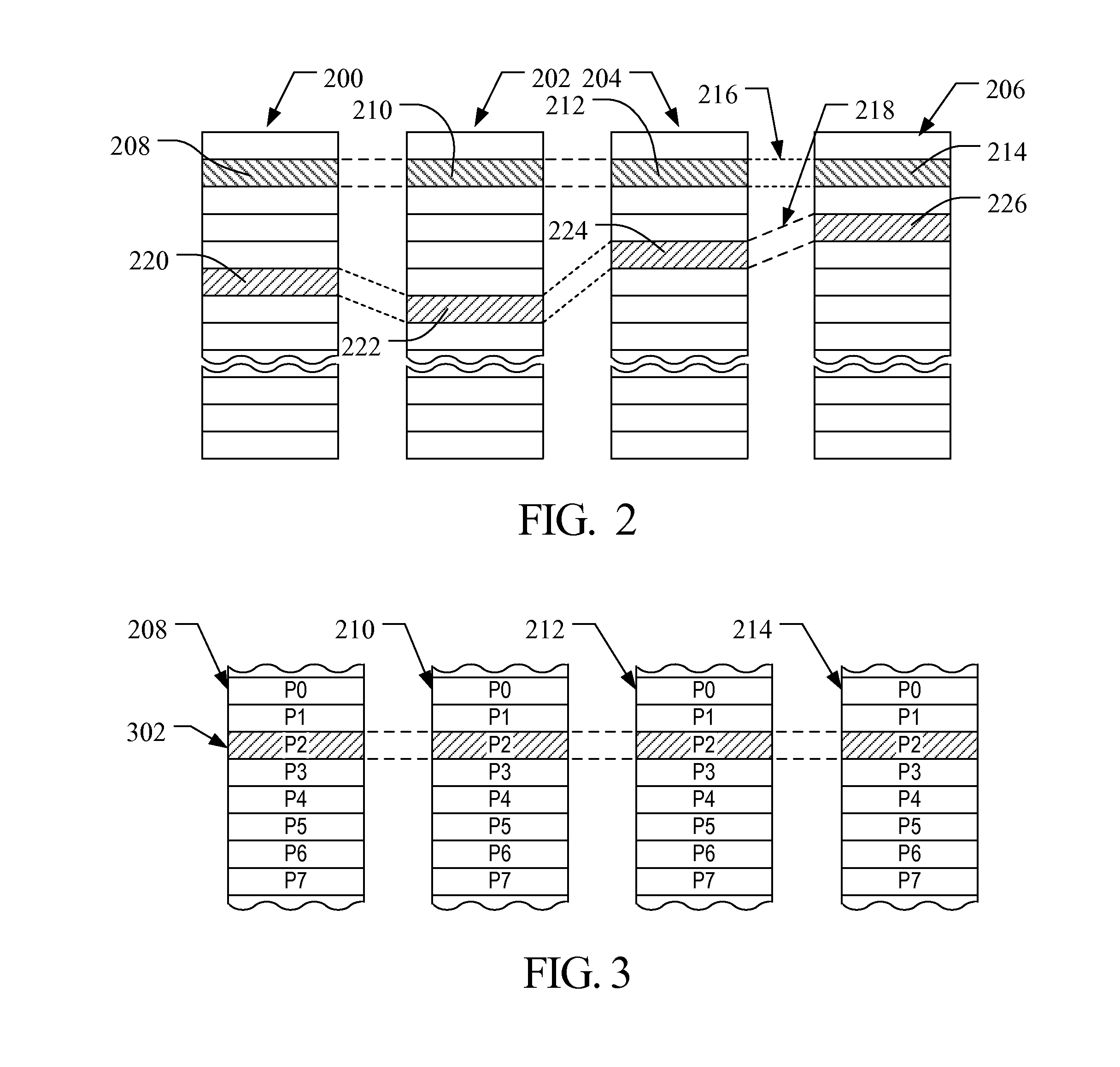

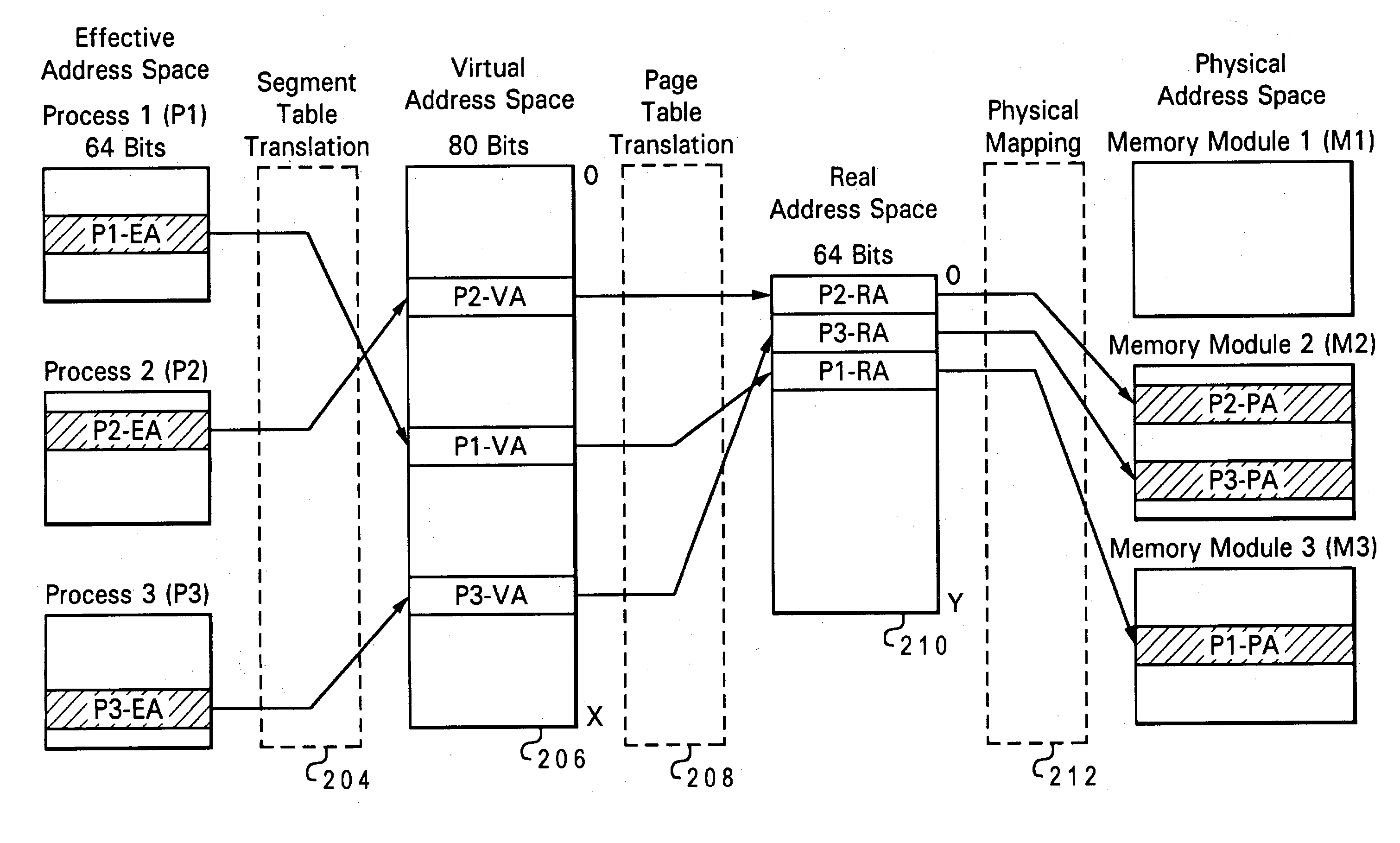

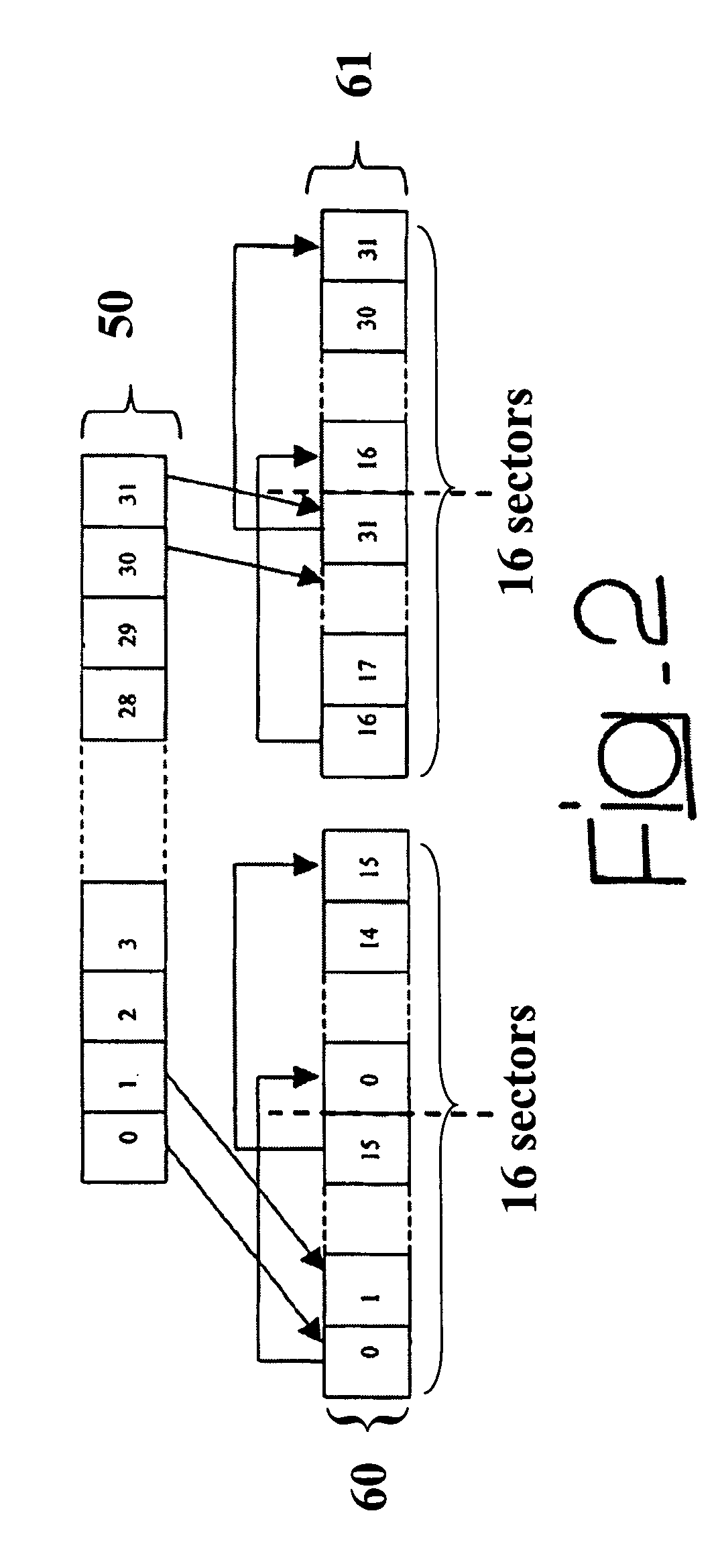

Controlling operation of flash memories

ActiveUS20060161723A1Convenient ArrangementMemory adressing/allocation/relocationMicro-instruction address formationParallel computingControl memory

A method controls write / erase operations in a memory device, such as a NAND flash memory. The method includes dividing the memory device in physical blocks, wherein each physical block is comprised of a number of pages; considering the memory device as comprising consecutive virtual blocks, each virtual block including consecutive sectors; associating to each virtual block a virtual block number; selecting the size of the virtual blocks equal to a multiple of the size of the physical blocks; and creating a virtual-to-physical mapping table having entries. Each entry in the mapping table stores a pointer to a root node of a tree structure that links logically a set of physical blocks in the memory device.

Owner:MICRON TECH INC

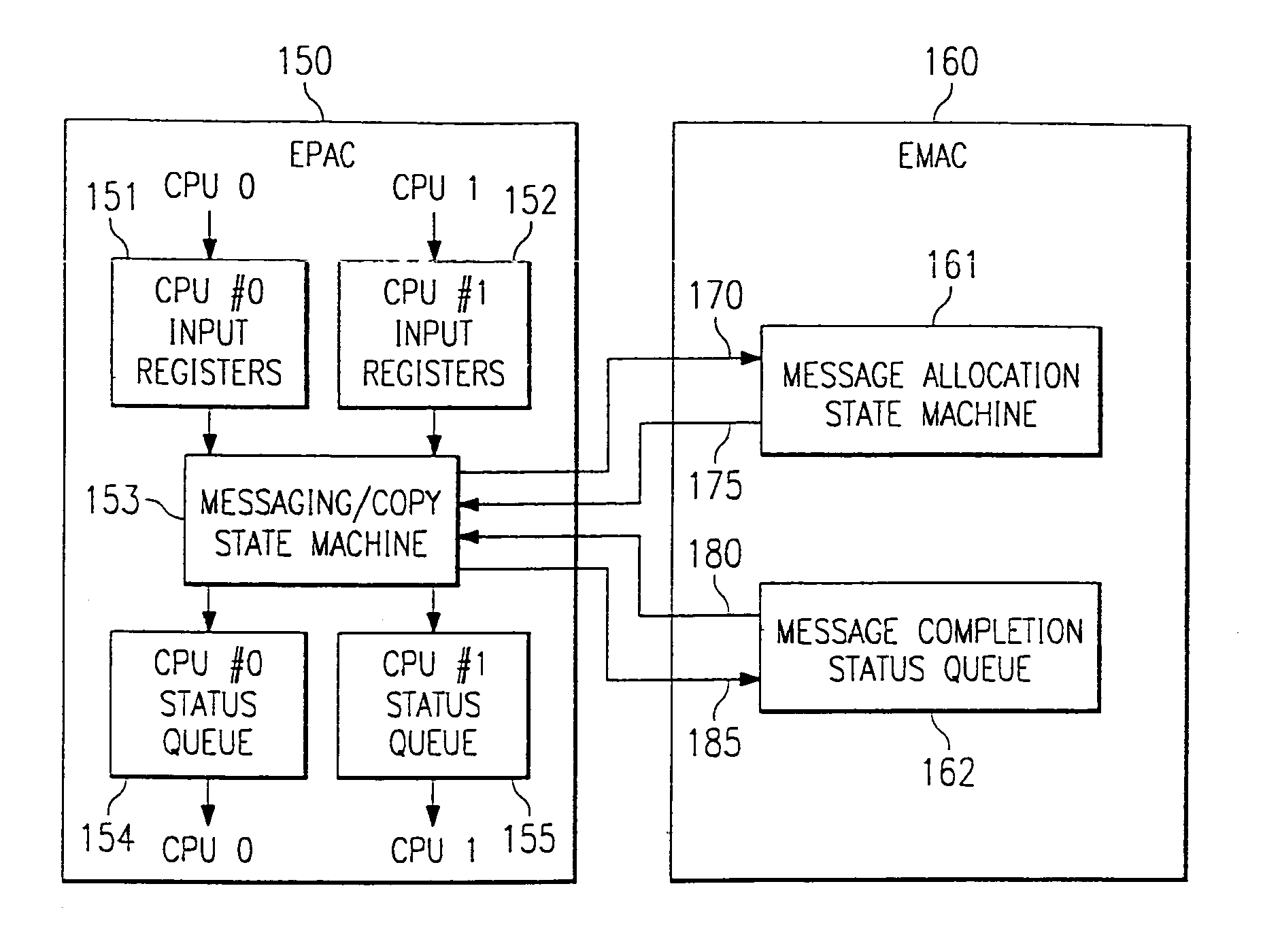

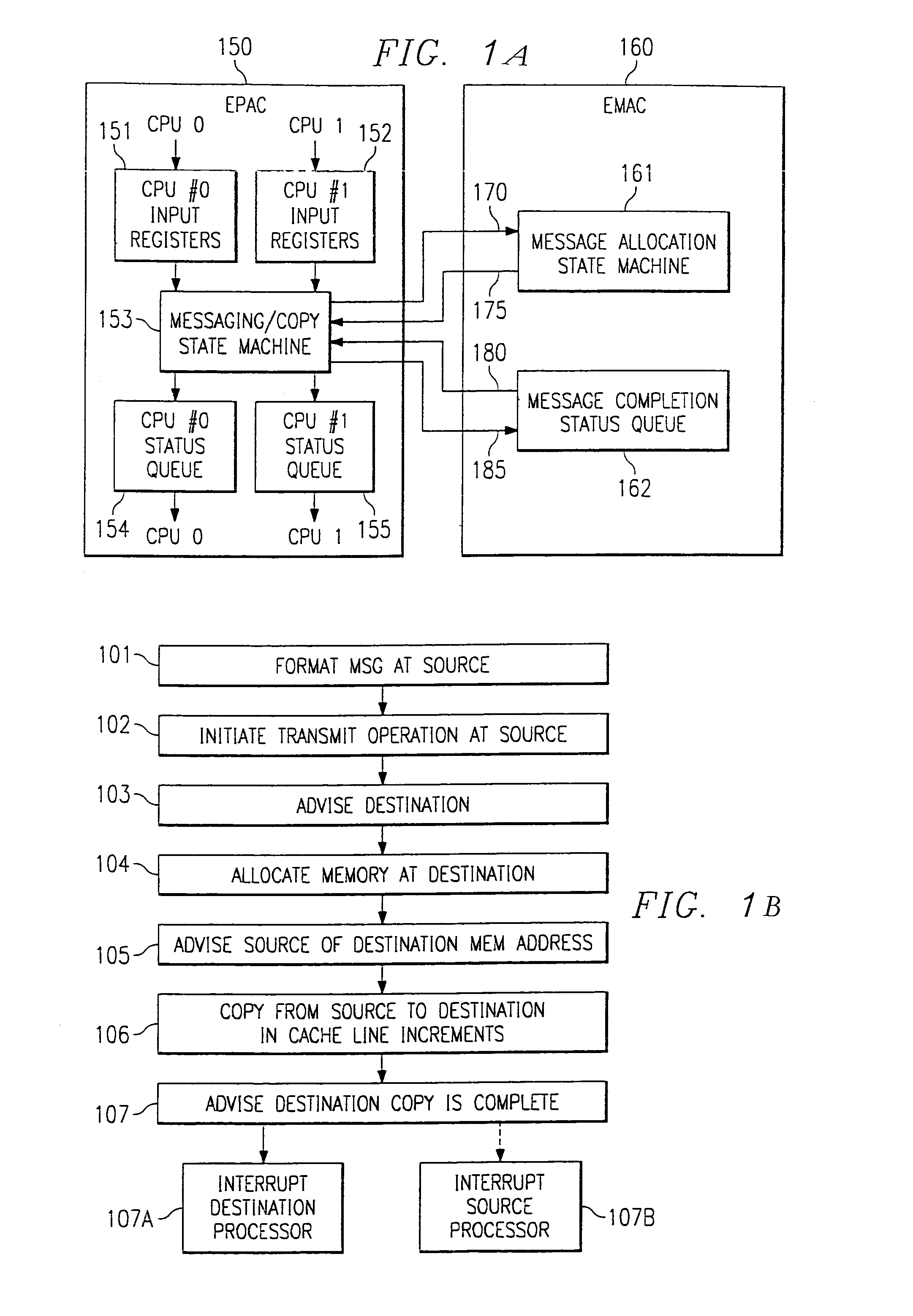

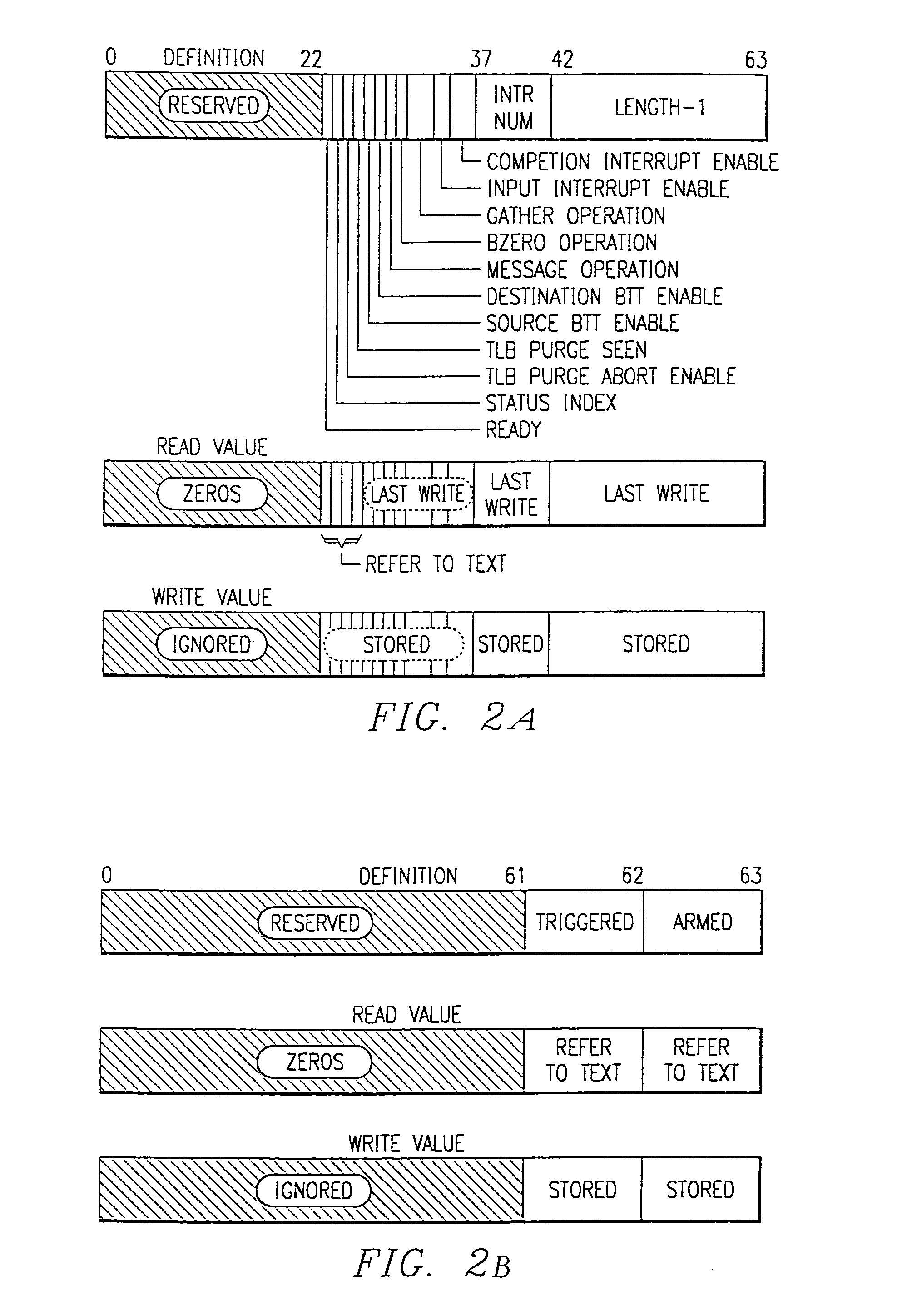

Virtual memory address translation control by TLB purge monitoring

InactiveUS7117338B2Optimize data movement operationEnsure integrityMemory adressing/allocation/relocationHardware monitoringVirtual memoryCompletion Status

In a computer system, an architecture is disclosed for optimizing aspects of data movement operations by performing functions such as memory allocation and notification on hardware rather than software. In this environment, the claimed invention is a method and apparatus for ensuring the integrity of data movement operations from virtual memory. The invention monitors and detects Translation Lookaside Buffer (“TLB”) purges, a hardware-based operation whose occurrence signals that virtual-to-physical mapping has changed. Responsive to detection of a TLB purge during the set up or execution of a data movement operation, the claimed invention aborts the operation, and then enqueues corresponding completion status information to notify processors of the event.

Owner:HEWLETT PACKARD DEV CO LP

Efficient error handling mechanisms in data storage systems

A data storage system configured to efficiently search and update system data is disclosed. In one embodiment, the data storage system can attempt to correct errors in retrieved data configured to index system data. Metadata stored along with user data in a memory location can be configured to indicate a logical address associated in a logical-to-physical location mapping with a physical address at which user data and metadata are stored. The data storage system can generate modified versions of logical address indicated by the metadata and determine whether such modified versions match the physical address in the logical-to-physical mapping. Modified versions of the logical address can be generated by flipping one or more bits in the logical address indicated by the metadata. Efficiency can be increased and improved performance can be attained.

Owner:WESTERN DIGITAL TECH INC

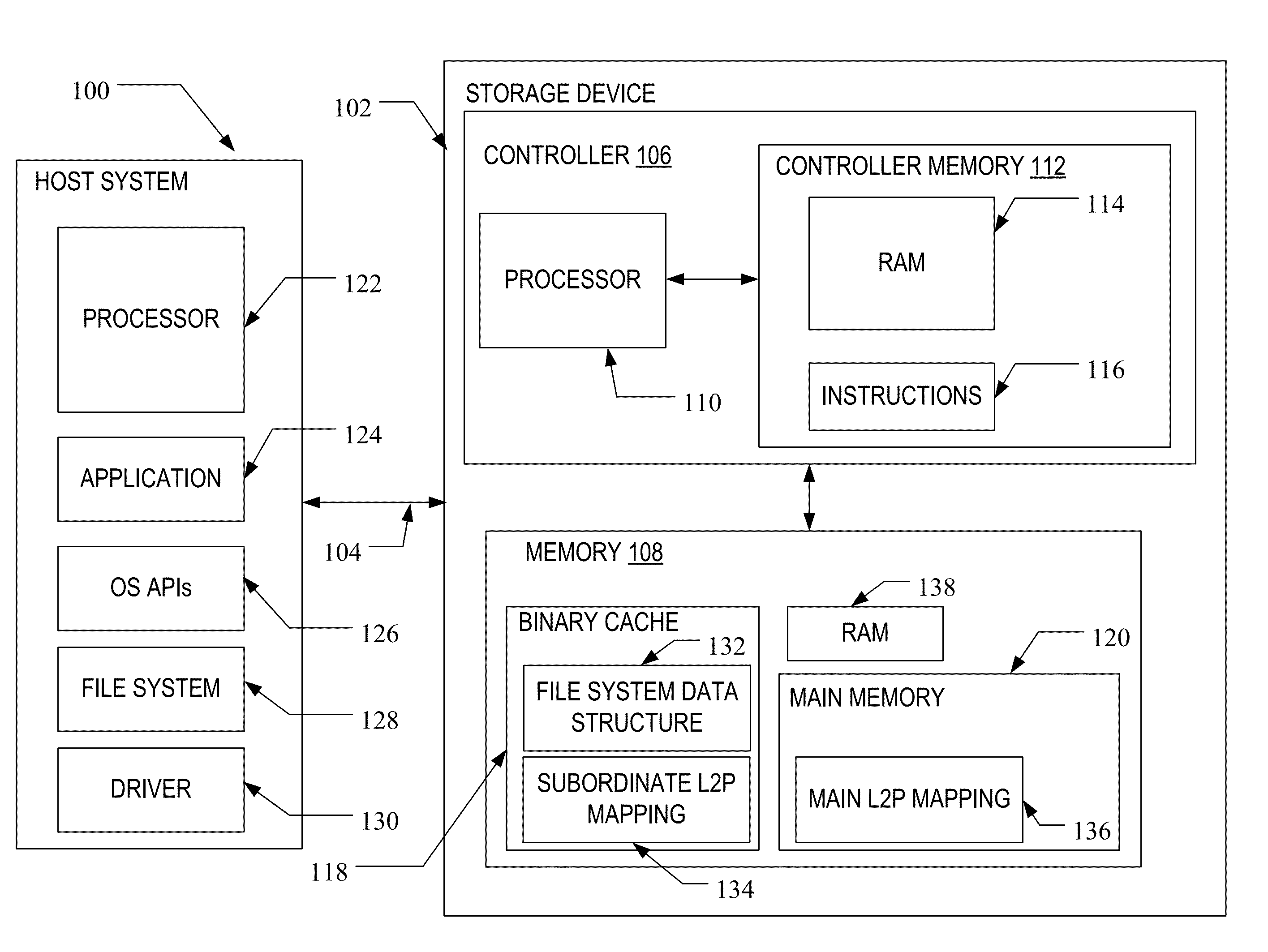

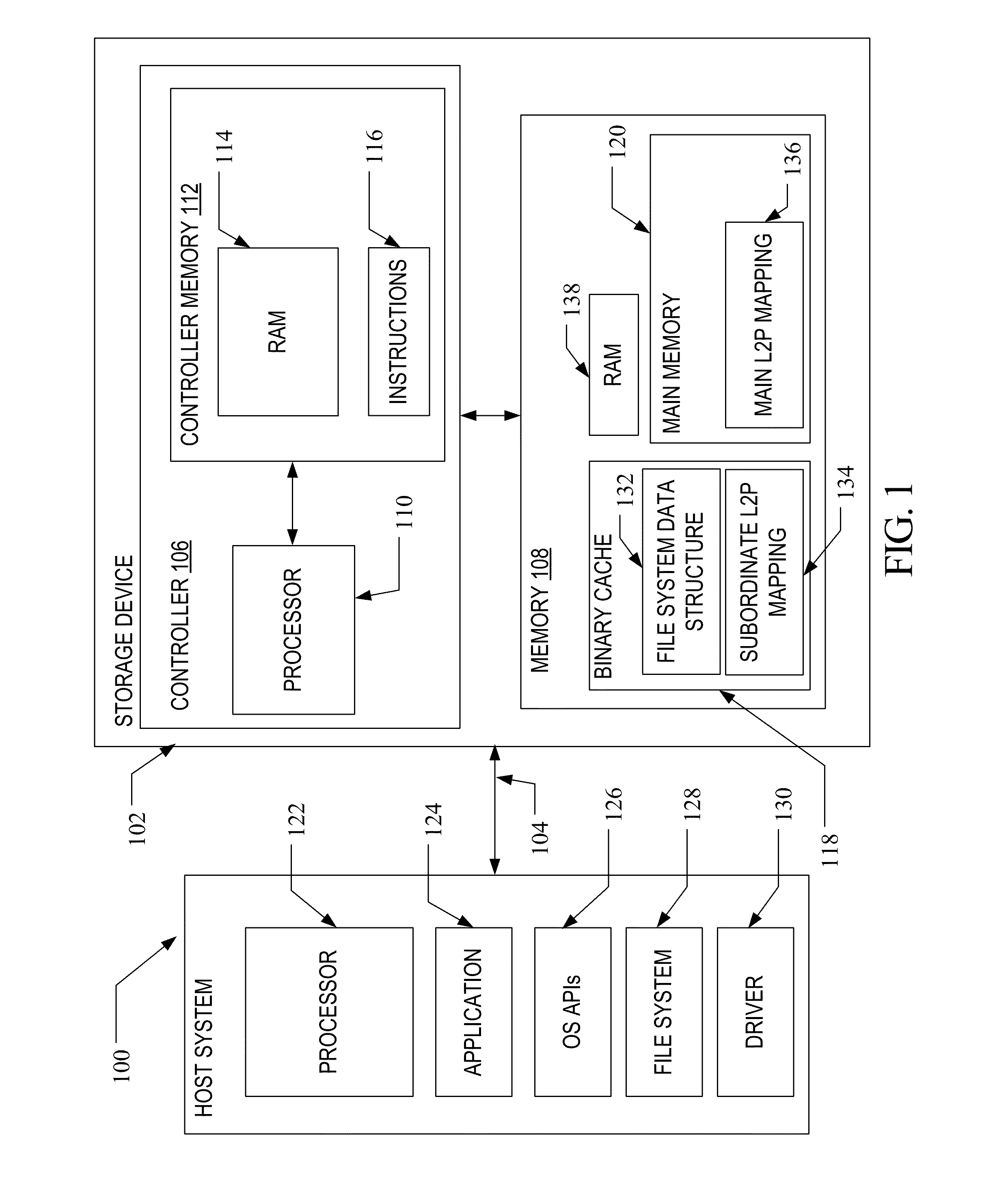

Usage of cache and write transaction information in a storage device

InactiveUS20140143476A1Memory adressing/allocation/relocationInput/output processes for data processingFile systemData structure

A method and system are disclosed for tracking write transactions in a manner to prevent corruption of file system during interruptions such as power failures between write commands. The method includes the storage device tracking transaction identifiers for write commands and delaying the update of a main memory logical-to-physical map until all of the write commands for a particular transaction have been received based on the transaction ID information. The system includes a storage device having a flash memory with a main logical-to-physical mapping data structure and a controller configured to track individual write commands of a write transaction and store data from those commands without updating the main logical-to-physical mapping data structure until all of the data for the write transaction has been received.

Owner:SANDISK TECH LLC

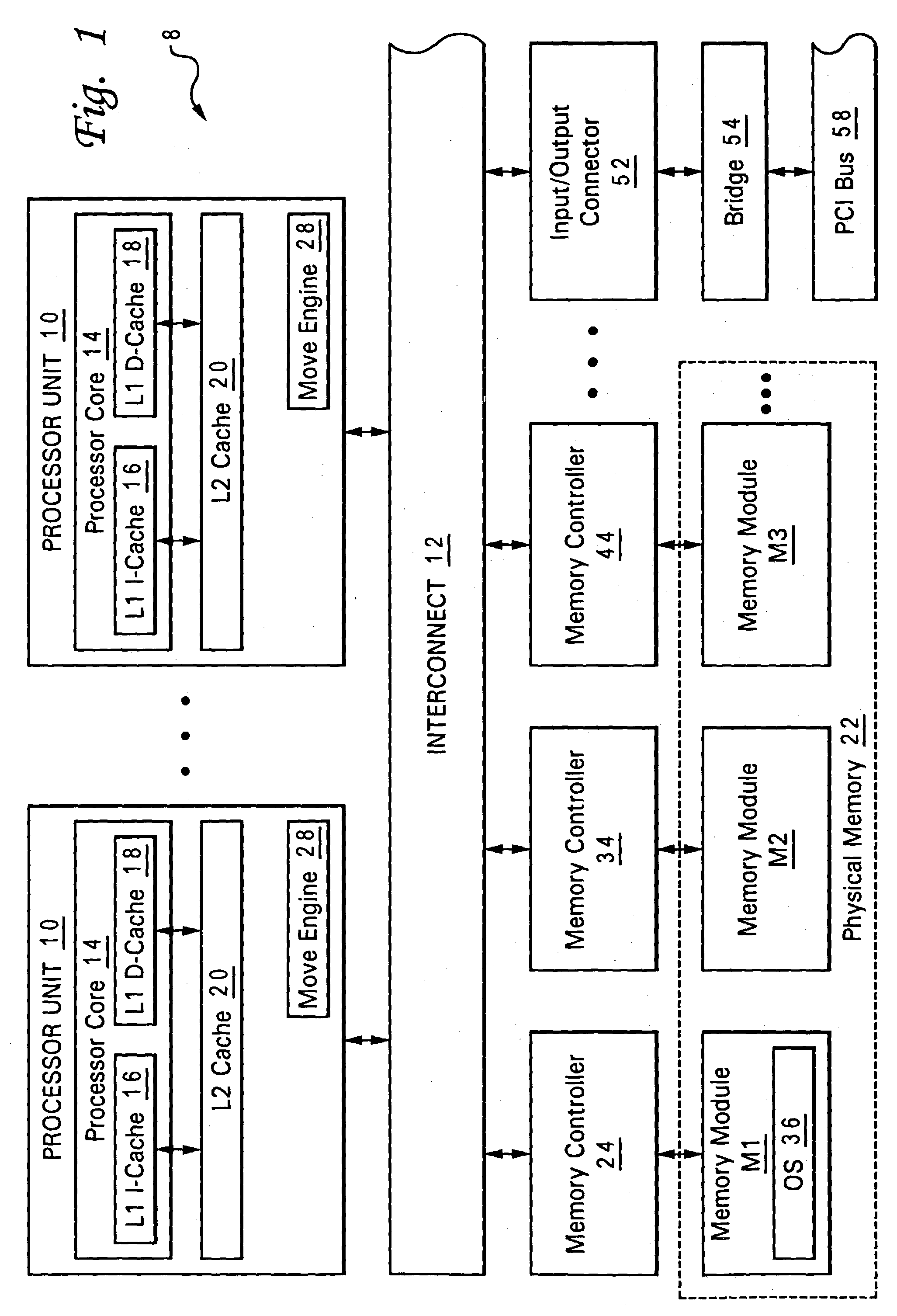

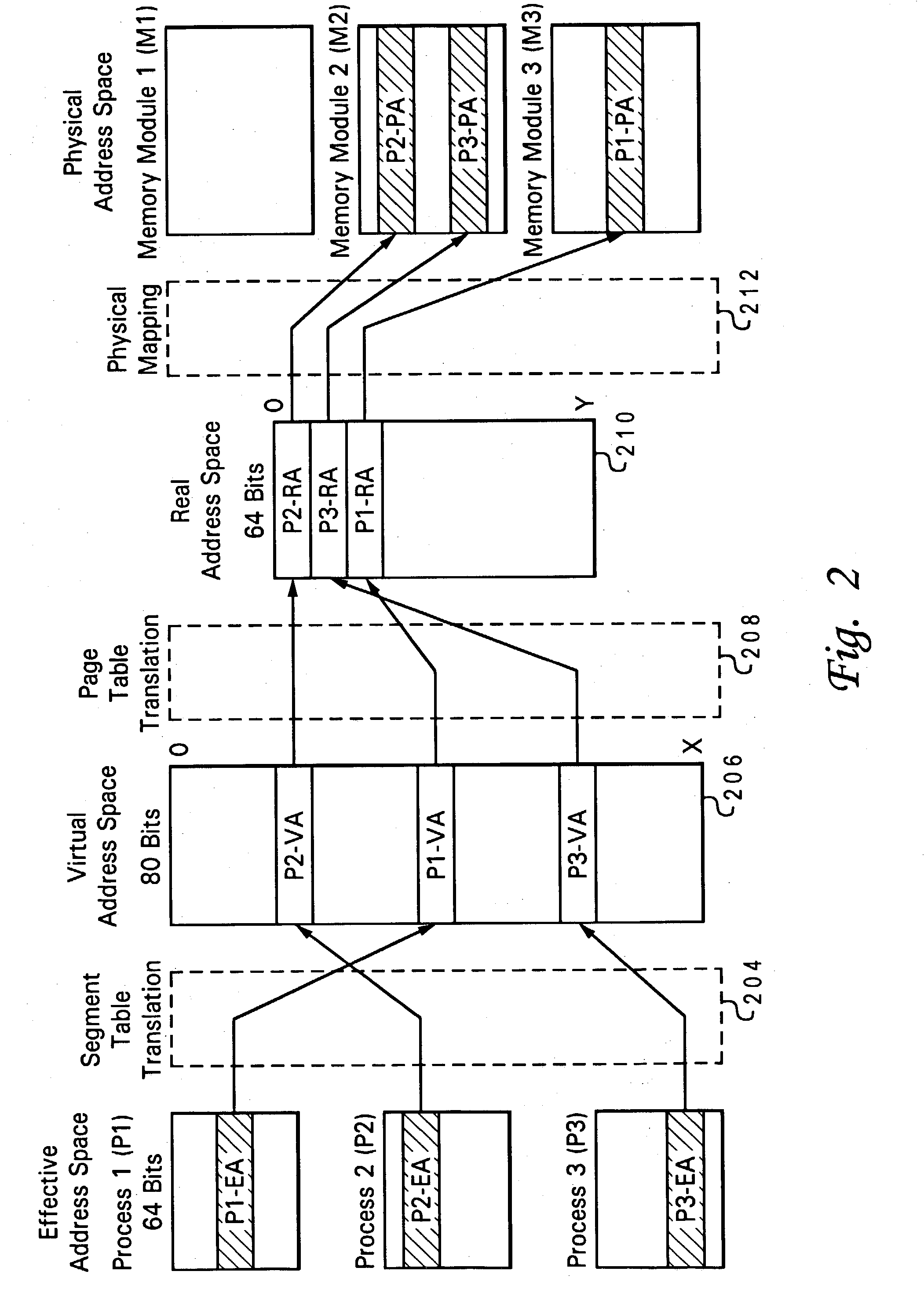

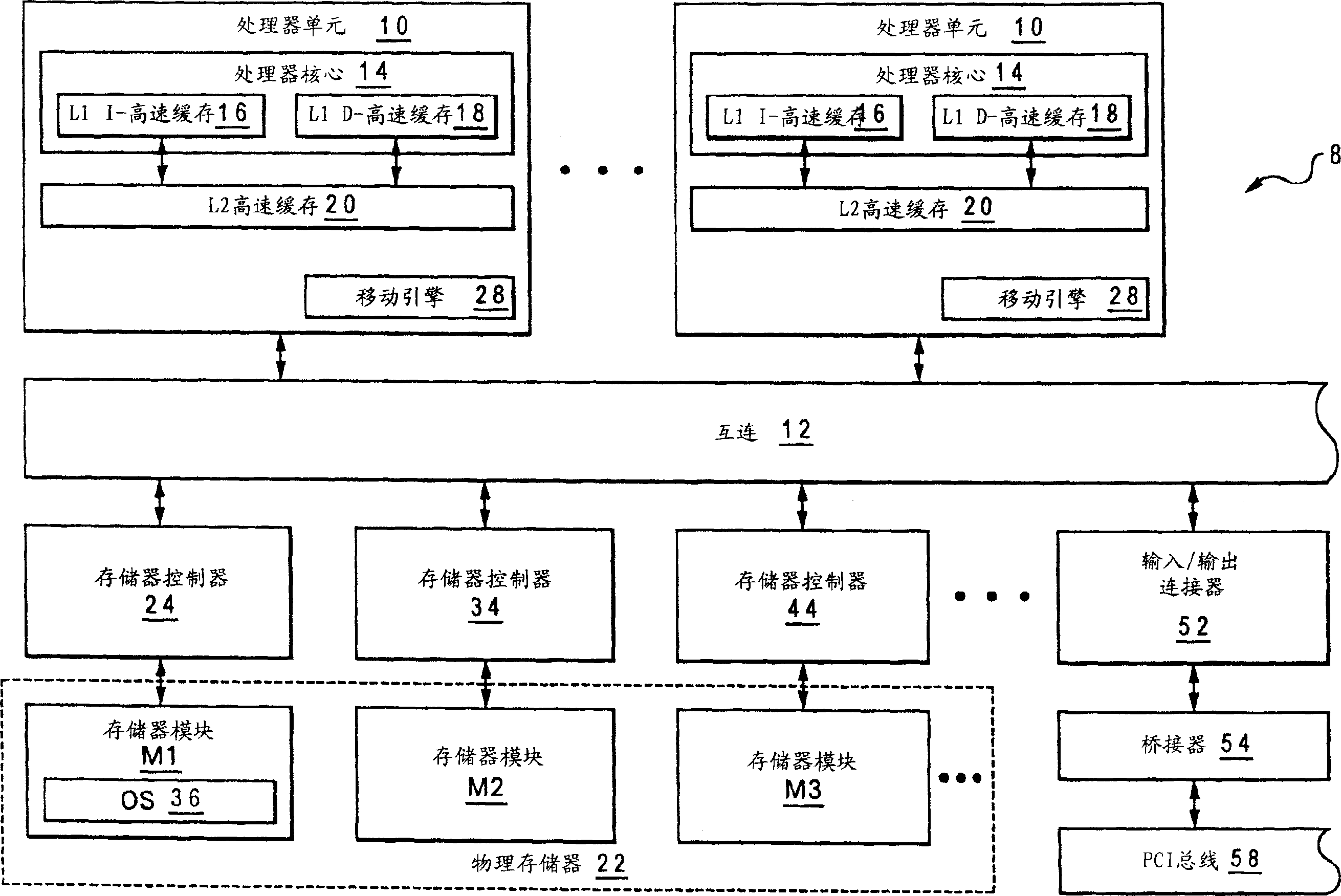

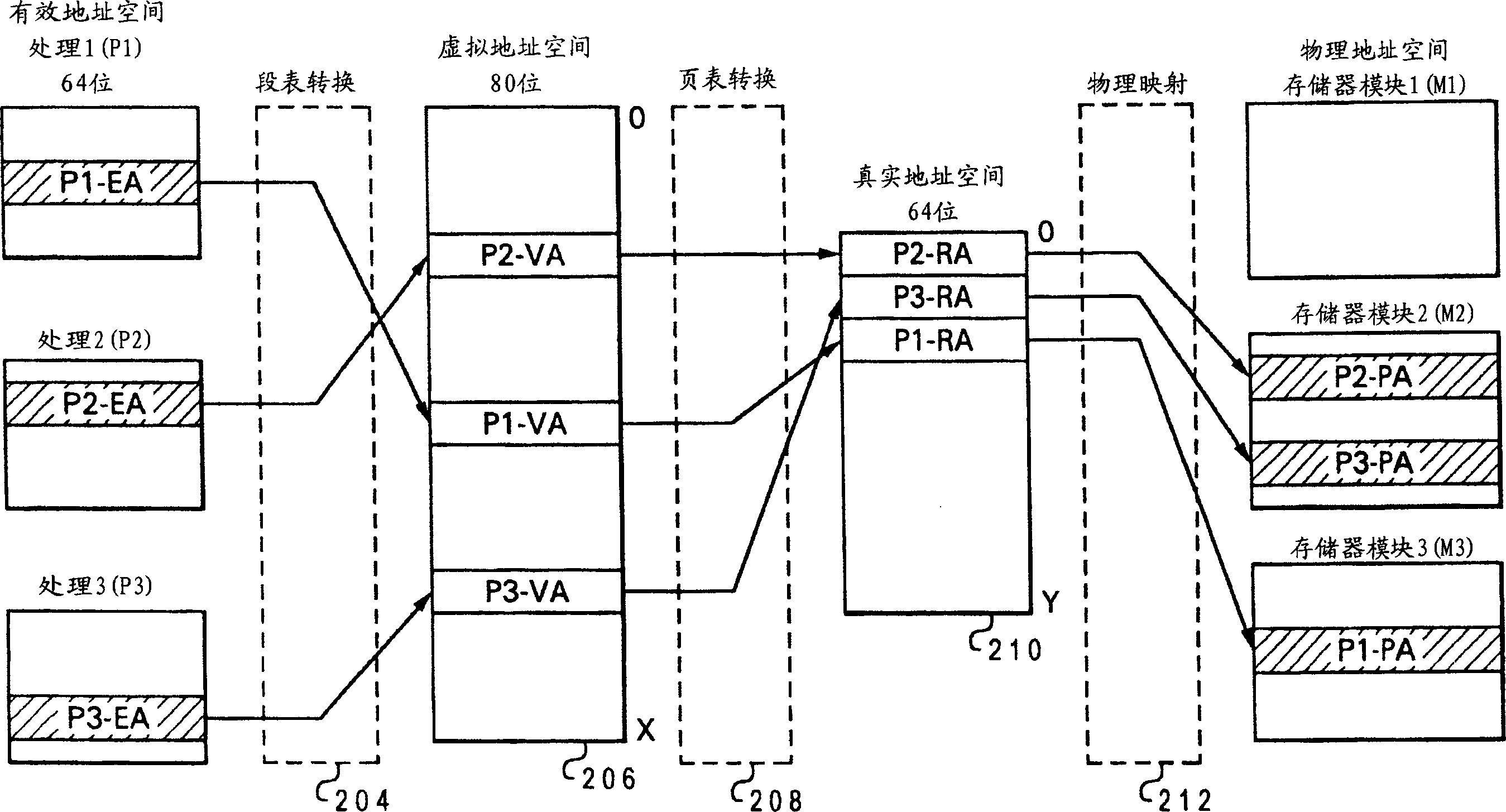

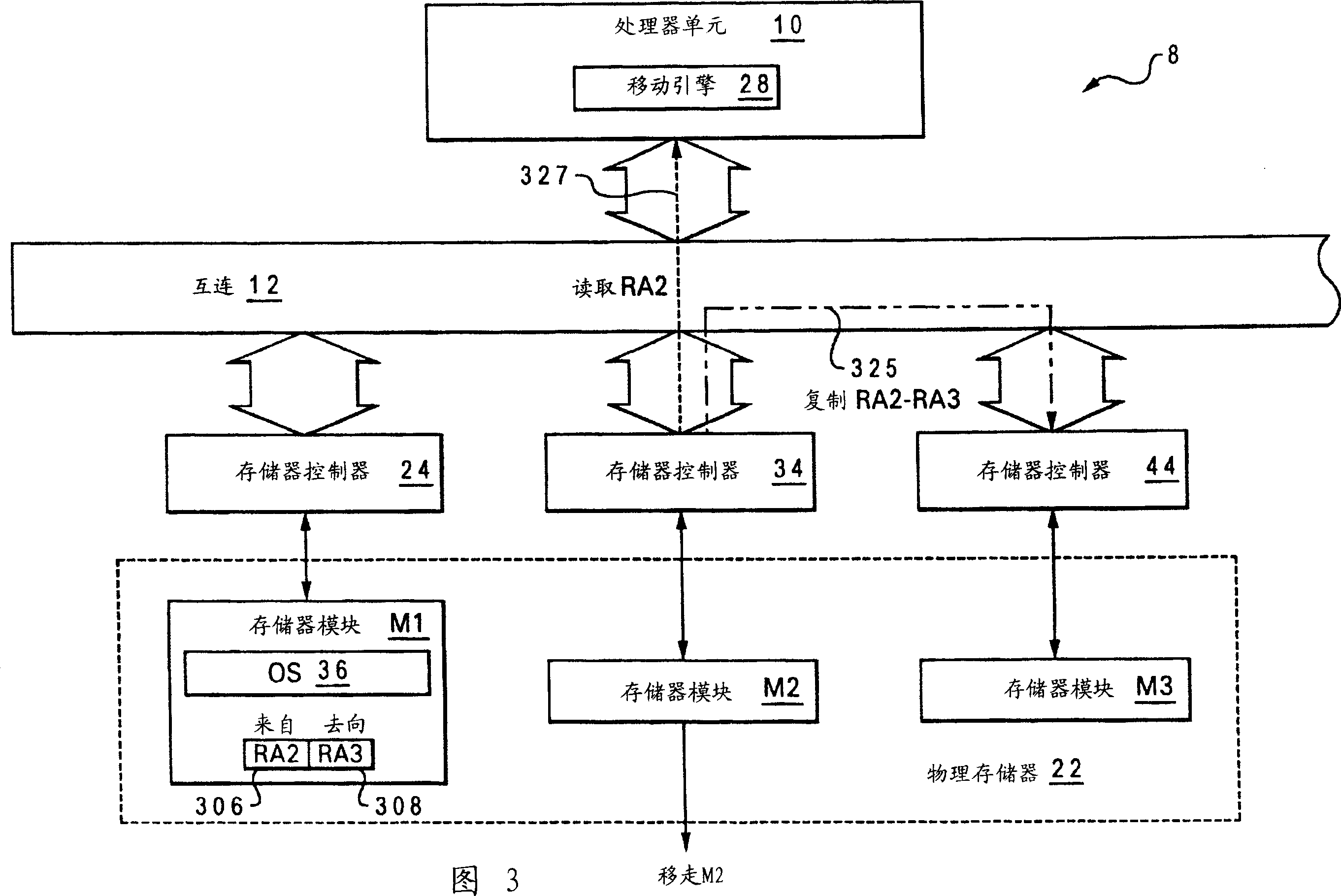

Method and system of managing virtualized physical memory in a data processing system

InactiveUS20040073742A1Input/output to record carriersMemory adressing/allocation/relocationOperational systemHandling system

A move engine and operating system transparently reconfigure physical memory to accomplish addition, subtraction, or replacement of a memory module. The operating system stores FROM and TO real addresses in unique fields in memory that are used to virtualize the physical address of the memory module being reconfigured and provide the reconfiguration in real-time through the use of hardware functionality and not software. Using the FROM and TO real addresses to select a source and a target, the move engine copies the contents of the memory module to be removed or reconfigured into the remaining or inserted memory module. Then, the real address associated with the reconfigured memory module is re-assigned to the memory module receiving the copied contents, thereby creating a virtualized physical mapping from the addressable real address space being utilized by the operating system into a virtual physical address space. During the process of moving the memory contents, the operating system stalls Write memory requests addressed to the real address space currently associated with the sourcing memory module indicated by either the FROM or TO real address space. As will be appreciated, a memory module can be inserted, removed or replaced in physical memory without the operating system having to stop all memory operations in the memory to accomplish the physical memory change.

Owner:IBM CORP

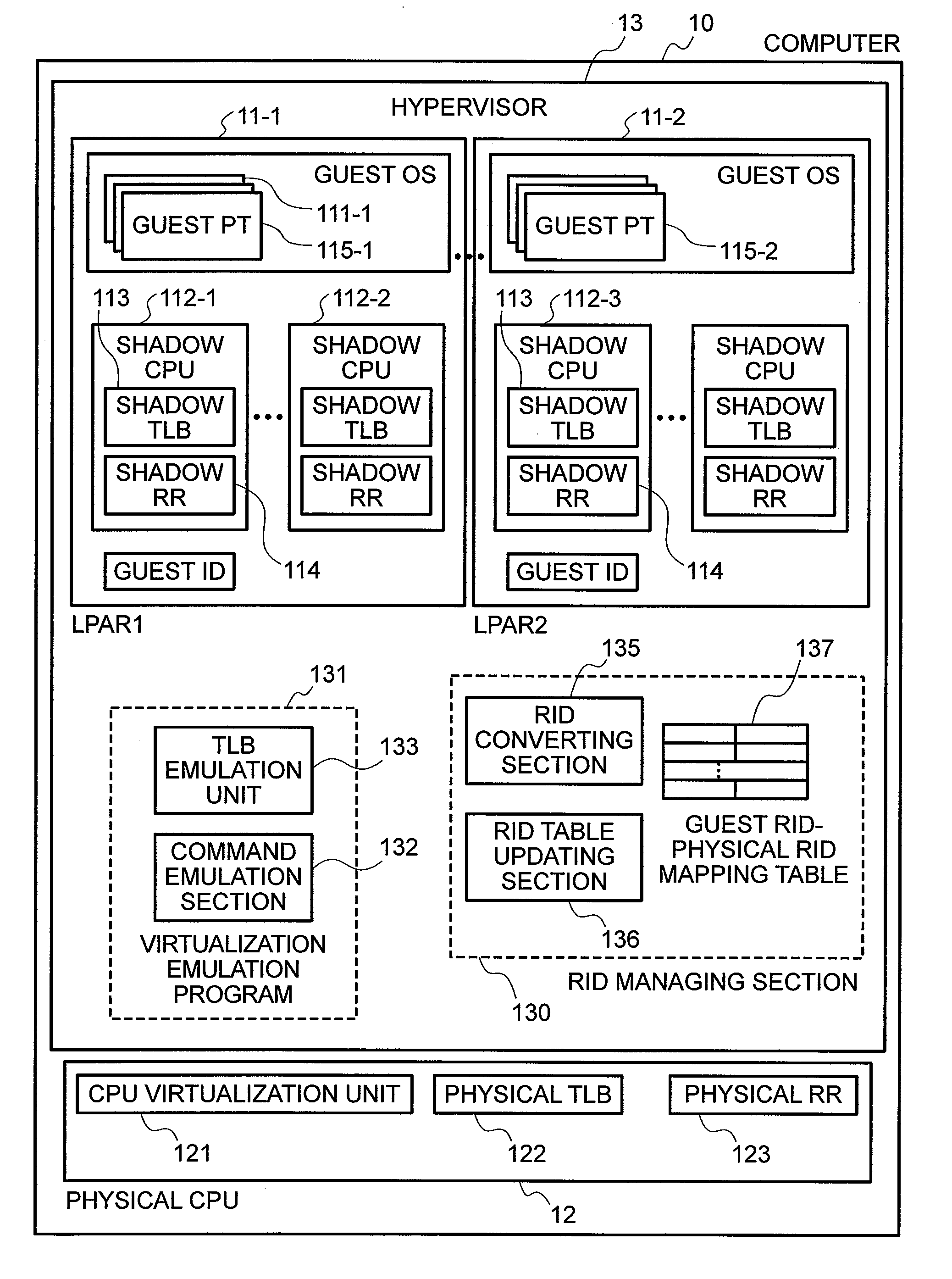

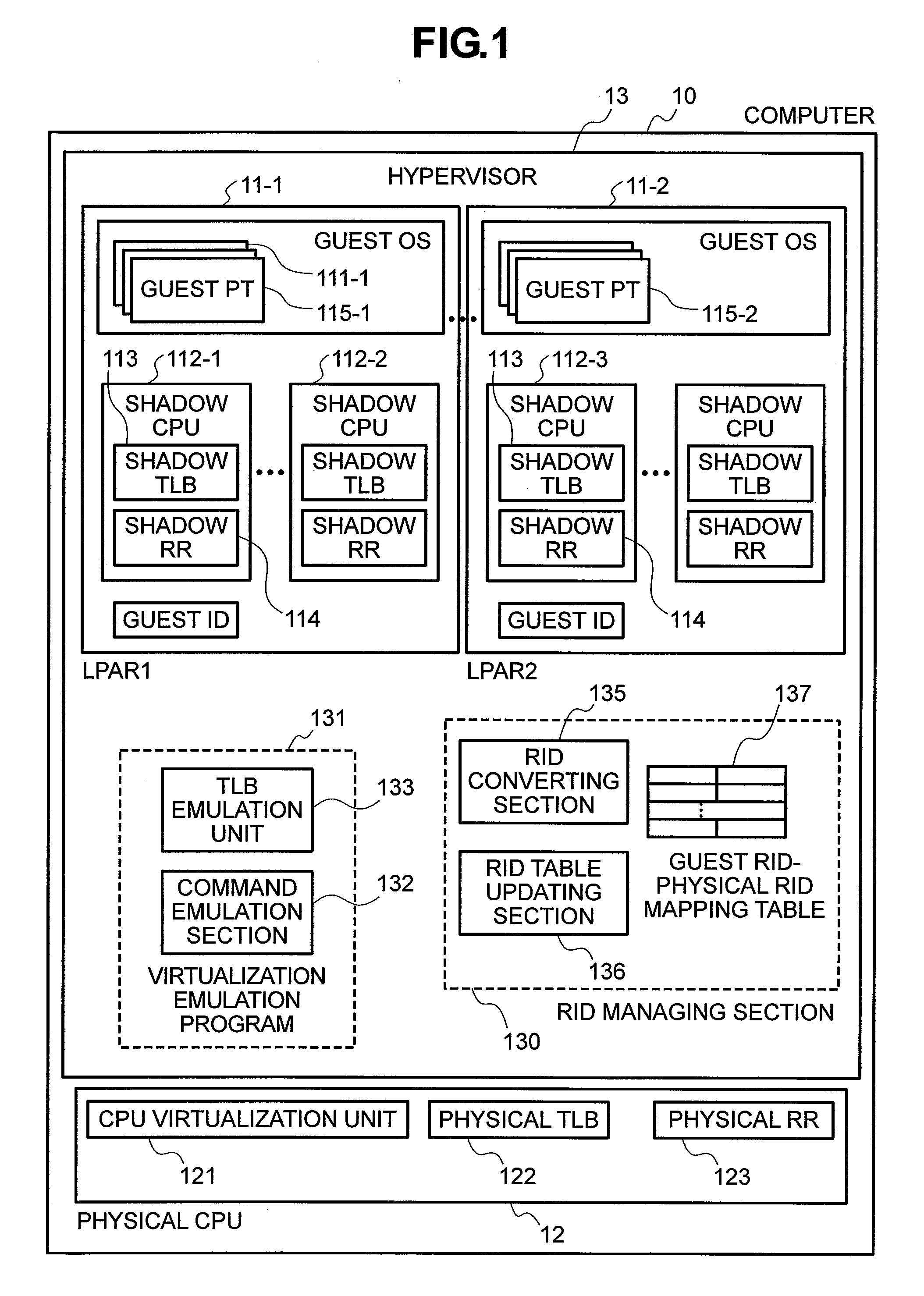

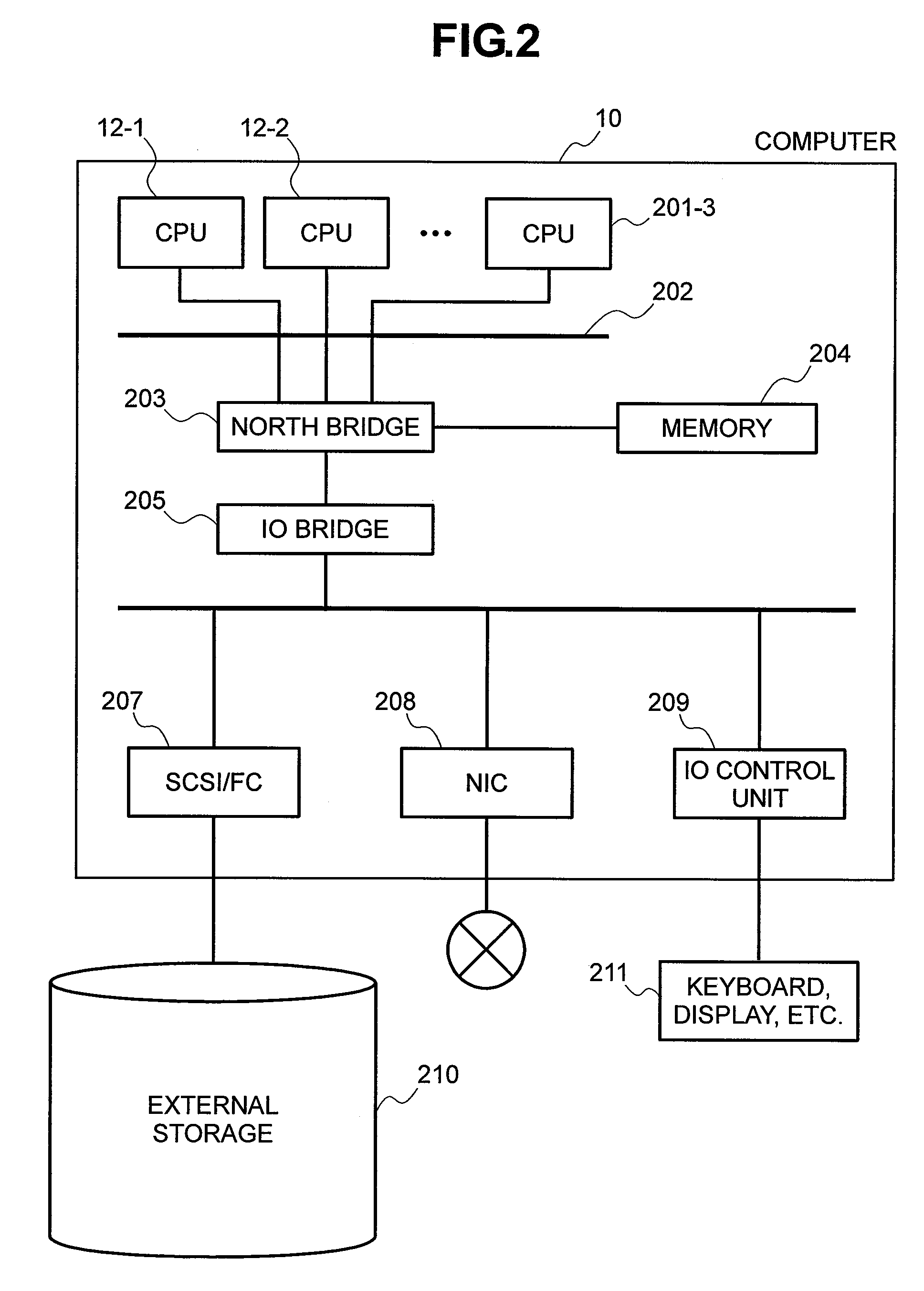

Computer virtualization apparatus and program and method therefor

ActiveUS20090164991A1Performance is not deterioratedMemory architecture accessing/allocationMemory adressing/allocation/relocationOperating systemHypervisor

A hypervisor prepares a guest RID-physical RID mapping table for dynamically registering and managing items and performs RID conversion using the guest RID-physical RID mapping table. When the mapping table is used, since it is unnecessary to provide a specific information area representing LPARs corresponding to respective guests in an RID to be converted, there is no limitation concerning the number of LPARs and a problem in operation can be eliminated.

Owner:HITACHI LTD

Controlling operation of flash memories

A method controls write / erase operations in a memory device, such as a NAND flash memory. The method includes dividing the memory device in physical blocks, wherein each physical block is comprised of a number of pages; considering the memory device as comprising consecutive virtual blocks, each virtual block including consecutive sectors; associating to each virtual block a virtual block number; selecting the size of the virtual blocks equal to a multiple of the size of the physical blocks; and creating a virtual-to-physical mapping table having entries. Each entry in the mapping table stores a pointer to a root node of a tree structure that links logically a set of physical blocks in the memory device.

Owner:MICRON TECH INC

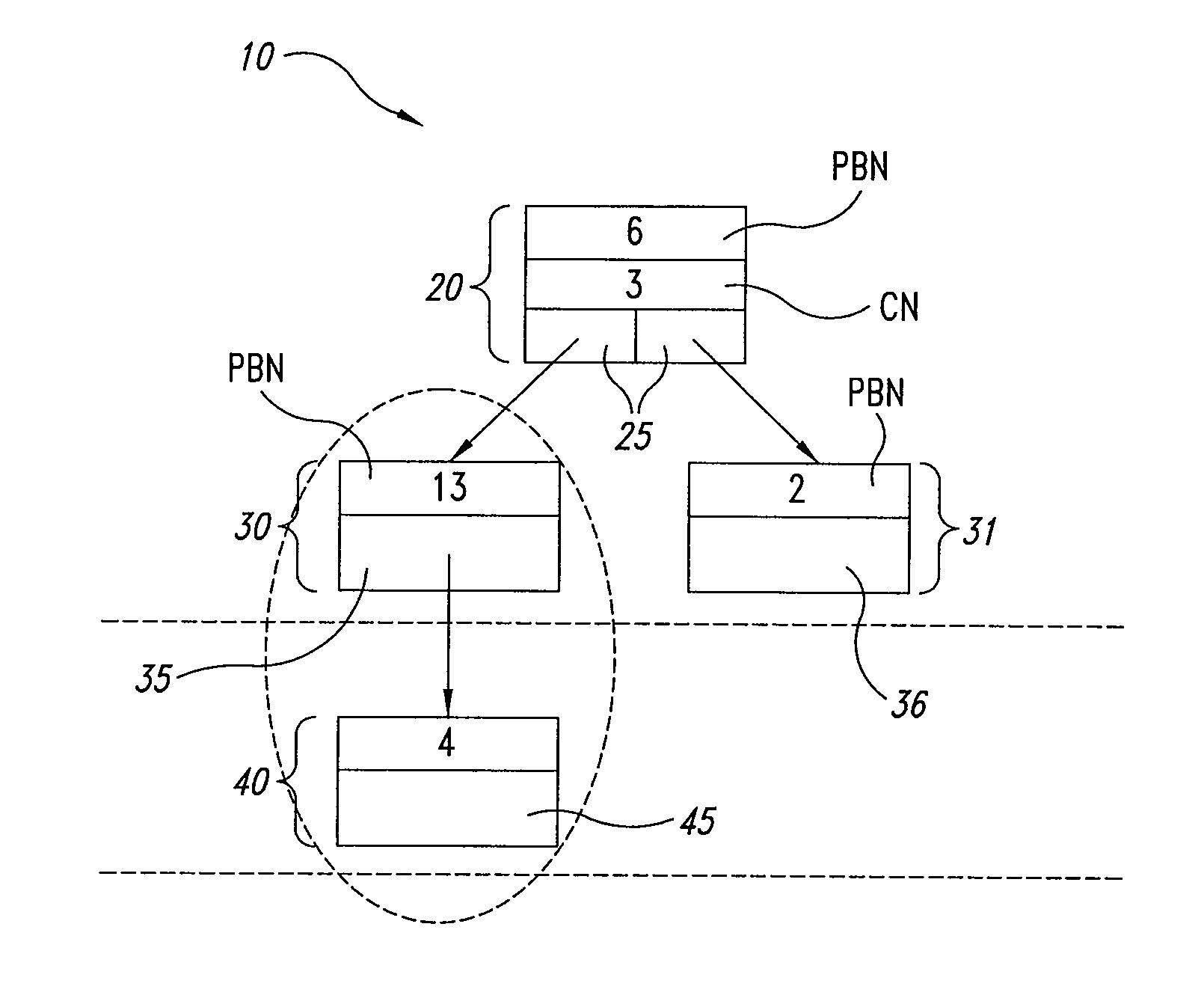

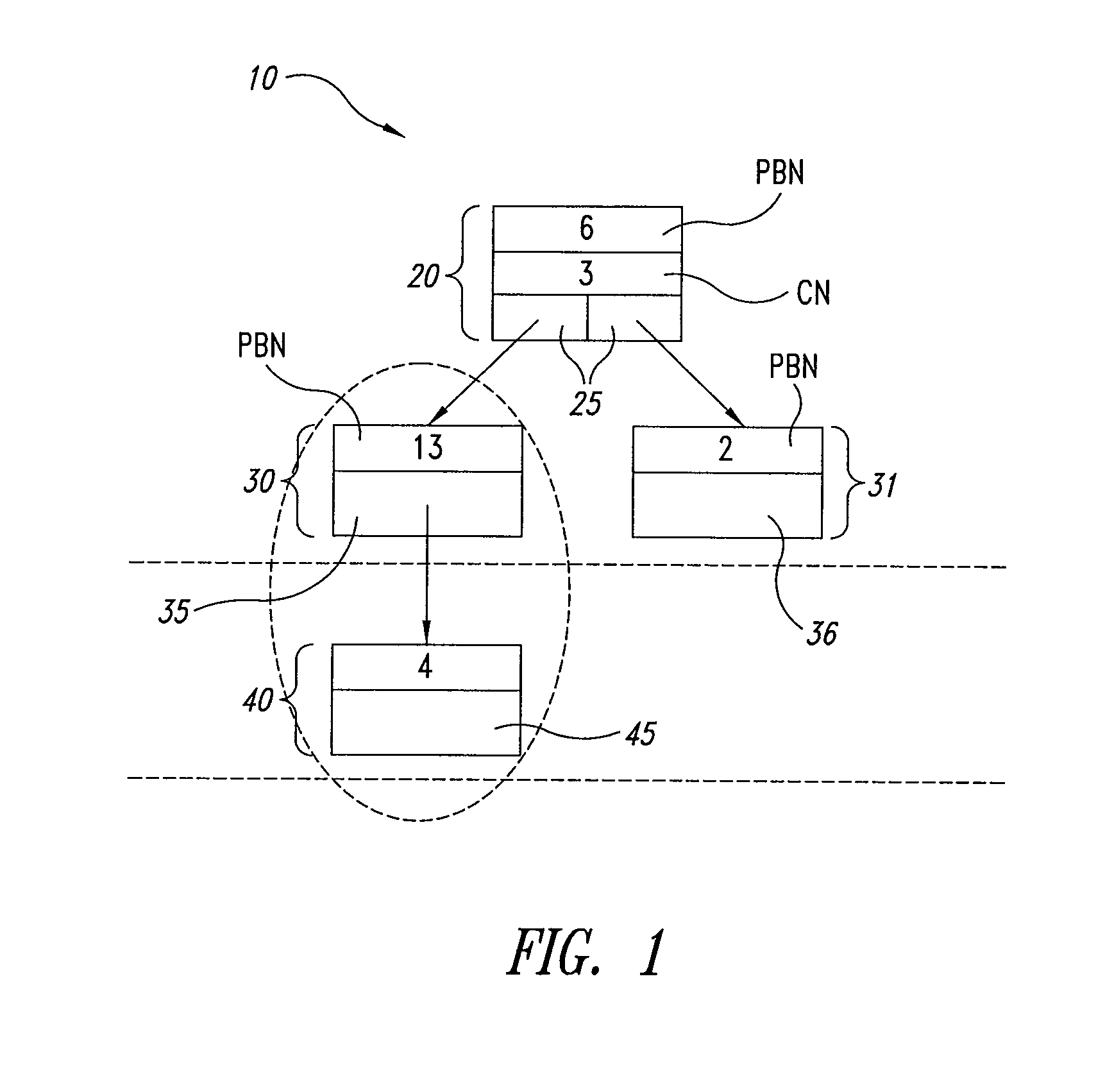

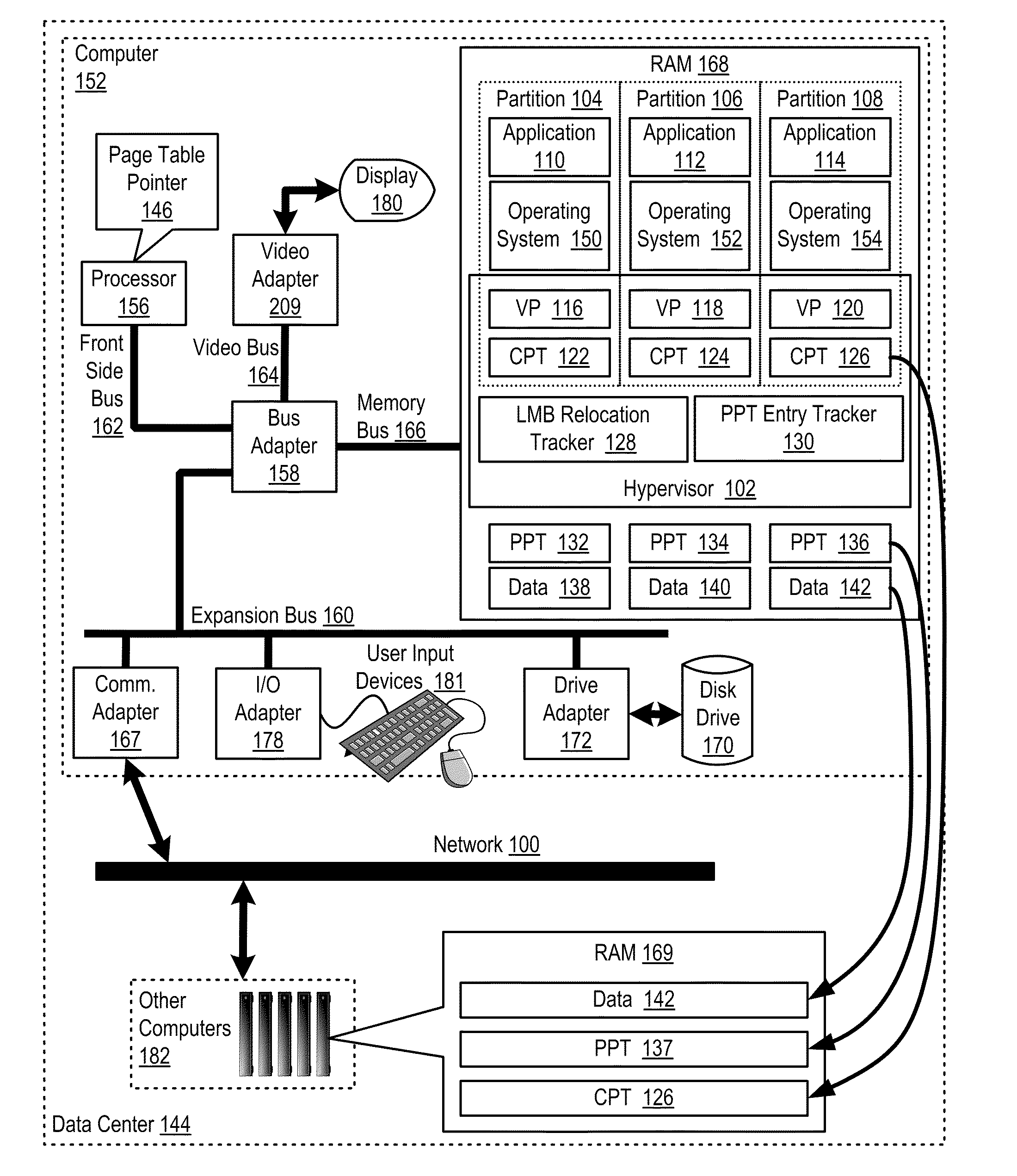

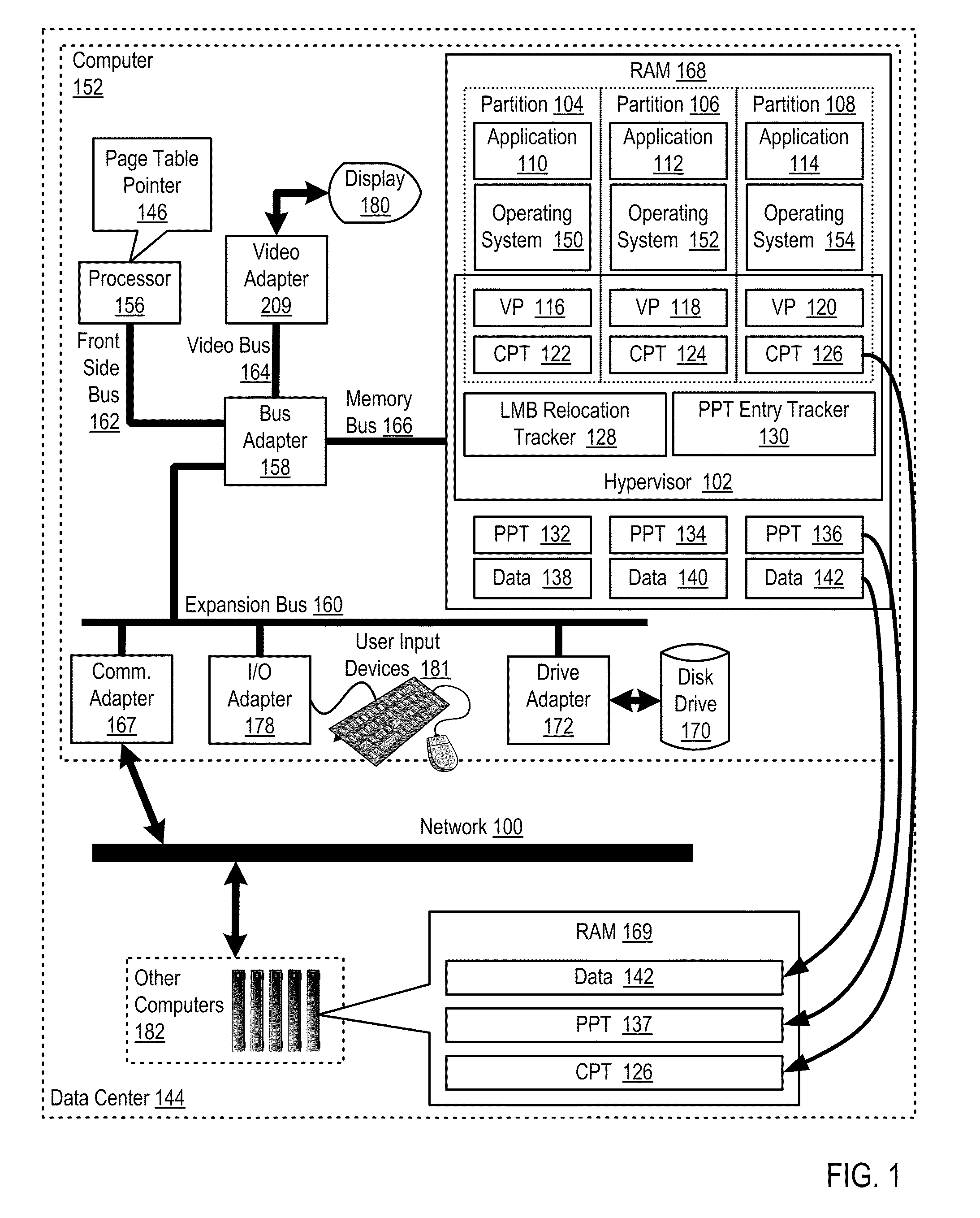

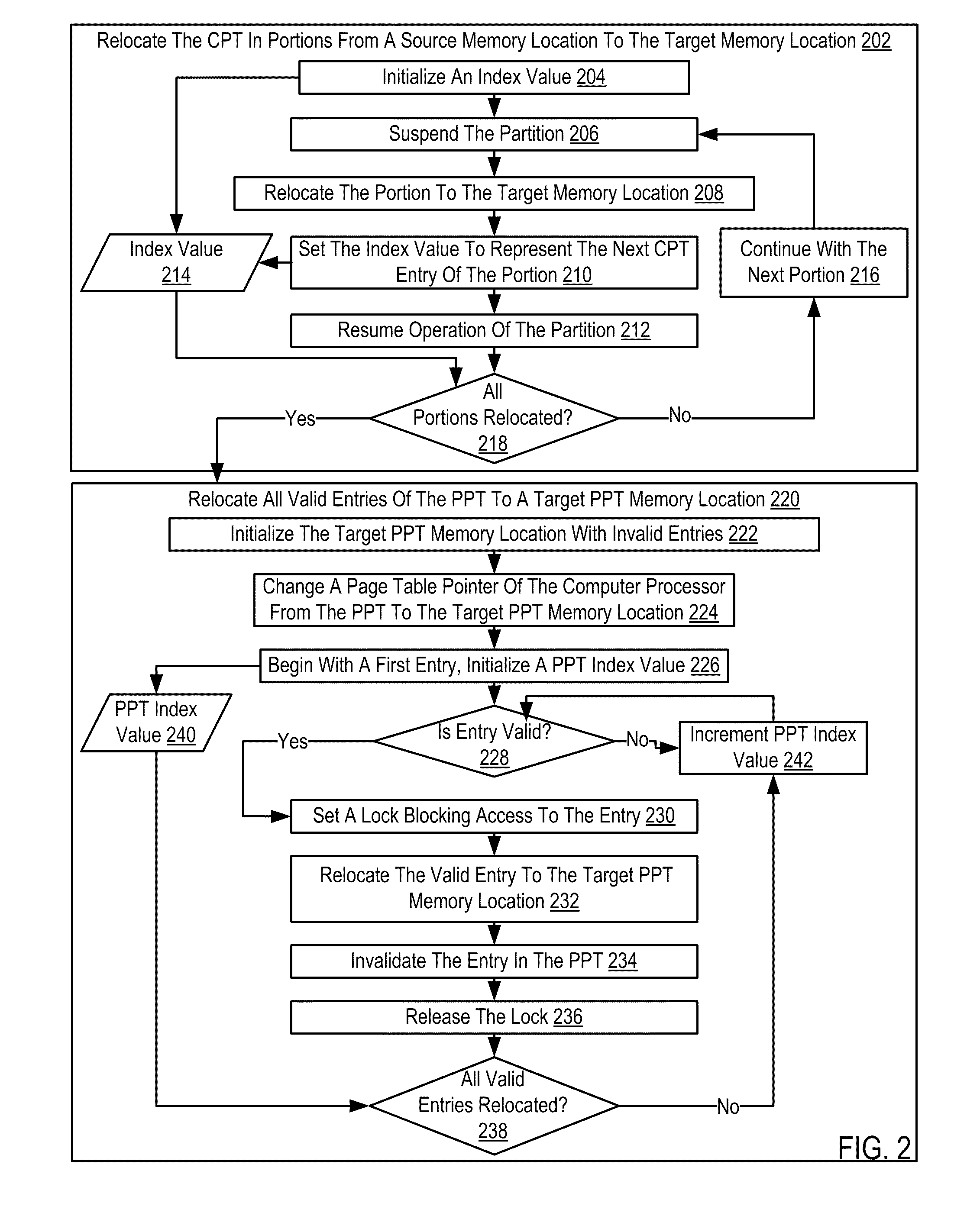

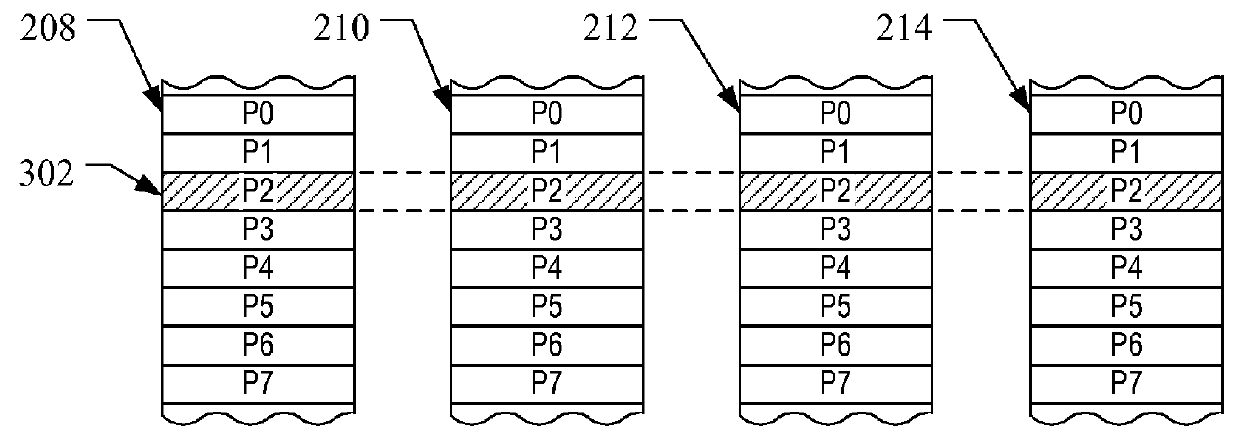

Relocating Page Tables And Data Amongst Memory Modules In A Virtualized Environment

InactiveUS20110173370A1Memory adressing/allocation/relocationMultiprogramming arrangementsLogical Memory IPage table

Relocating data in a virtualized environment maintained by a hypervisor administering access to memory with a Cache Page Table (‘CPT’) and a Physical Page Table (‘PPT’), the CPT and PPT including virtual to physical mappings. Relocating data includes converting the virtual to physical mappings of the CPT to virtual to logical mappings; establishing a Logical Memory Block (‘LMB’) relocation tracker that includes logical addresses of an LMB, source physical addresses of the LMB, target physical addresses of the LMB, a translation block indicator for each relocation granule, and a pin count associated with each relocation granule; establishing a PPT entry tracker including PPT entries corresponding to the LMB to be relocated; relocating the LMB in a number of relocation granules including blocking translations to the relocation granules during relocation; and removing the logical addresses from the LMB relocation tracker.

Owner:IBM CORP

Method and system for dynamic compression of address tables in a memory

ActiveUS9229876B2Memory architecture accessing/allocationInput/output to record carriersOperating systemVolatile memory

A method and system are disclosed for handling logical-to-physical mapping and increasing the amount of mapping table information that may be stored in a cache in volatile memory. The method includes the storage device storing in fast access memory, such as RAM, a copy of only a portion of the complete mapping information for non-volatile memory of the storage device using a compressed format by compressing the mapping data when a skip pattern of interleaved sequential writes to non-volatile memory are found in the mapping information. The system includes a storage device having volatile memory, non-volatile memory and a controller in communication with the volatile and non-volatile memory that is configured to carry out the method noted above.

Owner:SANDISK TECH LLC

Method and system for managing virtualized physical storage in data processor

A move engine and operating system transparently reconfigure physical memory to accomplish addition, subtraction, or replacement of a memory module. The operating system stores FROM and TO real addresses in unique fields in memory that are used to virtualize the physical address of the memory module being reconfigured and provide the reconfiguration in real-time through the use of hardware functionality and not software. Using the FROM and TO real addresses to select a source and a target, the move engine copies the contents of the memory module to be removed or reconfigured into the remaining or inserted memory module. Then, the real address associated with the reconfigured memory module is re-assigned to the memory module receiving the copied contents, thereby creating a virtualized physical mapping from the addressable real address space being utilized by the operating system into a virtual physical address space.

Owner:INT BUSINESS MASCH CORP

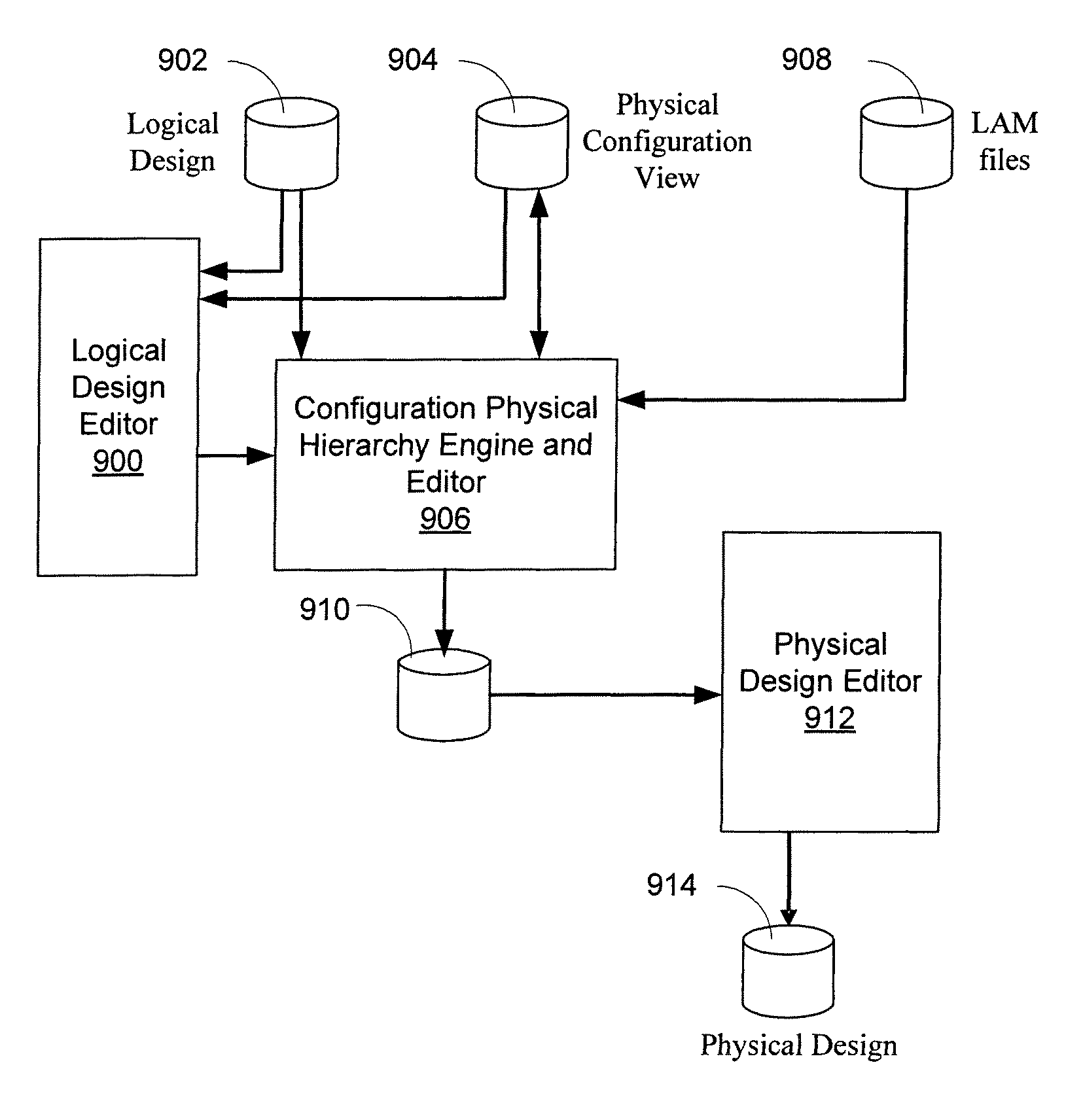

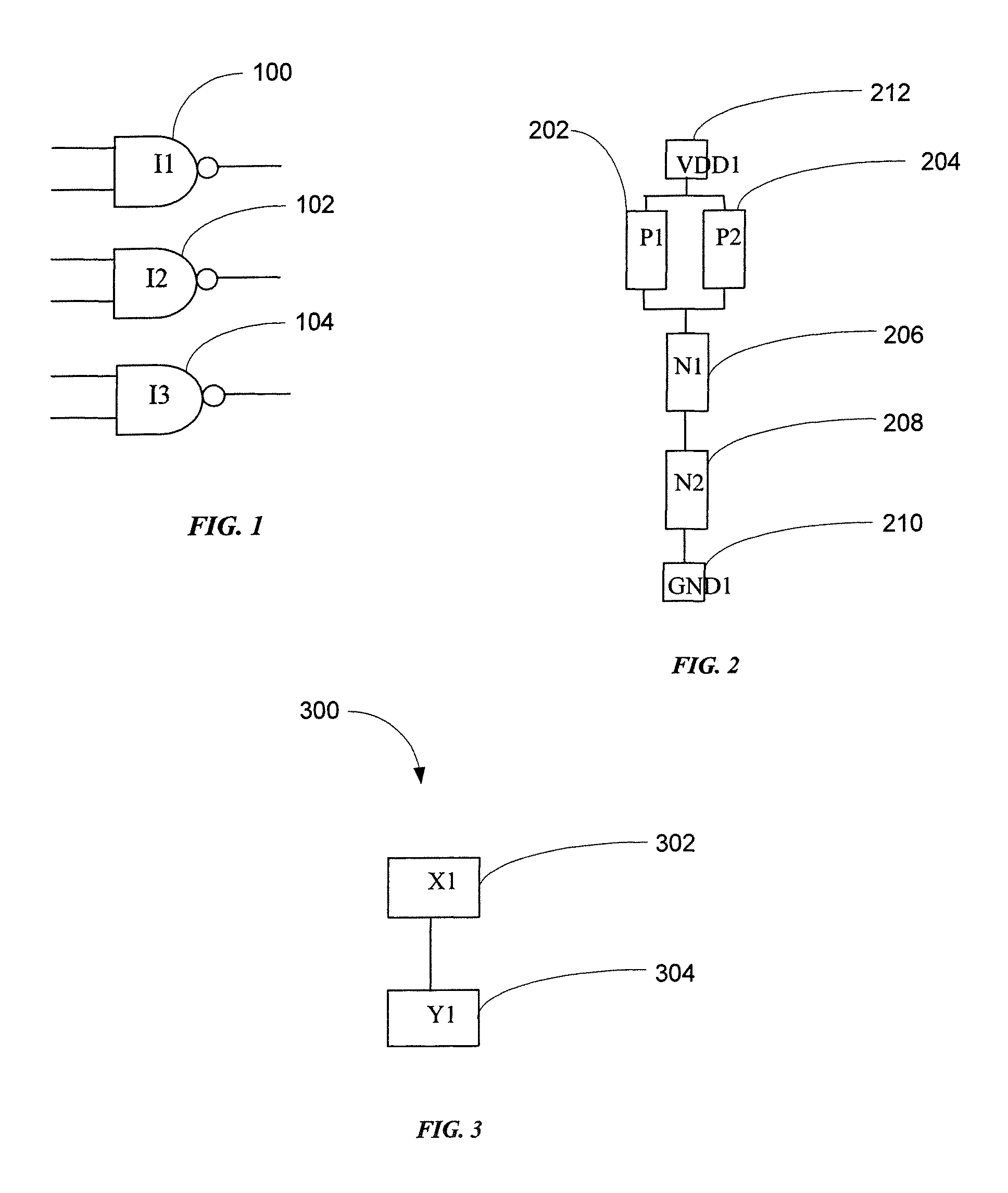

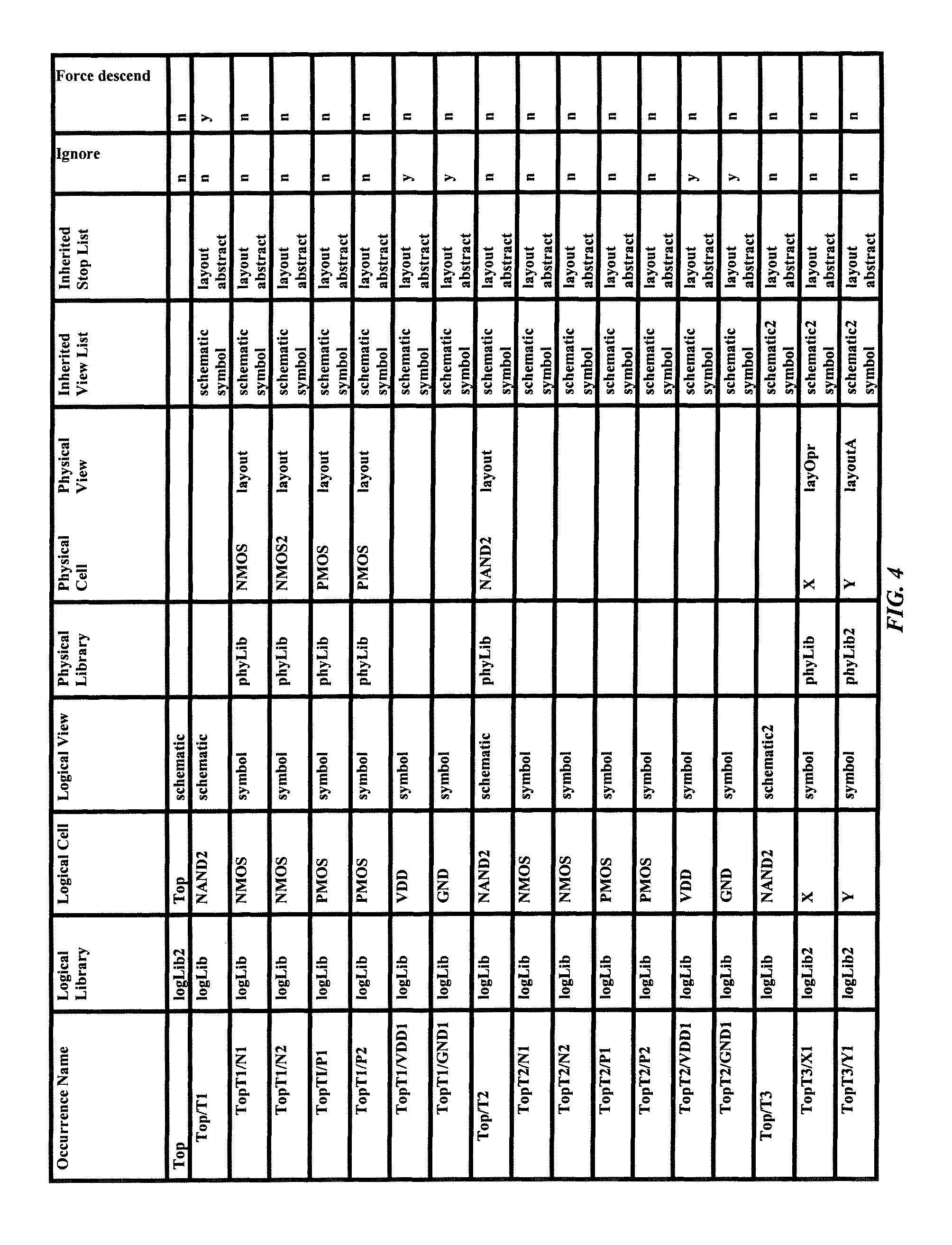

Methods and systems for physical hierarchy configuration engine and graphical editor

ActiveUS7805698B1Computer programmed simultaneously with data introductionProgram controlGraphicsComputer architecture

In one embodiment a new method to address configuring a logical design and libraries of design elements with additional information is proposed that may be used to create a physical design from that logical design. Logical designs may be generic, while physical design libraries are normally targeted towards specific technology. Consequently, there can be a mapping from the cells in a logical library to cells which correspond to their implementation in a physical library. In one embodiment, annotations required to map from logical design to physical design may be stored in a separate design view. In one embodiment the user can modify the physical mapping attributes of cells, instances, and occurrences in the logical design and save the modifications back to the physical configuration view.

Owner:CADENCE DESIGN SYST INC

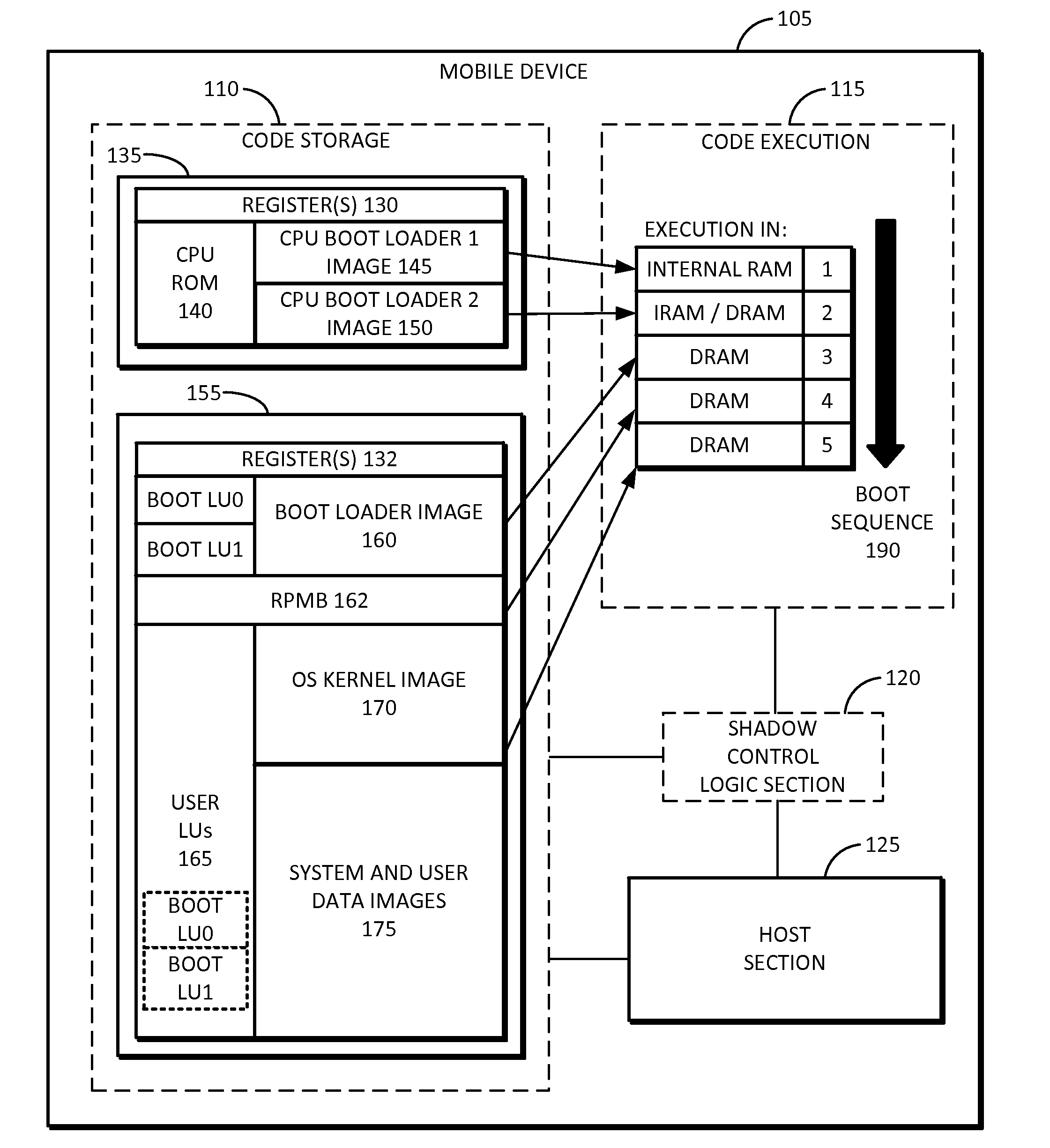

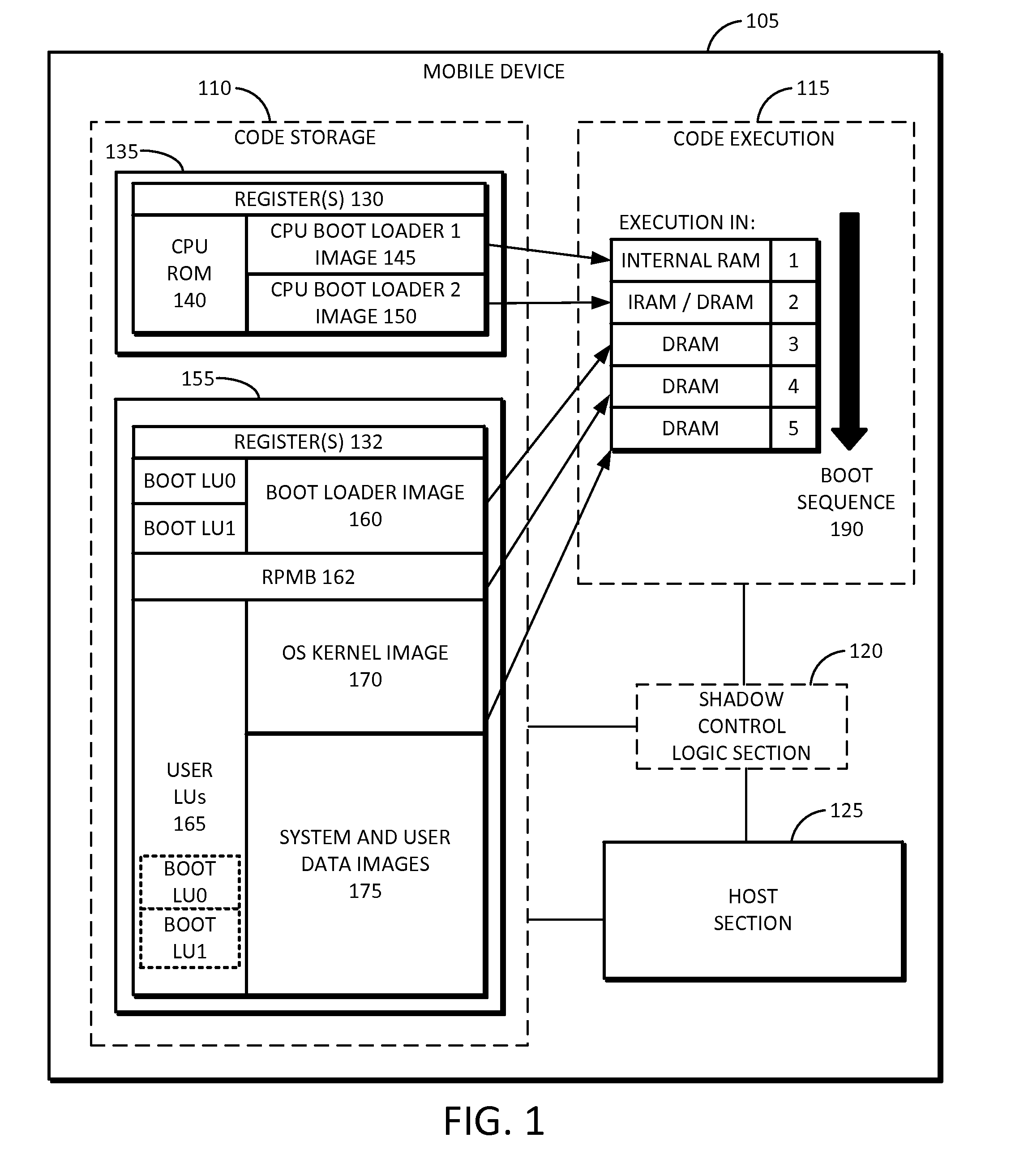

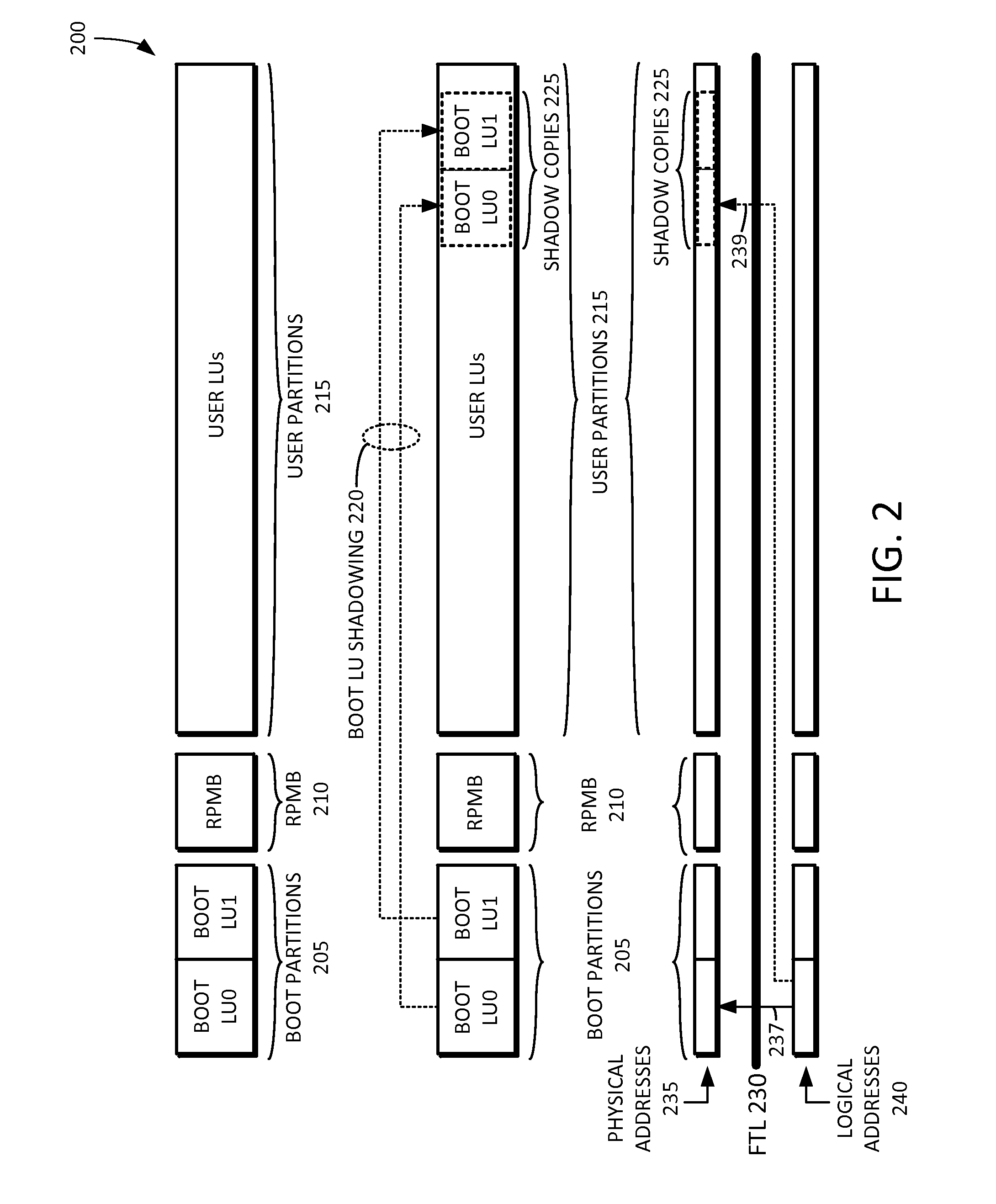

Mobile flash storage boot partition and/or logical unit shadowing

ActiveUS20160117225A1Redundant operation error correctionRedundant hardware error correctionShadowingsLogic cell

Embodiments of the inventive concept include computer-implemented method for shadowing one or more boot images of a mobile device. The technique can include duplicating boot images to shadow partitions in a user area of a non-volatile memory device such as a flash memory. The technique can include detecting boot image corruption, and causing a mobile device to boot from the shadow partitions. The technique can include dynamically shadowing and releasing blocks used by the shadow partitions. The technique can include boot failure recovery and bad image preservation through firmware flash translation layer (FTL) logical to physical mapping updates. Boot image corruption failures can be recovered from and / or debugged using the shadow partitions.

Owner:SAMSUNG ELECTRONICS CO LTD