Patents

Literature

1579 results about "Control memory" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

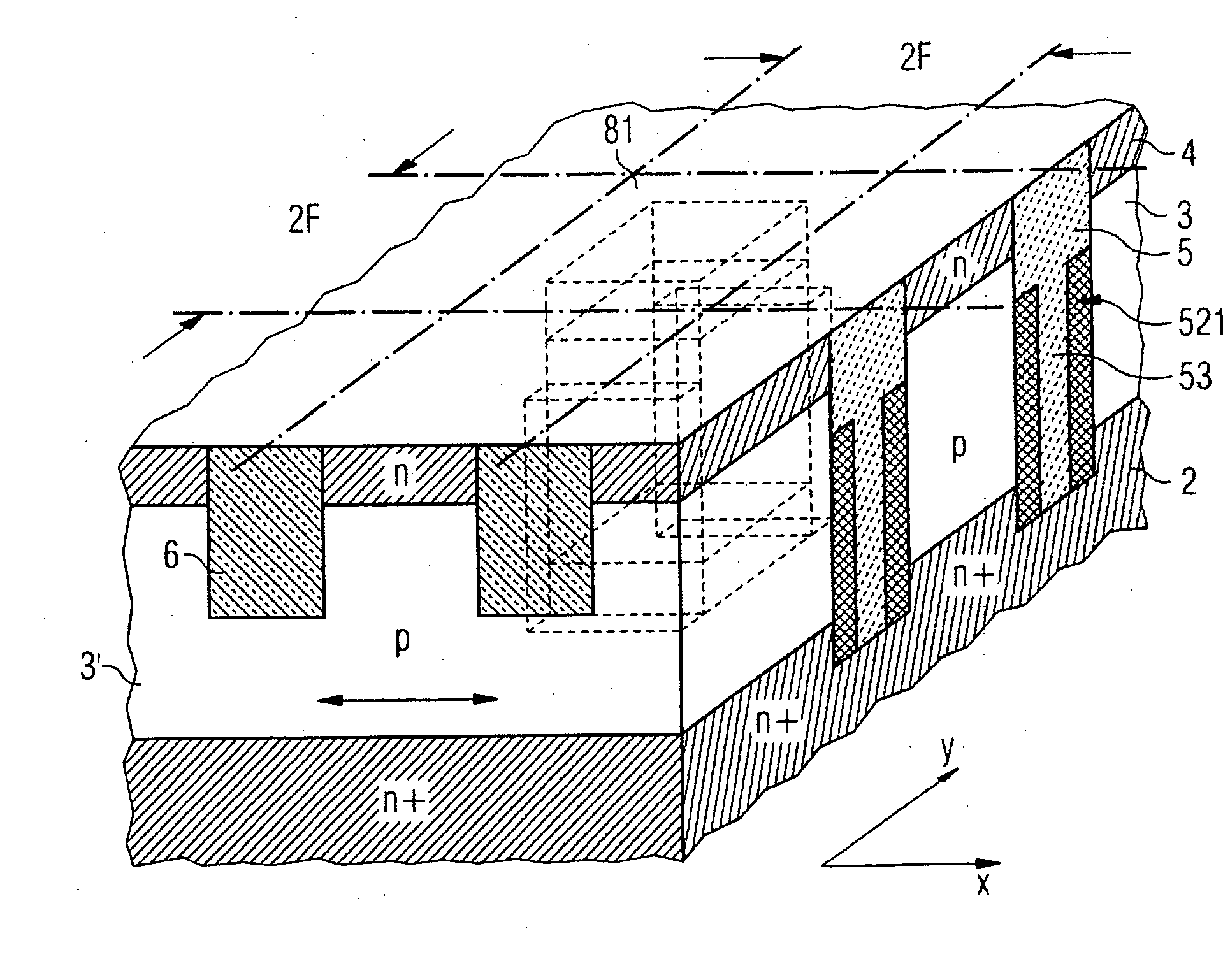

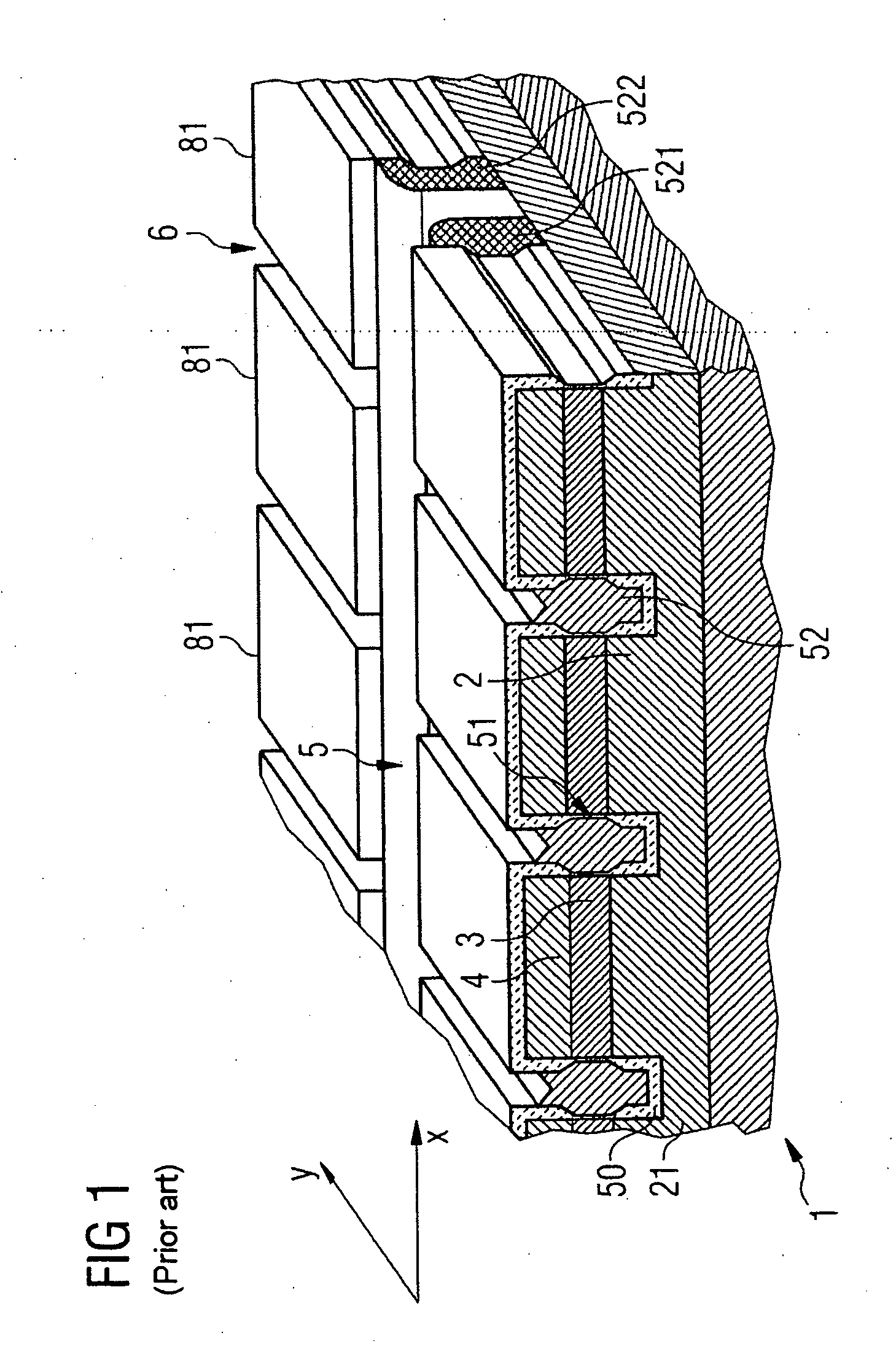

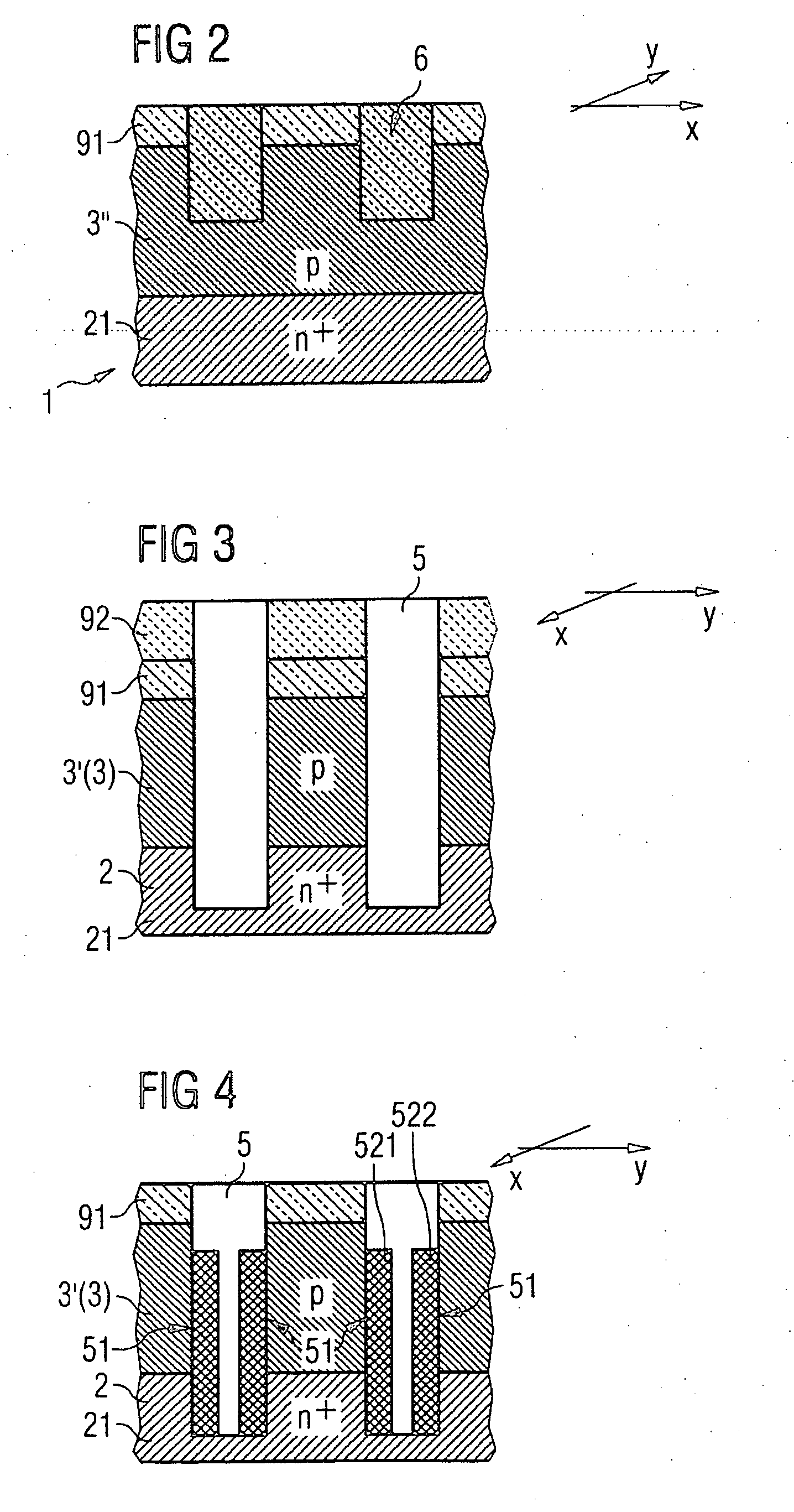

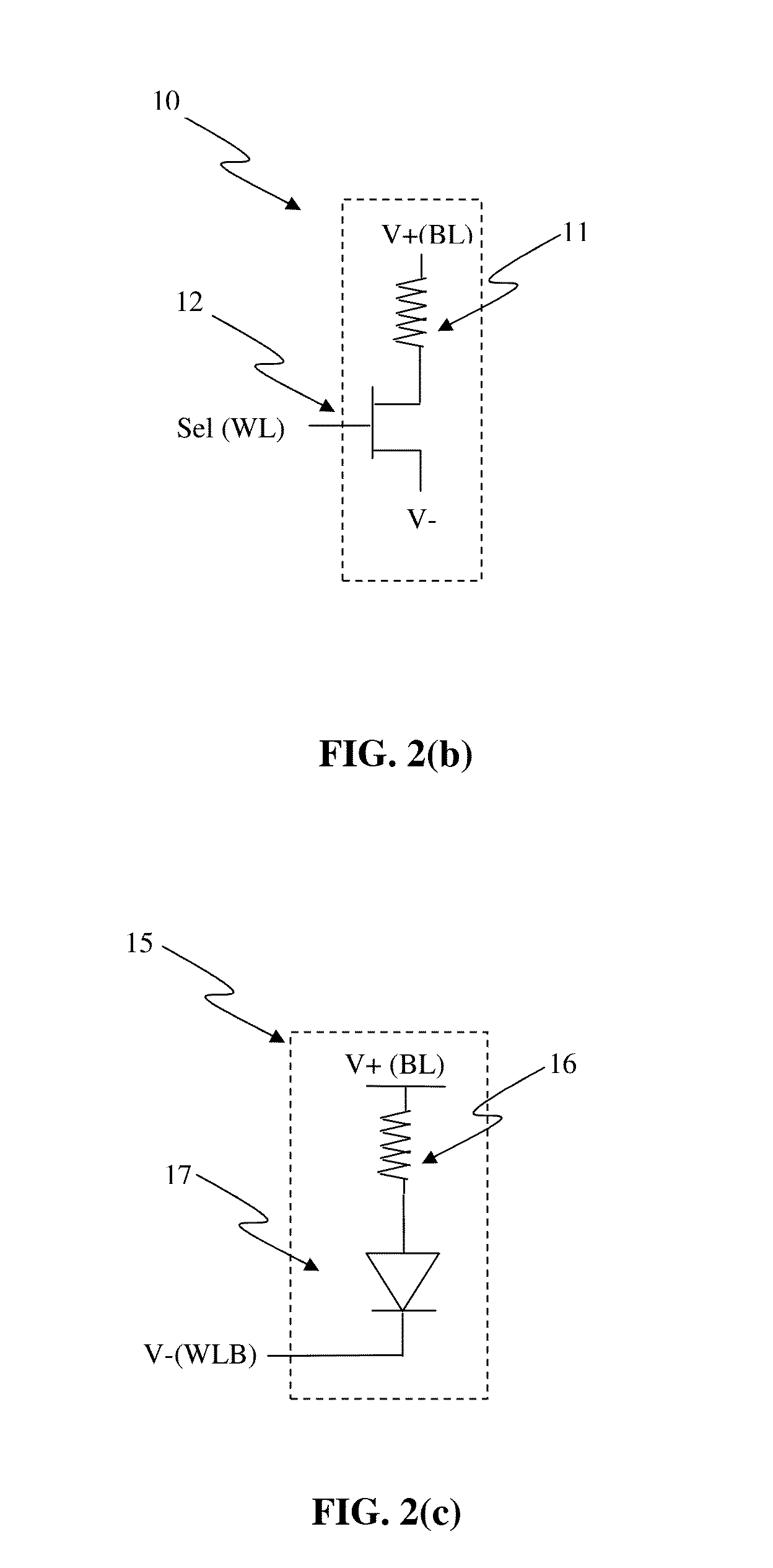

Method of fabricating and architecture for vertical transistor cells and transistor-controlled memory cells

InactiveUS20050001257A1Increased area requirementLimited functionTransistorSolid-state devicesFloating body effectDram memory

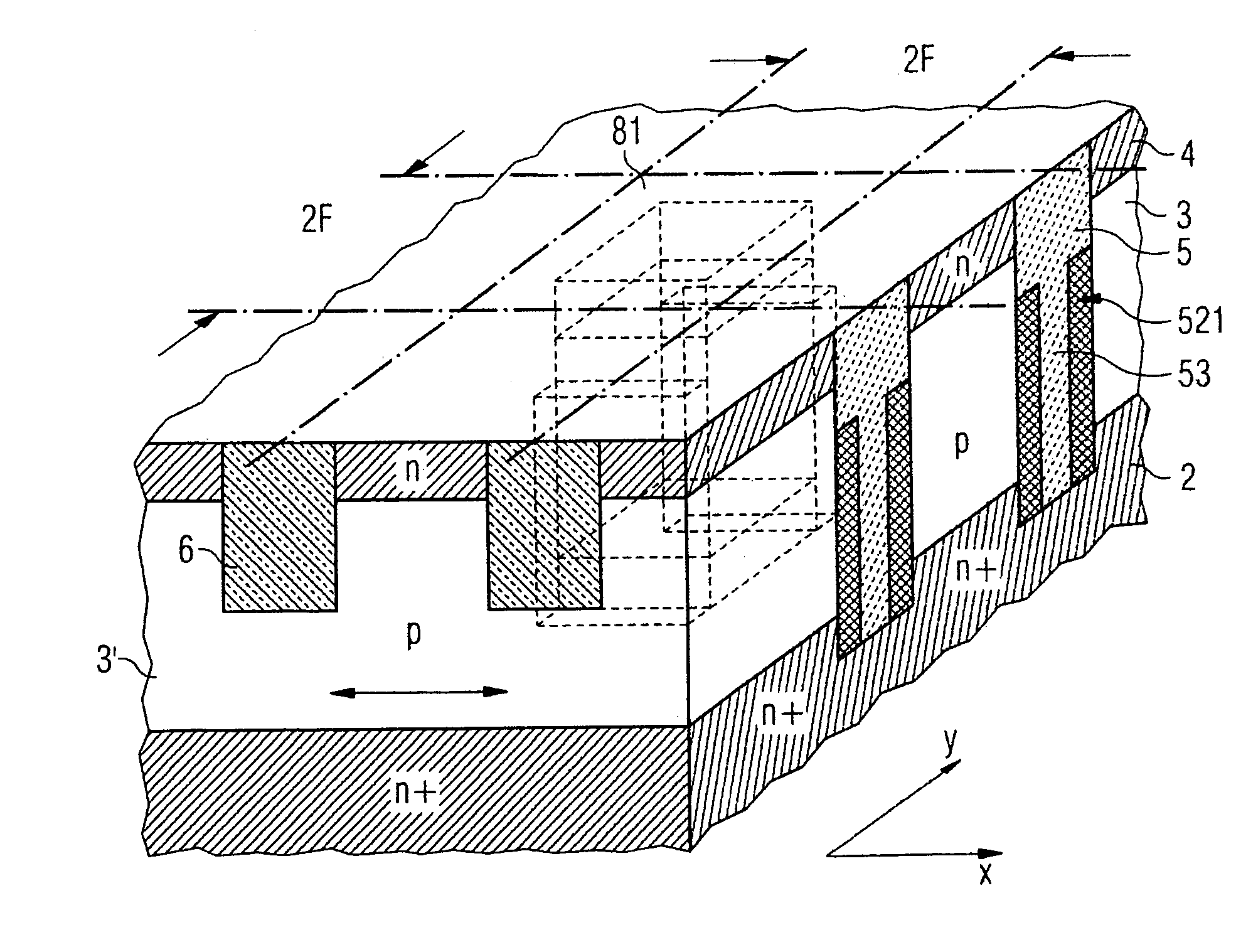

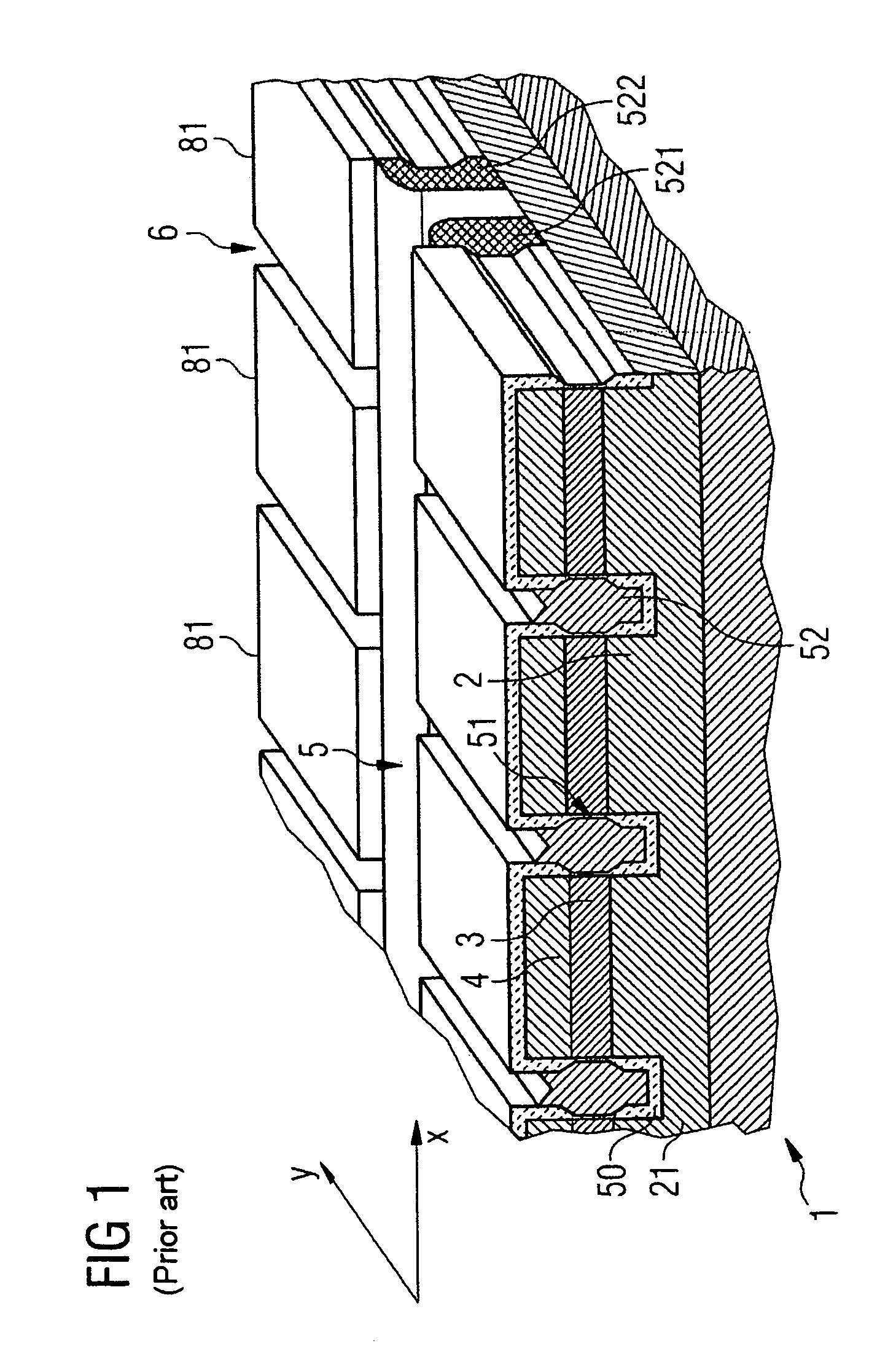

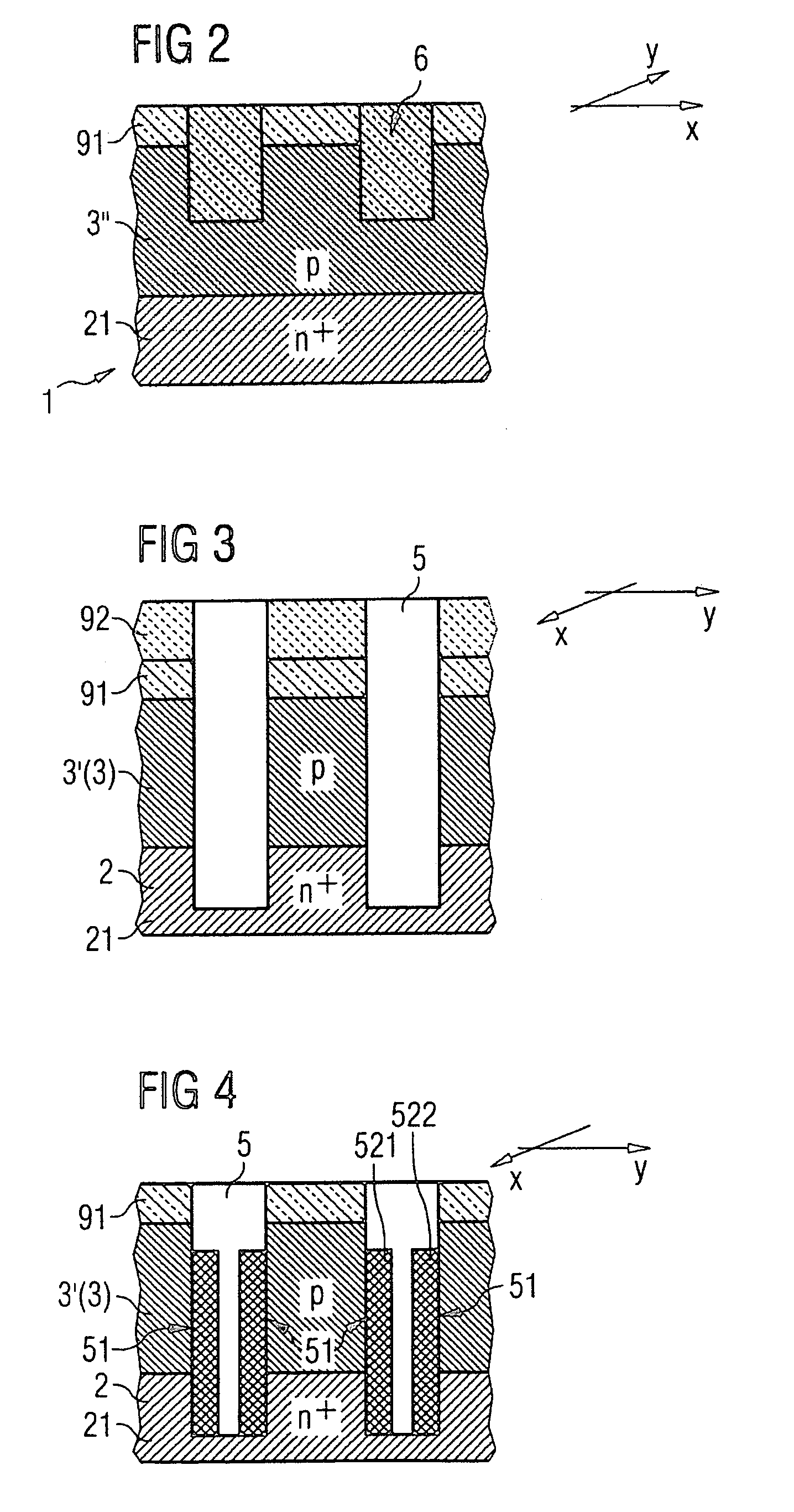

In a substrate vertical transistor cells are formed and are arranged, in a transistor cell array, row by row in an x direction and column by column in a y direction. Lower source / drain regions of the transistor cells are connected to a common connection plate. Upper source / drain regions of the transistor cells impart a contact connection for instance to a storage capacitor of a DRAM memory cell. Active trenches running between the transistor cells with word lines are formed along the x direction. The word lines form gate electrodes in sections. A potential at the gate electrode controls a conductive channel in an active region arranged in each case between the upper and the lower source / drain connection region. According to the invention, the active regions of adjacent transistor cells are sections of a contiguous layer body and are connected to one another. An accumulation of charge carriers in the active region and floating body effects are avoided without increasing the area requirement of a transistor cell.

Owner:POLARIS INNOVATIONS LTD

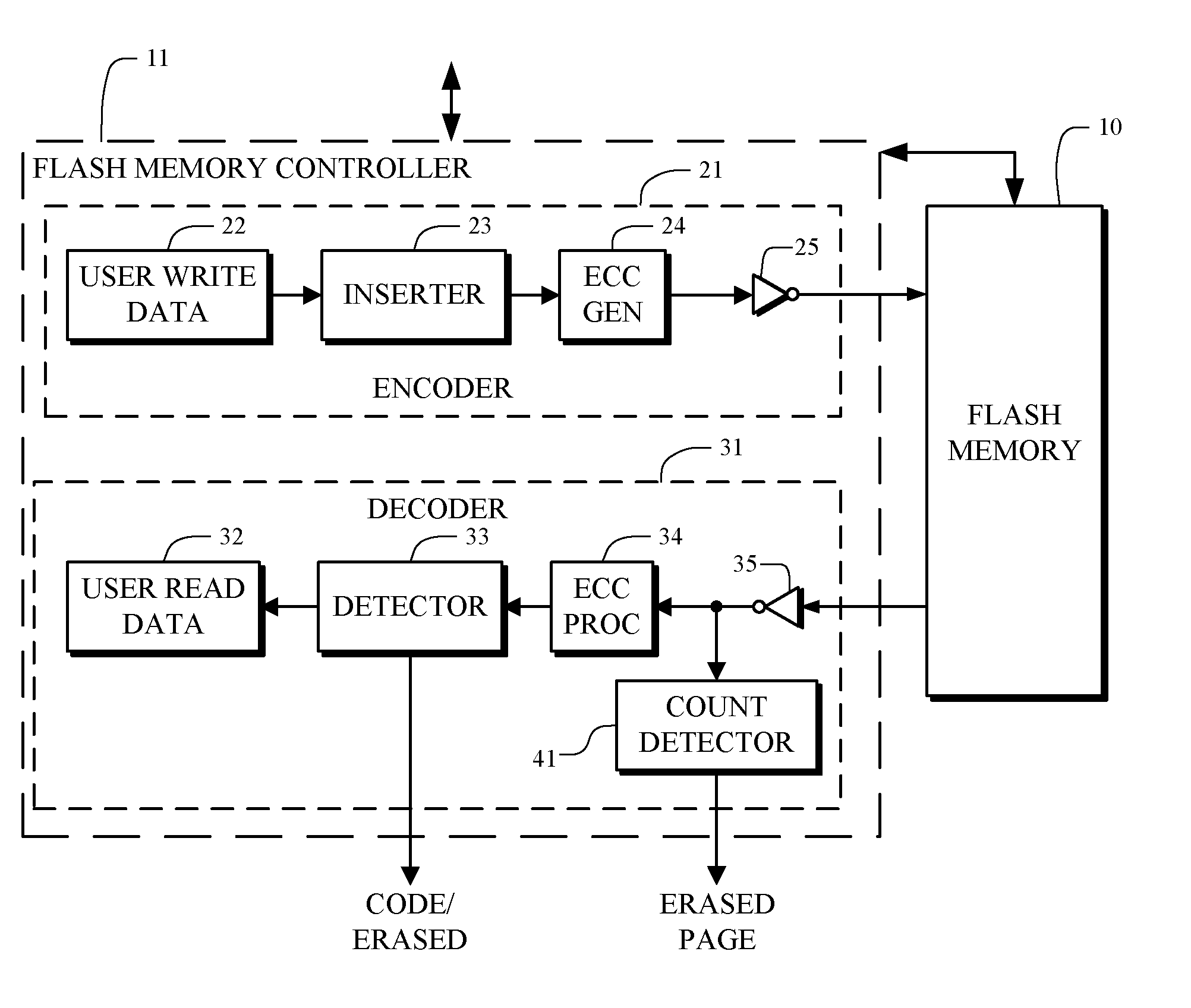

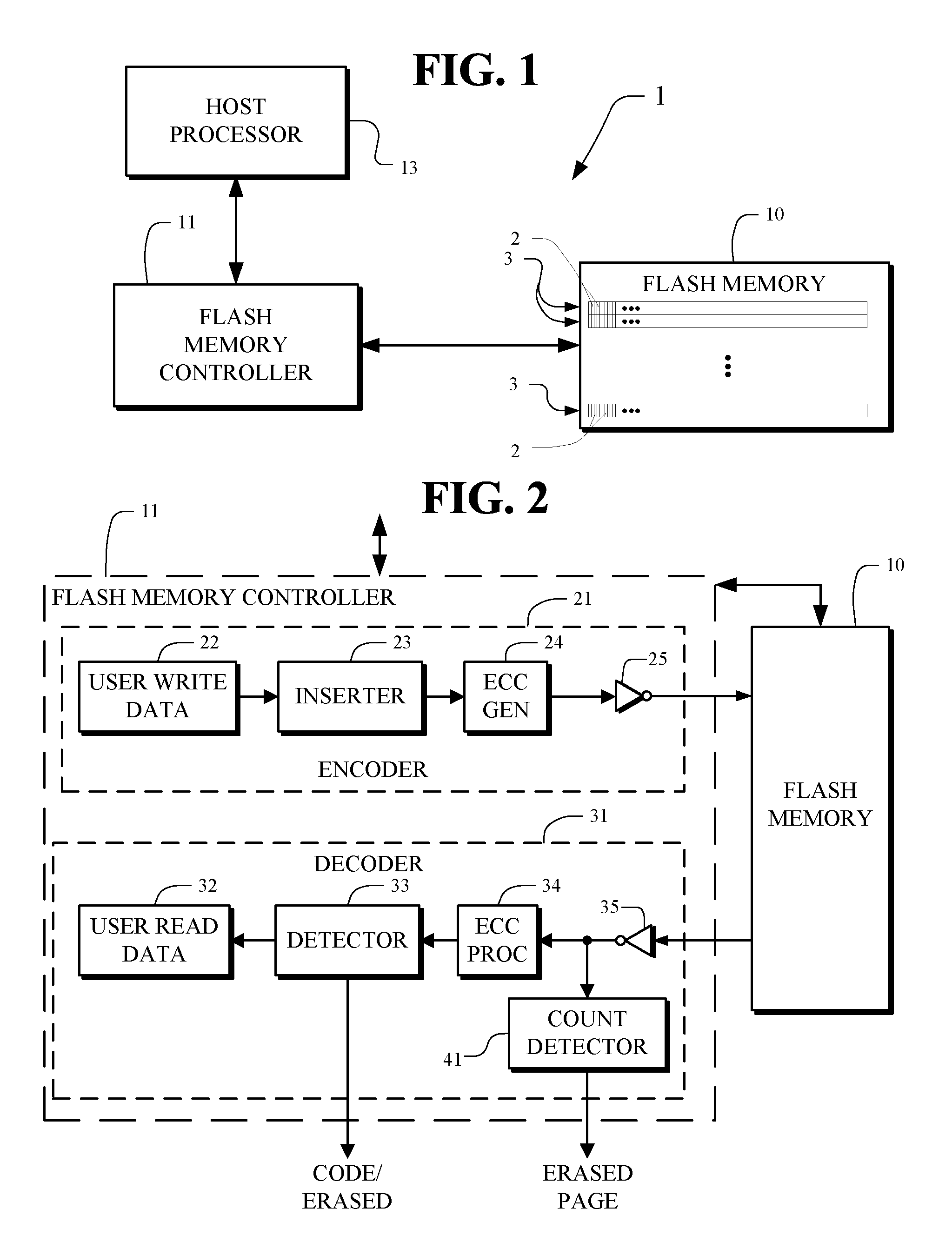

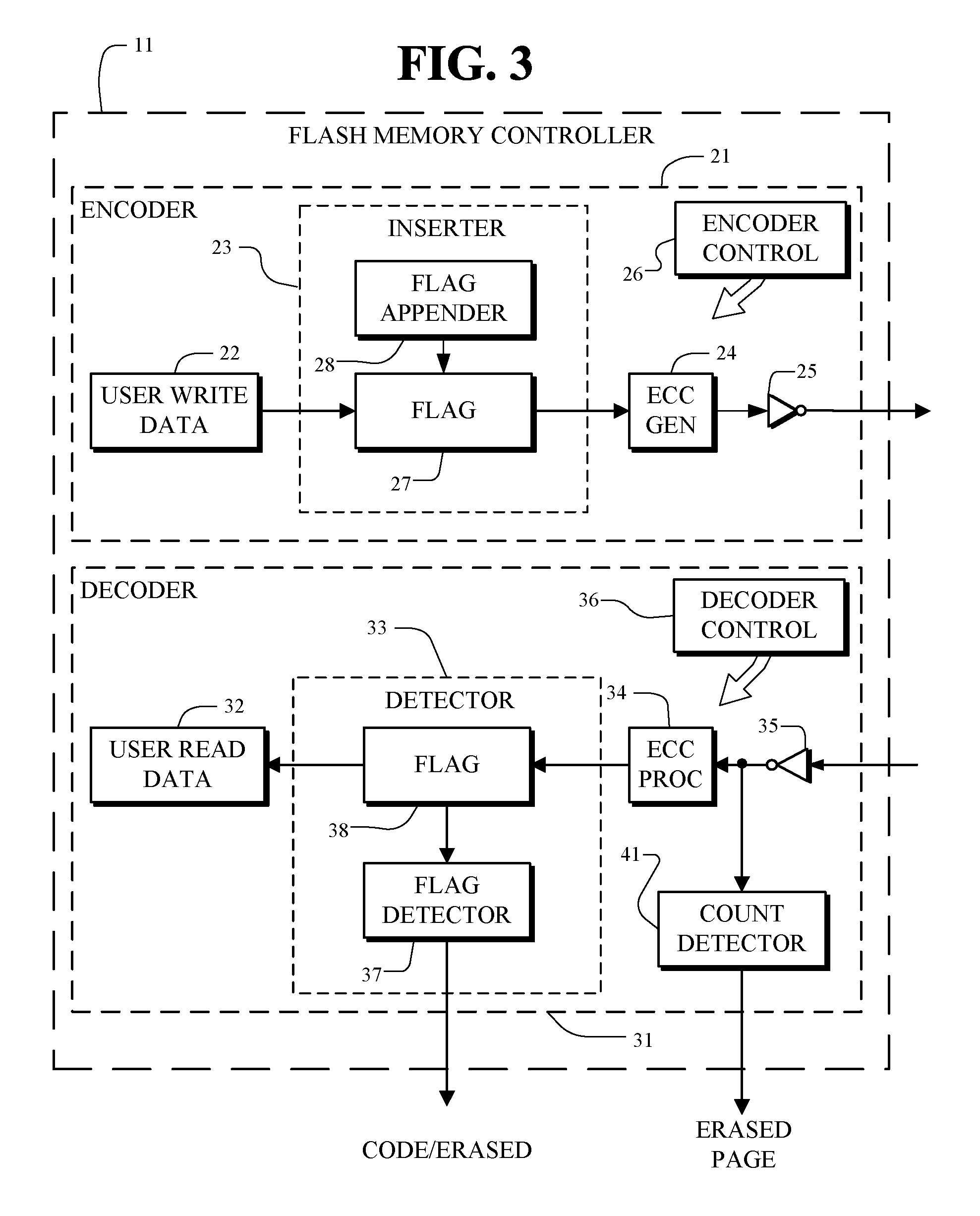

Erased page detection

A memory device and method, such as a flash memory device and method, includes a memory having a plurality of nonvolatile memory cells for storing stored values of user data. The memory device and method includes a memory controller for controlling the memory. The memory controller includes an encoder for encoding user write data for storage of code values as the stored values in the memory. The encoder includes an inserter for insertion of an indicator as part of the stored values for use in determining when the stored values are or are not in an erased state. The memory controller includes a decoder for reading the stored values from the memory to form user read data values when the stored values are not in the erased state.

Owner:MARVELL ASIA PTE LTD

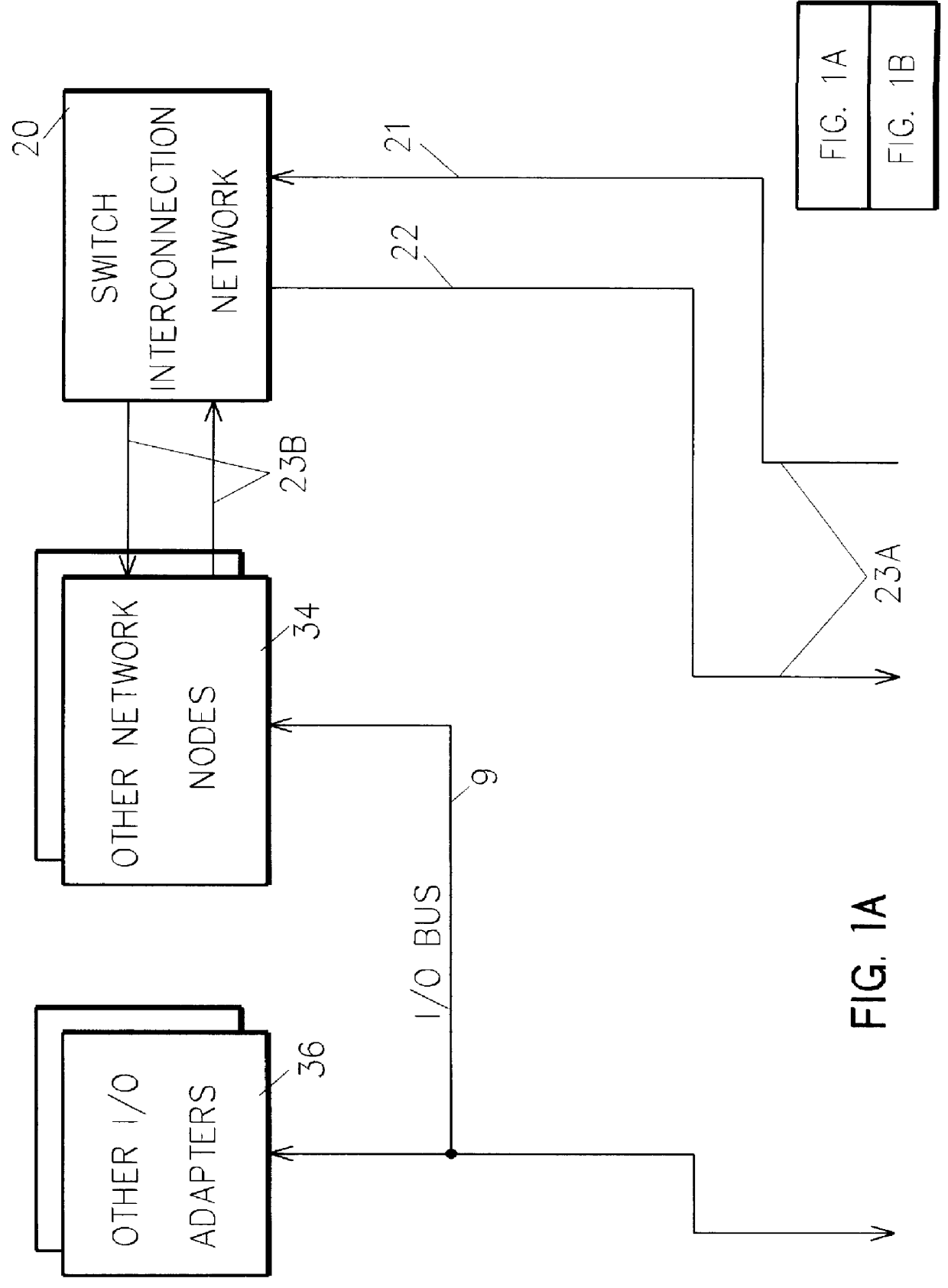

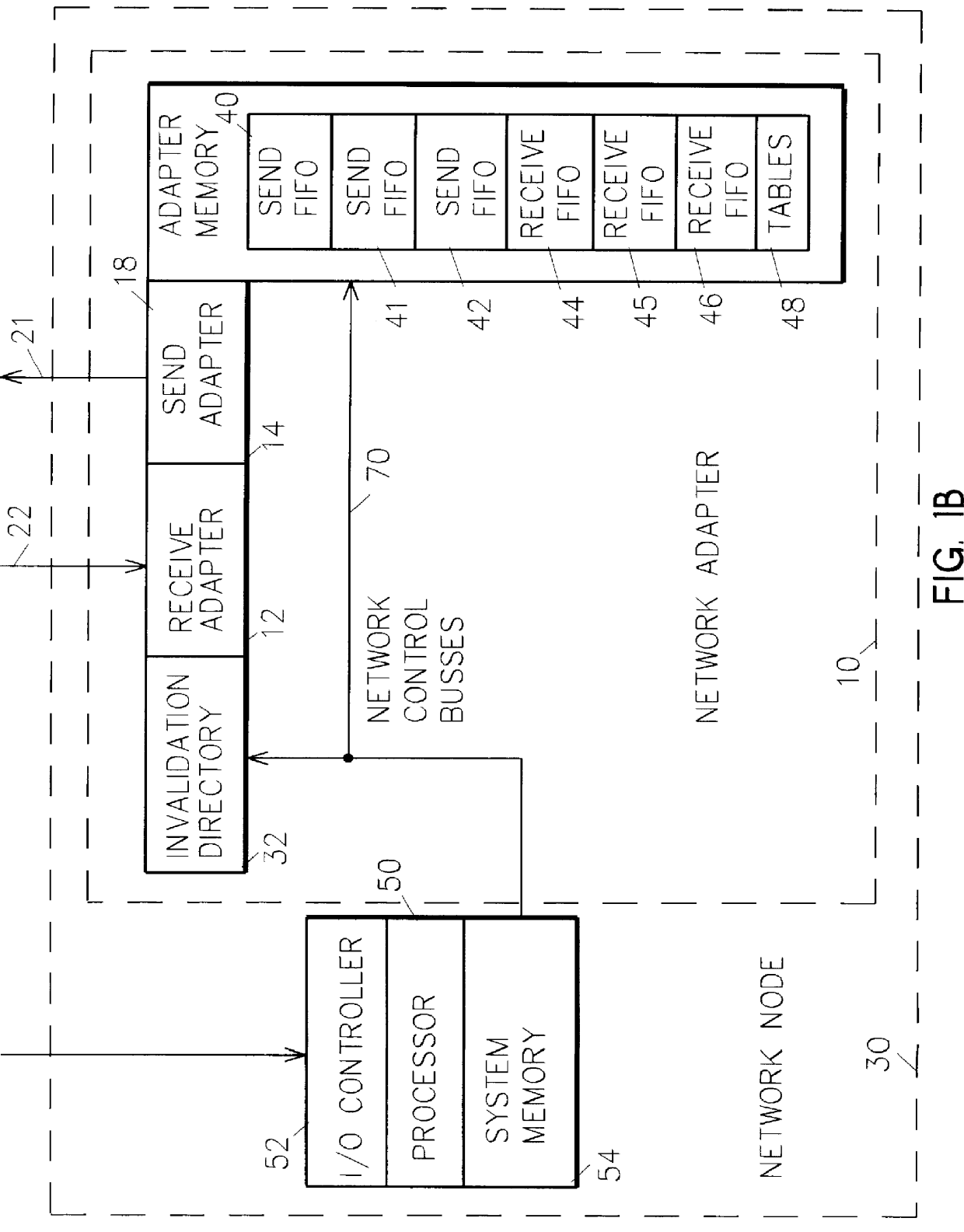

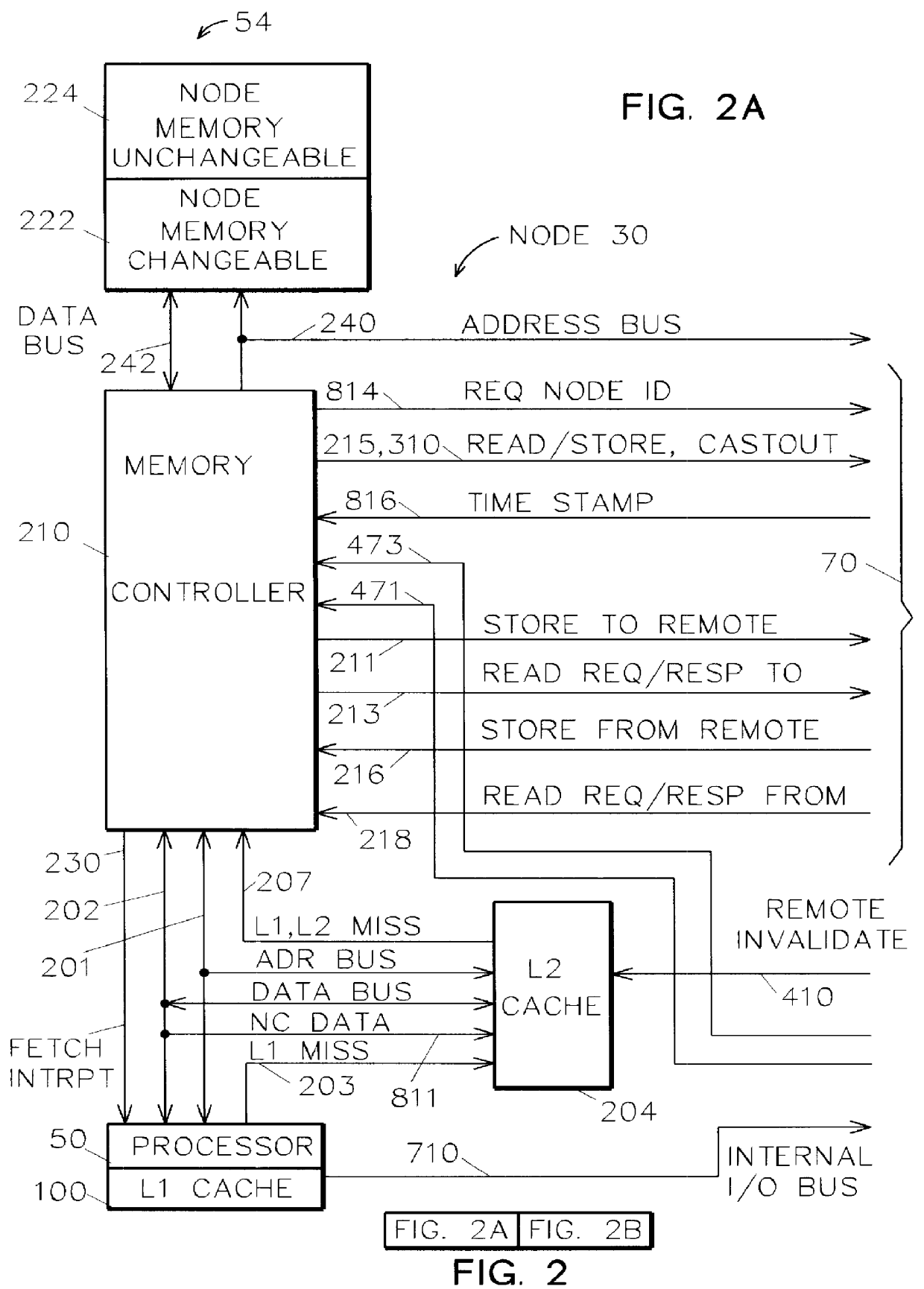

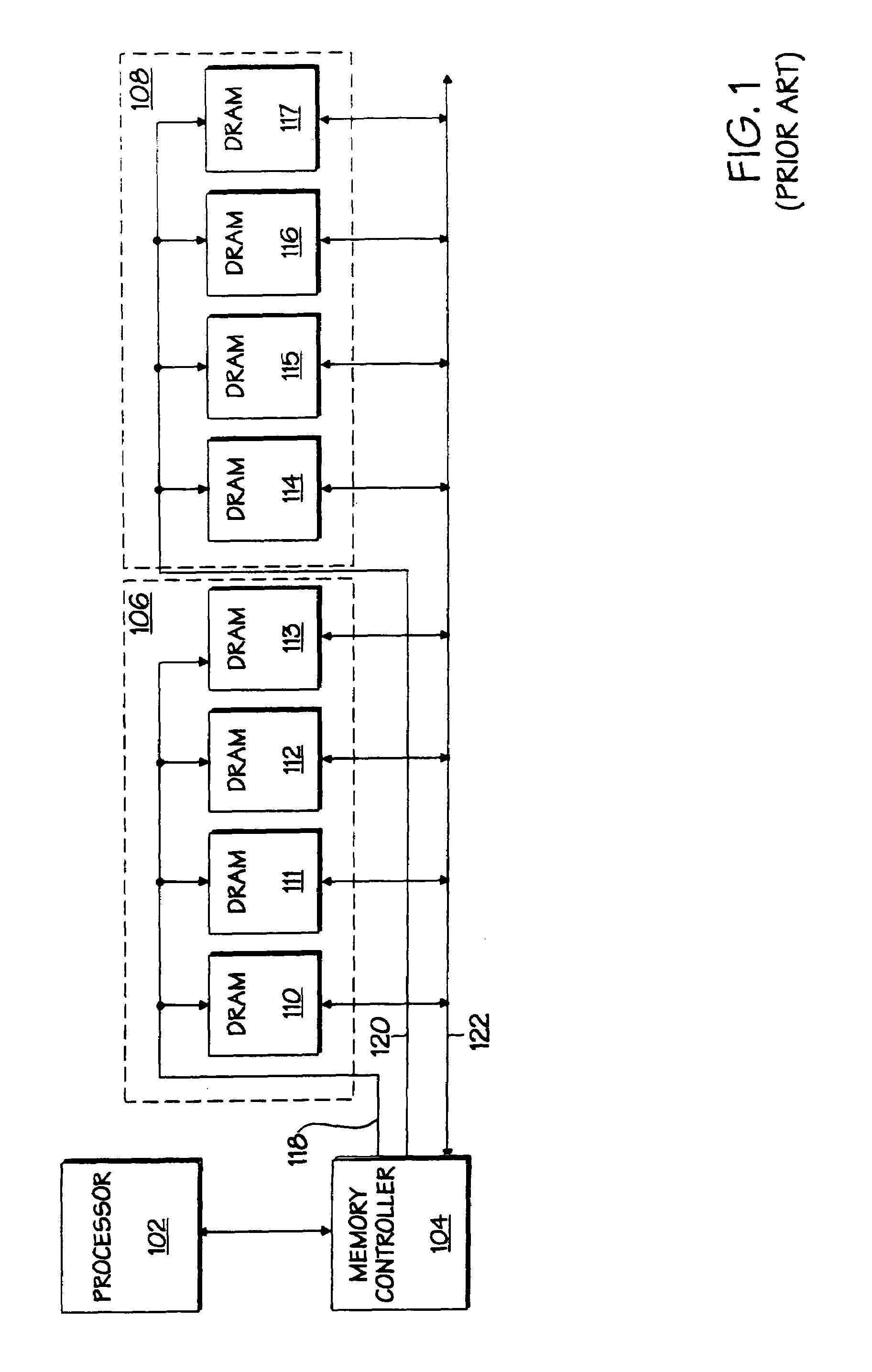

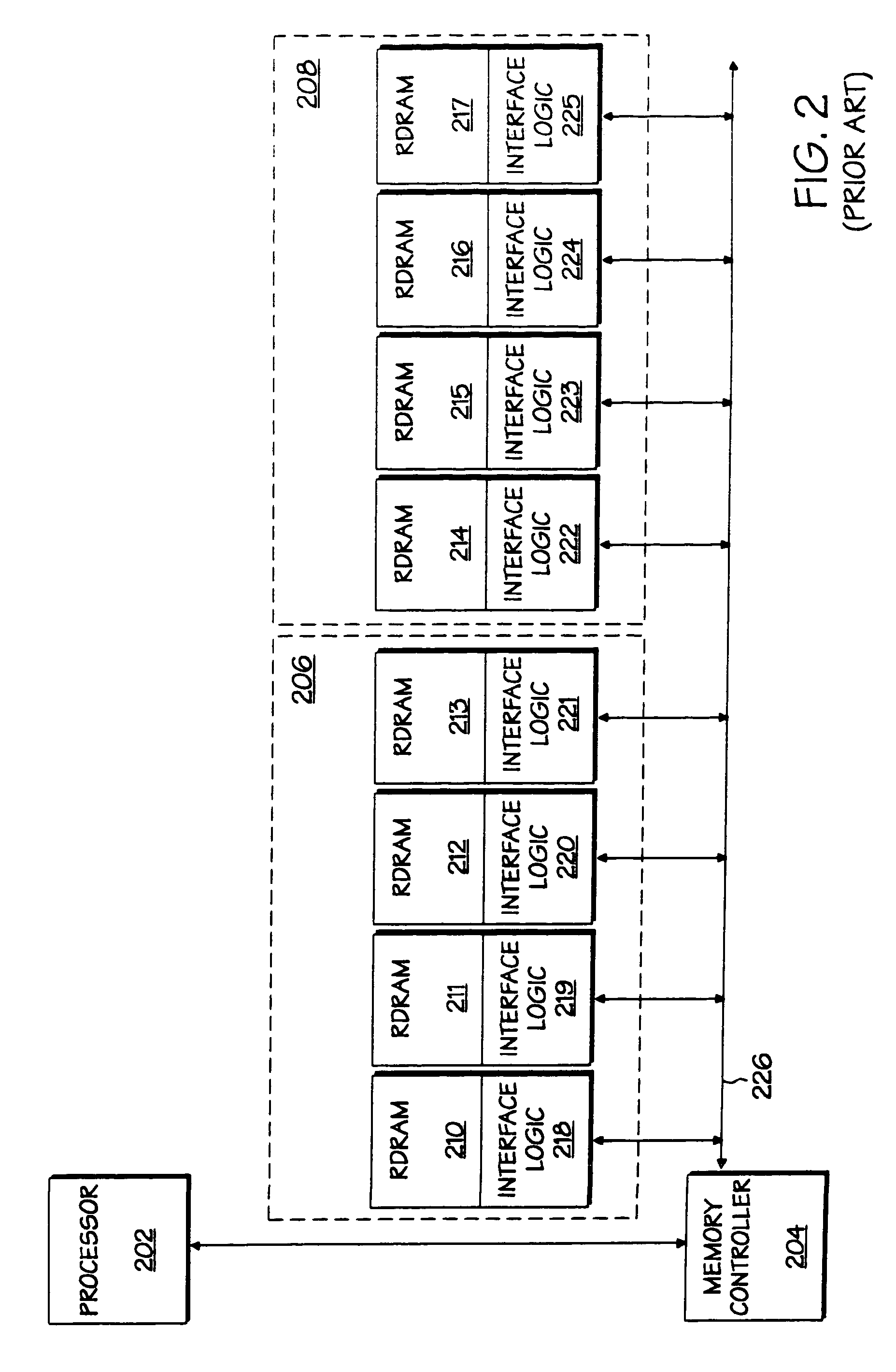

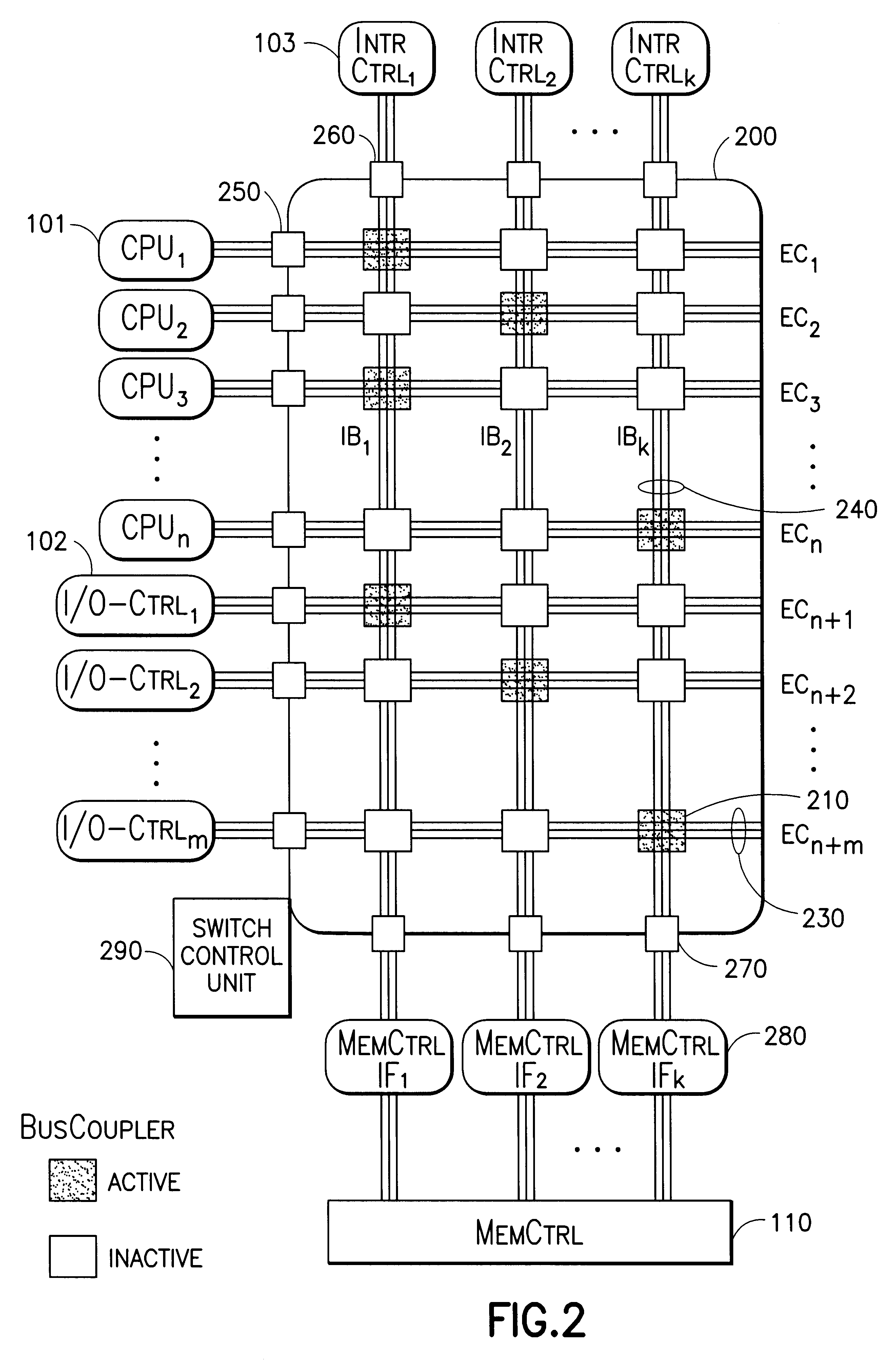

Memory controller for controlling memory accesses across networks in distributed shared memory processing systems

InactiveUS6044438AMore efficient cache coherent systemData processing applicationsMemory adressing/allocation/relocationRemote memory accessRemote direct memory access

A shared memory parallel processing system interconnected by a multi-stage network combines new system configuration techniques with special-purpose hardware to provide remote memory accesses across the network, while controlling cache coherency efficiently across the network. The system configuration techniques include a systematic method for partitioning and controlling the memory in relation to local verses remote accesses and changeable verses unchangeable data. Most of the special-purpose hardware is implemented in the memory controller and network adapter, which implements three send FIFOs and three receive FIFOs at each node to segregate and handle efficiently invalidate functions, remote stores, and remote accesses requiring cache coherency. The segregation of these three functions into different send and receive FIFOs greatly facilitates the cache coherency function over the network. In addition, the network itself is tailored to provide the best efficiency for remote accesses.

Owner:IBM CORP

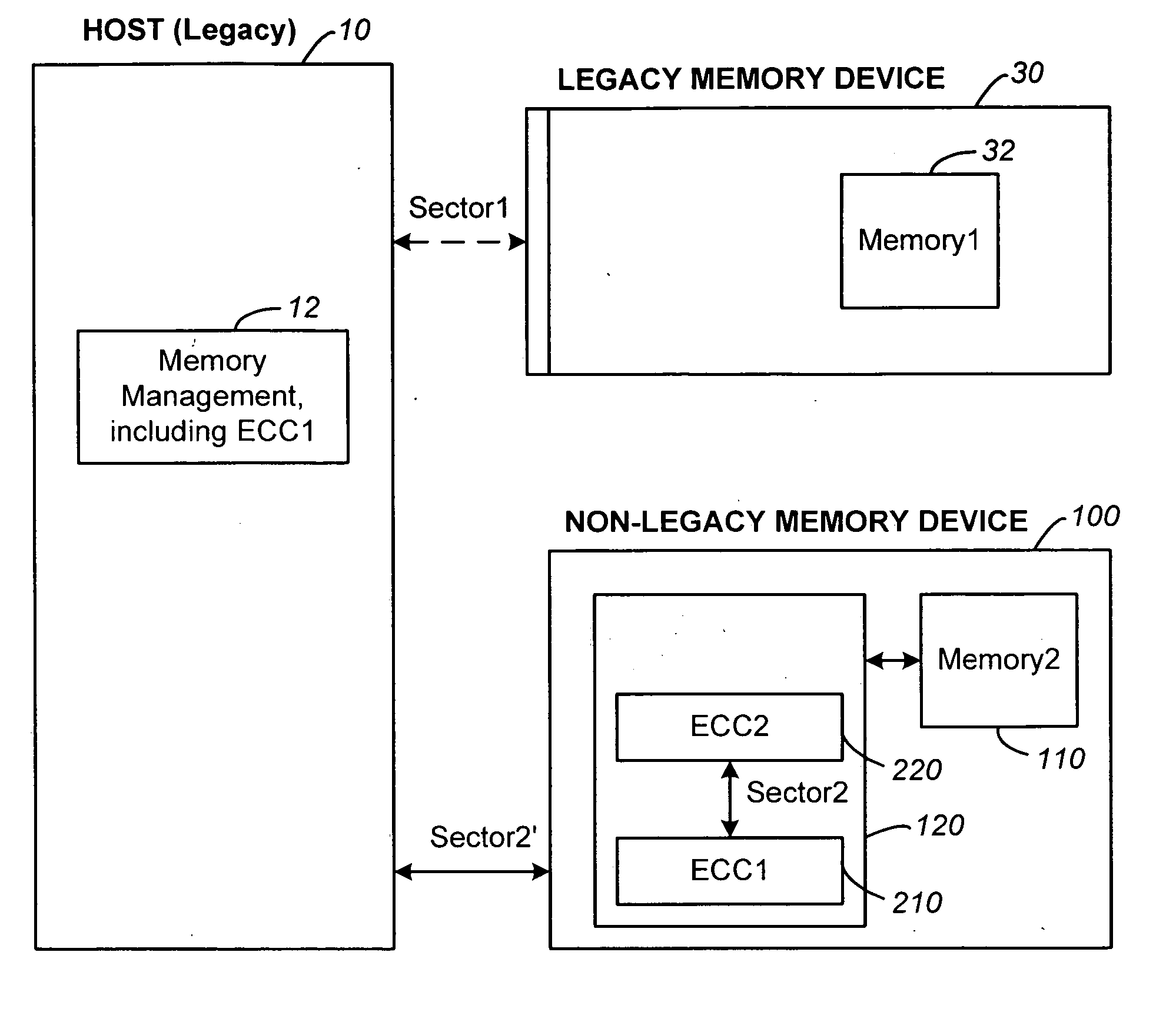

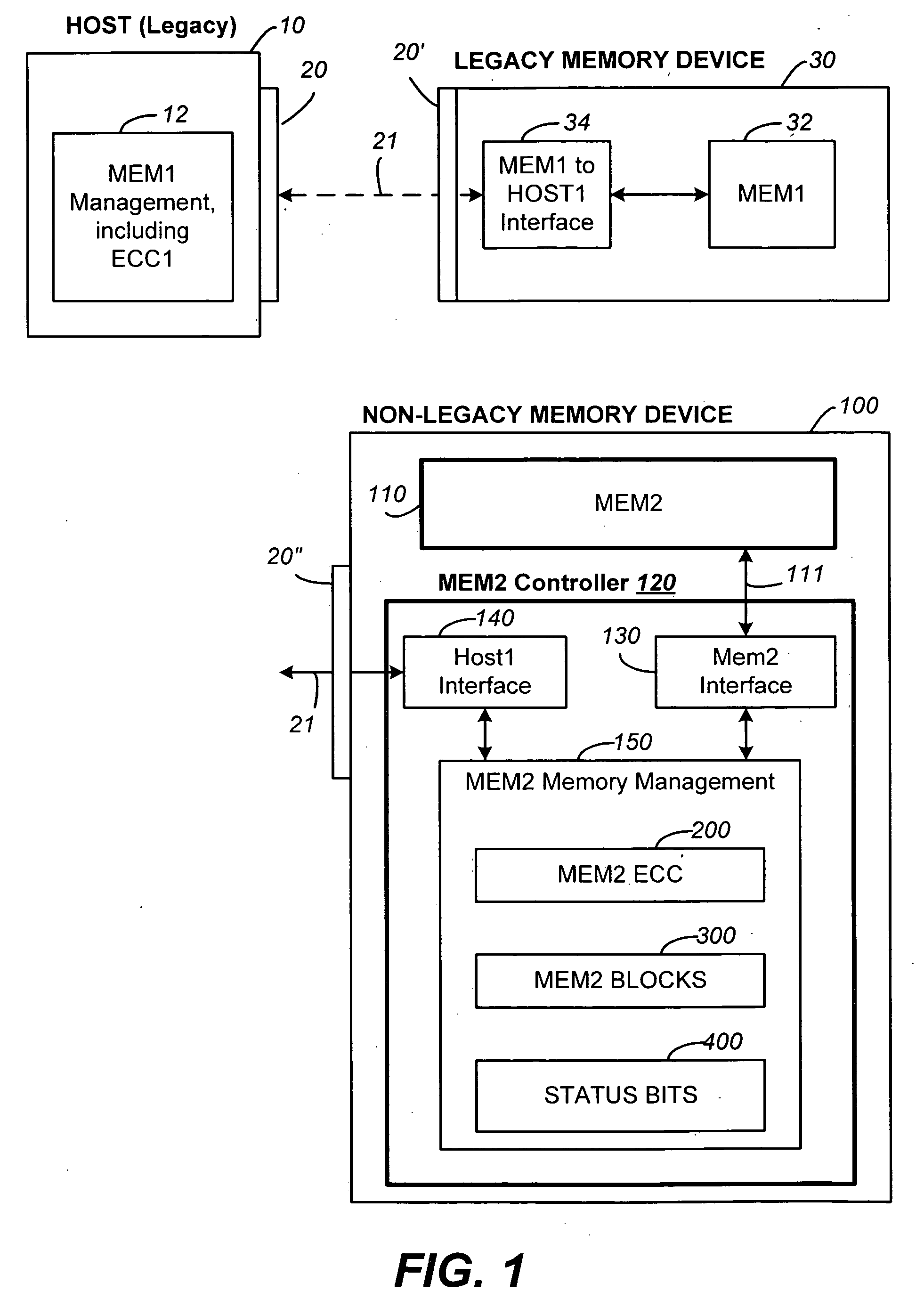

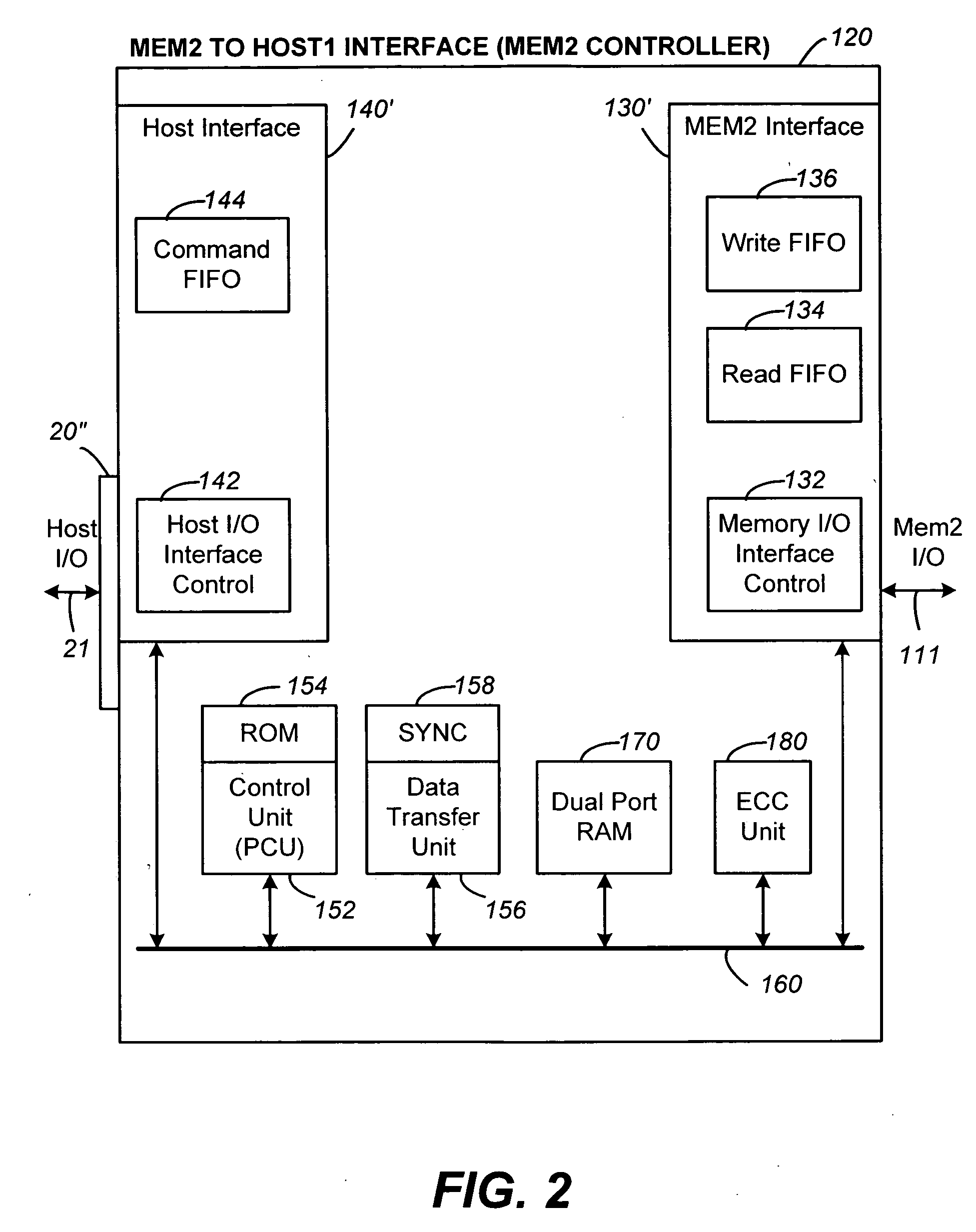

Memory system for legacy hosts

ActiveUS20070118713A1Maintain compatibilityError detection/correctionCode conversionTerm memoryControl memory

A non-volatile memory device is provided with a controller and includes method that controls memory operations and to emulate the memory and communication characteristics of a legacy memory device. In this way, the memory device is compatible with a host that was originally designed to operate the legacy memory device. In particular, the controller performs the emulation to the host taking into account differences such as multibit memory, error correction requirement, memory support of overwrites, and erasable block sizes.

Owner:SANDISK TECH LLC

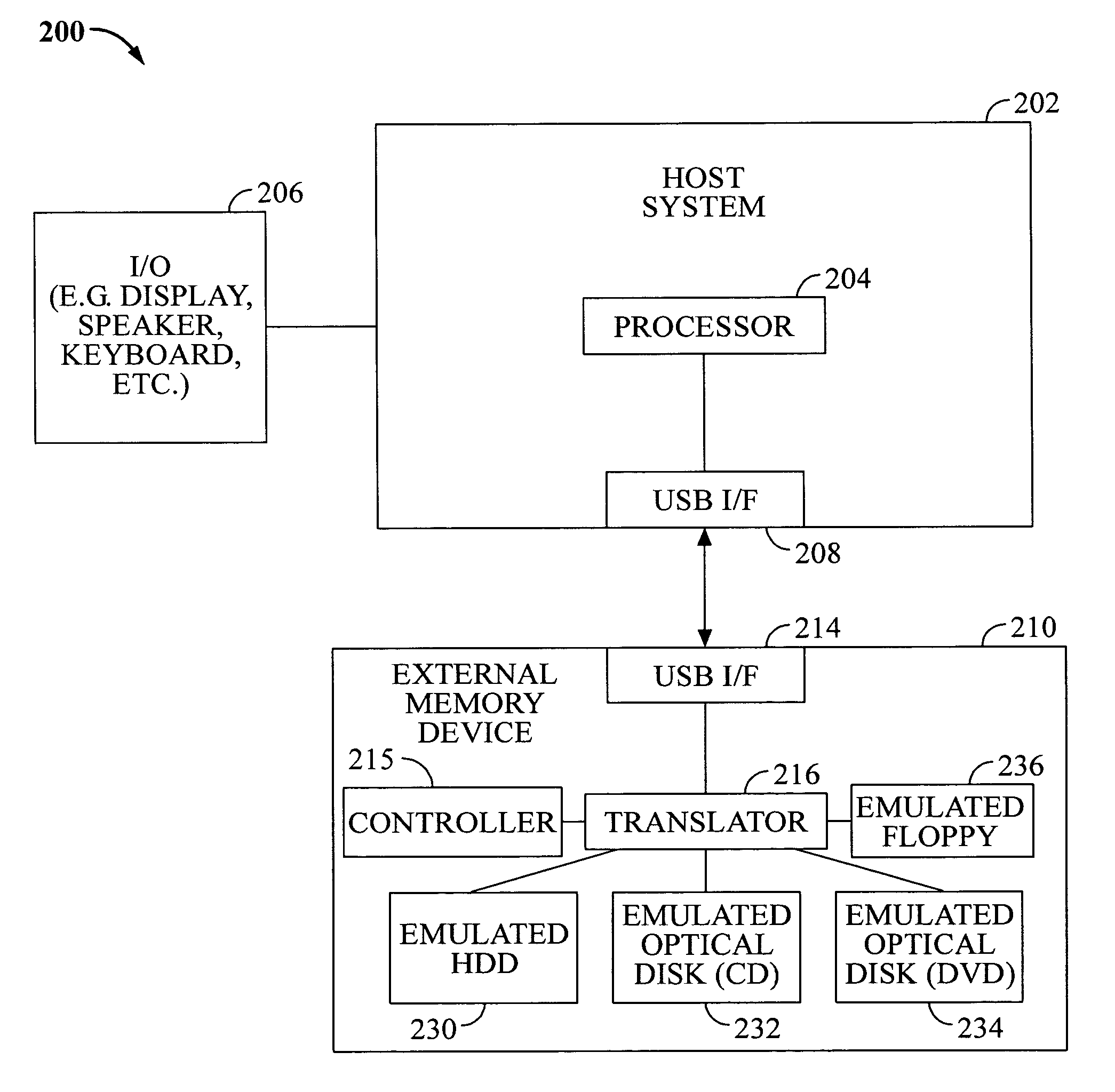

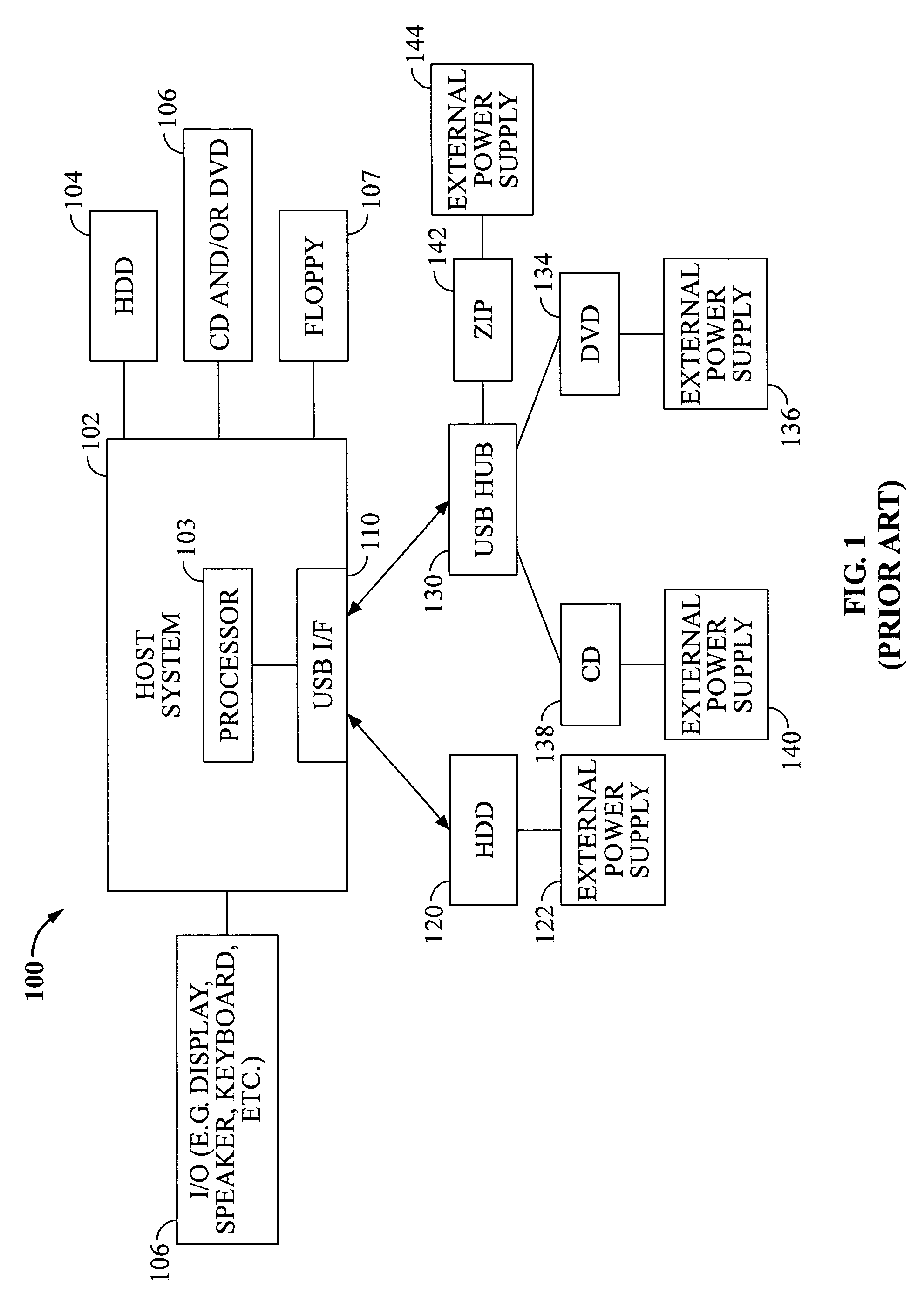

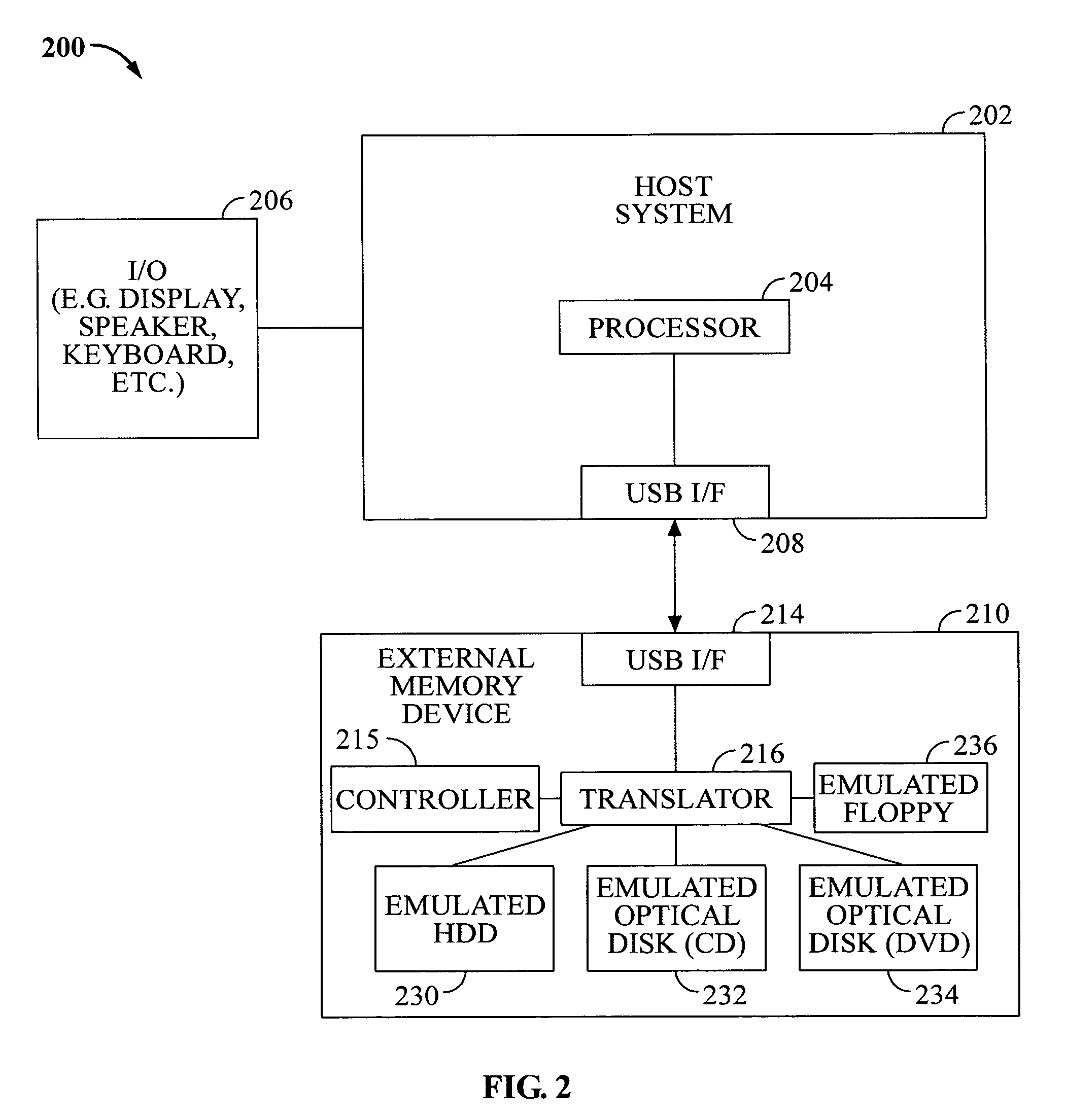

External memory device to provide disk device and optical device functionality

InactiveUS7496493B1Energy efficient ICTEnergy efficient computingExternal storageComputerized system

A memory device is attachable to a host computer system. The memory device includes an interface to couple the memory device to the host computer system. The memory device includes a controller for controlling operations in the memory device. The controller enables a first mode of operation in which the memory device communicates with the host computer system through the interface by emulating a disk device and a second mode of operation in which the memory device communicates through the interface by emulating an optical device.

Owner:WESTERN DIGITAL TECH INC

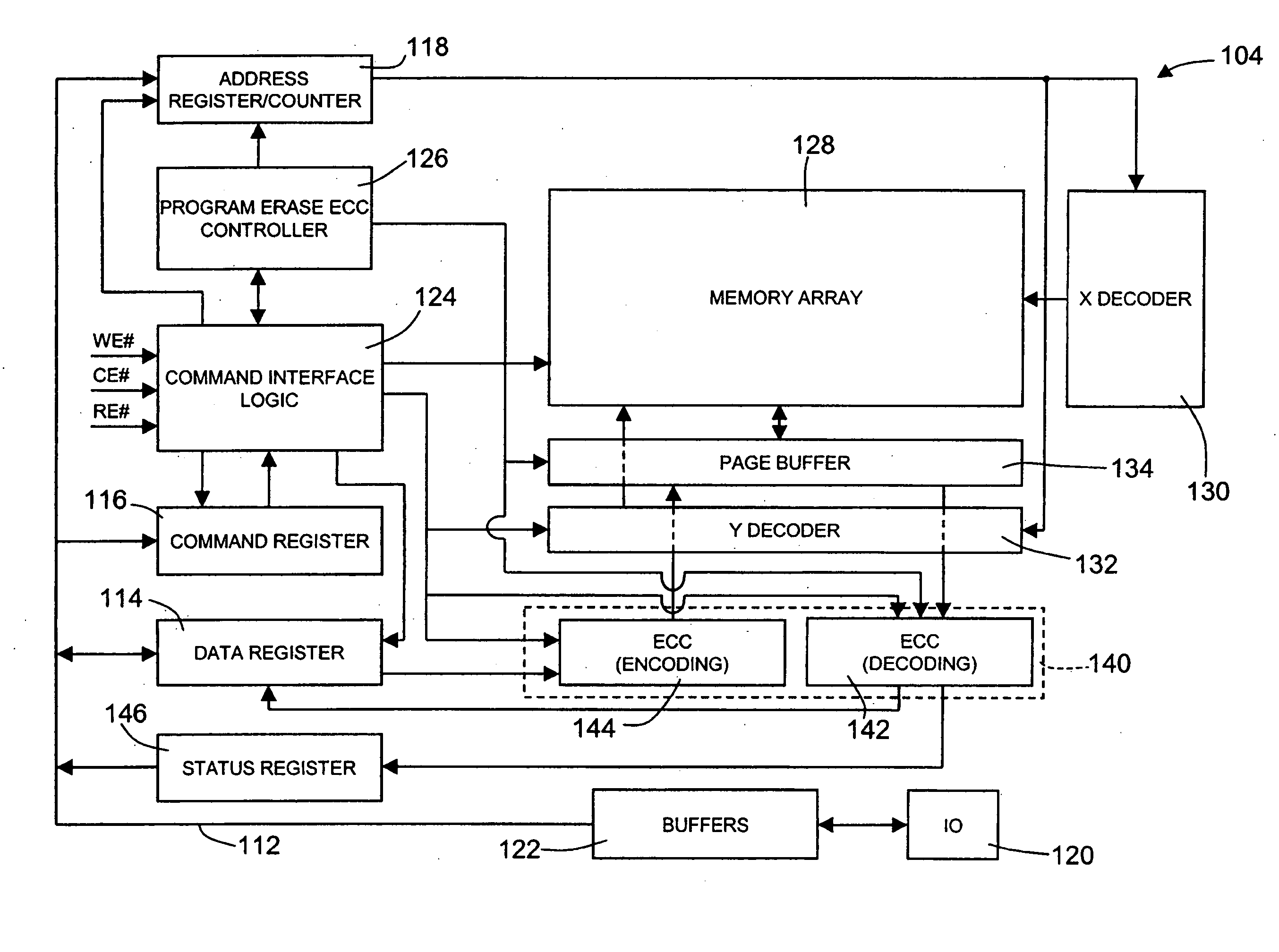

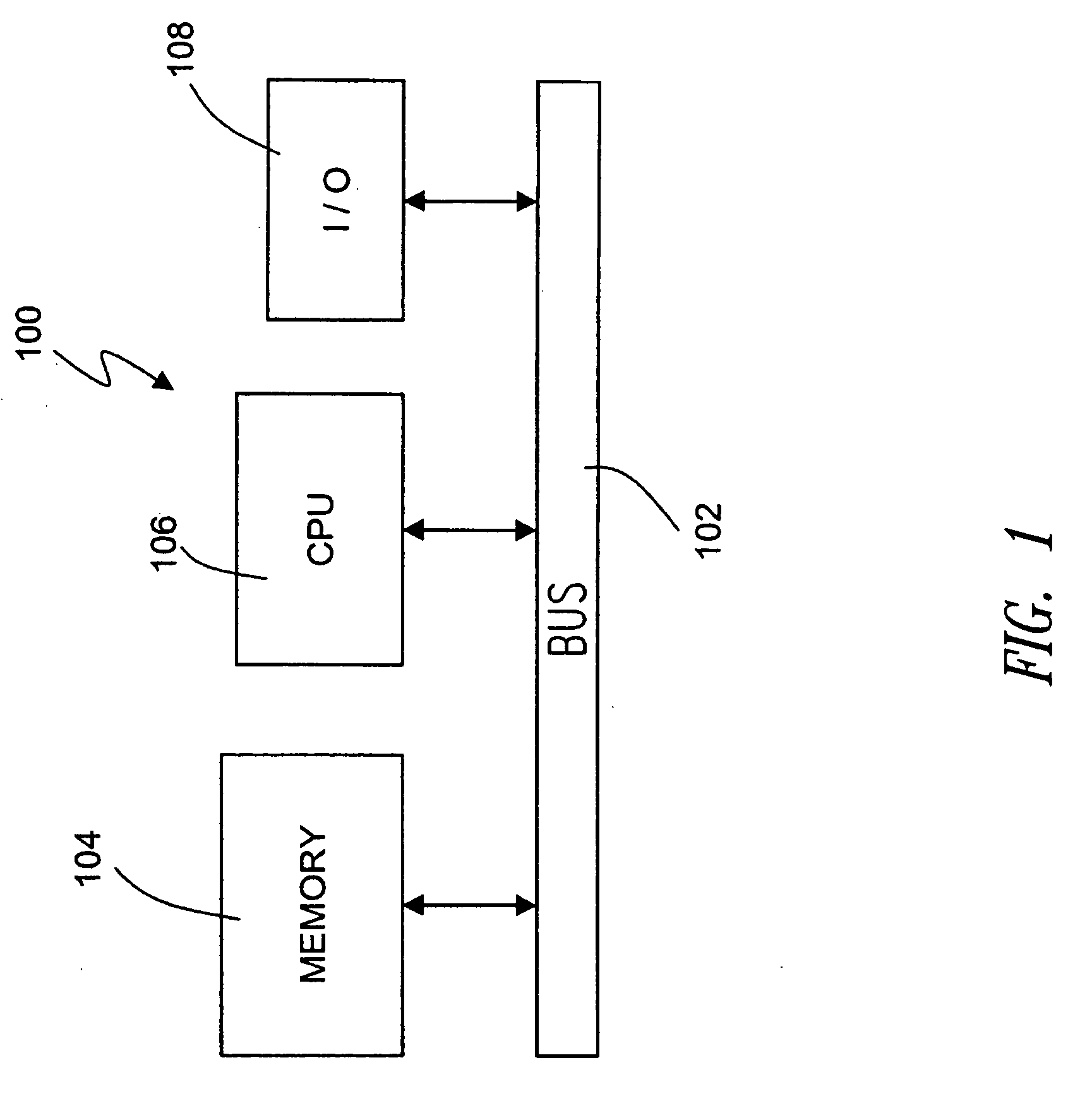

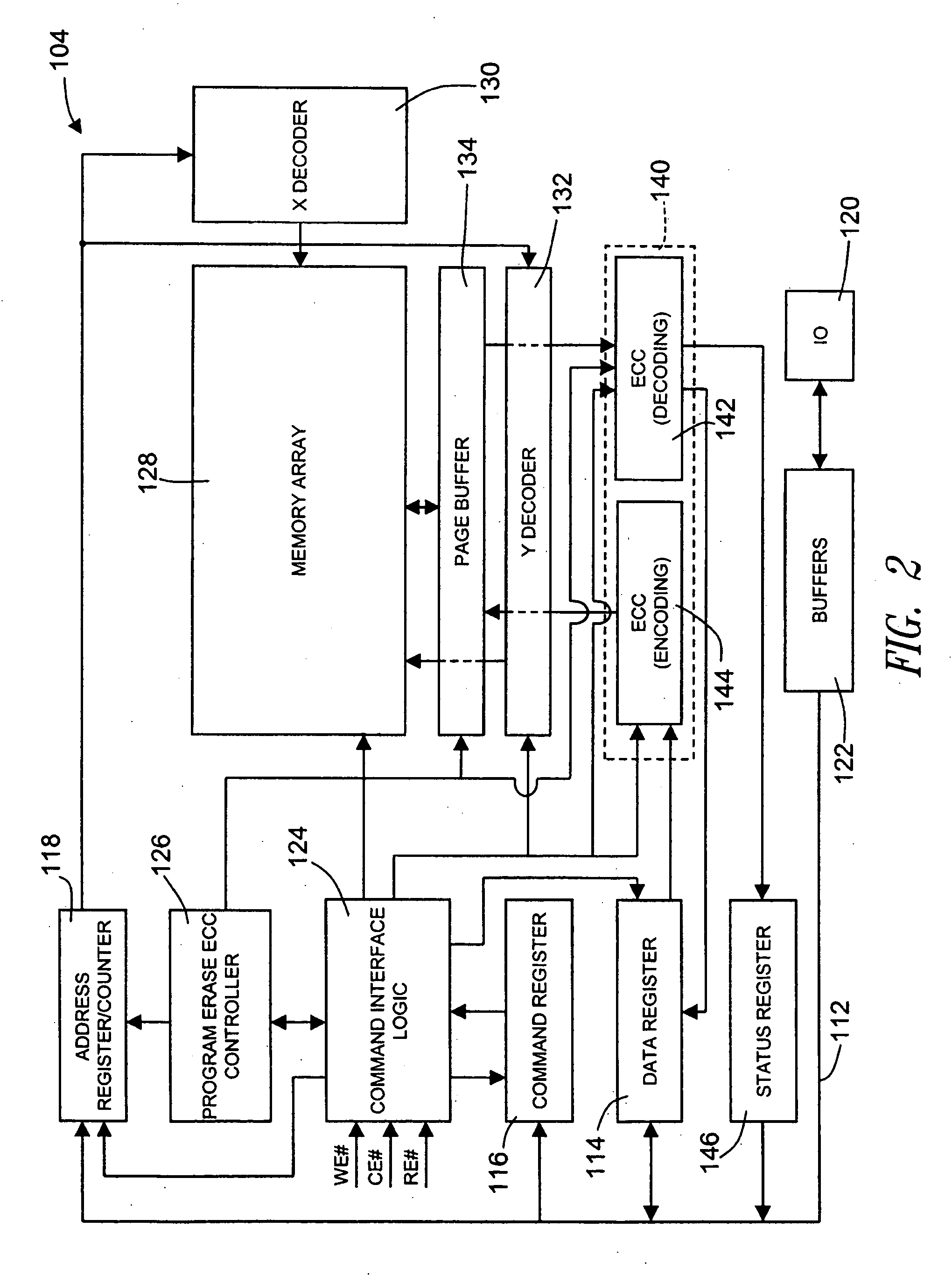

Memory with embedded error correction codes

A memory has one bus for data, addresses, and commands. A data register is coupled to the bus to store the data written to and read from the memory, a command register is coupled to the bus for receiving memory commands, and an address register is coupled to the bus to address the memory. The memory also includes an Error Correction Code circuit for calculating an ECC. The memory is configured to be responsive to external commands for controlling the operation of the ECC circuit for reading or writing of the ECC that are separate from external commands controlling reads or writes of the memory data. The memory may also include a status register that stores information regarding the passing or failing of the ECC.

Owner:STMICROELECTRONICS SRL +1

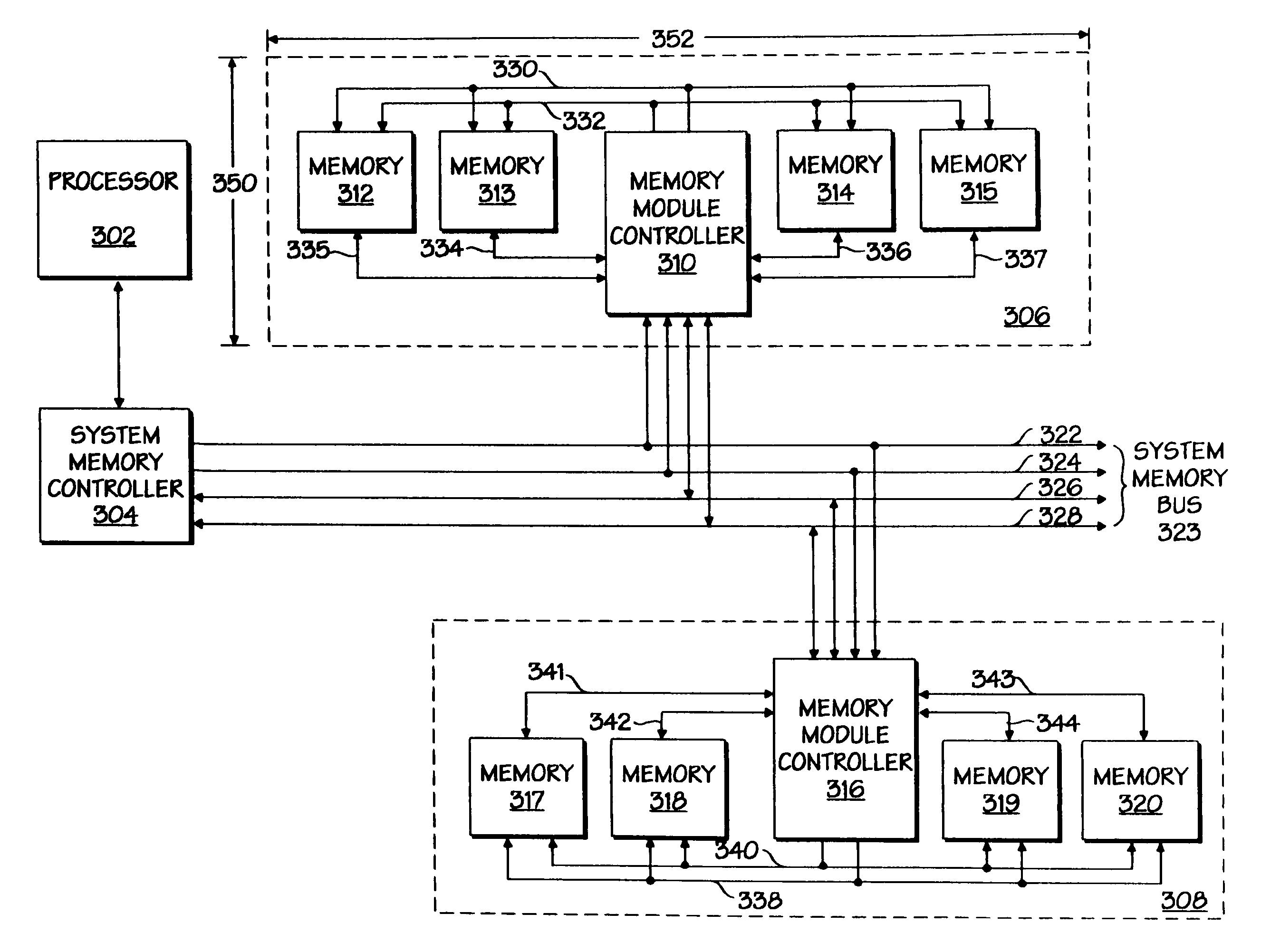

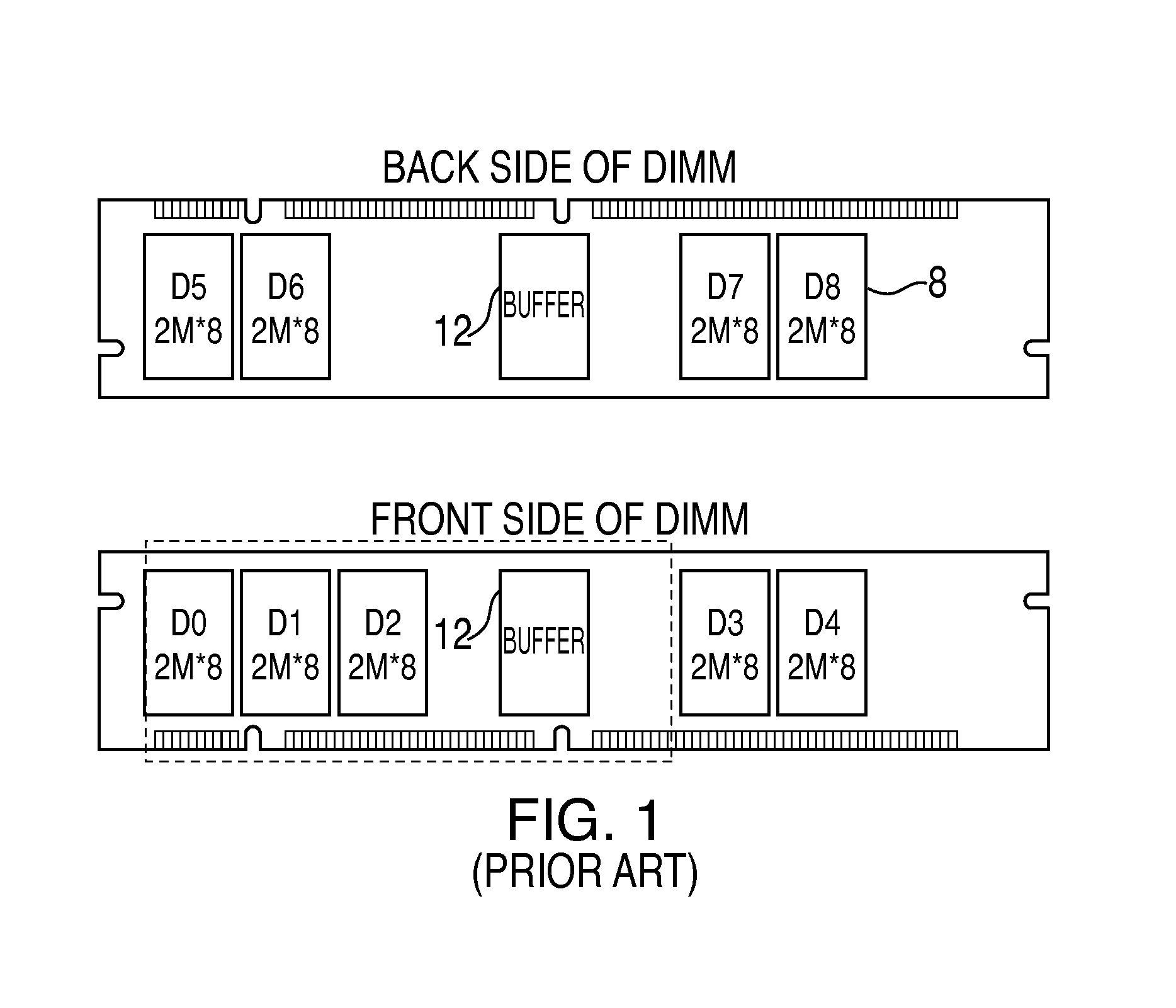

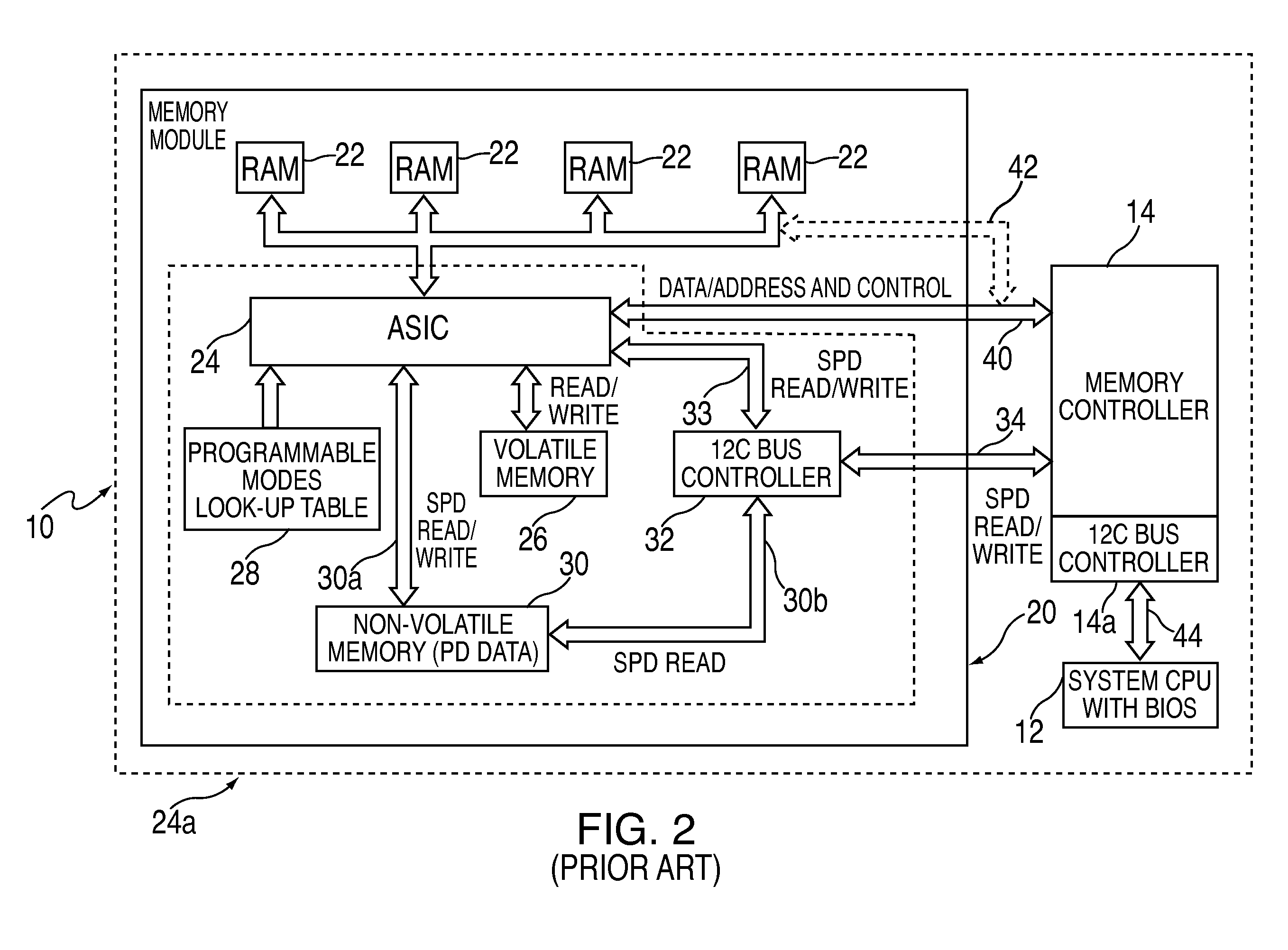

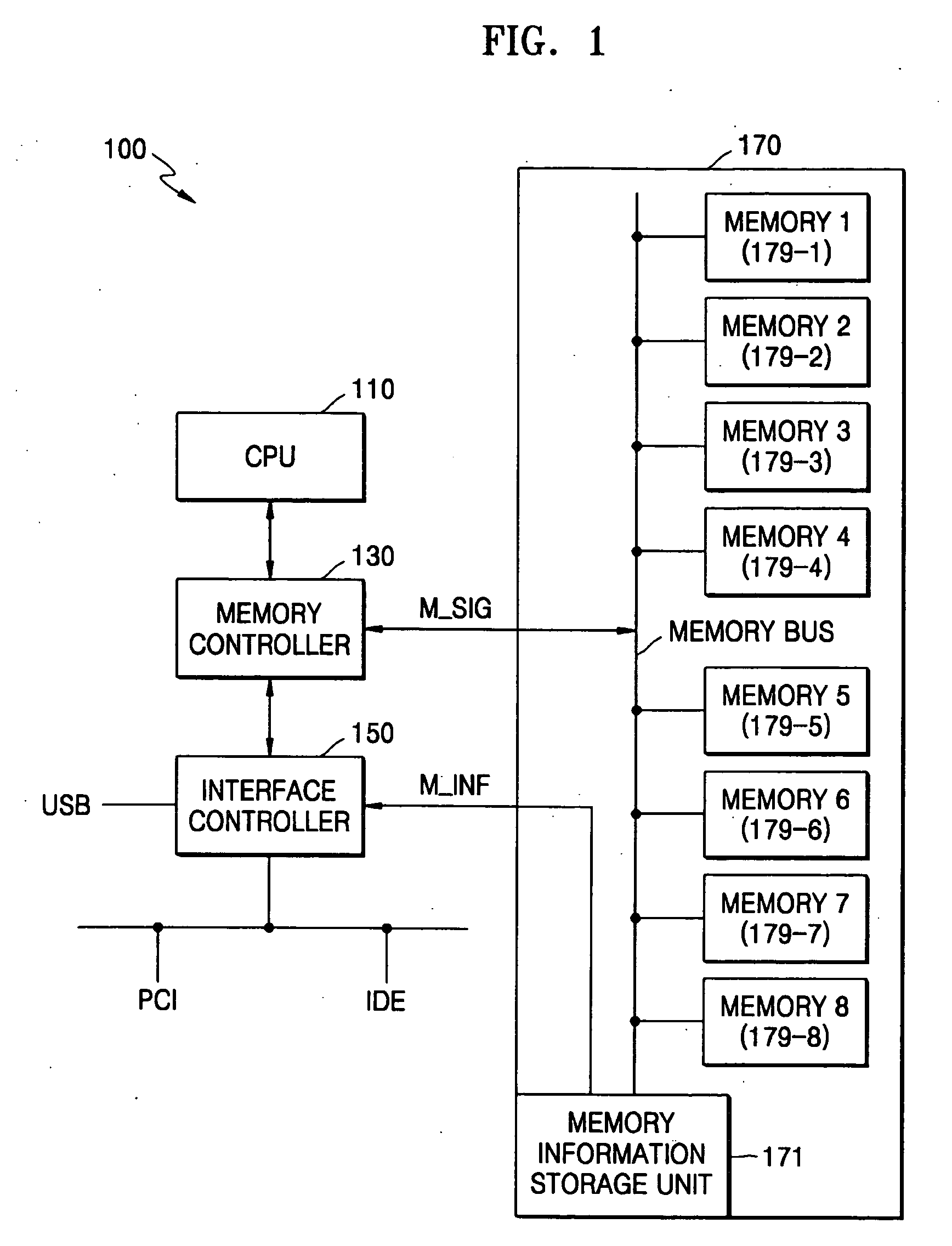

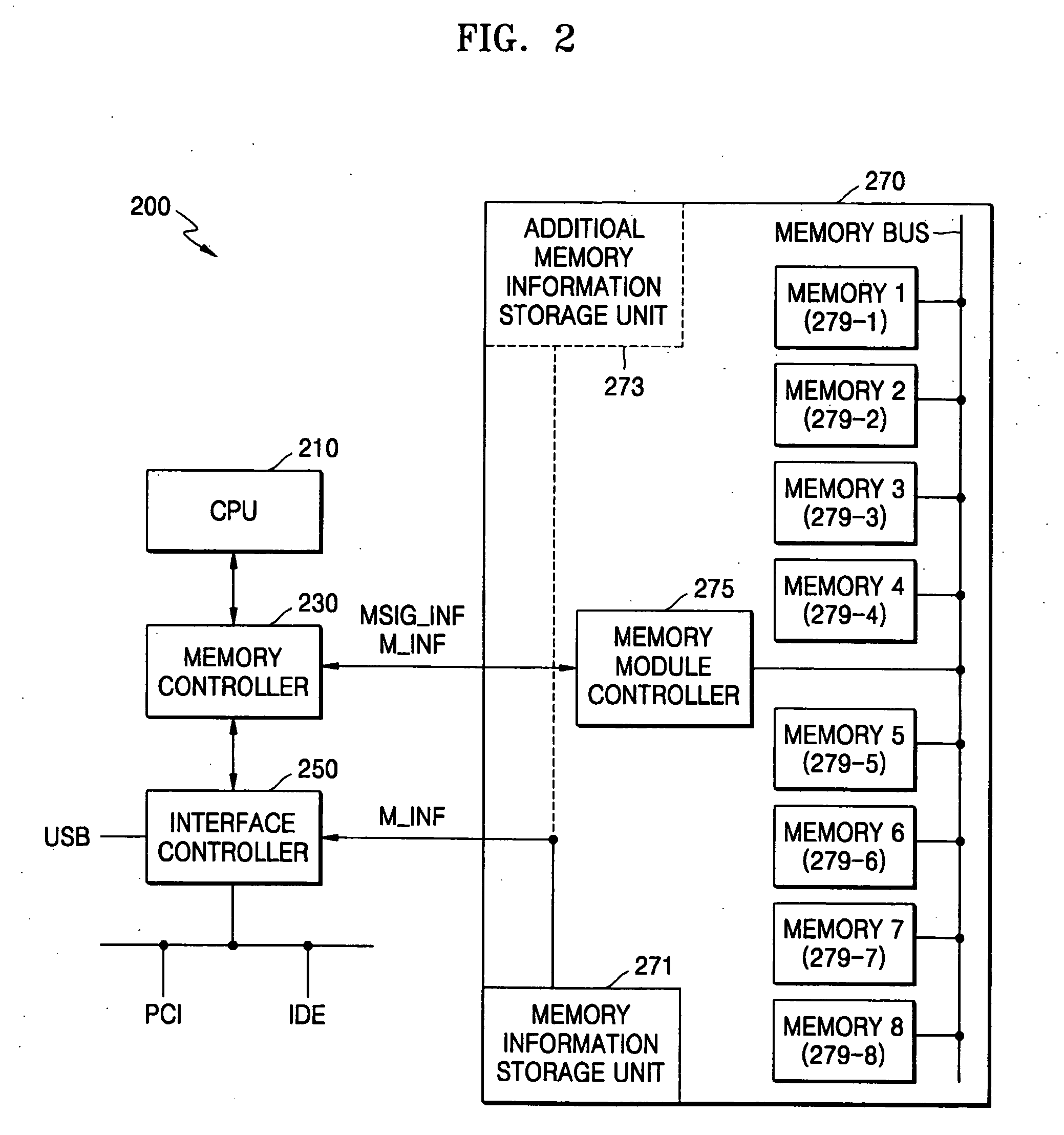

Memory module having a memory module controller controlling memory transactions for a plurality of memory devices

InactiveUS6968419B1Energy efficient ICTMemory adressing/allocation/relocationMemory busControl memory

A memory module that has a plurality of memory devices and a memory module controller configured to receive a memory transaction from a first memory bus and to control access to the plurality of memory devices.

Owner:INTEL CORP

Architecture for vertical transistor cells and transistor-controlled memory cells

InactiveUS7109544B2Meet growth requirementsFunctional restriction of the transistor cells by a floating body effect is reducedTransistorSolid-state devicesTransistor arrayFloating body effect

Owner:POLARIS INNOVATIONS LTD

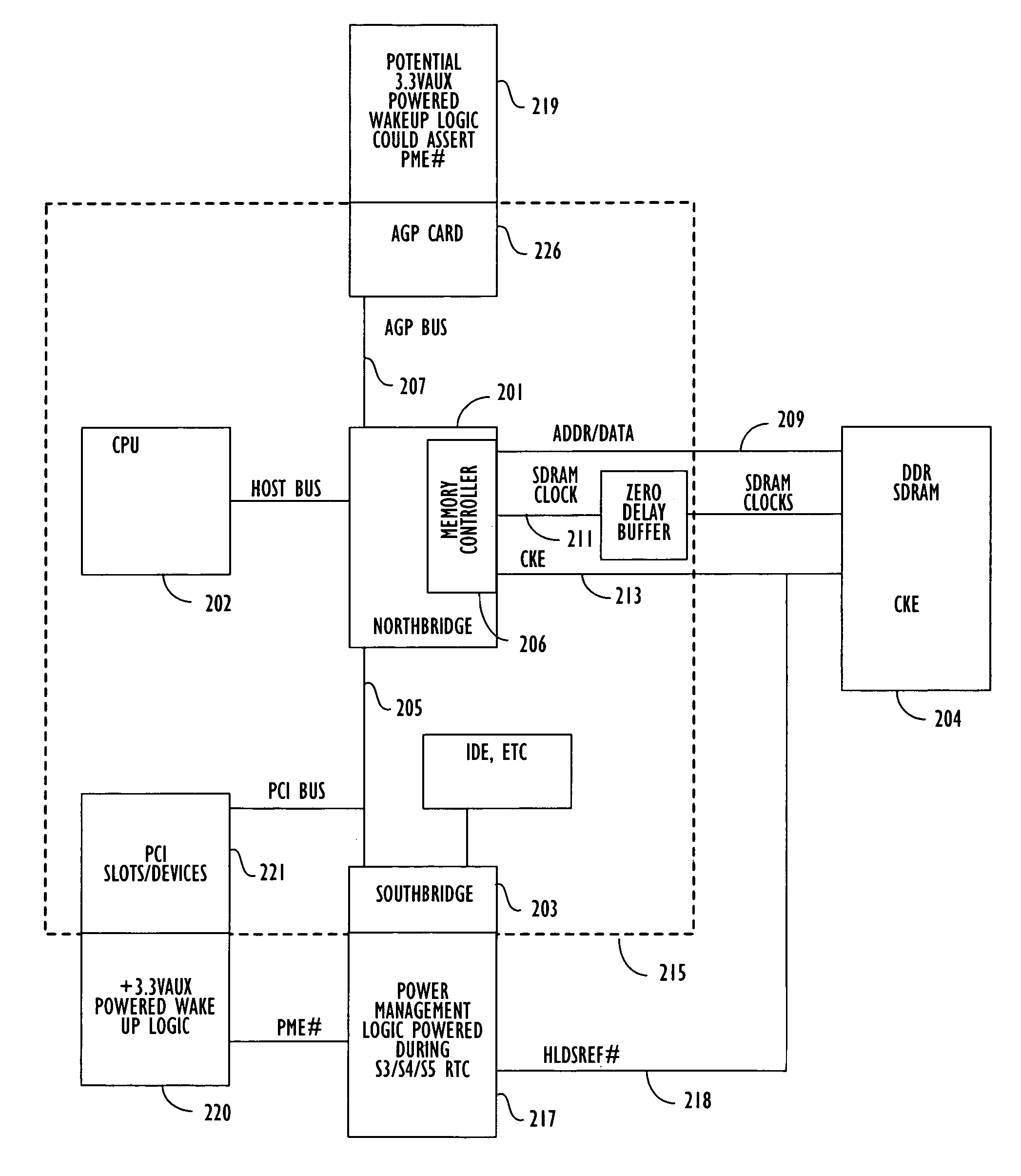

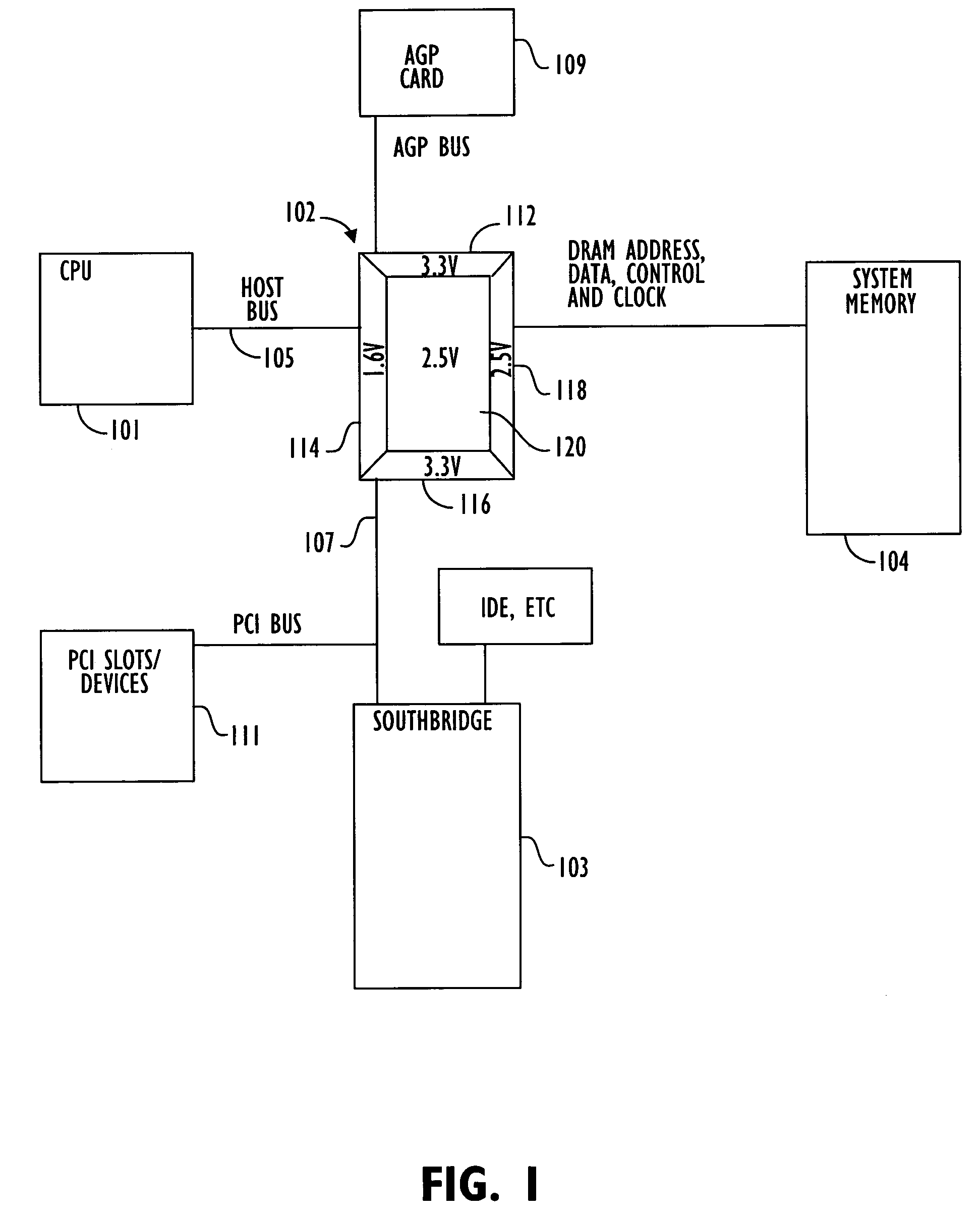

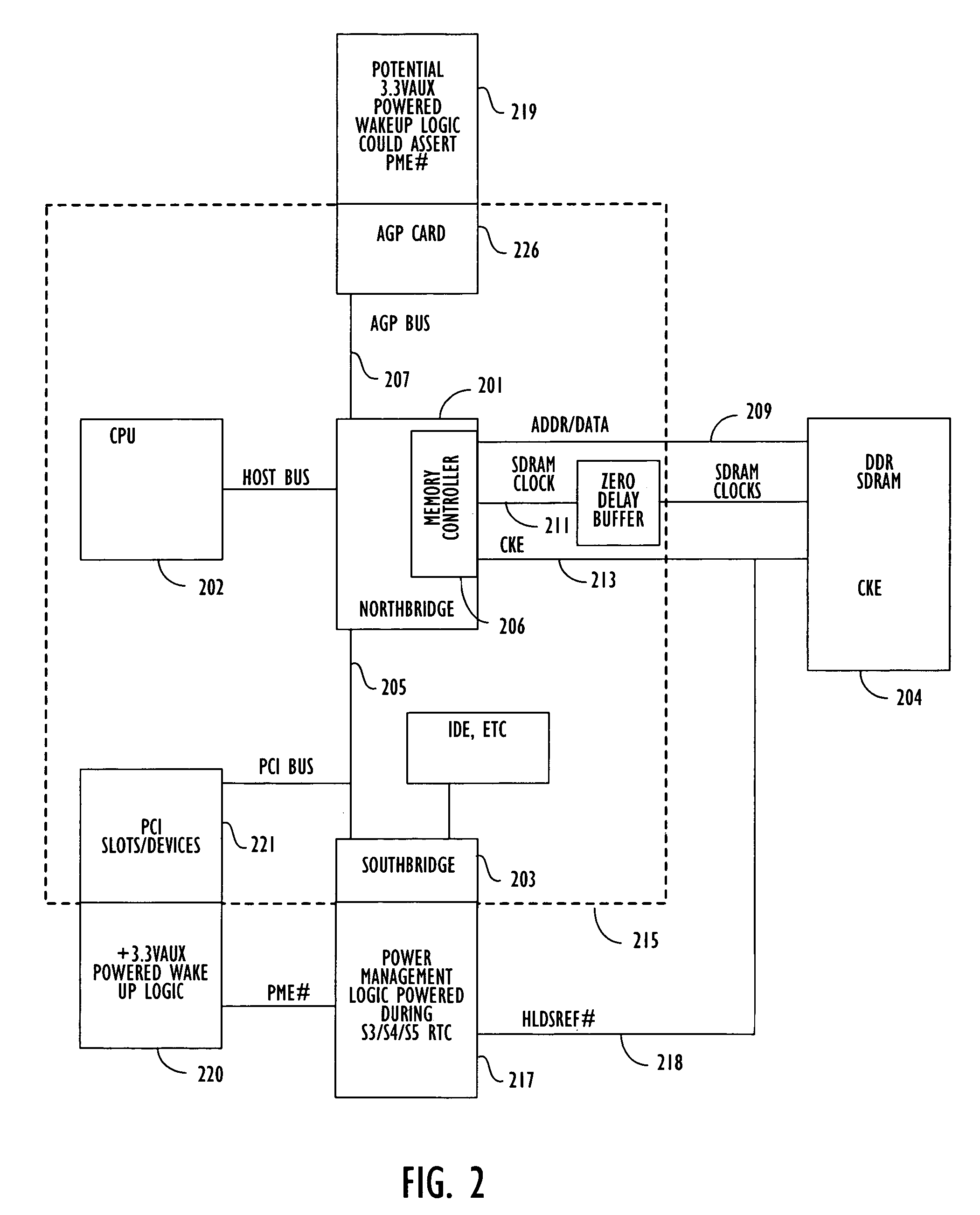

Method and apparatus for powering down the CPU/memory controller complex while preserving the self refresh state of memory in the system

Power management logic maintains memory in a computer system in the self refresh state during a power savings state in which power is removed from the memory controller. A memory control circuit, separate from the power management logic, controls the memory during other operational modes. The power management logic maintains the system memory in the self refresh state by driving memory control signal(s) at appropriate values during the power savings state.

Owner:MEDIATEK INC

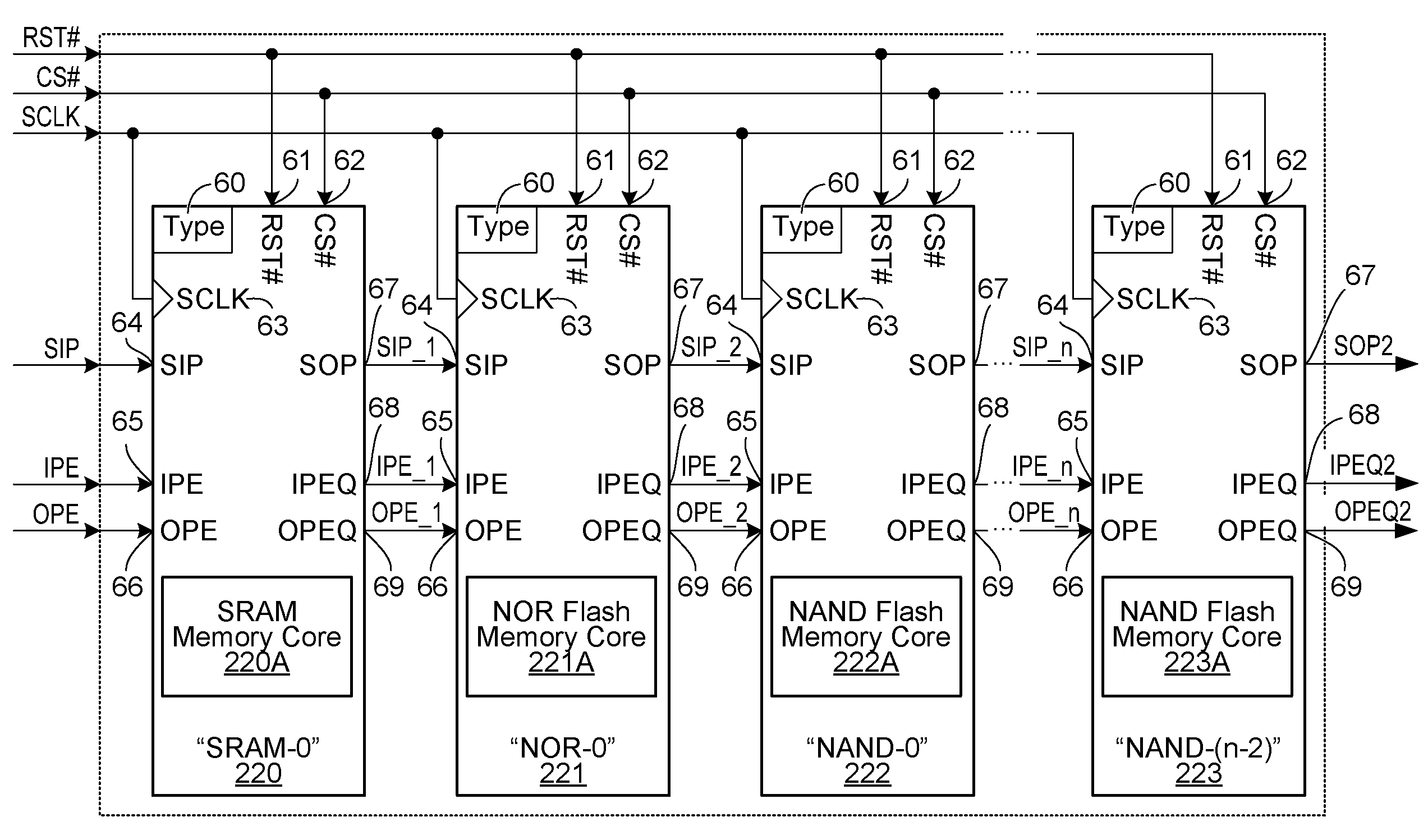

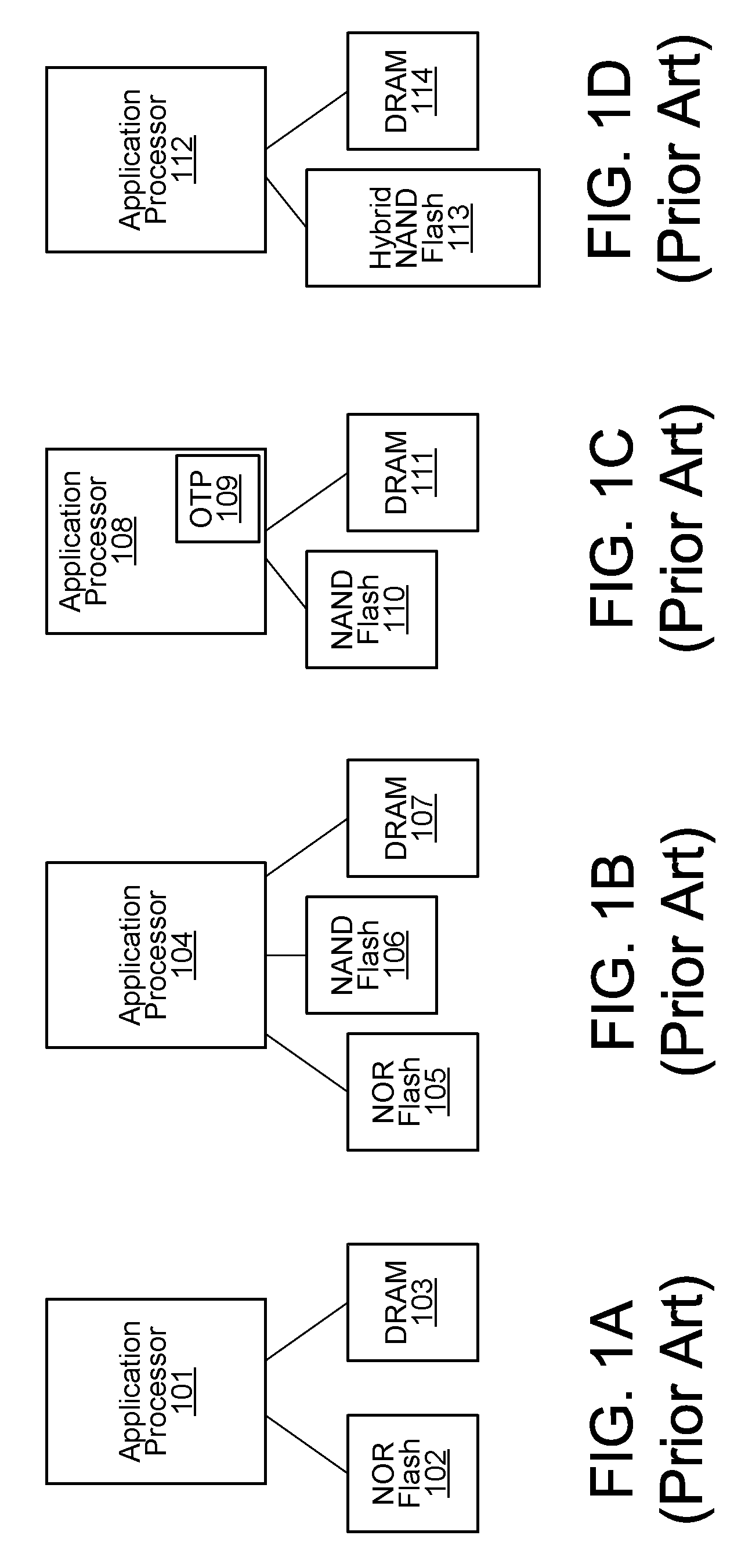

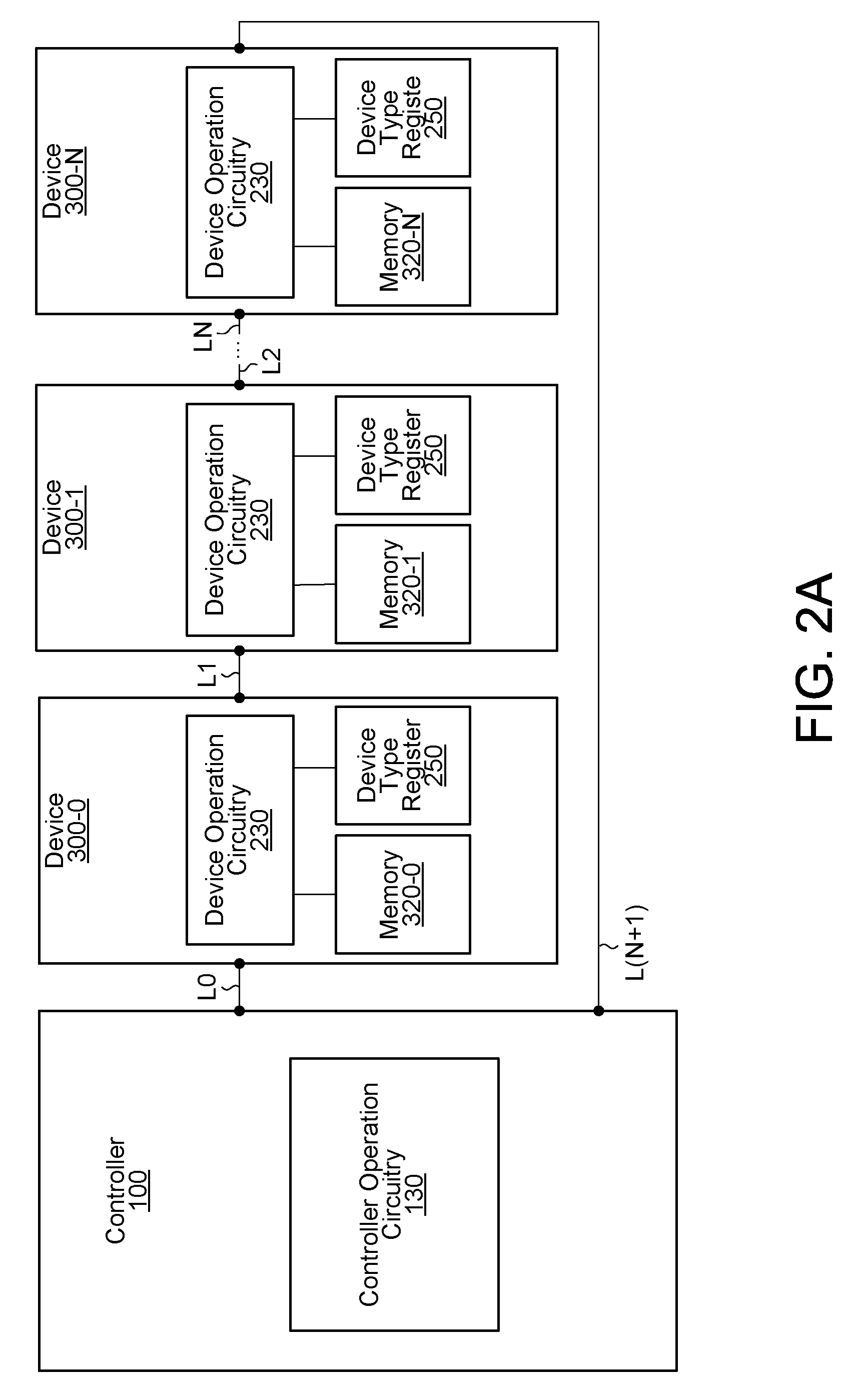

System and method of operating memory devices of mixed type

InactiveUS20080140916A1Memory adressing/allocation/relocationRead-only memoriesHybrid typeStatic random-access memory

A memory system architecture is provided in which a memory controller controls memory devices in a serial interconnection configuration. The memory controller has an output port for sending memory commands and an input port for receiving memory responses for those memory commands requisitioning such responses. Each memory device includes a memory, such as, for example, NAND-type flash memory, NOR-type flash memory, random access memory and static random access memory. Each memory command is specific to the memory type of a target memory device. A data path for the memory commands and the memory responses is provided by the interconnection. A given memory command traverses memory devices in order to reach its intended memory device of the serial interconnection configuration. Upon its receipt, the intended memory device executes the given memory command and, if appropriate, sends a memory response to a next memory device. The memory response is transferred to the memory controller.

Owner:CONVERSANT INTPROP MANAGEMENT INC

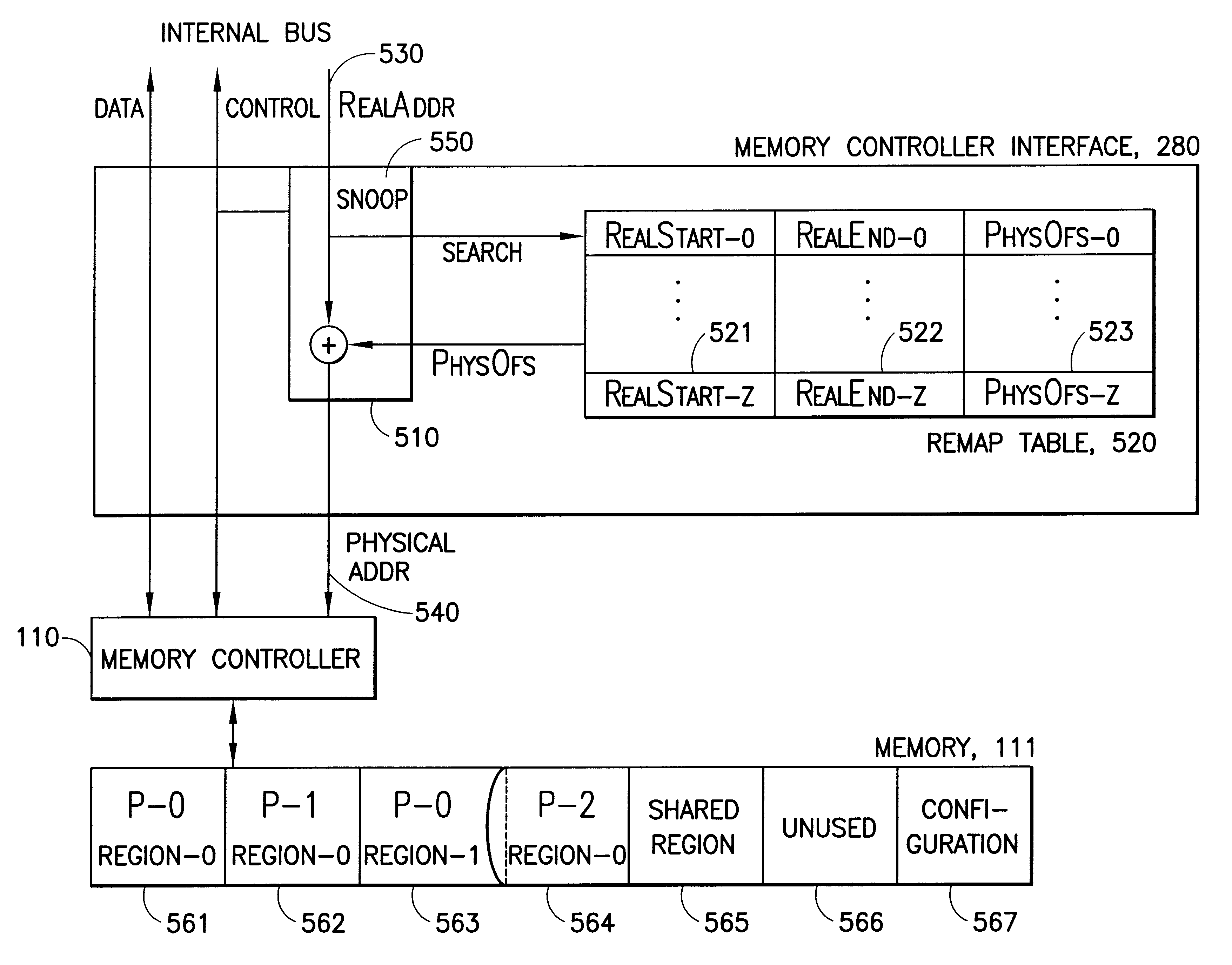

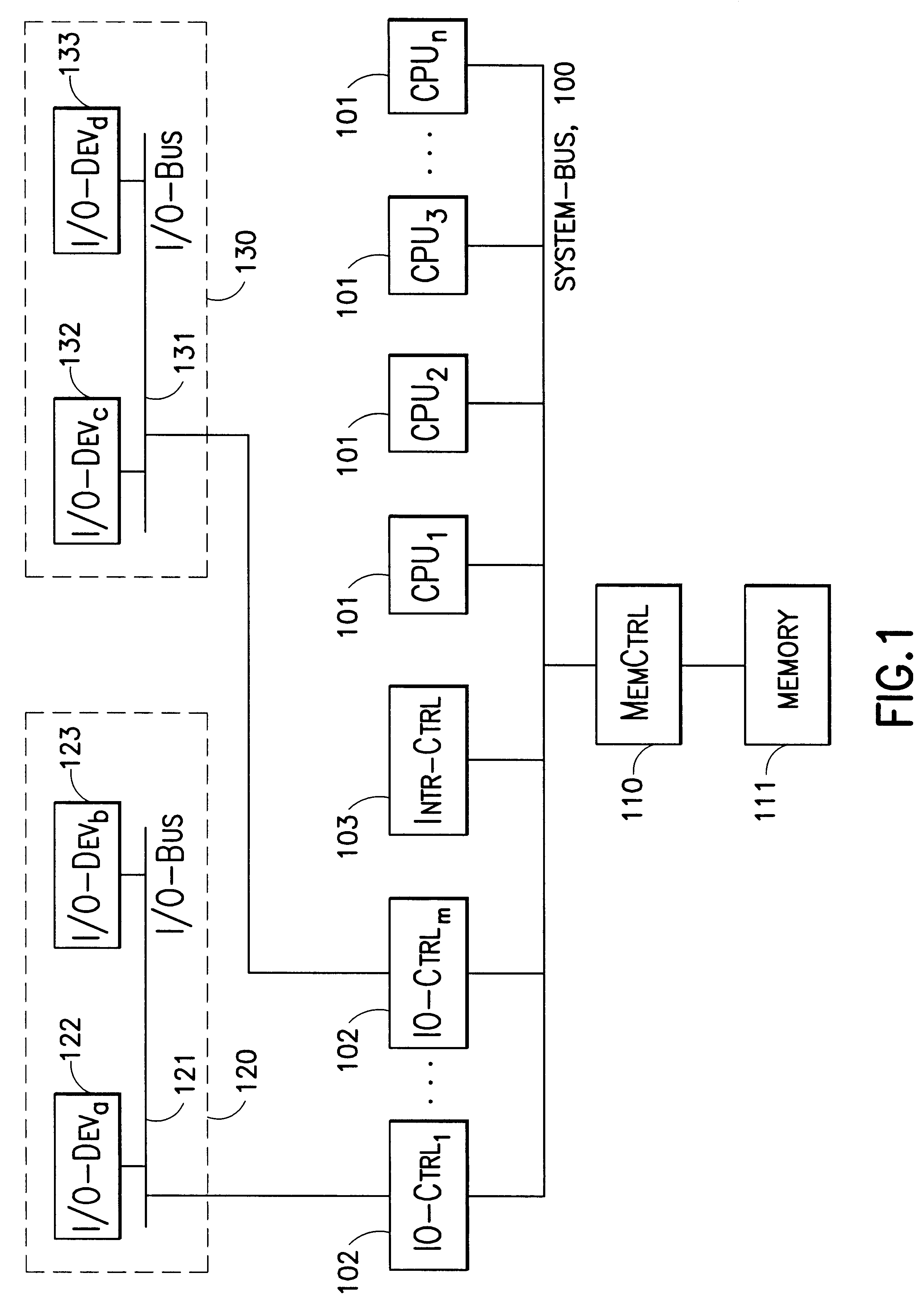

Secure partitioning of shared memory based multiprocessor system

InactiveUS6480941B1Flexible and secure partitioningMemory adressing/allocation/relocationMulti processorPhysical address

A method and apparatus for sharing memory in a multiprocessor computing system. More specifically, this invention provides a number of system buses with each bus being connected to a respective memory controller which controls a corresponding partition of the memory. Any one of the processors can use any one of the system buses to send real addresses to the connected memory controller which then converts the real addresses into physical addresses corresponding to the partition of memory that is controlled by the receiving memory controller. The processors can be dynamically assigned to different partitions of the memory by via a switching mechanism.

Owner:IBM CORP

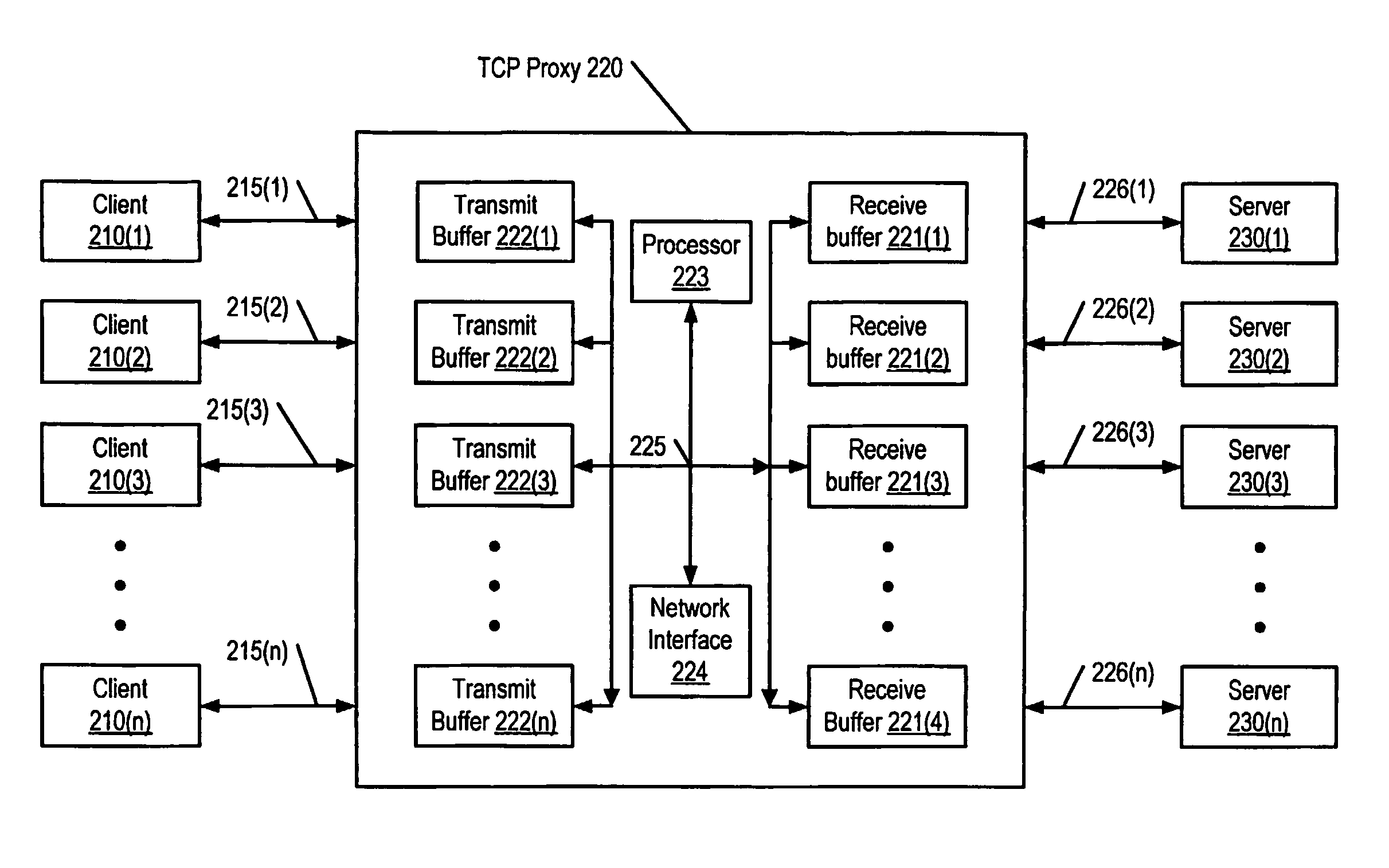

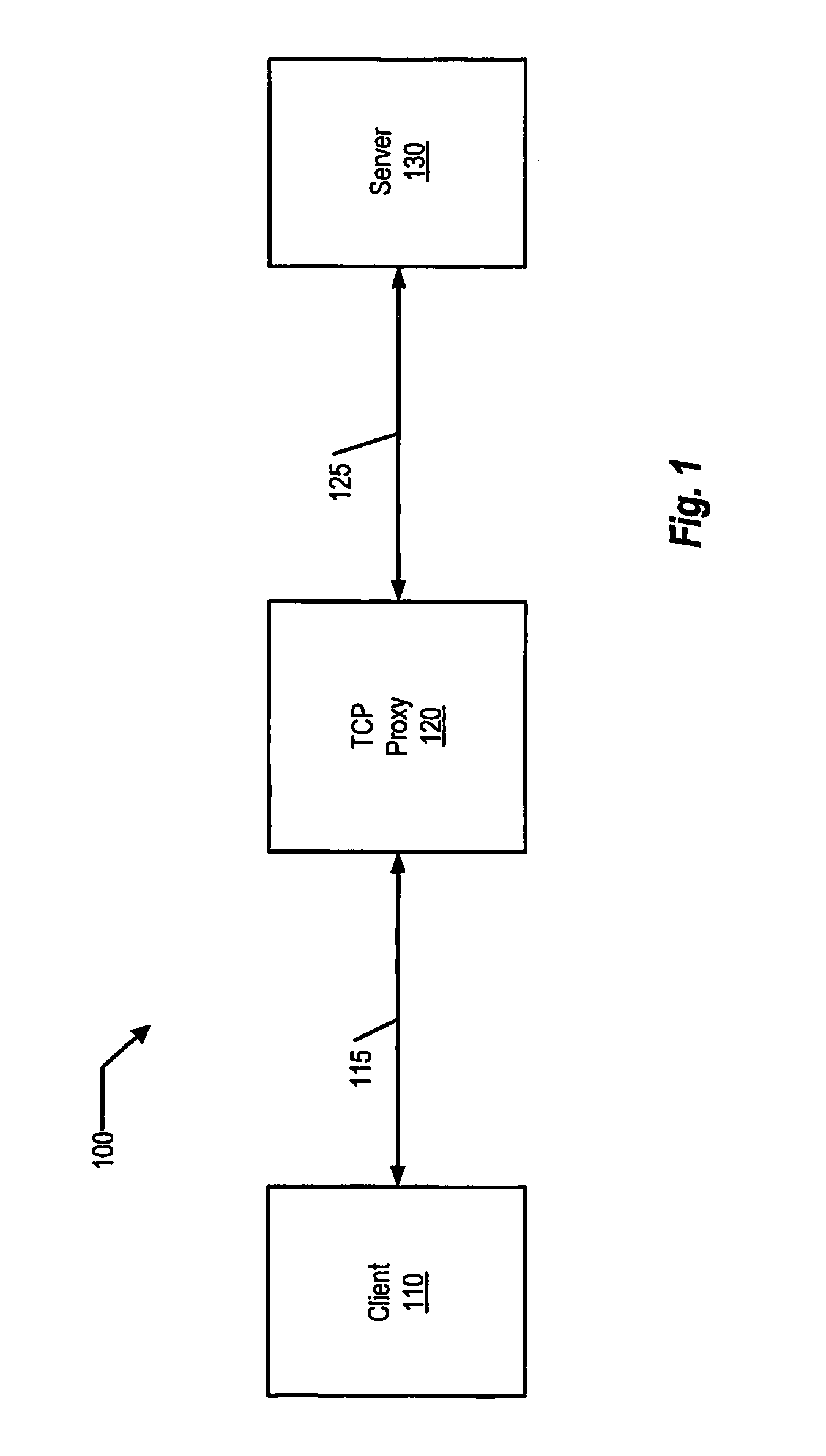

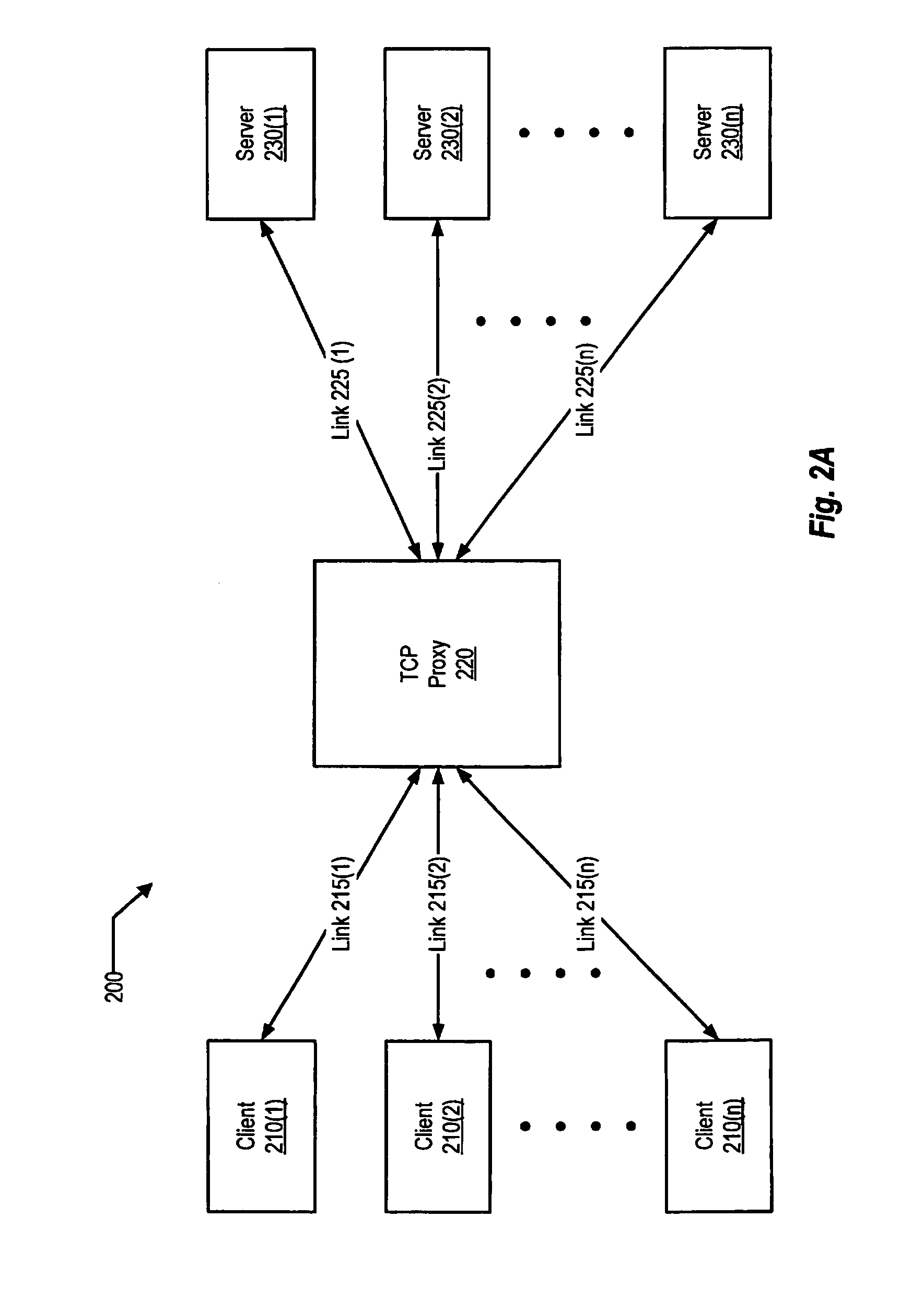

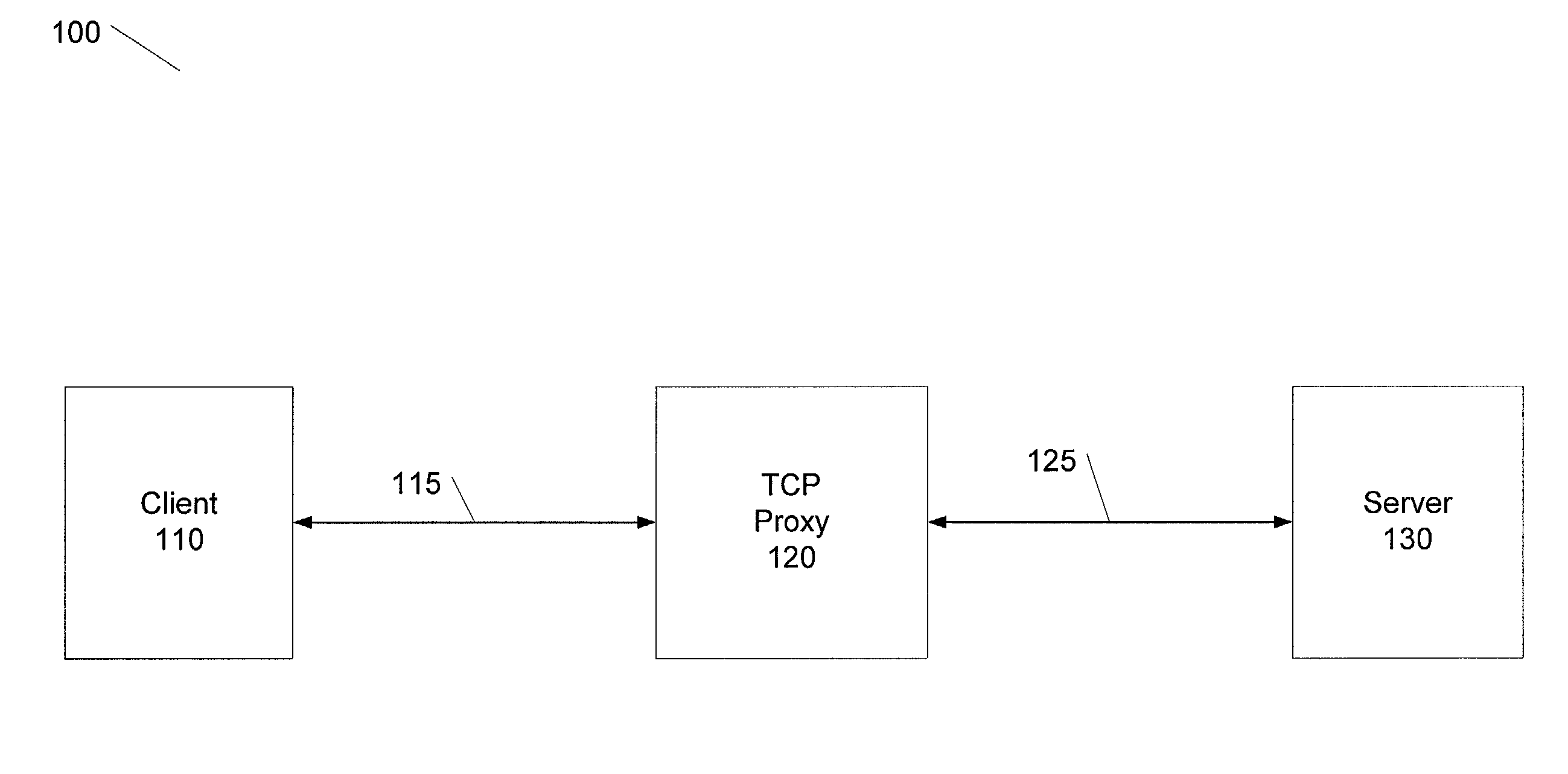

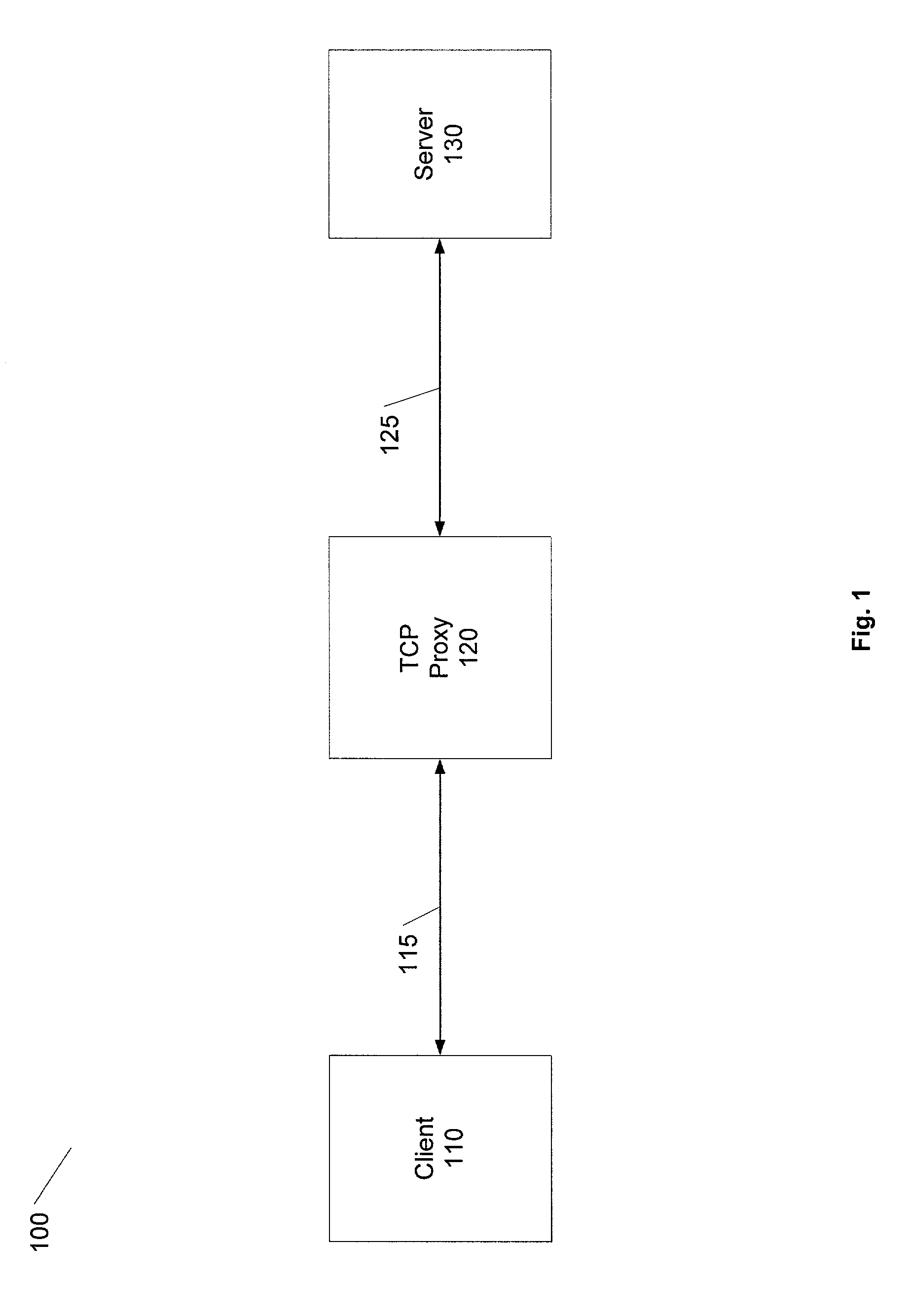

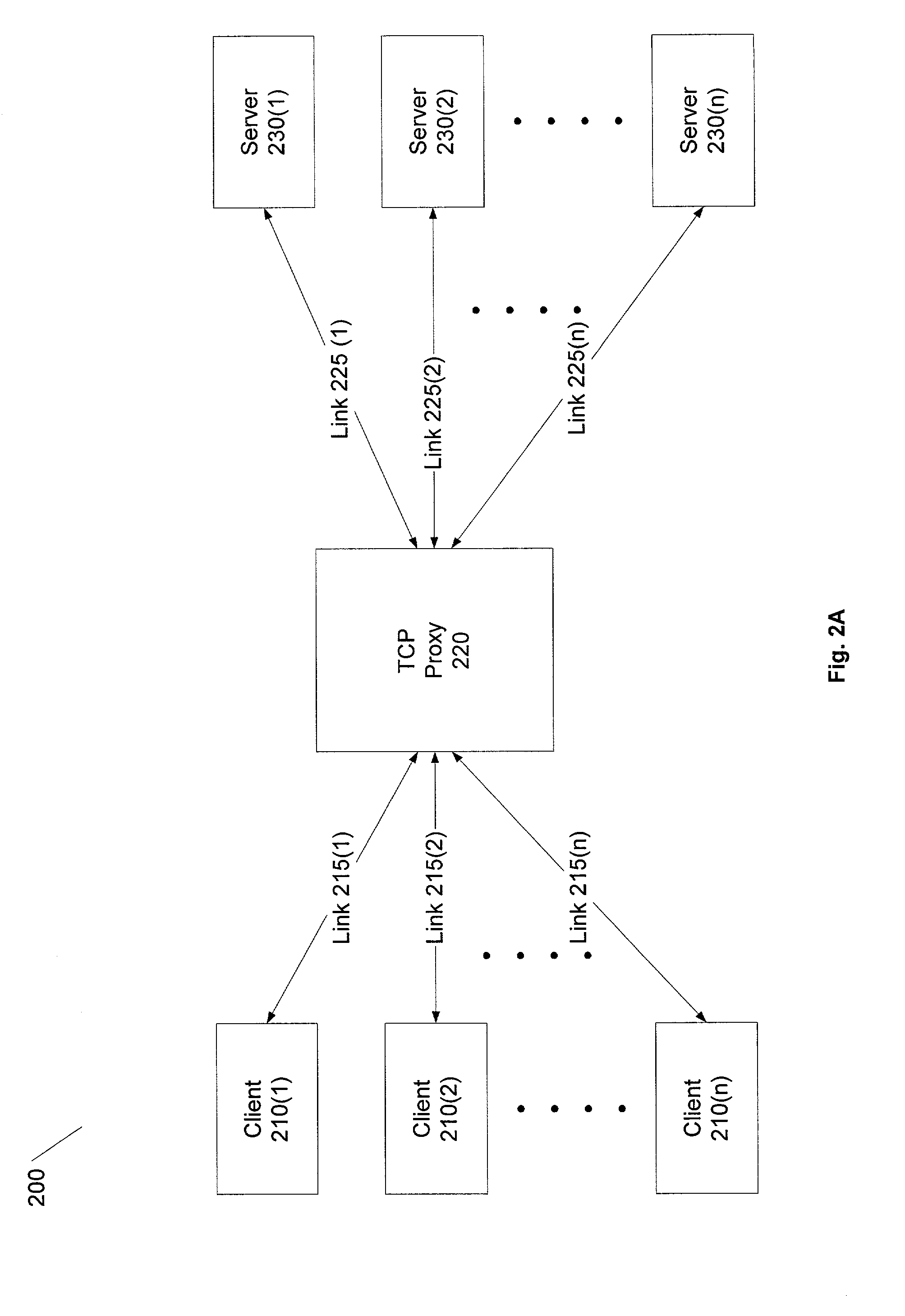

TCP proxy connection management in a gigabit environment

The present invention describes a method and apparatus to effectively manage data buffers for a client and a server connection in a multiple connection environment. The TCP processes of servers and clients are merged into an independent TCP process in a TCP ‘proxy’ server. The TCP proxy server includes a control unit and a data switching unit (the proxy application). The TCP proxy server terminates the client TCP connection and initiates a separate TCP connection with the server. The data switching unit binds the two individual connections. The TCP proxy server portrays the actual server TCP. The control unit in the TCP proxy server manages data buffers, control memory and supports multiple connections. The control unit ‘pushes’ the data into the buffers by monitoring the use of the buffers. The control unit does not wait for data requests from the data switching unit thus, eliminating the overhead of data request messages.

Owner:CISCO TECH INC

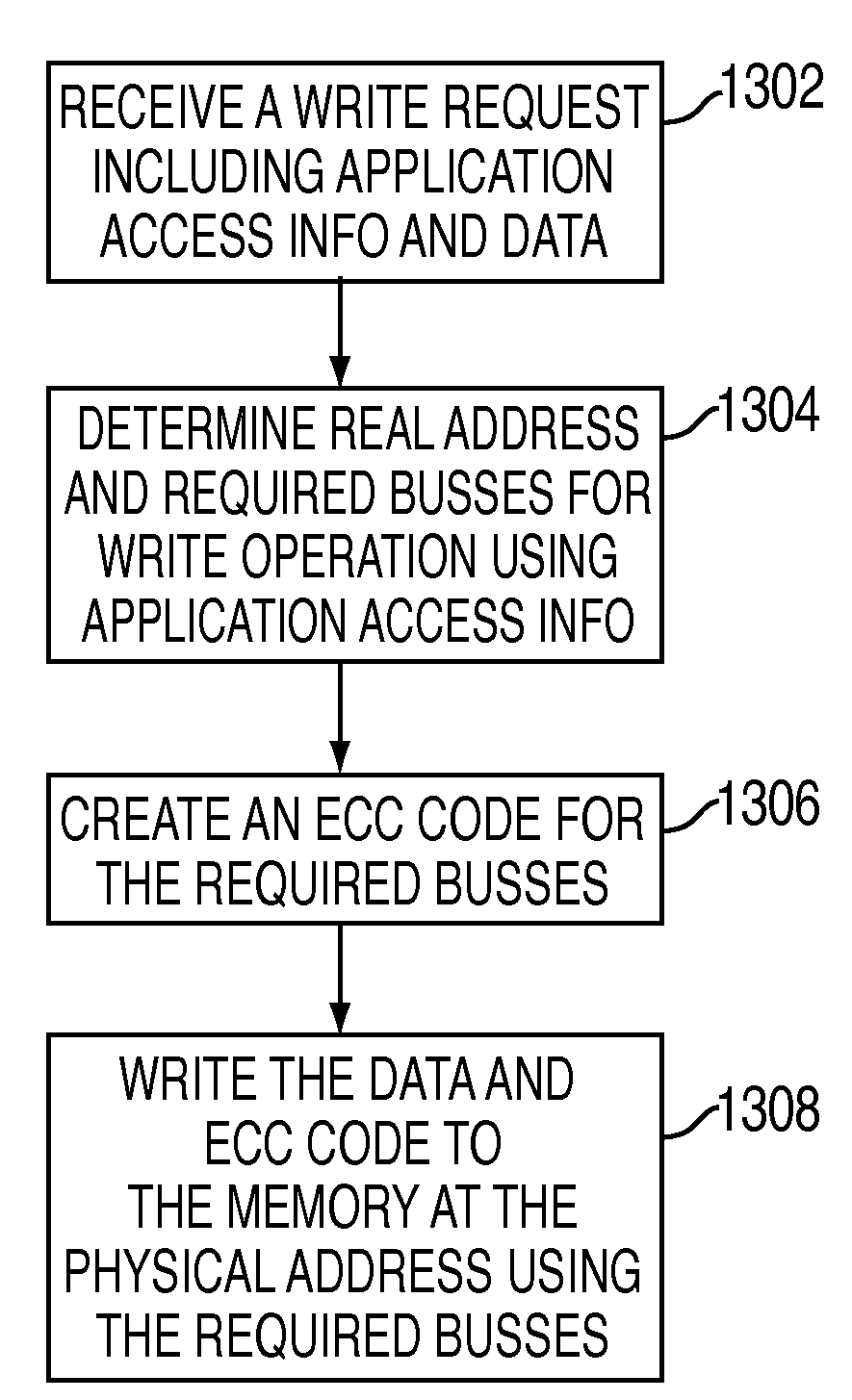

Systems and methods for program directed memory access patterns

InactiveUS20080046666A1Memory adressing/allocation/relocationMicro-instruction address formationDirect memory accessVirtual memory management

Systems and methods for program directed memory access patterns including a memory system with a memory, a memory controller and a virtual memory management system. The memory includes a plurality of memory devices organized into one or more physical groups accessible via associated busses for transferring data and control information. The memory controller receives and responds to memory access requests that contain application access information to control access pattern and data organization within the memory. Responding to memory access request includes accessing one or more memory devices. The virtual memory management system includes: a plurality of page table entries for mapping virtual memory addresses to real addresses in the memory; a hint state responsive to application access information for indicating how real memory for associated pages is to be physically organized within the memory; and a means for conveying the hint state to the memory controller.

Owner:IBM CORP

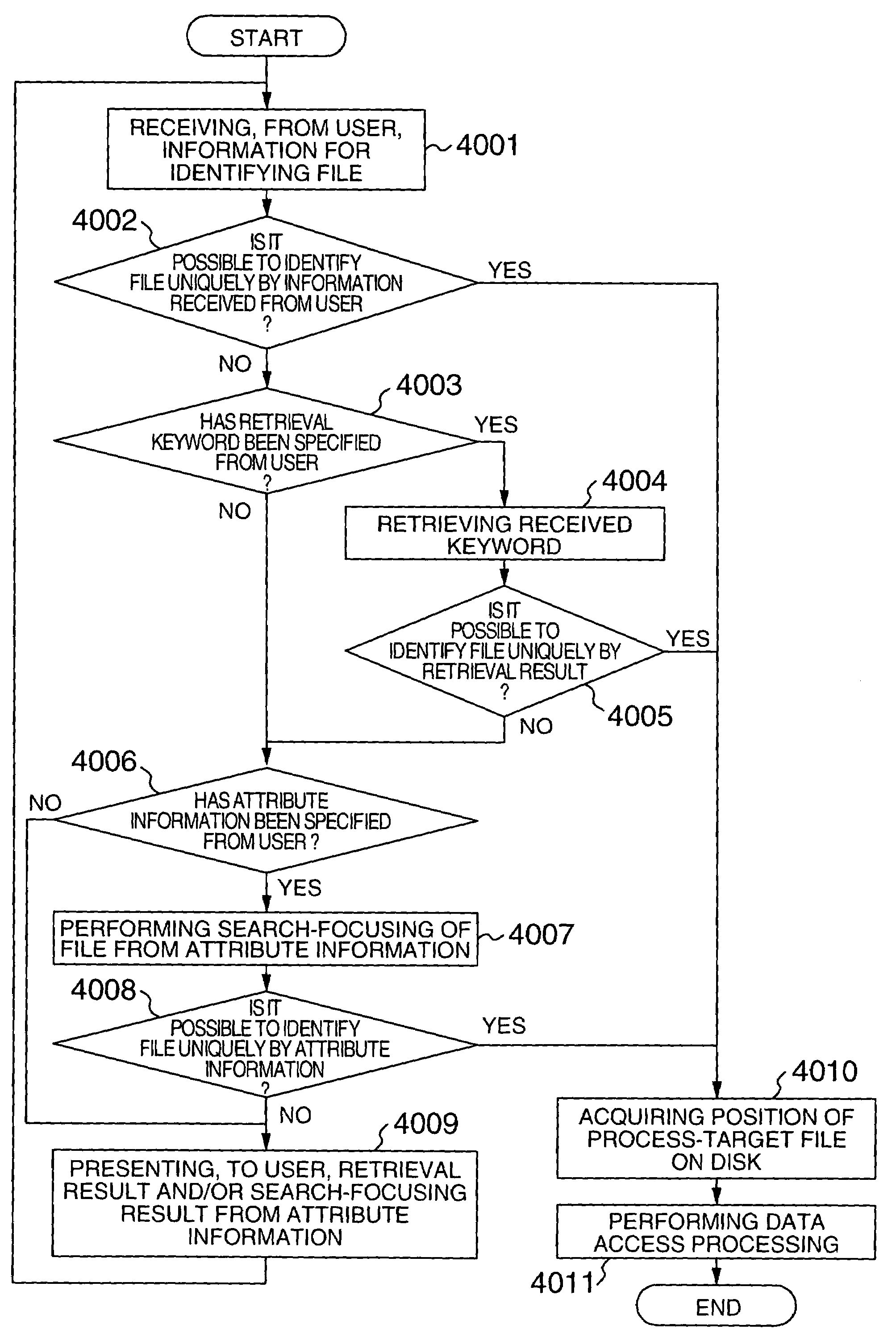

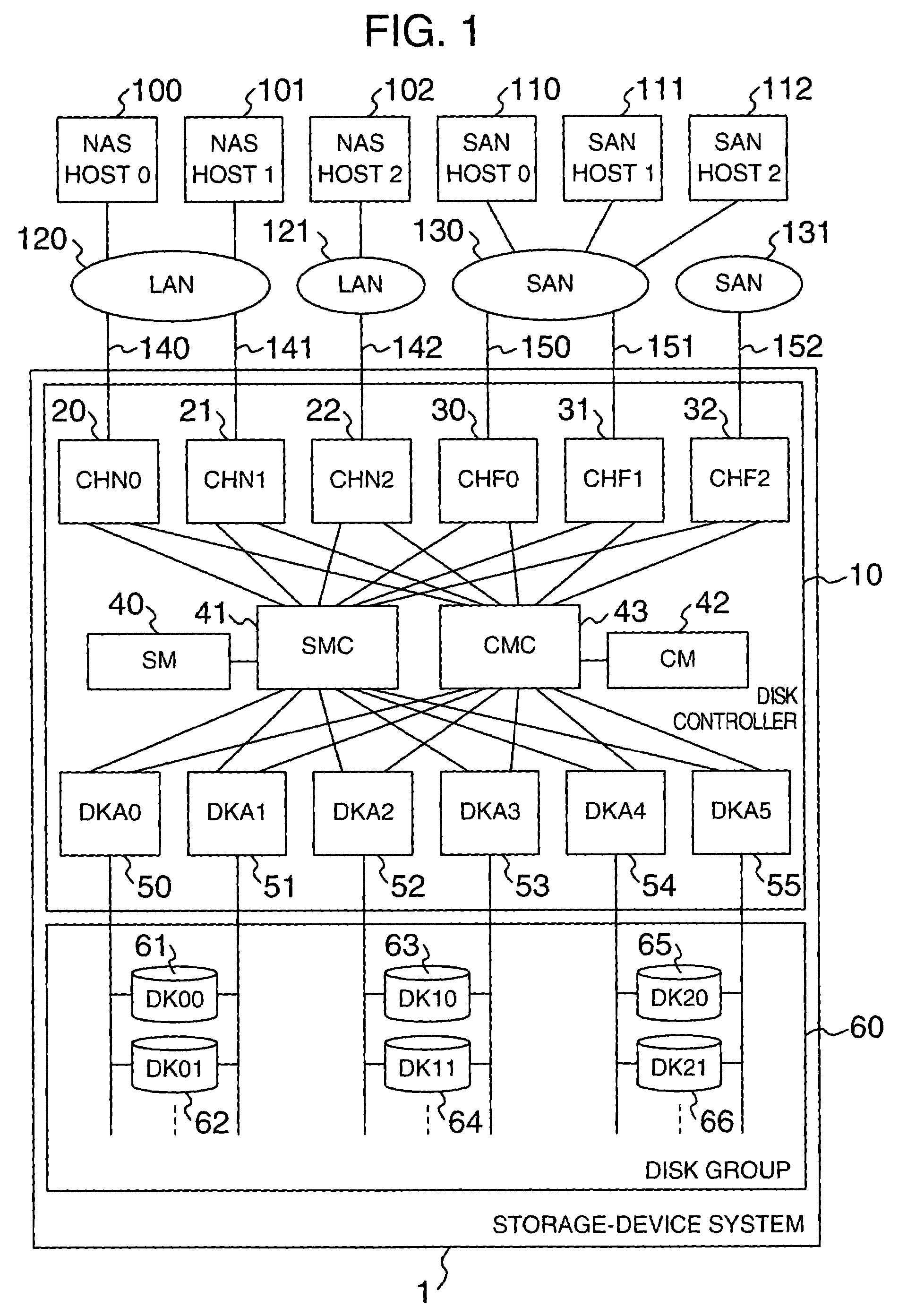

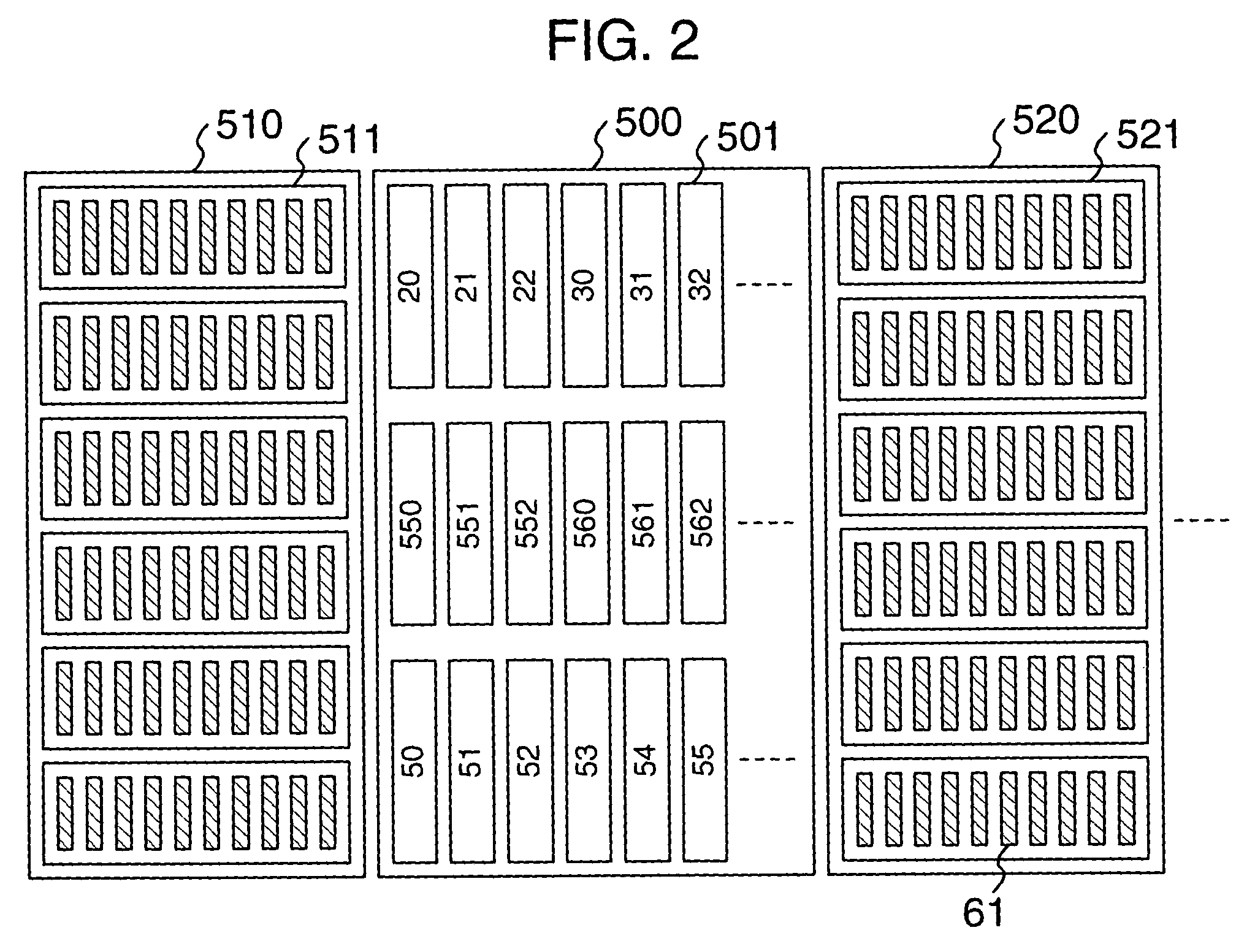

File access method in storage-device system, and programs for the file access

ActiveUS7069380B2Improve access performanceInput/output to record carriersData processing applicationsAccess methodControl memory

In order to manage the various types of attribute information within the storage-device system, the storage-device system includes the following databases within a file-access controlling memory: a database for managing index information for managing contents of the files, and an index retrieval program, a database for managing the attribute information on the files, and a database for managing storage positions of blocks configuring a file. When the storage-device system receives an access request to a file, the utilization of these databases allows the storage-device system to make the access to the access-target file.

Owner:RAKUTEN GRP INC

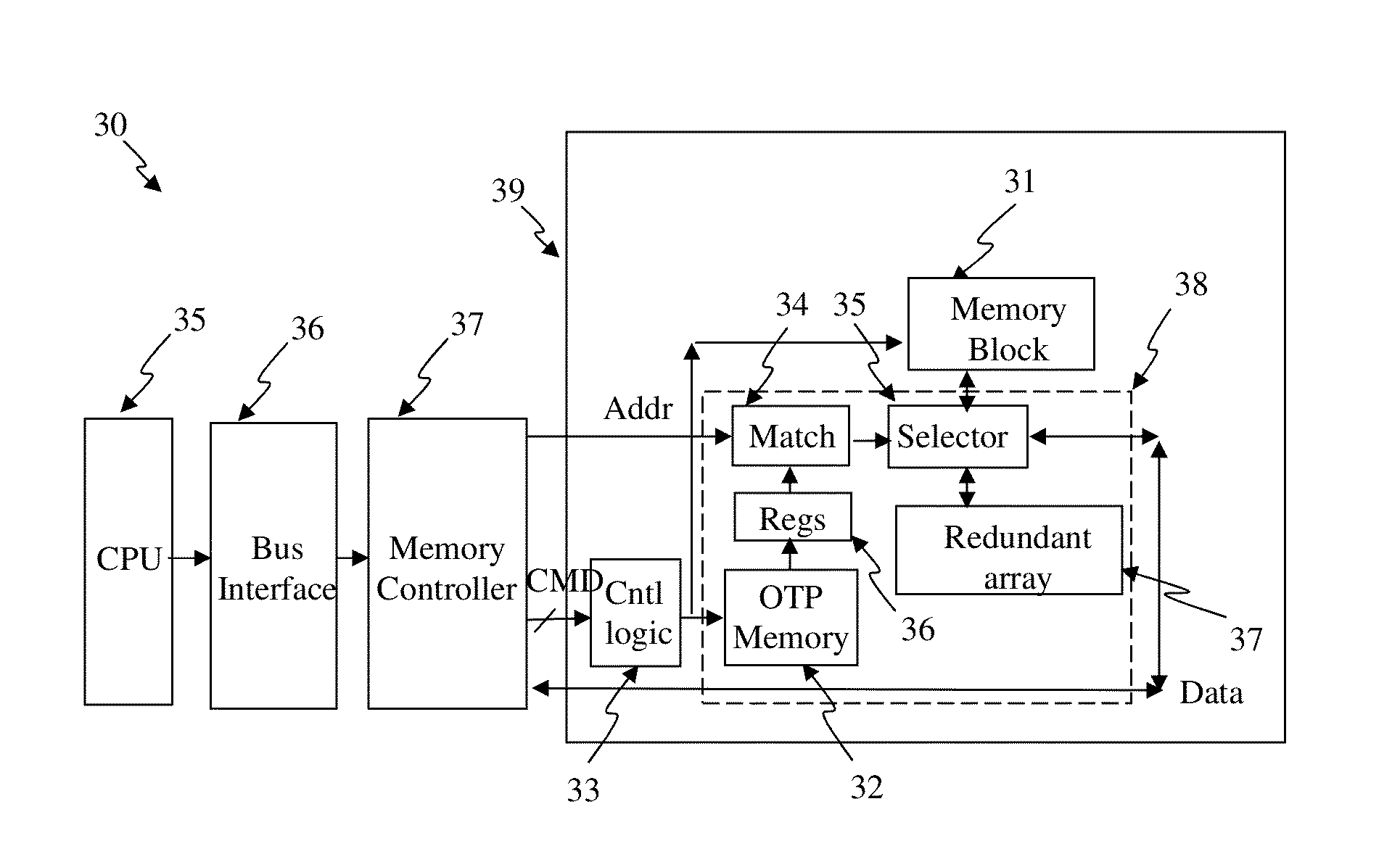

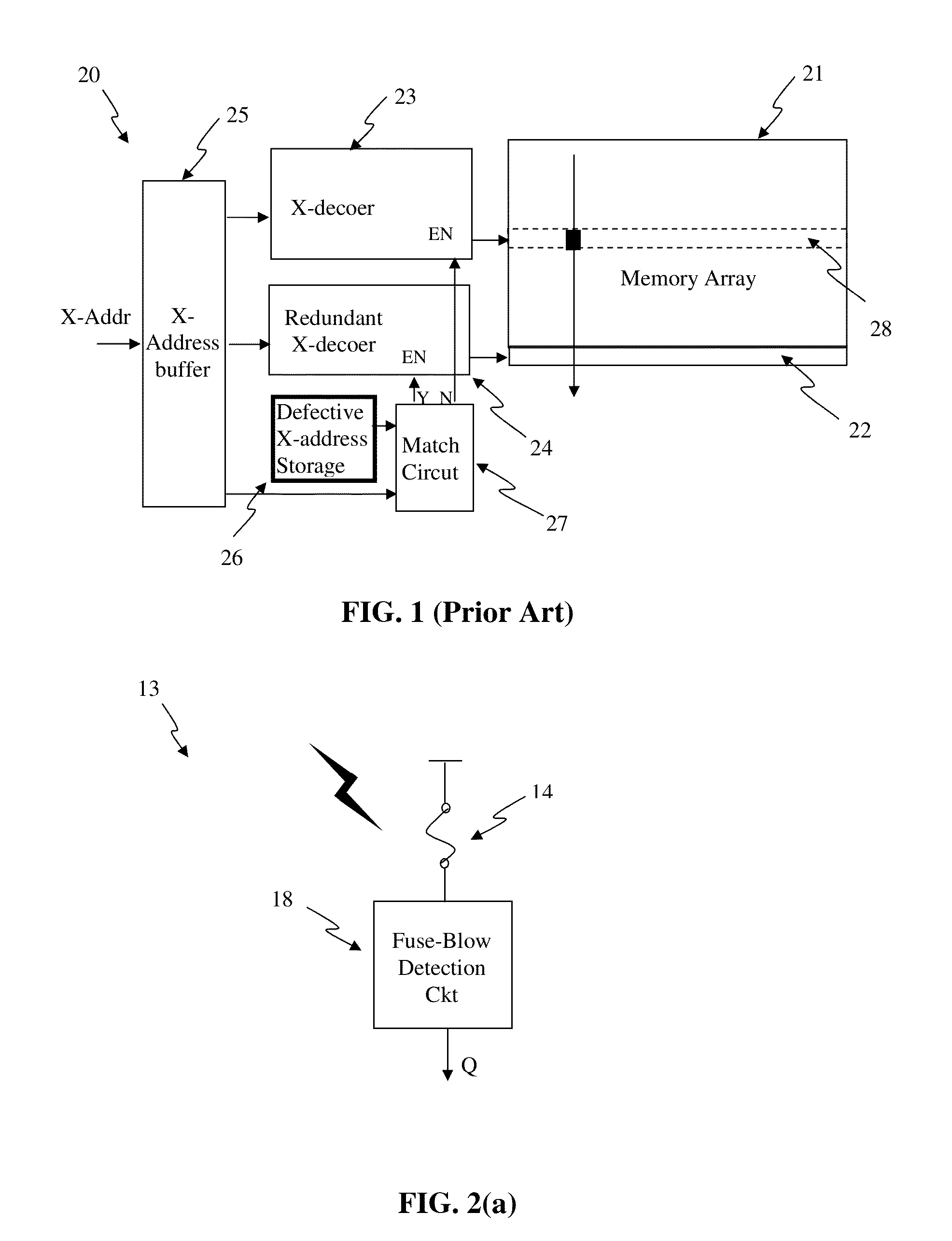

System and method of in-system repairs or configurations for memories

In-system repairing or configuring faulty memories after being used in a system are disclosed. In one embodiment, a memory chip can include at least one OTP memory to store defective addresses that are to be repaired. Advantageously, the OTP memory can operate without requiring additional I / O pins or high voltage supplies for reading or programming. The memory chip can also include control logic to control reading or programming of the OTP memory as needed.

Owner:ATTOPSEMI TECH CO LTD

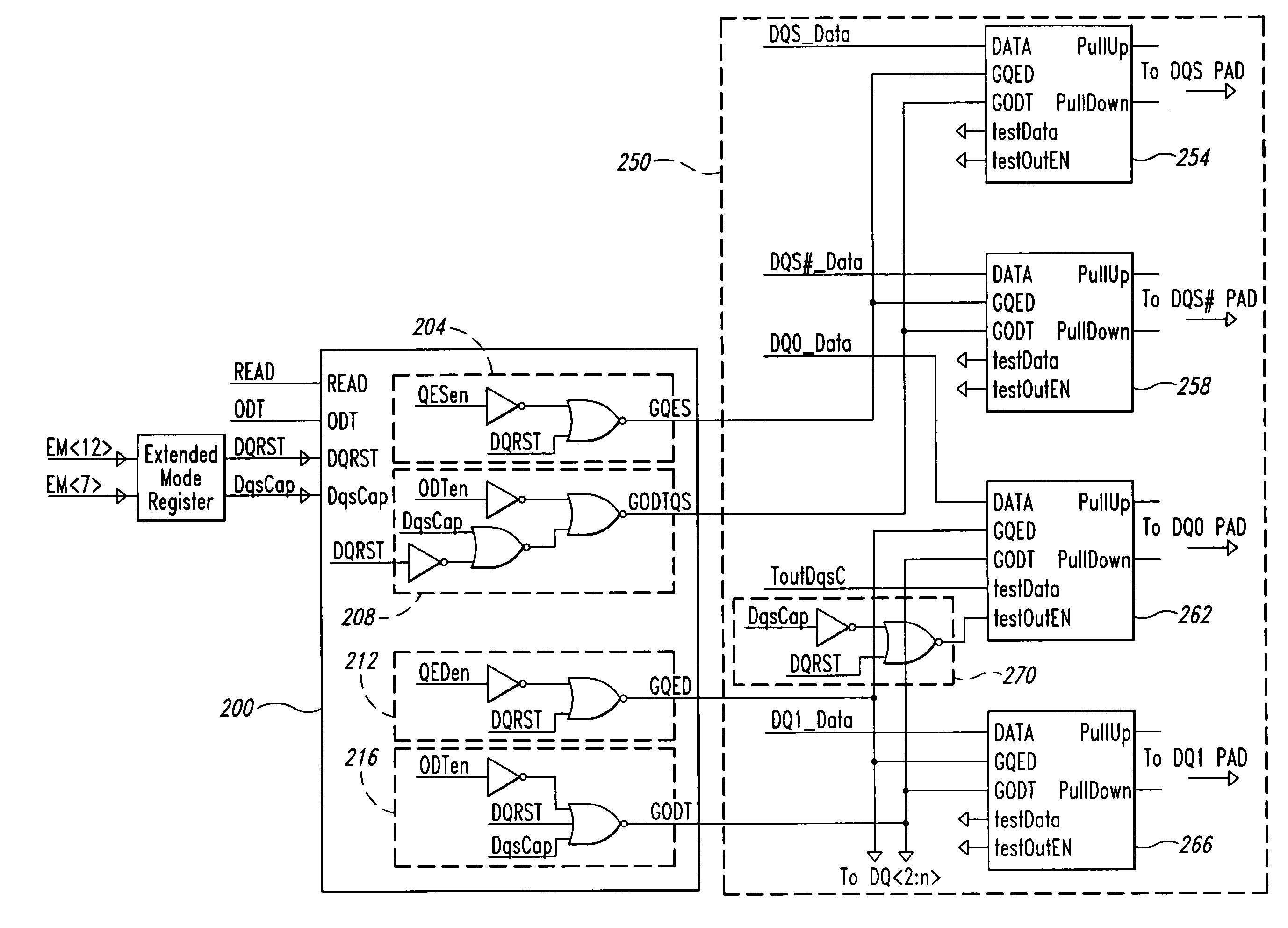

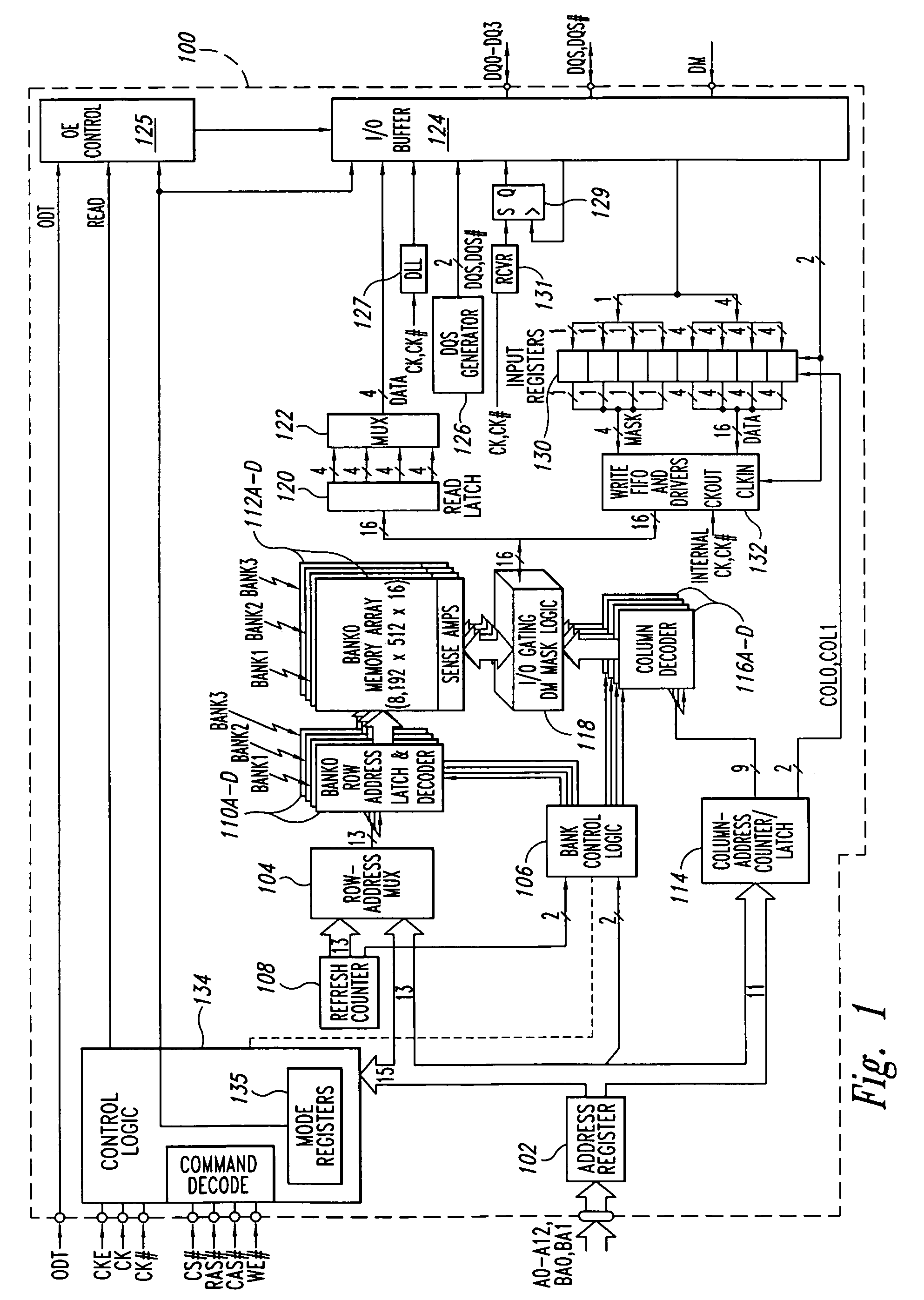

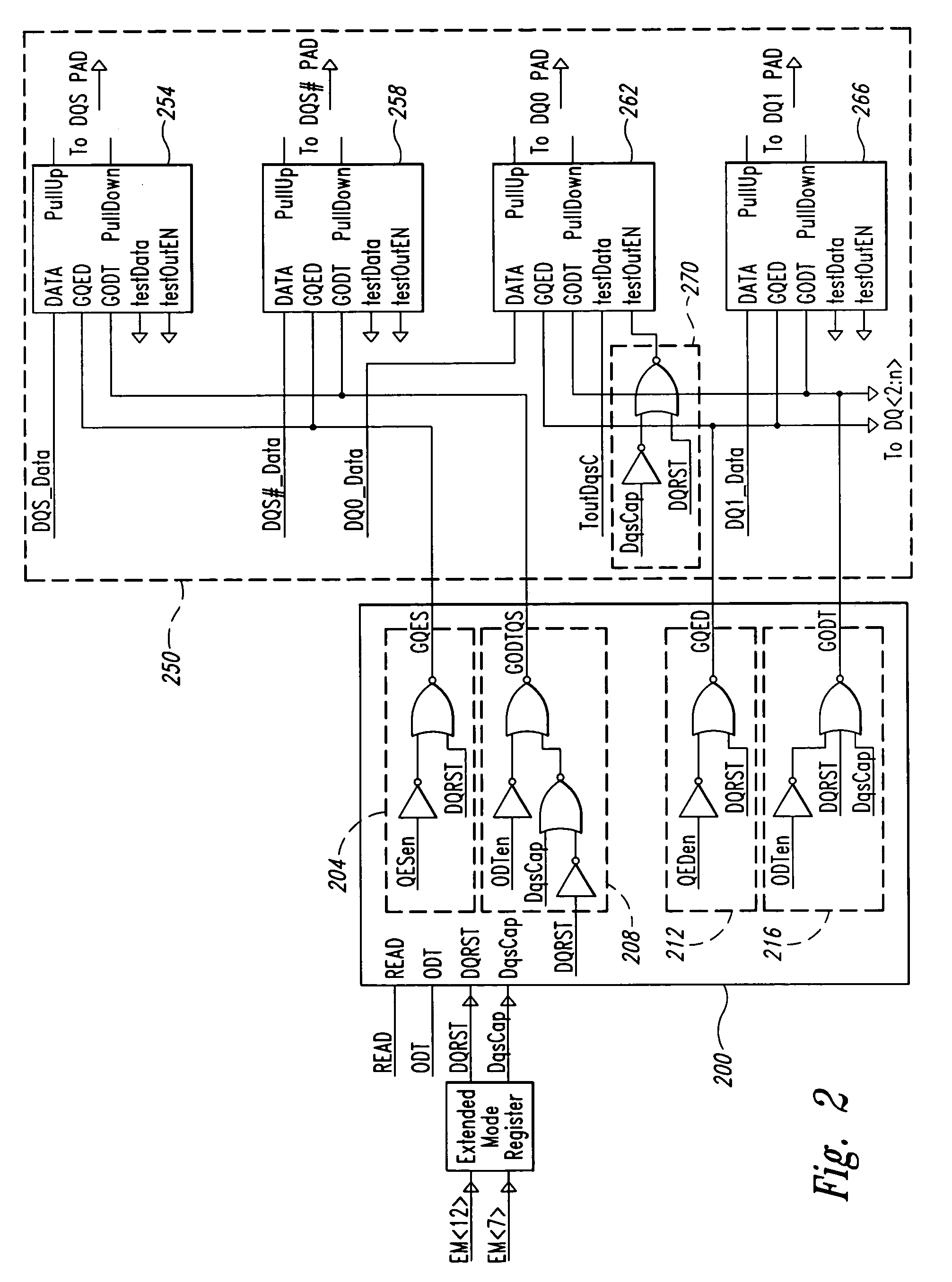

Apparatus and method for independent control of on-die termination for output buffers of a memory device

An apparatus and method providing independent control of on-die termination (ODT) of output buffers. The ODTs for the buffer circuits of an input / output (I / O) buffer can be enabled and disabled in response to an ODT control signal. Additionally, the ODTs for a first set of the buffer circuits can be enabled and disabled responsive to the ODT control signal and the ODT for at least one of a second set of the buffer circuits is disabled.

Owner:ROUND ROCK RES LLC

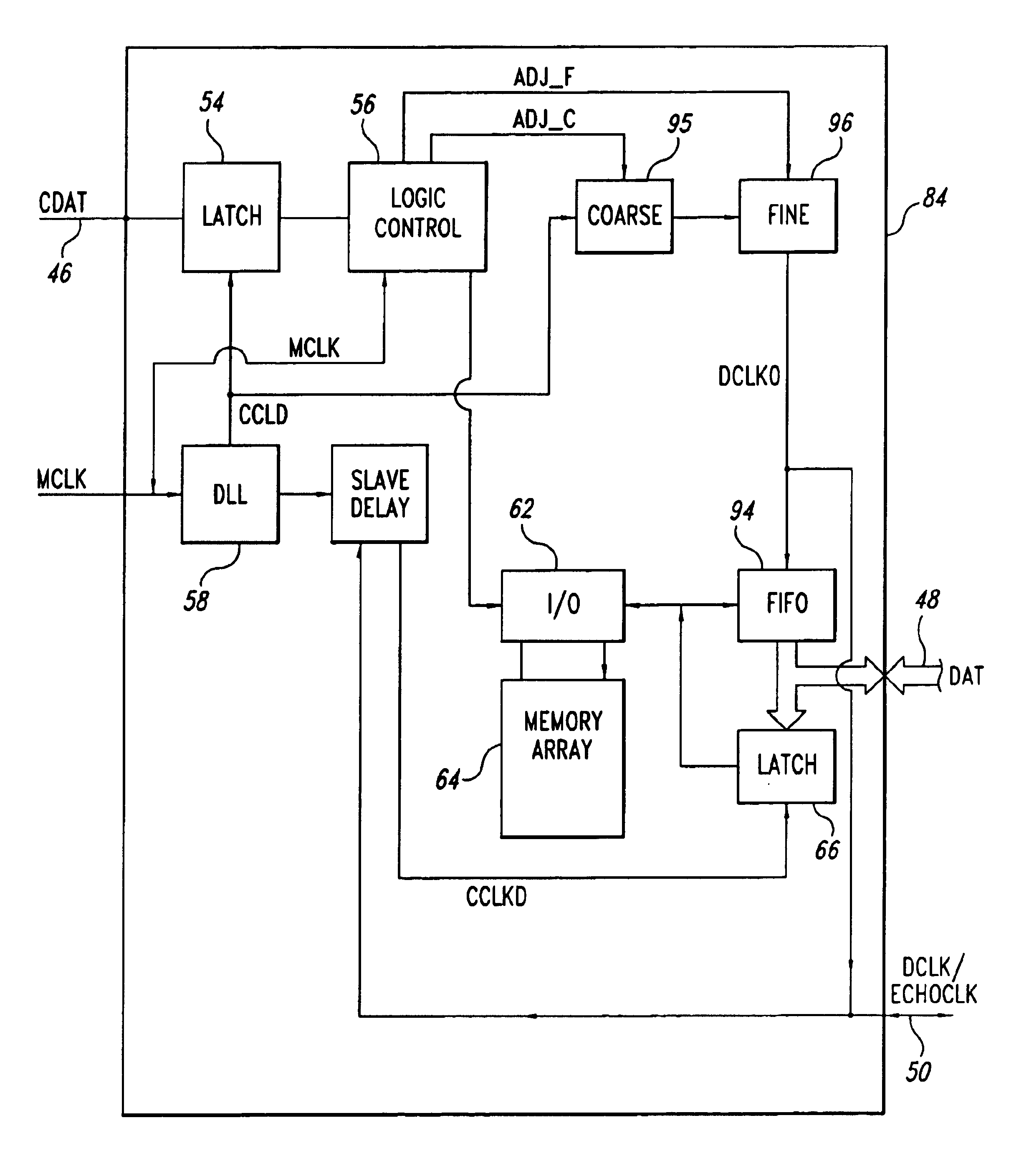

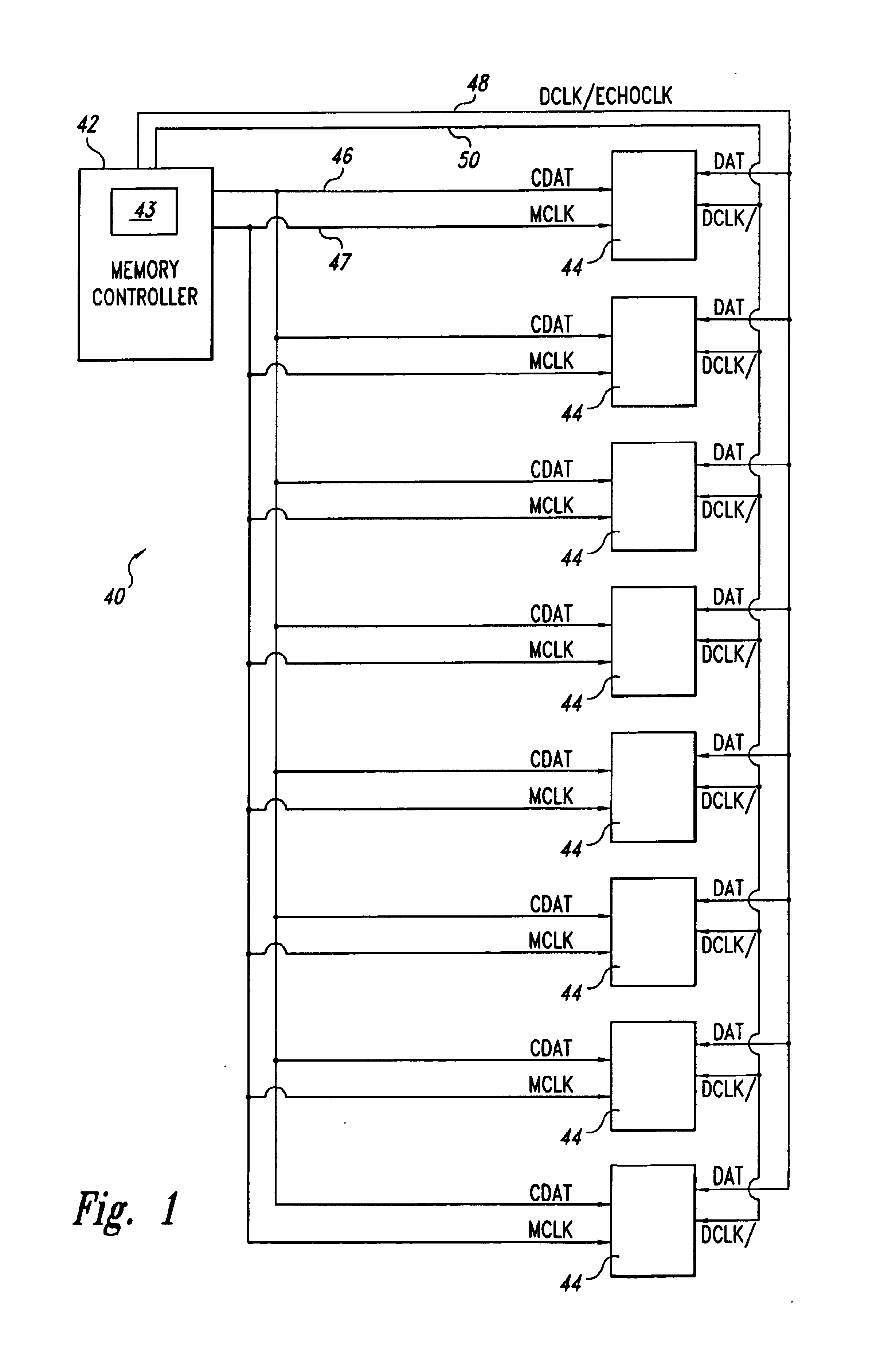

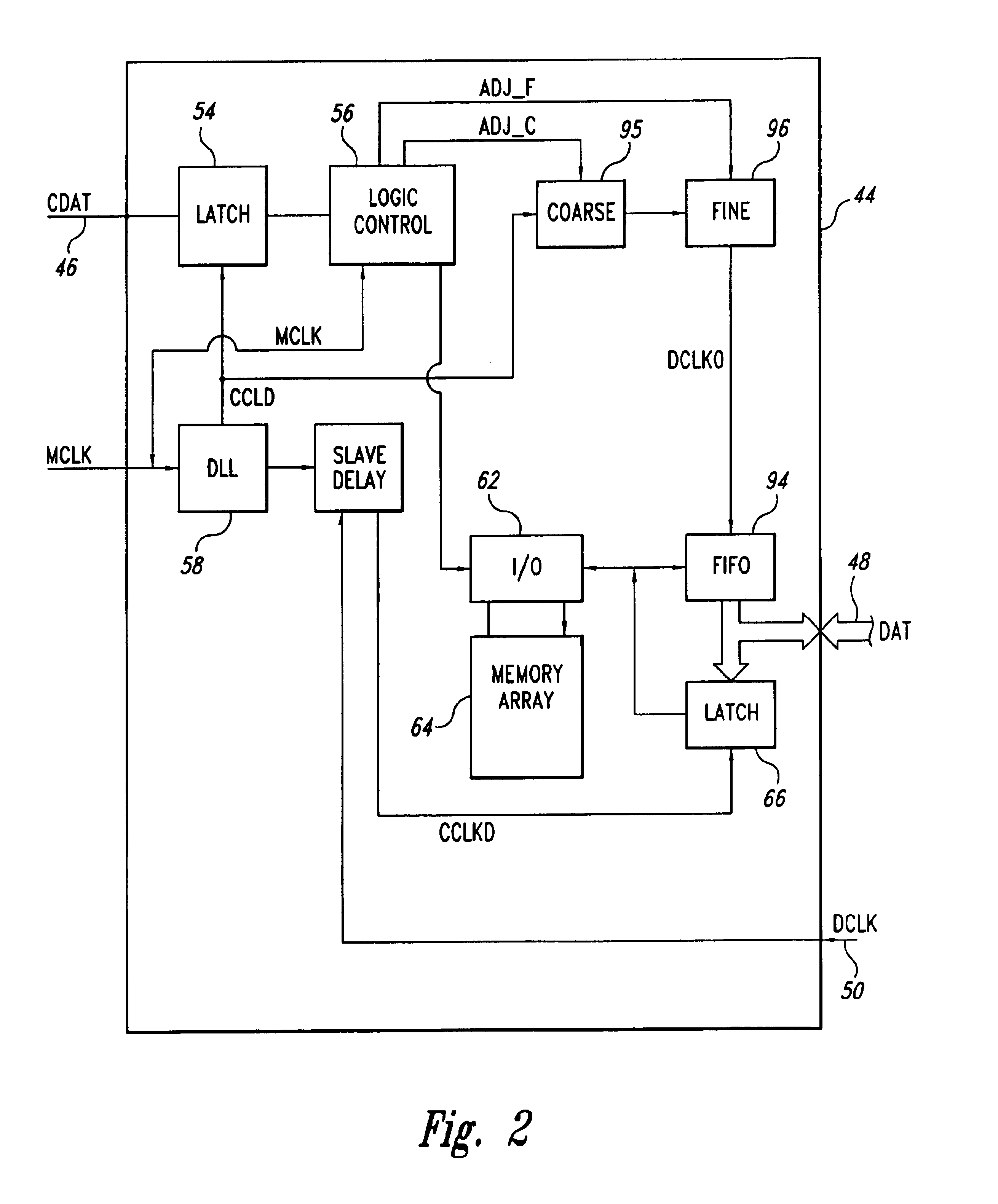

Memory system with dynamic timing correction

InactiveUS6912680B1Reducing the phase shiftElectronic circuit testingError detection/correctionNetwork packetControl data

A memory system includes a memory controller and a bank of memory devices. The memory controller controls the memory devices through packets of control data and a master clock signal. Each of the memory devices includes an adjustable output timing vernier that can be adjusted in response to commands from the memory controller. The vernier output controls timing of output data relative to the master clock signal. As each memory device transmits data to the memory controller, the memory device also transmits an echo clock signal coincident with the data. The memory controller receives the echo clock signal and compares the echo clock signal to the master clock signal to identify shifts in timing of the echo clock signal. If the echo clock signal shifts by more than one vernier increment from the master clock signal, the master controller issues a command to the memory device to adjust the output vernier to correct the timing drift of the echo clock signal. By correcting the timing drift of the echo clock signal, the memory controller also corrects timing drift of the output data, thereby assuring that the data arrive at the memory controller coincident with edges of the master clock signal.

Owner:ROUND ROCK RES LLC

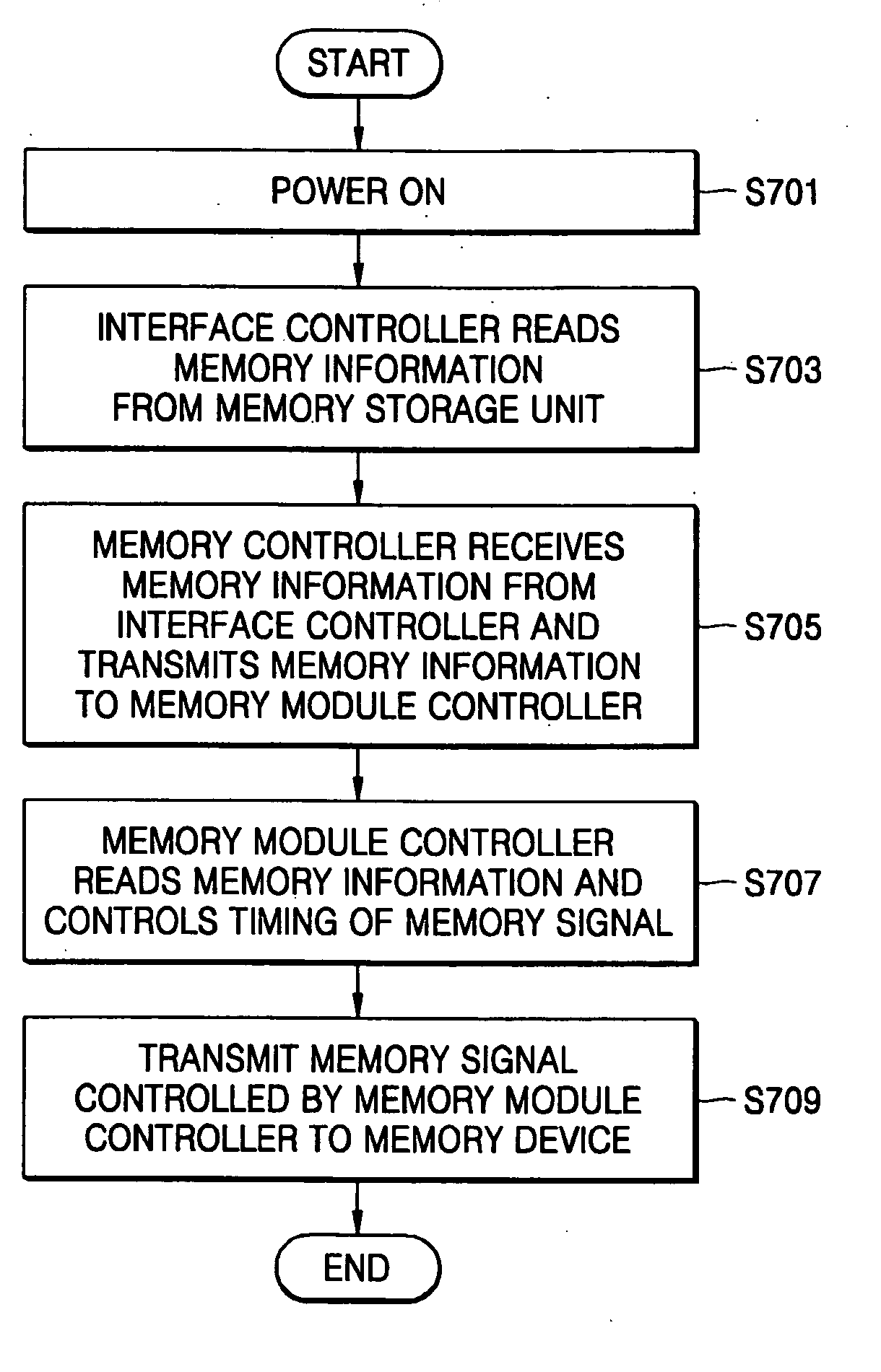

System controlling interface timing in memory module and related method

A memory system for controlling interface timing in a memory module and a related timing control method are disclosed. The memory system comprises a memory module having a memory module controller configured to control interface timing of a plurality of memory devices in accordance with memory information and memory signal information. The memory information includes memory initialization information and interface timing information for the plurality of memory devices.

Owner:SAMSUNG ELECTRONICS CO LTD

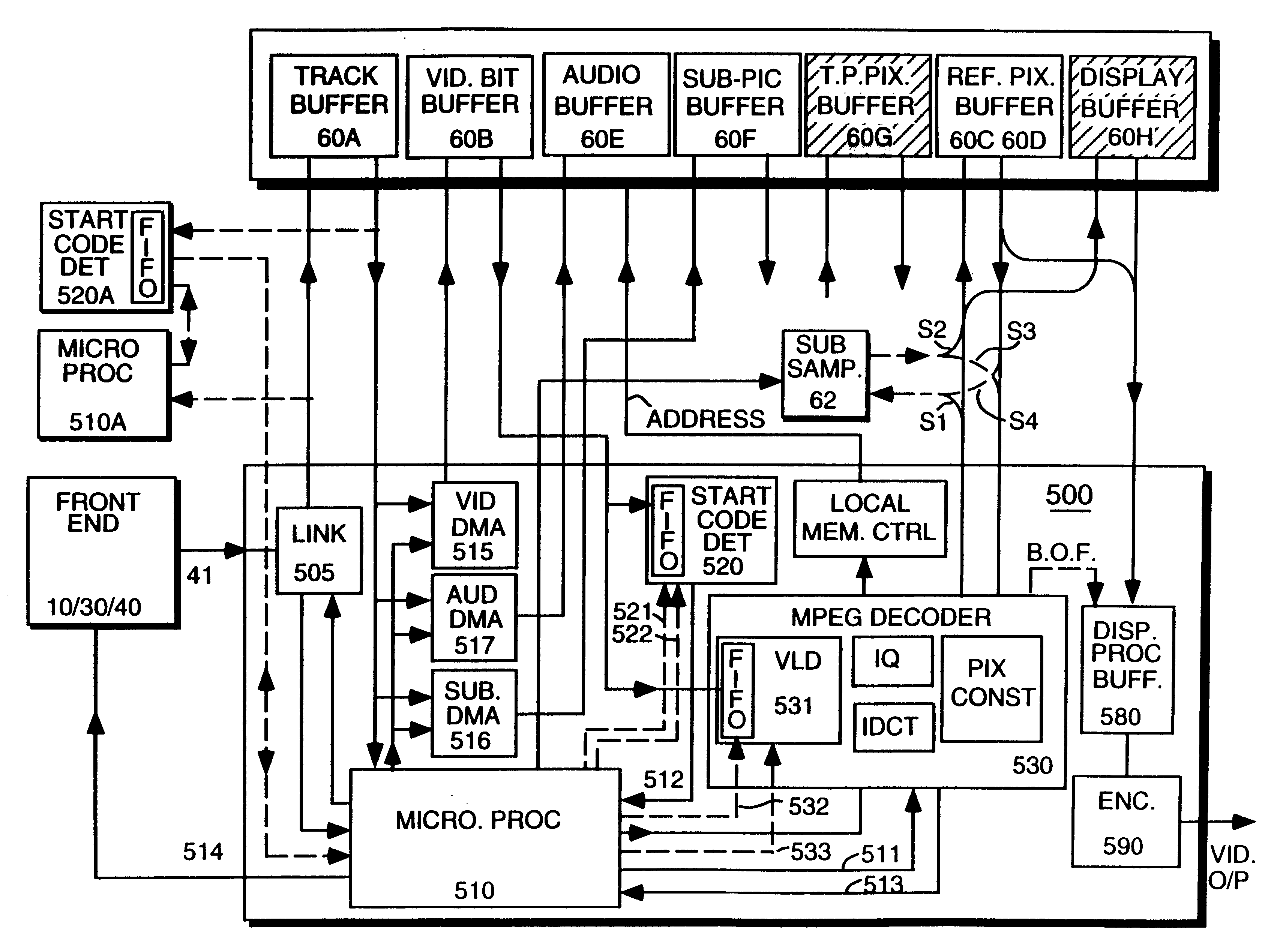

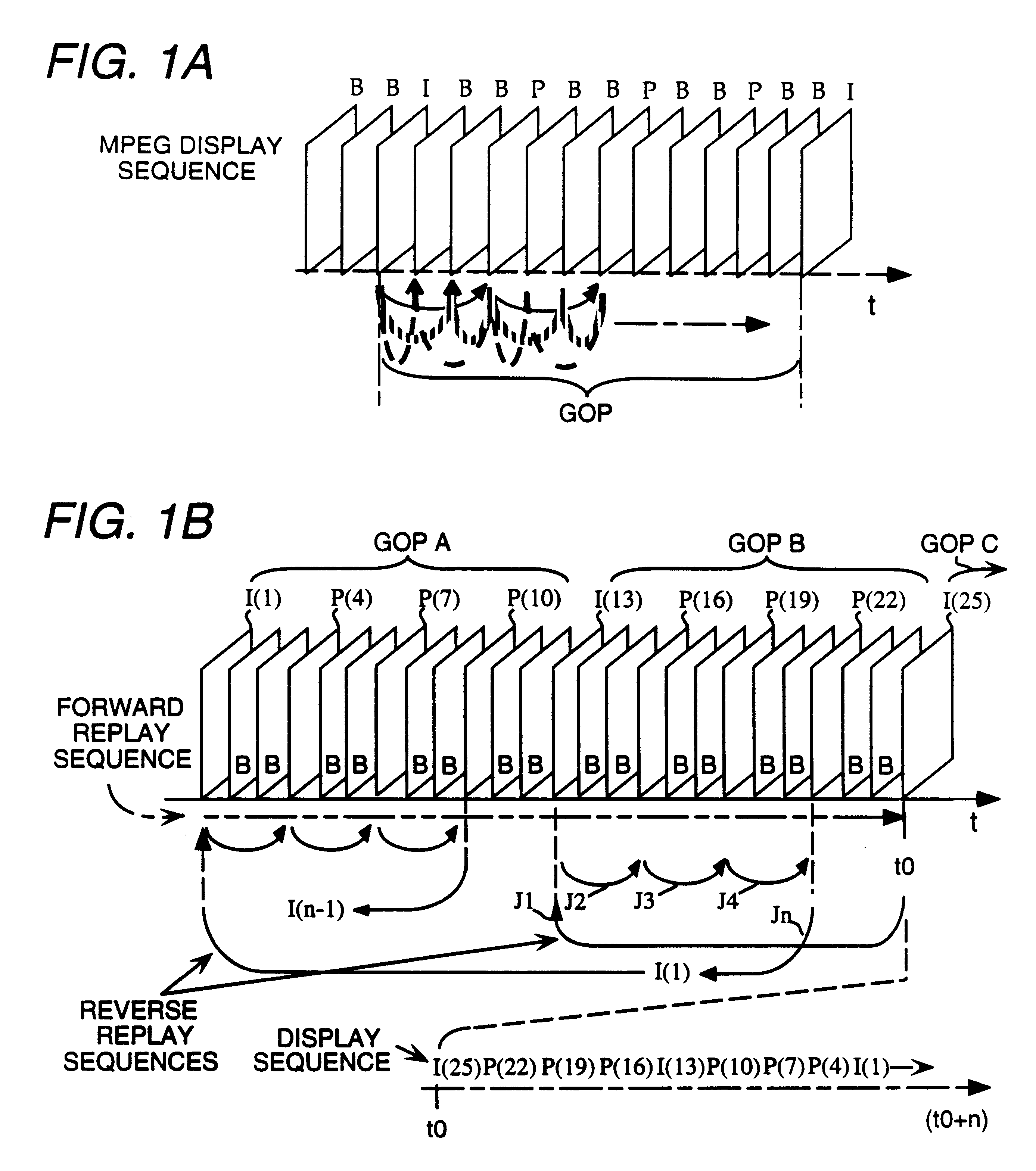

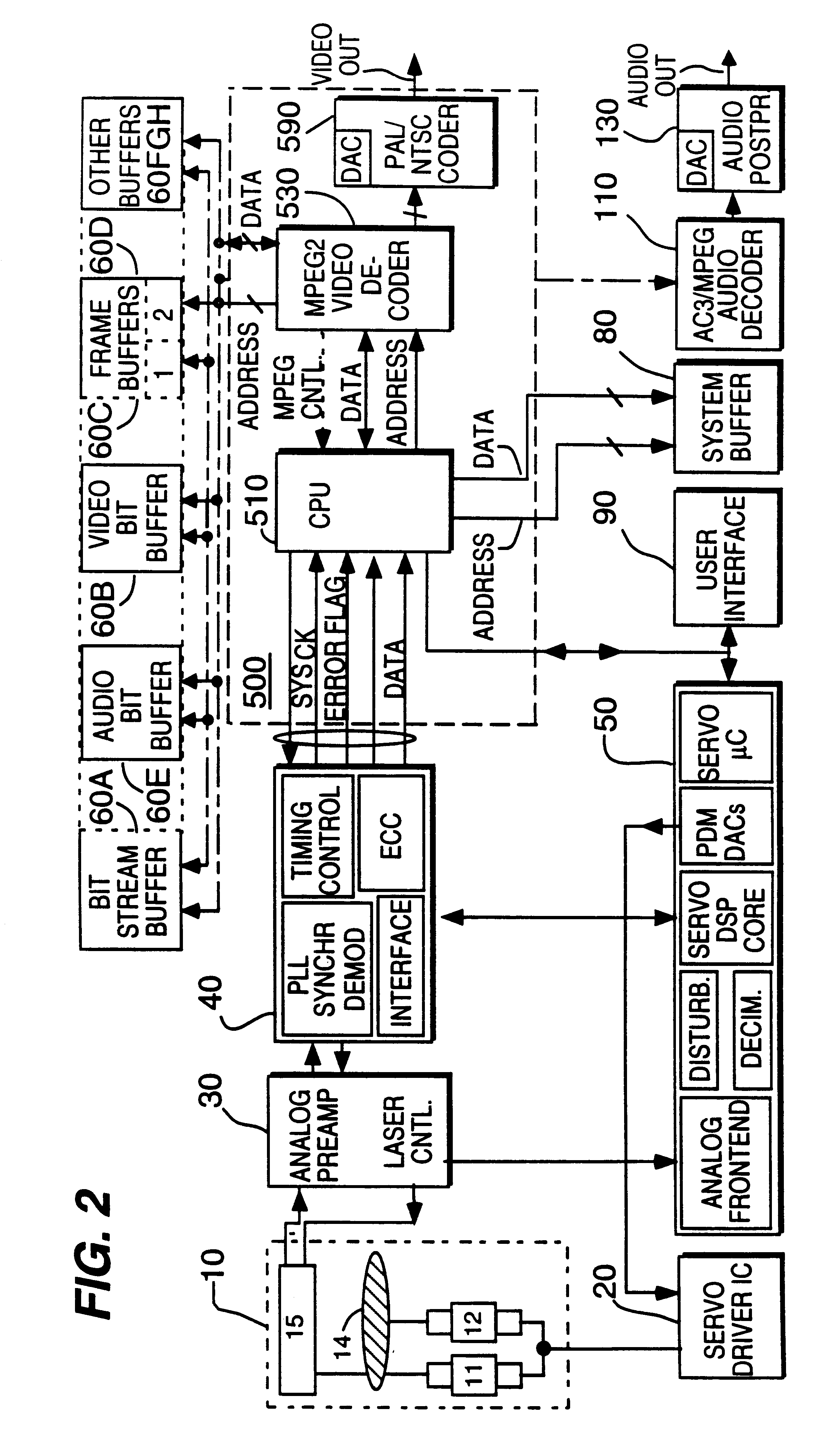

Memory control in trick play mode

InactiveUS6222979B1Television system detailsPulse modulation television signal transmissionControl memoryData type

An apparatus for reproducing a digitally encoded signal from a disk medium, comprises a source of a bitstream representative of the digitally encoded signal. A processor is coupled to the bitstream for processing the bitstream to extract at least a first and a second data type represented therein. A memory is controllably coupled to the processor for storing one of the first and a second data types. A controller is coupled to control allocation of the memory, wherein a first reproducing mode the controller allocates the memory for storing the first data type, and in a second reproducing mode the controller allocates the memory for storing the second data type.

Owner:THOMSON CONSUMER ELECTRONICS INC

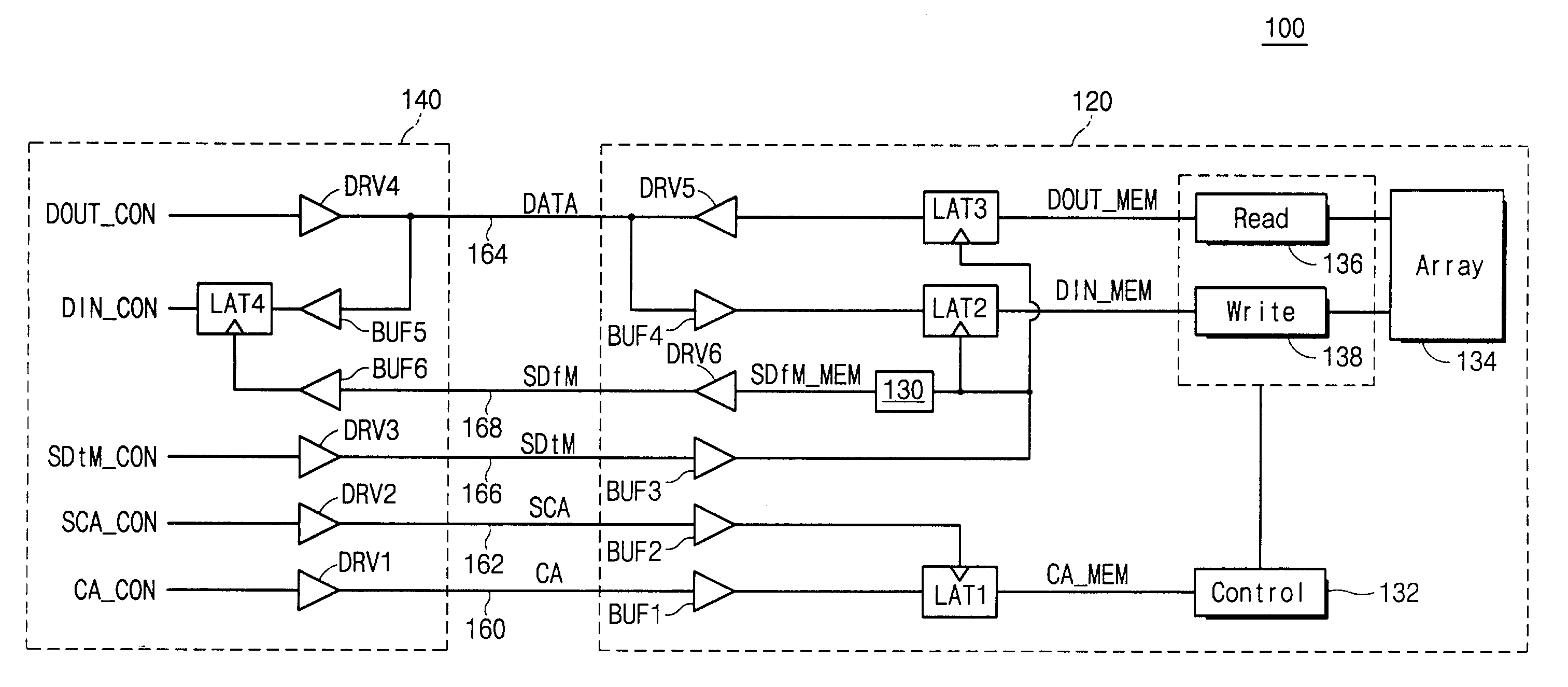

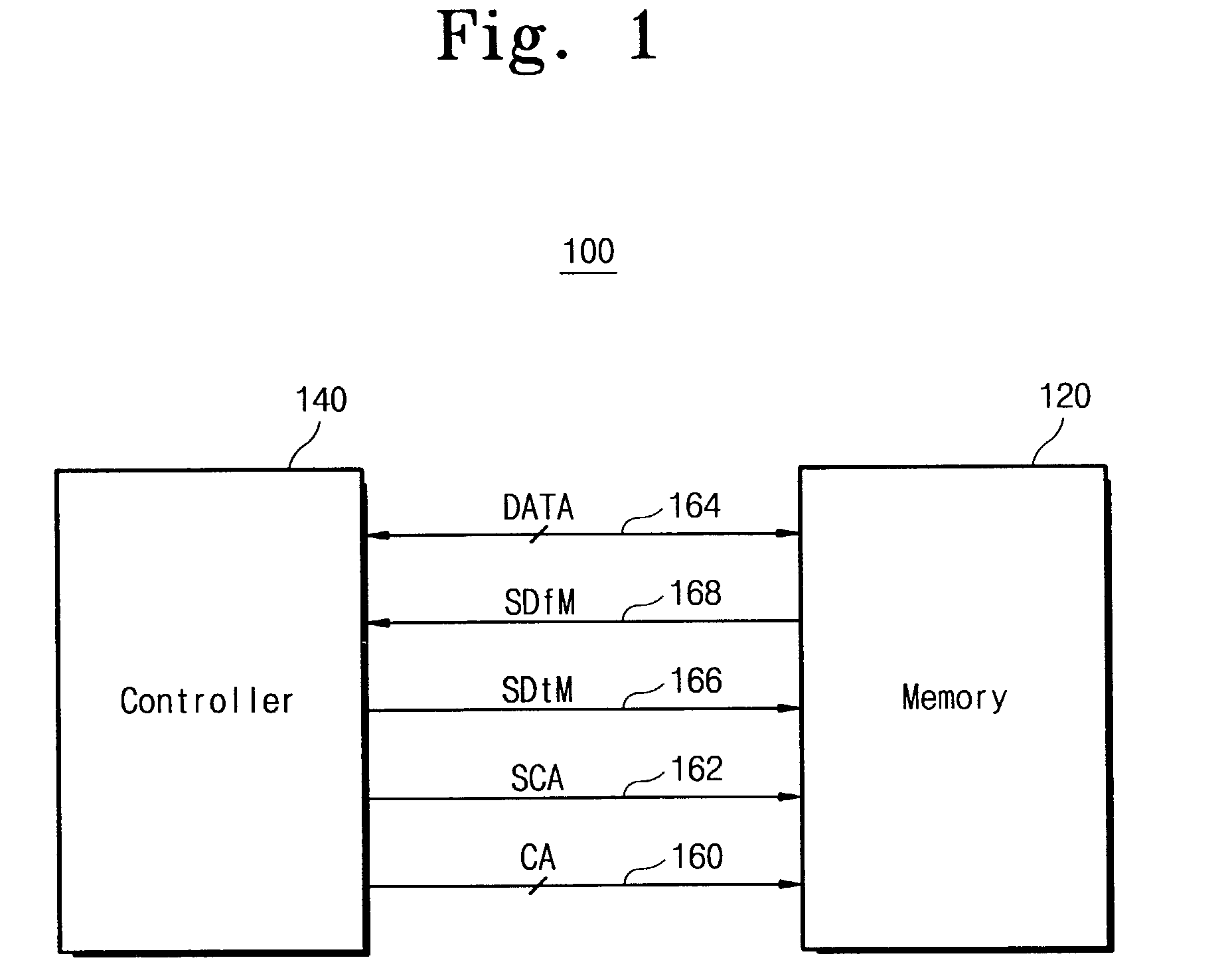

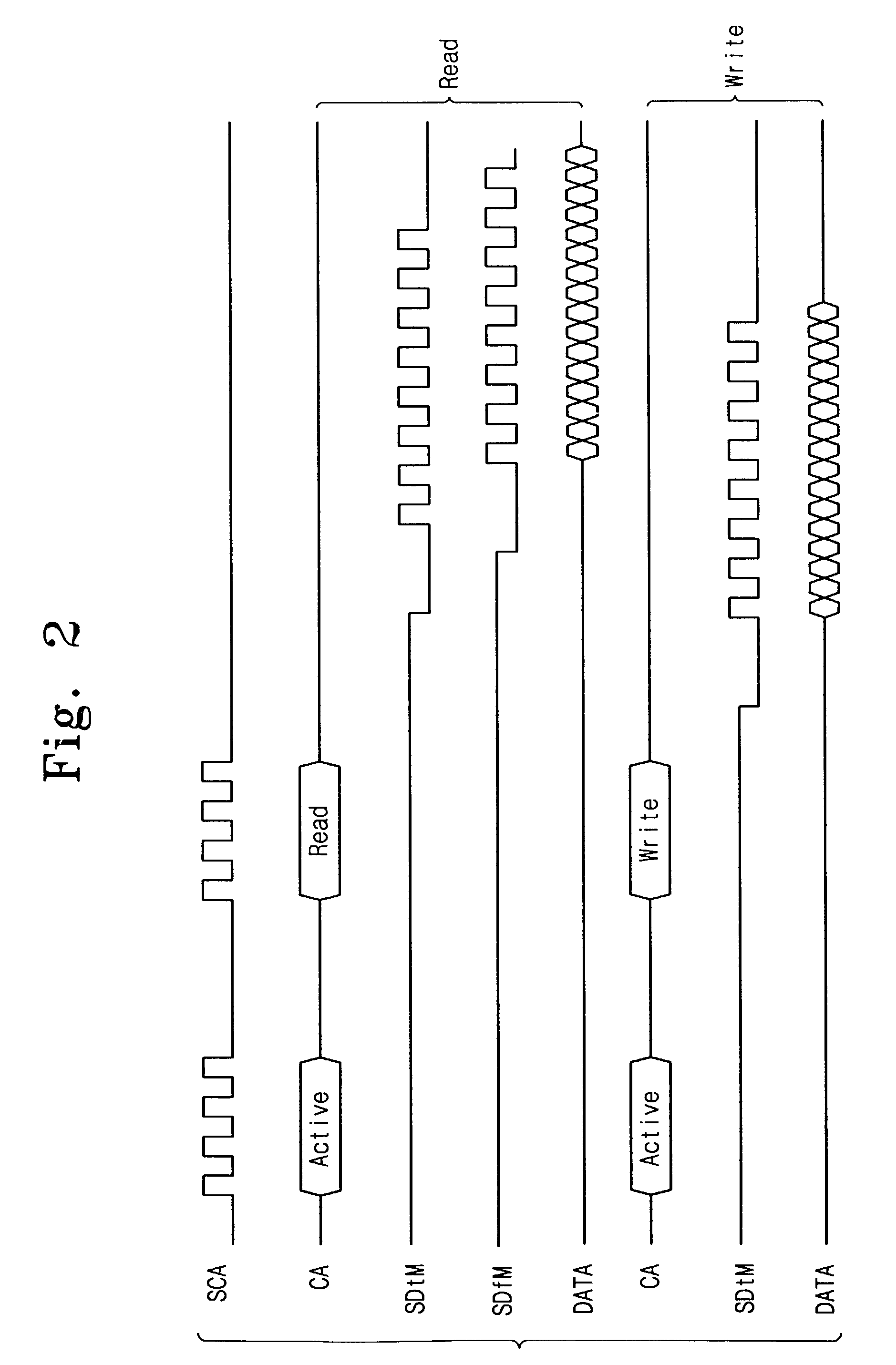

Asynchronous memory using source synchronous transfer and system employing the same

A memory for storing data information and / or a controller for controlling read / write operations of the memory based on a source synchronous interface are provided. During the read / write operations, a command and an address are provided to the memory together with the first strobe signal. The memory may latch the command and address in response to the first strobe signal. During a read operation, the memory responds to a received second strobe signal to generate a third strobe signal. The memory outputs data from the memory and the third strobe signal, for example, so that the output data may be latched with the third strobe signal by the memory controller.

Owner:SAMSUNG ELECTRONICS CO LTD

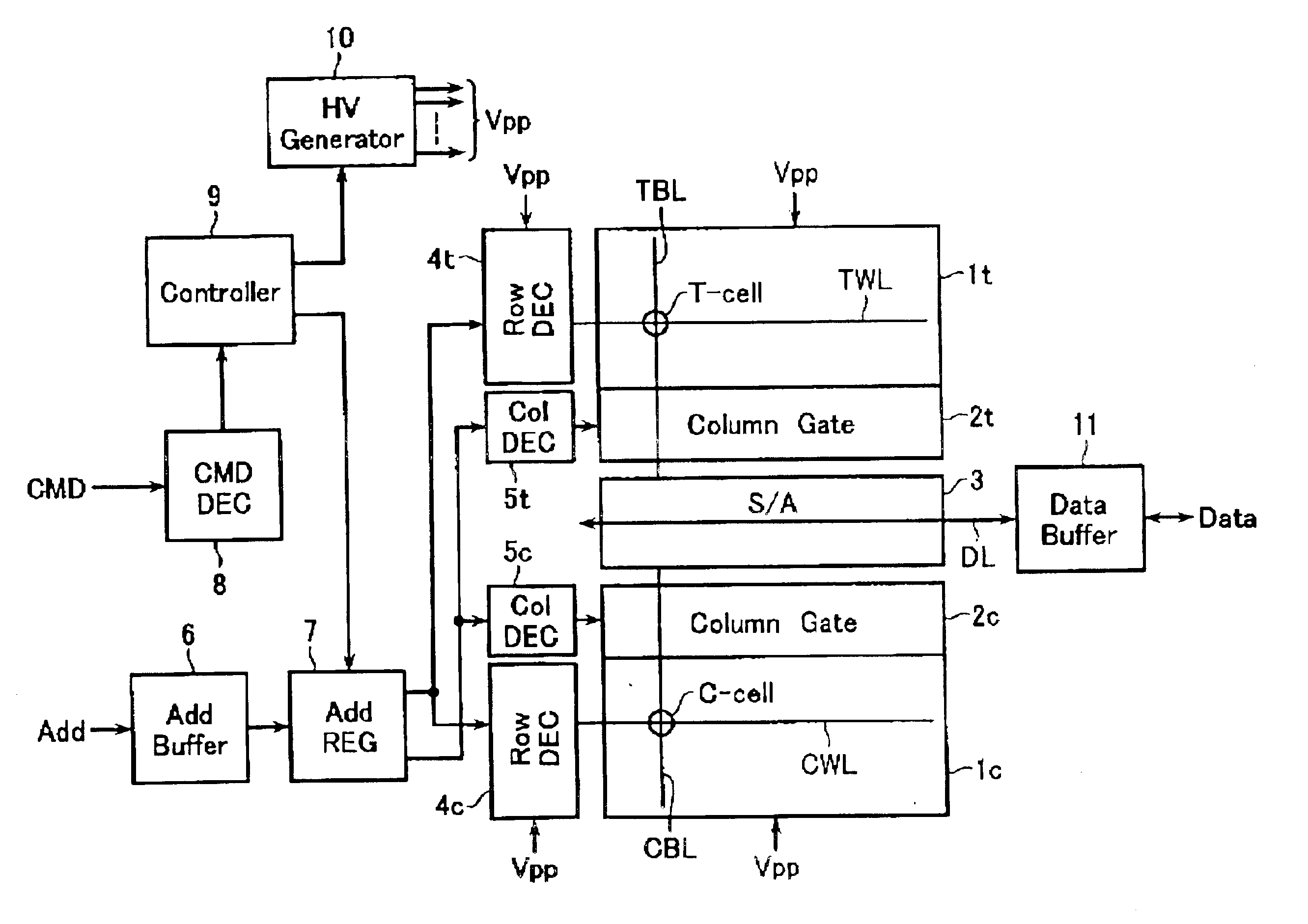

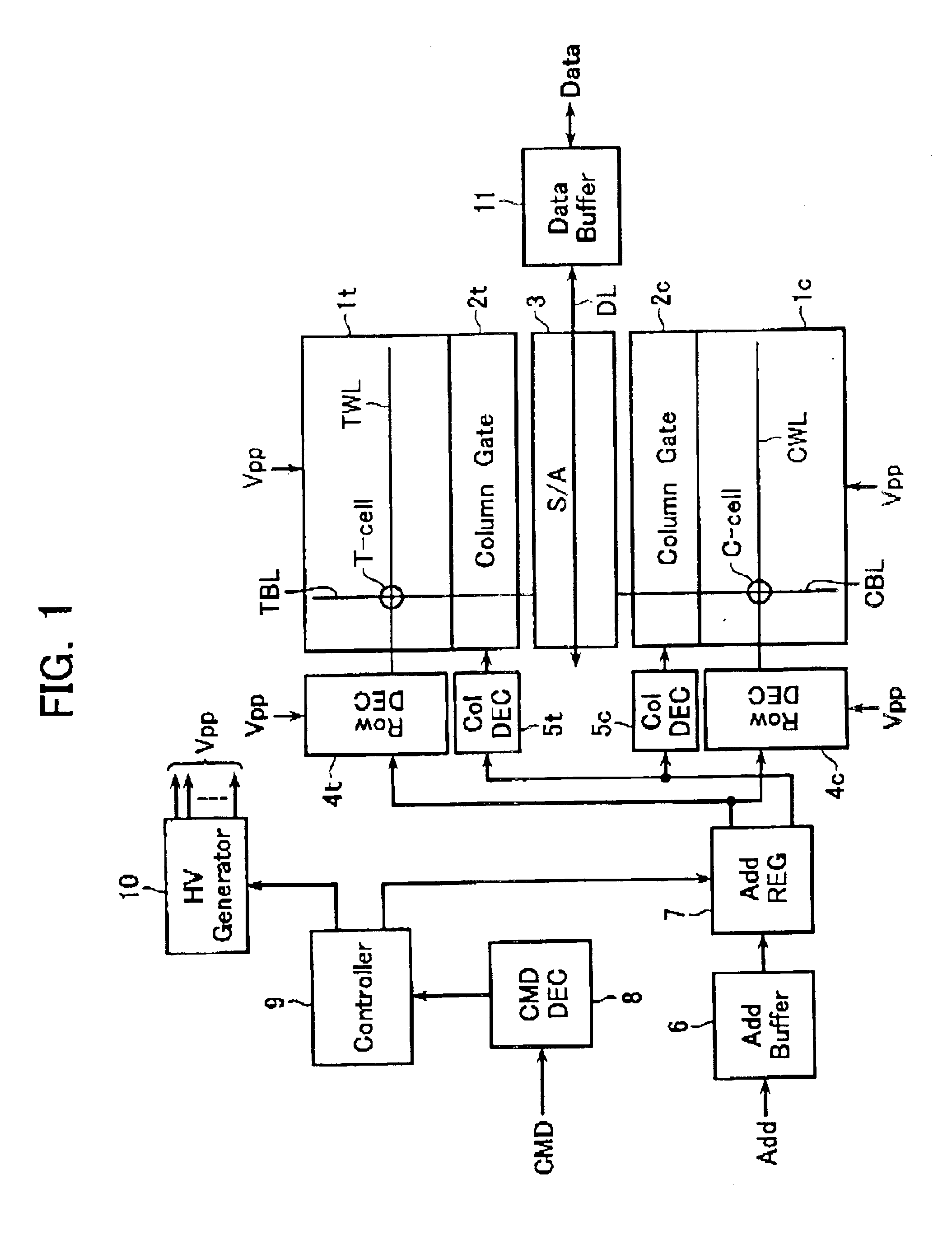

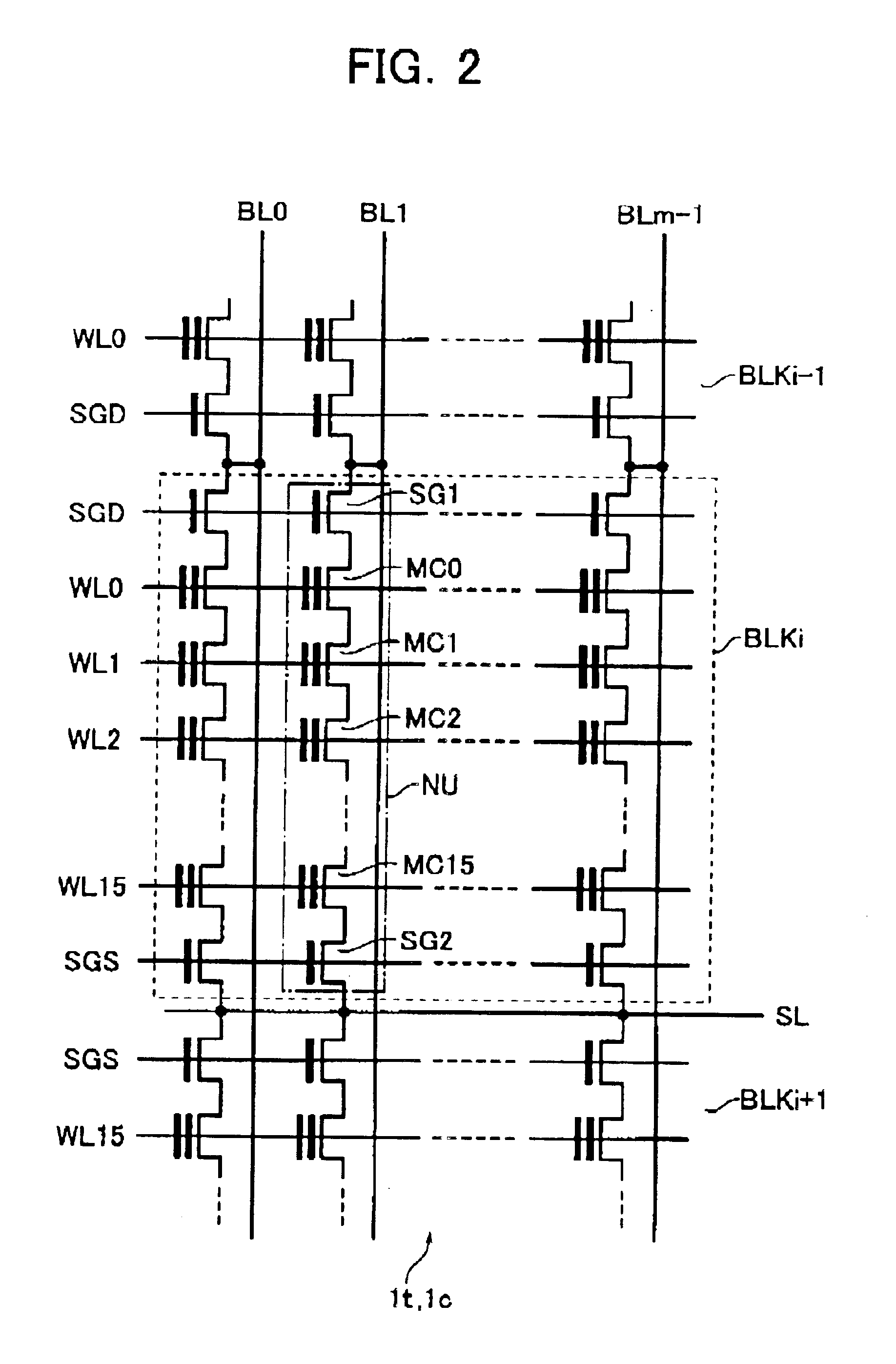

Non-volatile semiconductor memory device reading and writing multi-value data from and into pair-cells

A non-volatile semiconductor memory device includes: a memory cell array in which a plurality of electrically rewritable and non-volatile memory cells are arranged; a sense amplifier circuit configured to write M-value data (where, M is an integer equal to 4 or more) to pair-cells each constituted by simultaneously selected first and second memory cells connected to a pair of bit lines in the memory cell array, the M-value data being defined as a combination of different threshold levels of the first and second memory cells in M threshold levels to be set at each memory cell, and read M-value data stored in each pair-cell by sensing a difference between cell currents of the first and second memory cells; and a controller configured to control data write and read operations for the memory cell array.

Owner:KK TOSHIBA

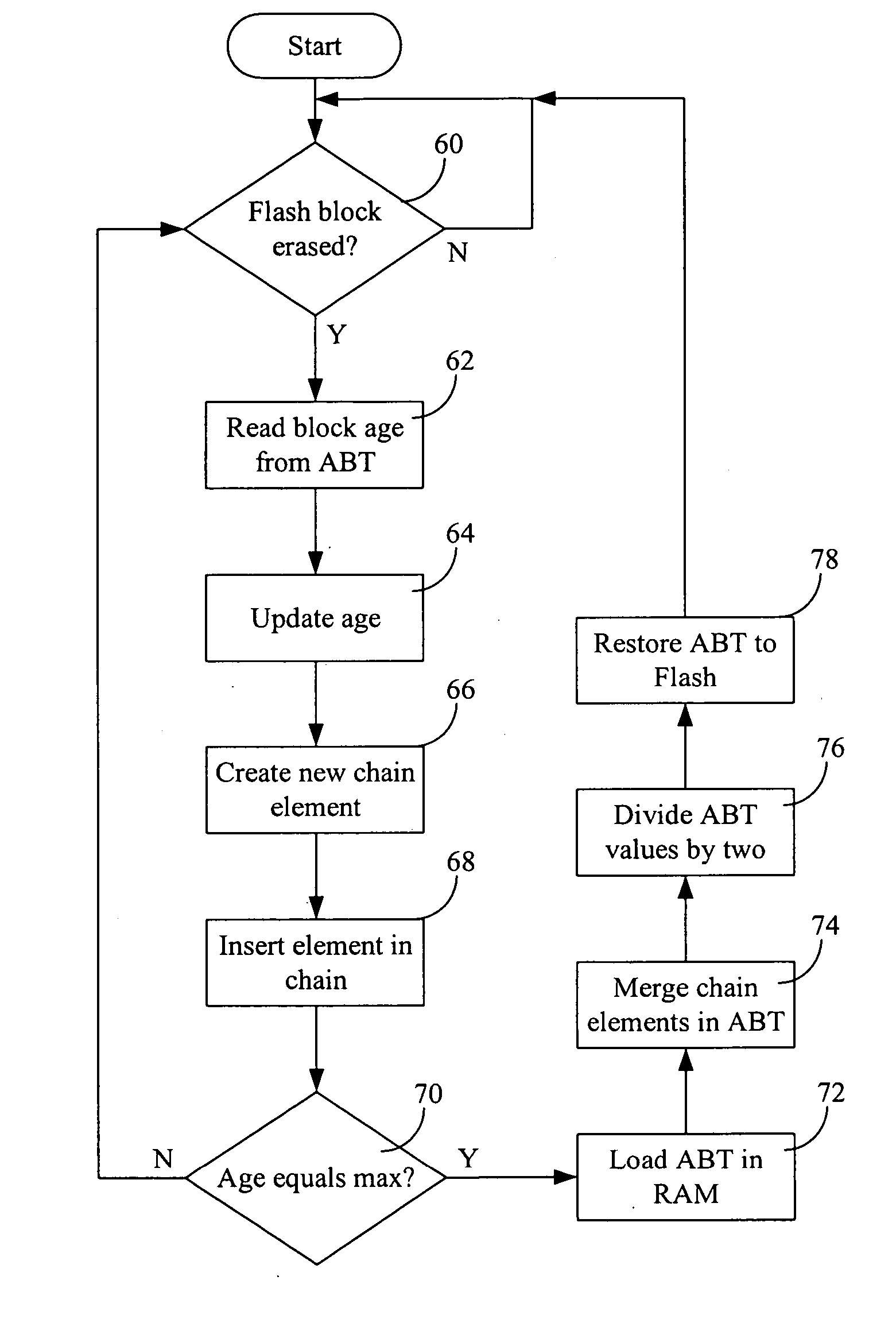

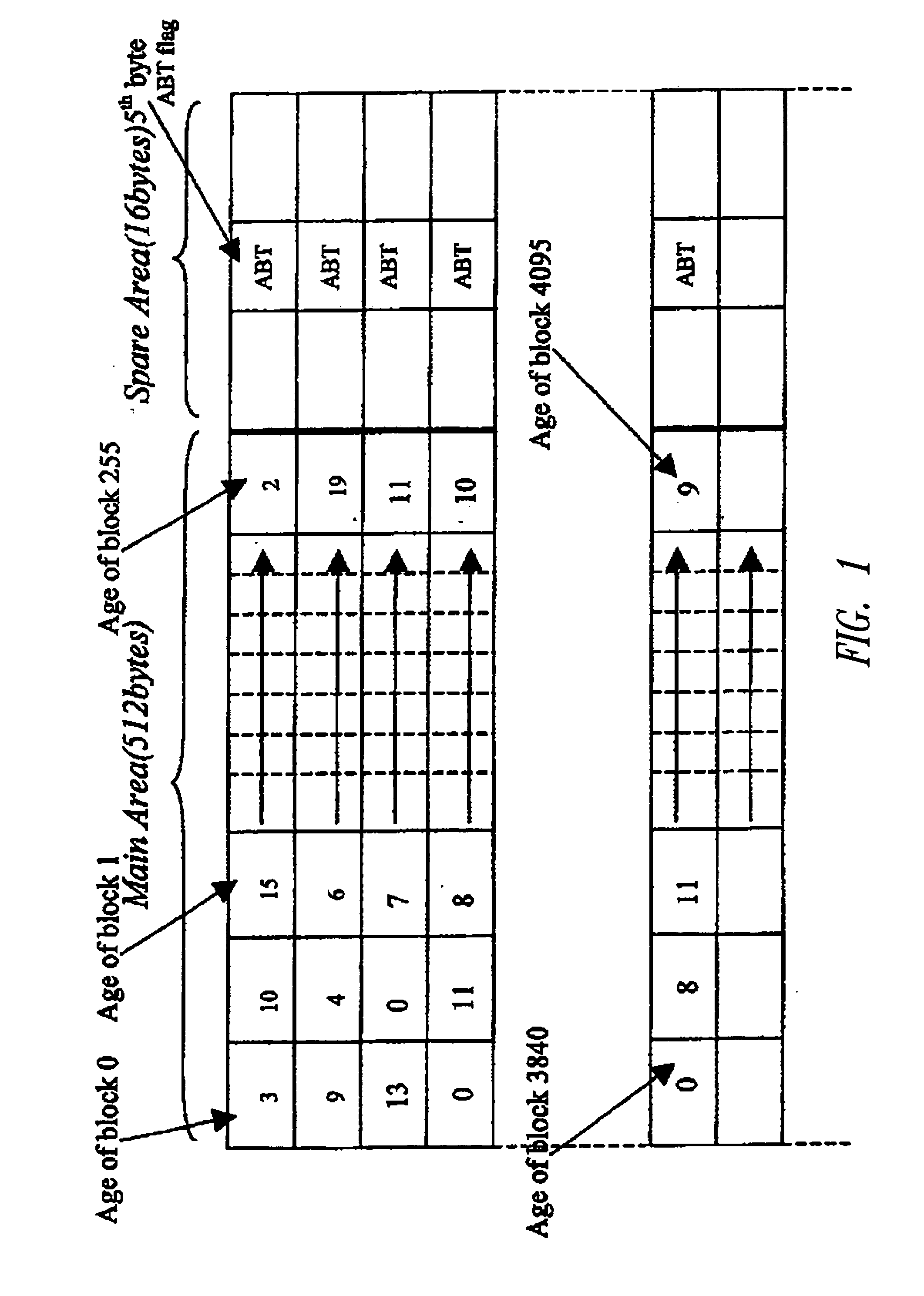

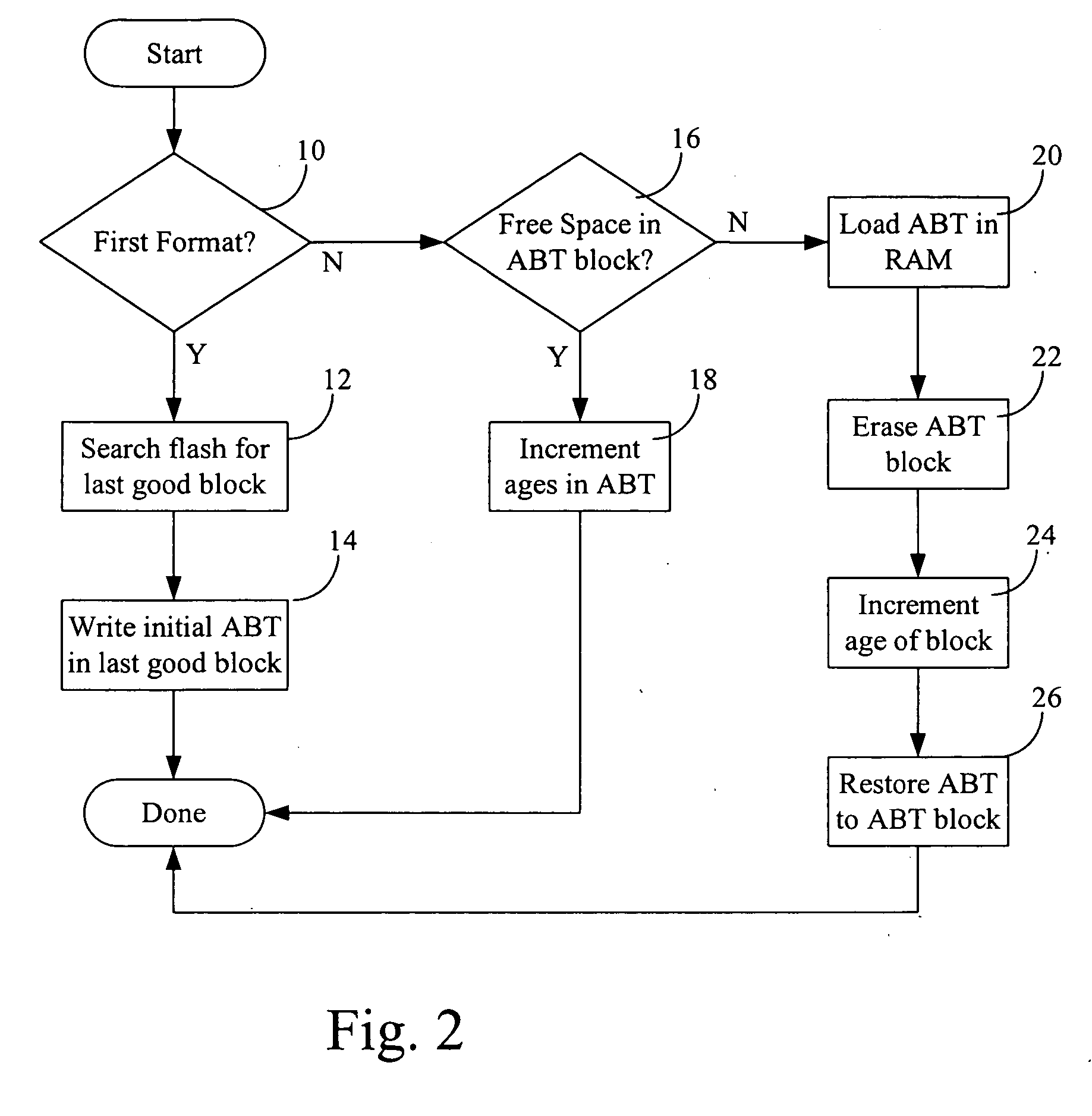

Optimizing write/erase operations in memory devices

ActiveUS20060155917A1Uniformity in useSatisfactory responseMemory architecture accessing/allocationRead-only memoriesControl memoryComputer science

Owner:MICRON TECH INC

TCP proxy connection management in a gigabit environment

The present invention describes a method and apparatus to effectively manage data buffers for a client and a server connection in a multiple connection environment. The TCP processes of servers and clients are merged into an independent TCP process in a TCP ‘proxy’ server. The TCP proxy server includes a control unit and a data switching unit (the proxy application). The TCP proxy server terminates the client TCP connection and initiates a separate TCP connection with the server. The data switching unit binds the two individual connections. The TCP proxy server portrays the actual server TCP. The control unit in the TCP proxy server manages data buffers, control memory and supports multiple connections. The control unit ‘pushes’ the data into the buffers by monitoring the use of the buffers. The control unit does not wait for data requests from the data switching unit thus, eliminating the overhead of data request messages.

Owner:CISCO TECH INC

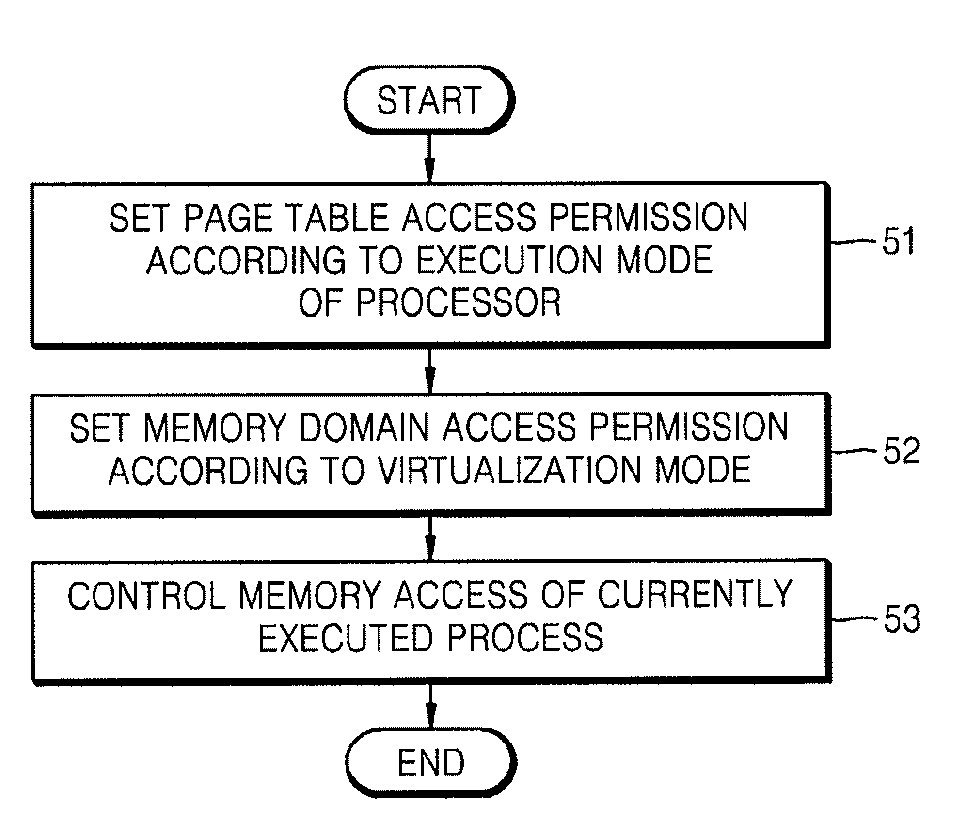

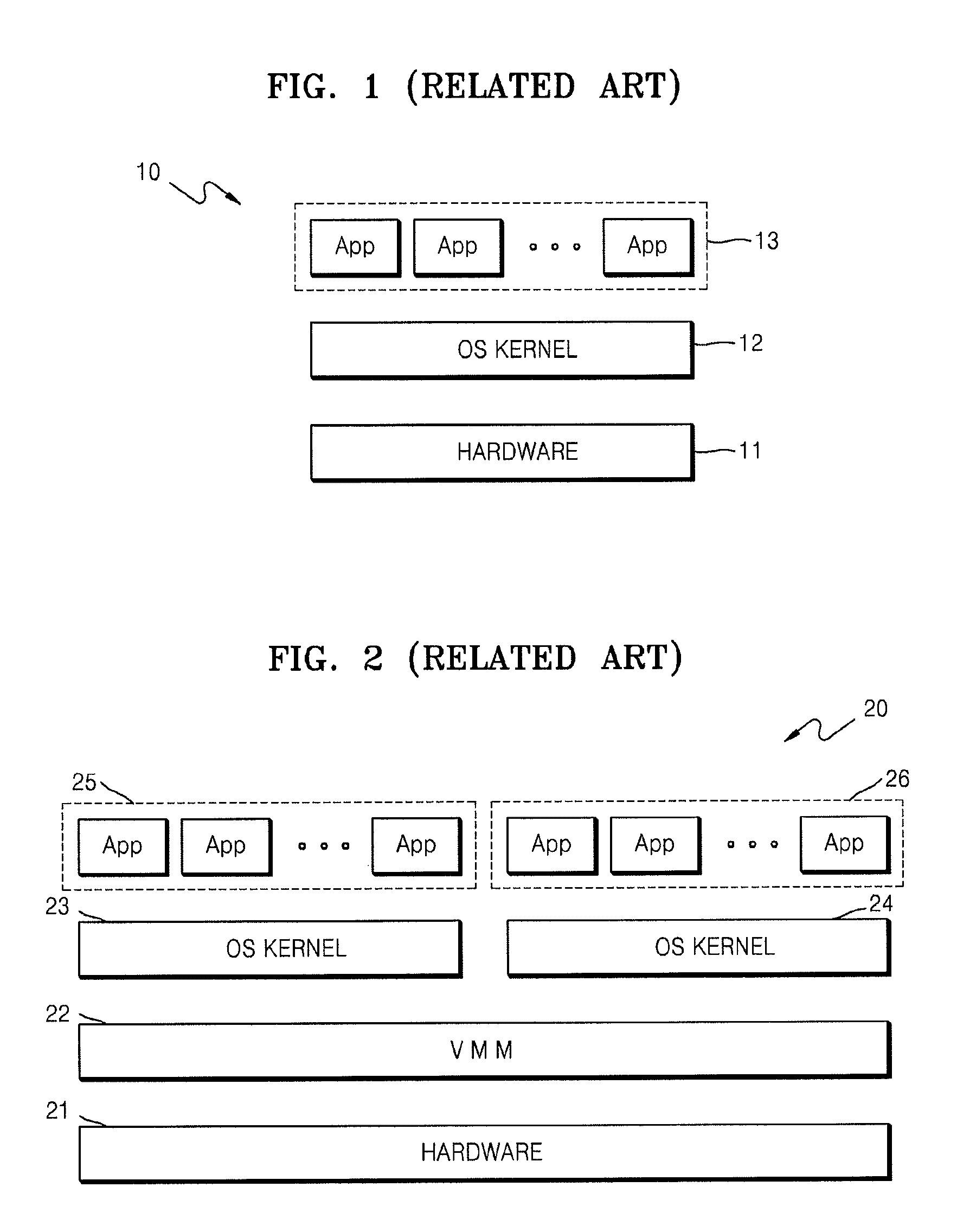

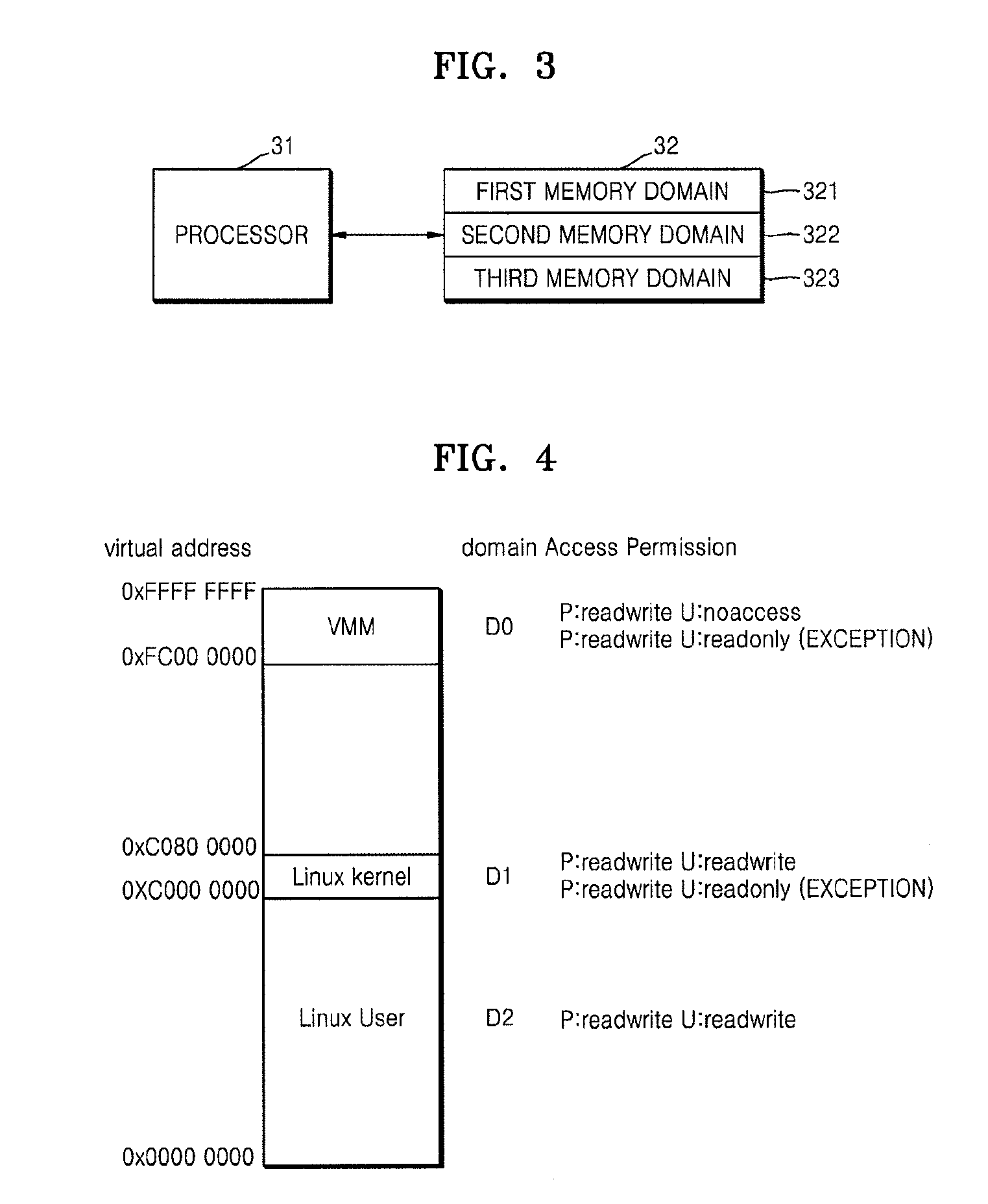

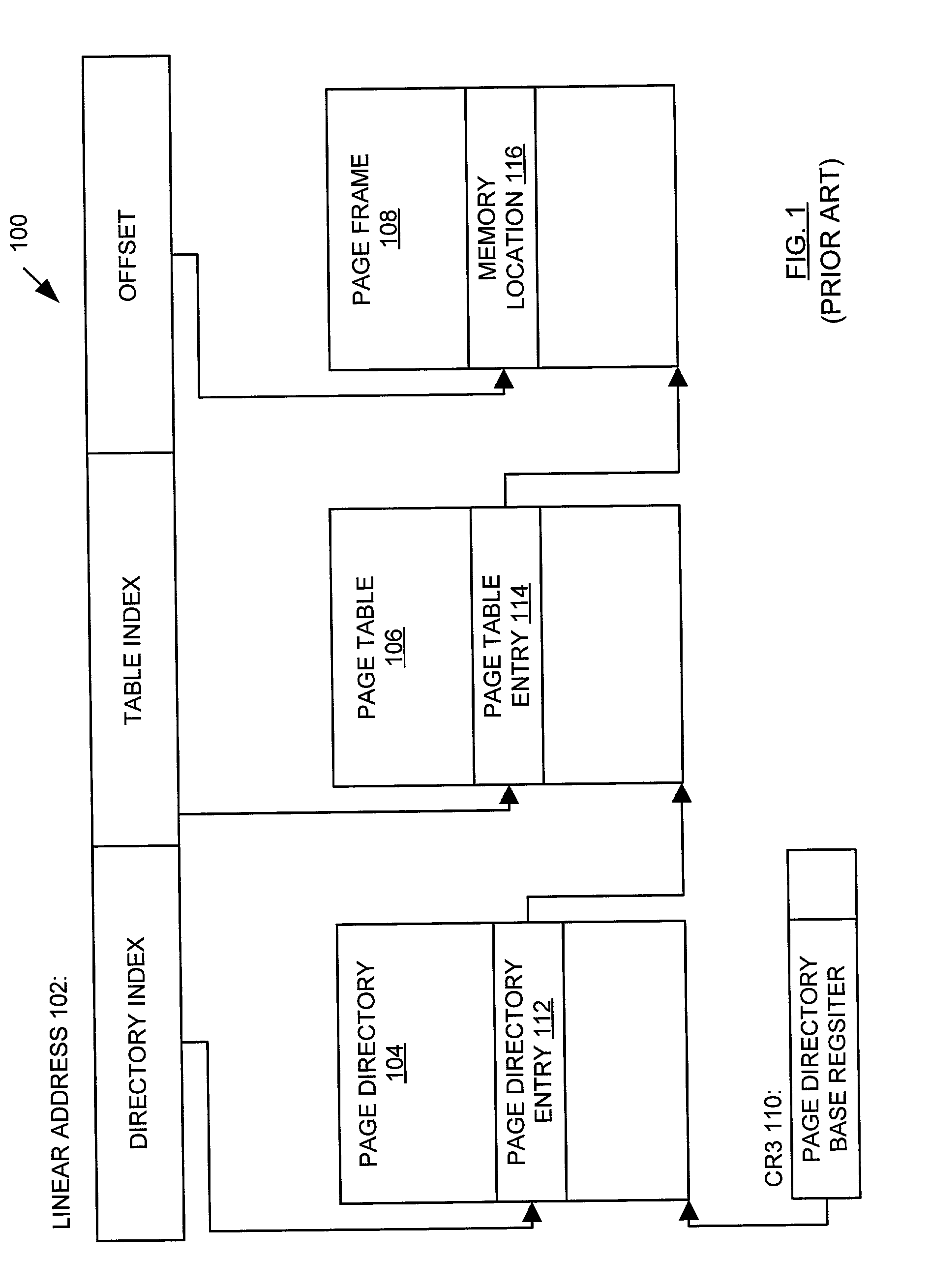

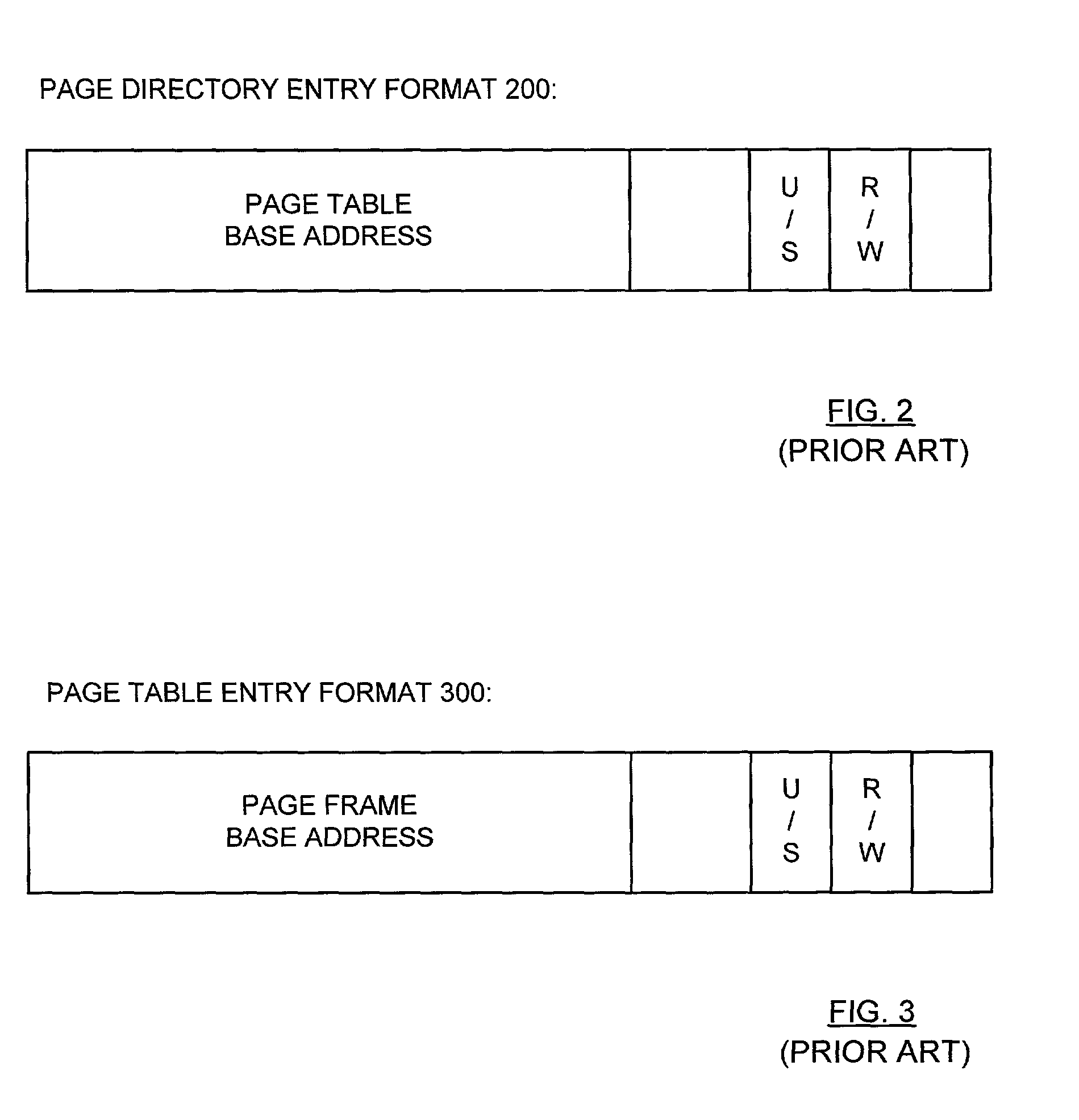

Method of controlling memory access

ActiveUS20080244206A1Unauthorized memory use protectionComputer security arrangementsOperational systemA domain

Provided is a method of controlling memory access. In a system including a first layer element executed in a privileged mode having a first priority of permission to access the entire region of a memory and second and third layer elements executed in an unprivileged mode having a second priority of permission to access a partial region of the memory, the method of controlling memory access determines whether the memory is accessible for each page that is an address space unit, based on which mode a layer element currently accessing the memory is executed in between the privileged mode and the unprivileged mode; and determines whether the memory is accessible based on which one of the first, second and third layer elements corresponds to a domain currently being attempted to be accessed from among a plurality of domains of the memory. Accordingly, a memory domain allocated to a guest operating system kernel is effectively protected from an application executed in the unprivileged mode in which the guest operating system kernel is executed.

Owner:SAMSUNG ELECTRONICS CO LTD

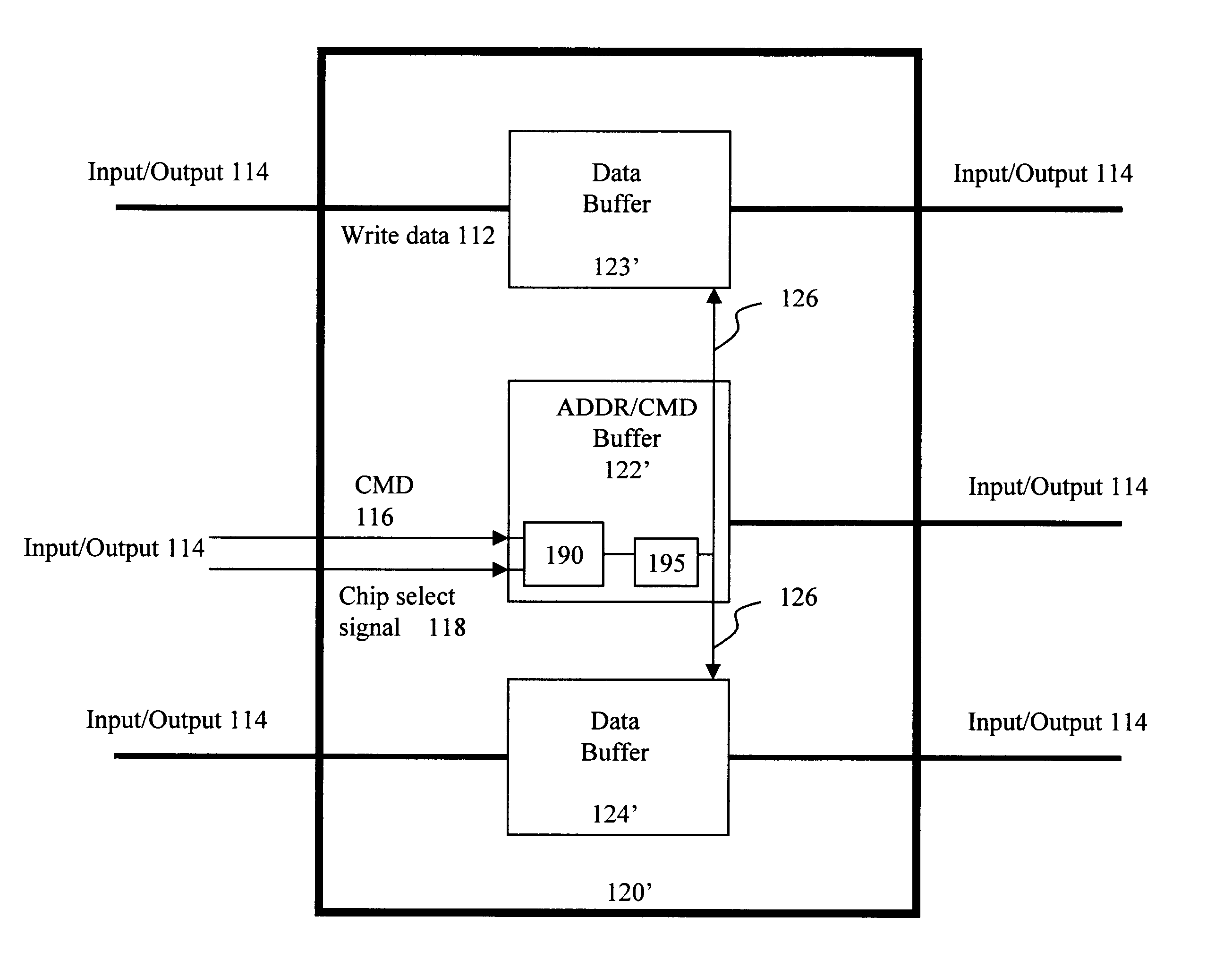

System and method for controlling data flow direction in a memory system

A system and method for controlling the direction of data flow in a memory system is provided. The system comprising memory devices, a memory controller, a buffering structure, and a data flow director. The memory controller sends data, such as read-data, write-data, address information and command information, to the memory devices and receives data from the memory devices. The buffering structure interconnects the memory device and the memory controller. The buffering structure is adapted to operate in a bi-directional manner for the direction of data flow therethrough. The data flow director, which may reside in the buffering structure, the memory controller, the memory devices, or an external device, controls the direction of data flow through the buffering structure based on the data transmitted from the memory controller or the memory device.

Owner:INTEL CORP

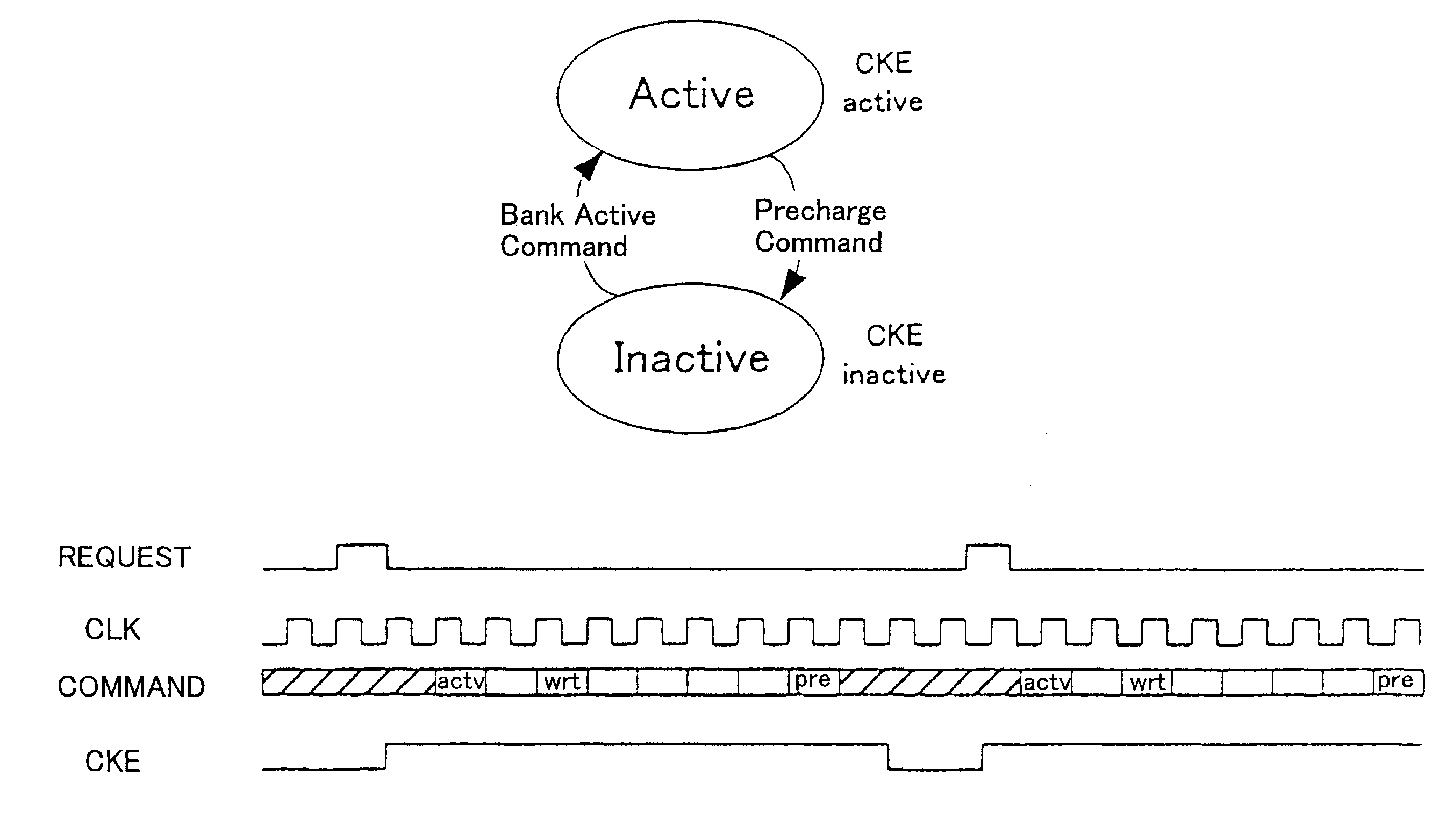

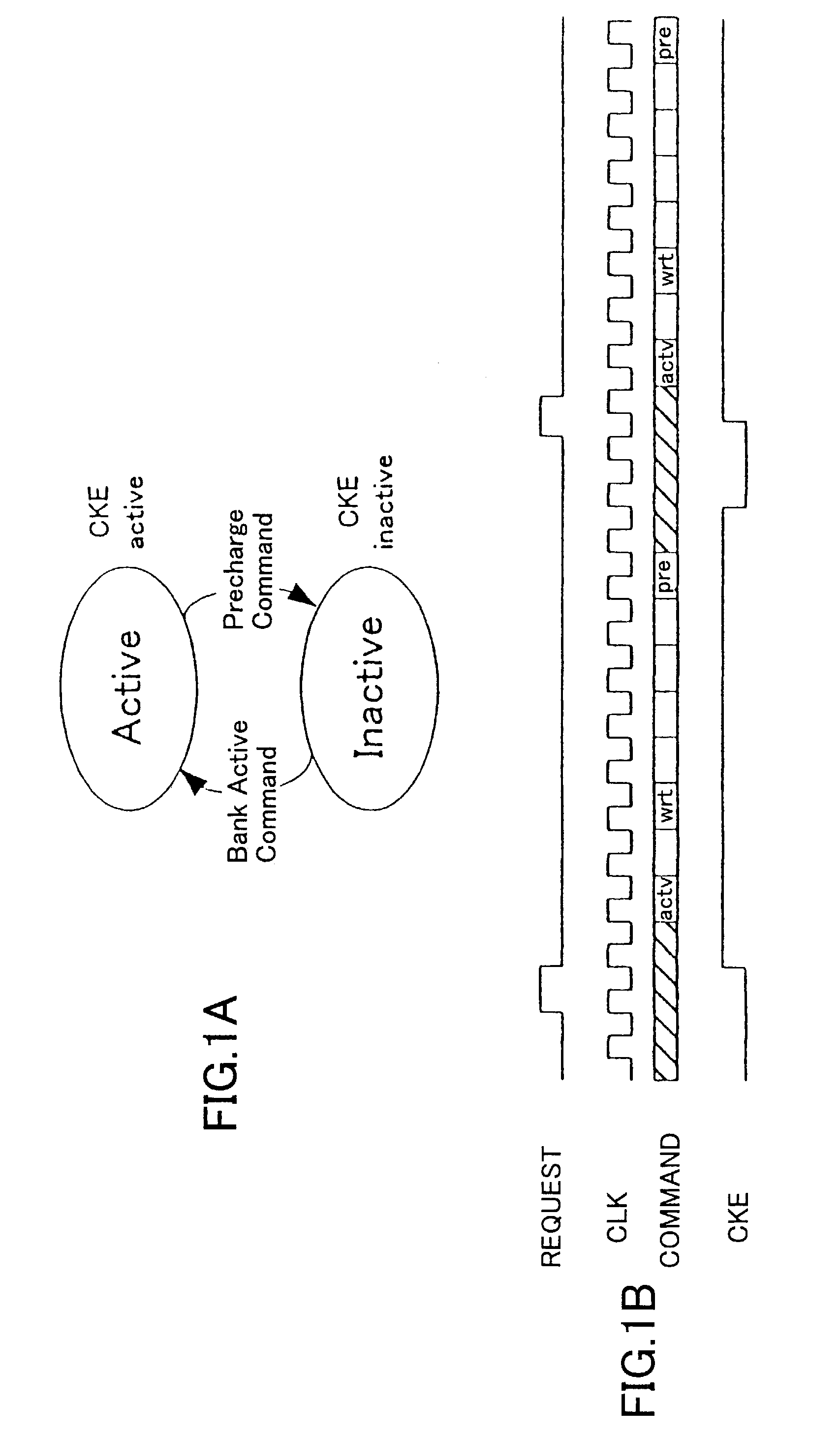

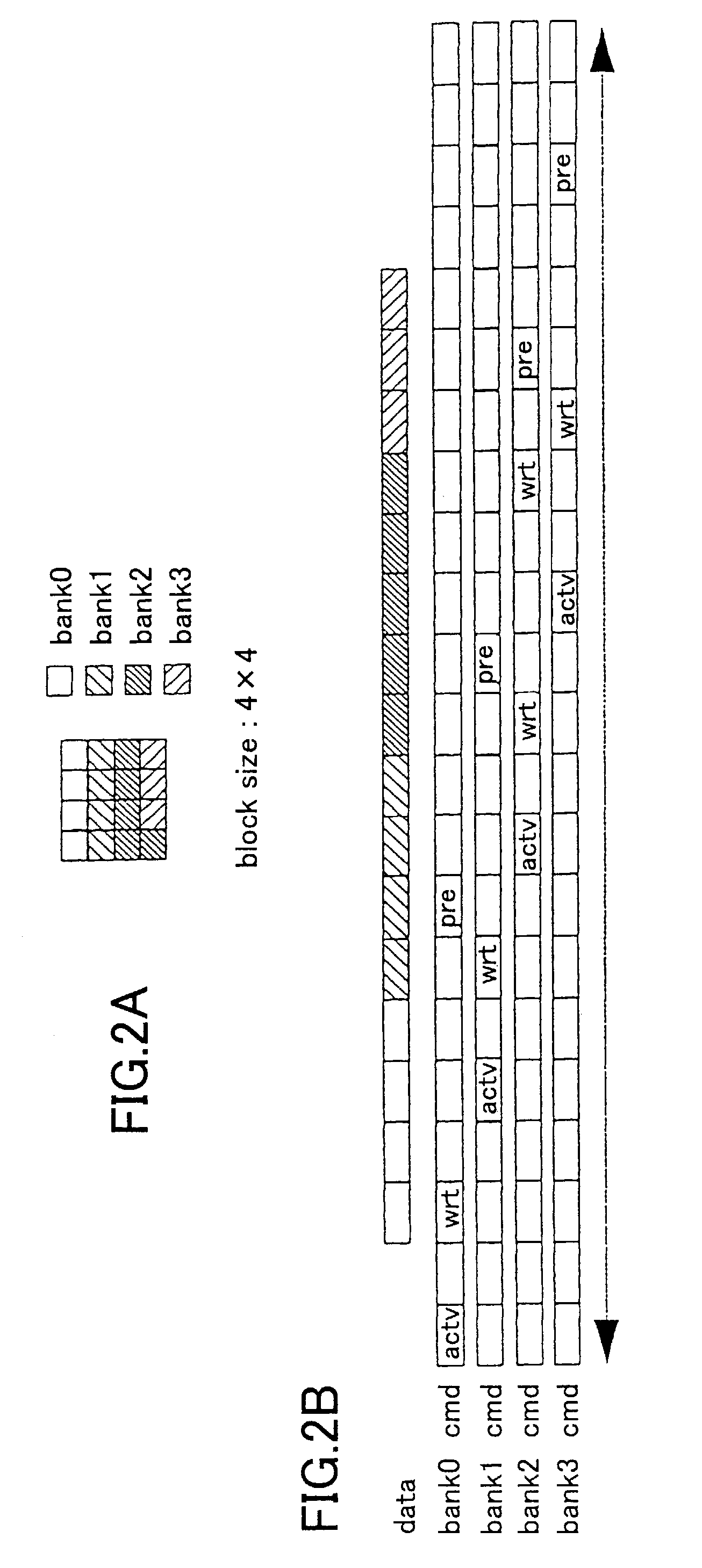

Clock control apparatus and method, for a memory controller, that processes a block access into single continuous macro access while minimizing power consumption

InactiveUS7085941B2Efficient executionReduce power consumptionEnergy efficient ICTVolume/mass flow measurementControl signalMemory controller

A clock control apparatus for a memory controller comprises an interface unit which processes a block access to a plurality of banks of an SDRAM as a single continuous macro access in order to perform arbitration of the macro access, the block access externally supplied to the memory controller. A power-saving control unit controls both a clock signal of an internal circuit of the memory controller and a clock enable signal of the SDRAM in response to a control signal supplied from the interface unit.

Owner:FUJITSU LTD

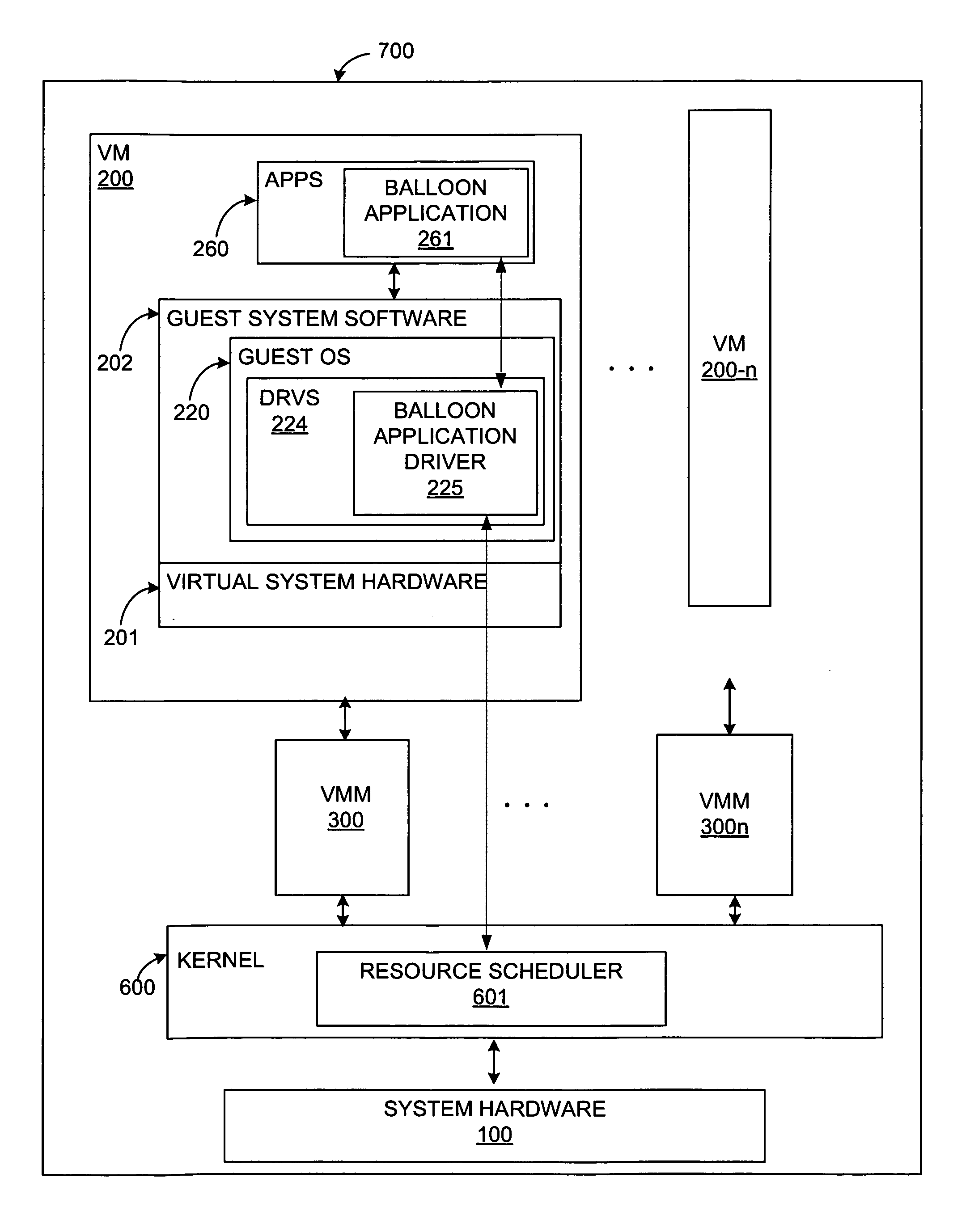

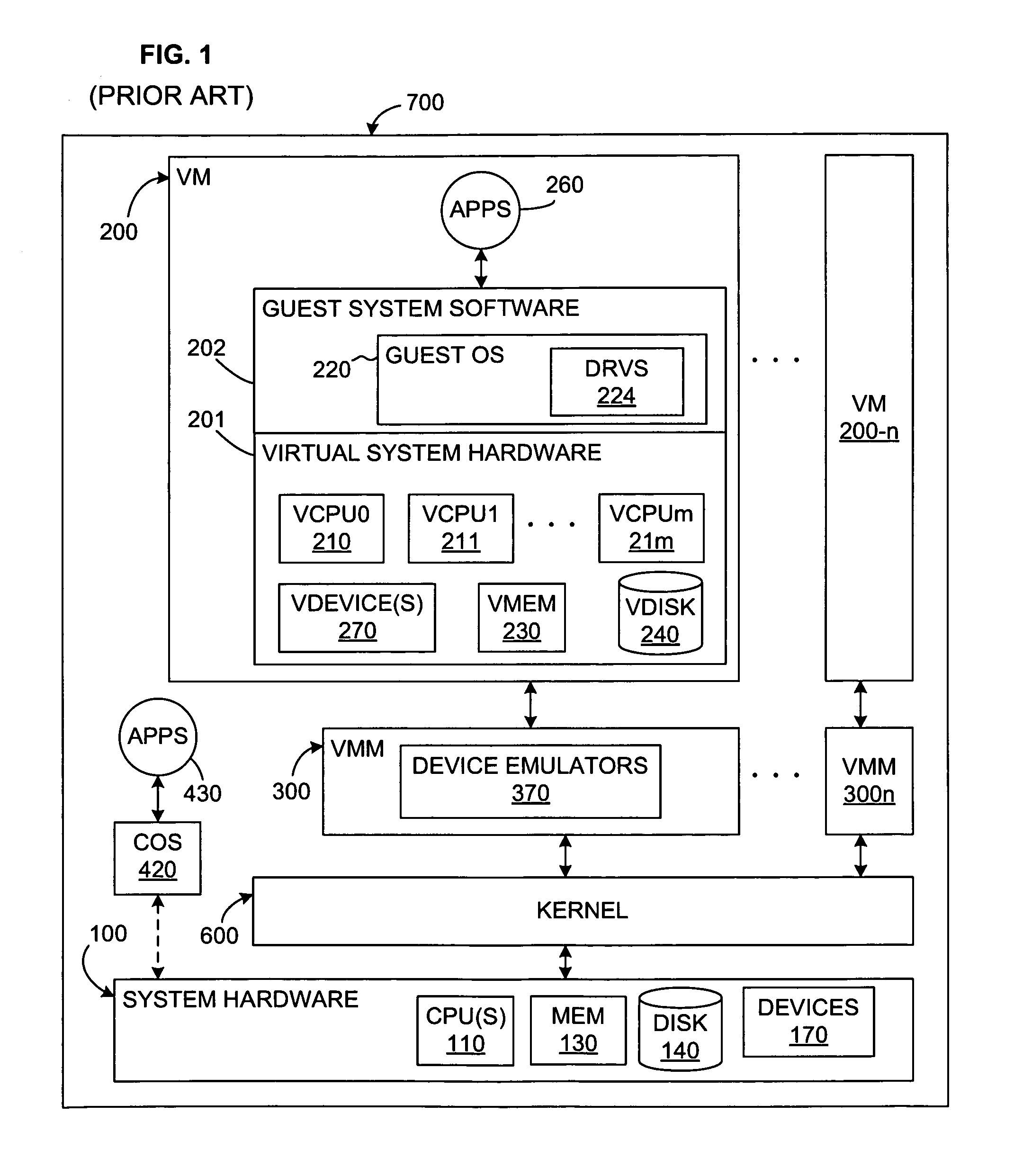

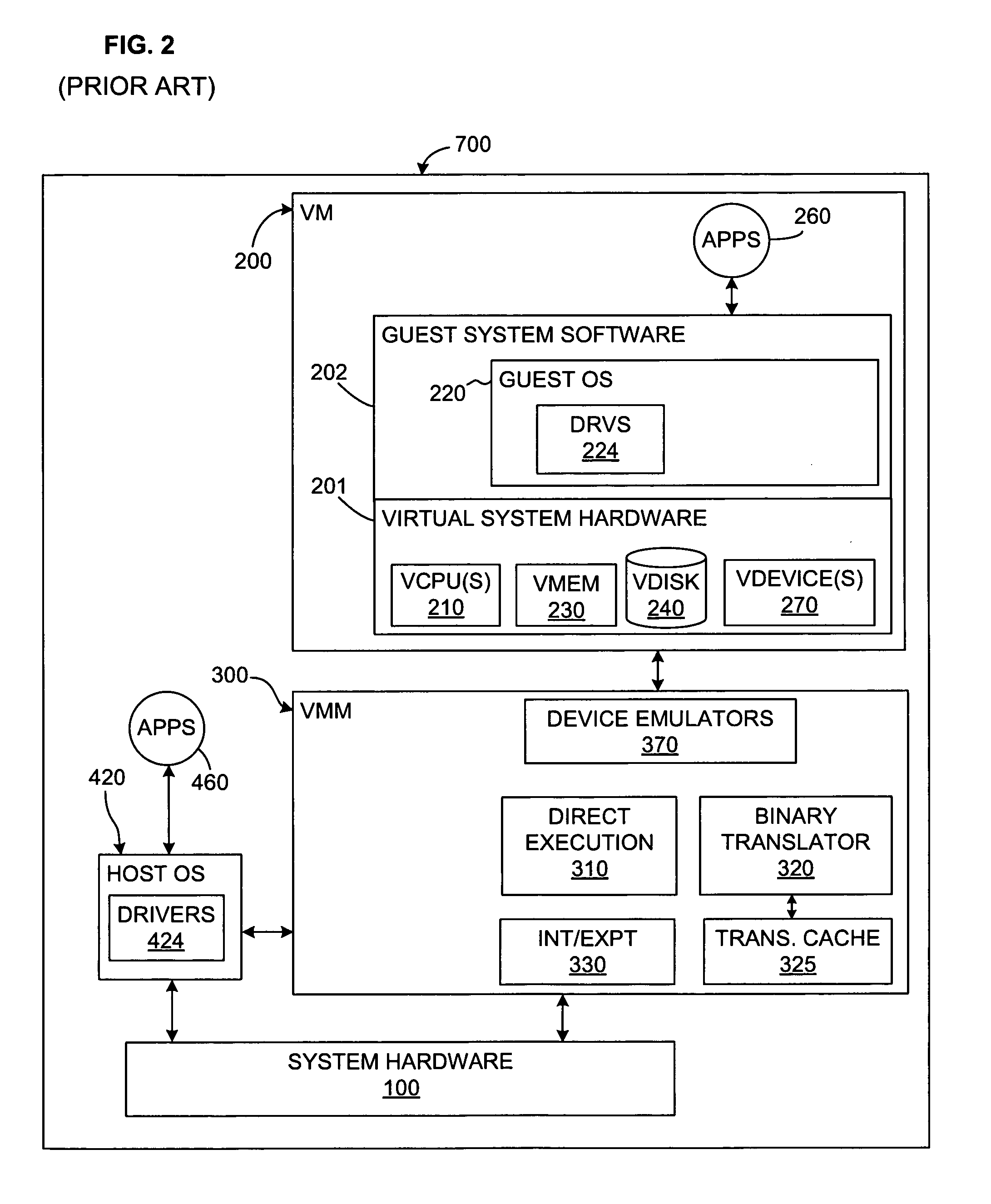

System and method for cooperative virtual machine memory scheduling

ActiveUS7716446B1Memory architecture accessing/allocationMemory adressing/allocation/relocationVirtual memoryOperational system

Memory assigned to a virtual machine is reclaimed. A resource reservation application running as a guest application on the virtual machine reserves a location in guest virtual memory. The corresponding physical memory can be reclaimed and allocated to another virtual machine. The resource reservation application allows detection of guest virtual memory page-out by the guest operating system. Measuring guest virtual memory page-out is useful for determining memory conditions inside the guest operating system. Given determined memory conditions, memory allocation and reclaiming can be used control memory conditions. Memory conditions in the virtual machine can be controlled with the objective of achieving some target memory conditions.

Owner:VMWARE INC

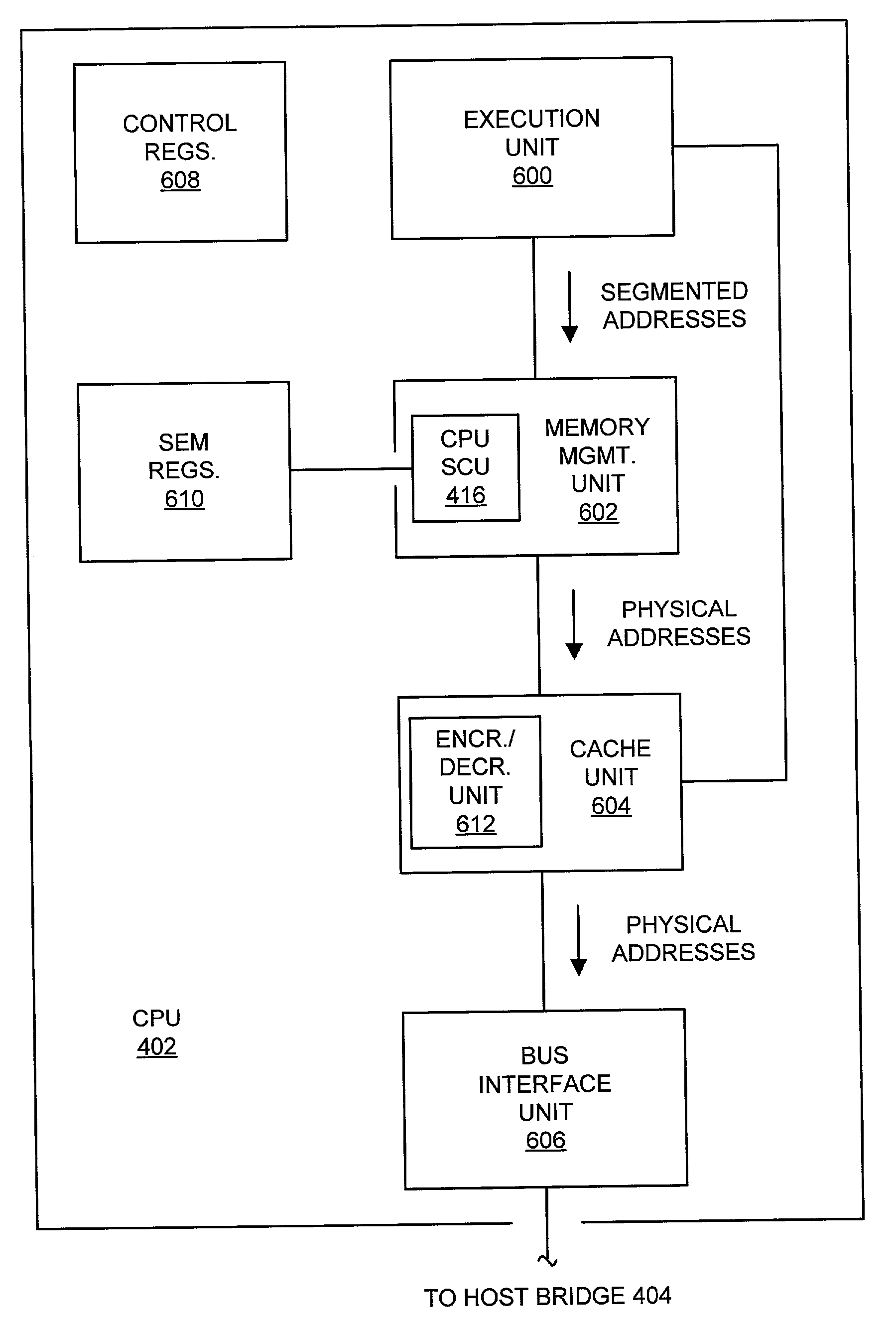

System and method providing region-granular, hardware-controlled memory encryption

ActiveUS20030188178A1User identity/authority verificationMemory adressing/allocation/relocationControl memoryData dependent

A memory, system, and method for providing security for data stored within a memory and arranged within a plurality of memory regions. The method includes receiving an address within a selected memory region and using the address to access an encryption indicator. The encryption indicator indicates whether data stored in the selected memory page are encrypted. The method also includes receiving a block of data from the selected memory region and the encryption indicator and decrypting the block of data dependent upon the encryption indicator.

Owner:MEDIATEK INC

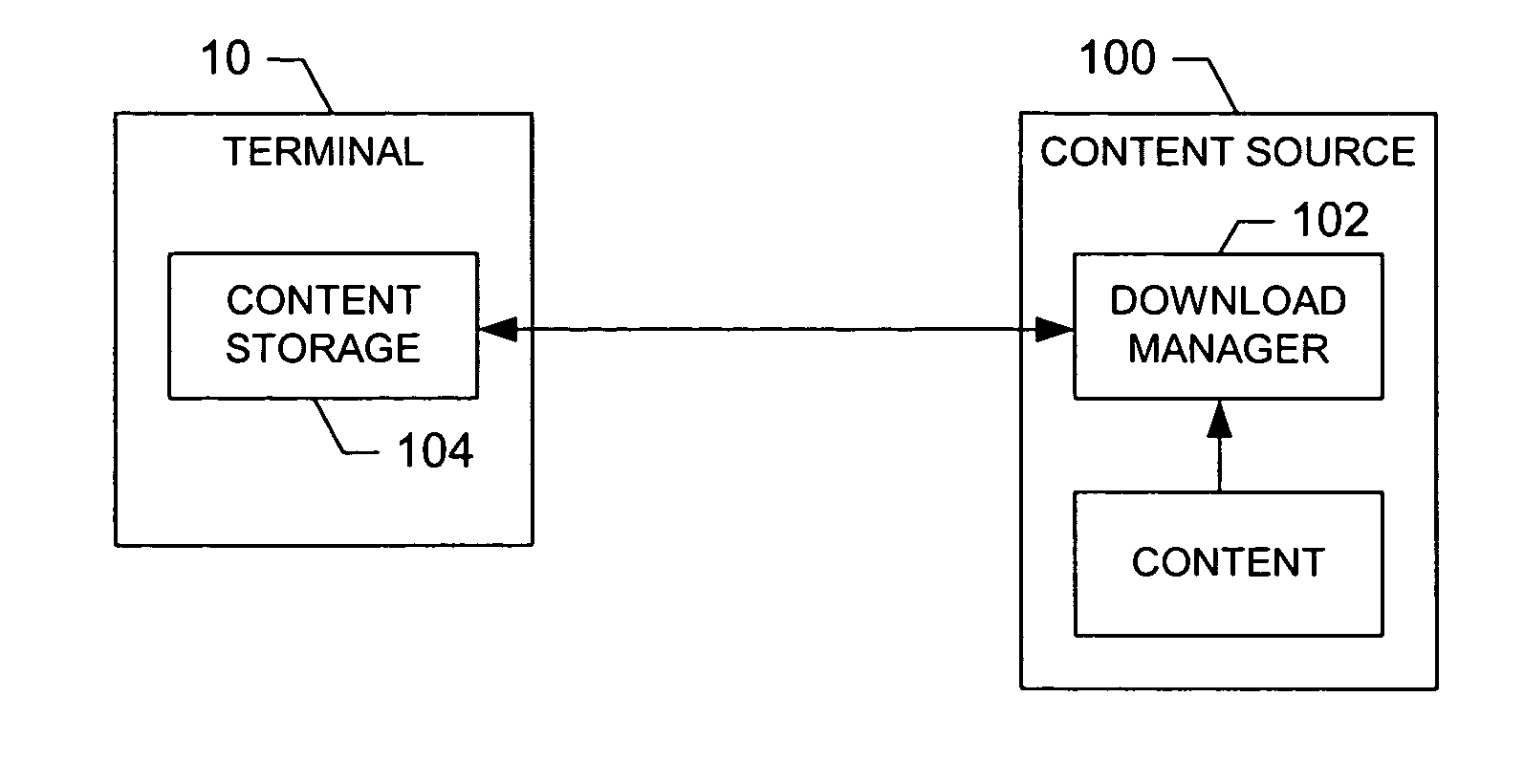

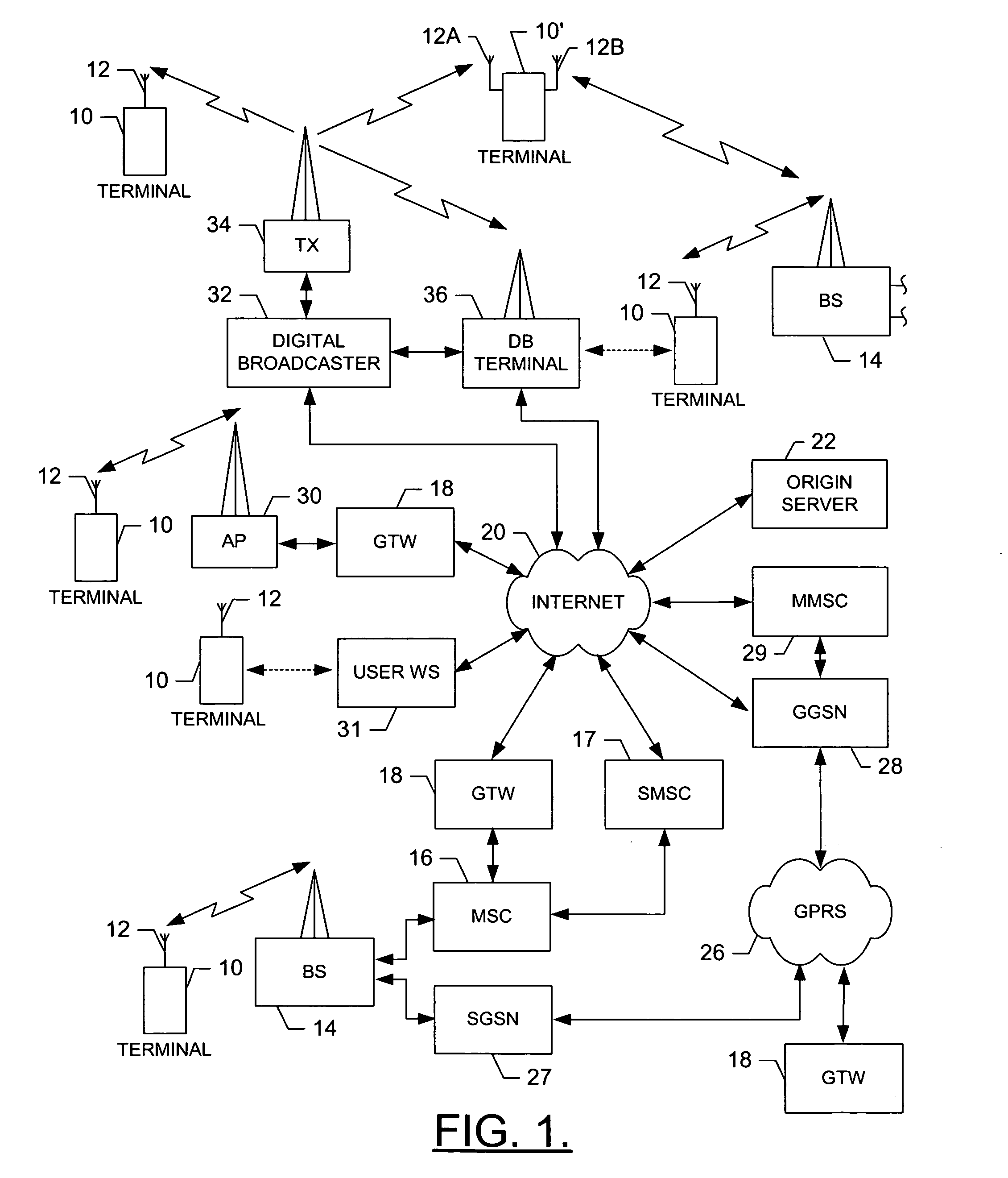

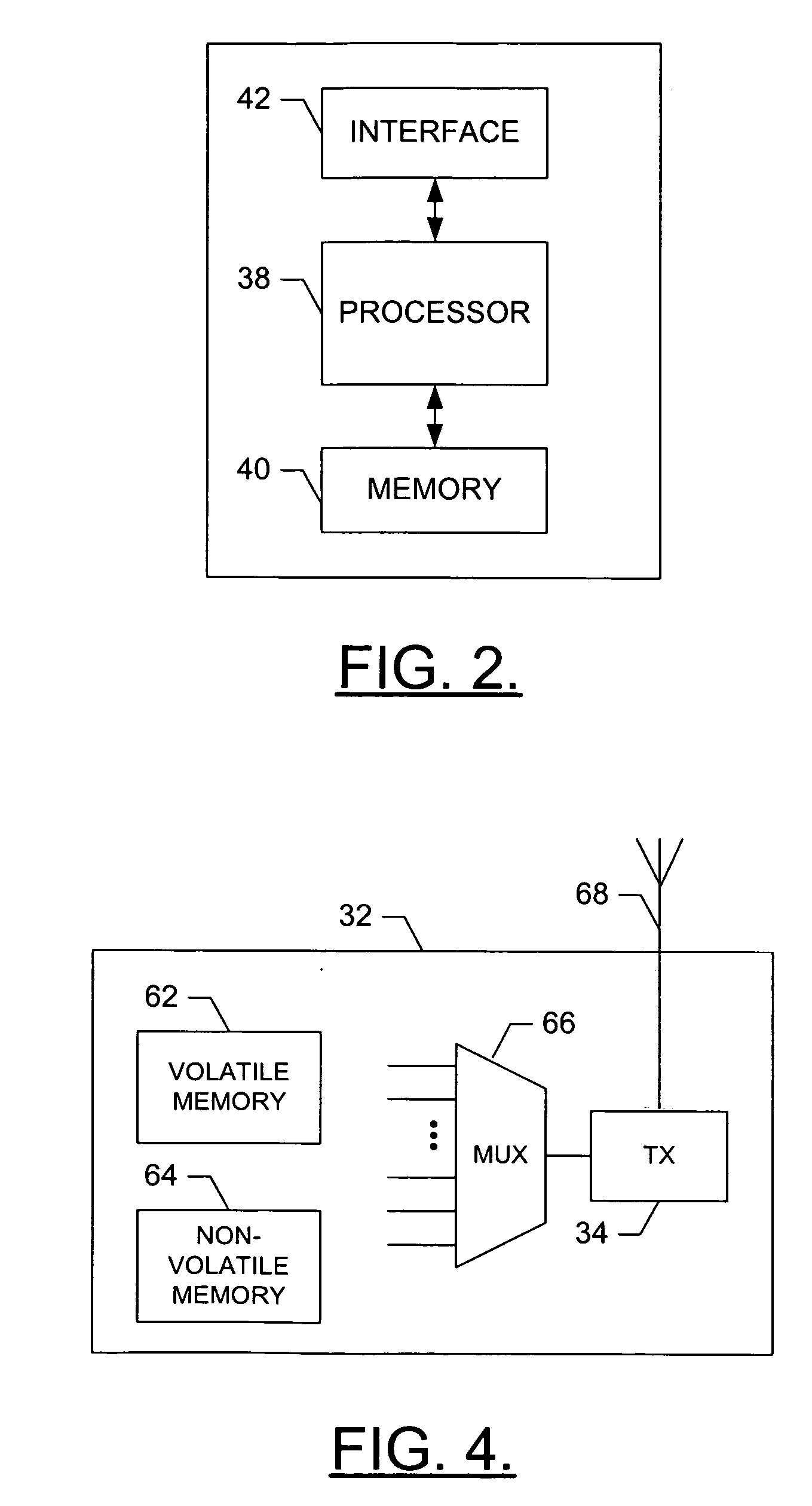

System and associated terminal, method and computer program product for controlling memory for storage of content

InactiveUS20050129042A1Increase storage capacityReduce the burden onAccumulation-type receiver broadcastData switching by path configurationExpiration TimeControl memory

A system for controlling memory for storage of content includes a network entitiy, such as a terminal or a content source. The network entity includes a download manager capable of receiving a selection of at least one piece of content. The download manager is also capable of reserving at least a portion of a storage capacity of memory of a terminal for at least one of the selected piece(s) of content such that the terminal can thereafter receive and store the selected piece(s) of content into the reserved storage capacity. To facilitate reserving storage capacity, the selected piece(s) of content and / or content stored in memory of the terminal includes a set of one or more parameters, such as an expiration time, a deletion priority value and / or a download priority value.

Owner:NOKIA CORP

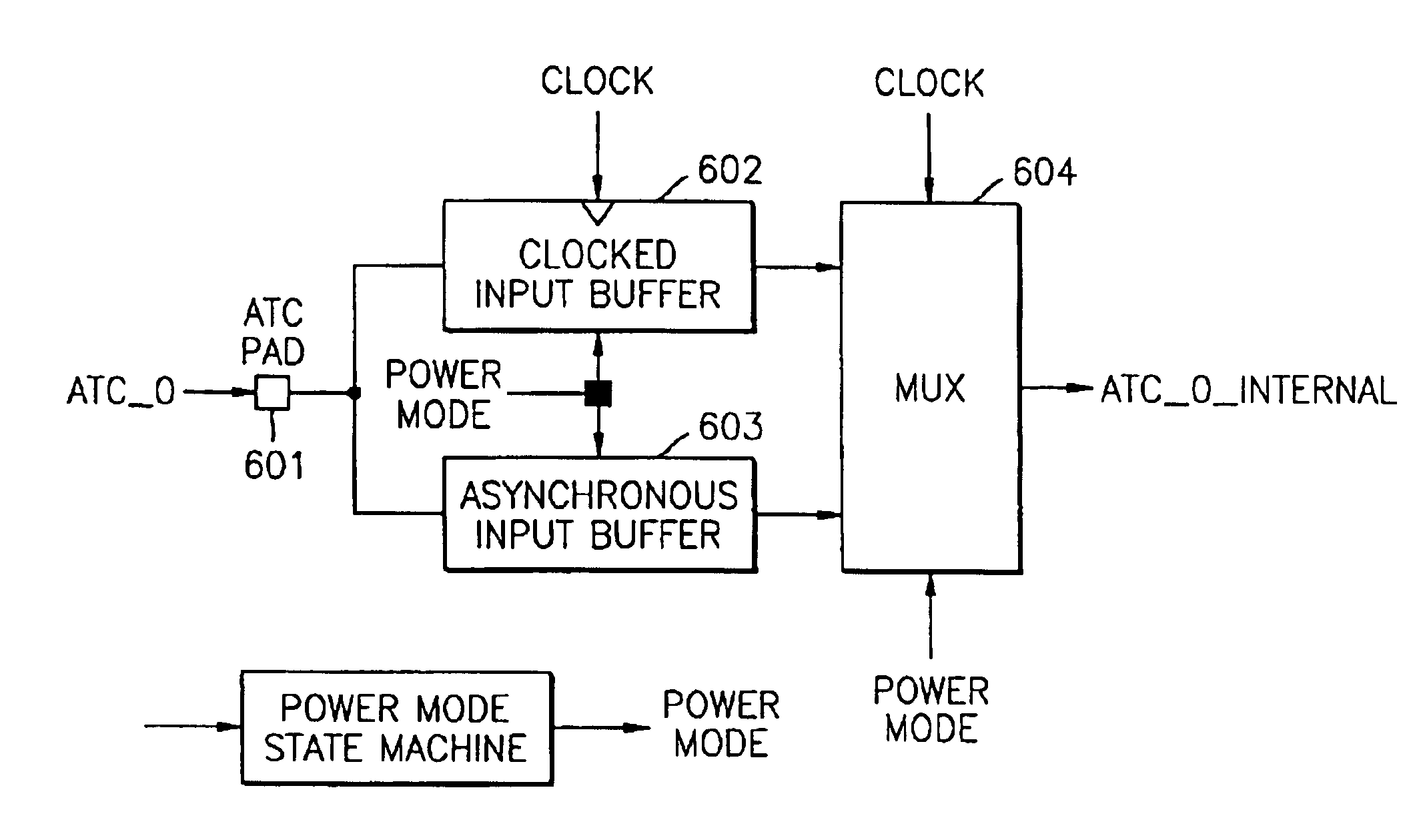

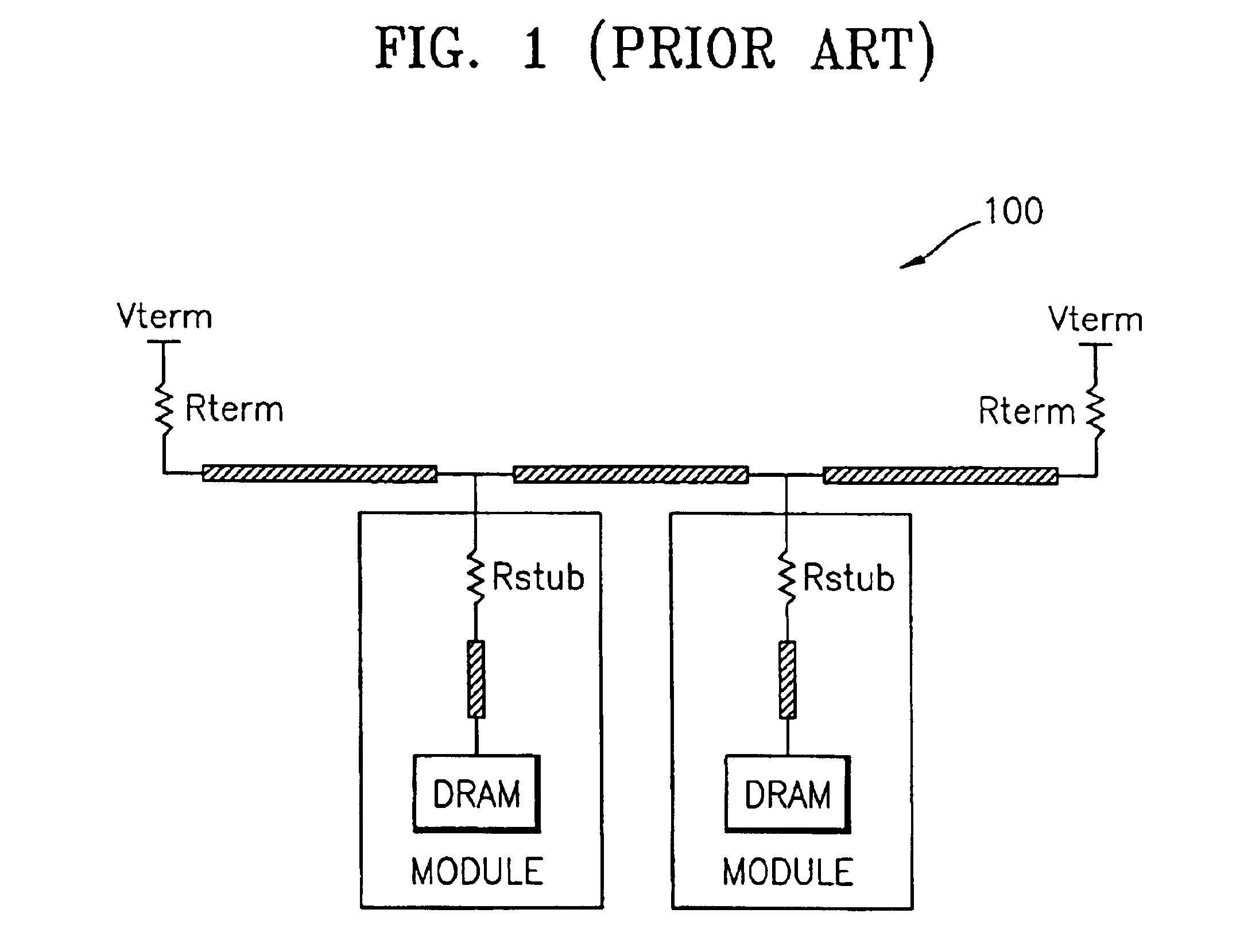

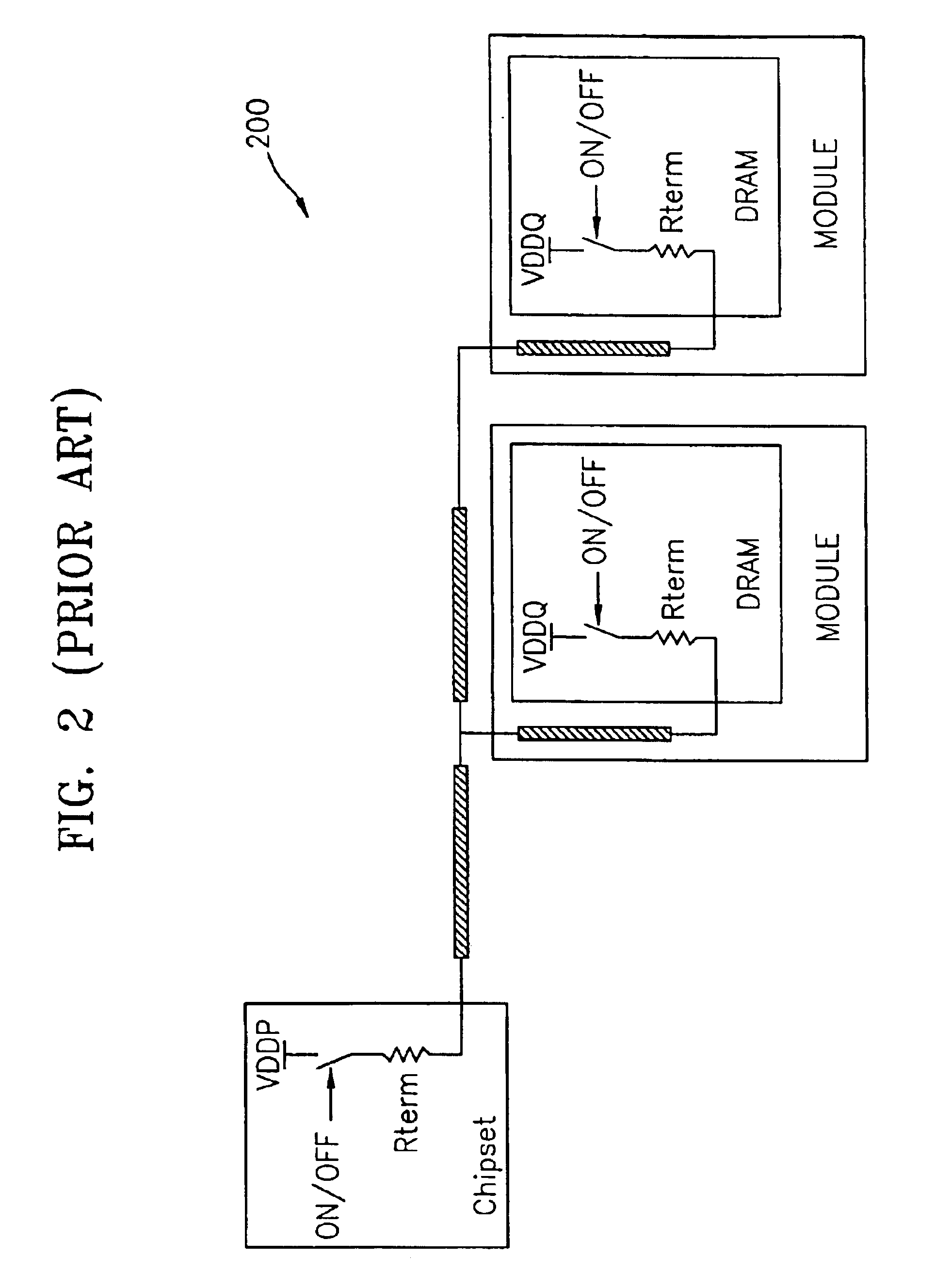

Devices and methods for controlling active termination resistors in a memory system

An active termination circuit is mounted in a memory circuit and includes a termination resistor which provides a termination resistance for the memory circuit, and a control circuit which receives an externally supplied active termination control signal, and which selectively switches on and off the termination resistor in response to the active termination control signal. The control circuit includes a synchronous input buffer and an asynchronous input buffer which each receive the active termination control signal, and a switching circuit which selectively outputs an output of said synchronous input buffer or an output of said asynchronous input buffer according to an operational mode of the memory circuit. The output of the switching circuit controls an on / off state of said termination resistor.

Owner:SAMSUNG ELECTRONICS CO LTD