Patents

Literature

286 results about "Floating body effect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

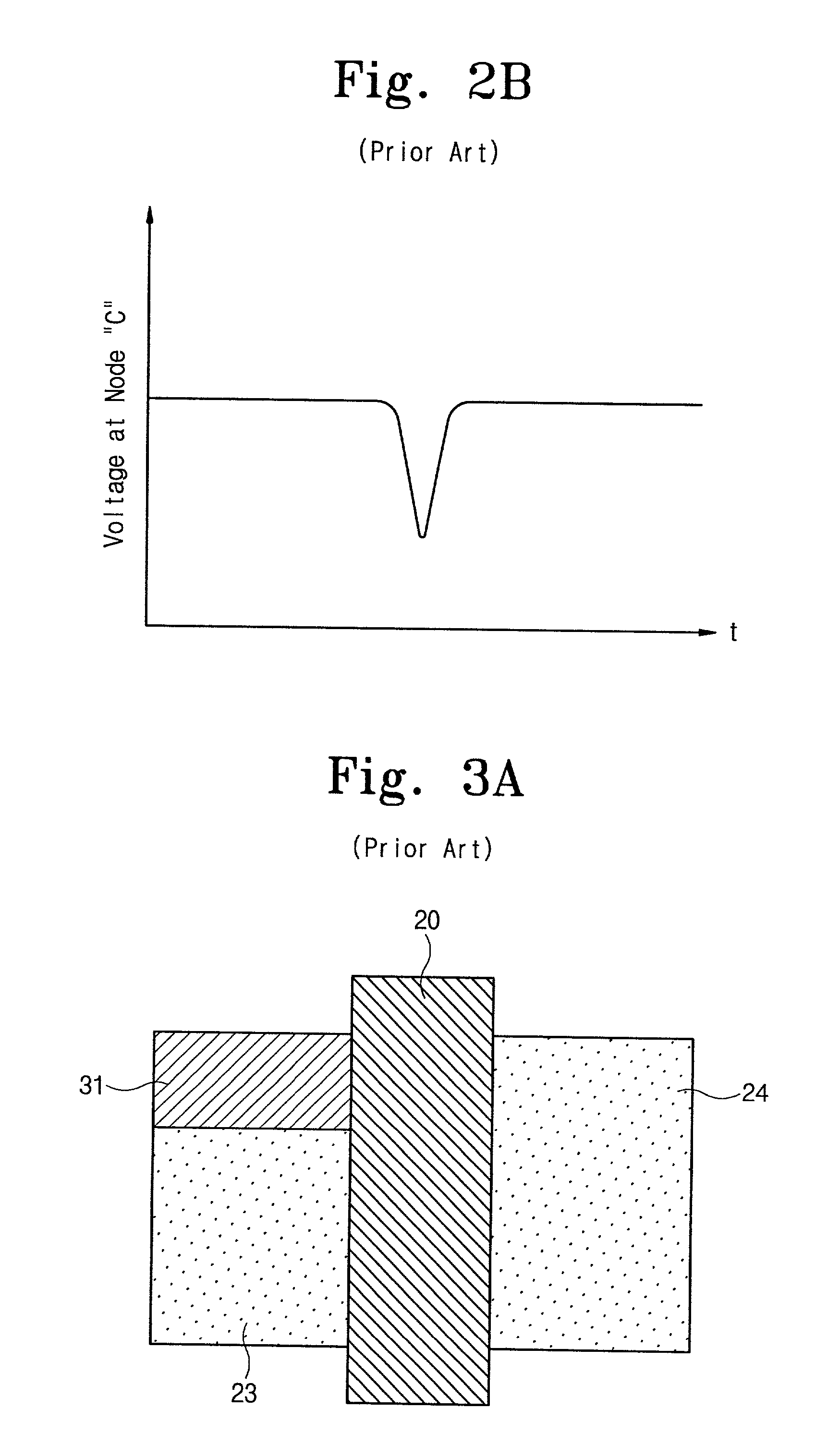

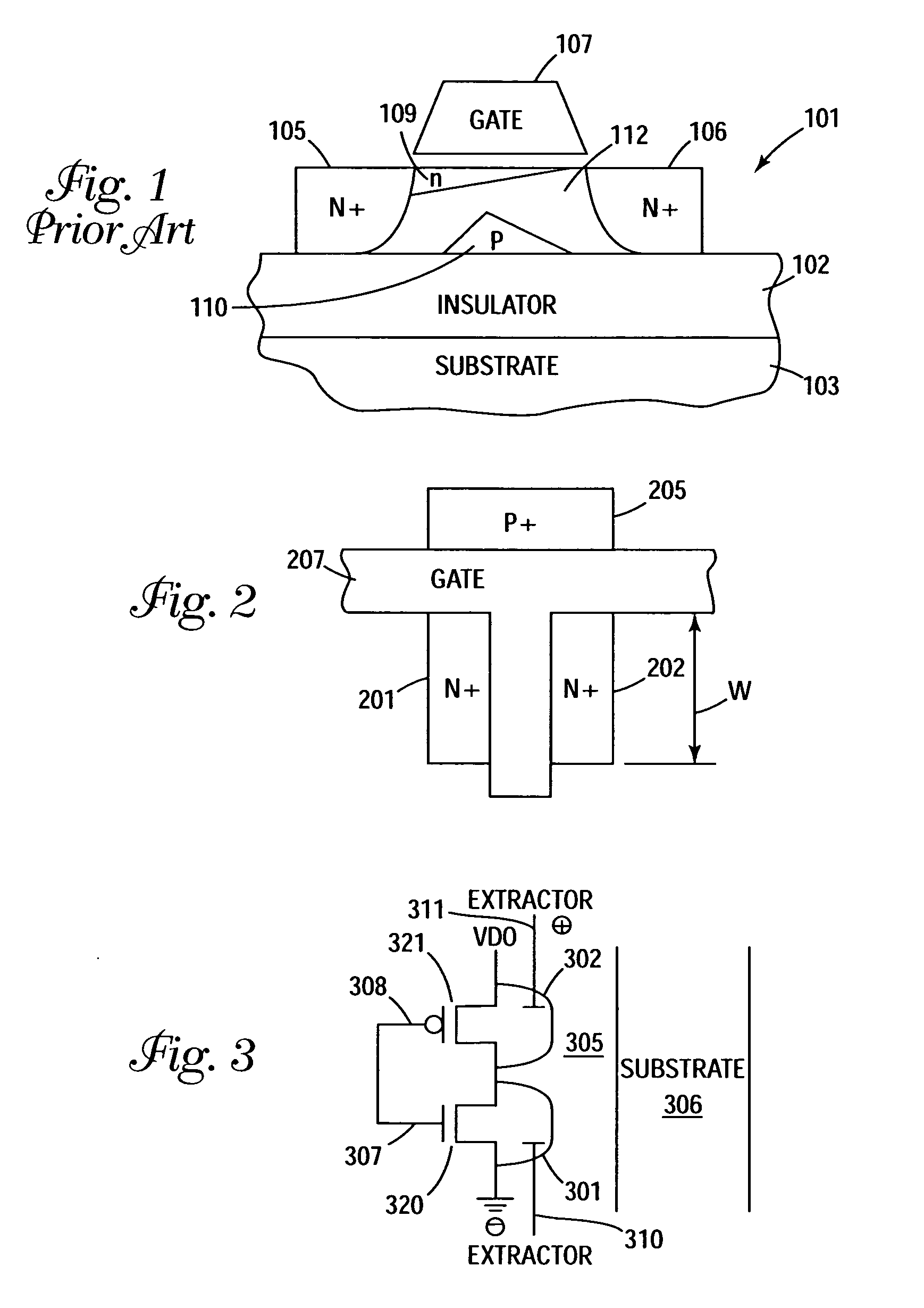

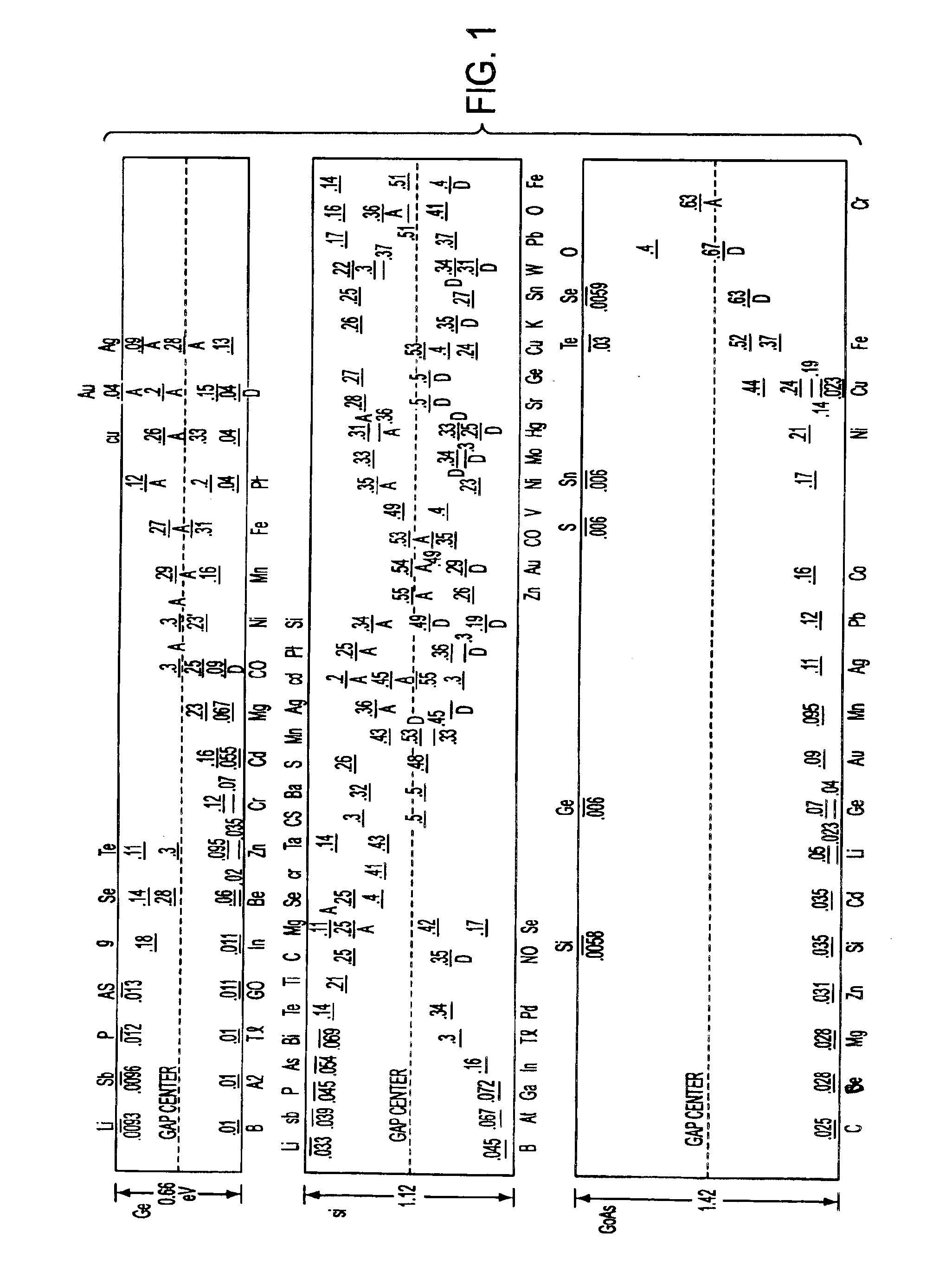

The floating body effect is the effect of dependence of the body potential of a transistor realized by the silicon on insulator (SOI) technology on the history of its biasing and the carrier recombination processes. The transistor's body forms a capacitor against the insulated substrate. The charge accumulates on this capacitor and may cause adverse effects, for example, opening of parasitic transistors in the structure and causing off-state leakages, resulting in higher current consumption and in case of DRAM in loss of information from the memory cells. It also causes the history effect, the dependence of the threshold voltage of the transistor on its previous states. In analog devices, the floating body effect is known as the kink effect.

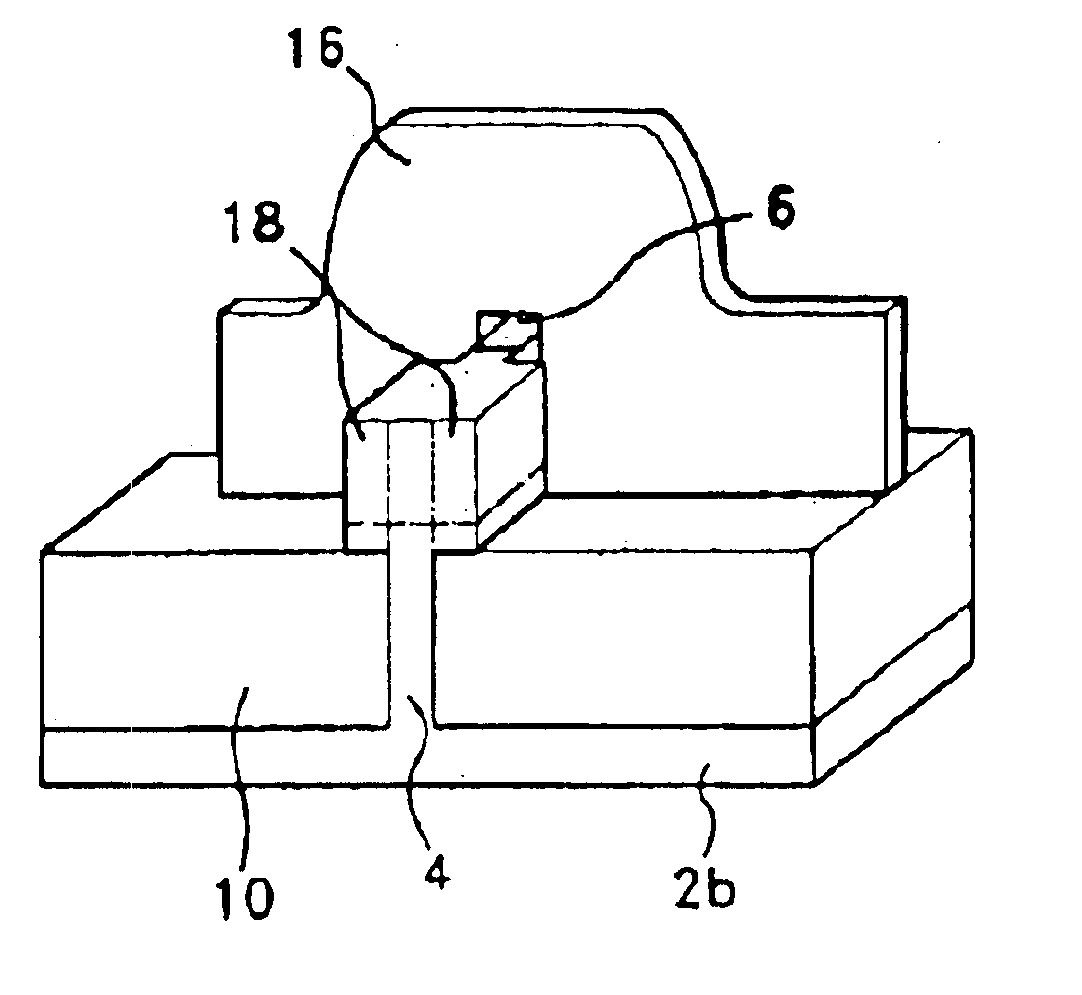

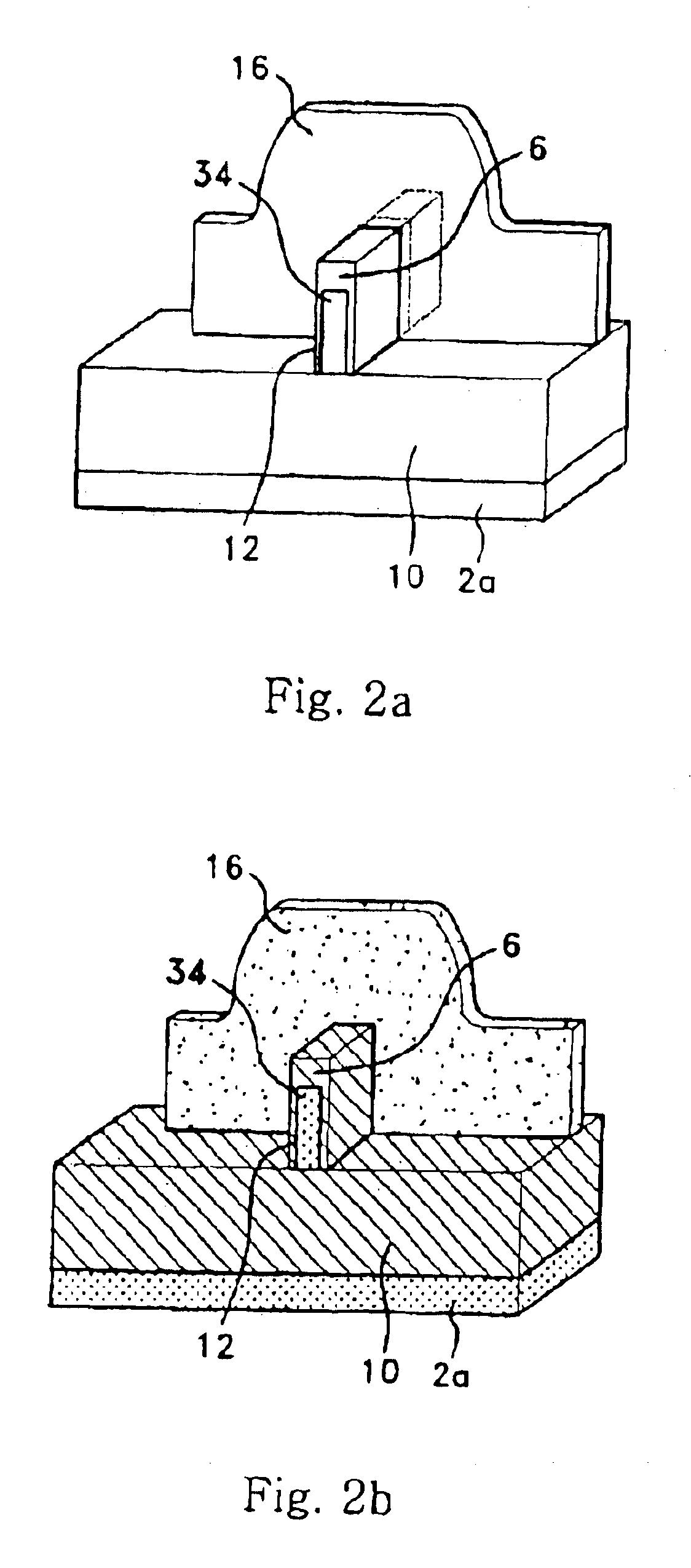

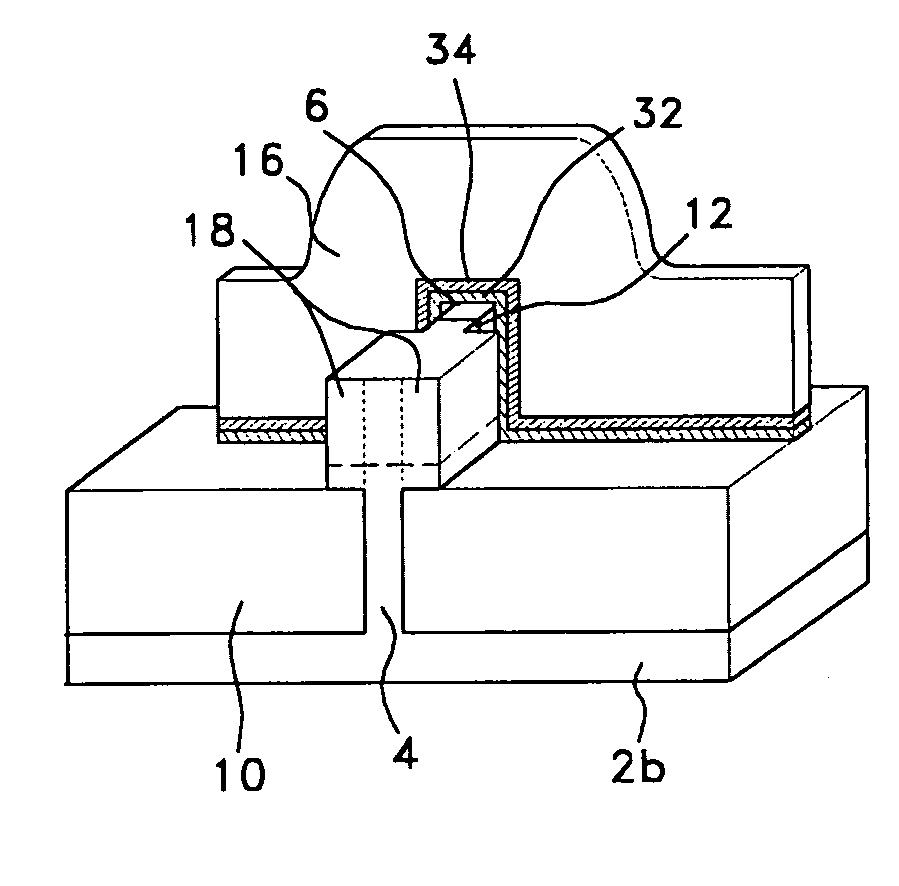

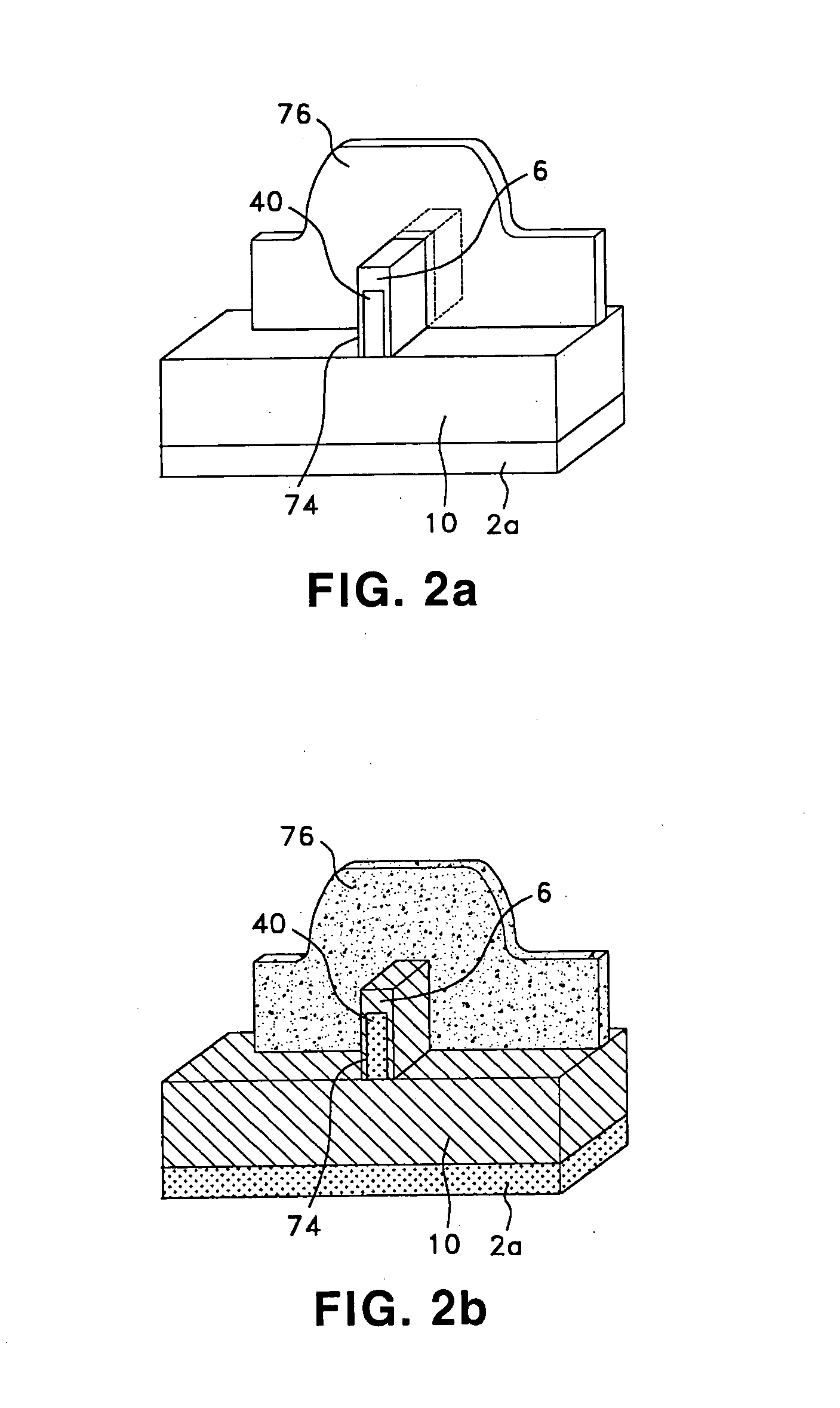

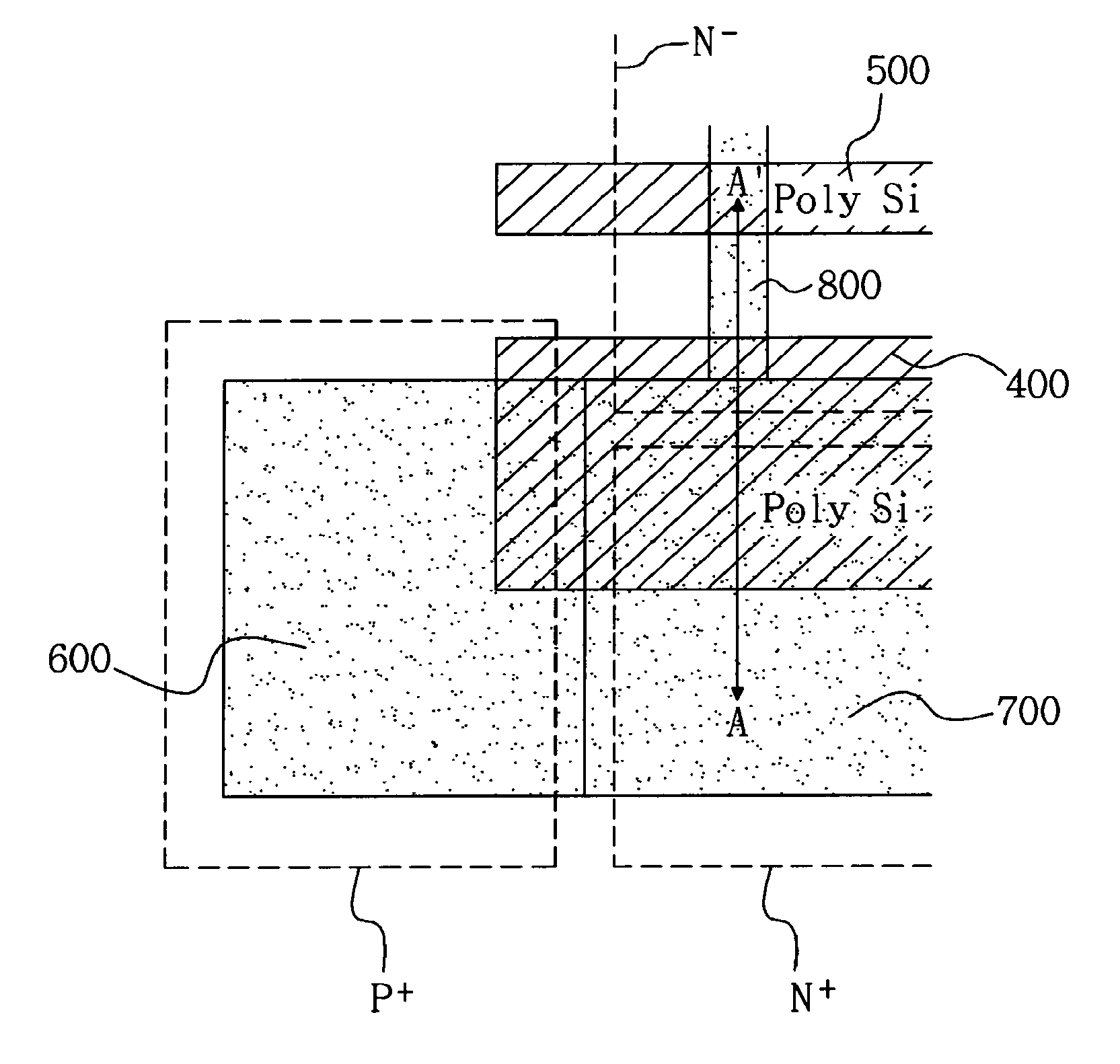

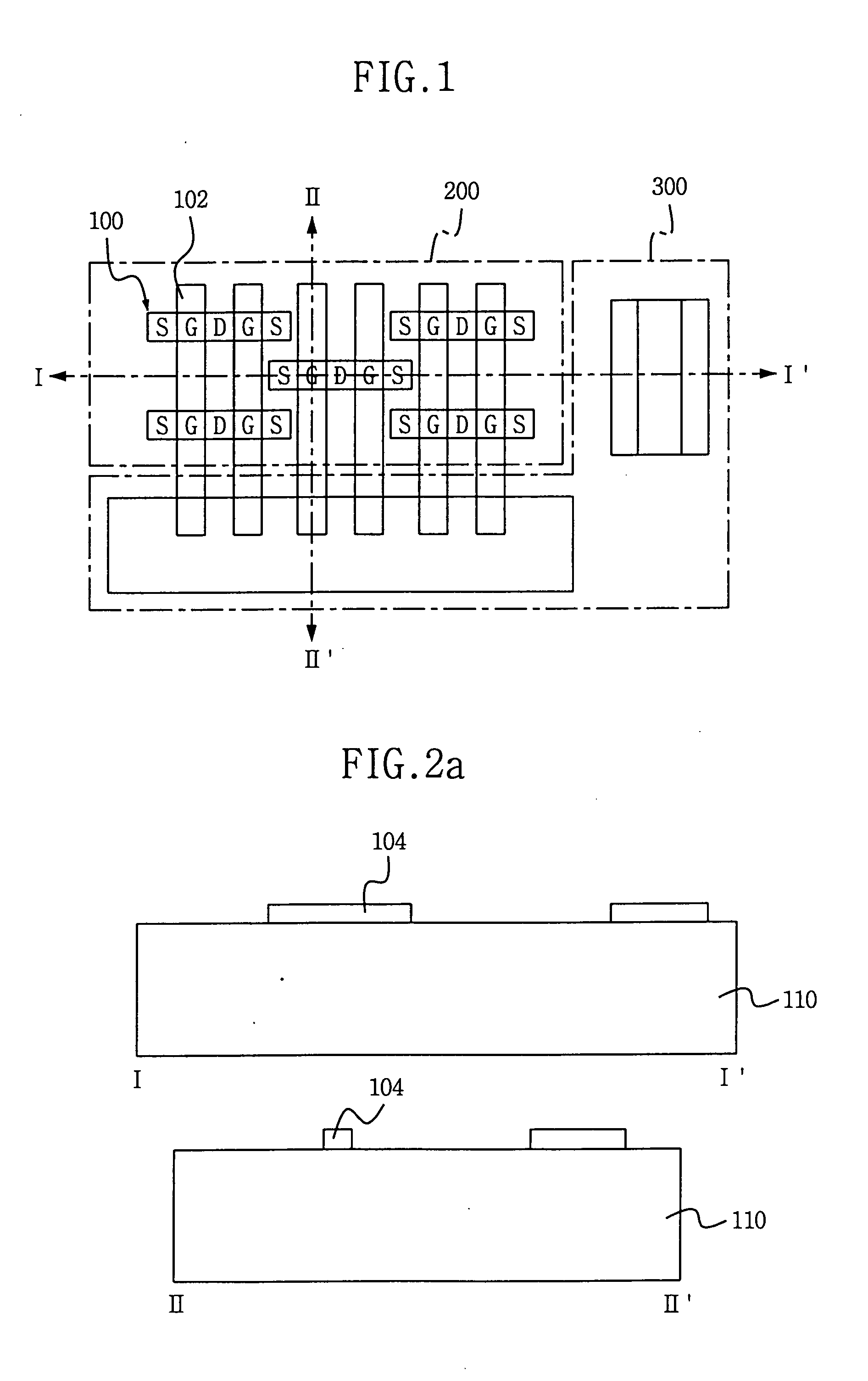

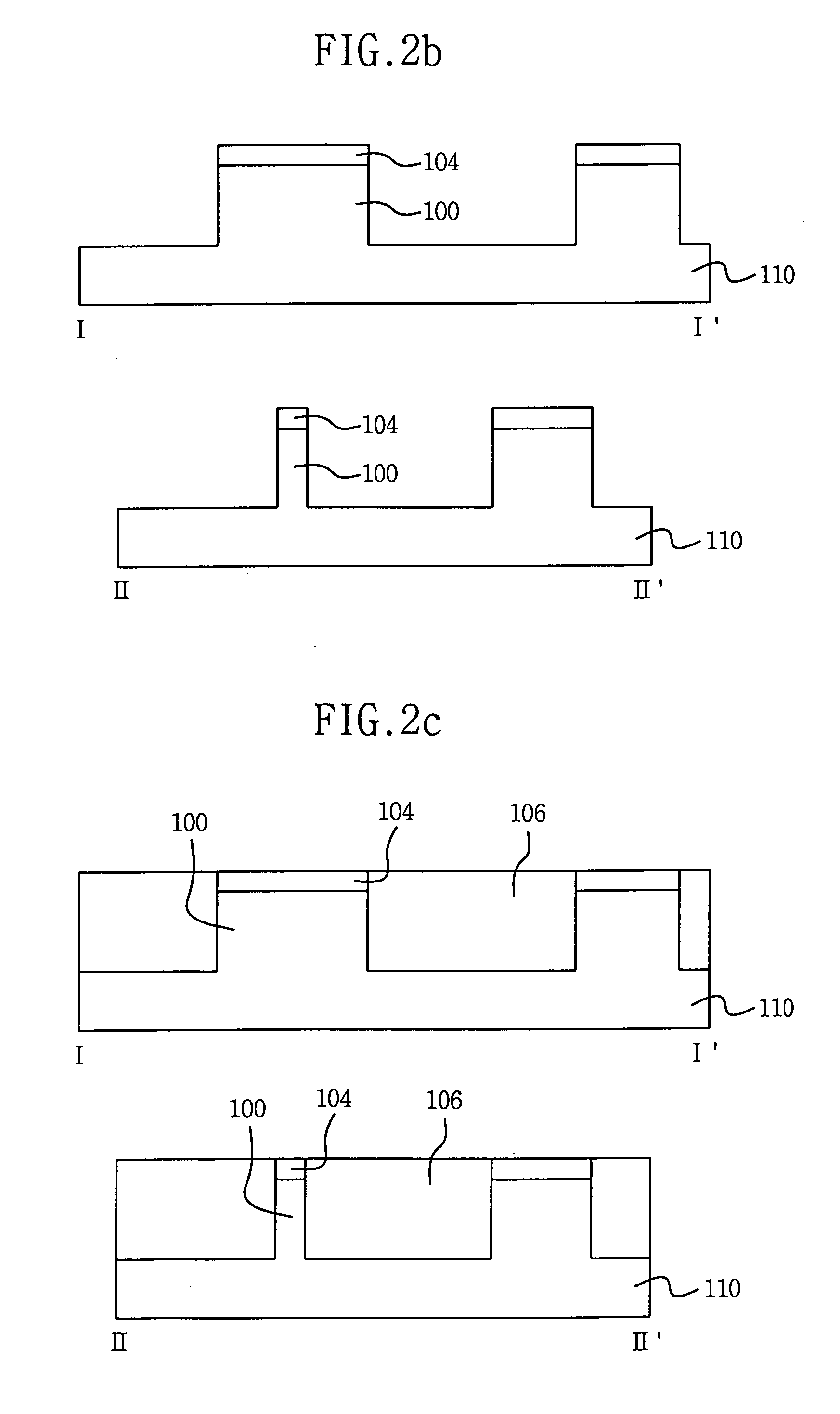

Double-gate FinFET device and fabricating method thereof

InactiveUS6885055B2Cost of wafer is decreasedImprove featuresTransistorSemiconductor/solid-state device detailsNano sizeFloating body effect

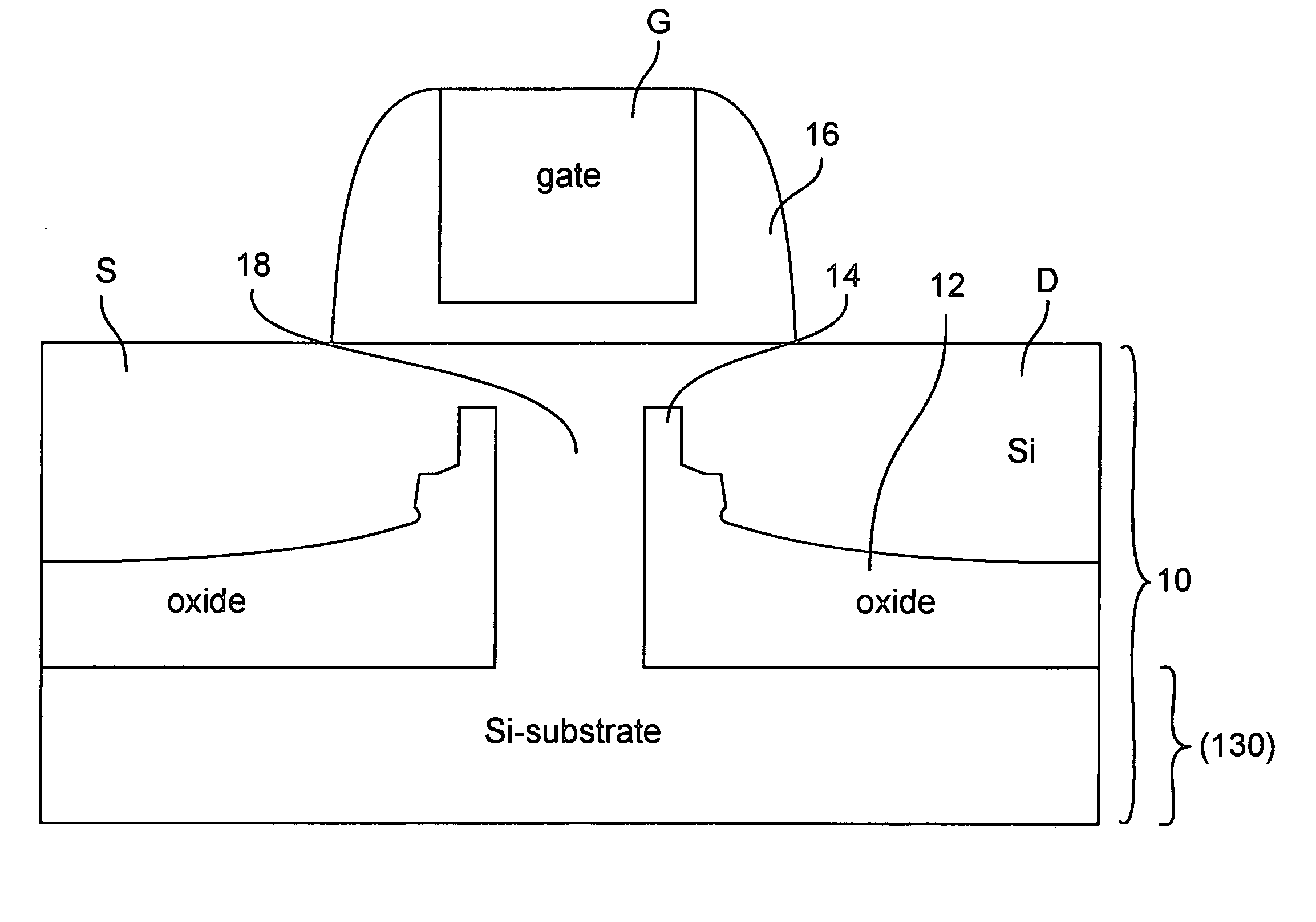

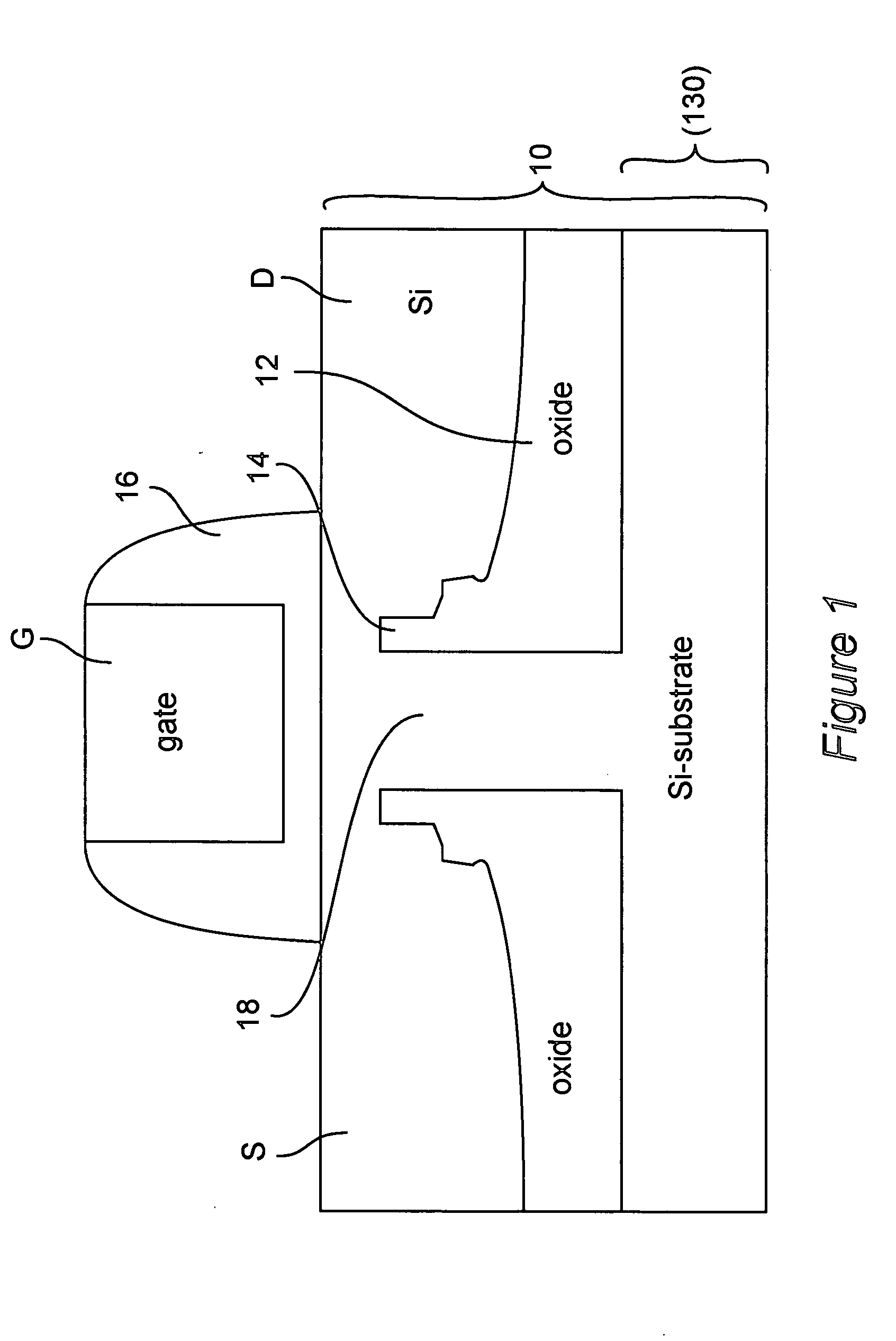

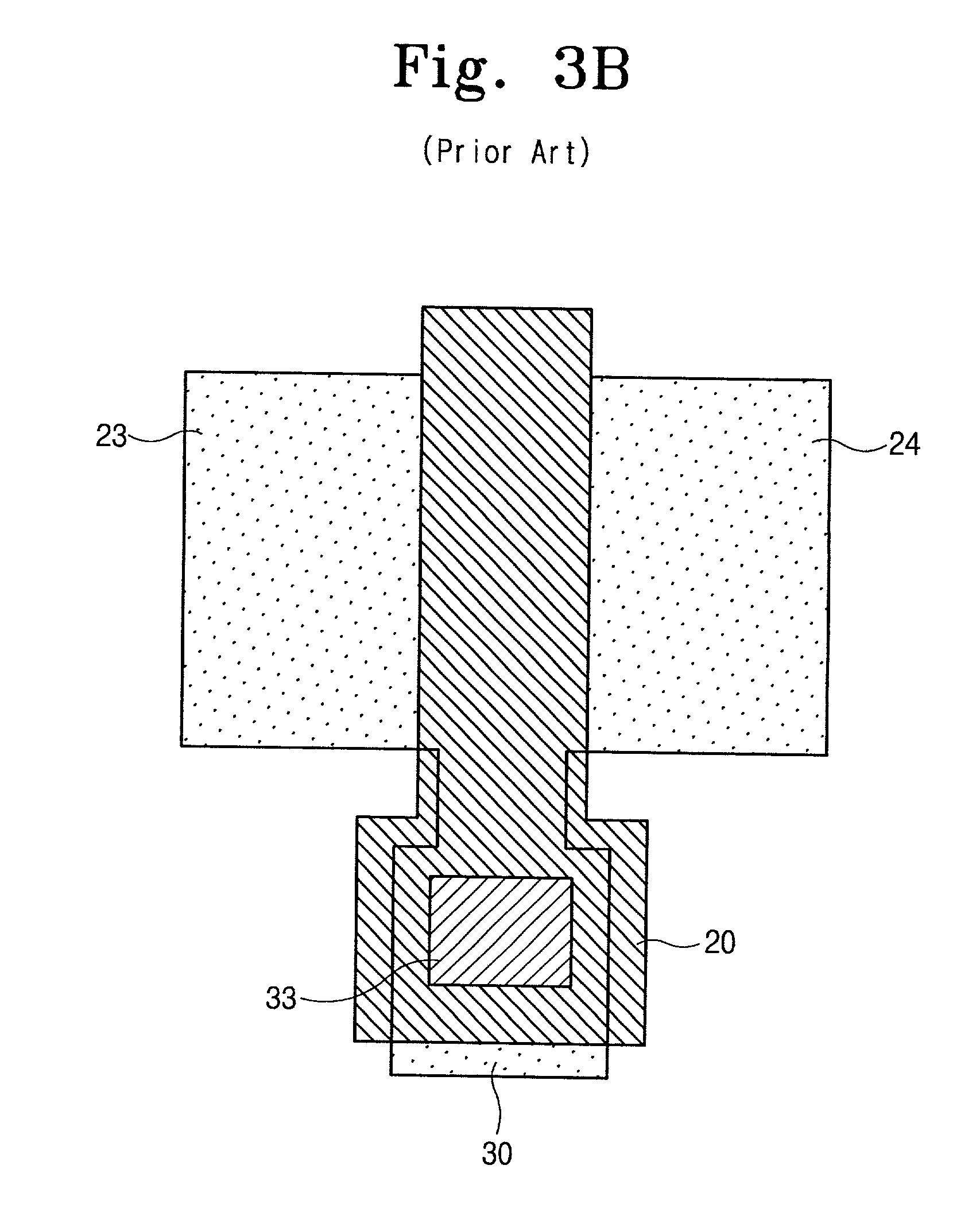

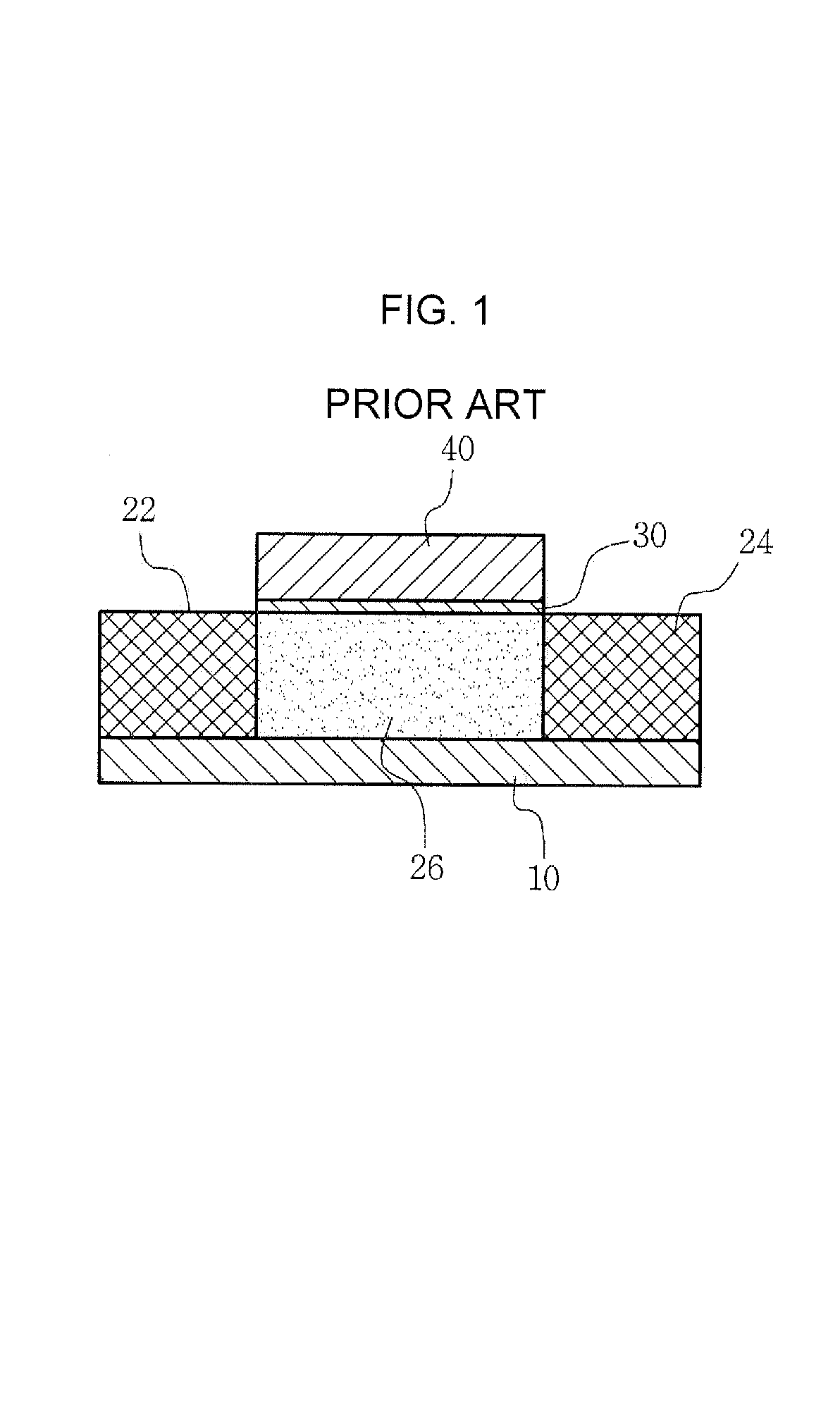

The present invention relates to double-gate FinFET devices and fabricating methods thereof. More particularly, the invention relates to an electrically stable double-gate FinFET device and the method of fabrication in which the Fin active region on a bulk silicon substrate where device channel and the body are to be formed has a nano-size width and is connected to the substrate and is formed with the shape of a wall along the channel length direction.The conventional double-gate MOS devices are fabricated using SOI wafers which are more expensive than bulk silicon wafers. It also has problems including the floating body effects, larger source / drain parasitic resistance, off-current increase, and deterioration in heat transfer to the substrate.

Owner:KIPB LLC

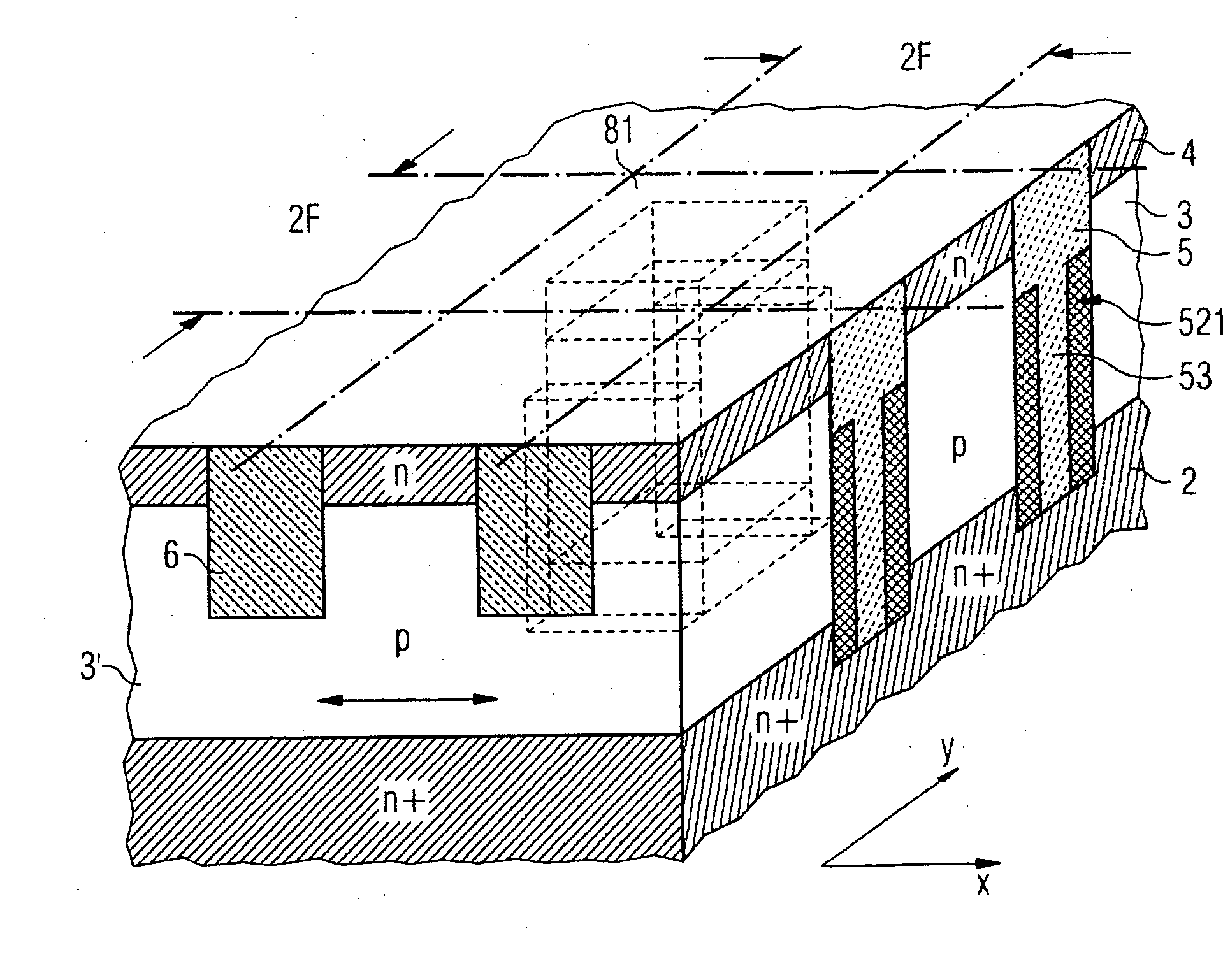

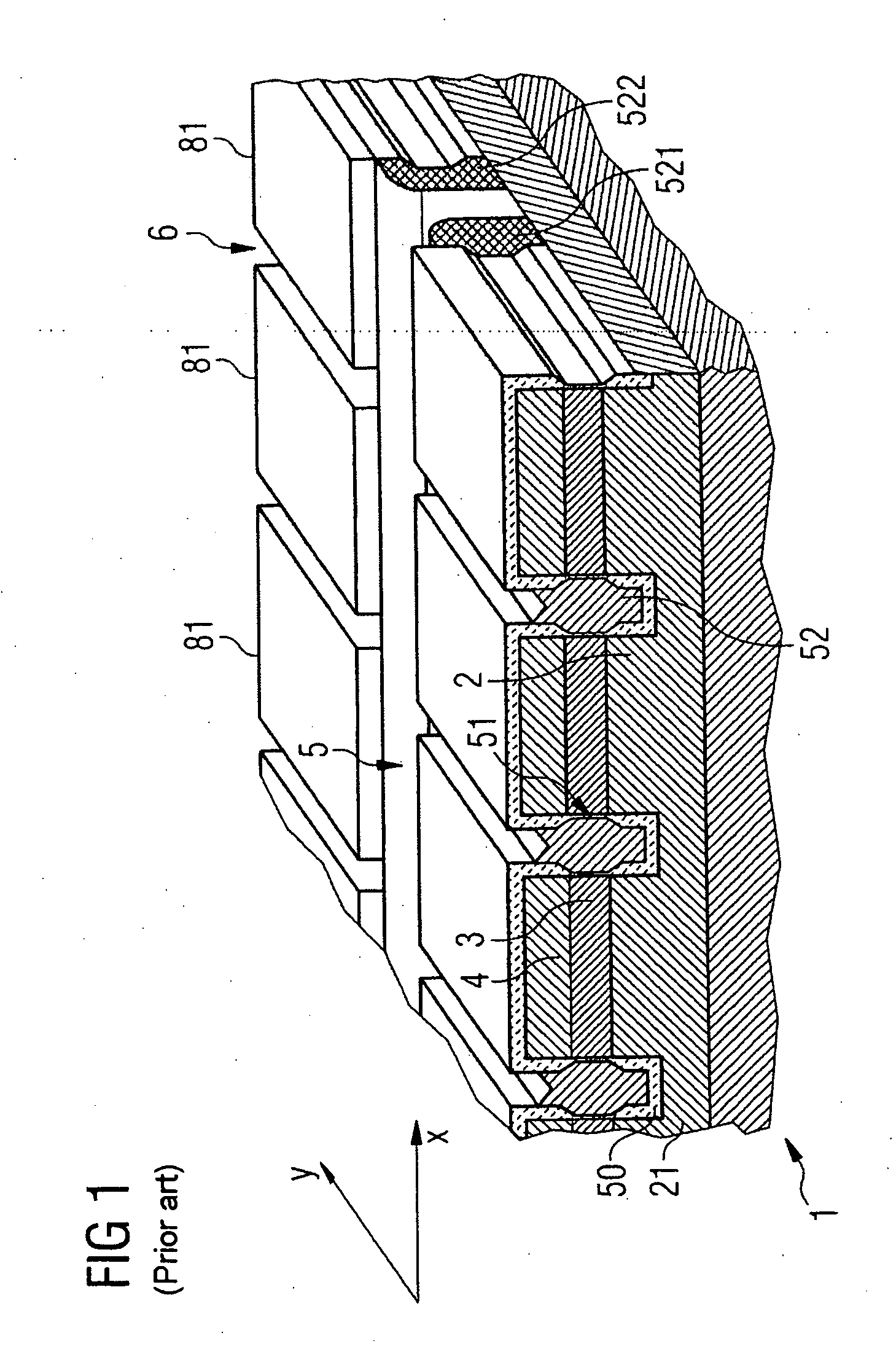

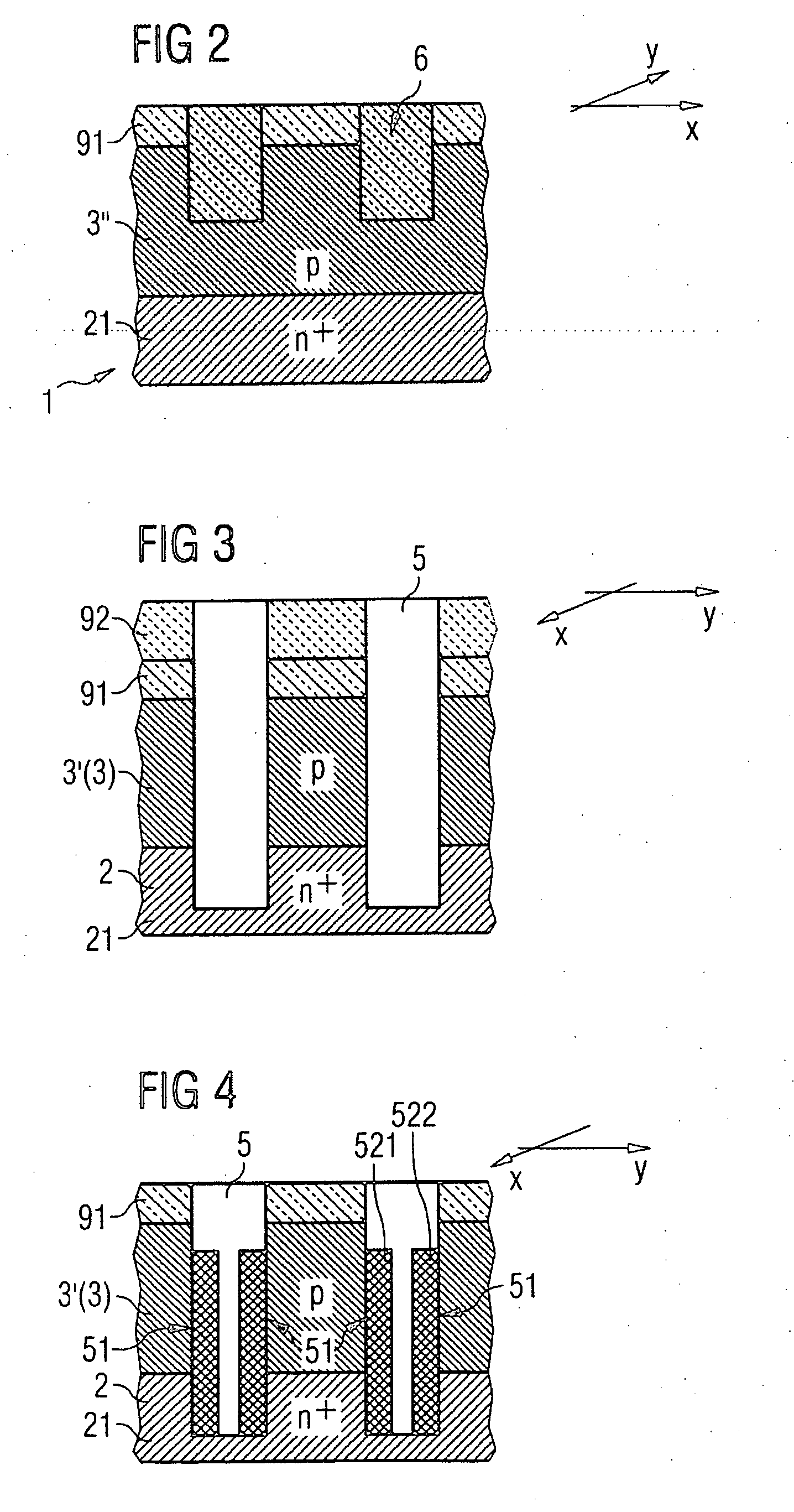

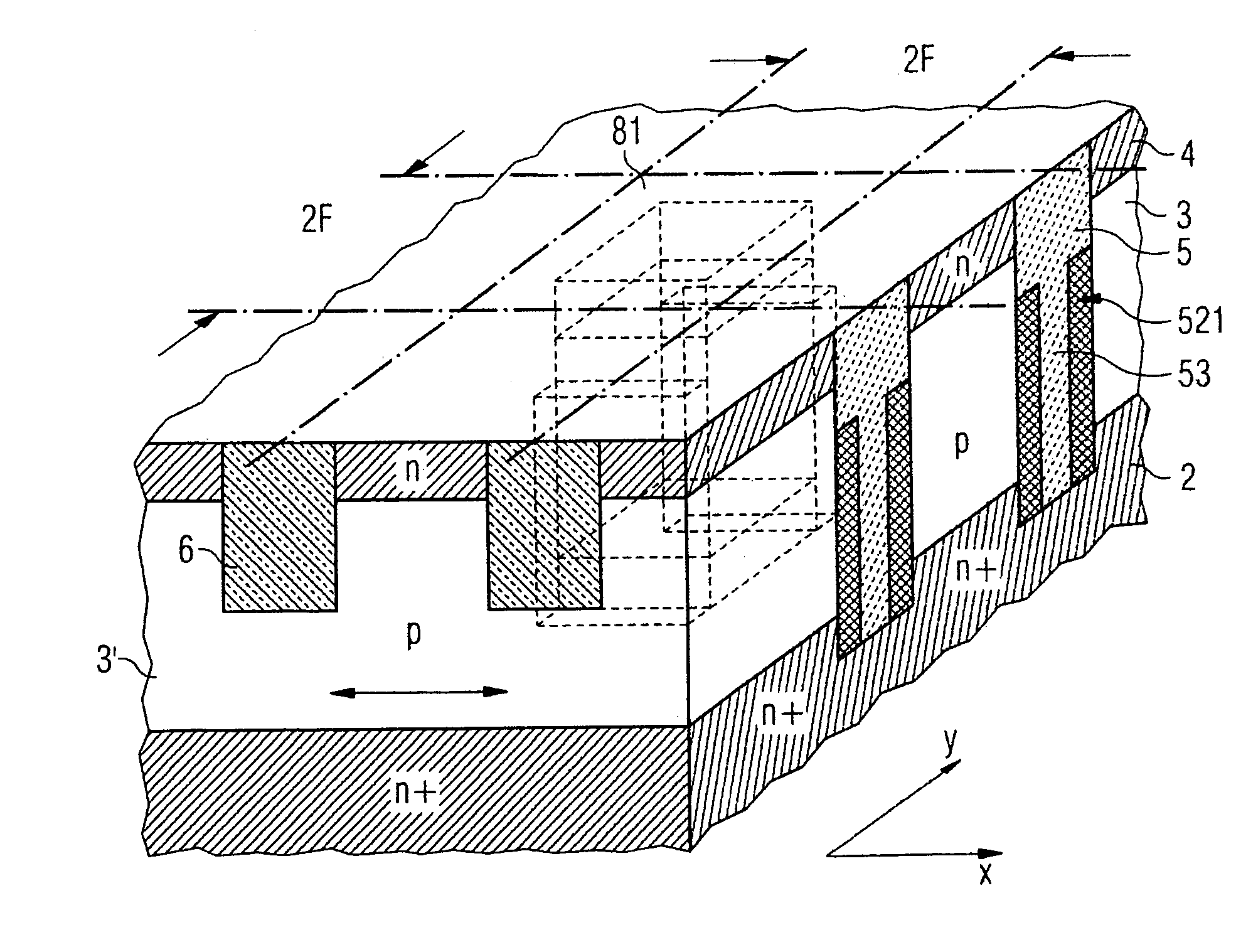

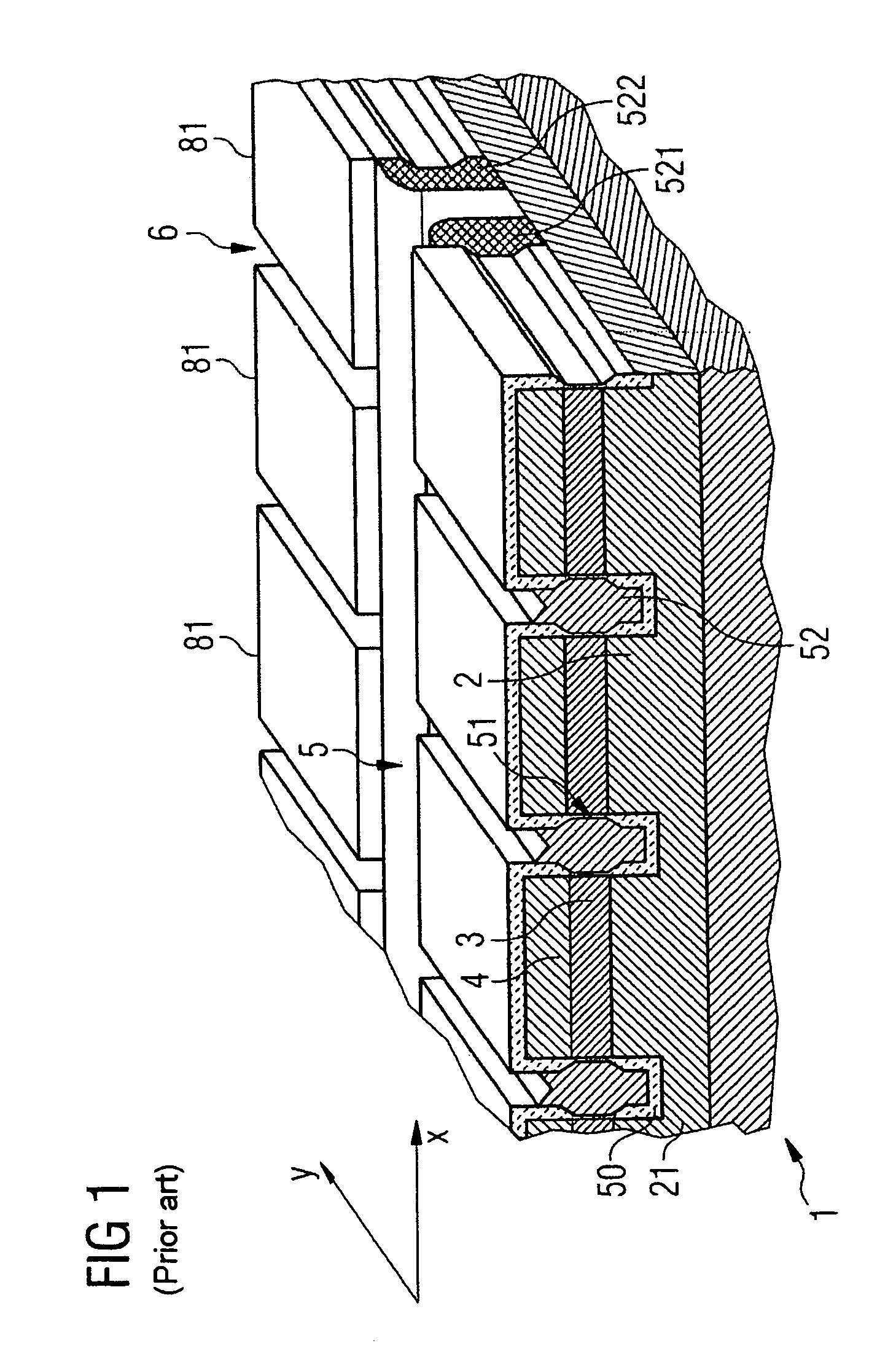

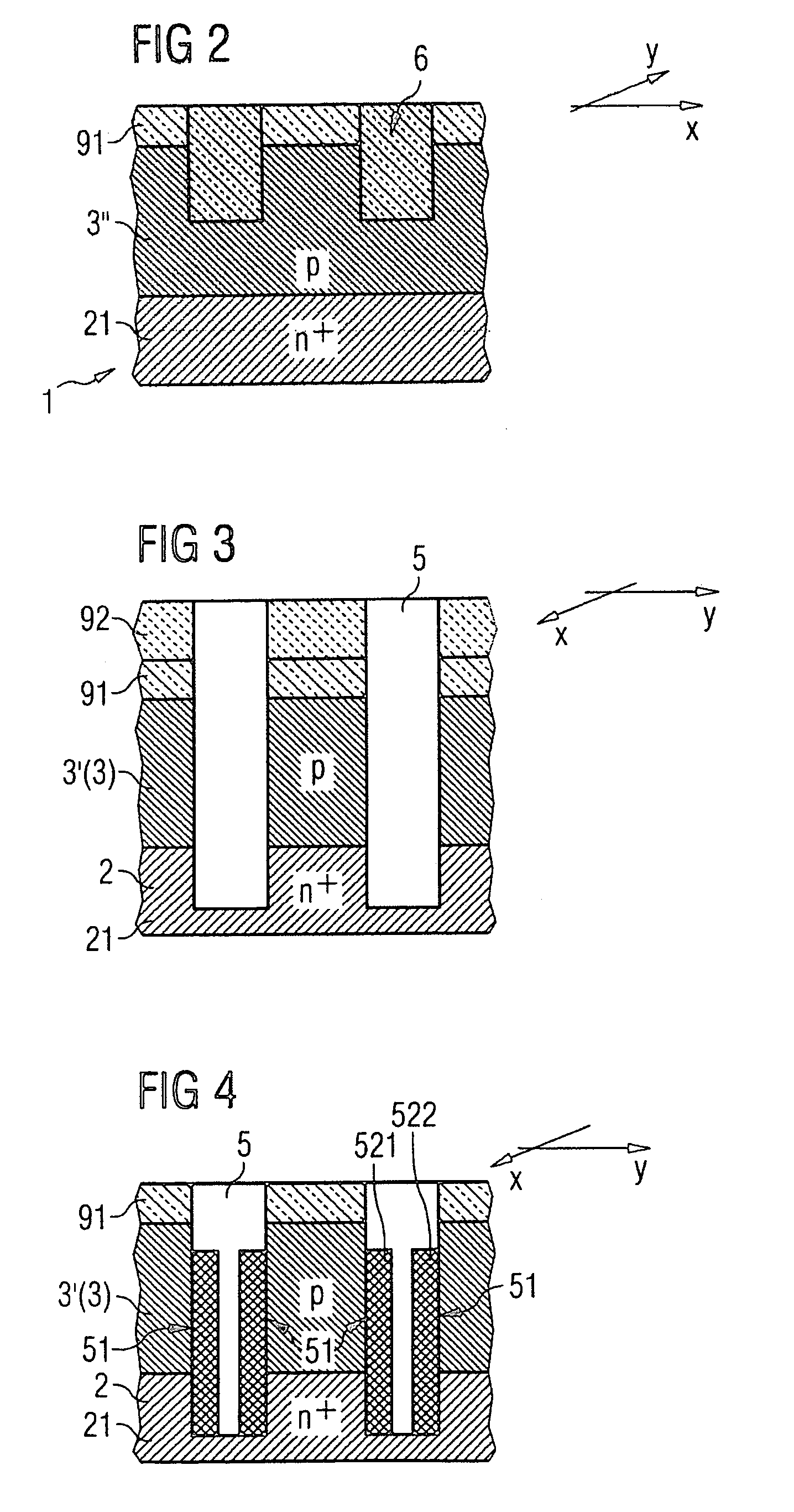

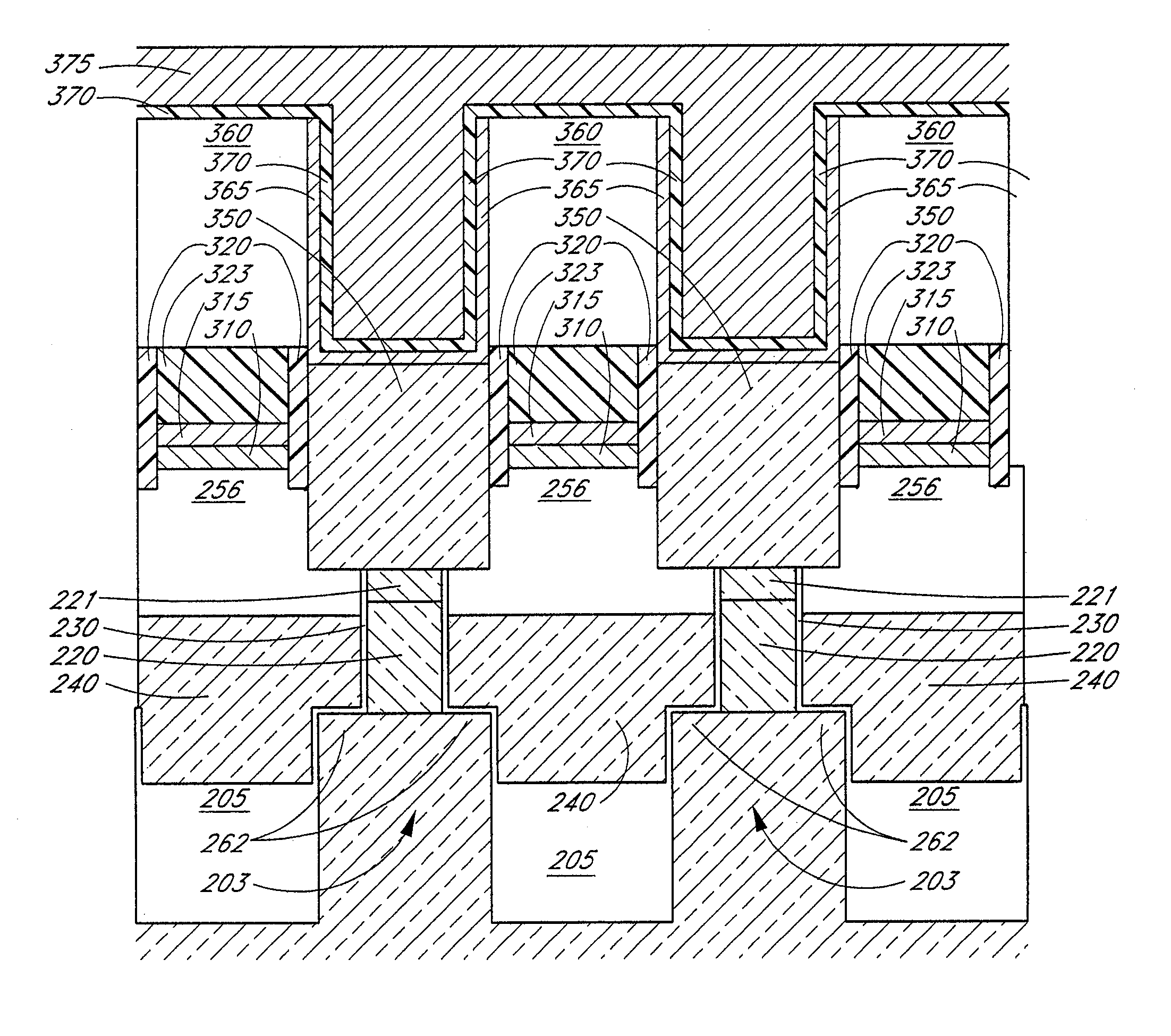

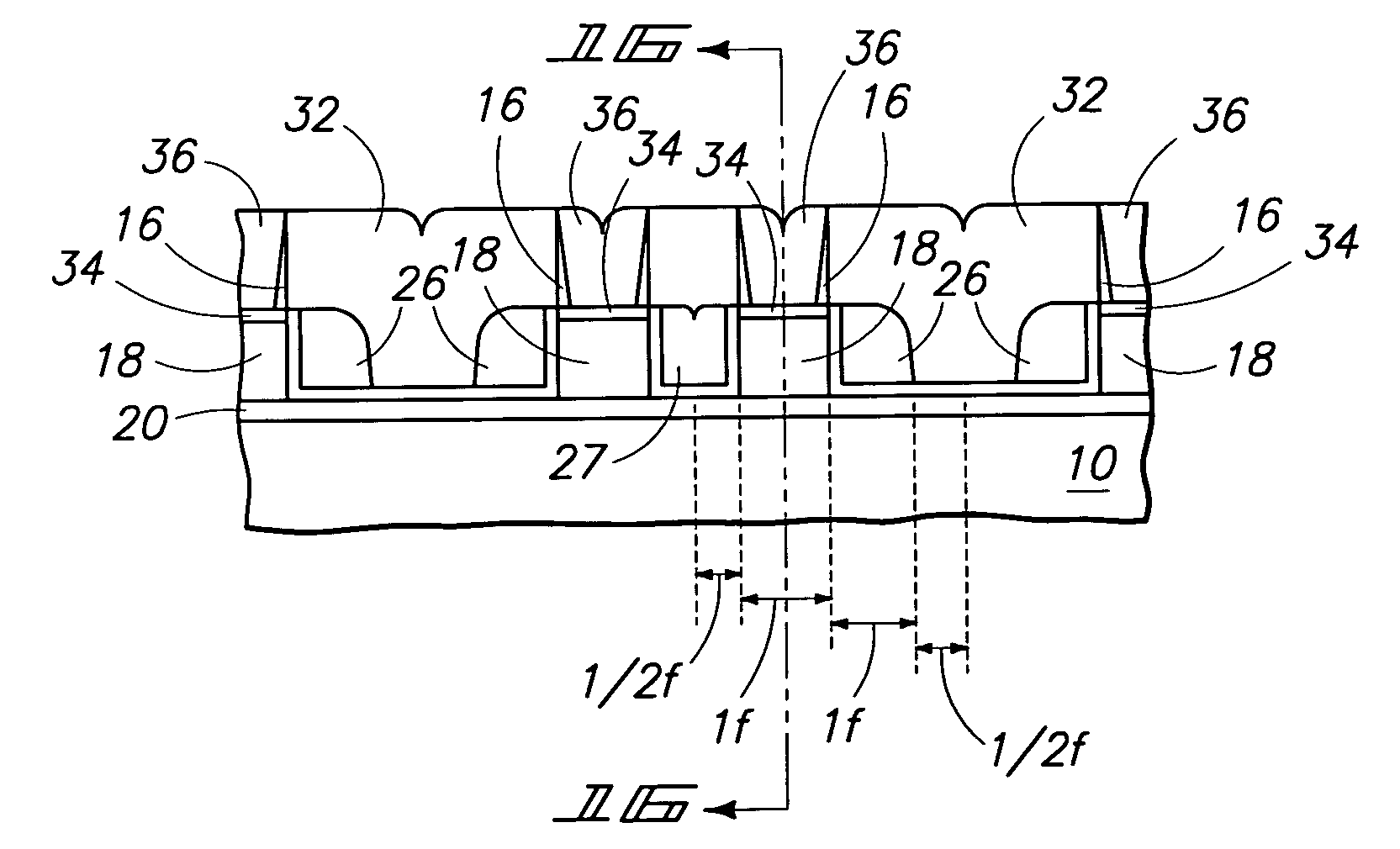

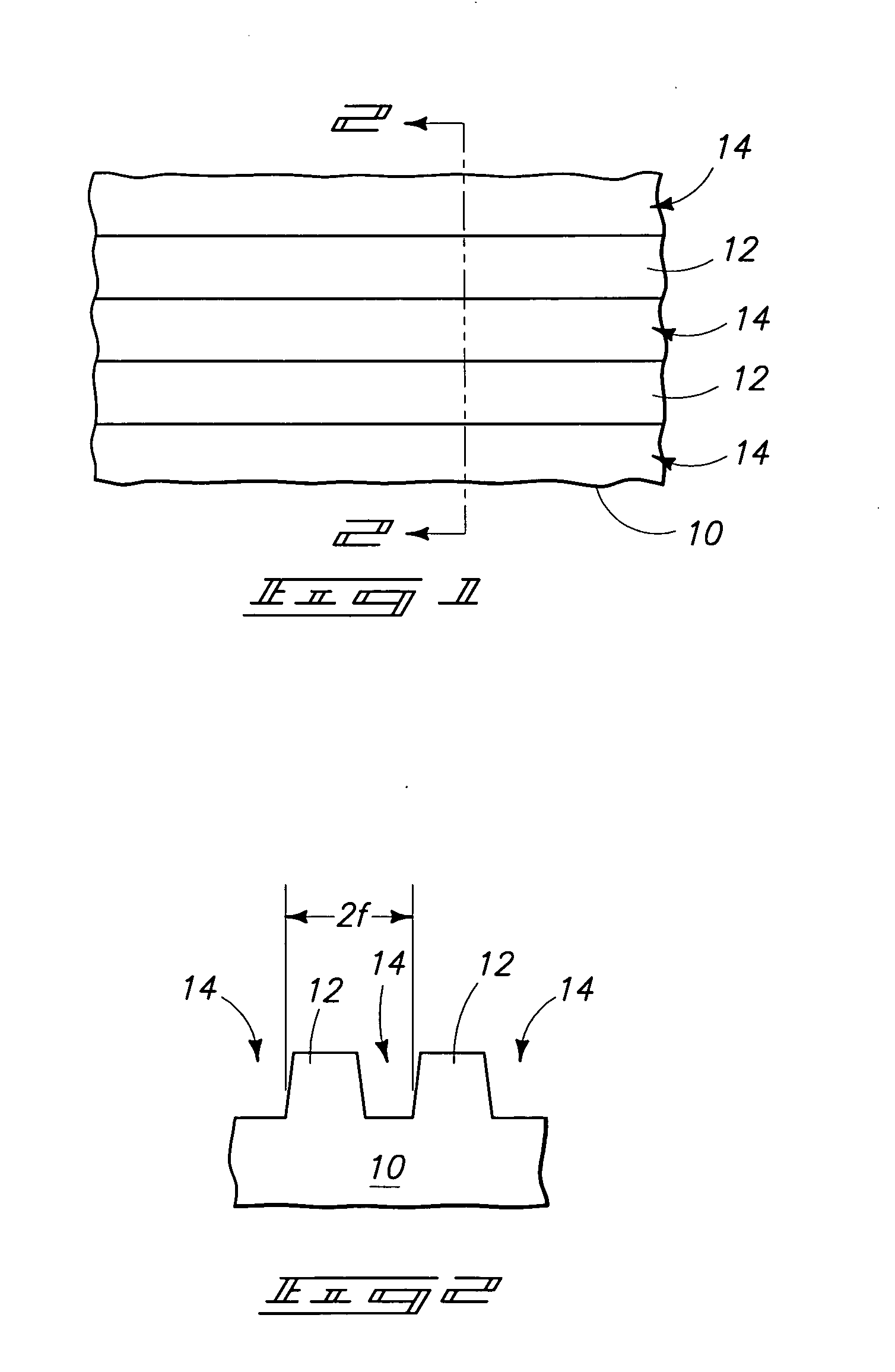

Method of fabricating and architecture for vertical transistor cells and transistor-controlled memory cells

InactiveUS20050001257A1Increased area requirementLimited functionTransistorSolid-state devicesFloating body effectDram memory

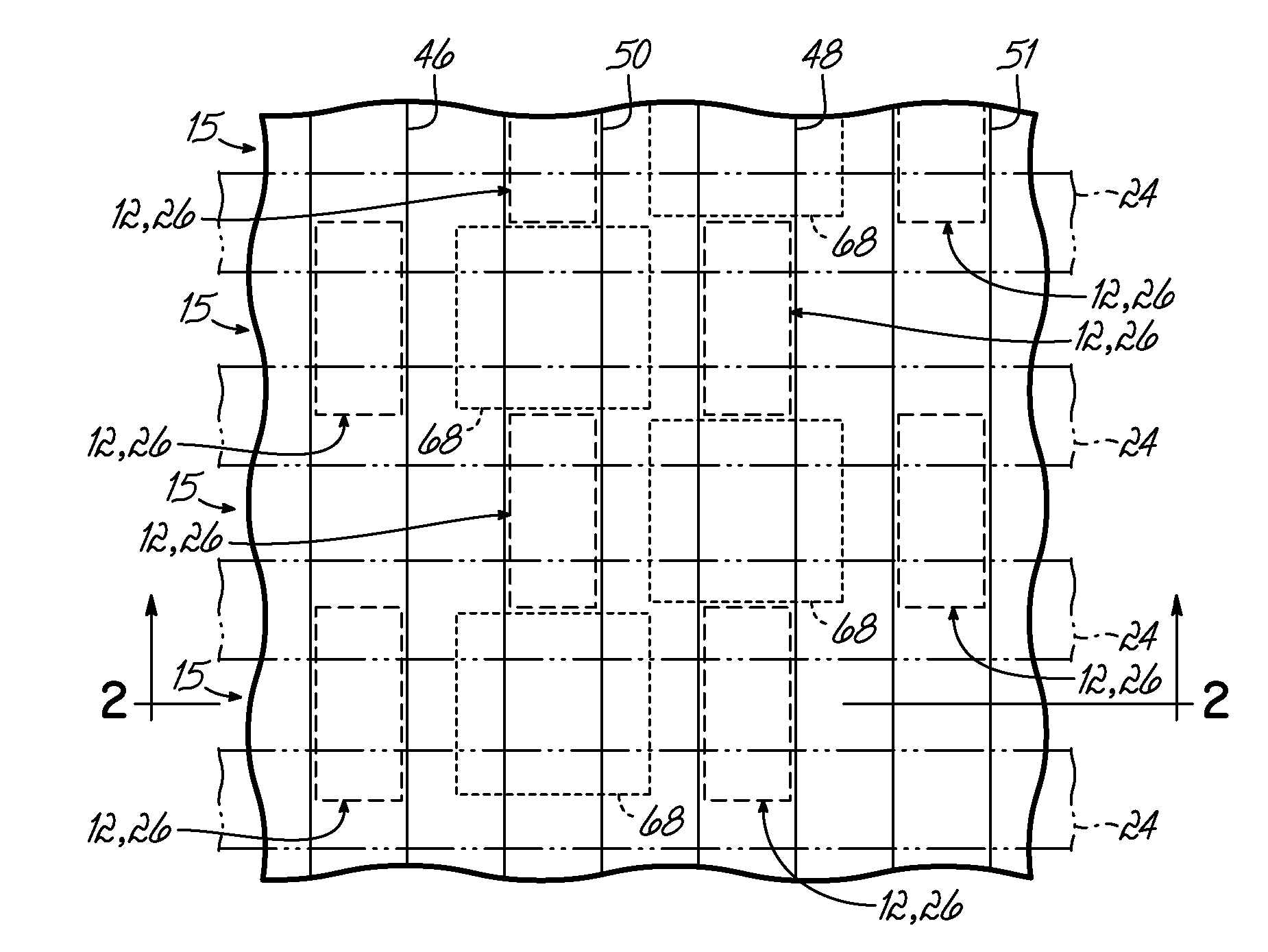

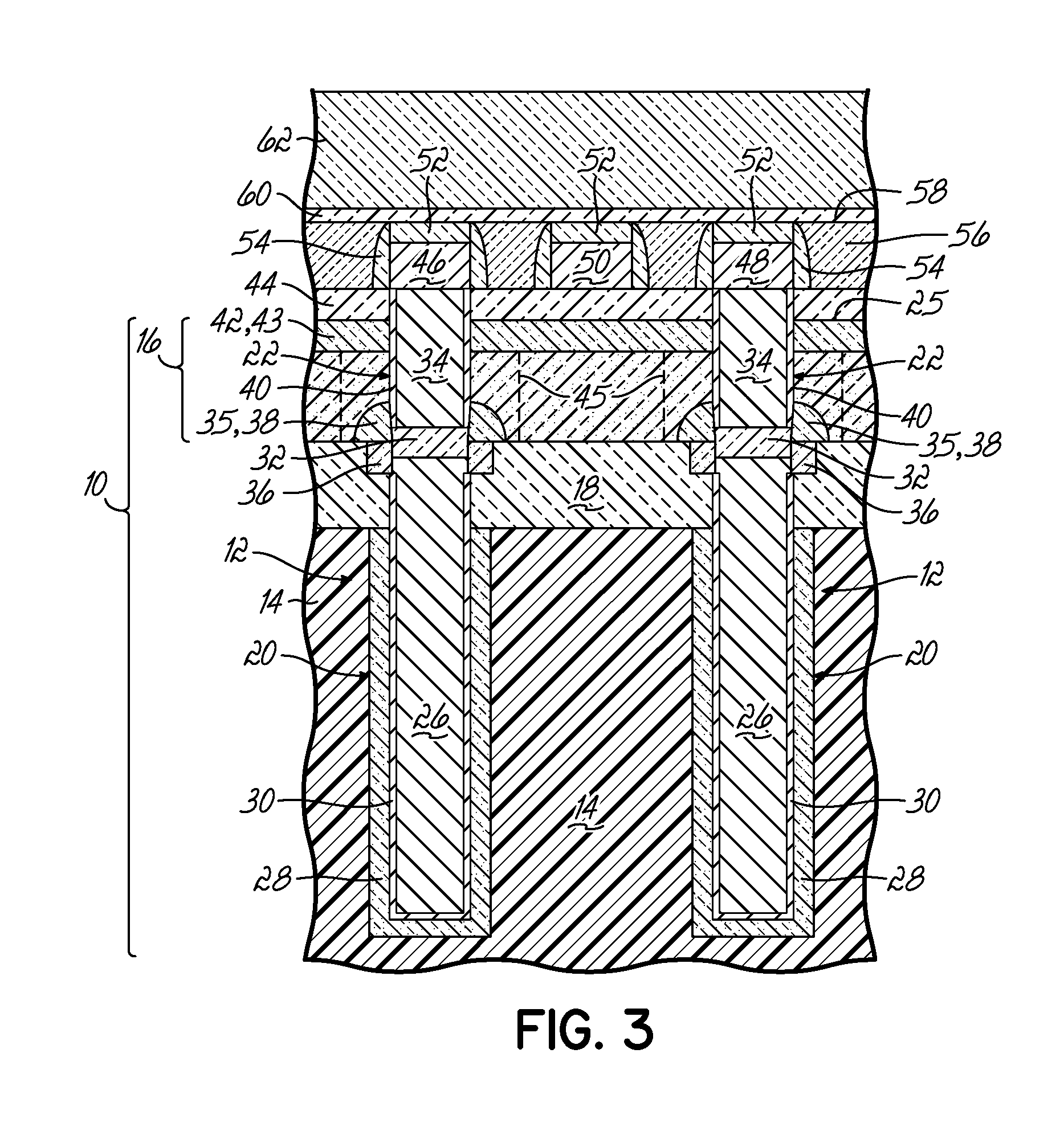

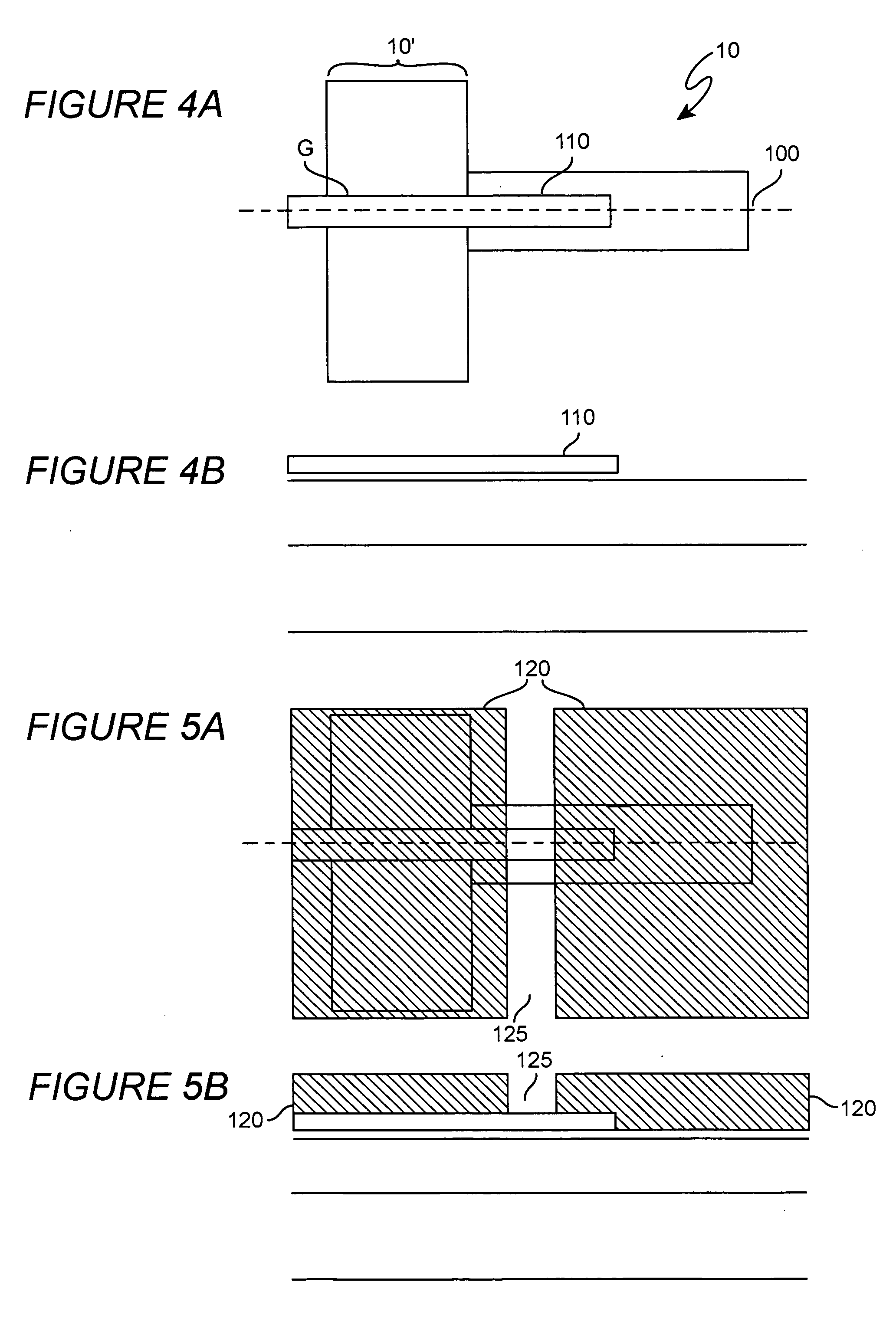

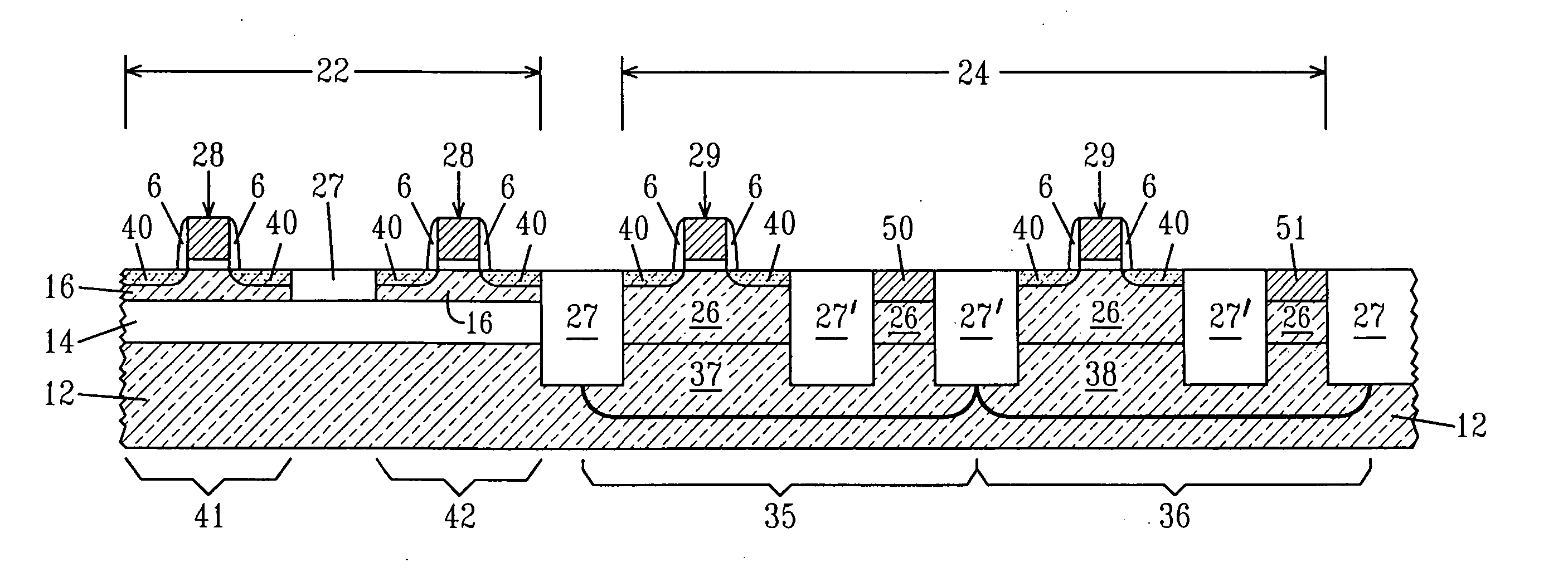

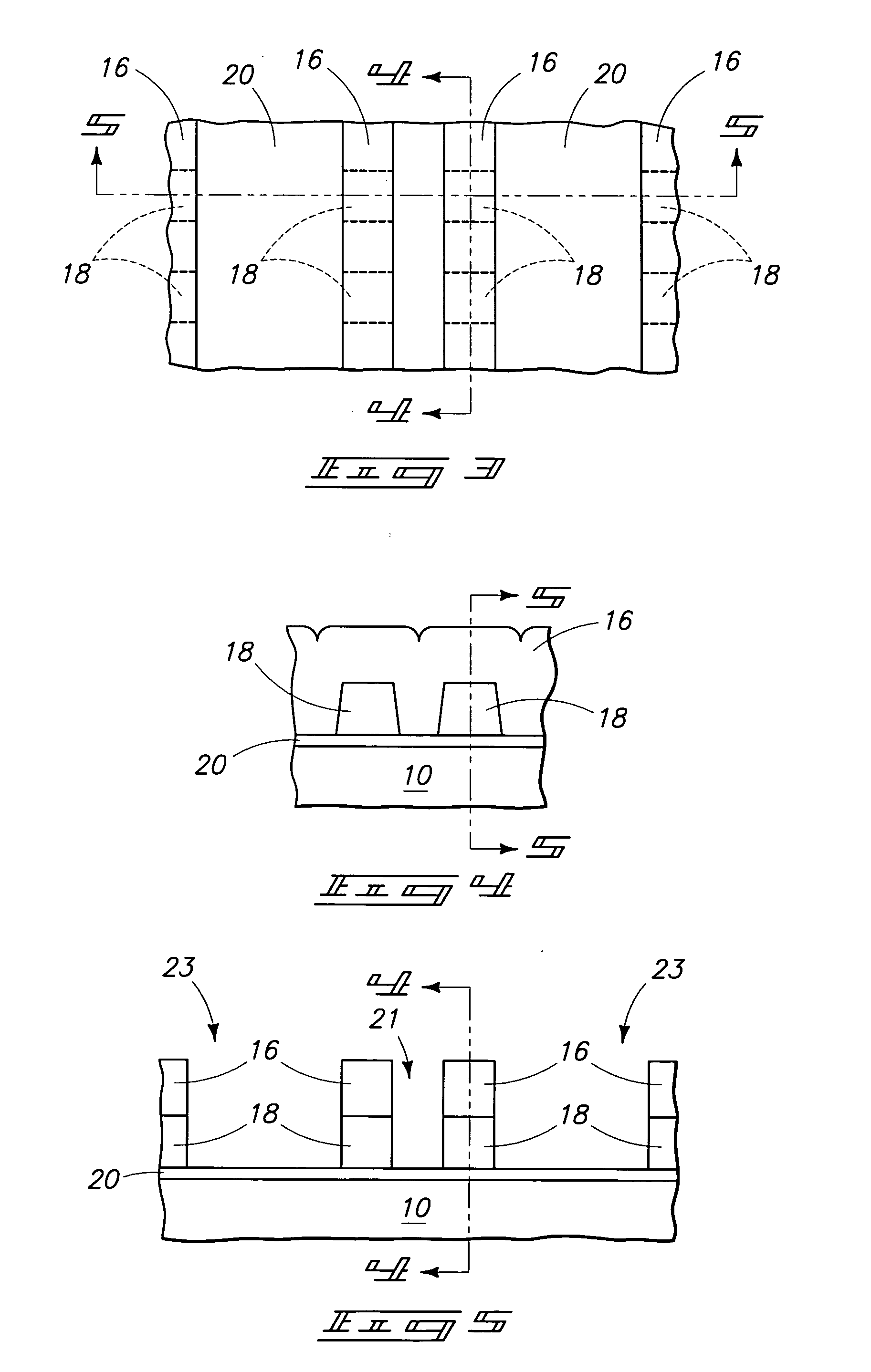

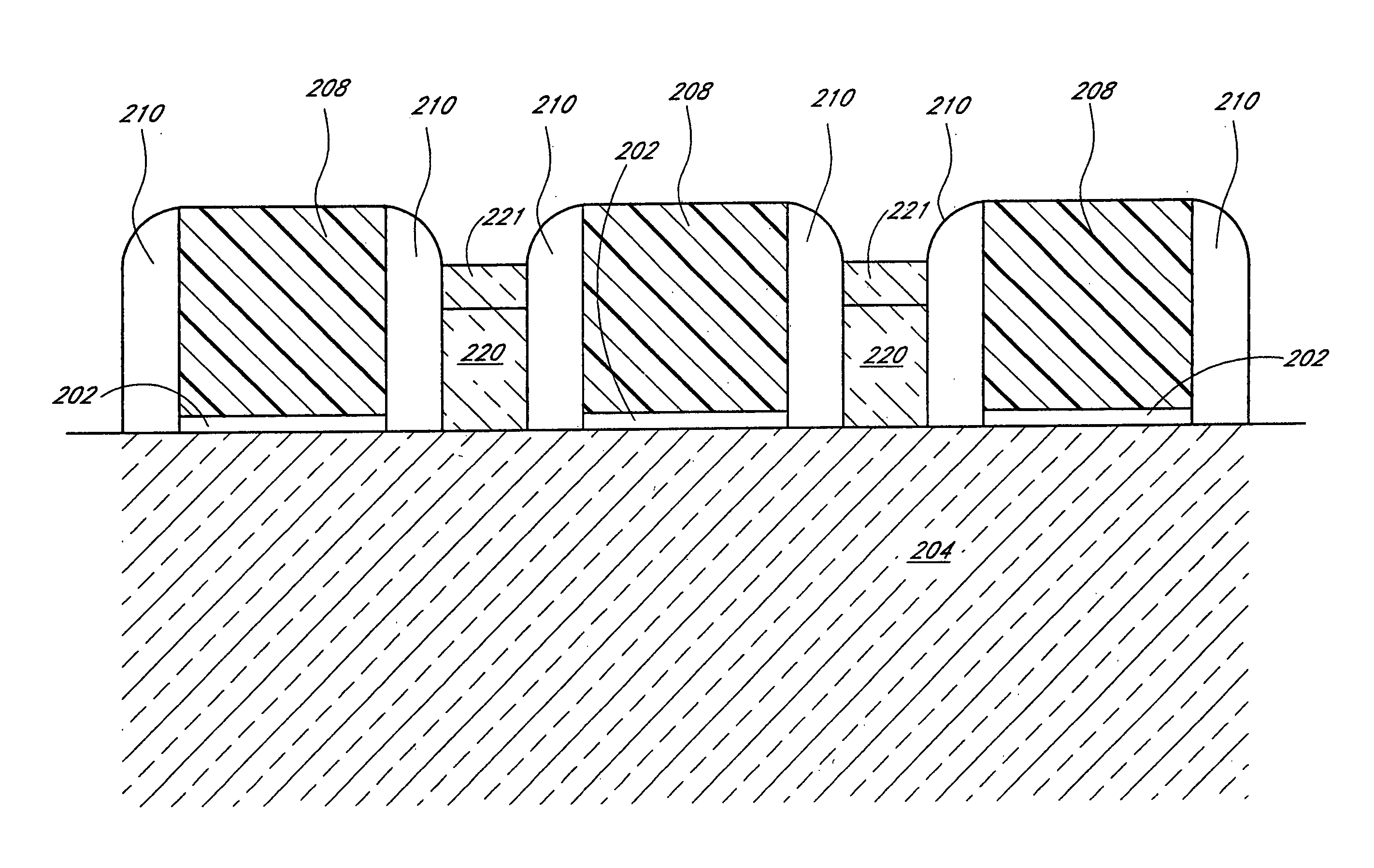

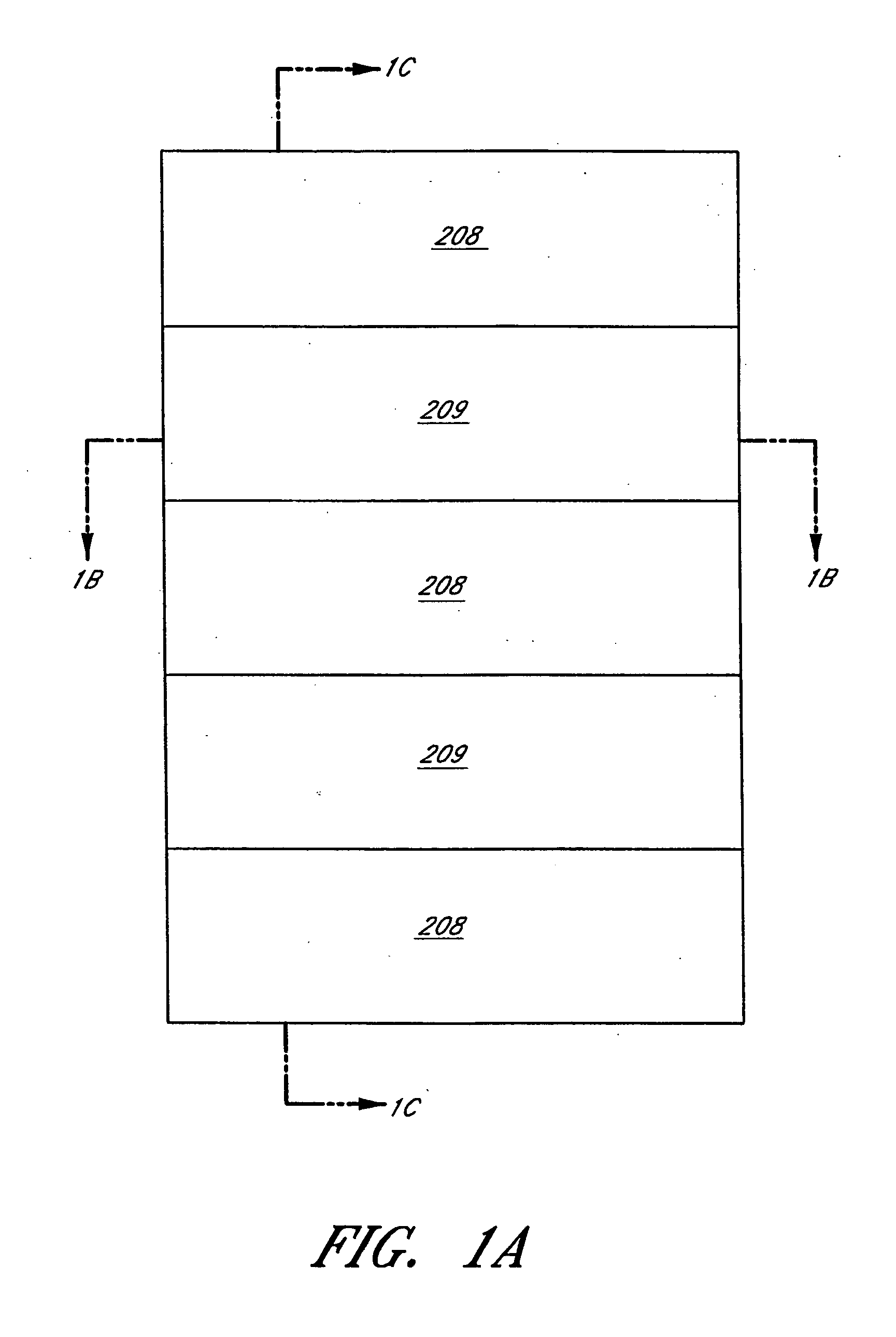

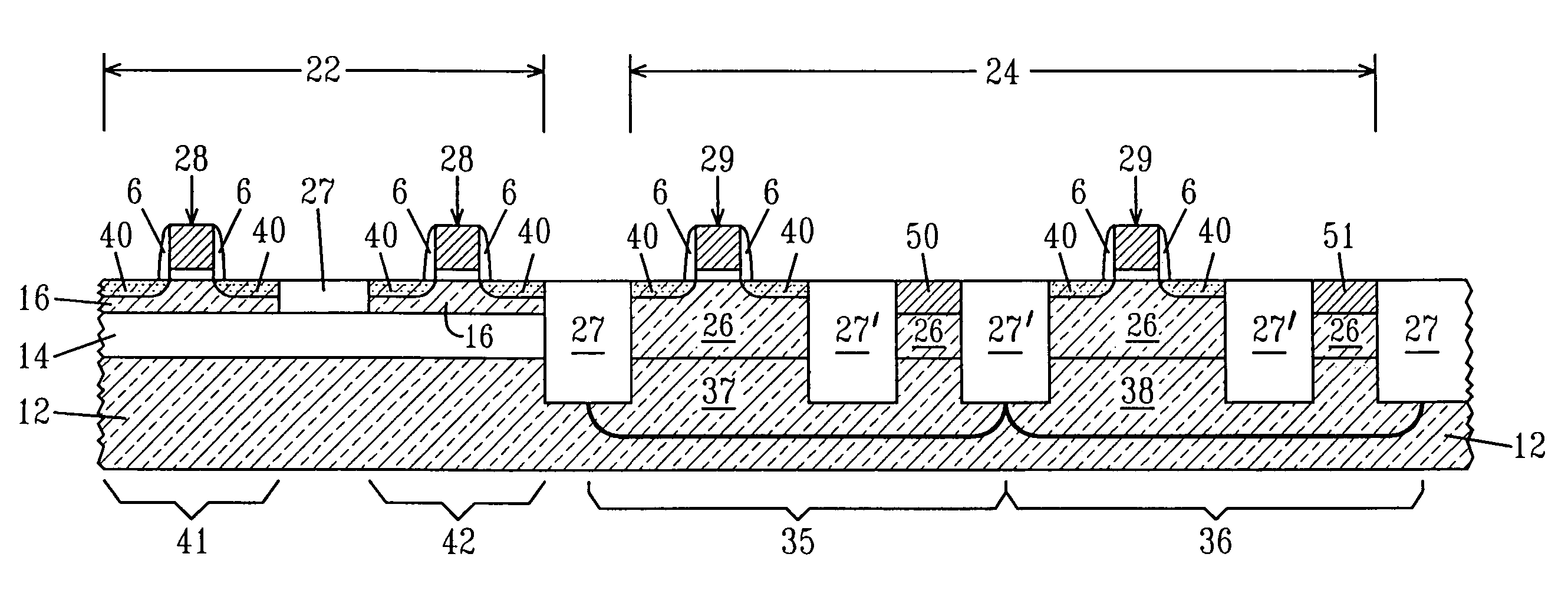

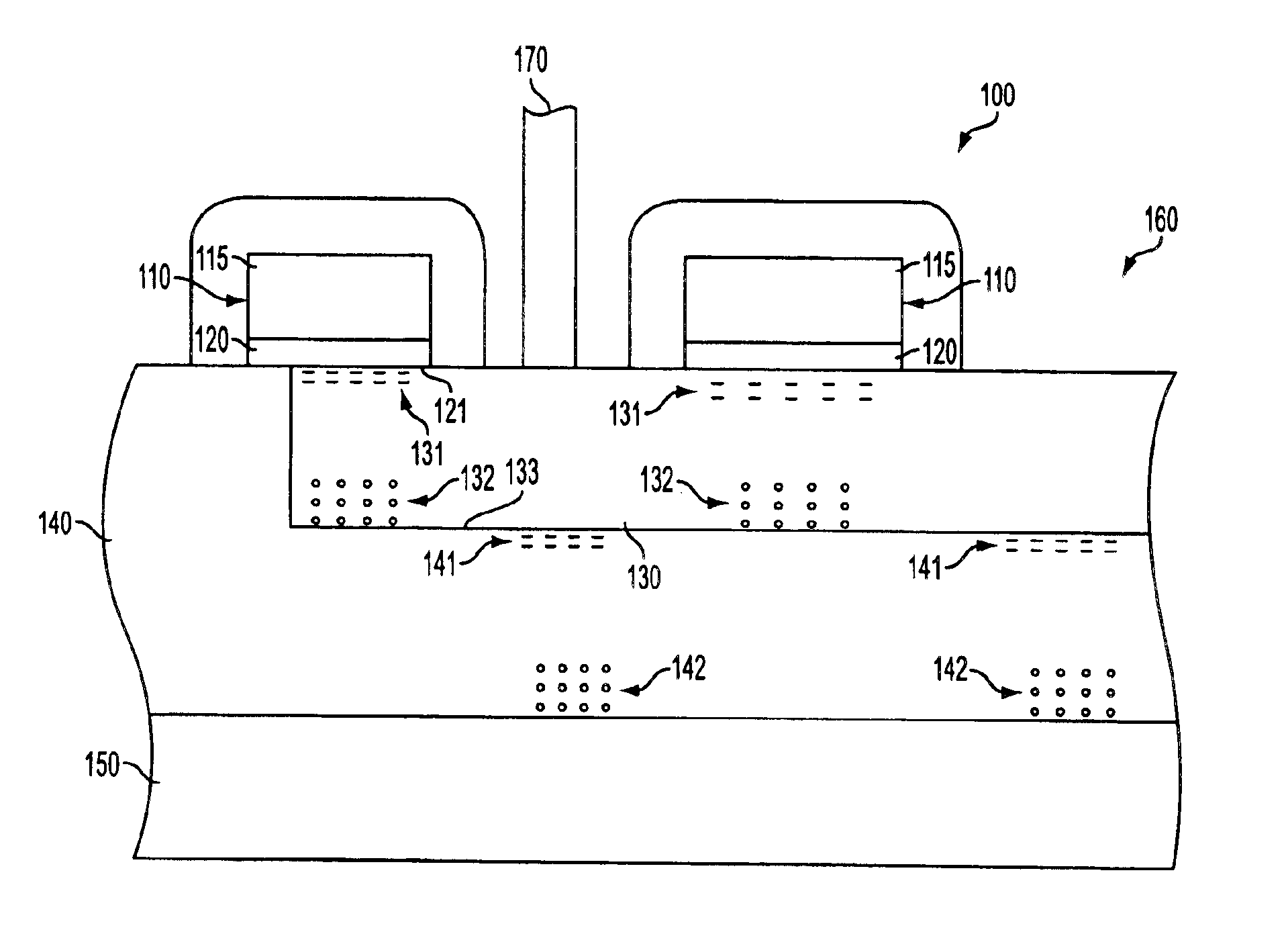

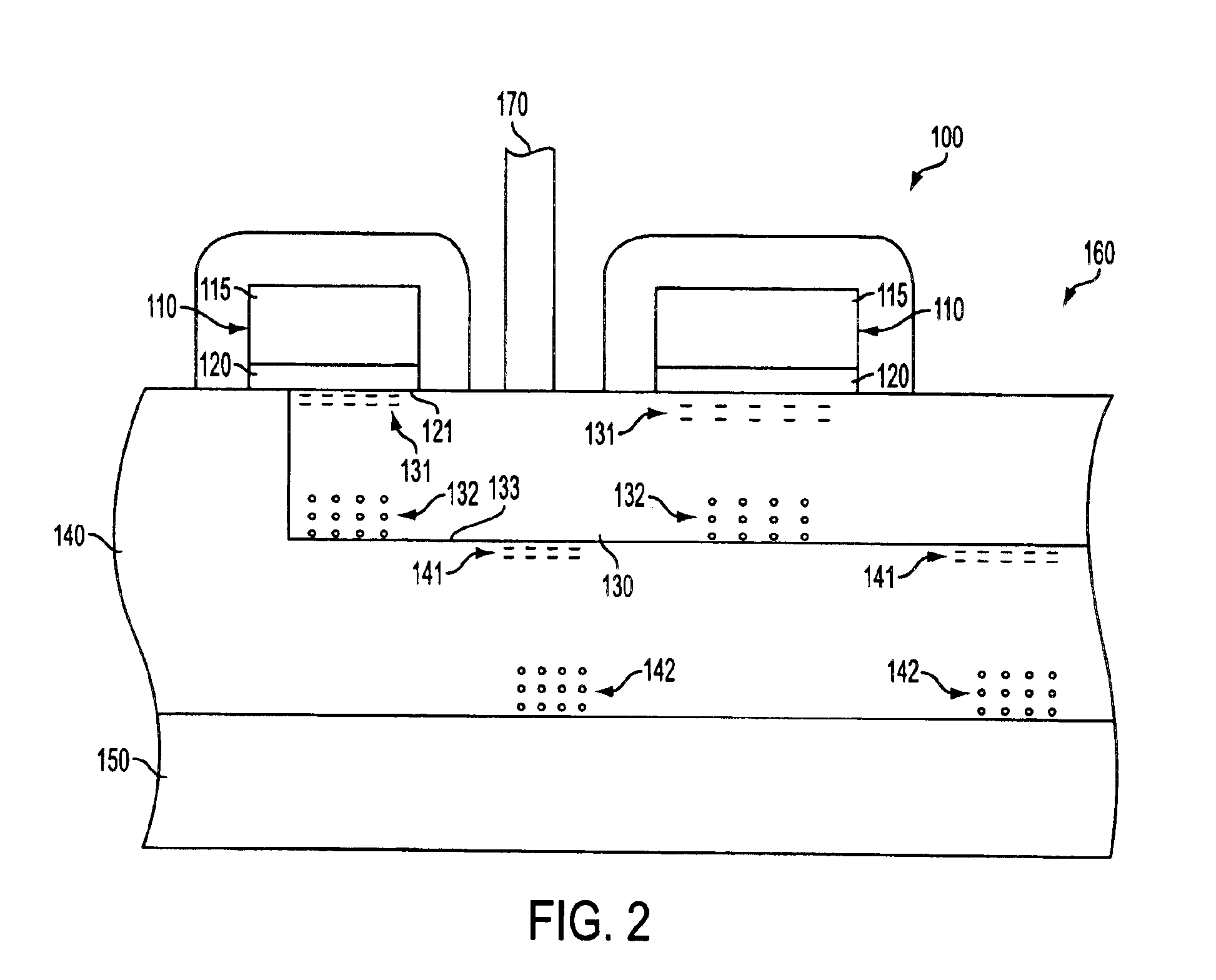

In a substrate vertical transistor cells are formed and are arranged, in a transistor cell array, row by row in an x direction and column by column in a y direction. Lower source / drain regions of the transistor cells are connected to a common connection plate. Upper source / drain regions of the transistor cells impart a contact connection for instance to a storage capacitor of a DRAM memory cell. Active trenches running between the transistor cells with word lines are formed along the x direction. The word lines form gate electrodes in sections. A potential at the gate electrode controls a conductive channel in an active region arranged in each case between the upper and the lower source / drain connection region. According to the invention, the active regions of adjacent transistor cells are sections of a contiguous layer body and are connected to one another. An accumulation of charge carriers in the active region and floating body effects are avoided without increasing the area requirement of a transistor cell.

Owner:POLARIS INNOVATIONS LTD

Architecture for vertical transistor cells and transistor-controlled memory cells

InactiveUS7109544B2Meet growth requirementsFunctional restriction of the transistor cells by a floating body effect is reducedTransistorSolid-state devicesTransistor arrayFloating body effect

Owner:POLARIS INNOVATIONS LTD

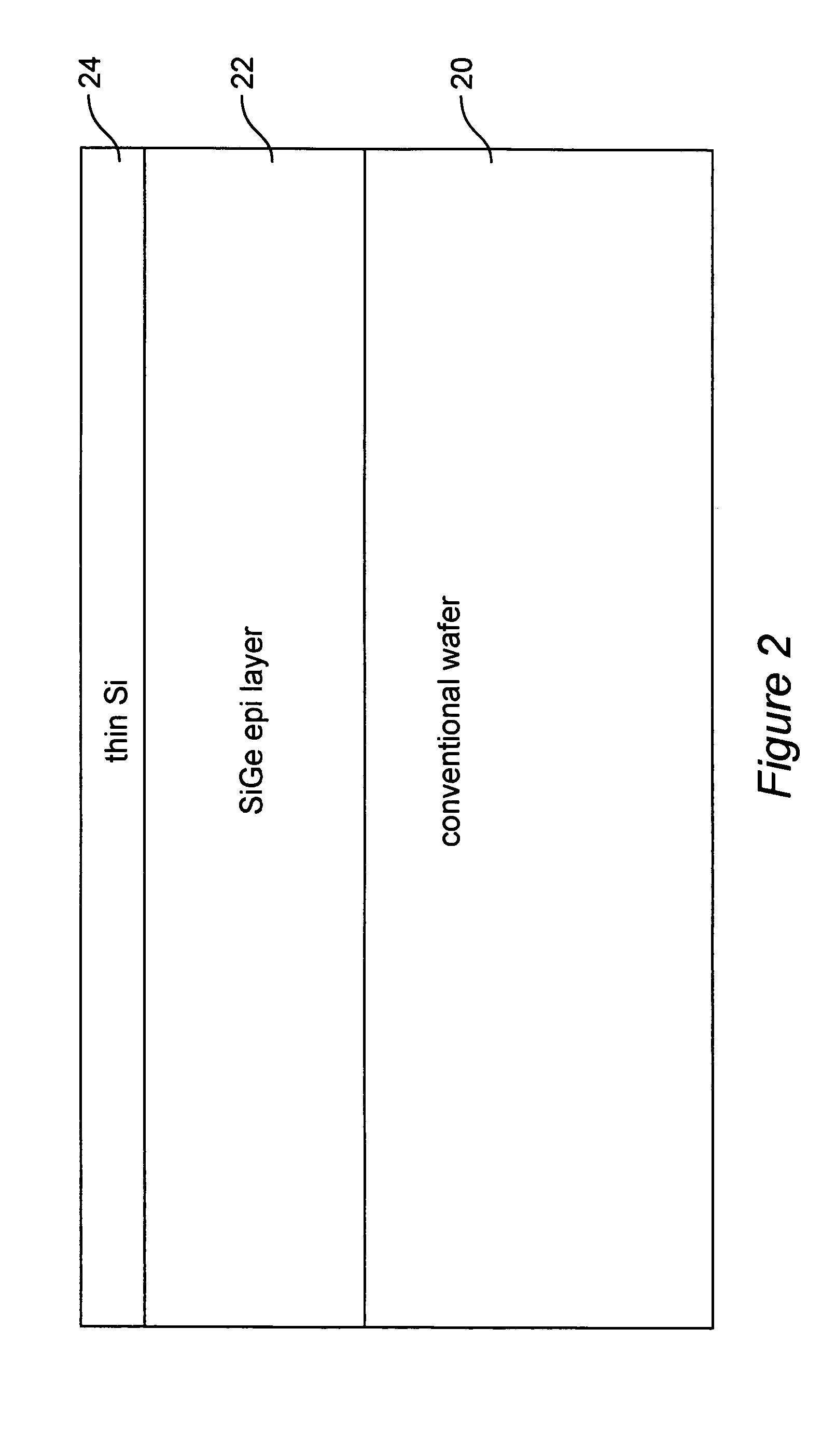

Hybrid SOI/bulk semiconductor transistors

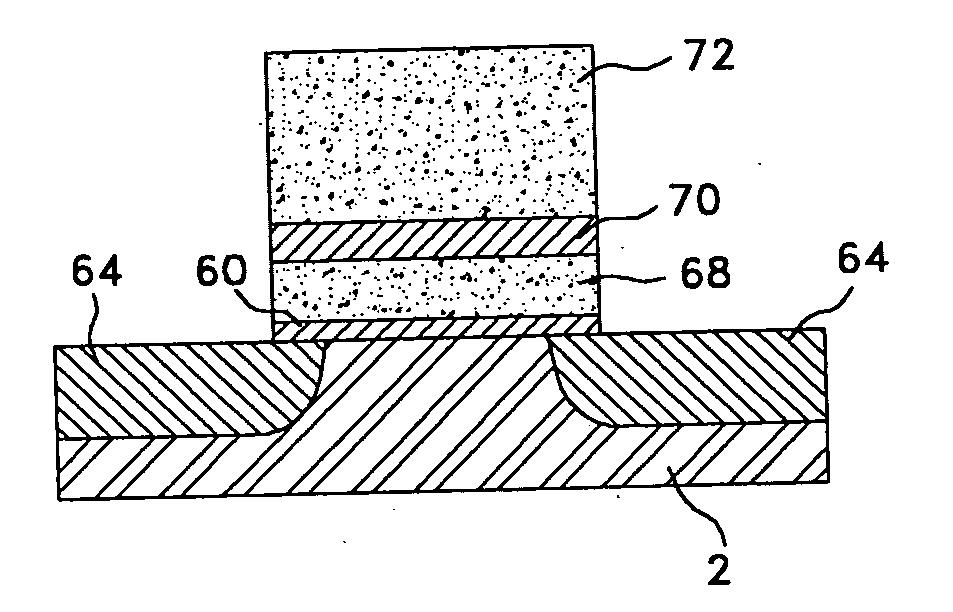

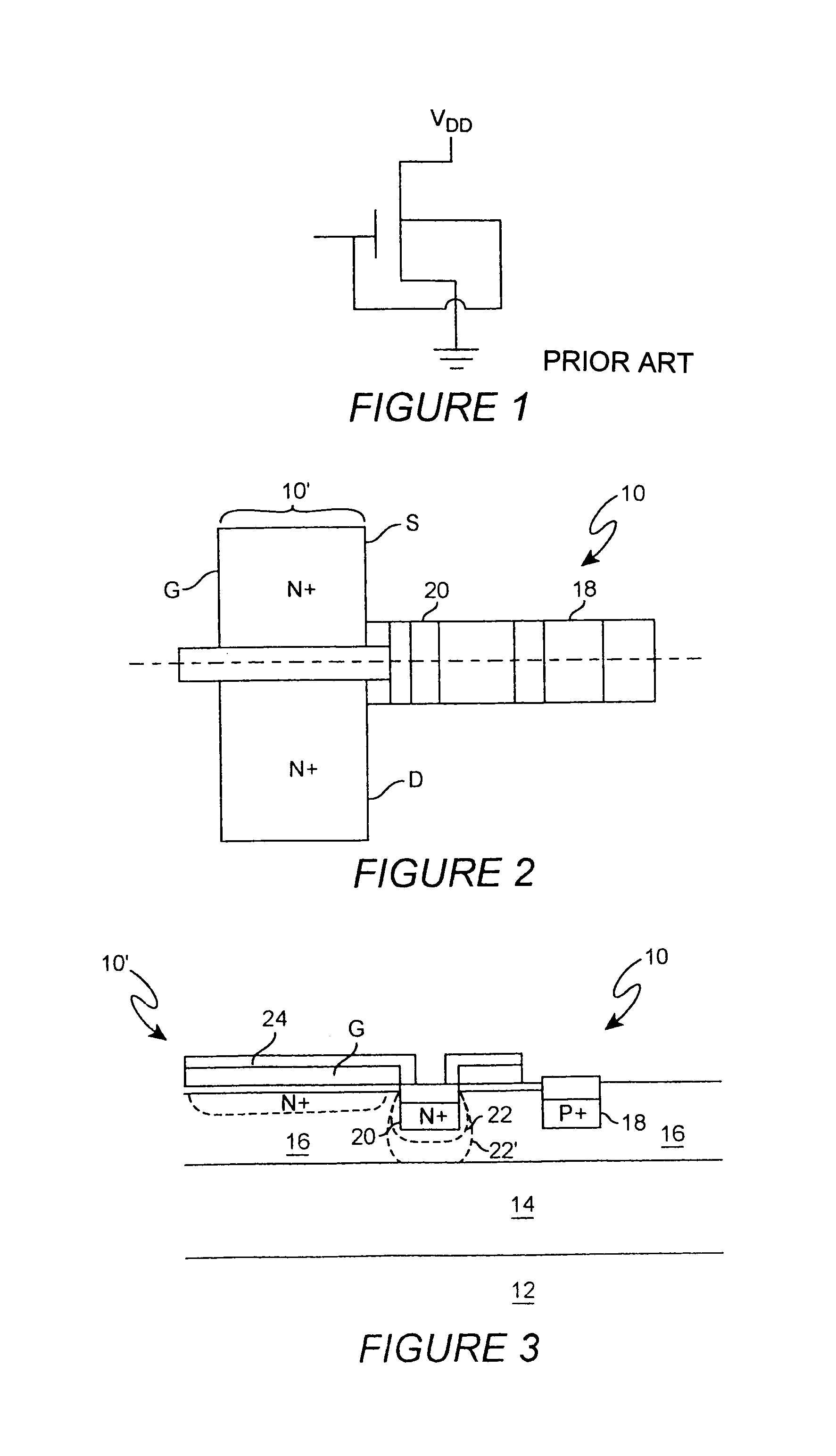

ActiveUS20050189589A1Increase resistanceDesirable propertyTransistorSolid-state devicesCapacitanceElectrical resistance and conductance

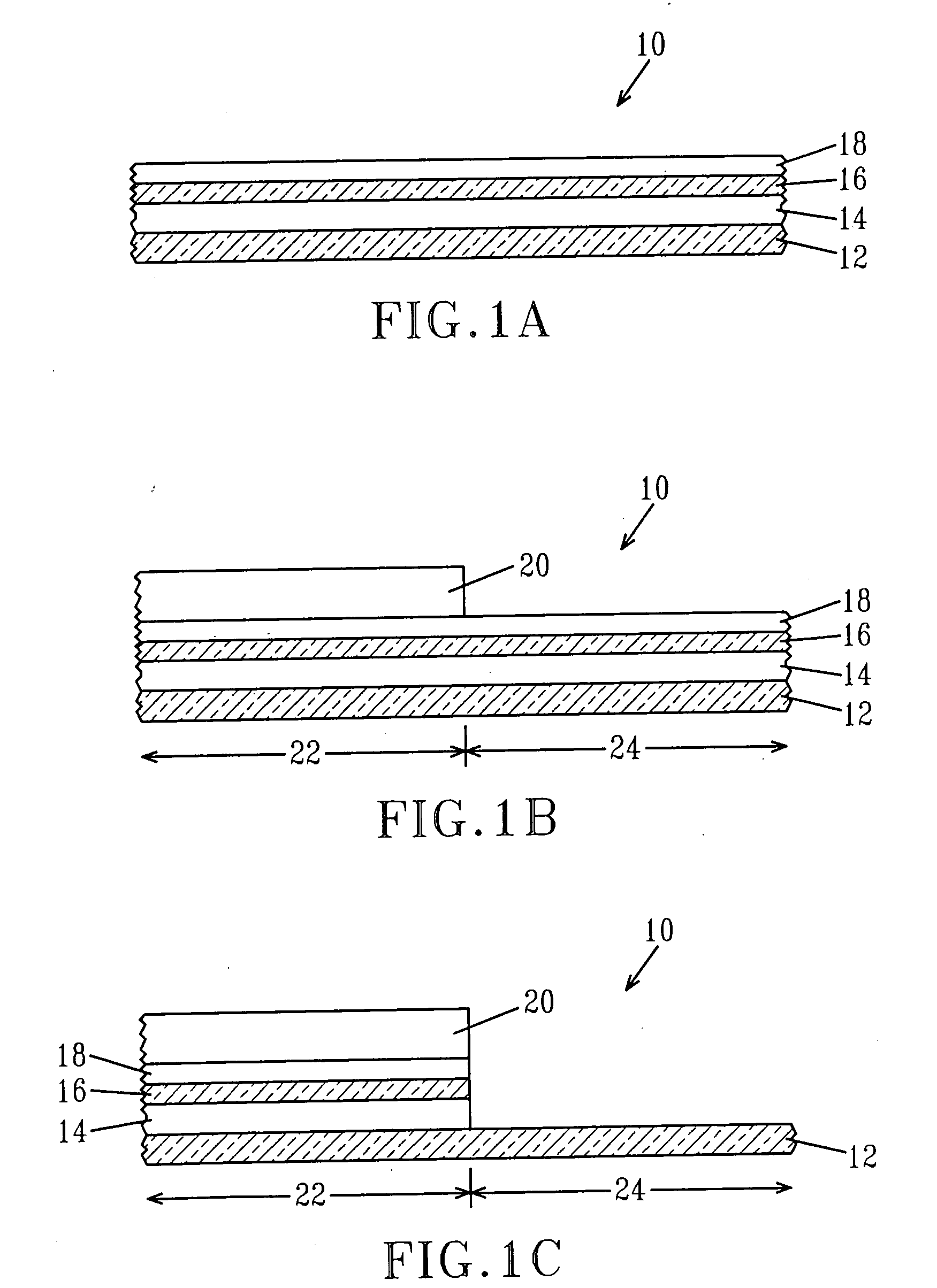

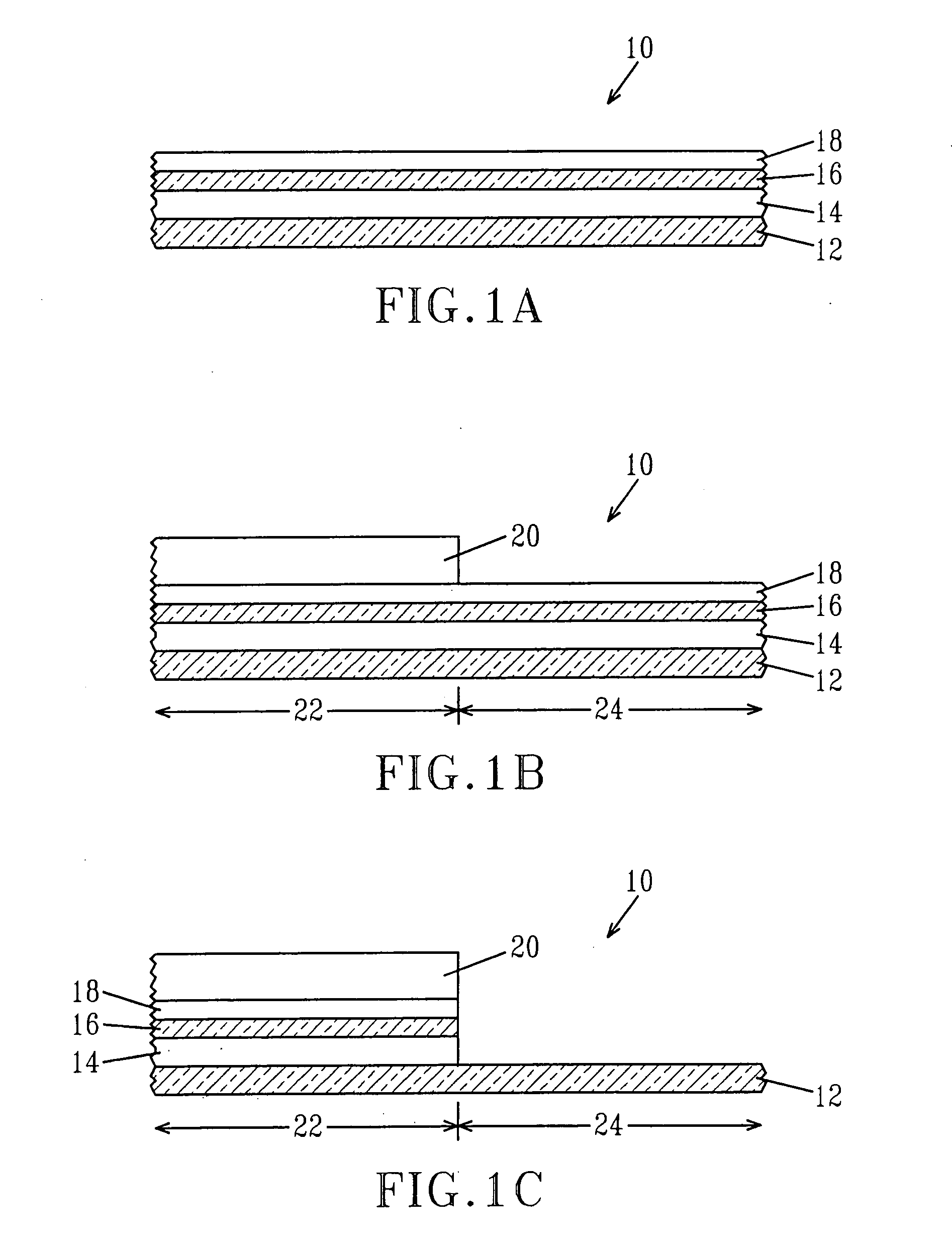

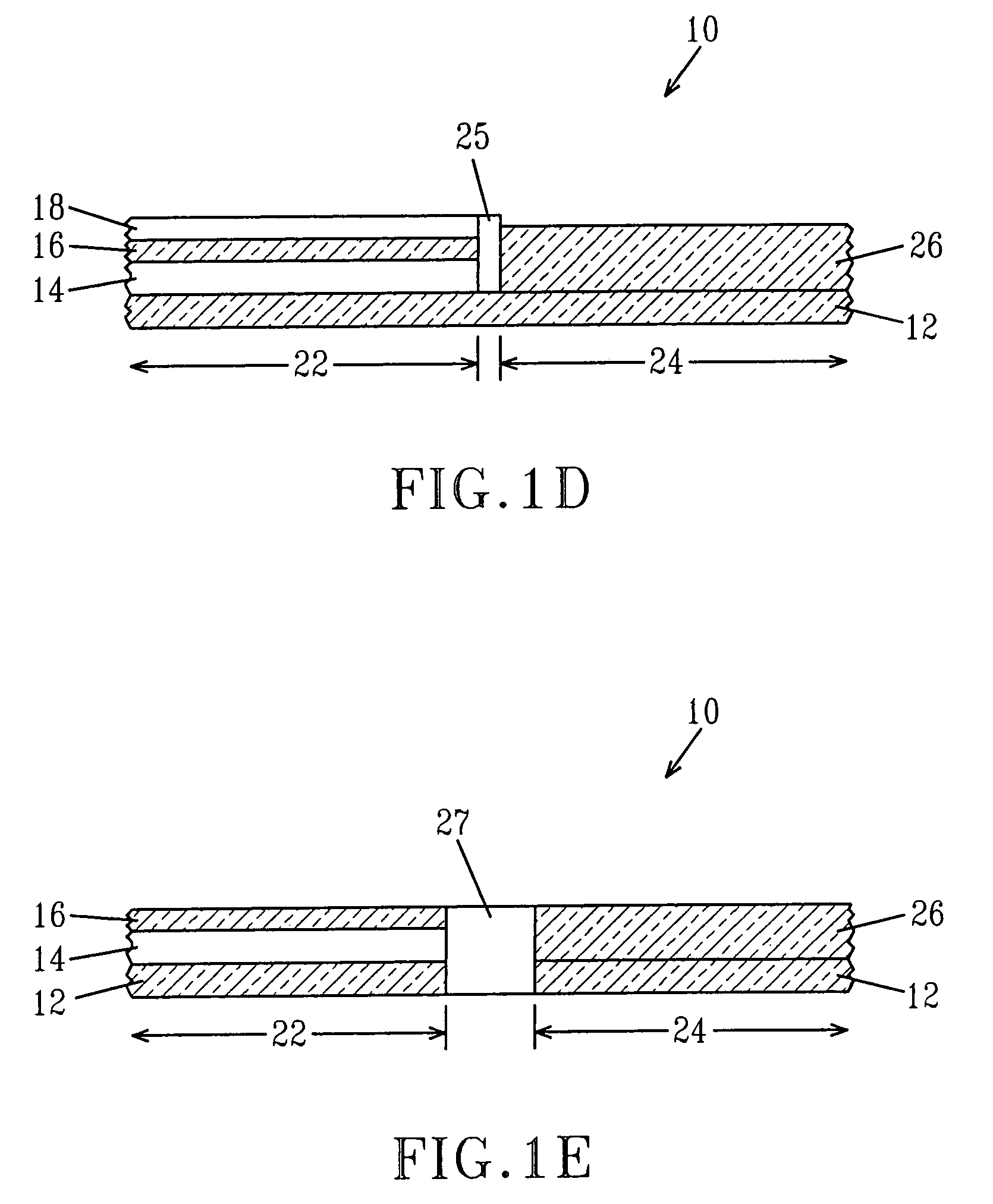

Channel depth in a field effect transistor is limited by an intra-layer structure including a discontinuous film or layer formed within a layer or substrate of semiconductor material. Channel depth can thus be controlled much in the manner of SOI or UT-SOI technology but with less expensive substrates and greater flexibility of channel depth control while avoiding floating body effects characteristic of SOI technology. The profile or cross-sectional shape of the discontinuous film may be controlled to an ogee or staircase shape to improve short channel effects and reduce source / drain and extension resistance without increase of capacitance. Materials for the discontinuous film may also be chosen to impose stress on the transistor channel from within the substrate or layer and provide increased levels of such stress to increase carrier mobility. Carrier mobility may be increased in combination with other meritorious effects.

Owner:GLOBALFOUNDRIES US INC

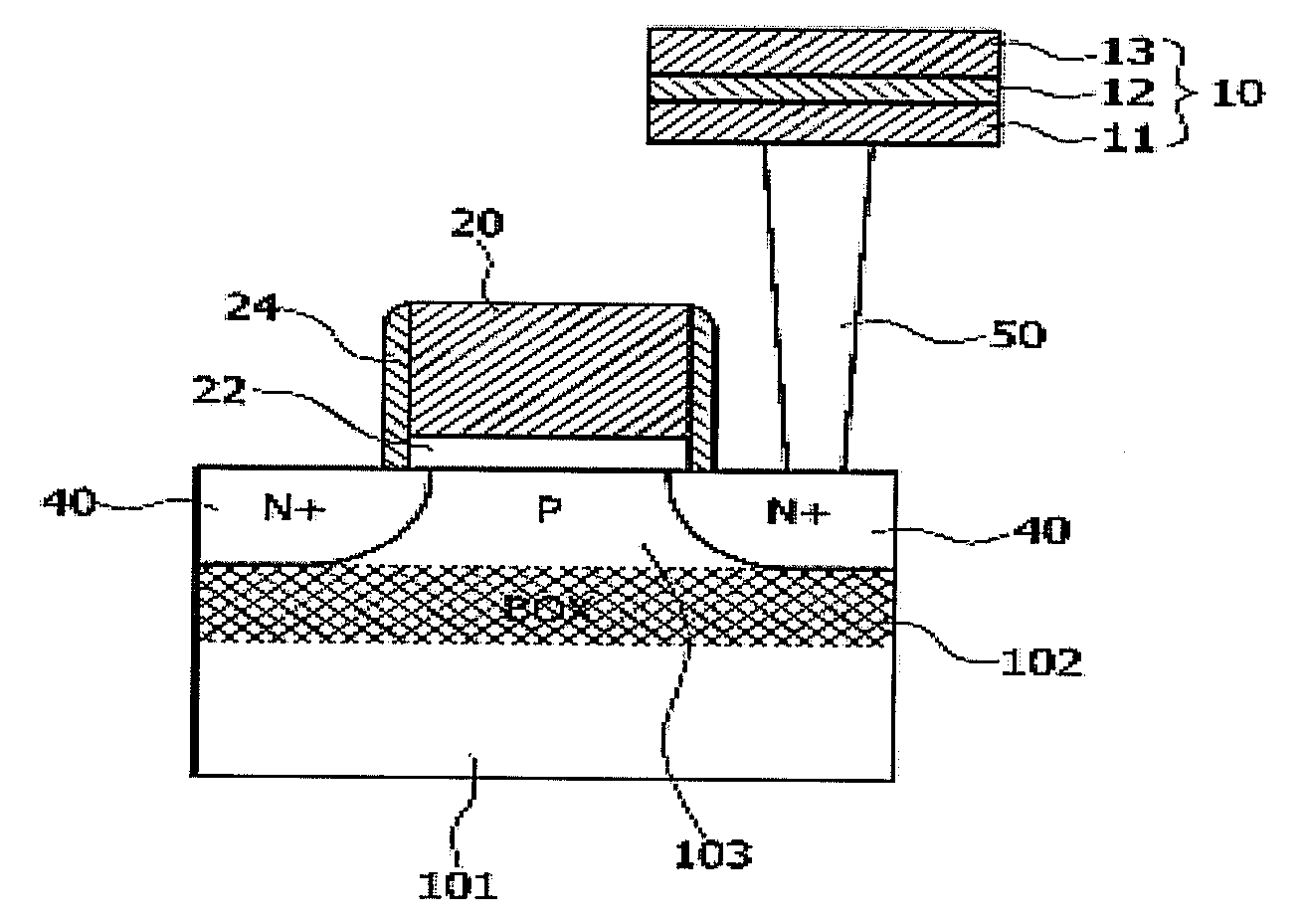

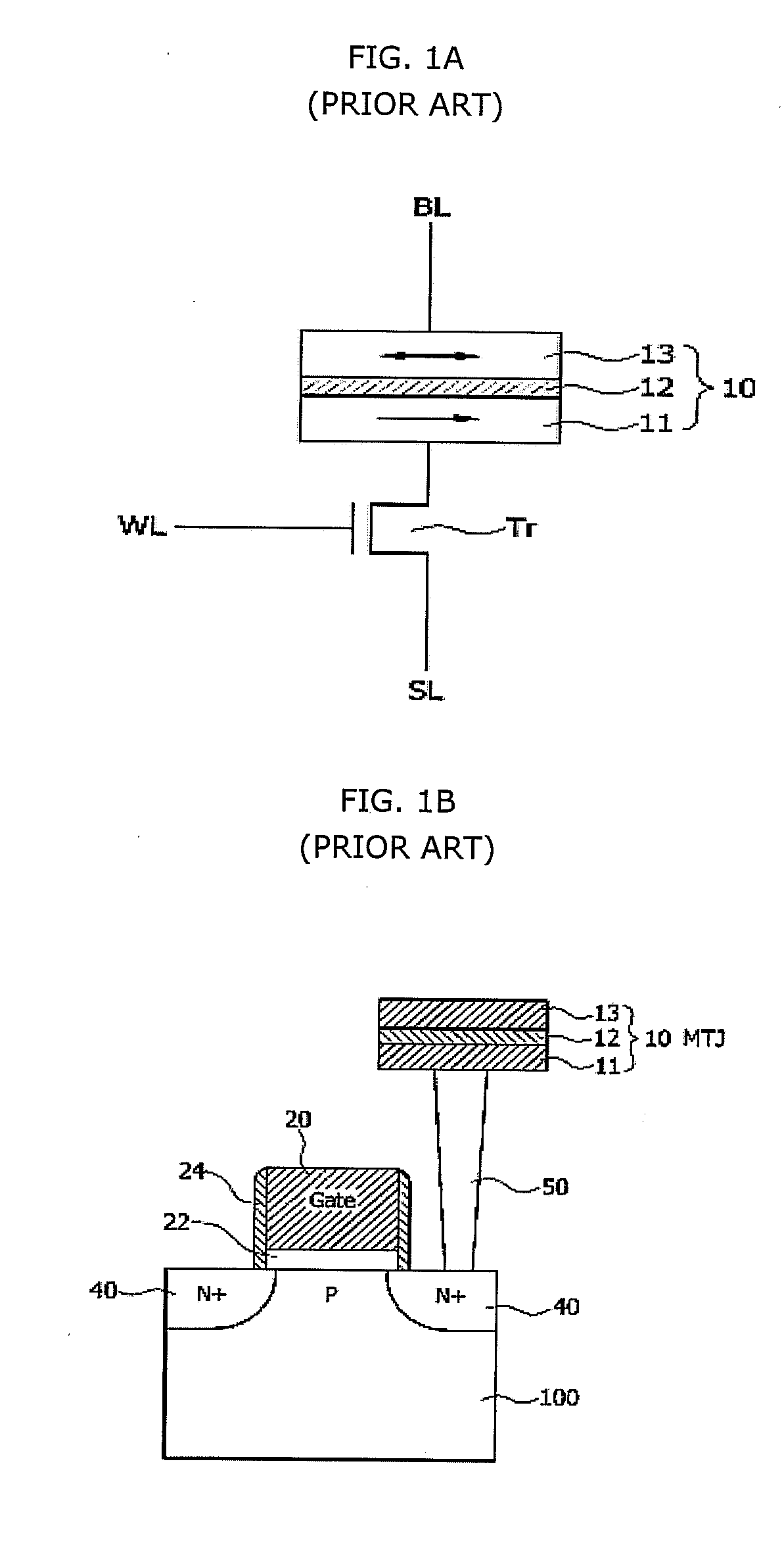

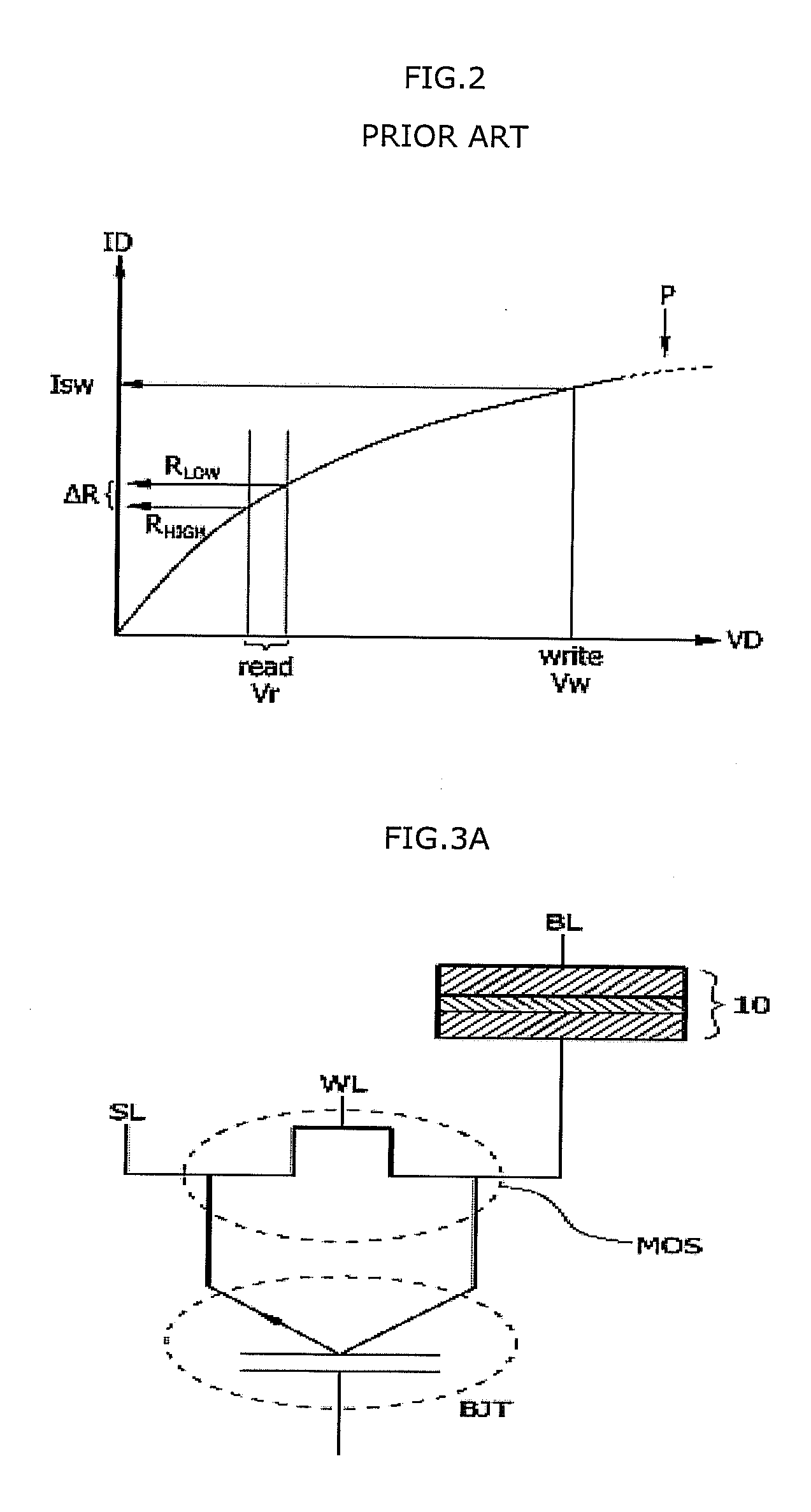

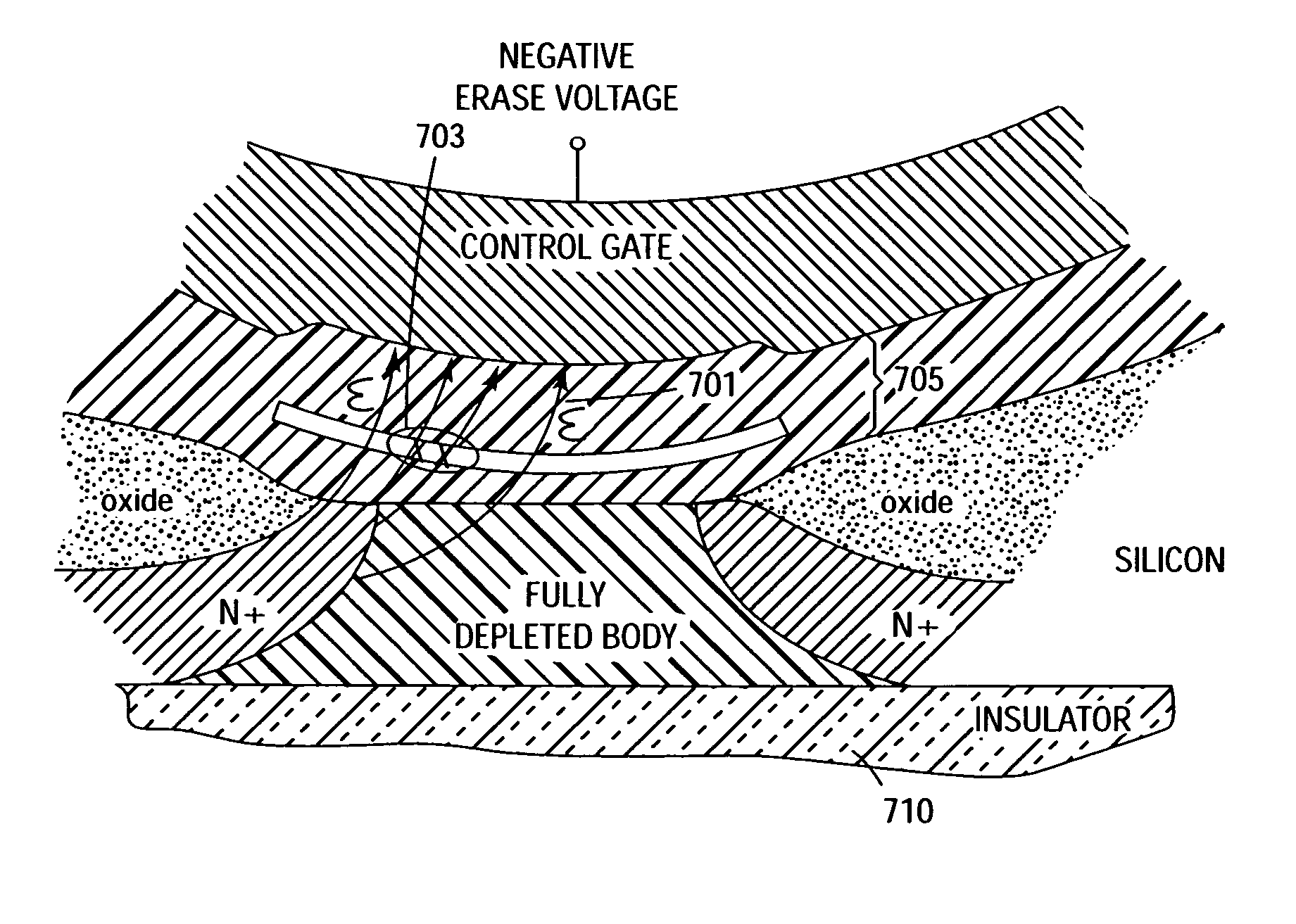

Magnetoresistive memory cell using floating body effect, memory device having the same, and method of operating the memory device

ActiveUS20100157664A1Drive capability can be improvedImprove rendering capabilitiesSolid-state devicesSemiconductor/solid-state device manufacturingDiffusionFloating body effect

A magnetoresistive memory cell includes an MTJ device and a select transistor. The select transistor includes a first conduction-type semiconductor layer, a gate electrode formed by disposing a gate insulating layer on top of the semiconductor layer, and first and second diffusion regions formed in the semiconductor layer to be spaced apart from each other and to have a second conduction type. A part of the semiconductor layer between the first and second diffusion regions is formed as an electrically floating body region. By using a high-performance select transistor with a floating body effect, high integration of a magnetoresistive memory device may be achieved.

Owner:SK HYNIX INC

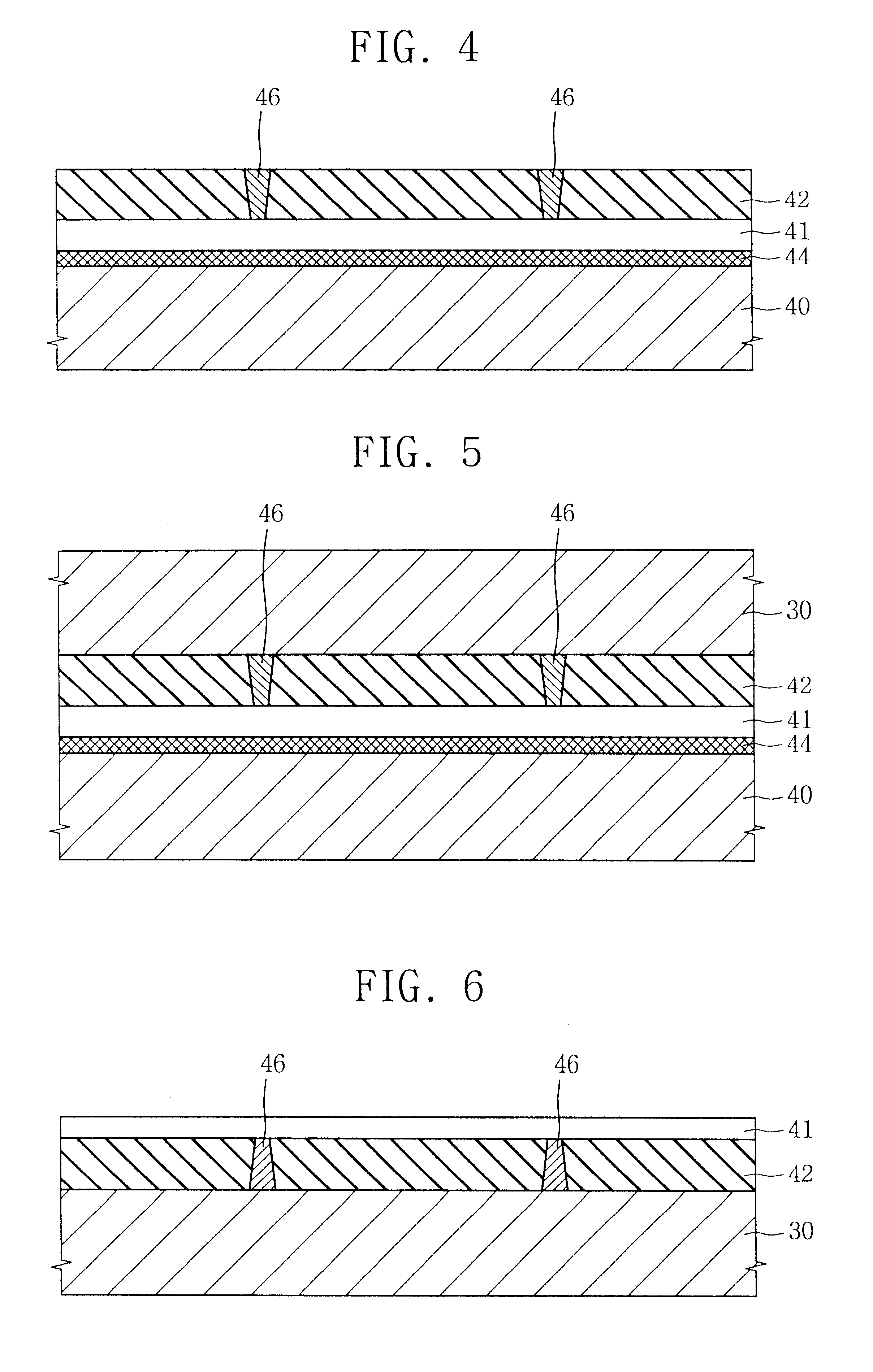

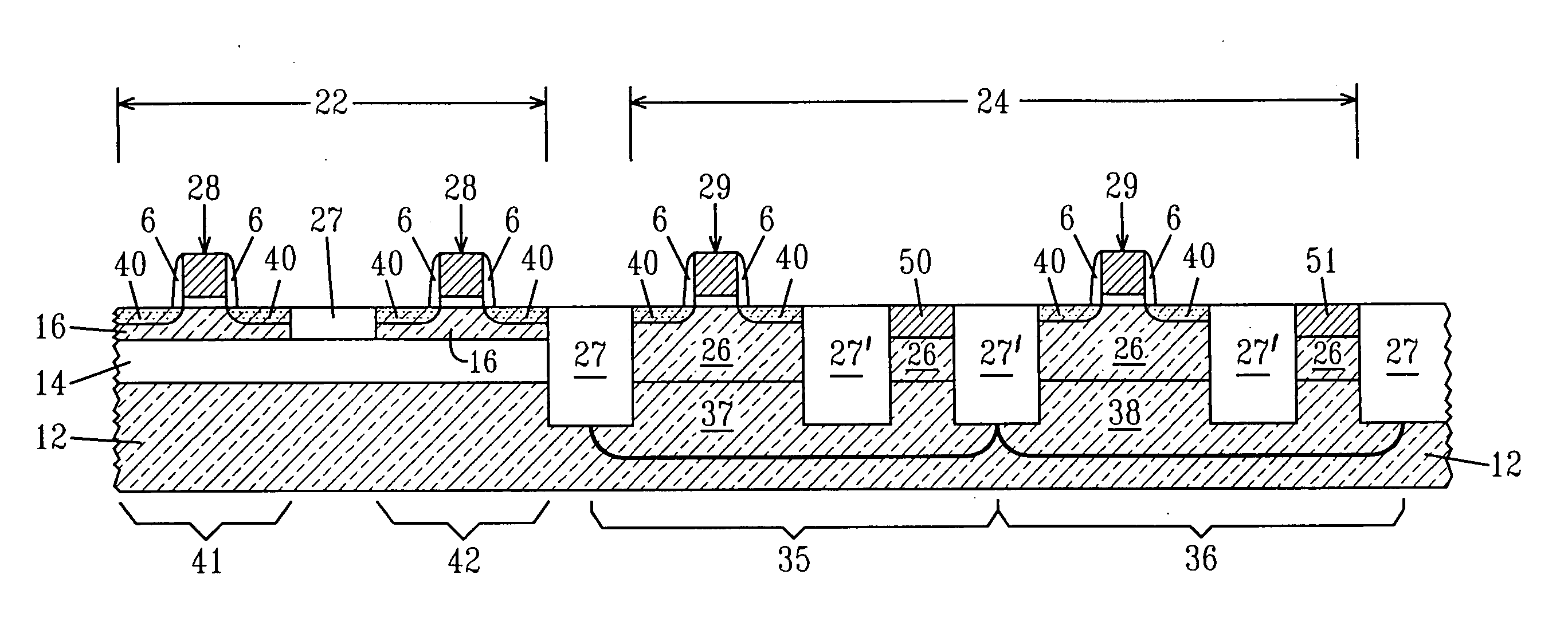

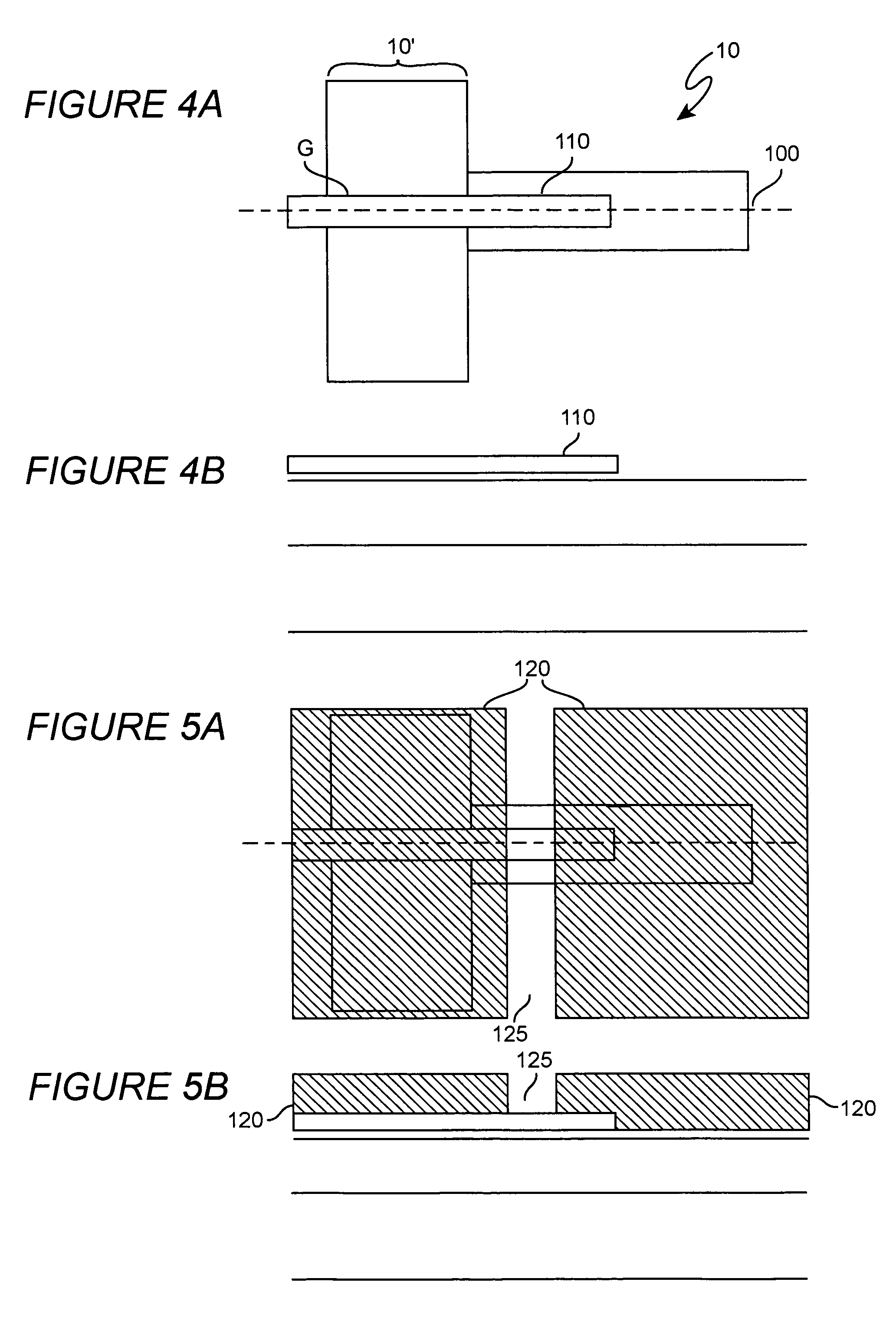

SOI semiconductor integrated circuit for eliminating floating body effects in SOI MOSFETs and method of fabricating the same

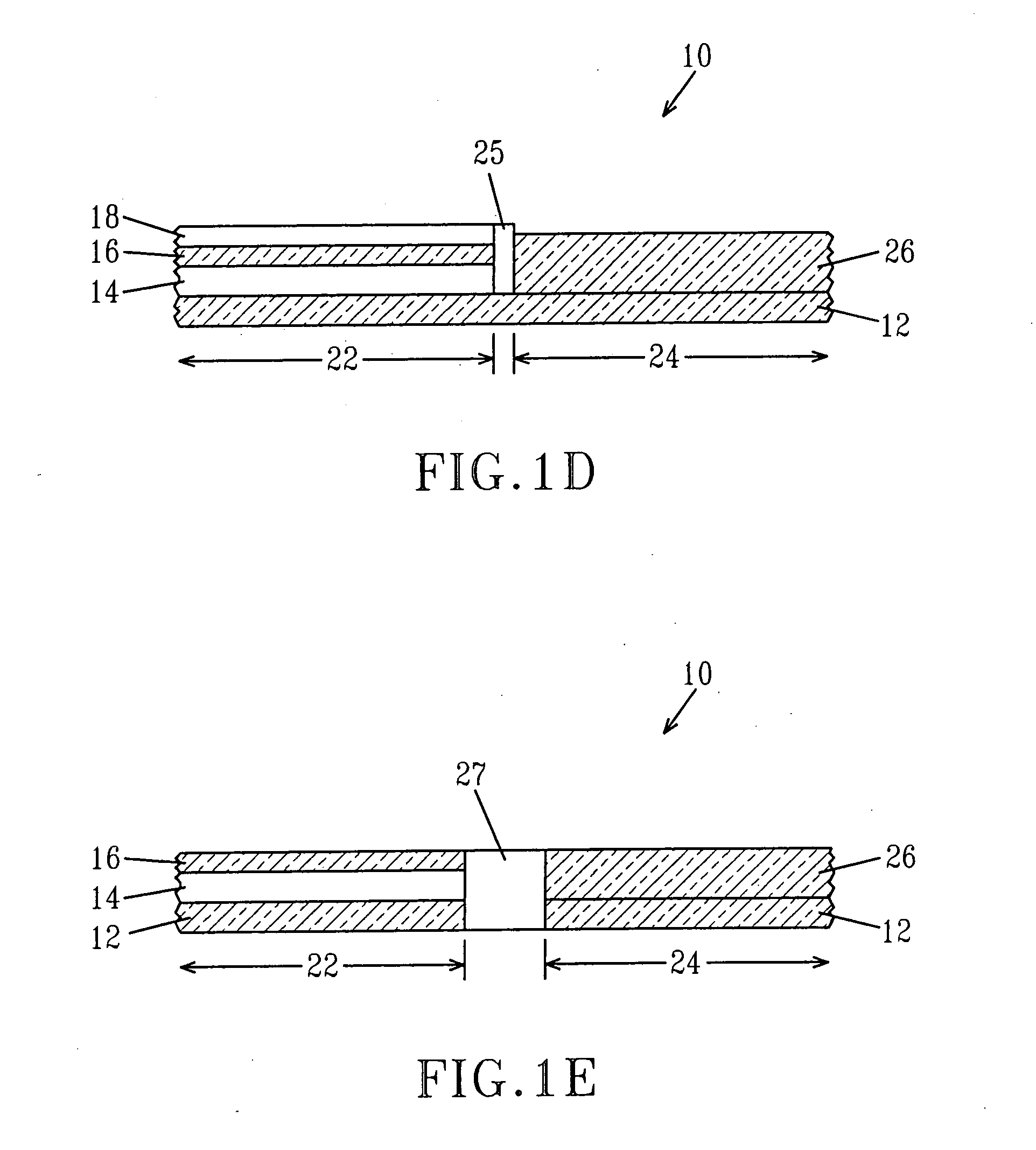

A silicon-on-insulator (SOI) integrated circuit and a method of fabricating the SOI integrated circuit are provided. At least one isolated transistor active region and a body line are formed on an SOI substrate. The transistor active region and the body line are surrounded by an isolation layer which is in contact with a buried insulating layer of the SOI substrate. A portion of the sidewall of the transistor active region is extended to the body line. Thus, the transistor active region is electrically connected to the body line through a body extension. The body extension is covered with a body insulating layer. An insulated gate pattern is formed over the transistor active region, and one end of the gate pattern is overlapped with the body insulating layer.

Owner:SAMSUNG ELECTRONICS CO LTD

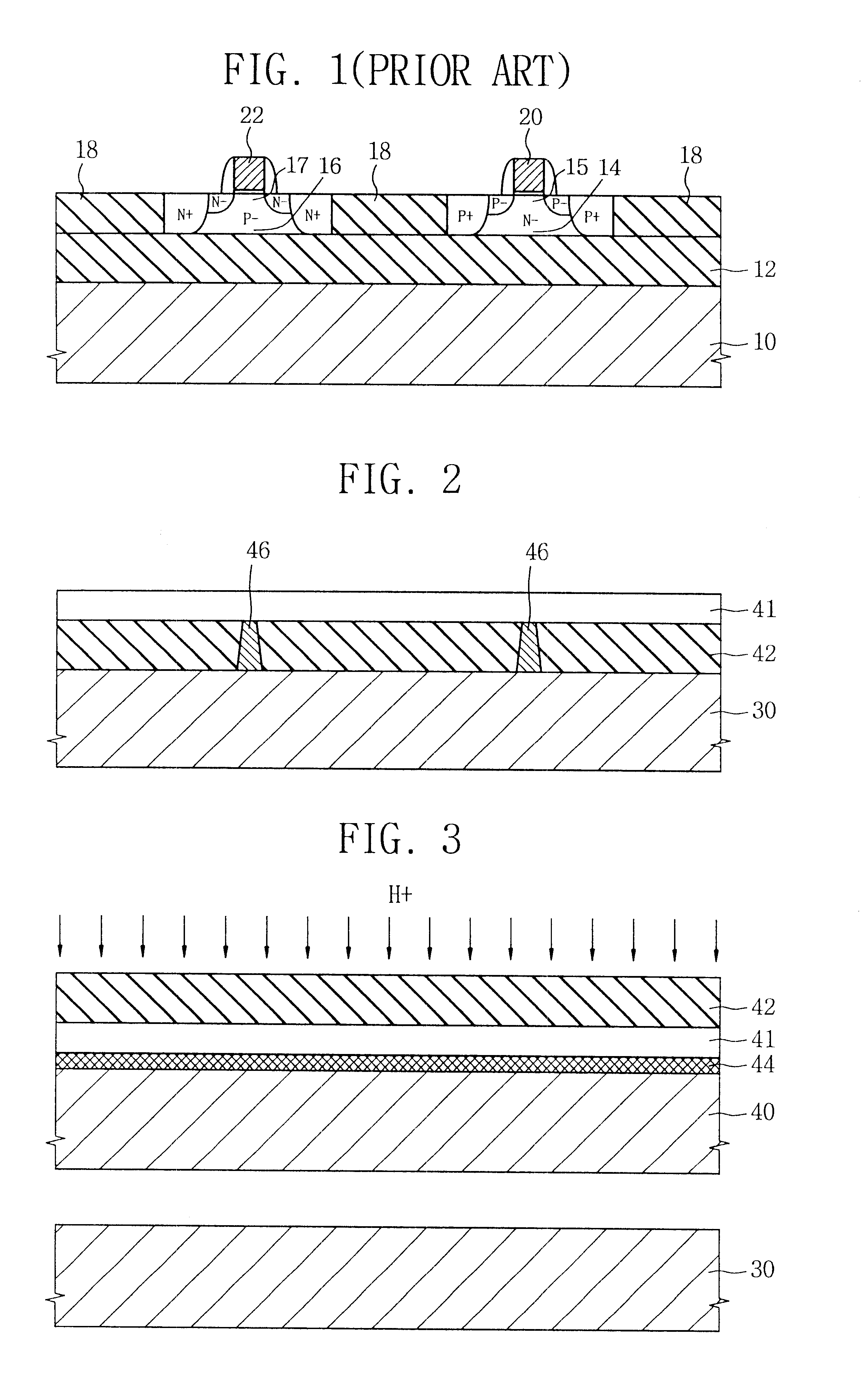

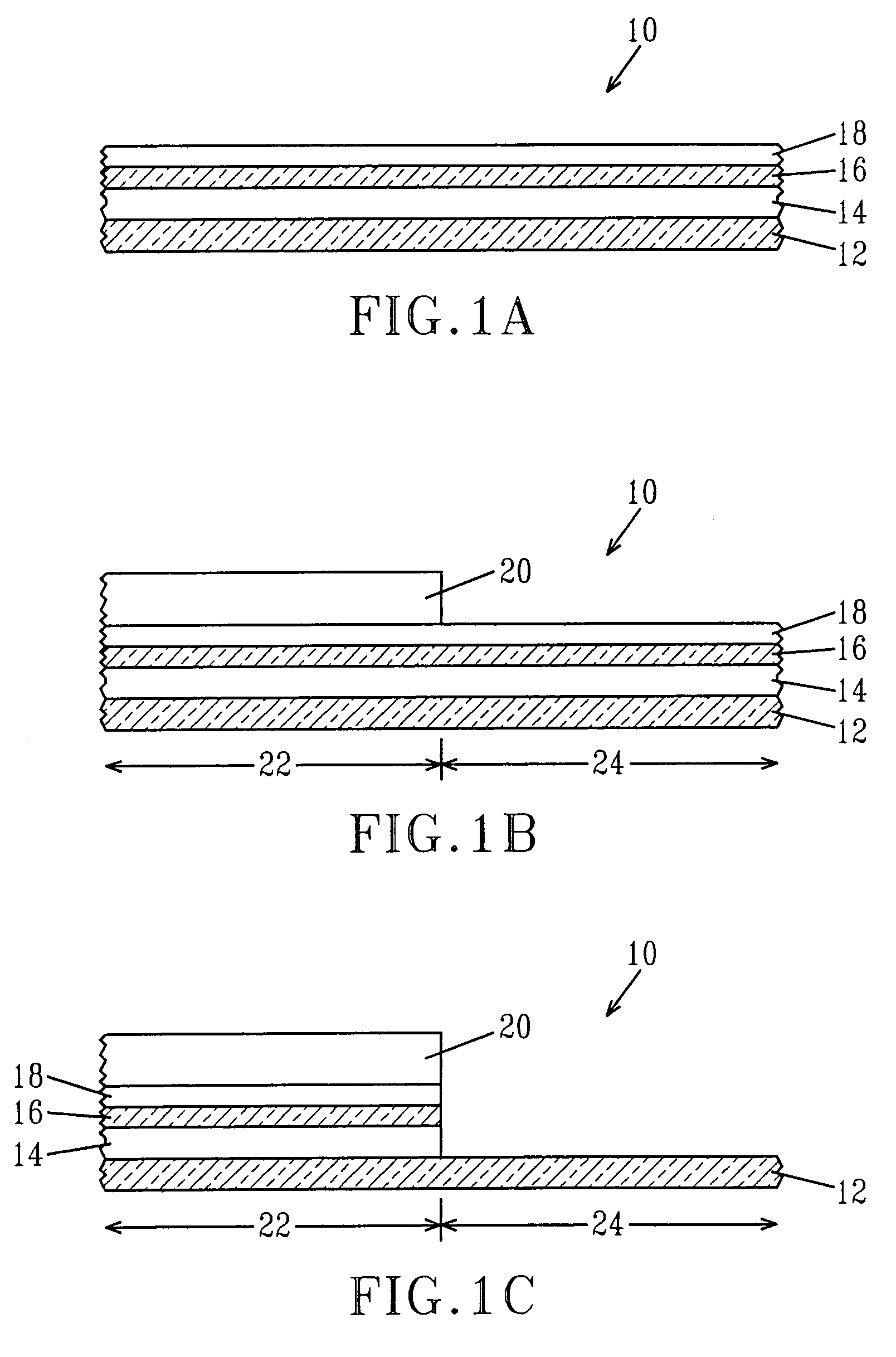

Silicon-on-insulator (SOI) substrate, method for fabricating SOI substrate and SOI MOSFET using the SOI substrate

InactiveUS6437405B2Simple processSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETFloating body effect

The present invention relates to a silicon-on-insulator (SOI) substrate, a method for fabricating the SOI substrate and a SOI MOSFET using the SOI substrate to easily migrate the design applied to a conventional bulk silicon substrate to the SOI design and to remove a floating body effect. The SOI substrate includes a mono-silicon substrate, a buried oxide layer formed over the surface of the mono-silicon substrate, and a thin mono-silicon layer formed over the surface of the buried oxide layer. Conductive layers are formed at through holes of the buried oxide layer positioned between the predetermined regions of the thin layer and the substrate for body contacts. Therefore, additional layout spaces are not needed for body contacts and the constant body contact resistance can allow the conventional circuit design applied to the bulk silicon substrate to be migrated to the circuit design applied to the SOI substrate without any modifications. Also, a variety of operational failures caused by the floating effect can be eliminated in the SOI substrate. As a consequence, additional effort is not required for designing or verifying the circuit of the present invention, so as to make it possible to construct a highly efficient, but low power consuming system.

Owner:SAMSUNG ELECTRONICS CO LTD

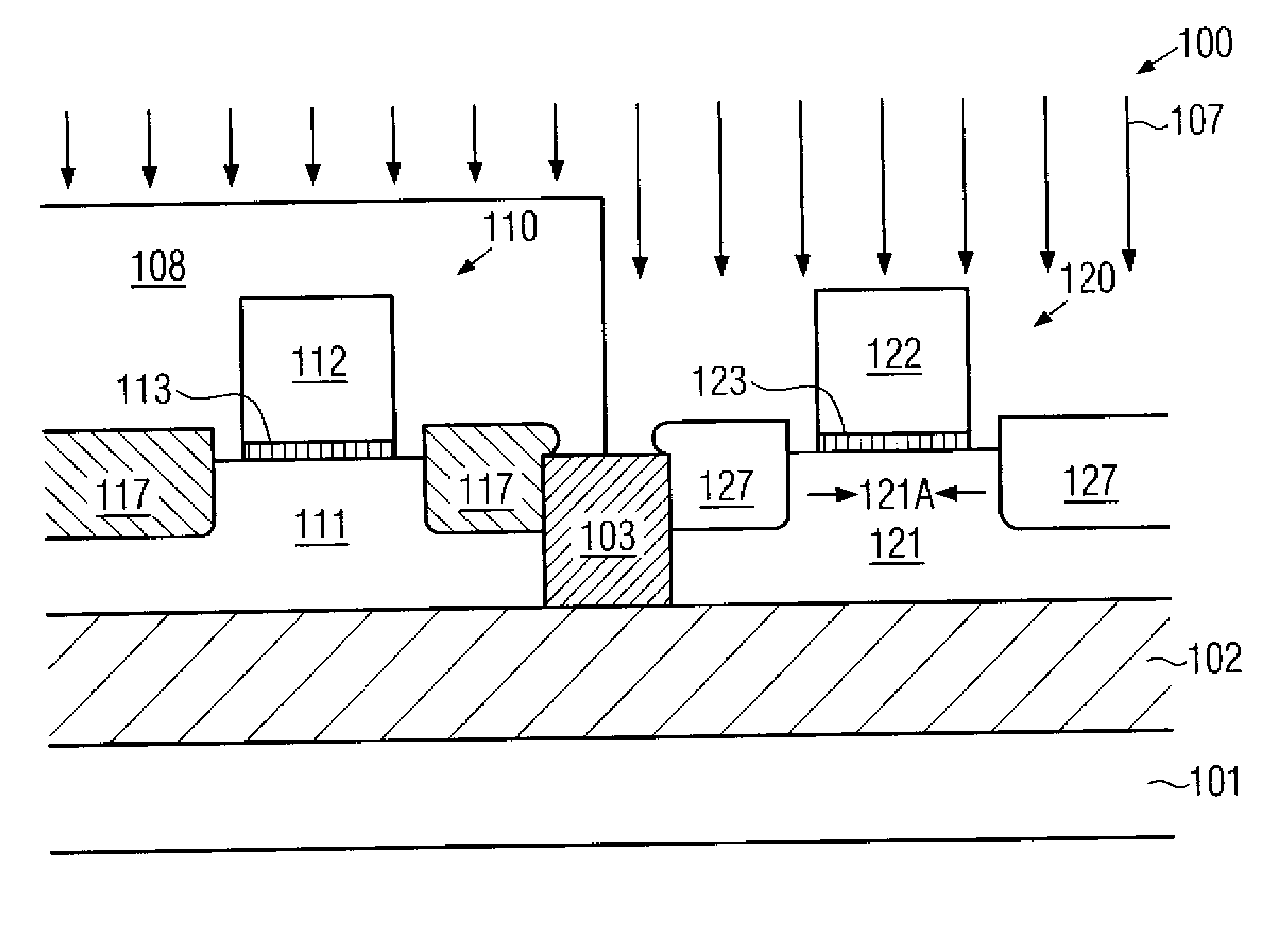

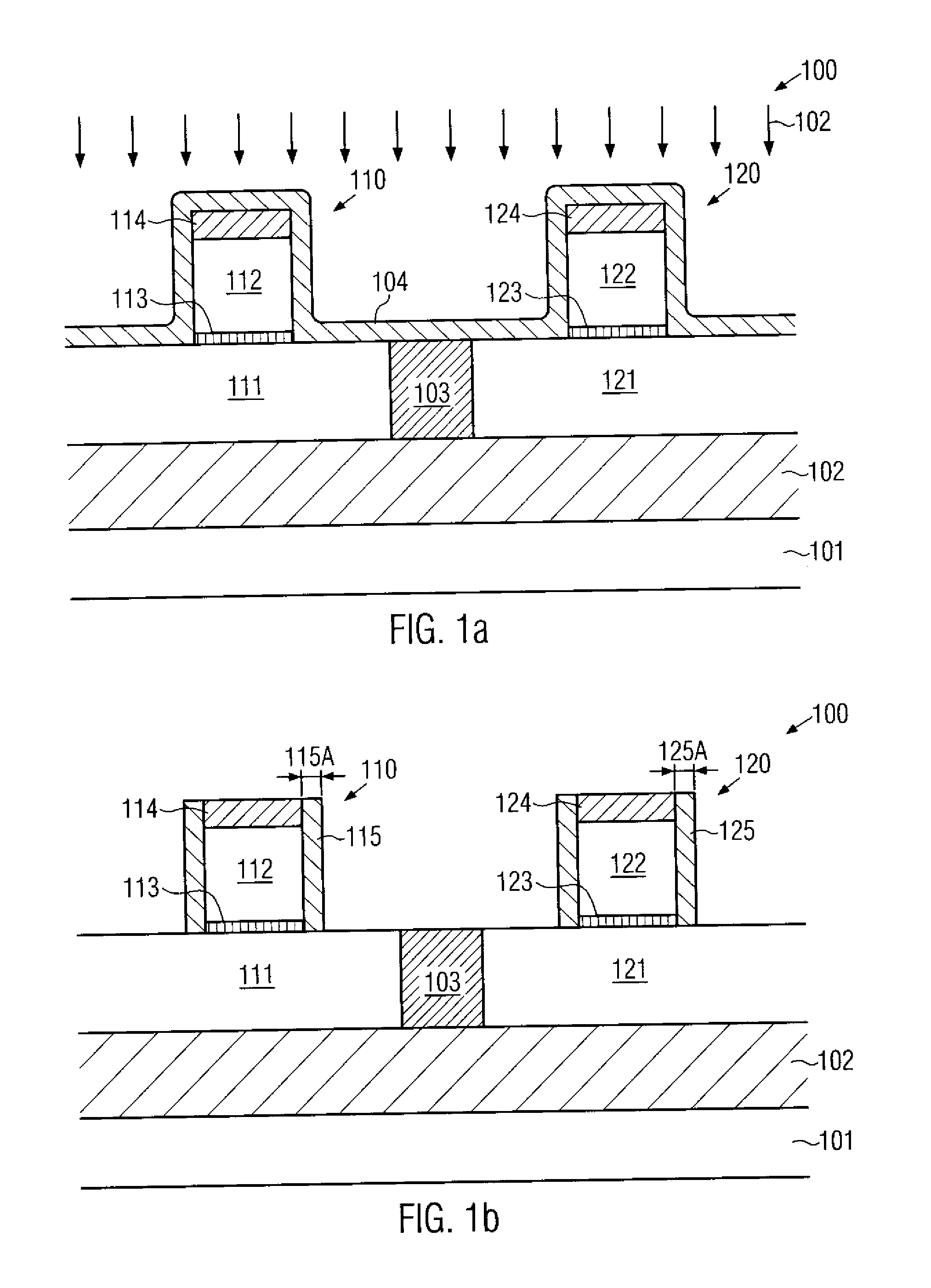

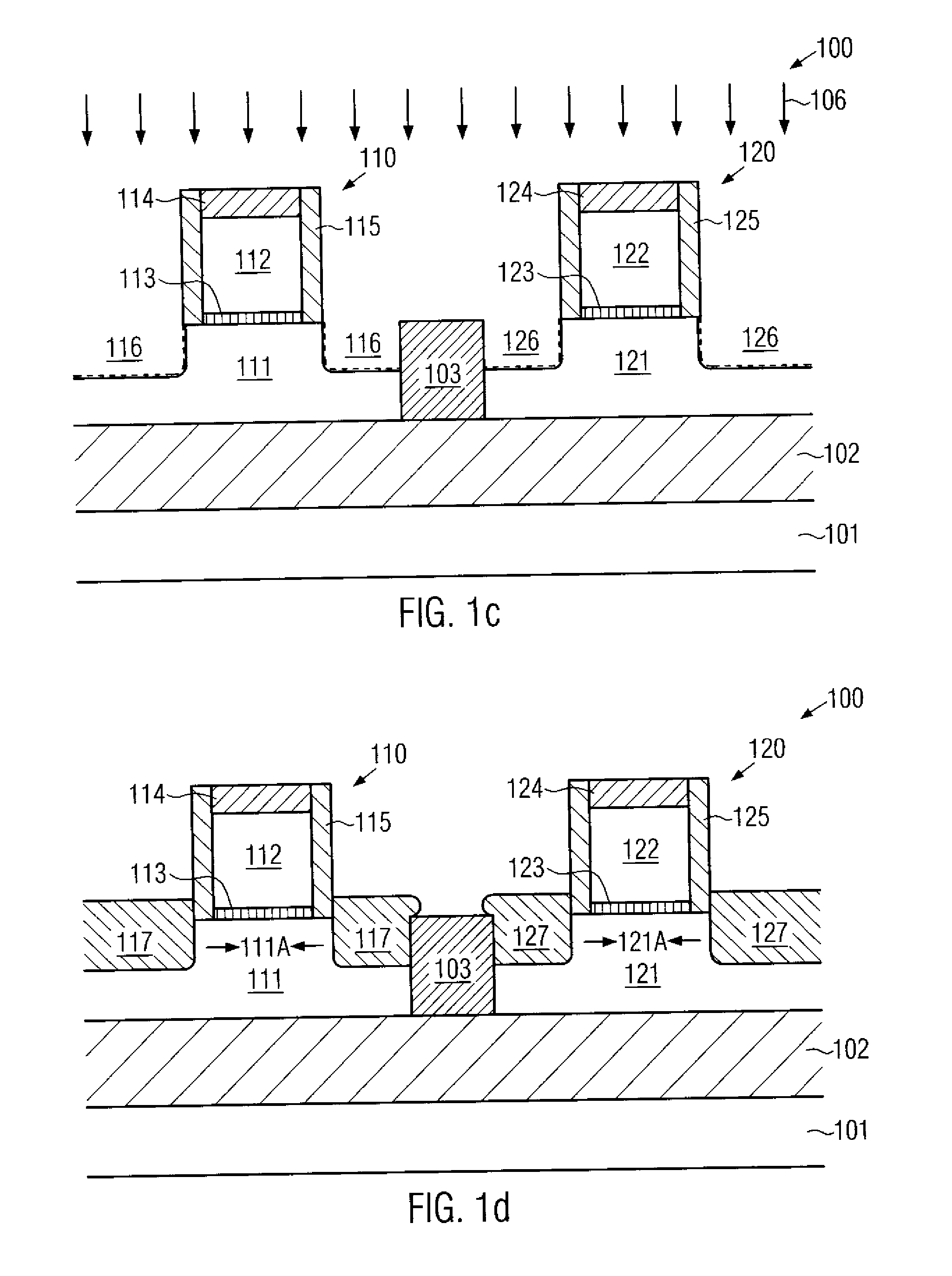

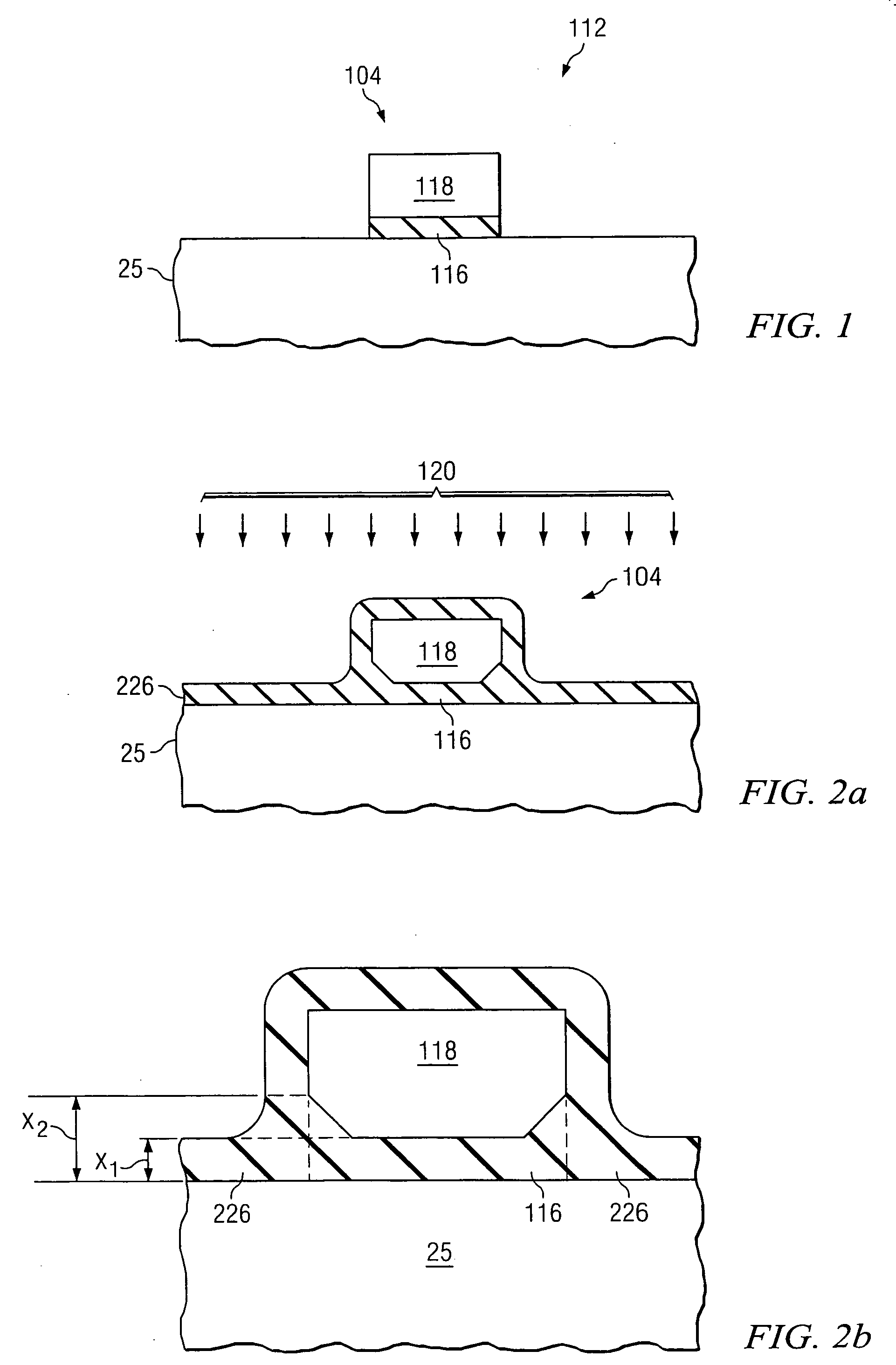

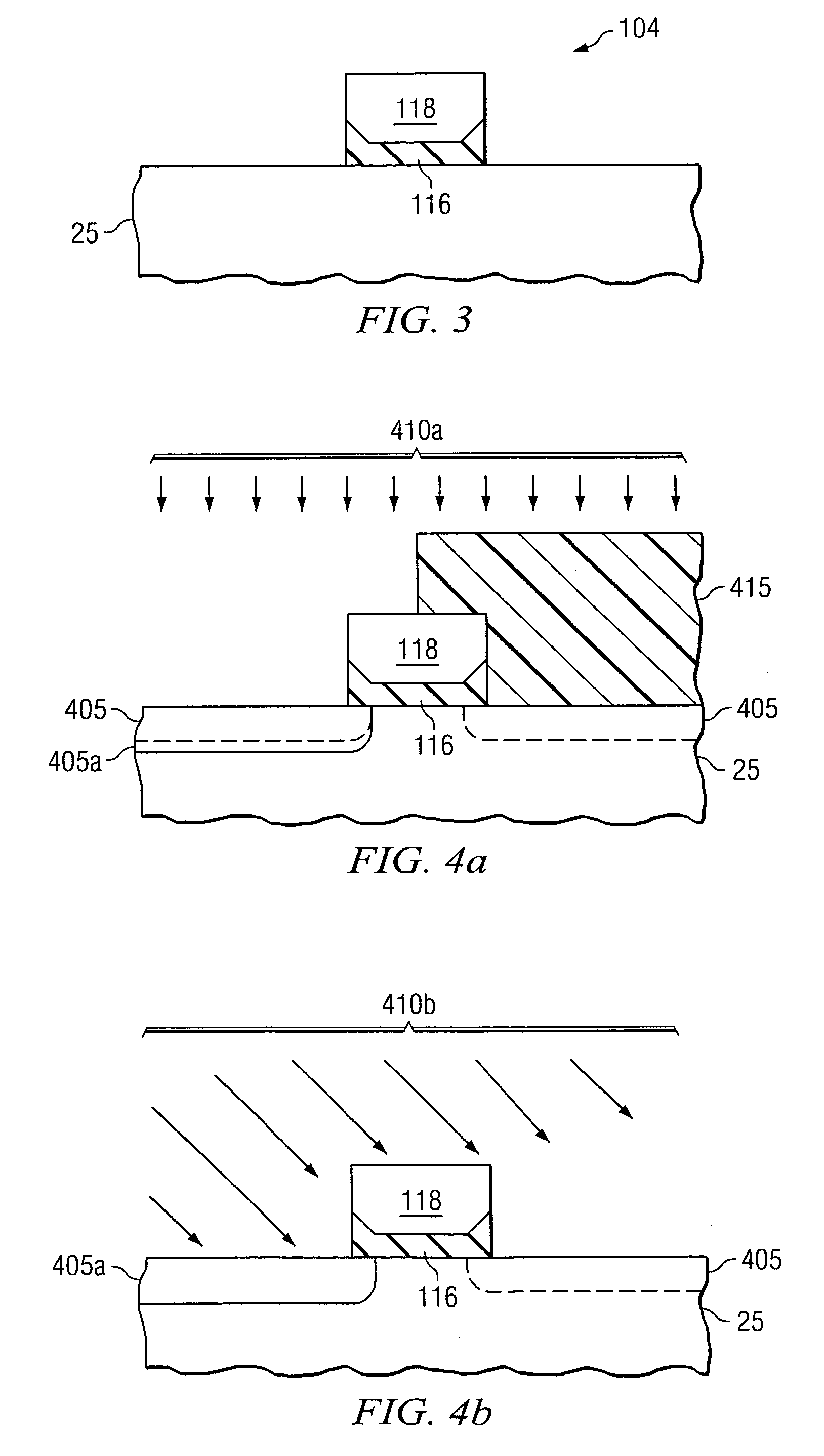

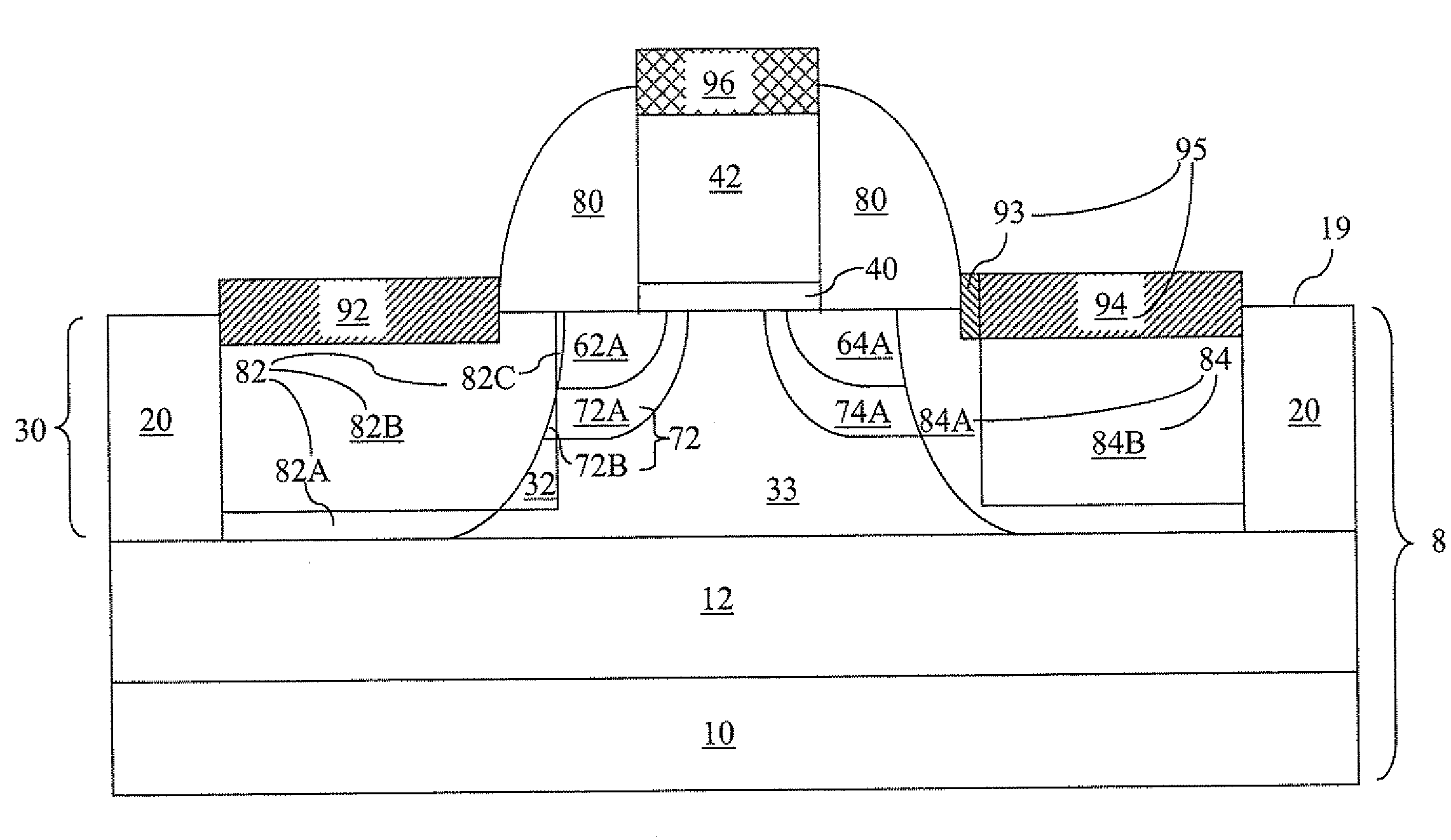

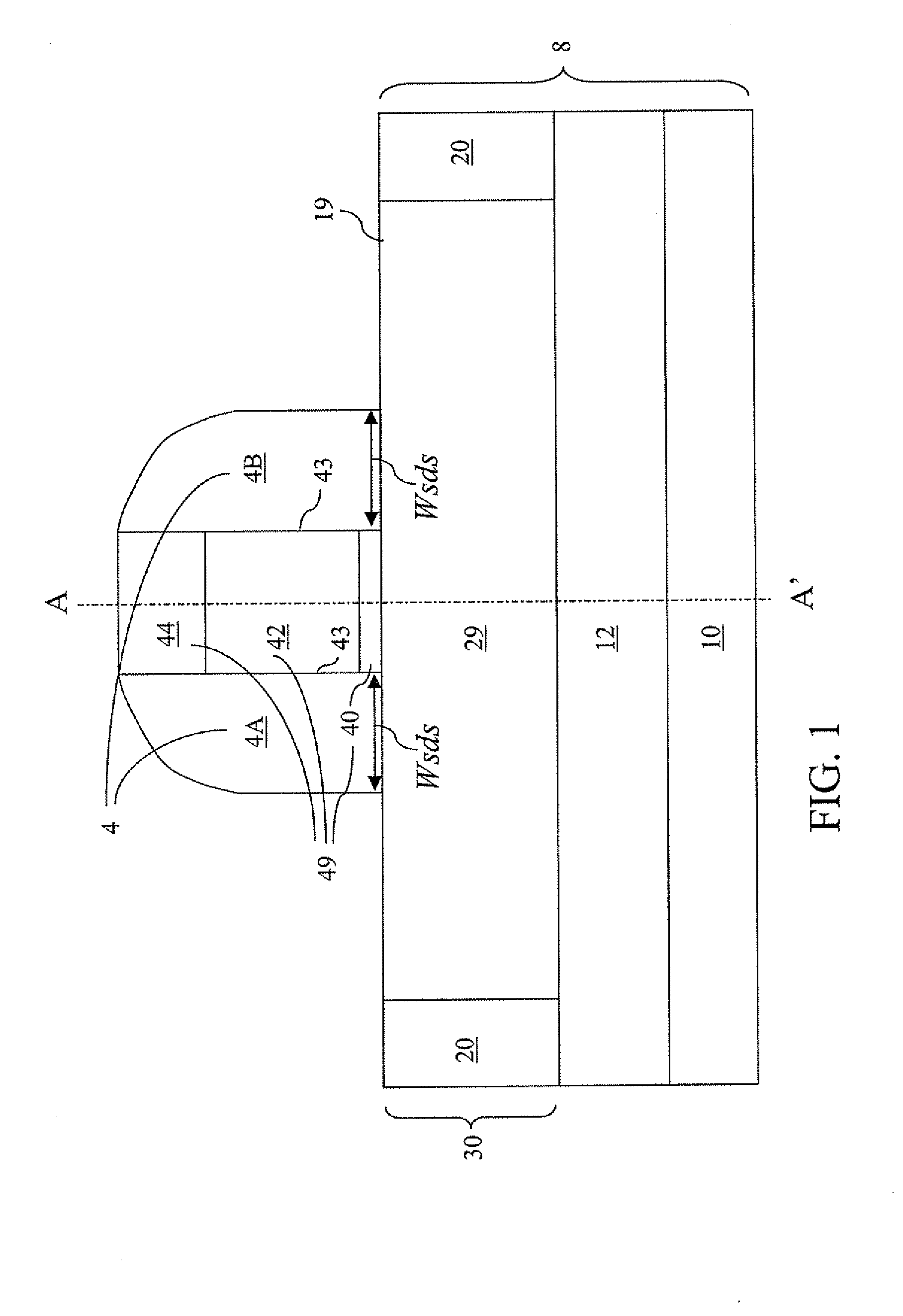

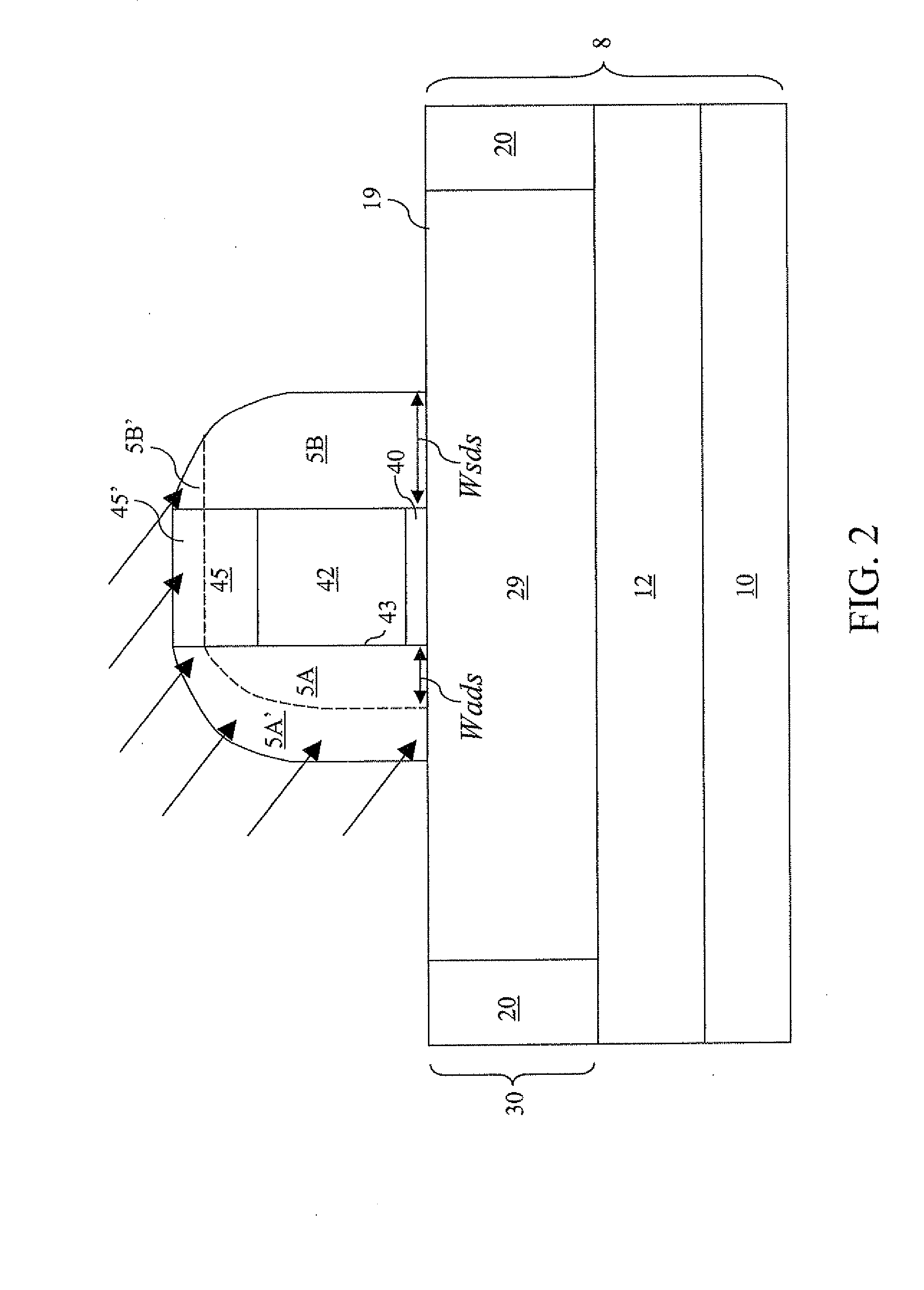

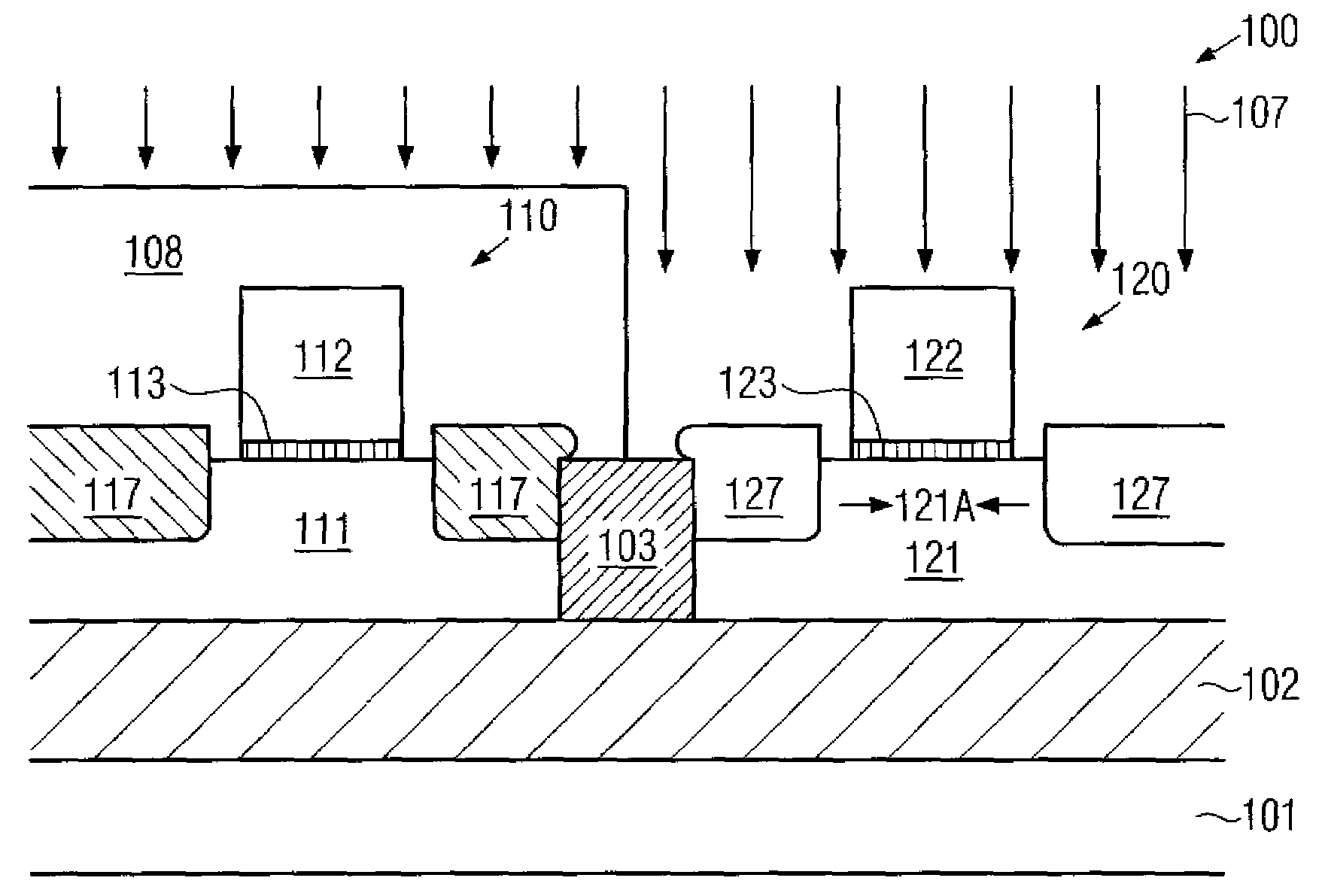

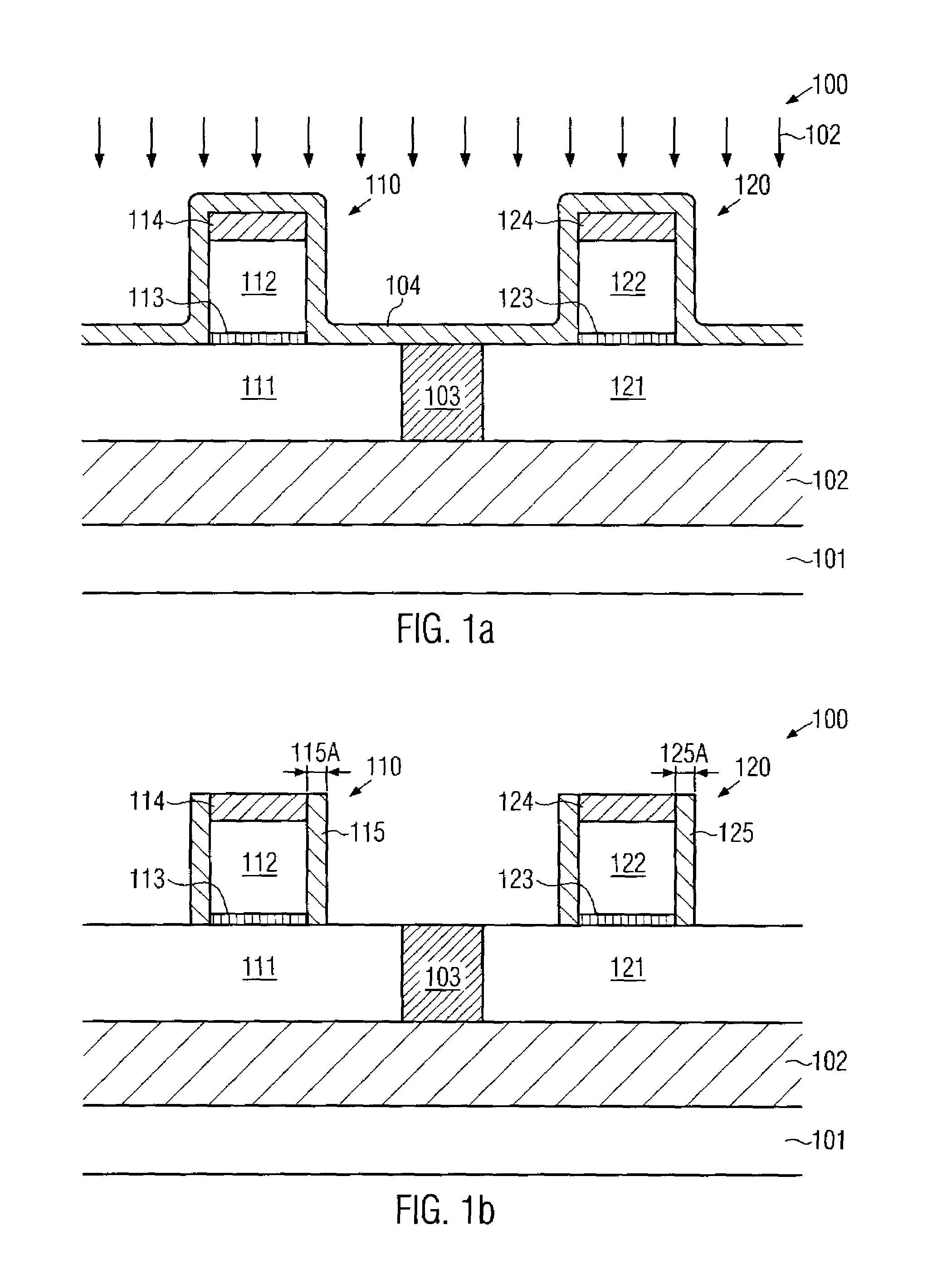

Technique for forming recessed strained drain/source regions in NMOS and PMOS transistors

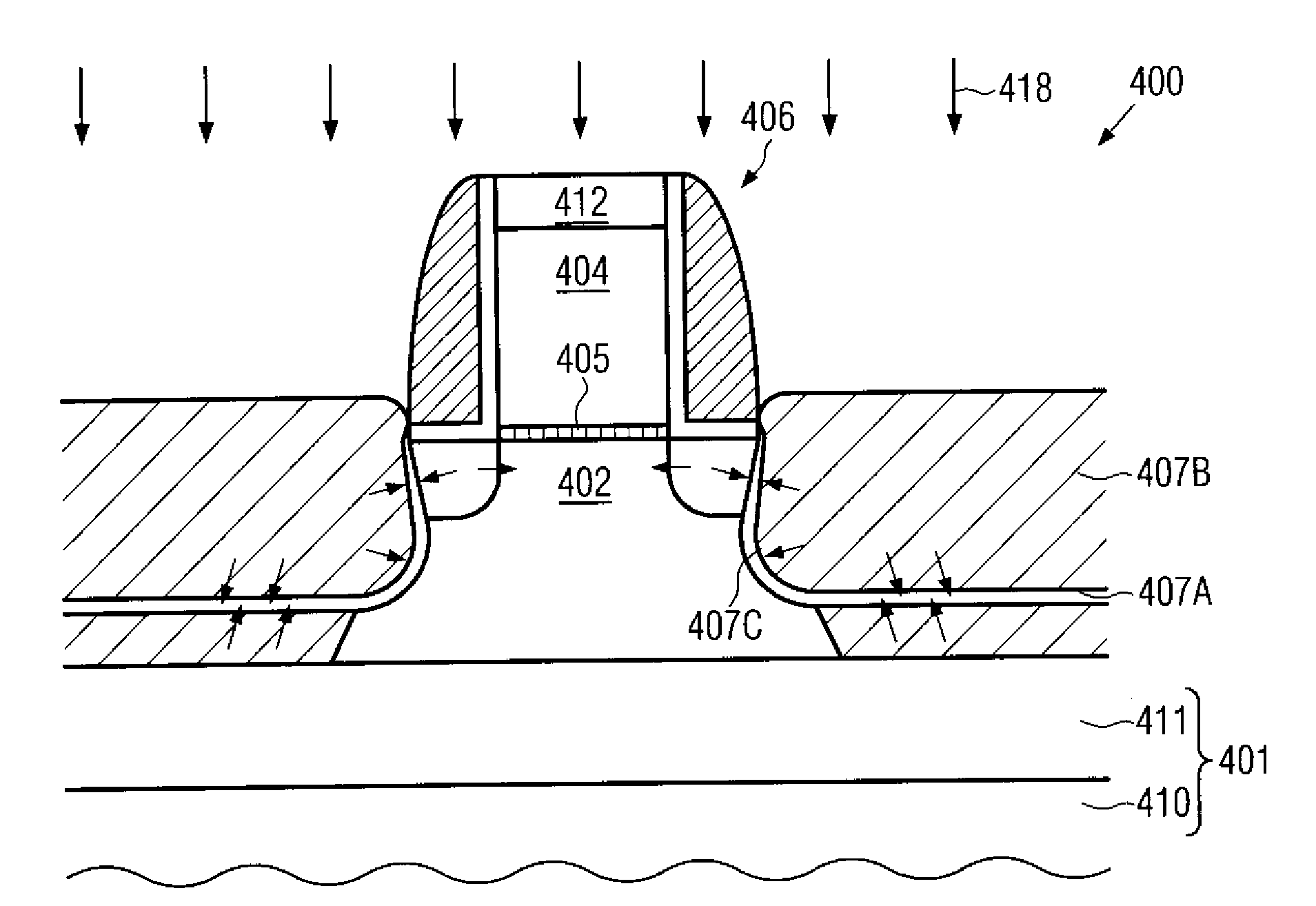

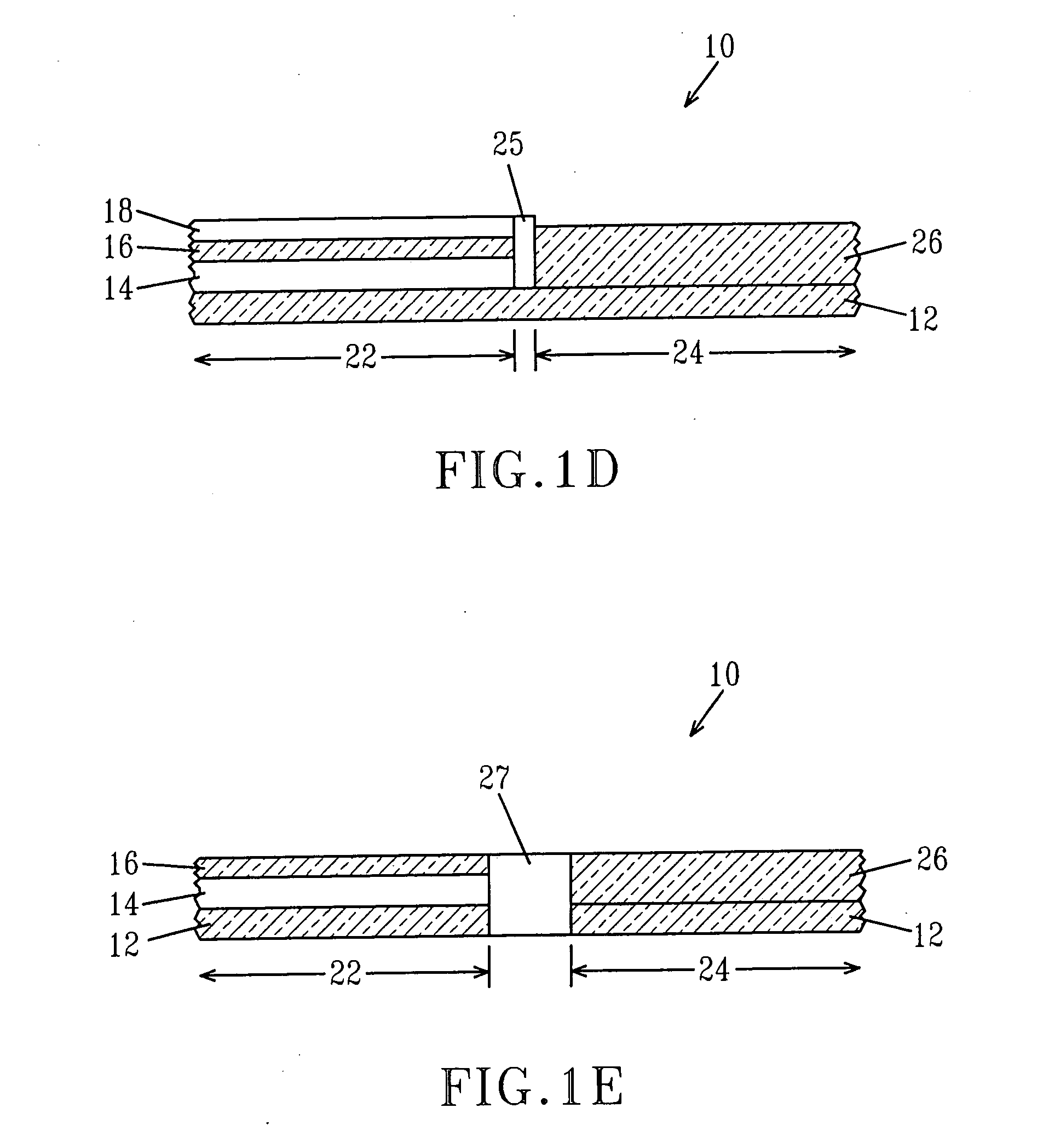

ActiveUS20070045729A1High carrier mobilityIncrease flexibilityTransistorSolid-state devicesFloating body effectEngineering

By forming a strained semiconductor layer in a PMOS transistor, a corresponding compressively strained channel region may be achieved, while, on the other hand, a corresponding strain in the NMOS transistor may be relaxed. Due to the reduced junction resistance caused by the reduced band gap of silicon / germanium in the NMOS transistor, an overall performance gain is accomplished, wherein, particularly in partially depleted SOI devices, the deleterious floating body effect is also reduced, due to the increased leakage currents generated by the silicon / germanium layer in the PMOS and NMOS transistor.

Owner:ADVANCED MICRO DEVICES INC

Soi semiconductor integrated circuit for eliminating floating body effects in soi mosfets and method of fabricating the same

A silicon-on-insulator (SOI) integrated circuit and a method of fabricating the SOI integrated circuit are provided. At least one isolated transistor active region and a body line are formed on an SOI substrate. The transistor active region and the body line are surrounded by an isolation layer which is in contact with a buried insulating layer of the SOI substrate. A portion of the sidewall of the transistor active region is extended to the body line. Thus, the transistor active region is electrically connected to the body line through a body extension. The body extension is covered with a body insulating layer. An insulated gate pattern is formed over the transistor active region, and one end of the gate pattern is overlapped with the body insulating layer.

Owner:SAMSUNG ELECTRONICS CO LTD

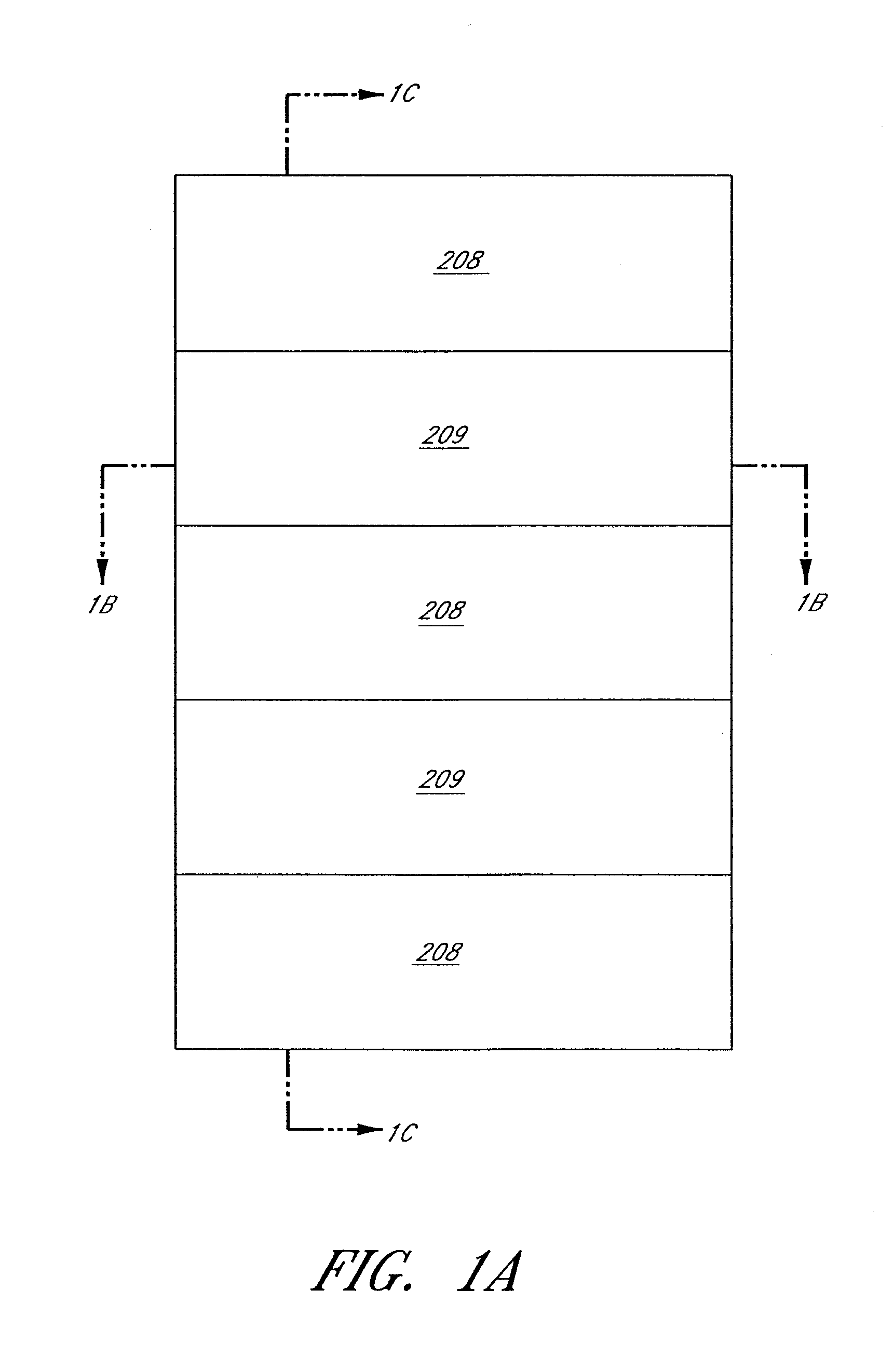

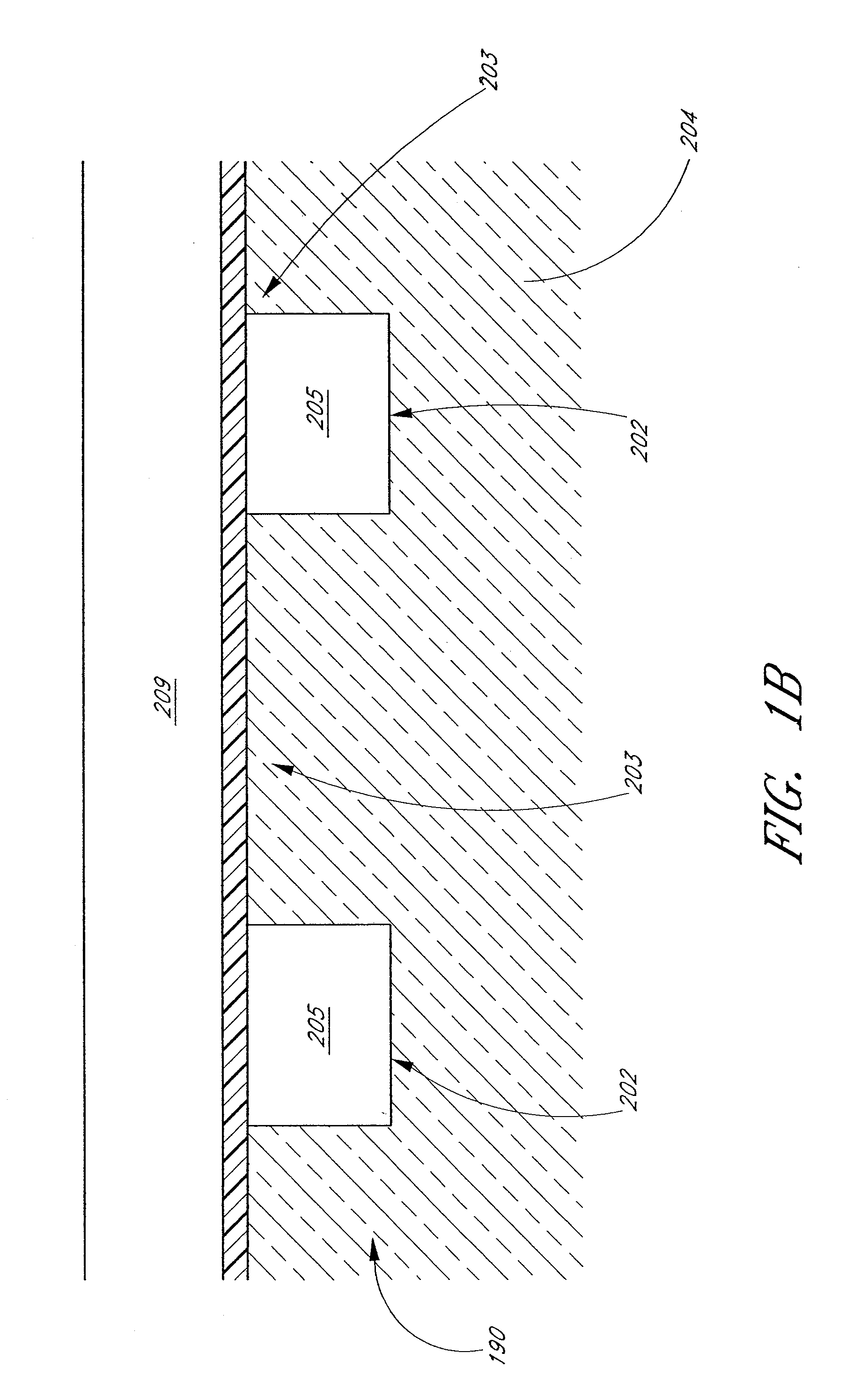

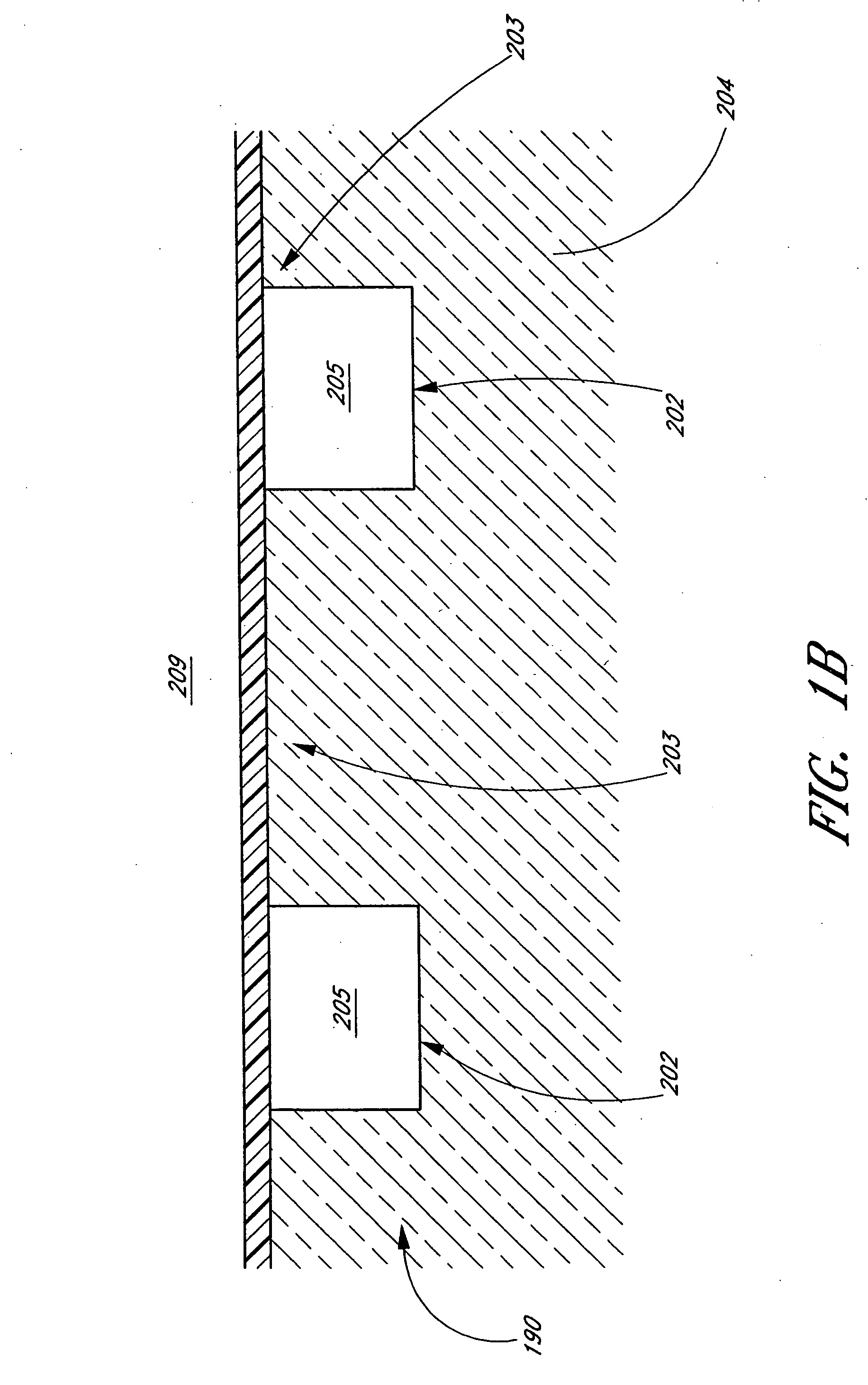

Body-contacted semiconductor structures and methods of fabricating such body-contacted semiconductor structures

InactiveUS20080044959A1Improves cell data retention timeEliminate the effects ofSolid-state devicesSemiconductor/solid-state device manufacturingHigh resistanceFloating body effect

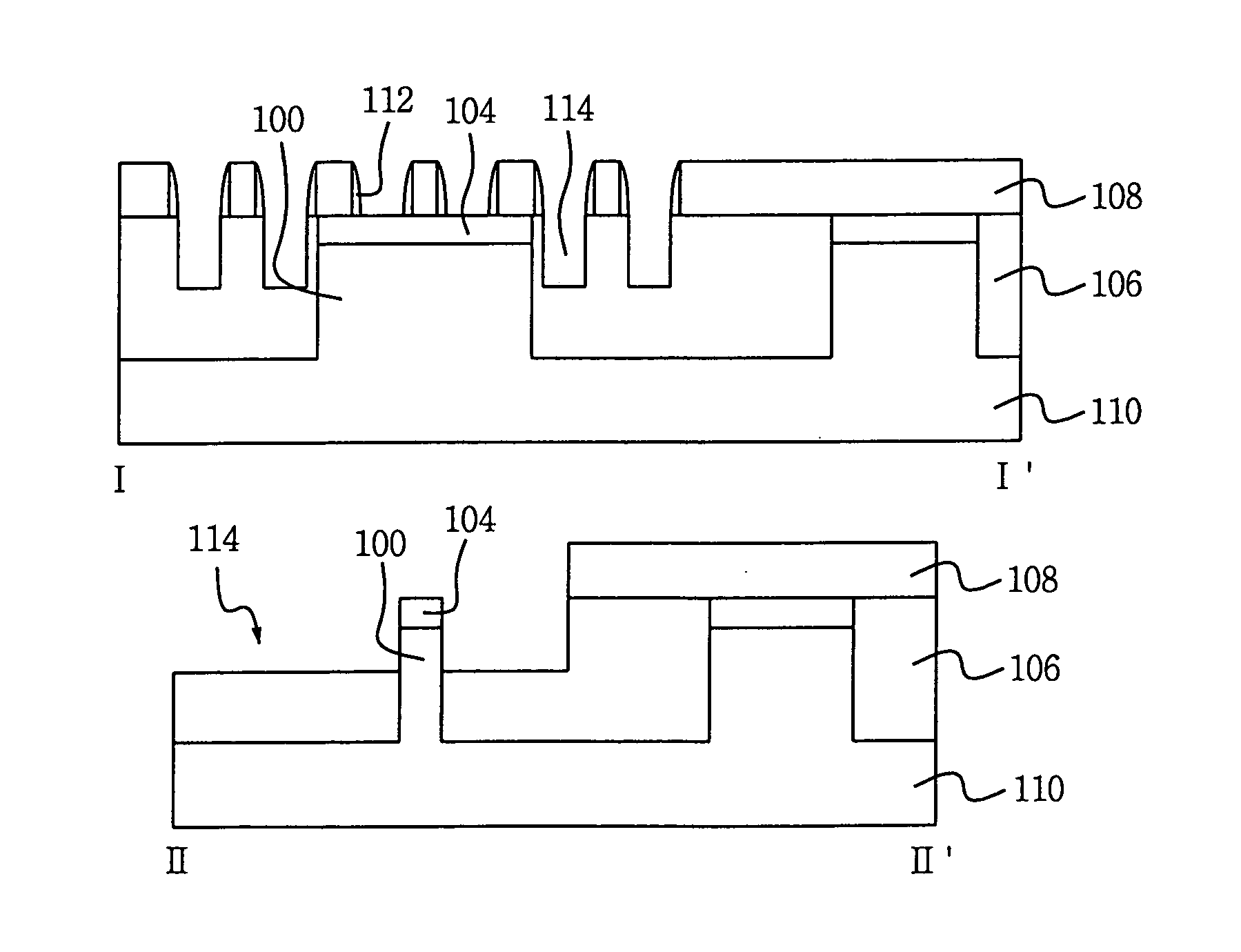

A semiconductor structure for a dynamic random access memory (DRAM) cell array that includes a plurality of vertical memory cells built on a semiconductor-on-insulator (SOI) wafer and a body contact in the buried dielectric layer of the SOI wafer. The body contact electrically couples a semiconductor body with a channel region of the access device of one vertical memory cell and a semiconductor substrate of the SOI wafer. The body contact provides a current leakage path that reduces the impact of floating body effects upon the vertical memory cell. The body contact may be formed by an ion implantation process that modifies the stoichiometry of a region of the buried dielectric layer so that the modified region becomes electrically conductive with a relatively high resistance.

Owner:IBM CORP

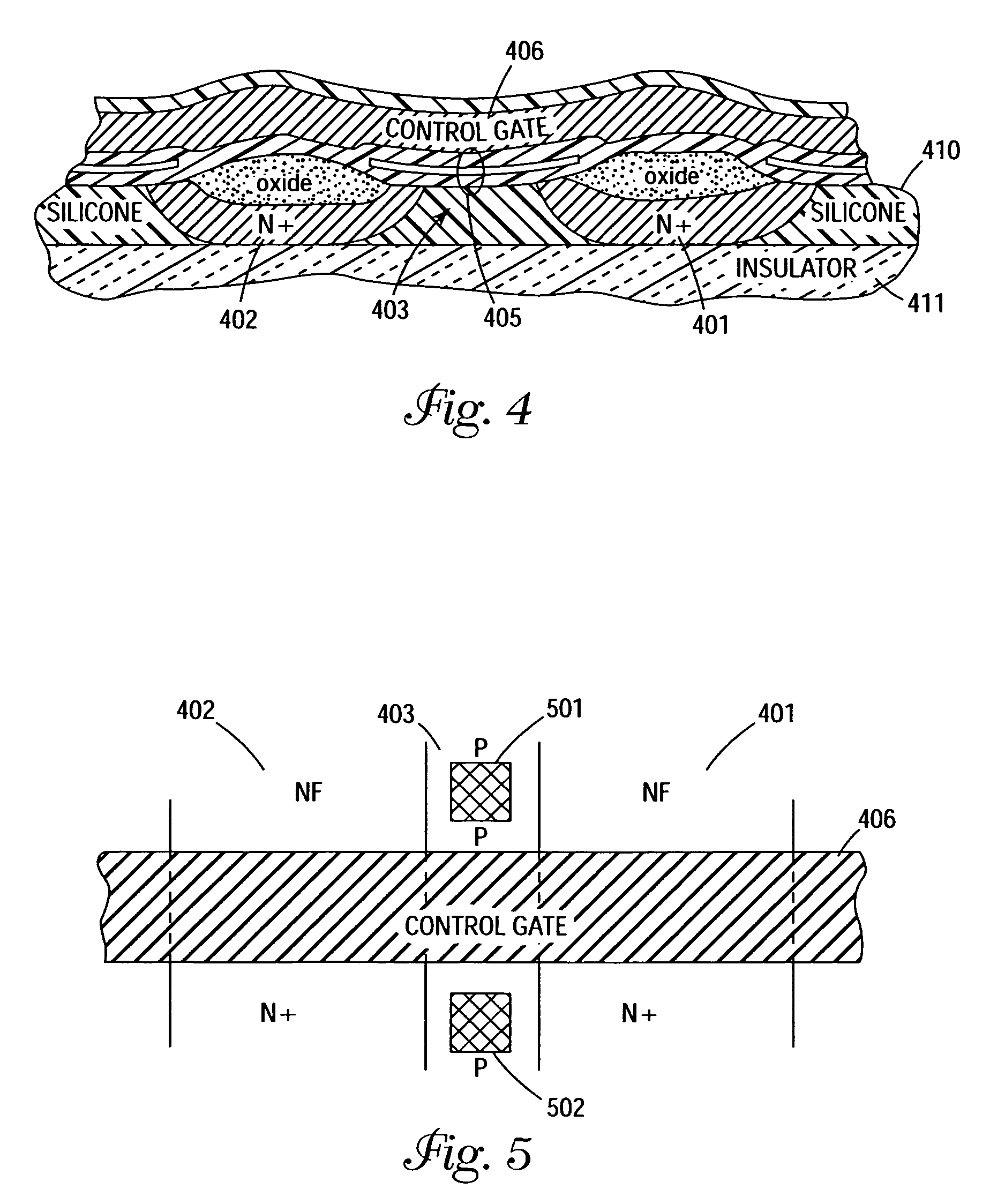

Double-gate flash memory device

The conventional flash memory device is fabricated by the MOS processing technology on a bulk substrate and has a similar configuration to an MOS device.While the conventional CMOS device has a superior scaling down characteristic, the scaling down characteristic of a flash memory device is poor due to the inability to reduce the thickness below 7 nm or 8 nm for the tunneling oxide film where the charges in the channel are tunneled into the floating electrode through the tunneling oxide.In order to resolve this problem, the present invention, instead of a SOI wafer, uses a cheaper bulk silicon wafer with lower defect density. A wall shape Fin active region where the channel and the source / drain are formed is connected to the bulk silicon substrate by which floating body effect and heat conduction problem are resolved. a flash memory device is fabricated by forming a tunneling oxide film on side surfaces of the Fin active and a floating (storage) electrode where the charges could be stored.The above structure has a superior scaling down characteristic and enhanced memory performance due to a double-gate flash memory device structure.

Owner:SEOUL NAT UNIV R&DB FOUND

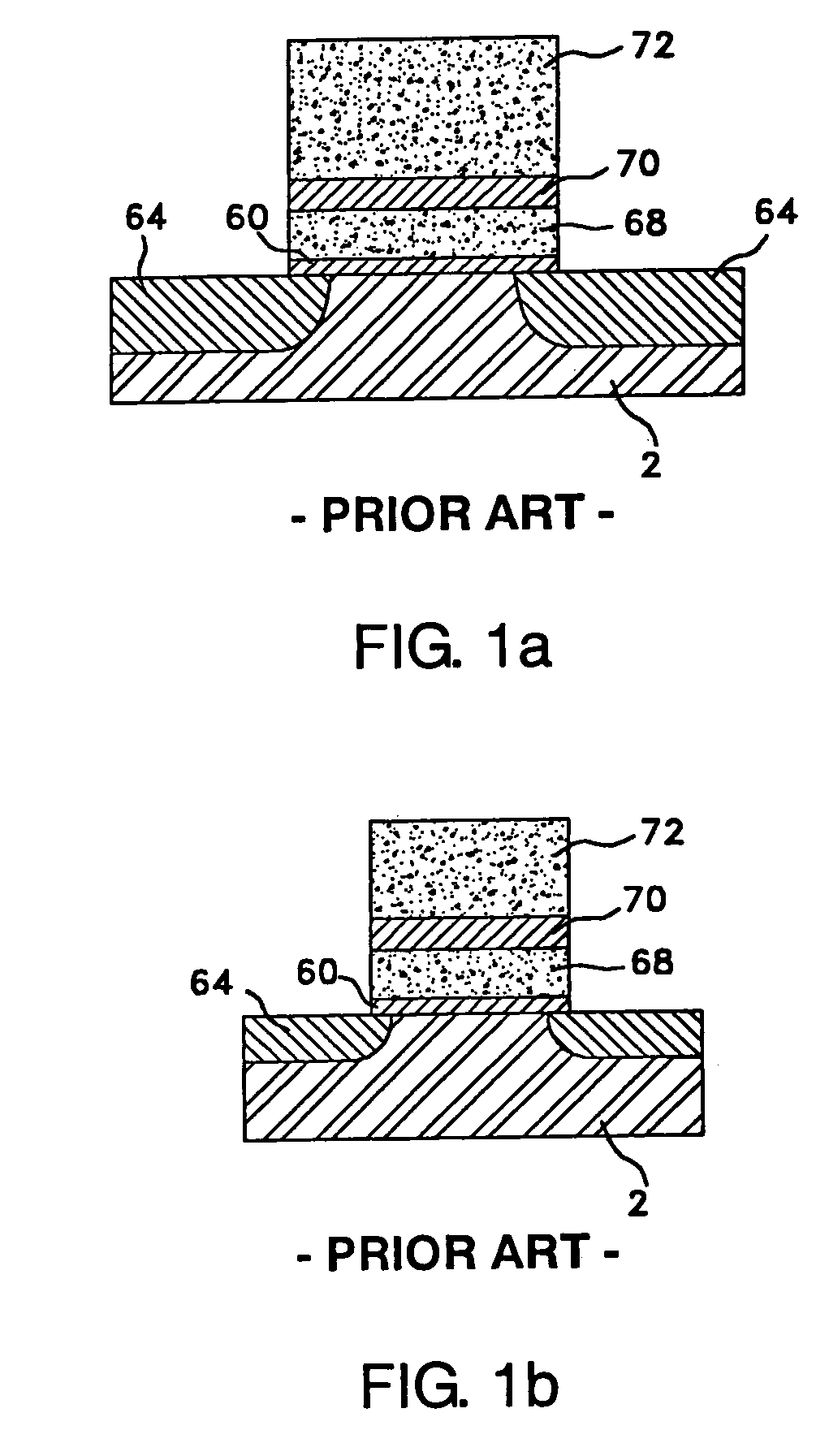

Fully depleted silicon-on-insulator CMOS logic

A extractor implanted region is used in a silicon-on-insulator CMOS memory device. The extractor region is reversed biased to remove minority carriers from the body region of partially depleted memory cells. This causes the body region to be fully depleted without the adverse floating body effects.

Owner:MICRON TECH INC

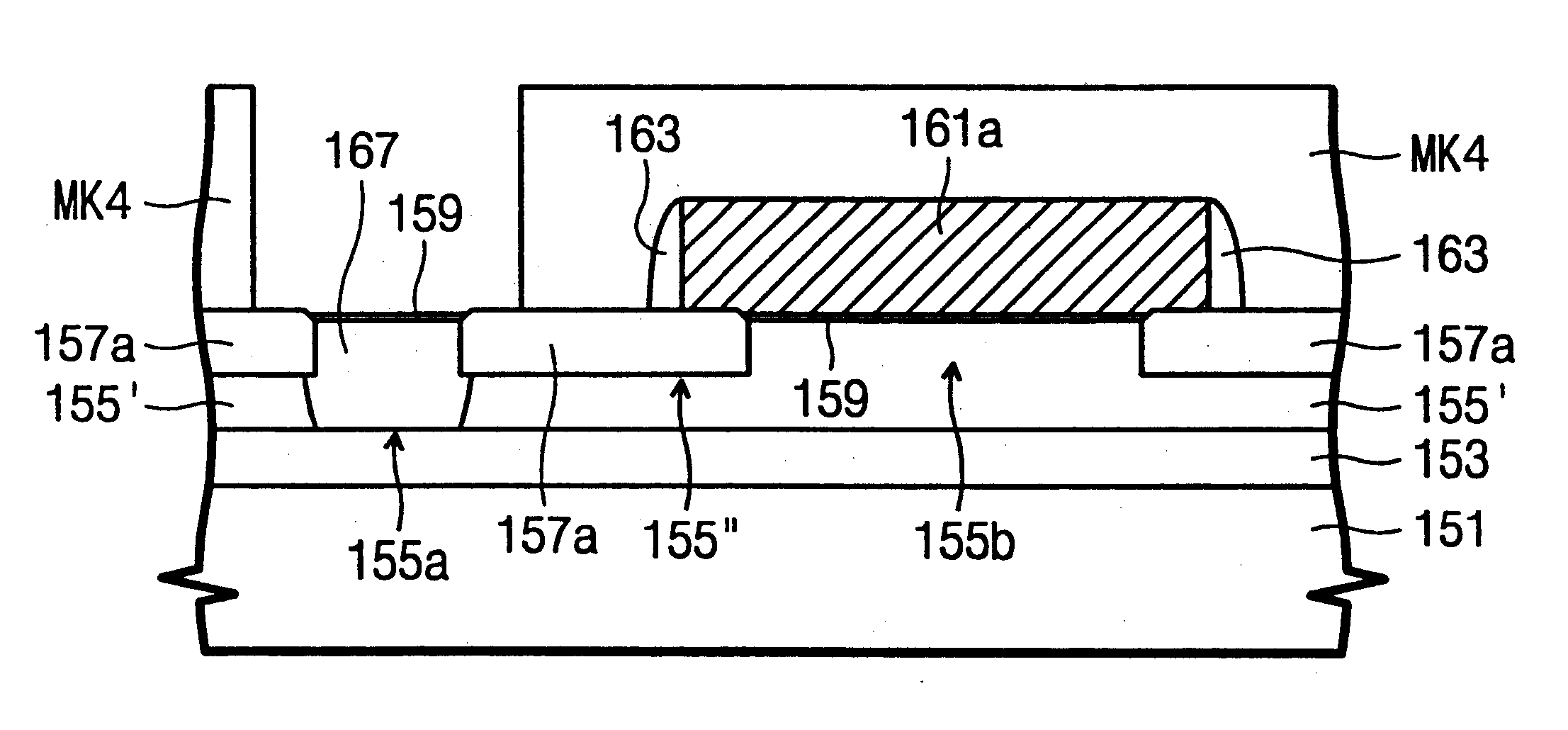

Double-gate flash memory device and fabrication method thereof

ActiveUS20050145926A1Improve featuresImprove integration densityTransistorNanoinformaticsFloating body effectEngineering

The conventional flash memory device is fabricated by the MOS processing technology on a bulk substrate and has a similar configuration to an MOS device. While the conventional CMOS device has a superior scaling down characteristic, the scaling down characteristic of a flash memory device is poor due to the inability to reduce the thickness below 7 nm or 8 nm for the tunneling oxide film where the charges in the channel are tunneled into the floating electrode through the tunneling oxide. In order to resolve this problem, the present invention, instead of a SOI wafer, uses a cheaper bulk silicon wafer with lower defect density. A wall shape Fin active region where the channel and the source / drain are formed is connected to the bulk silicon substrate by which floating body effect and heat conduction problem are resolved. a flash memory device is fabricated by forming a tunneling oxide film on side surfaces of the Fin active and a floating (storage) electrode where the charges could be stored. The above structure has a superior scaling down characteristic and enhanced memory performance due to a double-gate flash memory device structure.

Owner:SEOUL NAT UNIV R&DB FOUND

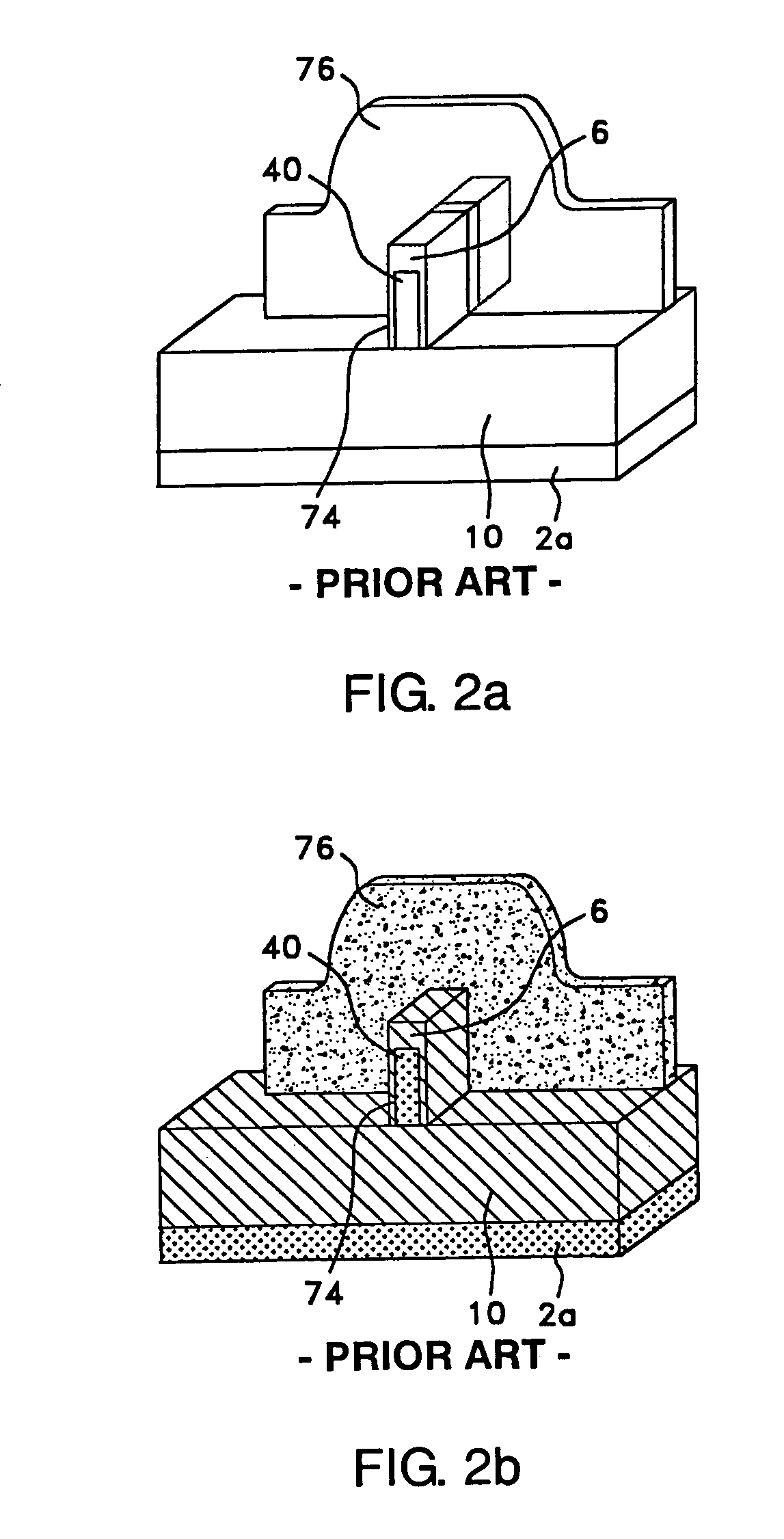

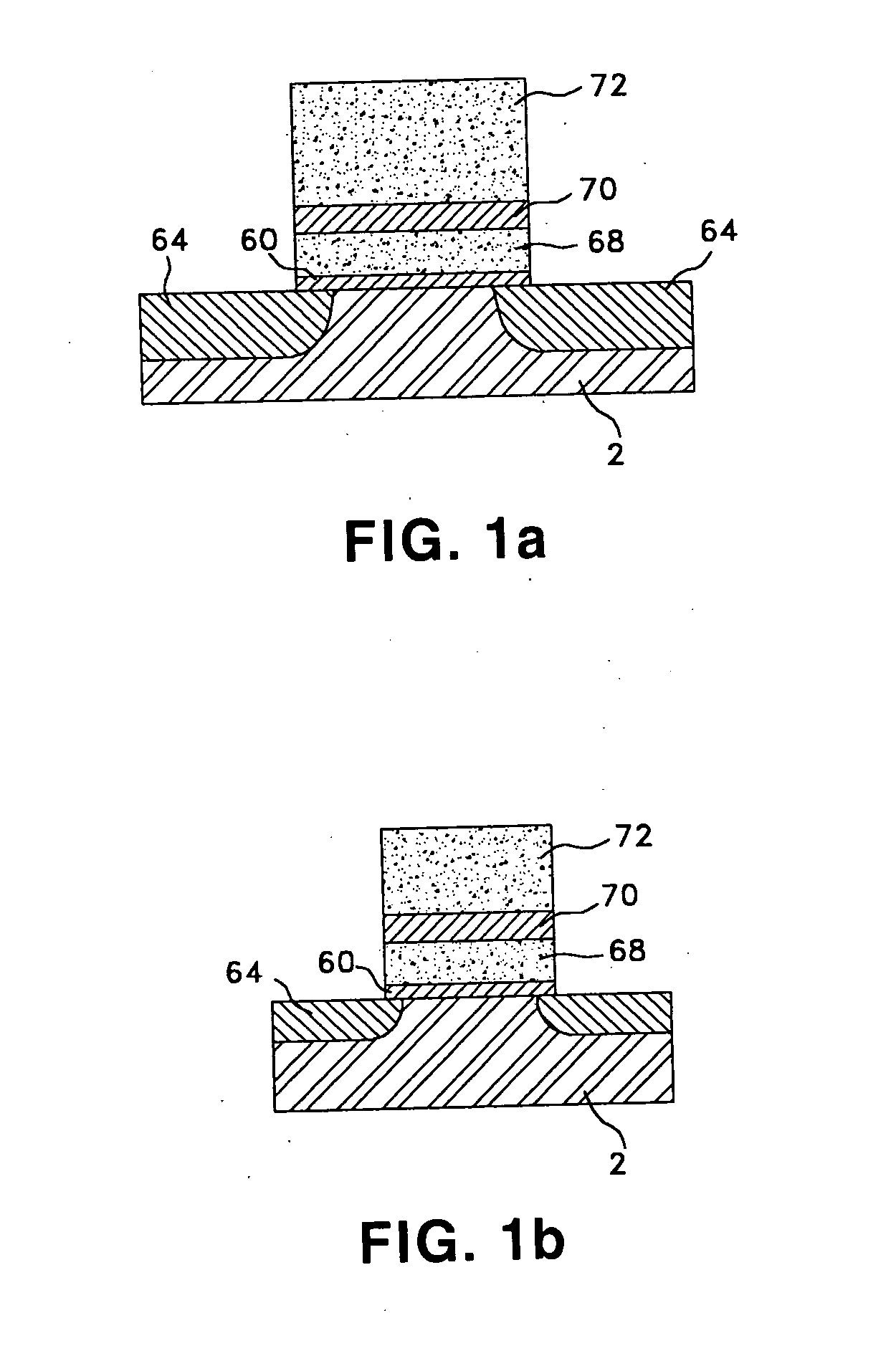

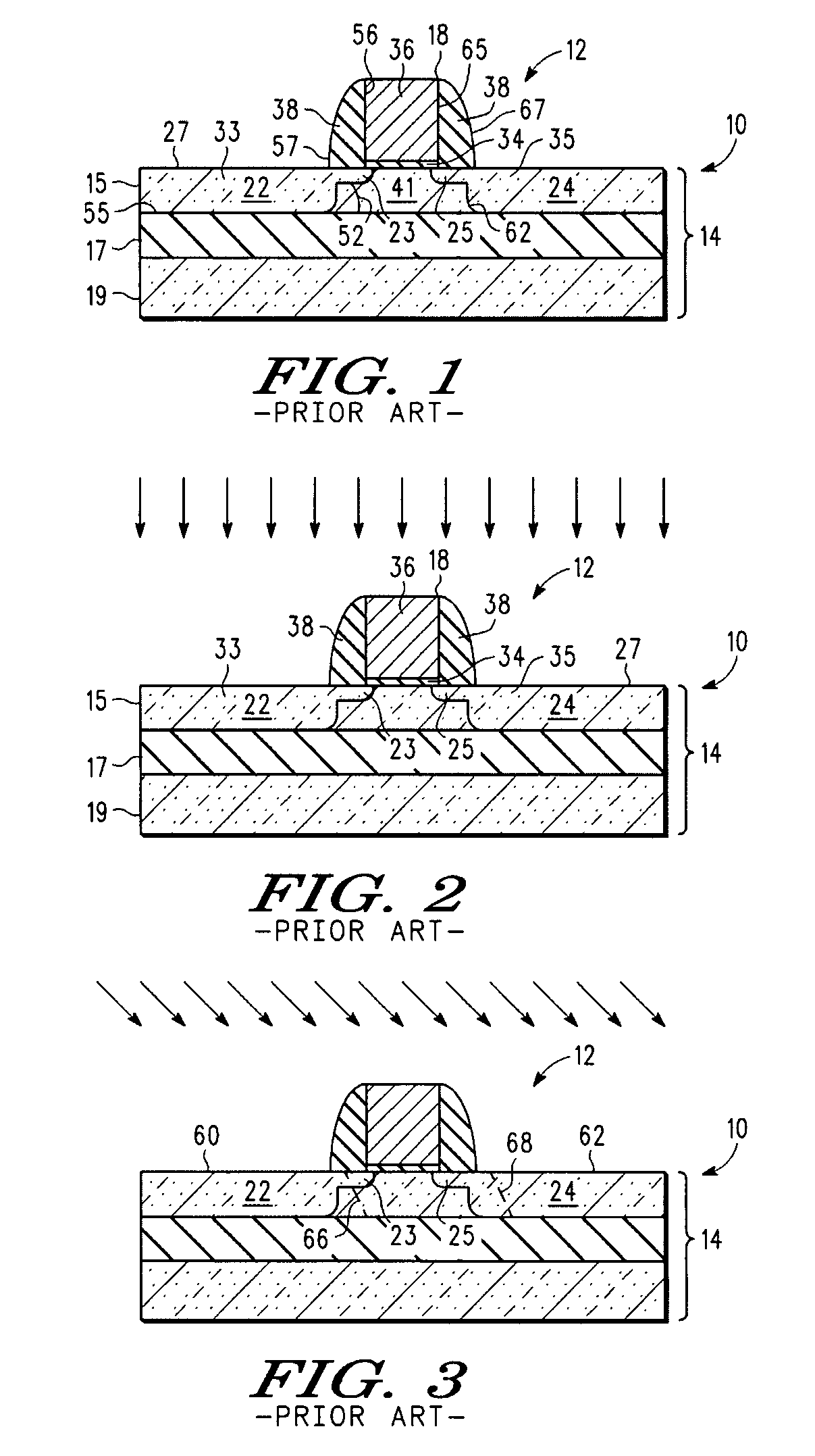

Methods of reducing floating body effect

Methods of reducing the floating body effect in vertical transistors are disclosed. The floating body effect occurs when an active region in a pillar is cut off from the substrate by a depletion region and the accompanying electrostatic potential created. In a preferred embodiment, a word line is recessed into the substrate to tie the upper active region to the substrate. The resulting memory cells are preferably used in dynamic random access memory (DRAM) devices.

Owner:MICRON TECH INC

Soi transistor having an embedded strain layer and a reduced floating body effect and a method for forming the same

InactiveUS20070252204A1Improve performanceEfficient dischargeTransistorSolid-state devicesDriving currentFloating body effect

By forming a portion of a PN junction within strained silicon / germanium material in SOI transistors with a floating body architecture, the junction leakage may be significantly increased, thereby reducing floating body effects. The positioning of a portion of the PN junction within the strained silicon / germanium material may be accomplished on the basis of implantation and anneal techniques, contrary to conventional approaches in which in situ doped silicon / germanium is epitaxially grown so as to form the deep drain and source regions. Consequently, high drive current capability may be combined with a reduction of floating body effects.

Owner:ADVANCED MICRO DEVICES INC

Body biasing structure of SOI

ActiveUS7432552B2Suppression of floating body effectTransistorSolid-state devicesMOSFETFloating body effect

Owner:SEOUL NAT UNIV R&DB FOUND +1

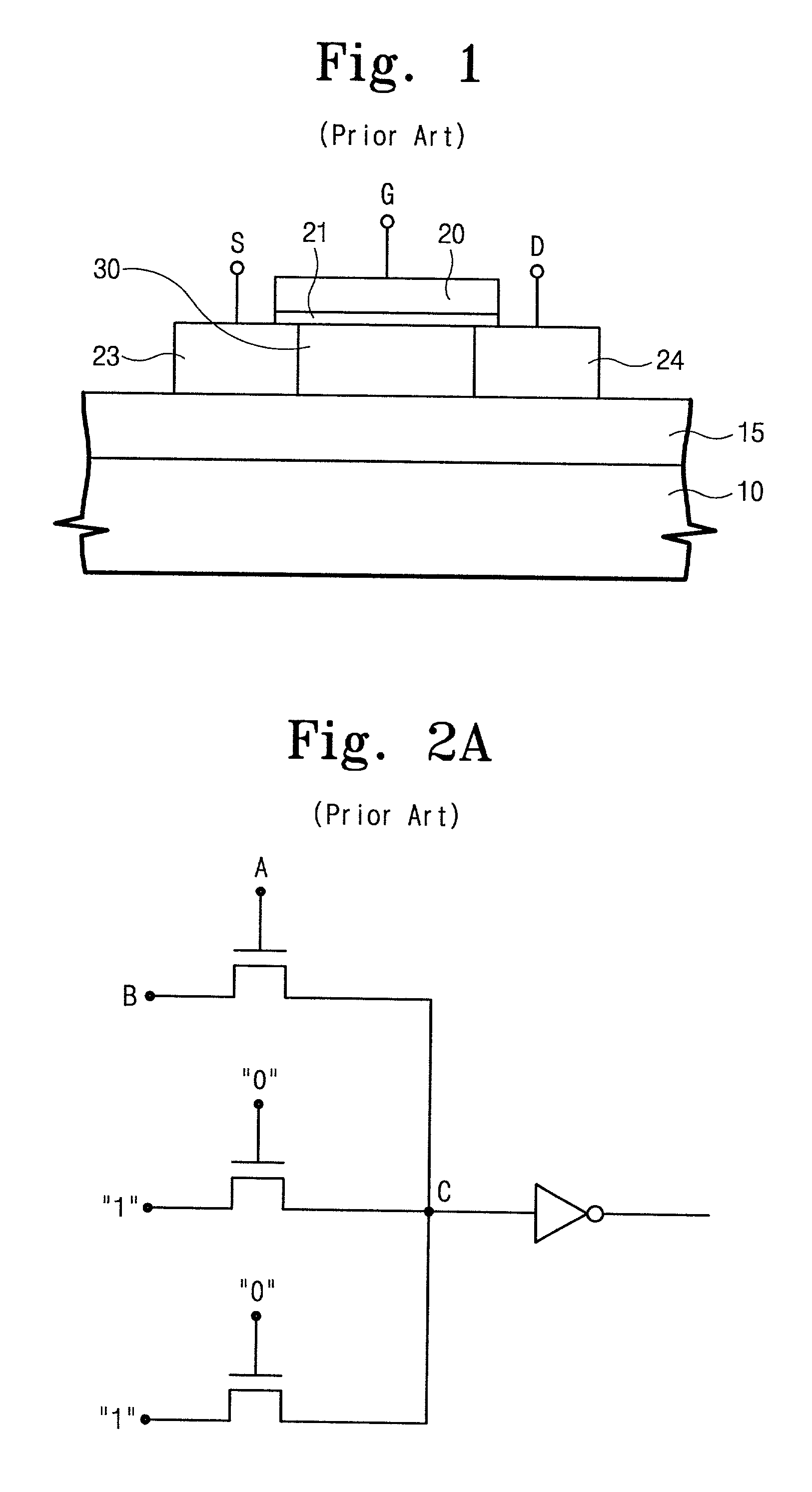

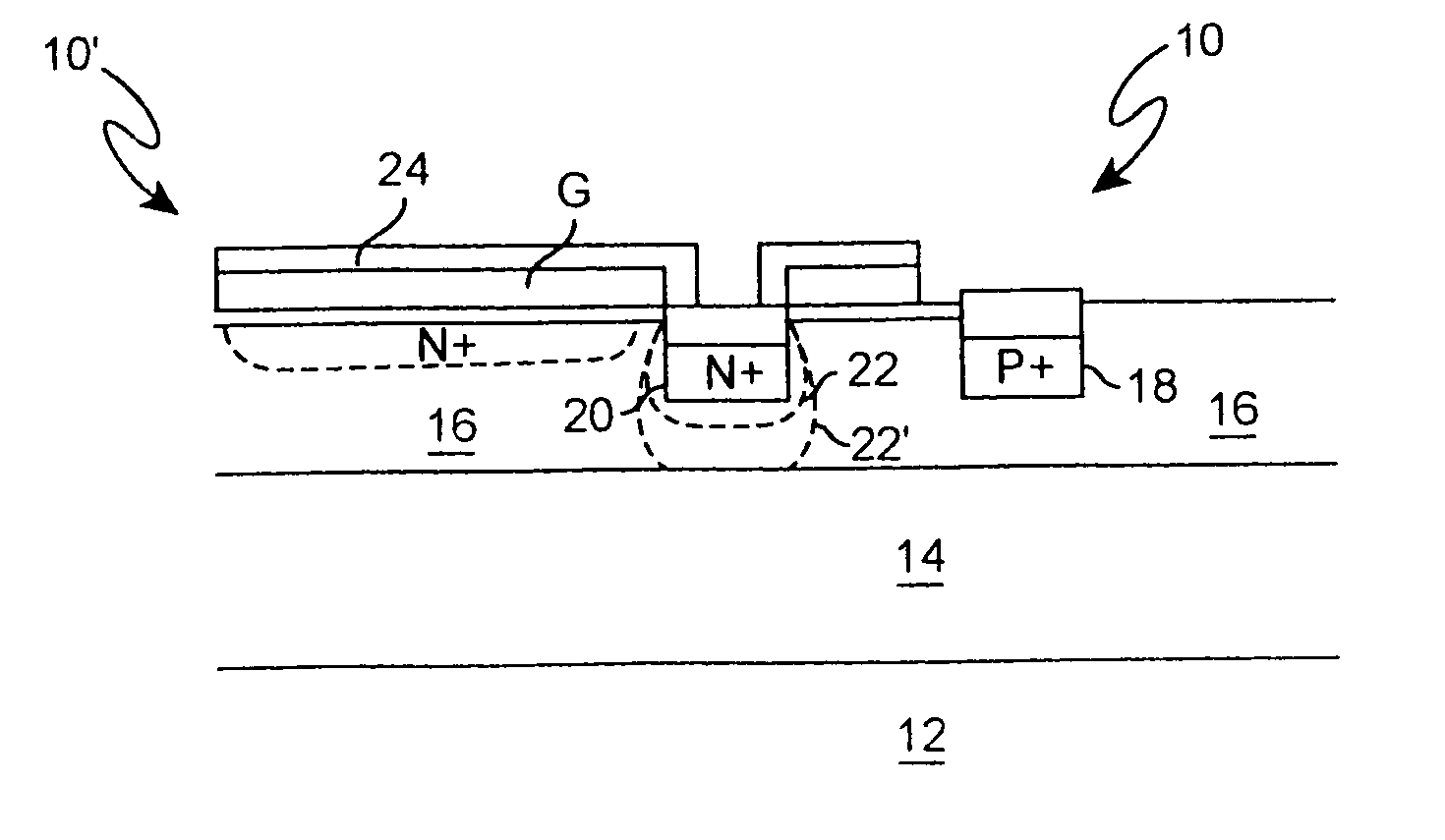

Dynamic threshold voltage MOSFET on SOI

ActiveUS20050121699A1Improve performanceReduce manufacturing costTransistorSolid-state devicesMOSFETFloating body effect

Provision of a body control contact adjacent a transistor and between the transistor and a contact to the substrate or well in which the transistor is formed allows connection and disconnection of the substrate of the transistor to and from a zero (ground) or substantially arbitrary low voltage in accordance with control signals applied to the gate of the transistor to cause the transistor to exhibit a variable threshold which maintains good performance at low supply voltages and reduces power consumption / dissipation which is particularly advantageous in portable electronic devices. Floating body effects (when the transistor substrate in disconnected from a voltage source in the “on” state) are avoided since the substrate is discharged when the transistor is switched to the “off” state. The transistor configuration can be employed with both n-type and p-type transistors which may be in complementary pairs.

Owner:GLOBALFOUNDRIES US INC

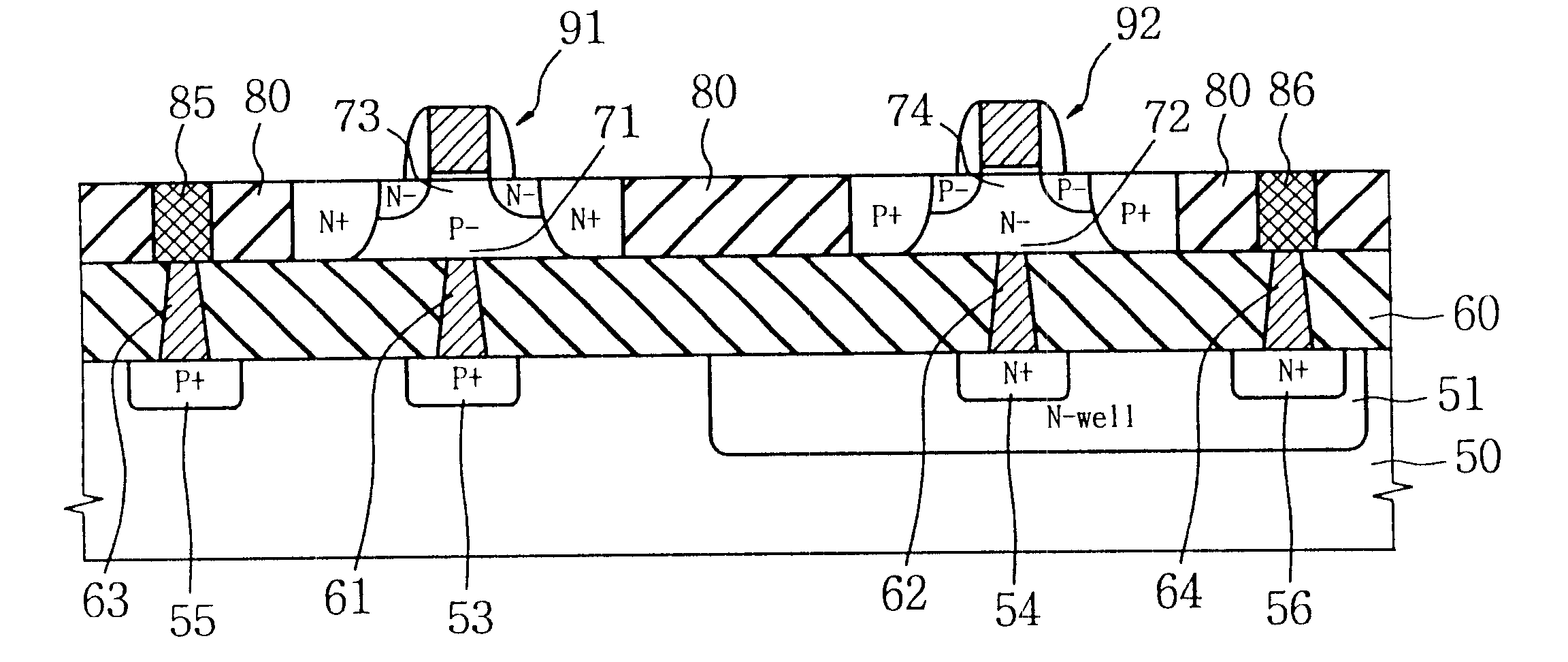

Hybrid crystal orientation CMOS structure for adaptive well biasing and for power and performance enhancement

ActiveUS20060231893A1Suppression of floating body effectAdjustable voltageTransistorSolid-state devicesPerformance enhancementFloating body effect

The present invention provides a semiconducting structure including a substrate having an SOI region and a bulk-Si region, wherein the SOI region and the bulk-Si region have a same or differing crystallographic orientation; an isolation region separating the SOI region from the bulk-Si region; and at least one first device located in the SOI region and at least one second device located in the bulk-Si region. The SOI region has an silicon layer atop an insulating layer. The bulk-Si region further comprises a well region underlying the second device and a contact to the well region, wherein the contact stabilizes floating body effects. The well contact is also used to control the threshold voltages of the FETs in the bulk-Si region to optimized the power and performance of circuits built from the combination of the SOI and bulk-Si region FETs.

Owner:GLOBALFOUNDRIES US INC

Hybrid bulk-SOI 6T-SRAM cell for improved cell stability and performance

ActiveUS20060231899A1Optimal NFET device performanceImprove device performanceTransistorSolid-state devicesFloating body effectSram cell

The present invention provides a 6T-SRAM semiconducting structure including a substrate having an SOI region and a bulk-Si region, wherein the SOI region and the bulk-Si region have a same or differing crystallographic orientation; an isolation region separating the SOI region from the bulk-Si region; and at least one first device located in the SOI region and at least one second device located in the bulk-Si region. The SOI region has an silicon layer atop an insulating layer. The bulk-Si region further comprises a well region underlying the second device and a contact to the well region, wherein the contact stabilizes floating body effects. The well contact is also used to control the threshold voltages of the FETs in the bulk-Si region to optimized the power and performance of the SRAM cell built from the combination of the SOI and bulk-Si region FETs.

Owner:GLOBALFOUNDRIES US INC

Method of manufacturing a fin field effect transistor

ActiveUS20050186746A1Improve productivityReduce manufacturing costTransistorSolid-state devicesFloating body effectProduction rate

In an exemplary embodiment, a fin active region is protruded along one direction from a bulk silicon substrate on which a shallow trench insulator is entirely formed so as to cover the fin active region. The shallow trench insulator is removed to selectively expose an upper part and sidewall of the fin active region, along a line shape that at least one time crosses with the fin active region, thus forming a trench. The fin active region is exposed by the trench and thereon a gate insulation layer is formed. Thereby, productivity is increased and performance of the device is improved. A fin FET employs a bulk silicon substrate of which a manufacturing cost is lower than that of a conventional SOI type silicon substrate. Also, a floating body effect can be prevented, or is substantially reduced.

Owner:SAMSUNG ELECTRONICS CO LTD

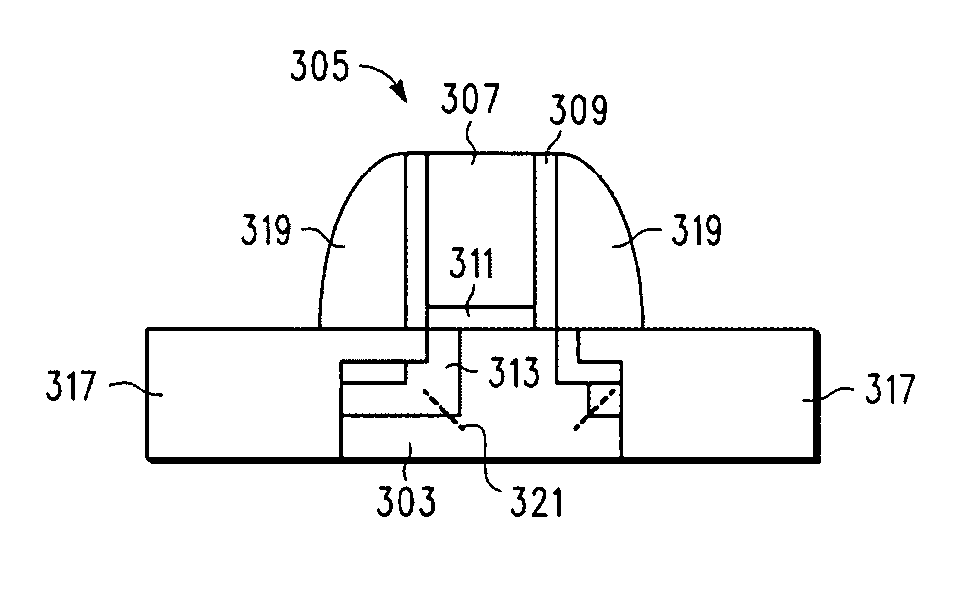

Methods of forming vertical transistors

A vertical transistor forming method includes forming a first pillar above a first source / drain and between second and third pillars, providing a first recess between the first and second pillars and a wider second recess between the first and third pillars, forming a gate insulator over the first pillar, forming a front gate and back gate over opposing sidewalls of the first pillar by depositing a gate conductor material within the first and second recesses and etching the gate conductor material to substantially fill the first recess, forming the back gate, and only partially fill the second recess, forming the front gate, forming a second source / drain elevationally above the first source / drain, and providing a transistor channel in the first pillar. The channel is operationally associated with the first and second sources / drains and with the front and back gates to form a vertical transistor configured to exhibit a floating body effect.

Owner:MICRON TECH INC

Dynamic threshold voltage MOSFET on SOI

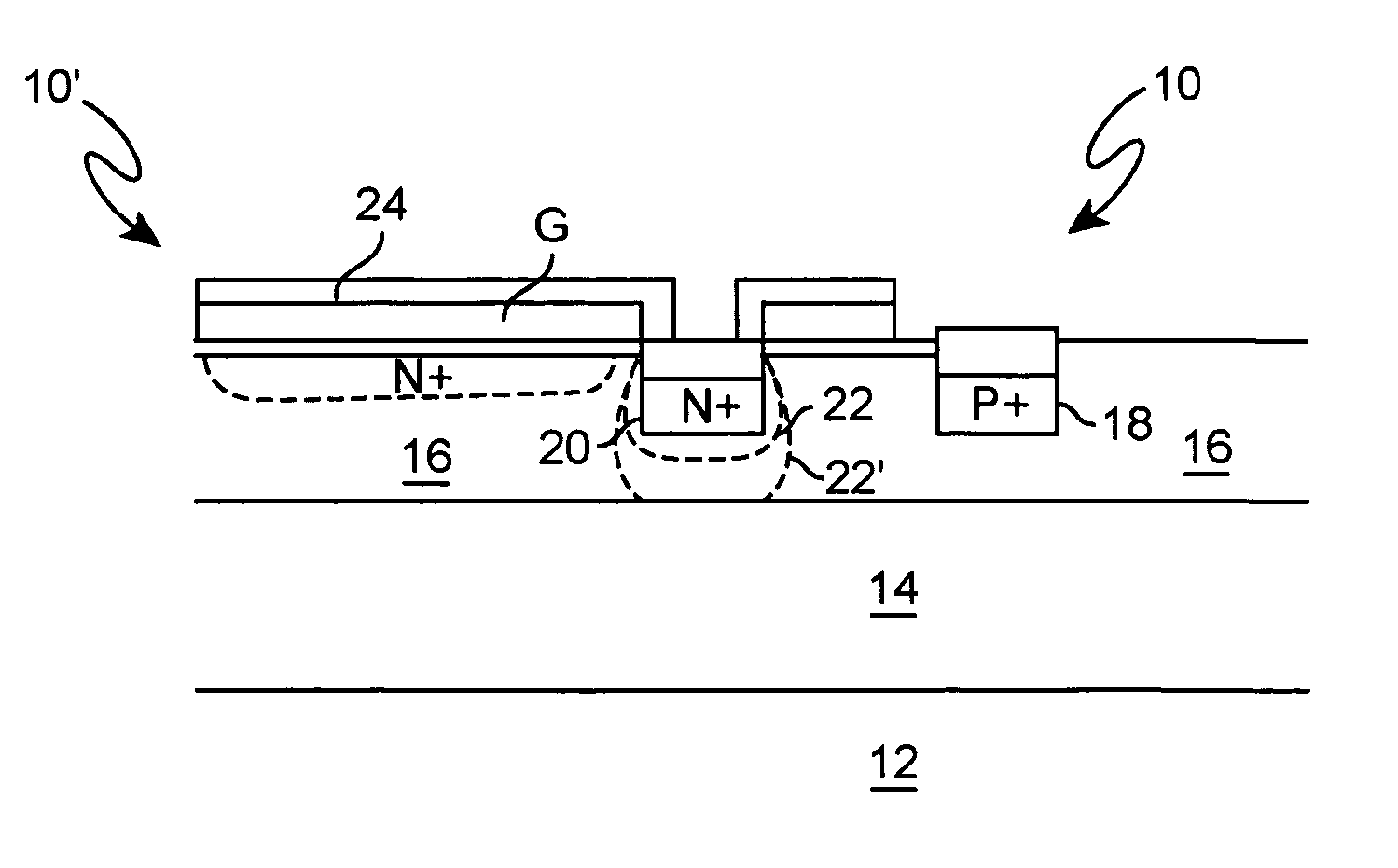

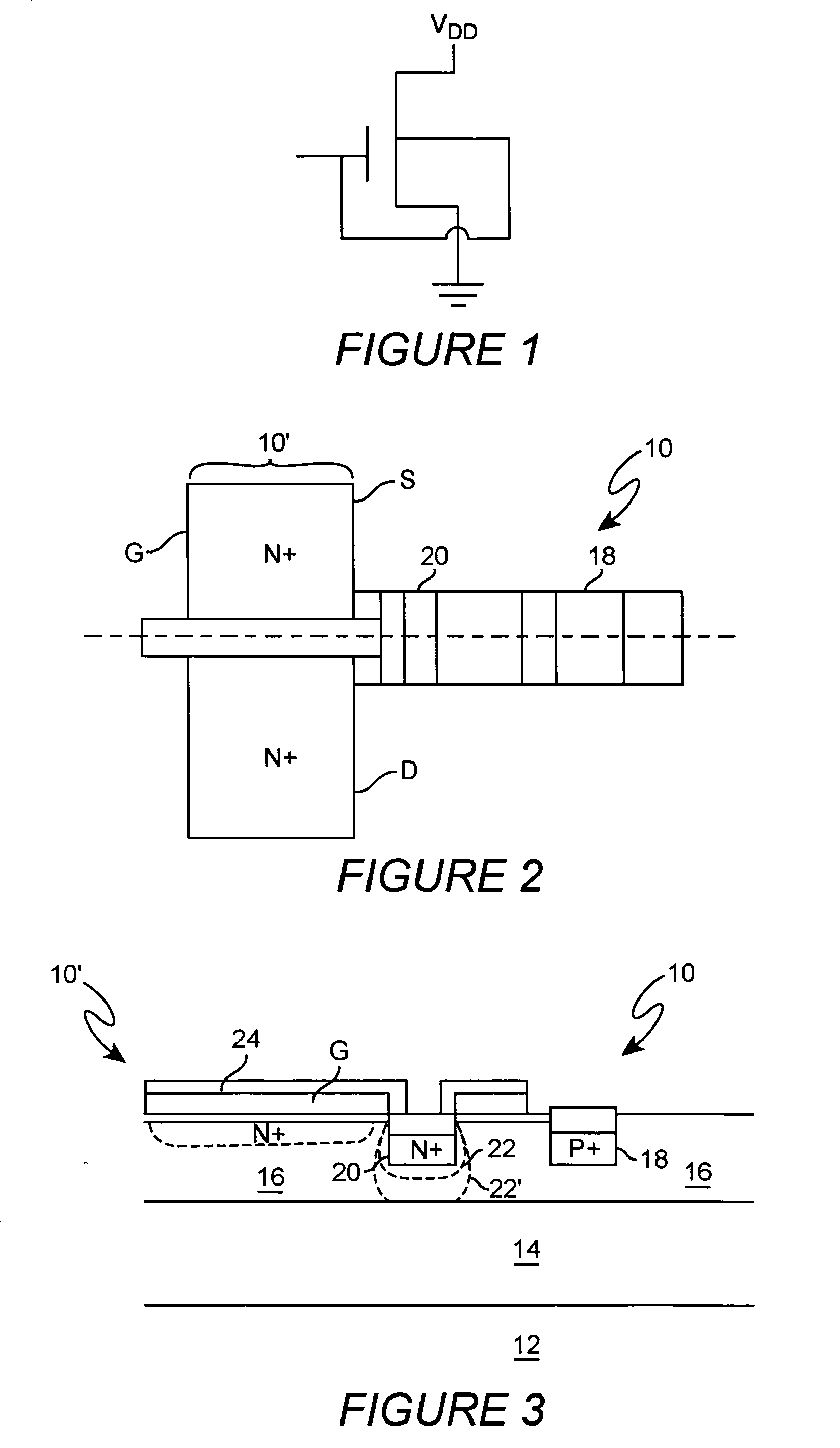

ActiveUS7045873B2Improve performanceReduce manufacturing costTransistorSolid-state devicesMOSFETFloating body effect

Provision of a body control contact adjacent a transistor and between the transistor and a contact to the substrate or well in which the transistor is formed allows connection and disconnection of the substrate of the transistor to and from a zero (ground) or substantially arbitrary low voltage in accordance with control signals applied to the gate of the transistor to cause the transistor to exhibit a variable threshold which maintains good performance at low supply voltages and reduces power consumption / dissipation which is particularly advantageous in portable electronic devices. Floating body effects (when the transistor substrate in disconnected from a voltage source in the “on” state) are avoided since the substrate is discharged when the transistor is switched to the “off” state. The transistor configuration can be employed with both n-type and p-type transistors which may be in complementary pairs.

Owner:GLOBALFOUNDRIES U S INC

Methods of reducing floating body effect

ActiveUS20060125044A1Solid-state devicesSemiconductor/solid-state device manufacturingFloating body effectDepletion region

Methods of reducing the floating body effect in vertical transistors are disclosed. The floating body effect occurs when an active region in a pillar is cut off from the substrate by a depletion region and the accompanying electrostatic potential created. In a preferred embodiment, a word line is recessed into the substrate to tie the upper active region to the substrate. The resulting memory cells are preferably used in dynamic random access memory (DRAM) devices.

Owner:MICRON TECH INC

CMOS devices for low power integrated circuits

InactiveUS20060273391A1Reducing off-state leakage currentTransistorSemiconductor/solid-state device manufacturingGate dielectricFloating body effect

A preferred embodiment of the invention provides a semiconductor fabrication method. An embodiment comprises forming a MOS device and thermally oxidizing the MOS device to form a gate dielectric substantially thicker at a gate dielectric edge than that at a gate dielectric center. Embodiments further comprise performing a source / drain ion implant to form an asymmetric source / drain, wherein the source region includes a high leakage source junction, and wherein the drain region includes a low leakage drain junction. Other embodiments of the invention comprise a MOS device formed in a semiconductor substrate, wherein the device has improved resistance to floating body effects. Still other embodiments include a CMOS device for low power integrated circuits.

Owner:TAIWAN SEMICON MFG CO LTD

Hybrid bulk-SOI 6T-SRAM cell for improved cell stability and performance

ActiveUS7274072B2Reduce power consumptionImprove performanceTransistorSolid-state devicesFloating body effectEngineering

The present invention provides a 6T-SRAM semiconducting structure including a substrate having an SOI region and a bulk-Si region, wherein the SOI region and the bulk-Si region have a same or differing crystallographic orientation; an isolation region separating the SOI region from the bulk-Si region; and at least one first device located in the SOI region and at least one second device located in the bulk-Si region. The SOI region has an silicon layer atop an insulating layer. The bulk-Si region further comprises a well region underlying the second device and a contact to the well region, wherein the contact stabilizes floating body effects. The well contact is also used to control the threshold voltages of the FETs in the bulk-Si region to optimized the power and performance of the SRAM cell built from the combination of the SOI and bulk-Si region FETs.

Owner:GLOBALFOUNDRIES US INC

Field-shielded SOI-MOS structure free from floating body effect, and method of fabrication therefor

InactiveUS6933572B2Enhancing recombinationReduced recombination time constantTransistorSolid-state devicesFloating body effectElectrical conductor

A silicon-on-insulator structure provides an effective drift field for holes, and simultaneously enhanced recombination centers for holes and electrons. The structure includes a silicon substrate, an oxide insulation layer disposed above the silicon substrate, a silicon body layer disposed above the oxide insulation layer, and a field shield gate disposed above the silicon body layer. The field shield gate includes a conductor portion, and an alumina insulation layer disposed beneath the conductor portion. The oxide insulation layer and the silicon body layer each include at least one channel stop region, and at least one recombination center for the recombination of positive- and negative-charge carriers. The effective drift field and enhanced recombination centers facilitate the rapid recombination of the charge carriers, leading to a very small recombination time constant, which overcomes the floating body effect associated with conventional silicon-on-insulator structures.

Owner:MICRON TECH INC

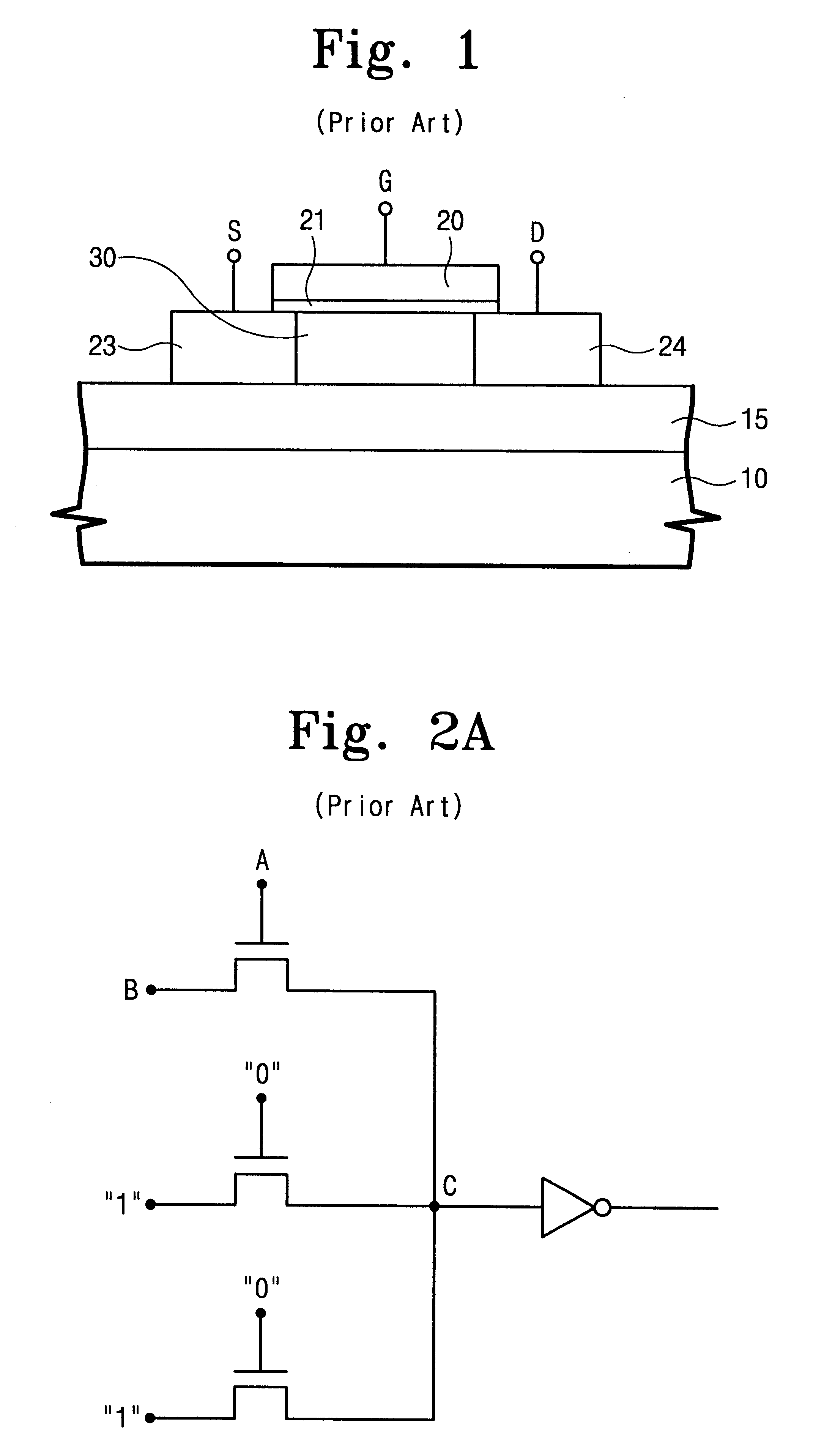

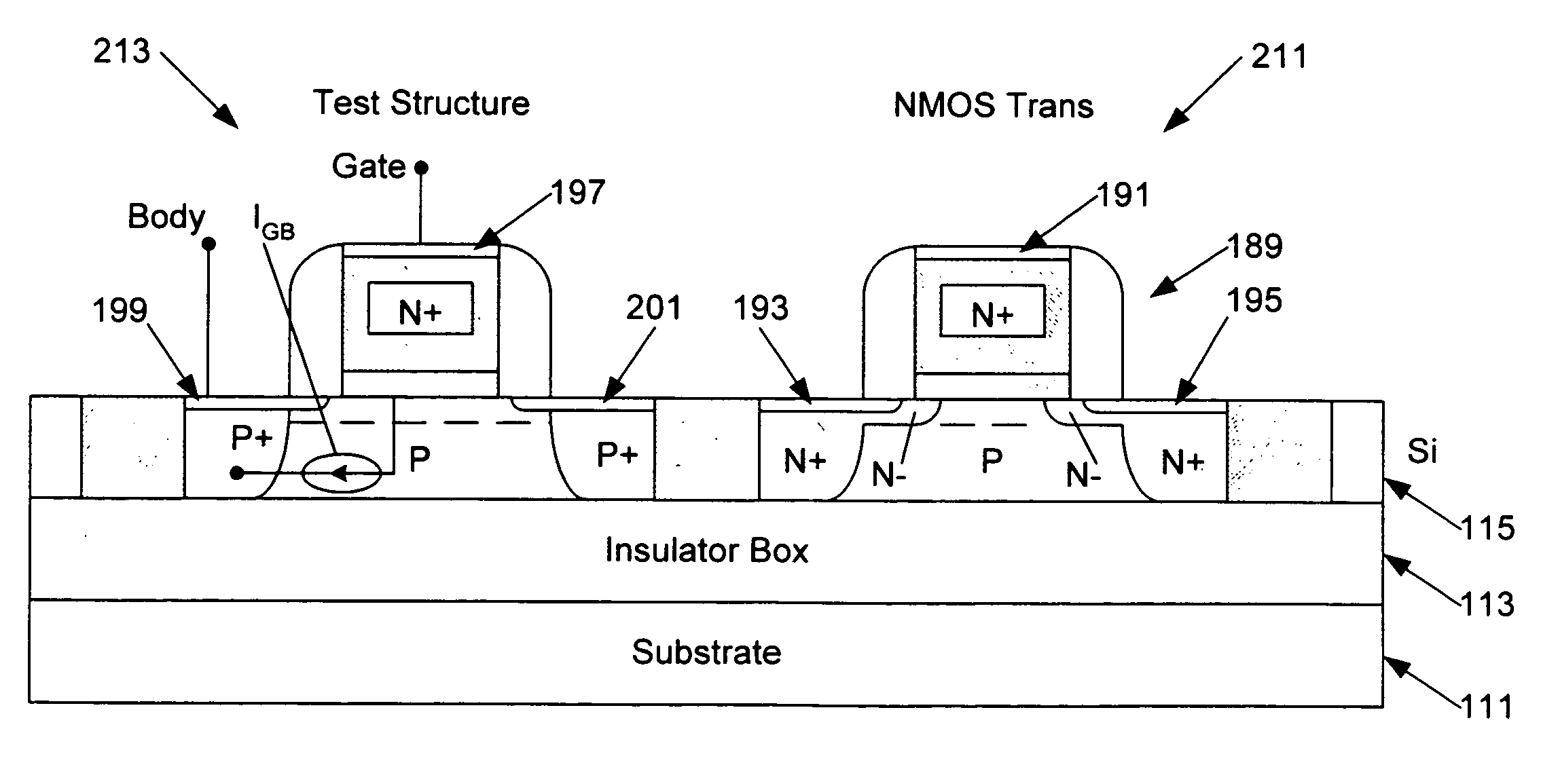

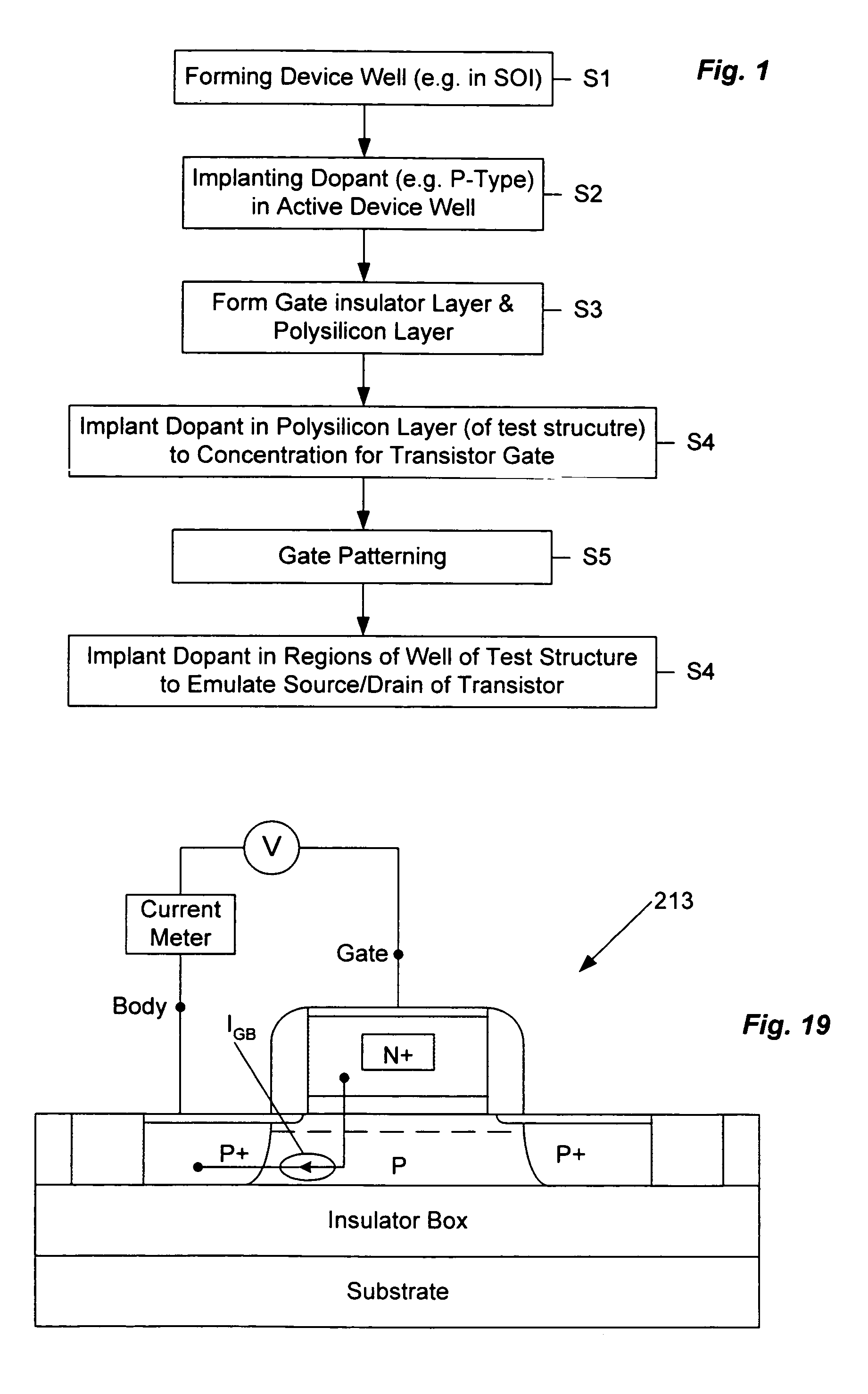

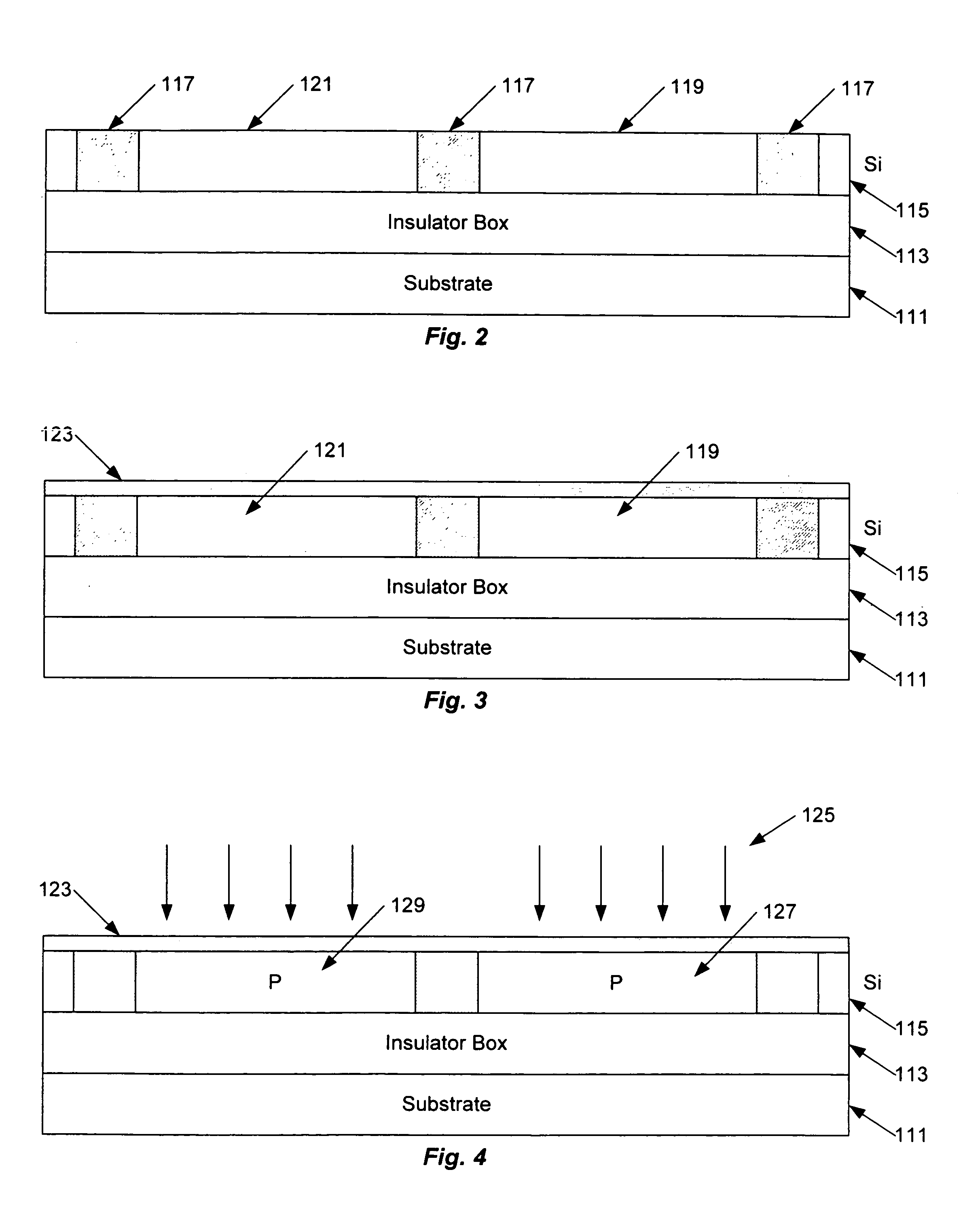

Method of making a test structure for gate-body current and direct extraction of physical gate length using conventional CMOS

InactiveUS7071044B1Efficient productionSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingDopantFloating body effect

Owner:GLOBALFOUNDRIES INC

Soi field effect transistor having asymmetric junction leakage

InactiveUS20090032845A1Narrow widthFloating body effect is reduced and eliminatedTransistorSemiconductor/solid-state device manufacturingFloating body effectJunction leakage

A source trench and a drain trench are asymmetrically formed in a top semiconductor layer comprising a first semiconductor in a semiconductor substrate. A second semiconductor material having a narrower band gap than the first semiconductor material is deposited in the source trench and the drain trench to form a source side narrow band gap region and a drain side narrow band gap region, respectively. A gate spacer is formed and source and drain regions are formed in the top semiconductor layer. A portion of the boundary between an extended source region and an extended body region is formed in the source side narrow band gap region. Due to the narrower band gap of the second semiconductor material compared to the band gap of the first semiconductor material, charge formed in the extended body region is discharged through the source and floating body effects are reduced or eliminated.

Owner:GLOBALFOUNDRIES INC

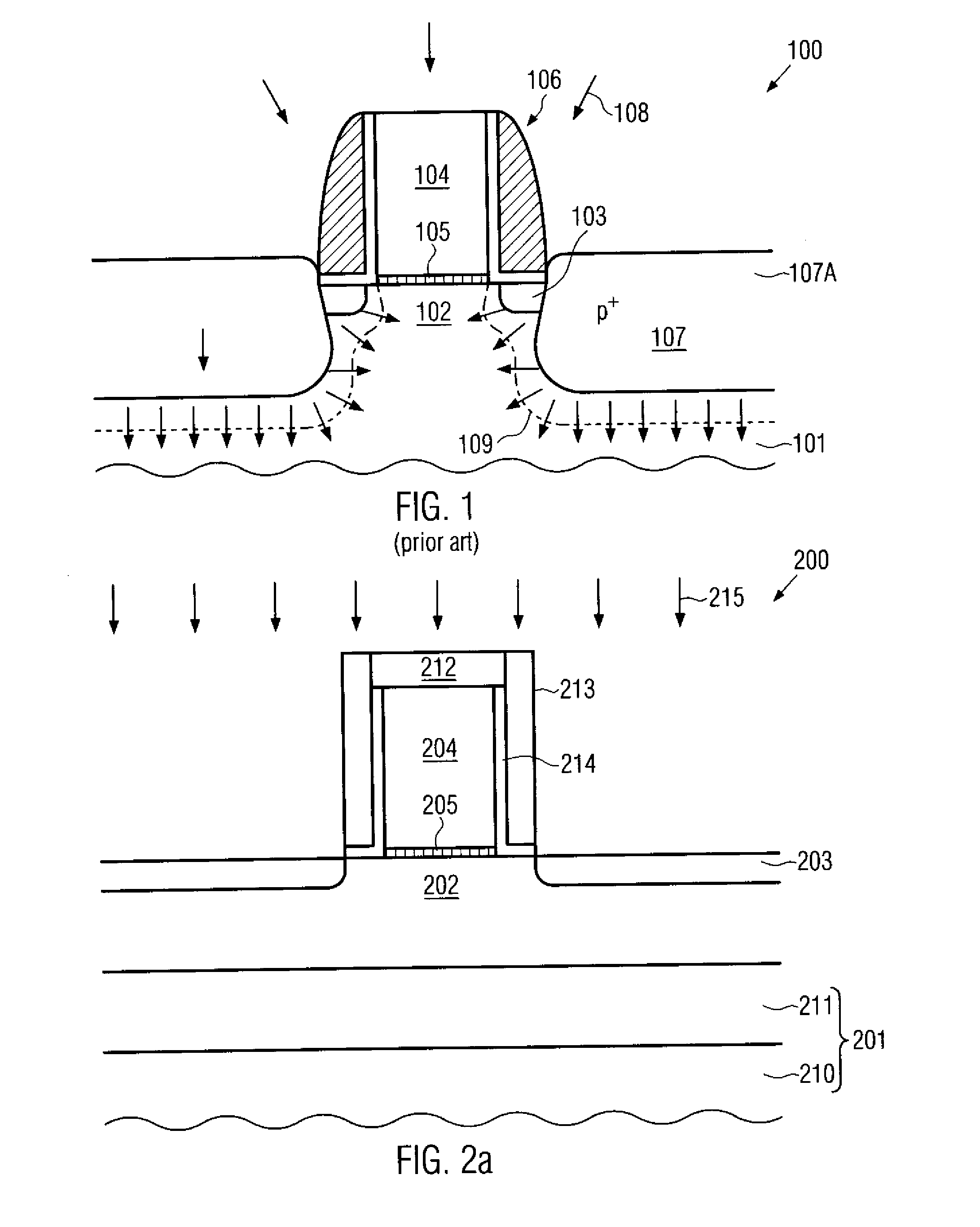

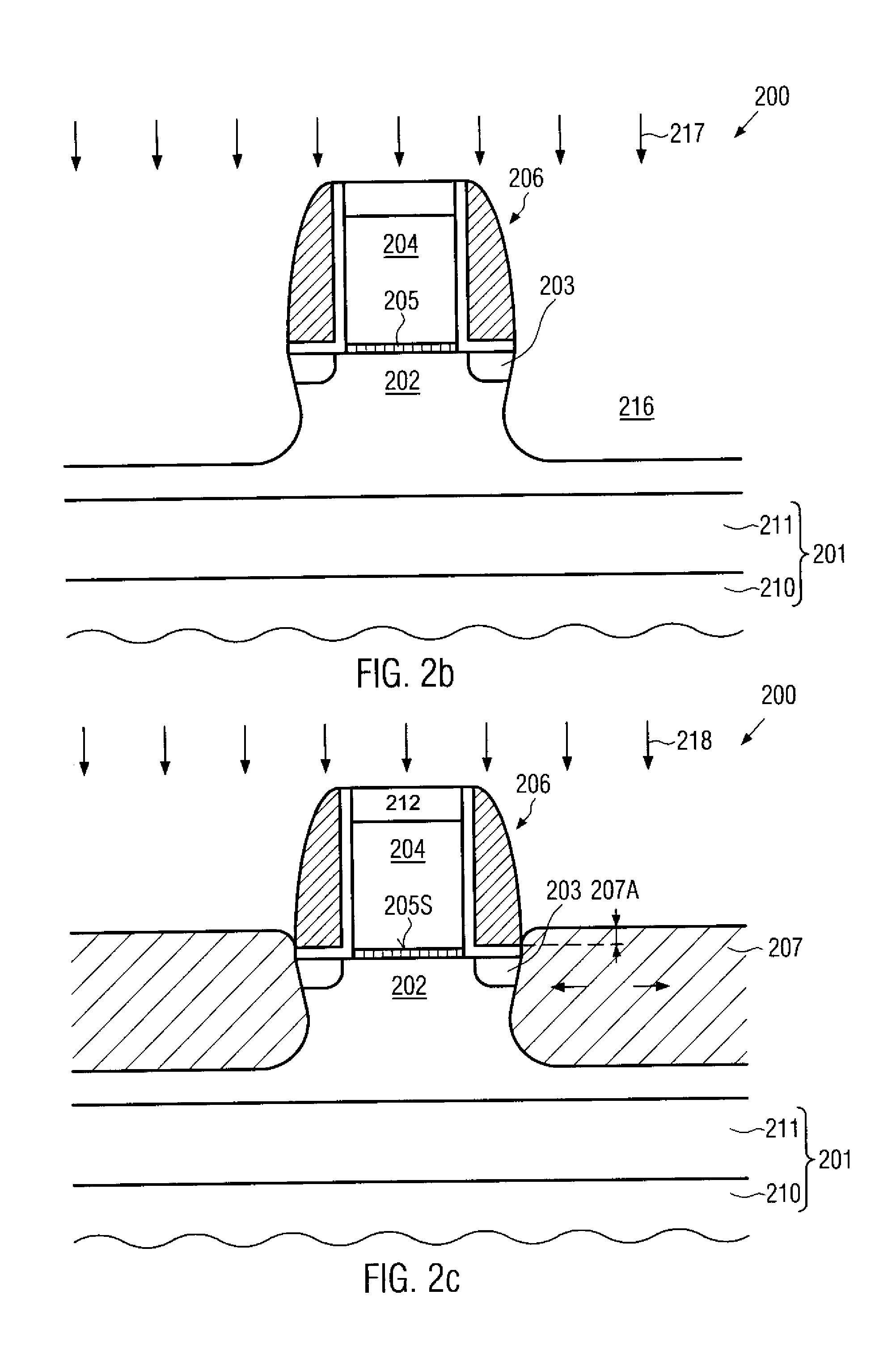

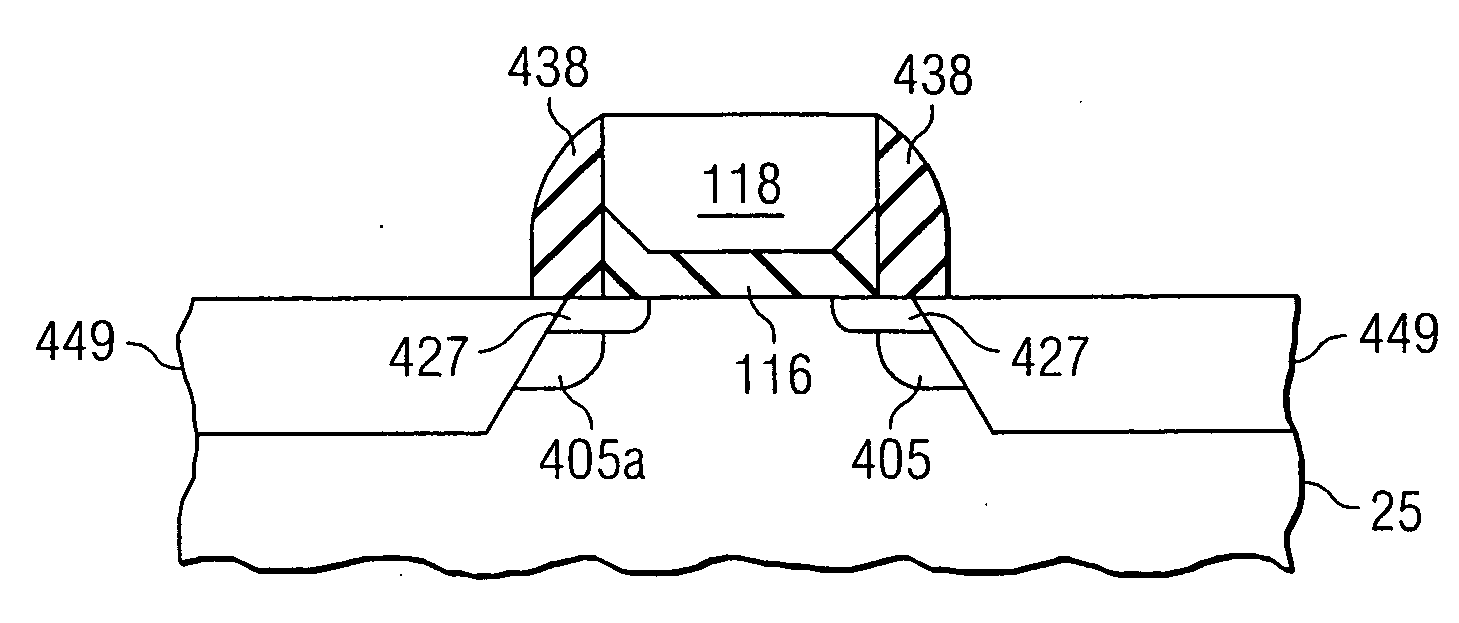

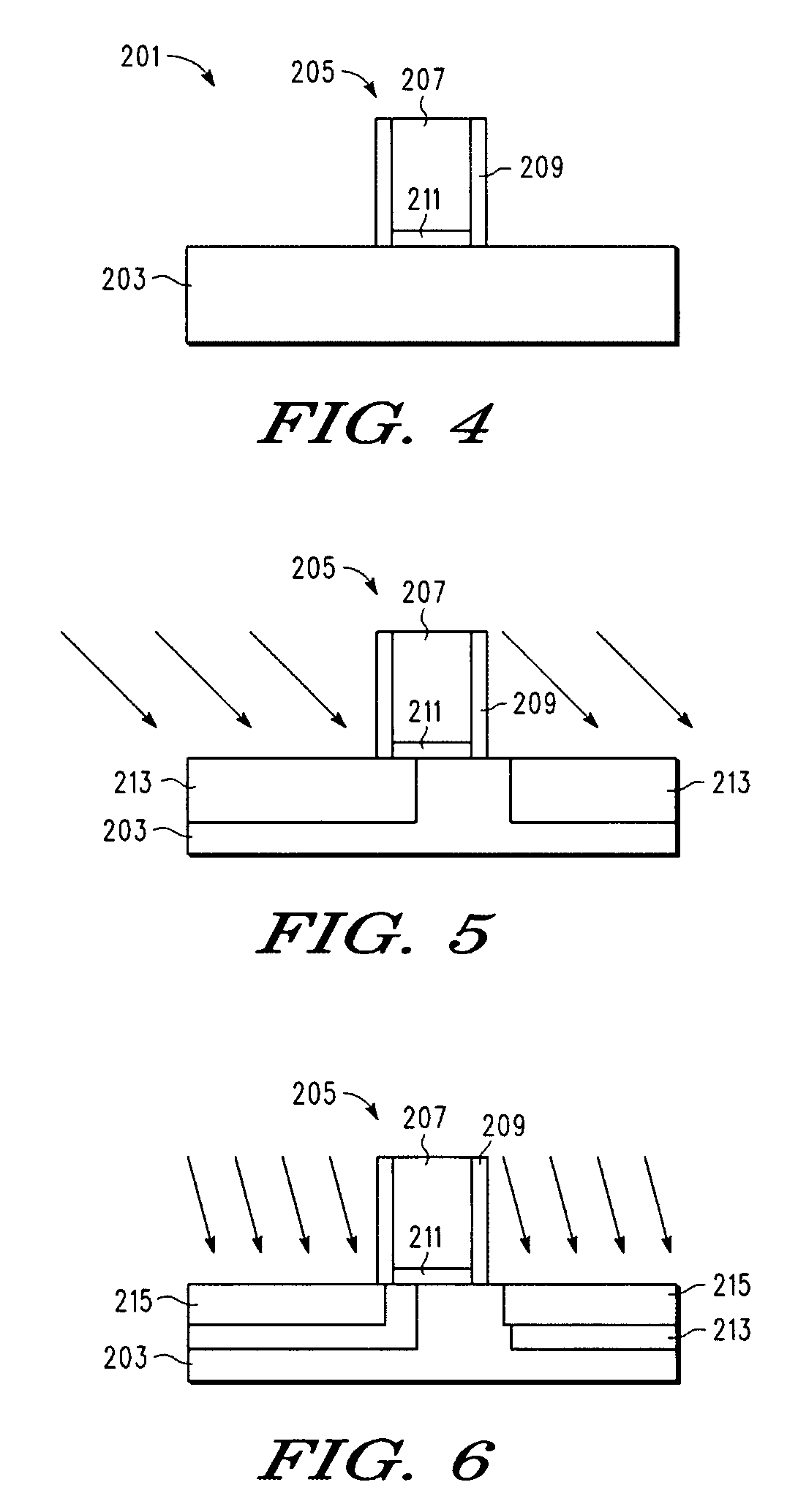

Methodology to reduce SOI floating-body effect

InactiveUS7410876B1Semiconductor/solid-state device manufacturingSemiconductor devicesFloating body effectSemiconductor

A method for making a semiconductor device, comprising (a) providing a structure comprising a gate electrode (207) disposed on a substrate (203); (b) creating first (213) and second (214) pre-amorphization implant regions in the substrate such that the first and second pre-amorphization implant regions are asymmetrically disposed with respect to said gate electrode; (c) creating first (219) and second (220) spacer structures adjacent to first and second sides of the gate electrode, wherein the first and second spacer structures overlap the first and second pre-amorphization implant regions; and (d) creating source (217) and drain (218) regions in the substrate adjacent, respectively, to the first and second spacer structures.

Owner:NORTH STAR INNOVATIONS

Technique for forming recessed strained drain/source regions in NMOS and PMOS transistors

ActiveUS7586153B2High carrier mobilityIncrease flexibilityTransistorSolid-state devicesFloating body effectEngineering

By forming a strained semiconductor layer in a PMOS transistor, a corresponding compressively strained channel region may be achieved, while, on the other hand, a corresponding strain in the NMOS transistor may be relaxed. Due to the reduced junction resistance caused by the reduced band gap of silicon / germanium in the NMOS transistor, an overall performance gain is accomplished, wherein, particularly in partially depleted SOI devices, the deleterious floating body effect is also reduced, due to the increased leakage currents generated by the silicon / germanium layer in the PMOS and NMOS transistor.

Owner:ADVANCED MICRO DEVICES INC