Patents

Literature

229 results about "Power integrated circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

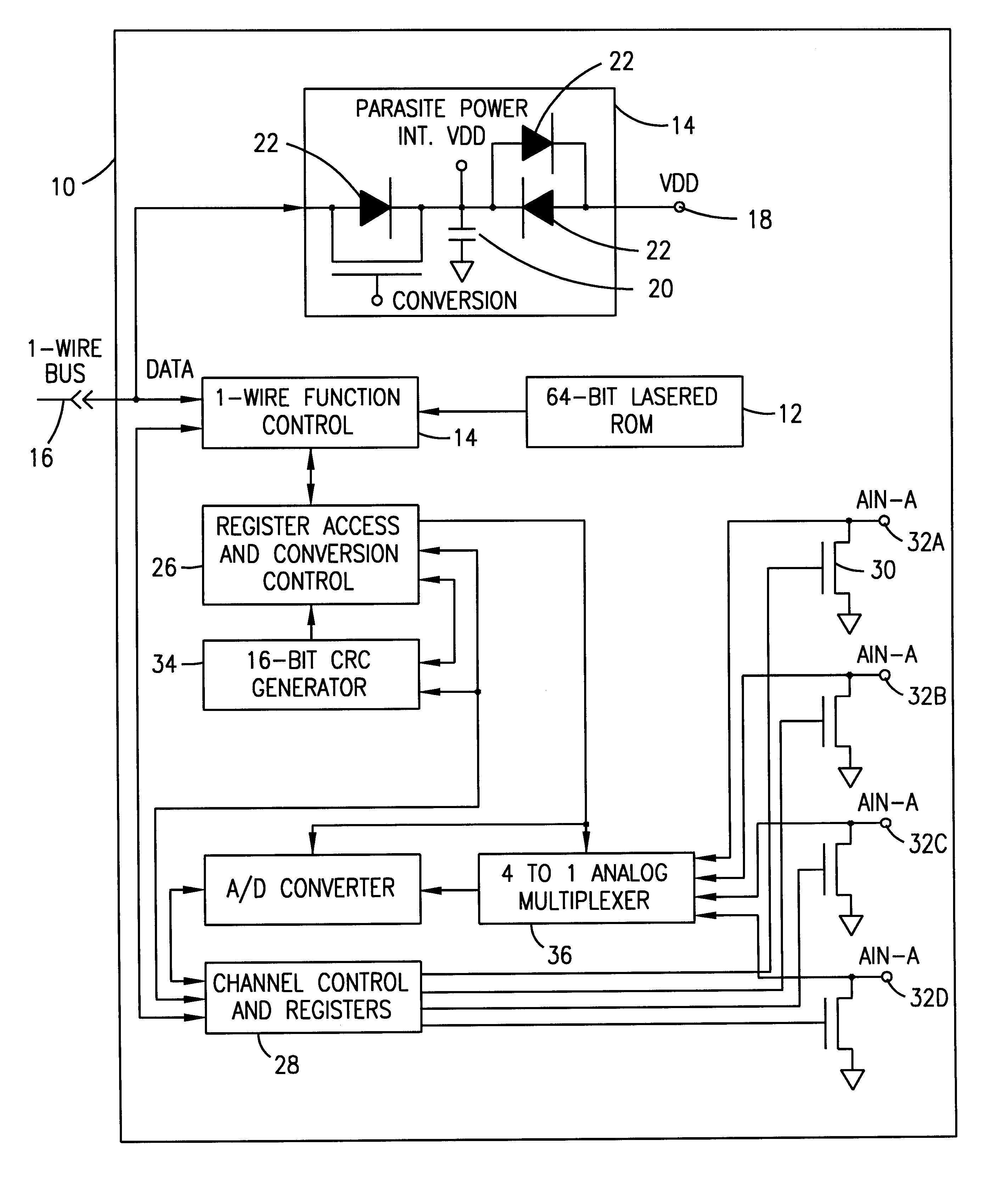

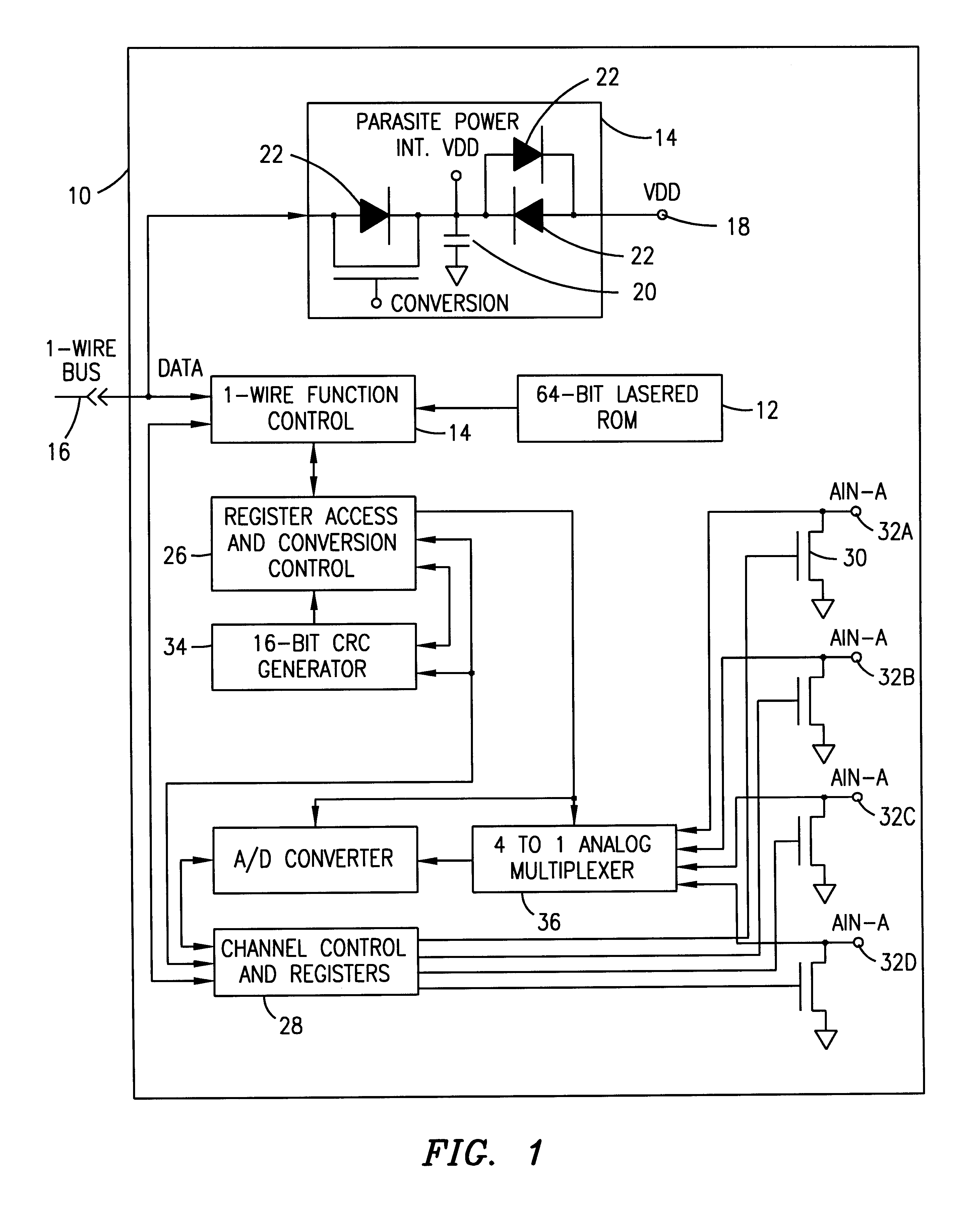

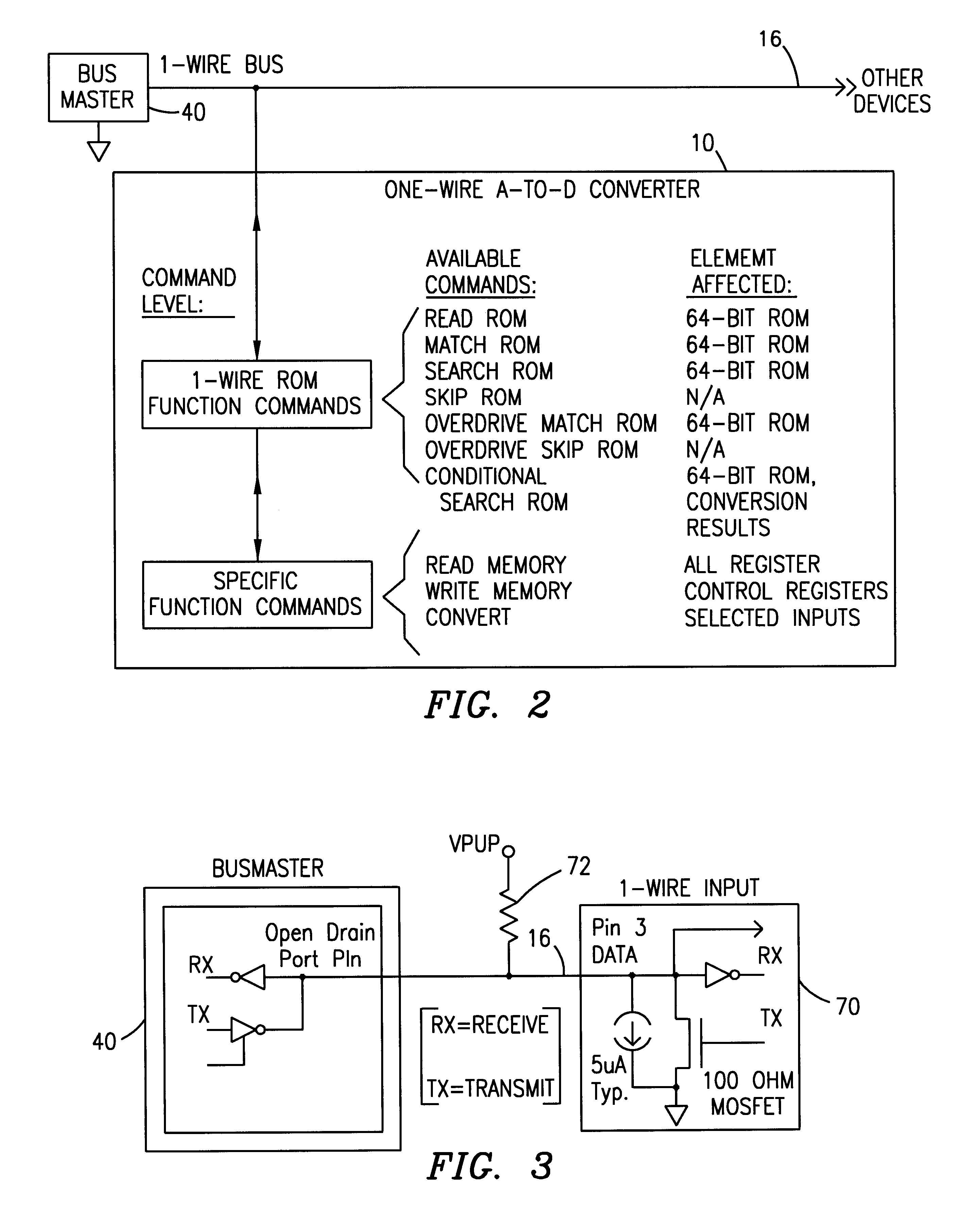

One-wire device with A-to-D converter

InactiveUS6239732B1Electric signal transmission systemsAnalogue-digital convertersĆuk converterAnalog signal

A low power integrated circuit having analog to digital conversion circuitry capable of receiving a plurality of analog signals and converting them to a digital value. The digital value is then transmitted, upon request, over a single wire bus. The accuracy of the analog to digital conversion circuitry can be calibrated via trim codes stored in an onboard EPROM.

Owner:MAXIM INTEGRATED PROD INC

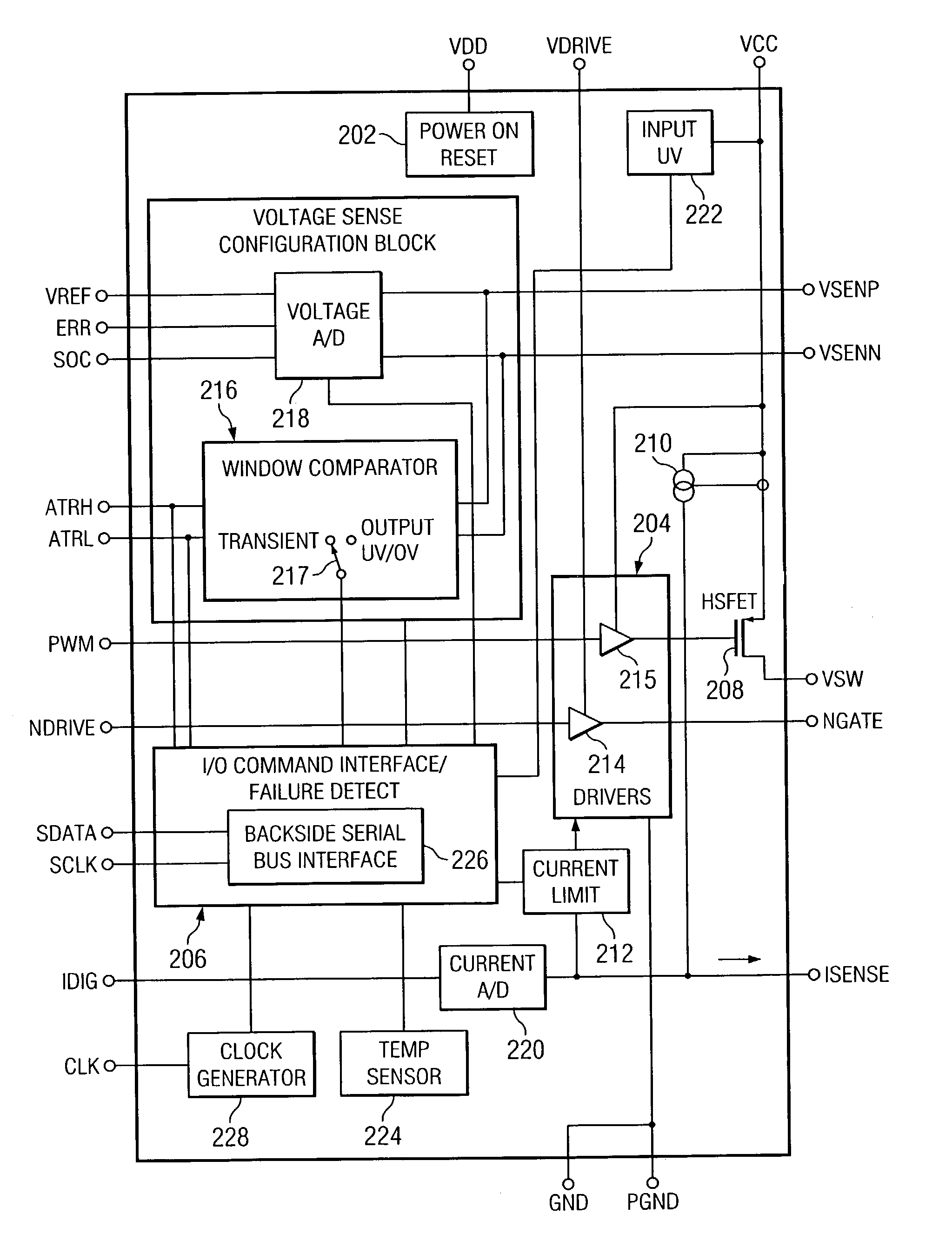

Digitally controlled voltage regulator

ActiveUS7023672B2Easy to customizePrecise power controlEfficient power electronics conversionDc-dc conversionControl signalOptimal control

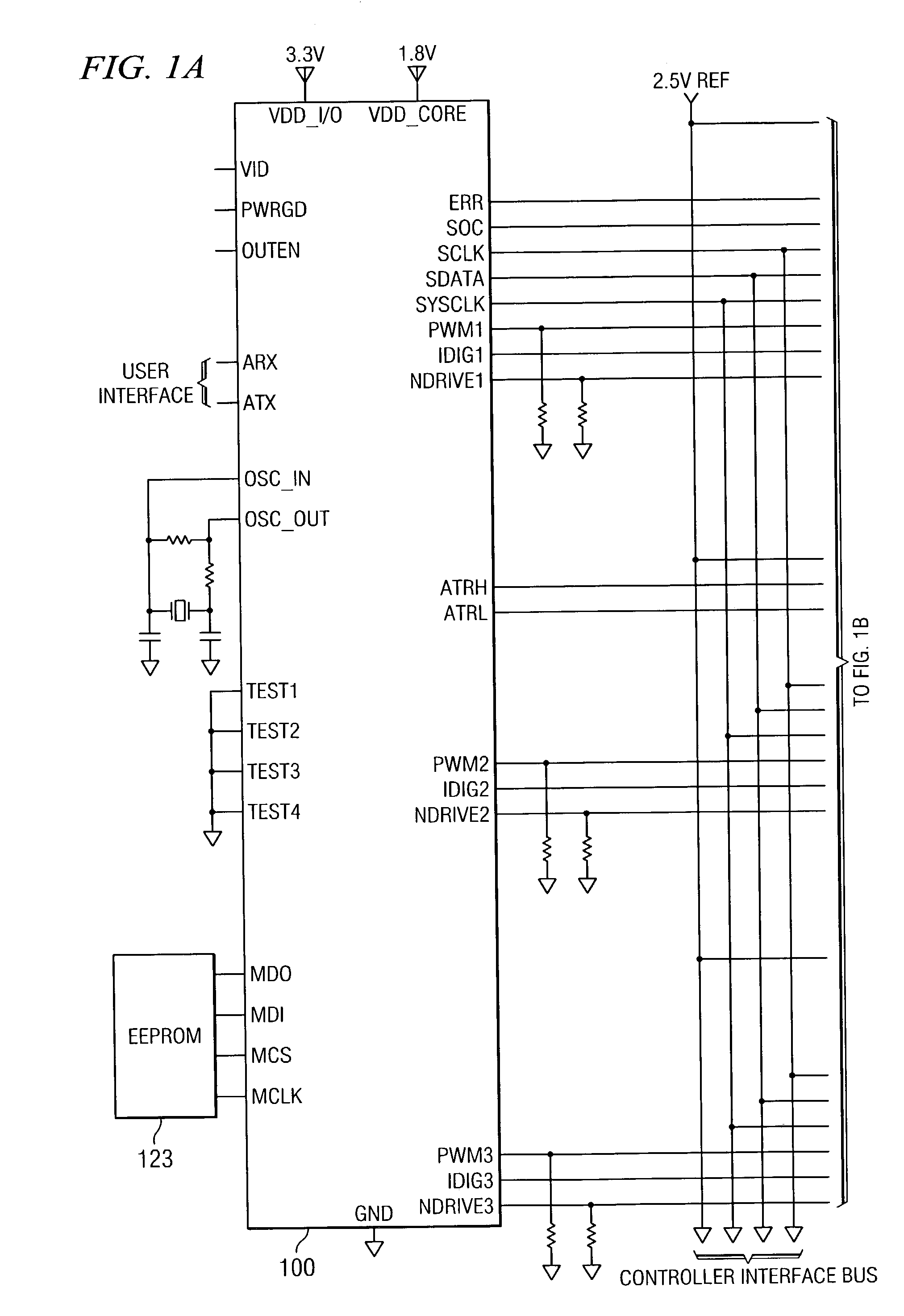

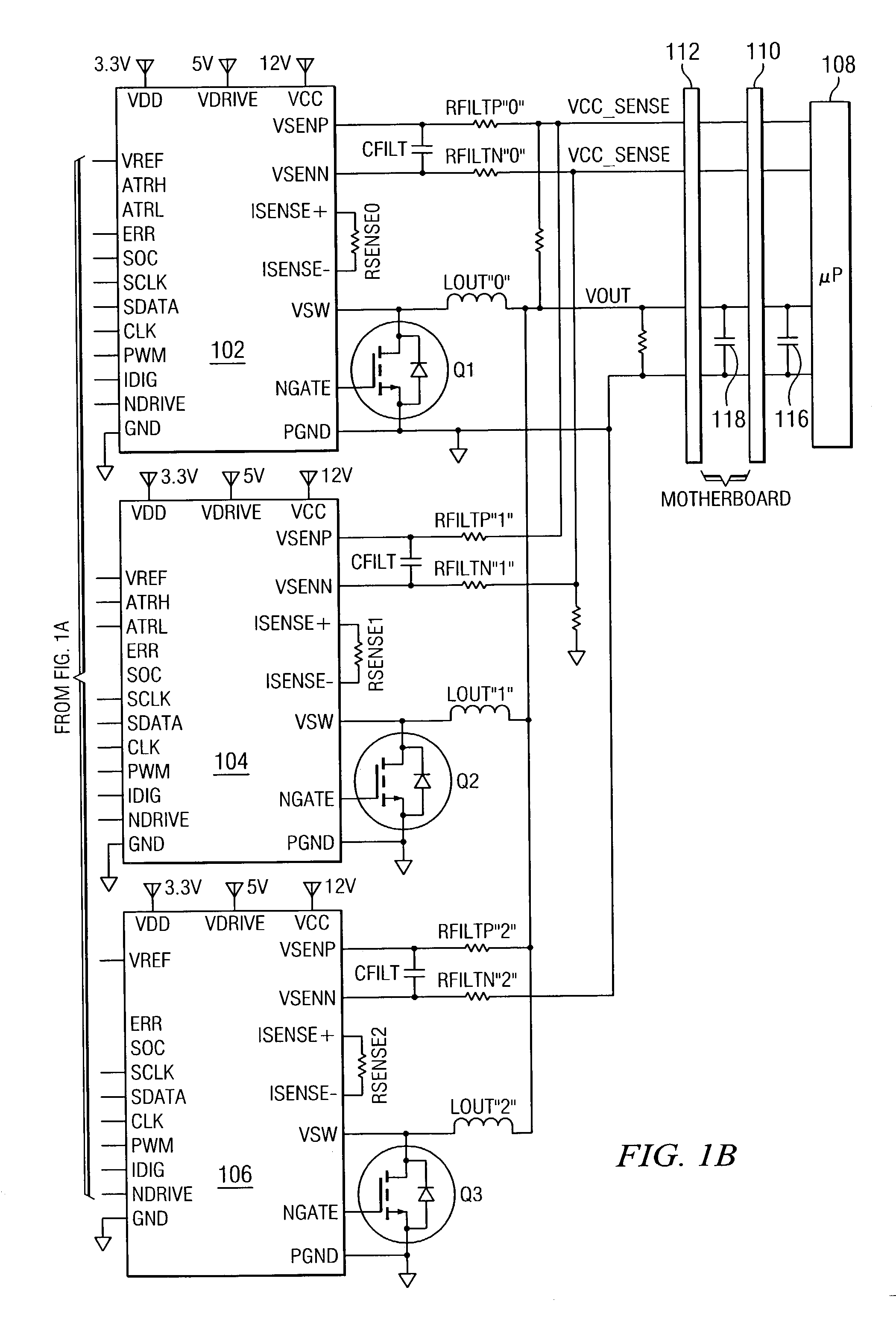

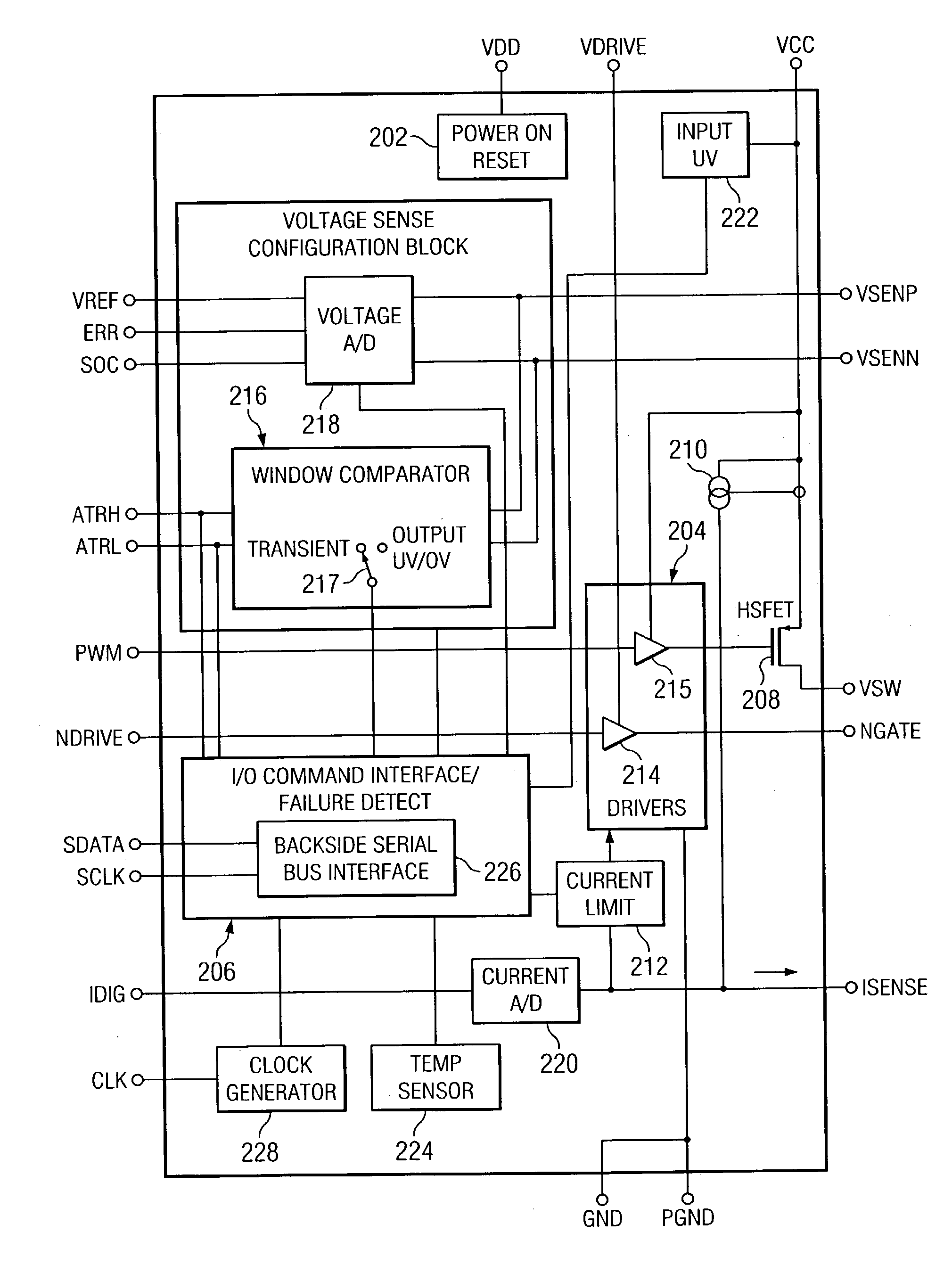

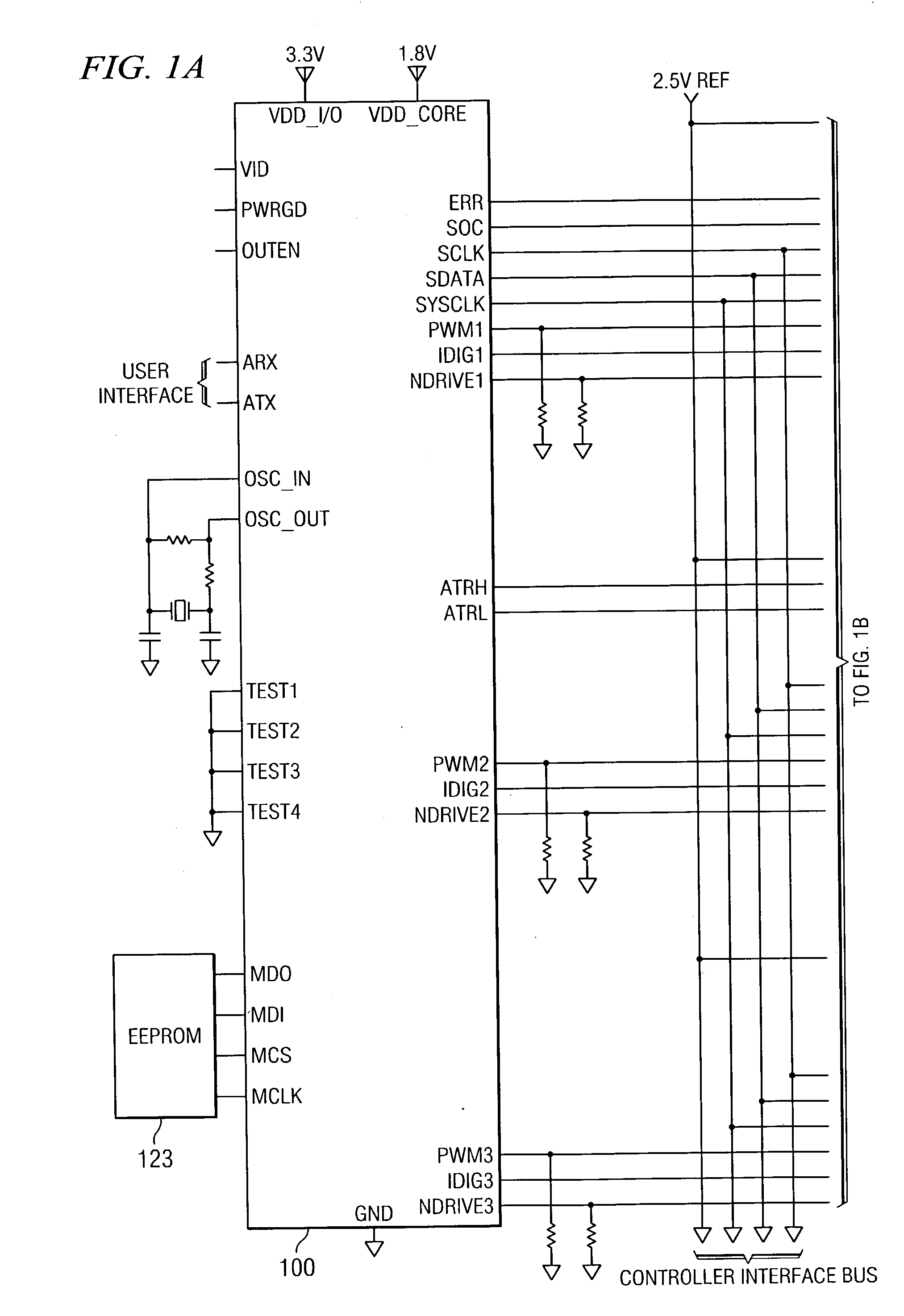

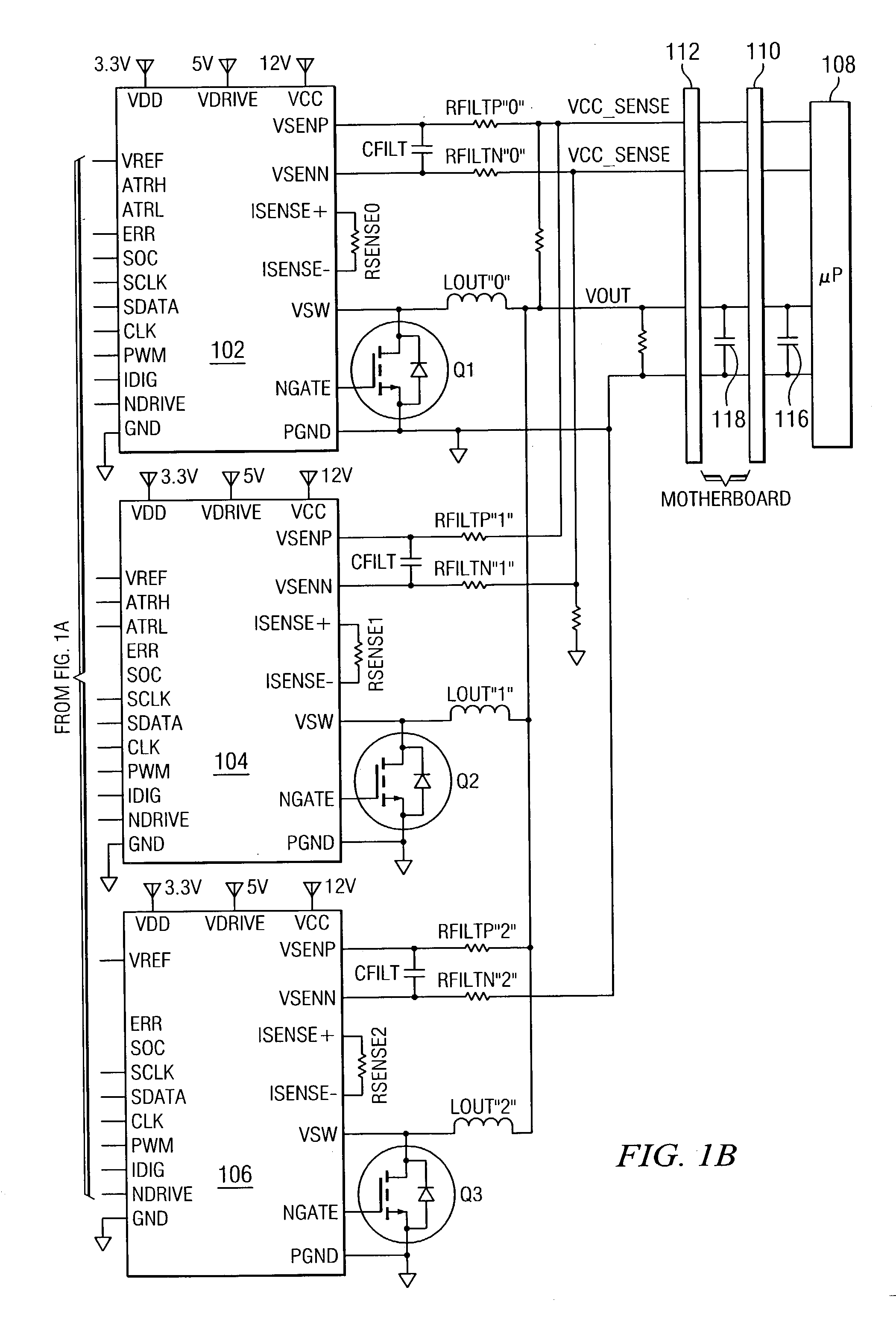

Disclosed is a digitally controlled multi-phase voltage regulator system providing regulated power to electronic components that have variable power requirements. Power is supplied by one or more power integrated circuits (IC) each having a high side power switch controlled by pulse width modulated signals and a low side power switch. The power IC senses voltage at the load and has an on-chip current mirror for generating a current that is a ratio of current delivered to the load. The power IC also has current limiting and on-chip temperature sensing components. The voltage and current information is digitized and provided to a control integrated circuit (IC). The control IC receives this digitized information as well as user provided parameters and, in the regulation mode of operation, provides digitized pulse width modulated control signals to the power IC. In an active transient response mode of operation, the control IC provides signals to turn either the high side switches or low side switches ON. Fault detection circuitry identifies over voltage, under voltage, and excessive temperatures. All communications between the control IC and the power IC are digital providing high bandwidth, optimal control frequency response, noise immunity and efficient active transient response.

Owner:INFINEON TECH AUSTRIA AG

Digitally controlled voltage regulator

ActiveUS20040150928A1Easy to customizePrecise power controlEfficient power electronics conversionDc-dc conversionControl signalOptimal control

Disclosed is a digitally controlled multi-phase voltage regulator system providing regulated power to electronic components that have variable power requirements. Power is supplied by one or more power integrated circuits (IC) each having a high side power switch controlled by pulse width modulated signals and a low side power switch. The power IC senses voltage at the load and has an on-chip current mirror for generating a current that is a ratio of current delivered to the load. The power IC also has current limiting and on-chip temperature sensing components. The voltage and current information is digitized and provided to a control integrated circuit (IC). The control IC receives this digitized information as well as user provided parameters and, in the regulation mode of operation, provides digitized pulse width modulated control signals to the power IC. In an active transient response mode of operation, the control IC provides signals to turn either the high side switches or low side switches ON. Fault detection circuitry identifies over voltage, under voltage, and excessive temperatures. All communications between the control IC and the power IC are digital providing high bandwidth, optimal control frequency response, noise immunity and efficient active transient response.

Owner:INFINEON TECH AUSTRIA AG

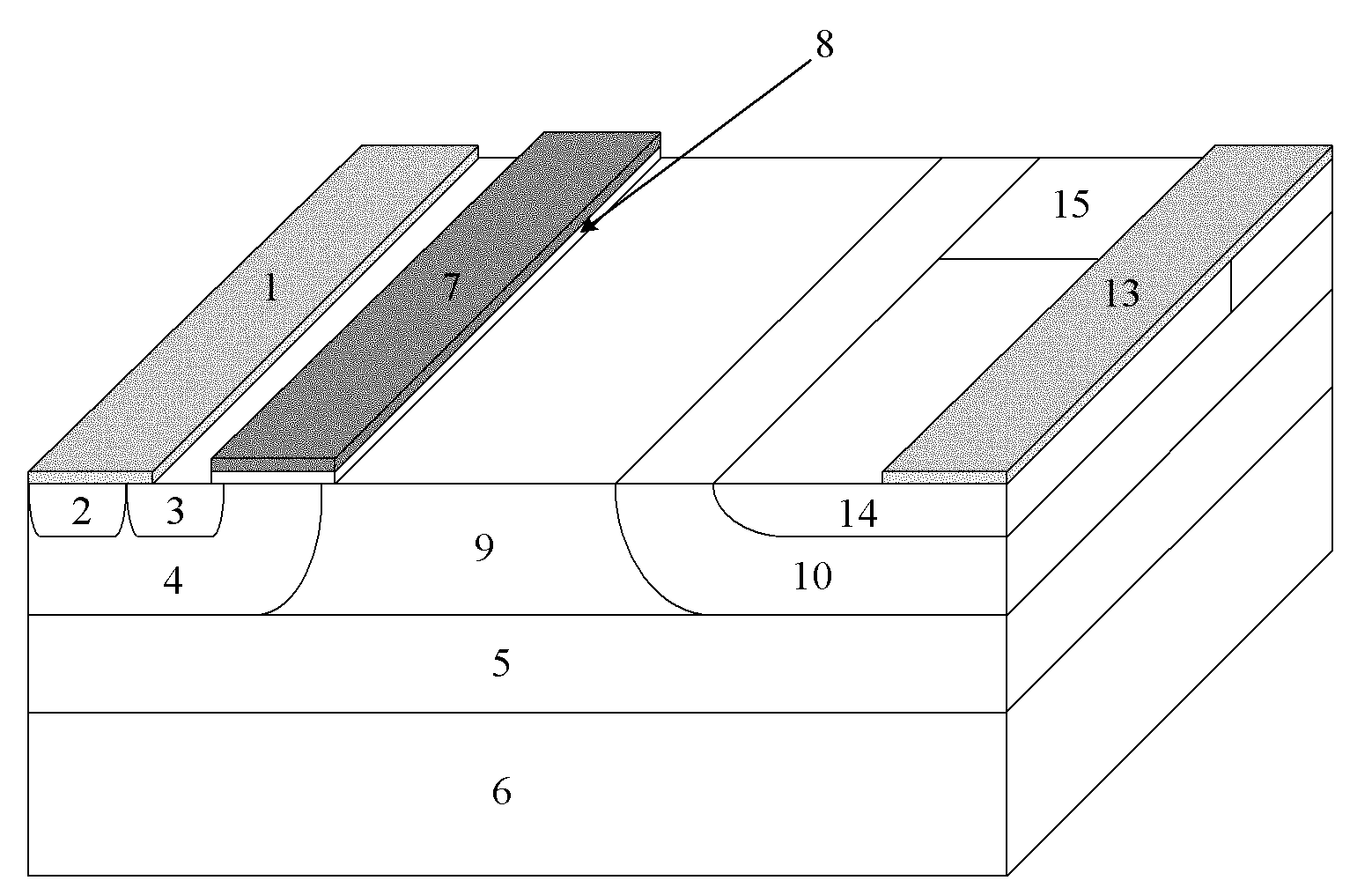

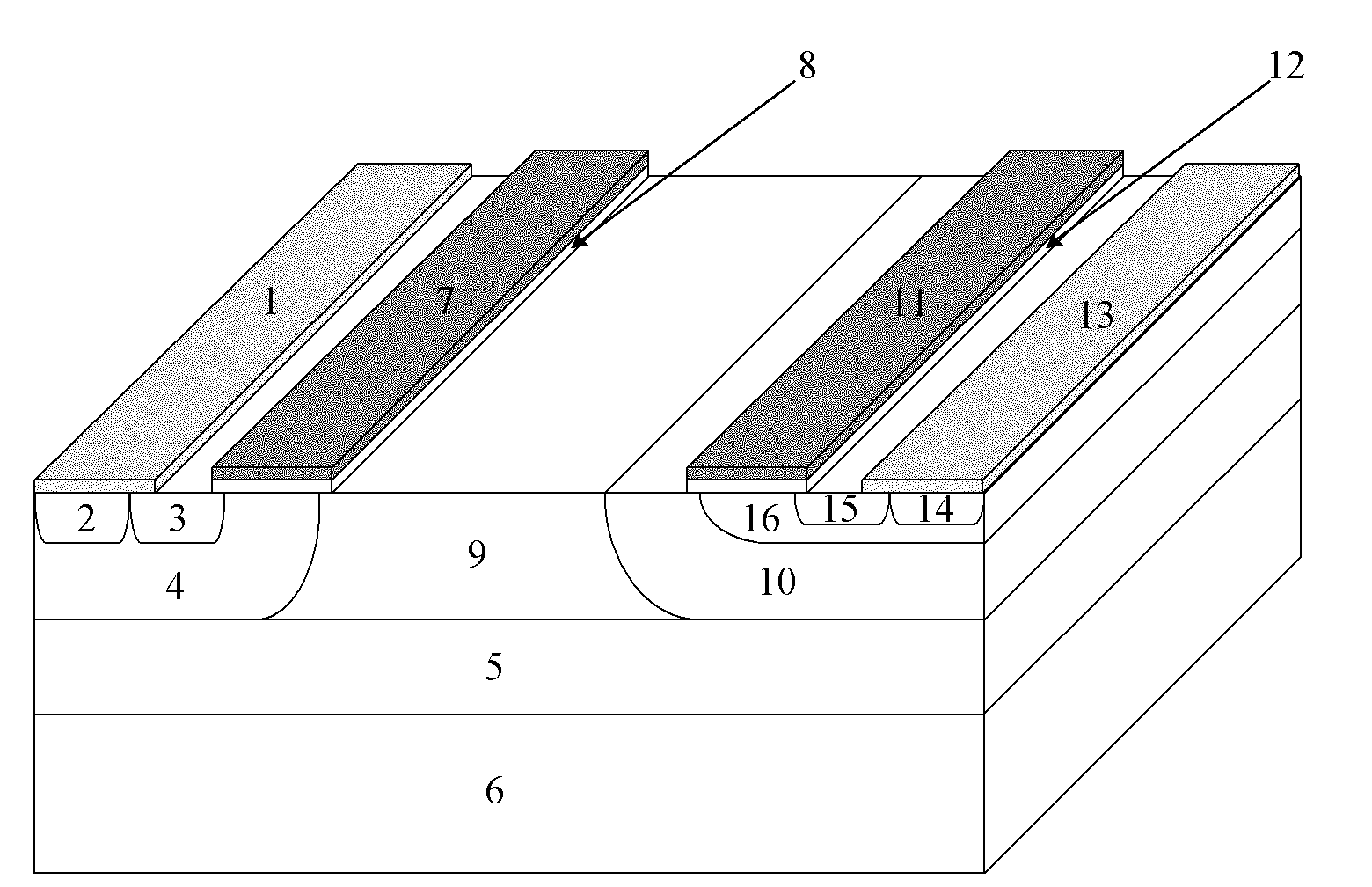

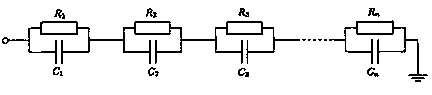

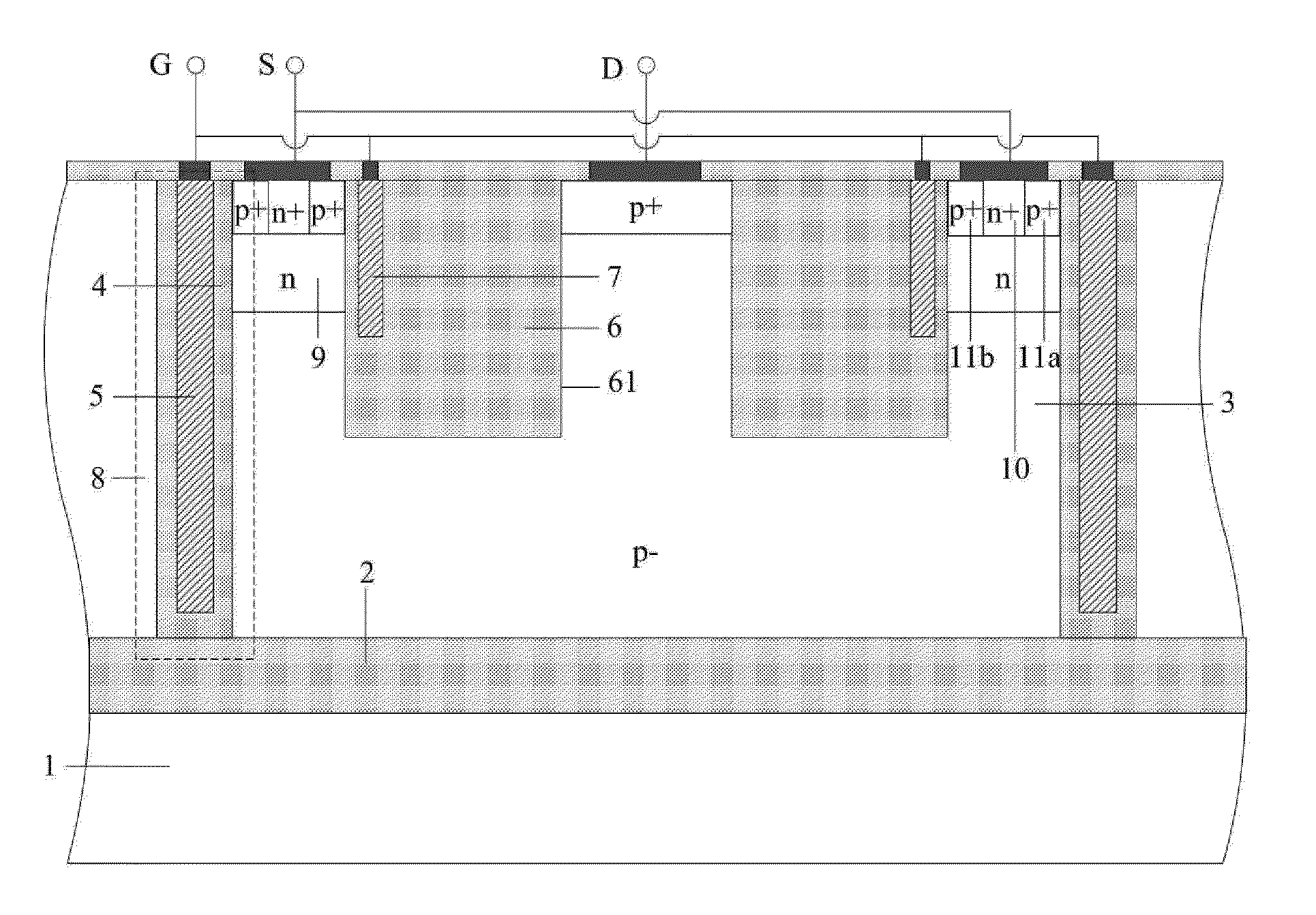

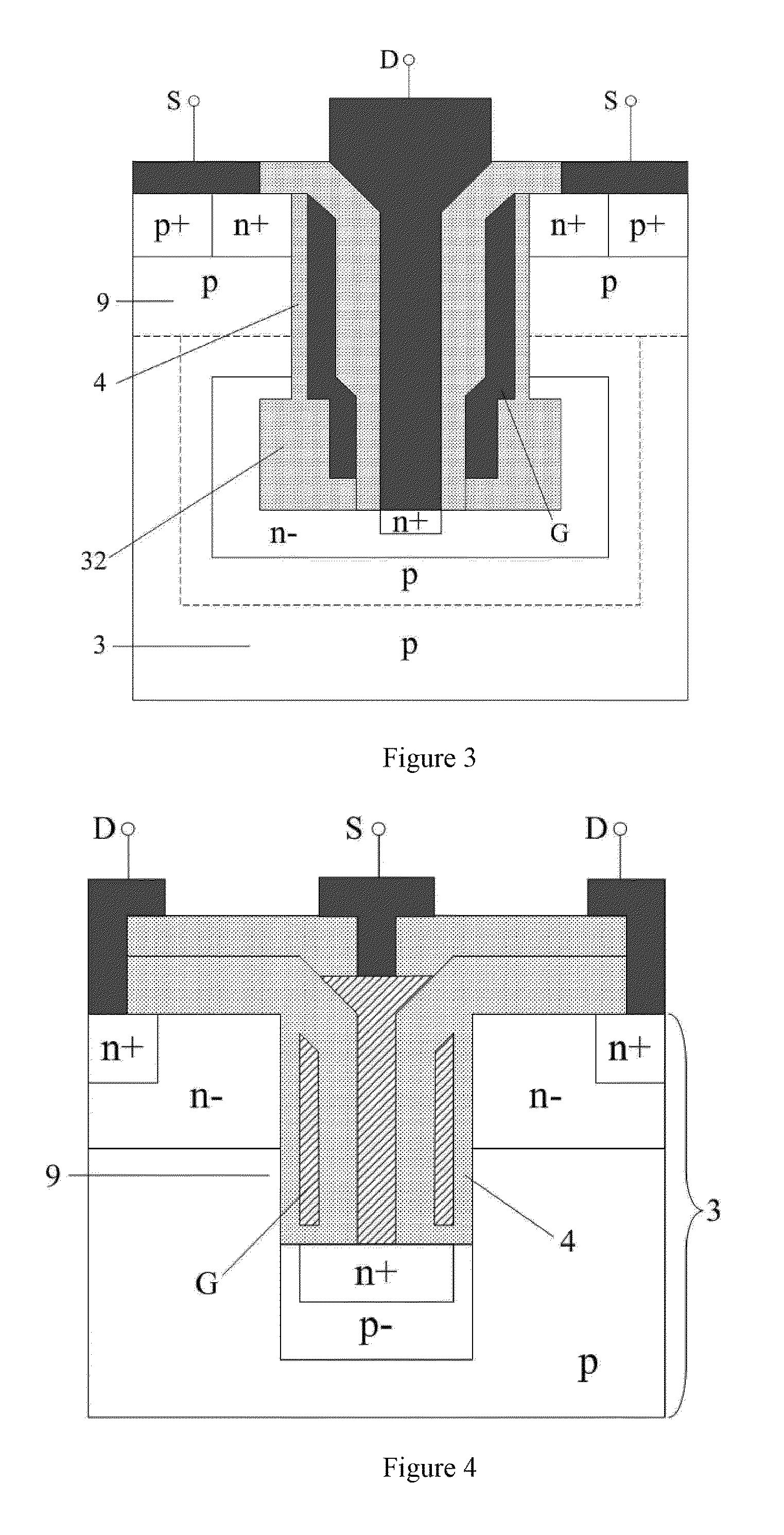

Super junction / resurf LDMOST (SJR-LDMOST)

InactiveUS7023050B2Reduce doping concentrationBreakdown voltage of deviceSemiconductor devicesMOSFETDisplay device

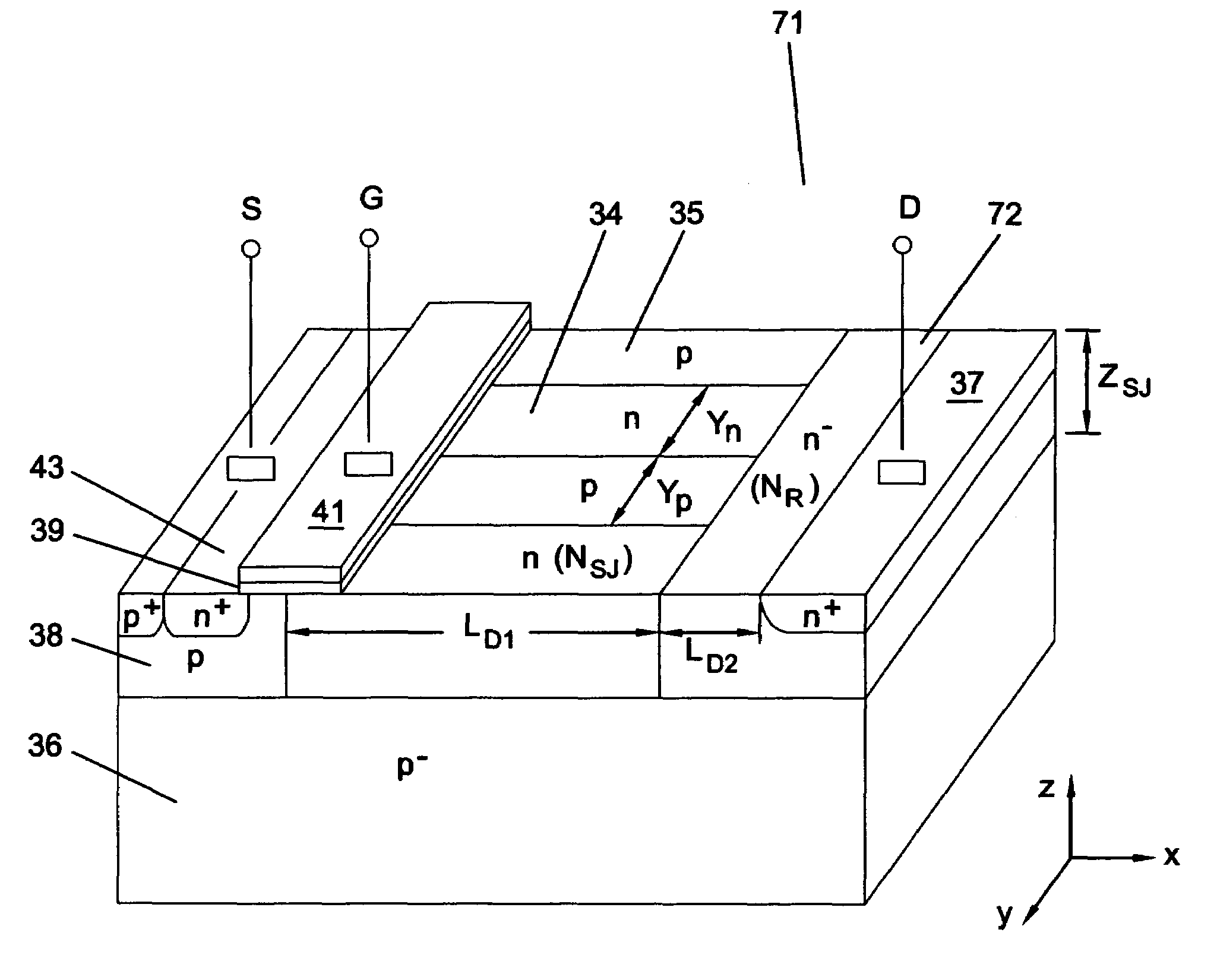

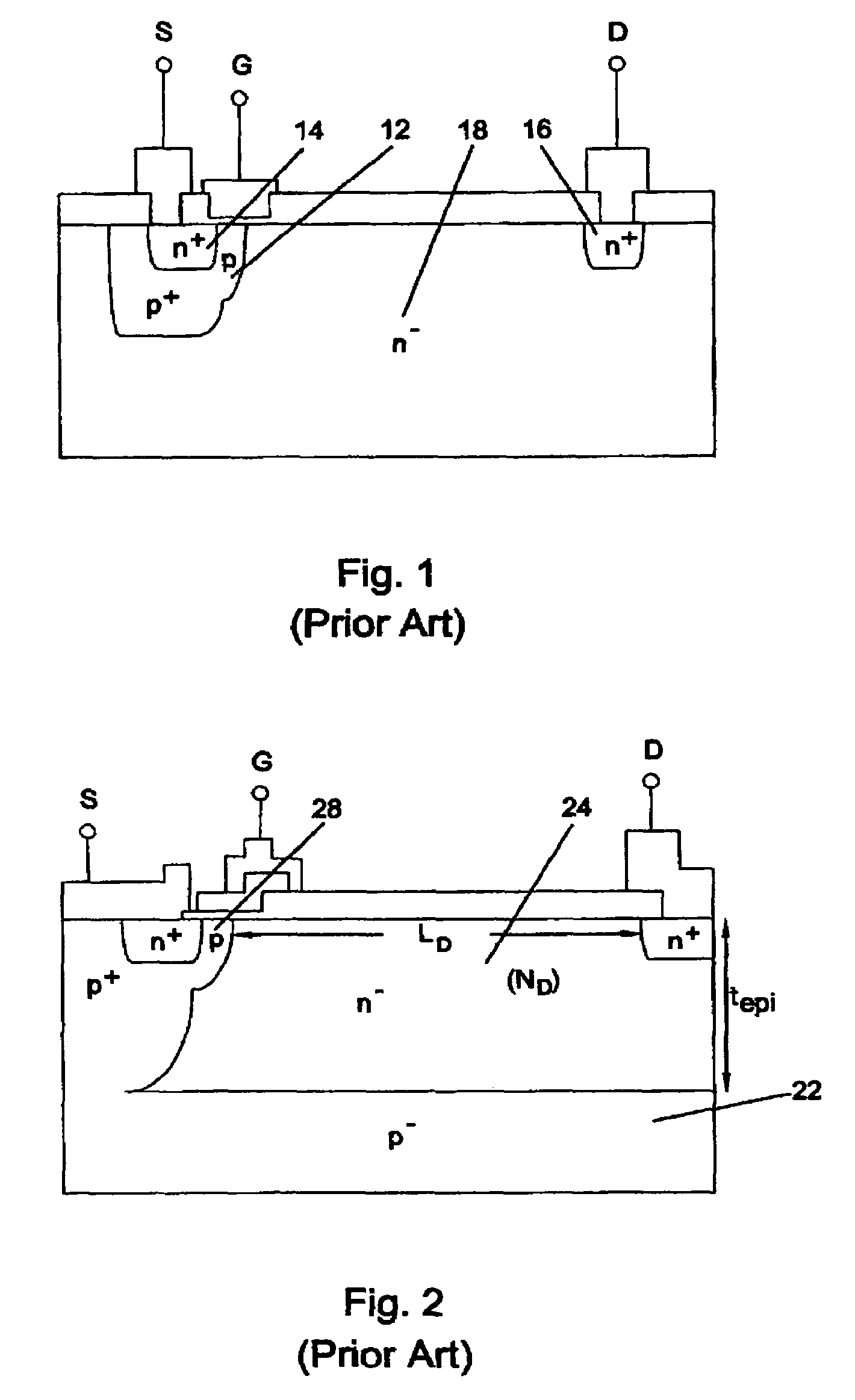

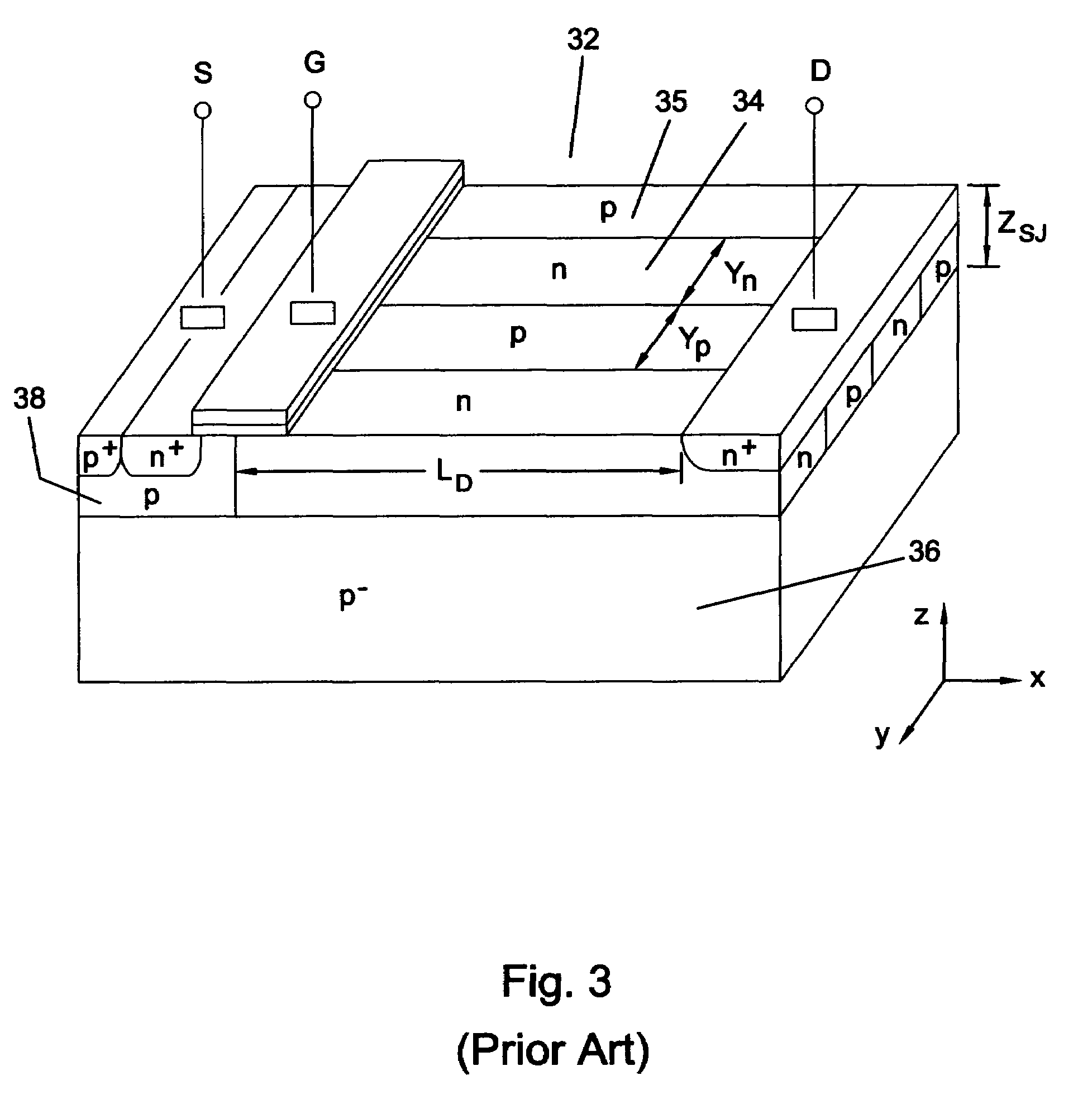

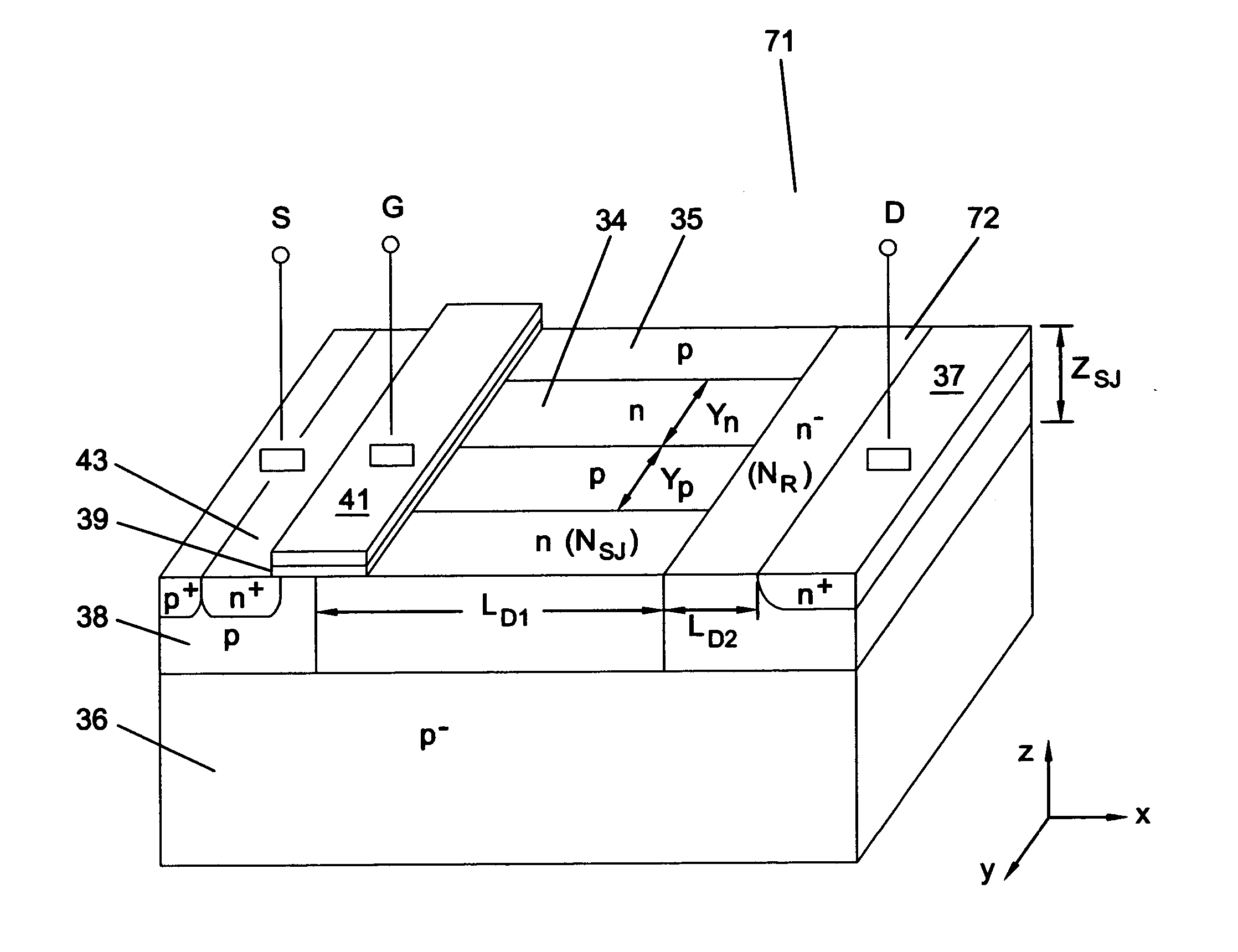

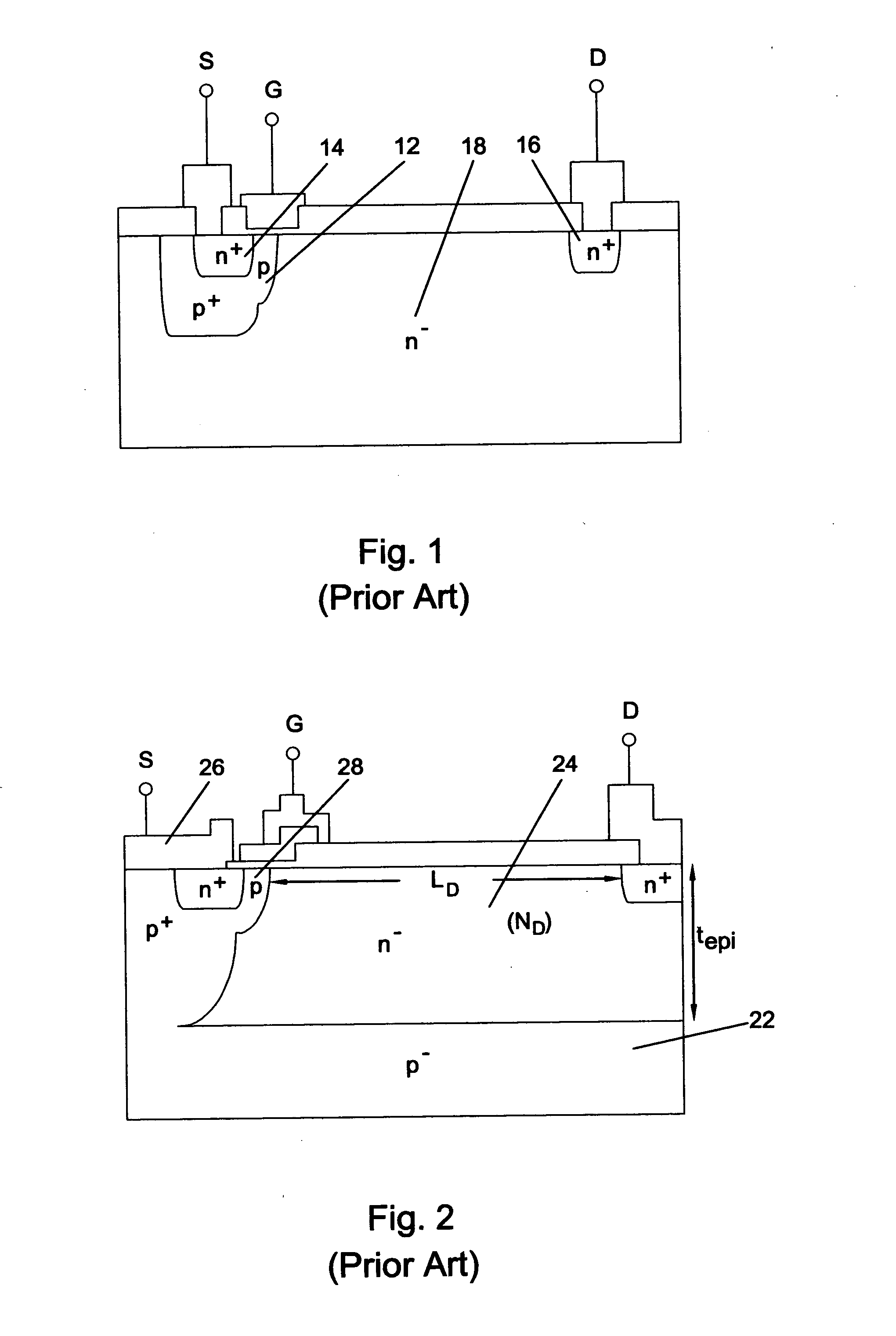

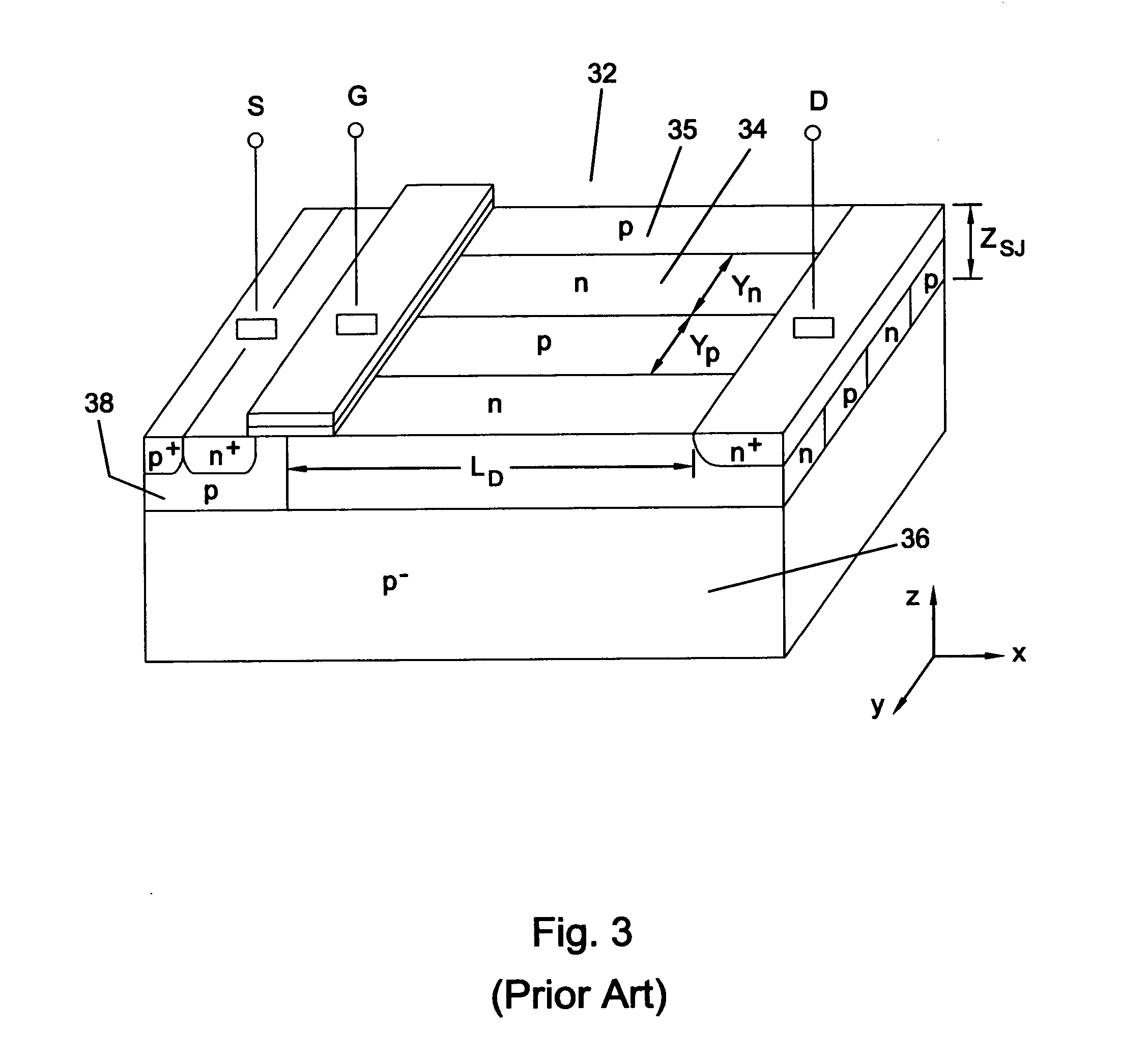

A lateral double diffused MOSFET (LDMOST) incorporates both the reduced surface field (RESURF) and super junction (SJ) in a split-drift region to significantly improve the on-state, off-state and switching characteristics in junction-isolated (JI) technology. The structure effectively suppresses substrate-assisted-depletion which is the main problem encountered when applying the SJ concept to lateral power devices. The device structure features a split-drift region formed of two parts: a SJ structure that extends over most of the drift region, and a terminating RESURF region occupying a portion of the drift region next to the drain. The structure offers improved breakdown voltage and reduced specific on resistance as compared to convention structures, and is useful in power integrated circuits suitable for a variety of applications including flat plasma panel display, automotive electronics, motor control, power supply and high voltage lamp ballasts.

Owner:SALAMA C ANDRE T +1

Super junction / resurf ldmost (sjr-LDMOST)

InactiveUS20050017300A1Reduce doping concentrationBreakdown voltage of deviceSemiconductor devicesMOSFETElectrical ballast

A lateral double diffused MOSFET (LDMOST) incorporates both the reduced surface field (RESURF) and super junction (SJ) in a split-drift region to significantly improve the on-state, off-state and switching characteristics in junction-isolated (JI) technology. The structure effectively suppresses substrate-assisted-depletion which is the main problem encountered when applying the SJ concept to lateral power devices. The device structure features a split-drift region formed of two parts: a SJ structure that extends over most of the drift region, and a terminating RESURF region occupying a portion of the drift region next to the drain. The structure offers improved breakdown voltage and reduced specific on resistance as compared to convention structures, and is useful in power integrated circuits suitable for a variety of applications including flat plasma panel display, automotive electronics, motor control, power supply and high voltage lamp ballasts.

Owner:SALAMA C ANDRE T +1

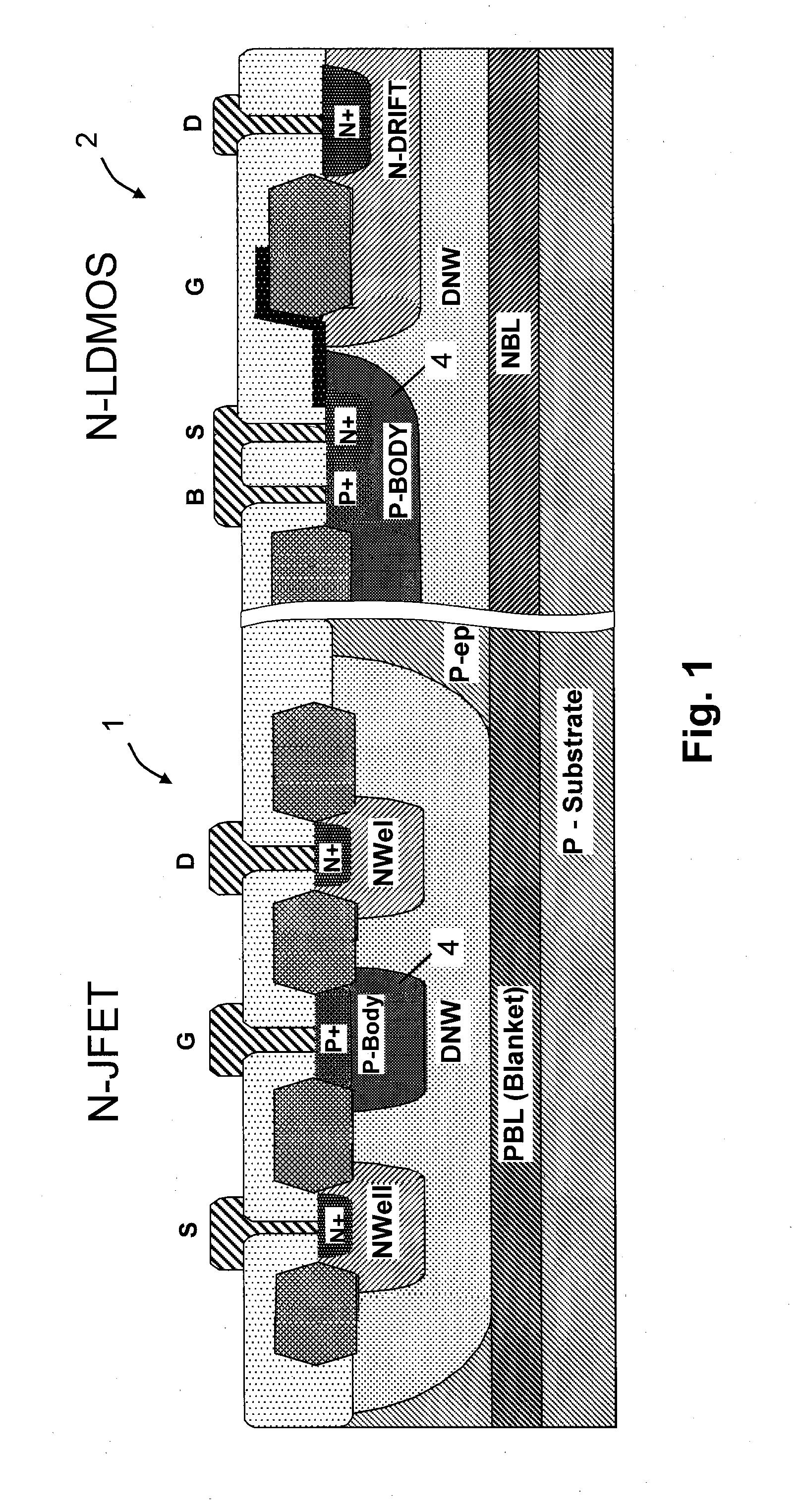

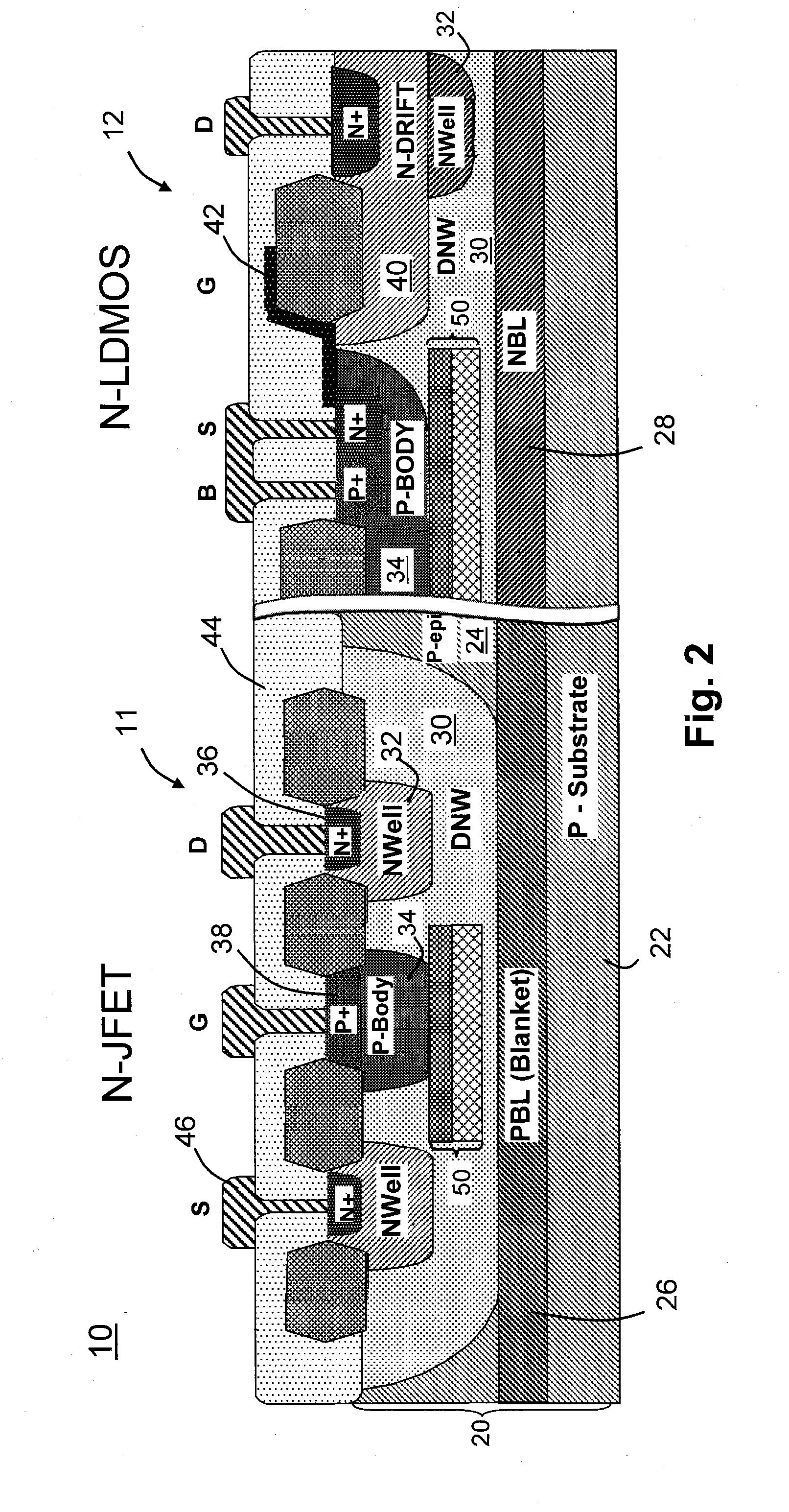

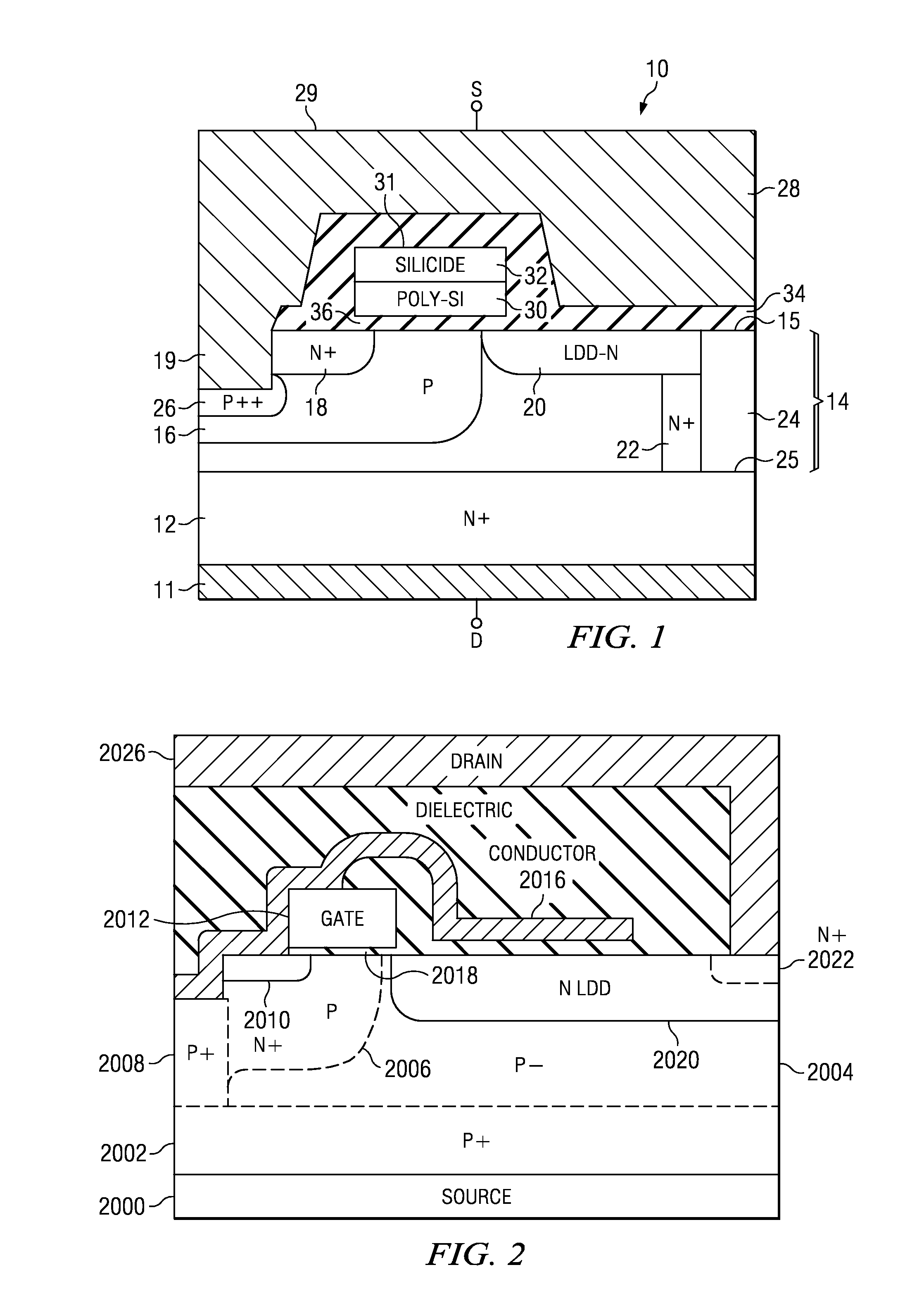

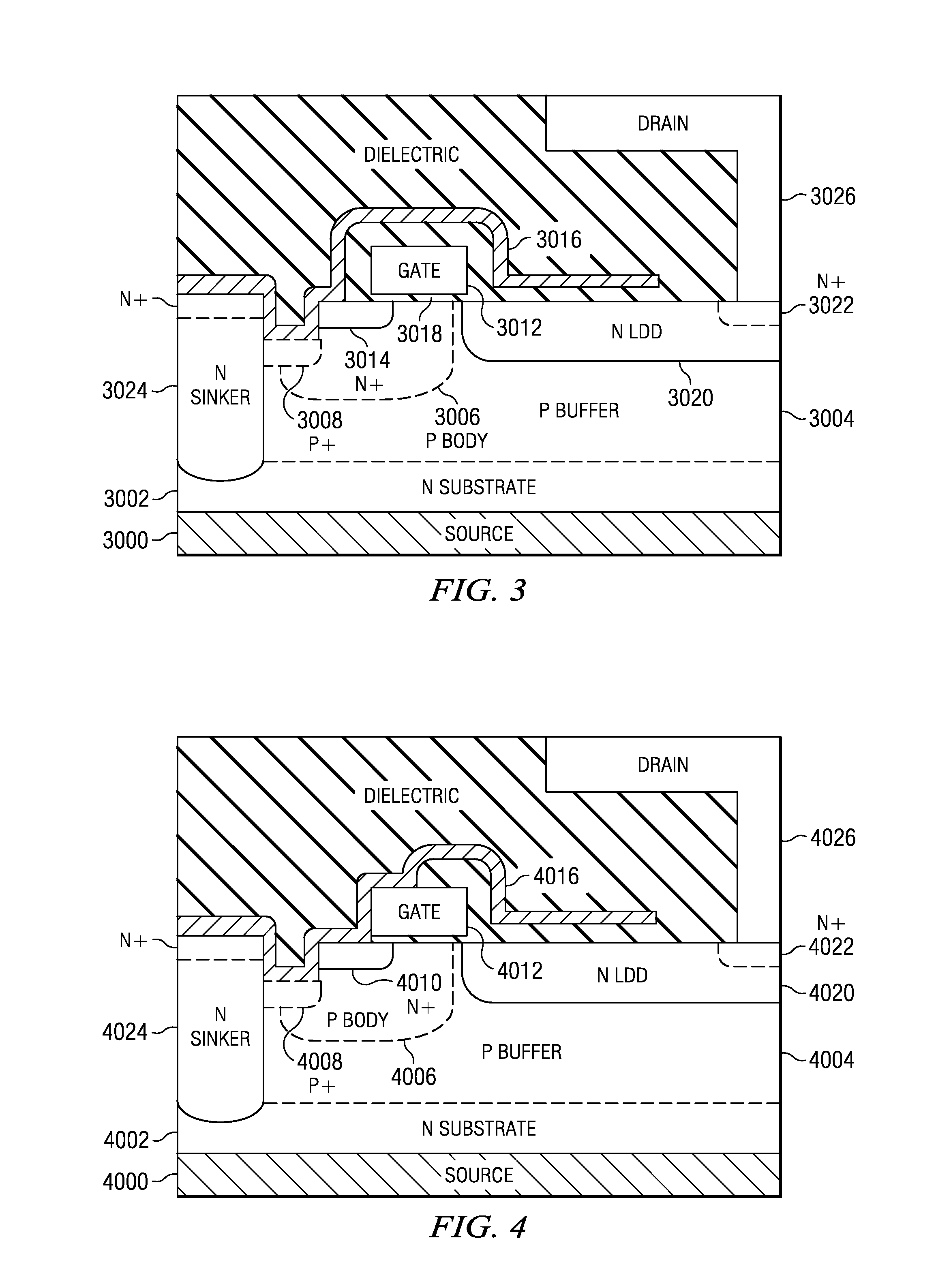

Forming jfet and ldmos transistor in monolithic power integrated circuit using deep diffusion regions

ActiveUS20150380398A1Solid-state devicesSemiconductor/solid-state device manufacturingLDMOSDevice form

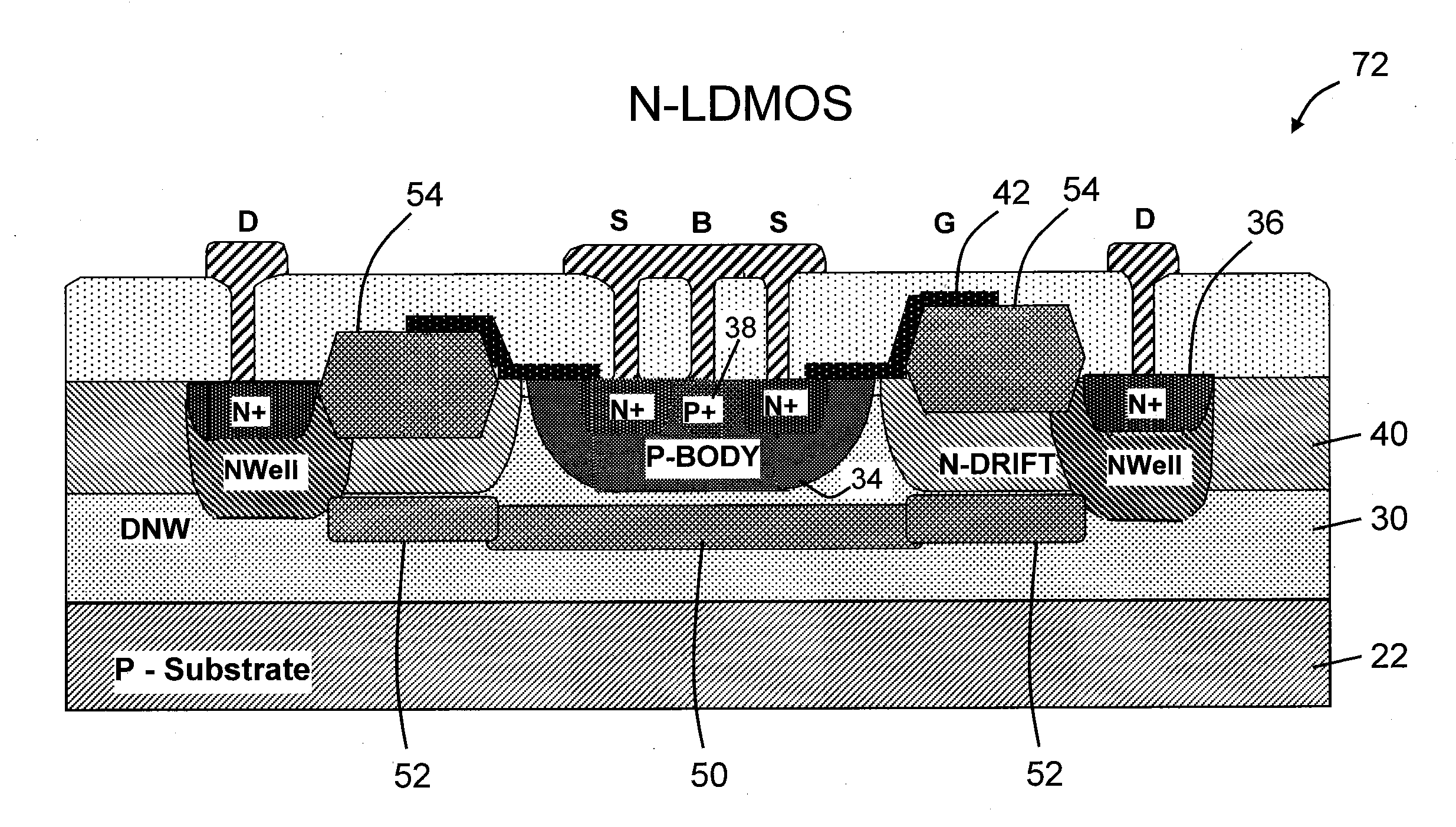

A power integrated circuit includes a junction field effect transistor (JFET) device formed in a first portion of a semiconductor layer with a gate region being formed using a first body region, and a double-diffused metal-oxide-semiconductor (LDMOS) transistor formed in a second portion of the semiconductor layer with a channel being formed in a second body region. The power integrated circuit includes a first deep diffusion region formed under the first body region and in electrical contact with the first body region where the first deep diffusion region together with the firs body region establish a pinch off voltage of the JFET device; and a second deep diffusion region formed under the second body region and in electrical contact with the second body region where the second deep diffusion region forms a reduced surface field (RESURF) structure in the LDMOS transistor.

Owner:ALPHA & OMEGA SEMICON INC

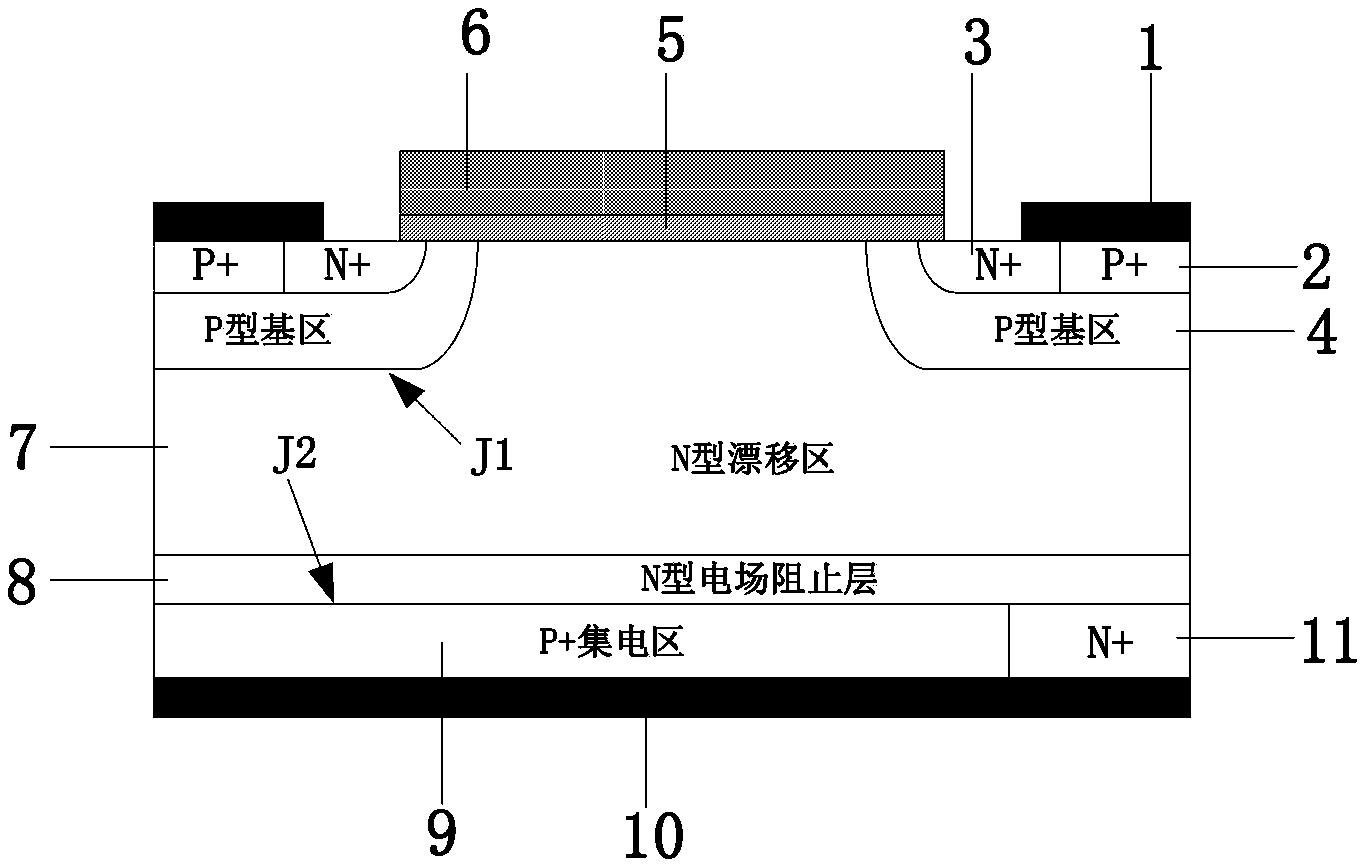

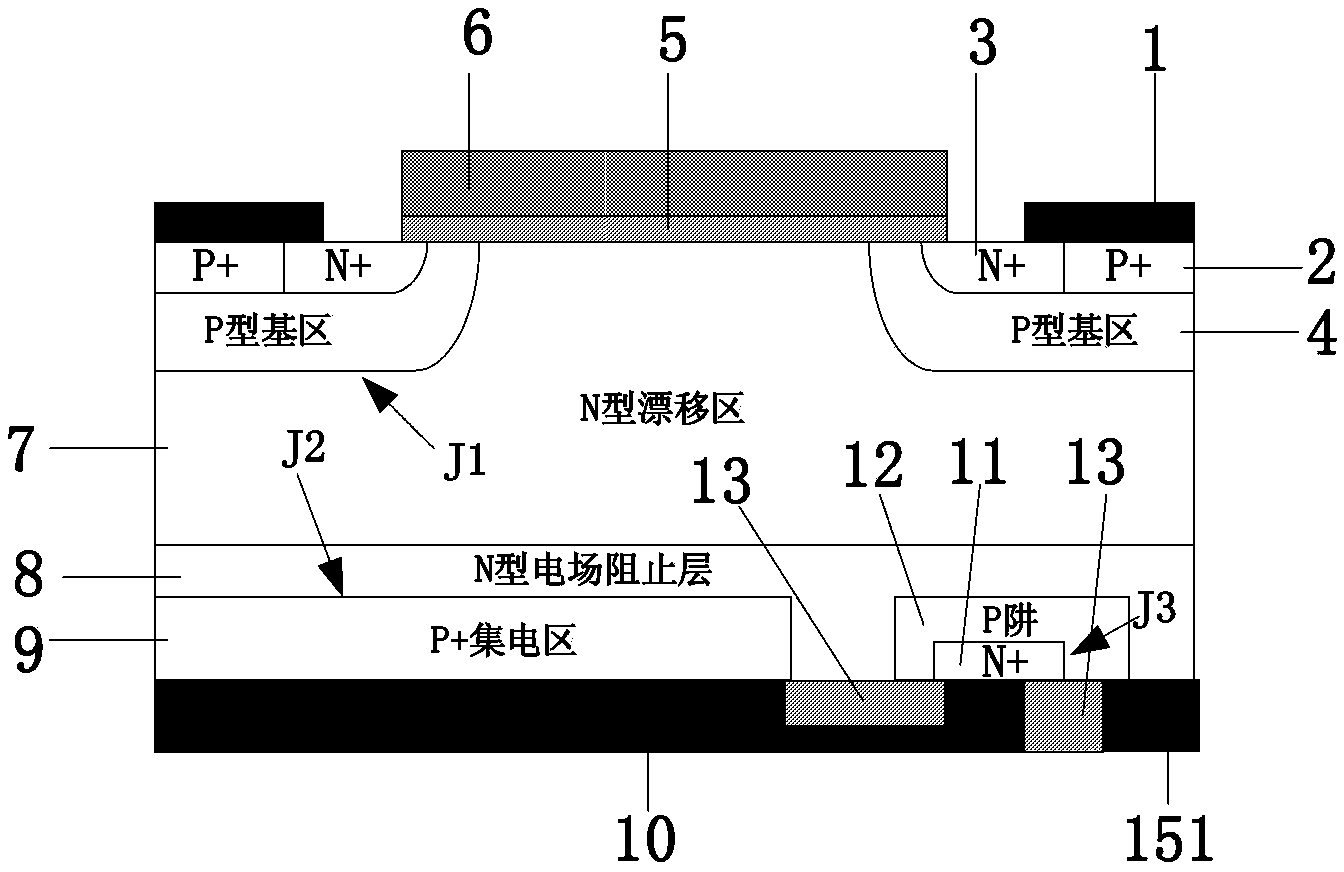

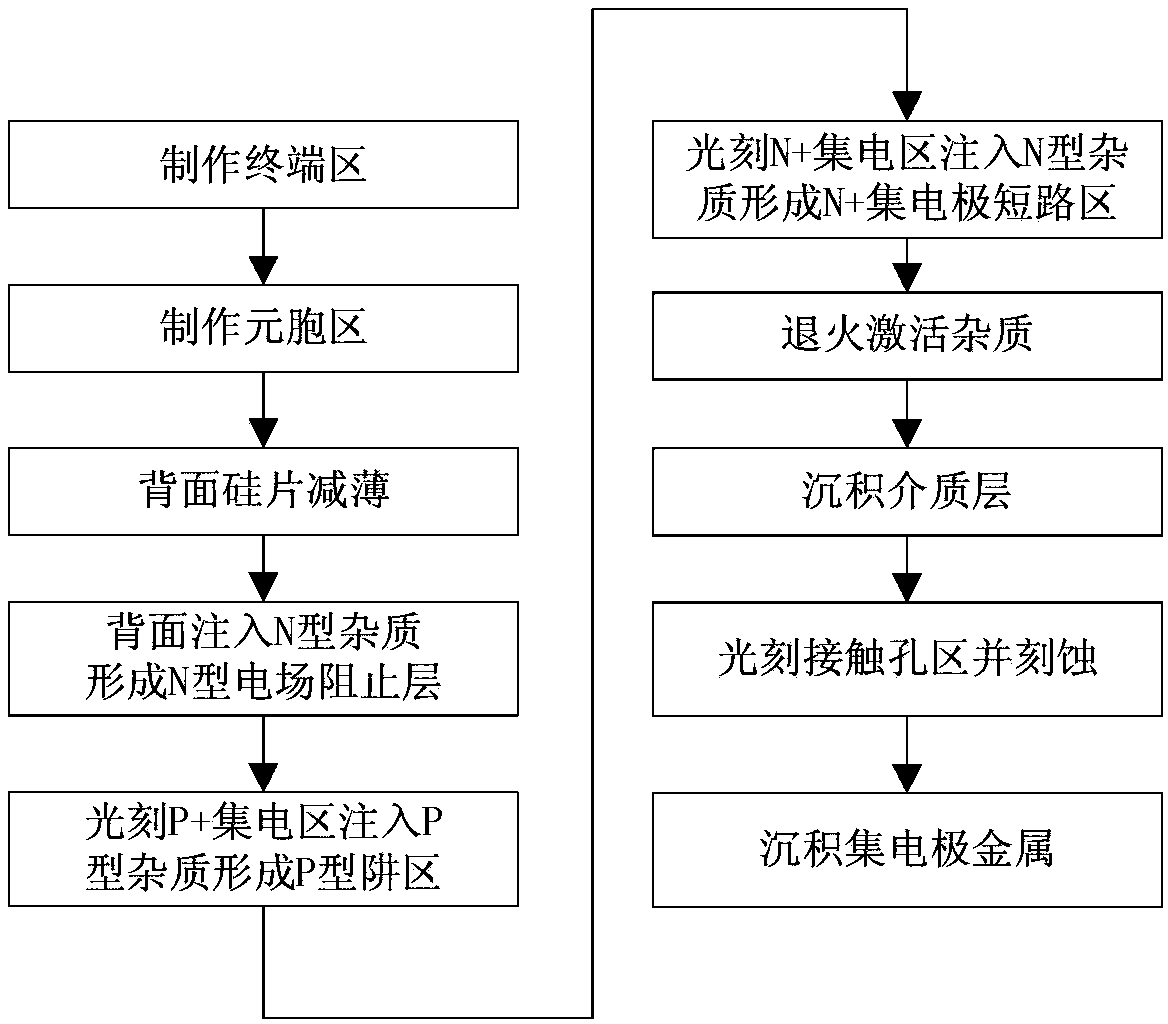

Reverse conducting (RC)-insulated gate bipolar transistor (IGBT) device and manufacturing method thereof

InactiveCN103383958AImprove reliabilityNo Snapback phenomenonSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringElectric field

A reverse conducting (RC)-insulated gate bipolar transistor (IGBT) device and a manufacturing method thereof belong to the technical field of power semi-conductor devices. On the basis of a traditional RC-IGBT device structure, a P-type well region 12 is introduced between an N+ collector short circuit area 11 and an N type electric field preventing layer 8, and the N type electric field preventing layer 8 and the P-type well region 12 are insulated from a metal collector 10 by adopting an isolation medium 13. On the basis of traditional RC-IGBT device characteristics, the device can fully eliminate an intrinsic Snap back phenomenon of a traditional RC-IGBT during connection in the positive direction and has a similar loss characteristic as the traditional RC-IGBT. The RC-IGBT device and the manufacturing method are applicable to the field of semi-conductor power devices from small power to large power and power integrated circuits.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

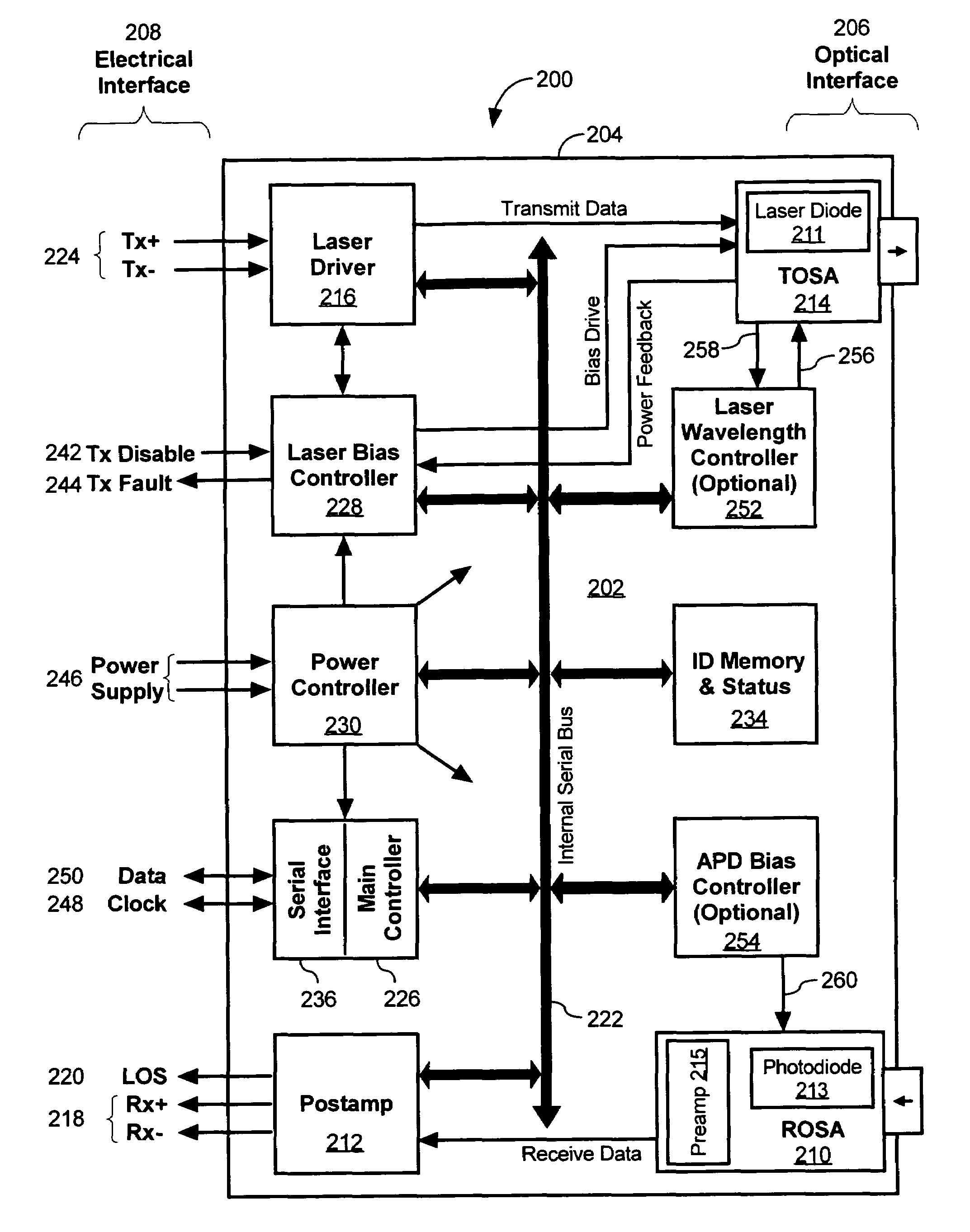

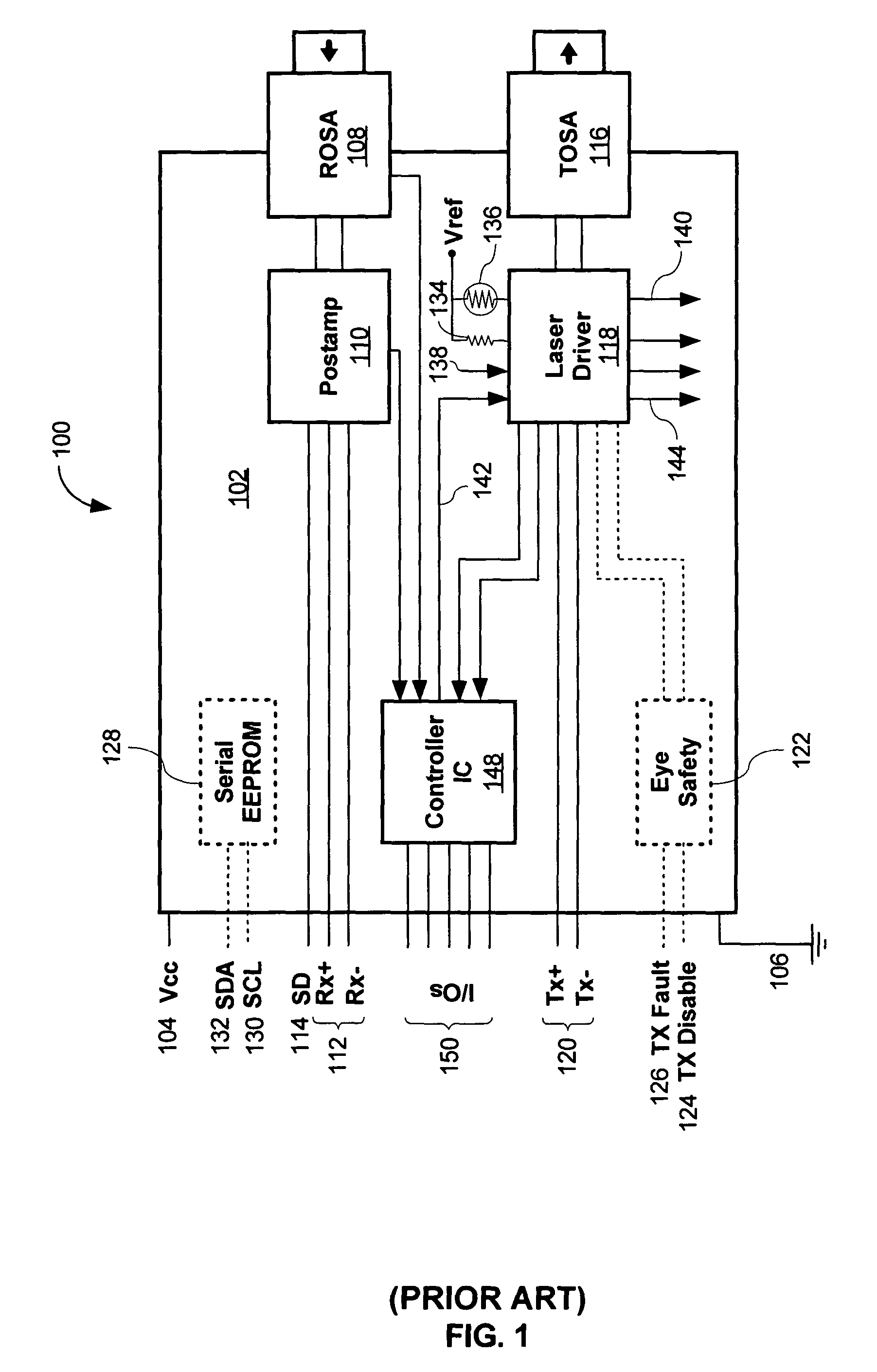

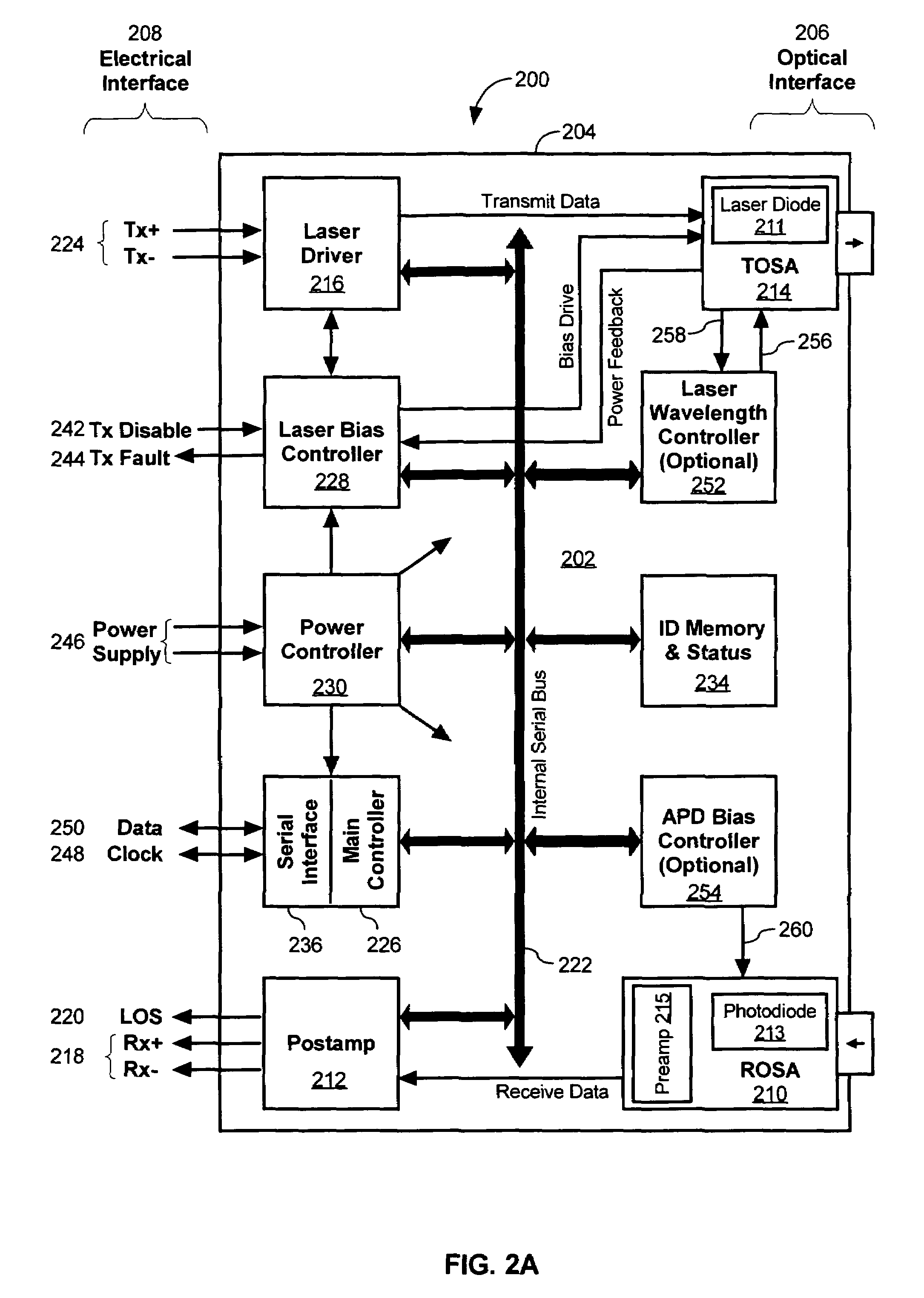

Optical transceiver module with power integrated circuit

InactiveUS7359643B2Reduce system complexityMore compact transceiver moduleCoupling light guidesTransmission monitoringPower controllerElectricity

The optical transceiver module includes a housing and a plurality of components disposed at least partially within the housing. The components include an optical transmitter, an optical receiver, and a power controller integrated circuit (IC). The power controller IC is electrically coupled to at least one of the plurality of components. The power controller IC is configured to perform power supply functions for the optical transceiver module. Also, the power controller IC includes multiple voltage regulators providing power to the components at two or more voltages.

Owner:II VI DELAWARE INC

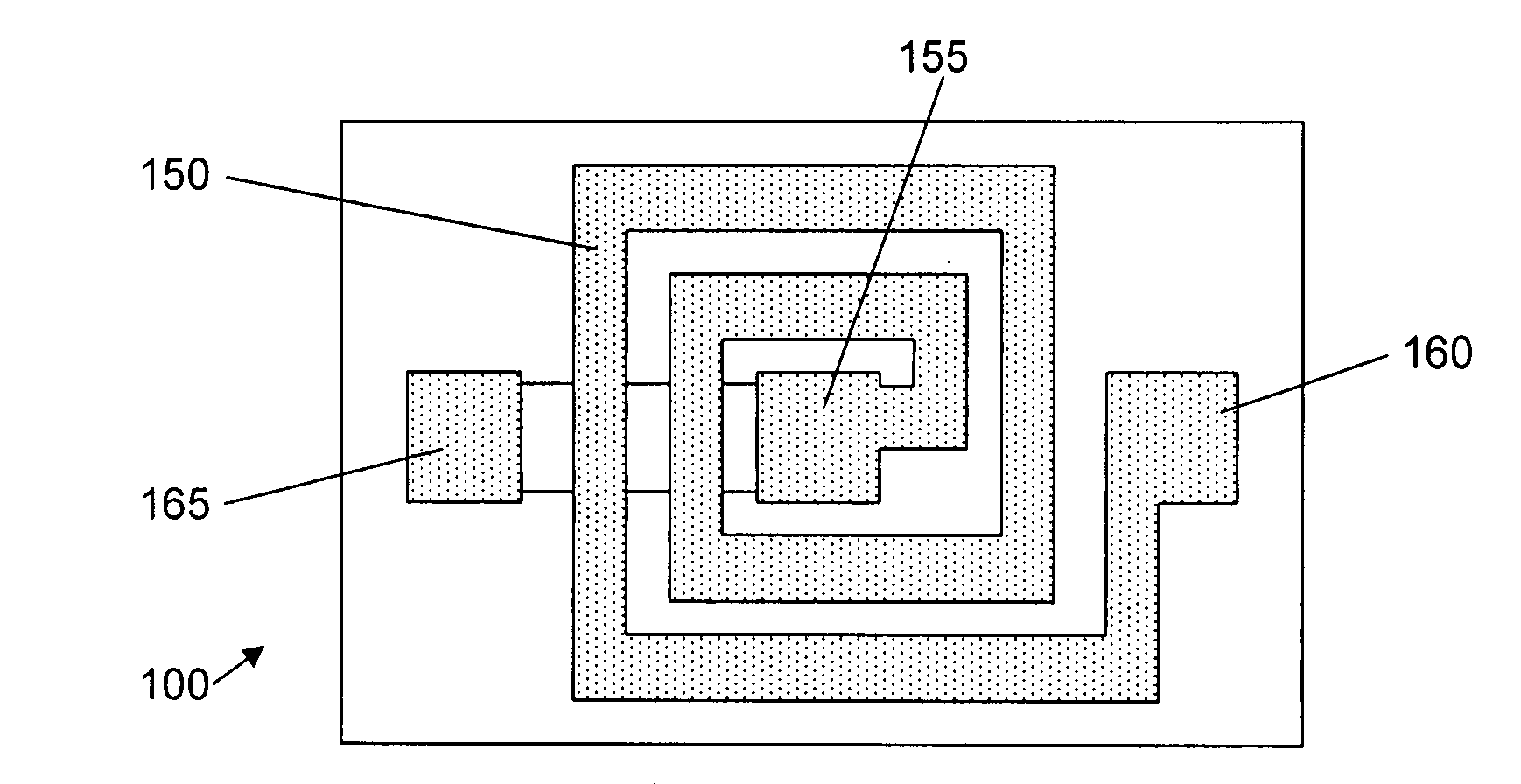

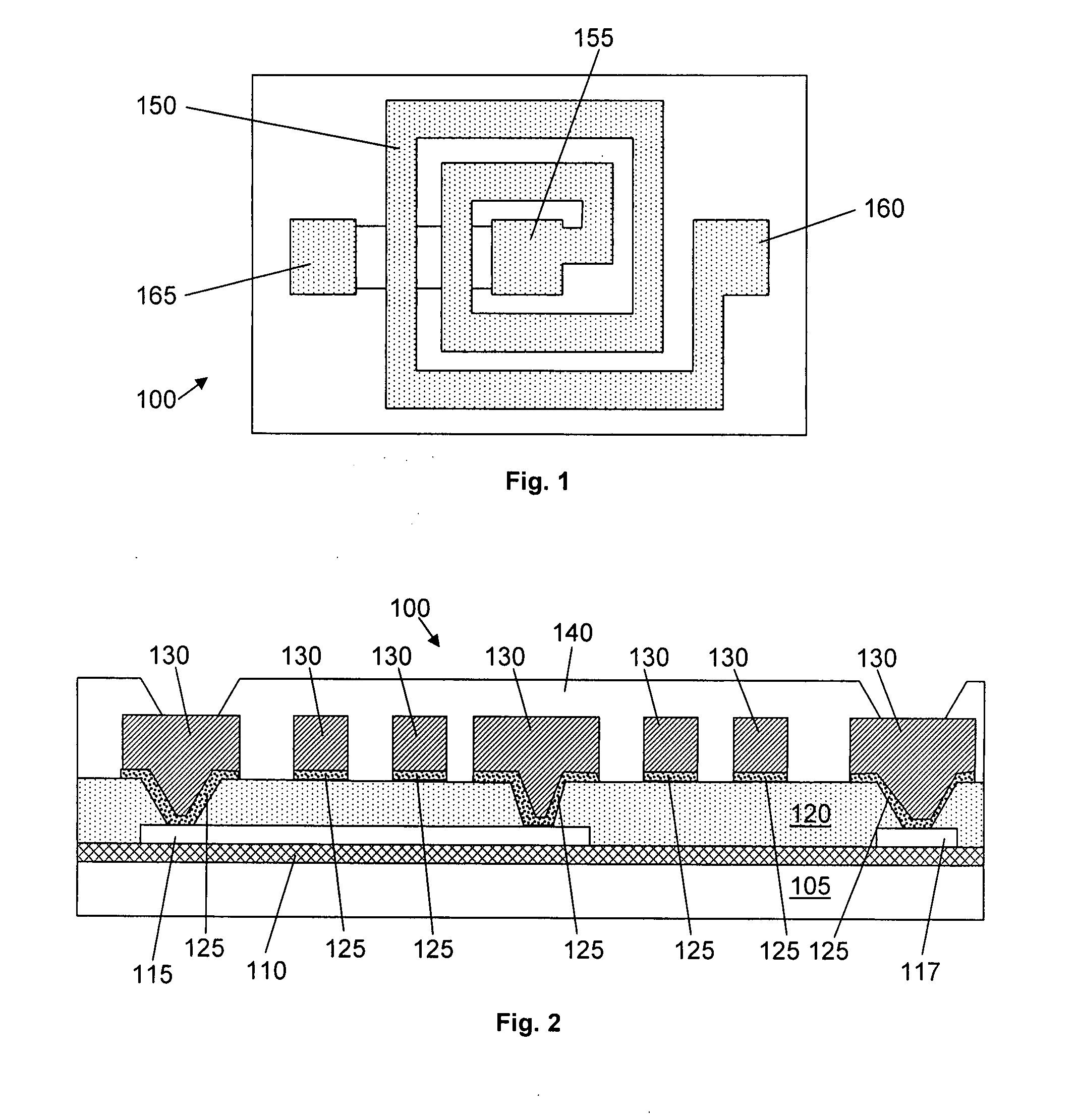

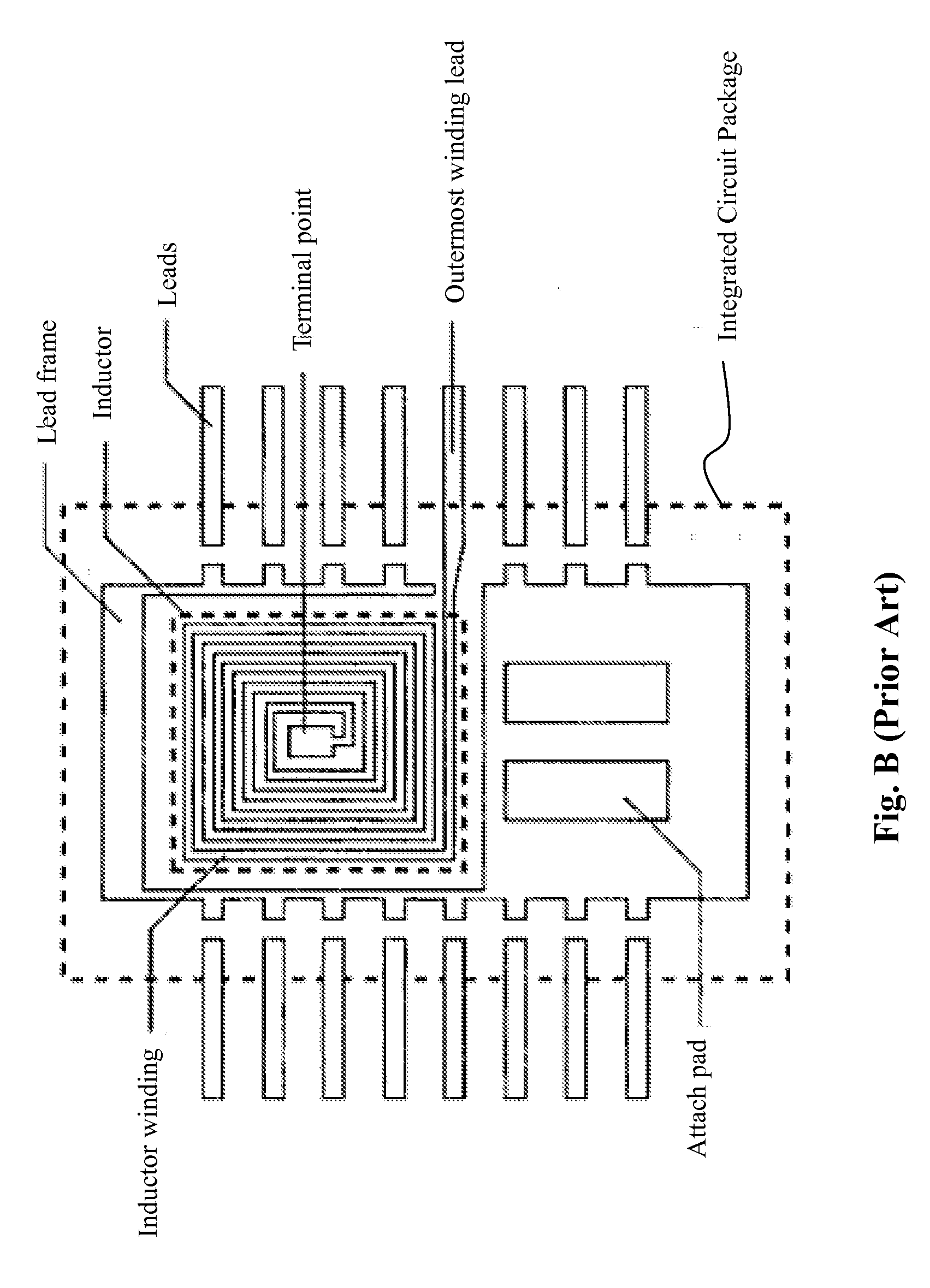

Chip scale power converter package having an inductor substrate

ActiveUS20080238599A1Improve efficiencySemiconductor/solid-state device detailsTransformers/inductances coils/windings/connectionsPlanar spiral inductorsInductor

A chip scale power converter package having an inductor substrate and a power integrated circuit flipped onto the inductor substrate is disclosed. The inductor substrate includes a high resistivity substrate having a planar spiral inductor formed thereon.

Owner:ALPHA & OMEGA SEMICON INC

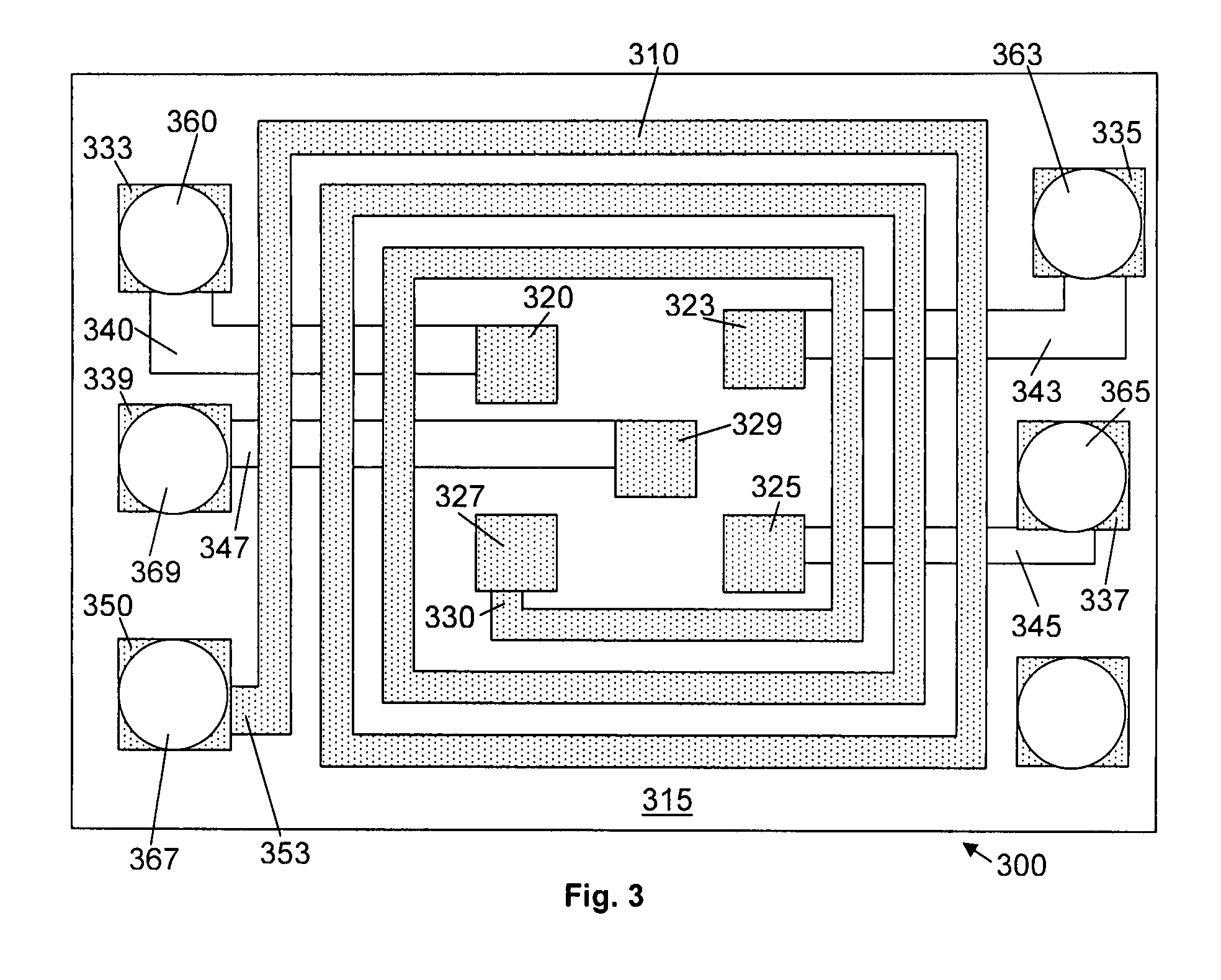

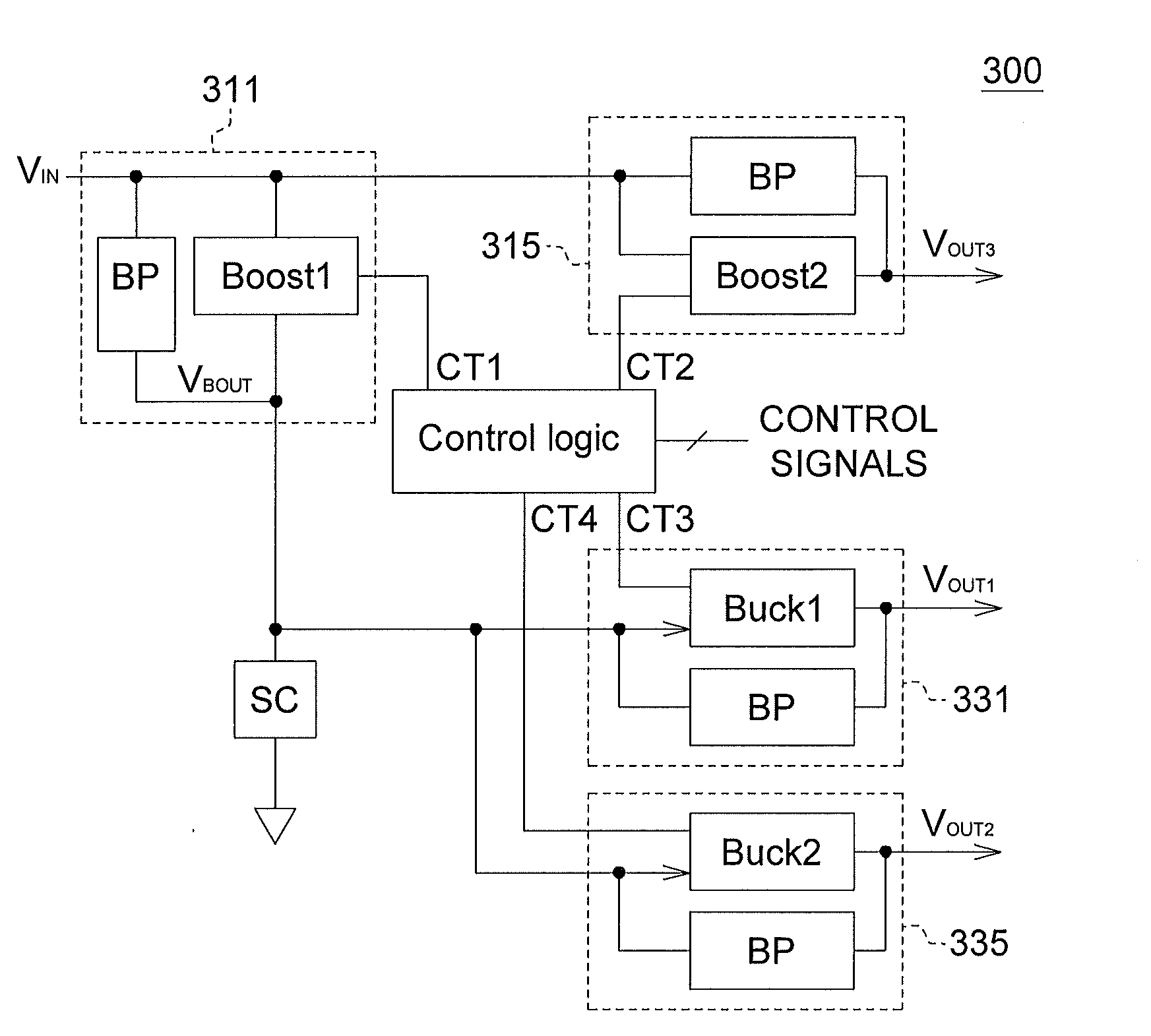

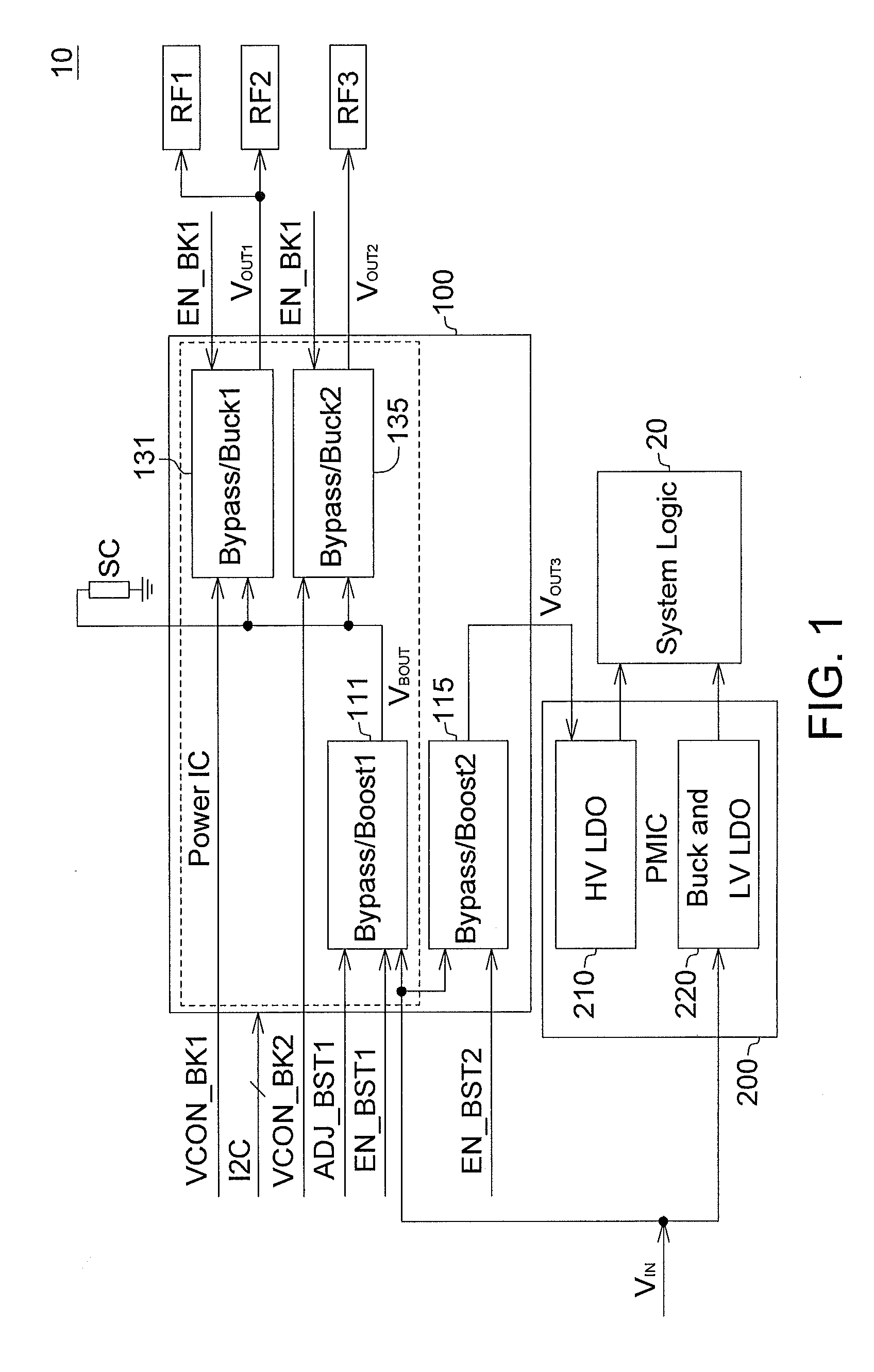

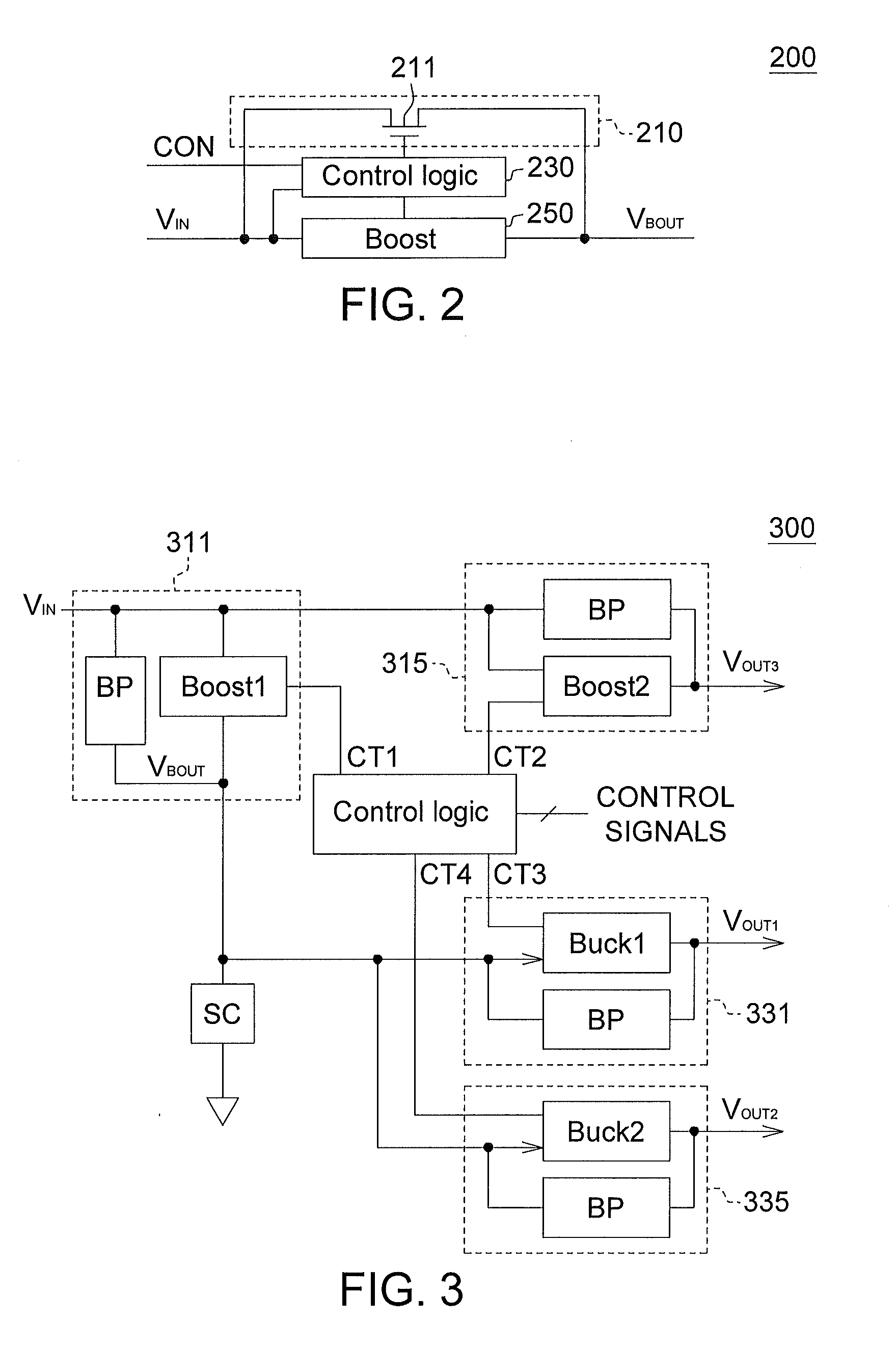

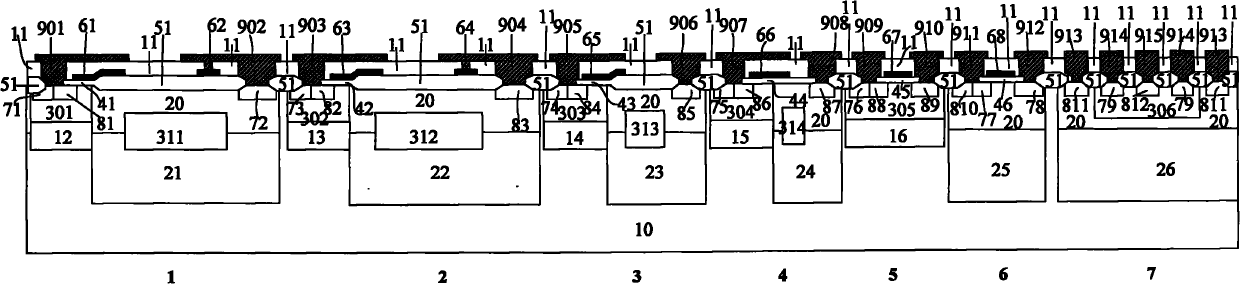

System power integrated circuit and architecture, management circuit, power supply arrangement, and portable apparatus

ActiveUS20130009470A1Dc network circuit arrangementsAc network voltage adjustmentComputer moduleEngineering

According to one embodiment, a management circuit for a portable device includes an input terminal, a first step-up converter, a first step-down converter, and a second step-down converter. The input terminal is coupled to receive a supply voltage from a power supply. The first step-up converter, coupled to the input terminal, selectively converts the supply voltage to a boosted voltage. The first step-down converter, coupled to the first step-up converter, selectively provides a first output power voltage to a first radio frequency (RF) module. The second step-down converter, coupled to the first step-up converter, selectively provides a second output power voltage to a second radio frequency (RF) module. The first step-up converter performs the conversion of the supply voltage when the supply voltage is under a threshold voltage.

Owner:HTC CORP

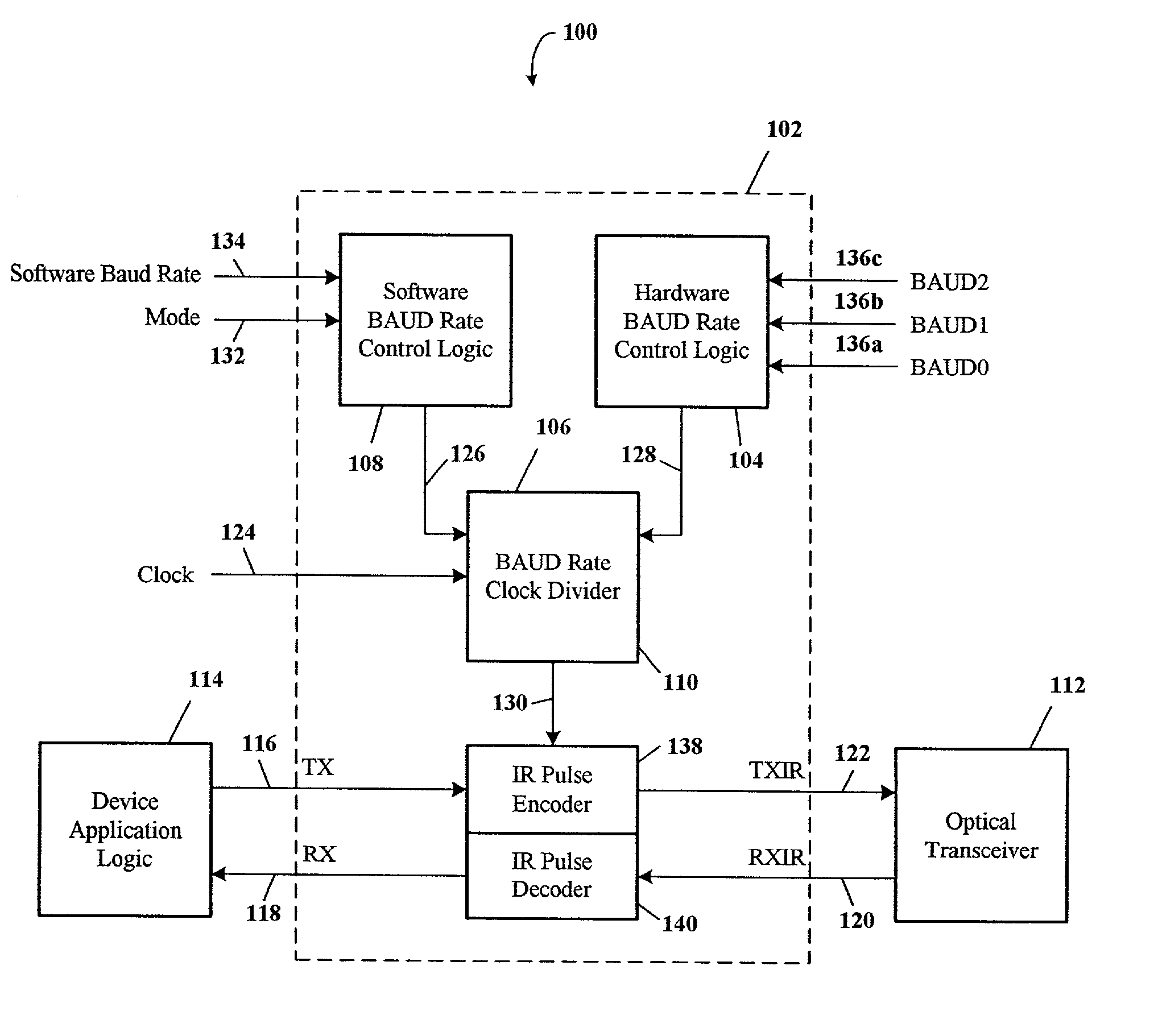

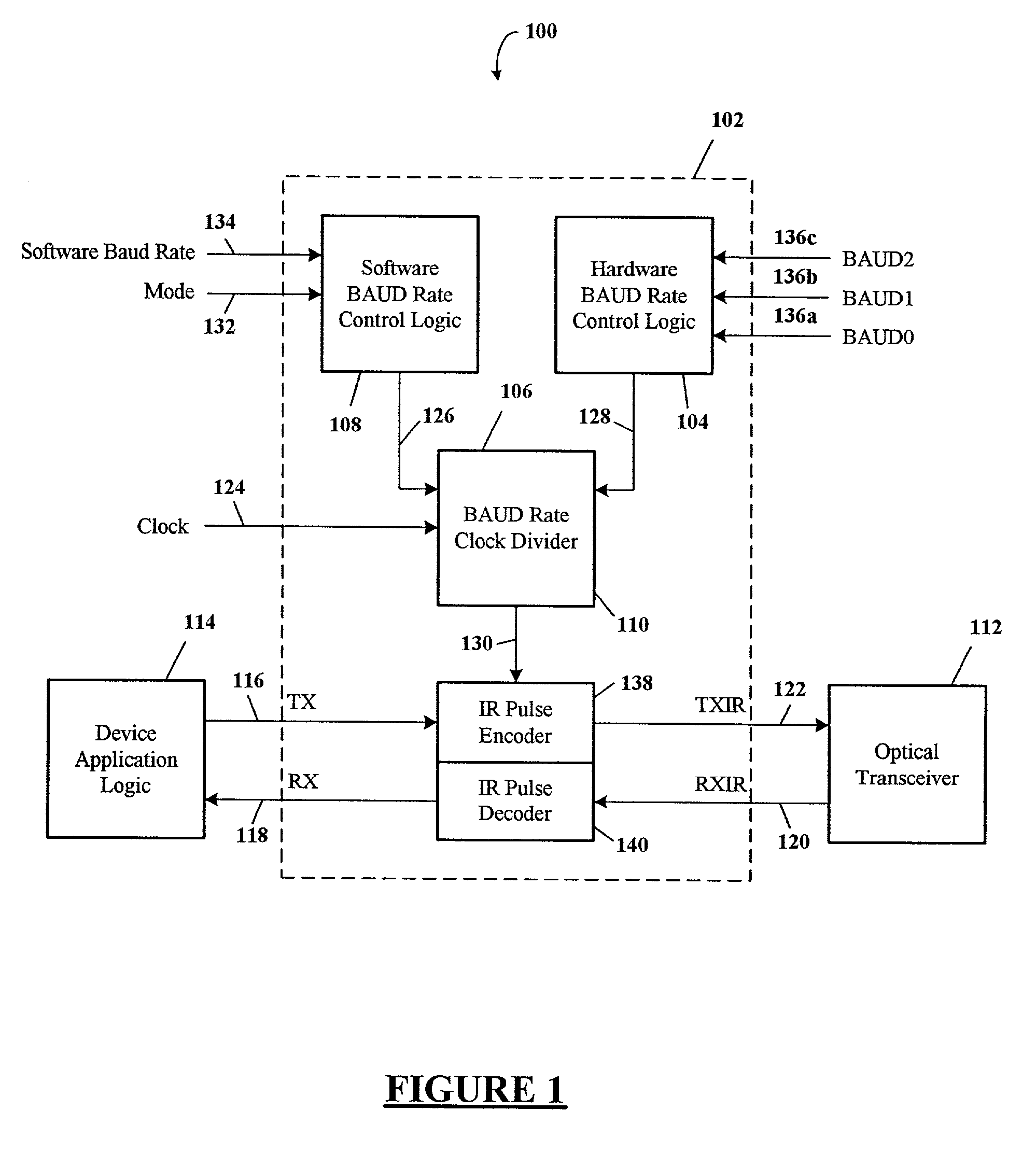

Infrared encoder/decoder having hardware and software data rate selection

InactiveUS20020176138A1Reduce system resourceClose-range type systemsElectromagnetic transmittersInfraredSerial transfer

An infrared encoder / decoder selects the data rate of a serial transmission of data by changing an input clock speed, setting the operating characteristics of a clock divider circuit by hardware inputs or selecting a clock speed by software commands that program the operating characteristics of a clock divider circuit. Having three alternate ways, two hardware and one software, of selecting the data rate of the serial transmission allows greater flexibility in the application and interfacing of a single integrated circuit package infrared encoder / decoder with all types of digital logic circuits and systems. An encoder / decoder having standard pulse width output and input compatibility with infrared industry standards, e.g., IrDA, and infrared transceivers is achieved in a flexible and cost effective low power integrated circuit package.

Owner:MICROCHIP TECH INC

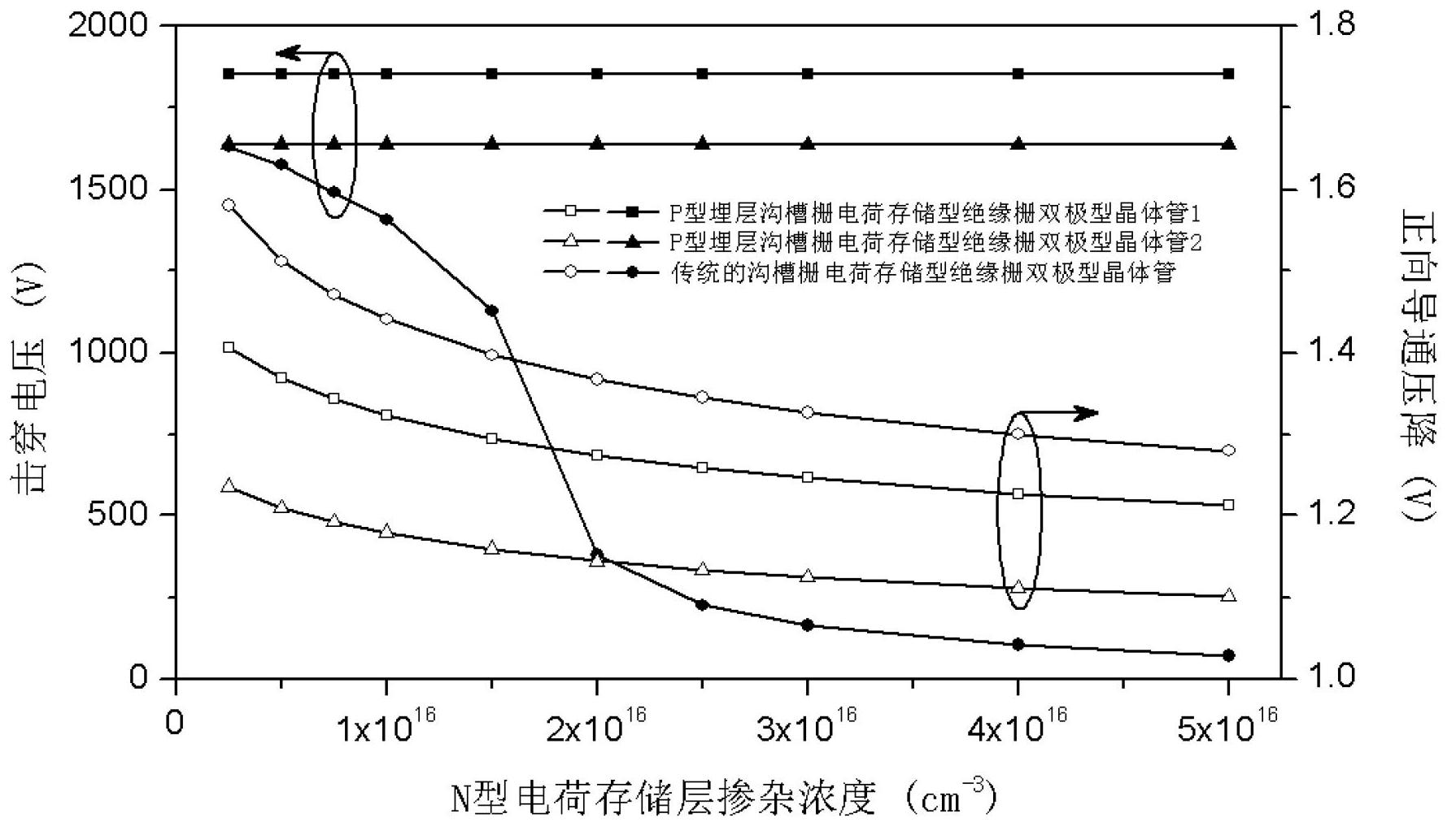

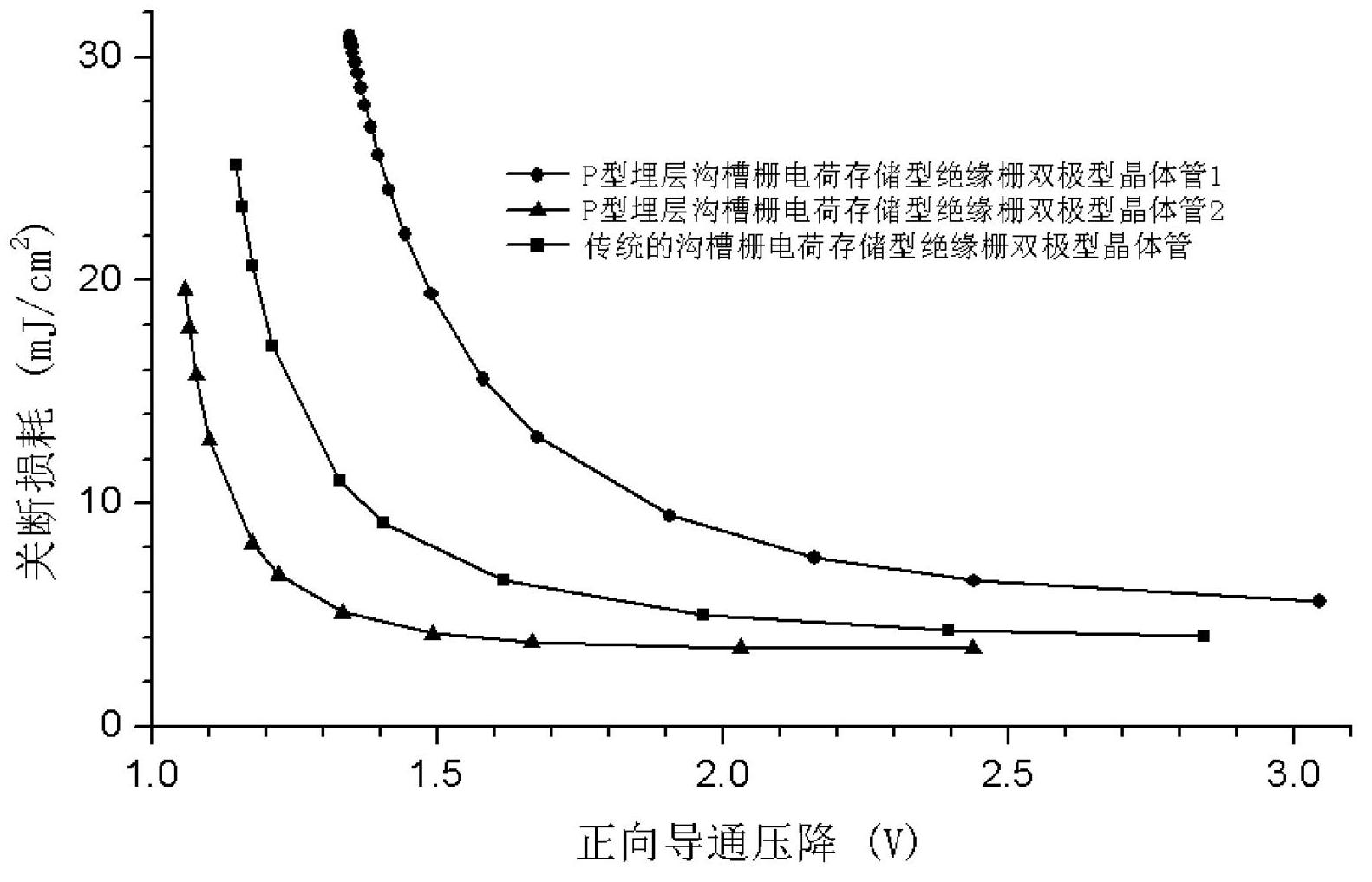

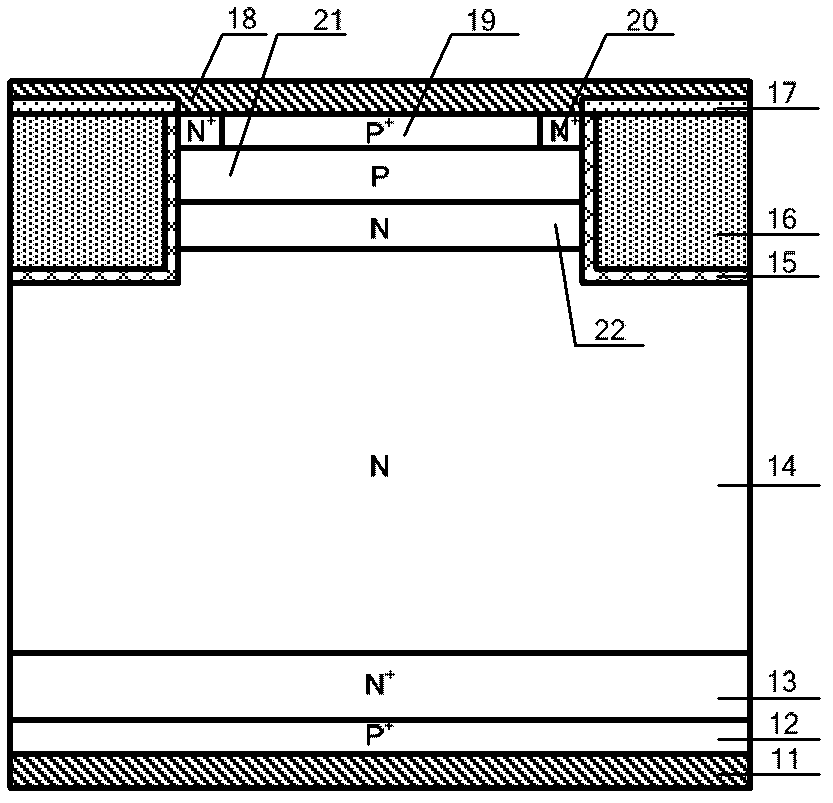

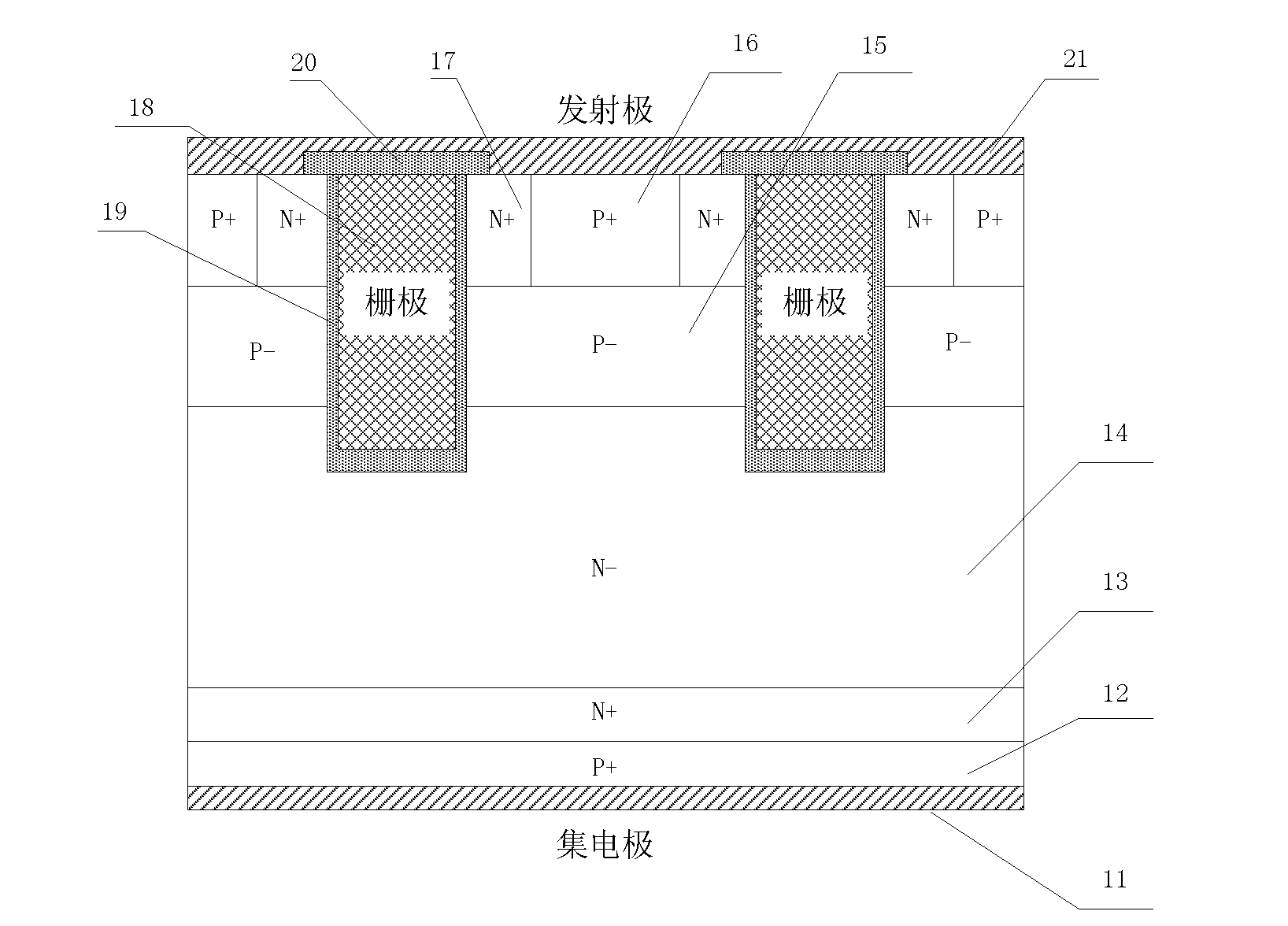

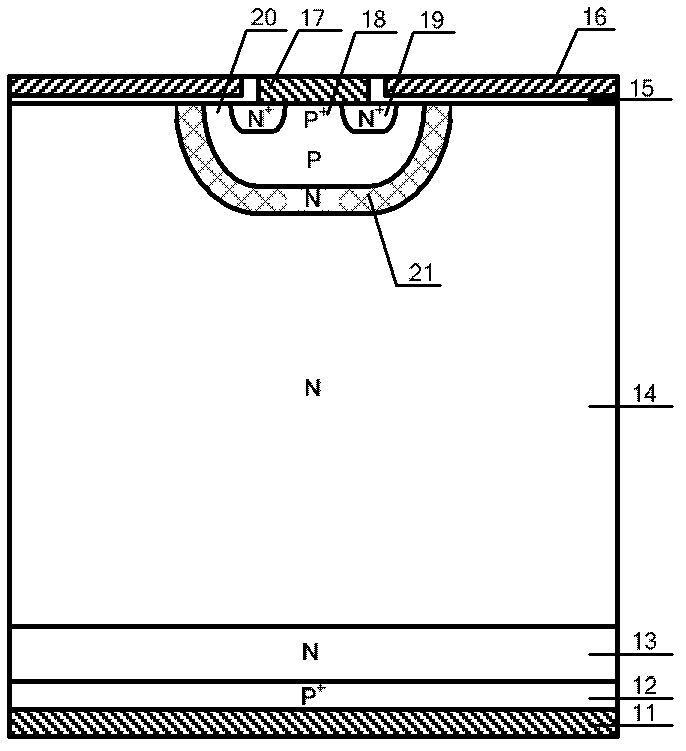

Trench gate charge storage type insulated gate bipolar transistor (IGBT)

InactiveCN102683403AImprove breakdown voltageGood forward voltage dropSemiconductor devicesConductivity modulationBreakdown voltage

The invention discloses a trench gate charge storage type IGBT and belongs to the technical field of power semiconductor devices. Based on traditional trench gate charge storage type IGBTs, a P-shaped buried layer is introduced on the upper portion of a N-shaped drifting area of a device, by the aid of an attached PN junction introduced by the P-shaped buried layer and the electric field modulating effect, negative influences of a highly doped N-shaped charge storage layer on the breakdown voltage of the device is shielded, and the device can acquire high breakdown voltage. The P-shaped buried layer has an electric field shielding effect on the N-shaped charge storage layer, high doping concentration of the N-shaped charge storage layer can be adopted, the conductivity modulation in the N-shaped drifting area of the device can be strengthened, and the distribution of current carriers in the N-shaped drifting area is optimized, so that the device can acquire low and good forward voltage drop and good turn-off loss compromise. The trench gate charge storage type IGBT is applicable to fields of semiconductor power devices ranging from low power to high power and power integrated circuits.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

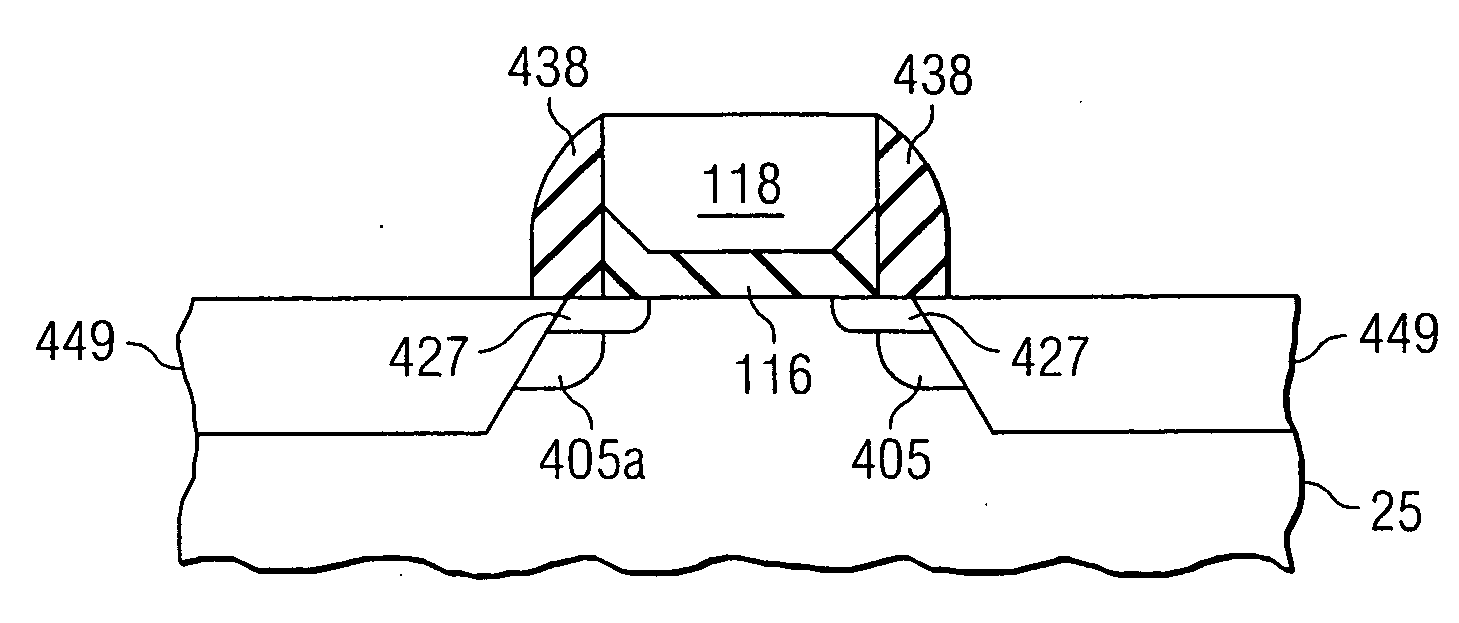

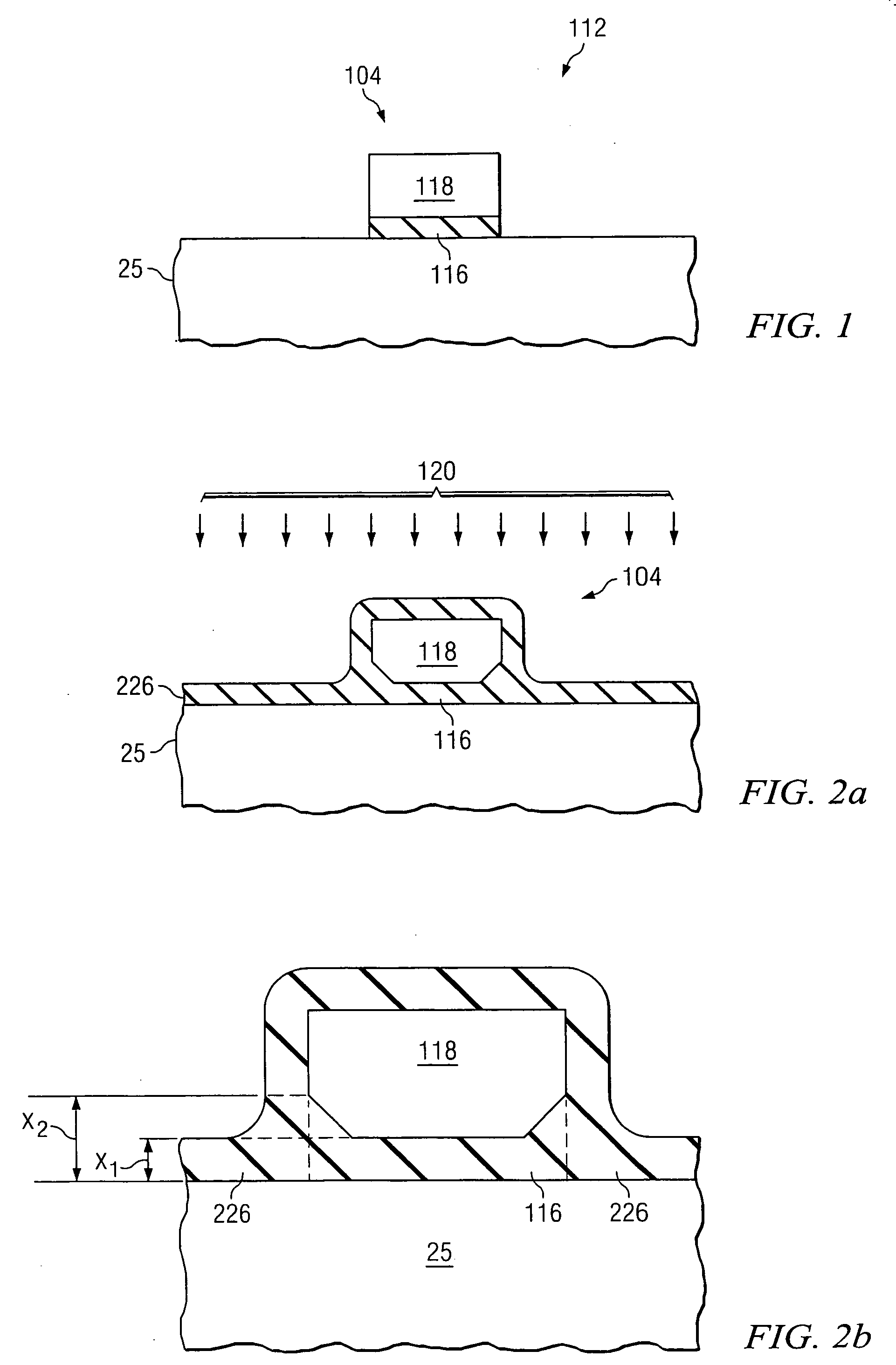

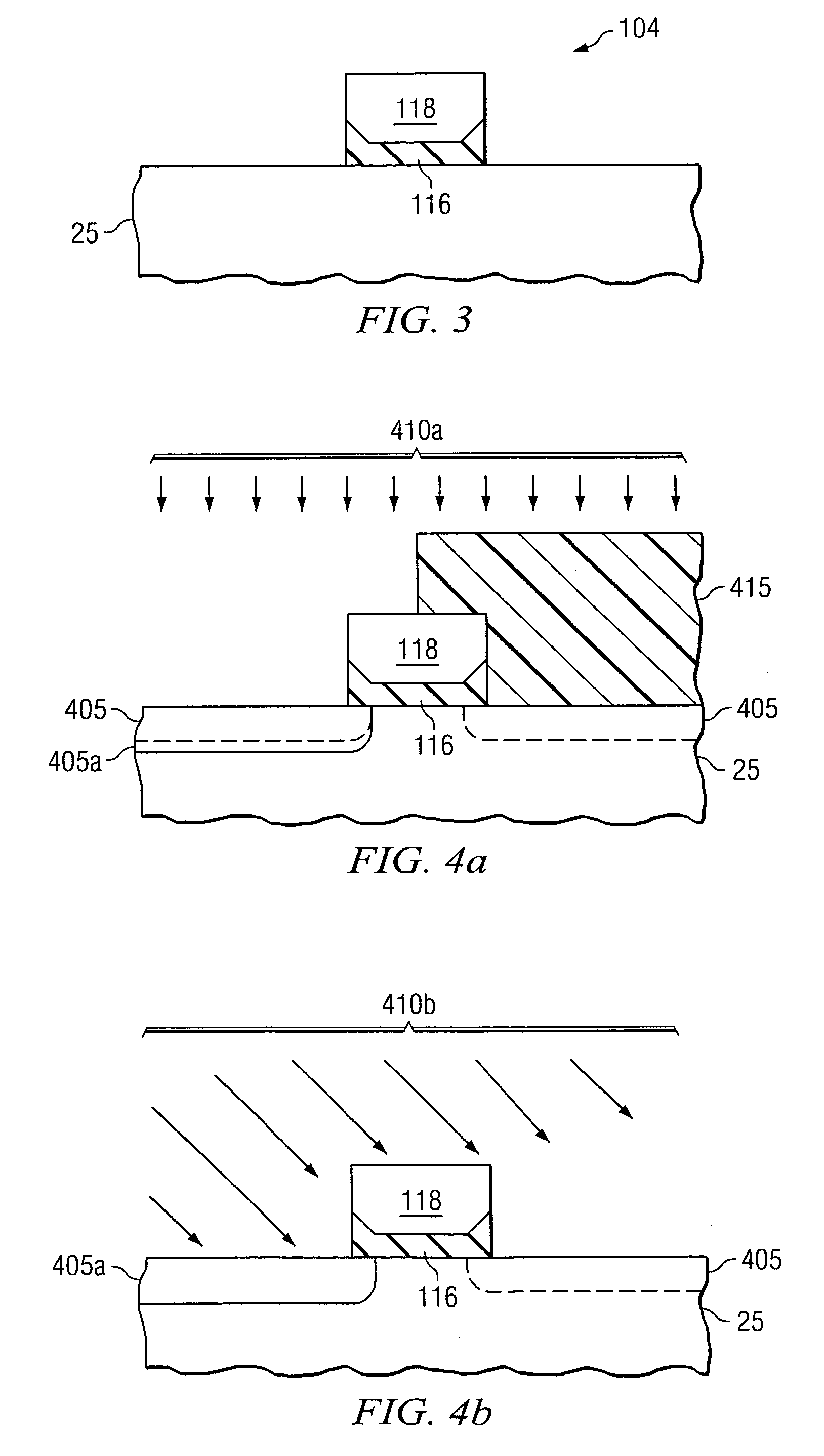

CMOS devices for low power integrated circuits

InactiveUS20060273391A1Reducing off-state leakage currentTransistorSemiconductor/solid-state device manufacturingGate dielectricFloating body effect

A preferred embodiment of the invention provides a semiconductor fabrication method. An embodiment comprises forming a MOS device and thermally oxidizing the MOS device to form a gate dielectric substantially thicker at a gate dielectric edge than that at a gate dielectric center. Embodiments further comprise performing a source / drain ion implant to form an asymmetric source / drain, wherein the source region includes a high leakage source junction, and wherein the drain region includes a low leakage drain junction. Other embodiments of the invention comprise a MOS device formed in a semiconductor substrate, wherein the device has improved resistance to floating body effects. Still other embodiments include a CMOS device for low power integrated circuits.

Owner:TAIWAN SEMICON MFG CO LTD

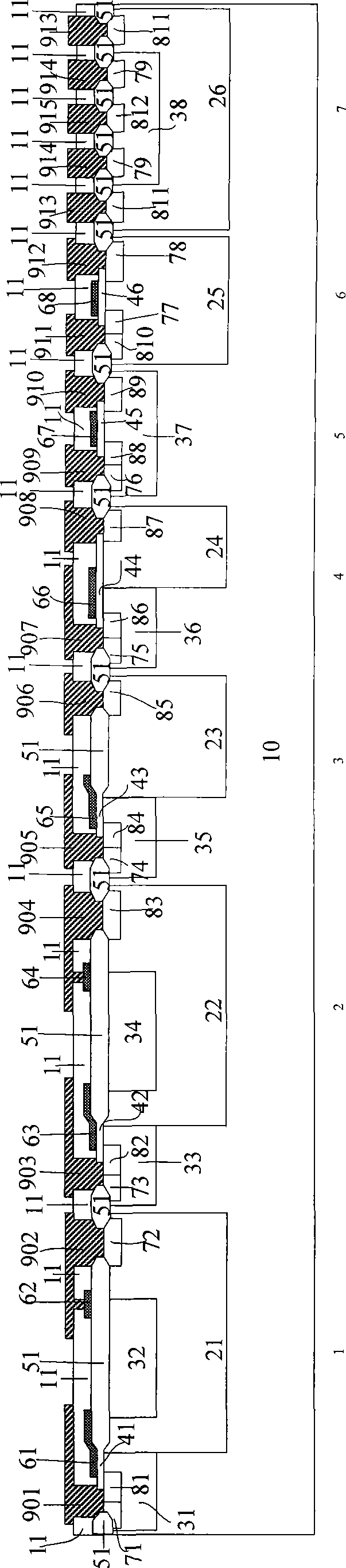

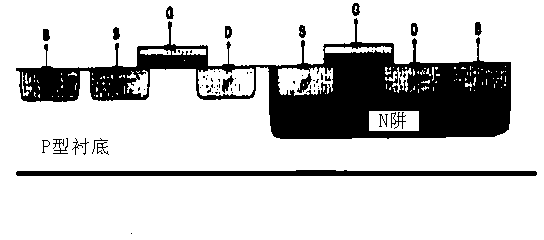

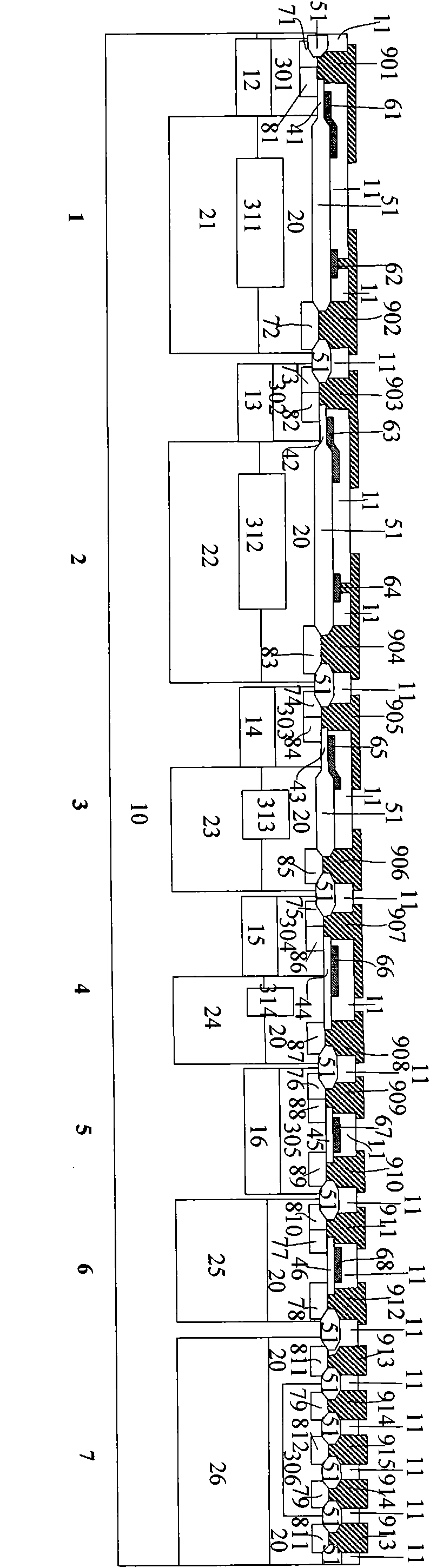

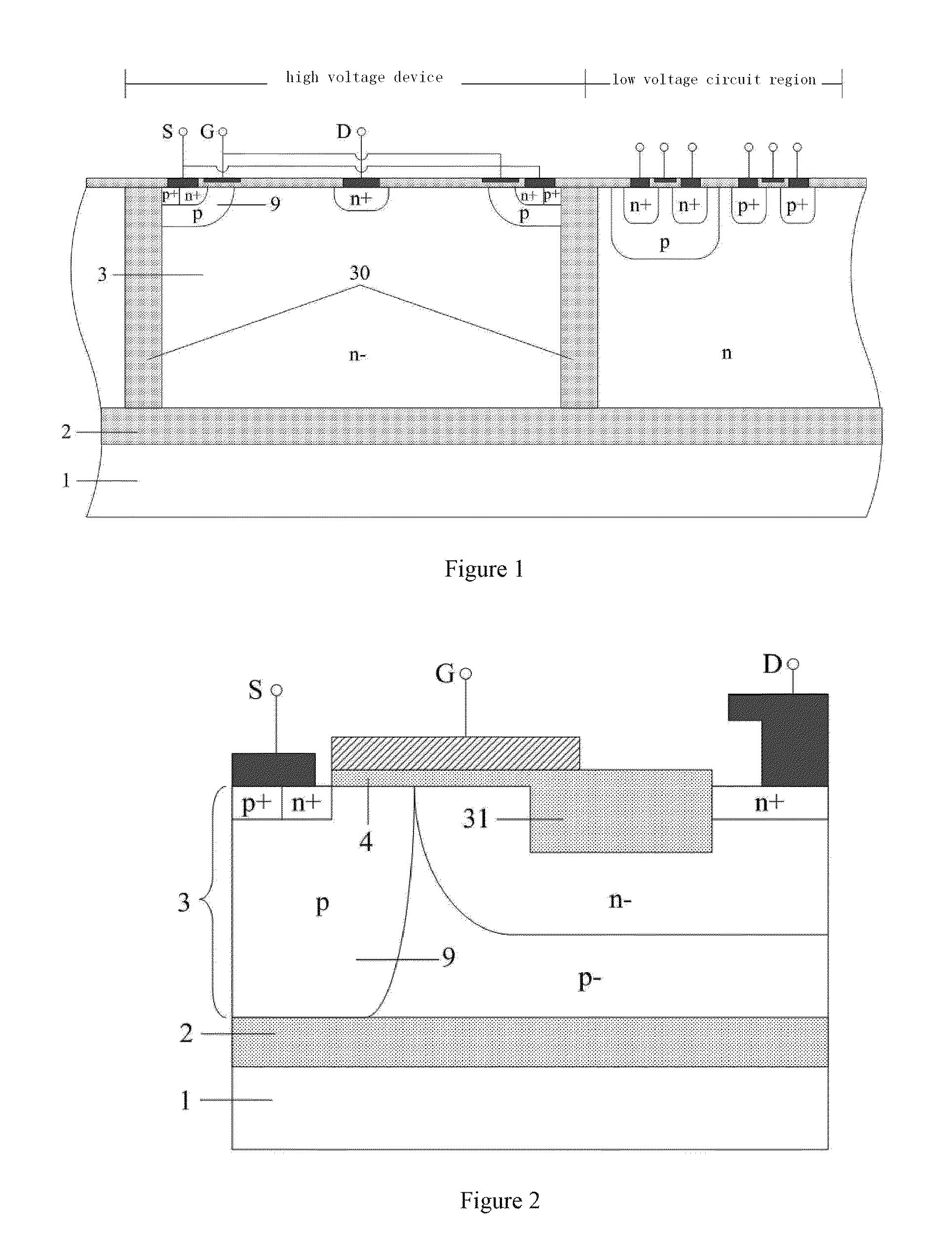

BCD semiconductor device and manufacturing method thereof

InactiveCN101452933AReduce conduction lossReduce manufacturing costSolid-state devicesSemiconductor/solid-state device manufacturingLow voltageElectric consumption

The invention provides a BCD semiconductor device and a method for producing the same, and belongs to the technical field of a semiconductor power device. The device comprises a high-voltage nLIGBT, a first-class high-voltage nLDMOS, a second-class high-voltage nLDMOS, a third-class high-voltage nLDMOS, a low-voltage NMOS, a low-voltage PMOS and a low-voltage NPN. The semiconductor device is directly arranged on a single crystal substrate. The high-voltage nLIGBT, the high-voltage nLDMOSes and the low-voltage NPN are directly arranged on a single crystal p-type substrate, the low-voltage NMOS is arranged in a p-type well, and the low-voltage PMOS is arranged in an n-type well. During the production, the epitaxial process is not required. Single chips of the nLIGBT, the NLDMOSes, the low-voltage NMOS, the low-voltage PMOS and the low-voltage NPN are successfully integrated on the single crystal substrate. Because the epitaxial process is not required, the chips are relatively low in production cost. The nLIGBT device and nLDMOS devices of the invention have the characteristics of high input impedance, low output impedance and the like, and a high-voltage power integrated circuit formed by the nLIGBT device and the nLDMOS devices can be applied to various products in fields of electric consumption, display drive and the like.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA +1

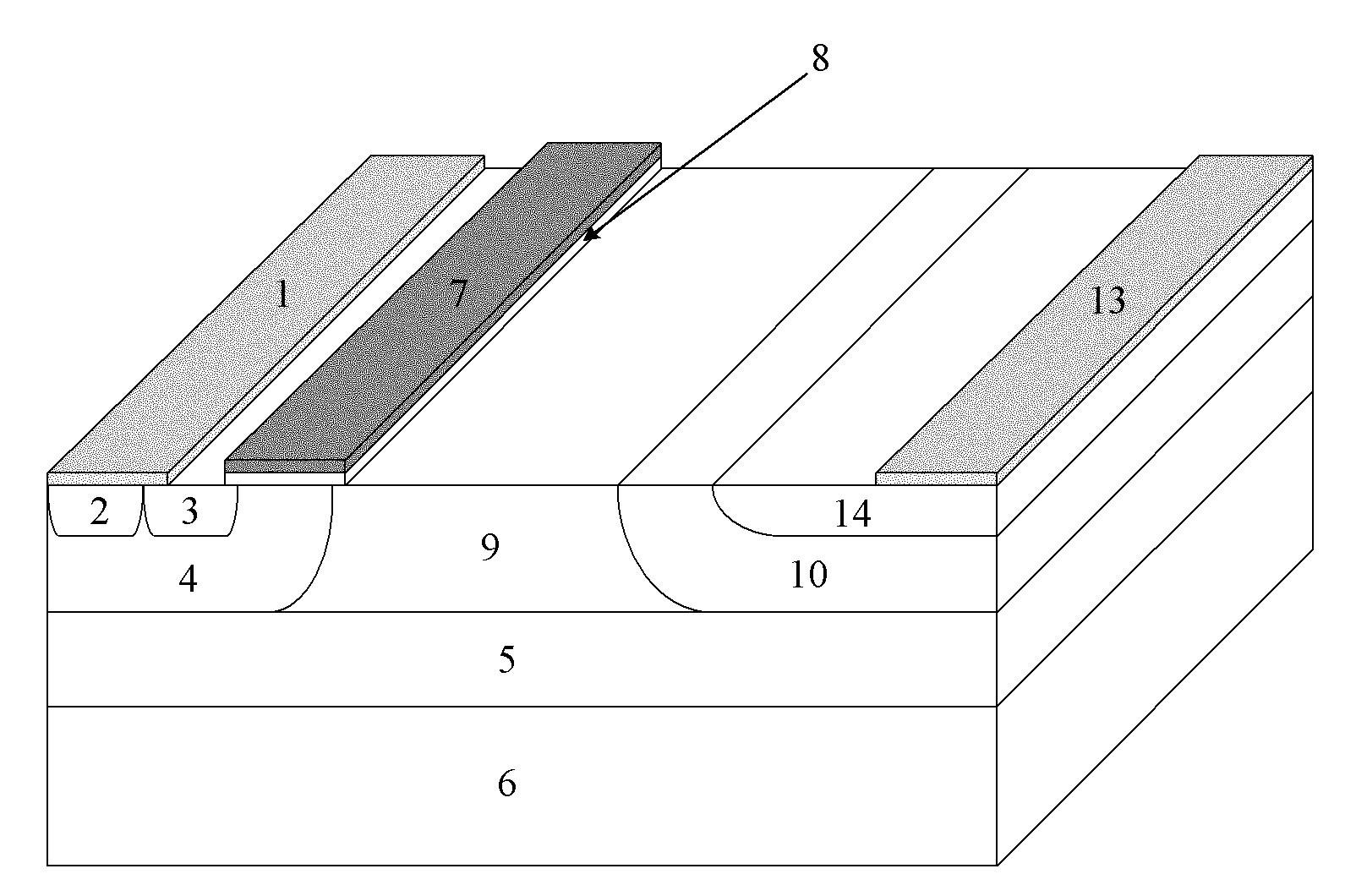

SOI-LIGBT (silicon on insulator-lateral insulated gate bipolar transistor) device with split anode structure

InactiveCN102148240ALow costImprove hole injection efficiencySemiconductor devicesElectronIntegrated circuit

The invention discloses an SOI-LIGBT (silicon on insulator-lateral insulated gate bipolar transistor) device with a split anode structure, belonging to the technical field of semiconductor power devices. The SOI-LIBGT device comprises a substrate layer, a buried oxide layer, an N-base region, a cathode region, an anode region and a gate region, wherein the cathode region and the anode region area are positioned on the two sides of the N-base region; and the gate region is positioned on the cathode region. The anode region is split into a first anode region and a second anode region by an isolation groove, but the first anode region and the second anode region are still kept in electric connection. The first anode region ensures high hole injection efficiency when the device works; and the second anode region has a function of eliminating the negative differential resistance (NDR) area when the device is opened and provides an electron extraction channel at the turn-off transient state of the device. Through the invention, the NDR area introduced into positive characteristics in the anode short-circuit structure is eliminated on one hand, and on the other hand, the on resistance is increased while the turn-off speed is increased, and a good eclectic relationship between the conduction loss and the turn-off loss is obtained; and moreover, the manufacturing process of the device is compatible with a conventional power integrated circuit process, and additional steps or cost is not increased.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

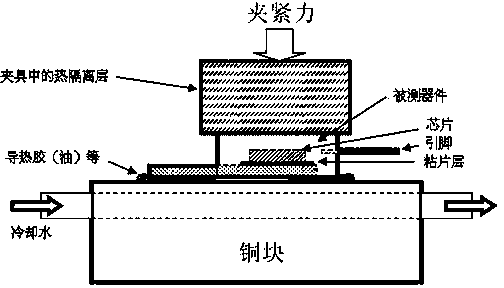

Thermal resistance measuring method for semiconductor device

ActiveCN103792476AMaterial heat developmentIndividual semiconductor device testingJunction temperatureHeat balance

The invention relates to a thermal resistance measuring method for a semiconductor device. The thermal resistance measuring method includes the following steps that (1) according to the structure of the semiconductor device, a main heat conduction channel is determined, and a constant temperature plane good in contact is arranged on the surface of a shell of the main heat conduction channel; (2) certain power is loaded to the semiconductor device, after the semiconductor device reaches heat balance, it is switched to the situation that measuring power is loaded to the semiconductor device, temperature-sensitive parameters of the semiconductor device are measured in real time to obtain the junction temperature for measuring the semiconductor device, and accordingly a transient thermal response curve of the semiconductor device is obtained; (3) according to the transient thermal response curve, the thermal resistance from a junction of the semiconductor device to the shell is determined. According to the thermal resistance measuring method for the semiconductor device, heating power is loaded through a P zone and an N zone of a substrate of the semiconductor device, the junction temperature is measured by the utilization of a PN junction assembly existing in the semiconductor device, and therefore the transient thermal resistance of integrated circuit products without temperature-sensitive diodes and the transient thermal resistance of non-power integrated circuit products can be measured accurately.

Owner:CHINA ACADEMY OF SPACE TECHNOLOGY

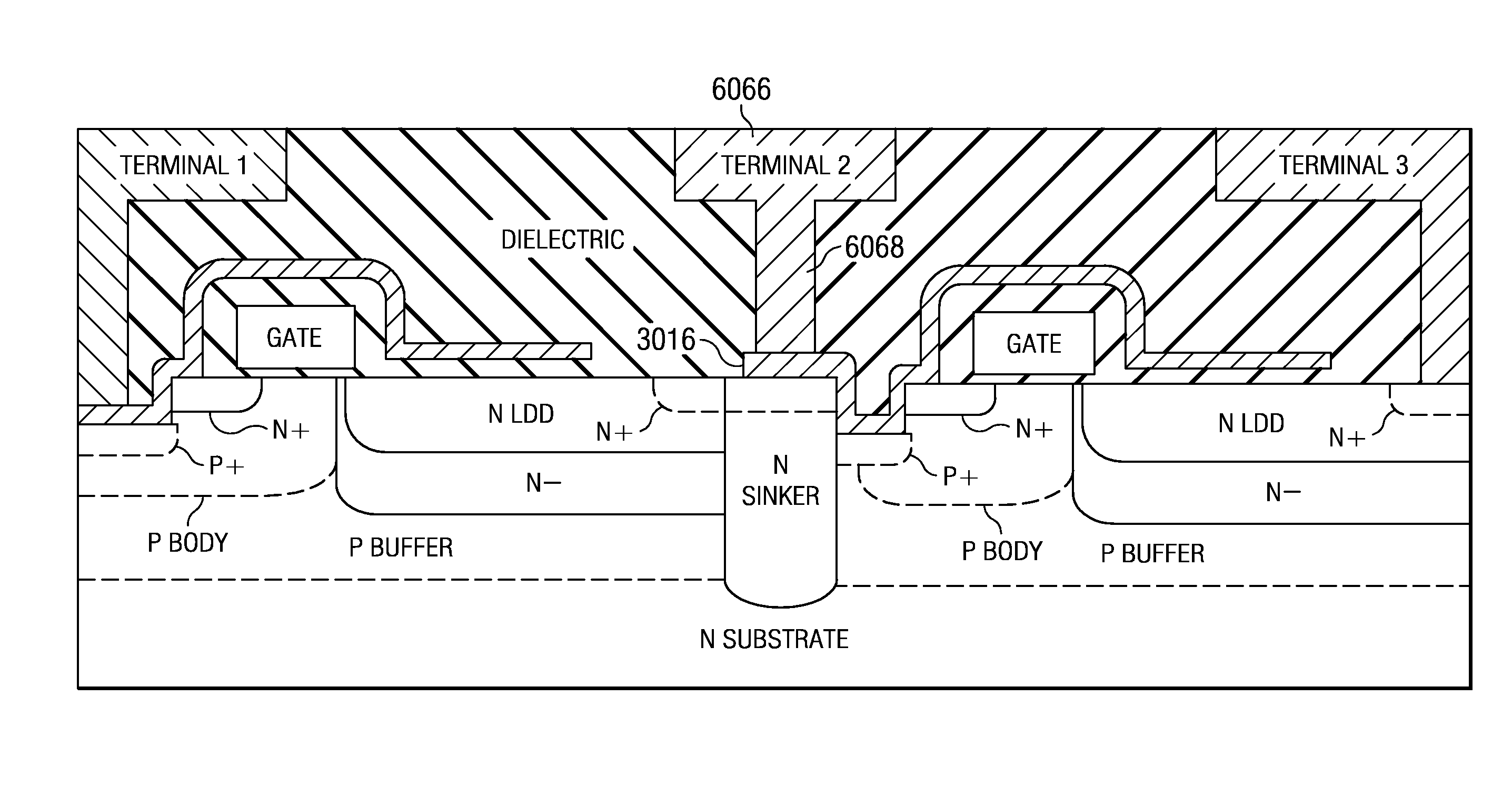

High voltage power integrated circuit

A high performance, power integrated circuit composed of two charge balanced, extended drain NMOS transistors (CBDEMOS) formed on an n-substrate. A CBDENMOS transistor with an n-type substrate source. A charge balanced channel diode (CBCD) with an n-type substrate. A process for forming a high performance, power integrated circuit composed of two CBDENMOS transistors formed on an n-substrate. A process for forming a power integrated circuit composed of one CBDENMOS transistor and one CBCD on an n-type substrate.

Owner:TEXAS INSTR INC

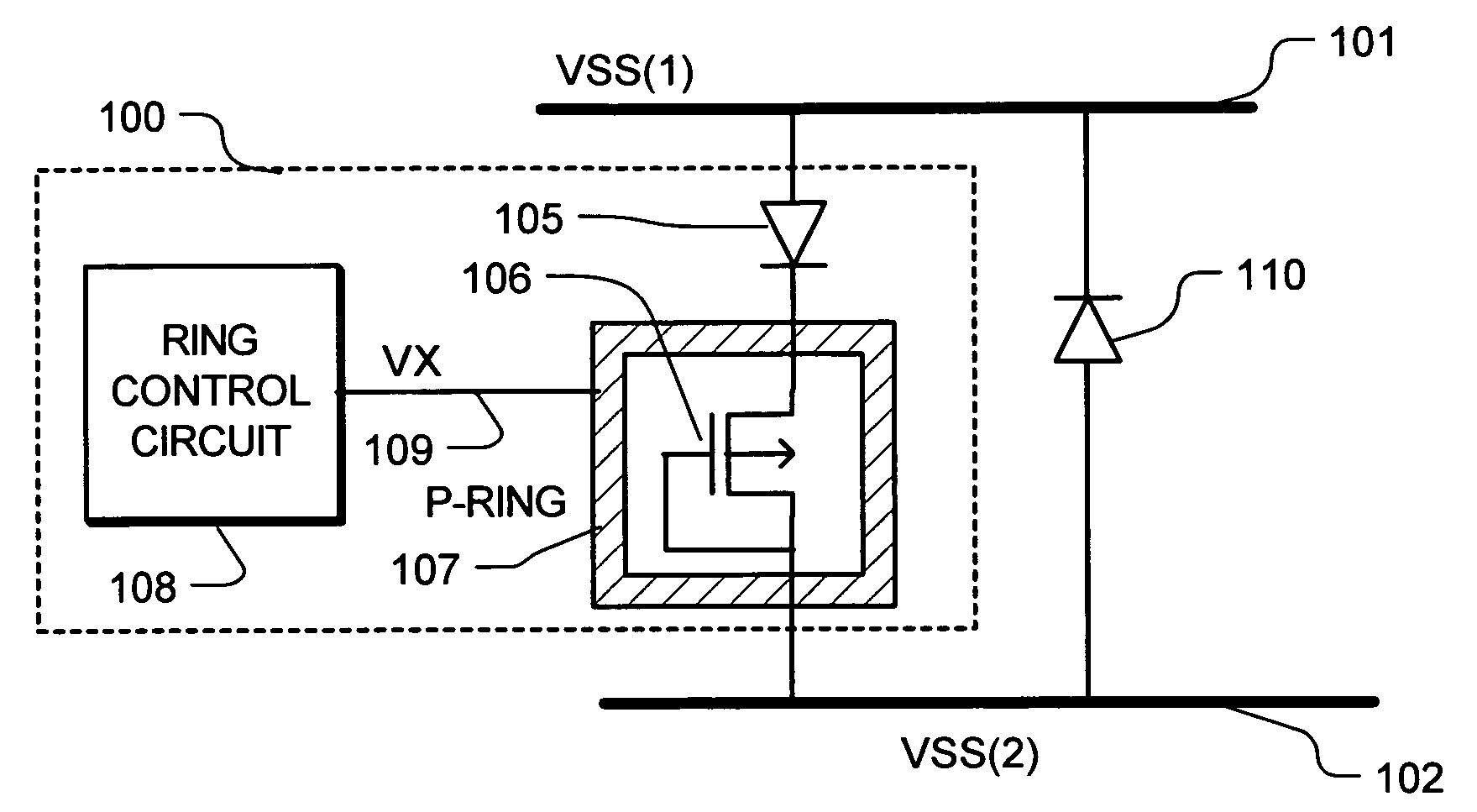

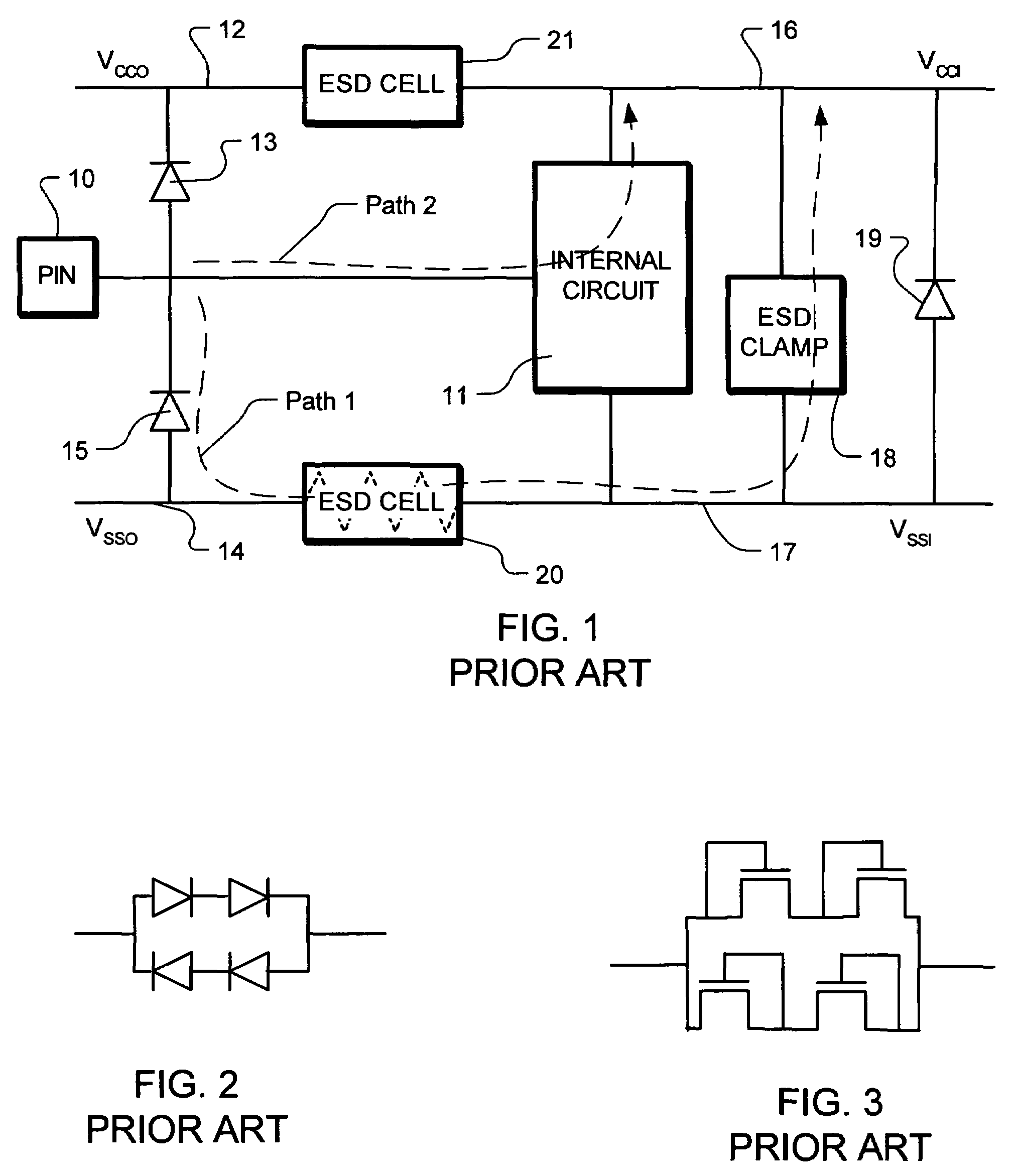

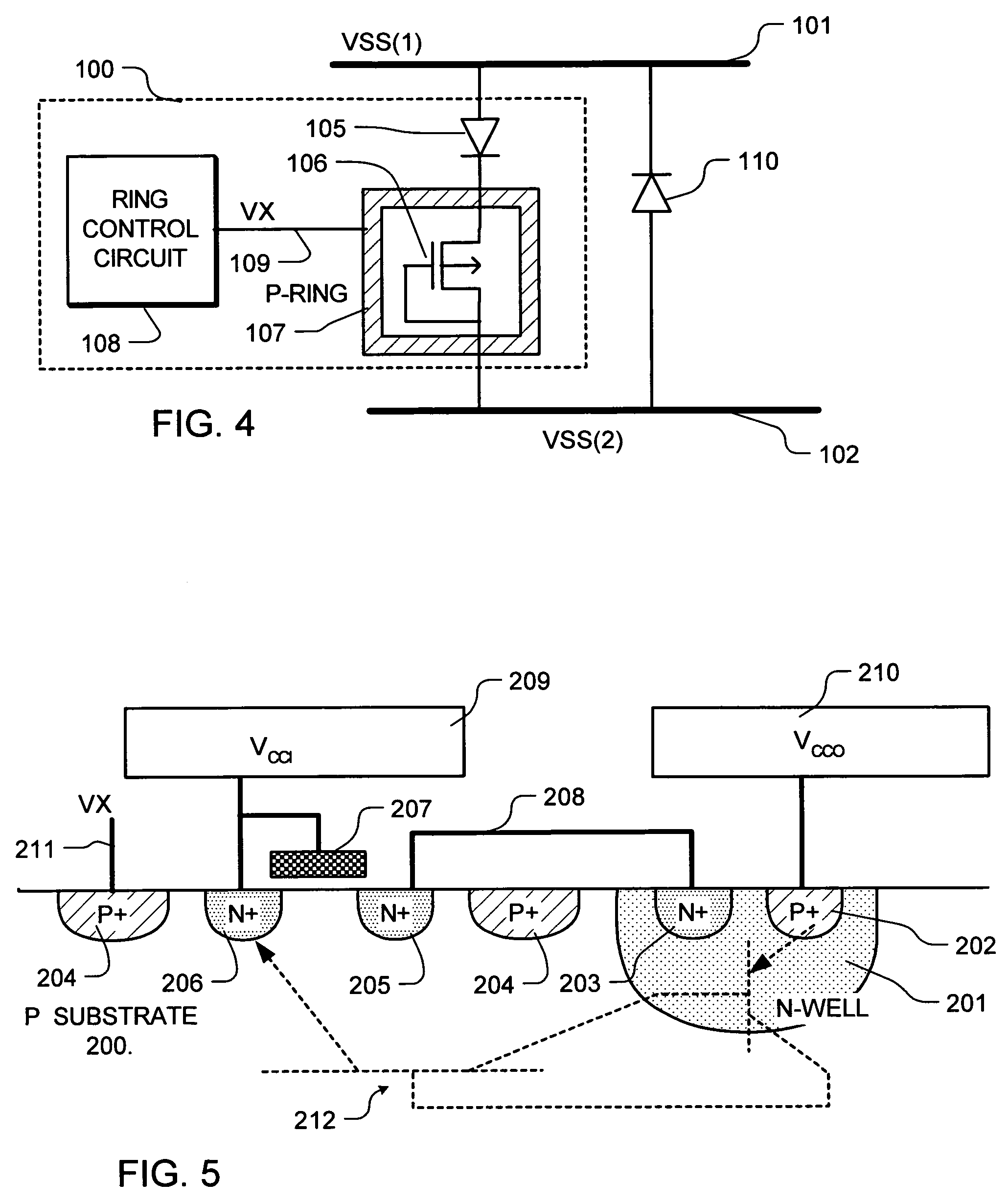

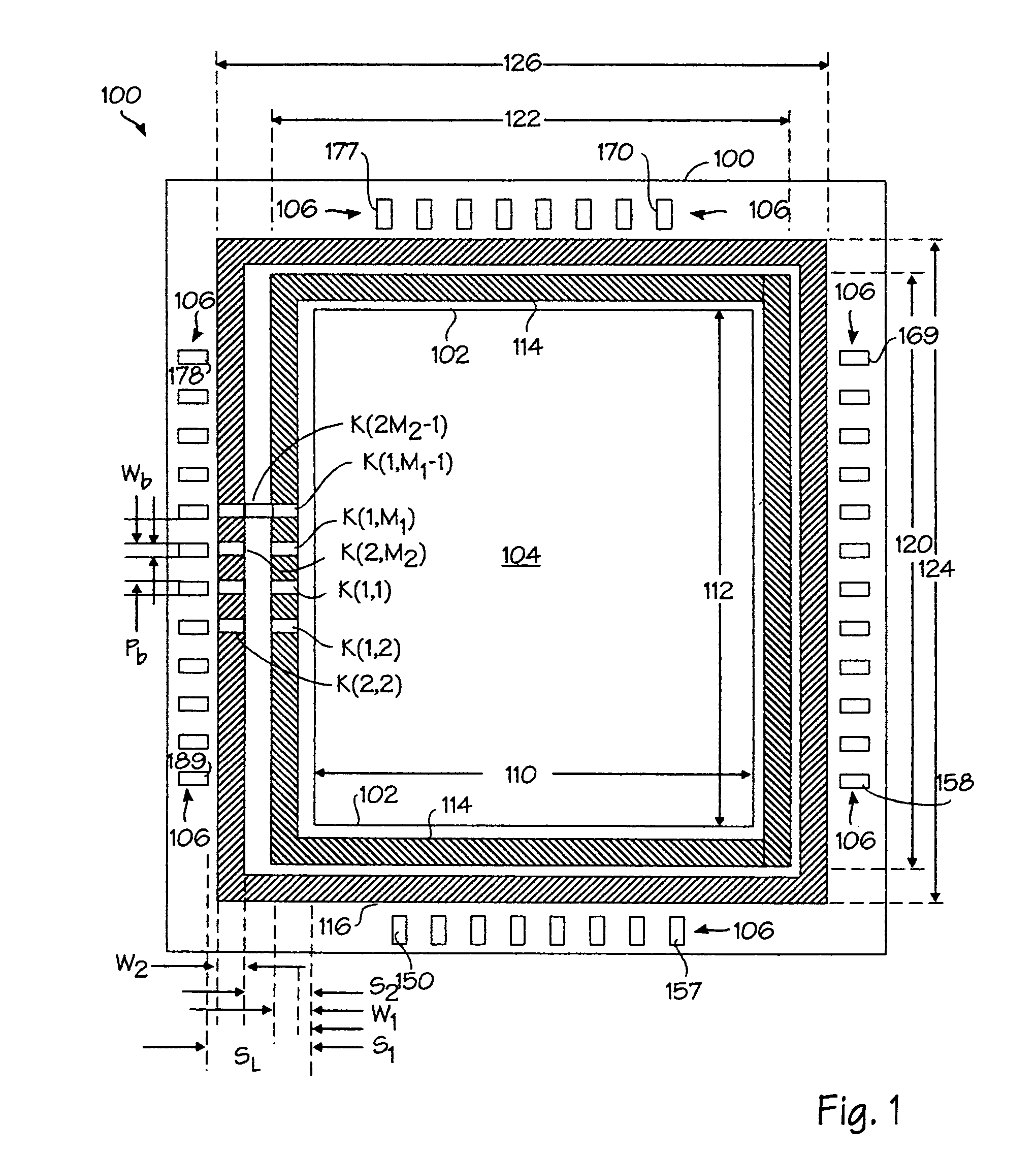

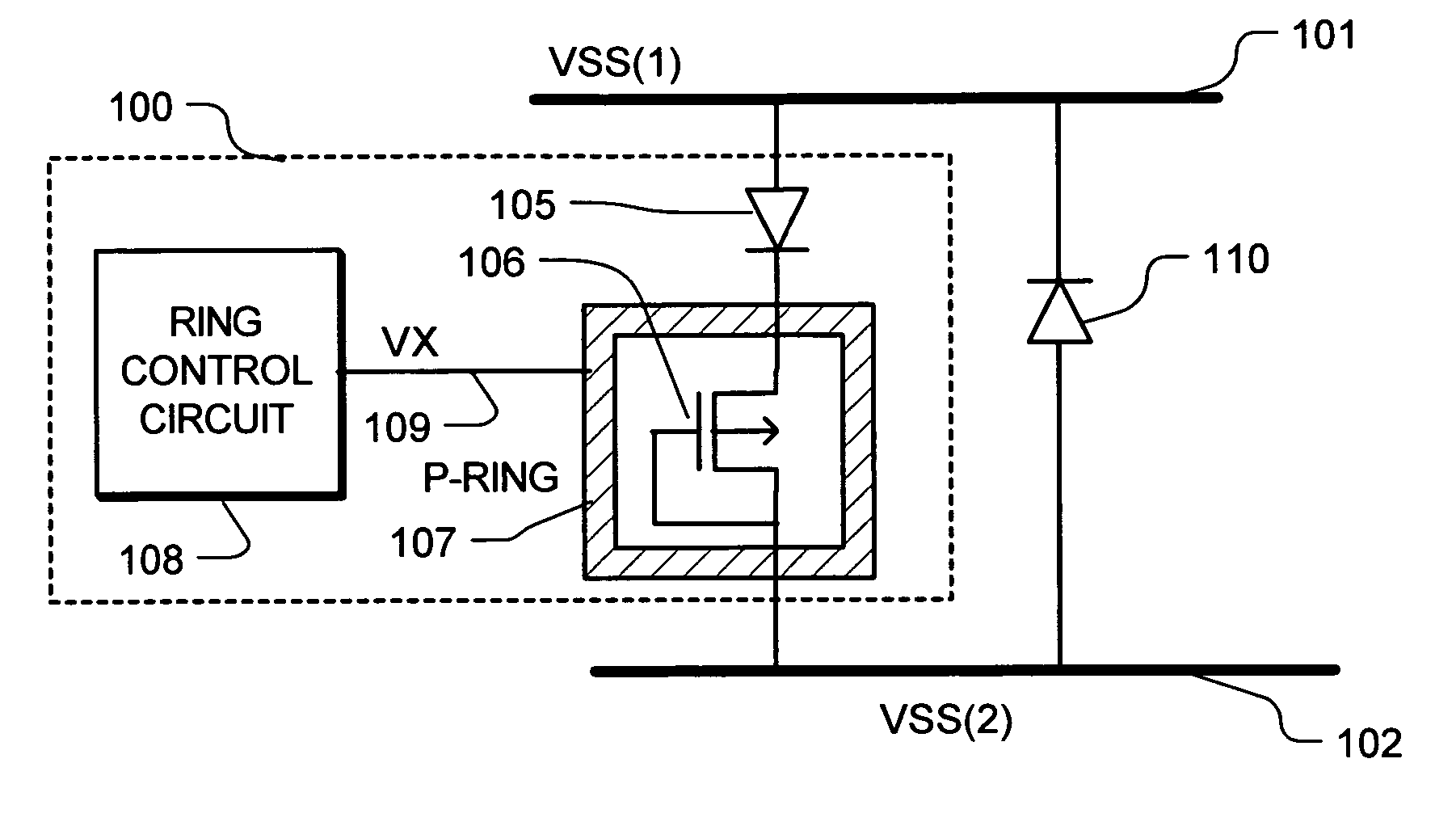

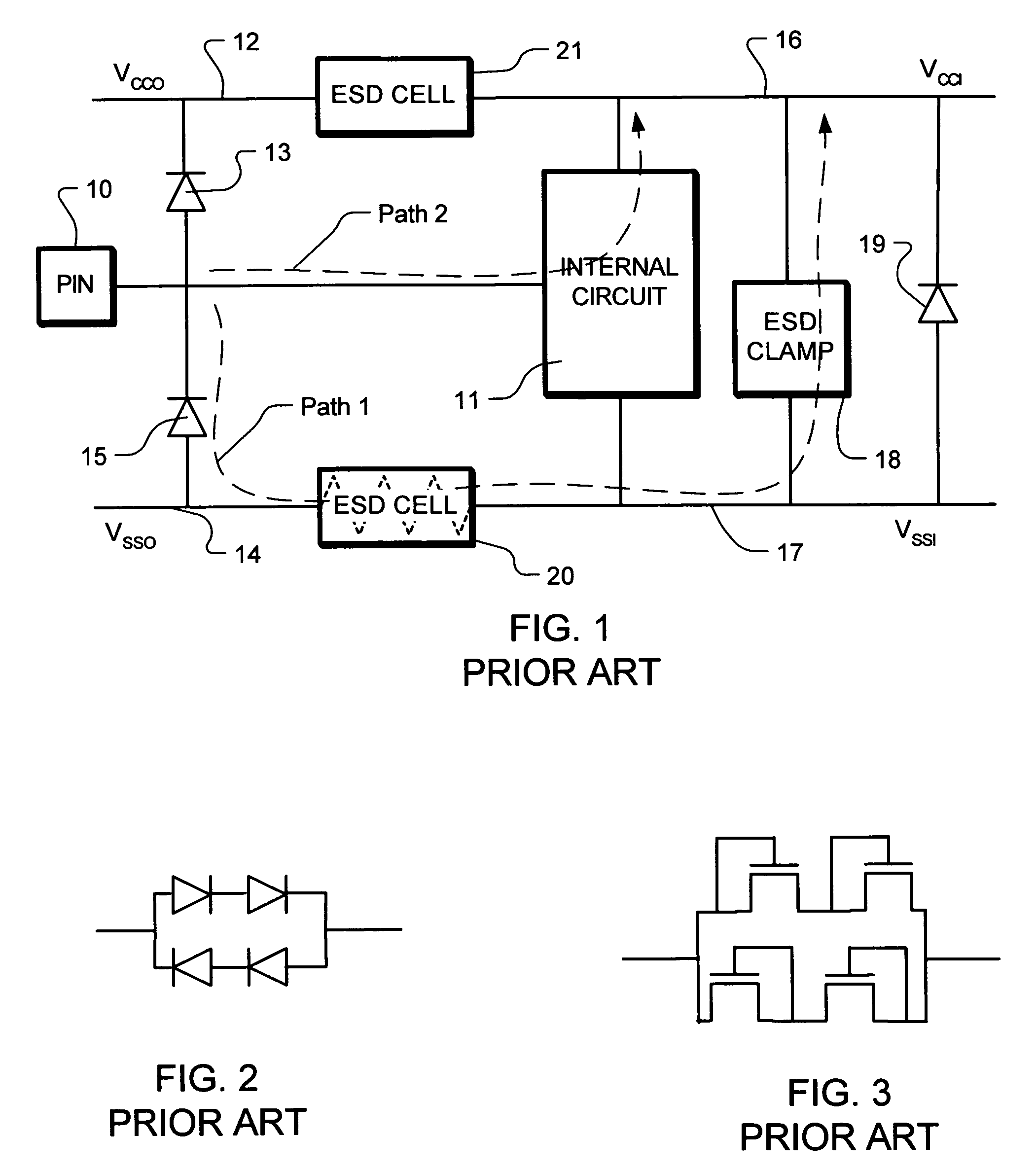

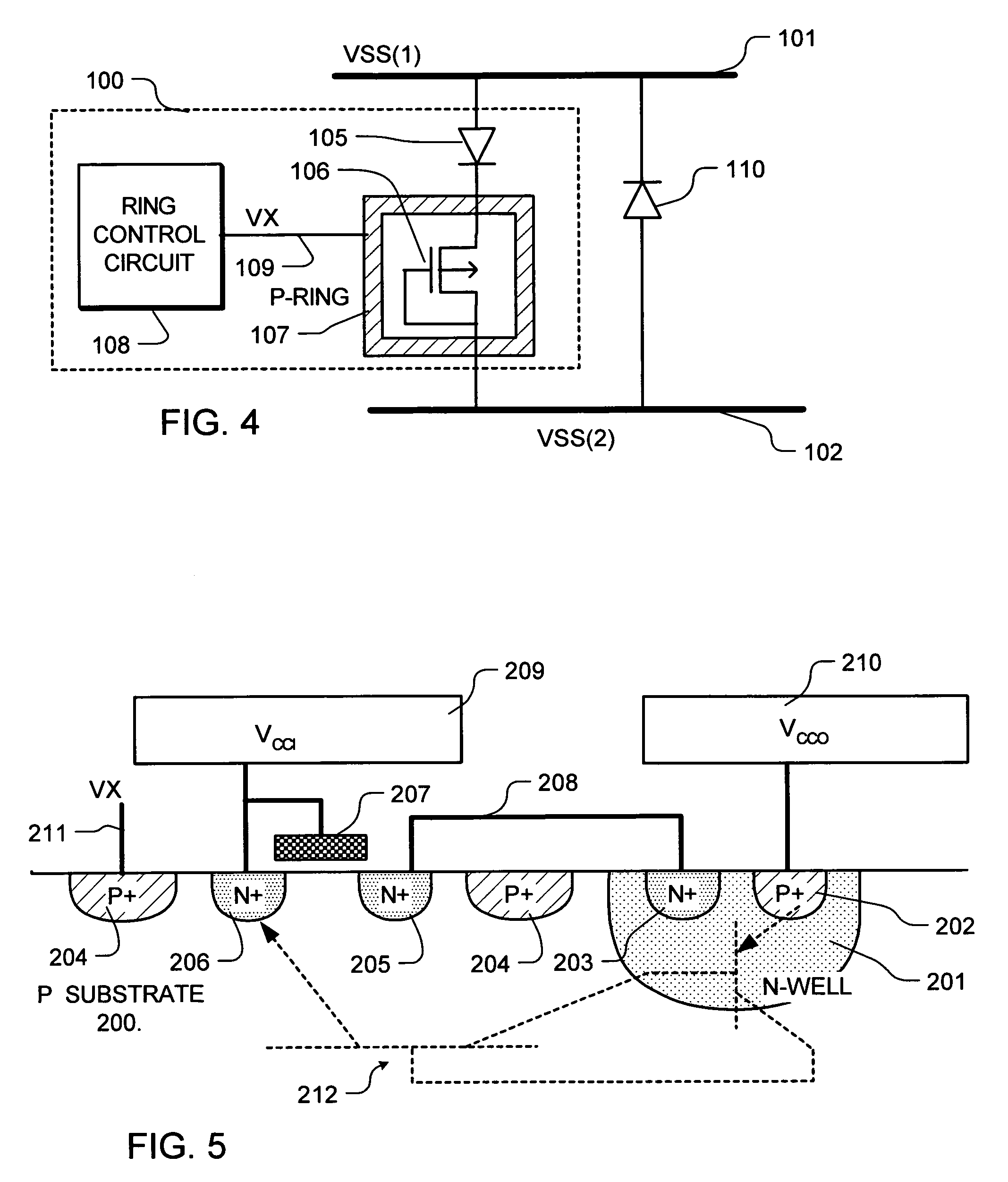

Electrostatic discharge conduction device and mixed power integrated circuits using same

ActiveUS7187527B2Reduce leakage currentEfficient dischargeSolid-state devicesEmergency protective arrangements for limiting excess voltage/currentElectrical conductorVoltage pulse

A device for connection between supply buses in mixed power integrated circuits includes a diode in series with a transistor with an active p-ring in a semiconductor substrate. The active p-ring surrounds the source and drain of the transistor with a conductive region having the same conductivity type as the semiconductor substrate. A control circuit coupled to the p-ring applies a bias voltage in response to an ESD event affecting the first and second conductors. The bias voltage tends to inject carriers into the semiconductor substrate which enables discharge of the short voltage pulse via a parasitic SCR in the substrate from the anode of the diode to the source of the transistor.

Owner:MACRONIX INT CO LTD

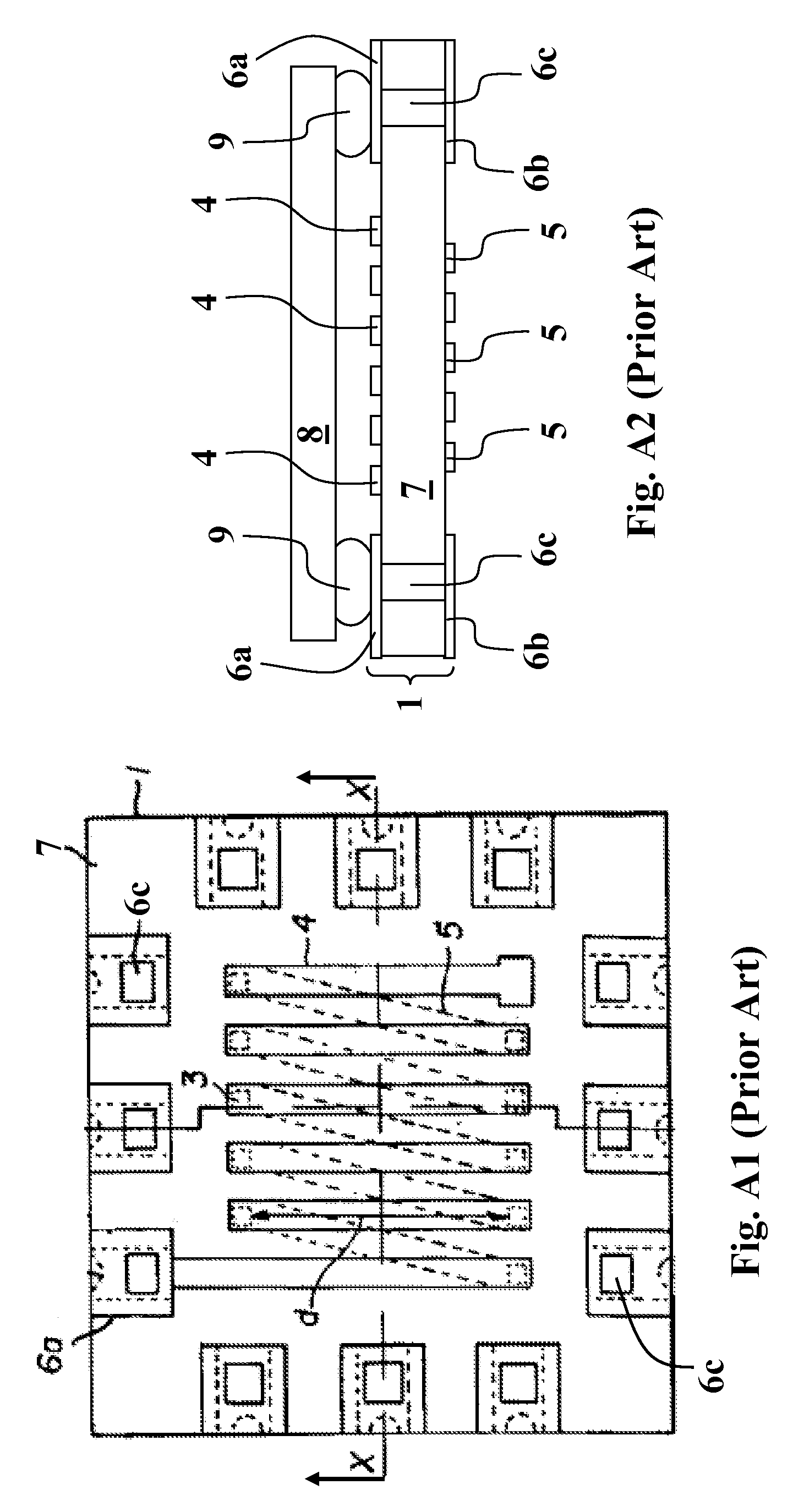

Semiconductor power device package having a lead frame-based integrated inductor

ActiveUS20090134503A1Increase inductanceReduce DC resistanceSemiconductor/solid-state device detailsSolid-state devicesInductorLead frame

A semiconductor power device package having a lead frame-based integrated inductor is disclosed. The semiconductor power device package includes a lead frame having a plurality of leads, a inductor core attached to the lead frame such that a plurality of lead ends are exposed through a window formed in the inductor core, a plurality of bonding wires, ones of the plurality of bonding wires coupling each of the plurality of lead ends to adjacent leads about the inductor core to form the inductor, and a power integrated circuit coupled to the inductor. In alternative embodiments, a top lead frame couples each of the plurality of lead ends to adjacent leads about the inductor core by means of a connection chip.

Owner:ALPHA & OMEGA SEMICON INC

Compact Inductive Power Electronics Package

ActiveUS20090167477A1Save package foot printSemiconductor/solid-state device detailsSolid-state devicesEngineeringInductor

An inductive power electronics package is disclosed. It has a circuit substrate with power inductor attached atop. The power inductor has inductor core of closed magnetic loop with an interior window. The closed magnetic loop can include air gap for inductance adjustment. The circuit substrate has bottom half-coil forming elements constituting a bottom half-coil beneath the inductor core. Also provided are top half-coil forming elements interconnected with the bottom half-coil forming elements to form an inductive coil enclosing the inductor core. An inner connection chip can be added in the interior window for interconnecting bottom half-coil forming elements with top half-coil forming elements. An outer connection chip can be added about the inductor core for interconnecting bottom half-coil forming elements with top half-coil forming elements outside the inductor core. A power Integrated Circuit can be attached to the top side of the circuit substrate as well.

Owner:ALPHA & OMEGA SEMICON INC

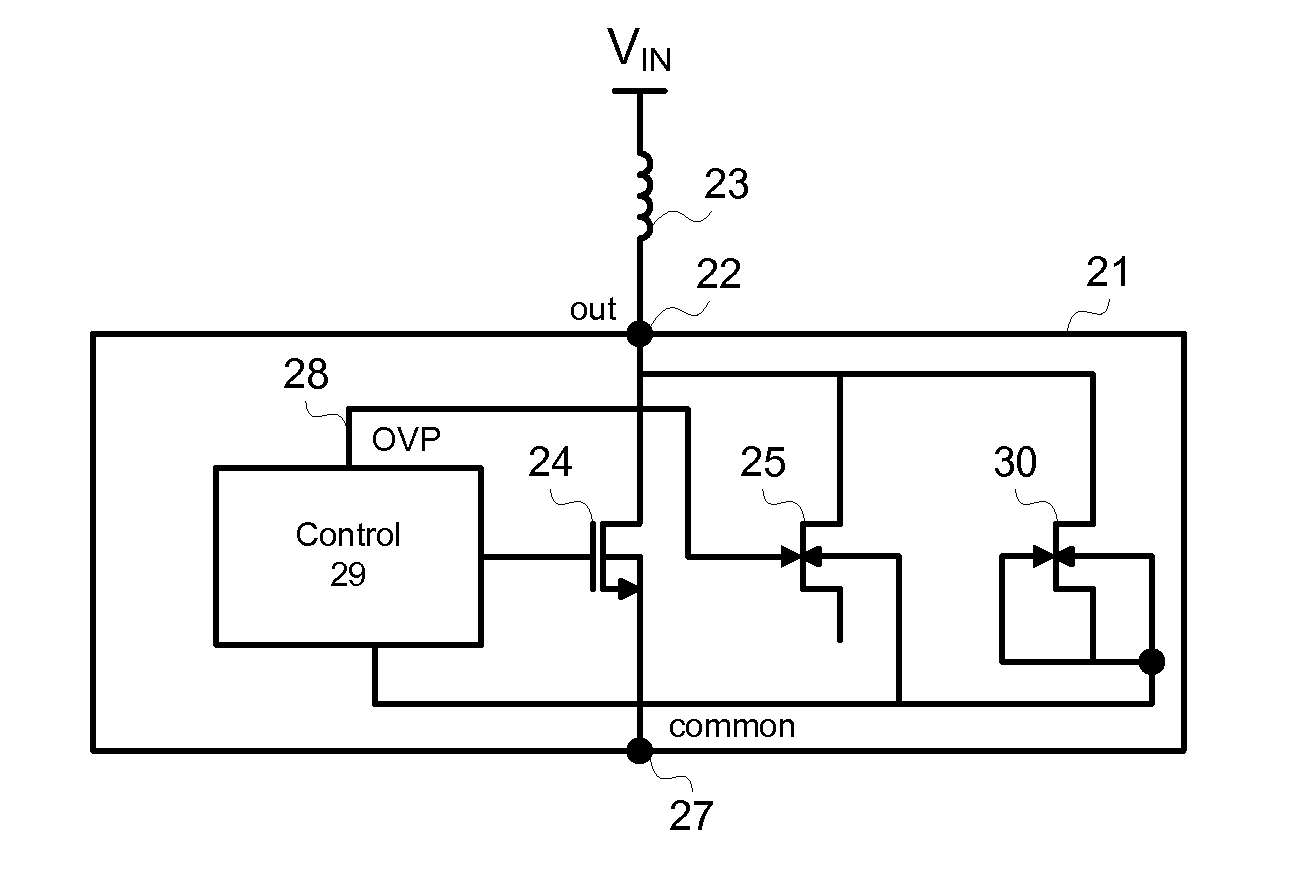

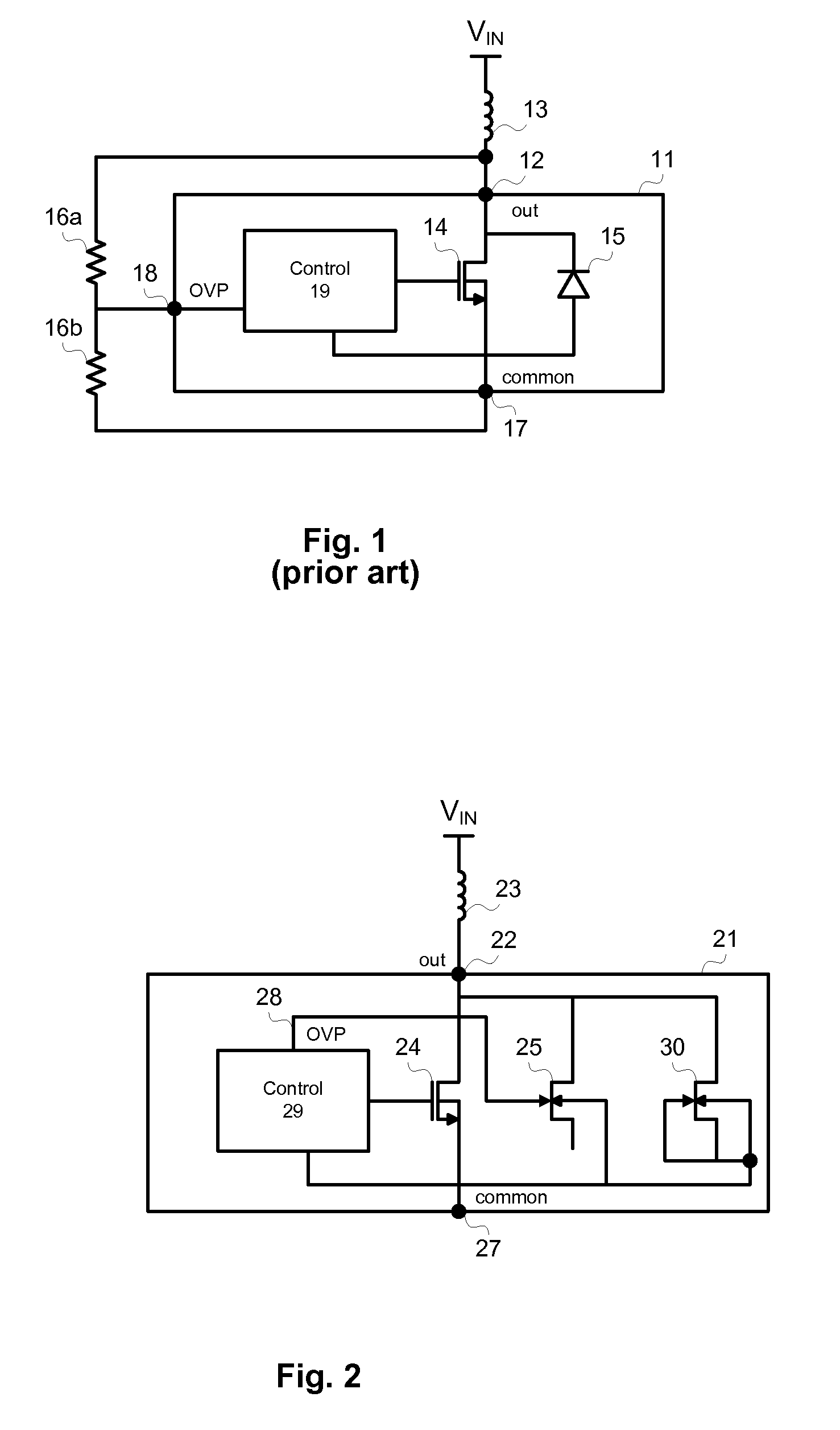

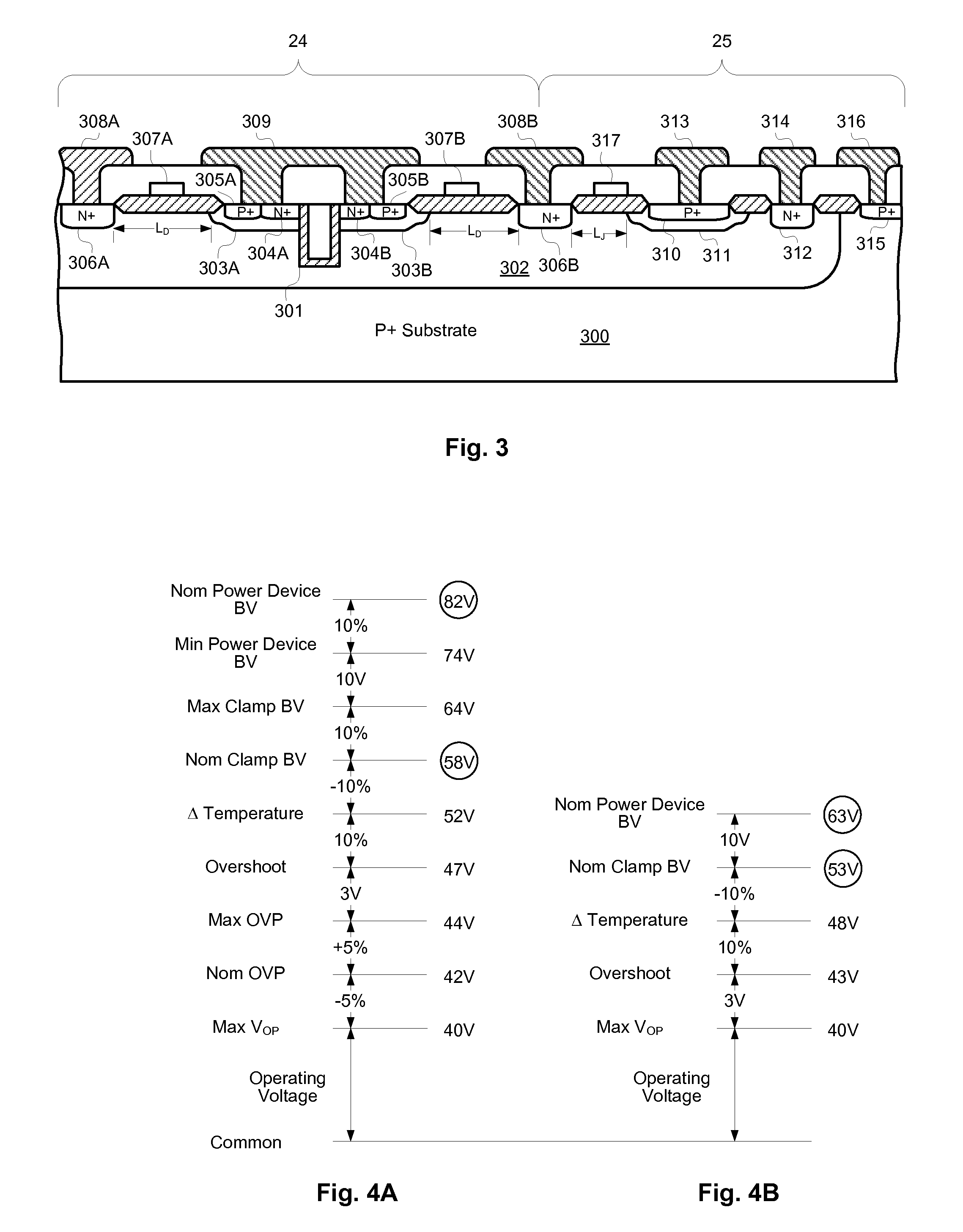

Method and Apparatus for Over-voltage Protection With Breakdown-Voltage Tracking Sense Element

InactiveUS20100232081A1Improve breakdown voltageProtection from damageTransistorSemiconductor/solid-state device manufacturingControl circuitPower integrated circuits

A power integrated circuit with internal over-voltage protection includes a power transistor monolithically integrated with a sense element and a control circuit. The power transistor is connected to an output terminal that is connected (or is connectable) to an external load. The sense element is connected to the output terminal in parallel with the power transistor. The sense element is constructed to be similar to the power transistor except that the sense element has a lower breakdown voltage. When the voltage of the output terminal exceeds the breakdown voltage of the sense element a breakdown current flows from the gate of the sense element to the control circuit. Inside the control circuit, a comparator or other over-voltage protection circuit monitors this feedback and controls the power transistor accordingly to protect the power integrated circuit from damage.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

BCD device and manufacturing method thereof

InactiveCN101771039ALower specific on-resistanceLower on-resistanceSolid-state devicesSemiconductor/solid-state device manufacturingLow voltageEngineering

The invention discloses a BCD device and a manufacturing method thereof, which belong to the technical field of semiconductor power devices. In the invention, semiconductor devices such as a high-voltage nLIGBT, three high-voltage nLDMOSs, a low-voltage NMOS, a low-voltage PMOS, a low-voltage NPN and the like are synchronously integrated on the same chip, wherein the high-voltage nLIGBT, the high-voltage nLDMOSs and the low-voltage NPN are directly arranged on a single-crystal p-type substrate; the low-voltage NMOS is arranged in a p-type well; and the low-voltage PMOS is arranged in an n-type epitaxial layer. As p-type reduced-field layers are respectively arranged between the n-type epitaxial layer and an n-type shift region well, the n-type epitaxial layer on a p-type buried layer supplies an extra surface conducting channel to high-voltage devices, the conducting channel is increased, the specific on resistance of the high-voltage devices is reduced, and the manufacturing cost of the chip is further reduced. The nLIGBT device and the nLDMOS devices of the invention further have the characteristics of high input impedance, low output impedance and the like, and a high-voltage power integrated circuit formed by the nLIGBT device and the nLDMOS devices can be used in a plurality of products, such as consumer electronics, display drivers and the like.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

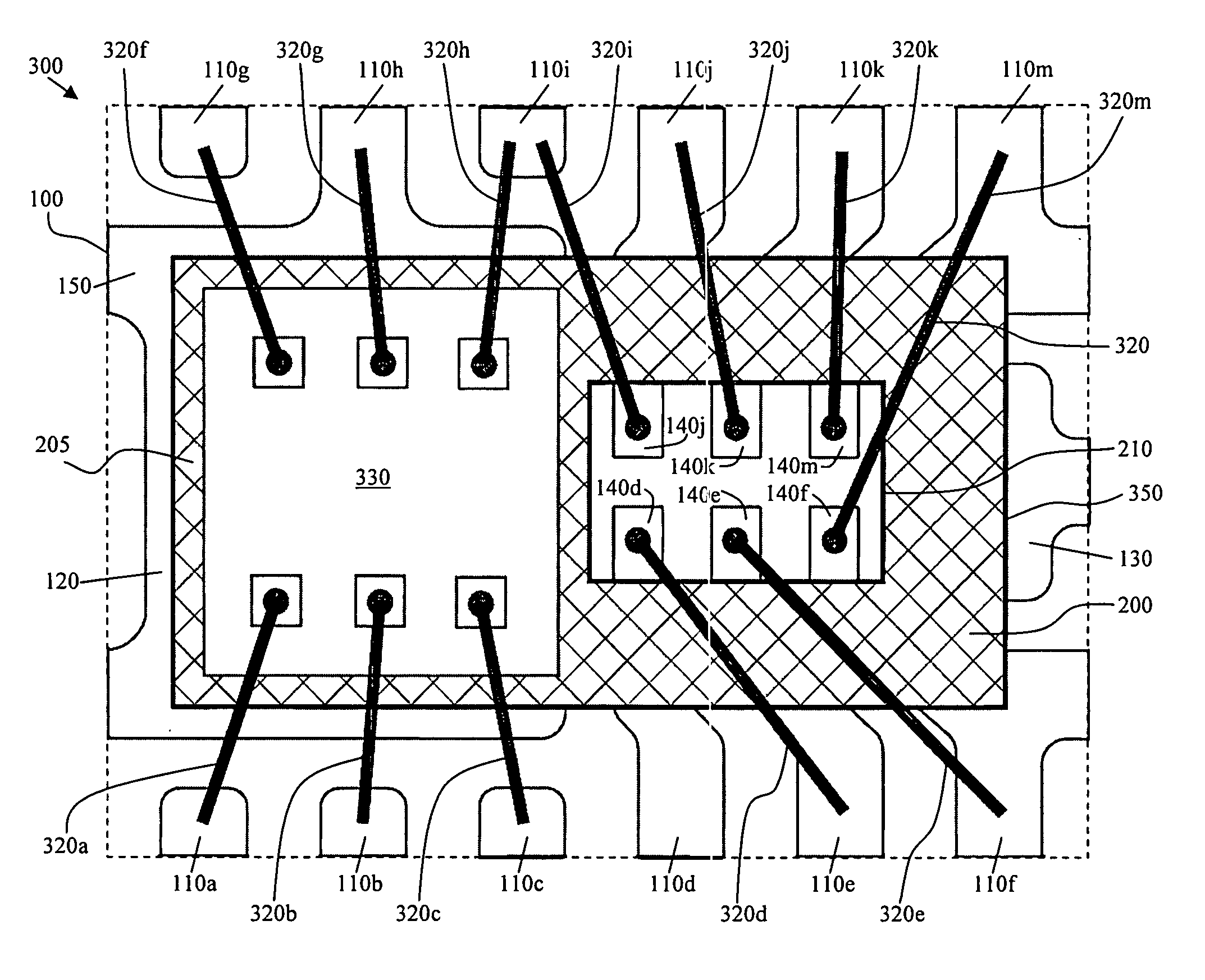

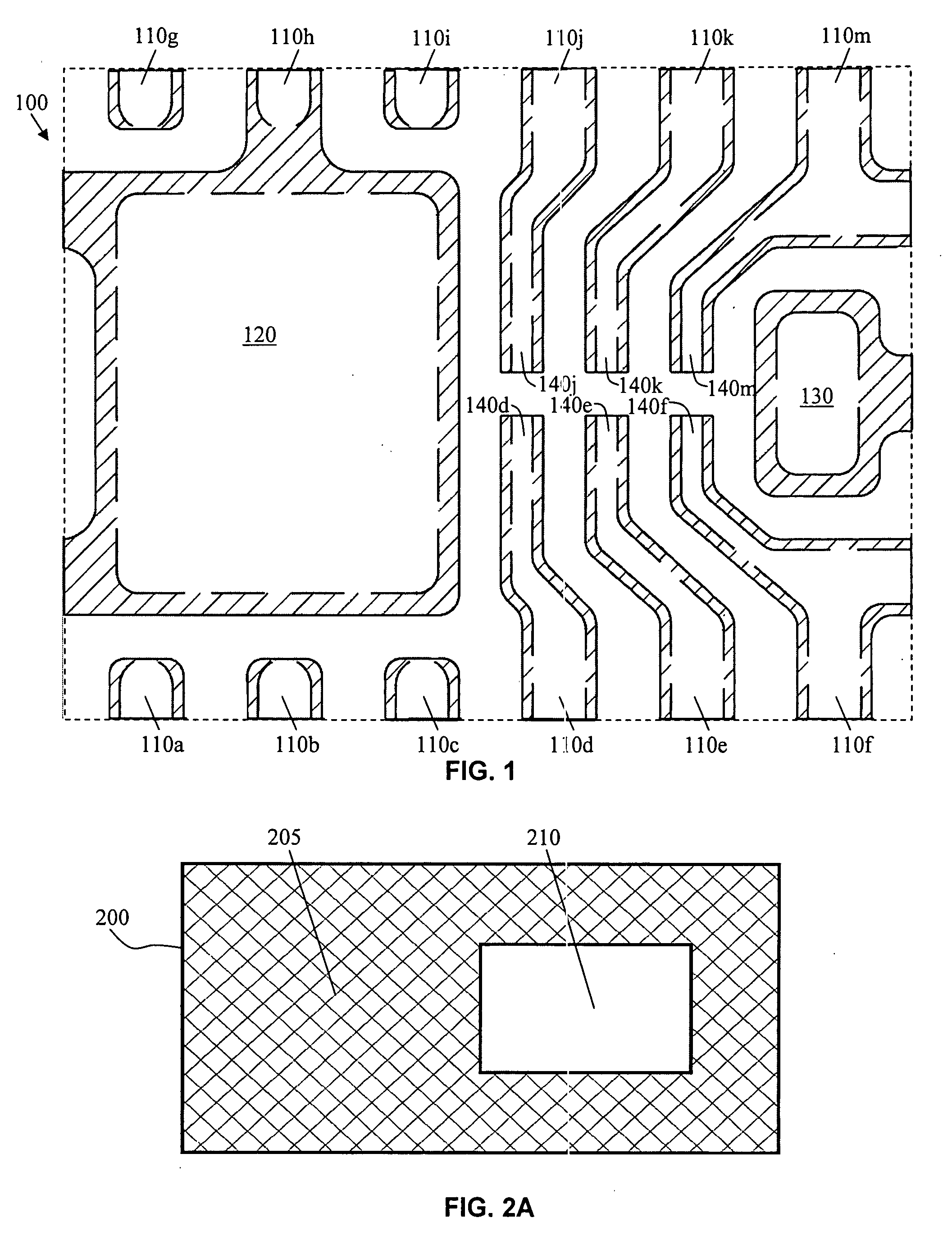

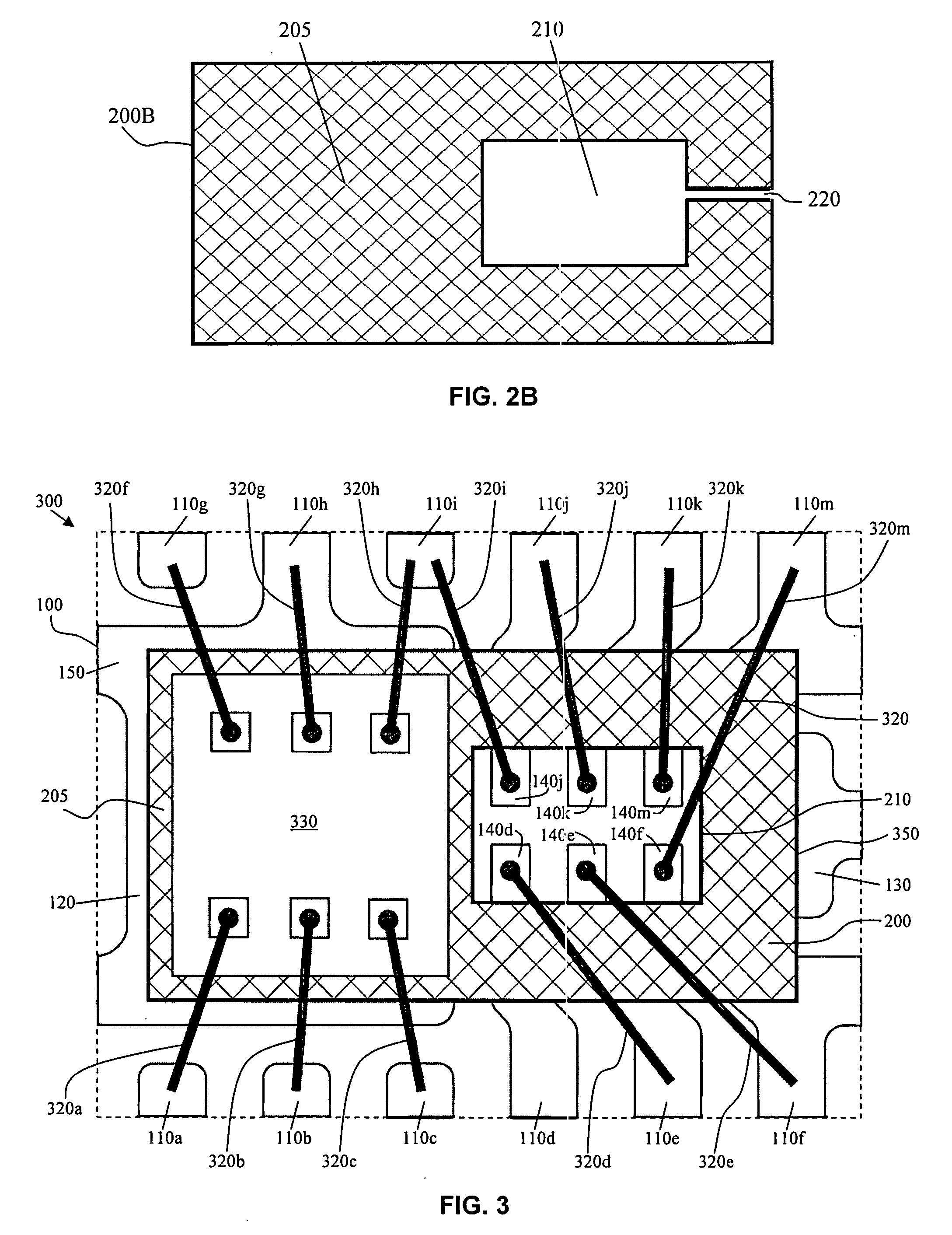

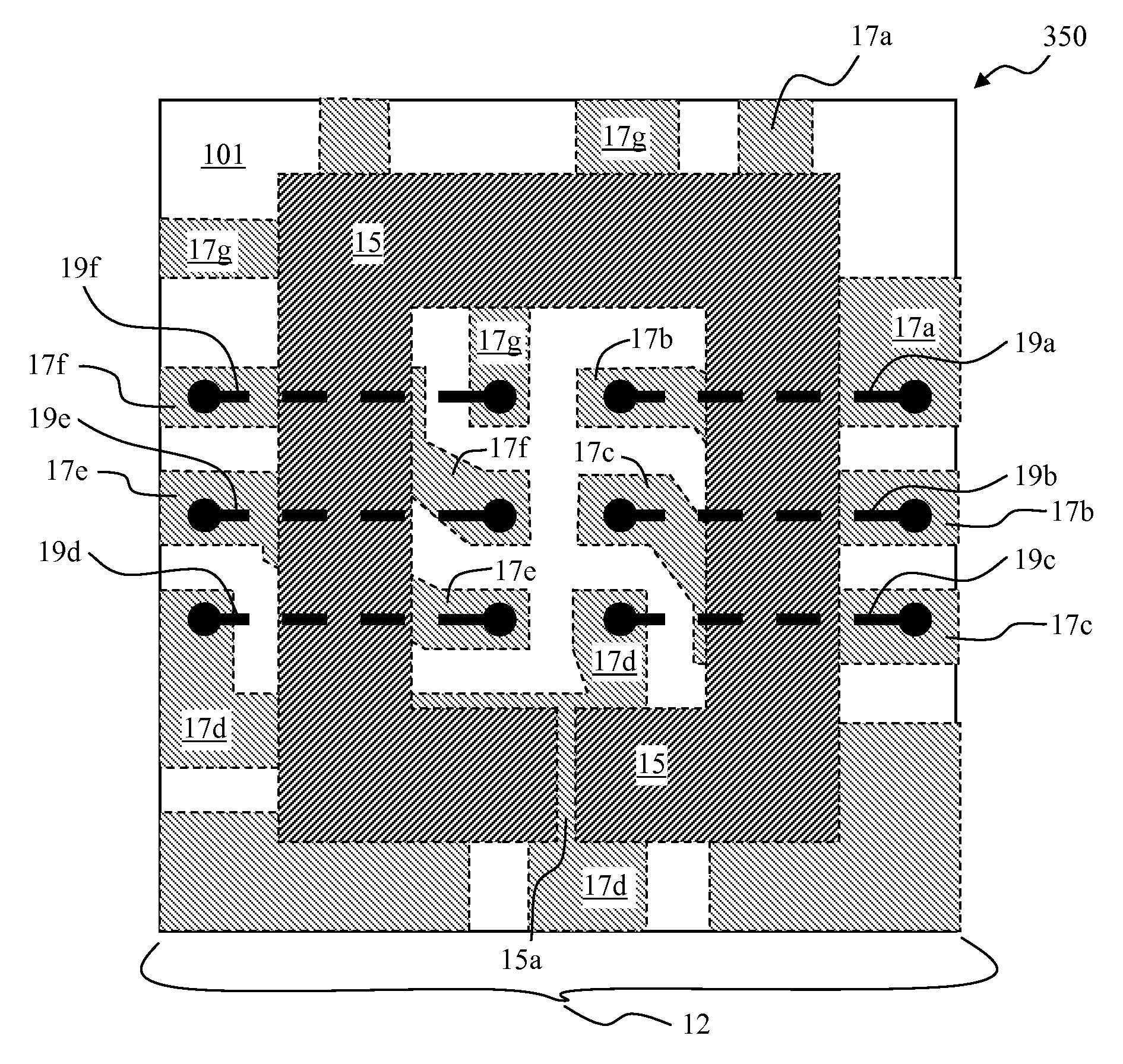

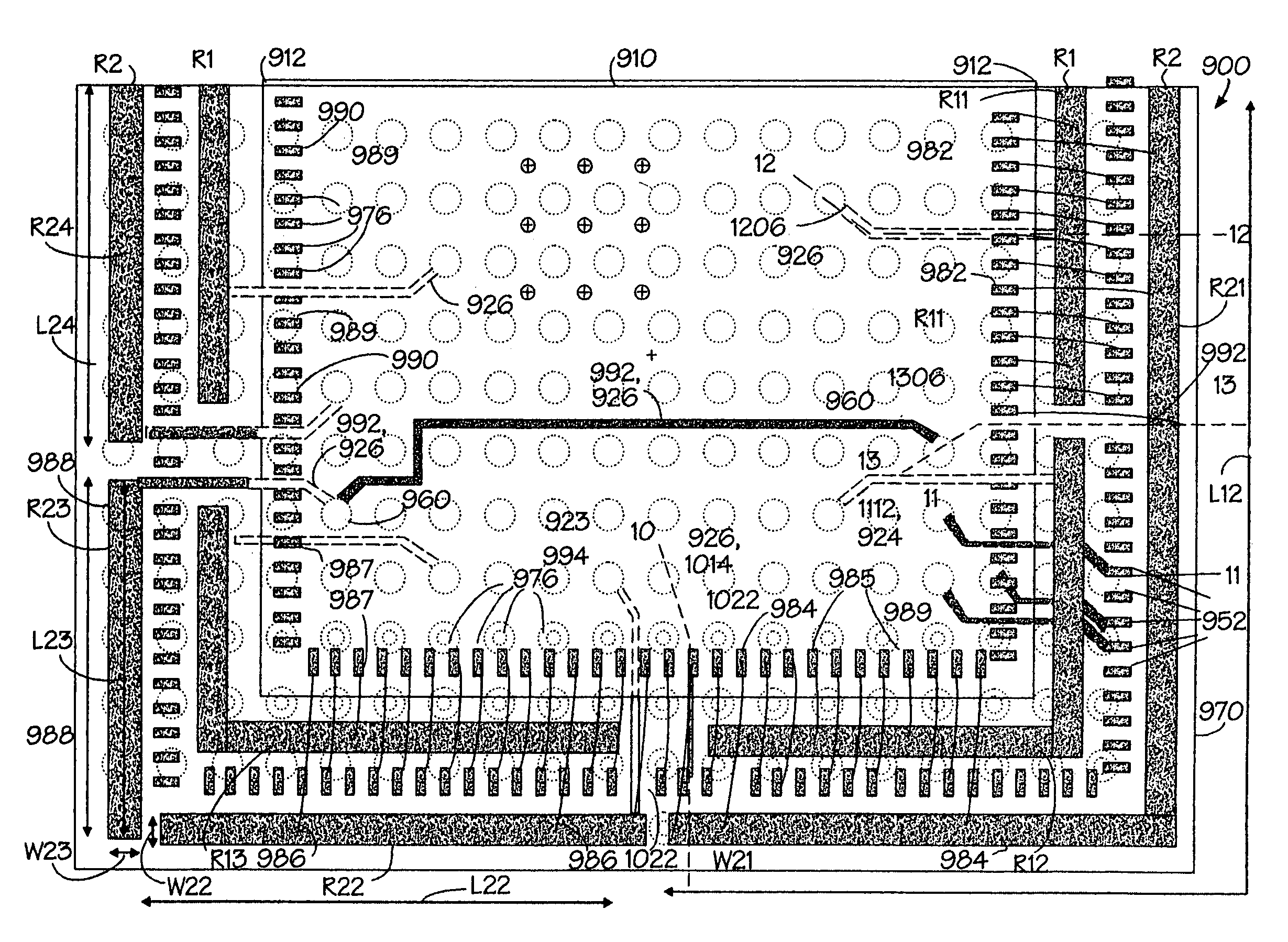

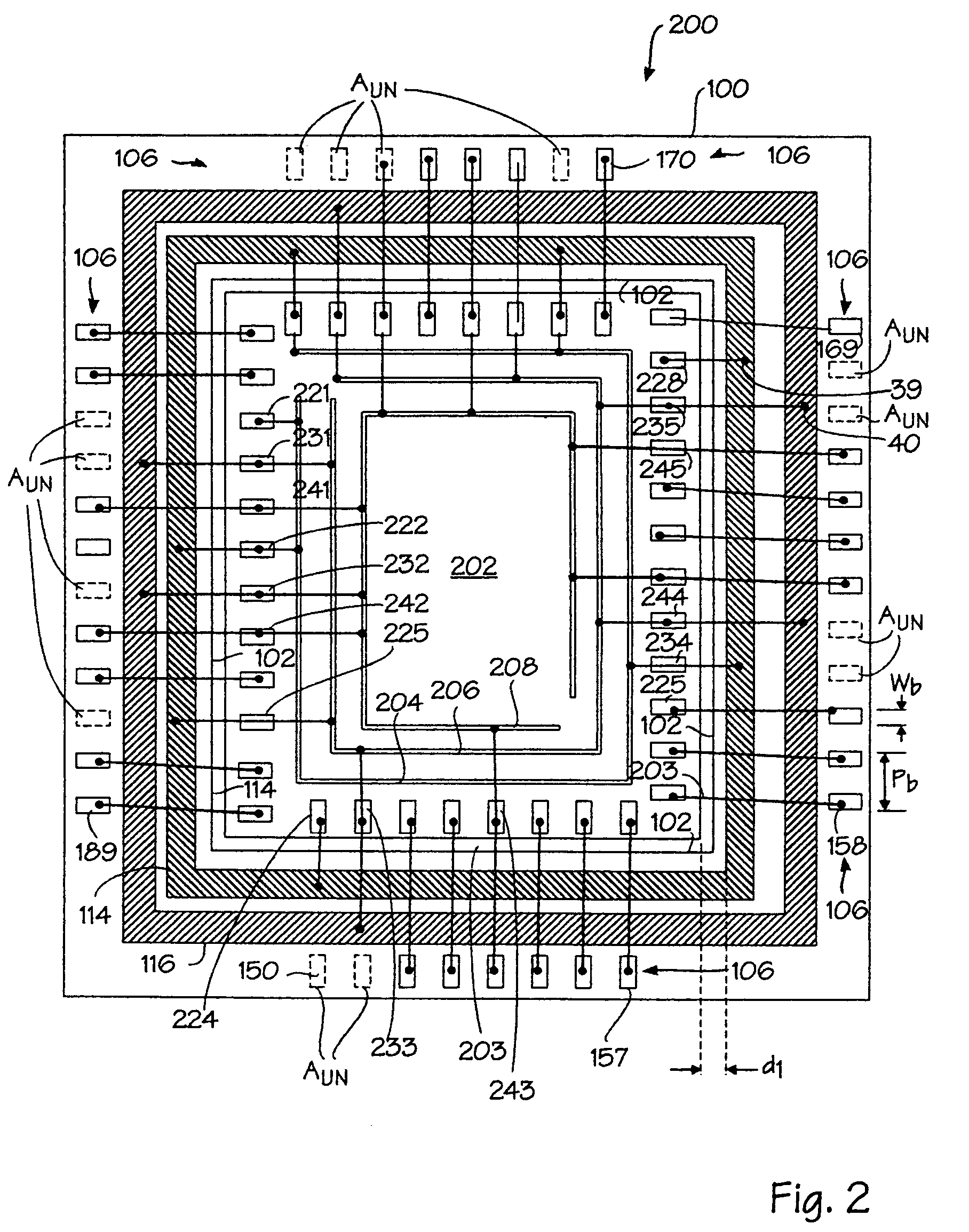

Multi-power ring chip scale package for system level integration

InactiveUS7129574B2Semiconductor/solid-state device detailsSolid-state devicesEngineeringDie bonding

A scalable multi-power integrated circuit package for integrated circuits having spaced apart first, second and third pluralities of respective spaced apart chip power bonding pads connected to-corresponding first, second, and third chip power supply nets, the chip power bonding pads disposed adjacent to a chip periphery defining the chip area, the scalable multi-power integrated circuit package comprising: a central chip mounting area for mounting one of said integrated circuits, said chip mounting area defining a chip mounting area periphery surrounding said chip mounting area; spaced apart first, second and third package power supply continuous conductive traces, each trace disposed adjacent to the chip area mounting periphery; corresponding first, second and third pluralities of spaced apart package bonding areas defined along each respective one of said first, second and third package power supply continuous conductive traces, each respective one of said package bonding areas disposed in bondable alignment with a corresponding one of said chip power bonding pads along said chip periphery such that a permanent conductive bond can be made between said package bonding area and said chip bonding pad. Alternatives include a chip scale package outline, in which one of the chip power supply nets is a common ground return for the other two power supply nets.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

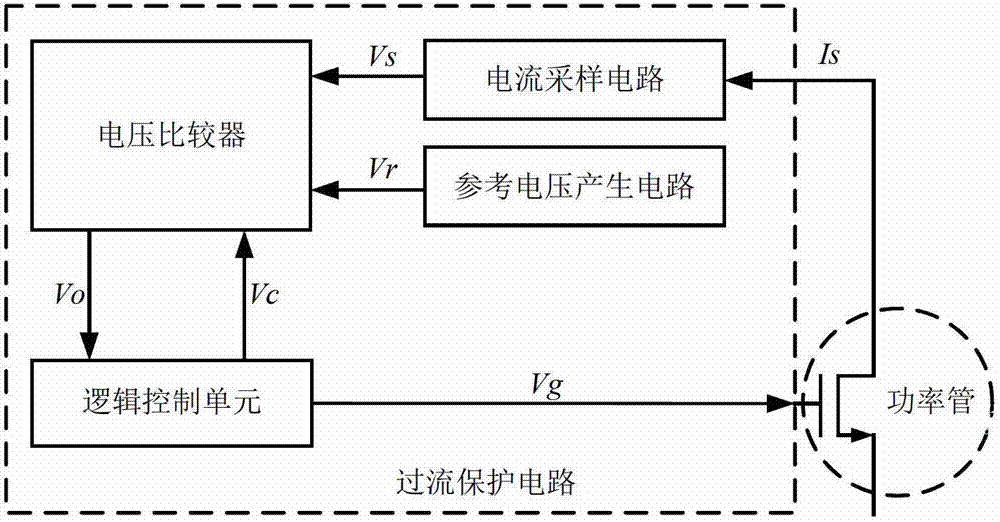

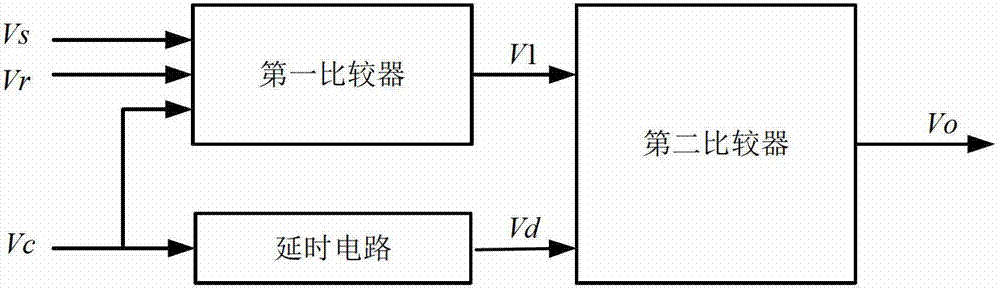

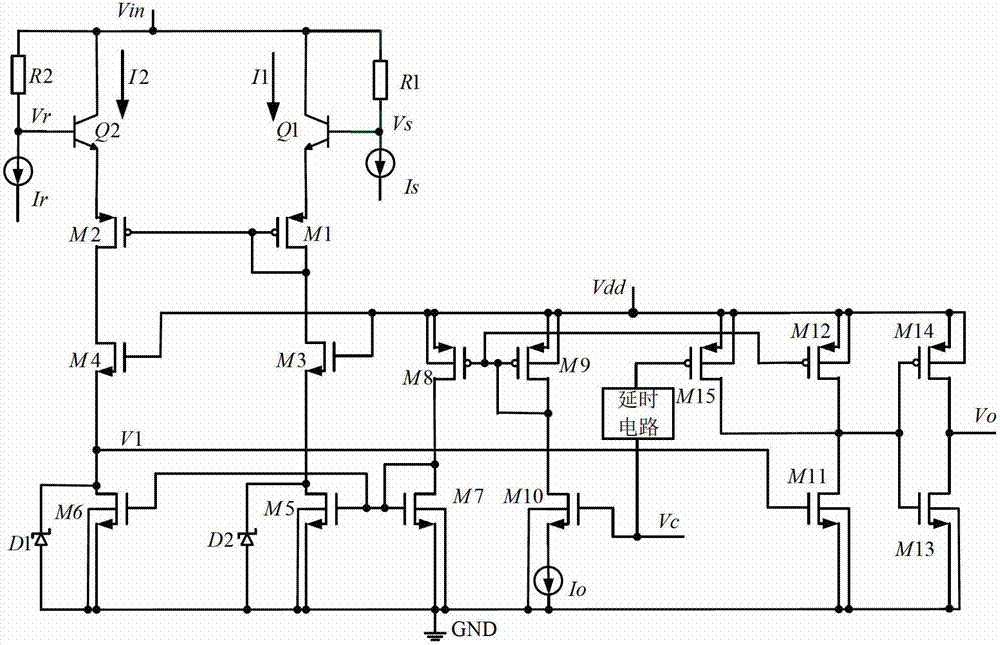

Over-current protection circuit

InactiveCN102832599AWith delay processing abilityAvoid influenceEmergency protective circuit arrangementsControl signalPeak current

The invention relates to the technology of power integrated circuit design and discloses an over-current protection circuit aiming at the shortcoming that an over-current protection circuit is susceptible to power tube peak current interference and unreliable in acquired data in the prior art. The over-current protection circuit mainly comprises a current sampling circuit, a reference voltage generation circuit, a voltage comparator and a logic control unit. Current flowing through a power tube is compared with set reference signals to generate over-current information, and control signals are outputted to control the power tube by means of delay. Since the voltage comparator has delayed processing capacity, influences of peak current can be avoided, reliability of over-current acquired data is improved, and misoperations are avoided. The over-current protection circuit is particularly suitable for integrated circuit products of high-voltage heavy-current power management chips, DC-DC converters and the like.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Trench-type insulated gate bipolar transistor (Trench IGBT) with enhanced internal conductivity modulation

InactiveCN102201439AReduce forward voltage dropImprove concentration distributionSemiconductor devicesTrench igbtParasitic bipolar transistor

The invention relates to a Trench IGBT with enhanced internal conductivity, belonging to the technical field of power semiconductor device. According to the invention, on the basis of the structure of the conventional Trench IGBT device, a dielectric layer is introduced between a P<-> base region and an N<-> drift region of the device so as to effectively prevent the P<-> base region from extracting minority carrier holes at the edge of the N<-> drift region during forward conduction, thereby greatly increasing electrons and hole density of the whole N<-> drift region, optimizing the density distribution of carriers in the drift region, enhancing the conductivity modulation in the device, lowering the forward conduction voltage drop of the device, and better compromising the forward conduction voltage drop and the turn-off loss. Meanwhile, the chip surface utilization rate is not reduced and the chip area is saved. The Trench IGBT is suitable for the field of semiconductor power devices and power integrated circuits from small power to large power.

Owner:INST OF ELECTRONICS & INFORMATION ENG IN

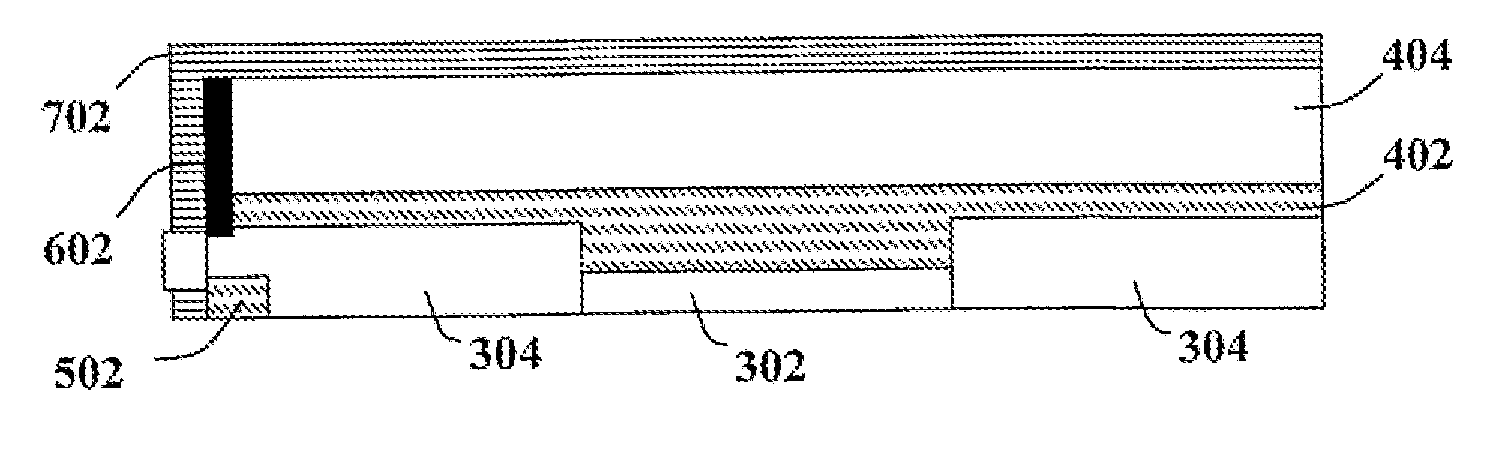

Integrated solar powered device

ActiveUS20110169554A1Solid-state devicesConductive pattern formationEngineeringPower integrated circuits

A system and method for fabricating a self-powering integrated circuit chip having an integrated circuit, which may be a MEMS or CMOS device or the like and a thin film photovoltaic cell stack overlayed thereupon or on the opposite side of the substrate on which the IC is manufactured upon.

Owner:SOL CHIP

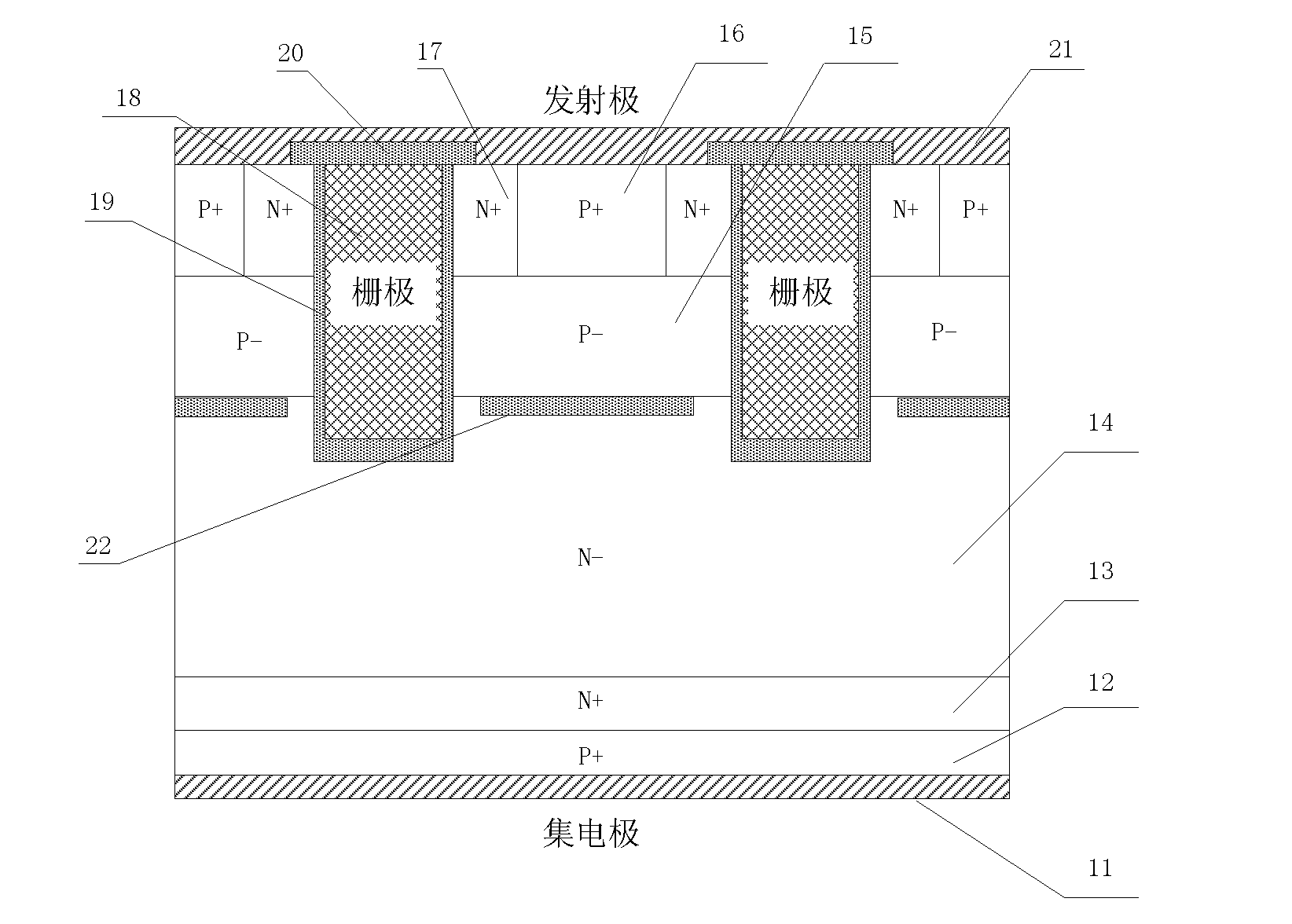

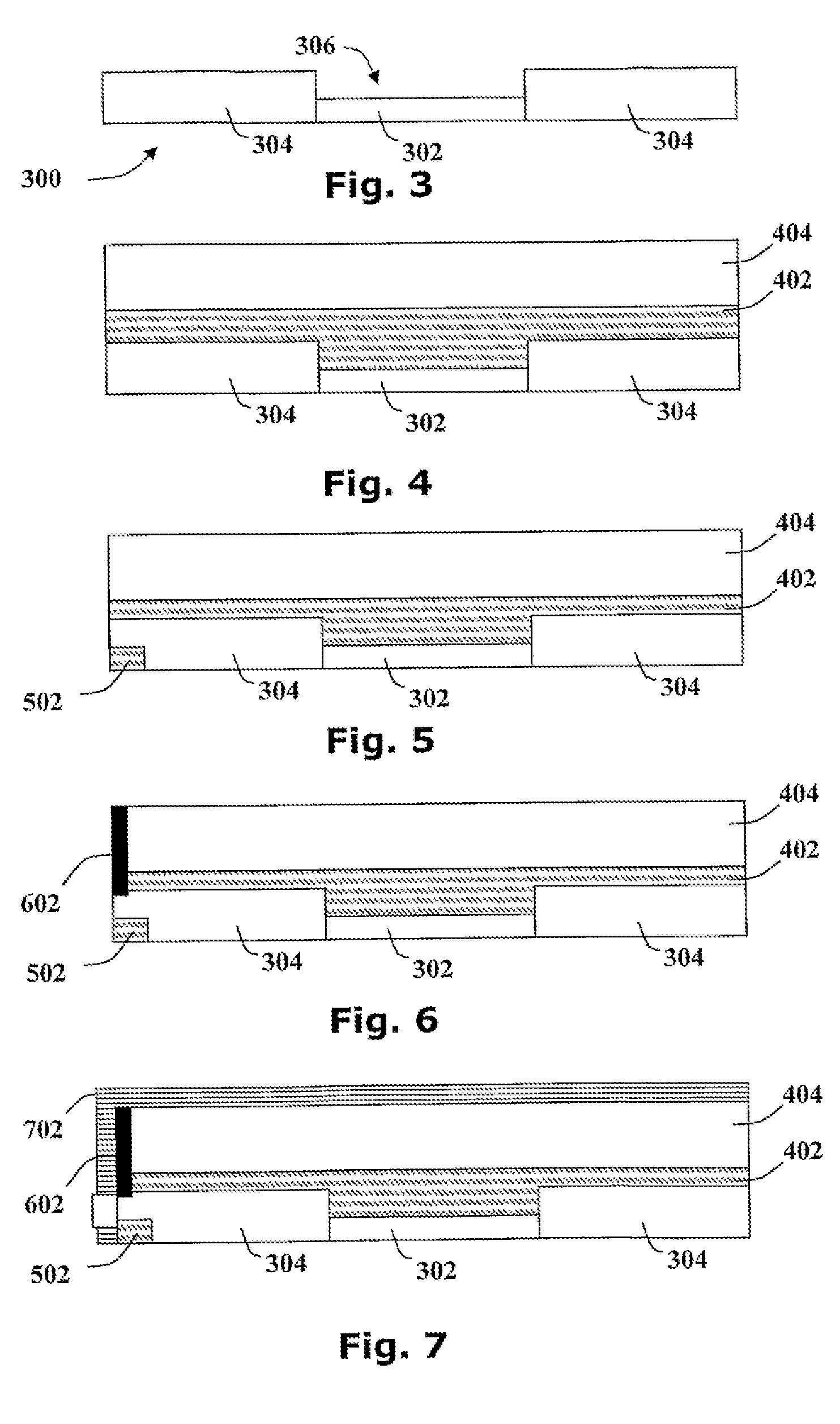

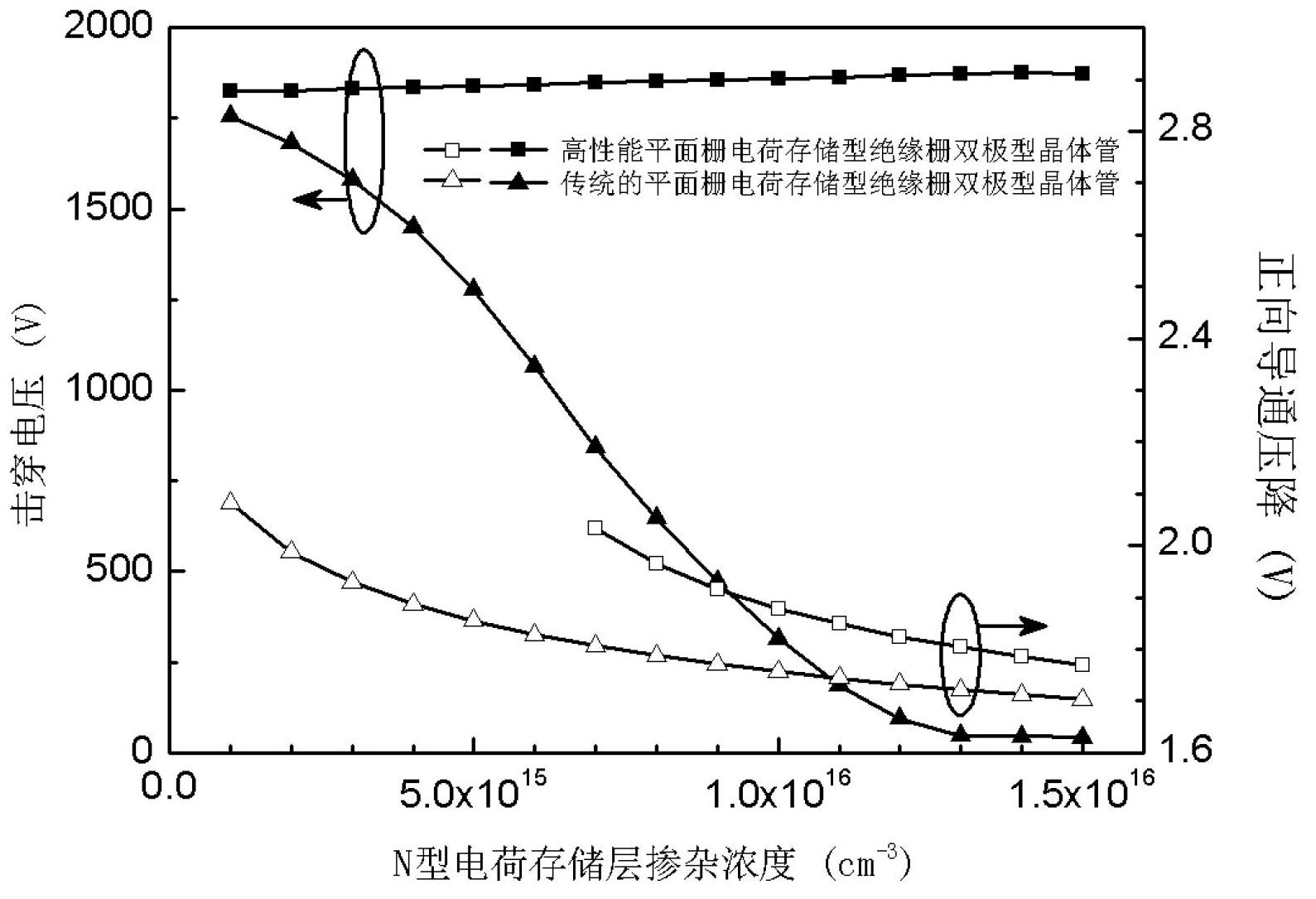

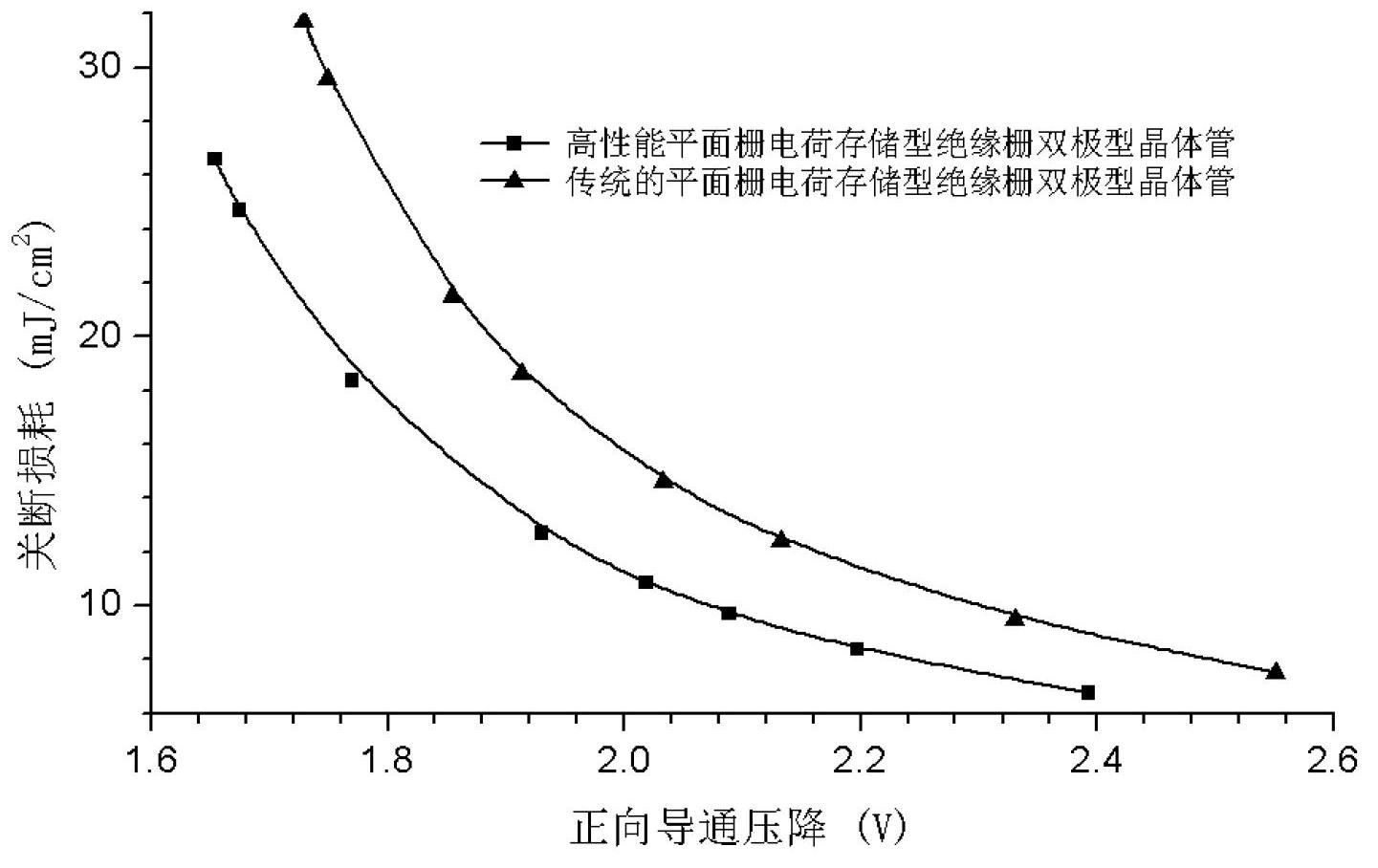

Flat-grid electric charge storage type IGBT (insulated gate bipolar translator)

InactiveCN102683402AImprove breakdown voltageGood forward voltage dropSemiconductor devicesConductivity modulationBreakdown voltage

The invention provides a flat-grid electric charge storage type IGBT (insulated gate bipolar translator), belonging to the technical field of a power semiconductor device. On the basis of the conventional flat-grid electric charge storage type IGBT, a layer of P type buried layer is induced between an N type drift region and an N type electric charge storage layer; due to the electric field modulating action of an additive PN (positive / negative) junction and the electric charge induced into the P type buried layer, the adverse impact of a highly-doped N type electric charge storage layer to the device is screened, so that the device can obtain high puncture voltage; and due to the electric field screening action of the P type buried layer to the N type electric charge storage layer, the IGBT can adopt higher N type electric charge storage layer doping concentration, so that the conductivity modulation of the N type drift region of the device can be enhanced, and the carrier distribution in the N type drift region can be optimized, and therefore, the device is lower in forward conductivity voltage drop and relatively good in compromises between the forward conductivity voltage drop and the turn-off loss. The IGBT is applicable to the filed of the semiconductor device and a power integrated circuit from small power to high power.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

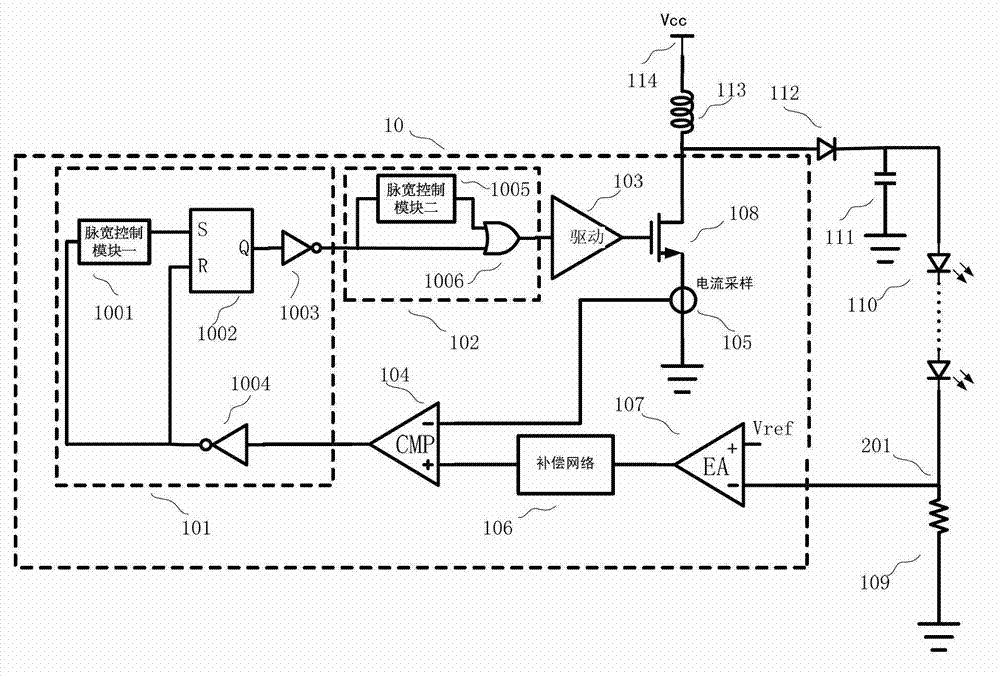

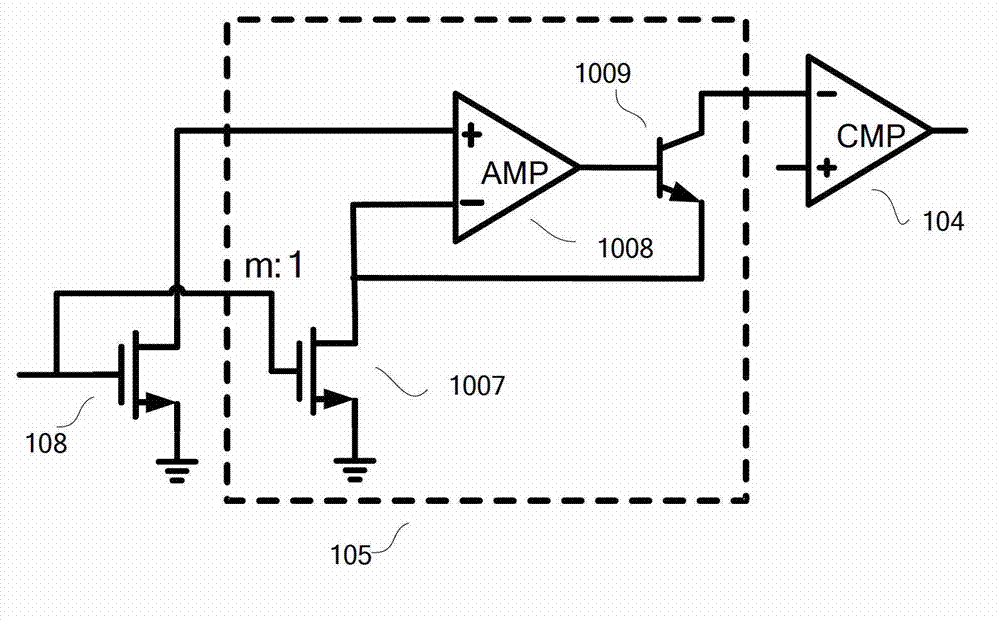

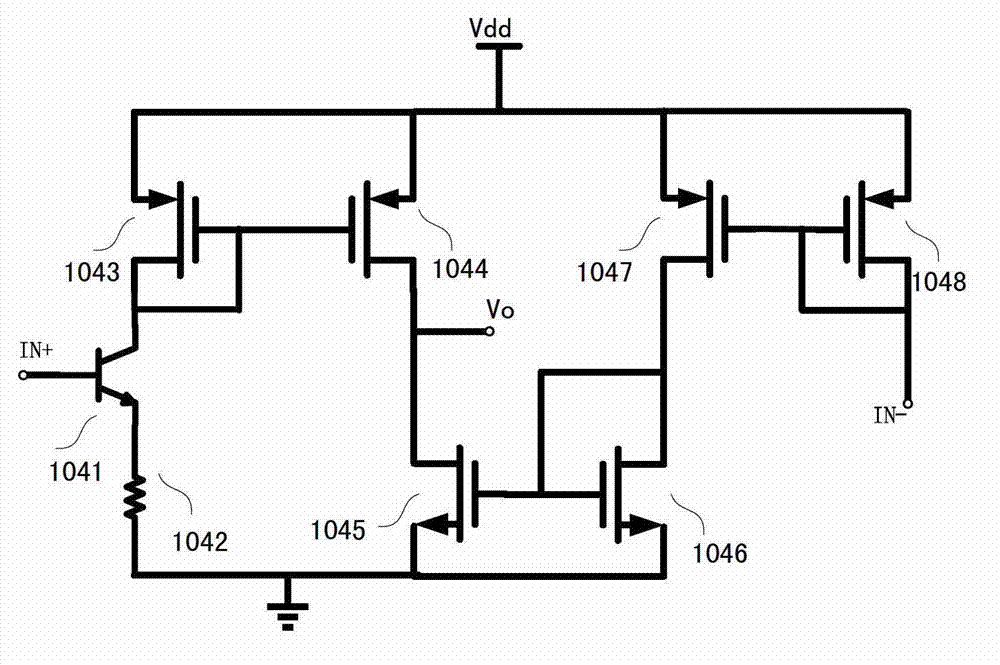

Deadline-fixed PFM (pulse frequency modulation) mode switching power supply controller

InactiveCN102868297ASimple structureReduce lossApparatus without intermediate ac conversionElectric light circuit arrangementController architectureExternal energy

The invention relates to a deadline-fixed PFM (pulse frequency modulation) mode switching power supply controller belonging to the technical field of power integrated circuits, and mainly relates to the application area of BOOST switching power supplies. The switching power supply controller comprises an error amplifier (107), a frequency compensation network (106), a comparator (104), a deadline-fixed PFM control module (101), a maximum frequency limit module (102), a power switching tube drive circuit (103), a current sampling module (105) and a power switch (108). The PFM controller architecture is simple in implementation mode, can work in an interrupted current mode and can also work in a continuous current mode; and in practical application, the controller has the advantages of small size of external energy storage elements, low ripple voltage in case of a light load, low switching loss and high efficiency in case of a heavy load, and the like.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

Electrostatic discharge conduction device and mixed power integrated circuits using same

ActiveUS20060044718A1Reduce leakage currentEfficient dischargeSolid-state devicesEmergency protective arrangements for limiting excess voltage/currentElectrical conductorVoltage pulse

A device for connection between supply buses in mixed power integrated circuits includes a diode in series with a transistor with an active p-ring in a semiconductor substrate. The active p-ring surrounds the source and drain of the transistor with a conductive region having the same conductivity type as the semiconductor substrate. A control circuit coupled to the p-ring applies a bias voltage in response to an ESD event affecting the first and second conductors. The bias voltage tends to inject carriers into the semiconductor substrate which enables discharge of the short voltage pulse via a parasitic SCR in the substrate from the anode of the diode to the source of the transistor.

Owner:MACRONIX INT CO LTD

SOI lateral MOSFET devices

InactiveUS8716794B2Improve breakdown voltageReduce areaSolid-state devicesSemiconductor devicesMOSFETEngineering

The present invention relates to a semiconductor power device and power integrated circuits (ICs). The lateral SOI MOSFET in the present comprises a trench gate extended to the dielectric buried layer, one or multiple dielectric trenches in the drift region, and a buried gate in said dielectric trench. The permittivity of the dielectric in said dielectric trench is lower than that of said active layer. Firstly, said dielectric trench not only greatly improves breakdown voltage, but also reduces pitch size. Secondly, the trench gate widens the effective conductive region in the vertical direction. Thirdly, dual gates of said trench gate and buried gate increase channel and current densities. Thereby, specific on-resistance and the power loss are reduced. The device of the present invention has many advantages, such as high voltage, high speed, low power loss, low cost and ease of integration. The device in the present invention is particularly suitable for power integrated circuits and RF power integrated circuits.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA