Patents

Literature

133 results about "Conductivity modulation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Answer Wiki. Conductivity modulation is the change in the conductivity of the material due to some external stimulus like temperature,sound,voltage,radiation etc. Like if we increase the temperature of the metal then its resistance will increase.

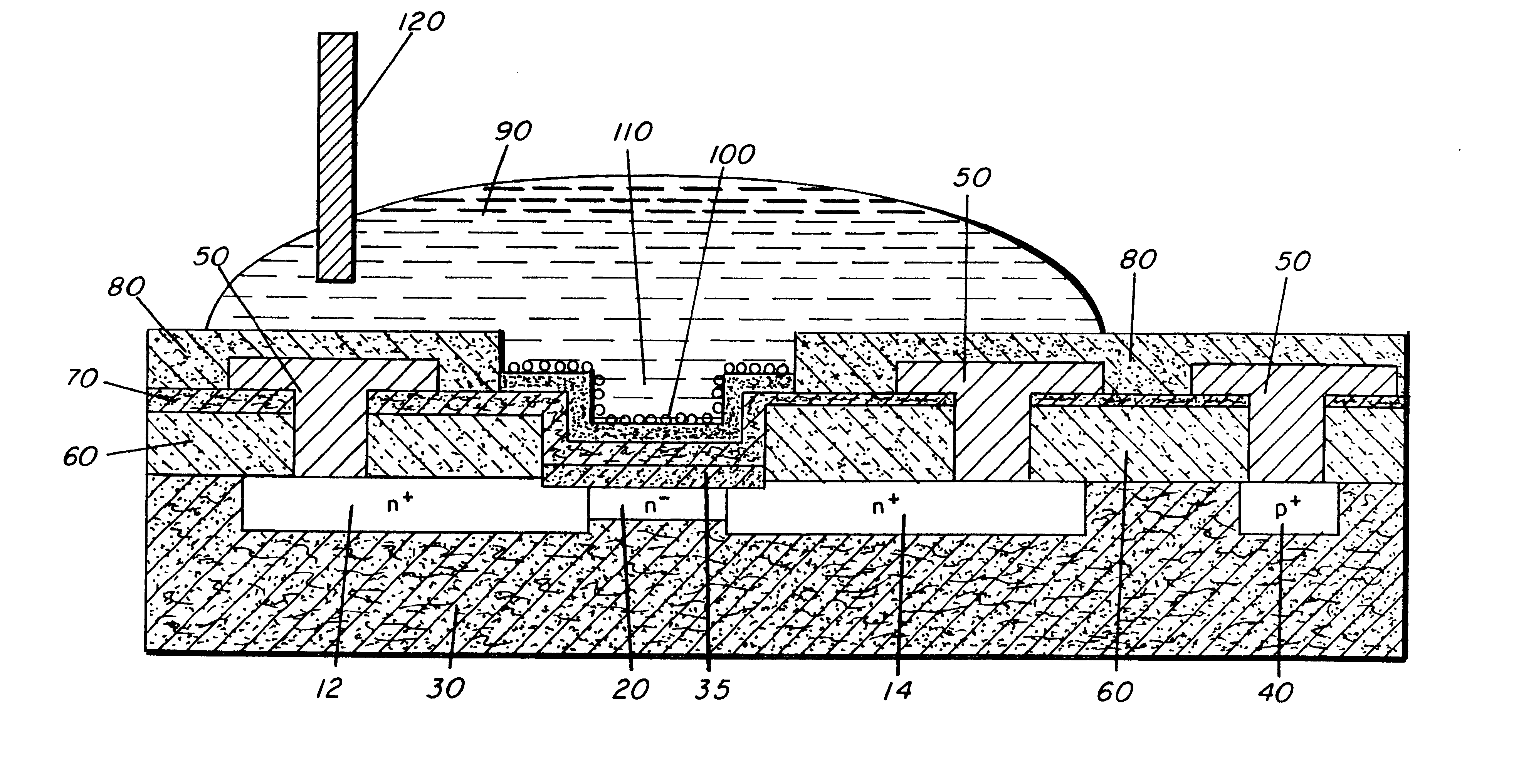

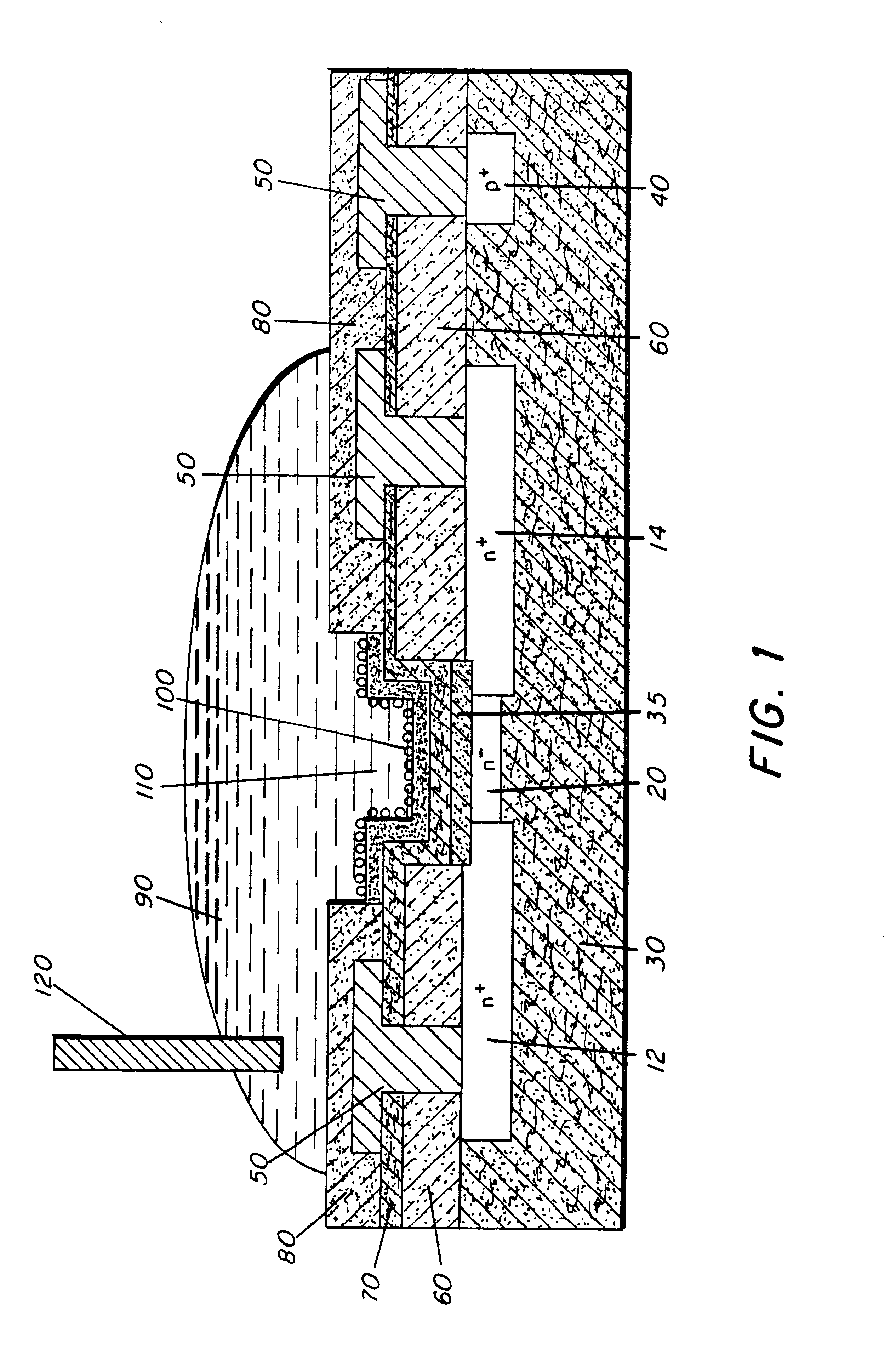

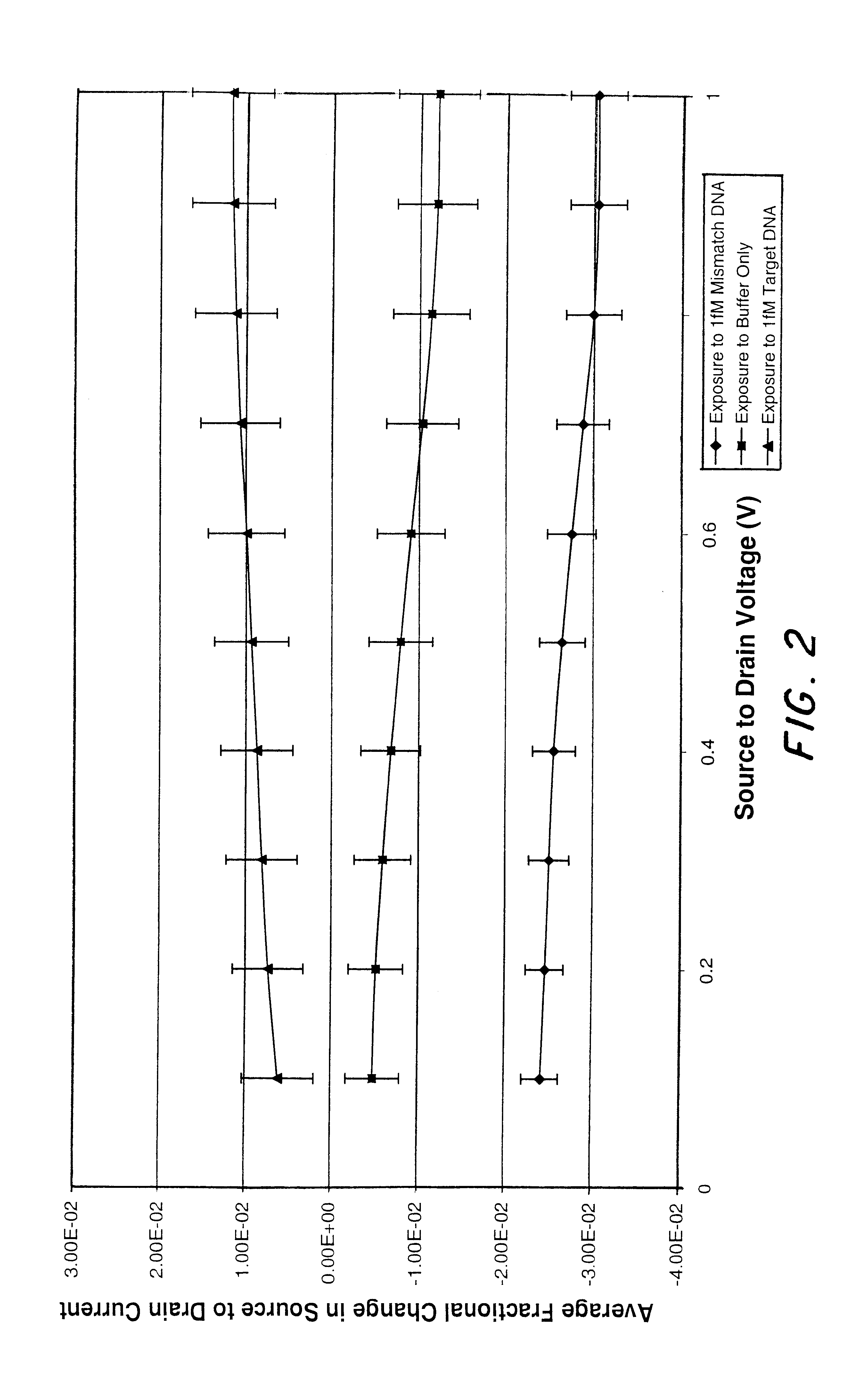

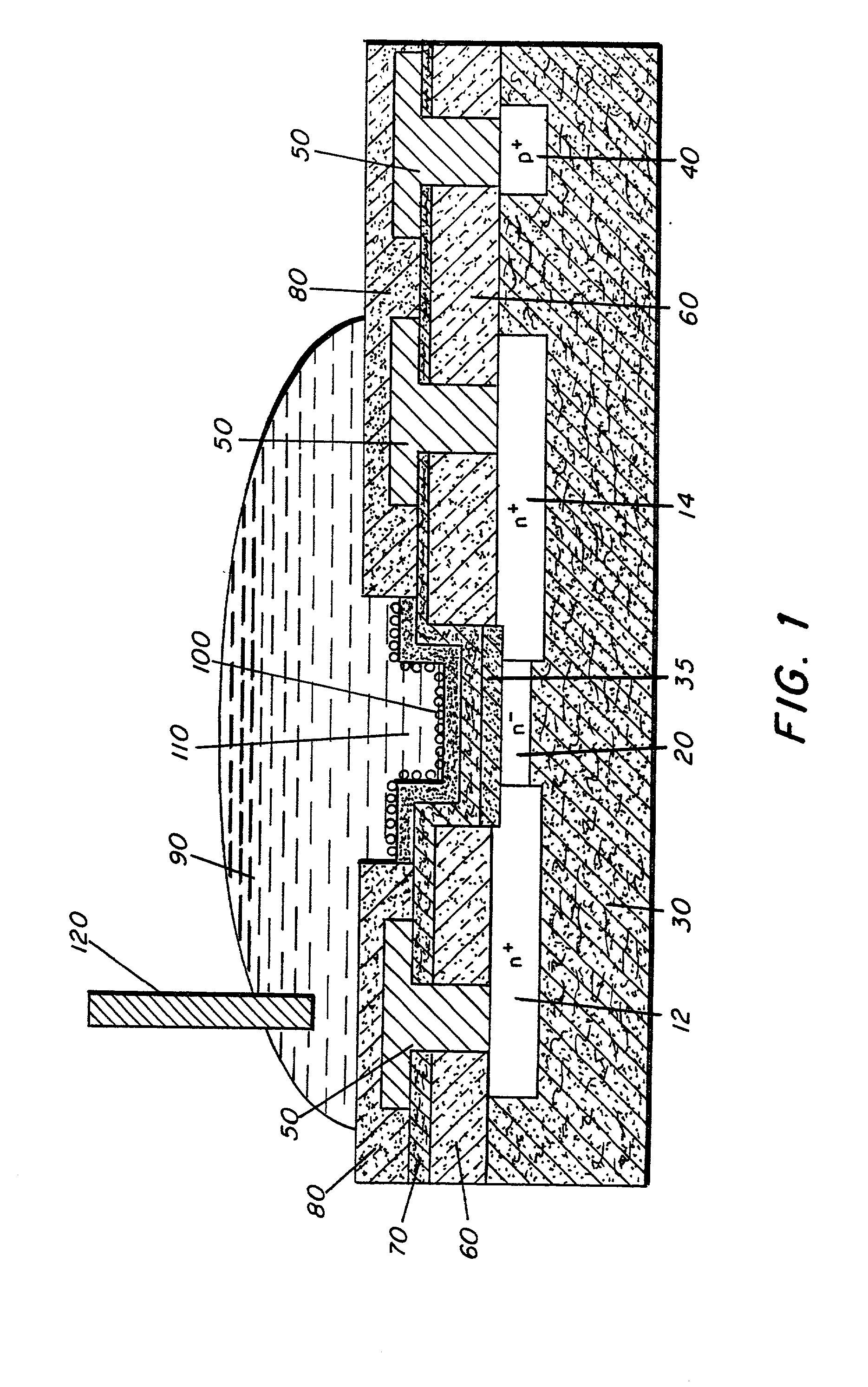

Microelectronic device and method for label-free detection and quantification of biological and chemical molecules

InactiveUS6482639B2Sensitive and accurate detectionWide scope of practical and worthwhile utilizationBioreactor/fermenter combinationsBiological substance pretreatmentsCapacitanceField-effect transistor

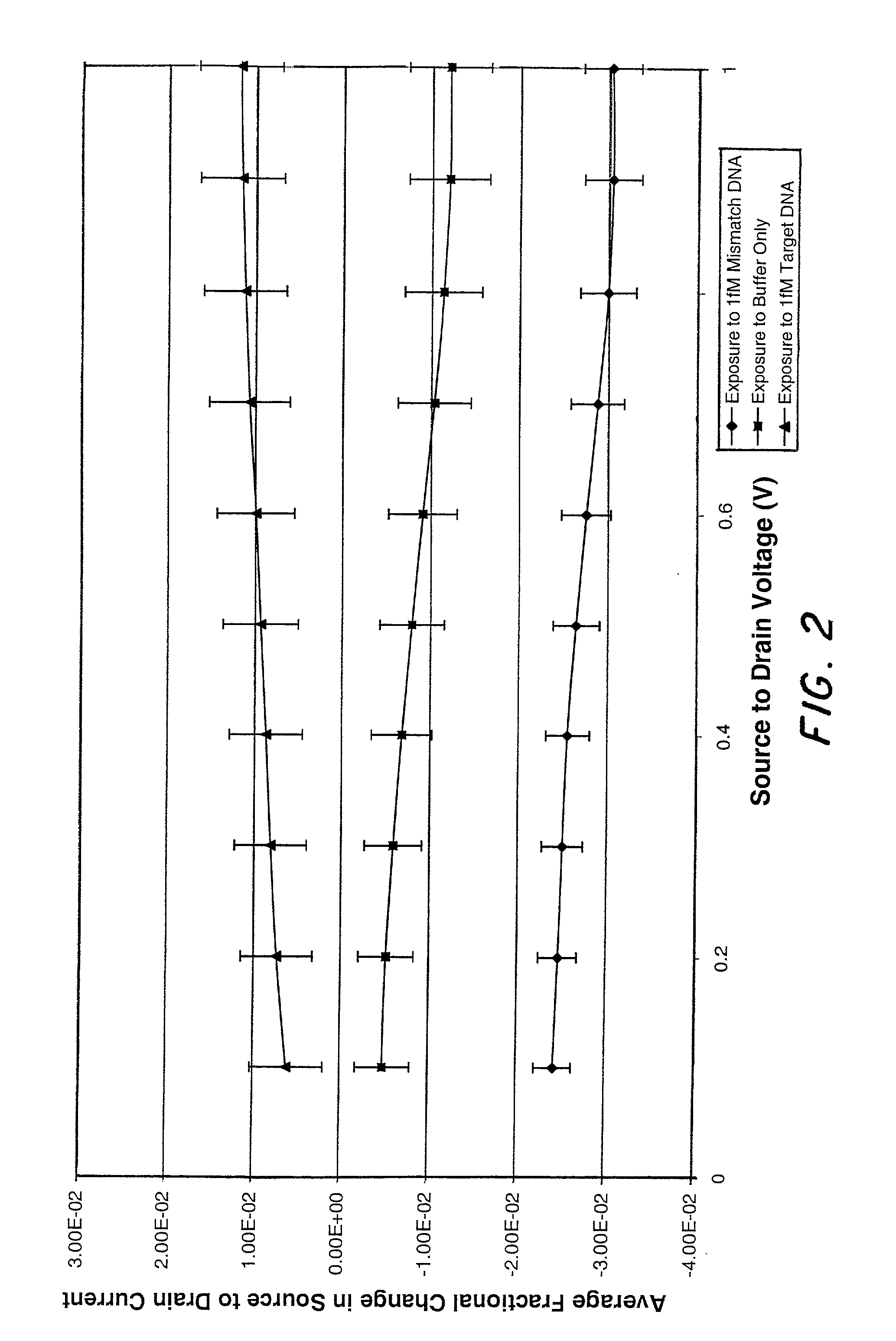

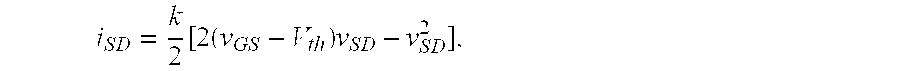

Molecular recognition-based electronic sensor, which is gateless, depletion mode field effect transistor consisting of source and drain diffusions, a depletion-mode implant, and insulating layer chemically modified by immobilized molecular receptors that enables miniaturized label-free molecular detection amenable to high-density array formats. The conductivity of the active channel modulates current flow through the active channel when a voltage is applied between the source and drain diffusions. The conductivity of the active channel is determined by the potential of the sample solution in which the device is immersed and the device-solution interfacial capacitance. The conductivity of the active channel modulates current flow through the active channel when a voltage is applied between the source and drain diffusions. The interfacial capacitance is determined by the extent of occupancy of the immobilized receptor molecules by target molecules. Target molecules can be either charged or uncharged. Change in interfacial capacitance upon target molecule binding results in modulation of an externally supplied current through the channel.

Owner:THE UNITED STATES OF AMERICA AS REPRESENTED BY THE SECRETARY OF THE NAVY

Microelectronic device and method for label-free detection and quantification of biological and chemical molecules

InactiveUS20020012937A1Wide scope of practicalWide scope of worthwhile utilizationBioreactor/fermenter combinationsBiological substance pretreatmentsCapacitanceField-effect transistor

Molecular recognition-based electronic sensor, which is gateless, depletion mode field effect transistor consisting of source and drain diffusions, a depletion-mode implant, and insulating layer chemically modified by immobilized molecular receptors that enables miniaturized label-free molecular detection amenable to high-density array formats. The conductivity of the active channel modulates current flow through the active channel when a voltage is applied between the source and drain diffusions. The conductivity of the active channel is determined by the potential of the sample solution in which the device is immersed and the device-solution interfacial capacitance. The conductivity of the active channel modulates current flow through the active channel when a voltage is applied between the source and drain diffusions. The interfacial capacitance is determined by the extent of occupancy of the immobilized receptor molecules by target molecules. Target molecules can be either charged or uncharged. Change in interfacial capacitance upon target molecule binding results in modulation of an externally supplied current through the channel.

Owner:THE UNITED STATES OF AMERICA AS REPRESENTED BY THE SECRETARY OF THE NAVY

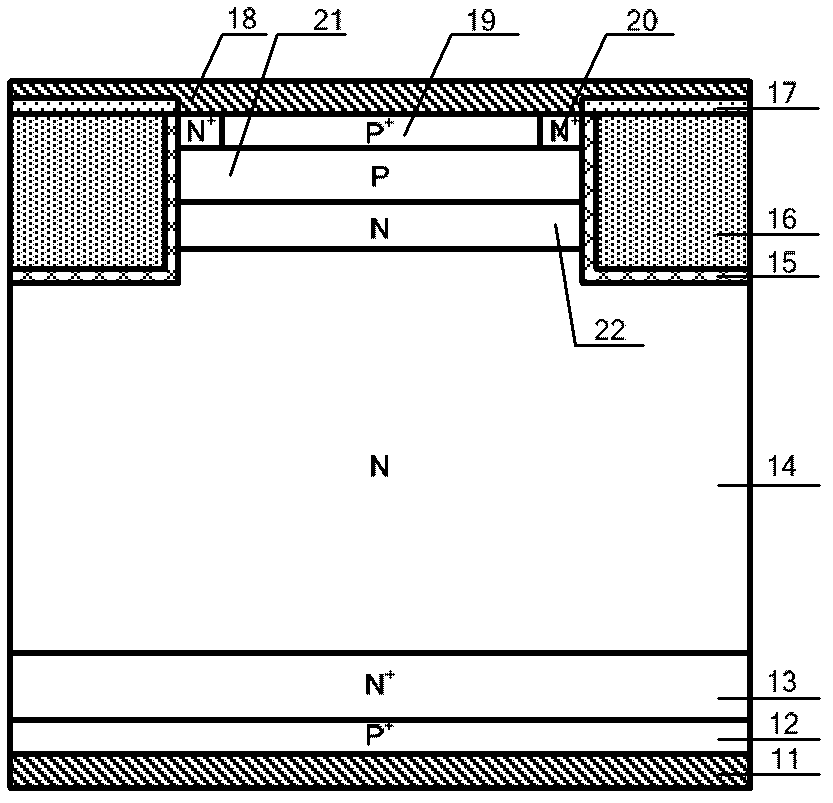

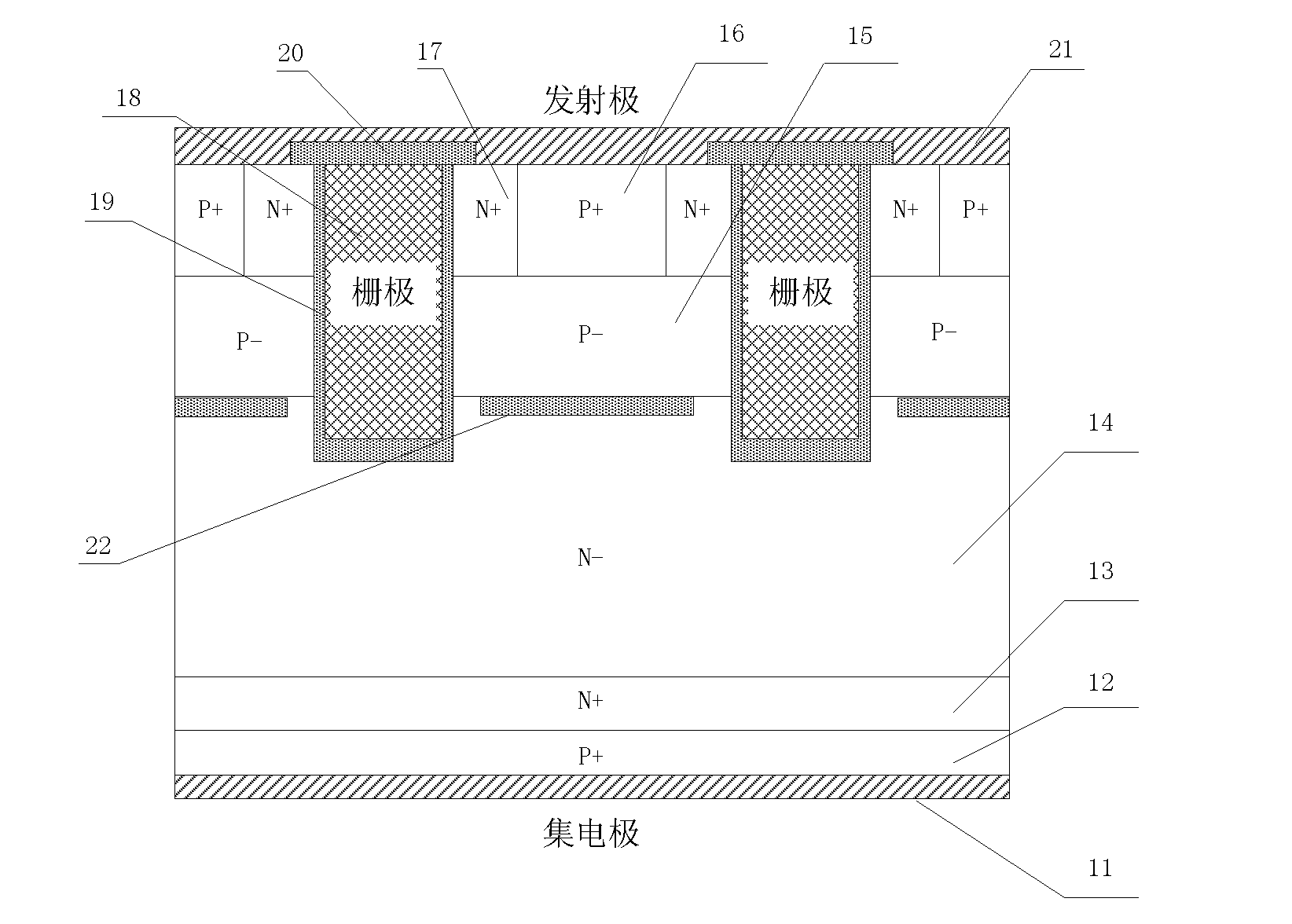

Trench gate charge storage type insulated gate bipolar transistor (IGBT)

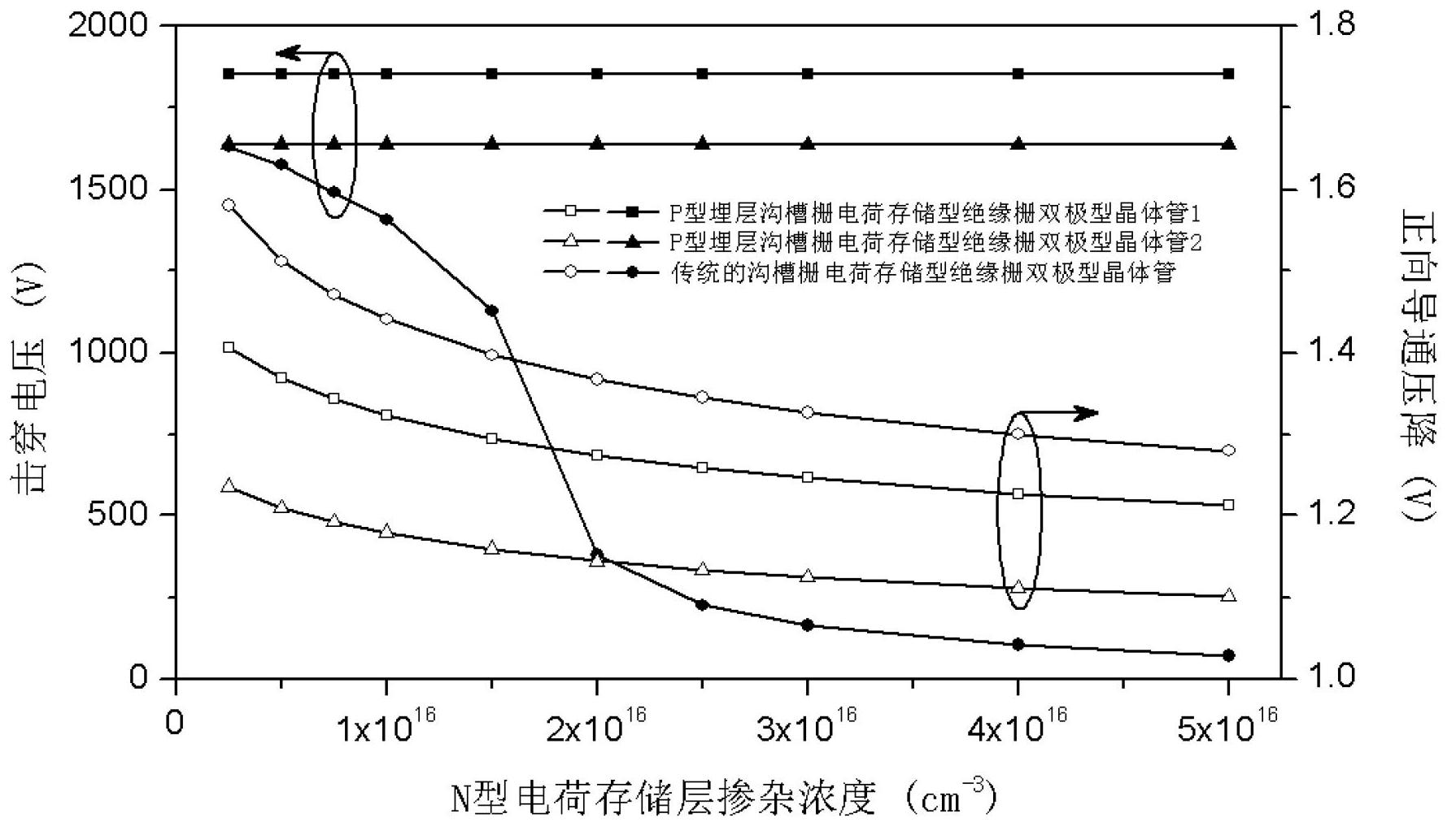

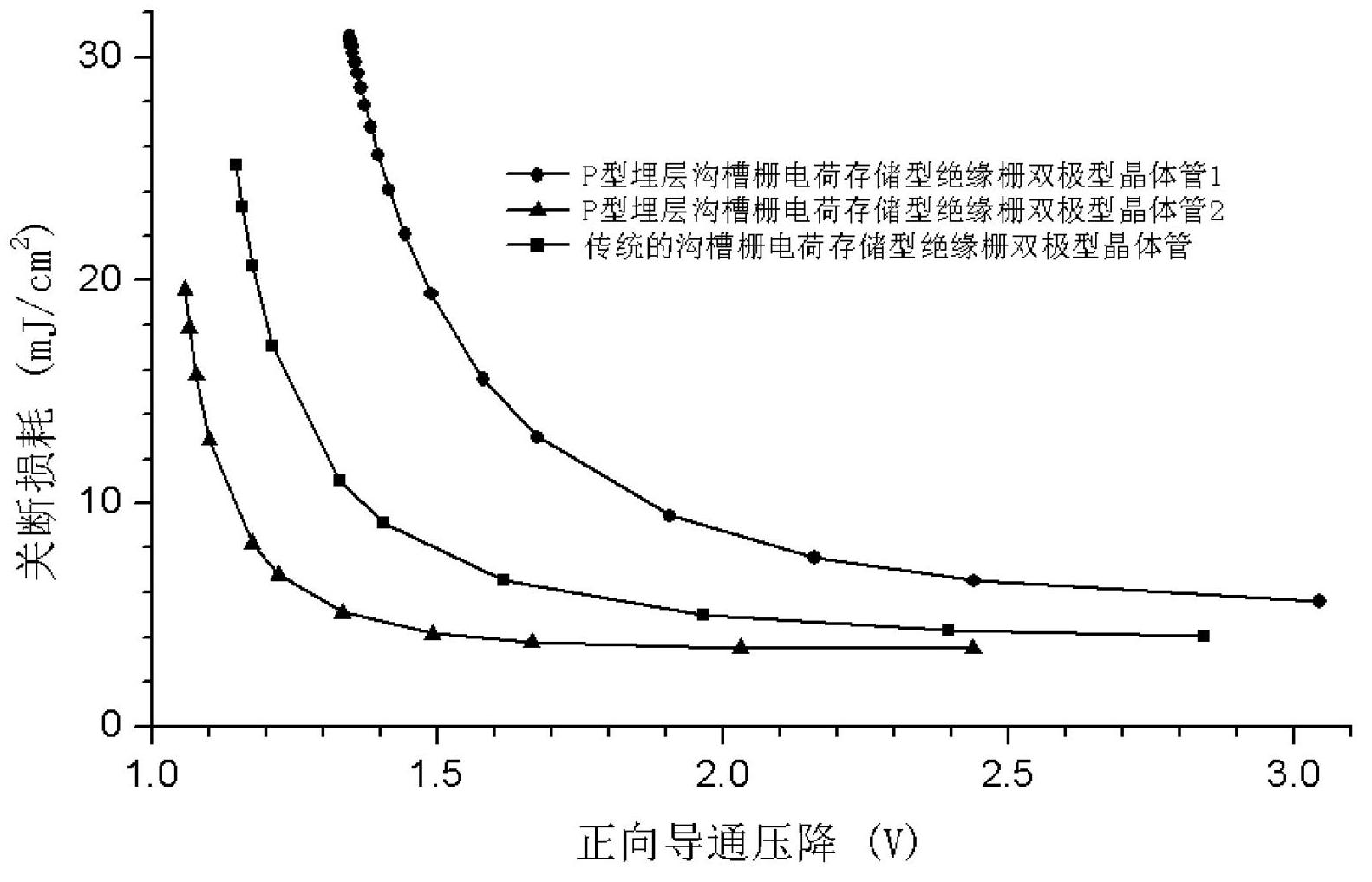

InactiveCN102683403AImprove breakdown voltageGood forward voltage dropSemiconductor devicesConductivity modulationBreakdown voltage

The invention discloses a trench gate charge storage type IGBT and belongs to the technical field of power semiconductor devices. Based on traditional trench gate charge storage type IGBTs, a P-shaped buried layer is introduced on the upper portion of a N-shaped drifting area of a device, by the aid of an attached PN junction introduced by the P-shaped buried layer and the electric field modulating effect, negative influences of a highly doped N-shaped charge storage layer on the breakdown voltage of the device is shielded, and the device can acquire high breakdown voltage. The P-shaped buried layer has an electric field shielding effect on the N-shaped charge storage layer, high doping concentration of the N-shaped charge storage layer can be adopted, the conductivity modulation in the N-shaped drifting area of the device can be strengthened, and the distribution of current carriers in the N-shaped drifting area is optimized, so that the device can acquire low and good forward voltage drop and good turn-off loss compromise. The trench gate charge storage type IGBT is applicable to fields of semiconductor power devices ranging from low power to high power and power integrated circuits.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

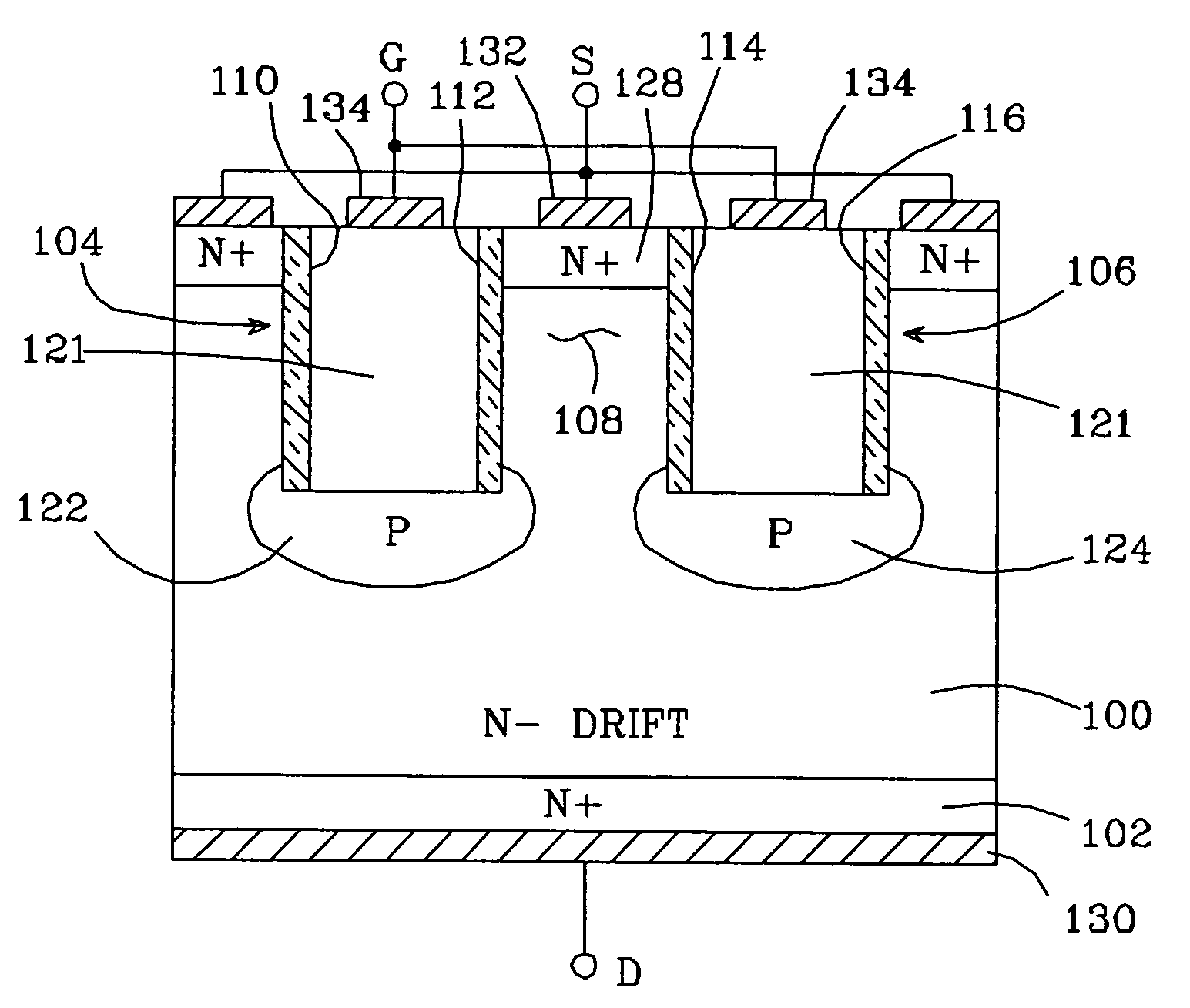

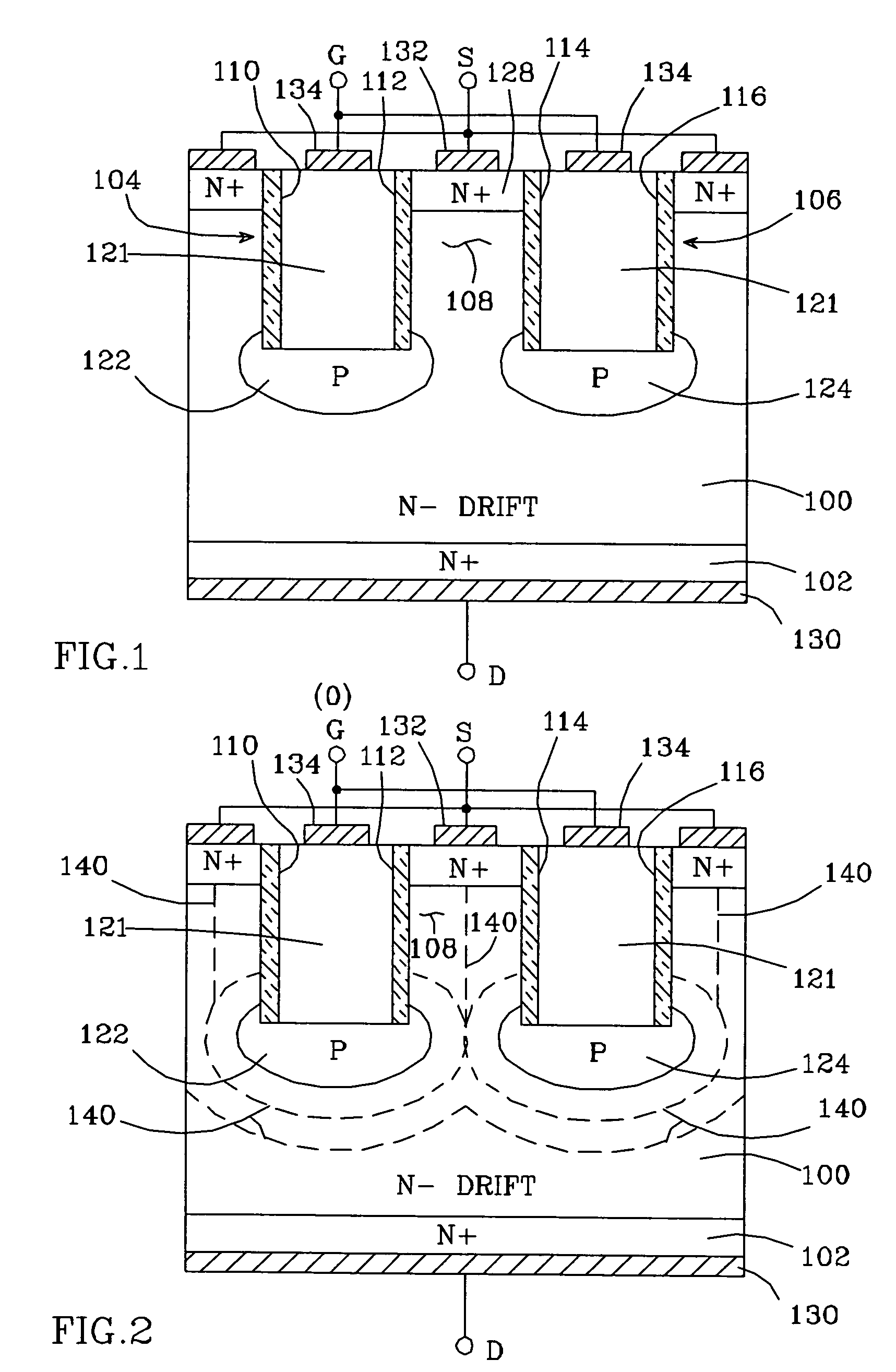

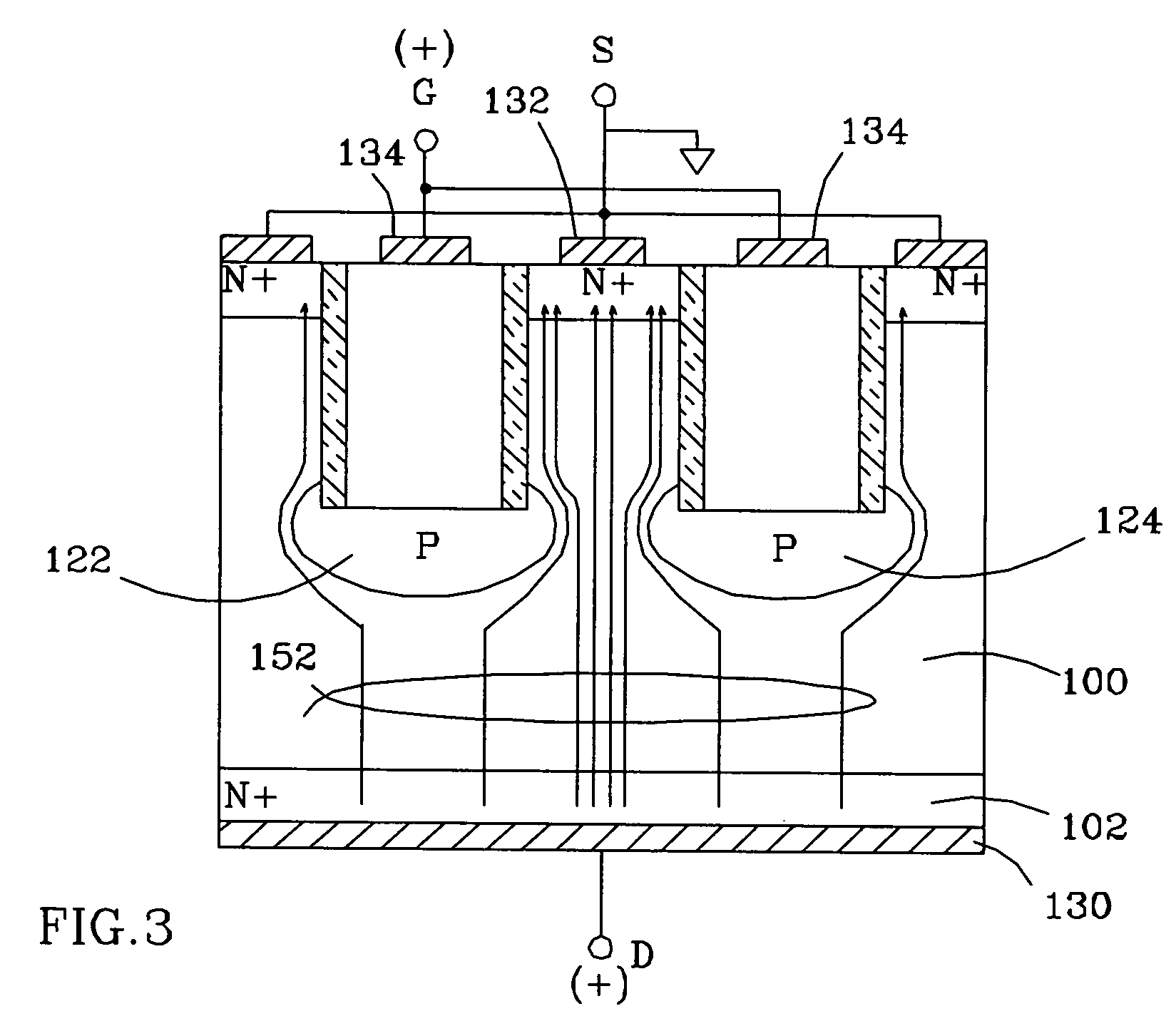

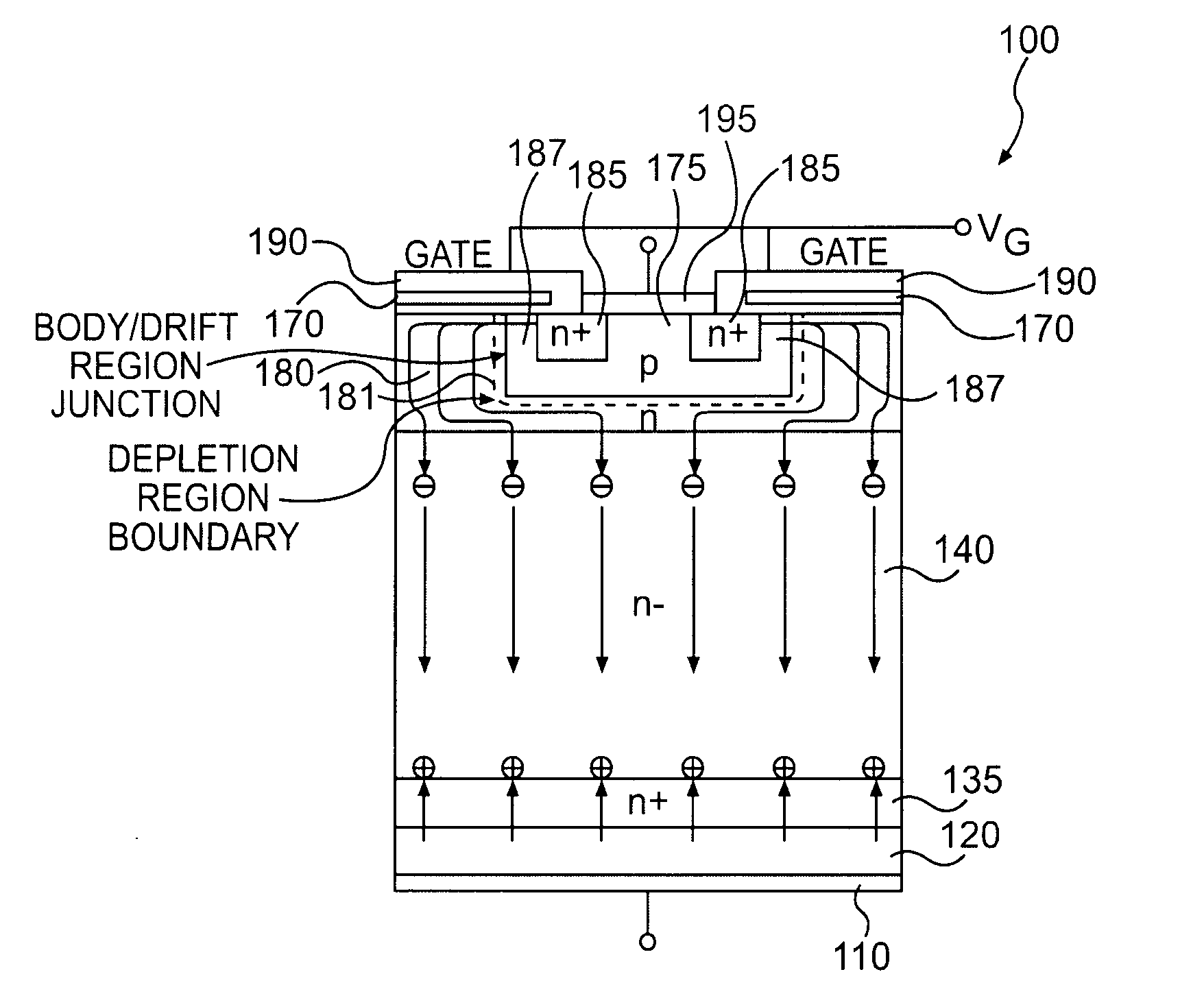

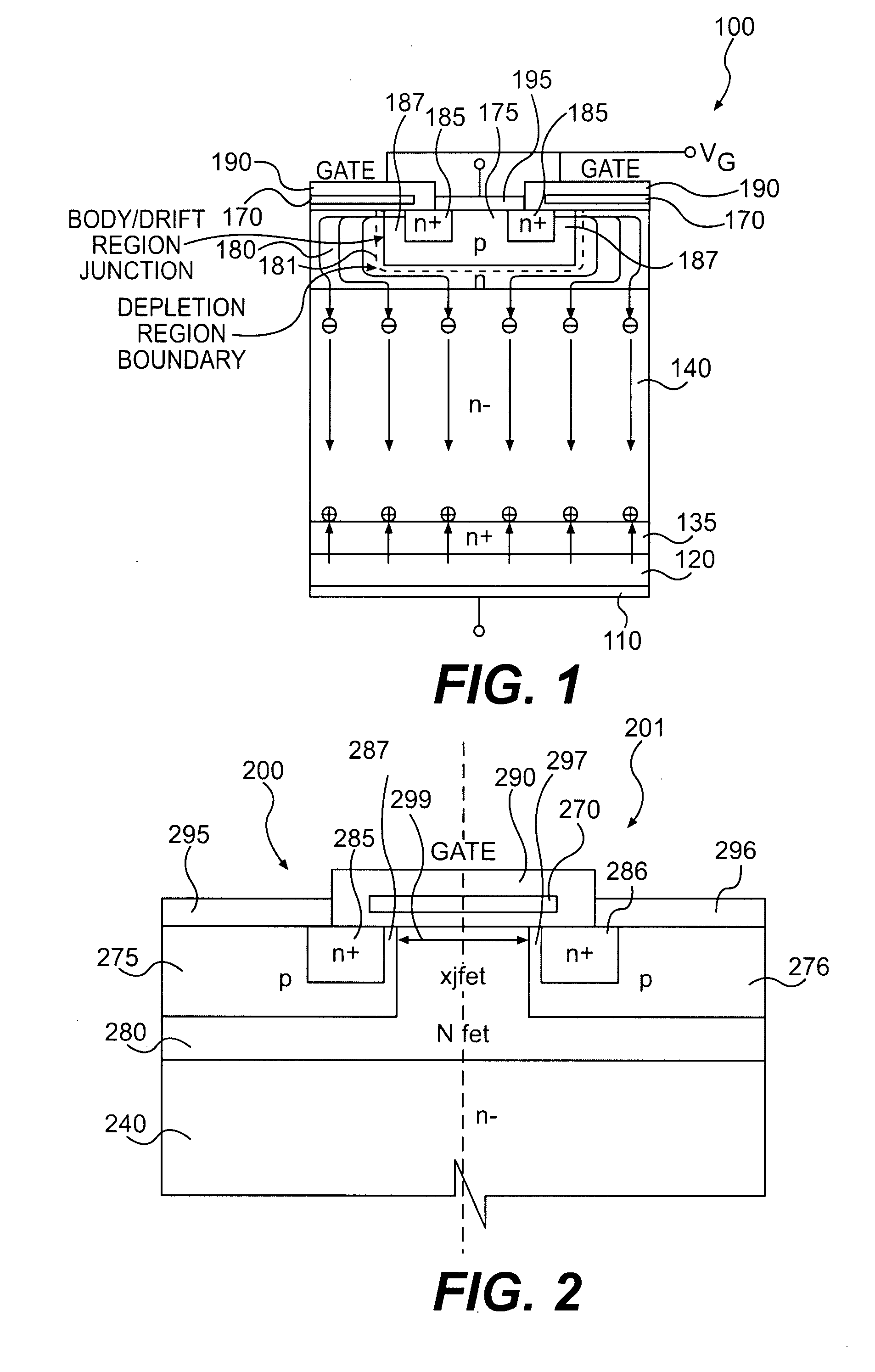

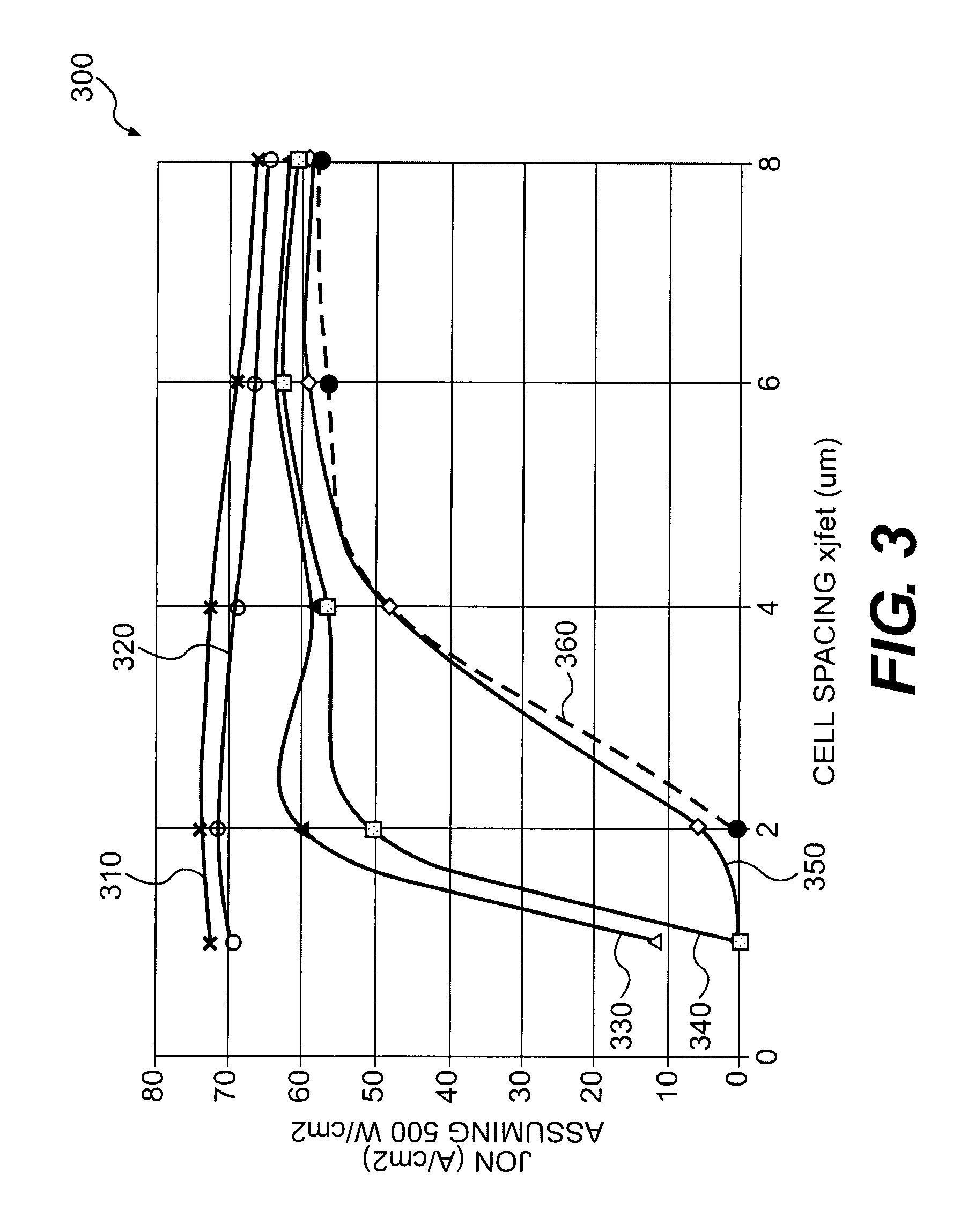

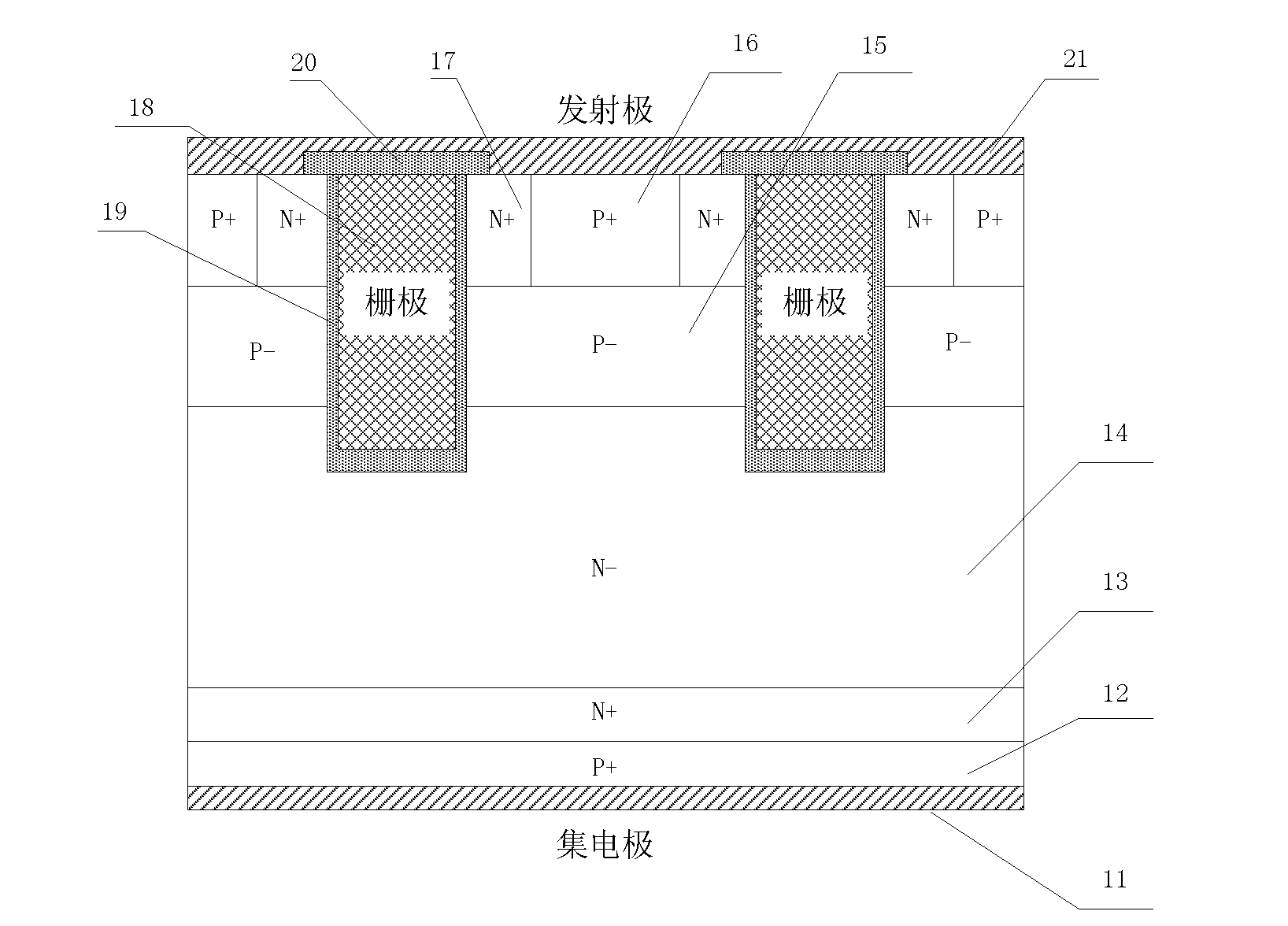

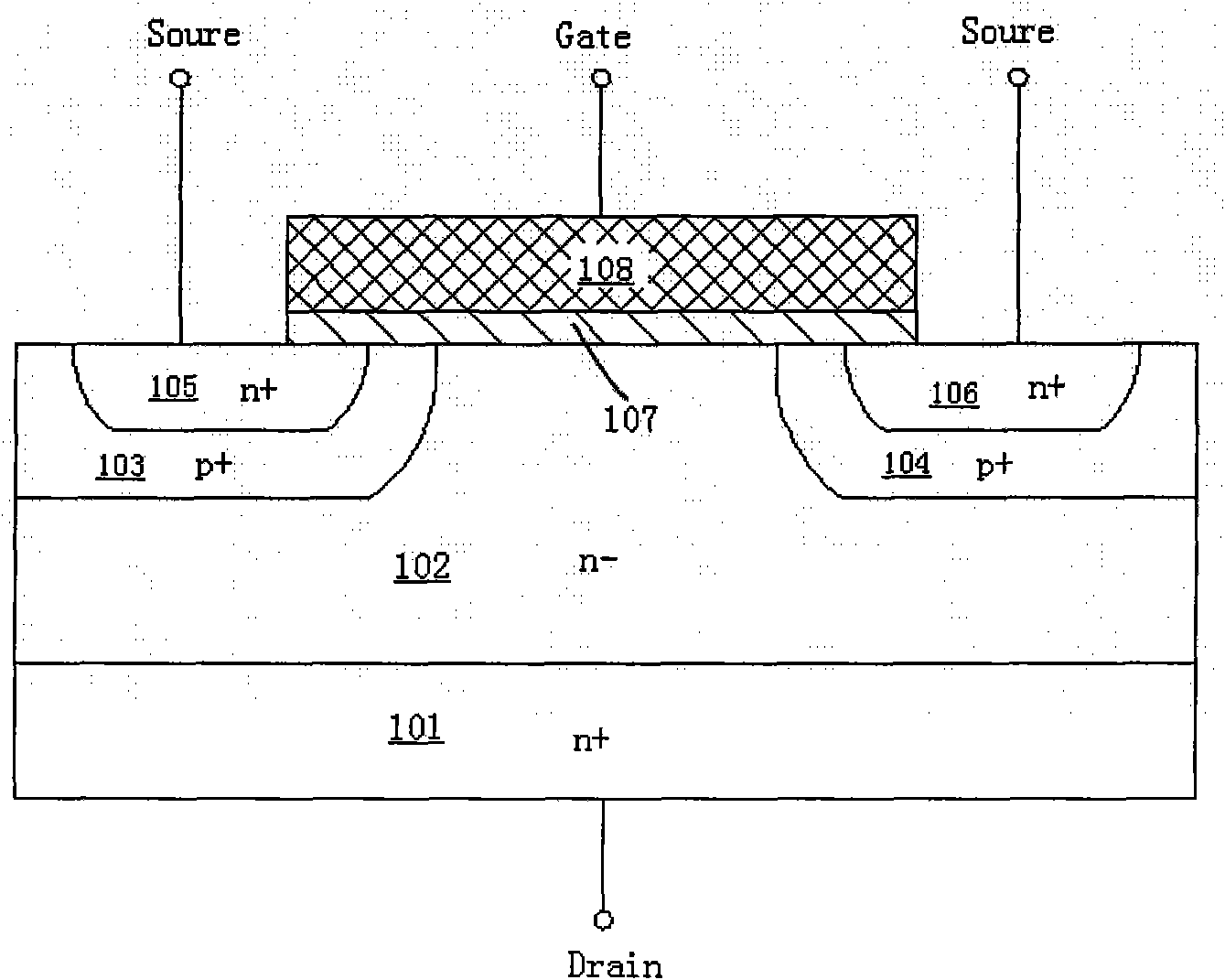

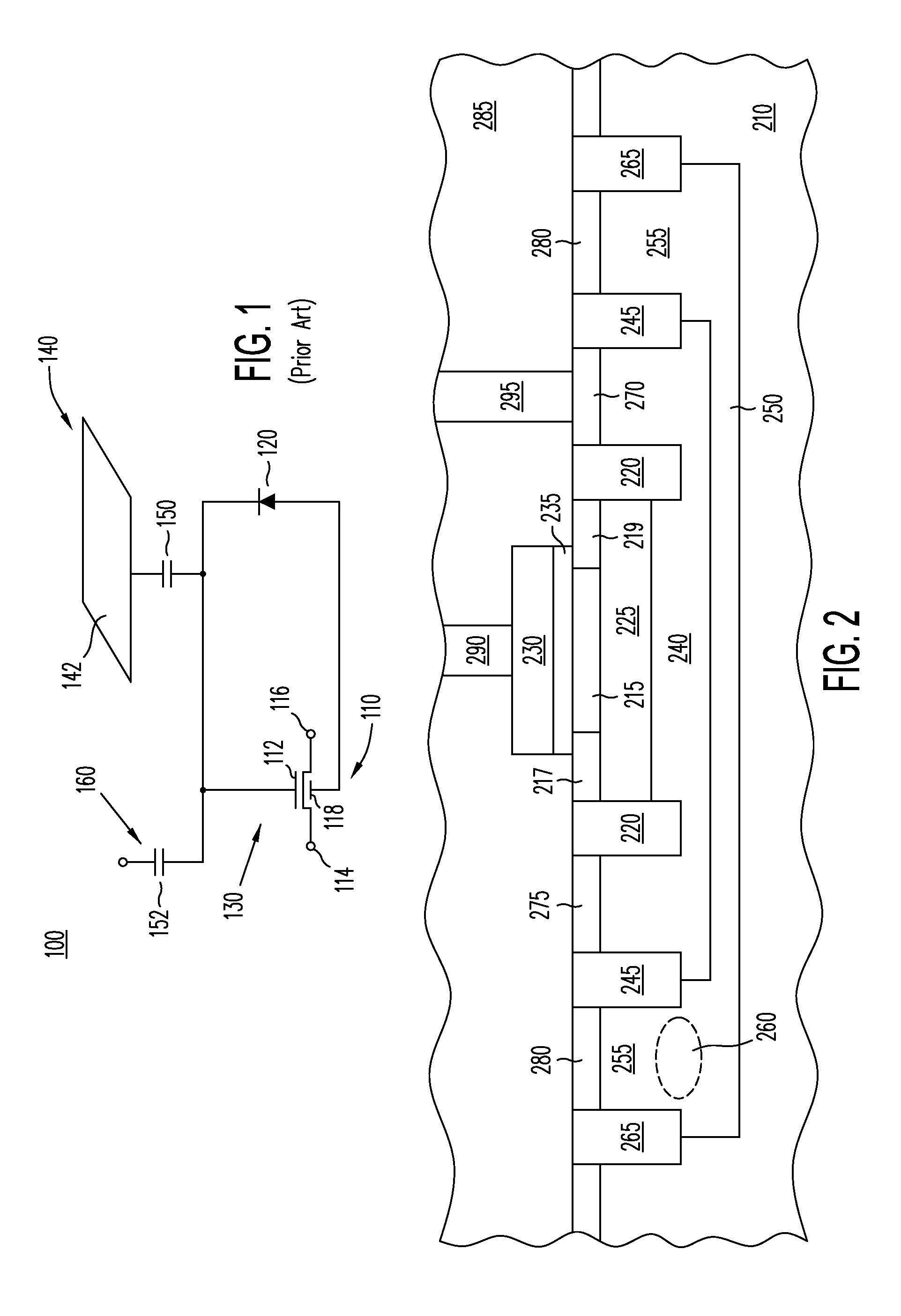

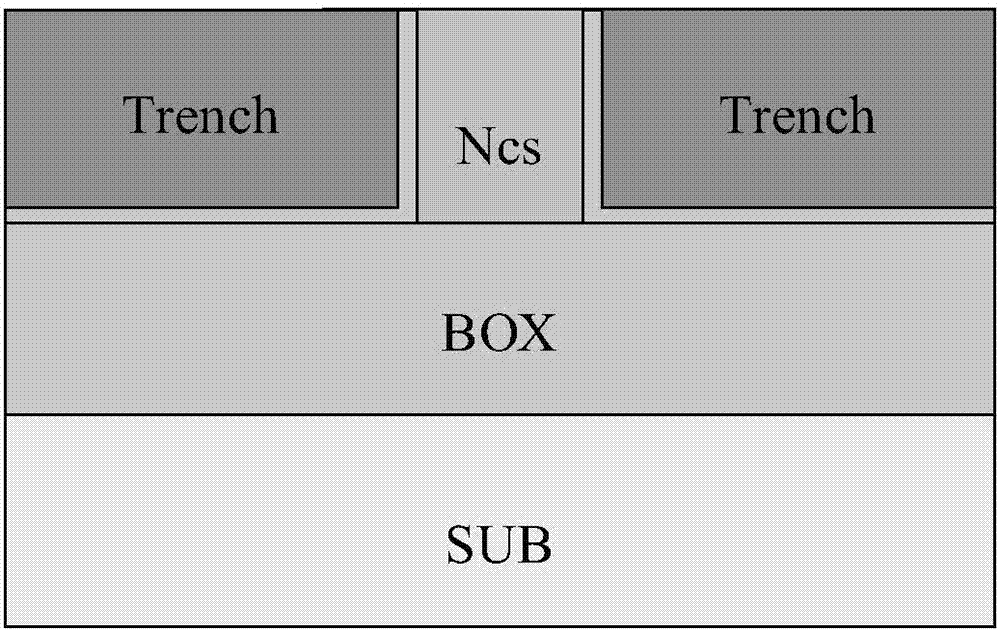

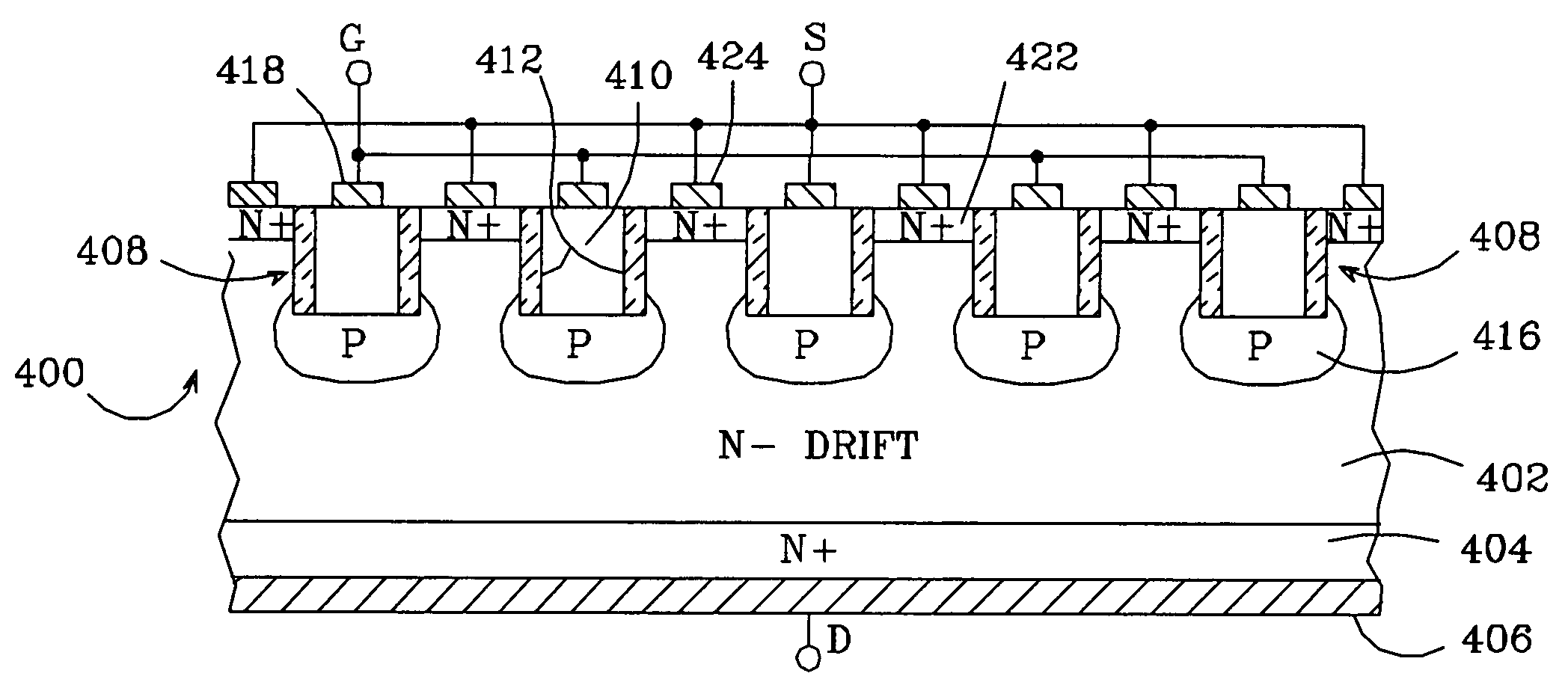

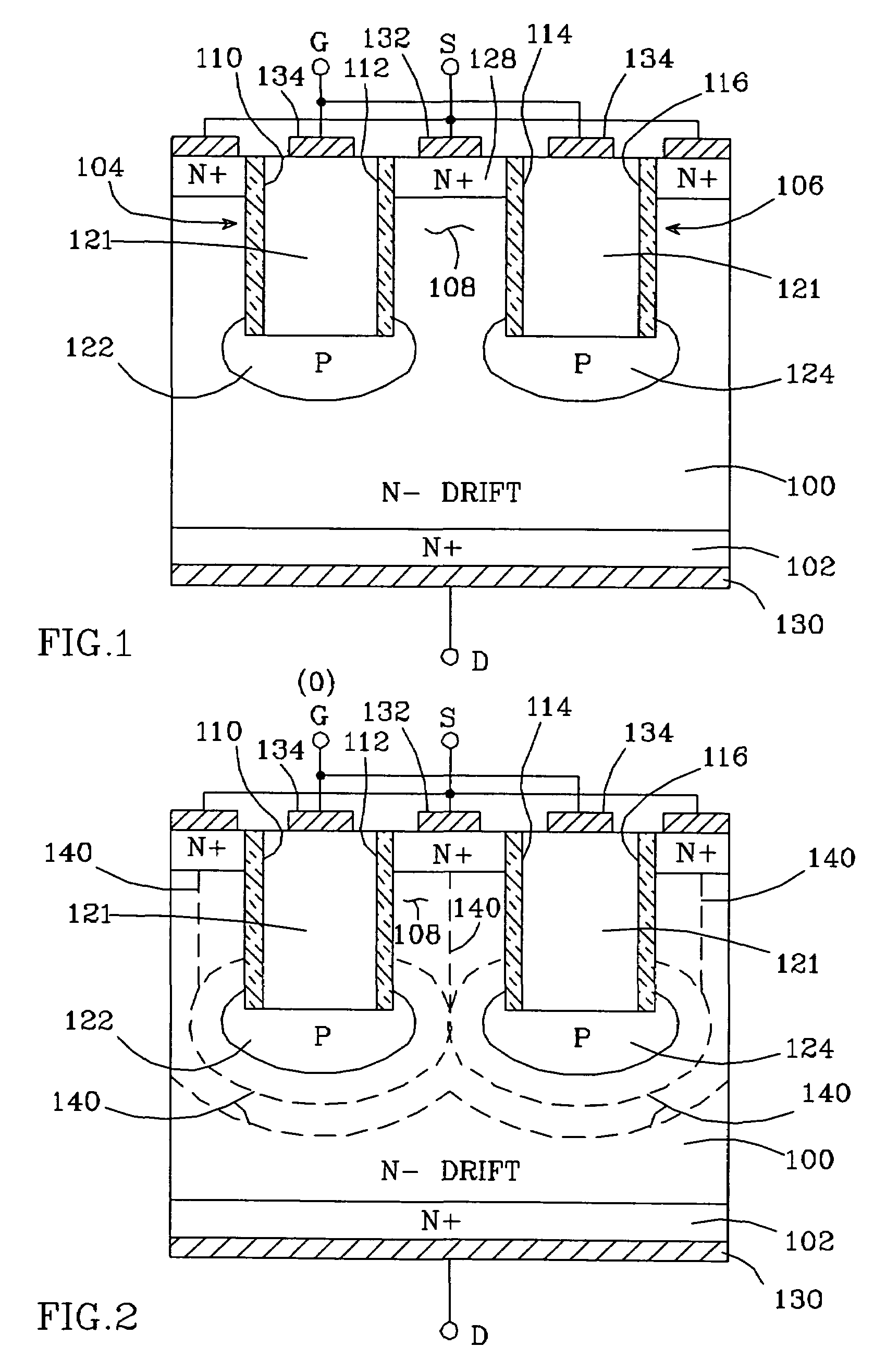

High voltage FET switch with conductivity modulation

ActiveUS20060071295A1Negligible switching lossLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesConductive materialsGate voltage

A high power FET switch comprises an N− drift layer, in which pairs of trenches are recessed to a predetermined depth; oxide side-walls extend to the trench bottoms, and each trench is filled with a conductive material. N+ and metal layers on opposite sides of the drift layer provide drain and source connections for the FET, and the conductive material in each trench is connected together to provide a gate connection. A shallow P region extends across the bottom and around the corners of each trench's side-walls into the drift layer. The application of a sufficient gate voltage causes holes to be injected from the shallow P regions into the N− drift layer, thereby modulating the drift layer's conductivity and lowering the device's on-resistance, and enabling current to flow between the drain and source connections.

Owner:CALLAHAN CELLULAR L L C

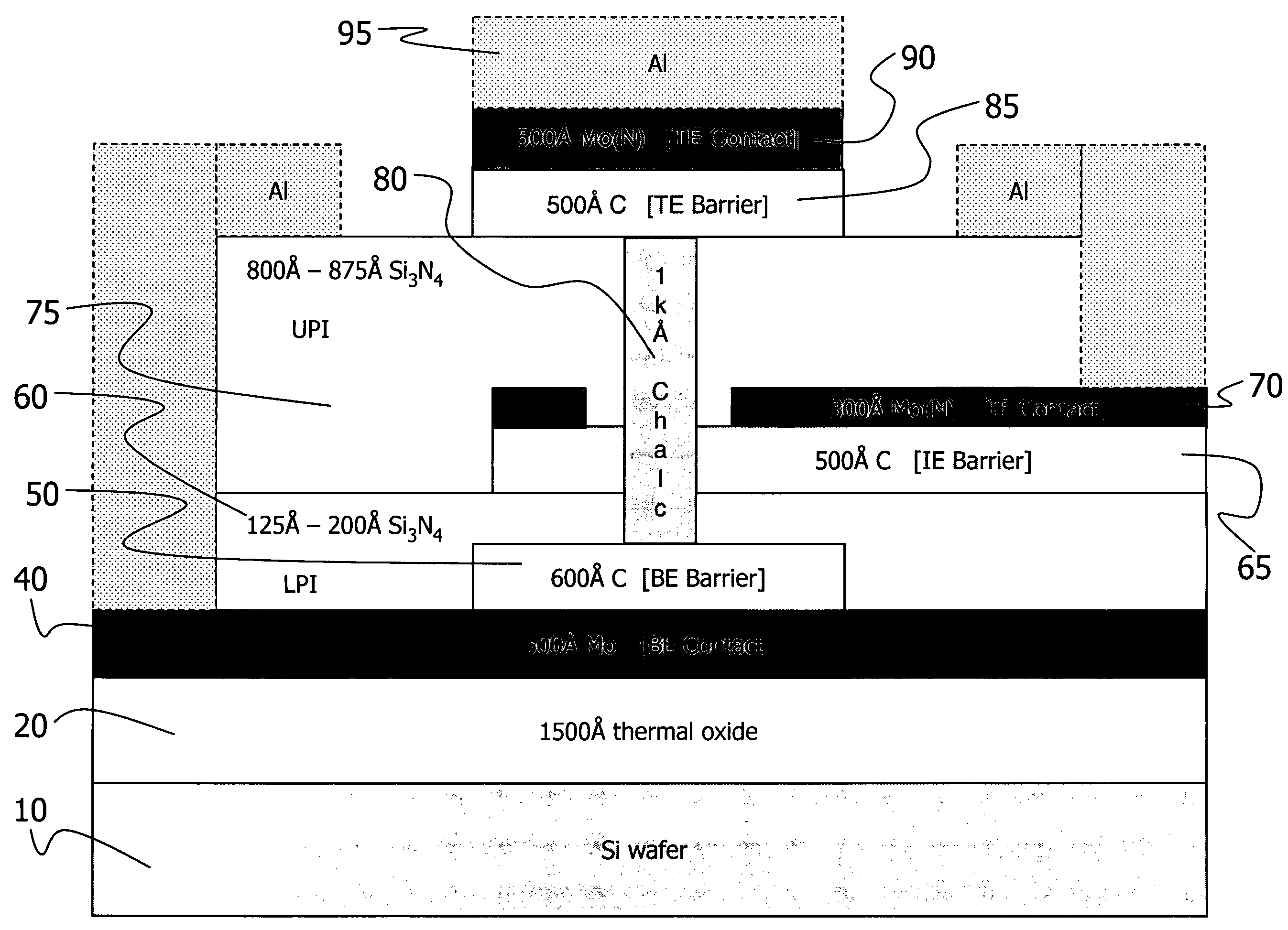

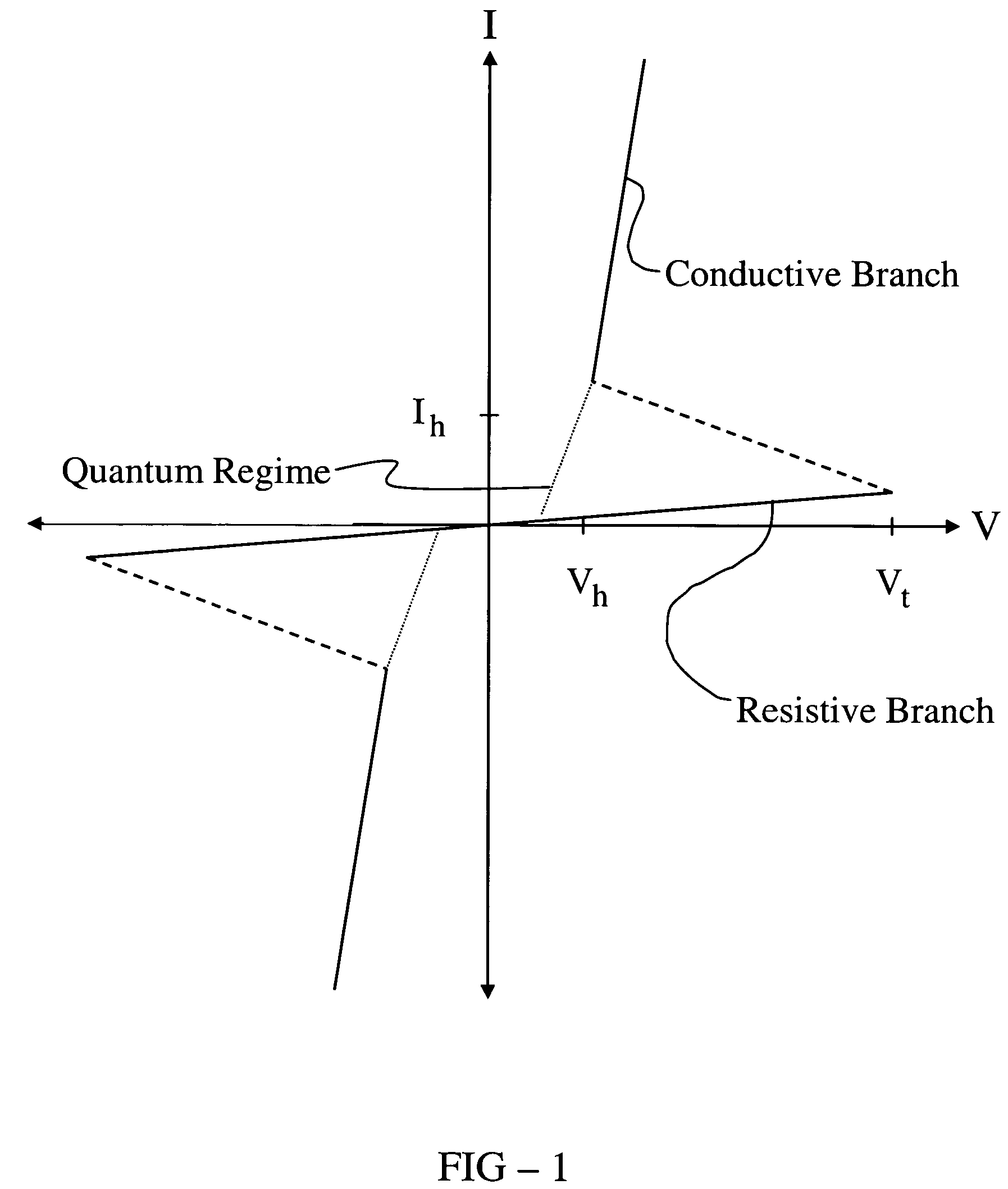

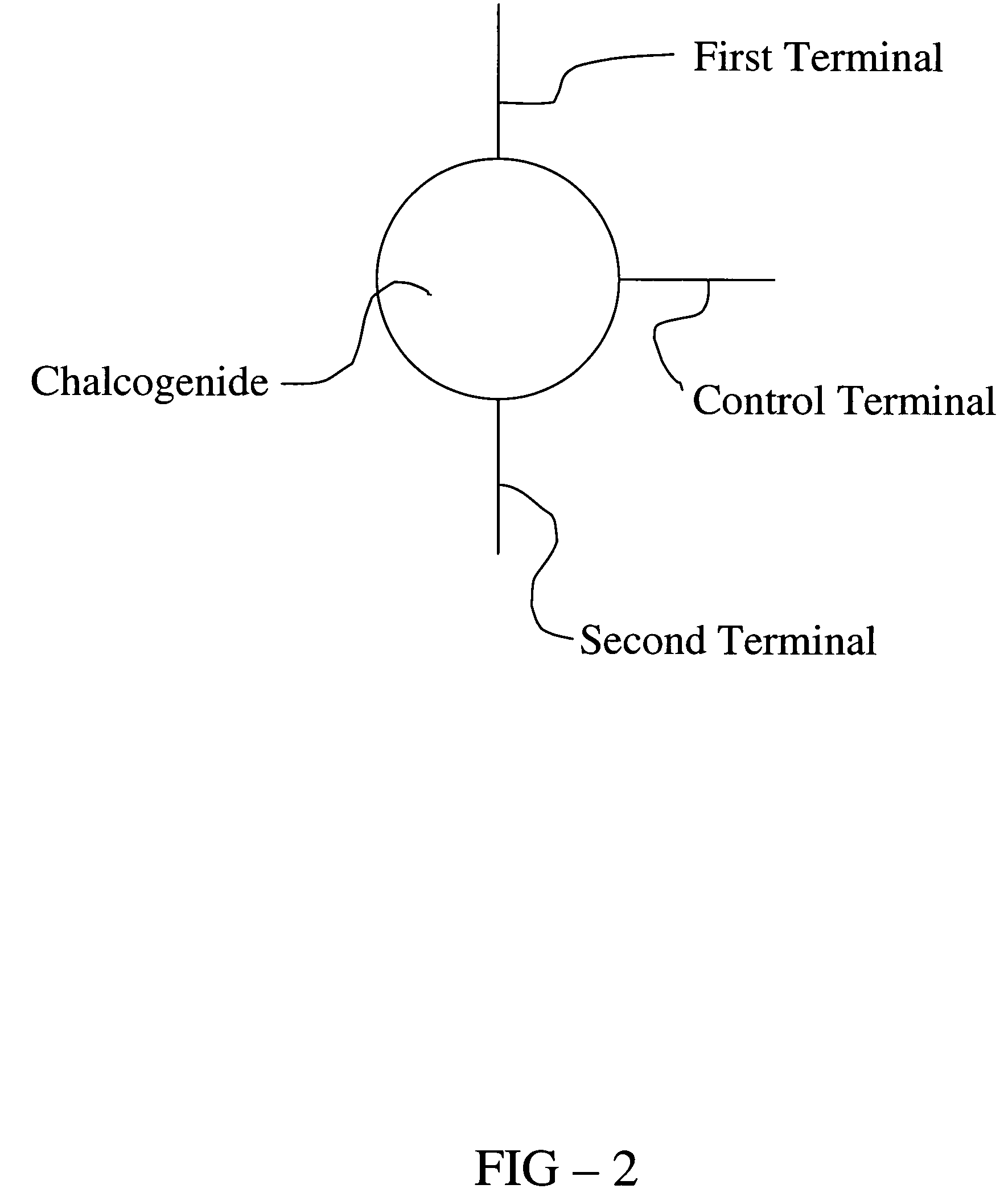

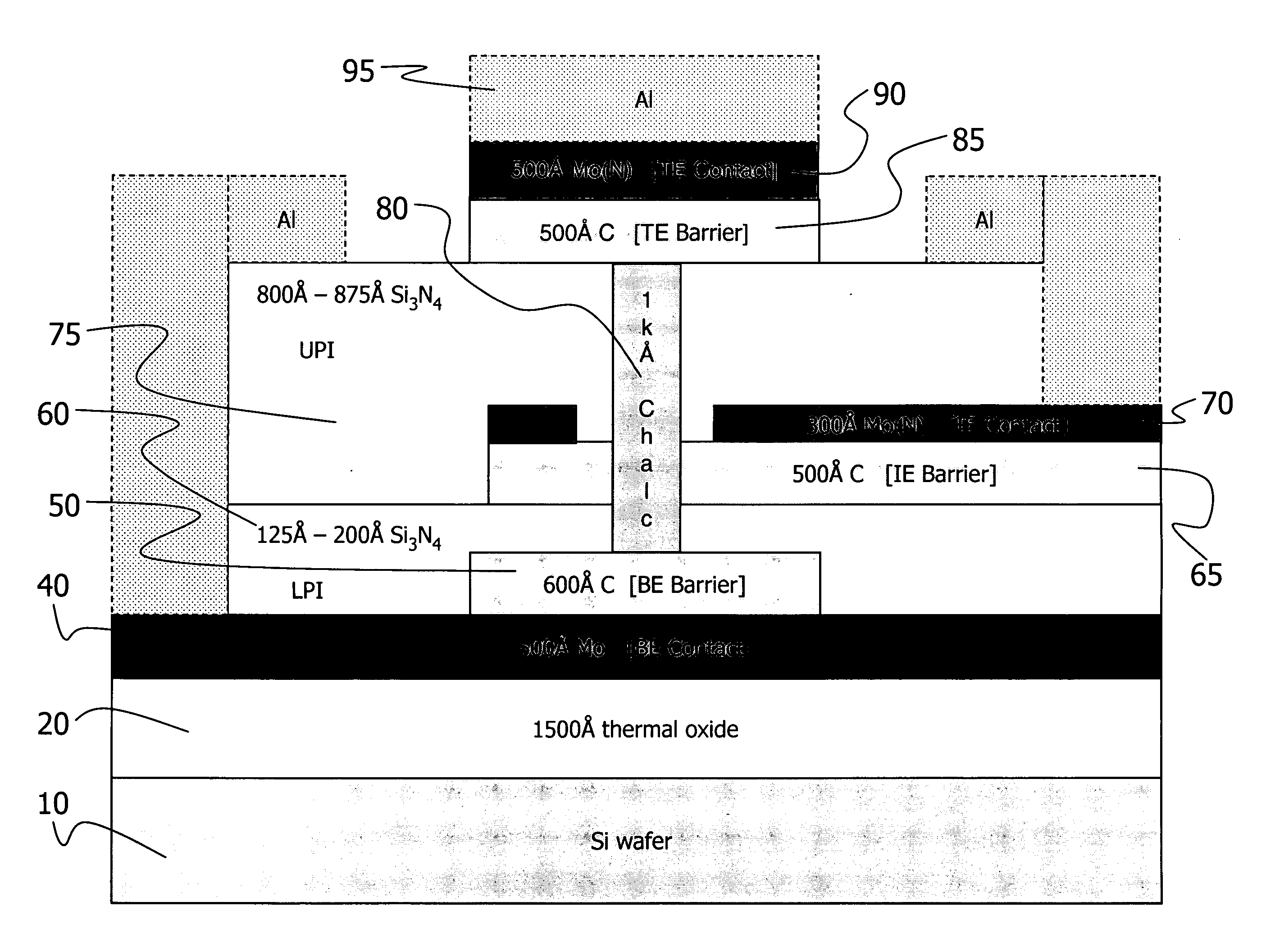

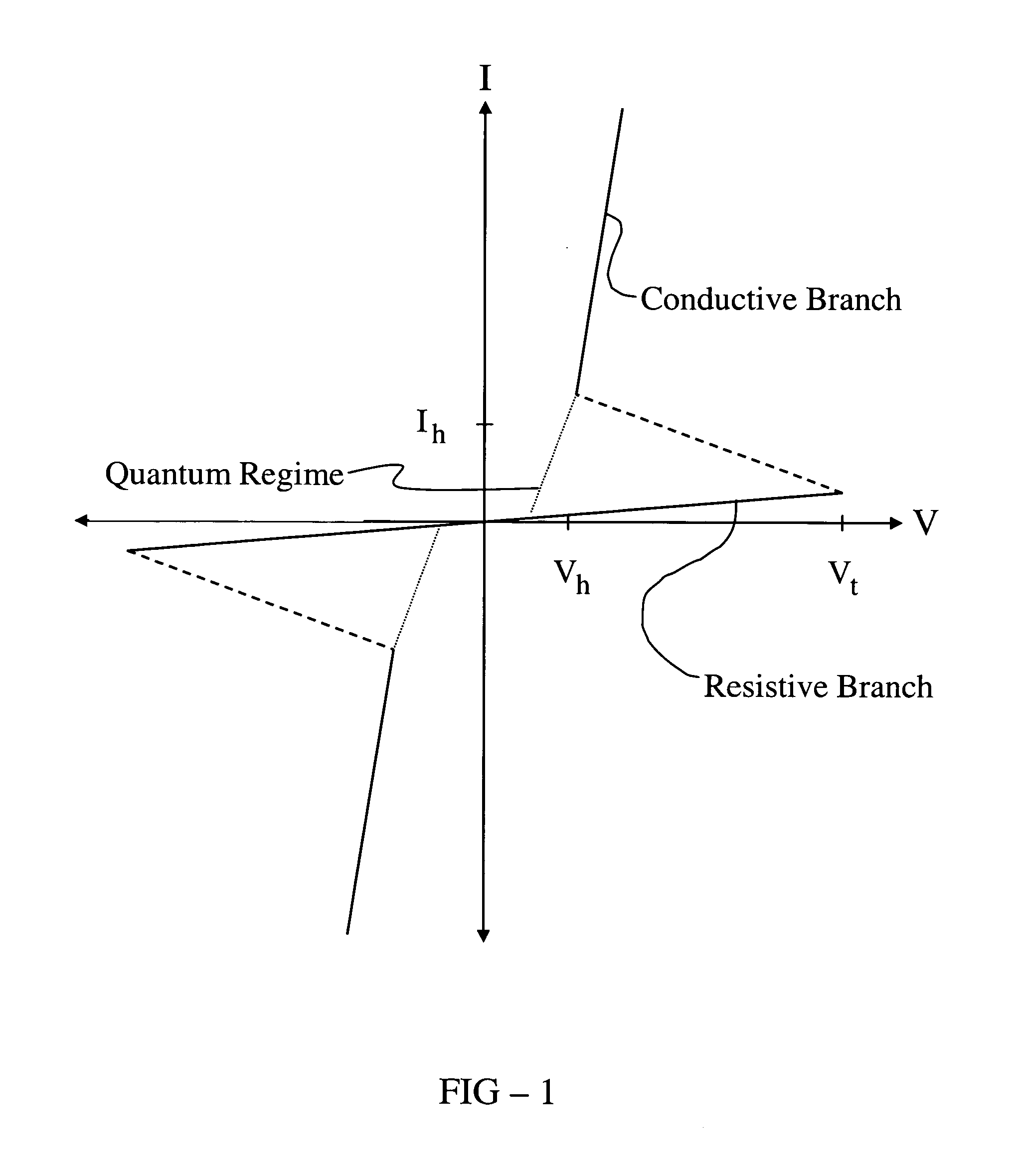

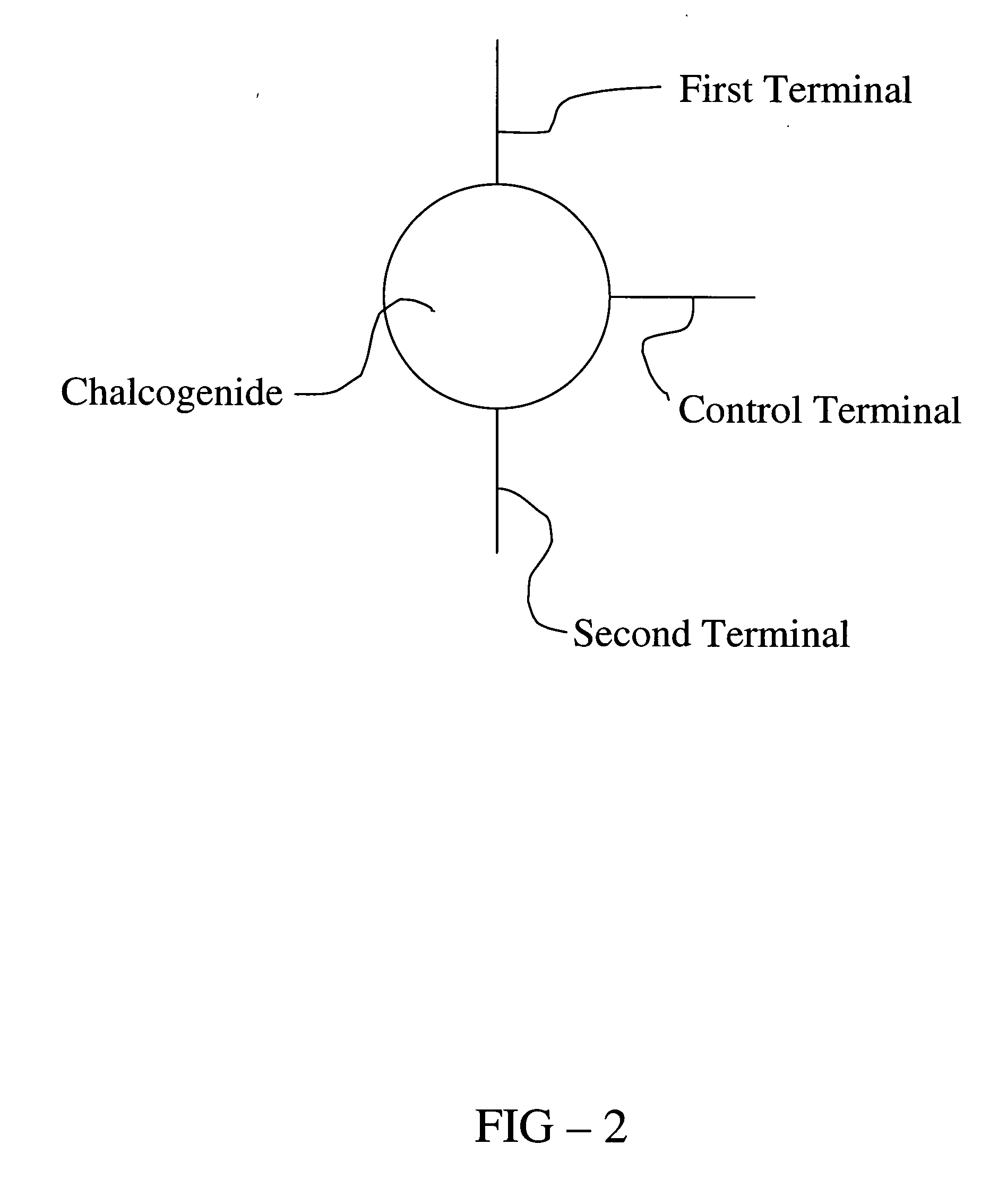

Multi-functional chalcogenide electronic devices having gain

ActiveUS7547906B2Bulk negative resistance effect devicesSemiconductor devicesElectrical resistance and conductanceControl signal

Multi-functional electronic switching and current control device comprising a chalcogenide material. The devices include a load terminal, a reference terminal and a control terminal. Application of a control signal to the control terminal permits the device to function in one or more of the following modes reversibly: (1) a gain mode in which gain is induced in the current passing between the load and reference terminals; (2) a conductivity modulation mode in which the conductivity of the chalcogenide material between the load and reference terminals is modulated; (3) a current modulation mode in which the current or current density between the load and reference terminals is modulated; and / or (4) a threshold modulation mode in which the voltage required to switch the chalcogenide material between the load and reference terminals from a resistive state to a conductive state is modulated. The devices may be used as interconnection devices or signal providing devices in circuits and networks.

Owner:OVONYX MEMORY TECH LLC

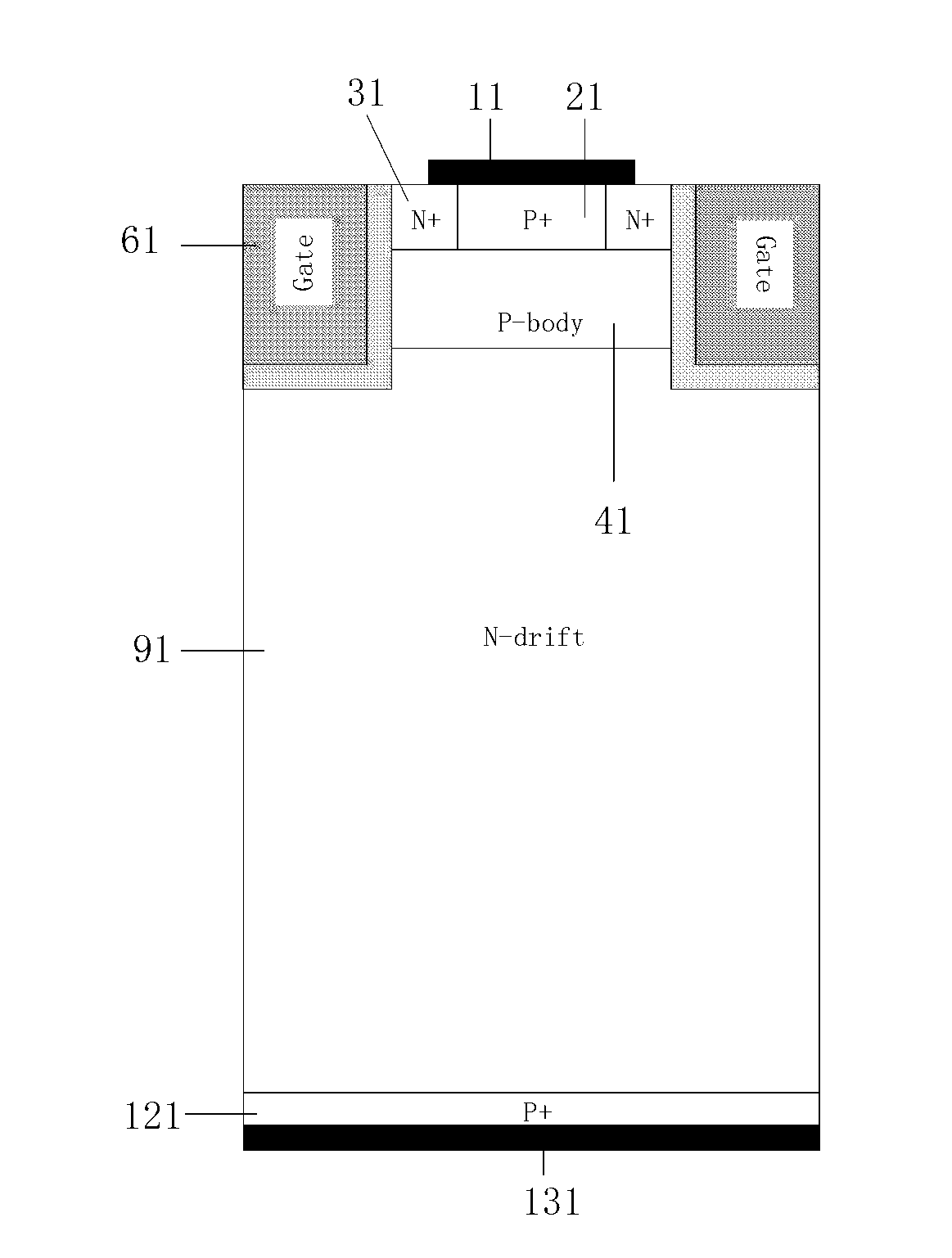

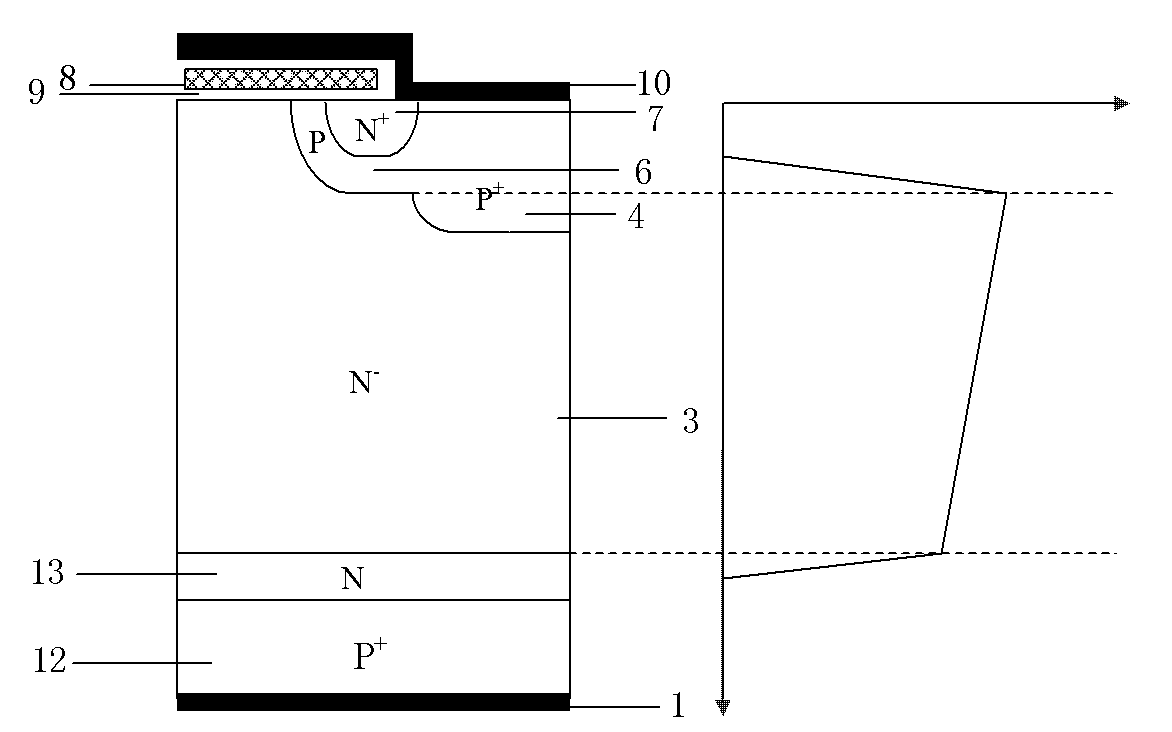

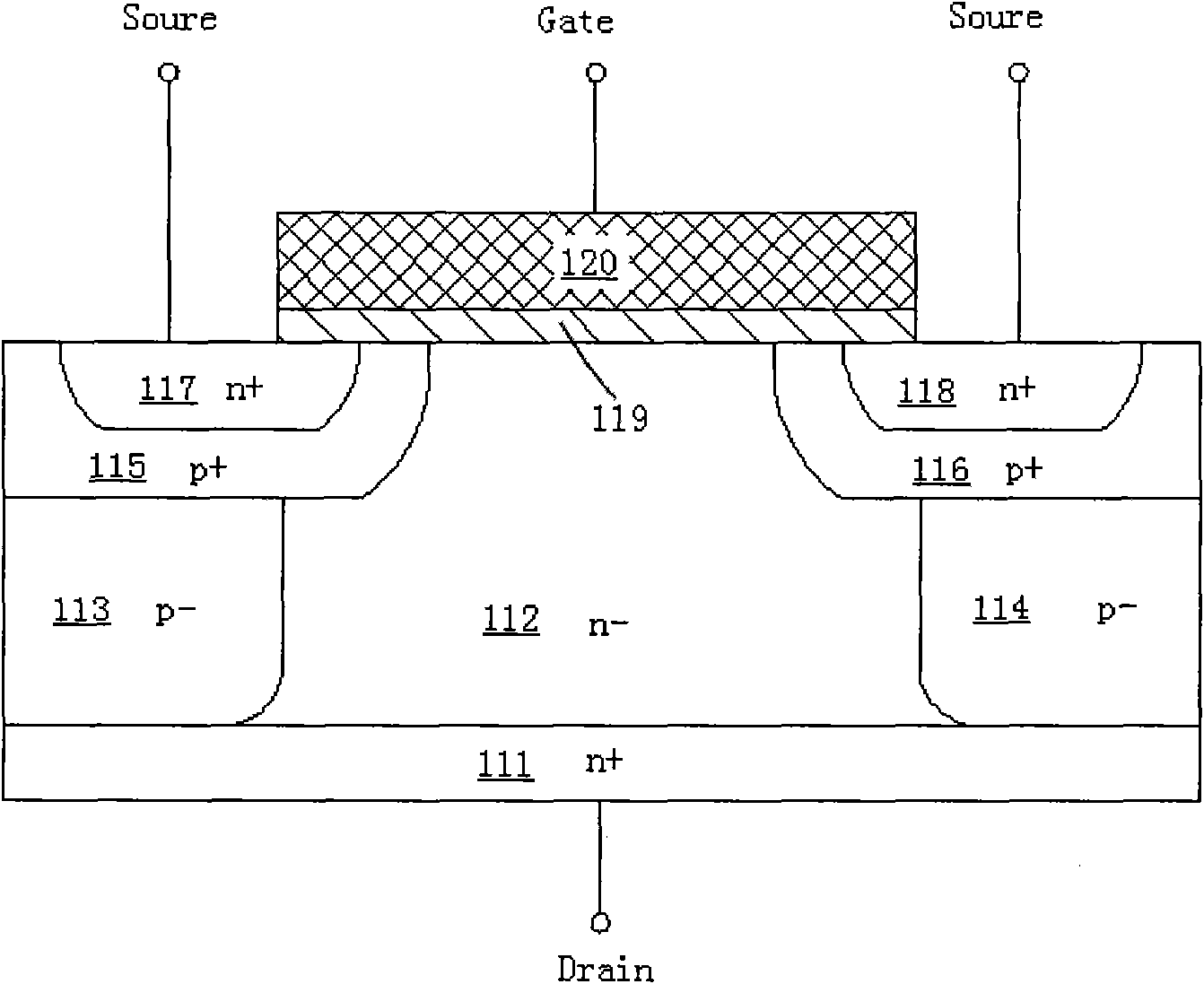

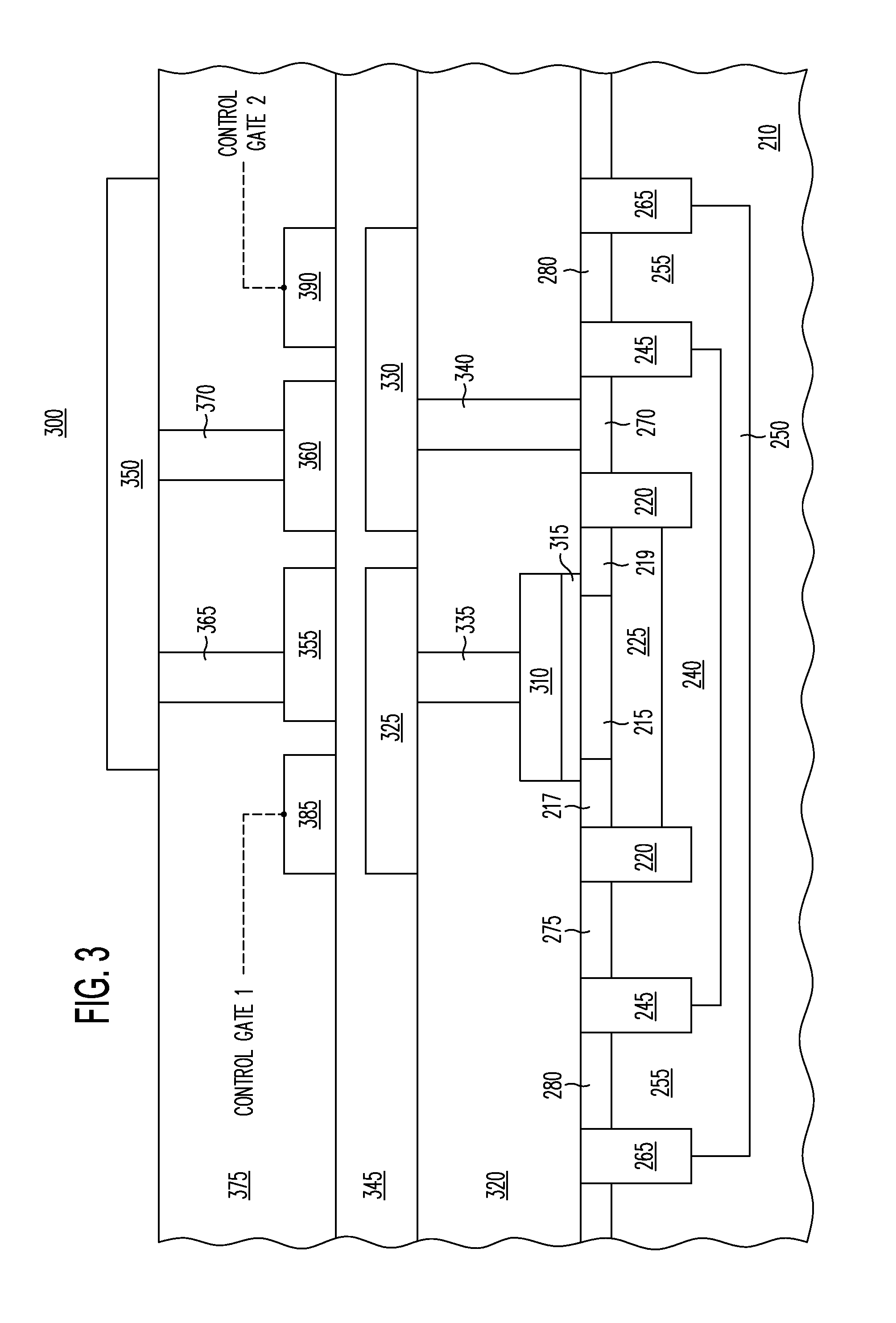

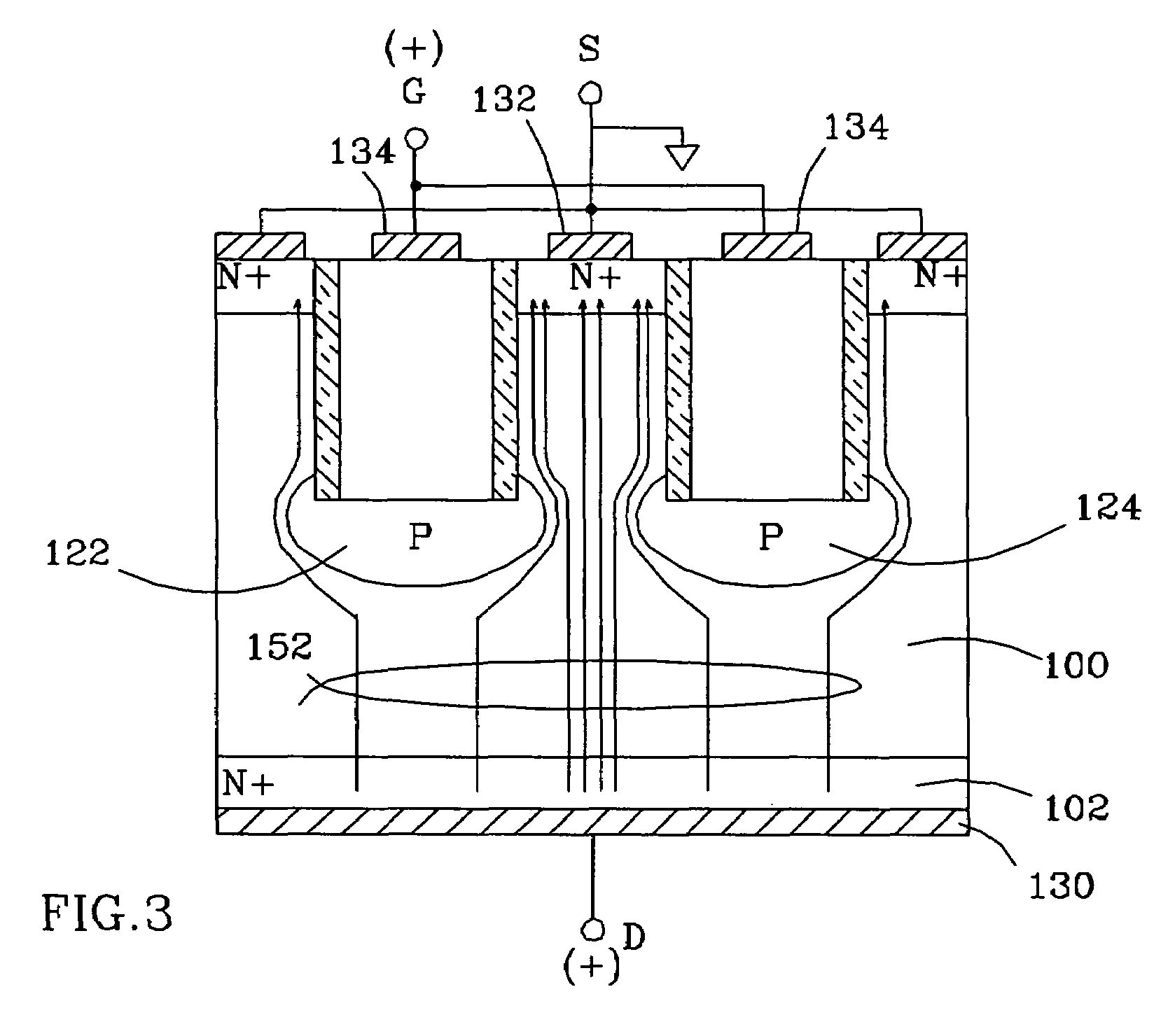

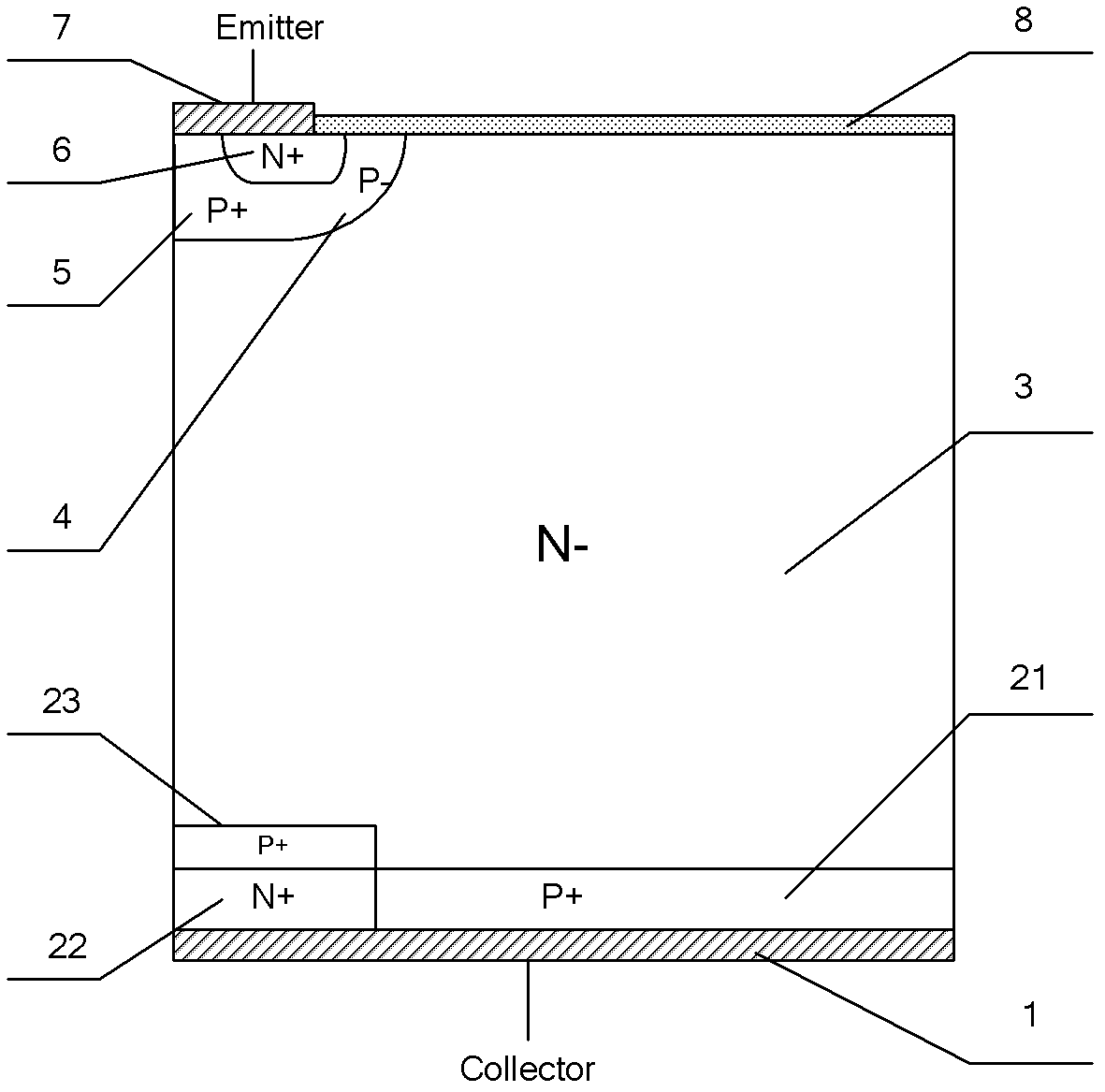

Insulated gate bipolar transistor with enhanced conductivity modulation

InactiveUS20080157117A1Reduced on-state power dissipationGood conductivity modulationThyristorSemiconductor/solid-state device manufacturingParasitic bipolar transistorConductivity modulation

A insulated gate bipolar transistors (IGBT) having an enhanced modulation layer provides reduced on-state power dissipation and better conductivity modulation than conventional devices. The IGBT includes an enhanced modulation layer disposed within a portion of the n− doped drift layer, in a n-type device, or p− doped drift layer, in a p-type device. The enhanced modulation layer contains a higher carrier concentration than the n− or p− doped drift layer. If the IGBT device is in an on state, the enhanced modulation layer decreases a size of a depletion region formed around the p well body region or n well body region. In a n-type enhanced modulation layer IGBT, electrons, traveling from the n+ region towards the emitter, are spread laterally and uniformly in the n− doped drift layer. In a p-type enhanced modulation layer IGBT, holes, traveling from the p+ region towards the emitter, are spread laterally and uniformly in the p− doped drift layer.

Owner:NORTHROP GRUMMAN SYST CORP

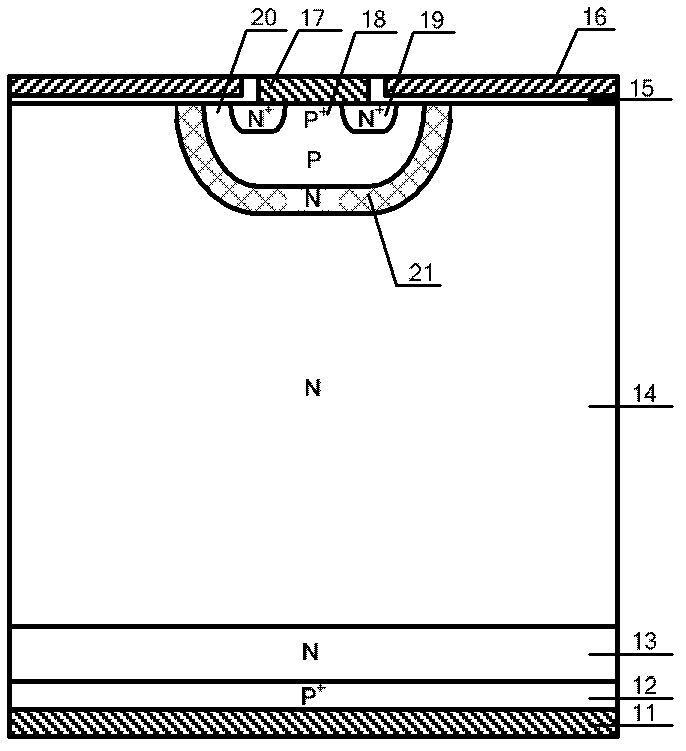

Trench-type insulated gate bipolar transistor (Trench IGBT) with enhanced internal conductivity modulation

InactiveCN102201439AReduce forward voltage dropImprove concentration distributionSemiconductor devicesTrench igbtParasitic bipolar transistor

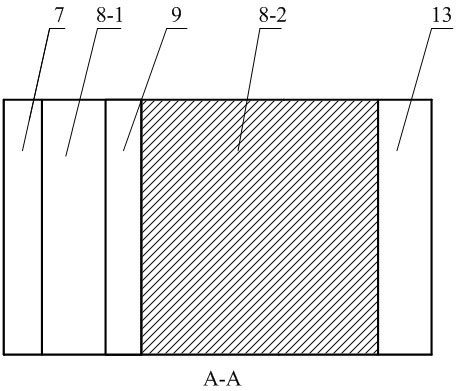

The invention relates to a Trench IGBT with enhanced internal conductivity, belonging to the technical field of power semiconductor device. According to the invention, on the basis of the structure of the conventional Trench IGBT device, a dielectric layer is introduced between a P<-> base region and an N<-> drift region of the device so as to effectively prevent the P<-> base region from extracting minority carrier holes at the edge of the N<-> drift region during forward conduction, thereby greatly increasing electrons and hole density of the whole N<-> drift region, optimizing the density distribution of carriers in the drift region, enhancing the conductivity modulation in the device, lowering the forward conduction voltage drop of the device, and better compromising the forward conduction voltage drop and the turn-off loss. Meanwhile, the chip surface utilization rate is not reduced and the chip area is saved. The Trench IGBT is suitable for the field of semiconductor power devices and power integrated circuits from small power to large power.

Owner:INST OF ELECTRONICS & INFORMATION ENG IN

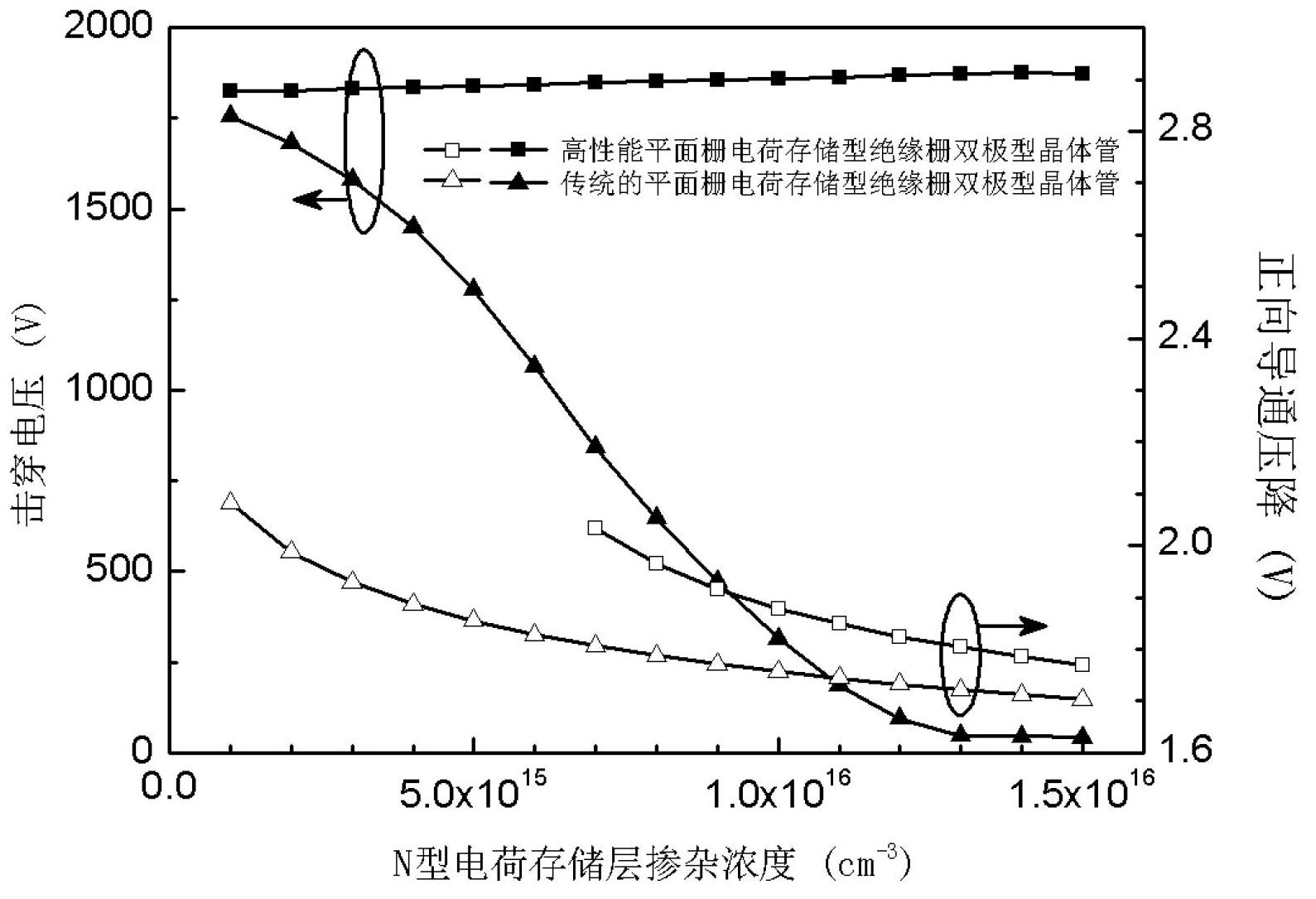

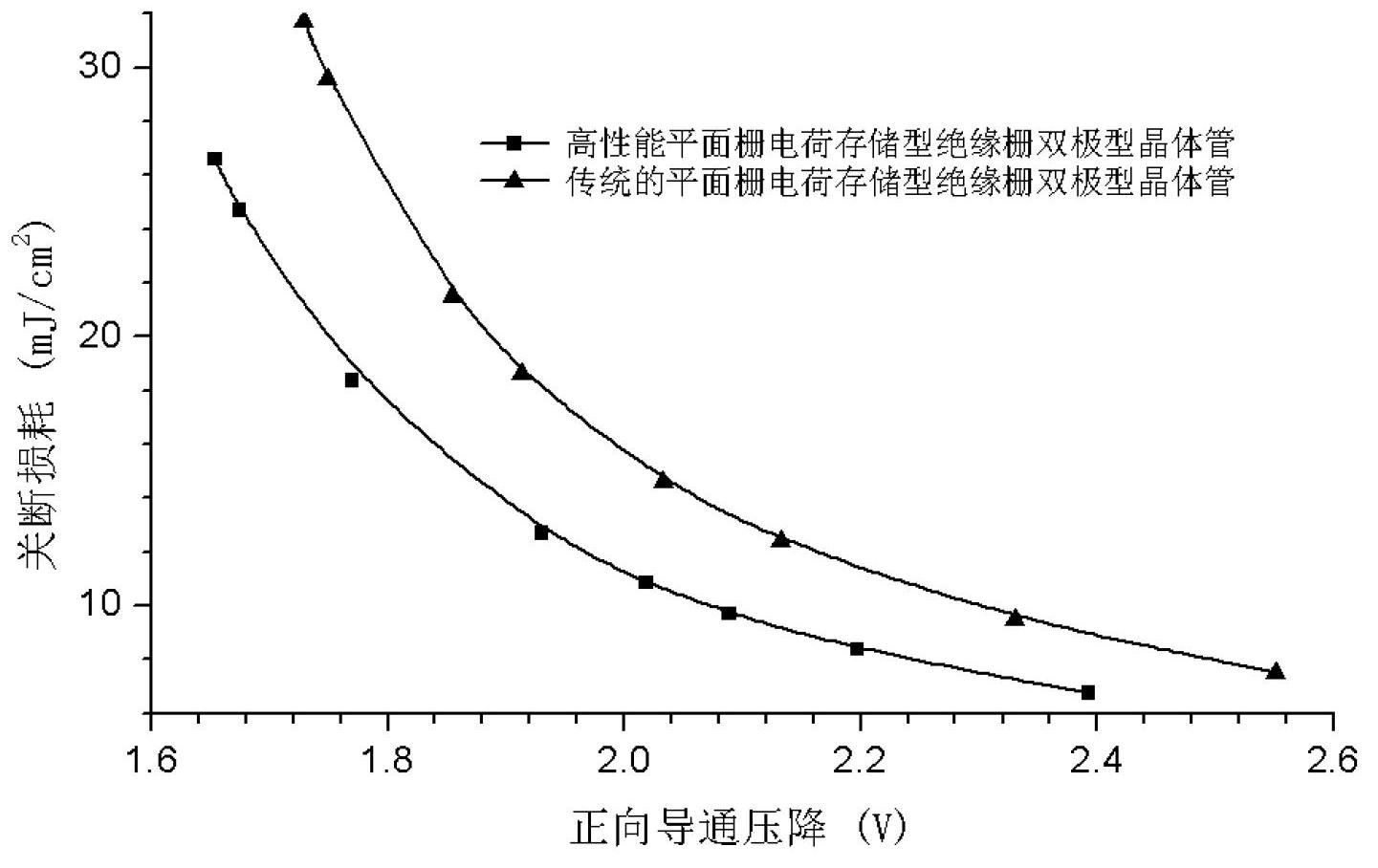

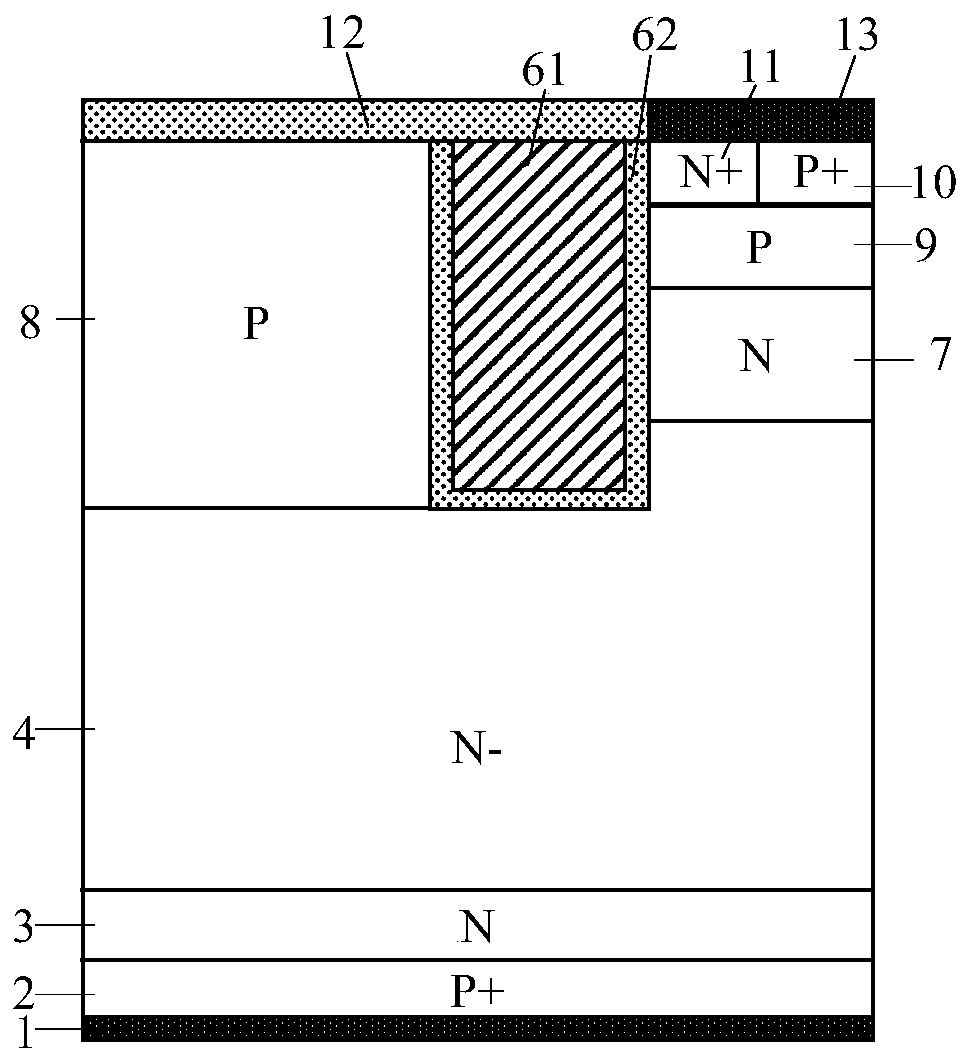

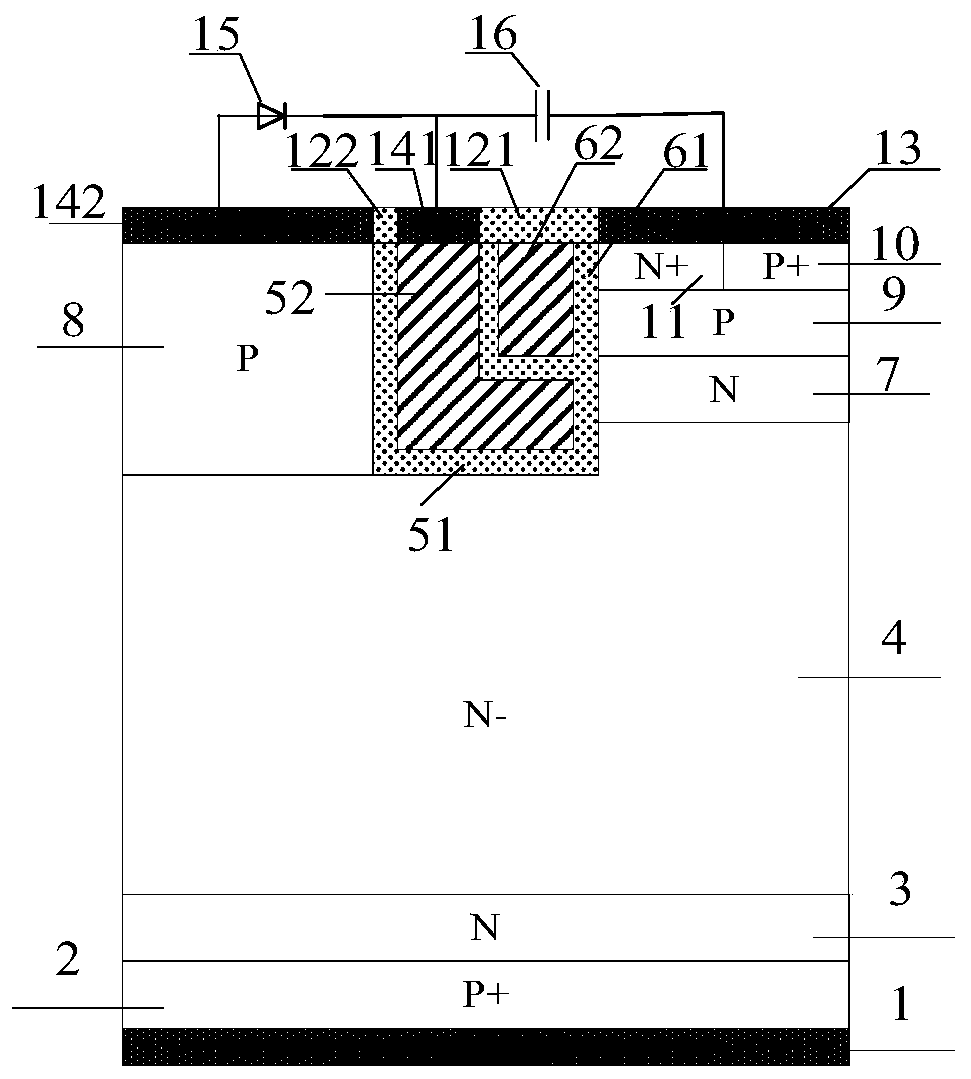

Flat-grid electric charge storage type IGBT (insulated gate bipolar translator)

InactiveCN102683402AImprove breakdown voltageGood forward voltage dropSemiconductor devicesConductivity modulationBreakdown voltage

The invention provides a flat-grid electric charge storage type IGBT (insulated gate bipolar translator), belonging to the technical field of a power semiconductor device. On the basis of the conventional flat-grid electric charge storage type IGBT, a layer of P type buried layer is induced between an N type drift region and an N type electric charge storage layer; due to the electric field modulating action of an additive PN (positive / negative) junction and the electric charge induced into the P type buried layer, the adverse impact of a highly-doped N type electric charge storage layer to the device is screened, so that the device can obtain high puncture voltage; and due to the electric field screening action of the P type buried layer to the N type electric charge storage layer, the IGBT can adopt higher N type electric charge storage layer doping concentration, so that the conductivity modulation of the N type drift region of the device can be enhanced, and the carrier distribution in the N type drift region can be optimized, and therefore, the device is lower in forward conductivity voltage drop and relatively good in compromises between the forward conductivity voltage drop and the turn-off loss. The IGBT is applicable to the filed of the semiconductor device and a power integrated circuit from small power to high power.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

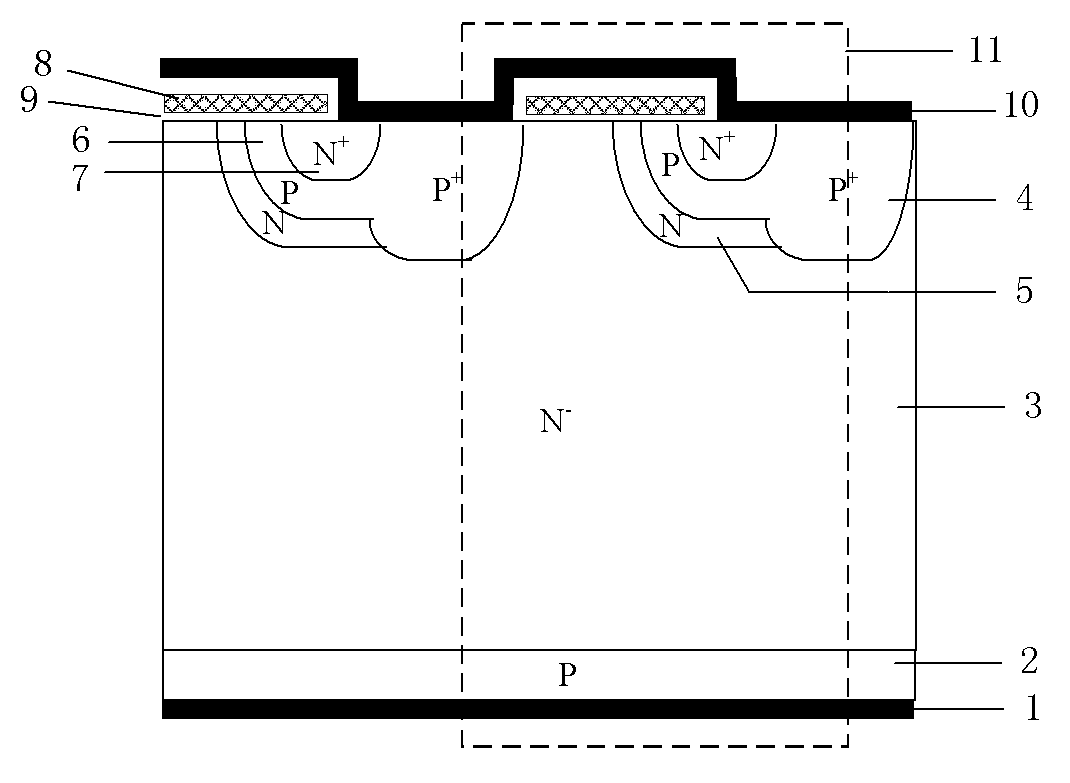

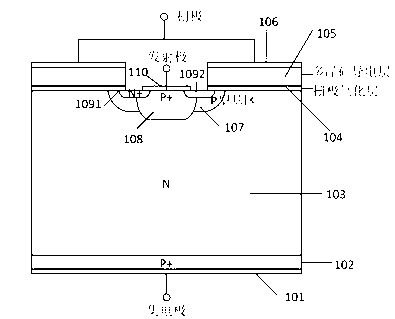

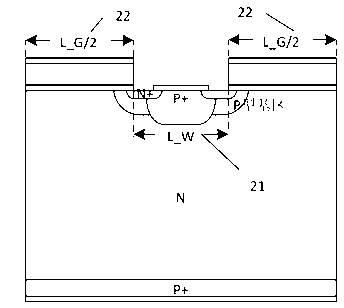

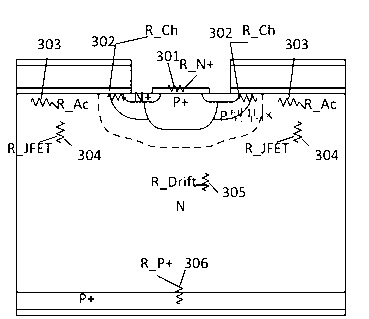

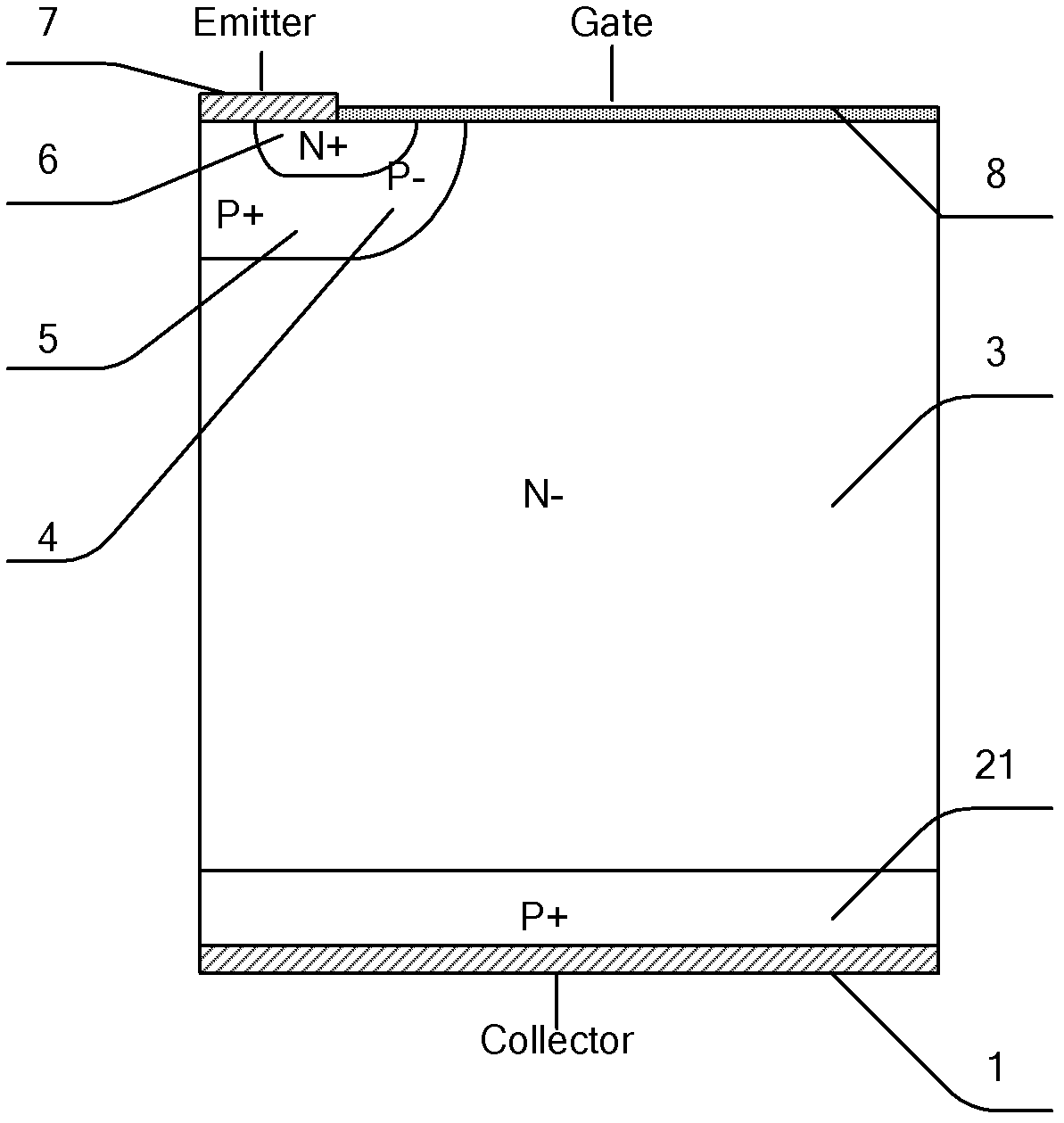

Enhancement mode planar insulated gate bipolar transistor (IGBT)

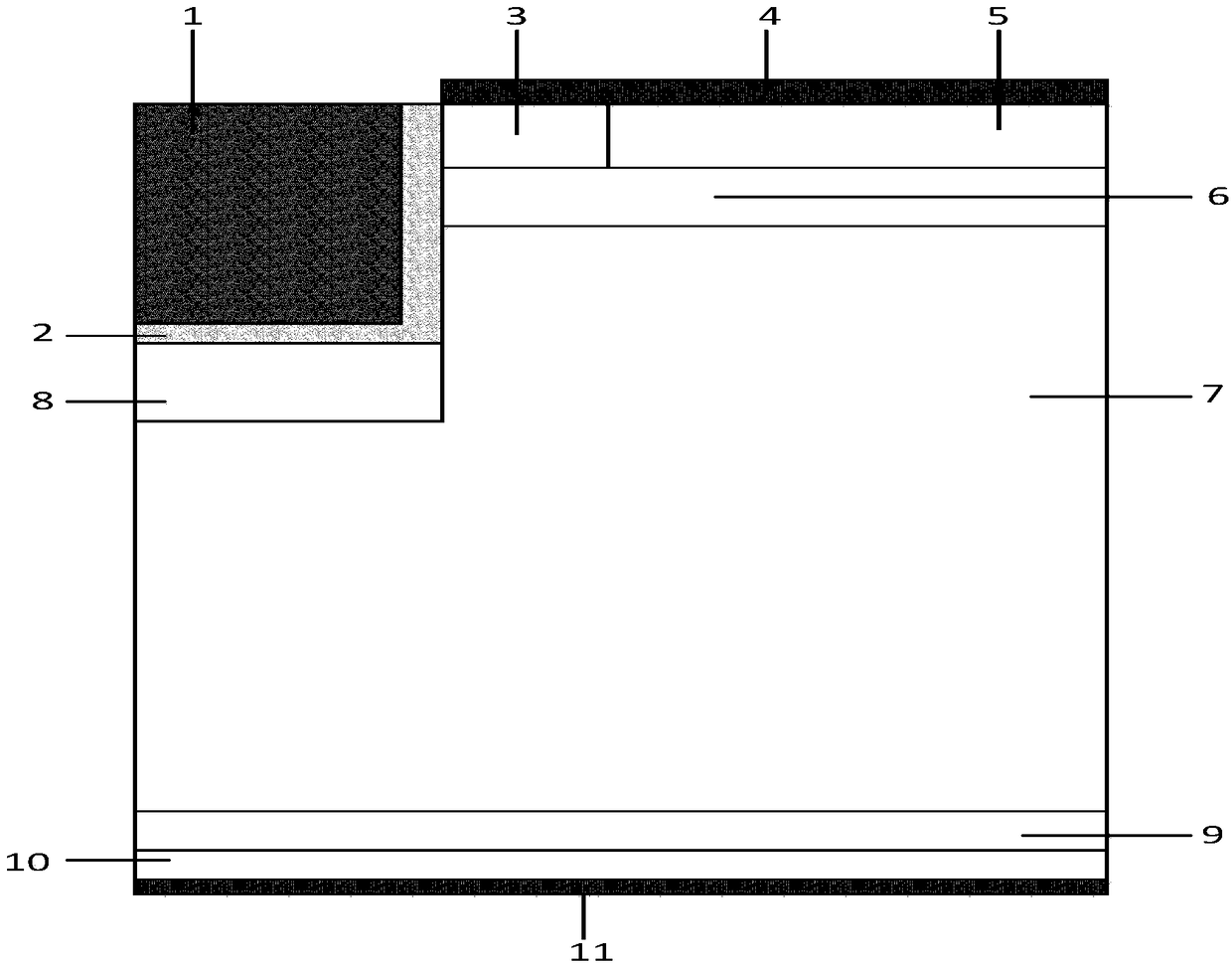

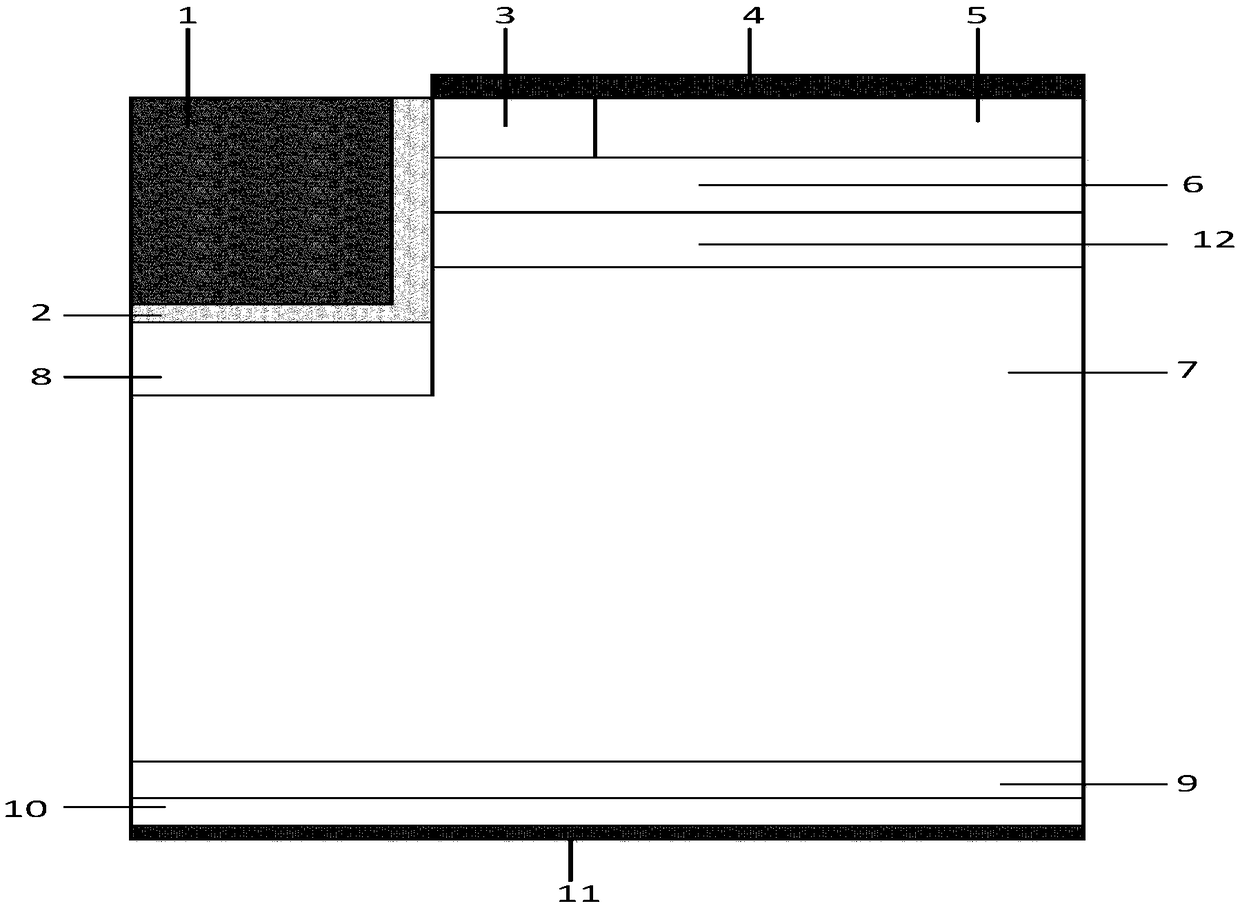

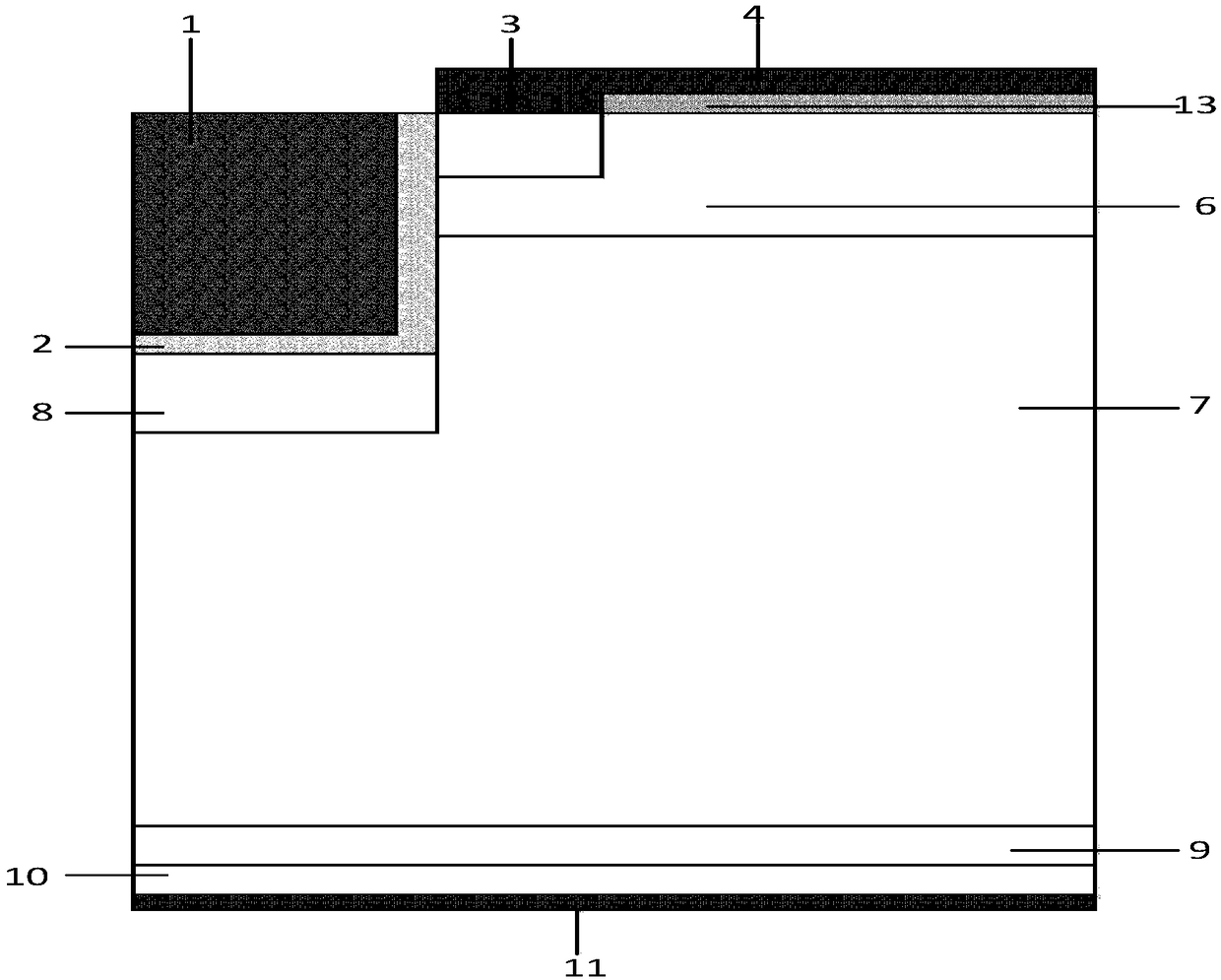

The invention discloses an enhancement mode planar insulated gate bipolar transistor (IGBT), belonging to the technical field of semiconductor power devices, wherein a hole bypass structure consisting of a P+ body region and a trench-type metallization emitter is introduced based on the traditional enhancement mode planar IGBT; and on the basis of the traditional non-through type planar IGBT, a JFET(Junction Field Effect Transistor) effect weakening structure consisting of an N type hole potential barrier layer and an N- draft region is introduced, and a path structure of expanded current formed by the N type hole potential barrier layer is introduced. Through the N type hole potential barrier layer, the conductivity modulation effect of one side of a device near the emitter can be enlarged, the JFET effect is reduced, the area flown through by electronic current is increased, therefore the on-state voltage drop is lowered; through the trench-type hole bypass structure, the current density of a latch can be increased, hole extraction is accelerated, and then the shutoff speed is enhanced; in addition, the area of an exhaustion region is increased by the P+ body region, thus the breakdown voltage is also increased; and the resistance of the device can be further lowered by the trench-type metallization emitter, thus the on-state voltage drop is reduced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

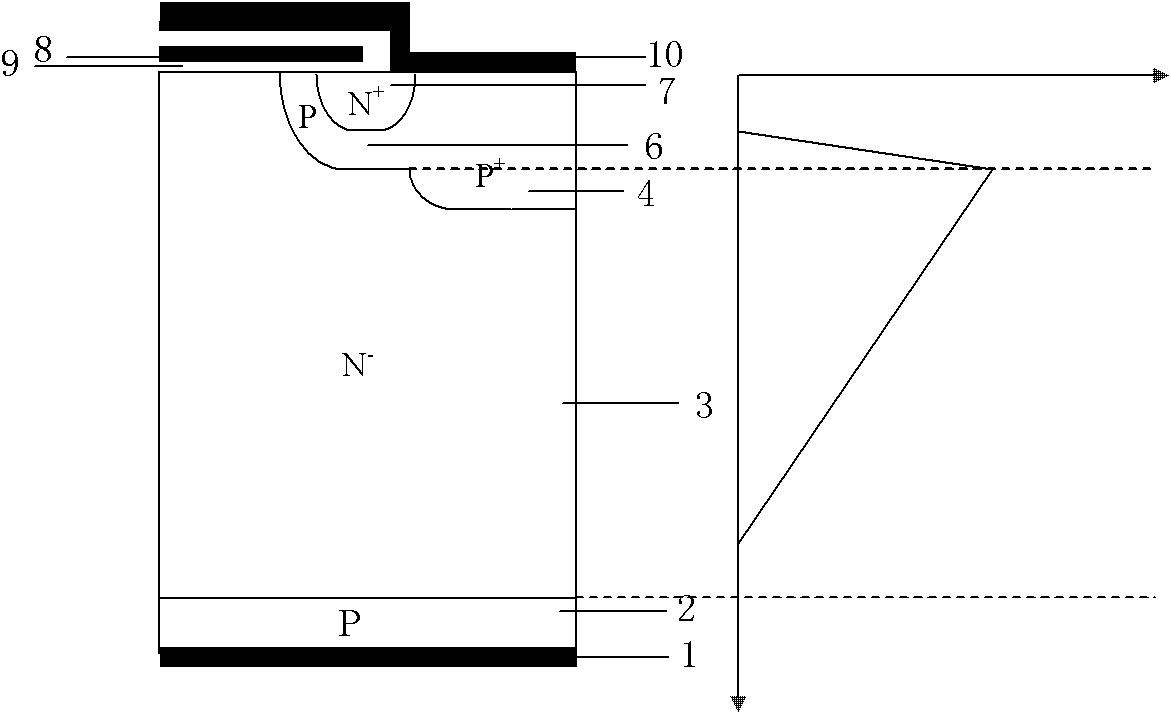

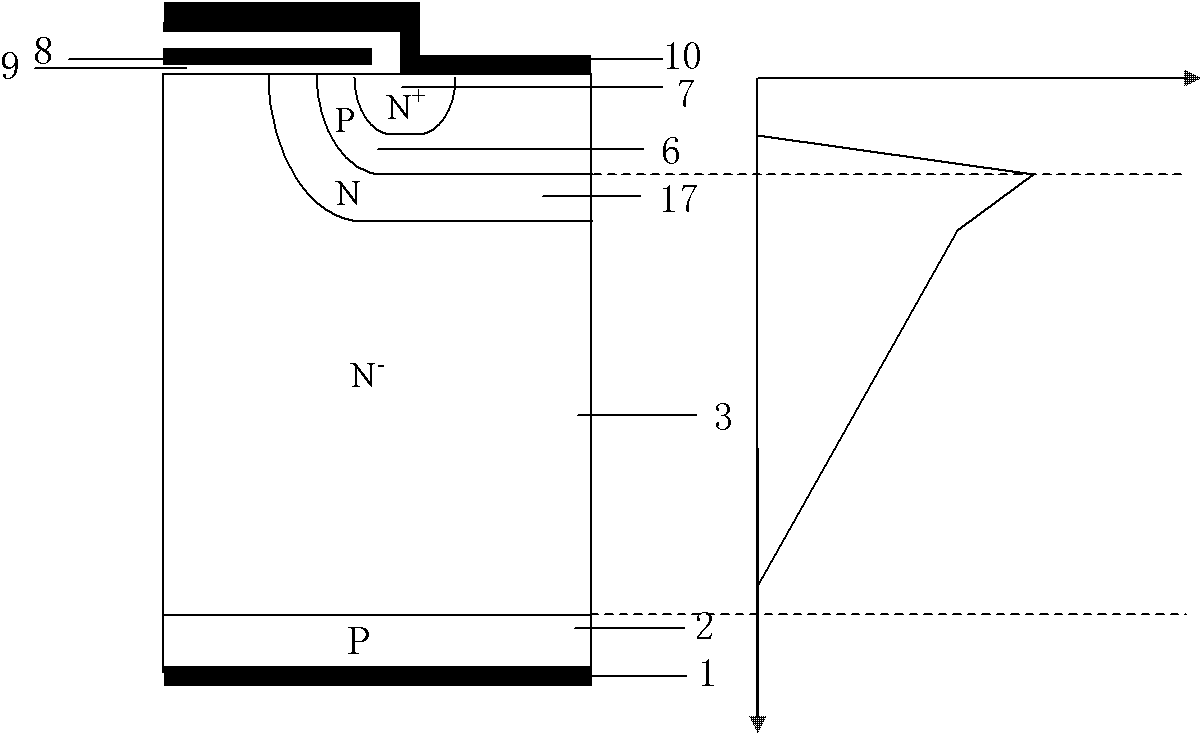

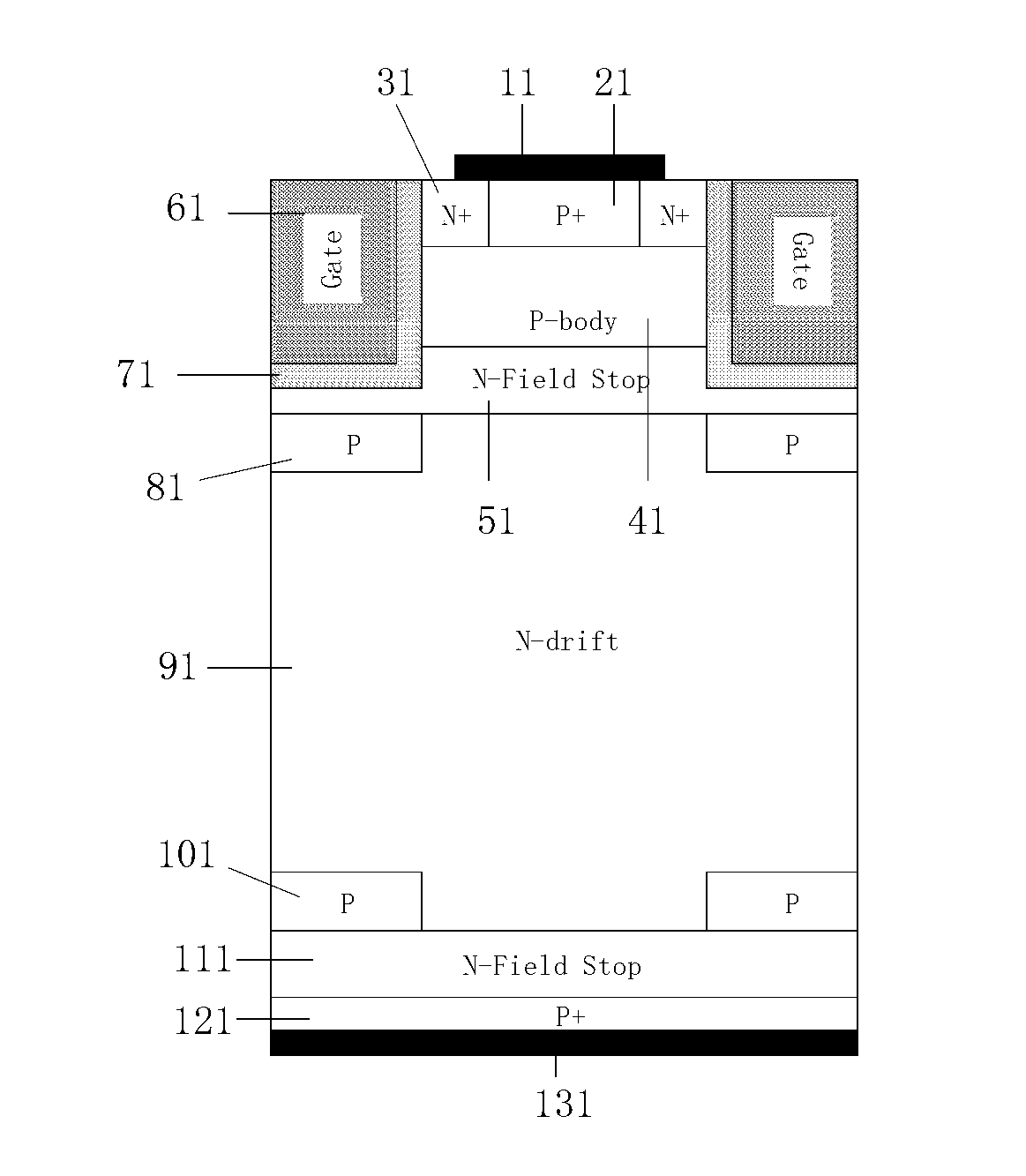

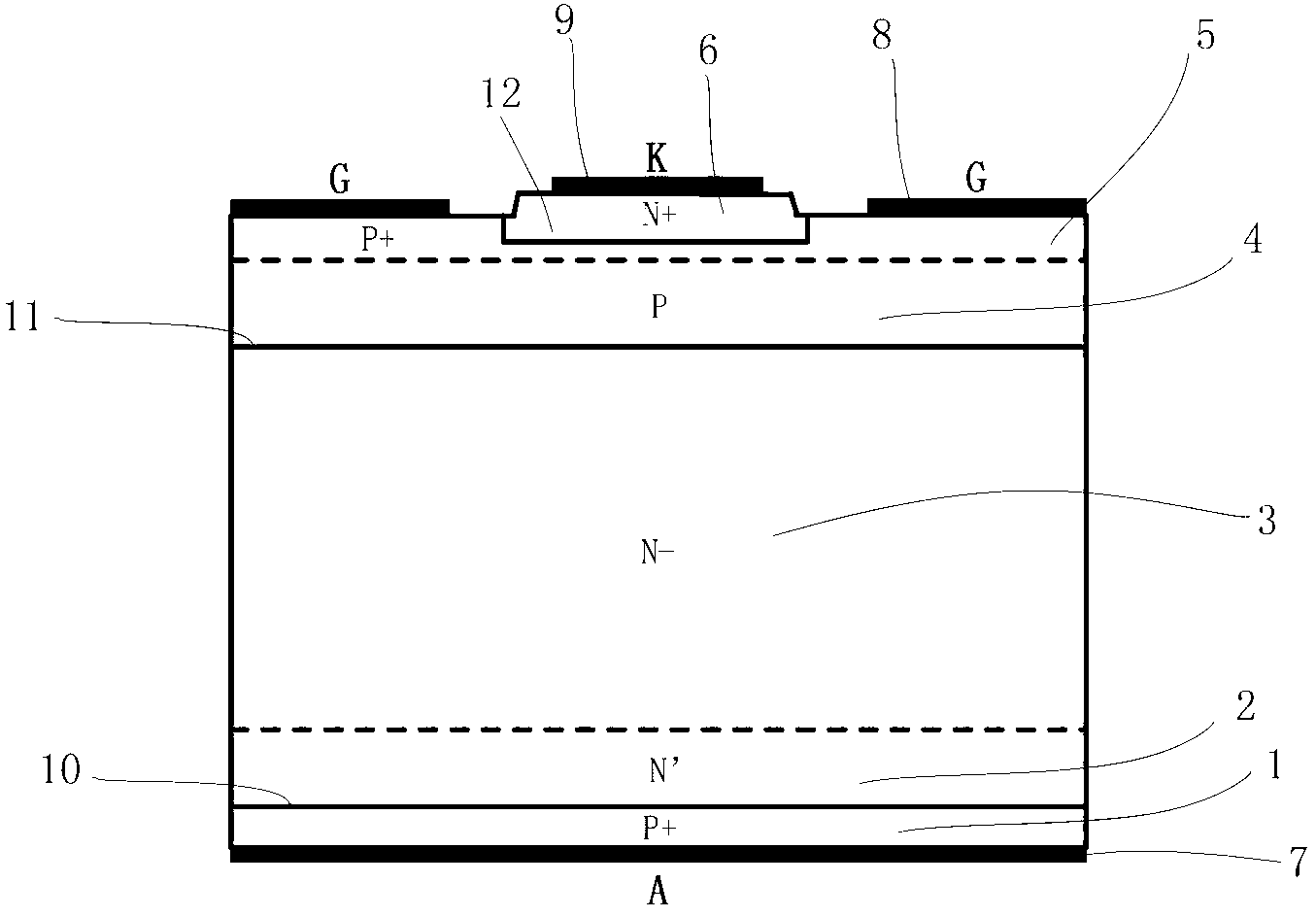

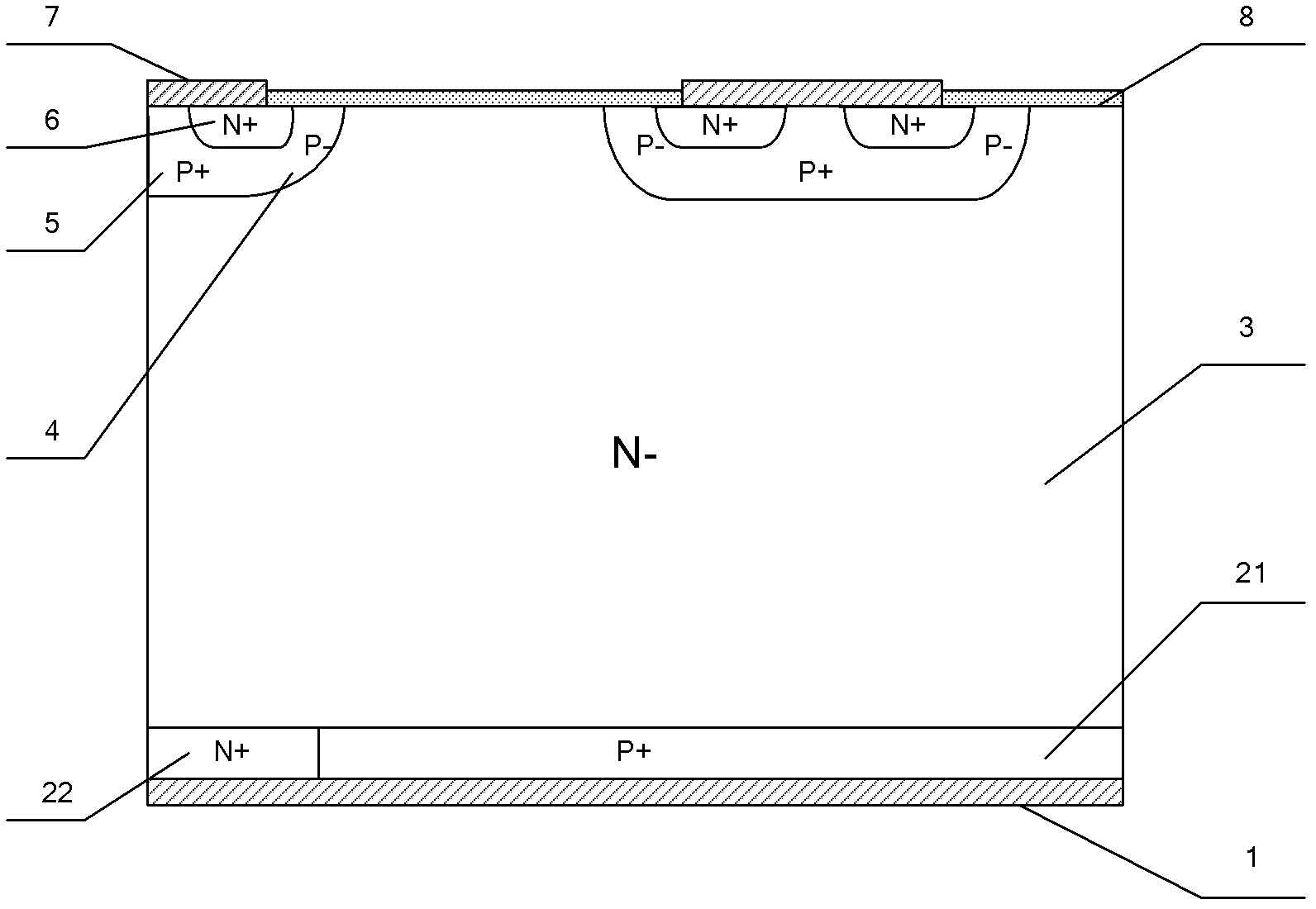

Reverse block (RB)-insulated gate bipolar transistor (IGBT) device provided with double-faced field stop with buried layers

InactiveCN103258847AImprove forward and reverse withstand voltage levelsReduce forward voltage dropSemiconductor devicesPower semiconductor deviceConductivity modulation

The invention discloses a reverse block (RB)-insulated gate bipolar transistor (IGBT) device provided with double-faced field stop with buried layers, and belongs to the technical field of power semiconductor devices. On the basis of a common RB-IGBT structure, an N-type FS ( Field Stop) layer is introduced between a P-type base region and an N-type drift region, an N-type FS ( Field Stop) layer is introduced between the N-type drift region and a P+ collector region, and meanwhile, P-type buried layers are introduced below a front field stop layer and above a back field stop layer. Under the condition that a device voltage withstanding requirement is met, the electric fields of the device are distributed in a trapezoid mode replacing a triangular mode by a manner that the thickness of the device is reduced. Carrier concentration distribution in the drift region is optimized, so that conductivity modulation in the device is enhanced, and forward direction breakover drop voltage and turn-off loss of the device are reduced.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA +1

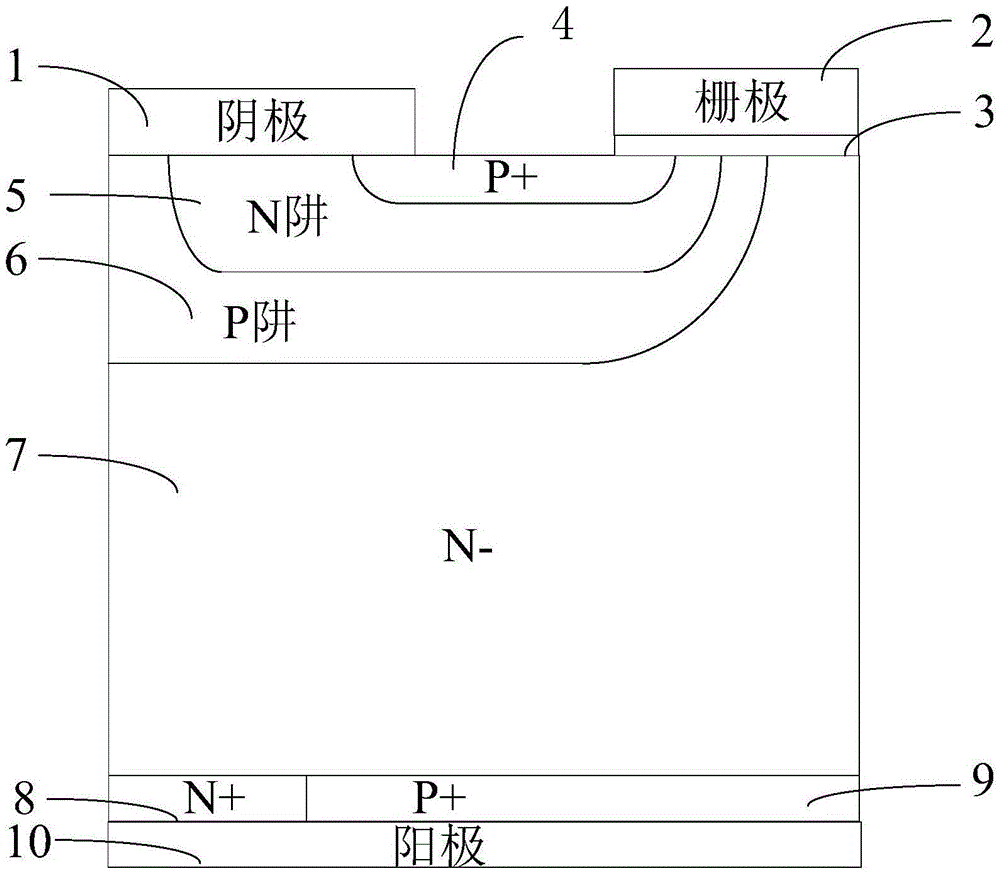

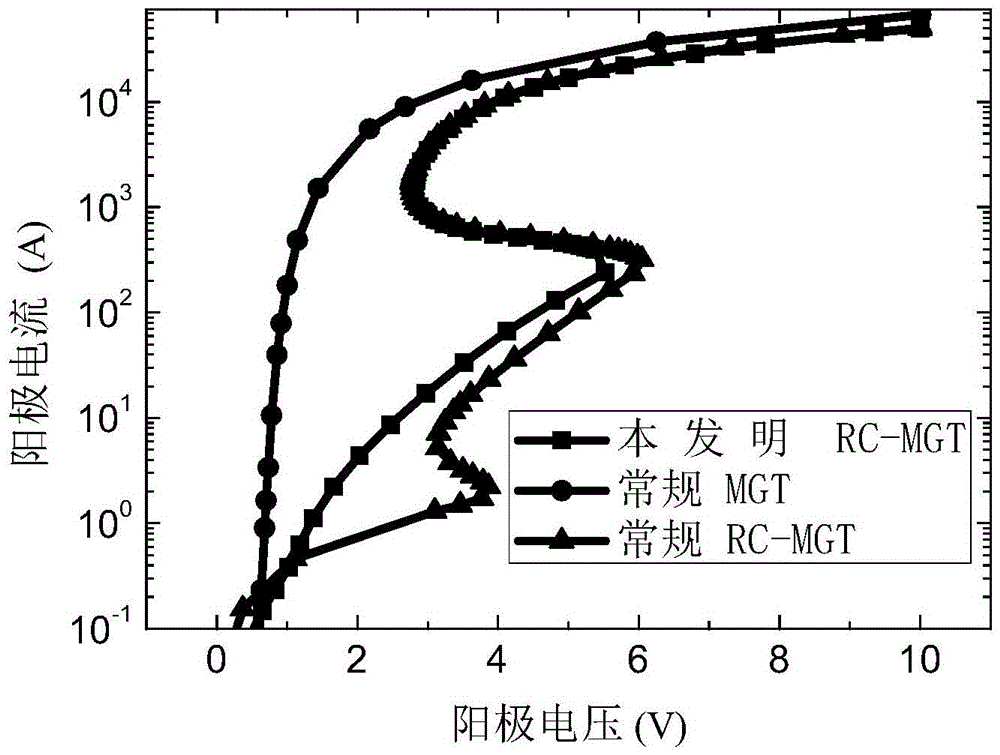

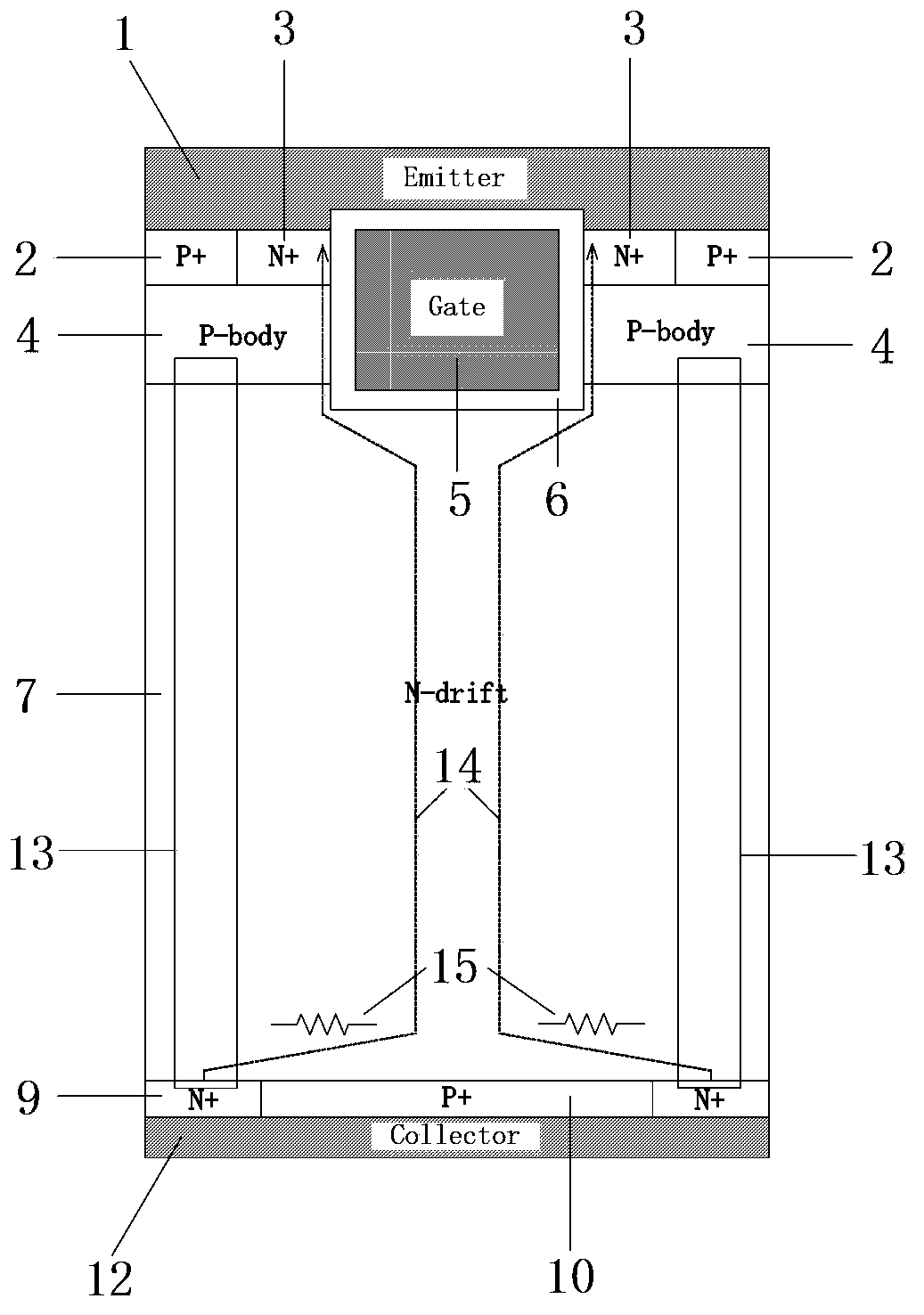

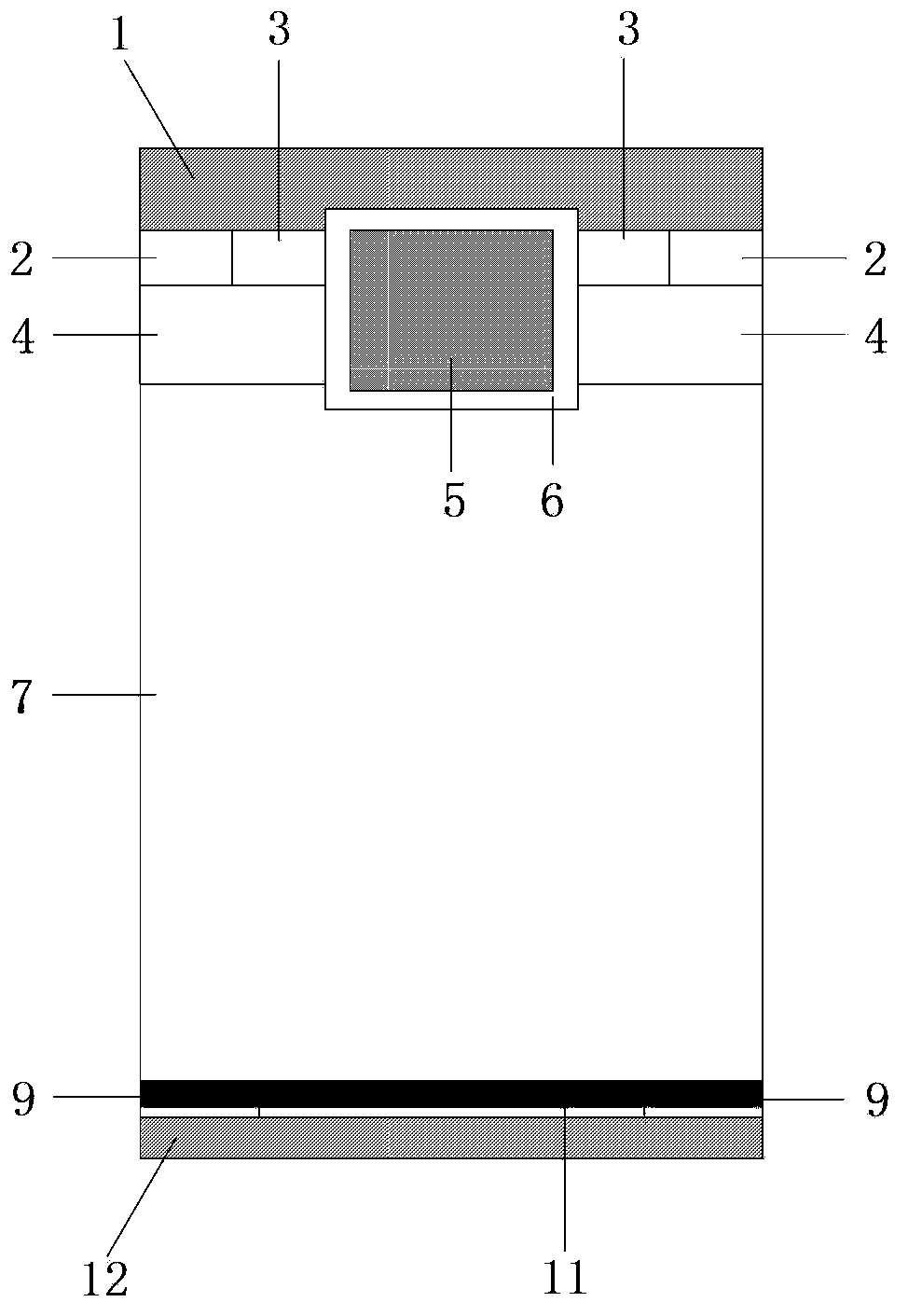

Reverse conducting MOS gate-controlled thyristor and fabrication method thereof

ActiveCN105679819AReduce cell lengthActs as an electron barrierThyristorSemiconductor/solid-state device manufacturingPower semiconductor deviceElectrical resistance and conductance

The invention belongs to the field of power semiconductor devices, and particularly relates to a reverse conducting MOS gate-controlled thyristor and a fabrication method thereof. The novel reverse conducting MOS gate-controlled thyristor provided by the invention can play a role of an electronic potential barrier when the current density is relatively low, so that the cell length of an N anode region is reduced; the effective area is reduced; the snapback effect is inhibited by greatly improving an anode short-circuit resistance; a P floating region also carries out hole emission towards an N drift region along with a voltage increase, so that conductivity modulation is carried out and the snapback effect is inhibited. Meanwhile, due to additionally introduced P floating region in reverse conduction, a parasitic PNPN structure is passed in conduction; the thyristor is conducted when a current reaches a certain magnitude; and the novel reverse conducting MOS gate-controlled thyristor also has high current conduction capability in the reverse direction.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

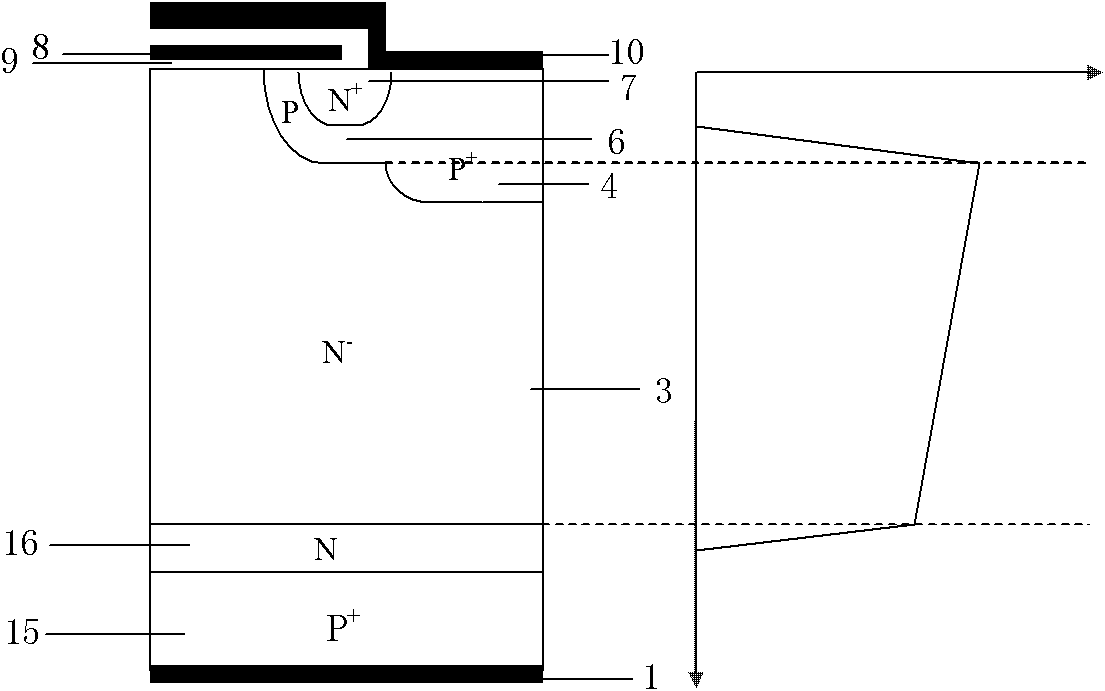

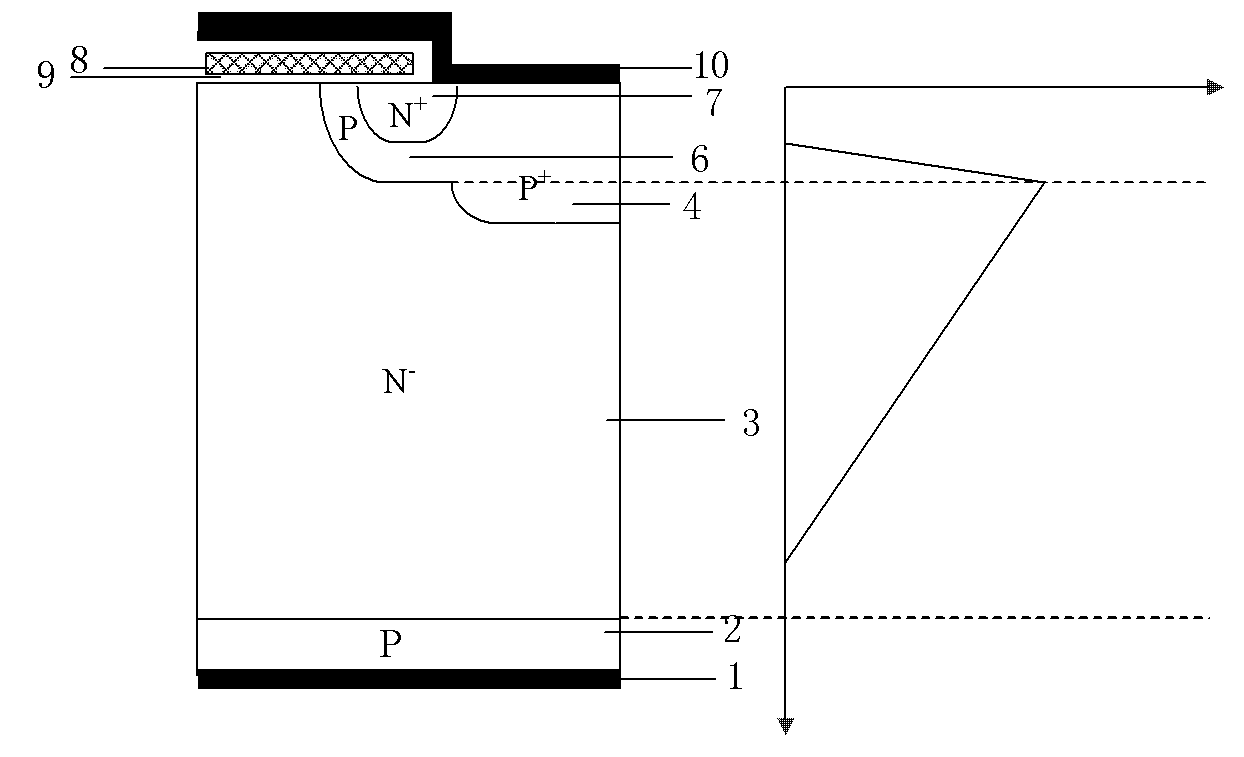

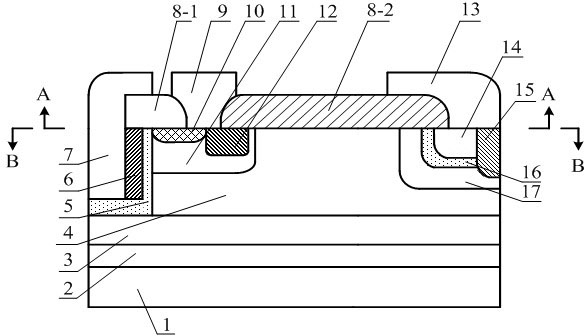

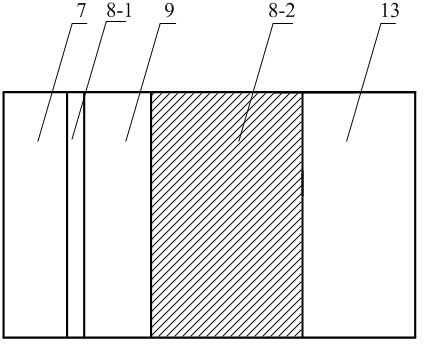

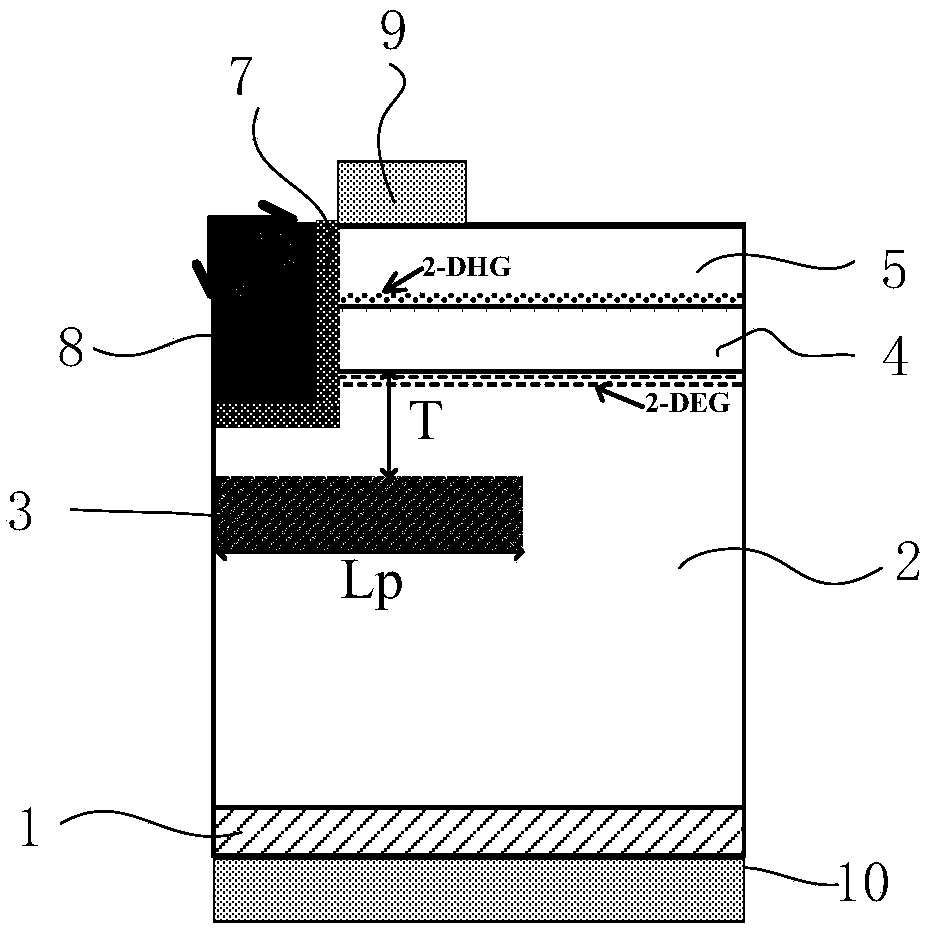

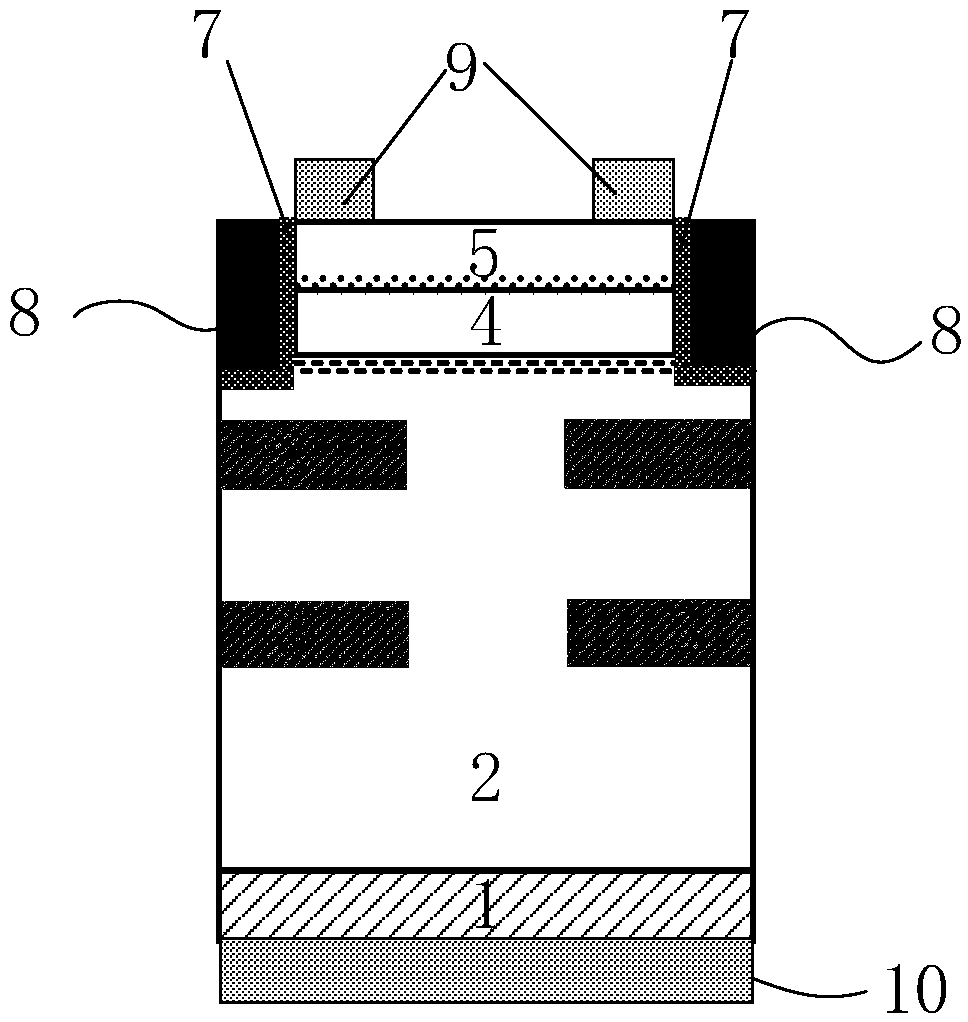

IGBT with current carrier storage layer and additional hole passage

InactiveCN102157551AIncrease the minority carrier concentrationPrevent openingSemiconductor devicesCharge carrierConductivity modulation

The invention discloses an insulate gate bipolar transistor (IGBT) with a current carrier storage layer and an additional hole passage, and belongs to the technical field of semiconductor power devices. In the IGBT, an N-type current carrier storage layer (5) and a large P<+> tagma (4) structure are introduced on the basis of a conventional planar non-pouch-through IGBT. The N-type current carrier storage layer (5) improves a conductivity modulation effect close to an emitter and the large P<+> tagma (4) structure plays a role in providing an additional passage for a hole so that the latch-up resistance is improved. Due to the design of the N-type current carrier storage layer (5) and the large P<+> tagma (4), the flow path of a hole current of the conventional IGBT is optimized, so that a safety operation area of a device is enlarged and the sensitivity of latch current density to a temperature is reduced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

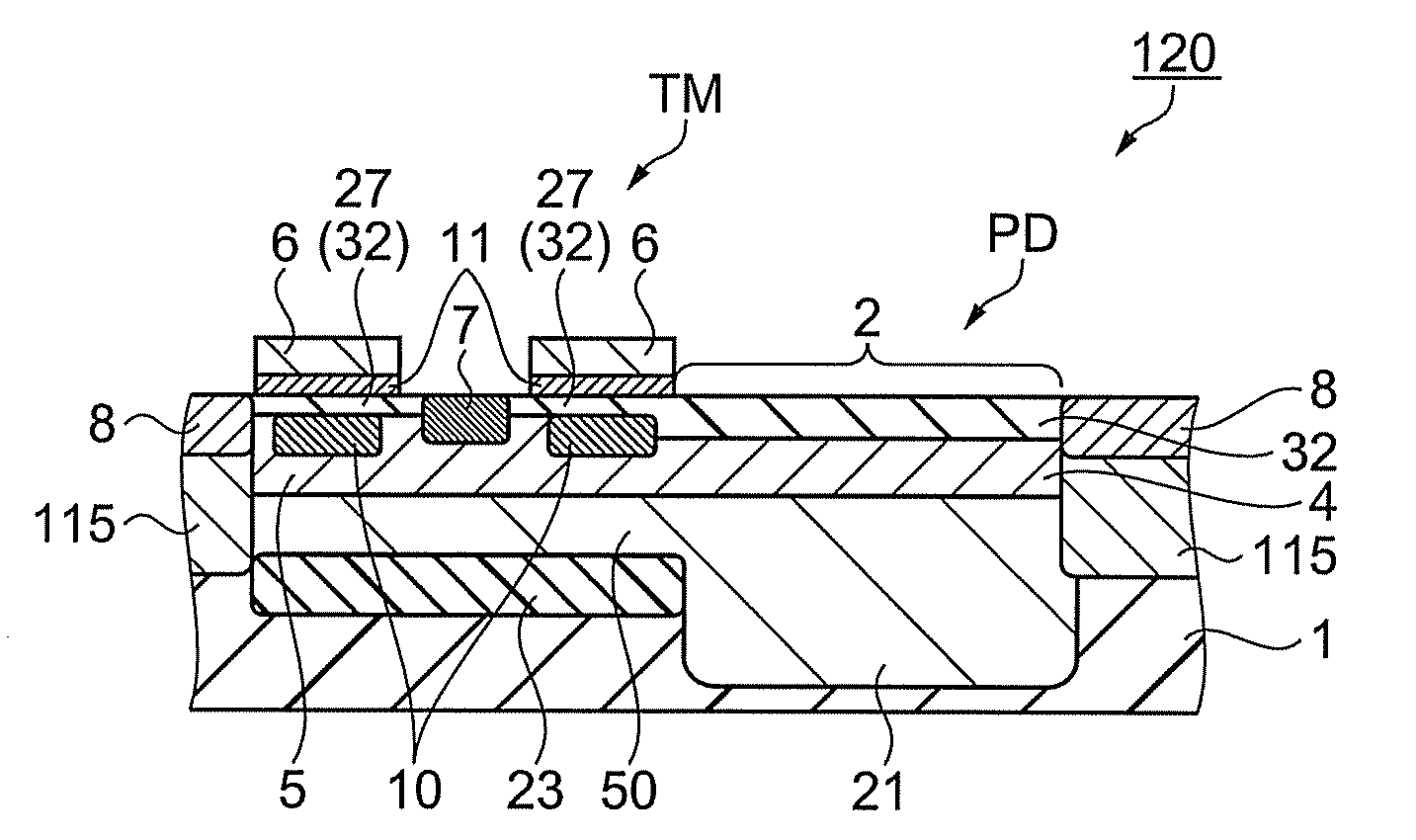

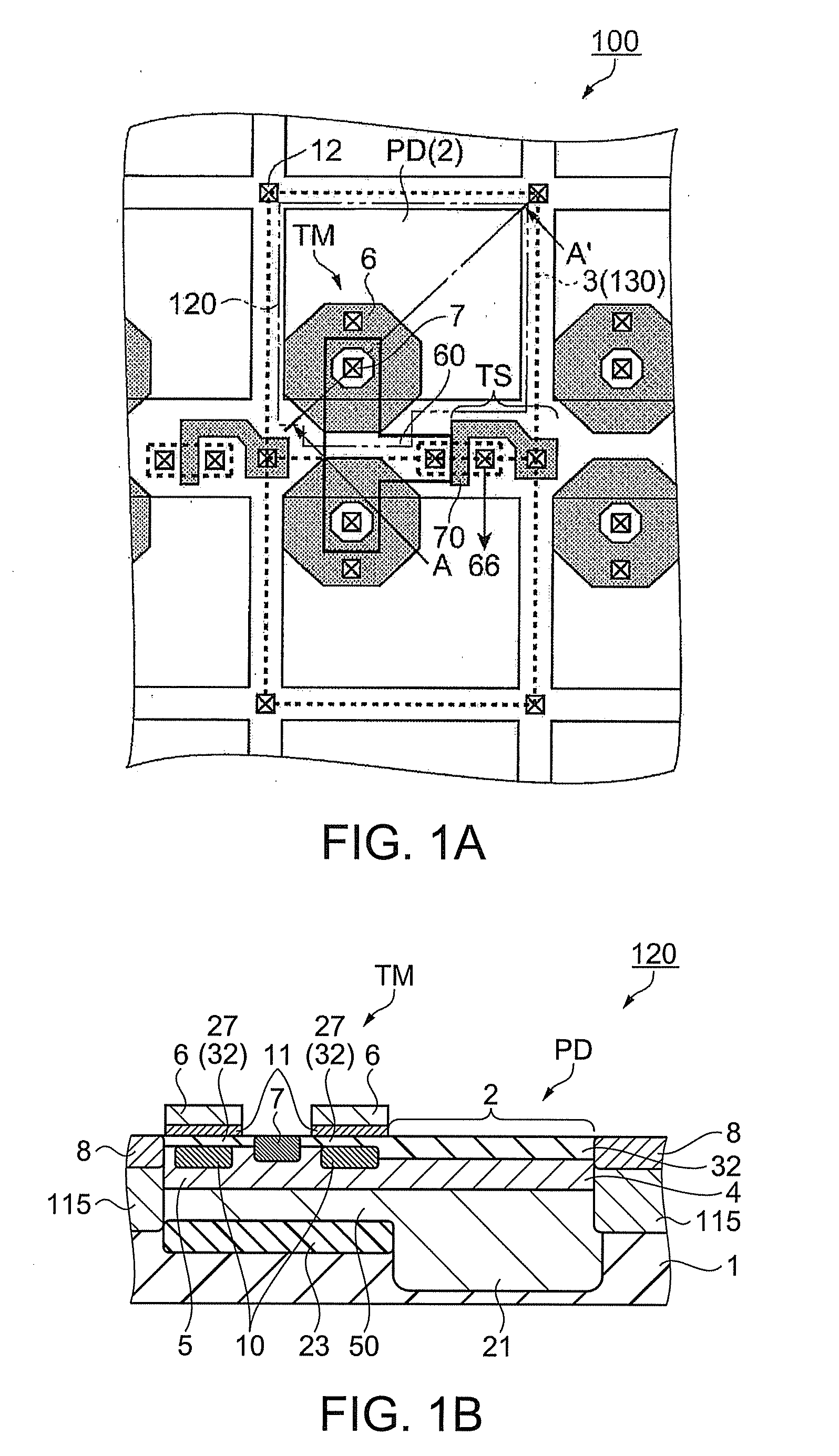

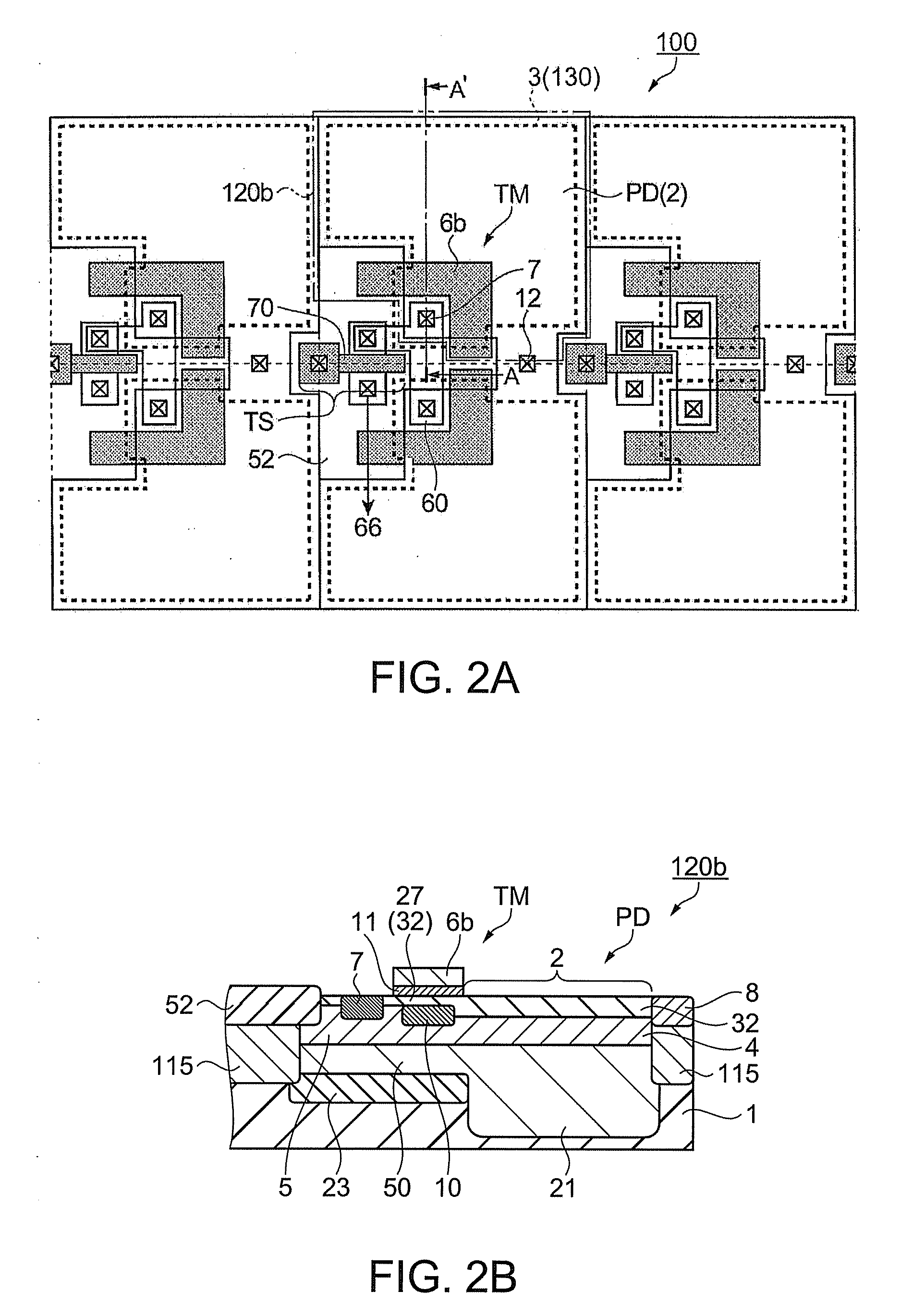

Image capturing apparatus

InactiveUS20090014628A1Improve image qualityIncrease the number ofTelevision system detailsTelevision system scanning detailsInsulation layerConductivity modulation

An apparatus including: a photodiode including: a first conductivity substrate; a second conductivity PD-well on the substrate's first surface side; and a first conductivity collection well inside the PD-well; a modulation transistor including: a second conductivity TR-well connected with the PD-well, and a junction depth shallower than that of the PD-well; a first conductivity modulation well inside the TR-well, and connected with the collection well; a second conductivity source inside the modulation well, and including a region contacting the first surface; a gate electrode in a region partially covering the modulation well and enclosing the source; a gate insulation layer between the gate and the first surface; and a second conductivity drain partially sandwiching the gate and opposing the source, and including a region contacting the first surface; and a transfer transistor connected to modulation transistors in pixels between the source and a connected source line.

Owner:SEIKO EPSON CORP

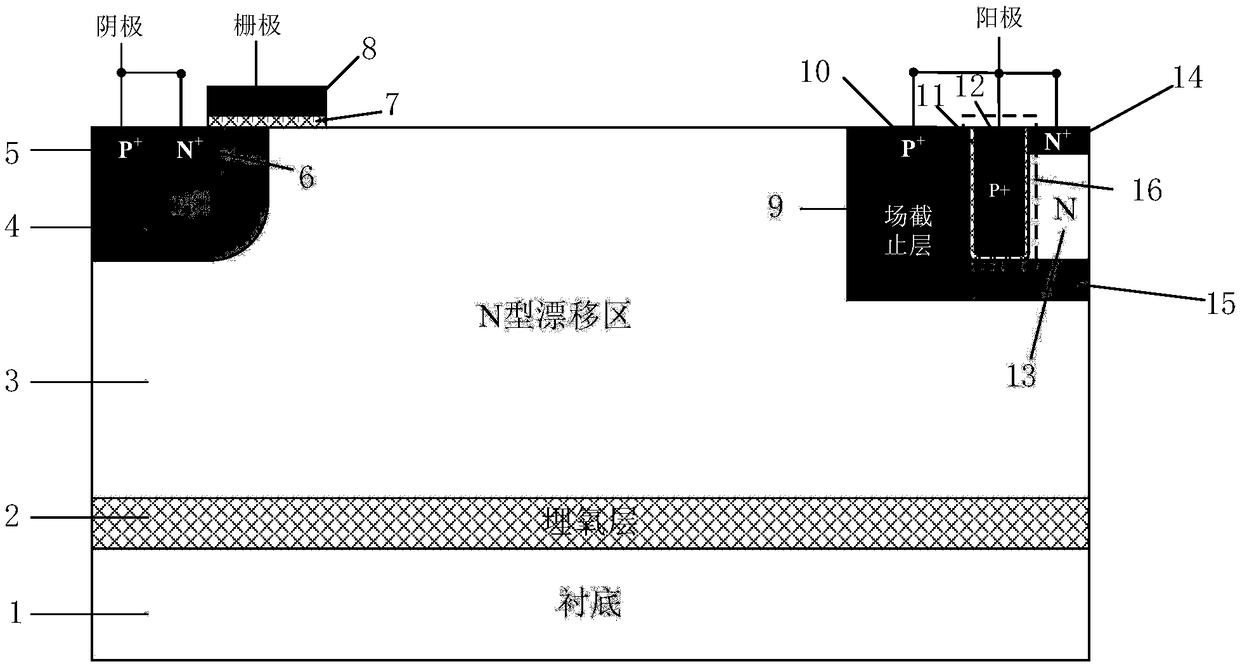

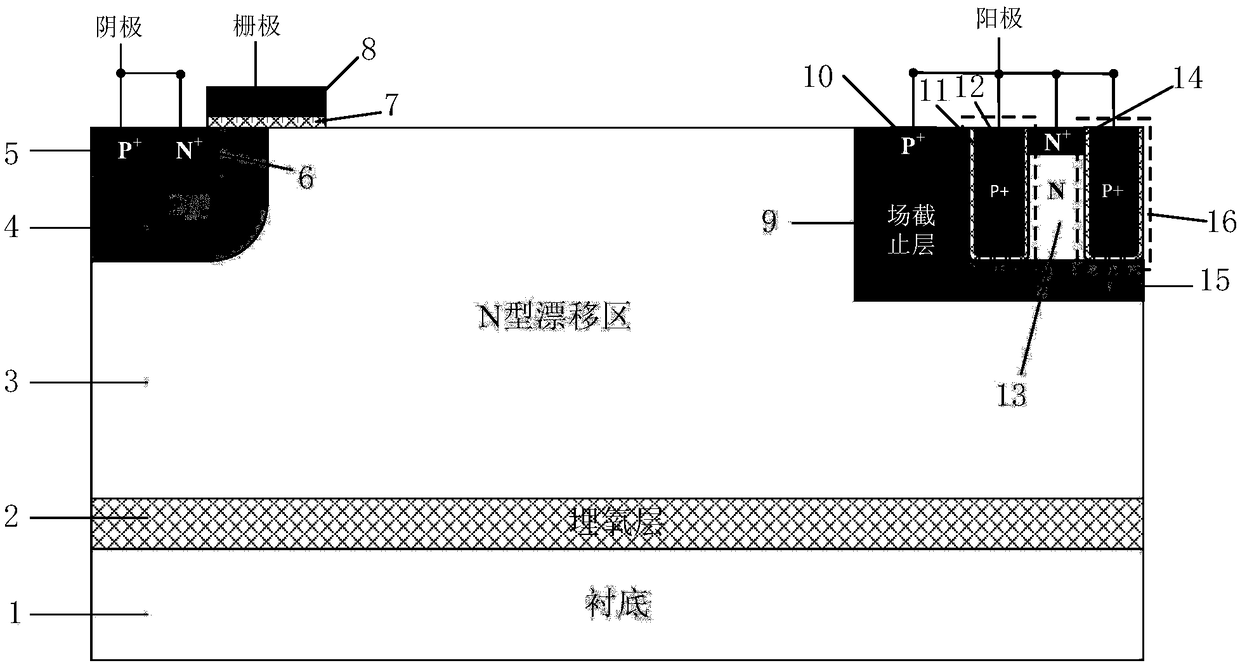

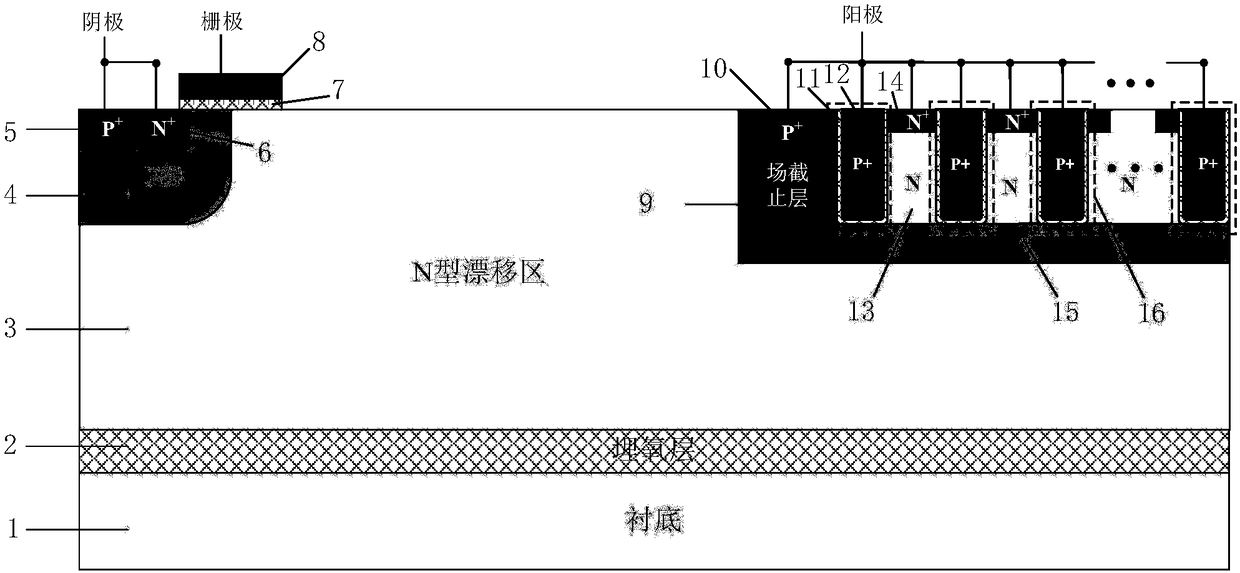

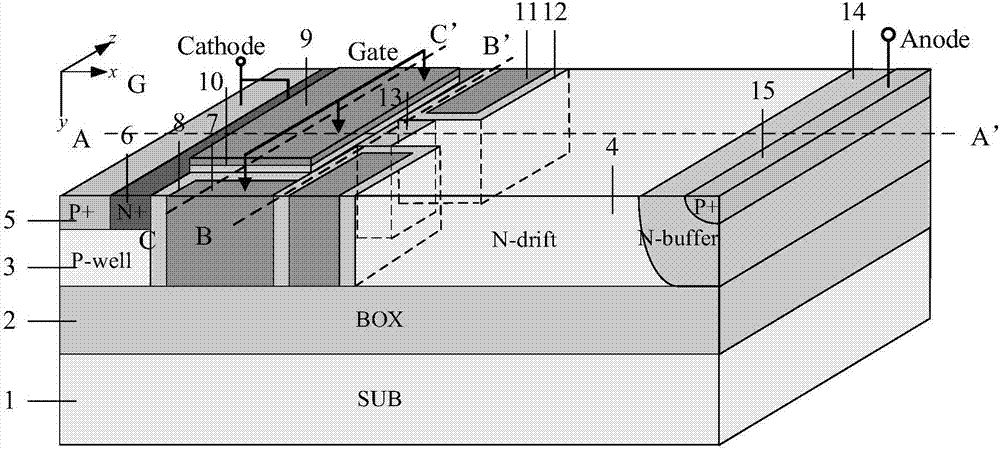

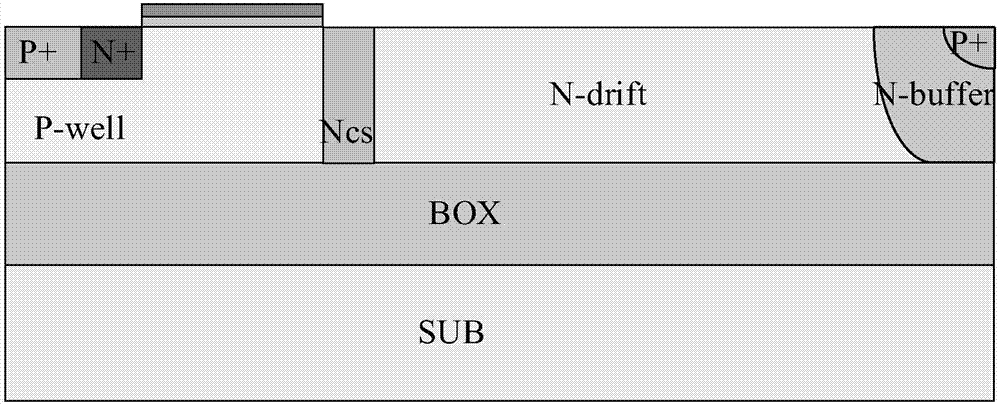

SOI (silicon on insulator) LIGBT (lateral insulated gate bipolar transistor) device unit with p buried layer and longitudinal channel

ActiveCN102157550AReduce adverse effectsImprove vertical pressure resistanceSemiconductor devicesMetal electrodesConductivity modulation

The invention relates to an SOI (silicon on insulator) LIGBT (lateral insulated gate bipolar transistor) device unit with a p buried layer and a longitudinal channel. The existing products restrict the improvement of the device structures and the electrical properties. The device unit comprises a p-type semiconductor substrate, a buried oxide layer and a p buried layer region in sequence, wherein a metal gate, an n-type heavily doped polysilicon gate, a gate oxide layer and an n-type lightly doped drift region are arranged at the top of the p buried layer region side by side in sequence; a first p-type well region and an n-type buffer region are respectively embedded at the two sides at the top of the n-type lightly doped drift region; an n-type cathode region and a first p well ohmic contact region are embedded at the top of the first p-type well region; a second p-type well region and an anode short-circuit point region are embedded at the top of the n-type buffer region; a second p well ohmic contact region is embedded at the top of the second p-type well region; and a first field oxide layer, a second field oxide layer, an anode metal electrode and a cathode metal electrode are arranged at the top of the device unit. The device unit has the beneficial effects of reducing the spreading resistance, improving the conductivity modulation effect of the drift region, reducing the on-state power consumption and obviously improving the thermal property of the device.

Owner:SERVICE CENT OF COMMLIZATION OF RES FINDINGS HAIAN COUNTY

A trench type insulated gate bipolar transistor and a preparation method thereof

ActiveCN109192772AImprove breakdown voltageImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionParasitic bipolar transistor

The invention relates to a trench-type insulated gate bipolar transistor and a preparation method thereof, belonging to the technical field of power semiconductors. A semiconductor layer or Schottky contact metal having a relatively small band gap is introduced into the upper surface of the base region of the device adjacent to the outer side of the emitter region, By using heterojunction or Schottky contact as minority carrier barrier to enhance the conductivity modulation effect, the conduction voltage drop is reduced and the tradeoff between forward voltage drop and turn-off loss is optimized. As the heterojunction or Schottky contact introduced by the invention can replace the CS layer functionally, the electric field strength of the PN junction formed in the base region and the driftregion is reduced to improve the breakdown voltage of the device; and the electric field intensity of the gate oxide layer is below the safe value (3MV / cm), so the reliability of the gate oxide layeris ensured. In addition, the fabrication process of the device is simple and controllable, and the device has strong compatibility with the existing process.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

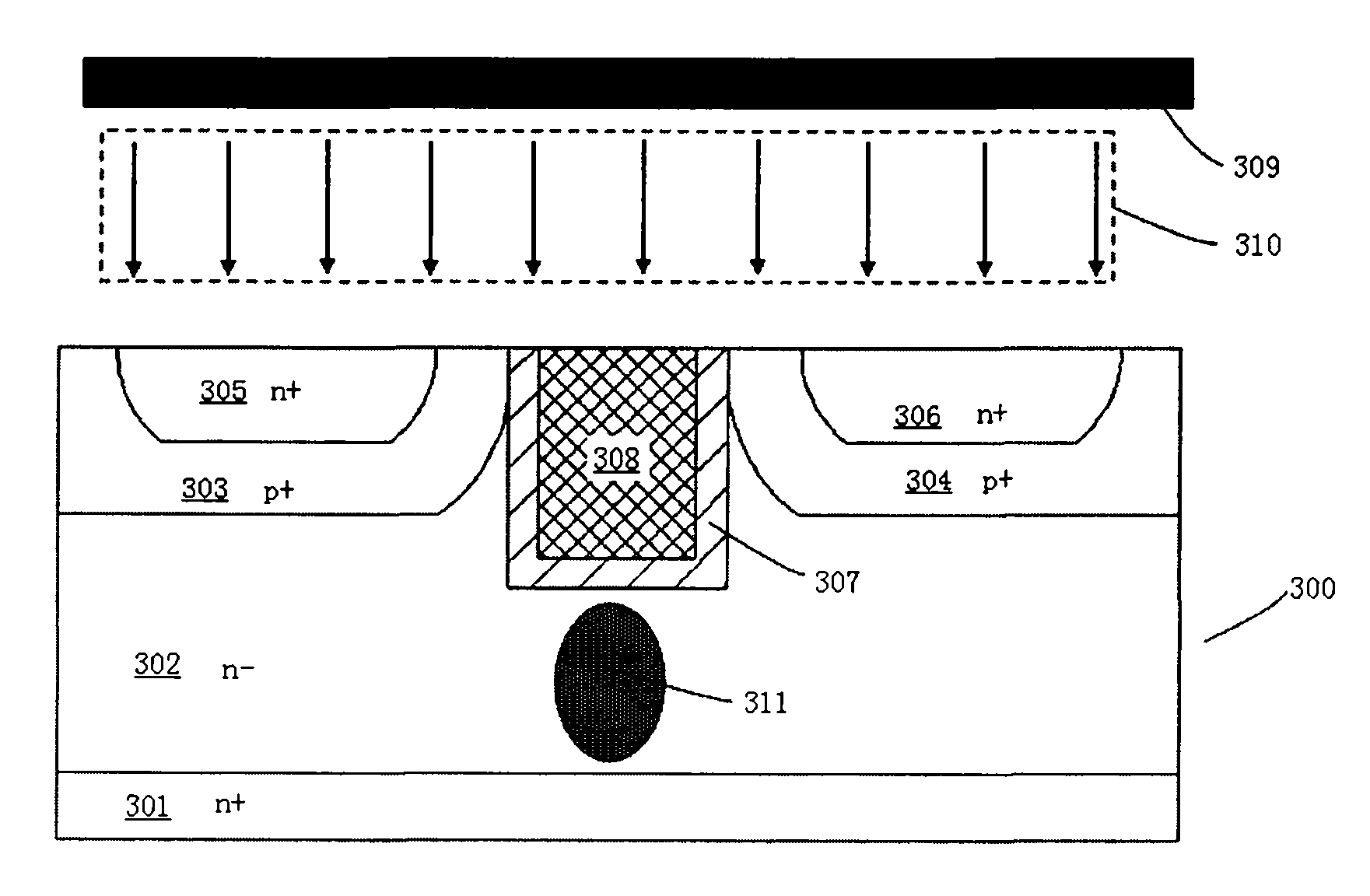

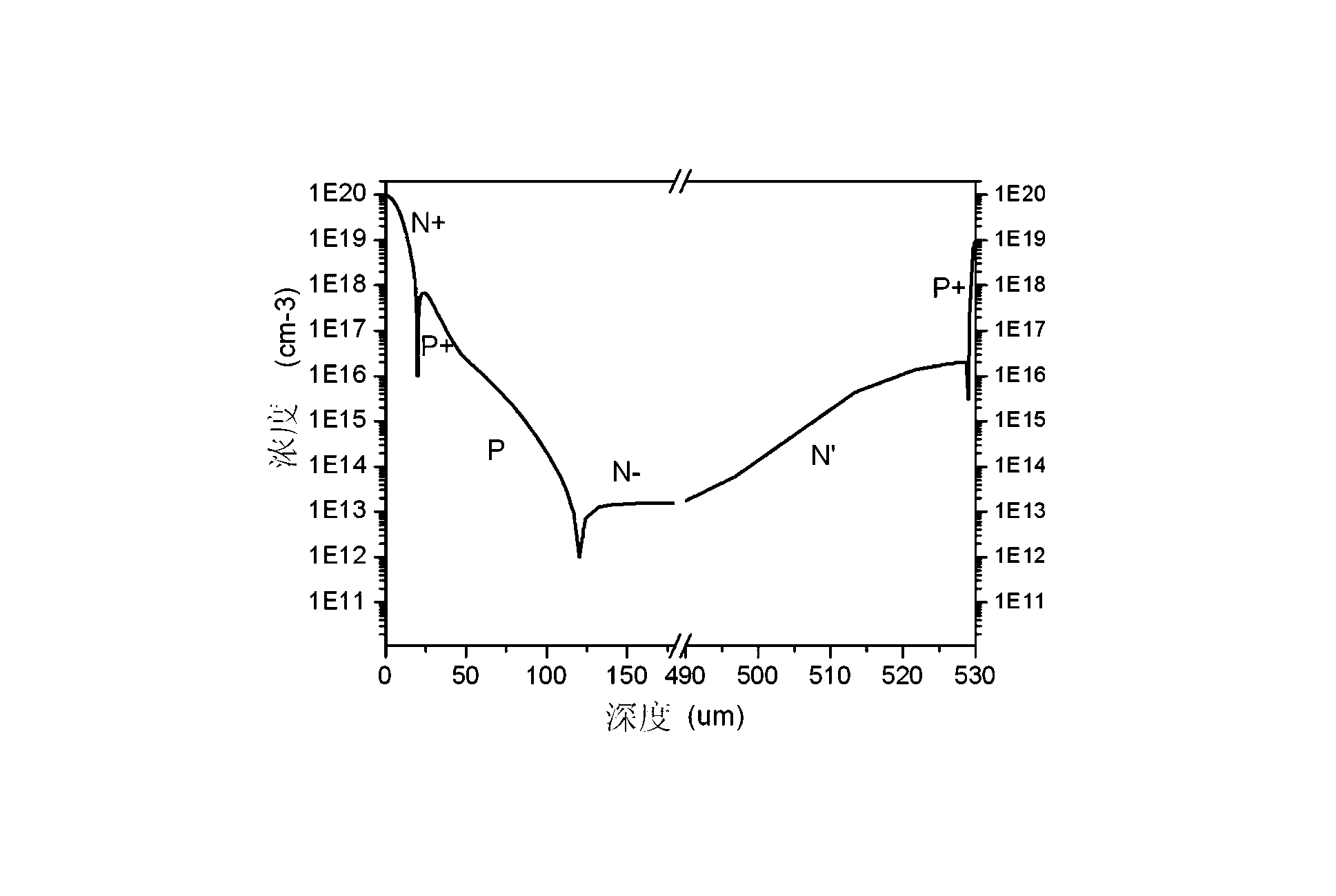

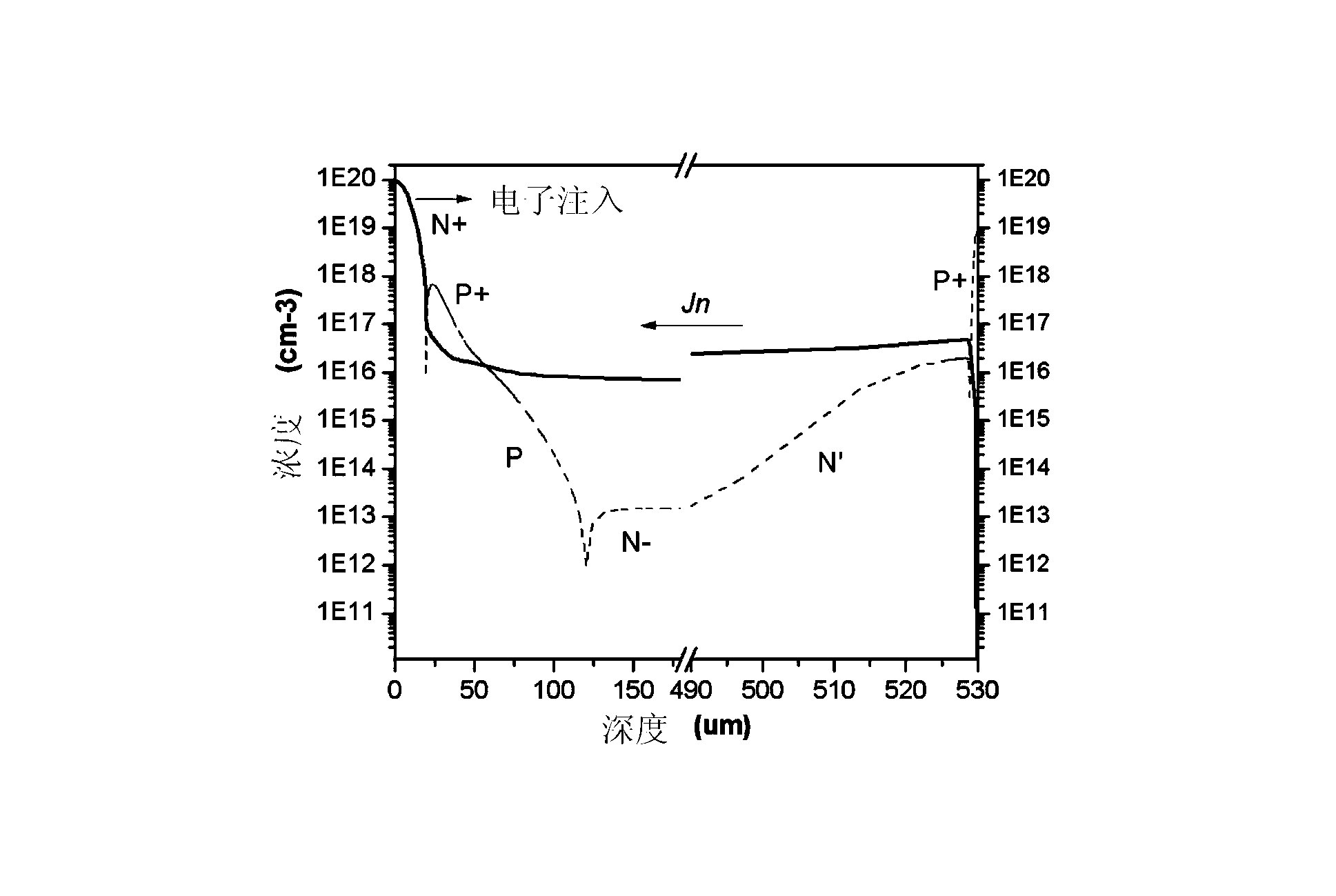

Power device and method for performing conductivity modulation by using photoelectron injection

InactiveCN101814527ALower characteristic on-resistanceImprove performanceSemiconductor devicesConductivity modulationElectron

The invention belongs to the technical filed of semiconductor devices, and in particular discloses a power device and a method for performing conductivity modulation by using photoelectron injection. The power device comprises at least one photoelectron injection light source and a power MOS transistor. By adopting a photoelectron injection method, current carriers are injected into a drift region below the gate of the power MOS transistor and the conductivity modulation is performed, so that the characteristic on-resistance of the power MOS transistor is reduced; and simultaneously the doping concentration of the drift region can be reduced and a blocking-voltage can be improved, so that the performance of the power MOS transistor is greatly improved and the application of the power MOS transistor is expanded to high-voltage fields.

Owner:FUDAN UNIV

Manufacturing method of self-aligned insulated gate bipolar transistor

ActiveCN103219237AReduce power consumptionReduce widthSemiconductor/solid-state device manufacturingDevice materialField effect

The invention relates to semiconductor devices in the technical field of power electronics, and particularly relates to a manufacturing method of a self-aligned insulated gate bipolar transistor applicable to a planar gate bipolar transistor. The manufacturing method adopts a window as a mask and realizes manufacturing of a first conduction type doped region of one side 431 of the window by first-time inclined implantation. The manufacturing method provides a technology which does not need photoetching and can control the width of an N+ emitter region, and further provides a set of full-self-aligned method for manufacturing an IGBT (Insulated Gate Bipolar Transistor) device. Compared with the traditional process, the method has the advantages that due to reduction of strict aligning times of photoetching, the width of a P-type base region can be effectively reduced, the concentration of minority carriers under a gate is increased, the conductivity modulation effect is improved, and the influence of a JEFT (Junction Field Effect Transistor) is reduced, so that the power consumption of the IGBT is reduced; and due to reduction of the strict aligning times of photoetching, the manufacturing cost is effectively reduced and the fault rate is reduced.

Owner:中国东方电气集团有限公司 +1

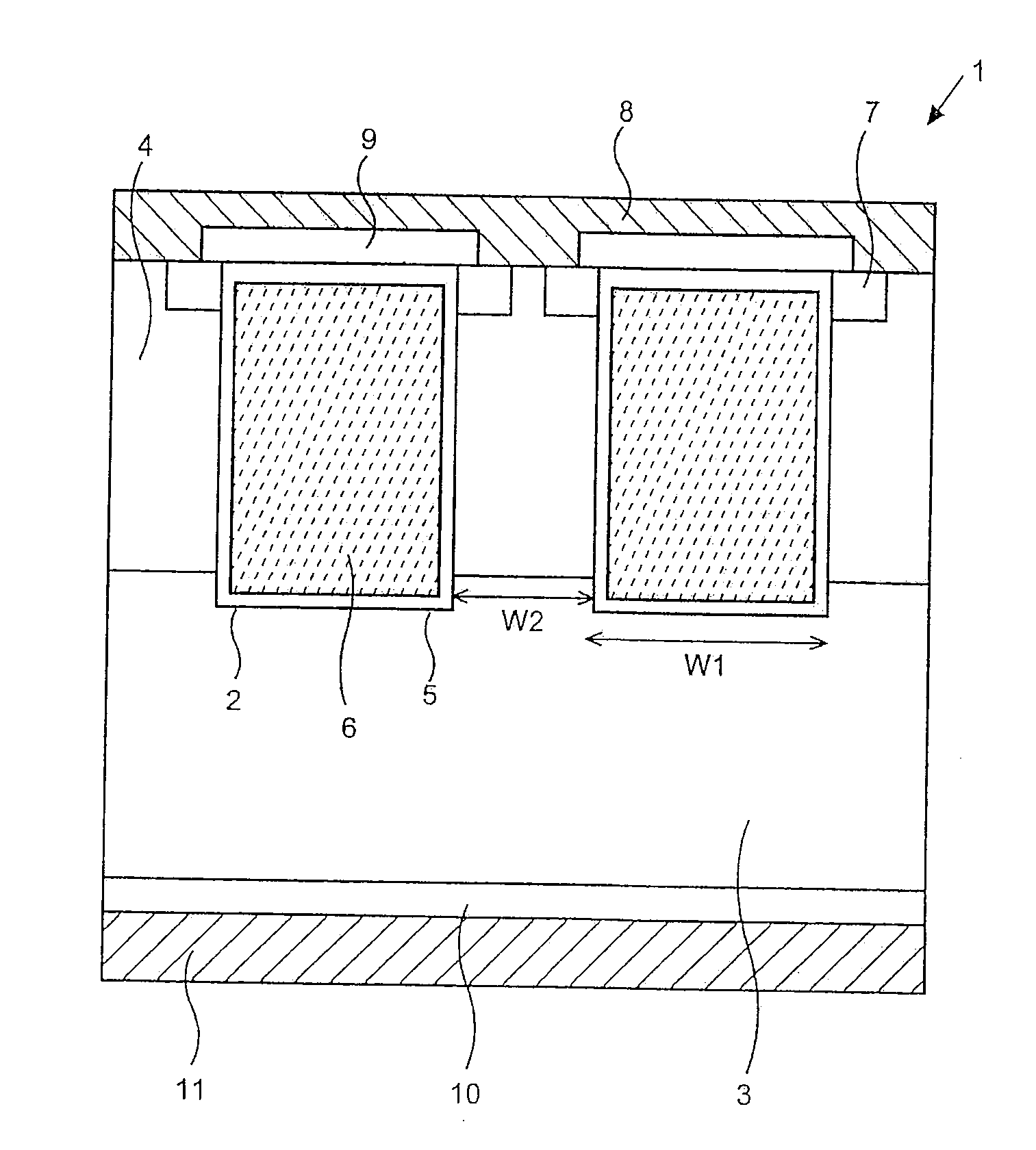

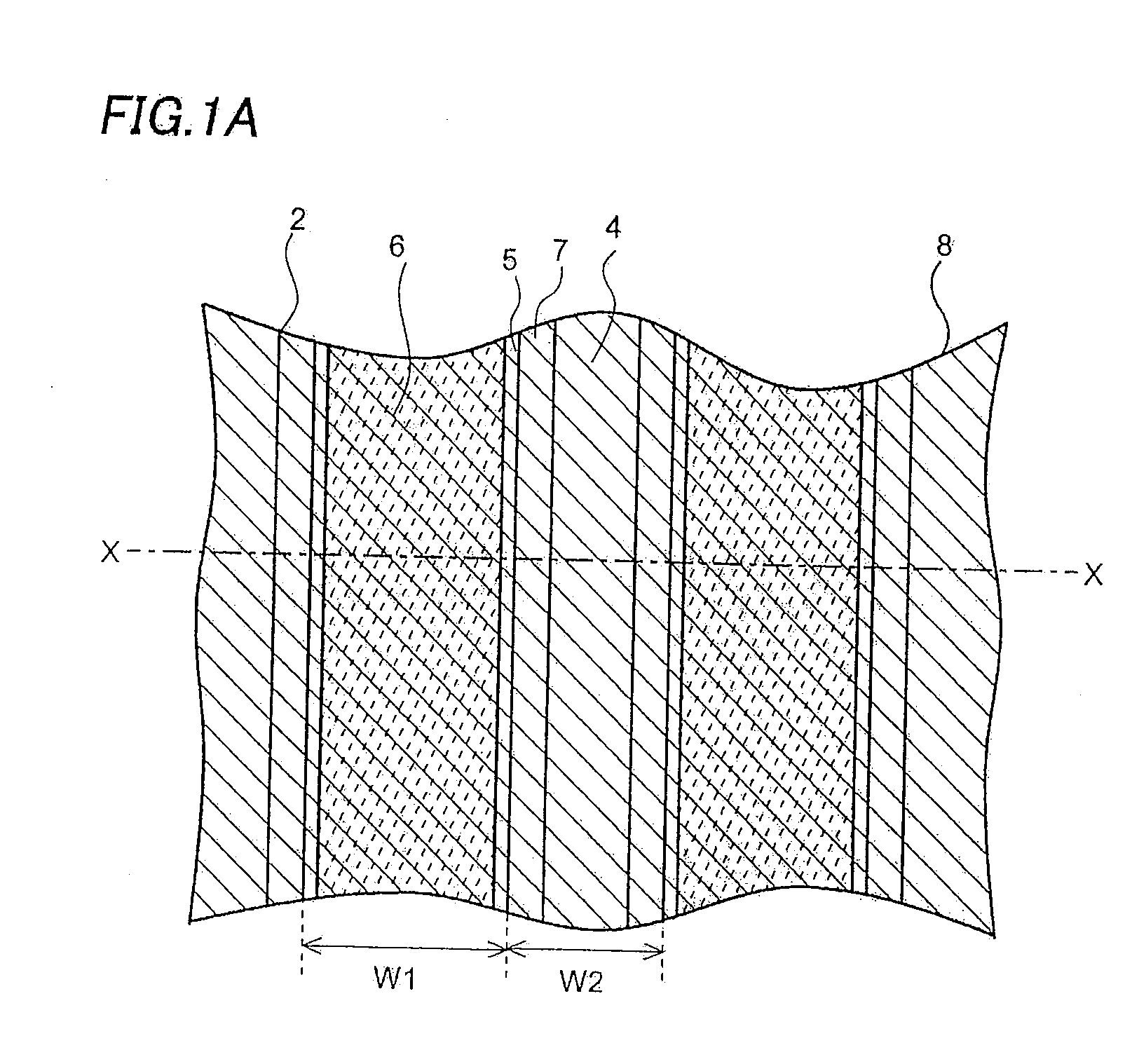

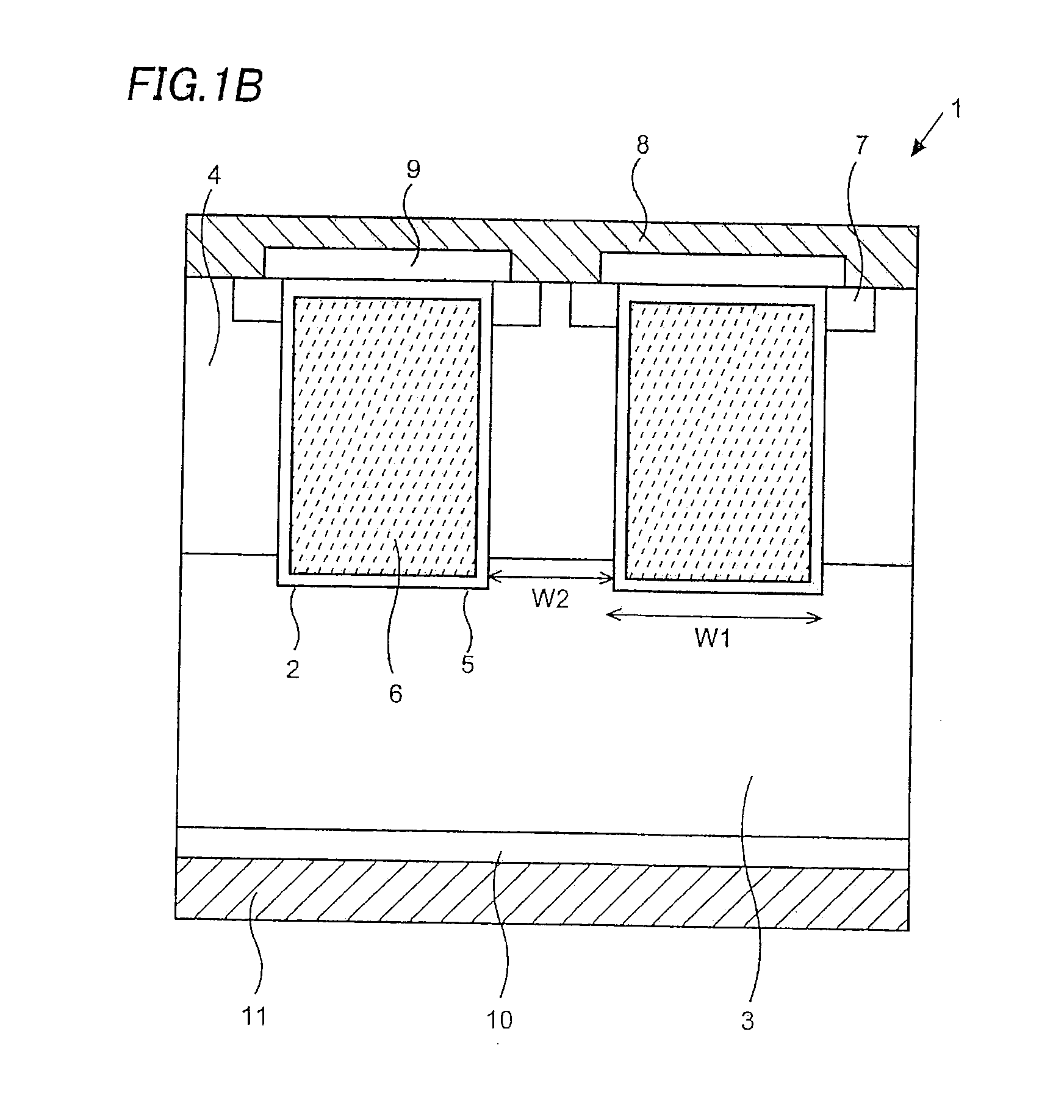

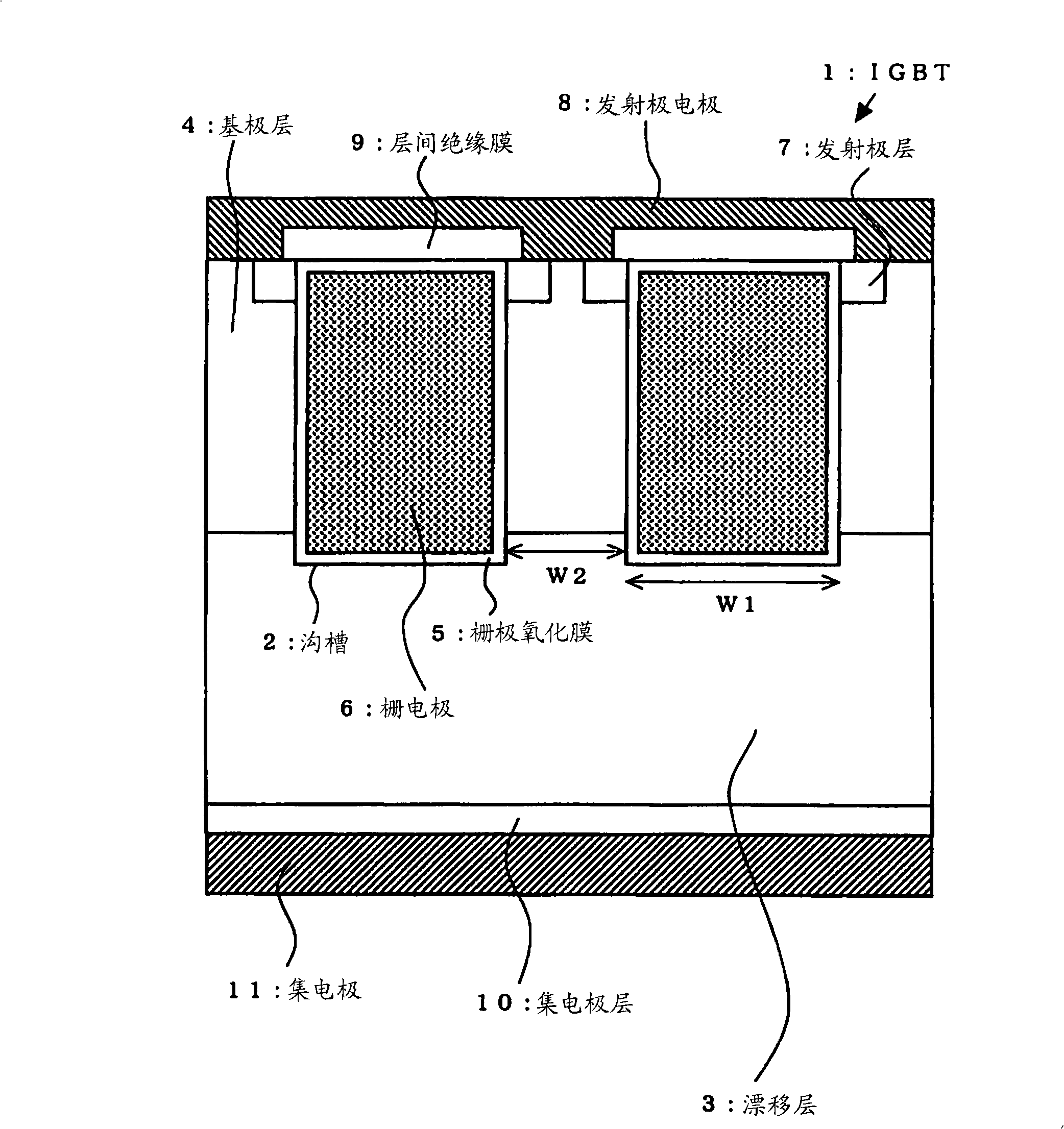

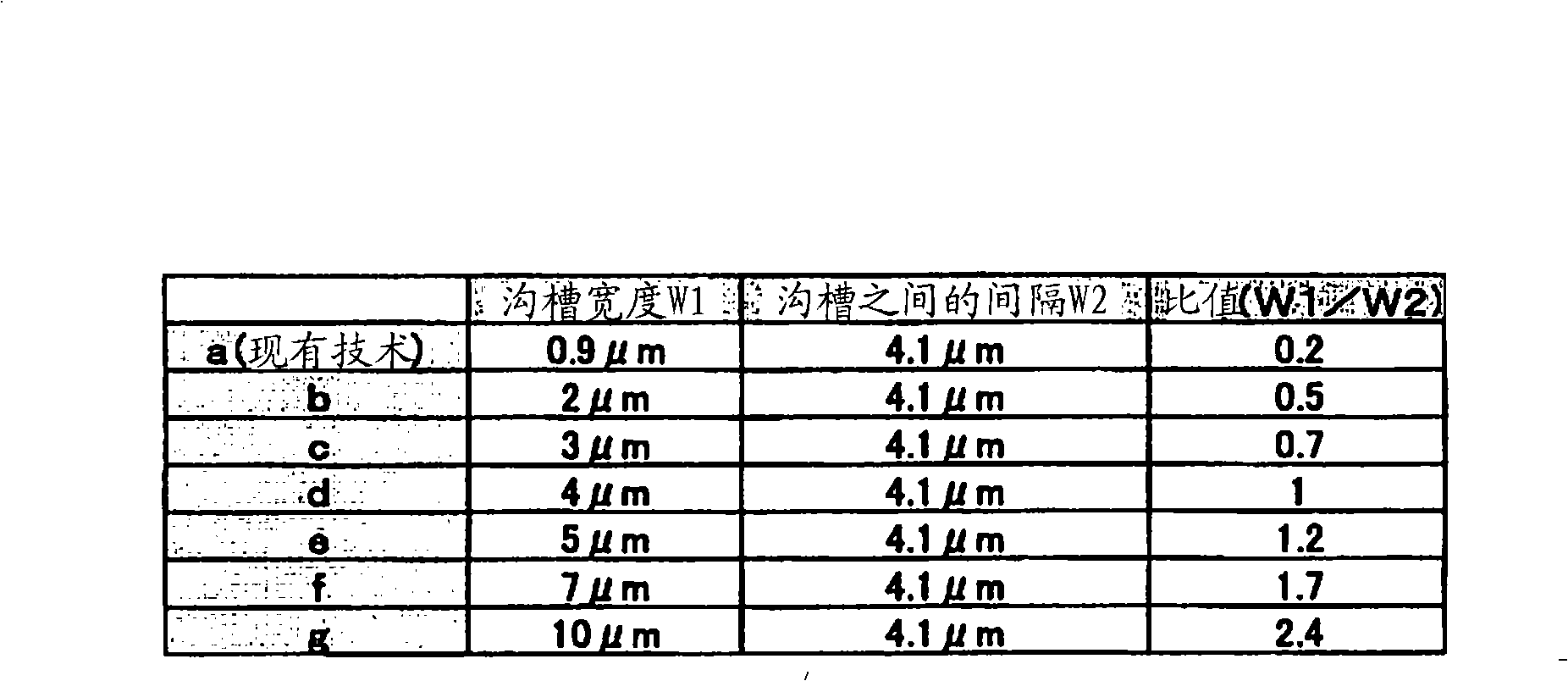

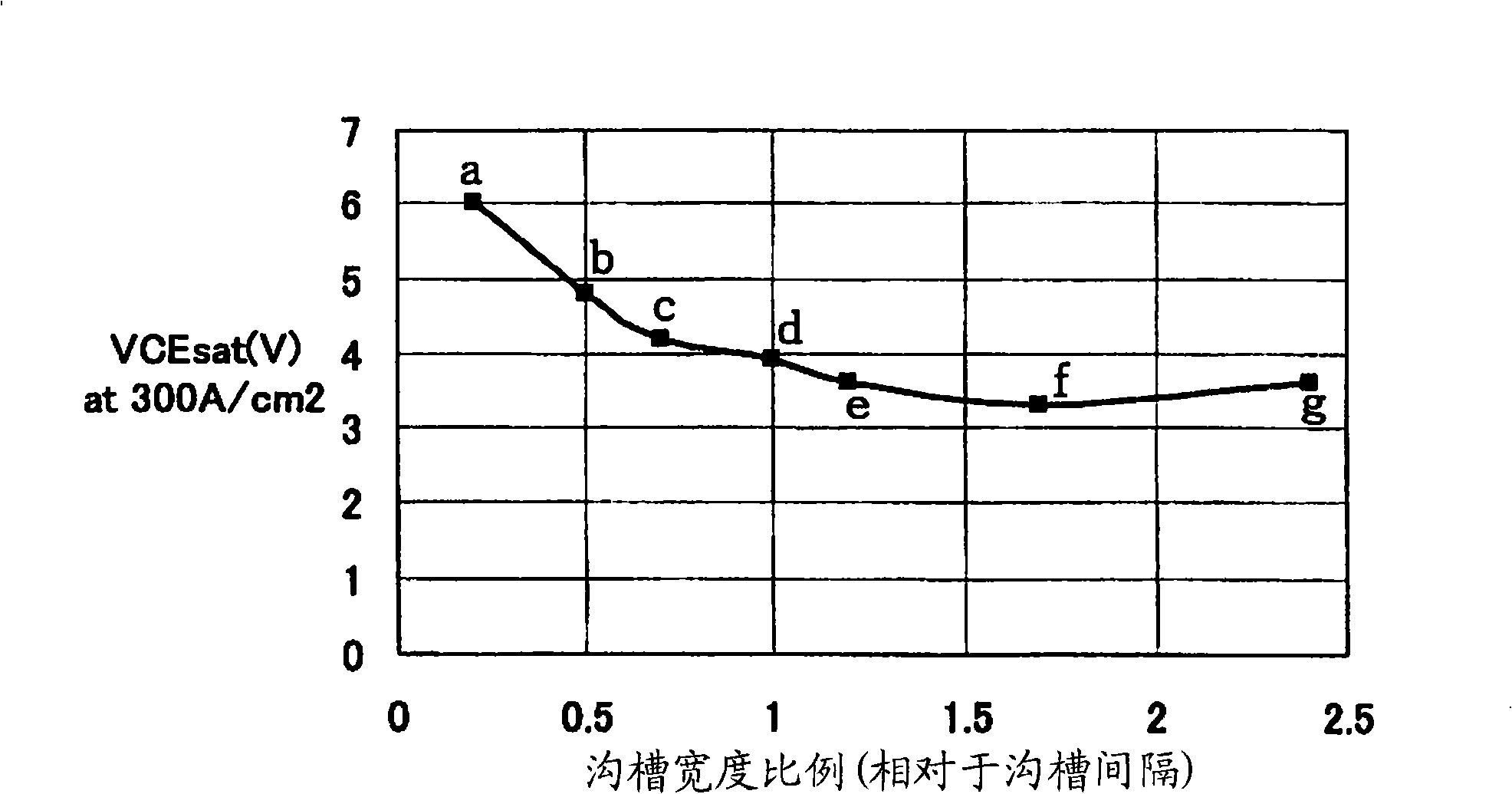

Insulated gate bipolar transistor

InactiveUS20080308839A1Reduce decreaseSuppress mutationTransistorSemiconductor/solid-state device manufacturingElectrical resistance and conductanceElectron current

The invention realizes IGBT having an NPT structure which has a smaller variation in switching characteristics and the like and lower on-resistance. In the IGBT of the invention, by setting a ratio of a width of a trench to an interval between the trenches within a range of 1 to 2, electron current density and a conductivity modulation effect are optimized, a breakdown voltage is secured, a variation in characteristics is minimized, and on-resistance is largely reduced.

Owner:SANYO ELECTRIC CO LTD +1

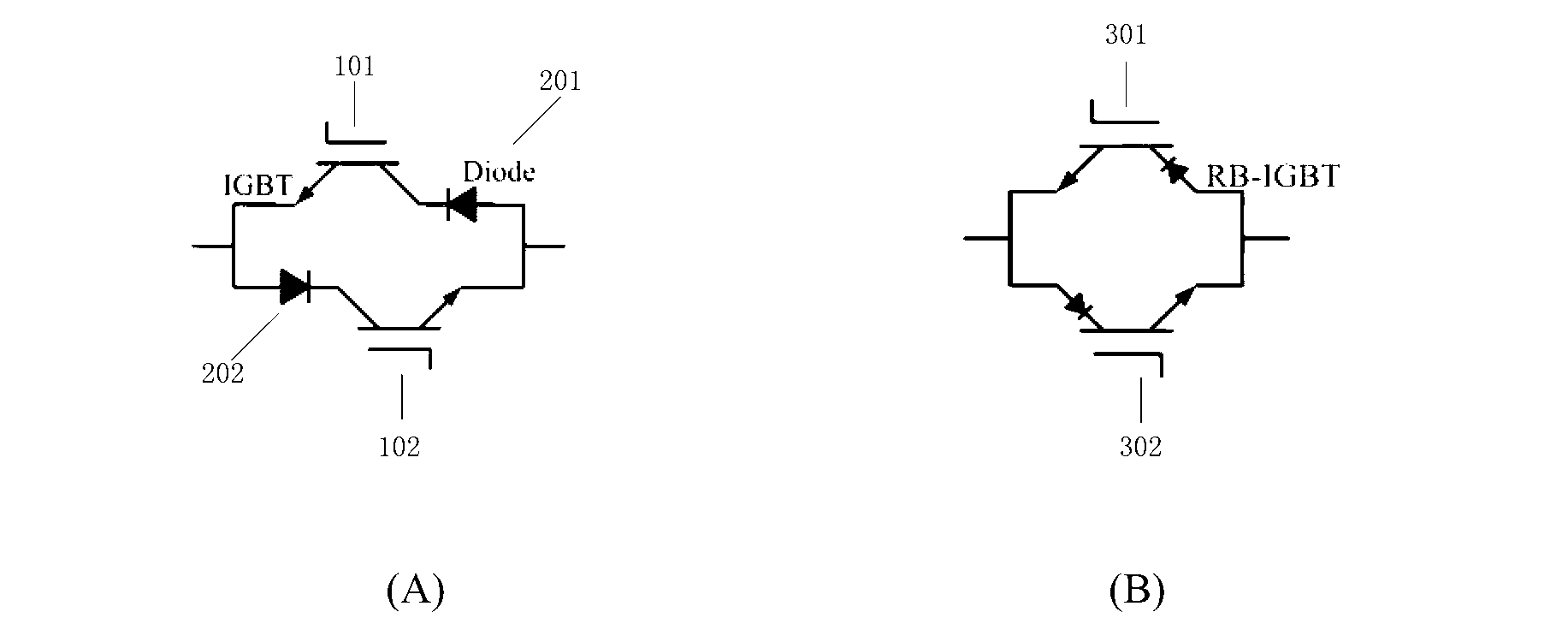

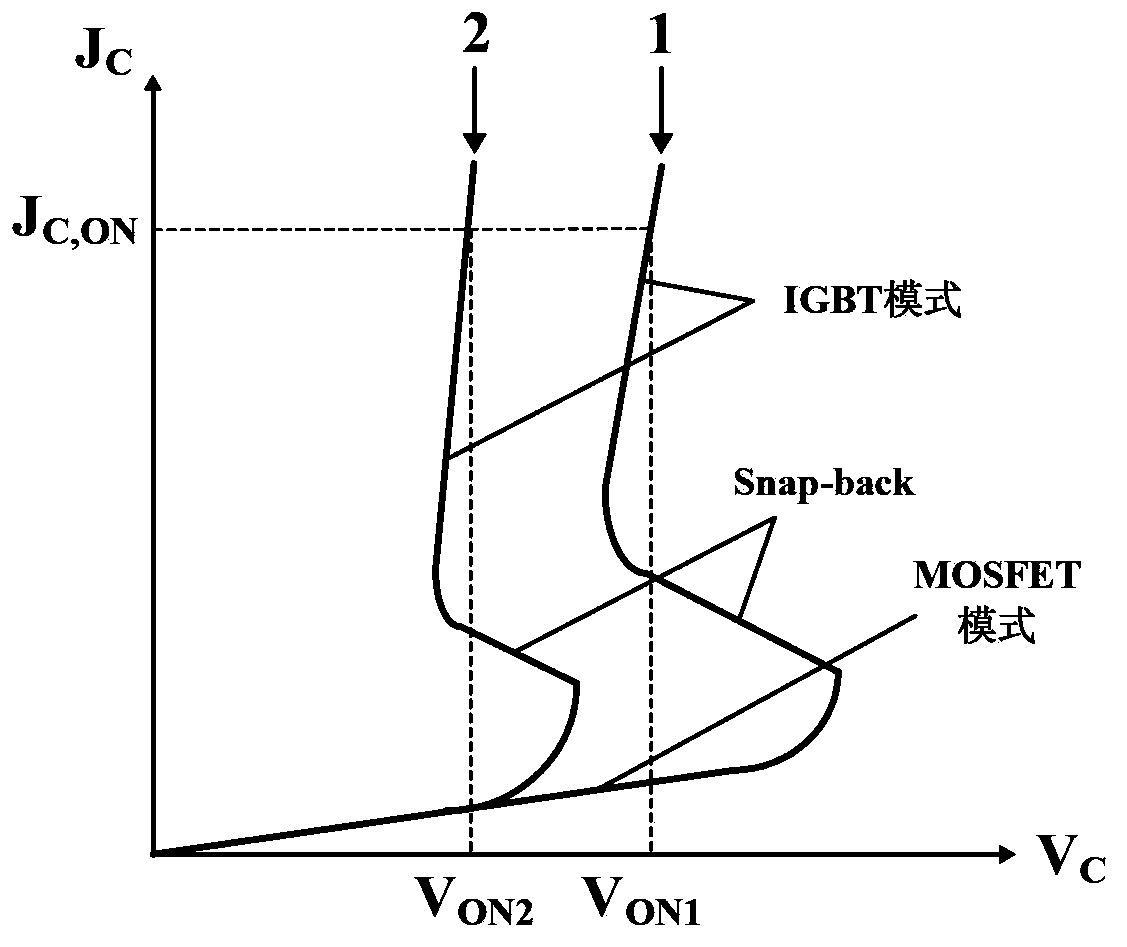

Reverse conducting insulated gate bipolar transistor (RC-IGBT) device

InactiveCN103383957AWeaken the snap-back phenomenonReduce forward voltage dropSemiconductor devicesPower semiconductor deviceVoltage drop

The invention relates to an RC-IGBT device and belongs to the technical field of power semi-conductor devices. Variable-component mixed crystals are used for producing a collector region of the IGBT to form an energy band structure with gradually variable forbidden bandwidth. The forbidden bandwidth is small at the junction of the collector region and a drift region, built-in electrical potentials of the collector region and the drift region are reduced, and the phenomenon of snap-back is relieved; meanwhile, the gradually variable forbidden bandwidth is formed due to the variable-component materials of the collector region, and a retarding field of minority carriers is generated in the collector region, so that injection of the minority carriers to the collector region by the drift region is reduced, the injection efficiency of the collector region to the drift region is improved, the strong conductivity modulation effect can be obtained, and the forward conducting voltage drop of the IGBT is reduced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

Short-circuit anode SOI LIGBT with anode pinch-off groove

ActiveCN108321195AIncreased shutdown speedReduce lossSemiconductor/solid-state device manufacturingSemiconductor devicesHigh concentrationConductive materials

The invention belongs to the technical field of power semiconductors, and relates to a short-circuit anode SOI LIGBT (Lateral Insulated Gate Bipolar Transistor) with an anode pinch-off groove. Compared with the traditional short-circuit anode LIGBT, anode grooves connected with the anode potential are introduced at the anode end, a conductive material of the anode grooves comprises high-concentration P-type doping, and a low-concentration N-type doped region is introduced one side of each groove wall. When the device is turned off, the outer wall of each anode groove accumulates electrons, low-resistance channels are provided, the extractions of electrons in a drift region is accelerated, and the turn-off time and the turn-off loss are reduced. When the device is just turned on, a P-type impurity in the anode grooves enable the low-concentration N-type doped regions to be exhausted, the electrons are prevented from being extracted by the N+ anode, a voltage turning-back effect is eliminated, a conductivity modulation effect is enhanced at the same time, and the conduction voltage drop is reduced. The beneficial effects are that the short-circuit anode SOI LIGBT has high turn-off speed and lower loss compared with the traditional LIGBT; and the short-circuit anode SOI LIGBT eliminates the voltage turning-back phenomenon under a smaller transverse cell size compared with the traditional short-circuit anode LIGBT, and has lower conduction voltage drop at the same time.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

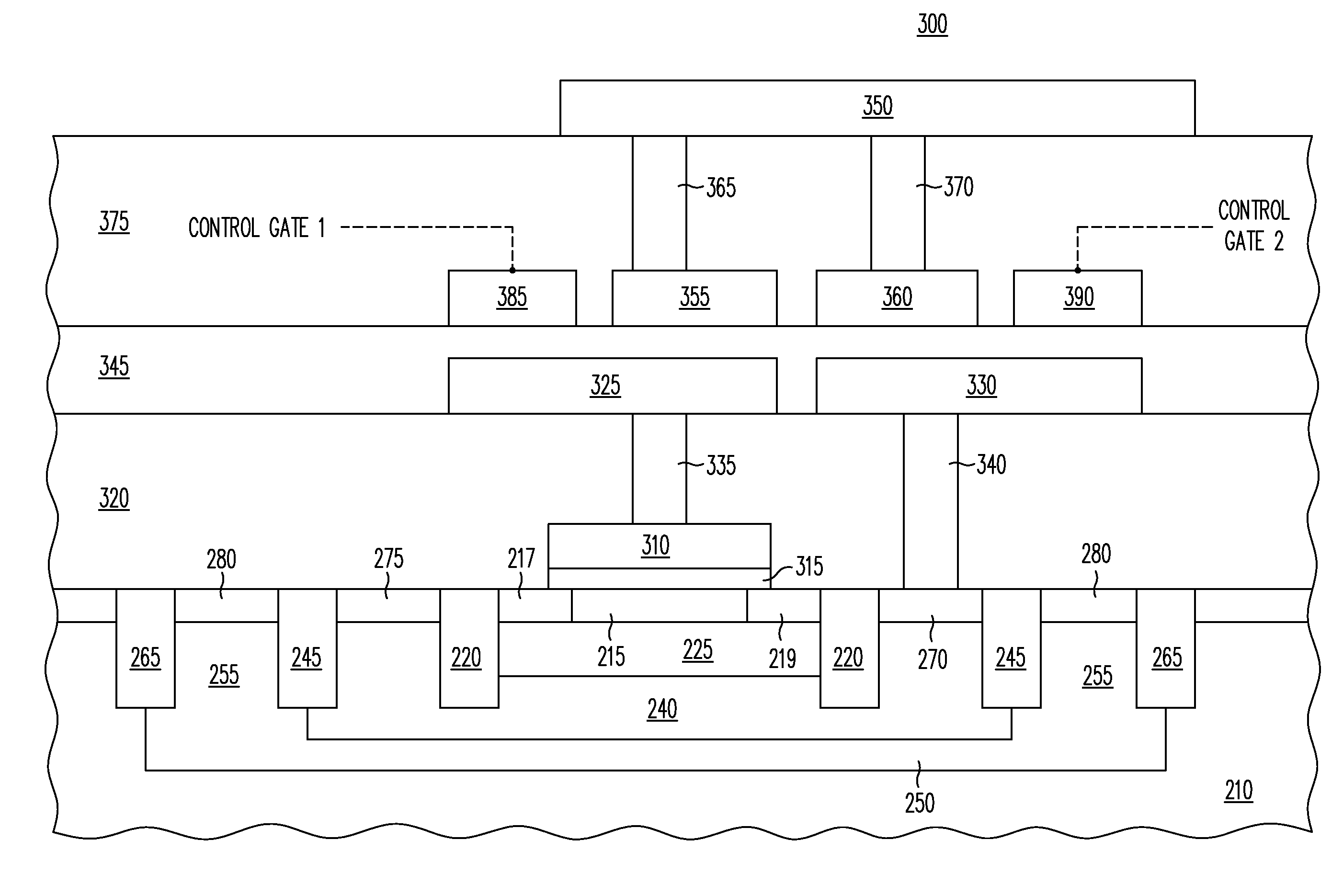

Enhanced sensitivity ion sensing devices

A mechanism is provided for enhancing the sensitivity of an ion-sensitive semiconductor device by creating a second gate coupled to a sense plate that can improve the amount of charge brought to the ion-sensitive semiconductor device conductivity modulated region (e.g., a channel region of an ISFET). This is accomplished by utilizing a buried dielectric layer associated with the ion-sensitive semiconductor device conductivity modulated region as the second gate dielectric. The buried dielectric layer is coupled to the sense plate using an isolated well region as a conductor that is coupled to metal layers extending to the sense plate. Some embodiments further use the buried dielectric layer as the sole gate dielectric for the semiconductor device, thereby allowing the traditional gate dielectric region to be coupled to a protection diode. This protection diode then protects the gate dielectric from plasma induced damage and electrostatic discharge.

Owner:NXP USA INC

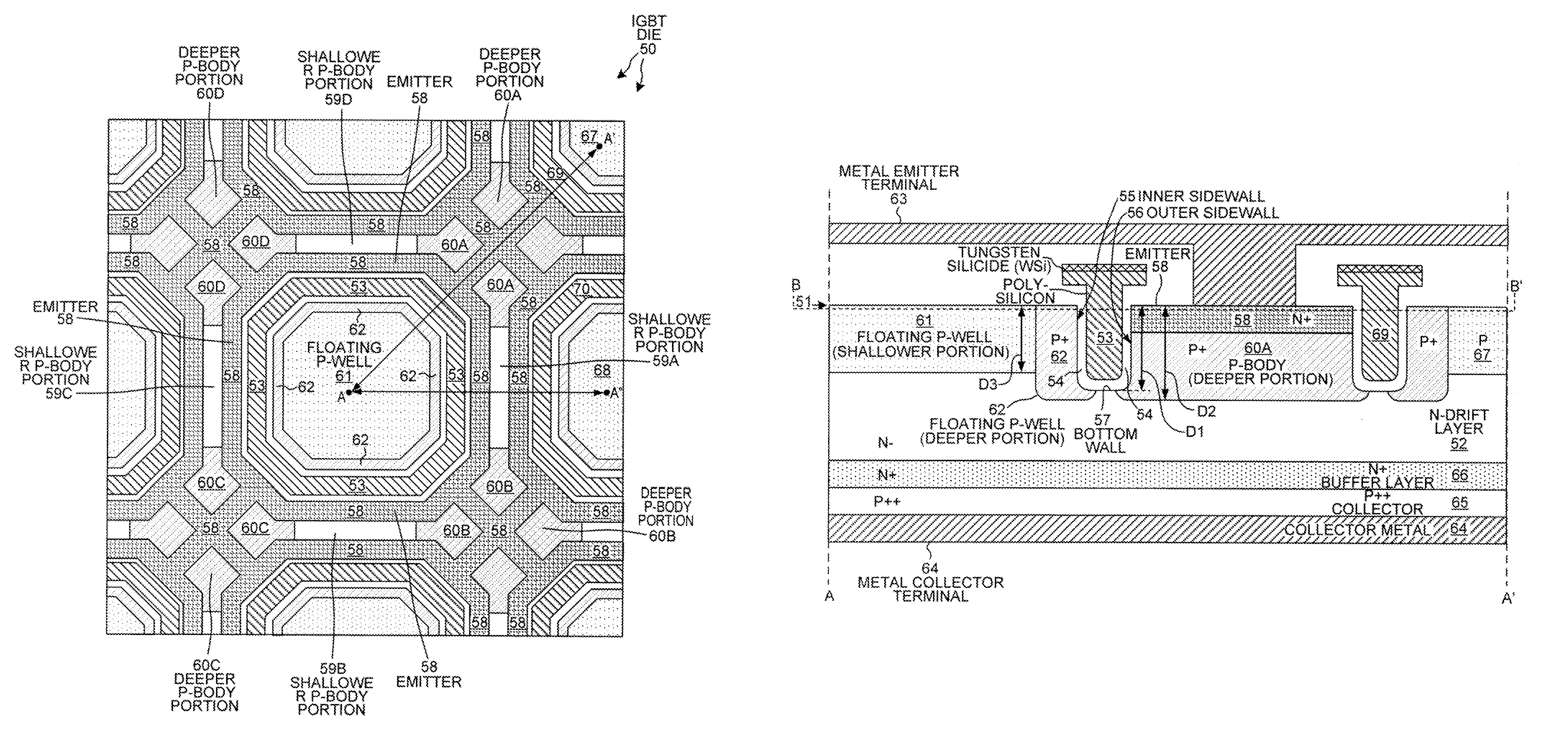

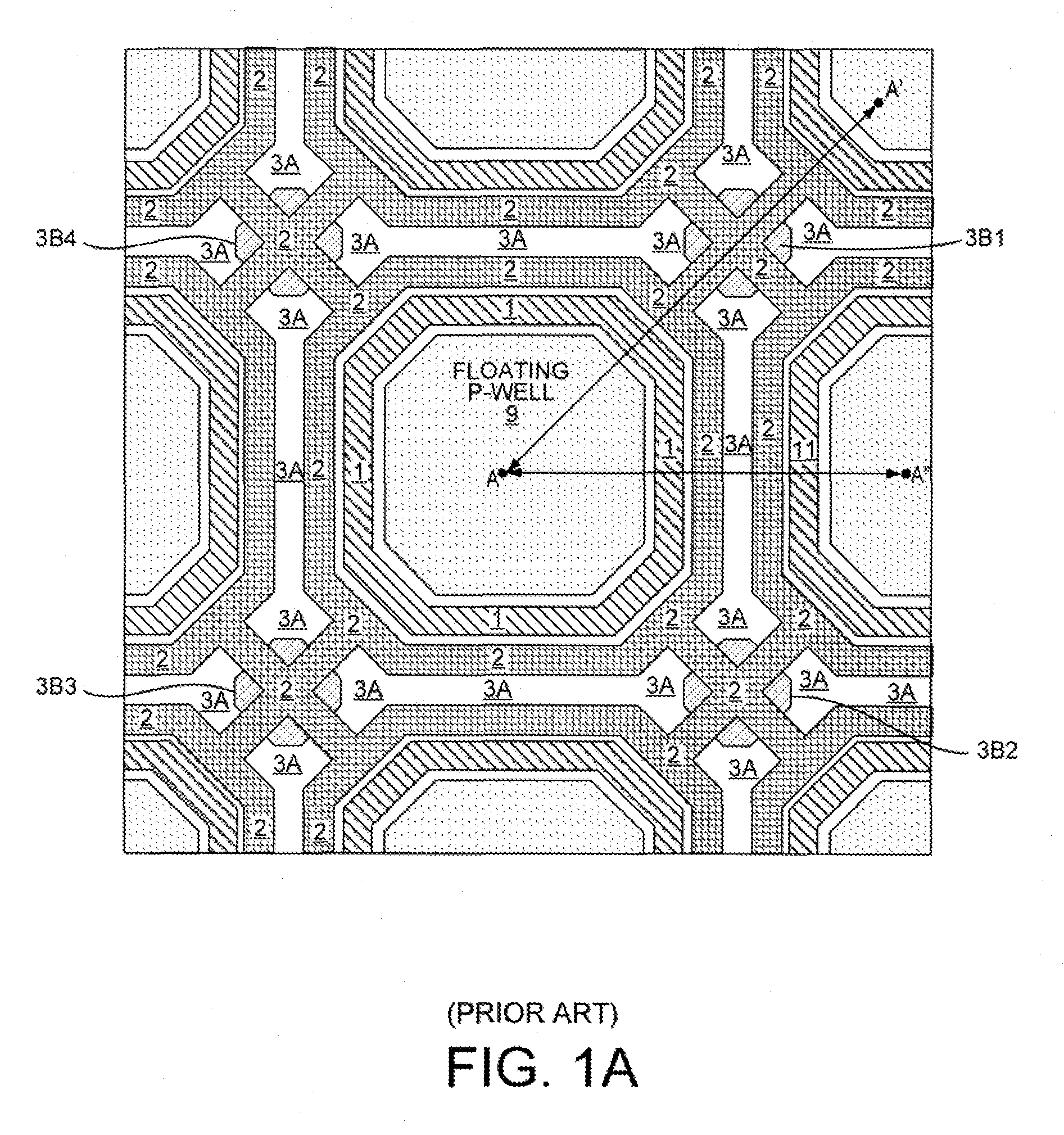

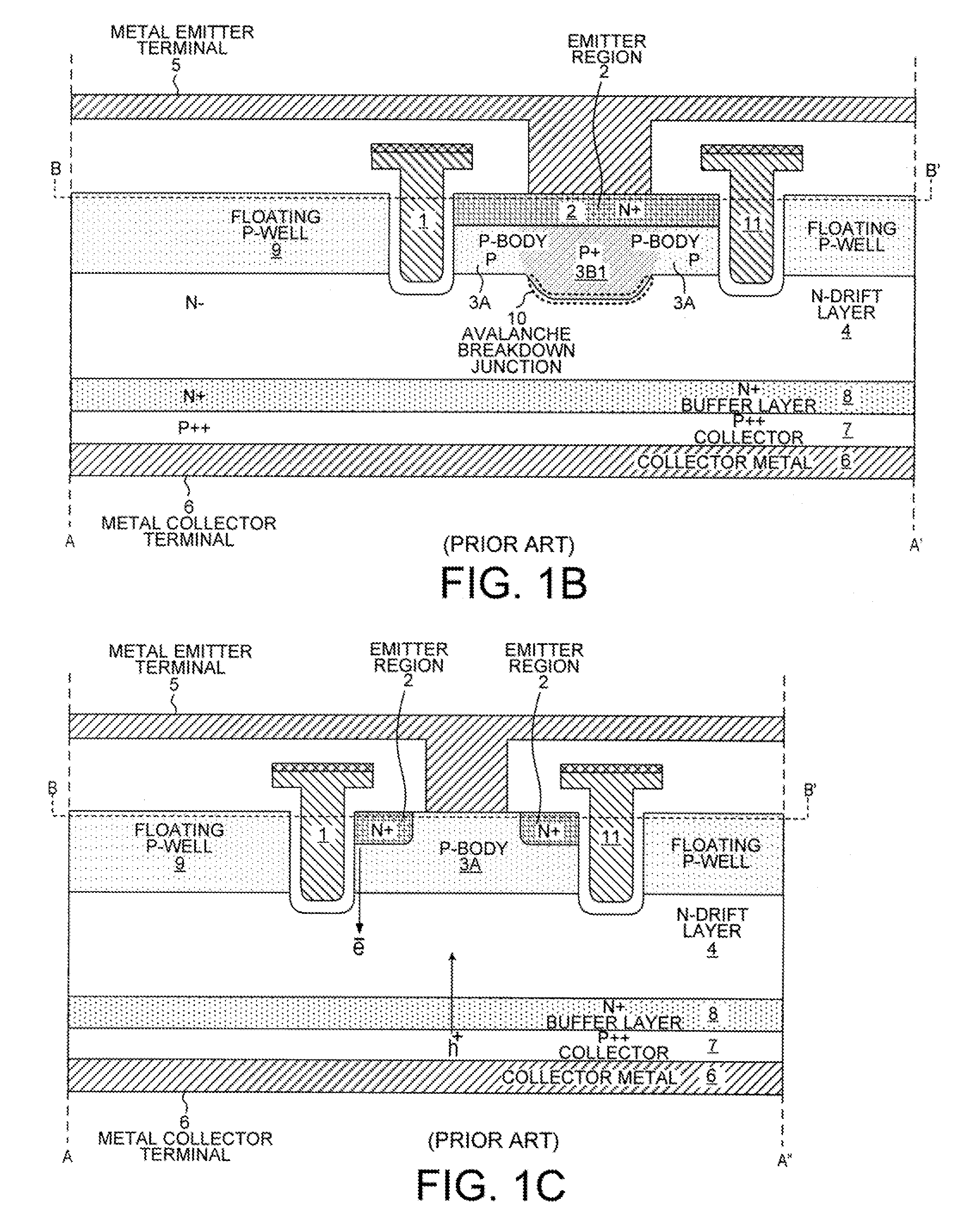

Trench IGBT with tub-shaped floating P-well and hole drains to P-body regions

A trench IGBT has a gate electrode disposed in a trench. A tub-shaped floating P-well is disposed on one side of the trench. The tub-shaped floating P-well has a central shallower portion and a peripheral deeper portion. An inner sidewall of the trench is semiconductor material of the peripheral deeper portion of the floating P-well. On the other side of the trench is a P type body region involving a plurality of deeper portions and a plurality of shallower portions. Each deeper portion extends to the trench such that some parts of the outer sidewall of the trench are semiconductor material of these deeper P-body portions. Other parts of the outer sidewall of the trench are semiconductor material of the shallower P-body portions. A shallow N+ emitter region is disposed at the top of the outer sidewall. The IGBT has fast turn off and enhanced on state conductivity modulation.

Owner:LITTELFUSE INC

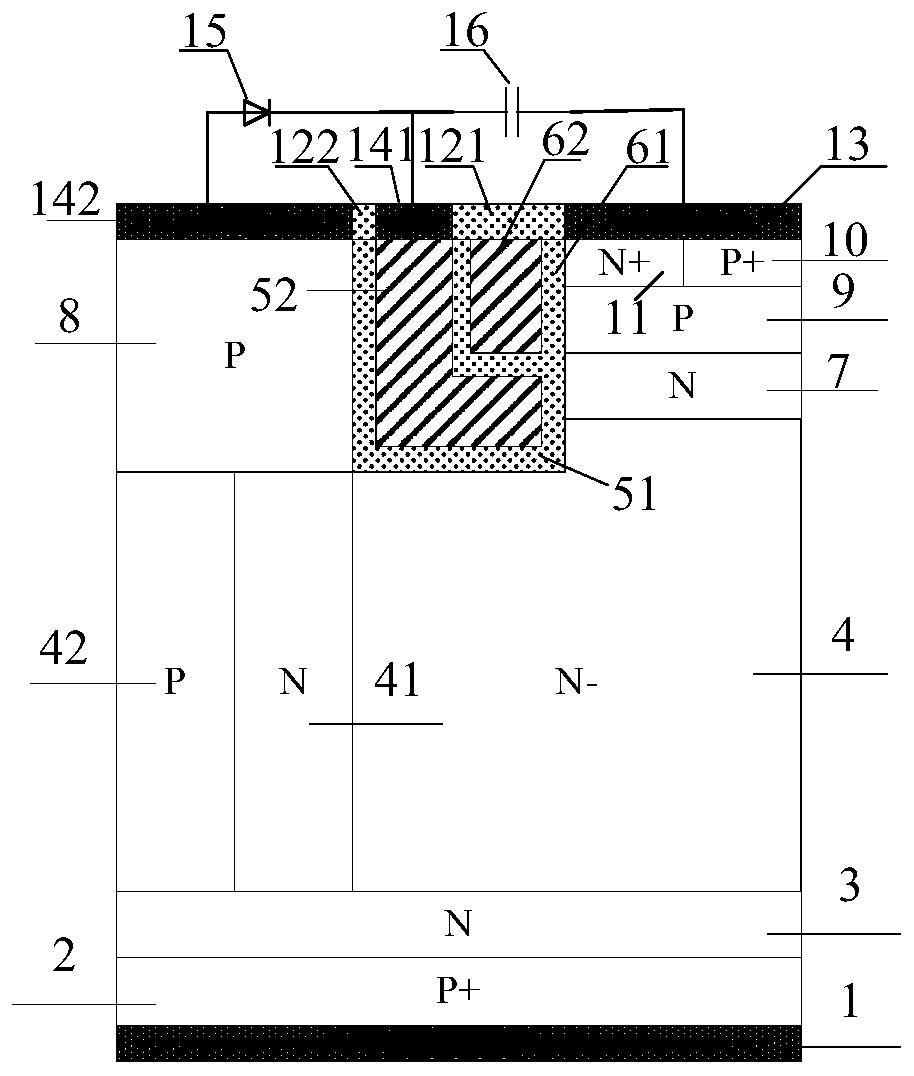

IGBT with self-biased separation gate structure

ActiveCN110491937AGuaranteed breakdown voltageFast switching speedSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceChannel density

The invention belongs to the technical field of power semiconductor devices, and relates to a separation gate TIGBT with a self-biased PMOS and a manufacturing method thereof. According to the invention, a PMOS structure is introduced on the basis of a traditional TIGBT; the channel density is not reduced; saturation current during forward conduction of the device is effectively improved, the short-circuit safety working capability of the device is improved, and meanwhile, an extra current discharge path provided by the PMOS structure accelerates the hole extraction speed of the device in a blocking state, so that the switching speed of the device is increased, and the switching loss of the device is reduced. Meanwhile, for the TIGBT with an N-type charge storage layer, a P-type buried layer can shield the influence of the N-type charge storage layer on the breakdown characteristic of the device; therefore, the doping concentration of the N-type charge storage layer can be improved tofurther improve the carrier distribution during forward conduction of the device, the conductivity modulation capability of a drift region is improved, and the compromise relationship between the forward conduction voltage drop Vce (on) and the turn-off loss Eoff of the device is further improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Insulated gate bipolar transistor

InactiveCN101325215AReduce current densityFull Conductivity Modulation EffectTransistorSemiconductor/solid-state device manufacturingElectron currentConductivity modulation

The invention realizes IGBT having an NPT structure which has a smaller variation in switching characteristics and the like and lower on-resistance. In the IGBT of the invention, by setting a ratio of a width of a trench to an interval between the trenches within a range of 1 to 2, electron current density and a conductivity modulation effect are optimized, a breakdown voltage is secured, a variation in characteristics is minimized, and on-resistance is largely reduced.

Owner:SANYO ELECTRIC CO LTD +1

Groove type SOI LIGBT comprising carrier storage layer

ActiveCN106920842AReduce conduction voltage dropImprove pressure resistanceSemiconductor devicesHigh concentrationChannel density

The invention belongs to the field of power semiconductor technology and relates to a groove type SOI LIGBT comprising a carrier storage layer. The groove type SOI LIGBT relative to a structure in the prior art comprises the following characteristics: 1, the groove type SOI LIGBT comprises the carrier storage layer in high concentration which blocks a hole in forward conduction, the concentration of the hole near an interface is increased, according to an electroneutrality principle, more electrons is injected to a drift region, the conductivity modulation effect is enhanced, and the forward conduction voltage drop of a device is reduced, simultaneously, a medium groove is introduced, the medium groove physically block a cathode to collect the hole and acts on further reduction of forward conduction voltage drop, and more importantly, the medium groove can assistant to drain the carrier storage layer in forward blocking, so that the device maintains high pressure resistance in the condition of high concentration carrier storage layer; 2. the groove type SOI LIGBT adopts tri-gate structure, and the channel density is improved; 3. tri-gate structure and the medium groove can be manufactured simultaneously without extra processing steps.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

Multi-functional chalcogenide electronic devices having gain

ActiveUS20070267624A1Function increaseBulk negative resistance effect devicesSemiconductor devicesElectrical resistance and conductanceControl signal

Multi-functional electronic switching and current control device comprising a chalcogenide material. The devices include a load terminal, a reference terminal and a control terminal. Application of a control signal to the control terminal permits the device to function in one or more of the following modes reversibly: (1) a gain mode in which gain is induced in the current passing between the load and reference terminals; (2) a conductivity modulation mode in which the conductivity of the chalcogenide material between the load and reference terminals is modulated; (3) a current modulation mode in which the current or current density between the load and reference terminals is modulated; and / or (4) a threshold modulation mode in which the voltage required to switch the chalcogenide material between the load and reference terminals from a resistive state to a conductive state is modulated. The devices may be used as interconnection devices or signal providing devices in circuits and networks.

Owner:OVONYX MEMORY TECH LLC

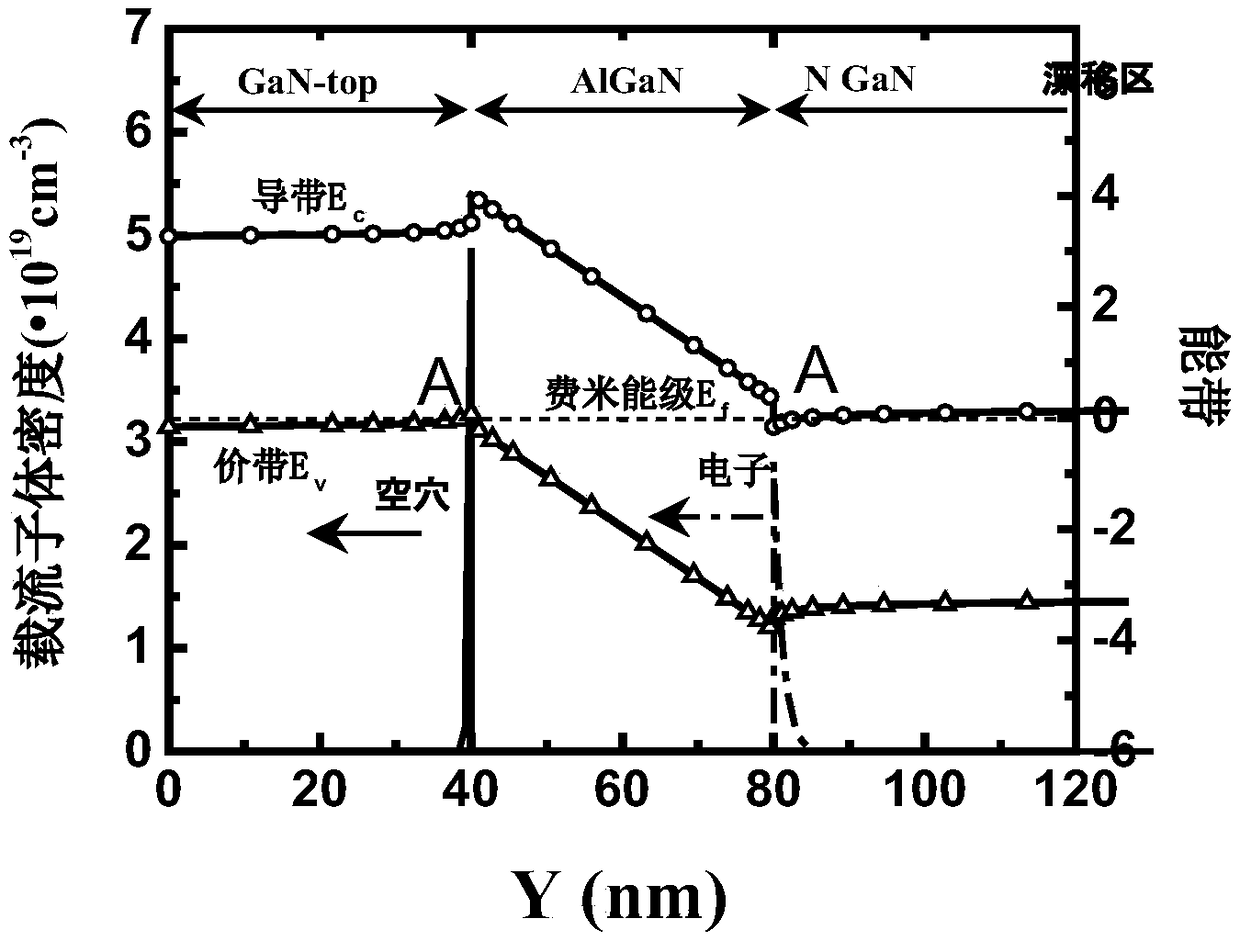

GaN heterojunction conductivity modulation field effect transistor

InactiveCN108649070AIncrease concentrationLower on-resistanceSemiconductor devicesHeterojunctionPower flow

The invention belongs to the technical field of power semiconductors and relates to a GaN heterojunction conductivity modulation field effect transistor. When the GaN heterojunction conductivity modulation field effect transistor is positively switched on, after positive voltage is applied to a drain, a large number of holes are injected into a lightly doped N-type GaN drift region from a P-type heavily doped GaN layer, a large injection phenomenon occurs in the lightly doped N-type GaN drift region, at that same time, a large number of electrons are injected into the drift region from a source electrode for maintaining charge balance, so that the carrier concentration in the orginally lightly doped drift region is increased, the conductivity modulation occurs in the lightly doped N-type GaN drift region, the drift region resistance of the lightly doped N-type GaN drift region is greatly reduced, and the novel structure can further obtain an excellent forward characteristic of low on-resistance and large on-current. During reverse voltage withstanding, a reverse-biased PN junction formed by the floating P-GaN and the N-type drift region is used as gate protection ring to reduce thepeak value of a gate electric field, and a depletion region of the reverse-biased PN junction expands continuously to uniformly distribute the device in the electric field when the reverse-biased PNjunction withstands reverse voltage, so that the reverse leakage current is reduced and the breakdown voltage of the device is increased.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Thyristor gate cathode structure and gate pole commutation thyristor with thyristor gate cathode structure

The invention discloses a thyristor gate cathode structure and a gate pole commutation thyristor with the thyristor gate cathode structure. The thyristor comprises an N-substrate, a P base region, a P+ short base region, an N+ emitter region, a door pole metal electrode and a cathode metal electrode. The N+ emitter region, the P+ short base region, the P base region and the N-substrate are sequentially distributed, the cathode metal electrode is arranged on the outer surface of the N+ emitter region, and the door pole metal electrode is arranged on the outer surface of the P+ short base region. The thyristor gate cathode structure is of a two-layer step structure, wherein the first layer of steps is a shallow step, and the bottom of the first layer of the steps is a P+N+ boundary. The second layer of the steps is a deep step, and the bottom of the second layer of the steps is a PN+ boundary. The gate pole commutation thyristor with the thyristor gate cathode structure further comprises an N' buffer layer and a P+ anode region. The combination of electrons injected in the N+ emitter region of the thyristor is reduced at the P+ short base region and the P base region, conductivity modulation effects of the thyristor are intensified, and connected currents and the starting speed can be further improved.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

High voltage FET switch with conductivity modulation

ActiveUS7135740B2Lower on-resistanceHigh blocking voltageSemiconductor/solid-state device manufacturingSemiconductor devicesConductive materialsEngineering

A high power FET switch comprises an N− drift layer, in which pairs of trenches are recessed to a predetermined depth; oxide side-walls extend to the trench bottoms, and each trench is filled with a conductive material. N+ and metal layers on opposite sides of the drift layer provide drain and source connections for the FET, and the conductive material in each trench is connected together to provide a gate connection. A shallow P region extends across the bottom and around the corners of each trench's side-walls into the drift layer. The application of a sufficient gate voltage causes holes to be injected from the shallow P regions into the N− drift layer, thereby modulating the drift layer's conductivity and lowering the device's on-resistance, and enabling current to flow between the drain and source connections.

Owner:CALLAHAN CELLULAR L L C

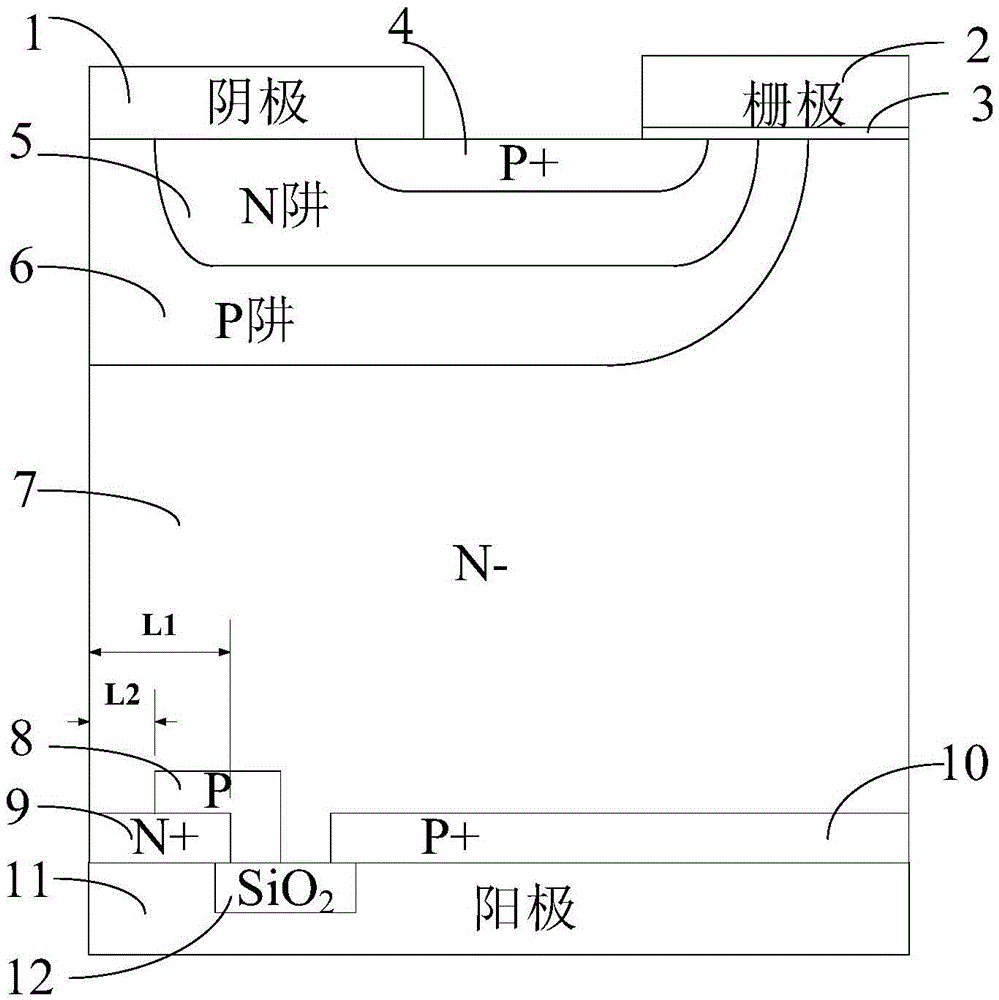

Insulated gate bipolar translator (IGBT) device with two short-circuit positive electrodes

InactiveCN102544084AAnode Structure ImprovementReduce forward voltage dropSemiconductor devicesConductivity modulationSilicon dioxide

The invention discloses an insulated gate bipolar translator (IGBT) device with two short-circuit positive electrodes, and belongs to the technical field of semiconductor power devices. A positive electrode structure of the device is a two-positive-electrode short-circuit structure. The IGBT device comprises a first P+ hole emission layer, a second P+ hole emission layer, a metal collector and a silicon dioxide barrier layer, wherein the silicon dioxide barrier layer is positioned on the back face of the first P+ hole emission layer; the metal collector is positioned on the side face of the first P+ hole emission layer and below the second P+ hole emission layer, and the two P+ hole emission layers are contacted with each other; the second P+ hole emission layer is positioned at the bottom of an N- drift region and staggered in parallel with the first P+ hole emission layer; and an electronic trench is formed between the first P+ hole emission layer and the second P+ hole emission layer. The positive electrode structure of the IGBT device is improved, so that the hole injection efficiency is improved, the current carrier concentration distribution in the drift region is optimized, the conductivity modulation performance in the device body is improved, a negative differential resistance (NDR) region is eliminated effectively, the cut-off loss of the IGBT device is reduced effectively, and finally, compromise optimization for conductivity pressure drop and cut-off loss is realized.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1