Patents

Literature

378 results about "Parasitic bipolar transistor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

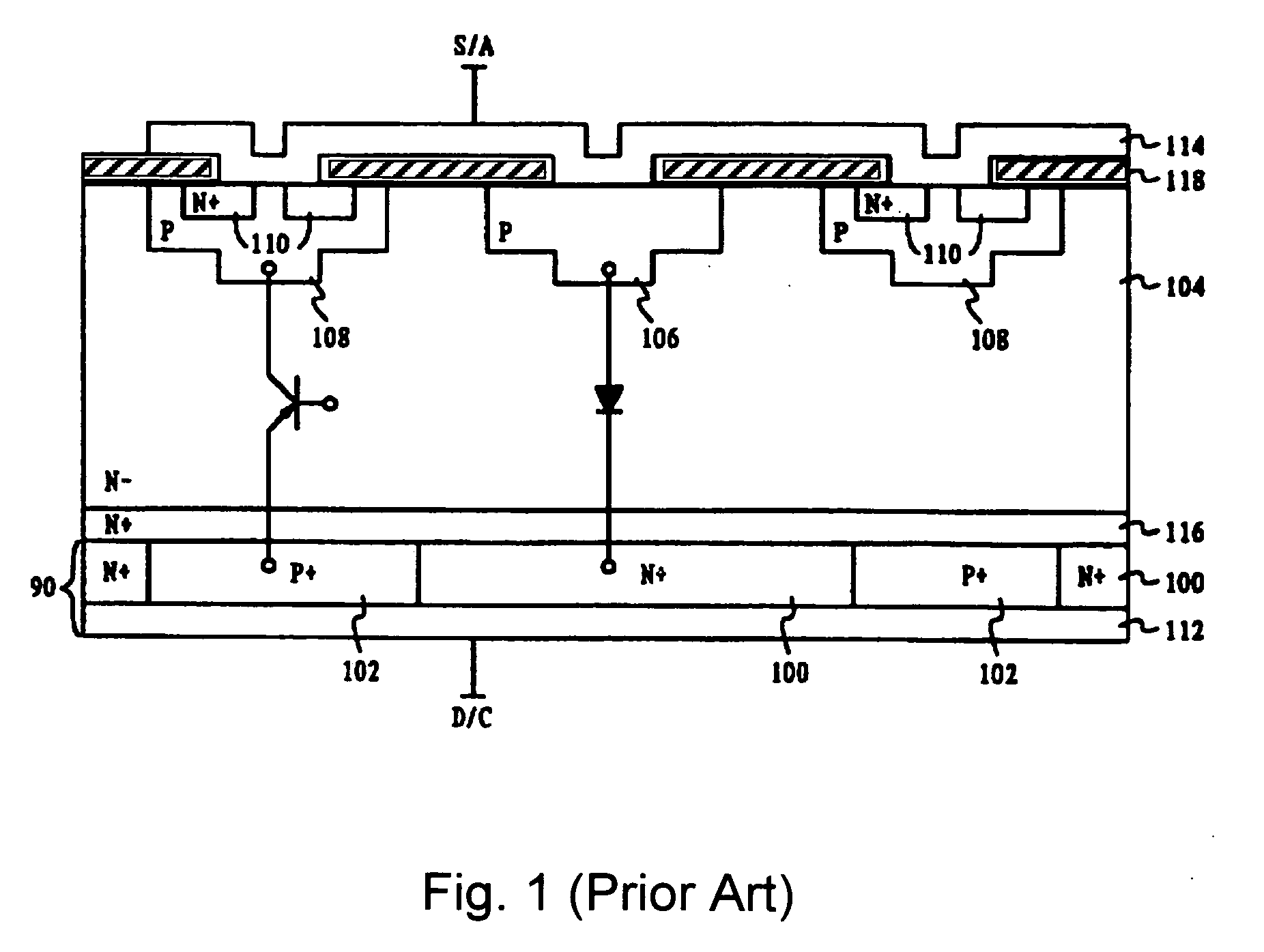

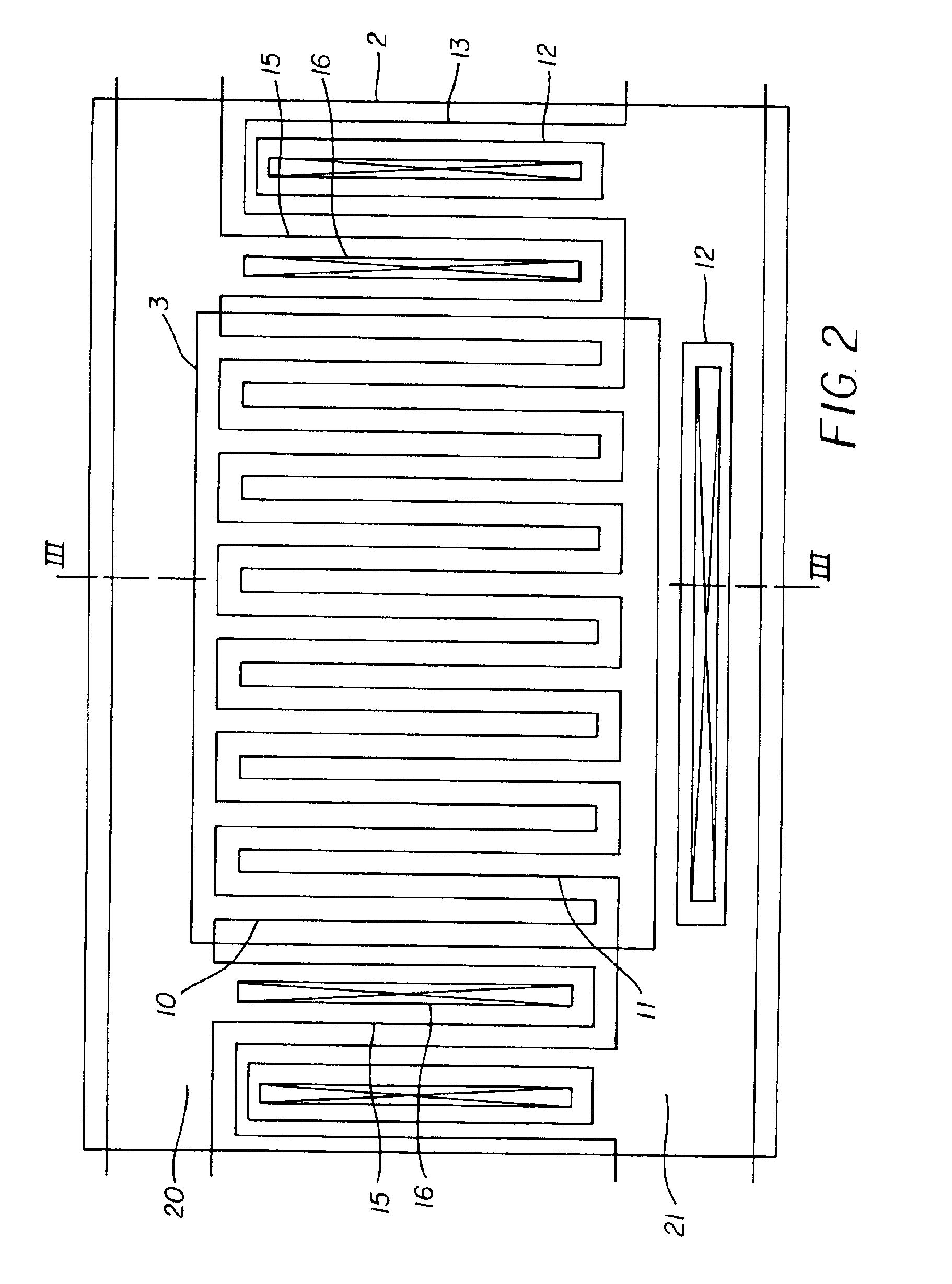

A parasitic vertical PNP bipolar transistor in BiCMOS process comprises a collector, a base and an emitter. The collector is formed by active region with p-type ion implanting layer (P type well in NMOS).

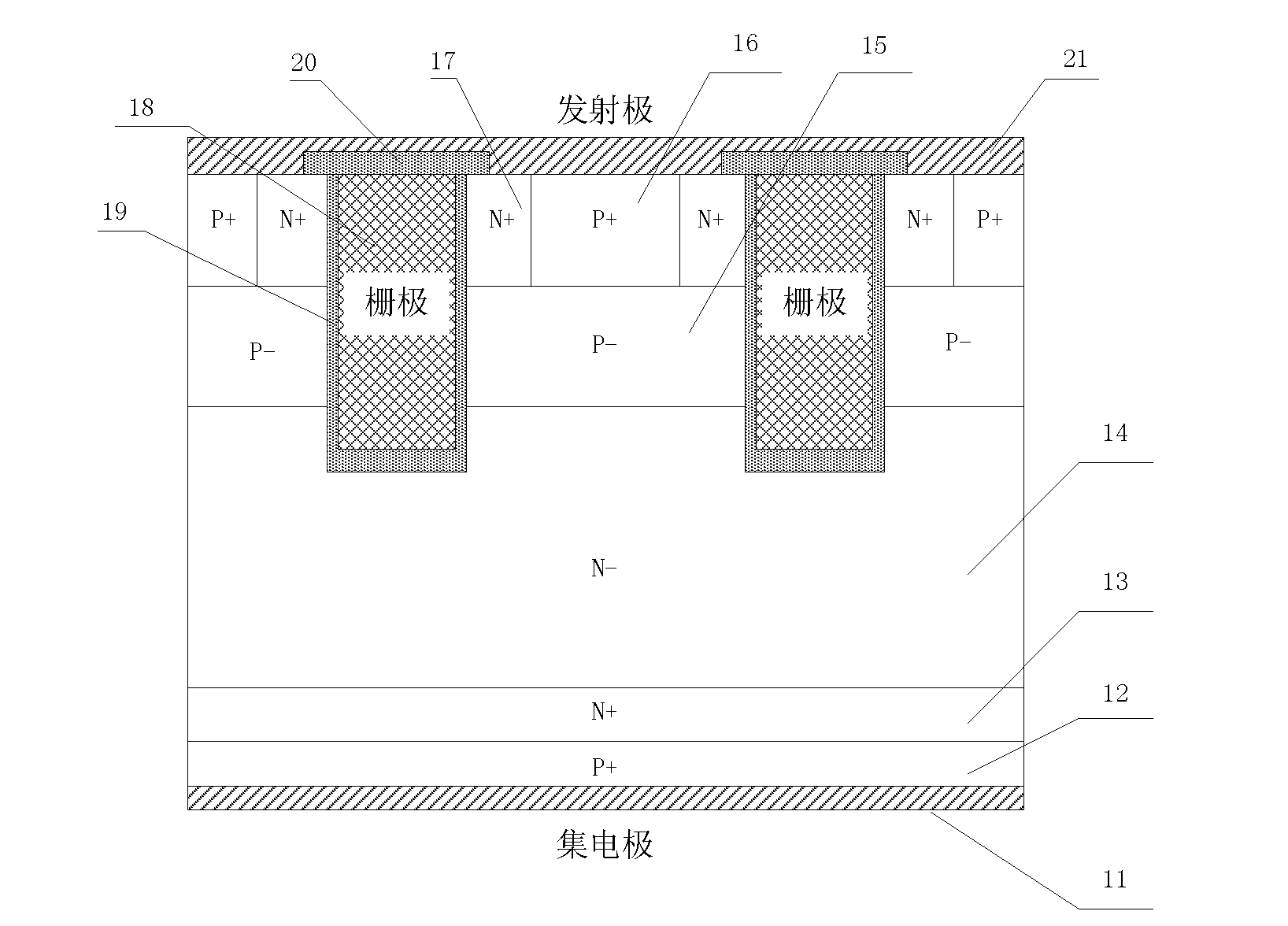

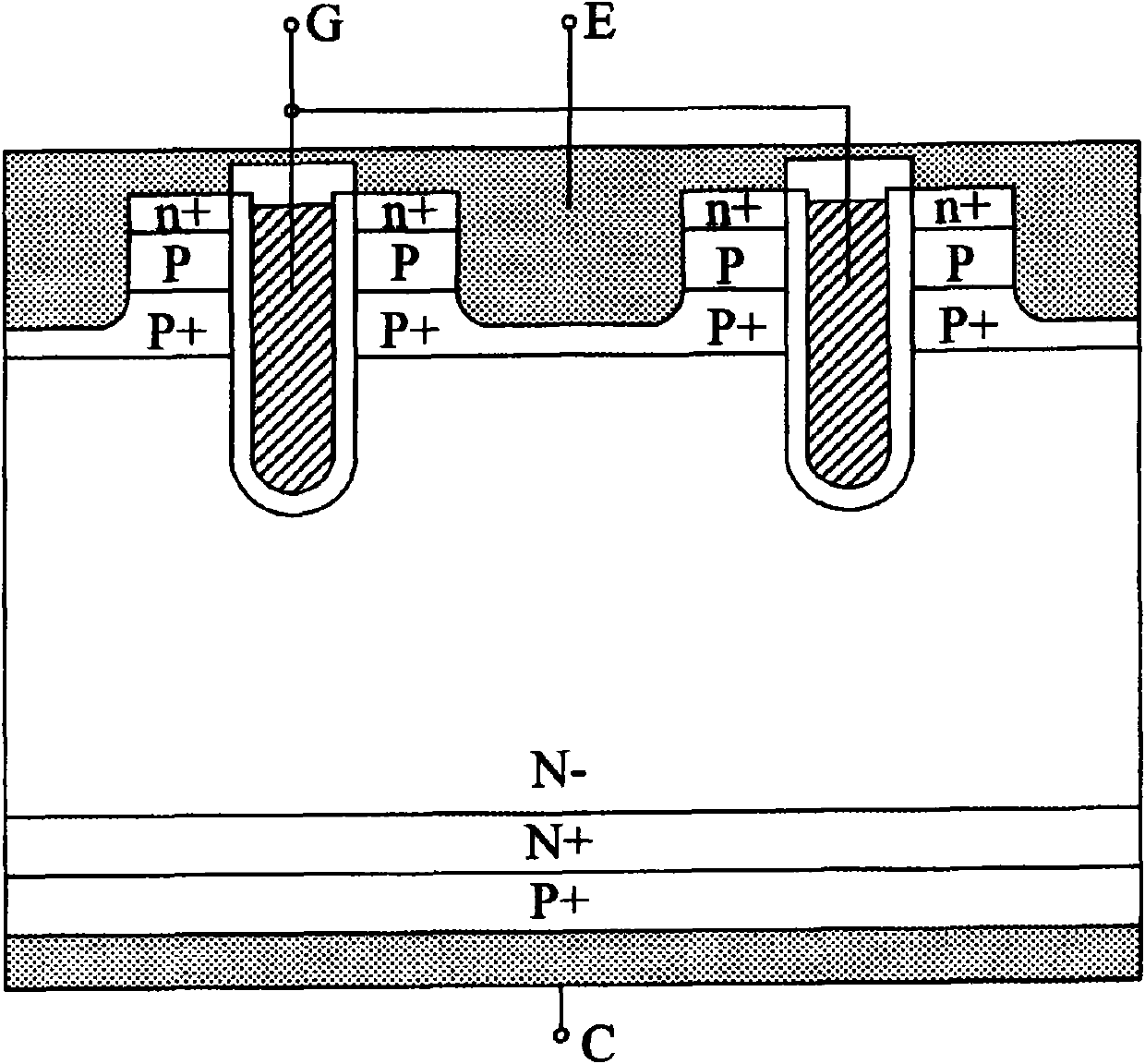

Double gate insulated gate bipolar transistor

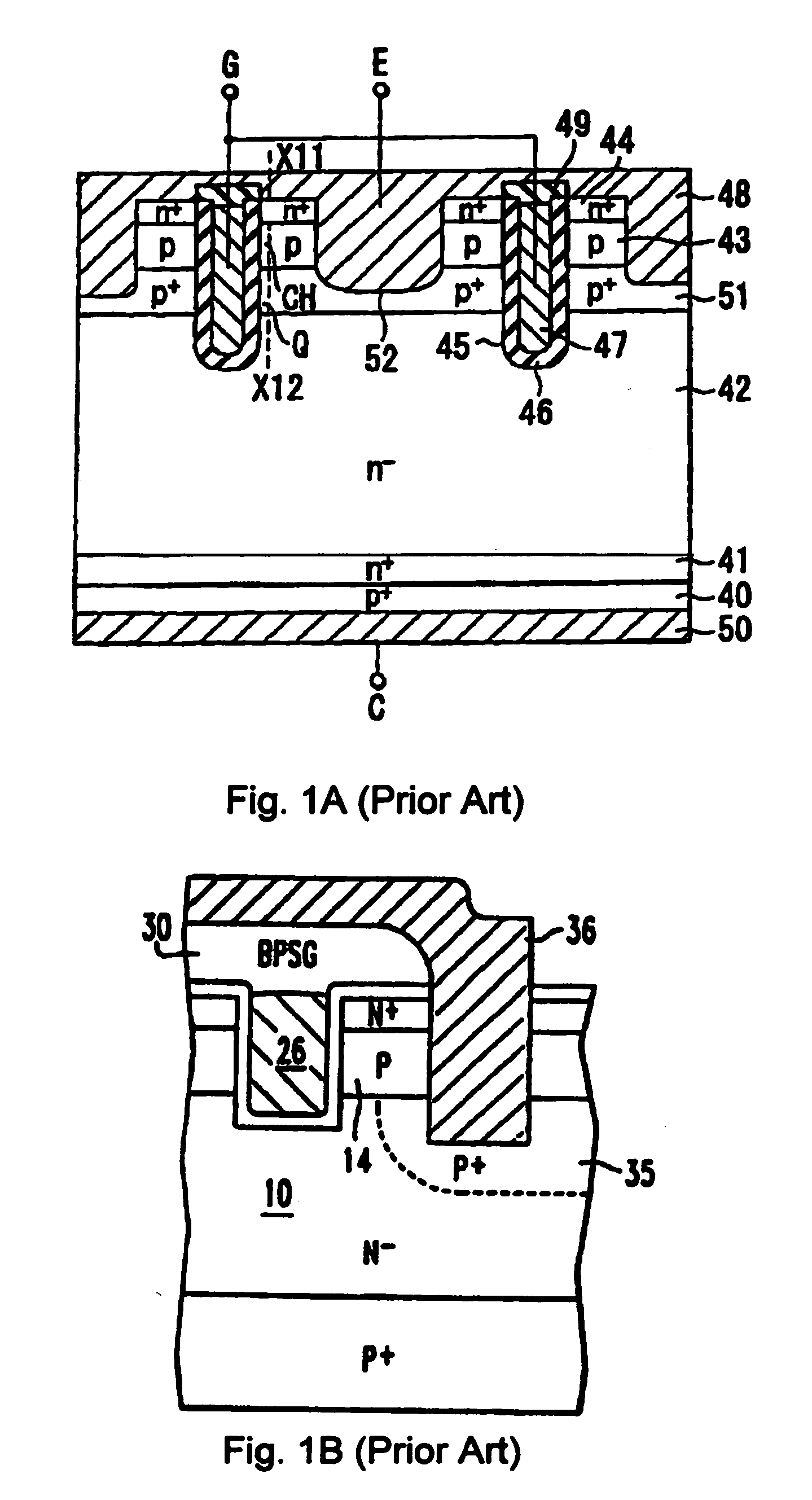

InactiveUS20090008674A1Reduce the number of holesReduce transportationTransistorSolid-state devicesParasitic bipolar transistorEngineering

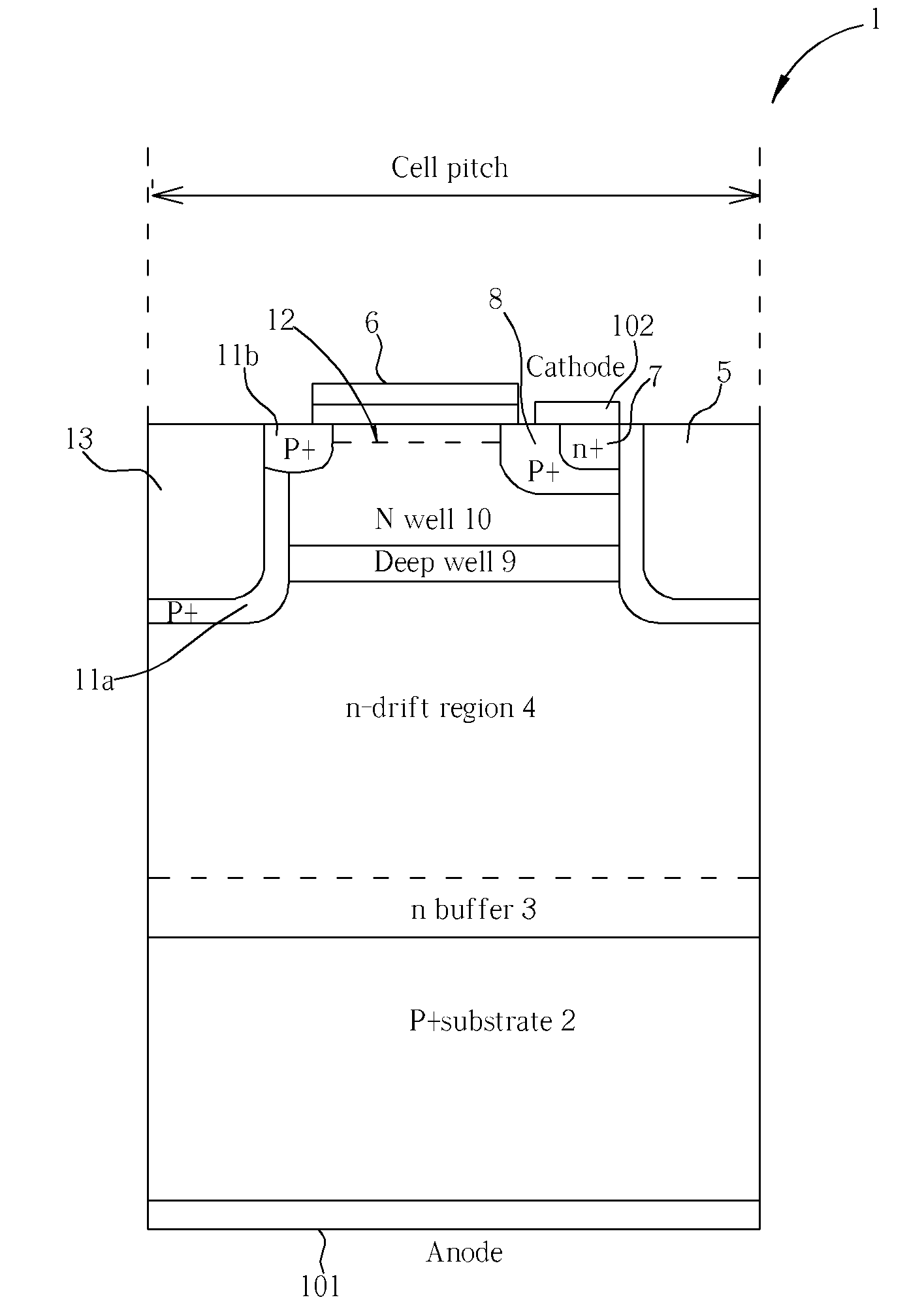

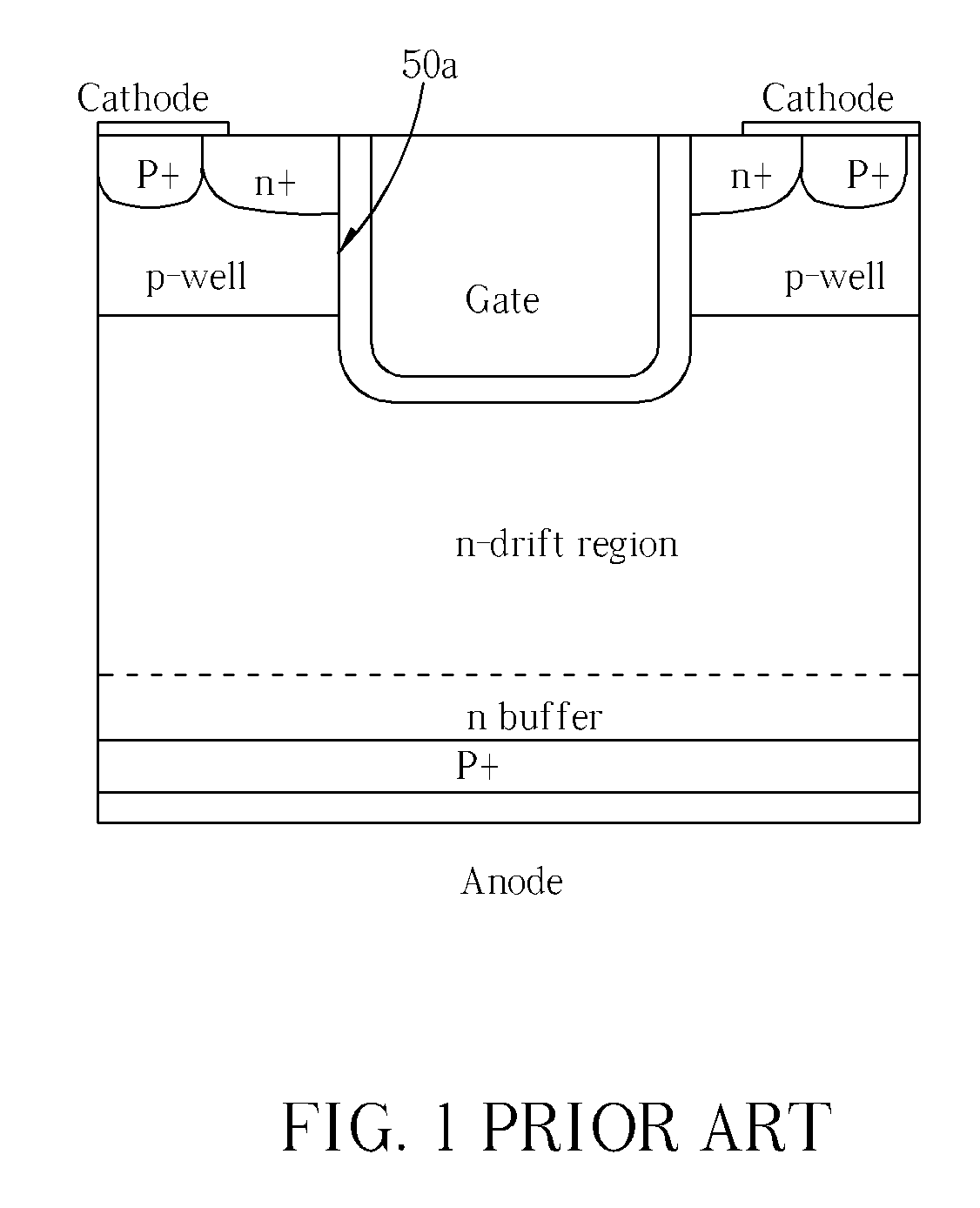

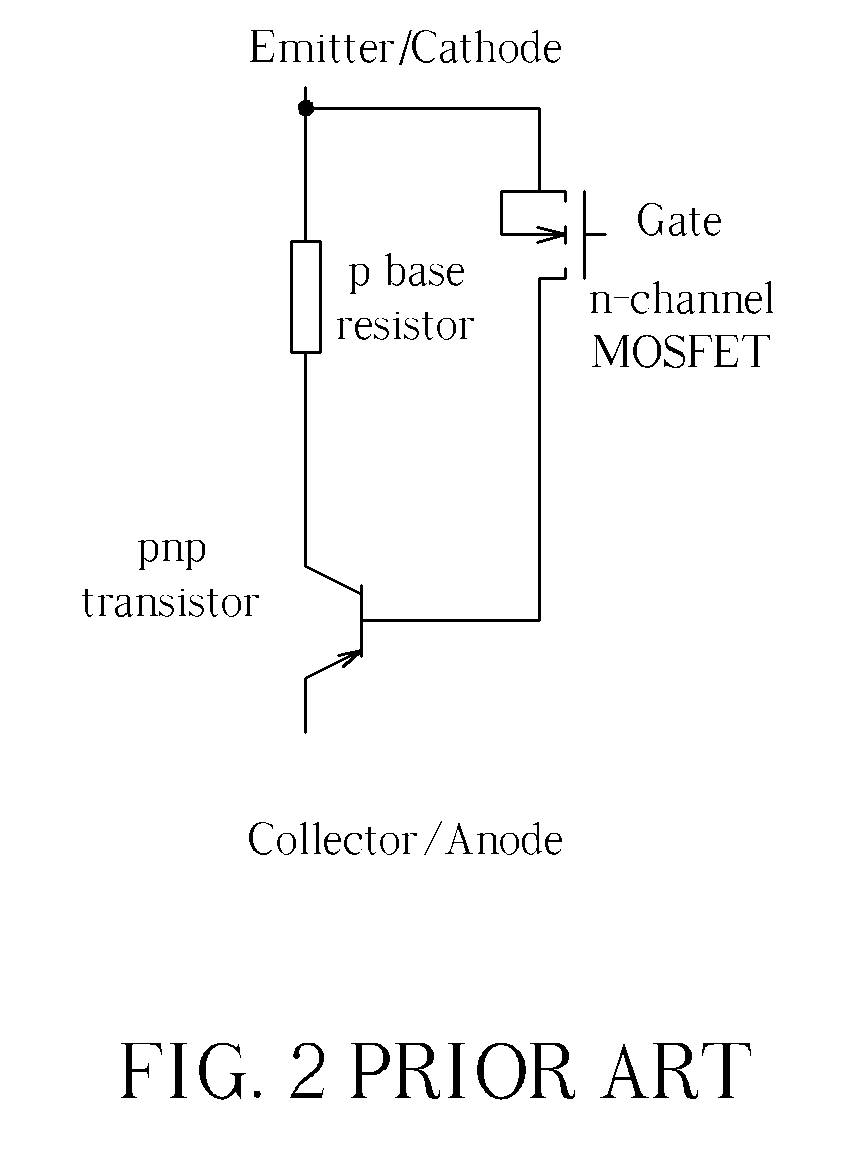

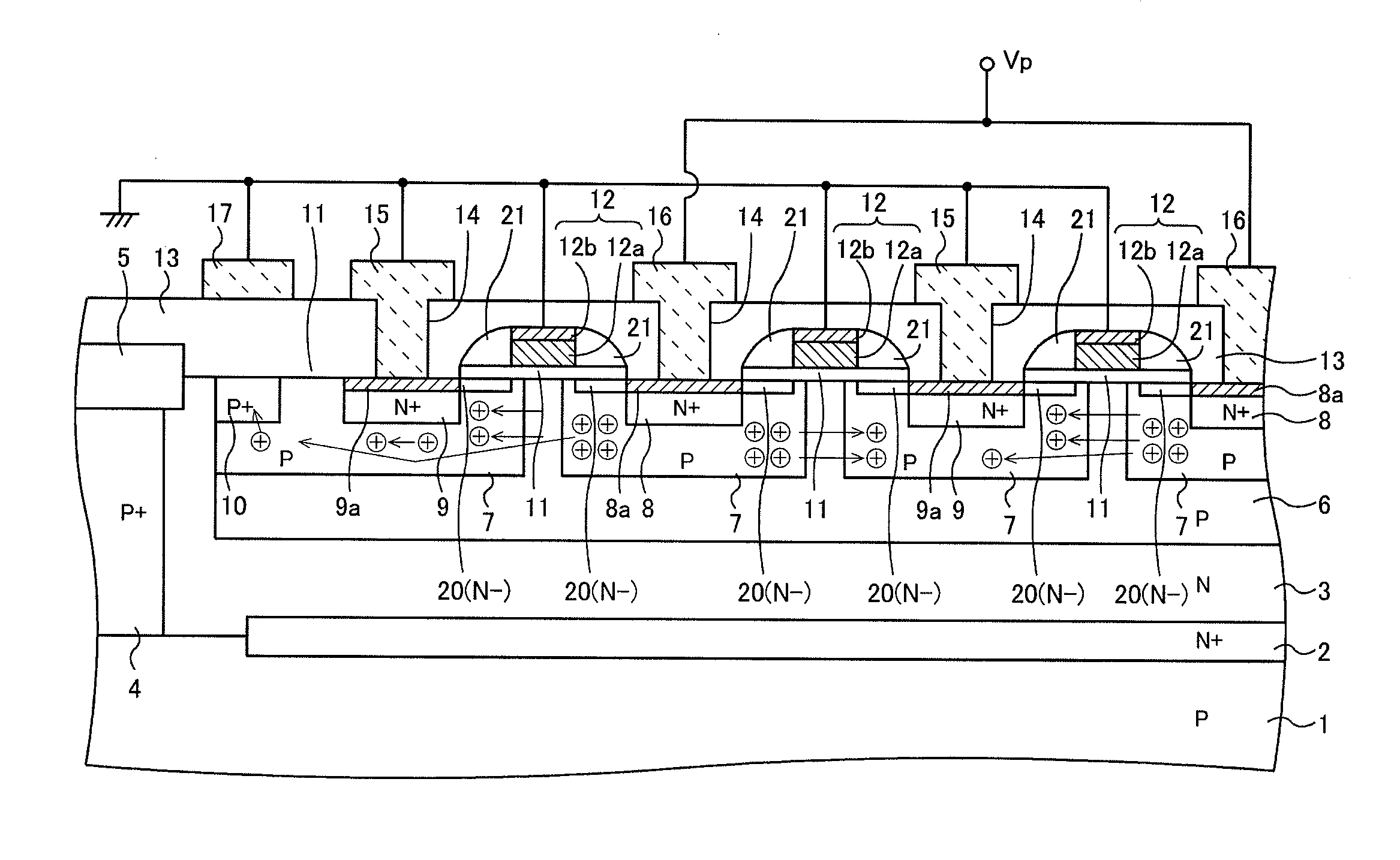

Double gate IGBT having both gates referred to a cathode in which a second gate is for controlling flow of hole current. In on-state, hole current can be largely suppressed. While during switching, hole current is allowed to flow through a second channel. Incorporating a depletion-mode p-channel MOSFET having a pre-formed hole channel that is turned ON when 0V or positive voltages below a specified threshold voltage are applied between second gate and cathode, negative voltages to the gate of p-channel are not used. Providing active control of holes amount that is collected in on-state by lowering base transport factor through increasing doping and width of n well or by reducing injection efficiency through decreasing doping of deep p well. Device includes at least anode, cathode, semiconductor substrate, n− drift region, first & second gates, n+ cathode region; p+ cathode short, deep p well, n well, and pre-formed hole channel.

Owner:ANPEC ELECTRONICS CORPORATION

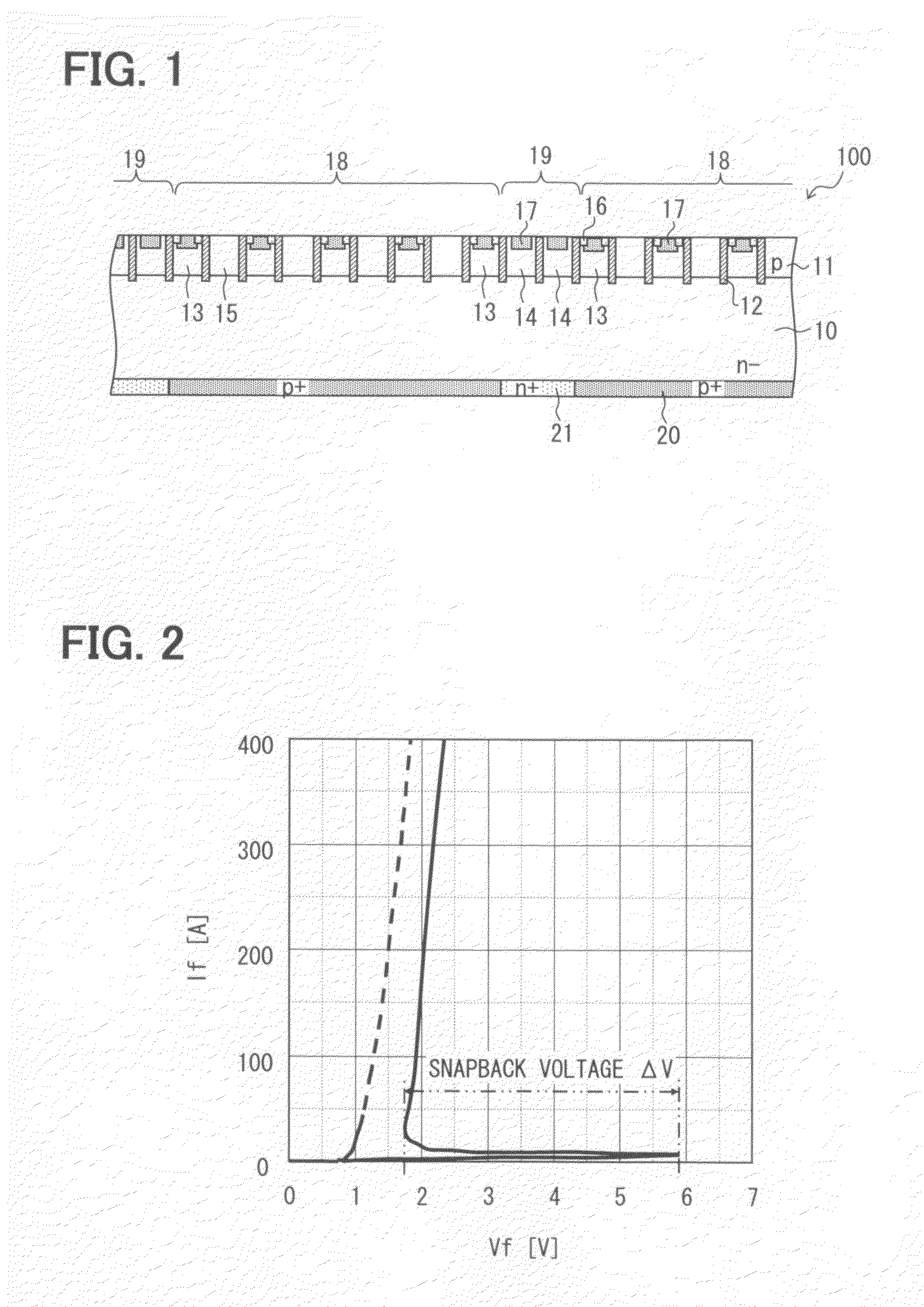

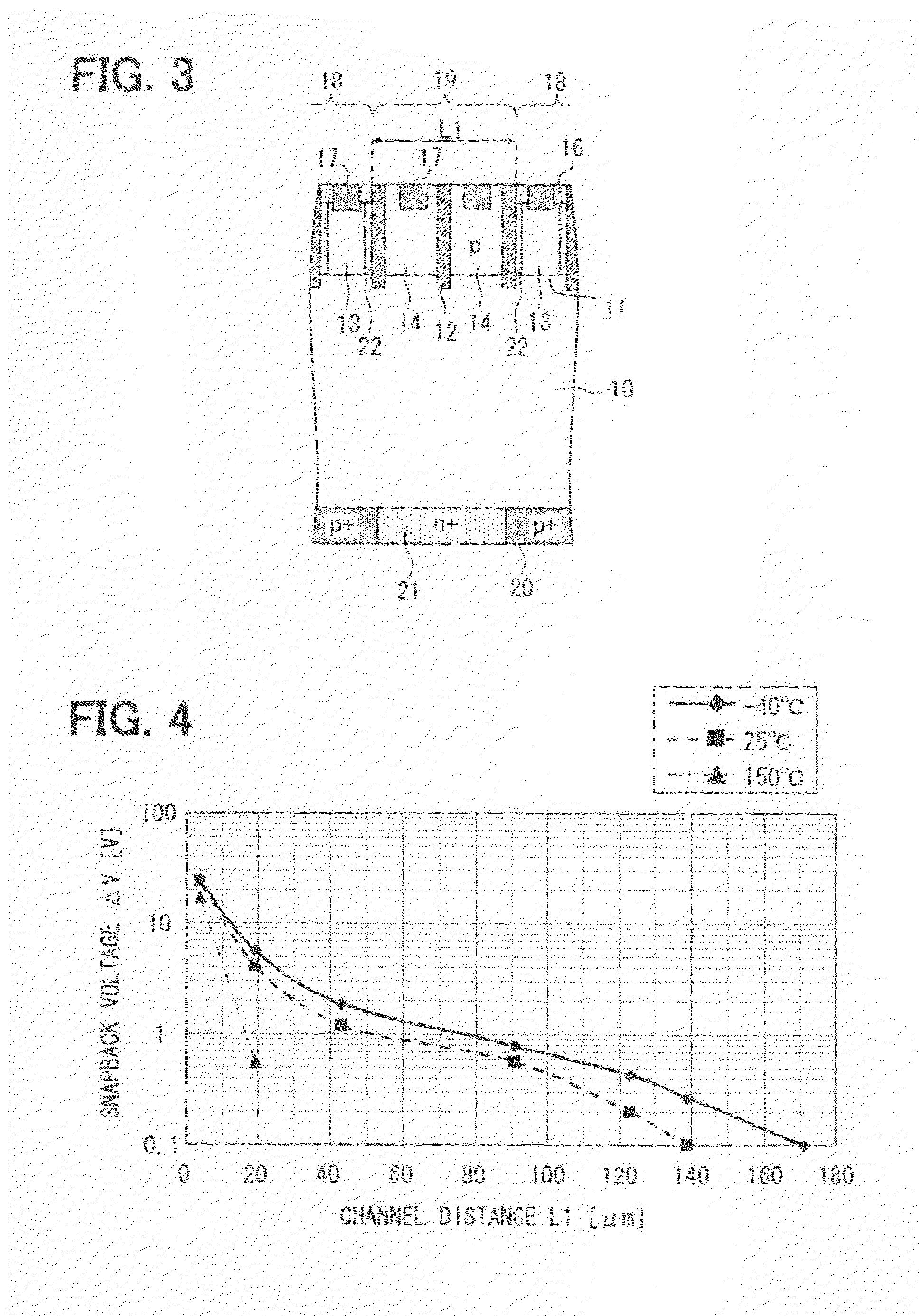

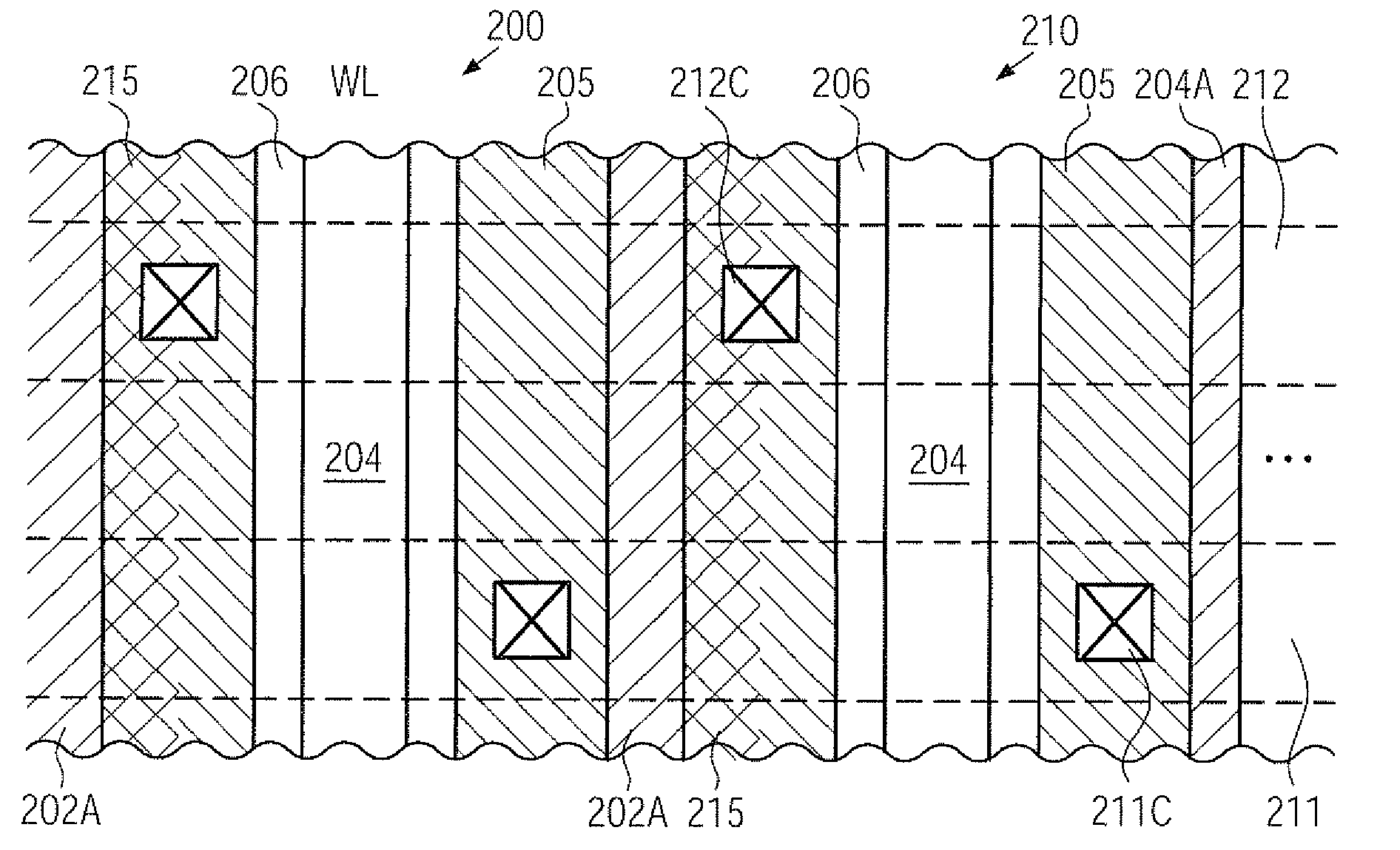

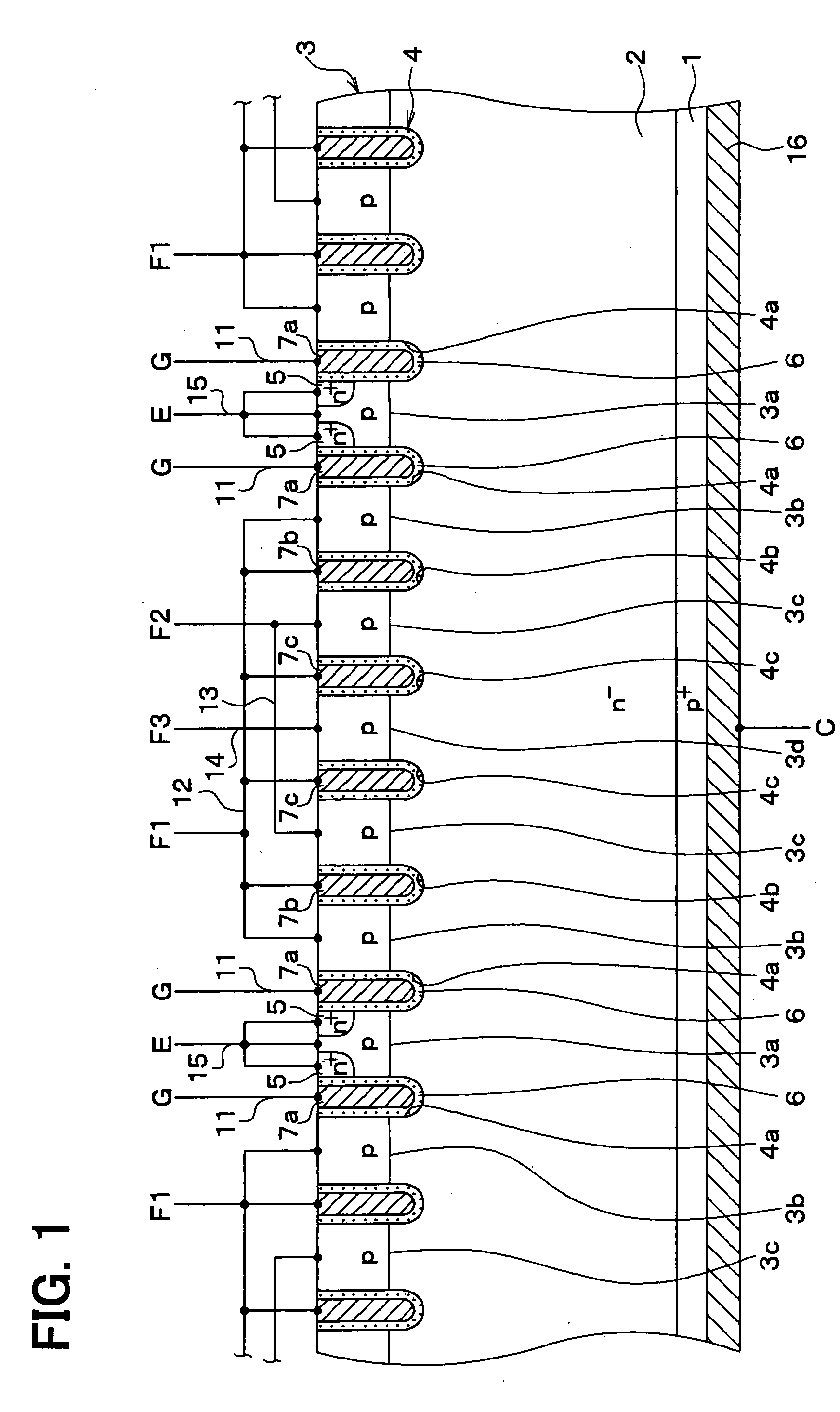

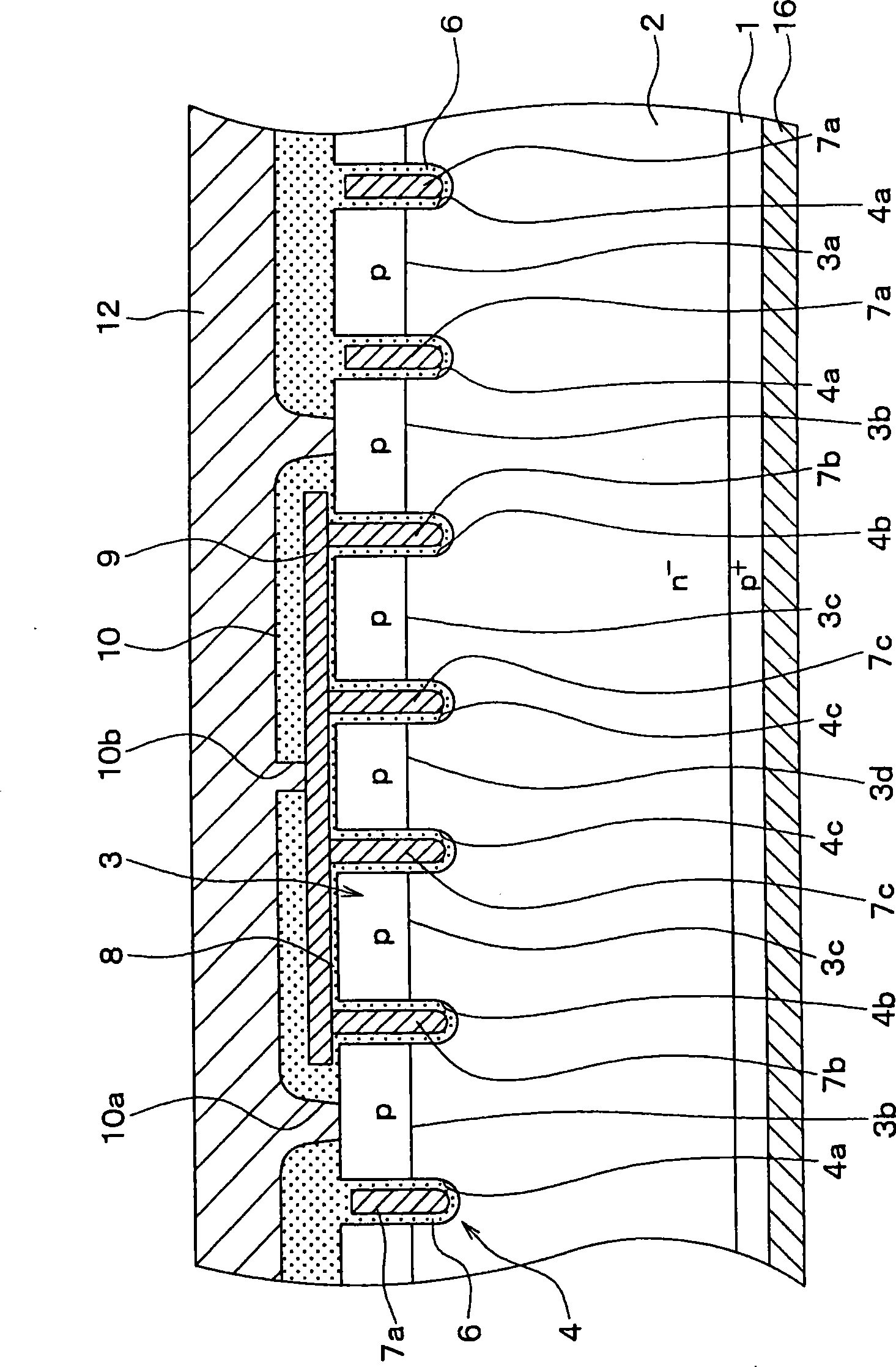

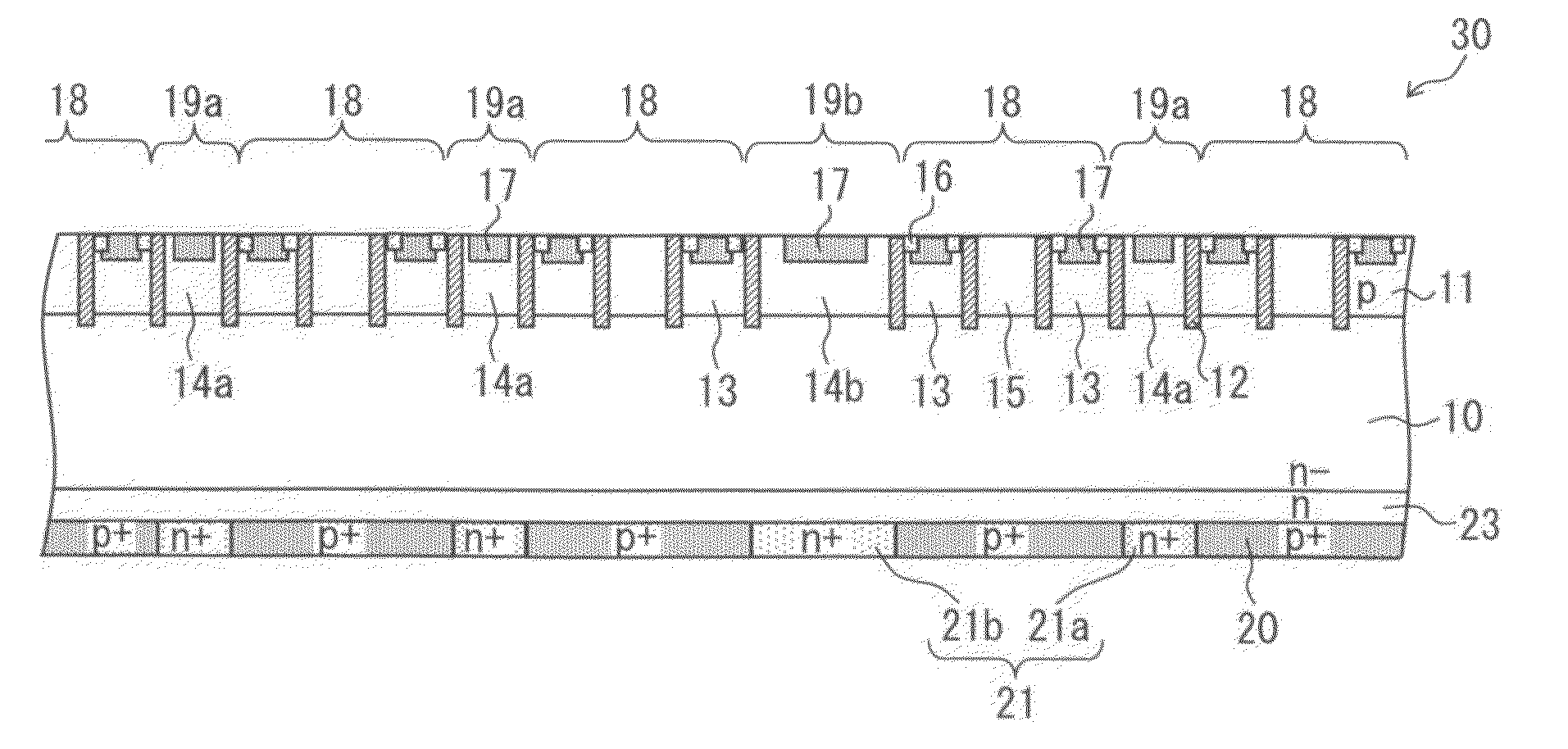

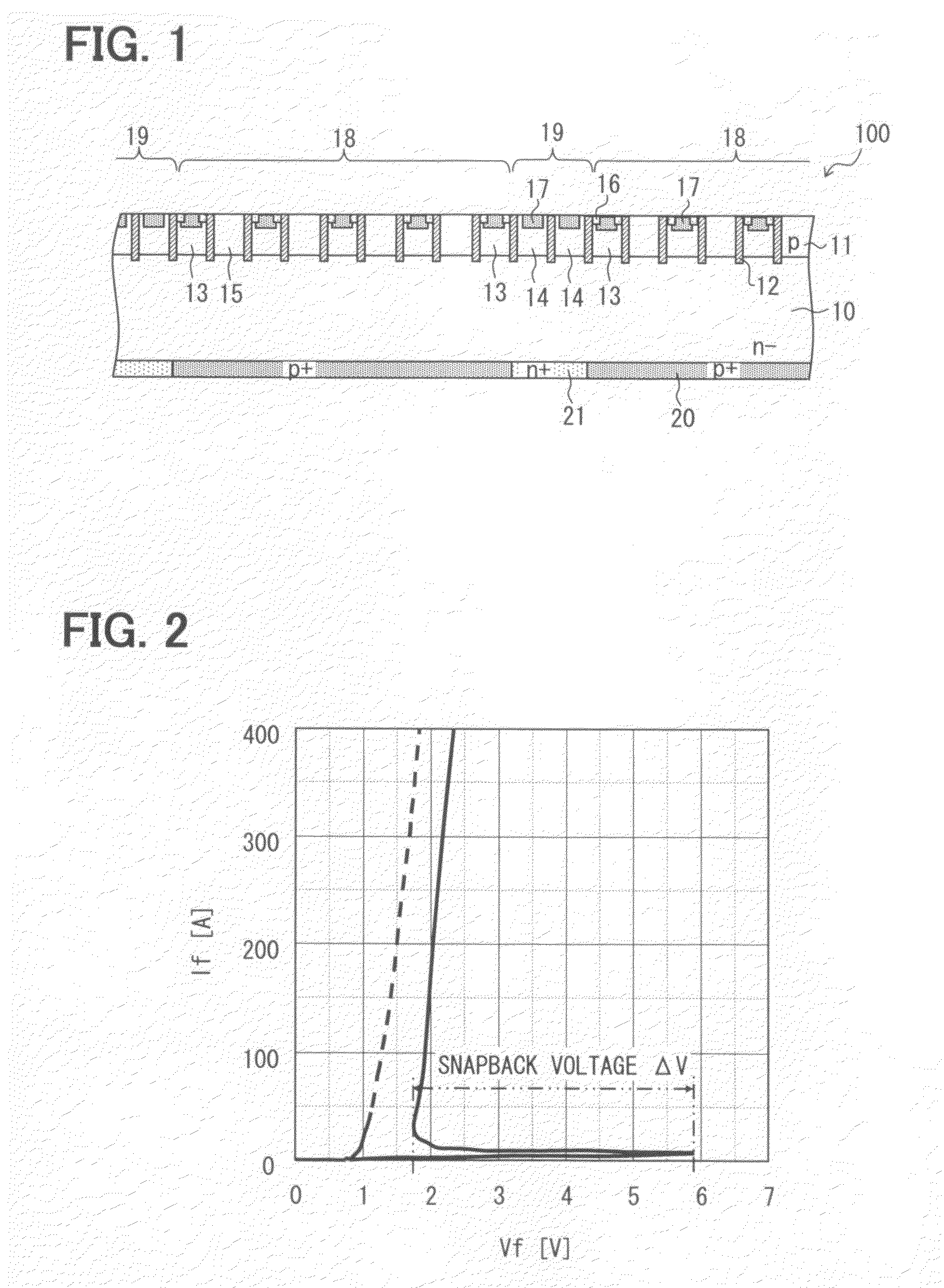

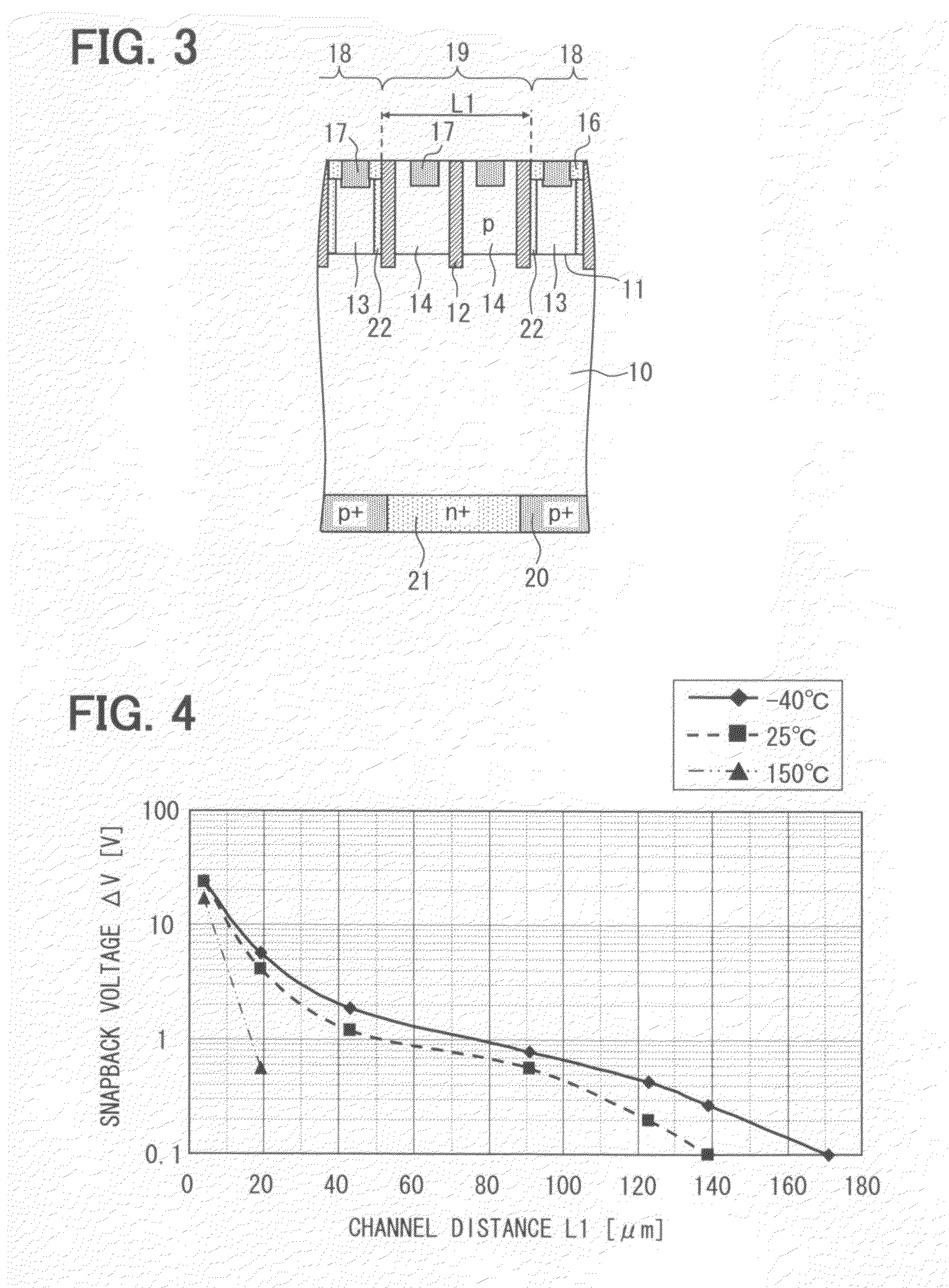

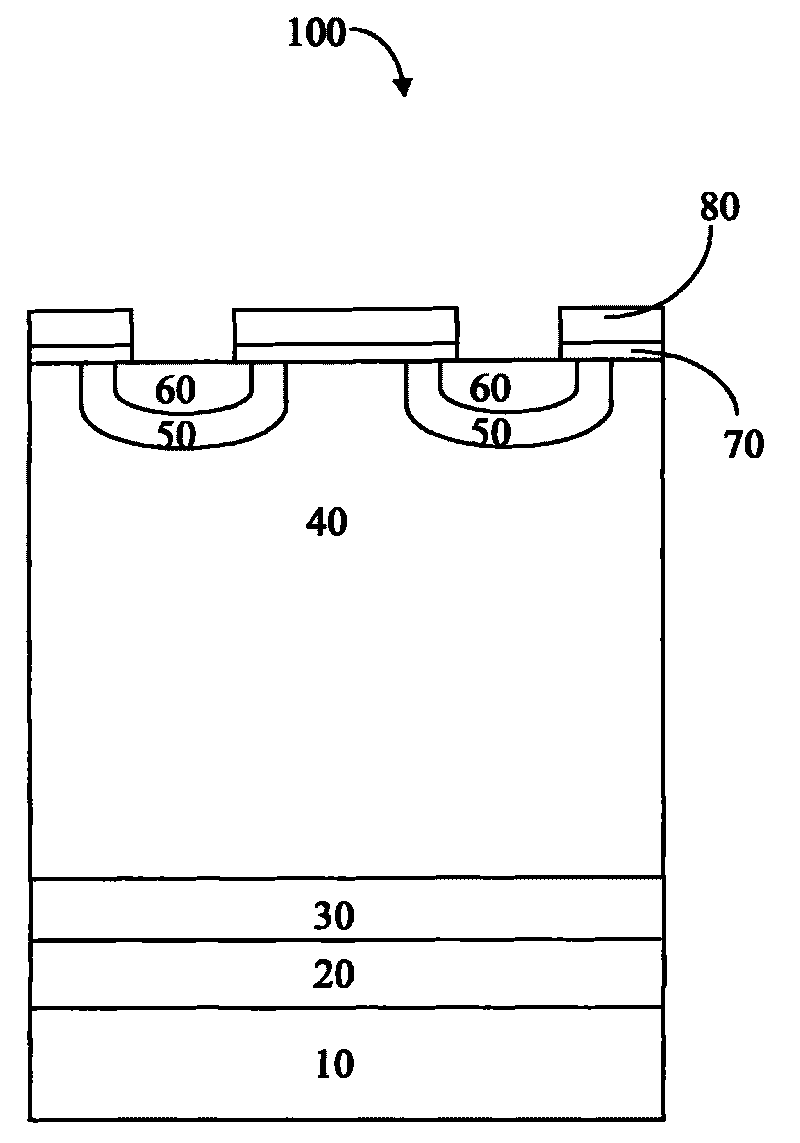

Semiconductor device including insulated gate bipolar transistor and diode

ActiveUS20100156506A1Unified operationReduce reboundTransistorSolid-state devicesParasitic bipolar transistorEngineering

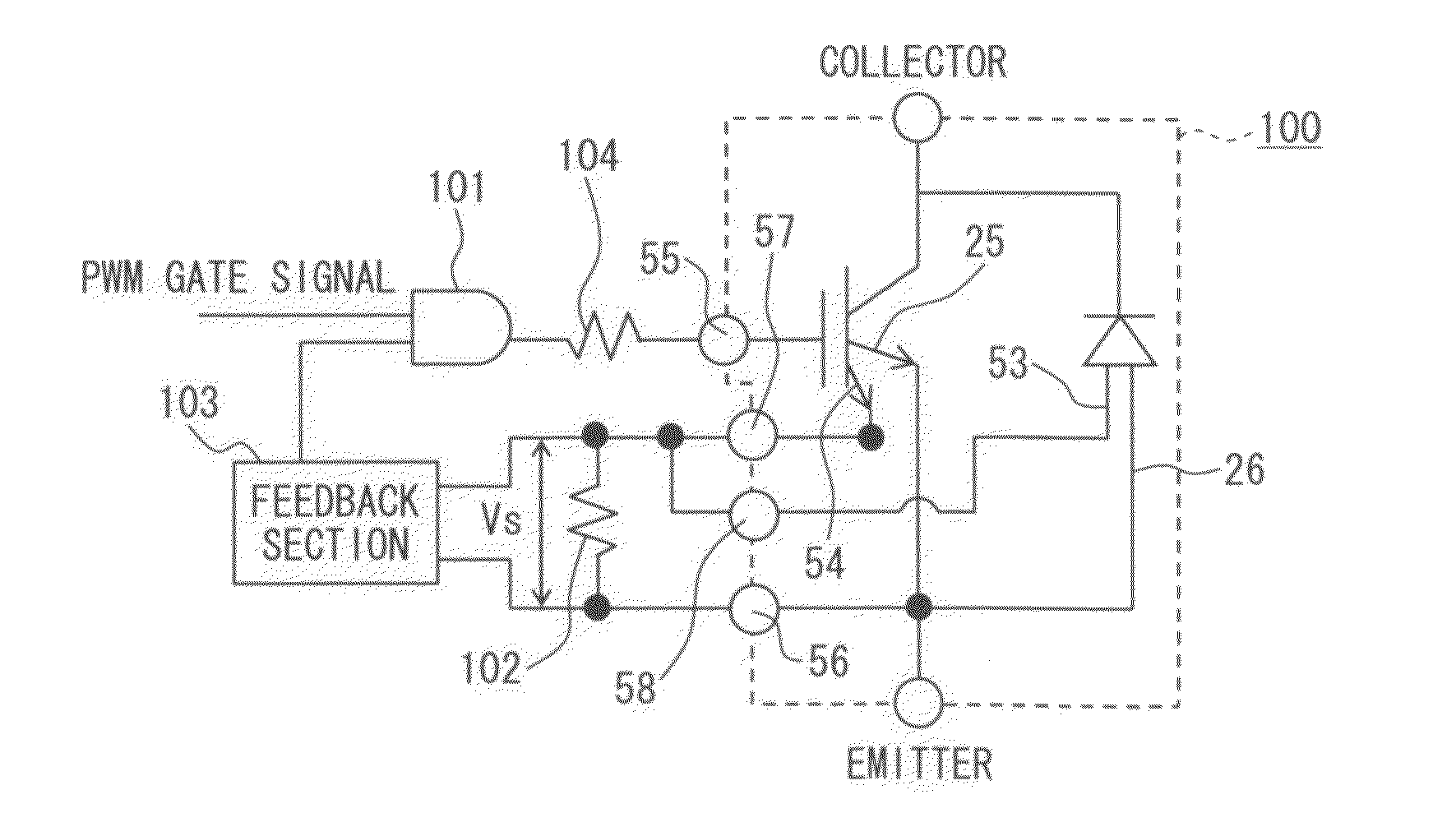

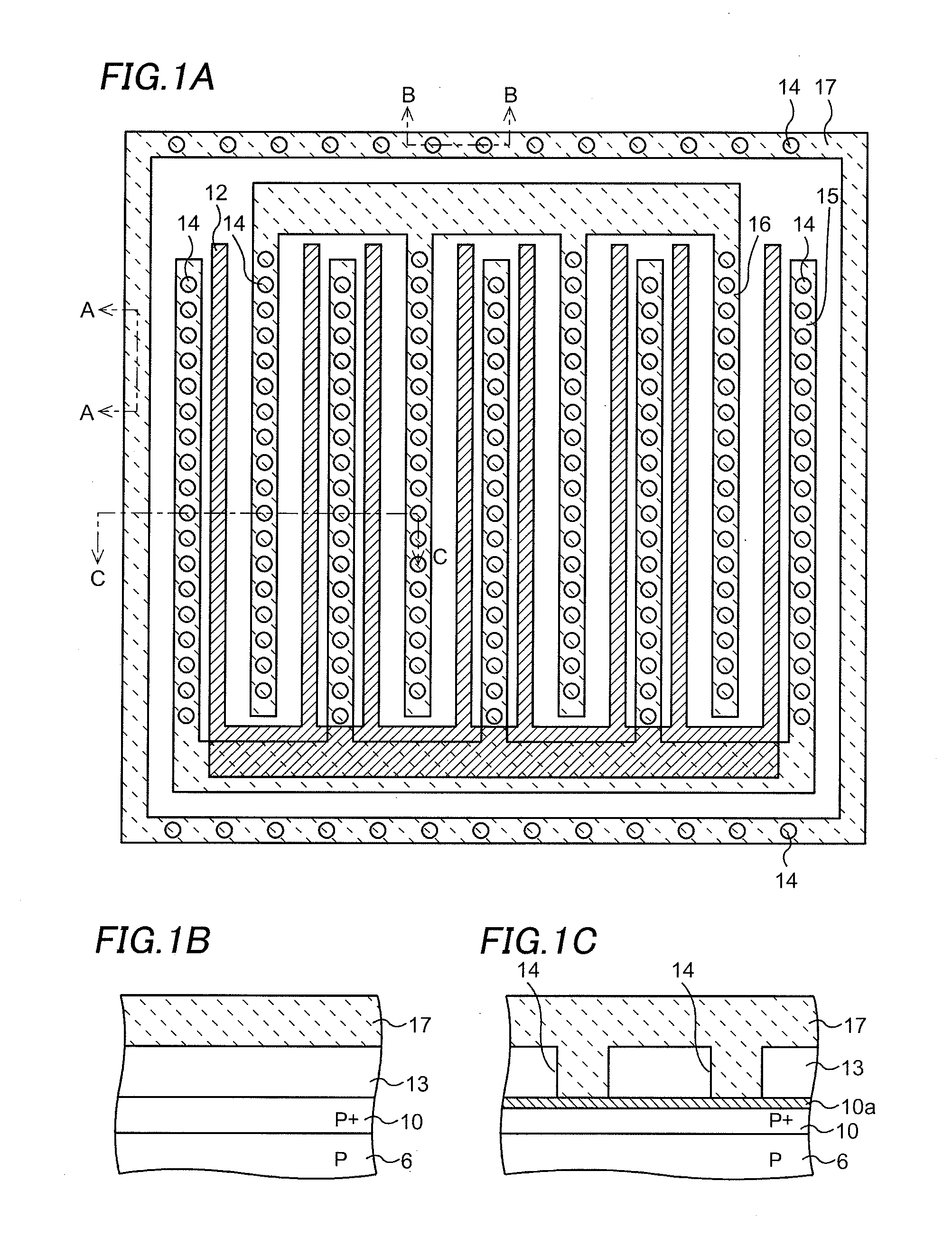

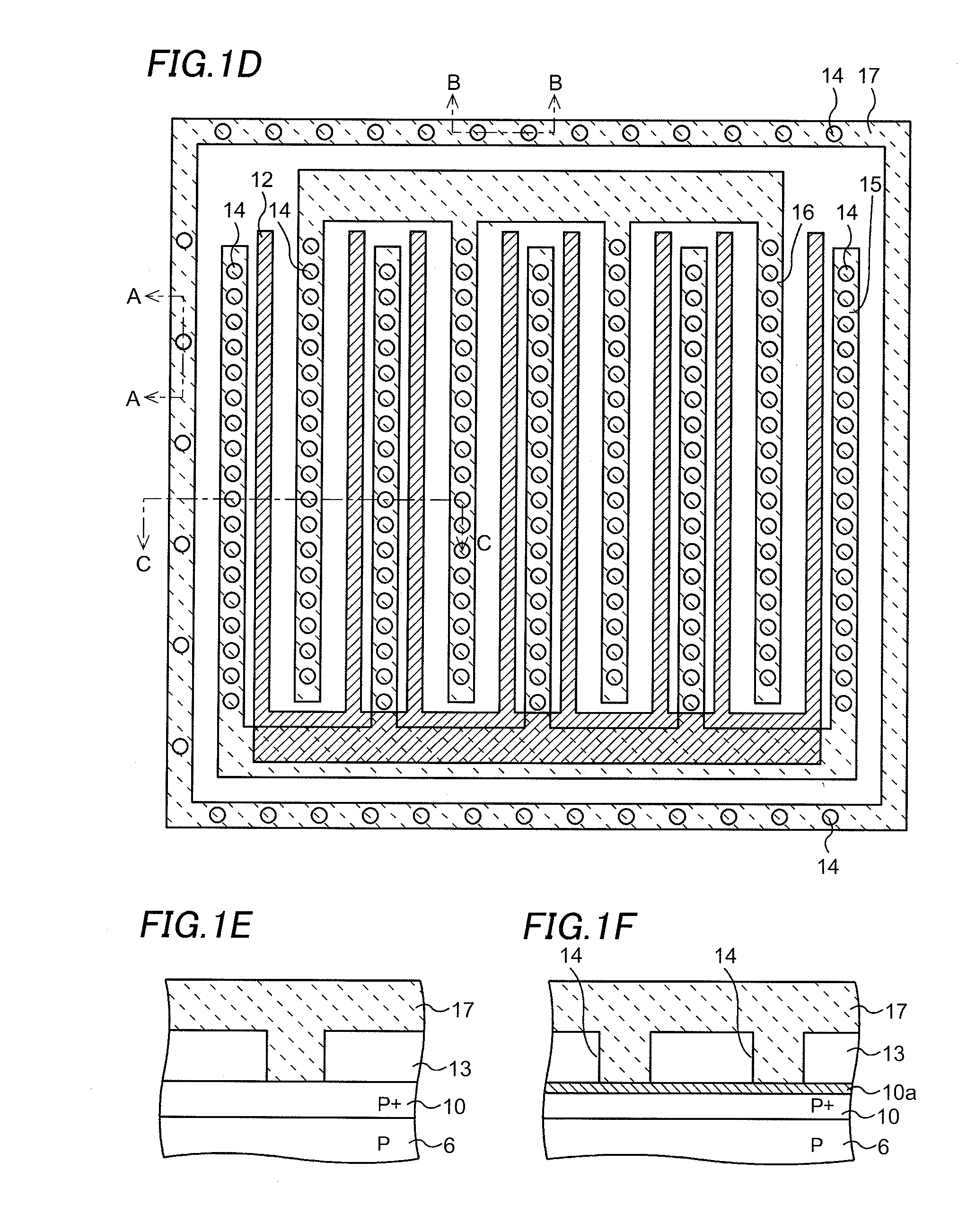

A semiconductor device includes a vertical IGBT and a vertical free-wheeling diode in a semiconductor substrate. A plurality of base regions is disposed at a first-surface side portion of the semiconductor substrate, and a plurality of collector regions and a plurality of cathode regions are alternately disposed in a second-surface side portion of the semiconductor substrate. The base regions include a plurality of regions where channels are provided when the vertical IGBT is in an operating state. The first-side portion of the semiconductor substrate include a plurality of IGBT regions each located between adjacent two of the channels, including one of the base regions electrically coupled with an emitter electrode, and being opposed to one of the cathode regions. The IGBT regions include a plurality of narrow regions and a plurality of wide regions.

Owner:DENSO CORP

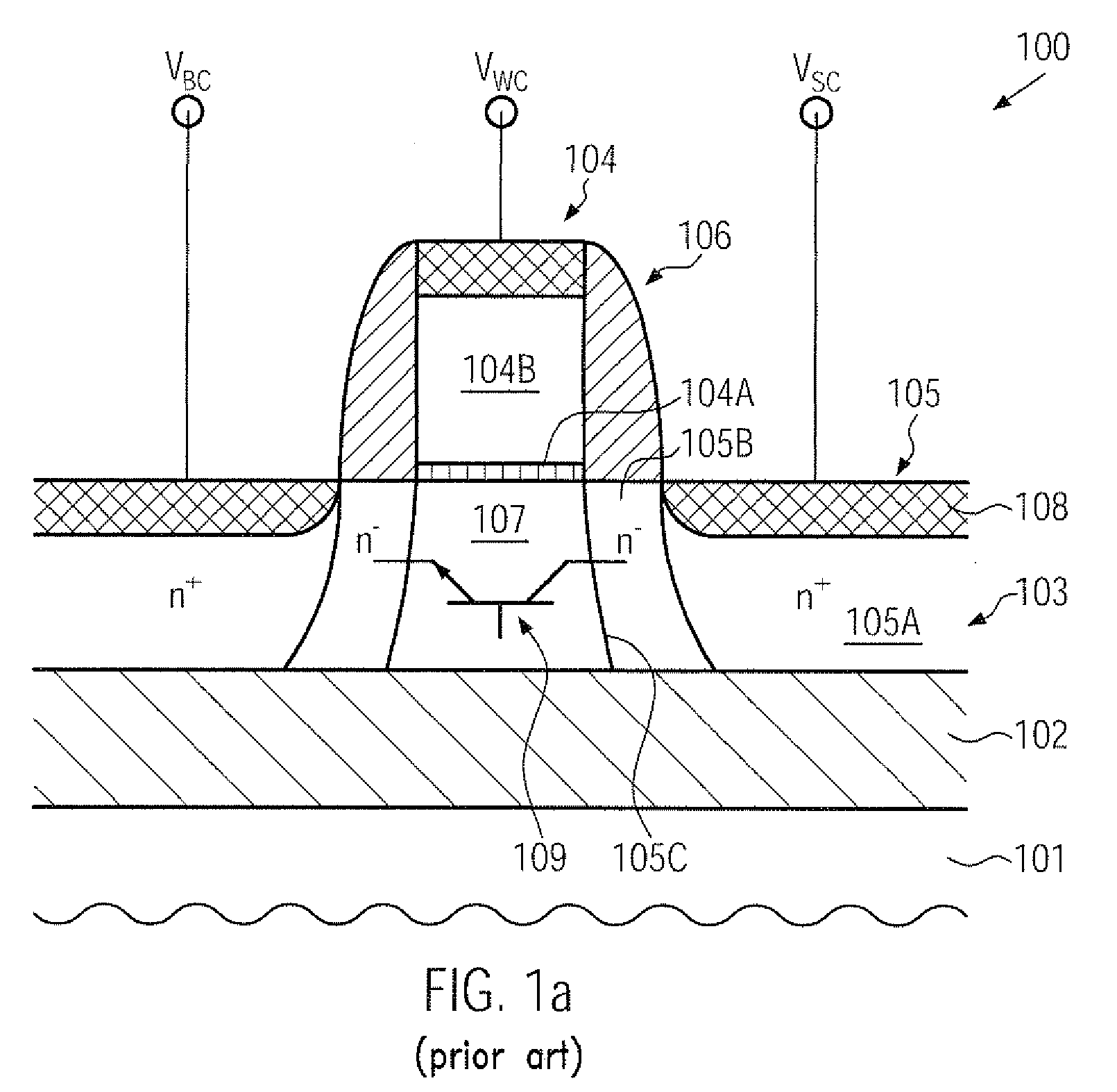

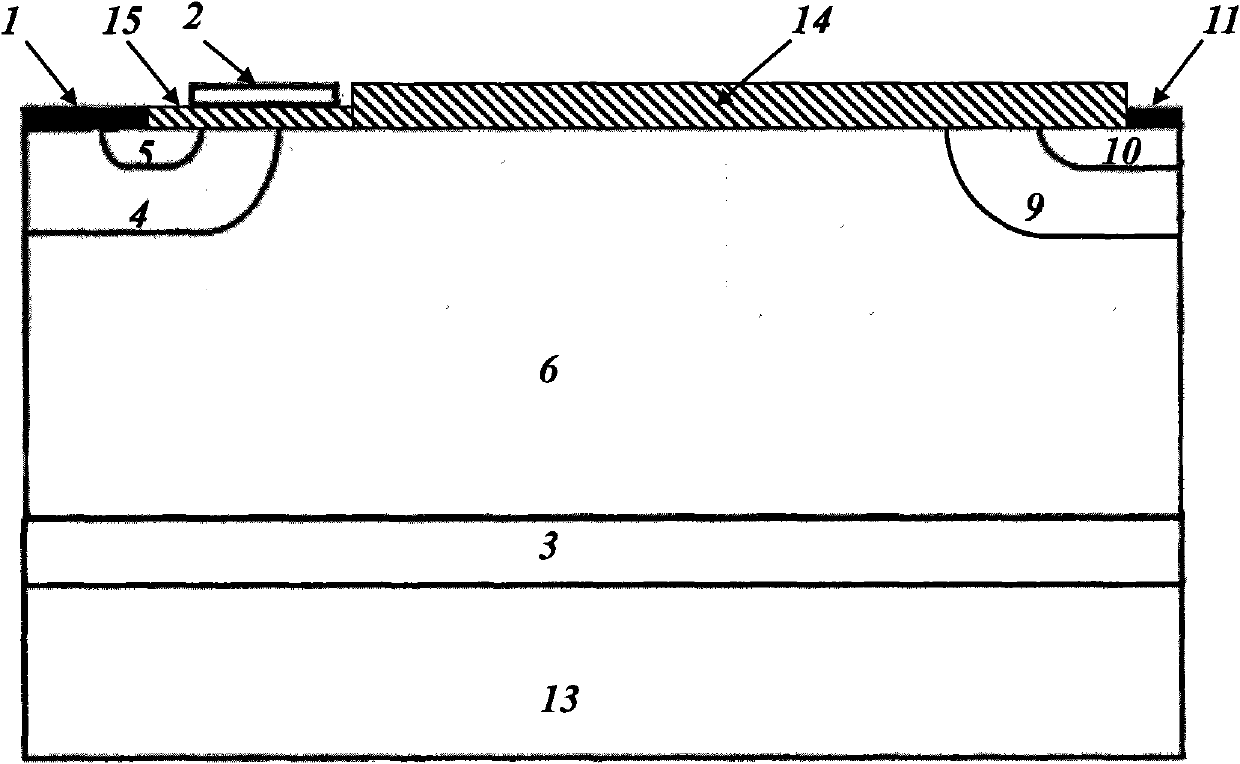

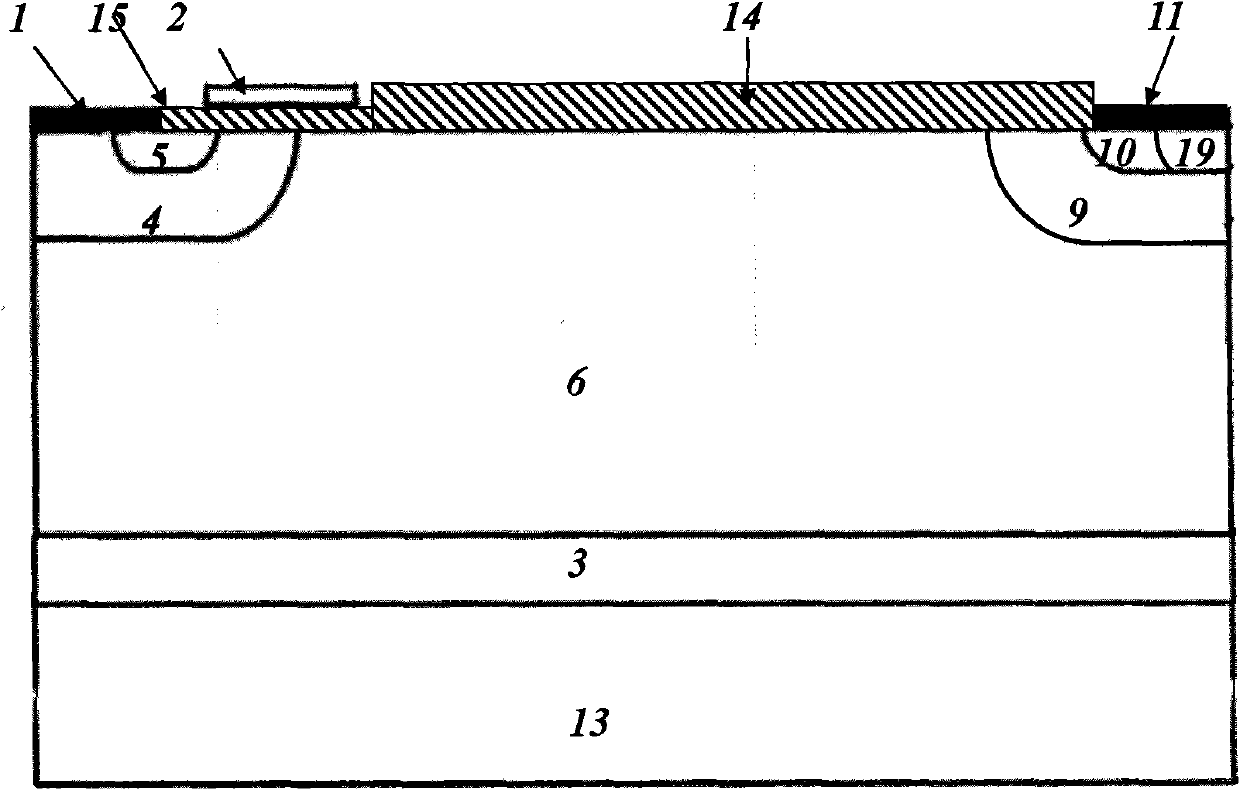

Soi transistor with floating body for information storage having asymmetric drain/source regions

InactiveUS20090242996A1Reduce probabilityEfficient switchingTransistorSolid-state devicesLateral asymmetrySymmetric design

By laterally asymmetrically defining the well dopant concentration in a floating body storage transistor, an increased well dopant concentration may be provided at the drain side, while a moderately low concentration may remain in the rest of the floating body region. Consequently, compared to conventional symmetric designs, a reduction in the read / write voltages for switching on the parasitic bipolar transistor may be accomplished, while the increased punch-through immunity may allow further scaling of the gate length of the floating body storage transistor.

Owner:GLOBALFOUNDRIES INC

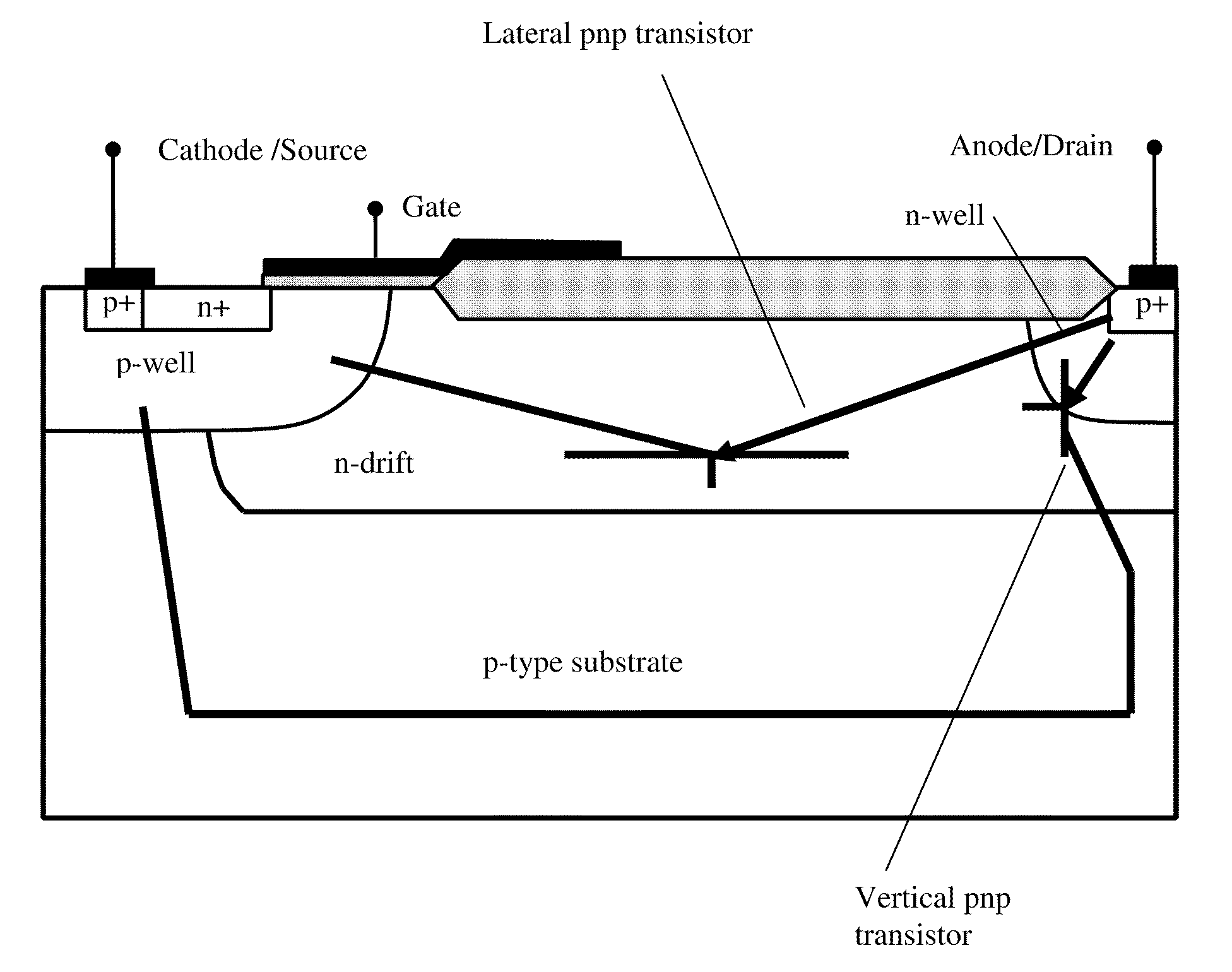

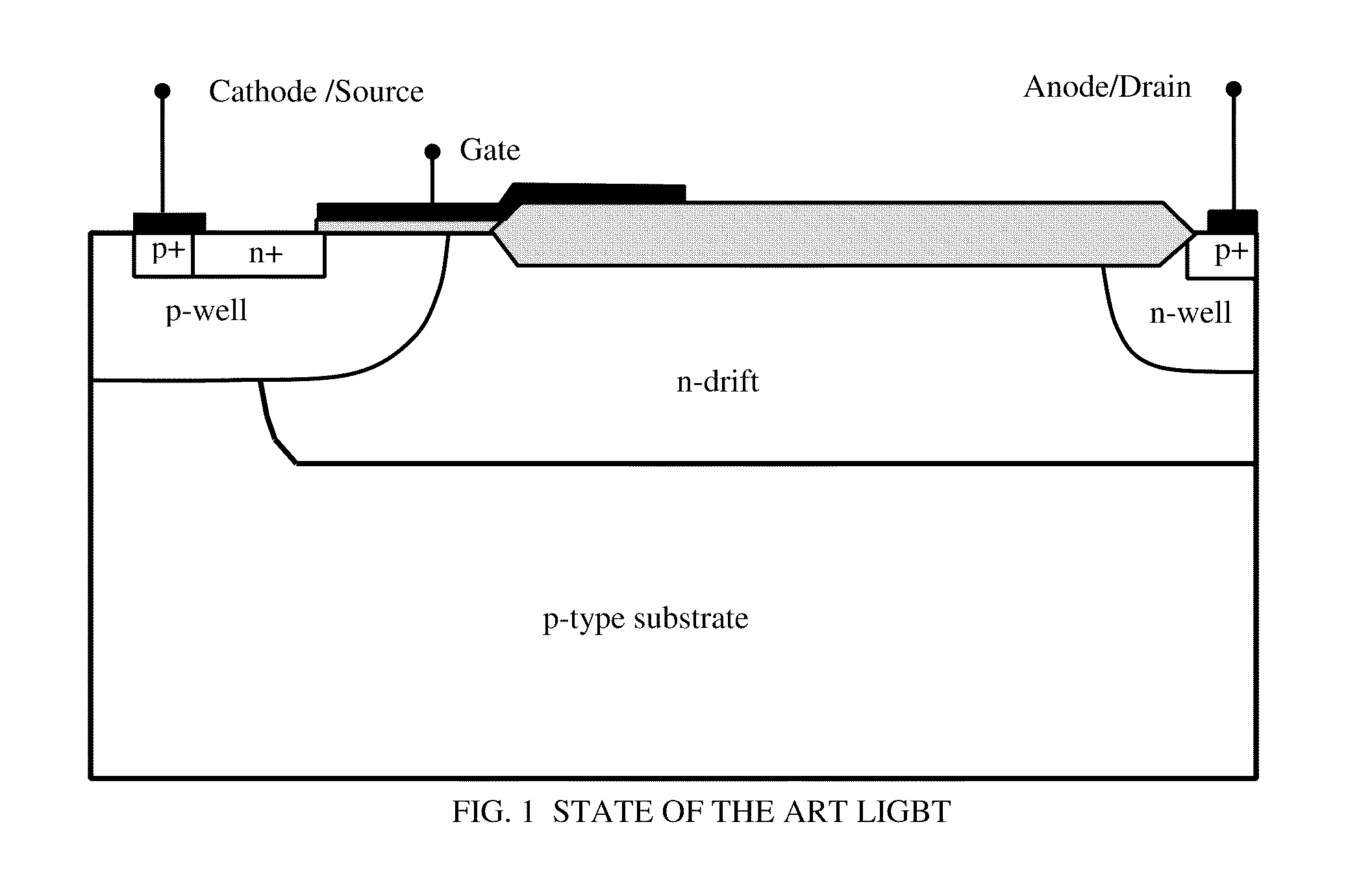

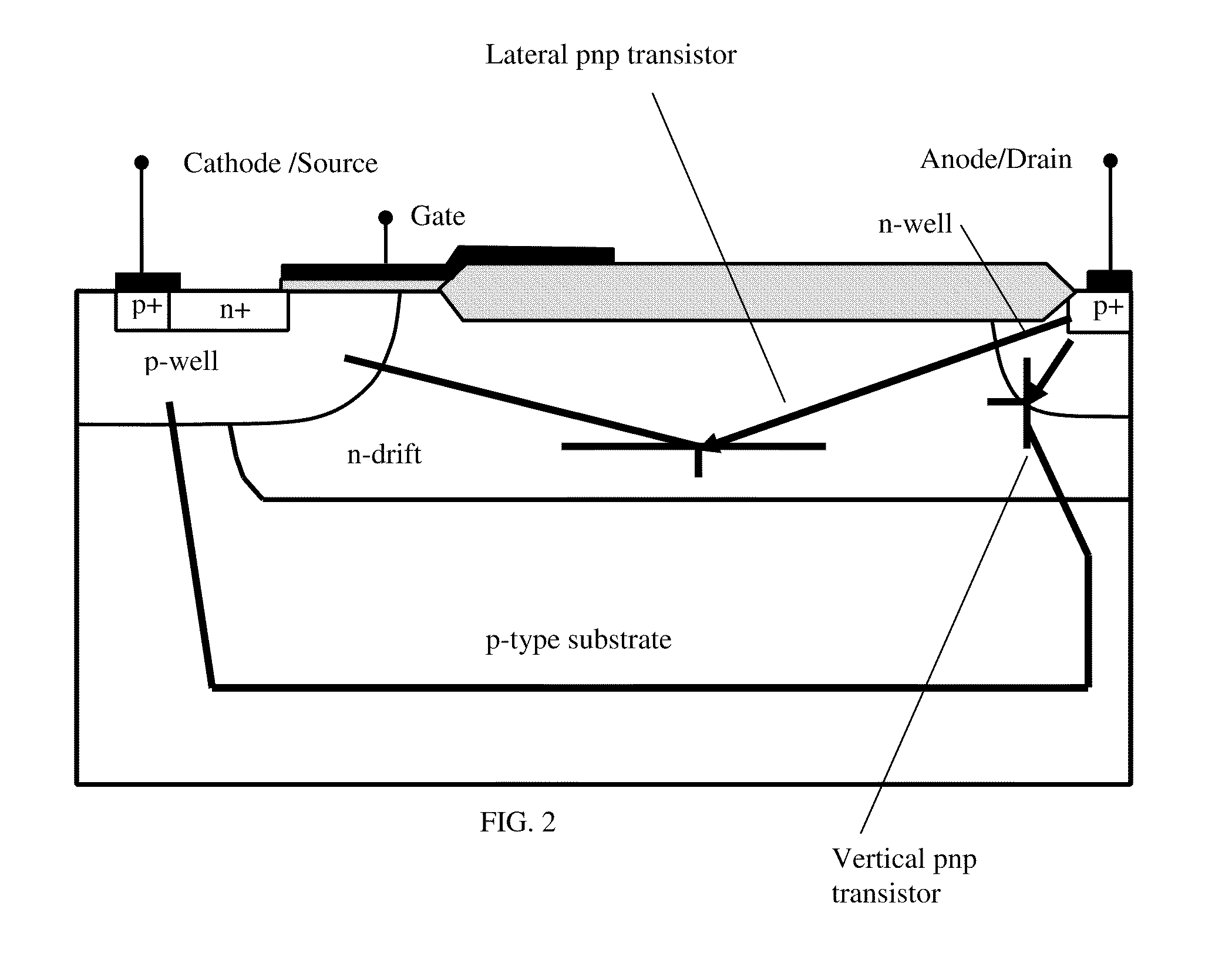

Lateral Insulated Gate Bipolar Transistors (LIGBTS)

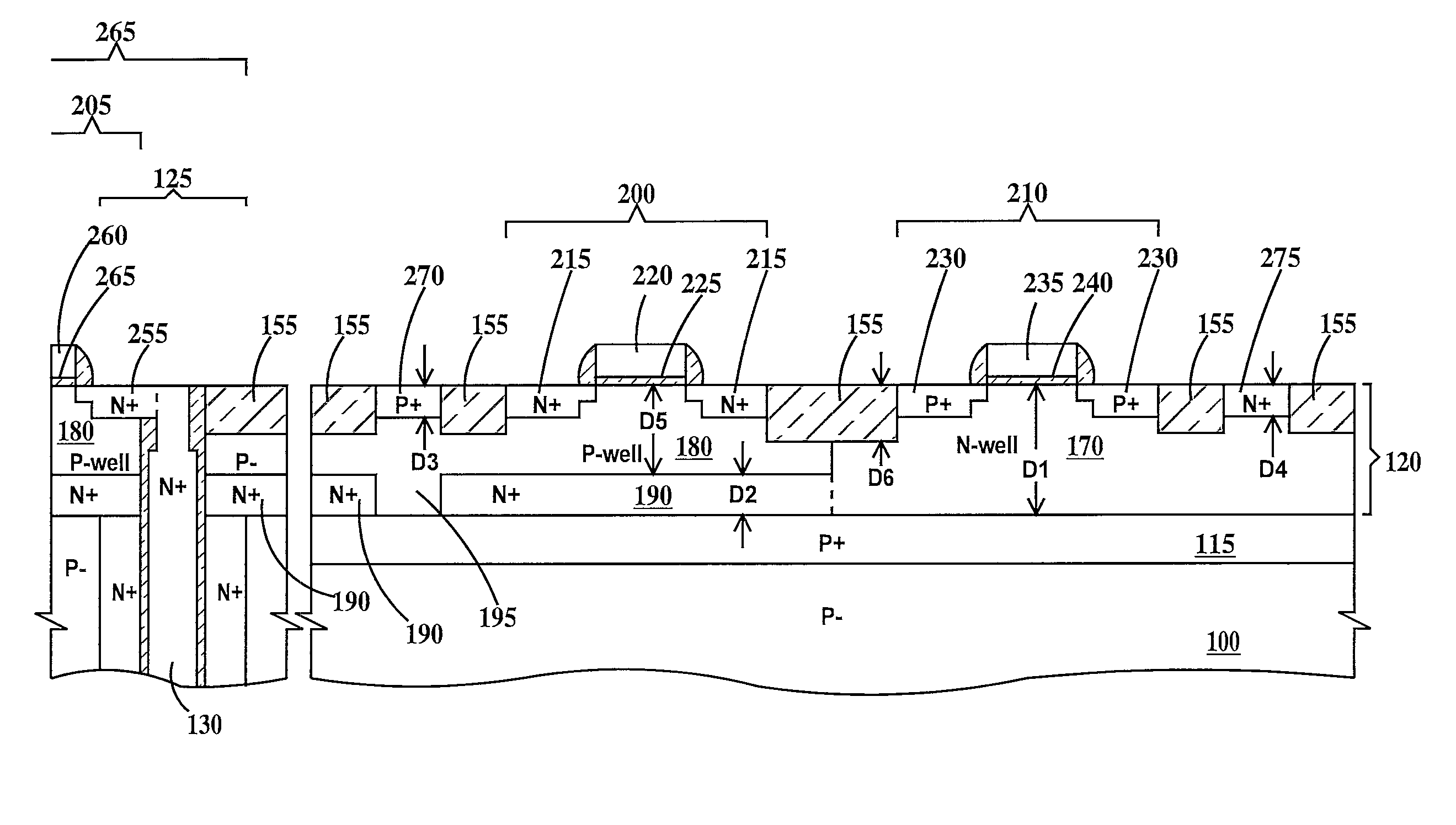

InactiveUS20110057230A1Reduce gainReduction in current gainSemiconductor/solid-state device manufacturingSemiconductor devicesEpoxyParasitic bipolar transistor

This invention generally relates to lateral insulated gate bipolar transistors (LIGBTs), for example in integrated circuits, methods of increasing switching speed of an LIGBT, a method of suppressing parasitic thyristor latch-up in a bulk silicon LIGBT, and methods of fabricating an LIGBT. In particular, a method of suppressing parasitic thyristor latch-up in a bulk silicon LIGBT comprises selecting a current gain αv for a vertical transistor of a parasitic thyristor of the LIGBT such that in at least one predetermined mode of operation of the LIGBT αv<1−αp where αp is a current gain of a parasitic bipolar transistor having a base-emitter junction formed by a Schottky contact between the a semiconductor surface and a metal enriched epoxy die attach.

Owner:POWER INTEGRATIONS INC

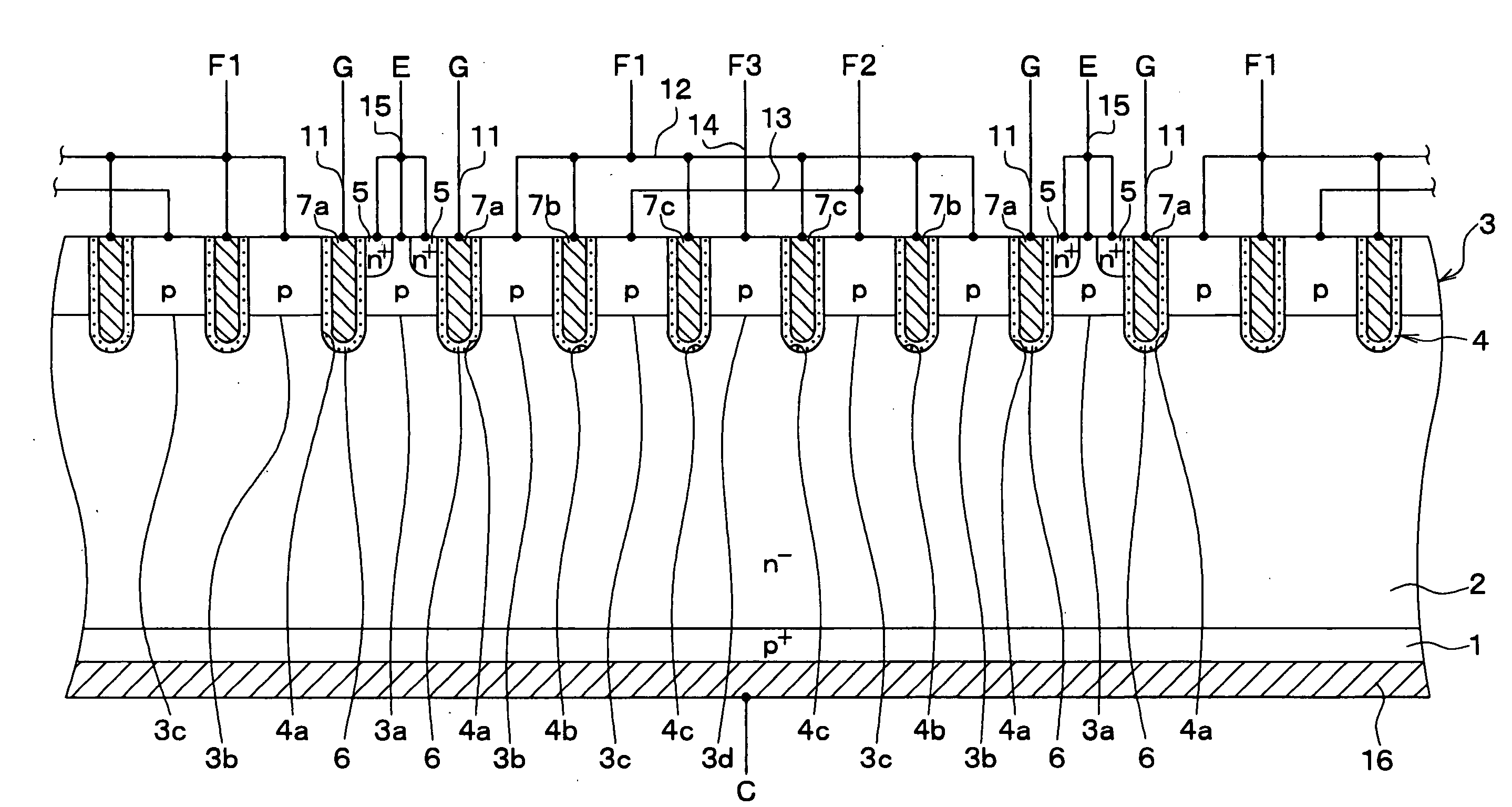

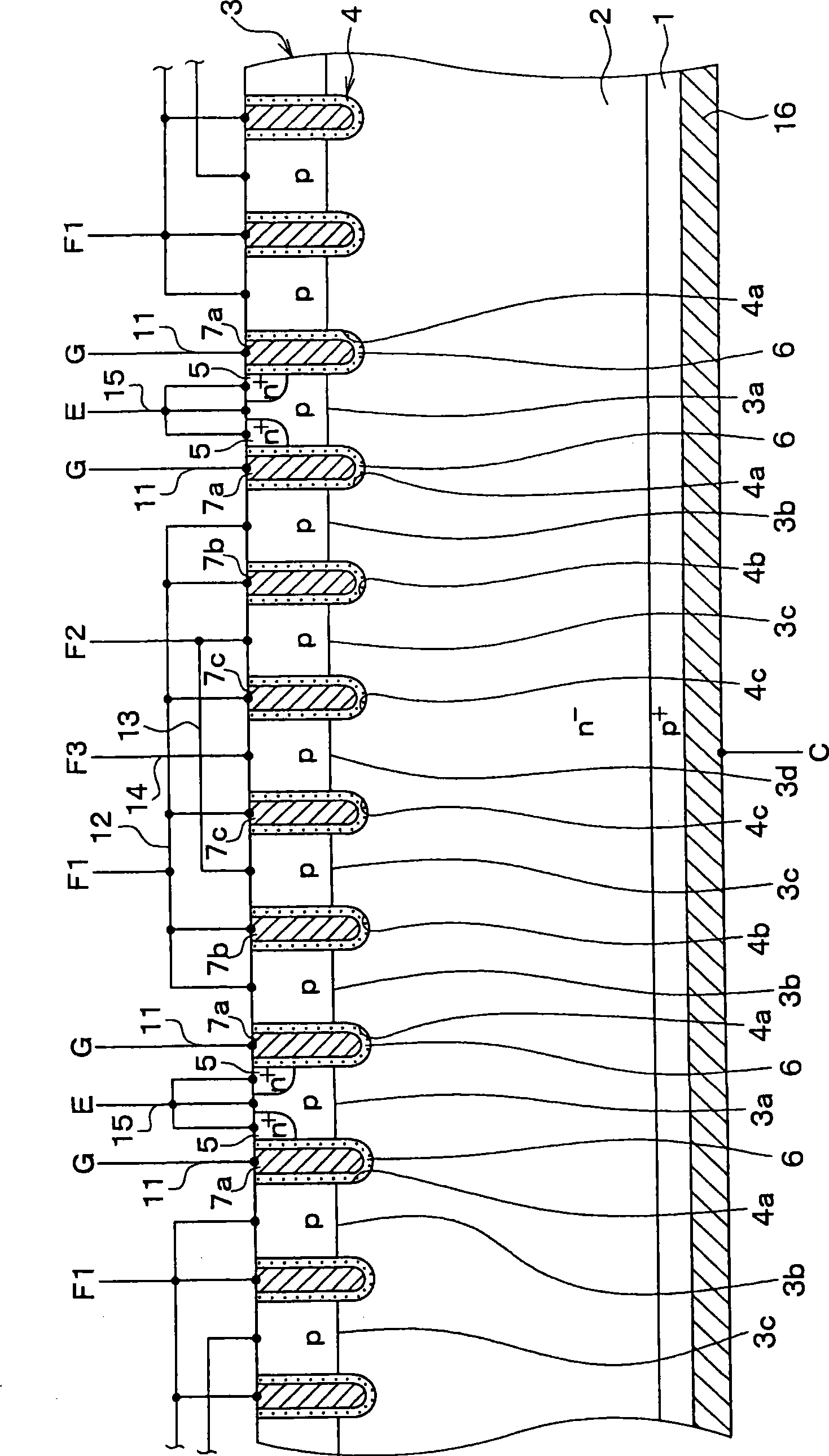

Semiconductor device having insulated gate semiconductor element, and insulated gate bipolar transistor

ActiveUS20090189181A1Improve breakdown voltageSoft switching characteristicSemiconductor devicesParasitic bipolar transistorEngineering

A semiconductor device having an IGBT includes: a substrate; a drift layer and a base layer on the substrate; trenches penetrating the base layer to divide the base layer into base parts; an emitter region in one base part; a gate element in the trenches; an emitter electrode; and a collector electrode. The one base part provides a channel layer, and another base part provides a float layer having no emitter region. The gate element includes a gate electrode next to the channel layer and a dummy gate electrode next to the float layer. The float layer includes a first float layer adjacent to the channel layer and a second float layer apart from the channel layer. The dummy gate electrode and the first float layer are coupled with a first float wiring on the base layer. The dummy gate electrode is isolated from the second float layer.

Owner:DENSO CORP +1

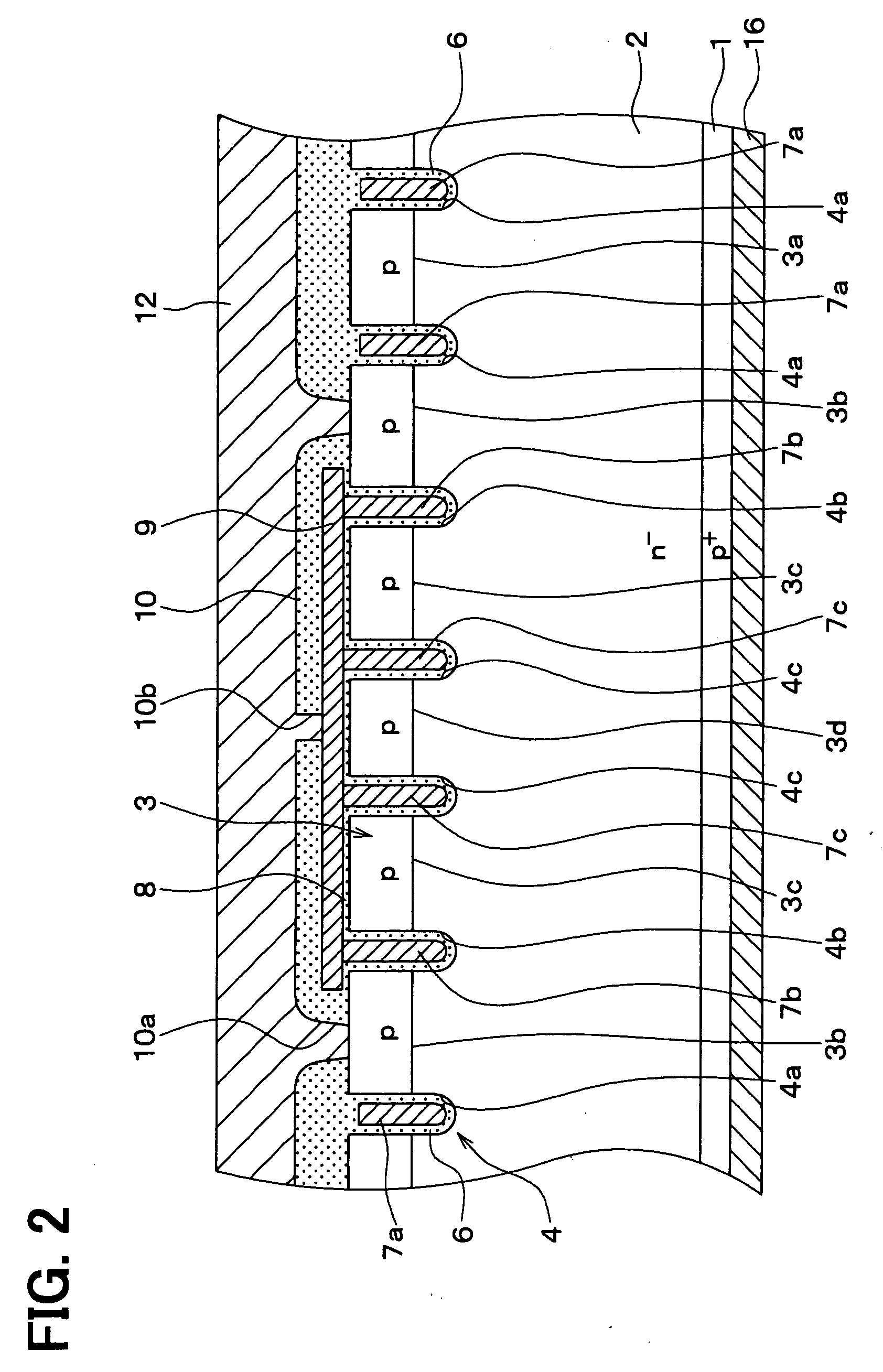

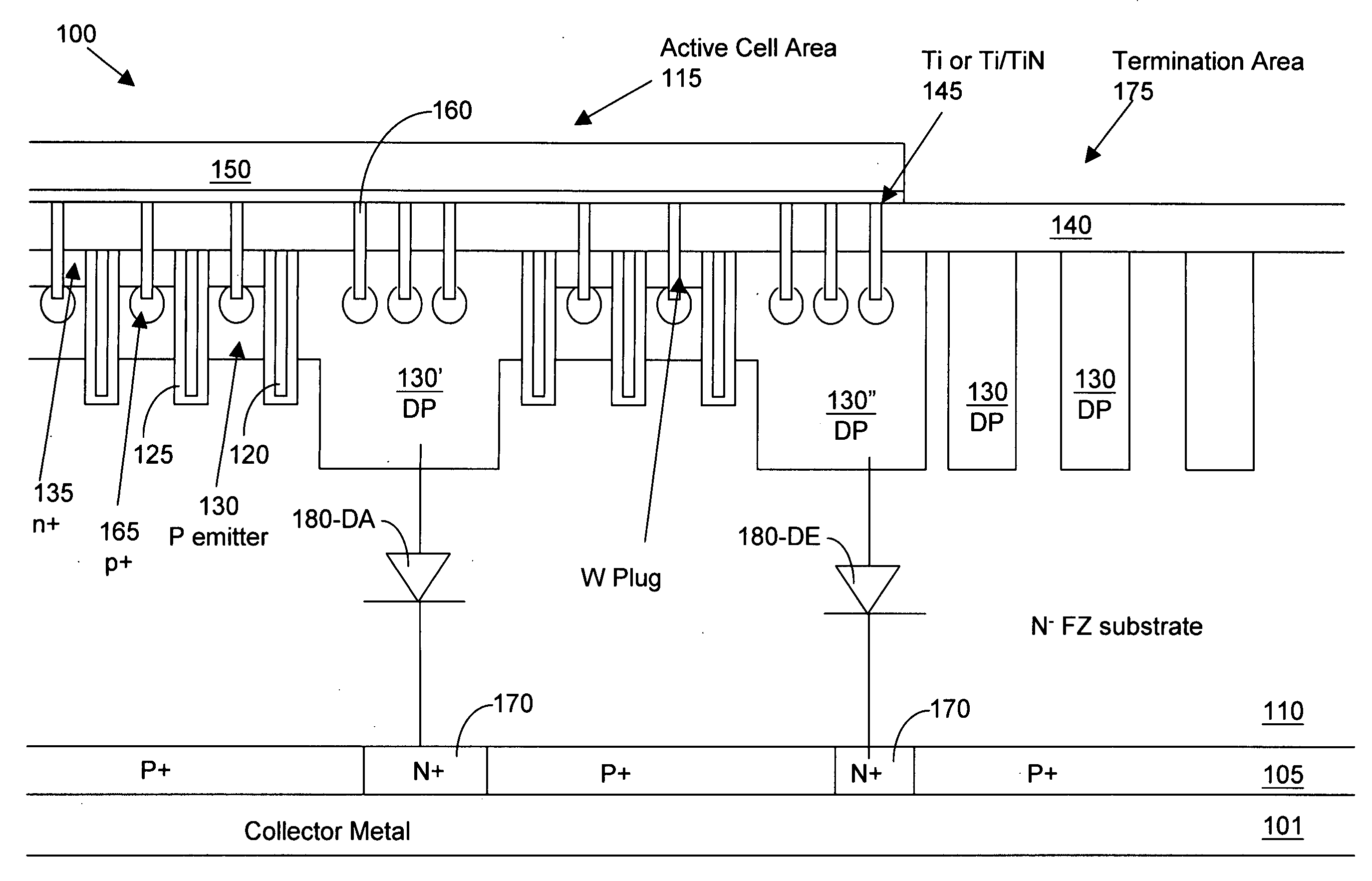

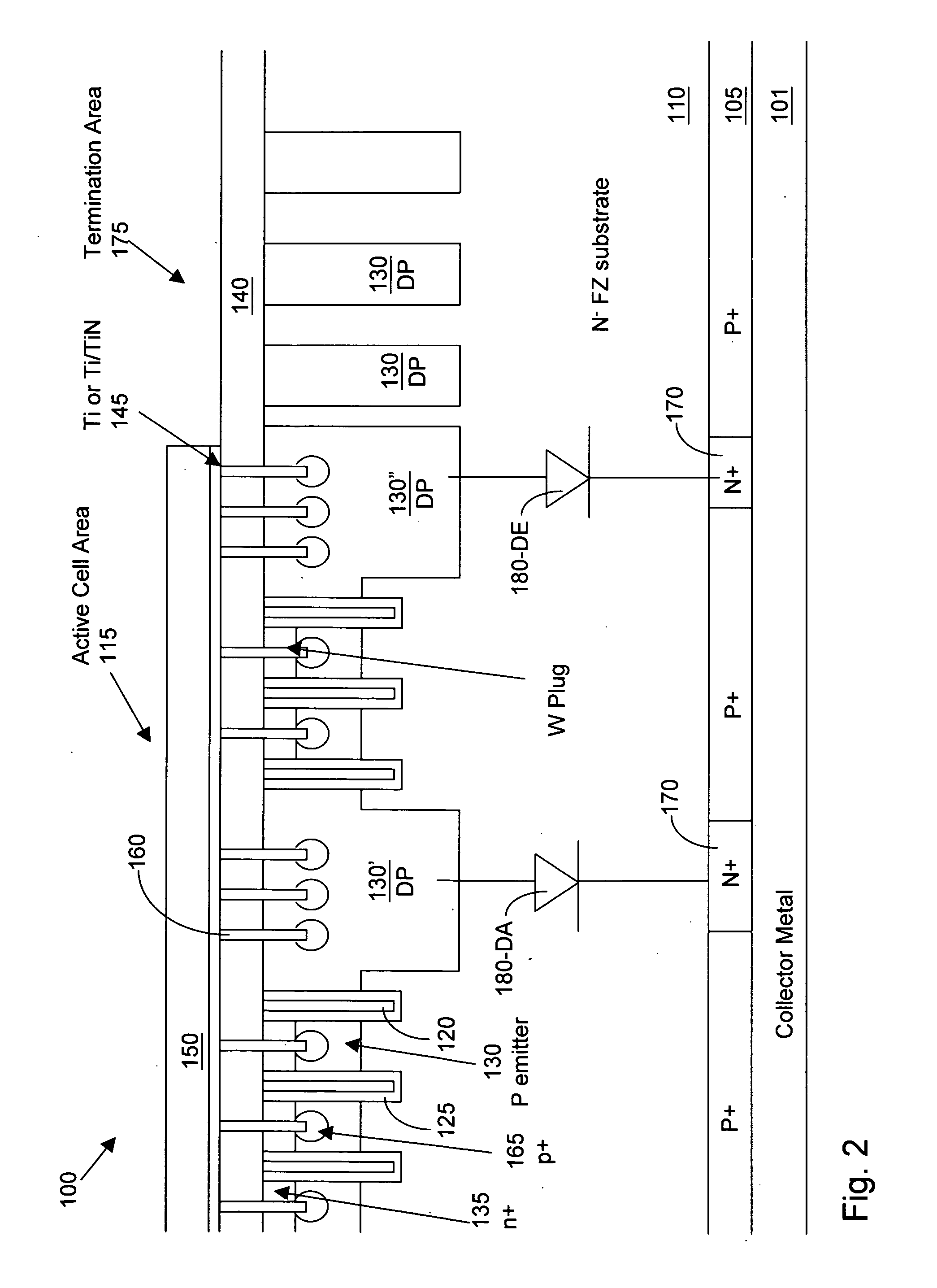

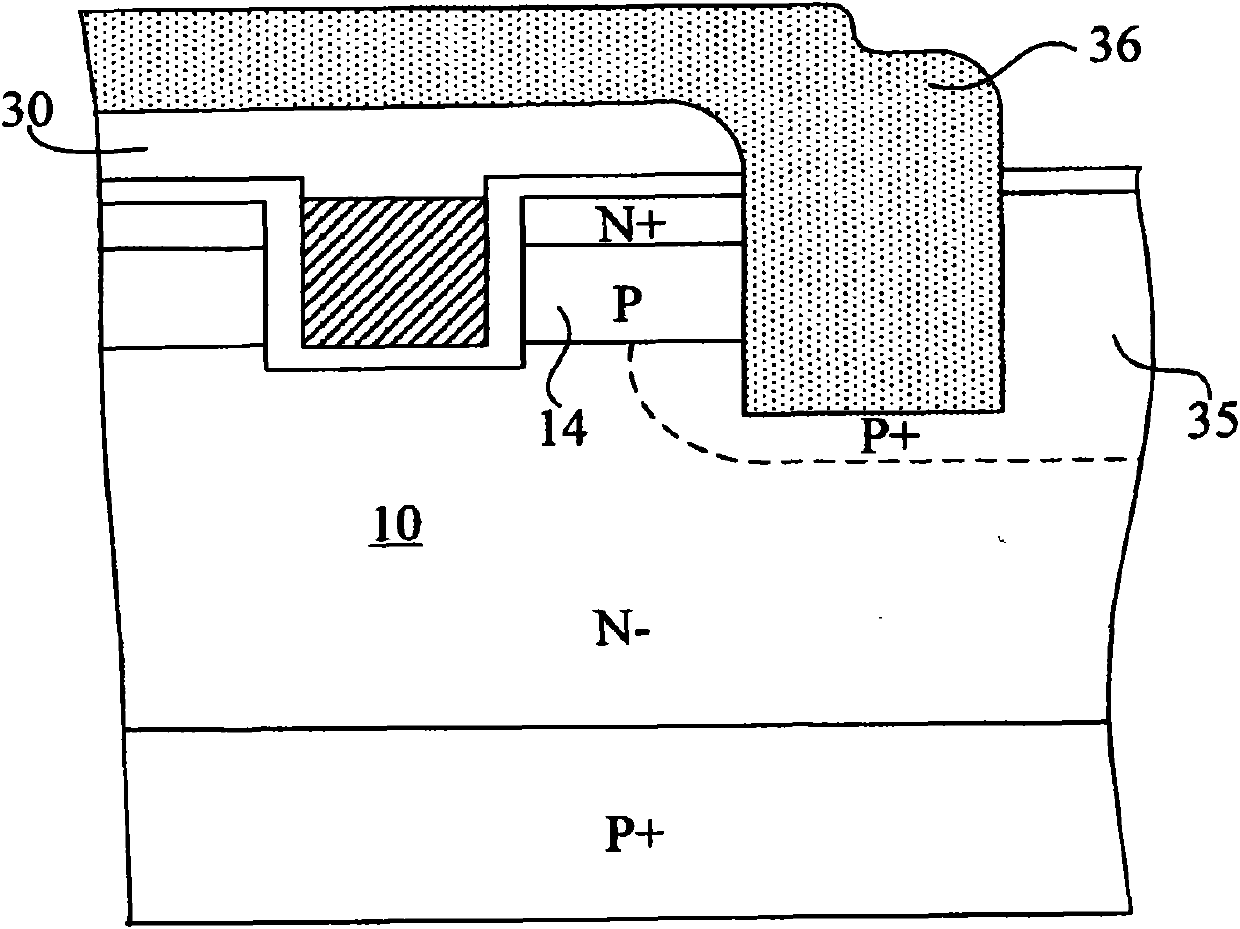

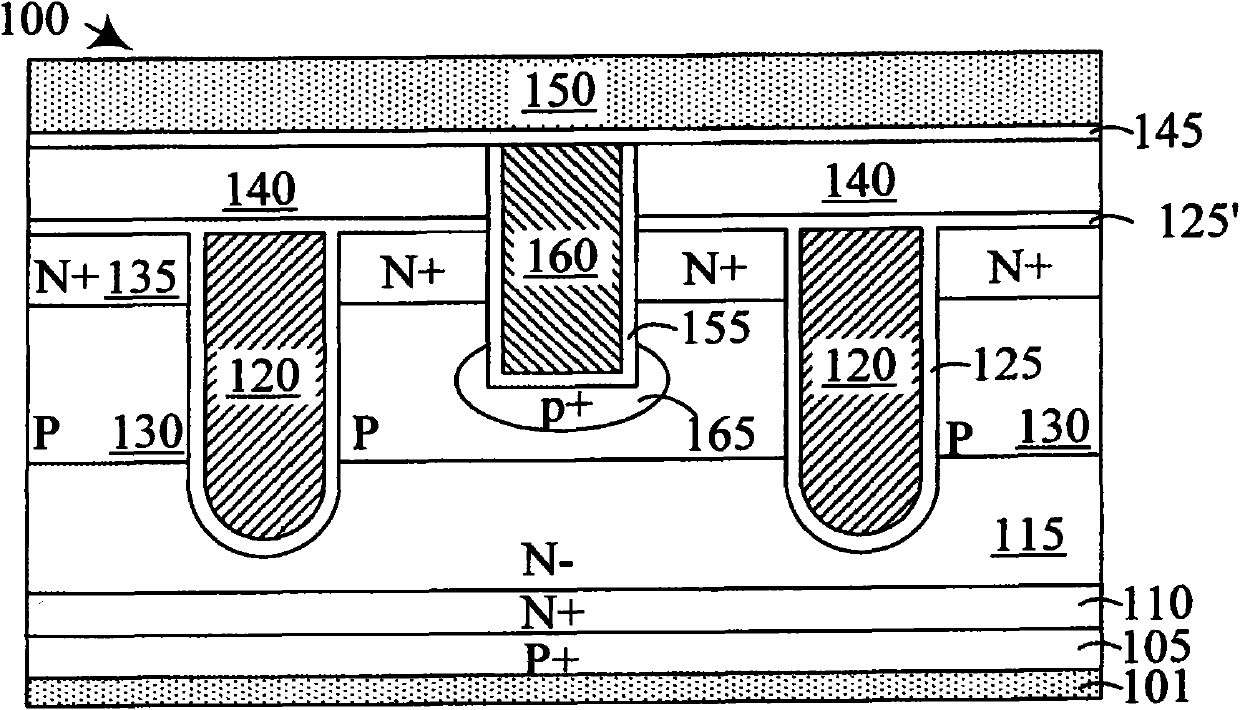

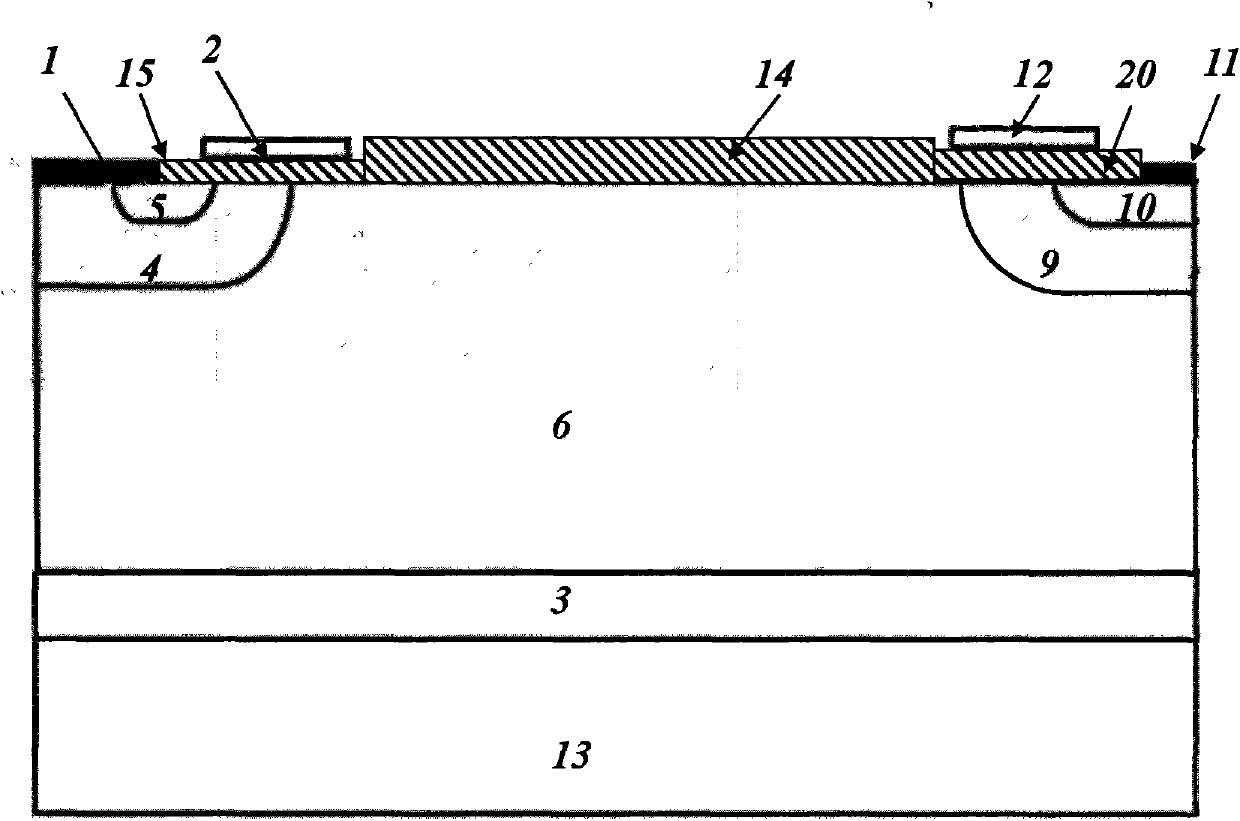

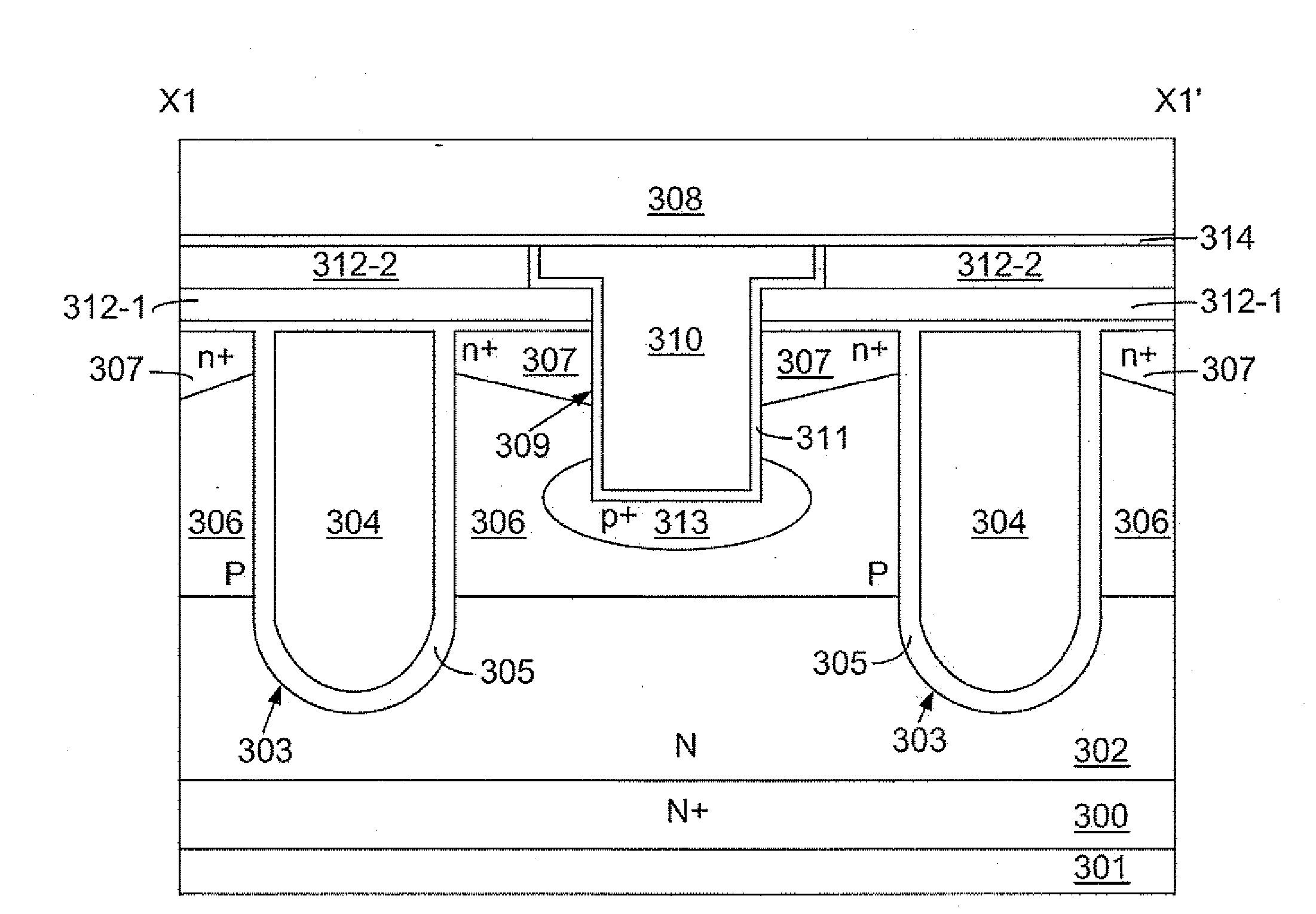

Trench insulated gate bipolar transistor (GBT) with improved emitter-base contacts and metal schemes

InactiveUS20100193835A1Reduce base contact resistanceEnhance latch-up immunity capabilitySemiconductor/solid-state device manufacturingSemiconductor devicesTrench igbtDopant

A trench insulation gate bipolar transistor (IGBT) power device includes a plurality of trench gates surrounded by emitter regions of a first conductivity type near a top surface of a semiconductor substrate encompassed in base regions of a second conductivity type and a collector layer disposed at a bottom surface of the semiconductor substrate. The trench IGBT power device further includes an insulation layer covering over the top surface over the trench gate and the emitter regions having emitter-base contact trenches opened therethrough between the trench gates and extending to the base regions and an emitter-base contact dopant region disposed in the base region of the second conductivity type surrounding a lower region of the contact trenches. The emitter-base contact dopant region is disposed at a distance away from a channel near the trench gates for reducing an emitter-base resistance without increasing a gate-emitter threshold voltage.

Owner:FORCE MOS TECH CO LTD

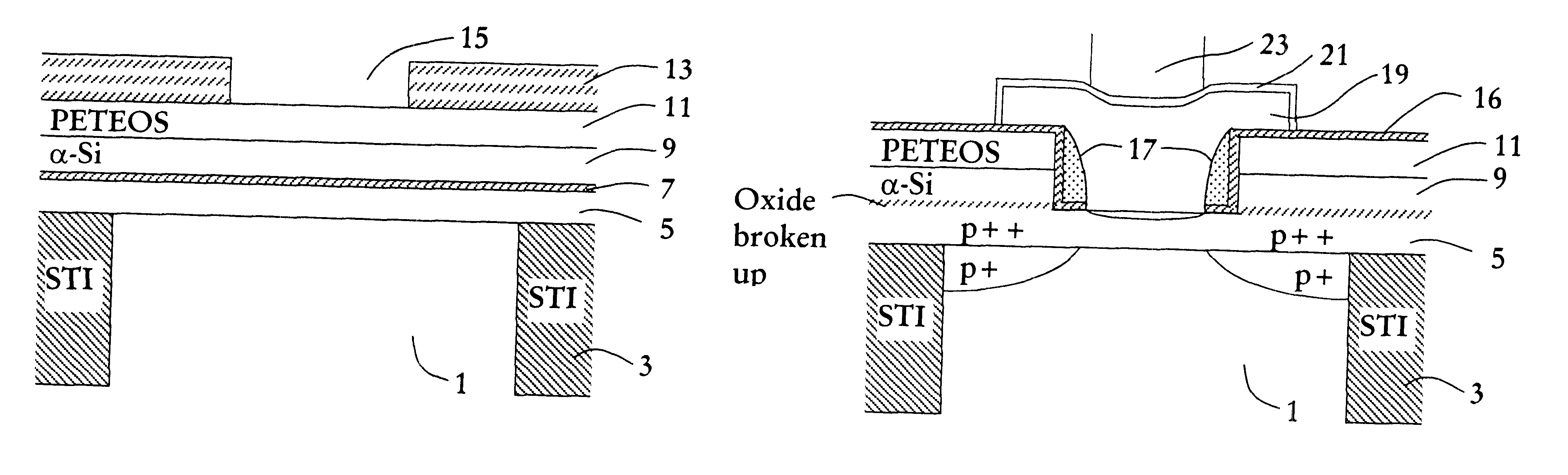

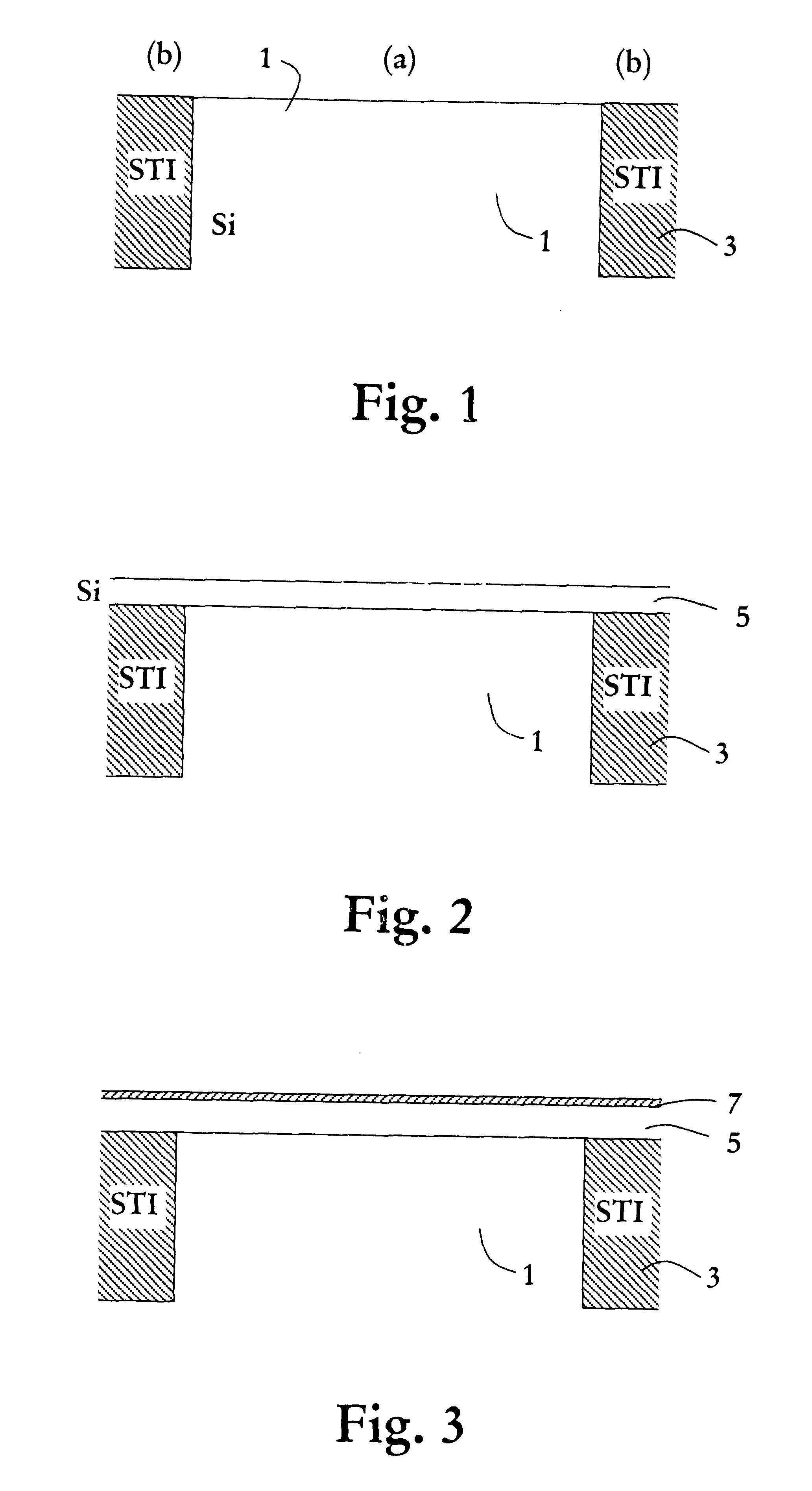

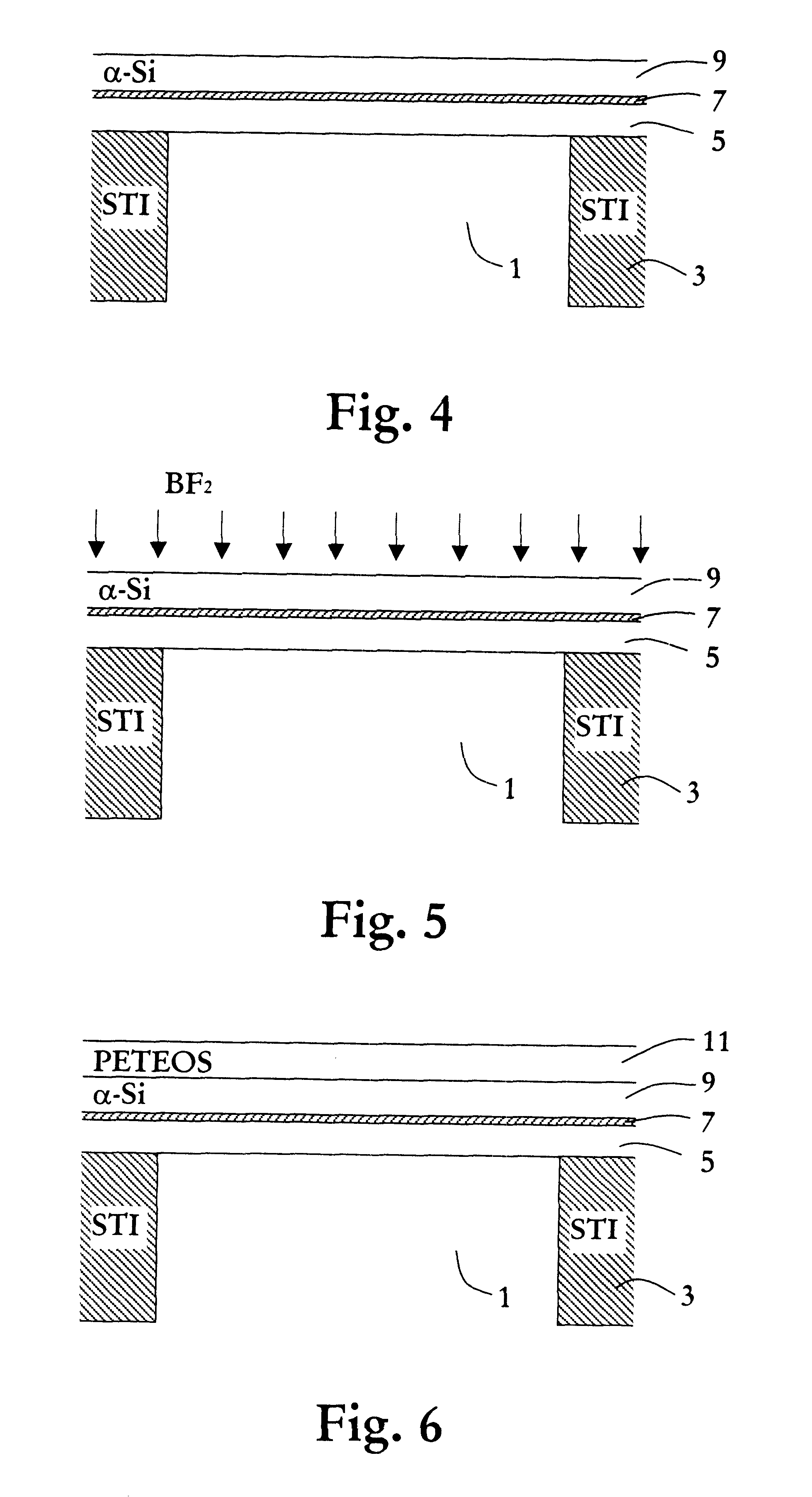

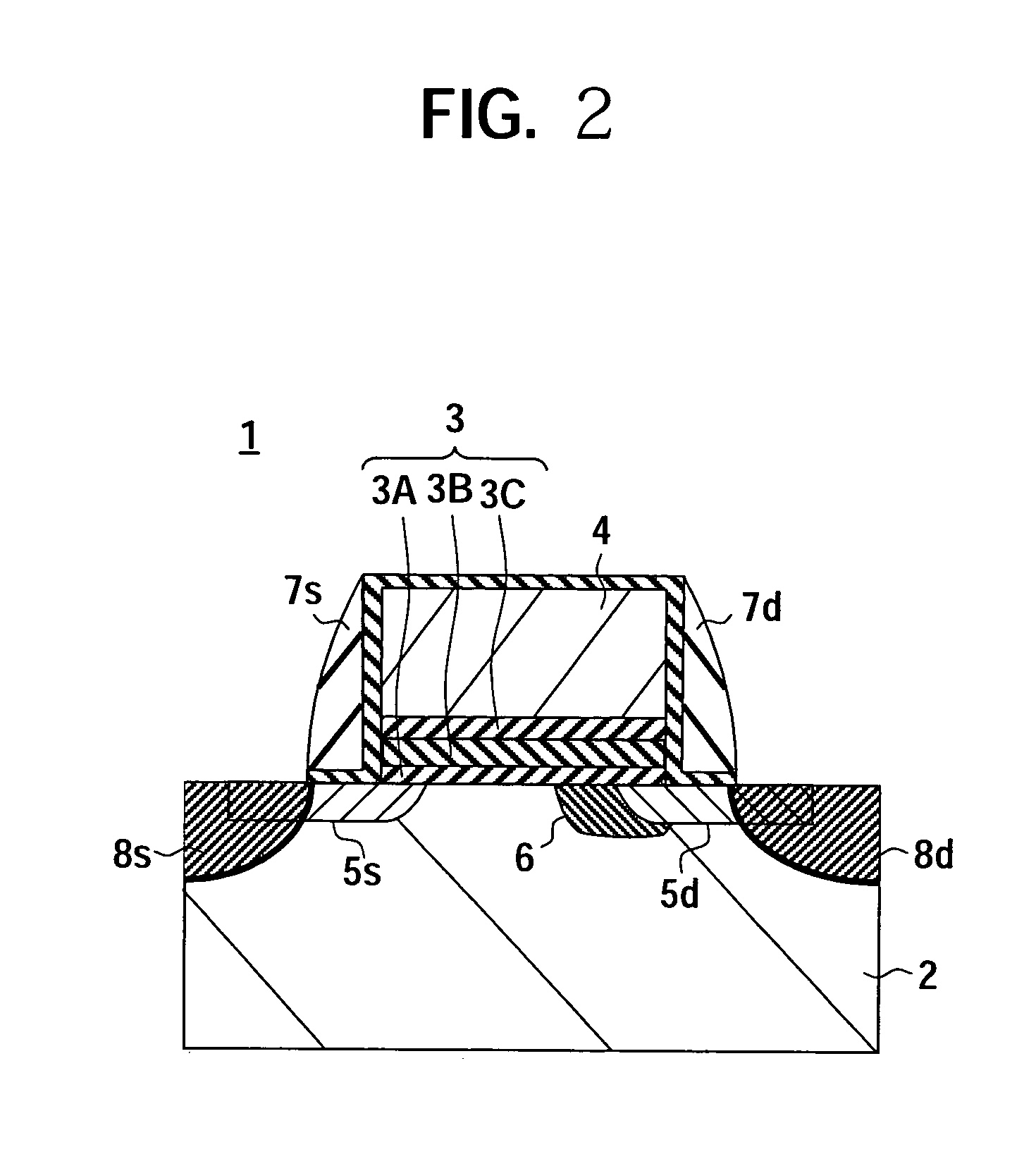

Method in the fabrication of a silicon bipolar transistor

InactiveUS6440810B1Reduce riskImproved profileSemiconductor/solid-state device manufacturingSemiconductor devicesThin oxideDielectric

In the fabrication of a silicon bipolar transistor, a method for forming base regions and for opening an emitter window is provided. A silicon substrate is provided with suitable device isolation. A first base region is formed in or on top of the substrate. A thin layer of oxide is formed on the first base region. A layer of silicon is formed on top of the thin oxide layer, the silicon layer is to be a second base region. The silicon layer is ion implanted. A layer of a dielectric is formed on top of the silicon layer, the dielectric is to isolate base and emitter regions of the transistor. The obtained structure is patterned in order to define the emitter window. The structure inside the defined emitter window area is etched and through the dielectric and silicon layers, wherein the thin oxide layer is used as etch stop, thus forming the emitter window. The structure is subsequently heat treated and thus break up the oxide such that the first and second base regions will contact each other.

Owner:INFINEON TECH AG

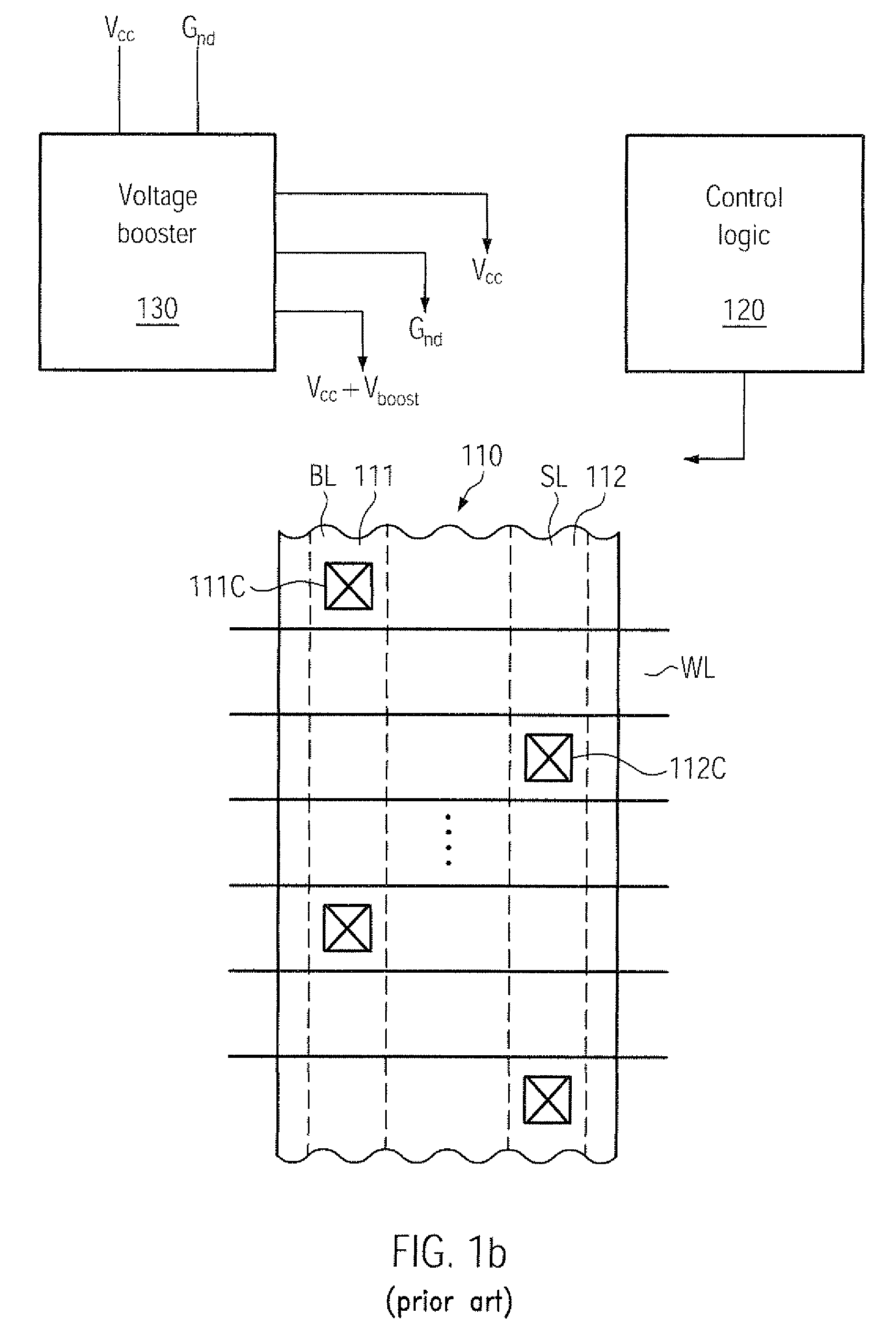

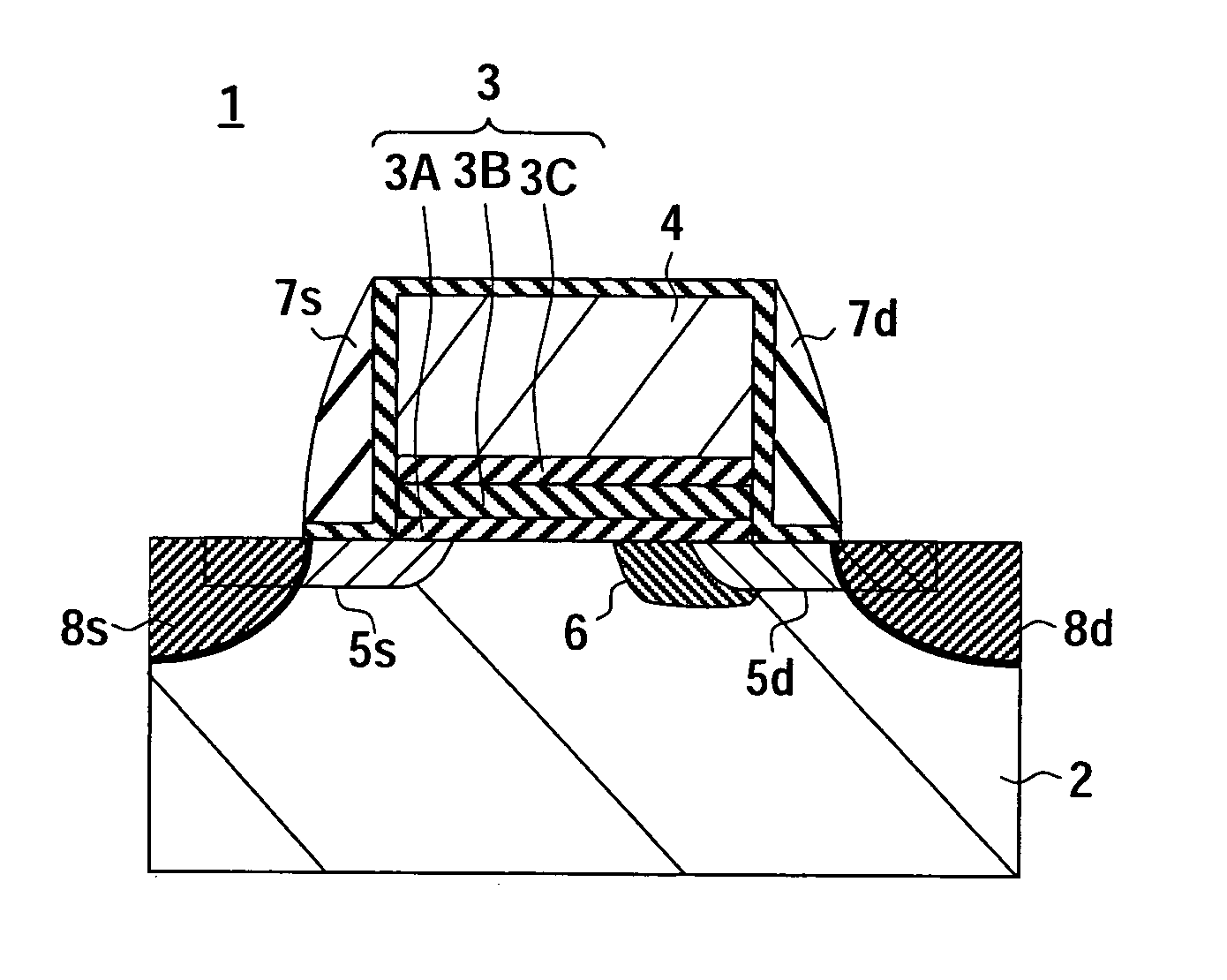

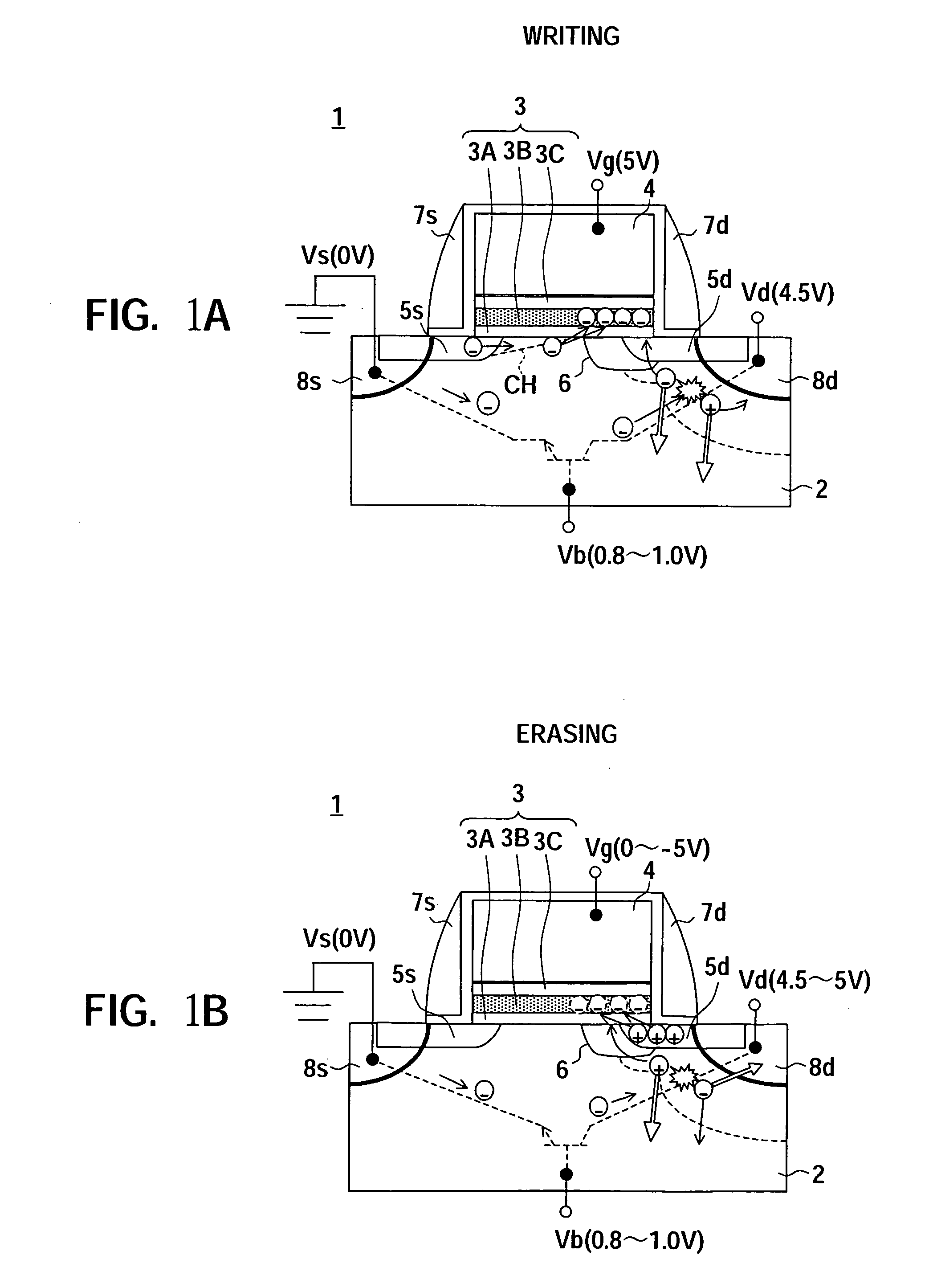

Nonvolatile semiconductor memory device, charge injection method thereof and electronic apparatus

InactiveUS20050194633A1High data re-writing speedLow ON voltage operationTransistorSolid-state devicesCharge injectionParasitic bipolar transistor

A charge injection method for improve efficiency of generating hot carrier, wherein, for example, electrons are injected at writing and holes are injected at erasing to a charge storage layer of a memory transistor. A positive voltage is applied to the drain region by using a voltage of the source region as a reference, and a voltage having a polarity in accordance with charges to be injected is applied to a gate electrode. A voltage having a voltage value between a source voltage and a drain voltage for turning on a diode made by an N-type source region and a P-type body region is applied to the body region. Then a parasitic bipolar transistor turns on, consequently, impact ionization arises on the drain side and an injection charge amount increases.

Owner:SONY CORP

Semiconductor device

ActiveUS20120326235A1TransistorSemiconductor/solid-state device detailsPower semiconductor deviceMetal silicide

A semiconductor device equally turns on the parasitic bipolar transistors in the finger portions of the finger form source and drain electrodes when a surge voltage is applied, even with the P+ type contact layer surrounding the N+ type source layers and the N+ type drain layers connected to the finger form source and drain electrodes. A P+ type contact layer surrounds N+ type source layers and N+ type drain layers. Metal silicide layers are formed on the N+ type source layers, the N+ type drain layers, and a portion of the P+ type contact layer. Finger form source electrodes, finger form drain electrodes, and a P+ type contact electrode surrounding these finger form electrodes are formed, being connected to the metal silicide layers respectively through contact holes formed in an interlayer insulation film deposited on the metal silicide layers.

Owner:SEMICON COMPONENTS IND LLC

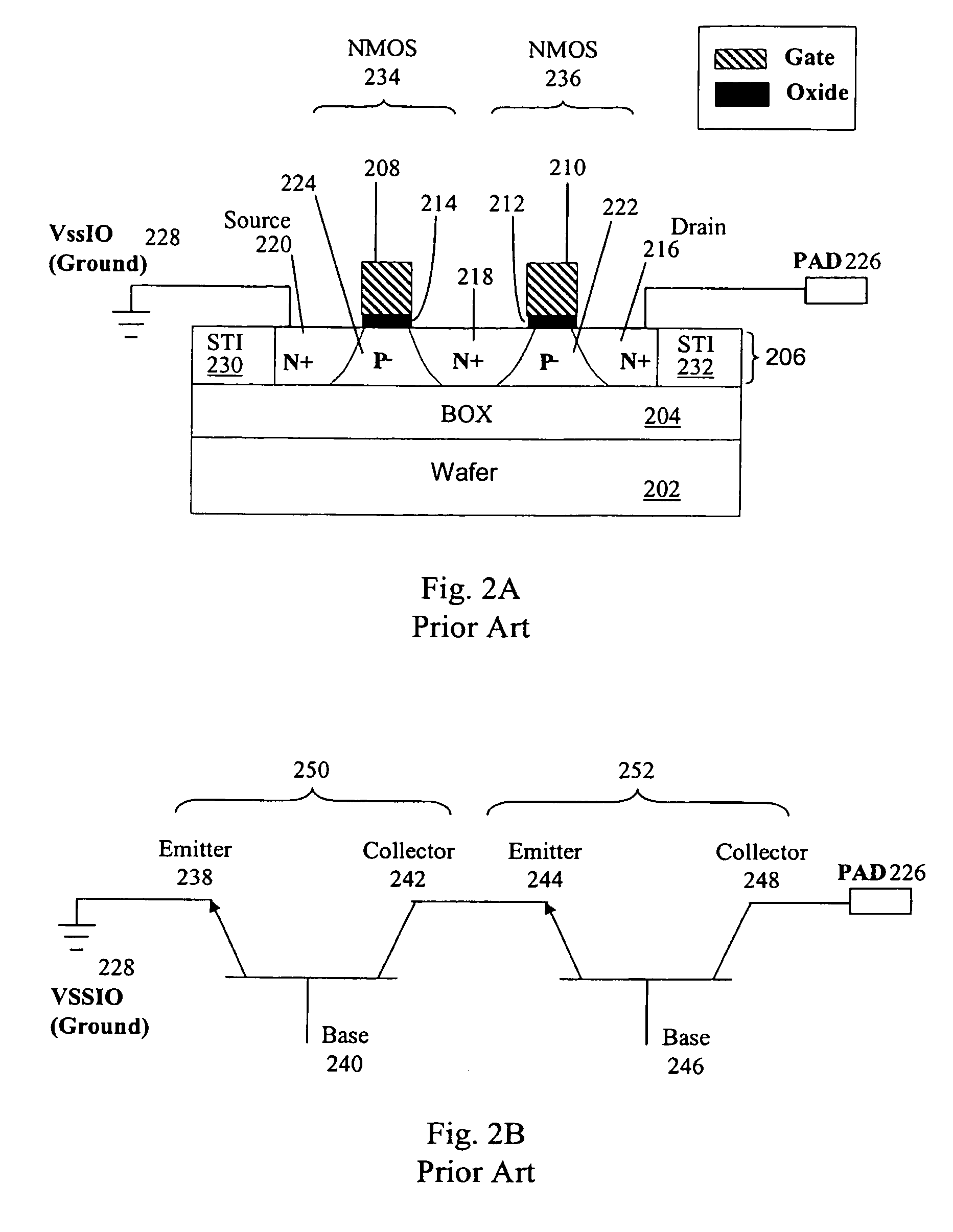

Method for implementing electro-static discharge protection in silicon-on-insulator devices

InactiveUS7125760B1Improve protectionControl depthTransistorSemiconductor/solid-state device detailsSalicideDopant

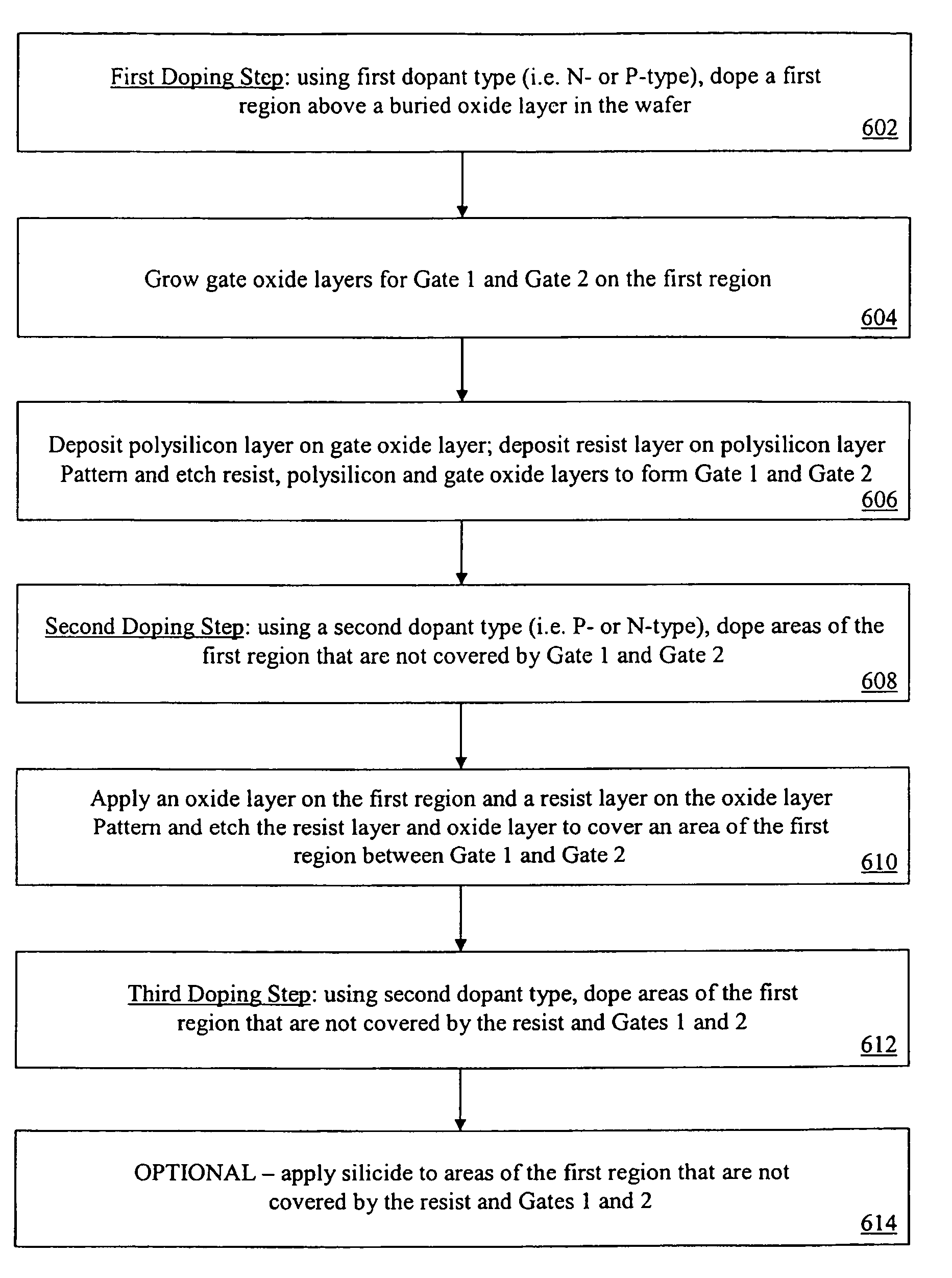

The present invention is a method and apparatus whereby two NMOS or PMOS devices connected in series in a stacked gate configuration formed on SOI exhibit improved ESD response characteristics. The shared source-drain region between the two devices is formed to have a dopant depth in the shared region that does not extend through the silicon layer to the BOX layer. This provides a common body for the two devices, and thus a single parasitic bipolar transistor is formed between the drain of one NMOS or PMOS device and the source of the second NMOS or PMOS device. Simultaneous snapback occurs for the two devices through the common body. A further embodiment includes a method of forming two or more stacked gate NMOS or PMOS devices on SOI. The method includes protecting the shared source-drain region between two NMOS or PMOS devices during a final doping step and silicide processing.

Owner:ALTERA CORP

Semiconductor device having insulated gate semiconductor element, and insulated gate bipolar transistor

ActiveCN101499473ATransistorSemiconductor/solid-state device detailsParasitic bipolar transistorEngineering

The invention discloses a semiconductor device with an insulated gate semiconductor component and an insulated gate bipolar transistor. A semiconductor device having an IGBT includes: a substrate; a drift layer and a base layer on the substrate; trenches penetrating the base layer to divide the base layer into base parts; an emitter region in one base part; a gate element in the trenches; an emitter electrode; and a collector electrode. The one base part provides a channel layer, and another base part provides a float layer having no emitter region. The gate element includes a gate electrode next to the channel layer and a dummy gate electrode next to the float layer. The float layer includes a first float layer adjacent to the channel layer and a second float layer apart from the channel layer. The dummy gate electrode and the first float layer are coupled with a first float wiring on the base layer. The dummy gate electrode is isolated from the second float layer.

Owner:DENSO CORP +1

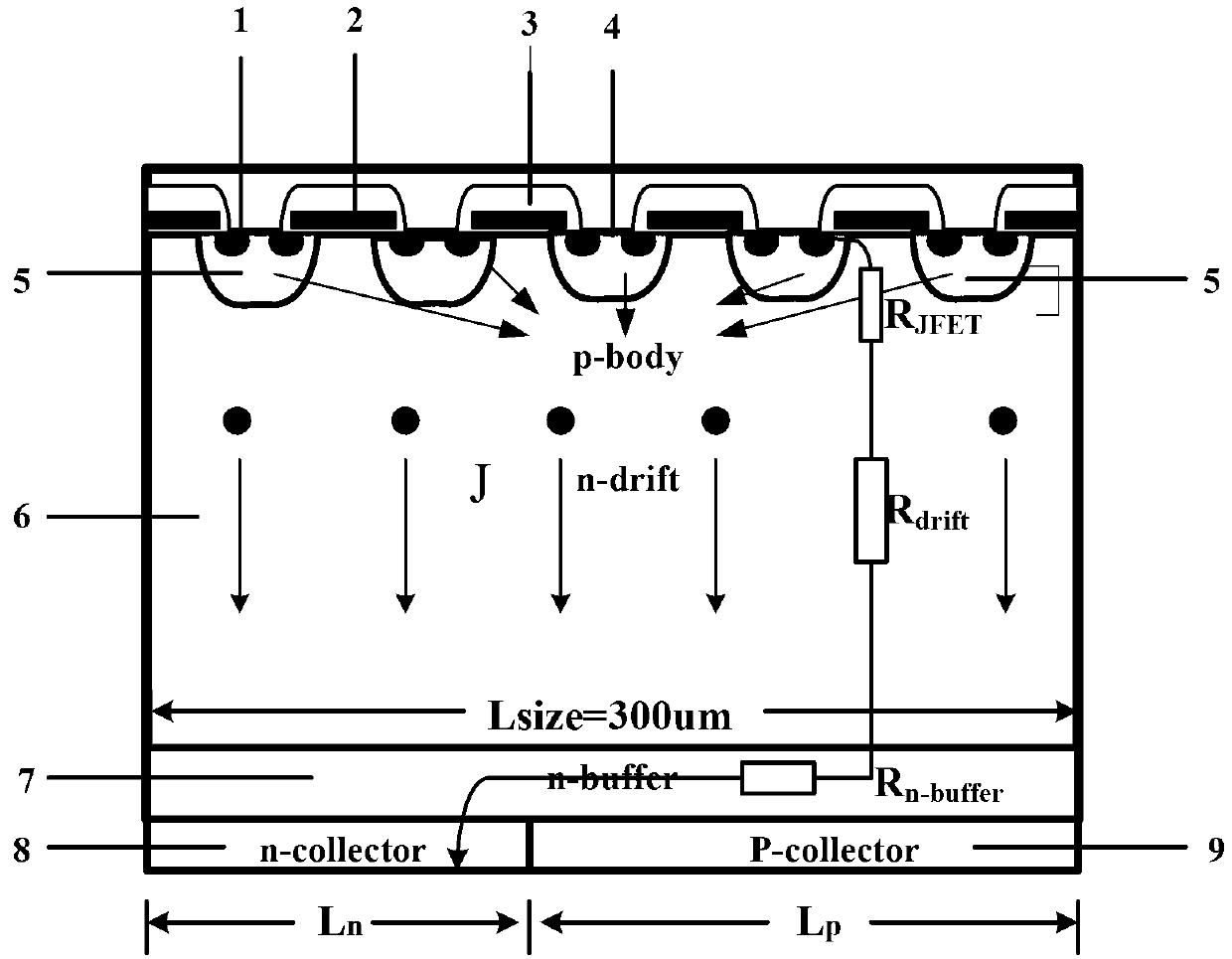

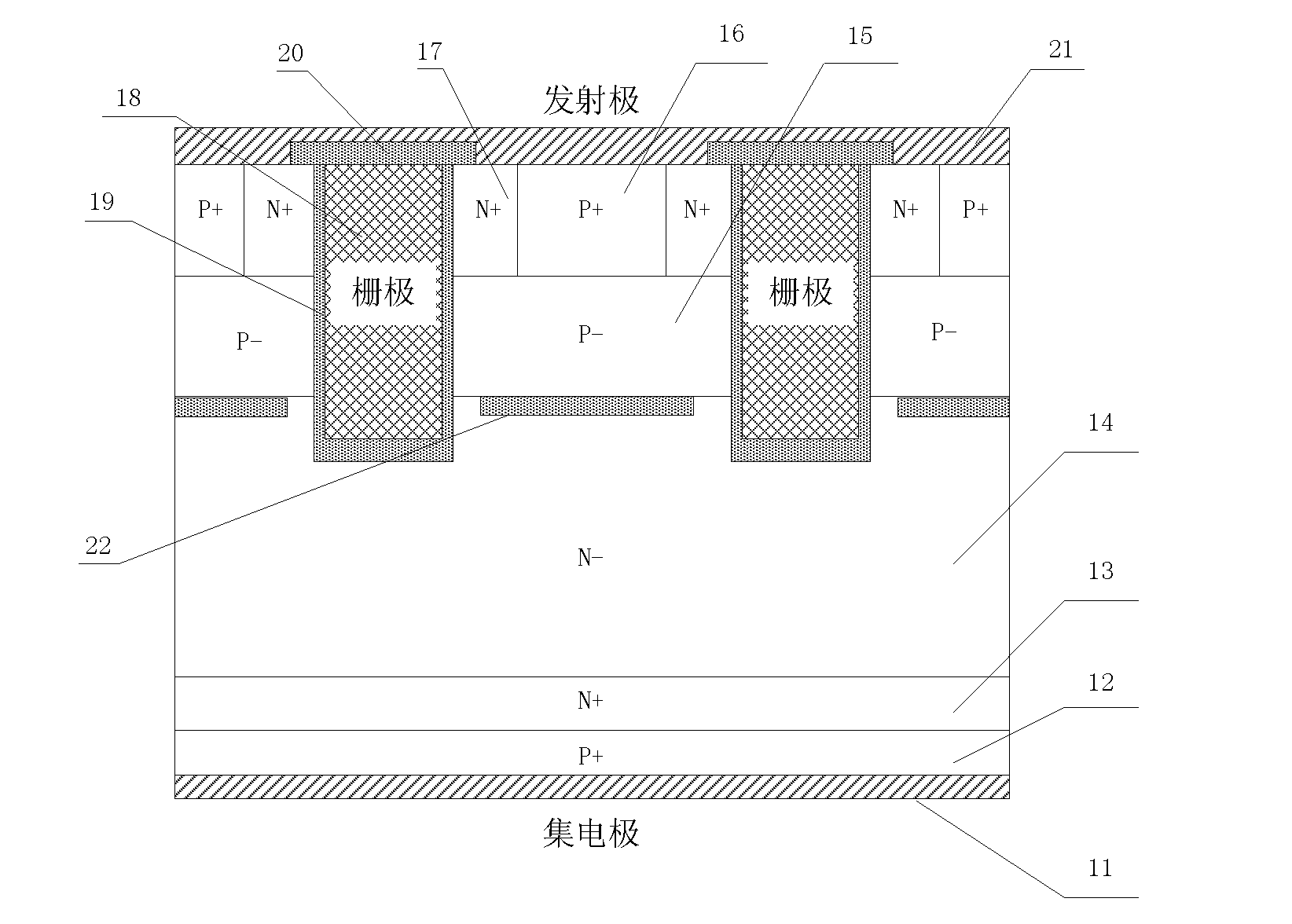

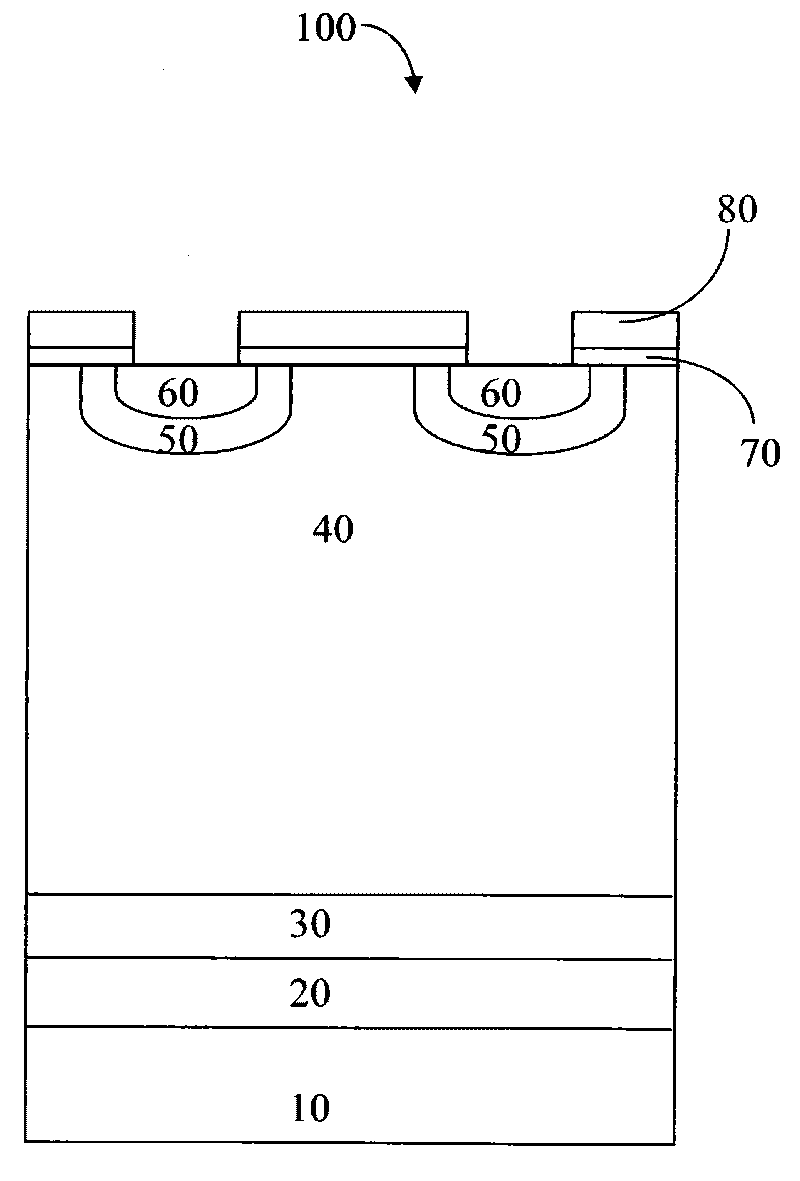

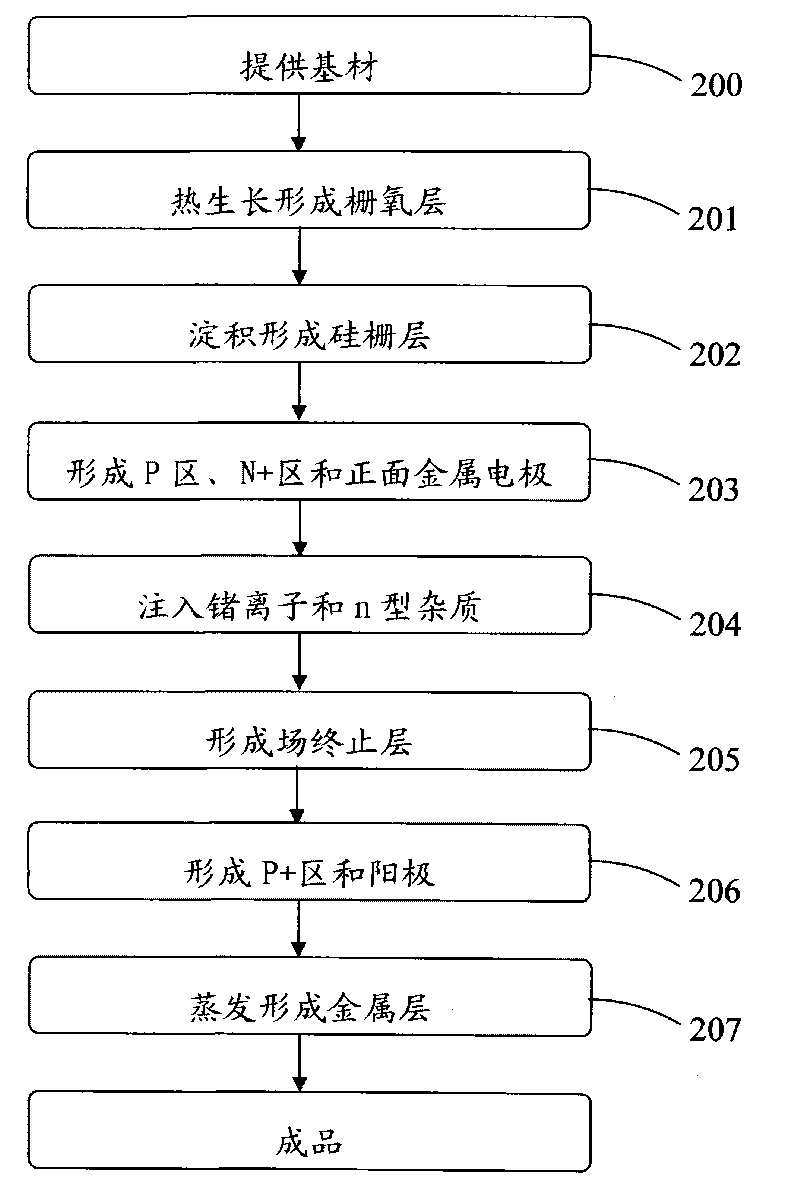

Insulated gate bipolar transistor and manufacturing method thereof

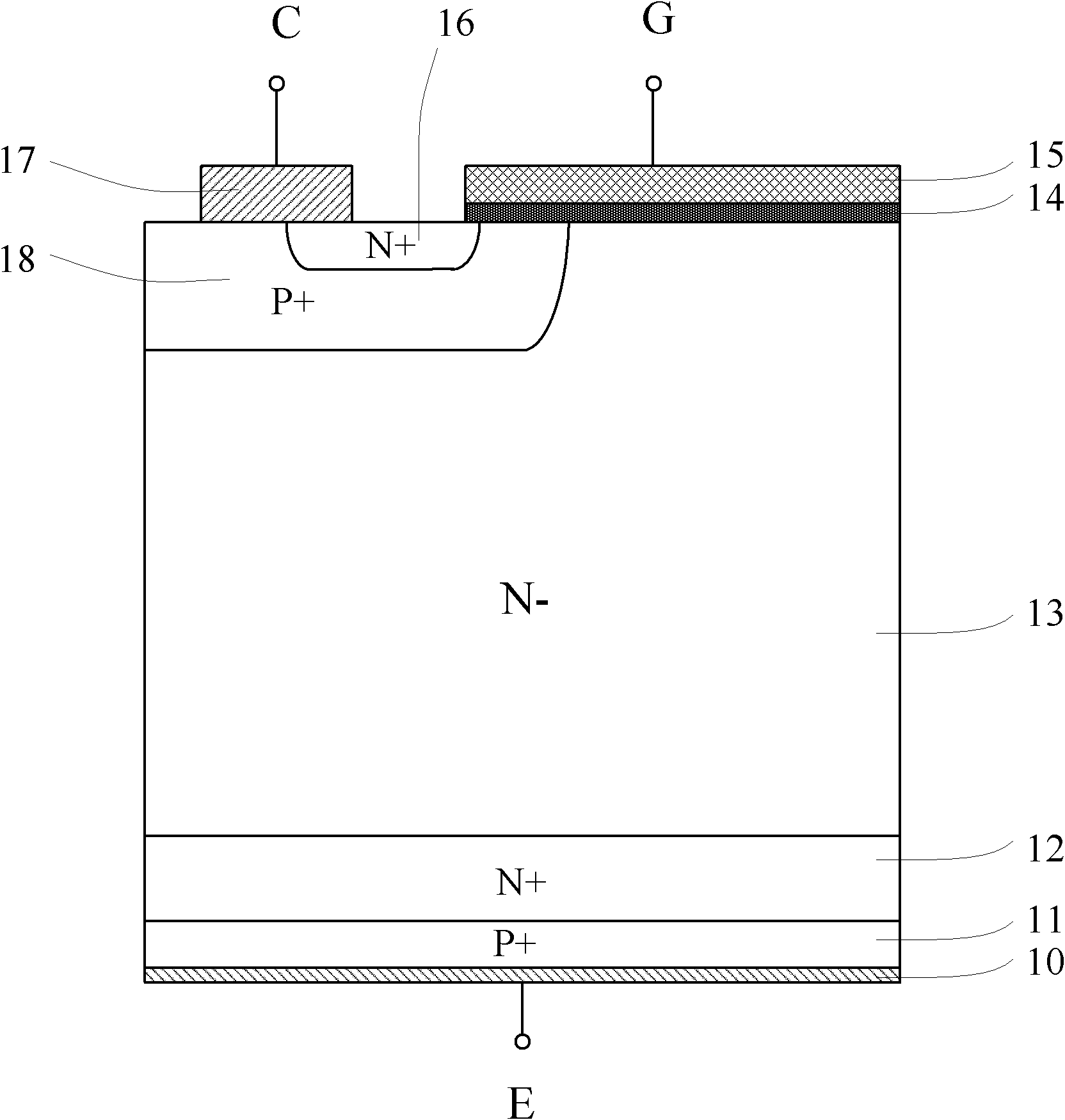

InactiveCN101976683AIncrease the doping concentrationEliminate the effect of resistanceTransistorSemiconductor/solid-state device manufacturingVoltage dropParasitic bipolar transistor

The invention discloses an insulated gate bipolar transistor (IGBT) and a manufacturing method thereof. The IGBT comprises an N-type base region, a P-type base region, a back P+ emitter region, an N+ collector region, a gate oxide, a collector electrode, a gate electrode and an emitter electrode; the N-type base region consists of a N+ diffusion residue layer, a N- base region and an N+ buffer layer which are sequentially laminated; and the dosage concentration of the N+ diffusion residue layer and the N+ buffer layer is gradually increased outwards from a boundary with the N- base region. In the IGBT of the invention, a front surface of the N- base region is provided with the N+ diffusion residue layer, so that the ion dosage concentration of a N-type front surface is improved and the influences on a Junction Field Effect Transistor (JEFT) resistor are reduced; therefore, the voltage drop of the IGBT under a conducting condition is effectively reduced.

Owner:ZHEJIANG UNIV

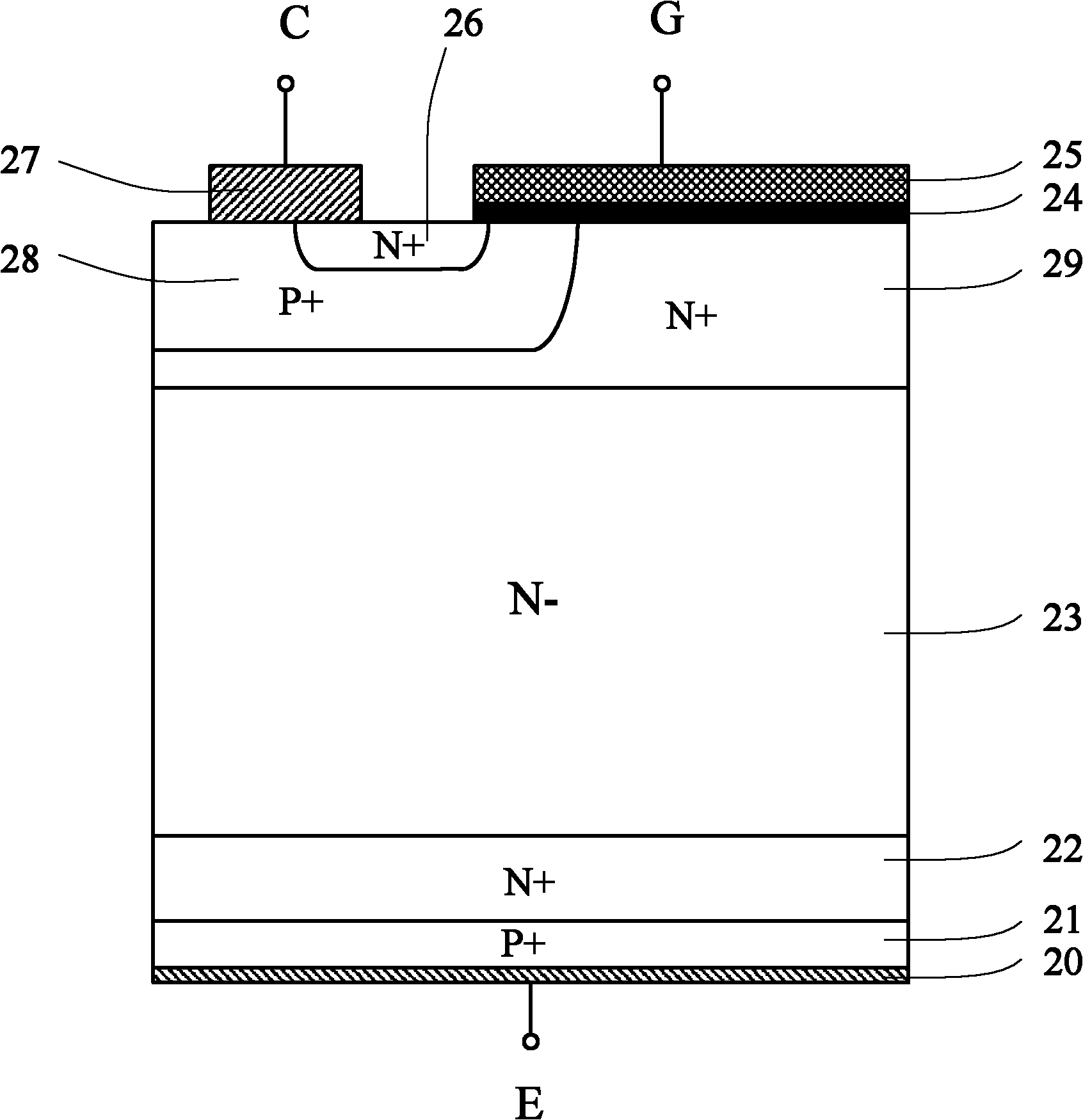

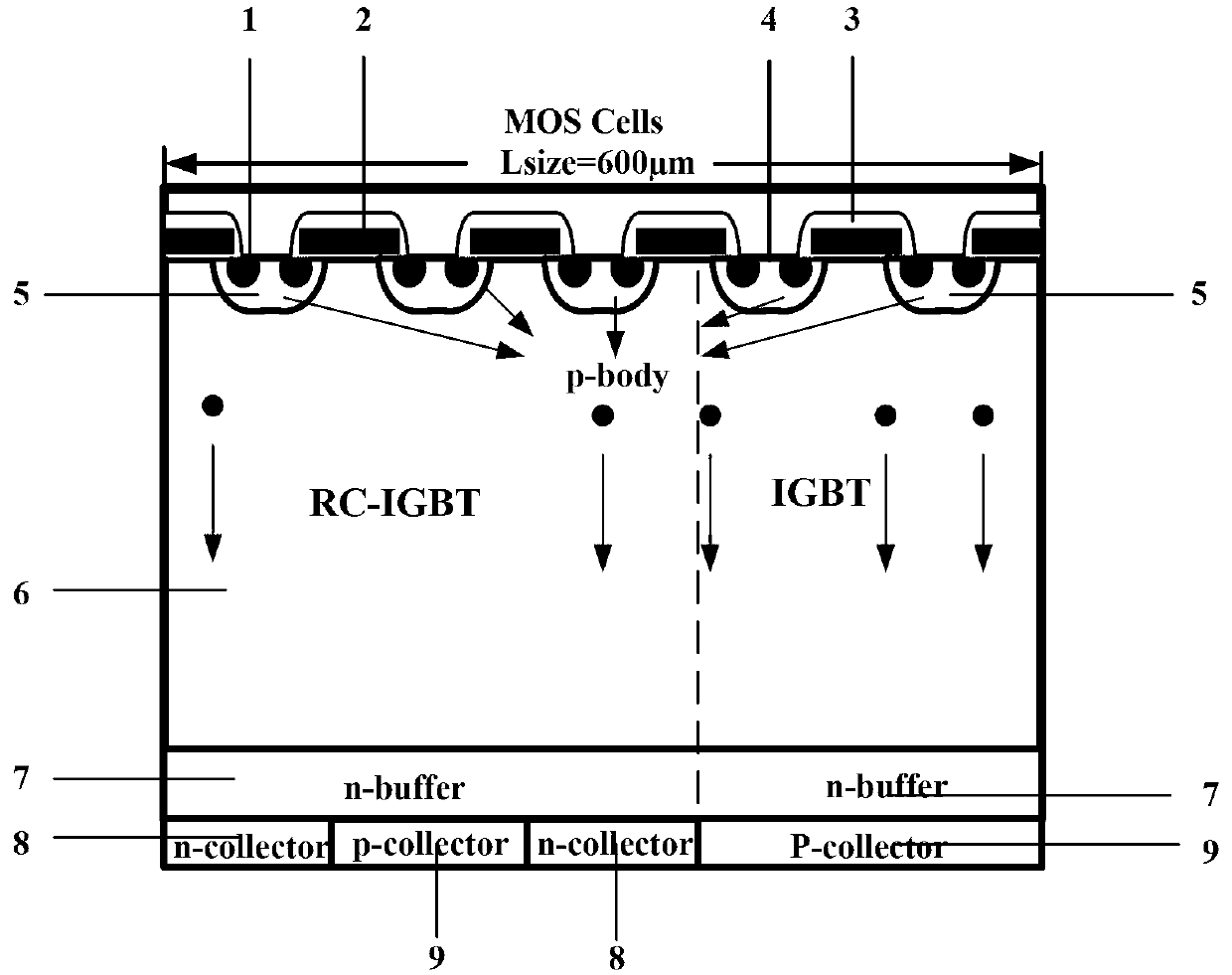

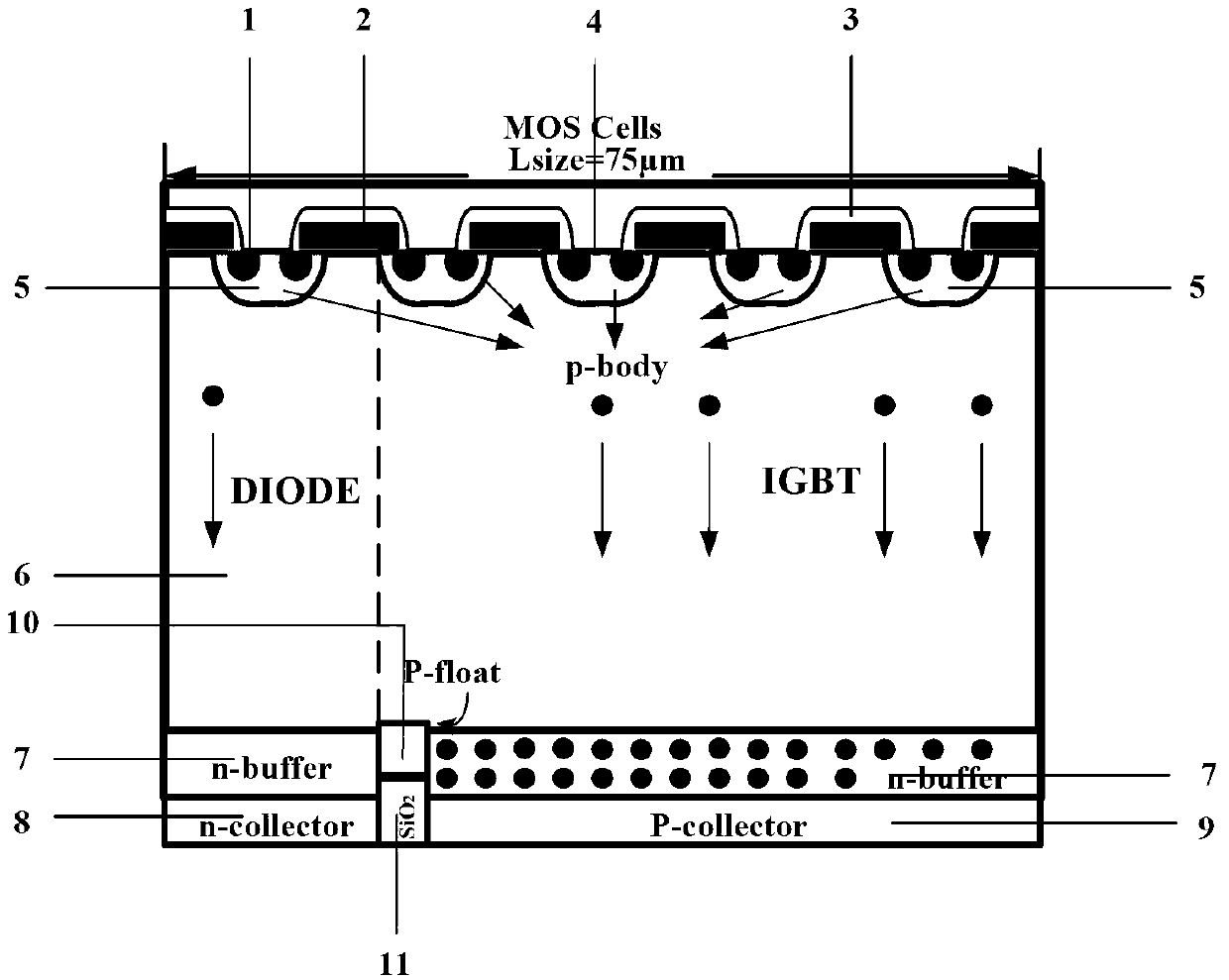

Reverse-conducting insulated-gate bipolar transistor (RC-IGBT) with P floating layer current bolt

InactiveCN103219370AGuaranteed uniformityLower breakover voltageSemiconductor devicesReverse recoveryParasitic bipolar transistor

The invention discloses a reverse-conducting insulated-gate bipolar transistor (RC-IGBT) with a P floating layer current bolt, and belongs to the field of semiconductor power elements. A medium buried layer is led in between an N collector region and a P collector region of a traditional RC-IGBT, and the P floating layer current bolt is led into an N-type buffering layer above the medium buried layer. According to the RC-IGBT with the P floating layer current bolt, other parameters of an element are not affected, break-over voltage of a snapback is obviously lowered, a reverse recovery soft factor is improved, current is distributed uniformly, local over-heating phenomenon is avoided, and the reliability of the RC-IGBT is improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

Insulated gate bipolar transistor (IGBT) with monolithic deep body clamp diode to prevent latch-up

ActiveUS20100308370A1Prevent lockoutFast switching speedSemiconductor devicesParasitic bipolar transistorP–n junction

A trench insulation gate bipolar transistor (IGBT) power device with a monolithic deep body clamp diode comprising a plurality of trench gates surrounded by emitter regions of a first conductivity type near a top surface of a semiconductor substrate of the first conductivity type encompassed in base regions of a second conductivity type. The trench semiconductor power device further comprises a collector region of the second conductivity type disposed on a rear side opposite from the top surface of the semiconductor substrate corresponding to and underneath the trench gates surrounded by the emitter regions encompassed in the base regions constituting a plurality of insulation gate bipolar transistors (IGBTs). The IGBT power device further includes a deep dopant region of the second conductivity type having P-N junction depth deeper than the base region, disposed between and extending below the trench gates in the base region of the first conductivity type. The IGBT power device further includes a dopant region of the first conductivity type disposed on the rear side of the semiconductor substrate corresponding to and underneath the deep dopant region disposed between the trench gates thus constituting a plurality of deep body diodes.

Owner:FORCE MOS TECH CO LTD

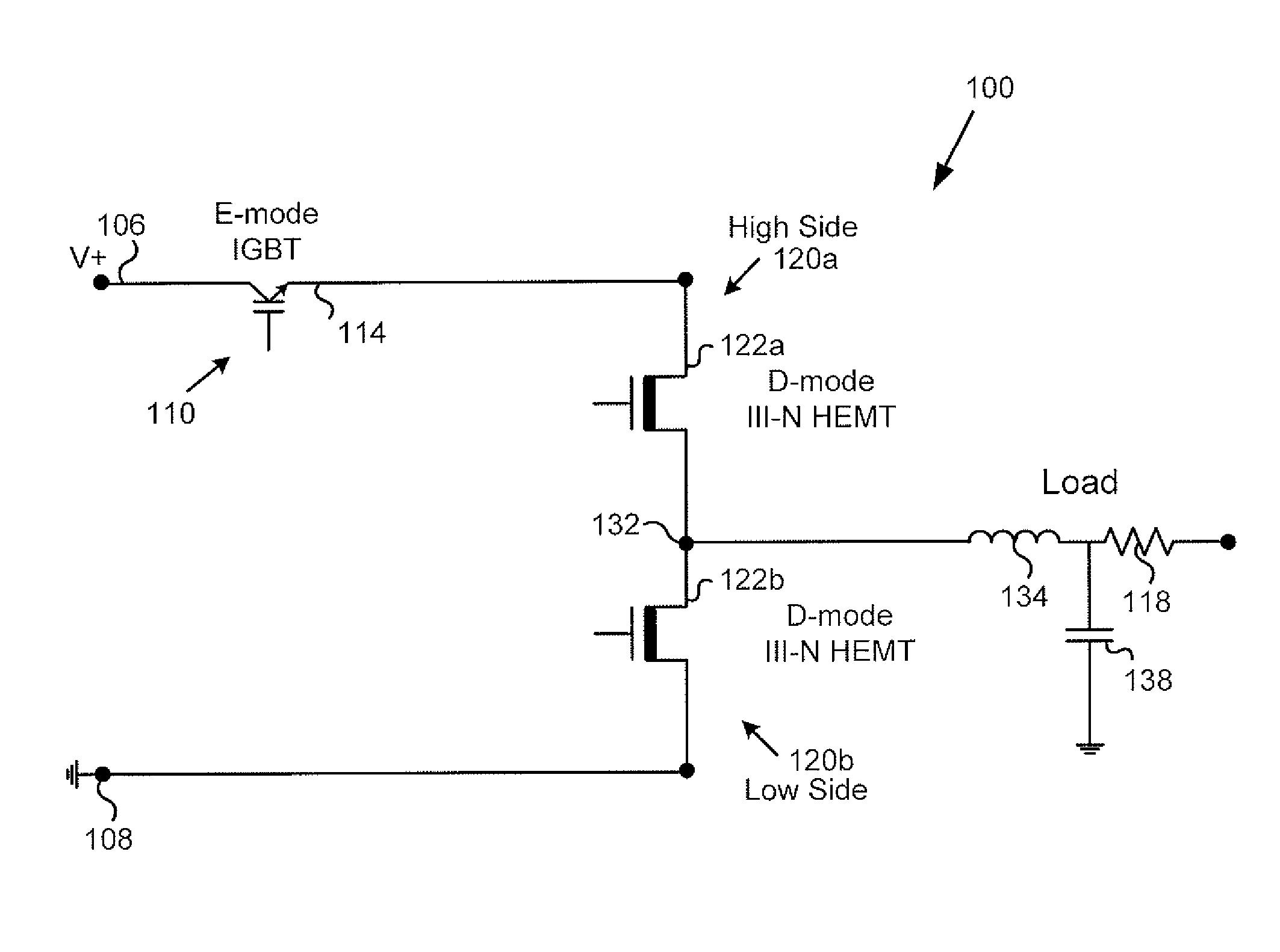

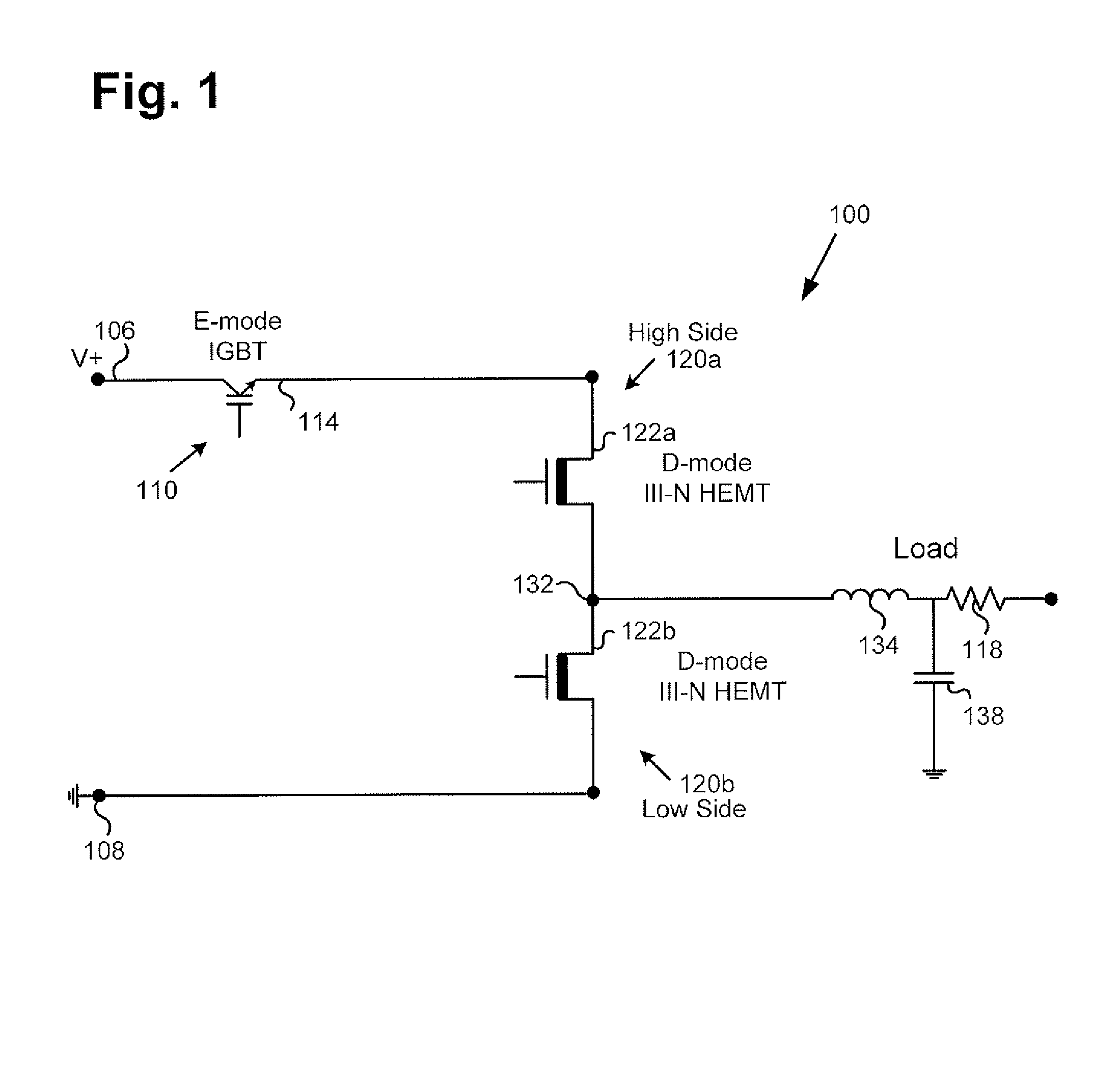

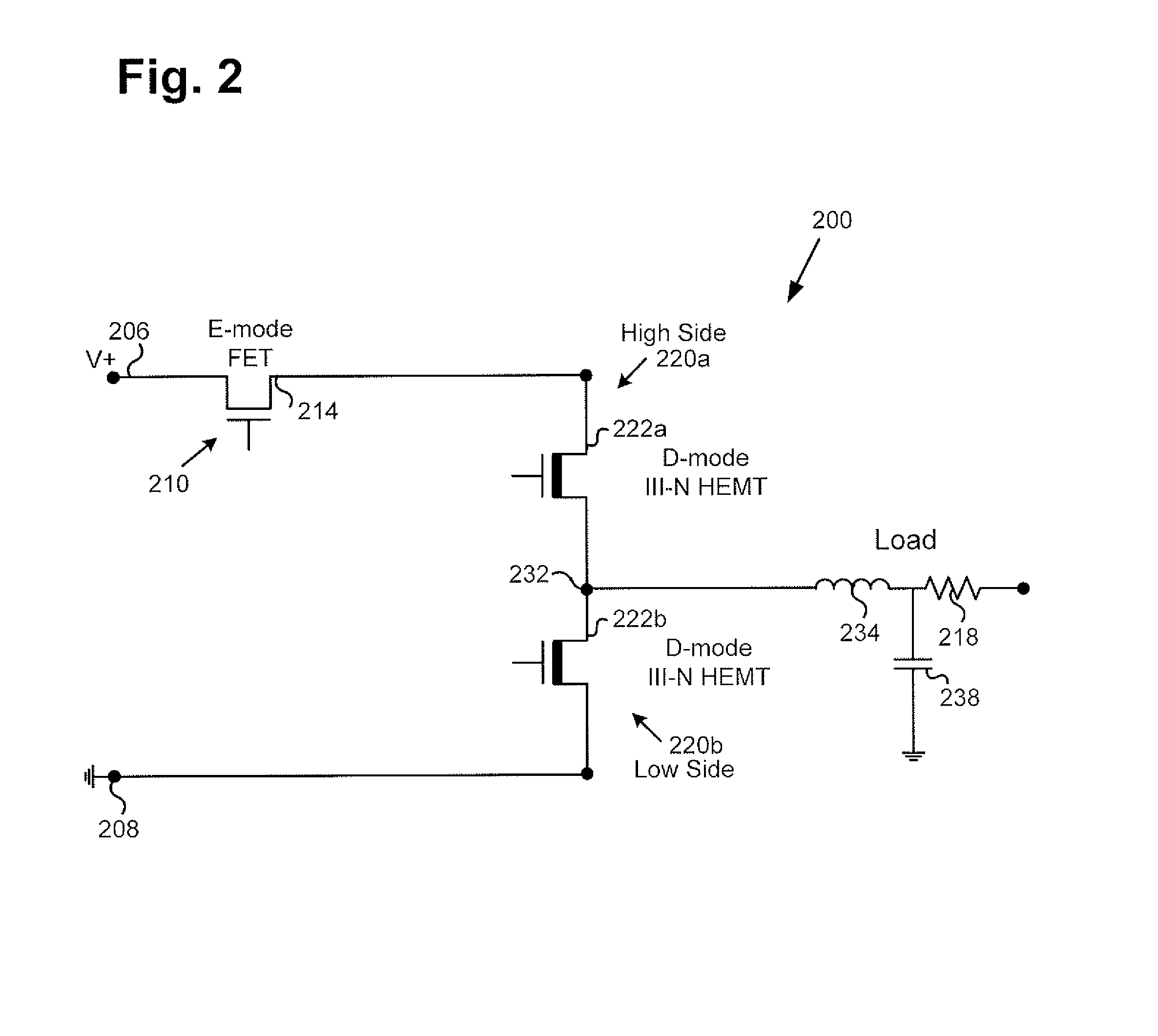

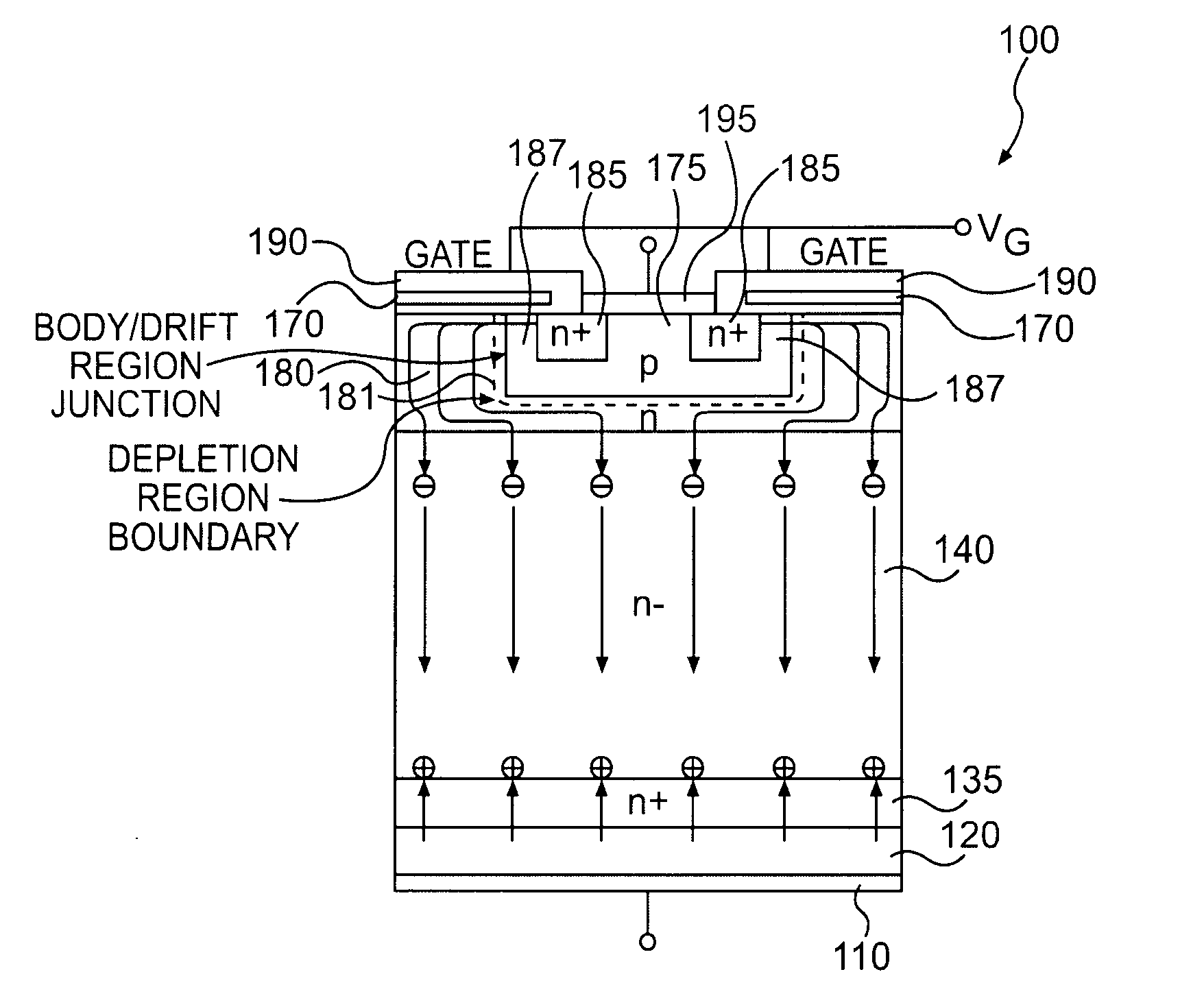

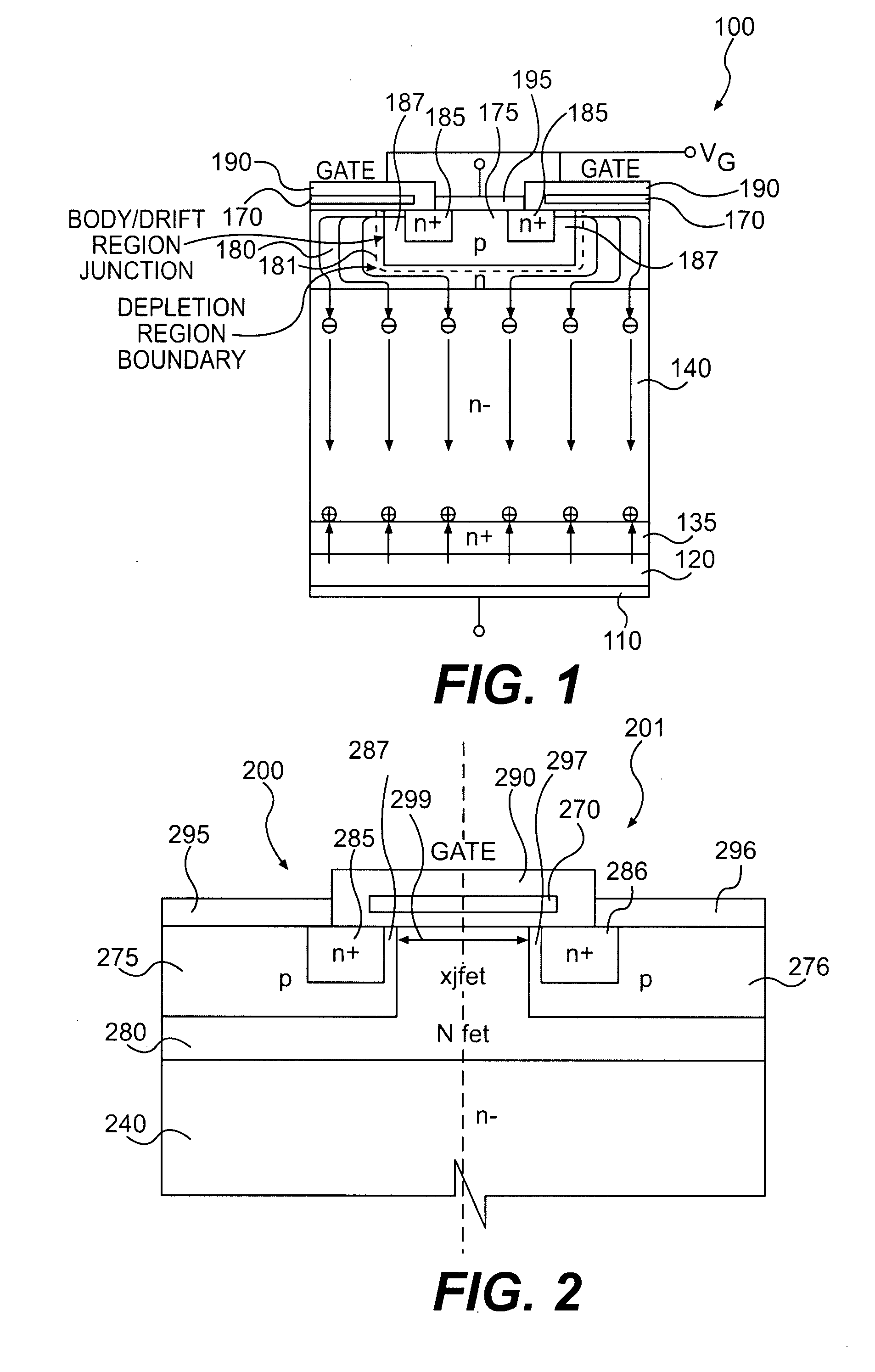

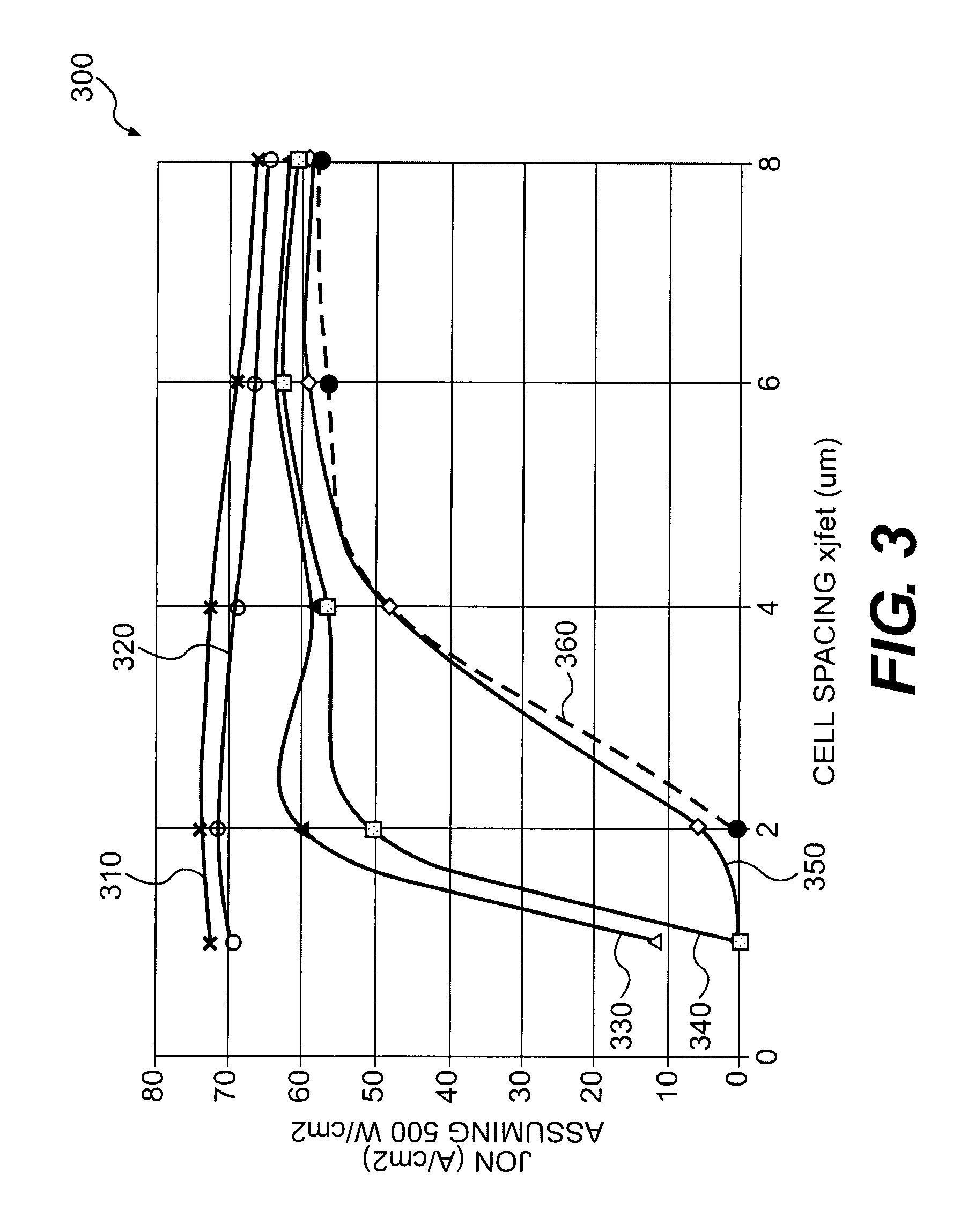

Monolithic Composite III-Nitride Transistor with High Voltage Group IV Enable Switch

ActiveUS20150014740A1Efficient power electronics conversionEmergency protective circuit arrangementsParasitic bipolar transistorNitride

There are disclosed herein various implementations of a monolithically integrated component. In one exemplary implementation, such a monolithically integrated component includes an enhancement mode group IV transistor and two or more depletion mode III-Nitride transistors. The enhancement mode group IV transistor may be implemented as a group IV insulated gate bipolar transistor (group IV IGBT). One or more of the III-Nitride transistor(s) may be situated over a body layer of the group IV IGBT, or the III-Nitride transistor(s) may be situated over a collector layer of the IGBT.

Owner:INFINEON TECH AMERICAS CORP

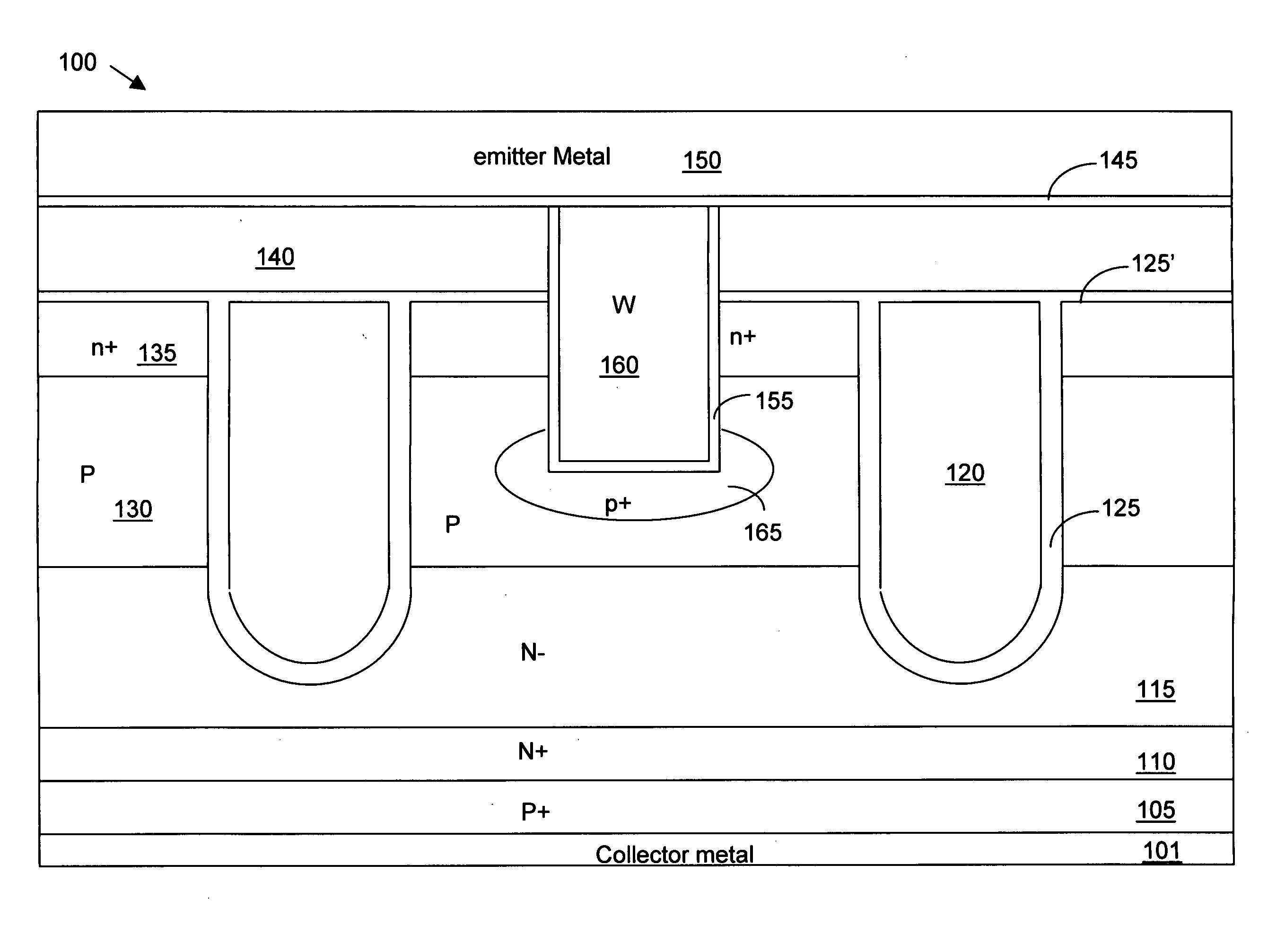

Insulated gate bipolar transistor with enhanced conductivity modulation

InactiveUS20080157117A1Reduced on-state power dissipationGood conductivity modulationThyristorSemiconductor/solid-state device manufacturingParasitic bipolar transistorConductivity modulation

A insulated gate bipolar transistors (IGBT) having an enhanced modulation layer provides reduced on-state power dissipation and better conductivity modulation than conventional devices. The IGBT includes an enhanced modulation layer disposed within a portion of the n− doped drift layer, in a n-type device, or p− doped drift layer, in a p-type device. The enhanced modulation layer contains a higher carrier concentration than the n− or p− doped drift layer. If the IGBT device is in an on state, the enhanced modulation layer decreases a size of a depletion region formed around the p well body region or n well body region. In a n-type enhanced modulation layer IGBT, electrons, traveling from the n+ region towards the emitter, are spread laterally and uniformly in the n− doped drift layer. In a p-type enhanced modulation layer IGBT, holes, traveling from the p+ region towards the emitter, are spread laterally and uniformly in the p− doped drift layer.

Owner:NORTHROP GRUMMAN SYST CORP

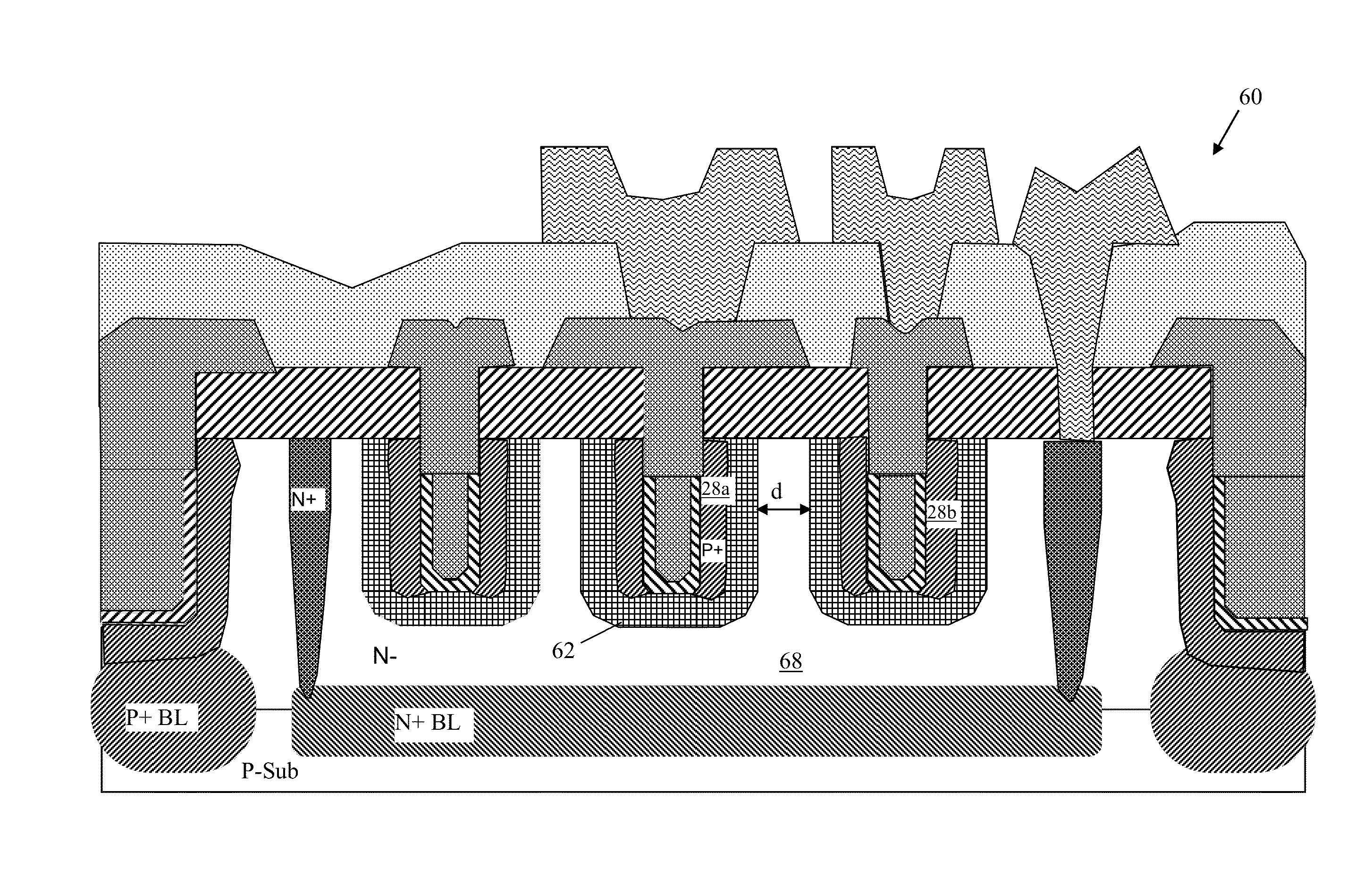

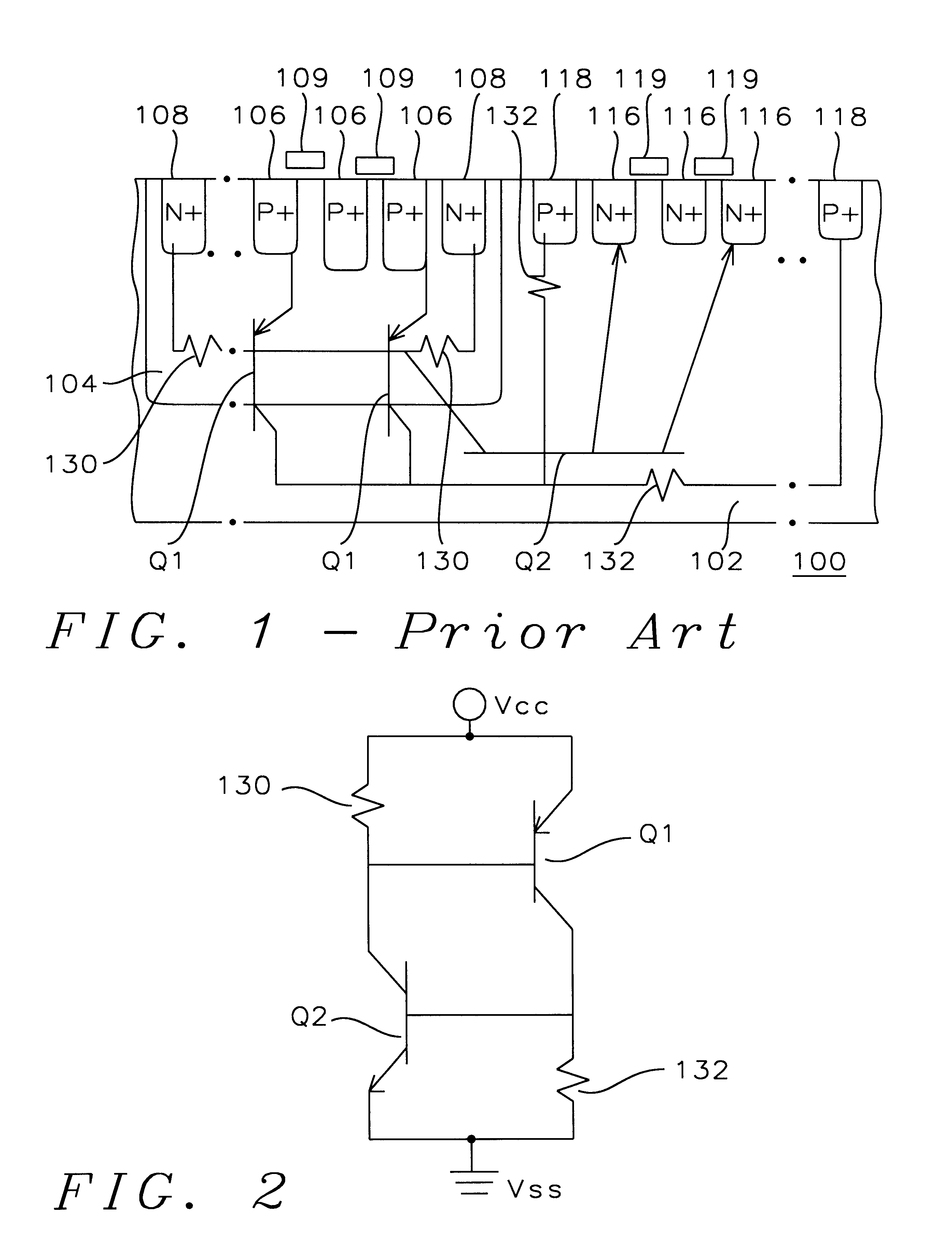

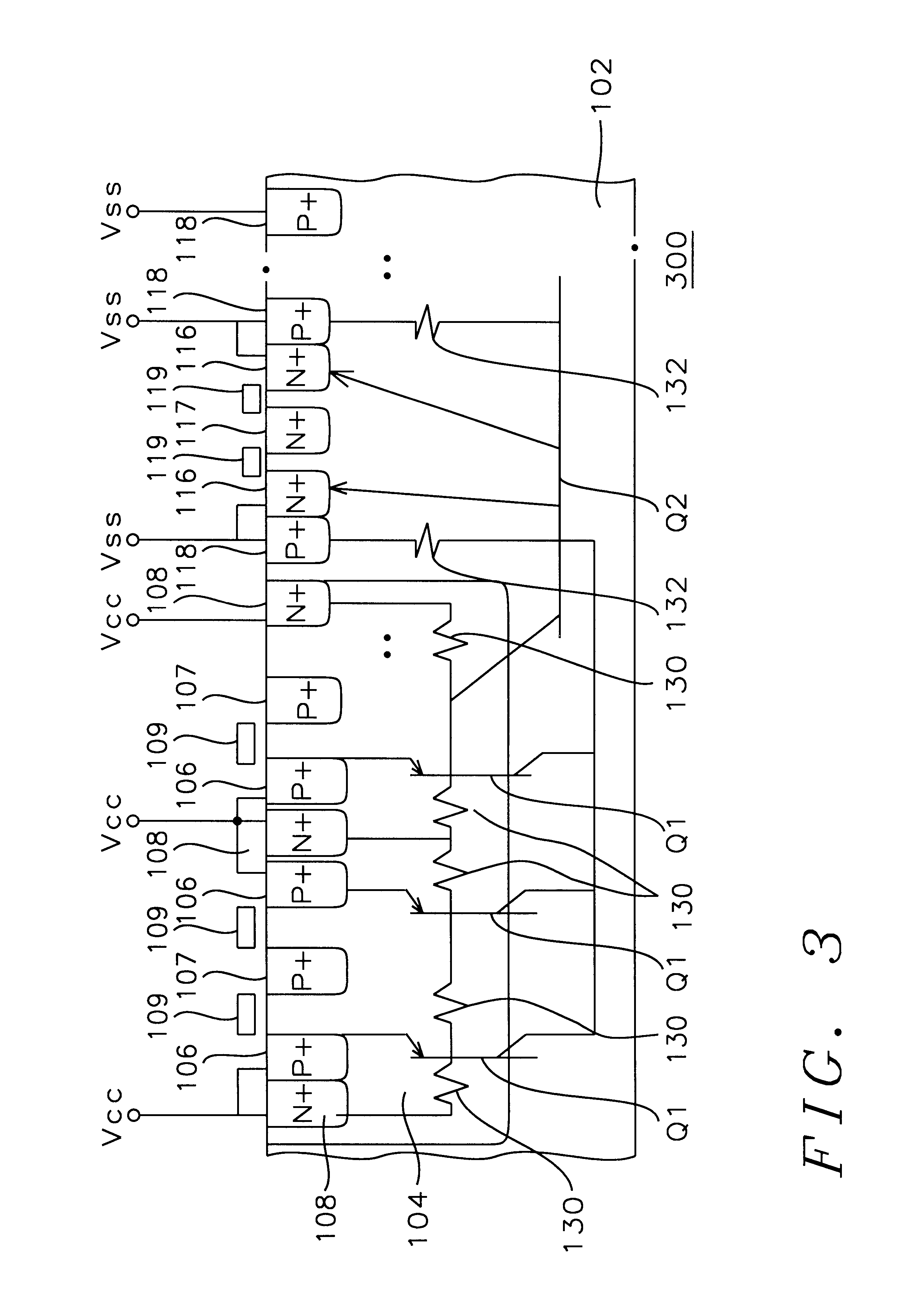

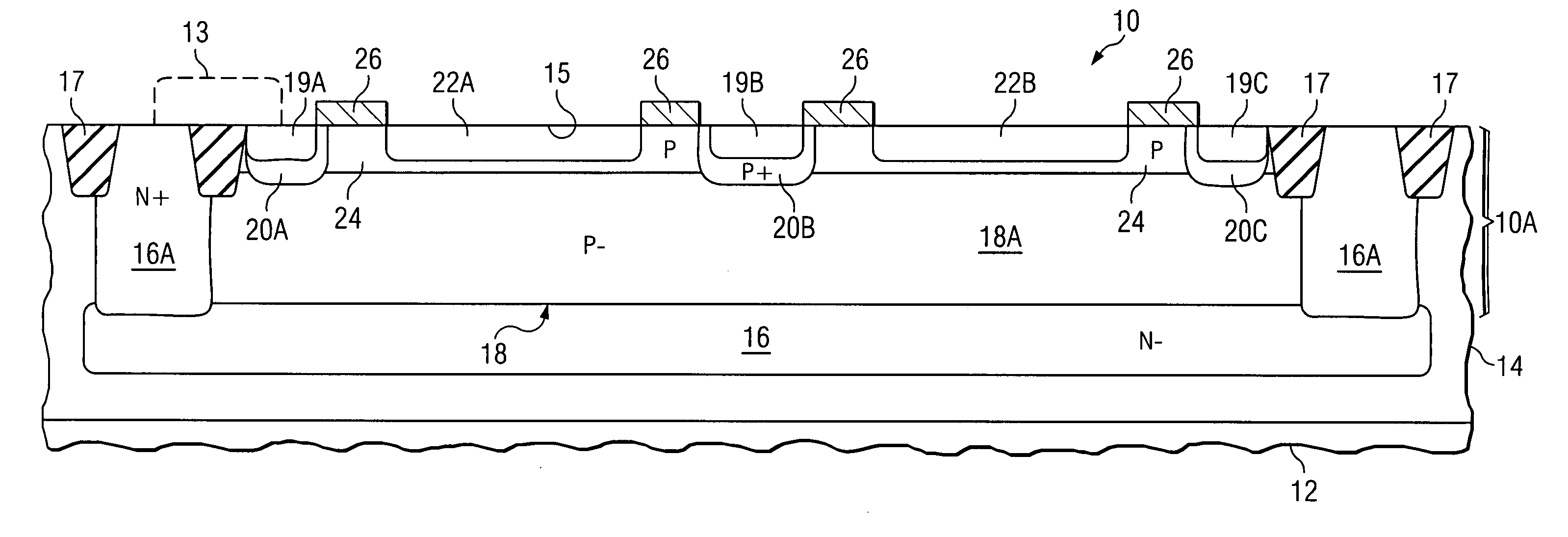

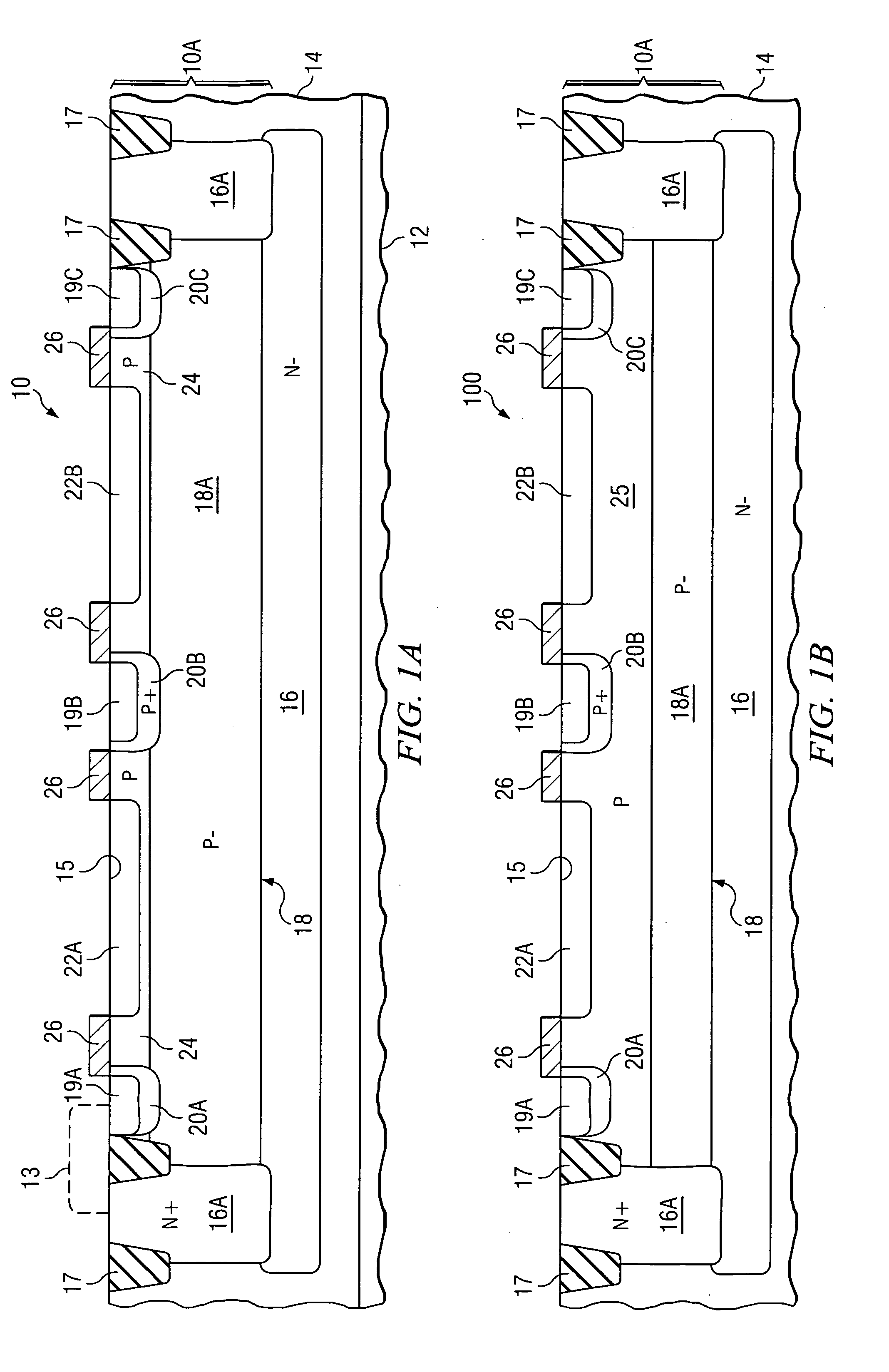

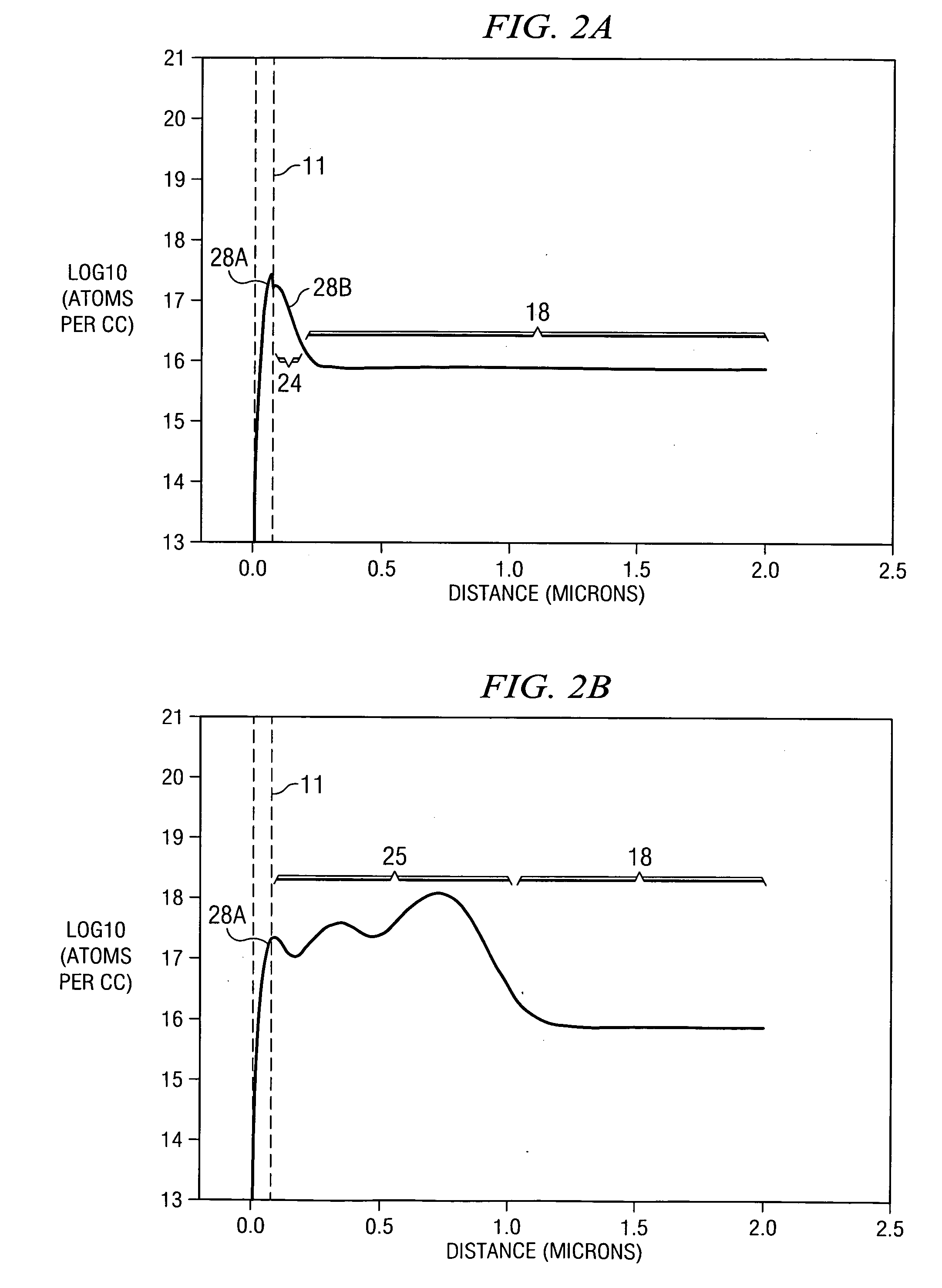

Triple-well CMOS devices with increased latch-up immunity and methods of fabricating same

Owner:INT BUSINESS MASCH CORP

Trench-type insulated gate bipolar transistor (Trench IGBT) with enhanced internal conductivity modulation

InactiveCN102201439AReduce forward voltage dropImprove concentration distributionSemiconductor devicesTrench igbtParasitic bipolar transistor

The invention relates to a Trench IGBT with enhanced internal conductivity, belonging to the technical field of power semiconductor device. According to the invention, on the basis of the structure of the conventional Trench IGBT device, a dielectric layer is introduced between a P<-> base region and an N<-> drift region of the device so as to effectively prevent the P<-> base region from extracting minority carrier holes at the edge of the N<-> drift region during forward conduction, thereby greatly increasing electrons and hole density of the whole N<-> drift region, optimizing the density distribution of carriers in the drift region, enhancing the conductivity modulation in the device, lowering the forward conduction voltage drop of the device, and better compromising the forward conduction voltage drop and the turn-off loss. Meanwhile, the chip surface utilization rate is not reduced and the chip area is saved. The Trench IGBT is suitable for the field of semiconductor power devices and power integrated circuits from small power to large power.

Owner:INST OF ELECTRONICS & INFORMATION ENG IN

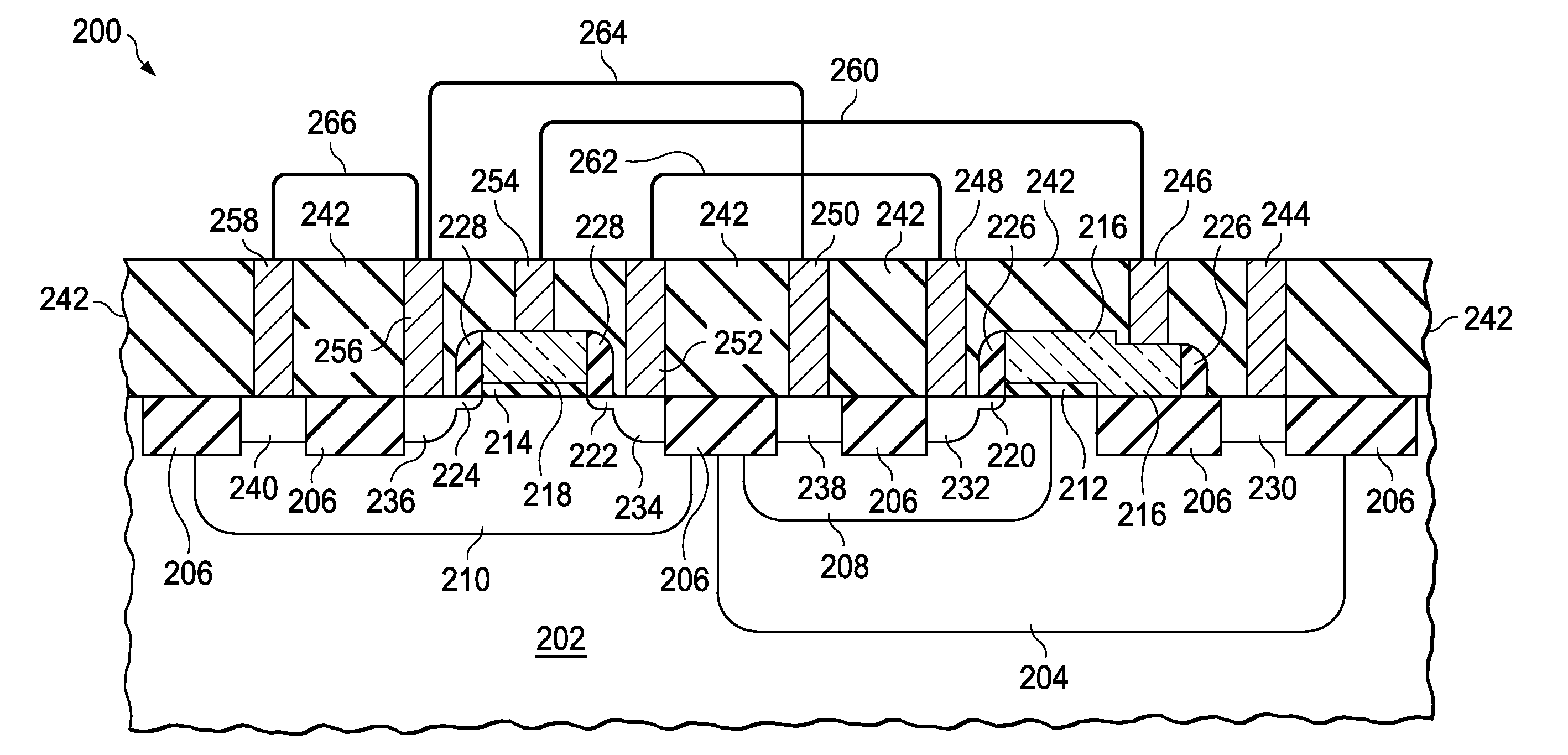

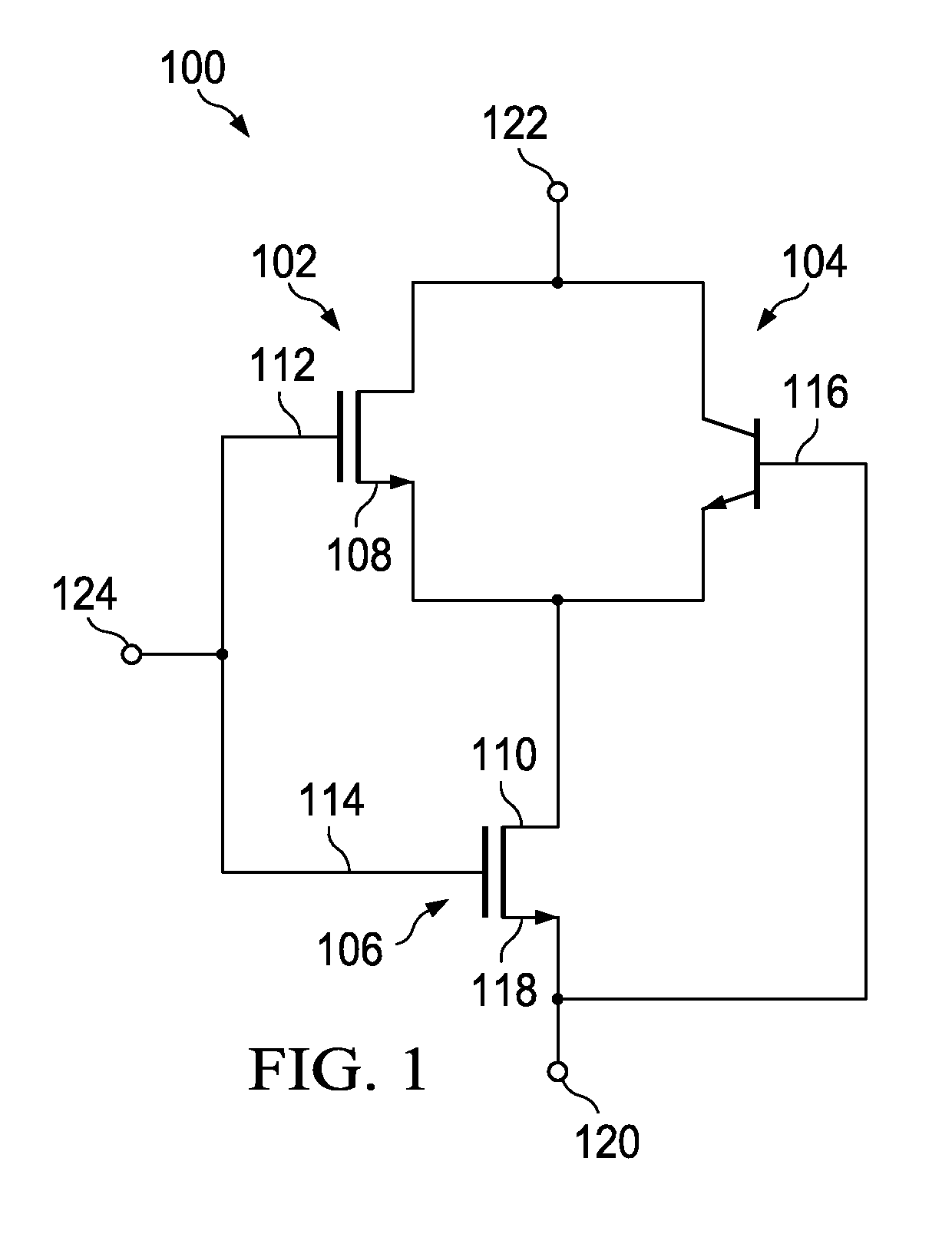

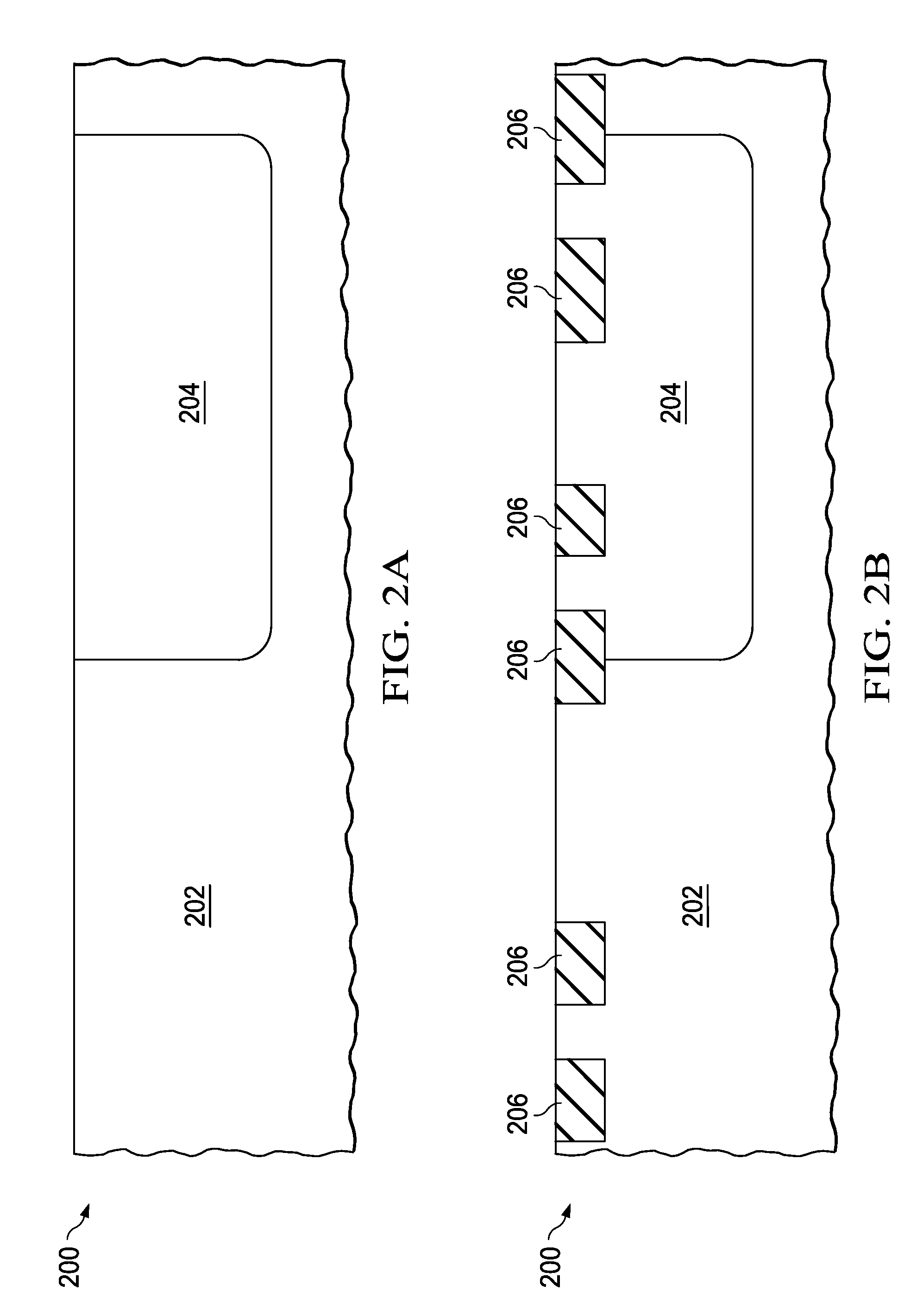

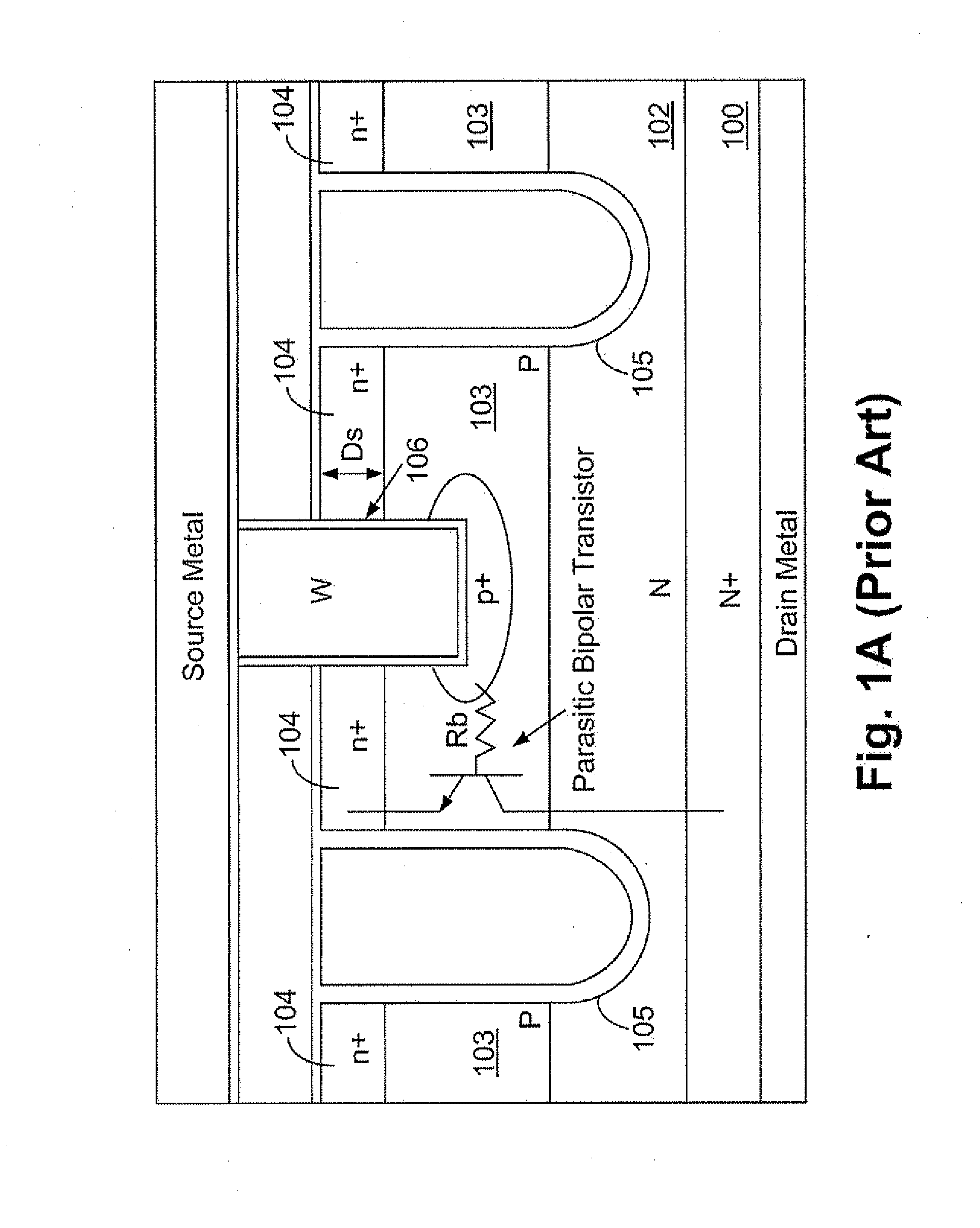

BVDII Enhancement with a Cascode DMOS

InactiveUS20090159968A1TransistorSemiconductor/solid-state device manufacturingCascodeParasitic bipolar transistor

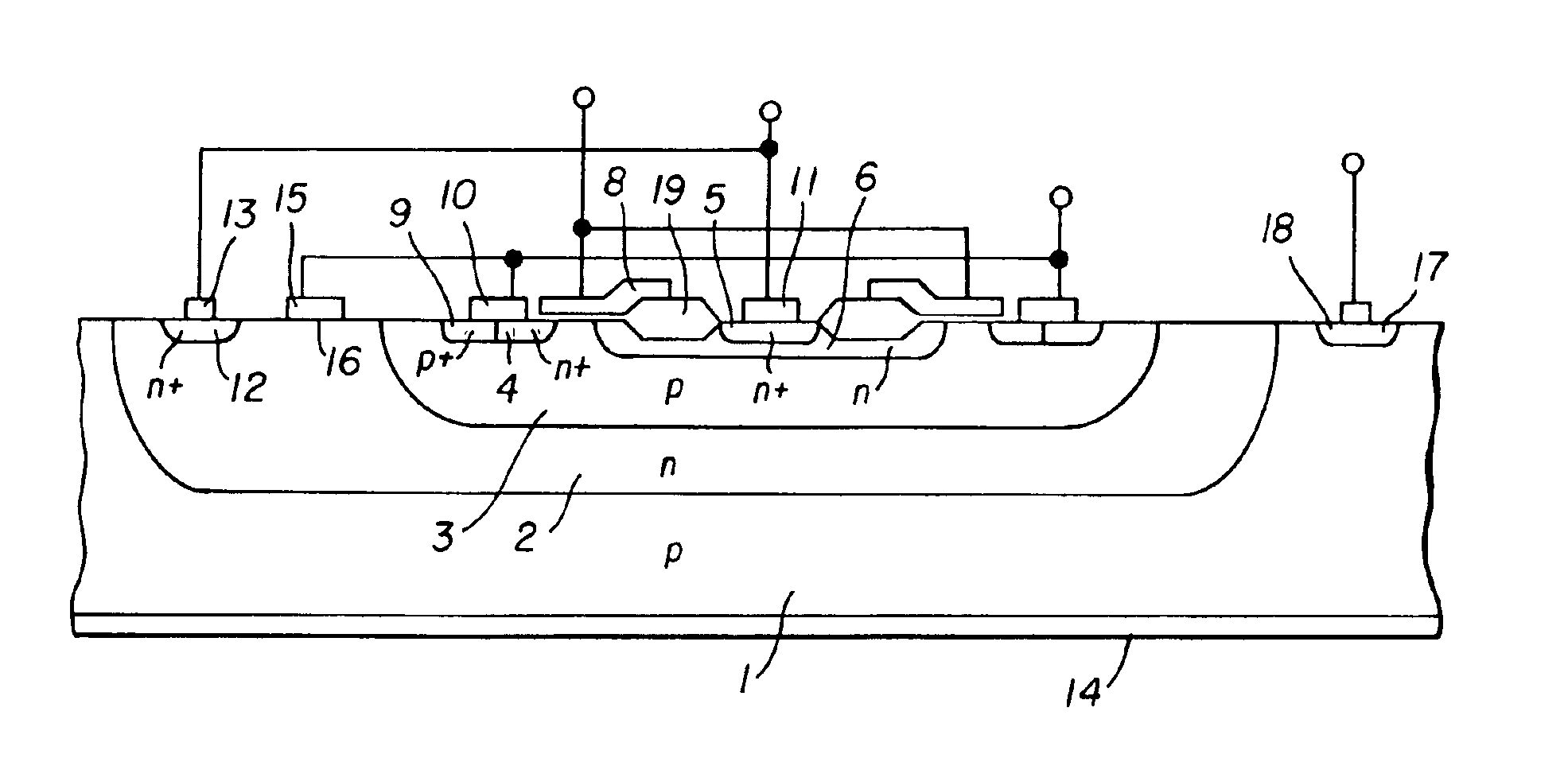

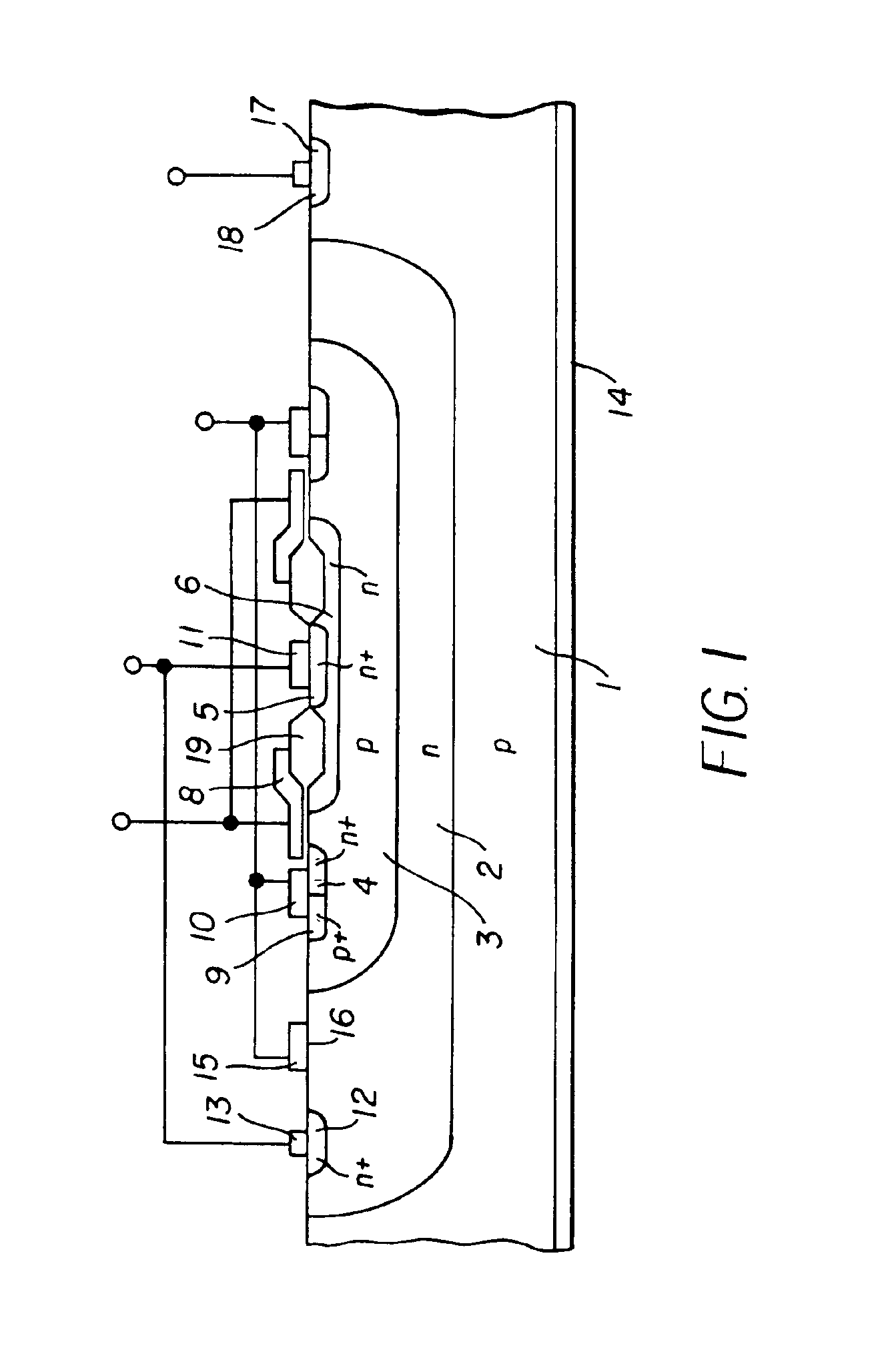

Double diffused MOS (DMOS) transistors feature extended drain regions to provide depletion regions which drop high drain voltages to lower voltages at the gate edges. DMOS transistors exhibit lower drain breakdown potential in the on-state than in the off-state than in the off-state due to snapback by a parasitic bipolar transistor that exists in parallel with the DMOS transistor. The instant invention is a cascoded DMOS transistor in an integrated circuit incorporating an NMOS transistor on the DMOS source node to reverse bias the parasitic emitter-base junction during on-state operation, eliminating snapback. The NMOS transistor may be integrated with the DMOS transistor by connections in the interconnect system of the integrated circuit, or the NMOS transistor and DMOS transistor may be fabricated in a common p-type well and integrated in the IC substrate. Methods of fabricating an integrated circuit with the incentive cascoded DMOS transistor are also disclosed.

Owner:TEXAS INSTR INC

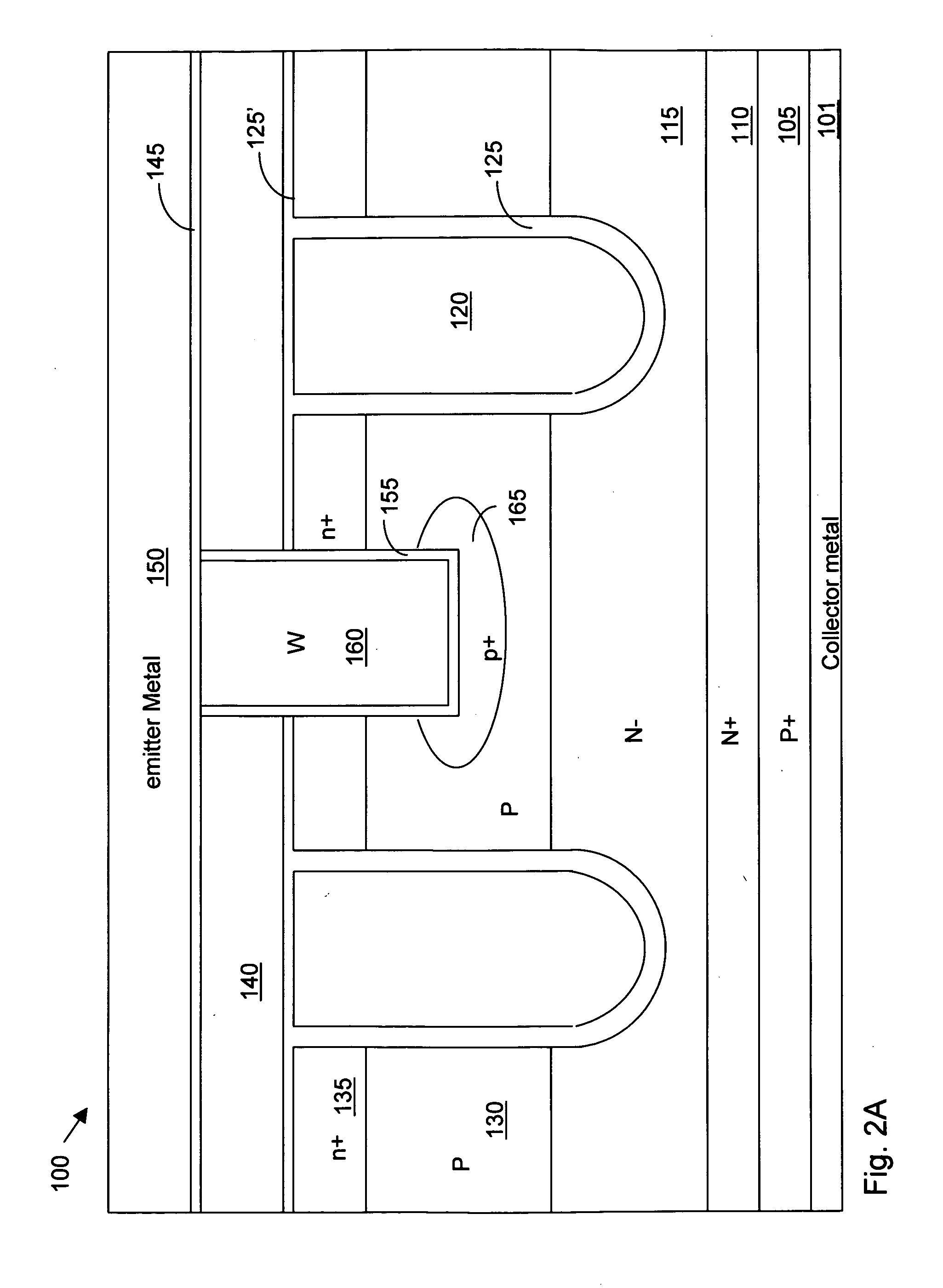

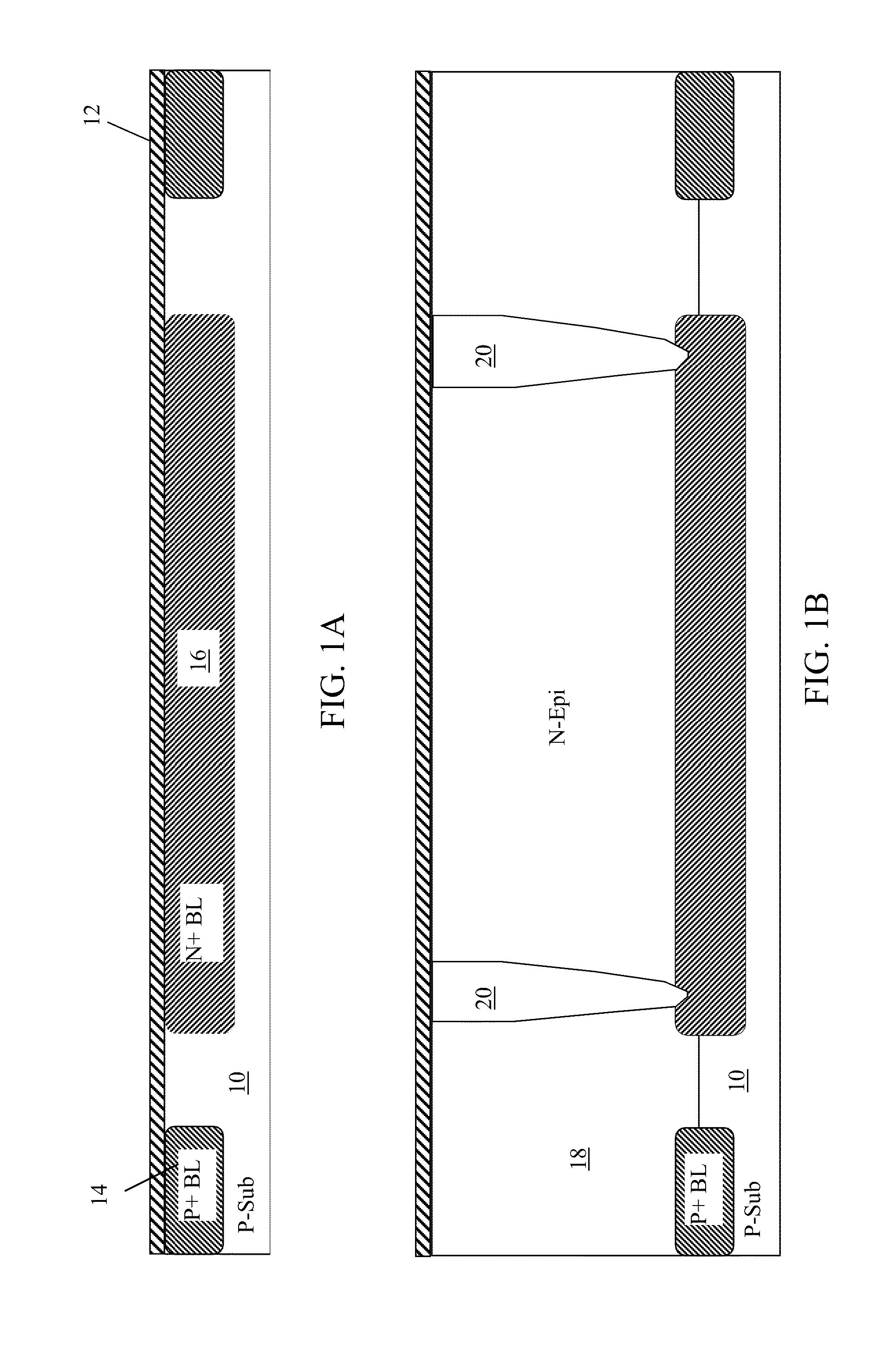

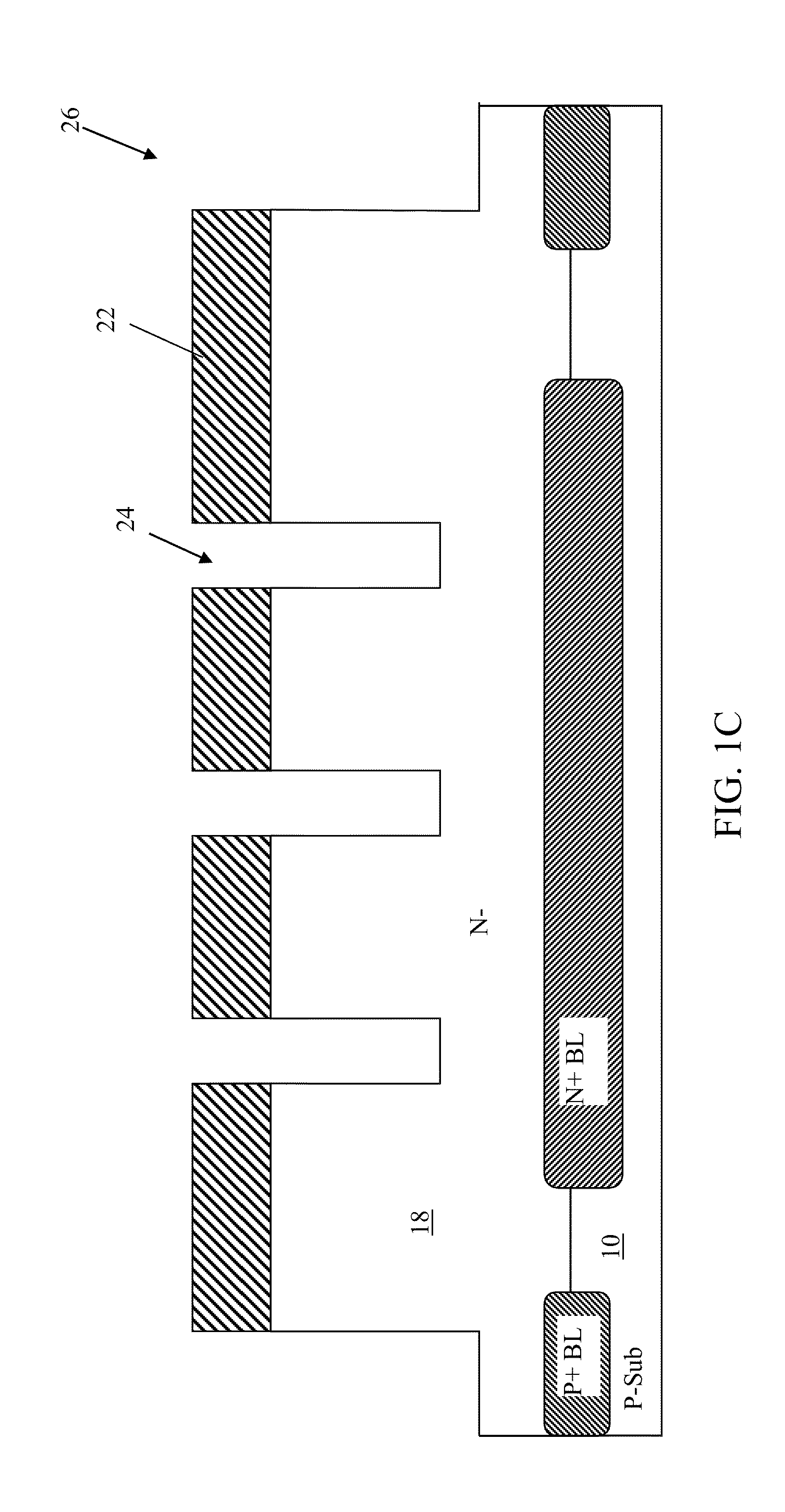

Lateral PNP Bipolar Transistor Formed with Multiple Epitaxial Layers

ActiveUS20130075741A1Improve performanceSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSParasitic bipolar transistor

A lateral bipolar transistor with deep emitter and deep collector regions is formed using multiple epitaxial layers of the same conductivity type. Deep emitter and deep collector regions are formed without the use of trenches. Vertically aligned diffusion regions are formed in each epitaxial layer so that the diffusion regions merged into a contiguous diffusion region after annealing to function as emitter or collector or isolation structures. In another embodiment, a lateral trench PNP bipolar transistor is formed using trench emitter and trench collector regions. In yet another embodiment, a lateral PNP bipolar transistor with a merged LDMOS transistor is formed to achieve high performance.

Owner:ALPHA & OMEGA SEMICON INC

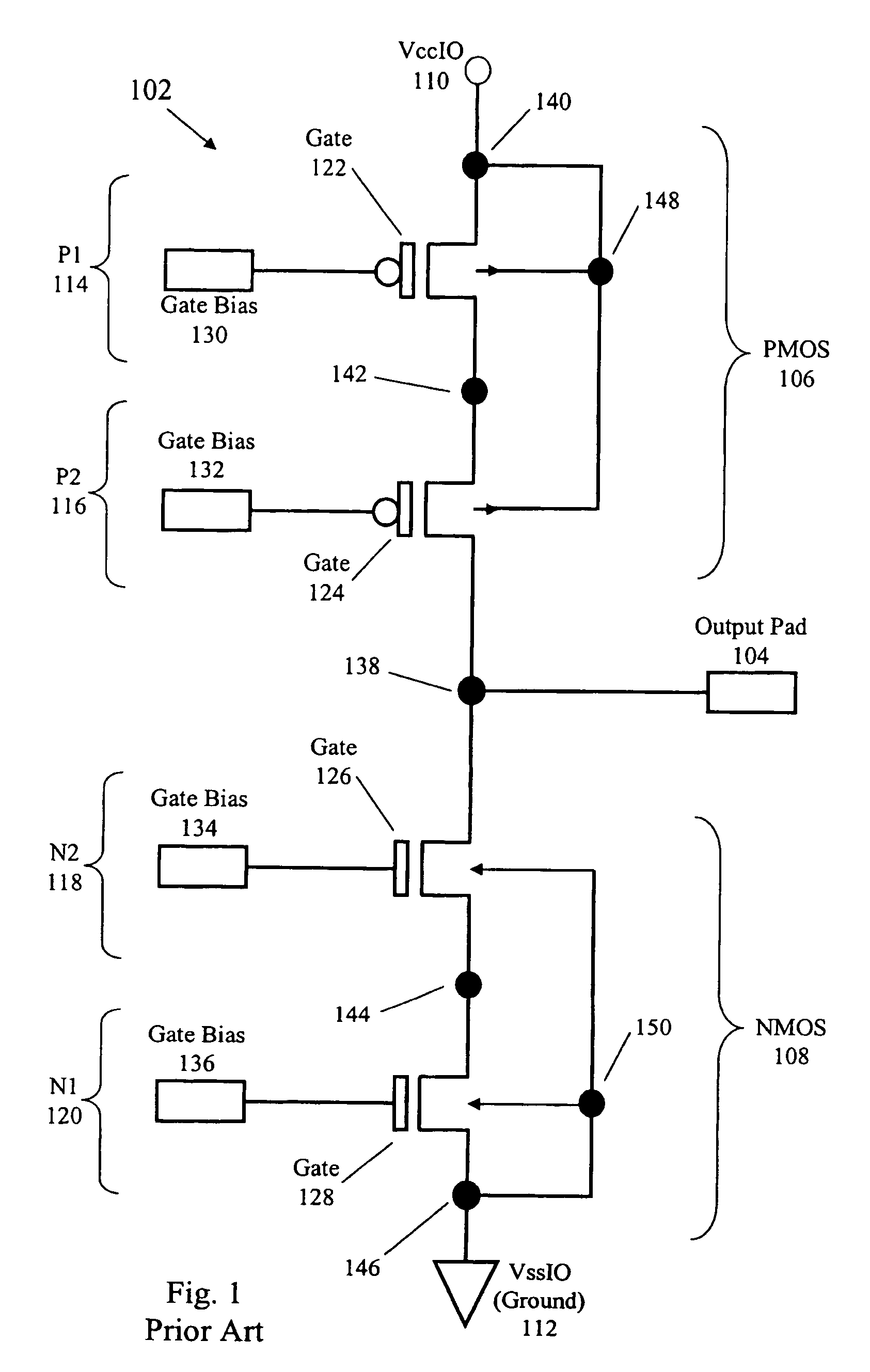

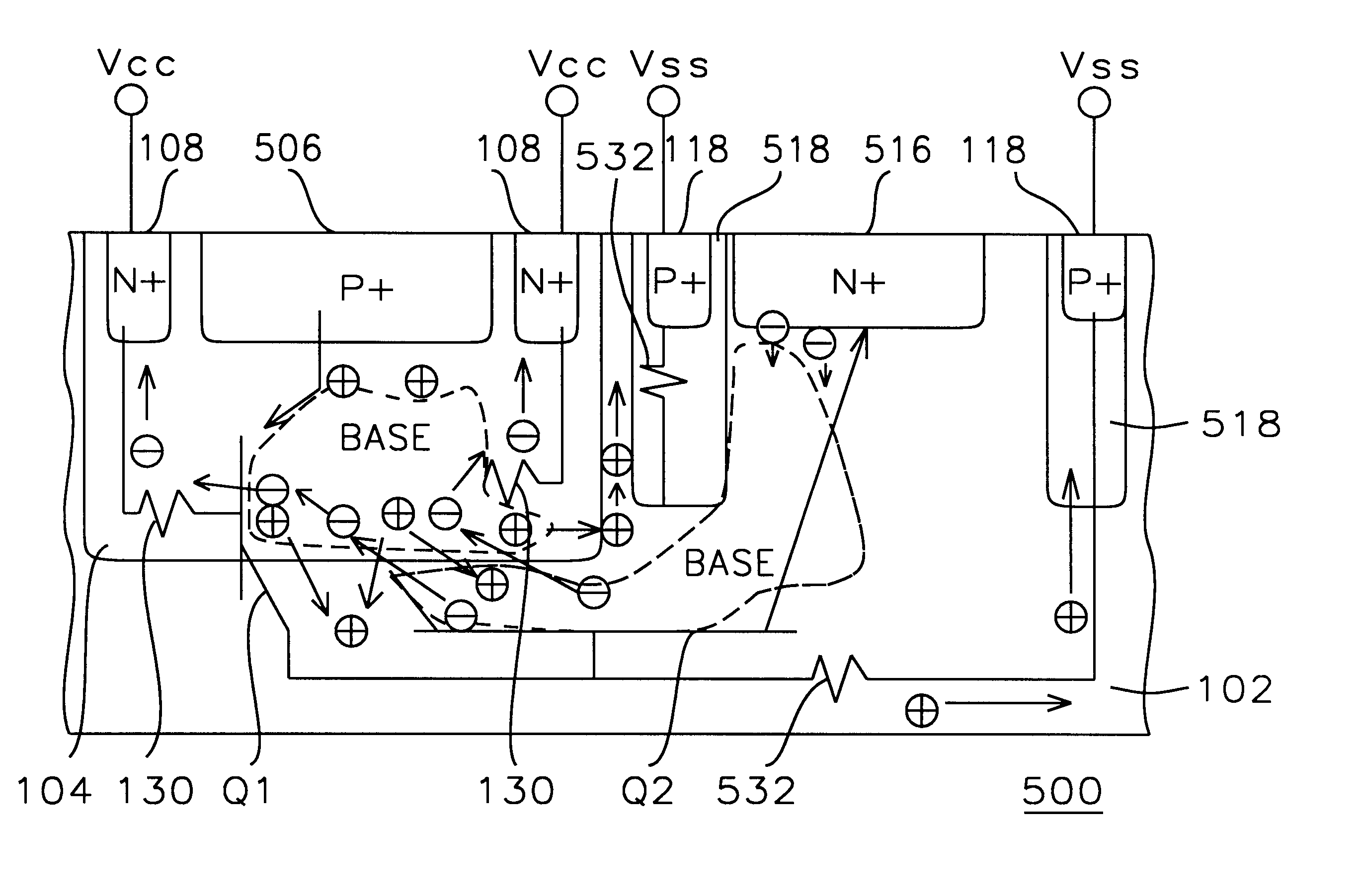

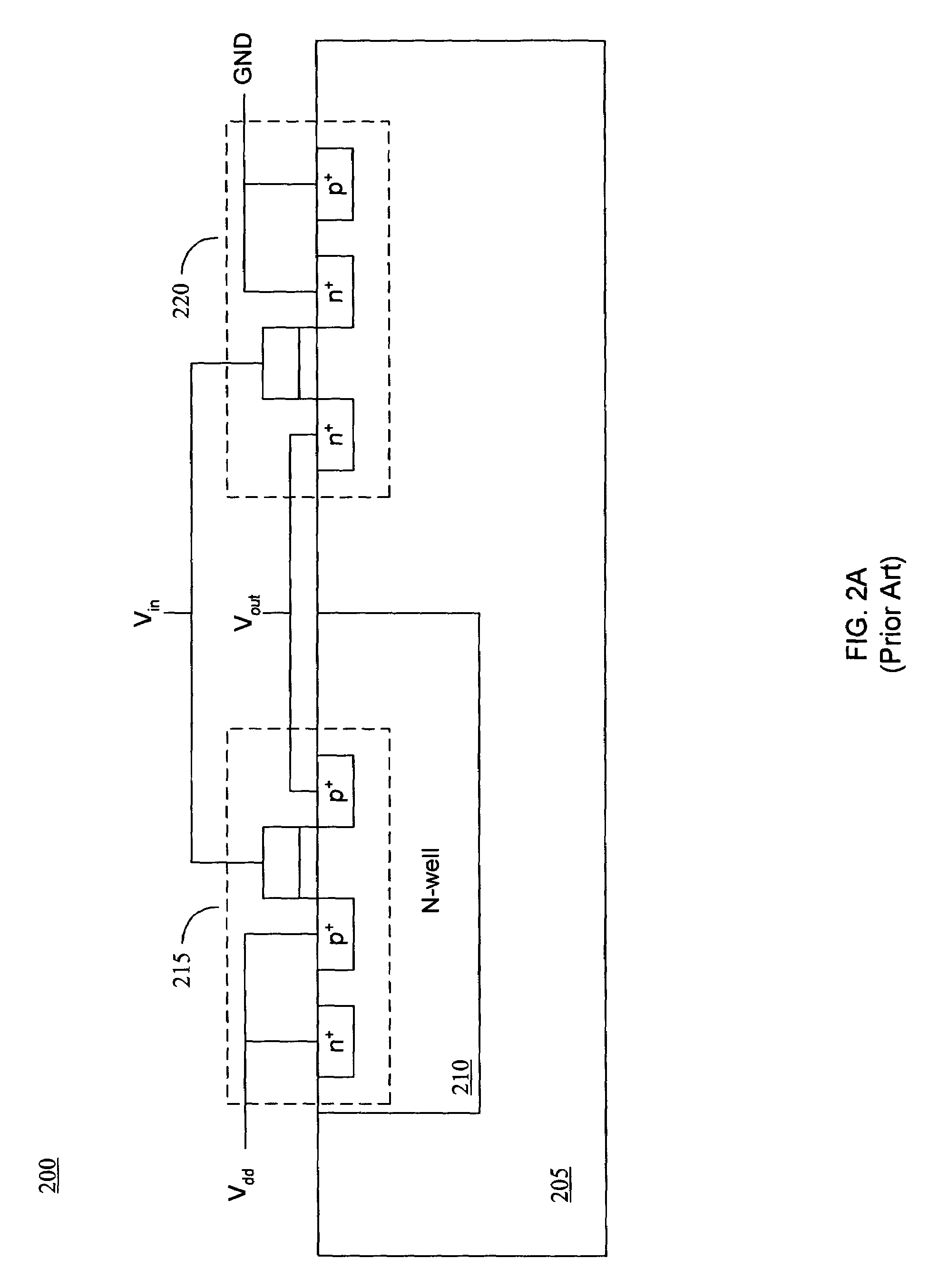

Highly latchup-immune CMOS I/O structures

InactiveUS6614078B2Improve their latchup immunityReduce spacingTransistorSolid-state devicesElectrical resistance and conductanceCMOS

CMOS I / O structures are described which are latchup-immune by inserting p+ and n+ diffusion guard-rings into the NMOS and PMOS source side of a semiconductor substrate, respectively. P+ diffusion guard-rings surround individual n-channel transistors and n+ diffusion guard-rings surround individual p-channel transistors. These guard-rings, connected to voltage supplies, reduce the shunt resistances of the parasitic SCRs, commonly associated with CMOS structures, from either the p-substrate to p+ guard-ring or the n-well to n+ guard-ring. In a second preferred embodiment a deep p+ implant is implanted into the p+ guard-ring or p-well pickup to decrease the shunt resistances of the parasitic SCRs. The n+ and p+ guard-rings, like the guard-rings of the first preferred embodiment, are connected to positive and negative voltage supplies, respectively. In either of the two preferred embodiments the reduced shunt resistances prevent the forward biasing of the parasitic bipolar transistors of the SCR, thus insuring that the holding voltage is larger than the supply voltage.

Owner:TAIWAN SEMICON MFG CO LTD

Trench insulated gate bipolar transistor and manufacturing method thereof

InactiveCN102201437AReduce contact resistanceImprove contact effectSemiconductor/solid-state device manufacturingSemiconductor devicesParasitic bipolar transistorEngineering

The invention discloses a trench insulated gate bipolar transistor (IGBT) device. According to the invention, an emitter region-base region contact doping zone with a P<+> type is included. The doping zone is in a P-type base and at least encompasses the lowest part of an emitter region-base region contact trench. The concentration of the majority carriers in the emitter region-base region contact doping zone is higher than that of the P-type base, and the emitter region-base region contact doping zone keeps a predetermined distance from a channel region nearby trench gates, so that it can be guaranteed that an emitter electrode-base electrode resistor can be reduced under the condition that a grid electrode- emitter electrode threshold voltage is not improved.

Owner:FORCE MOS TECH CO LTD

Semiconductor device including insulated gate bipolar transistor and diode

ActiveUS8080853B2Snapback of the FWD can be reducedUnified operationTransistorSolid-state devicesParasitic bipolar transistorEngineering

A semiconductor device includes a vertical IGBT and a vertical free-wheeling diode in a semiconductor substrate. A plurality of base regions is disposed at a first-surface side portion of the semiconductor substrate, and a plurality of collector regions and a plurality of cathode regions are alternately disposed in a second-surface side portion of the semiconductor substrate. The base regions include a plurality of regions where channels are provided when the vertical IGBT is in an operating state. The first-side portion of the semiconductor substrate include a plurality of IGBT regions each located between adjacent two of the channels, including one of the base regions electrically coupled with an emitter electrode, and being opposed to one of the cathode regions. The IGBT regions include a plurality of narrow regions and a plurality of wide regions.

Owner:DENSO CORP

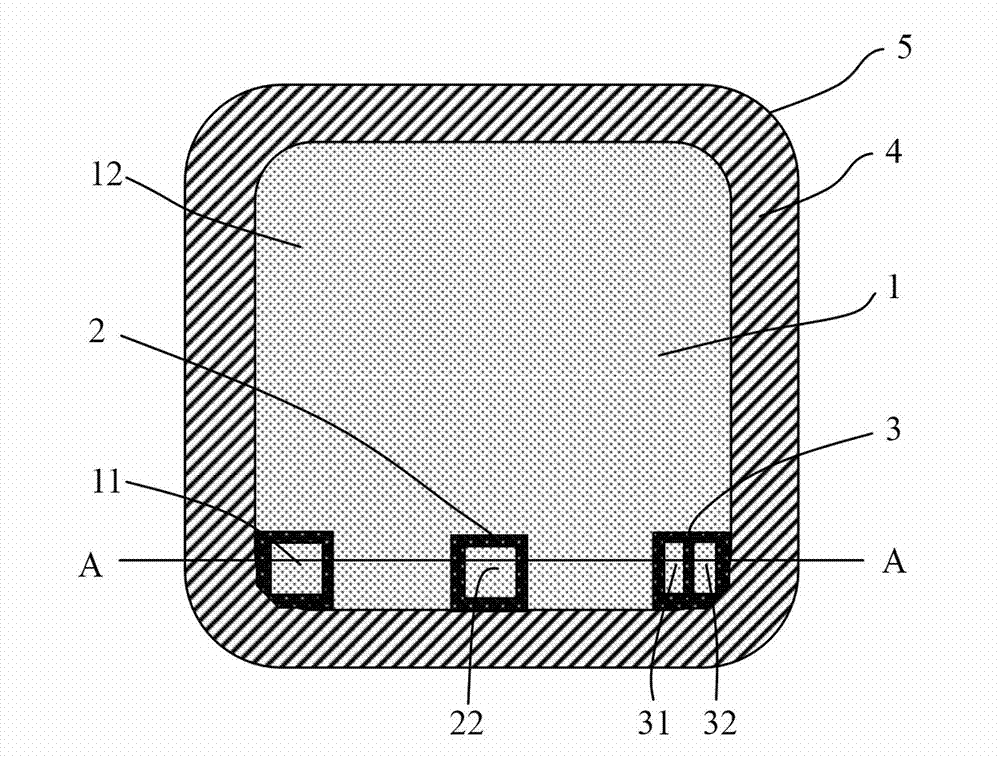

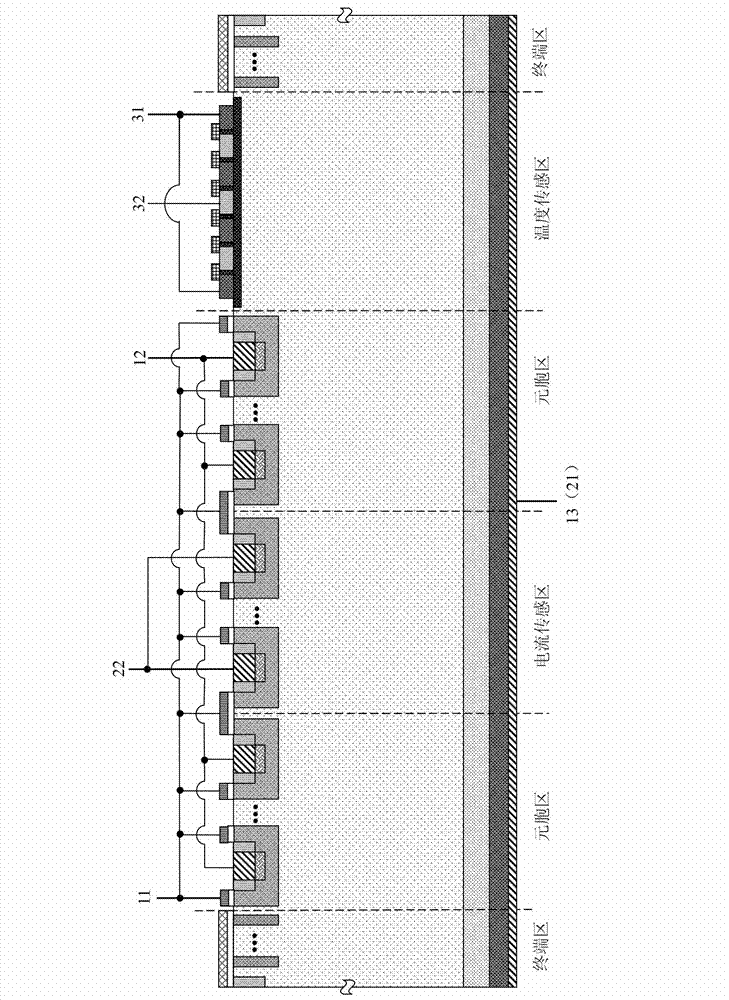

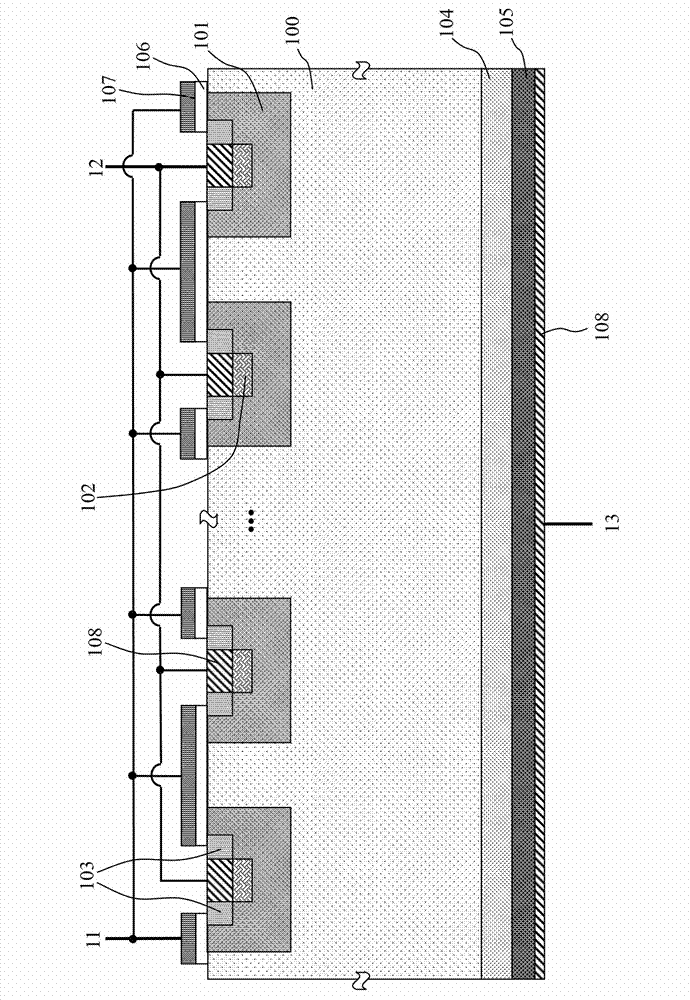

IGBT (insulated gate bipolar transistor) chip integrating temperature and current sensing function

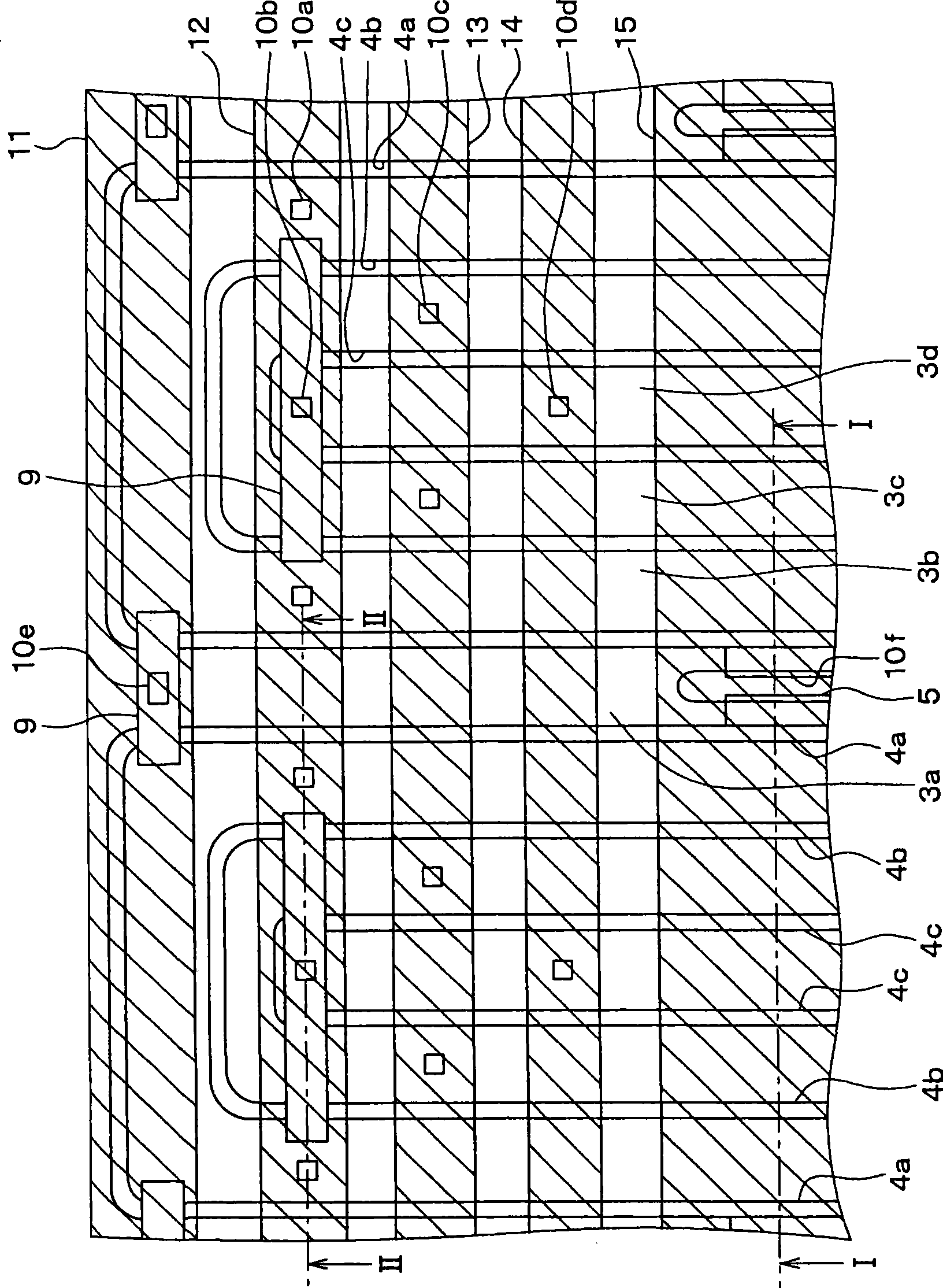

ActiveCN102881679AAccurate monitoringAccurate acquisitionTransistorSemiconductor/solid-state device detailsParasitic bipolar transistorCurrent sensor

The invention relates to an IGBT (insulated gate bipolar transistor) chip integrating a temperature and current sensing function, comprising a chip. The edge of the chip is provided with an IGBT terminal protection area, the middle part comprises an IGBT cellular area, a current sensing area and a temperature sensing area, and the front surface is provided with an IGBT chip grid electrode, IGBT chip emitting electrode, a current sensor negative electrode, a temperature sensor positive electrode and a temperature sensor negative electrode; the electrodes are separated by etching the metalized layer on the surface of the chip; the IGBT chip grid electrode and the IGBT chip emitting electrode are arranged in the IGBT cellular are; the current sensor negative electrode is arranged in the current sensing area; the temperature sensor positive electrode and the temperature sensor negative electrode are arranged in the temperature sensing area; and the back surface of the chip is provided with an IGBT chip collection electrode or current sensor positive electrode in the current sensing area, wherein the IGBT chip collection electrode and the current sensor positive electrode are same. The IGBT chip has the advantages of simpler and compacter structure and wider range of application. The temperature and current information of the chip can be accurately monitored and acquired when the chip works so that the chip in the module can be protected better.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

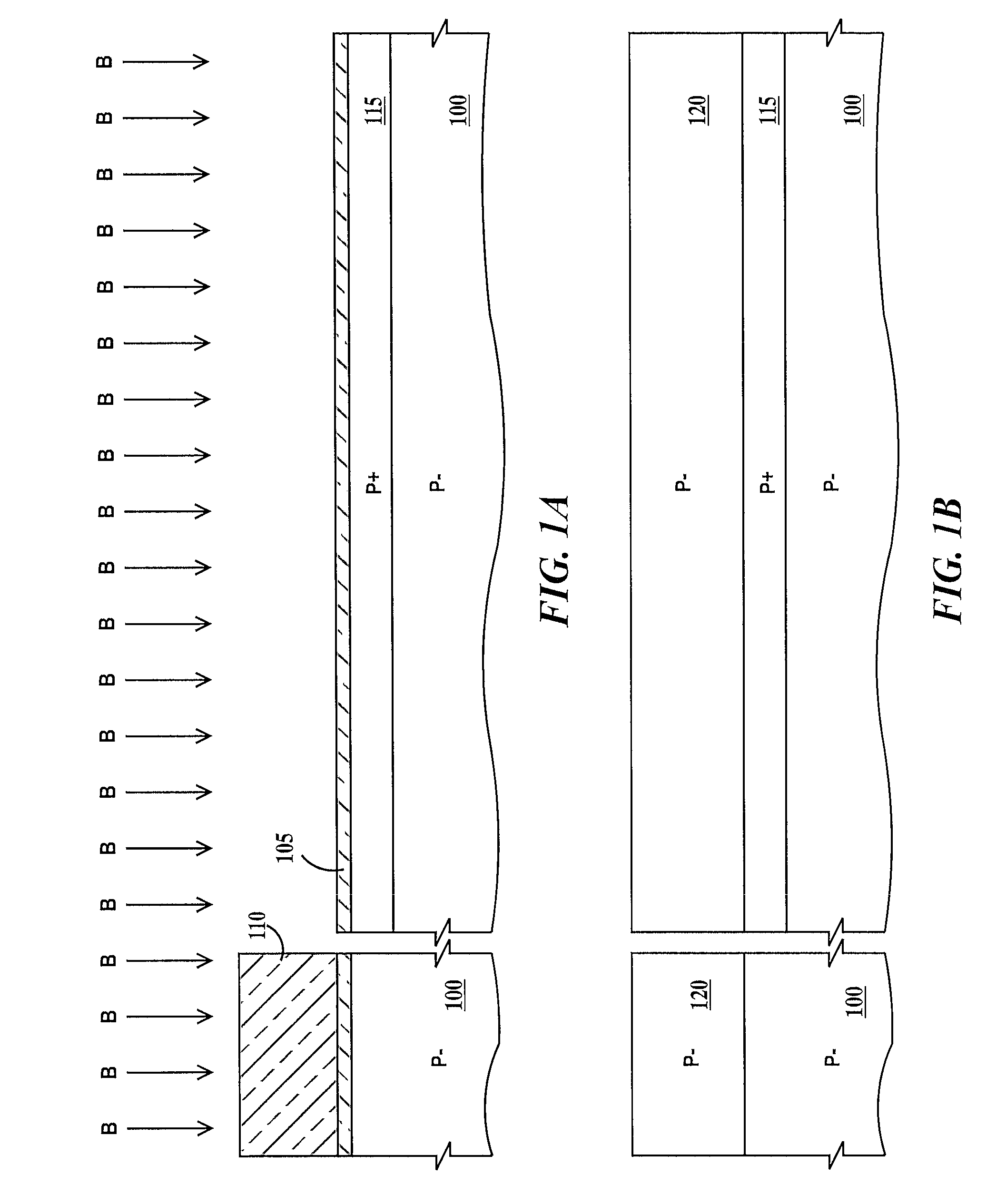

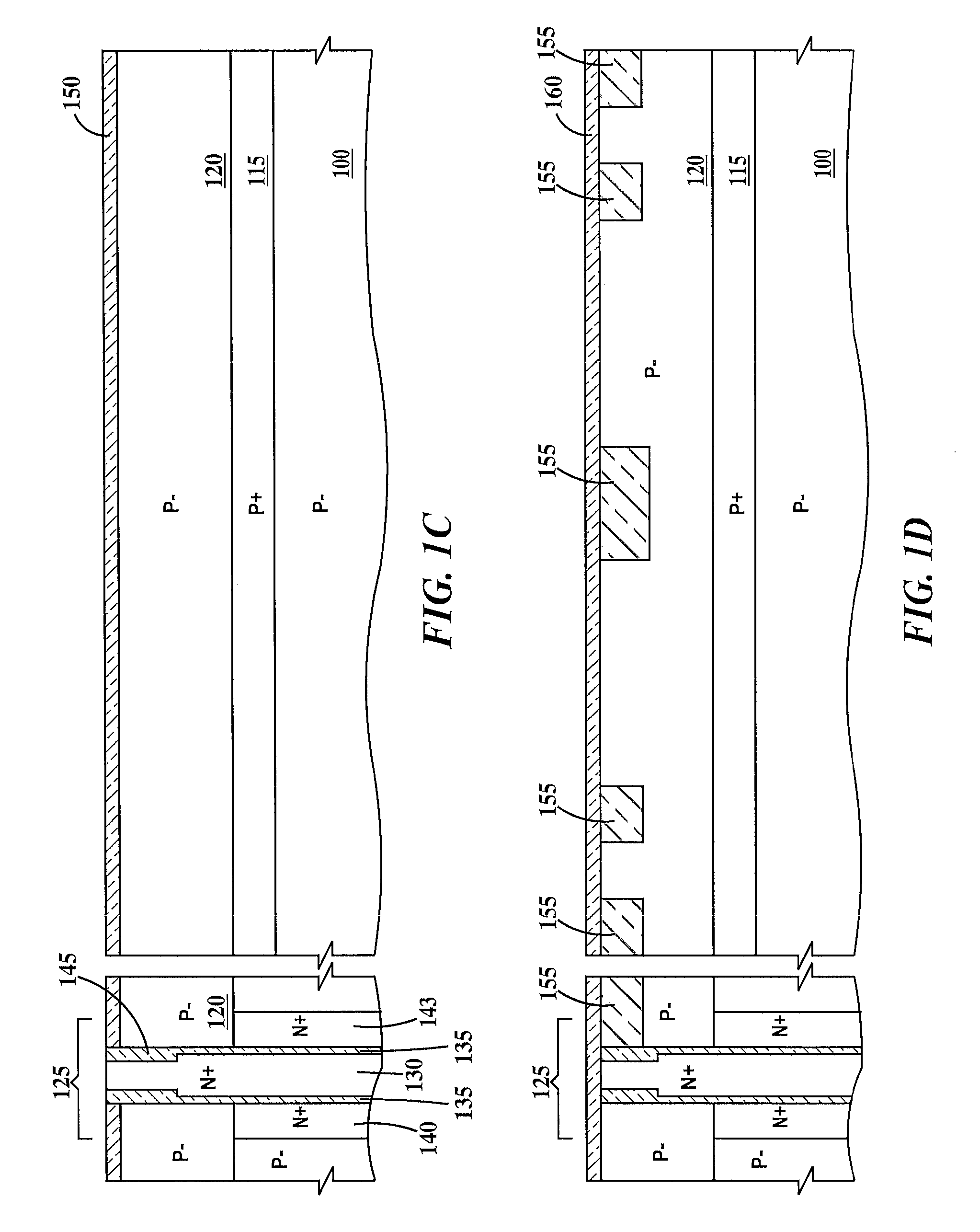

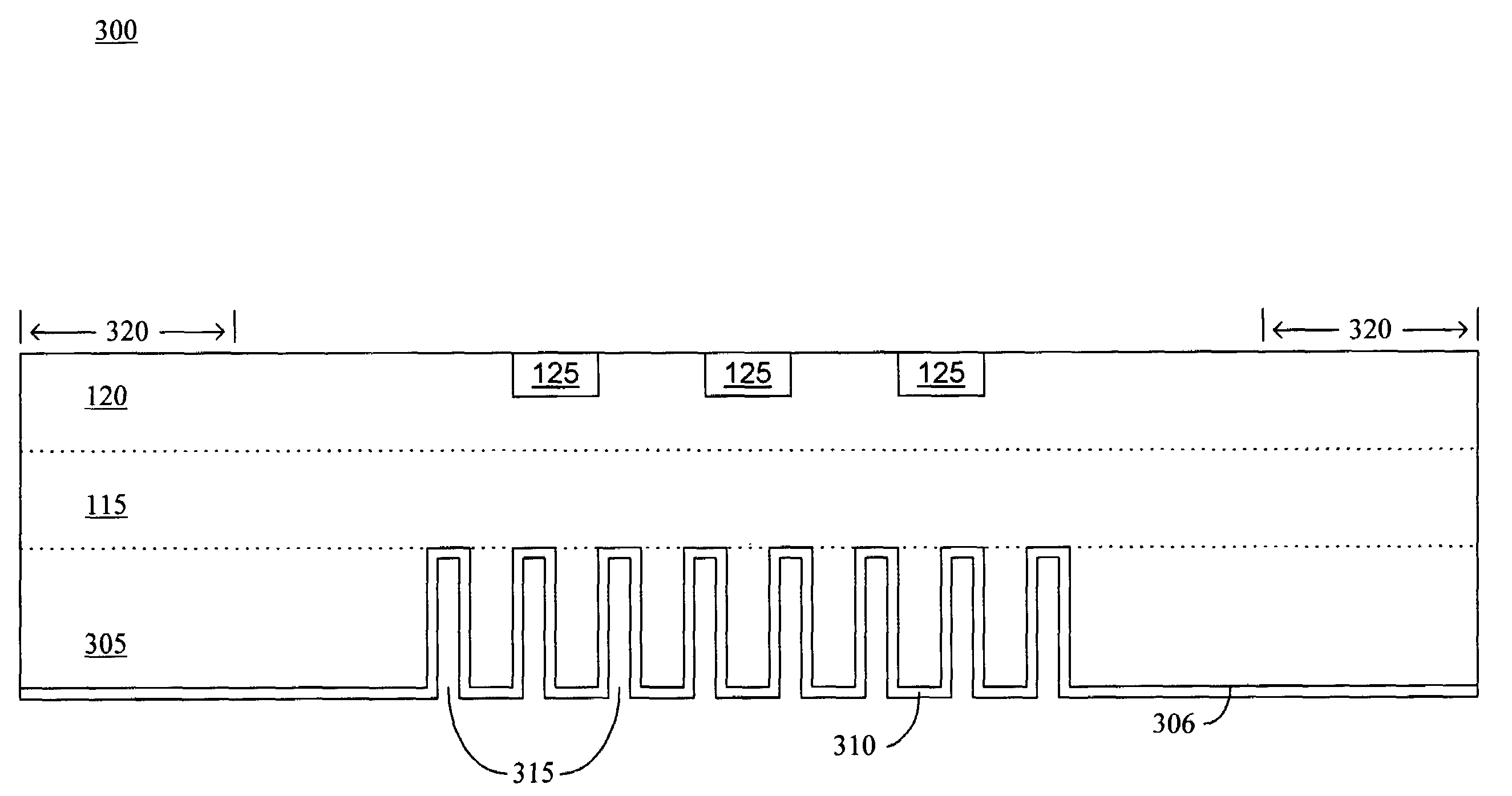

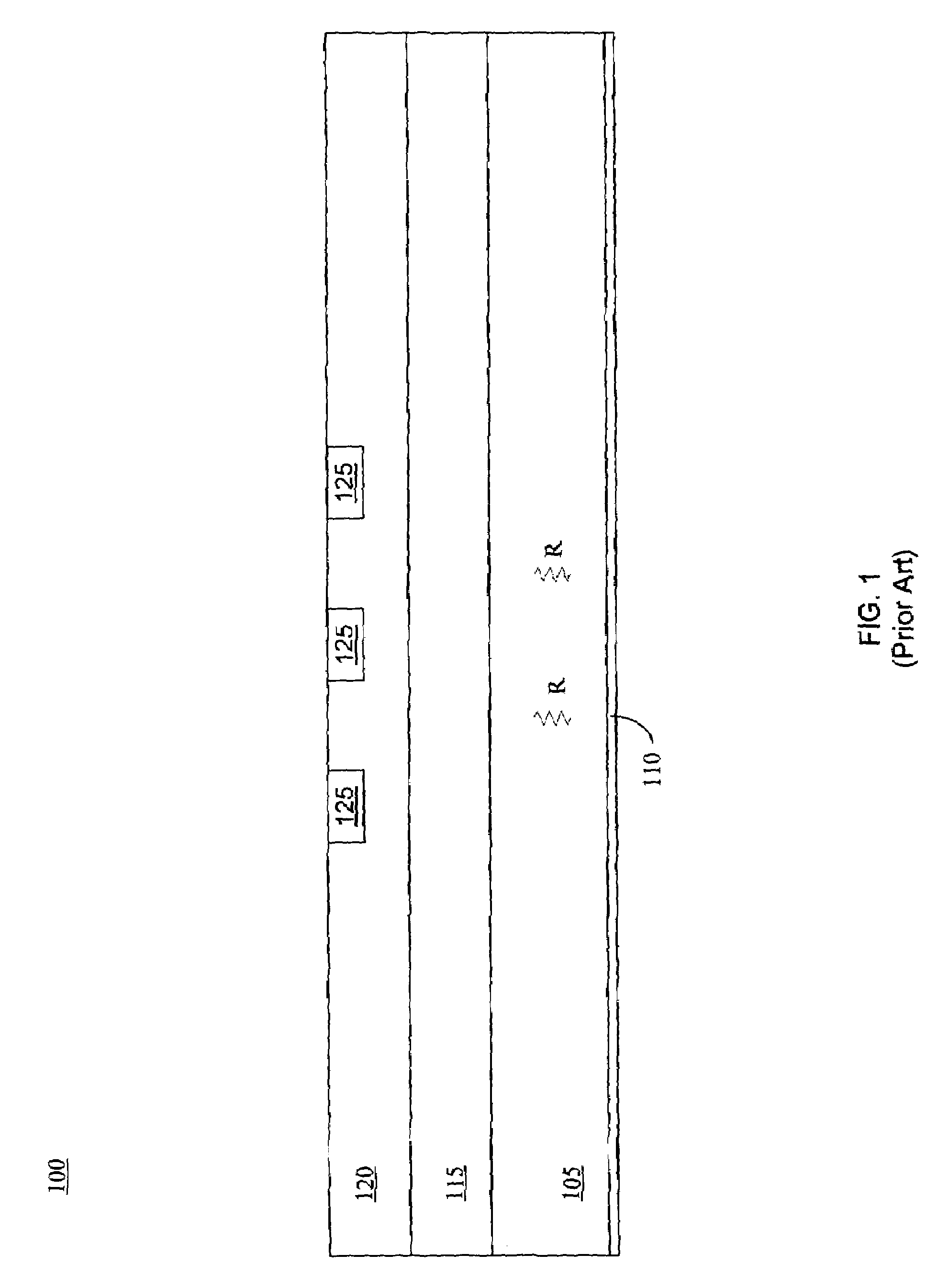

Structure and method for enhanced performance in semiconductor substrates

InactiveUS7227242B1Improve electrical performanceImprove cooling effectSolid-state devicesSemiconductor devicesSemiconductor materialsParasitic bipolar transistor

An etched substrate structure is augmented by conductive material to provide enhanced electrical and / or thermal performance. A semiconductor device substrate comprising active regions defined on a top surface is masked and etched to define a pattern of blind features in a bottom surface of the substrate. A conductive material is then deposited on the surface of the blind features. The replacement of semiconductor material with the conductive material lowers the resistance between the active elements on the top surface and the bottom surface. The blind features may be placed in proximity to parasitic bipolar transistors in order to increase immunity to latchup. During wafer processing, a pattern of grooves aligned opposite to a scribe street pattern may be etched on the wafer back side in order to facilitate the separation of individual devices.

Owner:POWER INTEGRATIONS INC

High-speed insulated gate bipolar transistor on lateral SOI

InactiveCN101771073AIncreased shutdown speedAvoid difficultiesSemiconductor devicesParasitic bipolar transistorField oxide

The invention relates to a high-speed insulated gate bipolar transistor on a lateral SOI. The insulated gate bipolar transistor comprises a buried oxide layer, an N-based region, a cathode region and an anode region which are respectively arranged at the two ends of the N-based region and a gate region, field oxide and an anode field plate which are arranged above the cathode region, wherein the anode region is partitioned into at least one group of a first anode region and a second anode region by an isolation groove; the isolation groove isolates the P+ anode region of a first anode from the P drift region and the N+ anode region of a second anode; the isolation groove extends downwards to the buried oxide layer; and the field oxide layer is attached on the anode region, and the anode field plate is attached on the field oxide and is electrically connected with the anode of the anode region. The invention has the beneficial effects that: an on-resistance is not added while the turn-off speed of lateral SOI IGBT is improved, and the high-speed insulated gate bipolar transistor on the lateral SOI is provided.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

Insulated gate bipolar transistor and method for producing same

InactiveCN101752415AShorten off timeEnhanced hole recombination probabilitySemiconductor/solid-state device manufacturingSemiconductor devicesParasitic bipolar transistorAlloy

The invention provides an insulated gate bipolar transistor comprises a metal layer, a P+ area, a field termination layer, an N- area, a P area, an N+ area, a gate oxide layer and a silicon gate layer. The field termination layer comprises N-type silicon germanium alloy. The invention also provides a method for producing the insulated gate bipolar transistor. The insulated gate bipolar transistor uses the field termination layer of the N-type silicon germanium alloy as a reverse breakdown termination layer, thus the excess minority carrier hole recombination probability is enhanced, the turn-off time of the insulated gate bipolar transistor is shortened, the turn-off speed of the insulated gate bipolar transistor is increased and further the circuit efficiency is improved.

Owner:商海涵

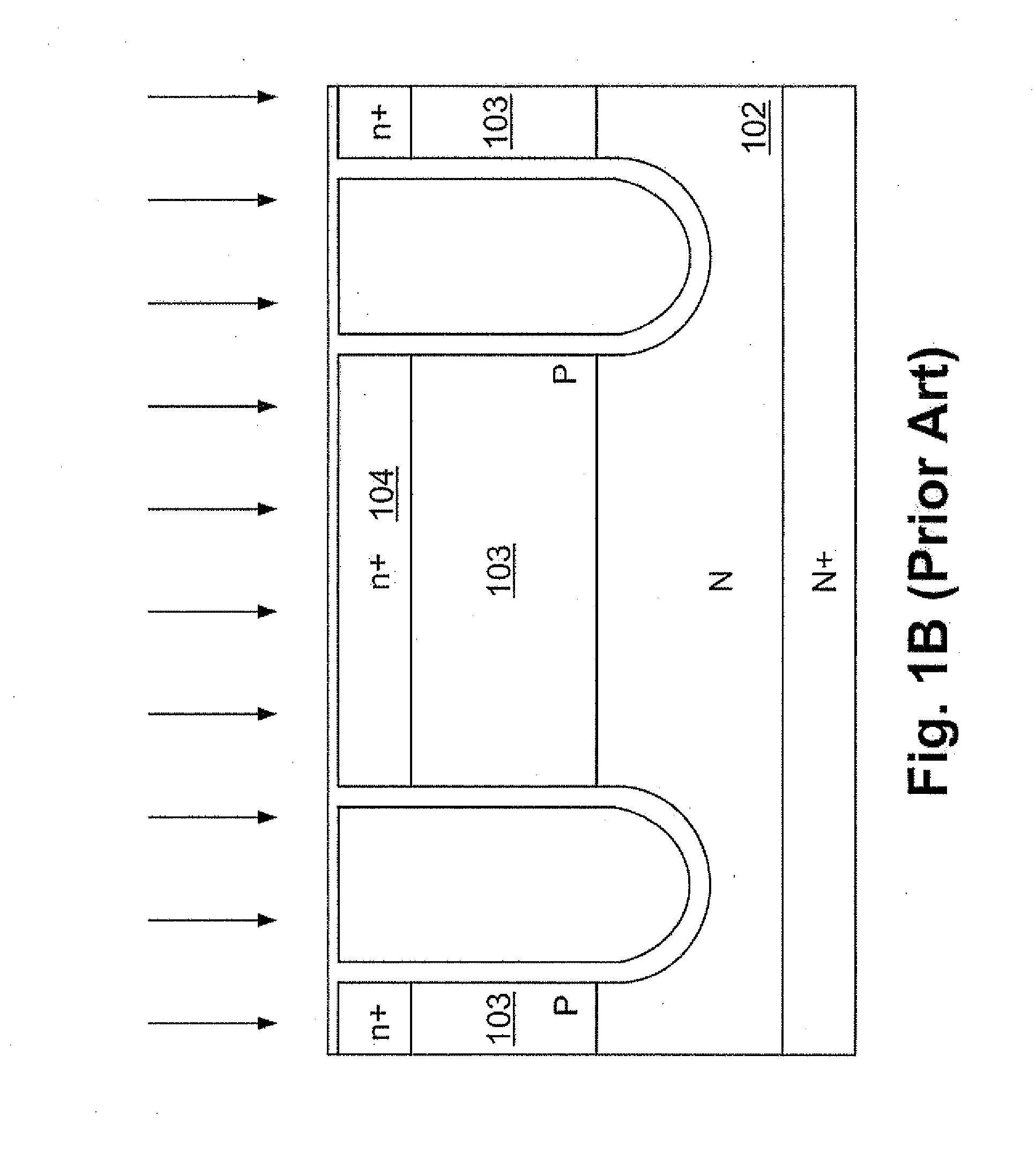

Trench mosfet having floating dummy cells for avalanche improvement

ActiveUS20120032261A1Improved device configurationTransistorSemiconductor/solid-state device manufacturingTrench mosfetParasitic bipolar transistor

A trench MOSFET comprising source regions having a doping profile of a Gaussian-distribution along the top surface of epitaxial layer and floating dummy cells formed between edge trench and active area is disclosed. A SBR of n region existing at cell corners renders the parasitic bipolar transistor difficult to turn on, and the floating dummy cells having no parasitic bipolar transistor act as buffer cells to absorb avalanche energy when gate bias is increasing for turning on channel, therefore, the UIS failure issue is avoided and the avalanche capability of the trench MOSFET is enhanced.

Owner:FORCE MOS TECH CO LTD

Method and Schottky diode structure for avoiding intrinsic NPM transistor operation

InactiveUS20070052057A1Avoid unnecessary operationsUndesired operationSolid-state devicesDiodeMetal silicideParasitic bipolar transistor

A Schottky diode includes an isolation region of a first conductivity type and an anode region of a second conductivity type isolated by the isolation region, the anode region including a lightly doped deep anode region of the second conductivity type and an increased dopant region of the second conductivity type, the increased dopant region including a shallow surface dopant spike region of the second conductivity type at a surface of the anode region. A heavily doped anode contact region of the second conductivity type electrically contacts the anode region, and a metal silicide cathode region is disposed in the surface dopant spike region. The peak dopant surface concentration is high enough to produce a predetermined saturation current density. The dopant concentration in the increased dopant region is sufficiently high to suppress the current gain of a parasitic bipolar transistor enough to adequately suppress operation of the parasitic bipolar transistor.

Owner:TEXAS INSTR INC

High power semiconductor device having a Schottky barrier diode

InactiveUS6870223B2Reduce parasitic effectsAvoid parasitic effectsTransistorSolid-state devicesPower semiconductor deviceSchottky barrier

A semiconductor device is configured to prevent destruction of elements and / or miss-operation of the circuit by parasitic effects produced by parasitic transistors when a MOSFET of a bridge circuit is formed on a single chip. A Schottky junction is formed by providing an anode electrode in an n well region where a source region, a drain region, and a p well region of a lateral MOSFET. A Schottky barrier diode constituting a majority carrier device is connected in parallel with a PN junction capable of being forward-biased so that the PN junction is not forward-biased so that minority carriers are not generated, and thereby suppressing parasitic effects.

Owner:FUJI ELECTRIC CO LTD