High-speed insulated gate bipolar transistor on lateral SOI

A bipolar transistor, insulated gate technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of slow turn-off time of lateral SOIIGBT, difficult to implement and manufacture, slow turn-off time, etc., to avoid auxiliary anode control circuit. , Increase the difficulty and cost of the process, and improve the effect of turning off the speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

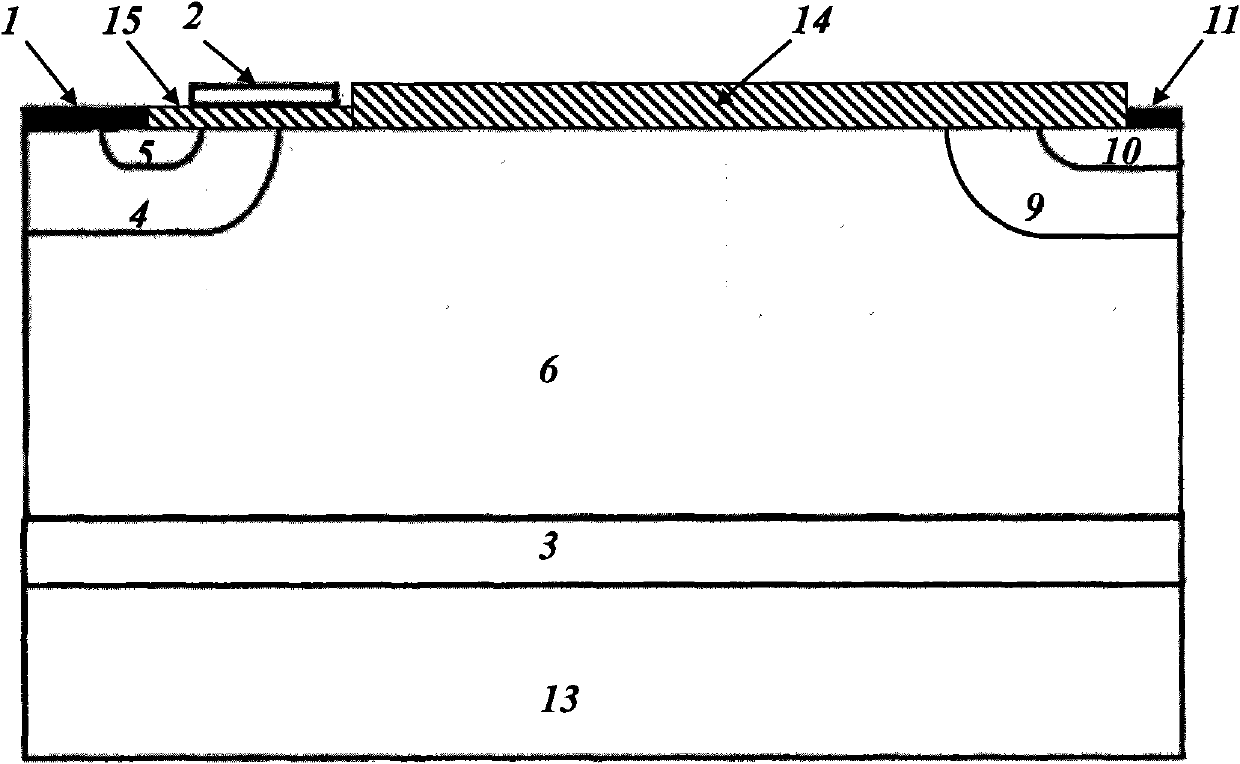

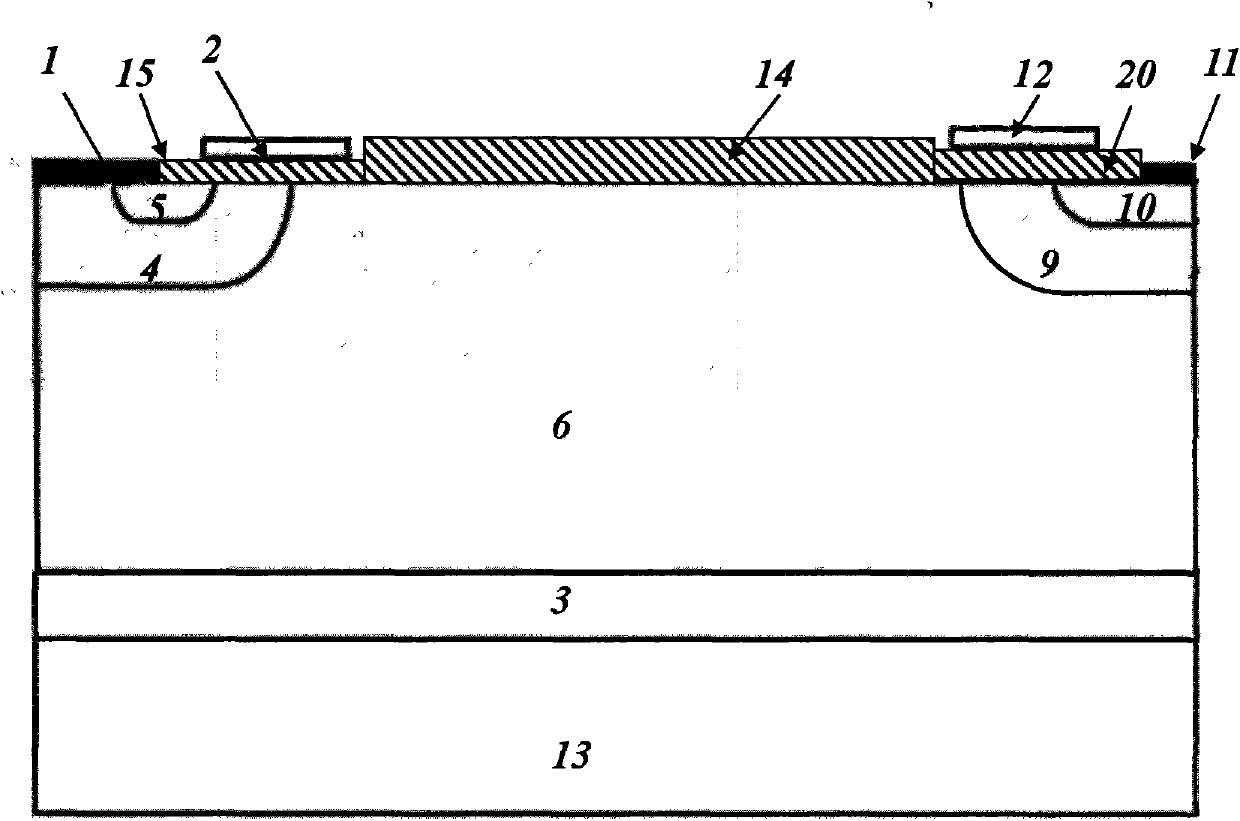

[0024] Embodiment 1: as Figure 4 , Figure 5 , Figure 6 and Figure 7 As shown, a high-speed lateral SOI insulated gate bipolar transistor, this embodiment is a non-punch-through (NPT, None-Punch-Through), including a substrate 13, a buried oxide layer 3, an N-base region 6, respectively located at the N The cathode region and the anode region at both ends of the base region 6 and the gate region above the cathode region are characterized in that the anode region is divided into a group of first anode region and second anode region by the isolation groove 8, and the first anode region An anode region includes P + anode region 10 and anode 11, the P + The anode region 10 is attached to the N base region 6, and the anode 11 is attached to the P + above the anode region 10; the second anode region includes the P drift region 7, the N + Anode region 17 and anode 11, the P drift region 7 and N + The anode region 17 is attached to the N base region 6, and the two ends of th...

Embodiment 2

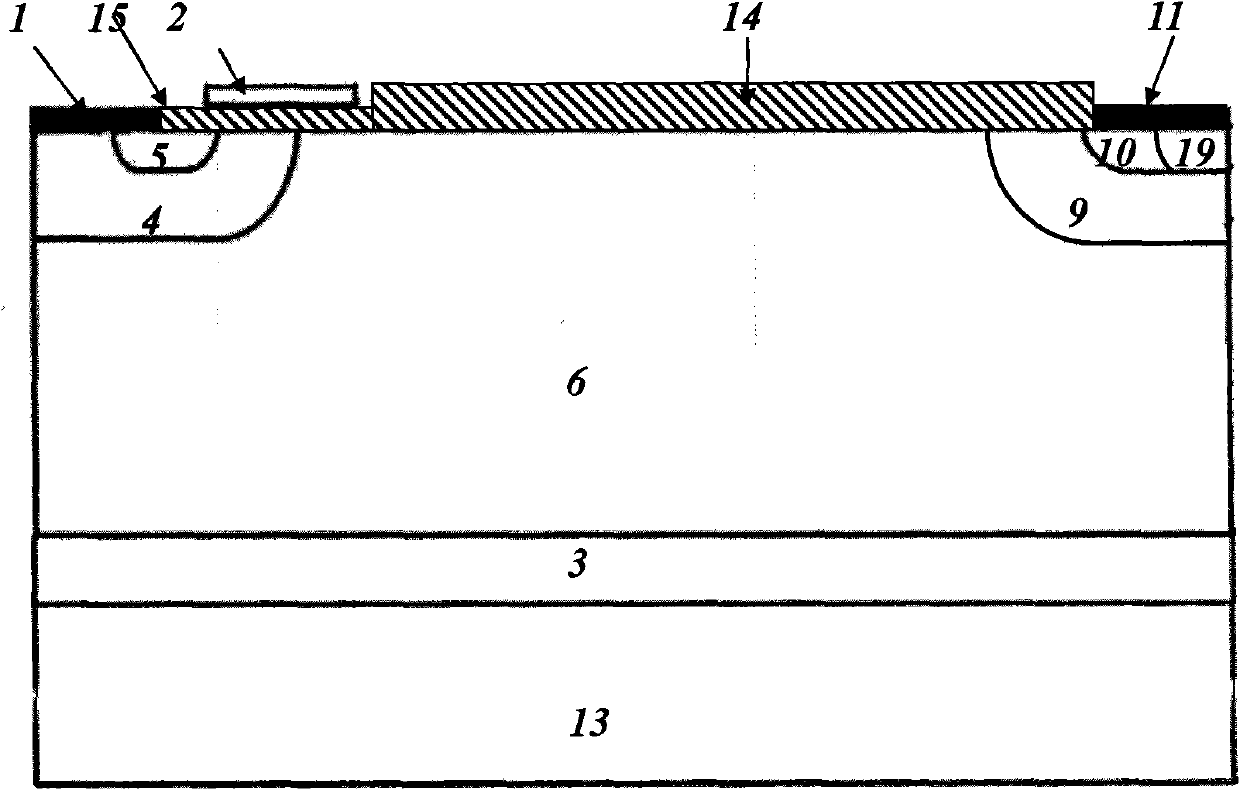

[0034] Embodiment 2: as Figure 8 , Figure 9 and Figure 10 As shown, a high-speed lateral SOI insulated gate bipolar transistor, this embodiment is a punch-through (PT, Punch-Through), this embodiment is based on the embodiment 1 in the N base region 6 of the first anode region and P + An N buffer zone 9 is added between the anodes 10, and the N buffer zone 9 is attached to the N base region 6, and the P + The anode region 10 is attached on the N buffer zone 9 and is separated from the N base region 6 . N buffer 9 to P + The hole injection from the anode 10 to the N-base region 6 has a regulating effect, so that the non-equilibrium carrier storage in the N-base region 6 is weakened, the device off-time is reduced, and the N buffer zone 9 can make the device block The withstand voltage structure of the device satisfies the RESURF condition, and under the same withstand voltage requirement, a shorter length of the N-base region 6 can be used.

[0035] In this embodiment,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More