Thin SOI LIGBT device with carrier storage layer

A carrier storage and device technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of SOIL IGBT's small current capacity, reduced conductance modulation efficiency in the drift region, large forward conduction voltage drop, etc., and achieve fast turn-off Effects of speed, low turn-off loss, and low forward voltage drop

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

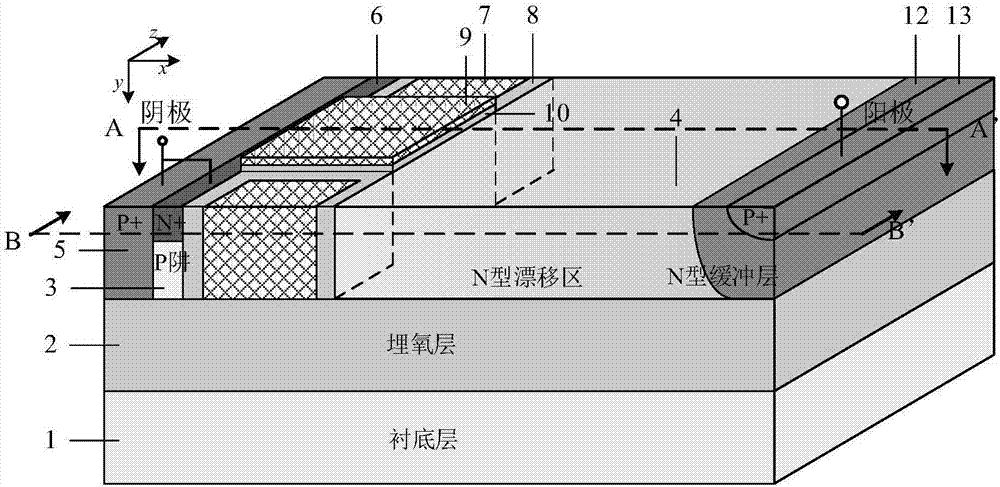

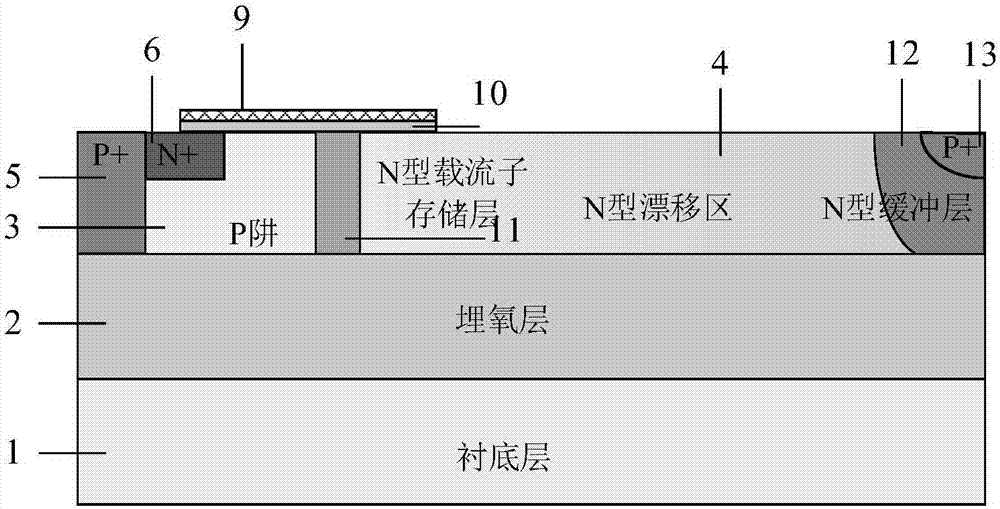

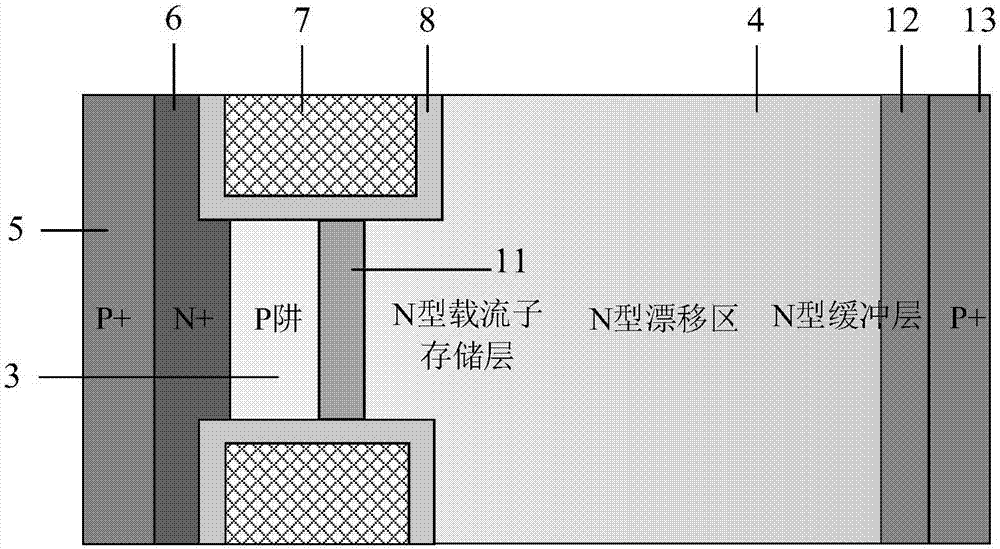

[0027] Such as figure 1 , 2 , 3, the thin SOI LIGBT device with the carrier storage layer of this example includes a substrate layer 1, a dielectric buried layer 2 and a top semiconductor layer that are sequentially stacked from bottom to top; along the lateral direction of the device, the The top semiconductor layer has a cathode structure, a trench gate structure, an N-type semiconductor drift region 4 and an anode structure in sequence from one side to the other;

[0028] The cathode structure includes a P-type well region 3 and a P-type heavily doped region 5 penetrating the top semiconductor layer along the vertical direction of the device, the P-type well region 3 and the P-type heavily doped region 5 are in contact with each other, and the P-type well region 3 is located at One side by the N-type semiconductor drift region 4; the upper layer of the P-type well region 3 has an N-type heavily doped region 6; the bottom of the P-type heavily doped region 5 and the P-type ...

Embodiment 2

[0037] Such as Figure 4 As shown, the difference between this example and Example 1 is that this example has a P-type layer 14 penetrating the top semiconductor layer along the vertical direction of the device on the side of the groove gate close to the N-type semiconductor drift region 4; Discontinuous distribution, the lengths of the two P-type layers 14 in the longitudinal direction are greater than or equal to the length of the corresponding groove grids in the longitudinal direction, and there is a distance between the P-type layers 14; The blocking effect of the carrier storage layer on the holes reduces the forward voltage drop; in the case of forward blocking, this example uses the depletion pinch-off effect of the P-type layer on the side of the trench gate close to the drift region on the drift region Realize normal withstand voltage; compared with embodiment 1, the doping concentration of the carrier storage layer in this example can be further increased, so that t...

Embodiment 3

[0039] Such as Figure 5 with 6 As shown, the difference between this example and Embodiments 1 and 2 is that, in this example, the planar gate structure and the grooved gates located on both sides of the planar gate structure along the device longitudinal direction constitute a three-gate structure. pole; such a gate connection method, the channel area becomes larger, the saturation current of the device increases, and the forward conduction voltage drop is reduced; compared with Examples 1 and 2, this example determines the position of the gate.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More