Patents

Literature

175results about How to "Increased current capability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

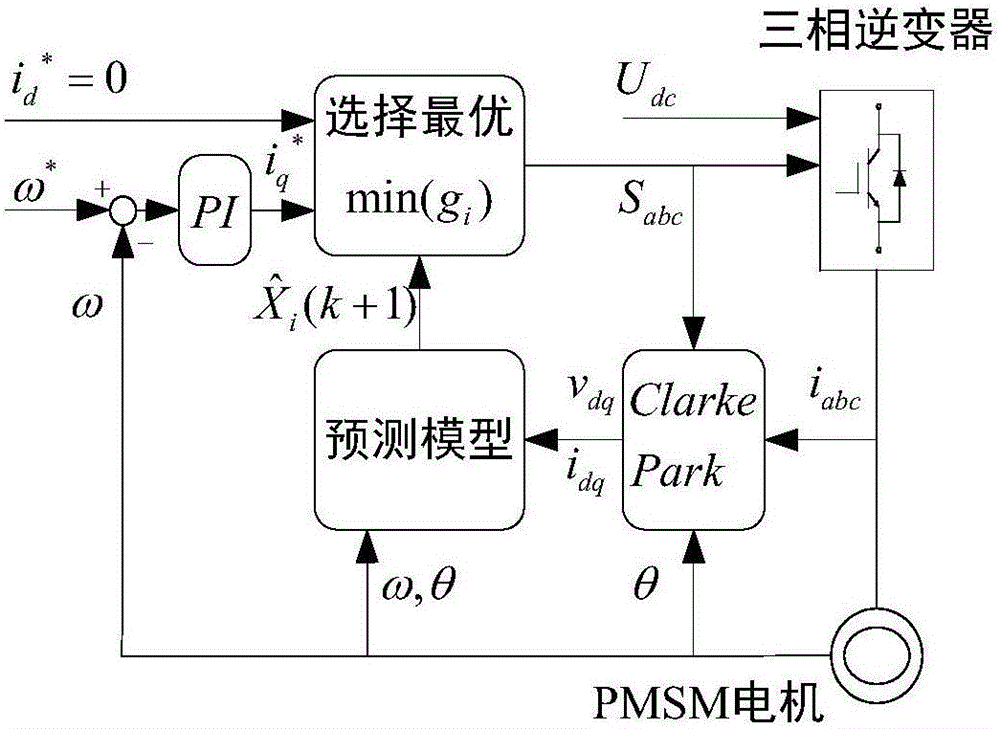

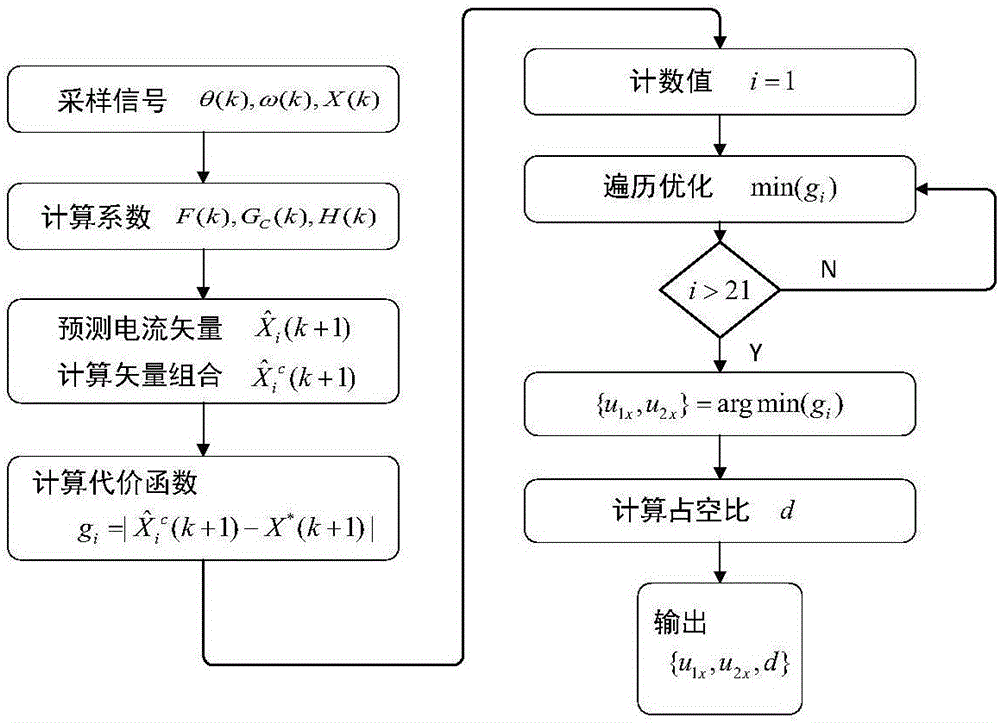

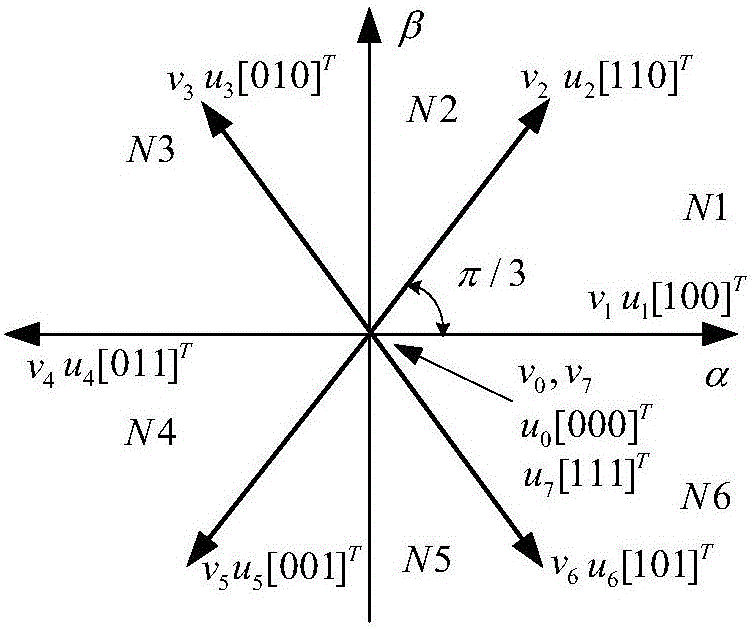

Optimal two-vector combination-based model predictive control method and system

ActiveCN106788027ASmall amount of calculationIncreased current capabilityElectronic commutation motor controlAC motor controlTwo-vectorControl system

The invention discloses an optimal two-vector combination-based model predictive control method and system. The method is applied to a permanent-magnet synchronous motor control system driven by a three-phase two-level inverter. A model predictive current control strategy is adopted, all two-vector combinations and resultant vector sets obtained under action time are considered at the same time, and a cost function is inspected and an optimal resultant vector is selected from all to-be-selected sets. In order to simplify the optimization process, an equivalent voltage equation is given, a sector transformation method is provided and to-be-selected two-vector combination sets are transformed into multiple fixed line segments; and a fast algorithm is given and partial complicated calculation is transformed to offline execution, so that the real-time calculated amount of the novel method is effectively reduced. The model predictive control method disclosed by the invention is simple in structure, small in real-time calculated amount and easy to implement; and the response speed of a motor is high, current ripples and distortion are small, the switching frequency is low and the dynamic and static performance of the system is excellent.

Owner:HUAZHONG UNIV OF SCI & TECH

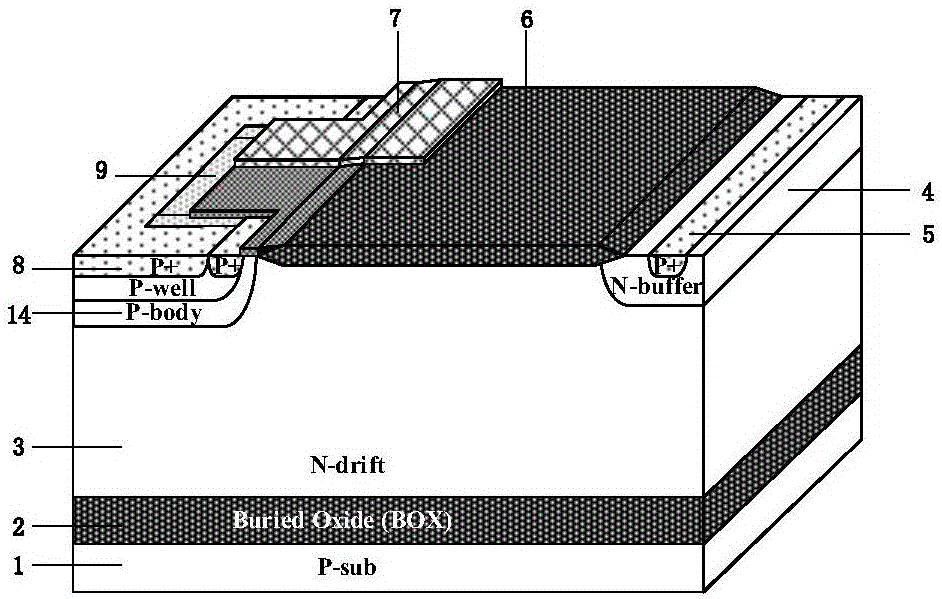

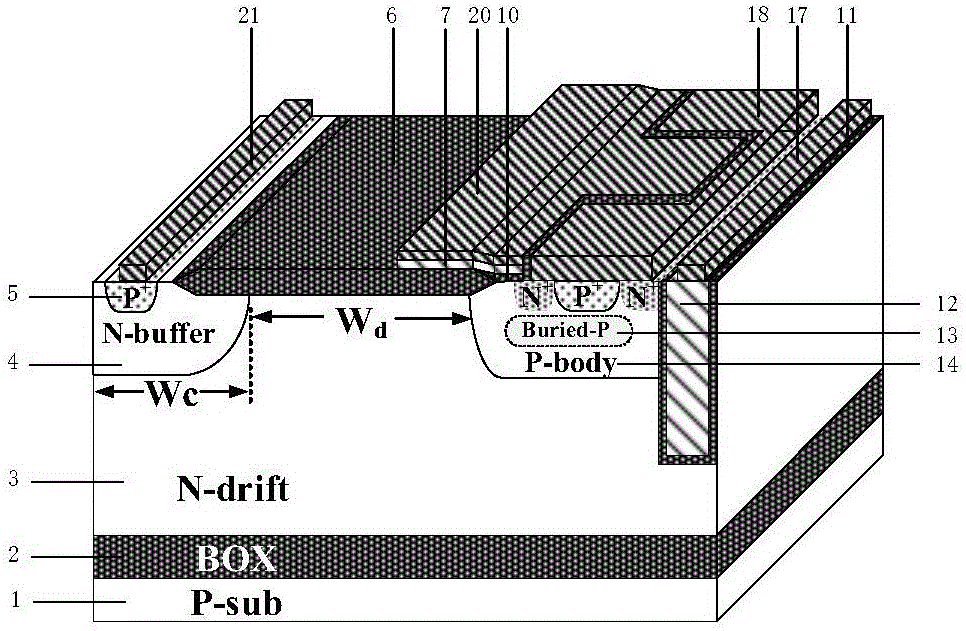

Large-current silicon on insulator lateral insulated gate bipolar transistor device

The invention discloses a novel large-current silicon on insulator lateral insulated gate bipolar transistor. According to the semiconductor, a buried oxide is arranged on a P-type substrate, an N-type drift region is arranged on the buried oxide, a P-type body region and an N-type buffer region are arranged on the N-type drift region, the N-type buffer region is internally provided with a P-type collector region, a collector metal is connected onto the P-type collector region, a field oxygen layer is arranged above the N-type drift region, the P-type body region is internally provided with a P-type emitter region, an N-type emitter region is arranged around, an emitter metal is connected onto the N-type emitter region and the P-type emitter region, a gate oxide is arranged between the field oxygen layer and the N-type emitter region, a first polysilicon layer is arranged on the surface of the gate oxide, a first gate metal is connected onto the surface of the first polysilicon layer, a longitudinal groove is arranged outside the P-type body region, the longitudinal groove is internally provided with silicon dioxide and a second polysilicon layer coated by other medium, and a second gate metal is connected onto the second polysilicon layer.

Owner:SOUTHEAST UNIV

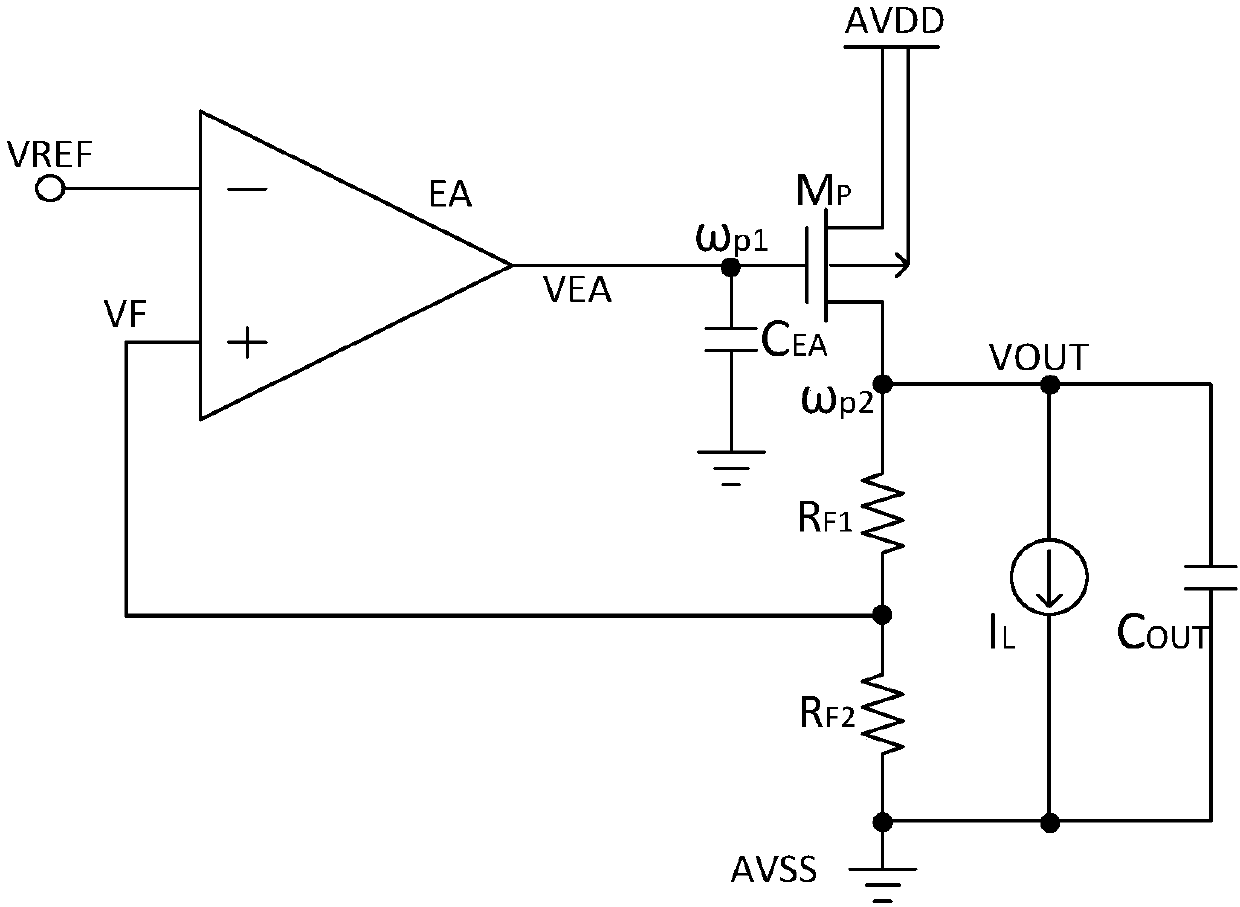

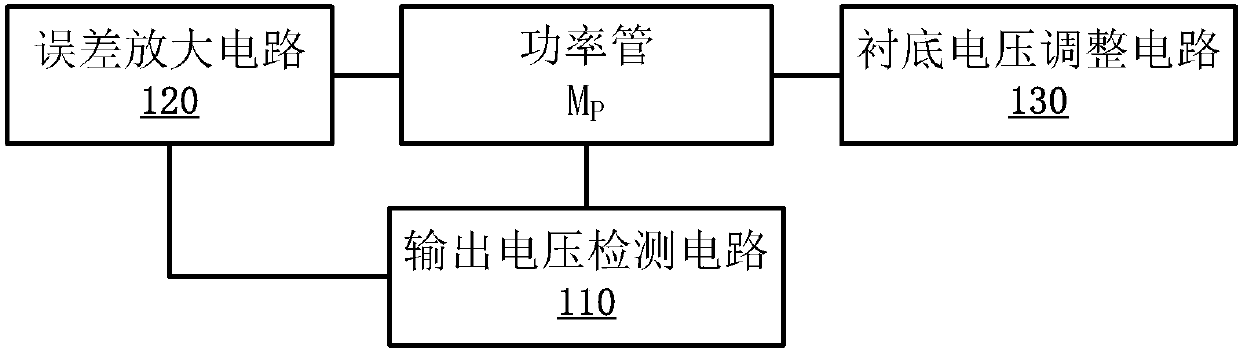

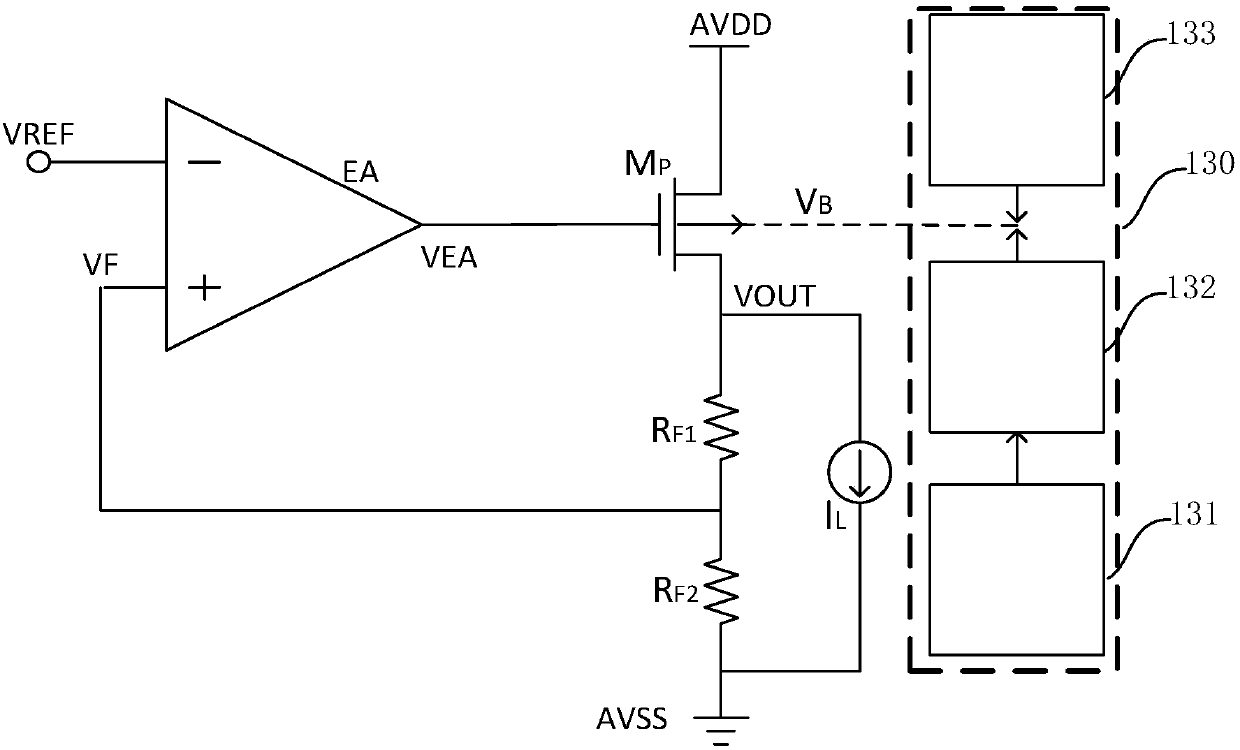

Low-dropout linear regulator circuit

ActiveCN108235744AIncrease the maximum output currentLower threshold voltageElectric variable regulationLinear regulatorPower flow

Embodiments of the present invention provide a low-dropout linear regulator circuit. The low-dropout linear voltage stabilizing circuit comprises: an output voltage detecting circuit for detecting anoutput voltage of the low-dropout linear voltage stabilizing circuit and generating a corresponding feedback voltage; and an error amplifying circuit for comparing the feedback voltage and the reference voltage, and Generating a corresponding error voltage; a power tube, the output current of the power tube is adjusted according to the error voltage; and a substrate voltage adjustment circuit connected to the power tube and configured to be adjusted according to an output current of the power tube The substrate voltage of the power tube is such that the substrate voltage decreases with the increase of the output current within a predetermined fluctuation range, thereby appropriately reducing the threshold voltage of the power tube, and substantially increasing the maximum output current ofthe low-dropout linear regulator circuit.

Owner:SHENZHEN GOODIX TECH CO LTD

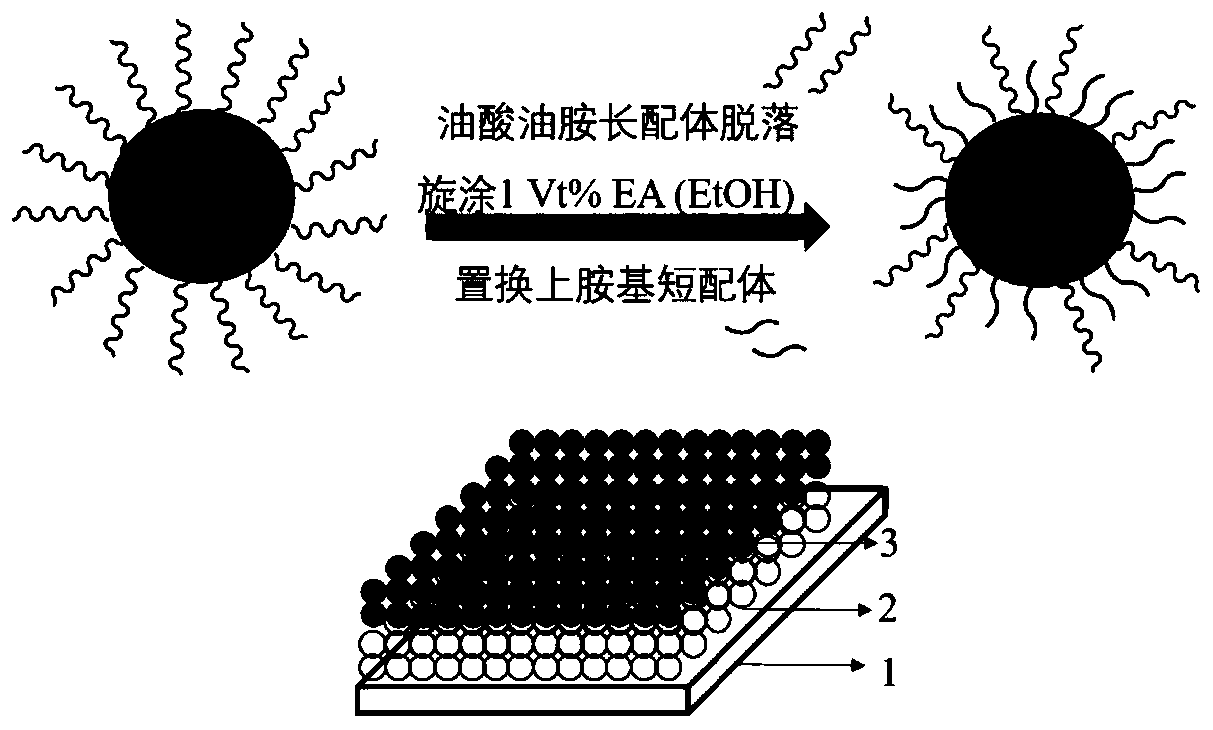

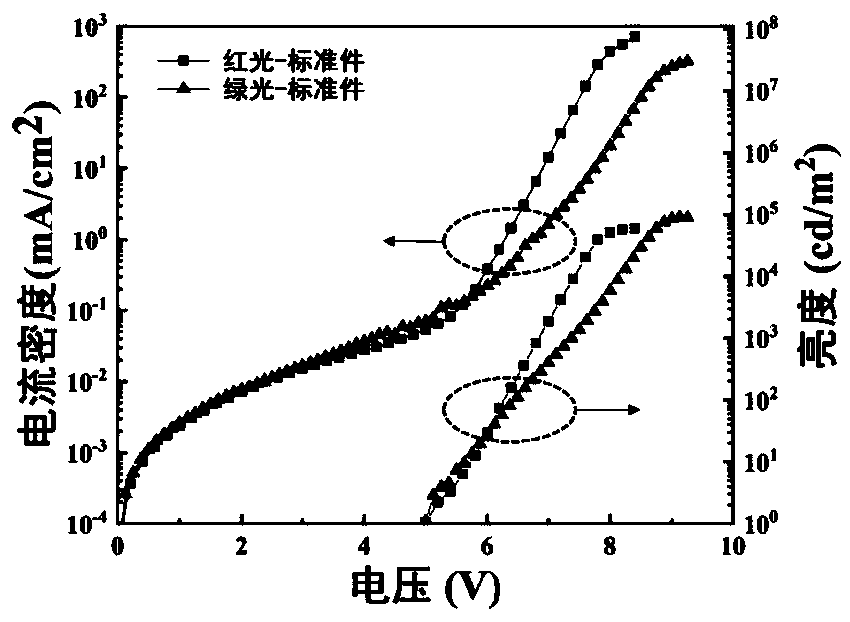

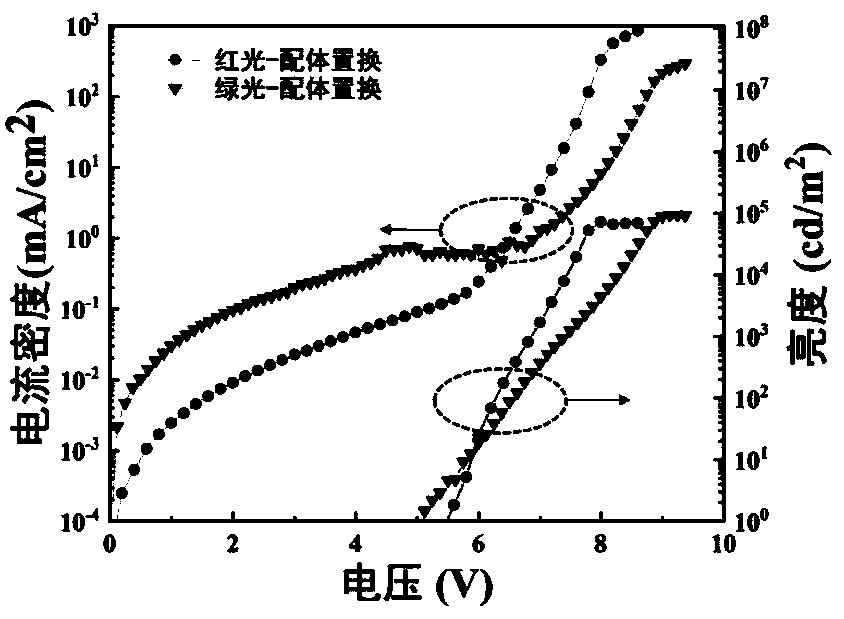

Quantum dot electroluminescent device and preparation method thereof

InactiveCN110224074ALower hole injection barrierBalanced hole electron flowSolid-state devicesSemiconductor/solid-state device manufacturingSolventQuantum dot

The invention discloses a quantum dot electroluminescent device and a preparation method thereof. In order to reduce the hole injection barrier of a quantum dot light emitting diode device, small molecular materials containing polar coordination groups of lone pair electrons, such as materials containing amino groups, mercapto groups or phosphorus groups, are dissolved in a proton solvent throughin-situ ligand replacement and the obtained product is applied to a filmed quantum dot layer after heat treatment during the preparation of the quantum dot light emitting diode device. Because of thepolar coordination groups (amino groups, mercapto groups and phosphorus groups) of lone pair electrons, a larger interface dipole is introduced, the hole injection barrier is reduced, the hole electron flow is balanced, and the device performance is improved. The surface defects of the quantum dot film are passivated, and exciton quenching is reduced. The method has the characteristics of wide applicability, high efficiency and simplicity.

Owner:SOUTH CHINA UNIV OF TECH

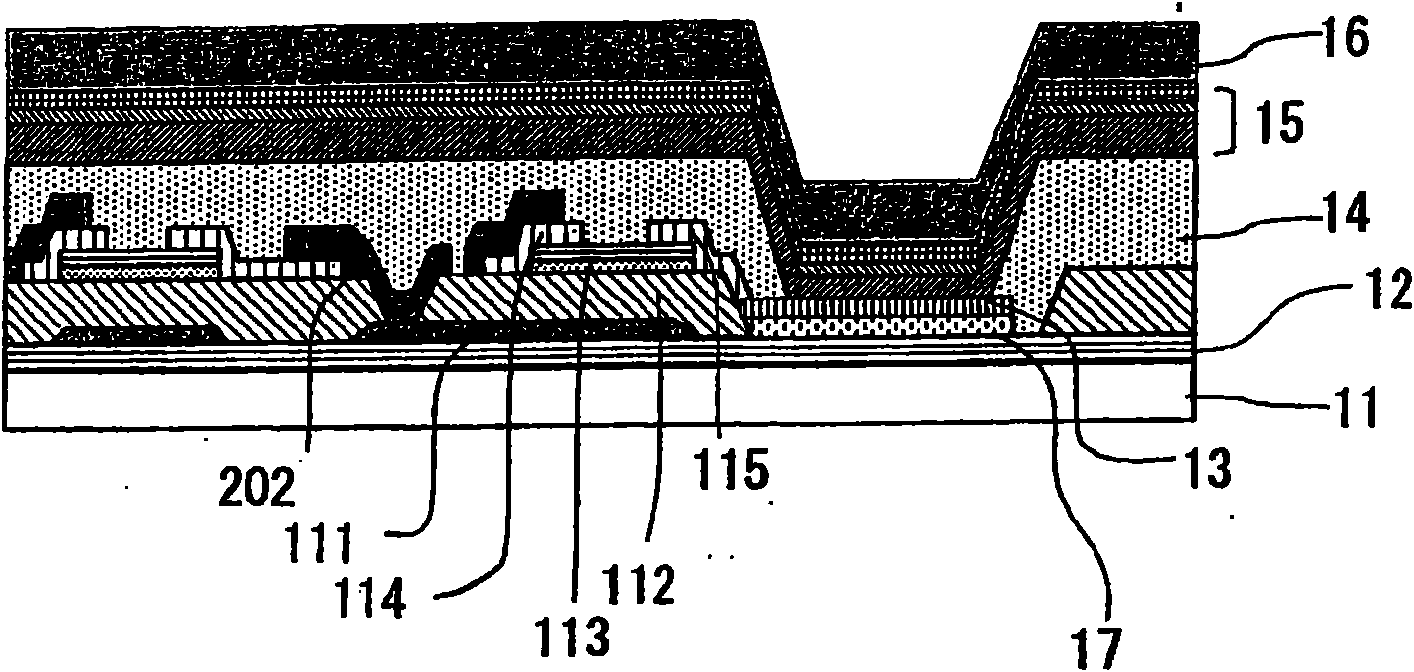

Organic electroluminescent display device

ActiveCN101641795AIncreased current capabilityHigh Field Effect MobilityTransistorElectroluminescent light sourcesEngineeringOrganic electroluminescence

An organic electroluminescent display device includes at least a driving TFT and pixels which are formed by organic electroluminescent elements and are provided on a substrate of the TFT. The drivingTFT includes at least a substrate, a gate electrode, a gate insulating film, an active layer, a source electrode, and a drain electrode. The driving TFT further includes a resistive layer between theactive layer and at least one of the source electrode and the drain electrode. The pixels include at least one color-modified pixel which has a color filter that modifies the emission color of the color-modified pixel, and which emits light of the modified color.

Owner:UDC IRELAND

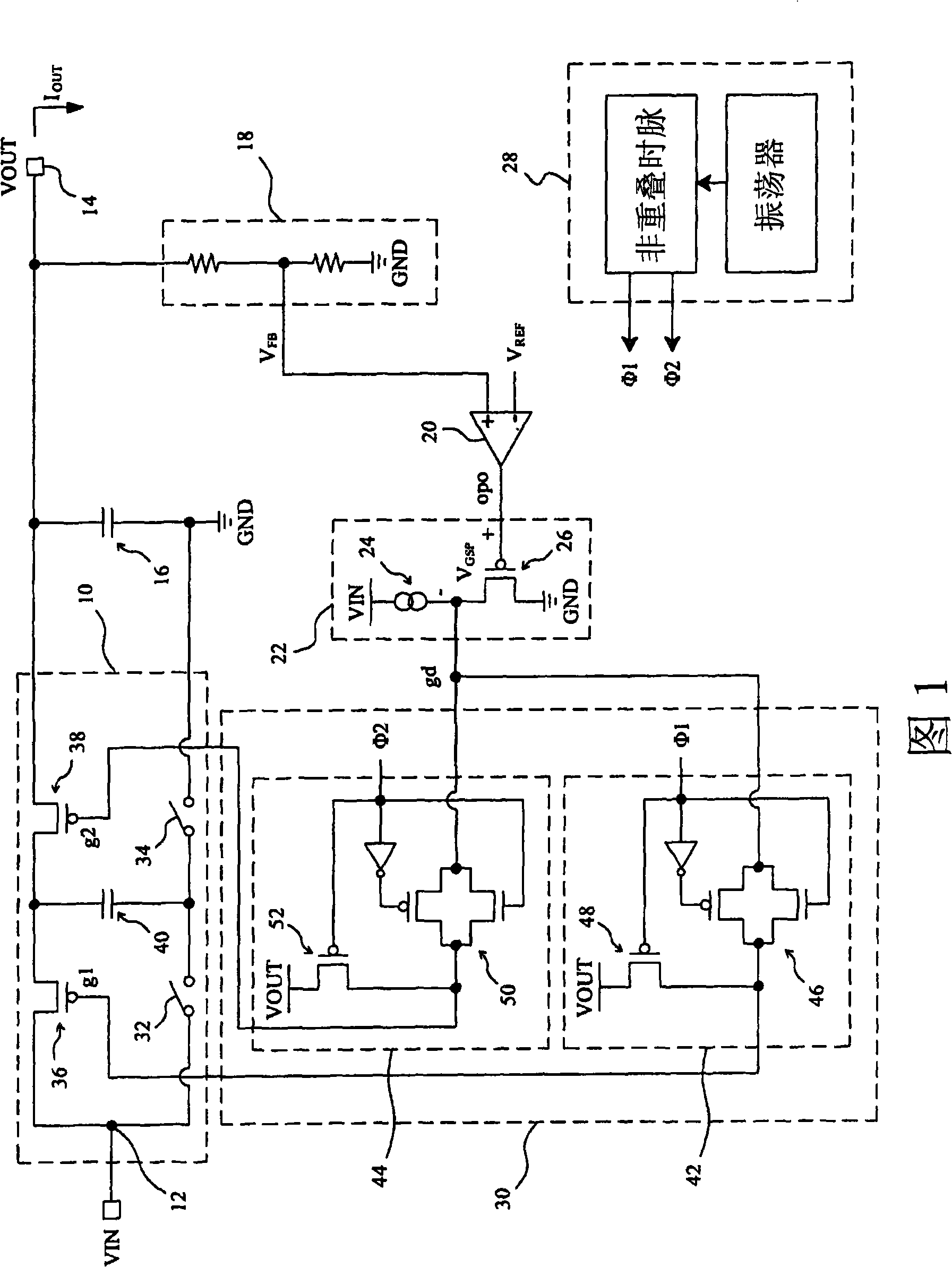

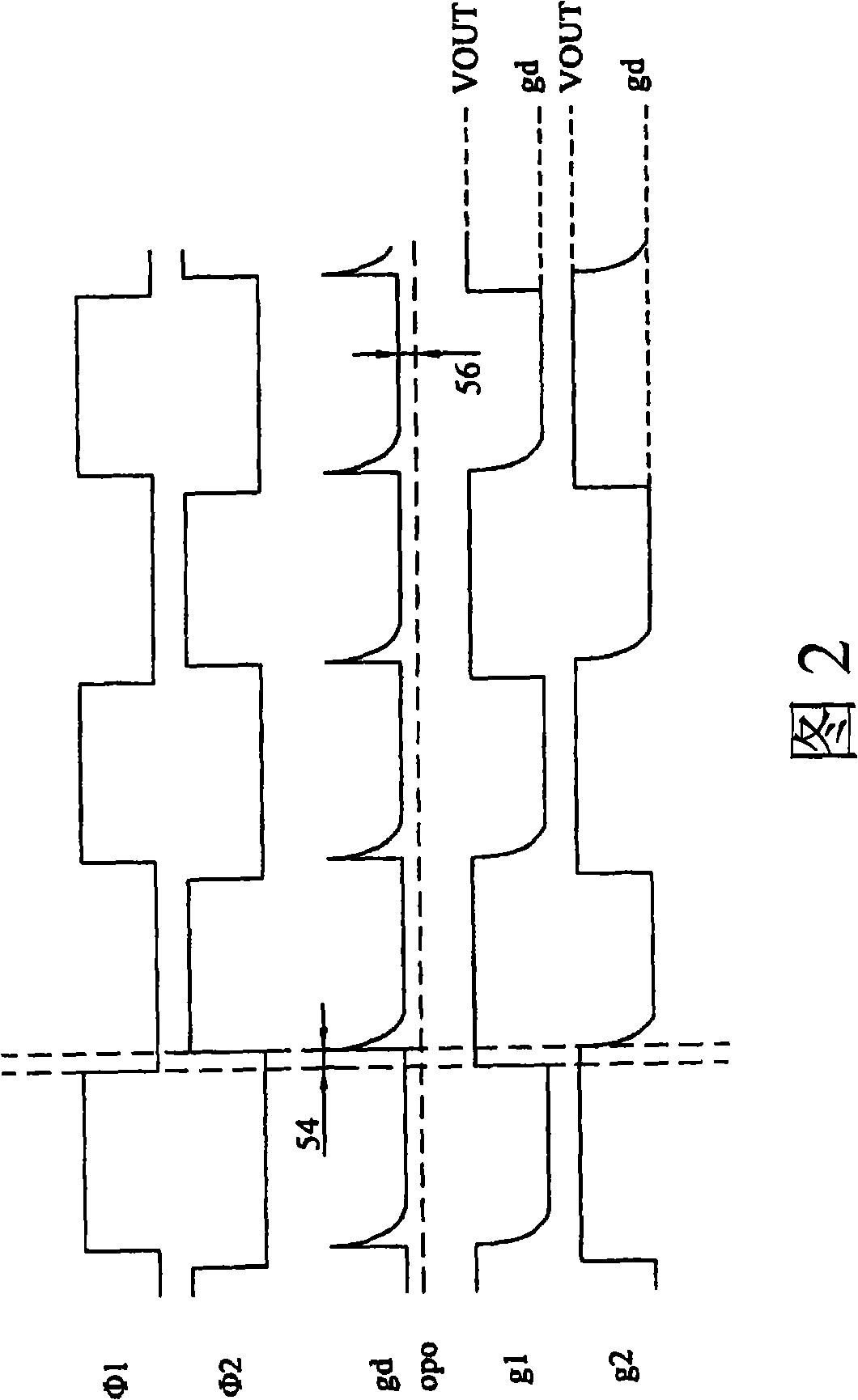

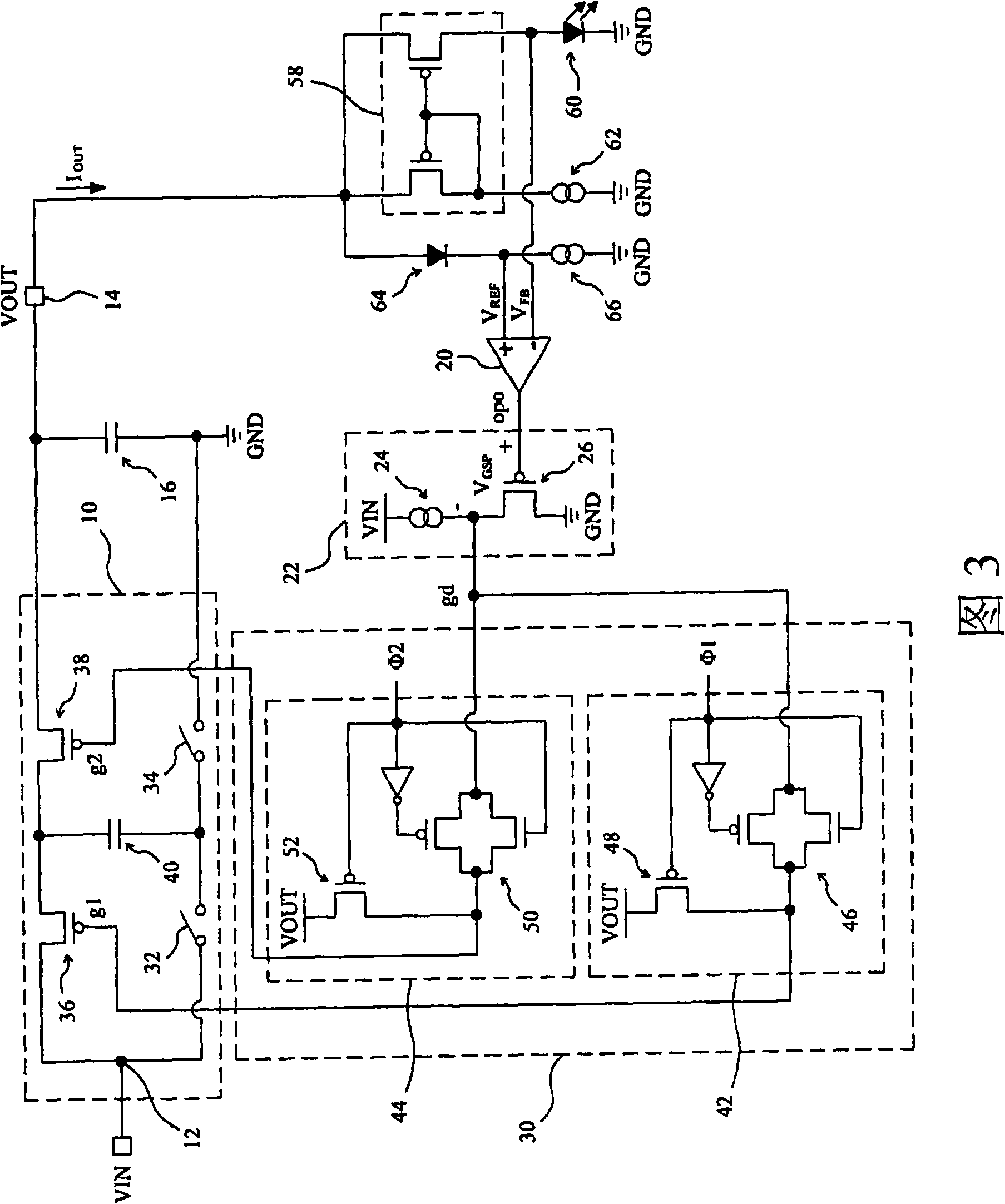

Charge pump regulator and method for generating regulated voltage

ActiveCN101286693AReduce power lossImprove performanceApparatus without intermediate ac conversionElectrical resistance and conductanceSignal on

The invention provides a charge pump regulator and a method for generating a regulated voltage. The charge pump regulator is used for regulating the voltage on an output end and comprises an input end used for connecting with a power source, a charge pump connected between the input end and the output end, in which a charge path and a discharge path can be interactively operated and established, and a feedback loop used for generating an output interdependent feedback signal, wherein, the charge pump contains at least one flow control component used for controlling passing current according to the driving signal derived form the output interdependent feedback signal on the charge path or the discharge path. The charge pump regulator and the method for generating the regulated voltage can reduce input ripple and output ripple without increasing the series resistance of the paths, thereby improving the efficiency; moreover, the area of the chips required by a whole circuit is relatively small. Relatively low open-loop resistance also increases current capability.

Owner:RICHTEK TECH

Semiconductor device

InactiveCN101359688AIncreased current capabilityLower on-resistanceTransistorSemiconductor/solid-state device manufacturingDopantSemiconductor

A semiconductor device includes a source region and a drain region disposed in a substrate wherein the source and drain regions have a first type of dopant; a gate electrode formed on the substrate interposed laterally between the source and drain regions; a gate spacer disposed on the substrate and laterally between the source region and the gate electrode, adjacent a side of the gate electrode; and a conductive feature embedded in the gate spacer.

Owner:TAIWAN SEMICON MFG CO LTD

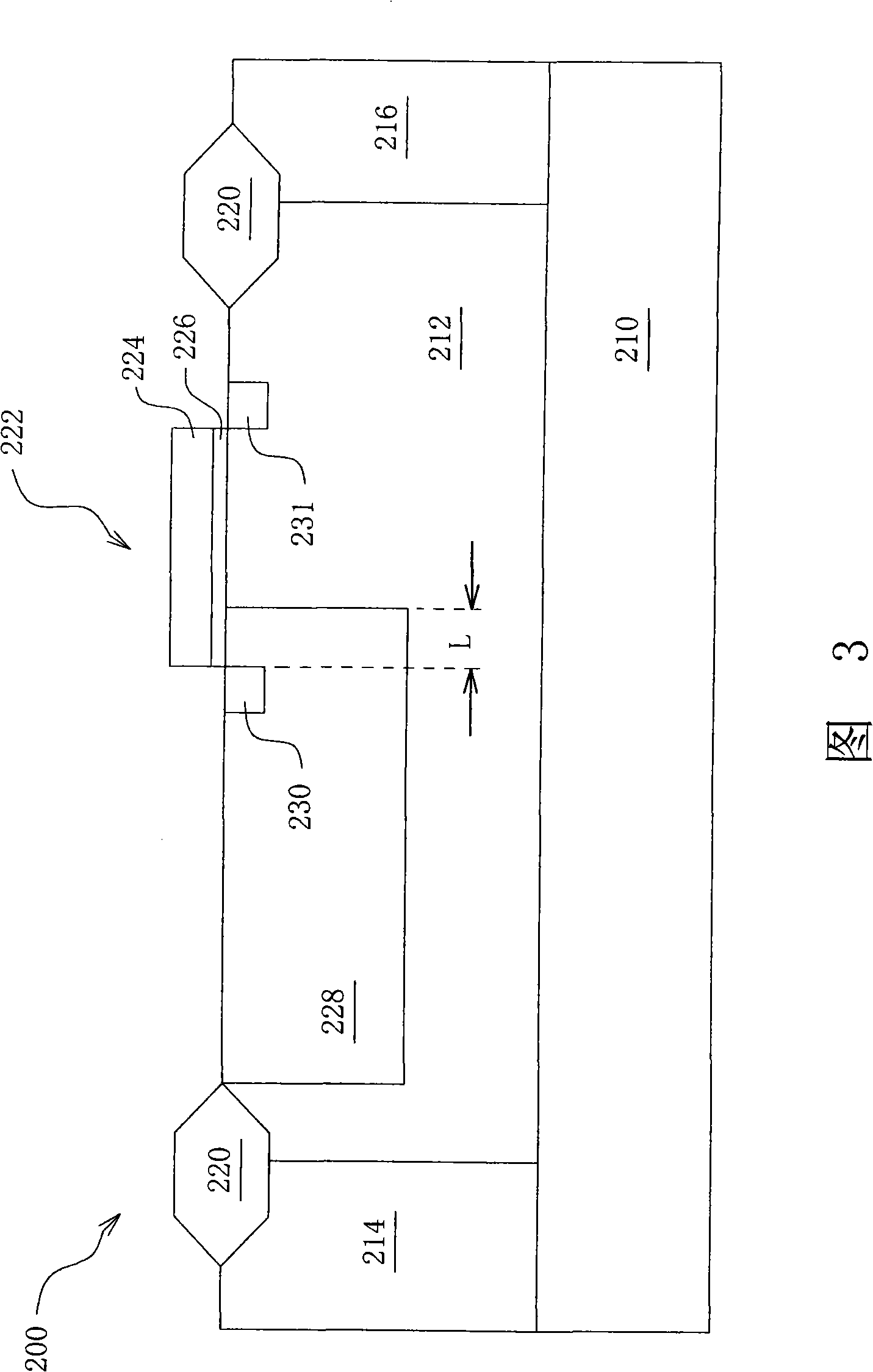

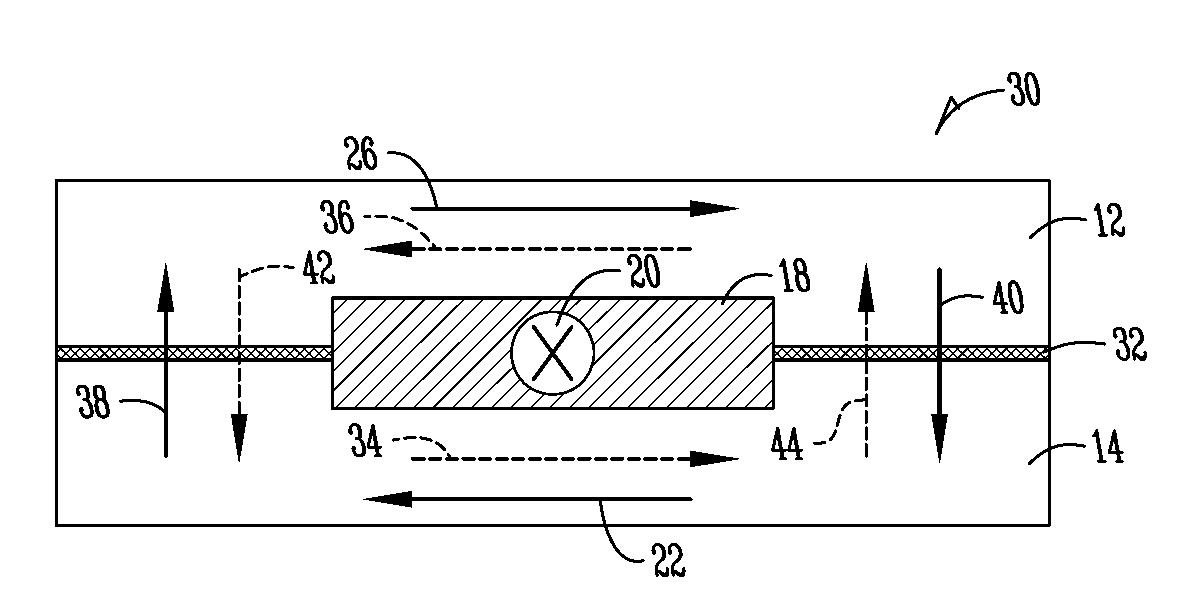

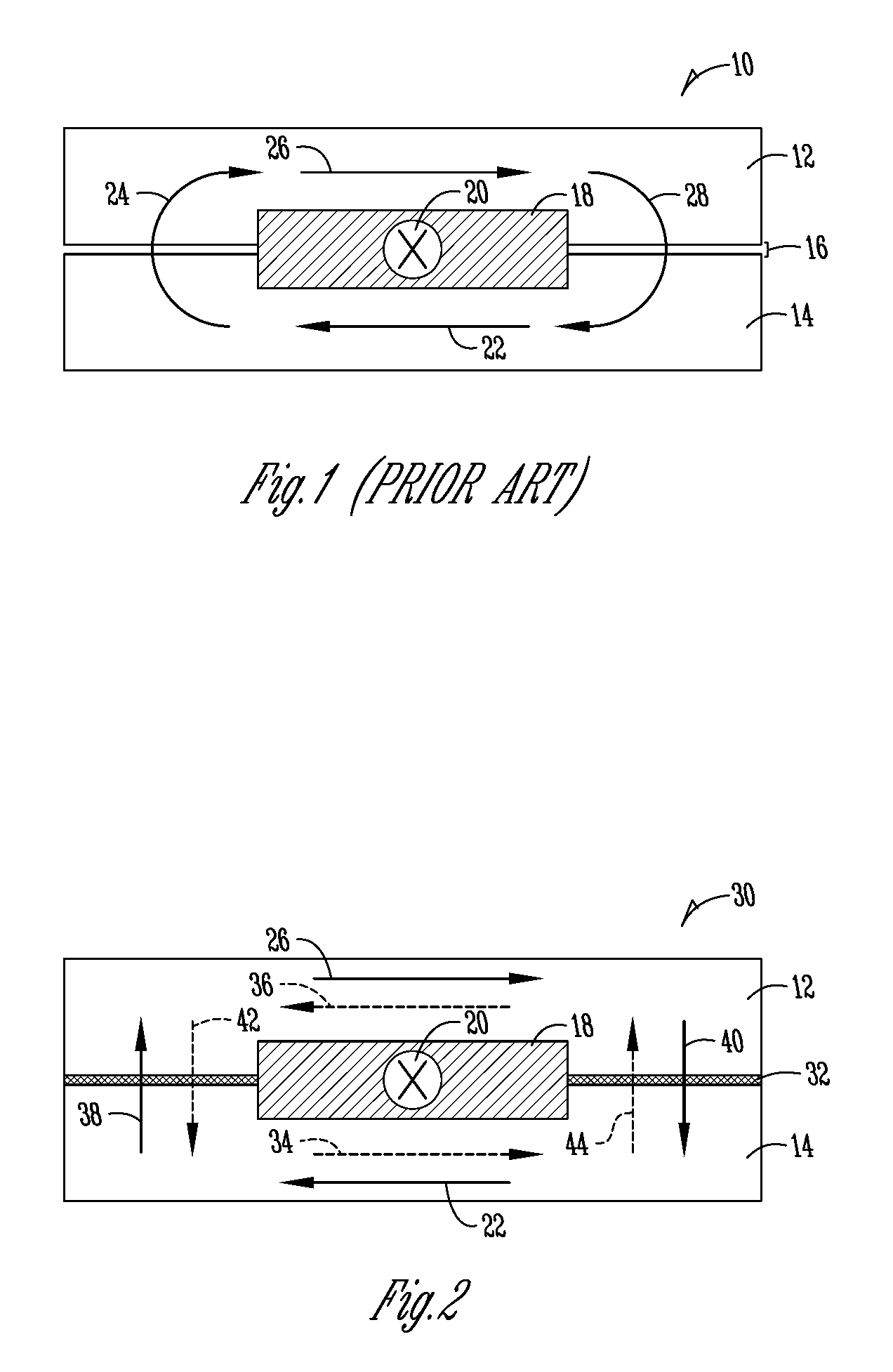

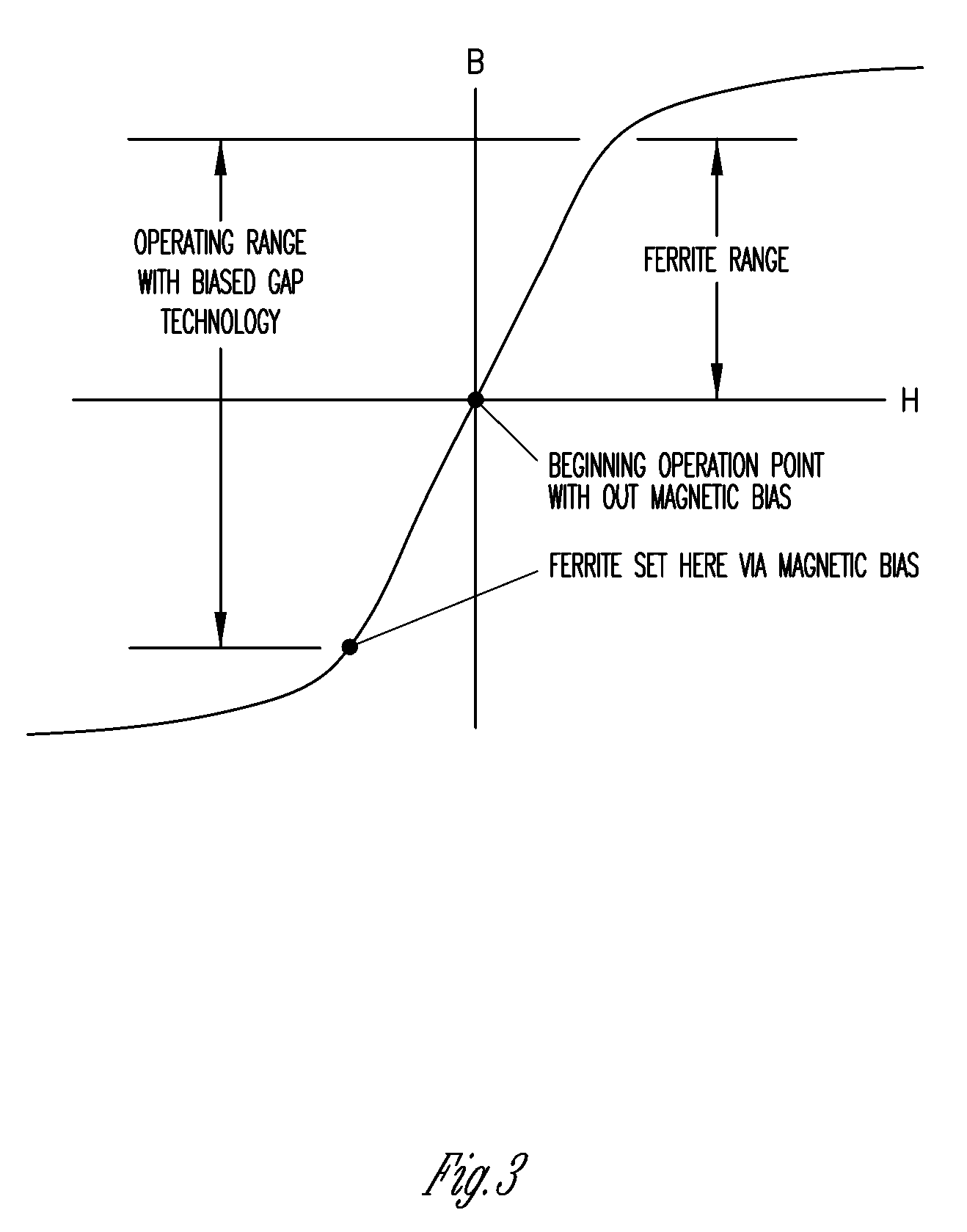

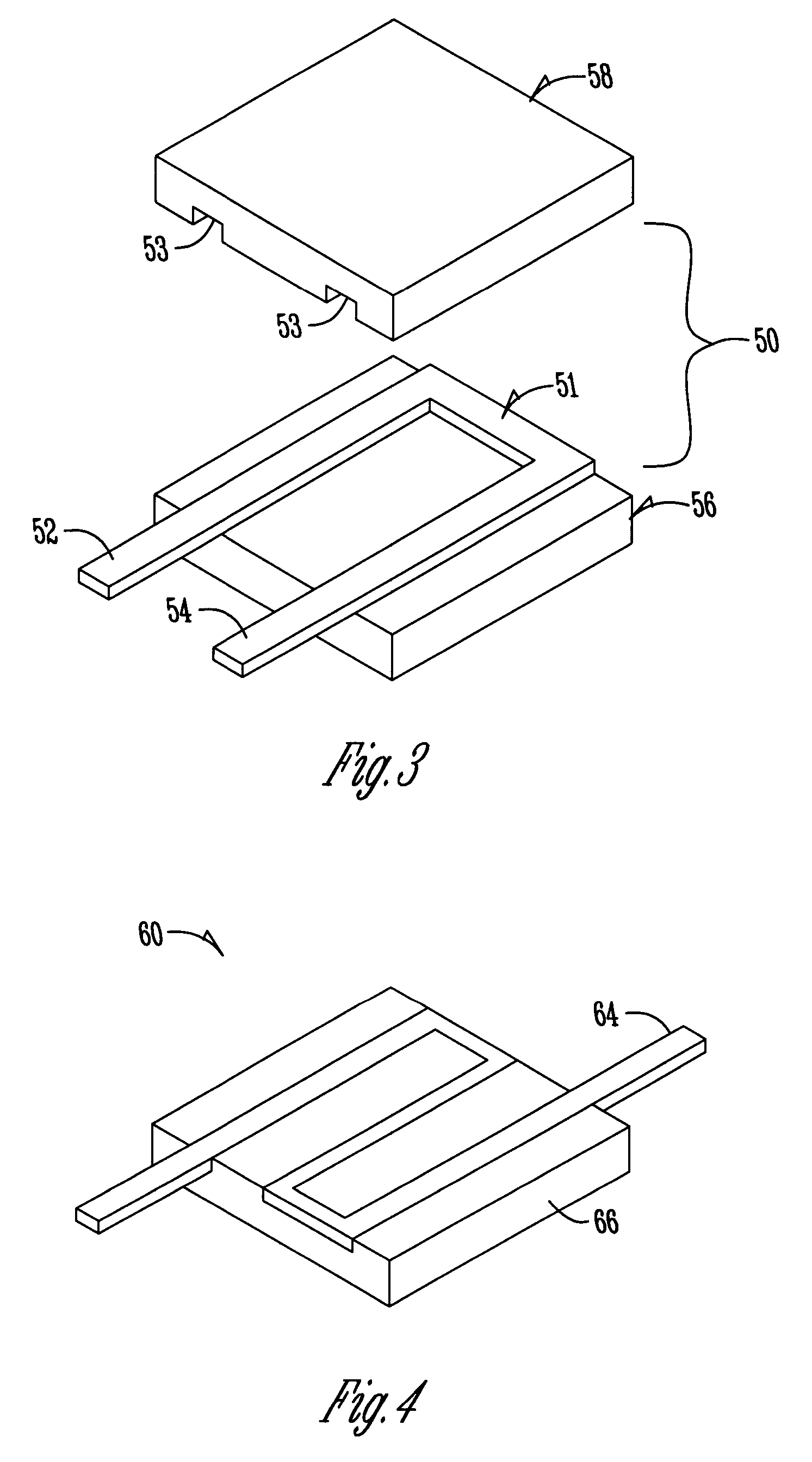

High powered inductors using a magnetic basis

InactiveUS20090066454A1Core lossIncreased current capabilityTransformers/inductances casingsTransformers/inductances coils/windings/connectionsElectrical conductorAdhesive

A biased gap inductor includes a first ferromagnetic plate, a second ferromagnetic plate, a conductor sandwiched between the first ferromagnetic plate and the second ferromagnetic plate, and an adhesive between the first ferromagnetic plate and the second ferromagnetic plate, the adhesive comprising magnet powder to thereby form at least one magnetic gap. A method of forming an inductor includes providing a first ferromagnetic plate and a second ferromagnetic plate and a conductor, placing the conductor between the first ferromagnetic plate and the second ferromagnetic plate, adhering the first ferromagnetic plate to the second ferromagnetic plate with a composition comprising an adhesive and a magnet powder to form magnetic gaps, and magnetizing the inductor.

Owner:VISHAY DALE ELECTRONICS INC

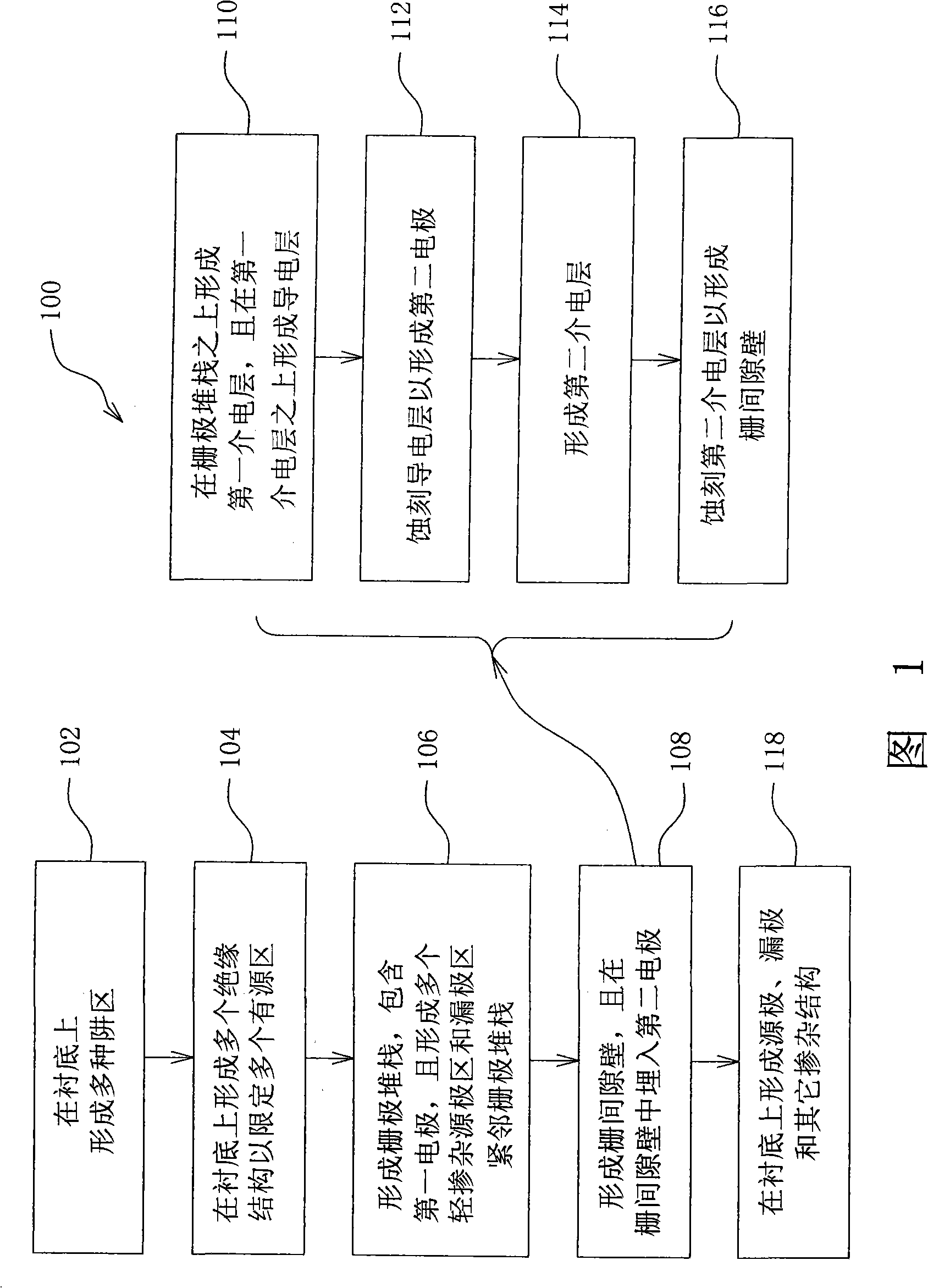

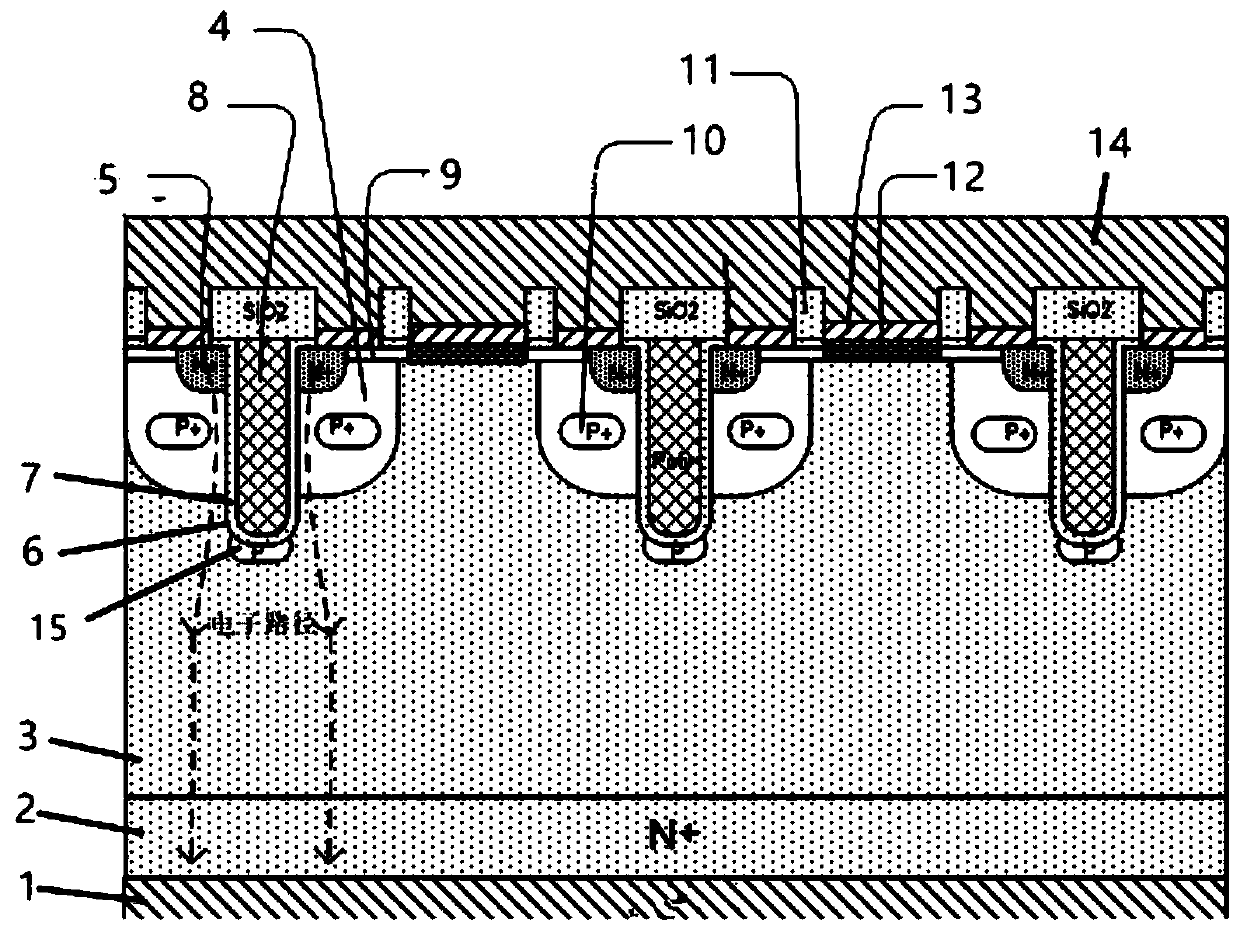

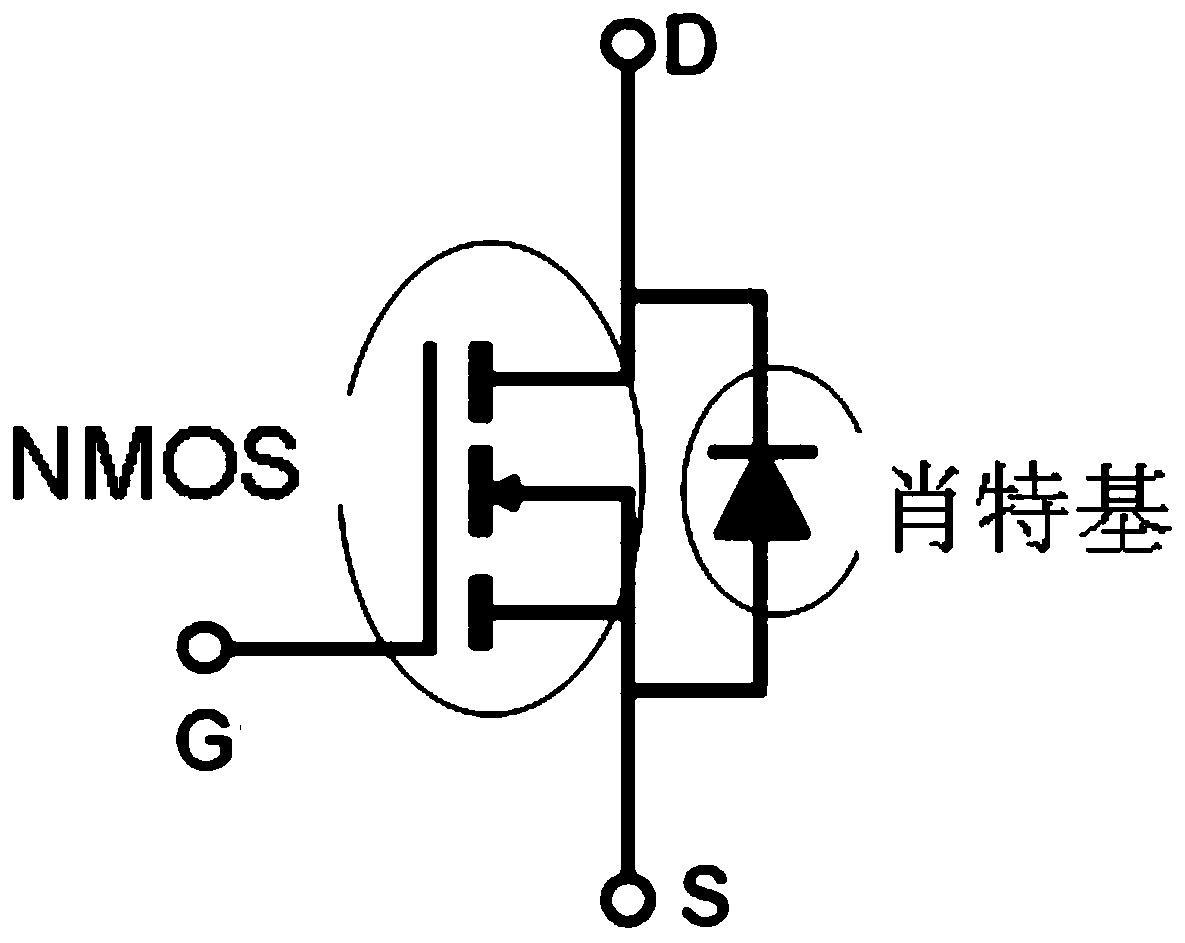

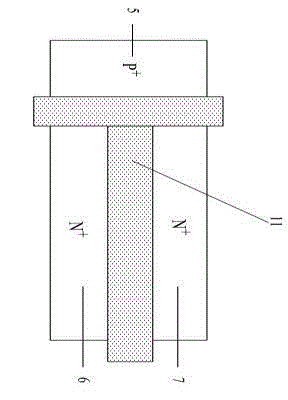

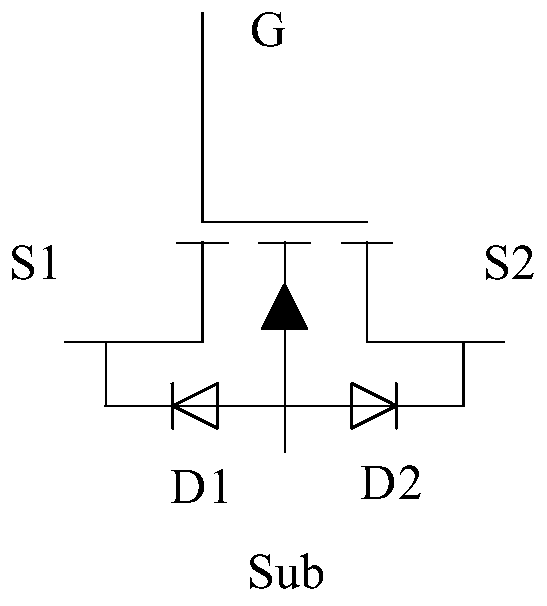

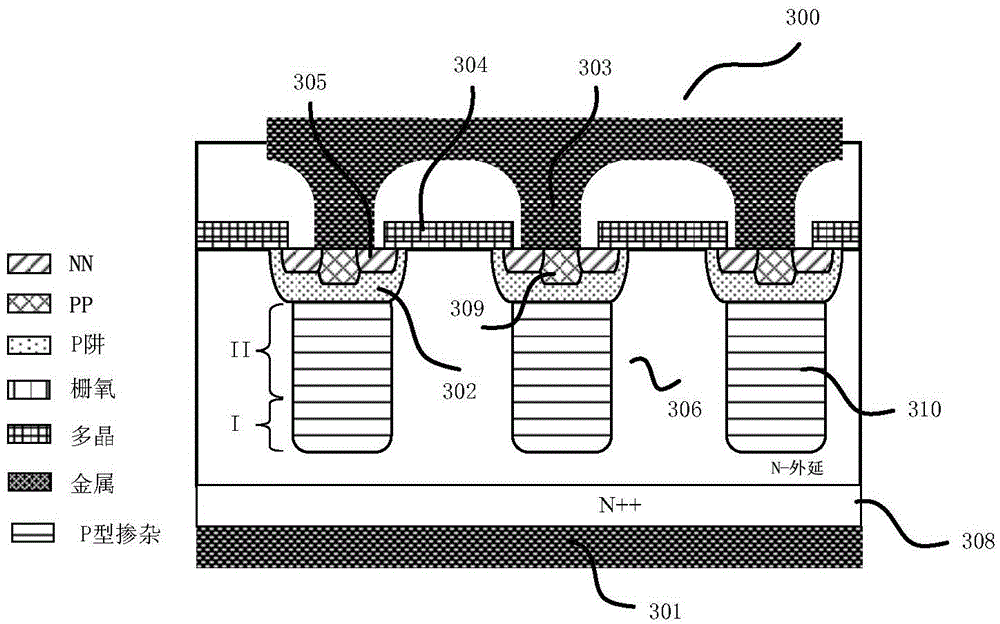

Enhanced silicon carbide MOSFET device and manufacturing method thereof

ActiveCN111081759AFast switching speedImprove performanceTransistorSolid-state devicesMOSFETSchottky barrier

The invention discloses an enhanced silicon carbide MOSFET device. The enhanced silicon carbide MOSFET device sequentially comprises back metal, an N+ type heavily doped SiC substrate, an N- epitaxiallayer, an insulating dielectric layer and front metal from bottom to top. According to the invention, a Schottky diode is integrated into the MOSFET device, and the area of a Schottky barrier metal layer is flexibly increased or decreased to adjust and adapt to the current and specification of the MOSFET and the Schottky diode, so that the effects of increasing the switching speed of the MOSFET,reducing the switching loss and the like are achieved, the performance and the reliability of the device can be greatly improved, and the application cost of the device is reduced. The enhanced silicon carbide MOSFET device adopts a trench SiC MOSFET design, and a conductive channel is changed from the traditional horizontal direction to the vertical direction, so that a JFET effect between primitive cells of the traditional MOSFET is eliminated, and the current capability of the device is improved. The gate bottom P region at the bottom of the trench can protect and weaken an electric field at the bottom of the trench, thereby playing a certain role in electrostatic shielding of gate oxide at the bottom of the trench, and improving the reliability of the device. Meanwhile, certain help isprovided for voltage resistance of the device.

Owner:SOUTH UNIVERSITY OF SCIENCE AND TECHNOLOGY OF CHINA

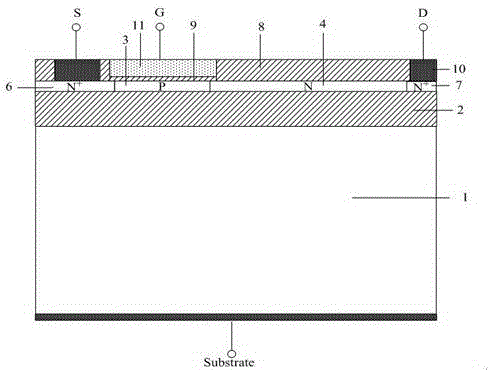

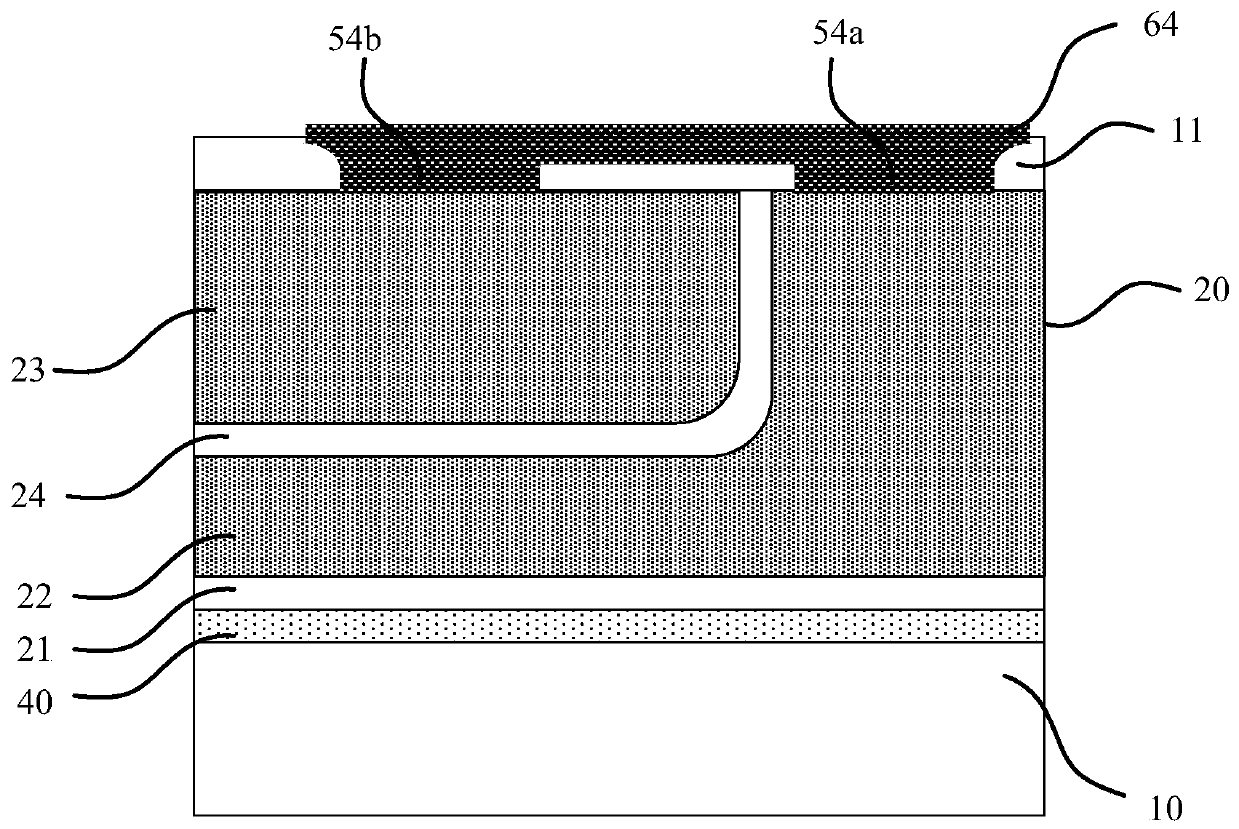

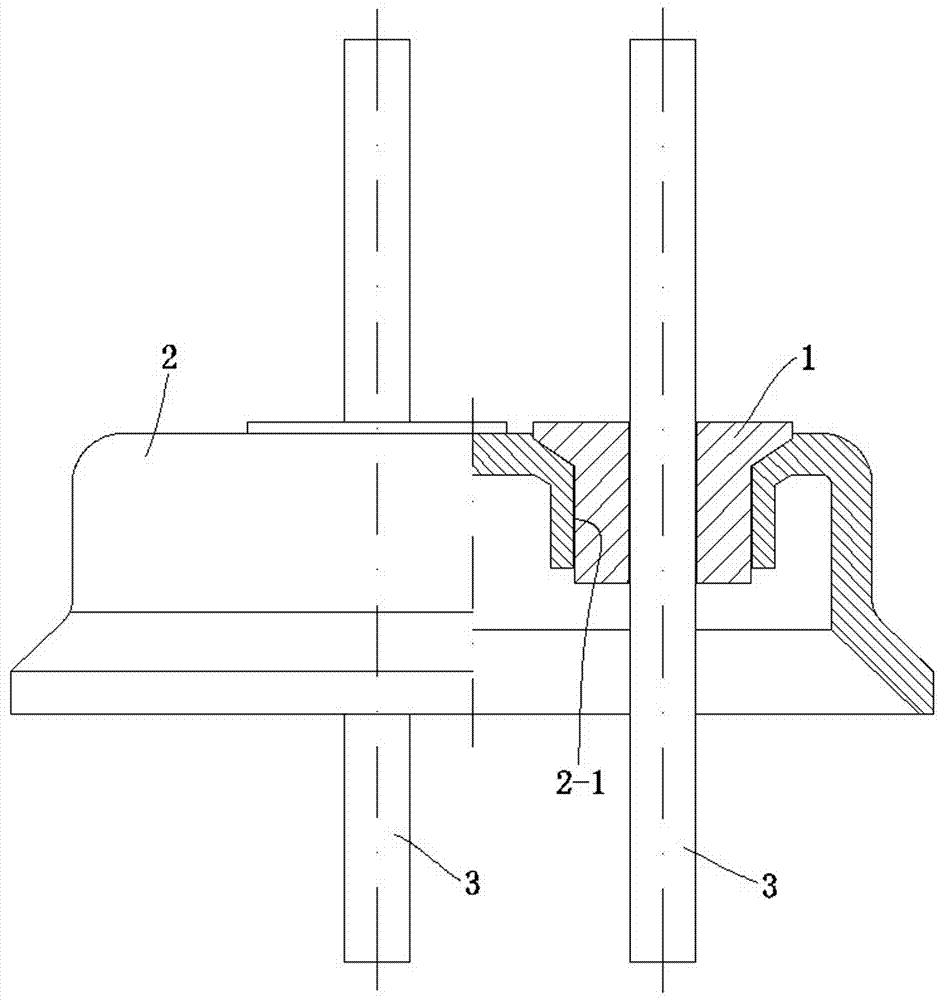

Transverse signal operation instruction (SOI) power device

InactiveCN102751316AImprove pressure resistanceIncreased current capabilityTransistorFloating body effectMemory effect

The invention discloses a transverse signal operation instruction (SOI) power device. The transverse SOI power device comprises a semiconductor substrate, an insulating medium layer and a semiconductor active layer, wherein a body region and a drain region are arranged on the surface of the semiconductor active layer, an interval exists between the body region and the drain region to form a drift region of the device, a body contact region and a source region are sequentially formed on the surface of the body region, a silicon window is arranged on the insulating medium layer, the bottom of the body region is located in the silicon window or enters into the semiconductor substrate through the silicon window, the bottom of the body contact region enters into the silicon window, and a common leading-out end of the source region and the body contact region serves as a source electrode. The transverse SOI power device has the advantages that the body region is effectively led out, floating body effects of a Kink effect, a parasitic triode effect, memory effect and the like are eliminated, the off state withstand voltage and gate control capacity are improved, simultaneously the puncture voltage in an on state is boosted, characteristics of the SOI device are improved, and the possibility of a partial appendage effect appearing in a T-shaped gate structure and a base transceiver station (BTS) structure is eliminated.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

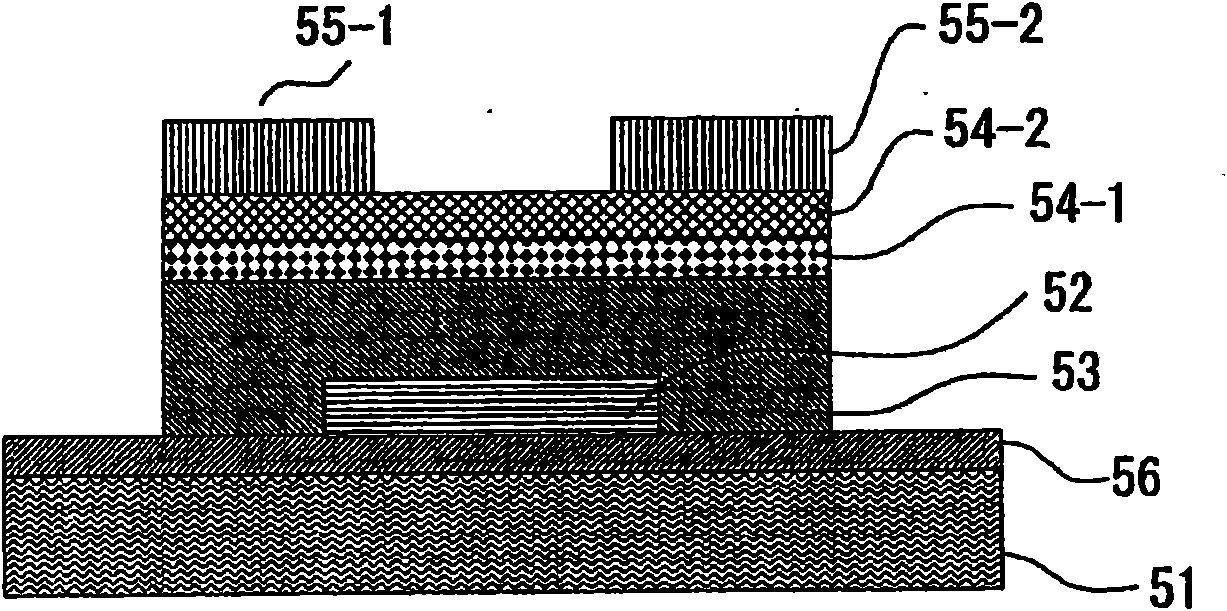

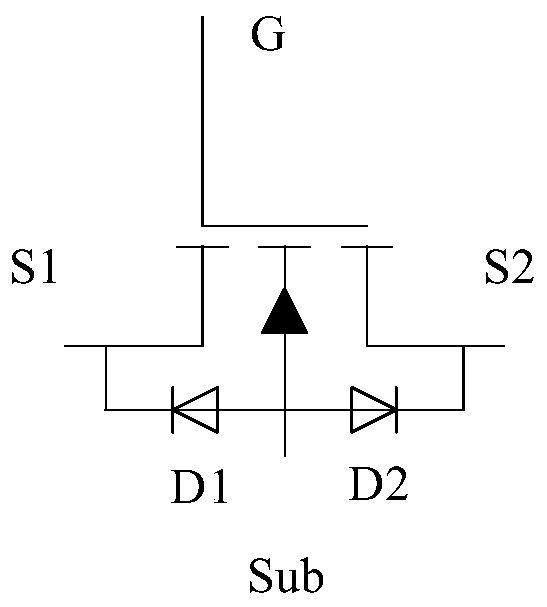

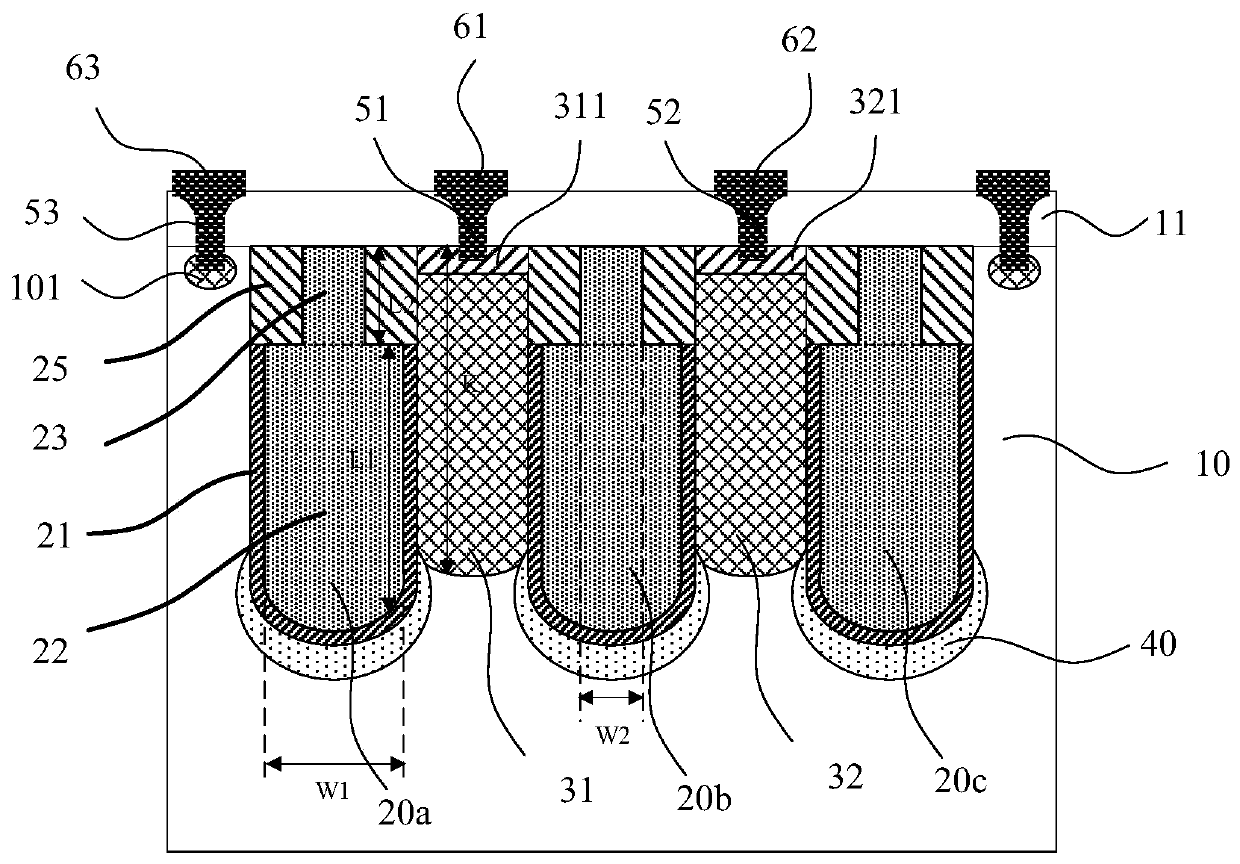

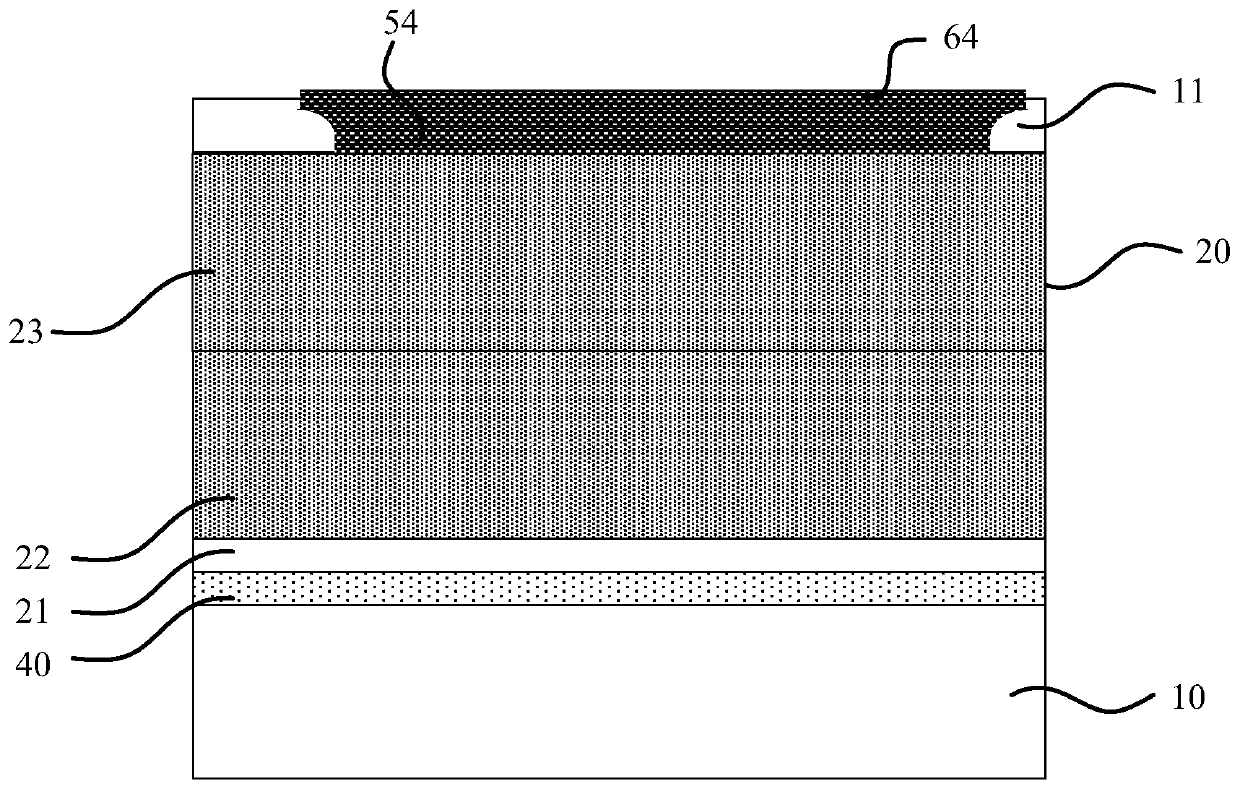

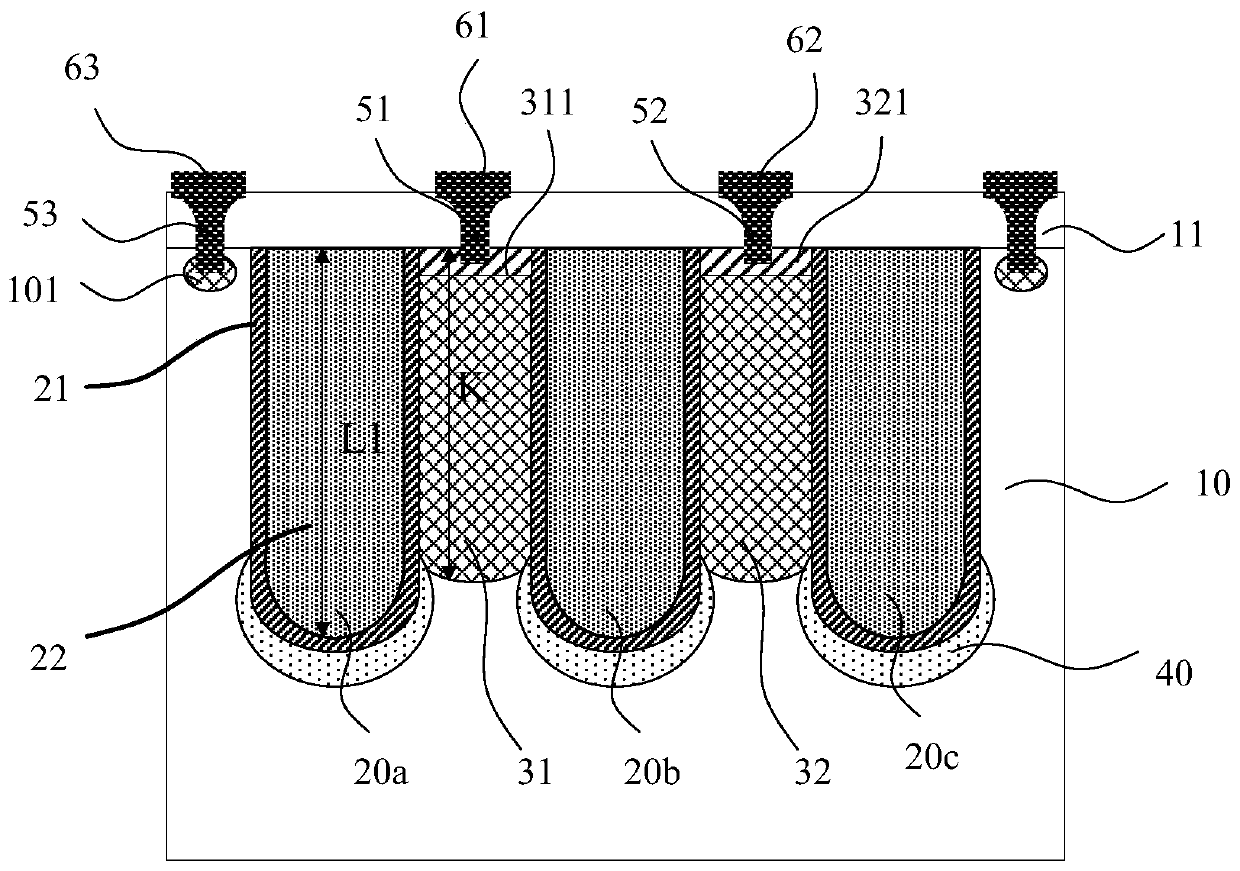

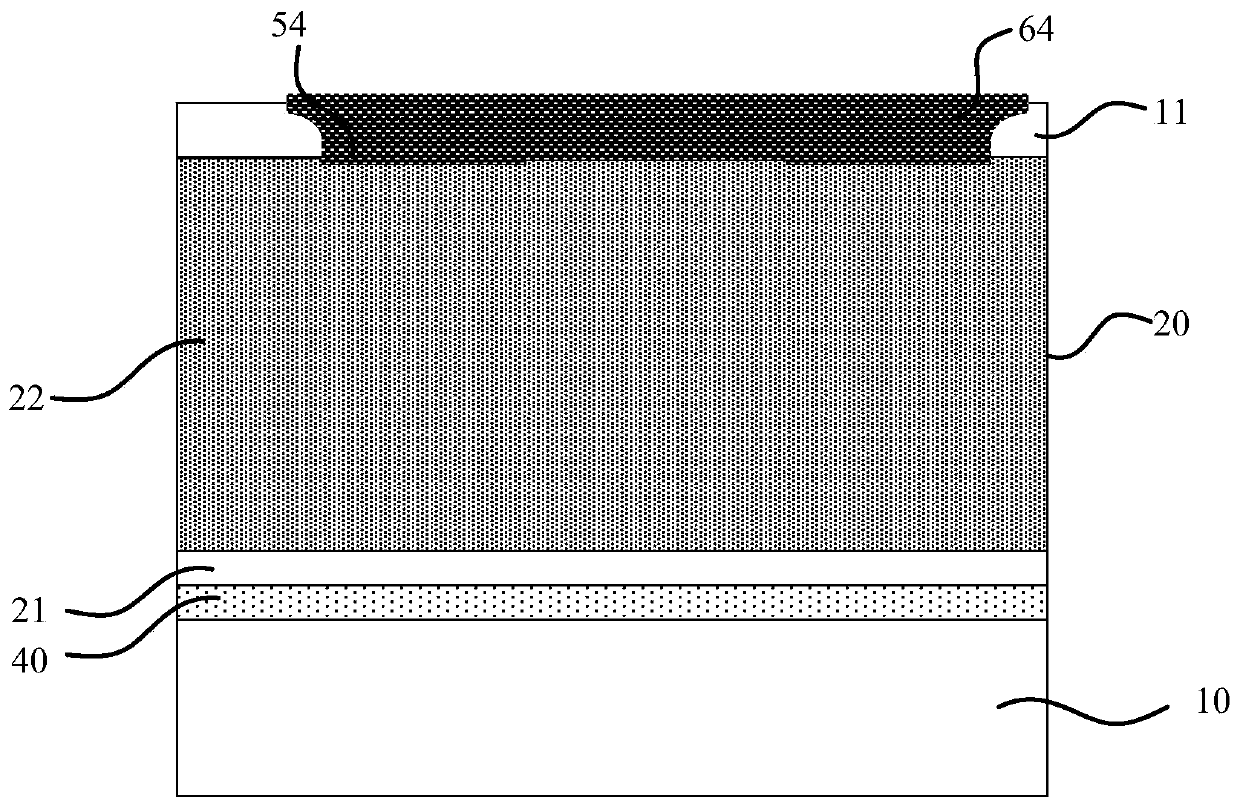

Bidirectional power device and manufacturing method thereof

PendingCN110137243AImprove withstand voltage characteristicsLower impedanceSemiconductor devicesGate dielectricDielectric layer

The invention discloses a bidirectional power device and a manufacturing method thereof. The bidirectional power device comprises: a semiconductor layer; a groove located in the semiconductor layer; agate dielectric layer located at the side wall of the groove; a control gate located at the lower portion of the groove; a shielding gate located at the upper portion of the groove; and an isolationlayer located between the control gate and the shielding gate, wherein the control gate is separated from the semiconductor layer by the gate dielectric layer. The shielding gate is located at the upper portion of the control gate which is mutually separated from the shielding gate, and is separated from a source and a drain through a shielding dielectric layer, and when the bidirectional power device is cut off, the shielding gate depletes charges of a second doped region through the shielding dielectric layer, and the voltage-withstanding characteristic is improved. When the bidirectional power device is conducted, the source and / or the drain and the semiconductor layer provide a low-impedance conduction path.

Owner:HANGZHOU SILAN MICROELECTRONICS

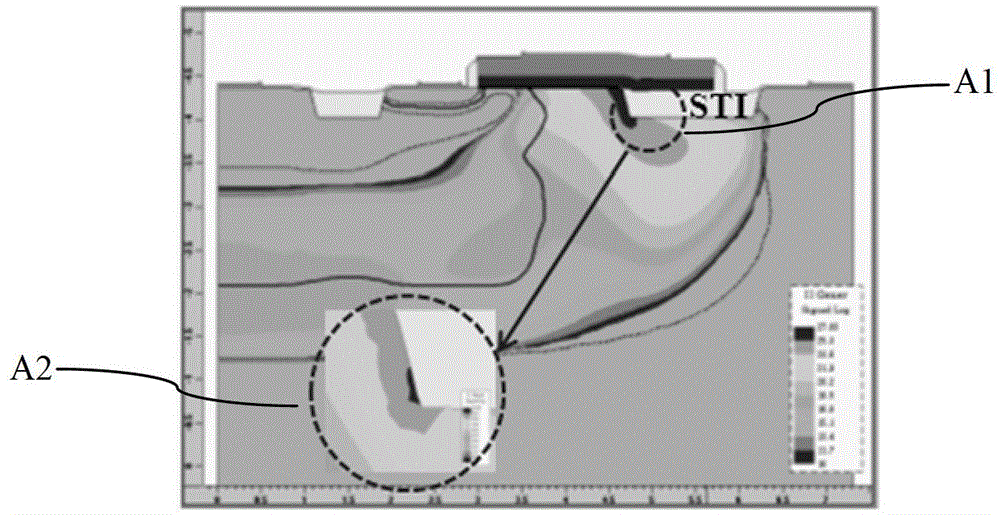

LDMOS device and manufacturing method thereof

InactiveCN104377242AImprove breakdown voltageEvenly distributedSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSElectricity

The invention discloses an LDMOS device formed on a silicon substrate. An active area is isolated by a shallow groove field oxide, a partial field oxide is adopted in a drain region field oxide in a drift region between a channel region and a drain region, the partial field oxide is formed by partial field oxidation after silicon in the partial field oxide region is etched by a certain depth, and the depth of the partial field oxide is defined by the depth of the etched silicon in the partial field oxide region. The invention further discloses a manufacturing method of the LDMOS device. According to the LDMOS device and the manufacturing method of the LDMOS device, a smooth bottom is formed in the drain area through partial field oxide, and therefore the problem that current and an electricity field are centralized at the bottom of the field oxide of the drain region can be solved, and the breakdown voltage of the device can be improved; the length of the current path of the drain region of the device can be shortened, so the specific on-resistance of the device can be lowered, and the current performance of the device can be improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

PVC (polyvinyl chloride) home decorative sheet and preparation method thereof

InactiveCN106380738AInhibition of premature decompositionAvoid breakingWeather resistanceFoaming agent

The invention discloses a PVC (polyvinyl chloride) home decorative sheet which is prepared from the following raw materials according to a weight proportion: 20 to 30 of PVC resin powder; 10 to 30 of colloidal calcium carbonate; 90 to 150 of PVC recycled materials; 1.5 to 2.0 of composite stabilizer; 6 to 9 of foaming control agent; 1 to 1.8 of composite foaming agent; 0.2 to 0.5 of plasticizer, 0.5 to 0.7 of internal lubricant, 0.1 to 0.3 of external lubricant, and 0.025 to 0.035 of whitening agent. The PVC recycled materials comprise a PVC decorative template recycled material, a white PVC plastic steel window recycled material and a white PVC pipe recycled material; the composite foaming agent is formed by mixing a white foaming agent and a yellow foaming agent. The invention further discloses a preparation method of the PVC home decorative sheet. According to the PVC home decorative sheet and the preparation method thereof, which are disclosed by the invention, the PVC recycled materials are used as one of the main raw materials, wastes are changed into treasures, production cost is reduced, energy is saved, hardness and weather resistance of the product are improved, recycling times are increased, the recycling times can reach 35 times or above, moreover, the preparation method is easy to operate, and the prepared product is smooth and attractive in surface. The PVC home decorative sheet disclosed by the invention is energy-saving, environmental-friendly, low in production cost and long in service life.

Owner:江苏旺科新材料有限公司

Glass insulator

ActiveCN102881386AStable physical propertiesStable chemical propertiesLead-in/lead-through insulatorsAlternating currentMetal

The invention discloses a glass insulator used for encapsulation connection between the metal end cover and the metal conductive columns of the wiring terminal of a compressor. The glass insulator comprises the components with the weight percentage as follows: 92-94 percent of SiO2, 3-4 percent of Al2O3, 0.5-1 percent of Bi2O3, 0.5-1 percent of TiO2 and 1.5-2.5 percent of SrO, preferably, 93 percent of SiO2, 33.3 percent of Al2O3, 0.7 percent of Bi2O3, 0.8 percent of TiO2 and 2.2 percent of SrO. The glass insulator not only has favorable insulating performance and avoids flashover generated during operation, but also has low probability of generation of crackle under the long-term action of the alternating current of the metal columns, therefore an explosion hazard of the compressor is avoided, and the glass insulator is suitable for widely applied in the wiring terminal of the compressor.

Owner:JIANGSU CHANGRONG ELECTRICAL APPLIANCE CO LTD

Bidirectional power device and manufacturing method thereof

PendingCN110137242AImprove withstand voltage characteristicsLower impedanceSemiconductor devicesGate dielectricSemiconductor package

The invention discloses a bidirectional power device and a manufacturing method thereof. The bidirectional power device comprises: a semiconductor layer; a groove located in the semiconductor layer; agate dielectric layer located at the side wall of the groove; a control gate located at the lower portion of the groove; and a shielding gate located at the upper portion of the groove, wherein the control gate is in mutual contact with the shielding gate, and the control gate is separated from the semiconductor layer by the gate dielectric layer. The shielding gate is located on the control gatewhich is in mutual contact with the shielding gate, and is separated from a source and a drain through a shielding dielectric layer, and when the bidirectional power device is cut off, the shieldinggate depletes charges of a second doped region through the shielding dielectric layer, and the voltage-withstanding characteristic is improved. When the bidirectional power device is conducted, the source and / or the drain and the semiconductor layer provide a low-impedance conduction path.

Owner:HANGZHOU SILAN MICROELECTRONICS

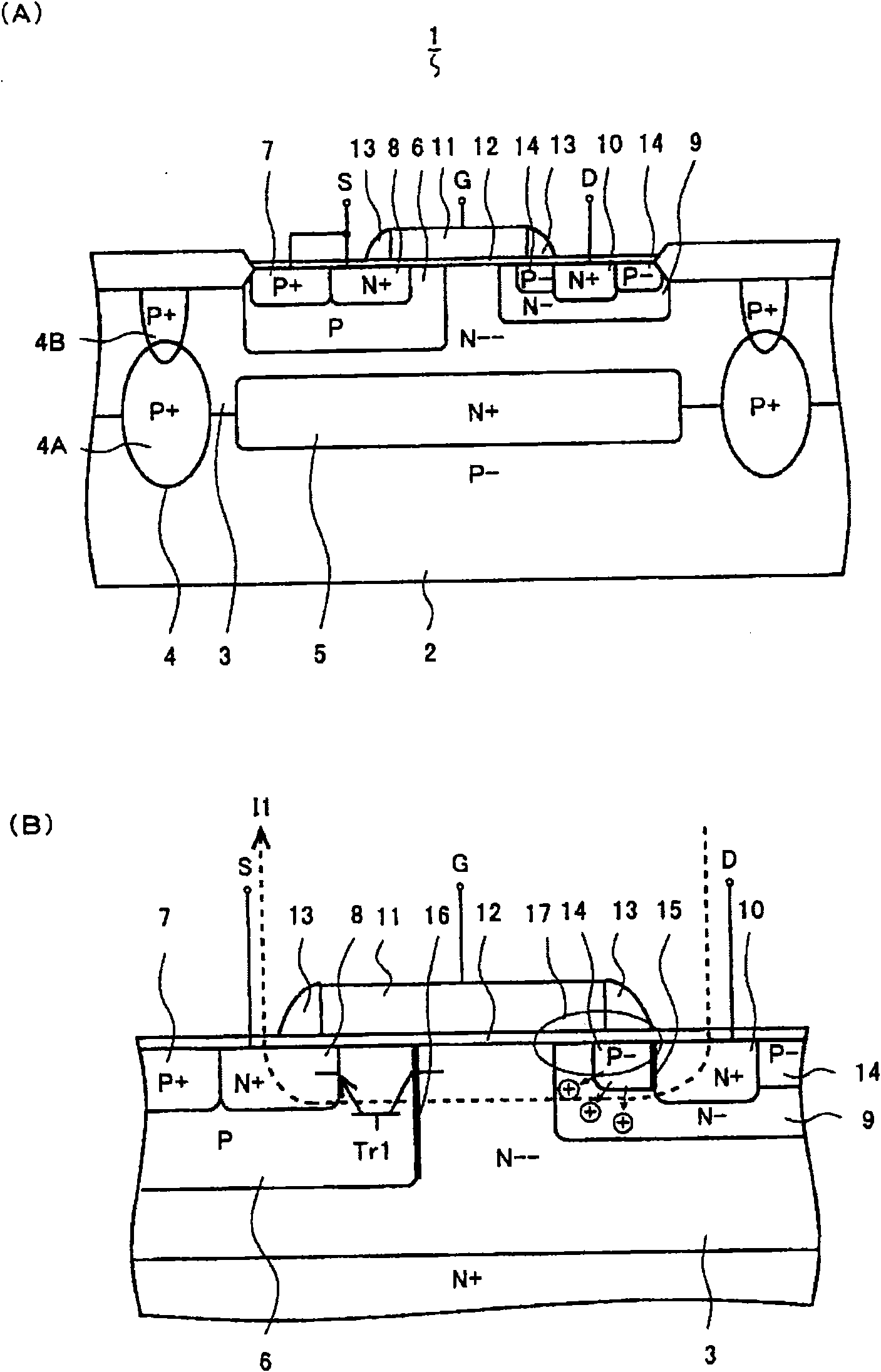

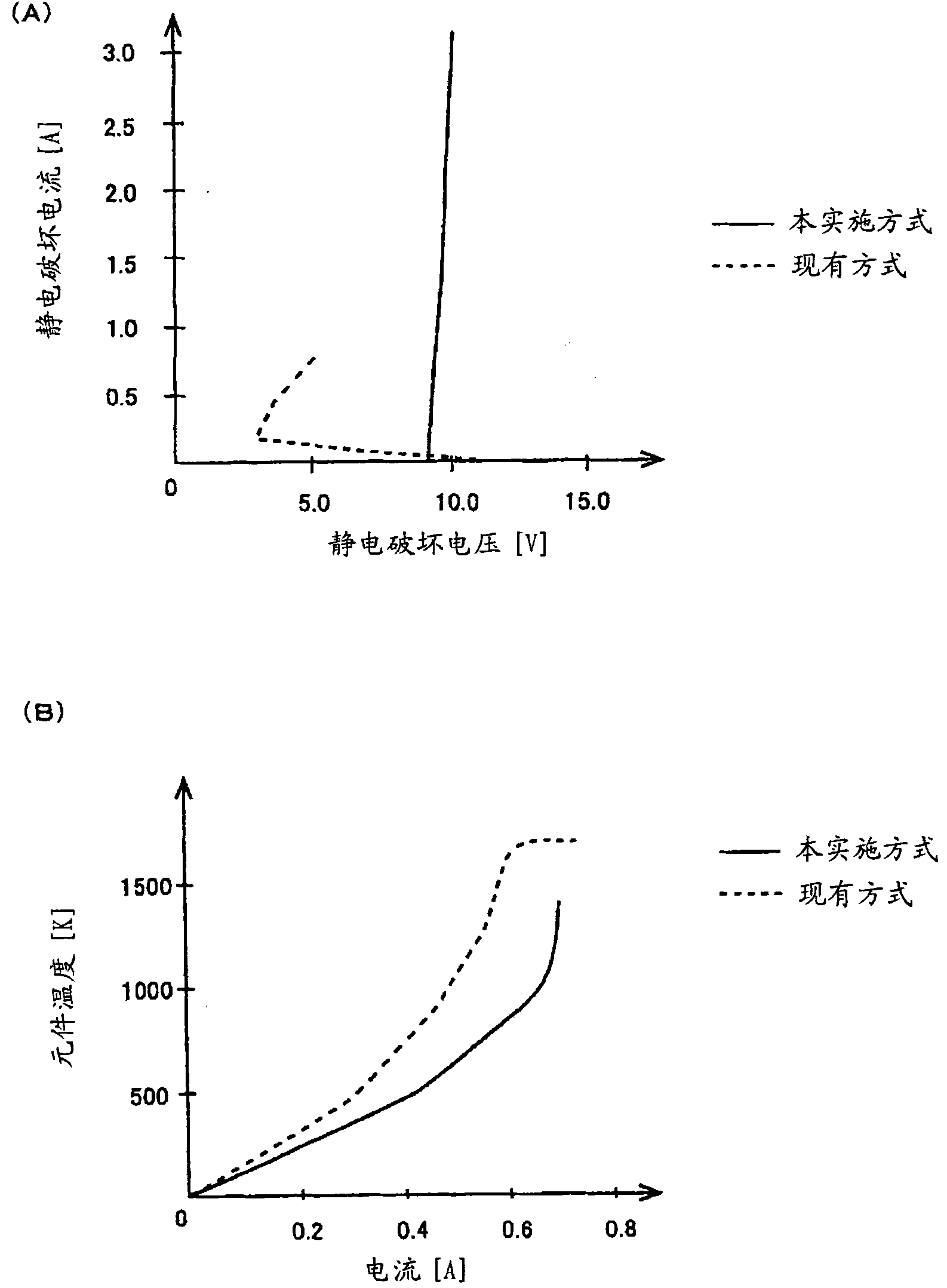

Semiconductor device and method of manufacturing the same

InactiveCN101807599AAvoid thermal damageAvoid destructionThyristorSemiconductor/solid-state device detailsDiffusion layerSemiconductor

In the semiconductor device according to the present invention, a P type diffusion layer and an N type diffusion layer as a drain lead region are formed on an N type diffusion layer as a drain region. The P type diffusion layer is disposed between a source region and the drain region of the MOS transistor. When a positive ESD surge is applied to a drain electrode, causing an on-current of a parasite transistor to flow, this structure allows the on-current of the parasite transistor to take a path flowing through a deep portion of an epitaxial layer. Thus, the heat breakdown of the MOS transistor is prevented.

Owner:SANYO ELECTRIC CO LTD +1

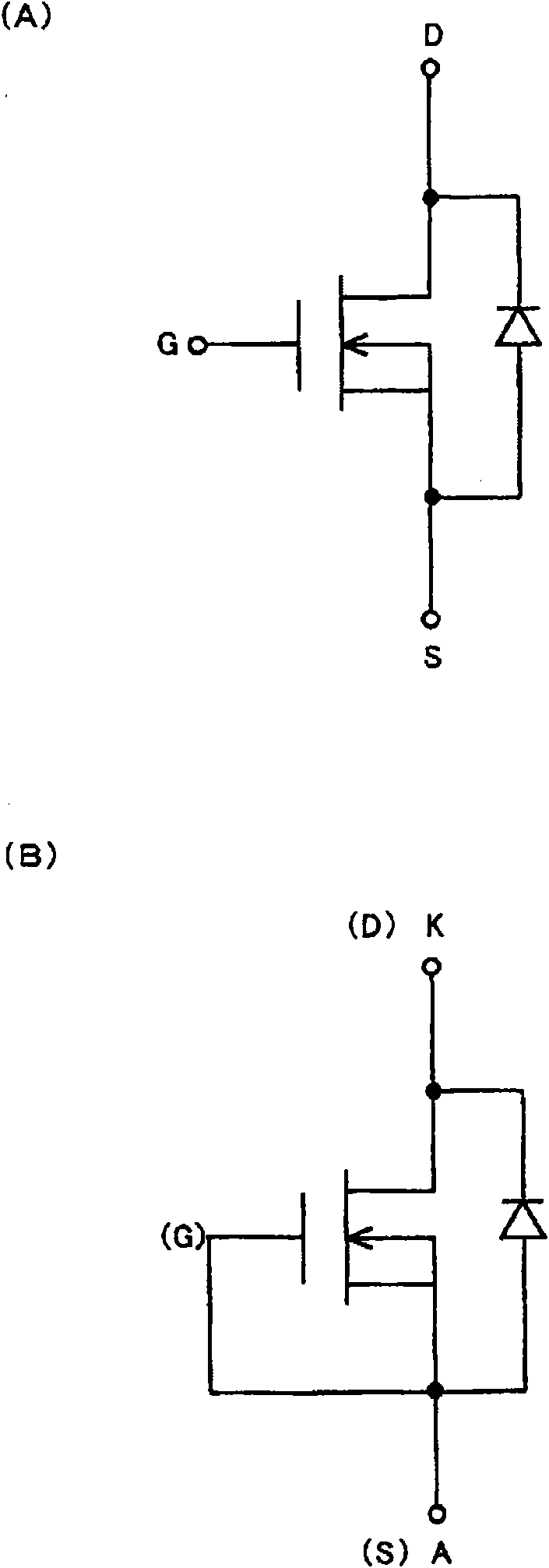

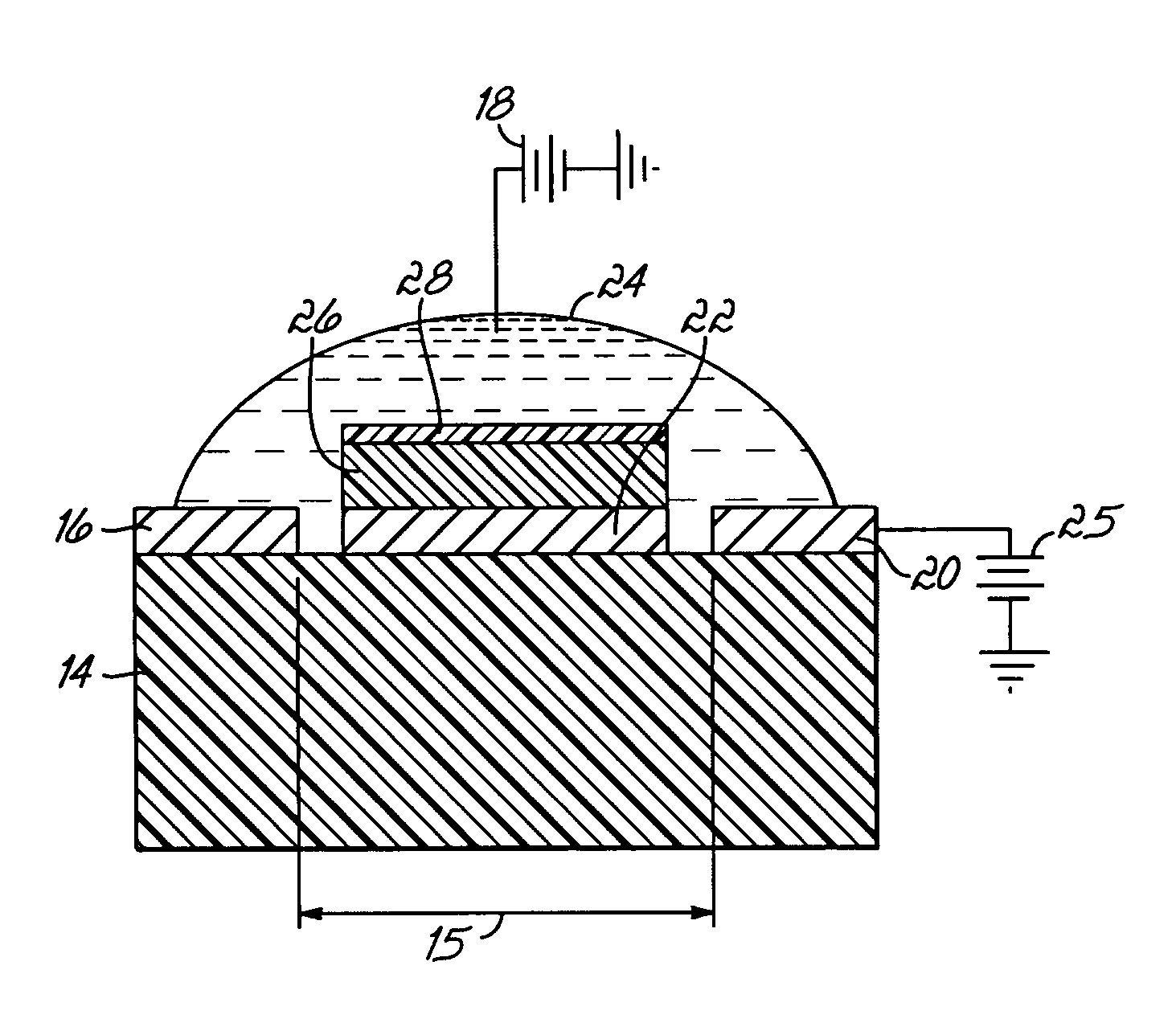

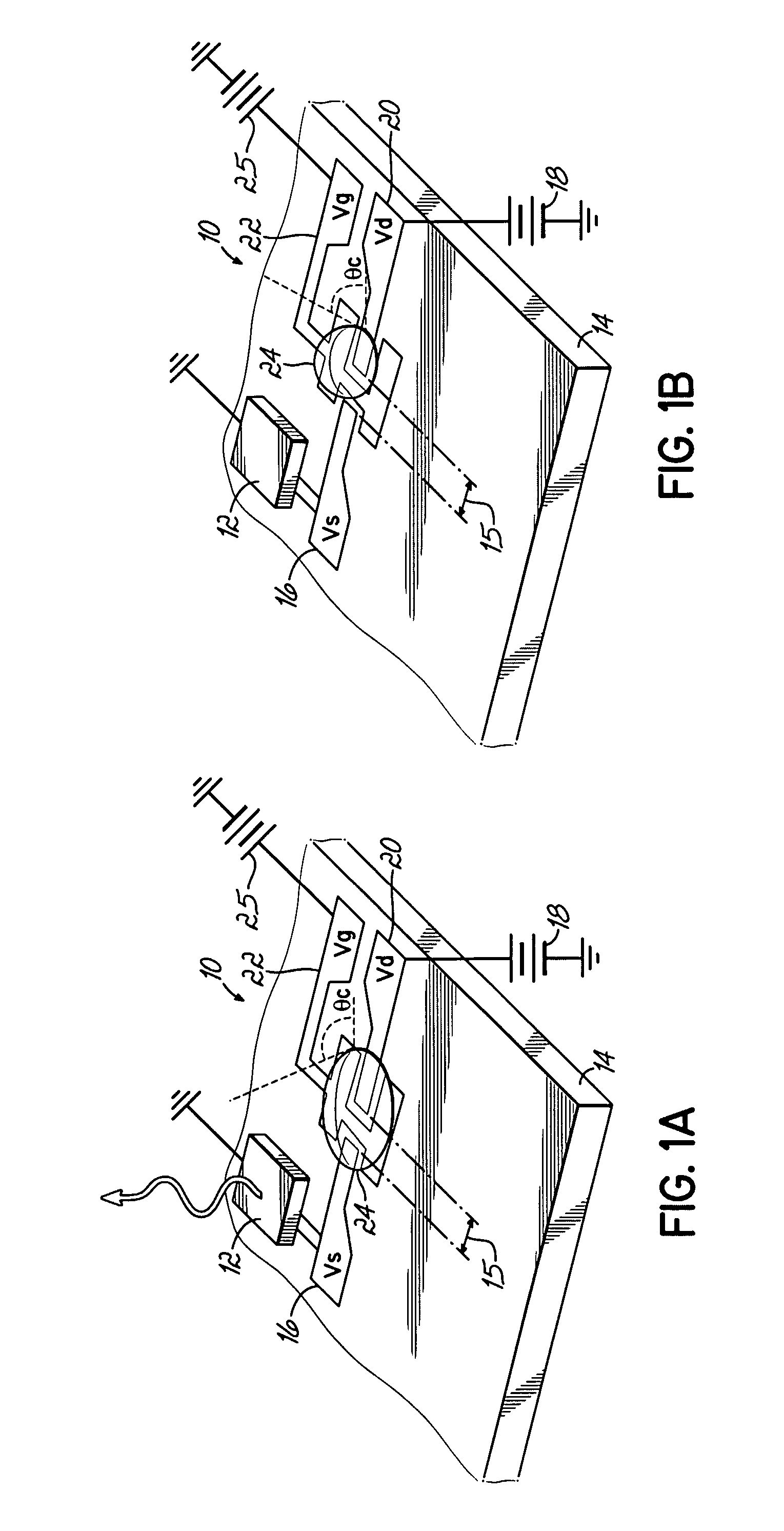

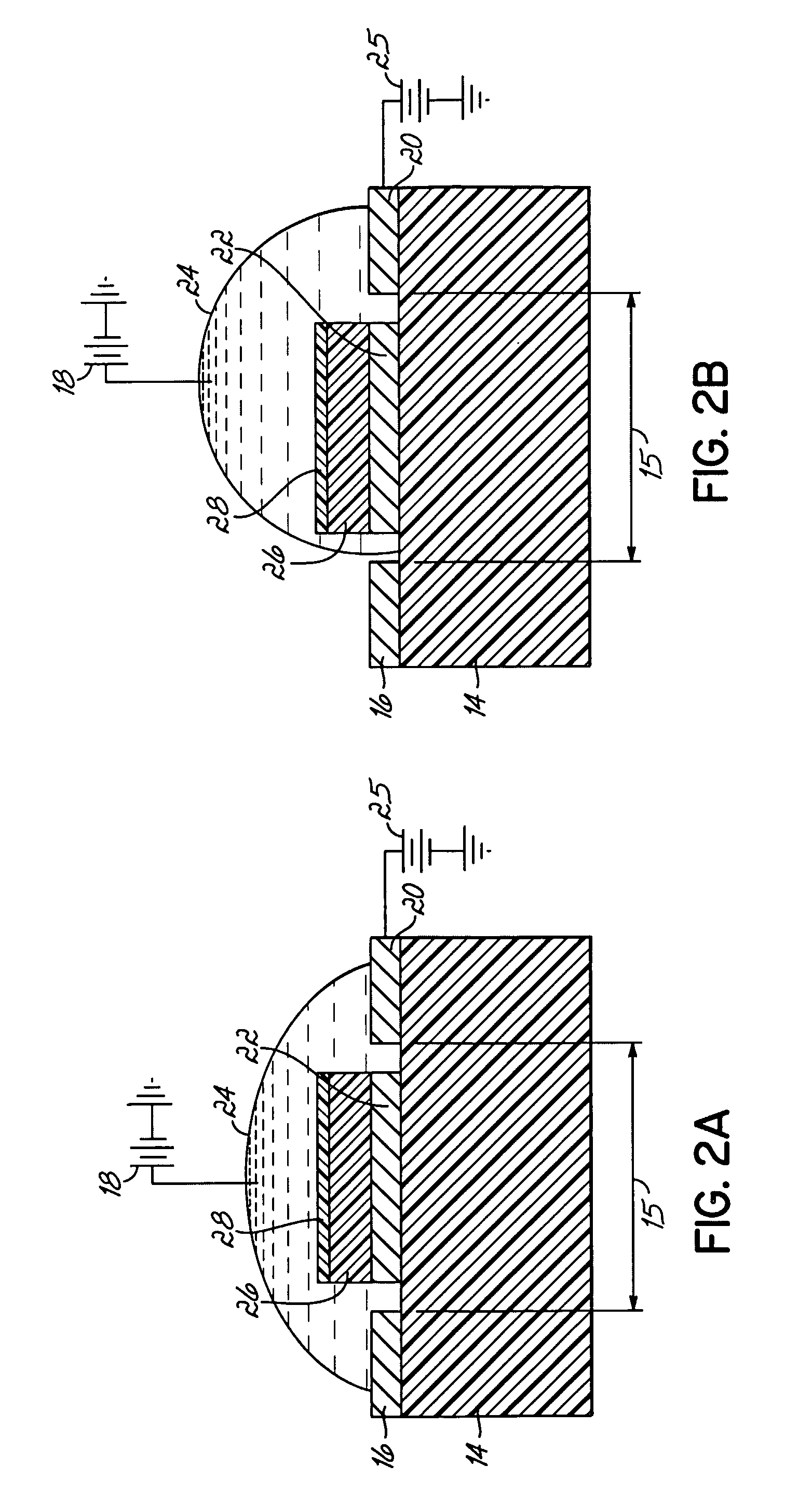

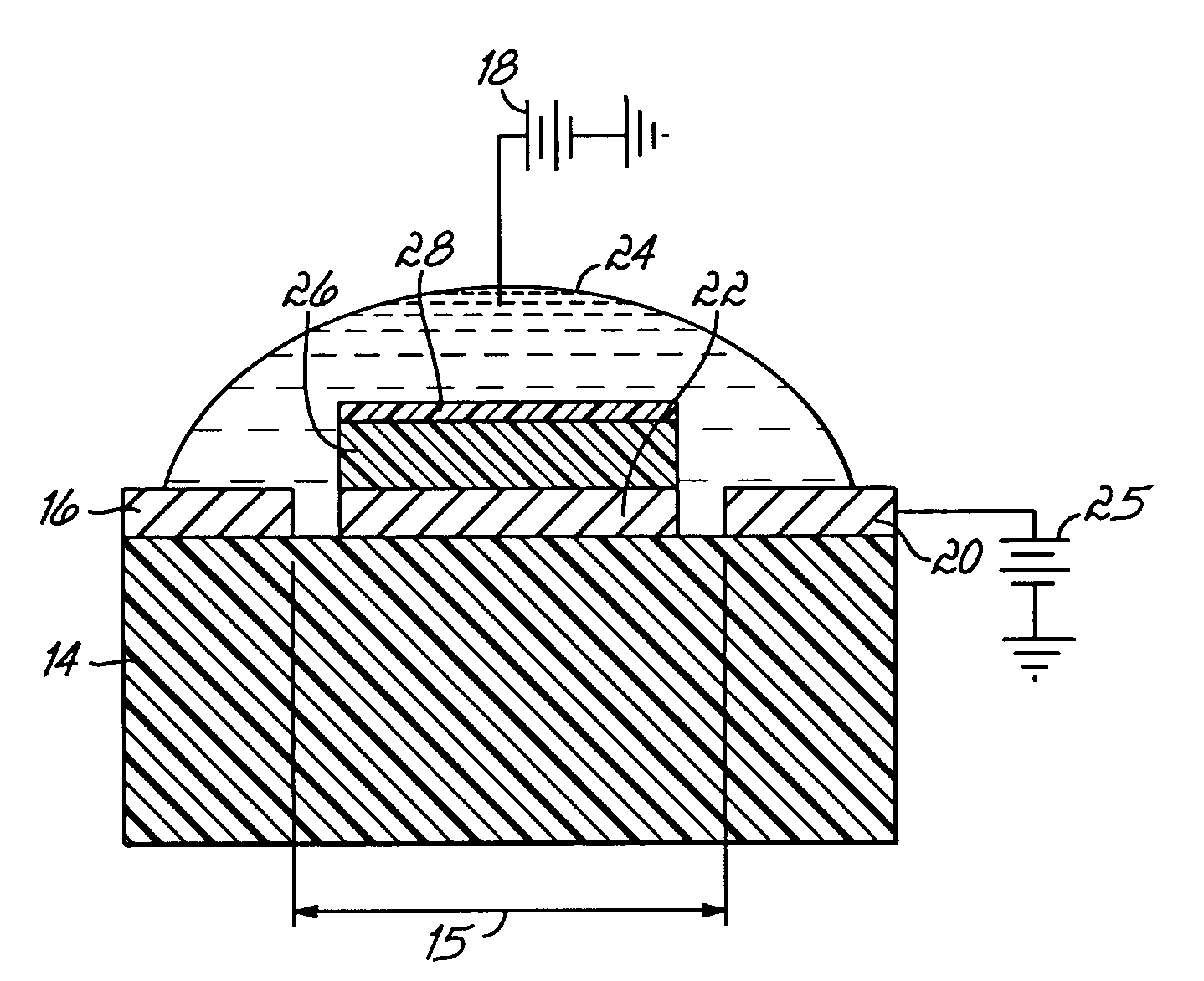

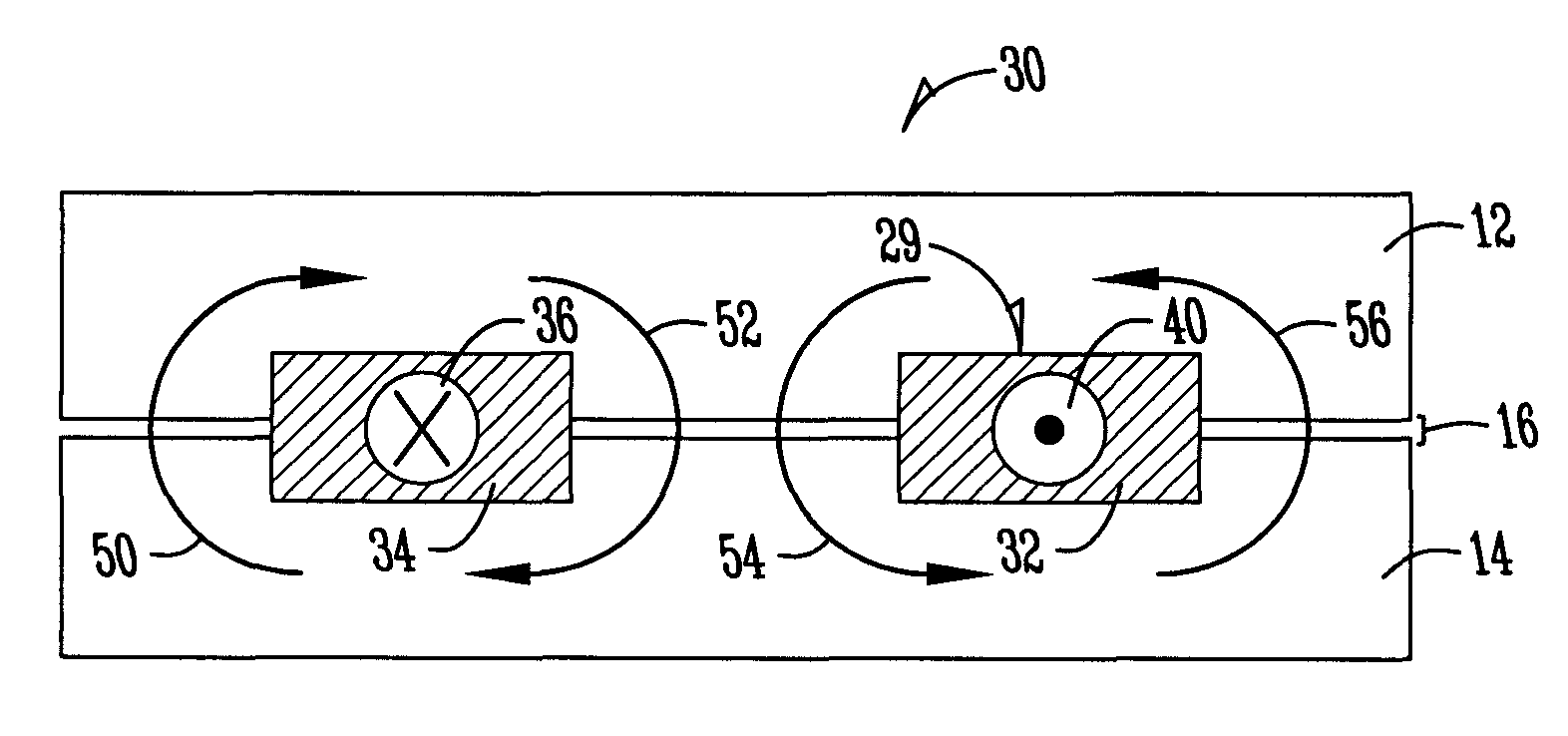

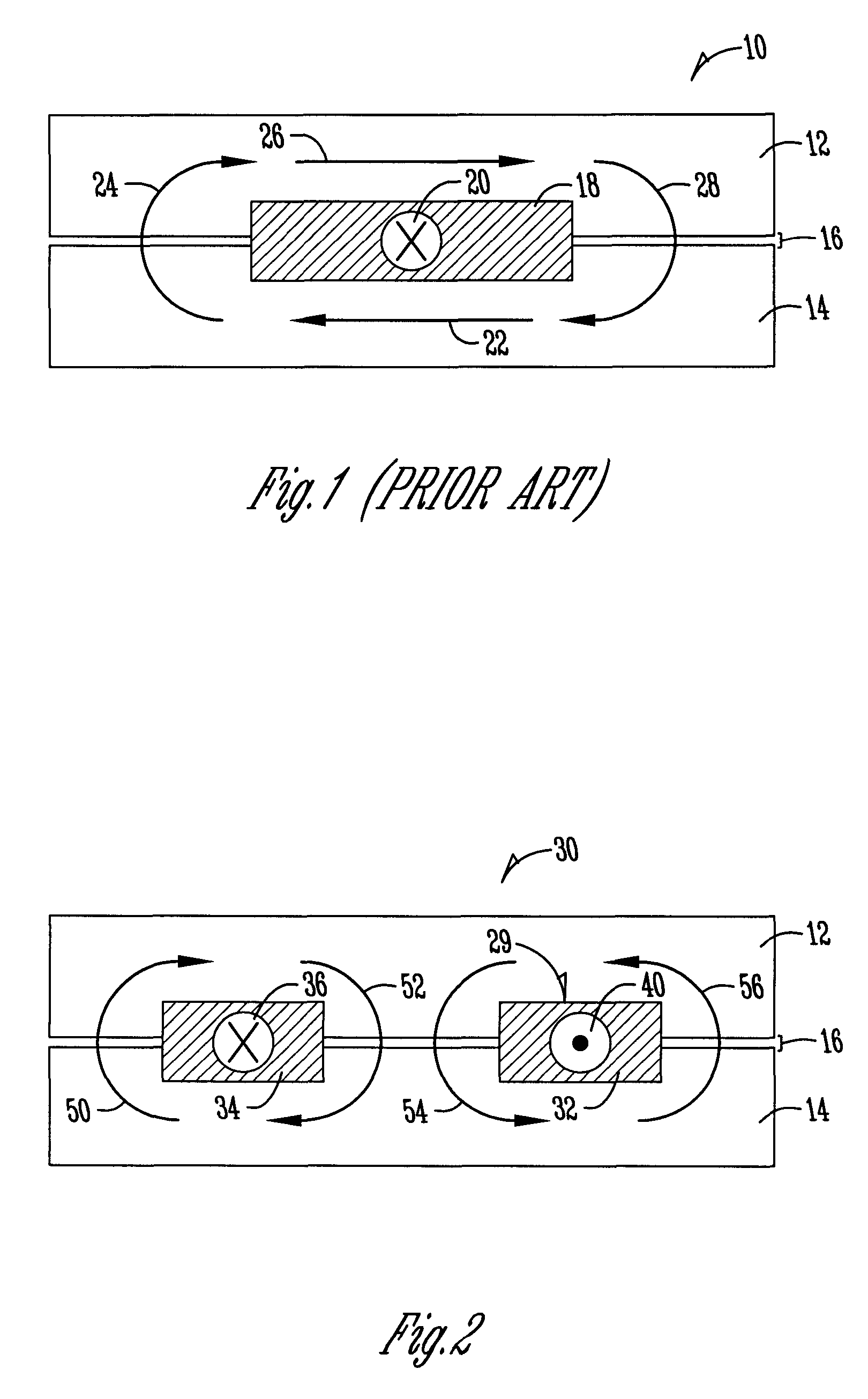

Liquid Logic Structures for Electronic Device Applications

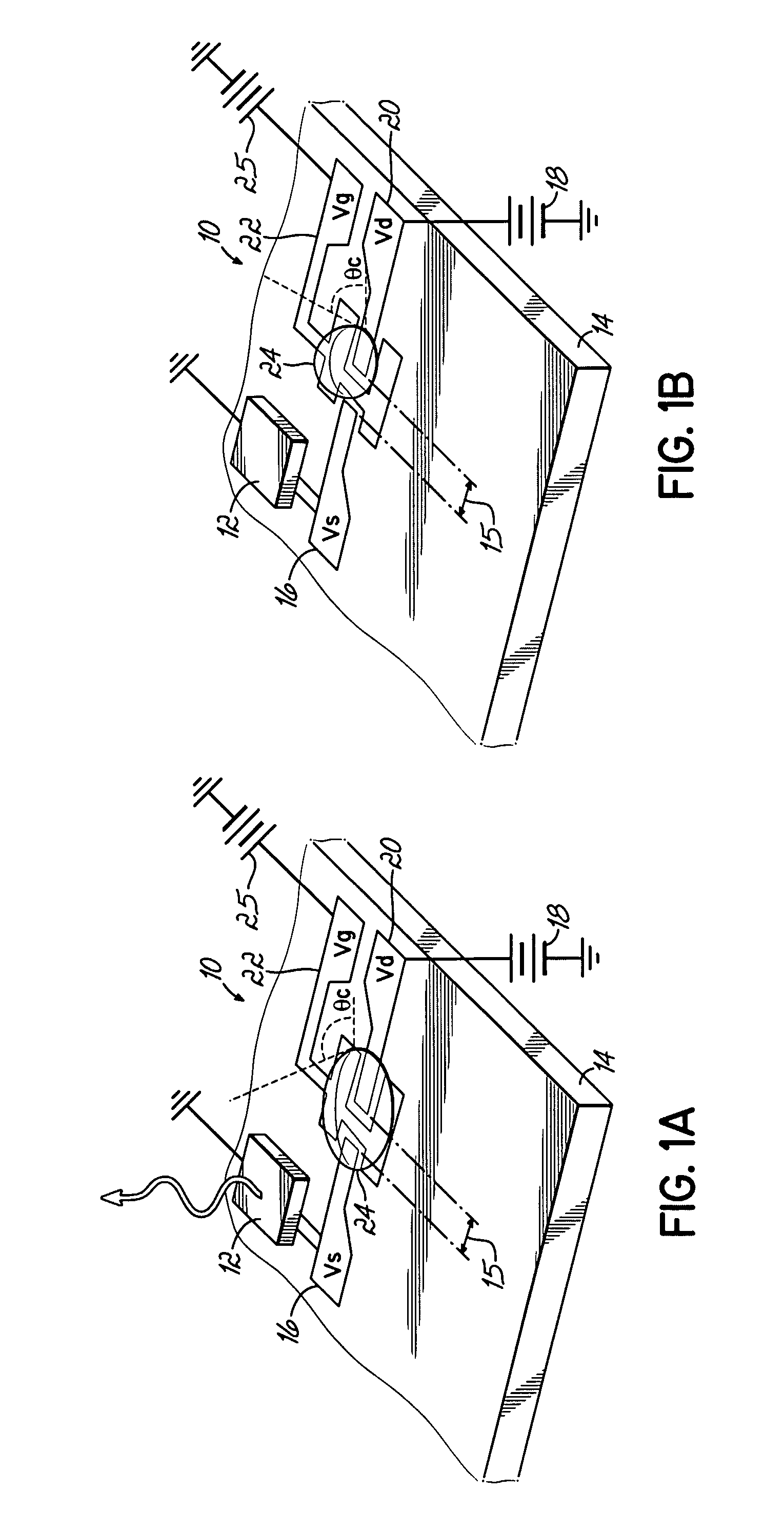

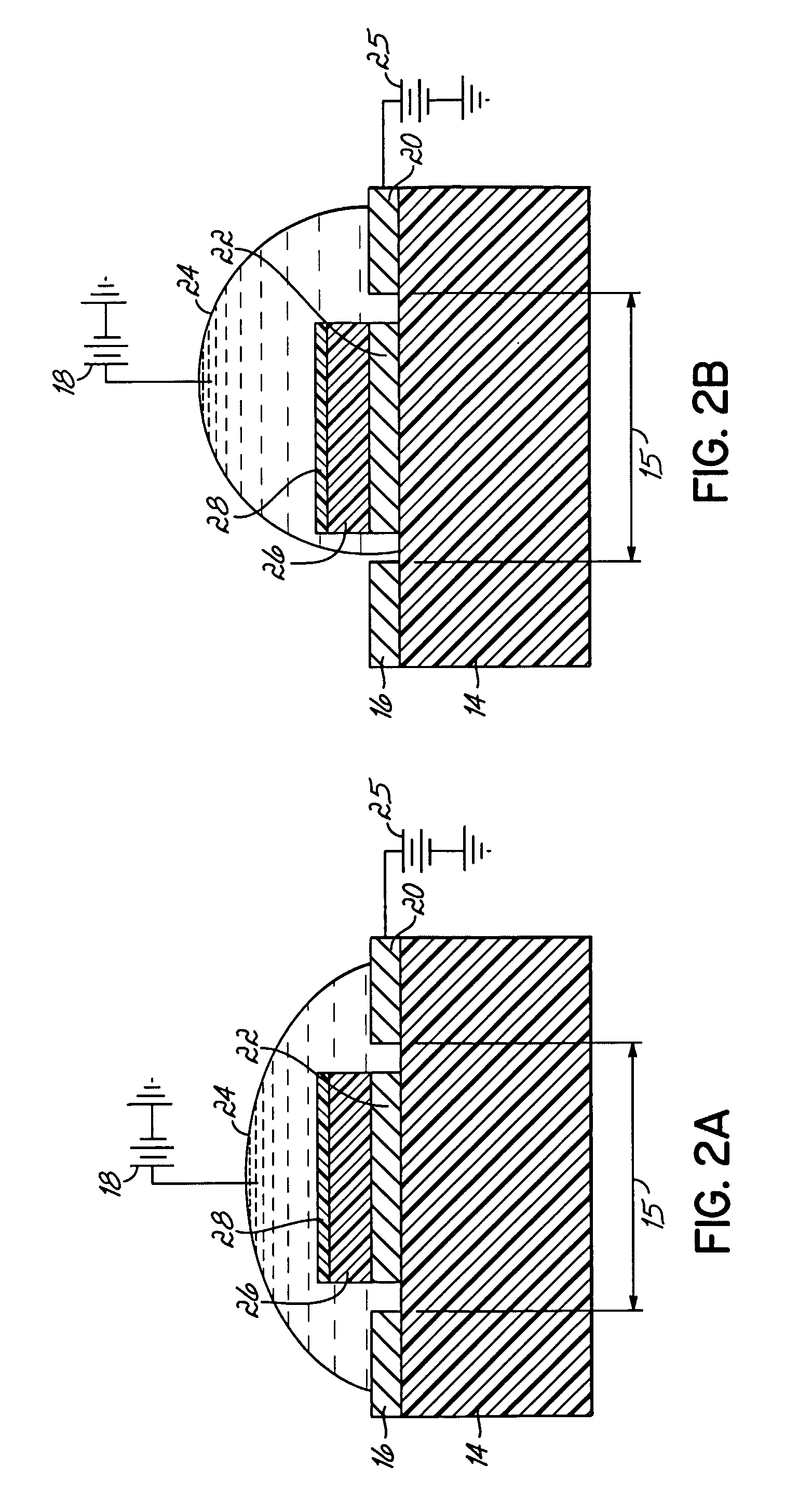

ActiveUS20070221484A1Function increaseHigh bulk densityTransistorElectrostatic/electro-adhesion relaysEngineeringElectric field

Electronic devices (10, 30, 50) utilizing electrically-controlled liquid components to accomplish device switching. Electric fields are used in a device structure to manipulate the position and / or geometrical shape of a conductive fluid or liquid (60, 24) using electrowetting. This manipulation regulates the flow of current between electrodes of the device structure, such as the source and drain regions (16, 20) of a transistor construction, by bridging a non-conductive channel (15) separating the electrodes (16, 20) so that the electrodes (16, 20) are electrically coupled.

Owner:UNIVERSITY OF CINCINNATI

PVC (polyvinyl chloride) advertisement template and preparation method thereof

The invention provides a PVC (polyvinyl chloride) advertisement template. The PVC advertisement template is prepared from, by weight, 60-90 parts of PVC resin powder, 20-50 parts of PVC reclaimed materials, 30-60 parts of active light calcium carbonate, 2.5-4 parts of compound stabilizer, 5-12 parts of foaming control agent, 1.2-2.25 parts of compound foaming agent, 0.2-0.6 part of plasticizer, 0.7-1.5 parts of lubricant, 0.3-1 part of titanium dioxide and 0.01-0.04 part of brightening agent, wherein the compound foaming agent is formed by mixing an inorganic foaming agent with an organic foaming agent, and the lubricant is formed by mixing PE wax, stearic acid and an internal lubricant ZB-60. The invention further provides a preparation method of the PVC advertisement template. The PVC advertisement template and the preparation method thereof have the advantages that since the PVC reclaimed materials are used as one of main raw materials, turning waste into wealth, production cost reduction and energy saving are achieved, hardness and weather fastness of the PVC advertisement template are improved, the number of recycling times can be increased and reach more than 35, and the PVC advertisement template is smooth and attractive in surface; the preparation method is easy to operate.

Owner:江苏旺科新材料有限公司

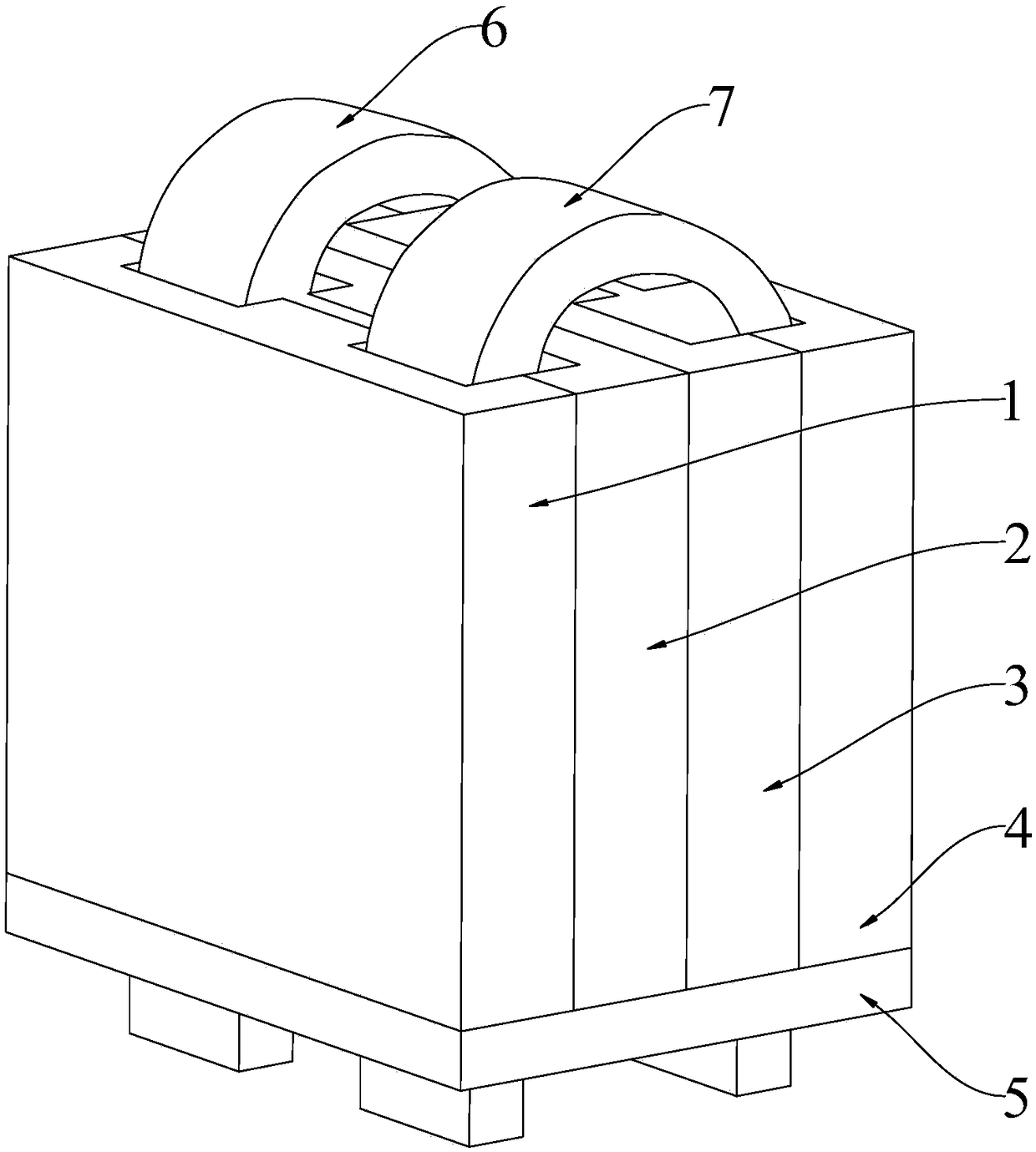

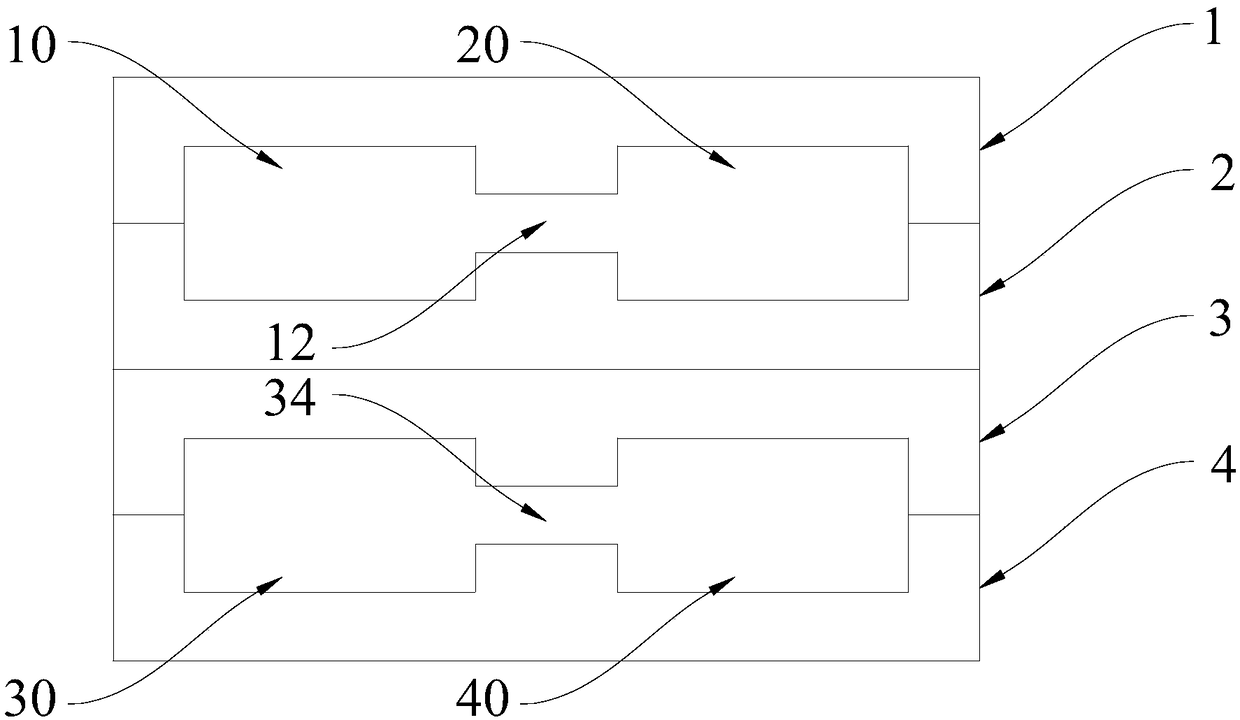

Novel differential- and common-mode filter inductance structure

InactiveCN108492965AReduce manufacturing costCompact structureTransformers/inductances coils/windings/connectionsTransformers/inductances magnetic coresInductorEngineering

The invention discloses a novel differential- and common-mode filter inductor structure. The filter inductor structure comprises a first magnetic core, a second magnetic core, a third magnetic core, afourth magnetic core, a first copper strip and a second copper strip, wherein the first magnetic core is attached onto the second magnetic core, a first through hole and a second through hole are simultaneously formed between the first magnetic core and the second magnetic core and communicate with each other via a first air gap, the third magnetic core is attached onto the fourth magnetic core,a third through hole and a fourth through hole are simultaneously formed between the third magnetic core and the fourth magnetic core and communicate with each other via a second air gap, the first copper strip and the second copper strip are used as windings, the first copper strip penetrates through the second through hole and the fourth through hole, and the second copper strip penetrates through the first through hole and the third through hole. The differential- and common-mode filter has the advantages of compact structure, high current through capability and good filtering performance,moreover, filtering characteristics can be configured, and modular expansion can be performed.

Owner:BEIJING INST OF SPACE LAUNCH TECH +1

Liquid logic structures for electronic device applications

ActiveUS8089013B2High densityFunction increaseTransistorElectrostatic/electro-adhesion relaysElectricityEngineering

Electronic devices (10, 30, 50) utilizing electrically-controlled liquid components to accomplish device switching. Electric fields are used in a device structure to manipulate the position and / or geometrical shape of a conductive fluid or liquid (60, 24) using electrowetting. This manipulation regulates the flow of current between electrodes of the device structure, such as the source and drain regions (16, 20) of a transistor construction, by bridging a non-conductive channel (15) separating the electrodes (16, 20) so that the electrodes (16, 20) are electrically coupled.

Owner:UNIVERSITY OF CINCINNATI

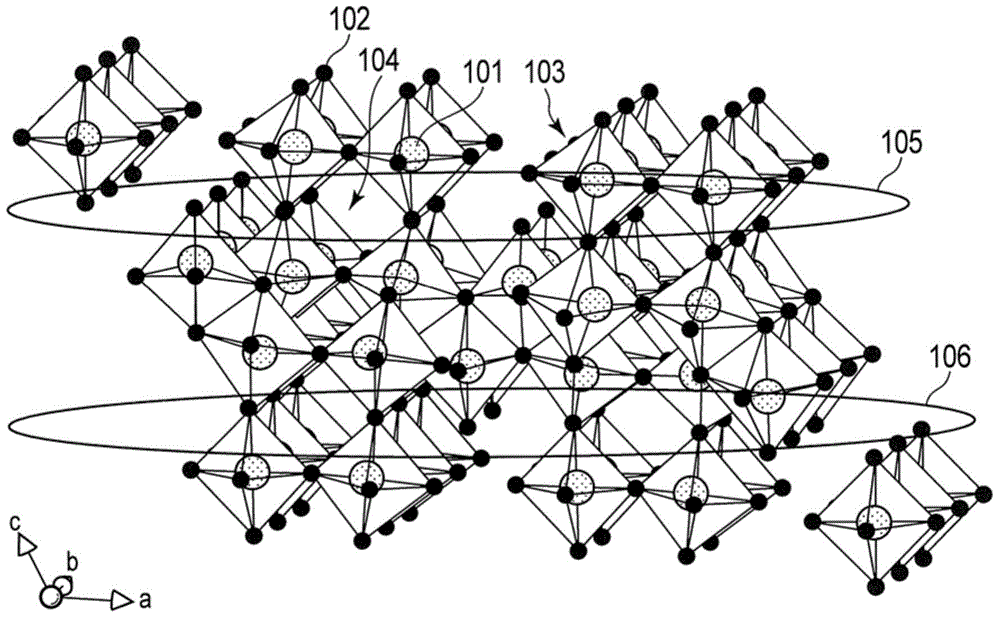

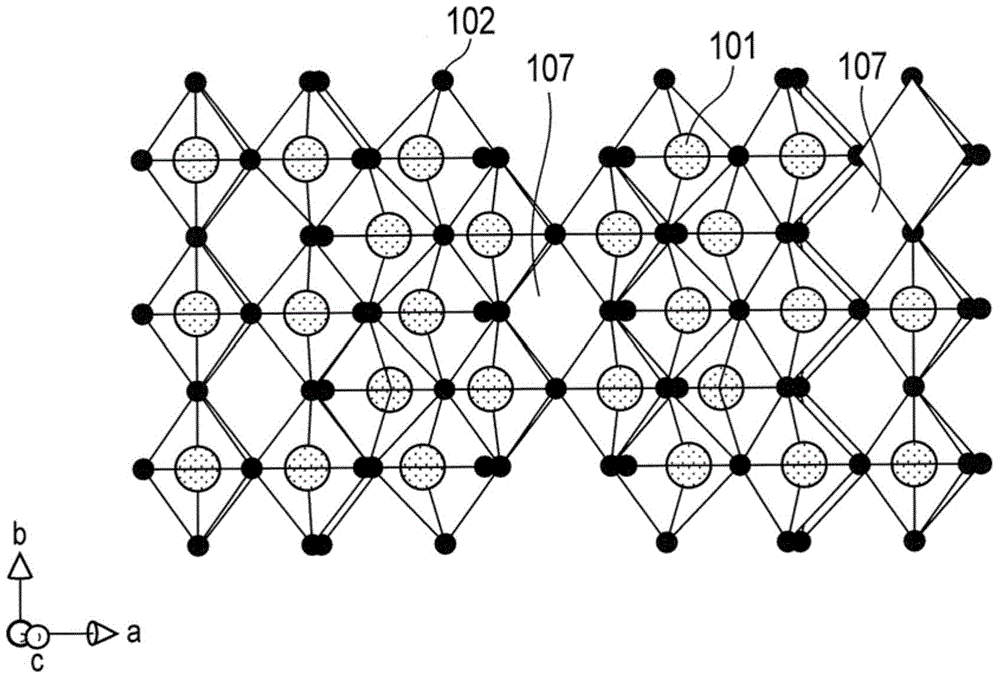

Active substance

InactiveCN104466151AIncrease capacityIncreased current capabilityCurrent conducting connectionsCell electrodesNiobiumUltimate tensile strength

According to one embodiment, there is provided an active substance. The active substance includes secondary particles and a carbon material phase formed on at least a part of a surface of each of the secondary particles. Each of the secondary particles is constructed by aggregated primary particles of an active material. The primary particles of the active material includes a niobium composite oxide represented by LixM(1-y)NbyNb2O(7+[delta]), wherein M is at least one selected from the group consisting of Ti and Zr, and x, y, and [delta] respectively satisfy 0!<=x!<=6, 0!<=y!<=1, and -1 PRG [delta]!<=1. The secondary particles have a compression fracture strength of 10 MPa or more.

Owner:KK TOSHIBA

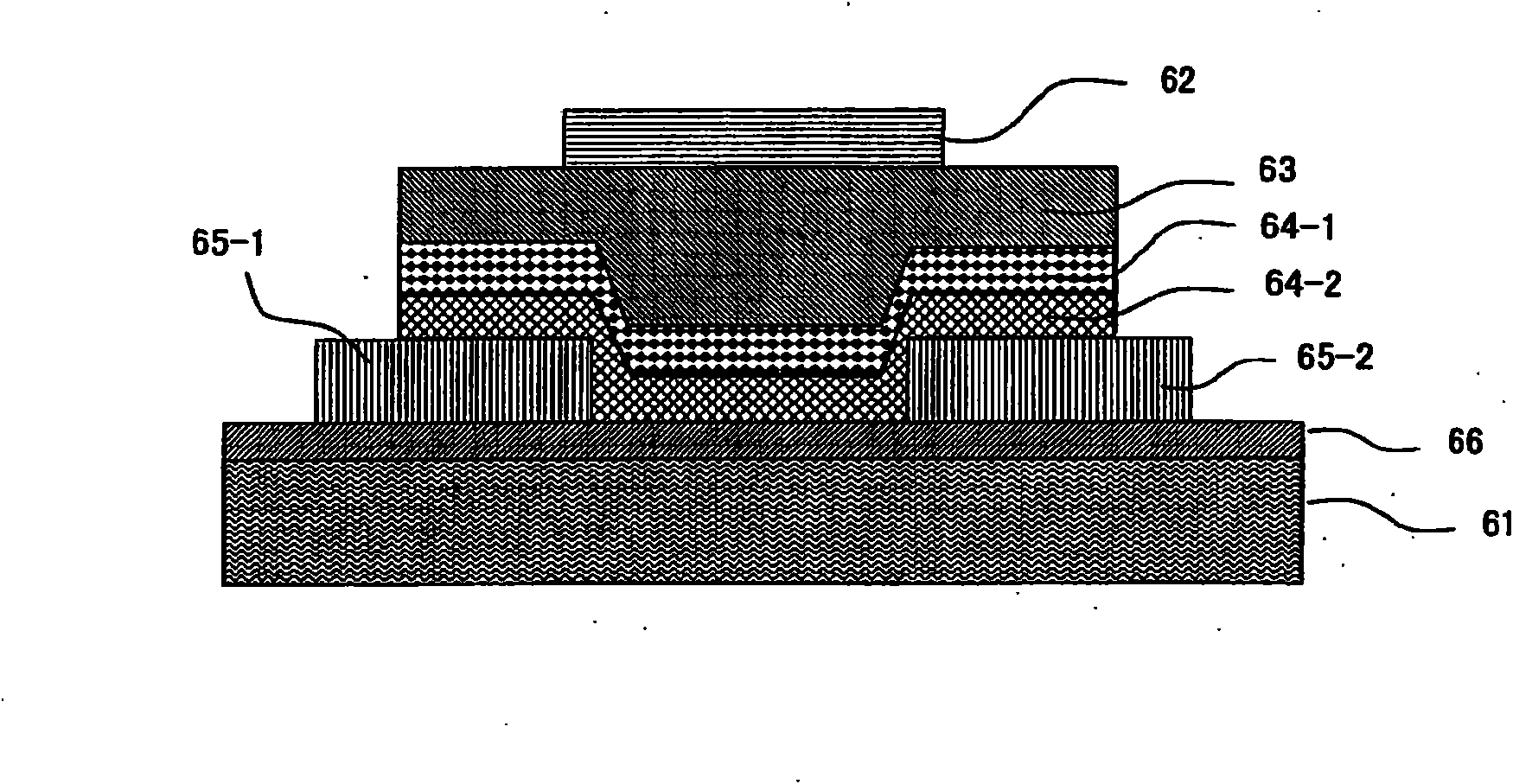

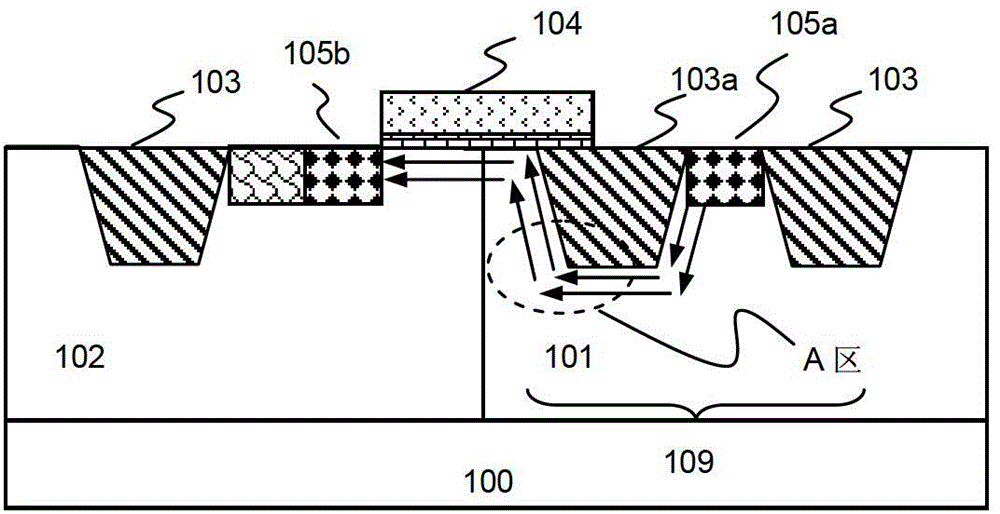

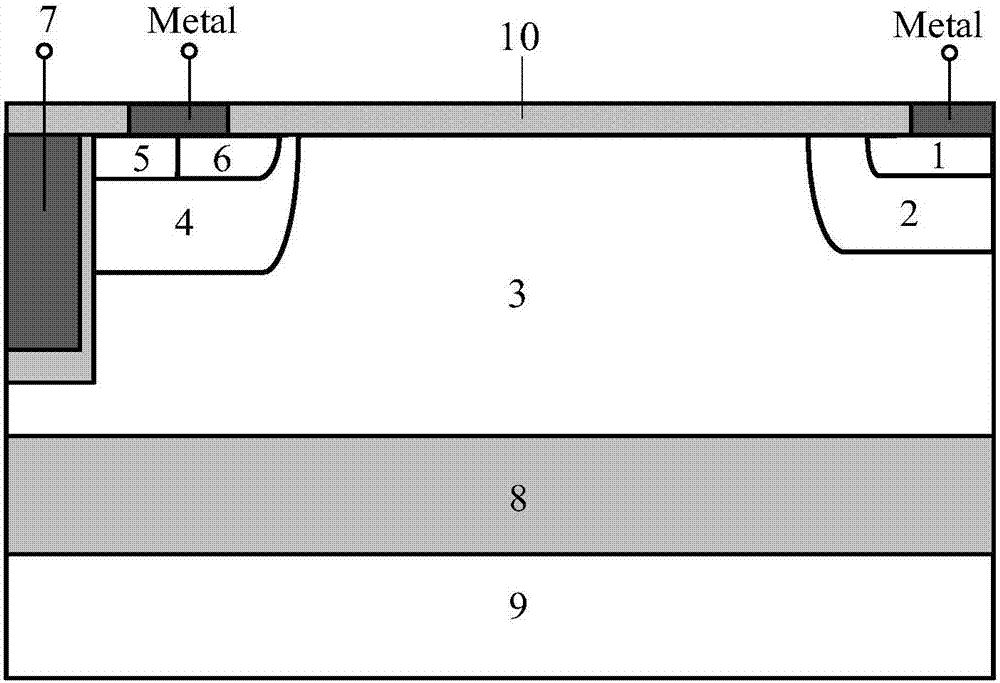

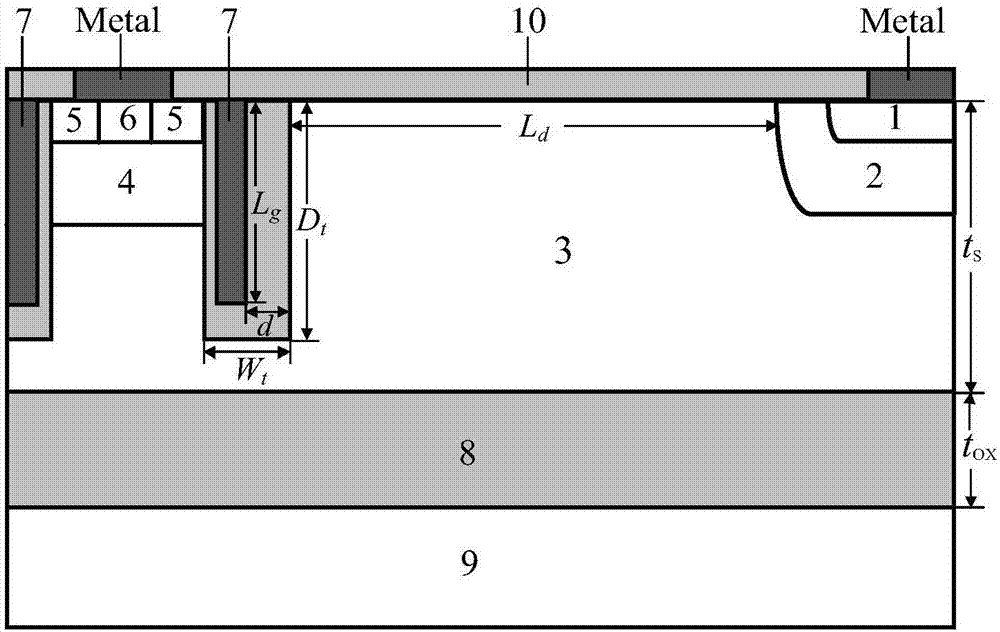

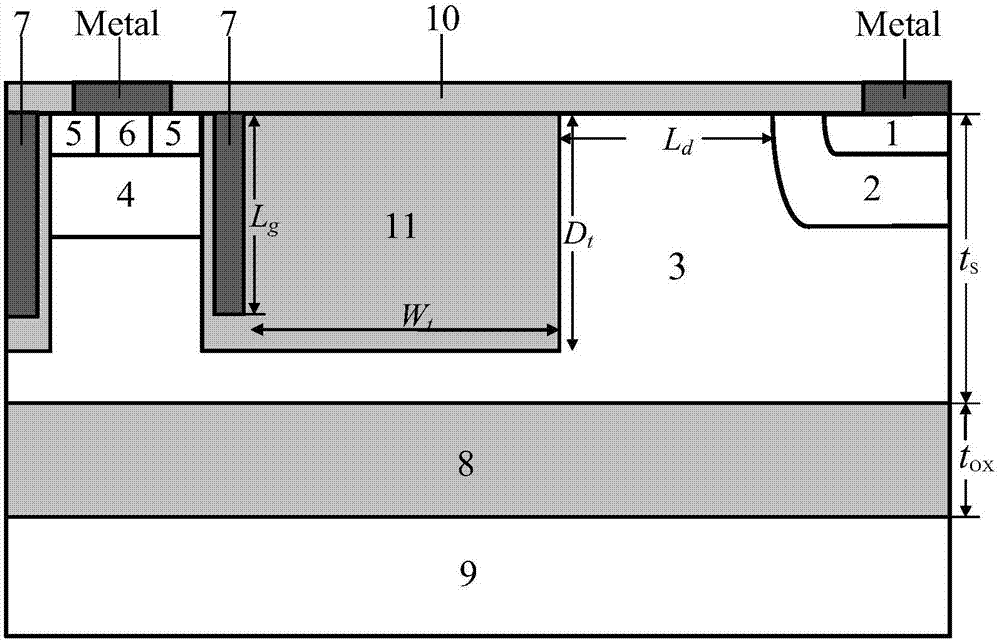

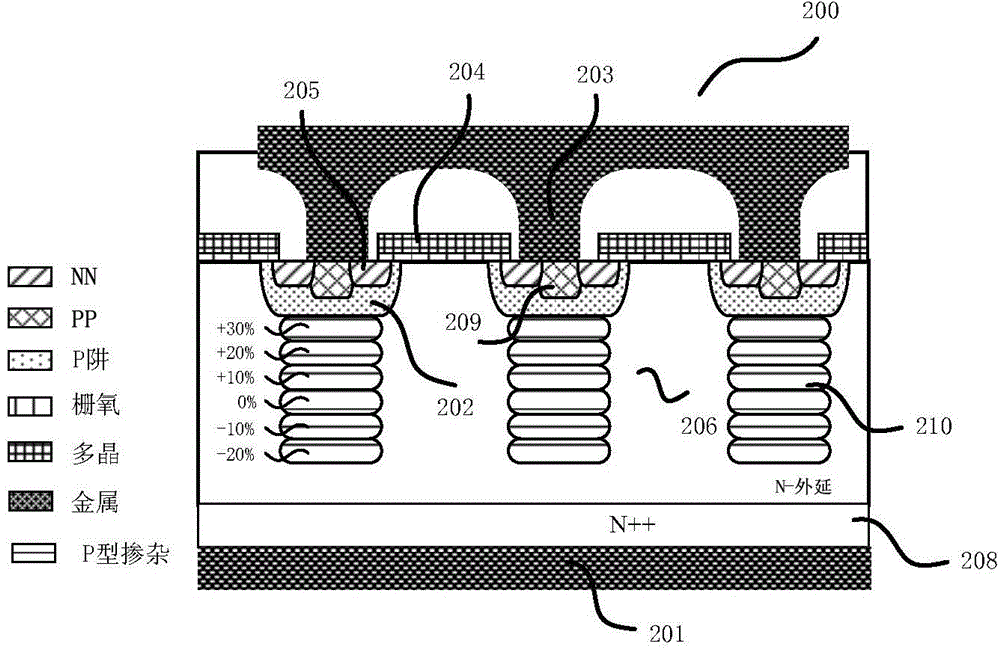

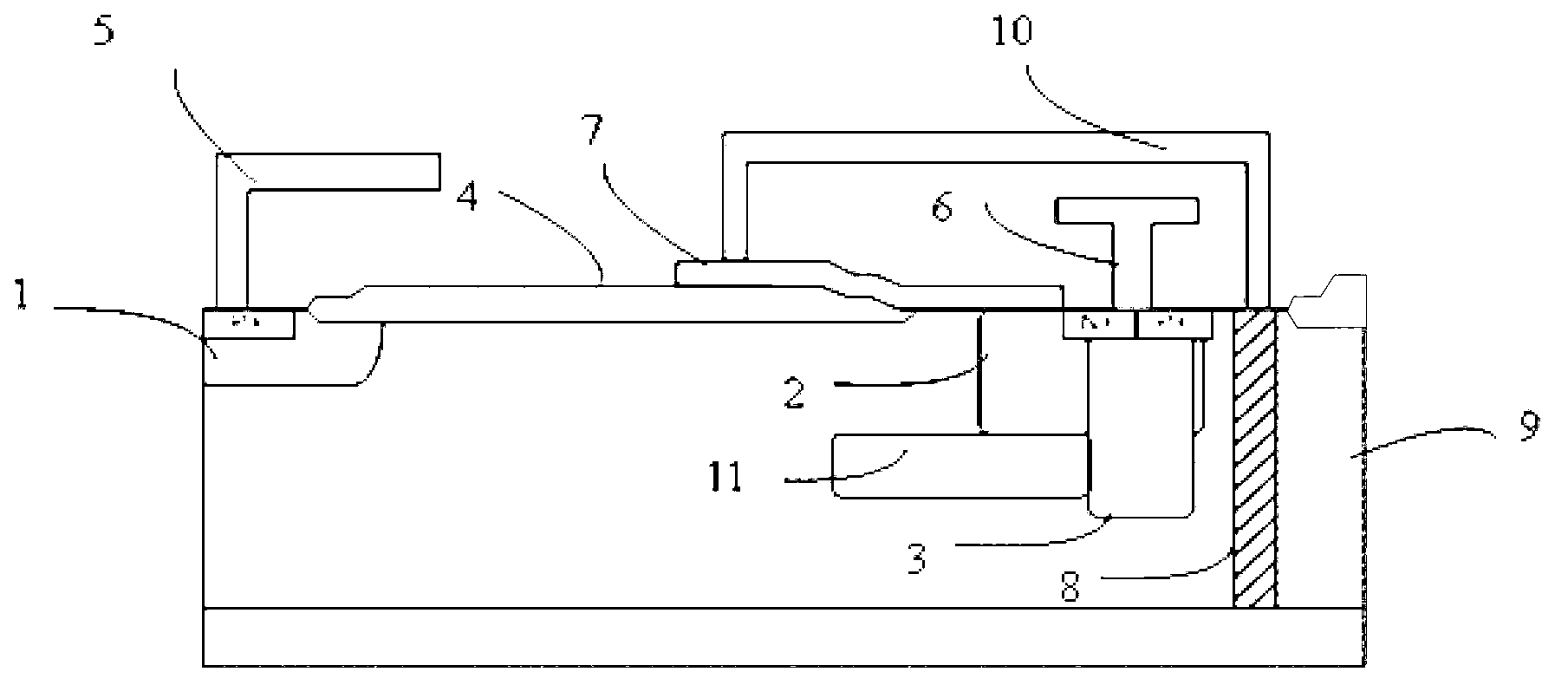

Silicon on insulator-lateral insulated gate bipolar transistor (SOI-LIGBT) device structure with low switch-off loss and dual groove gates

InactiveCN106876455AEvenly distributedPromote recombinationSemiconductor devicesSilicon dioxidePolycrystalline silicon

The invention provides a silicon on insulator-lateral insulated gate bipolar transistor (SOI-LIGBT) device structure with low switch-off loss and dual groove gates. The SOI-LIGBT device structure comprises a P-type substrate, buried oxide layer SiO2, an N-type drift region, a P-type well region, an N-buffer layer, an oxide layer, two N-type source ends, a P-type contact region and an N-type positive electrode region, wherein the P-type contact region is arranged between the two N-type source ends, gate oxide layers are arranged at two sides of a channel between the source ends and the P-type well region, and poly-silicon is arranged aside the gate oxide layers and is arranged at two sides of the P-type well region and at a left side of the N-buffer layer. The SOI-LIGBT device structure possesses a dual-gate structure and has higher current capability under the same condition, holes directly injected to the P-type well region are reduced by the introduction of an N-type carrier storage layer, so that the carrier distribution is more uniform, the carrier combination during switch off is facilitated, and the switch-off time is reduced; the effective space of the N-type drift region is reduced by groove medium SiO2, the injection of carriers at a right side is also simultaneously blocked, and a carrier accumulation layer is formed; and based on two effects, the switch-off loss of the structure is substantially reduced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

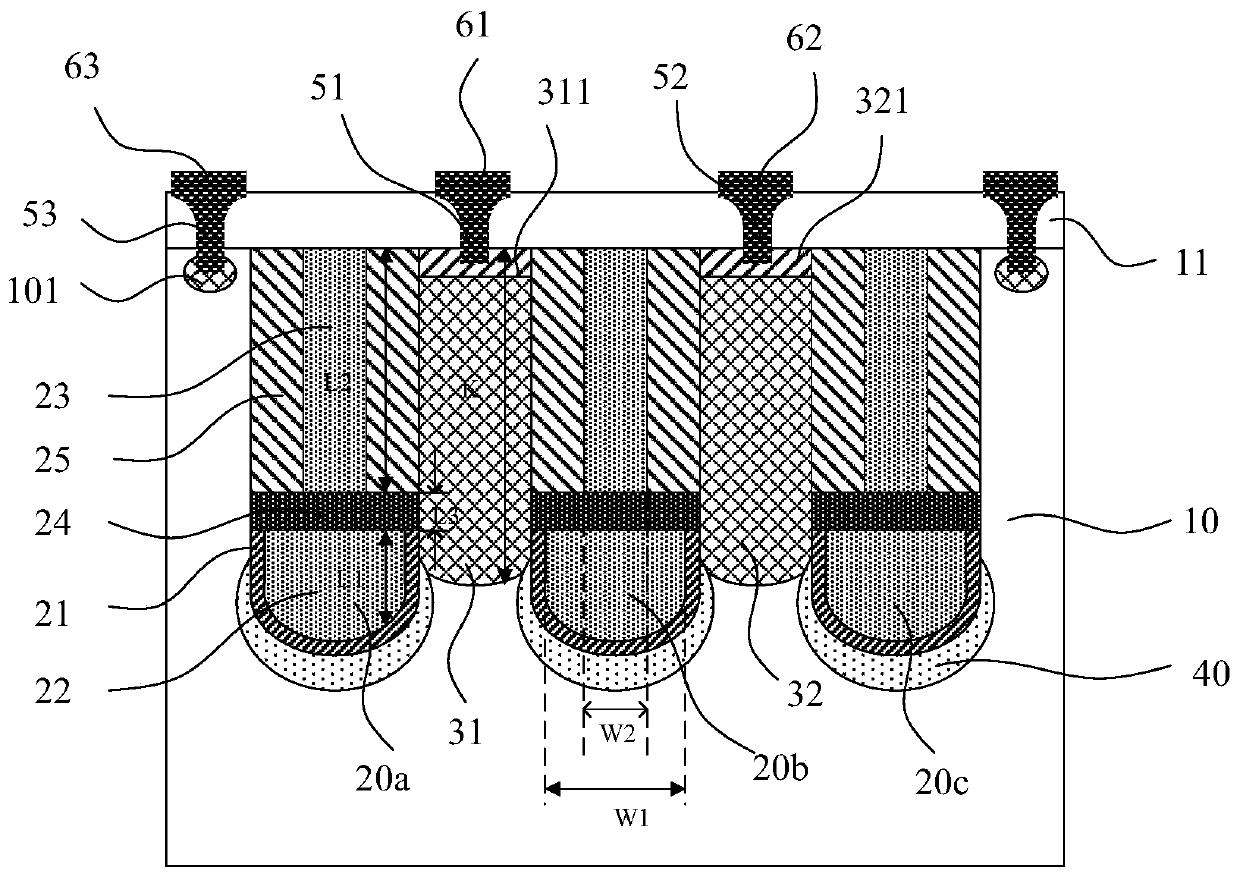

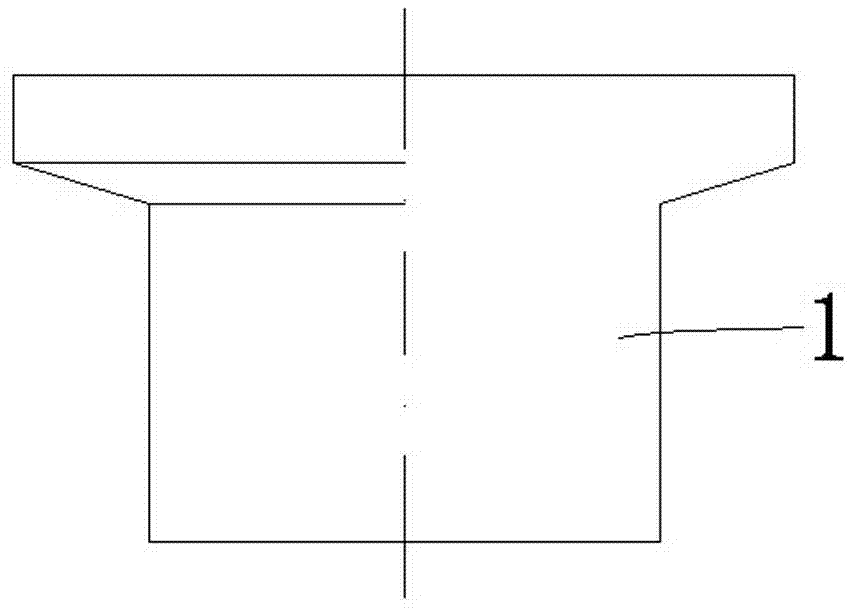

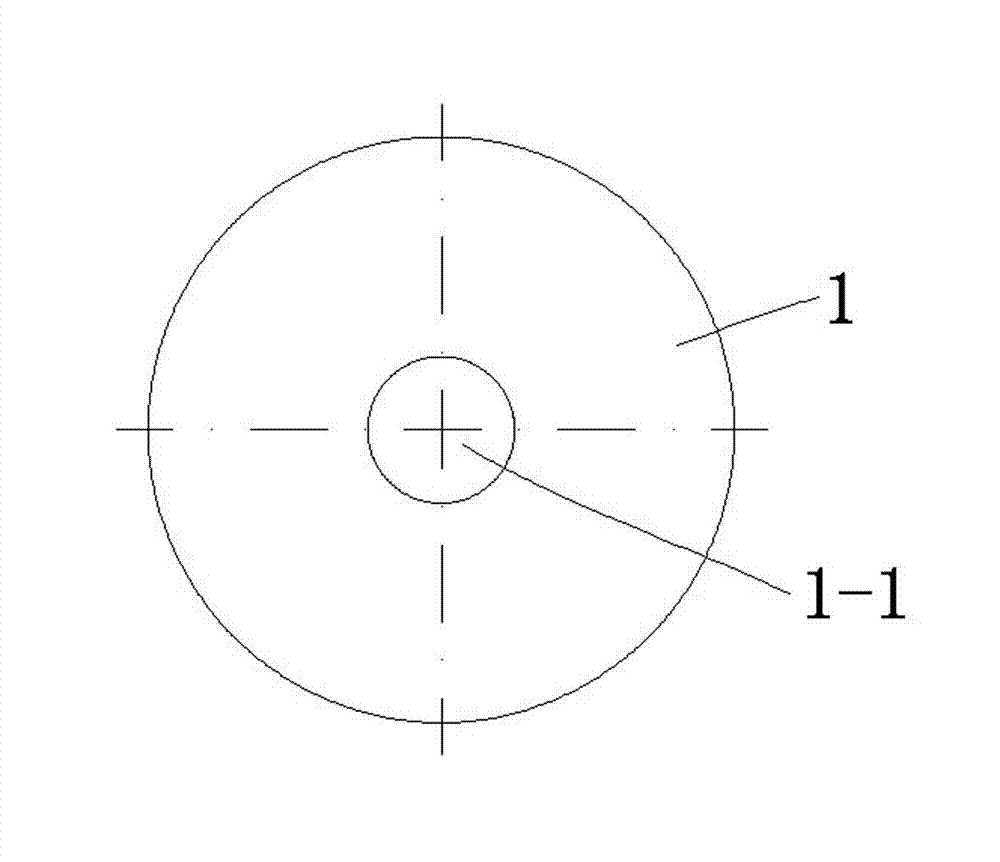

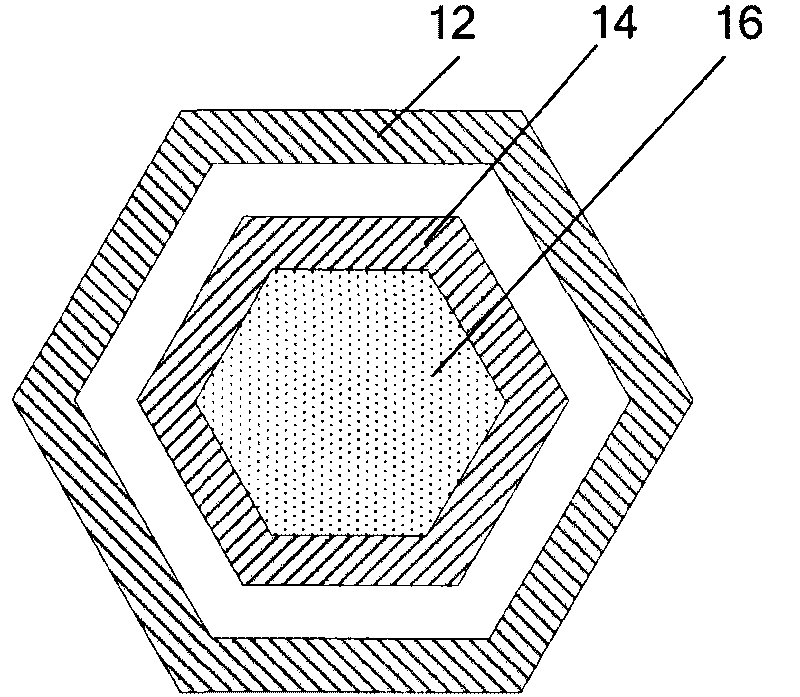

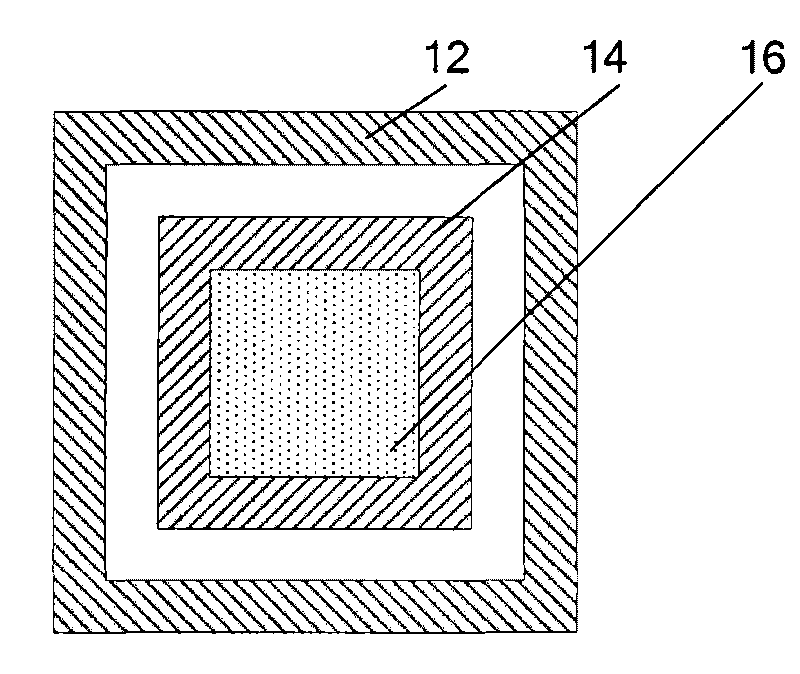

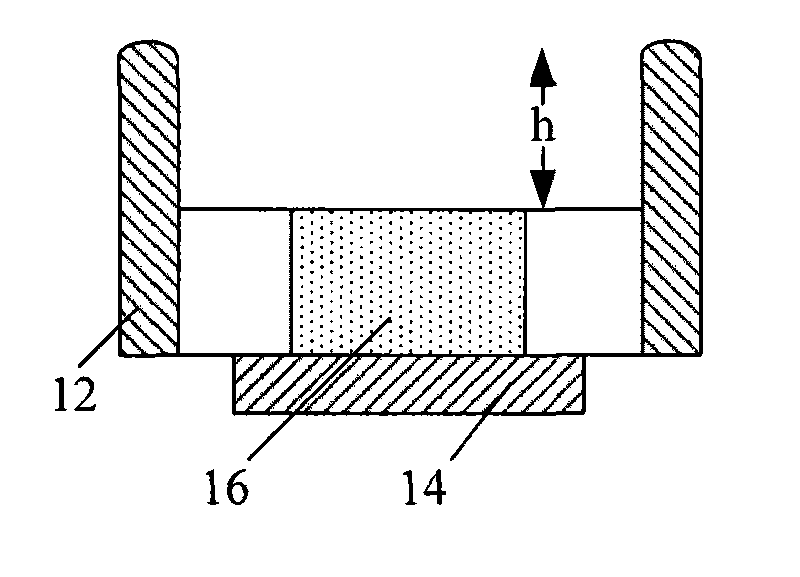

Power device chip

InactiveCN101728382AHigh aspect ratioIncreased current capabilityTransistorSolid-state devicesMedia layerElectric current

The embodiment of the invention discloses a power device chip and aims to improve the current capability of the power device chip. The chip comprises a plurality of unit cells which are in the same shape and are seamlessly jointed on a plane; a unit cell grid medium layer on the plane is in a shape that the perimeter of the unit cell grid medium layer is larger than the perimeter of a square when the area of the unit cell grid medium layer is same as that of the square, because the ratio of the width to the length of a groove in a unit area is an important factor for deciding the current capability of the chip. Under the condition that the process is fixed, the length of the groove is fixed and the width of the groove is approximately similar to the perimeter of the unit cells, thus the scheme provided by the embodiment of the invention improves the current capability of the power device chip.

Owner:PEKING UNIV FOUNDER GRP CO LTD +1

High-voltage power device and forming method thereof

ActiveCN105097932AMaintain pressure stabilityIncrease current channelSemiconductor/solid-state device manufacturingSemiconductor devicesHigh pressureComputer science

The invention provides a high-voltage power device and a forming method thereof. The device comprises a first doped area having a first doped type; one or a plurality of device doped areas arranged in the upper surface of the first doped area, wherein the device doped area has a second doped type opposite to the first doped type; and one or a plurality of second doped areas of the second doped type, wherein one end of the second doped area is in electric contact with a corresponding device doped area, the other end of the second doped area longitudinally extends to the first doped area, and in the transverse direction, the second doped areas and the first doped areas are alternatively distributed. The impurity concentration of each second doped area changes in a non-linear manner with the change of the longitudinal depth, and the total impurity concentration of the second doped areas is lower than the total impurity concentration of the first doped areas. According to the invention, the withstand voltage of the device is stabilized, and the conduction resistance of the device is reduced.

Owner:HANGZHOU SILAN MICROELECTRONICS

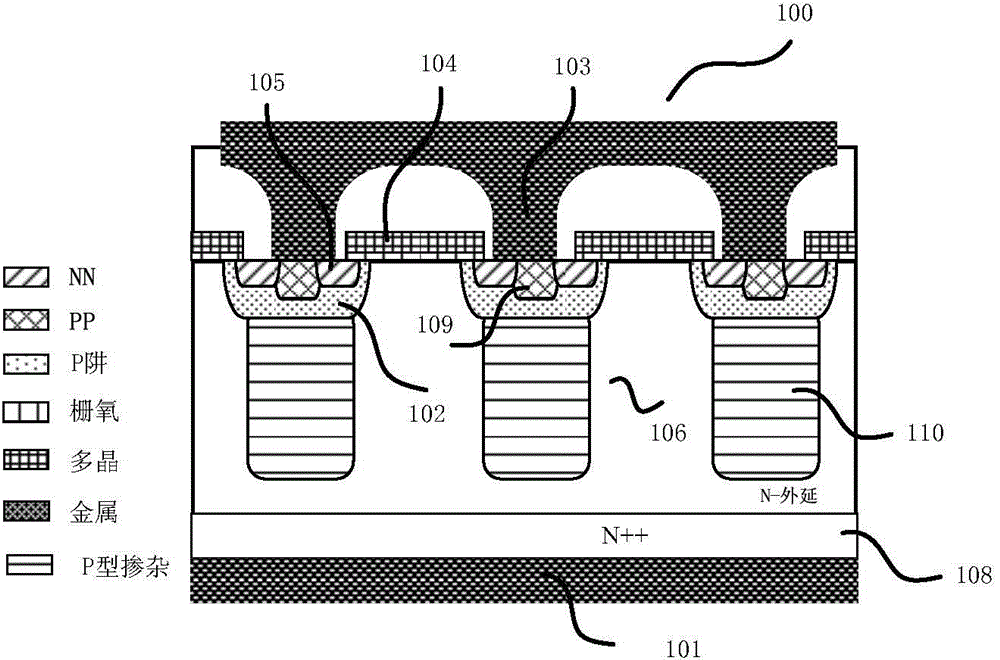

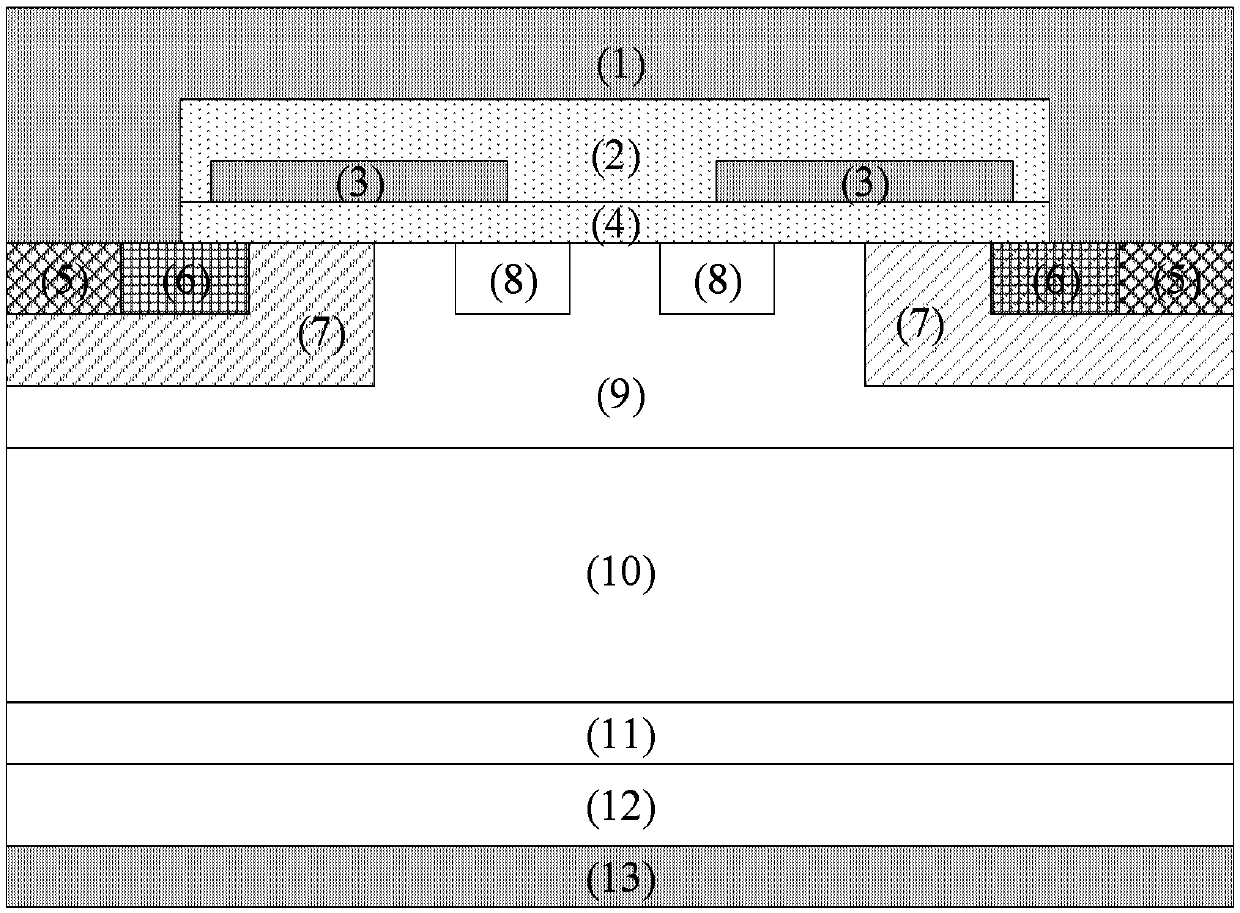

4H-SiC MOSFET power device and manufacturing method thereof

ActiveCN109616523AImprove switching characteristicsReduce areaSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricMOSFET

The invention discloses a 4H-SiC MOSFET power device and a manufacturing method thereof. The power device comprises a source electrode (1), an SiO2 interlayer dielectric (2), a grid electrode (3), a gate oxide layer (4), a P + contact region (5), an N+ source region (6), a P well (7), an additionally injected P-type region (8), an N type epitaxial layer (9), an N-epitaxial layer (10), a buffer layer (11), an N+ substrate (12) and a drain electrode (13). The 4H-SiC MOSFET power device disclosed in the invention adopts a separation grid structure, and by virtue of the structure the input capacitance and the grid leakage capacitance can be effectively lowered, and the switching performance of the device is improved; by introducing P type doping in a JFET region, the electric field intensity of a gate oxide layer can be effectively reduced, and the reliability of the device is improved; and in addition, a current expanding layer structure is adopted, so that the current capability of the device can be considered.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

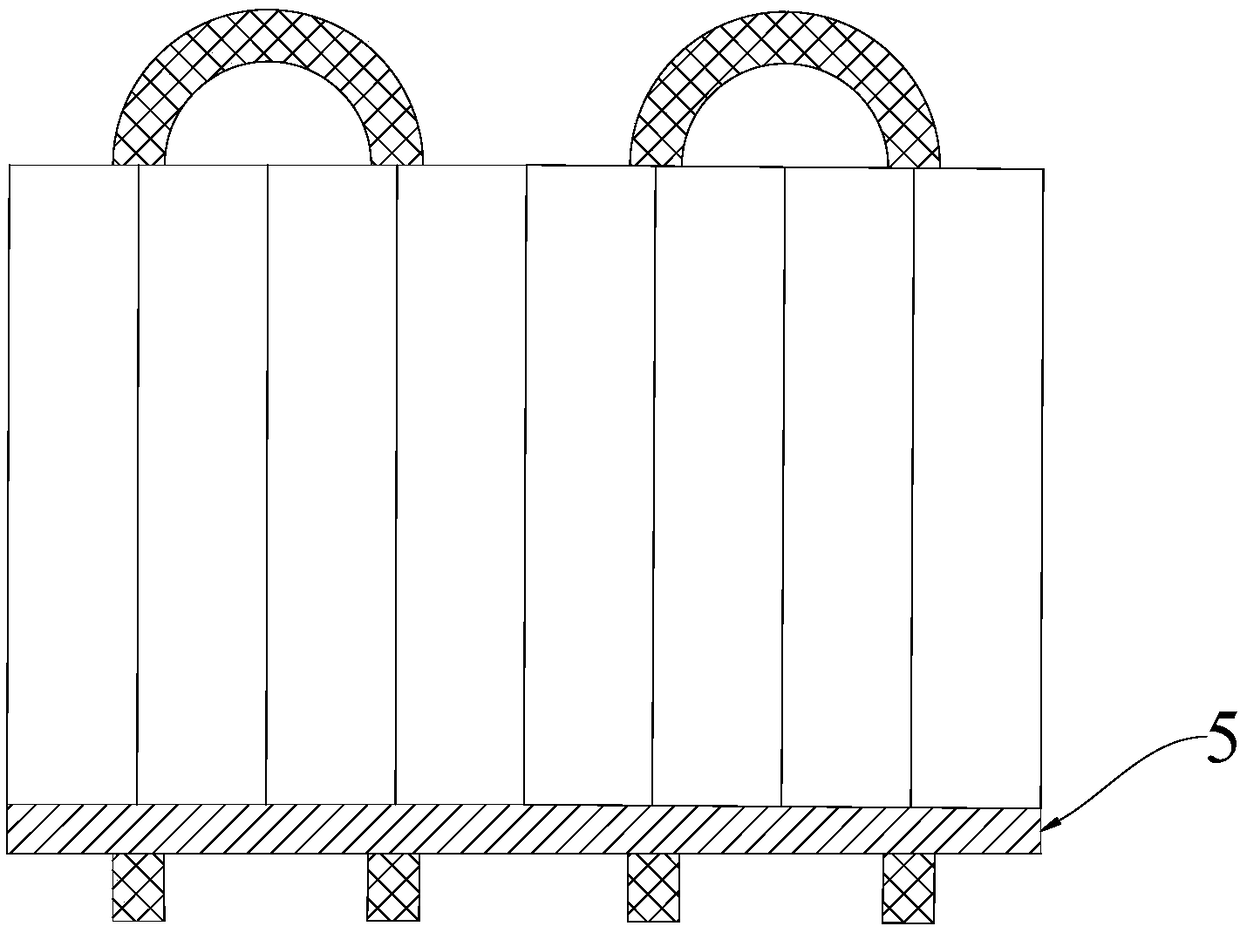

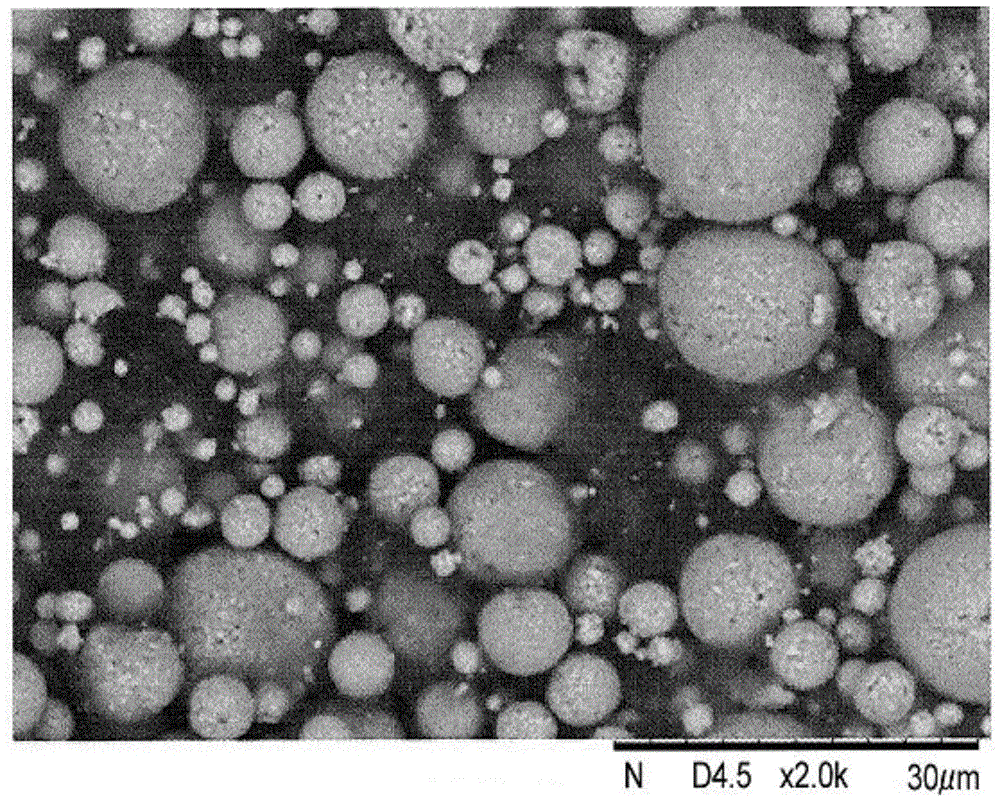

Flux channeled, high current inductor

InactiveUS7864015B2Core lossIncreased current capabilityTransformers/inductances magnetic coresCores/yokesElectrical conductorInductor

A flux-channeled high current inductor includes an inductor body having a first end and an opposite second end and a conductor extending through the inductor body. The conductor includes a plurality of separate channels through a cross-sectional area of the inductor body thereby directing magnetic flux inducted by a current flowing through the conductor into two or more cross-sectional areas and reducing flux density of a given single area. The inductor body may be formed of a first ferromagnetic plate and a second ferromagnetic plate. The inductor may be formed from a single component magnetic core and have one or more slits to define inductance. The inductor may be formed of a magnetic powder. A method is provided for manufacturing flux-channeled high current inductors.

Owner:VISHAY DALE ELECTRONICS INC

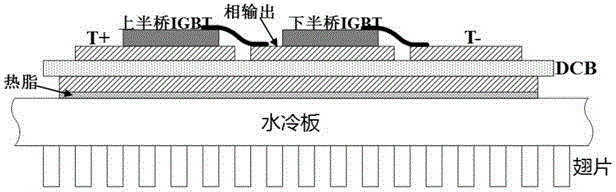

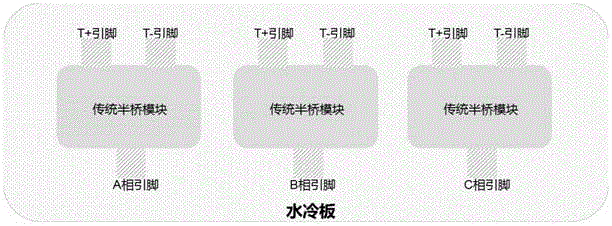

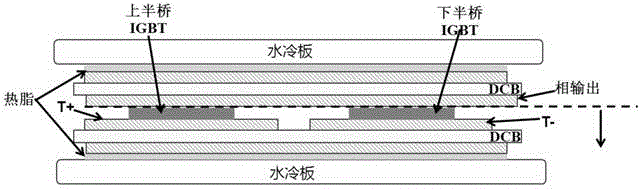

IGBT module packaging structure of inverter

ActiveCN104952859ALow costShort qualifyingSolid-state devicesSemiconductor devicesPower inverterParasitic capacitance

The invention discloses an IGBT module packaging structure of an inverter. The positive input end and the negative input end of each half-bridge IGBT module are respectively arranged on the lower surface of a chip. A buffer capacitor can be respectively welded on the surfaces of the positive input end area and the negative input end area on the surface of a first insulation ceramic substrate, thereby maximally eliminating pin inductance of the IGBT module through short-circuit. An E pole of an upper half-bridge IGBT chip and a C pole of the lower half-bridge IGBT chip of each half-bridge IGBT module are respectively arranged on the upper surface of the chip, and can be located far from a water cooling board, thereby reducing an equivalent parasitic capacitance, reducing earth common-mode interference current, and improving EMC performance of the inverter. A binding line of each phase half-bridge IGBT module is saved, thereby improving current capability and prolonging service life time, reducing chip area and lowering inverter cost. Electric pins of each phase half-bridge IGBT module are directly welded on the insulation ceramic substrate and a chip. The distances among the positive input end, the negative input end and phase output pin of each phase half-bridge IGBT module are small, thereby realizing short outlet wire of the inverter, simplifying wiring and ensuring no easy heating of an inner chamber by copper bars.

Owner:UNITED AUTOMOTIVE ELECTRONICS SYST

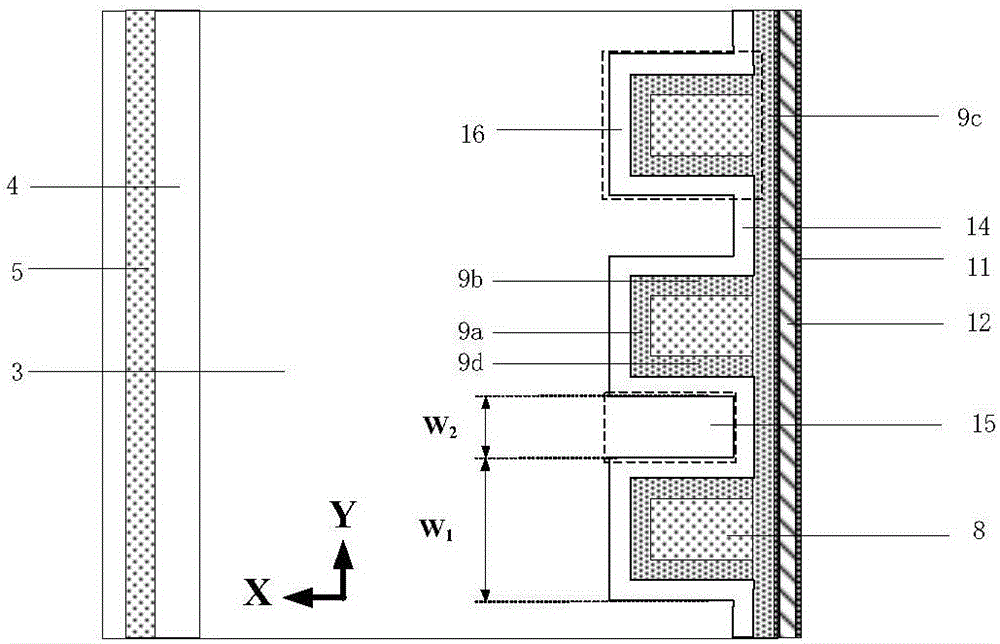

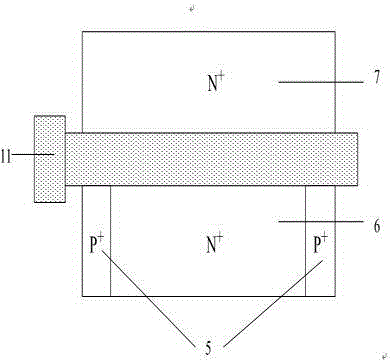

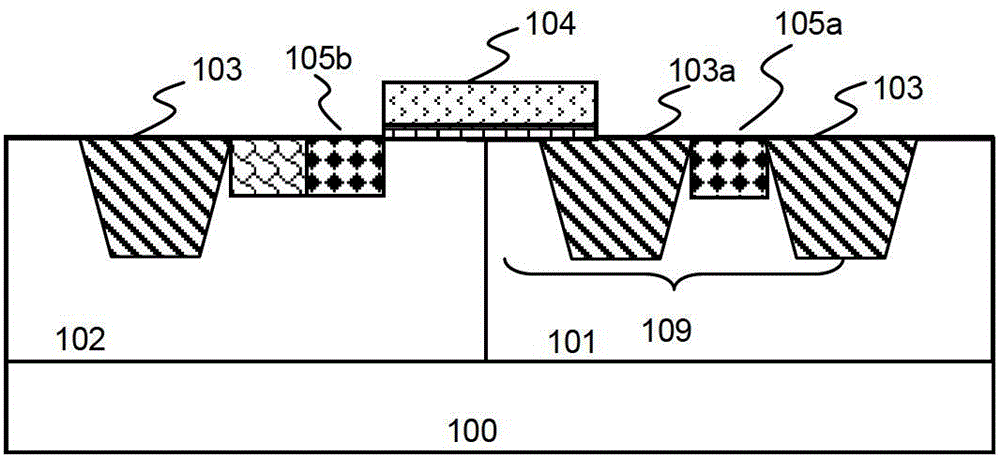

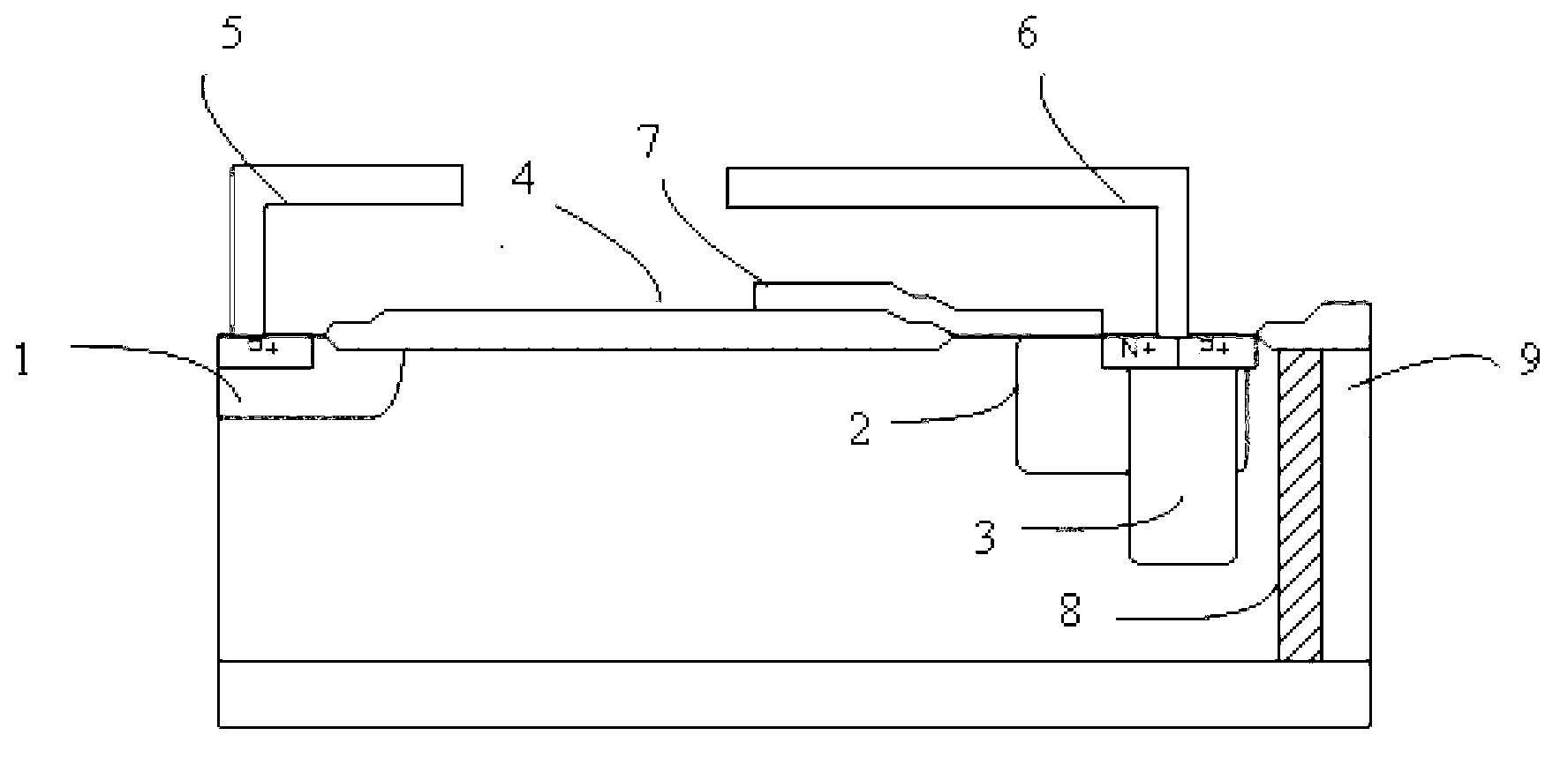

Double-gate SOI-LIGBT device with P-type buried layer

InactiveCN103325820ASmall sizeIncreased current capabilitySemiconductor devicesFilling materialsBody area

The invention relates to a semiconductor device and discloses a double-gate SOI-LIGBT device with a P-type buried layer. Under the condition that voltage resistance is ensured, the current capacity of the device is enhanced. According to the double-gate SOI-LIGBT device, the P-type buried layer is additionally arranged, traditional bulk silicon is changed into polycrystalline silicon for serving as filling materials of a separation groove, the separation groove is connected with a gate end electrode through a metal structure and accordingly serves as a gate electrode in the lateral direction of the device. The double-gate SOI-LIGBT device not only can serve as a gate field plate to be shrunk into an electric field near a channel region for meeting the voltage resistance requirement. Meanwhile, the double-gate SOI-LIGBT device can serve as a longitudinal gate electrode so that the current can stream on the surface and can also stream below the P-type buried layer in a device body area, the current capacity is enhanced, on-resistance is reduced, and therefore the size of the device in the width direction can be shortened under the condition that the voltage resistance is ensured. The double-gate SOI-LIGBT device with the P-type buried layer is suitable for a PDP scanning driving chip.

Owner:SICHUAN CHANGHONG ELECTRIC CO LTD

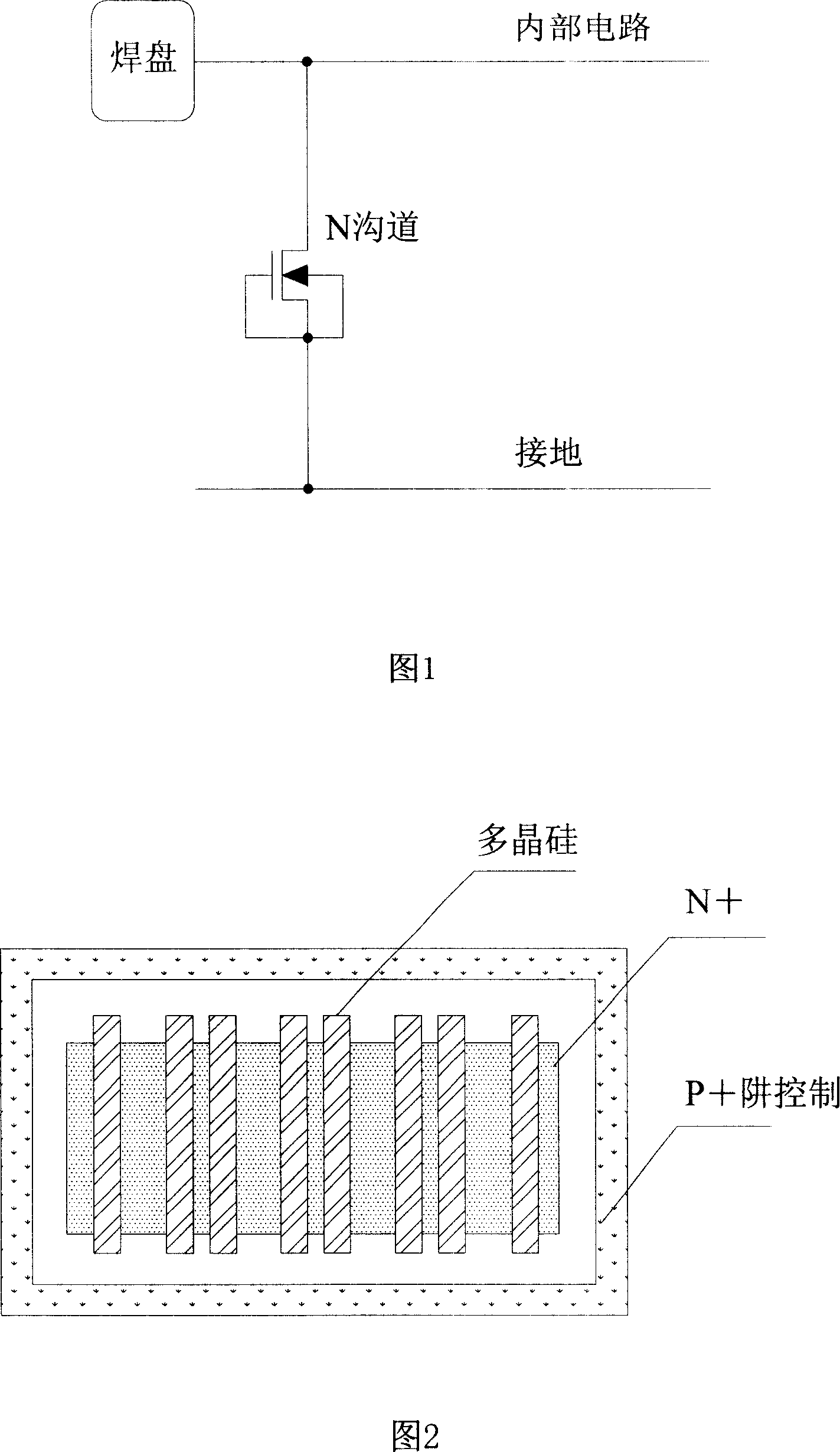

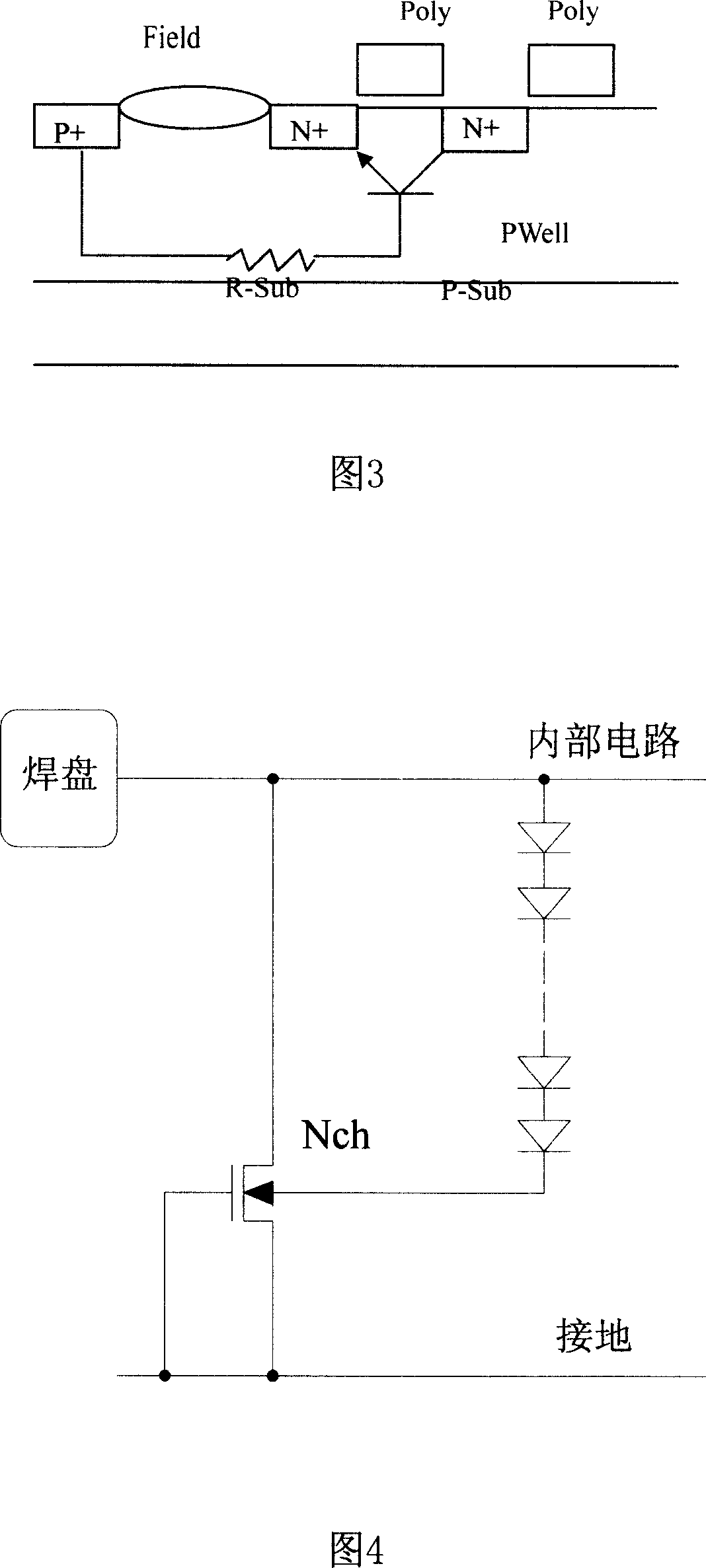

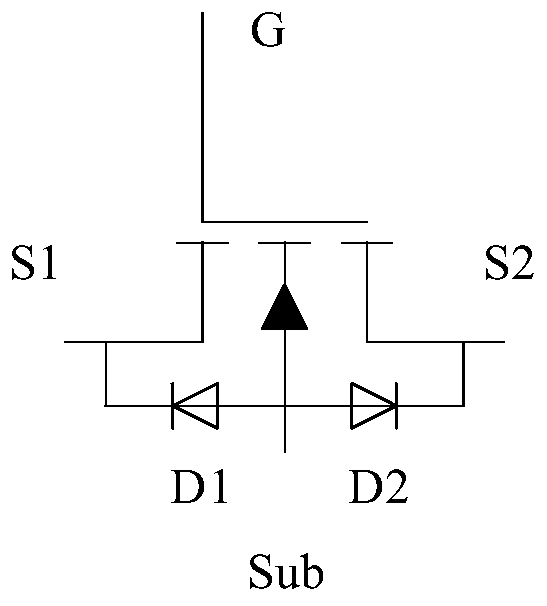

Electrostatic discharging protection circuit triggered by lining-bottom

InactiveCN1979842AQuick trigger onOpen smoothlySemiconductor/solid-state device detailsSolid-state devicesEngineeringSubstrate bias voltage

The protection circuit includes N type metallic oxide buffer (Nch Buffer) transistor, and a diode string. Grid of (Nch Buffer) transistor is connected to ground. Substrate is connected to cathode of diode at tail of the diode string. Anode of diode at header of the diode string is connected to previous stage of the internal circuit. When static discharge occurs, before Nch Buffer transistor turns on, the diode string generates current, which provides substrate current for Nch Buffer transistor, and generates substrate bias voltage so as to trigger Nch Buffer transistor. When static discharge occurs, the invention triggers and turns transistor to on quicker, provides larger current release capability, and turns transistor to on uniformly.

Owner:SHANGHAI HUA HONG NEC ELECTRONICS

Bidirectional power device and manufacturing method thereof

PendingCN110120416AImprove withstand voltage characteristicsShorten the lengthSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricHigh pressure

The invention discloses a bidirectional power device and a manufacturing method thereof. The bidirectional power device comprises a semiconductor layer; a trench in the semiconductor layer; a gate dielectric layer which is positioned on the side wall of the trench; a control gate which is positioned in the trench and extends from the first surface of the semiconductor layer to the lower part of the trench, wherein the control gate and the semiconductor layer are separated by the gate dielectric layer. According to the invention, the control gate in the trench extends from a first surface of asemiconductor layer to a lower portion of the trench, and a source region and a drain region extend from the first surface of the semiconductor layer to overlap the control gate at the lower portion of the trench. The extending lengths of the source region and the drain region are greater, so that the source region and the drain region can bear a high voltage applied to the source region and the drain region in the longitudinal direction when the bidirectional power device is cut off, and the voltage withstanding characteristic of the bidirectional power device is improved.

Owner:HANGZHOU SILAN MICROELECTRONICS