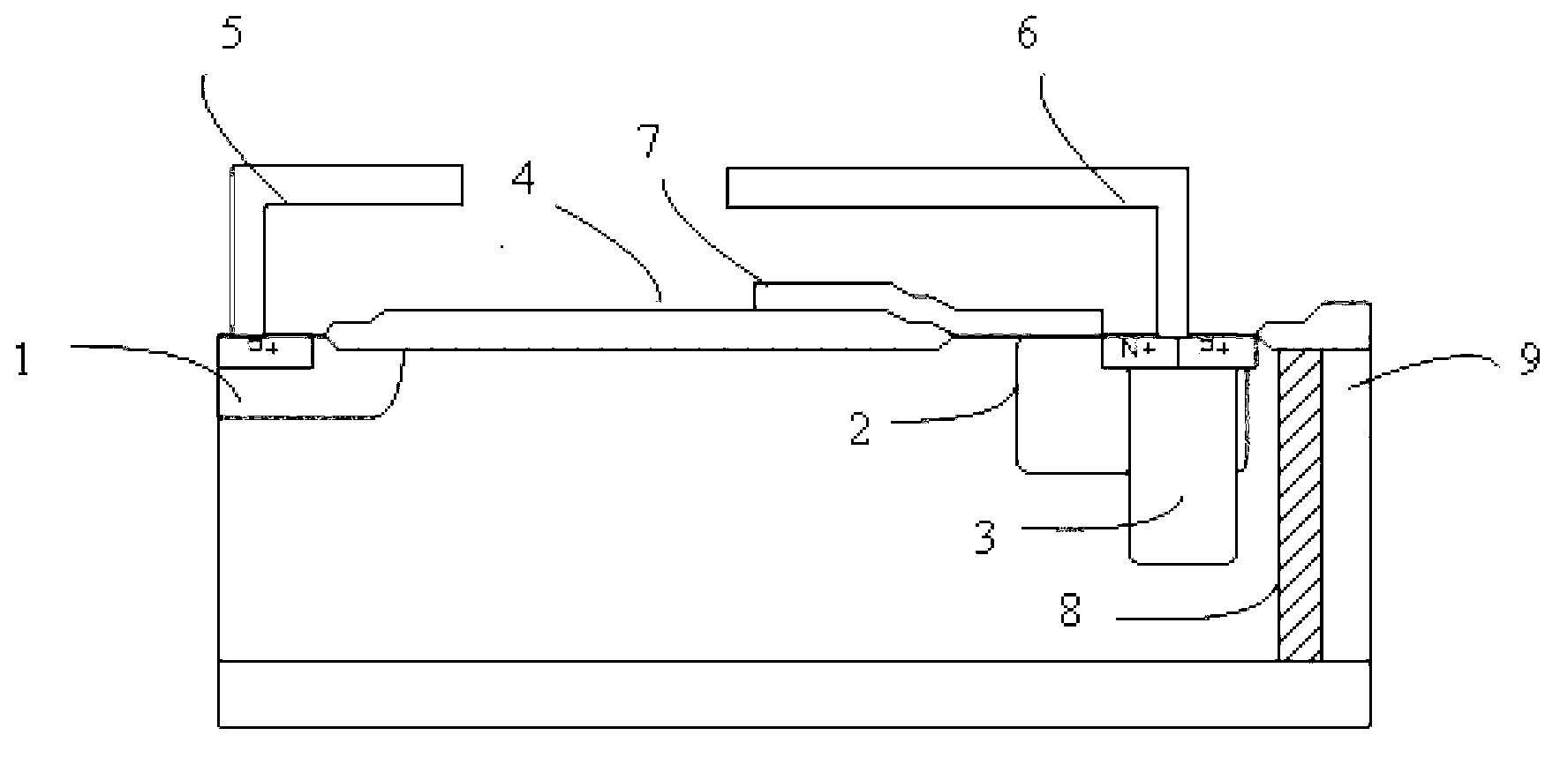

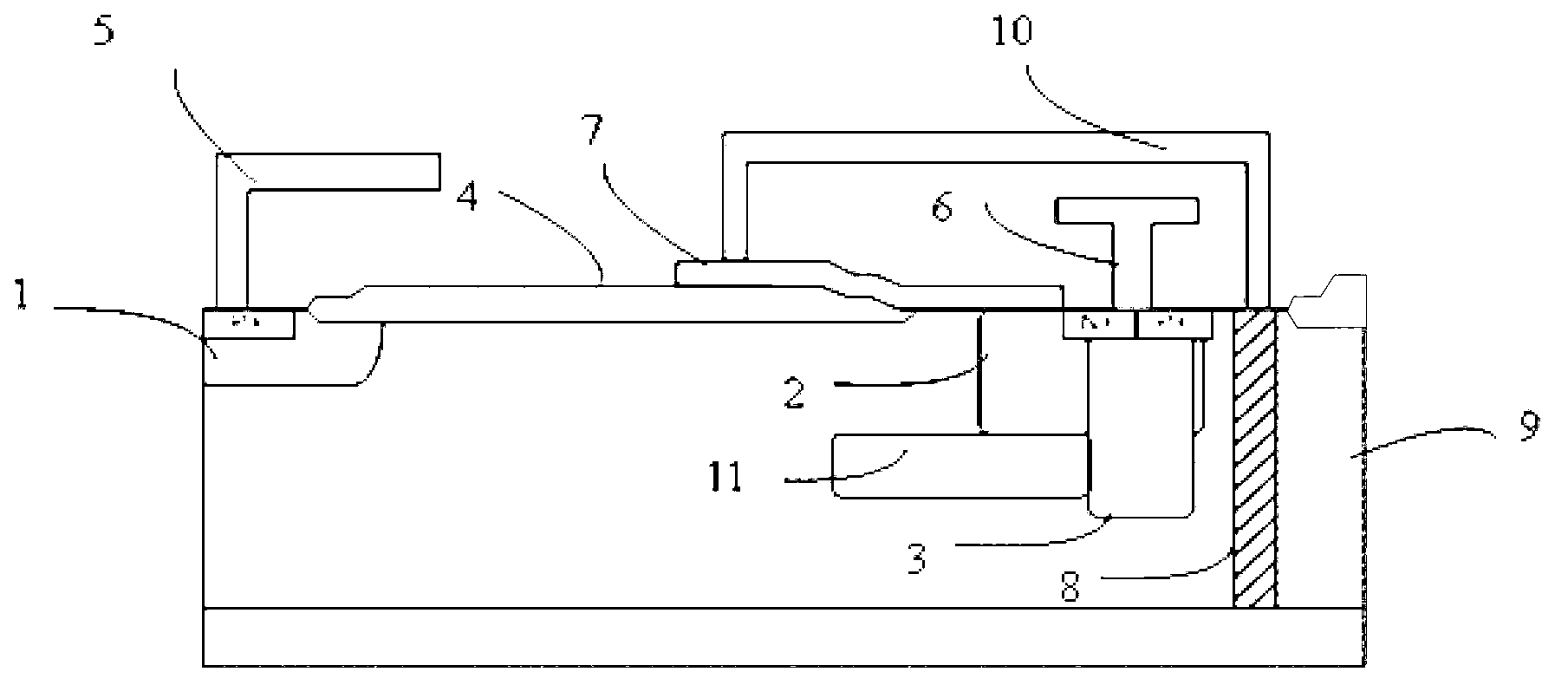

Double-gate SOI-LIGBT device with P-type buried layer

A device, N-type technology, applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve the problems of increasing the current capacity of the device, and no good solution has appeared, to increase the current capacity, reduce the size, and reduce the on-resistance. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013] The traditional LIGBT device introduces RESURF technology, and its source, drain, and gate field plates smooth the high electric field peaks formed at the surface field oxygen and drift regions of the device, making the electric field closer to the rectangular distribution and achieving higher resistance. However, in the on-state process, the current line mainly flows from the surface of the device, and the current in the body area is small, causing a certain waste; in response to this problem, the present invention proposes a new type of SOI-LIGBT device, by increasing P-type buried layer, and the filling material in the isolation trench is converted from traditional bulk silicon to filled polysilicon, and the isolation trench is connected to the gate terminal electrode through a metal structure, thereby using it as a gate electrode in the side direction of the device, making it It can be used as a gate field plate to reduce the electric field near the channel region to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More