Patents

Literature

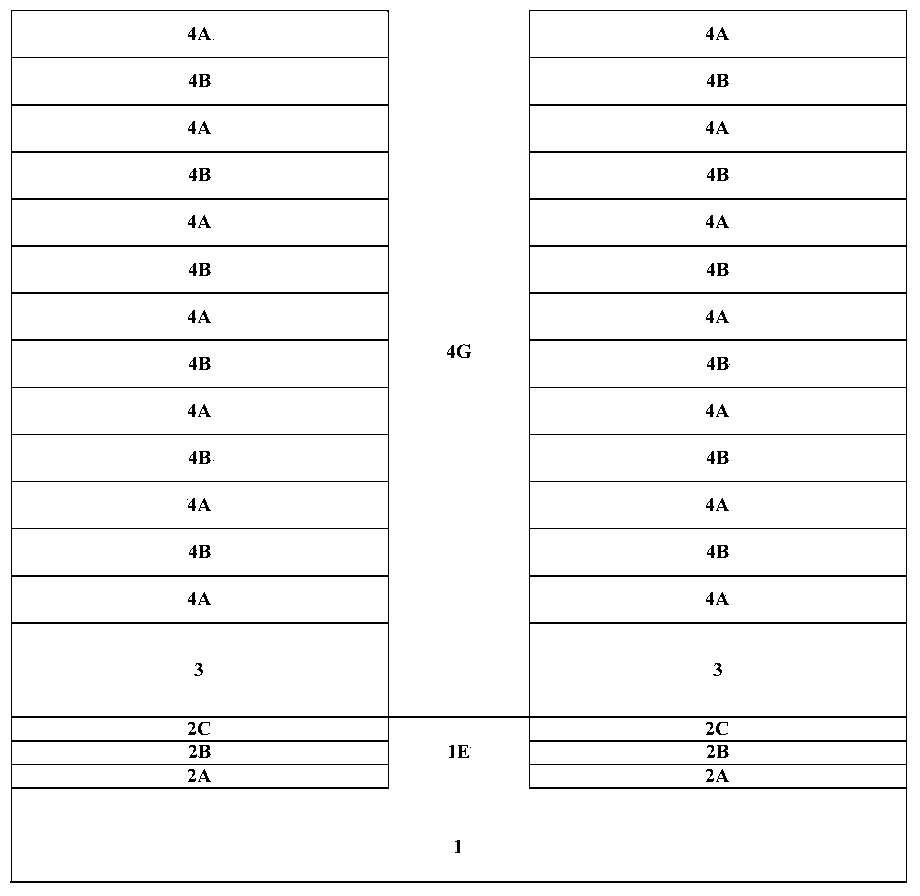

44results about How to "Increase current channel" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

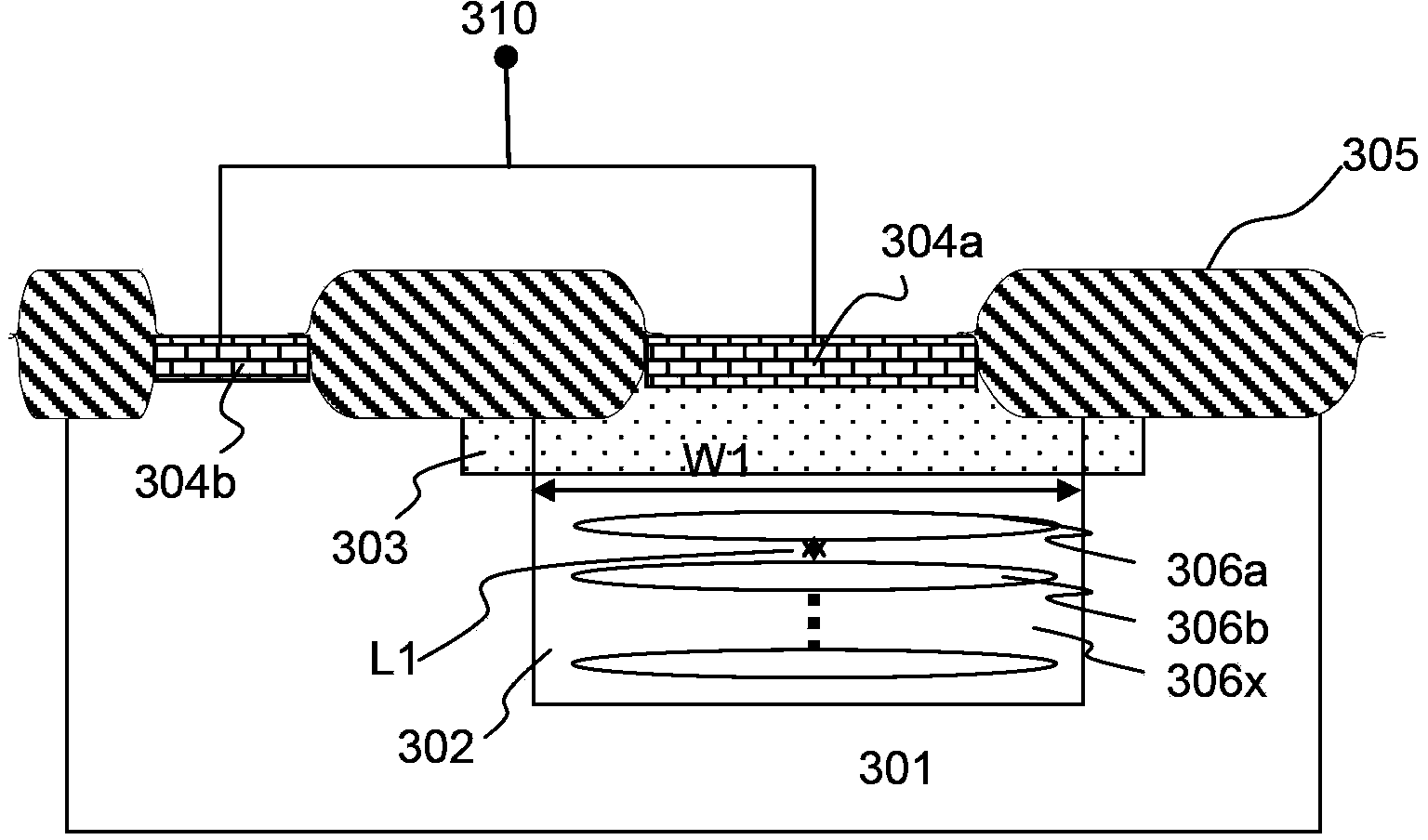

Method of manufacturing three-dimensional semiconductor device

ActiveUS20170250193A1Reduce channel surface roughnessEnhance channel carrier mobilitySolid-state devicesSemiconductor/solid-state device manufacturingCharge carrier mobilitySurface roughness

A method of manufacturing three-dimensional semiconductor device, comprising the steps of: forming a stack structure of a plurality of a first material layers and a second material layers on a substrate in the memory cell region; etching said stack structure to form a plurality of trenches; forming channel layers in said plurality of trenches; performing annealing treatment to at least one surface of the channel layers to reduce the surface roughness and the interface state. In accordance with the three-dimensional semiconductor device manufacturing method of the present invention, the formation of interface states is depressed by introducing a dummy channel sacrificial layer for the interface treatment on the channel surface and back surface, and / or the channel surface roughness is reduced by introducing a buffer layer on the channel surface and back surface during the treatment, which can improve the channel carrier mobility, improve the channel current as well as the reliability of the memory cell.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

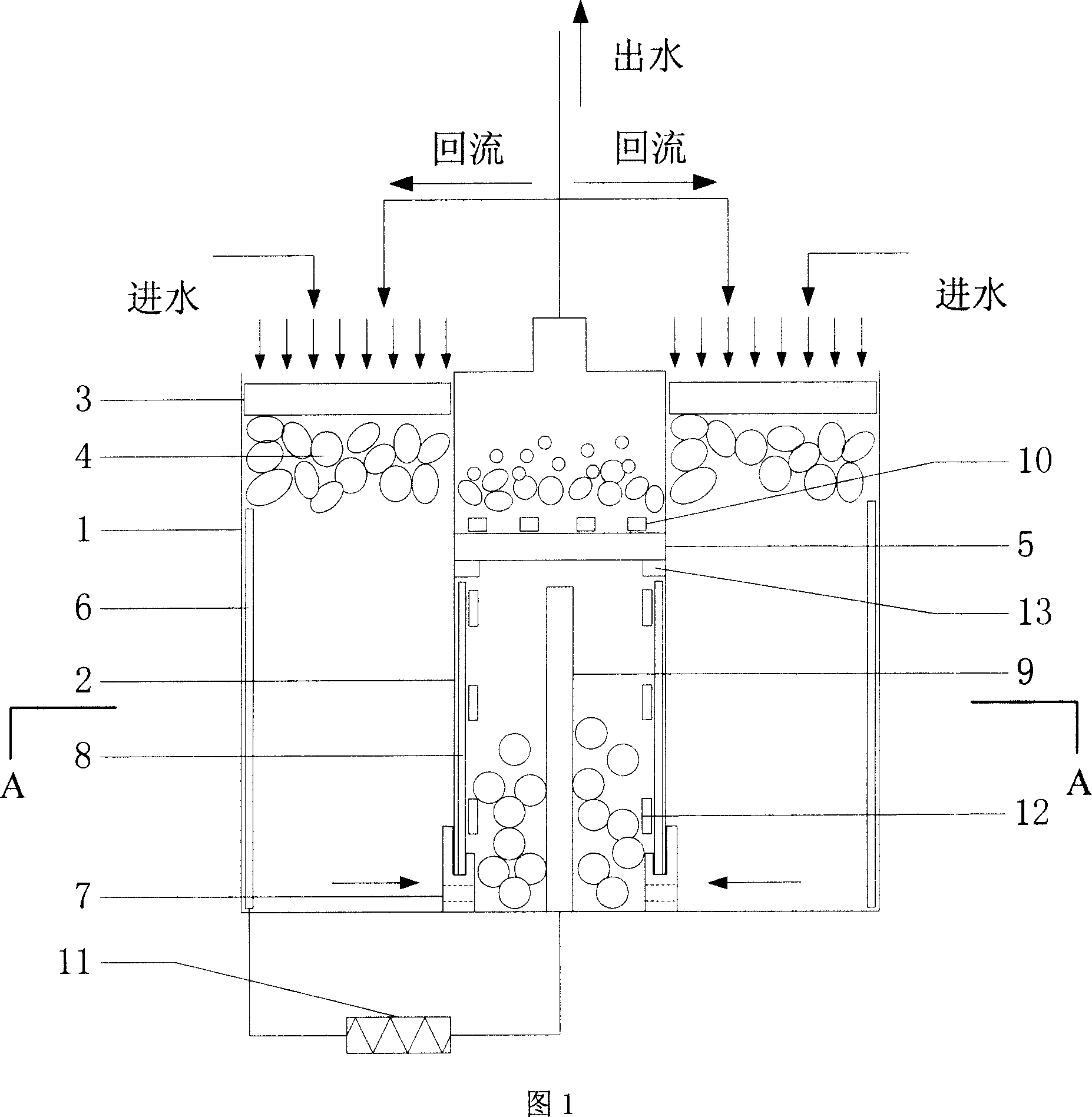

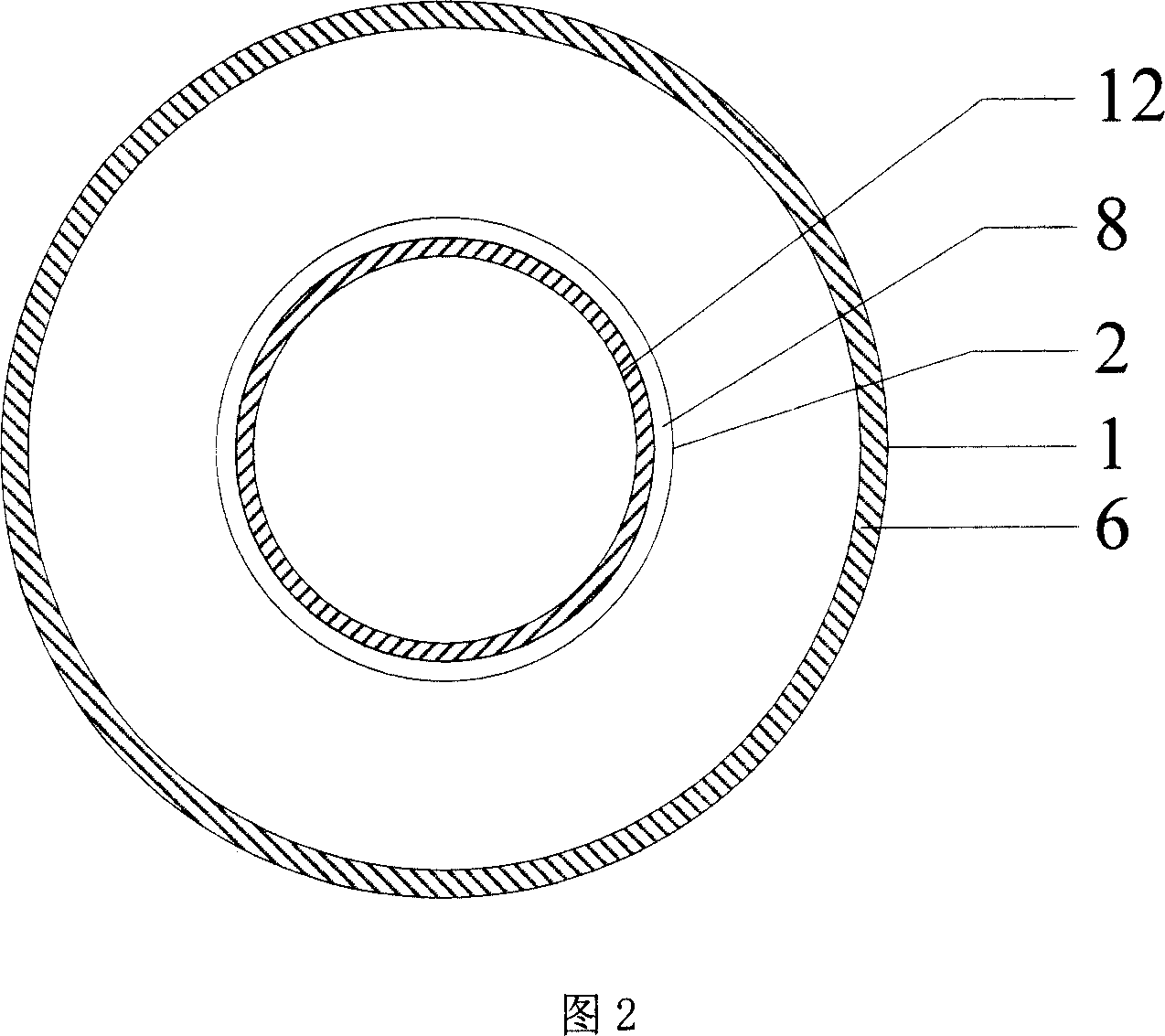

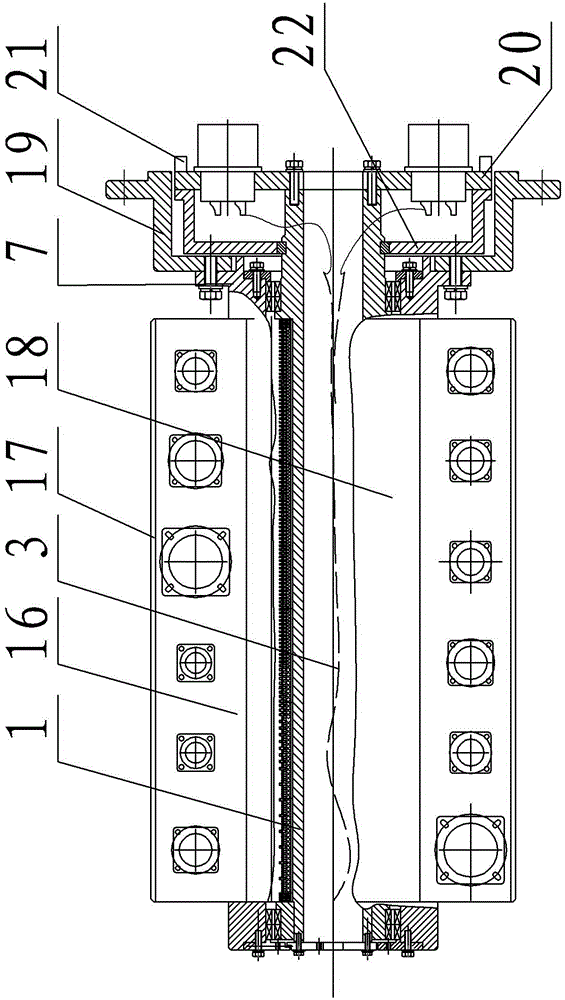

Double-drum microbial fuel cell

InactiveCN1937297ALow costLower internal resistanceBiochemical fuel cellsHigh concentrationInternal resistance

The fuel cell is composed of outer tube, inner tube, even water distributor, filler, graphite, graphite rod, and load etc. Anode chamber is surrounded by outer tube and inner tube. Sewage enters into anode chamber from the even water distributor, and flows to cathode chamber through diversion trench. Being filled to the outer tube, the filler is as carrier for microbe. Being pasted on inner wall of the outer tube, flexible graphite is in use for collecting anode current. Graphite rod setup inside cathode chamber is in use for collecting cathode current. Graphite rod, flexible graphite, and load constitute external circuit. The invention is suitable to degrading organic wastewater in high concentration, and generating electricity, or cleansing domestic sewage. The fuel cell is suitable to continuous running for long-term. Features are: low cost, low internal resistance, large capacity for generating electricity and capable of denitrifying at same time.

Owner:TSINGHUA UNIV

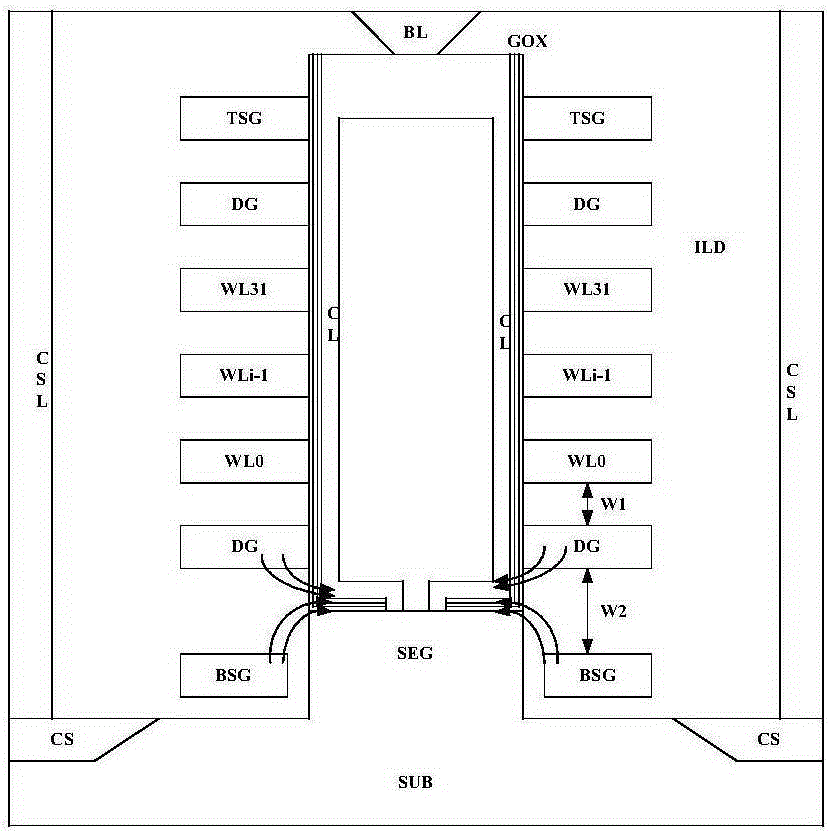

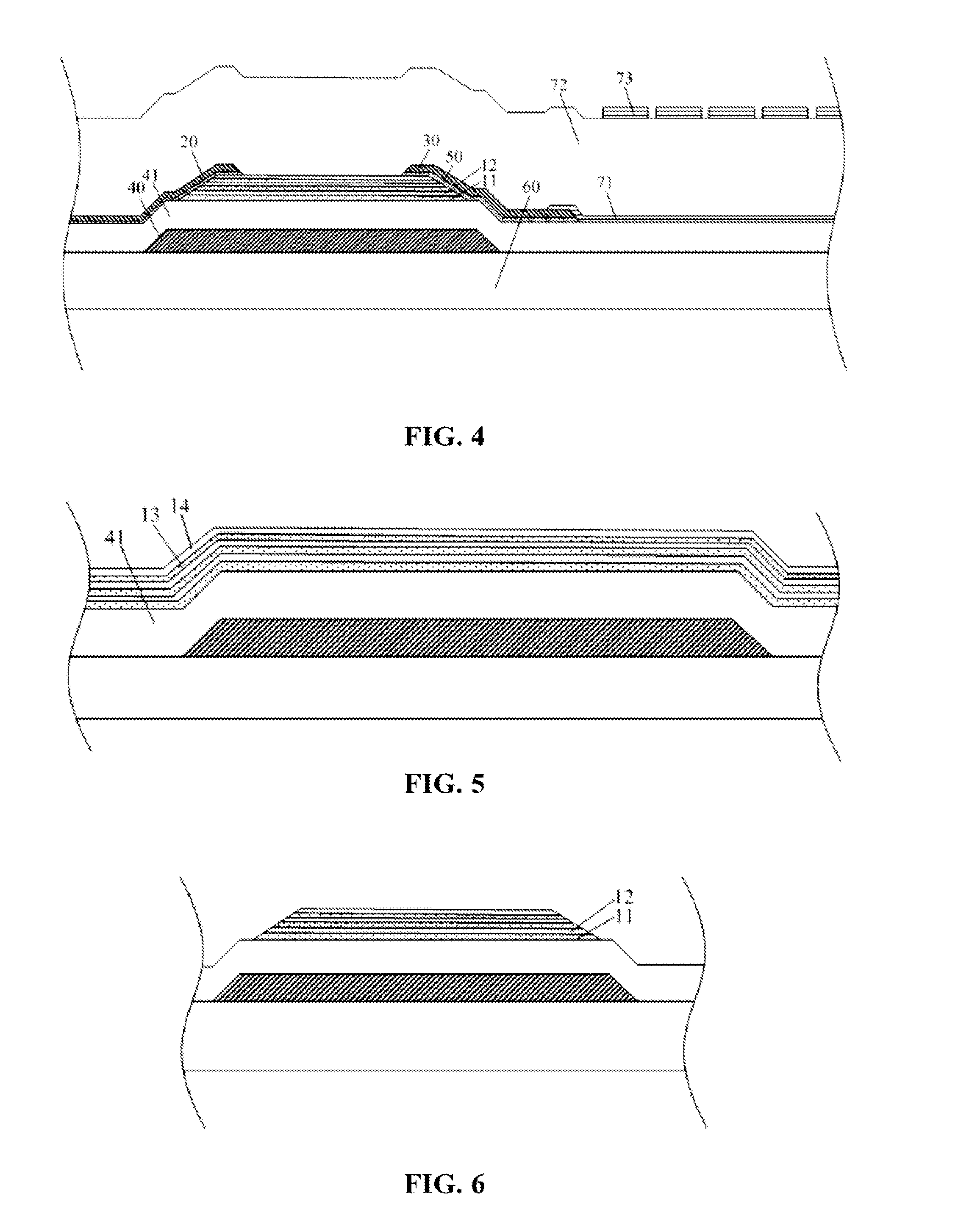

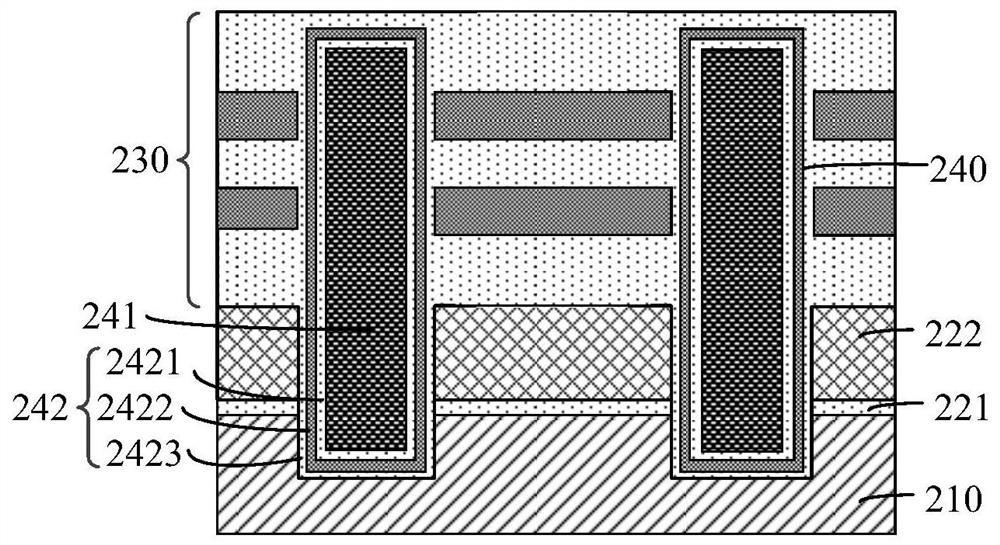

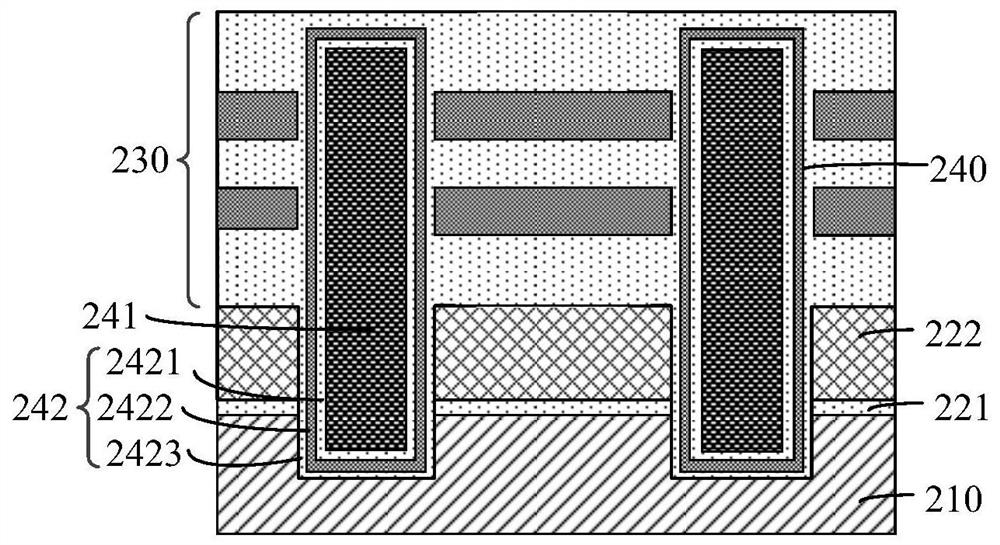

Three-dimensional semiconductor device and fabrication method thereof

ActiveCN105355602AControl consistencyOvercome the current bottleneckSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerPower flow

A three-dimensional semiconductor device comprises a plurality of storage units. Each storage unit comprises a channel layer, a bottom grid conductive layer, a floating gate layer, a plurality of second insulation layers, a plurality of grid conductive layers, a grid dielectric layer, a drain and a source, wherein the channel layer is arranged in a direction perpendicular to the surface of a substrate; the bottom grid conductive layer is arranged in a first insulation layer stack and arranged on a side wall of the channel layer; the floating gate layer is arranged on the first insulation layer stack and arranged on the side wall of the channel layer; the plurality of second insulation layer and the plurality of grid conductive layer are arranged on the floating grid layer and alternatively stacked along the side wall of the channel layer; the grid dielectric layer is arranged on the side wall of the channel layer; the drain is arranged at the top of the channel layer; and the source is arranged in the substrate between adjacent two storage units of the plurality of storage units. A floating gate which is not led out is embedded into the three-dimensional semiconductor device, a voltage is induced on the floating gate through voltage coupling on a near leading-out grid, thus, silicon epitaxial growth (SEG) and channel inversion of a poly-silicon contact region are assistantly completed, the current bottleneck of the region is overcome, the channel current is increased, and the consistency of threshold voltages of a field effect transistor (FET) near to the floating gate is effectively controlled.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

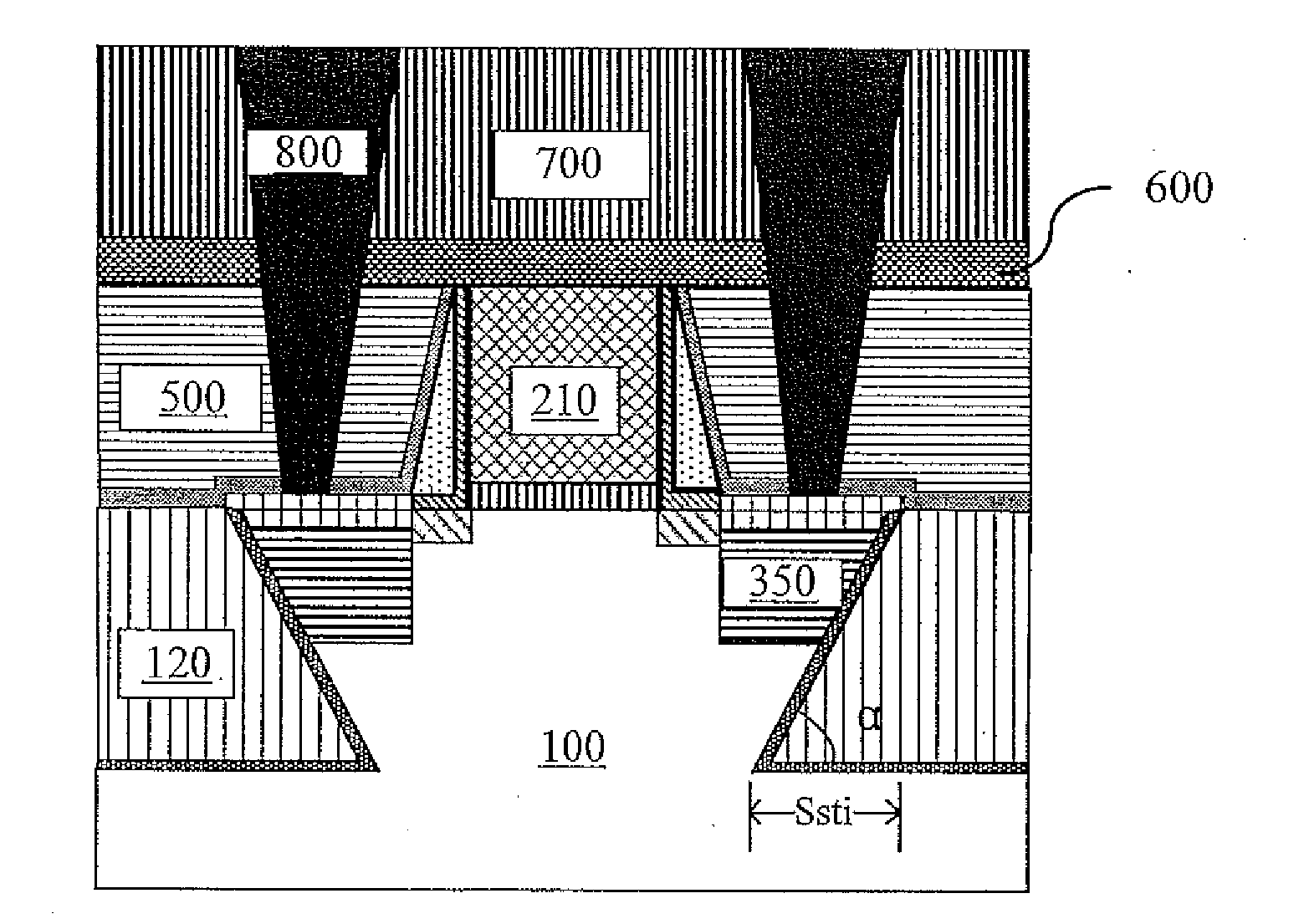

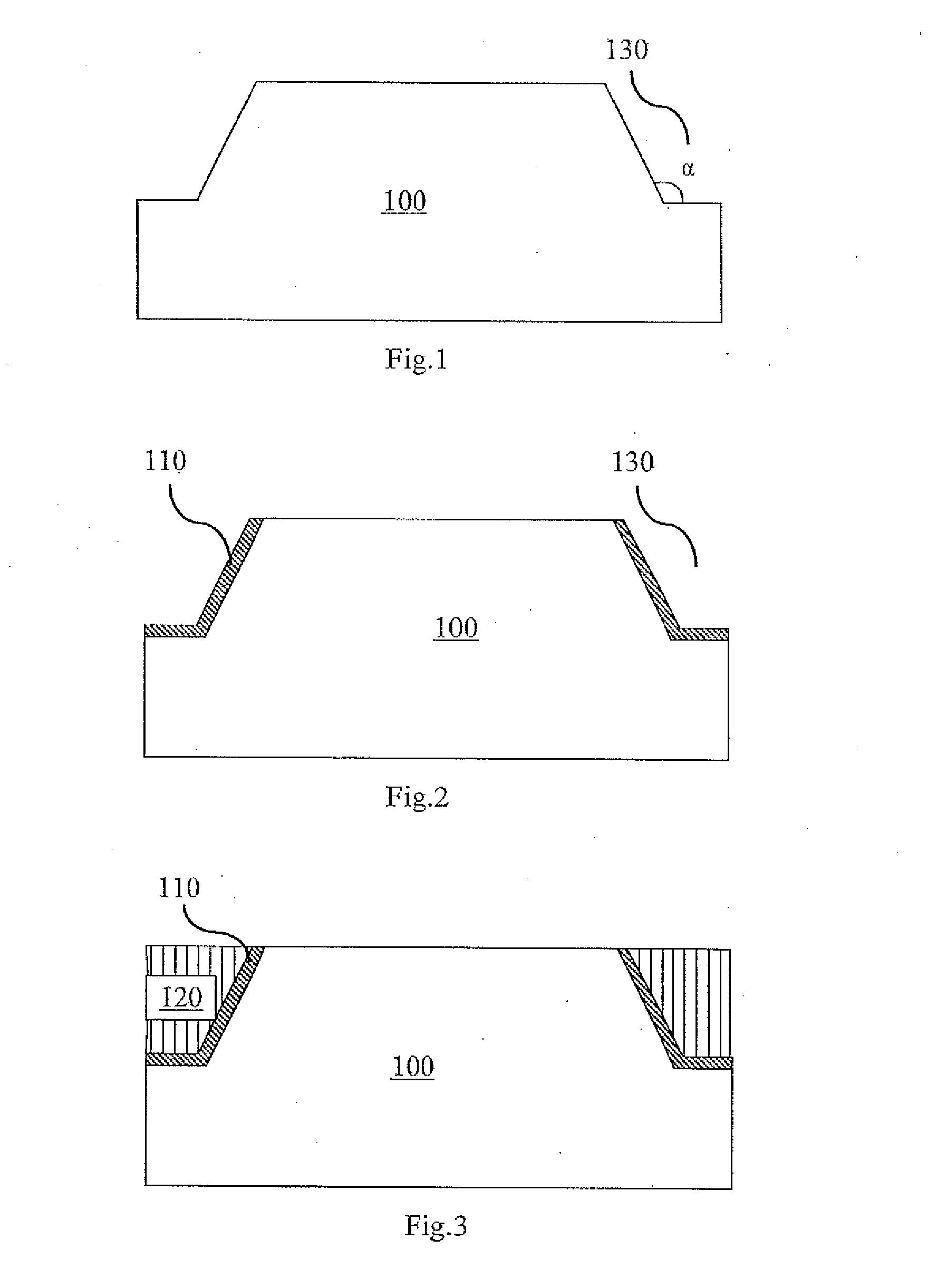

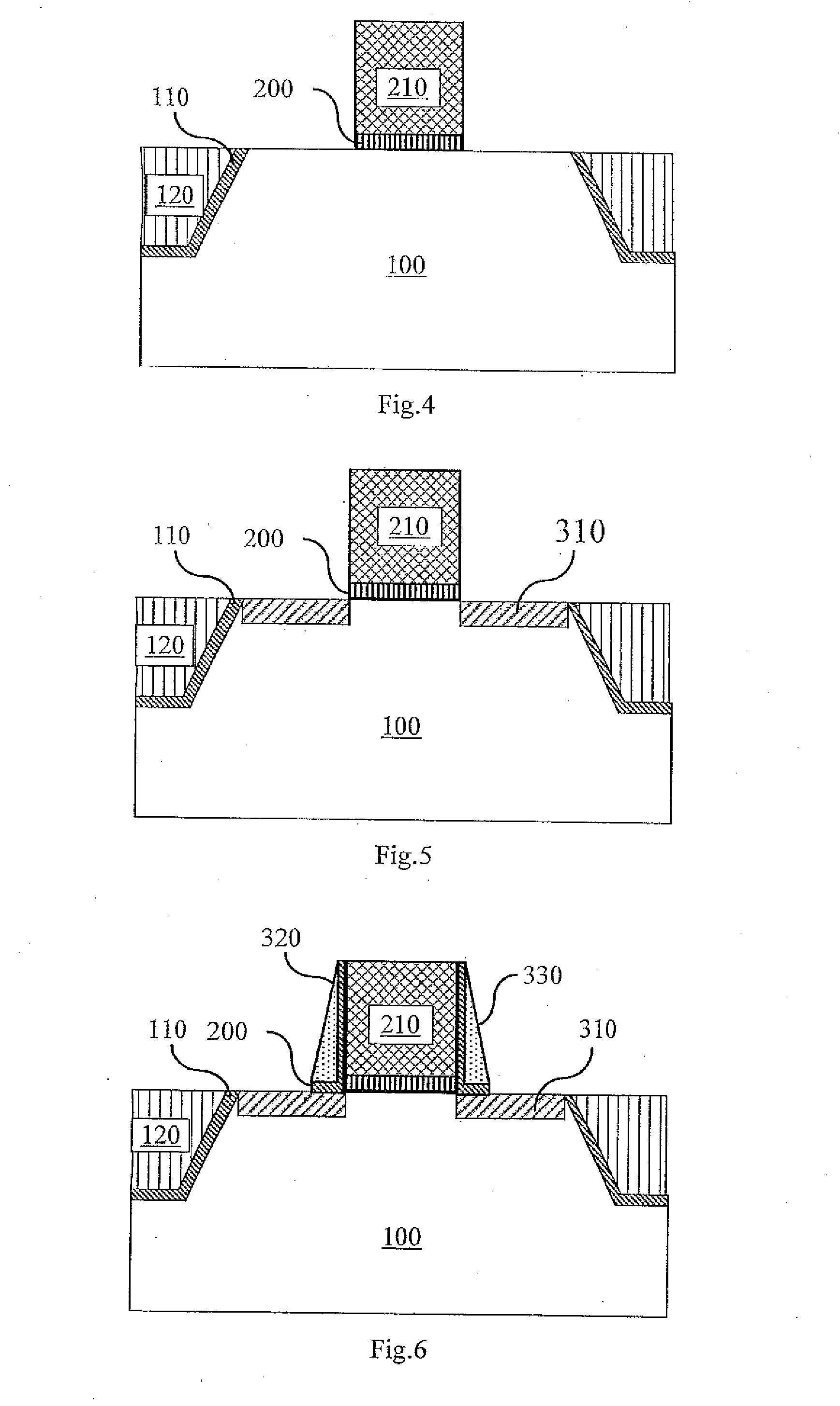

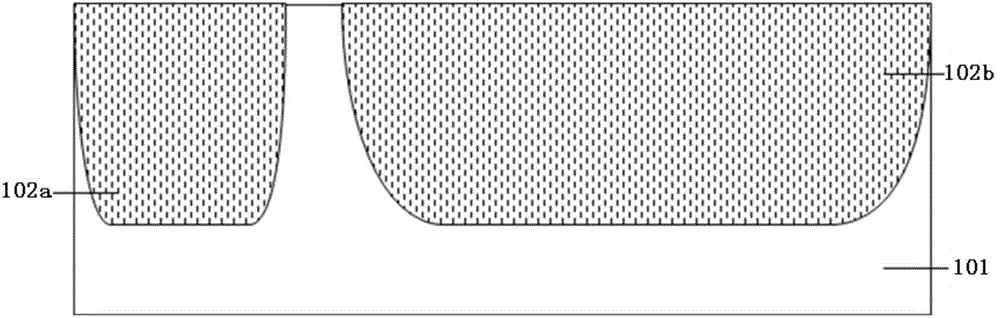

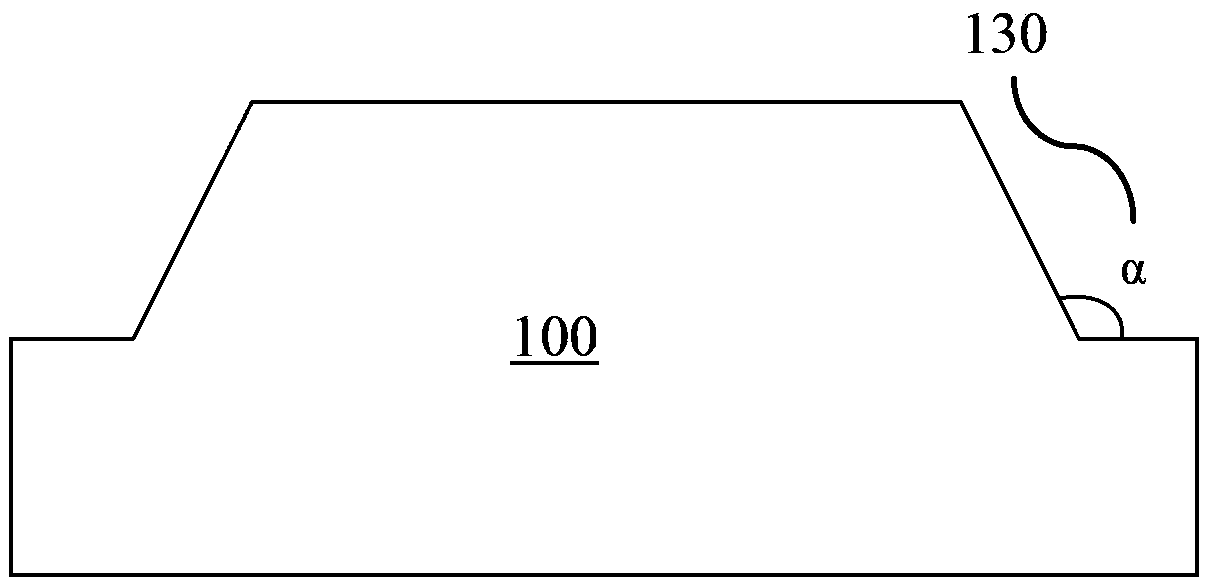

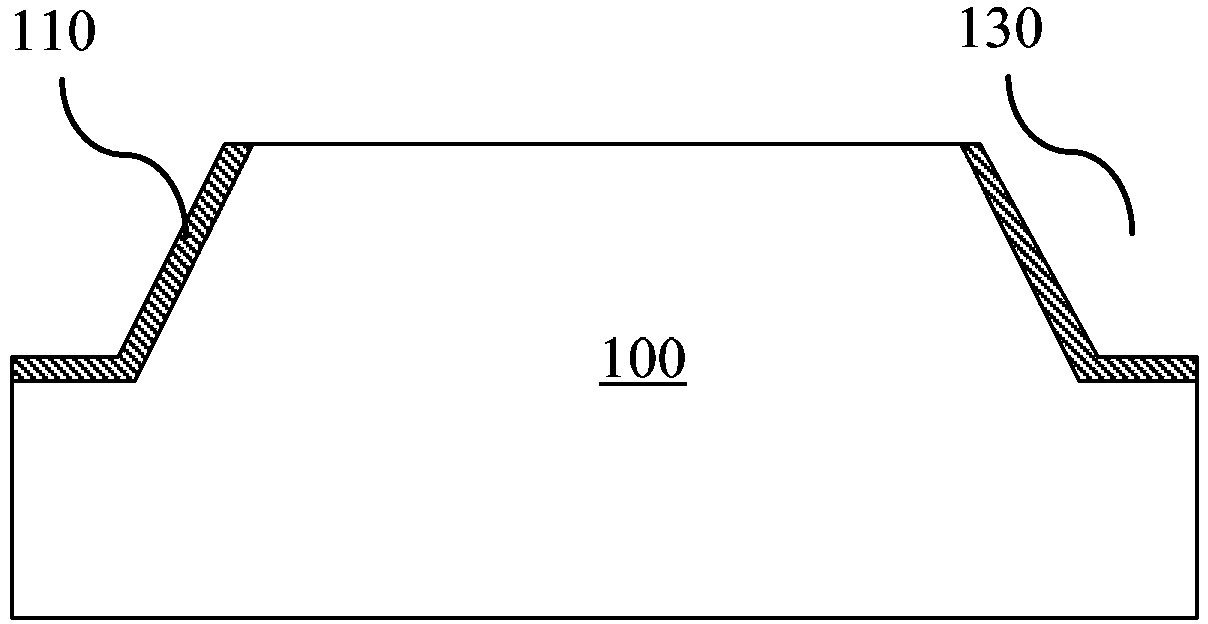

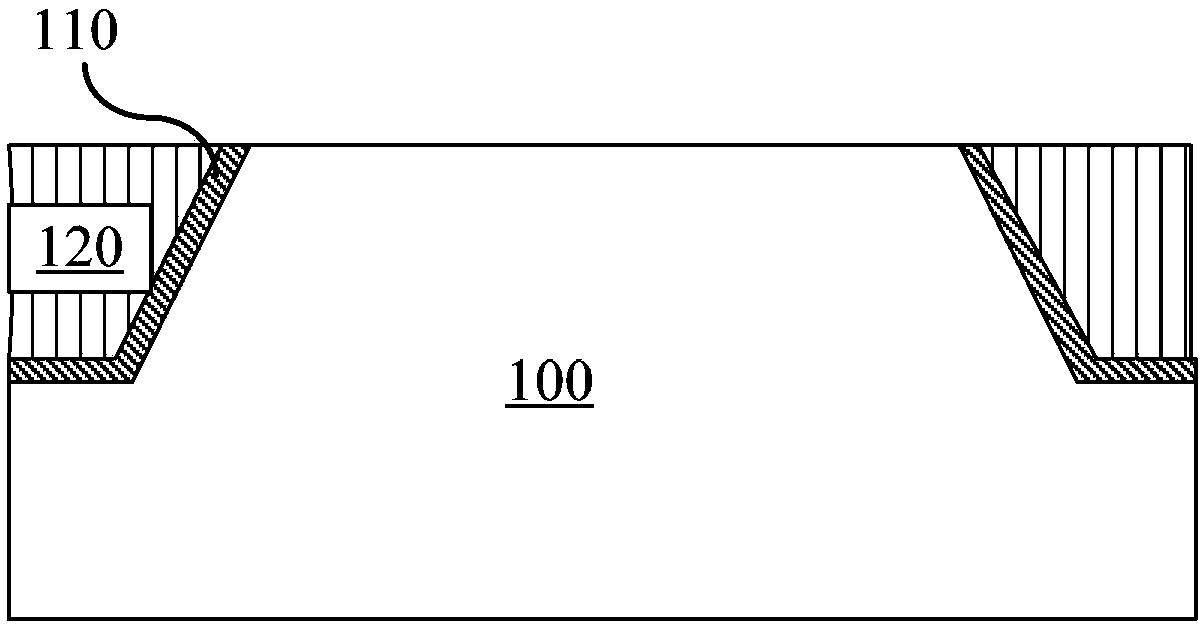

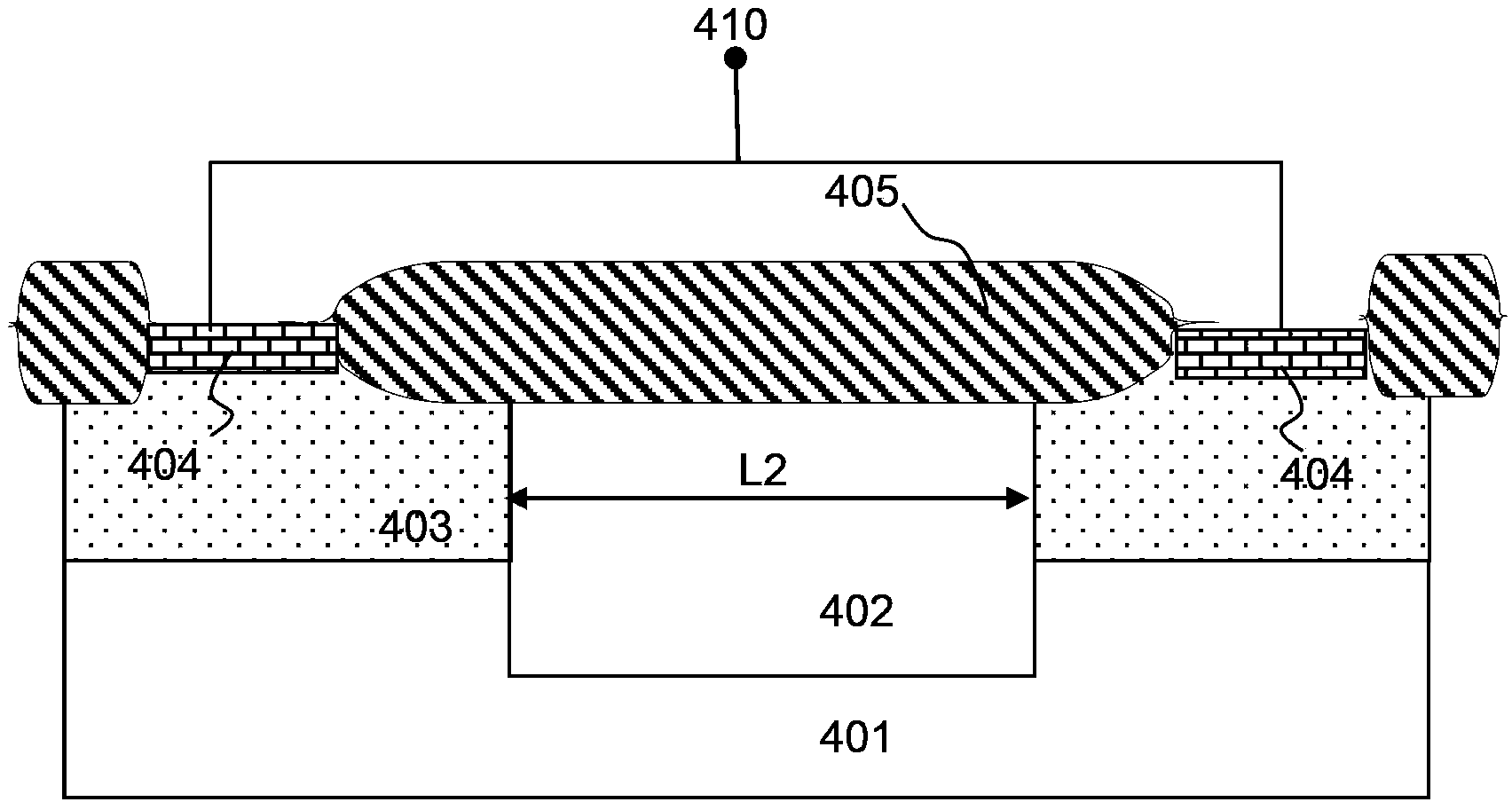

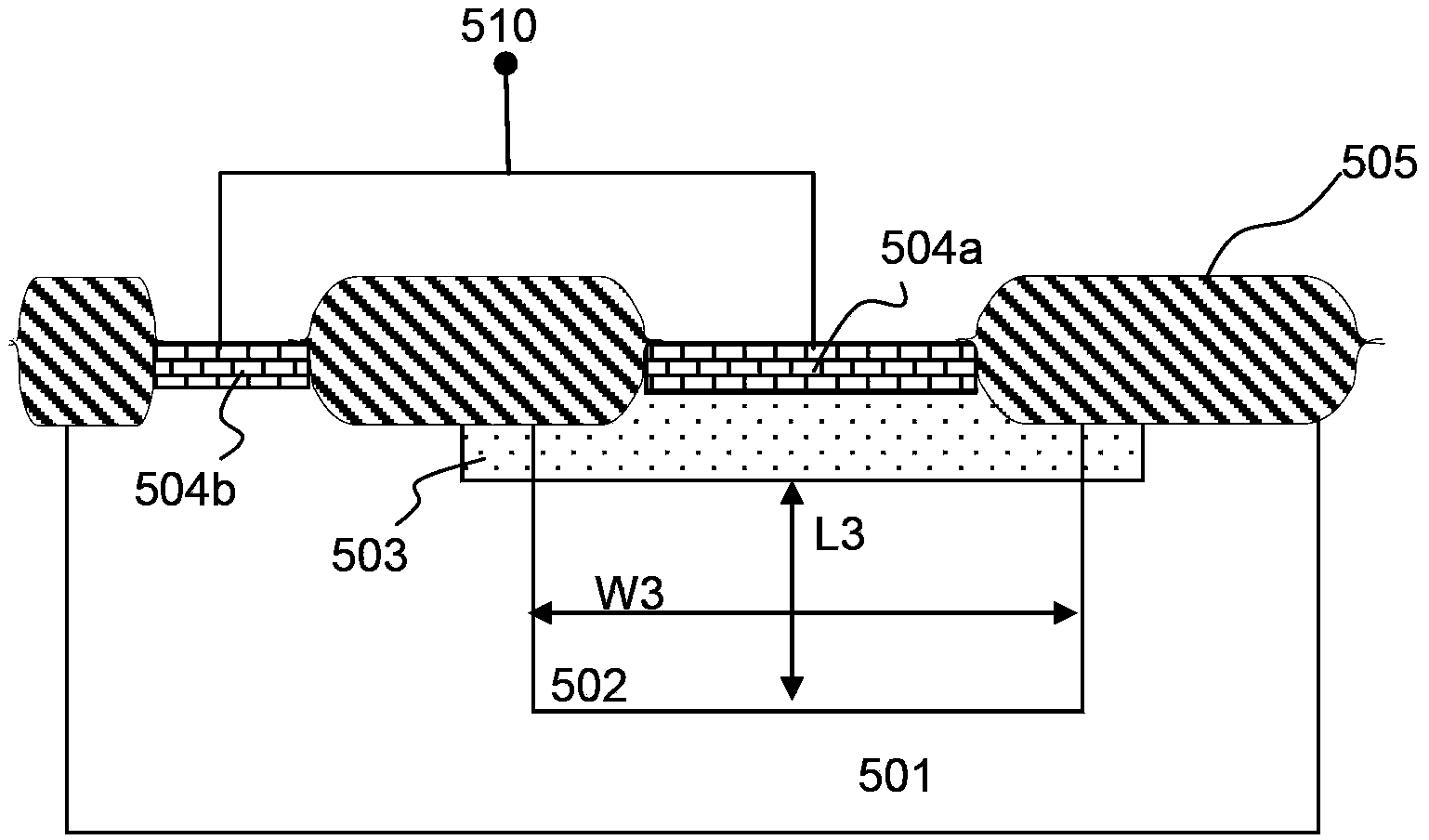

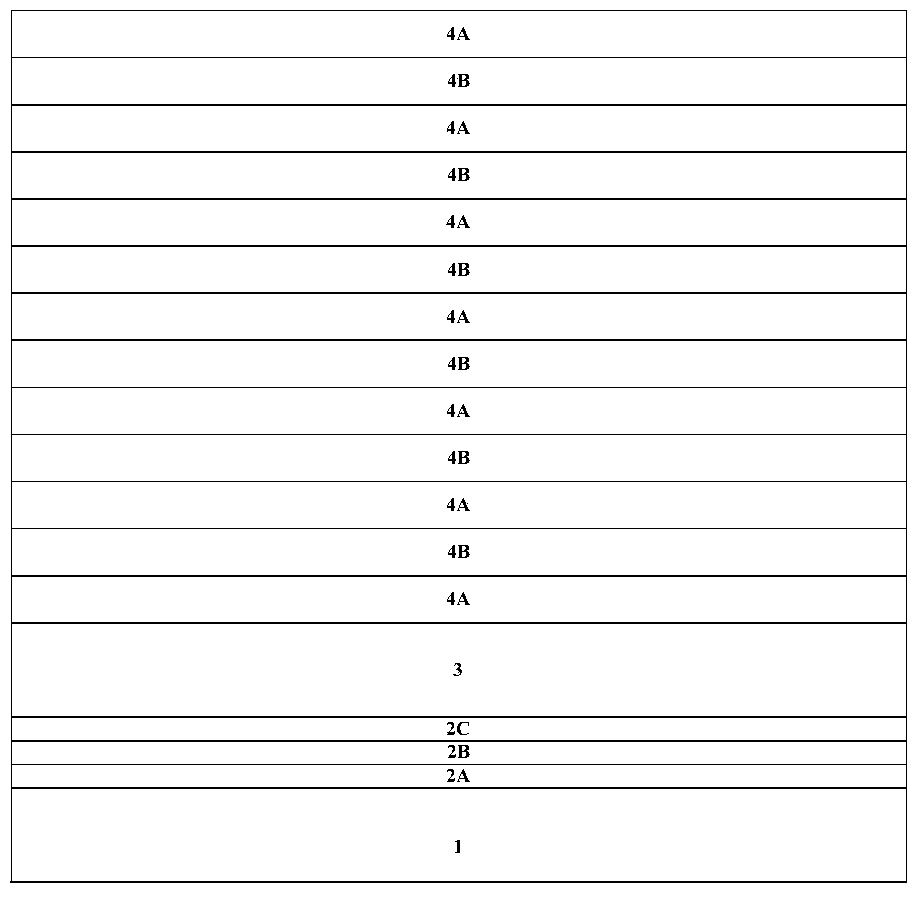

Semiconductor structure and method for manufacturing the same

InactiveUS20140231923A1Improve device performanceImprove impactTransistorSemiconductor/solid-state device manufacturingGate dielectricSemiconductor structure

The present invention provides a semiconductor structure, comprising: a substrate; a gate stack located on the substrate and comprising at least a gate dielectric layer and a gate electrode layer; source / drain regions, located in the substrate on both sides of the gate stack; an STI structure, located in the substrate on both sides of the source / drain regions, wherein the cross-section of the STI structure is trapezoidal, Sigma-shaped or inverted trapezoidal depending on the type of the semiconductor structure. Correspondingly, the present invention further to provides a method of manufacturing the semiconductor structure. In the present invention, STI structures having different shapes can be combined with different stress fillers to apply tensile stress or compressive stress laterally to the channel, which will produce a positive impact on the electron mobility of NMOS and the hole mobility of PMOS and increase the channel current of the device, thereby effectively improving the performance of the semiconductor structure.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

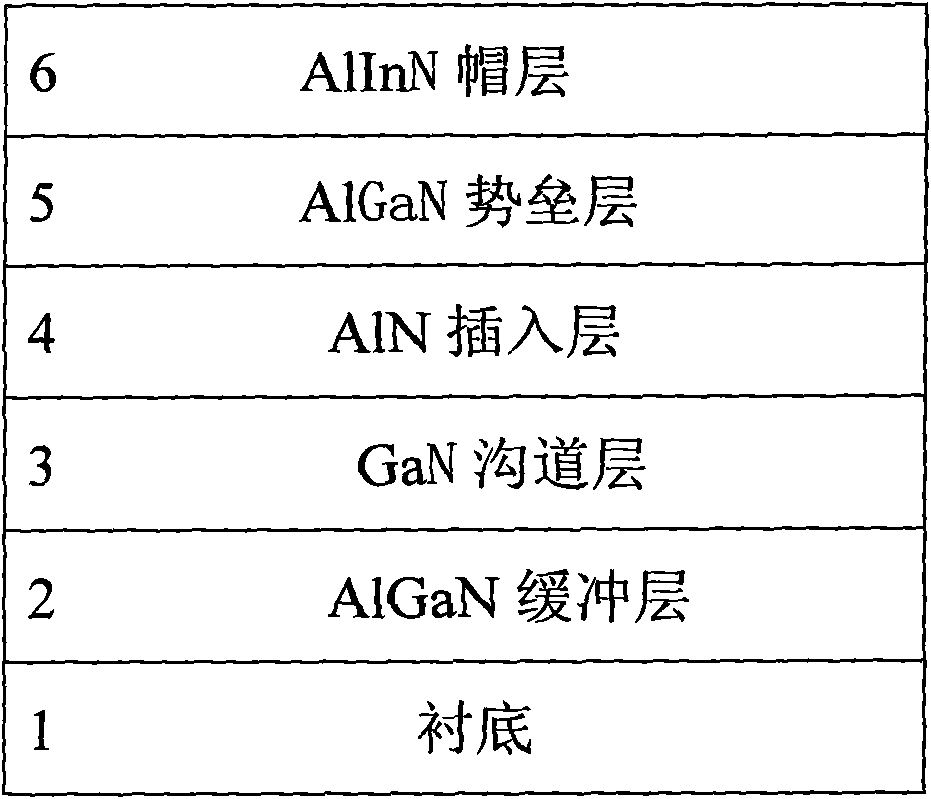

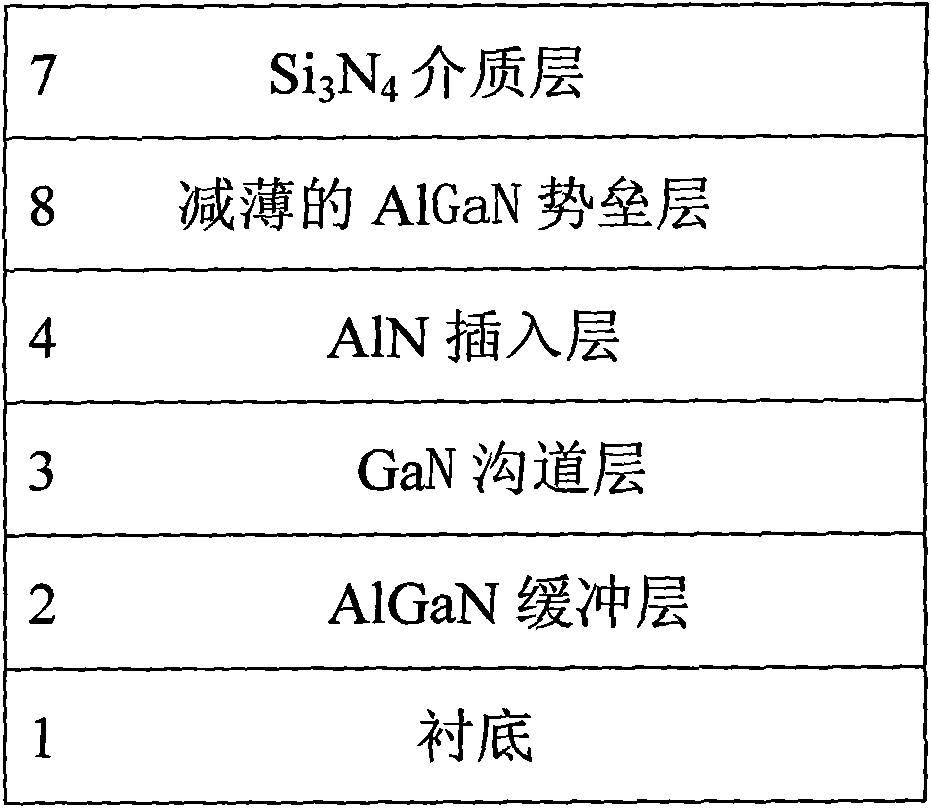

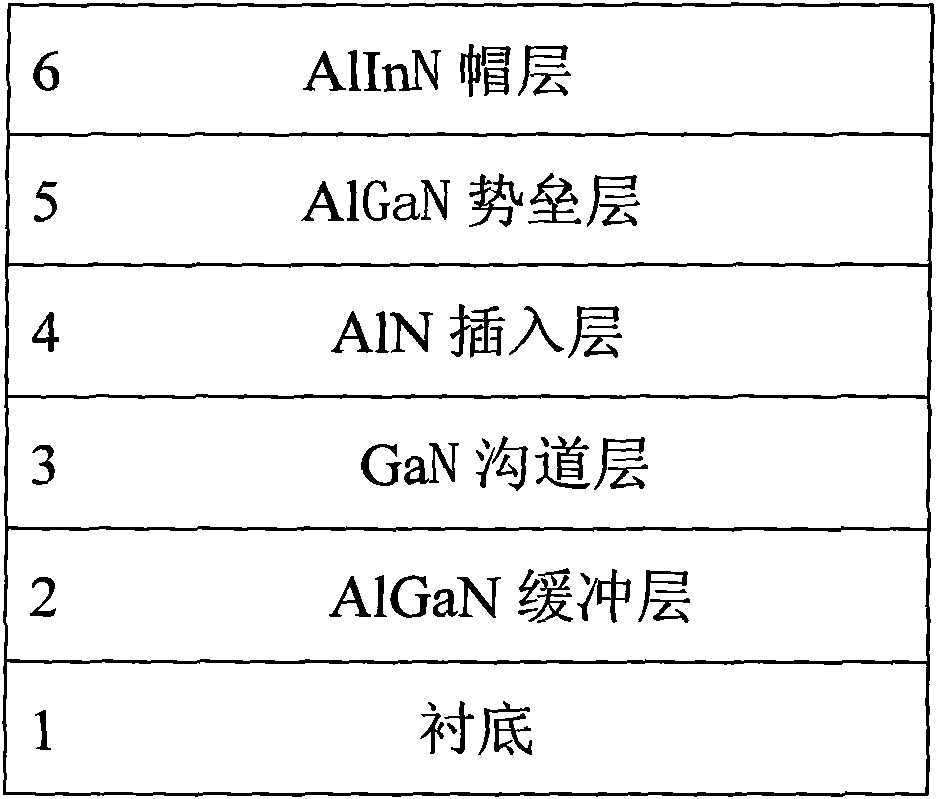

Method for manufacturing medium/nitride composite structure enhanced field effect transistor

ActiveCN102064108AHigh densityReduced series resistanceSemiconductor/solid-state device manufacturingHeterojunctionEngineering

The invention discloses a method for manufacturing a medium / nitride composite structure enhanced field effect transistor, which comprises the steps of: sequentially growing a AlGaN buffer layer, a GaN channel layer, a AlN inserting layer, a AlGaN barrier layer and a AlInN cap layer on a substrate; and forming a AlInN / AlGaN / AlN composite front barrier and a GaN / AlGaN back barrier into a high electronic air tightness external channel well limited by strong electrons. The thick AlInN cap layer with lattice match remarkably improves the electronic air tightness of an external channel, and the high and wide barriers provided by the AlInN cap layer strengthen the quantum restriction of the channel well, thus the serial resistance of the external channel is lowered and the ohmic contact resistance is reduced. After the AlInN layer is corroded by using a dry method channeling process and the AlGaN barrier layer is thinned, a Si3N4 medium layer with set thickness is deposited by using an atom layer deposition (ALD) process, thus the quantum restriction of an internal channel well is strengthened, and the ON state current of the element is improved by band distortion of a heterojunction, caused in a way that an electron wave function does not permeate into the barrier layer, under the condition that a large grid voltage change is ensured. A negative space charge is introduced on the surface of the Si3N4 medium layer by using a fluorine plasma process, thus the barrier height is increased, electron air in the internal channel well is consumed fully to ensure that the inner channel is pinched off under zero grid voltage. An ideal module enhancing work is realized.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

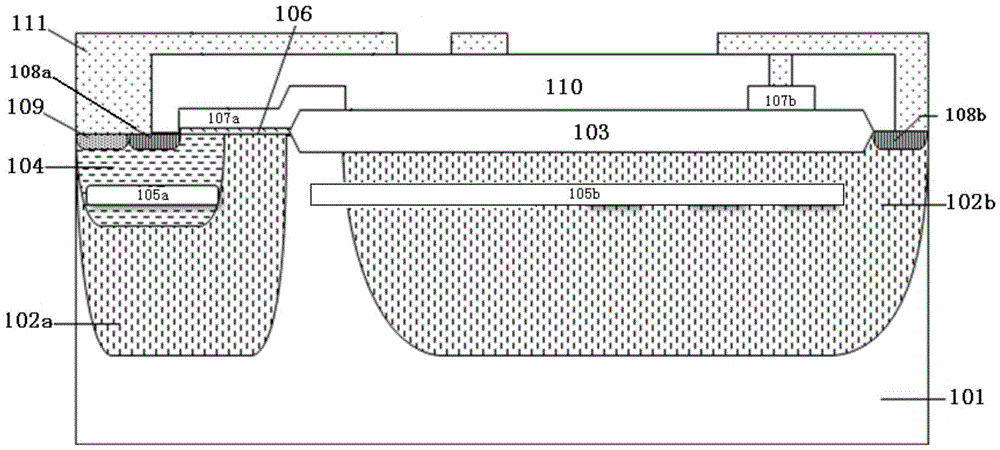

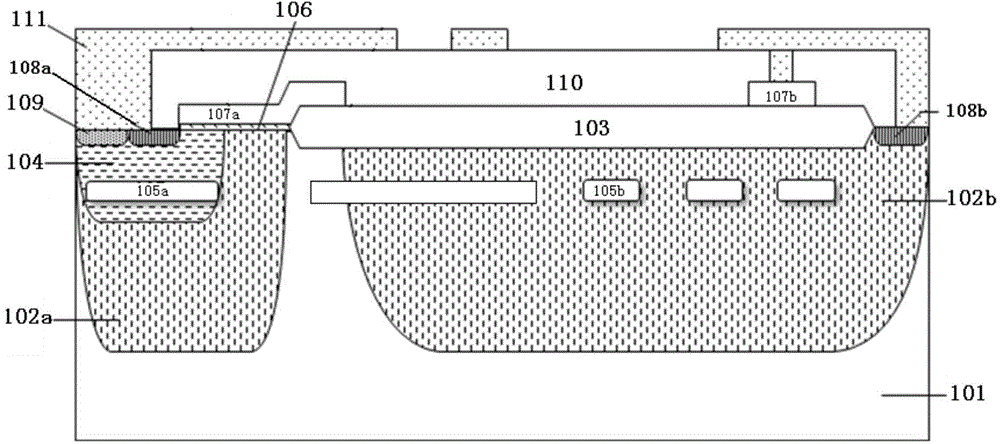

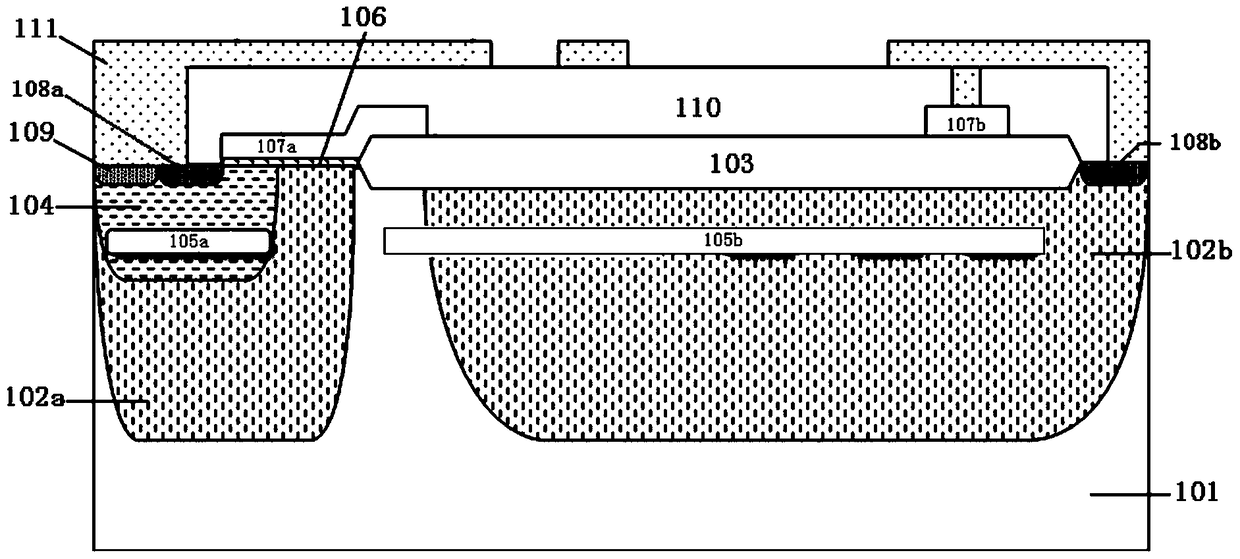

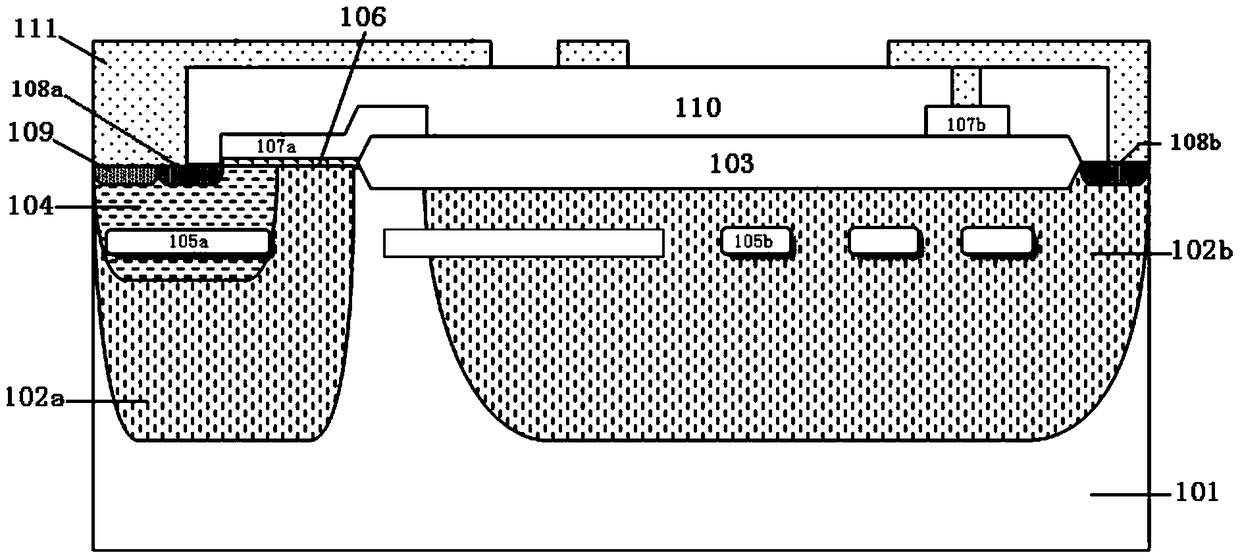

Isolation N-type laterally diffused metal oxide semiconductor (NLDMOS) device and manufacturing method thereof

ActiveCN104617149ALower on-resistanceIncrease the effective doping concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesP type siliconBreakdown voltage

The invention discloses an isolation N-type laterally diffused metal oxide semiconductor (NLDMOS) device. Two separate N-type deep well are formed on the P-type silicon substrate; left N-type deep well left portion is formed with a P-well; P-well left portion is formed with a P-type heavily doped region and an N-type heavily doped source miscellaneous areas; over the top and left-right portion of the N-type deep well P-well right portion formed with a gate oxide layer; N-type deep well with left and right P-type silicon N-type deep well between the top and right-left portion of the N-type deep well substrate above the field oxide is formed; the right N-type deep well right portion is formed with a drain terminal N-type heavily doped region; and a gate oxide layer over the top of the left part of the field oxide is formed with a gate polysilicon; P-type silicon substrate and the bottom of the field oxide Right N-type deep well formed in P-type implant drift region, the right of the P-type implant drift region as a staging interval shape. The invention also discloses a method for producing the isolated NLDMOS devices. The method can be isolated in ensuring NLDMOS device breakdown voltage does not decrease at the same time makes the device on-resistance is reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

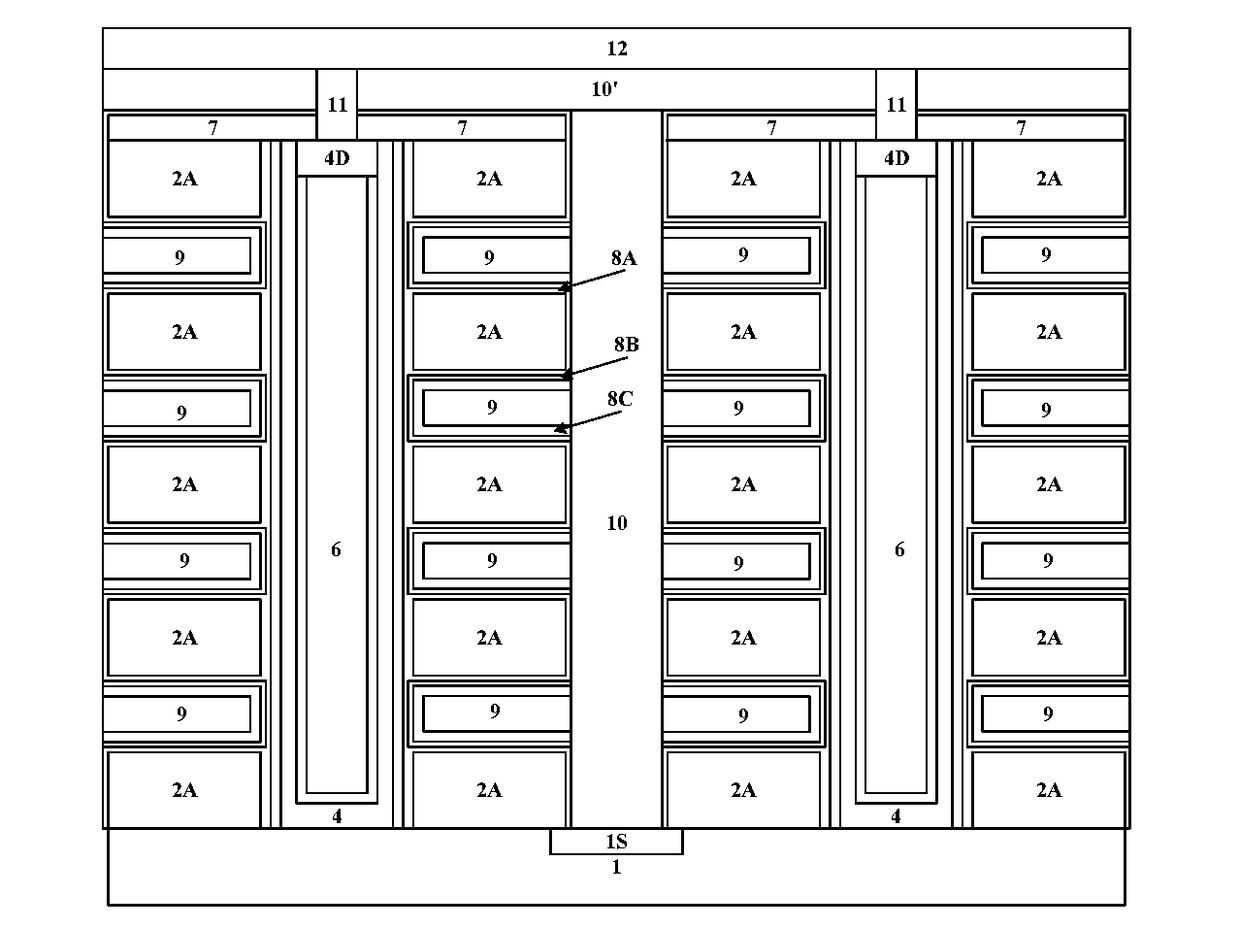

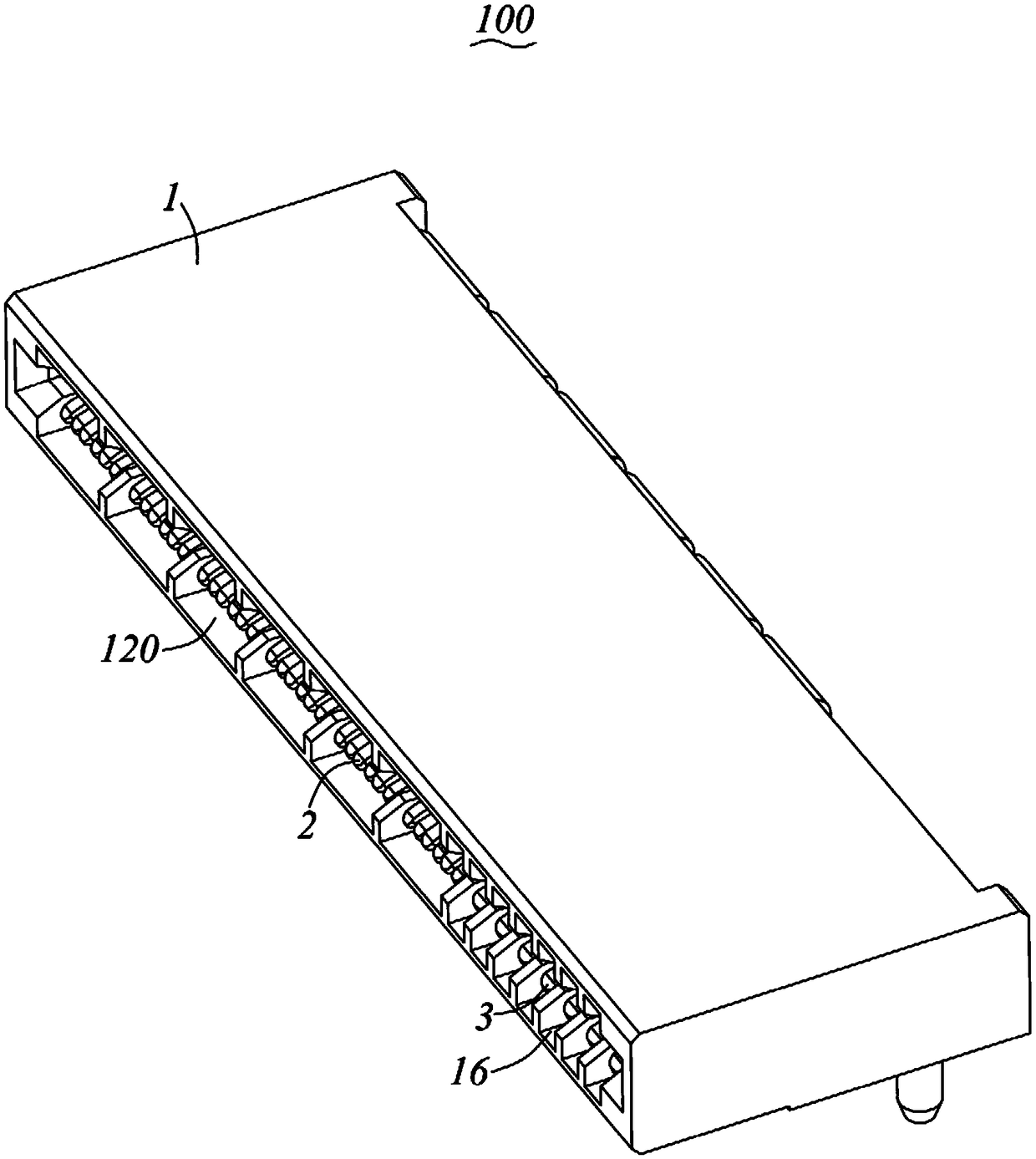

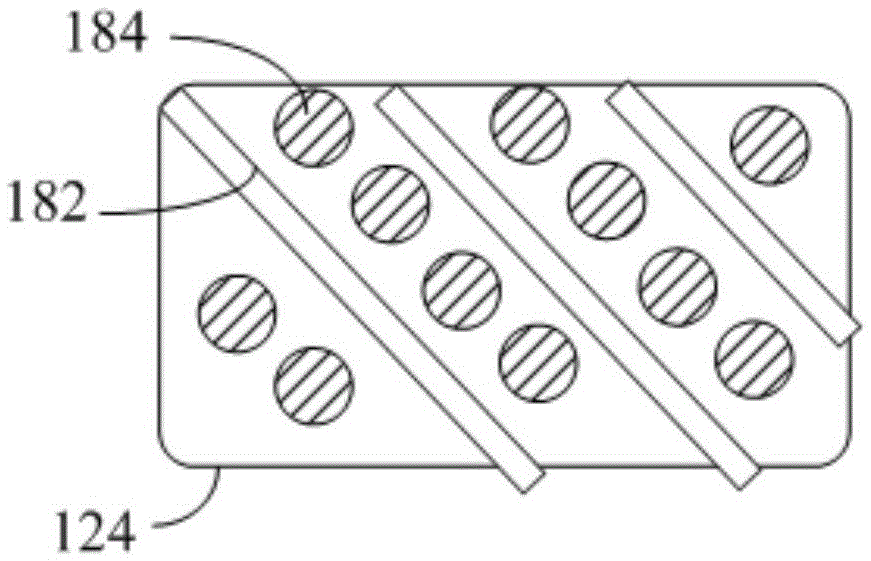

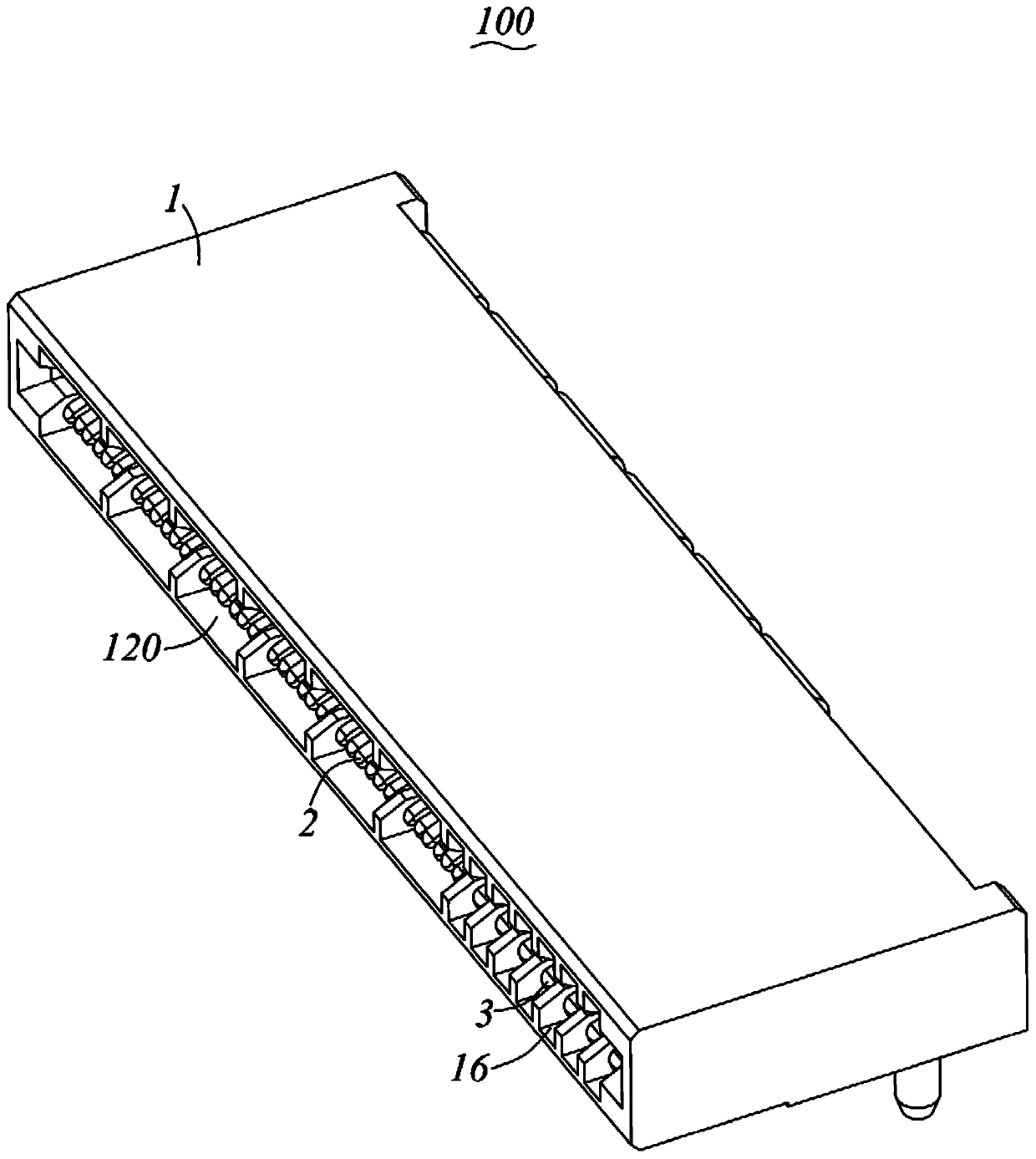

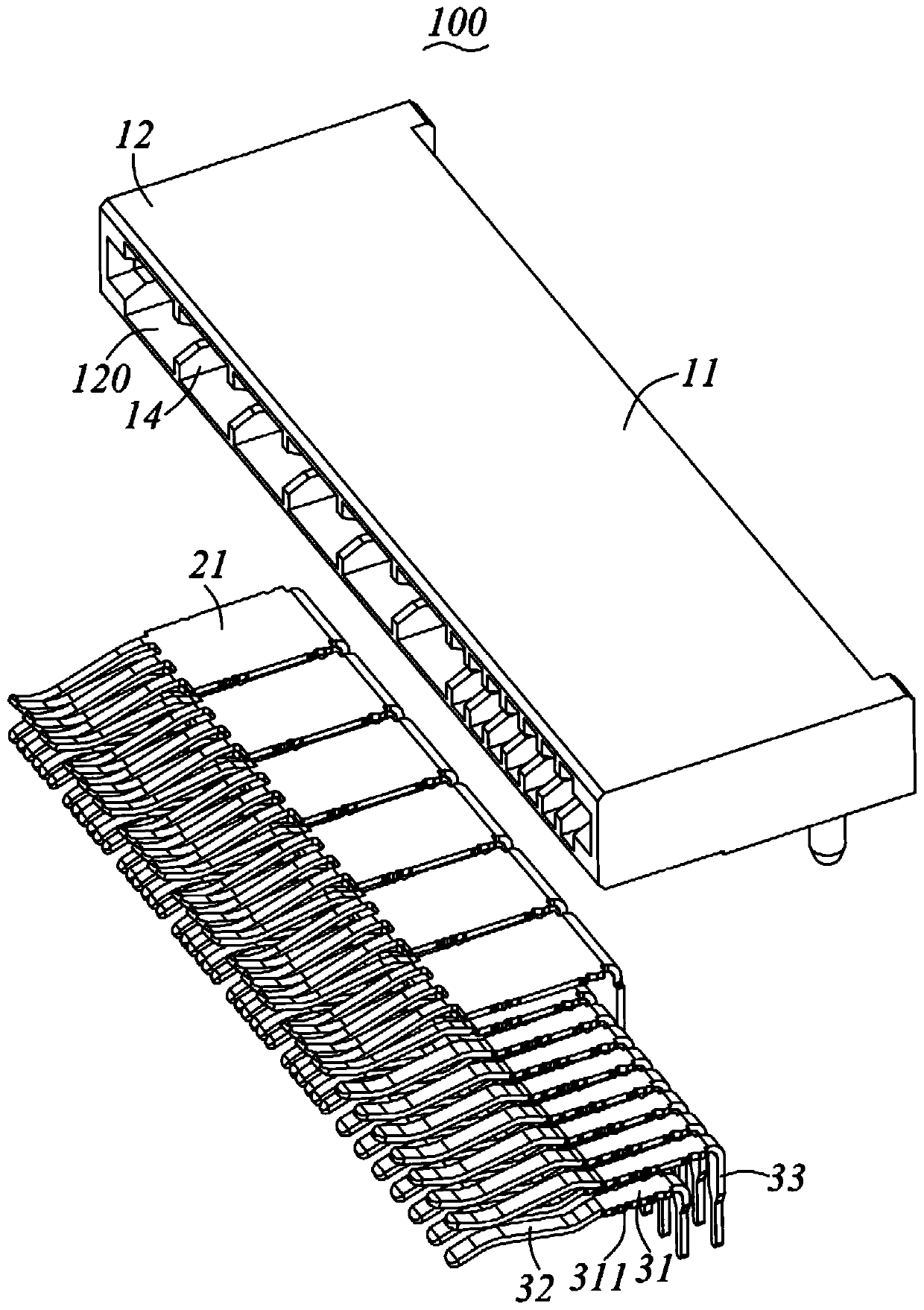

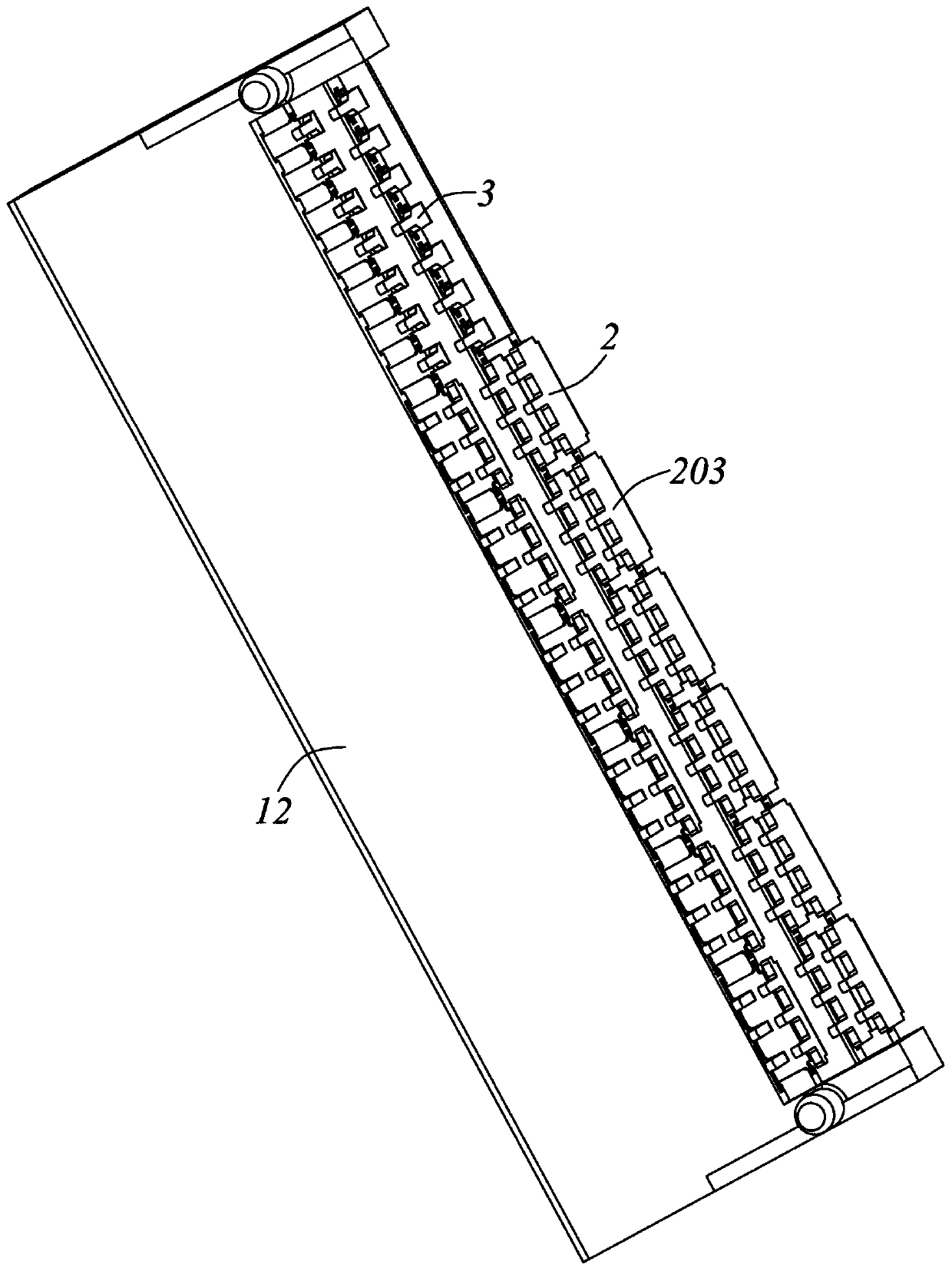

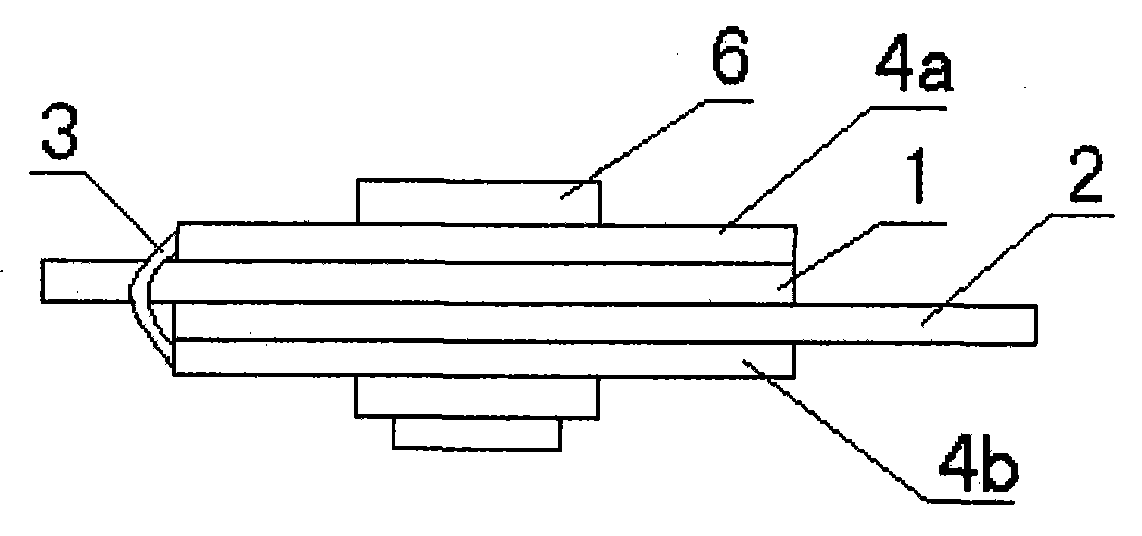

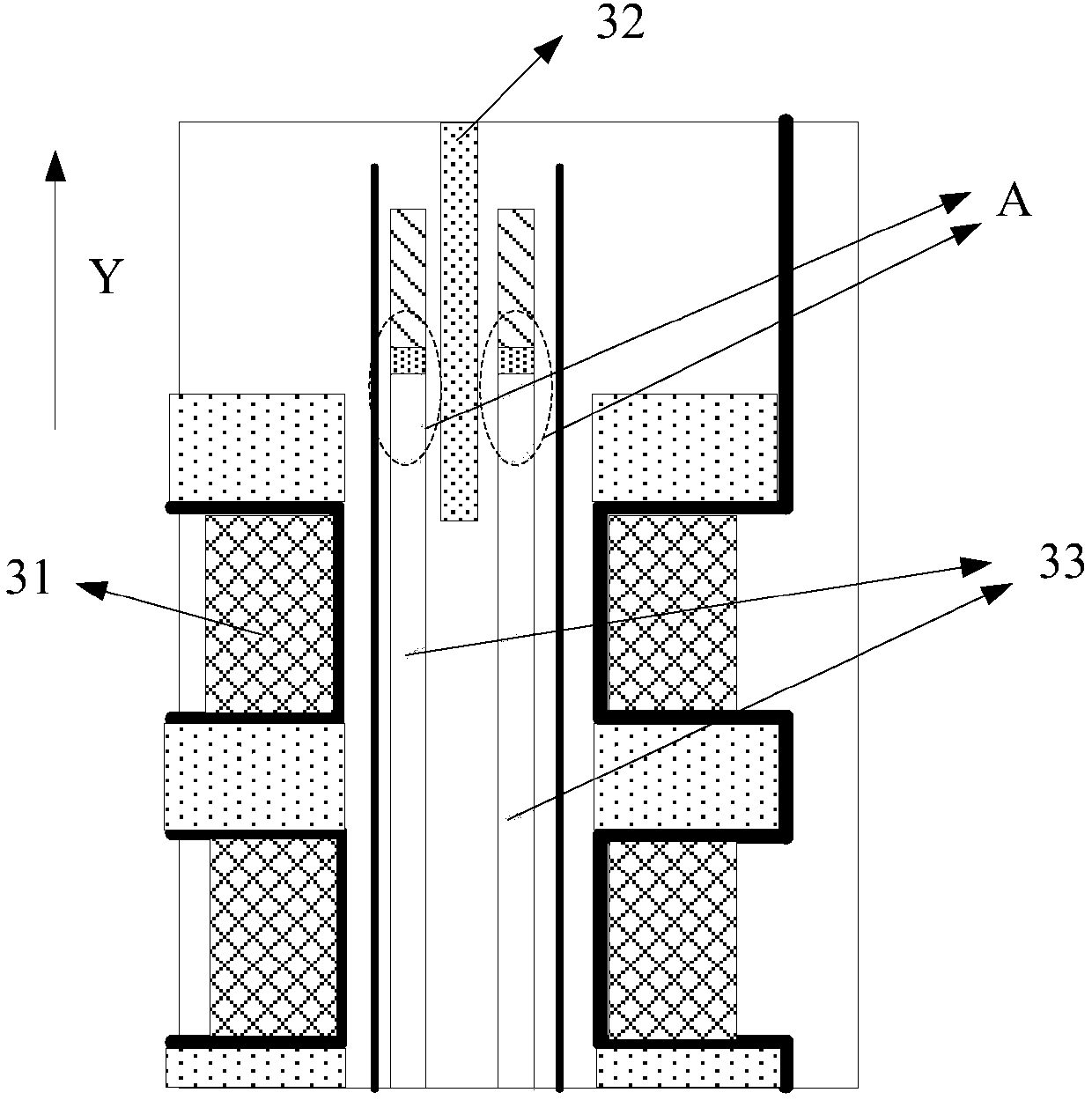

Electrical connector

InactiveCN109038003AImprove transmission reliabilityReduce feverCoupling contact membersModifications by conduction heat transferElectricityElectrical connector

An electrical connector which is provided with an insulating body and a plurality of power terminal pairs fixed to the insulating body, the insulating body has a base portion, a butt portion extendingforwardly from the base portion and a plurality of first terminal grooves extending in the front-rear direction, the power supply terminal pair is accommodated in a corresponding first terminal groove, and each of the power supply terminal pairs comprises two power supply terminals, each of the power supply terminals is provided with a retaining portion retained in the first terminal groove, A plurality of contact portions extending forward from one end of the retaining portion and a welding portion extending from the other end of the retaining portion are arranged in a row in the height direction of the contact portions of two power supply terminals in each pair of power supply terminals, and the plurality of contact portions of the two power supply terminals are alternately arranged inthe lateral direction and circularly. The electric connector of the invention can effectively improve the heating condition of a pair of power supply terminals.

Owner:ALLTOP ELECTRONICS SU ZHOU +1

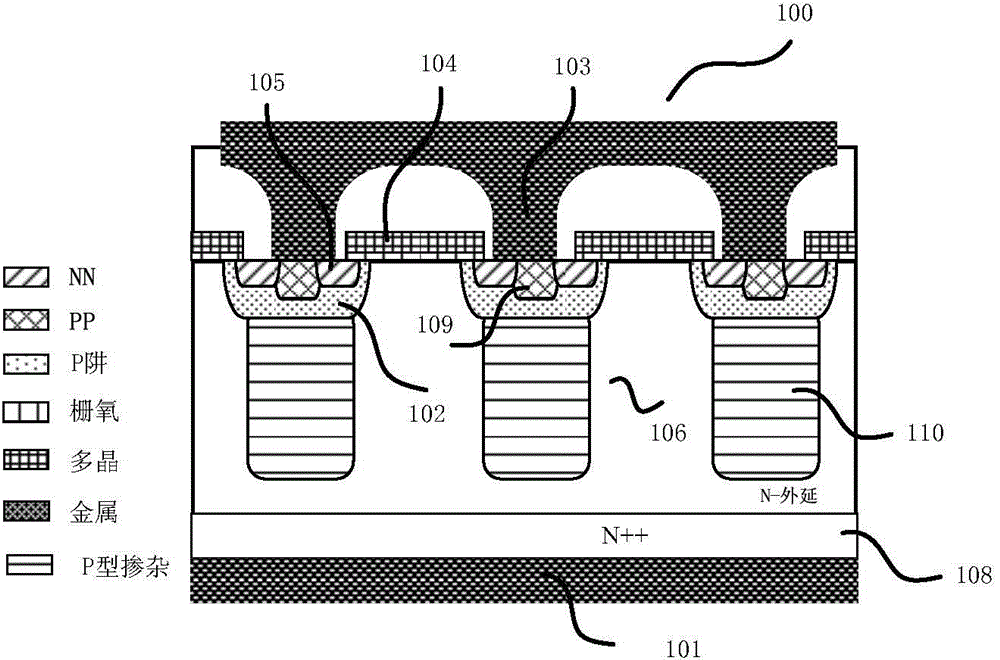

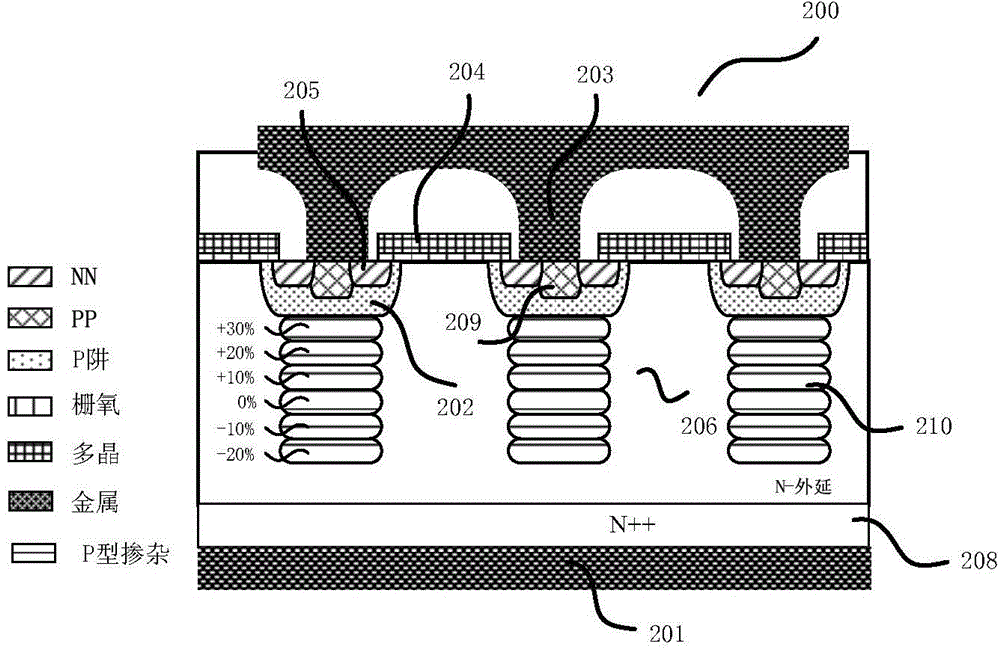

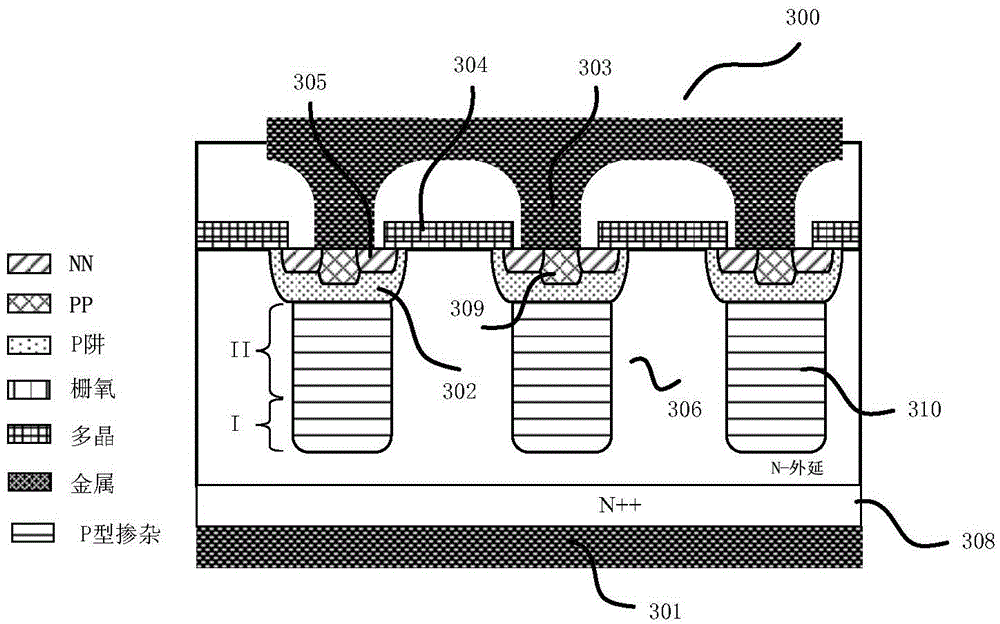

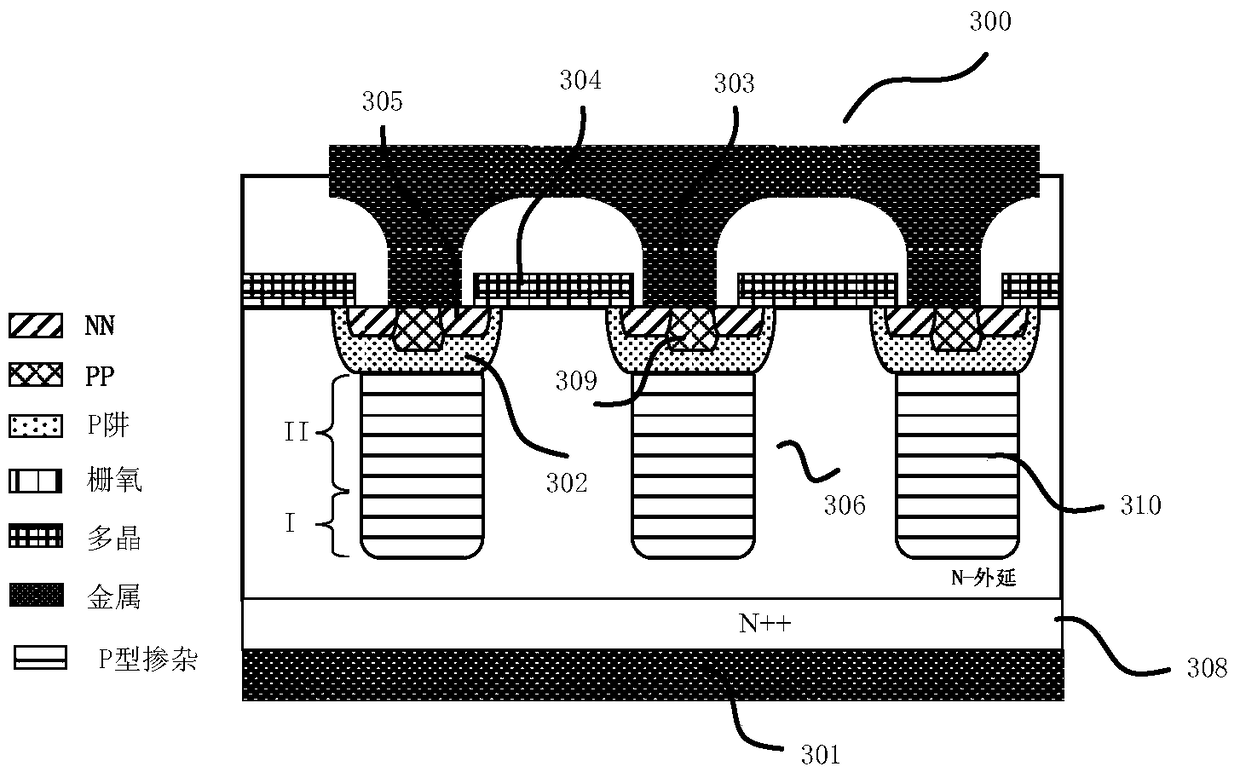

High-voltage power device and forming method thereof

ActiveCN105097932AMaintain pressure stabilityIncrease current channelSemiconductor/solid-state device manufacturingSemiconductor devicesHigh pressureComputer science

The invention provides a high-voltage power device and a forming method thereof. The device comprises a first doped area having a first doped type; one or a plurality of device doped areas arranged in the upper surface of the first doped area, wherein the device doped area has a second doped type opposite to the first doped type; and one or a plurality of second doped areas of the second doped type, wherein one end of the second doped area is in electric contact with a corresponding device doped area, the other end of the second doped area longitudinally extends to the first doped area, and in the transverse direction, the second doped areas and the first doped areas are alternatively distributed. The impurity concentration of each second doped area changes in a non-linear manner with the change of the longitudinal depth, and the total impurity concentration of the second doped areas is lower than the total impurity concentration of the first doped areas. According to the invention, the withstand voltage of the device is stabilized, and the conduction resistance of the device is reduced.

Owner:HANGZHOU SILAN MICROELECTRONICS

Laterally diffused metal oxide semiconductor field effect transistor with RESURF (reduced surface field) structure

ActiveCN106816468AIncrease the number ofImprove the optimization spaceSemiconductor devicesOxide semiconductorBody region

The present invention relates to a laterally diffused metal oxide semiconductor field effect transistor with an RESURF (reduced surface field) structure. The laterally diffused metal oxide semiconductor field effect transistor includes a substrate, a gate, a source, a drain, a body region, a field oxide region which is located between the source and the drain, as well as a first well region and a second well region which are located on the substrate; a plurality of gate doped regions are arranged in the second well region below the gate; the polysilicon gate of the gate is of a multi-section structure; the sections of the polysilicon gate are separated from one another; the gate doped regions are arranged below gaps between the sections of the polysilicon gate; and each gate doped region is electrically connected with one of two sections of the polysilicon gate which are located at two sides of the gate doped region, wherein the one section of the polysilicon gate electrically connected with the gate doped region is adjacent to the source. According to the laterally diffused metal oxide semiconductor field effect transistor with the RESURF structure of the invention, the number of trench electrons is increased, and the electrons are accelerated a plurality of times during a process of flowing from the source to the drain, equivalently, and a trench electric field and trench current can be improved, and therefore, trench resistance is reduced, and on-resistance can be reduced.

Owner:CSMC TECH FAB2 CO LTD

Semiconductor structure and manufacturing method thereof

ActiveCN103383962AIncrease current channelImprove performanceTransistorSemiconductor/solid-state device manufacturingSemiconductor structureGate stack

The invention provides a semiconductor structure. The semiconductor structure comprises a substrate, a gate stack, source / drain areas and STI structures, wherein the gate stack is located on the substrate and comprises at least a gate medium layer and a gate electrode layer, the source / drain areas are located in the portions, arranged at the two sides of the gate stack, of the substrate, the STI structures are located in the portions, arranged at the two sides of the source / drain areas, of the substrate, and according to the type of the semiconductor structure, the shape of the section of each STI structure is a regular trapezoid or a Sigma shape or a reverse trapezoid. Correspondingly, the invention further provides a manufacturing method of the semiconductor structure. According to the semiconductor structure, through the combination of the STI structures of different shapes and fillers with different kinds of stress, different kinds of tensile stress or pressure stress on a channel can be generated in the transverse direction, so that positive influence on the electron mobility of an NMOS and the hole mobility of a PMOS is generated, and the channel current of a device is increased. Therefore, the performance of the semiconductor structure is effectively improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

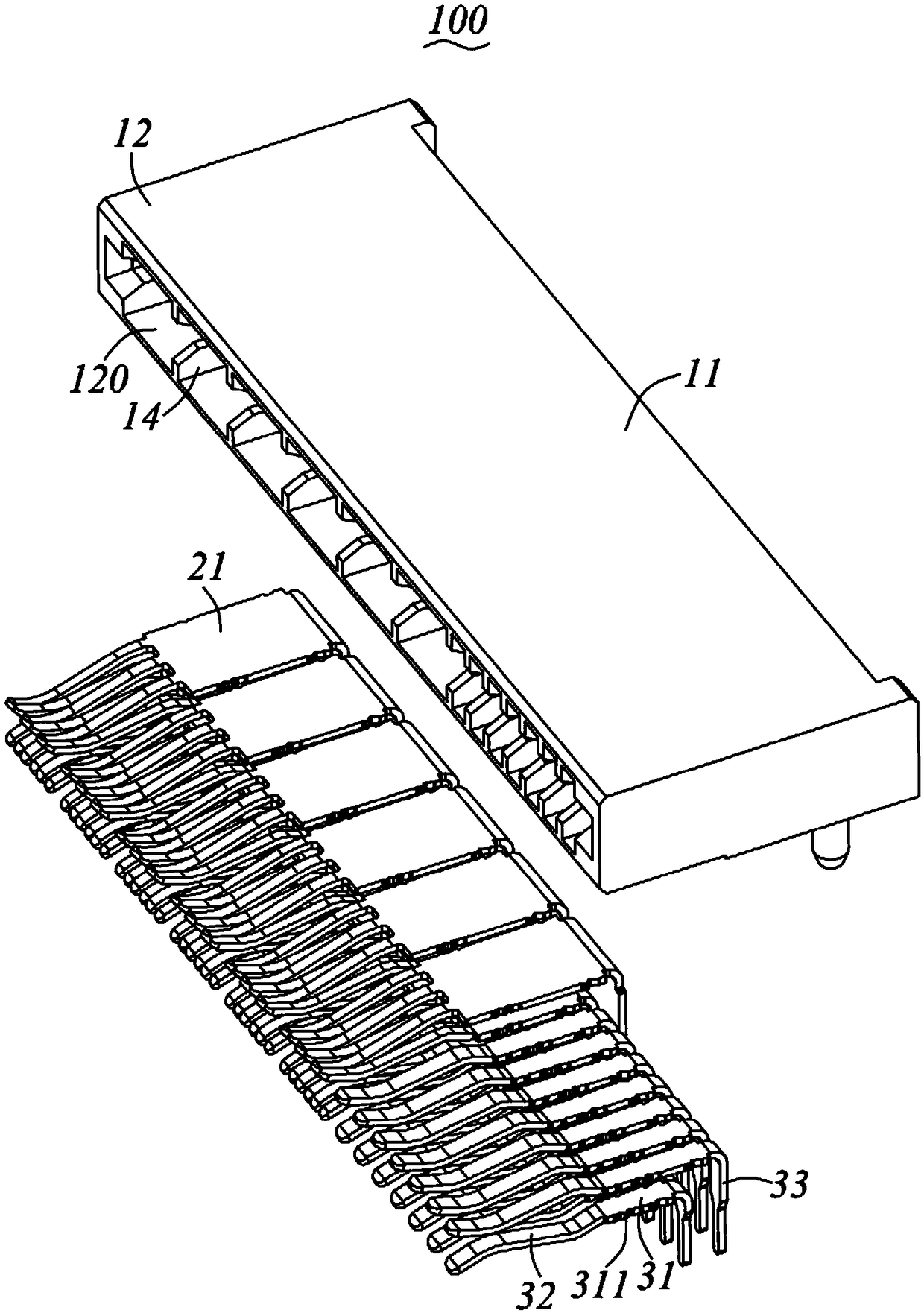

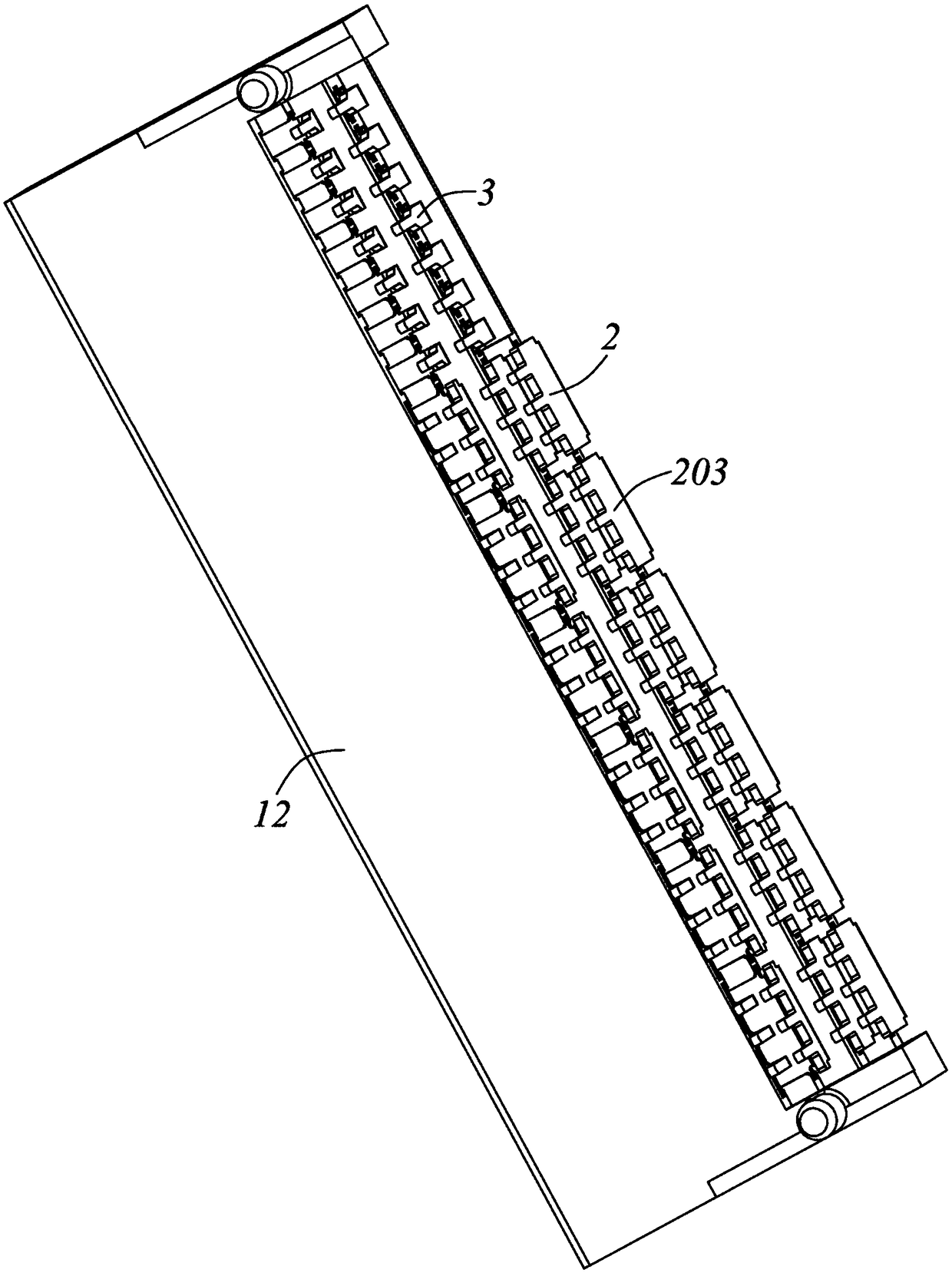

Electrical connector

PendingCN110391528AImprove transmission reliabilityReduce feverCoupling contact membersModifications by conduction heat transferElectricityEngineering

The invention provides an electrical connector. The electrical connector comprises an insulative body and a number of power supply terminal pairs fixed on the insulative body. The insulative body comprises a mounting portion mounted on a circuit board, an abutting portion which extends forward from the mounting portion and a number of terminal slots extending in the front-rear direction. The powersupply terminal pairs are fixed in corresponding terminal slots of the insulative body and divided into at least two rows arranged in the height direction. Each power supply terminal pair in each rowcomprises two power supply terminals. Each power supply terminal comprises a holding portion held in a corresponding terminal slot, a number of contact portions extending forward from the front end of the holding portion, and a soldering portion extending from the rear end of the holding portion. The contact portions of two power supply terminals in each power supply terminal pair are alternatelyand circularly arranged in the lateral direction. The electrical connector provided by the invention can effectively improve heat generation of the power supply terminal pairs.

Owner:ALLTOP ELECTRONICS SU ZHOU +1

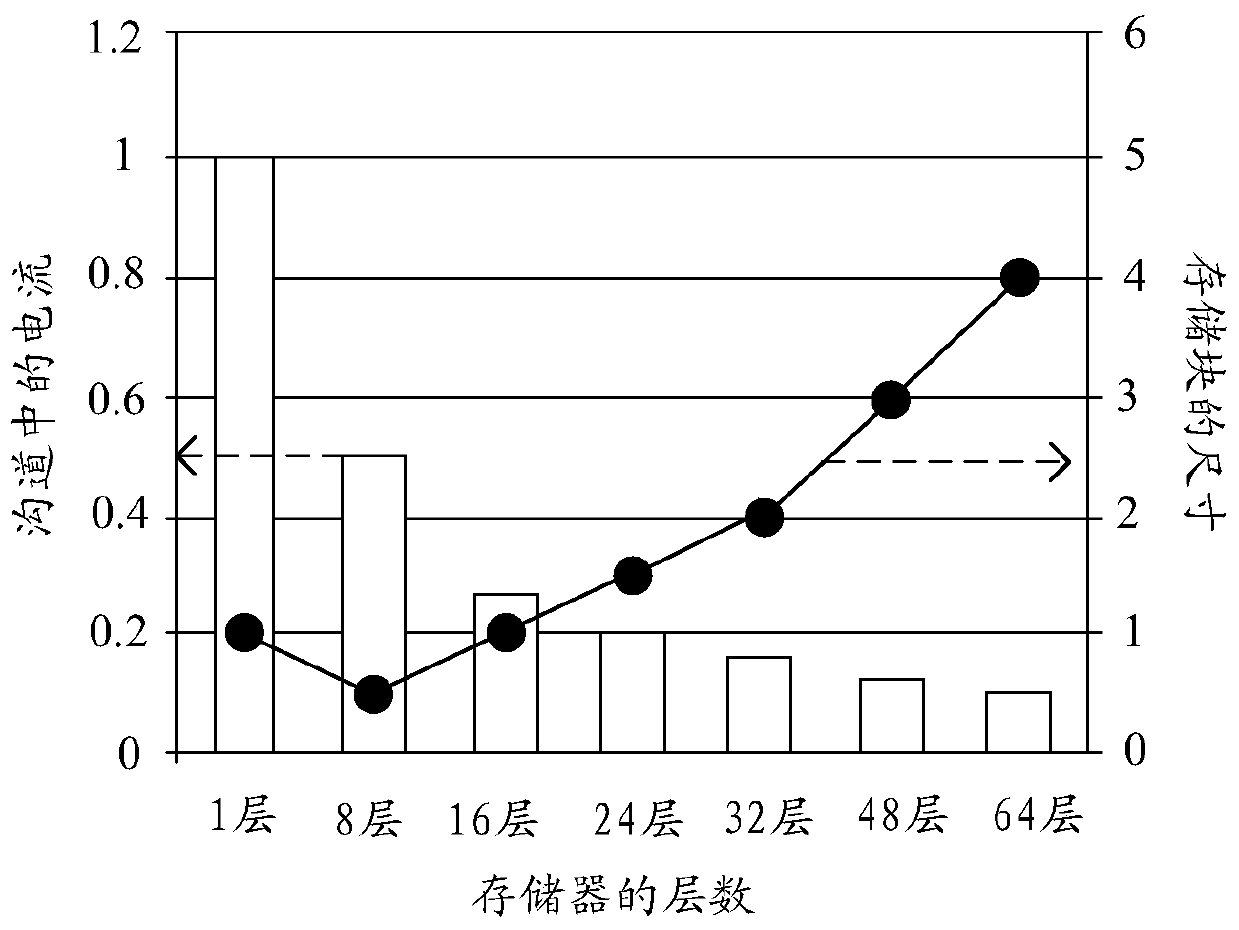

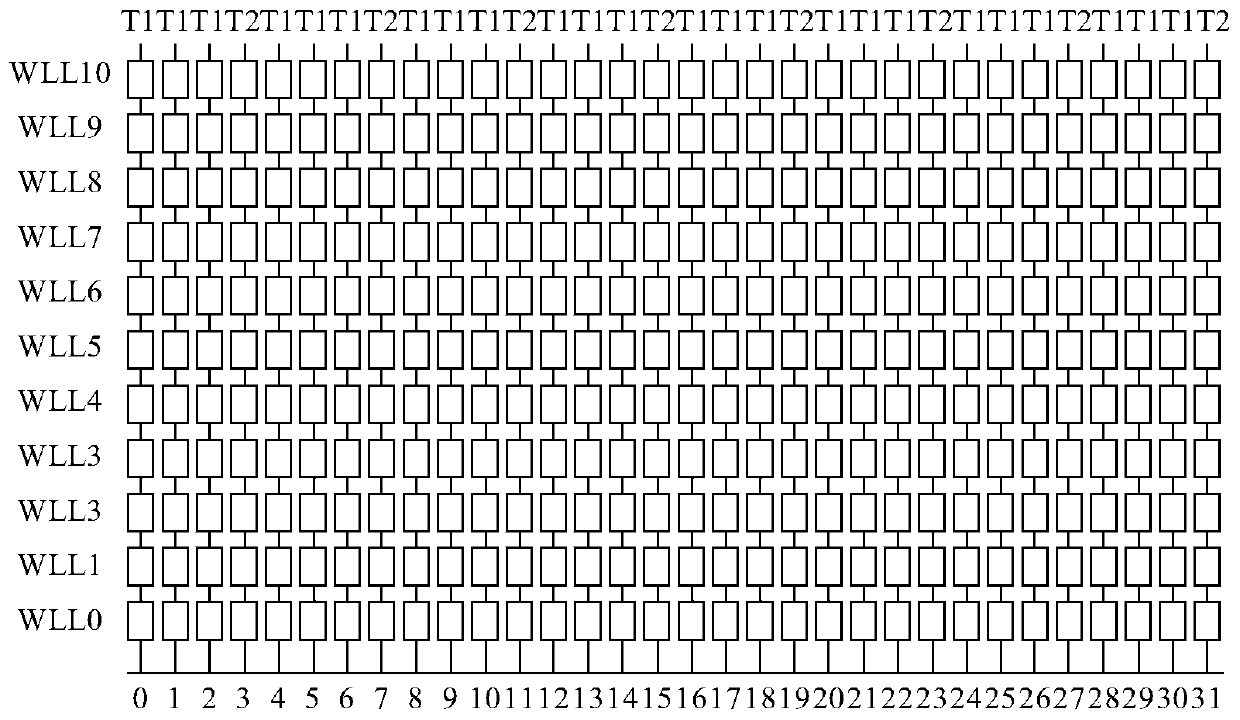

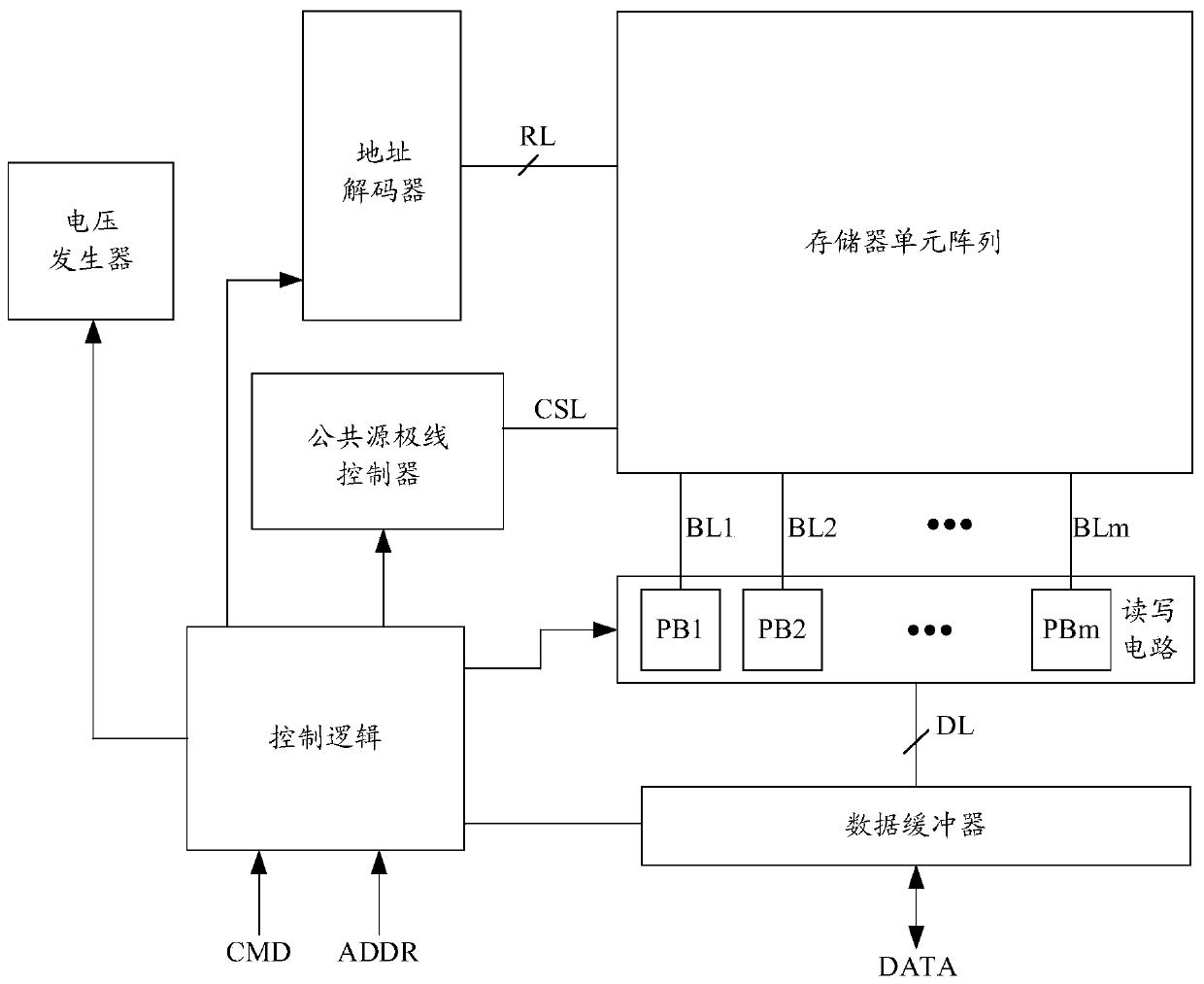

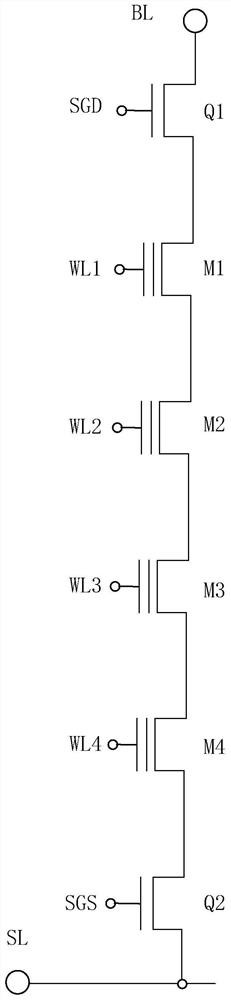

Control method and device of three-dimensional memory and storage medium

ActiveCN110580928AIncrease the read turn-on voltageHigh currentRead-only memoriesComputer scienceElectrical current

The embodiment of the invention provides a control method and device of a three-dimensional memory and a storage medium. The method comprises the following steps: determining to carry out reading operation on a selected first word line; wherein the selected first word line is at least one of a plurality of word lines of the three-dimensional memory; applying a first voltage to the first word line,wherein the first voltage is used for conducting a memory cell tube on the first word line, the first voltage is higher than the second voltage, the second voltage is a voltage applied to other wordlines when it is determined that reading operation is performed on other word lines except the first word line; and the second voltage is used for conducting the memory cell tubes on the other word lines. According to the embodiment of the invention, when the first word line is read, the read conduction voltage on the first word line selected in the three-dimensional memory is increased to increase the current flowing through the memory cell tube on the first word line, so that the channel current in the three-dimensional memory is increased.

Owner:YANGTZE MEMORY TECH CO LTD

Junction field effect transistor and manufacturing method thereof

InactiveCN103730517AReduce doping concentrationLower pinch-off voltageSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsVoltage

The invention discloses a junction field effect transistor. A channel region is arranged between two adjacent same-doped well regions, the channel region is doped through diffusion of the two adjacent well regions, and well regions with the opposite doping types are arranged above the channel region and used for longitudinal depleting the channel region. According to the junction field effect transistor, the doping concentration of the channel region can be reduced, the pinch-off voltage of the channel region is lowered, and thus the pinch-off voltage of the channel region can be adjusted, a small pinch-off voltage is obtained and extra cost does not need to be added. The width requirement of the channel region can be met just by adjusting the widths of the two adjacent same-doped well regions on the two sides of the channel region, and thus the channel current of the device can be adjusted; moreover, the channel current can be enlarged easily, and thus a large channel current is obtained. The invention further discloses a manufacturing method of the junction field effect transistor.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

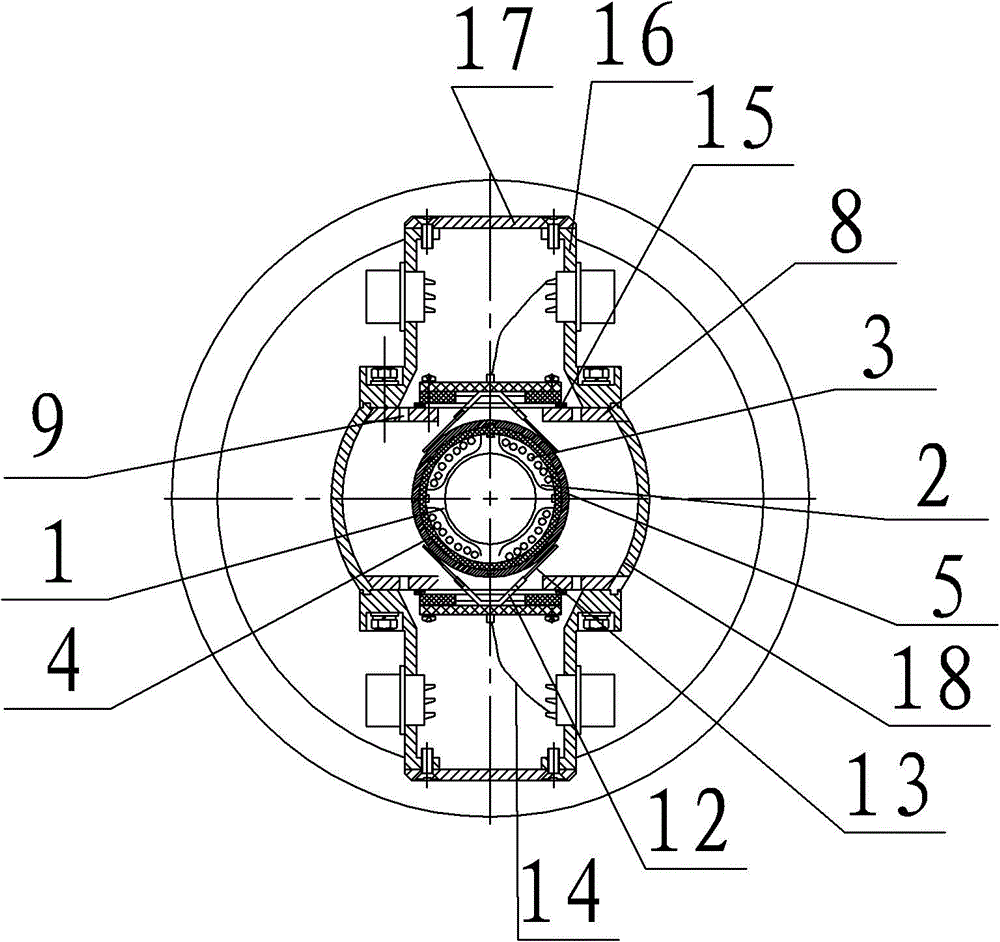

Hollow electric-rotating connector

InactiveCN101958498BAvoid crush damageSmall currentRotary current collectorElectrical conductorEngineering

The invention relates to a hollow electric-rotating connector. Electric sliding rings are sleeved on a sliding ring shaft sleeve, two ends of the sliding ring shaft sleeve are rotatably assembled with supporting devices connected through a bridging beam, the bridging beam is fixedly provided with an electric connector installing box corresponding to an electric brush group, an electric connector is fixedly arranged on the vertical wall of the electric connector installing box, an electric connector installing board is fixedly arranged on one end of the sliding ring shaft sleeve, an end part electric connector is fixedly arranged on the electric connector installing board, one side of each electric sliding ring close to the sliding ring shaft sleeve is connected with the end part electric connector through a corresponding sliding ring conductor, and the sliding ring conductors are arranged on the outer wall of the sliding ring shaft sleeve. According to the hollow electric-heating connector, the conductors used for connecting the electric sliding rings and the end part electric connector are arranged on the outer wall of the sliding ring shaft sleeve, the inner hole wiring of the traditional sliding ring shaft sleeve is changed into the outer wall wiring, thus the space inside the sliding ring shaft sleeve is remained, and can be used for installing parts needing installing.

Owner:CHINA AVIATION OPTICAL-ELECTRICAL TECH CO LTD

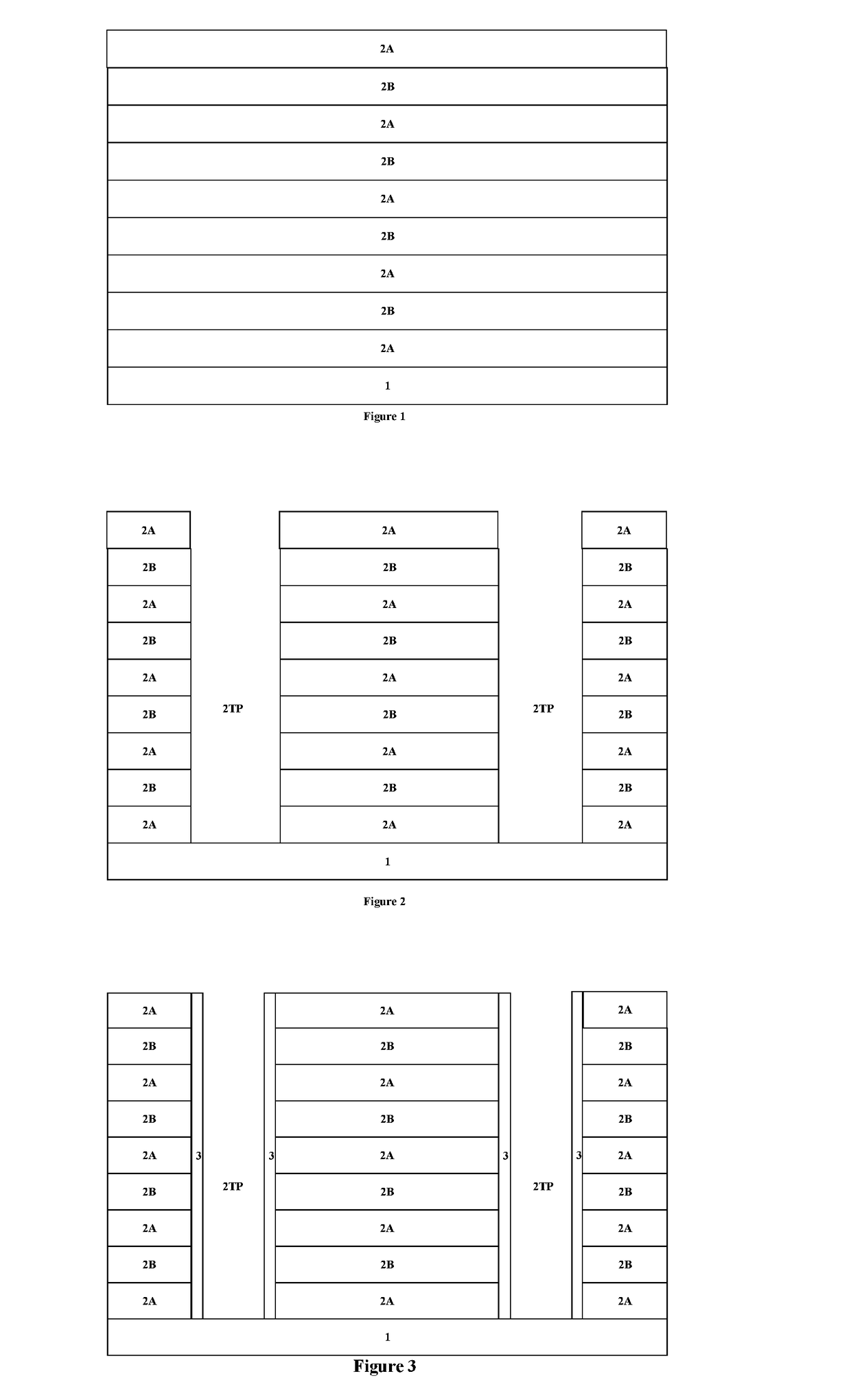

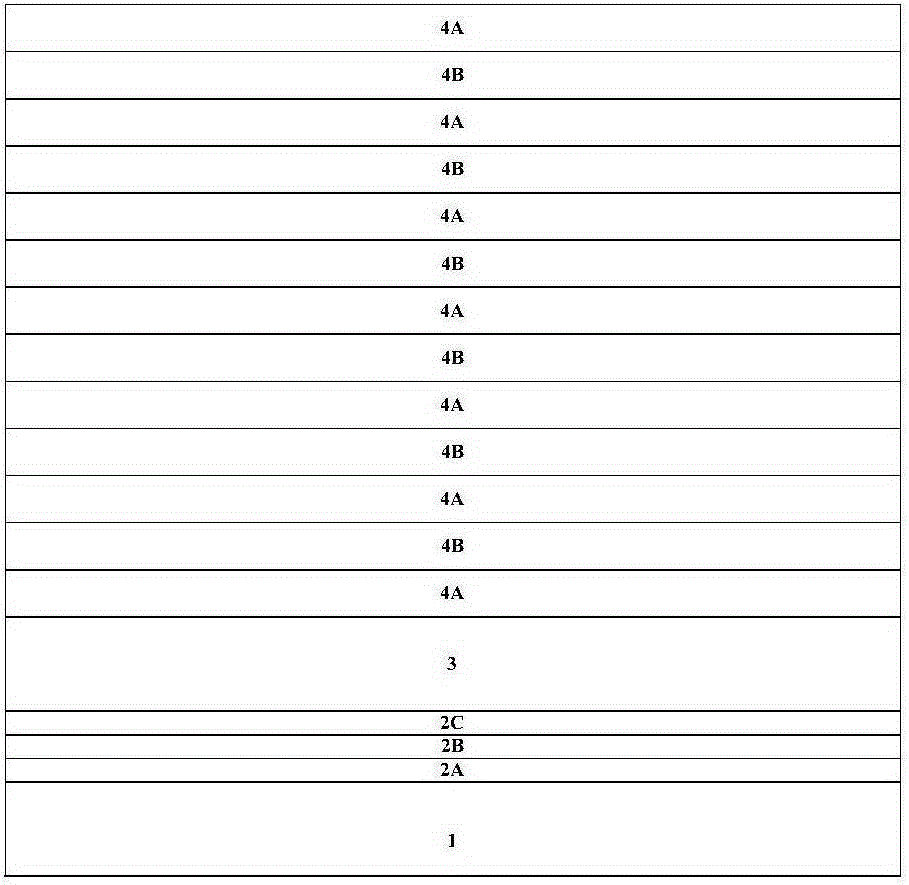

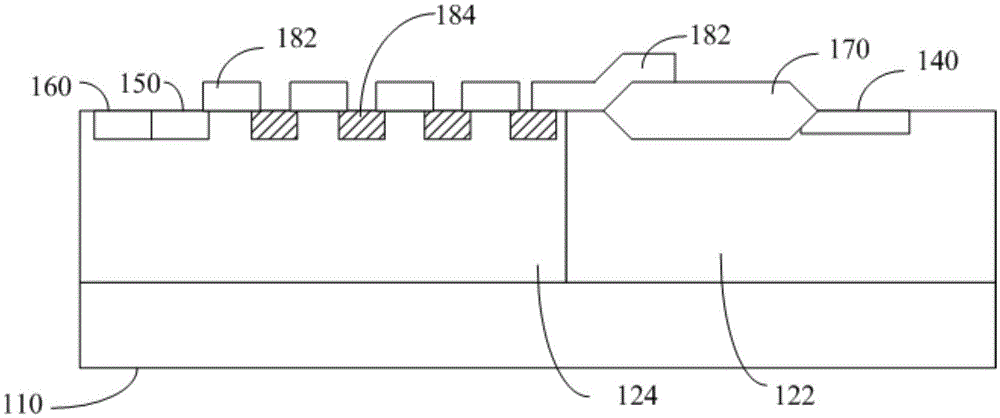

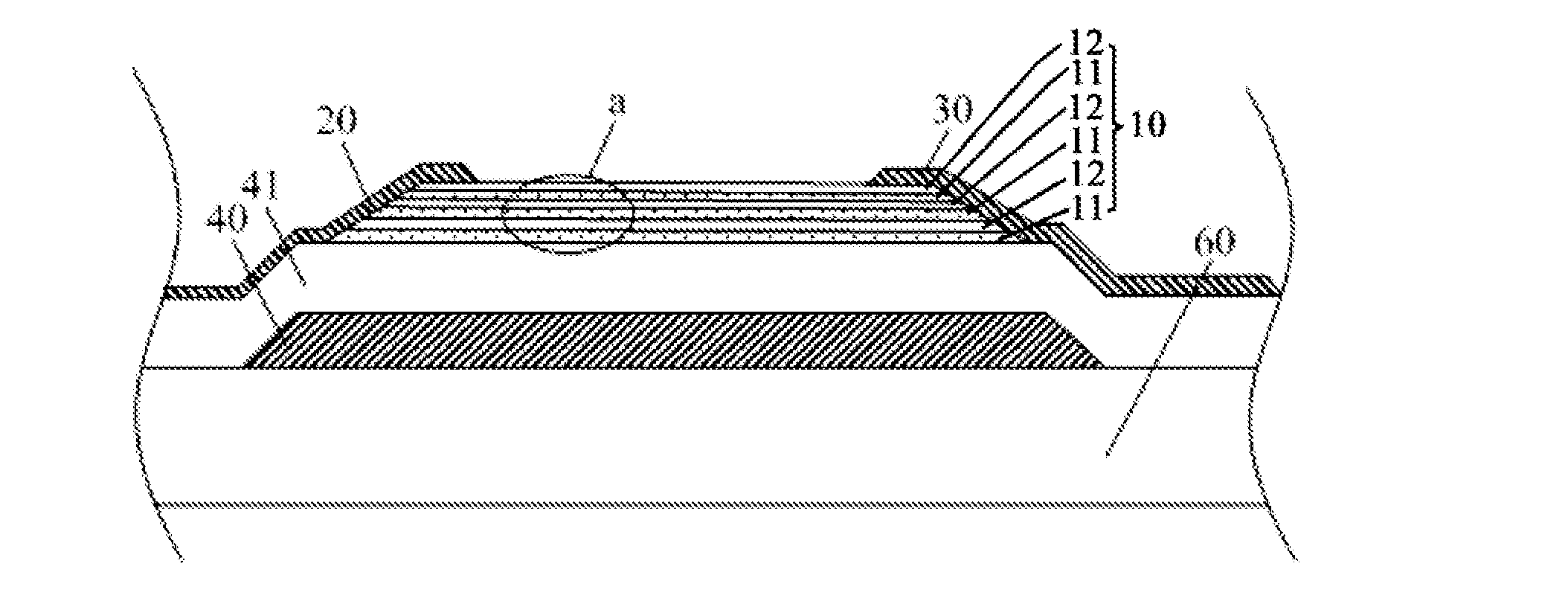

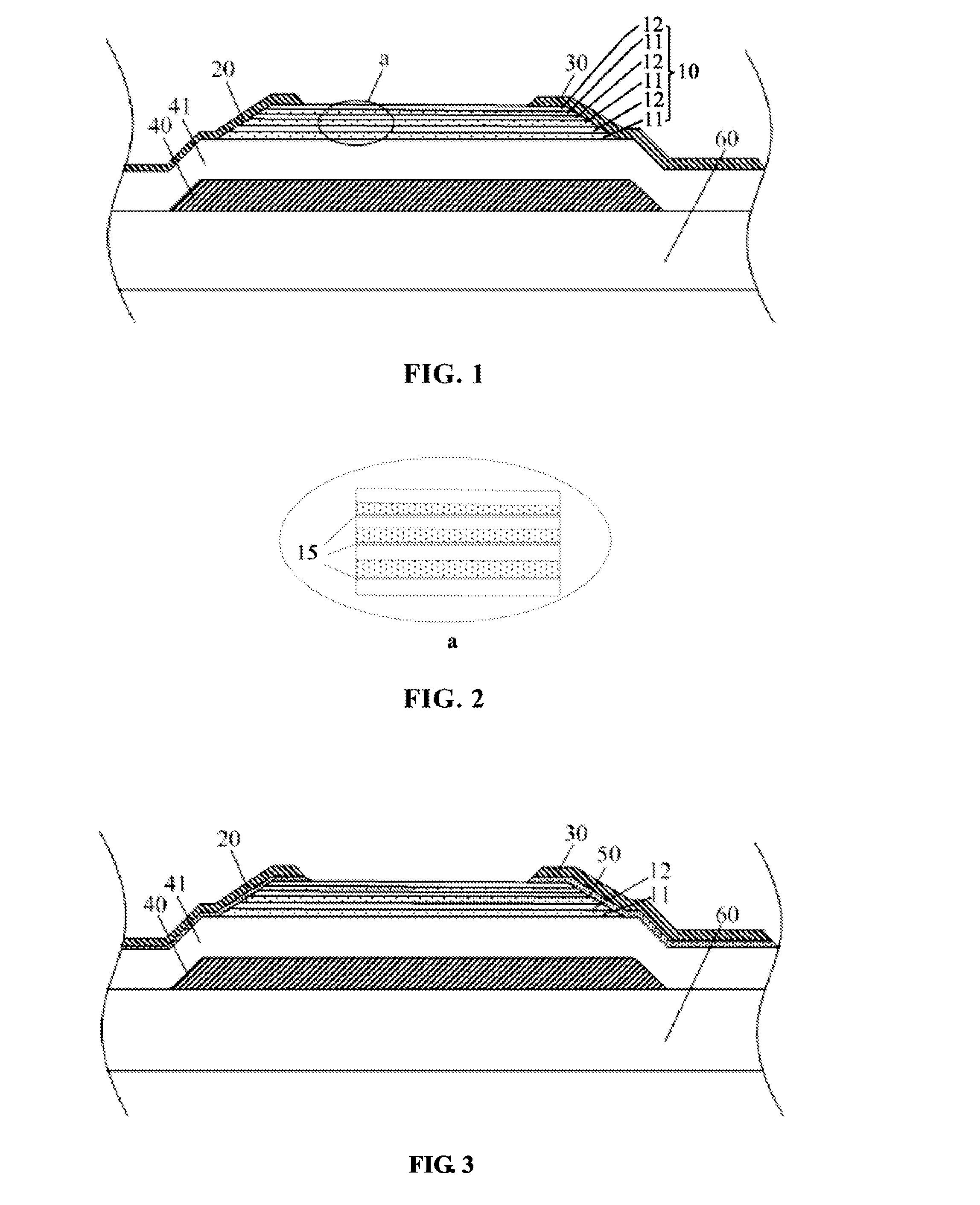

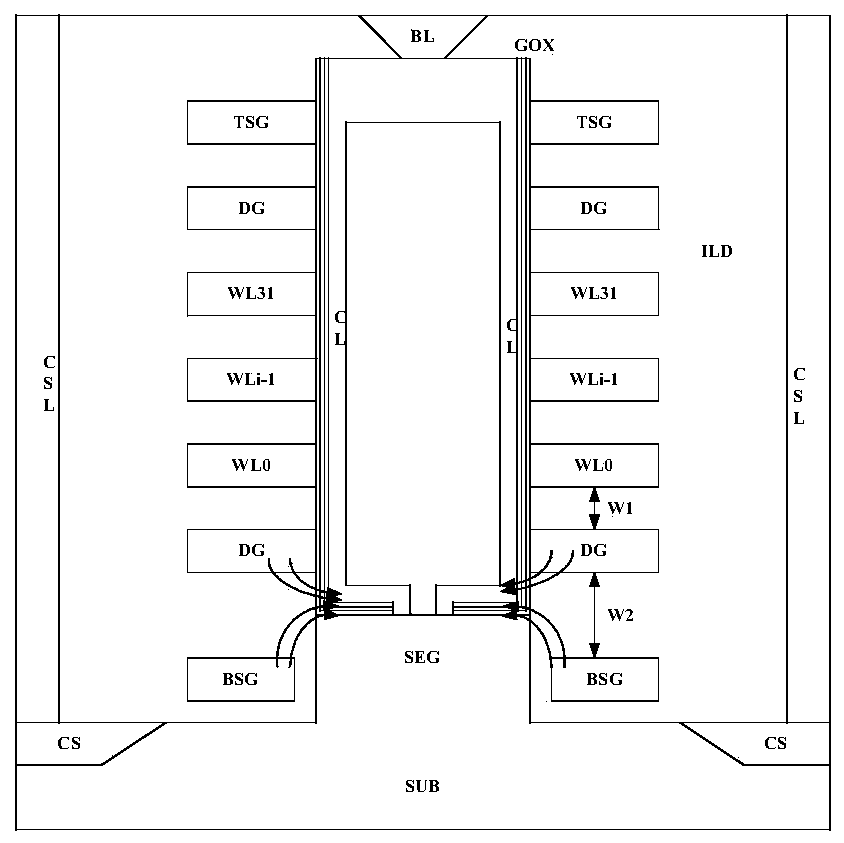

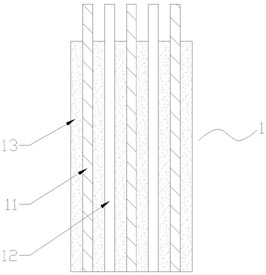

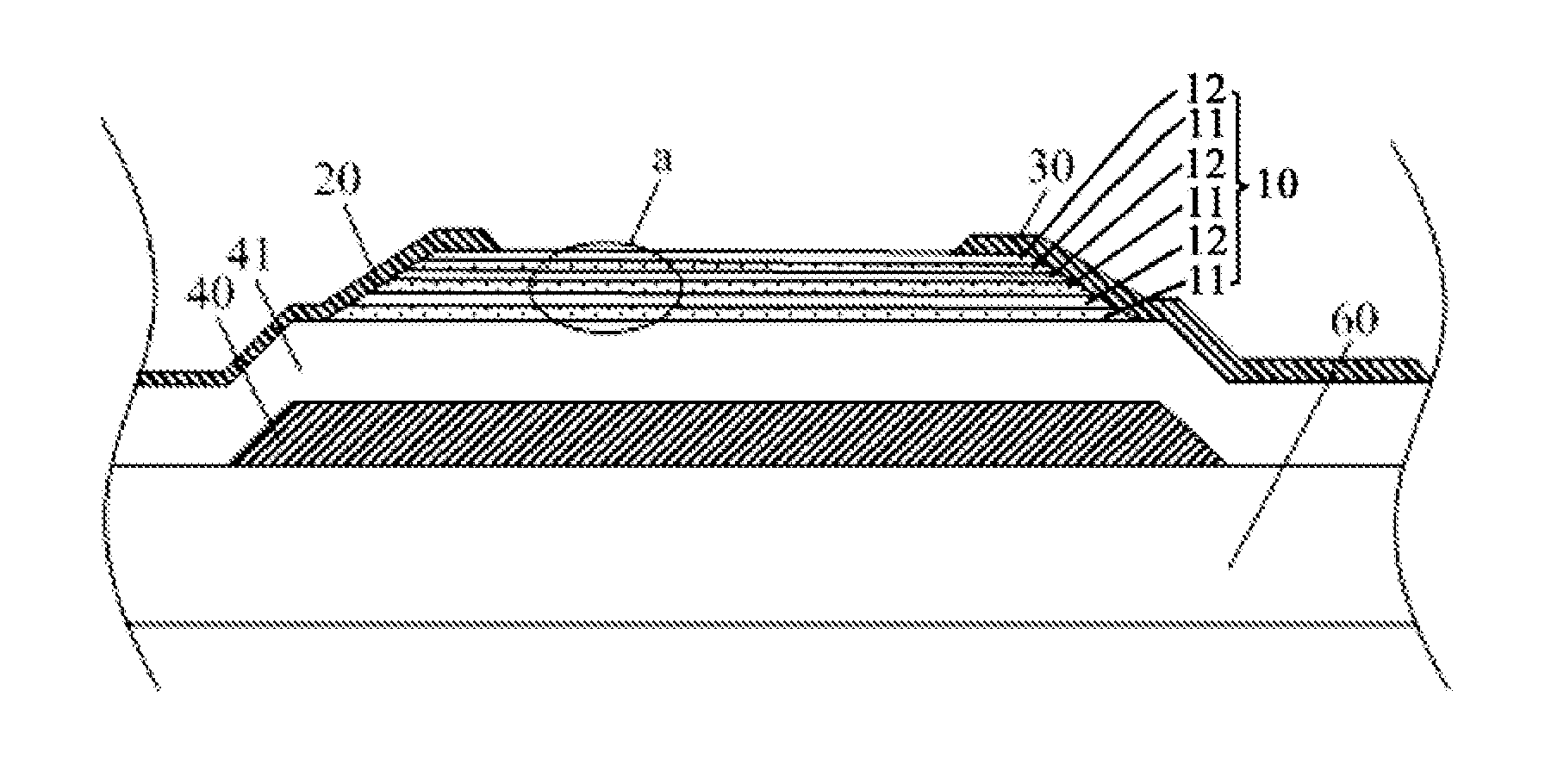

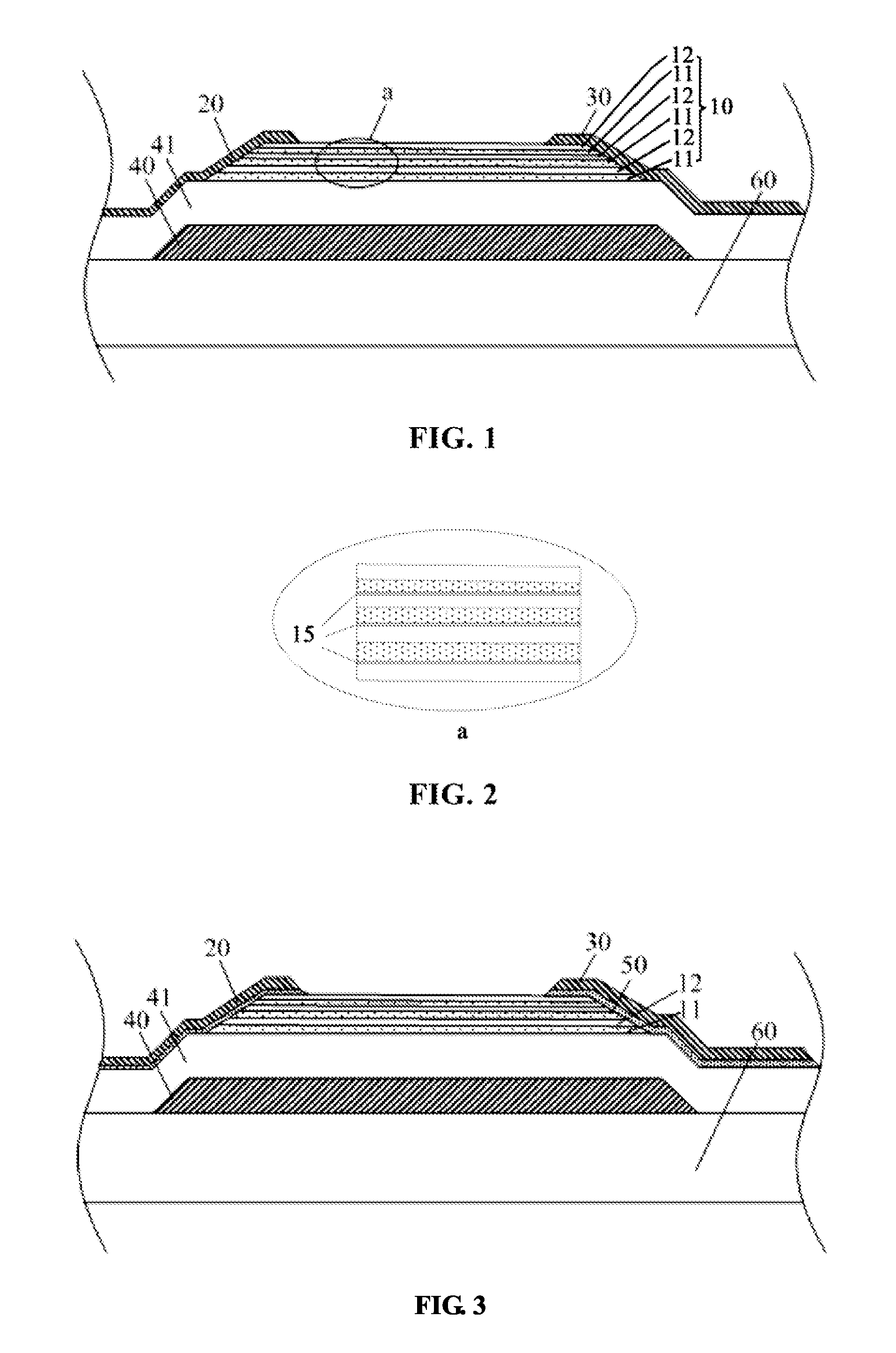

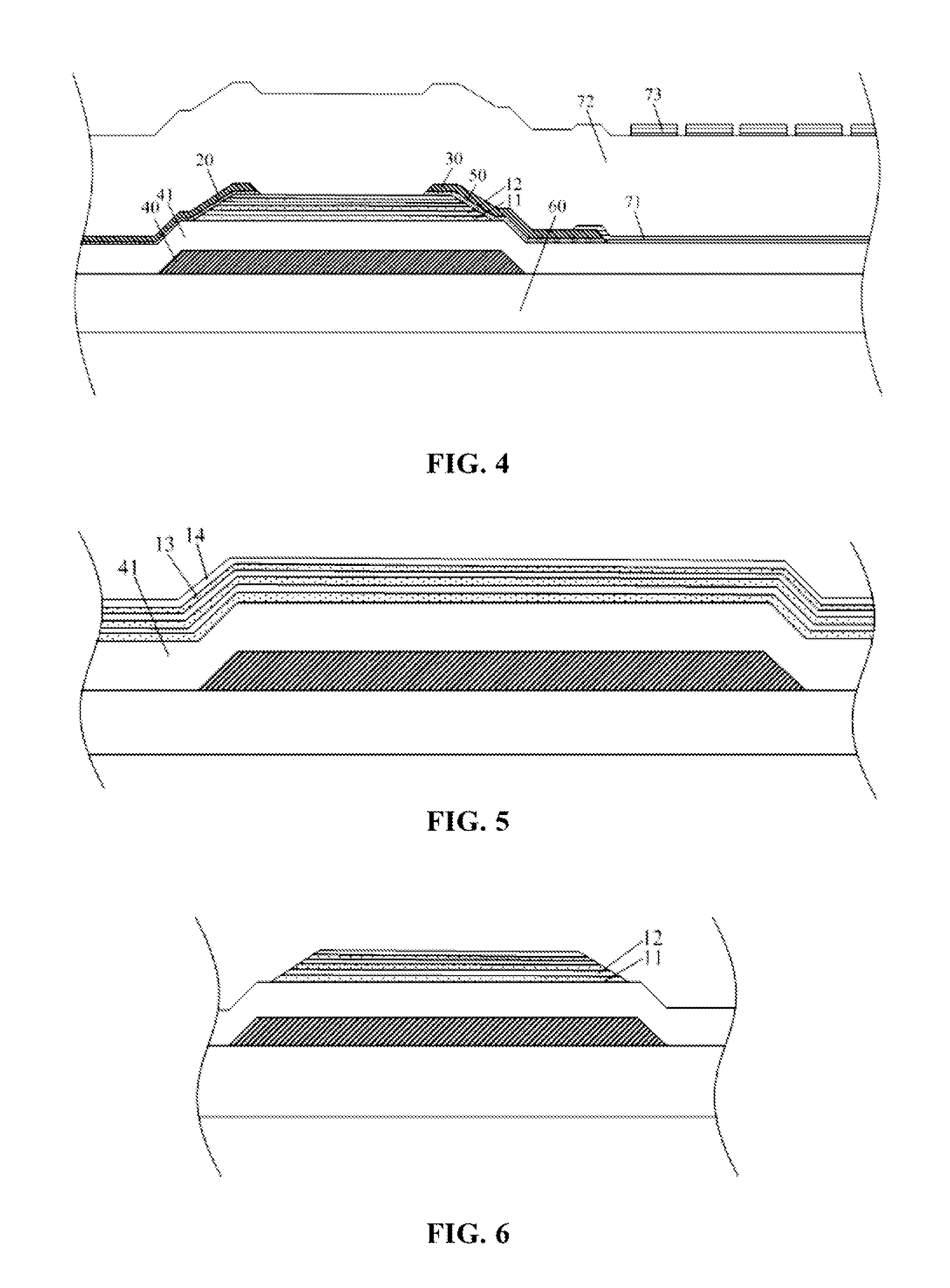

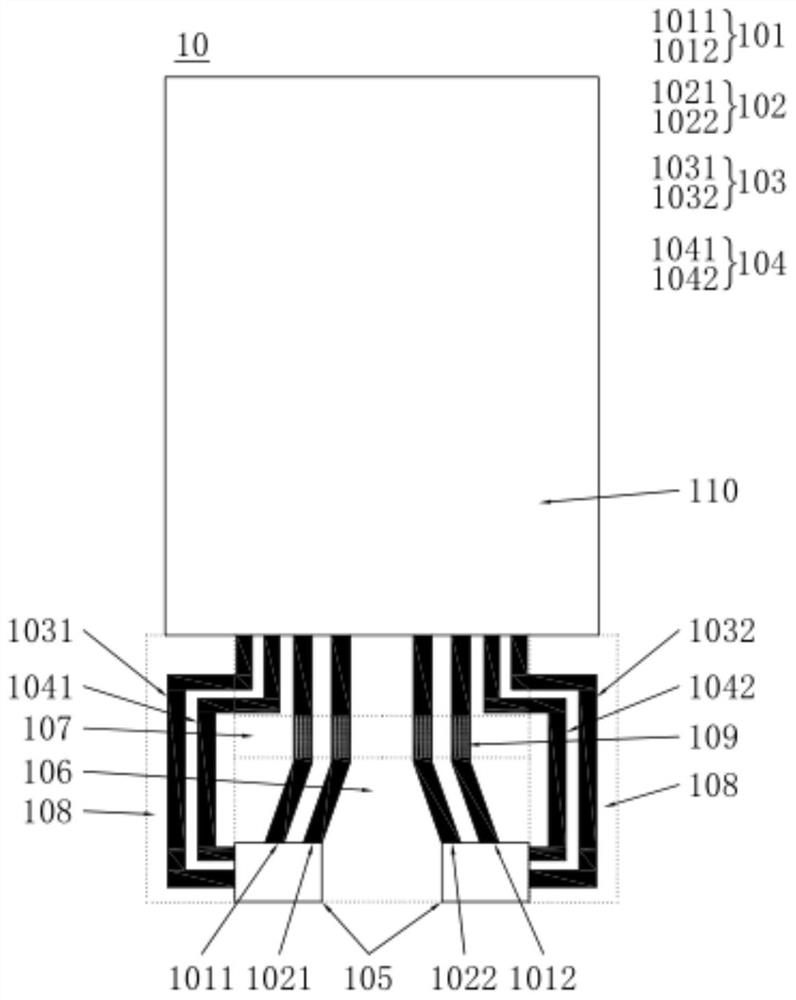

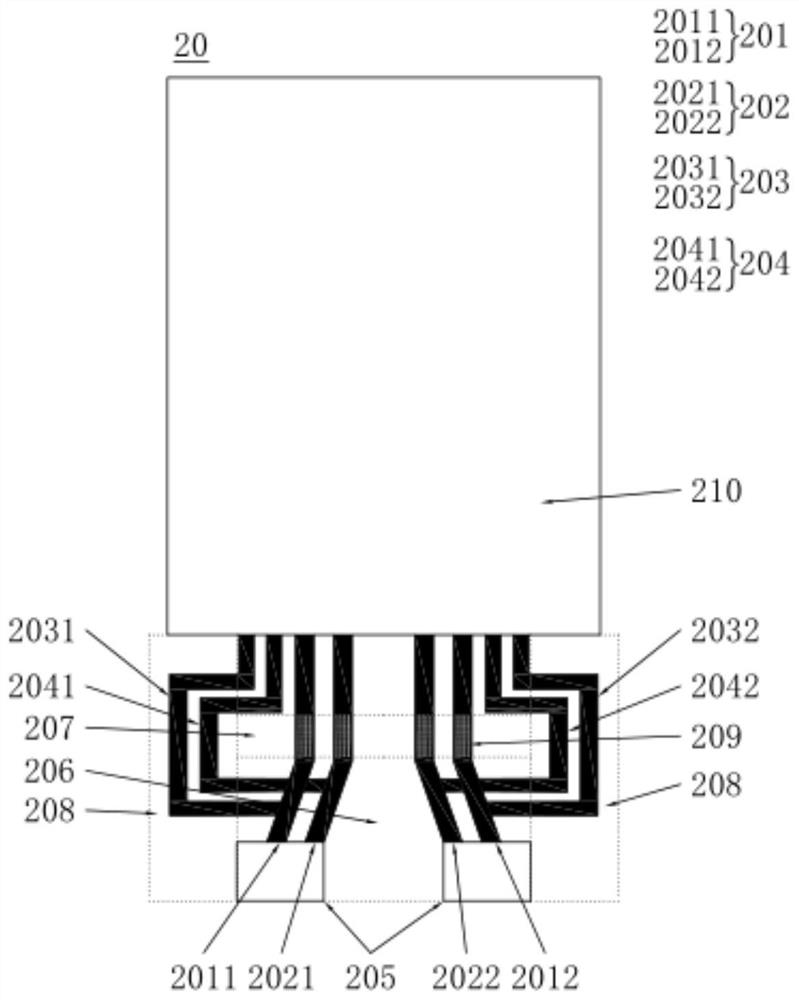

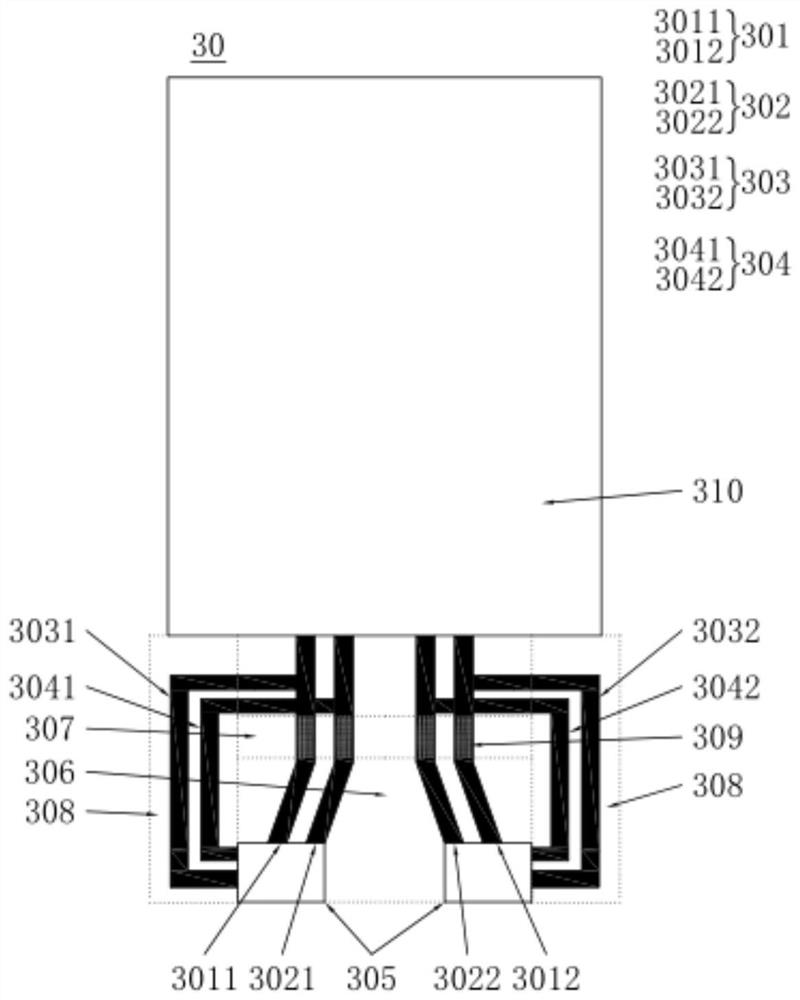

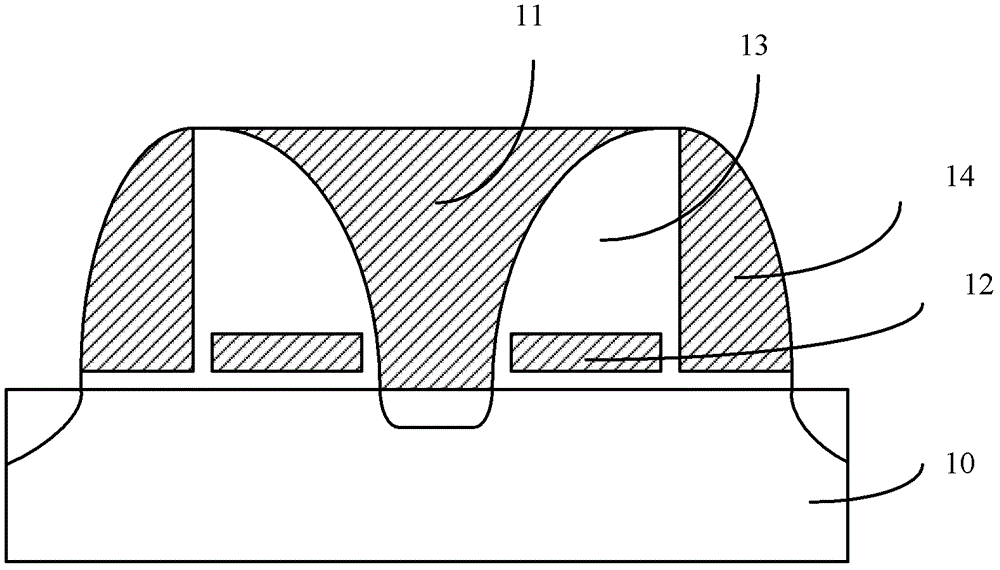

TFT and Manufacturing Method Thereof, Array Substrate and Display Device

ActiveUS20150243677A1Increase current channelMaximum compactnessTransistorSolid-state devicesDisplay deviceCharge carrier mobility

The present invention provides a thin film transistor. An active layer of the thin film transistor comprises a plurality of active semiconductor sub-layers and a plurality of insulation sub-layers, which are stacked alternately. A source and a drain of the thin film transistor are electrically connected to the plurality of active semiconductor sub-layers. Correspondingly, the present invention further provides a method for manufacturing a thin film transistor, and an array substrate. The present invention can effectively increase channel current of the active layer in a thin film transistor, and solves the problem of small channel current resulted from low carrier mobility of the active layer.

Owner:BOE TECH GRP CO LTD +1

Three-dimensional semiconductor device and manufacturing method thereof

ActiveCN105355602BControl consistencyOvercome the current bottleneckSolid-state devicesSemiconductor devicesGate dielectricMemory cell

A three-dimensional semiconductor device comprising a plurality of memory cells, each comprising: a channel layer distributed along a direction perpendicular to a substrate surface; a bottom gate conductive layer located in a first insulating layer stack and distributed on the side of the channel layer On the wall; the floating gate layer is located on the first insulating layer stack and distributed on the sidewall of the channel layer; a plurality of second insulating layers and a plurality of gate conductive layers are located on the floating gate layer and along the channel Layer sidewalls are stacked alternately; the gate dielectric layer is distributed on the sidewalls of the channel layer; the drain is located on the top of the channel layer; and the source is located in the substrate between two adjacent storage units of multiple storage units . The non-extracted floating gate is embedded inside, and the voltage is induced on the floating gate through the coupling of the voltage on the adjacent extraction gate to assist in completing the channel inversion of the contact area between the SEG and the polysilicon, thereby overcoming the current bottleneck in this area and increasing the channel current. Effectively control the threshold voltage consistency of the floating gate adjacent FETs.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Manufacturing method of 3D memory device

PendingCN112151553AIncrease current channelAffects the threshold voltageSolid-state devicesSemiconductor devicesDopingEngineering

The invention discloses a manufacturing method of a 3D memory device. The manufacturing method comprises the steps: forming a laminated structure on a substrate, wherein the laminated structure comprises interlayer dielectric layers and interlayer sacrificial layers which are alternately stacked; forming a channel hole passing through the laminated structure; forming a functional layer and a channel layer in the channel hole; forming a doped layer covering the channel layer; and annealing the doped layer so as to enable impurities in the doped layer to enter the channel layer. According to themanufacturing method, doped impurities are provided for the channel layer through the doped layer, and low-concentration doping of the channel layer is realized, so that the influence on other electrical properties of the 3D memory device is reduced while the channel current is improved.

Owner:YANGTZE MEMORY TECH CO LTD

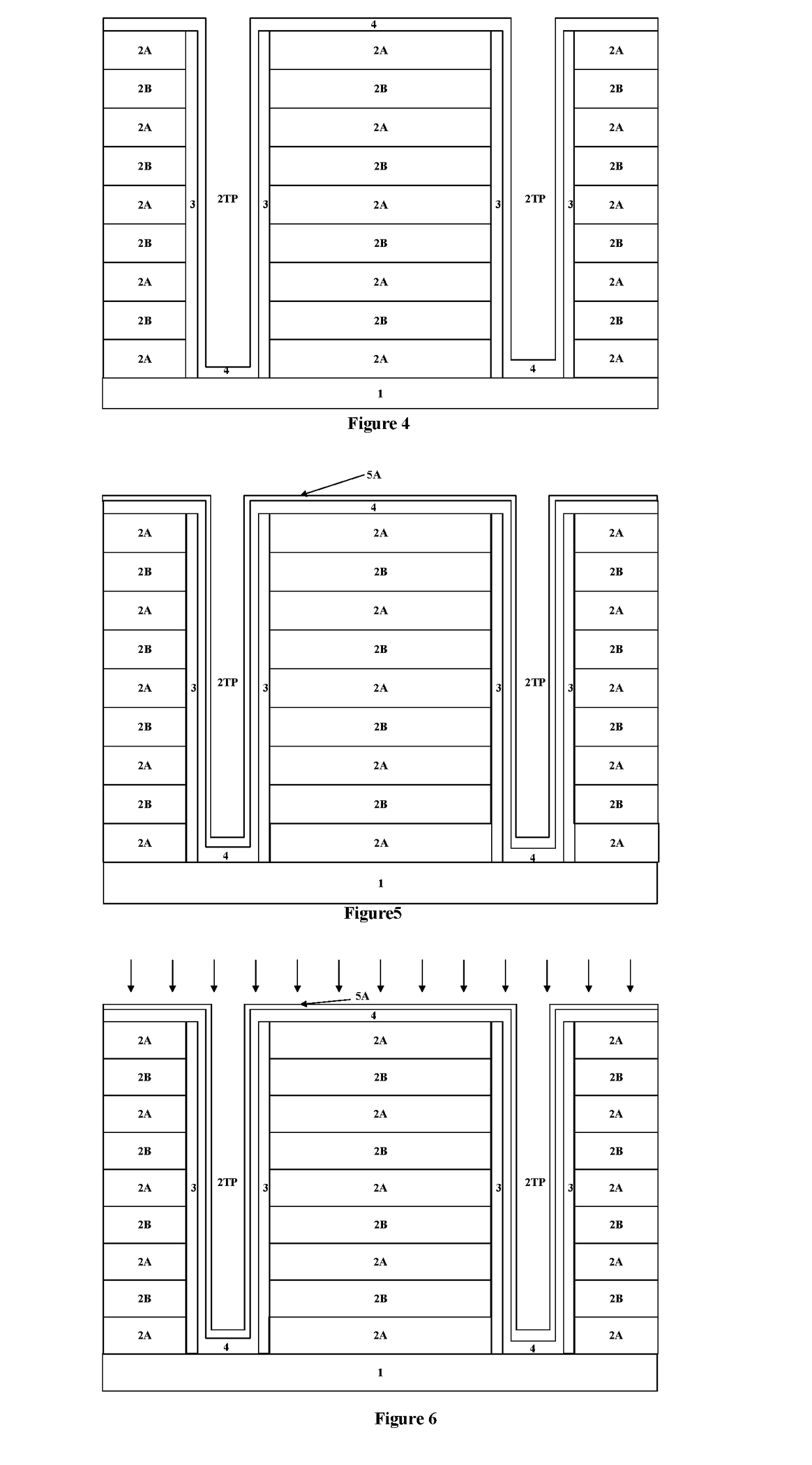

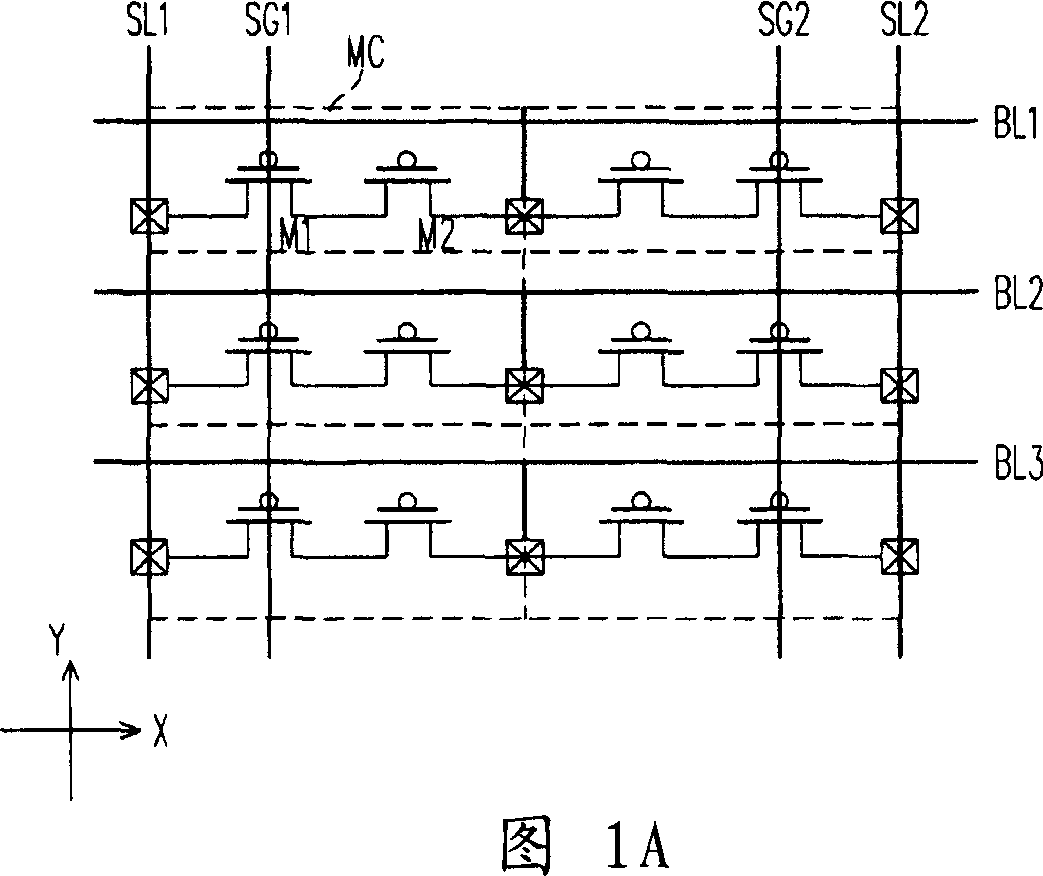

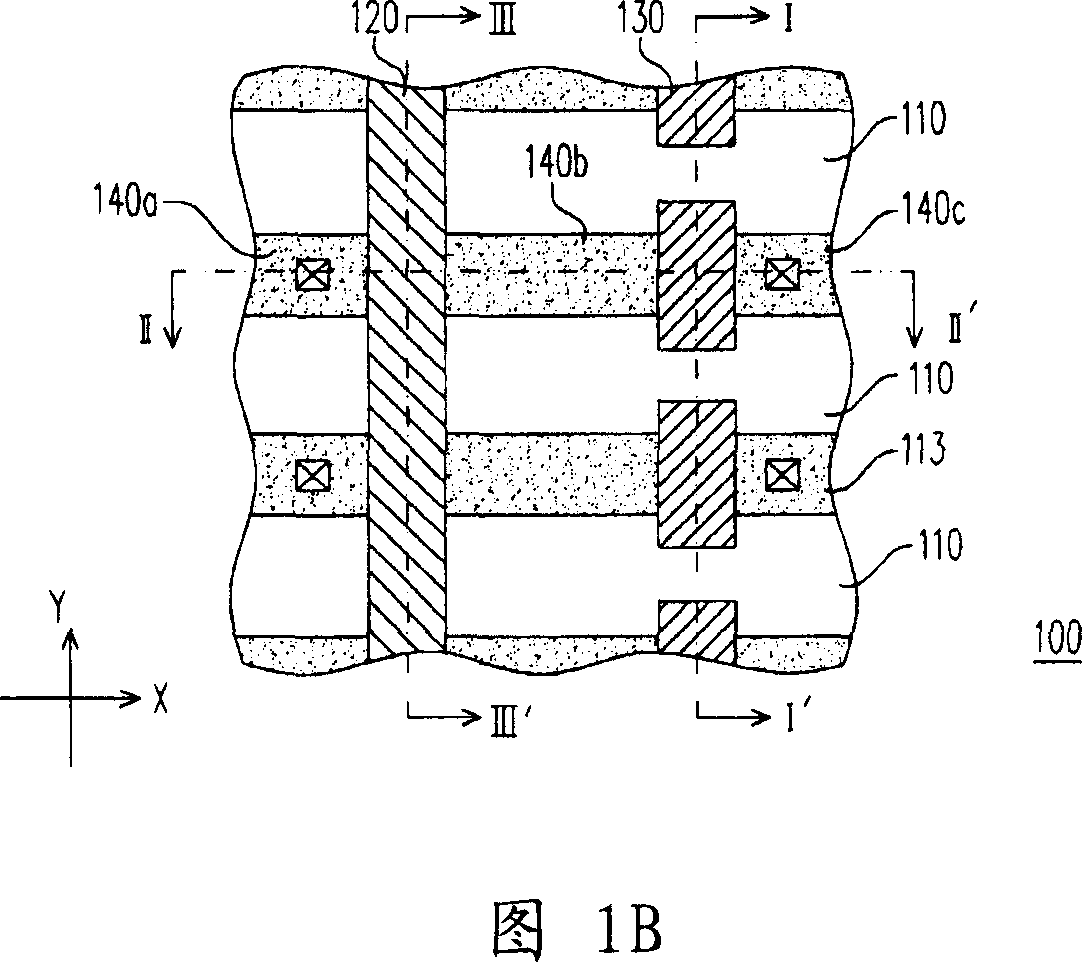

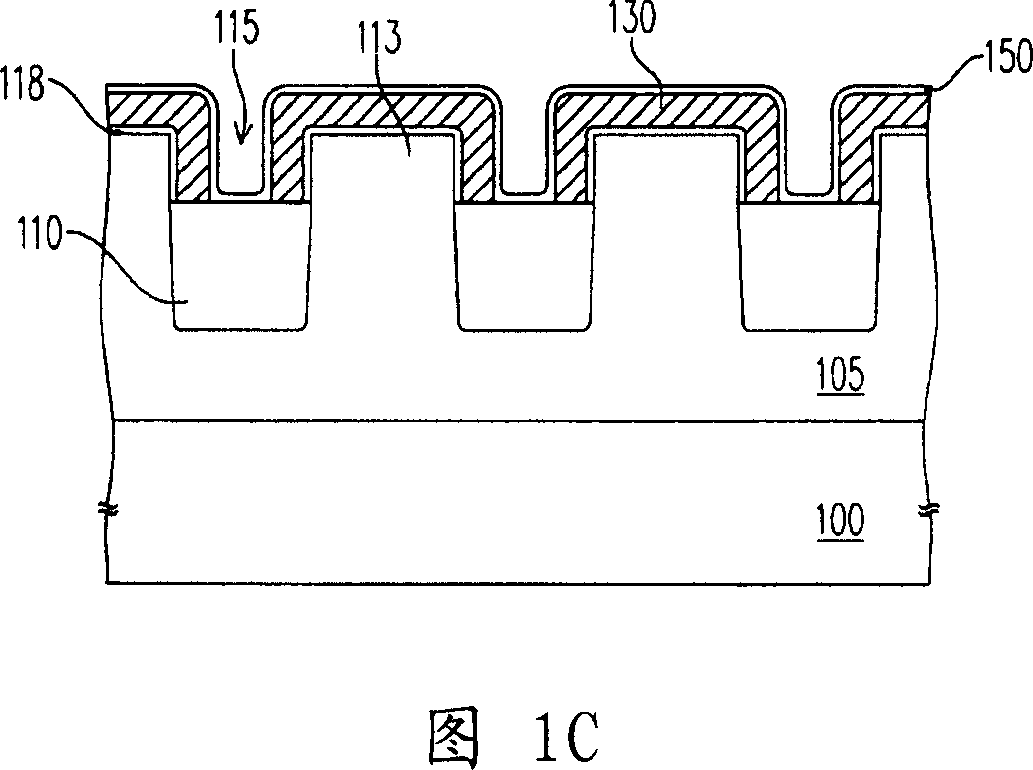

Single programmable memory and its making method

InactiveCN101064315AIncrease widthIncrease channel currentSolid-state devicesSemiconductor/solid-state device manufacturingTransistorElectrical and Electronics engineering

The invention discloses a single-time programmable memory that comprises basis, several separation configurations, the first transistor and the second transistor. The separation configurations are set on the basis to define the active area. Each of the separation configurations possesses depression to make the top surface of the separation configuration lower than the basis. The first transistor is set on the active area of the basis, and extends to the sidewall of the depression, the gate electrode of the first transistor is selecting gate electrode. The second transistor is set on the active area of the basis, serially connected with the first transistor. The gate electrode of the second transistor is float gate electrode which is block type and bestrides over the basis of the separation configurations, and extends to the sidewall of the depression.

Owner:POWERCHIP SEMICON CORP

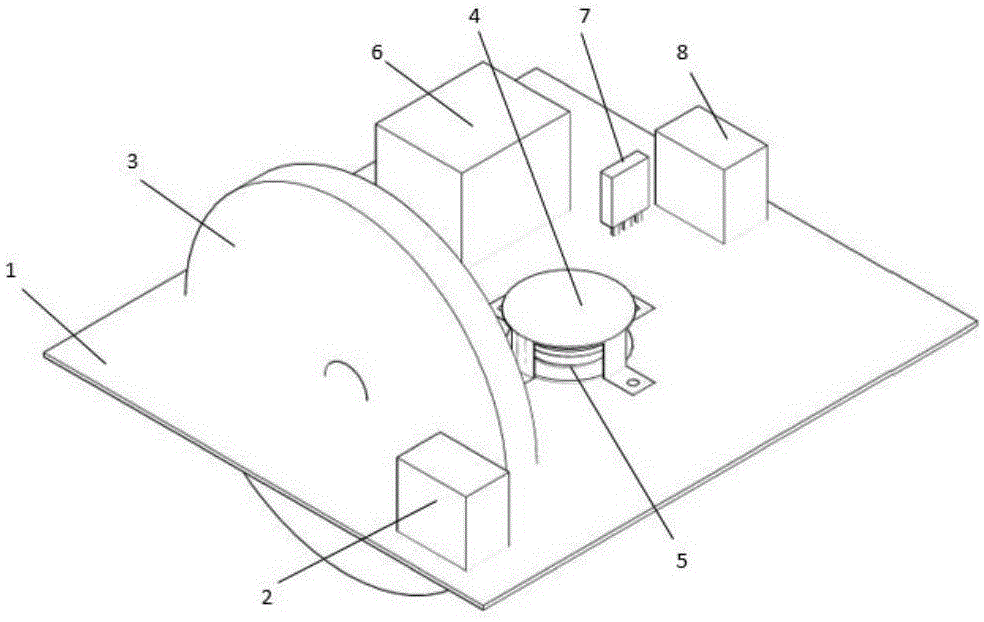

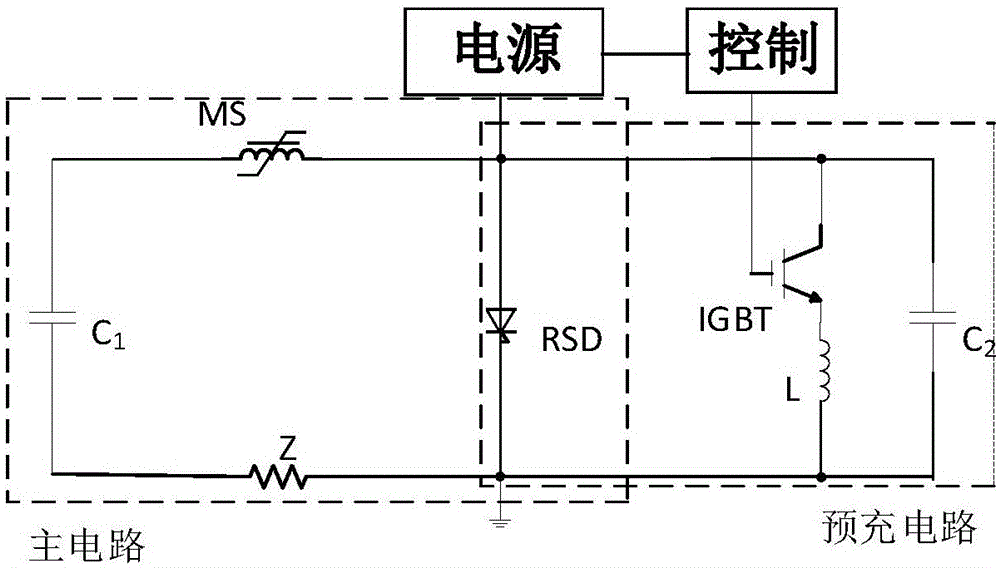

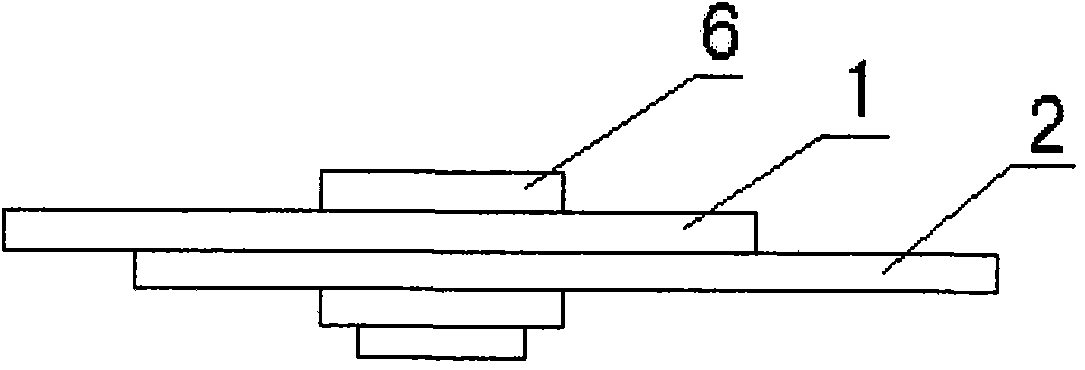

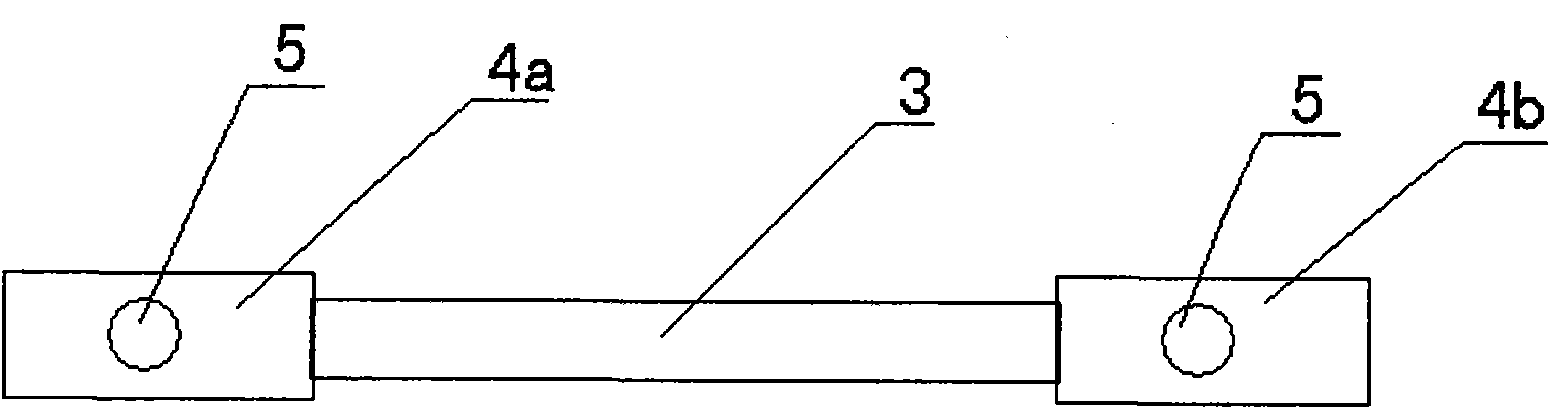

RSD-based pulse power supply module

ActiveCN105141293AReduce parasitic inductanceImprove on-state current rise ratePulse generation by energy-accumulating elementCapacitancePre-charge

The invention discloses an RSD-based pulse power supply module. The module comprises a main capacitor, a magnetic switch, an RSD, a charging power supply, a switch pipe, a pre-charge capacitor, a pre-charge inductor and a control module and is characterized in that the main capacitor, the magnetic switch, the RSD, the charging power supply, the switch pipe, the pre-charge capacitor and the pre-charge inductor are integrated in one PCB; and the RSD is fixed on the PCB by a surrounded copper foil. By integrating the RSD power switch, the charging power supply, the capacitor and the magnetic switch in the PCB, all elements work cooperatively and length of a wire is reduced, so stray parameters like parasitic inductance of the power supply is reduced; the rate of rise di / dt of on-state current of the RSD is increased; in addition, the surrounded copper foil is used for welding and fixing the RSD, thereby facilitating acceleration of heat radiation of the RSD and increasing of current channels on the PCB; and copper foil is capable of equally distributing current trends, so current carrying capacity of the pulse power supply module is improved.

Owner:HUAZHONG UNIV OF SCI & TECH

Method for preventing connection point of cable lug and knife switch from overheating during current carrying

InactiveCN101770889AEasy to manufactureIncrease effective touch pointsAir-break switch detailsContact electric connectionElectricityCurrent channel

The invention discloses a method for preventing a connection point of a cable lug and a knife switch from overheating during current carrying. The method is characterized in that a bypass conductive belt is arranged on the connection point of the cable lug and a knife switch type terminal board; and one end of the bypass conductive belt contacts the upper surface of the cable lug to form electrical connection, and the other end contacts the lower surface of the knife switch type terminal board form electrical connection. The method not only enlarges the contact area of the cable lug and the knife switch type terminal board but also increases current channels of connection point, thereby more uniformly distributing load current, reducing contact resistance and effectively preventing the connection point of the cable lug and the knife switch from overheating in the process of current carrying operation. The invention has the advantages of simple method, easy manufacture of the bypass conductive belt, no change of the original structure of electrical equipment during construction and convenient field construction.

Owner:HANZHONG POWER SUPPLY BUREAU

Lithium iron phosphate polymer lithium battery capable of realizing large current charging and discharging

InactiveCN110137577ALower internal resistanceLower cut-off voltageCell seperators/membranes/diaphragms/spacersCell electrodesLithium iron phosphateEngineering

The invention discloses a lithium iron phosphate polymer lithium battery capable of realizing large current charging and discharging and is to provide the lithium iron phosphate polymer lithium battery capable of realizing large current charging and discharging and having good discharge capacity, good safety, good durability and high temperature resistance. The lithium iron phosphate polymer lithium battery comprises a battery core body, a battery housing wrapping the battery core body and an electrolyte filled inside the battery housing. The battery core body adopts a laminated structure, andcomprises a plurality of anode sheets and cathode sheets, which are stacked up. Each cathode sheet is located between two adjacent anode sheets; a diaphragm is arranged between the adjacent anode andcathode sheets; each anode sheet is formed by coating anode paste on an anode current collector; and each cathode sheet is formed by coating cathode paste on a cathode current collector. The invention is applied to the technical field of a lithium battery.

Owner:广东省飞驰新能源科技有限公司

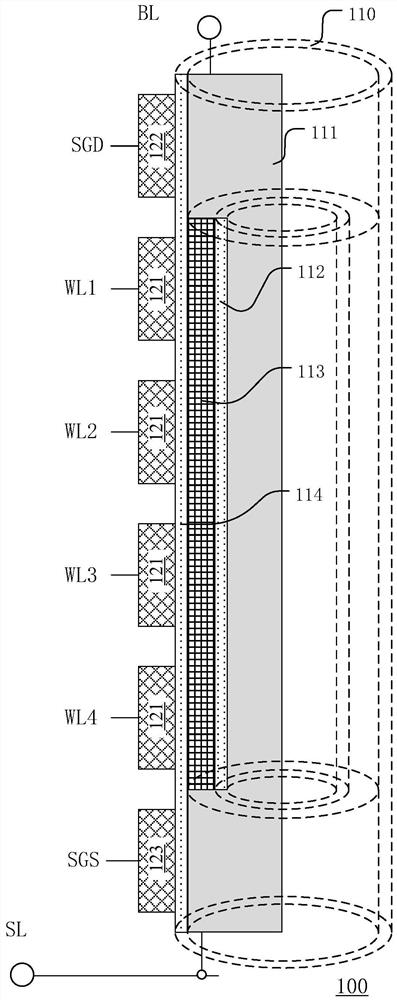

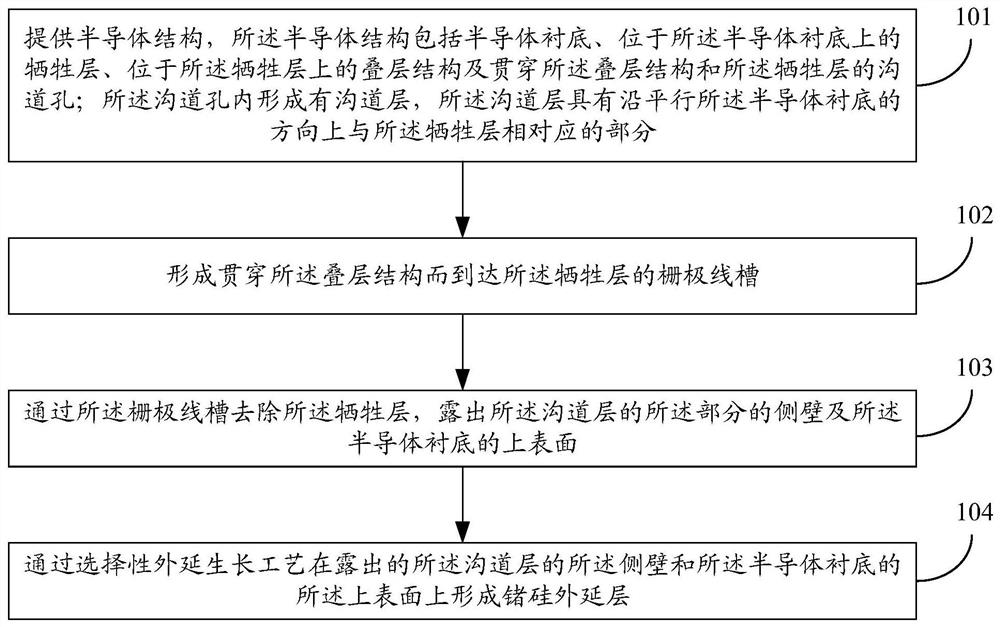

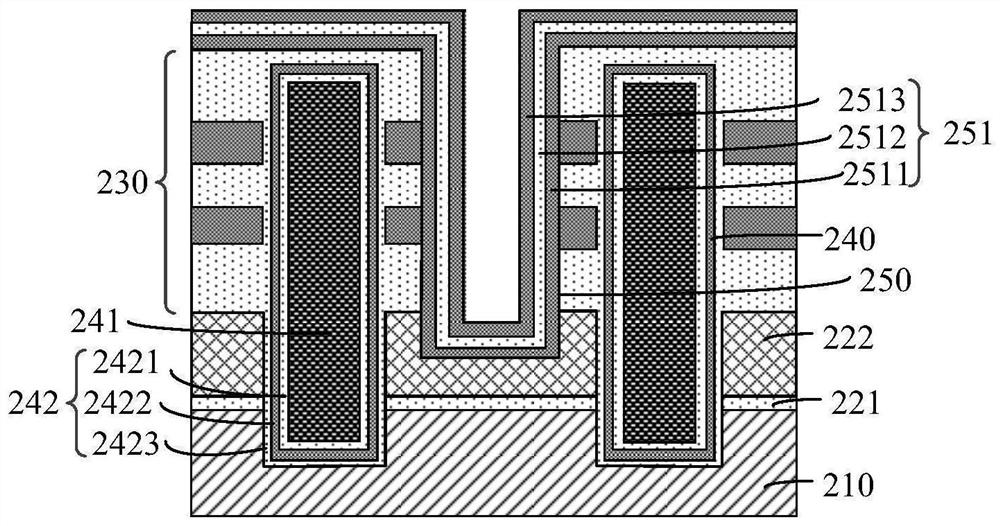

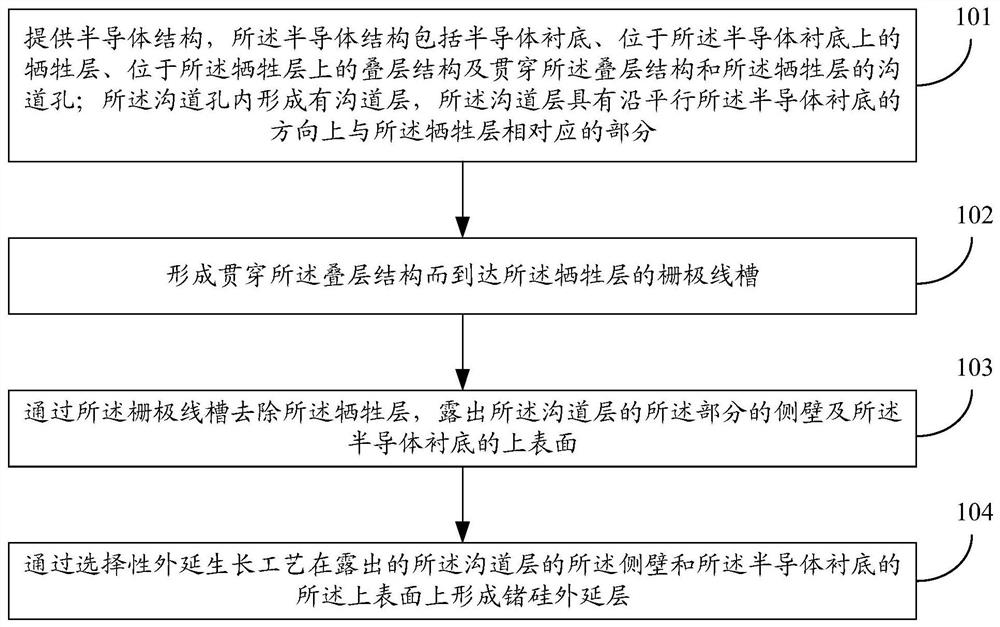

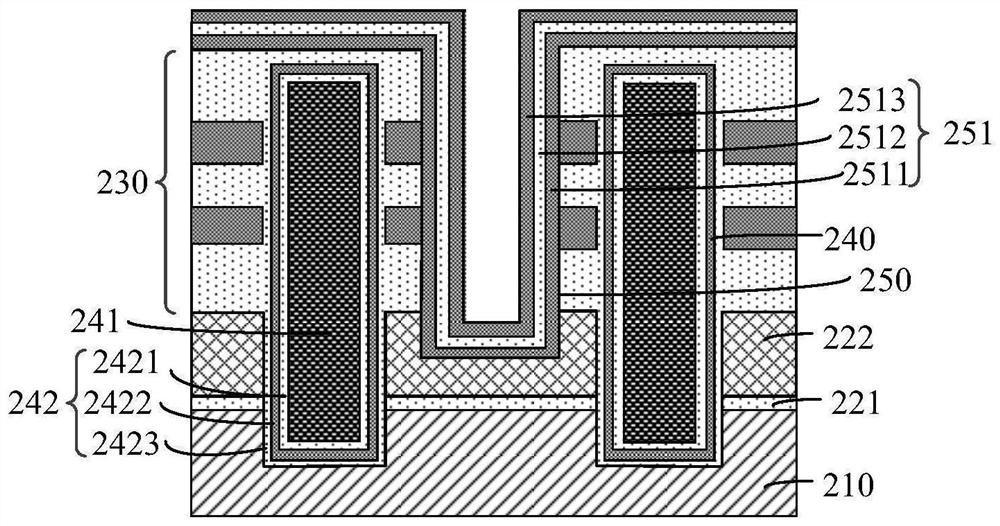

Three-dimensional memory and manufacturing method thereof

ActiveCN111769117AImprove mobilityIncrease current channelSolid-state devicesSemiconductor devicesSemiconductor structureEngineering

The embodiment of the invention discloses a three-dimensional memory and a manufacturing method thereof, and the method comprises the steps: providing a semiconductor structure which comprises a semiconductor substrate, a sacrificial layer located on the semiconductor substrate, a laminated structure located on the sacrificial layer, and a channel hole passing through the laminated structure and the sacrificial layer, wherein a channel layer is formed in the channel hole, and the channel layer is provided with a part corresponding to the sacrificial layer in the direction parallel to the semiconductor substrate; forming a gate line groove which penetrates through the laminated structure and reaches the sacrificial layer; removing the sacrificial layer through the gate line groove to exposethe side wall of the part of the channel layer and the upper surface of the semiconductor substrate; and forming a germanium-silicon epitaxial layer on the exposed side wall of the channel layer andthe upper surface of the semiconductor substrate through a selective epitaxial growth process.

Owner:YANGTZE MEMORY TECH CO LTD

Isolated nldmos device and manufacturing method thereof

ActiveCN104617149BLower on-resistanceIncrease the effective doping concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesP type siliconBreakdown voltage

The invention discloses an isolation N-type laterally diffused metal oxide semiconductor (NLDMOS) device. Two separate N-type deep well are formed on the P-type silicon substrate; left N-type deep well left portion is formed with a P-well; P-well left portion is formed with a P-type heavily doped region and an N-type heavily doped source miscellaneous areas; over the top and left-right portion of the N-type deep well P-well right portion formed with a gate oxide layer; N-type deep well with left and right P-type silicon N-type deep well between the top and right-left portion of the N-type deep well substrate above the field oxide is formed; the right N-type deep well right portion is formed with a drain terminal N-type heavily doped region; and a gate oxide layer over the top of the left part of the field oxide is formed with a gate polysilicon; P-type silicon substrate and the bottom of the field oxide Right N-type deep well formed in P-type implant drift region, the right of the P-type implant drift region as a staging interval shape. The invention also discloses a method for producing the isolated NLDMOS devices. The method can be isolated in ensuring NLDMOS device breakdown voltage does not decrease at the same time makes the device on-resistance is reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

A Lithium Iron Phosphate Lithium Polymer Lithium Battery Capable of High Current Charge and Discharge

InactiveCN110137577BLower internal resistanceLower cut-off voltageCell seperators/membranes/diaphragms/spacersFinal product manufactureLithium iron phosphateElectrical battery

Owner:广东省飞驰新能源科技有限公司

A kind of three-dimensional memory and its manufacturing method

ActiveCN111769117BImprove mobilityIncrease current channelSolid-state devicesSemiconductor devicesSemiconductor structureEngineering

The embodiment of the present application discloses a three-dimensional memory and a manufacturing method thereof. The method includes: providing a semiconductor structure, the semiconductor structure including a semiconductor substrate, a sacrificial layer on the semiconductor substrate, and a sacrificial layer on the sacrificial layer. A stacked structure and a channel hole penetrating through the stacked structure and the sacrificial layer; a channel layer is formed in the channel hole, and the channel layer has a direction parallel to the semiconductor substrate and The part corresponding to the sacrificial layer; forming a gate line groove through the laminated structure to reach the sacrificial layer; removing the sacrificial layer through the gate line groove, exposing the channel layer part of the sidewall and the upper surface of the semiconductor substrate; forming a silicon germanium epitaxial layer on the exposed sidewall of the channel layer and the upper surface of the semiconductor substrate by a selective epitaxial growth process .

Owner:YANGTZE MEMORY TECH CO LTD

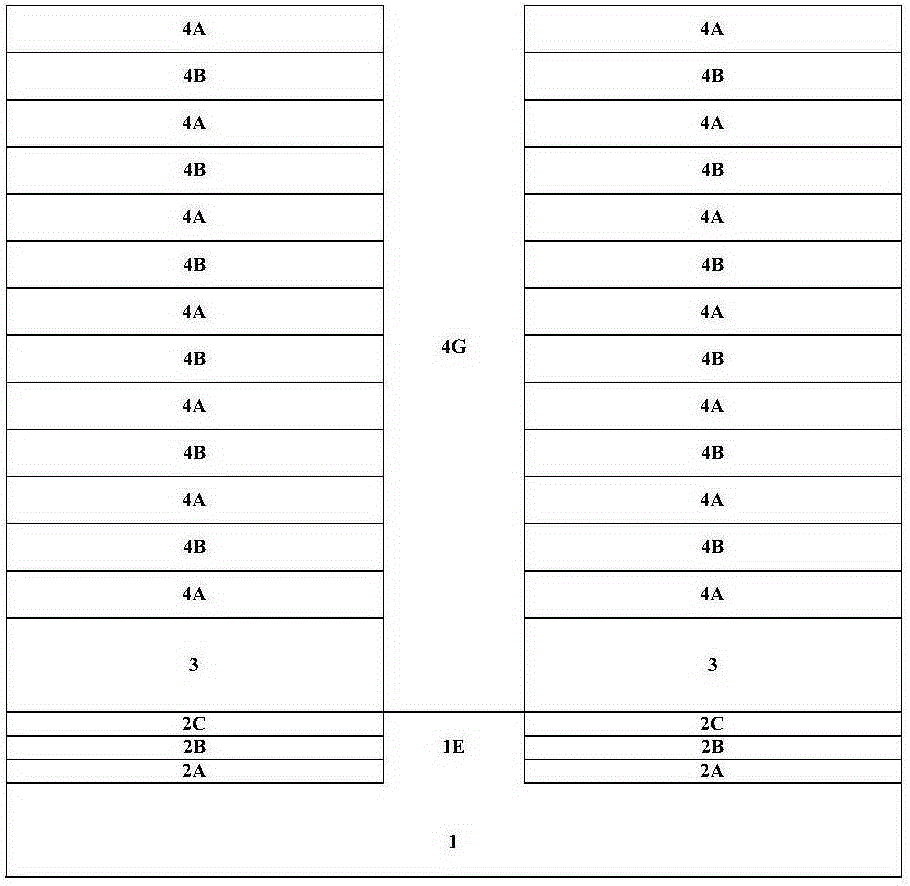

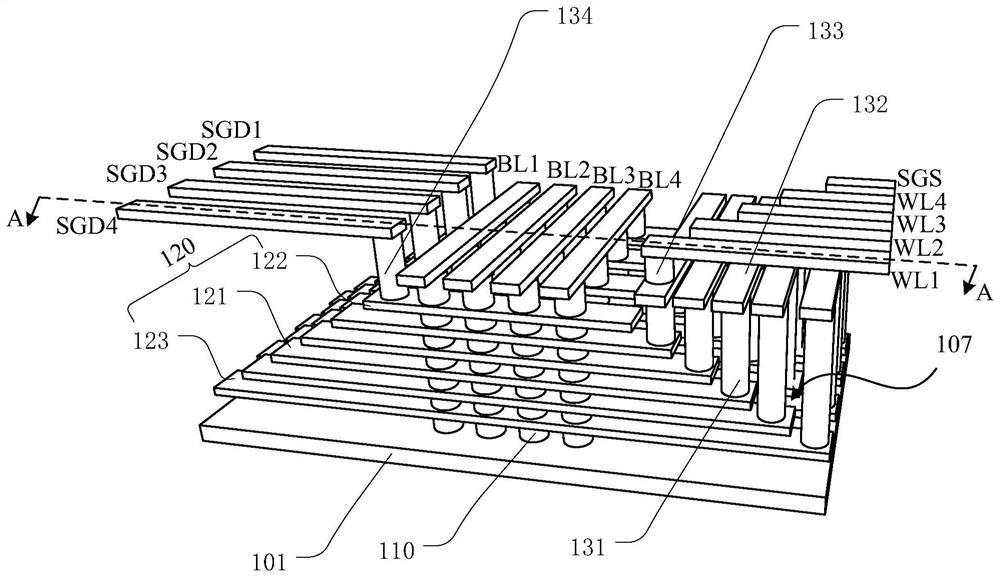

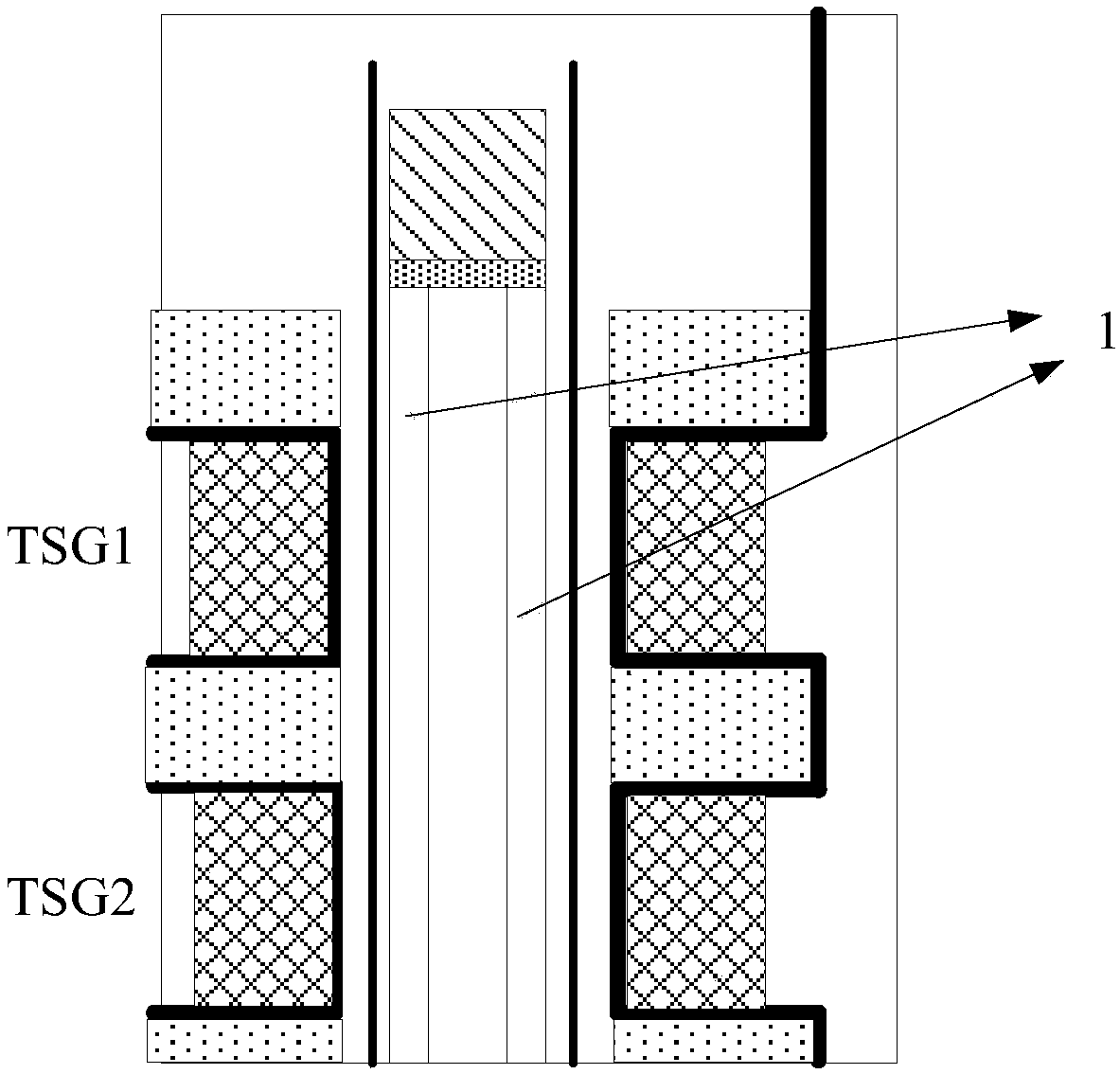

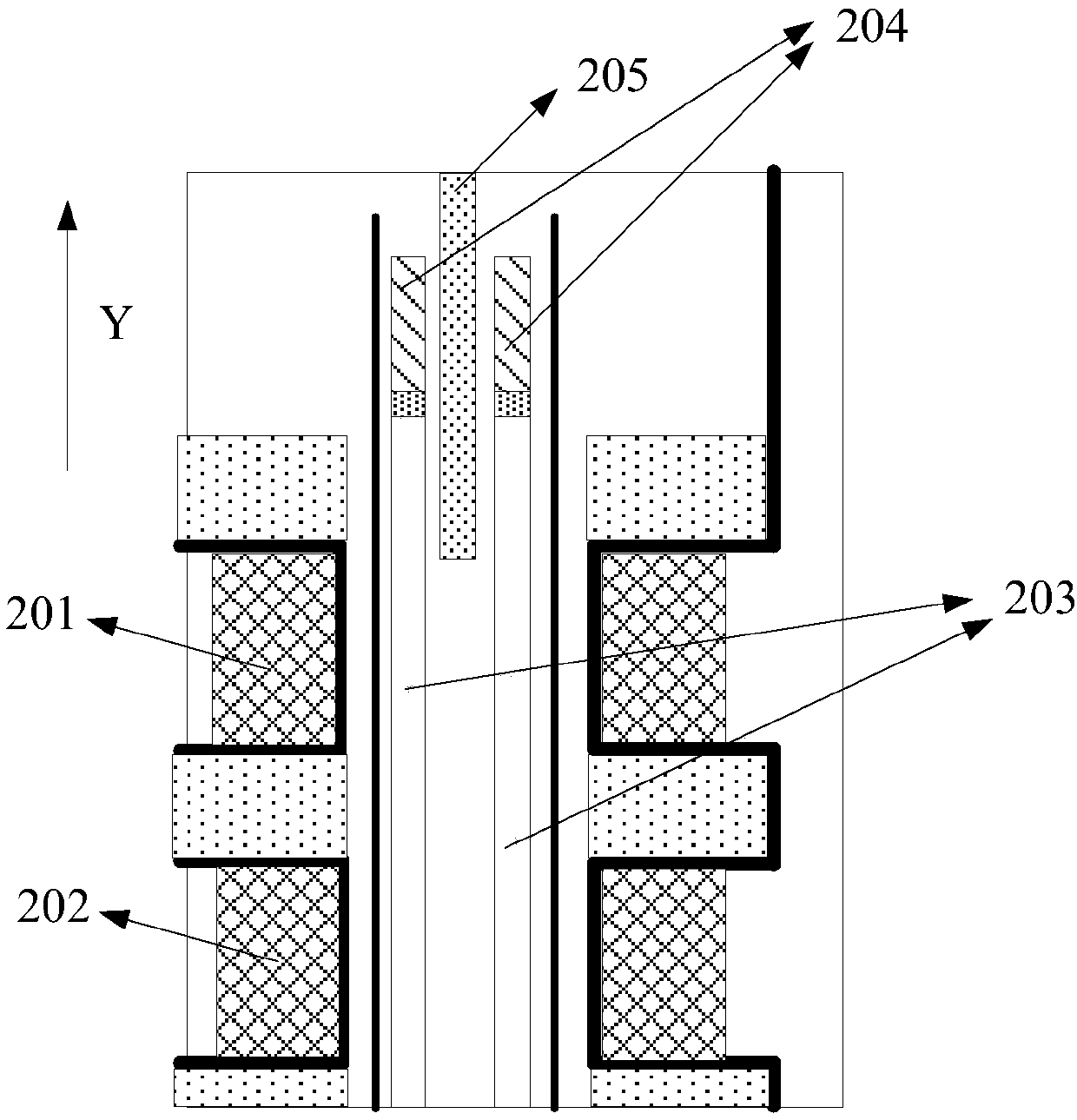

Dual-grid three-dimensional storage device and fabrication method thereof

ActiveCN107799527AHigh densityIncrease the number ofSolid-state devicesSemiconductor devicesHigh concentrationEngineering

The embodiment of the invention provides a dual-grid three-dimensional storage device and a fabrication method thereof. The three-dimensional storage device comprises a TSG and a storage unit, whereintwo channels are formed in the three-dimensional storage device, a doping plug is formed on each channel, a grid structure is arranged between the two doping plugs, and the doping plugs are isolatedby the grid structure. In the three-dimensional storage device, the doping plug is arranged on each channel, thus, the current resistance can be reduced, and the current passage is improved; by increasing the number of the doping plug, only a TSG is needed, and the problem of excessively large threshold voltage amplitude generated between two TSGs is prevented; the current passage is improved, thus, no boron is injected into the channels, and the problem of threshold value interference generated by the storage device caused by high-concentration doping is further prevented; and moreover, sincethe three-dimensional storage device only comprises the TSG, the density of the storage unit can be improved.

Owner:YANGTZE MEMORY TECH CO LTD

TFT and manufacturing method thereof, array substrate and display device

ActiveUS9196636B2Increase current channelMaximum compactnessTransistorSolid-state devicesPower flowCharge carrier mobility

The present invention provides a thin film transistor. An active layer of the thin film transistor comprises a plurality of active semiconductor sub-layers and a plurality of insulation sub-layers, which are stacked alternately. A source and a drain of the thin film transistor are electrically connected to the plurality of active semiconductor sub-layers. Correspondingly, the present invention further provides a method for manufacturing a thin film transistor, and an array substrate. The present invention can effectively increase channel current of the active layer in a thin film transistor, and solves the problem of small channel current resulted from low carrier mobility of the active layer.

Owner:BOE TECH GRP CO LTD +1

Display panel and display device

ActiveCN111081739BDoes not affect normal displayIncrease current channelSolid-state devicesSemiconductor devicesDisplay deviceEngineering

The invention discloses a display panel and a display device. The display panel includes a display area and a non-display area, and the non-display area includes a terminal area and a cut-out area surrounding the display area and the terminal area. Signal wires are arranged in the terminal area for connecting the TFT layer in the display area and the functional circuit located in the terminal area, auxiliary wires are arranged in the cut-out area and partly extend to the terminal area, and The auxiliary wire is connected in parallel with the signal wire. In the present invention, the auxiliary wire connected in parallel with the signal wire is arranged in the cut-off area to increase the current channel, reduce the impedance, and prevent the signal wire from heating, fusing and burning the film layer, and the auxiliary wire is arranged in the cut-out area. It can be removed, does not affect the normal display of the display panel, and improves the yield rate.

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

Storage unit of flash memory and method for forming same

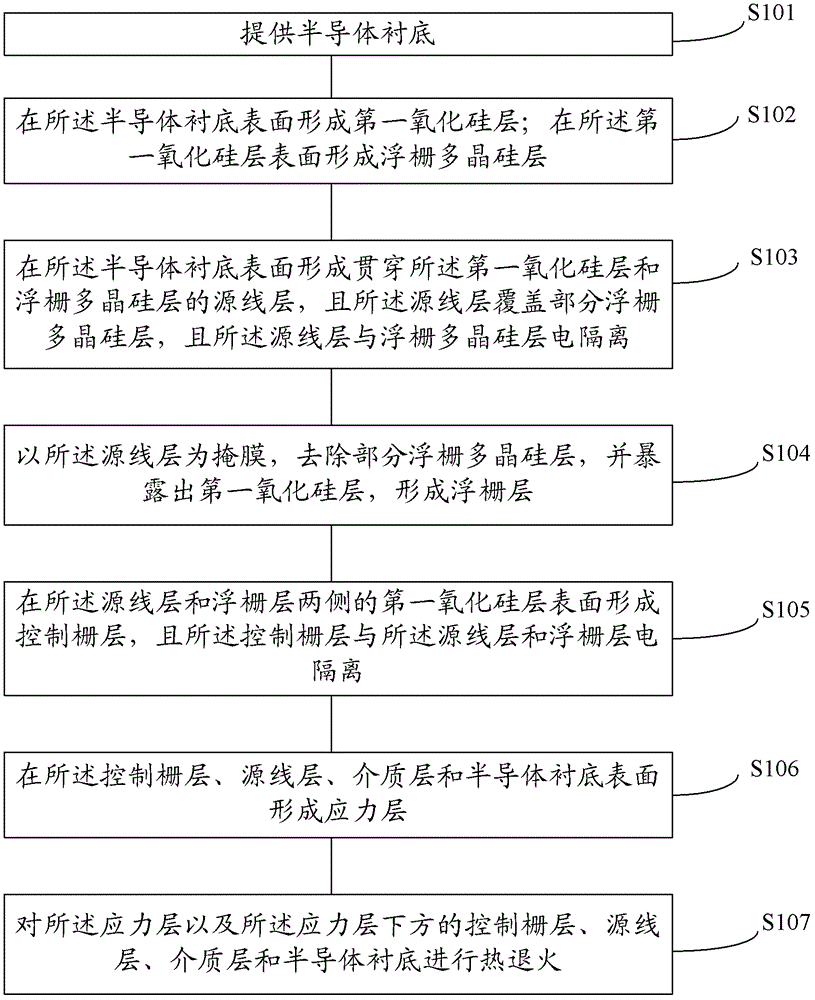

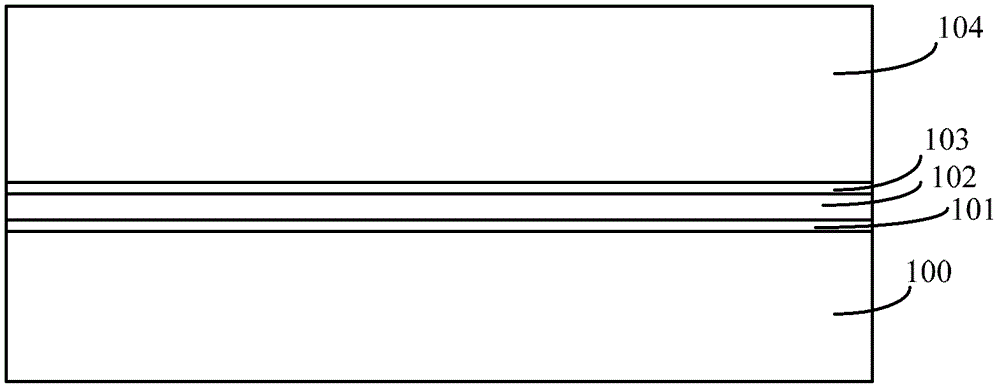

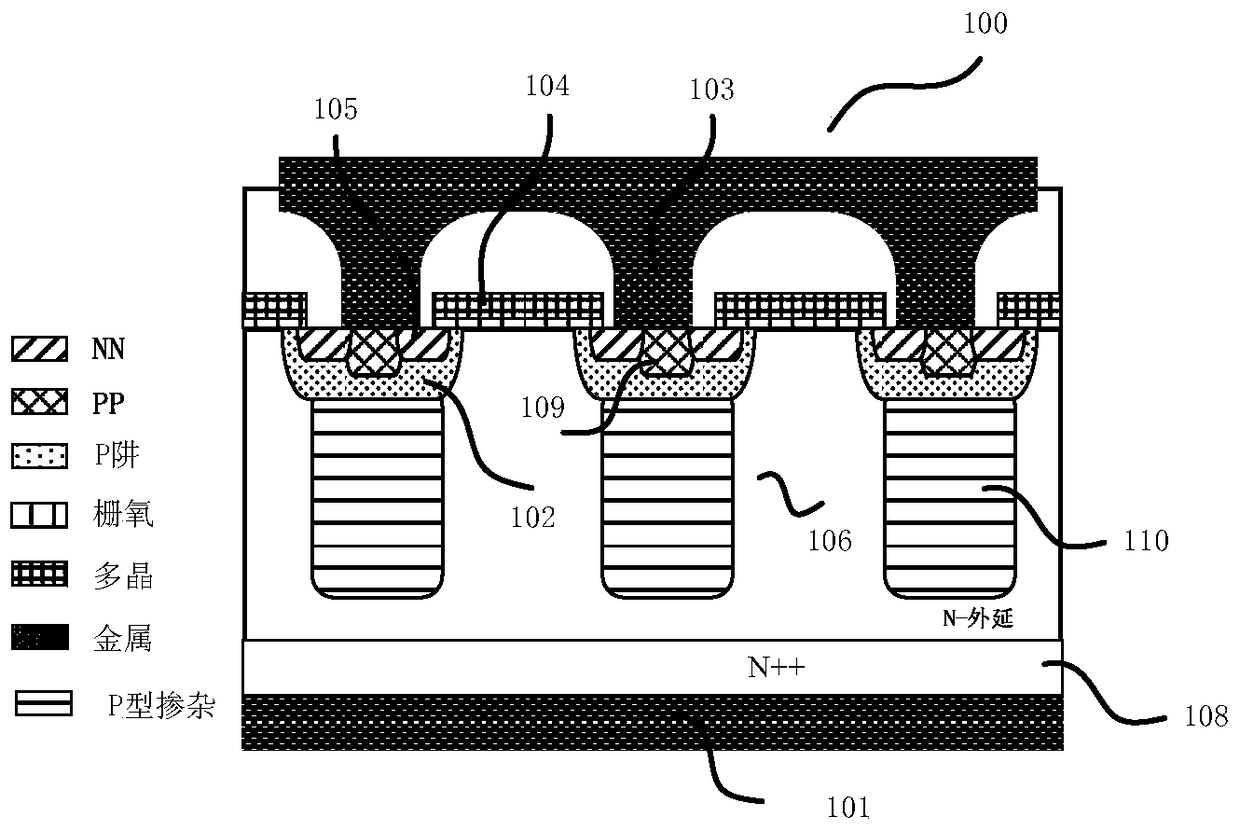

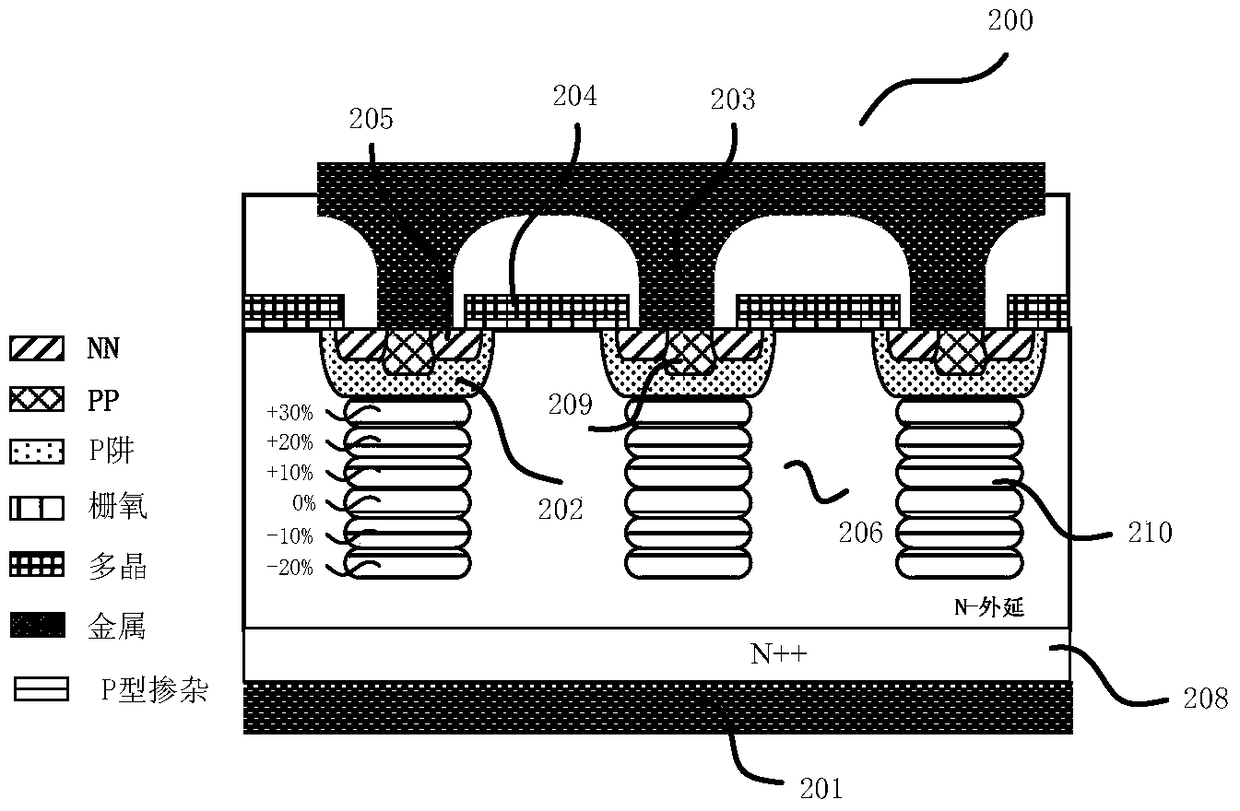

ActiveCN102637696BImprove retentionIncreased durabilitySolid-state devicesSemiconductor/solid-state device manufacturingSurface layerCell size

A storage unit of flash memory and a method for forming the same, wherein the storage unit of flash memory comprises: a semiconductor substrate; an insulating layer located on the surface of the semiconductor substrate; a floating gate layer located on the surface of the insulating layer; The bottom surface and the source line layer that runs through the floating gate layer and the insulating layer, and the source line layer covers the floating gate layer, and the source line layer is electrically isolated from the floating gate layer; Both sides of the line layer, and the control gate layer on the surface of the insulating layer, and the control gate layer is electrically isolated from the source line layer and the floating gate layer; the stress layer located on the control gate layer, the source line layer and the surface of the semiconductor substrate. The storage unit of the flash memory uses the stress effect to improve the programming efficiency and read efficiency of data, improve the retention and durability of data, and further reduce the size of the storage unit of the flash memory.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

High voltage power device and method of forming the same

ActiveCN105097932BMaintain pressure stabilityIncrease current channelSemiconductor/solid-state device manufacturingSemiconductor devicesHigh pressureComputer science

The invention provides a high-voltage power device and a forming method thereof. The device comprises a first doped area having a first doped type; one or a plurality of device doped areas arranged in the upper surface of the first doped area, wherein the device doped area has a second doped type opposite to the first doped type; and one or a plurality of second doped areas of the second doped type, wherein one end of the second doped area is in electric contact with a corresponding device doped area, the other end of the second doped area longitudinally extends to the first doped area, and in the transverse direction, the second doped areas and the first doped areas are alternatively distributed. The impurity concentration of each second doped area changes in a non-linear manner with the change of the longitudinal depth, and the total impurity concentration of the second doped areas is lower than the total impurity concentration of the first doped areas. According to the invention, the withstand voltage of the device is stabilized, and the conduction resistance of the device is reduced.

Owner:HANGZHOU SILAN MICROELECTRONICS