Single programmable memory and its making method

A manufacturing method and memory technology, which are used in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve the problems of reducing memory operation efficiency and small channel current, and achieve the effect of increasing the width and improving the channel current.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

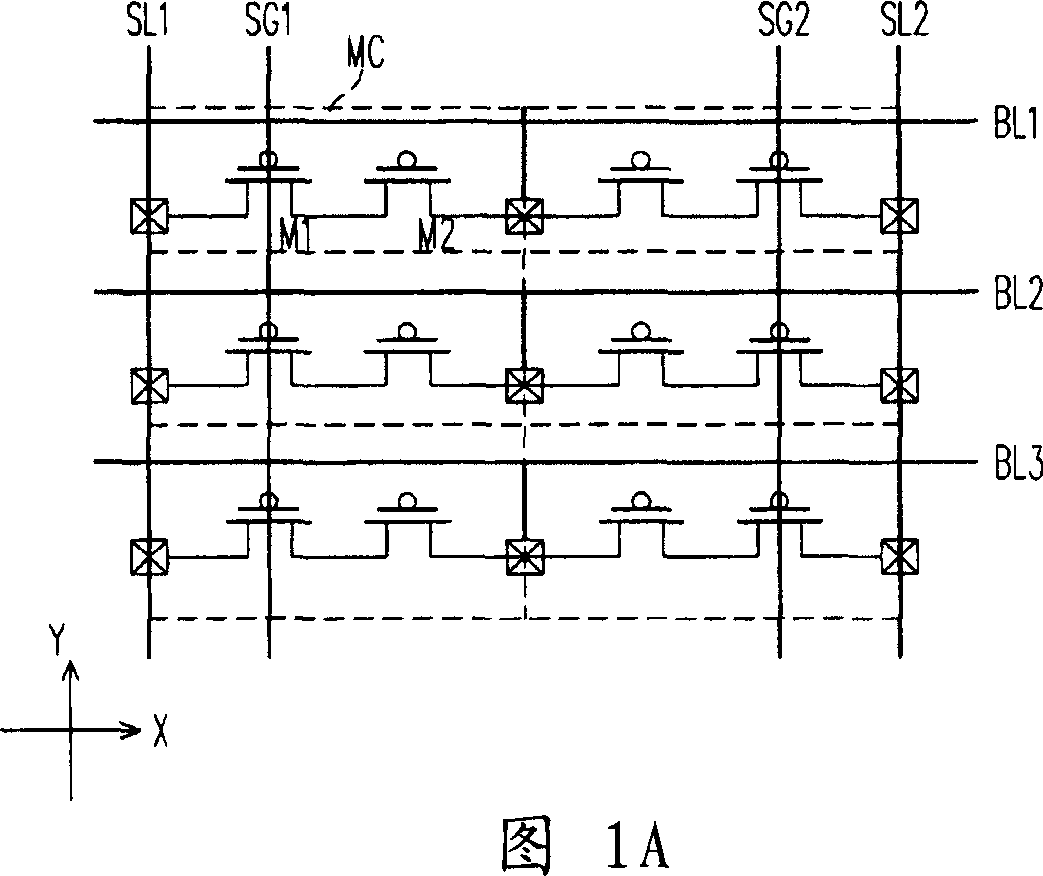

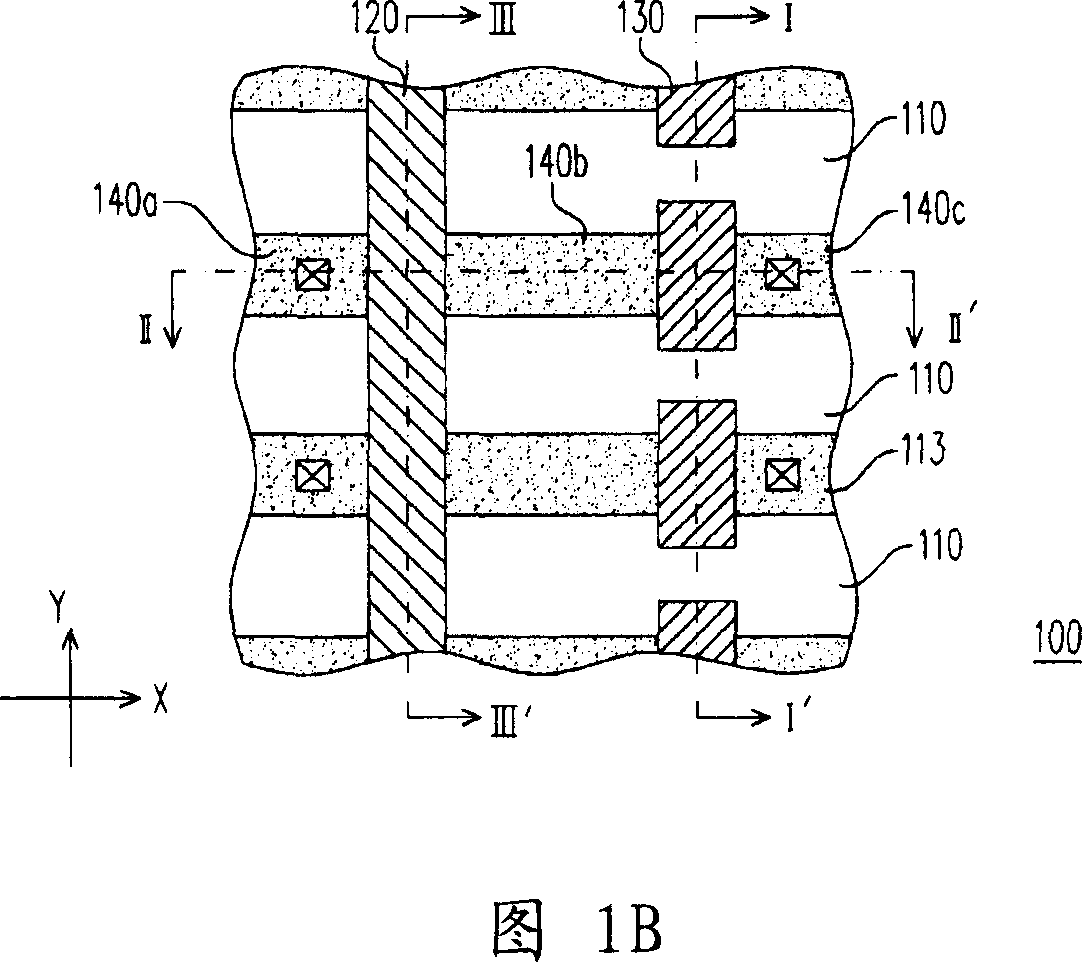

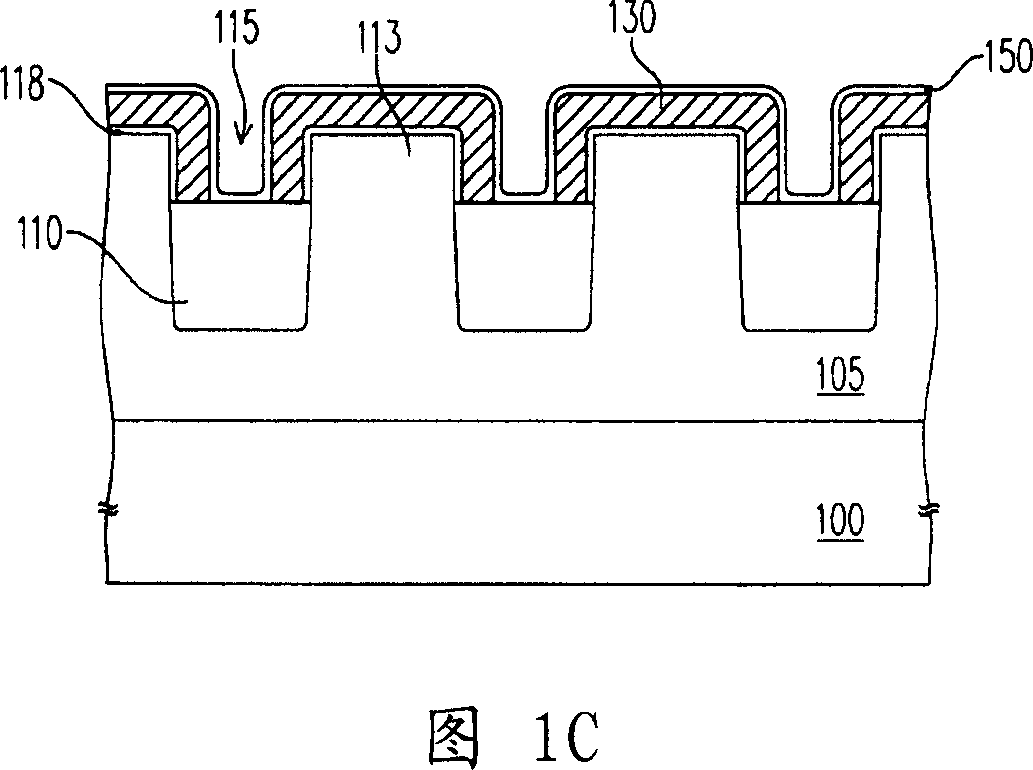

[0054] FIG. 1A is a schematic circuit diagram of a one-time programmable memory according to an embodiment of the present invention. FIG. 1B is a top view illustrating a one-time programmable memory according to an embodiment of the present invention. Fig. 1C is a schematic cross-sectional view along line I-I' of Fig. 1B. Fig. 1D is a schematic cross-sectional view along line II-II' of Fig. 1B. Fig. 1E is a schematic cross-sectional view along line III-III' of Fig. B.

[0055]Please refer to FIG. 1A , FIG. 1B , FIG. 1C , FIG. 1D and FIG. 1E . The one-time programmable memory proposed by the present invention is, for example, composed of a substrate 100, a plurality of isolation structures 110, a plurality of memory cells MC, selection gate lines SG1, SG2, source lines SL1, SL2, and bit lines BL1, BL2, BL3. consist of.

[0056] The substrate 100 is, for example, a silicon substrate. The isolation structure 110 is, for example, disposed in parallel in the substrate 100 and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More