Patents

Literature

2834 results about "Source lines" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Sources line is an italian factory that deals with equipments for the acoustic measurement, employed in the architectural acoustic and in the research and development fields. Sources line is an italian factory that deals with equipments for the acoustic measurement, employed in the architectural acoustic and in the research and development fields.

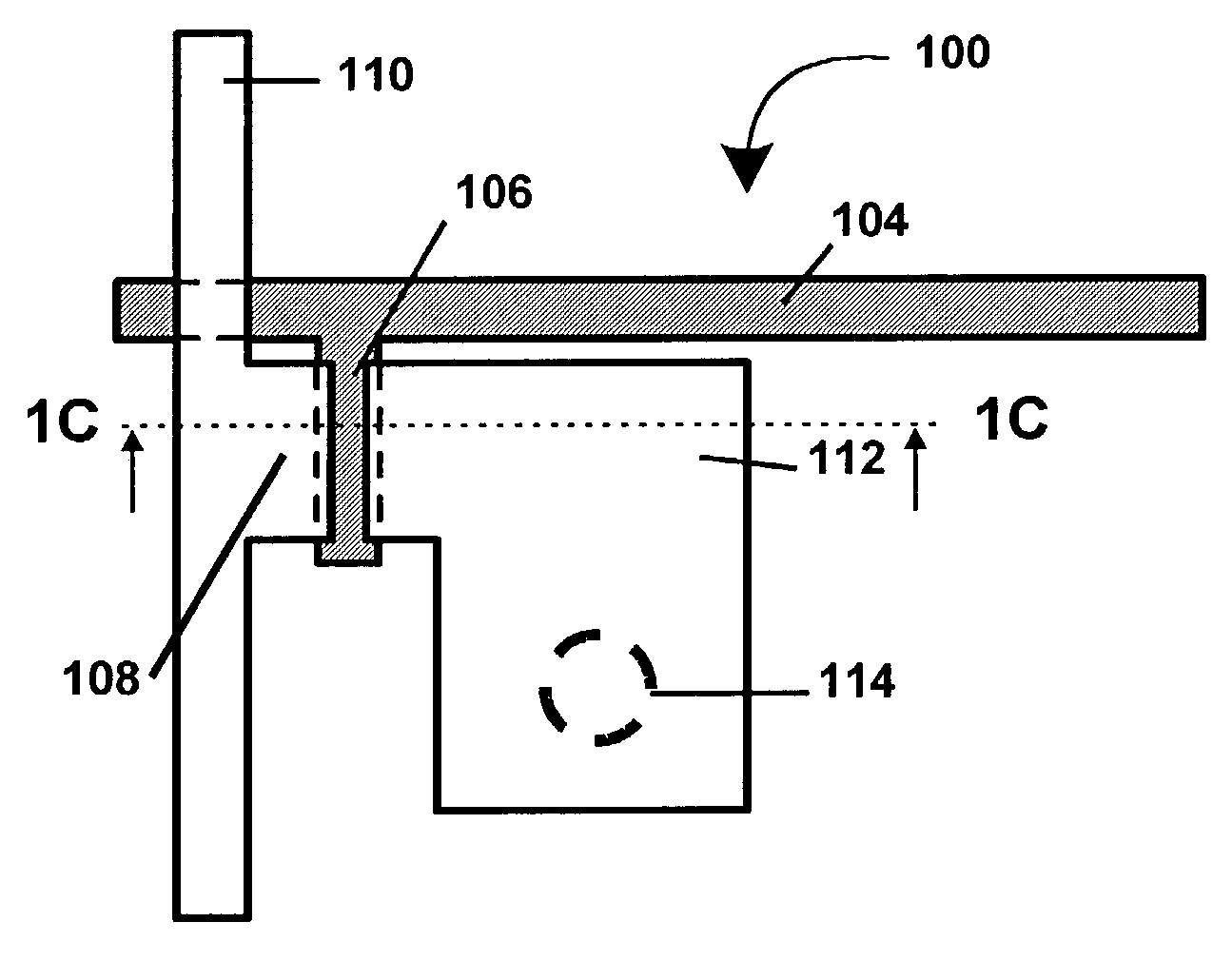

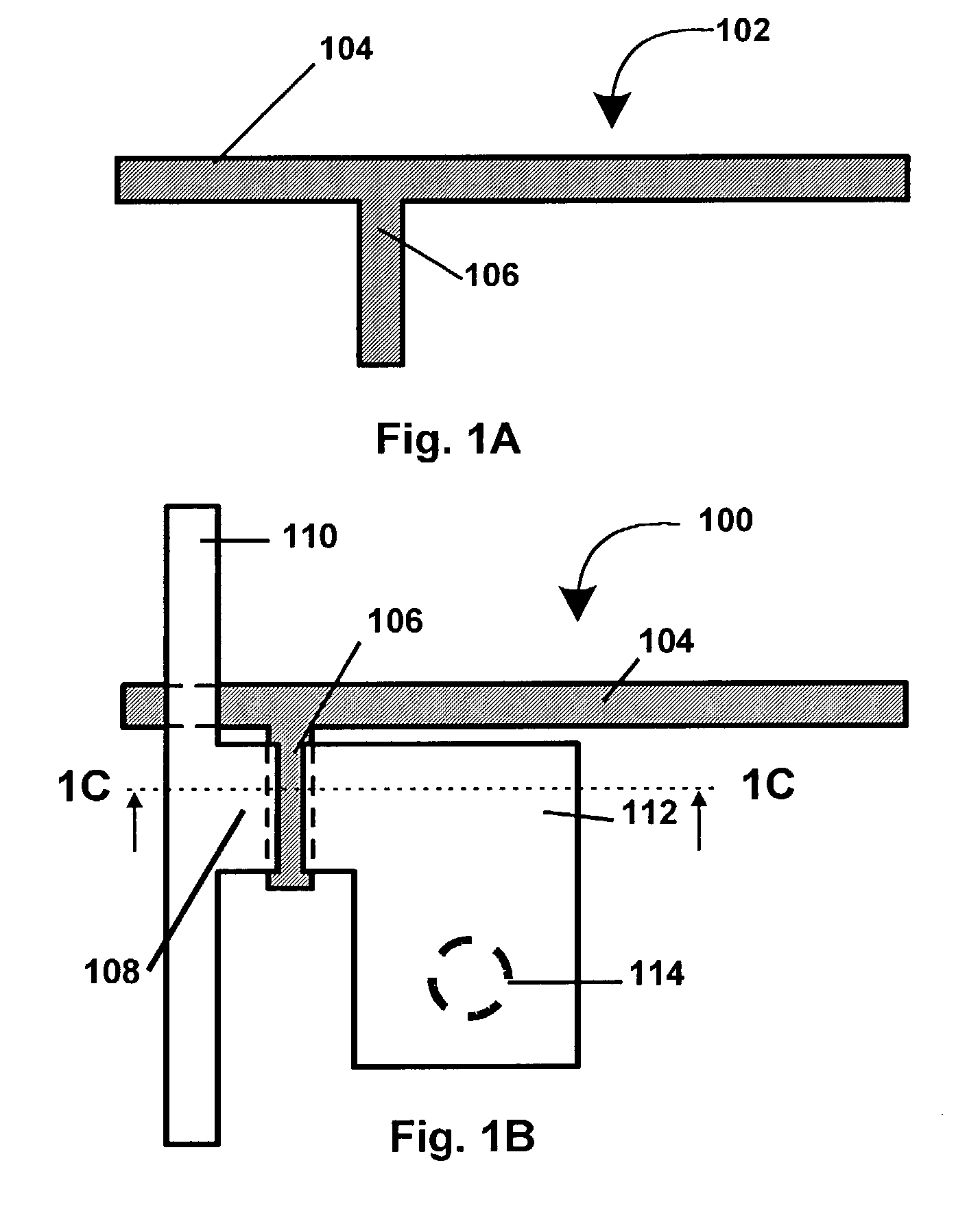

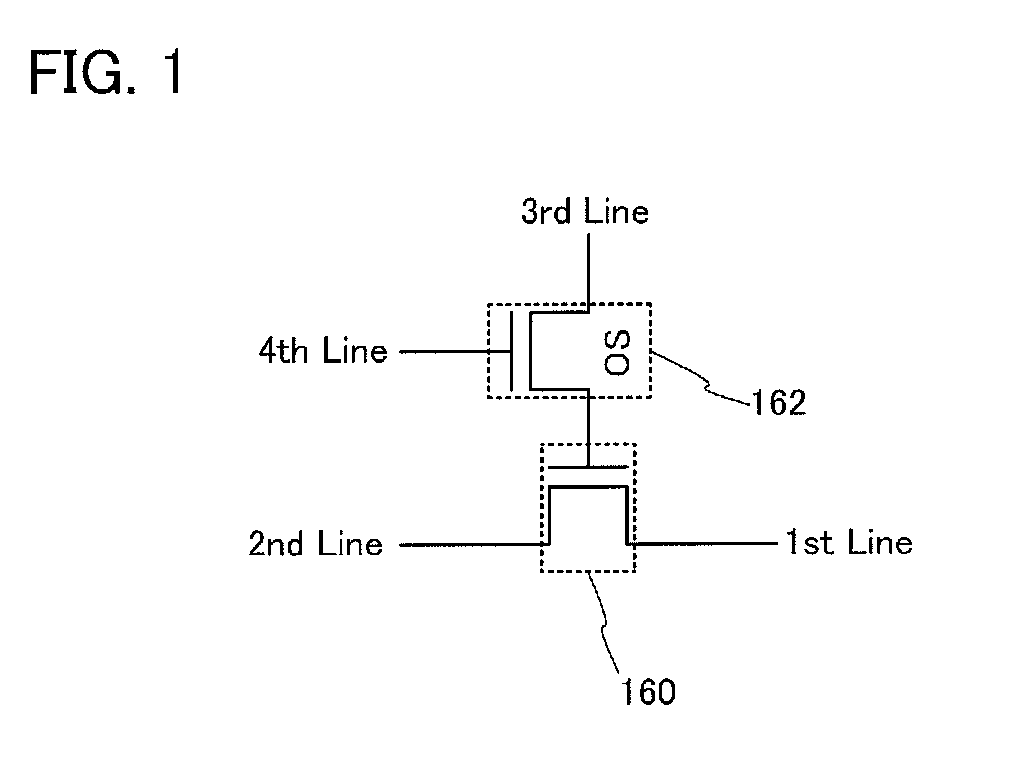

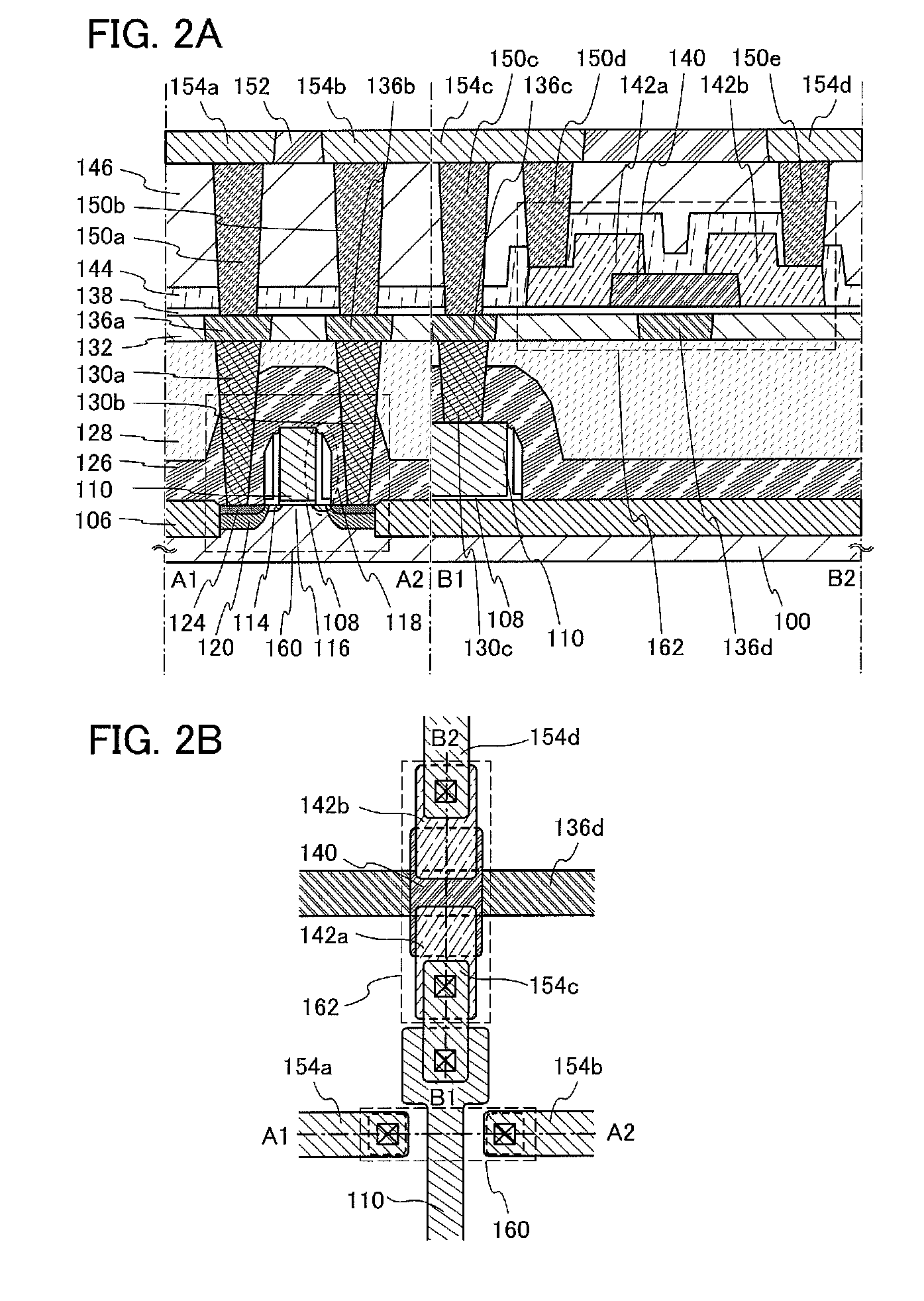

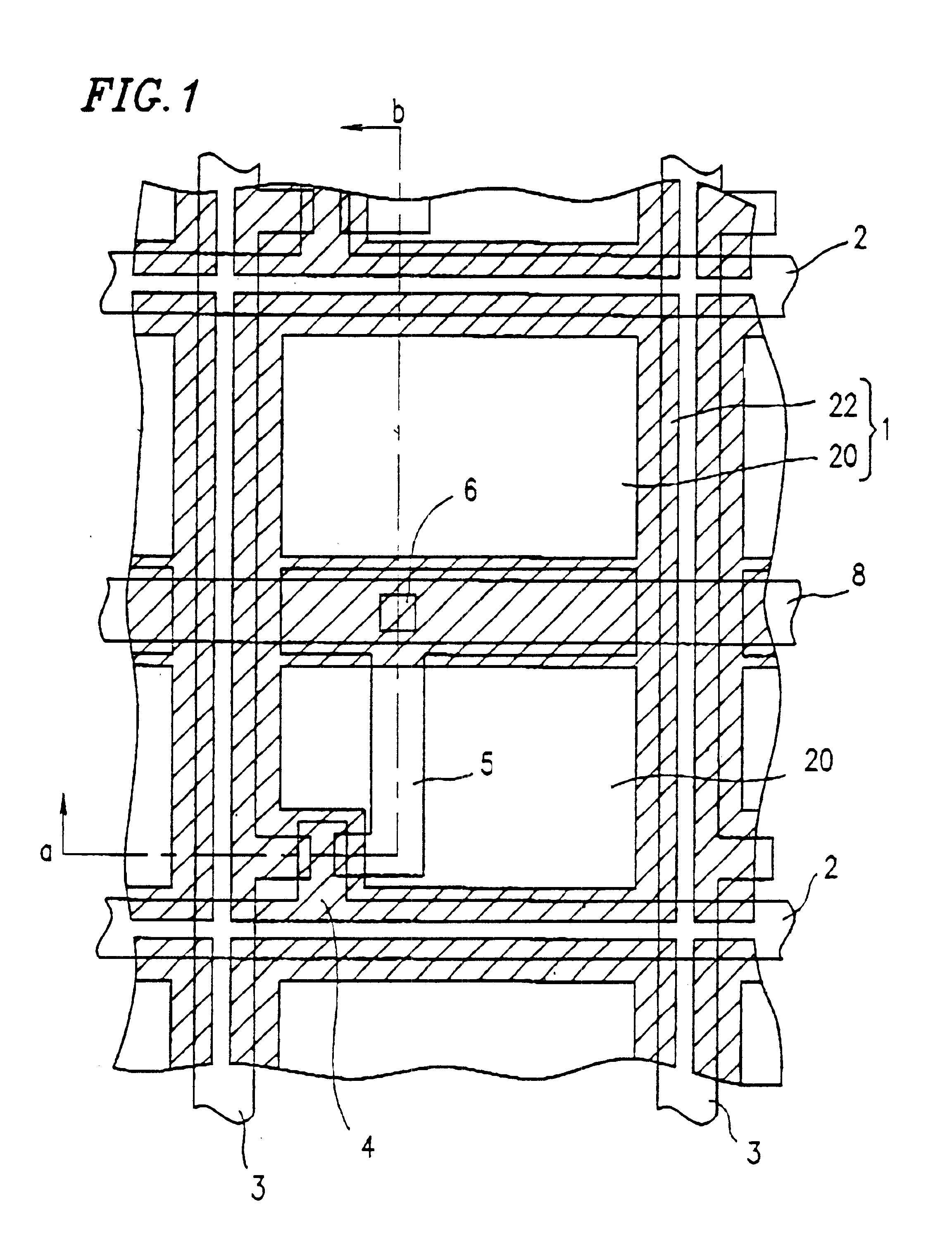

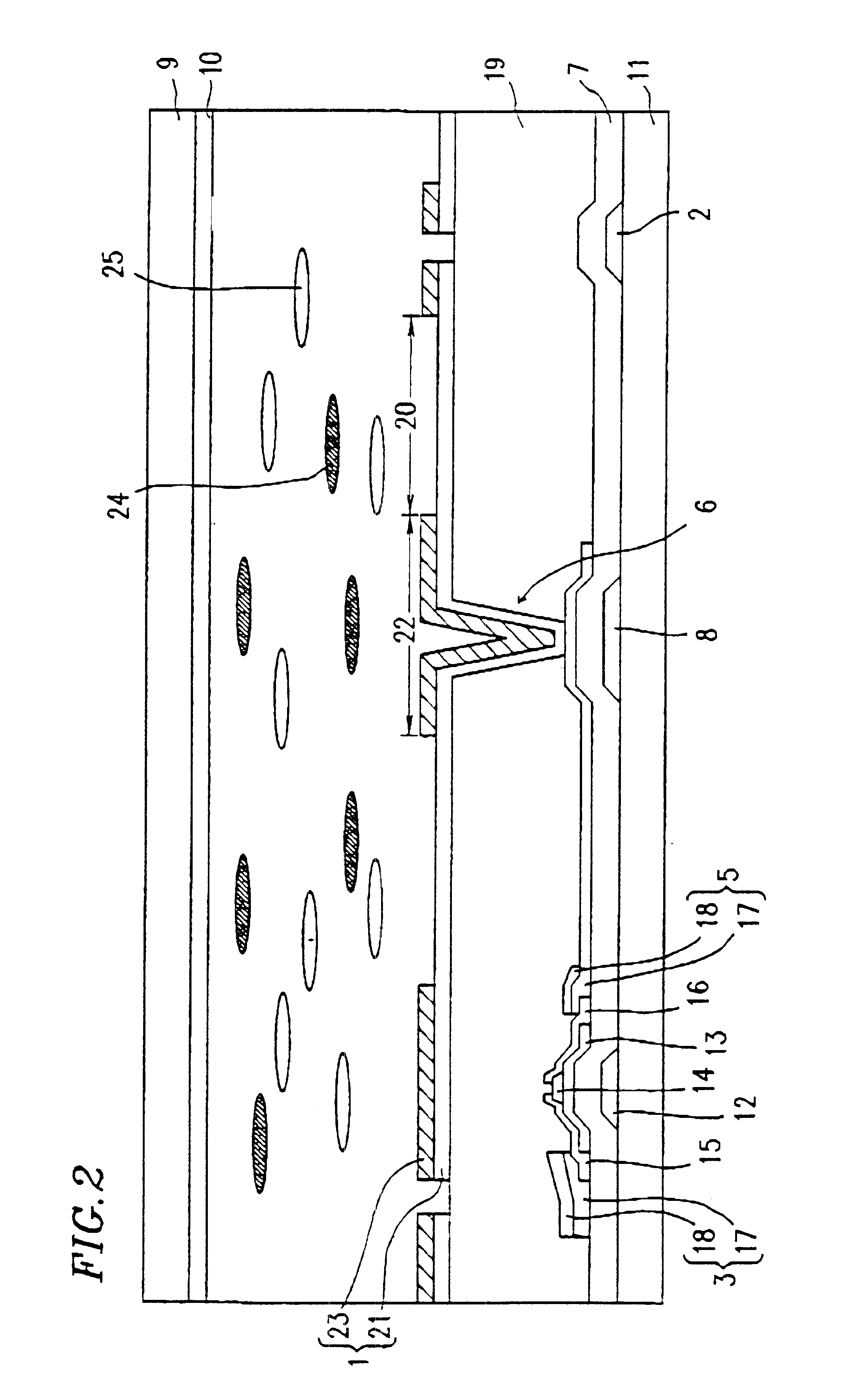

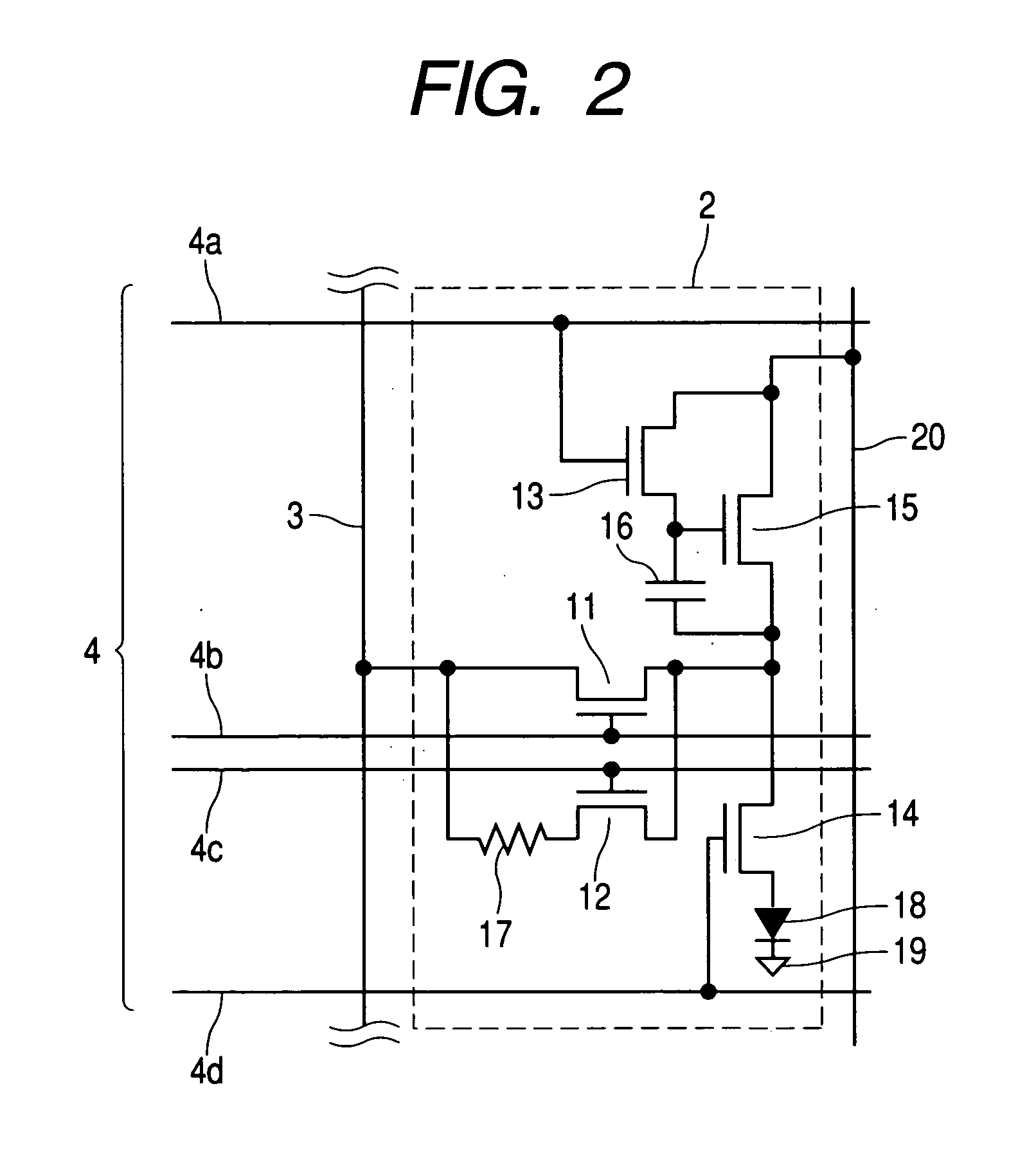

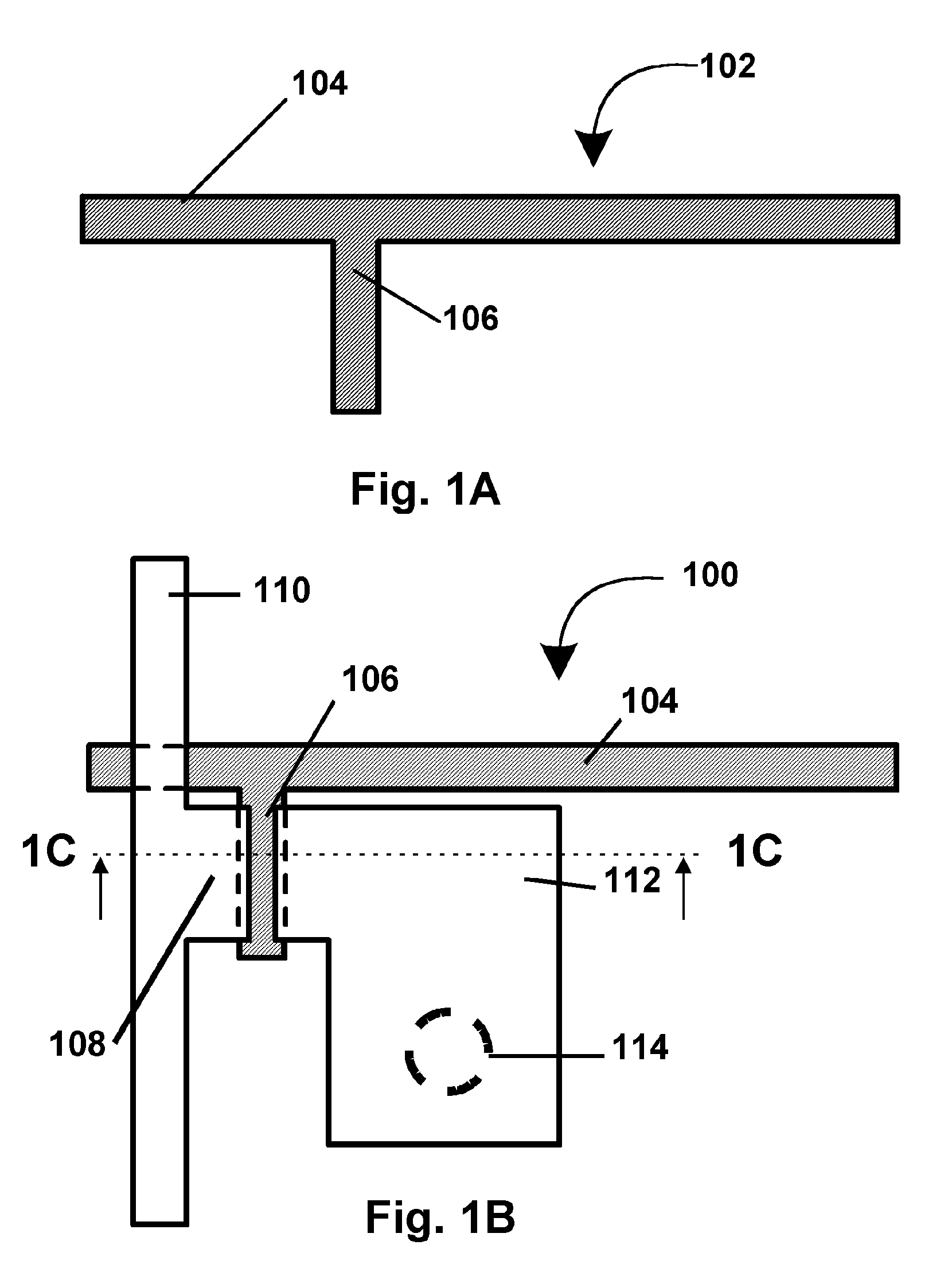

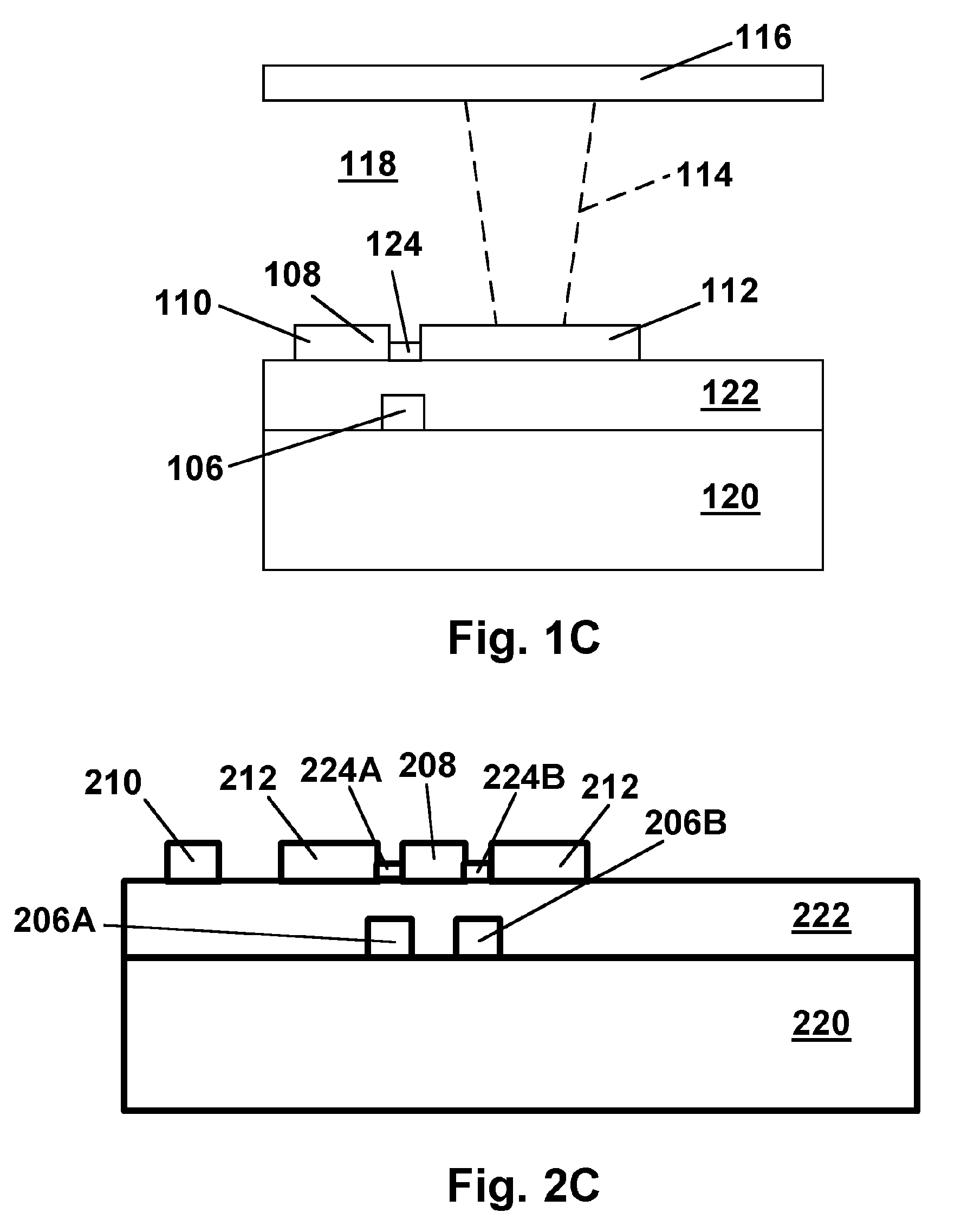

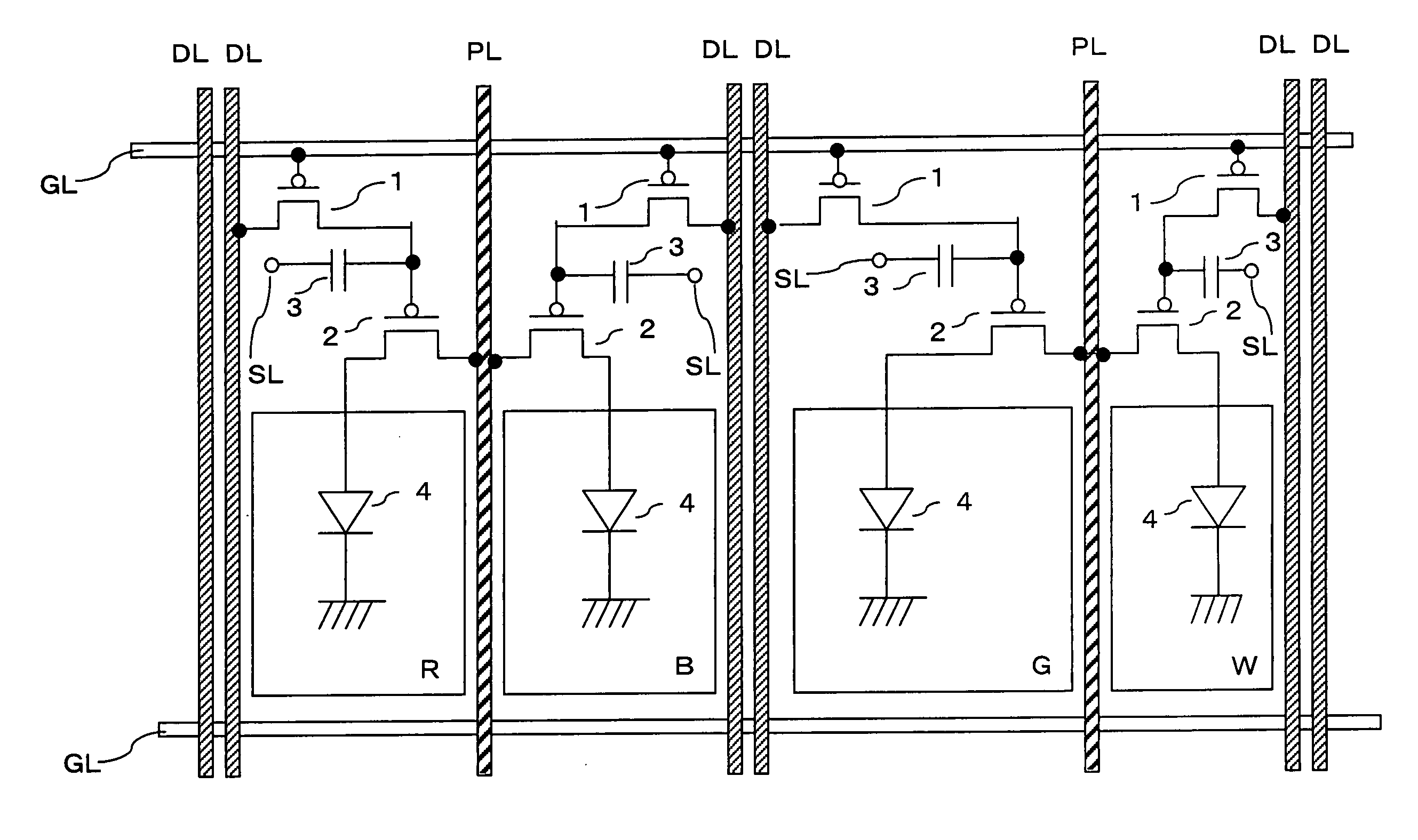

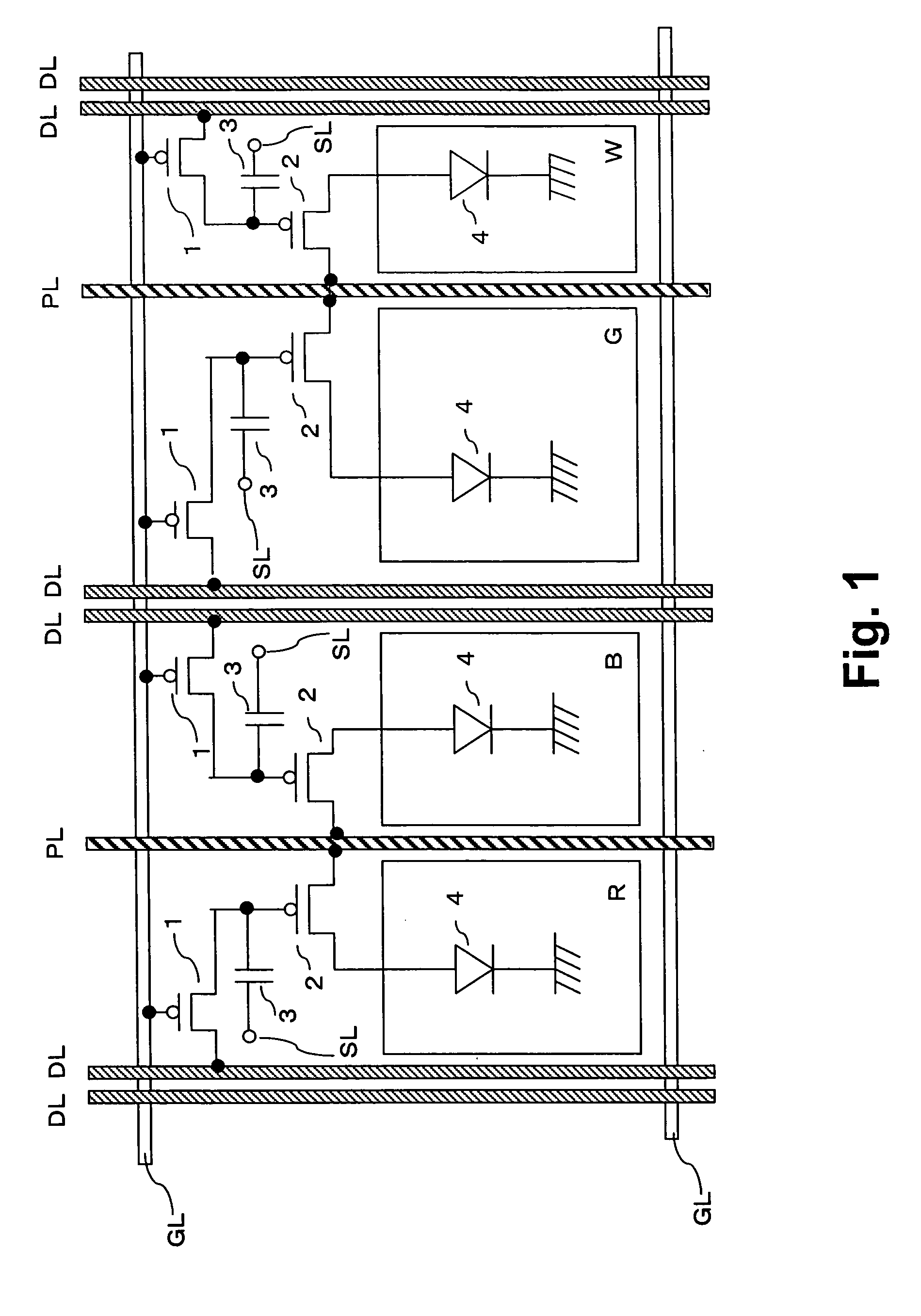

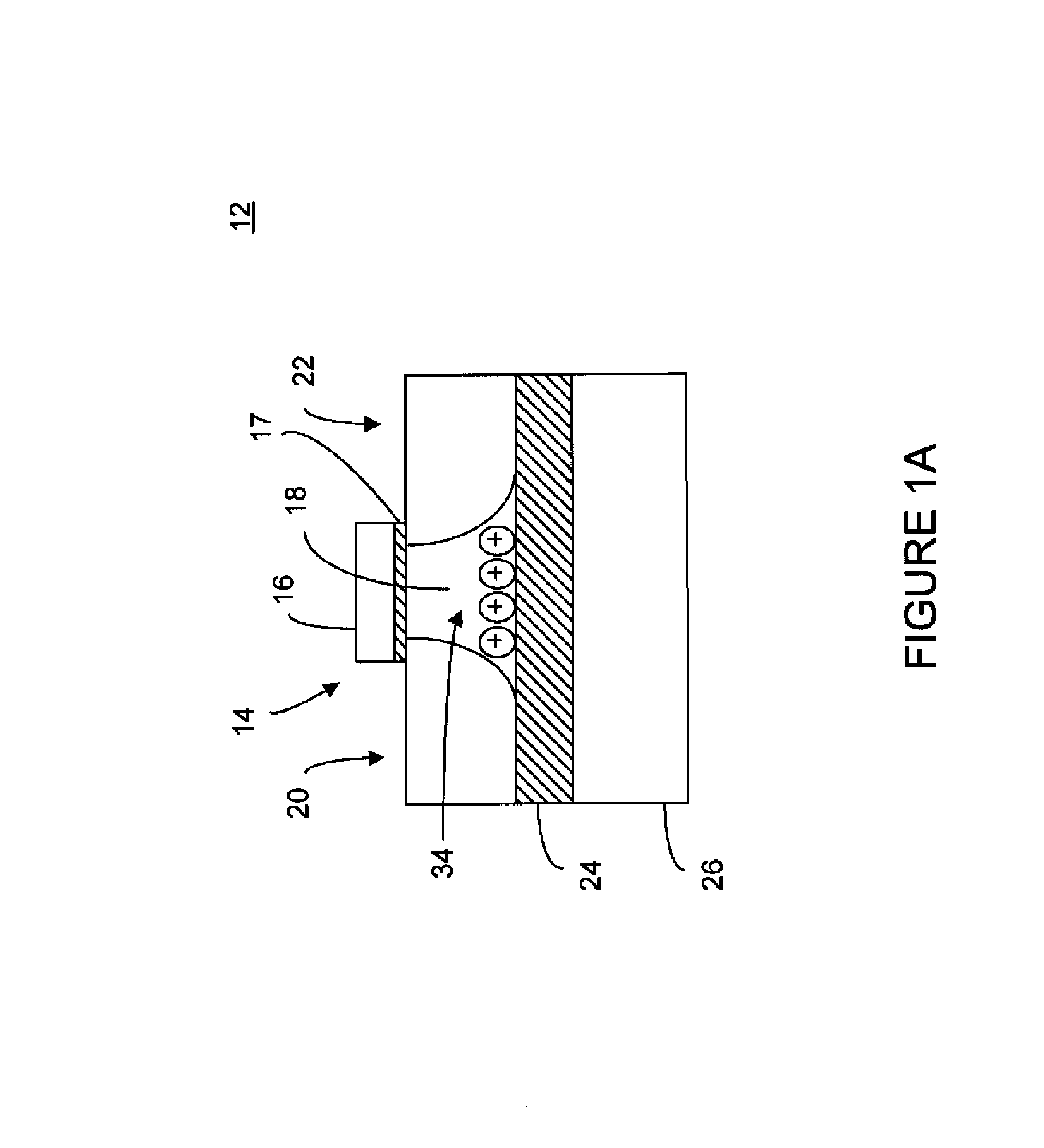

Backplanes for display applications, and components for use therein

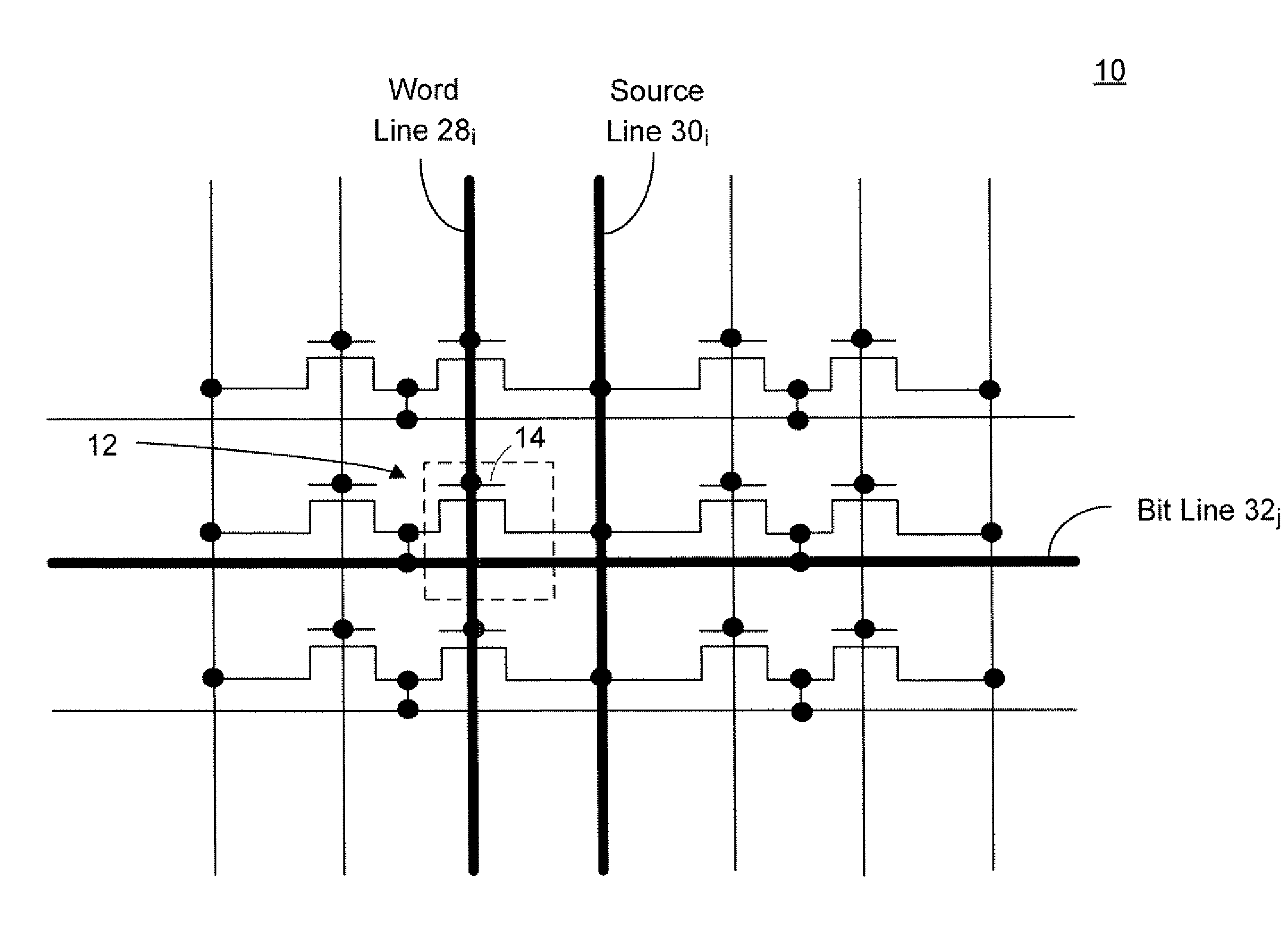

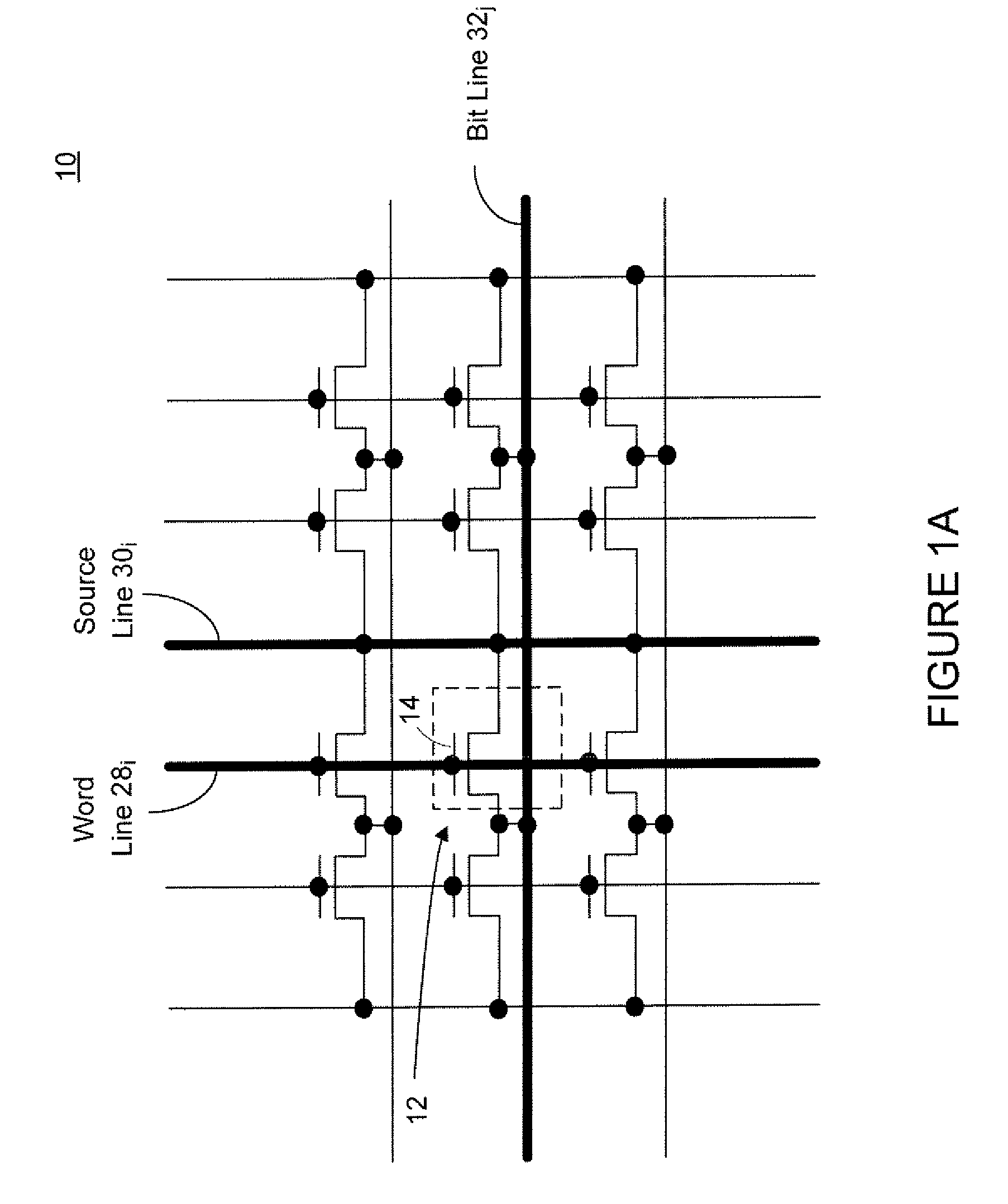

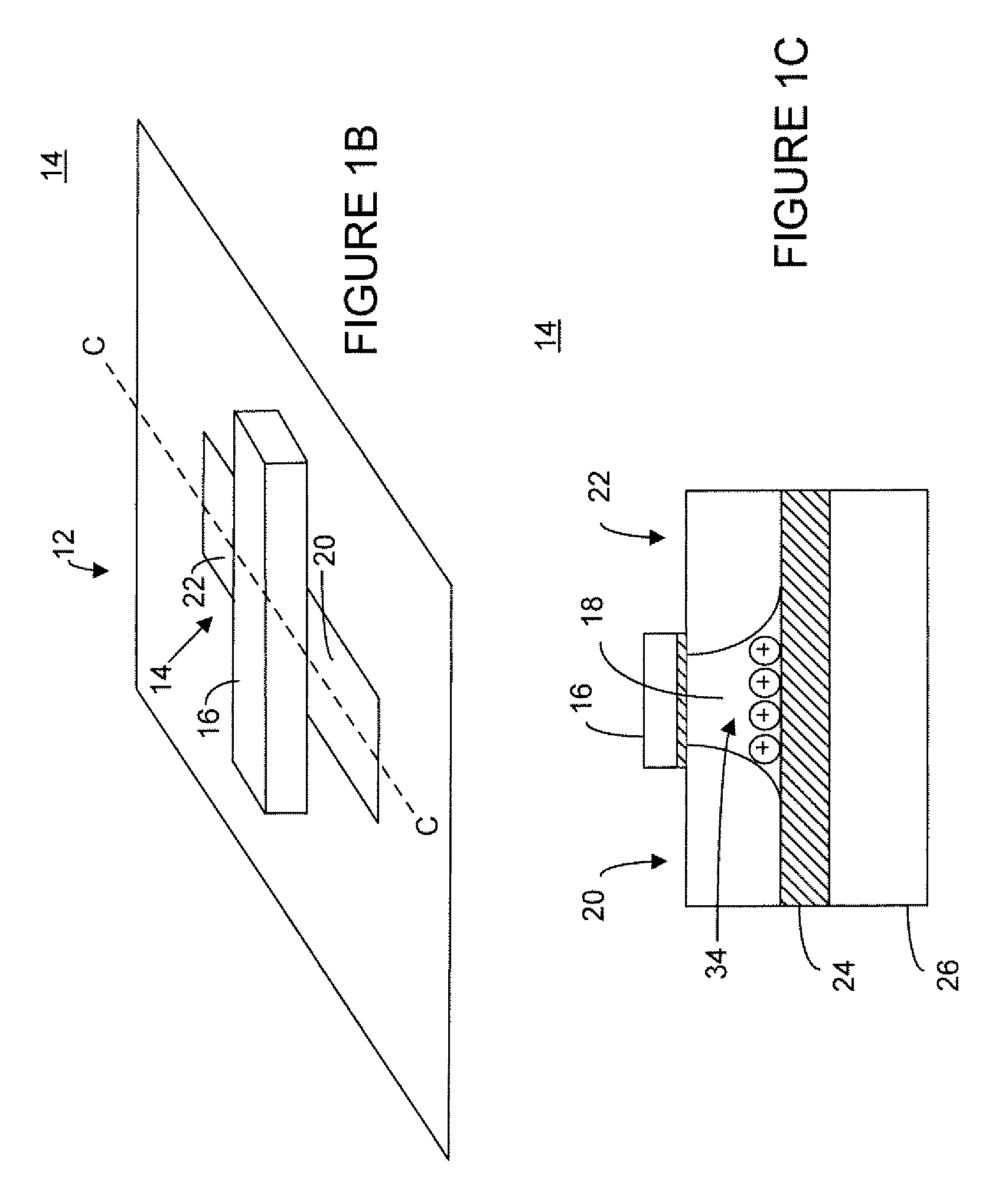

ActiveUS7116318B2Reduce manufacturing costThe process steps are simpleTransistorSolid-state devicesCapacitanceCoupling

A display pixel unit provides reduced capacitative coupling between a pixel electrode and a source line. The unit includes a transistor, the pixel electrode, and the source line. The source line includes an extension that provides a source for the transistor. A patterned conductive portion is disposed adjacent to the source line.

Owner:E INK CORPORATION

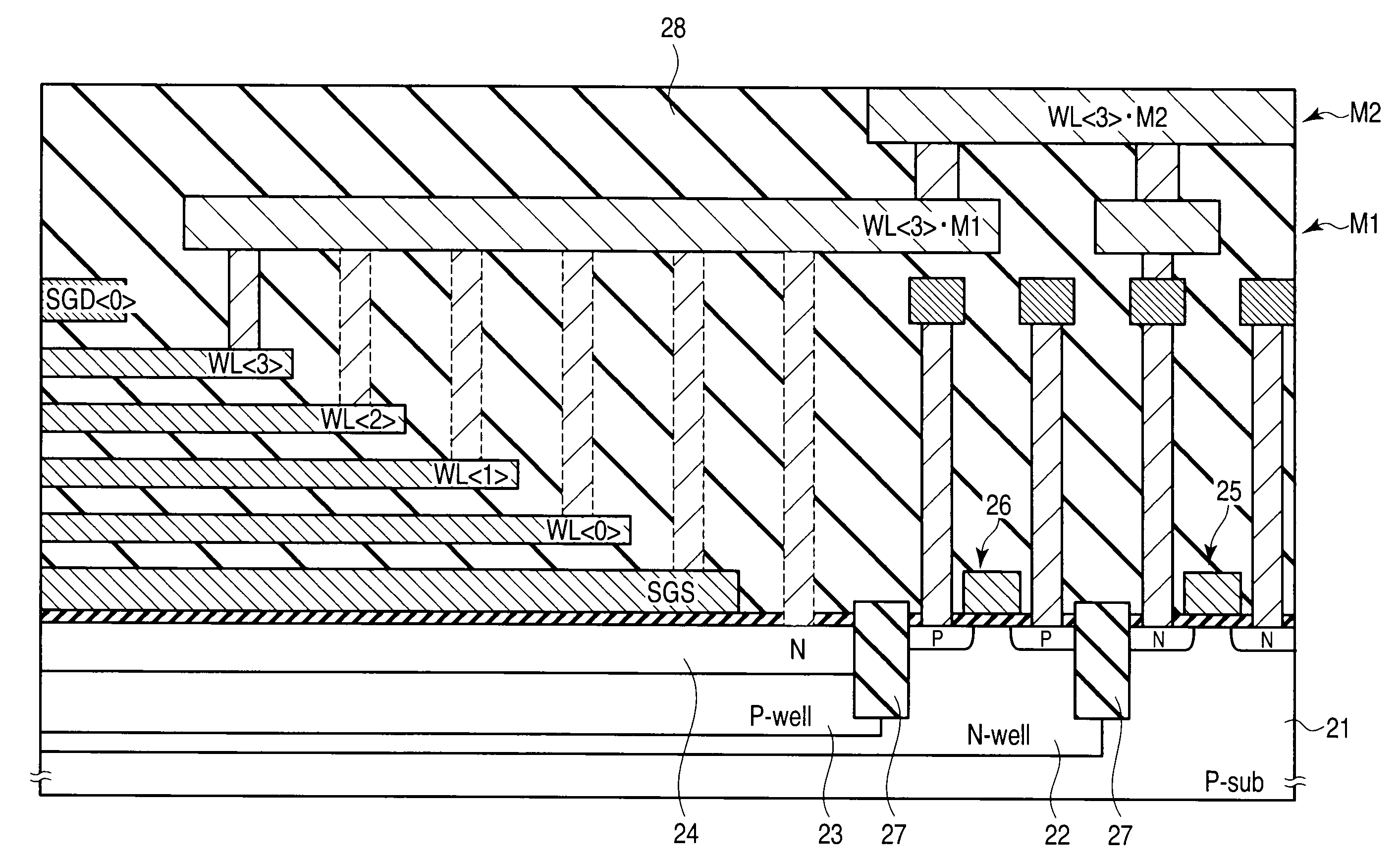

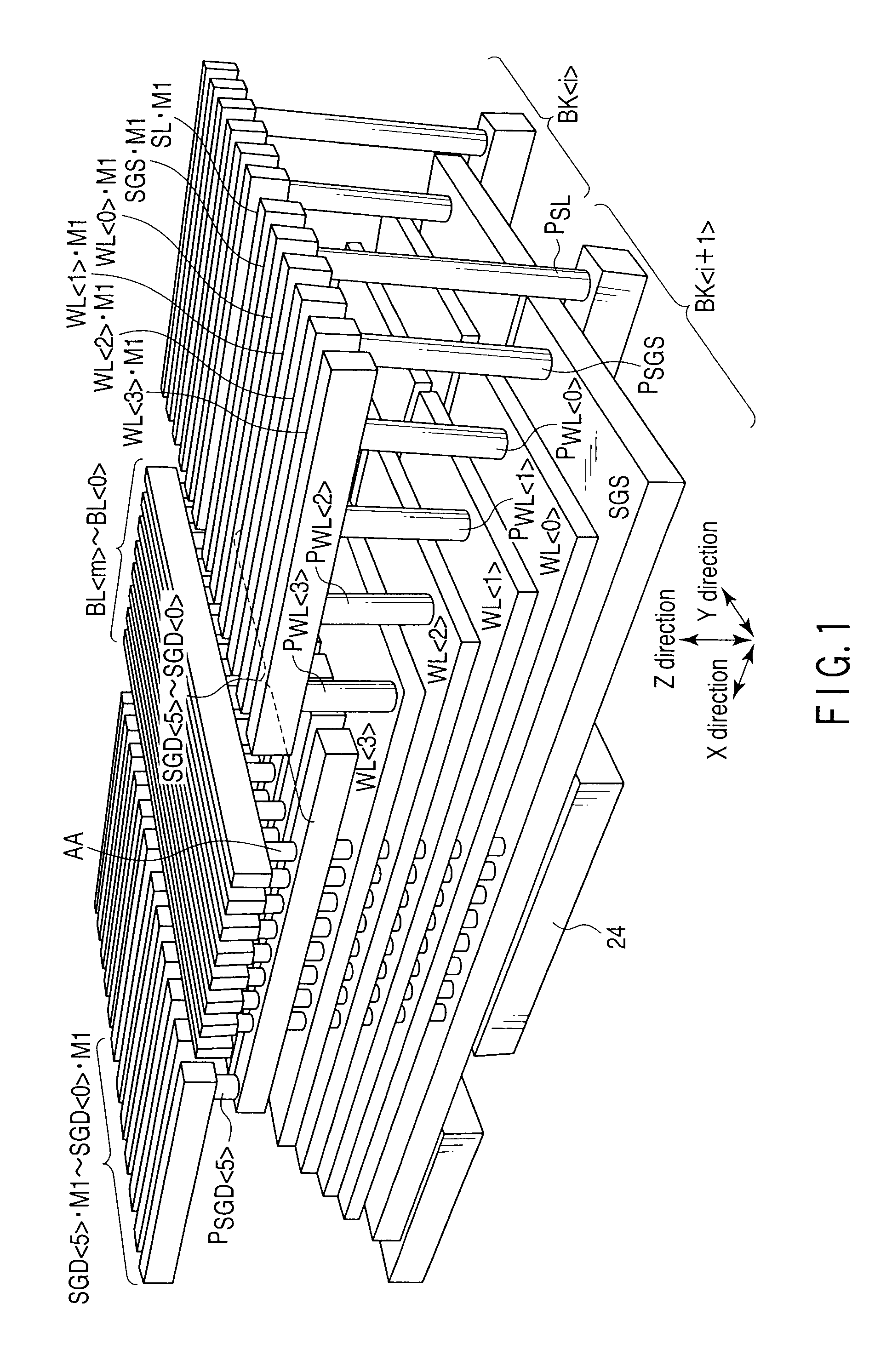

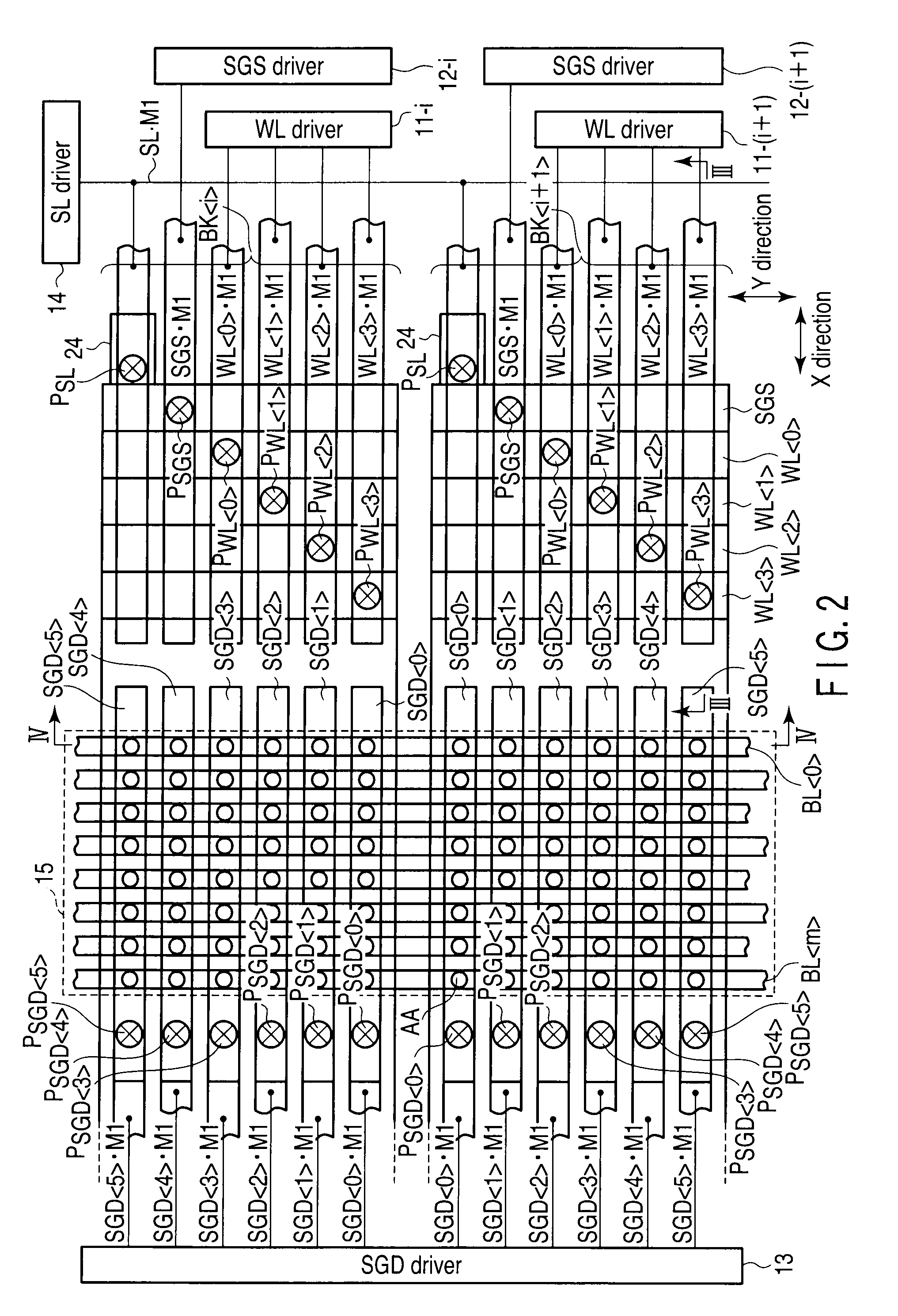

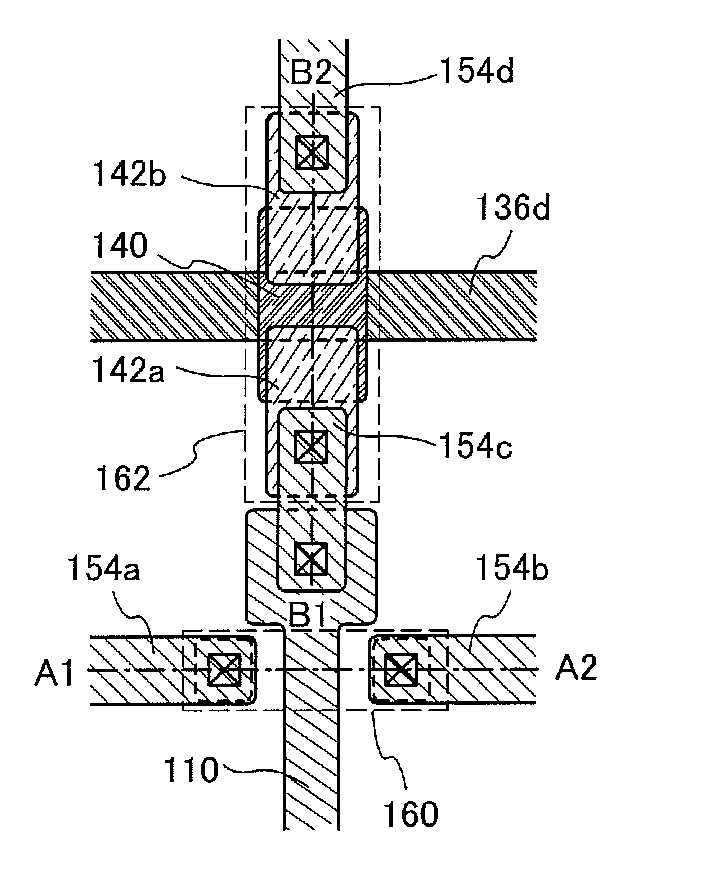

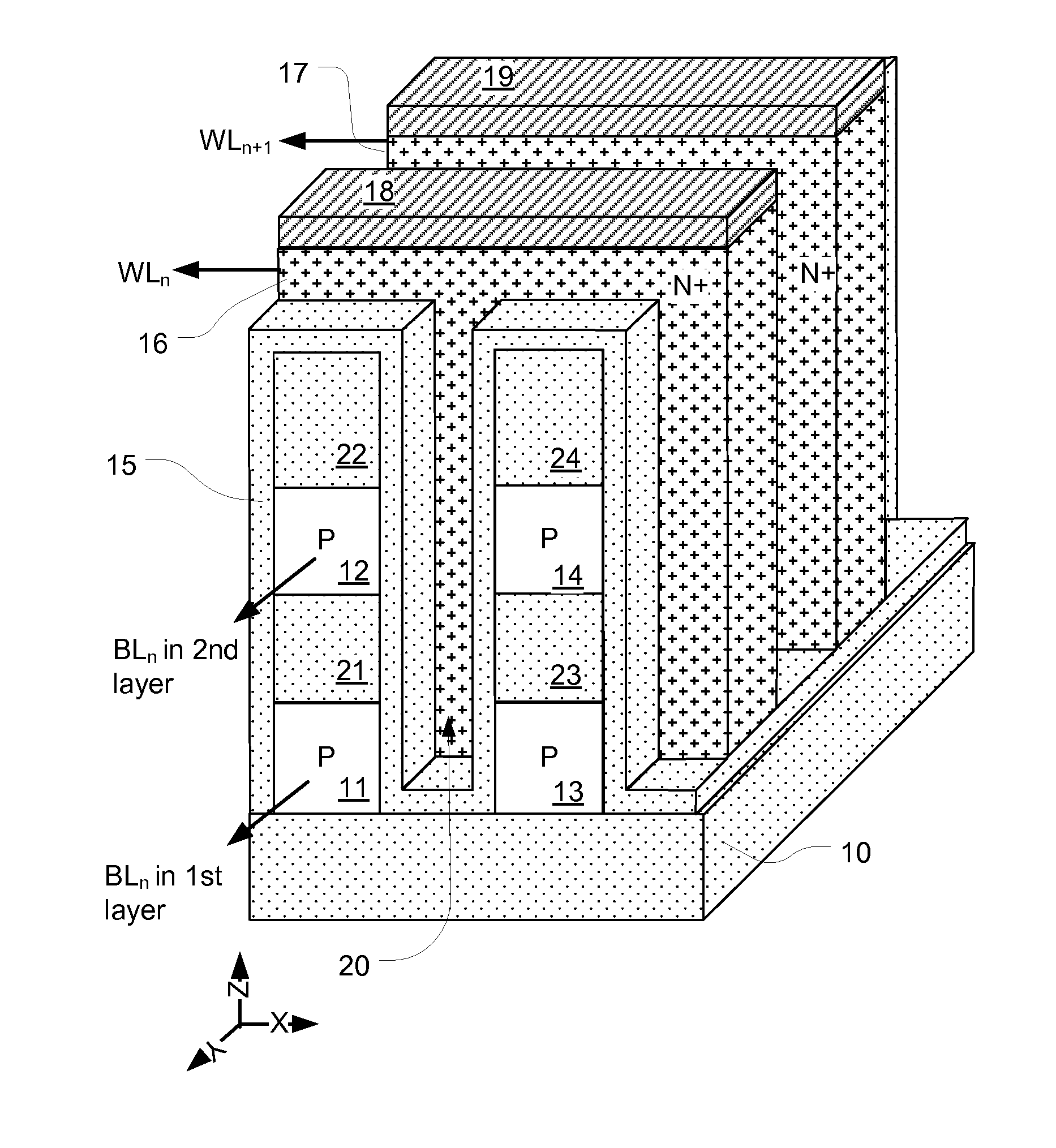

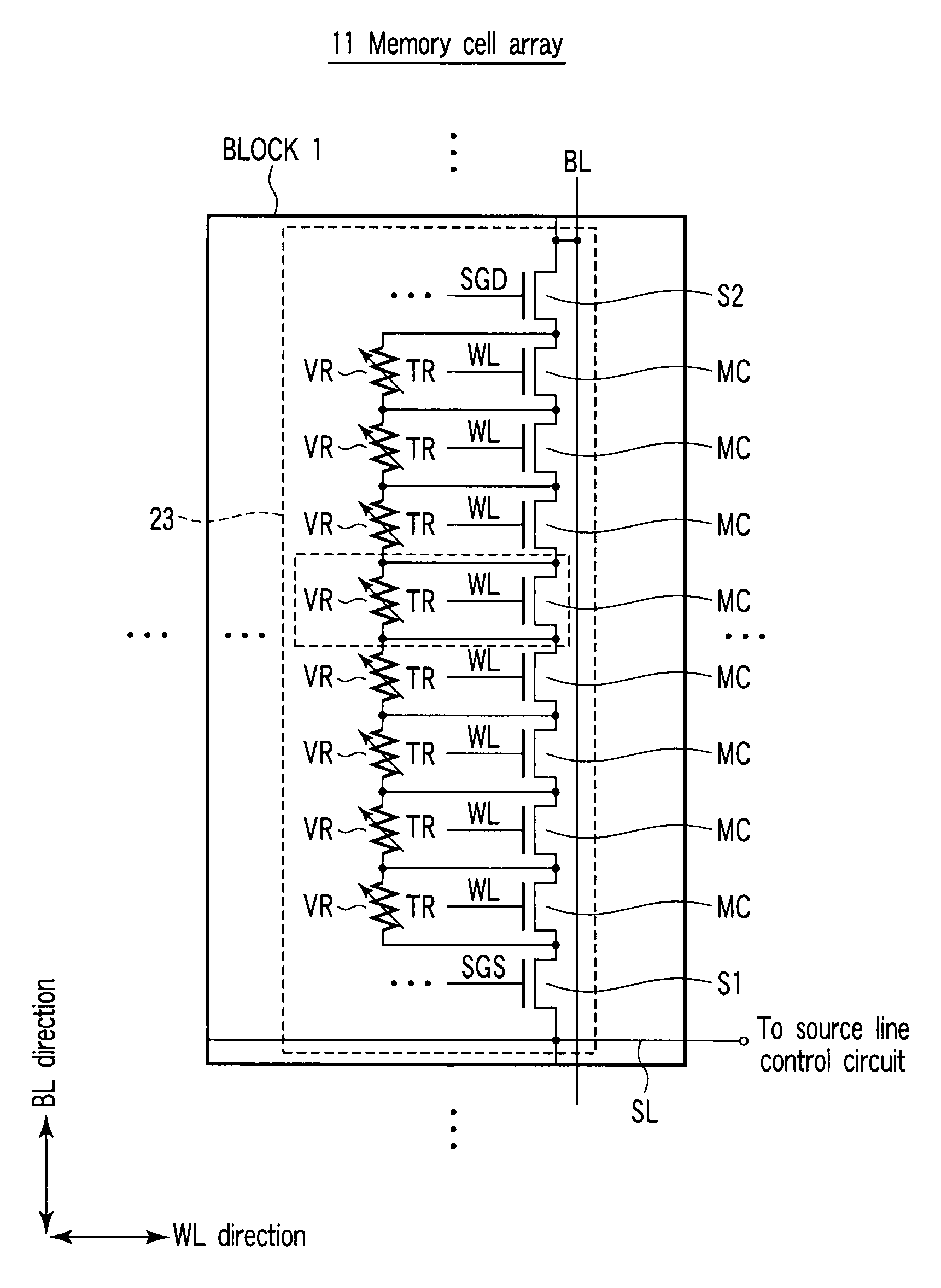

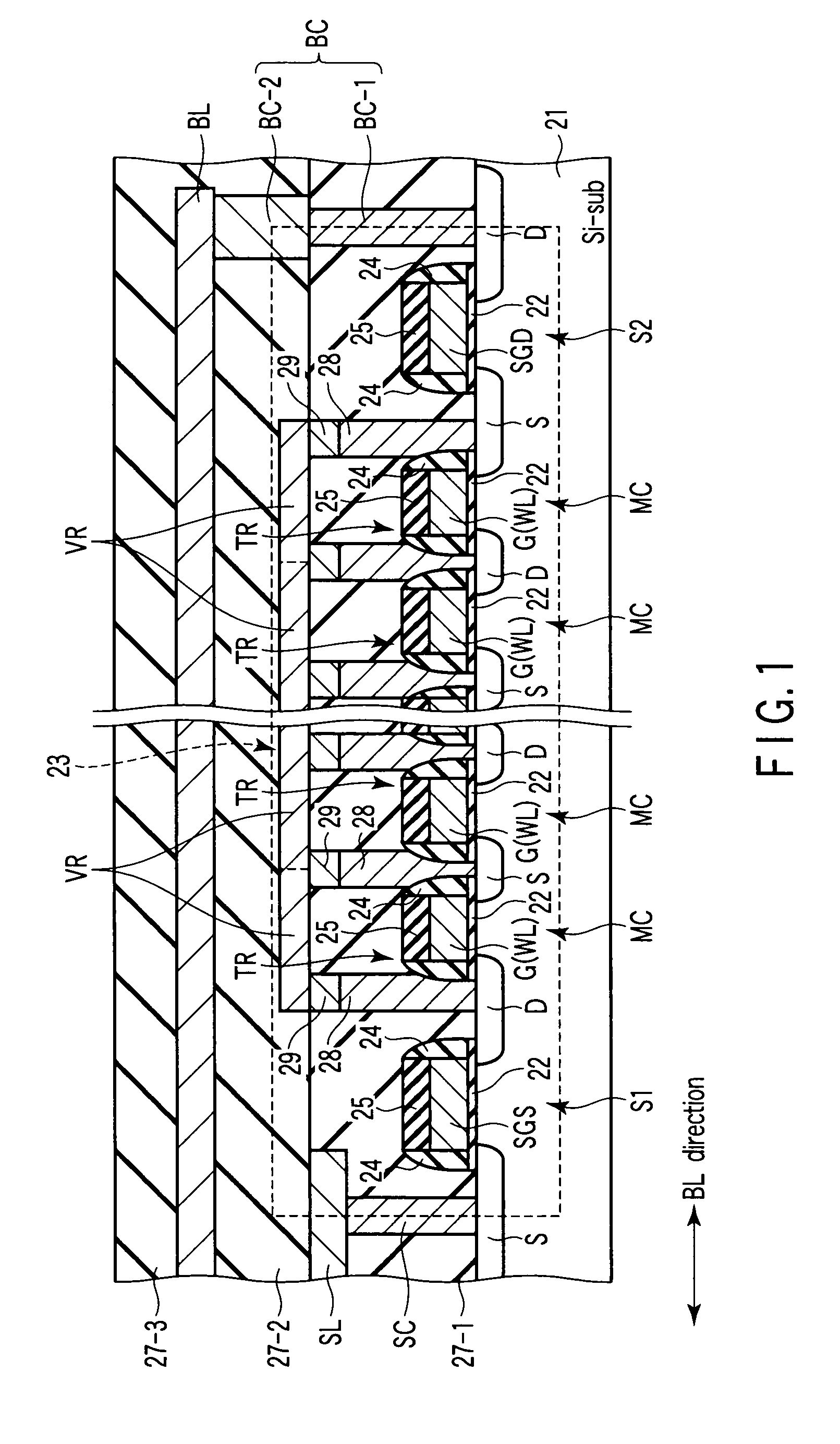

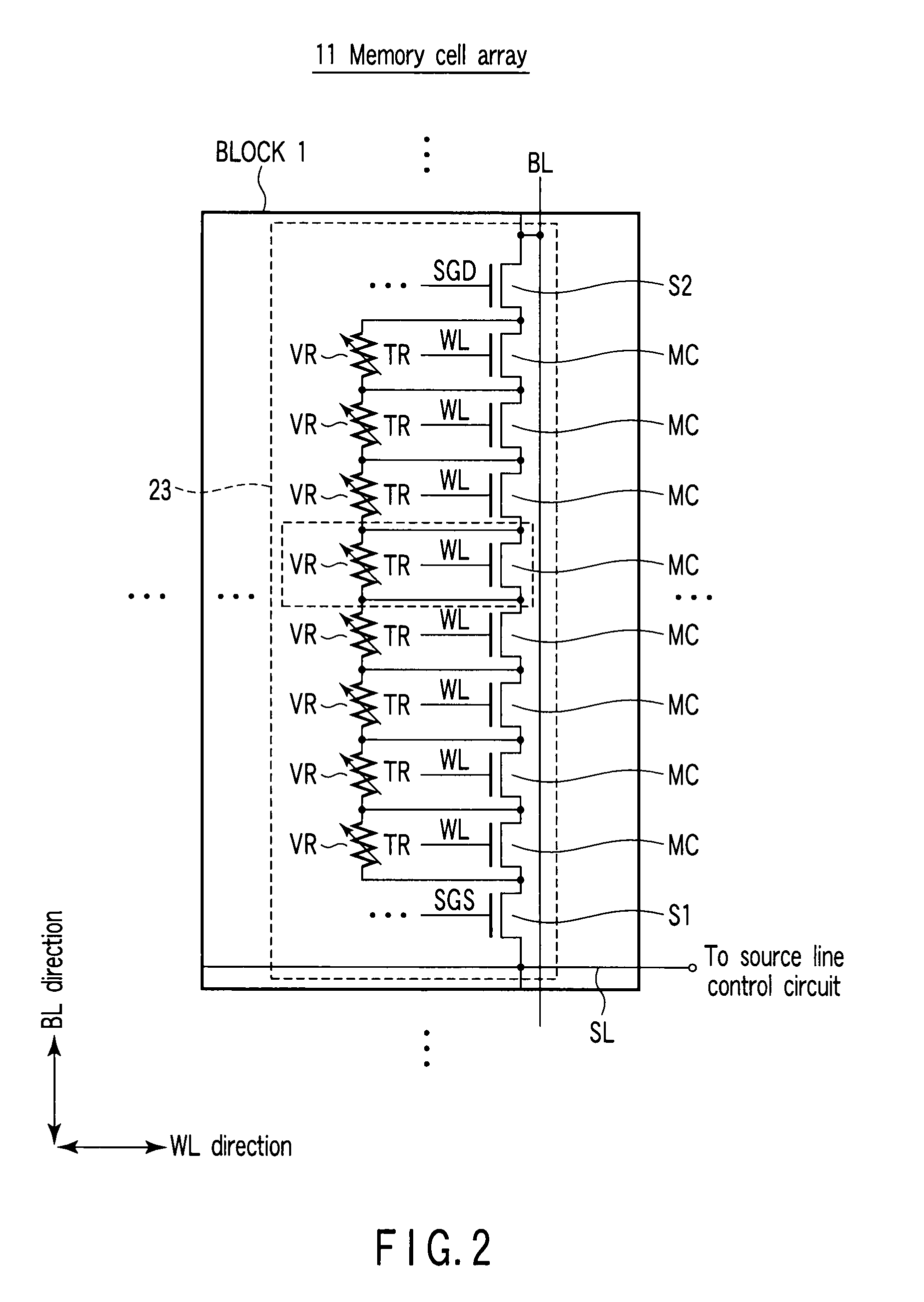

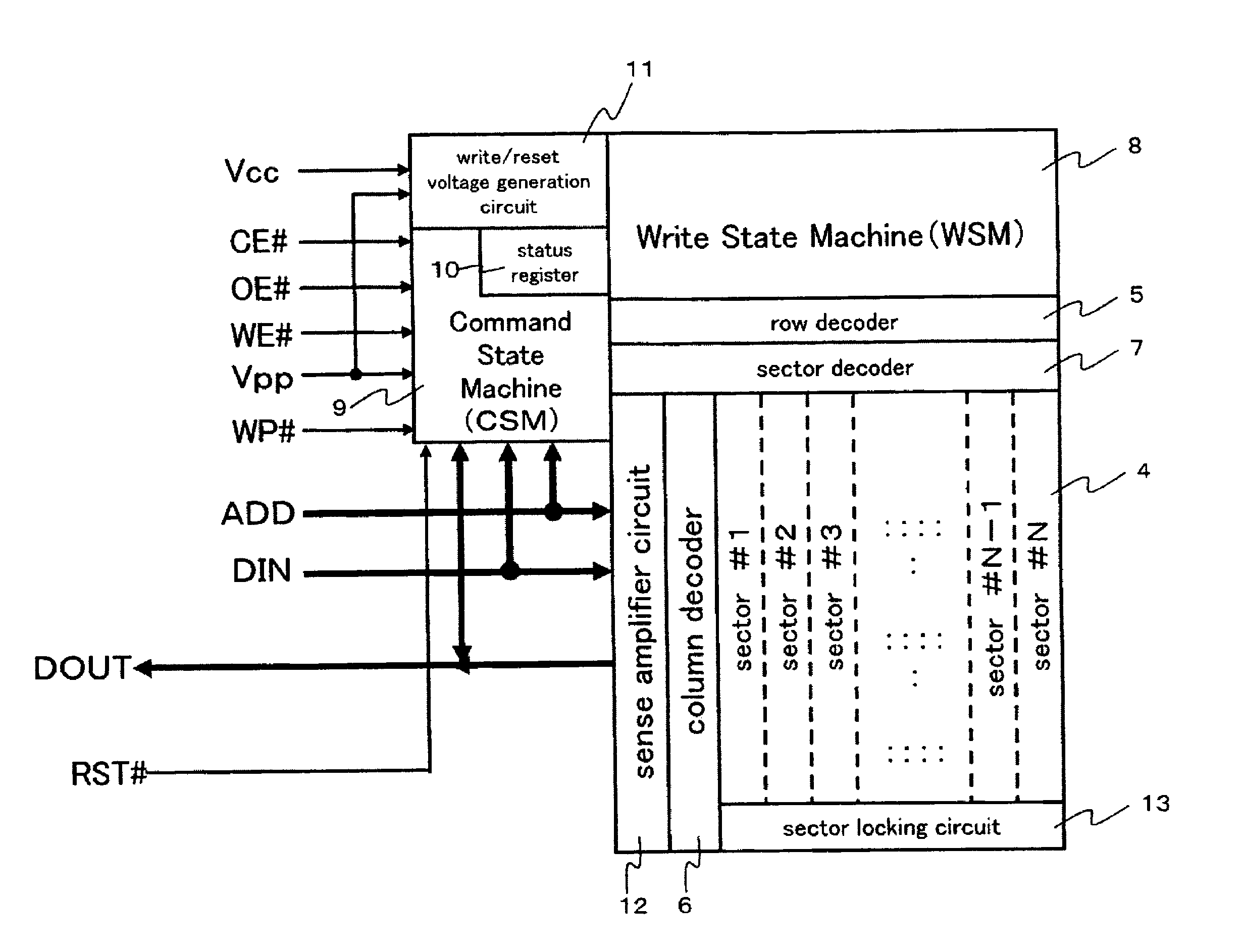

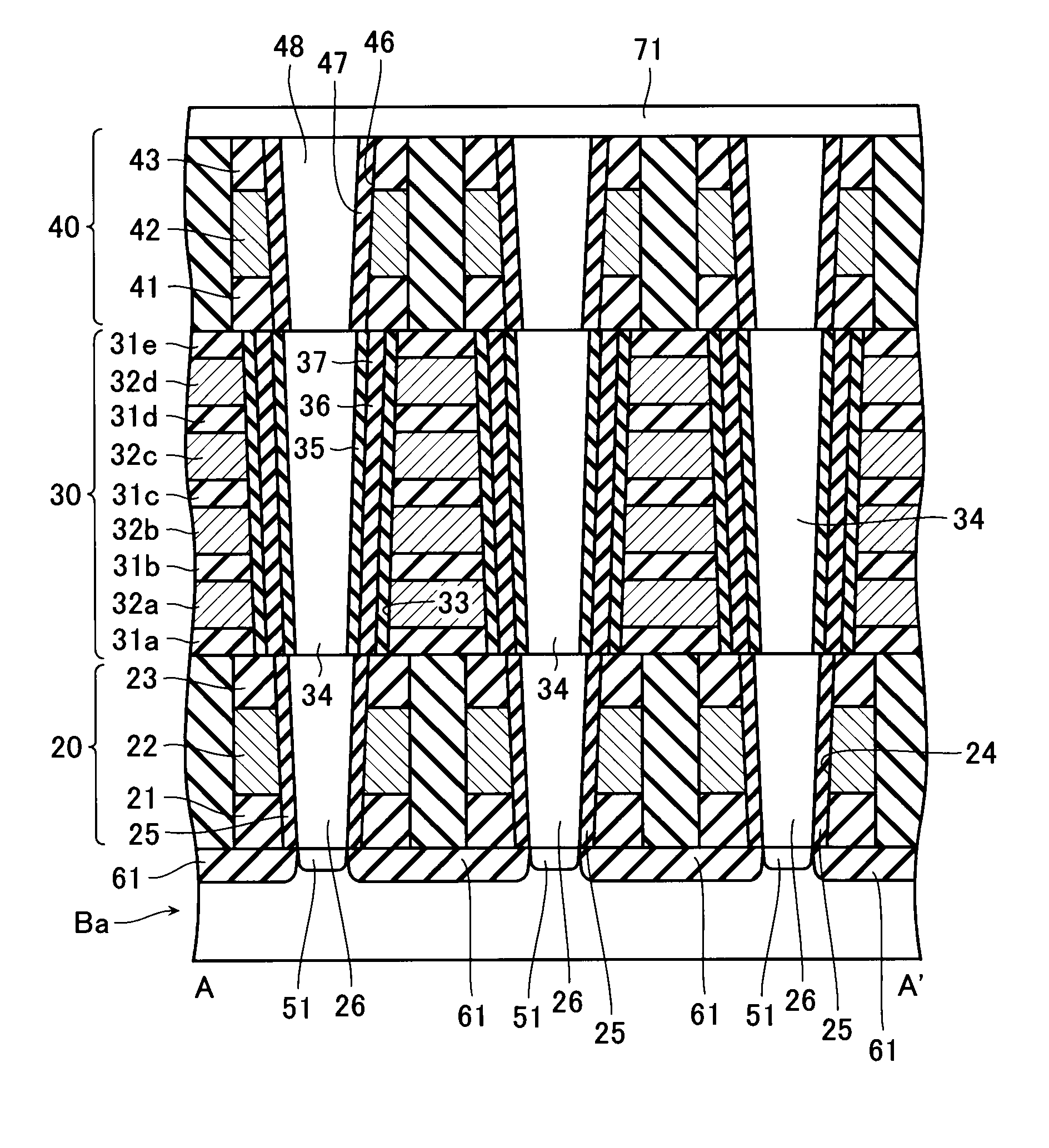

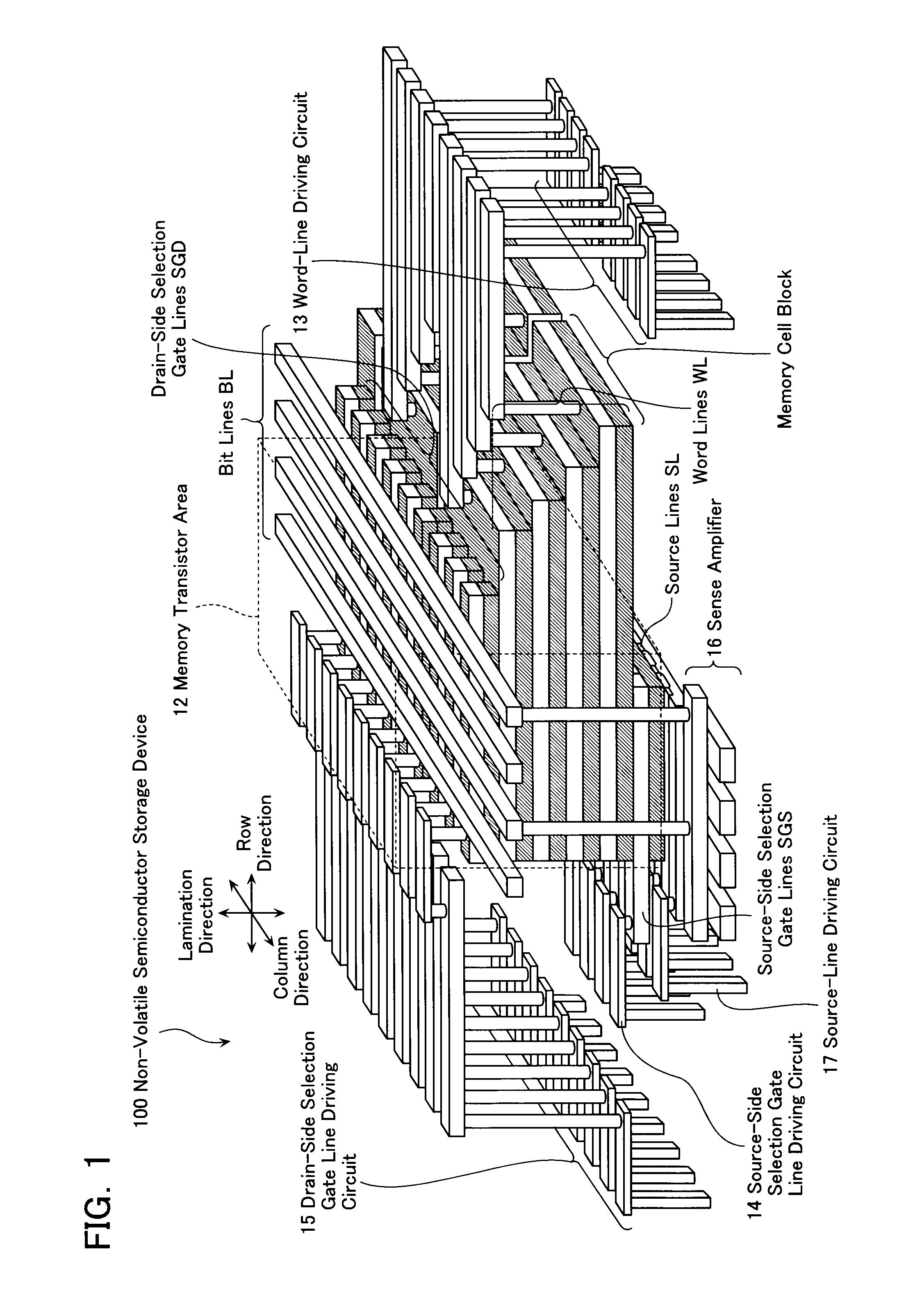

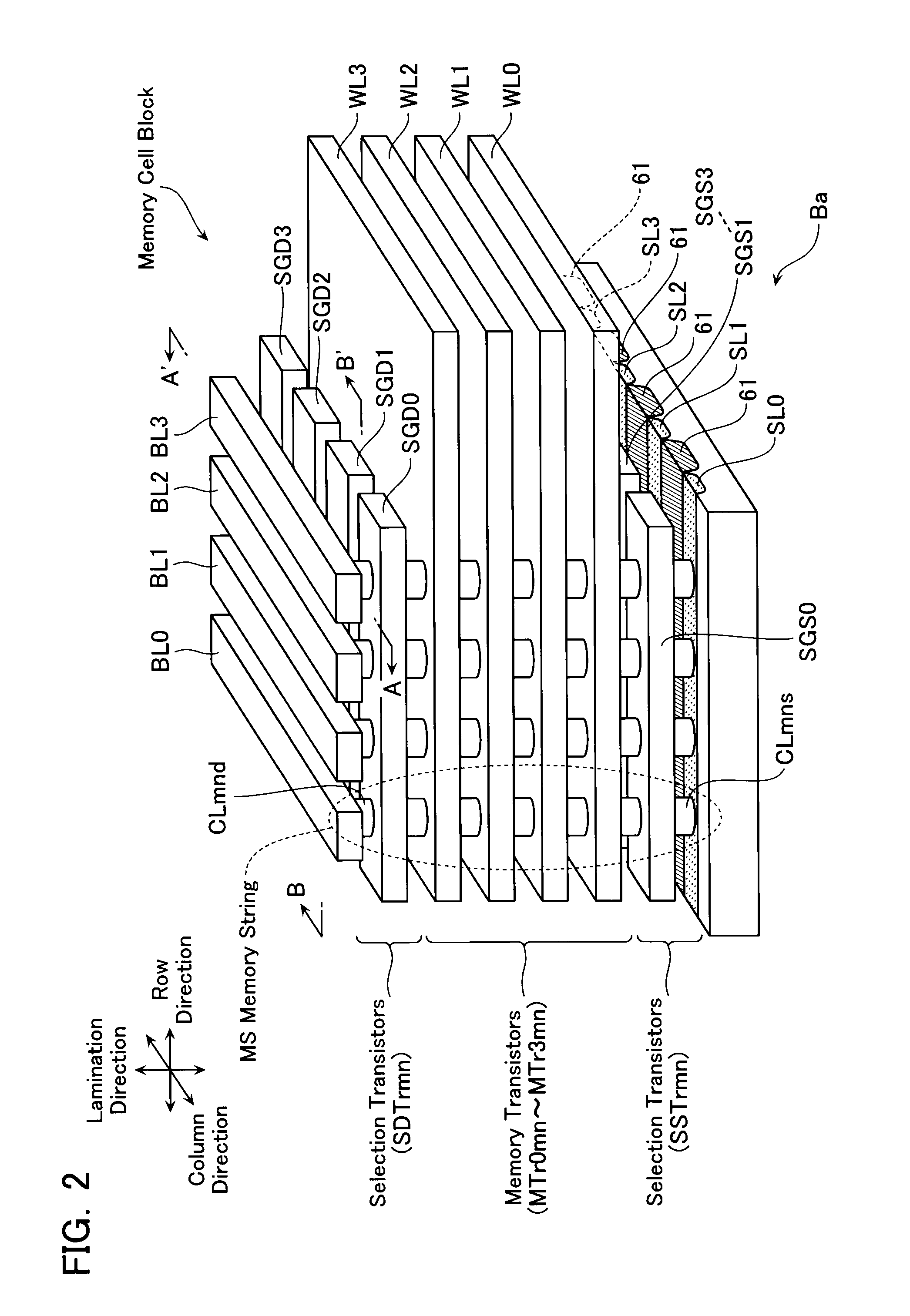

Three dimensional stacked nonvolatile semiconductor memory

A three dimensional stacked nonvolatile semiconductor memory according to an example of the present invention includes a memory cell array comprised of first and second blocks disposed side by side in a first direction, and a driver disposed on one end of the memory cell array in a second direction orthogonal to the first direction. A source diffusion layer, which is common to the first and second blocks, is disposed in a semiconductor substrate, and a contact plug, which has a lower end connected to the source diffusion layer and an upper end connected to a source line disposed above at least three conductive layers, is interposed between the first and second blocks.

Owner:KIOXIA CORP

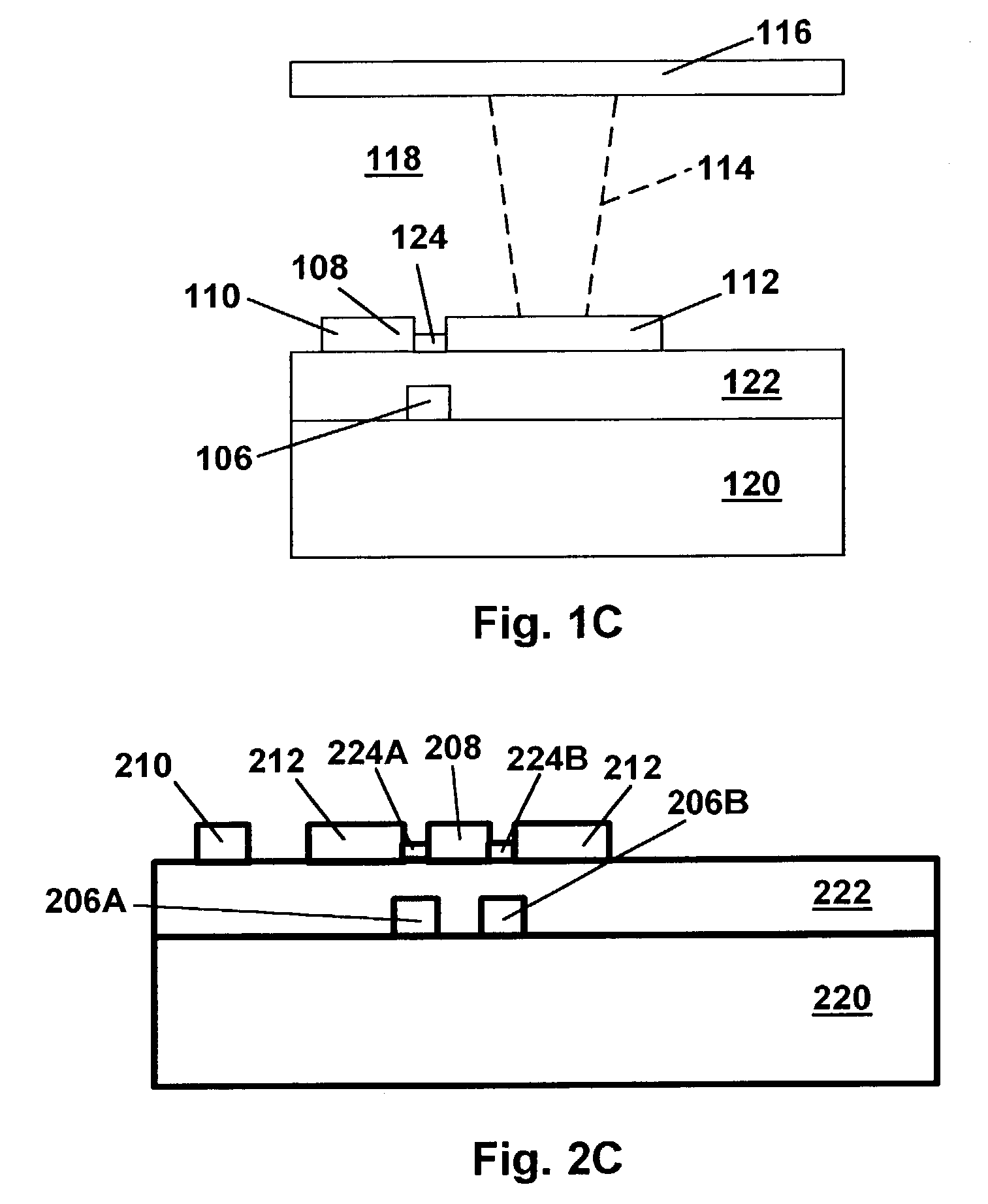

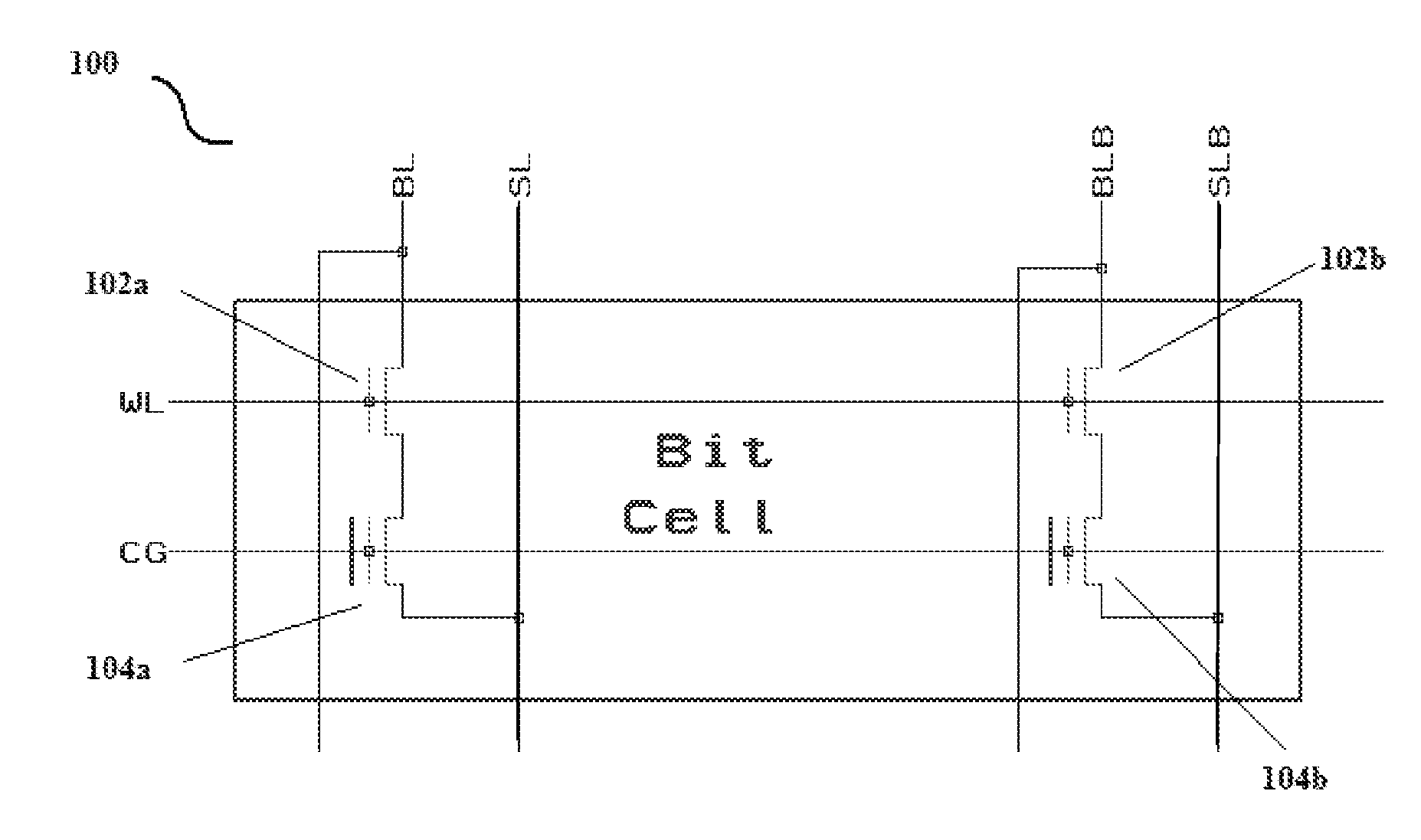

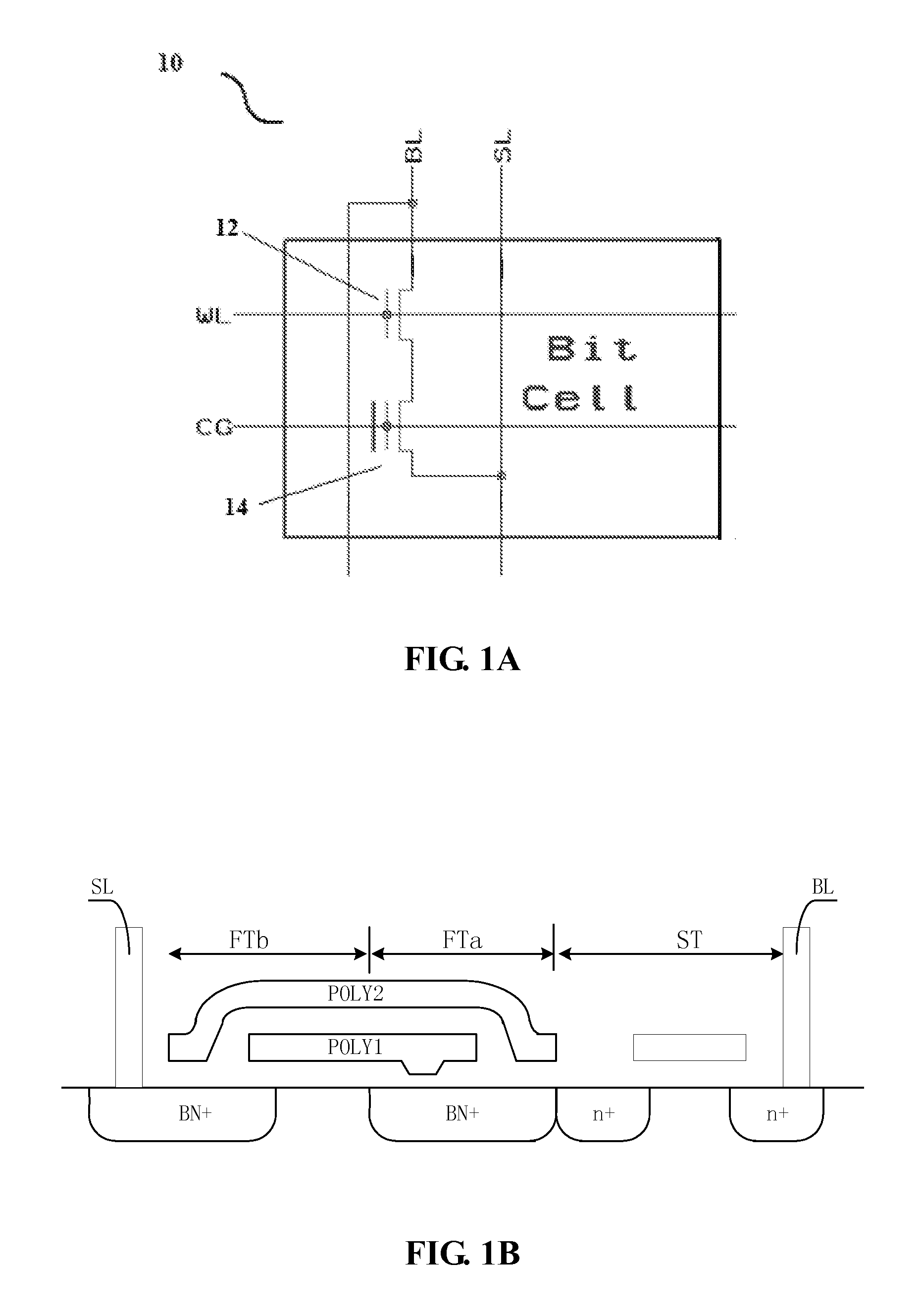

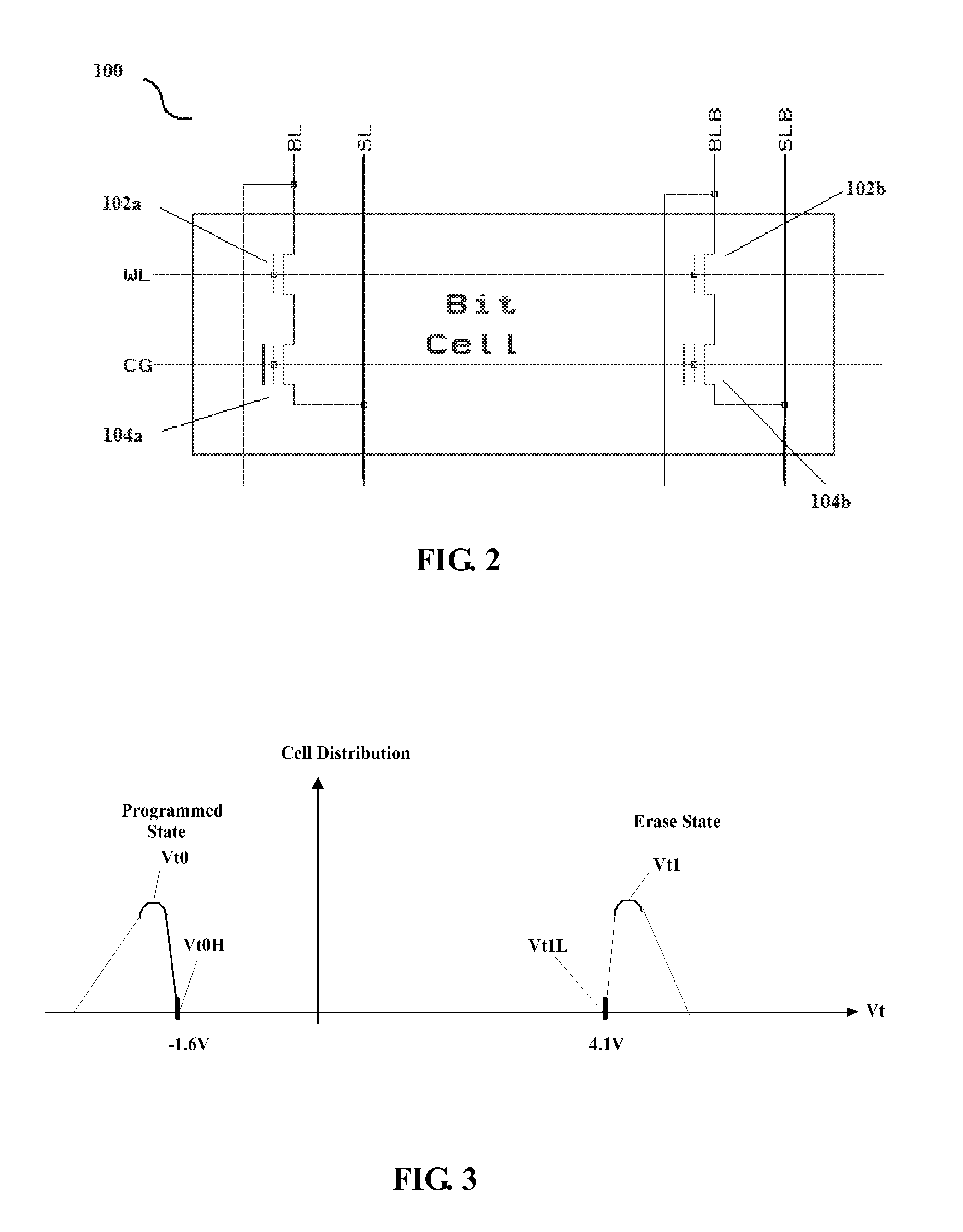

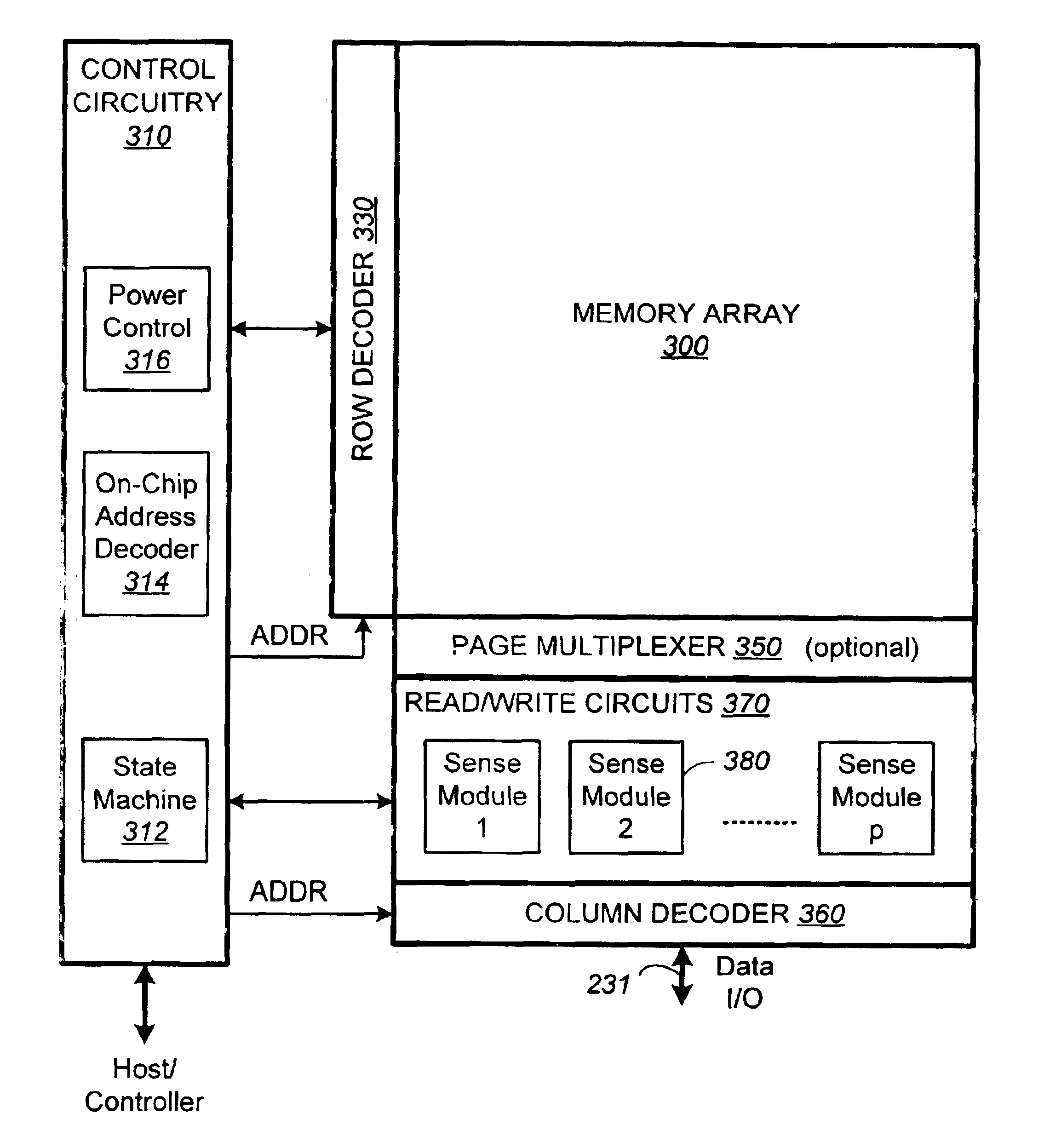

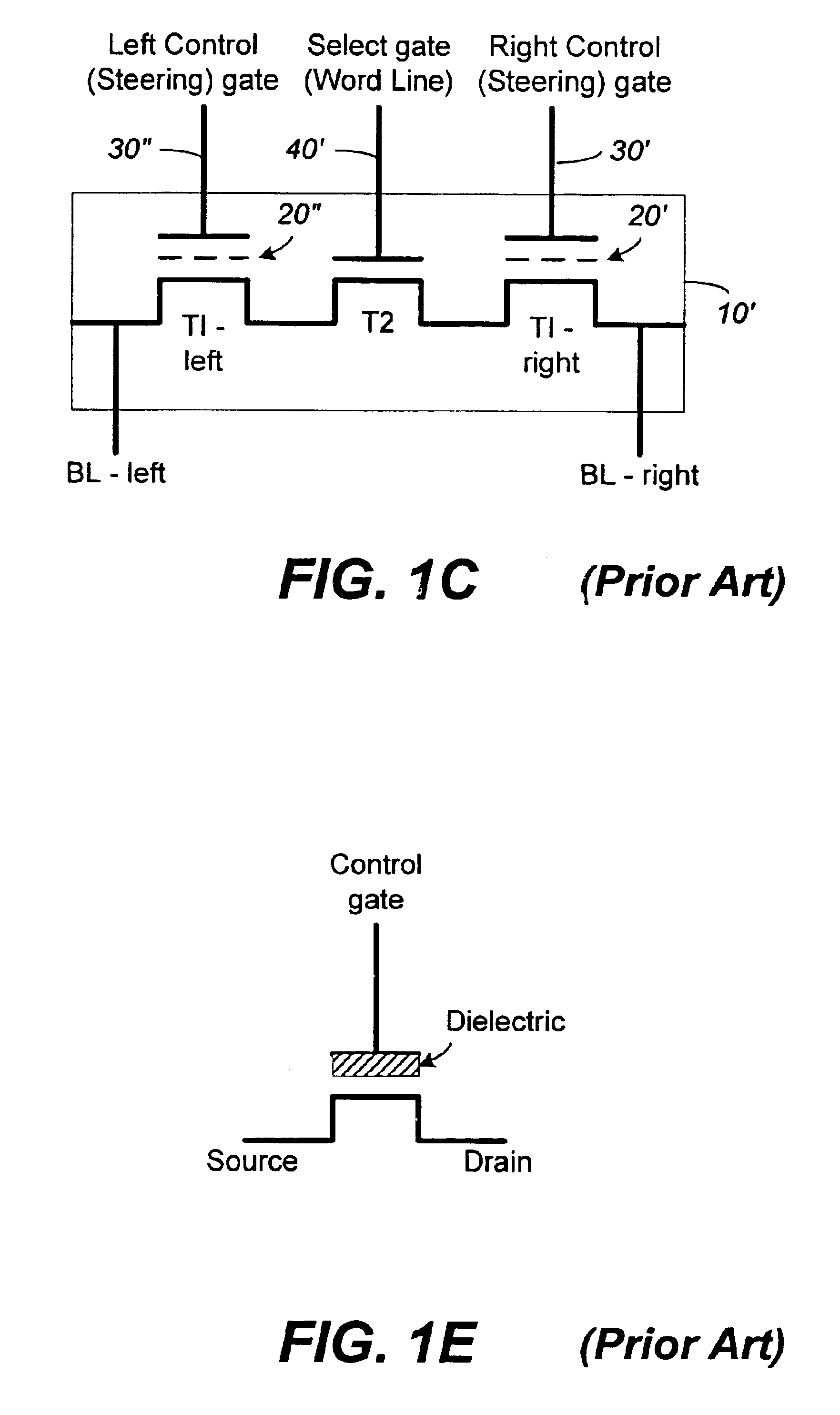

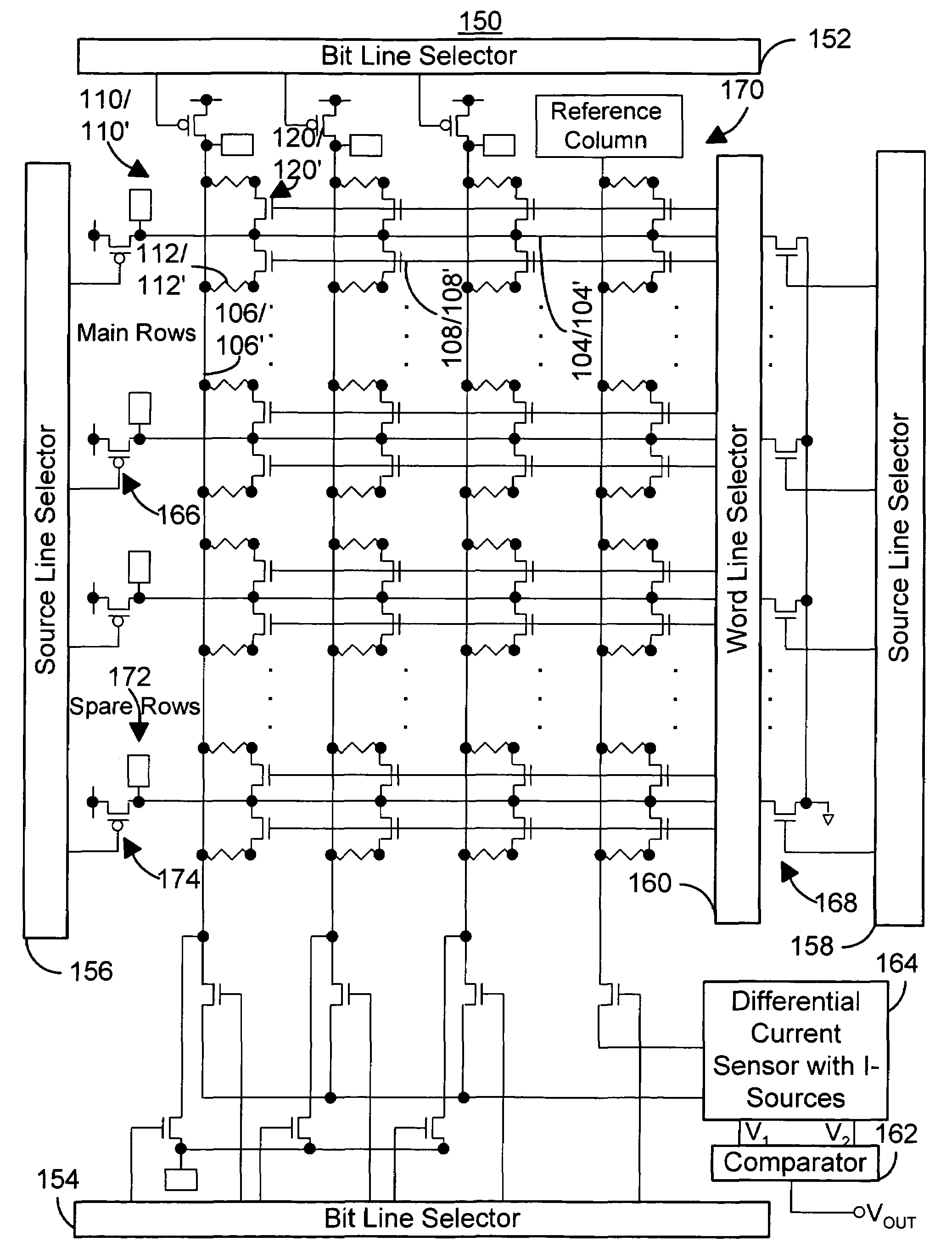

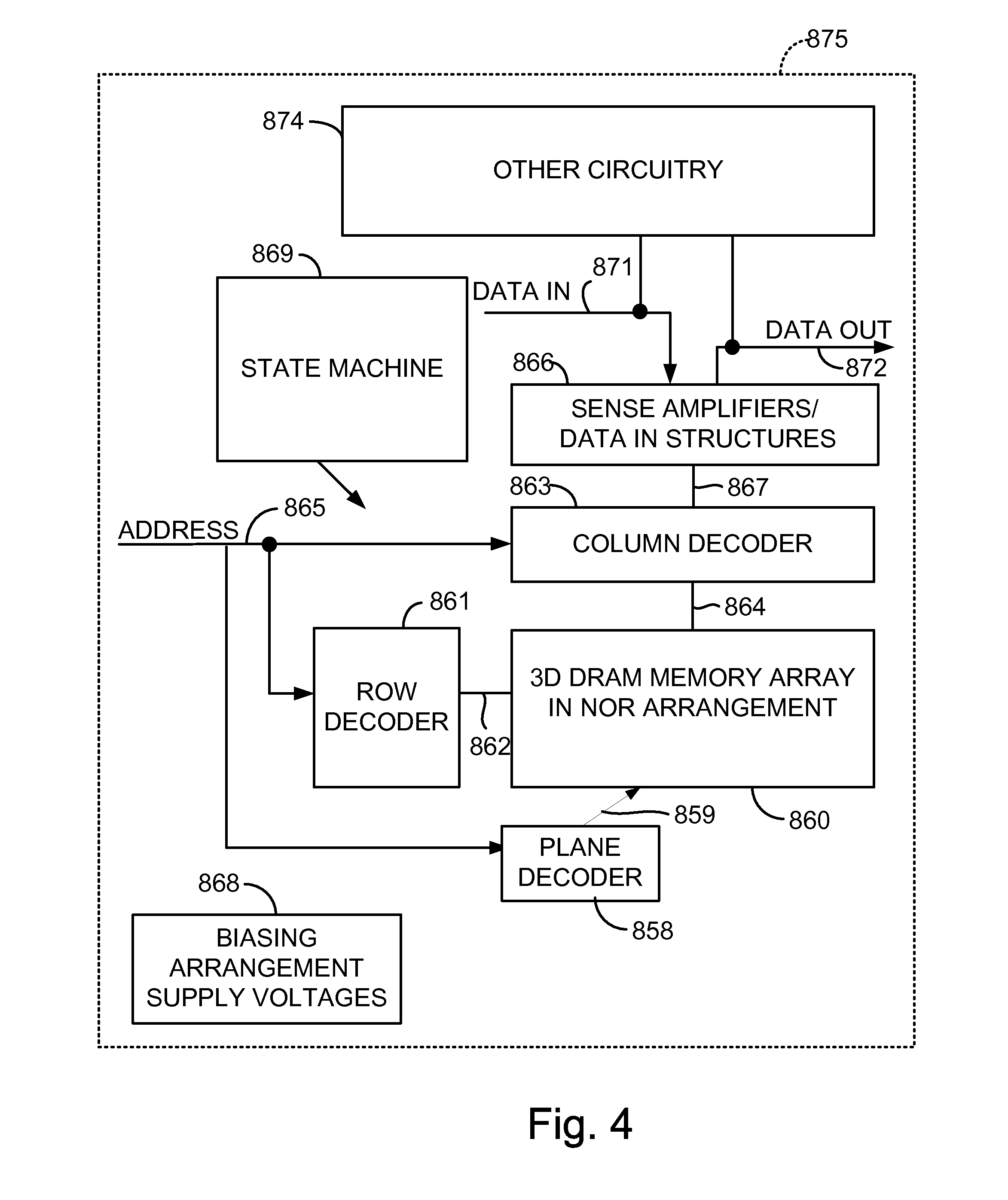

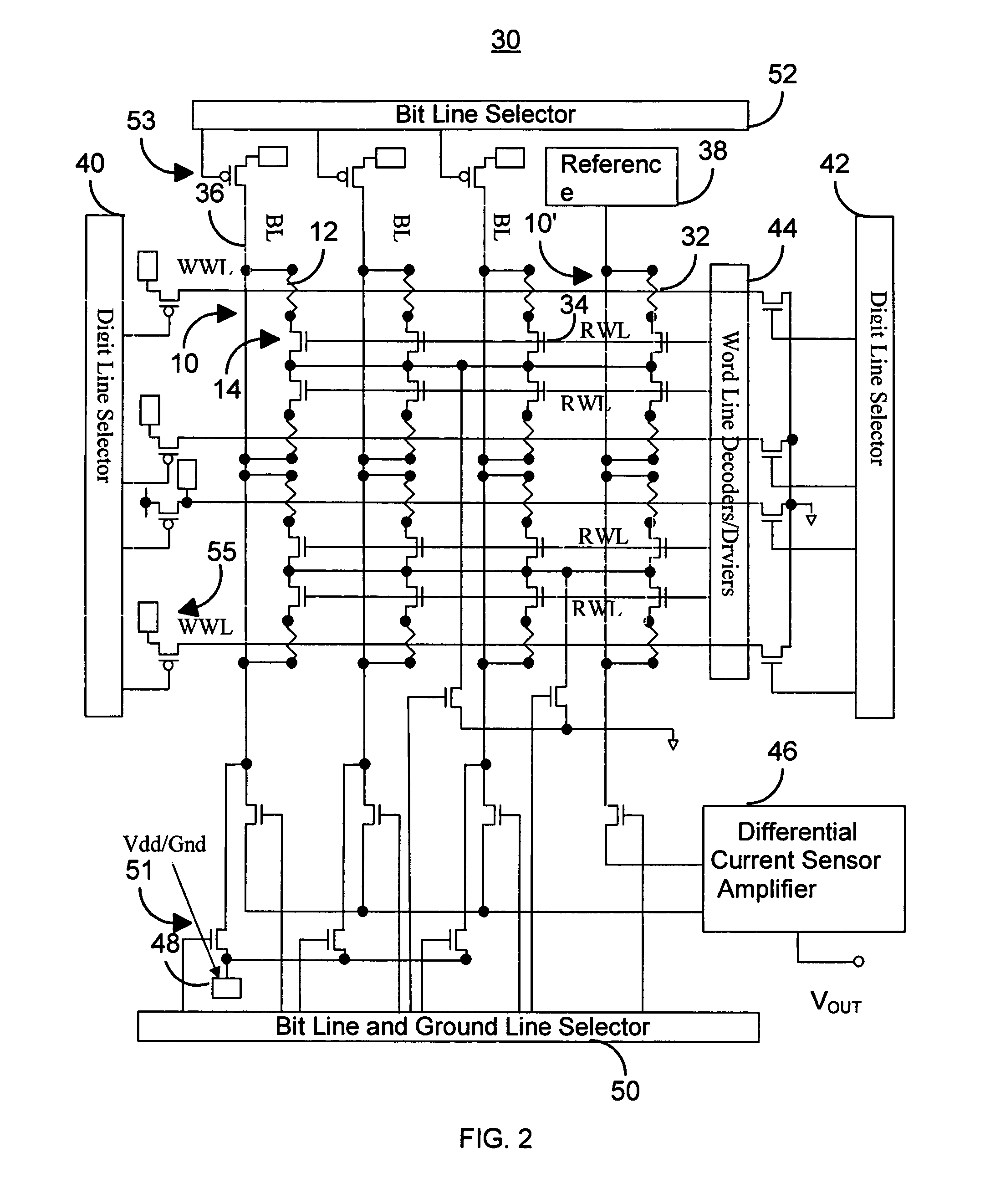

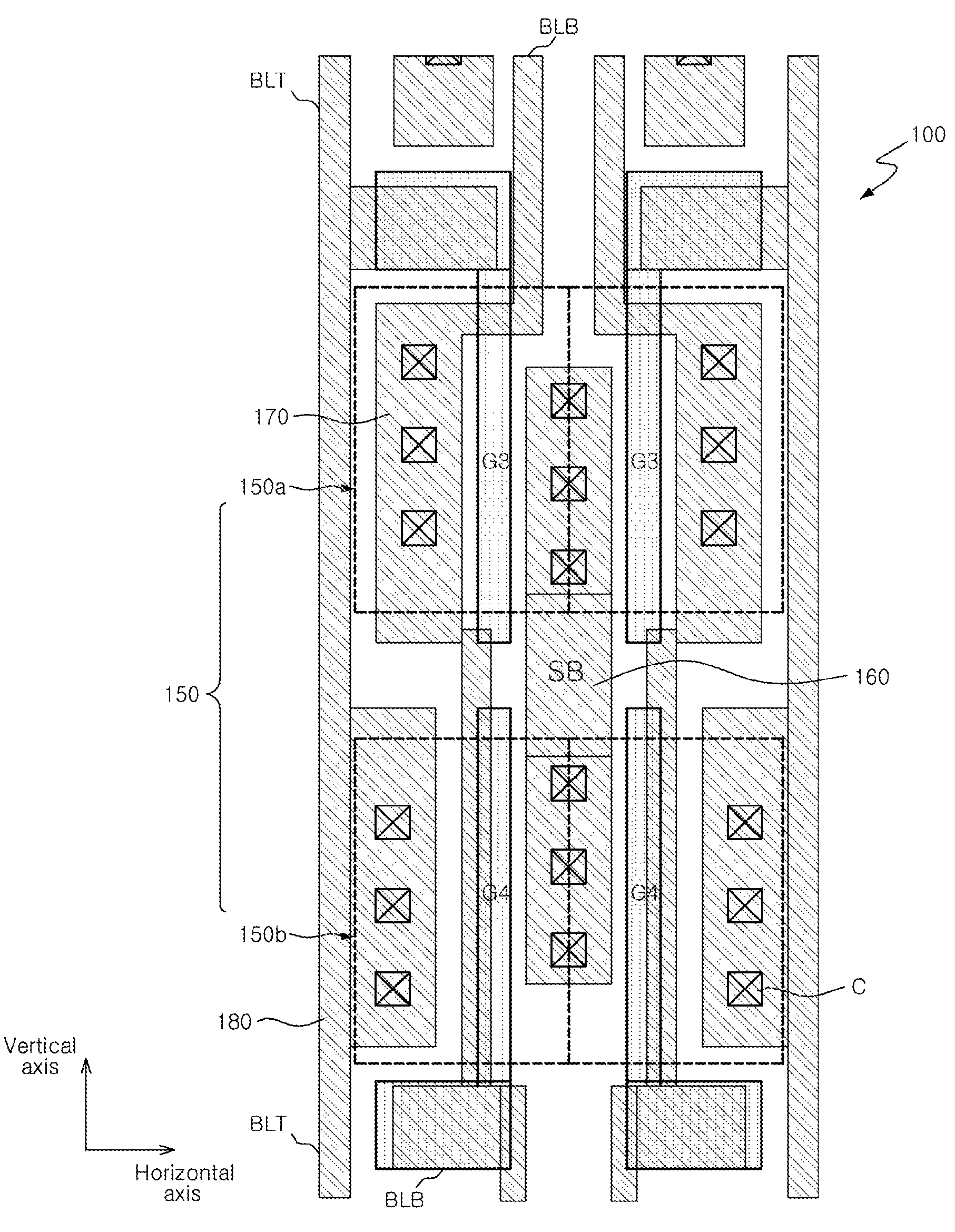

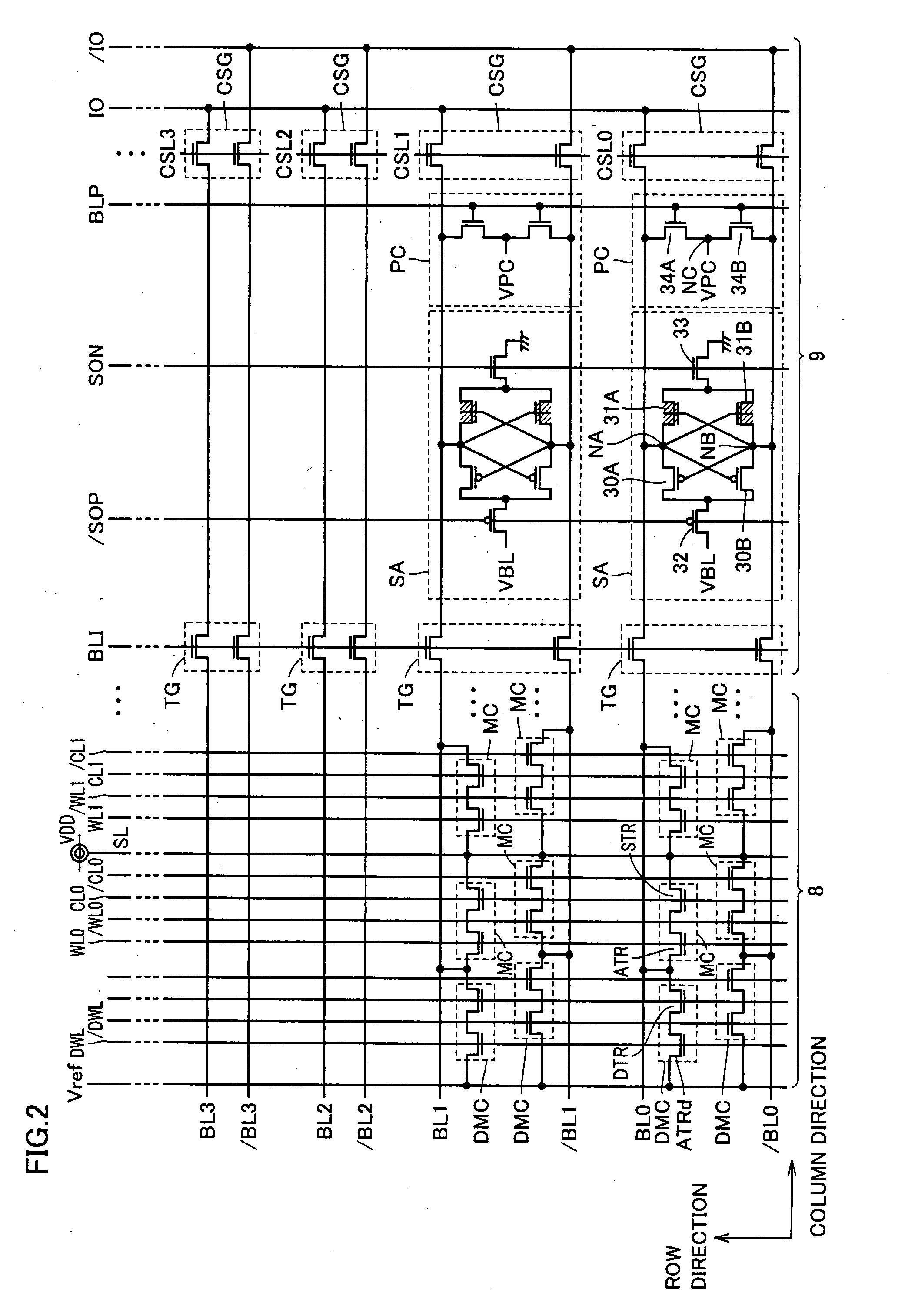

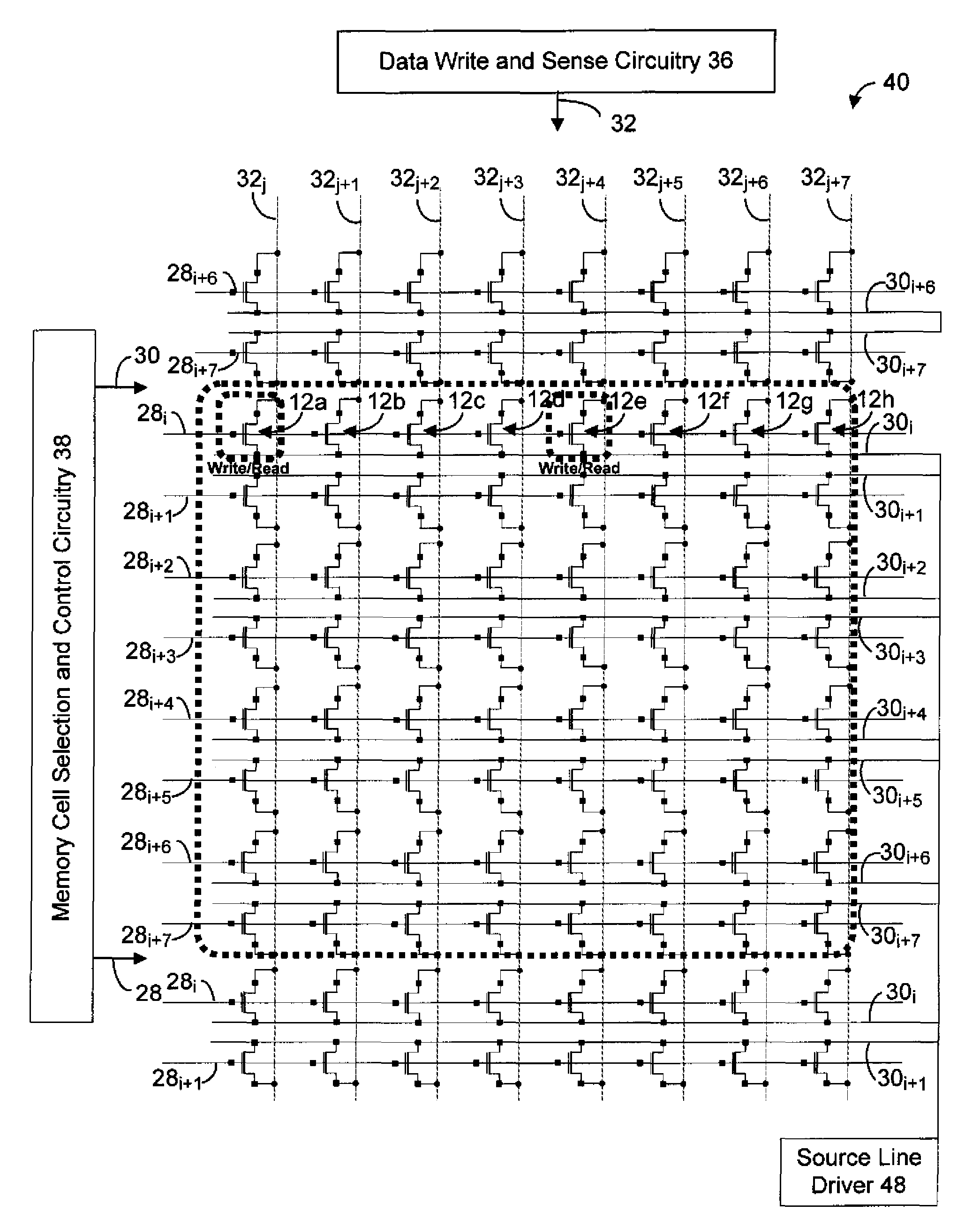

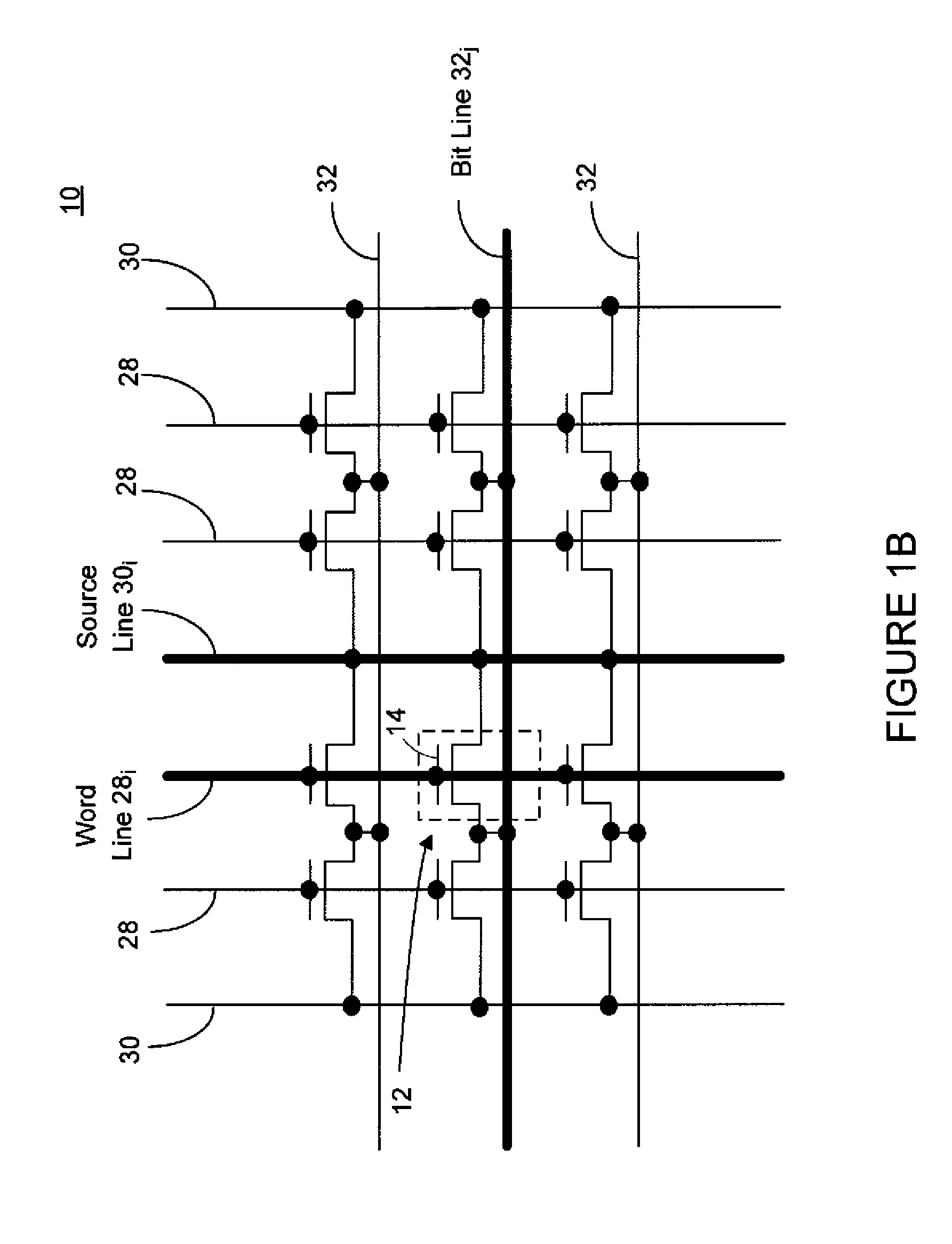

Dram-like nvm memory array and sense amplifier design for high temperature and high endurance operation

InactiveUS20110267883A1Improve threshold voltage sensing marginLarge silicon areaRead-only memoriesDigital storageBit lineAudio power amplifier

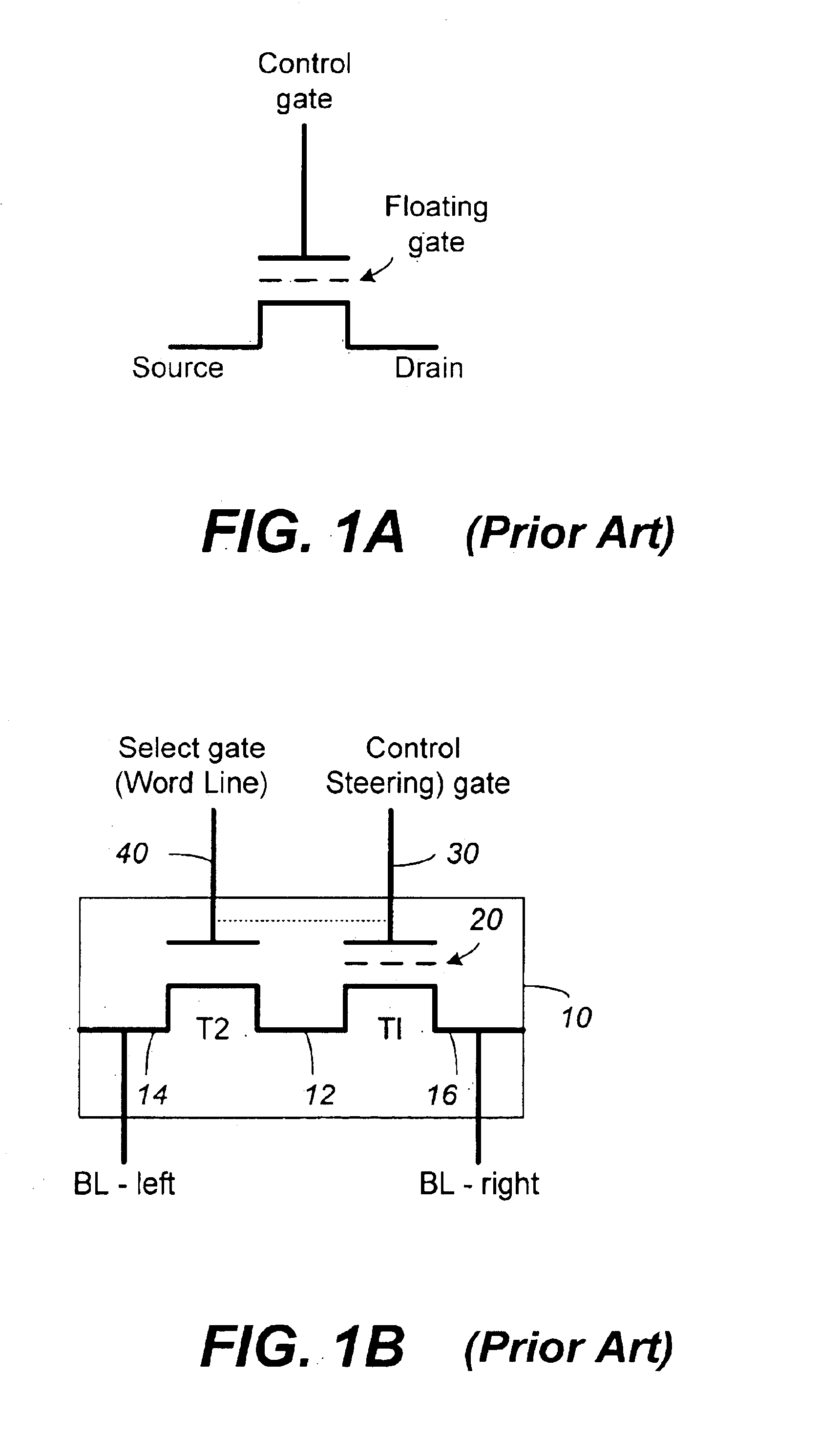

A DRAM-like non-volatile memory array includes a cell array of non-volatile cell units with a DRAM-like cross-coupled latch-type sense amplifier. Each non-volatile cell unit has two non-volatile cell devices with respective bit lines and source lines running in parallel and laid out perpendicular to the word line associated with the non-volatile cell unit. The two non-volatile cell devices are programmed with erased and programmed threshold voltages as a pair for storing a single bit of binary data. The two bit lines of each non-volatile cell unit are coupled through a Y-decoder and a latch device to the two respective inputs of the latch-type sense amplifier which provides a large sensing margin for the cell array to operate properly even with a narrowed threshold voltage gap. Each non-volatile cell device may be a 2 T FLOTOX-based EEPROM cell, a 2 T flash cell, 11 T flash cell or a 1.5 T split-gate flash cell.

Owner:APLUS FLASH TECH

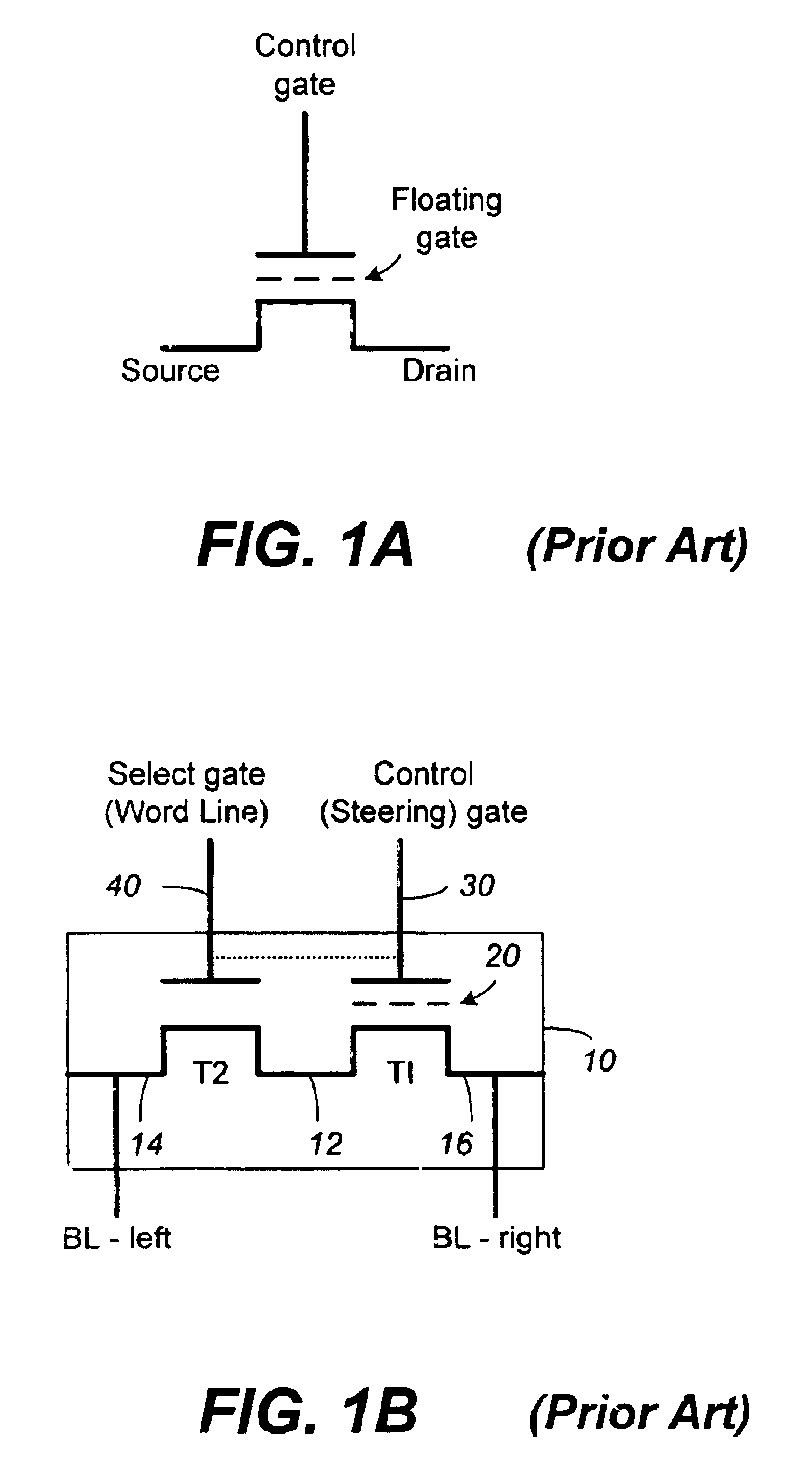

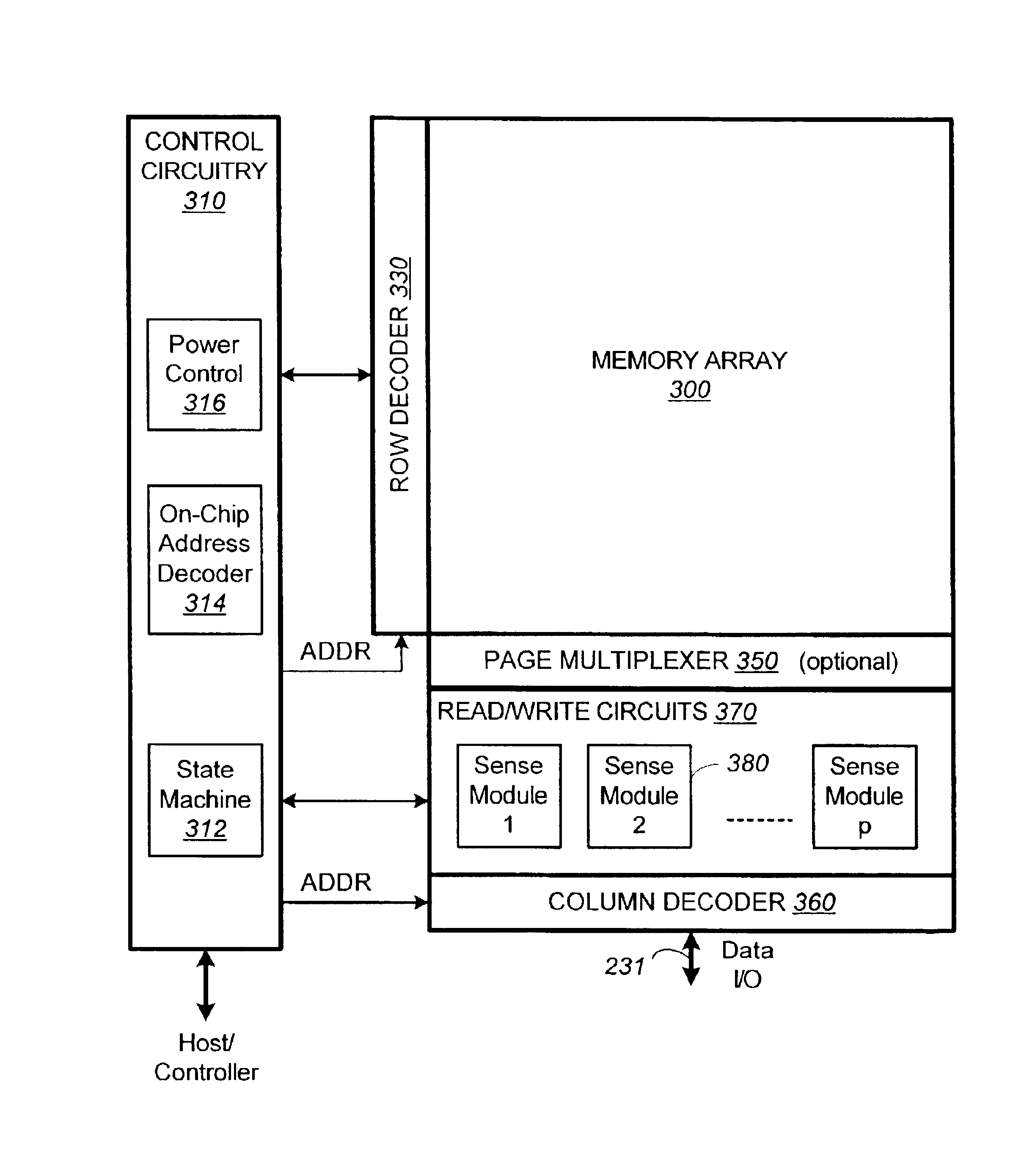

Non-volatile memory and method with improved sensing

InactiveUS7023736B2Large capacityImprove performanceRead-only memoriesDigital storageAudio power amplifierMultiple pass

A method for reducing source line bias is accomplished by read / write circuits with features and techniques for multi-pass sensing. When a page of memory cells are being sensed in parallel, each pass helps to identify and shut down the memory cells with conduction current higher than a given demarcation current value. In particular, the identified memory cells are shut down after all sensing in the current pass have been completed. In this way the shutting down operation does not disturb the sensing operation. Sensing in subsequent passes will be less affected by source line bias since the total amount of current flow is significantly reduced by eliminating contributions from the higher current cells. In another aspect of sensing improvement, a reference sense amplifier is employed to control multiple sense amplifiers to reduce their dependence on power supply and environmental variations.

Owner:SANDISK TECH LLC

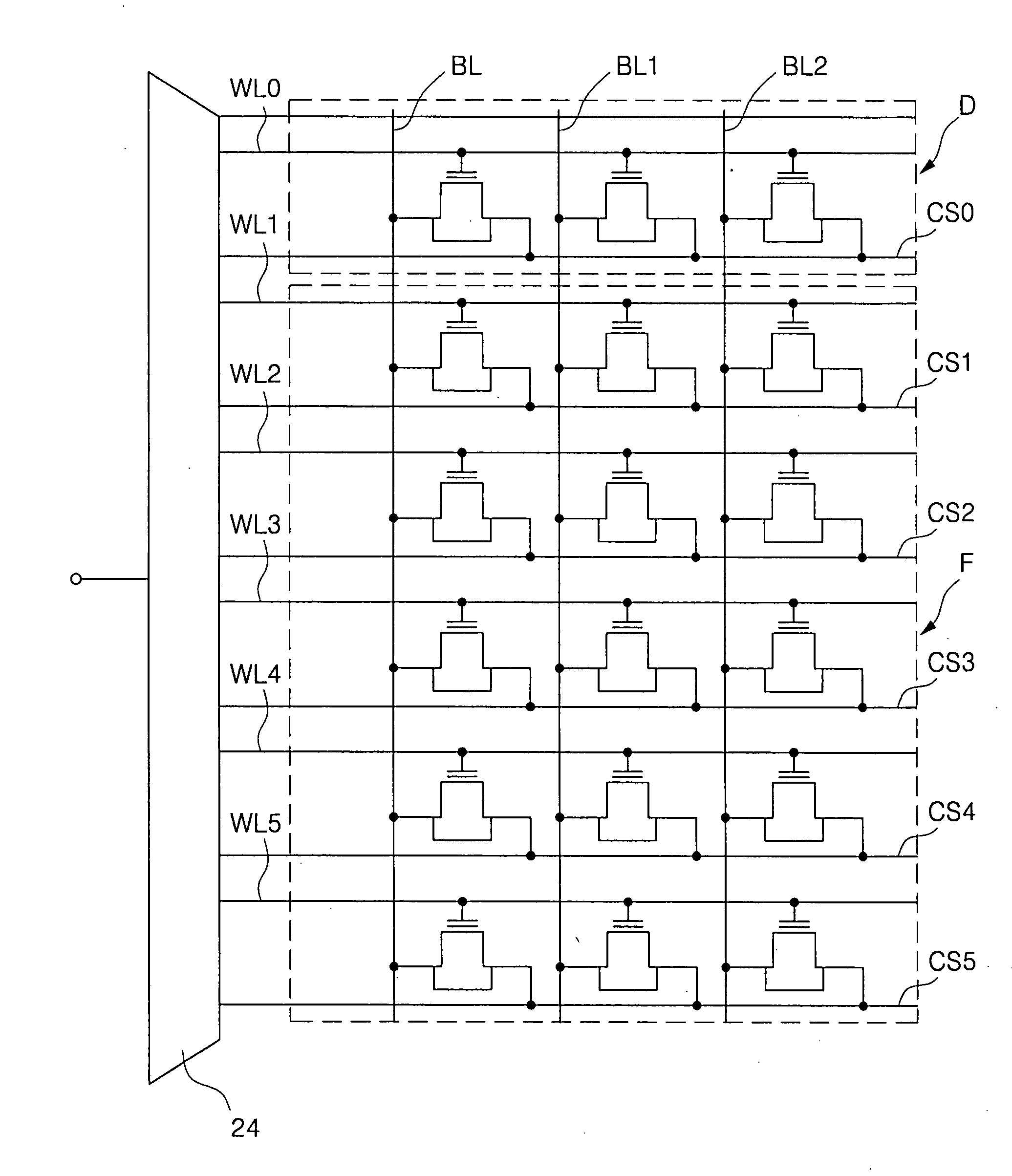

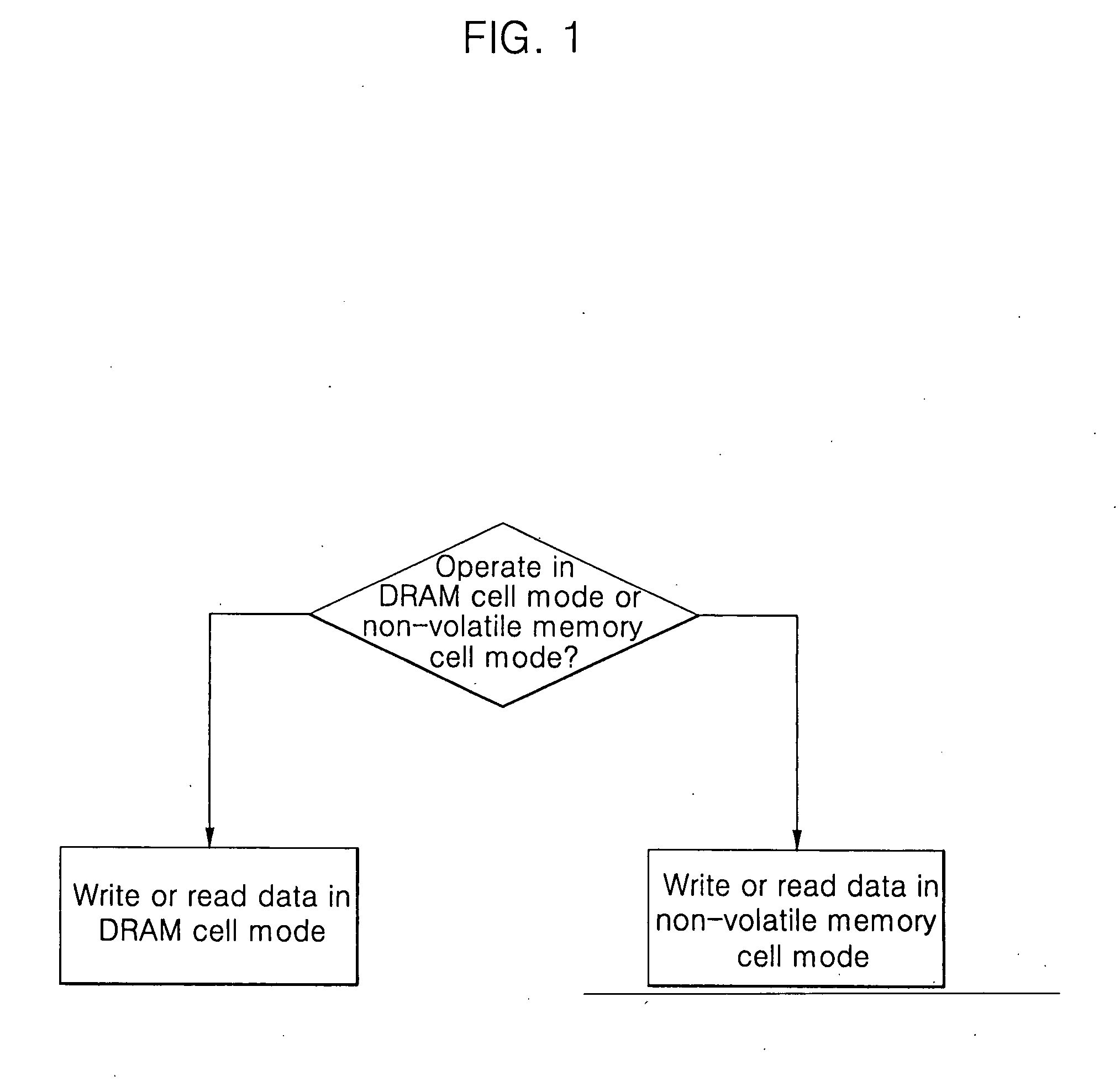

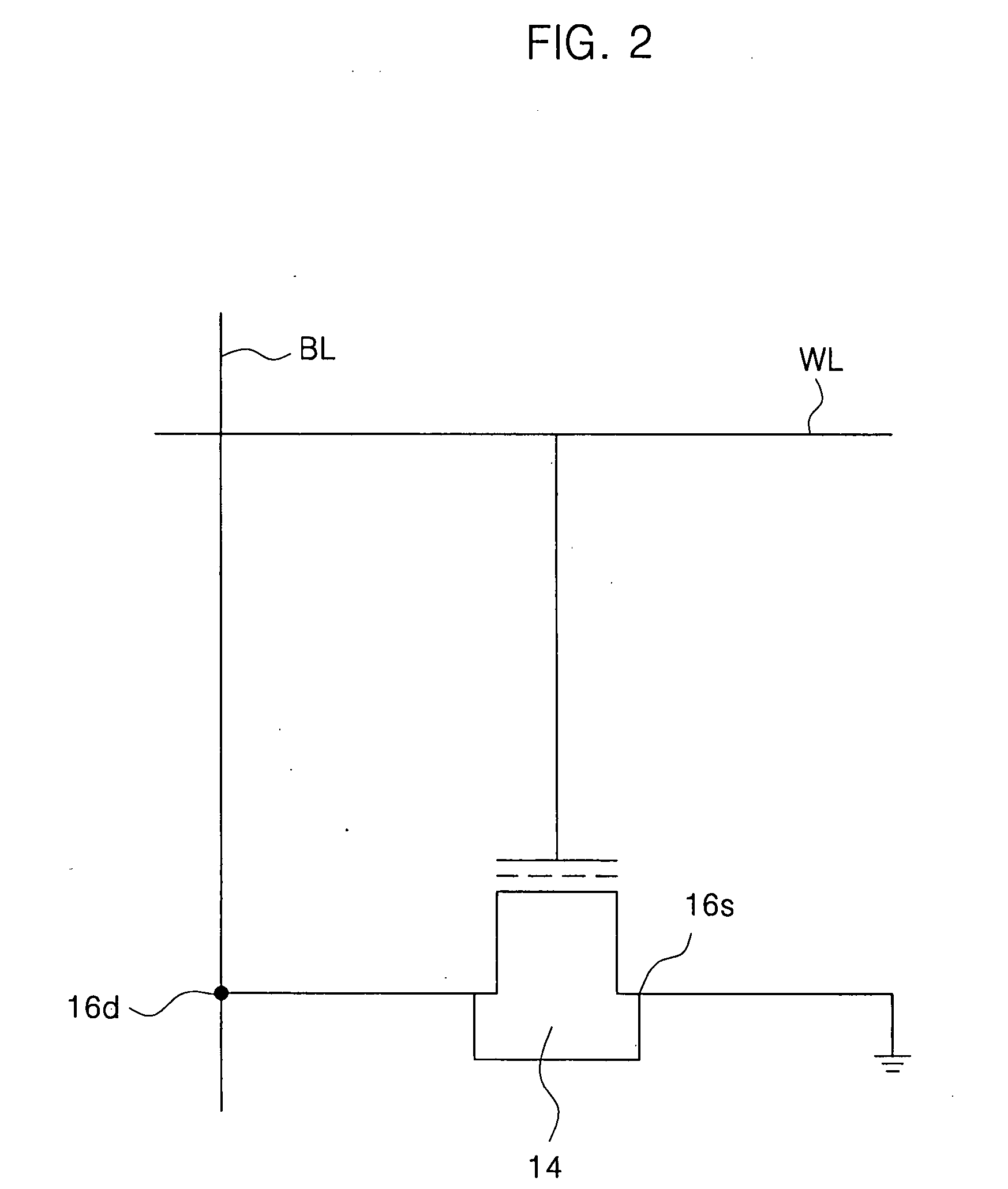

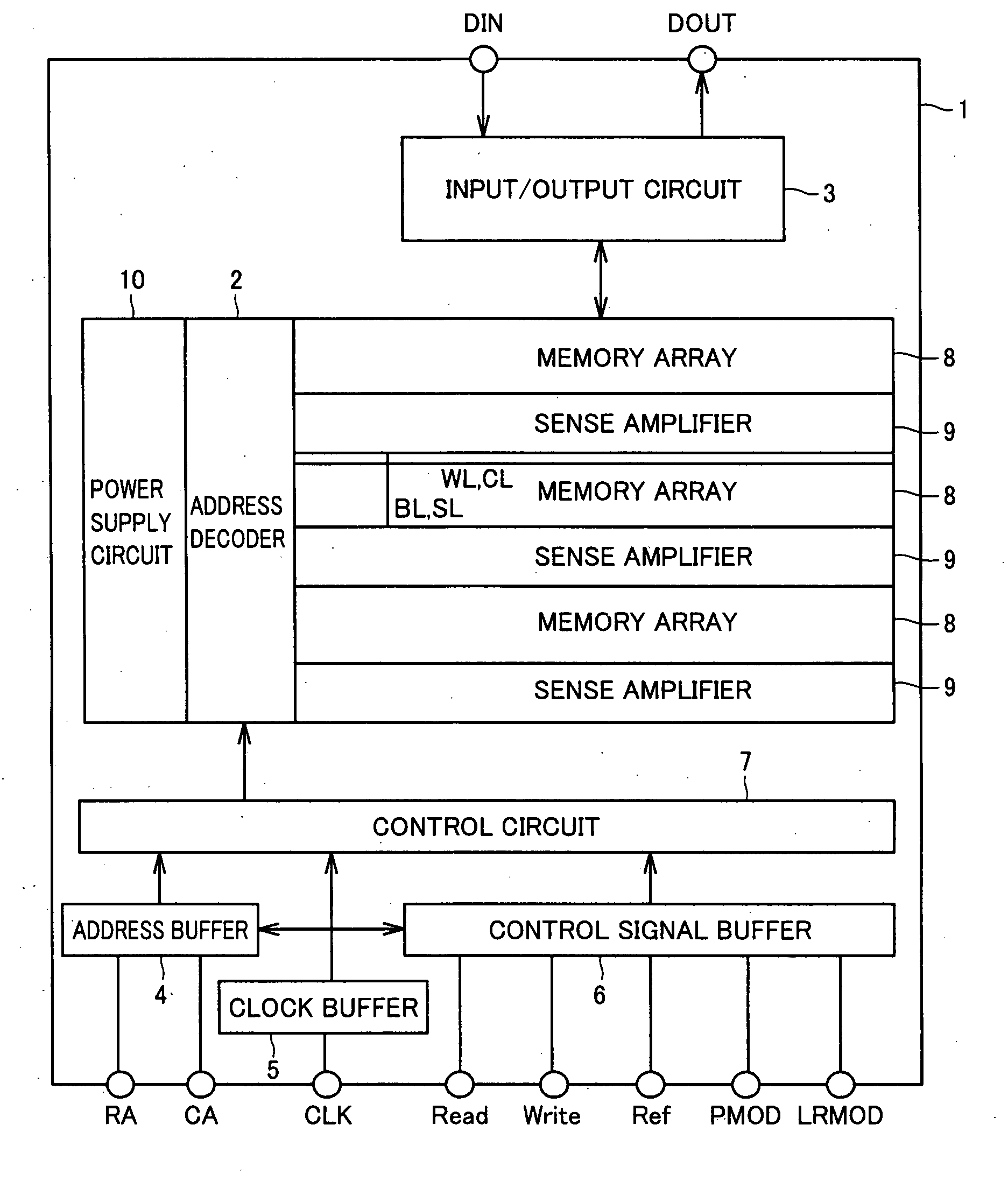

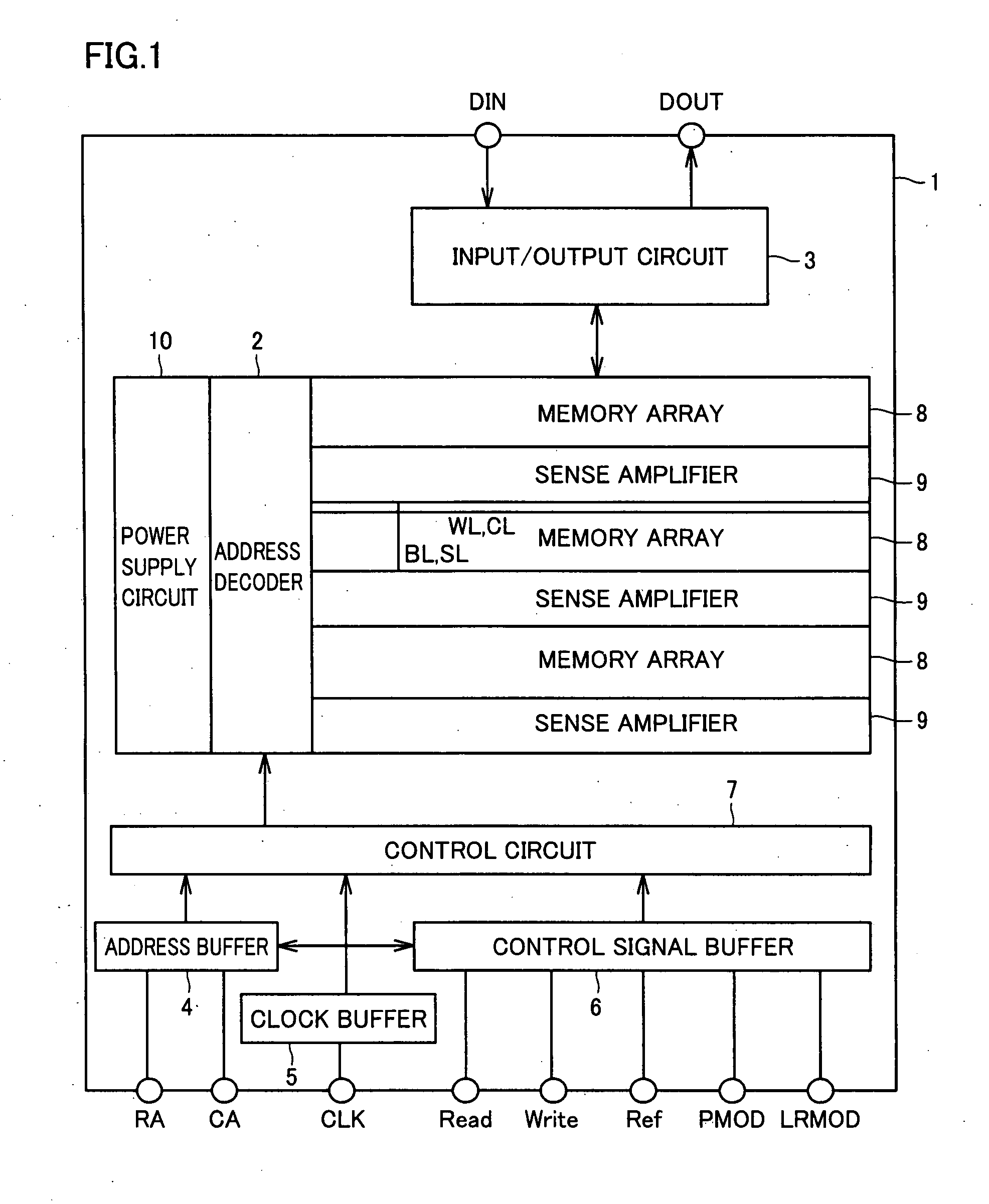

Semiconductor memory device having DRAM cell mode and non-volatile memory cell mode and operation method thereof

A semiconductor memory device may have a DRAM cell mode and a non-volatile memory cell mode without a capacitor, including multiple transistors arranged in an array and having floating bodies, word lines connected to gate electrodes of the transistors, bit lines at a first side of the gate electrodes connected to drains of the transistors, source lines at a second side of the gate electrodes, different from the first side, and connected to sources of the transistors on the semiconductor substrate, and charge storage regions between the gate electrodes and the floating bodies.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor device

ActiveUS20110134683A1Easily multivaluedNovel structureTransistorSolid-state devicesPower semiconductor deviceDriver circuit

Disclosed is a semiconductor device functioning as a multivalued memory device including: memory cells connected in series; a driver circuit selecting a memory cell and driving a second signal line and a word line; a driver circuit selecting any of writing potentials and outputting it to a first signal line; a reading circuit comparing a potential of a bit line and a reference potential; and a potential generating circuit generating the writing potential and the reference potential. One of the memory cells includes: a first transistor connected to the bit line and a source line; a second transistor connected to the first and second signal line; and a third transistor connected to the word line, bit line, and source line. The second transistor includes an oxide semiconductor layer. A gate electrode of the first transistor is connected to one of source and drain electrodes of the second transistor.

Owner:SEMICON ENERGY LAB CO LTD

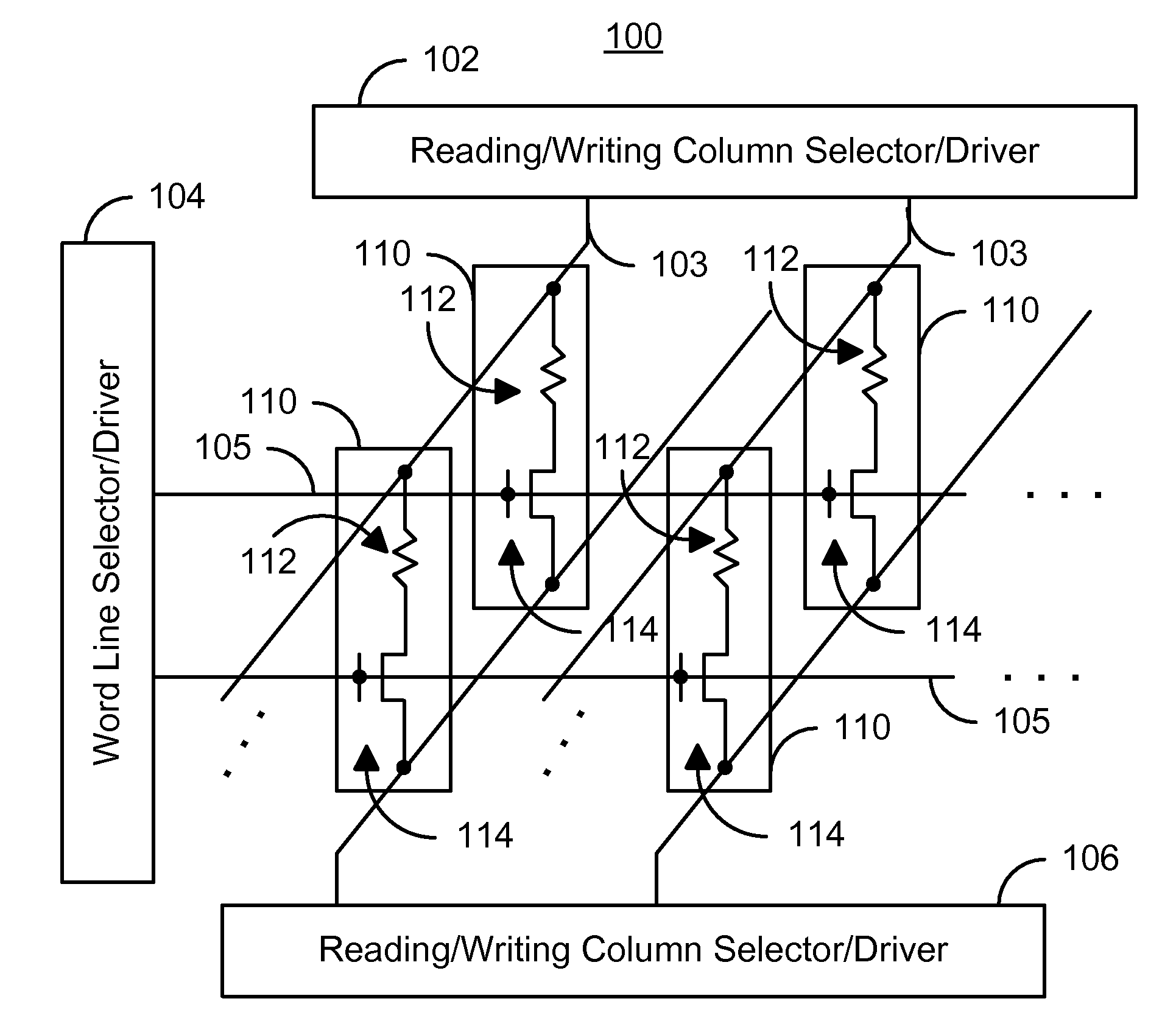

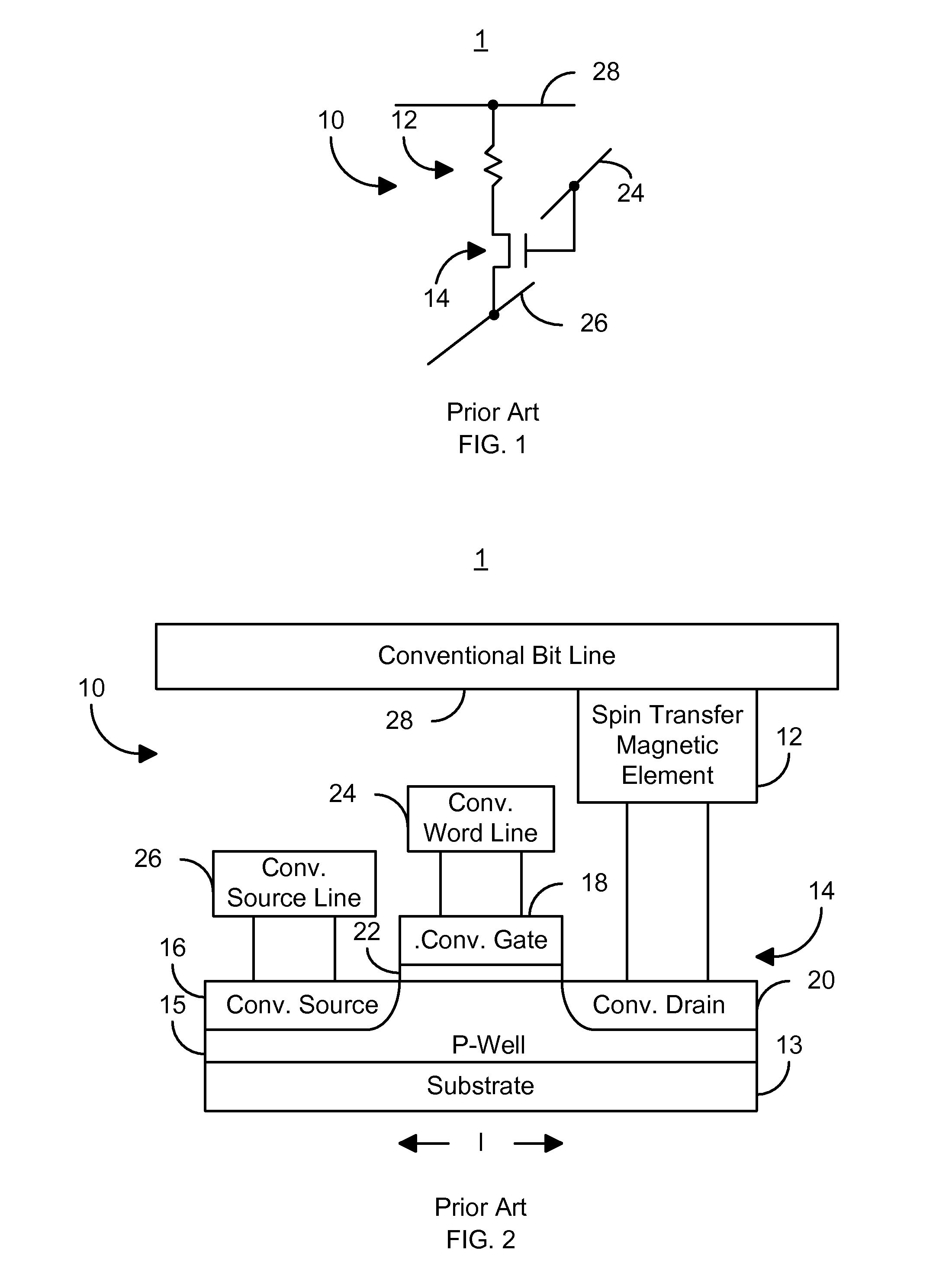

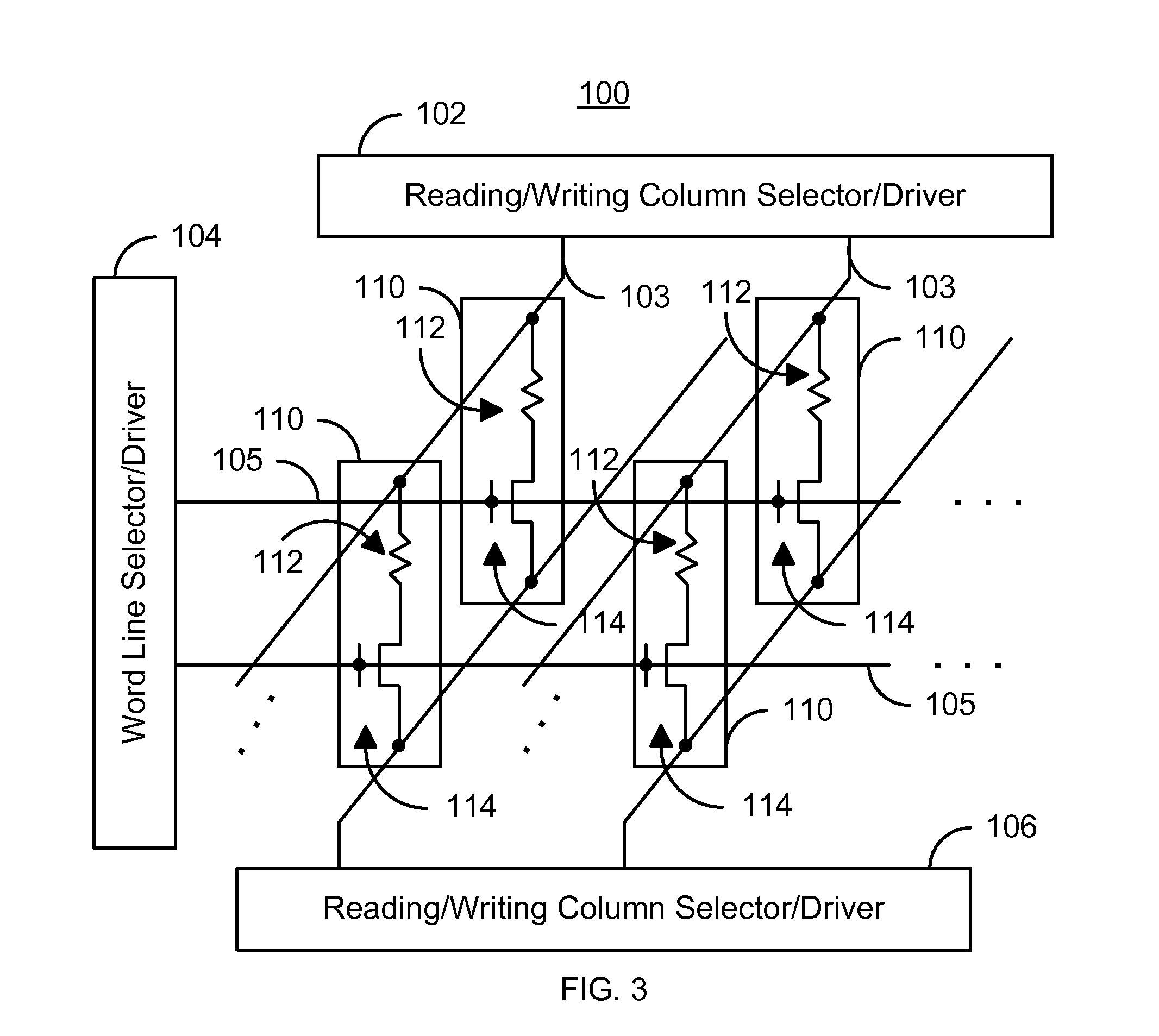

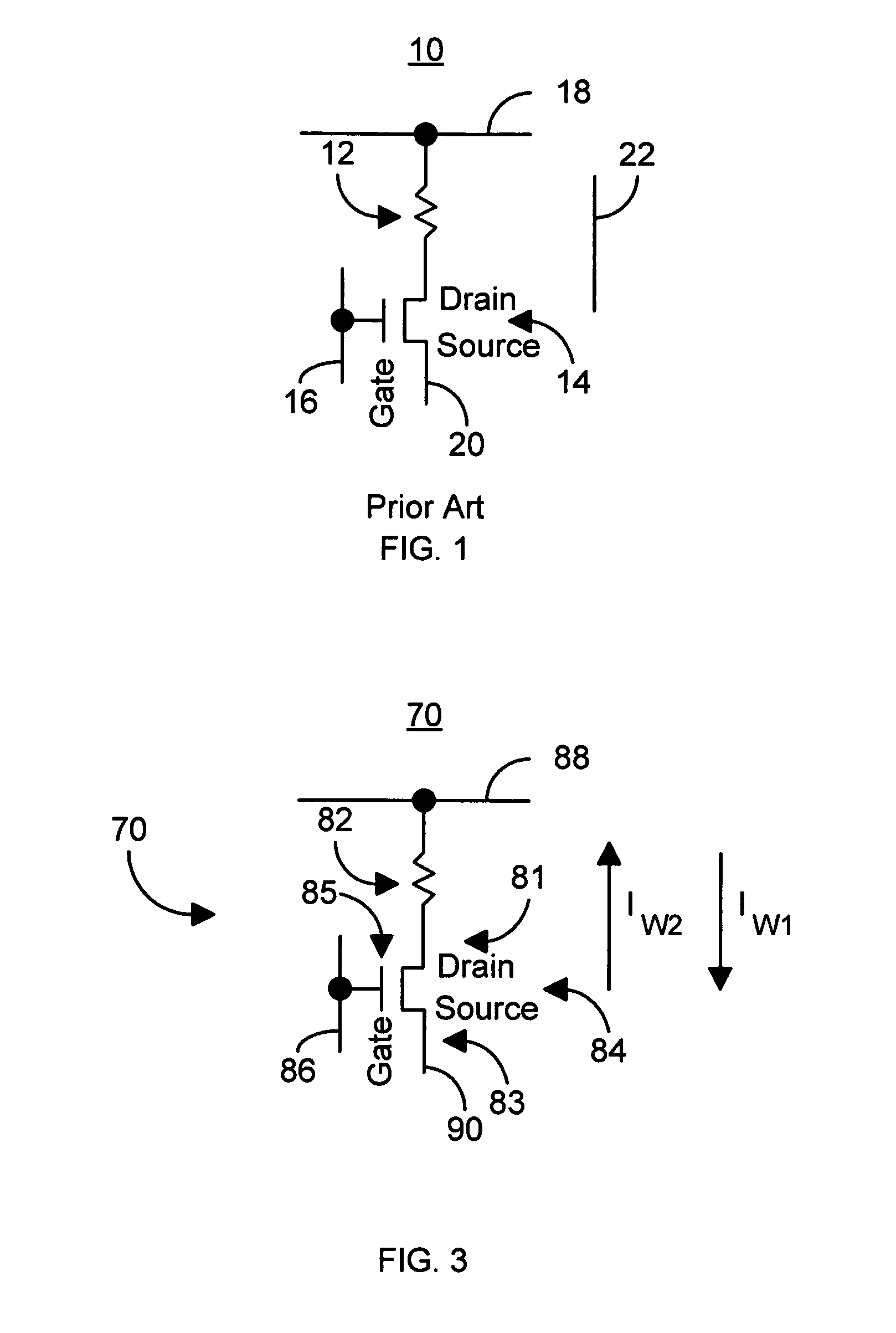

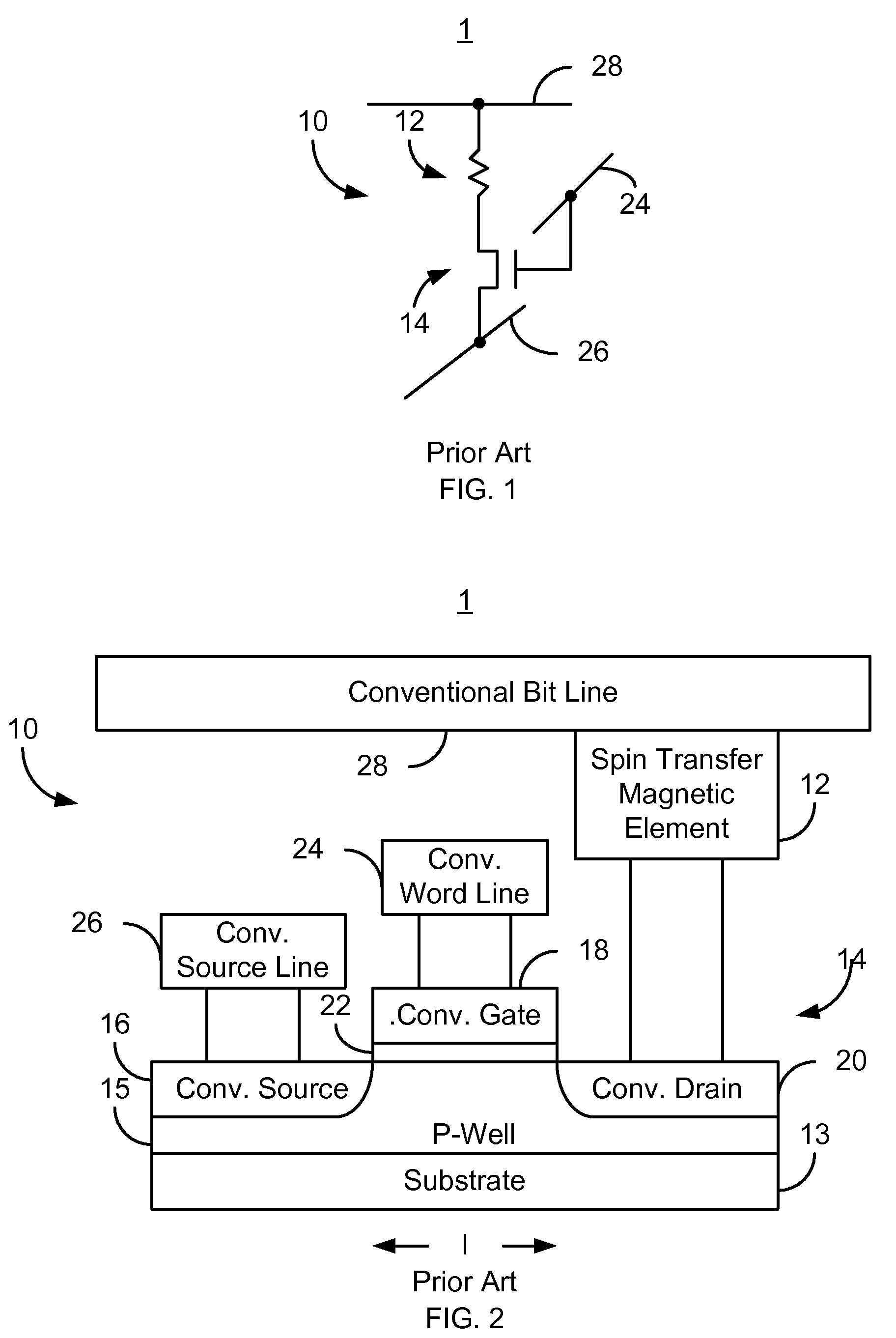

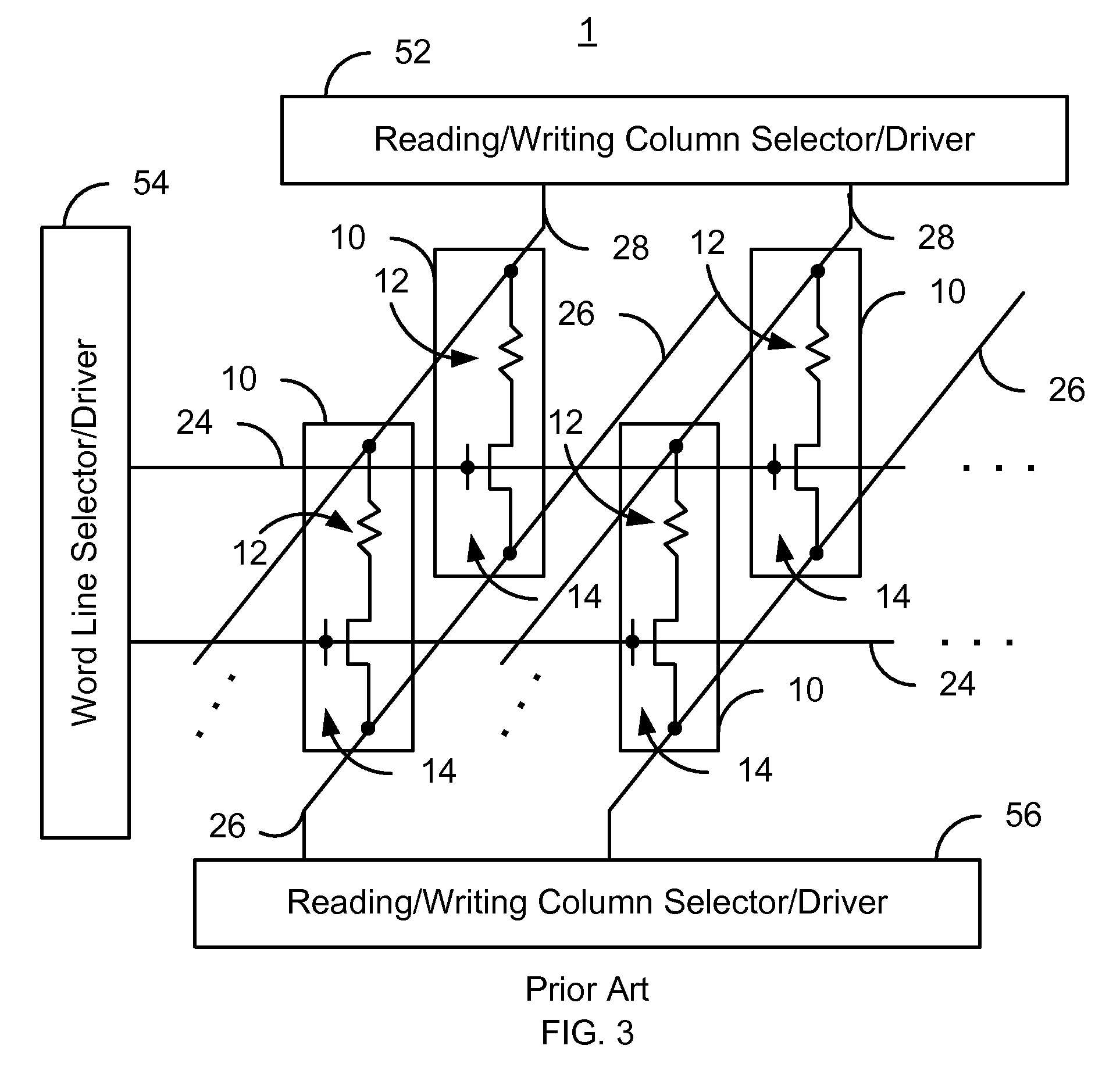

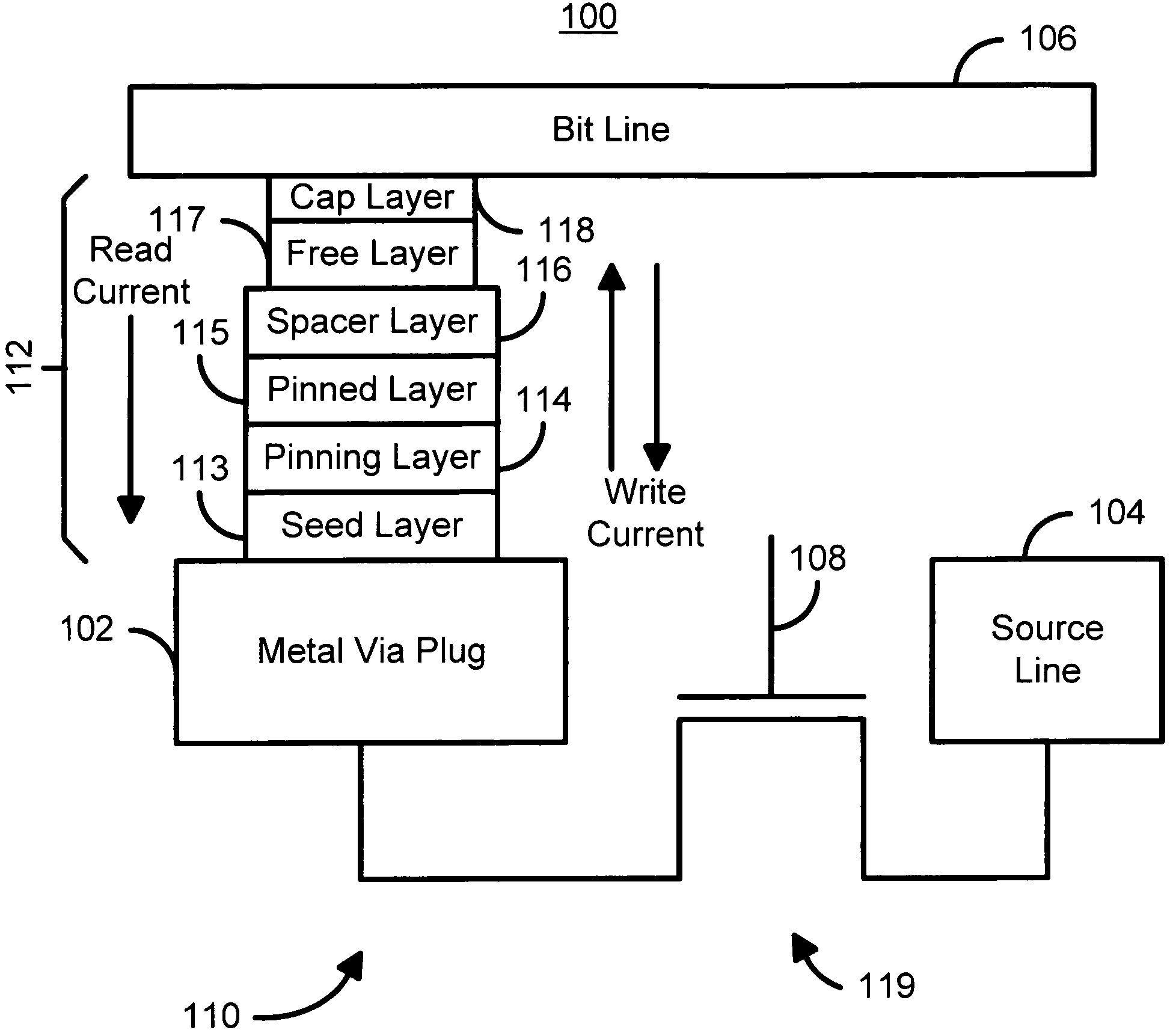

Method and system for providing spin transfer tunneling magnetic memories utilizing non-planar transistors

A magnetic memory cell and a magnetic memory incorporating the cell are described. The magnetic memory cell includes at least one magnetic element and at least one non-planar selection device. The magnetic element(s) are programmable using write current(s) driven through the magnetic element. The magnetic memory may include a plurality of magnetic storage cells, a plurality of bit lines corresponding to the plurality of magnetic storage cells, and a plurality of source lines corresponding to the plurality of magnetic storage cells.

Owner:SAMSUNG SEMICON

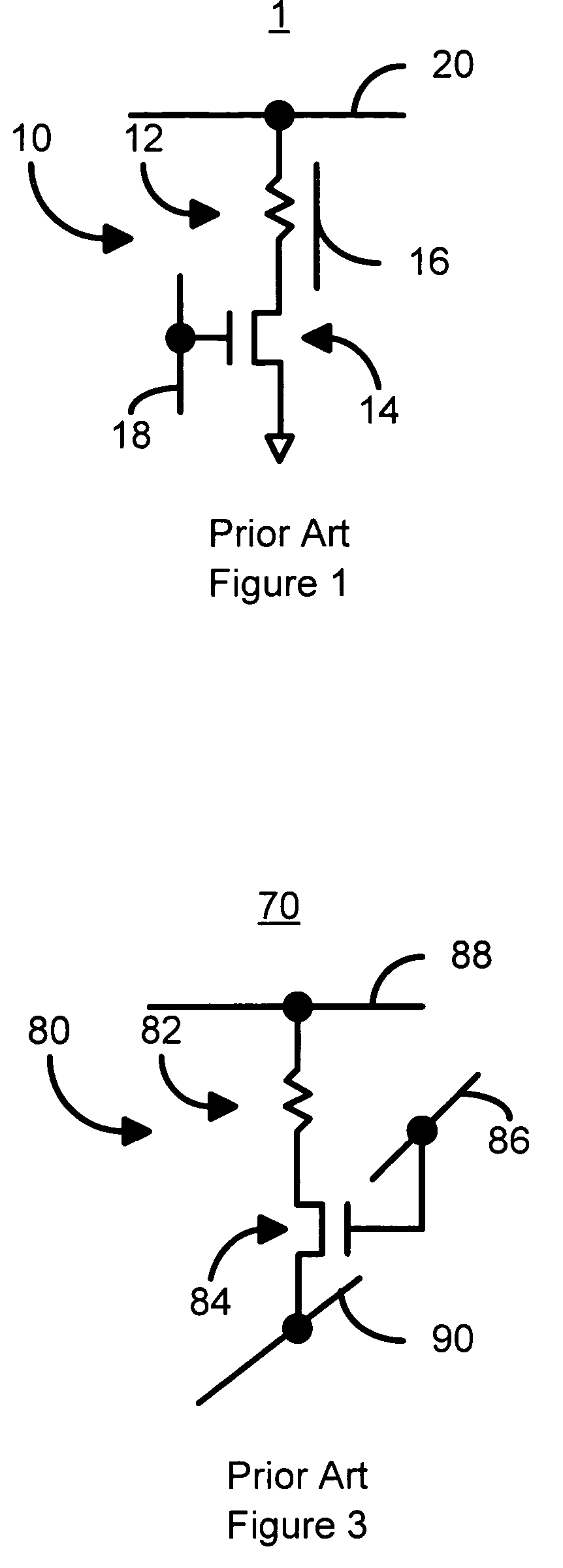

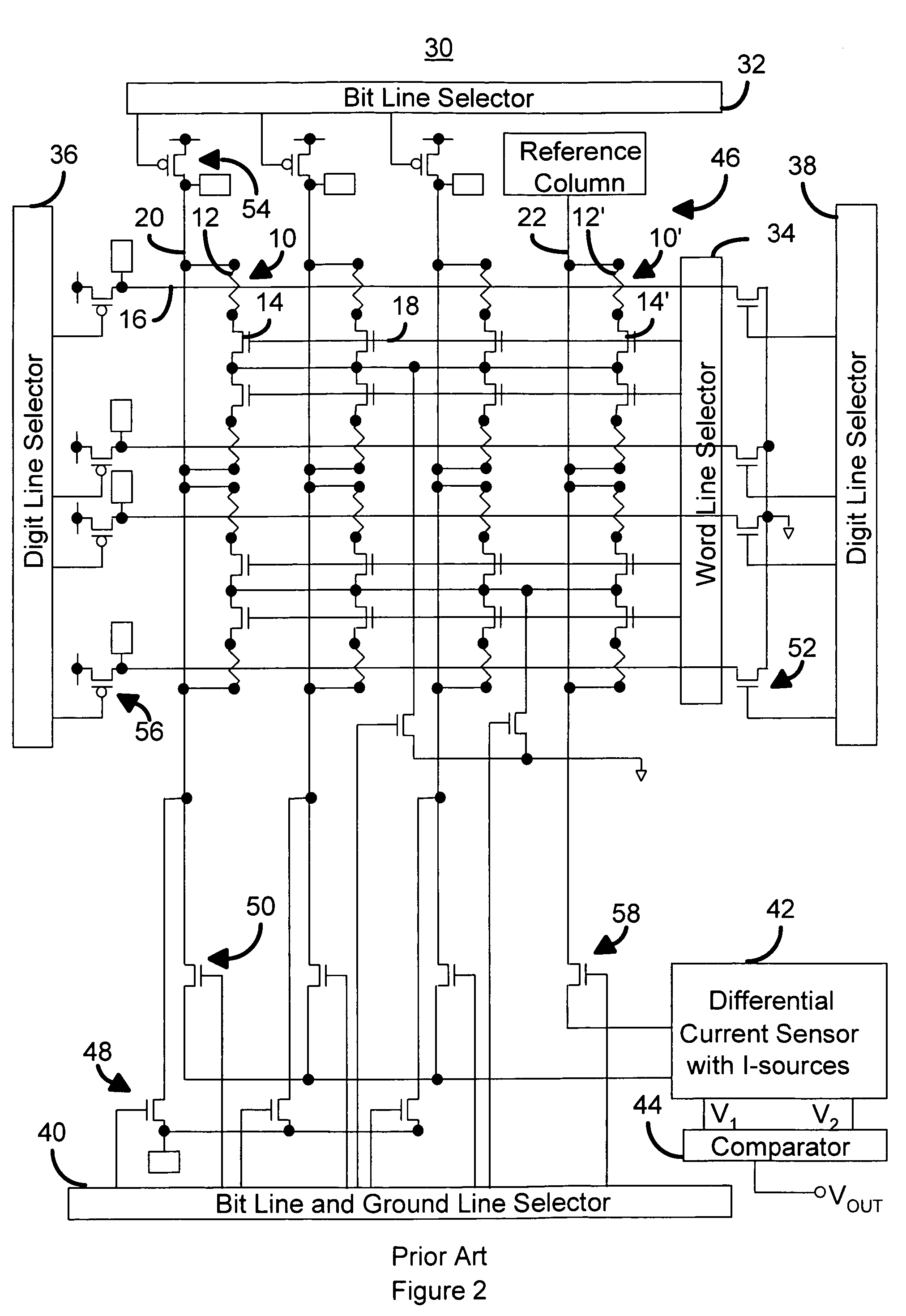

Current driven switching of magnetic storage cells utilizing spin transfer and magnetic memories using such cells having enhanced read and write margins

ActiveUS7379327B2Higher read and write marginDigital storageHigh resistanceElectrical resistance and conductance

A method and system for providing a magnetic memory. The magnetic memory includes magnetic storage cells in an array, bit lines, and source lines. Each magnetic storage cell includes at least one magnetic element. The magnetic element(s) are programmable by write currents driven through the magnetic element(s). Each magnetic element has free and pinned layer(s) and a dominant spacer. The magnetic memory is configured such that either the read current(s) flow from the free layer(s) to the dominant spacer if the maximum low resistance state read current divided by the minimum low resistance state write current is greater than the maximum high resistance state read current divided by the minimum high resistance state write current or the read current(s) flow from the dominant spacer to the free layer(s) if the maximum low resistance state read current divided by the minimum low resistance state write current is less than the maximum high resistance state read current divided by the minimum high resistance state write current.

Owner:SAMSUNG SEMICON +1

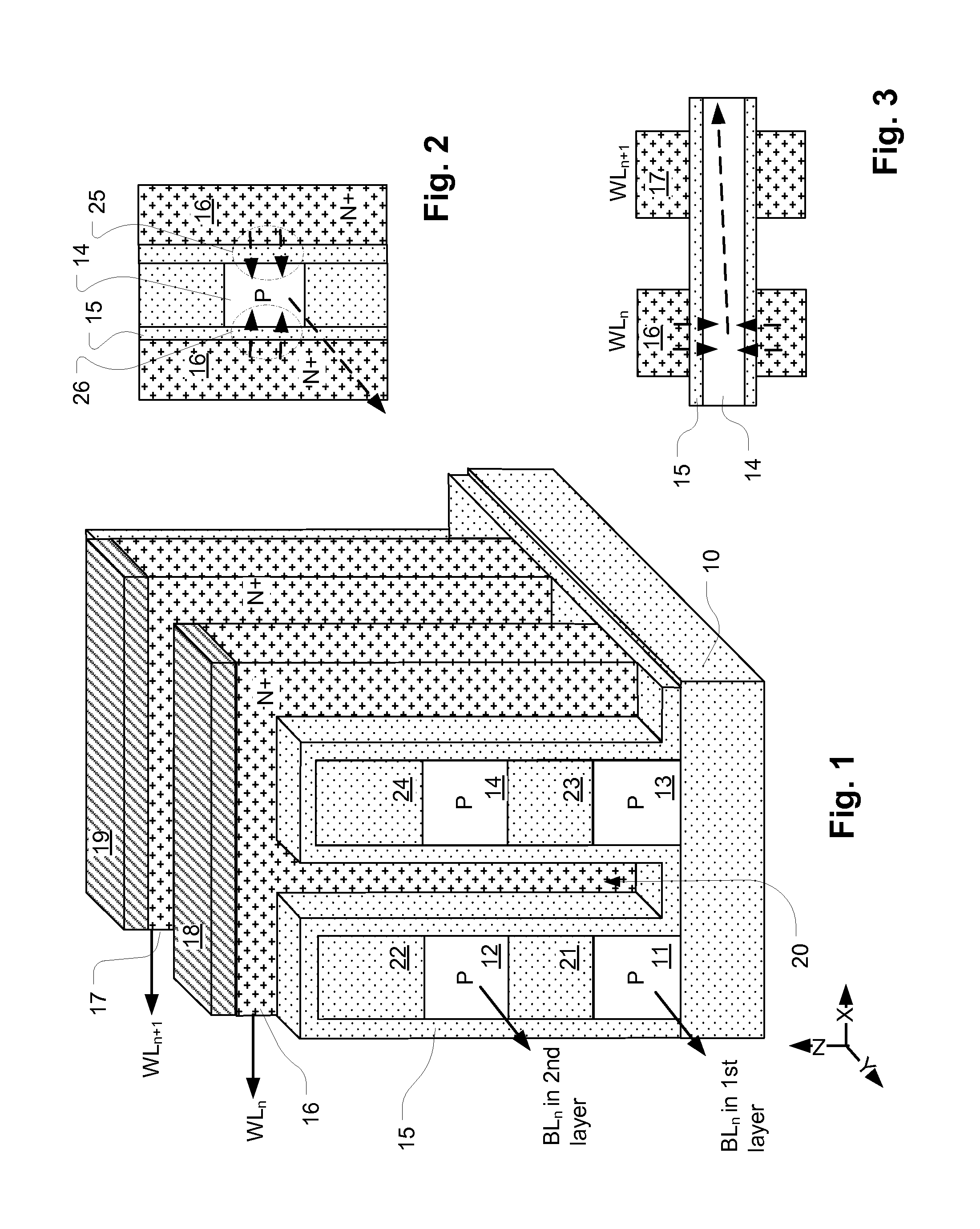

Memory Architecture of 3D NOR Array

A 3D memory device includes a plurality of ridge-shaped stacks of memory cells. Word lines are arranged over the stacks of memory cells. Bit lines structures are coupled to multiple locations along the stacks of memory cells. Source line structures are coupled to multiple locations along each of the semiconductor material strips of the stacks. The bit line structures and the source line structures are between adjacent ones of the word lines.

Owner:MACRONIX INT CO LTD

Non-volatile memory and method with reduced source line bias errors

ActiveUS7196931B2Large capacityImprove performanceRead-only memoriesDigital storageVoltage dropEngineering

Source line bias is an error introduced by a non-zero resistance in the ground loop of the read / write circuits. During sensing the control gate voltage of a memory cell is erroneously biased by a voltage drop across the resistance. This error is minimized when the current flowing though the ground loop is reduced. A method for reducing source line bias is accomplished by read / write circuits with features and techniques for multi-pass sensing. When a page of memory cells are being sensed in parallel, each pass helps to identify and shut down the memory cells with conduction current higher than a given demarcation current value. In this way, sensing in subsequent passes will be less affected by source line bias since the total amount of current flow is significantly reduced by eliminating contributions from the higher current cells.

Owner:SANDISK TECH LLC

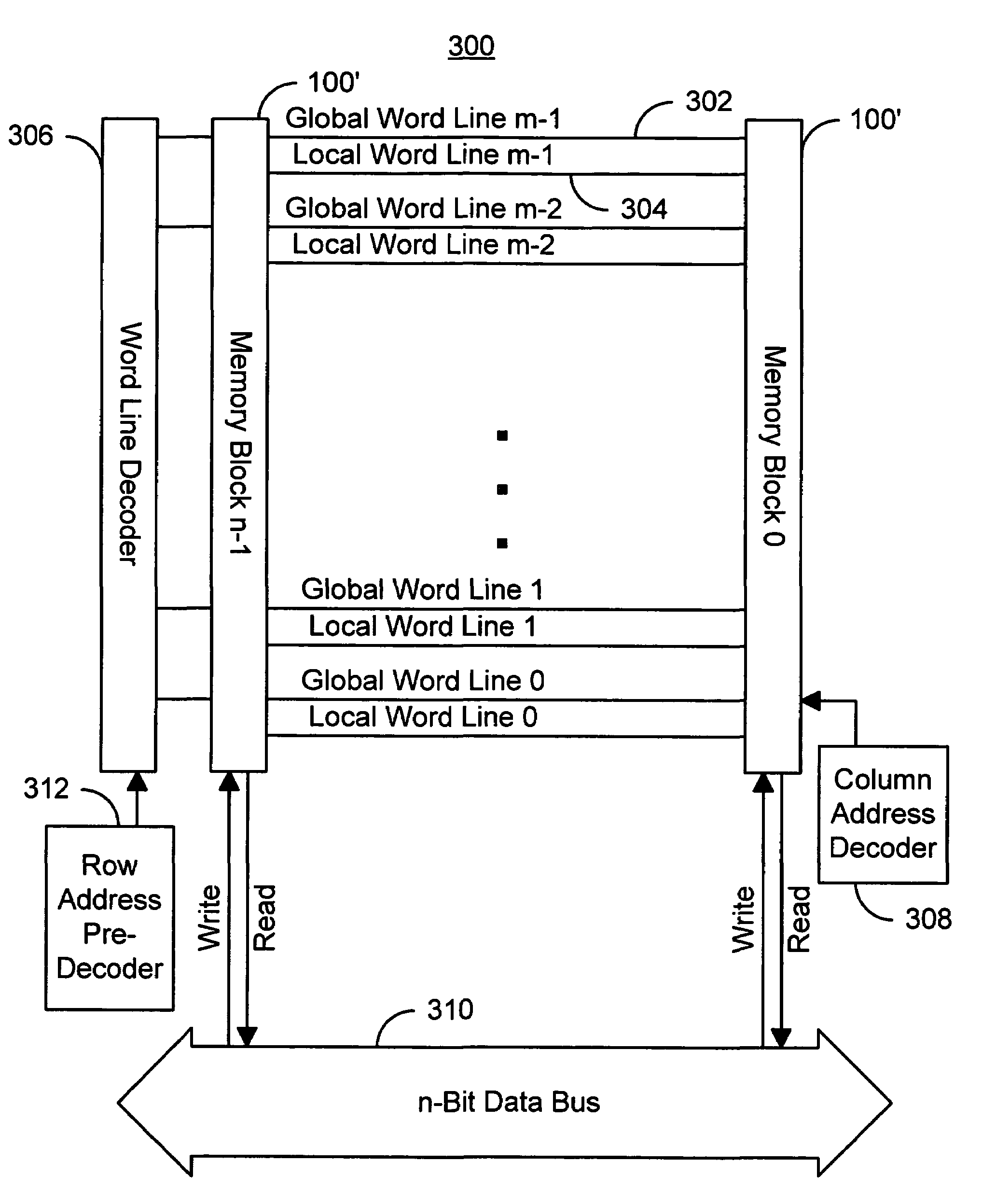

Method and system for providing a magnetic memory structure utilizing spin transfer

A method and system for providing a magnetic memory is described. The method and system include providing magnetic memory cells, local and global word lines, bit lines, and source lines. Each magnetic memory cell includes a magnetic element and a selection device connected with the magnetic element. The magnetic element is programmed by first and second write currents driven through the magnetic element in first and second directions. The local word lines are connected with the selection device of and have a first resistivity. Each global word line corresponds to a portion of the local word lines and has a resistivity lower than the first resistivity. The bit lines are connected with the magnetic element. The source lines are connected with the selection device. Each source line corresponds to a more than one of the magnetic memory cells and carries the first and second write currents.

Owner:RENESAS ELECTRONICS CORP +1

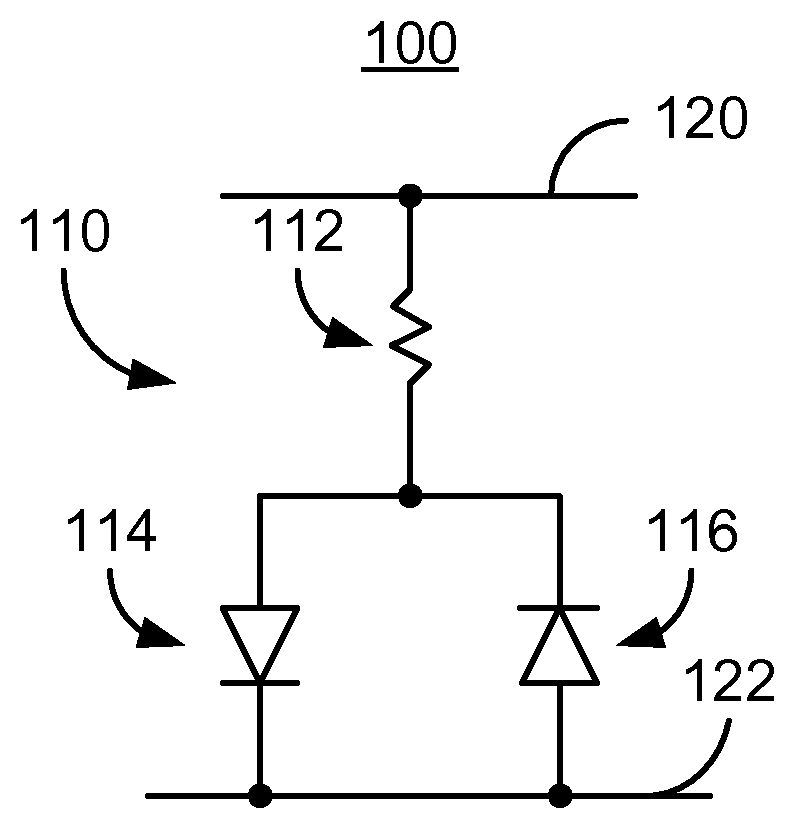

Method and system for providing spin transfer tunneling magnetic memories utilizing unidirectional polarity selection devices

A magnetic memory cell and a magnetic memory incorporating the cell are described. The magnetic memory cell includes at least one magnetic element and a plurality of unidirectional polarity selection devices. The magnetic element(s) are programmable using write current(s) driven through the magnetic element. The unidirectional polarity selection devices are connected in parallel and such that they have opposing polarities. The magnetic memory may include a plurality of magnetic storage cells, a plurality of bit lines corresponding to the plurality of magnetic storage cells, and a plurality of source lines corresponding to the plurality of magnetic storage cells.

Owner:GRANDIS

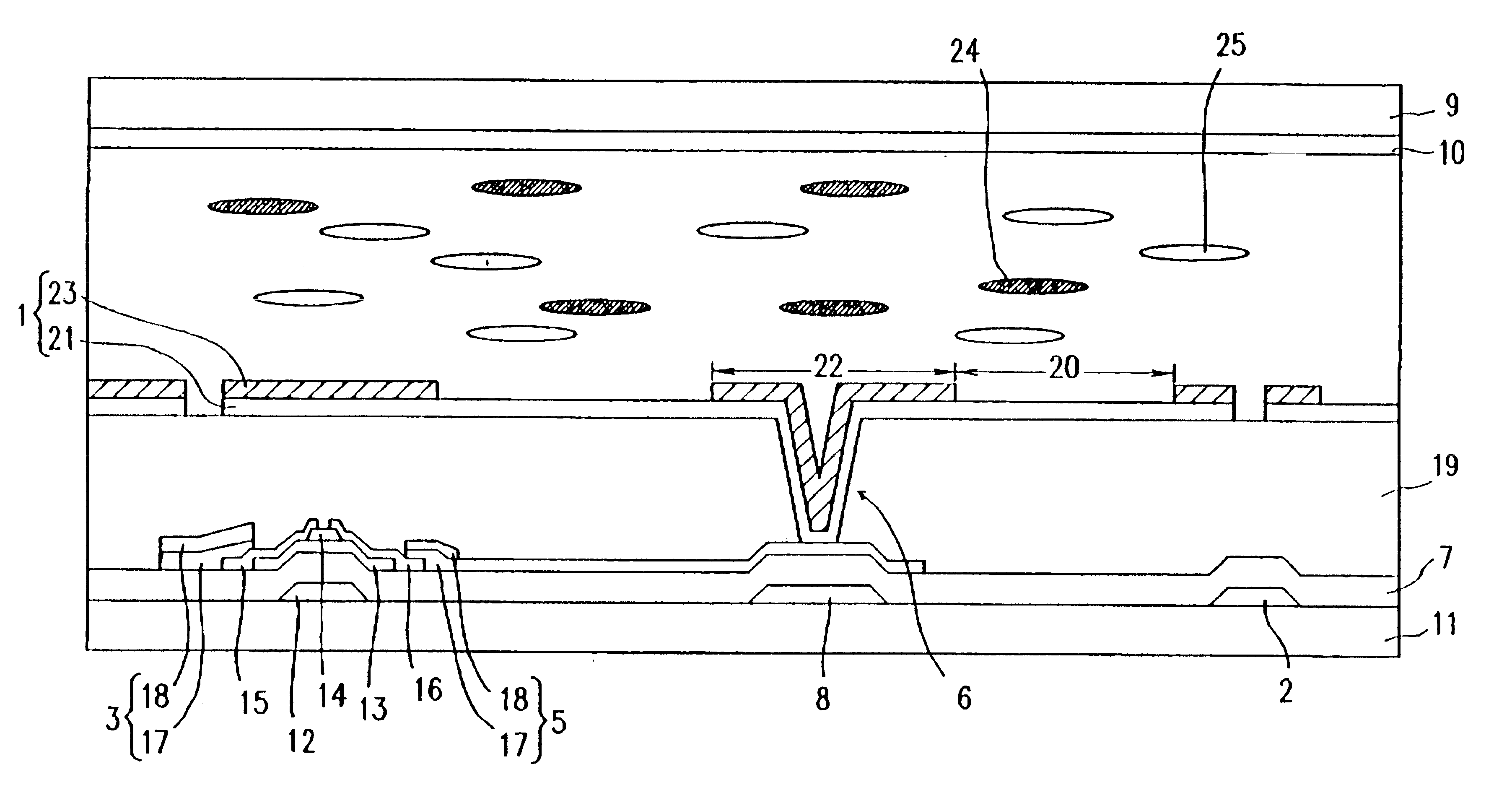

Liquid crystal display in which at least one pixel includes both a transmissive region and a reflective region

InactiveUS6452654B2Effective lightingImprove display qualityStatic indicating devicesNon-linear opticsLiquid-crystal displayTransmittance

A liquid crystal display device according to the present invention includes a first substrate, a second substrate, and a liquid crystal layer interposed between the first substrate and the second substrate. The first substrate includes: a plurality of gate lines; a plurality of source lines arranged to cross with the plurality of gate lines; a plurality of switching elements disposed in the vicinity of crossings of the plurality of gate lines and the plurality of source lines; and a plurality of pixel electrodes connected to the plurality of switching elements. The second substrate includes a counter electrode. A plurality of pixel regions are defined by the plurality of pixel electrodes, the counter electrode, and the liquid crystal layer interposed between the plurality of pixel electrodes and the counter electrode, and each of the plurality of pixel regions includes a reflection region and a transmission region.

Owner:SHARP KK

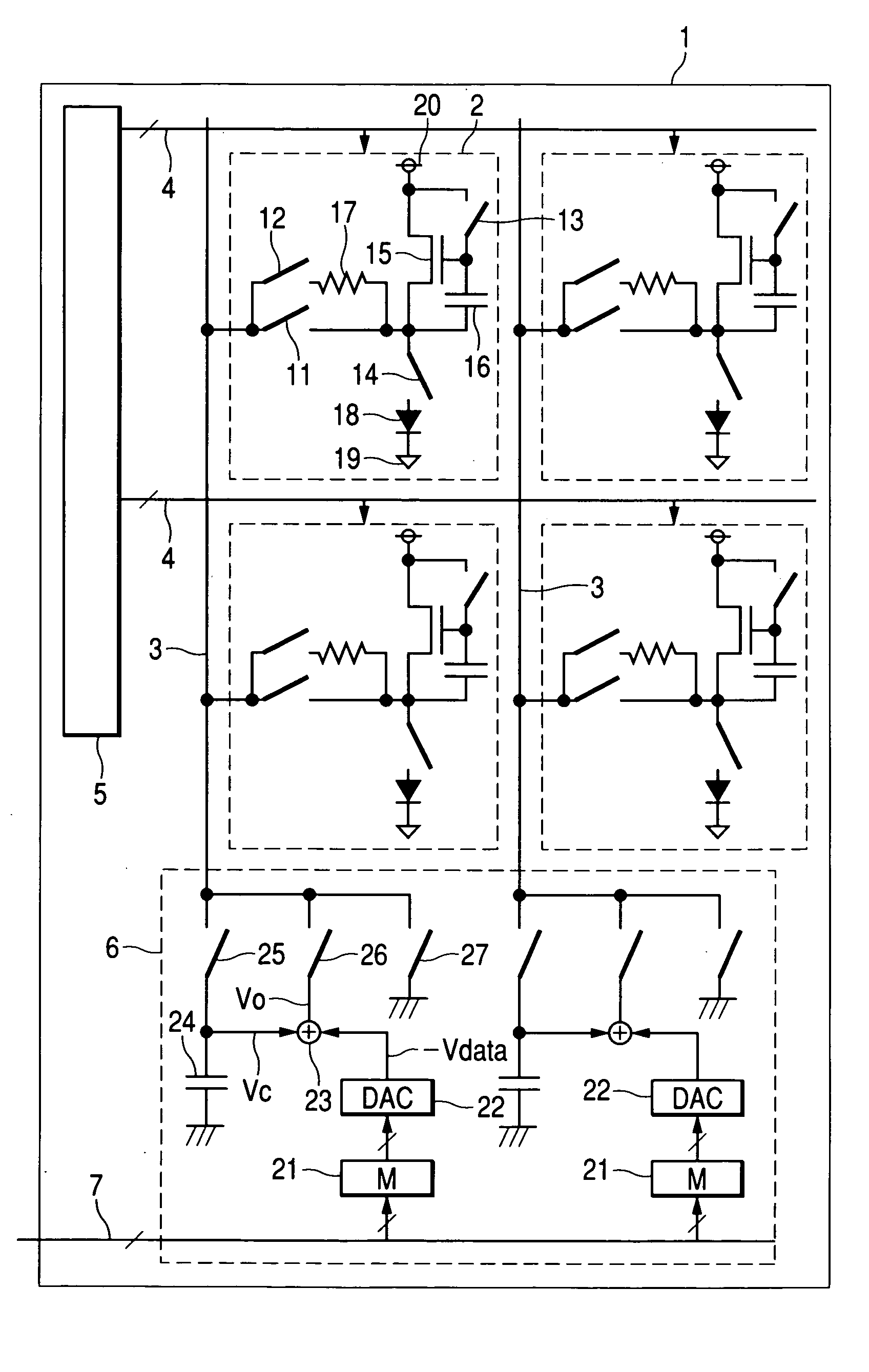

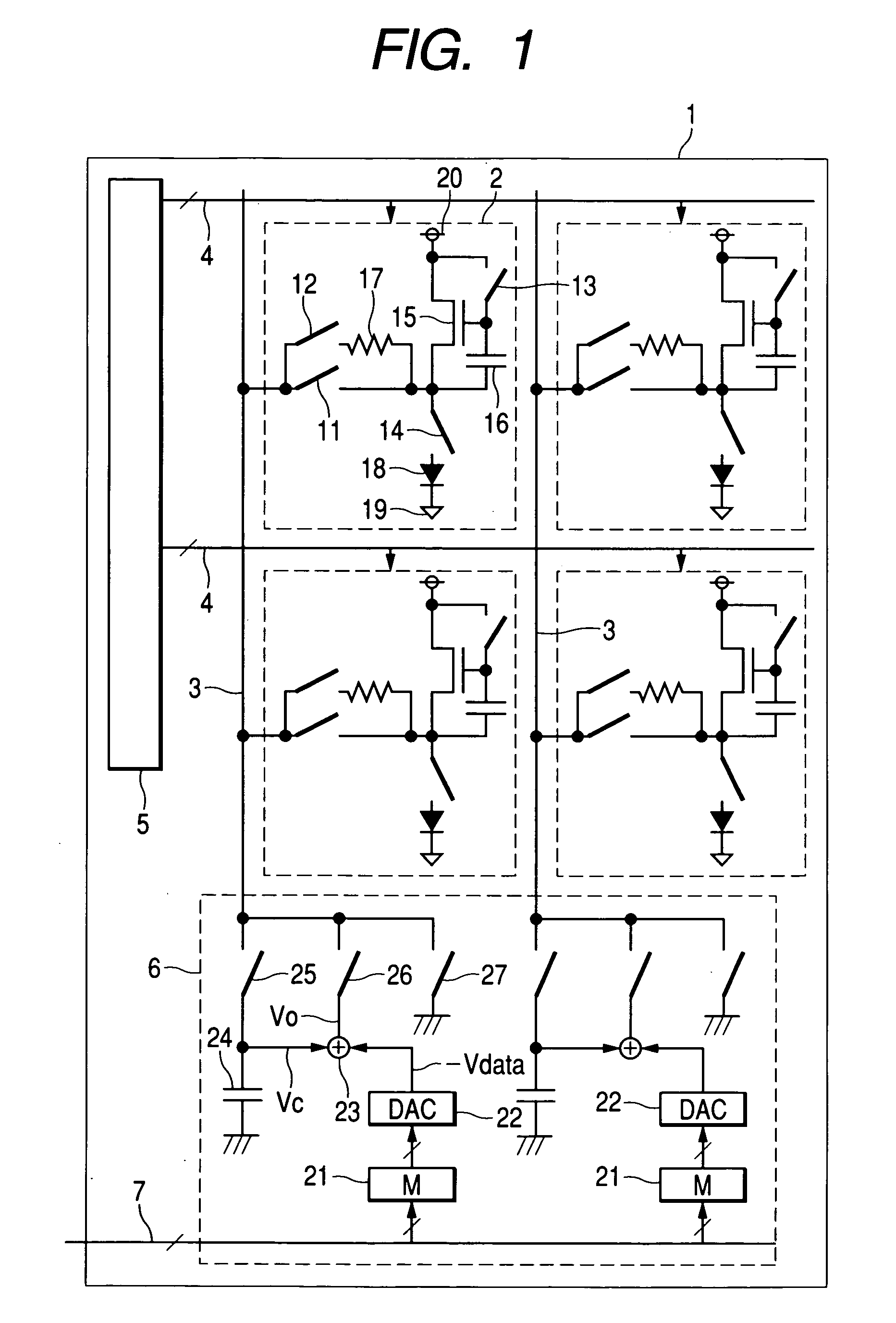

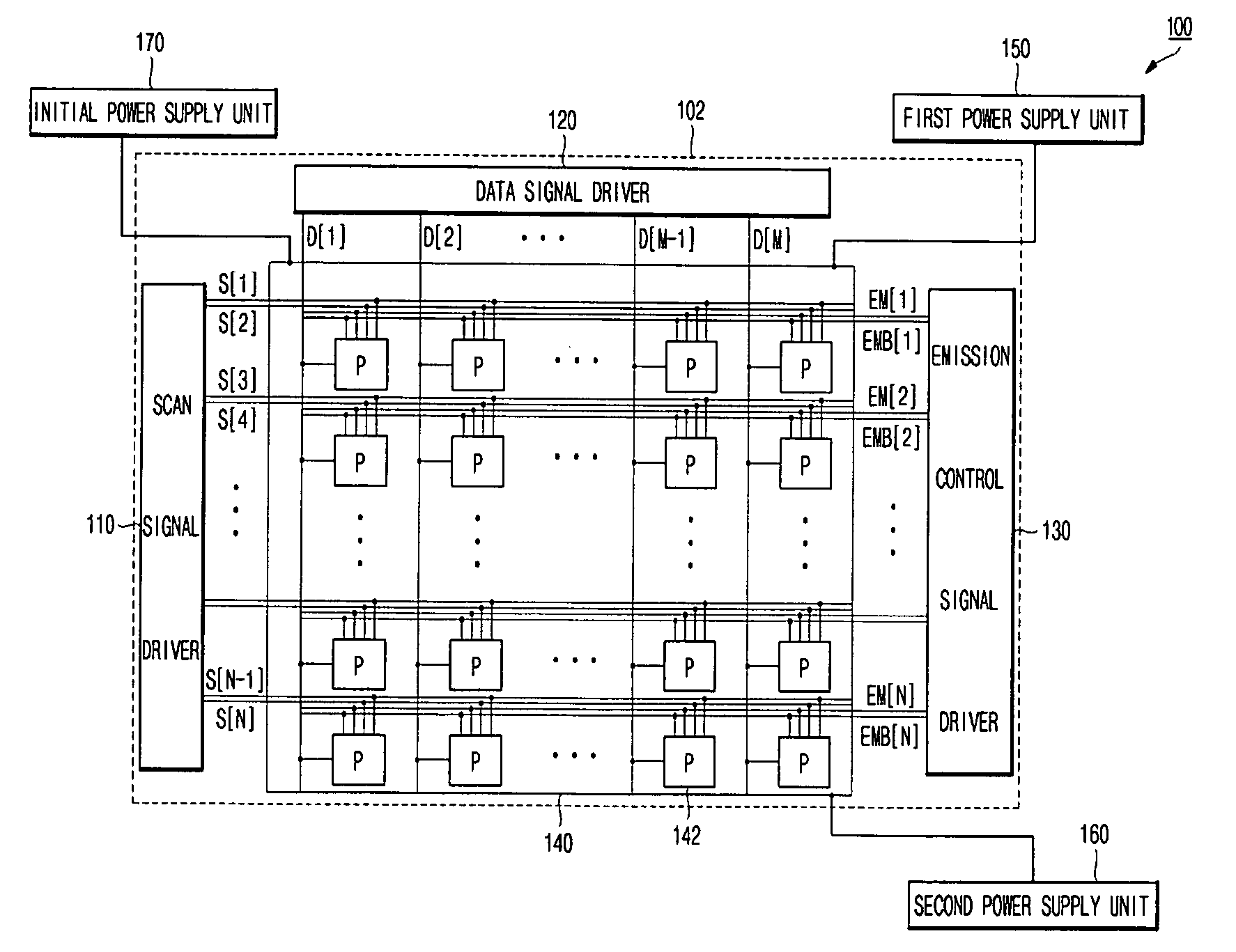

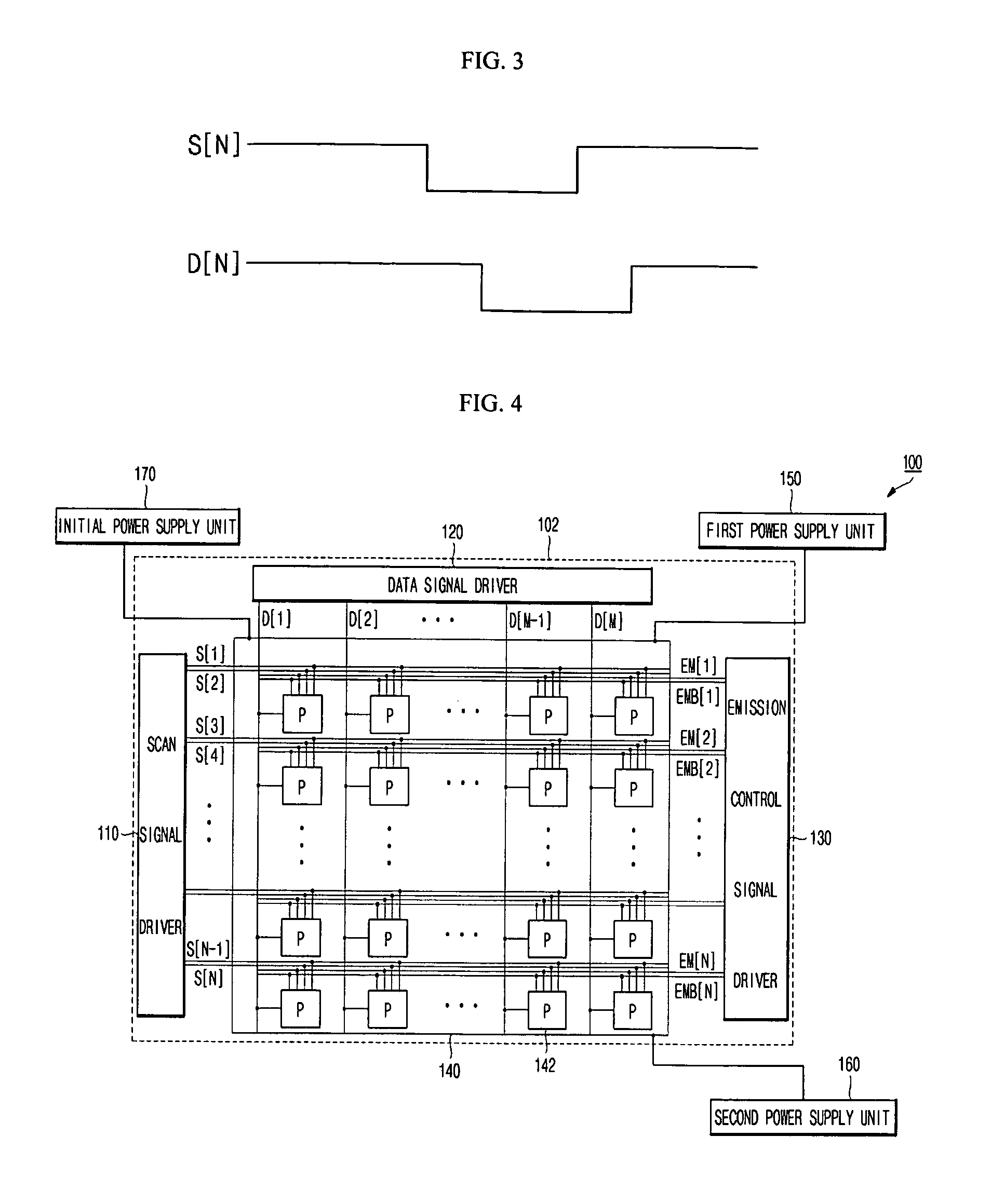

Image display device

ActiveUS20050088103A1Reduces variation brightnessGood quality imageRoad vehicles traffic controlElectroluminescent light sourcesVoltage dropImaging data

The present invention provides an image display device that reduces variations in brightness of the light emitting elements included in the device due to a voltage drop on the power source line of the device and TFT threshold voltage variations and displays good quality images. The image display device is equipped with a pixel circuit voltage detecting means to selectively output a voltage internal to a pixel circuit included in each of a plurality of pixels of the device to a signal line to which the pixel circuit connects. Its drive circuit is equipped with a voltage addition means to add the signal line voltage and a signal voltage corresponding to image data to be displayed and output a sum voltage to the signal line again.

Owner:SAMSUNG DISPLAY CO LTD +1

Current driven switched magnetic storage cells having improved read and write margins and magnetic memories using such cells

A method and system for providing a magnetic memory is described. The magnetic memory includes a plurality of magnetic storage cell and at least one bit line and a plurality of source lines corresponding to the plurality of magnetic storage cells. Each magnetic storage cell includes a magnetic element that is programmed to a high resistance state by a first write current driven through the magnetic element in a first direction and to a low resistance state by a second write current driven through the magnetic element in a second direction. The bit line(s) and the source lines are configured to drive the first write current through the magnetic element in the first direction, to drive the second write current through the magnetic element in the second direction, and to drive at least one read current through the magnetic element in a third direction that does not destabilize the low resistance state.

Owner:SAMSUNG SEMICON

Techniques for reducing a voltage swing

Techniques for reducing a voltage swing are disclosed. In one particular exemplary embodiment, the techniques may be realized as an apparatus for reducing a voltage swing comprising: a plurality of dynamic random access memory cells arranged in arrays of rows and columns, each dynamic random access memory cell including one or more memory transistors. The one or more memory transistors of the apparatus for reducing a voltage swing may comprise: a first region coupled to a source line, a second region coupled to a bit line, a first body region disposed between the first region and the second region, wherein the first body region may be electrically floating, and a first gate coupled to a word line spaced apart from, and capacitively coupled to, the first body region. The apparatus for reducing a voltage swing may also comprise a first voltage supply coupled to the source line configured to supply a first voltage and a second voltage to the source line, wherein a difference between the first voltage and the second voltage may be less than 3.5V.

Owner:MICRON TECH INC

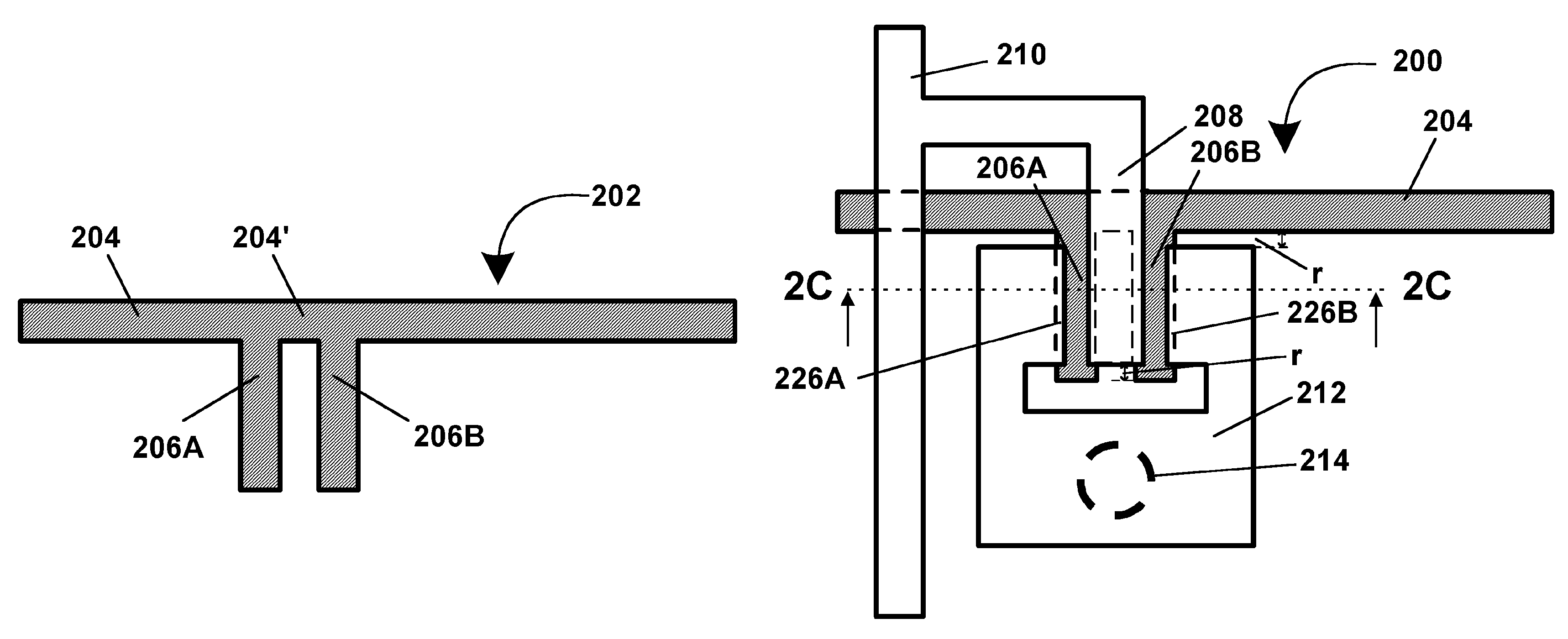

Backplanes for display applications, and components for use therein

InactiveUS7605799B2Slow changeLow cost manufacturingTransistorStatic indicating devicesCapacitanceDisplay device

A thin-film transistor includes a gate electrode having first and second gate electrode edges on opposed sides, and a drain electrode having a first edge that overlaps the first gate electrode edge, and a second edge that overlaps the second gate electrode edge. A diode array is fabricated by successive deposition of a conductive layer, a doped semiconductor layer and an undoped semiconductor layer adjacent to the substrate. A display pixel unit provides reduced capacitative coupling between a pixel electrode and a source line. The source line includes an extension that provides a source for the transistor. A patterned conductive portion is disposed adjacent to the source line. Another display pixel unit provides reduced pixel electrode voltage shifts using a source line and a balance line.

Owner:E INK CORPORATION

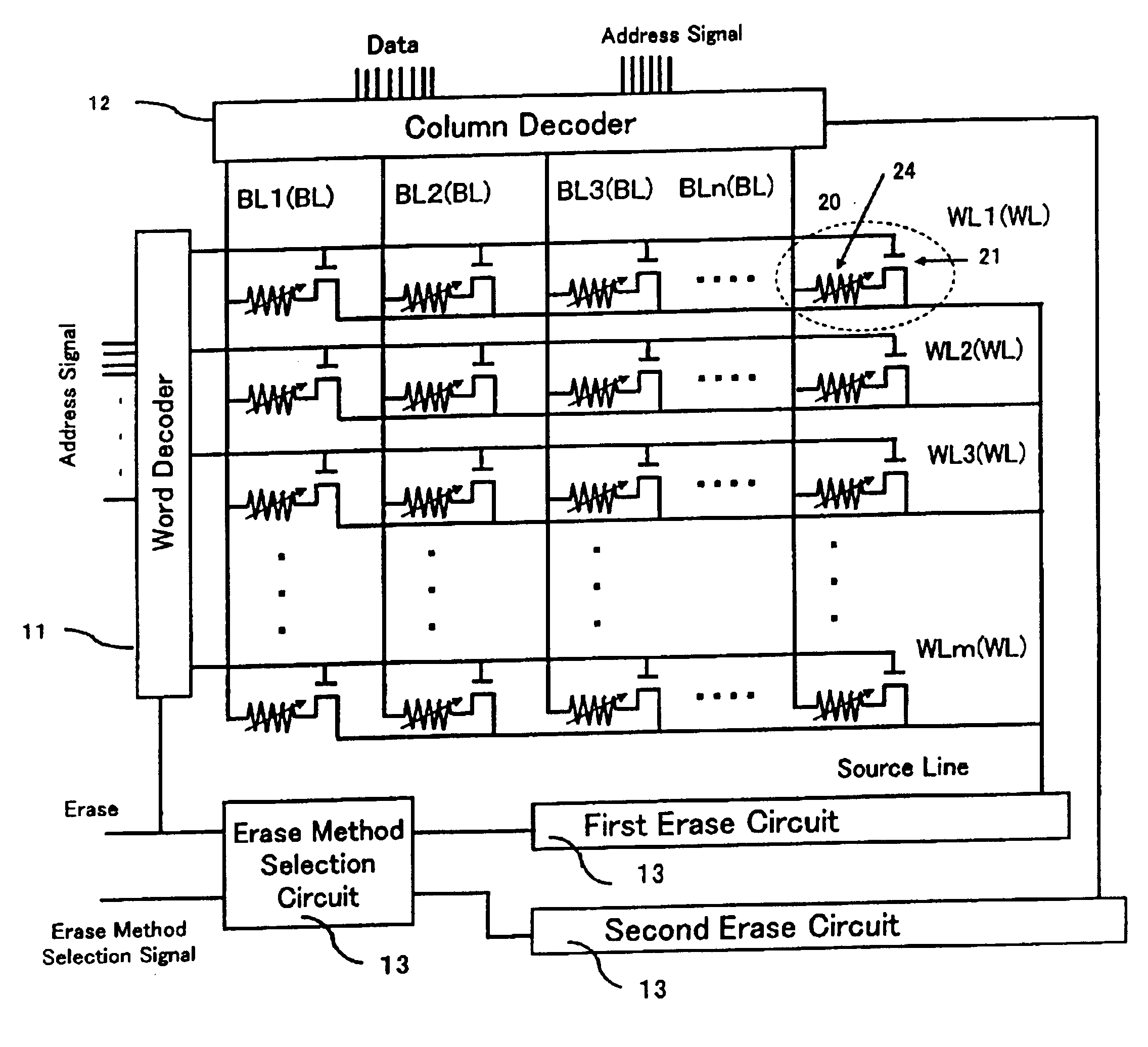

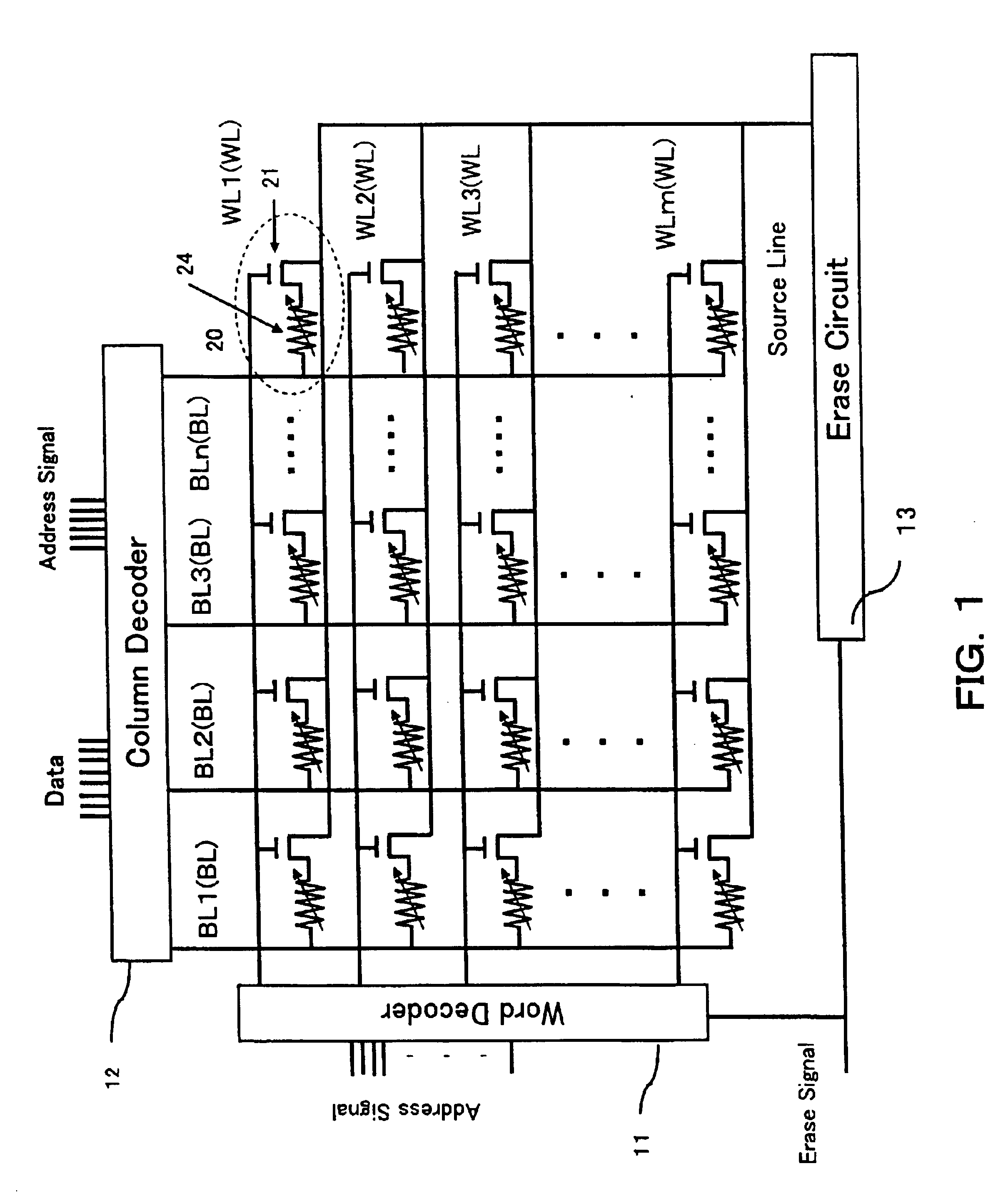

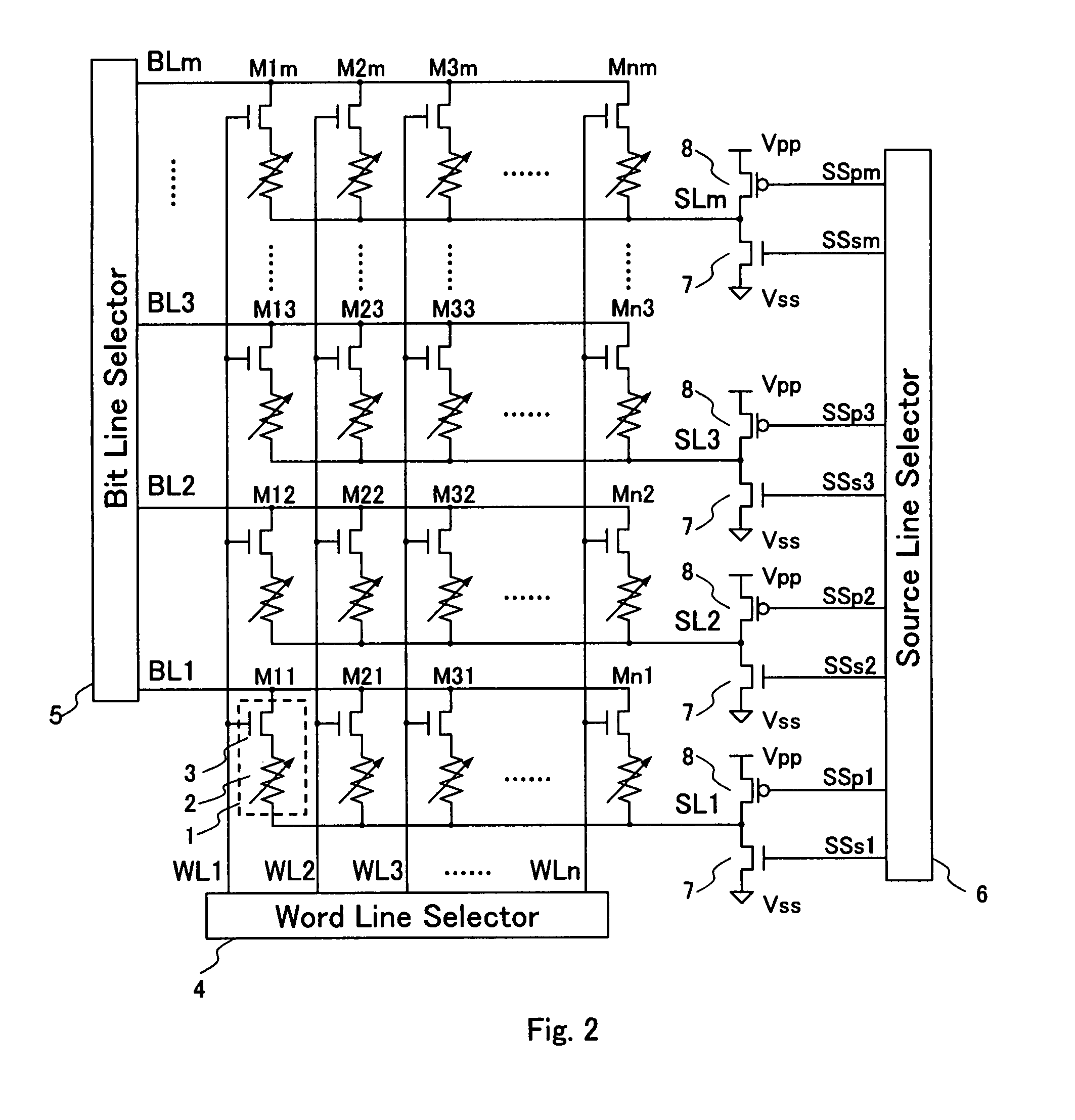

Semiconductor memory device and erase method for memory array

ActiveUS6888773B2Reduce unevennessEasy to useSolid-state devicesRead-only memoriesBit lineSemiconductor

An object of the invention is to provide a nonvolatile semiconductor memory device and an erase method for a memory cell array that have high degree of freedom and that are capable of quickly and securely implementing data erase and reprogramming. In a memory cell array, memory cells each configured of a variable resistor element for storing information through variations in electric resistance and a selected transistor are arranged in a matrix, and word lines (WL1, . . . , WLm) and bit lines (BL1, . . . , BLn) are arranged to select a predetermined memory cell. For the memory cell array, erase means is provided that sets the electric resistance of the variable resistor element to a predetermined erased state by applying voltage under a predetermined application condition to the word line (WL), bit line (BL), and source line (SL). The erase means switches between a batch-erase mode and an individual-erase mode. The batch-erase mode is used to perform batch erase of all the memory cells in the memory cell array, and the individual-erase mode is used to perform individual erase of a part of the memory cells in the memory cell array.

Owner:SHARP KK

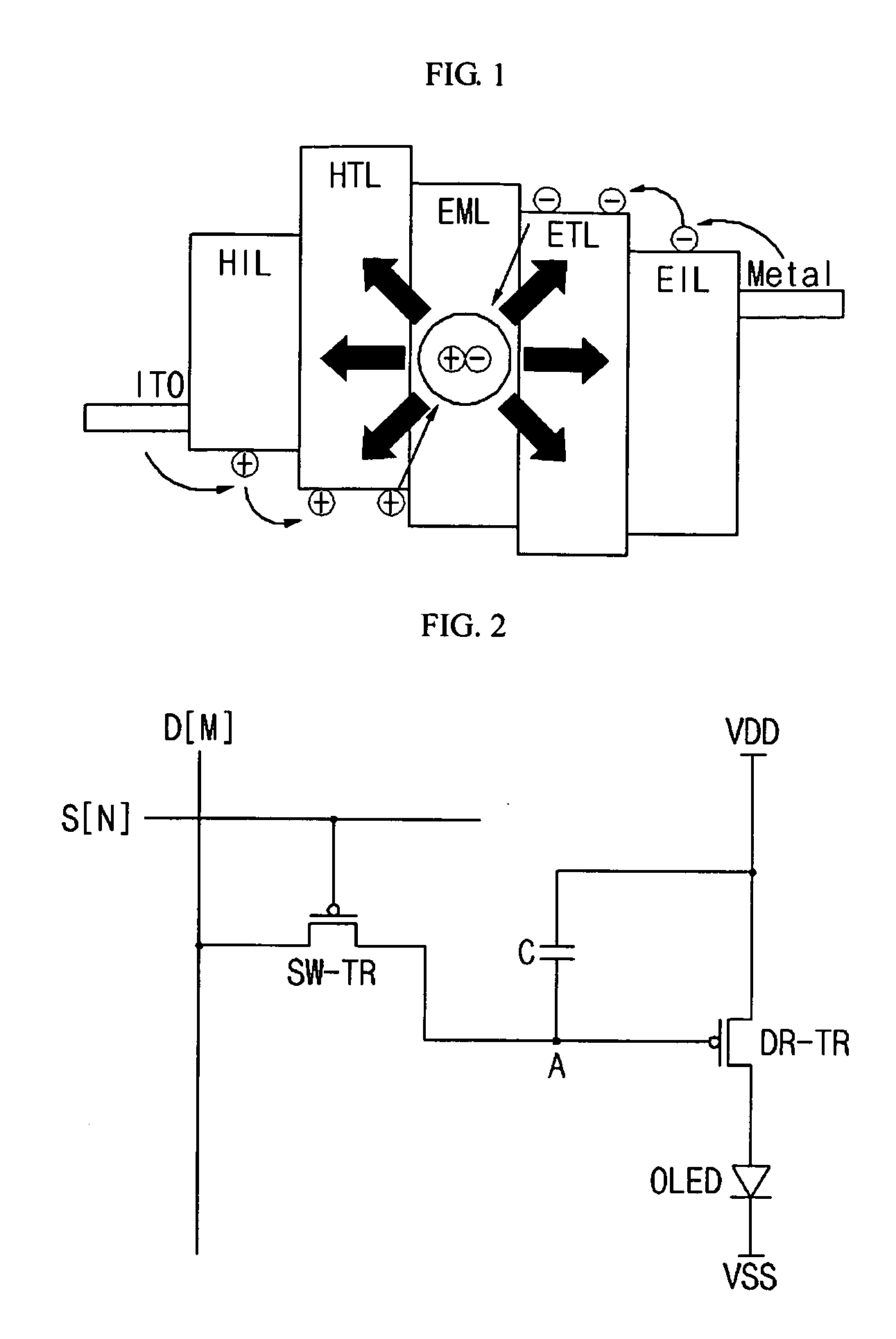

Organic light emitting display and driving method thereof

ActiveUS20080150846A1Operation margin can be ensuredAvoid voltage dropStatic indicating devicesDisplay deviceLight-emitting diode

An organic light emitting display including a scan signal line forwarding a scan signal, a data line sending a data signal and a pixel coupled to the scan signal line and the data line, the organic light emitting diode display, wherein the pixel includes a first switching transistor transmitting a data signal from the data line in response to the scan signal of the scan signal line, a driving transistor, coupled to the first switching transistor, controlling driving current from a first power source line, a storage capacitor coupled between the driving transistor and the first power source line, an organic light emitting diode, coupled between the driving transistor and a second power source line, displaying an image with the driving current controlled by the driving transistor, an initial switching transistor, coupled between the storage capacitor and an initial power source line, initializing the storage capacitor, and a switching transistor for applying a reverse bias, coupled between the second power source line and the initial power source line, applying a reverse bias voltage to the organic light emitting diode.

Owner:SAMSUNG DISPLAY CO LTD

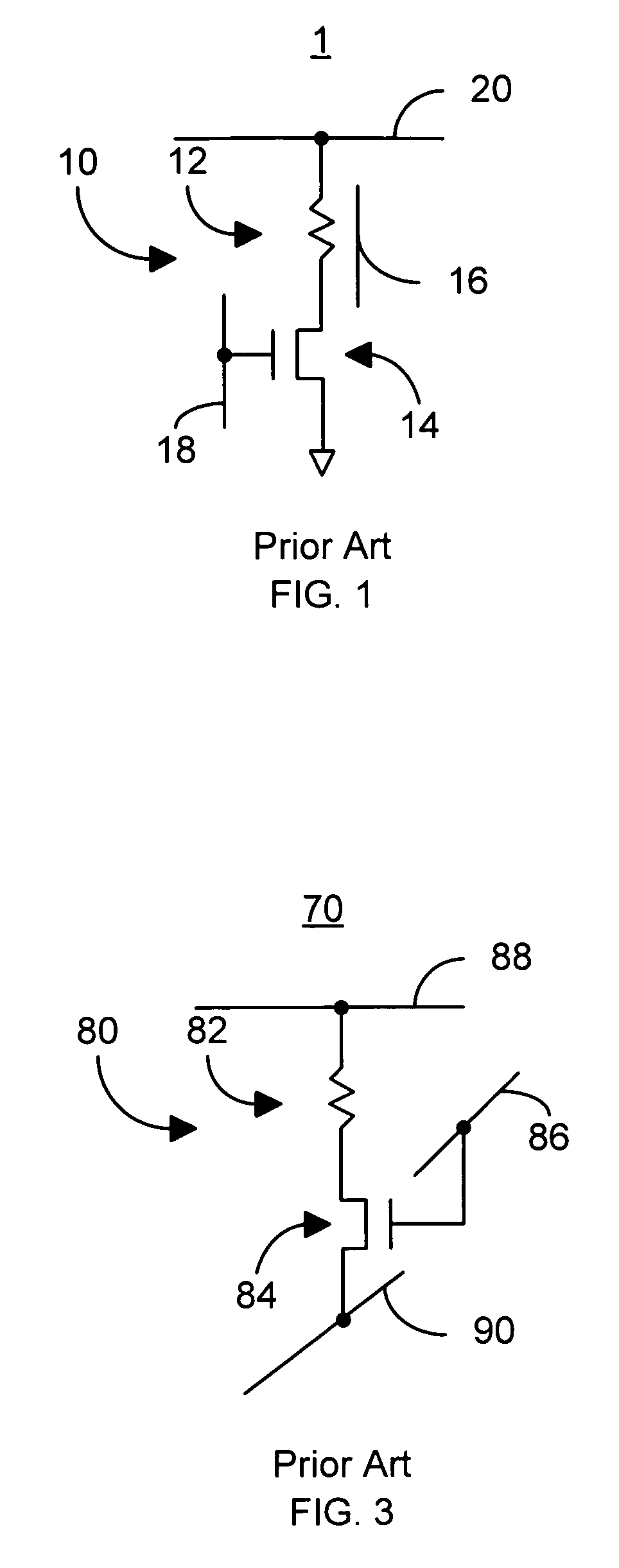

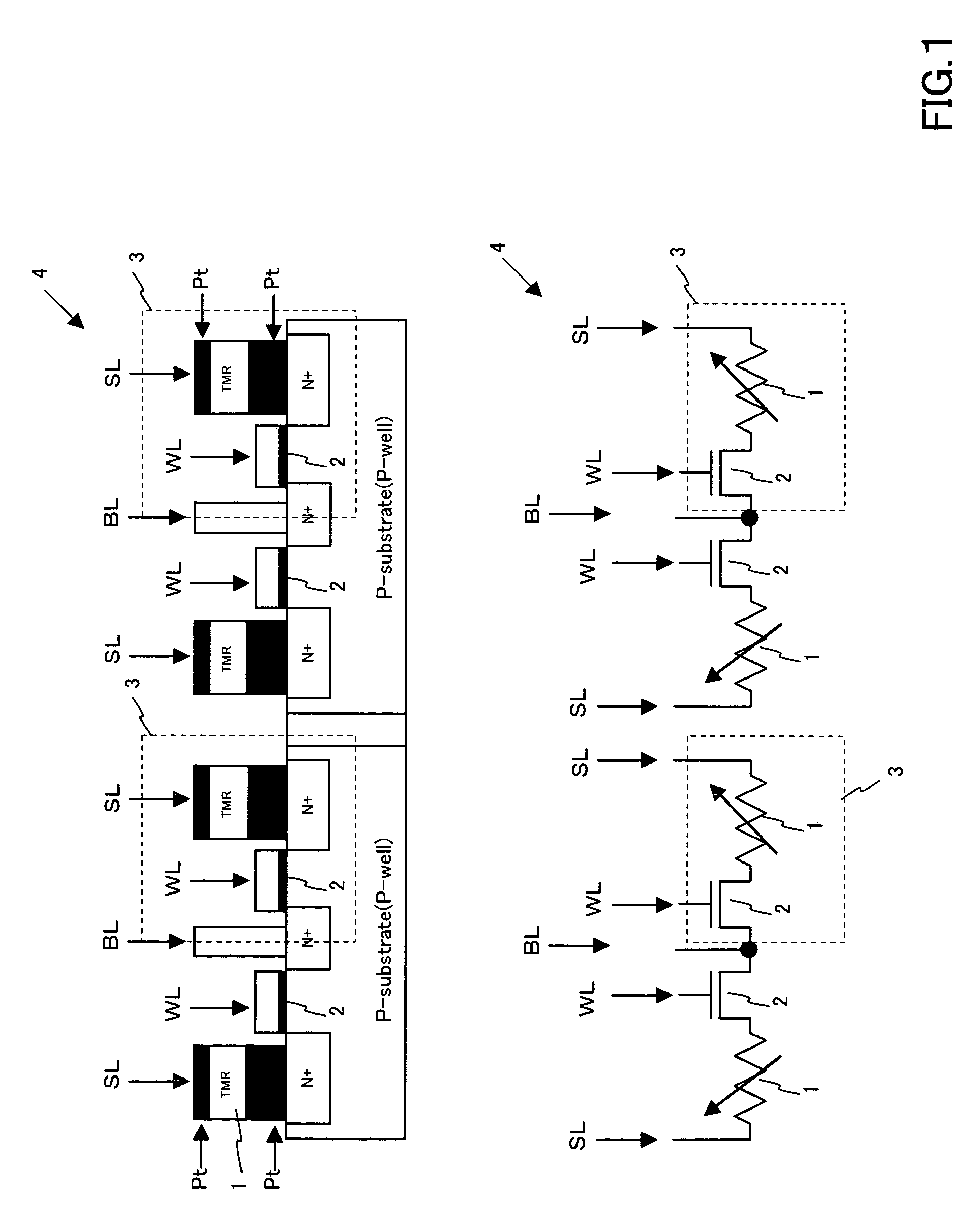

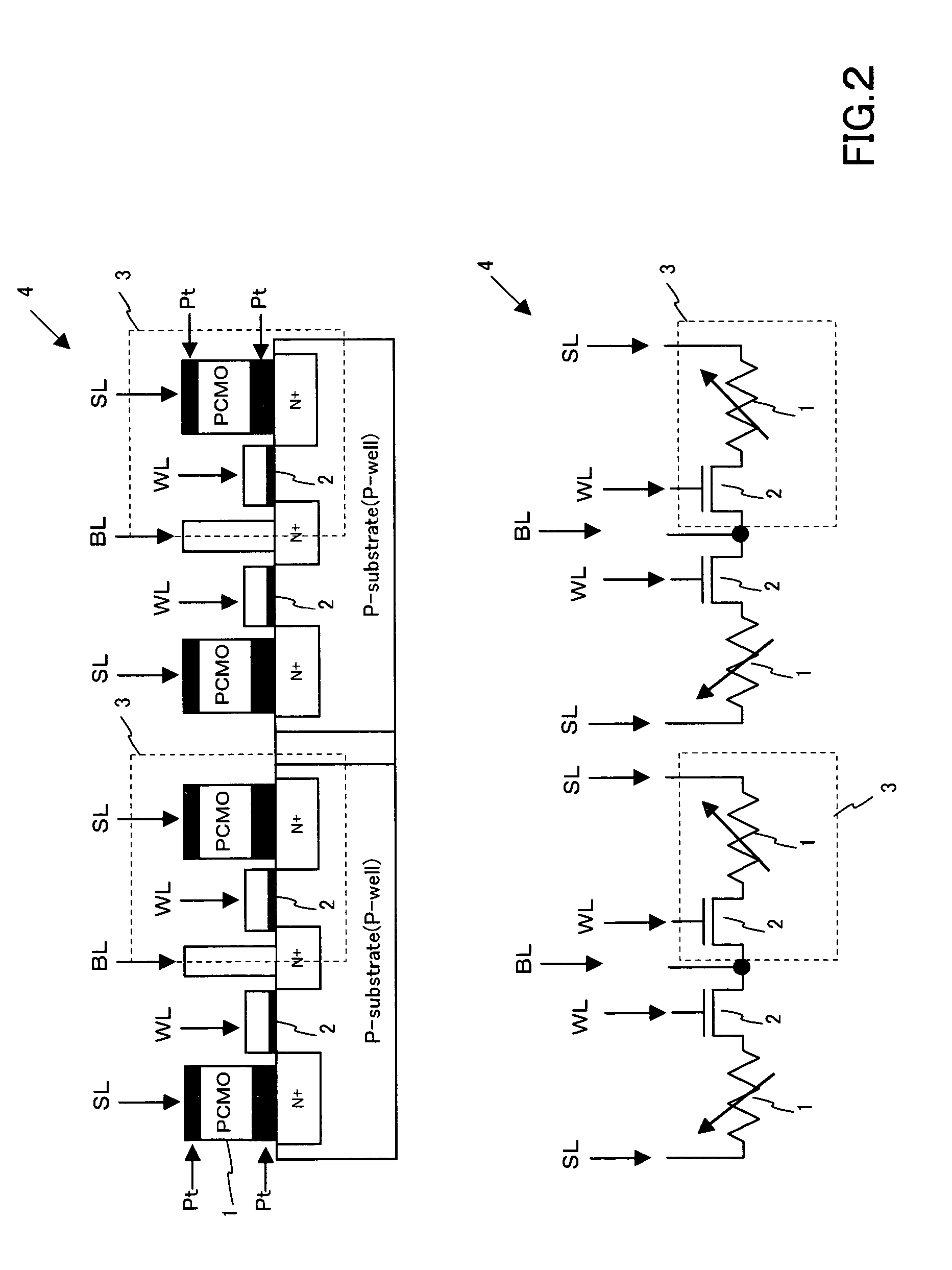

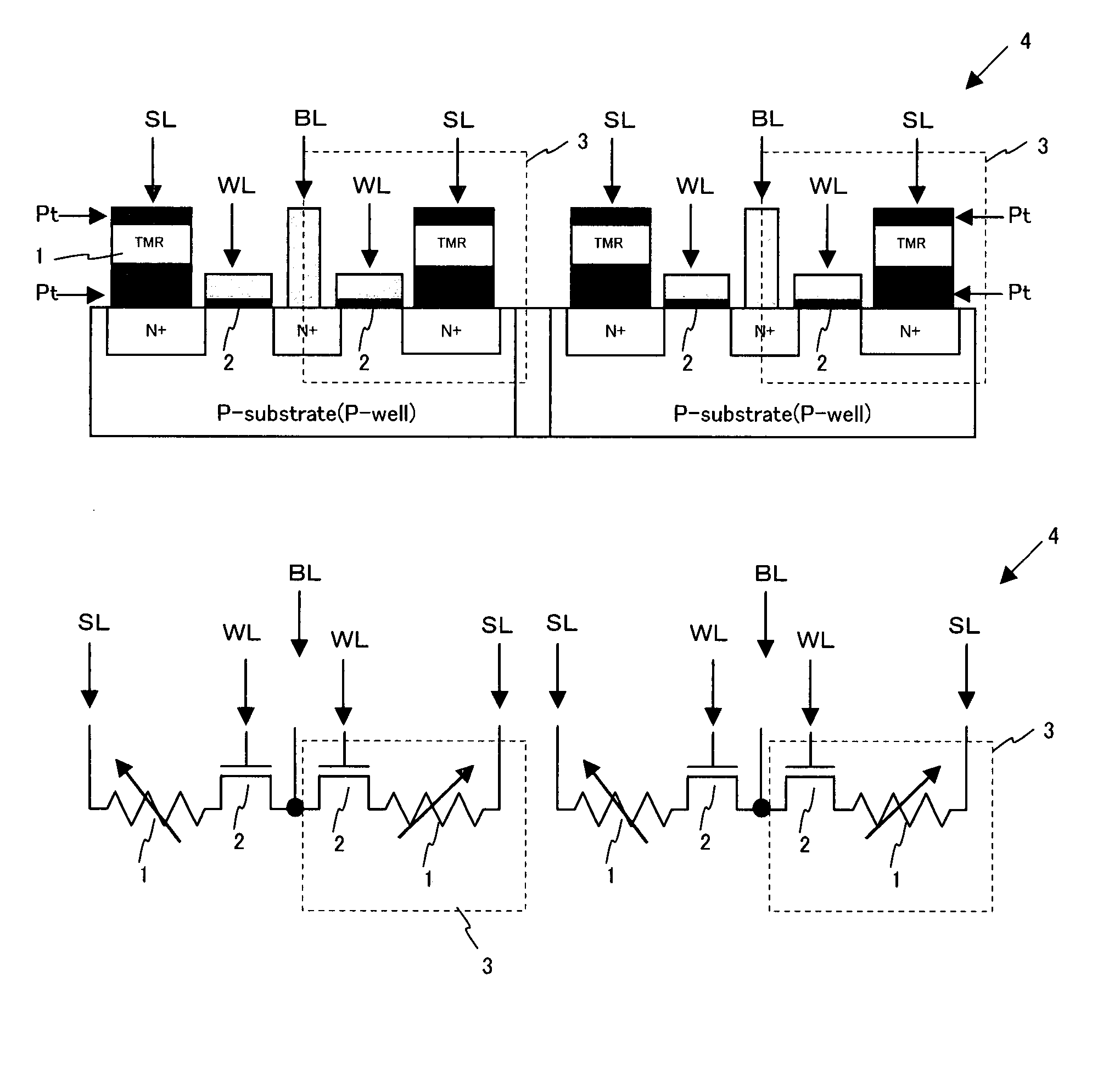

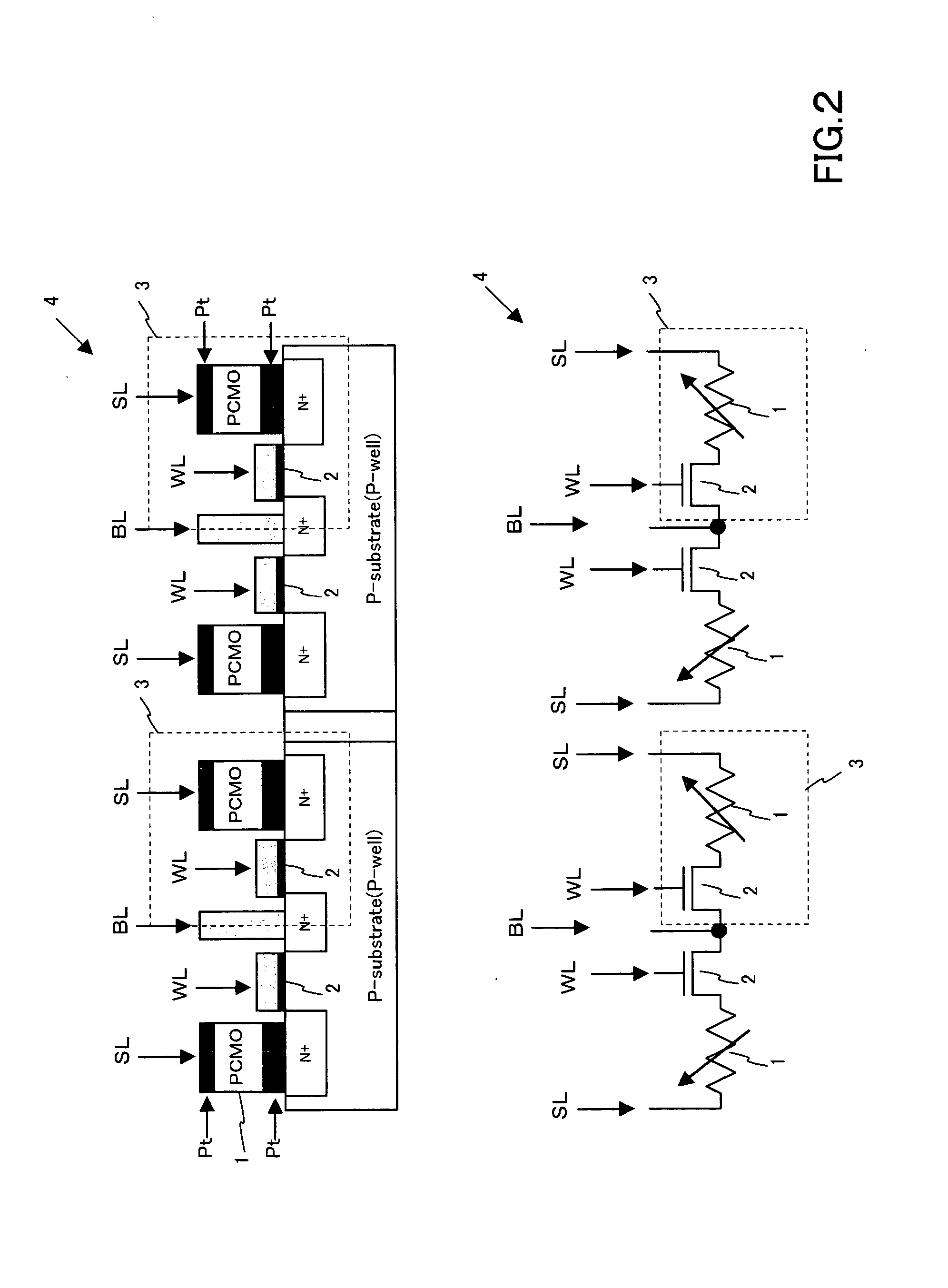

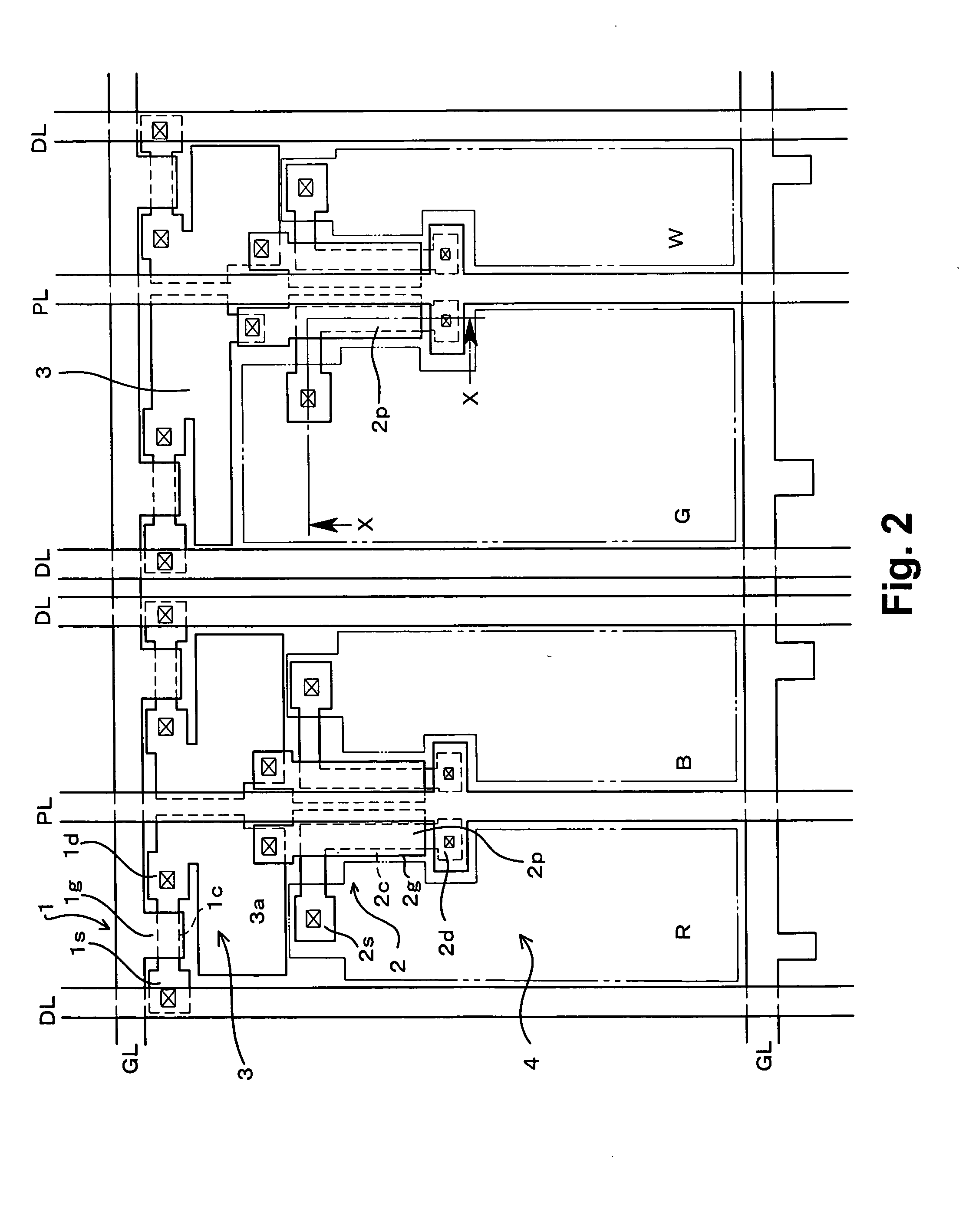

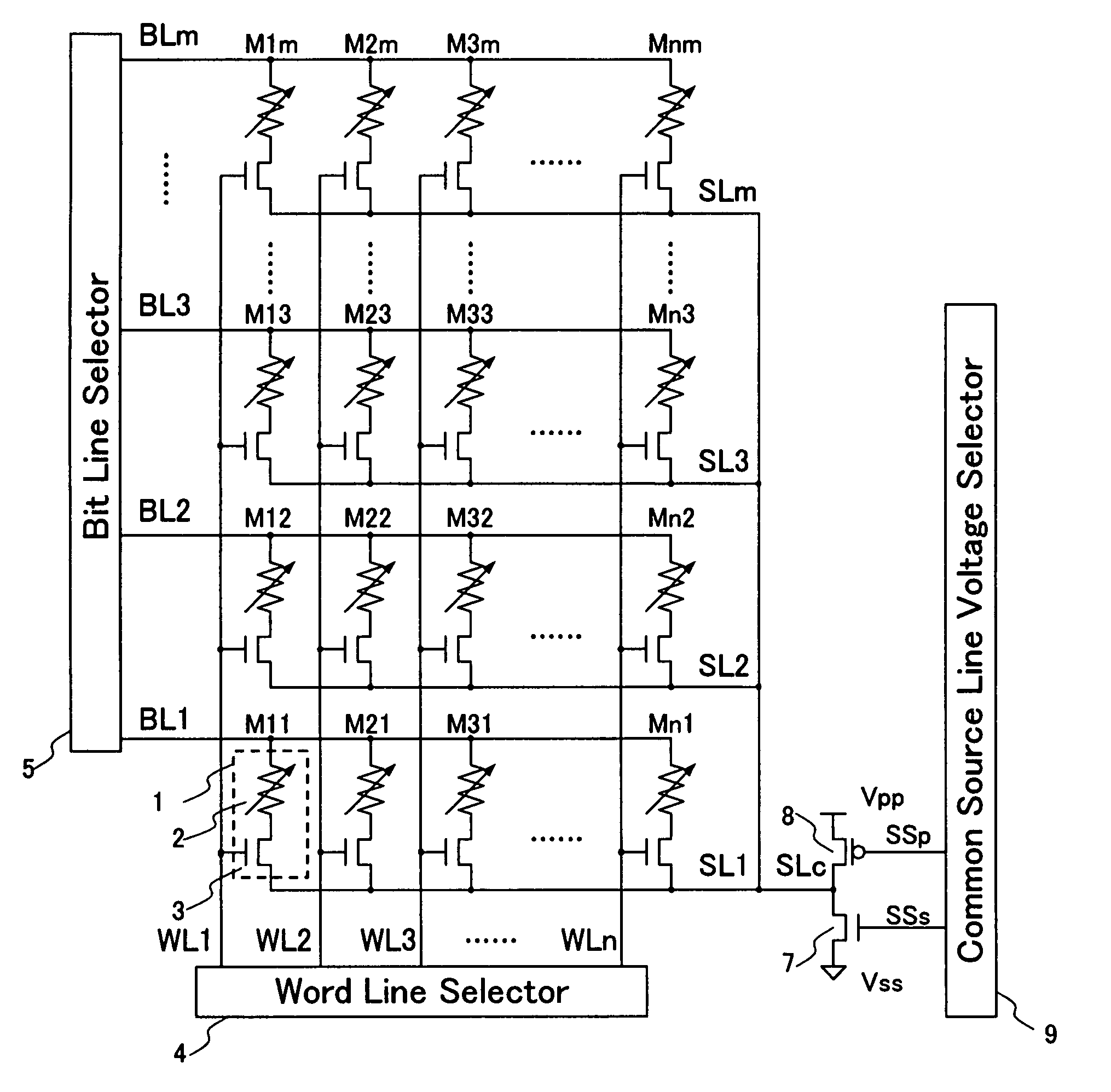

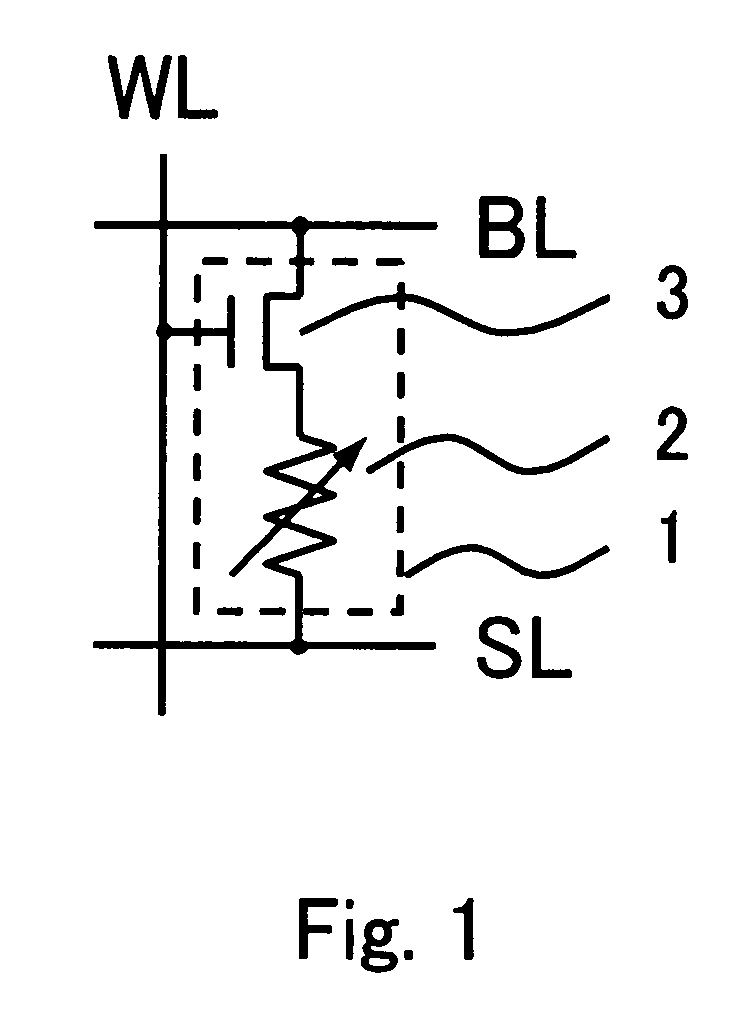

Nonvolatile semiconductor memory device

ActiveUS7057922B2Stress minimizationReliable dataNanoinformaticsSolid-state devicesBit lineEngineering

The present invention employs a memory cell structure in that one end of a variable resistance element (1) for storing information by change of electric resistance is connected to a source of a selection transistor (2) to form a memory cell (3) and, in a memory cell array (4), a drain of the selection transistor (2) is connected to a common bit line (BL) in a column direction, the other end of the variable resistance element (1) is connected to a source line (SL) and a gate of the selection transistor (2) is connected to a common word line (WL) in a row direction. In the memory cell structure, an operation of resetting data stored in the memory cell (3) is carried out for each of sectors including the plural memory cells (3) commonly connected to the source line (SL).

Owner:SAMSUNG ELECTRONICS CO LTD

Nonvolatile semiconductor memory device

ActiveUS20050122768A1Minimize of currentMinimize stress of voltageNanoinformaticsSolid-state devicesBit lineCommon word

The present invention employs a memory cell structure in that one end of a variable resistance element (1) for storing information by change of electric resistance is connected to a source of a selection transistor (2) to form a memory cell (3) and, in a memory cell array (4), a drain of the selection transistor (2) is connected to a common bit line (BL) in a column direction, the other end of the variable resistance element (1) is connected to a source line (SL) and a gate of the selection transistor (2) is connected to a common word line (WL) in a row direction. In the memory cell structure, an operation of resetting data stored in the memory cell (3) is carried out for each of sectors including the plural memory cells (3) commonly connected to the source line (SL).

Owner:SAMSUNG ELECTRONICS CO LTD

Organic EL panel

ActiveUS20050073264A1Increase freedomIncrease the aperture ratioTransistorDischarge tube luminescnet screensEngineeringAperture ratio

A drive transistor is connected, via its drain region, to a power supply line, and, via its source region, to a transparent electrode of an organic EL element. The channel region is formed bent into a substantially L shape. This arrangement is able to simplify the arrangement of a gate electrode by providing the gate electrode so as to run straight over a channel region in parallel to the power source line. Accordingly, the aperture ratio is increased.

Owner:SANYO ELECTRIC CO LTD

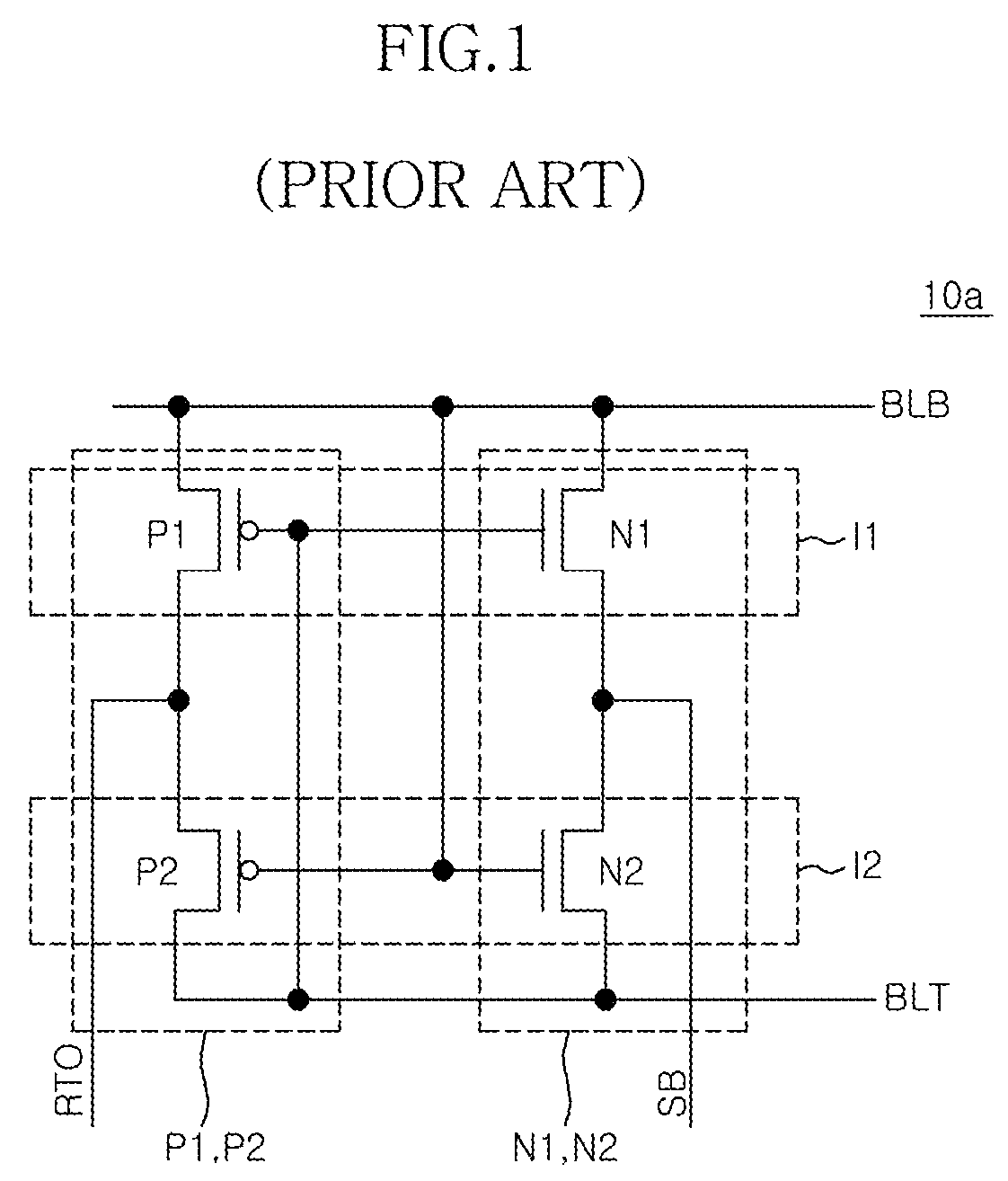

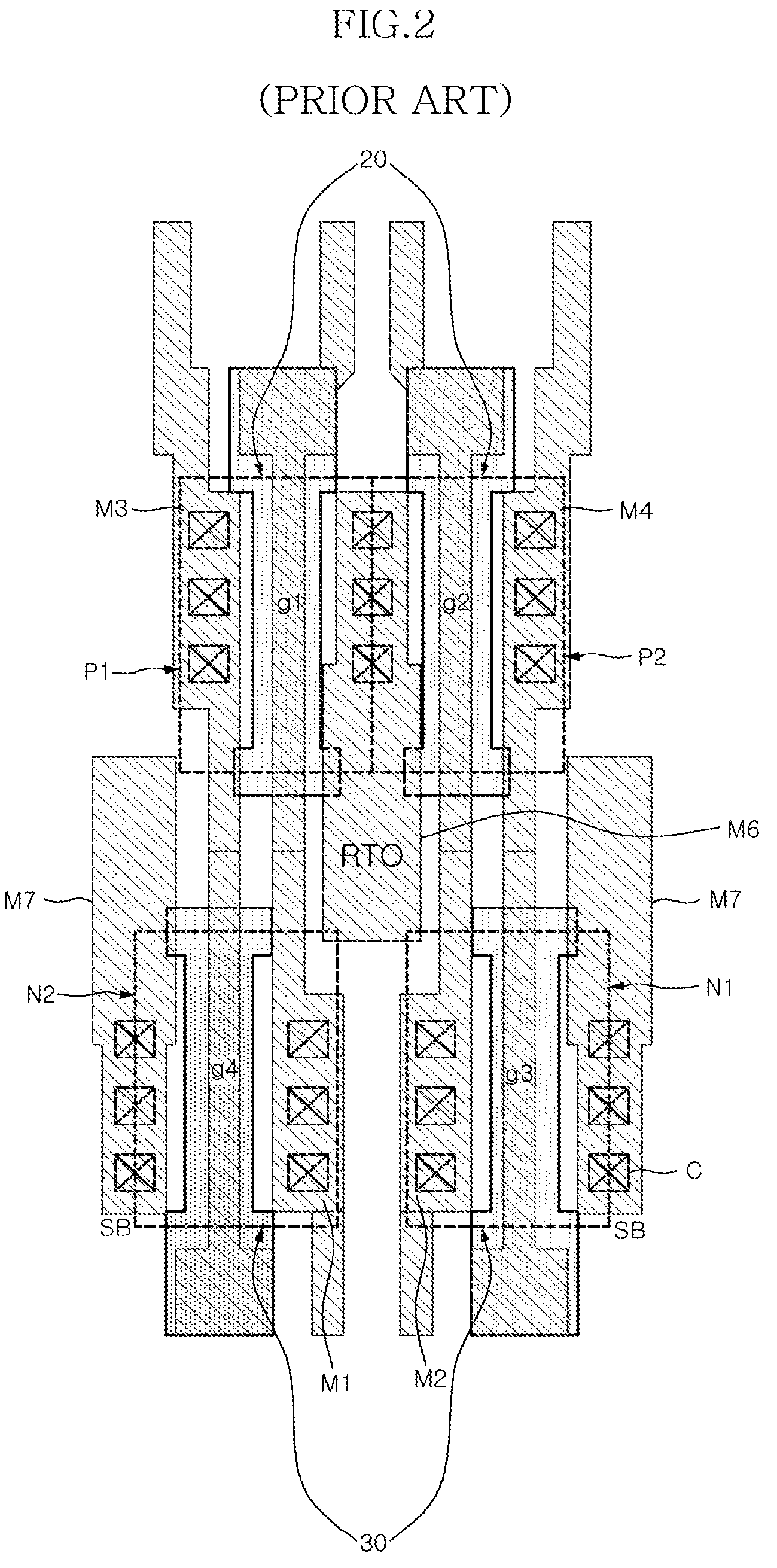

Latch structure and bit line sense amplifier structure including the same

ActiveUS7646651B2Reduce variationAvoid mistakesTransistorSolid-state devicesBit lineAudio power amplifier

Owner:SK HYNIX INC

Semiconductor memory device

ActiveUS20070263466A1Improve retentionRetaining capability of stored data in data readoutSolid-state devicesSemiconductor/solid-state device manufacturingBit lineControl line

When data “1” is stored in a memory cell, a bit line is driven to an H level (control line drive potential) and the other bit line is driven to an L level (reference potential) when a sense operation is completed. When a verify write operation is initiated, a charge line is driven from an H level (power supply potential) to an L level (reference potential). By the GIDL current from a source line, accumulation of holes is initiated again for a storage node subsequent to discharge of holes, whereby the potential of the storage node rises towards an H level (period α). When the charge line is driven to an H level from an L level, the potential of the storage node further rises (period β).

Owner:RENESAS ELECTRONICS CORP

Semiconductor memory device

A semiconductor memory device comprises an array of memory cells each comprising a variable resistance element and a cell access transistor, and a voltage supplying means for applying the first voltage between the bit and source lines connected to the selected memory cell, the third voltage to the word line to apply the first write voltage between the two ports of the variable resistance element for shifting the resistance from the first state to the second state, and the second voltage opposite in polarity to the first voltage between the bit and source lines, the third voltage to the word line to apply the second write voltage opposite in polarity to and different in the absolute value from the first write voltage between the two ports for shifting the resistance from the second state to the first state, the voltage supplying means comprising an n-channel MOSFET and a p-channel MOSFET.

Owner:SAMSUNG ELECTRONICS CO LTD

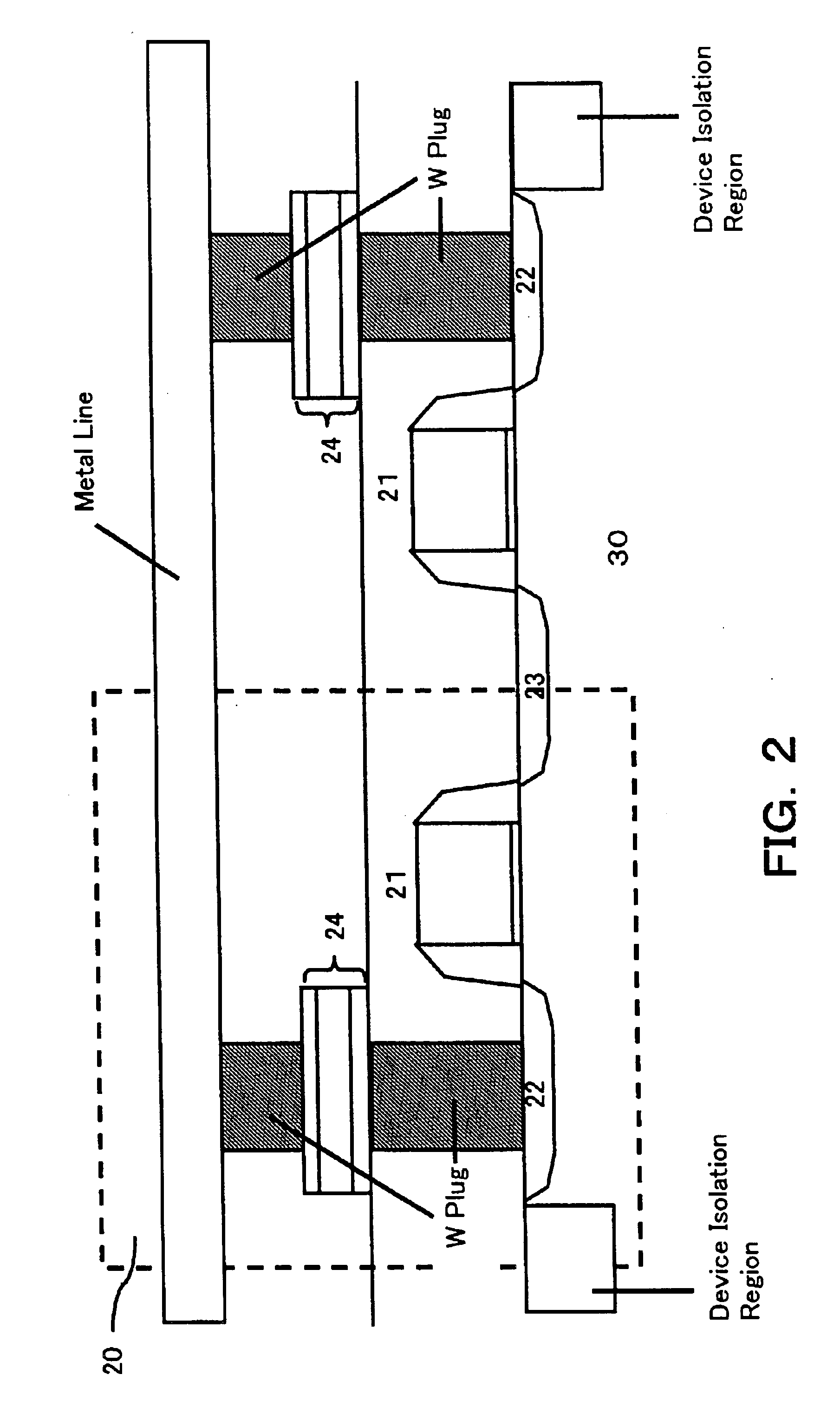

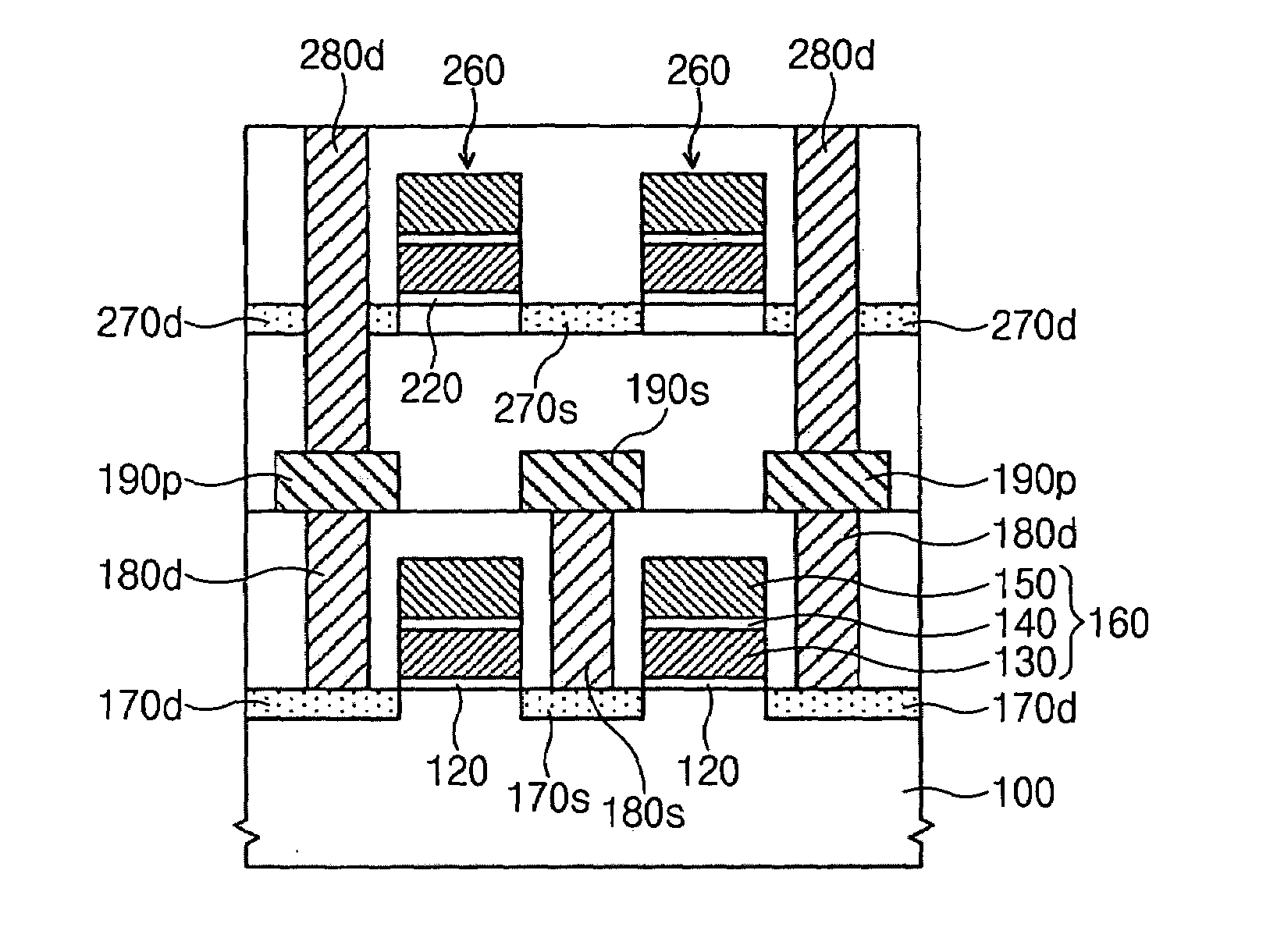

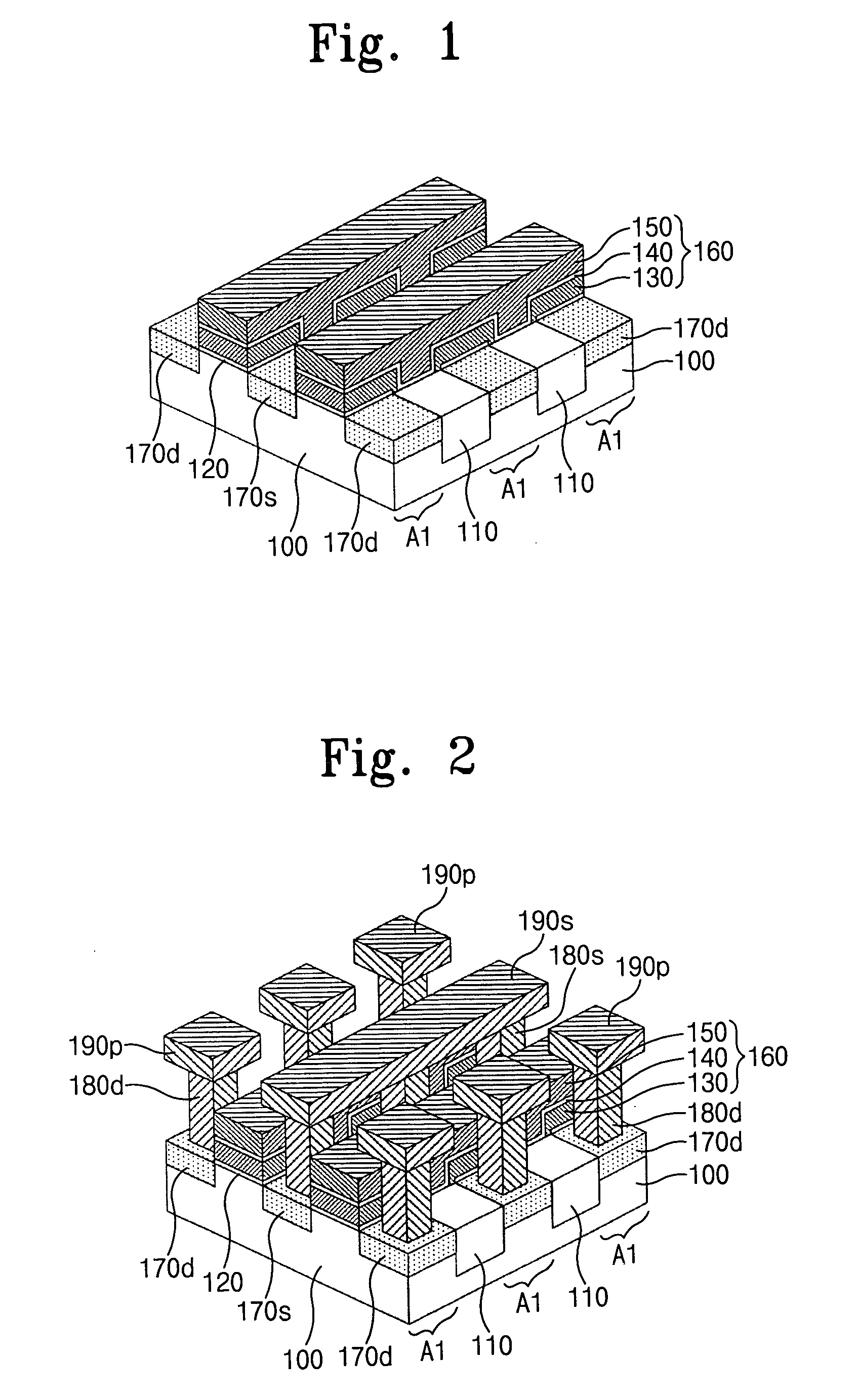

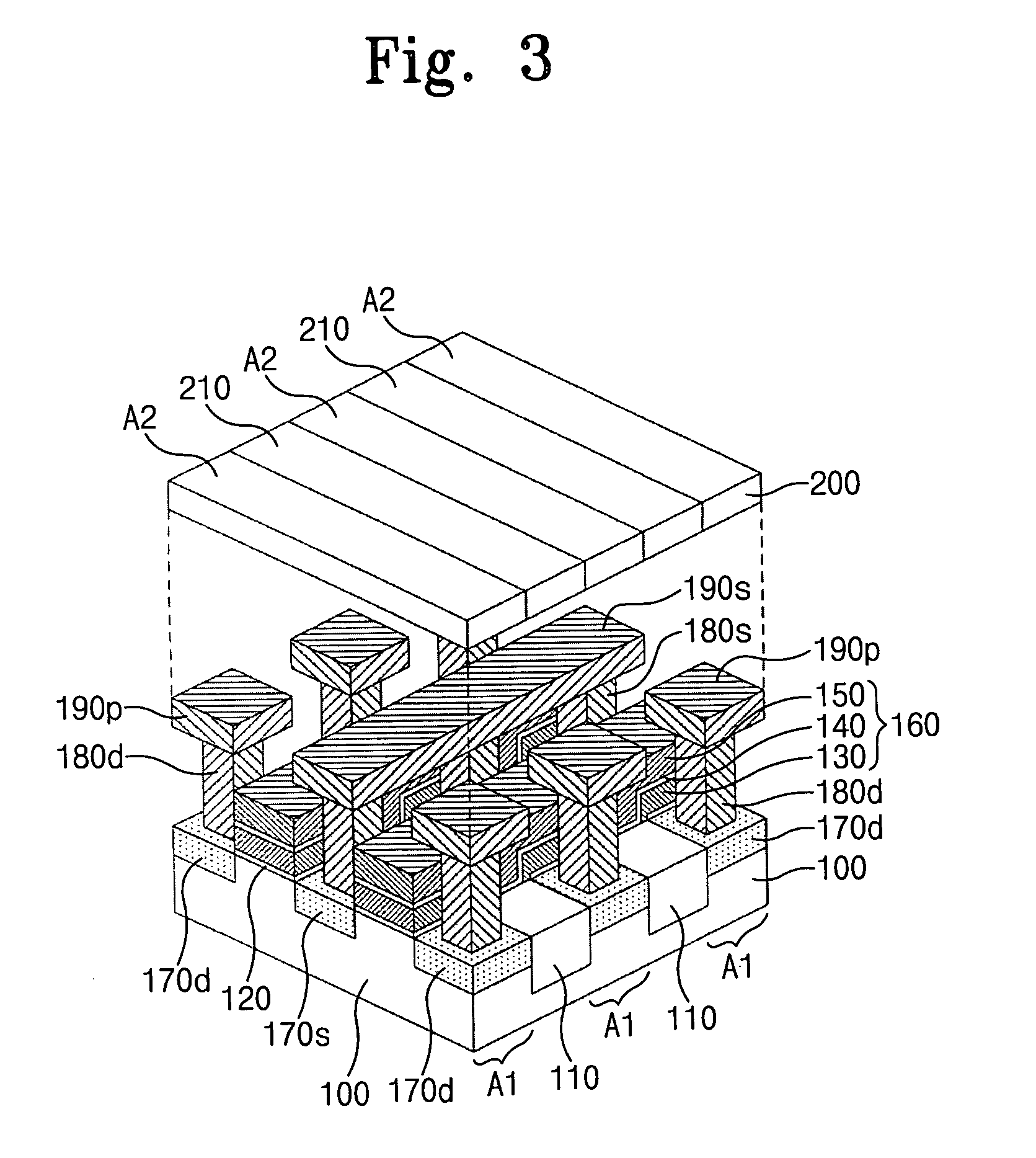

Multilevel integrated circuit devices and methods of forming the same

ActiveUS20070176214A1Solid-state devicesSemiconductor/solid-state device manufacturingSemiconductorIntegrated circuit

Semiconductor devices including a plurality of semiconductor layers. A plurality of transistors are on each of the semiconductor layers. The transistors include gate lines and have source regions and drain regions formed between the gate lines in the respective semiconductor layer including the transistors. The semiconductor devices further include a plurality of local source line structures. Each of the local source line structures is positioned on a corresponding one of the semiconductor layers and connects a plurality of the source regions formed on the corresponding one of the semiconductor layers. Methods of forming the semiconductor devices are also provided.

Owner:SAMSUNG ELECTRONICS CO LTD

Techniques for simultaneously driving a plurality of source lines

Techniques for simultaneously driving a plurality of source lines are disclosed. In one particular exemplary embodiment, the techniques may be realized as an apparatus for simultaneously driving a plurality of source lines. The apparatus may include a plurality of source lines coupled to a single source line driver. The apparatus may also include a plurality of dynamic random access memory cells arranged in an array of rows and columns, each dynamic random access memory cell including one or more memory transistors. Each of the one or more memory transistors may include a first region coupled to a first source line of the plurality of source lines, a second region coupled to a bit line, a body region disposed between the first region and the second region, wherein the body region may be electrically floating, and a gate coupled to a word line and spaced apart from, and capacitively coupled to, the body region.

Owner:MICRON TECH INC

Non-volatile semiconductor storage device

When a data erase operation is performed in one memory cell block, a first voltage is applied to one source line selected from m source lines in the one memory cell block. A second voltage equal to a voltage of the source lines before the data erase operation begins is applied to the other source lines. Then, after a certain time delay from application of the first voltage, a third voltage smaller than the first voltage is applied to a third conductive layer of a source-side selection transistor connected to a selected source line. Then, a hole current is produced near a third gate insulation layer due to a potential difference between the first and third voltage. A fourth voltage is applied to one of first conductive layers connected to one of the memory transistor to be erased. The other first conductive layers are brought into a floating state.

Owner:TOSHIBA MEMORY CORP

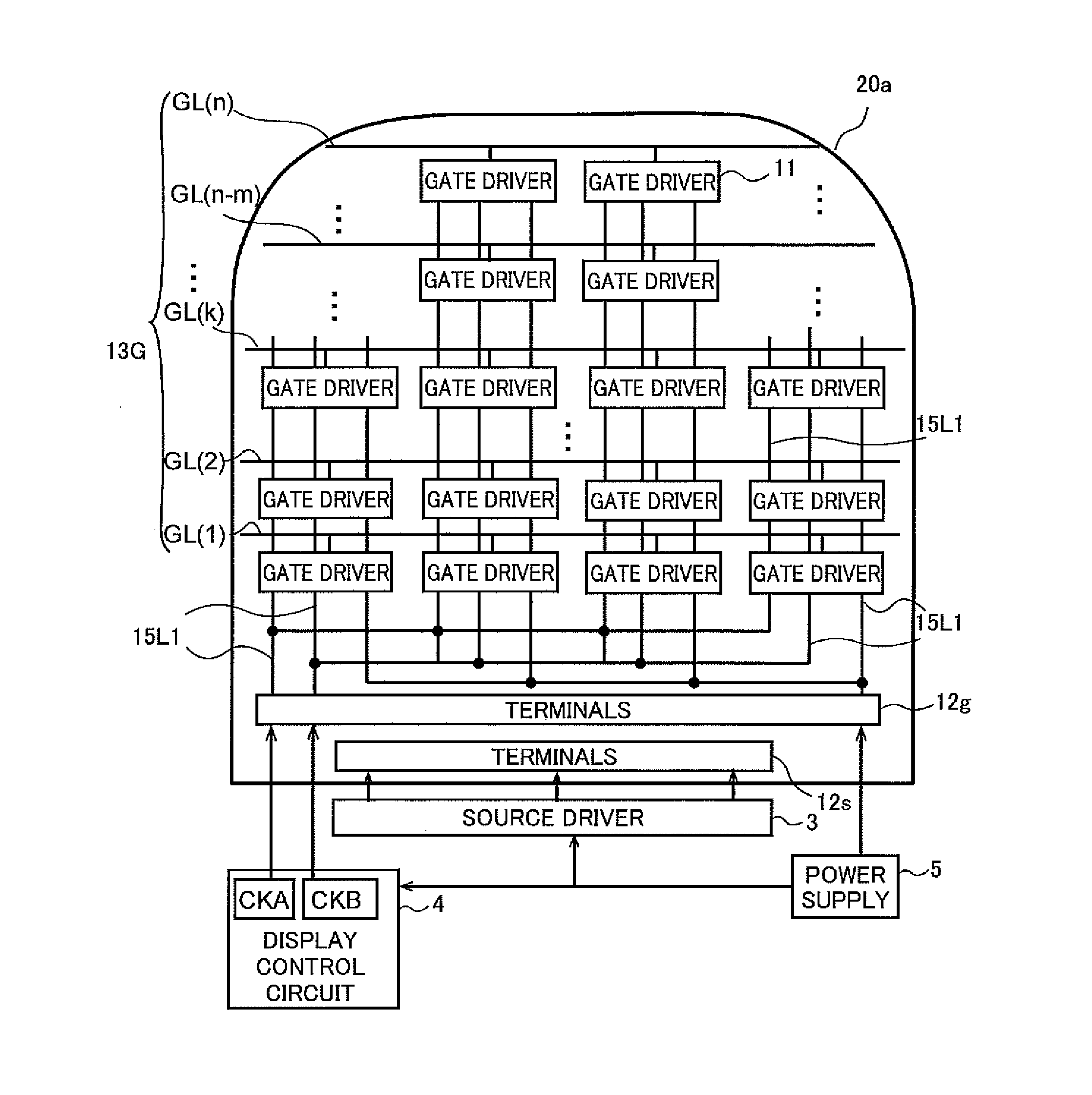

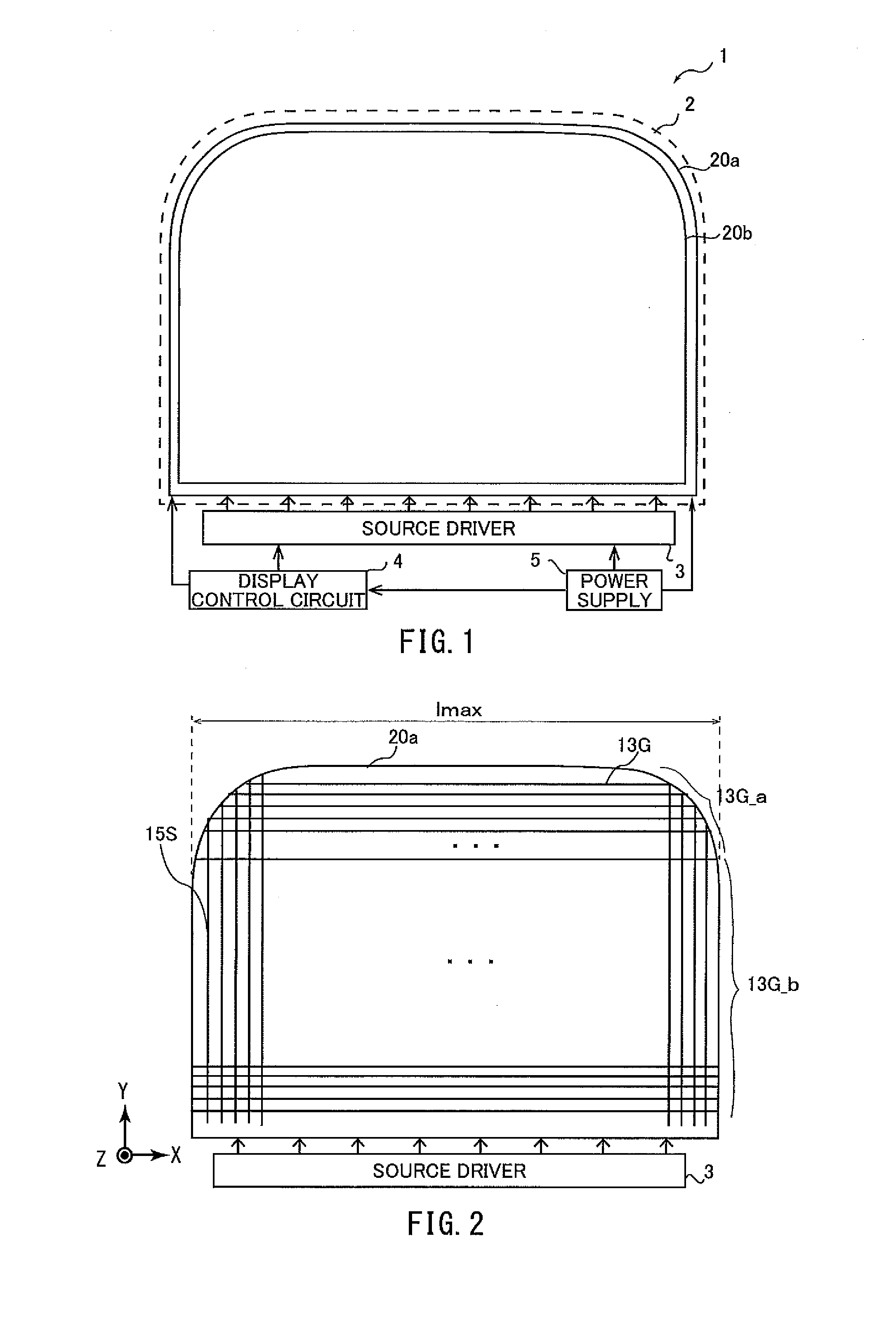

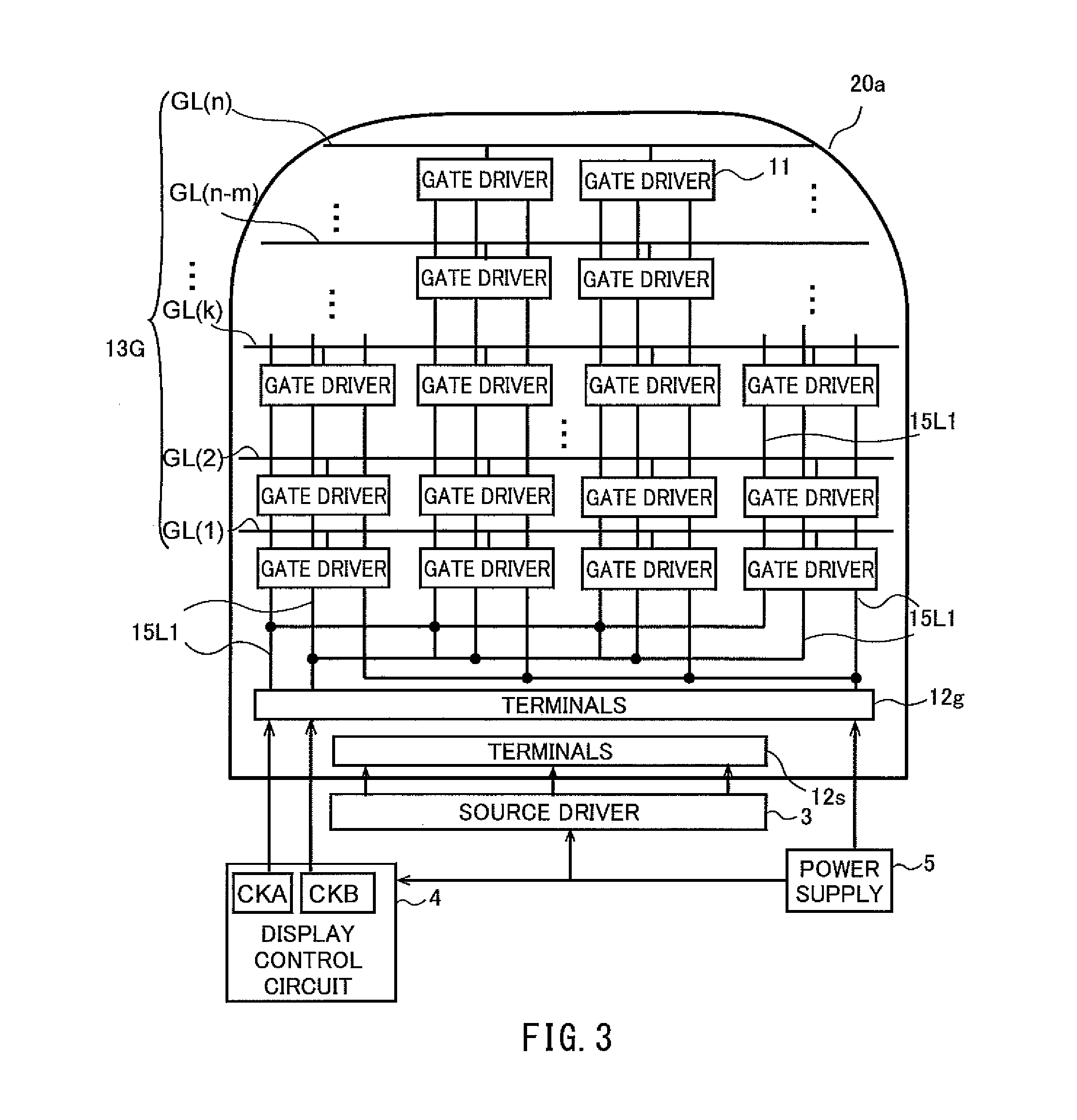

Active-matrix substrate, method of manufacturing active-matrix substrate, and display panel

ActiveUS20160019856A1Small sizeIncreased Design FreedomCathode-ray tube indicatorsNon-linear opticsControl signalActive matrix

An objective is to provide a technique for reducing the size of the picture-frame region of the active-matrix substrate and improve the freedom of design, such as the freedom in designing the active-matrix substrate. An active-matrix substrate includes a group of gate lines and a group of source lines crossing the gate lines. At least some of the gate lines have a length that is smaller than the maximum value of the width of the active-matrix substrate as measured in the direction in which the gate lines extend. The active-matrix substrate further includes pixel electrodes connected with the gate lines and source lines, and gate line driving units (11) provided in the display region for switching the gate lines to the selected or non-selected state in response to a supplied control signal. First terminals (12s) for providing data signals from the source driver and second terminals (12g) for providing control signals from the display control circuit are provided in the portion of the picture-frame region that is adjacent a side of the display region.

Owner:SHARP KK