Patents

Literature

3440 results about "Variable resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A string potentiometer is a multi-turn potentiometer operated by an attached reel of wire turning against a spring, enabling it to convert linear position to a variable resistance. User-accessible rotary potentiometers can be fitted with a switch which operates usually at the anti-clockwise extreme of rotation.

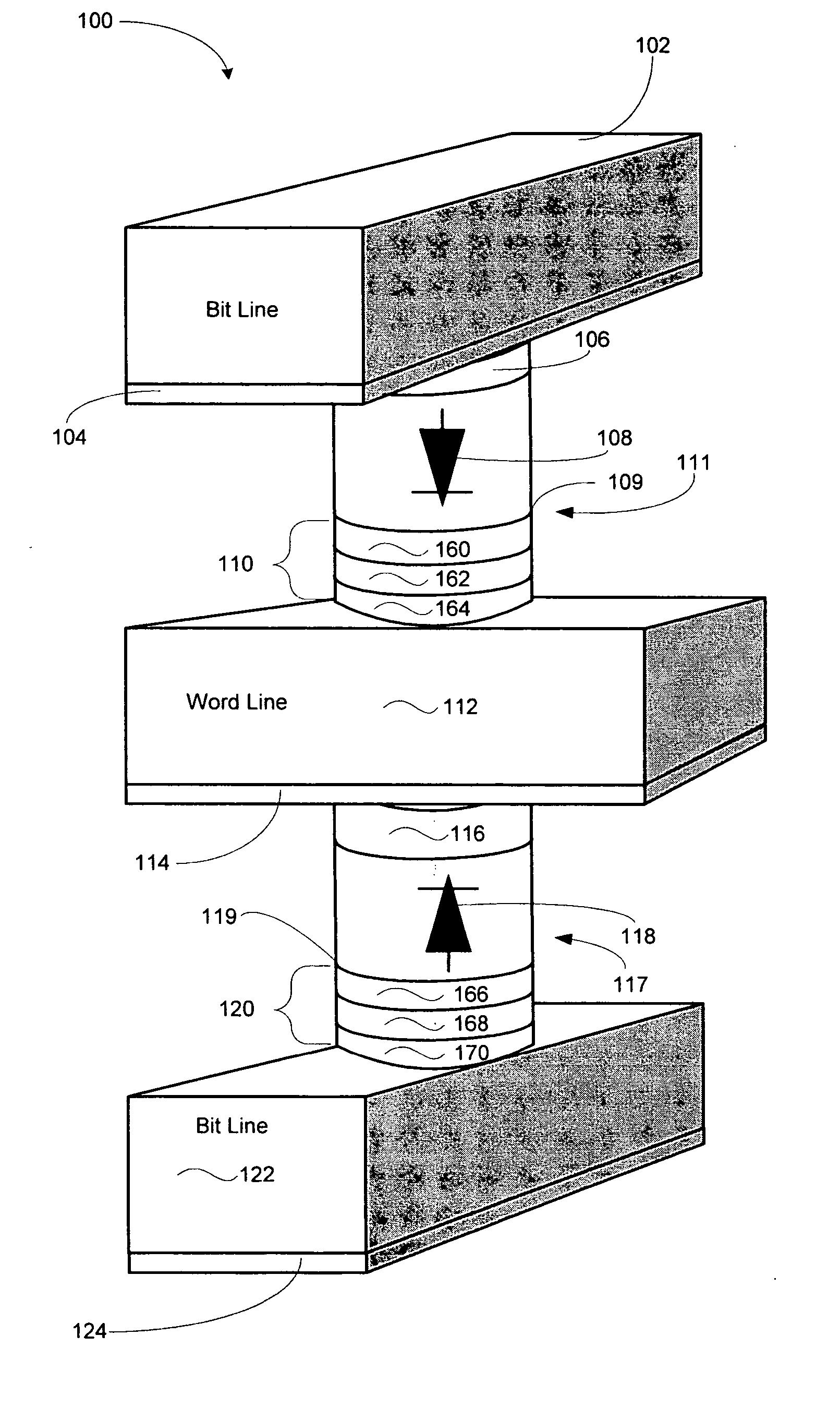

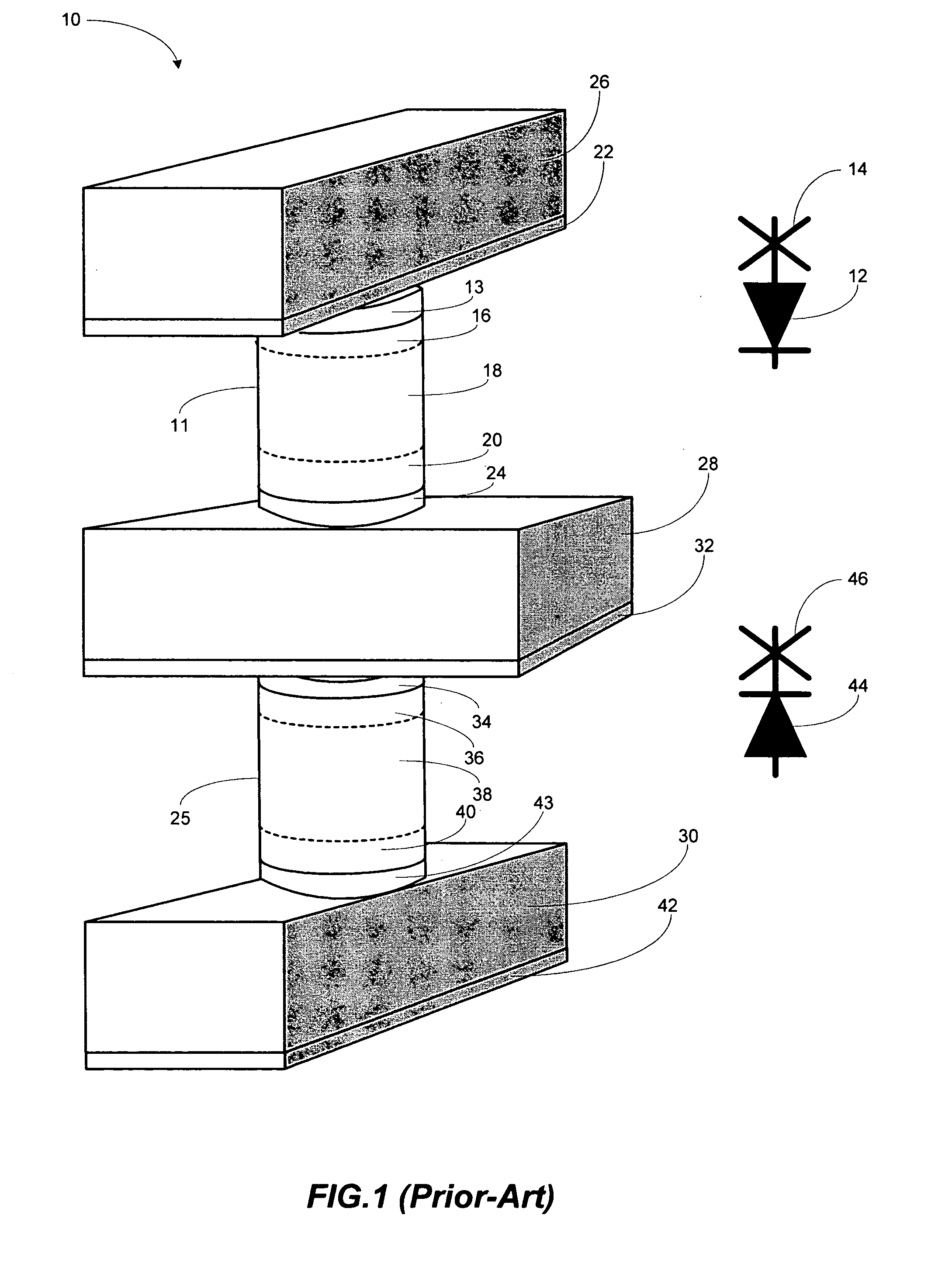

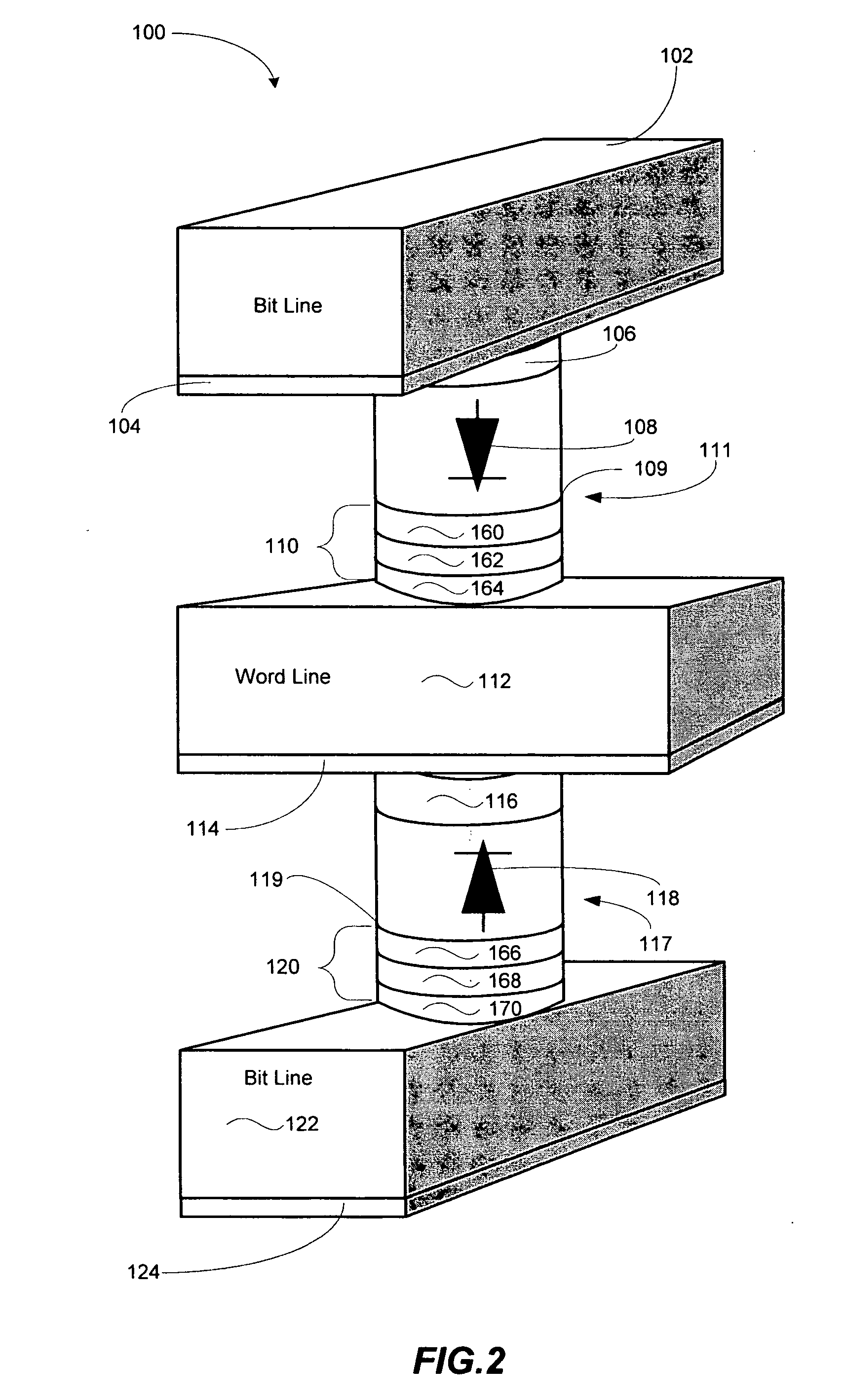

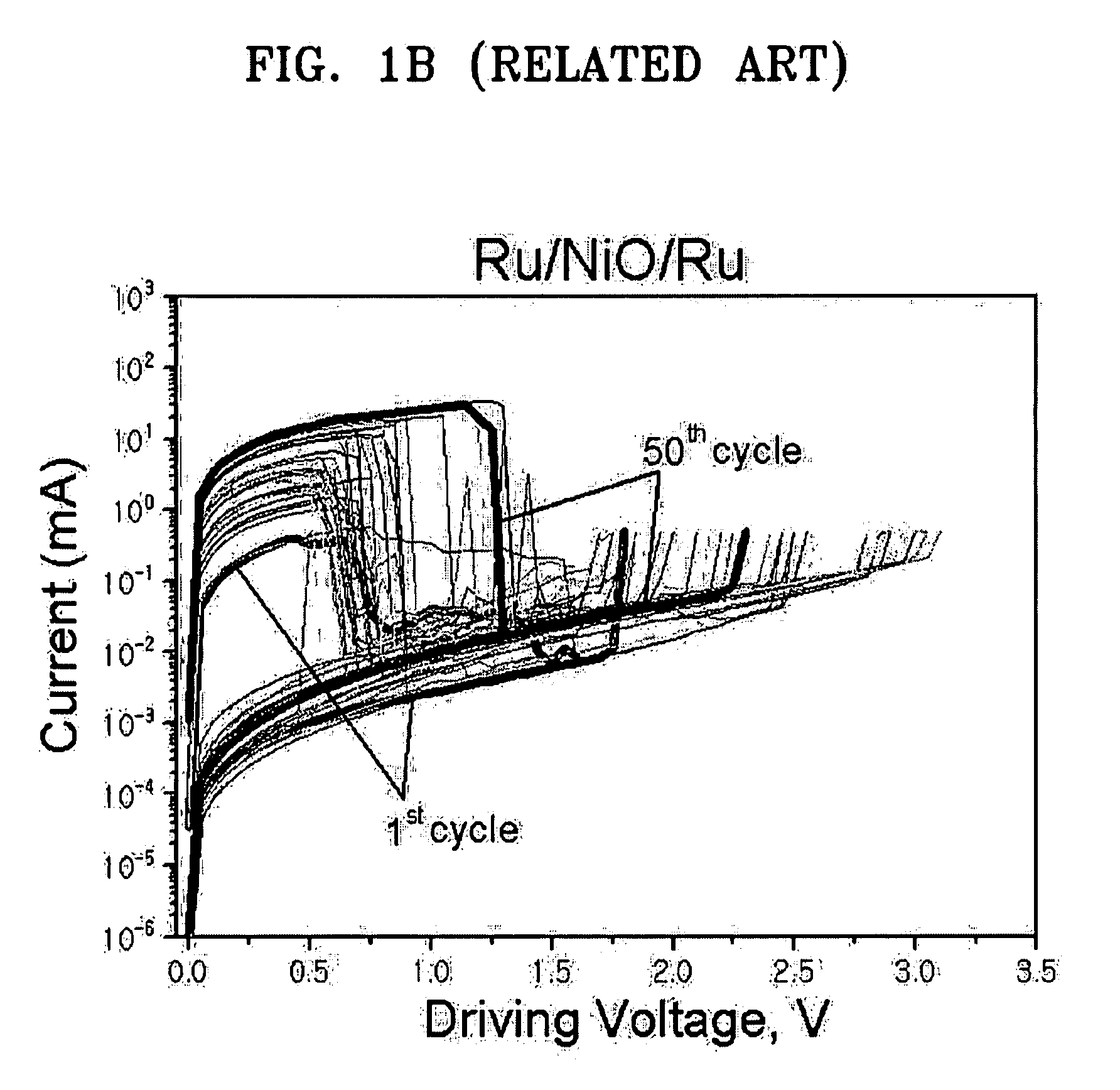

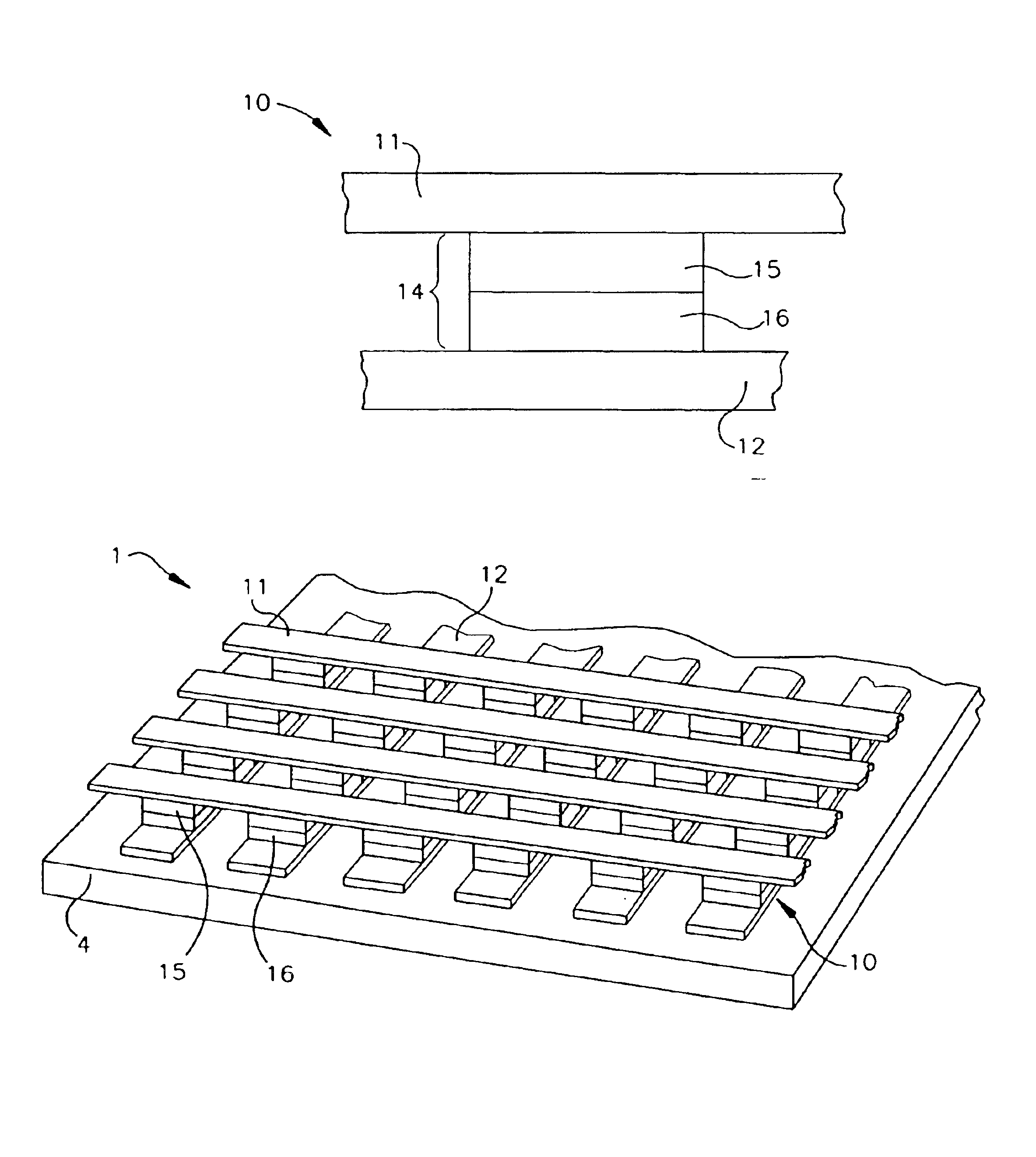

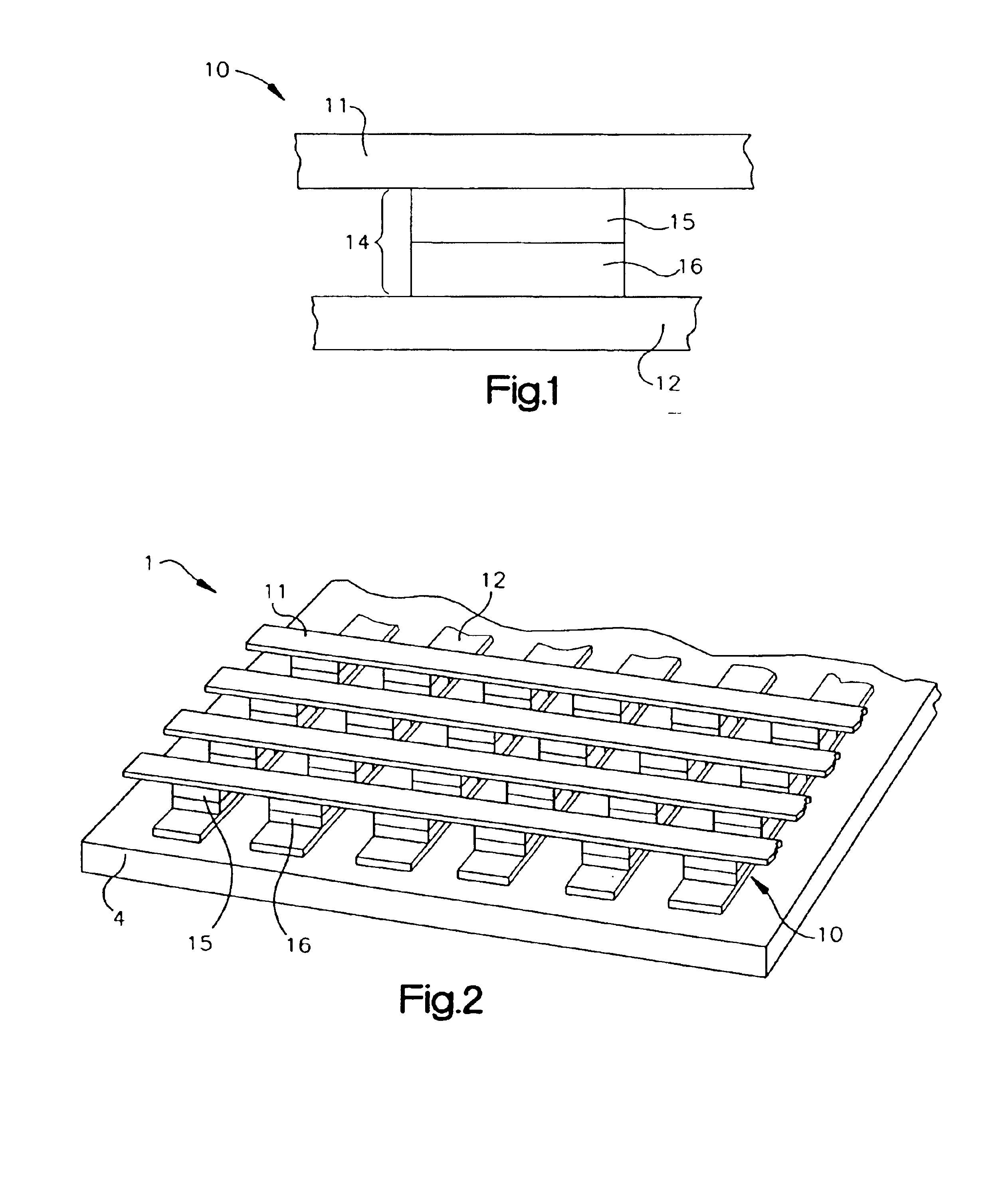

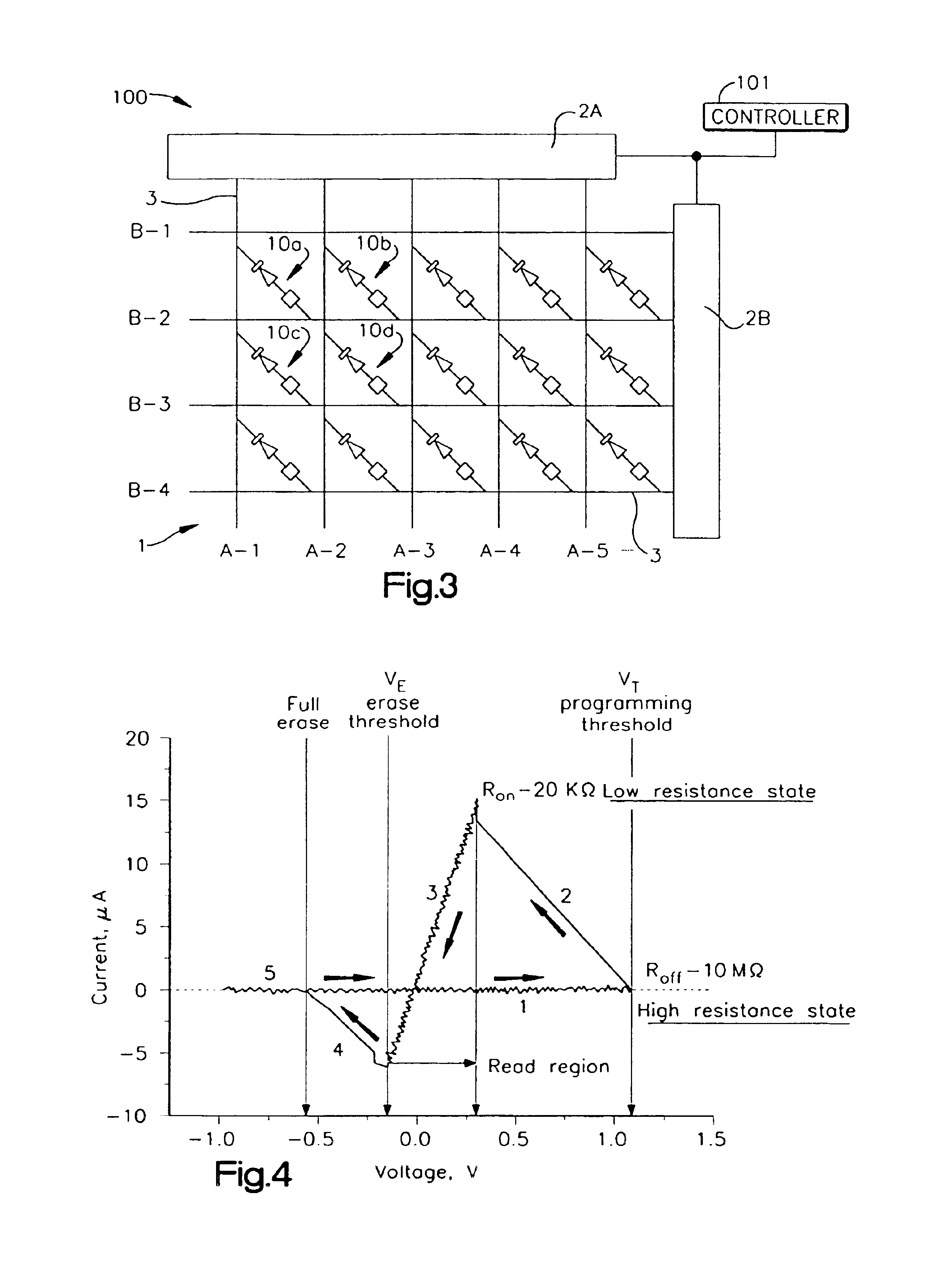

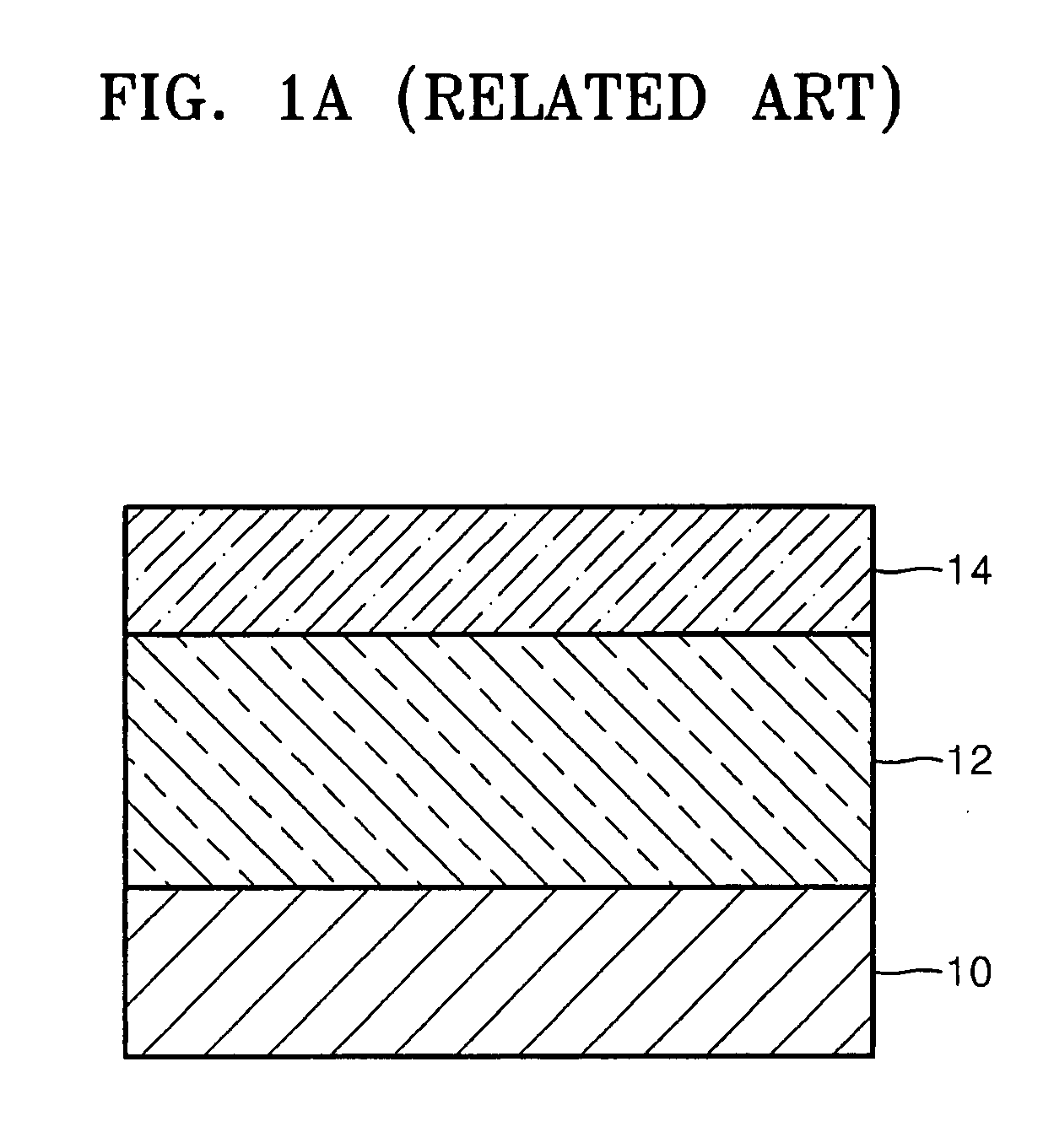

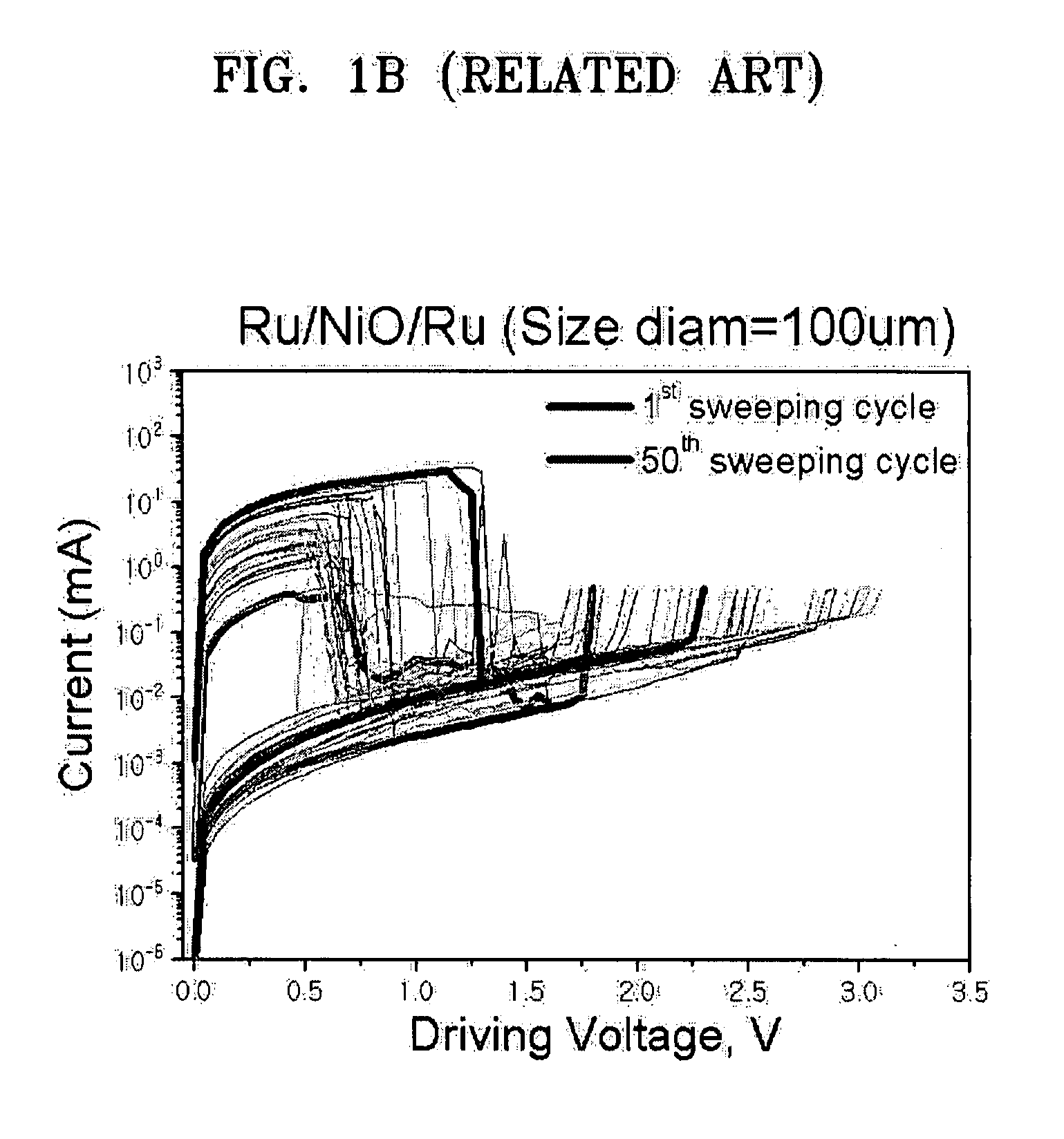

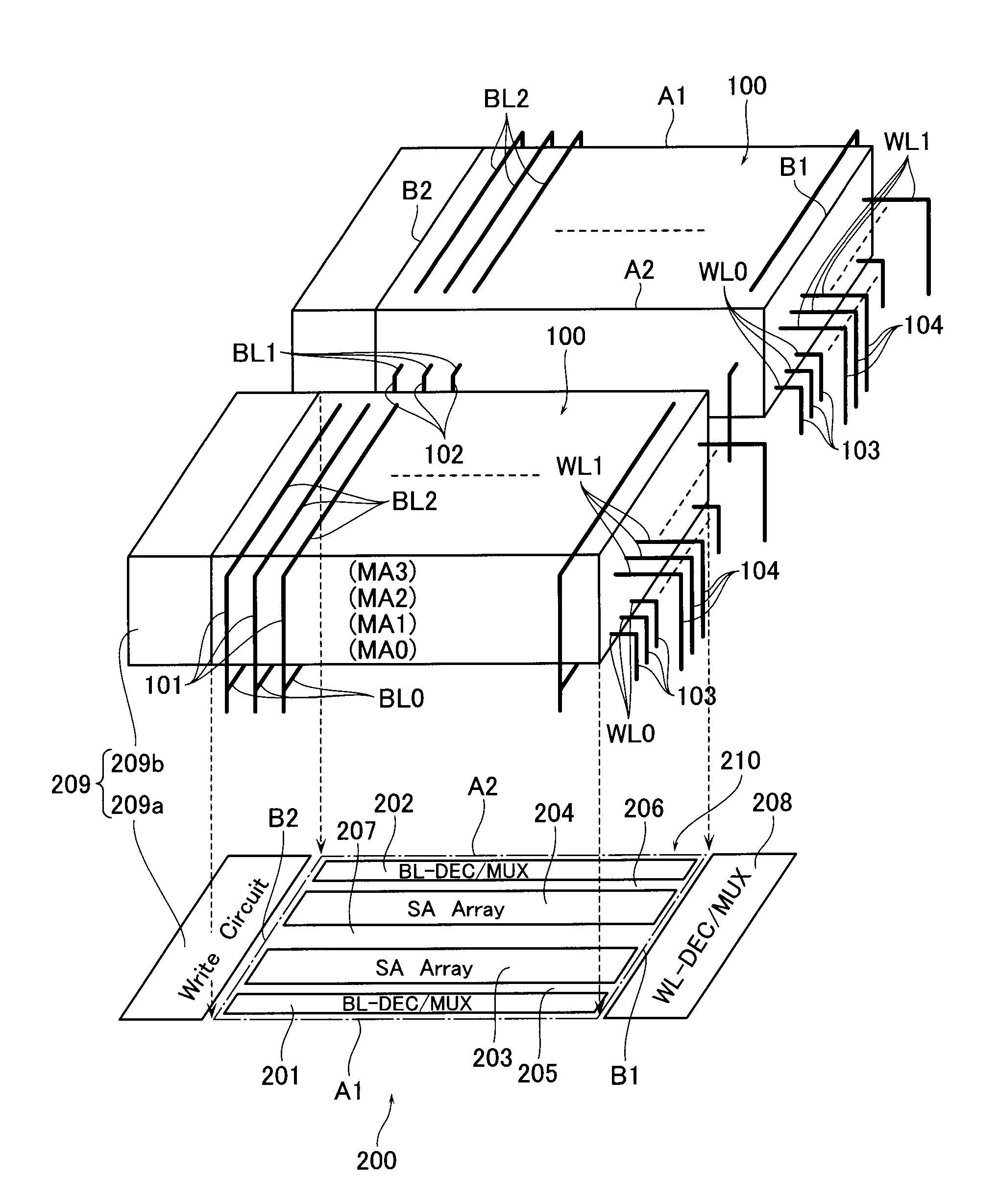

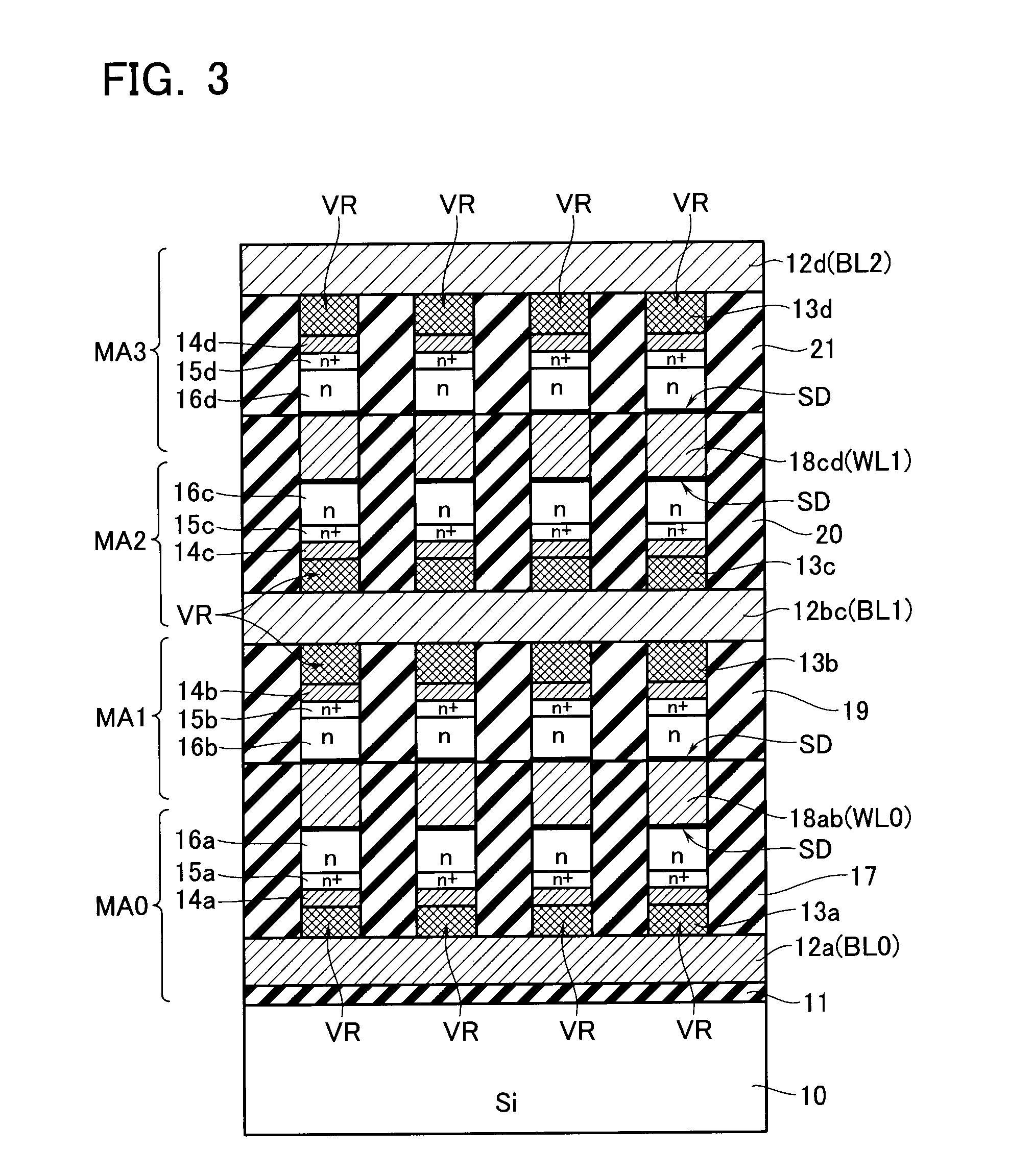

Unipolar resistance random access memory (RRAM) device and vertically stacked architecture

InactiveUS20070132049A1Improve performanceGalvano-magnetic devicesSolid-state devicesRandom access memoryEngineering

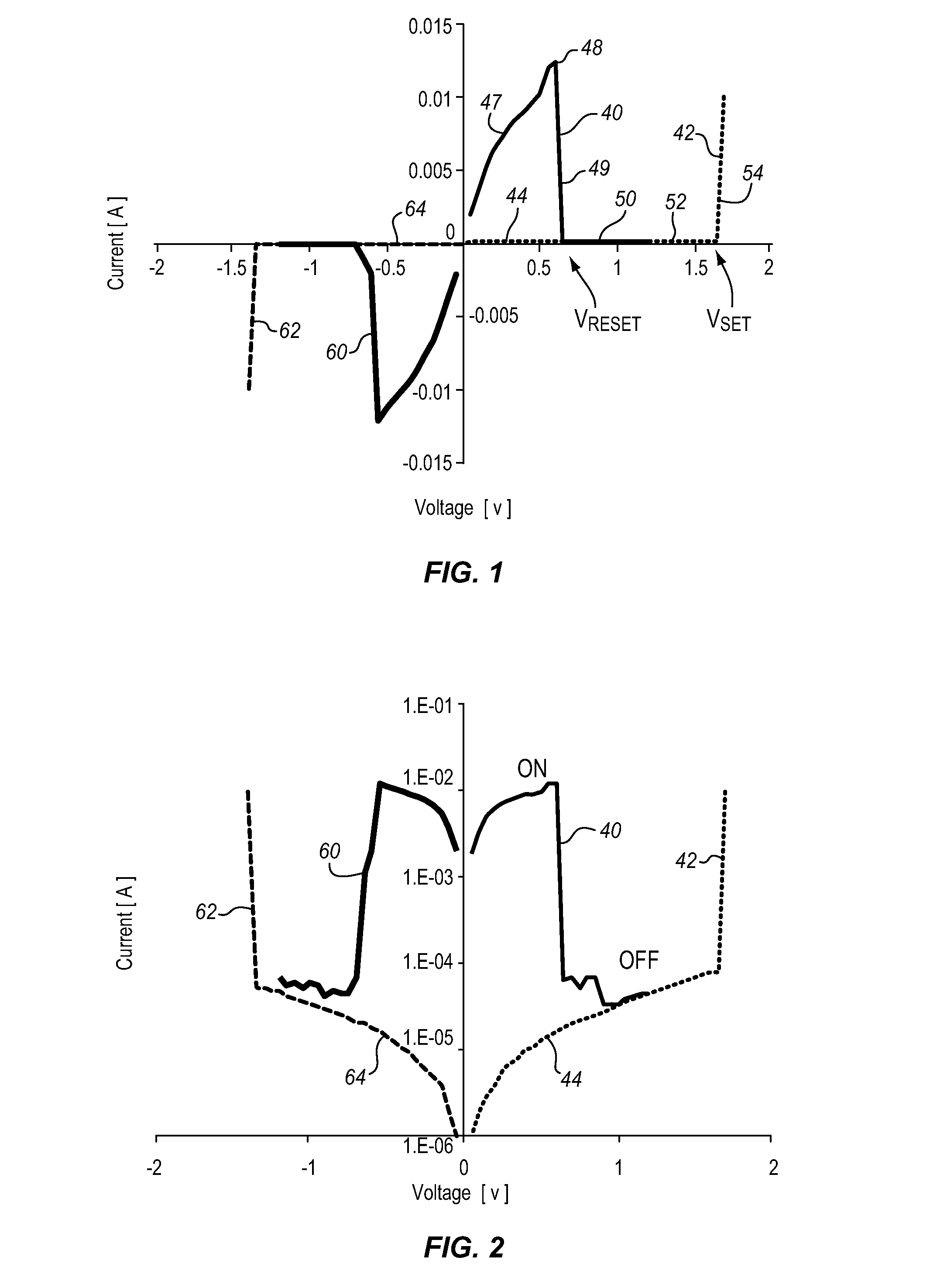

One embodiment of the present invention includes a low-cost unipolar rewritable variable-resistance memory device, made of cross-point arrays of memory cells, vertically stacked on top of one another and compatible with a polycrystalline silicon diode.

Owner:HITACHI GLOBAL STORAGE TECH NETHERLANDS BV

Electrosurgical instrument and method

InactiveUS7517349B2Lower base resistanceRule out the possibilityDiagnosticsSurgical instruments for heatingElectrical resistance and conductanceVaricose veins

Owner:TYCO HEALTHCARE GRP LP

Non-volatile resistance switching memories and methods of making same

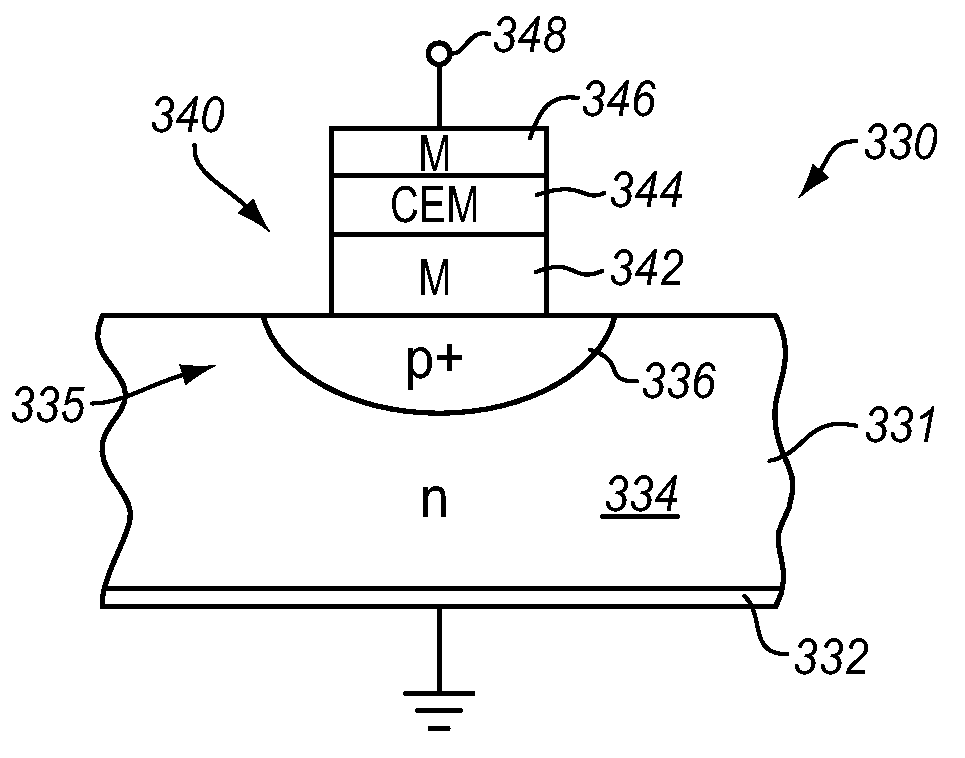

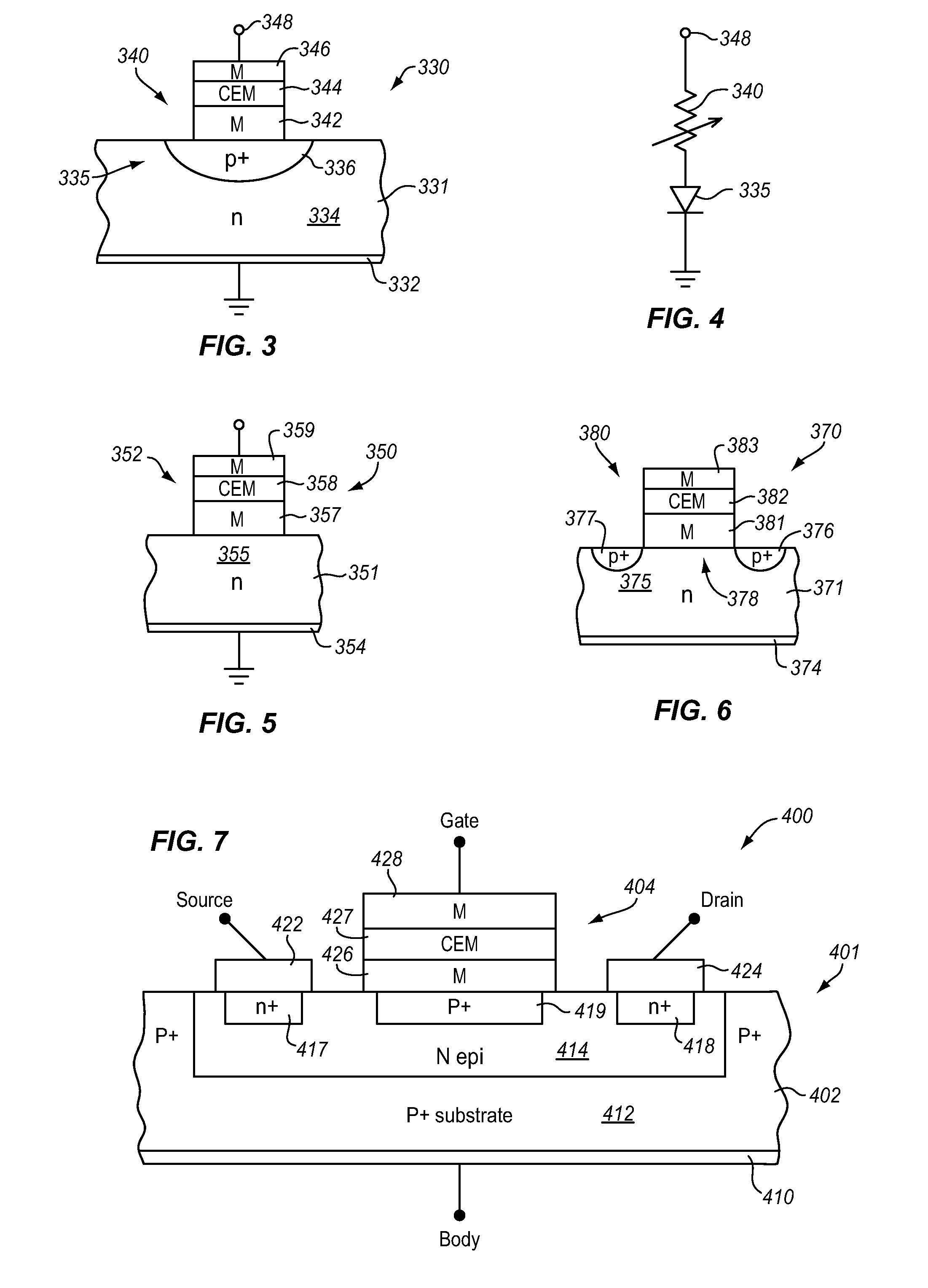

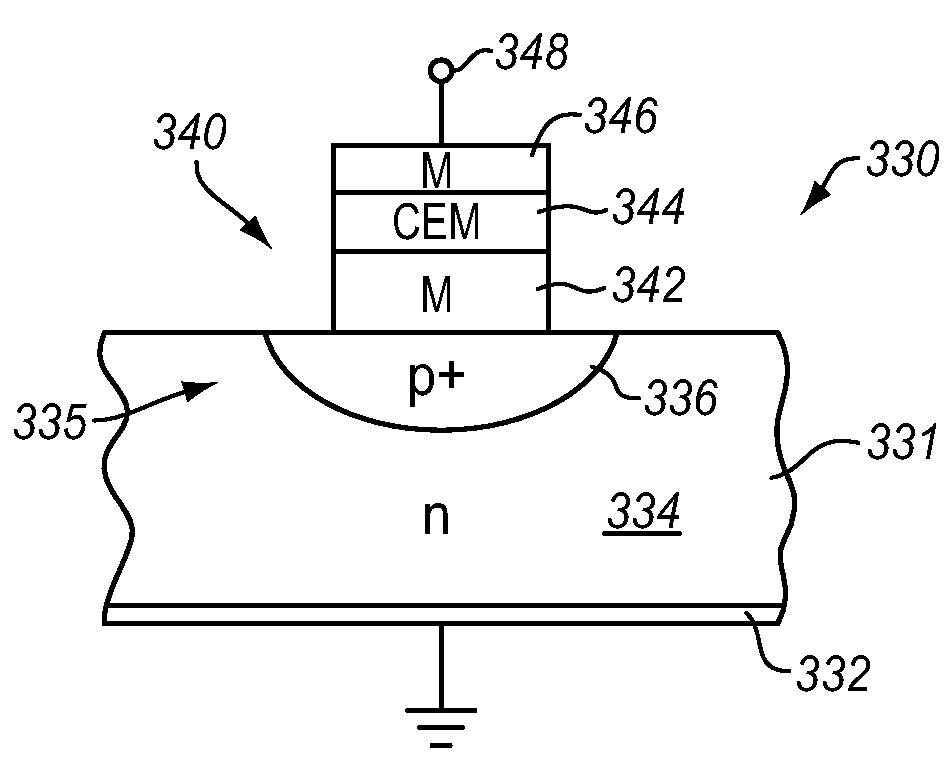

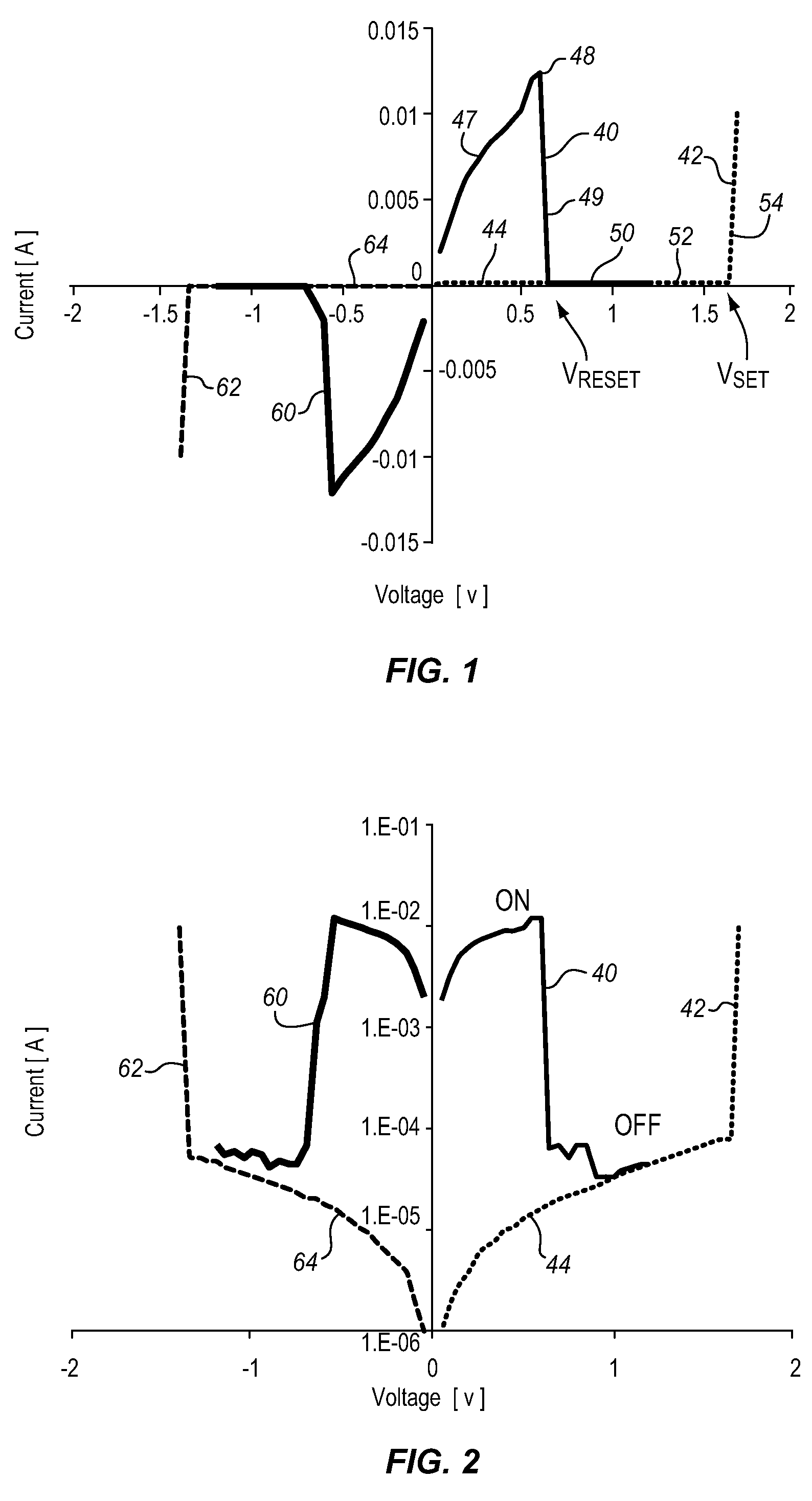

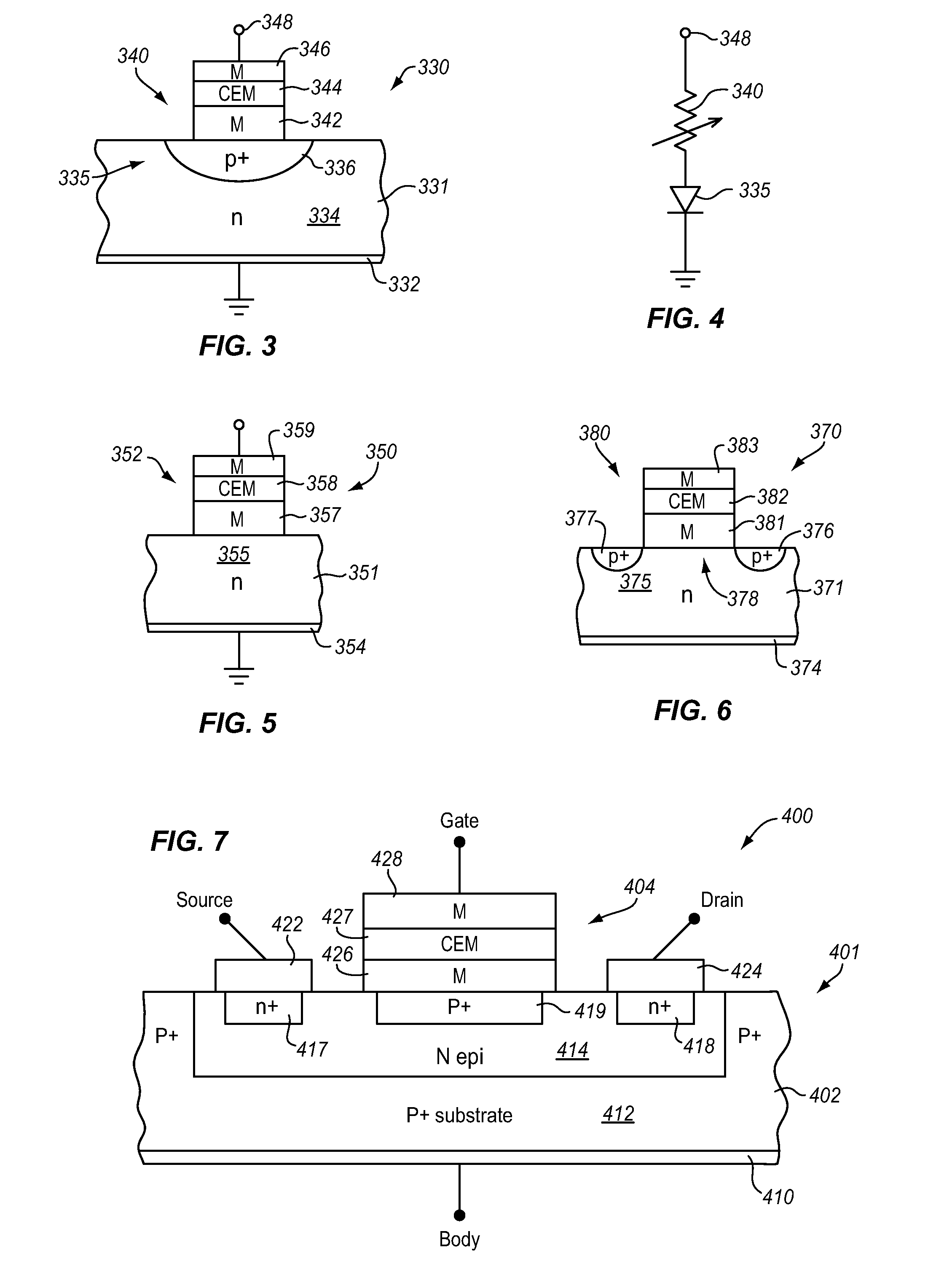

An integrated circuit memory cell including: a semiconductor having a first active area, a second active area, and a channel between the active areas; and a layer of a variable resistance material (VRM) directly above the channel. In one embodiment, there is a first conductive layer between the VRM and the channel and a second conductive layer directly above the VRM layer. The VRM preferably is a correlated electron material (CEM). The memory cell comprises a FET, such as a JFET or a MESFET. In another embodiment, there is a layer of an insulating material between the VRM and the channel. In this case, the memory cell may include a MOSFET structure.

Owner:SYMETRIX MEMORY

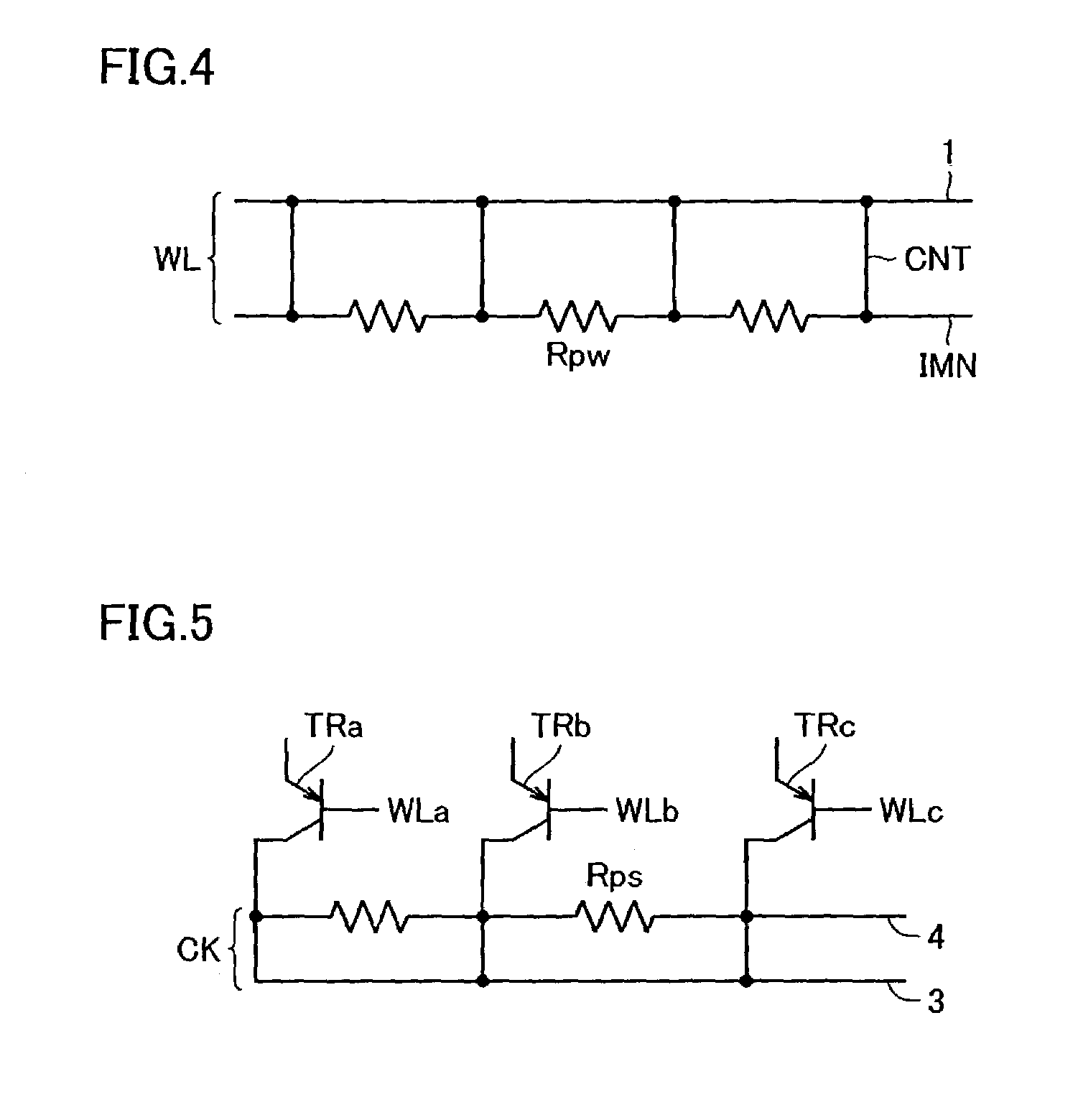

Semiconductor device

InactiveUS20050045919A1Increase the areaFine granularitySemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

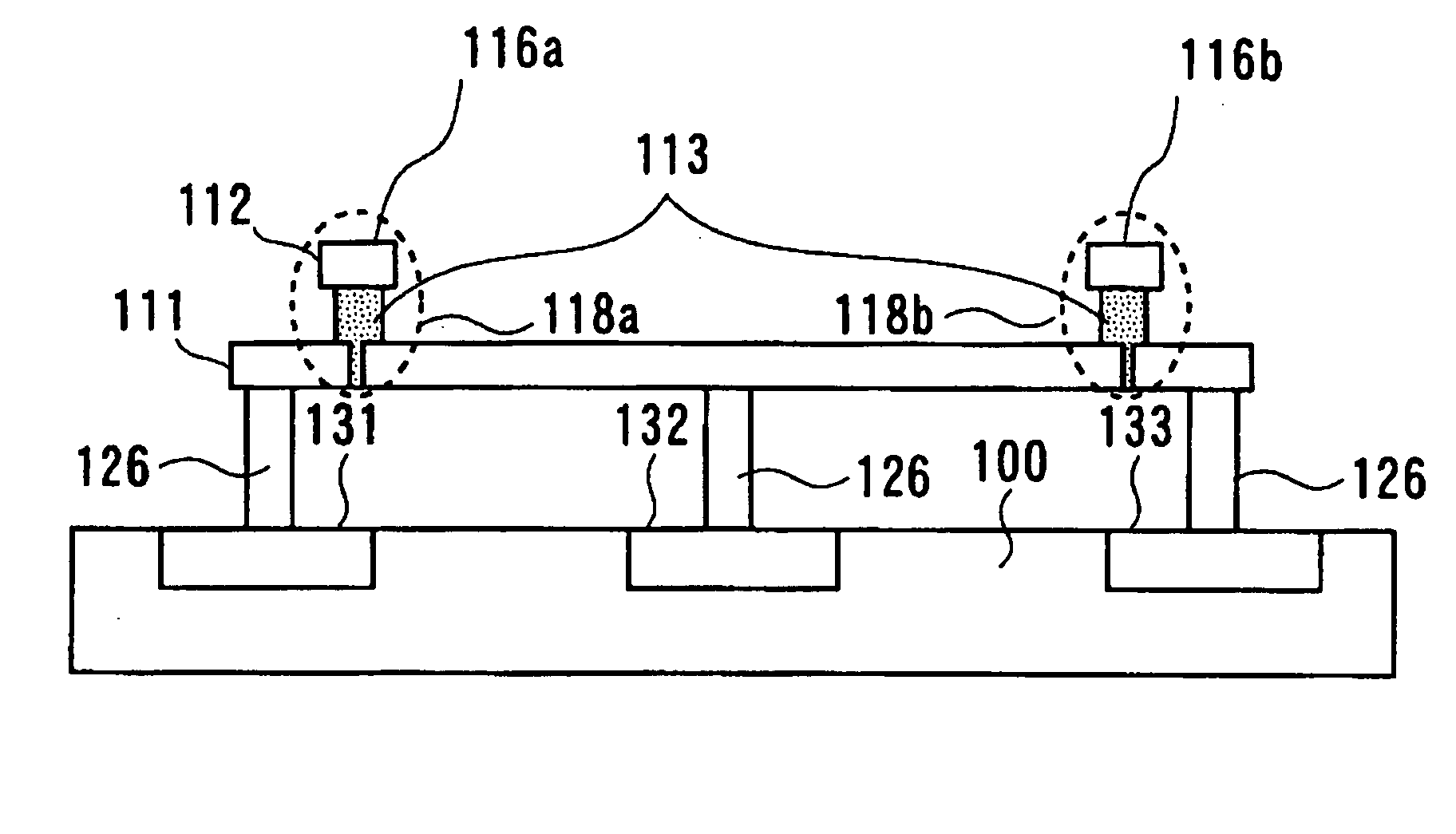

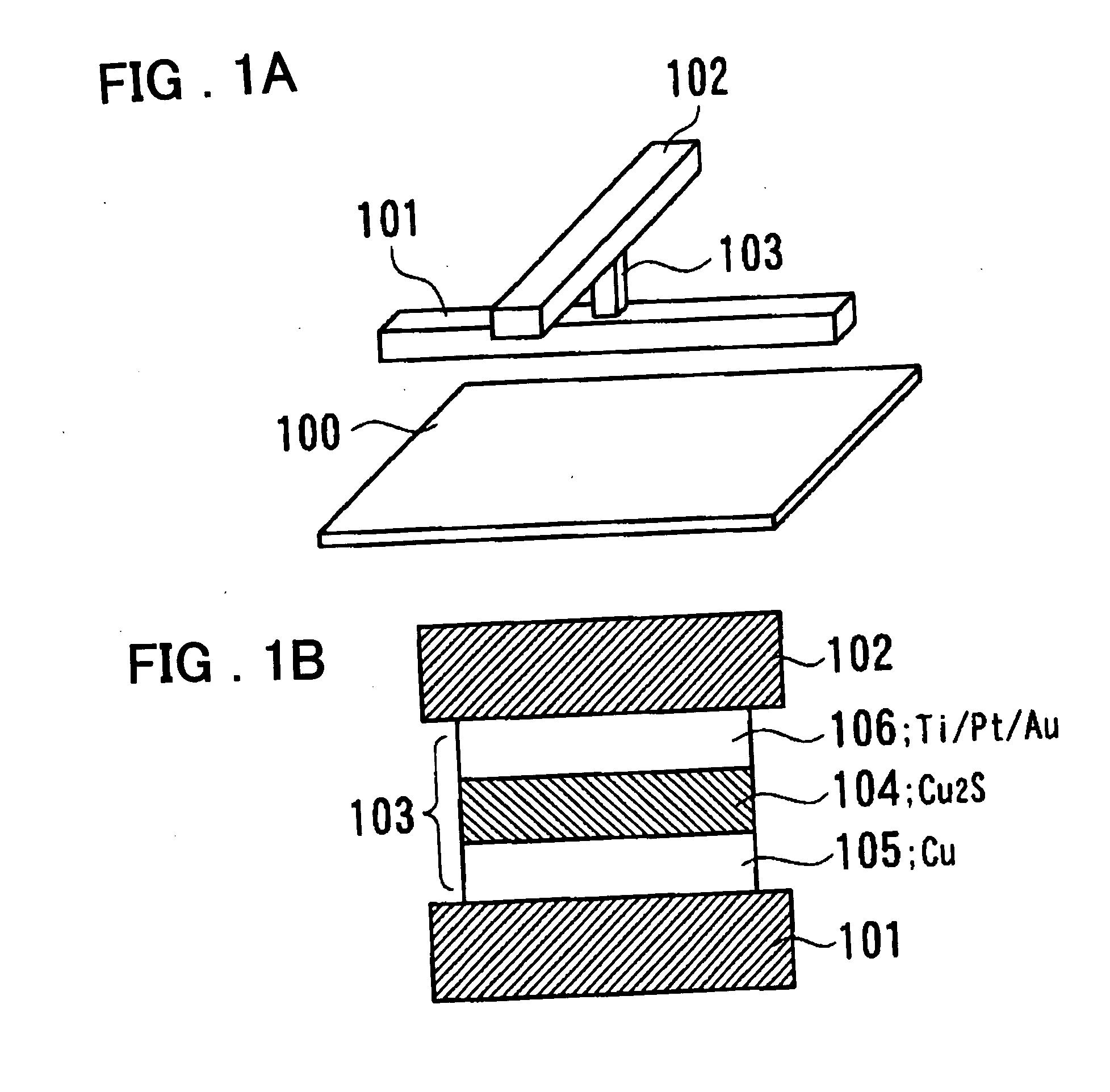

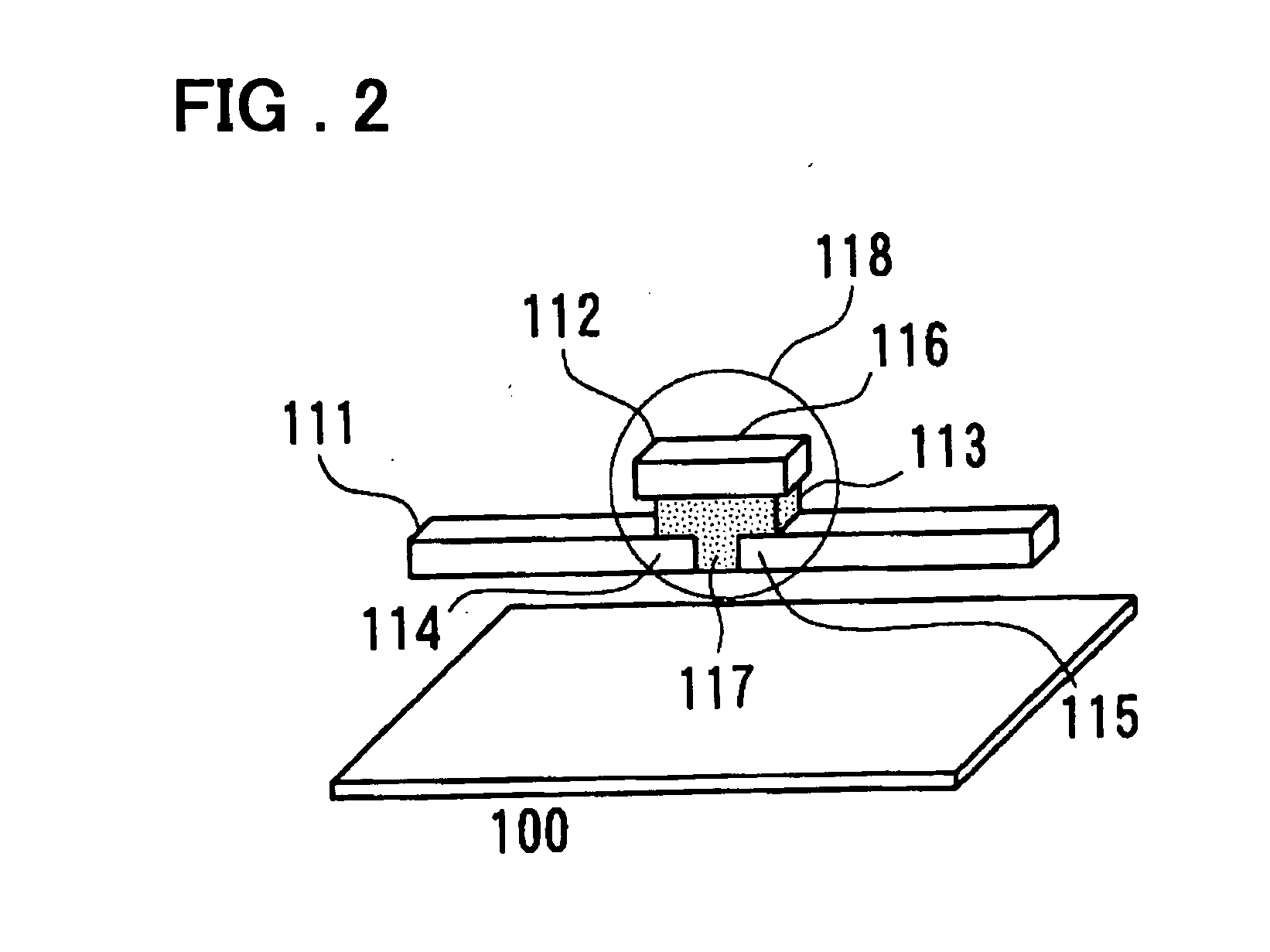

A programmable semiconductor device has a switch element in an interconnection layer, wherein in at least one of the inside of a via, interconnecting a wire of a first interconnection layer and a wire of a second interconnection layer, a contact part of the via with the wire of the first interconnection layer and a contact part of the via with the wire of the second interconnection layer, there is provided a variable electrical conductivity member, such as a member of an electrolyte material. The via is used as a variable electrical conductivity type switch element or as a variable resistance device having a contact part with the wire of the first interconnection layer as a first terminal and having a contact part with the wire of the second interconnection layer as a second terminal. By varying the electrical conductivity of the switch element, the state of connection of the via with the wire of the first interconnection layer and the state of connection of the via with the wire of the second interconnection layer may be variably set to a shorted state, an open-circuited state or to an intermediate state A two-state switch element includes an ion conductor for conducting metal ions interposed between the first and second electrodes. The second electrode is formed of a material lower in reactivity than the first electrode. The electrical conductivity across the first and second electrodes is changed by the oxidation-reduction reaction of the metal ions. There are provided first and second transistors of opposite polarities, connected to the first electrode, and third and fourth transistors of opposite polarities, connected to the second electrode.

Owner:NEC CORP

Non-volatile resistance switching memories and methods of making same

An integrated circuit memory cell including: a semiconductor having a first active area, a second active area, and a channel between the active areas; and a layer of a variable resistance material (VRM) directly above the channel. In one embodiment, there is a first conductive layer between the VRM and the channel and a second conductive layer directly above the VRM layer. The VRM preferably is a correlated electron material (CEM). The memory cell comprises a FET, such as a JFET or a MESFET. In another embodiment, there is a layer of an insulating material between the VRM and the channel. In this case, the memory cell may include a MOSFET structure.

Owner:SYMETRIX MEMORY

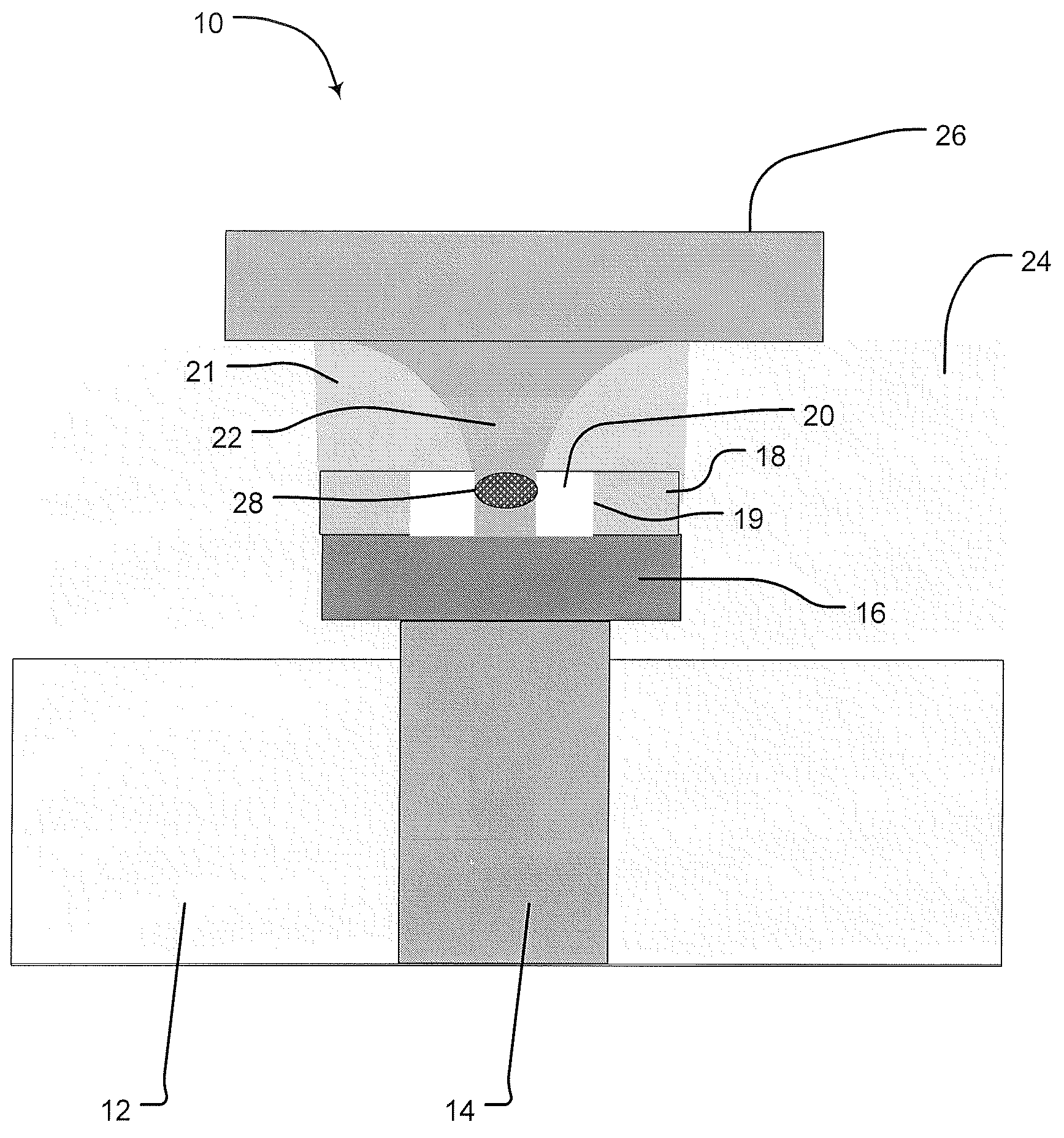

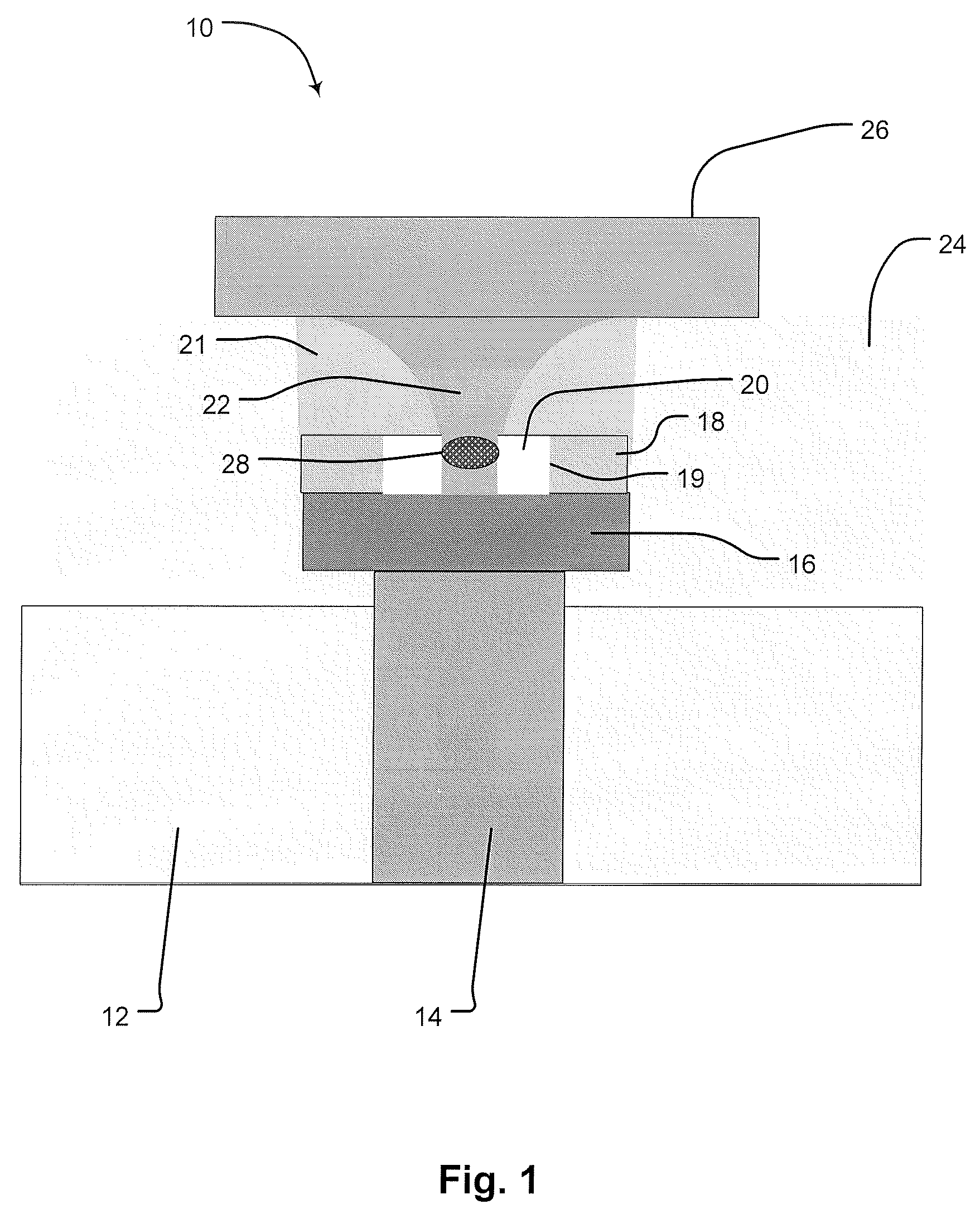

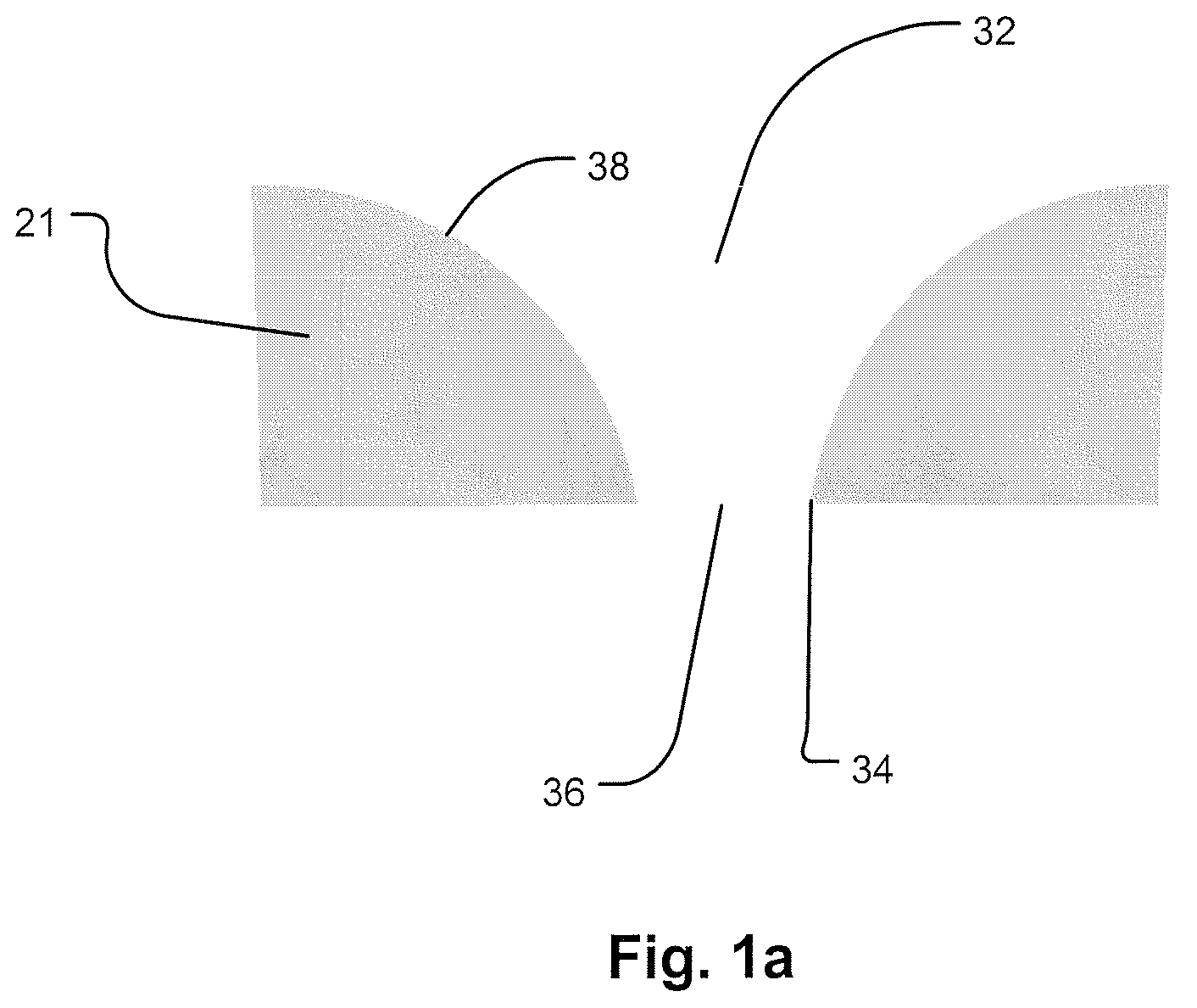

Method for Forming Self-Aligned Thermal Isolation Cell for a Variable Resistance Memory Array

A non-volatile method with a self-aligned RRAM element. The method includes a lower electrode element, generally planar in form, having an inner contact surface. At the top of the device is a upper electrode element, spaced from the lower electrode element. A containment structure extends between the upper electrode element and the lower electrode element, and this element includes a sidewall spacer element having an inner surface defining a generally funnel-shaped central cavity, terminating at a terminal edge to define a central aperture; and a spandrel element positioned between the sidewall spacer element and the lower electrode, having an inner surface defining a thermal isolation cell, the spandrel inner walls being spaced radially outward from the sidewall spacer terminal edge, such that the sidewall spacer terminal edge projects radially inward from the spandrel element inner surface. ARRAM element extends between the lower electrode element and the upper electrode, occupying at least a portion of the sidewall spacer element central cavity and projecting from the sidewall spacer terminal edge toward and making contact with the lower electrode. In this manner, the spandrel element inner surface is spaced from the RRAM element to define a thermal isolation cell adjacent the RRAM element.

Owner:MACRONIX INT CO LTD

Non-volatile semiconductor memory device allowing shrinking of memory cell

InactiveUS7208751B2Reducing memory cell sizeSmall sizeSemiconductor/solid-state device detailsSolid-state devicesComputer scienceStorage cell

Dummy cells are disposed in alignment with memory cells arranged in rows and columns in a memory array. The memory cell includes a variable resistance element and a select transistor having a collector connected to a substrate region and selecting the variable resistance element in response to a row select signal. Corresponding to a row of memory cells, there is provided a word line connecting to memory cells on corresponding row and transmitting the row select signal, and a word line shunting line electrically connected at predetermined intervals to each word line. Moreover, corresponding to a row of dummy cells and a column of dummy cells, there is provided substrate shunt lines electrically connected to the substrate region. The voltage distribution in the substrate region is eliminated to achieve stable operating characteristics of the memory cell transistor. In addition, a word line is driven at high speed by a word line shunt structure.

Owner:RENESAS ELECTRONICS CORP

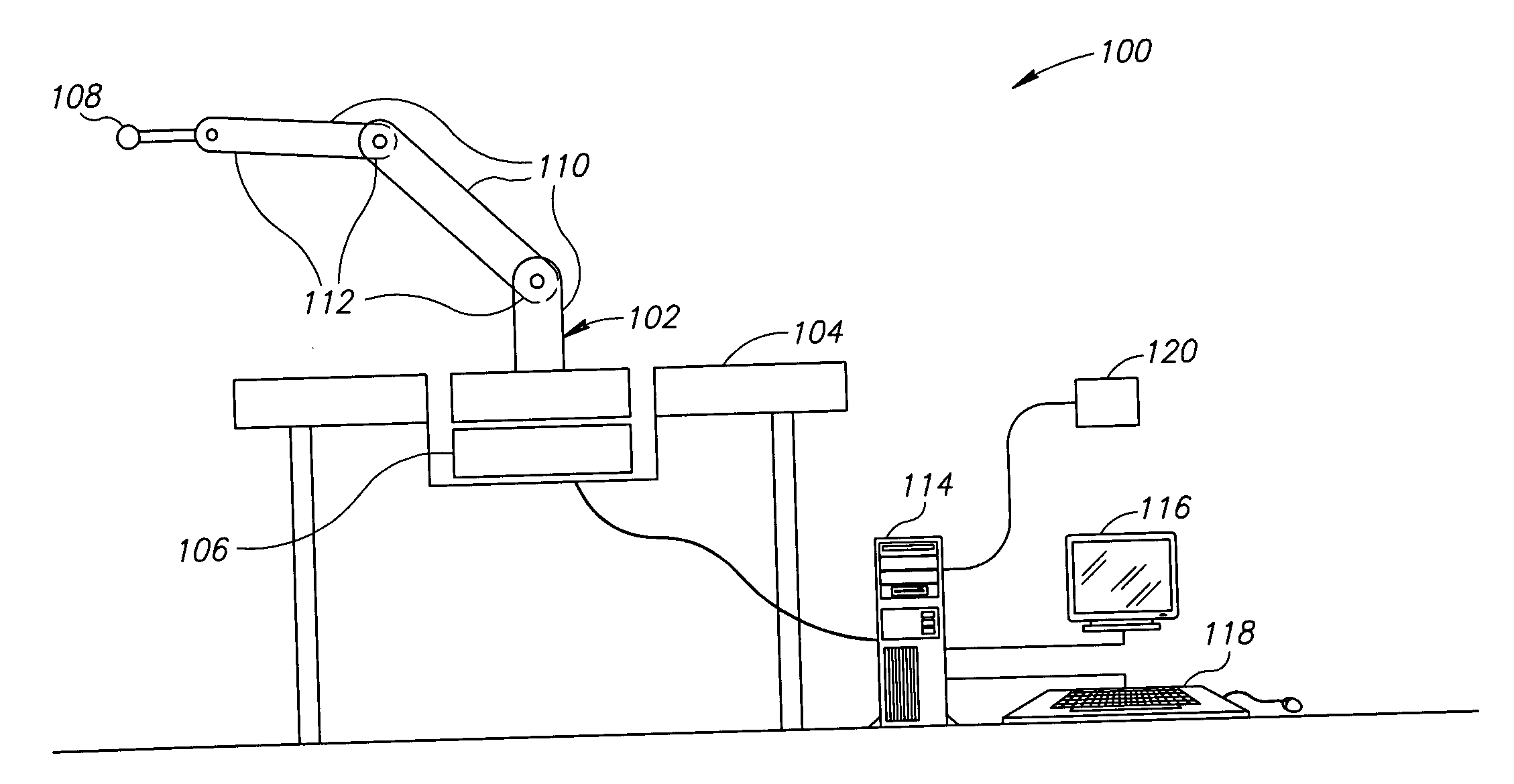

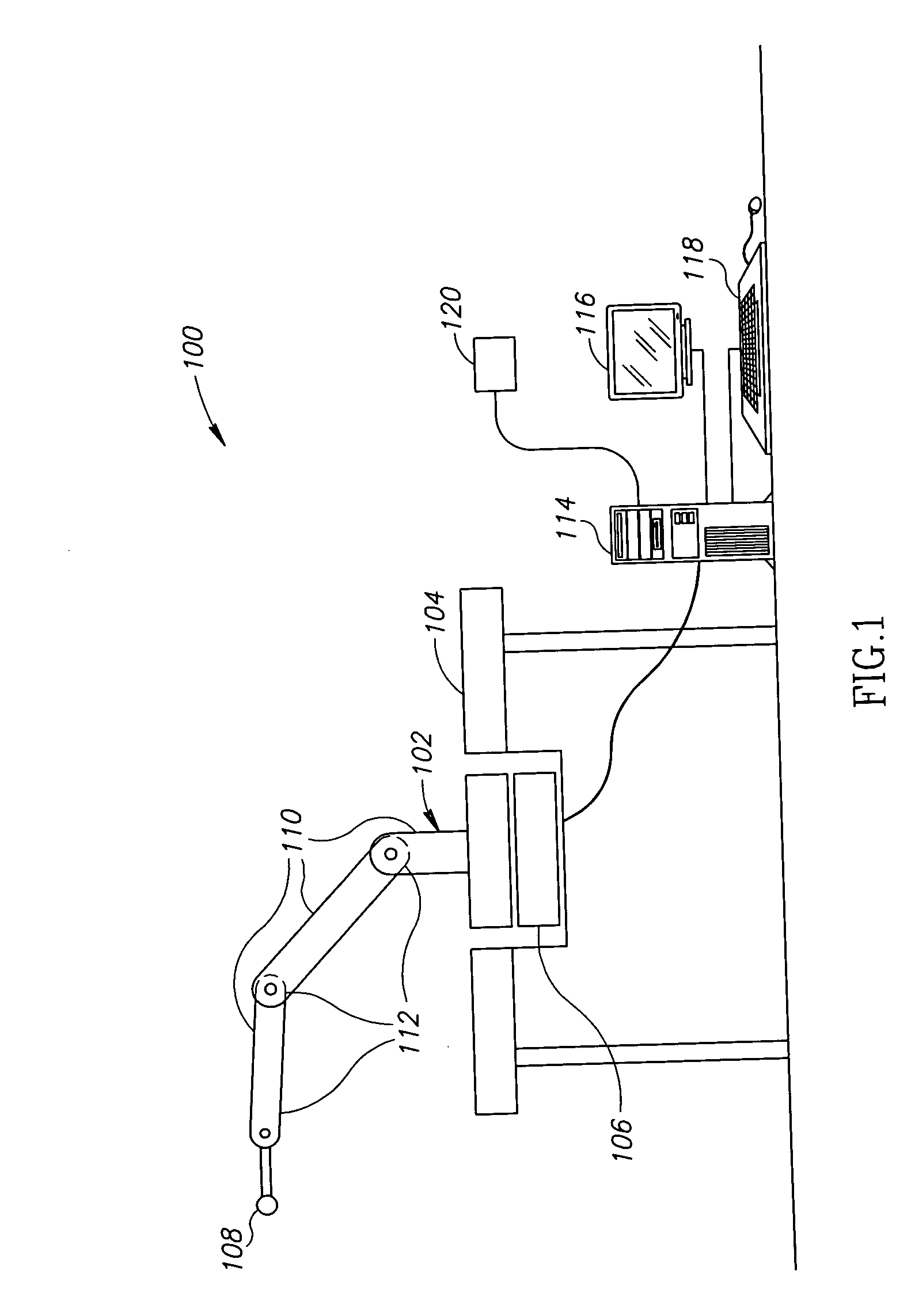

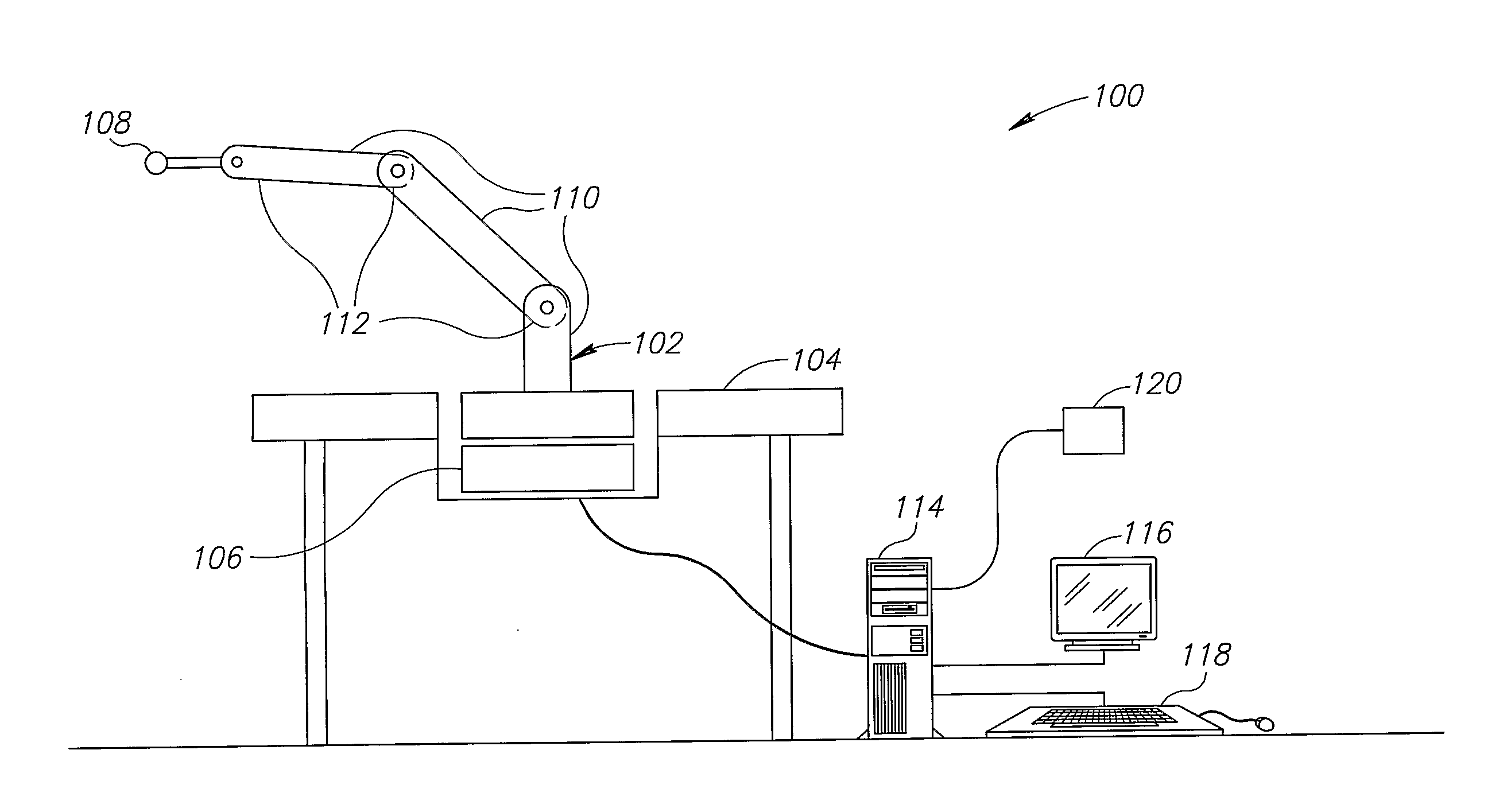

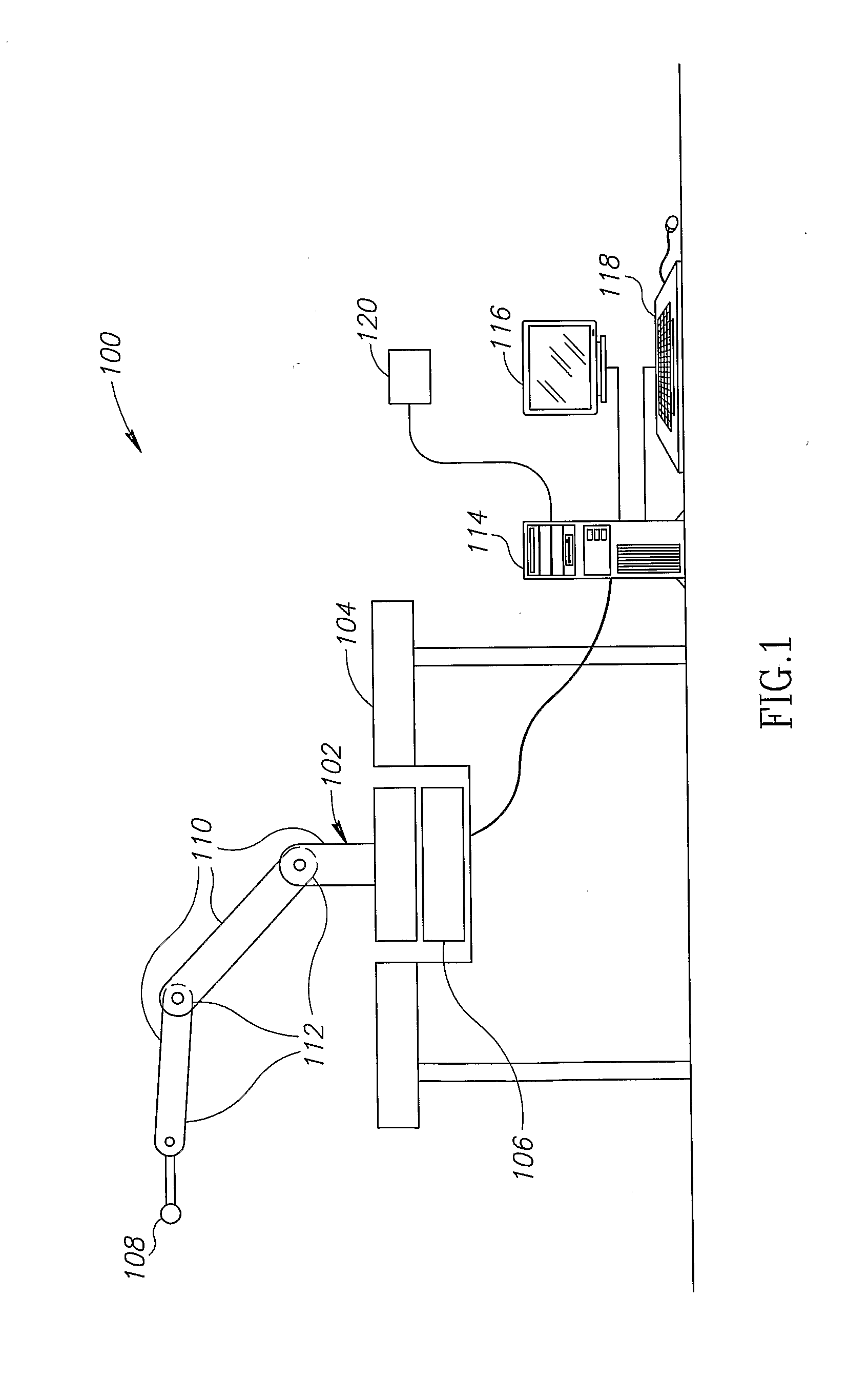

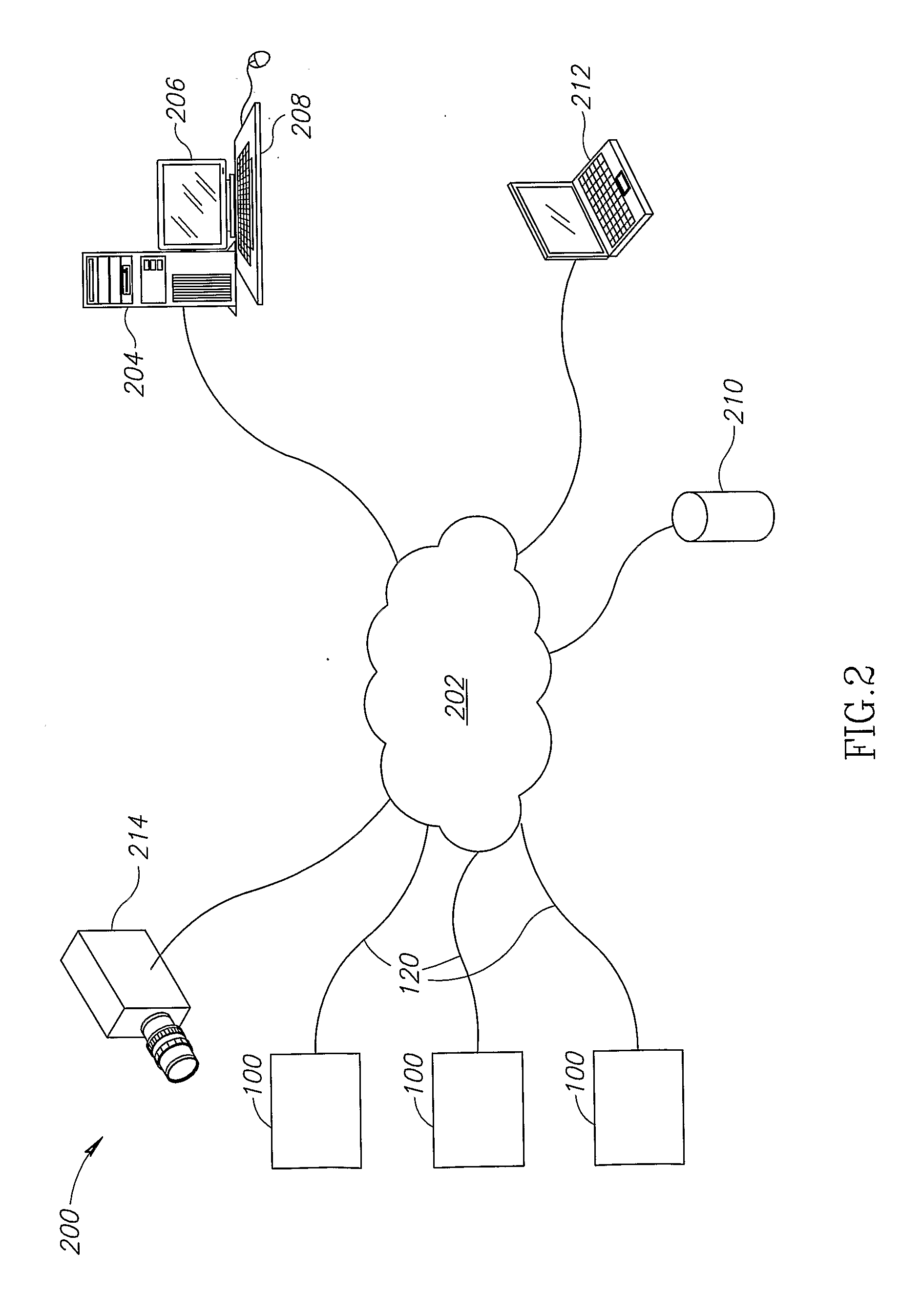

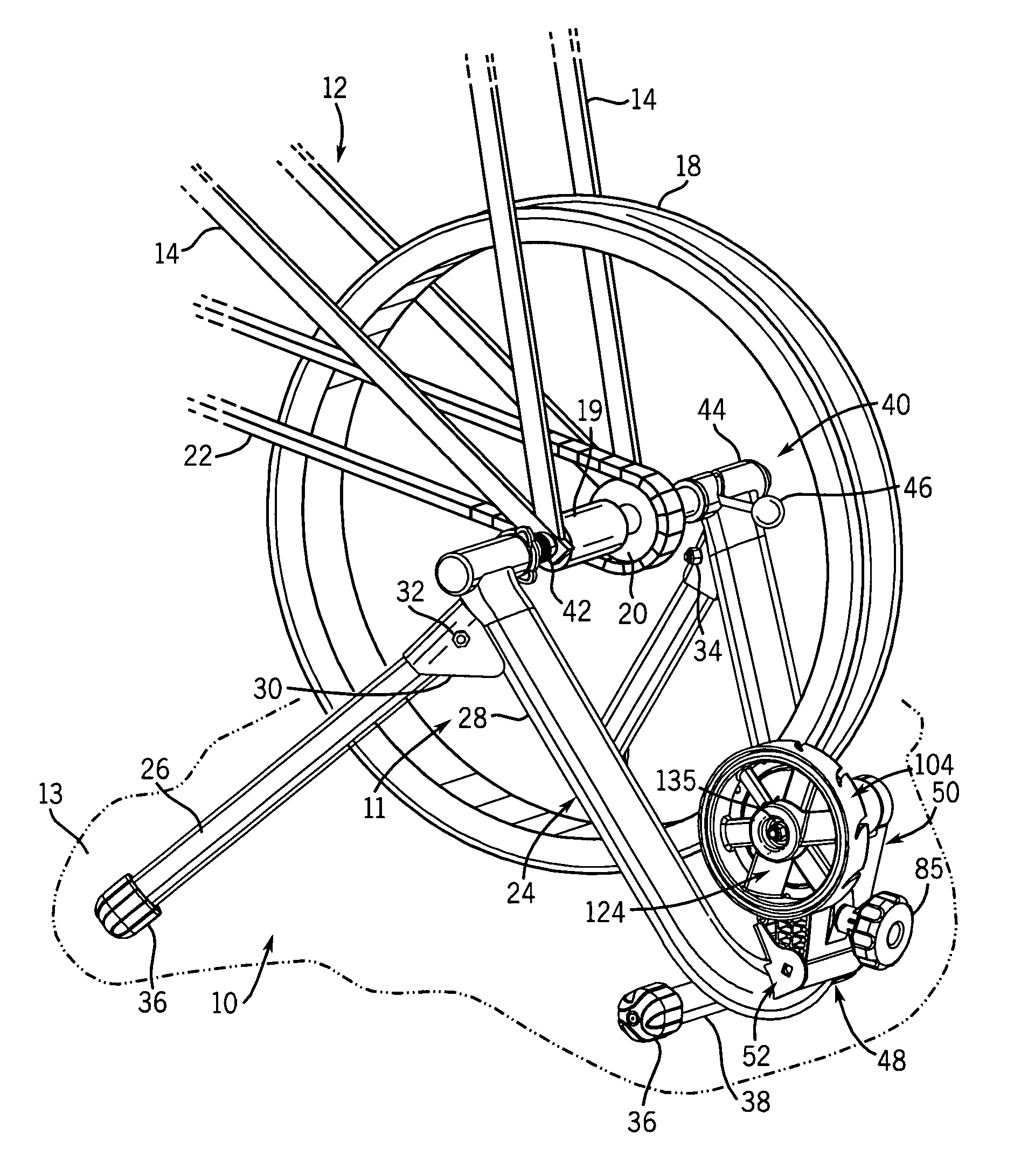

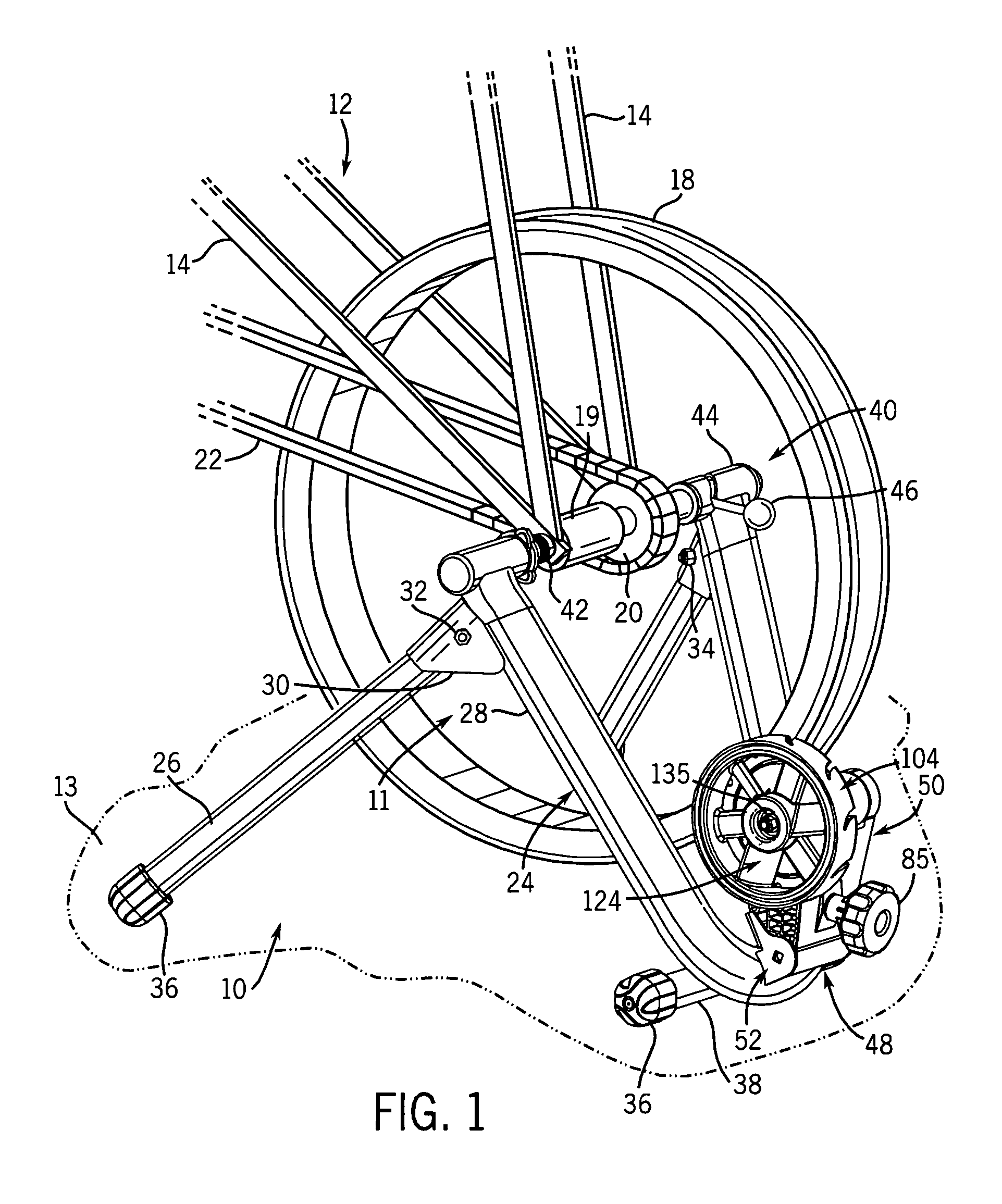

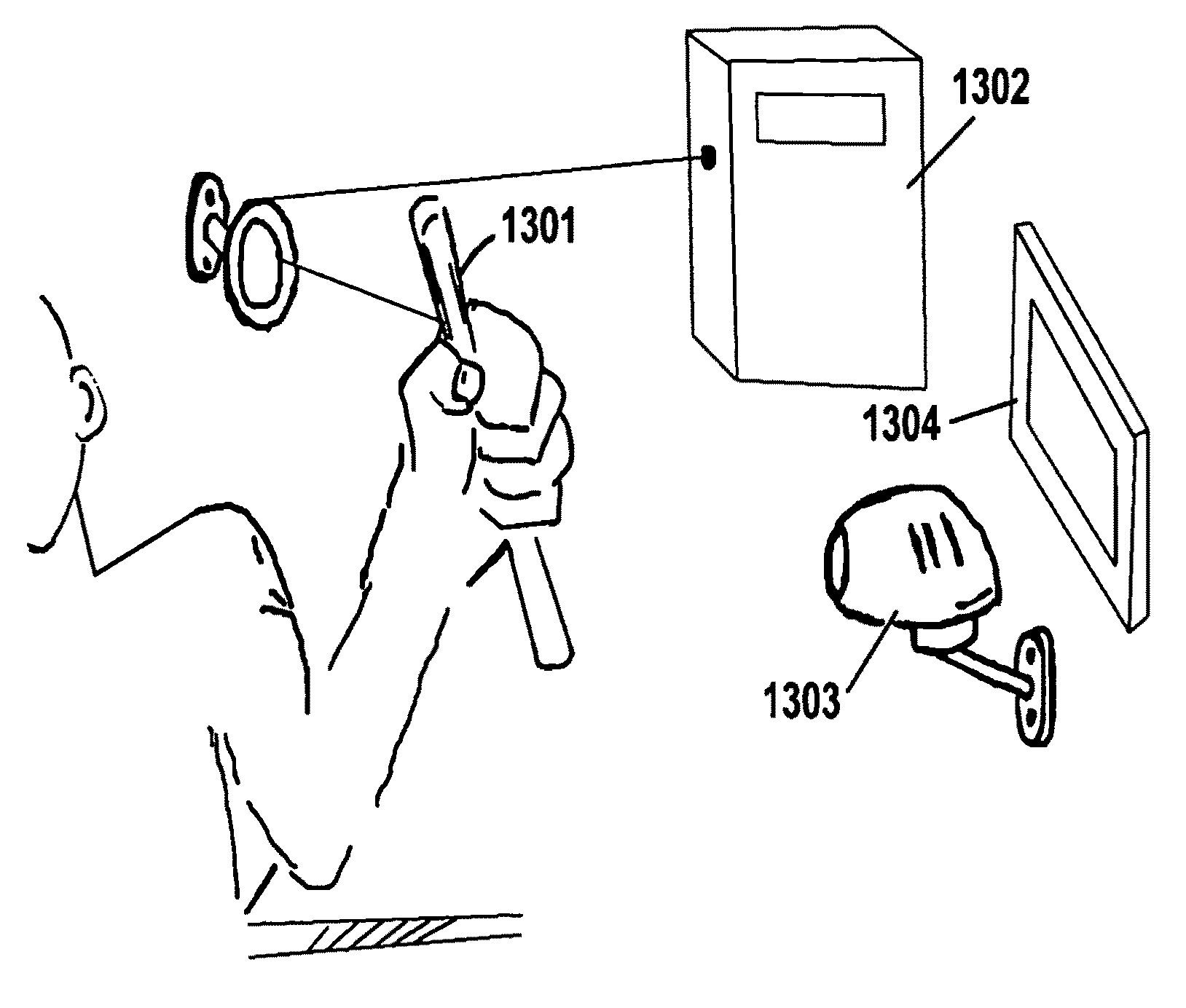

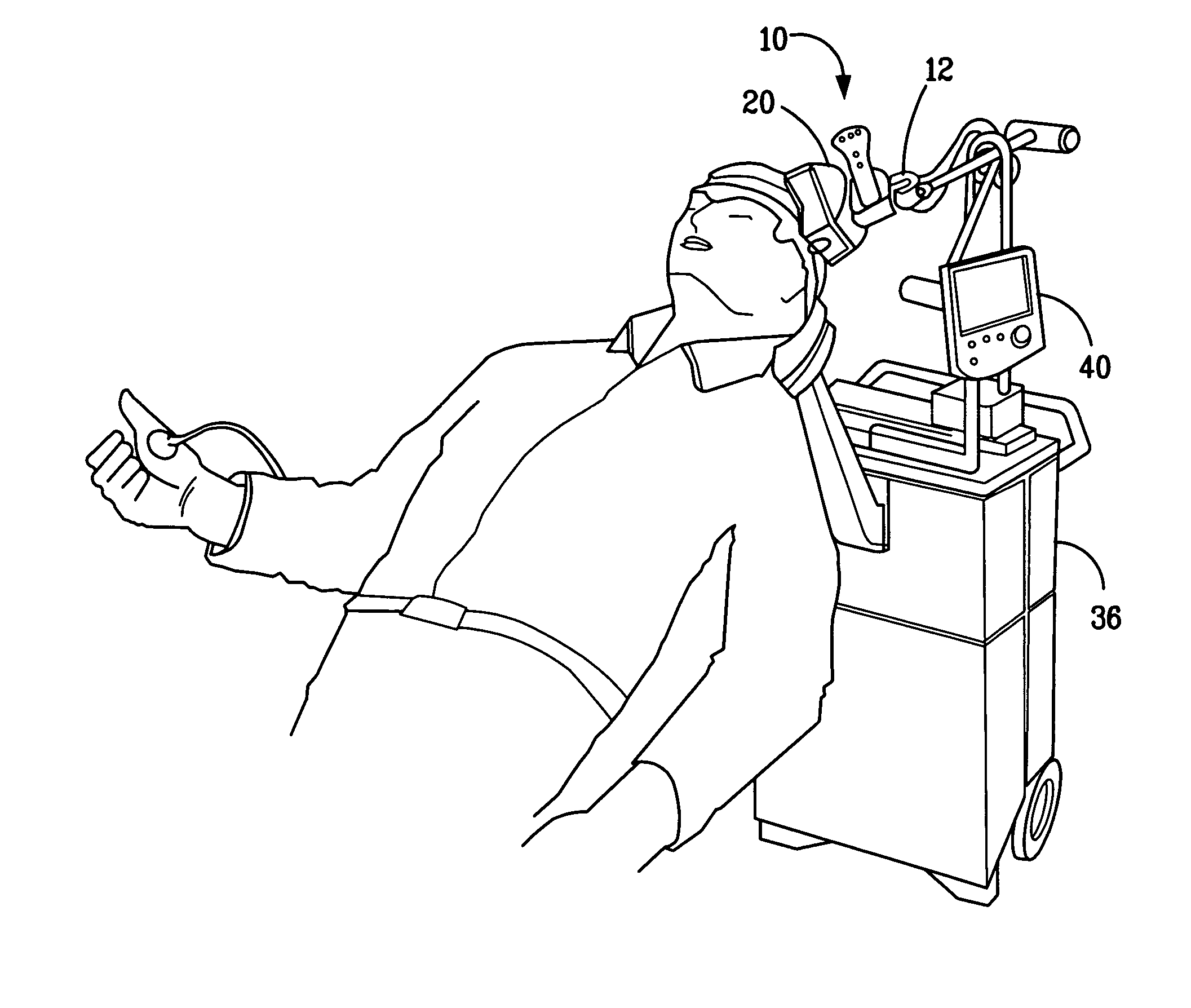

Methods and apparatuses for rehabilitation and training

InactiveUS20060293617A1Significant motionAvoid structural overloadingPhysical therapies and activitiesLocal control/monitoringThree degrees of freedomEngineering

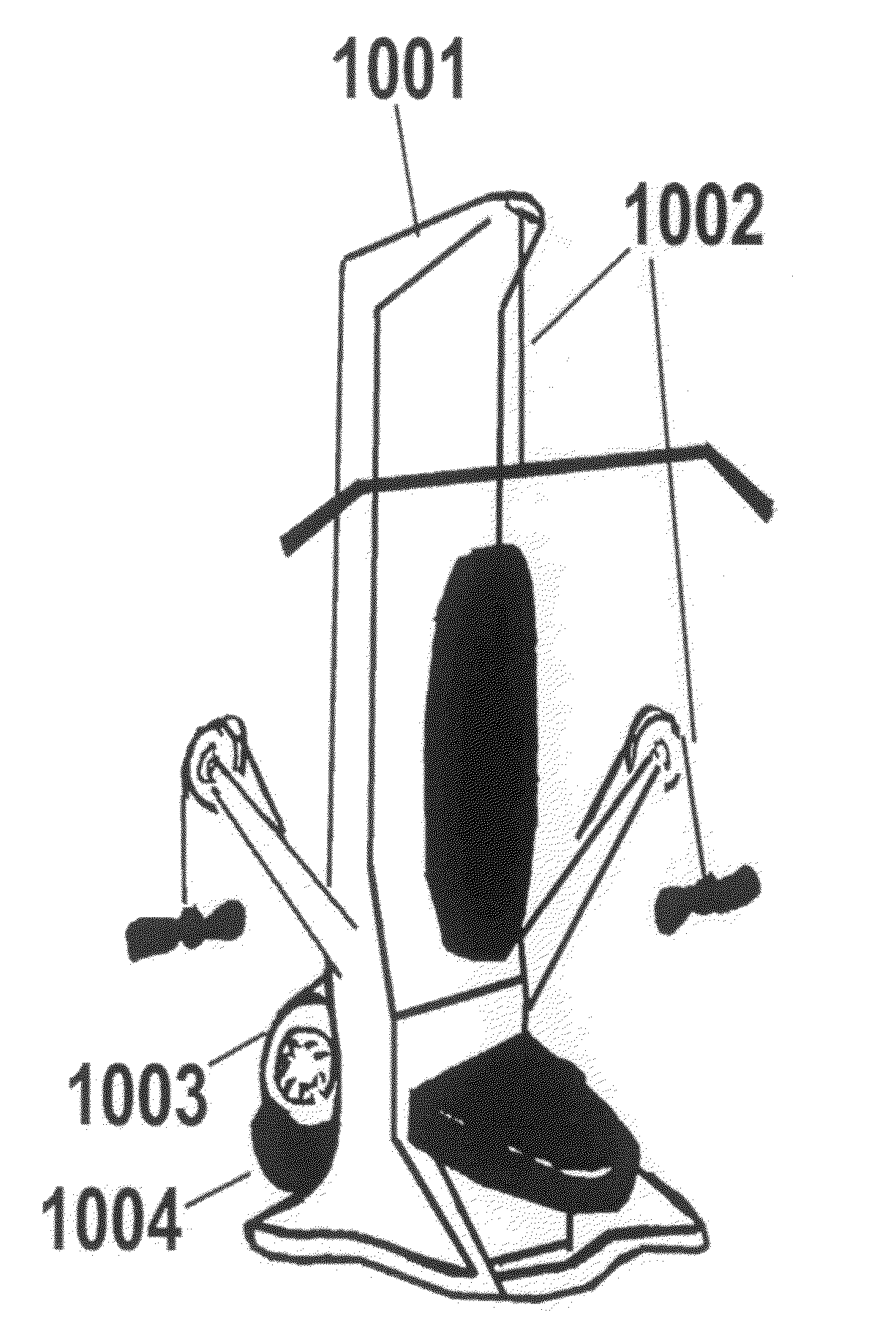

A rehabilitation apparatus with at least three degrees of freedom of motion, comprising: a plurality of brakes; a motor, wherein the motor is operationally connected to the brakes; a plurality of surfaces, wherein each of a plurality of the surfaces correlates to a brake; and, wherein when the motor is activated, the brakes are selectively advanced to make contact with the surfaces causing friction between the brakes and the surfaces and thus causing variable resistance in the three degrees of freedom to the apparatus based on the extent of advancement of the brakes.

Owner:MOTORIKA

Methods and Apparatuses for Rehabilitation and Training

ActiveUS20080161733A1Avoid structural overloadingPhysical therapies and activitiesLocal control/monitoringThree degrees of freedomEngineering

A rehabilitation apparatus with at least three degrees of freedom of motion, comprising: a plurality of brakes; a motor, wherein the motor is operationally connected to the brakes; a plurality of surfaces, wherein each of a plurality of the surfaces correlates to a brake; and, wherein when the motor is activated, the brakes are selectively advanced to make contact with the surfaces causing friction between the brakes and the surfaces and thus causing variable resistance in the three degrees of freedom to the apparatus based on the extent of advancement of the brakes.

Owner:MOTORIKA

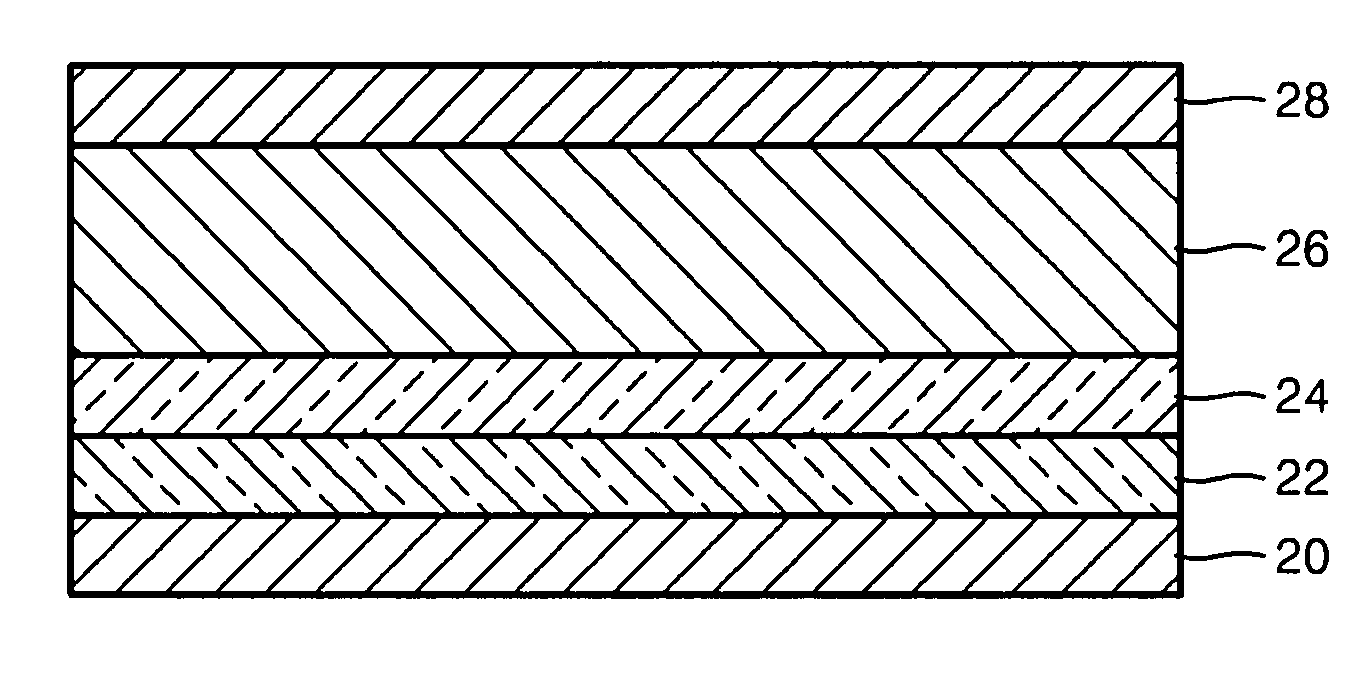

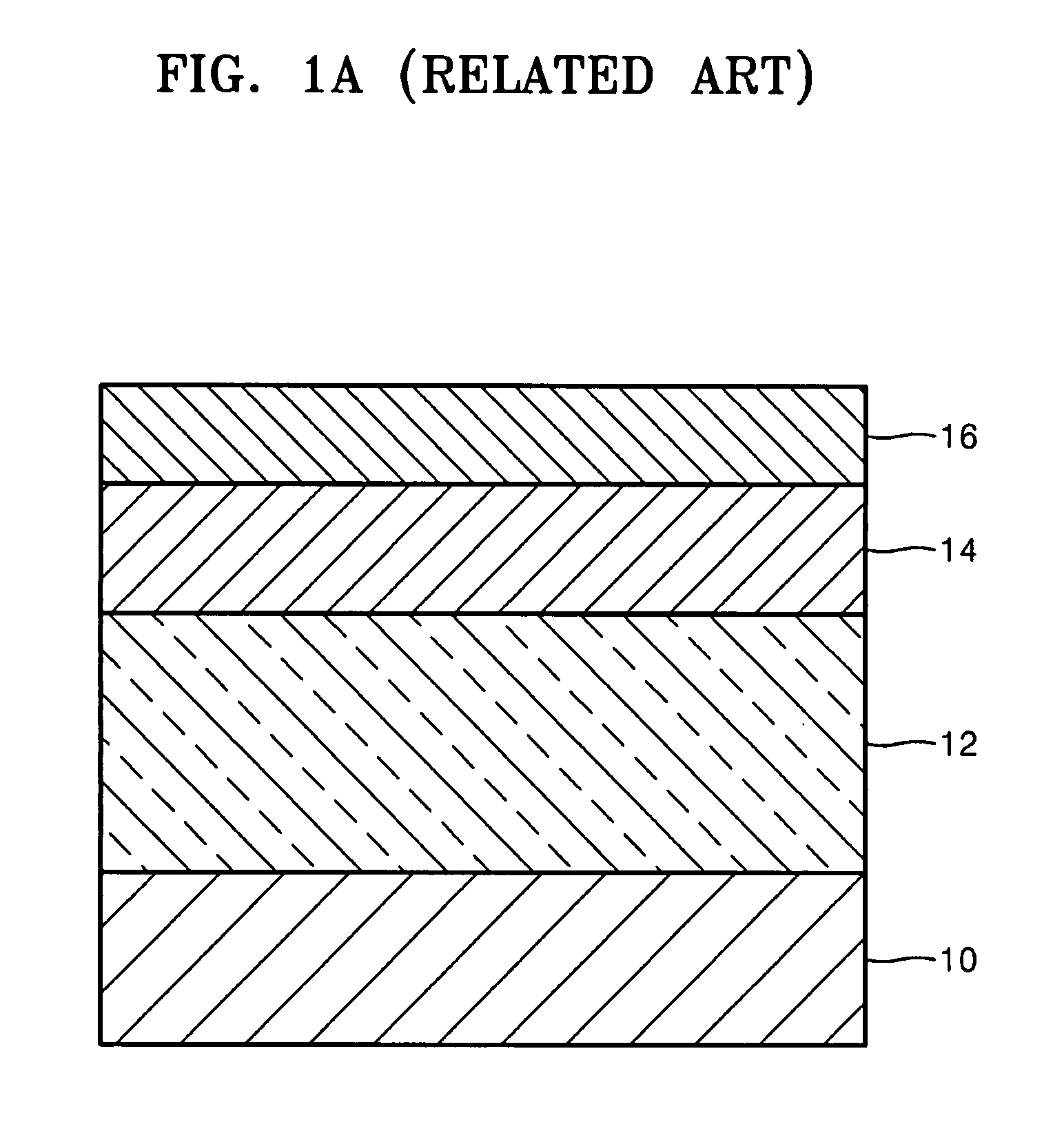

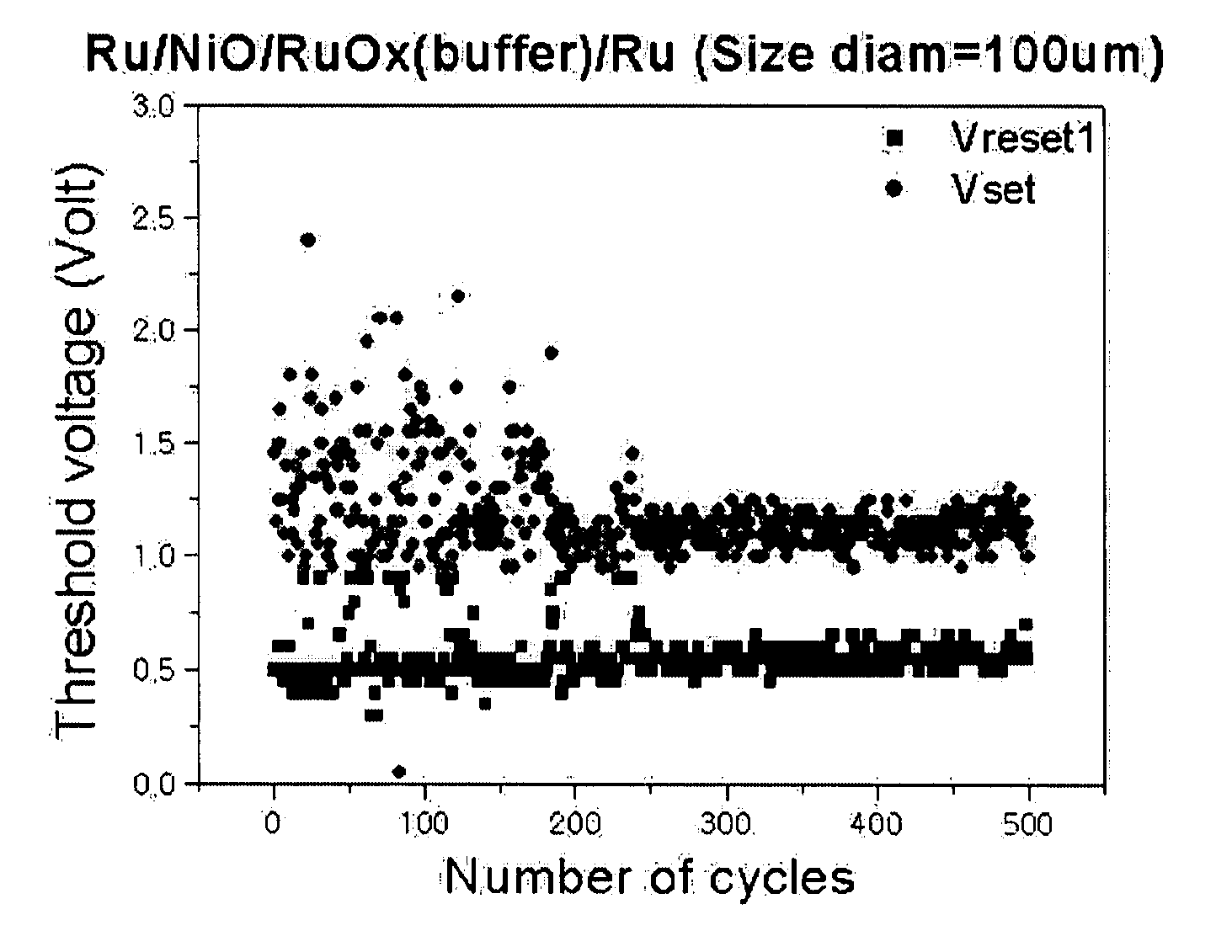

Variable resistance random access memory device and a method of fabricating the same

ActiveUS20070295950A1Stable reset currentIncrease heightSemiconductor/solid-state device manufacturingDigital storageRandom access memoryComputer science

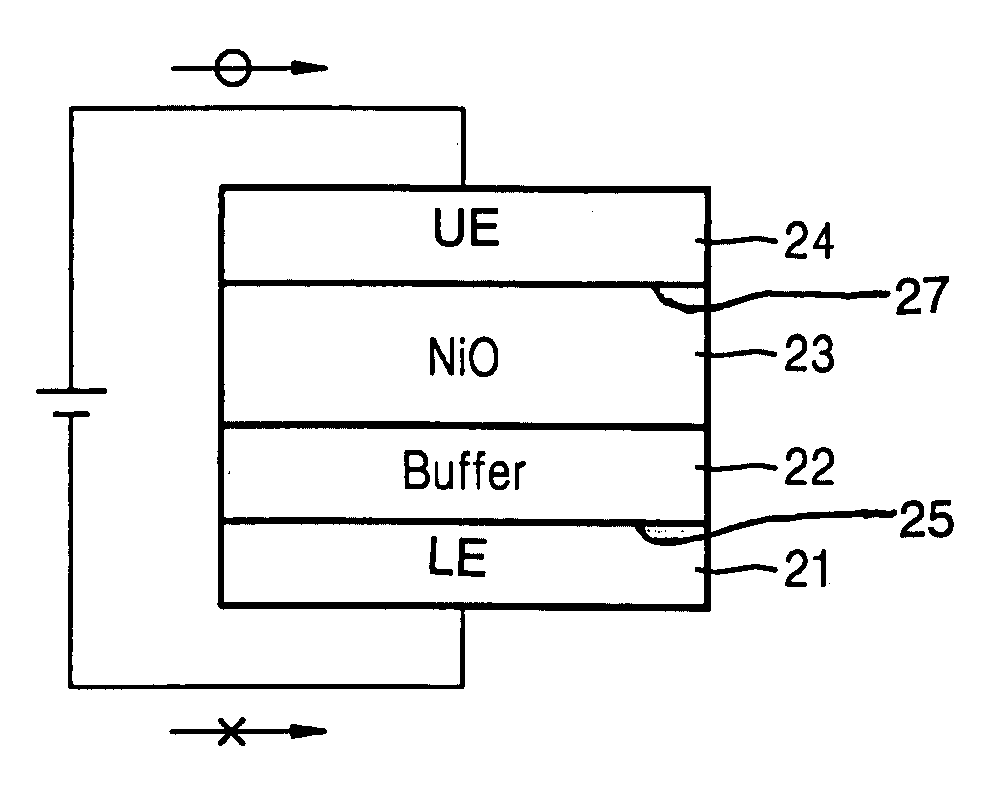

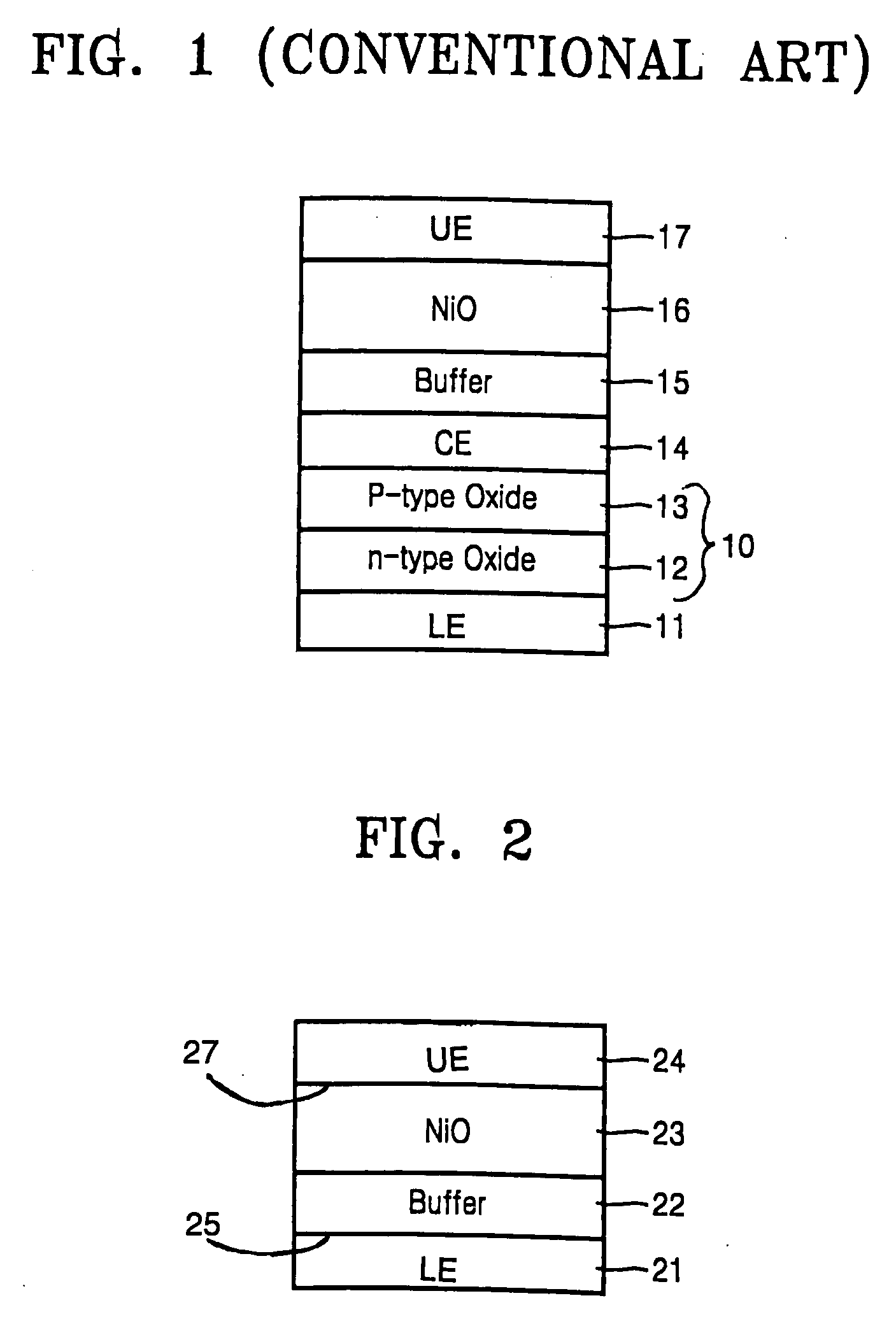

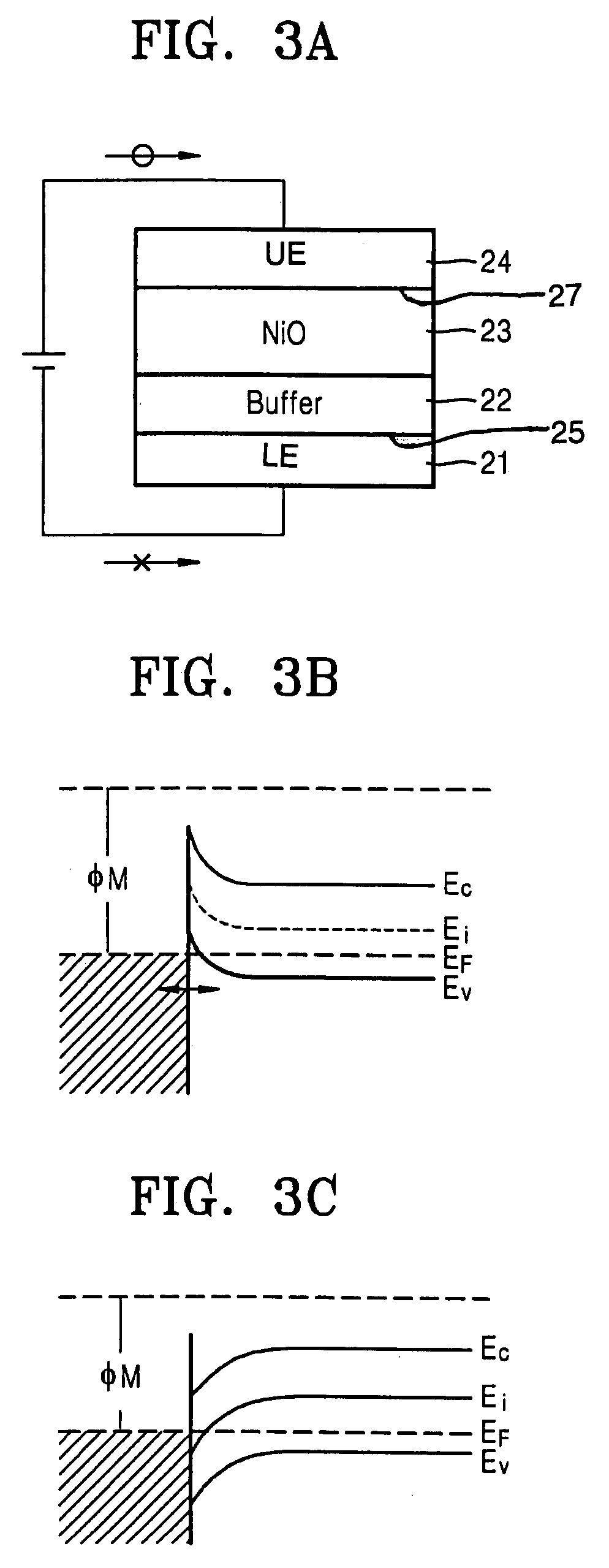

Provided is a variable resistance random access memory device having an n+ interfacial layer and a method of fabricating the same. The variable resistance random access memory device may include a lower electrode, an n+ interfacial layer on the lower electrode, a buffer layer on the n+ interfacial layer, an oxide layer on the buffer layer and having a variable resistance characteristic and an upper electrode on the oxide layer.

Owner:SAMSUNG ELECTRONICS CO LTD

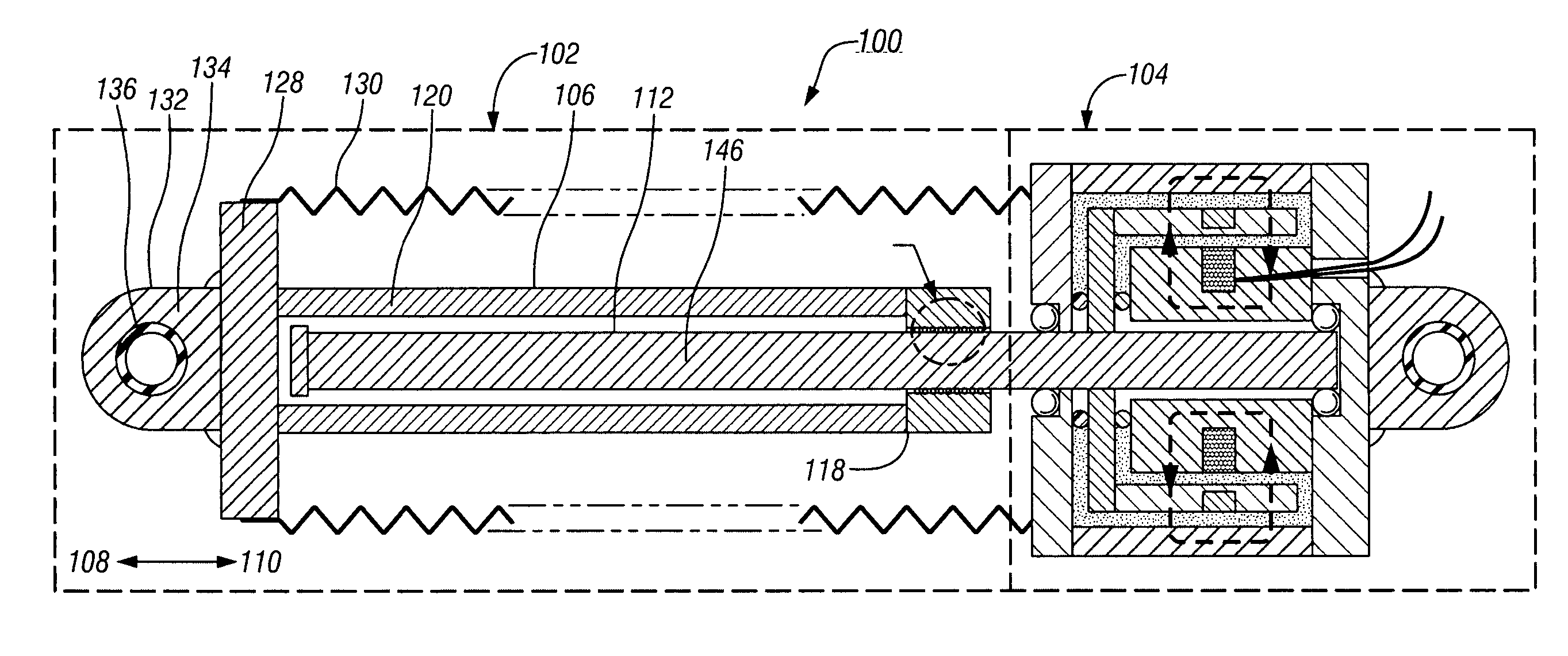

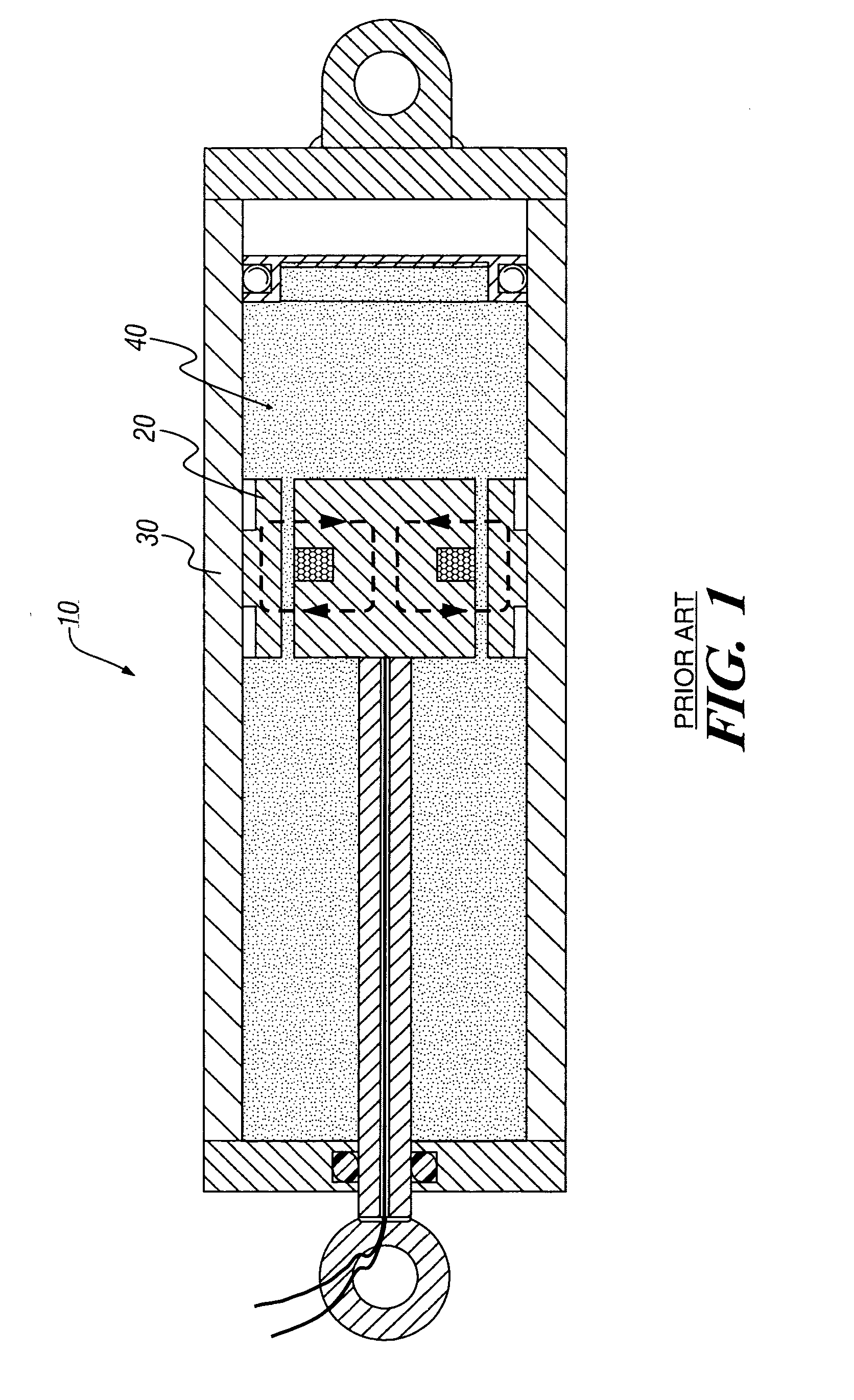

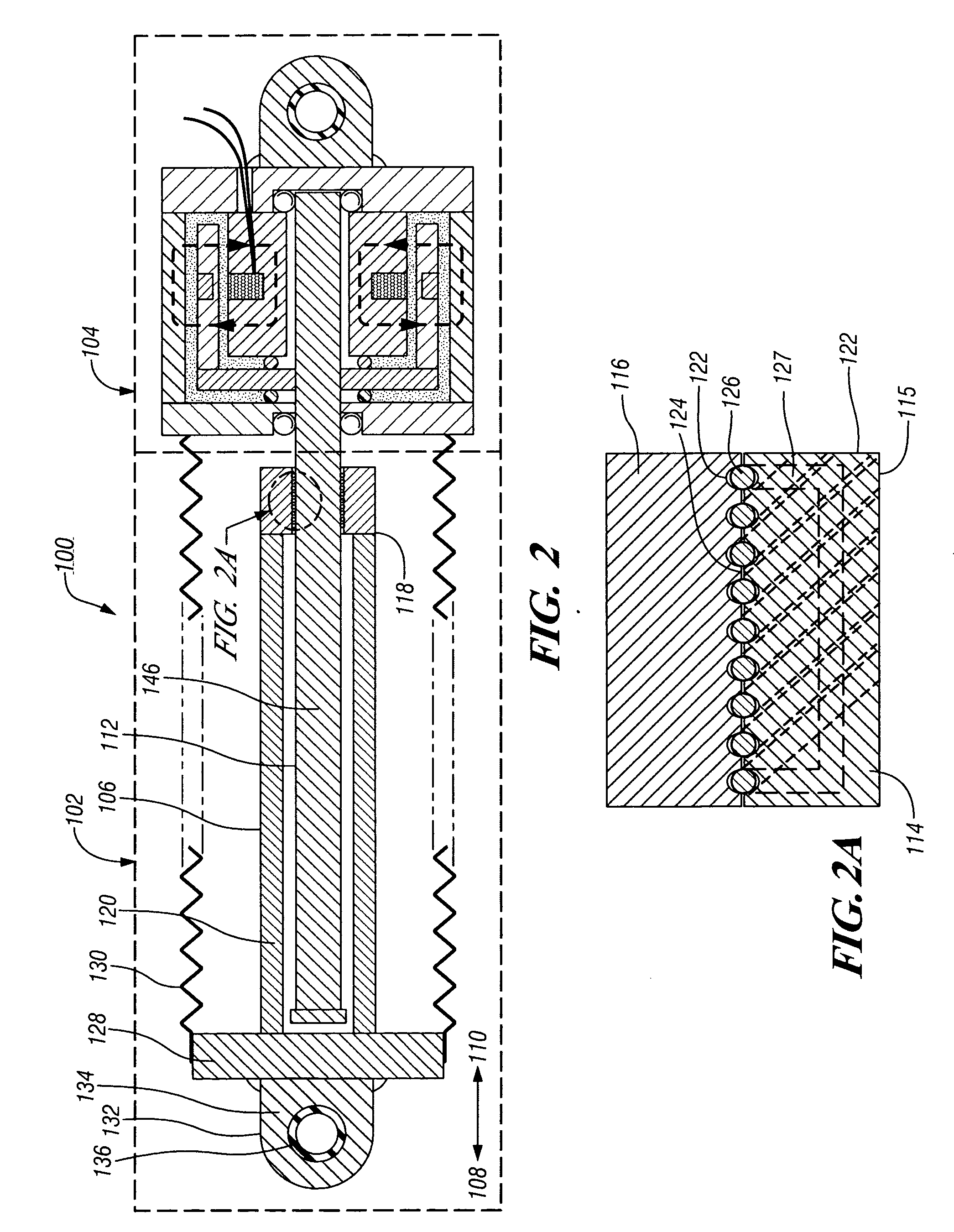

Fluid damper having continuously variable damping response

ActiveUS20050121269A1Reduce manufacturing costLower the volumeSpringsNon-rotating vibration suppressionMagnetorheological fluidEngineering

An improved damping apparatus that utilizes a fluid having a viscosity that may be varied by the application of an electromagnetic field, such as a magnetorheological fluid or an electrorheological fluid, to provide the damping response. The damping apparatus includes a linear to rotary conversion mechanism which comprises a translatable member that is adapted for linear translation in a forward and a reverse direction and a rotatable member comprising a rotatable shaft that is rotatably coupled to the translatable member; wherein translation of the translatable member in one of the forward or the reverse directions produces a forward or a reverse rotation of the rotatable member and shaft, respectively. The damping apparatus also includes a damping mechanism which comprises a hub that is fixed to the shaft, a means for generating a variable electromagnetic field in response to an applied electrical signal that may be continuously varied in response to an input signal that is representative of a desired damping force and a fluid having a viscosity that may be continuously varied by application of the electromagnetic field that is in touching contact with the hub. Application of the variable electromagnetic field to the fluid produces changes in the viscosity of the fluid that in turn provides variable resistance to rotation of the hub and resistance to translation of the translatable member, thereby providing a damping apparatus with a continuously variable damping response.

Owner:GM GLOBAL TECH OPERATIONS LLC

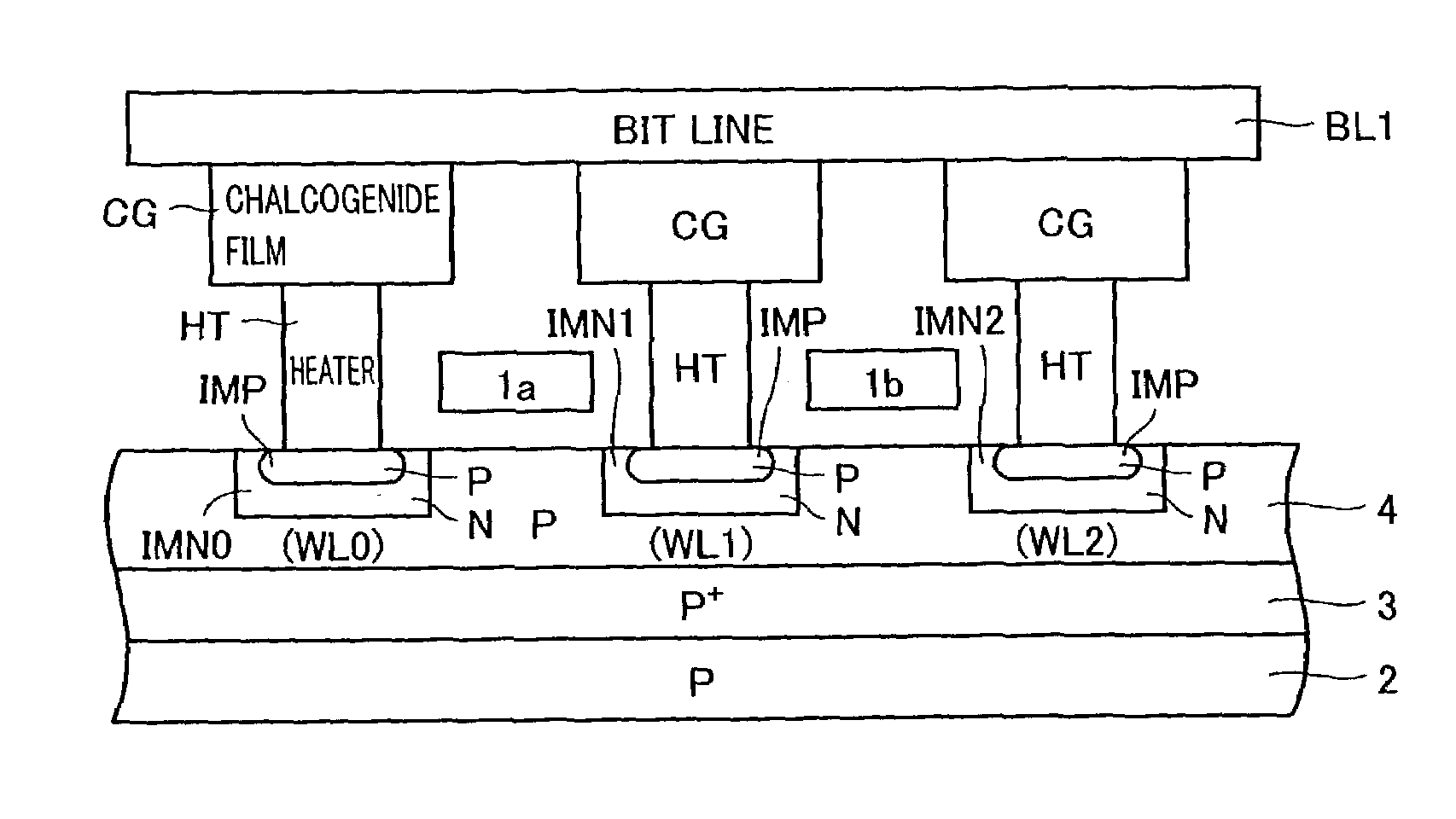

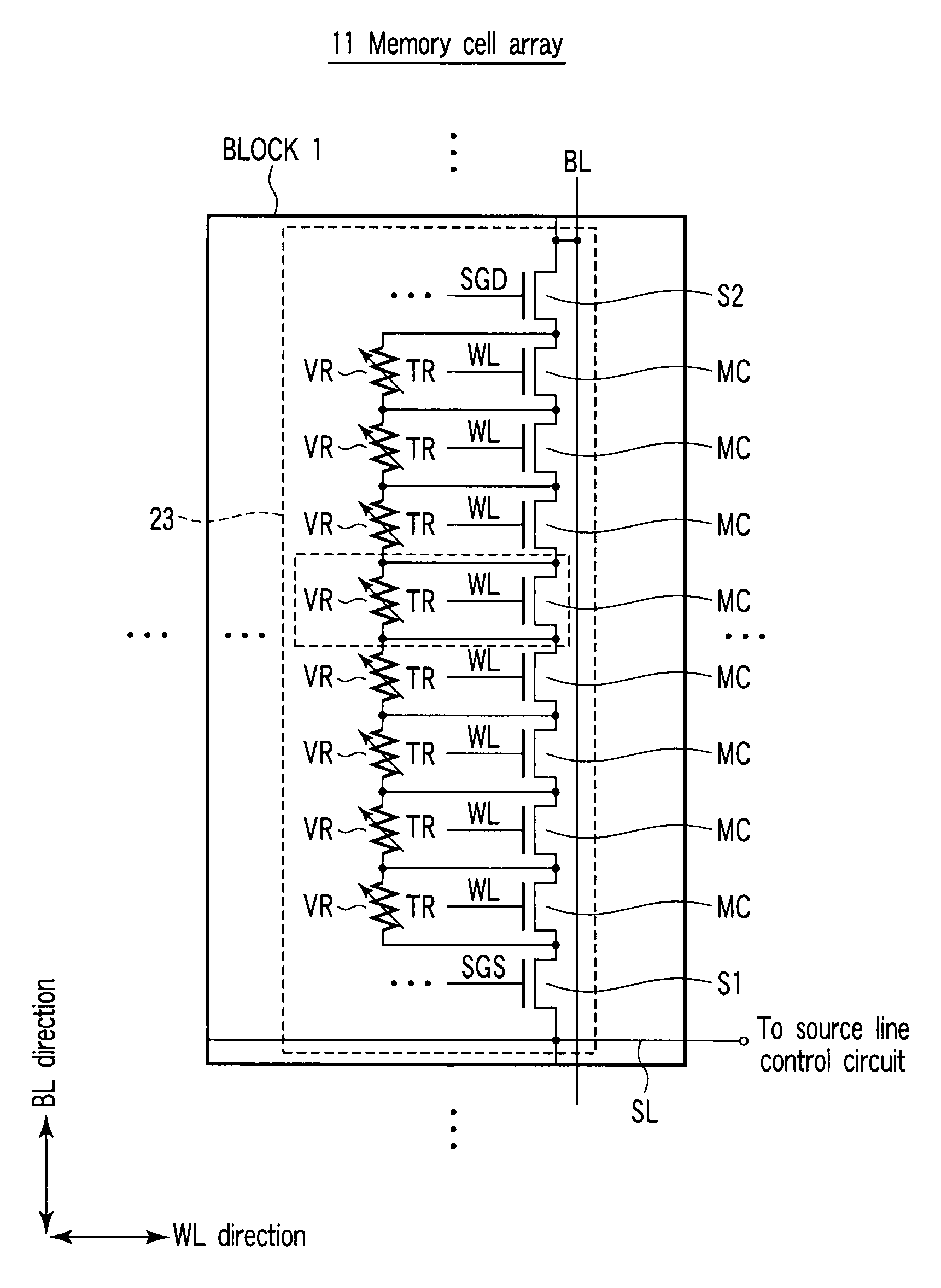

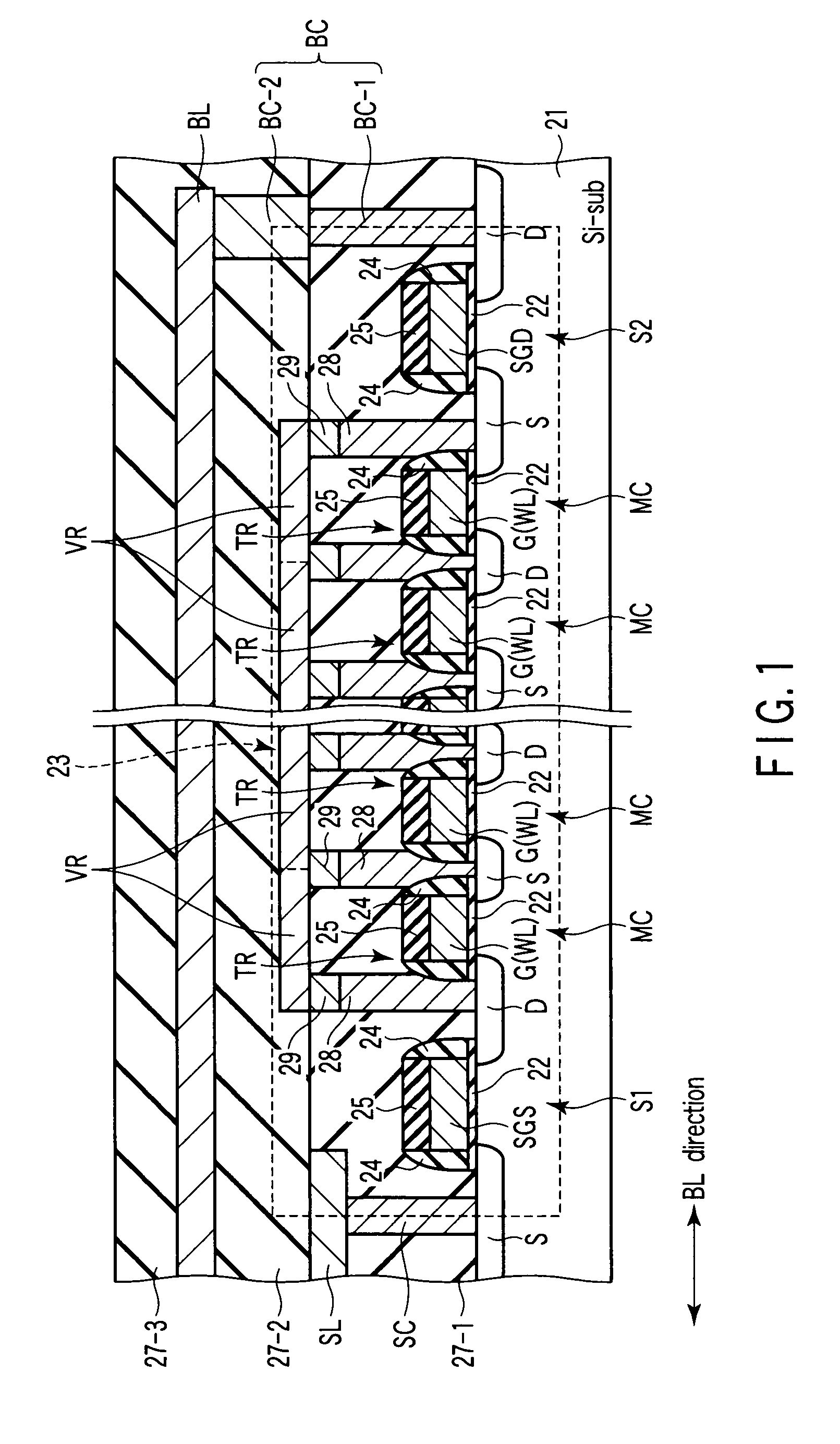

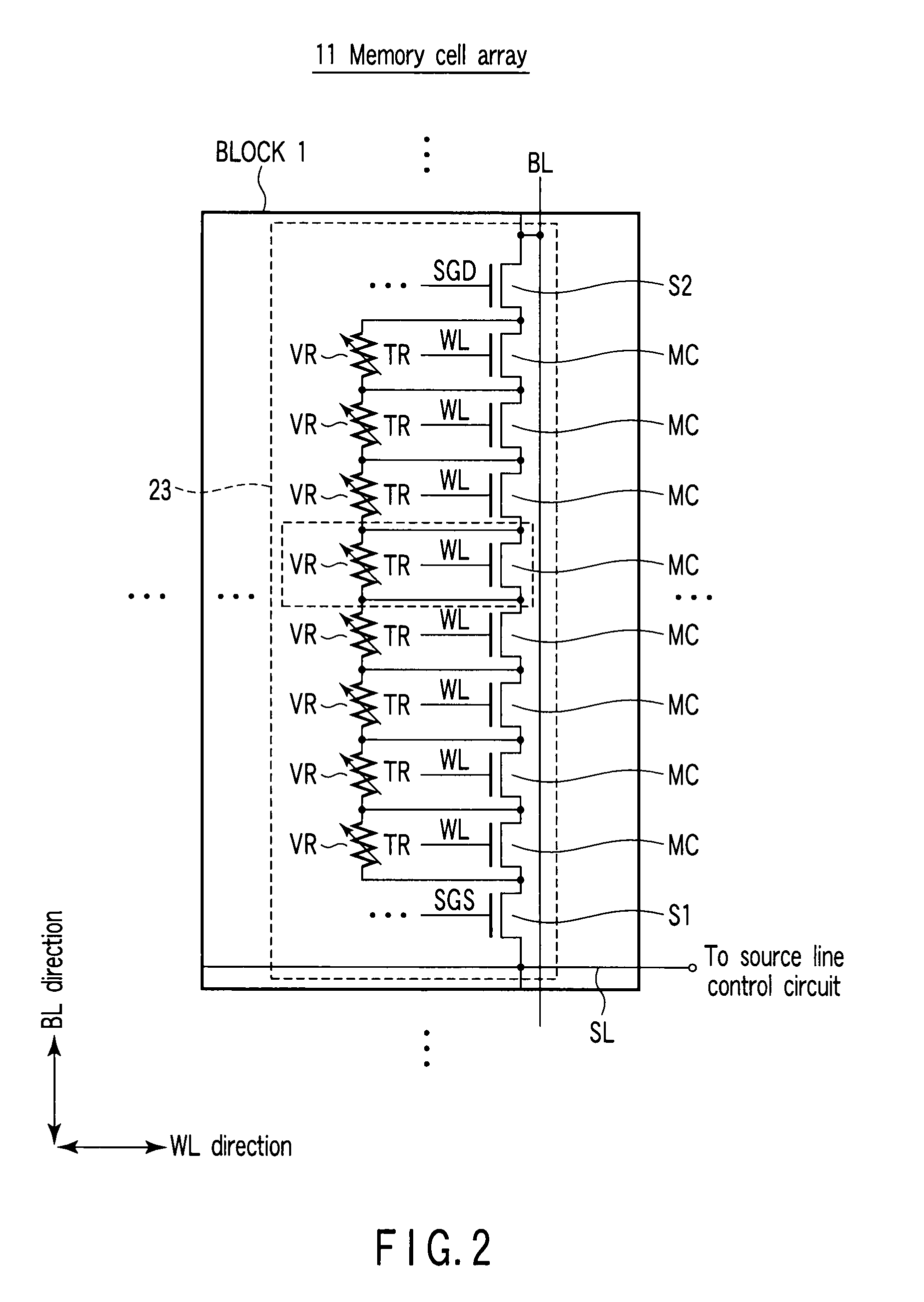

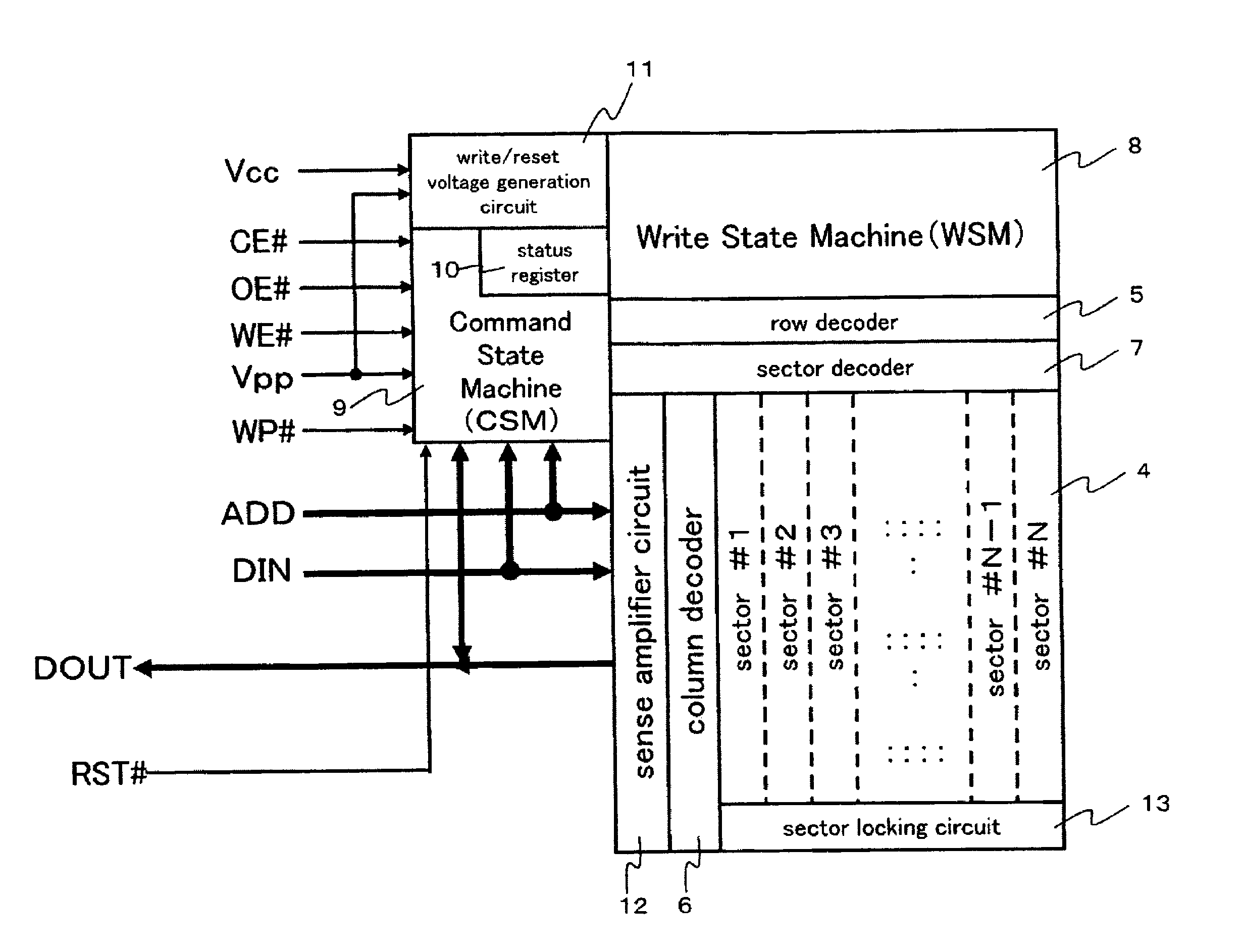

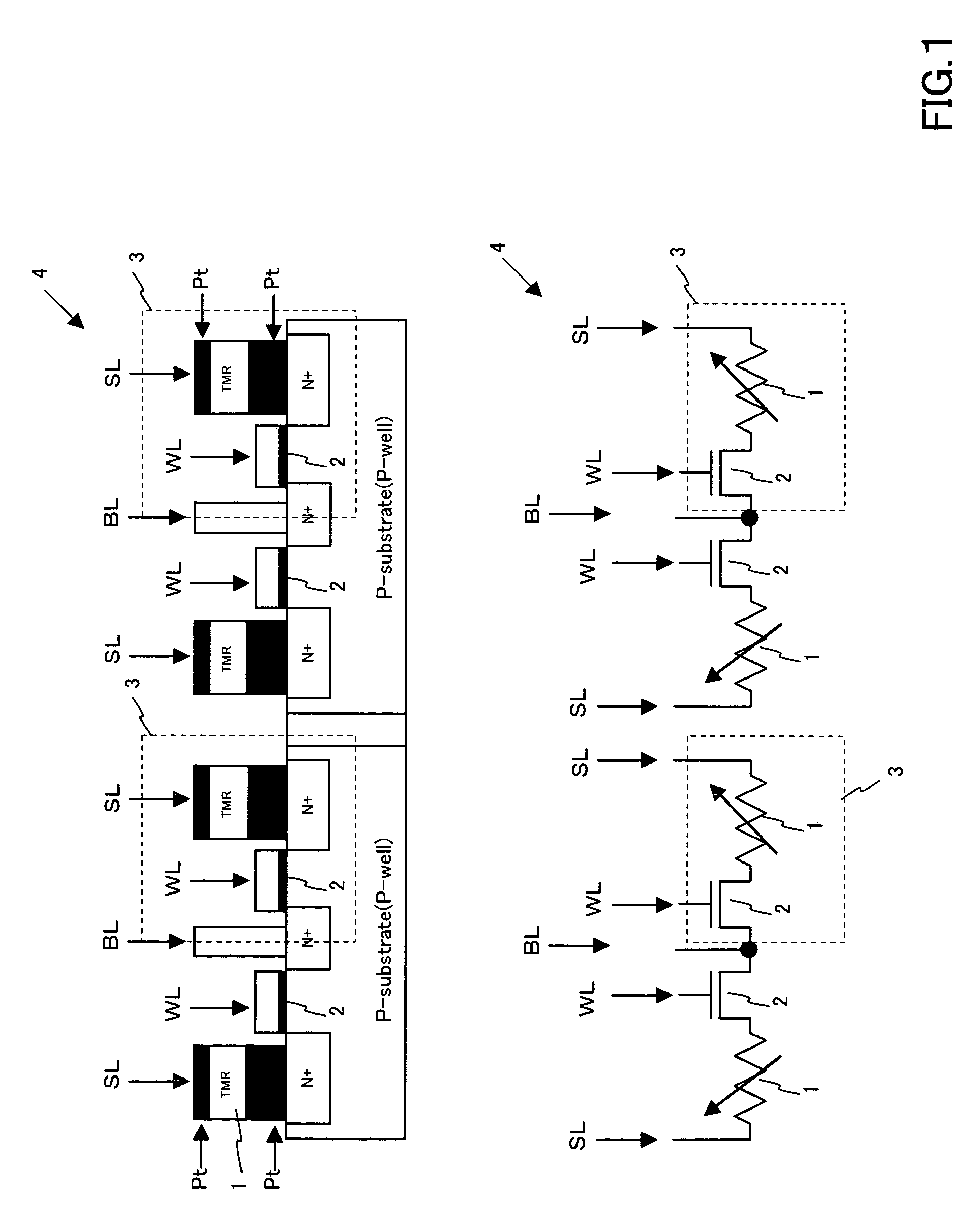

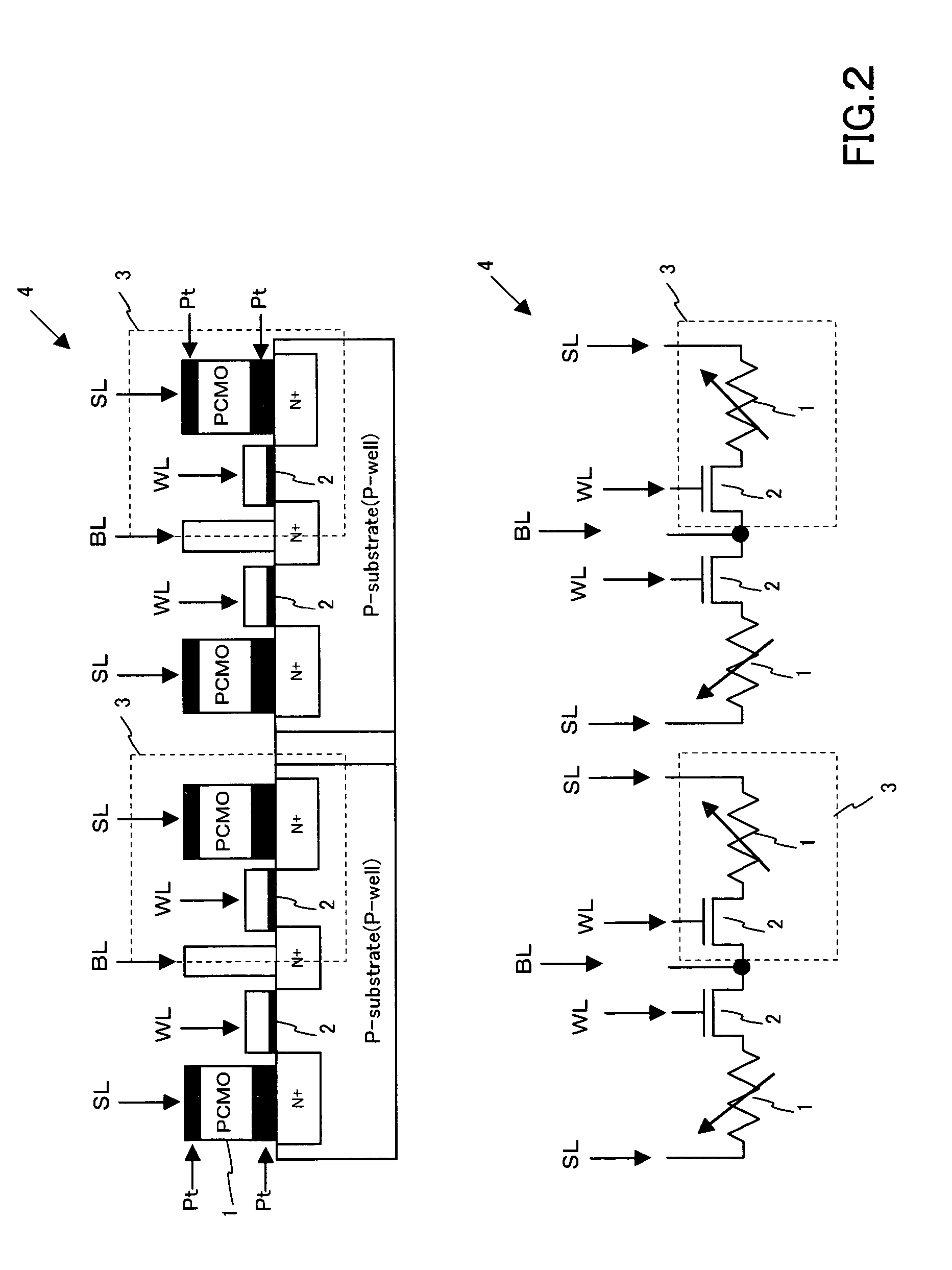

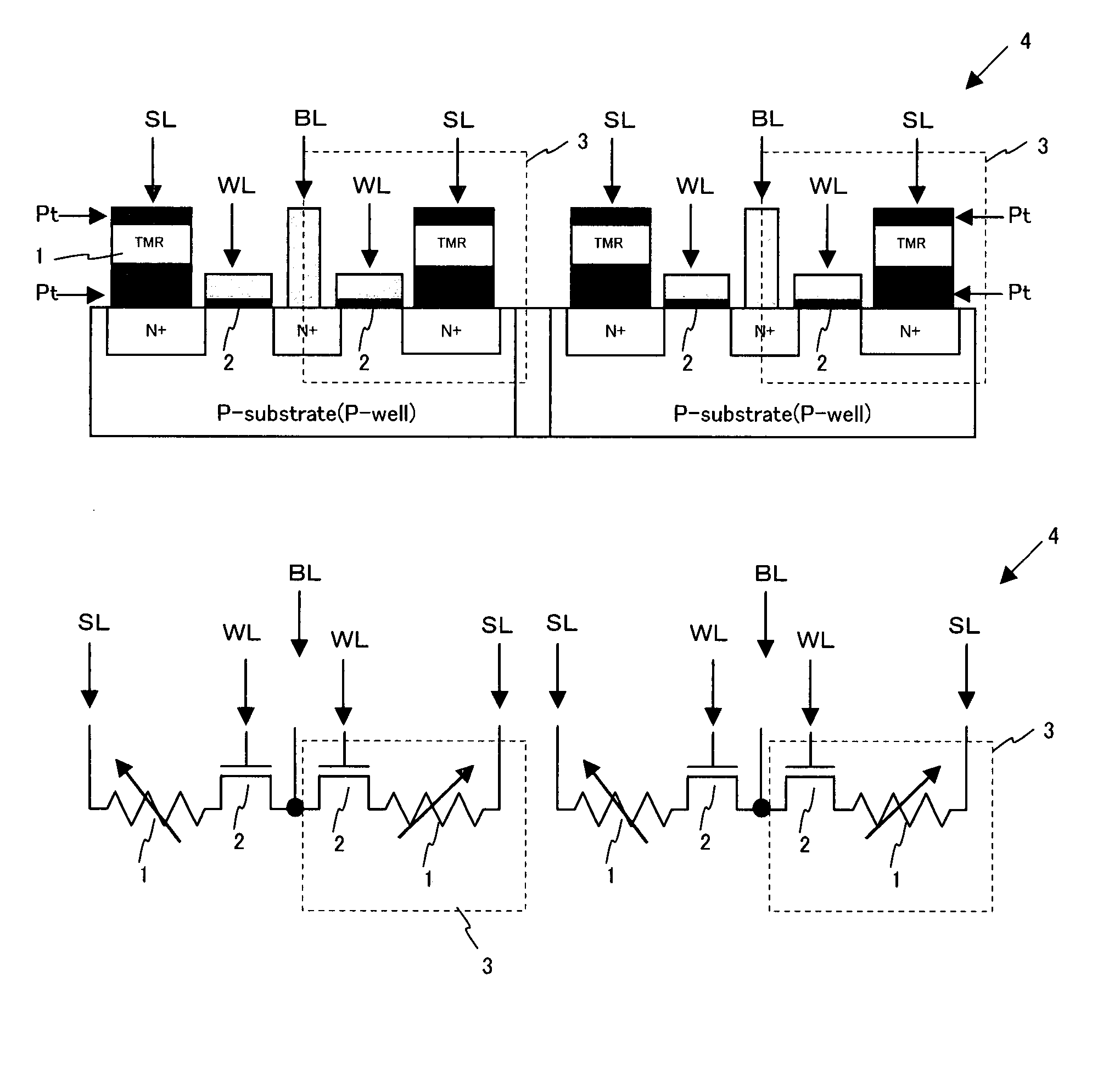

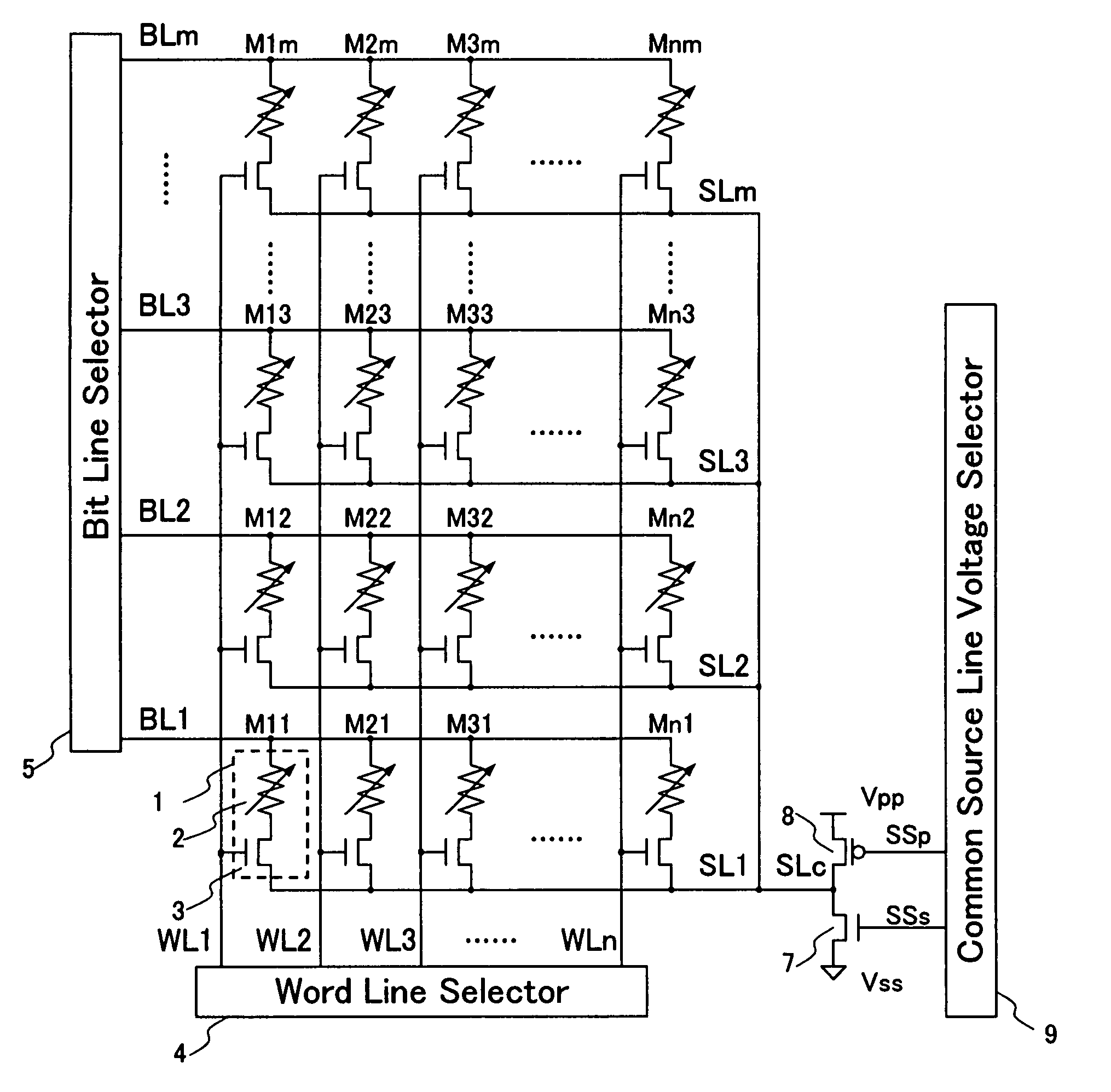

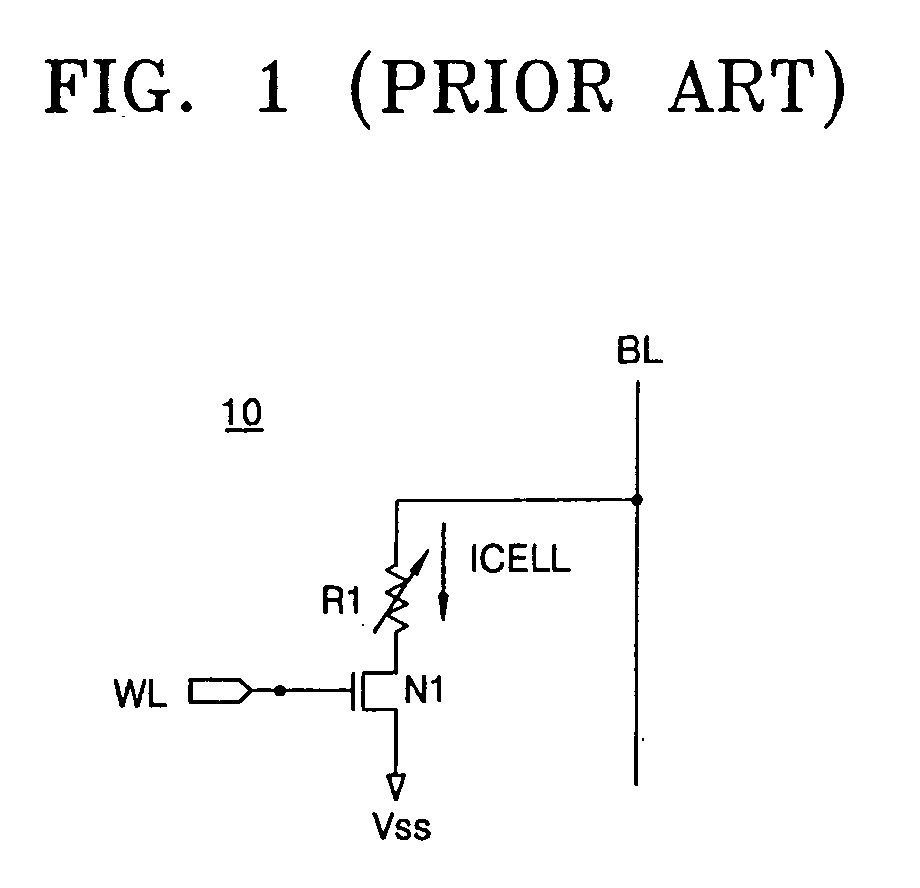

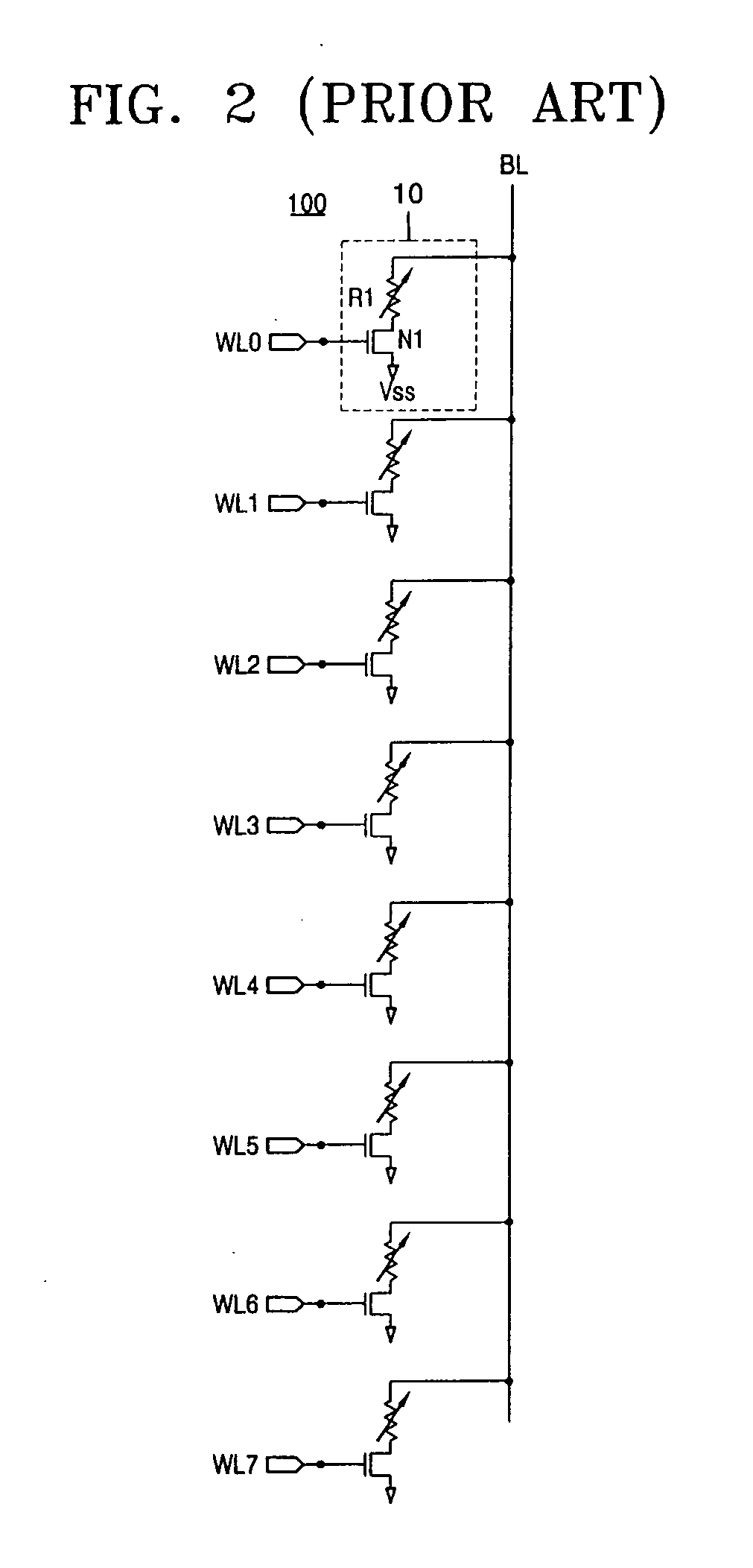

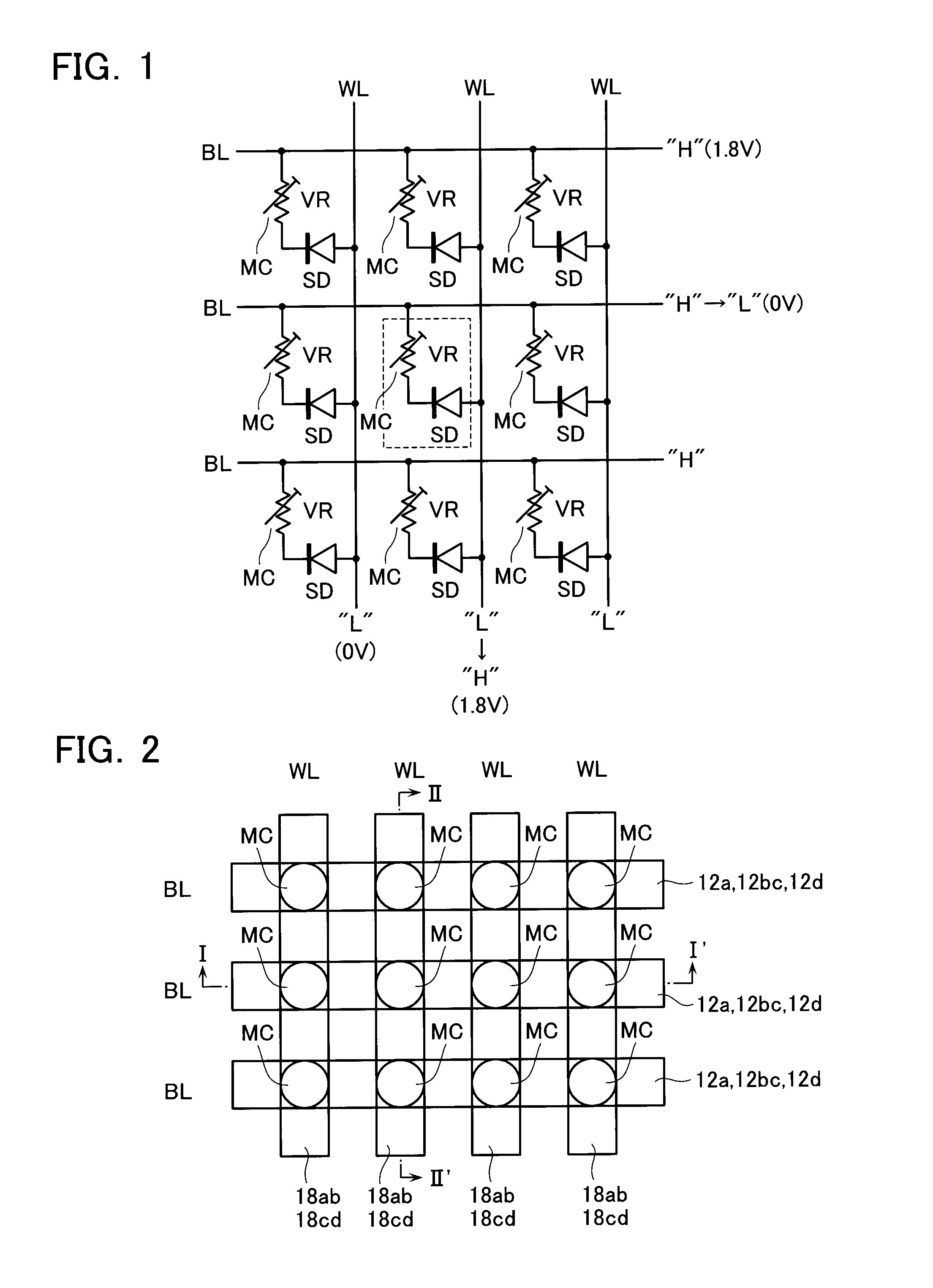

Nonvolatile semiconductor memory device

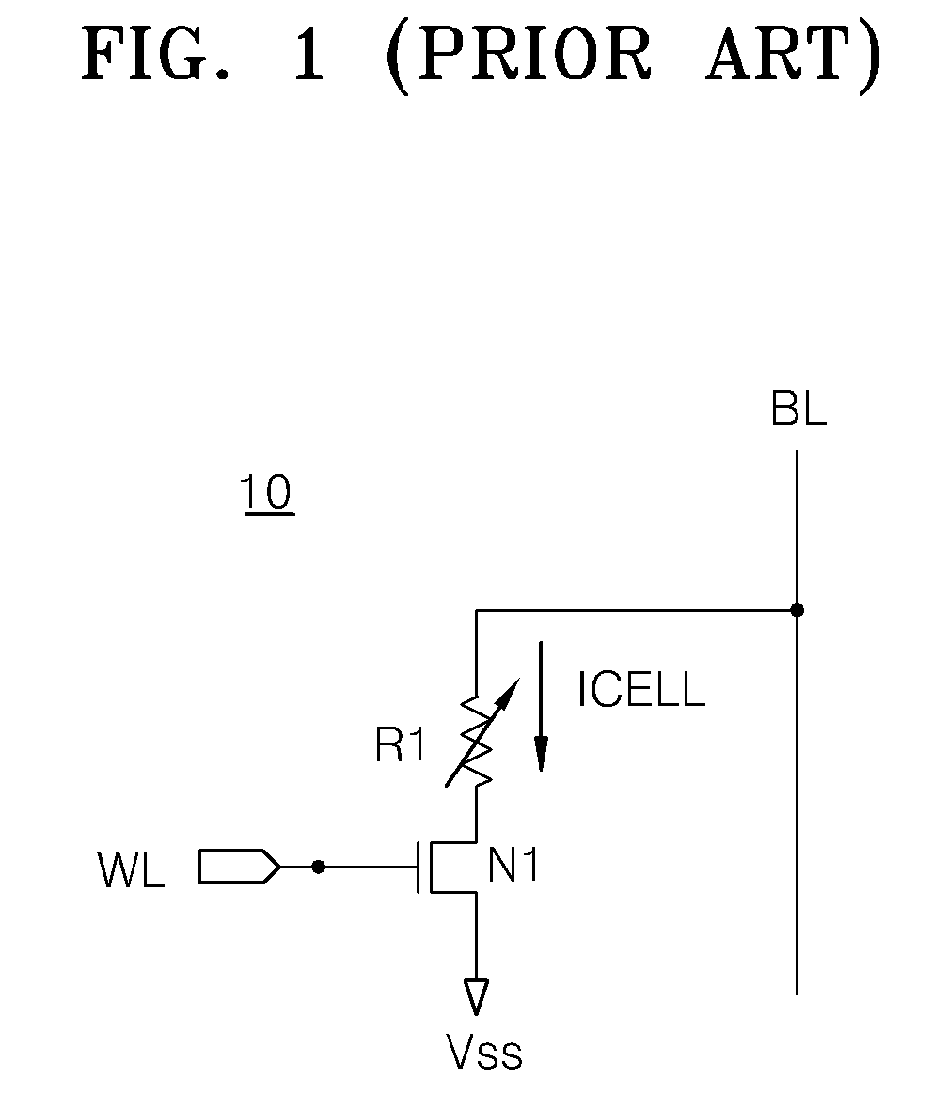

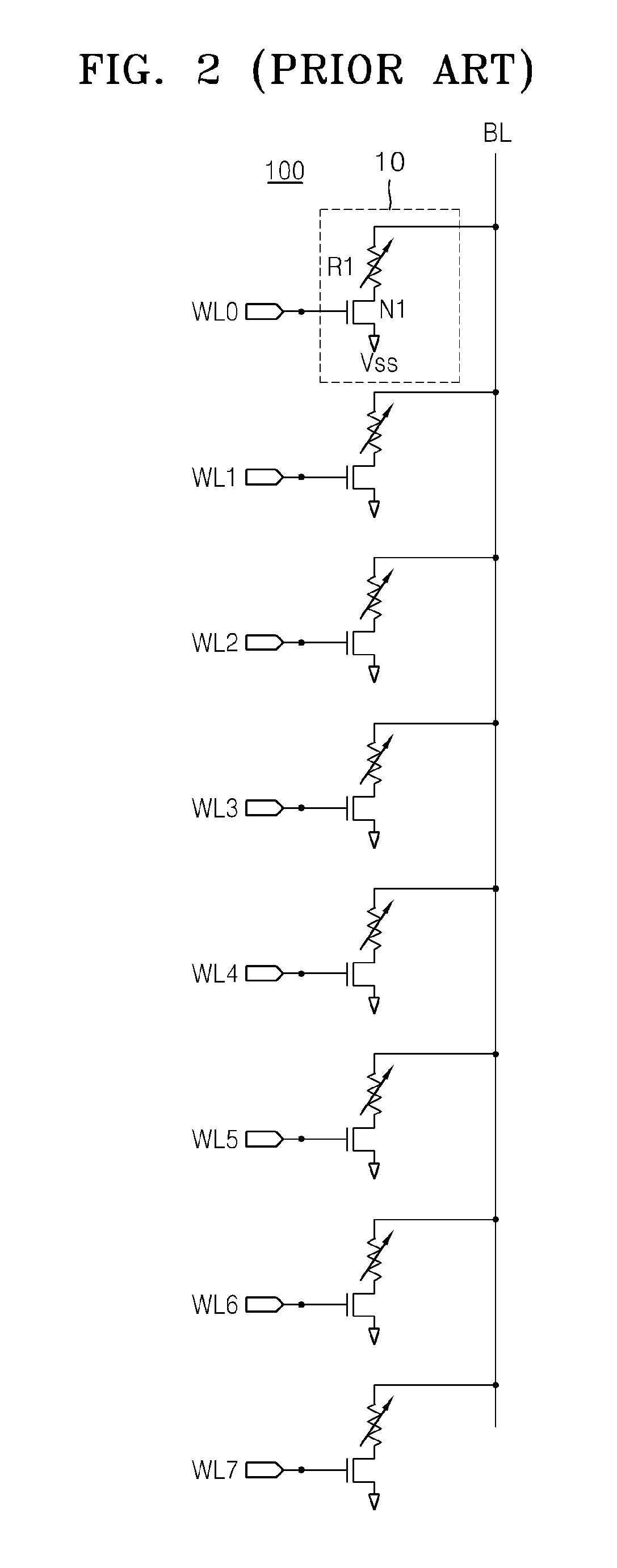

ActiveUS7057922B2Stress minimizationReliable dataNanoinformaticsSolid-state devicesBit lineEngineering

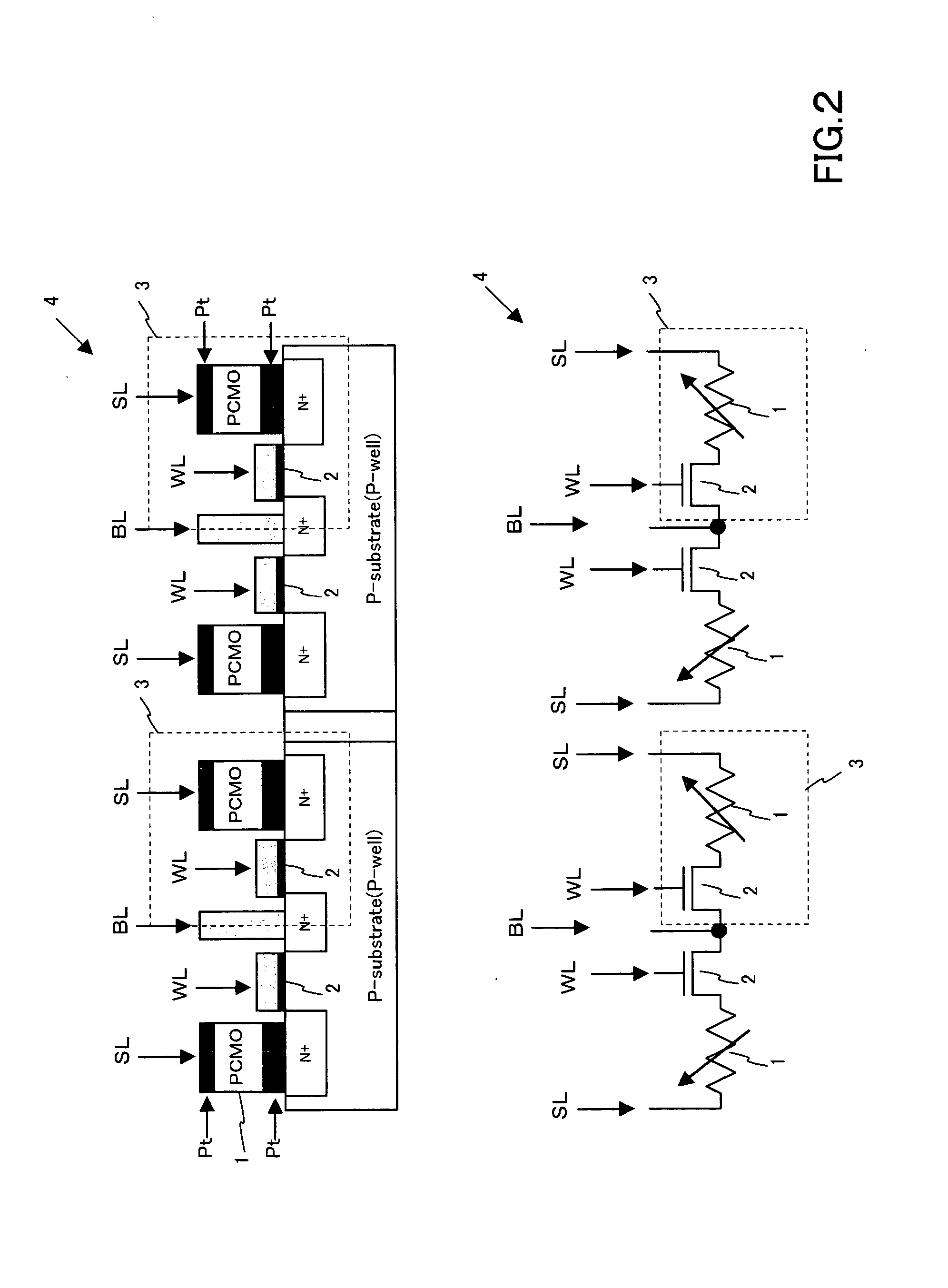

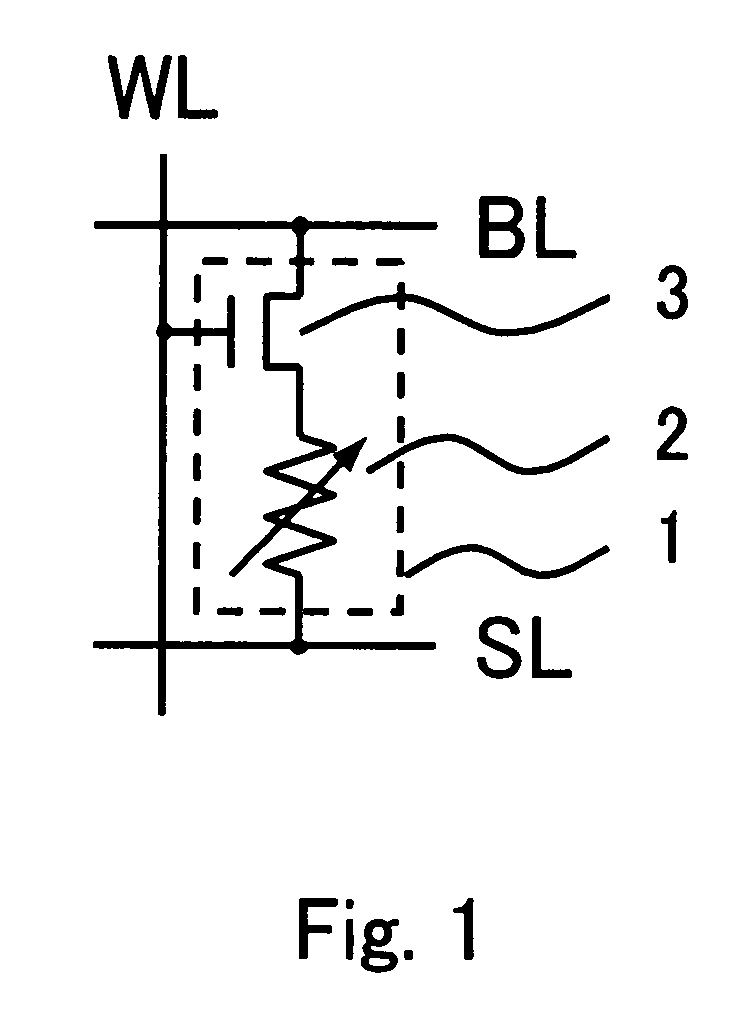

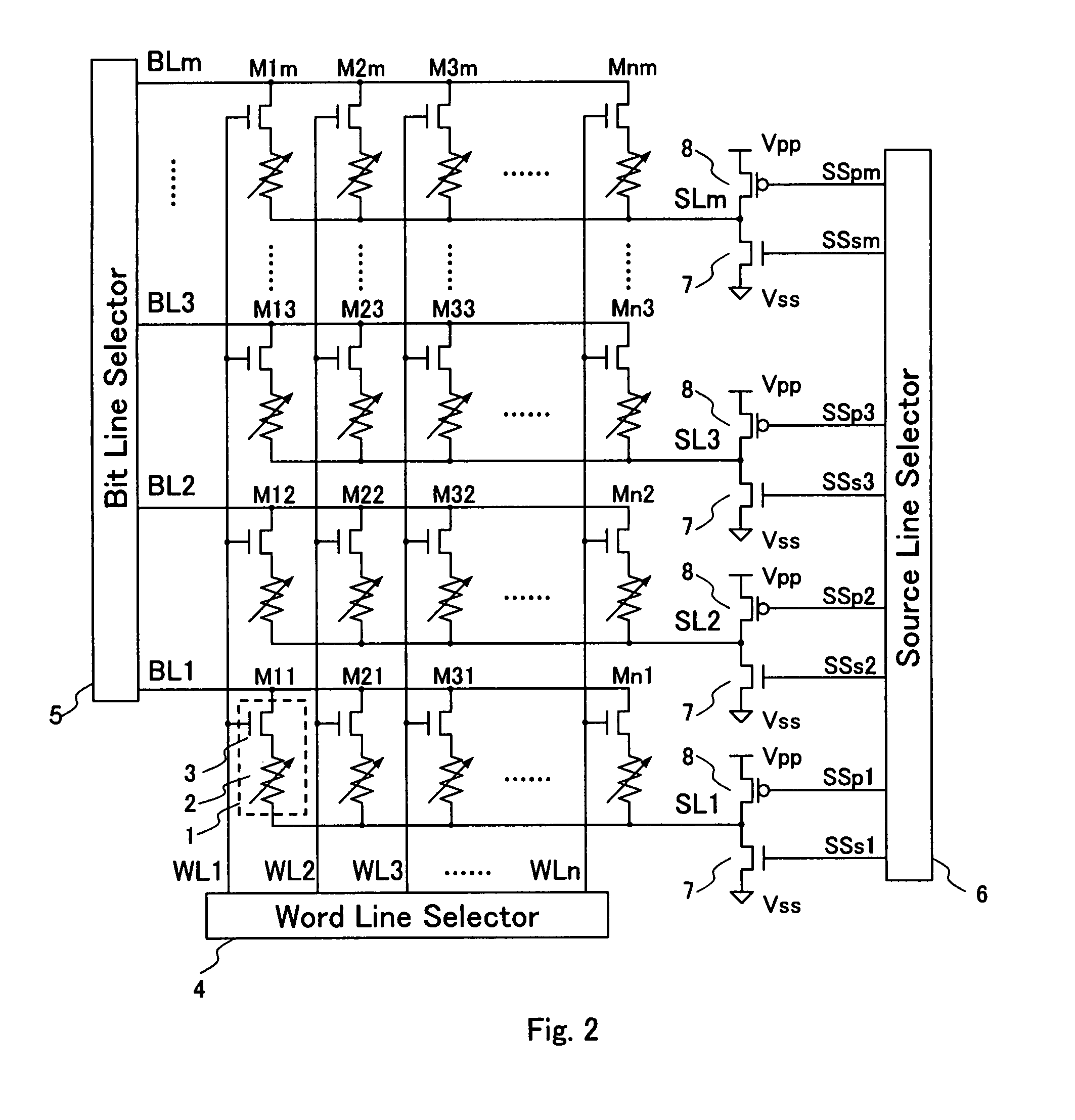

The present invention employs a memory cell structure in that one end of a variable resistance element (1) for storing information by change of electric resistance is connected to a source of a selection transistor (2) to form a memory cell (3) and, in a memory cell array (4), a drain of the selection transistor (2) is connected to a common bit line (BL) in a column direction, the other end of the variable resistance element (1) is connected to a source line (SL) and a gate of the selection transistor (2) is connected to a common word line (WL) in a row direction. In the memory cell structure, an operation of resetting data stored in the memory cell (3) is carried out for each of sectors including the plural memory cells (3) commonly connected to the source line (SL).

Owner:SAMSUNG ELECTRONICS CO LTD

Nonvolatile semiconductor memory device

ActiveUS20050122768A1Minimize of currentMinimize stress of voltageNanoinformaticsSolid-state devicesBit lineCommon word

The present invention employs a memory cell structure in that one end of a variable resistance element (1) for storing information by change of electric resistance is connected to a source of a selection transistor (2) to form a memory cell (3) and, in a memory cell array (4), a drain of the selection transistor (2) is connected to a common bit line (BL) in a column direction, the other end of the variable resistance element (1) is connected to a source line (SL) and a gate of the selection transistor (2) is connected to a common word line (WL) in a row direction. In the memory cell structure, an operation of resetting data stored in the memory cell (3) is carried out for each of sectors including the plural memory cells (3) commonly connected to the source line (SL).

Owner:SAMSUNG ELECTRONICS CO LTD

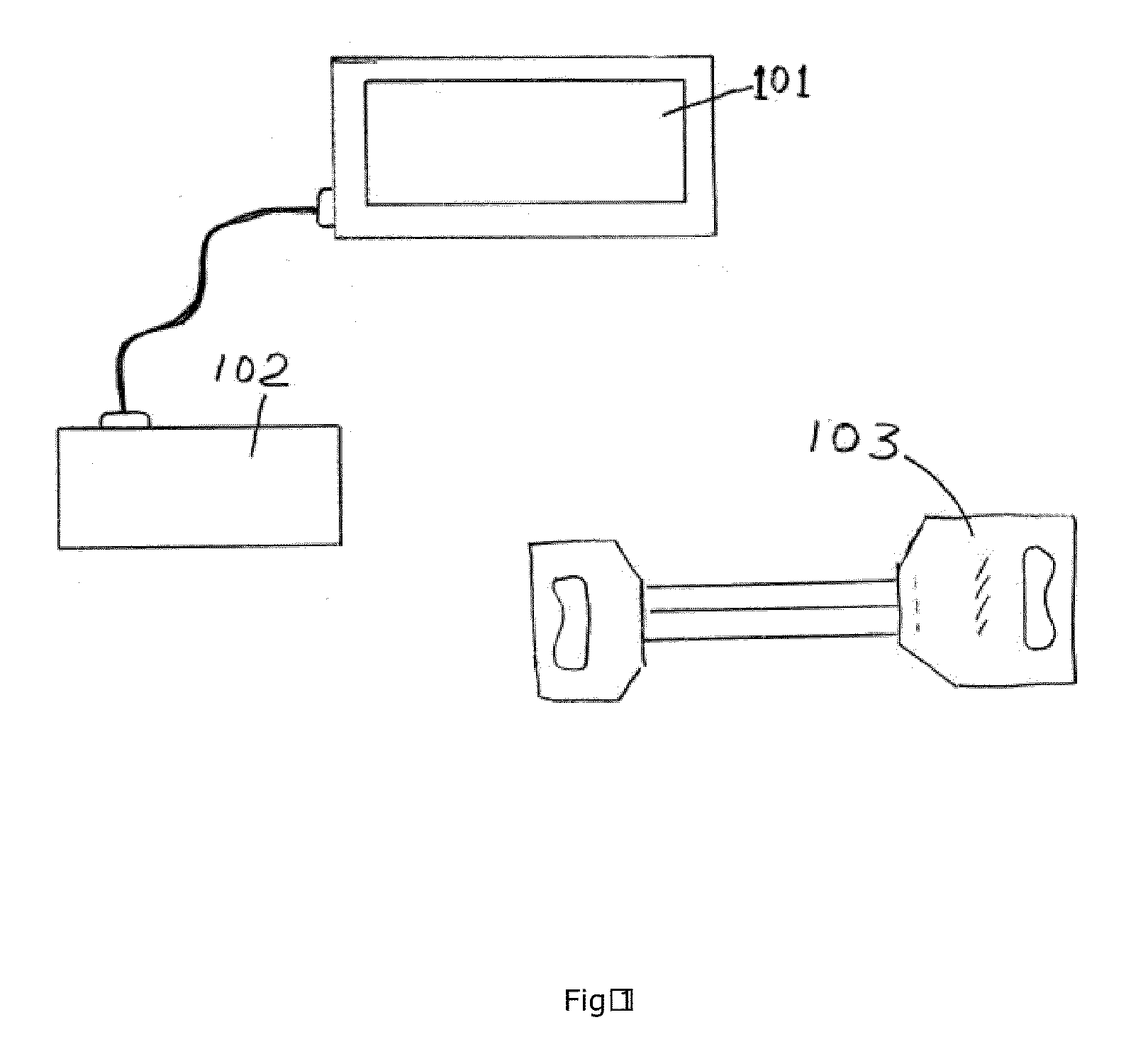

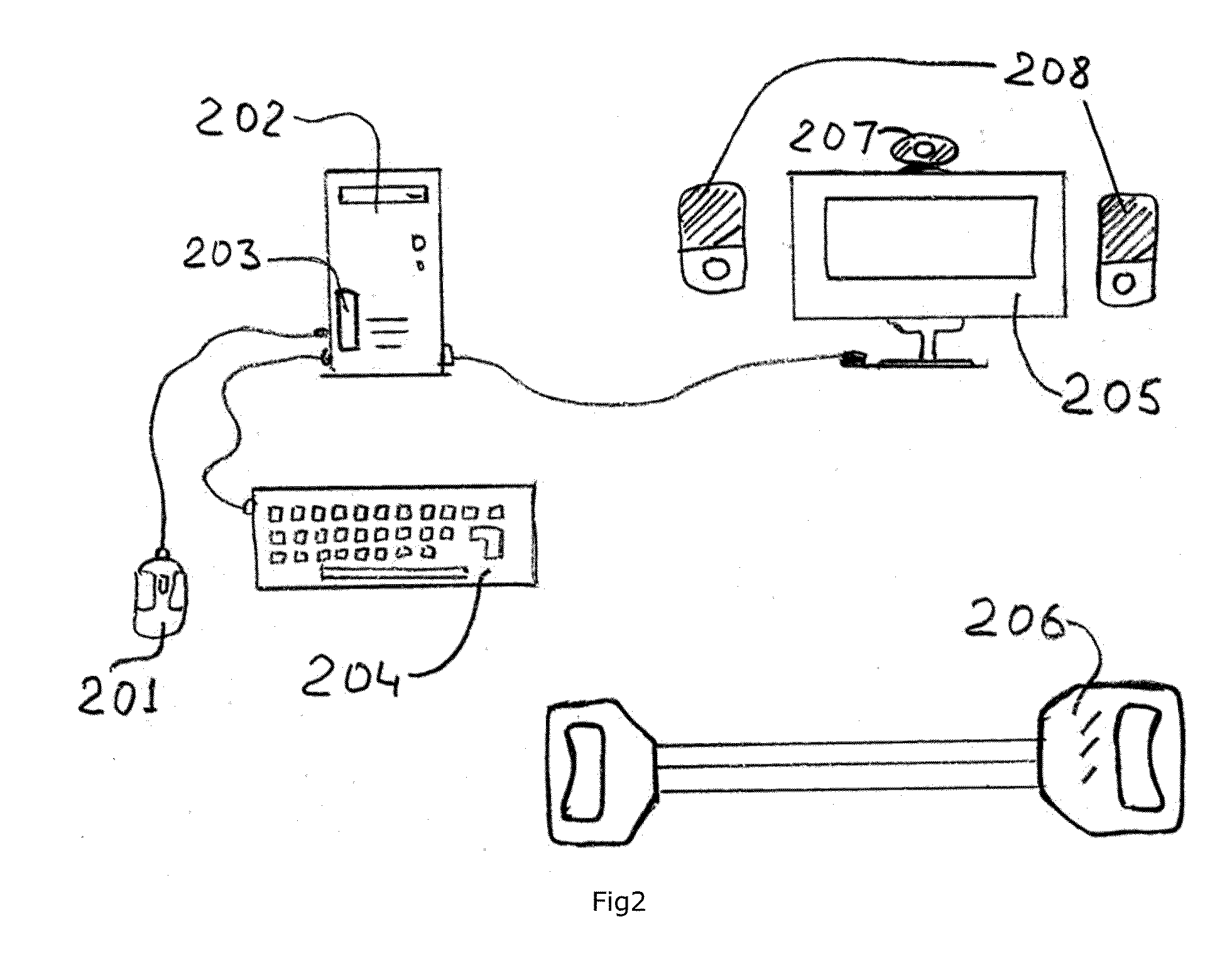

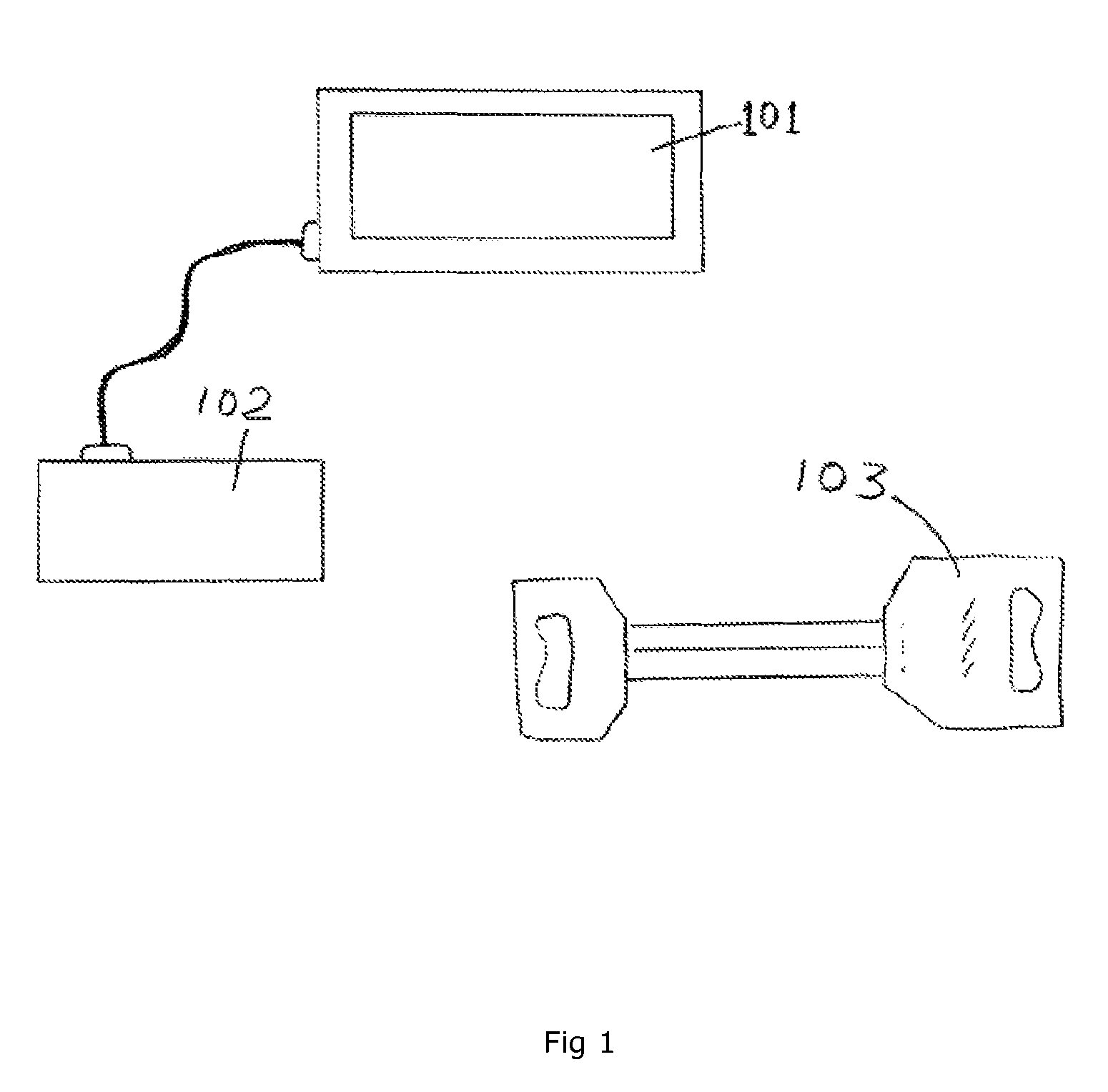

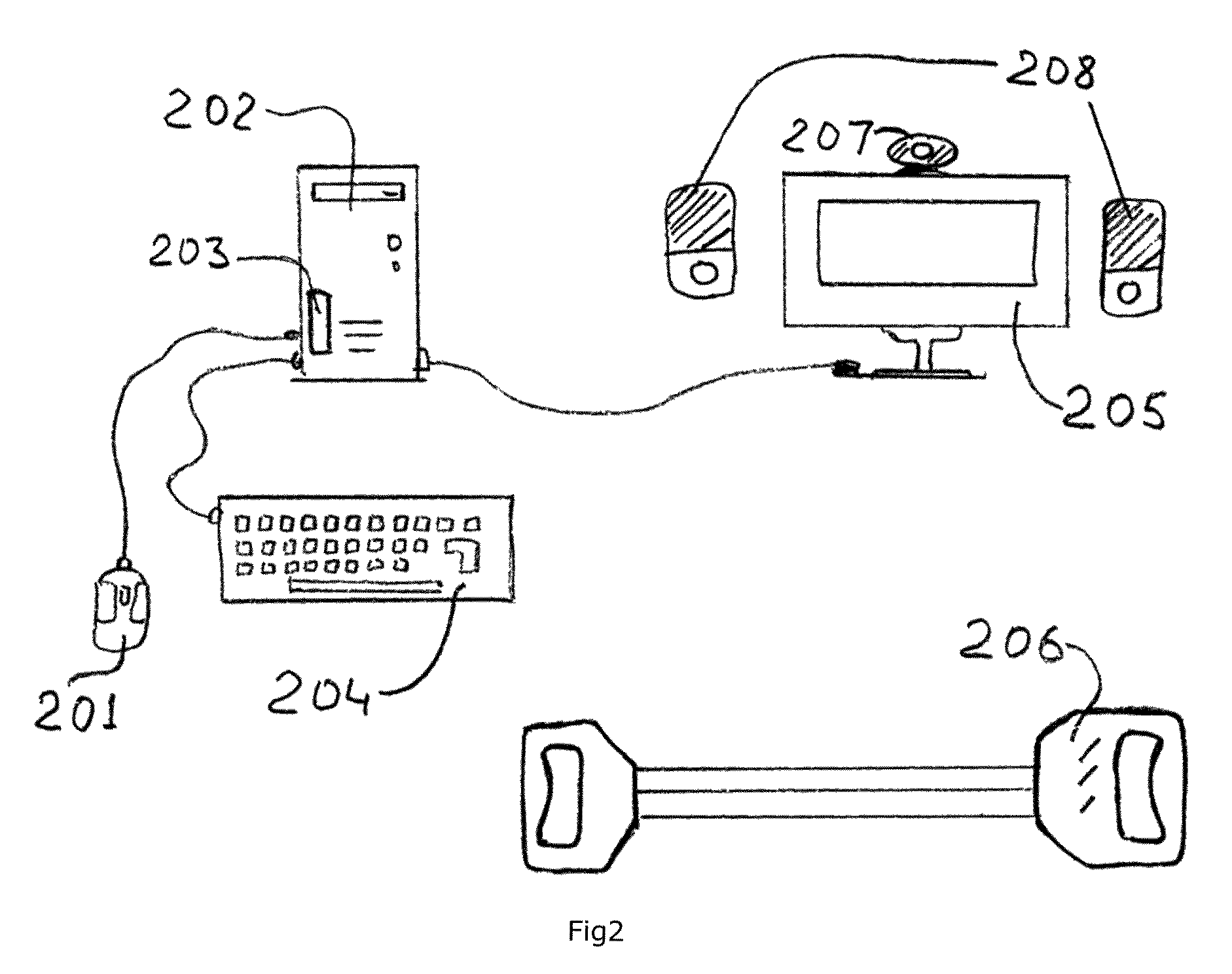

Wireless game controller for strength training and physiotherapy

Wireless game controller can provide variable resistance during strength training exercise and is coupled with off the shelf video gaming system such as Nintendo WII or personal computer by bluetooth or WiFI connection. The resistance is provided by a motor / generator. Electrical recuperation occurs between eccentric and concentric steps of the exercise, electrical energy is stored in a super capacitor between the steps. Video gaming system is configurable to run exercise software that provide reinforcing game experience, coaching, and physical therapy to the user. Exercise software tracks user's pose using fiduciary marks on the controller and data from 3d accelerometer embedded in the controller. The resistance is computed as a function of one or more the following: exercise type, position, velocity, user profile, and repetition number.

Owner:TONAL SYST INC

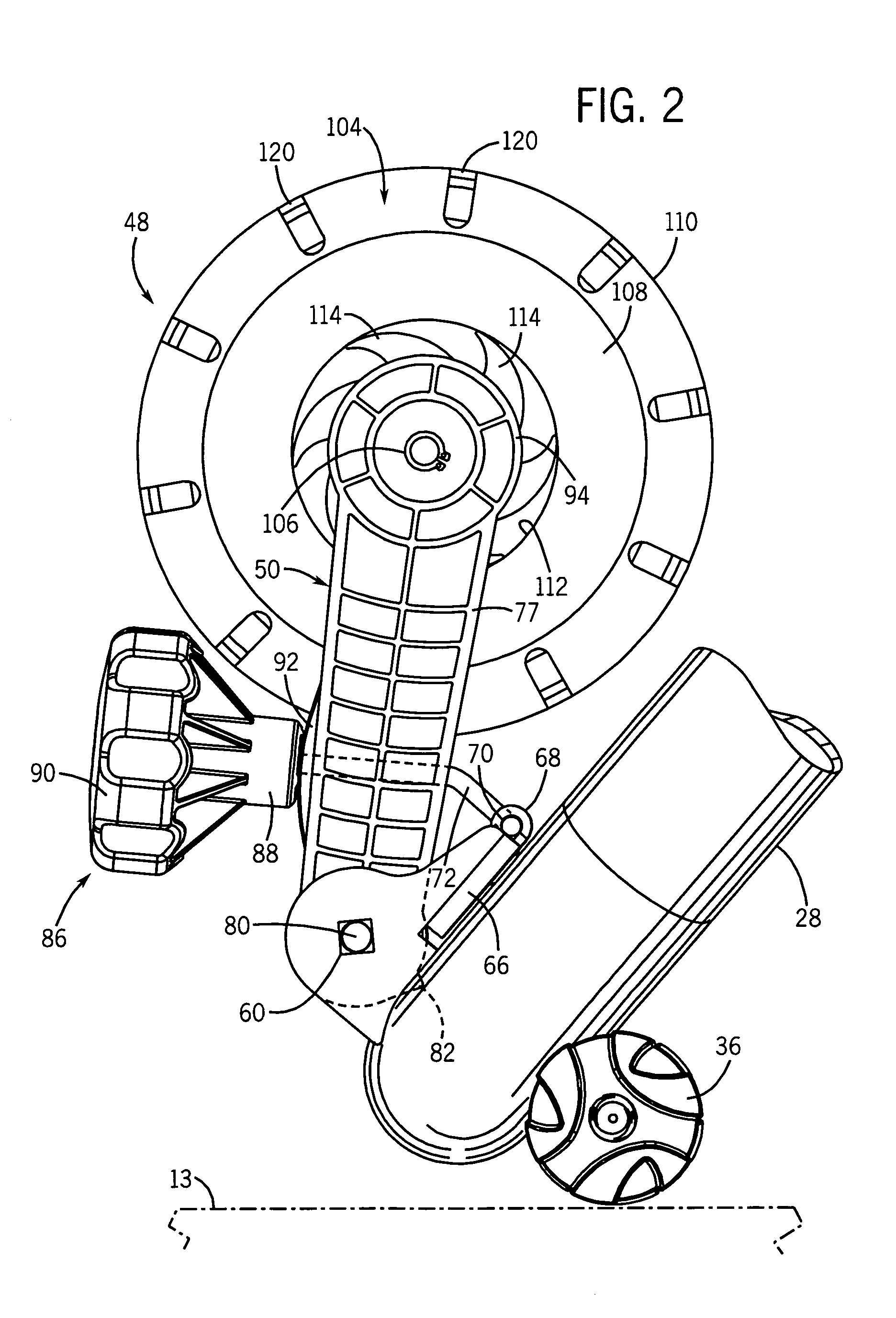

Variable magnetic resistance unit for an exercise device

InactiveUS7011607B2Realize automatic adjustmentRegulation stabilityMuscle exercising devicesMovement coordination devicesFreewheelRotation velocity

An automatically adjusting magnetic resistance unit for an exercise device such as a bicycle trainer, in which the degree of resistance is automatically and non-linearly adjusted in relation to the rotational speed of a rotating member caused by the input of a user. The rotating member may be in the form of a flywheel having a number of supports extending between a hub and a rim. The supports define longitudinal grooves which slidably retain magnets that are biased inwardly toward the hub by biasing members. An electrically conductive member is located adjacent the flywheel. As the flywheel rotates in response to rotation of the bicycle wheel, the magnets interact with the conductive member to establish eddy currents that provide resistance to the rotation of the flywheel. The speed of rotation of the flywheel increases as the speed of rotation of the bicycle wheel increases, and centrifugal forces act on the magnets to cause the magnets to slide outwardly along the grooves in opposition to the bias of the biasing members. The outward movement of the magnets causes outward movement of the eddy current forces, to increase the resistance provided to rotation of the flywheel and the bicycle wheel. The variable resistance due to the increased or decreased rotational speed of the flywheel is smooth, based on the constant interaction of the counteracting forces of the biasing members and the centrifugal forces acting on the magnets.

Owner:SARIS EQUIP LLC

Semiconductor memory device

A semiconductor memory device comprises an array of memory cells each comprising a variable resistance element and a cell access transistor, and a voltage supplying means for applying the first voltage between the bit and source lines connected to the selected memory cell, the third voltage to the word line to apply the first write voltage between the two ports of the variable resistance element for shifting the resistance from the first state to the second state, and the second voltage opposite in polarity to the first voltage between the bit and source lines, the third voltage to the word line to apply the second write voltage opposite in polarity to and different in the absolute value from the first write voltage between the two ports for shifting the resistance from the second state to the first state, the voltage supplying means comprising an n-channel MOSFET and a p-channel MOSFET.

Owner:SAMSUNG ELECTRONICS CO LTD

Non-volatile memory device including a variable resistance material

A non-volatile memory device including a variable resistance material is provided. The non-volatile memory device may include a buffer layer, a variable resistance material layer and / or an upper electrode, for example, sequentially formed on a lower electrode. A schottky barrier may be formed on an interface between the buffer layer and the lower electrode. The variable resistance material layer may be formed with a variable resistance property.

Owner:SAMSUNG ELECTRONICS CO LTD

Memory device with active passive layers

InactiveUS6838720B2Improve read and write speedLong-term data retentionTransistorNanoinformaticsActive layerElectron mobility

A memory including memory cells having active and passive layers may store multiple information bits. The active layer may include an organic polymer that has a variable resistance based on the movement of charged species (ions or ions and electrons) between the passive layer and the active layer. The passive layer may be a super-ionic material that has high ion and electron mobility. The active layer may be self-assembled from a monomer in a liquid or gas.

Owner:SPANSION LLC

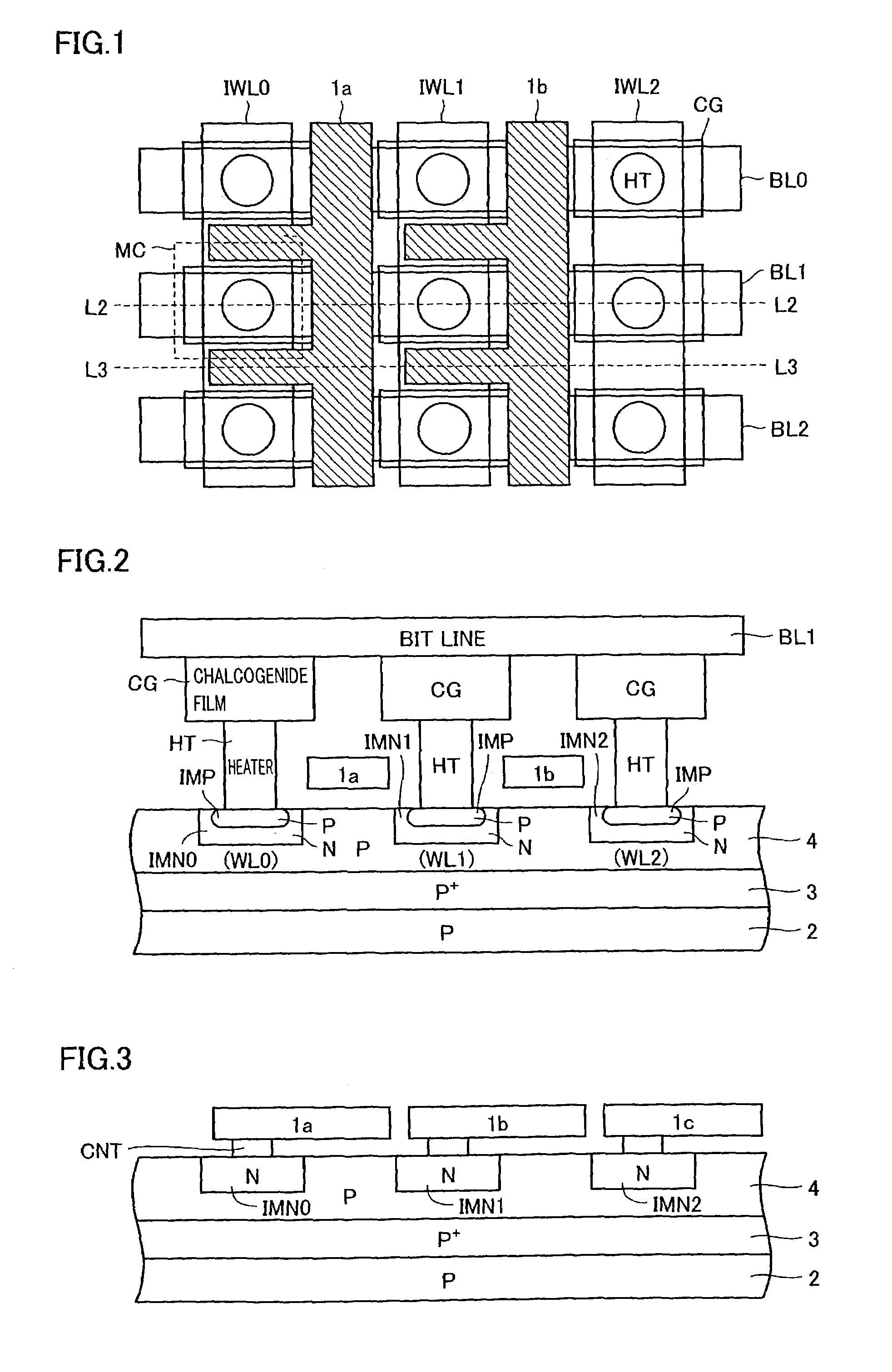

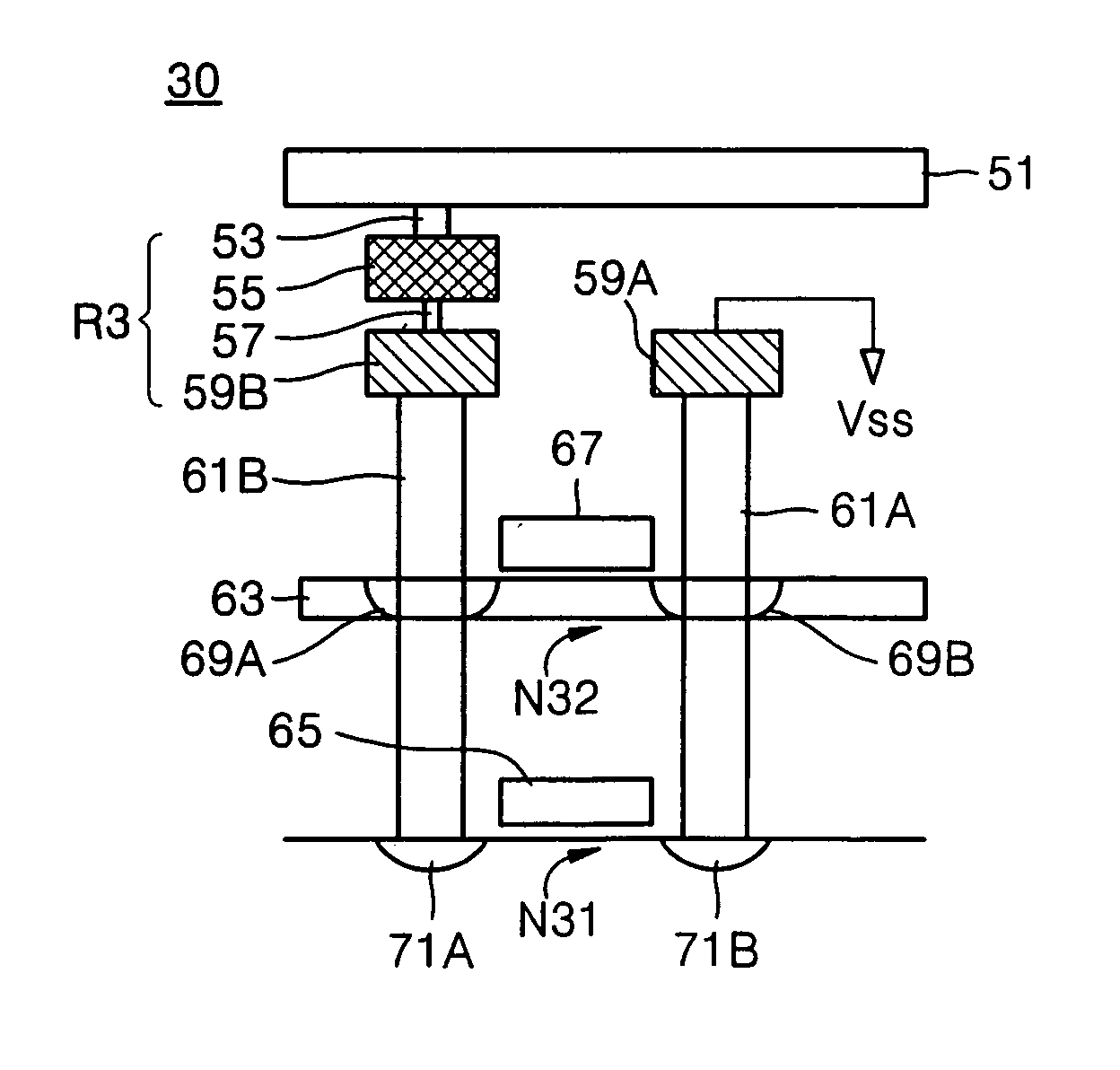

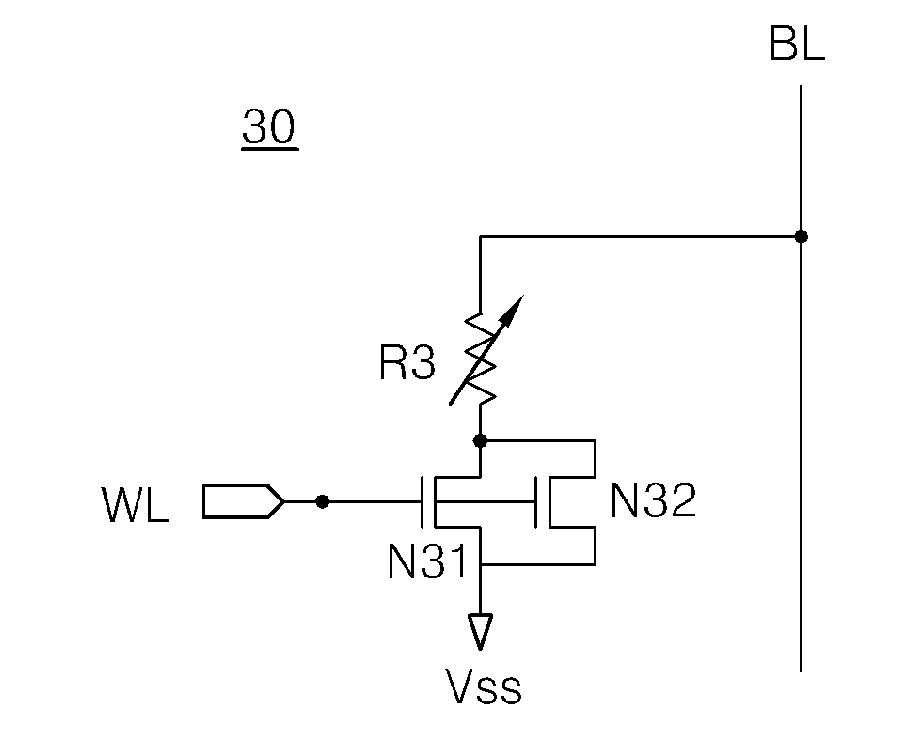

Semiconductor memory device with stacked memory cell and method of manufacturing the stacked memory cell

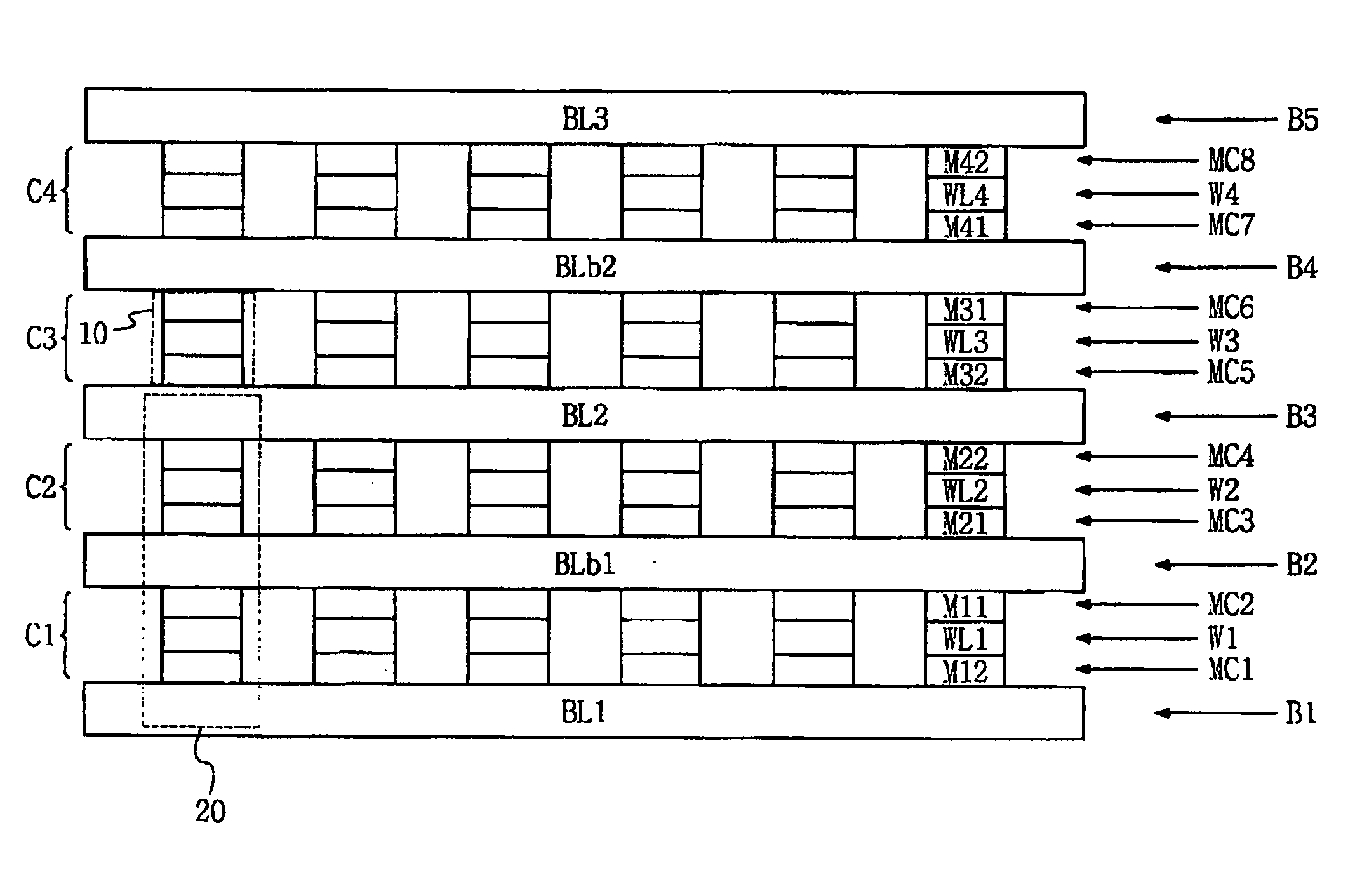

ActiveUS20060120148A1Improve integration densitySolid-state devicesDigital storageBit linePhase-change memory

In a semiconductor memory device and method, phase-change memory cells are provided, each including a plurality of control transistors formed on different layers and variable resistance devices formed of a phase-change material. Each phase-change memory cell includes a plurality of control transistors formed on different layers, and a variable resistance device formed of a phase-change material. In one example, the number of the control transistors is two. The semiconductor memory device includes a global bit line; a plurality of local bit lines connected to or disconnected from the global bit line via local bit line selection circuits which correspond to the local bit lines, respectively; and a plurality of phase-change memory cell groups storing data while being connected to the local bit lines, respectively. Each of the phase-change memory cells of each of the phase-change memory cell groups comprises a plurality of control transistors formed on different layers, and a variable resistance device formed of a phase-change material. In addition, the semiconductor memory device has a hierarchical bit line structure that uses a global bit line and local bit lines. Accordingly, it is possible to increase both the integration density of the semiconductor memory device and the amount of current flowing through each of the phase-change memory cells.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor memory device with stacked memory cell and method of manufacturing the stacked memory cell

In a semiconductor memory device and method, resistive-change memory cells are provided, each including a plurality of control transistors formed on different layers and variable resistance devices comprising a resistive-change memory. Each resistive-change memory cell includes a plurality of control transistors formed on different layers, and a variable resistance device formed of a resistive-change memory. In one example, the number of the control transistors is two. The semiconductor memory device includes a global bit line; a plurality of local bit lines connected to or disconnected from the global bit line via local bit line selection circuits which correspond to the local bit lines, respectively; and a plurality of resistive-change memory cell groups storing data while being connected to the local bit lines, respectively. Each of the resistive-change memory cells of each of the resistive-change memory cell groups comprises a plurality of control transistors formed on different layers, and a variable resistance device formed of a resistive-change memory. In addition, the semiconductor memory device has a hierarchical bit line structure that uses a global bit line and local bit lines. Accordingly, it is possible to increase both the integration density of the semiconductor memory device and the amount of current flowing through each of the resistive-change memory cells.

Owner:SAMSUNG ELECTRONICS CO LTD

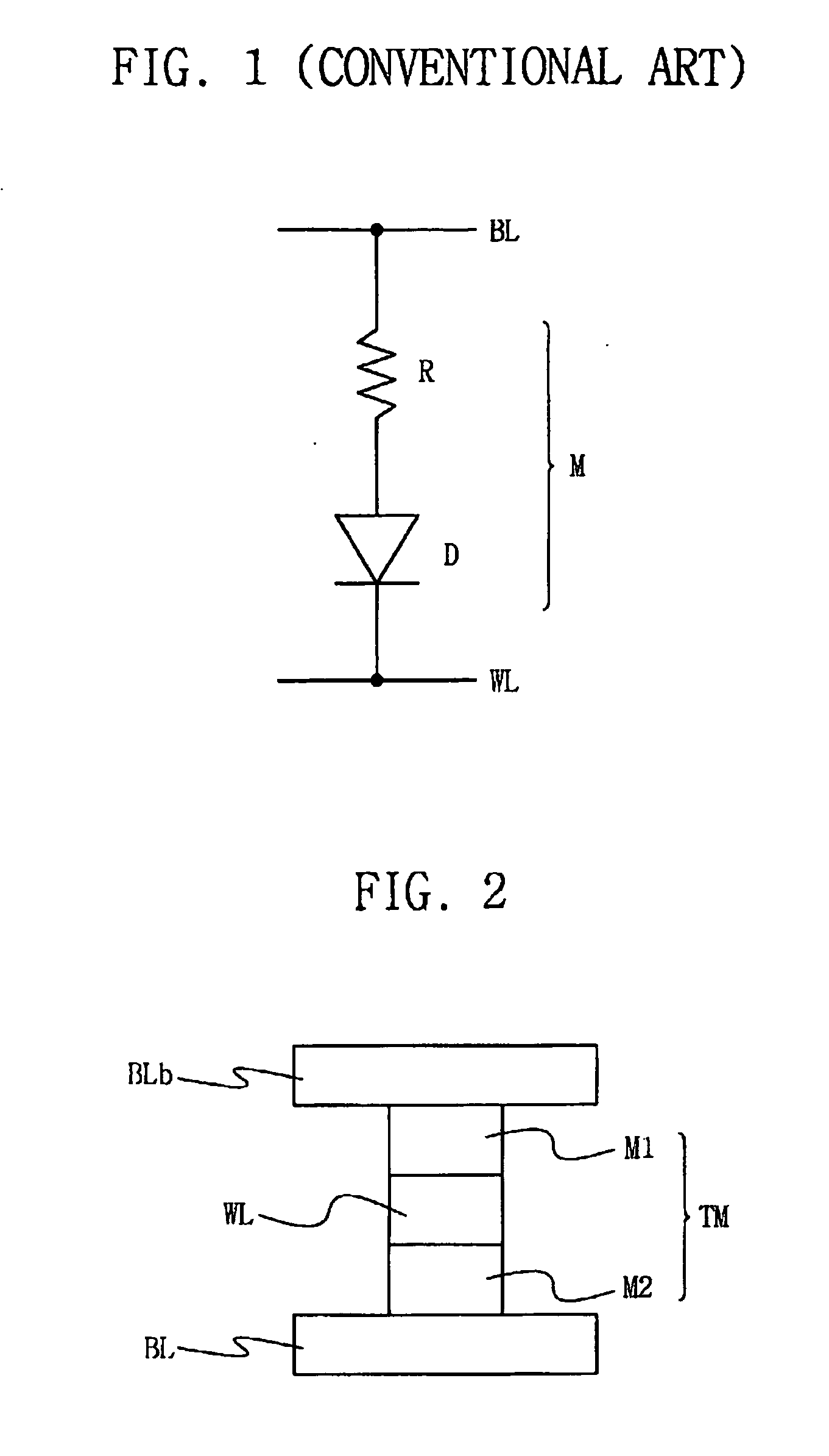

Memory cell of a resistive semiconductor memory device, a resistive semiconductor memory device having a three-dimensional stack structure, and related methods

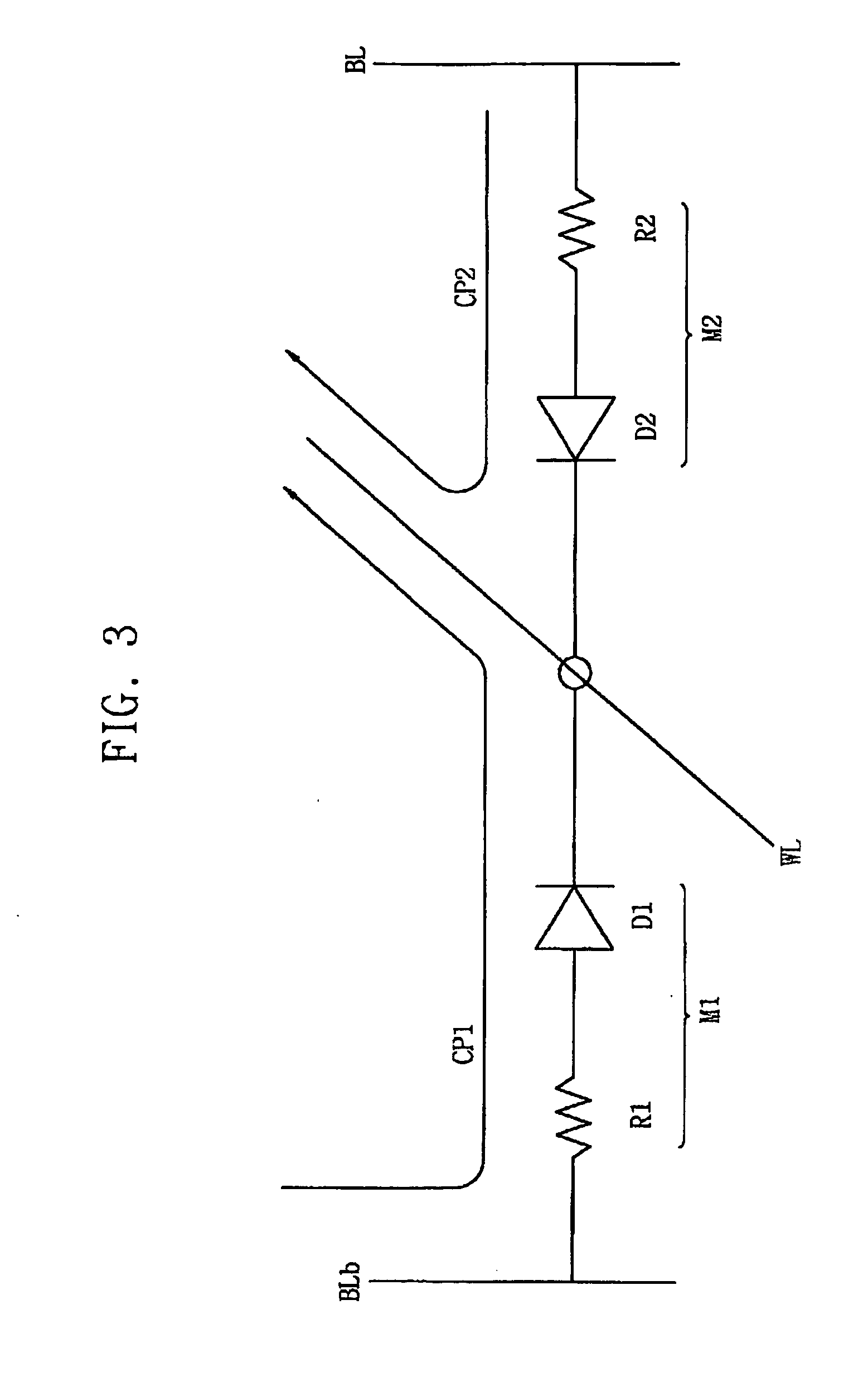

A memory cell of a resistive semiconductor memory device, a resistive semiconductor memory device having a three-dimensional stack structure, and related methods are provided. The memory cell of a resistive semiconductor memory device includes a twin cell, wherein the twin cell stores data values representing one bit of data. The twin cell includes a main unit cell connected to a main bit line and a word line, and a sub unit cell connected to a sub bit line and the word line. Also, the main unit cell includes a first variable resistor and a first diode, and the sub unit cell includes a second variable resistor and a second diode.

Owner:SAMSUNG ELECTRONICS CO LTD

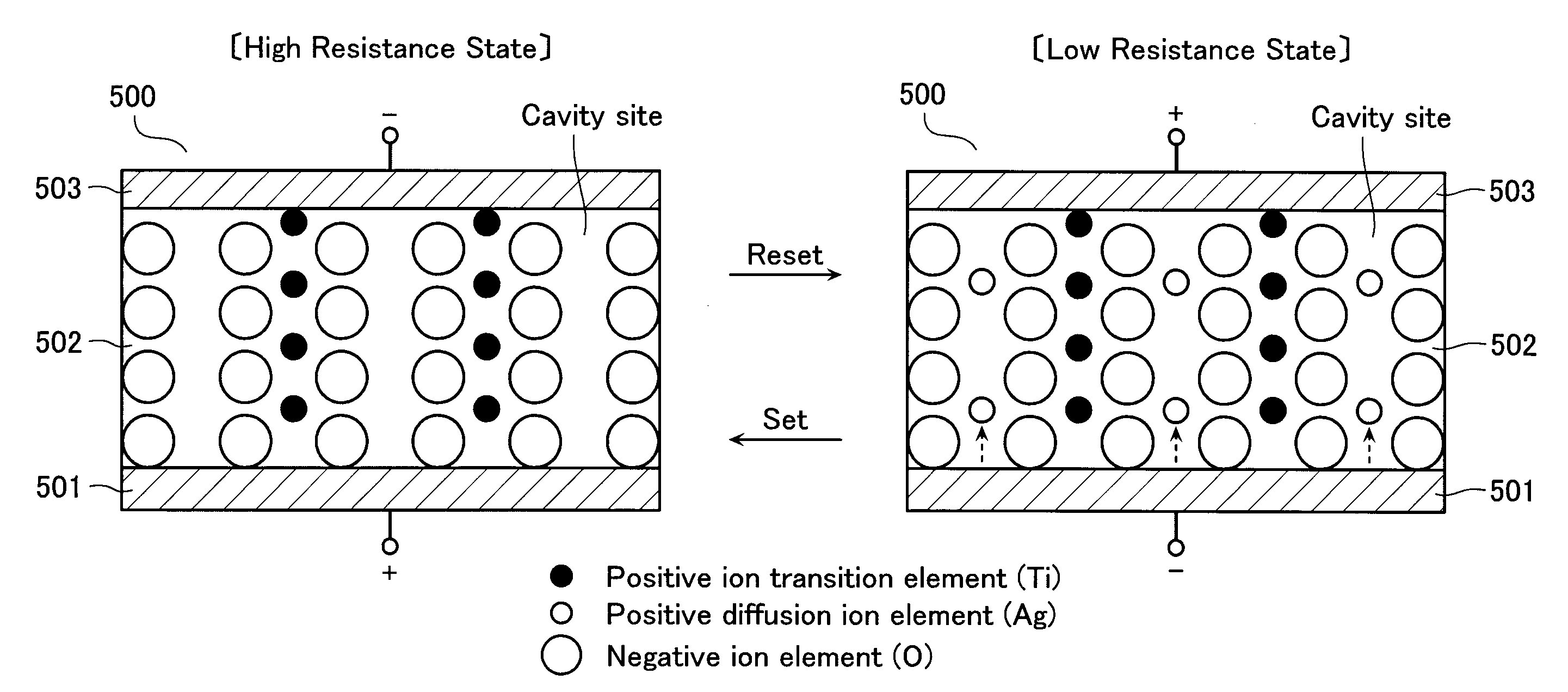

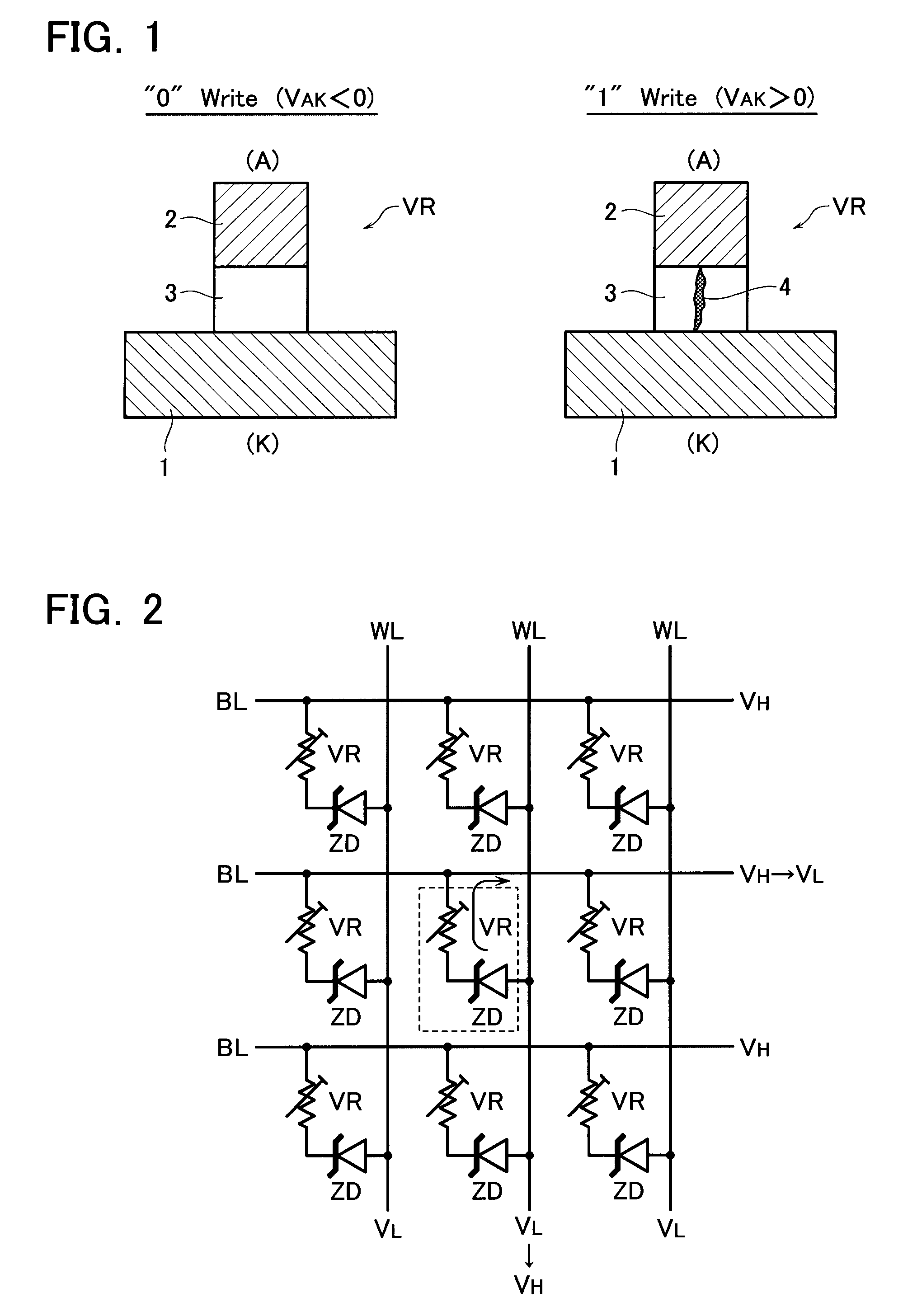

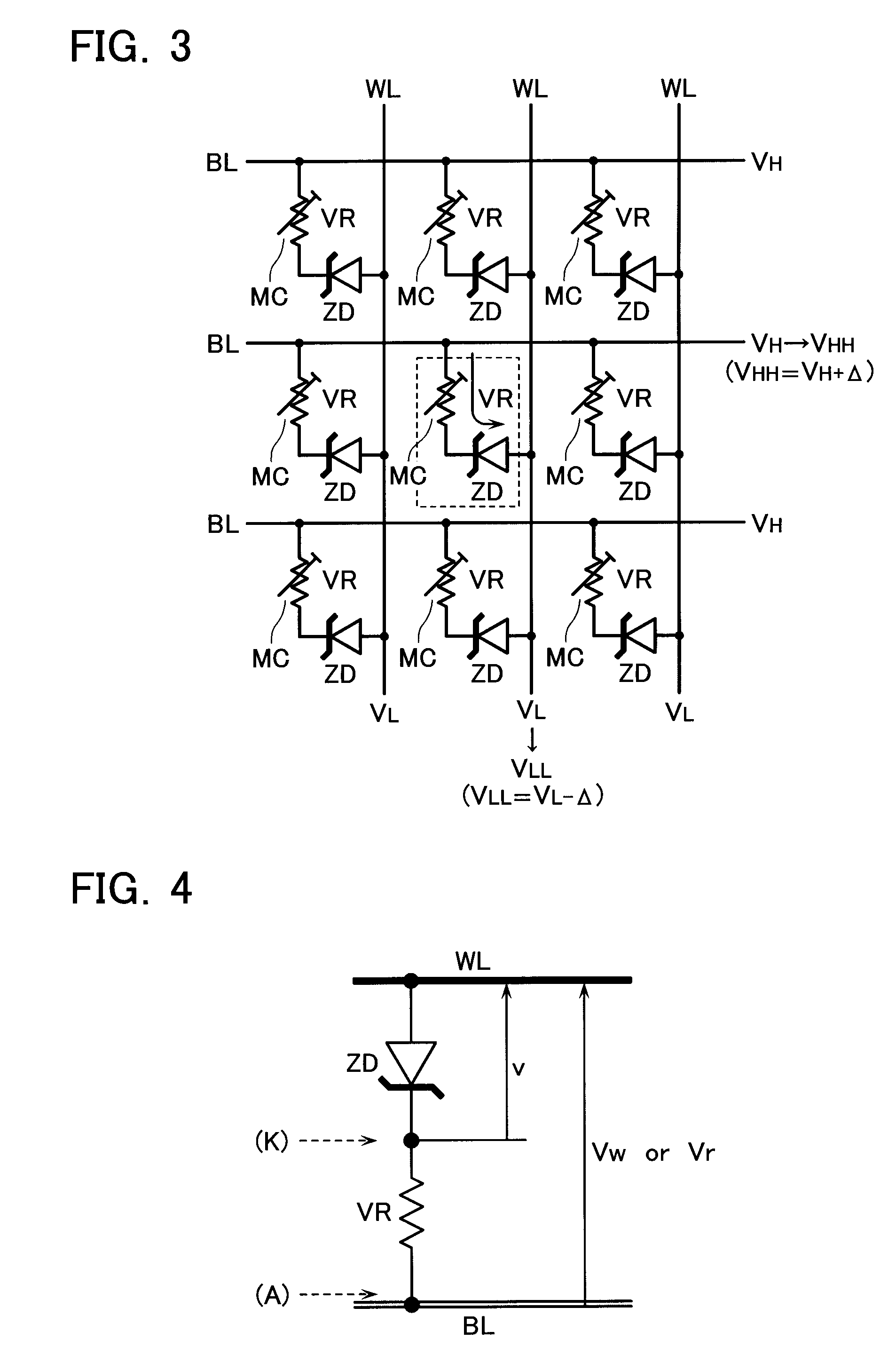

Resistance change memory device having a variable resistance element with a recording layer electrode served as a cation source in a write or erase mode

A resistance change memory device including: a semiconductor substrate; at least one cell array formed above the semiconductor substrate to have a stack structure of a variable resistance element and an access element, the variable resistance element storing a high resistance state or a low resistance state in a non-volatile manner, the access element having such an off-state resistance value in a certain voltage range that is ten times or more as high as that in a select state; and a read / write circuit formed on the semiconductor substrate, wherein the variable resistance element includes: a recording layer formed of a composite compound containing at least one transition element and a cavity site for housing a cation ion; and electrodes formed on the opposite sides of the recording layer, one of the electrodes serving as a cation source in a write or erase mode for supplying a cation to the recording layer to be housed in the cavity site.

Owner:TOSHIBA MEMORY CORP

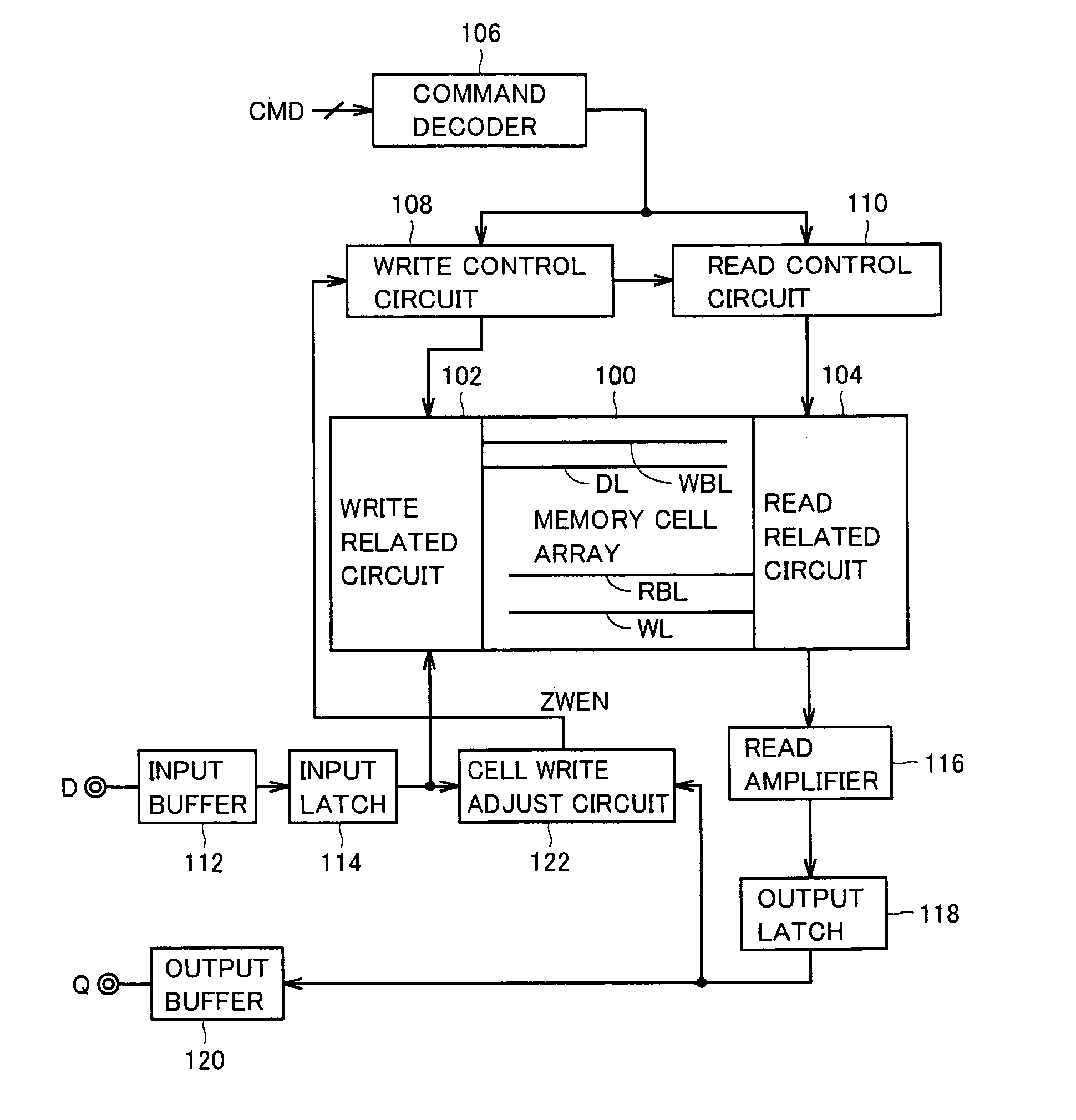

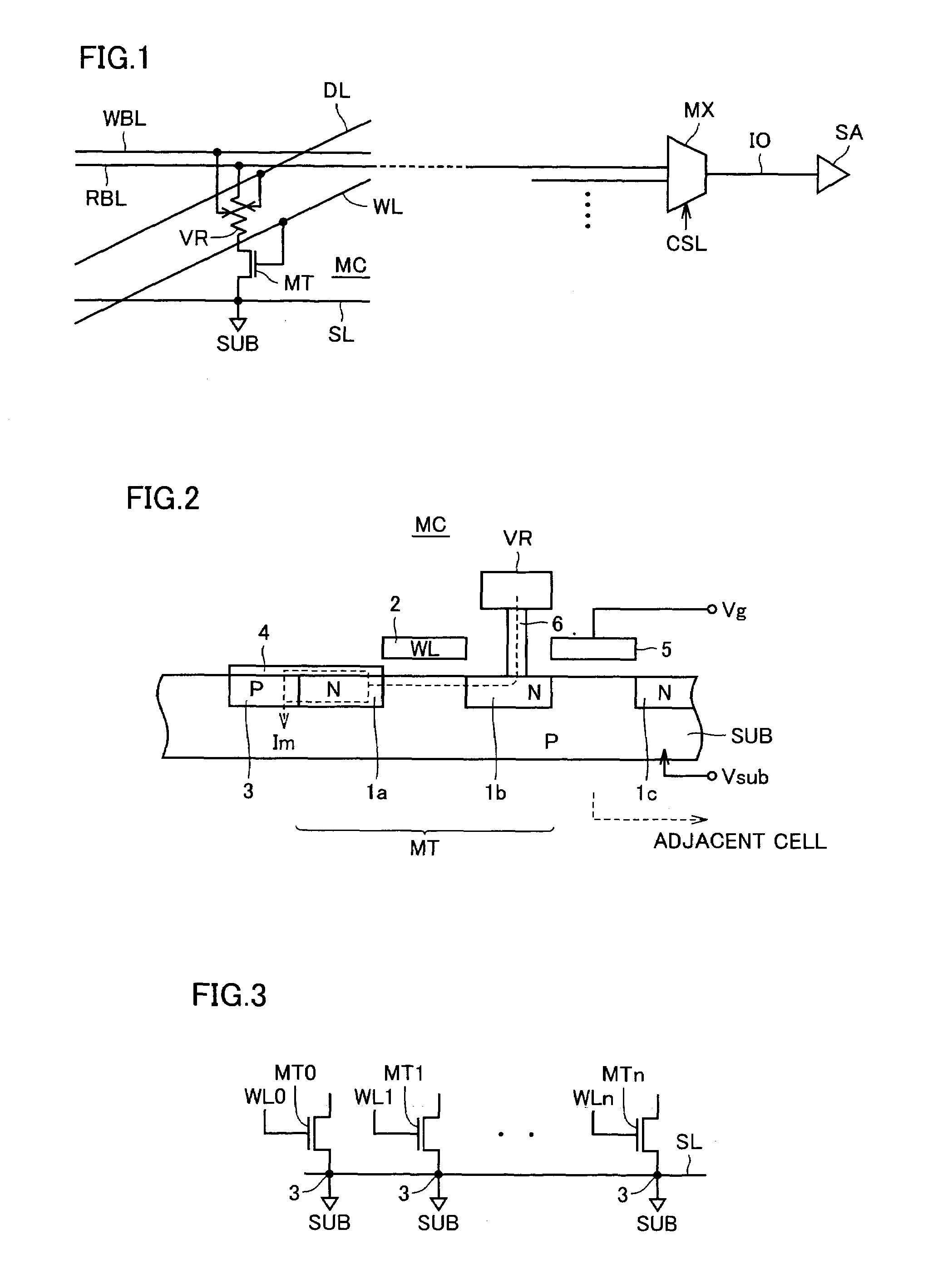

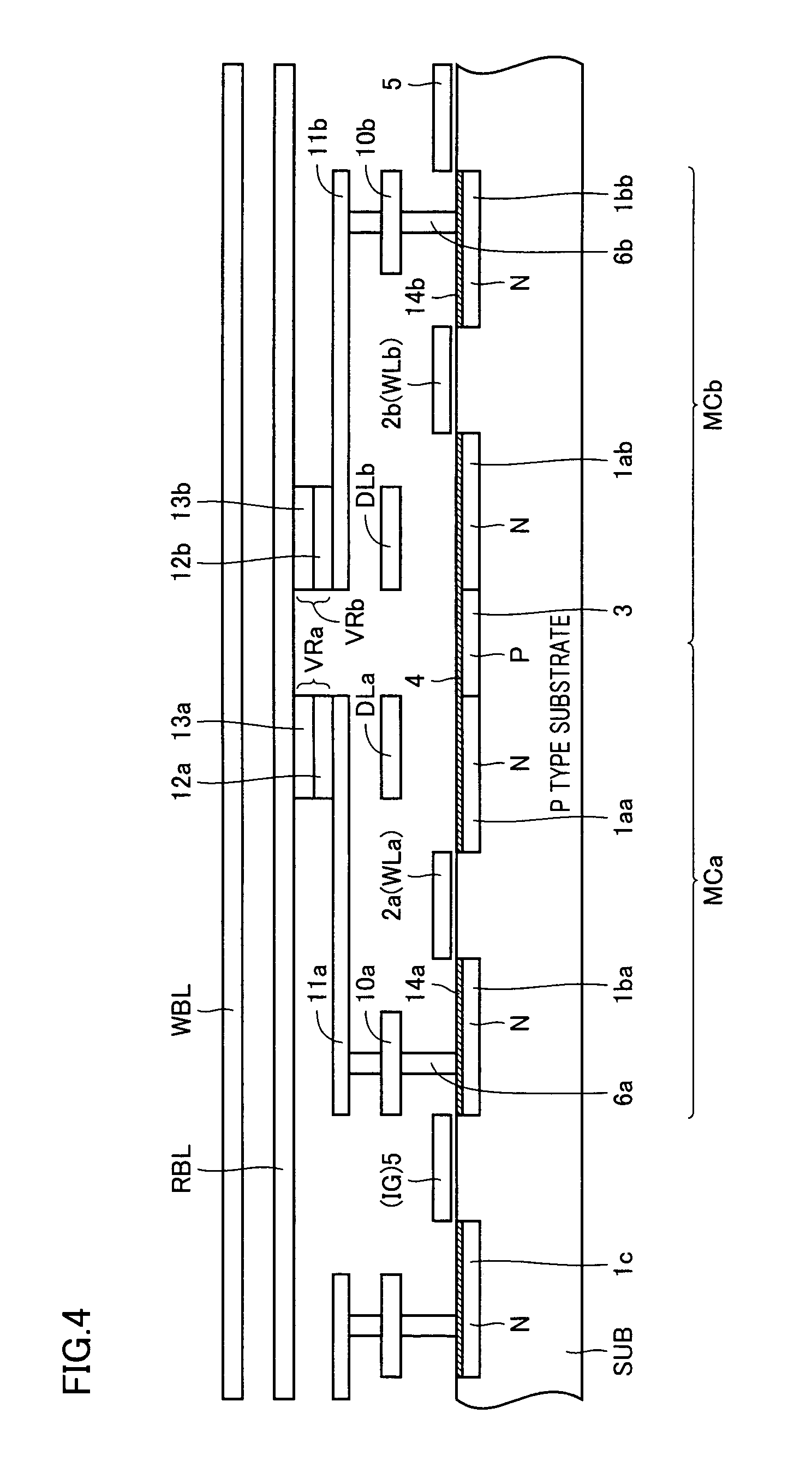

Non-volatile semiconductor memory device allowing concurrent data writing and data reading

A write bit line and a read bit line are provided separately for a memory cell. A source line connecting to the memory cell is formed of a source impurity region the same in conductivity type as a substrate region. A memory cell transistor and the source impurity region are connected by a metal interconnection line of a low resistance. A rise in the source line potential can be prevented, and a memory cell current can reliably be generated according to storage data. Further, fast data reading can be achieved. Additionally, by performing precharging and data amplification in a unit of read bit line, the load of the read bit line can be alleviated to achieve fast reading. An accessing time of a non-volatile semiconductor memory device that uses a variable resistance element as a storage element is reduced without increasing the current consumption.

Owner:RENESAS ELECTRONICS CORP

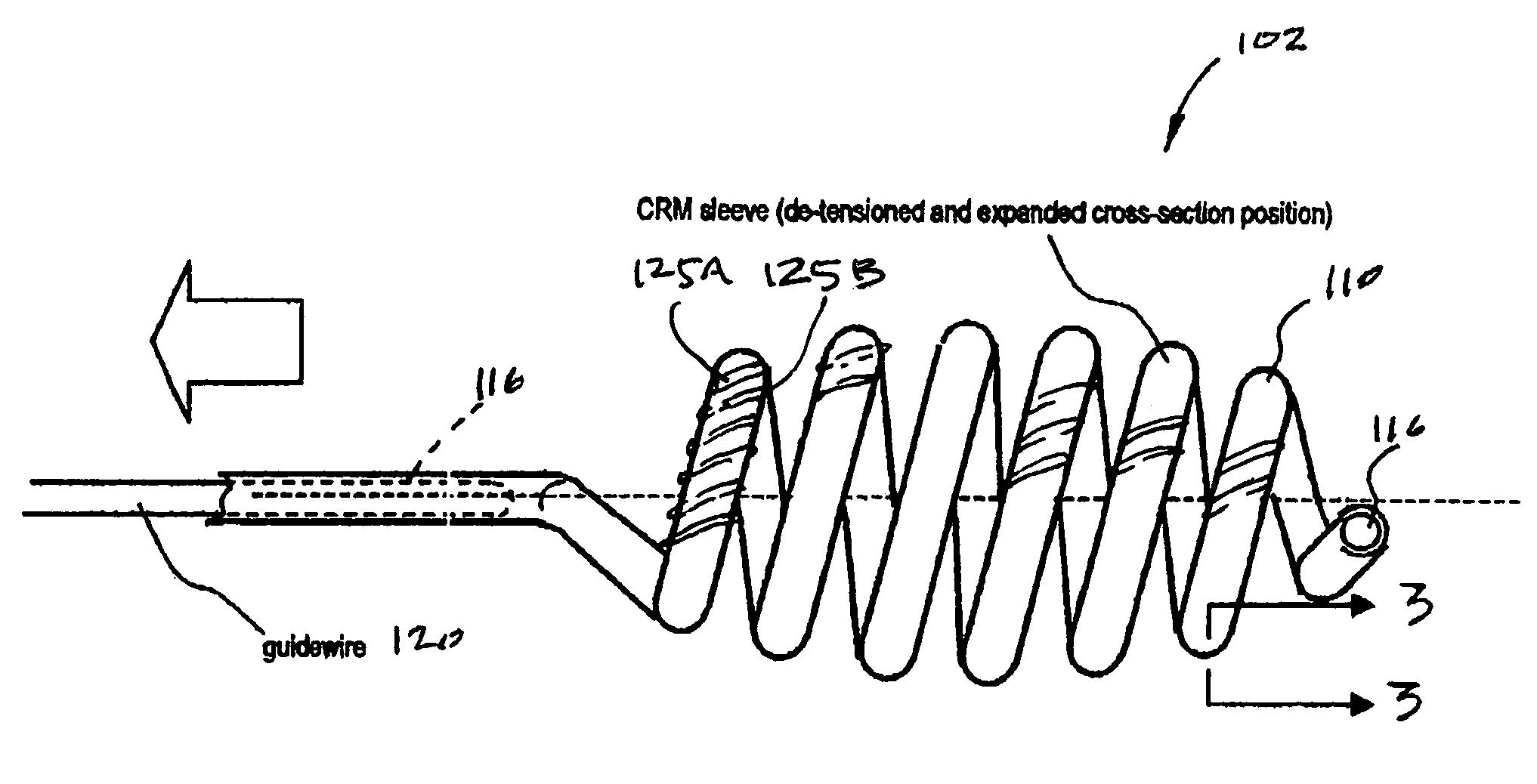

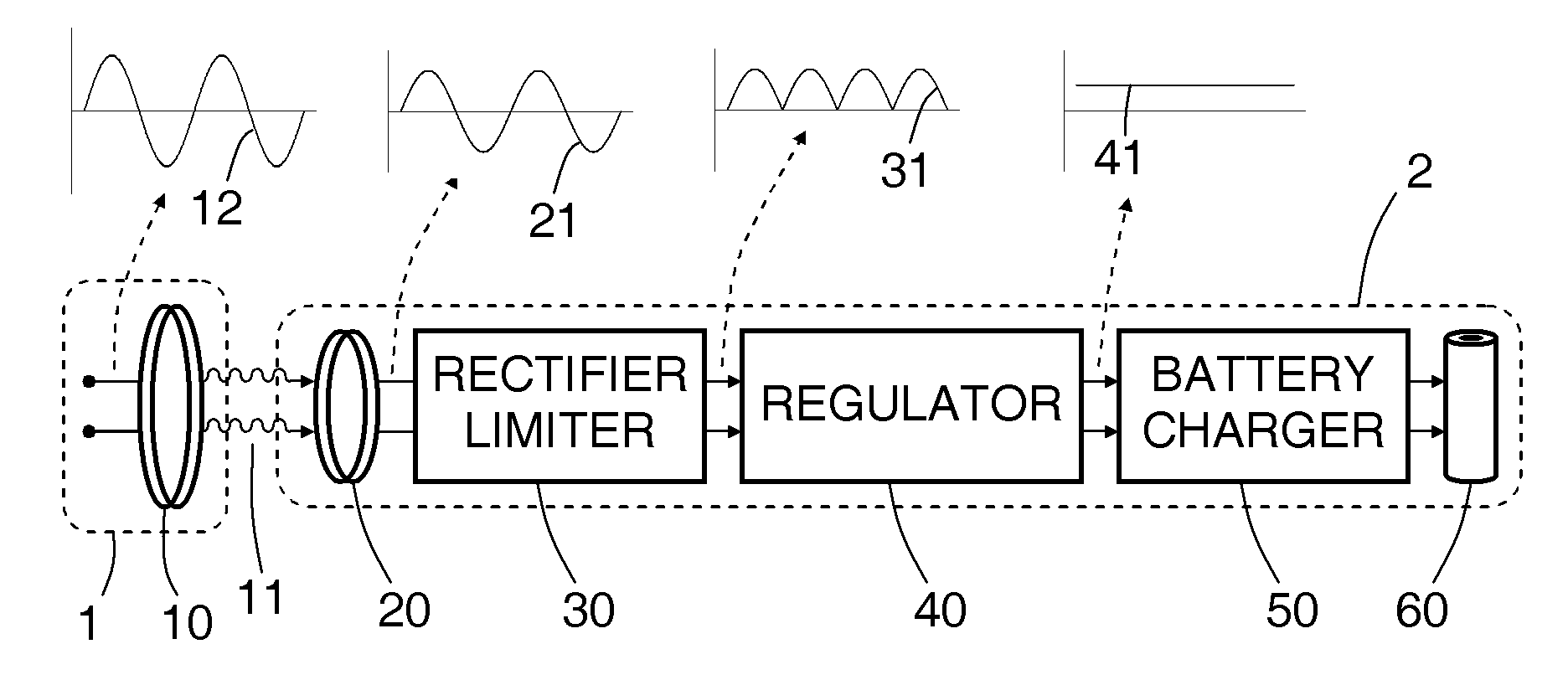

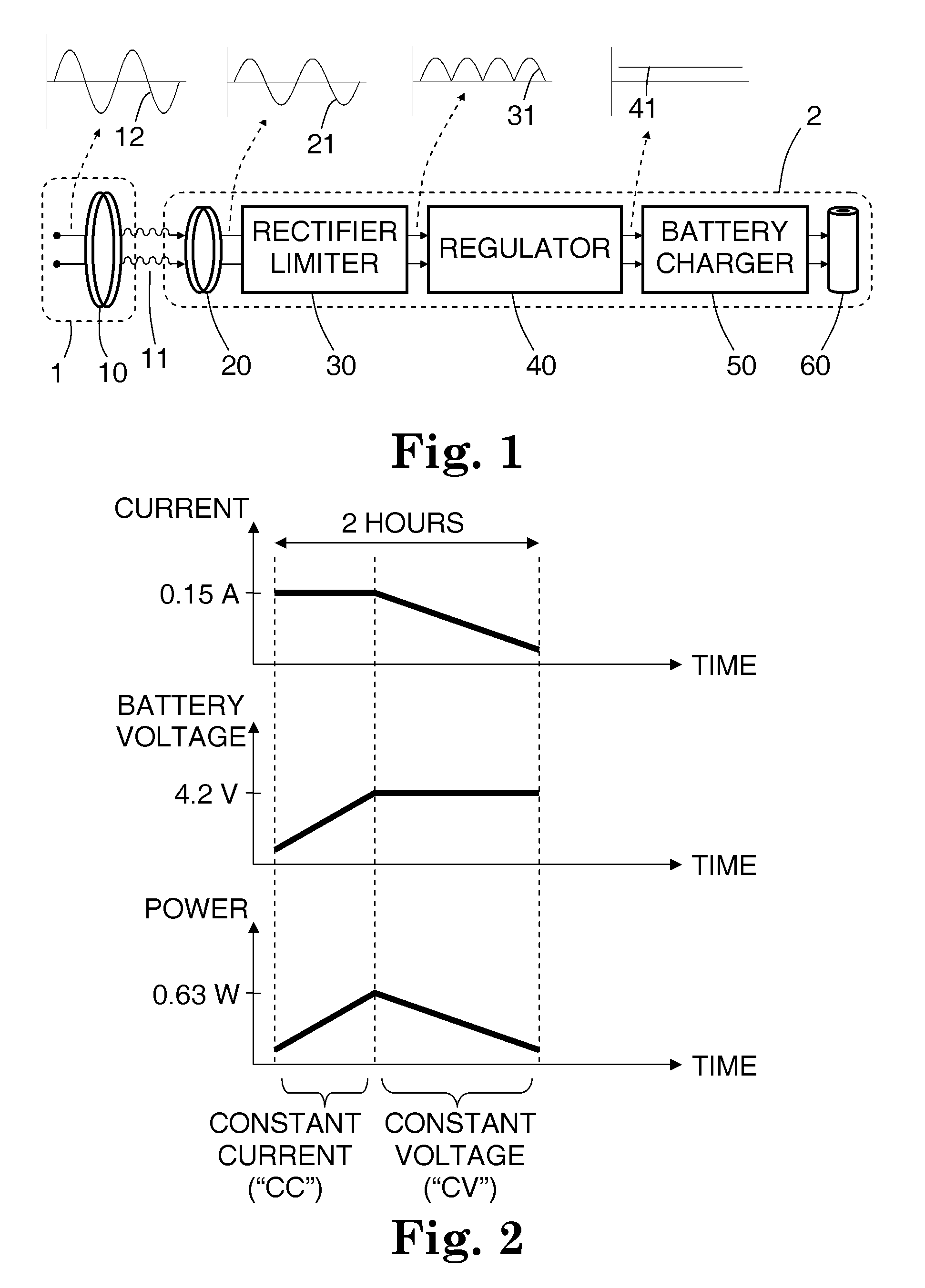

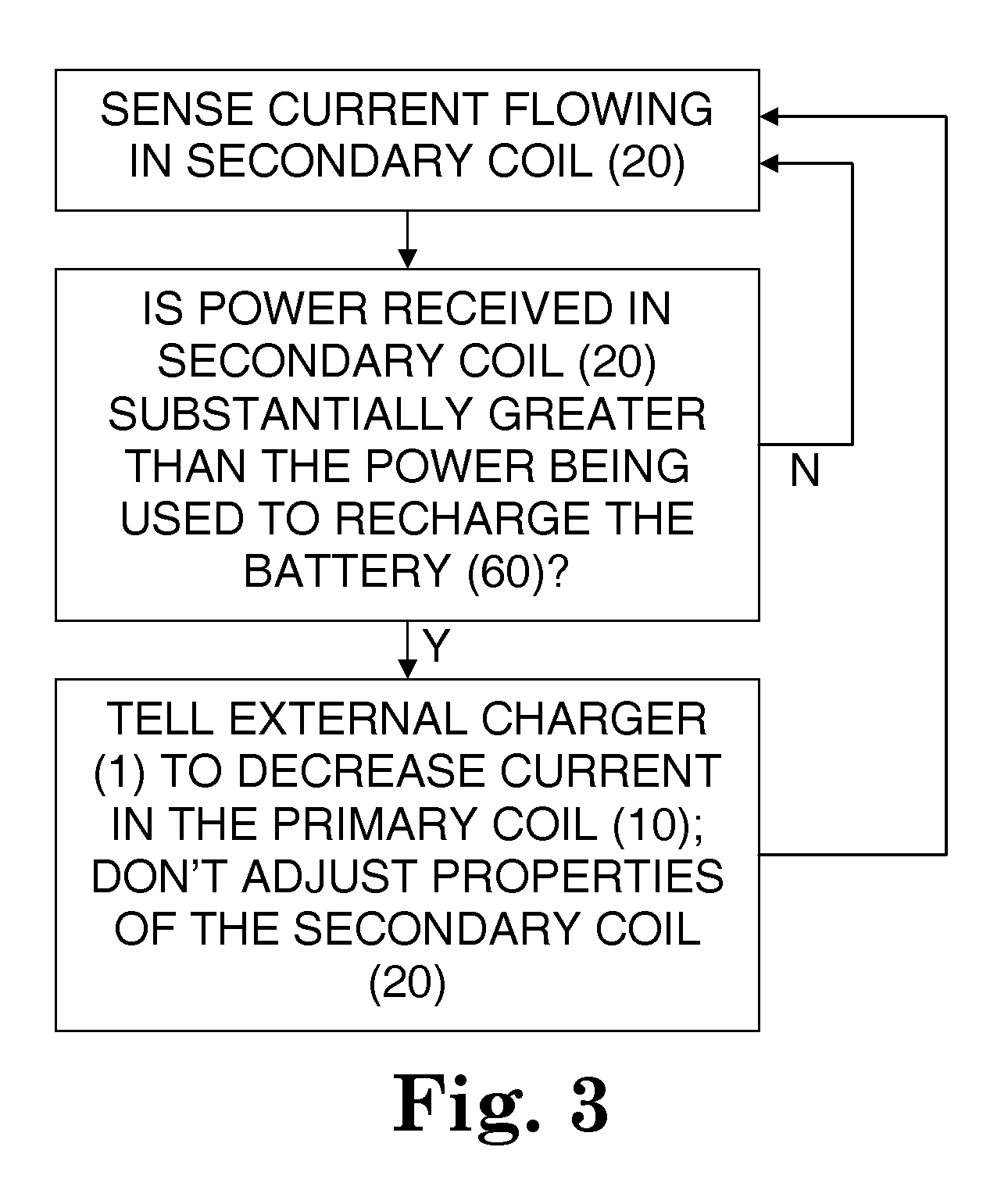

Self-regulating transcutaneous energy transfer

A rechargeable battery system and method are disclosed, in which an implantable medical device (IMD) regulates its transfer of energy from a separate charger unit. For recharging, a charger unit is brought into proximity to the implanted device. An oscillating current is generated in a primary coil, located in the charger. By inductive coupling through an oscillating magnetic field, an alternating current is generated in a secondary coil, which is implanted in or near the implanted device. The alternating current then passes through a half-wave or full-wave rectifier to form a one-sided current, then passes through a regulator to form an essentially direct current, which is in turn directed to the rechargeable battery in the implanted device. The secondary coil has a controllable damped resonant frequency, which can be dynamically tuned away from the driving frequency of the primary coil by a variable resistor and / or by varying a duty cycle of a rapidly switched electrical element. If a control loop in the implant senses that more power is being received at the second coil than is actually being used to recharge the battery, the control loop temporarily changes the variable resistance. When this happens, the resonant frequency of the secondary coil is detuned slightly away from the driving frequency, so that less of the incoming power is absorbed by the secondary coil. Alternatively, the secondary coil may be temporarily short-circuited. With less or no excess power entering the circuitry of the implant, the problem of overheating is mitigated.

Owner:ST CROIX MEDICAL

Wireless game controller for strength training and physiotherapy

Wireless game controller can provide variable resistance during strength training exercise and is coupled with off the shelf video gaming system such as Nintendo WII or personal computer by bluetooth or WiFI connection. The resistance is provided by a motor / generator. Electrical recuperation occurs between eccentric and concentric steps of the exercise, electrical energy is stored in a super capacitor between the steps. Video gaming system is configurable to run exercise software that provide reinforcing game experience, coaching, and physical therapy to the user. Exercise software tracks user's pose using fiduciary marks on the controller and data from 3d accelerometer embedded in the controller. The resistance is computed as a function of one or more the following: exercise type, position, velocity, user profile, and repetition number.

Owner:TONAL SYST INC

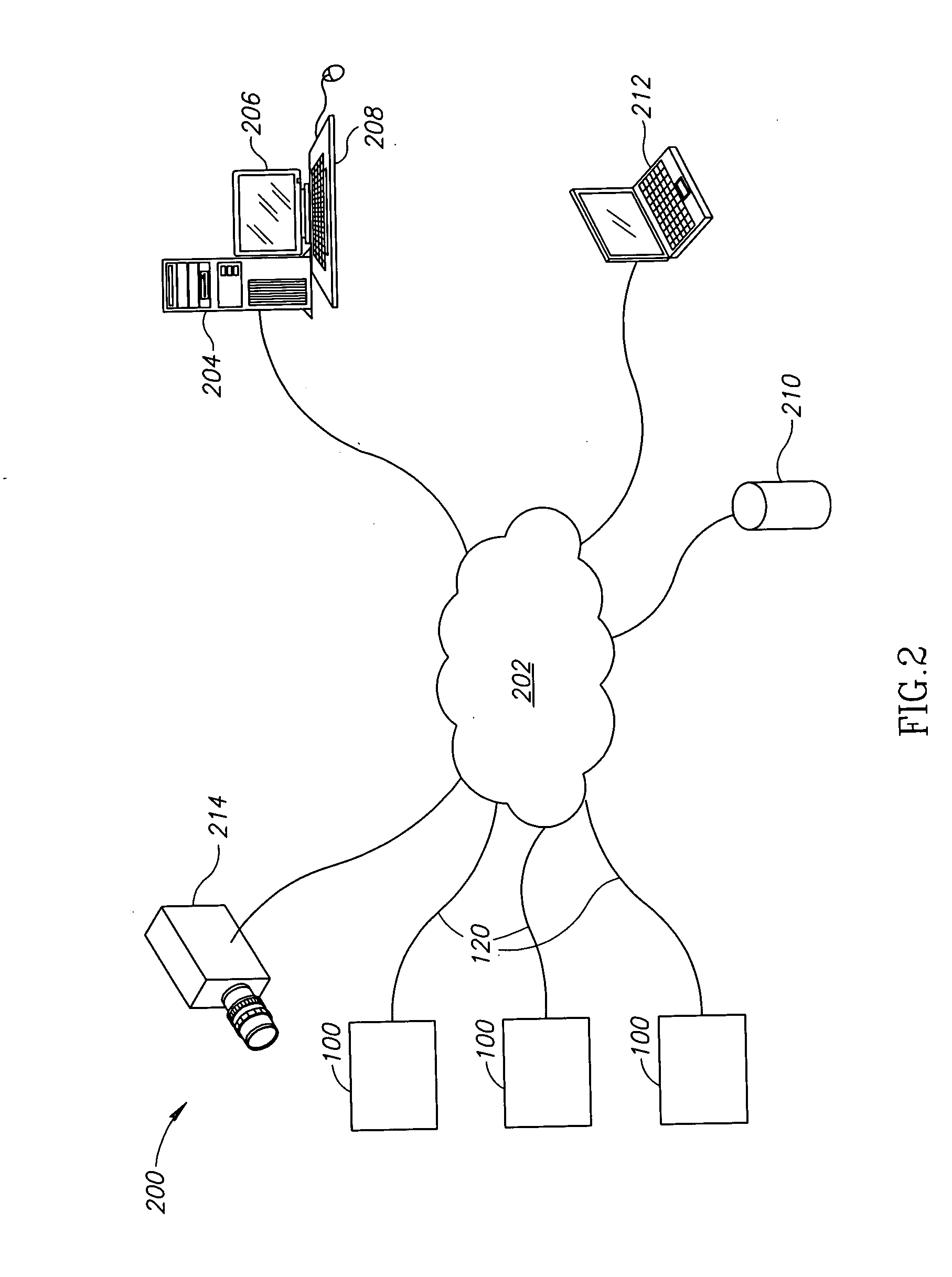

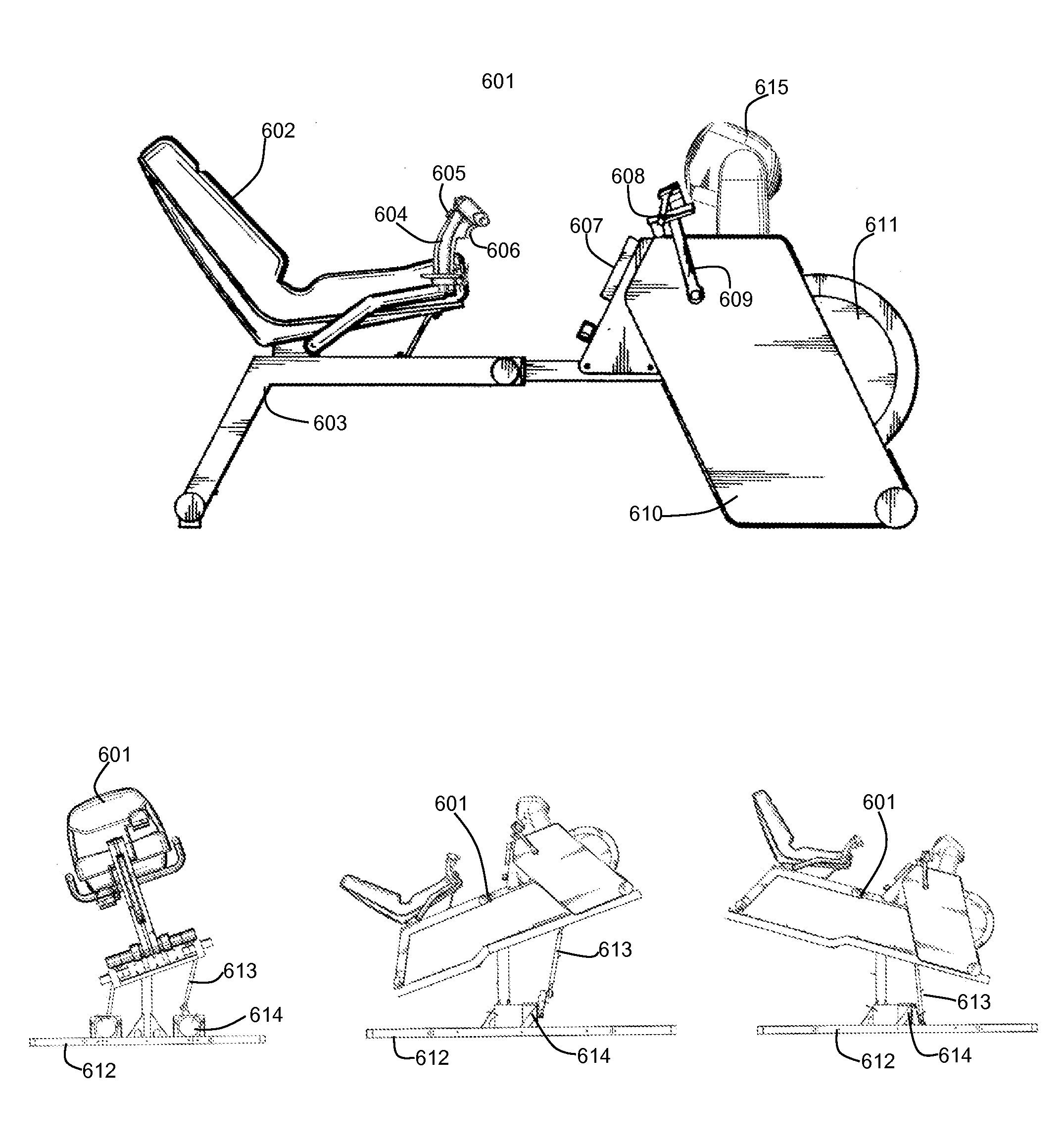

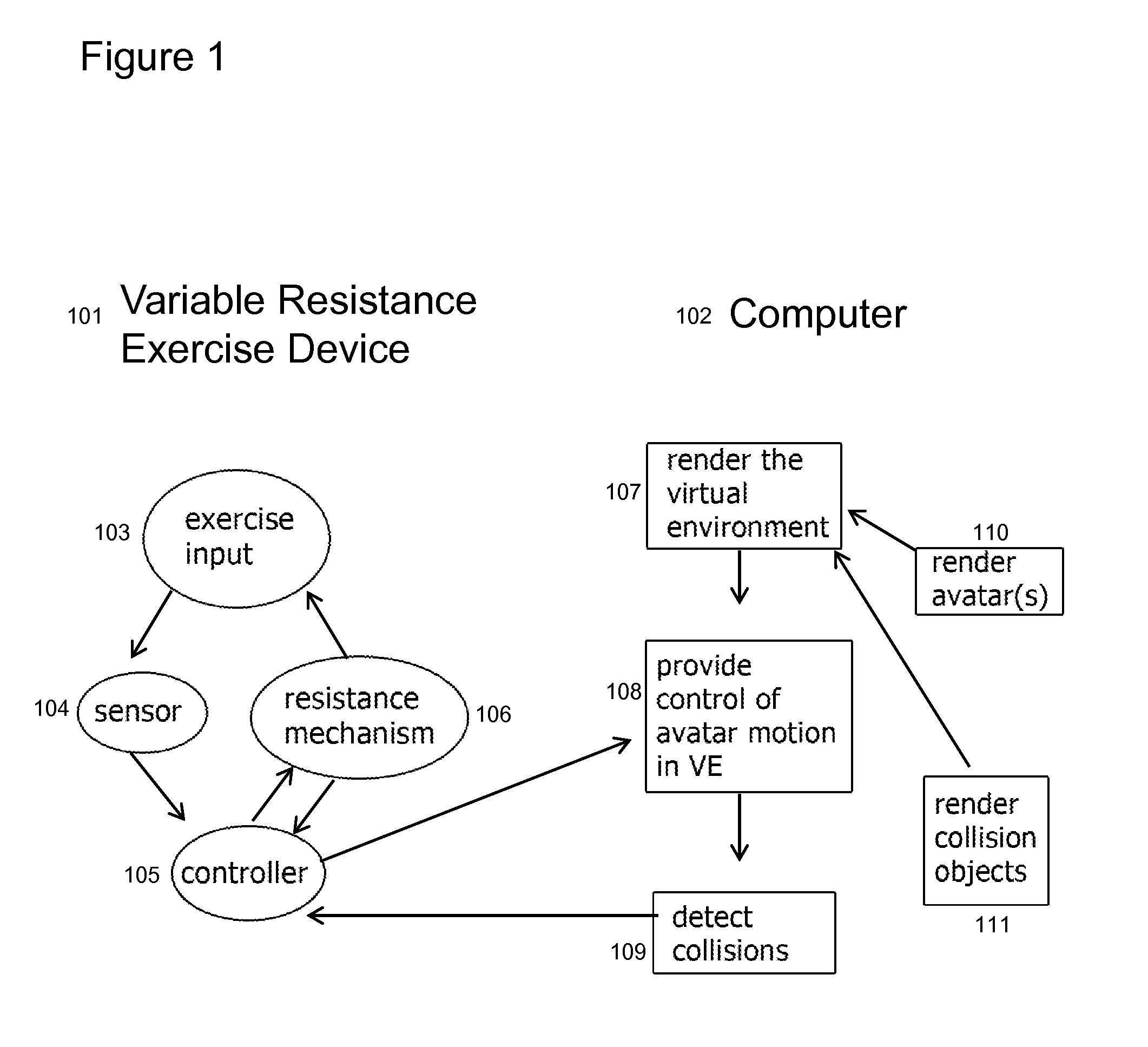

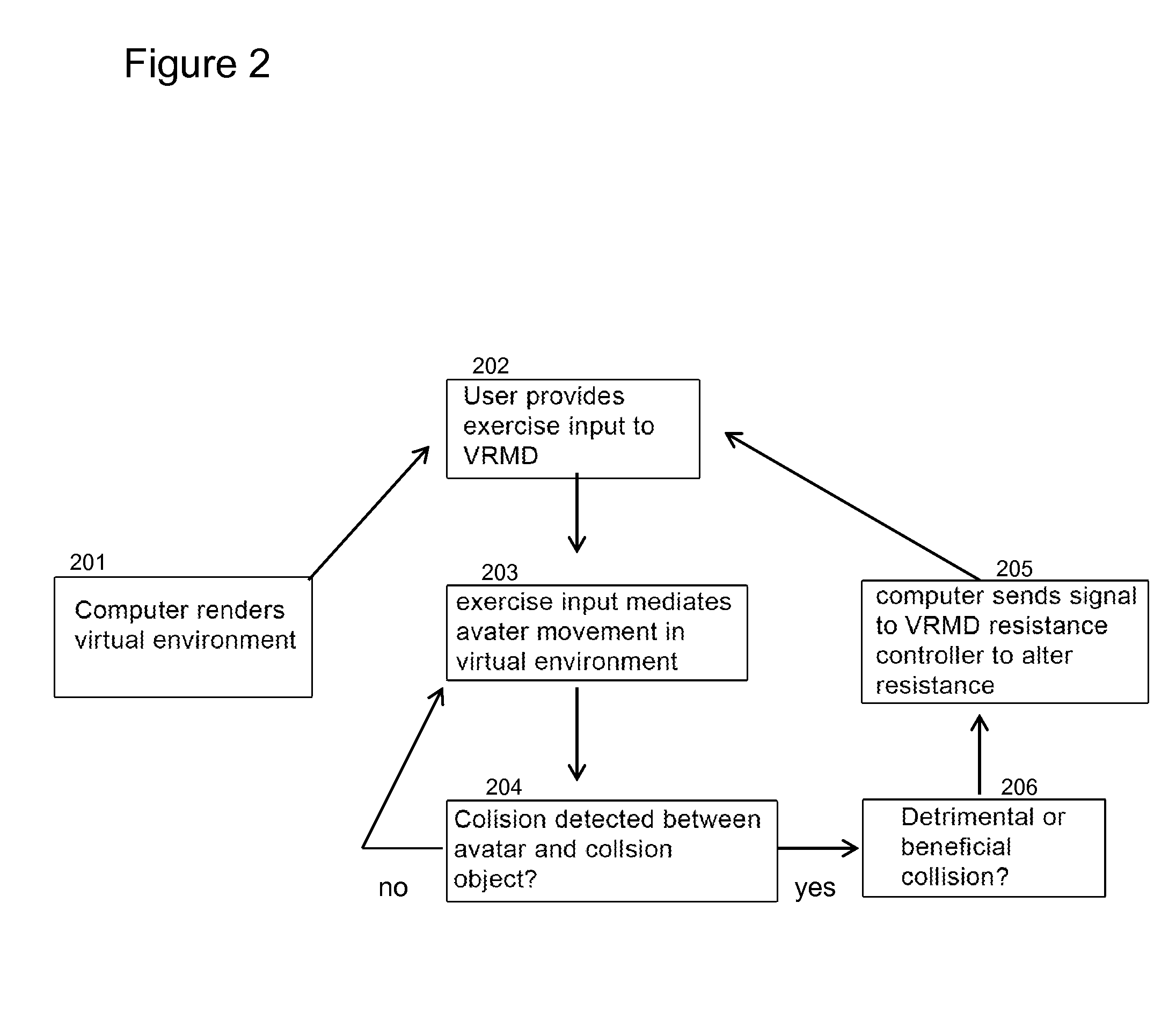

Devices, systems and methods for interaction in a virtual environment

The present disclosure provides a systems devices and methods for an exercise gaming platform particularly suited for multiple users. The exercise gaming platform has a variable resistance exercise device operatively coupled to a virtual reality environment rendered by a computer such that user exercise motion on the variable resistance exercise device translates to movement of an avatar representing the user in the virtual reality environment and wherein the virtual reality environment has collision objects capable of a collision with the avatar representing the user in the virtual environment, and wherein the collision of a collision object with the avatar representing the user in the virtual environment causes the resistance level of the user's variable resistance exercise device to change. Also disclosed are methods for providing power to virtual machines and methods for procedurally generating virtual terrain changes in response to changes of resistance on a variable resistance exercise device.

Owner:GREENBAUM ERIC A

Non-volatile variable resistance memory device and method of fabricating the same

ActiveUS20070290186A1Stable reset currentResistance characteristicSemiconductor/solid-state device manufacturingBulk negative resistance effect devicesOptoelectronicsVariable resistance

A non-volatile variable resistance memory device and a method of fabricating the same are provided. The non-volatile variable resistance memory device may include a lower electrode, a buffer layer on the lower electrode, an oxide layer on the buffer layer and an upper electrode on the oxide layer. The buffer layer may be composed of an oxide and the oxide layer may have variable resistance characteristics.

Owner:SAMSUNG ELECTRONICS CO LTD

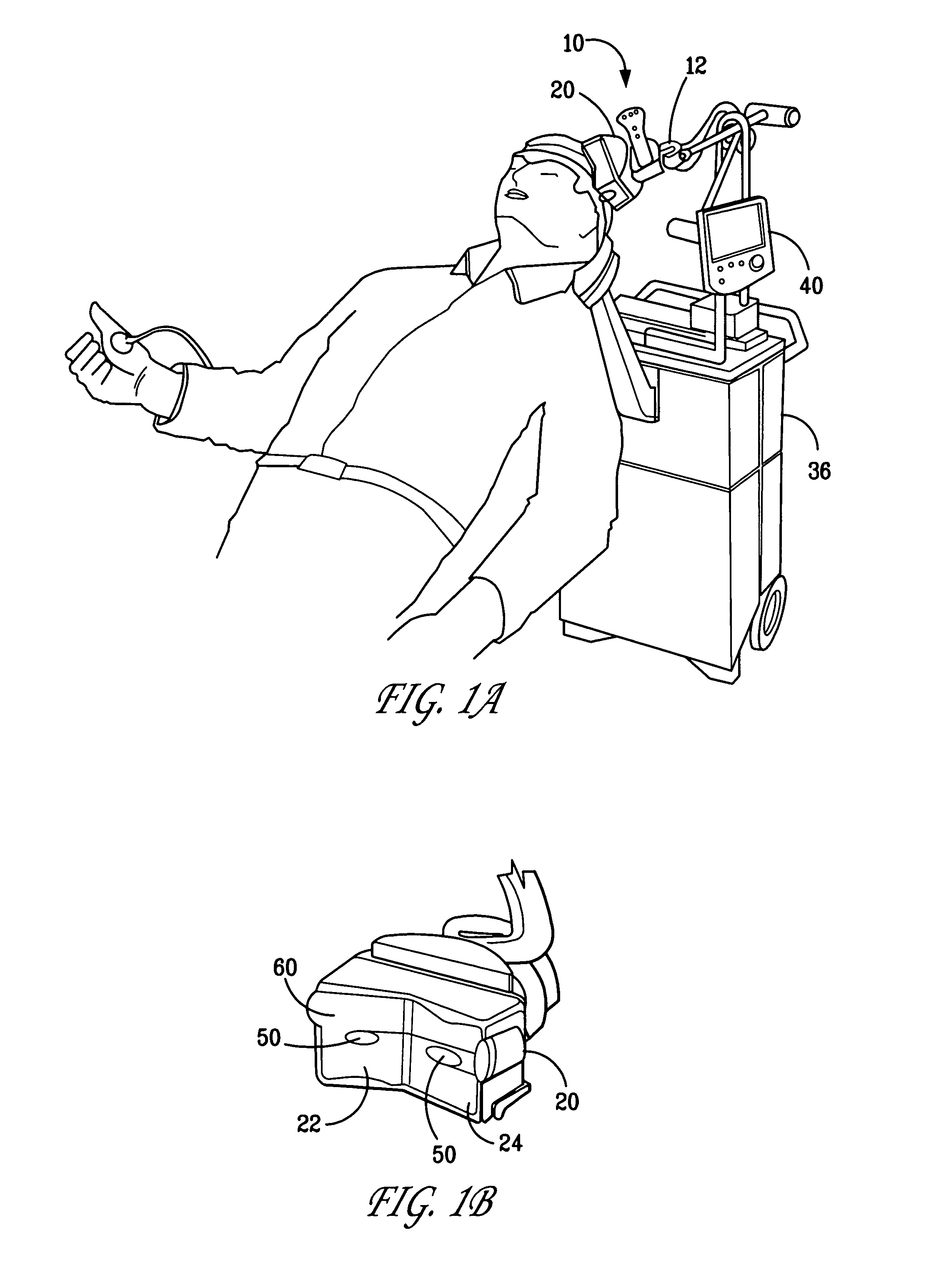

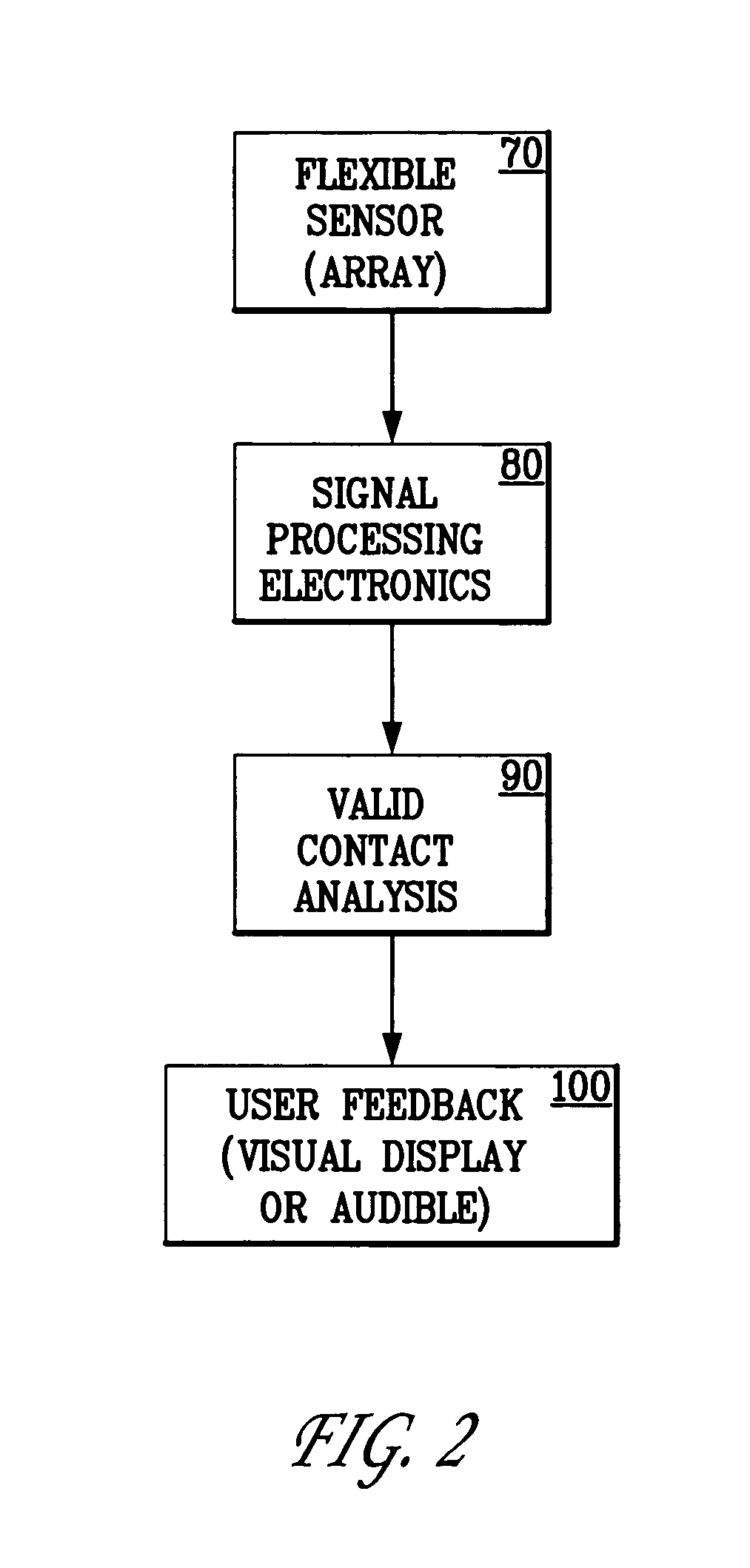

Method and apparatus for determining the proximity of a TMS coil to a subject's head

A proximity sensor for a transcranial magnetic stimulation (TMS) system detects the proximity of a TMS coil assembly to a position at which the coil is to receive pulses during TMS treatment and provides feedback to the operator so that the operator may adjust the TMS coil assembly as necessary to maintain optimal positioning during treatment. A flexible substrate containing a sensor or sensor array is disposed between the TMS coil assembly and the position such that the coupling of the TMS coil assembly to the position may be detected by the sensor(s). Sensor outputs are processed by signal processing circuitry to provide an indication of whether the TMS coil assembly is properly disposed with respect to the position during TMS treatment. A display may be used to provide an indication of how to adjust the TMS coil assembly to improve the positioning of the TMS coil assembly. On the other hand, a sound generator may be used to generate a sound that indicates to an operator whether the TMS coil assembly is properly positioned at the position. Many different types of sensor devices may be used to detect proximity, including membrane switches, variable resistance sensors, resistive strips, touch screens, pickup loops, fluid displacement sensors, optical sensors, acoustic sensors, inductive coupling sensors, capacitive coupling sensors, temperature sensors, and the like.

Owner:NEURONETICS

Resistance change memory device

A resistance change memory device including: a semiconductor substrate; cell arrays stacked above the substrate, each having memory cells, bit lines and word lines; a read / write circuit formed on the semiconductor substrate; first and second vertical wirings disposed to connect the bit lines to the read / write circuit; and third vertical wirings disposed the word lines to the read / write circuit. The memory cell includes a variable resistance element for storing as information a resistance value, which has a recording layer composed of a composite compound containing at least two types of cation elements, at least one type of the cation element being a transition element having “d” orbit, in which electrons are incompletely filled, the shortest distance between adjacent cation elements being 0.32 nm or less.

Owner:TOSHIBA MEMORY CORP