Memory cell of a resistive semiconductor memory device, a resistive semiconductor memory device having a three-dimensional stack structure, and related methods

a memory cell and semiconductor technology, applied in the direction of information storage, static storage, digital storage, etc., can solve the problems of high operation speed, low power consumption, and the degree of integration of a semiconductor memory device having a two-dimensional structure is approaching an upper limit, so as to improve reliability and high degree of integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040]In the drawings, like reference symbols indicate like or similar components throughout.

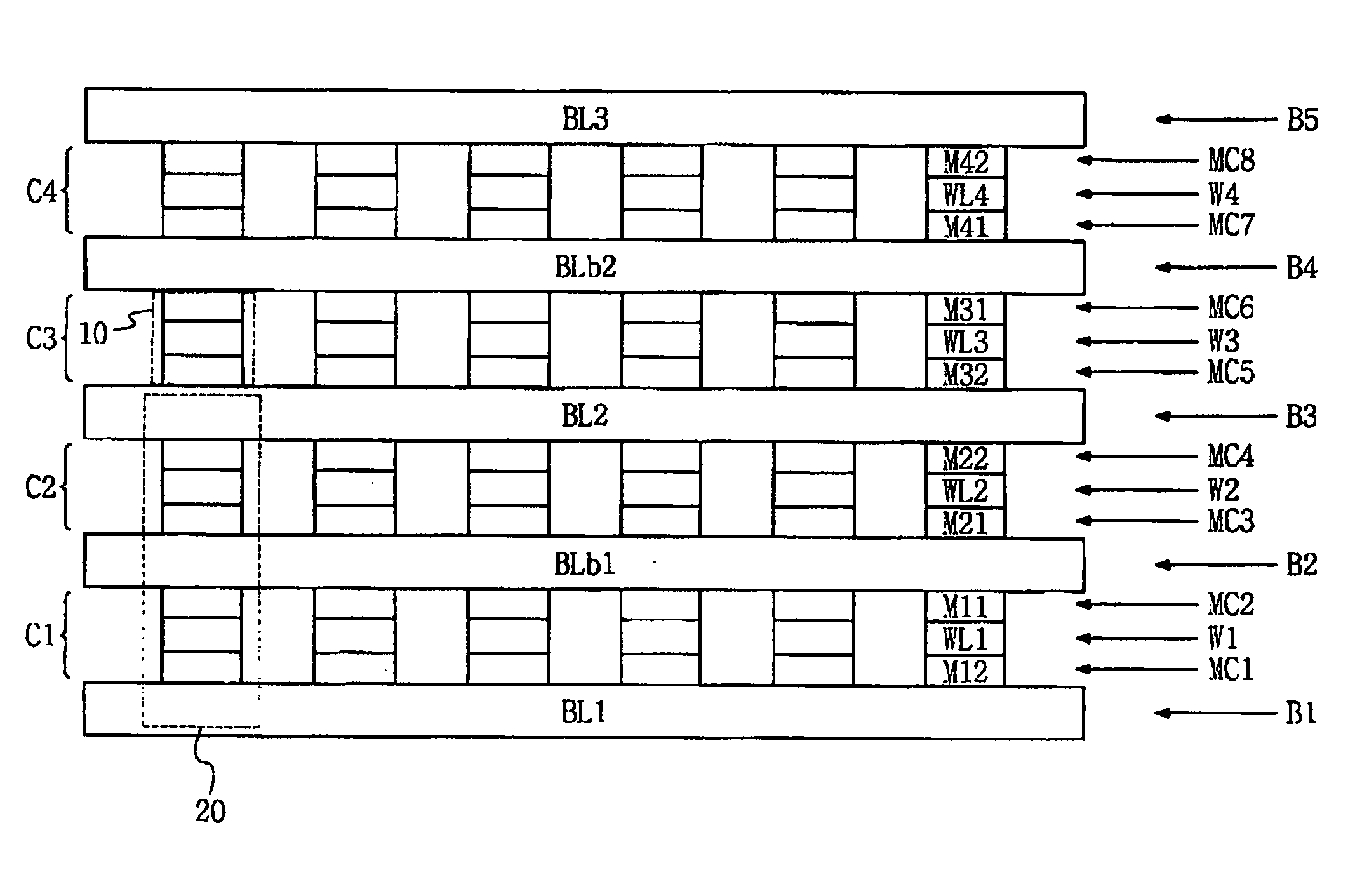

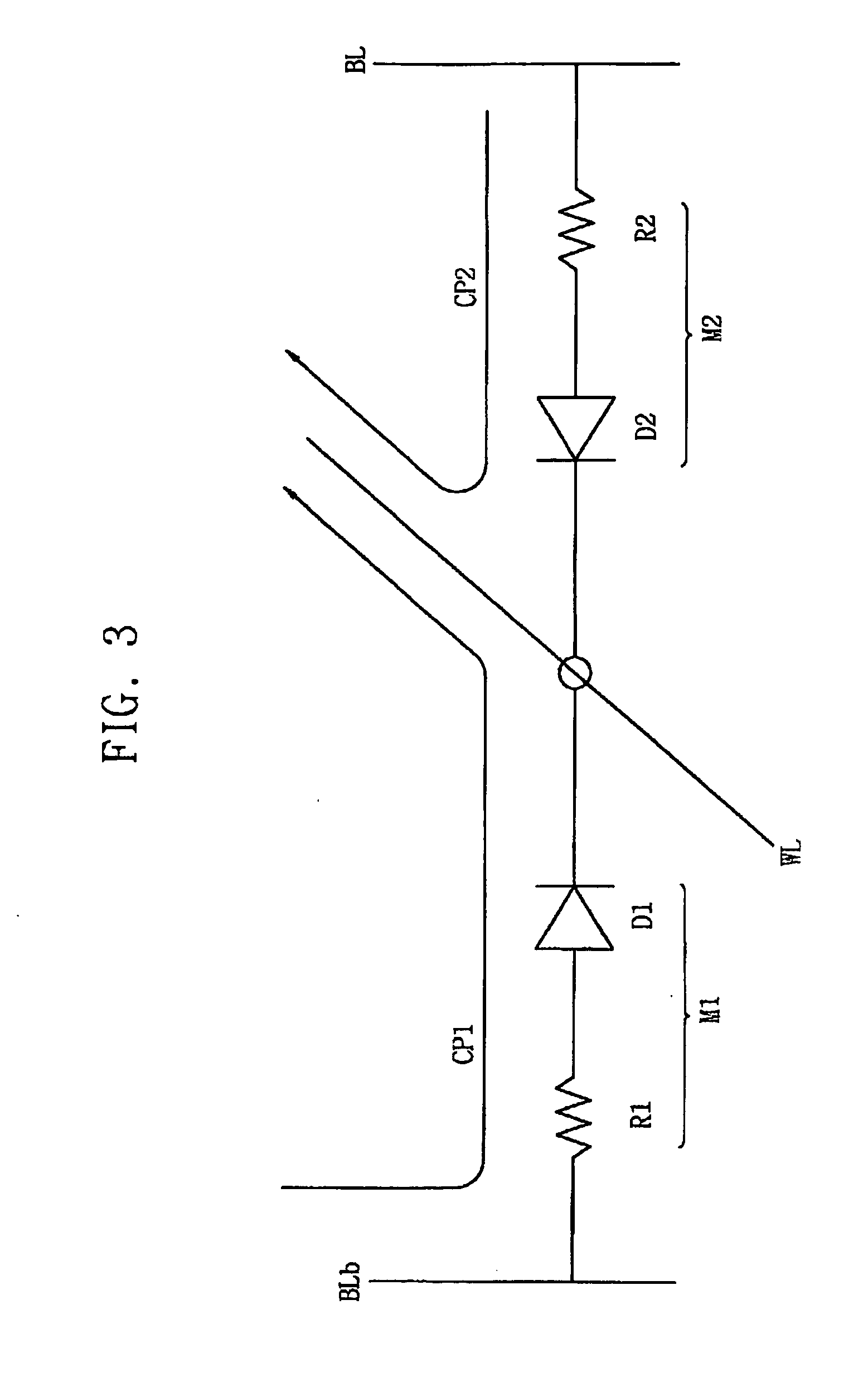

[0041]FIG. 2 illustrates the structure of a memory cell of a resistive semiconductor memory device in accordance with an embodiment of the invention.

[0042]As shown in FIG. 2, a memory cell TM in accordance with an embodiment of the invention has a twin cell structure. Thus, memory cell TM can store one more bit of data than a conventional memory cell (e.g., conventional memory cell M of FIG. 1). Memory cell TM comprises a main unit cell M2 connected to a main bit line BL and a sub unit cell M1 connected to a sub bit line BLb. In addition, main unit cell M2 and sub unit cell M1 are each connected to a word line WL (that is, they are each connected to the same word line WL). While the conventional memory cell M described above (with reference to FIG. 1) has one diode D and one variable resistor R, memory cell TM in accordance with an embodiment of the invention has a structure in which main un...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More