Patents

Literature

2845 results about "Cell structure" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Process for making and programming and operating a dual-bit multi-level ballistic MONOS memory

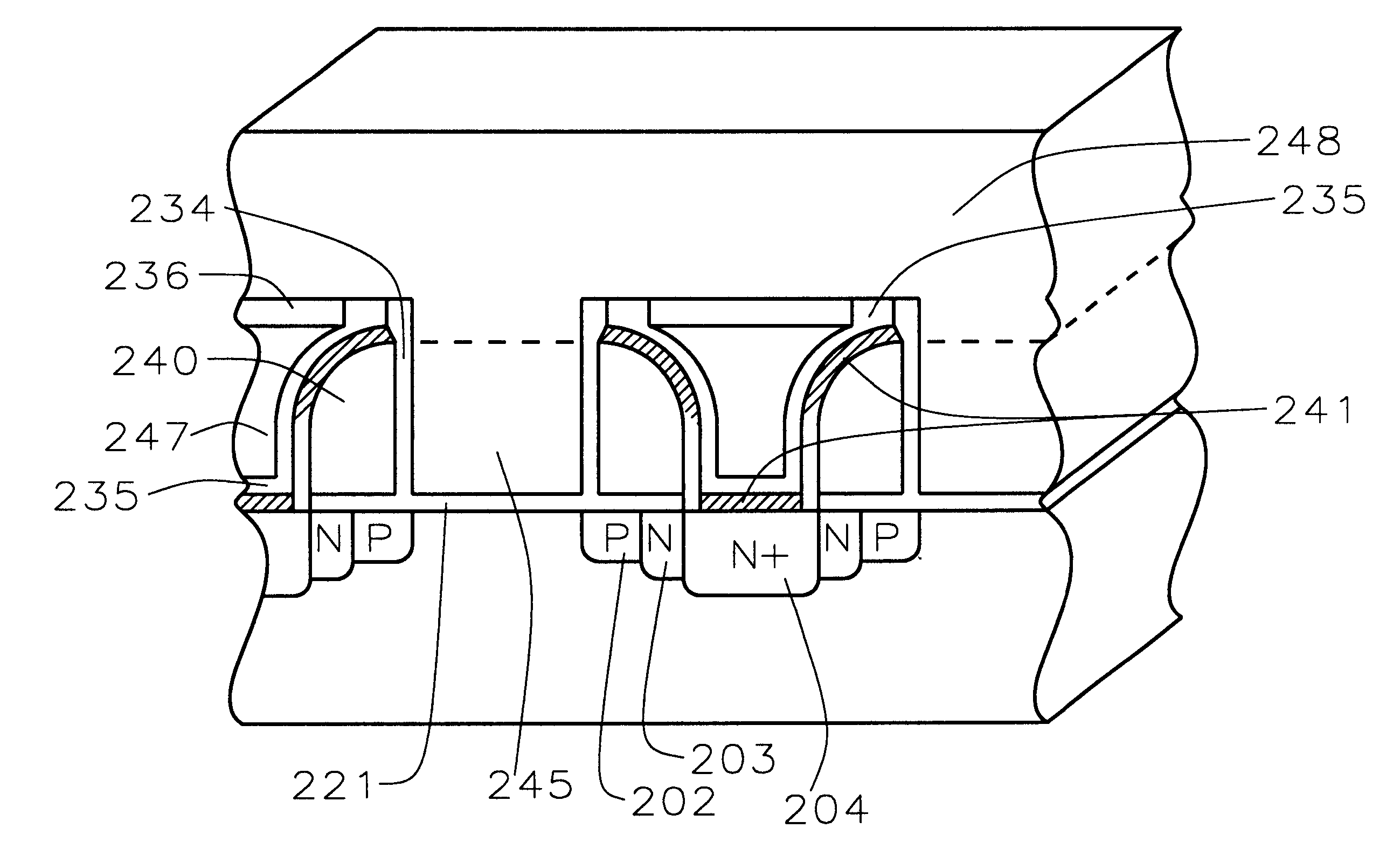

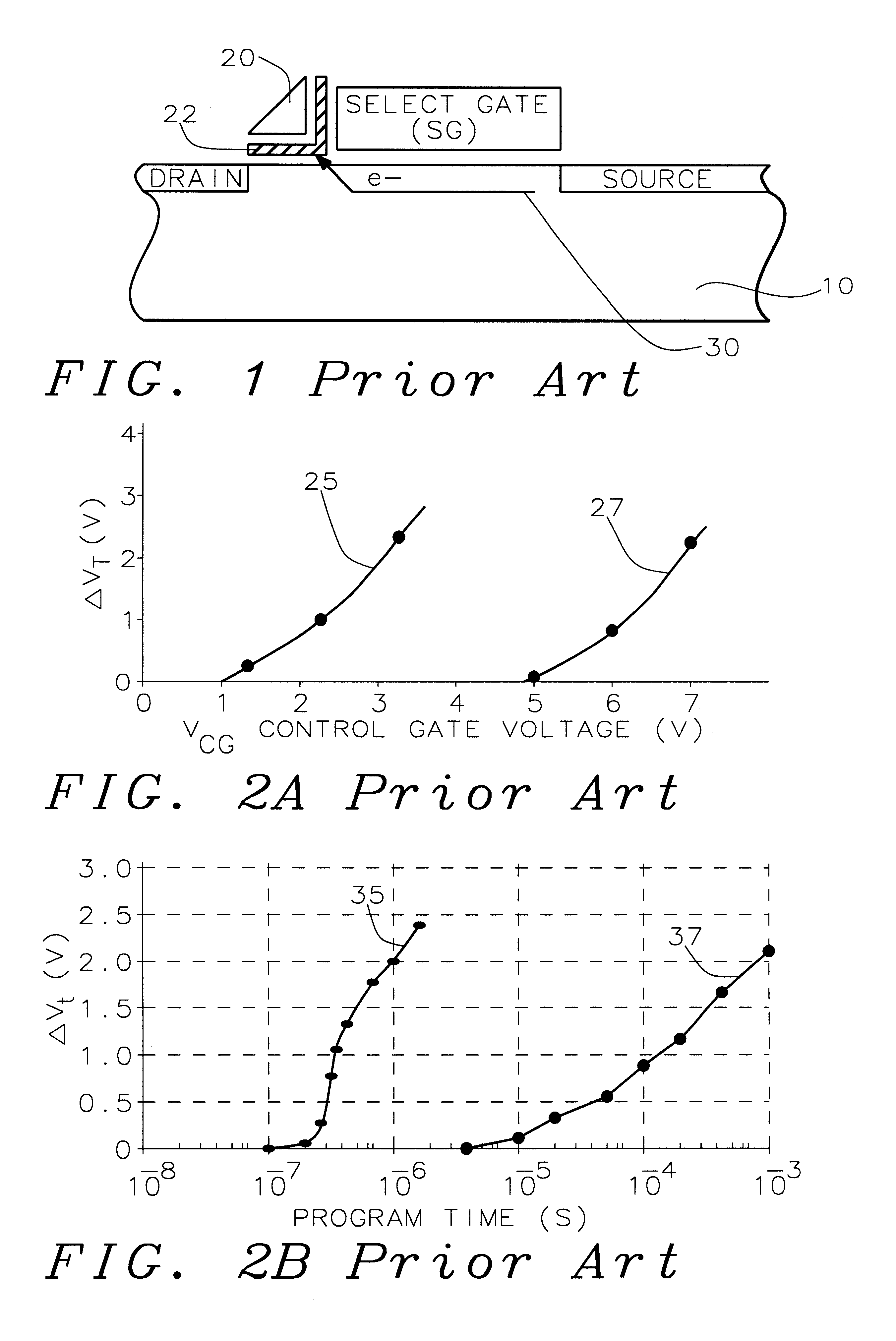

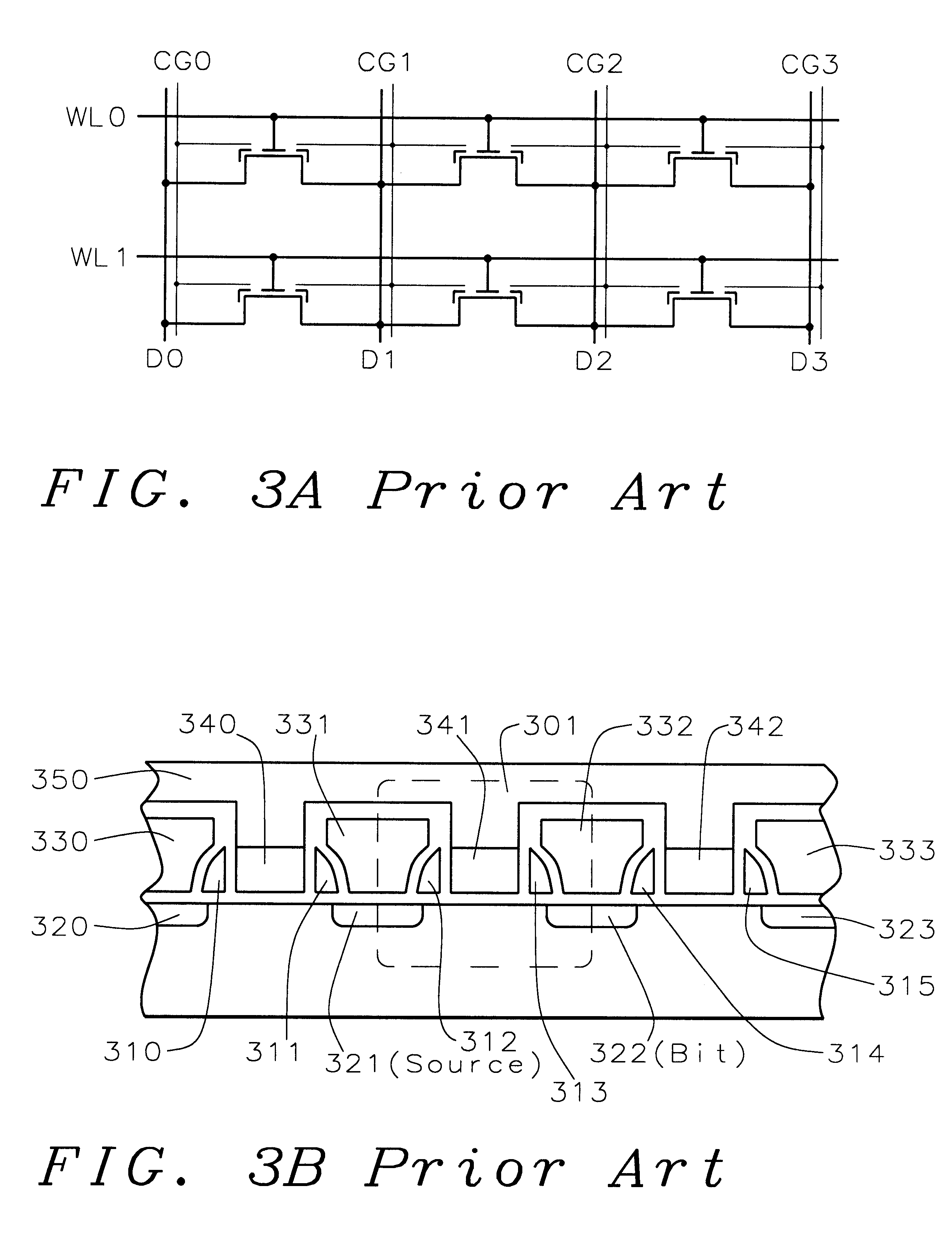

A fast low voltage ballistic program, ultra-short channel, ultra-high density, dual-bit multi-level flash memory is described with a two or three polysilicon split gate side wall process. The structure and operation of this invention is enabled by a twin MONOS cell structure having an ultra-short control gate channel of less than 40nm, with ballistic injection which provides high electron injection efficiency and very fast program at low program voltages of 3~5V. The cell structure is realized by (i) placing side wall control gates over a composite of Oxide-Nitride-Oxide (ONO) on both sides of the word gate, and (ii) forming the control gates and bit diffusion by self-alignment and sharing the control gates and bit diffusions between memory cells for high density. Key elements used in this process are: 1) Disposable side wall process to fabricate the ultra short channel and the side wall control gate with or without a step structure, and 2) Self-aligned definition of the control gate over the storage nitride and the bit line diffusion, which also runs in the same direction as the control gate. The features of fast program, low voltage, ultra-high density, dual-bit, multi-level MONOS NVRAM of the present invention include: 1) Electron memory storage in nitride regions within an ONO layer underlying the control gates, 2) high density dual-bit cell in which there are two nitride memory storage elements per cell, 3) high density dual-bit cell can store multi-levels in each of the nitride regions, 4) low current program controlled by the word gate and control gate, 5) fast, low voltage program by ballistic injection utilizing the controllable ultra-short channel MONOS, and 6) side wall control poly gates to program and read multi-levels while masking out memory storage state effects of the unselected adjacent nitride regions and memory cells. The ballistic MONOS memory cell is arranged in the following array: each memory cell contains two nitride regions for one word gate, and ½ a source diffusion and ½ a bit diffusion. Control gates can be defined separately or shared together over the same diffusion. Diffusions are shared between cells and run in parallel to the side wall control gates, and perpendicular to the word line.

Owner:HALO LSI INC

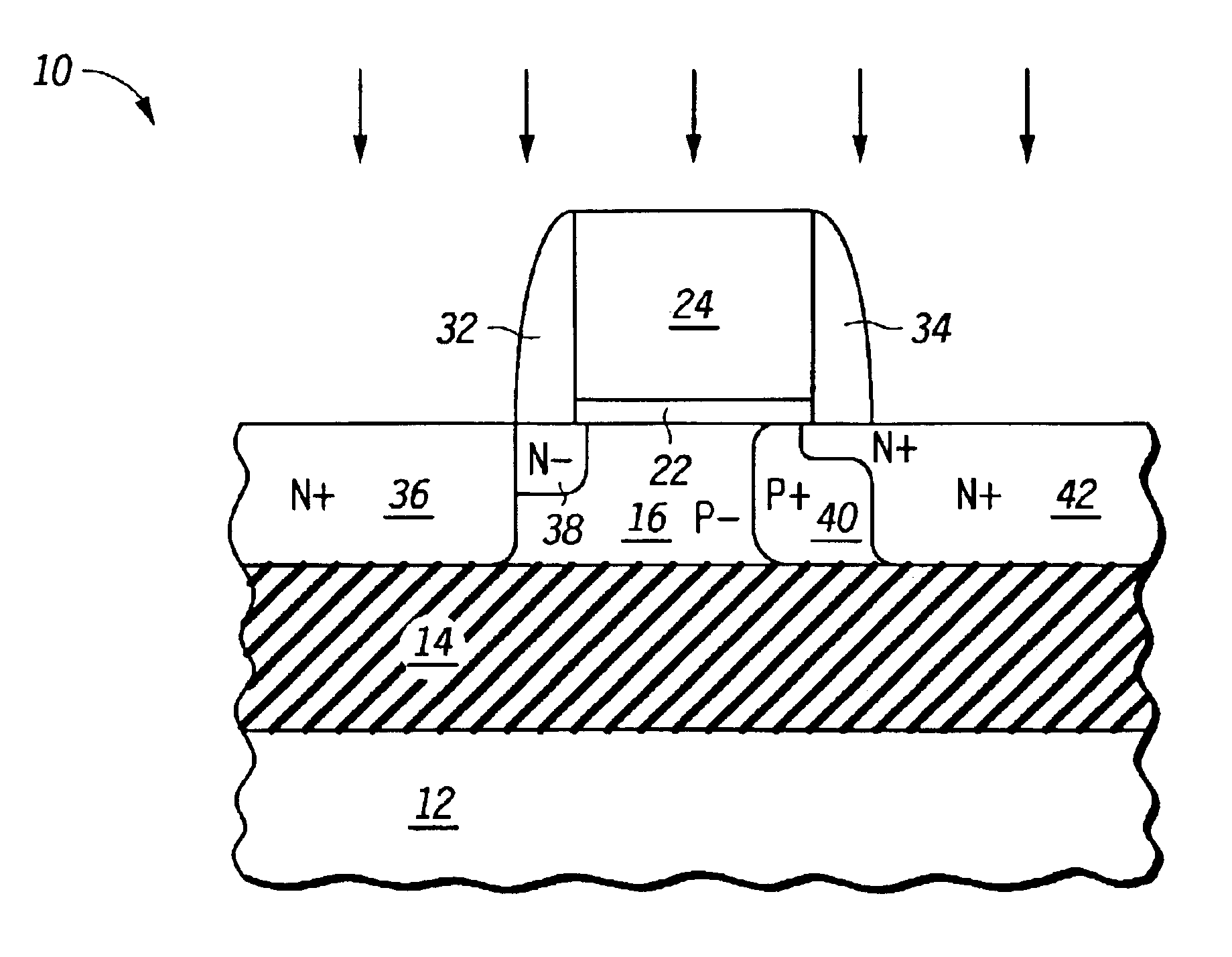

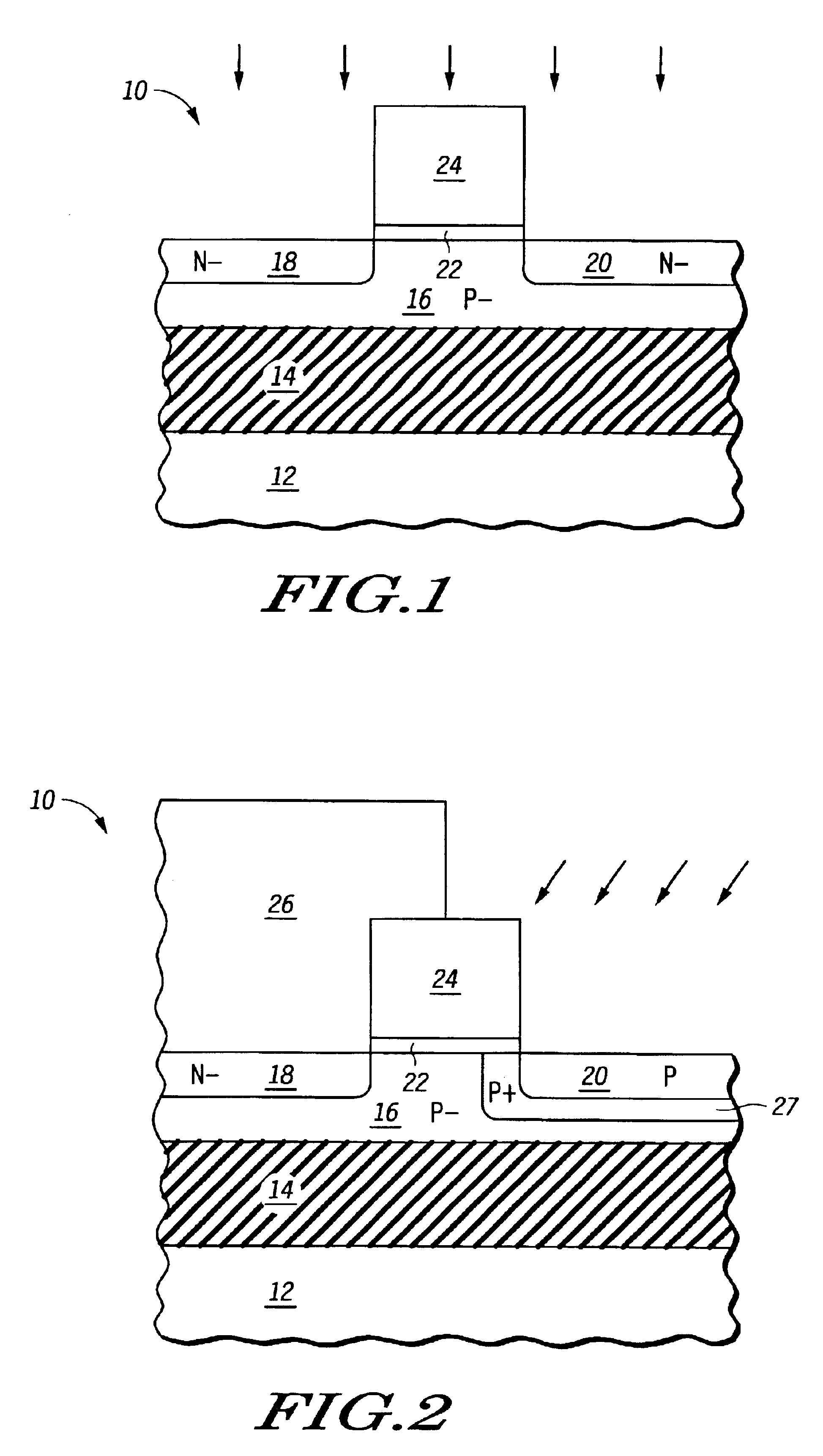

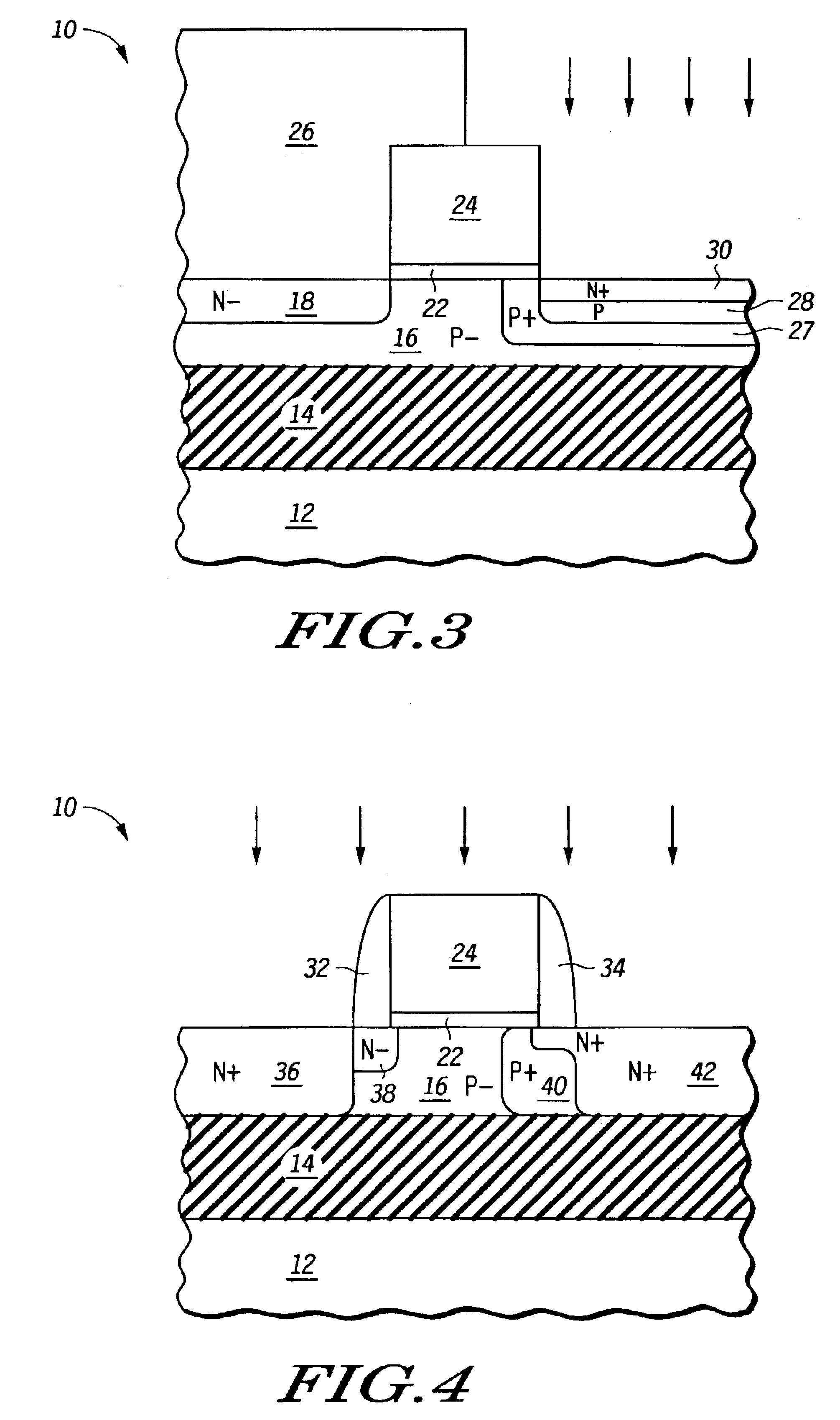

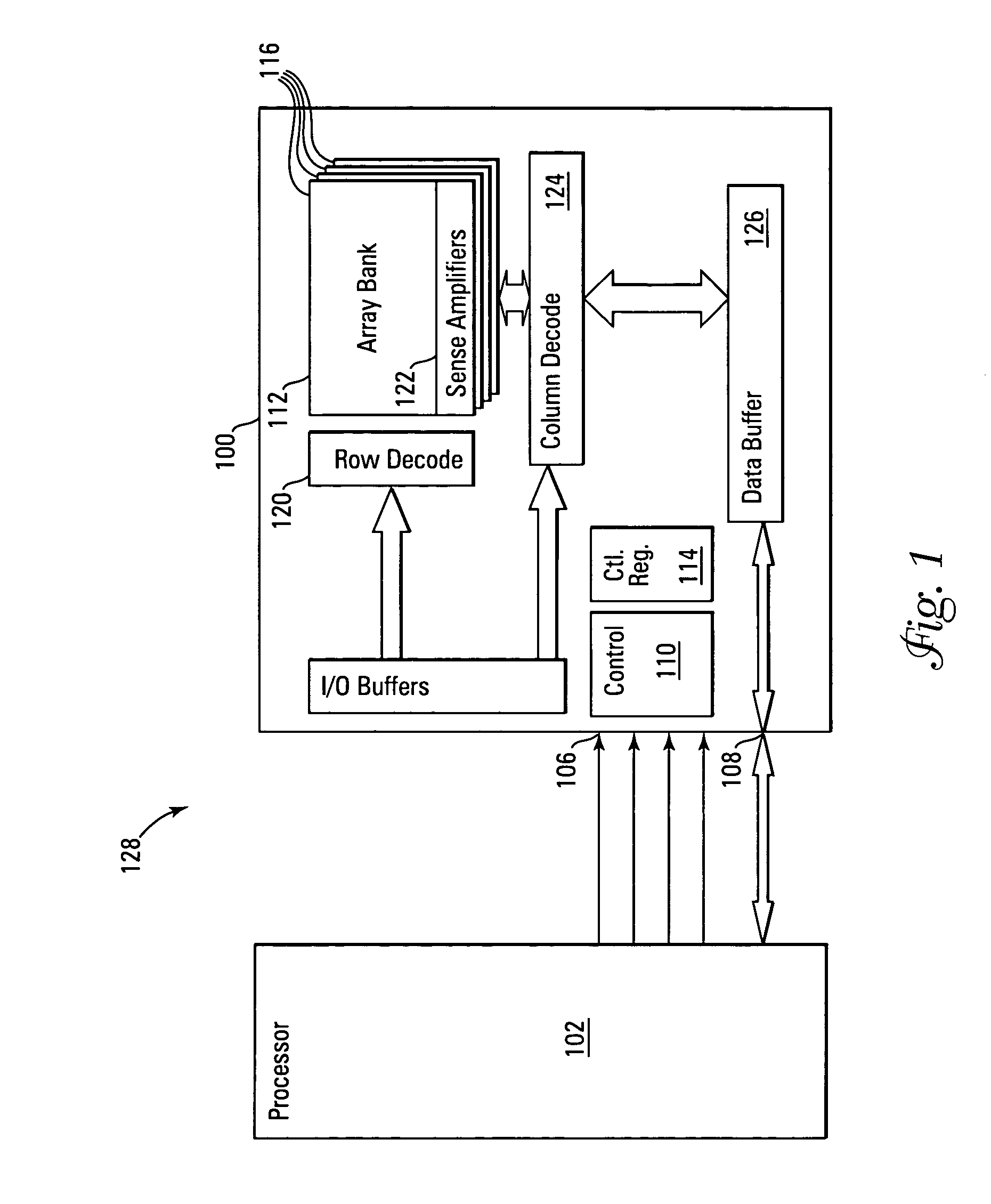

One transistor DRAM cell structure and method for forming

A single transistor DRAM cell is formed in a SOI substrate so that the DRAM cells are formed in bodies that are electrically isolated from each other. Each cell has doped regions that act as source and drain contacts. Between the drain contact and the body is a region, which aids in impact ionization and thus electron / hole formation during programming that is the same conductivity type as the body but of a higher concentration than the body. Adjacent to the source contact and to the body is a region, which aids in diode current during erase, that is the same conductivity type as the source contact but of a lower concentration than the source contact.

Owner:III HLDG 12 LLC

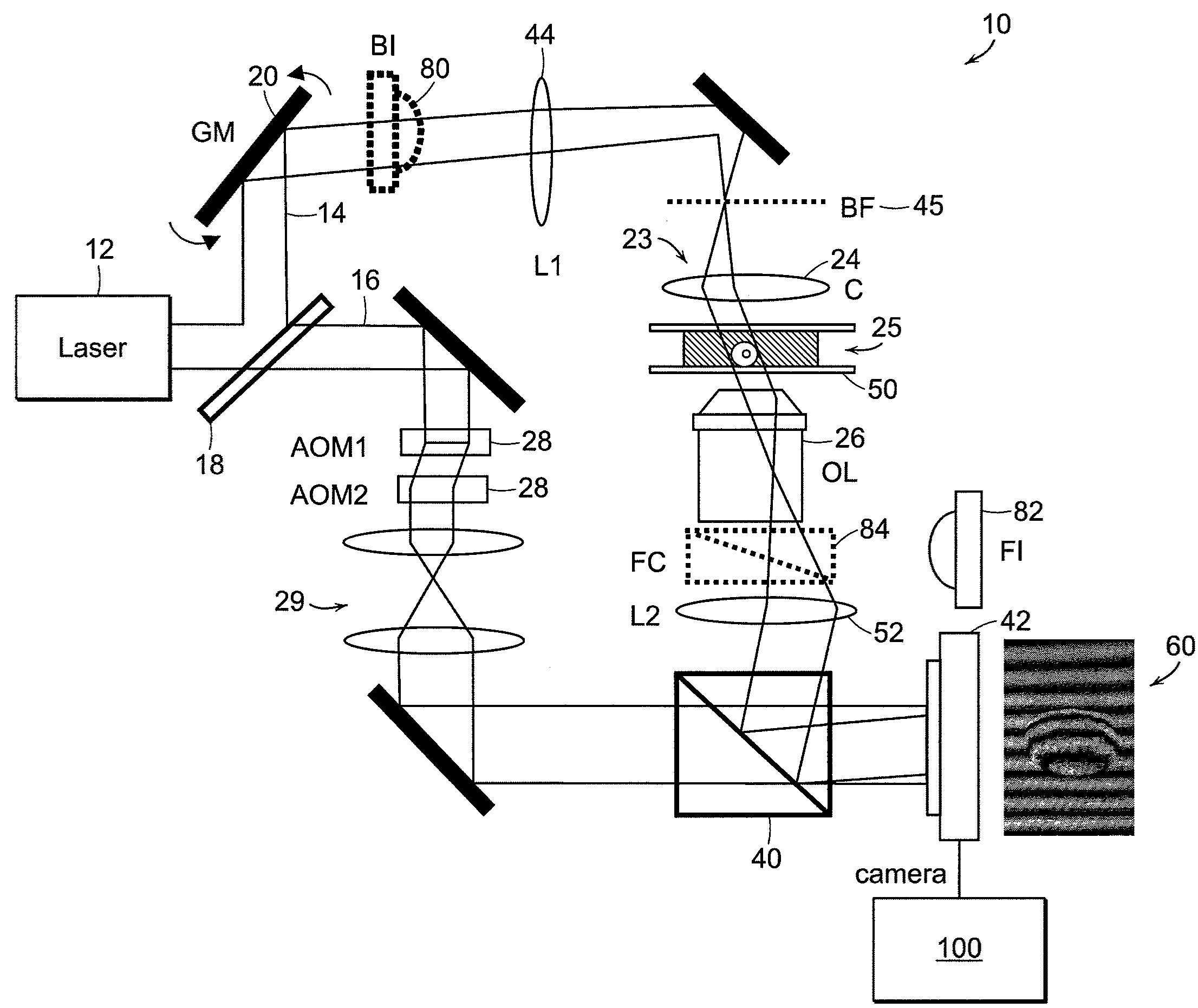

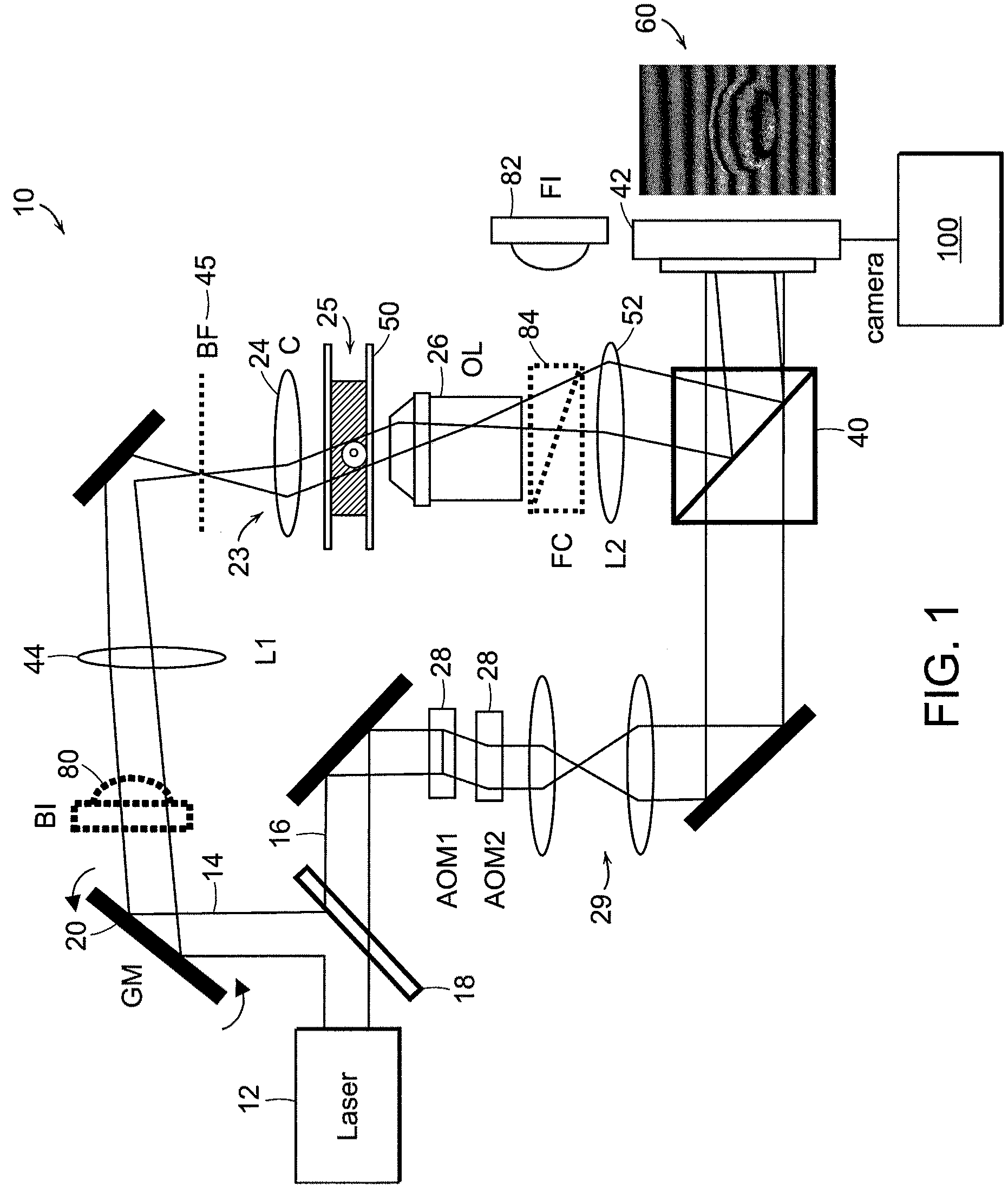

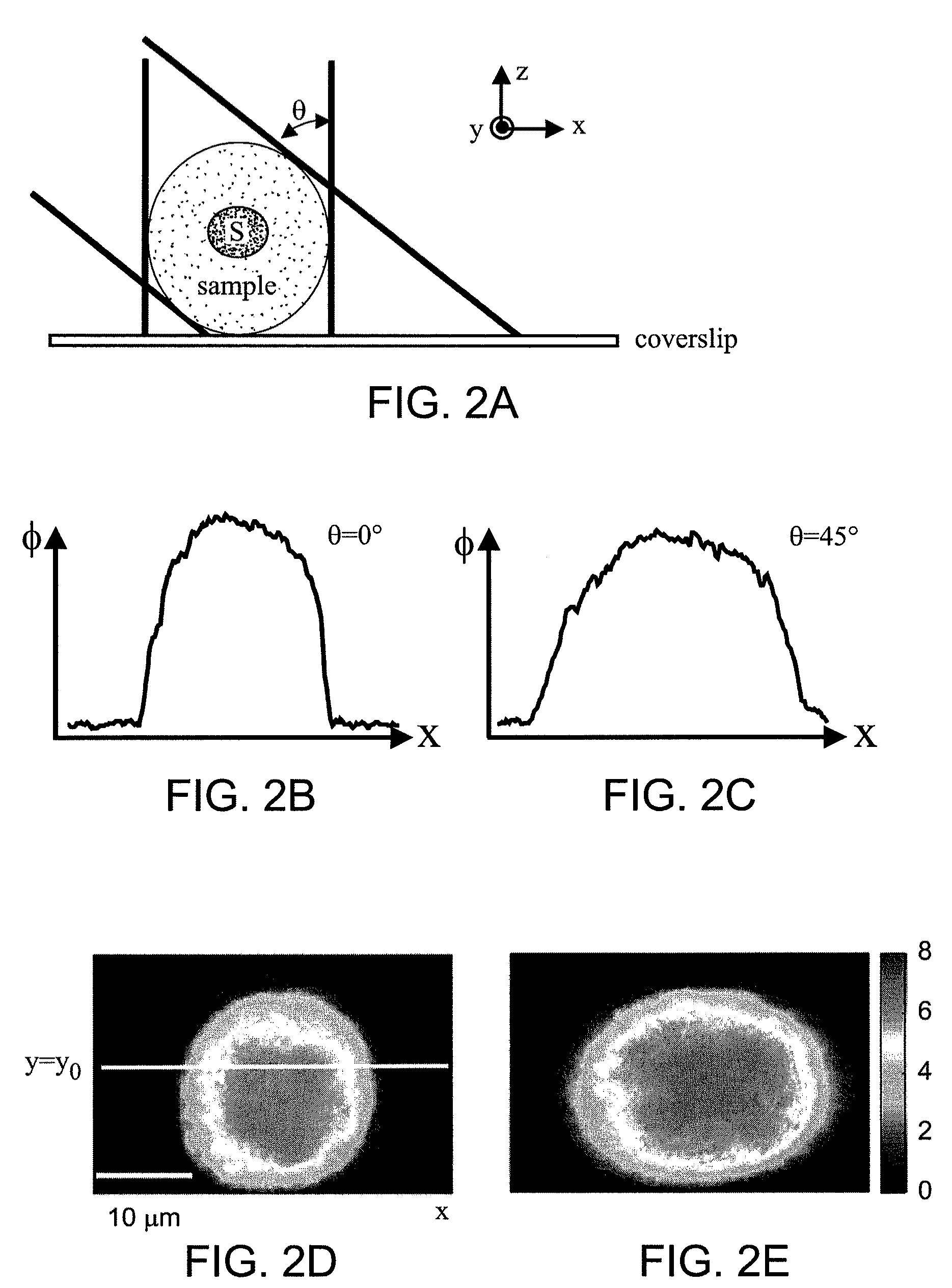

Tomographic phase microscopy

ActiveUS20090125242A1Phase-affecting property measurementsScattering properties measurementsRefractive indexOrganism

The present invention relates to systems and methods for quantitative three-dimensional mapping of refractive index in living or non-living cells, tissues, or organisms using a phase-shifting laser interferometric microscope with variable illumination angle. A preferred embodiment provides tomographic imaging of cells and multicellular organisms, and time-dependent changes in cell structure and the quantitative characterization of specimen-induced aberrations in high-resolution microscopy with multiple applications in tissue light scattering.

Owner:MASSACHUSETTS INST OF TECH

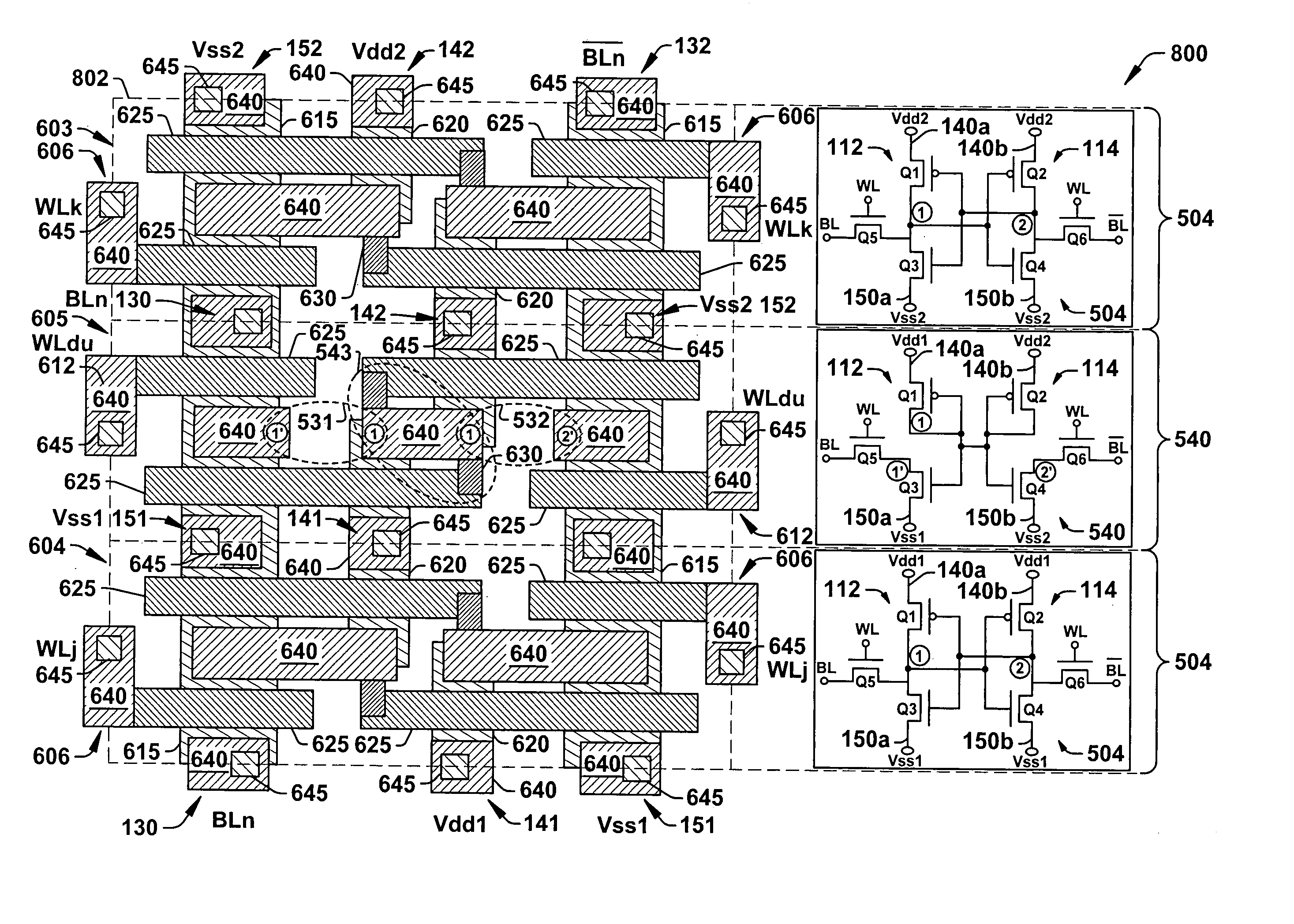

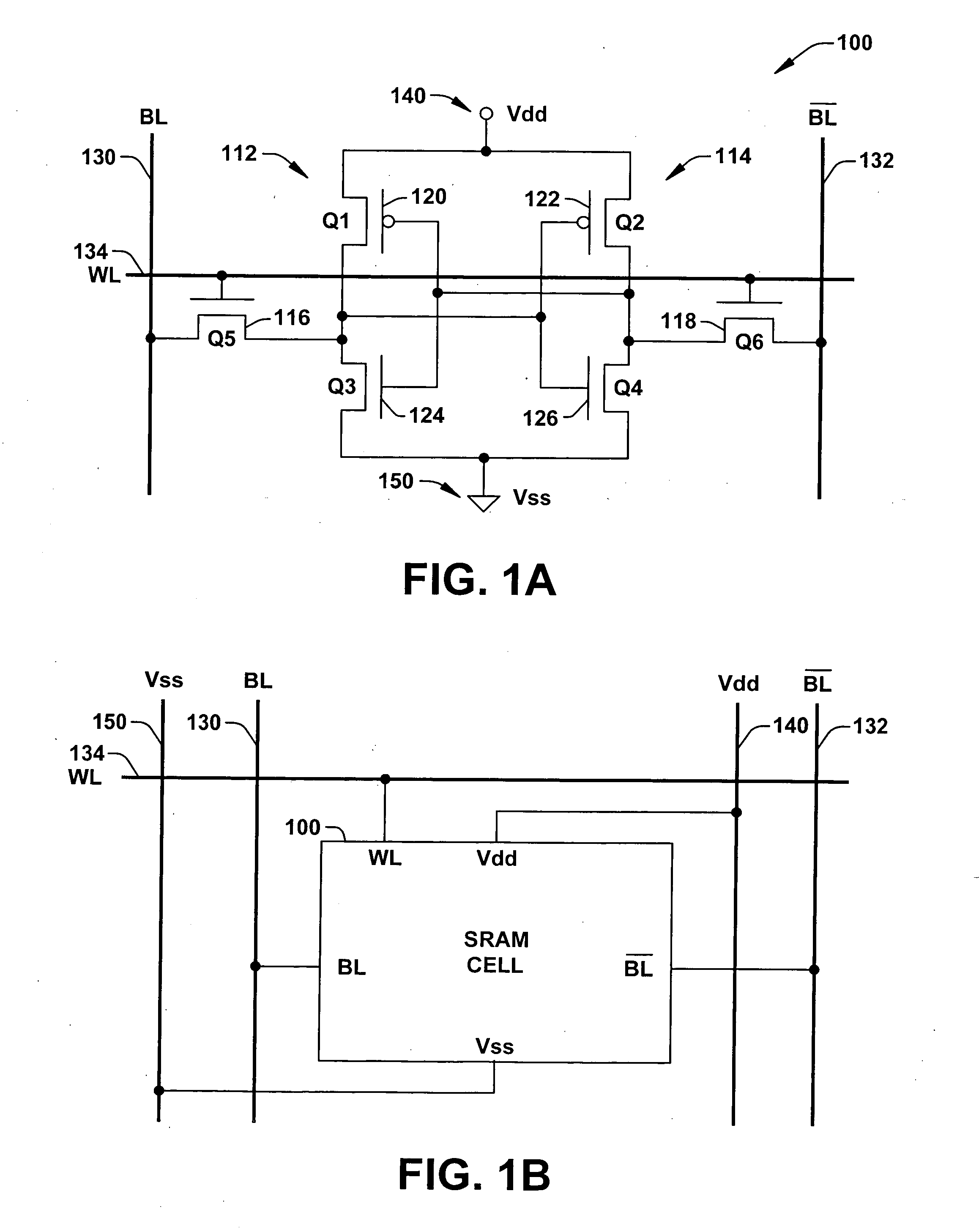

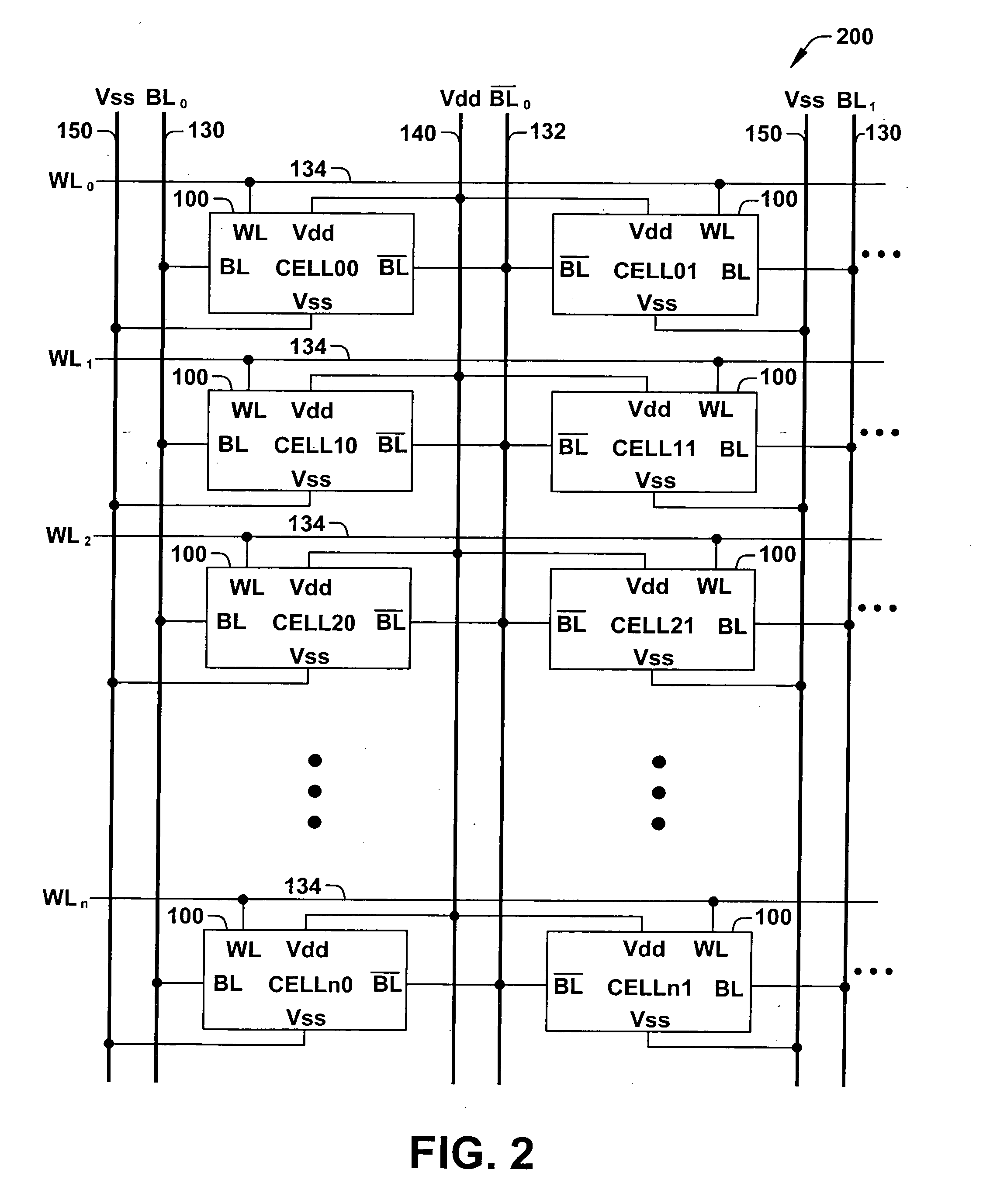

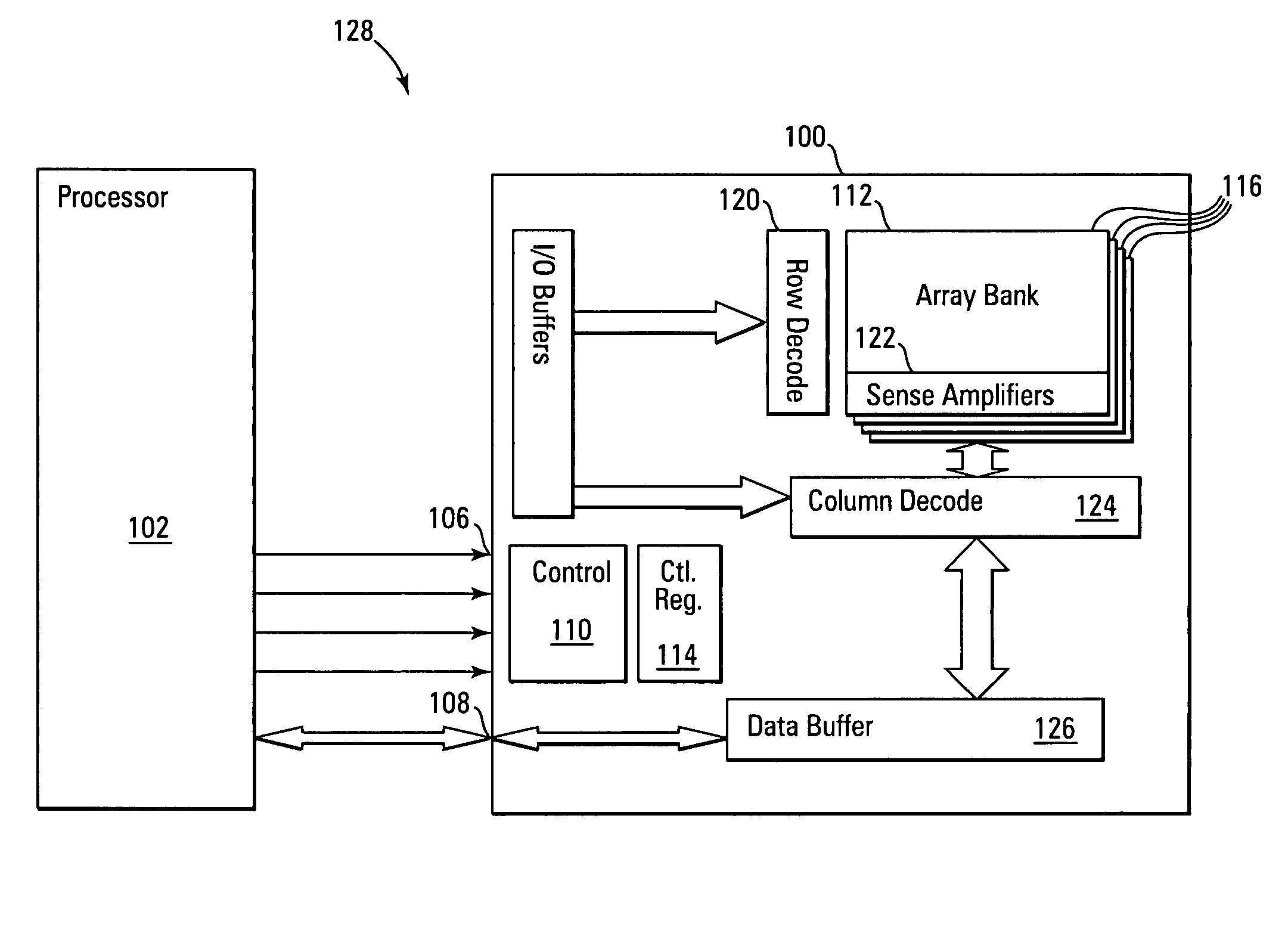

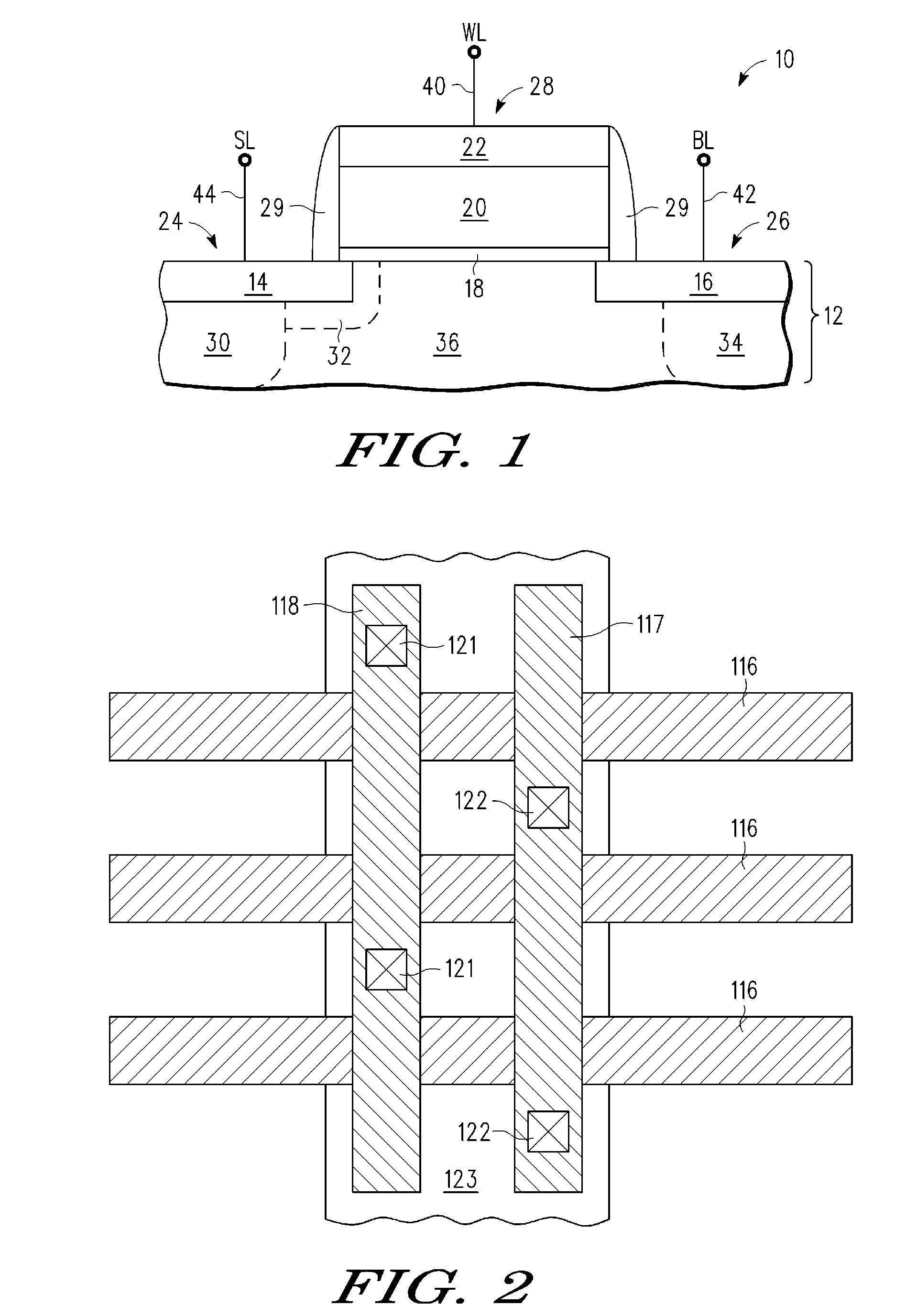

Area efficient implementation of small blocks in an SRAM array

ActiveUS20070002617A1Minimize changesImprove device performanceTransistorSolid-state devicesBit lineCell pattern

An SRAM array and a dummy cell row structure is discussed that permits an SRAM array to be divided into segments isolated by a row pattern of dummy cells. The dummy cell structure avoids the use of special OPC conditions at the power supply line and block boundaries by providing a continuous cell array at the lower cell patterning levels in an area efficient implementation. In one implementation, the SRAM array comprises a first and second array block each comprising an SRAM cell having a first layout configuration, one or more of the dummy cells having a second layout configuration arranged along the row pattern associated with a wordline of the SRAM array, a first power supply voltage line connected to the first array block, and a second different power supply voltage line connected to the second array block. The first and second power supply voltage lines of the array blocks are further connected to the one or more dummy cells. Beneficially, the bitlines of the array may be continuous across the first and second array blocks and a dummy cell associated therewith.

Owner:TEXAS INSTR INC

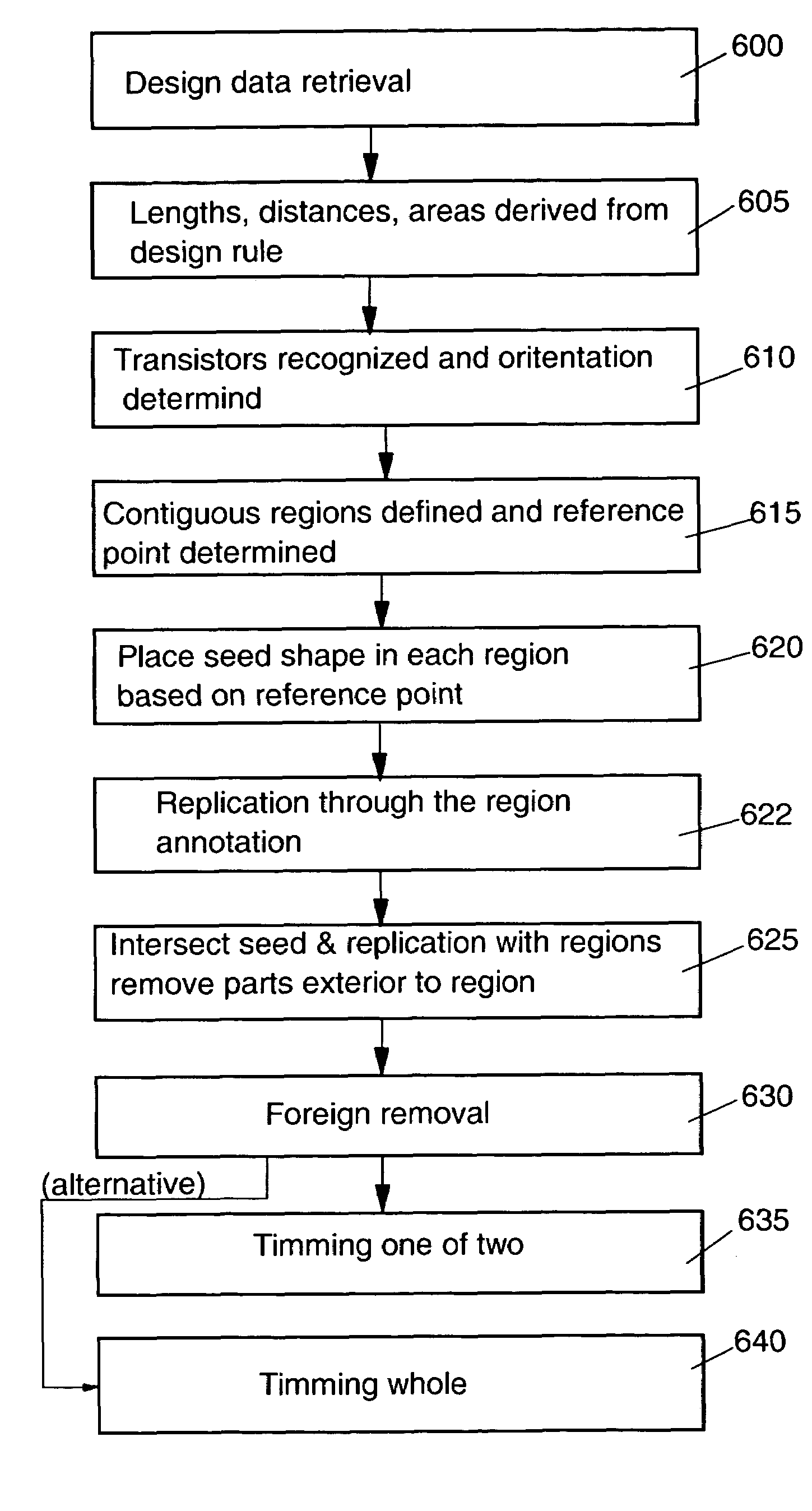

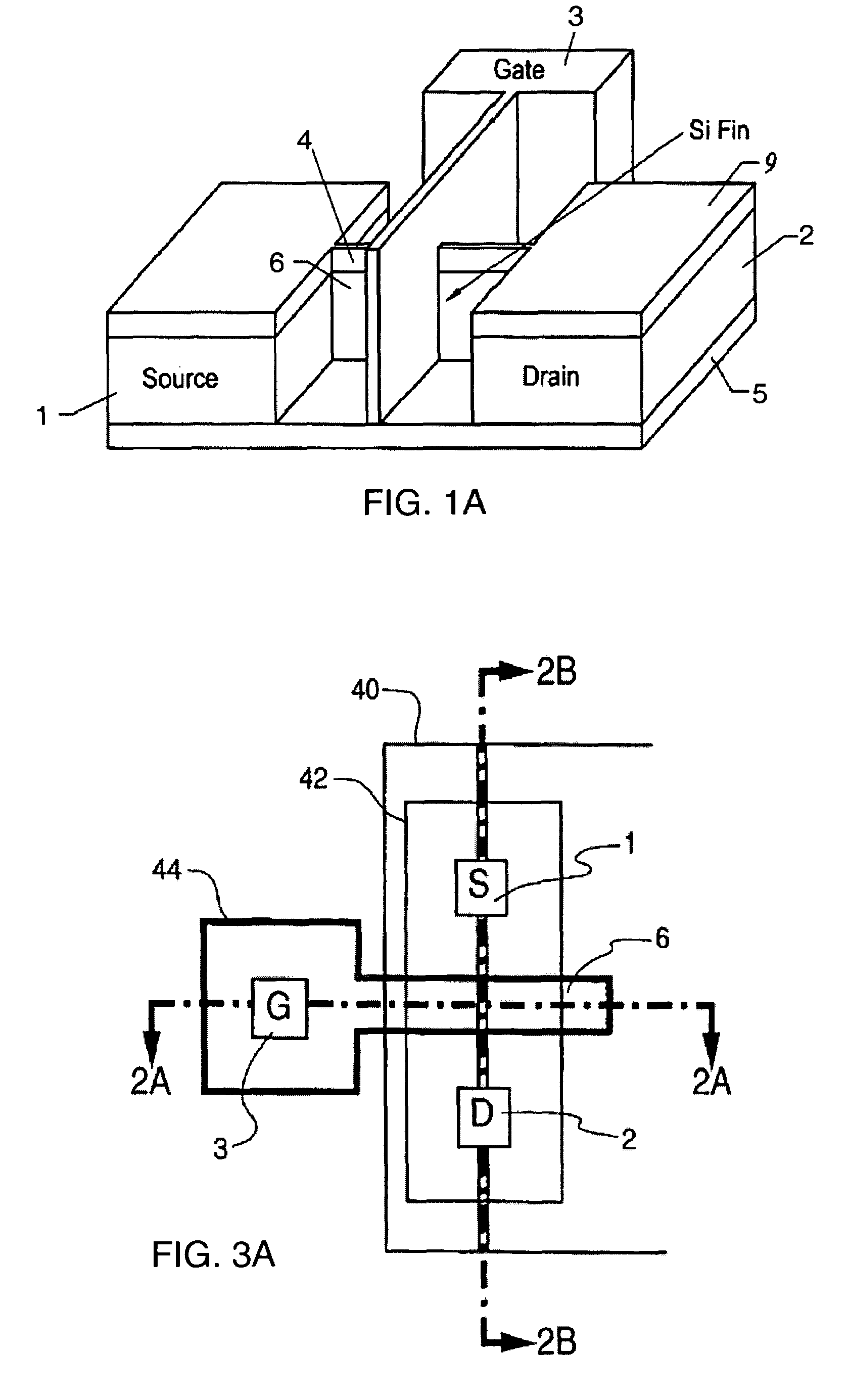

Method and device for automated layer generation for double-gate FinFET designs

InactiveUS7315994B2Reduce effortEnhance layeringTransistorSolid-state devicesEngineeringUnit structure

Owner:INT BUSINESS MASCH CORP

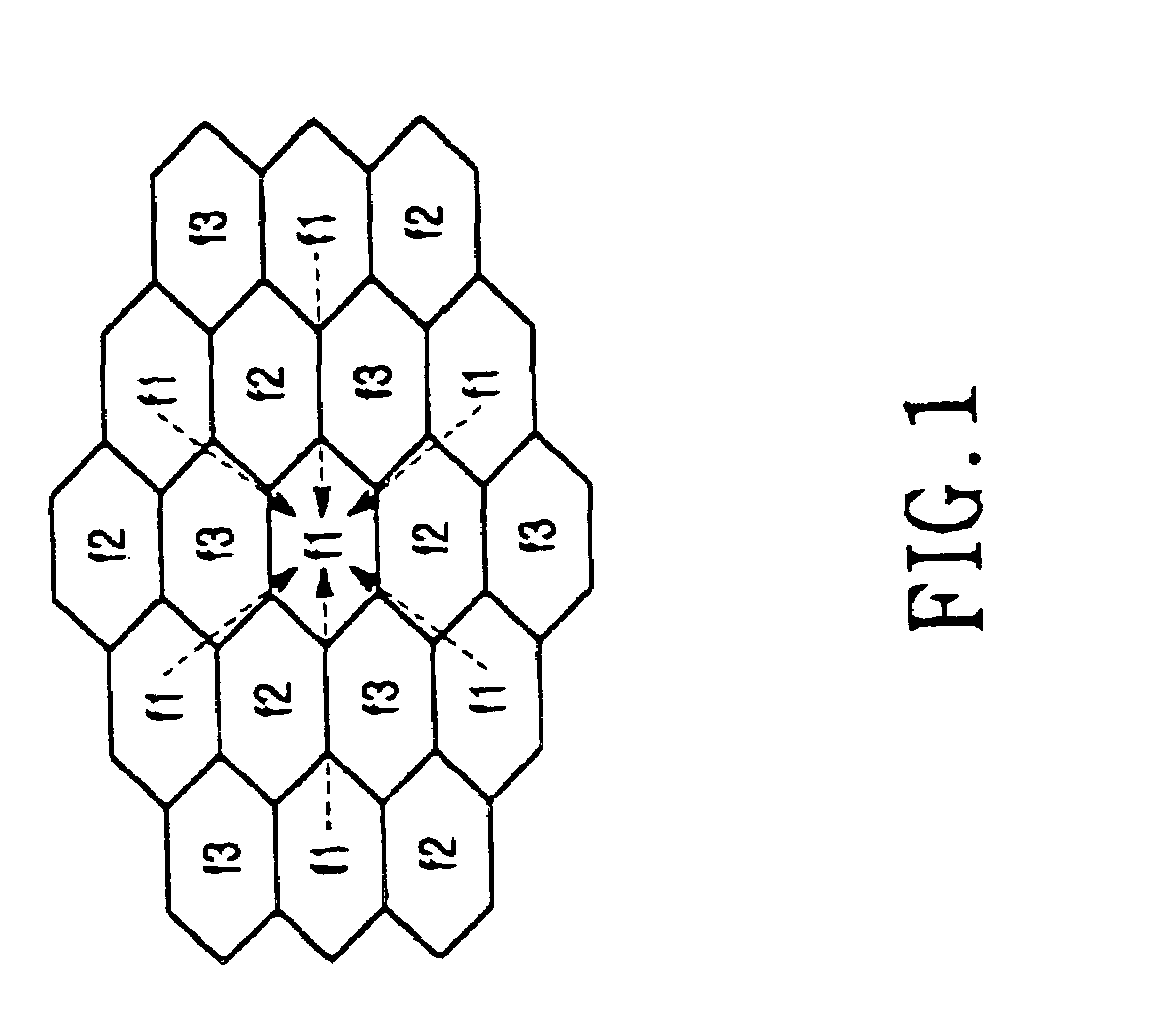

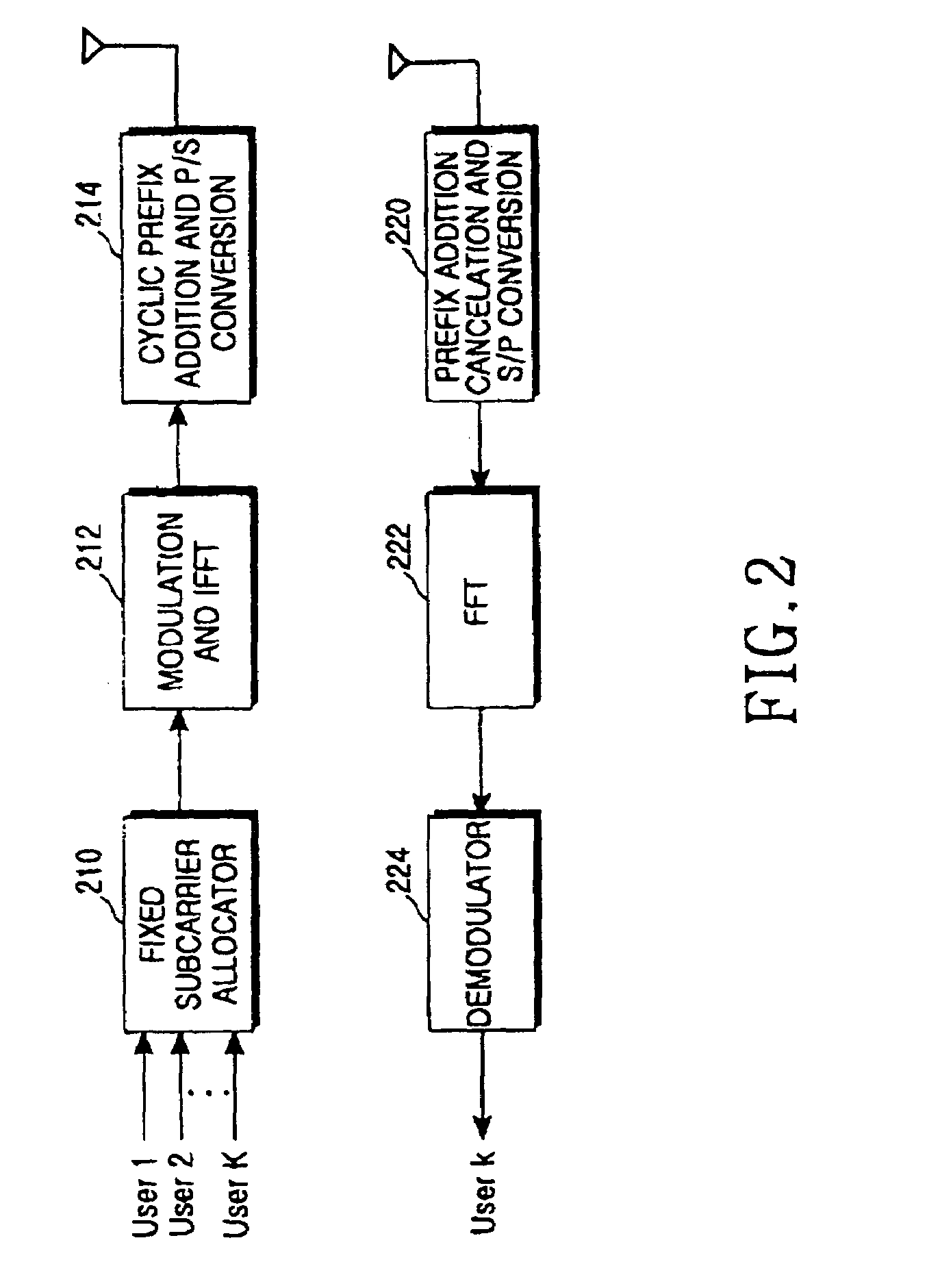

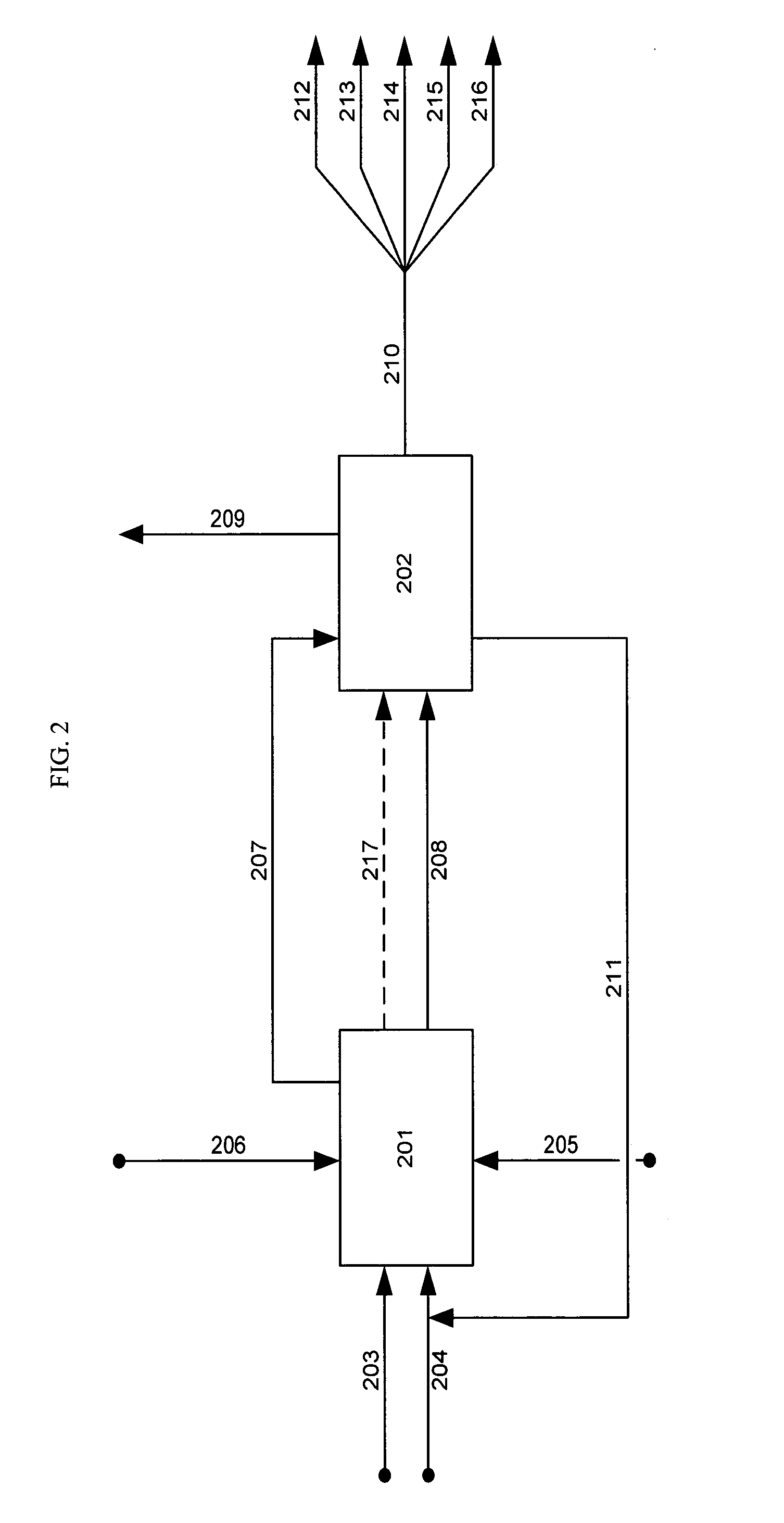

Apparatus and method for allocating resources of a virtual cell in an OFDM mobile communication system

ActiveUS7069009B2Improve efficiencyIncrease powerEnergy efficient ICTSite diversityCommunications systemVirtual cell

A virtual cell management apparatus and method using sectors in an orthogonal frequency division multiplexing mobile communication system including a cell structure having cells each comprised of a plurality of sectors, the cells performing data communication with mobile terminals within a corresponding cell through at least one subchannel having orthogonality. The method comprises forming a virtual cell with a particular one of sectors constituting a particular cell and sectors of two other cells neighboring the particular sector; transmitting, by three base stations forming the virtual cell, an interference measurement value and a channel parameter estimation value from a mobile terminal located in the virtual cell to a base station controller that controls the virtual cell, thereby allocating wireless resource including frequency bandwidth, initial bits, subcarriers and refined bits in the virtual cell; transmitting the allocated wireless resource to the three base stations so that the base stations allocate a same subchannel to each mobile terminal located in the virtual cell; and transmitting same data over the allocated subchannel.

Owner:SAMSUNG ELECTRONICS CO LTD

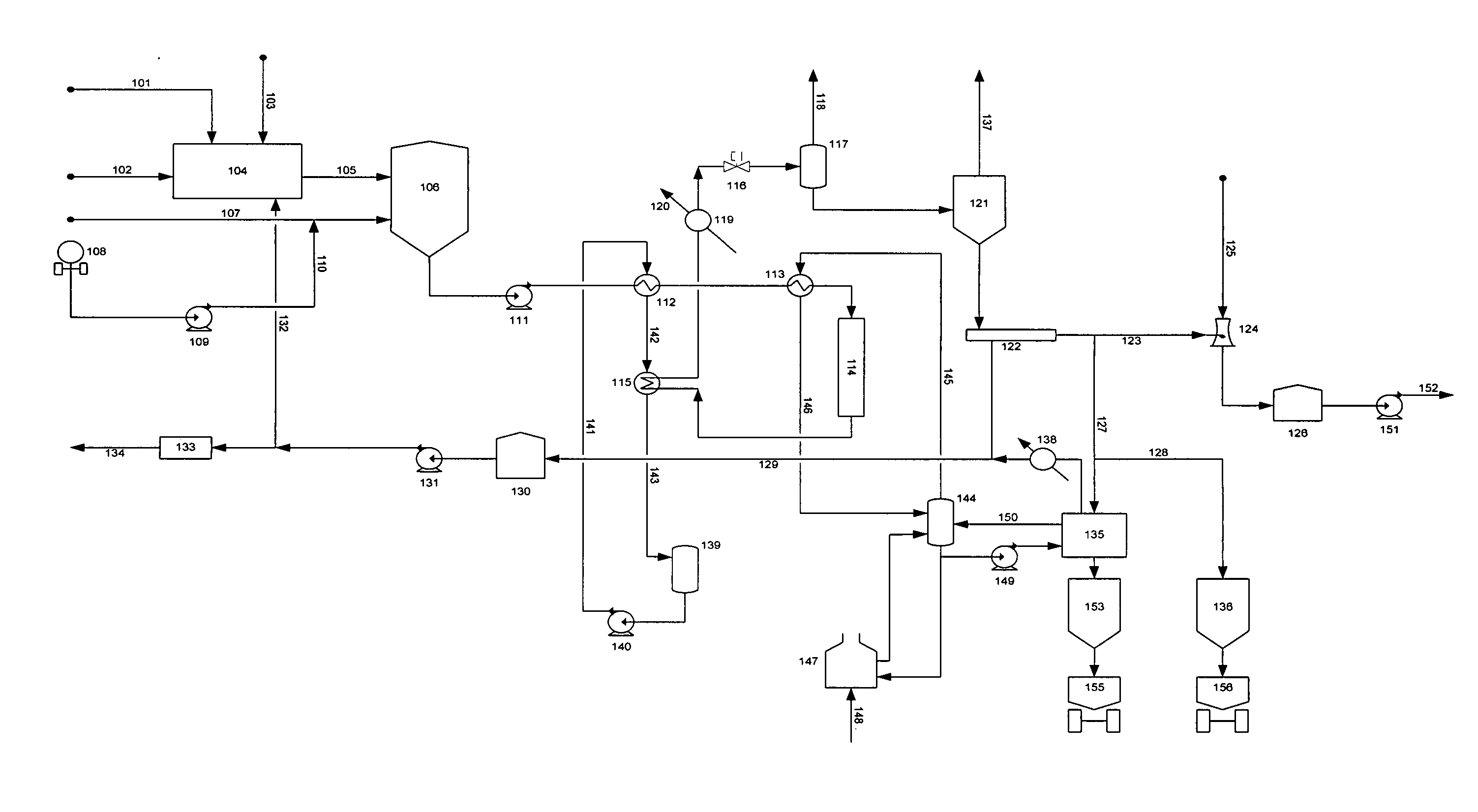

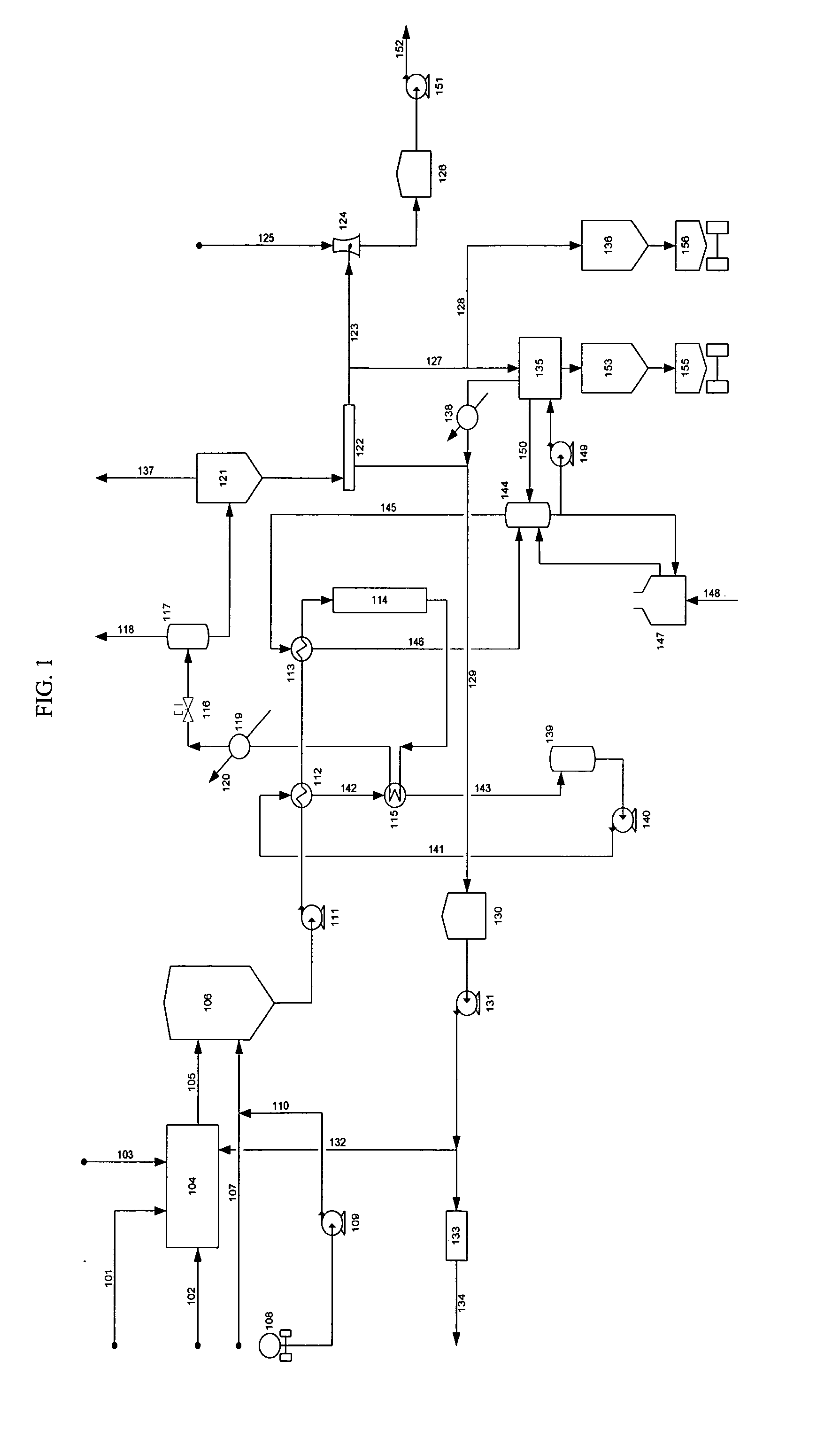

Slurry dewatering and conversion of biosolids to a renewable fuel

ActiveUS20060096163A1Readily removed mechanicallyLow oxygenBio-organic fraction processingBiofuelsEmission standardSlurry

In the processes for treating municipal sewage and storm water containing biosolids to discharge standards, biosolids, even after dewatering, contain typically about 80% water bound in the dead cells of the biosolids, which gives biosolids a negative heating value. It can be incinerated only at the expense of purchased fuel. Biosolids are heated to a temperature at which their cell structure is destroyed and, preferably, at which carbon dioxide is split off to lower the oxygen content of the biosolids. The resulting char is not hydrophilic, and it can be efficiently dewatered and / or dried and is a viable renewable fuel. This renewable fuel can be supplemented by also charging conventional biomass (yard and crop waste, etc.) in the same or in parallel facilities. Similarly, non-renewable hydrophilic fuels can be so processed in conjunction with the processing of biosolids to further augment the energy supply.

Owner:SGC ADVISORS

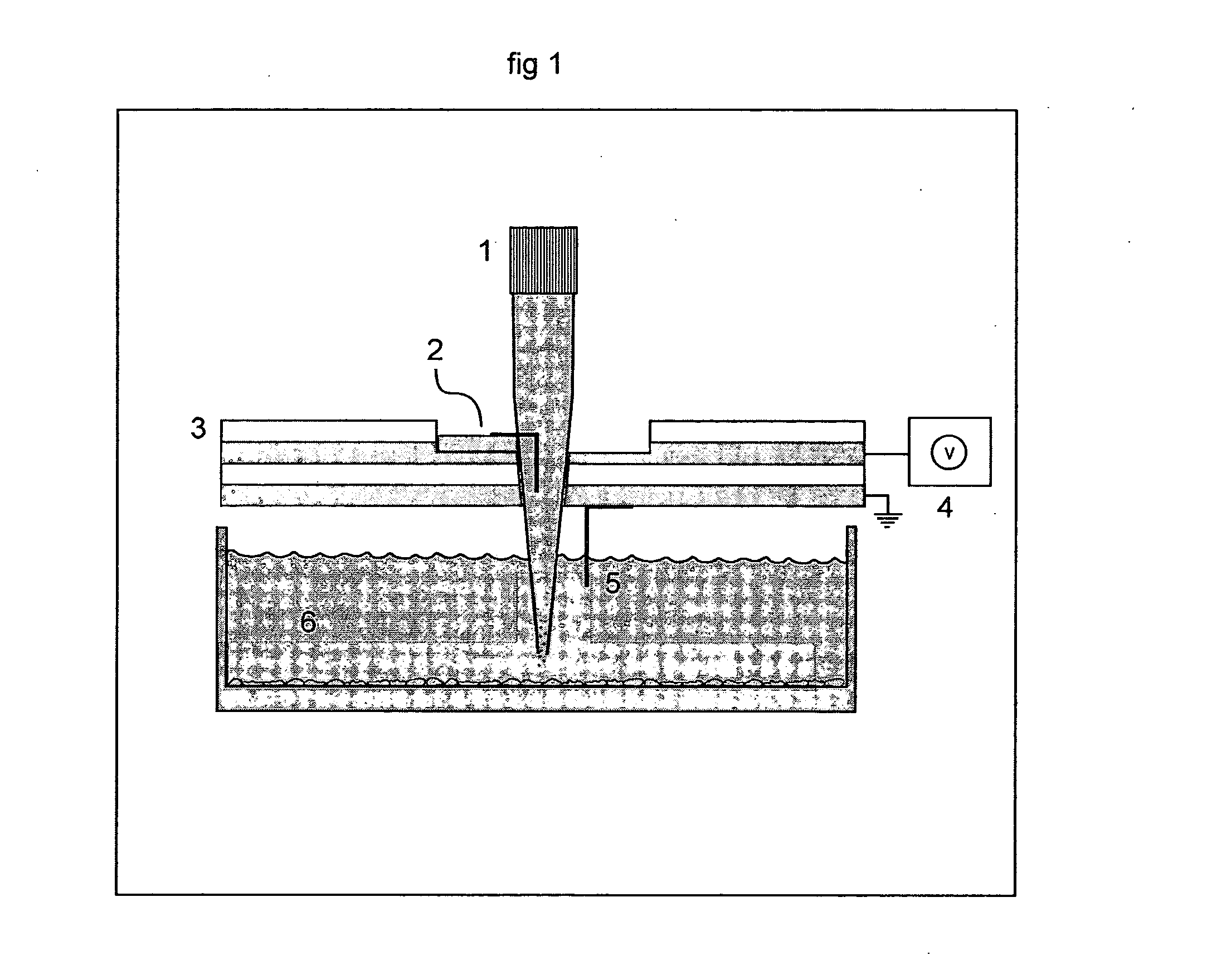

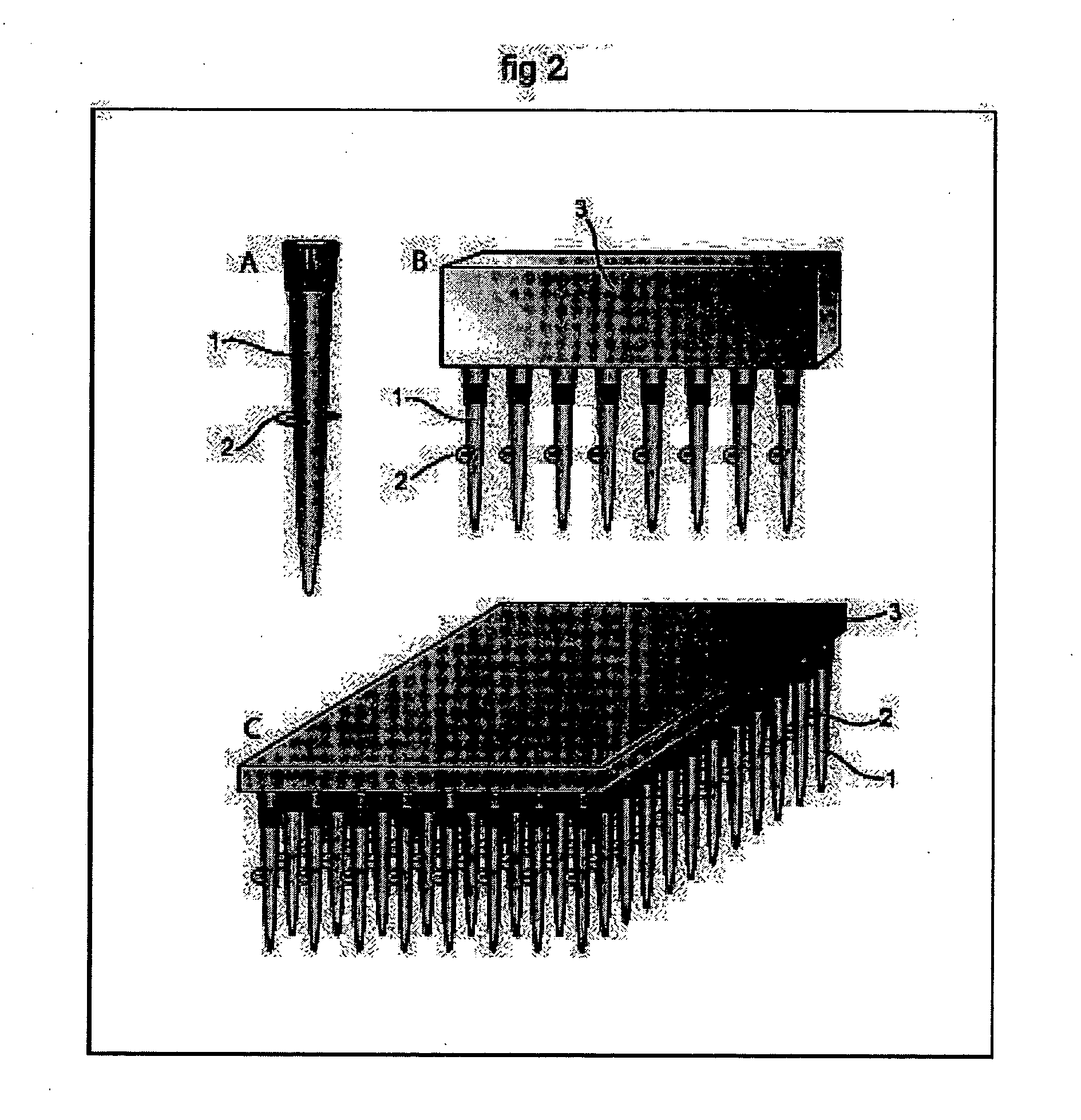

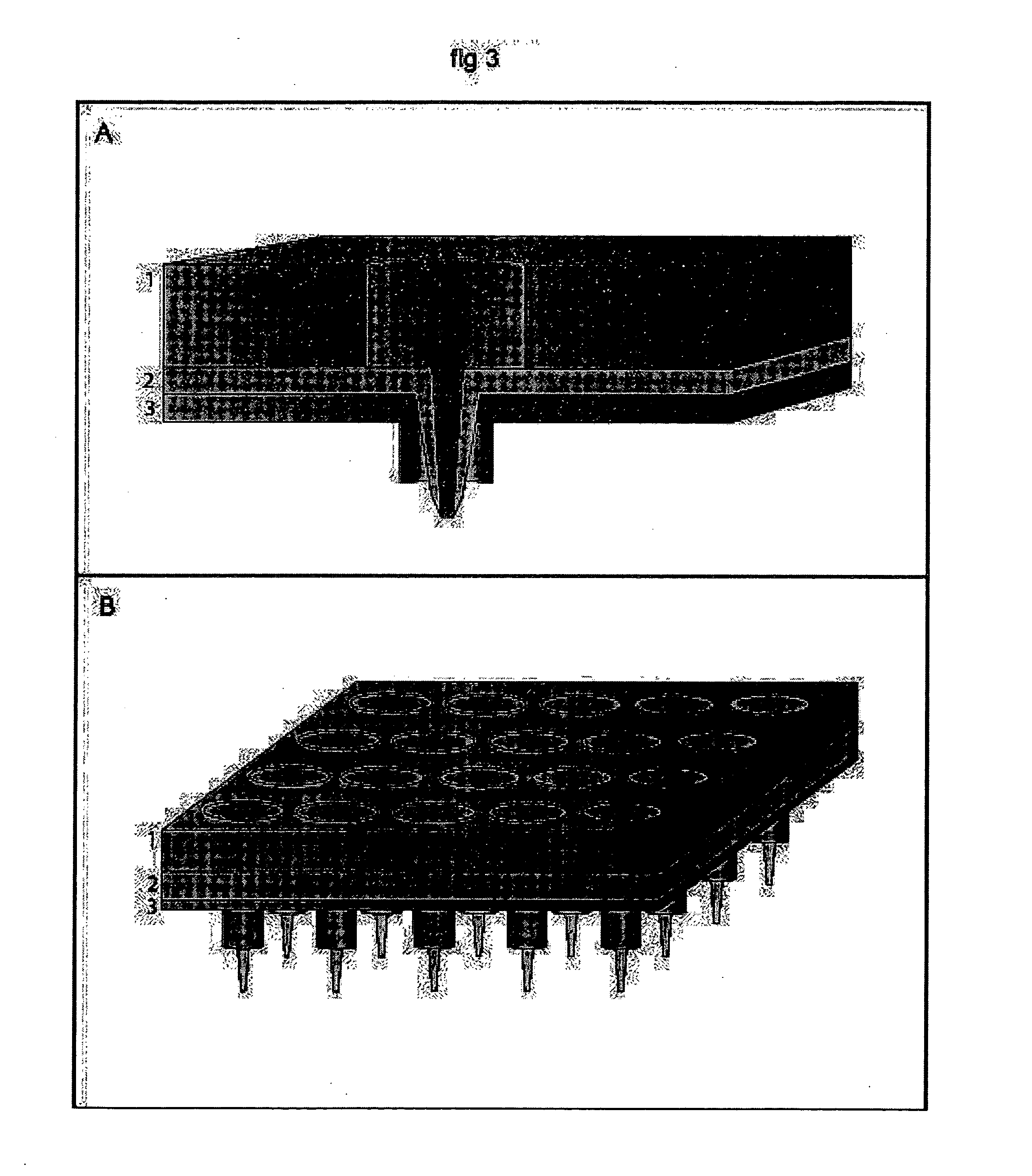

Method and apparatus for spatially confined electroporation

InactiveUS20050048651A1Bioreactor/fermenter combinationsElectrotherapyBiological targetElectroporation

The invention provides hollow-tip-electrodes for spatially localized delivery of substances to one or more biological targets present in a population comprising target and non-target molecules, macromolecules, and / or cells. The invention also provides electrode plates for receiving one or more of such tips, tip-electrode plates comprising electrode plates comprising one or more electrode tips, and systems comprising tip-electrodes and containers for containing one or more biological targets, e.g., such as molecules, macromolecules, and / or cells. The invention further provides methods for using such systems and components thereof. In one preferred aspect, the systems are used for spatially confined electroporation of cells and cell structures. The invention facilitates high throughput screening of agents (e.g., such as drugs) that act on intracellular targets.

Owner:CELLECTRICON

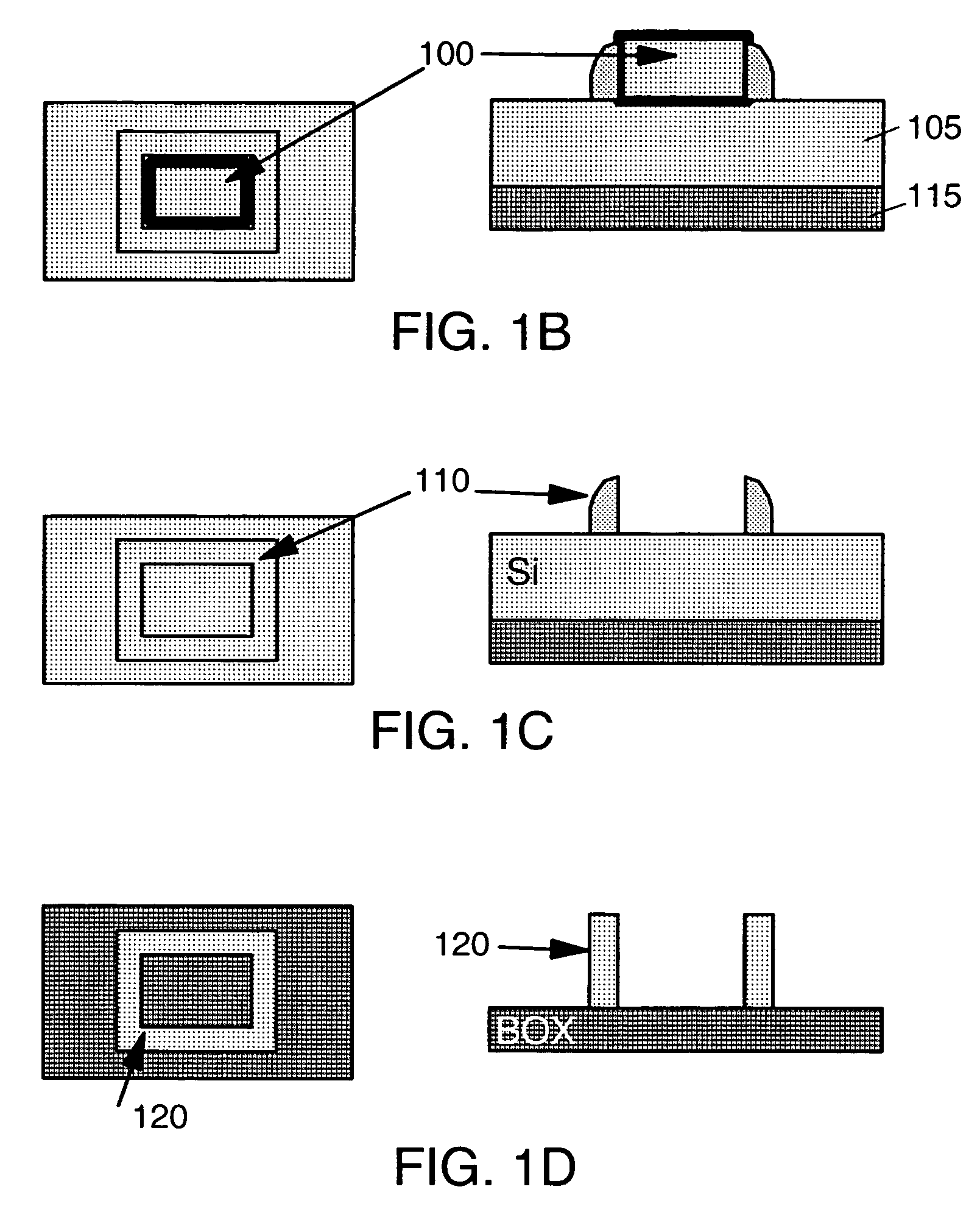

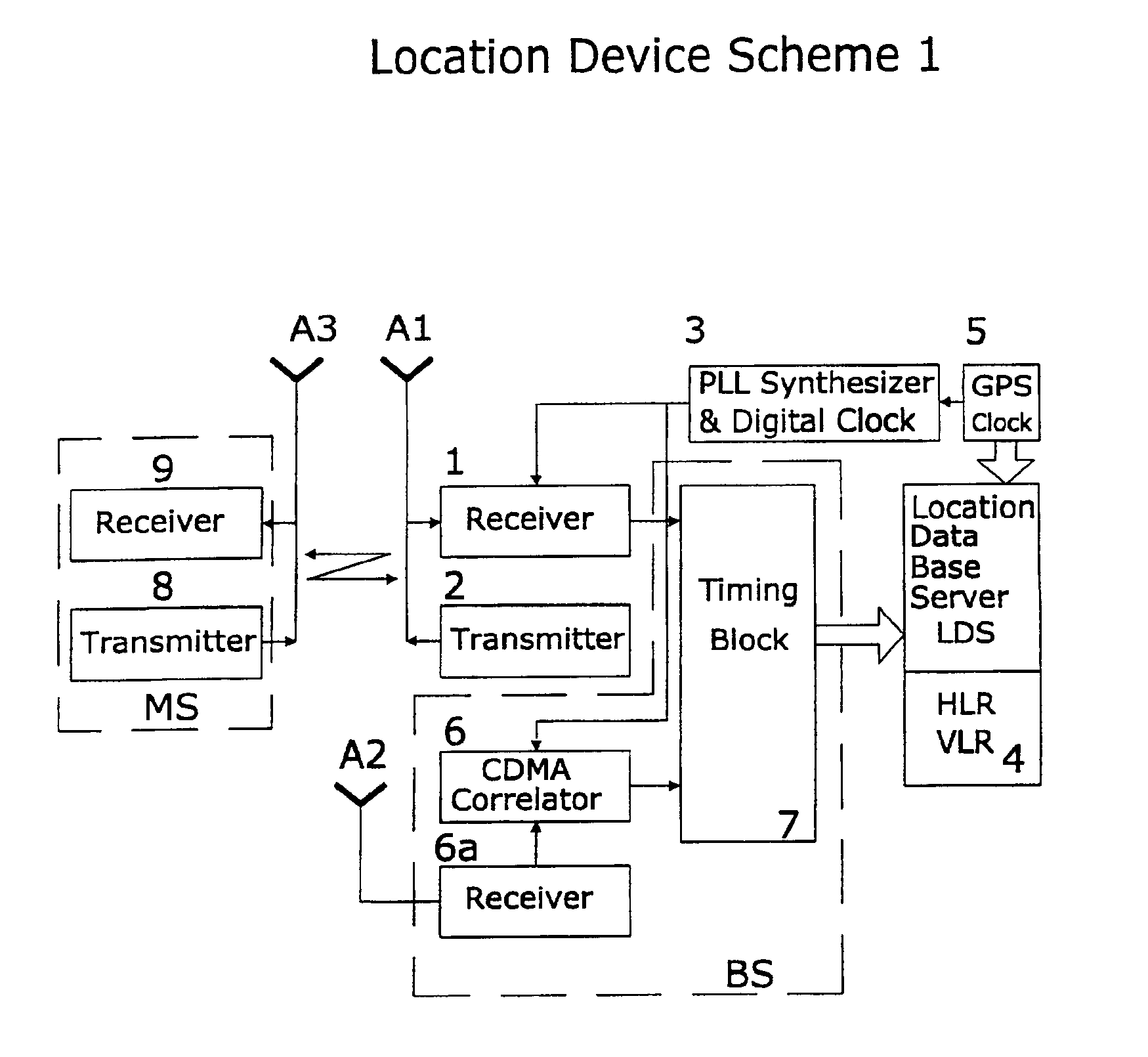

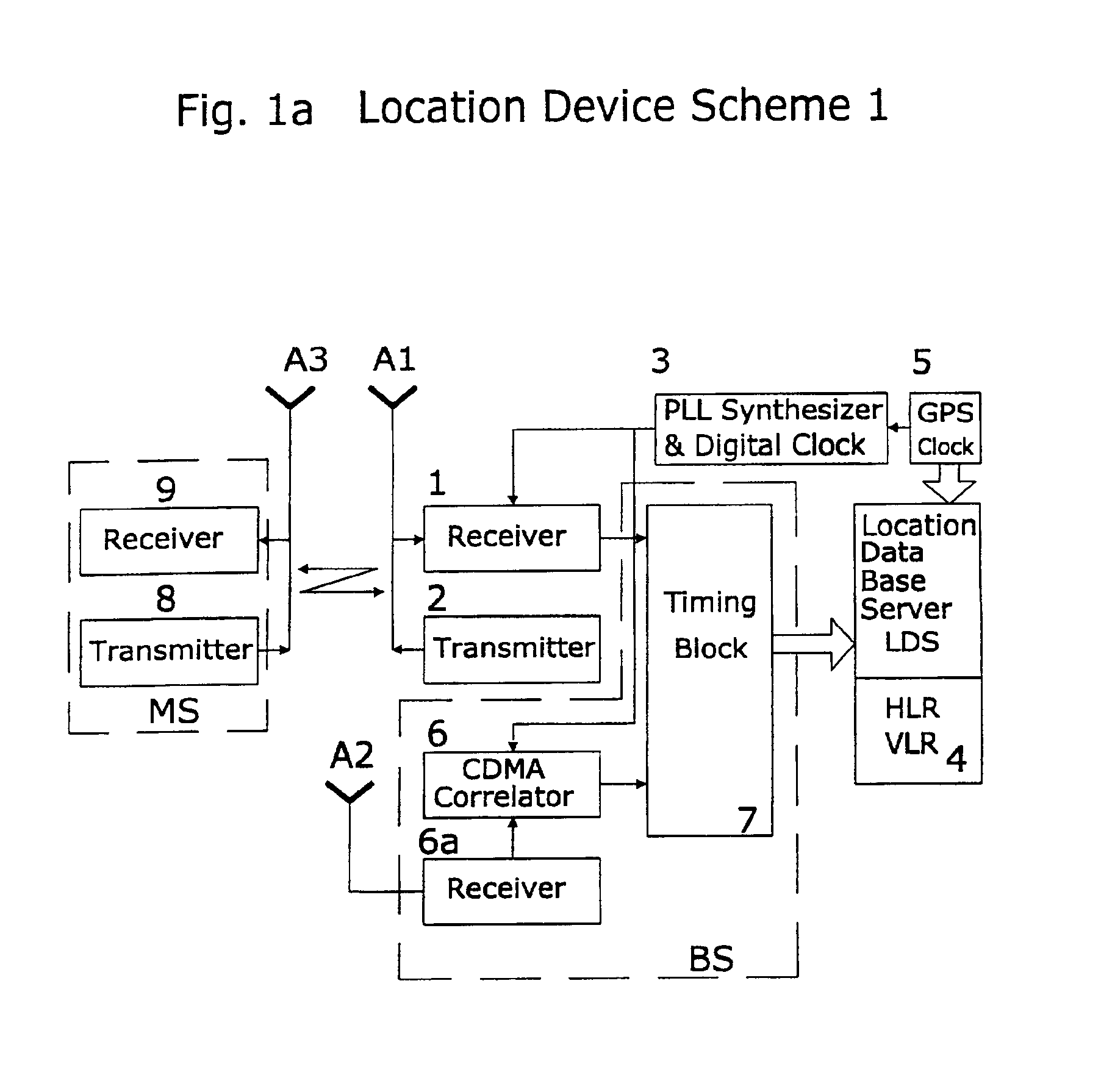

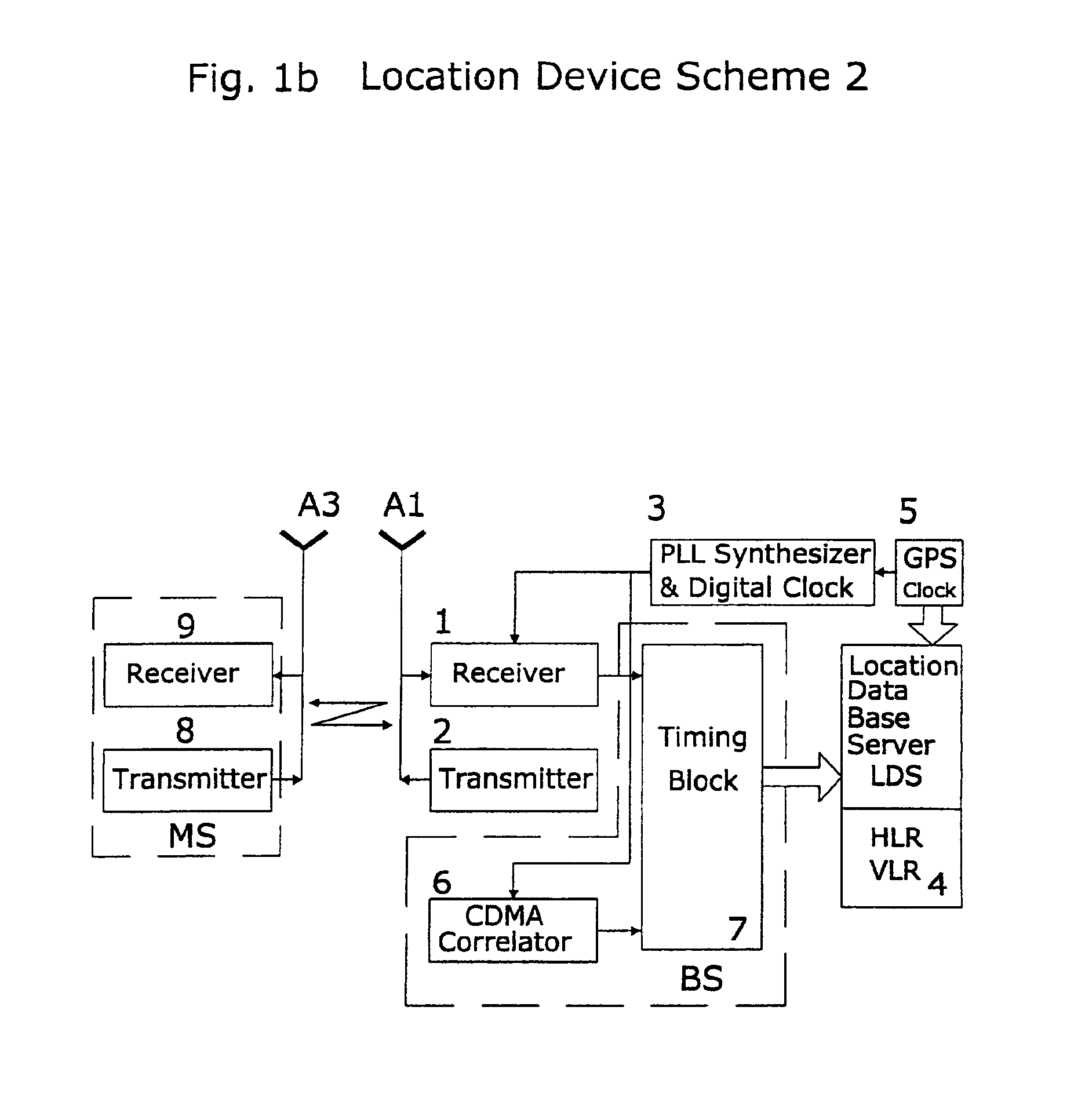

Method and system for mobile station positioning in cellular communication networks

InactiveUS6901264B2Improve accuracy of manyExpand coverageDirection finders using radio wavesNavigation instrumentsMultilaterationMobile station

A system of cell phone positioning in real time is provided with specialized location device installations on multiplicity of base stations BSs in CDMA and TDMA cellular communication networks. The purpose of the positioning system is to enable tracking and locating large quantities of anonymous mobile cell phones MS in any number of network cells to be used for real time traffic-forecasting systems, emergency services E911, and other client-initiated position requests. Location data thus obtained can be continuously updated from vehicular-based cellular phones, collected, processed and used as a basis for input to intelligent transportation systems, such as real time urban traffic guidance for vehicular congestion and intelligent traffic control systems. The system is capable of covering large urban geographical areas and number of independent cell structures serving thousands of mobile cell phone clients. It is an independent plug-in solution with specialized synchronized location device installations in each cell BS. Centrally located specialized location software based on Time of Arrival (TOA) and Time Difference of Arrival (TDOA) methods for high speed location processing in central Location Database Server (LDS). The inventive system consists of number of component functions: Operator-initiated functions, location device functions and software enabled positioning functions.

Owner:MAKOR ISSUES & RIGHTS

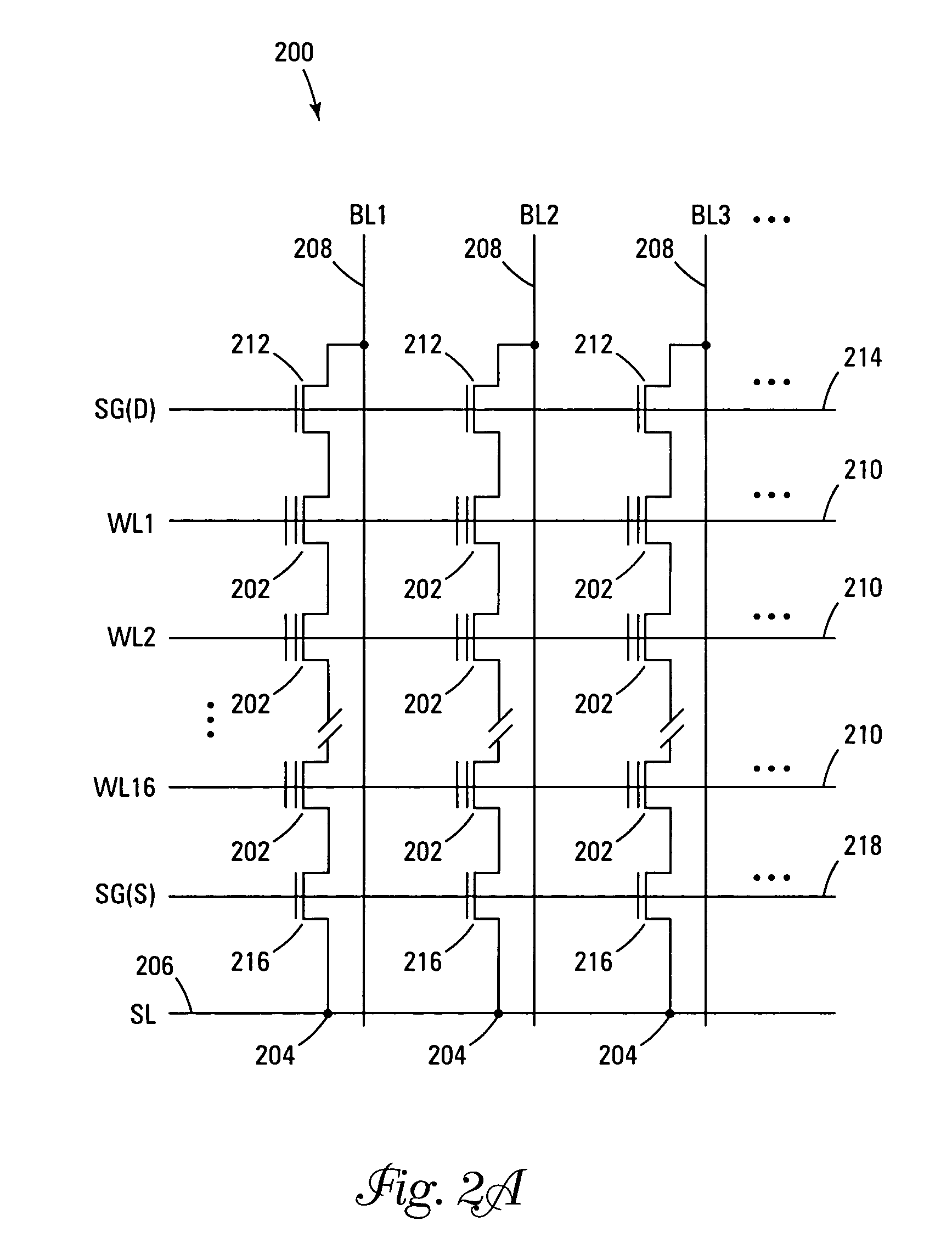

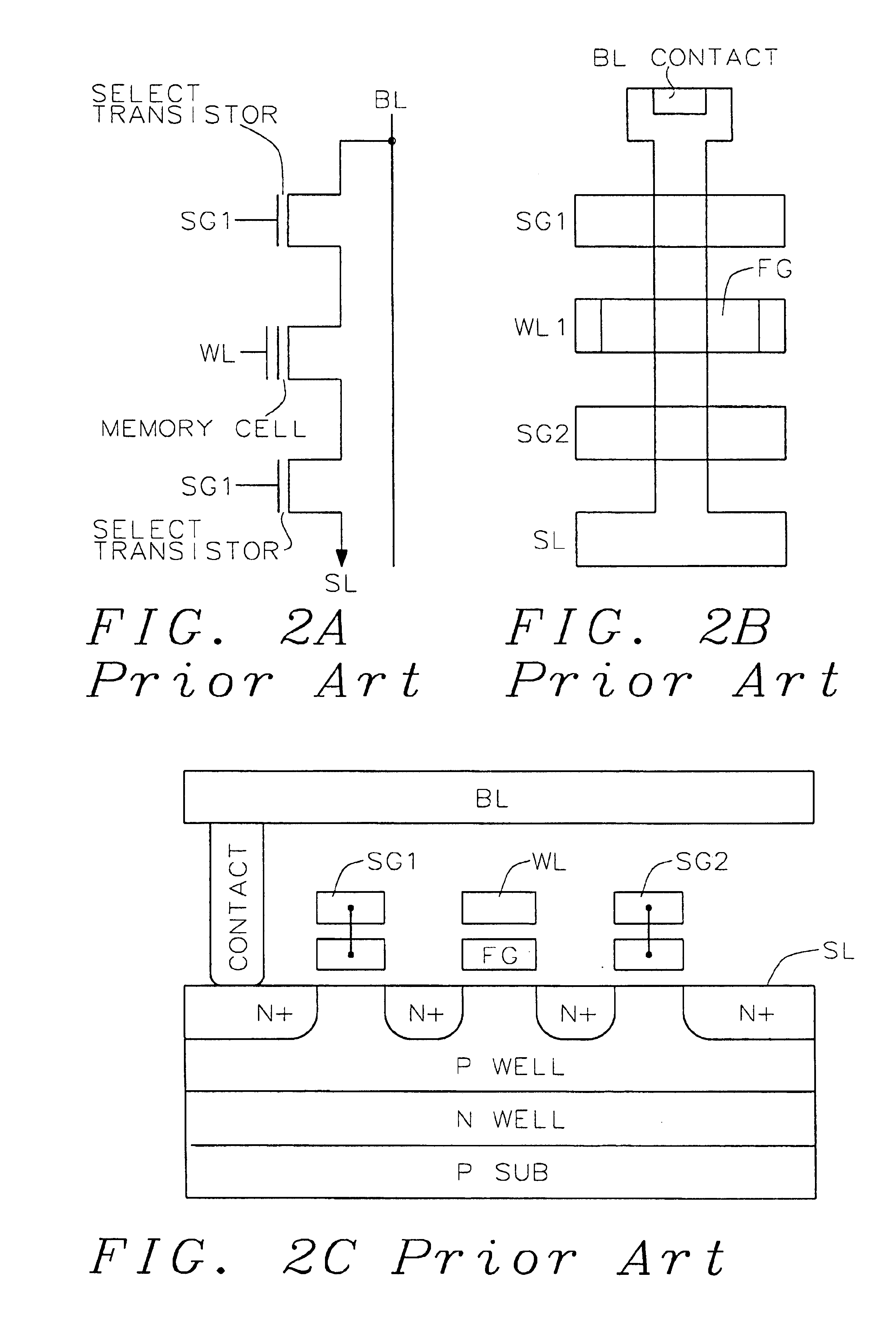

NAND flash depletion cell structure

InactiveUS20060044872A1Scale upIncrease supplyRead-only memoriesDigital storageCapacitanceRC time constant

NAND architecture Flash memory strings, memory arrays, and memory devices are described that utilize depletion mode floating gate memory cells. Depletion mode floating gate memory cells allow for increased cell current through lower channel rdS resistance and decreased “narrow width” effect, allowing for increased scaling of NAND memory cell strings. In addition, the required voltages for reading and programming operations are reduced, allowing the use of more efficient, lower voltage charge pumps and a reduction circuit element feature sizes and layouts. Cell inhibit of unselected cells is also increased, reducing the likelihood of cell disturb in the memory array. Operation speed is improved by increasing read current of the selected NAND string and by increasing the ability to overcome the RC time constants of circuit lines and capacitances through lowered voltage swings and increased current supplies.

Owner:MICRON TECH INC

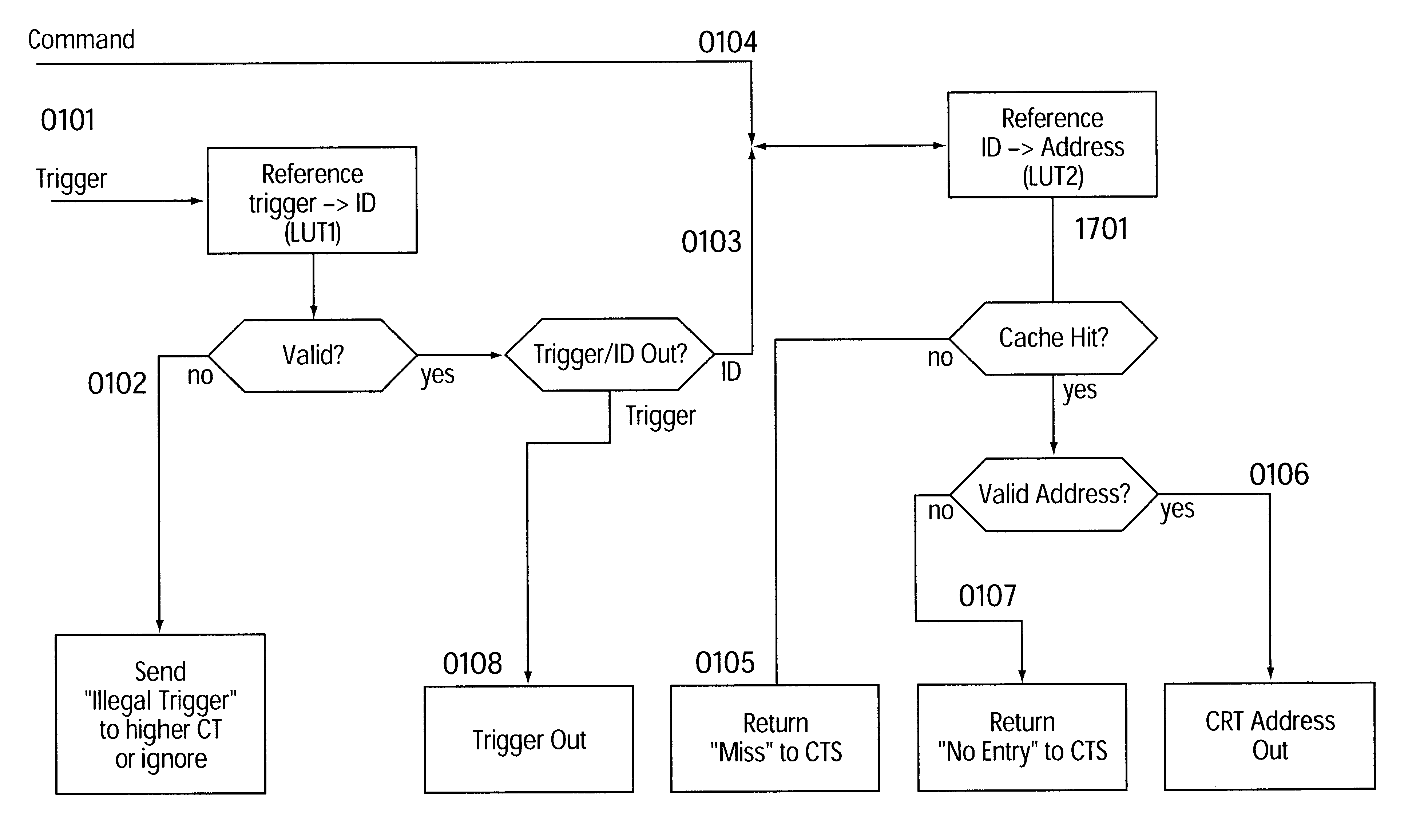

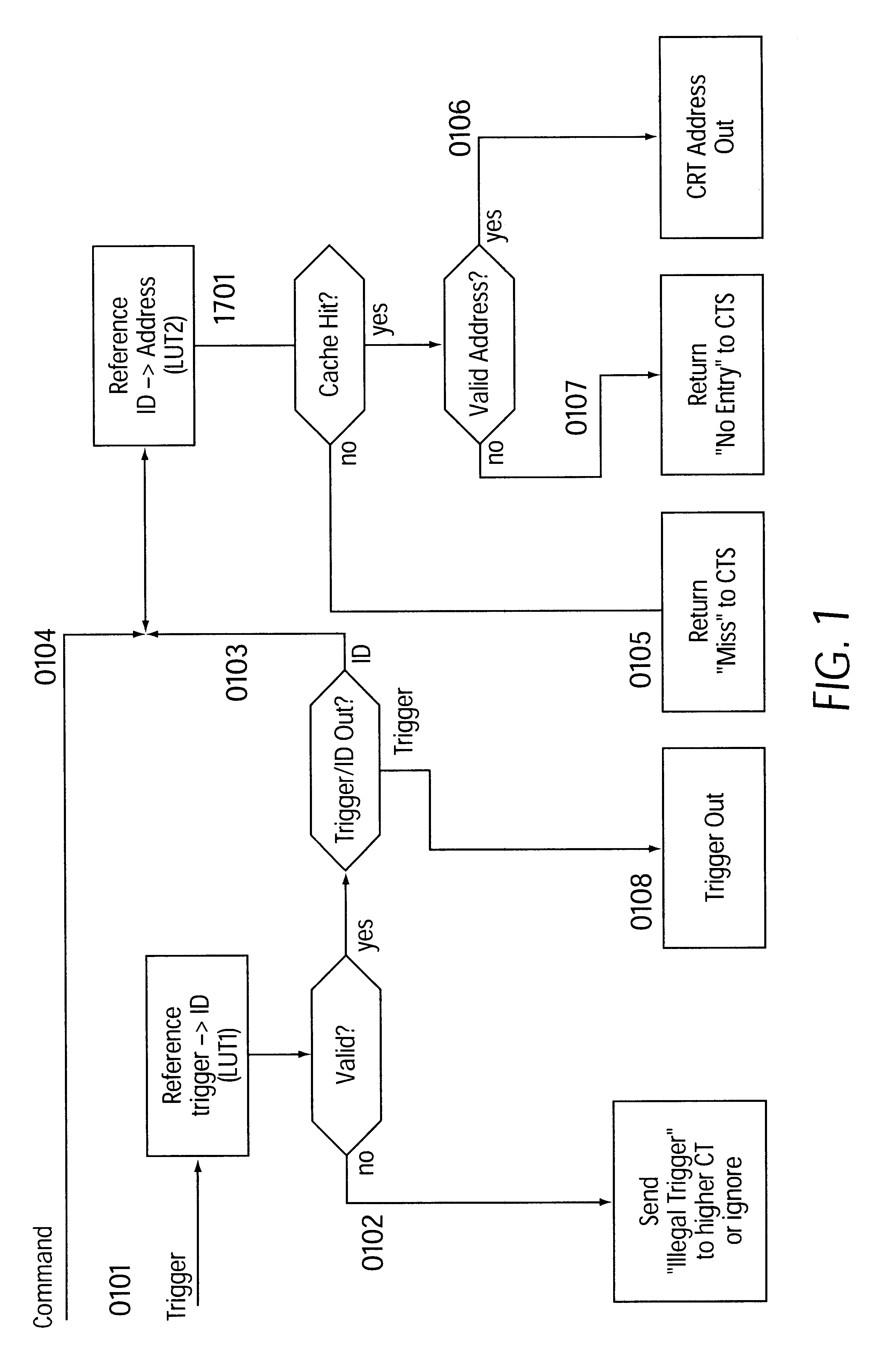

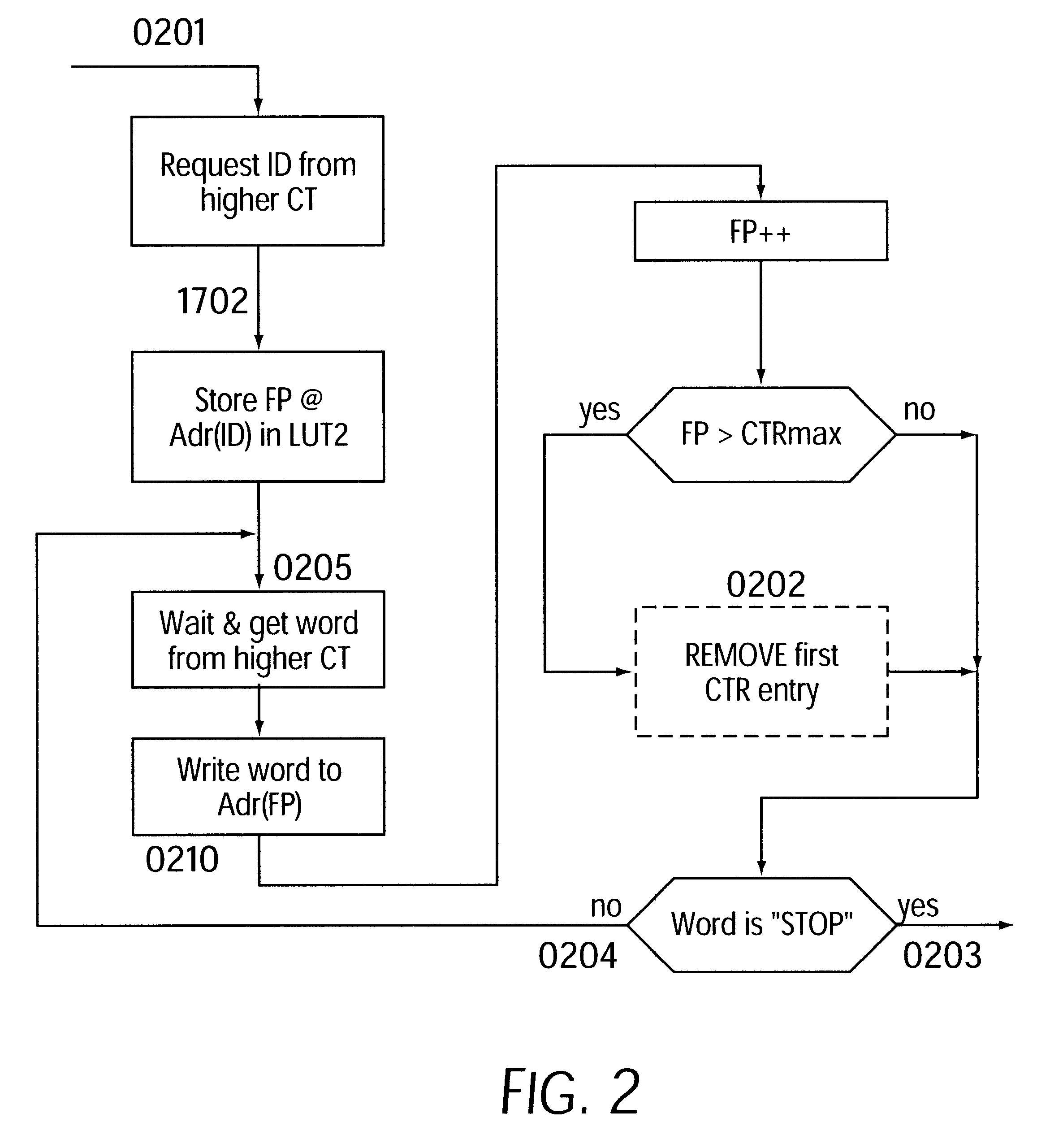

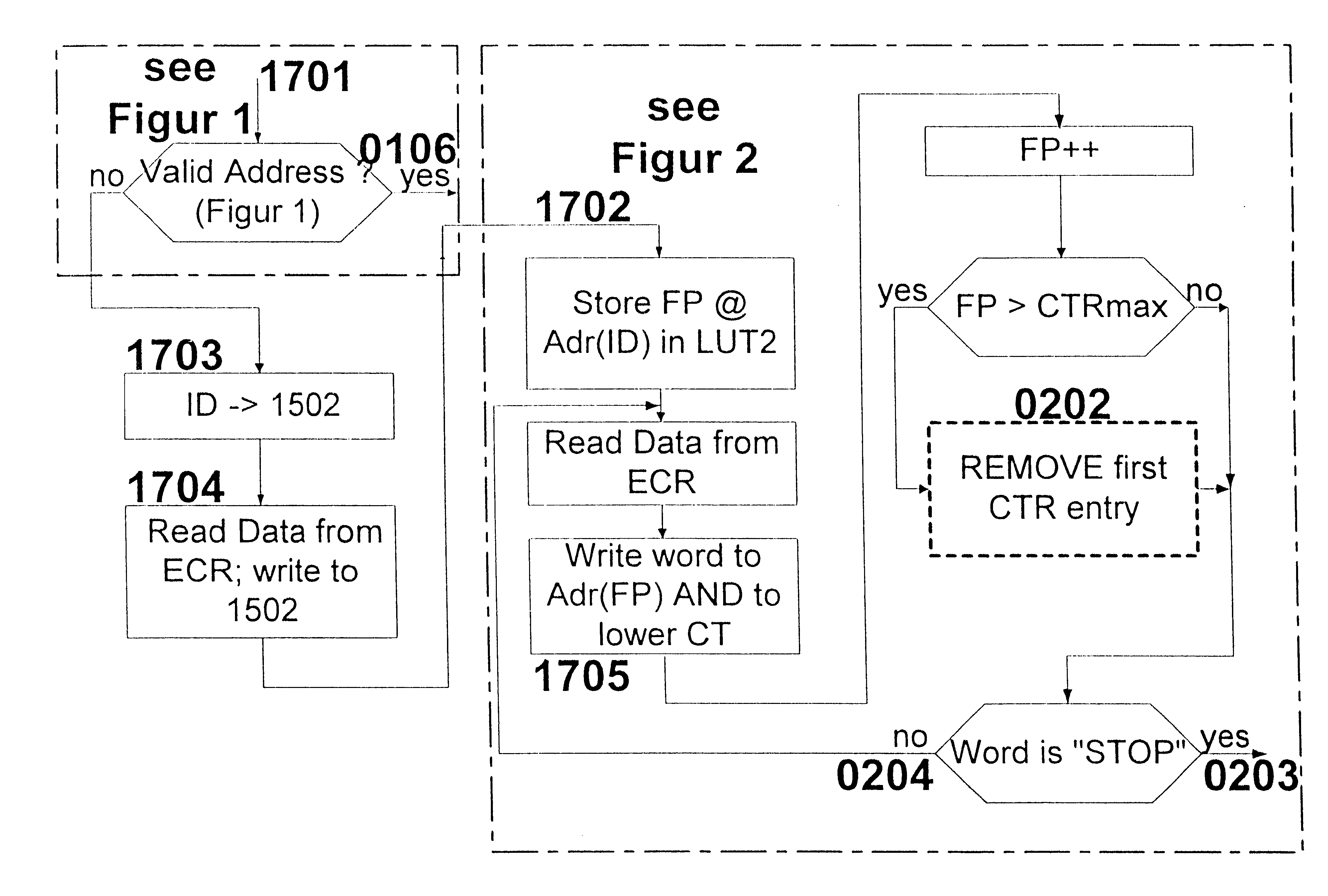

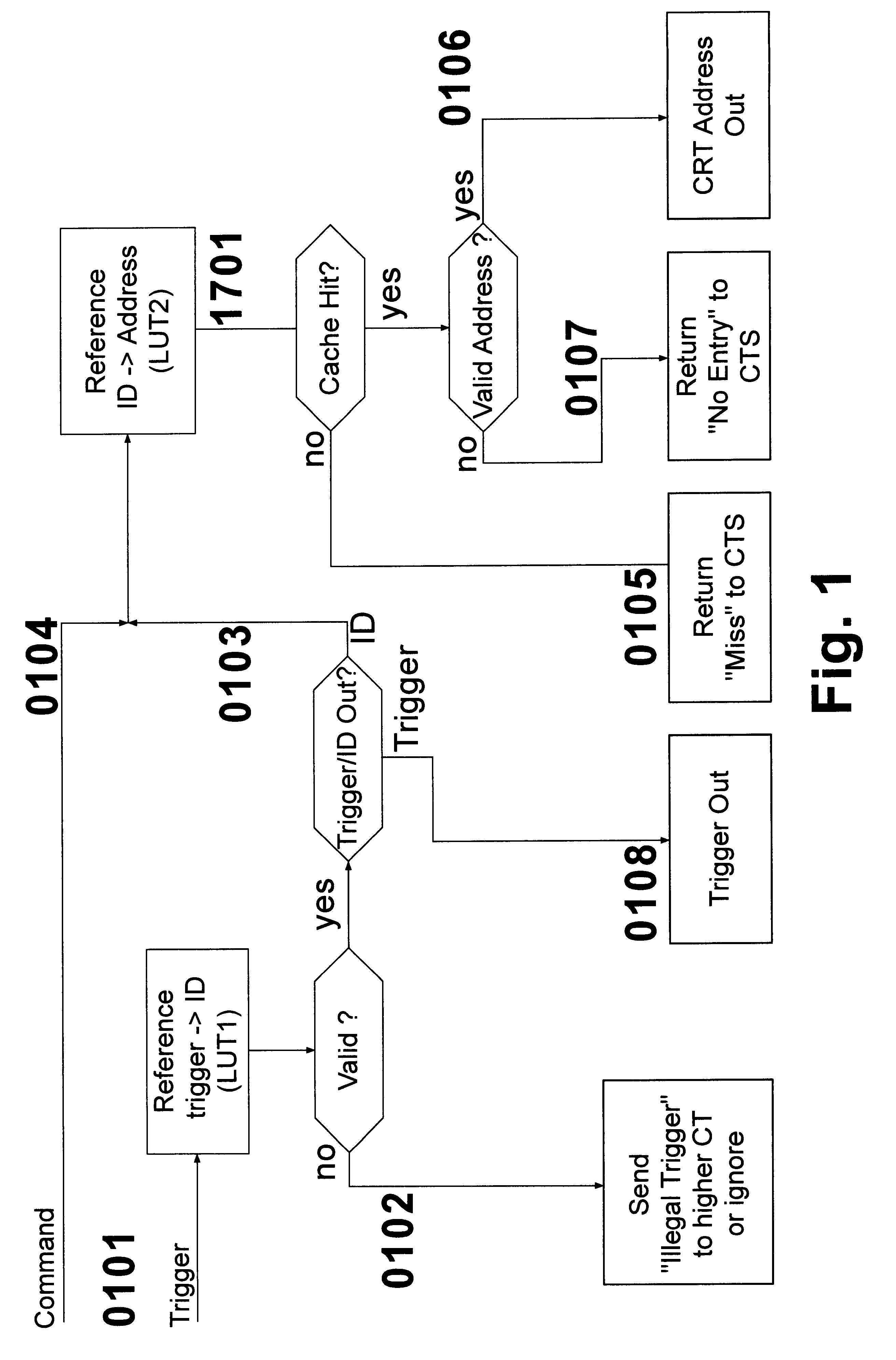

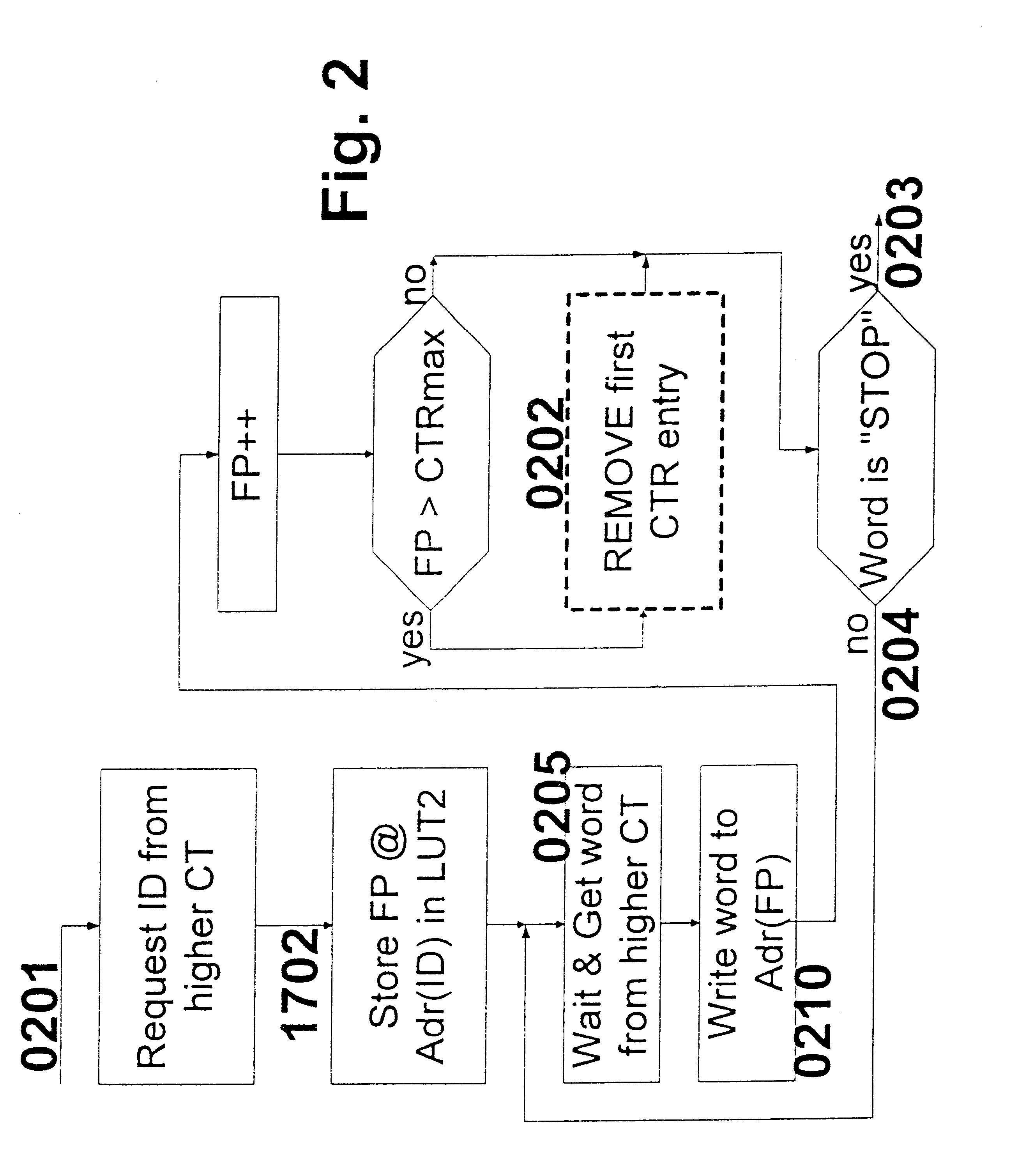

Method for hierarchical caching of configuration data having dataflow processors and modules having two-or multidimensional programmable cell structure (FPGAs, DPGAs, etc.)--

InactiveUS6480937B1Improve performanceEasy transferMemory adressing/allocation/relocationProgram controlData stream processingComputer module

A method of caching commands in microprocessors having a plurality of arithmetic units and in modules having a two- or multidimensional cell arrangement is provided. The method includes combining a plurality of cells and arithmetic units to form a plurality of groups, assigning a cache unit to a group, and connecting the cache unit to a higher level unit via a tree structure. The cache unit may send requests for required commands to the higher level cache unit, which may return a command sequence including the required command, if the higher level cache unit holds the first command sequence including the required command in the higher level cache unit's local memory.

Owner:SCIENTIA SOL MENTIS AG +1

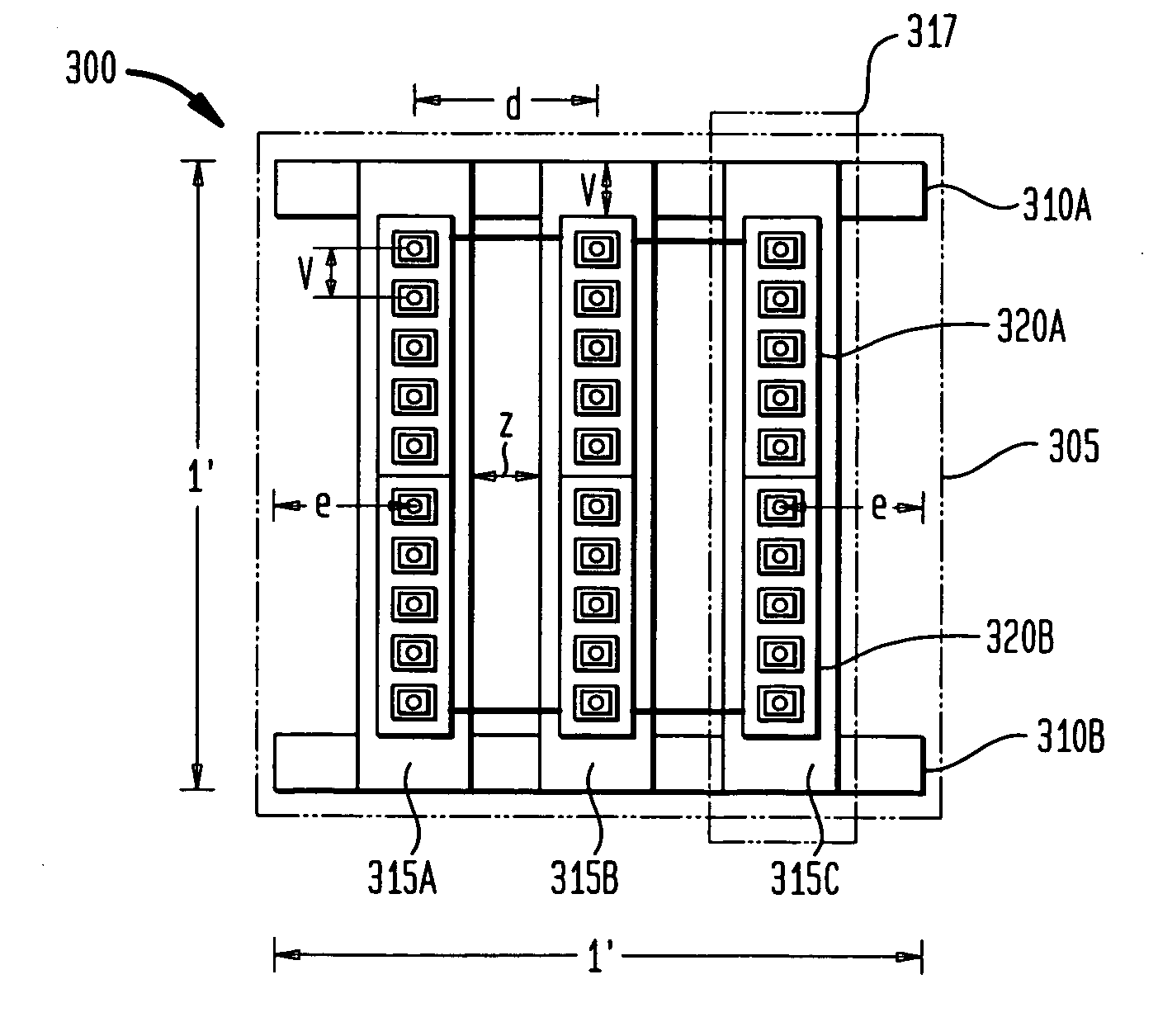

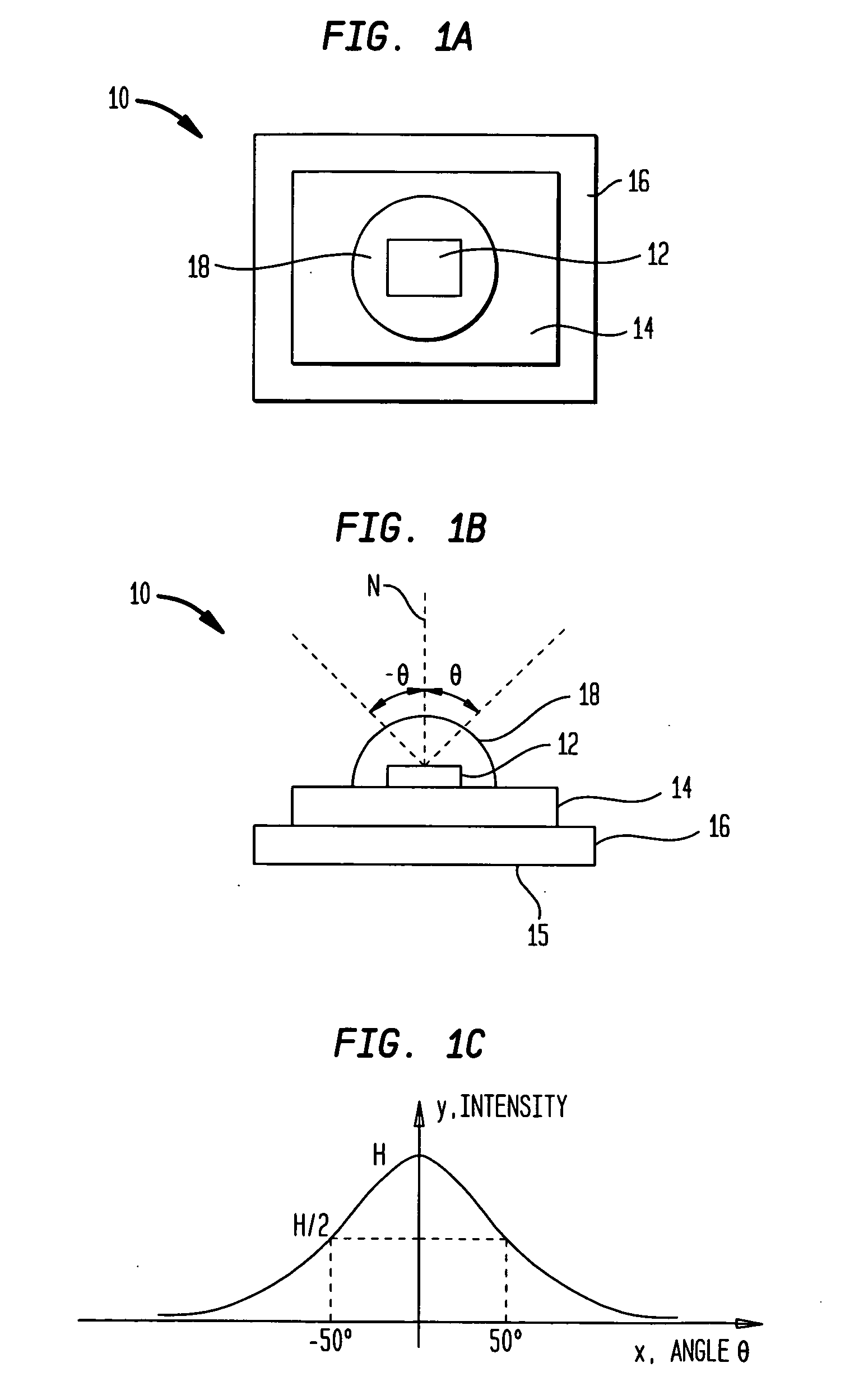

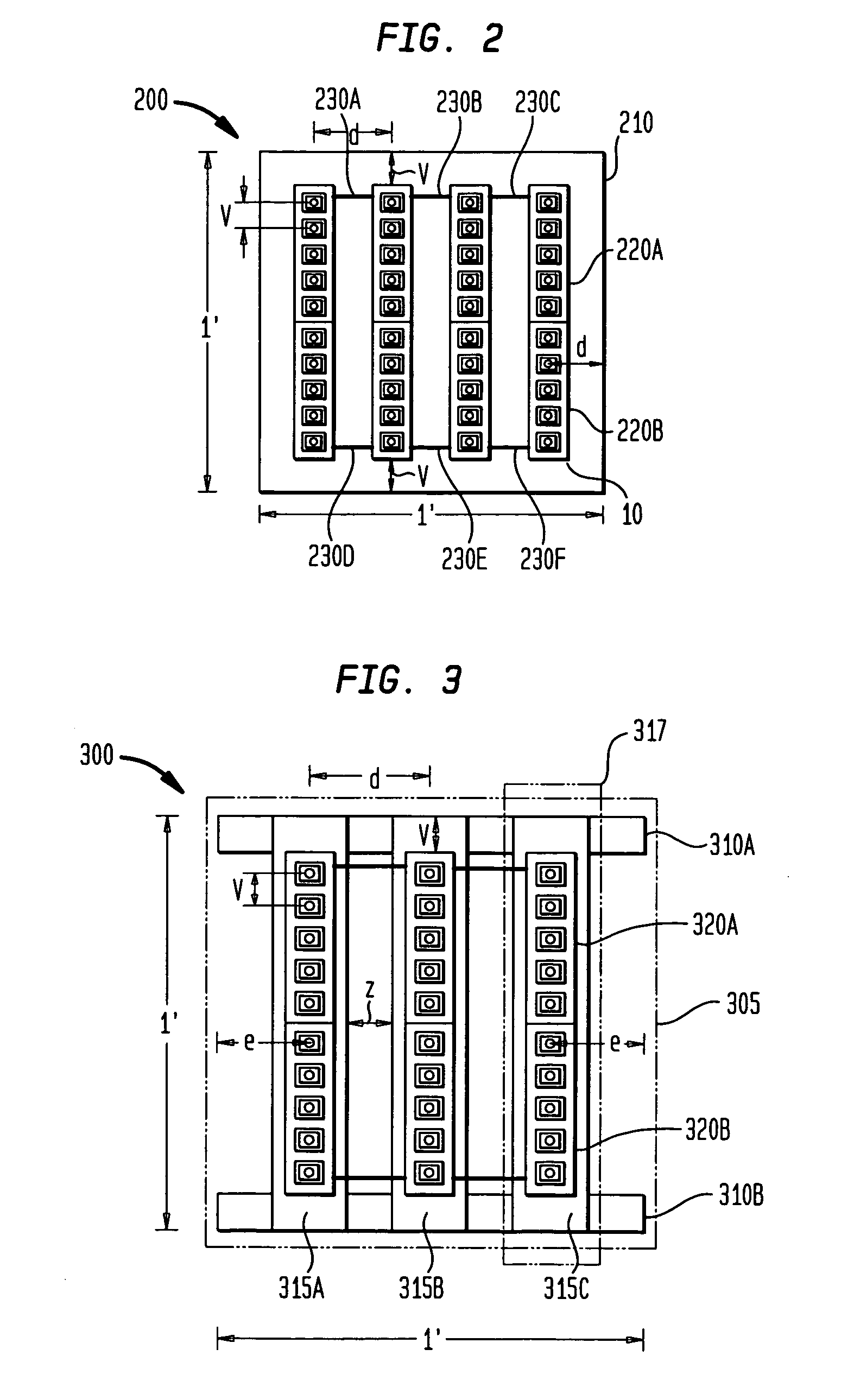

Light Emitting Diode Lighting Package With Improved Heat Sink

InactiveUS20070247851A1Lighting support devicesLighting heating/cooling arrangementsLed arrayEffect light

Improved lighting packages are described for light emitting diode (LED) lighting solutions having a wide variety of applications which seek to balance criteria such as heat dissipation, brightness, and color uniformity. The present approach includes a backing of thermally conductive material. The backing includes a cell structure. The cell structure comprises a plurality of hollow cells contiguously positioned in a side by side manner. The present approach also includes an array of LEDs. The array of LEDs is mounted to a printed circuit board (PCB). The PCB is attached to the cell structure to balance heat dissipation and color uniformity of the LEDs.

Owner:CREE INC

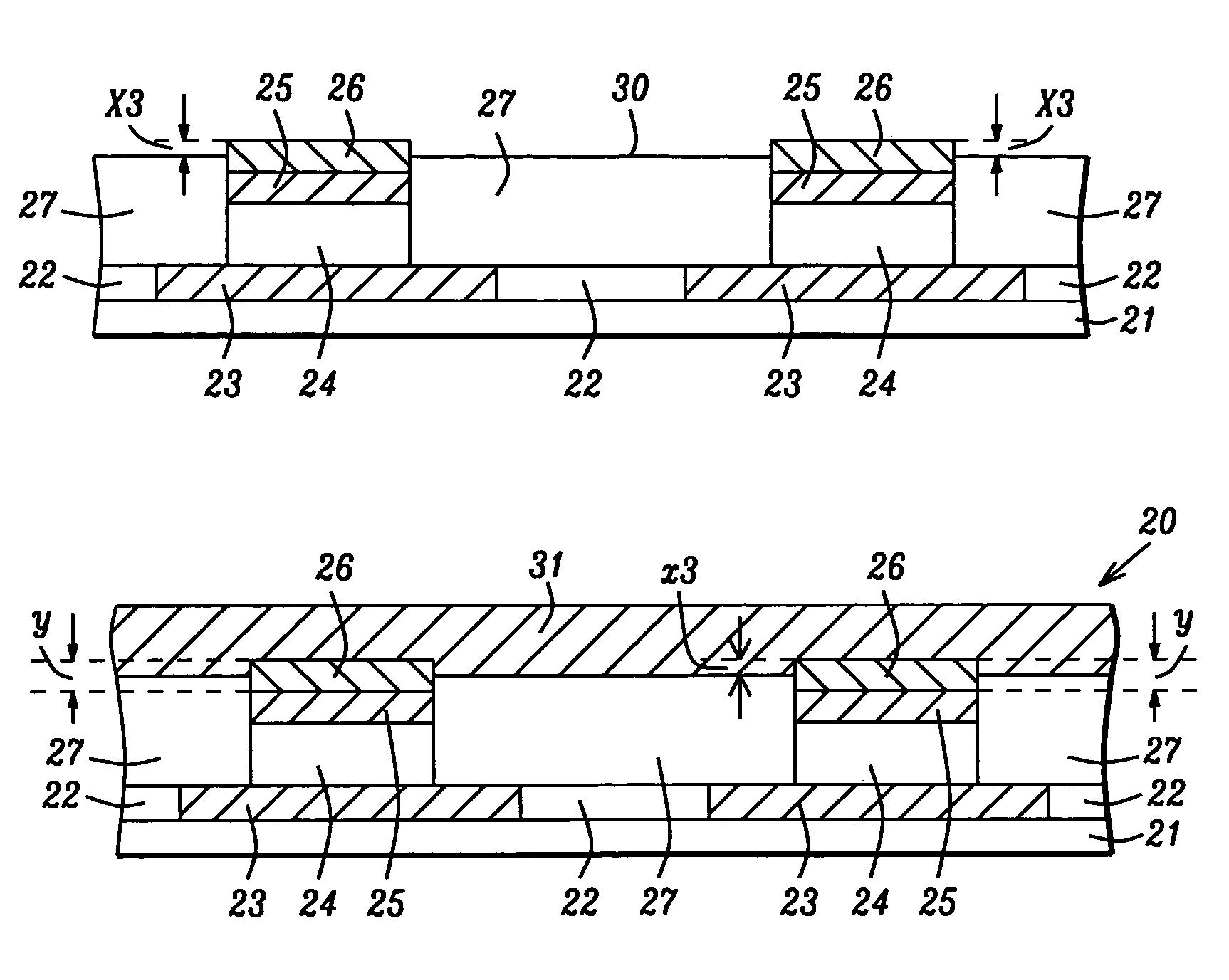

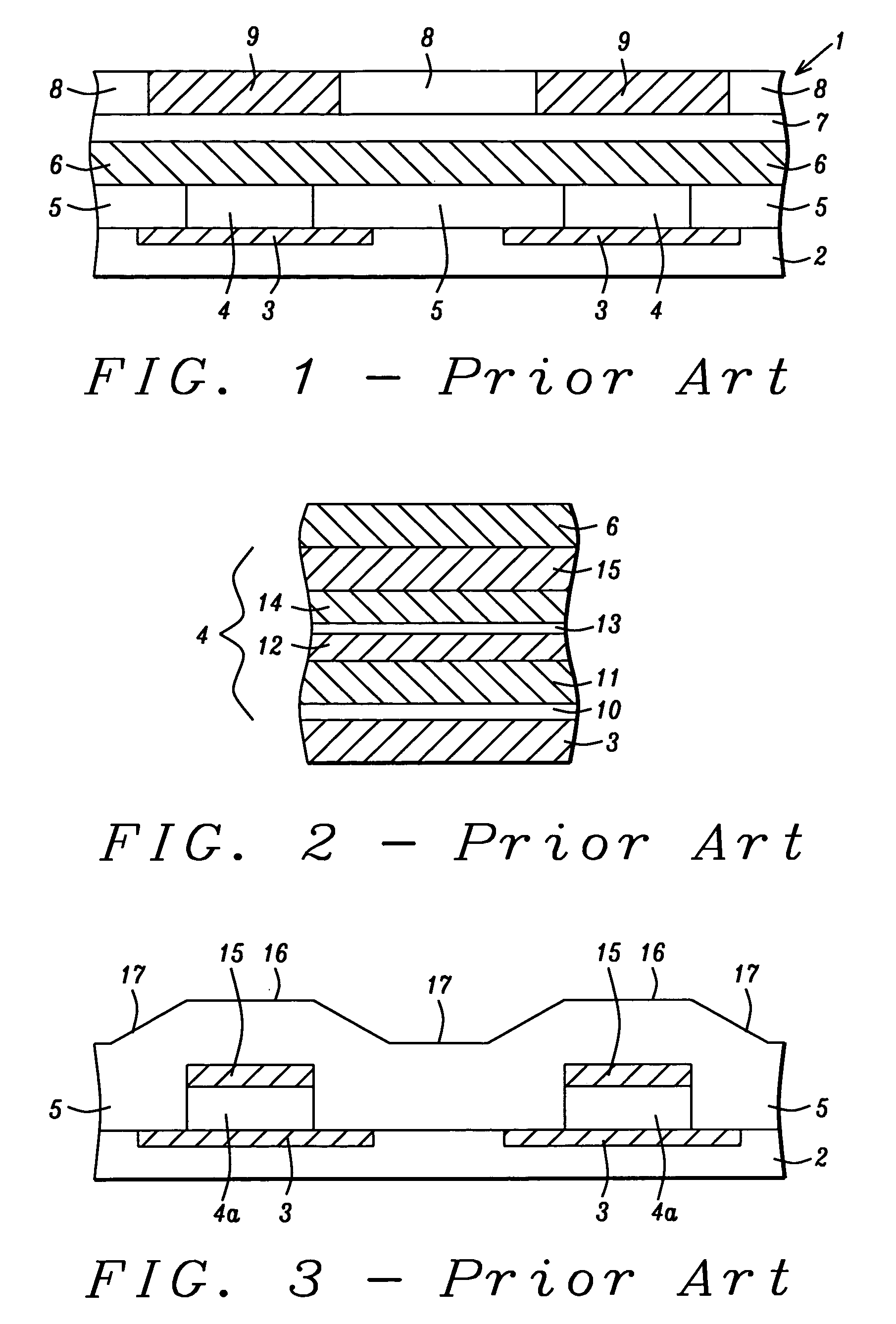

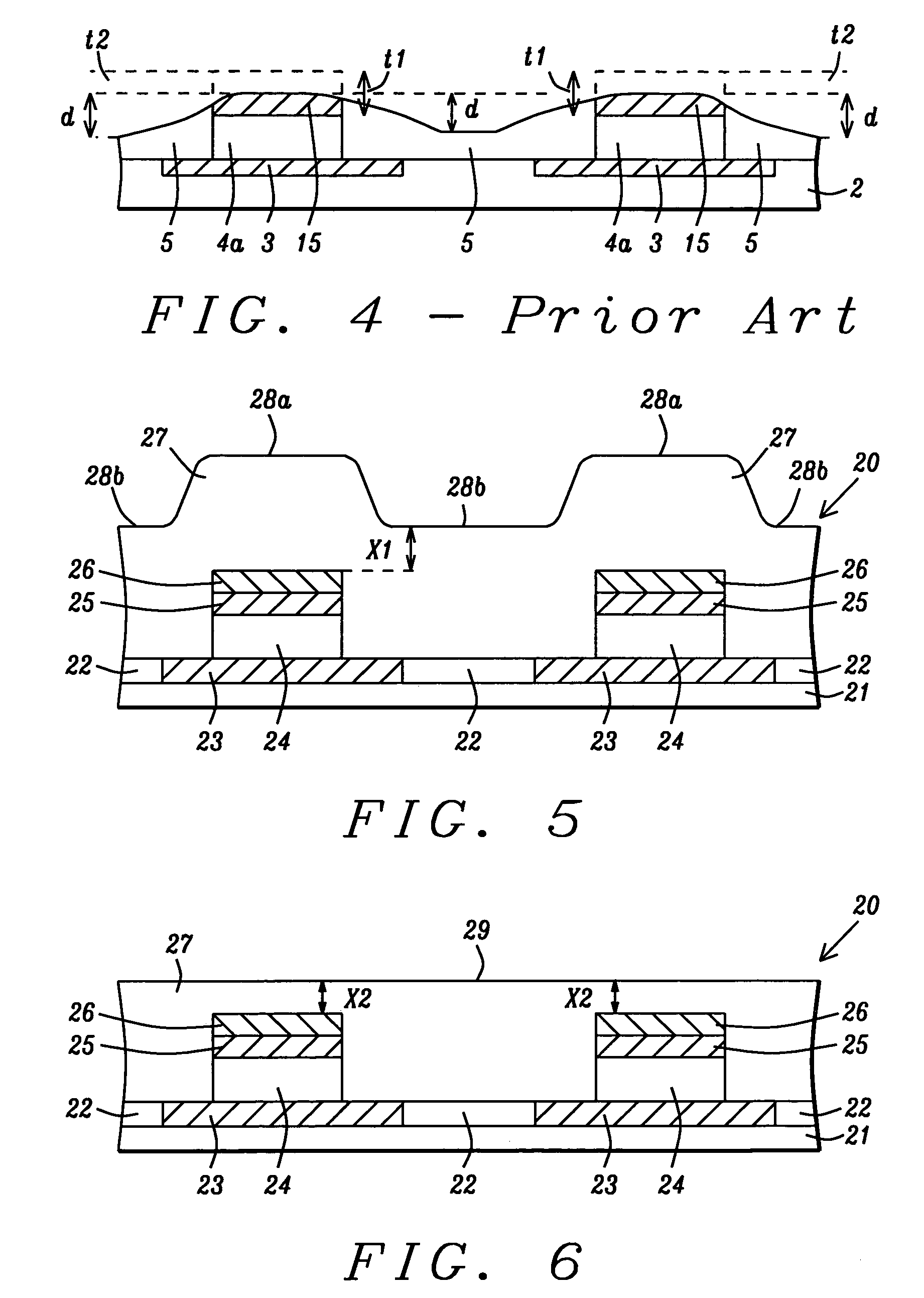

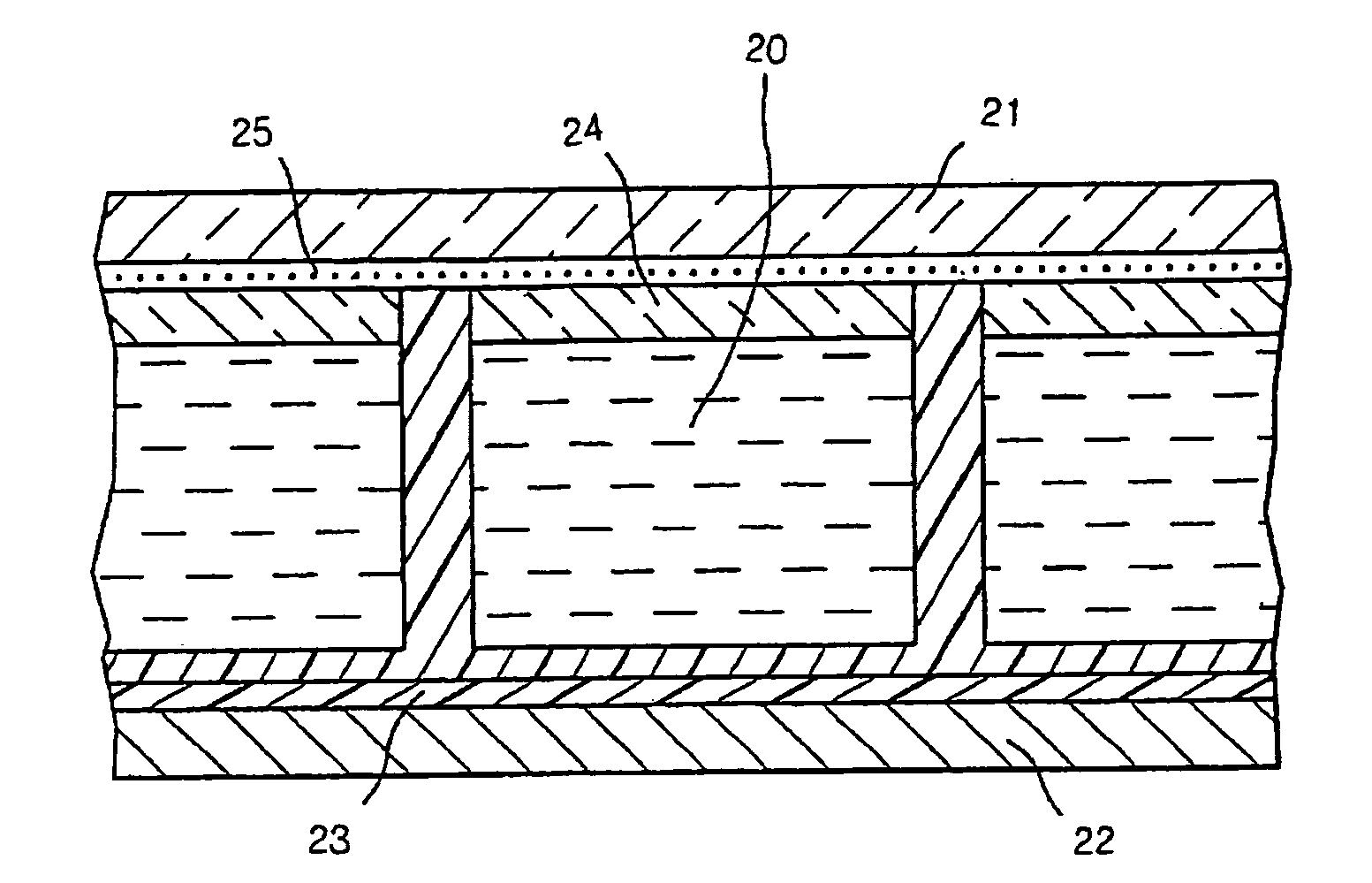

MRAM cell structure and method of fabrication

ActiveUS7045368B2Solid-state devicesSemiconductor/solid-state device manufacturingBit lineInsulation layer

An MRAM structure is disclosed where the distance from a bit line or word line to an underlying free layer in an MTJ is small and well controlled. As a result, the bit line or word line switching current is reduced and tightly distributed for better device performance. A key feature in the method of forming the MRAM cell structure is a two step planarization of an insulation layer deposited on the MTJ array. A CMP step flattens the insulation layer at a distance about 60 to 200 Angstroms above the cap layer in the MTJ. Then an etch back step thins the insulation layer to a level about 50 to 190 Angstroms below the top of the cap layer. Less than 5 Angstroms of the cap layer is removed. The distance variation from the free layer to an overlying bit line or word line is within + / −5 Angstroms.

Owner:TAIWAN SEMICON MFG CO LTD

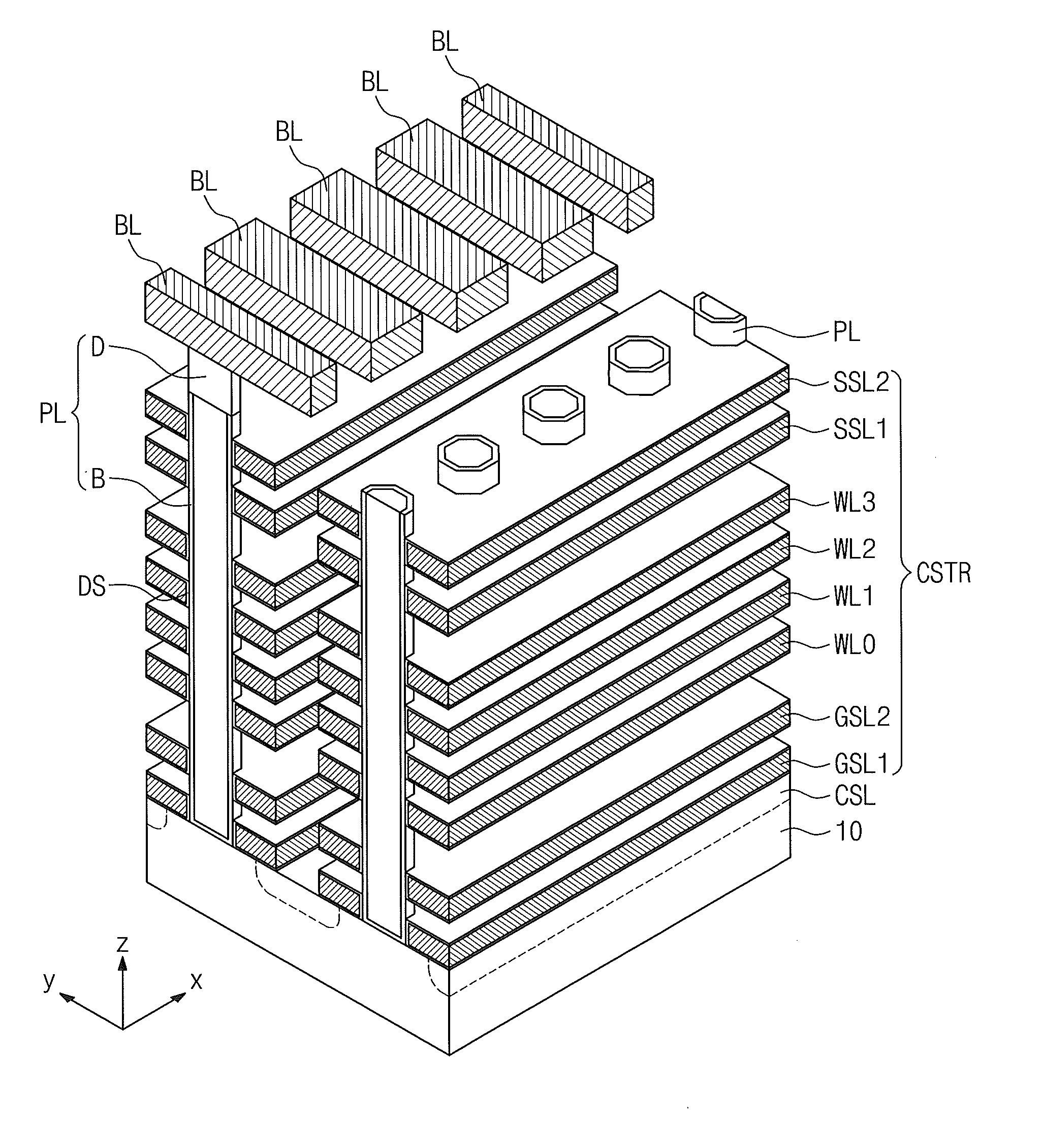

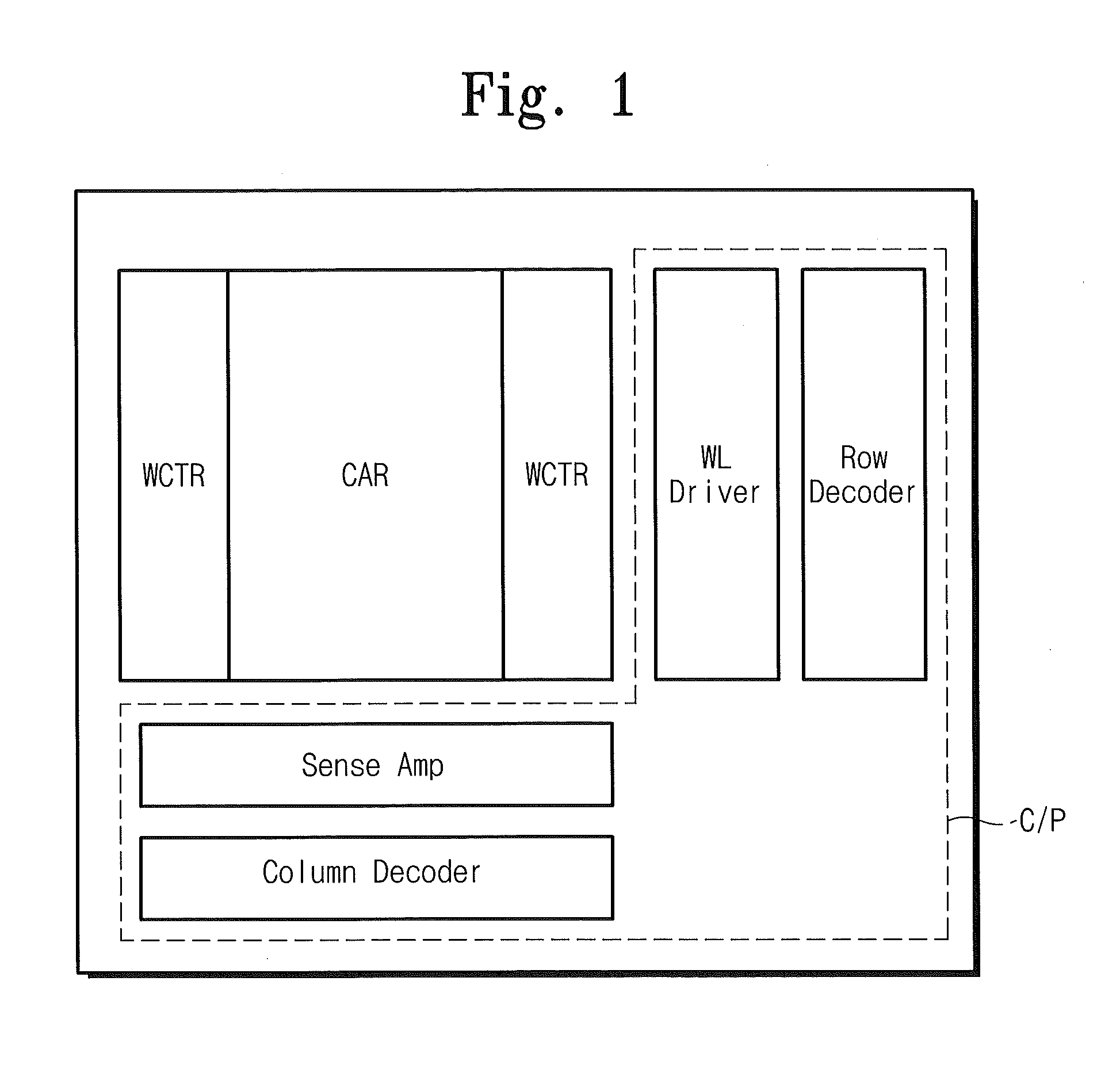

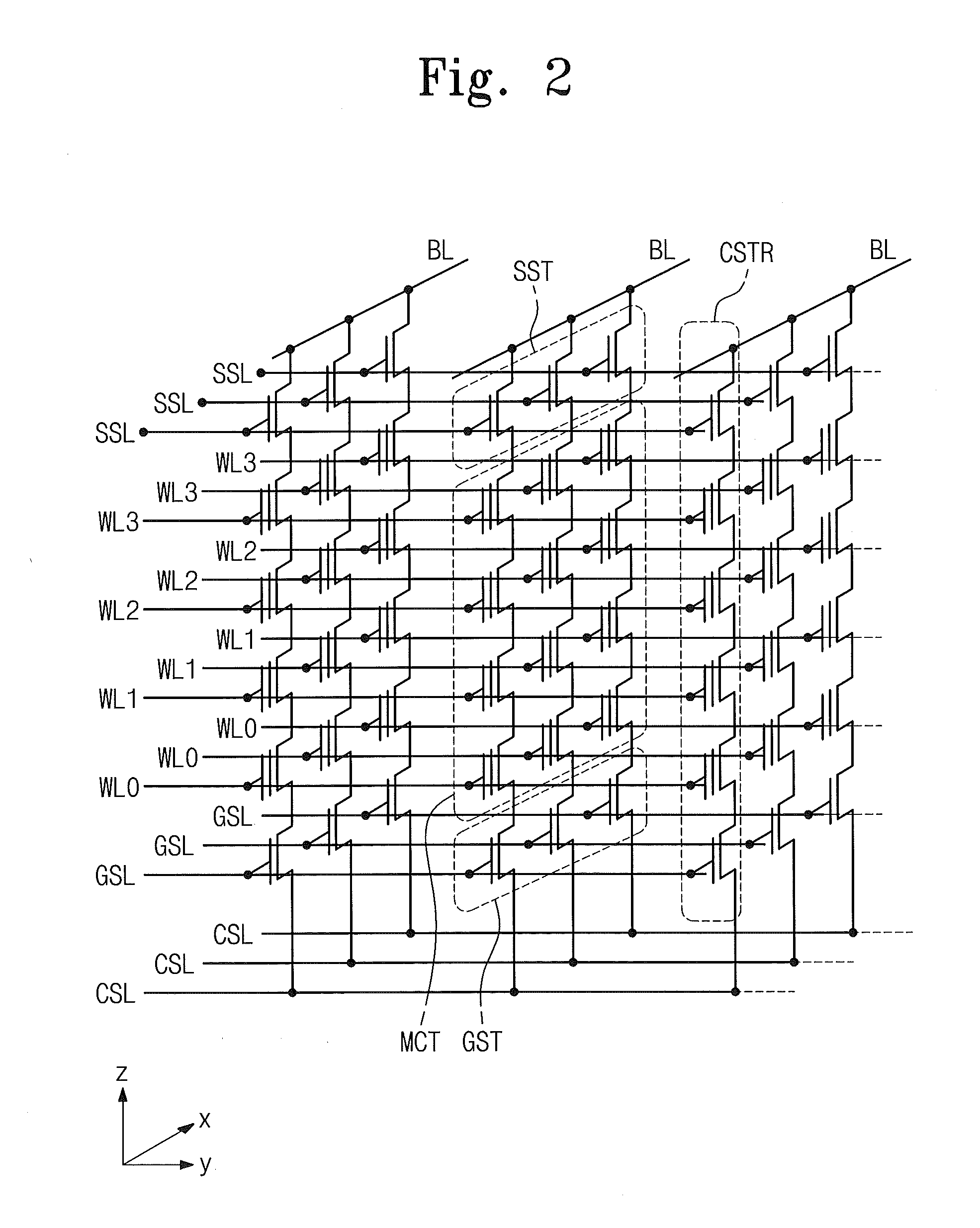

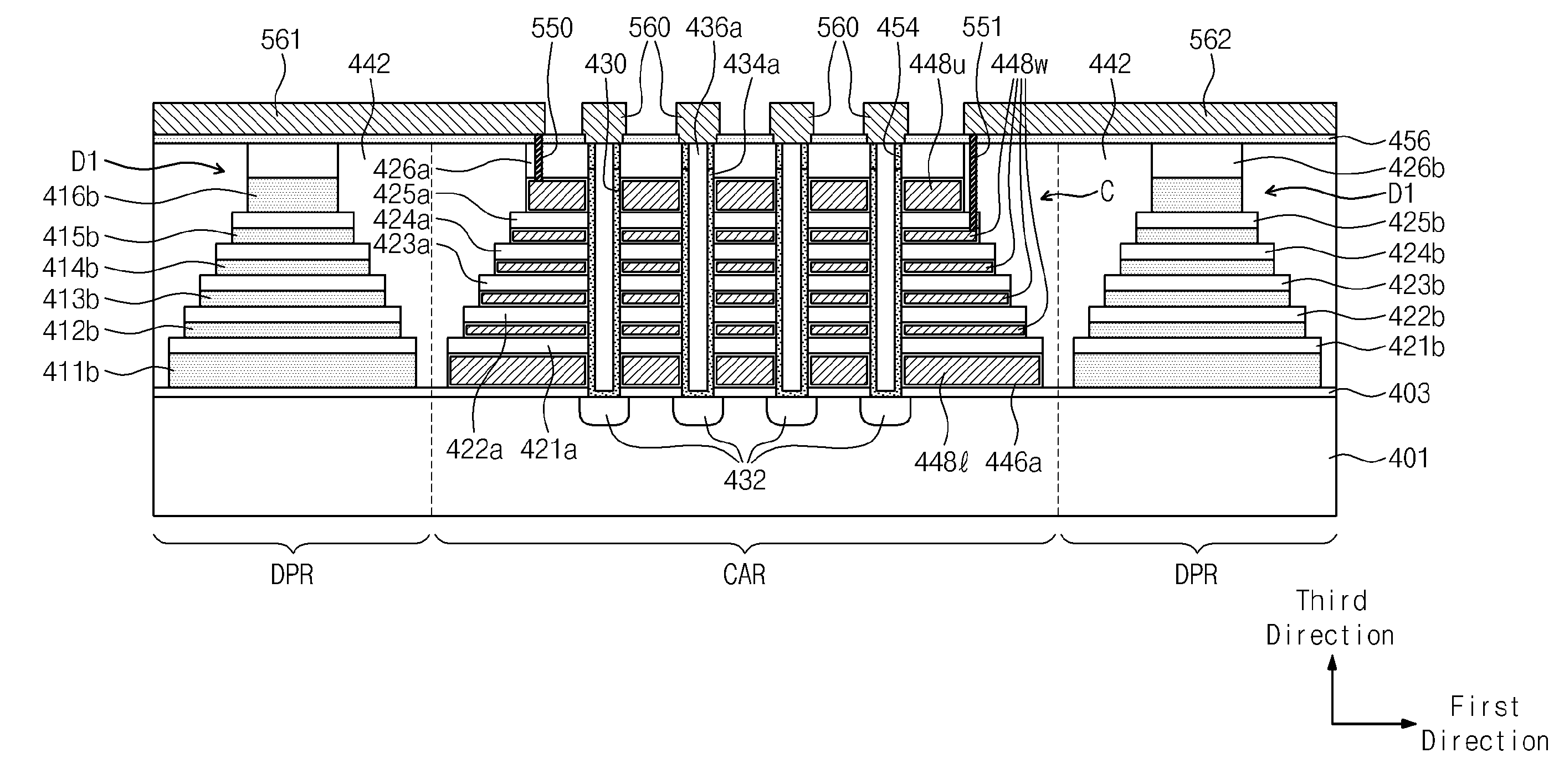

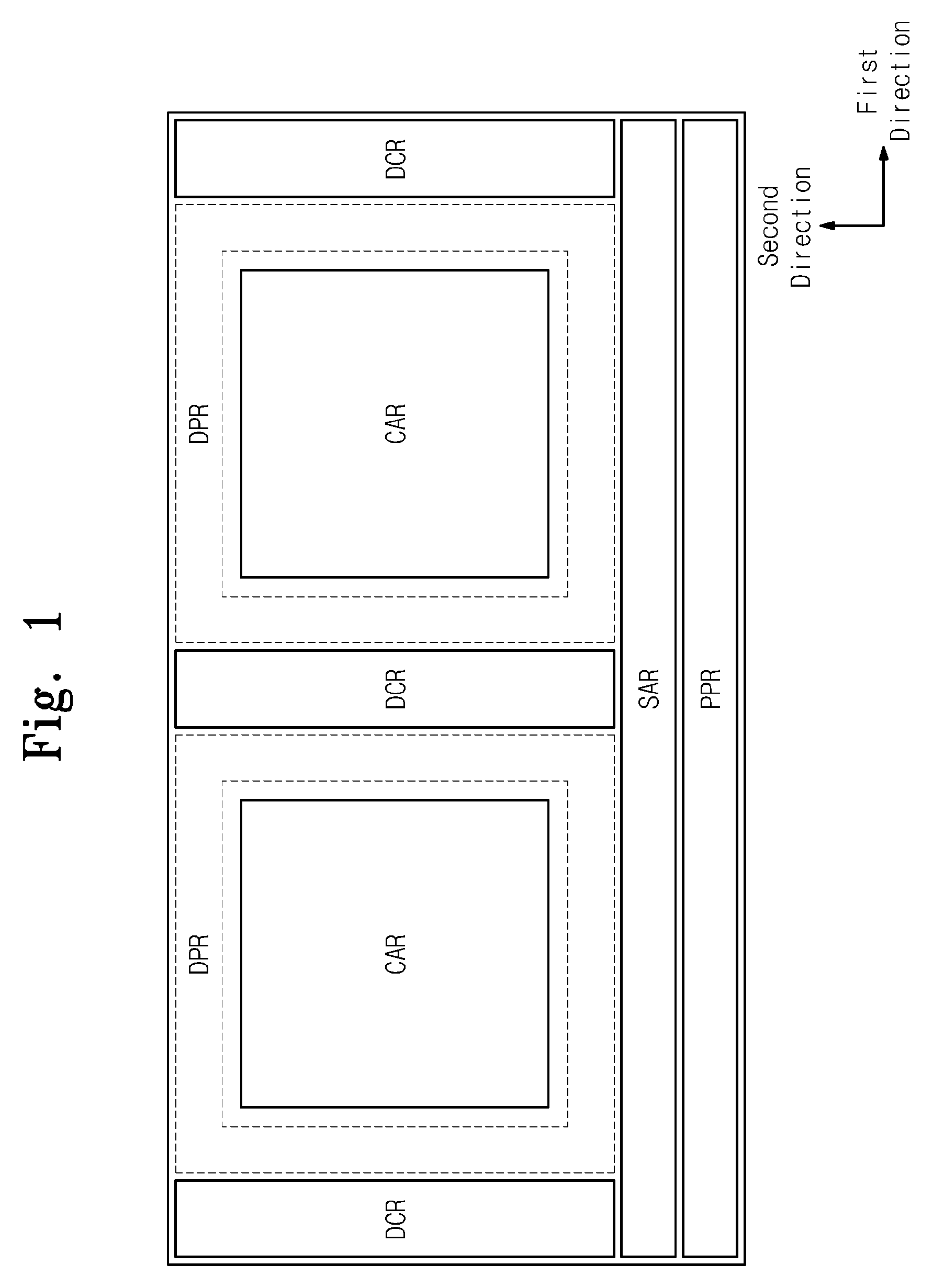

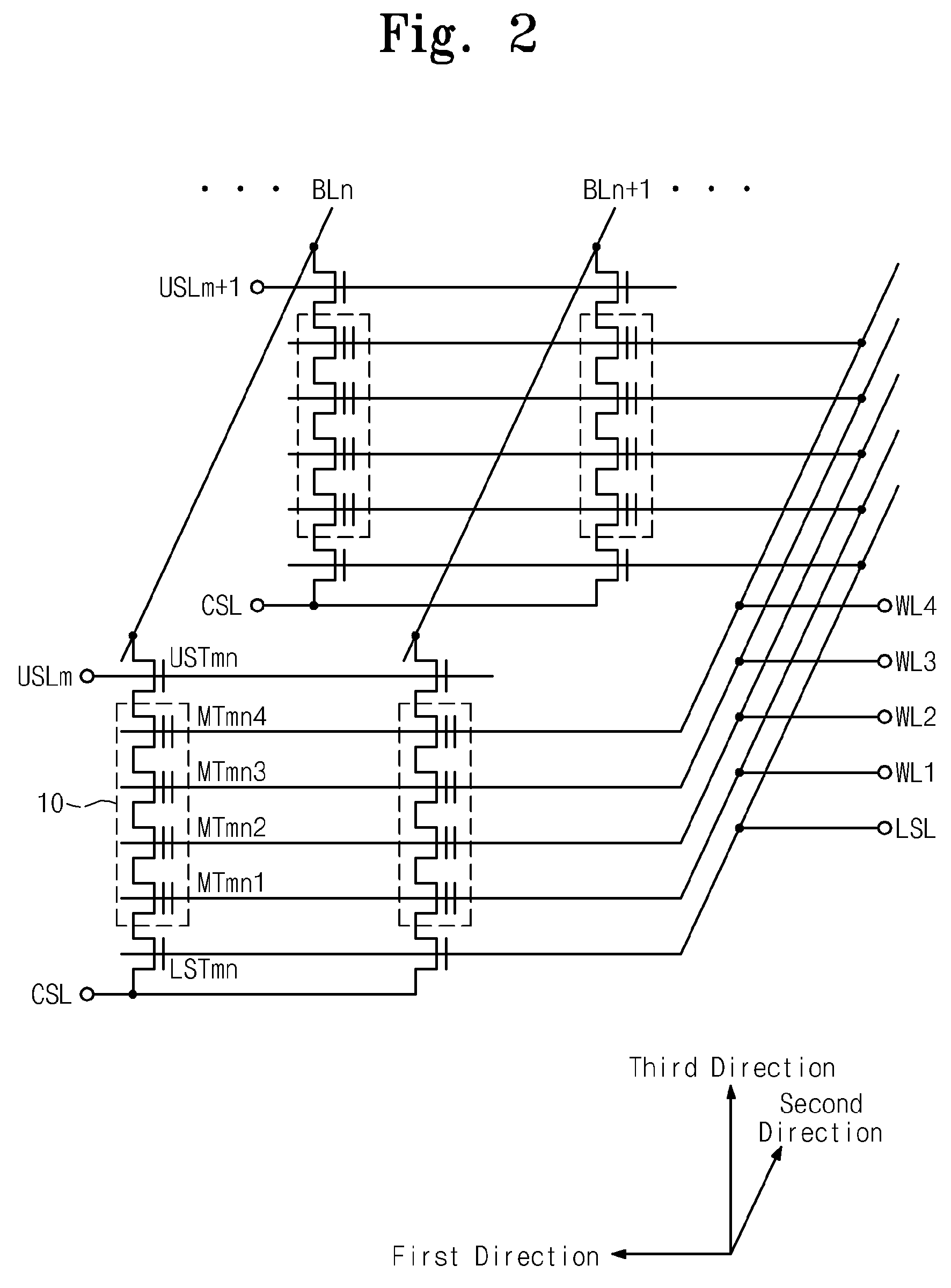

Methods of Manufacturing Three Dimensional Semiconductor Devices

InactiveUS20120070944A1Easy to manufactureSolid-state devicesSemiconductor/solid-state device manufacturingDielectricEngineering

Provided are methods of manufacturing a three dimensional semiconductor device. The method includes providing a substrate including a cell array region and a peripheral circuit region, forming a peripheral structure on the peripheral circuit region, forming a cell structure being thicker than the peripheral structure in the cell array region, forming an interlayer dielectric to cover the peripheral structure and the cell structure, forming a polishing stop layer on the interlayer dielectric, and planarizing the interlayer dielectric using the polishing stop layer as a planarization stop.

Owner:SAMSUNG ELECTRONICS CO LTD

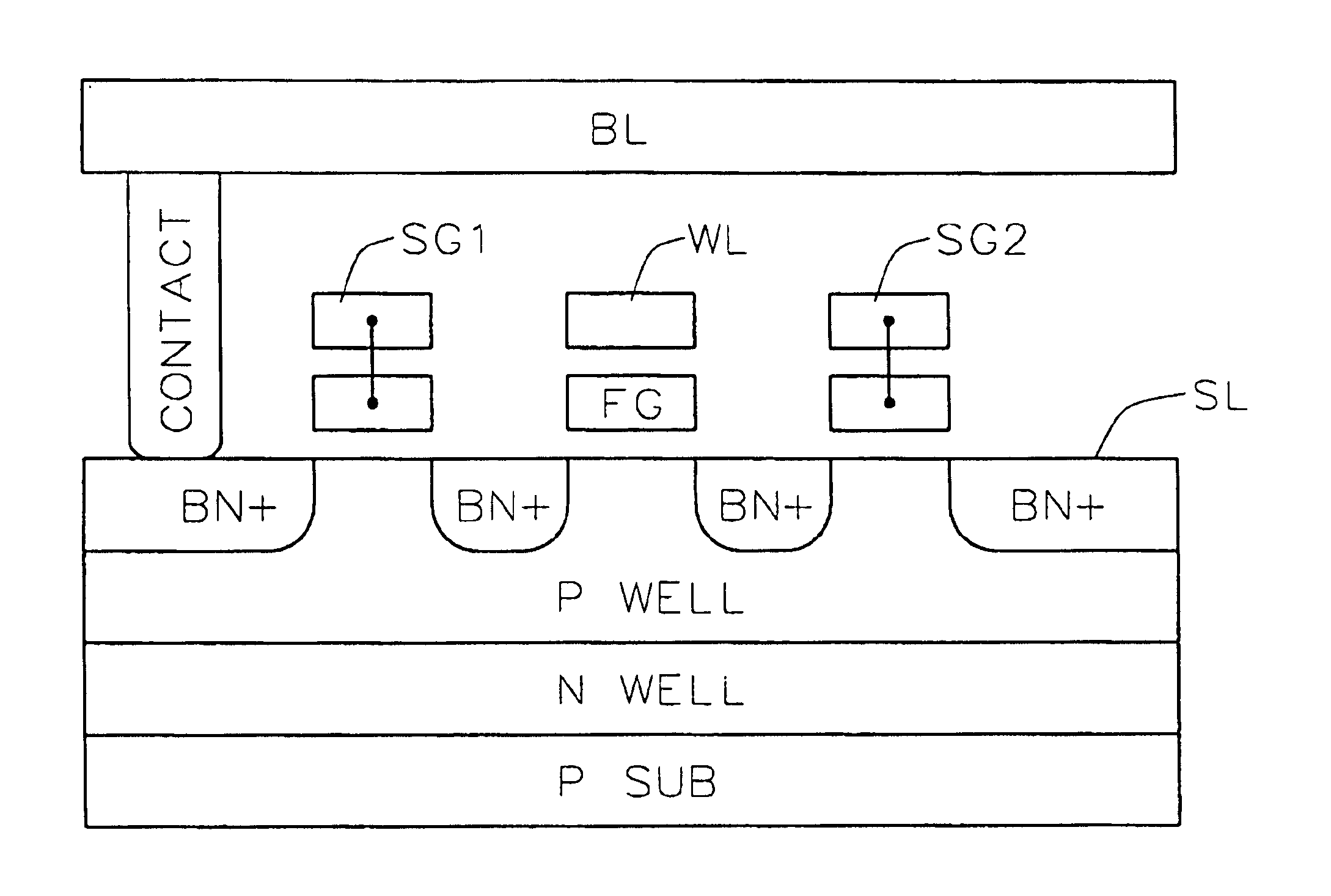

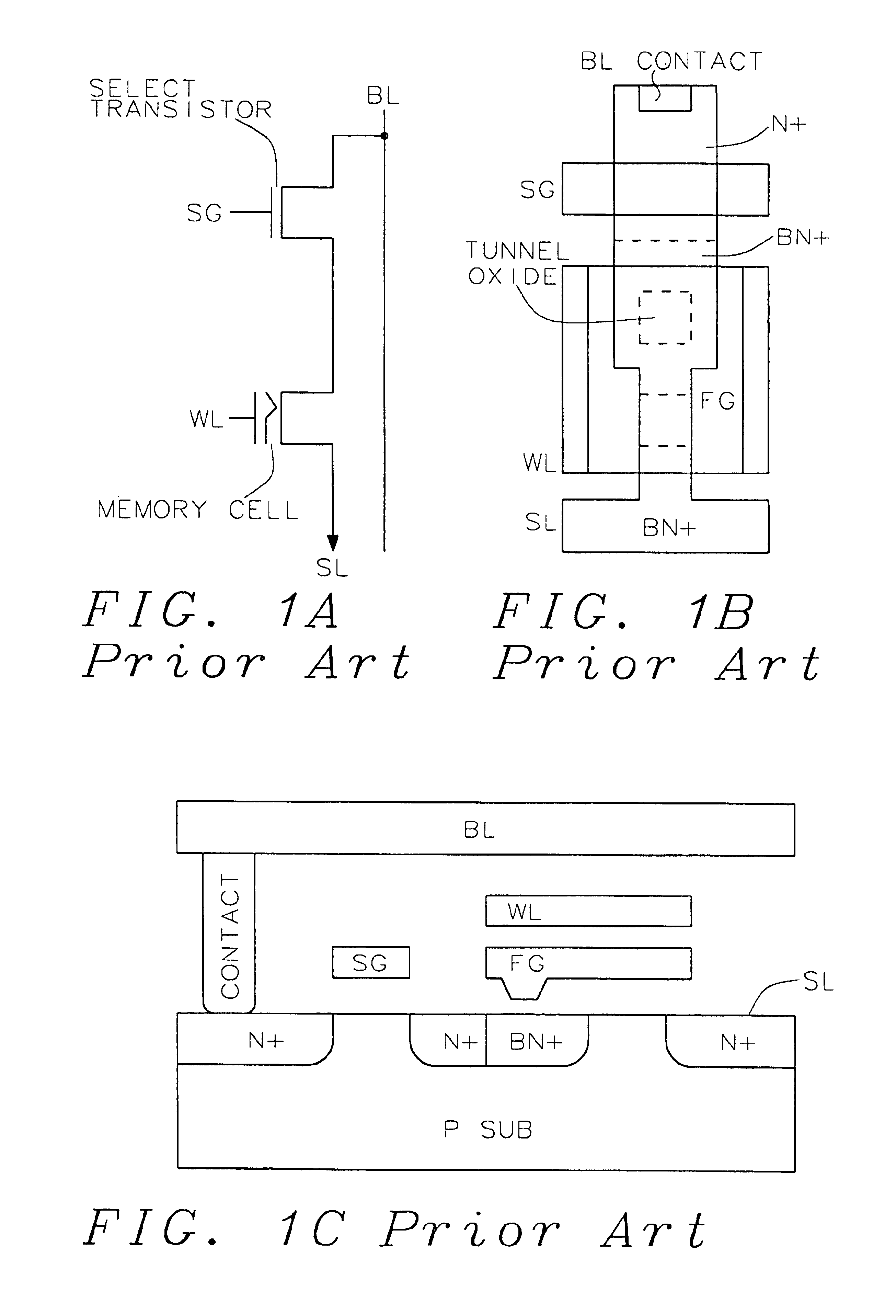

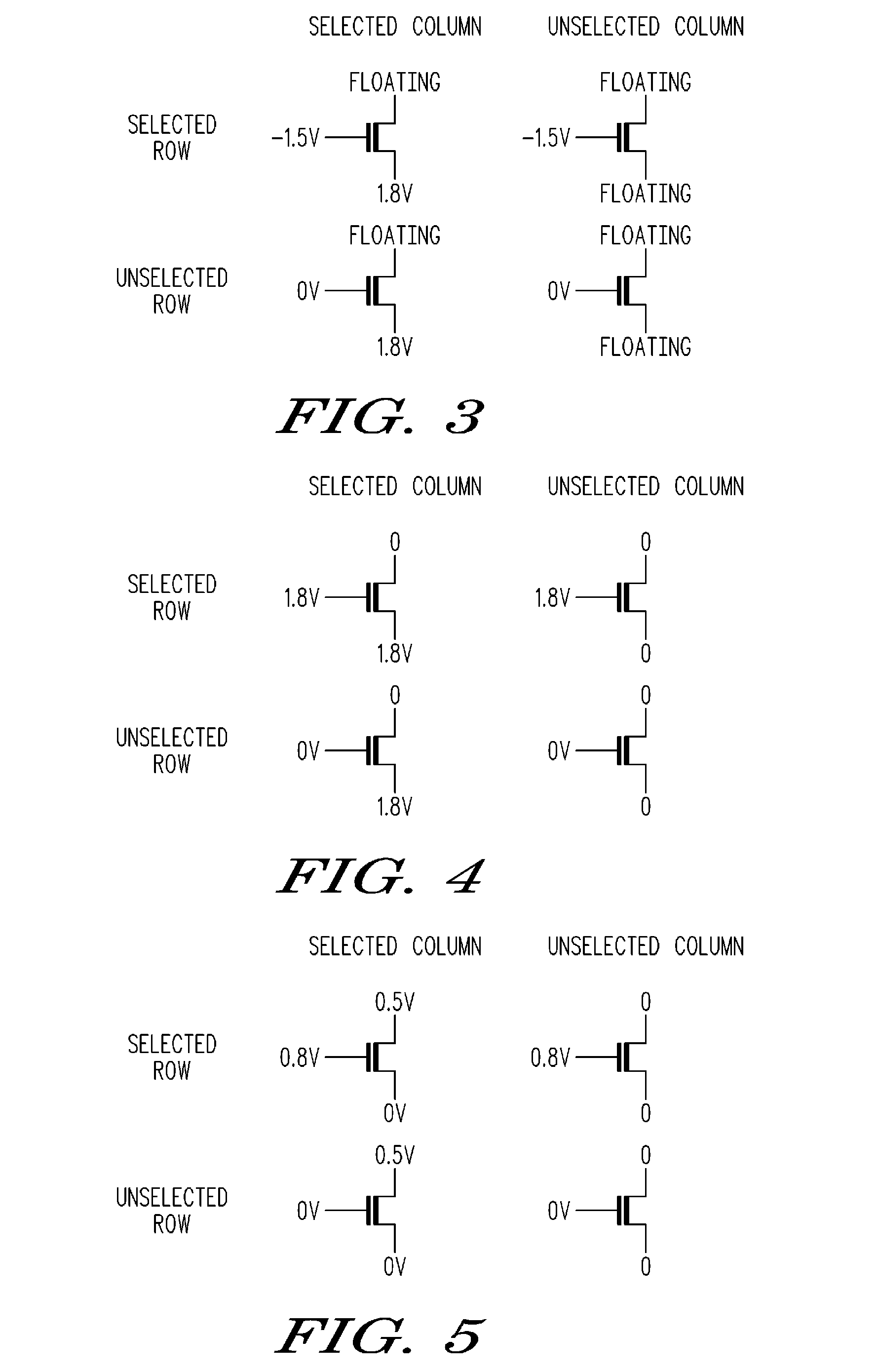

Monolithic, combo nonvolatile memory allowing byte, page and block write with no disturb and divided-well in the cell array using a unified cell structure and technology with a new scheme of decoder and layout

InactiveUS6862223B1Eliminate area-consuming divided triple-wellSuperior combo, monolithic, nonvolatile memorySolid-state devicesRead-only memoriesUnit structureByte

A novel FLASH-based EEPROM cell, decoder, and layout scheme are disclosed to eliminate the area-consuming divided triple-well in cell array and allows byte-erase and byte-program for high P / E cycles. Furthermore, the process-compatible FLASH cell for EEPROM part can be integrated with FLASH and ROM parts so that a superior combo, monolithic, nonvolatile memory is achieved. Unlike all previous arts, the novel combo nonvolatile memory of the present invention of ROM, EEPROM and FLASH or combination of any two is made of one unified, fully compatible, highly-scalable BN+cell and unified process. In addition, its cell operation schemes have zero array overhead and zero disturbance during P / E operations. The novel combo nonvolatile memory is designed to meet the need in those markets requiring flexible write size in units of bytes, pages and blocks at a lower cost.

Owner:CALLAHAN CELLULAR L L C

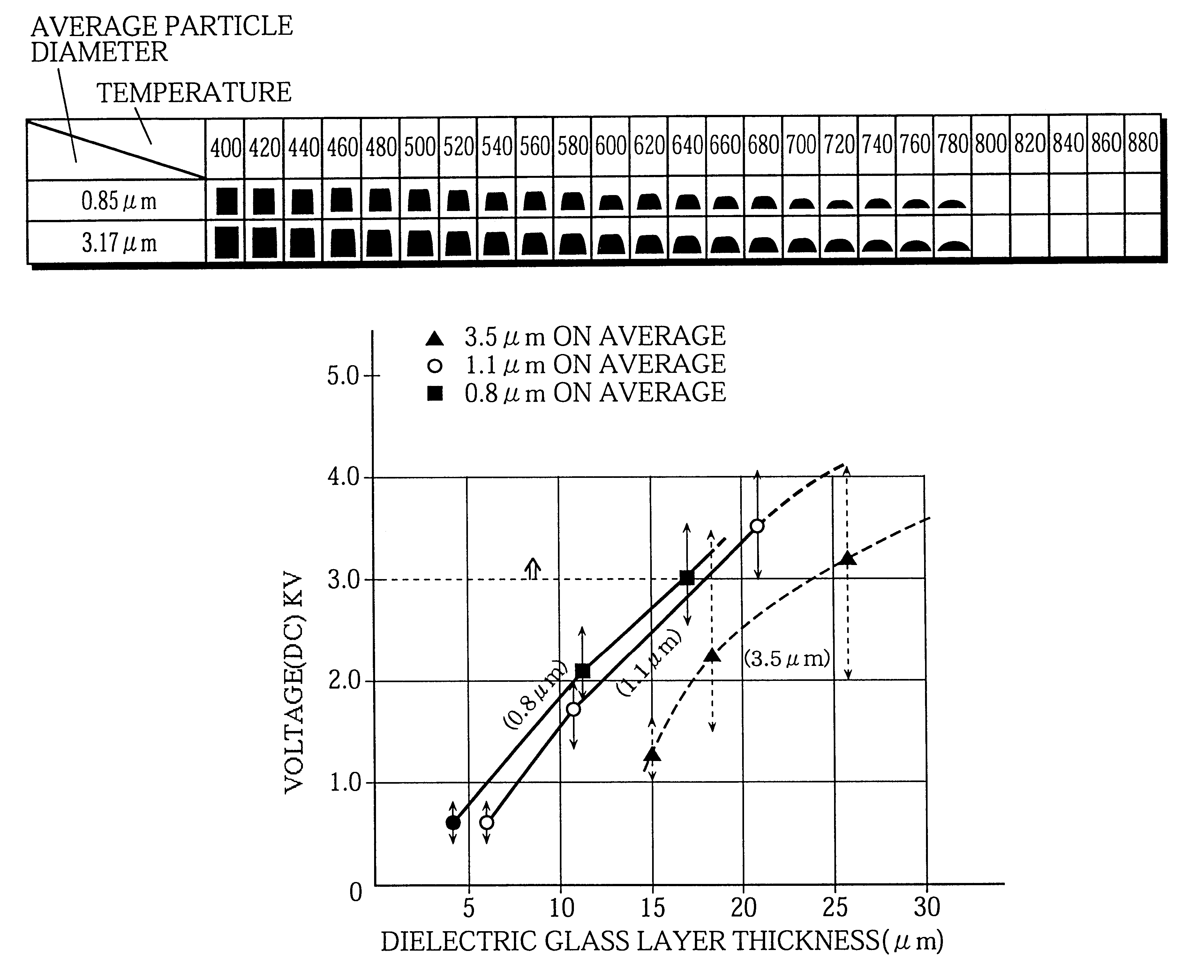

Manufacturing method of plasma display panel that includes adielectric glass layer having small particle sizes

InactiveUS6439943B1Alternating current plasma display panelsVessels or leading-in conductors manufactureScreen printingMetallurgy

The object of the present invention is to provide a high-intensity, reliable plasma display panel even when the cell structure is fine by resolving the problems such as a low visible light transmittance and low voltage endurance of a dielectric glass layer. The object is realized by forming the dielectric glass layer in the manner given below. A glass paste including a glass powder is applied on the front glass substrate or the back glass substrate, according to a screen printing method, a die coating method, a spray coating method, a spin coating method, or a blade coating method, on each of which electrodes have been formed, and the glass powder in the applied glass paste is fired. The average particle diameter of the glass powder is 0.1 to 1.5 mum and the maximum particle diameter is equal to or smaller than three times the average particle diameter.

Owner:PANASONIC CORP

Method of self-synchronization of configurable elements of a programmable module

InactiveUS6542998B1Generating/distributing signalsTransmission path multiple useIndependent elementComputer architecture

A method which permits self-synchronization of elements to be synchronized. Synchronization is neither implemented nor managed by a central entity. By shifting synchronization into each element, more synchronization tasks can also be performed simultaneously, because independent elements no longer interfere with one another when accessing the central synchronization entity. In a module with a two- or multi-dimensionally arranged programmable cell structure, each configurable element can access the configuration and status register of other configurable elements over an interconnecting structure and thus can have an active influence on their function and operation. The configuration can thus be accomplished by a load logic from a processing array.

Owner:SCIENTIA SOL MENTIS AG

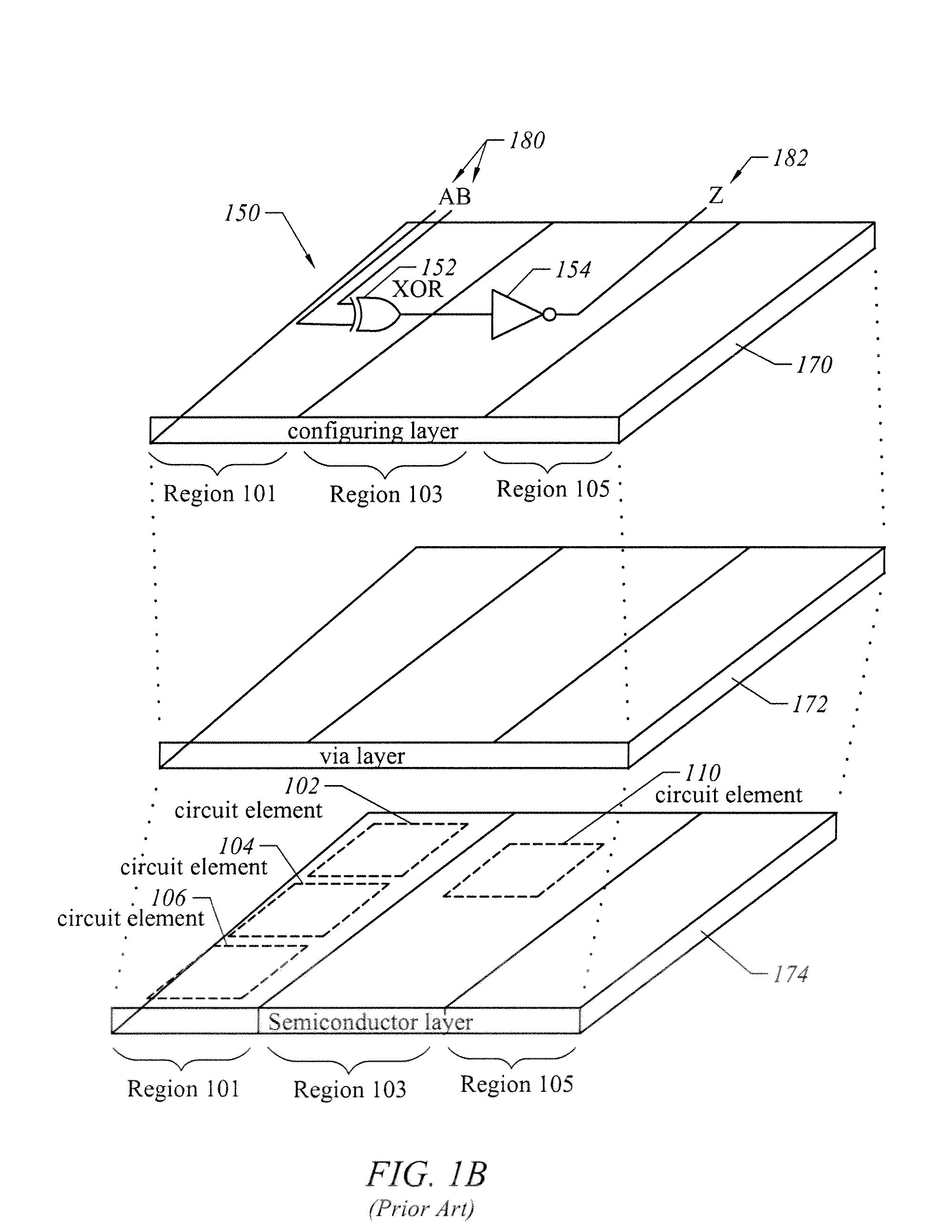

Cells of a customizable logic array device having independently accessible circuit elements

InactiveUS20080030228A1Easy to useReduce in quantitySolid-state devicesLogic circuits using elementary logic circuit componentsUnit structureElectrical and Electronics engineering

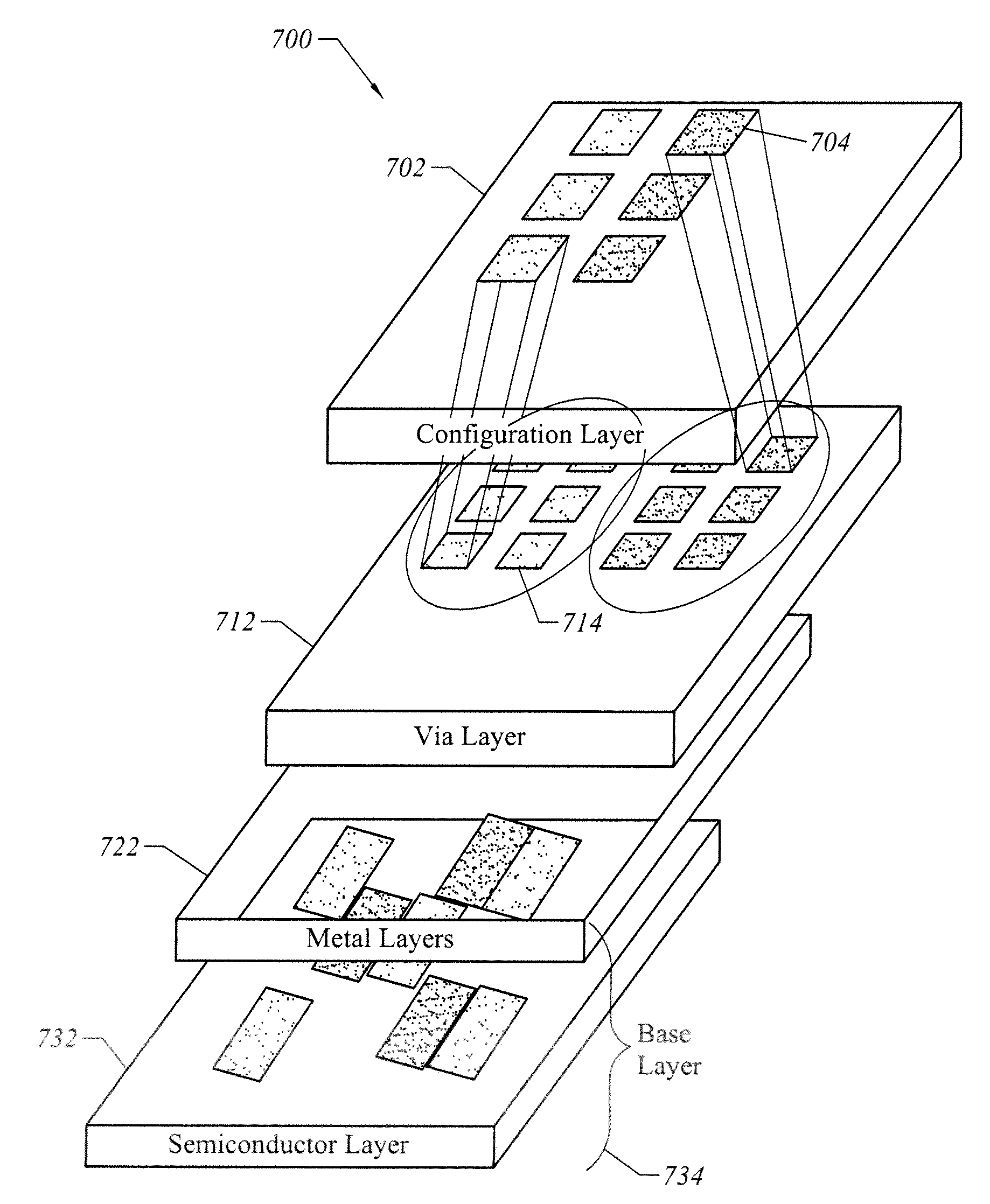

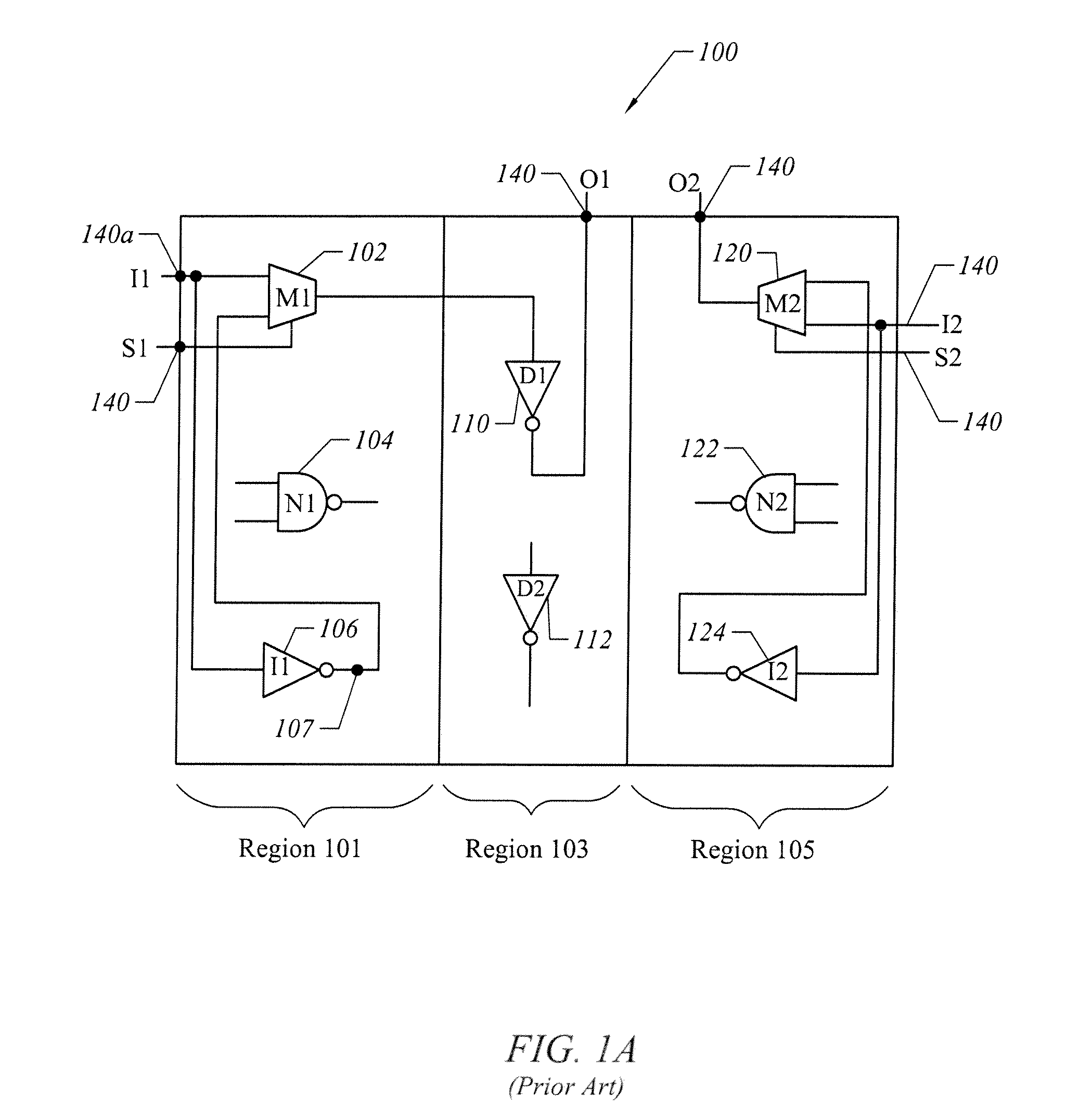

Various embodiments of the invention provide for cell structures having independently accessible circuit elements as a part of a customizable logic array device. In one embodiment, a cell forming a portion of a customizable logic array device includes a base layer, which, in turn, including circuit elements each having one or more inputs and one or more outputs. The cell also includes a configuration layer configured to form a logic device from one or more of the circuit elements. Further, the cell includes an interlayer connection layer configured to connect each of the inputs and the outputs to the configuration layer so as to enable each of the circuit elements to be independently accessible. Advantageously, the interlayer connection layer facilitates usage of each of the circuit elements to reduce the number of unused circuit elements in the cell.

Owner:SILICON VALLEY BANK

Method for deadlock-free configuration of dataflow processors and modules with a two- or multidimensional programmable cell structure (FPGAs, DPGAs, etc.)

InactiveUS6571381B1Memory adressing/allocation/relocationData resettingAuto-configurationData stream processing

A method of deadlock-free, automatic configuration and reconfiguration of modules having a two- or multidimensional cell arrangement, in which a unit for controlling the configuration and reconfiguration manages a set of associated configurable elements, the set being a subset or the total set of all configurable elements, and the management takes place as follows: reconfiguration requests from the associated configurable elements are sent to the unit; the unit processes the requests; the unit processes the configuration data of the command sequence; and after the configuration data has been fully processed, new requests are accepted again, the configuration data still to be loaded of the existing previous requests being loaded from a buffer memory (FILMO) into the configurable elements until a new request occurs.

Owner:SCIENTIA SOL MENTIS AG

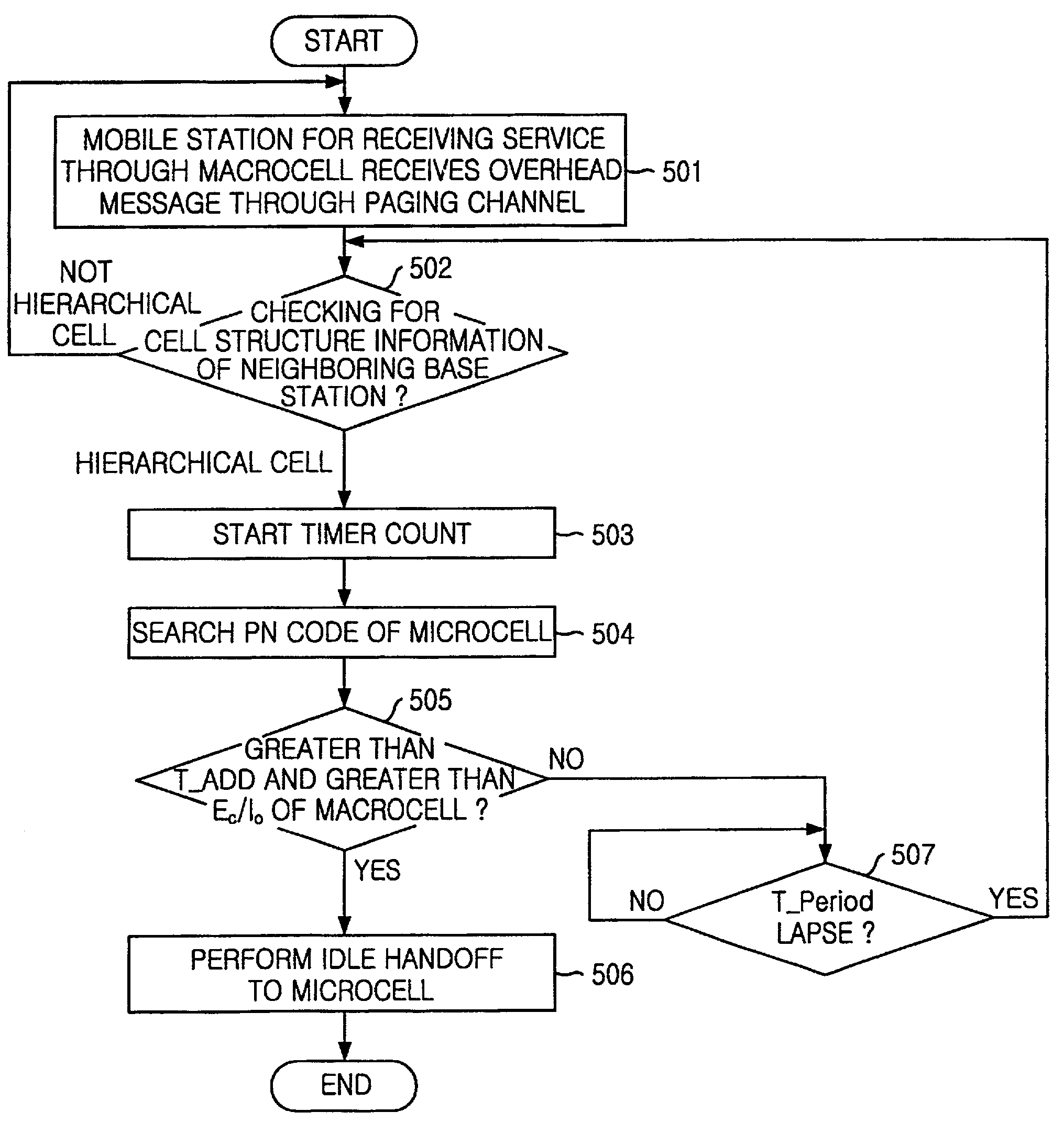

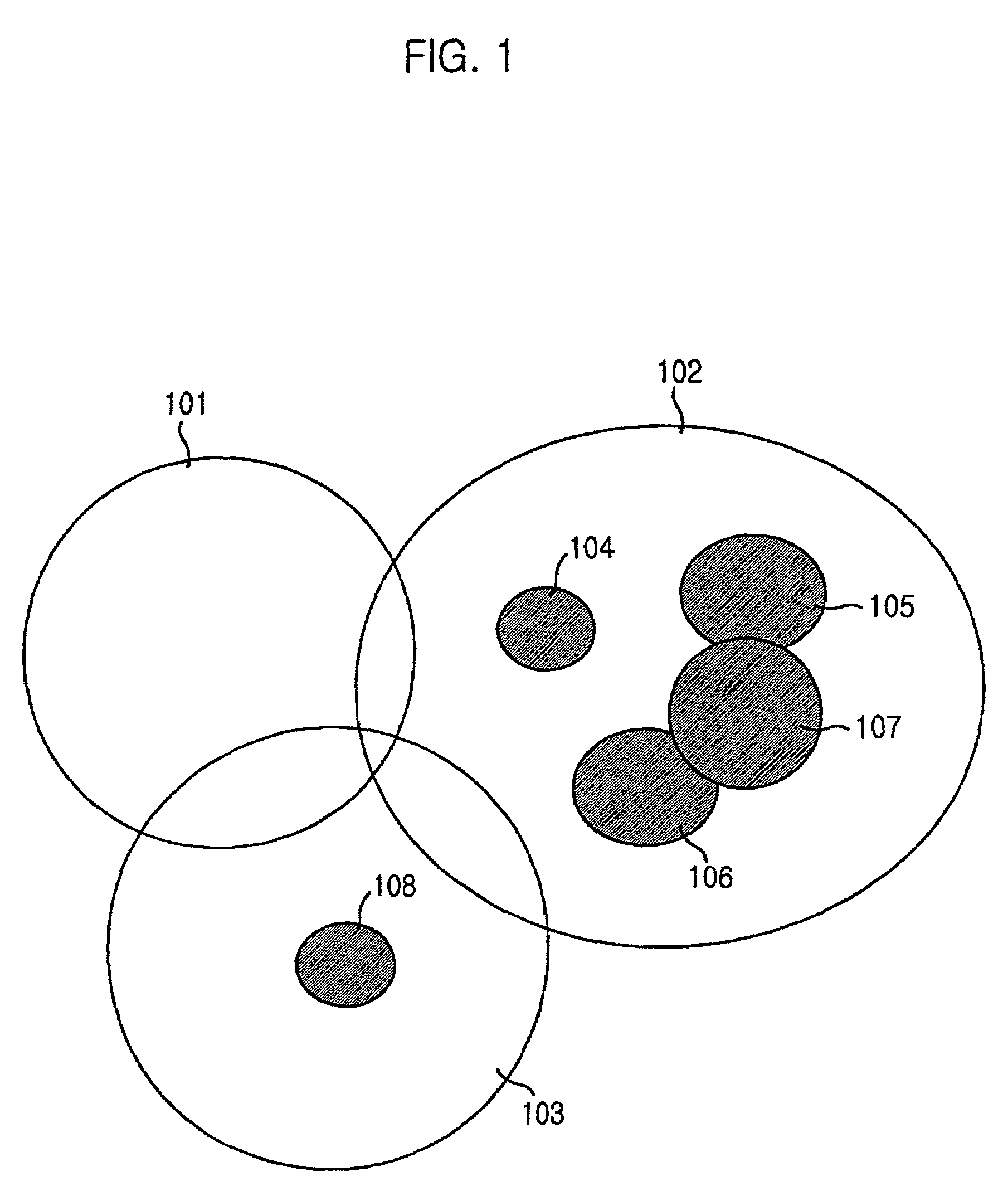

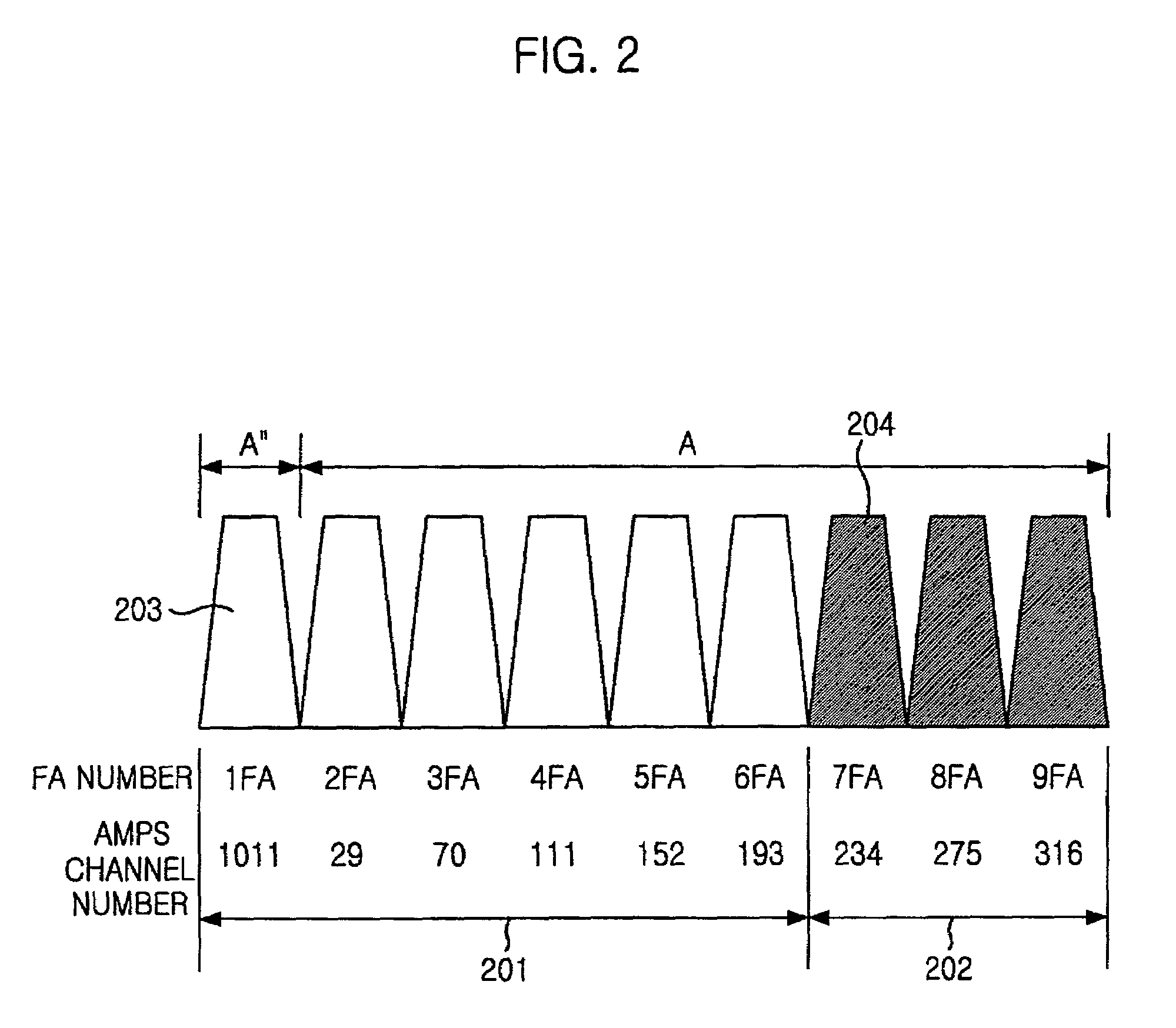

Method for carrying out handoff between macrocell and microcell in hierarchical cell structure

A method for carrying out an idle handoff from a macrocell to a microcell (picocell) in a hierarchical cell structure includes the steps of: a) allocating different frequency assignments (FA) to the macrocell and the microcell in a same service band, to construct the hierarchical cell structure; b) transmitting cell structure information of neighboring base stations and pseudo noise (PN) code from base station to mobile station; c) checking whether the mobile station is in the hierarchical cell by using the cell structure information of neighboring base station; and d) checking whether a value of the pseudo noise (PN) code is greater than T_ADD and greater than Ec / Io of the macrocell by periodically searching the pseudo noise (PN) code of the microcell, to carry out an idle handoff to the microcell, wherein the T_ADD represents a value of base station pilot strength required for the base station of neighboring set to be included in a candidate set, the Ec represents an pilot energy accumulated during one pseudo noise (PN) chip period, and the Io represents a total power spectrum density within a reception bandwidth.

Owner:SK TELECOM CO LTD

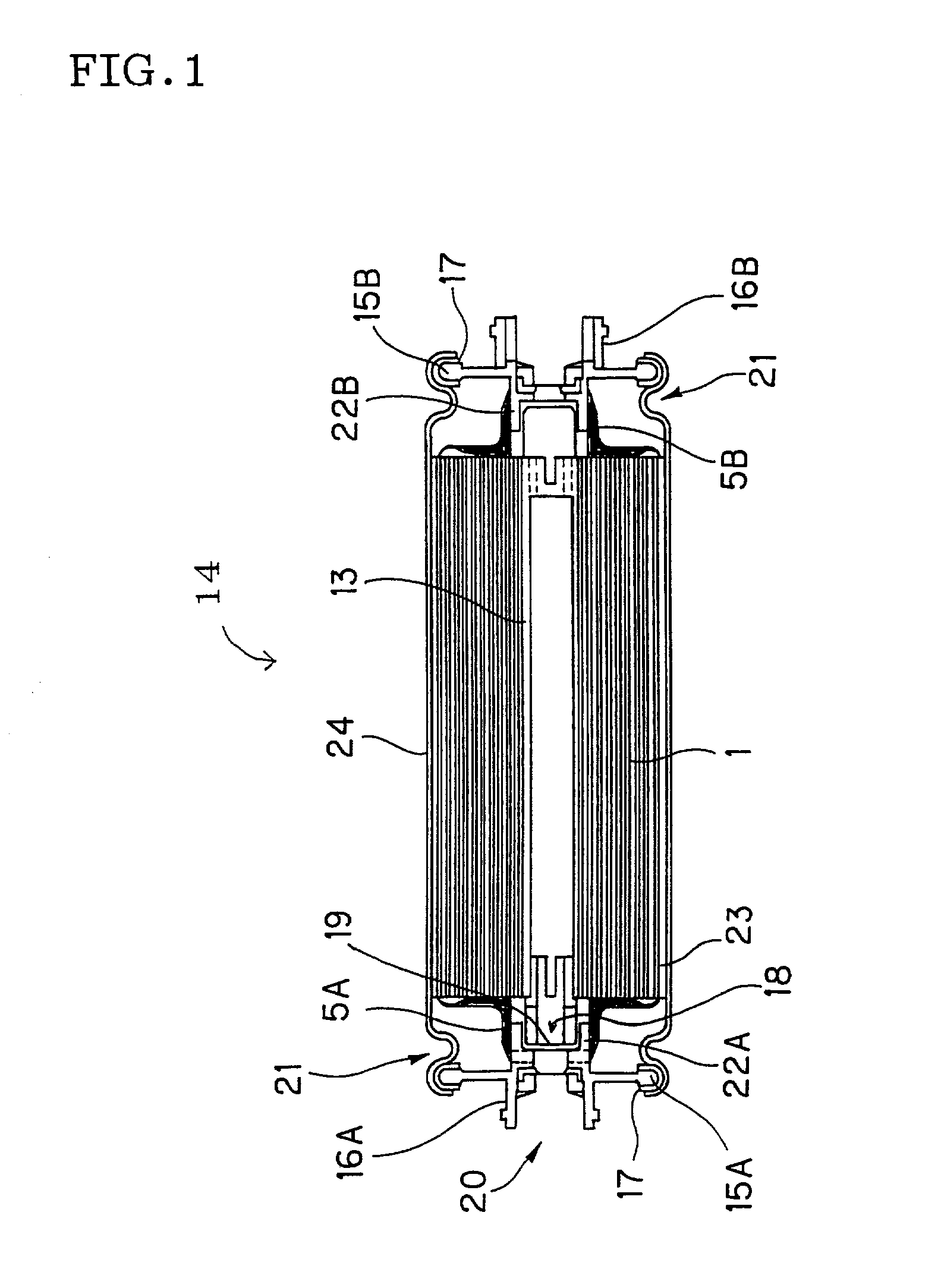

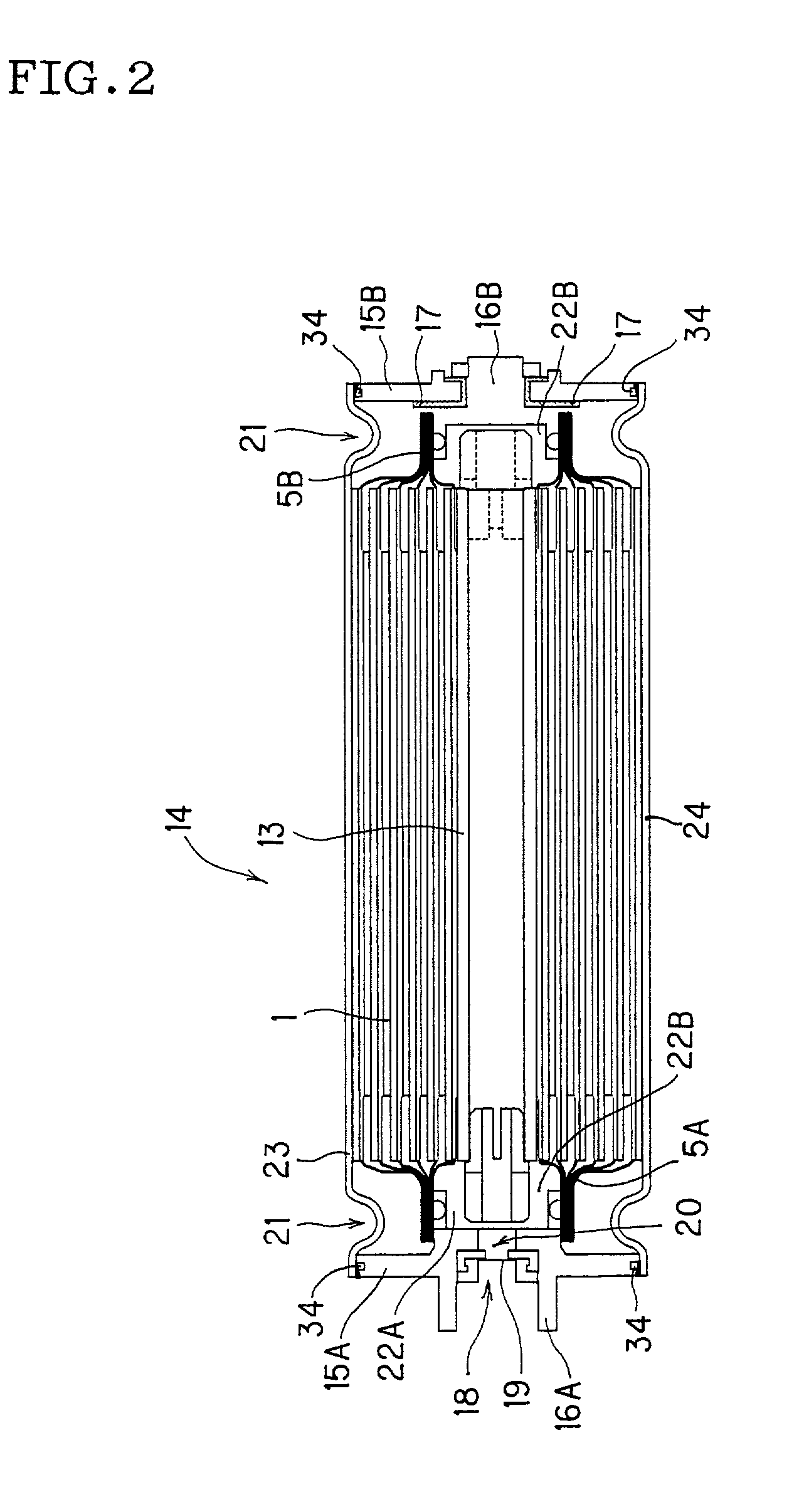

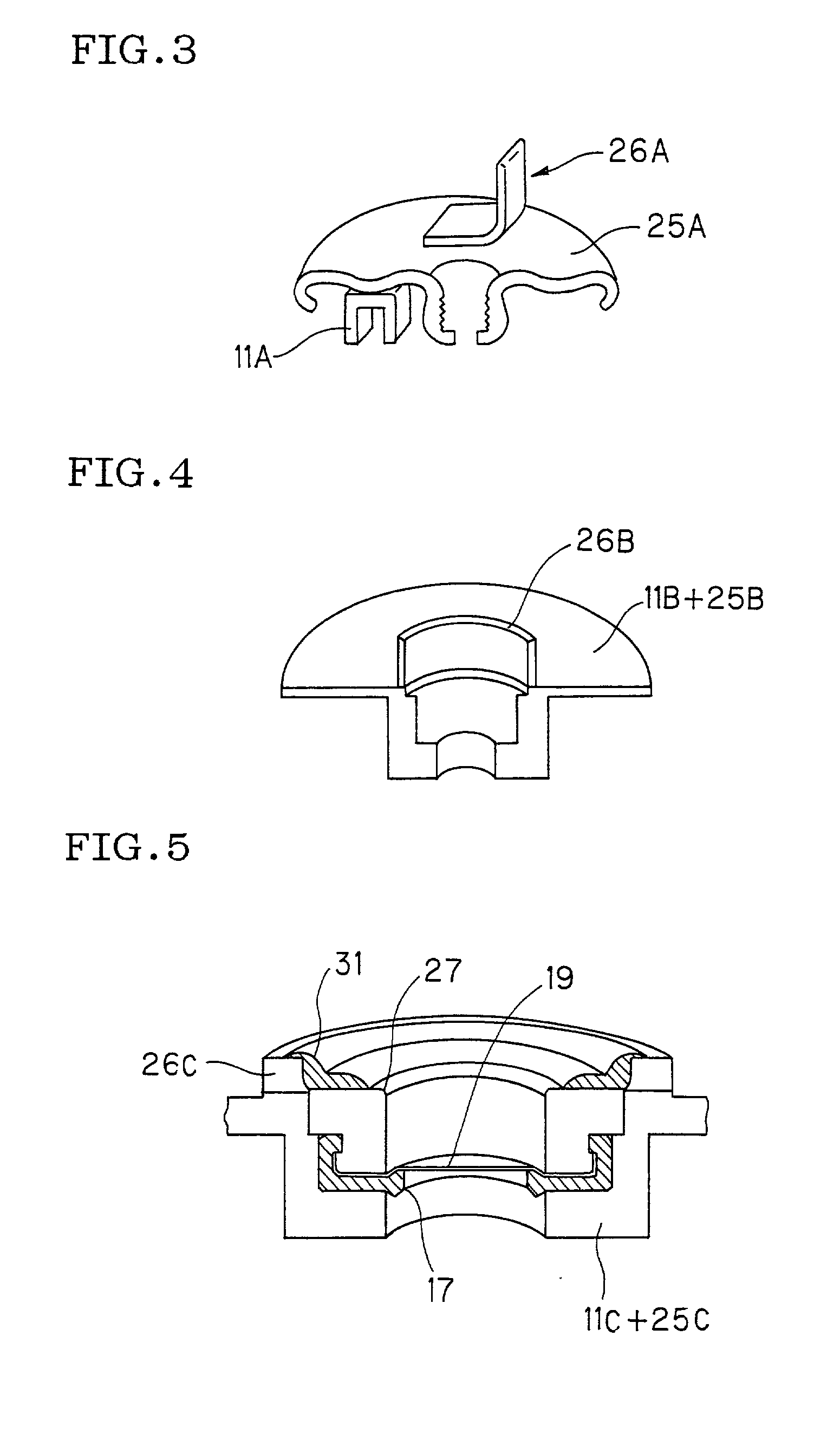

Lithium secondary cell and assembly thereof

InactiveUS20010049054A1Primary cell to battery groupingNon-aqueous electrolyte accumulatorsElastomerLithium

To provide a lithium secondary cell, which is excellent in productivity since a cell structure is simple and easy for assembly. Provided is a lithium secondary cell having: an internal electrode body including a positive electrode plate, a negative electrode plate, the positive electrode plate and the negative electrode plate being wound and laminated around an external periphery wall of a hollow cylindrical winding core, and inside the internal electrode body a nonaqueous electrolyte solution being impregnated, a cylindrical cell case contained in this internal electrode body 1 with both ends being opened, and two electrode caps sealing the above described internal electrode body 1 at both the open ends of this cell case. The electrode cap has a plate member sealing the internal electrode body and disposed so as to seal both the open ends of the above described cell case, an external terminal member protruding onto the surface of the electrode caps to lead out currents to outside, and an internal terminal member brought into connection with the internal electrode body and taking out currents from the internal electrode body, and an elastic body and at least two of the above described plate member, the external terminal member and the internal terminal member are joined together for construction. Furthermore, there is also provided an assembly of lithium secondary cells.

Owner:NGK INSULATORS LTD

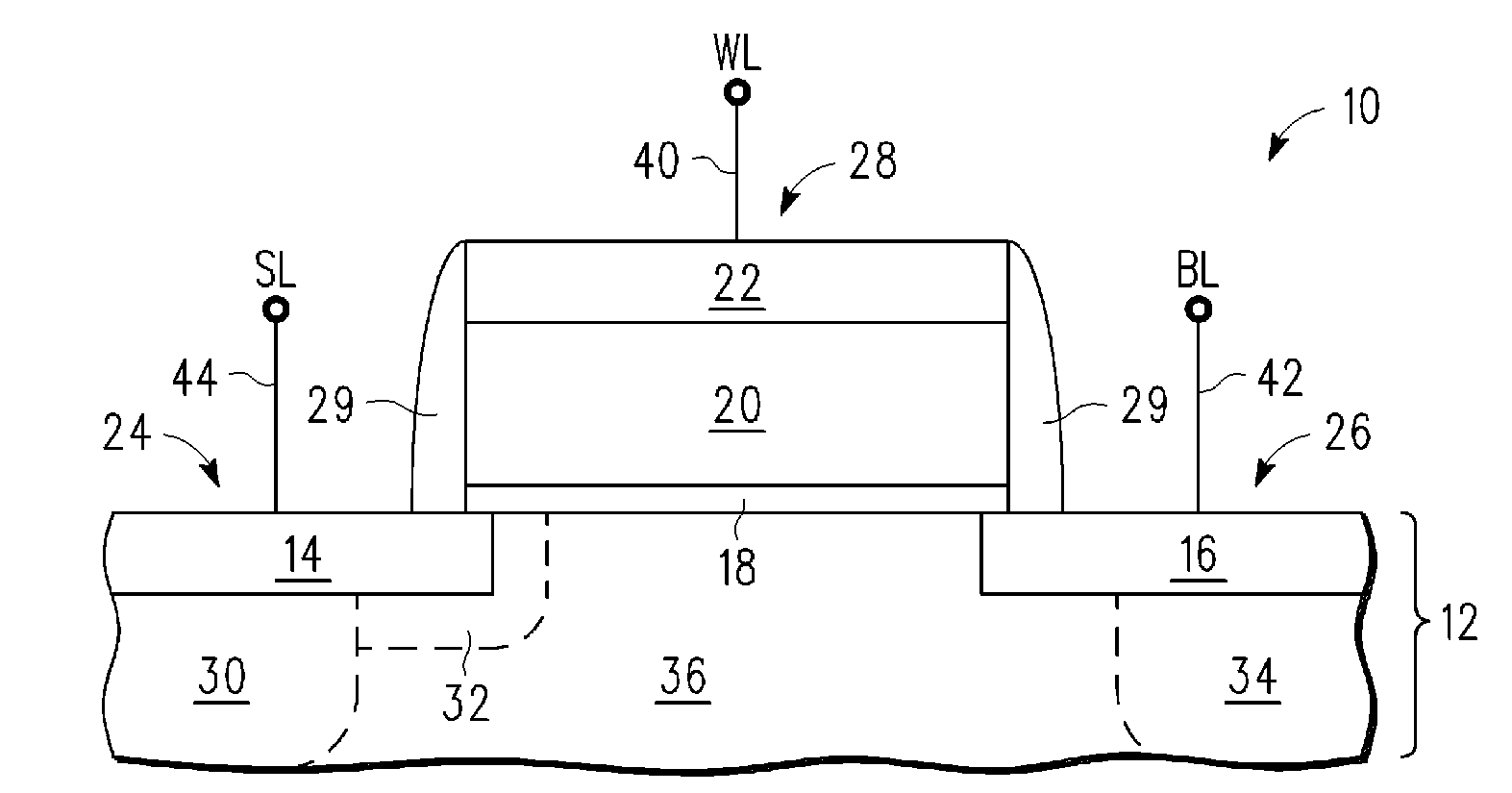

One transistor dram cell structure and method for forming

ActiveUS20080099808A1Simple and compact designGuaranteed uptimeTransistorSolid-state devicesSchottky diodeBody region

A one-transistor dynamic random access memory (DRAM) cell includes a transistor which has a first source / drain region, a second source / drain region, a body region between the first and second source / drain regions, and a gate over the body region. The first source / drain region includes a Schottky diode junction with the body region and the second source / drain region includes an n-p diode junction with the body region.

Owner:NXP USA INC

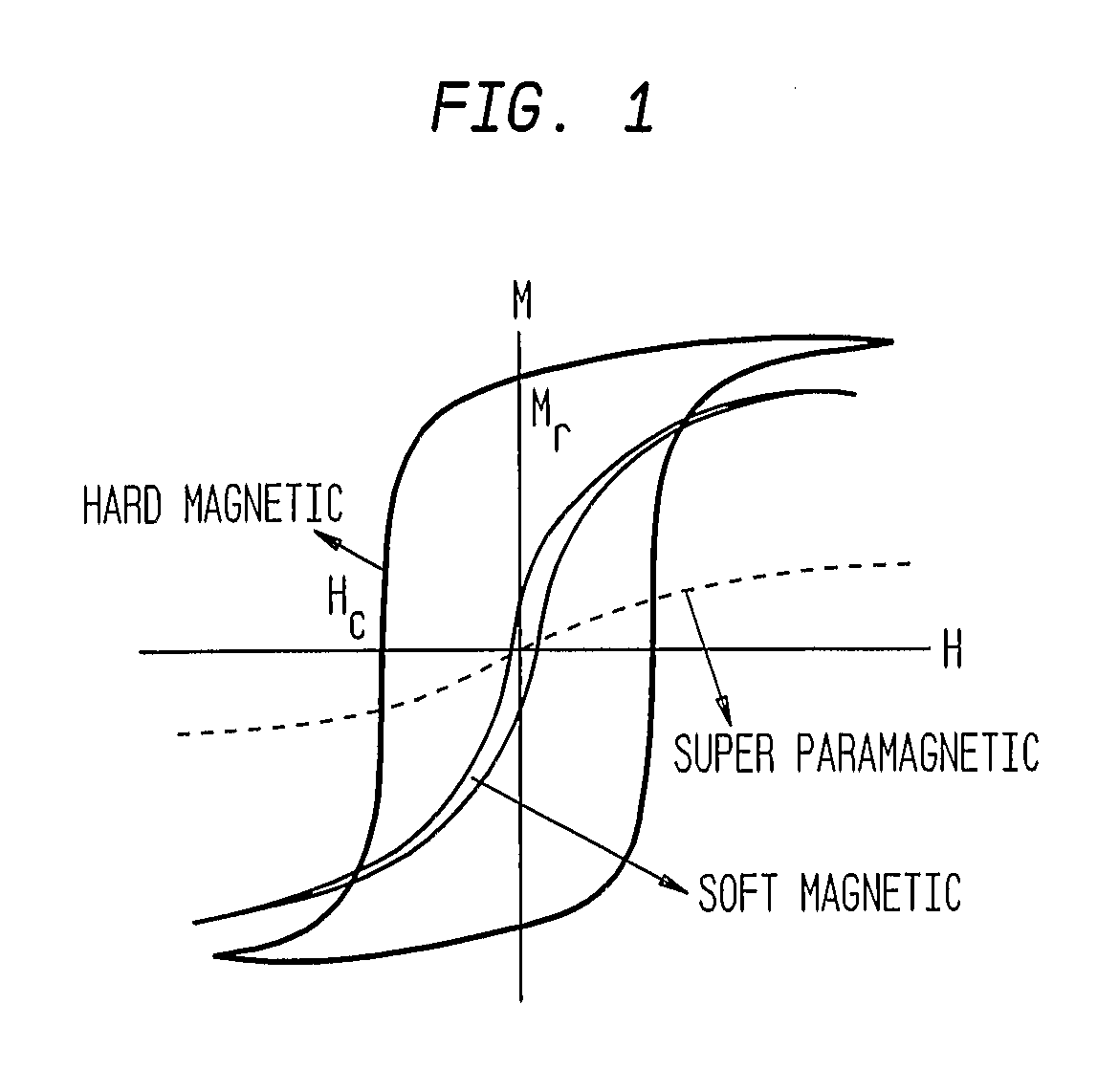

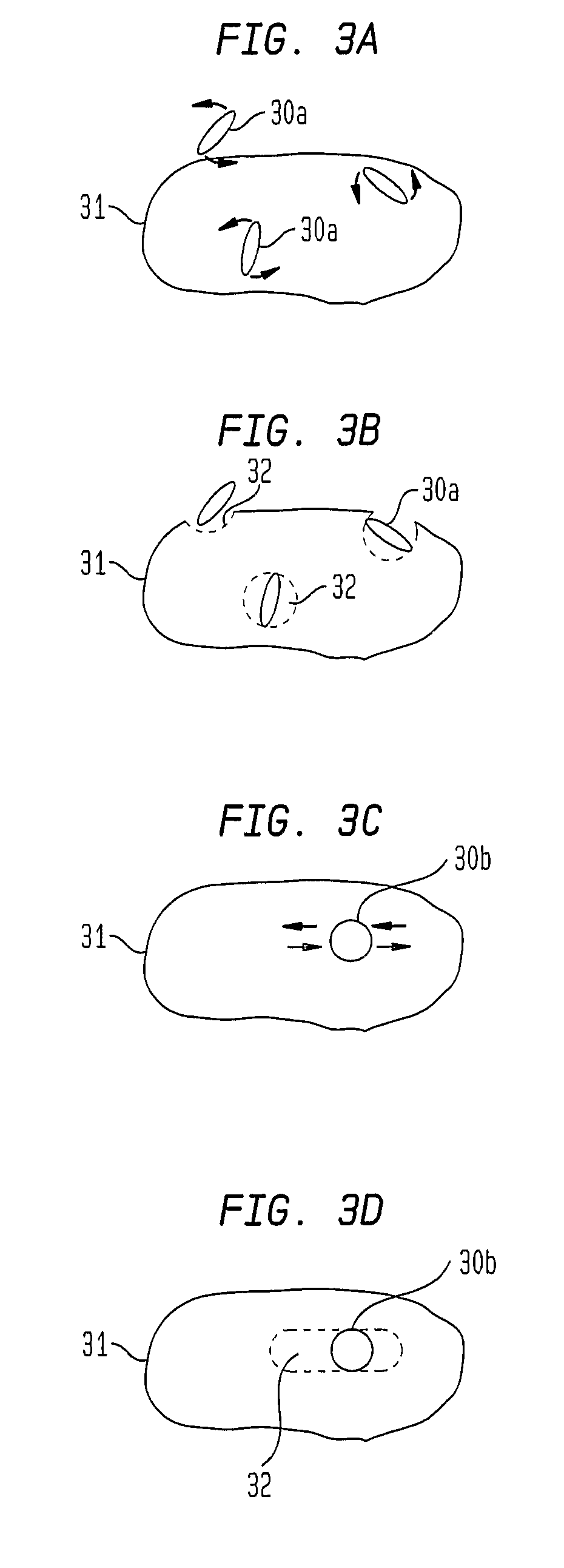

Method and articles for remote magnetically induced treatment of cancer and other diseases, and method for operating such article

InactiveUS20070196281A1Avoid damagePowder deliveryHeart defibrillatorsAbnormal tissue growthCancer cell

This invention describes unique treatment methods and innovative articles that can be placed in a human or animal body to enable controlled destruction of diseased tissue. The methods include destruction of diseased cells and tissues by magnetically controlled motion and an externally controllable drug delivery process with a capability to start and stop the drug delivery at any time, for any duration. This invention provides two approaches to diseased cell destruction, (1) magneto-mechanical disturbance of cell structure (e.g. cancer cells) for cell lysis and (2) magnetically activated drug release at local regions (e.g. tumors) from a magnetic-particle-containing drug reservoir. The invention also provides combinations of both the above treatments for dual therapy. It further combines one or both of the treatments with magnetic hyperthermia for multifunctional cell destruction therapy. The approaches can be combined with magnetic MRI for monitoring the accuracy of placement as well as for following up the cancer destruction progress and appropriate reprogramming of the magneto-mechanical therapy and remote-controlled drug release.

Owner:RGT UNIV OF CALIFORNIA

Semiconductor device and method of fabricating the same

A semiconductor device has a substrate that includes a cell array region and a dummy pattern region surrounding the cell array region. The cell array region includes a cell structure having a plurality of cell active pillars extending in a vertical direction from the cell array region of the substrate and includes cell gate patterns and cell gate interlayer insulating patterns alternately stacked on the substrate. The cell gate patterns and cell gate interlayer insulating patterns have sides facing the cell active pillars. The dummy pattern region includes a damp-proof structure.

Owner:SAMSUNG ELECTRONICS CO LTD

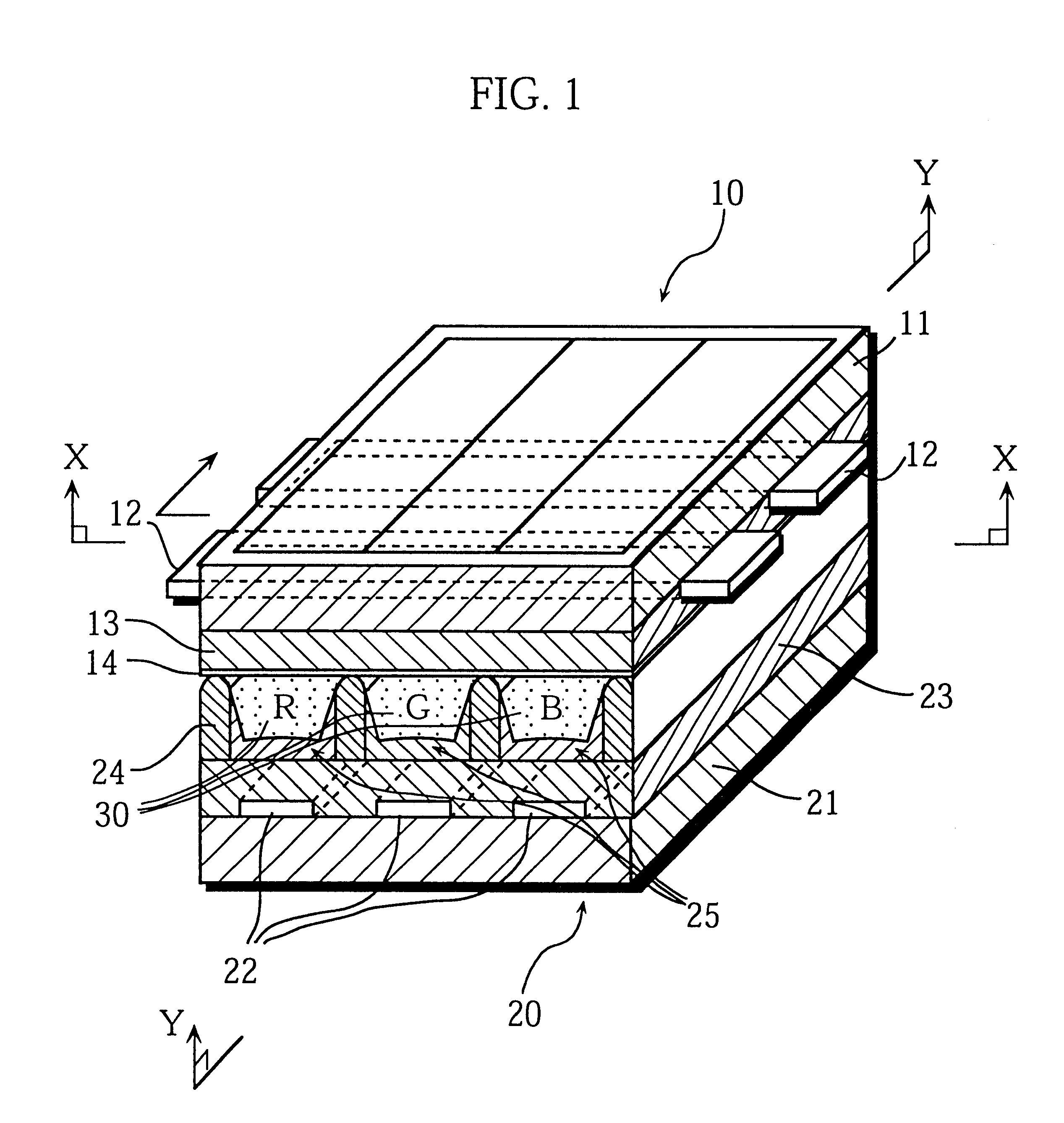

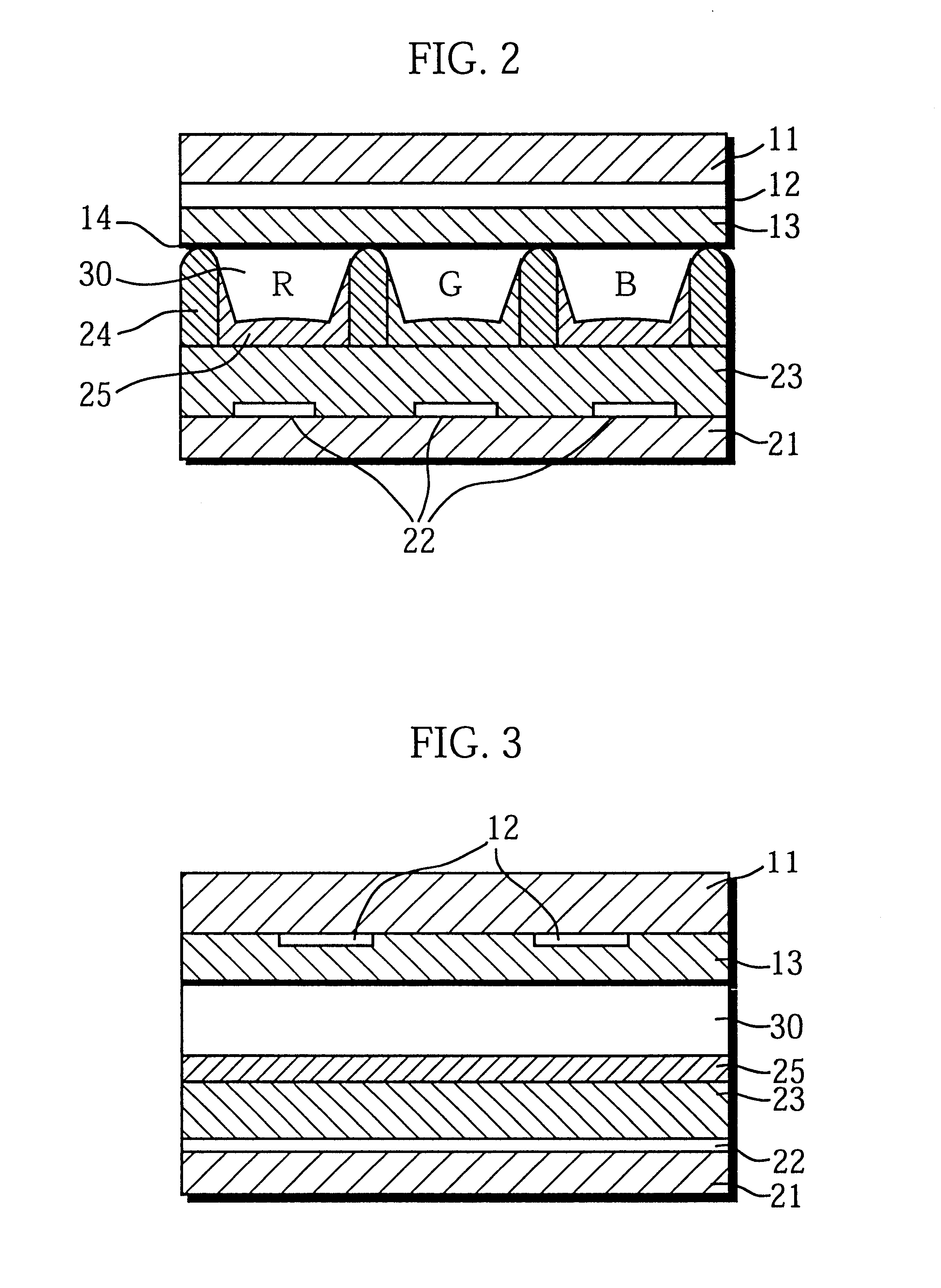

Display cell structure and electrode protecting layer compositions

ActiveUS7880958B2Improve the display effectImprove performanceLiquid crystal compositionsStatic indicating devicesVitrificationElectrical battery

Owner:E INK CORPORATION

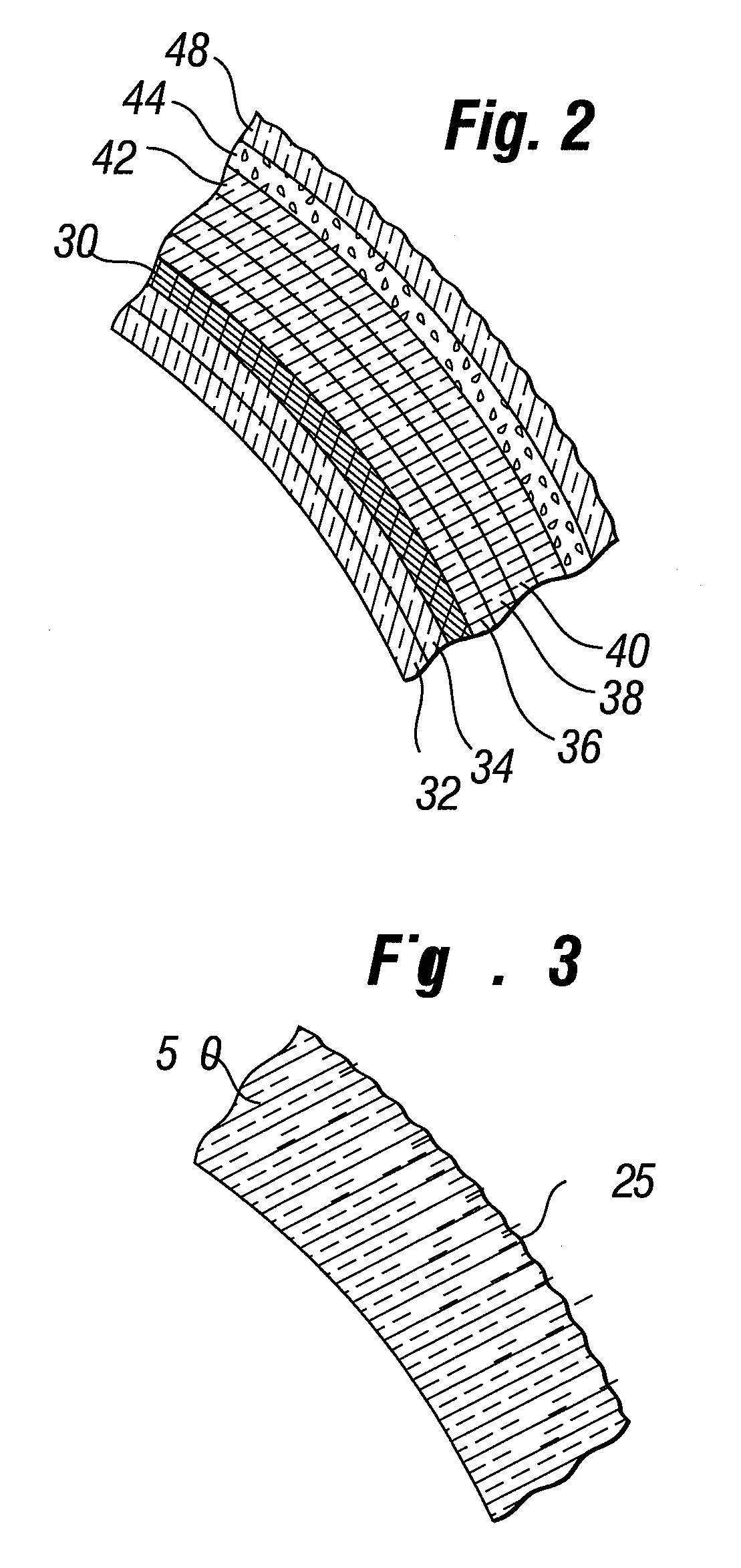

Soft prosthesis shell texturing method

A method of texturing a soft prosthetic implant shell, such as a silicone breast implant shell. A soft prosthetic implant with a textured external surface layer of silicone elastomer and having an open-cell structure is made by adhering and then dissolving round salt crystals. The resulting roughened surface has enhanced physical properties relative to surfaces formed with angular salt crystals. An implant having such a textured external surface layer is expected to help prevent capsular contraction, to help prevent scar formation, and to help in anchoring the implant within the body.

Owner:ALLERGAN INC

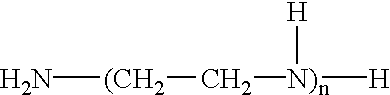

Two component thermosettable compositions useful for producing structural reinforcing adhesives

InactiveUS6451876B1Uniform cell structureExcessive heat dissipationEpoxy resin adhesivesEpoxyPartial system

A two part system for producing structural reinforcing adhesives is provided wherein one component containing epoxy resin is combined with a second component containing a specified curative system. An aliphatic polyamine, an amidoamine, an alcohol and an adduct of a polyamine and an epoxide are present in the curative system. When a thermally activated blowing agent is utilized, the resulting foam is remarkably uniform in cell structure and has improved strength and modulus. Hollow inorganic microspheres are employed to reduce the density of the thermoset produced from the two part system.

Owner:HENKEL KGAA

Stabilization of polyurethane foam polyol premixes containing halogenated olefin blowing agents

ActiveUS20090099272A1Reduced responseQuality improvementPreparation by halogen halide additionOrganic acidFoaming agent

The invention provides polyurethane and polyisocyanurate foams and methods for the preparation thereof More particularly, the invention relates to open-celled, polyurethane and polyisocyanurate foams and methods for their preparation. The foams are characterized by a fine uniform cell structure and little or no foam collapse. The foams are produced with a polyol premix composition which comprises a combination of a hydrohaloolefin blowing agent, a polyol, a silicone surfactant, and a catalyst which is an adduct of an amine and an organic acid.

Owner:HONEYWELL INT INC

Amine catalysts for polyurethane foams

The invention provides polyurethane and polyisocyanurate foams and methods for the preparation thereof More particularly, the invention relates to open-celled, polyurethane and polyisocyanurate foams and methods for their preparation. The foams are characterized by a fine uniform cell structure and little or no foam collapse. The foams are produced with a polyol premix composition which comprises a combination of a hydrohaloolefin blowing agent, a polyol, a silicone surfactant, and a sterically hindered amine catalyst.

Owner:HONEYWELL INT INC

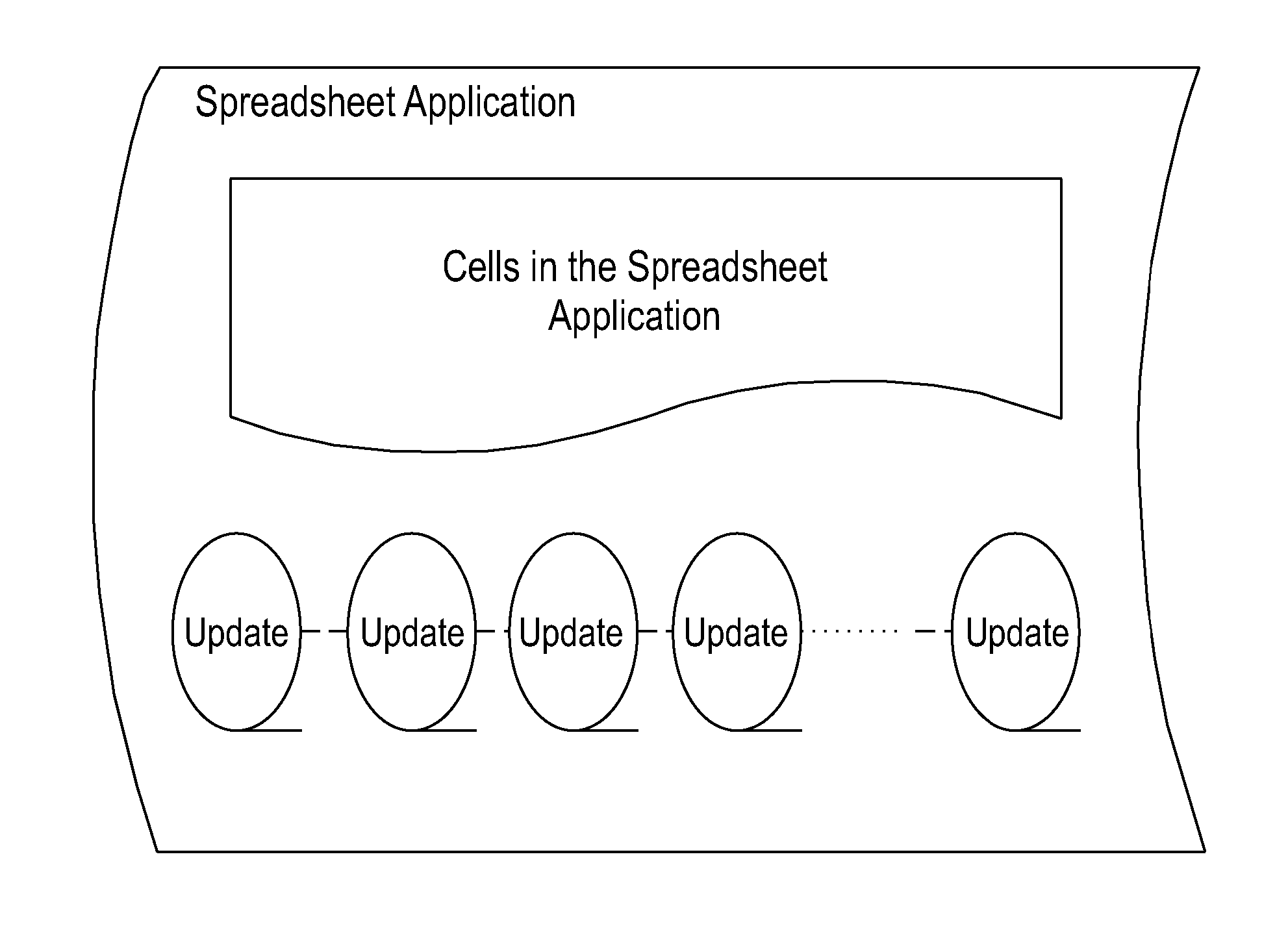

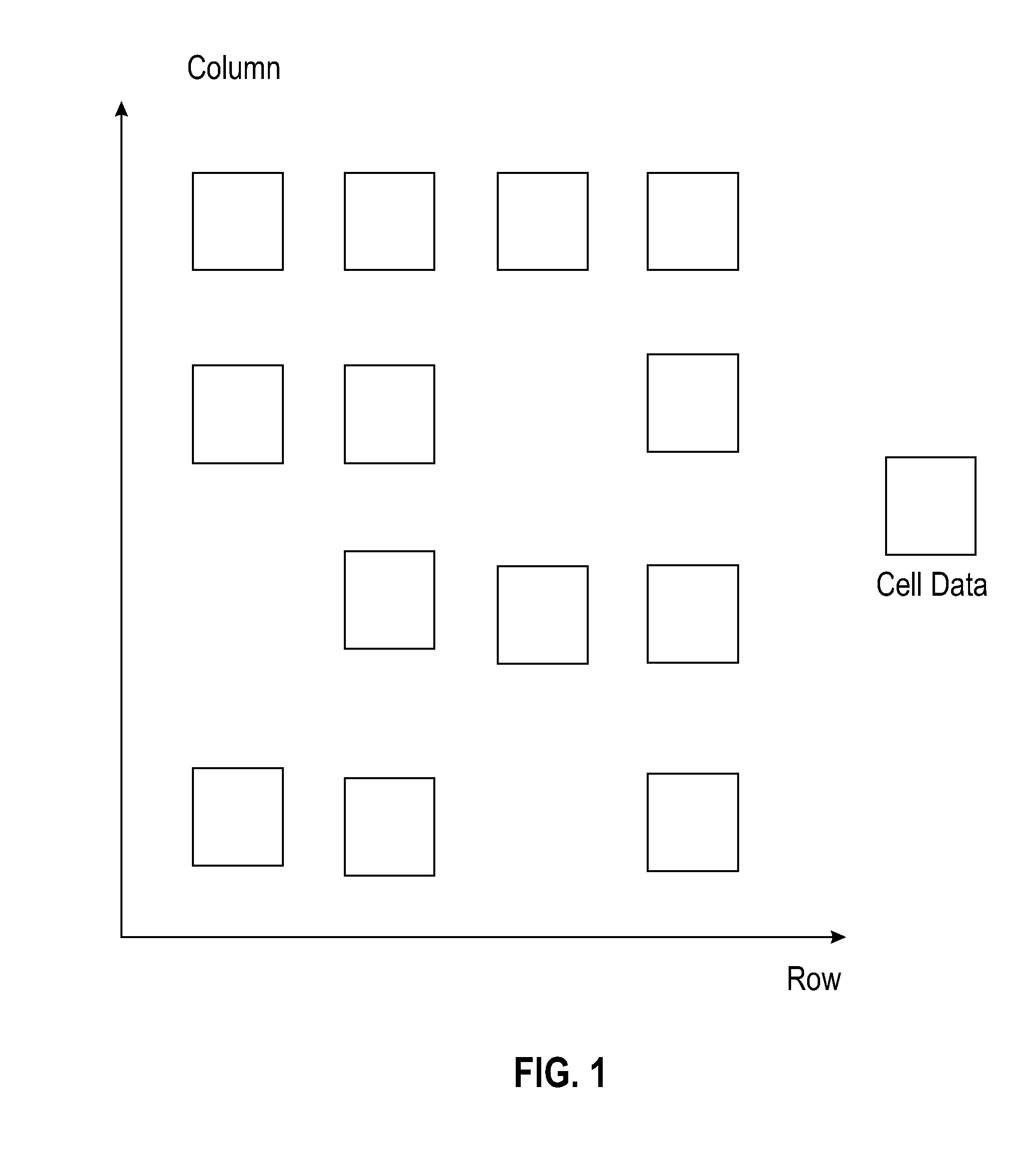

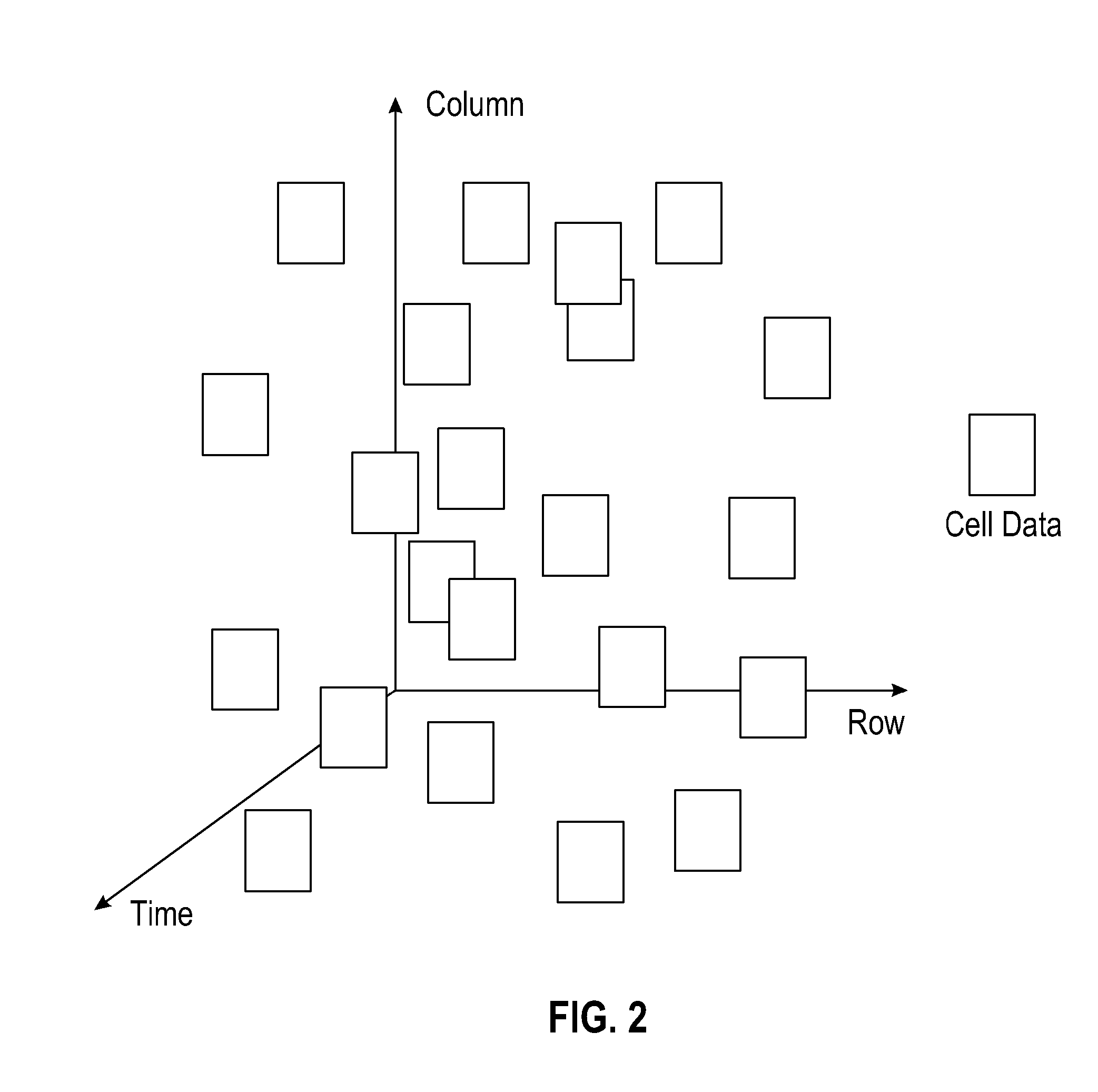

Change-oriented spreadsheet application

The invention discloses a data organization method for a change oriented spreadsheet application. In one embodiment, the valid updates to cells and the update times are stored with the cell positions as the primary index, and the valid updates to the same cell are arranged in the order of time. In another embodiment, the valid updates to cells are stored with the update time points of the valid updates of the cells as the primary index, and all the valid updates at the same valid update time point are arranged into an update table, the update table having the same cell structure as the spreadsheet file. In yet another embodiment, data structures organized in both manners are maintained at the same time.

Owner:IBM CORP