Methods of Manufacturing Three Dimensional Semiconductor Devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

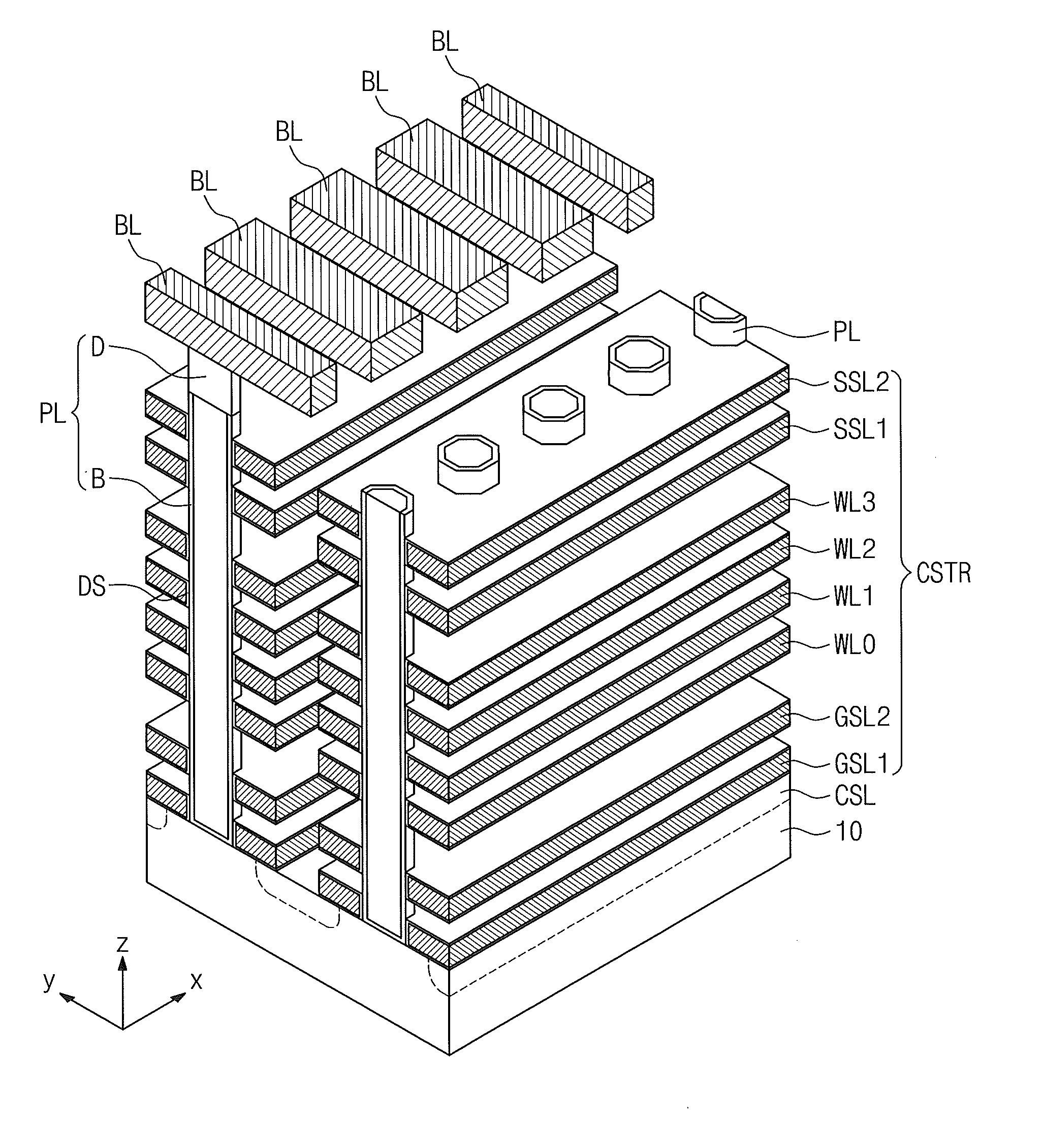

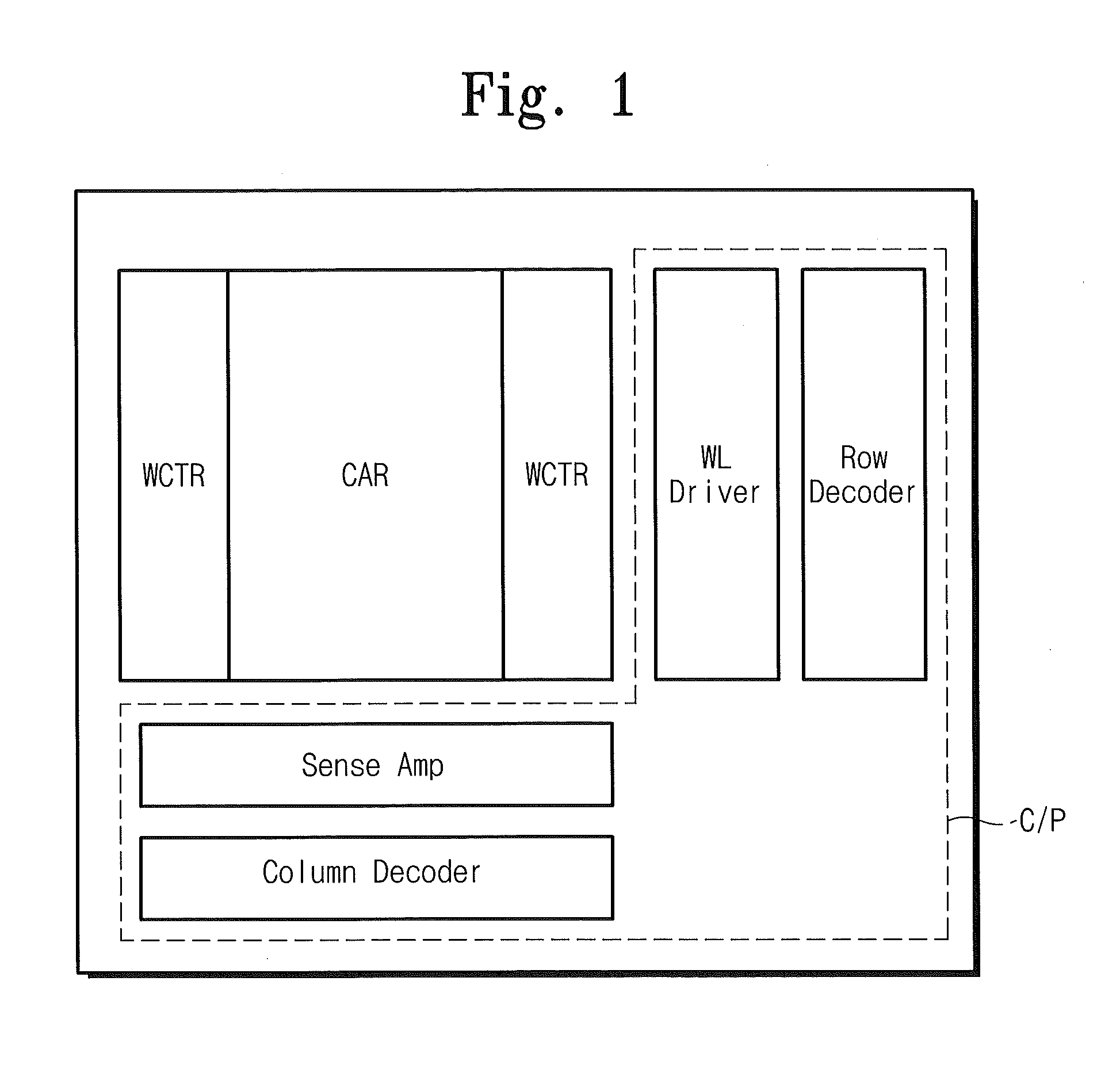

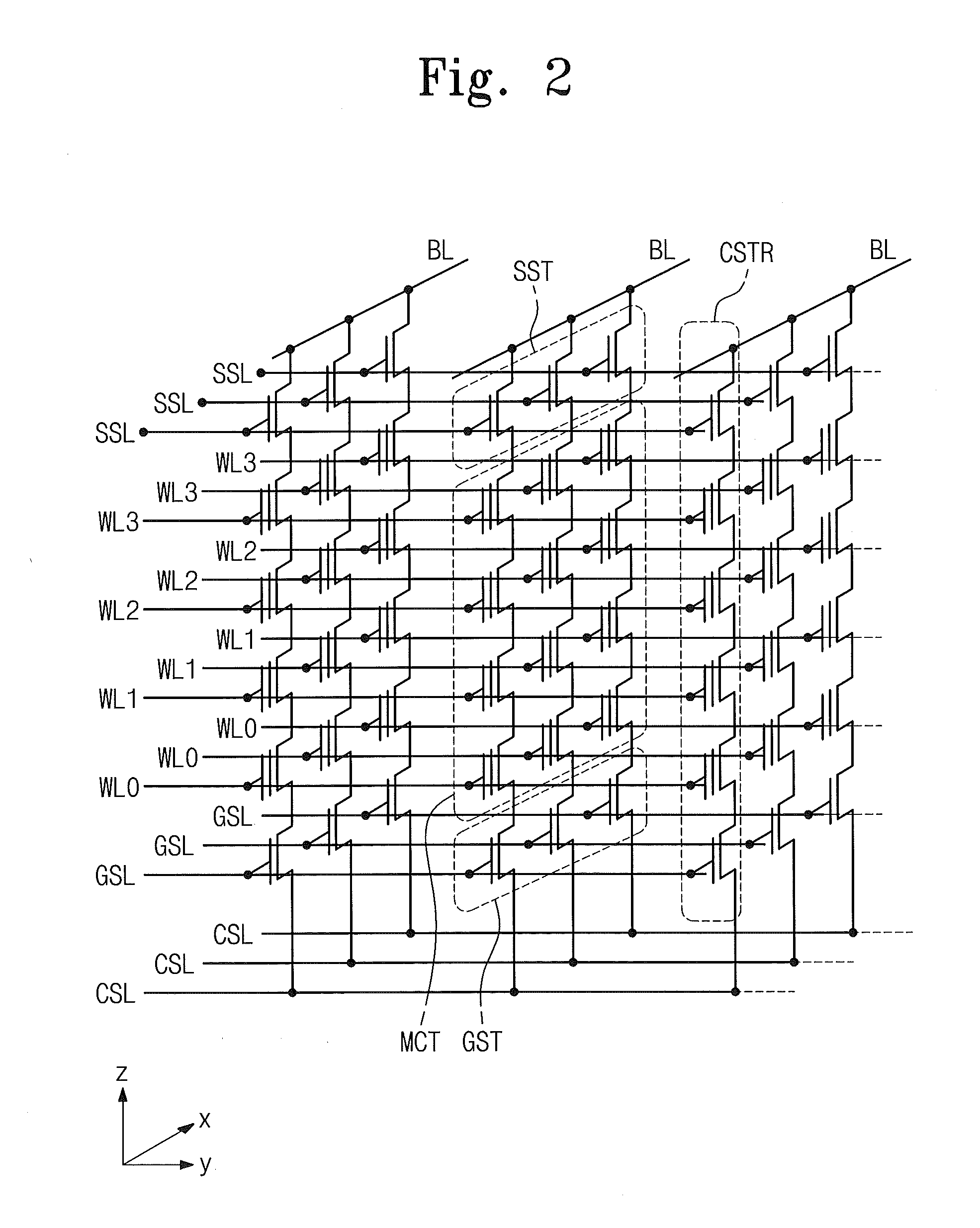

Embodiment Construction

[0024]In a three-dimensional semiconductor memory device, forming a plurality of vertically stacked memory cells in a cell array region may result in a significant height difference between structures in the cell array region and structures in a peripheral circuit region. Thus, an interlayer dielectric formed on both the cell array region and the peripheral circuit region may have a different height (relative to the substrate) in the cell array region than in the peripheral circuit region.

[0025]It may be desirable to planarize the interlayer dielectric to reduce this height difference. However, process control for planarization of an interlayer dielectric may be difficult, resulting in undesirably small process margins. In addition, dishing may occur over the peripheral circuit region and a contact region adjacent the cell array region when planarizing the interlayer dielectric.

[0026]According to example embodiments of the inventive concepts, a polishing stop layer may be selectivel...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More