Patents

Literature

2421 results about "Self alignment" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Self-Aligning System. a self-adaptive control system in which adaptation to randomly varying conditions is provided by an automatic change in the alignment parameters or by an automatic search for the optimum alignment.

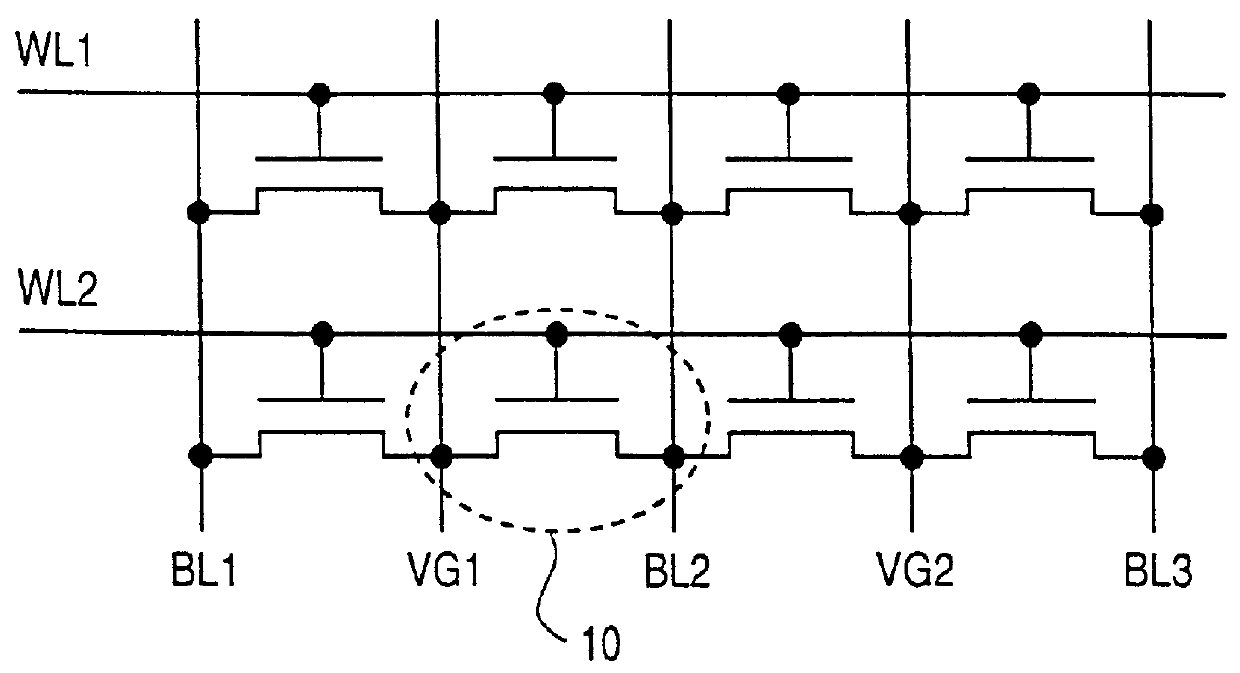

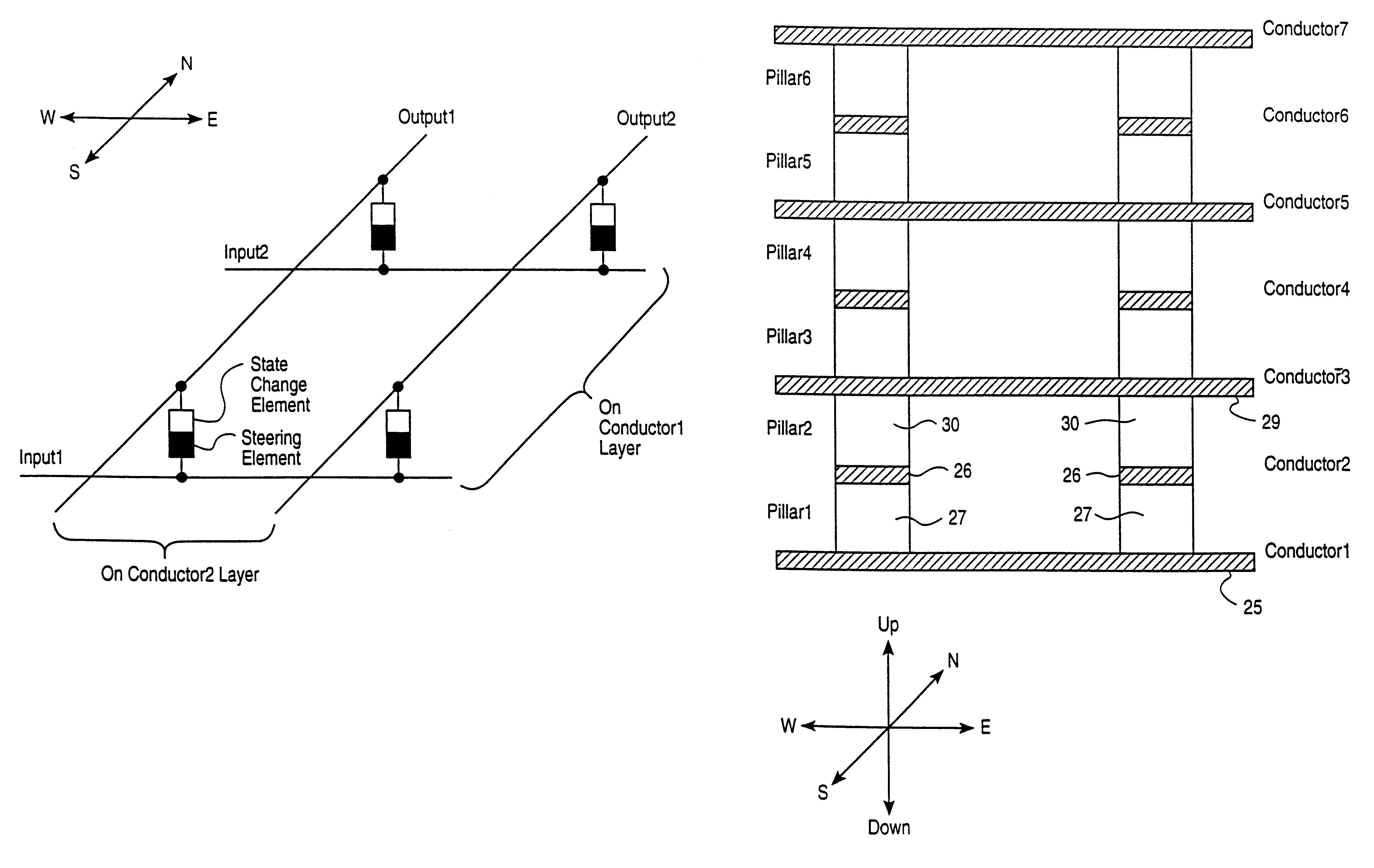

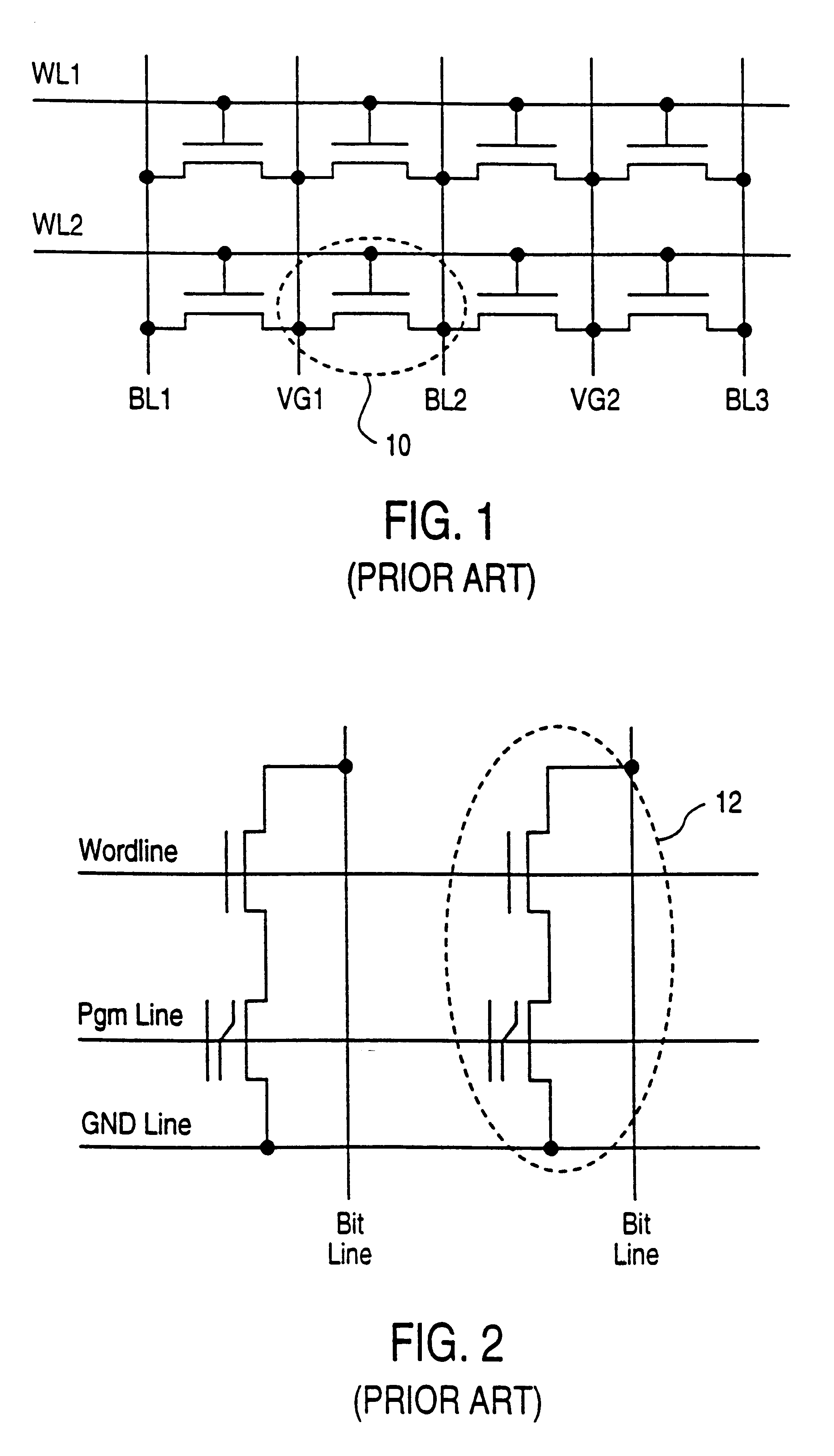

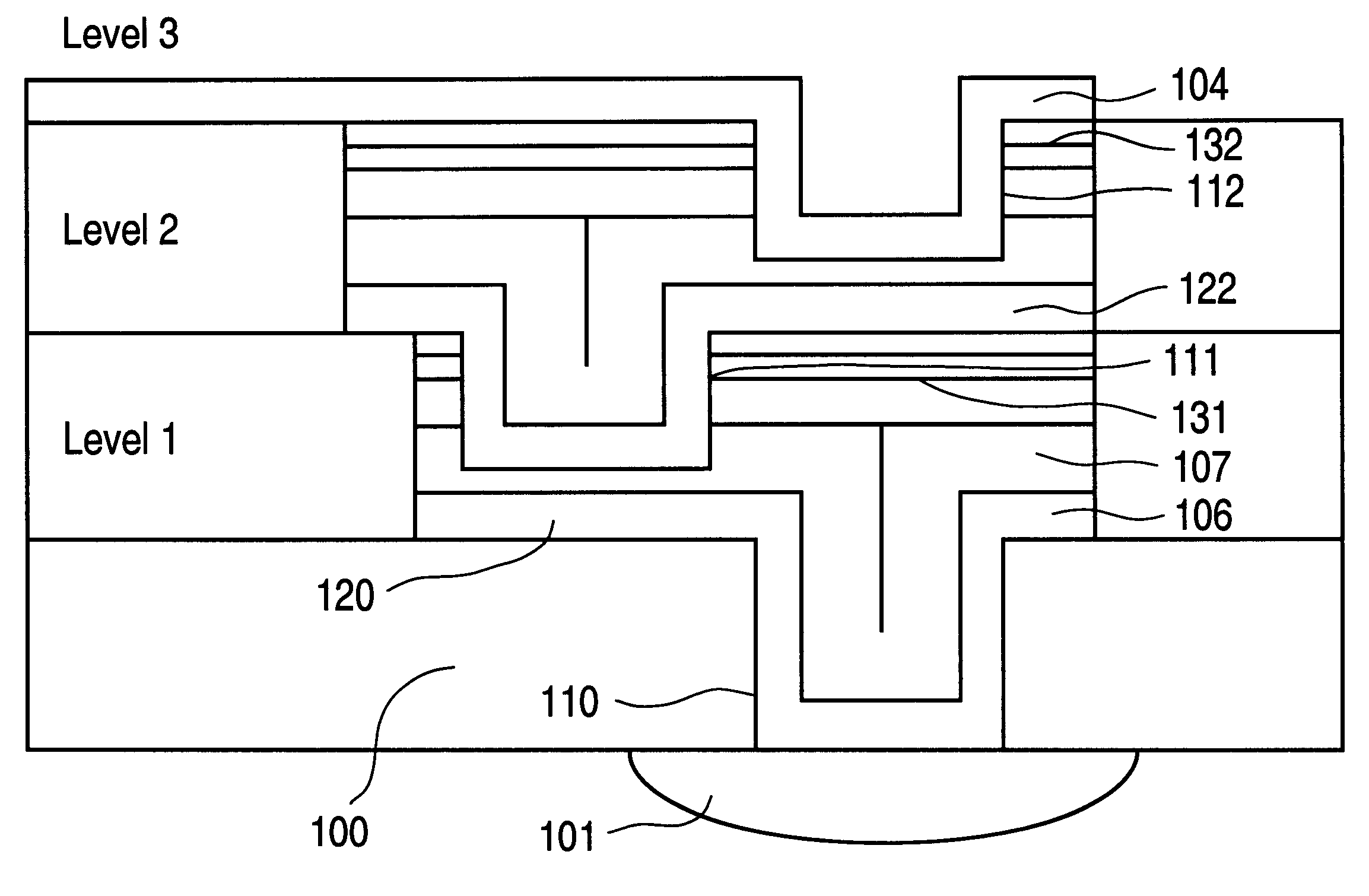

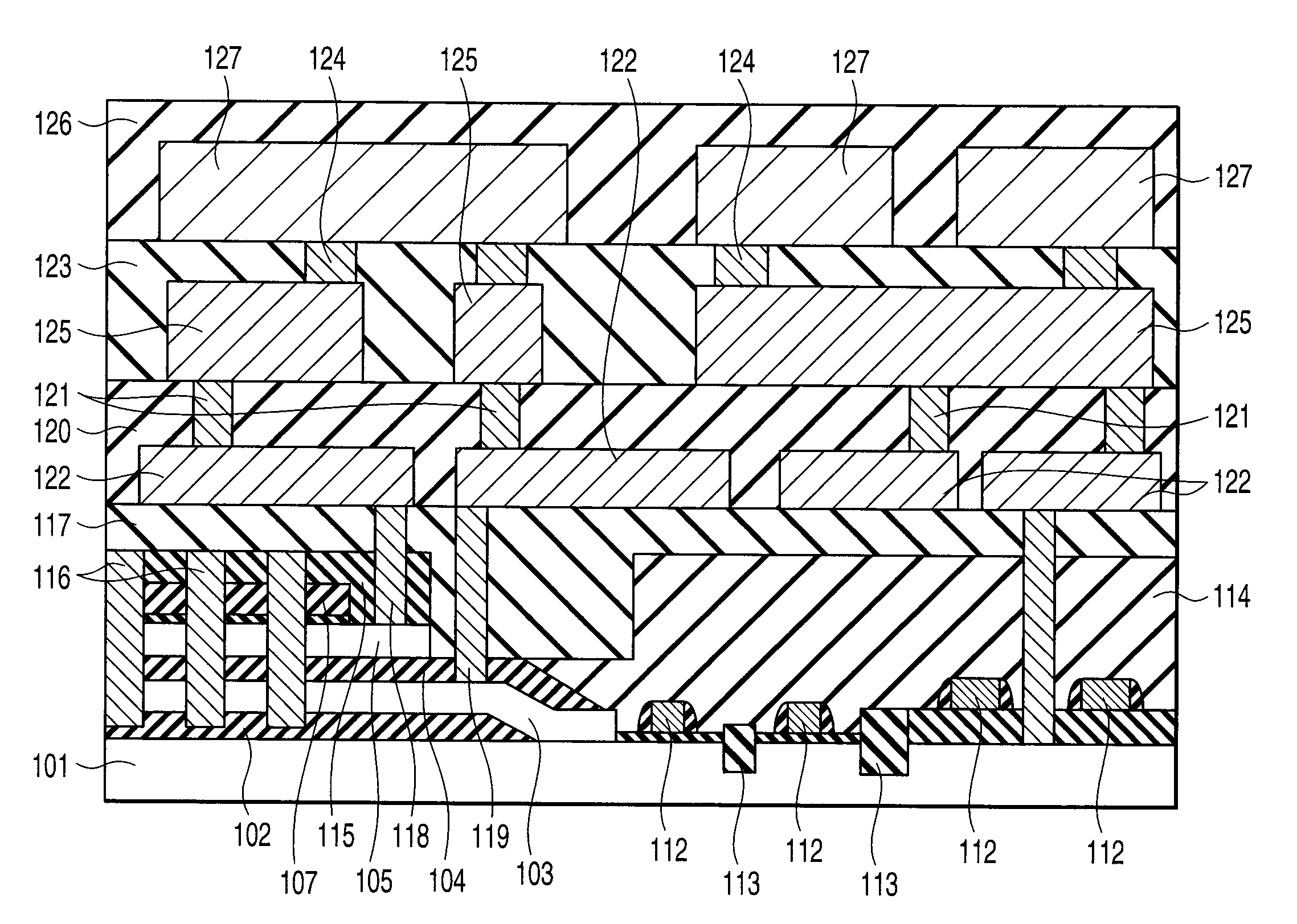

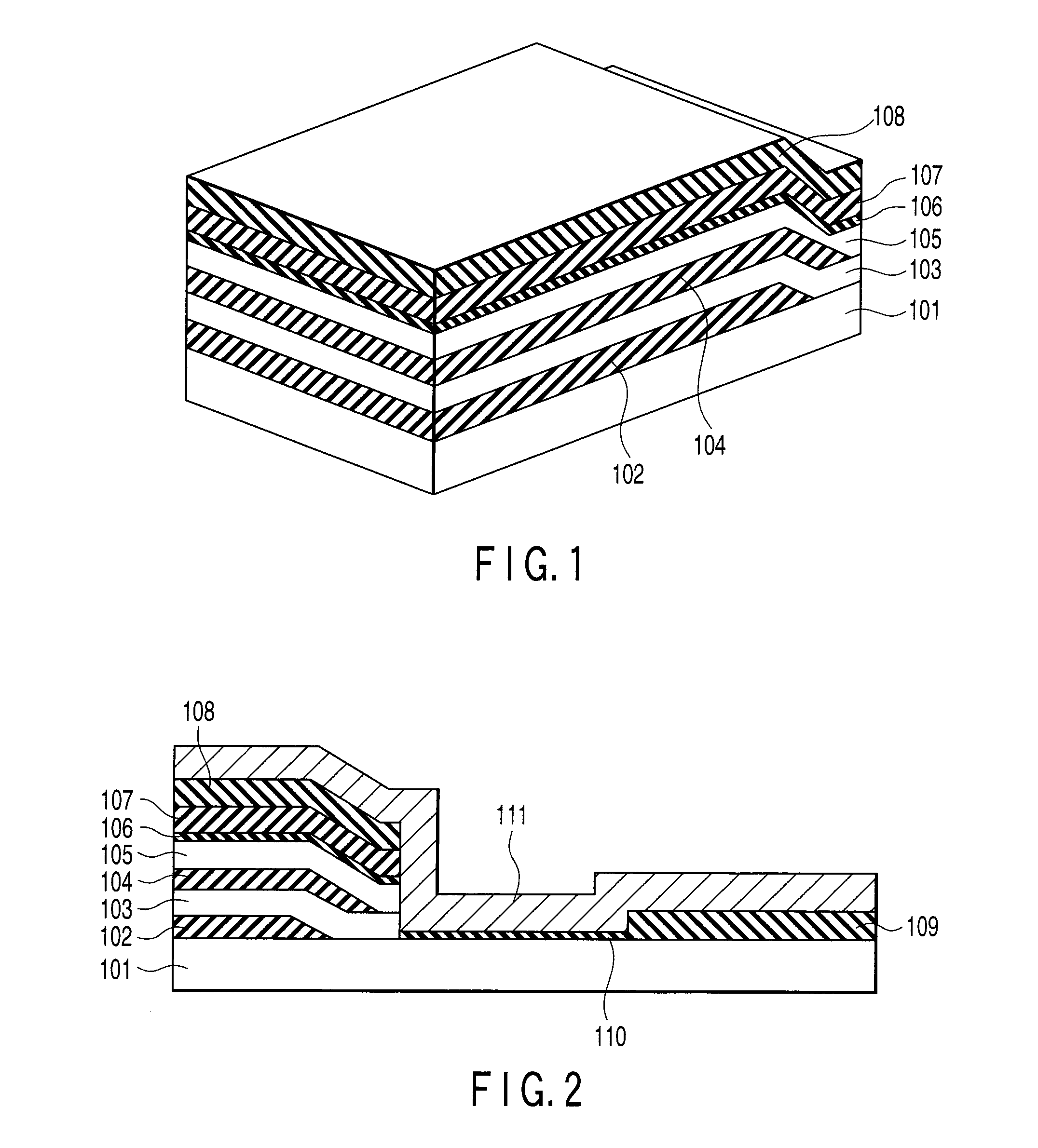

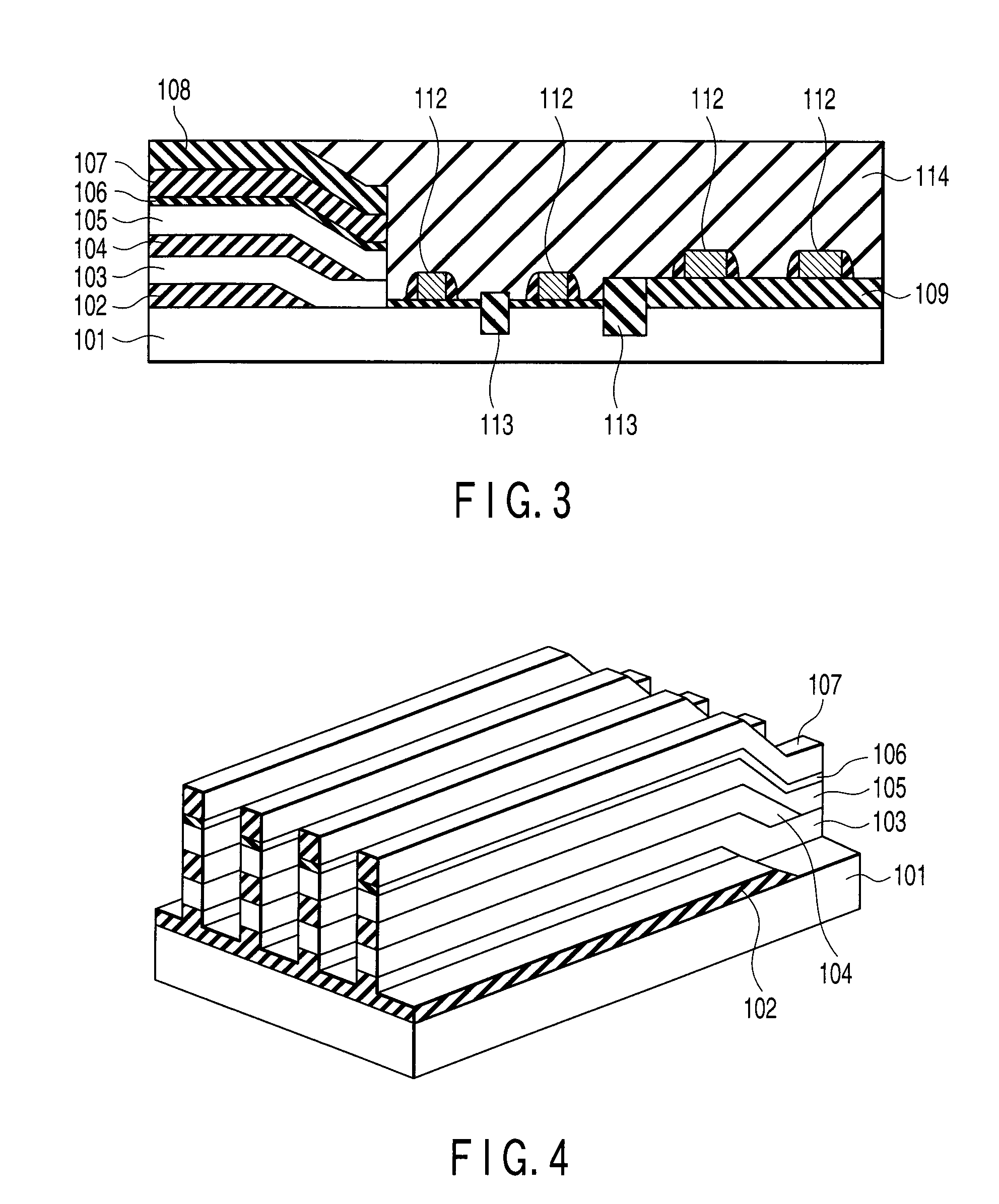

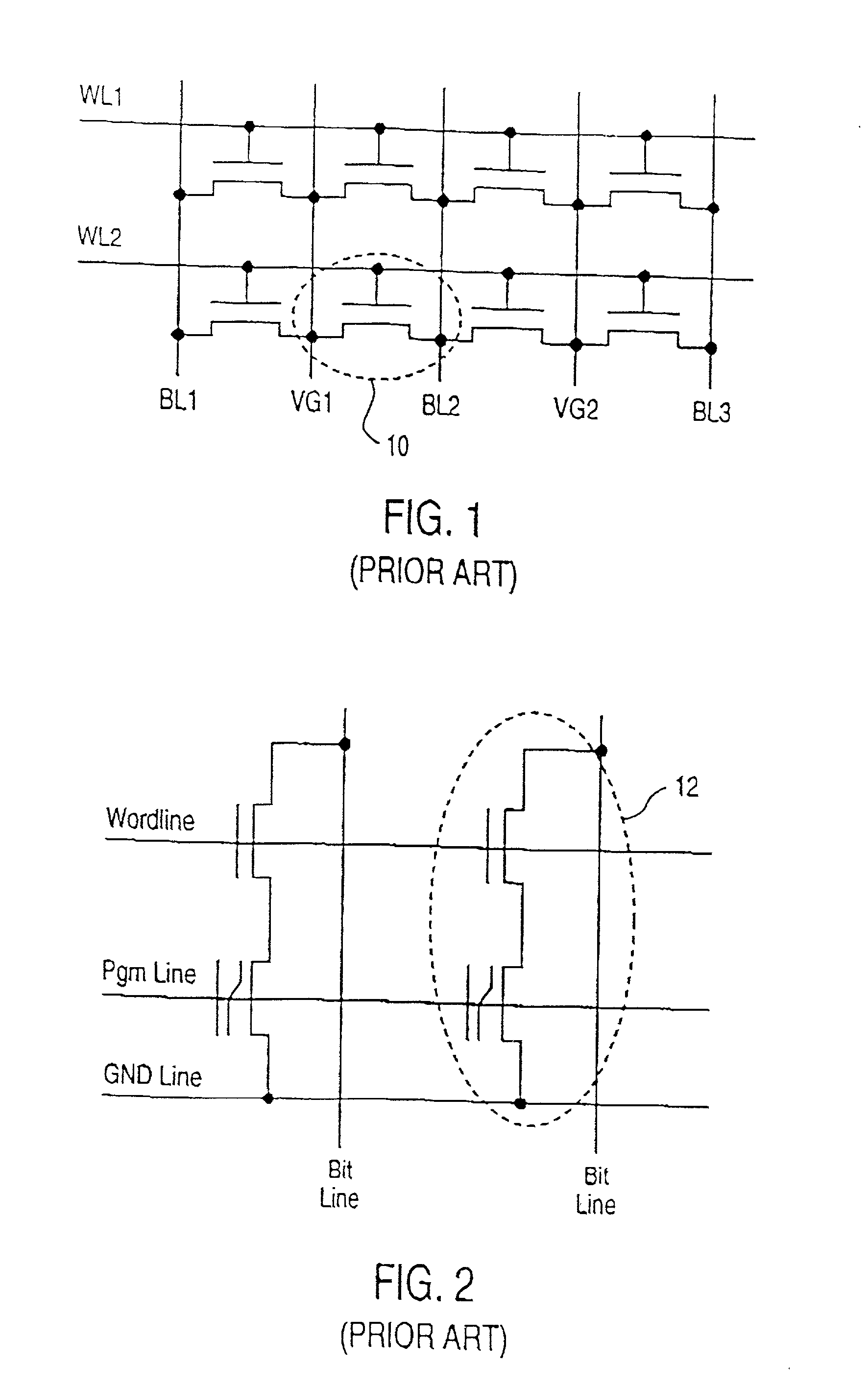

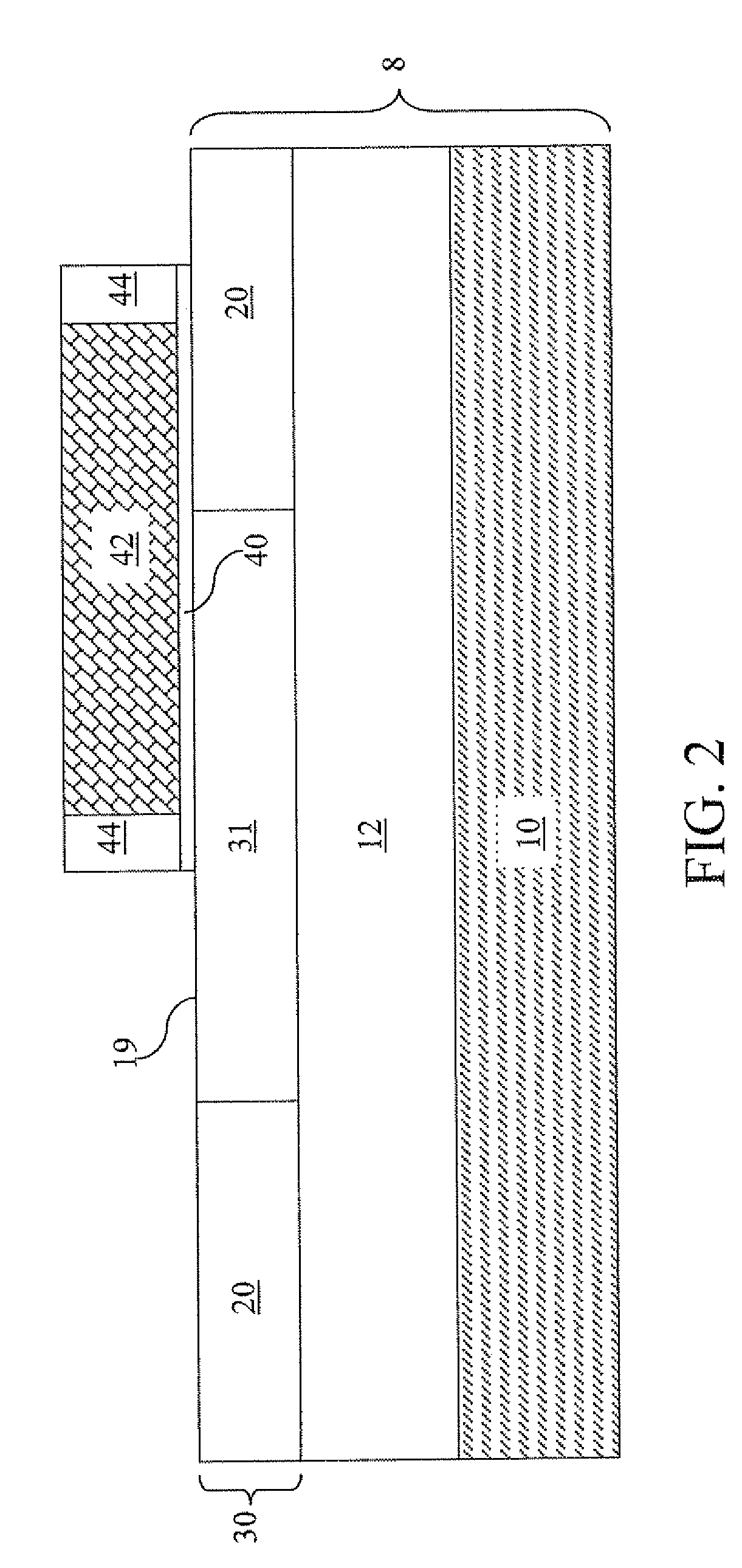

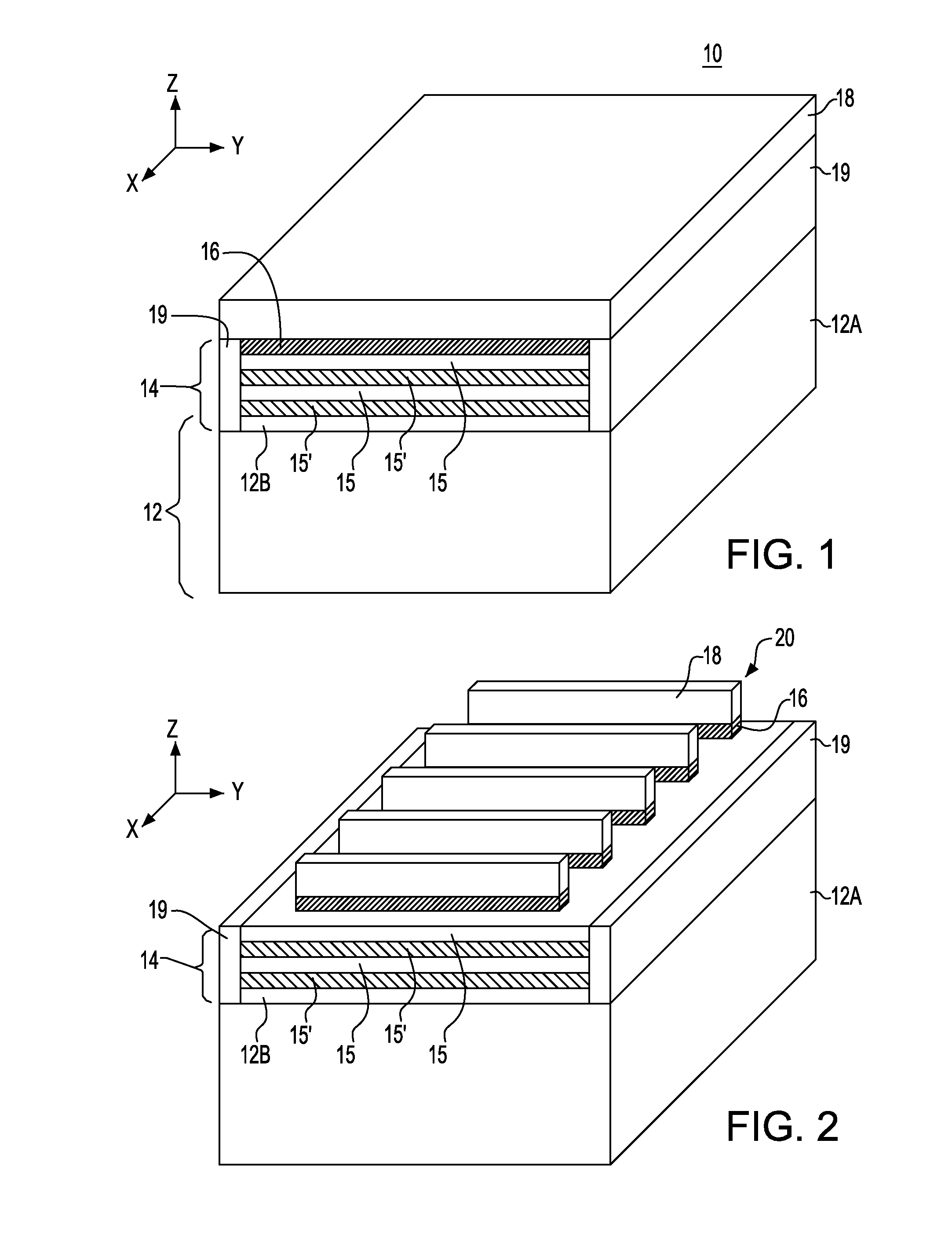

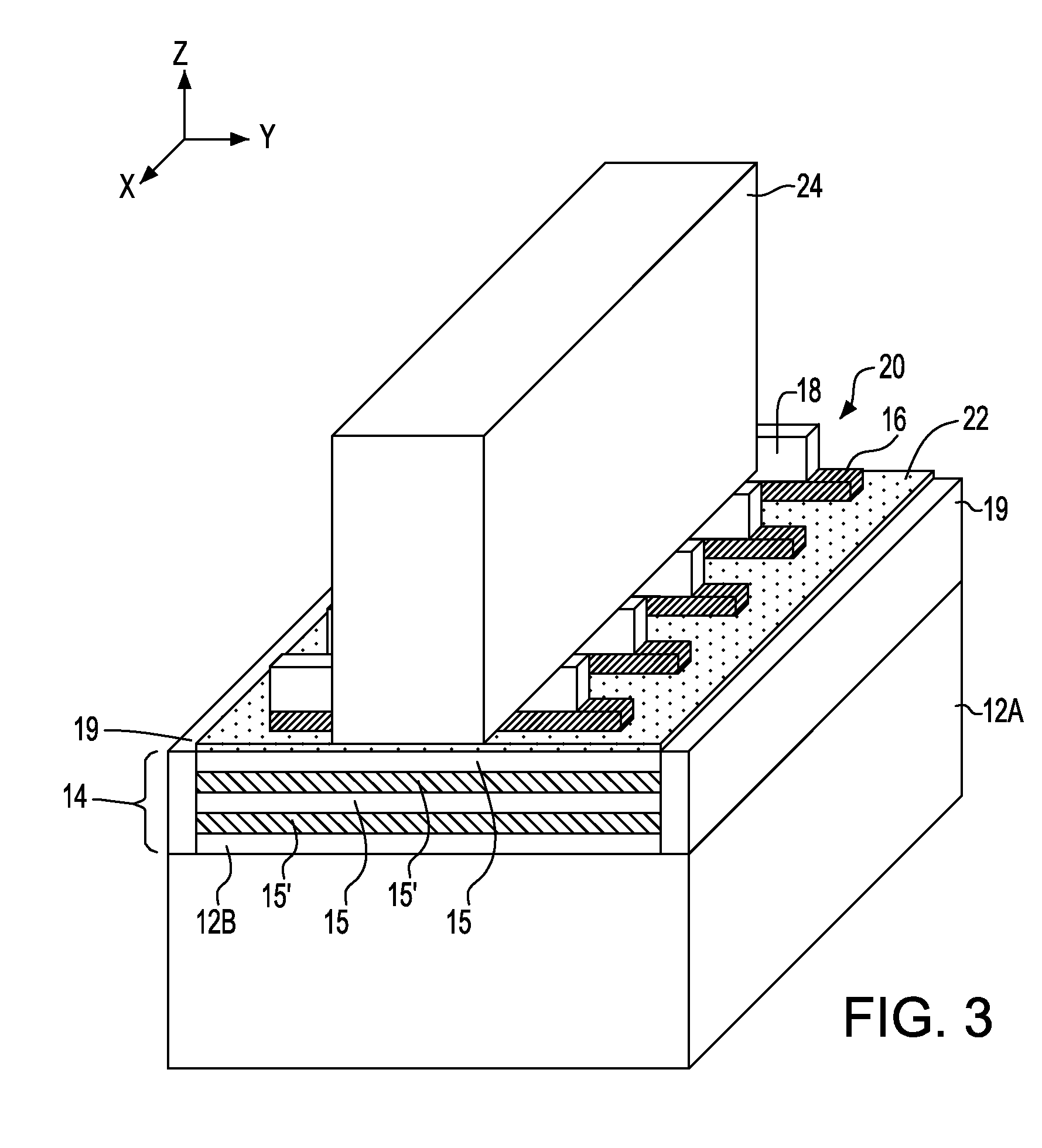

Vertically stacked field programmable nonvolatile memory and method of fabrication

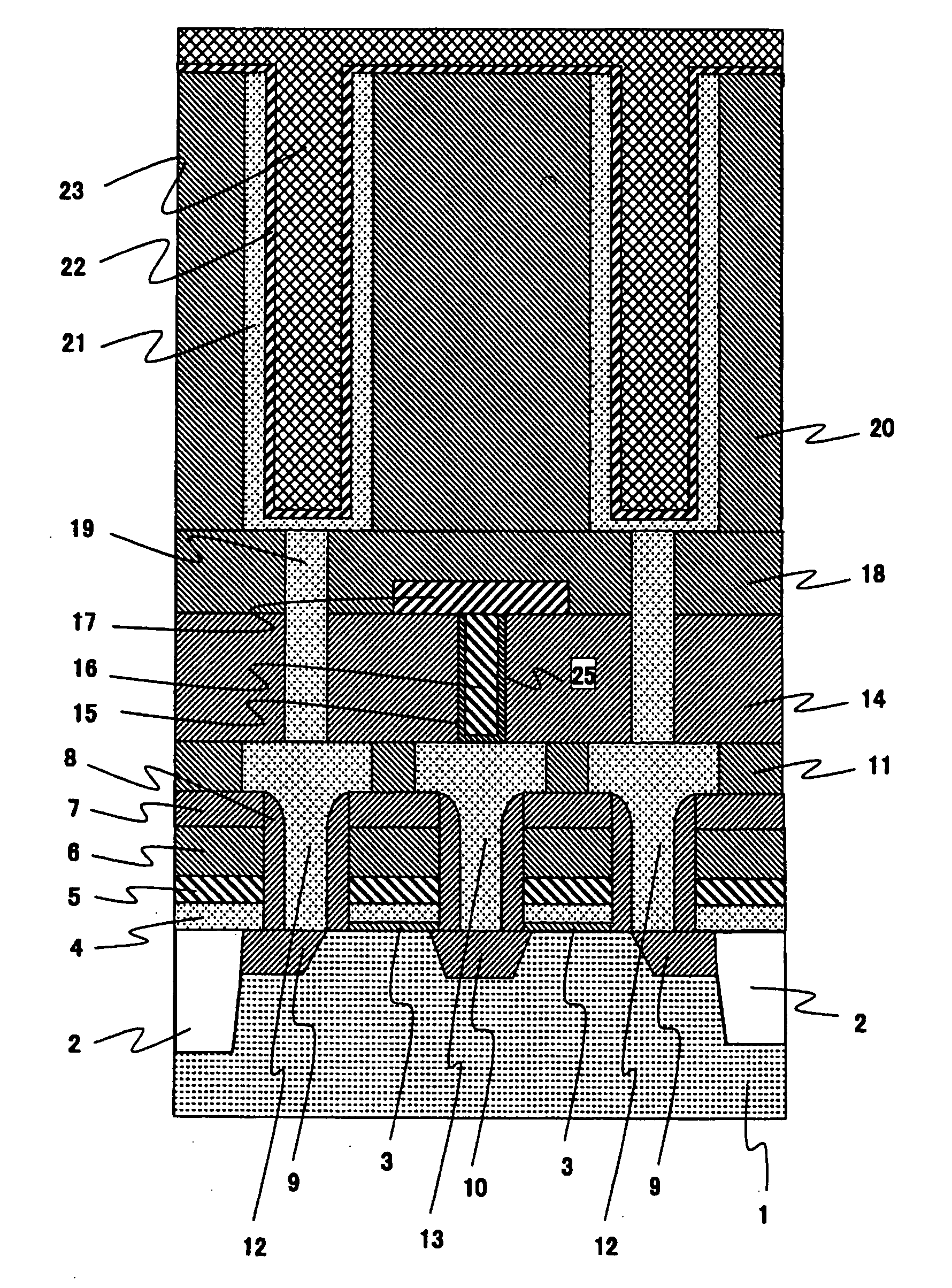

A very high density field programmable memory is disclosed. An array is formed vertically above a substrate using several layers, each layer of which includes vertically fabricated memory cells. The cell in an N level array may be formed with N+1 masking steps plus masking steps needed for contacts. Maximum use of self alignment techniques minimizes photolithographic limitations. In one embodiment the peripheral circuits are formed in a silicon substrate and an N level array is fabricated above the substrate.

Owner:RHOMBUS

Vertically stacked field programmable nonvolatile memory and method of fabrication

A very high density field programmable memory is disclosed. An array is formed vertically above a substrate using several layers, each layer of which includes vertically fabricated memory cells. The cell in an N level array may be formed with N+1 masking steps plus masking steps needed for contacts. Maximum use of self alignment techniques minimizes photolithographic limitations. In one embodiment the peripheral circuits are formed in a silicon substrate and an N level array is fabricated above the substrate.

Owner:SANDISK TECH LLC

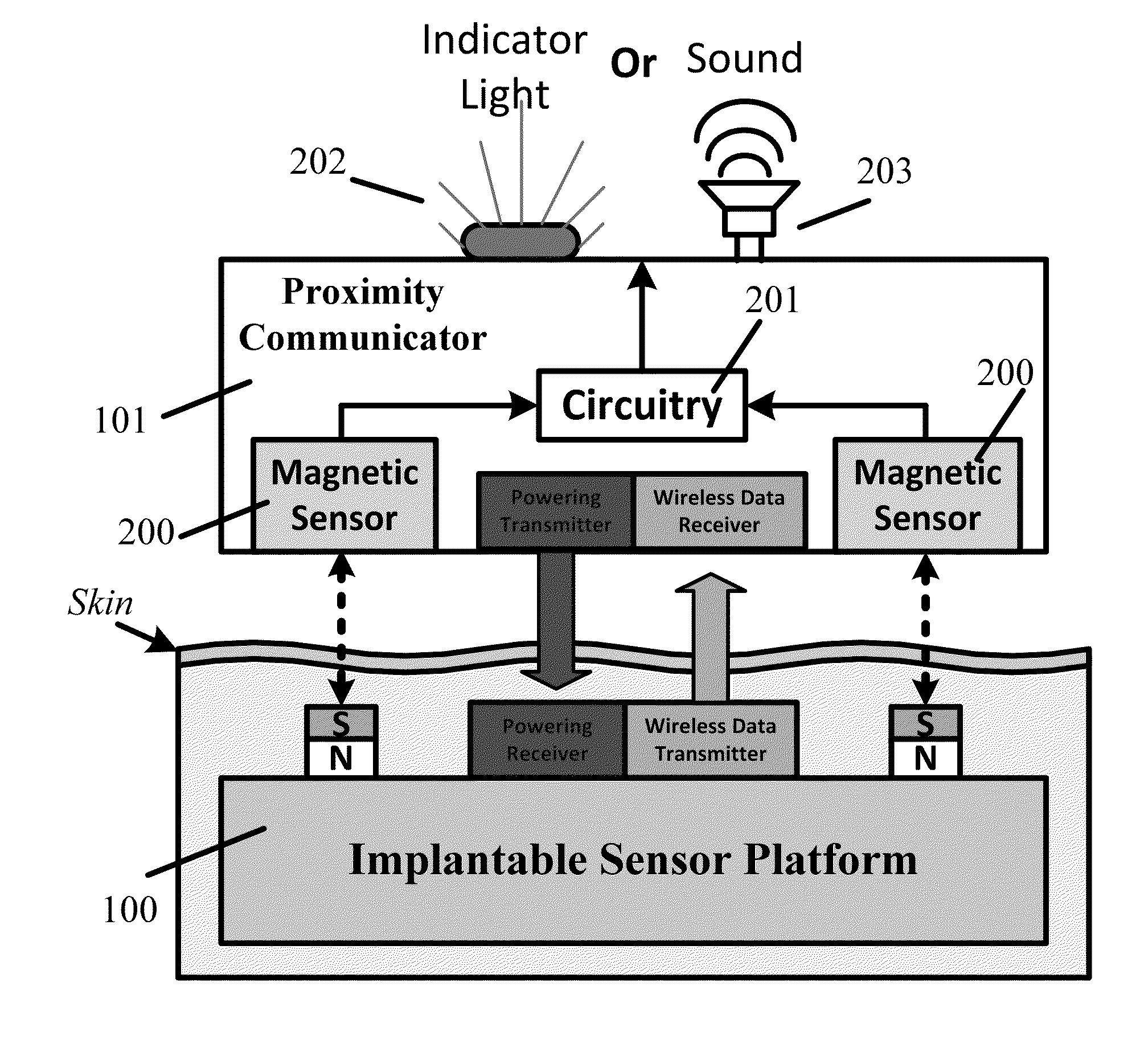

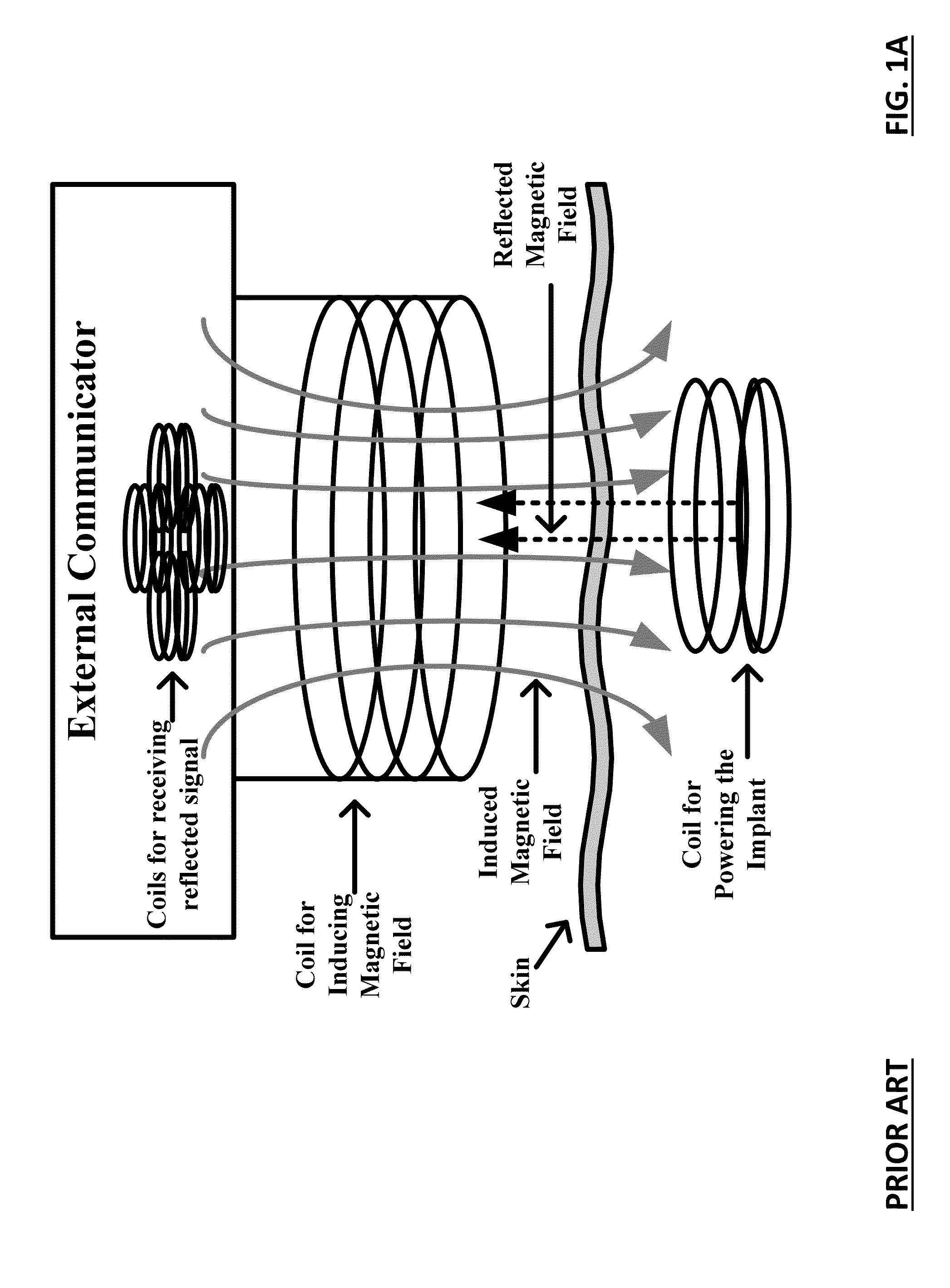

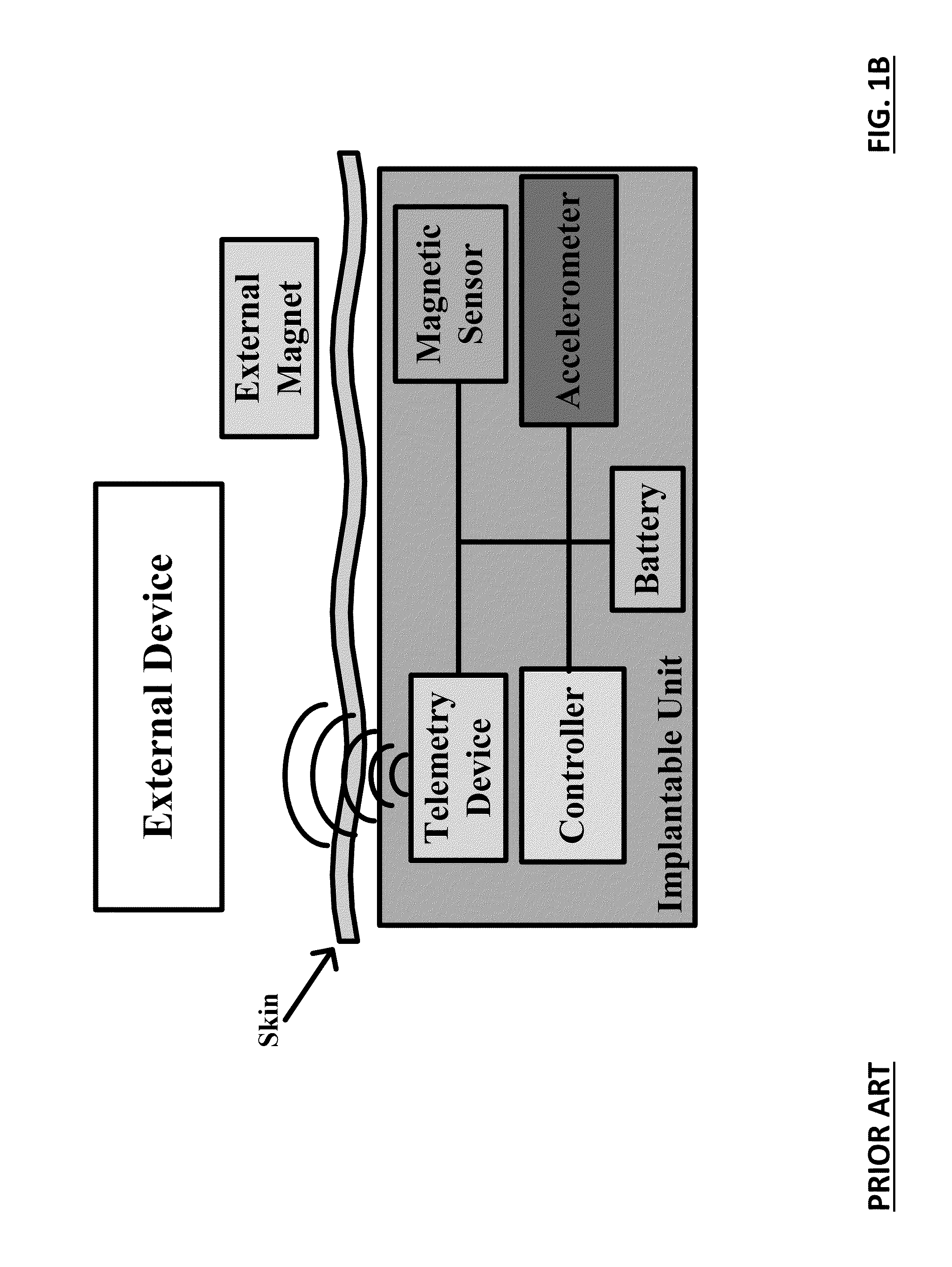

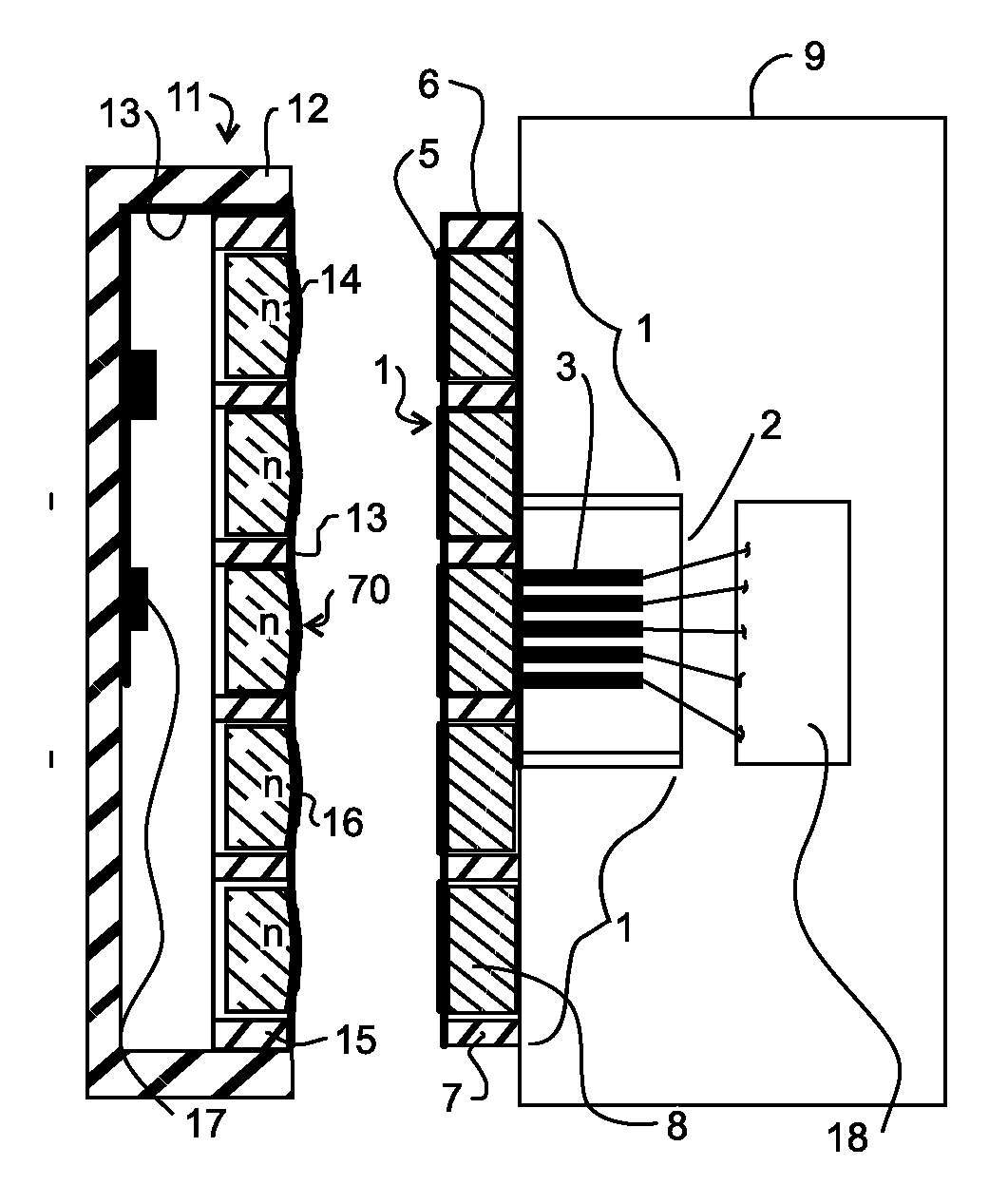

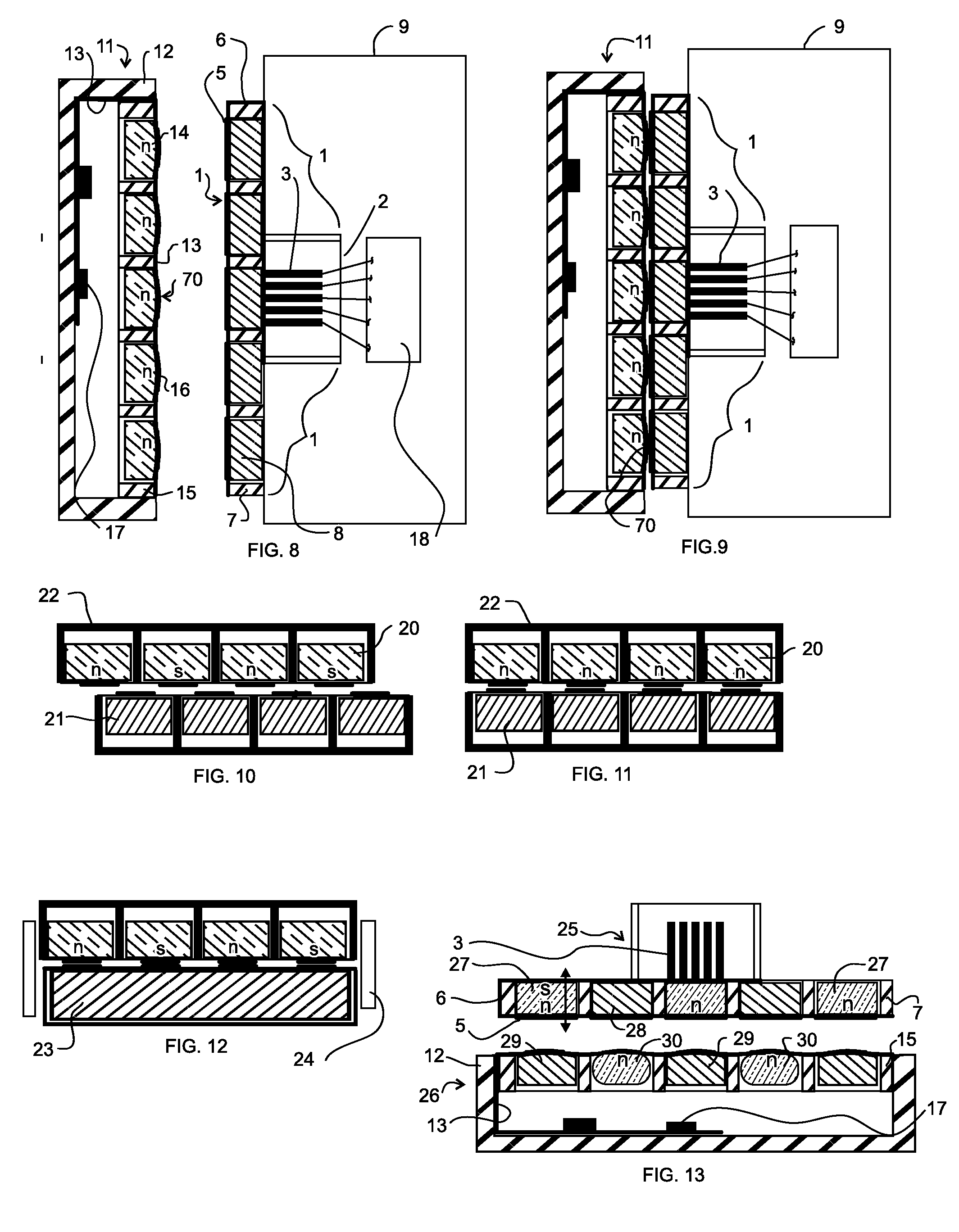

Detection of the spatial location of an implantable biosensing platform and method thereof

A methodology used to pinpoint the location of an implantable biomedical sensing device is provided and is carried out by integrating miniaturized magnets, or materials with magnetic properties into the implantable bio-sensing chip to detect the position of the implant by sensing the induced magnetic field via an external communication unit. Presented here are various configurations in which magnetic positional detection can be carried out. The positional information collected from these detection motifs can be used to provide feedback to the user about alignment status as well as activate a self-alignment methodology. With respect to the former, based on the positional information received the user manually adjusts the location of the external communicator into place to align with the implantable platform. In the latter scenario, various configurations allow the wireless powering and communication components on the proximity communicator to automatically find and align with the implantable biomedical sensing chip.

Owner:BIORASIS

Vertically stacked field programmable nonvolatile memory and method of fabrication

A very high density field programmable memory is disclosed. An array is formed vertically above a substrate using several layers, each layer of which includes vertically fabricated memory cells. The cell in an N level array may be formed with N+1 masking steps plus masking steps needed for contacts. Maximum use of self alignment techniques minimizes photolithographic limitations. In one embodiment the peripheral circuits are formed in a silicon substrate and an N level array is fabricated above the substrate.

Owner:SANDISK TECH LLC

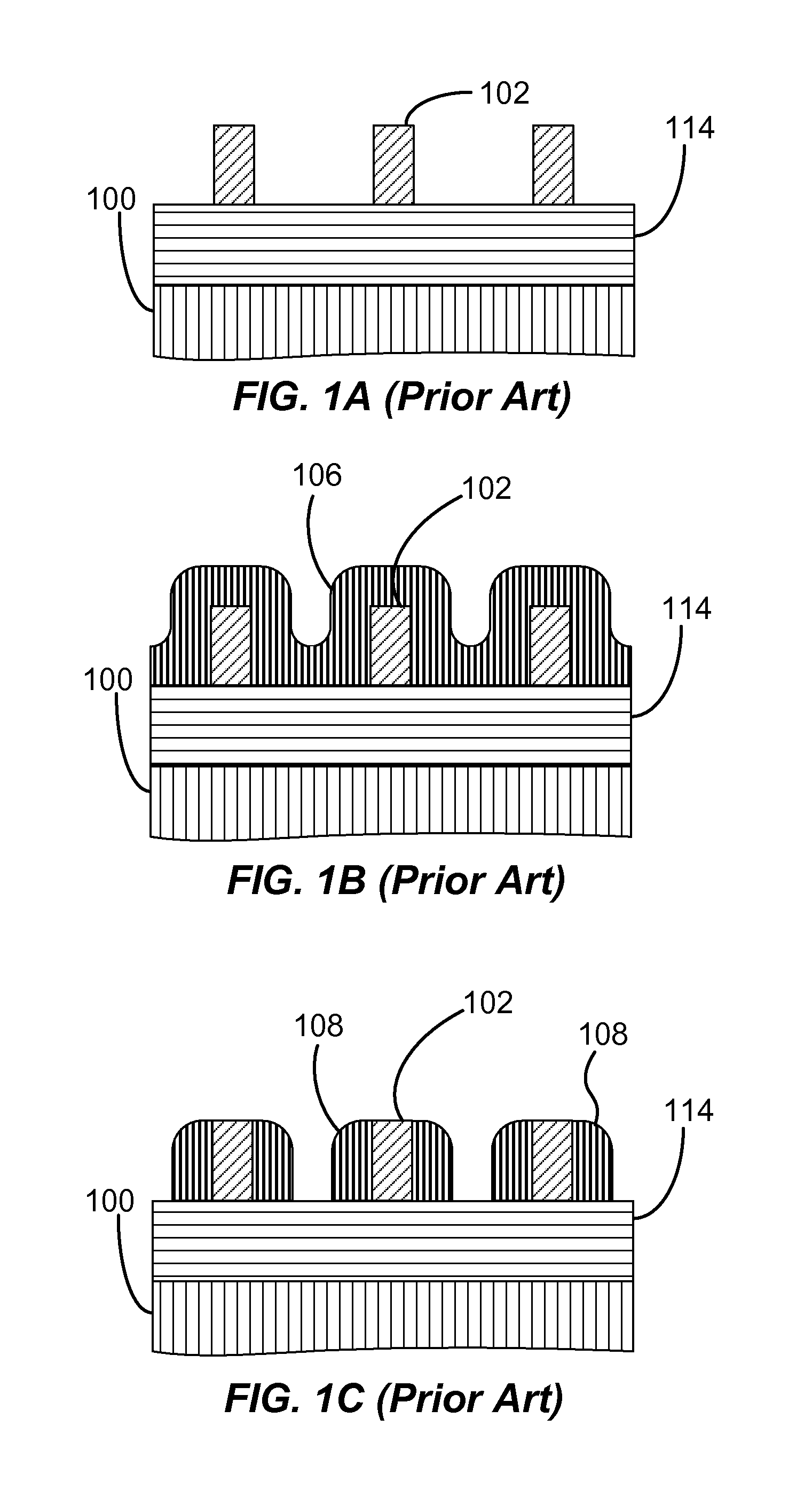

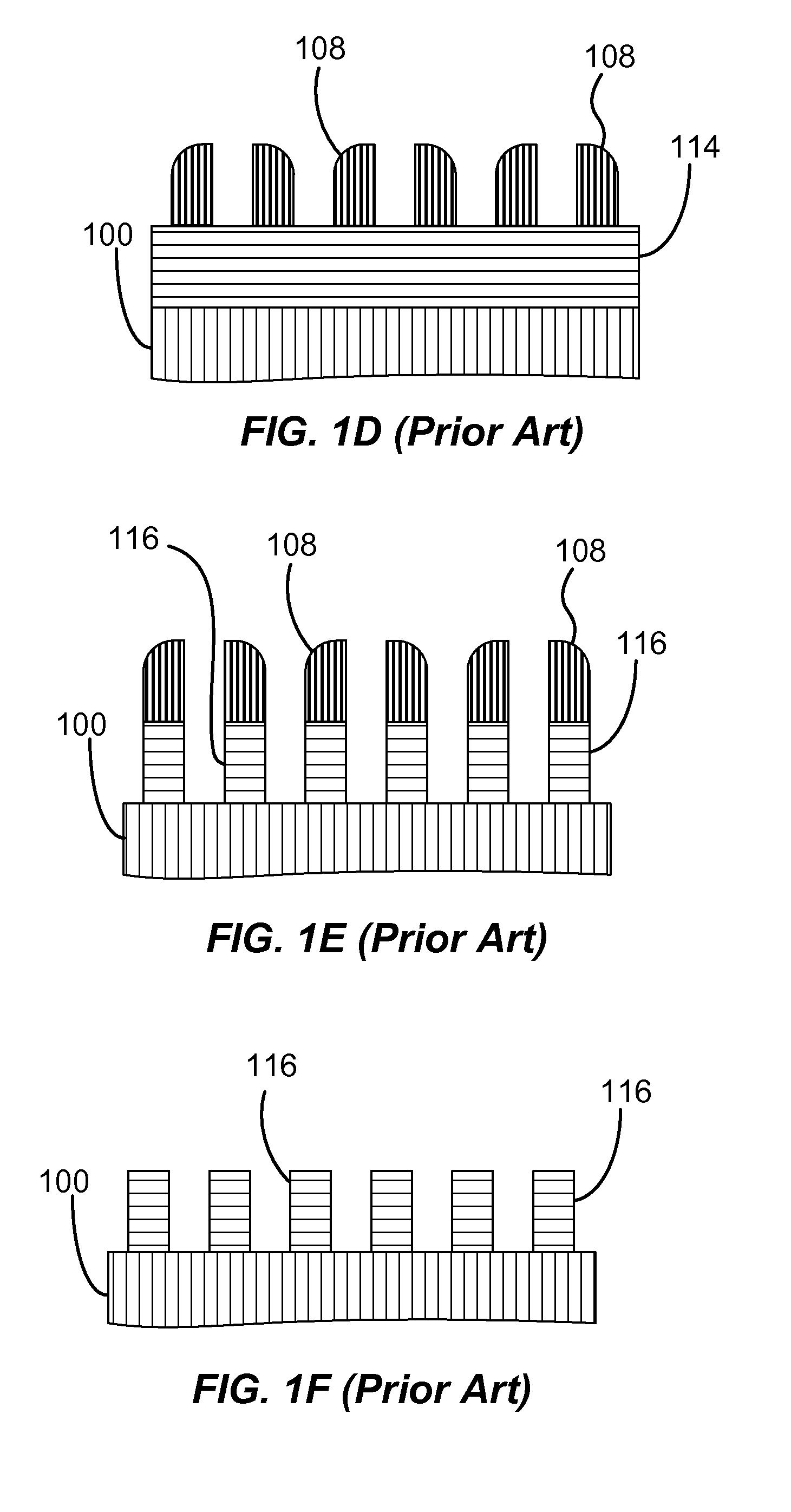

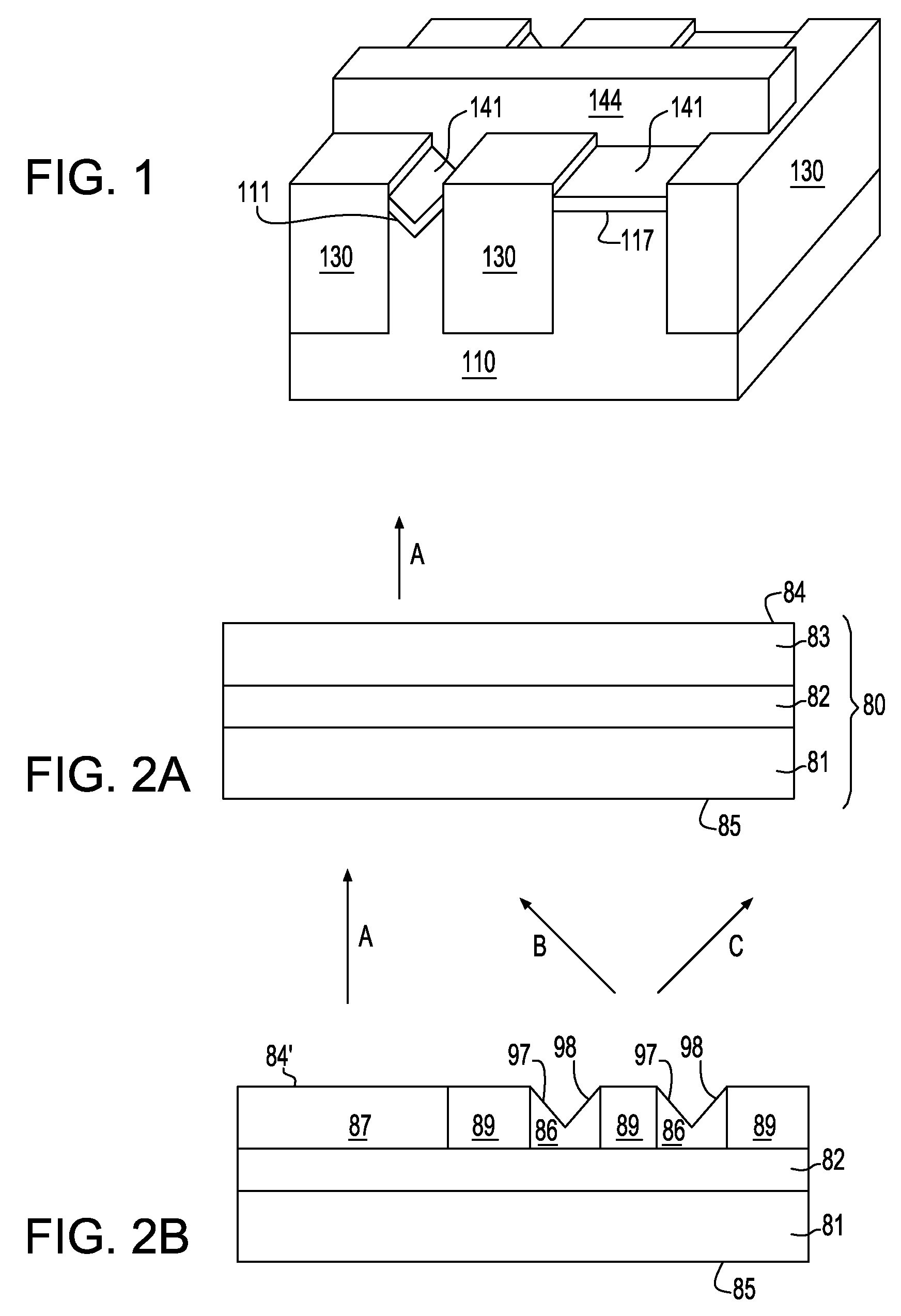

Spacer formation

ActiveUS20150287612A1Semiconductor/solid-state device manufacturingImage resolutionOptical resolution

Embodiments of the present invention pertain to methods of forming more symmetric spacers which may be used for self-aligned multi-patterning processes. A conformal spacer layer of spacer material is formed over mandrels patterned near the optical resolution of a photolithography system using a high-resolution photomask. A carbon-containing layer is further formed over the conformal spacer layer. The carbon-containing layer is anisotropically etched to expose the high points of the conformal spacer layer while retaining carbon side panels. The conformal spacer layer may then be etched to form spacers without the traditional skewing of the profile towards one side or the other.

Owner:APPLIED MATERIALS INC

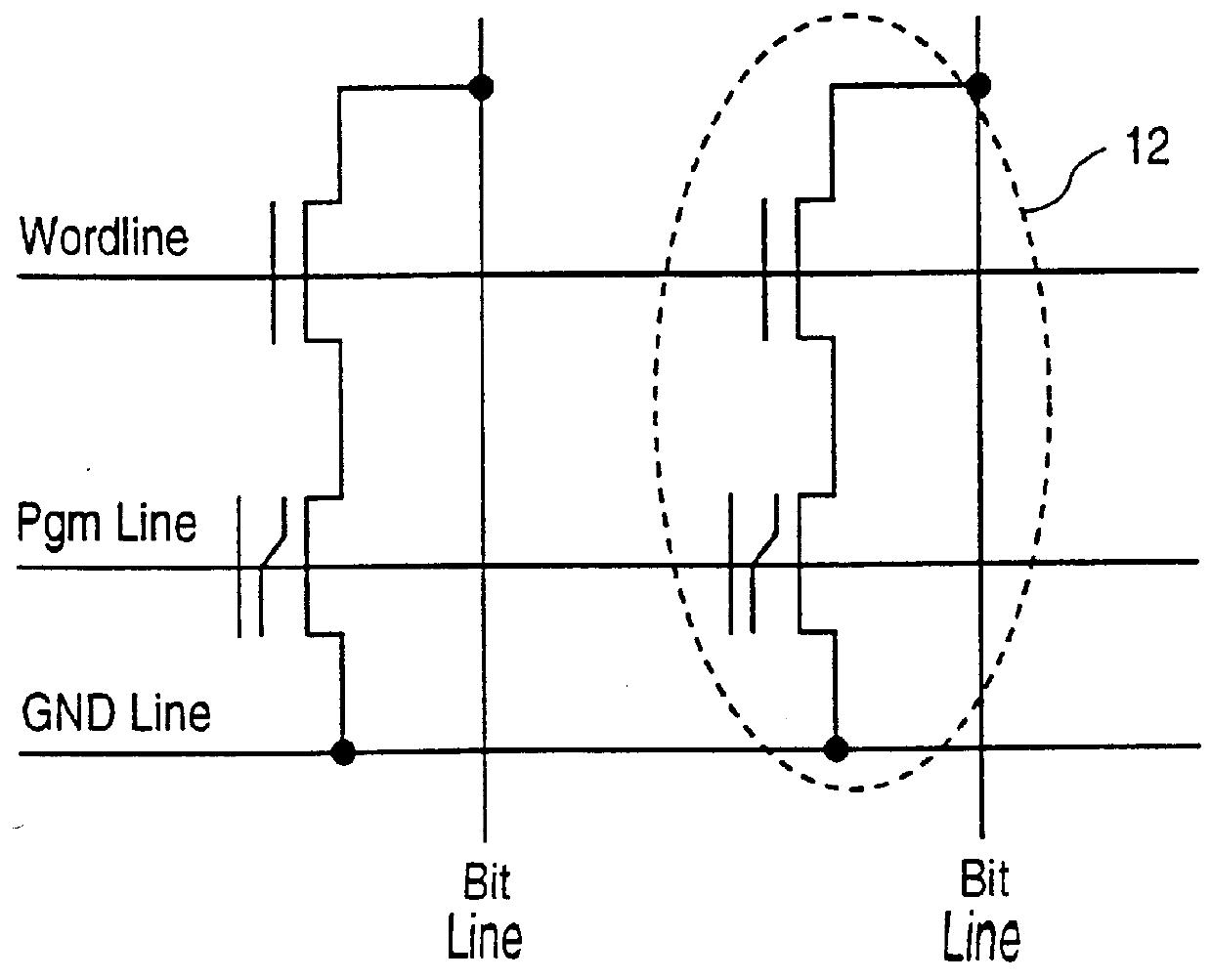

Process for making and programming and operating a dual-bit multi-level ballistic MONOS memory

A fast low voltage ballistic program, ultra-short channel, ultra-high density, dual-bit multi-level flash memory is described with a two or three polysilicon split gate side wall process. The structure and operation of this invention is enabled by a twin MONOS cell structure having an ultra-short control gate channel of less than 40nm, with ballistic injection which provides high electron injection efficiency and very fast program at low program voltages of 3~5V. The cell structure is realized by (i) placing side wall control gates over a composite of Oxide-Nitride-Oxide (ONO) on both sides of the word gate, and (ii) forming the control gates and bit diffusion by self-alignment and sharing the control gates and bit diffusions between memory cells for high density. Key elements used in this process are: 1) Disposable side wall process to fabricate the ultra short channel and the side wall control gate with or without a step structure, and 2) Self-aligned definition of the control gate over the storage nitride and the bit line diffusion, which also runs in the same direction as the control gate. The features of fast program, low voltage, ultra-high density, dual-bit, multi-level MONOS NVRAM of the present invention include: 1) Electron memory storage in nitride regions within an ONO layer underlying the control gates, 2) high density dual-bit cell in which there are two nitride memory storage elements per cell, 3) high density dual-bit cell can store multi-levels in each of the nitride regions, 4) low current program controlled by the word gate and control gate, 5) fast, low voltage program by ballistic injection utilizing the controllable ultra-short channel MONOS, and 6) side wall control poly gates to program and read multi-levels while masking out memory storage state effects of the unselected adjacent nitride regions and memory cells. The ballistic MONOS memory cell is arranged in the following array: each memory cell contains two nitride regions for one word gate, and ½ a source diffusion and ½ a bit diffusion. Control gates can be defined separately or shared together over the same diffusion. Diffusions are shared between cells and run in parallel to the side wall control gates, and perpendicular to the word line.

Owner:HALO LSI INC

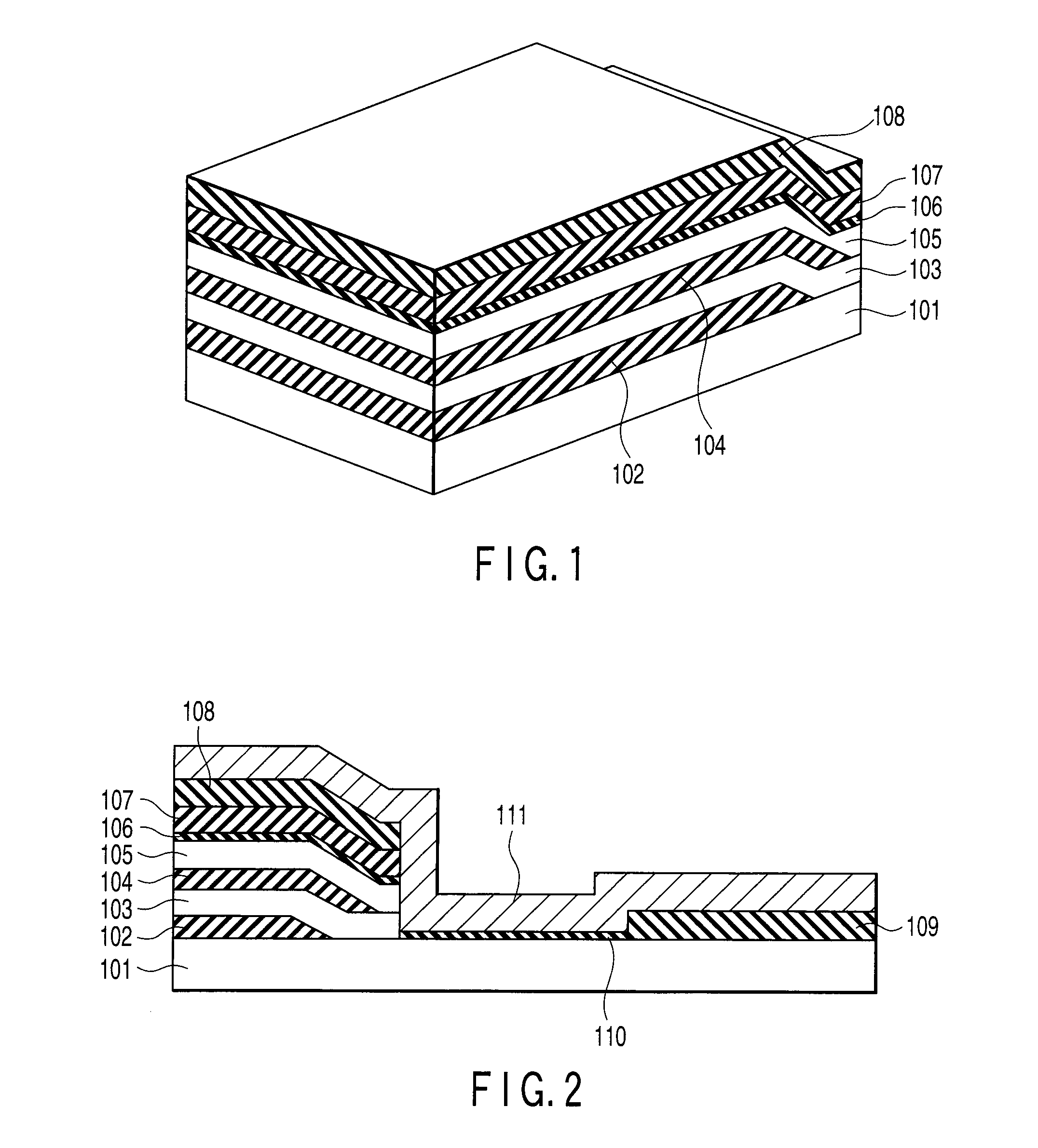

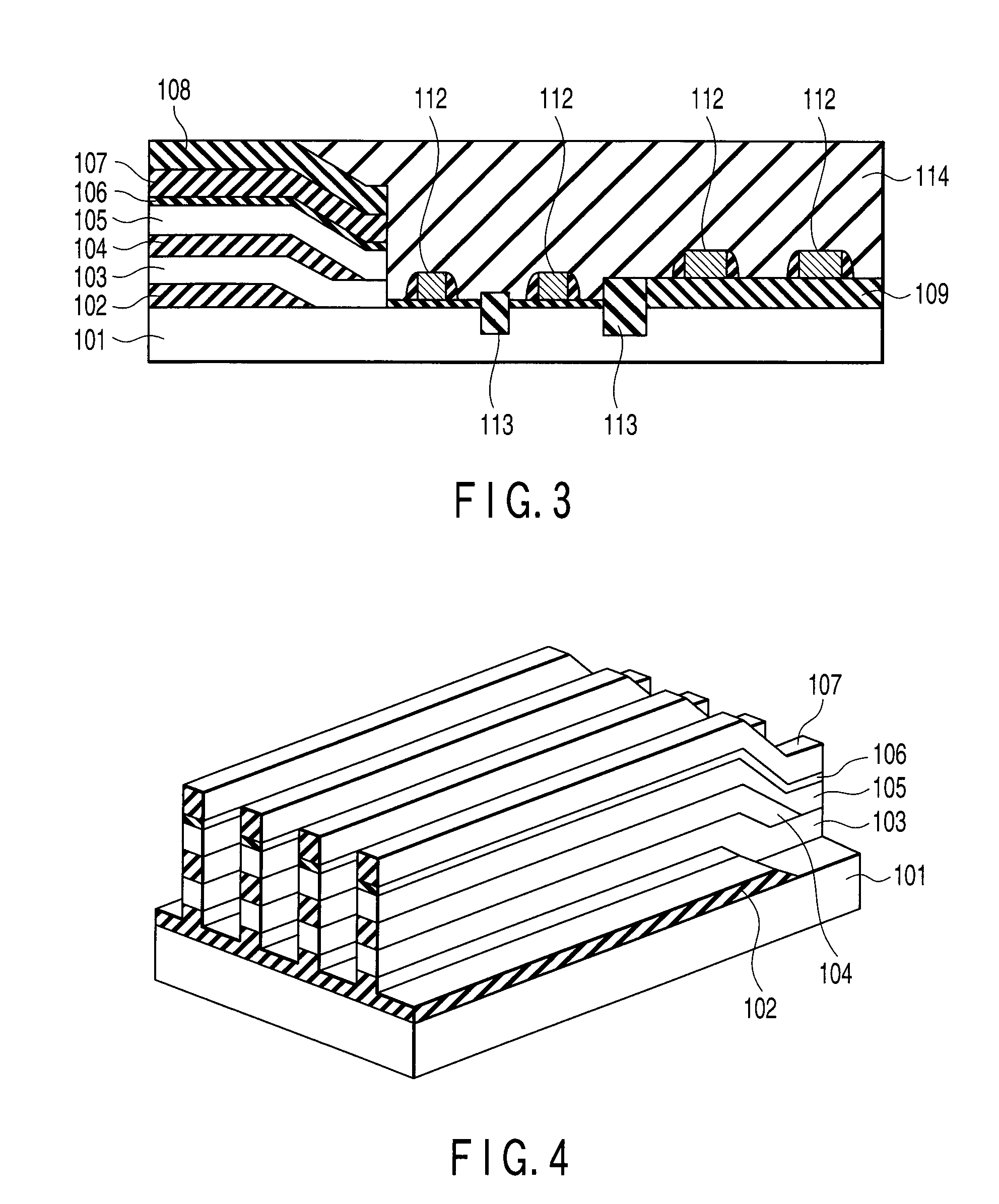

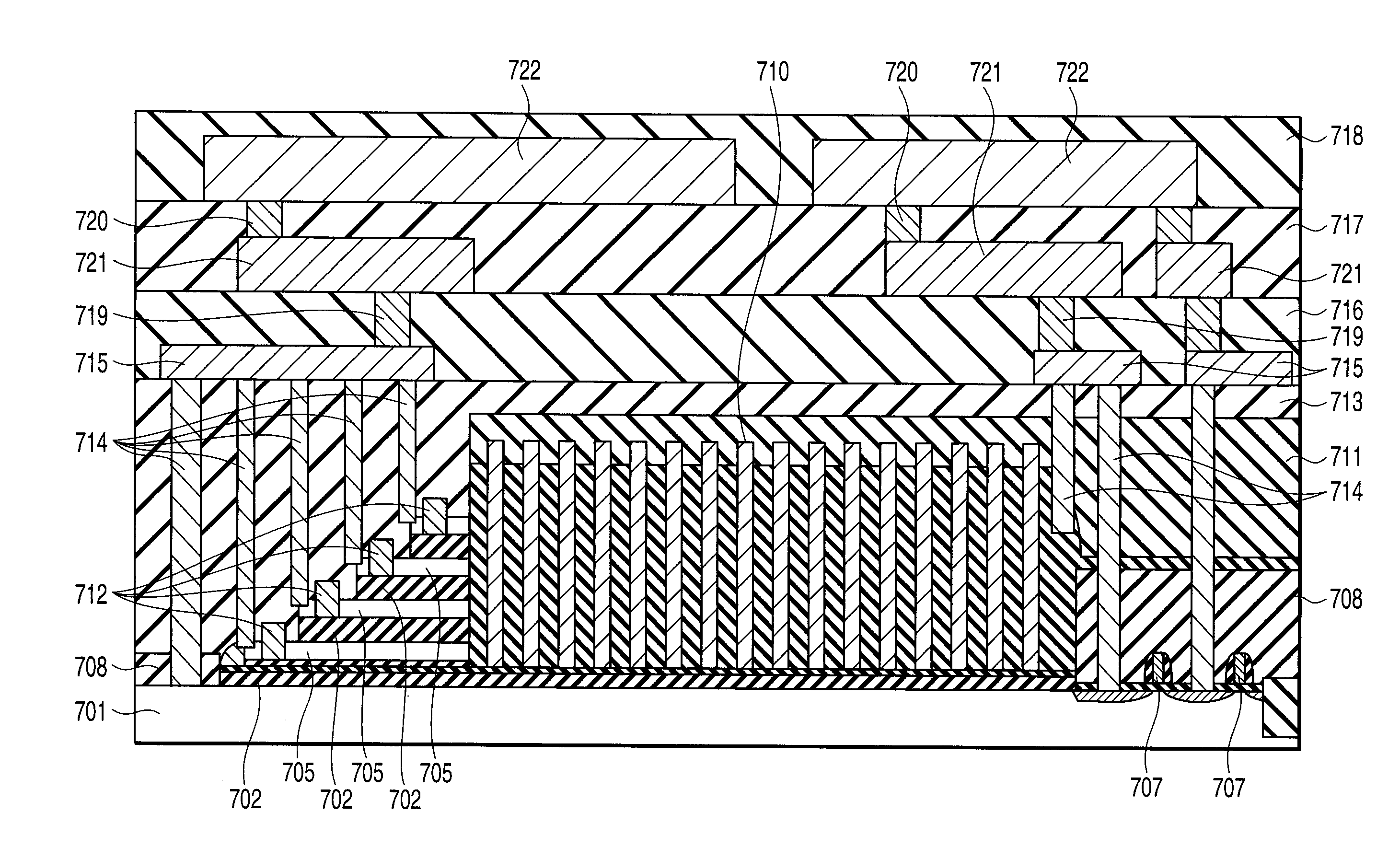

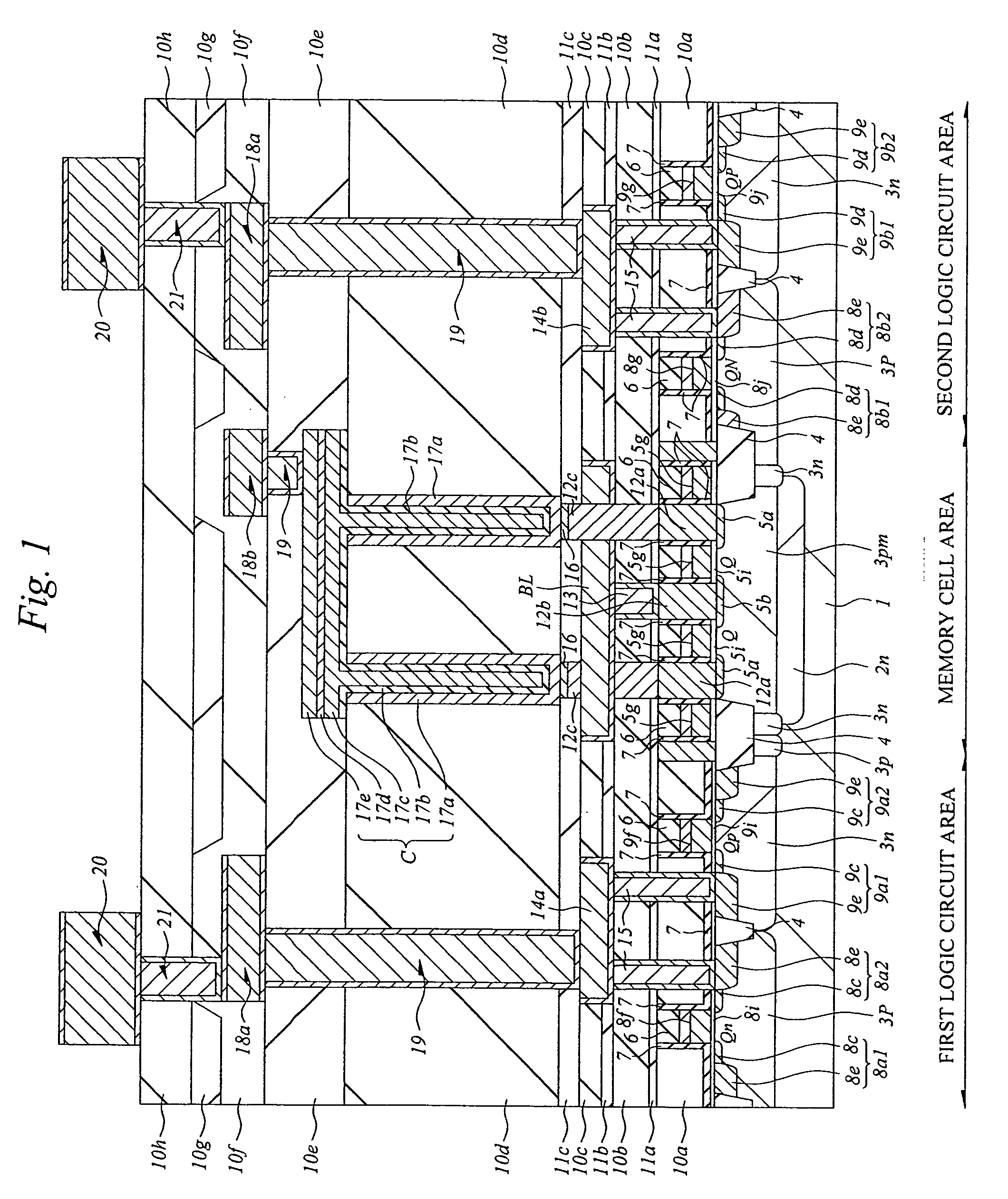

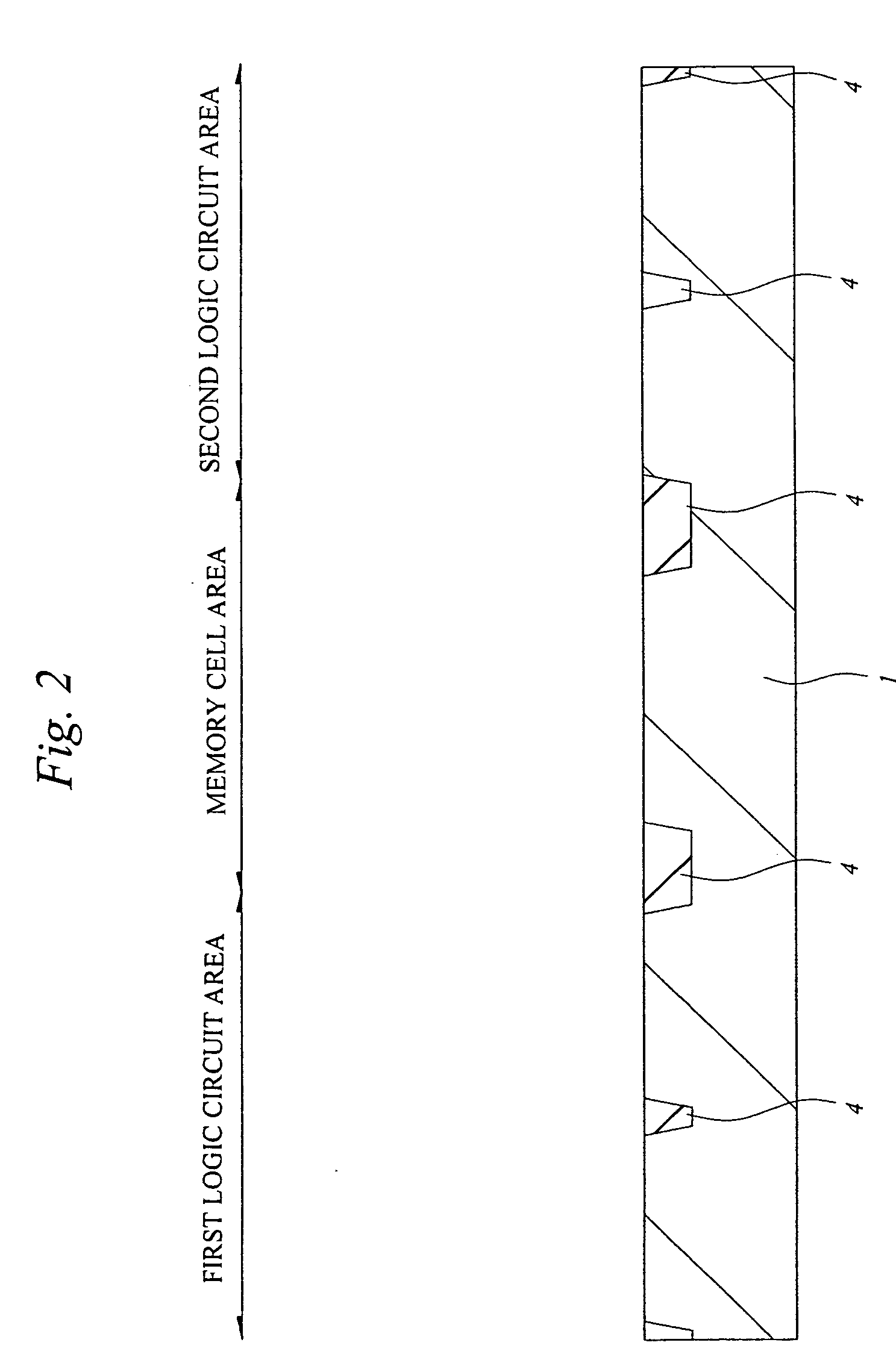

Semiconductor Memory and Method of Manufacturing the Same

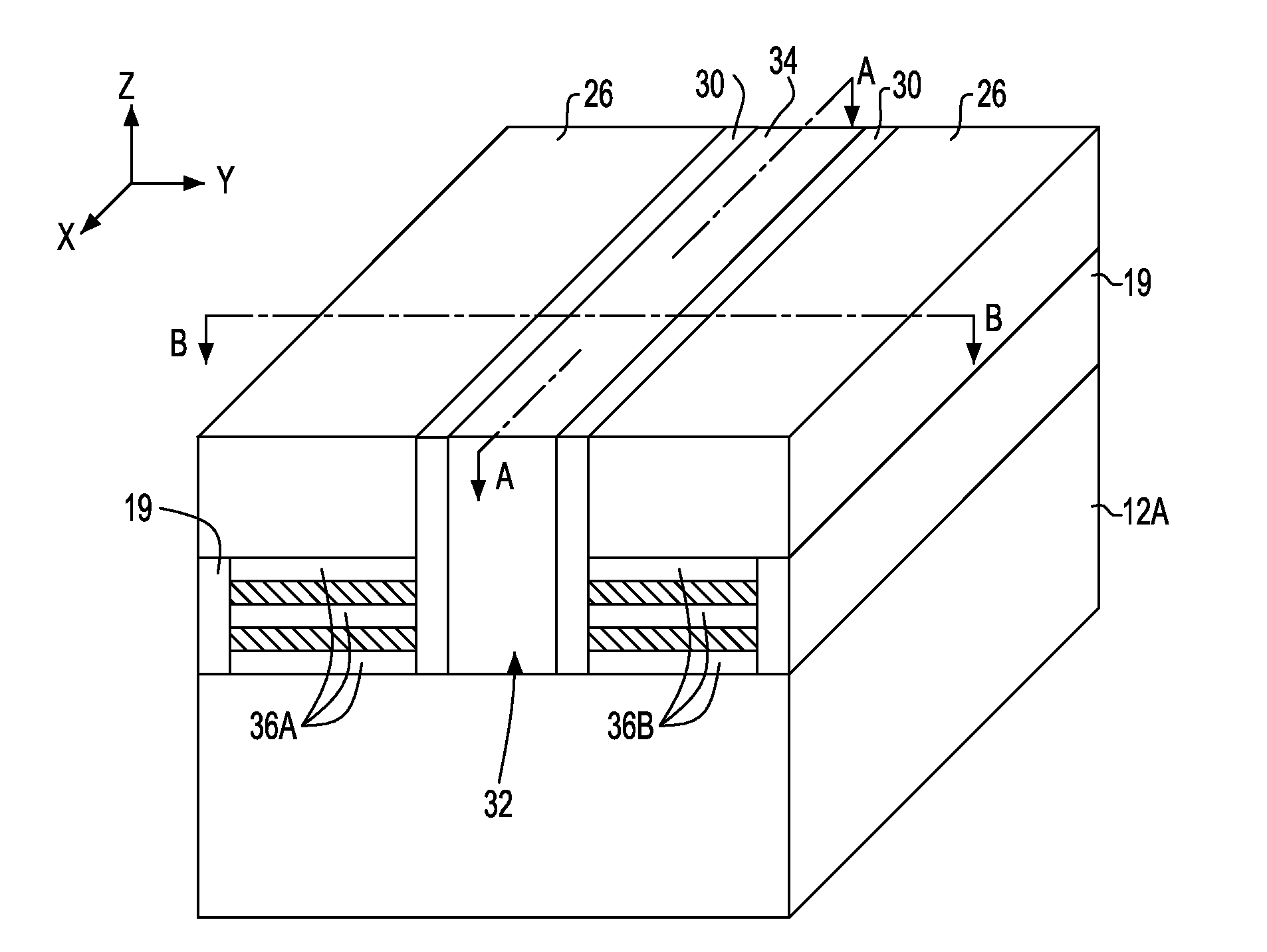

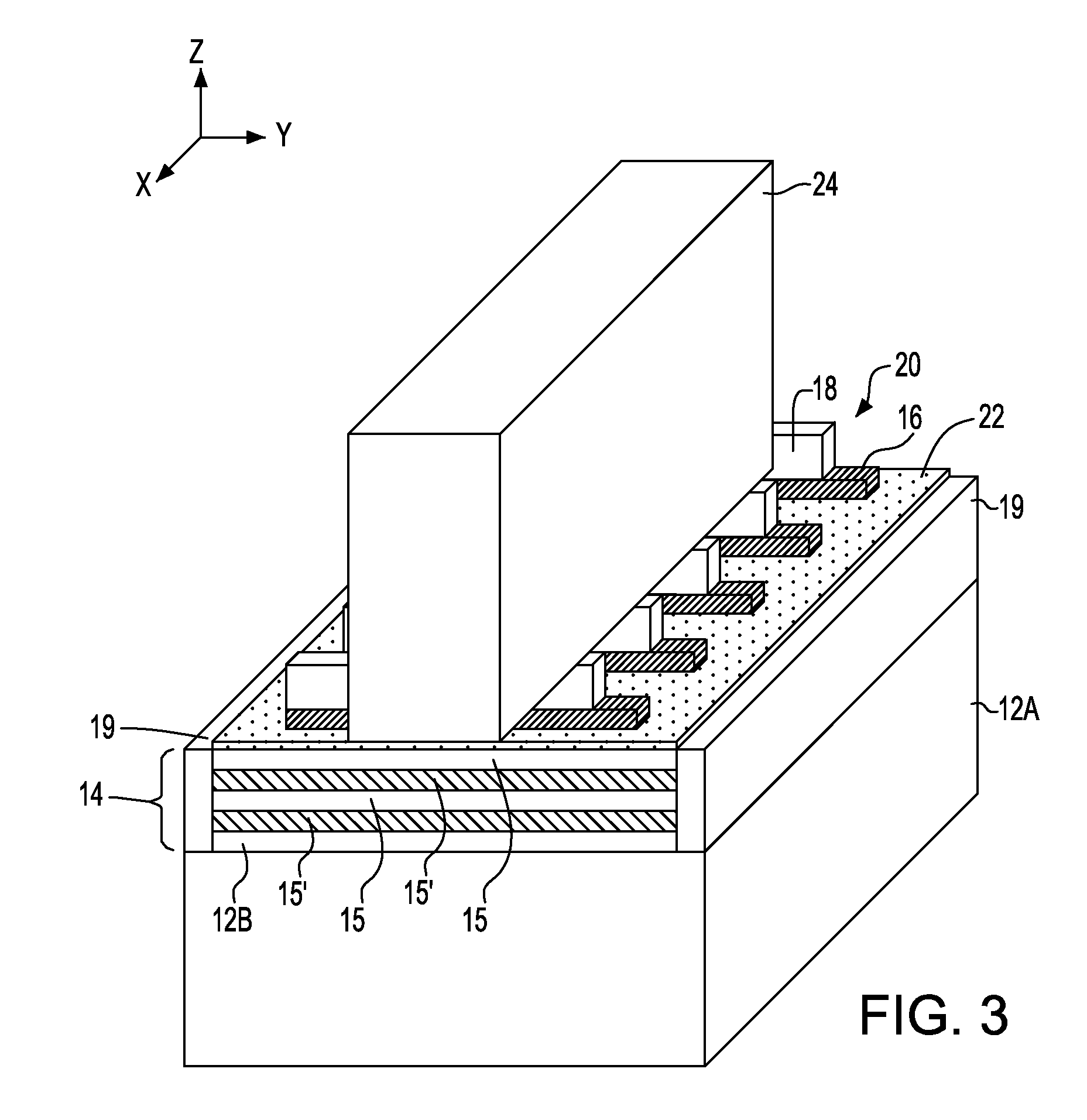

ActiveUS20080073635A1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

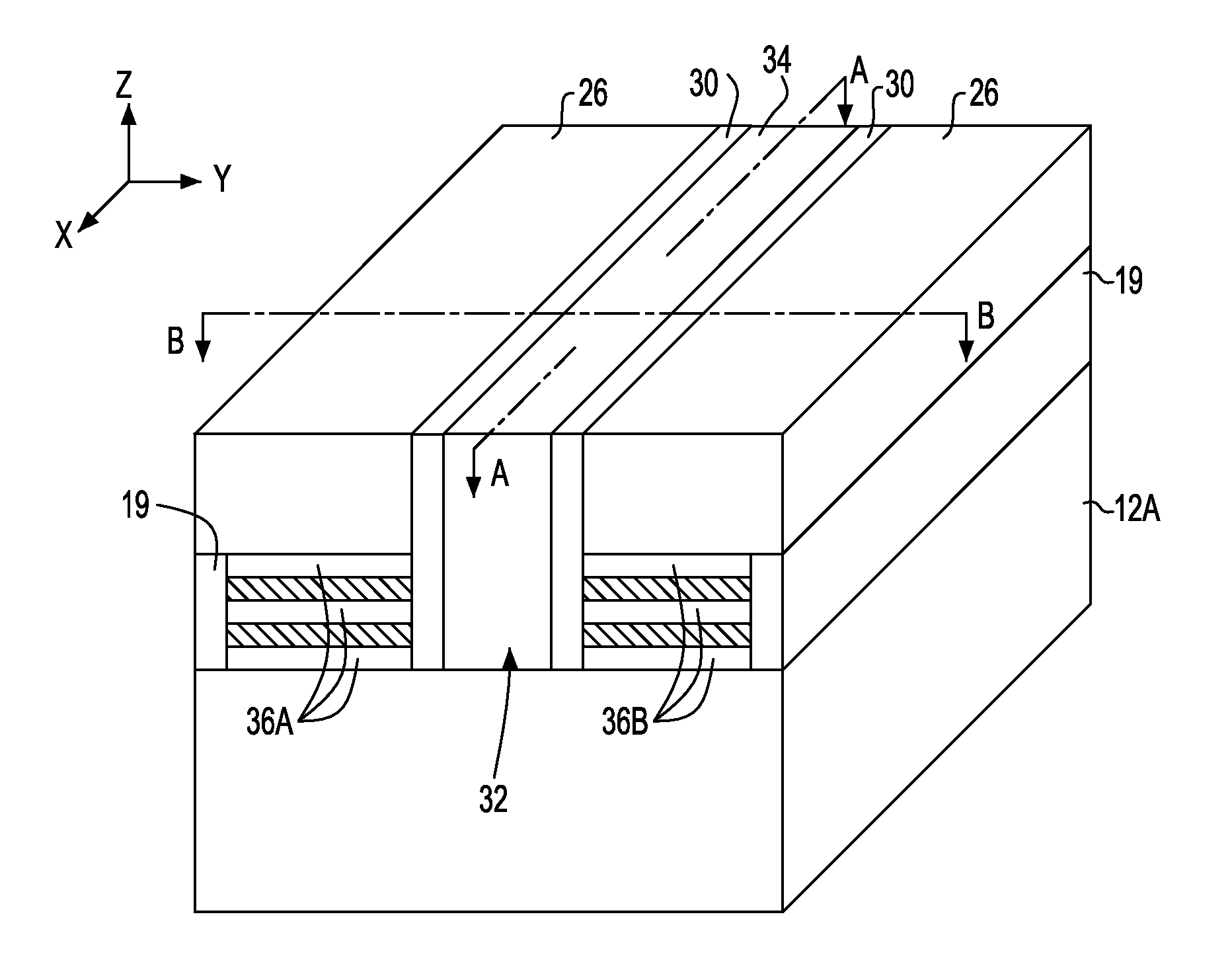

A semiconductor memory includes a plurality of stripe-like active areas formed by stacking, in a direction perpendicular to a substrate, a plurality of layers extending parallel to the substrate, a first gate electrode formed on first side surfaces of the active areas, the first side surfaces being perpendicular to the substrate, a second gate electrode formed on second side surfaces of the active areas, the second side surfaces being perpendicular to the substrate. The layers are patterned in self-alignment with each other, intersections of the active areas and the first gate electrode form a plurality of memory cells, and the plurality of memory cells in an intersecting plane share the first gate electrode.

Owner:KIOXIA CORP

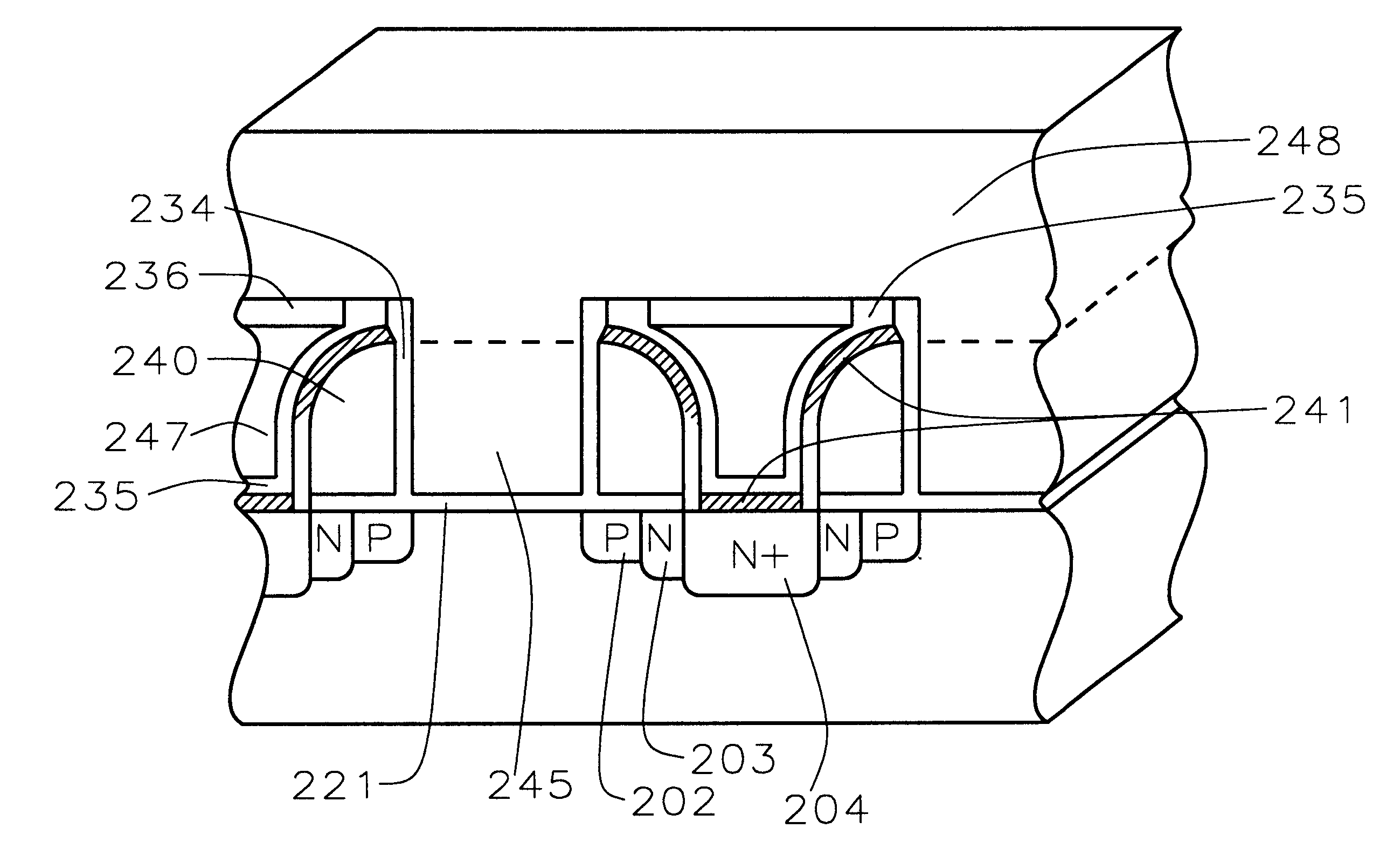

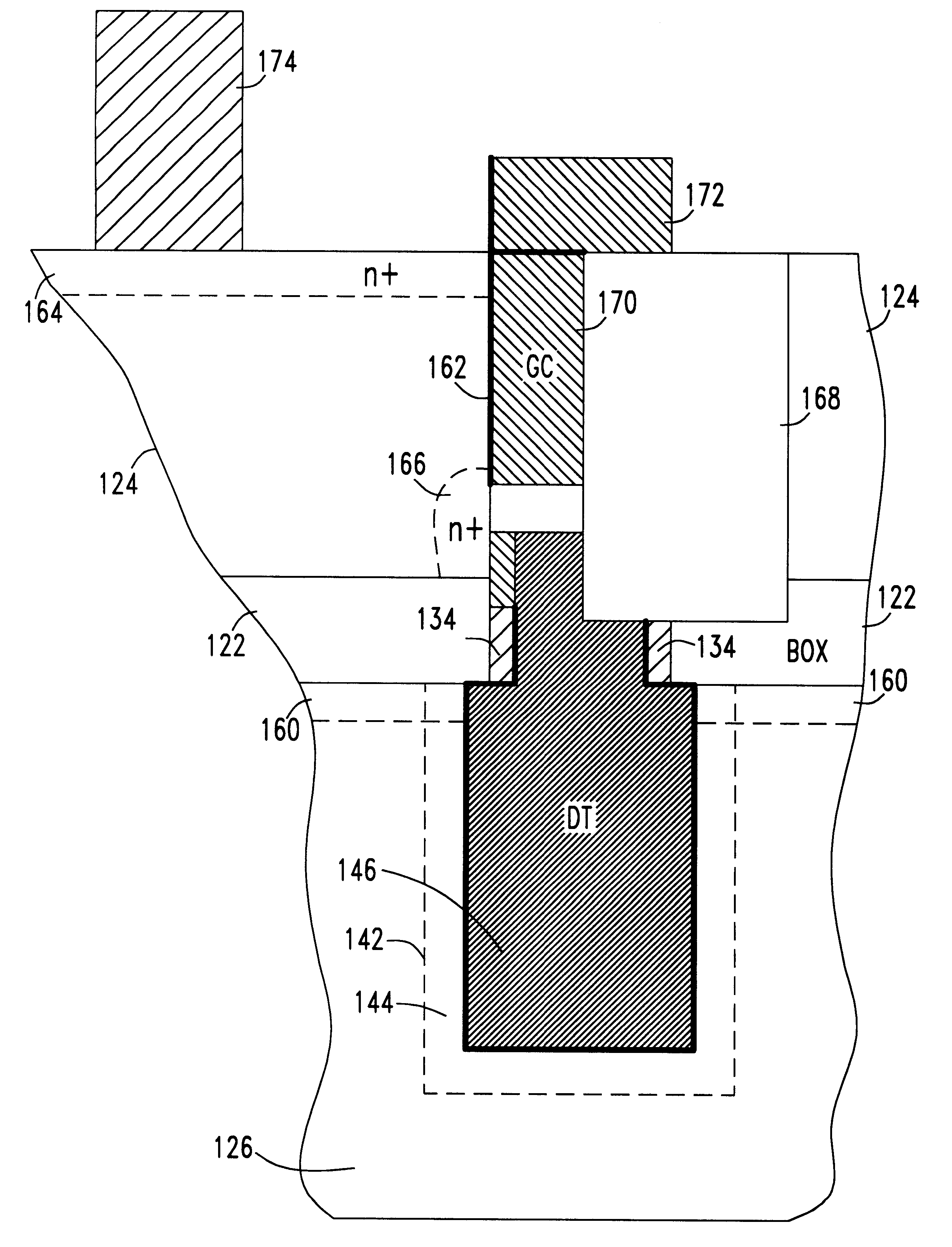

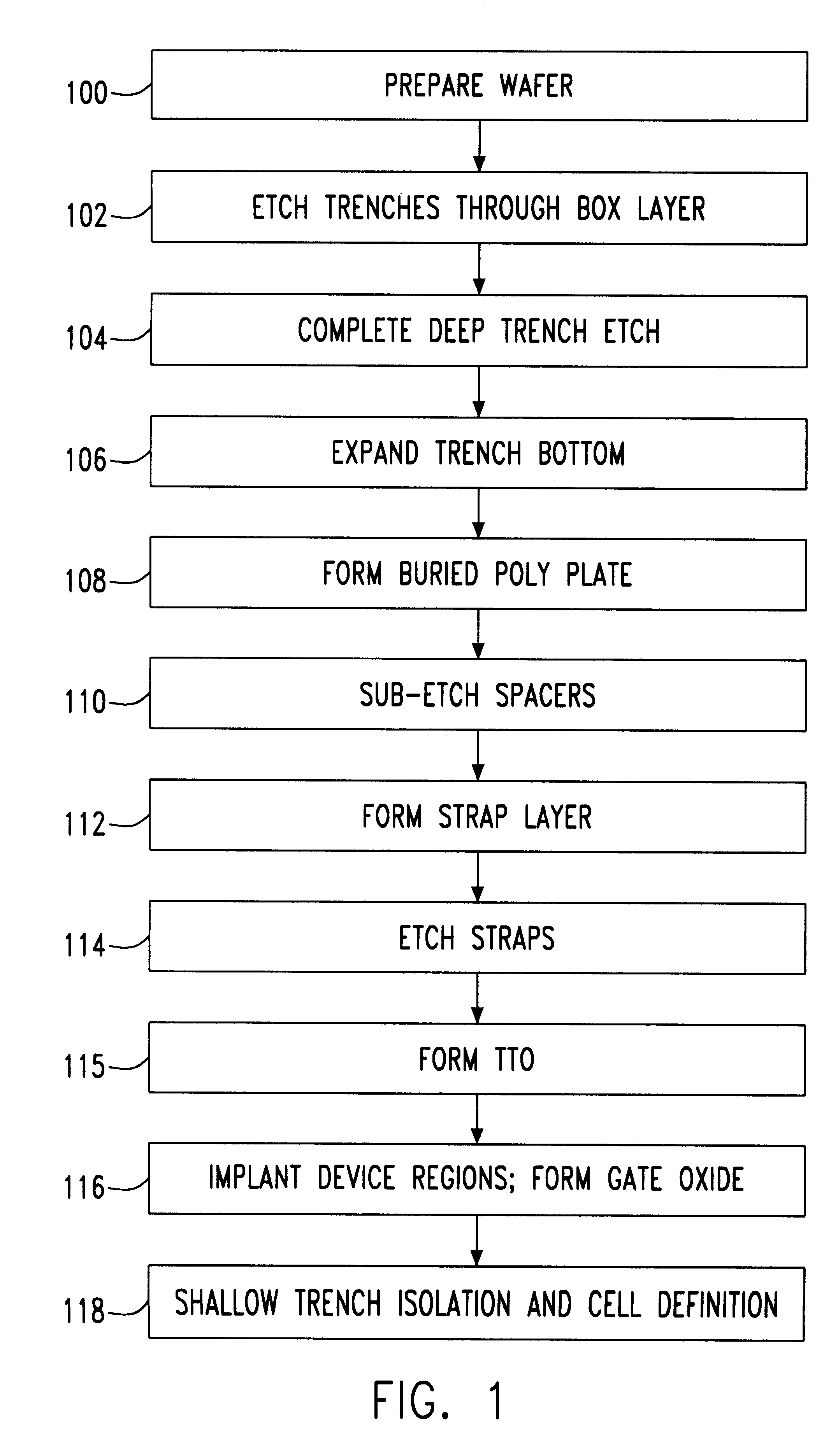

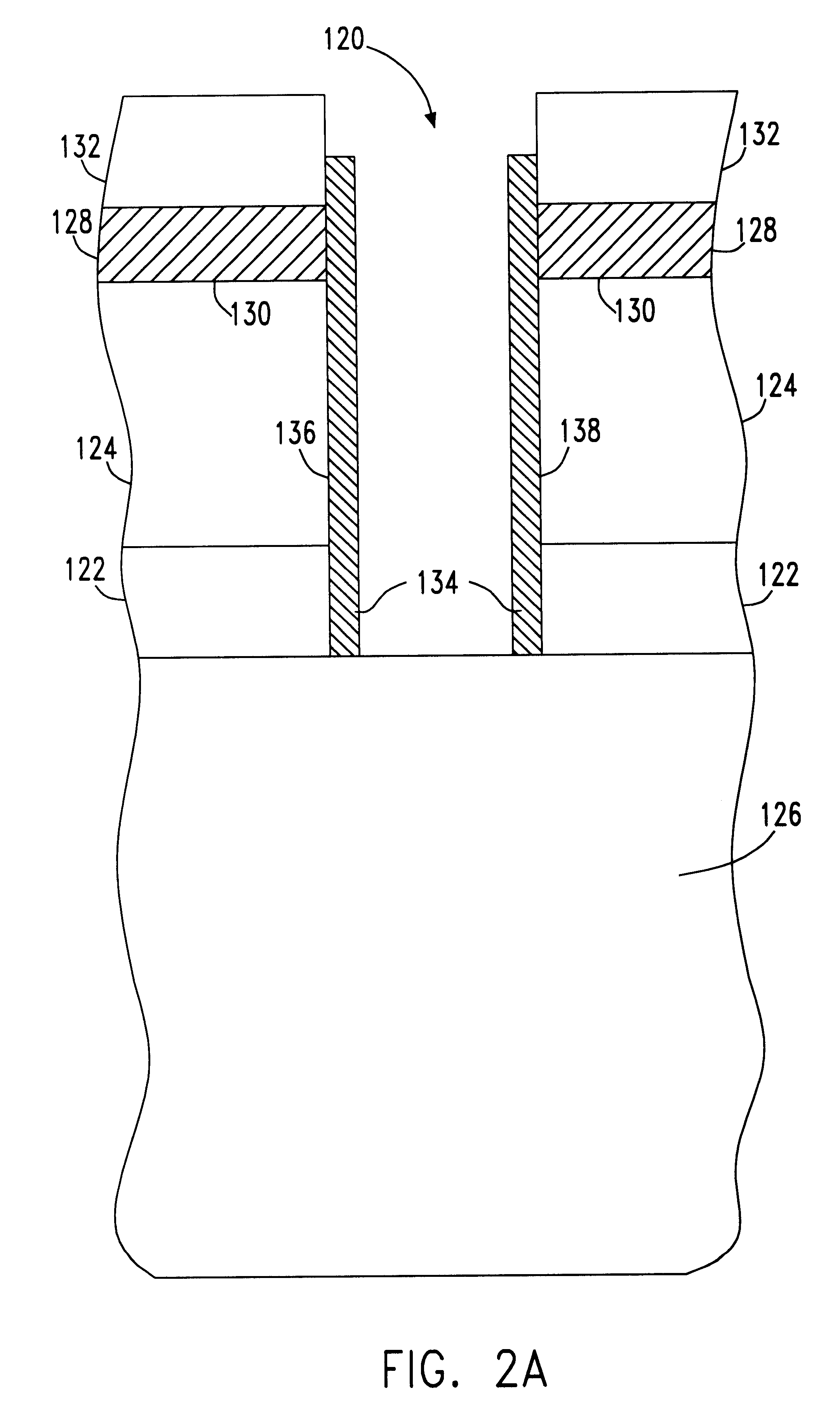

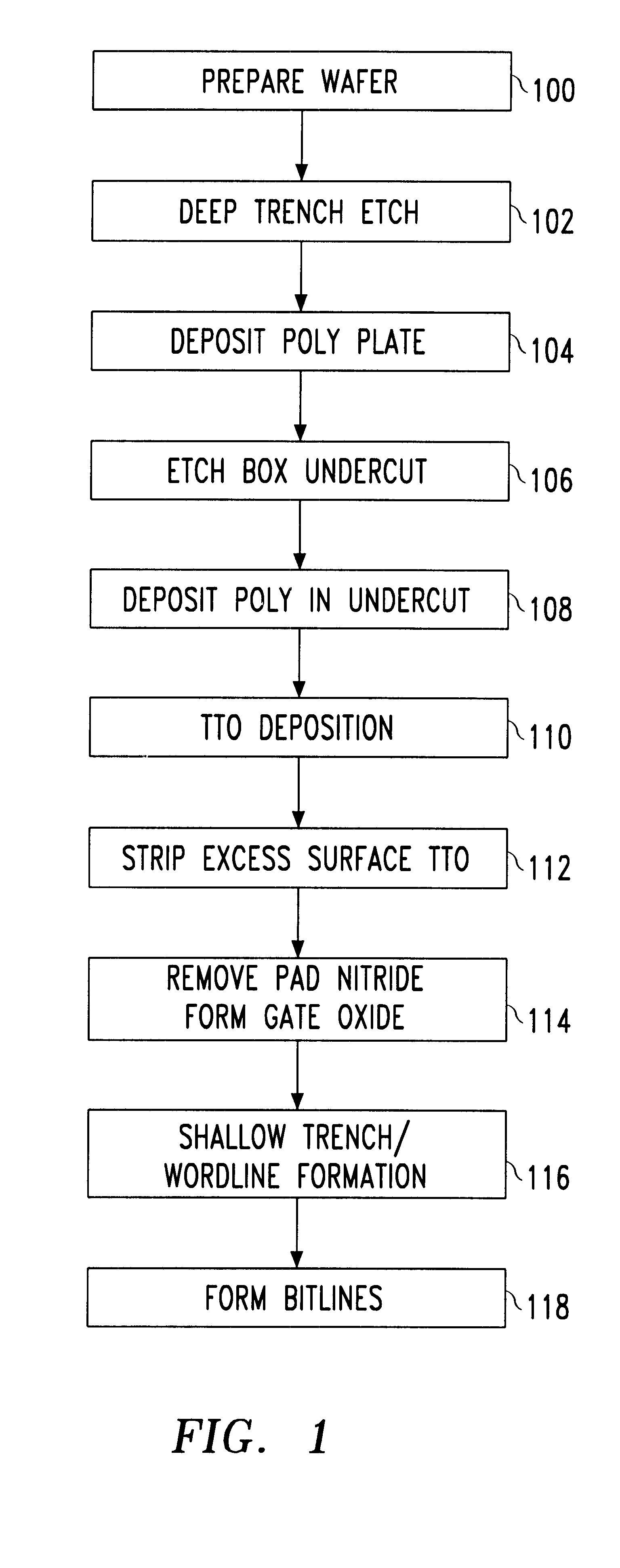

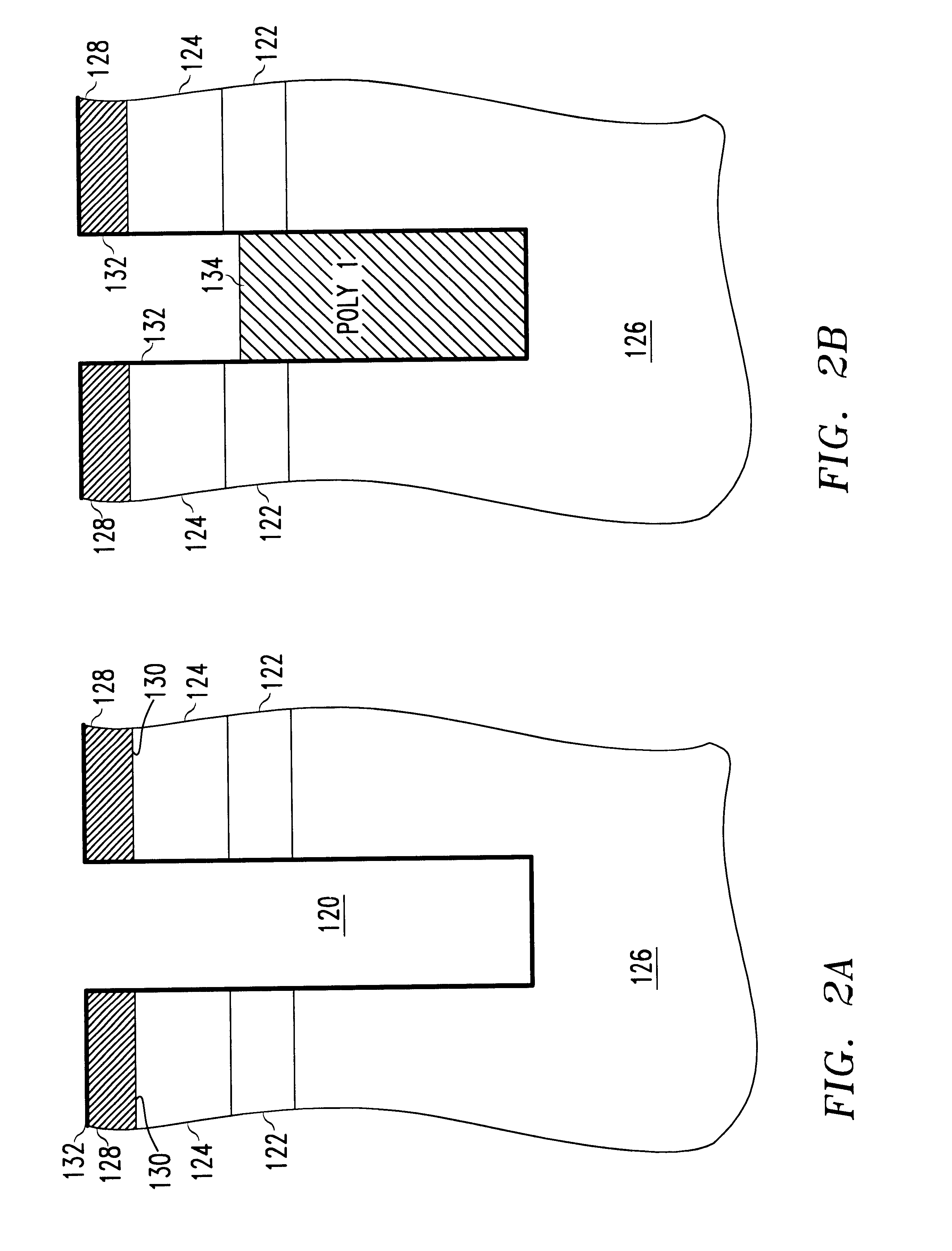

Silicon-on-insulator vertical array device trench capacitor DRAM

InactiveUS6566177B1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringBottle

A silicon on insulator (SOI) dynamic random access memory (DRAM) cell and array and method of manufacture. The memory cell includes a trench storage capacitor connected by a self aligned buried strap to a vertical access transistor. A buried oxide layer isolates an SOI layer from a silicon substrate. The trench capacitor is formed in the substrate and the access transistor is formed on a sidewall of the SOI layer. A polysilicon strap connected to the polysilicon plate of the storage capacitor provides a self-aligned contact to the source of the access transistor. Initially, the buried oxide layer is formed in the wafer. Deep trenches are etched, initially just through the SOI layer and the BOX layer. Protective sidewalls are formed in the trenches. Then, the deep trenches are etched into the substrate. The volume in the substrate is expanded to form a bottle shaped trench. A polysilicon capacitor plate is formed in the deep trenches and conductive polysilicon straps are formed in the trenches between the capacitor plates and the SOI sidewalls. Device regions are defined in the wafer and a sidewall gate is formed in the deep trenches. Shallow trenches isolation (STI) is used to isolate and define cells. Bitlines and wordlines are formed on the wafer.

Owner:GOOGLE LLC

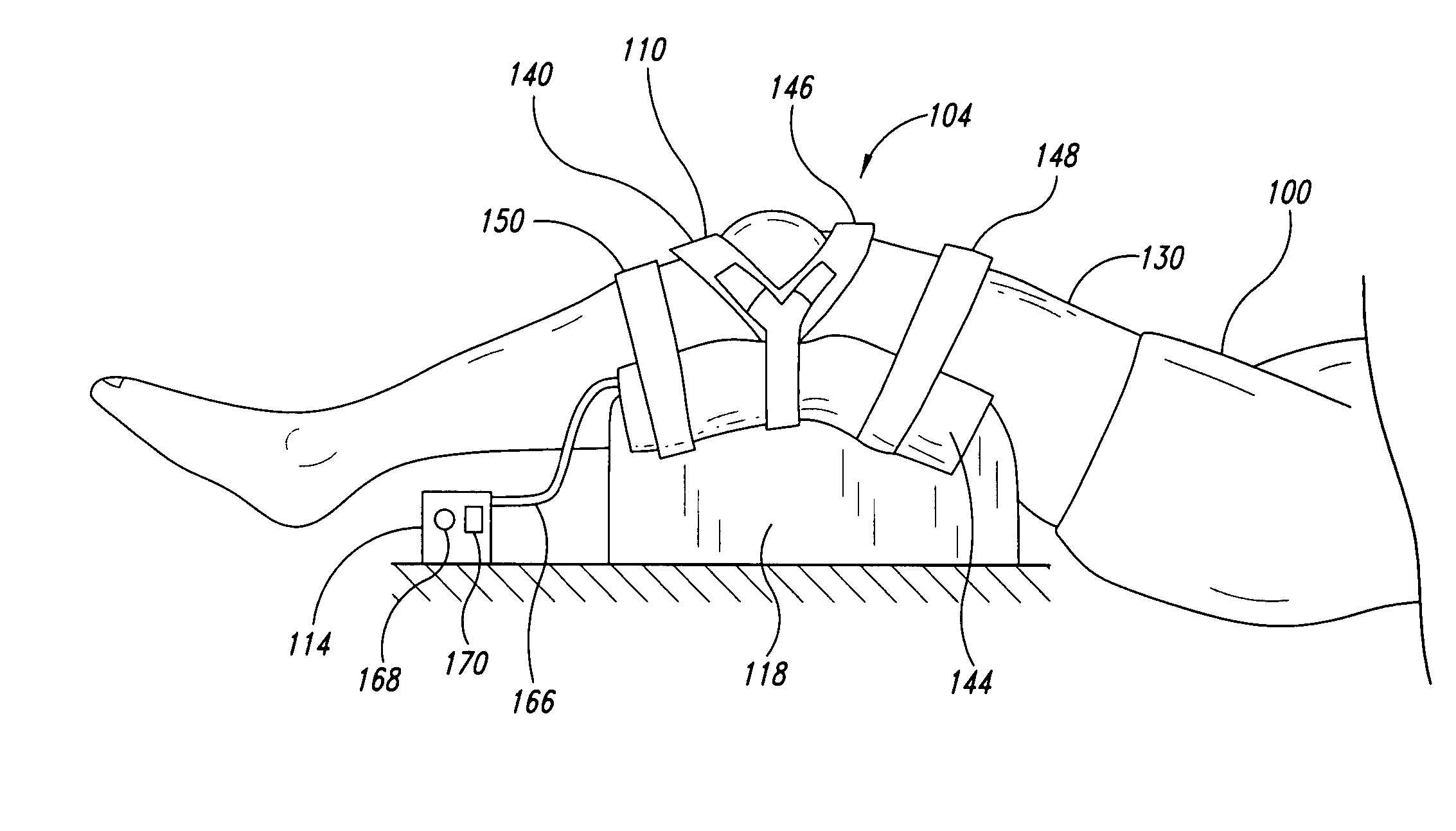

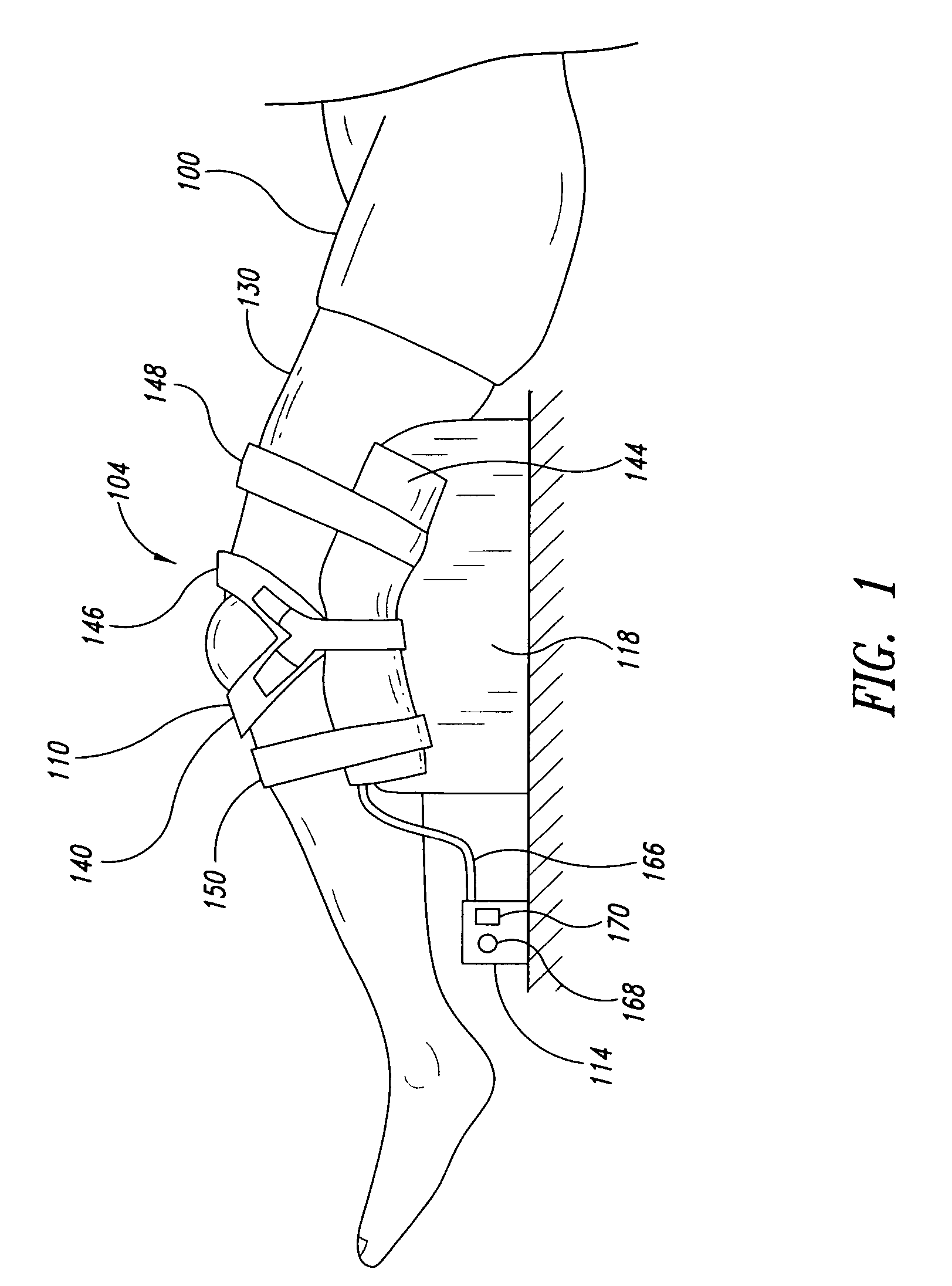

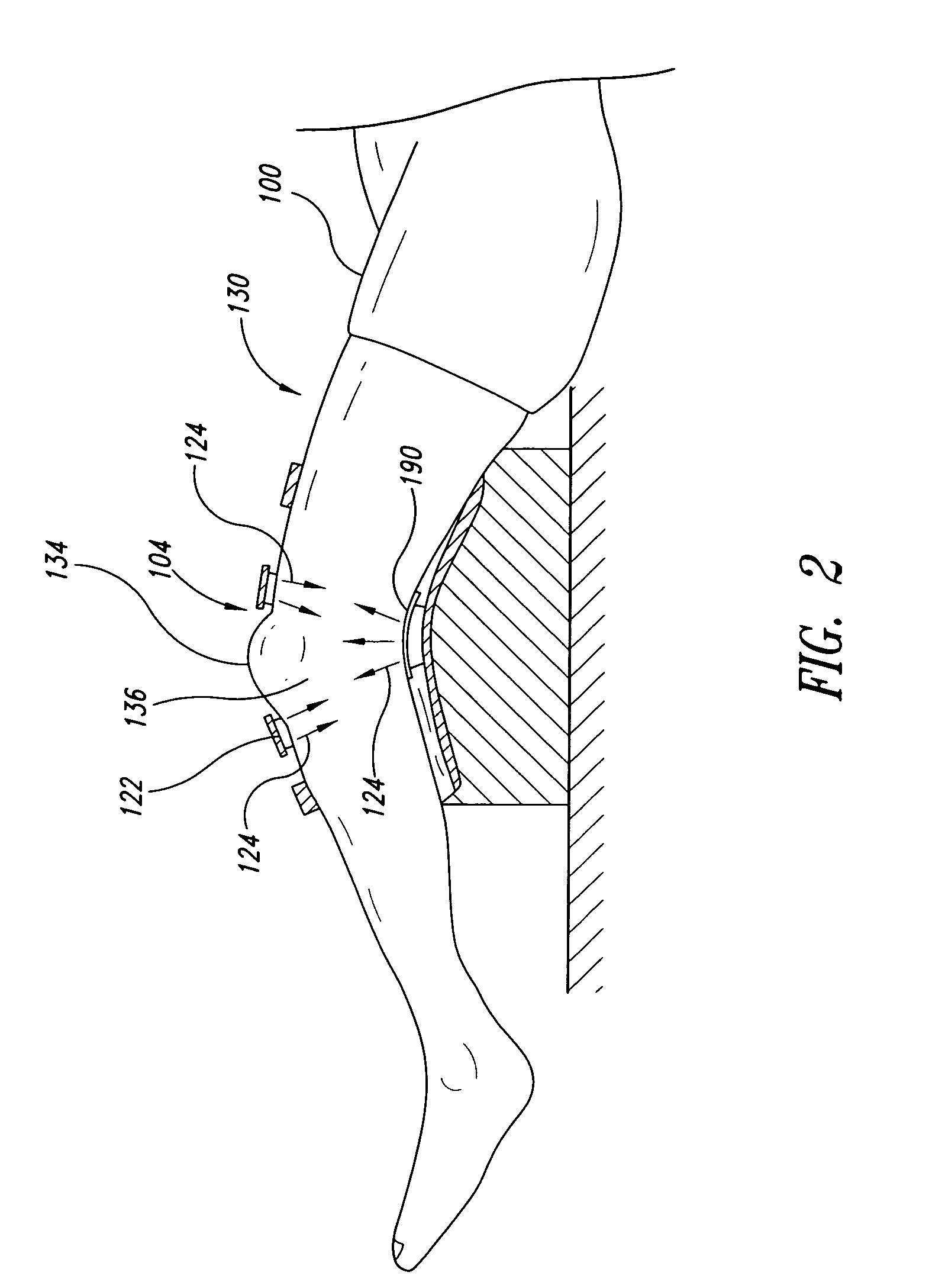

External wearable light therapy treatment systems

InactiveUS20070129776A1Reinforced jointsImprove abilitiesDiagnosticsSurgeryLight therapyLight energy

A light therapy system provides for self-alignment or positioning with respect to a joint of a subject. The light therapy system can provide light therapy to a body part of a subject. The therapy system has a main body configured to be placed adjacent a target site and an activatable light emitting system is coupled to the main body. The light emitting system is capable of delivering a therapeutic amount of light energy to the target site when the main body is placed adjacent the target site.

Owner:LIGHT SCI ONCOLOGY

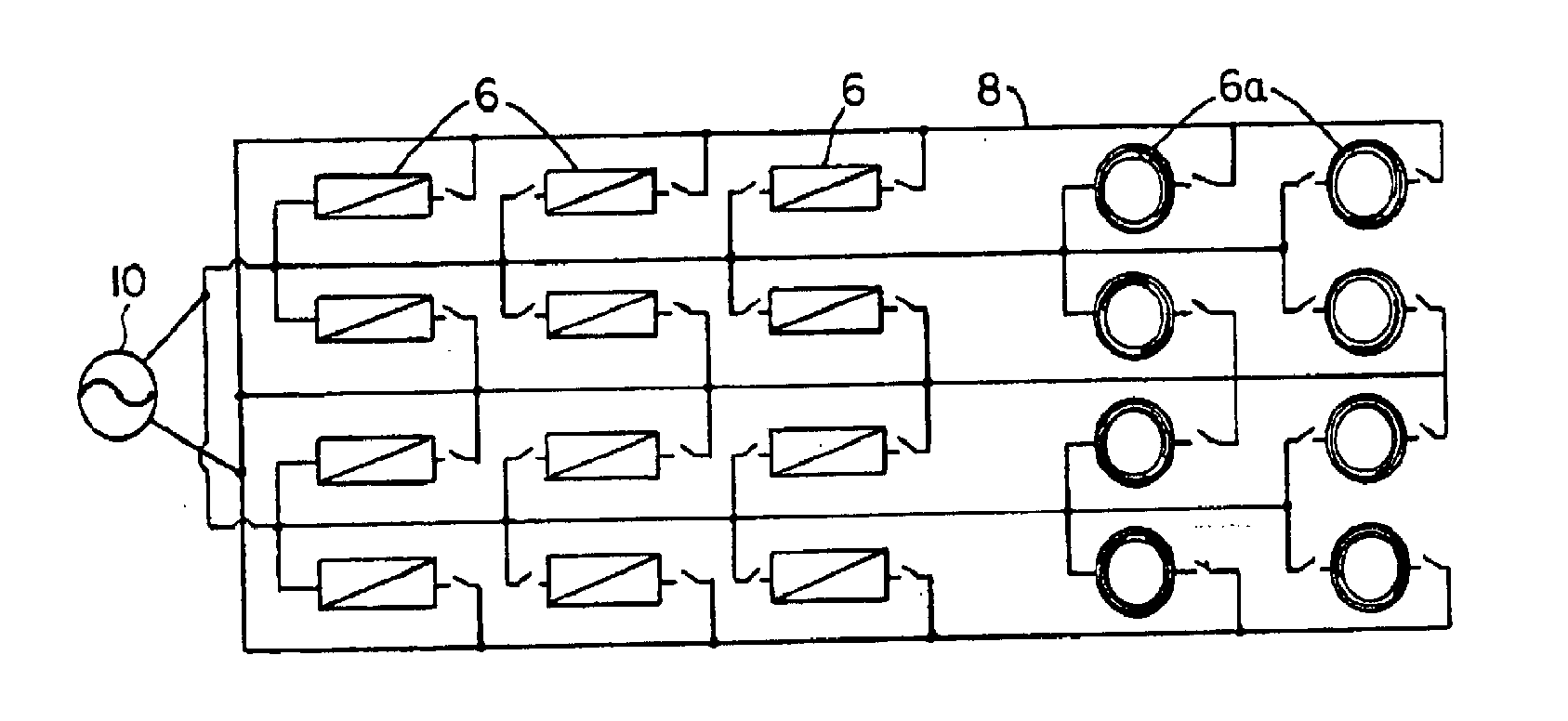

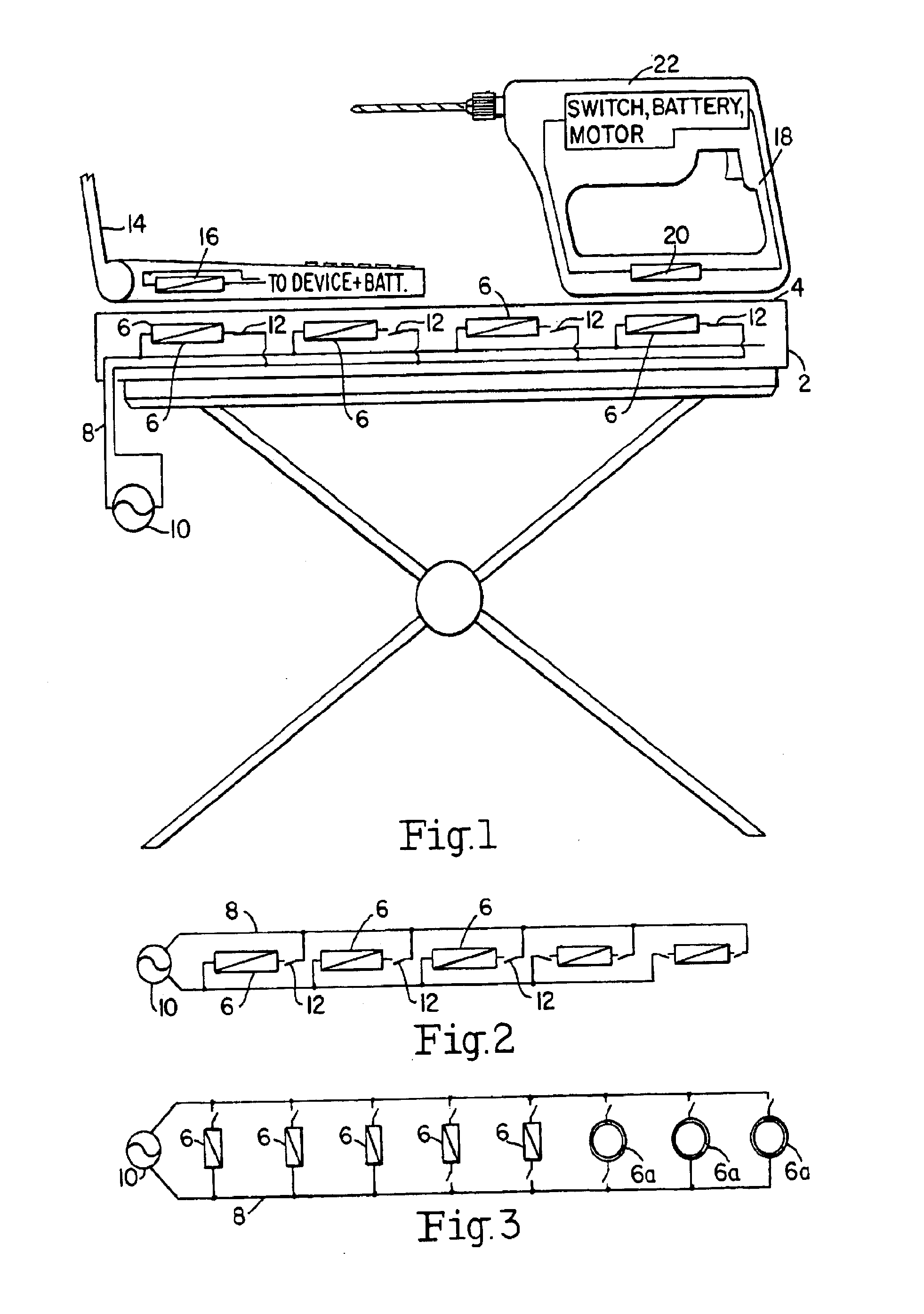

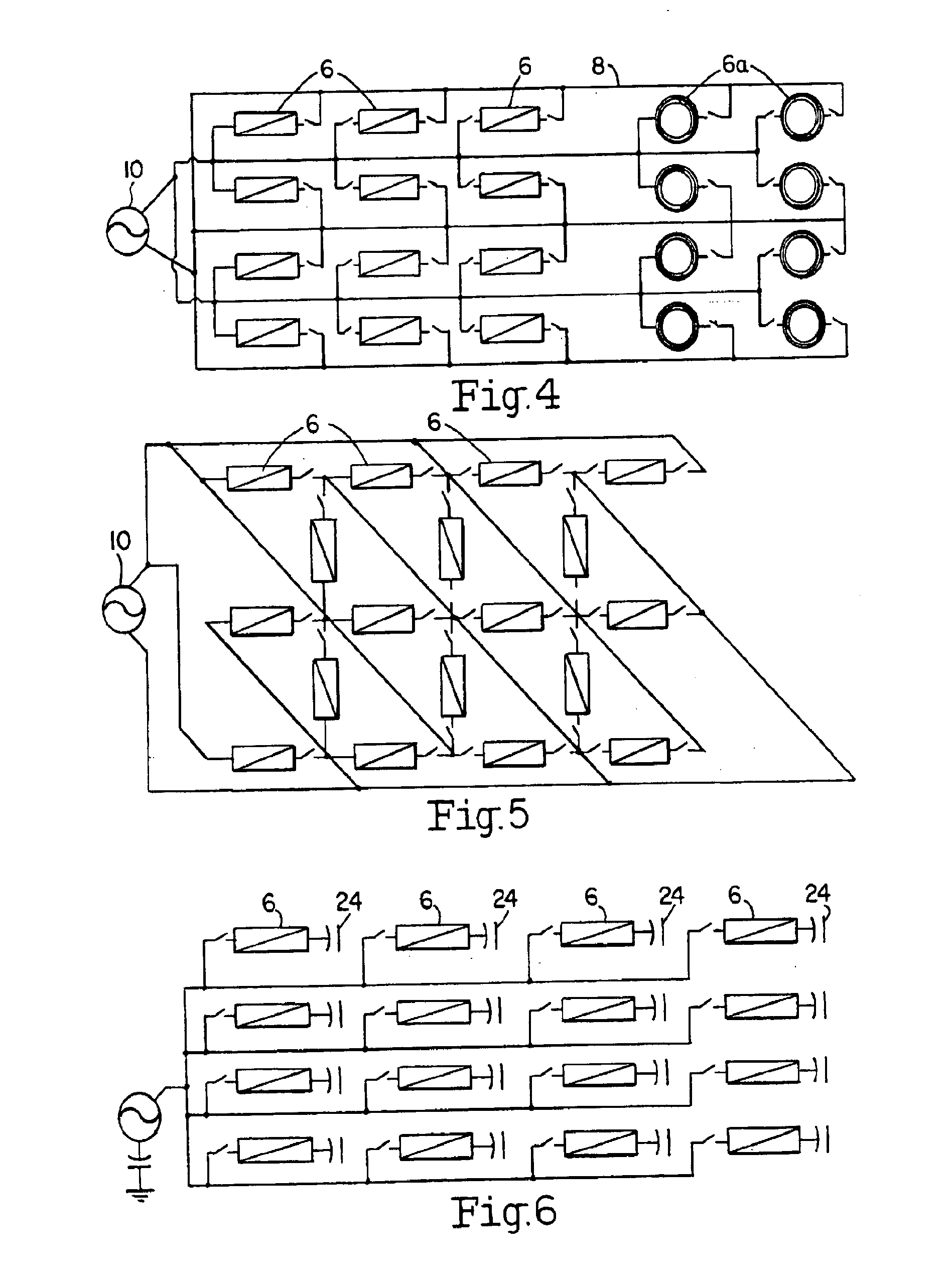

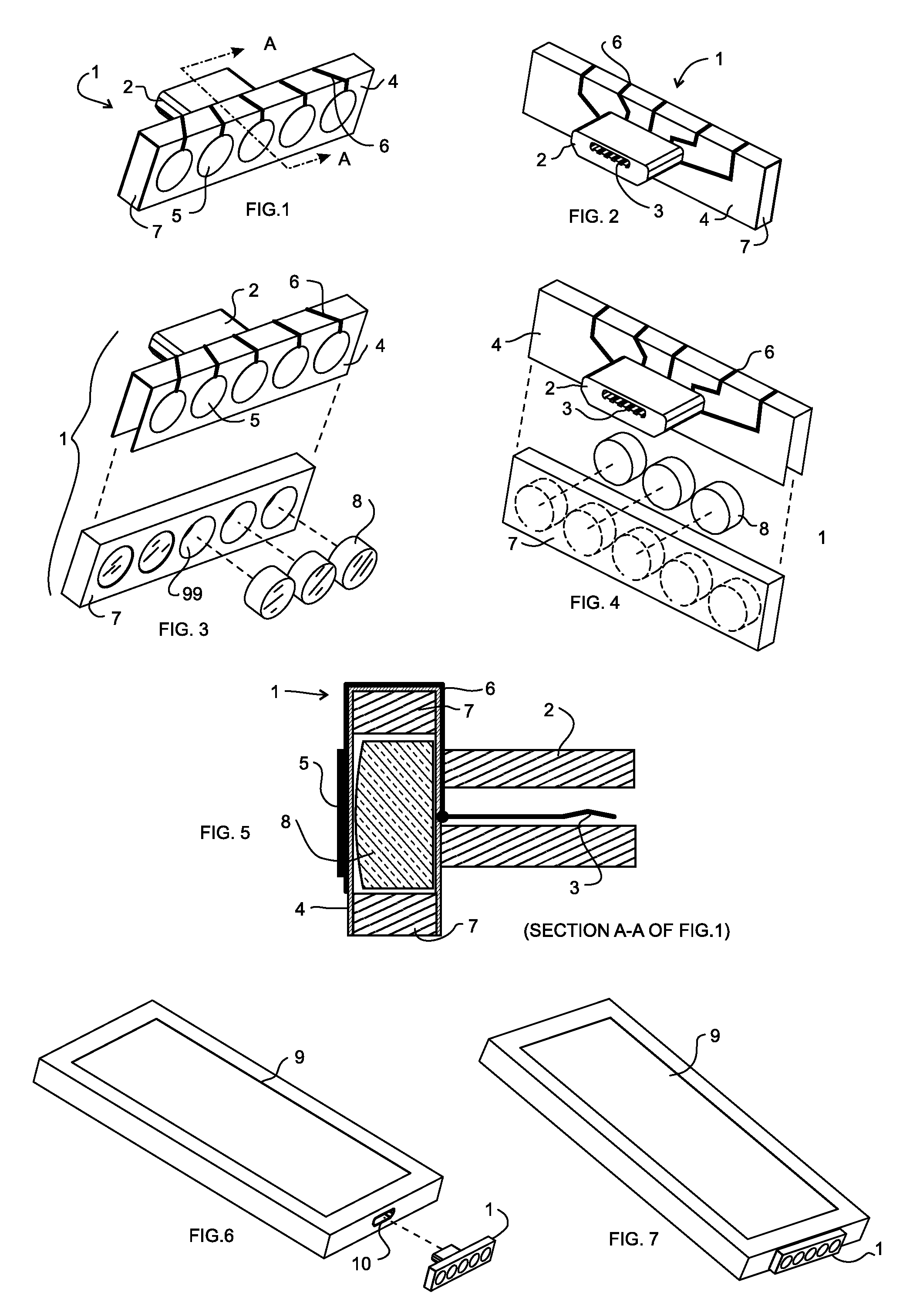

Alignment independent and self-aligning inductive power transfer system

InactiveUS20120146426A1Easy transferTransformersTransformers/inductances circuitsTransfer systemTransformer

An inductive power transfer device is provided for recharging cordless appliances. The device includes a plurality of inductors arranged in an array and connected with a power supply via switches which are selectively operable to activate the respective inductors. The inductors serve as the primary coil of a transformer. The secondary coil of the transformer is arranged in the appliance. When the appliance is arranged proximate to the power transfer device with the respective coils in alignment, power is inductively transferred from the device to the appliance via the transformer.

Owner:SABO ANTHONY

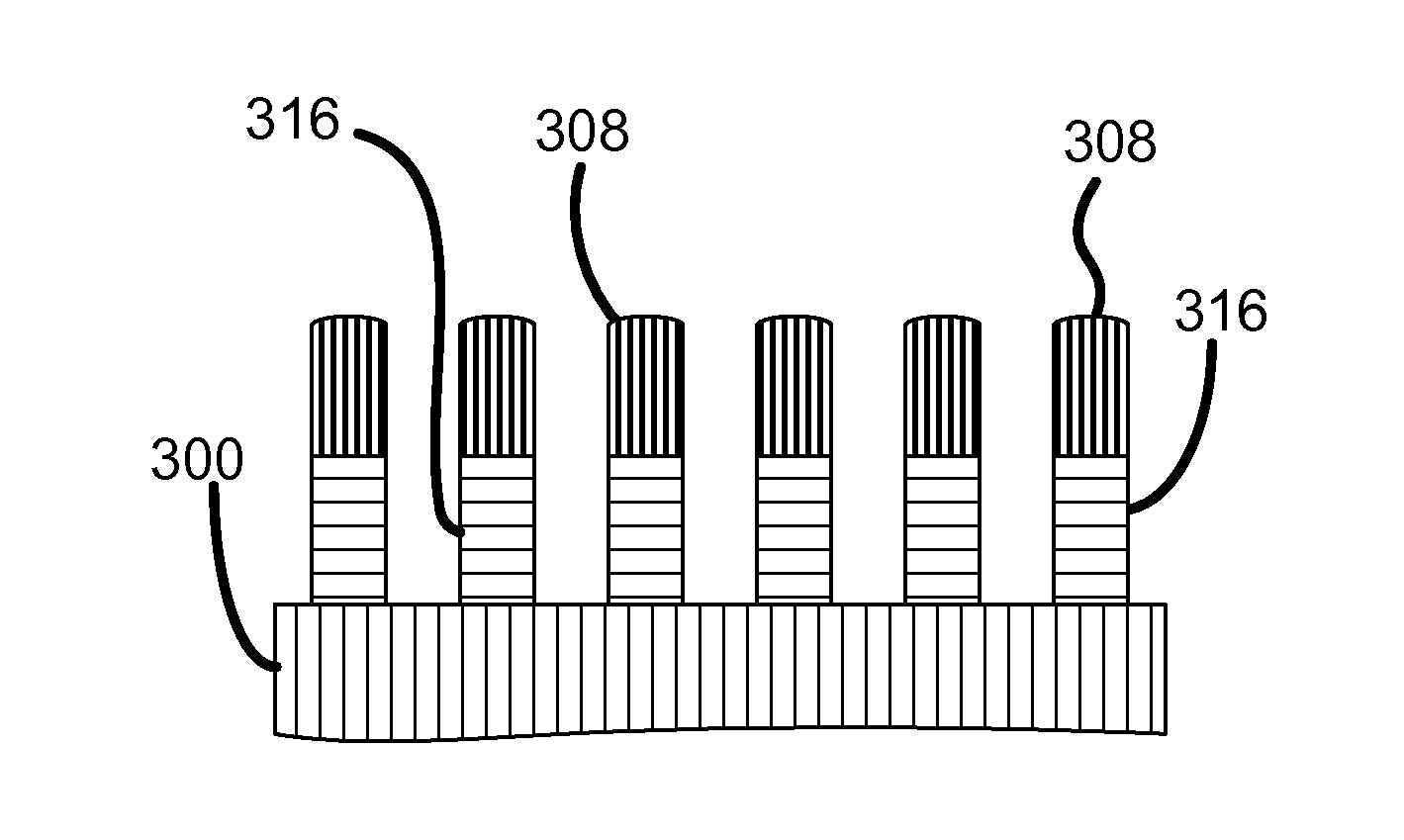

Nanowire mesh device and method of fabricating same

ActiveUS20100207208A1Improved contact schemeImprove scalabilityNanoinformaticsSemiconductor/solid-state device manufacturingNanowireGate dielectric

A semiconductor structure is provided that includes a plurality of vertically stacked and vertically spaced apart semiconductor nanowires (e.g., a semiconductor nanowire mesh) located on a surface of a substrate. One end segment of each vertically stacked and vertically spaced apart semiconductor nanowires is connected to a source region and another end segment of each vertically stacked and vertically spaced apart semiconductor nanowires is connected to a drain region. A gate region including a gate dielectric and a gate conductor abuts the plurality of vertically stacked and vertically spaced apart semiconductor nanowires, and the source regions and the drain regions are self-aligned with the gate region.

Owner:GLOBALFOUNDRIES US INC

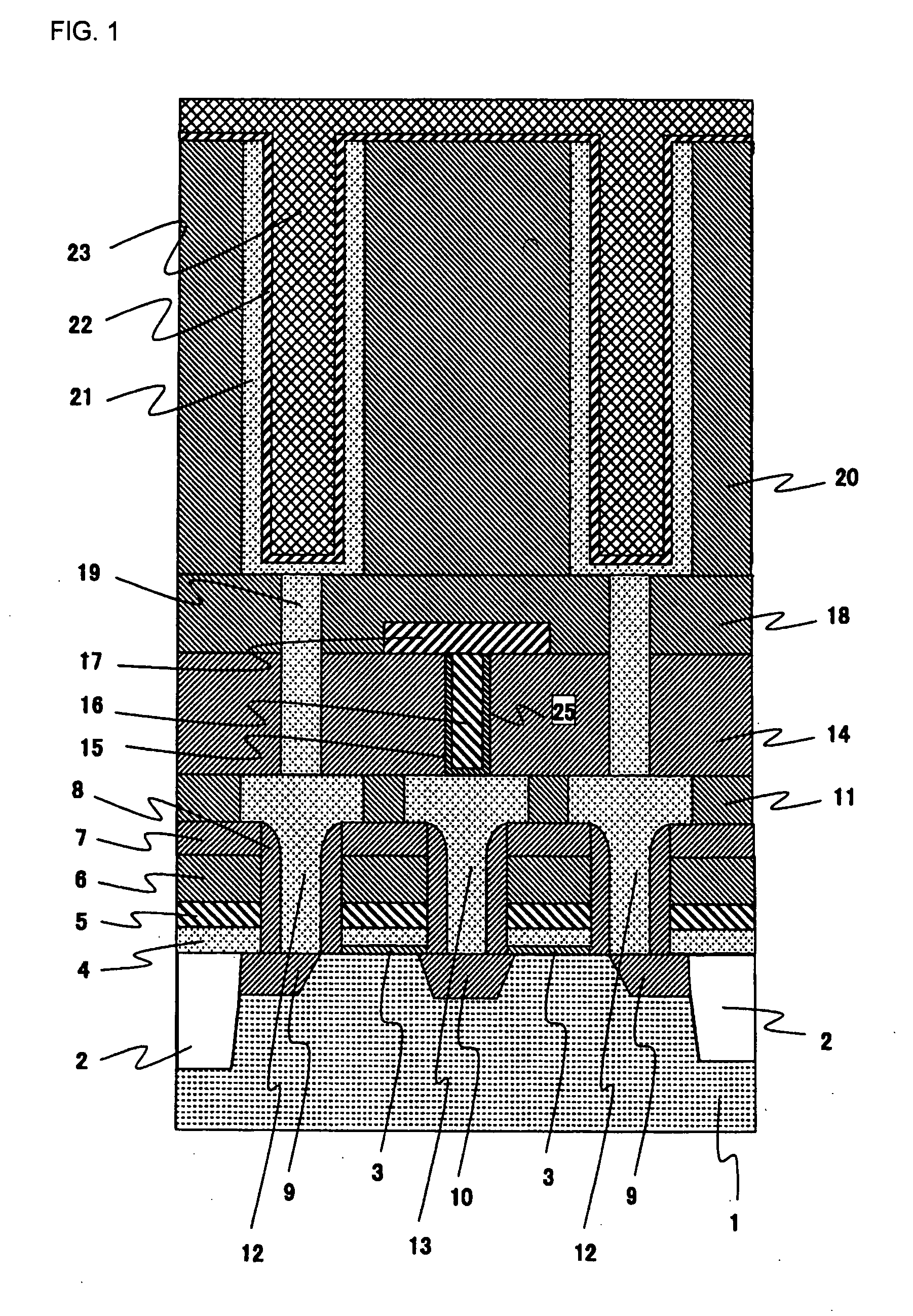

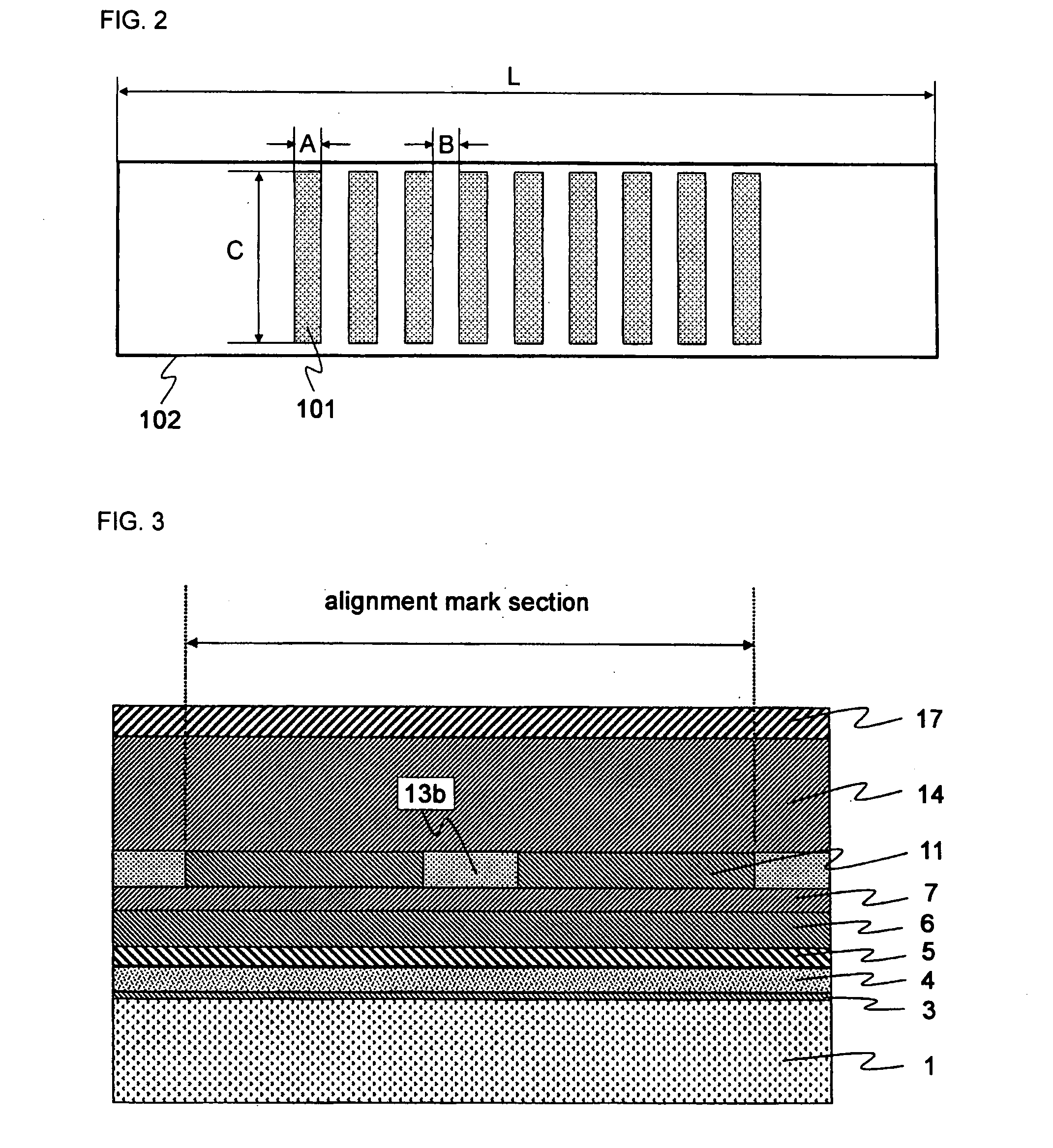

Method of manufacturing semiconductor device

InactiveUS20070275520A1Easy alignmentSolid-state devicesSemiconductor/solid-state device manufacturingPhotoresistSemiconductor

An object of the present inventions is to overcome a problem that the presence of a metal film, which is opaque to a visible light, between a lower layer alignment mark and a photoresist prevents the detection of the lower layer alignment mark, to make the pattern formation difficult. In the present inventions, an insulating film is placed beneath the alignment mark in structure; an alignment mark consisting of said multi-layered film comprising an alignment mark layer and the insulating film, which constitutes a stepped part with an increased difference in level, is first formed, inside a mark hole, in a manner of self-alignment; and then the metal film which is the very cause of the above problem is formed thereon. Since the metal film itself has a stepped shape corresponding to the alignment mark, alignment can be made with great accuracy.

Owner:LONGITUDE SEMICON S A R L

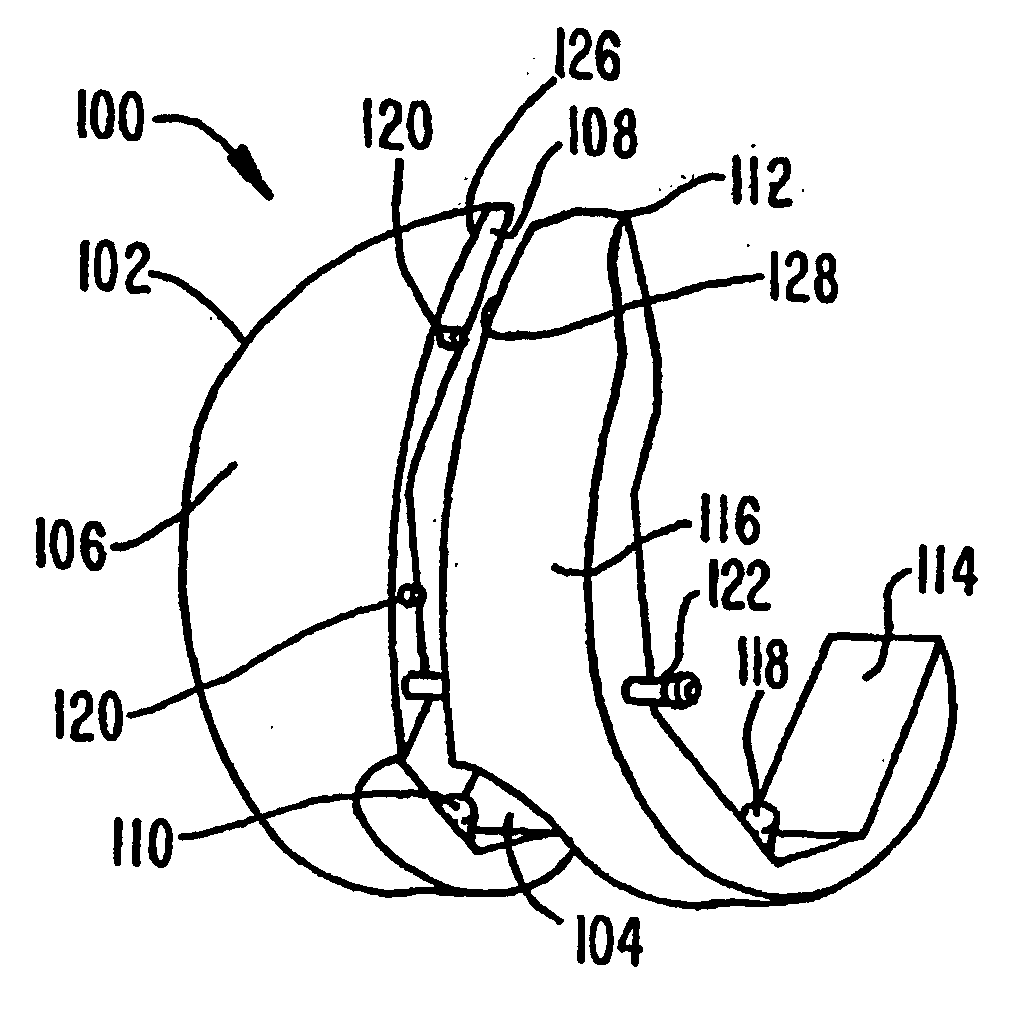

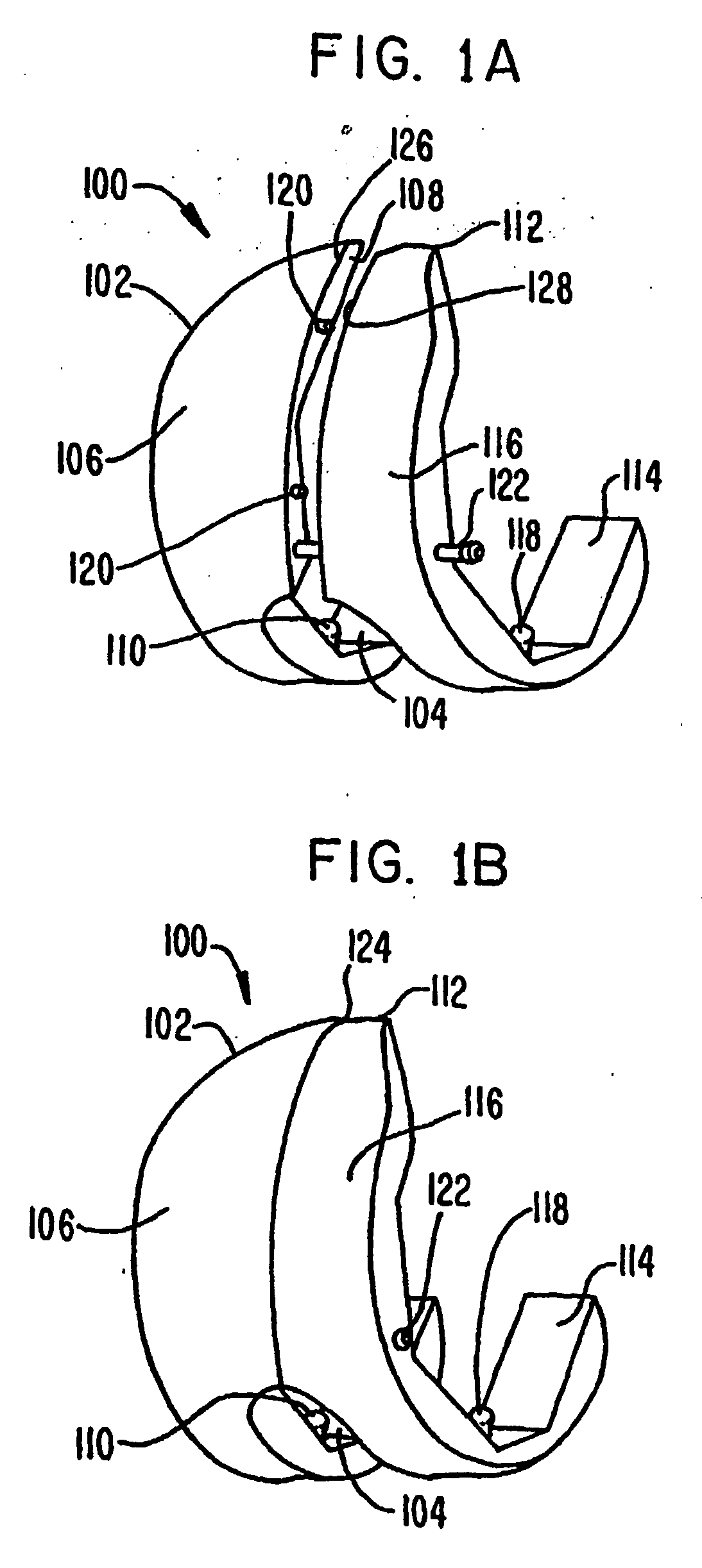

Modular femoral component for a total knee joint replacement for minimally invasive implantation

A femoral component (100) for a total knee joint replacement has a modular structure including a number of segments (102, 112), each of the segments (102, 112) having a femoral fixation surface (104, 114) for attachment to the distal end of a femur and at least one assembly surface (108) for joining with an adjacent segment (102, 112) of the modular femoral component (100). The assembly surfaces (108) are generally planar and arranged to be oriented generally in a plane extending in a proximal-distal direction and in an anterior-posterior direction when the femoral fixation surface (104, 114) is positioned on the distal end of the femur. Although the assembly surfaces (108) are generally planar, they may be shaped or provided with complementary structures (120) to assure self-alignment when the segments (102, 112) are assembled.

Owner:MAKO SURGICAL CORP

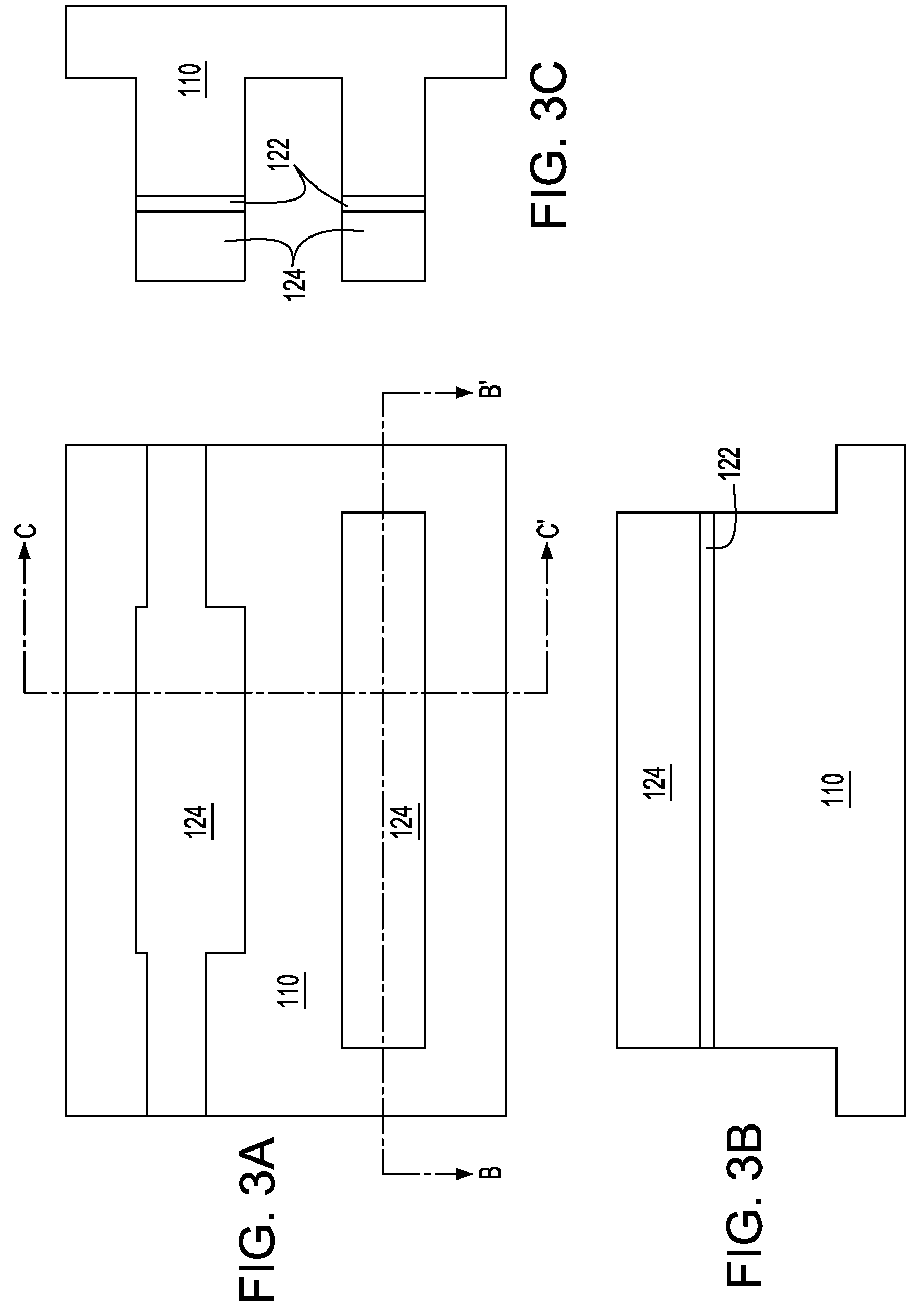

Semiconductor memory and method of manufacturing the same

A semiconductor memory includes a plurality of stripe-like active areas formed by stacking, in a direction perpendicular to a substrate, a plurality of layers extending parallel to the substrate, a first gate electrode formed on first side surfaces of the active areas, the first side surfaces being perpendicular to the substrate, a second gate electrode formed on second side surfaces of the active areas, the second side surfaces being perpendicular to the substrate. The layers are patterned in self-alignment with each other, intersections of the active areas and the first gate electrode form a plurality of memory cells, and the plurality of memory cells in an intersecting plane share the first gate electrode.

Owner:KIOXIA CORP

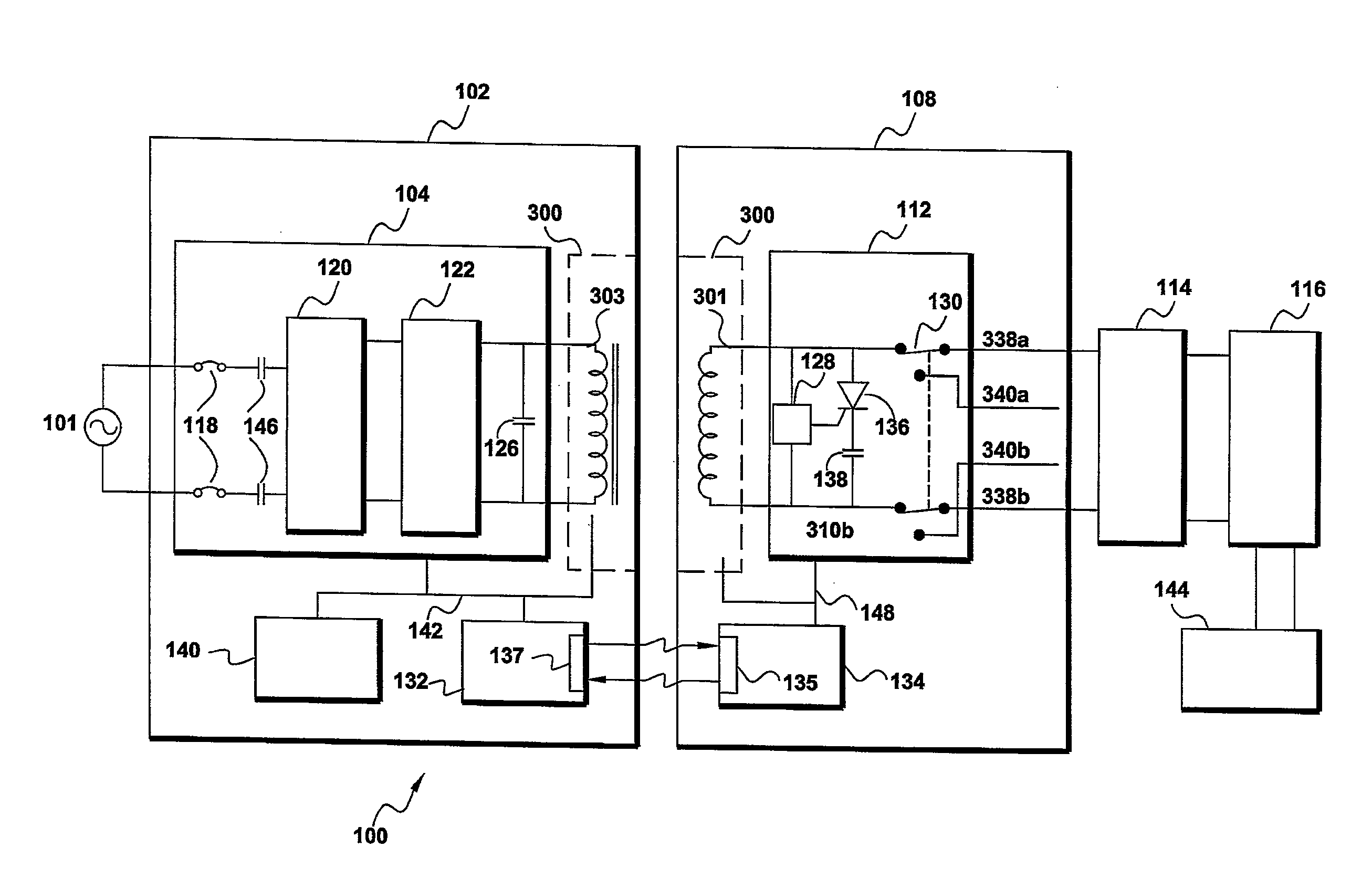

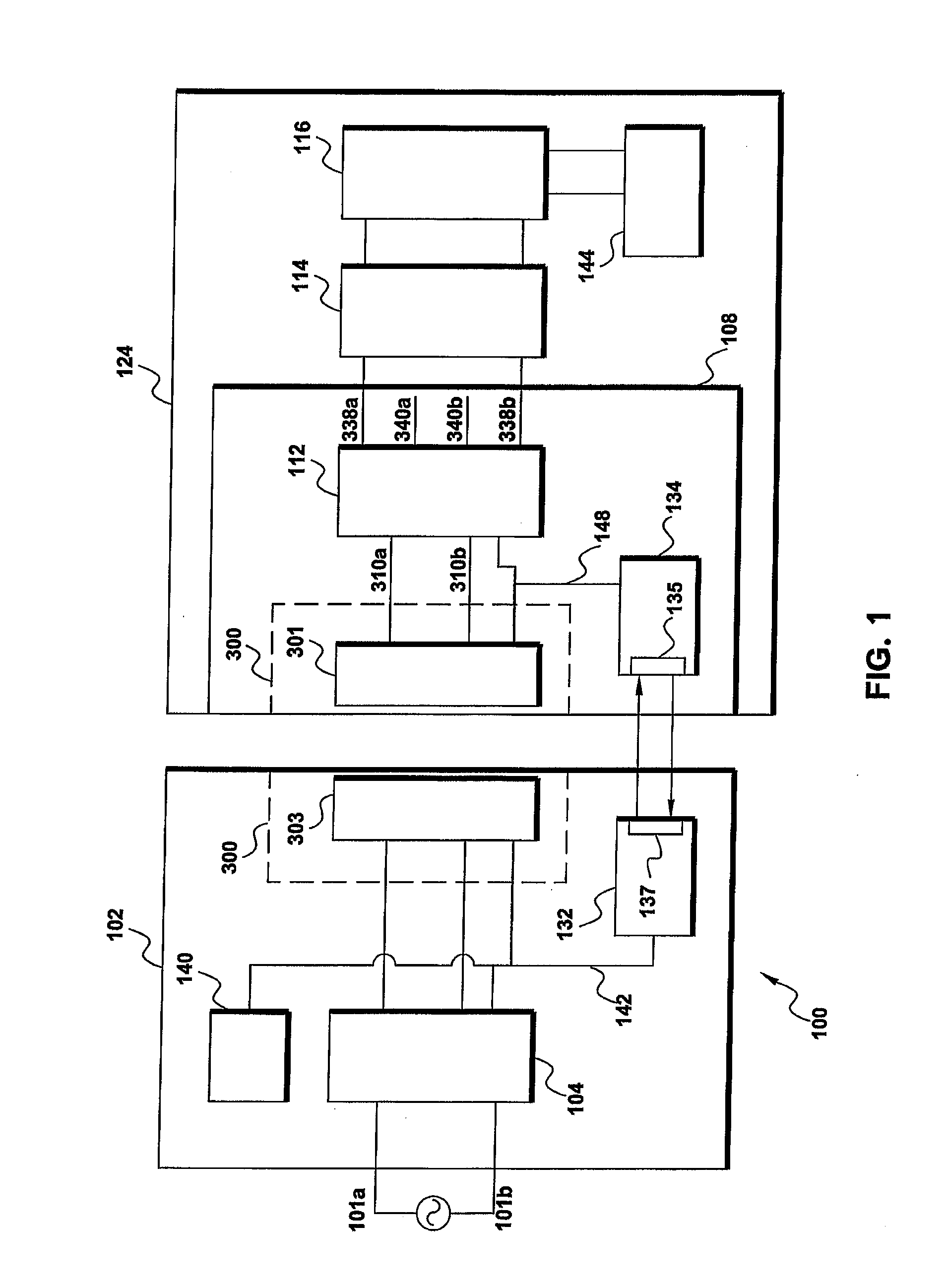

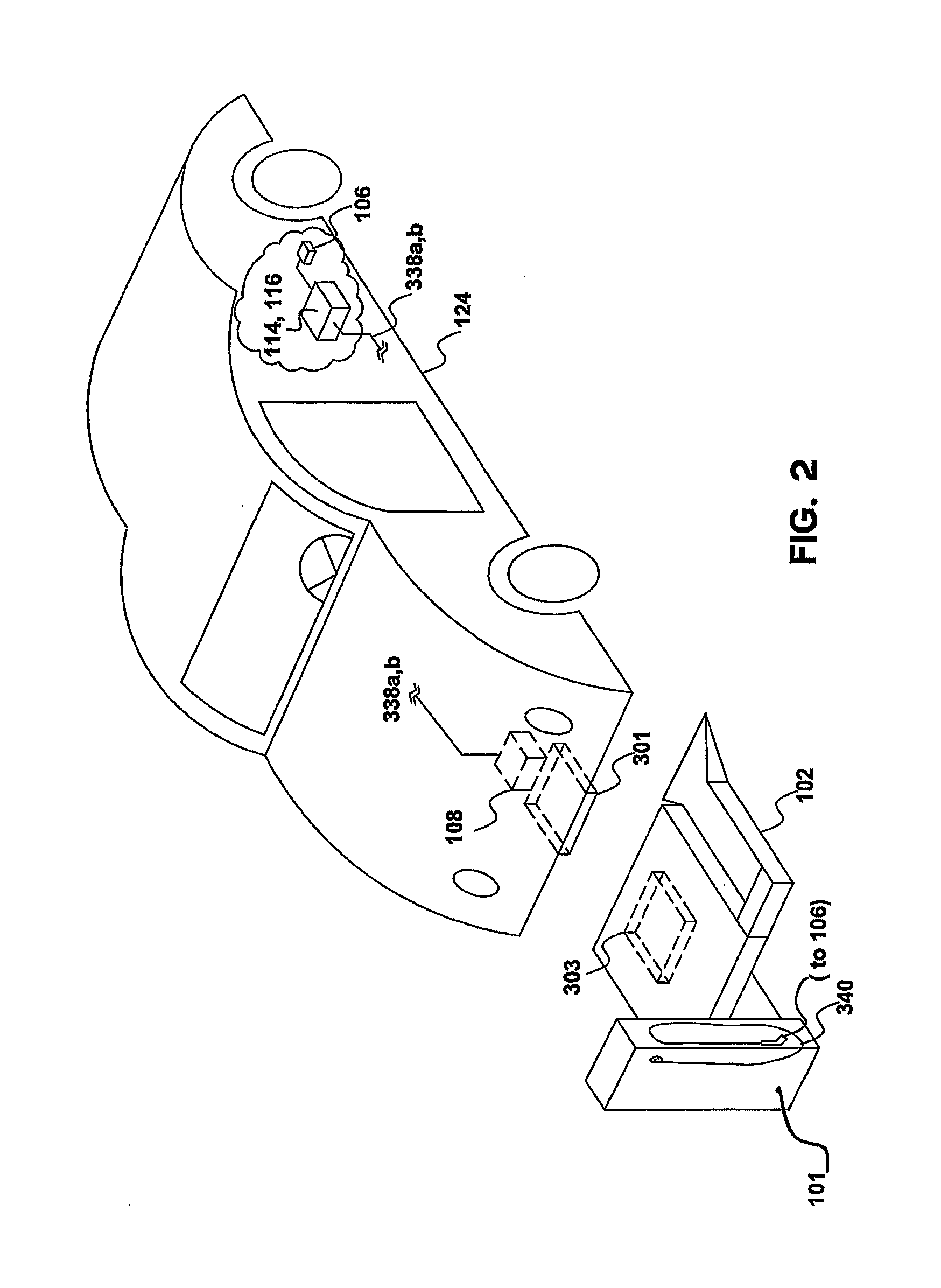

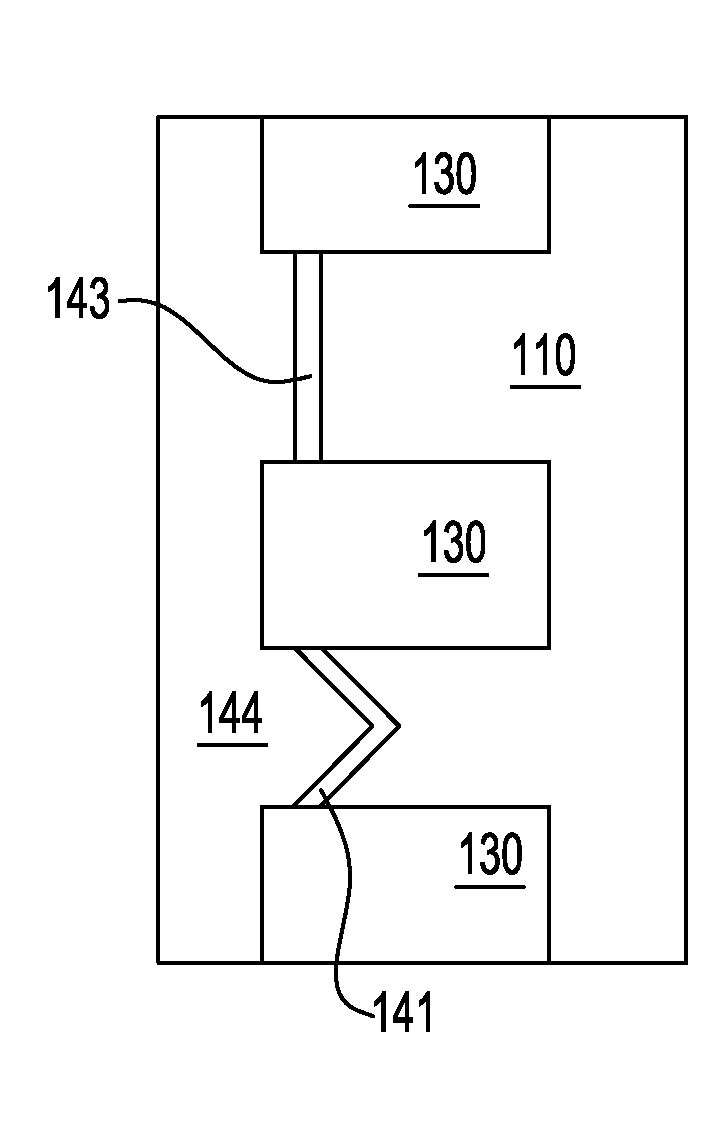

System and method for inductively transferring ac power and self alignment between a vehicle and a recharging station

InactiveUS20110204845A1Reducing induced noiseImprove efficiencyBatteries circuit arrangementsCharging stationsElectrical batteryTransformer

A method and apparatus for hands free inductive charging of batteries for an electric vehicle is characterized by the use of a transformer having a primary coil connected with a charging station and a secondary coil connected with a vehicle. More particularly, the when the vehicle is parked adjacent to the charging station, the primary coil is displaced via a self alignment mechanism to position the primary coil adjacent to the secondary coil to maximize the inductive transfer of charging current to the secondary coil. The self alignment mechanism preferably utilizes feedback signals from the secondary coil to automatically displace the primary coil in three directions to position the primary coil for maximum efficiency of the transformer.

Owner:PLUGLESS POWER INC

Enhanced mobility CMOS transistors with a v-shaped channel with self-alignment to shallow trench isolation

InactiveUS20080173906A1Improve performanceIncrease the on-currentTransistorSolid-state devicesCMOSCharge carrier mobility

The present invention provides structures and methods for a transistor formed on a V-shaped groove. The V-shaped groove contains two crystallographic facets joined by a ridge. The facets have different crystallographic orientations than what a semiconductor substrate normally provides such as the substrate orientation or orientations orthogonal to the substrate orientation. Unlike the prior art, the V-shaped groove is formed self-aligned to the shallow trench isolation, eliminating the need to precisely align the V-shaped grooves with lithographic means. The electrical properties of the new facets, specifically, the enhanced carrier mobility, are utilized to enhance the performance of transistors. In a transistor with a channel on the facets that are joined to form a V-shaped profile, the current flows in the direction of the ridge joining the facets avoiding any inflection in the direction of the current.

Owner:GLOBALFOUNDRIES INC

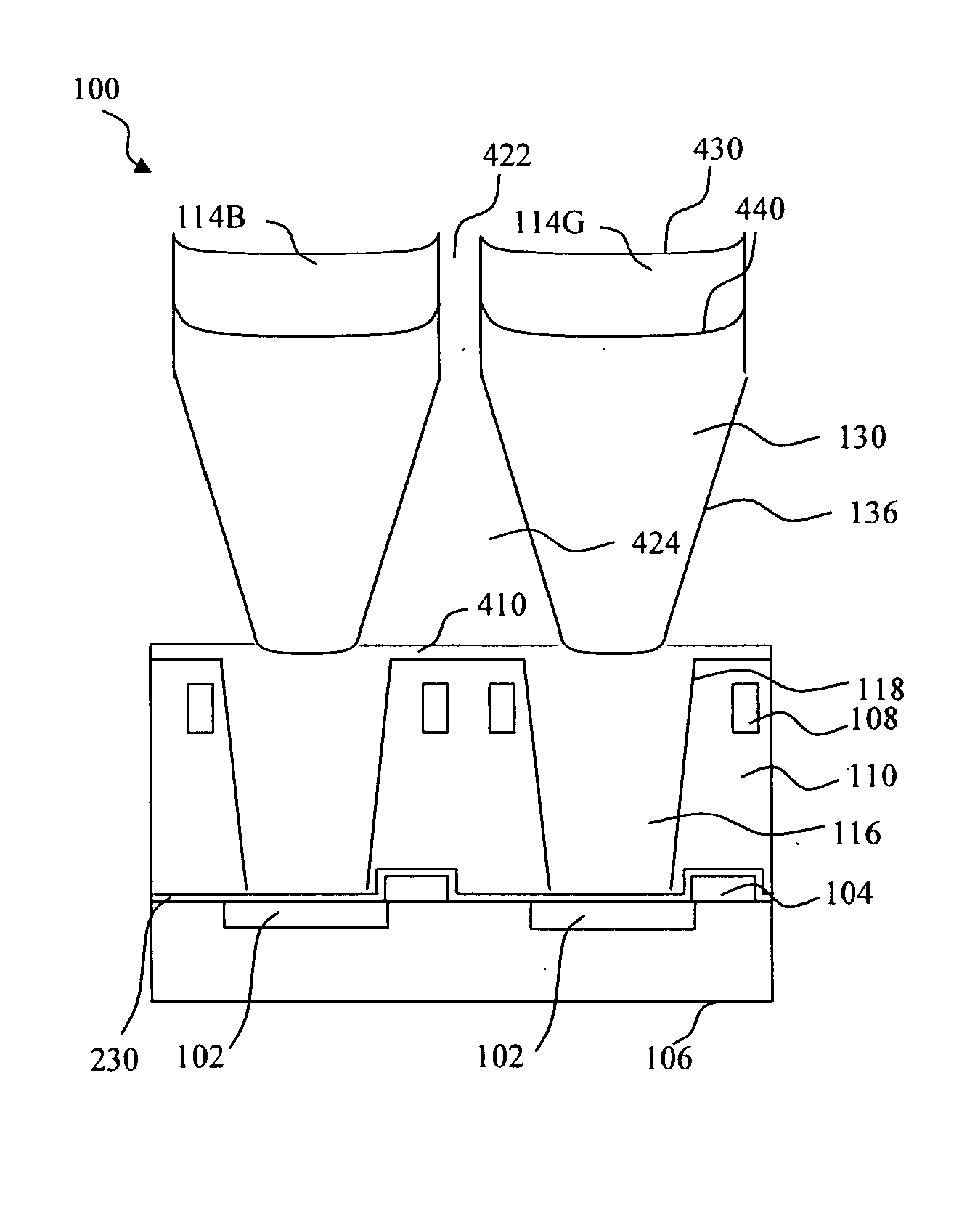

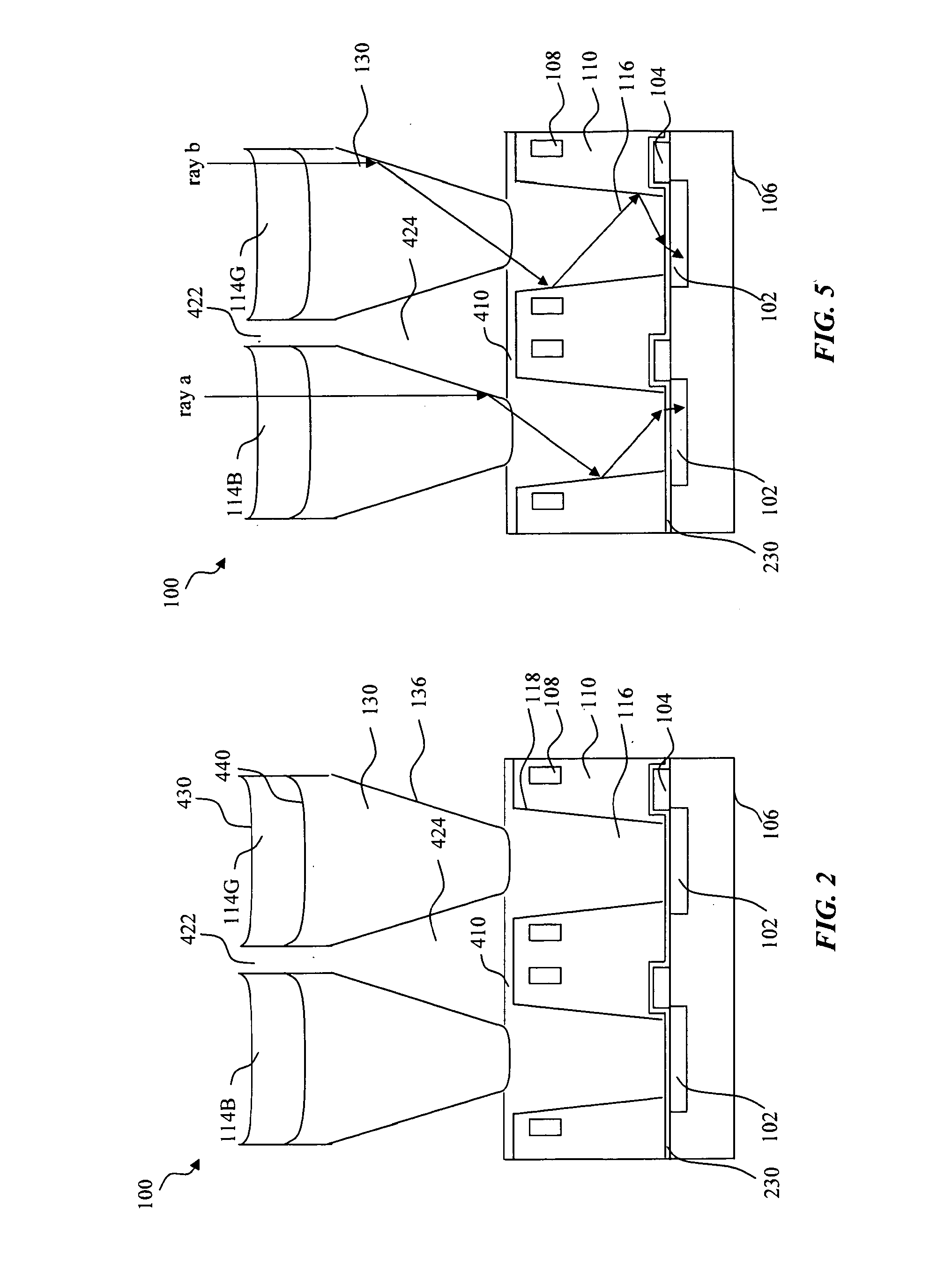

Light guide array for an image sensor

An image sensor pixel that includes a photoelectric conversion unit supported by a substrate and an insulator adjacent to the substrate. The pixel includes a cascaded light guide that is located within an opening of the insulator and extends above the insulator such that a portion of the cascaded light guide has an air interface. The air interface improves the internal reflection of the cascaded light guide. The cascaded light guide may include a self-aligned color filter having air-gaps between adjacent color filters. Air-gaps may be sealed from above by a transparent sealing film. The transparent sealing film may have a concave surface over the air-gap to diverge light that cross the concave surface into the air-gap away from the air-gap into adjacent color filters. These characteristics of the light guide eliminate the need for a microlens. Additionally, a portion of a support wall between a pair of color filters may have a larger width above than below to form a necking to hold down the color filters for better retention.

Owner:TAY HIOK NAM +1

Vertically stacked field programmable nonvolatile memory and method of fabrication

A very high density field programmable memory is disclosed. An array is formed vertically above a substrate using several layers, each layer of which includes vertically fabricated memory cells. The cell in an N level array may be formed with N+1 masking steps plus masking steps needed for contacts. Maximum use of self alignment techniques minimizes photolithographic limitations. In one embodiment the peripheral circuits are formed in a silicon substrate and an N level array is fabricated above the substrate.

Owner:SANDISK TECH LLC

Interposer connectors with magnetic components

ActiveUS20130273752A1Low-profile designLarge dimensional tolerances insensitivityEngagement/disengagement of coupling partsElectric connection structural associationsTablet computerElectrical connection

Disclosed are interposer electrical connector embodiments including magnetic components used to facilitate interconnection of peripheral devices to standard input / output, or “I / O”, connectors (such as USB connectors) of devices such as mobile communications products (e.g. smart phones, tablets, and personal computers). The interposer connector embodiments disclosed include those in which a plurality of discrete permanent magnets are arranged with magnetic poles aligned in the same orientation perpendicular to and on one side of the electrical interface. Other embodiments include a plurality of bar permanent magnets located on opposite sides of the interface with all poles of the same type directed at the interface, but each one opposing a ferromagnetic element. These arrangements provide self-aligning capabilities useful for electrical connections that have restrictions on visibility or connection approach geometries. Other embodiments have a single magnet per mated connector pair and magnetic pole pieces and / or actuators to concentrate magnetic flux providing the magnetic attractive force for a plurality of electrical connections.

Owner:APEX TECH INC

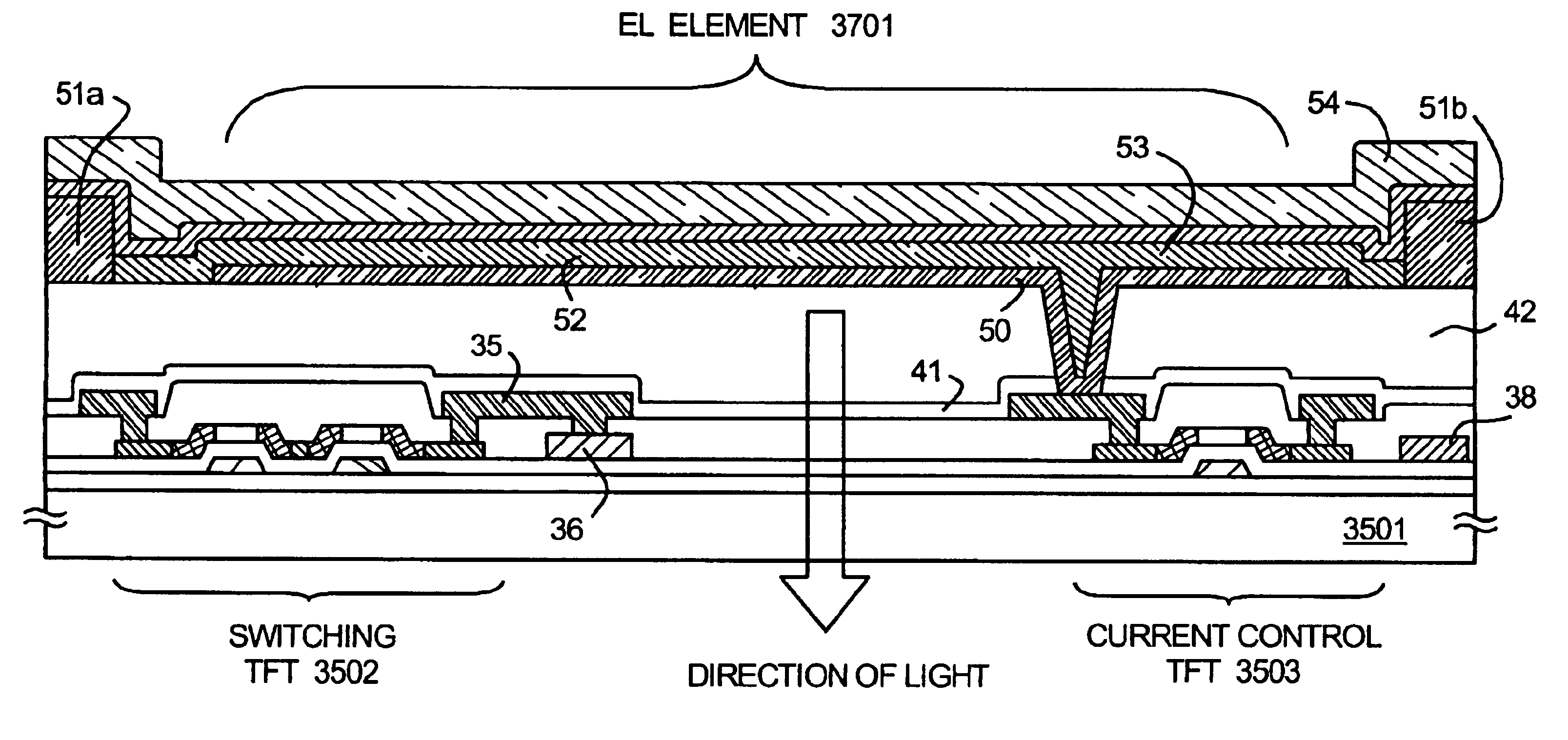

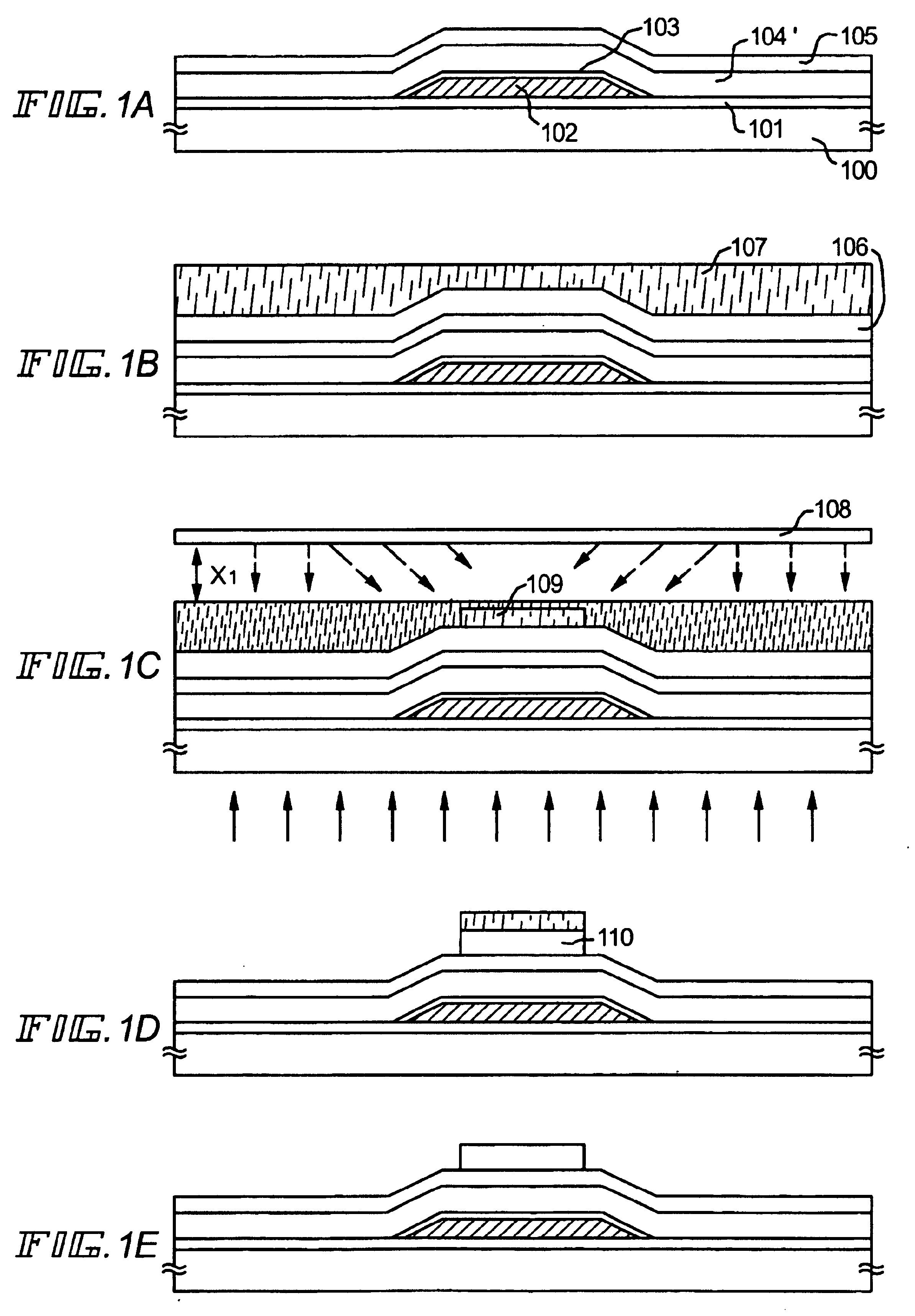

Exposure device, exposure method and method of manufacturing semiconductor device

Owner:SEMICON ENERGY LAB CO LTD

Tunneling effect transistor with self-aligned gate

ActiveUS7700466B2Semiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingField-effect transistorP–n junction

In one embodiment, a mandrel and an outer dummy spacer may be employed to form a first conductivity type region. The mandrel is removed to form a recessed region wherein a second conductivity type region is formed. In another embodiment, a mandrel is removed from within shallow trench isolation to form a recessed region, in which an inner dummy spacer is formed. A first conductivity type region and a second conductivity region are formed within the remainder of the recessed region. An anneal is performed so that the first conductivity type region and the second conductivity type region abut each other by diffusion. A gate electrode is formed in self-alignment to the p-n junction between the first and second conductivity regions. The p-n junction controlled by the gate electrode, which may be sublithographic, constitutes an inventive tunneling effect transistor.

Owner:TWITTER INC

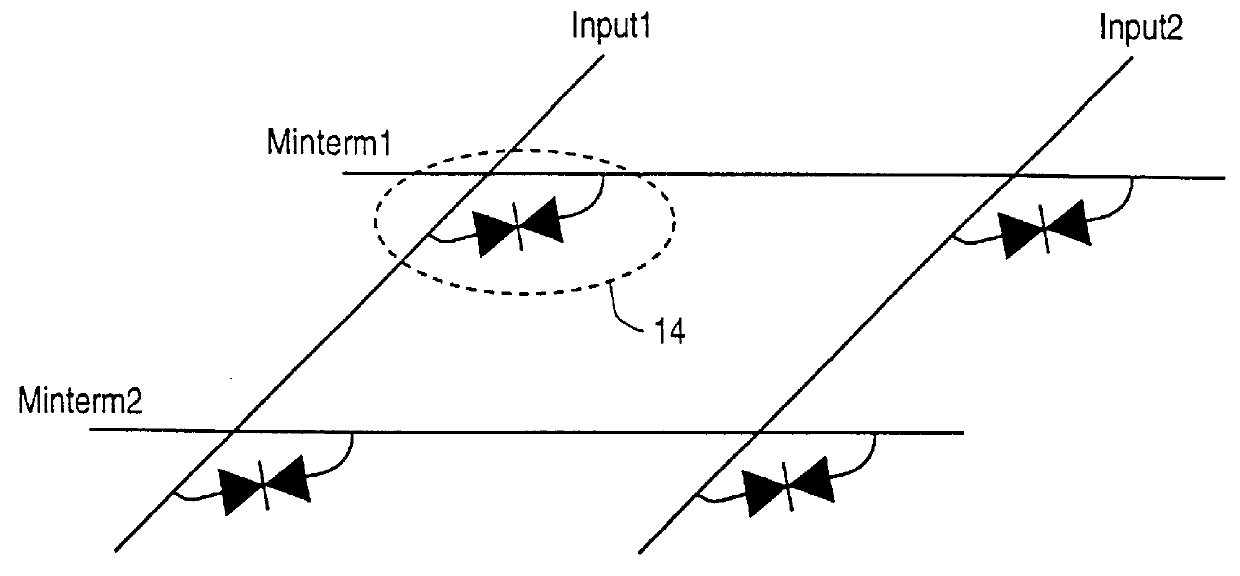

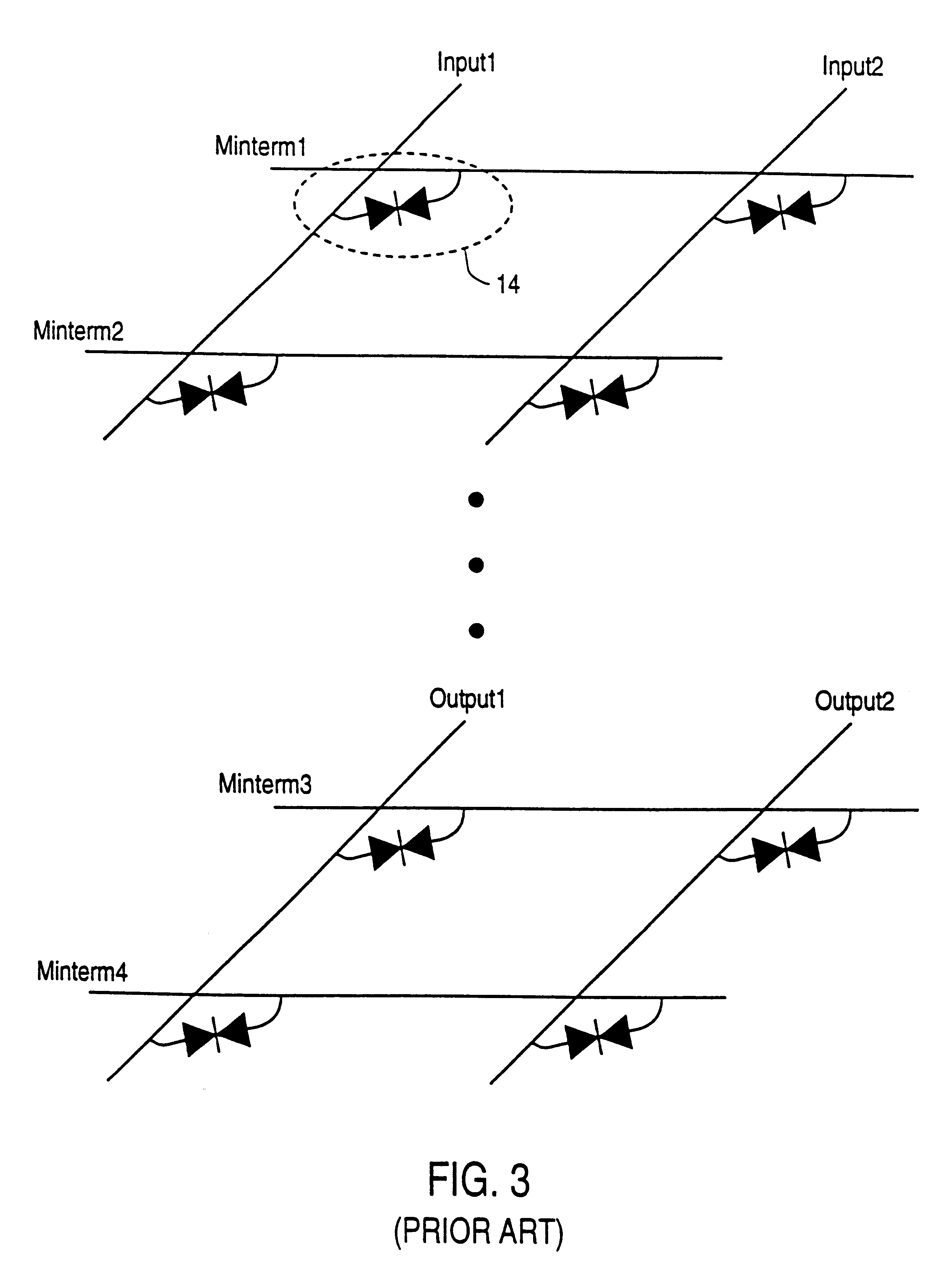

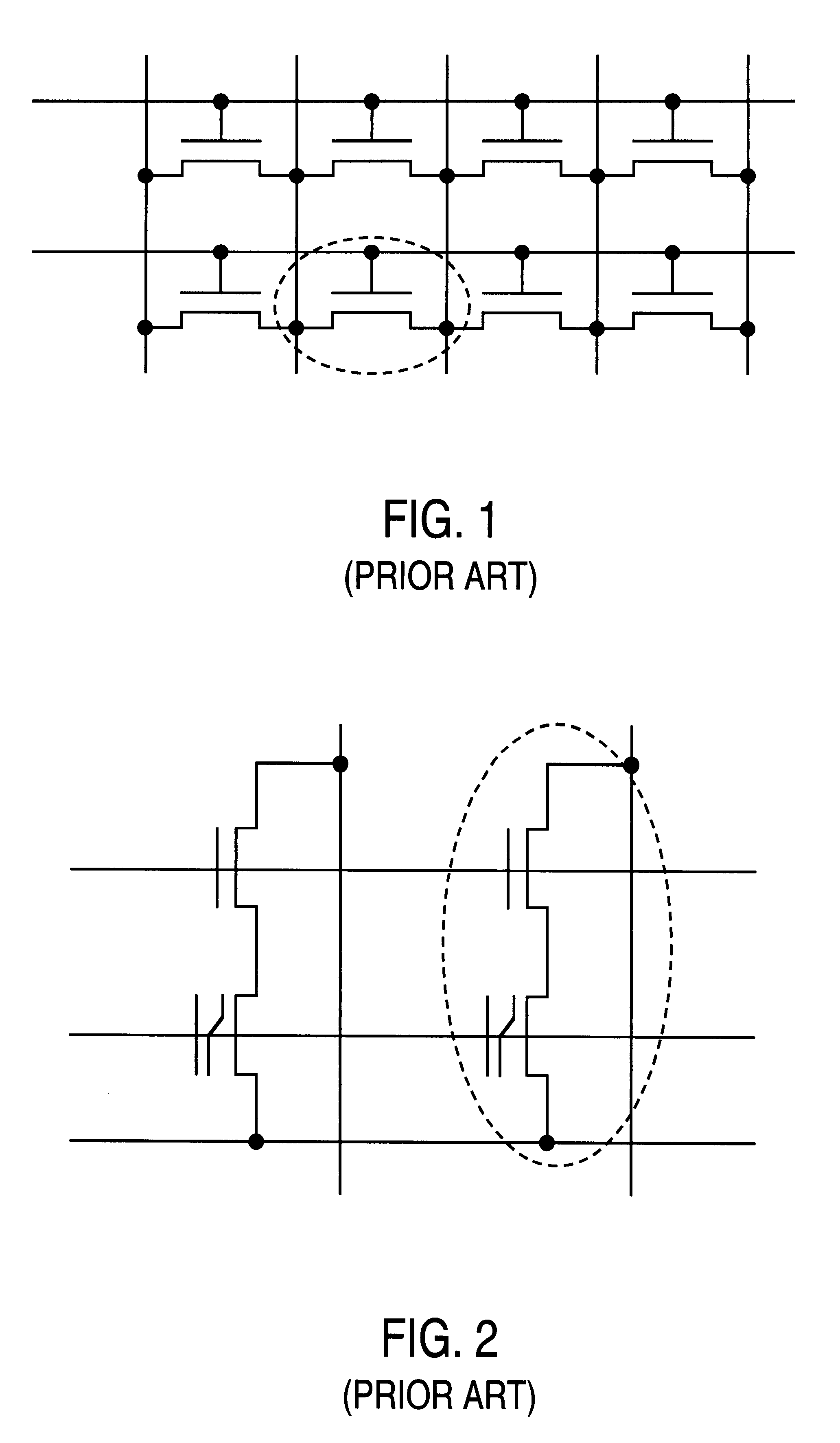

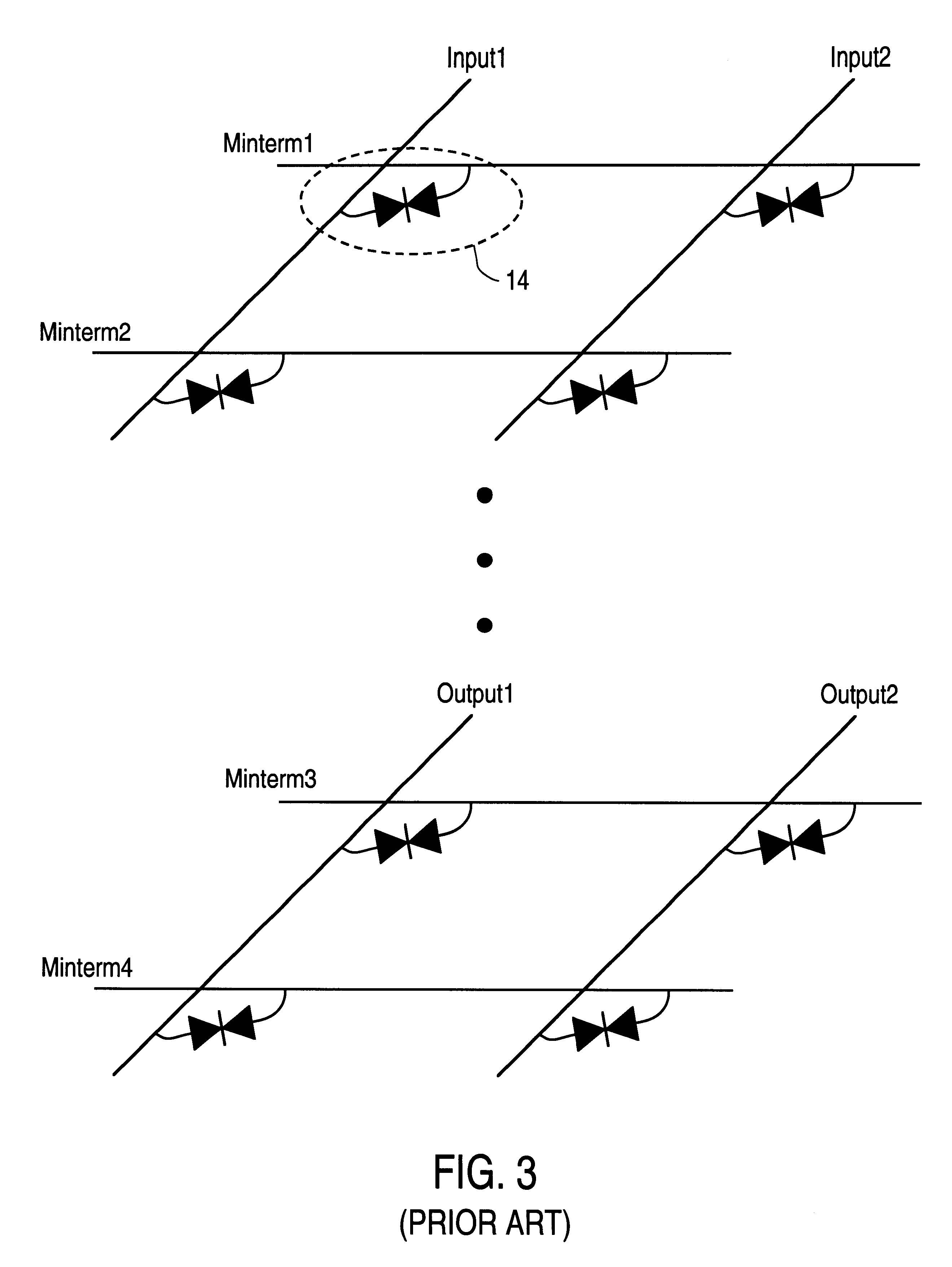

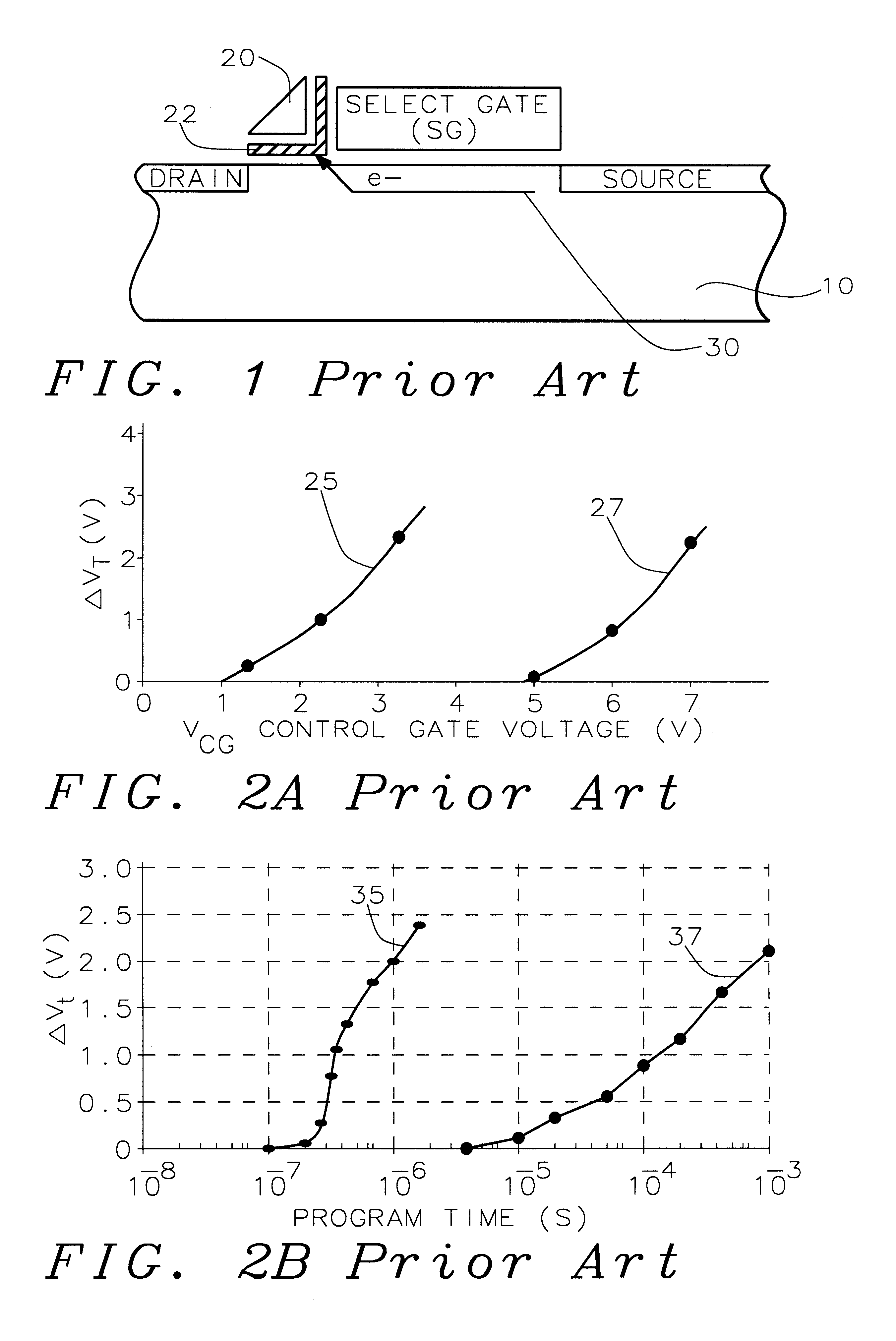

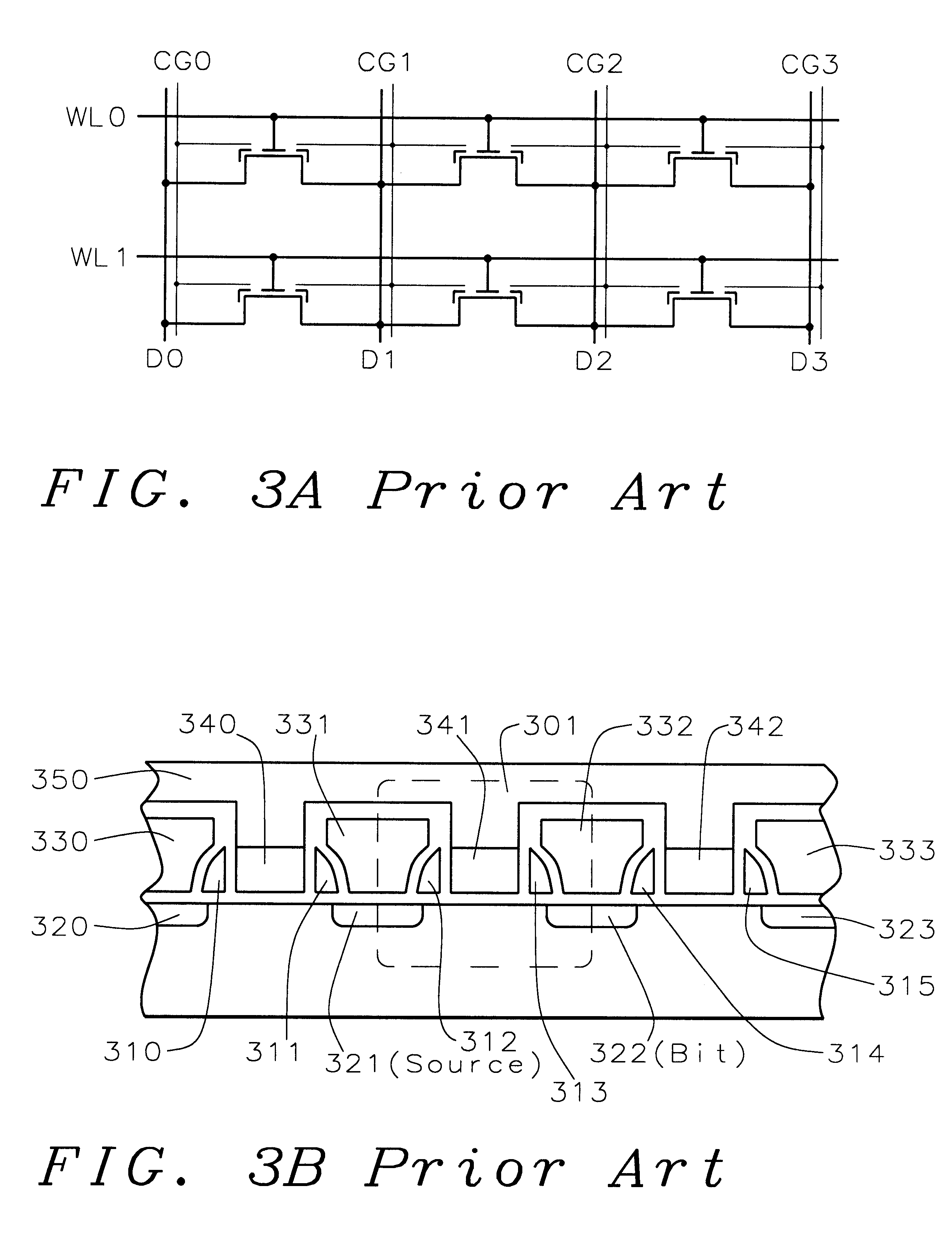

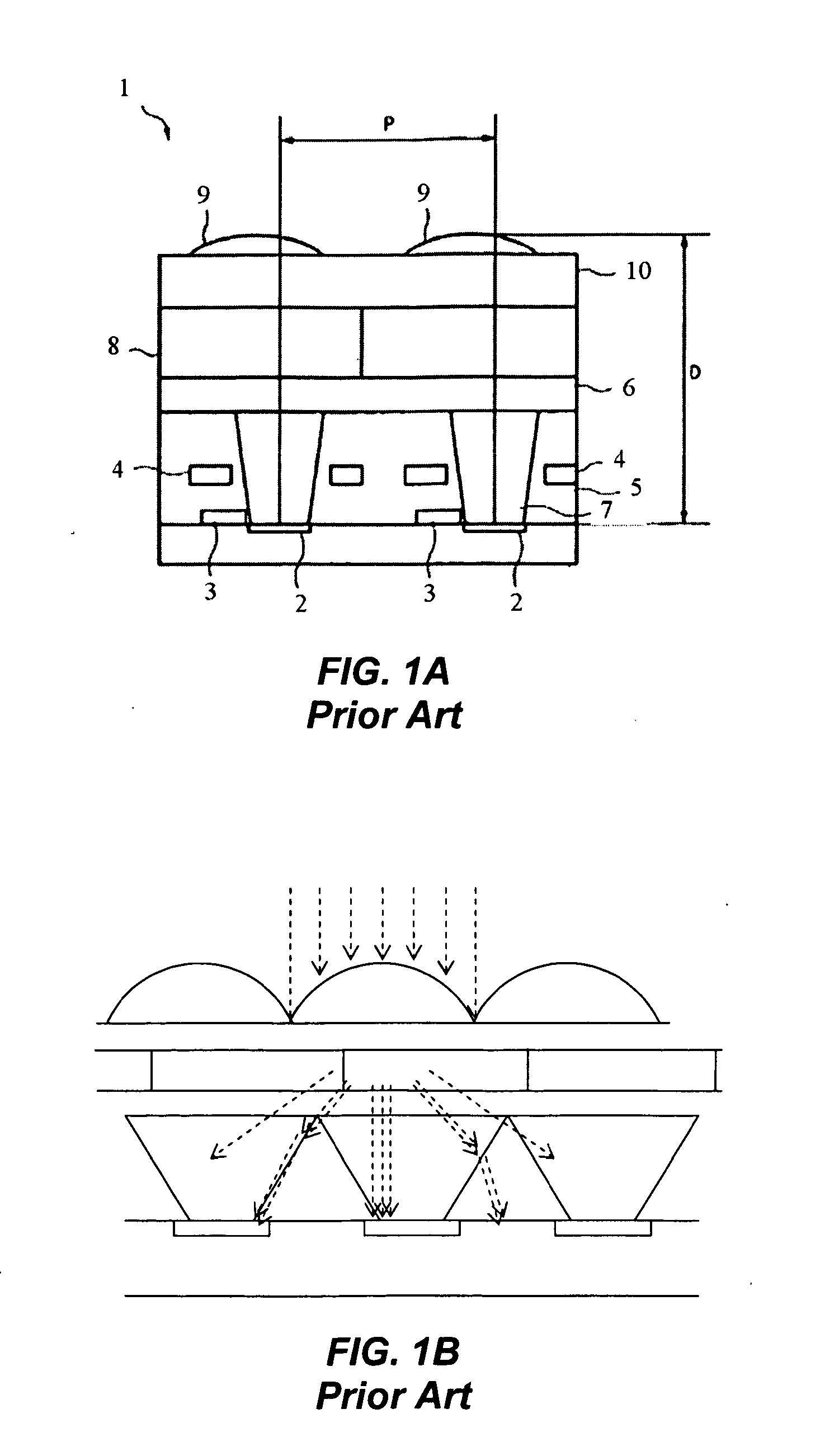

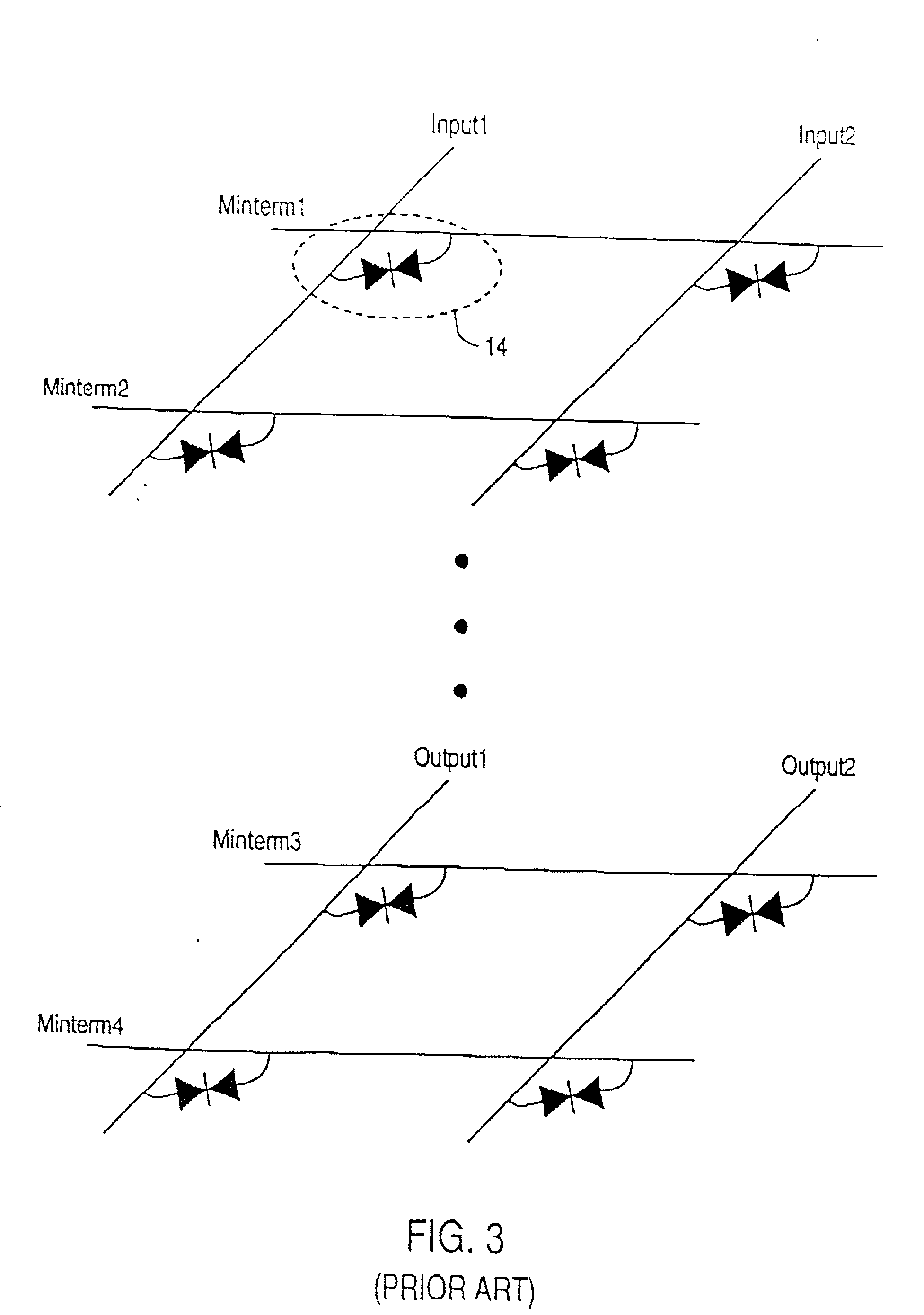

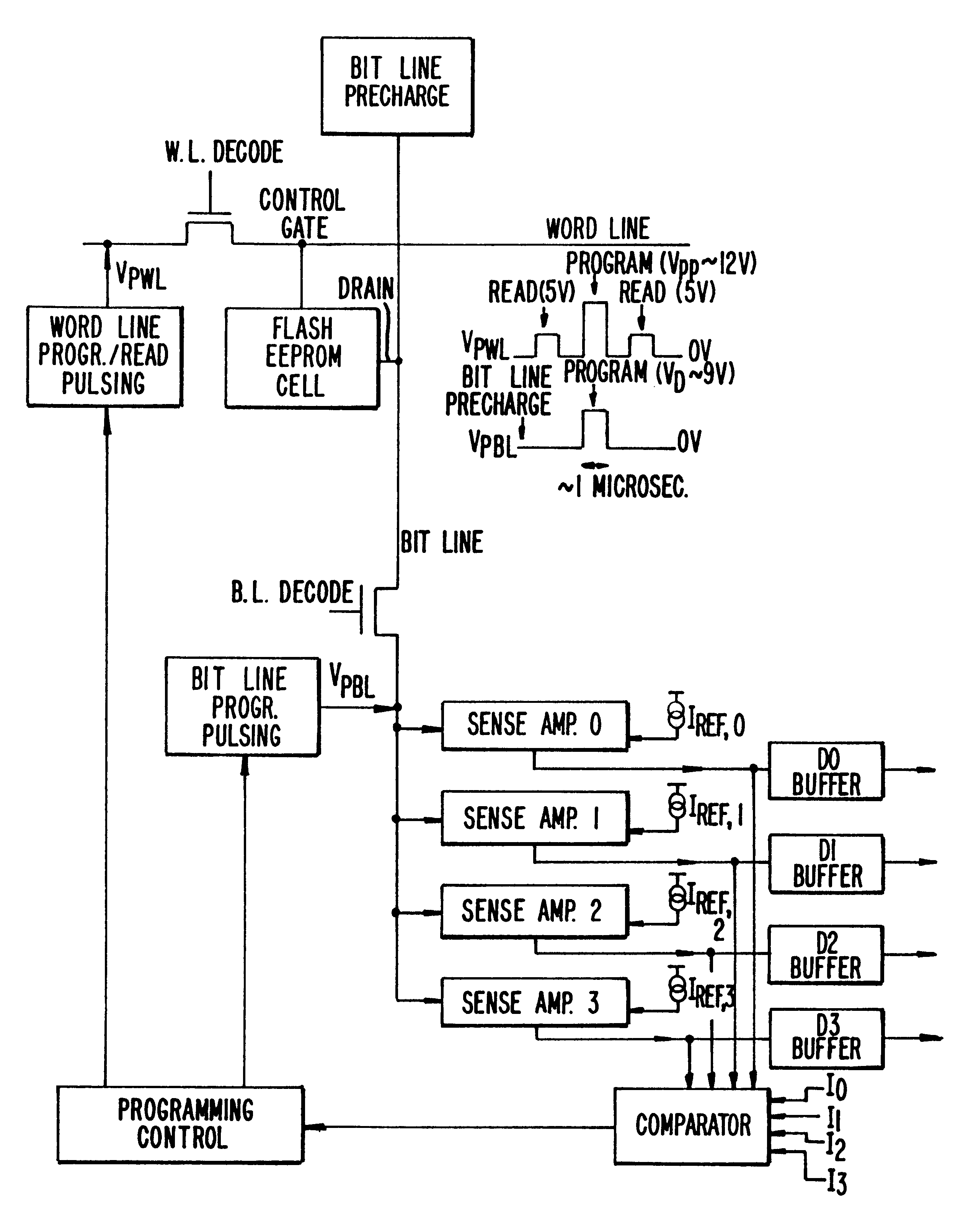

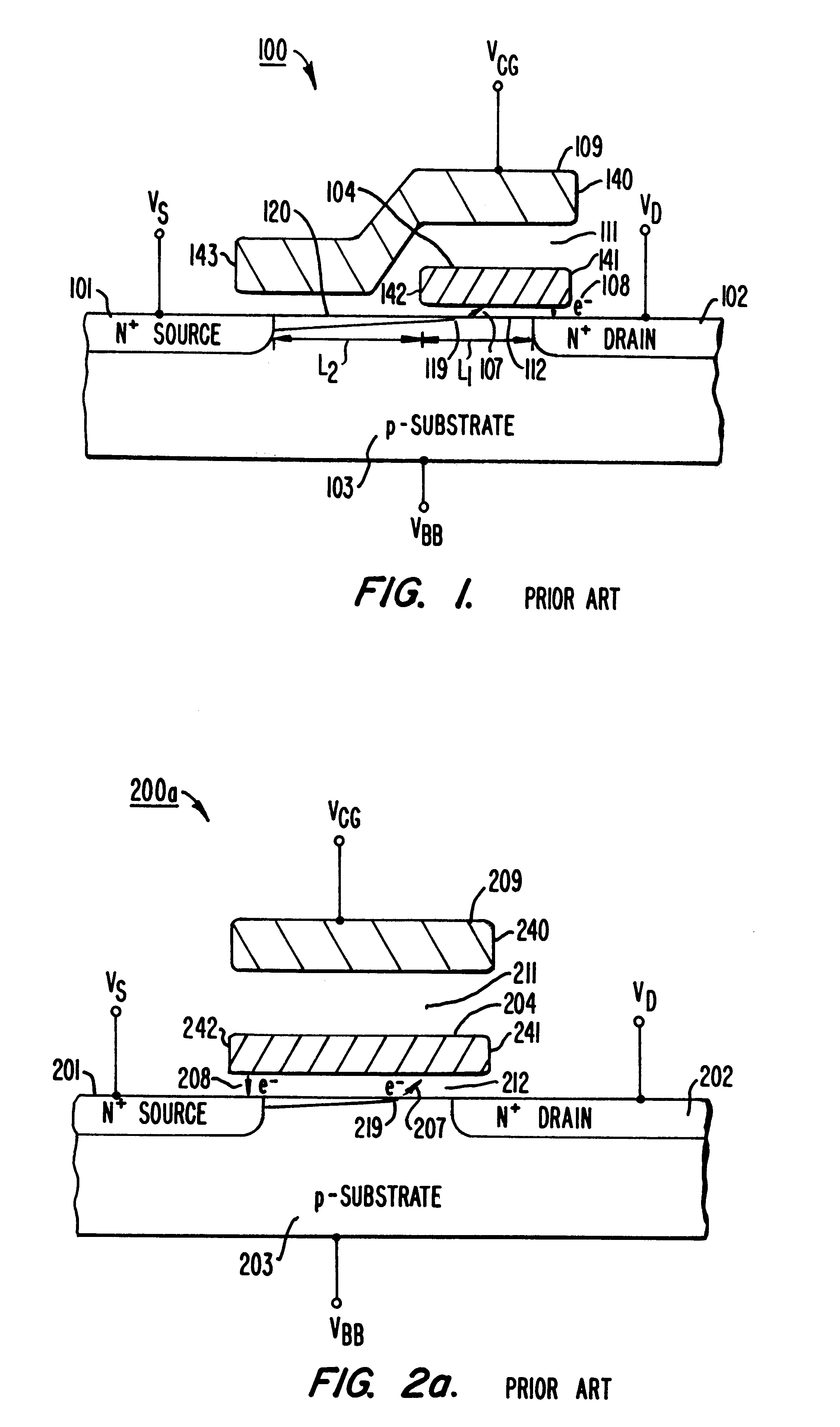

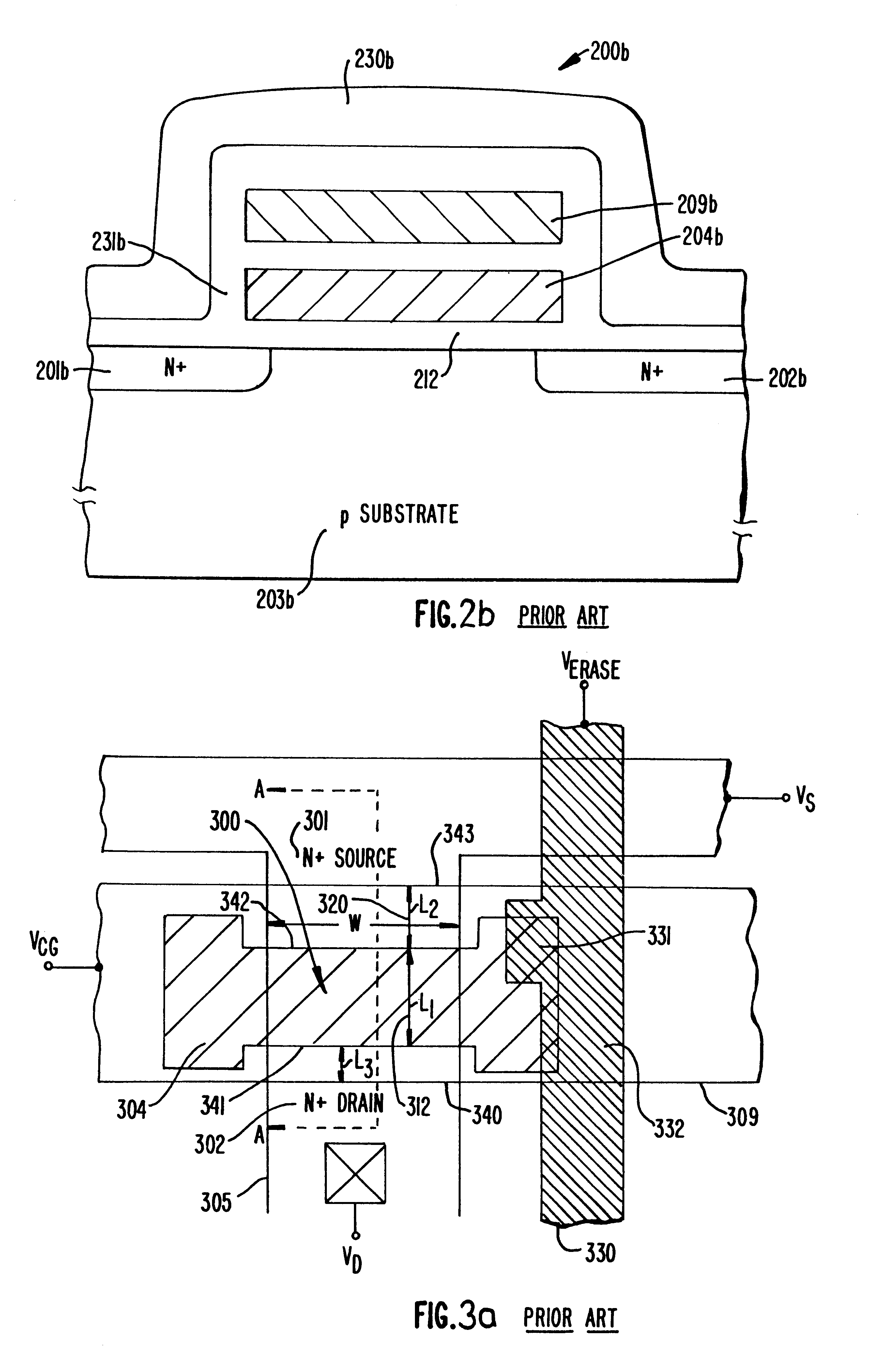

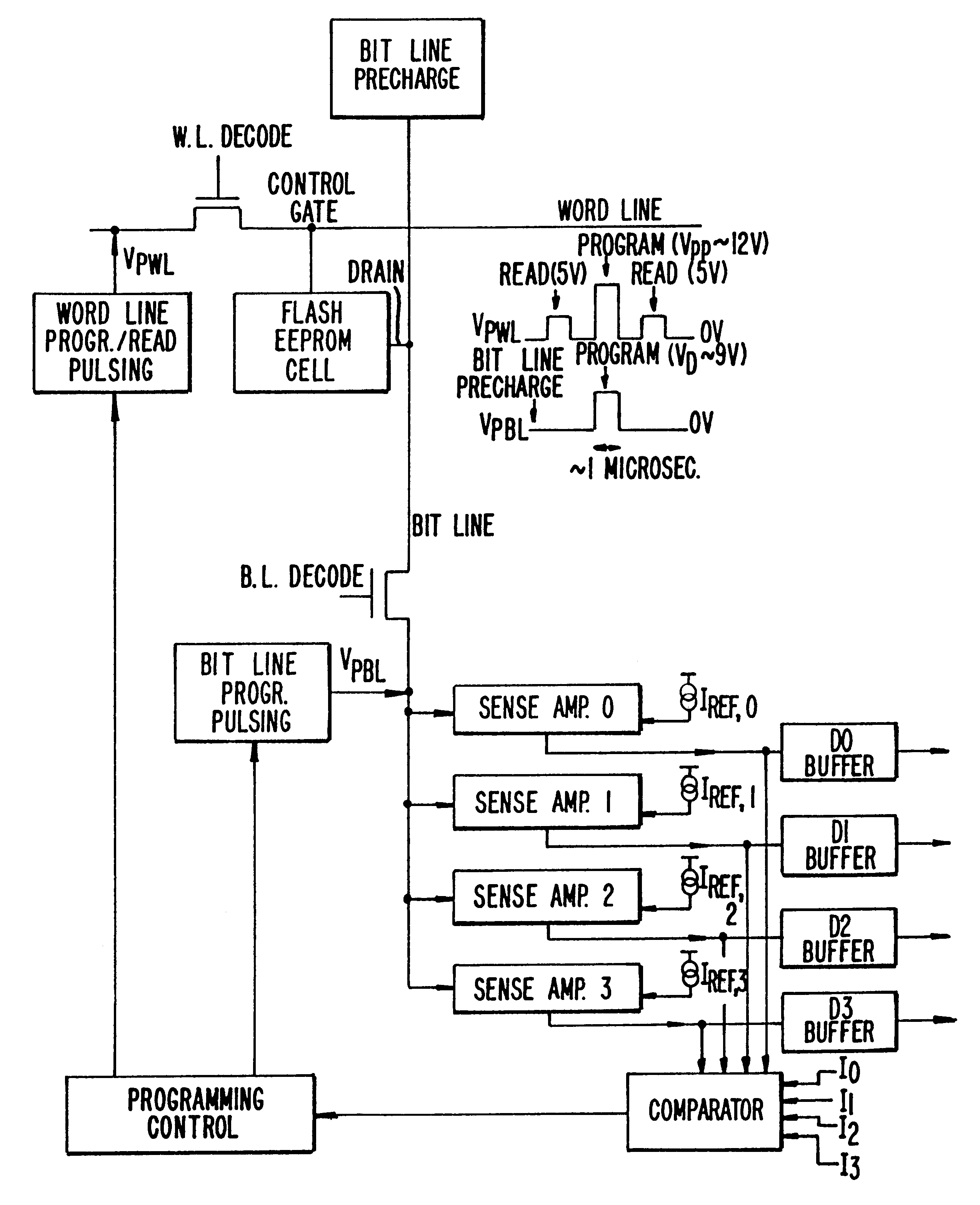

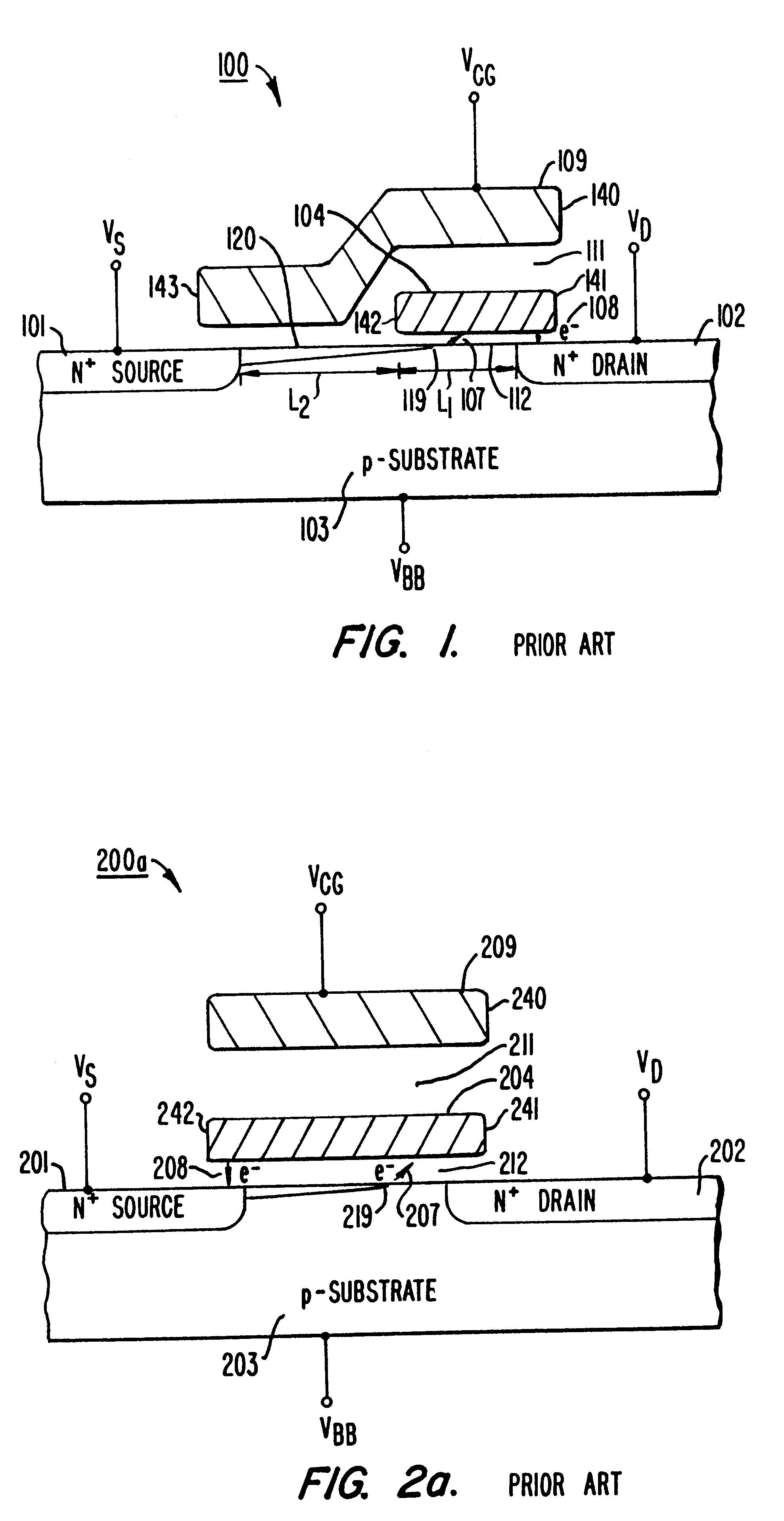

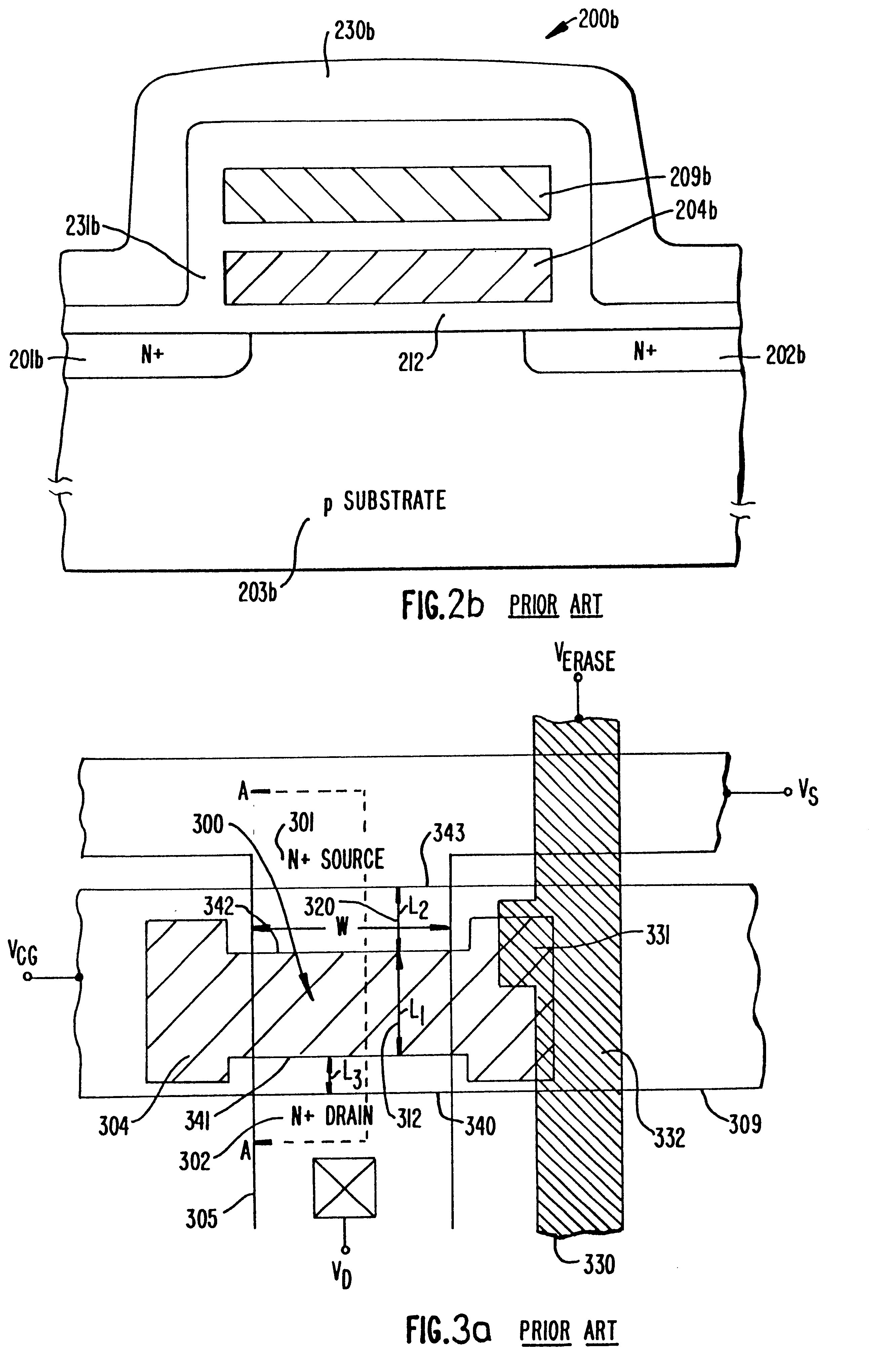

Highly compact EPROM and flash EEPROM devices

Structures, methods of manufacturing and methods of use of electrically programmable read only memories (EPROM) and flash electrically erasable and programmable read only memories (EEPROM) include split channel and other cell configurations. An arrangement of elements and cooperative processes of manufacture provide self-alignment of the elements. An intelligent programming technique allows each memory cell to store more than the usual one bit of information. An intelligent erase algorithm prolongs the useful life of the memory cells. Use of these various features provides a memory having a very high storage density and a long life, making it particularly useful as a solid state memory in place of magnetic disk storage devices in computer systems.

Owner:SANDISK TECH LLC

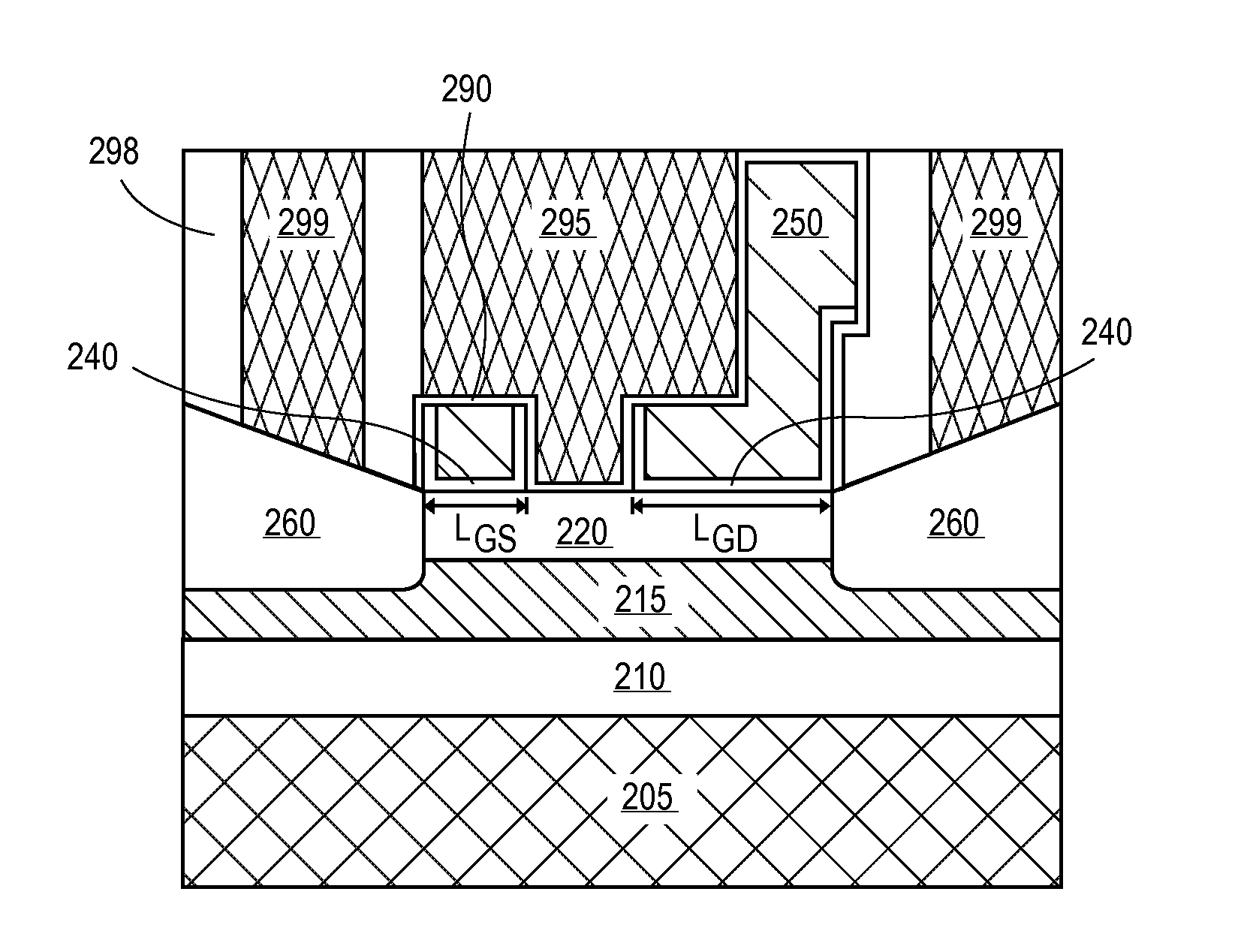

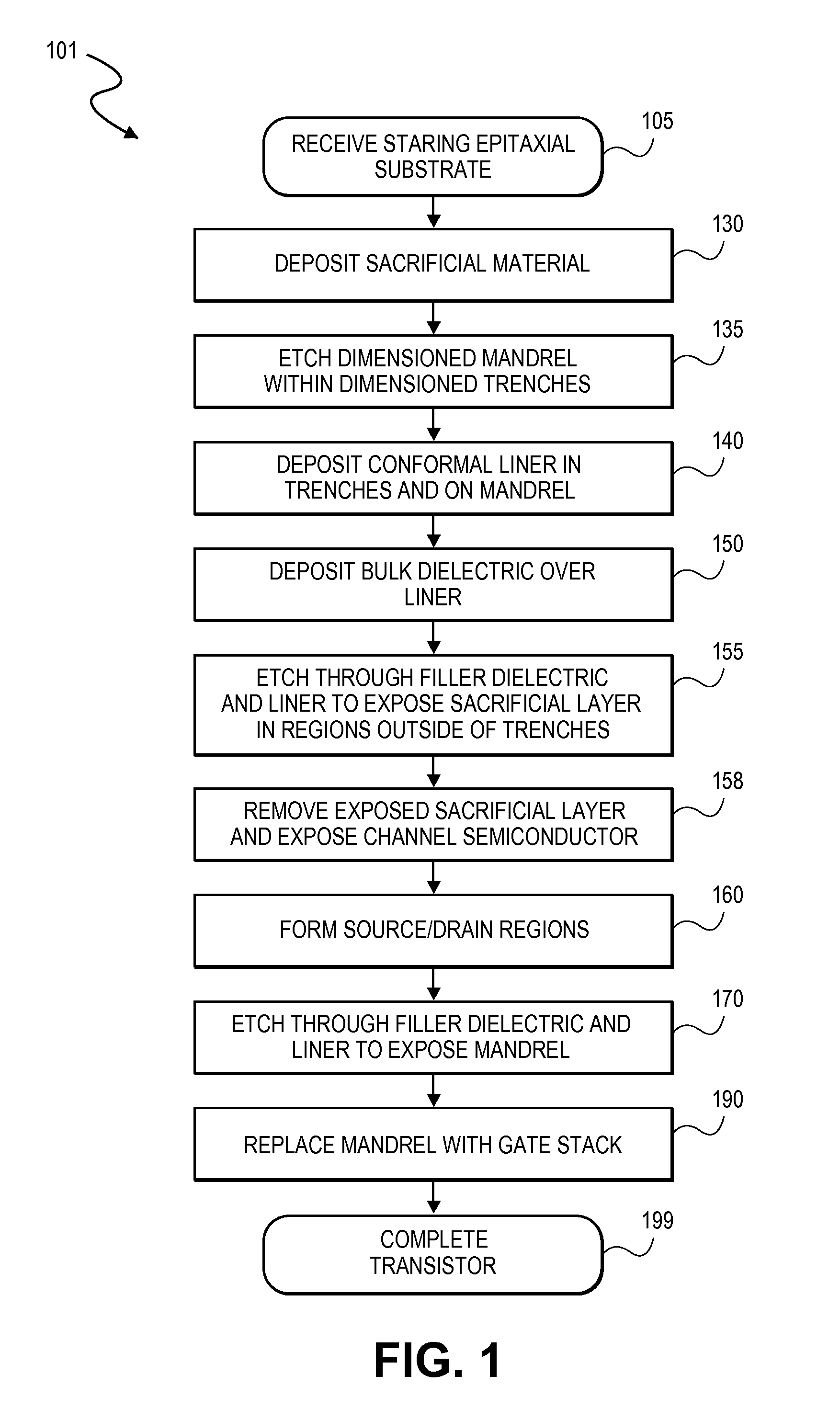

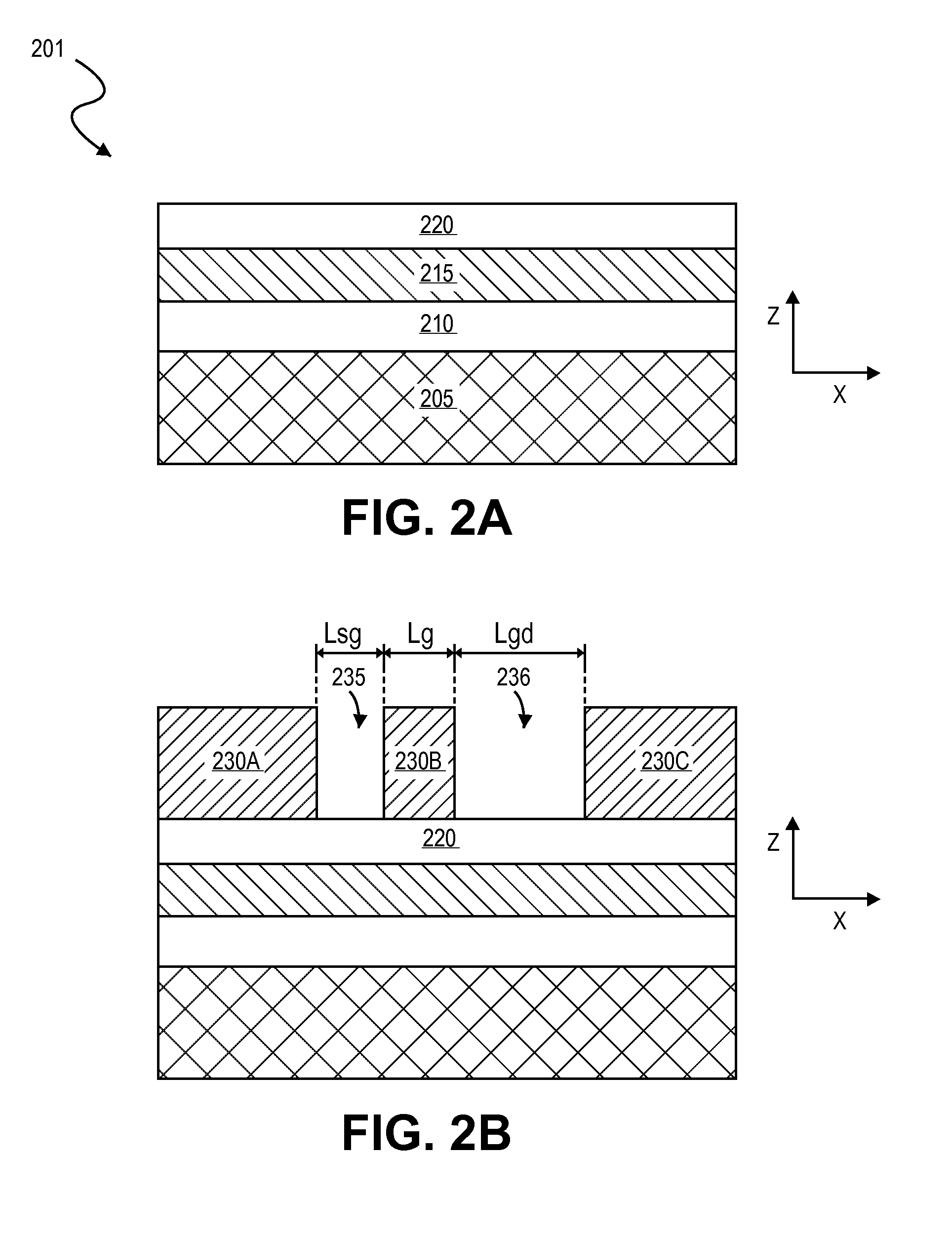

Self-aligned structures and methods for asymmetric GAN transistors & enhancement mode operation

ActiveUS20140091308A1Semiconductor/solid-state device manufacturingSemiconductor devicesNon symmetricEngineering

Embodiments include high electron mobility transistors (HEMT). In embodiments, a gate electrode is spaced apart by different distances from a source and drain semiconductor region to provide high breakdown voltage and low on-state resistance. In embodiments, self-alignment techniques are applied to form a dielectric liner in trenches and over an intervening mandrel to independently define a gate length, gate-source length, and gate-drain length with a single masking operation. In embodiments, III-N HEMTs include fluorine doped semiconductor barrier layers for threshold voltage tuning and / or enhancement mode operation.

Owner:INTEL CORP

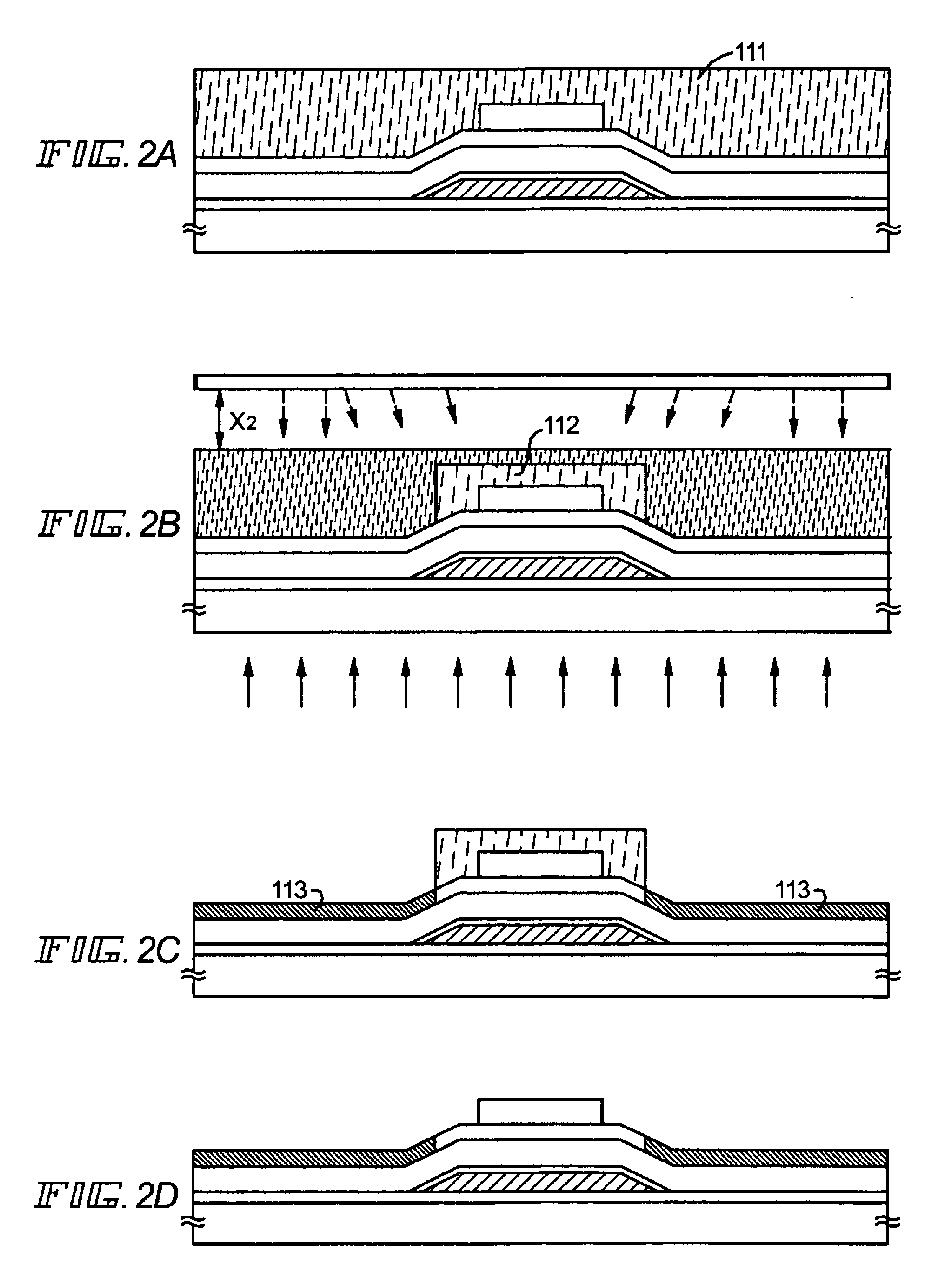

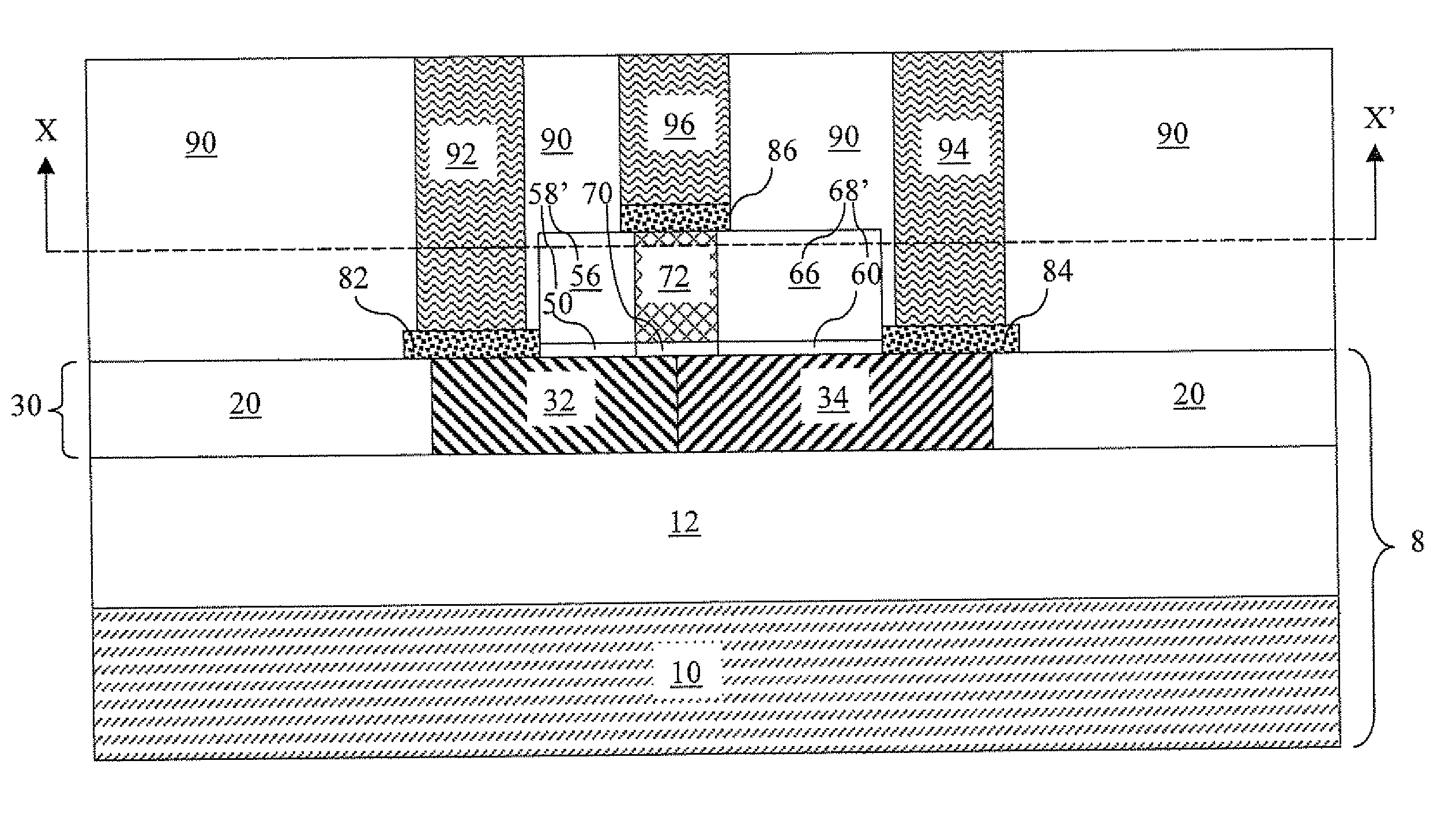

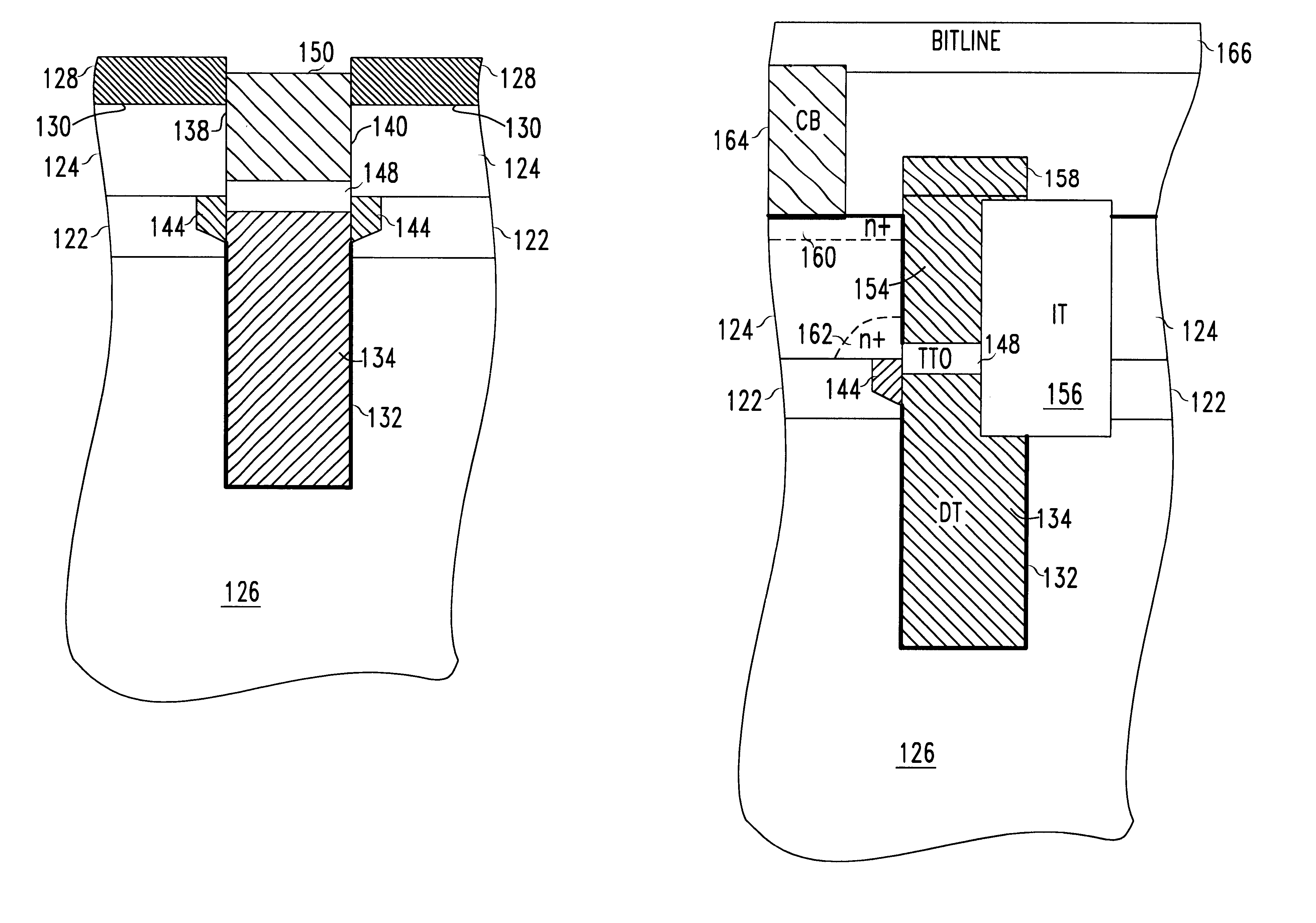

Silicon-on-insulator vertical array DRAM cell with self-aligned buried strap

InactiveUS6426252B1Solid-state devicesSemiconductor/solid-state device manufacturingVertical arrayBuried oxide

A silicon on insulator (SOI) dynamic random access memory (DRAM) cell, array and method of manufacture. The memory cell includes a vertical access transistor above a trench storage capacitor in a layered wafer. A buried oxide (BOX) layer formed in a silicon wafer isolates an SOI layer from a silicon substrate. Deep trenches are etched through the upper surface SOI layer, the BOX layer and into the substrate. Each trench capacitor is formed in the substrate and, the access transistor is formed on a sidewall of the SOI layer. Recesses are formed in the BOX layer at the SOI layer. A polysilicon strap recessed in the BOX layer connects each polysilicon storage capacitor plate to a self-aligned contact at the source of the access transistor. Dopant is implanted into the wafer to define device regions. Access transistor gates are formed along the SOI layer sidewalls. Shallow trenches are formed and filled with insulating material to isolate cells from adjacent cells. Wordlines and bitlines are formed to complete the memory array.

Owner:IBM CORP

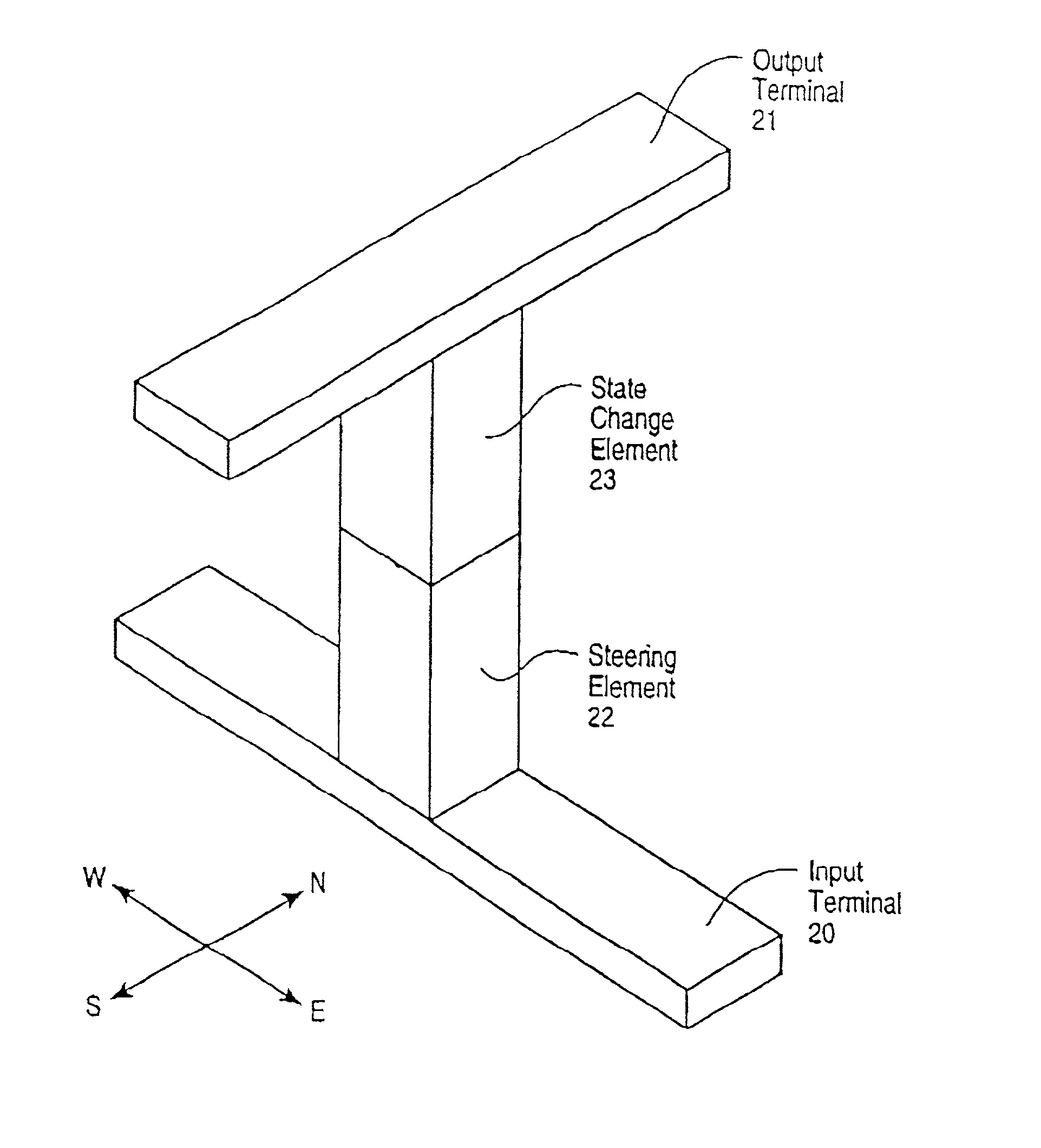

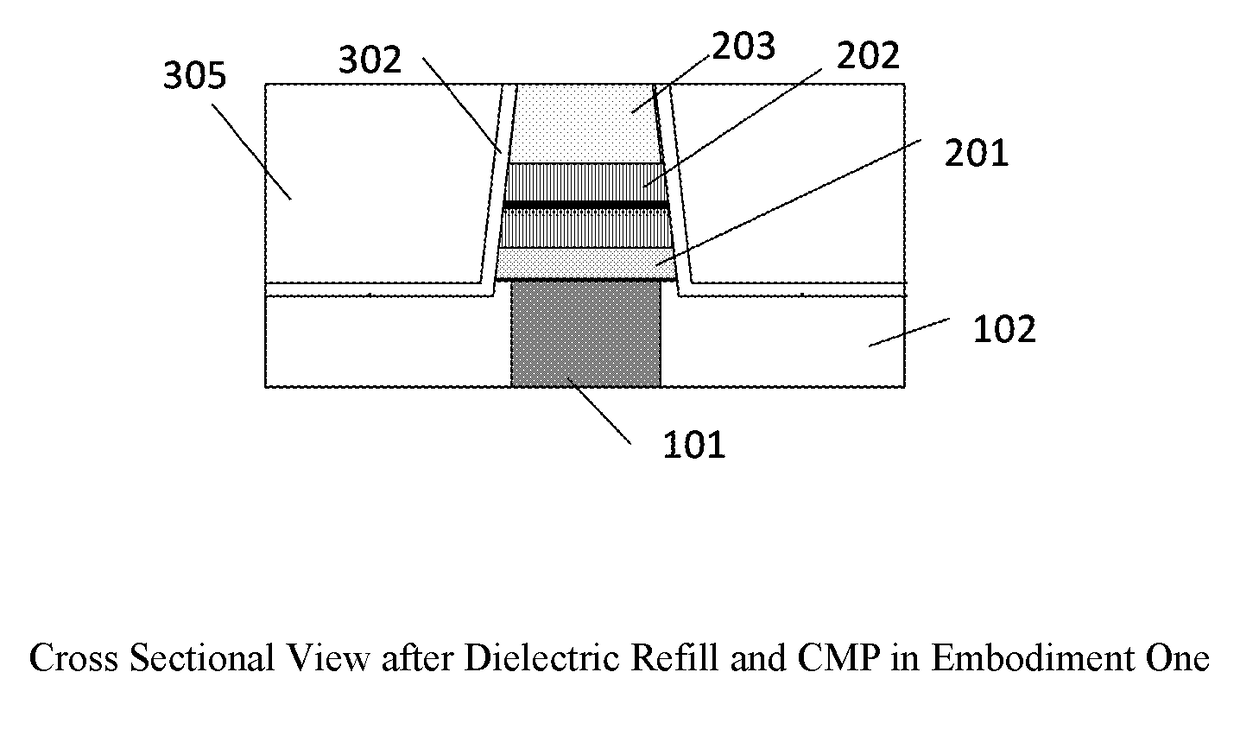

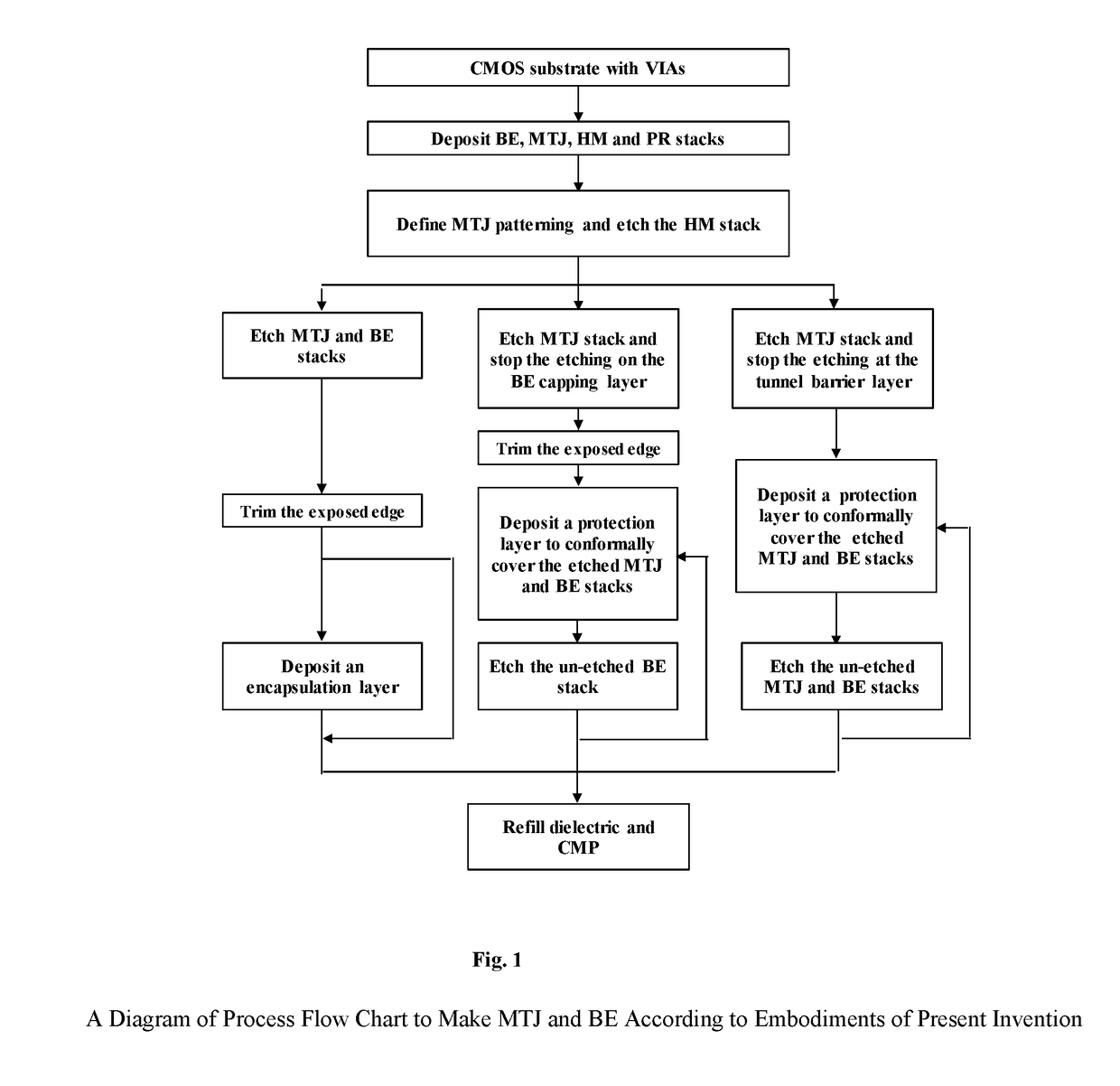

Method to make magnetic ramdom accesss memroy array with small footprint

InactiveUS20180033957A1Increase productionImprove propertiesMagnetic-field-controlled resistorsSolid-state devicesCMOSRandom access memory

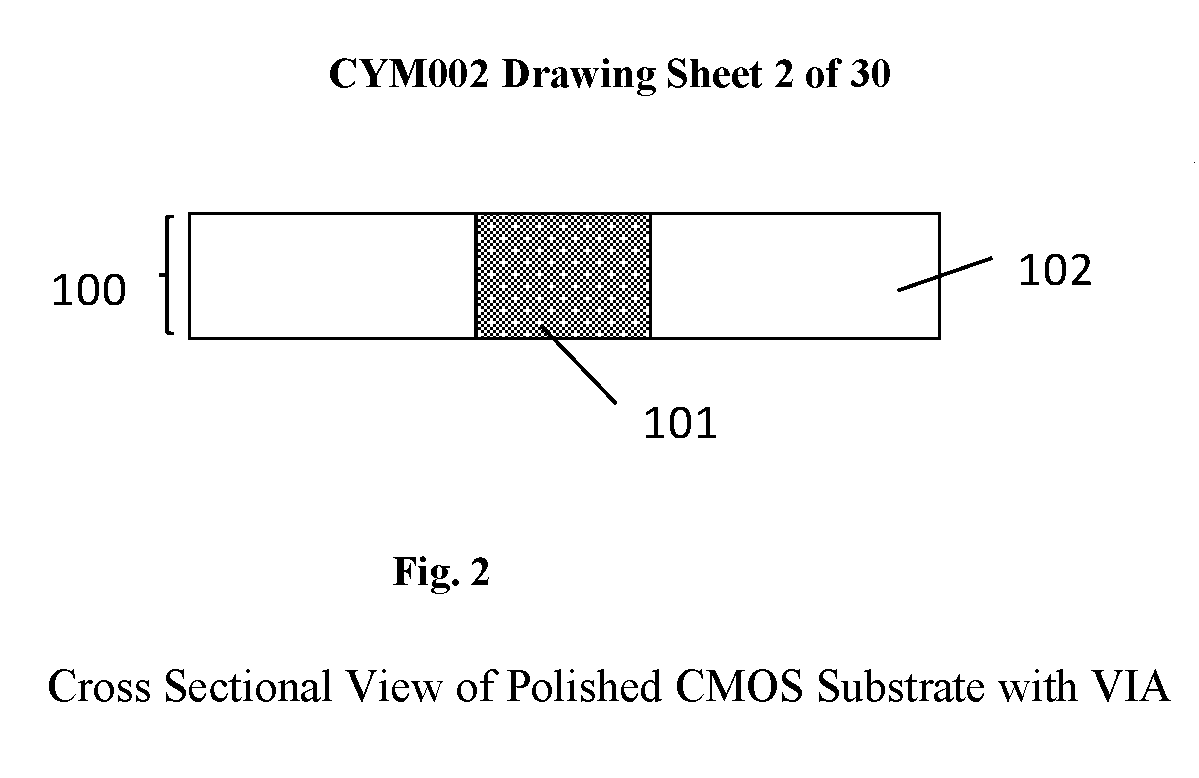

This invention is about a method to make magnetic random access memory with small footprint directly on CMOS VIA with a self-aligned etching process. The process schemes of the method proceeds as: (1) Etch MTJ and BE using one or more of RIE and / or IBE processes with Ta as hard mask; (2) Etch BE using one or more of RIE and / or IBE processes with Ta & sidewall protection layer on MTJ as hard mask; and (3) Etch a part of MTJ and BE using one or more of RIE and / or IBE processes with Ta & sidewall protection layer on top portion of MTJ as hard mask. All the three schemes lead the BE to be self-aligned to MTJ cells, the photo overlay margin is not necessary and circuits could be made extremely small with lower manufacturing cost; The invention also provides schemes to prevent the electrical shorting across the tunnel barrier layer. Through trimming and sidewall protection deposition process, device performance and electrical / magnetic properties could be greatly improved.

Owner:SHANGHAI CIYU INFORMATION TECH

Highly compact EPROM and flash EEPROM devices

Structures, methods of manufacturing and methods of use of electrically programmable read only memories (EPROM) and flash electrically erasable and programmable read only memories (EEPROM) include split channel and other cell configurations. An arrangement of elements and cooperative processes of manufacture provide self-alignment of the elements. An intelligent programming technique allows each memory cell to store more than the usual one bit of information. An intelligent erase algorithm prolongs the useful life of the memory cells. Use of these various features provides a memory having a very high storage density and a long life, making it particularly useful as a solid state memory in place of magnetic disk storage devices in computer systems.

Owner:SANDISK TECH LLC

Nanowire mesh device and method of fabricating same

InactiveUS20100297816A1Improved contact scheme and scalabilityImprove uniformityNanoinformaticsSemiconductor/solid-state device manufacturingGate dielectricNanowire

A semiconductor structure is provided that includes a plurality of vertically stacked and vertically spaced apart semiconductor nanowires (e.g., a semiconductor nanowire mesh) located on a surface of a substrate. One end segment of each vertically stacked and vertically spaced apart semiconductor nanowires is connected to a source region and another end segment of each vertically stacked and vertically spaced apart semiconductor nanowires is connected to a drain region. A gate region including a gate dielectric and a gate conductor abuts the plurality of vertically stacked and vertically spaced apart semiconductor nanowires, and the source regions and the drain regions are self-aligned with the gate region.

Owner:GLOBALFOUNDRIES U S INC

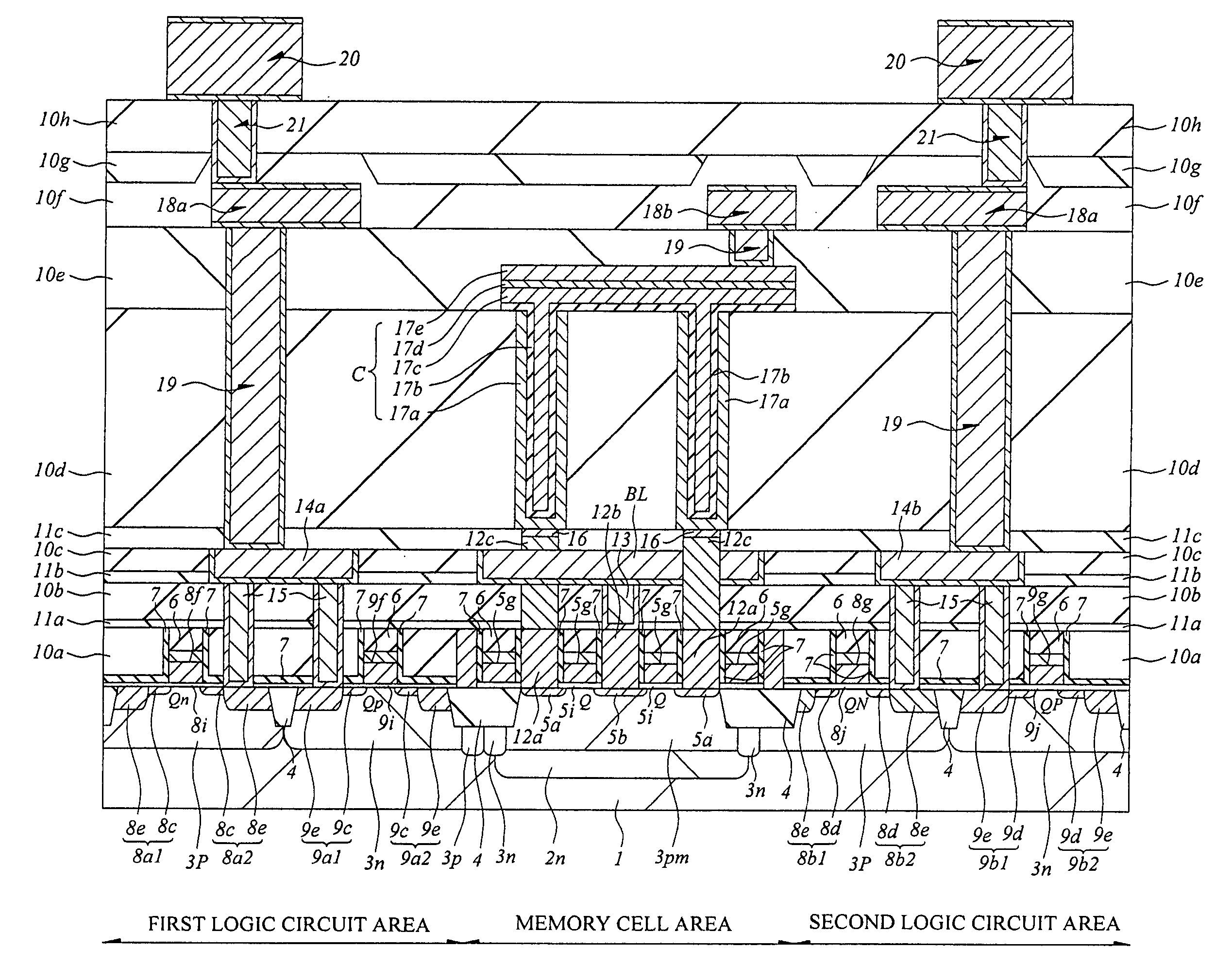

Semiconductor integrated circuit device and production method thereof

InactiveUS20050208716A1Improve refresh featureEasy to integrateTransistorSolid-state devicesDram memoryEngineering

A refresh characteristic of a DRAM memory cell is improved and the performance of a MISFET formed in the periphery thereof and constituting a logic circuit is improved. Each gate electrode in a memory cell area is formed of p type polycrystalline silicon, and a cap insulating film on each gate electrode and a sidewall film on the sidewall thereof are formed of a silicon oxide film. A polycrystalline silicon film formed on the gate electrodes and between the gate electrodes is polished by a CMP method, and thereby contact electrodes are formed. Also, sidewall films each composed of a laminated film of the silicon oxide film and the polycrystalline silicon film are formed on the sidewall of the gate electrodes in the logic circuit area, and these films are used as a mask to form semiconductor areas. As a result, it is possible to reduce the boron penetration and form contact electrodes in a self-alignment manner. In addition, the performance of the MISFET constituting the logic circuit can be improved.

Owner:ELPIDA MEMORY INC

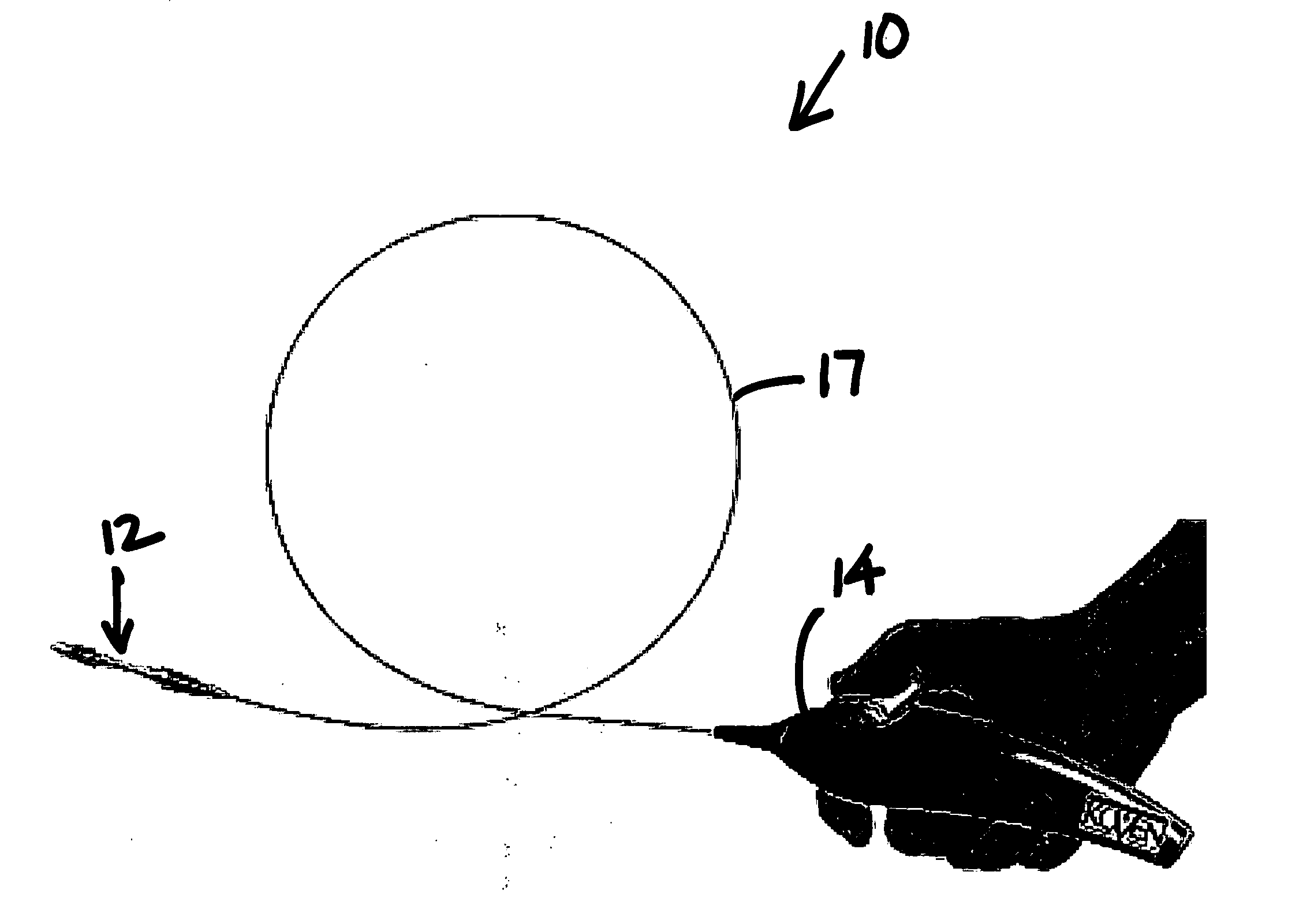

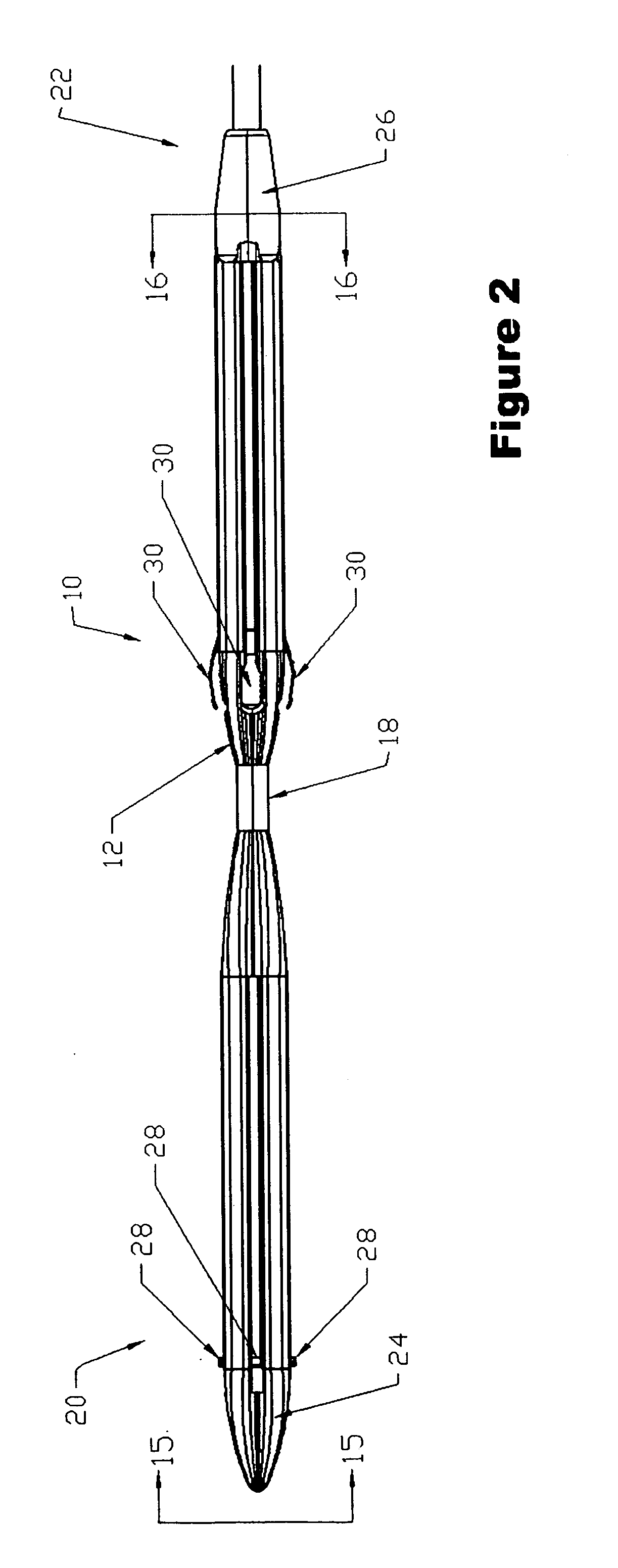

Valvulotome

A valvulotome device having retractable cutting blades and guide fins which permits continual centralizing, self-alignment of the cutting blades within the lumen of the vein is disclosed. The valvulotome device comprises a bifurcated assembly having a cutter head and guide head joined by a conduit member permitting communication of a catheter wire running longitudinally through the device. The cutter head and guide head each define a chamber adapted to receive the catheter wire therein. First and second wedge members are operatively engaged to the catheter wire and disposed inside a respective chamber of the cutter head and guide head which permit the surgeon to remotely manipulate the degree to which the cutting blades and guide fins emerge from the cutter head and guide head, respectively, as well as allow rotation of the device about its axis thereby increasing the maneuverability of the device as it is pulled through the vein.

Owner:KOVEN PAUL +2

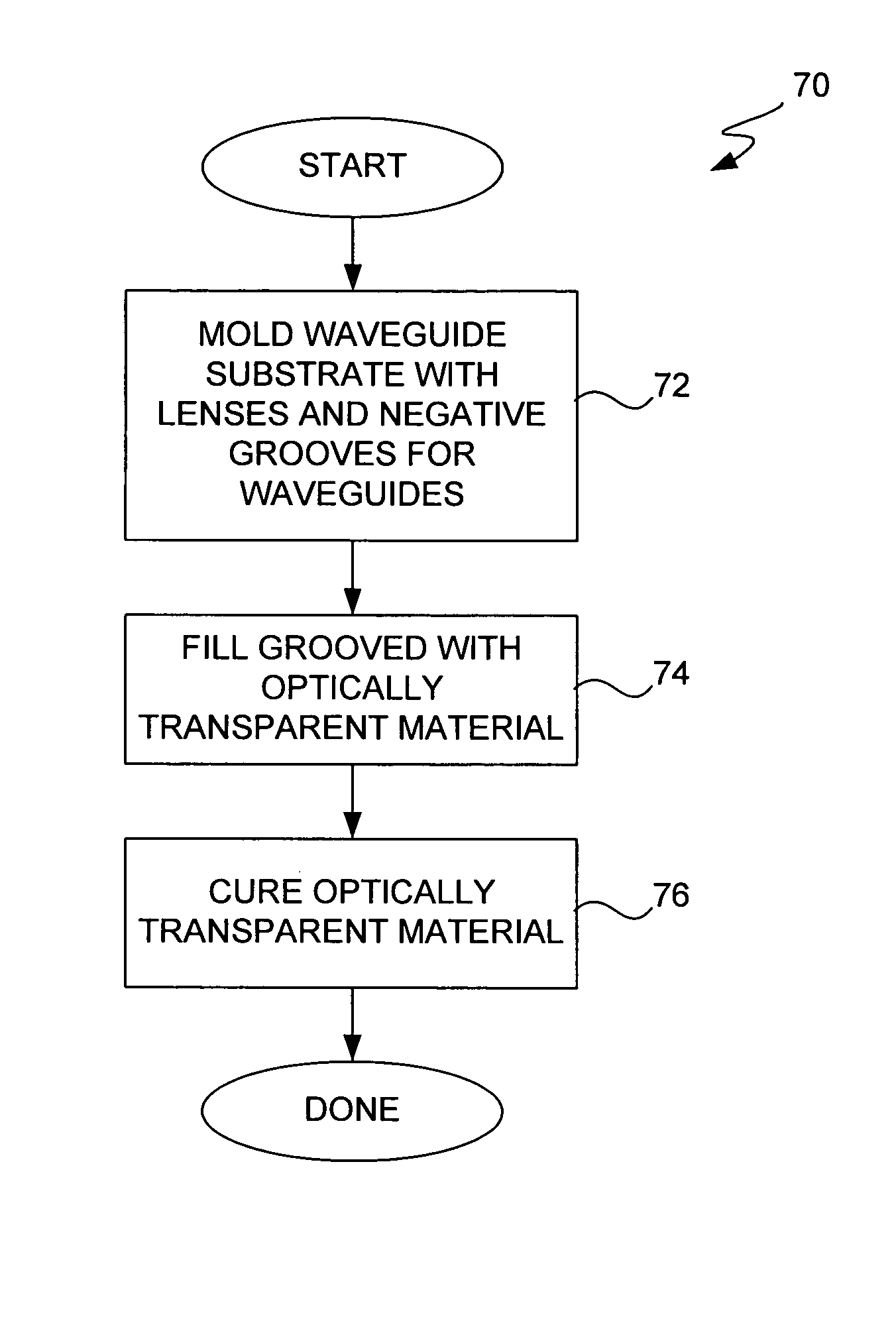

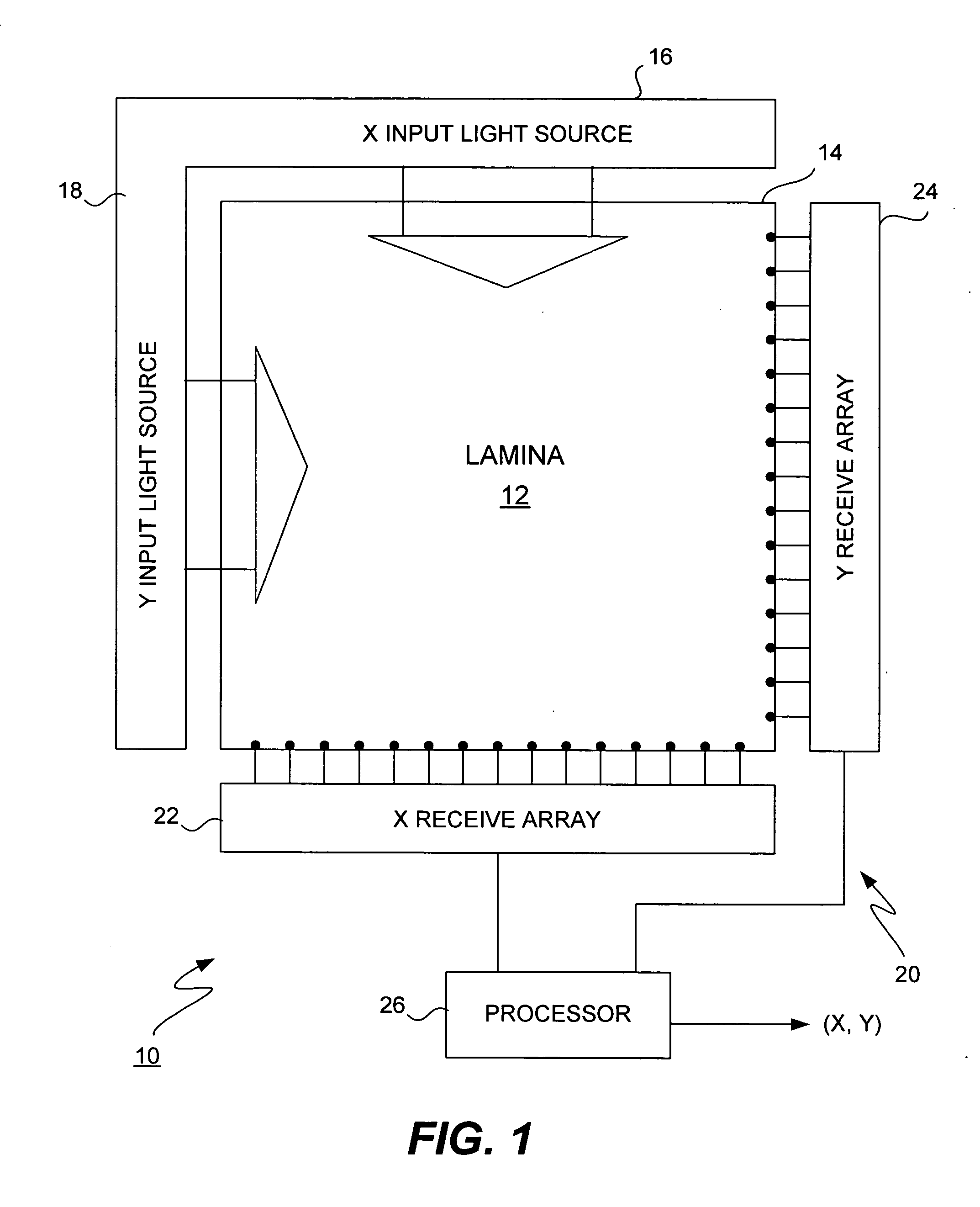

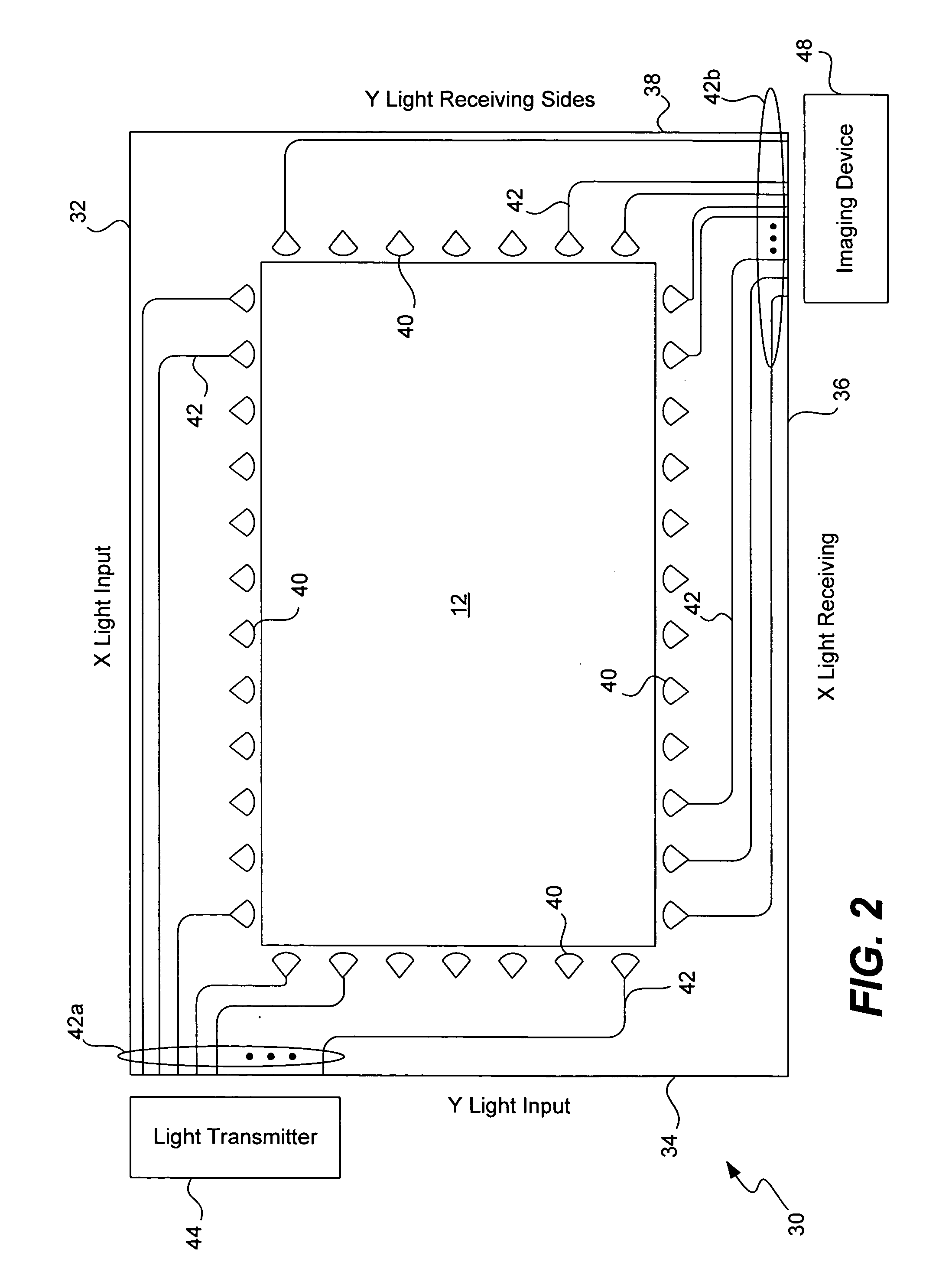

Apparatus and method for a molded waveguide for use with touch screen displays

InactiveUS20050271319A1Input/output for user-computer interactionOptical articlesGratingDisplay device

An apparatus and method for an inexpensive, simple to make, self-aligning molded waveguide made of an optically transparent material and that can be used to generate a grid or lamina of light for use with touch screen displays. The molded waveguide substrate includes a plurality of lenses and a plurality of waveguide grooves corresponding to the plurality of integral lenses respectively. After the substrate is molded, the grooves are filled with an optically transparent material to optically couple and align the plurality of lenses and the plurality of grooves respectively. In one application, the molded waveguide substrate is positioned adjacent a touch screen device. A light transmitter and an imaging device are optically coupled to the molded waveguide substrate, and a processing device is coupled to the imaging device. The processing device is configured to determine a data entry to the touch screen by deciphering the coordinates of an interrupt in the light created in the free space adjacent the touch screen device when a data entry is being made to the touch screen device.

Owner:POA SANA LIQUIDATING TRUST