Patents

Literature

36results about How to "Improve refresh feature" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

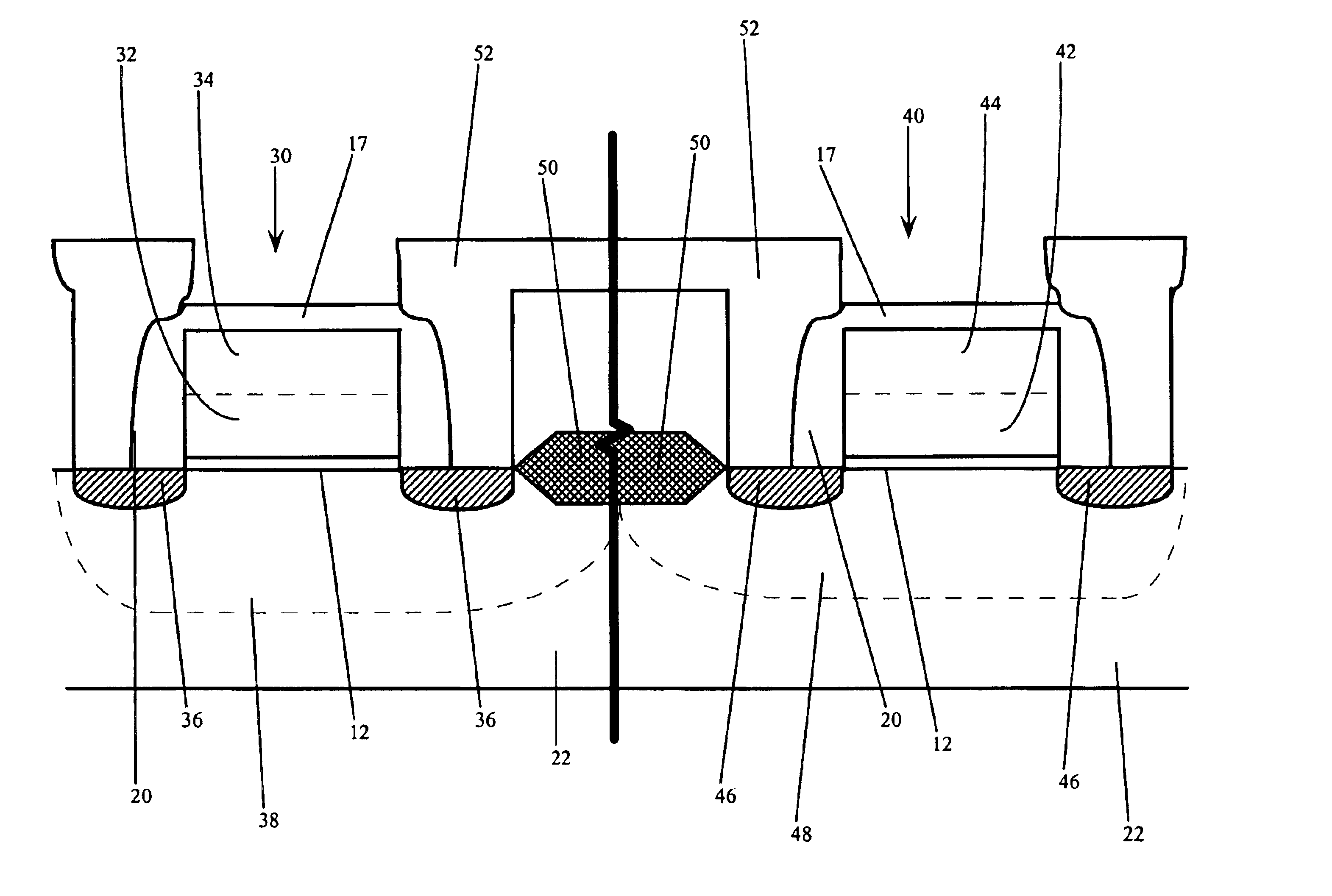

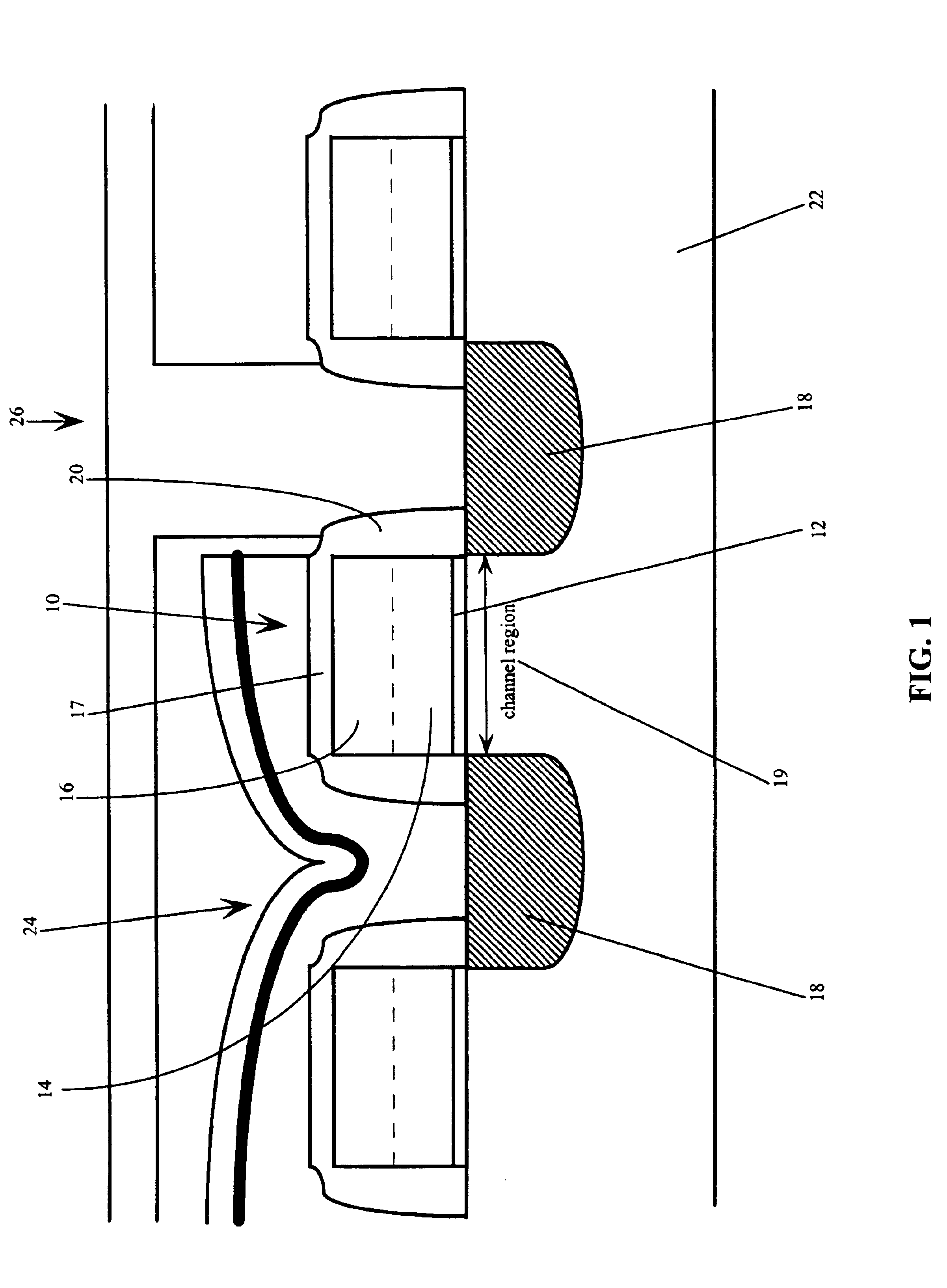

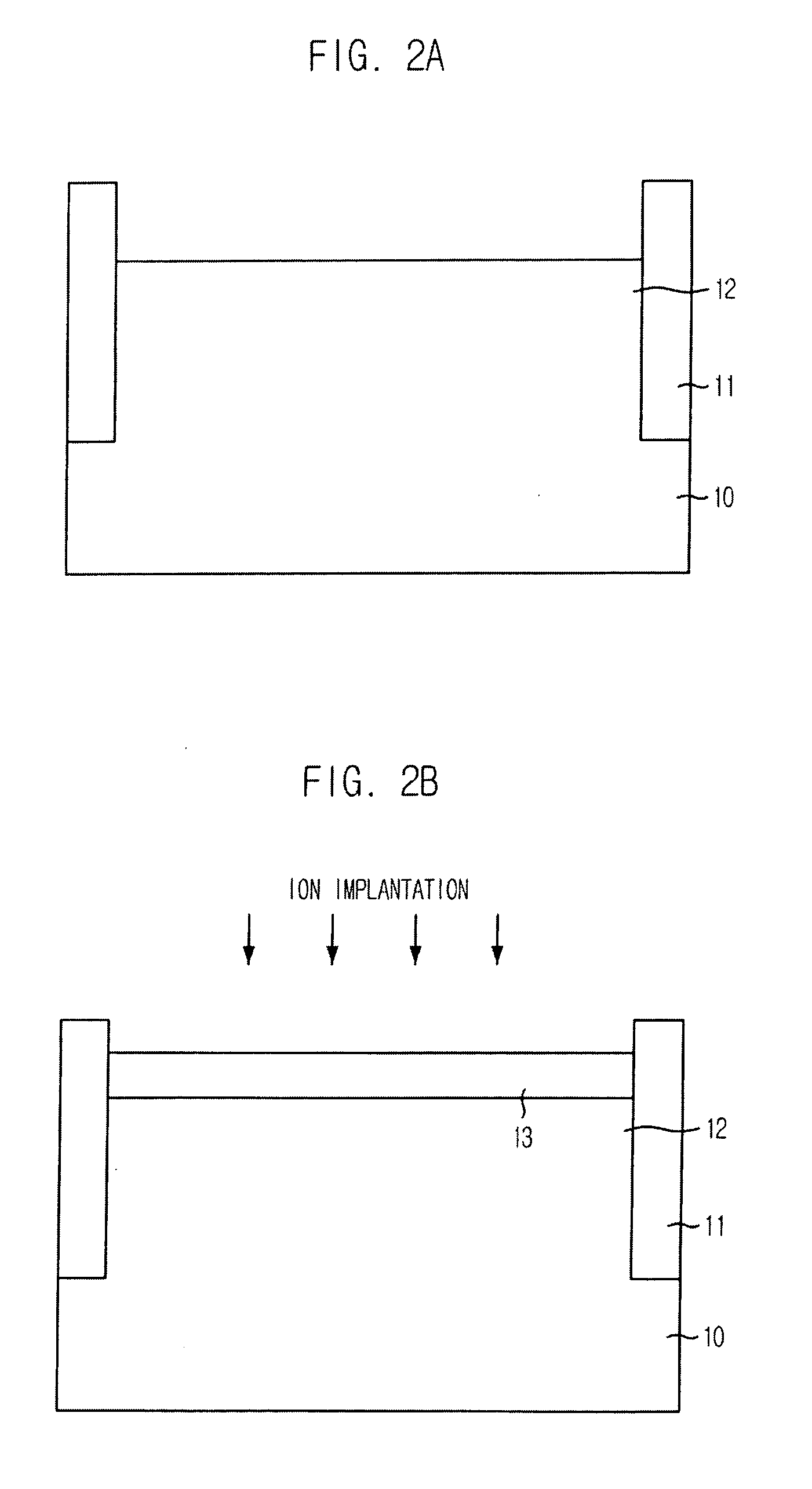

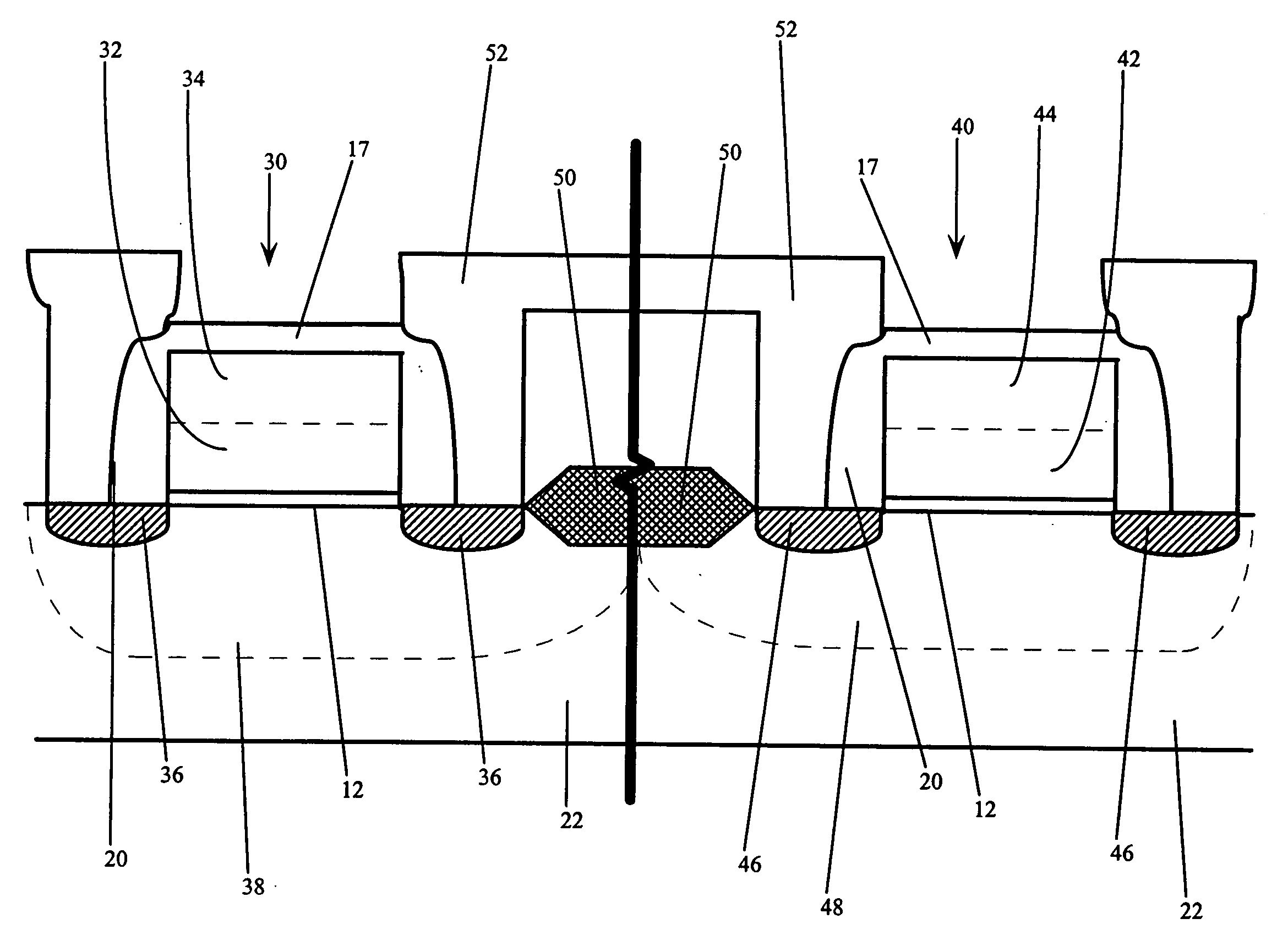

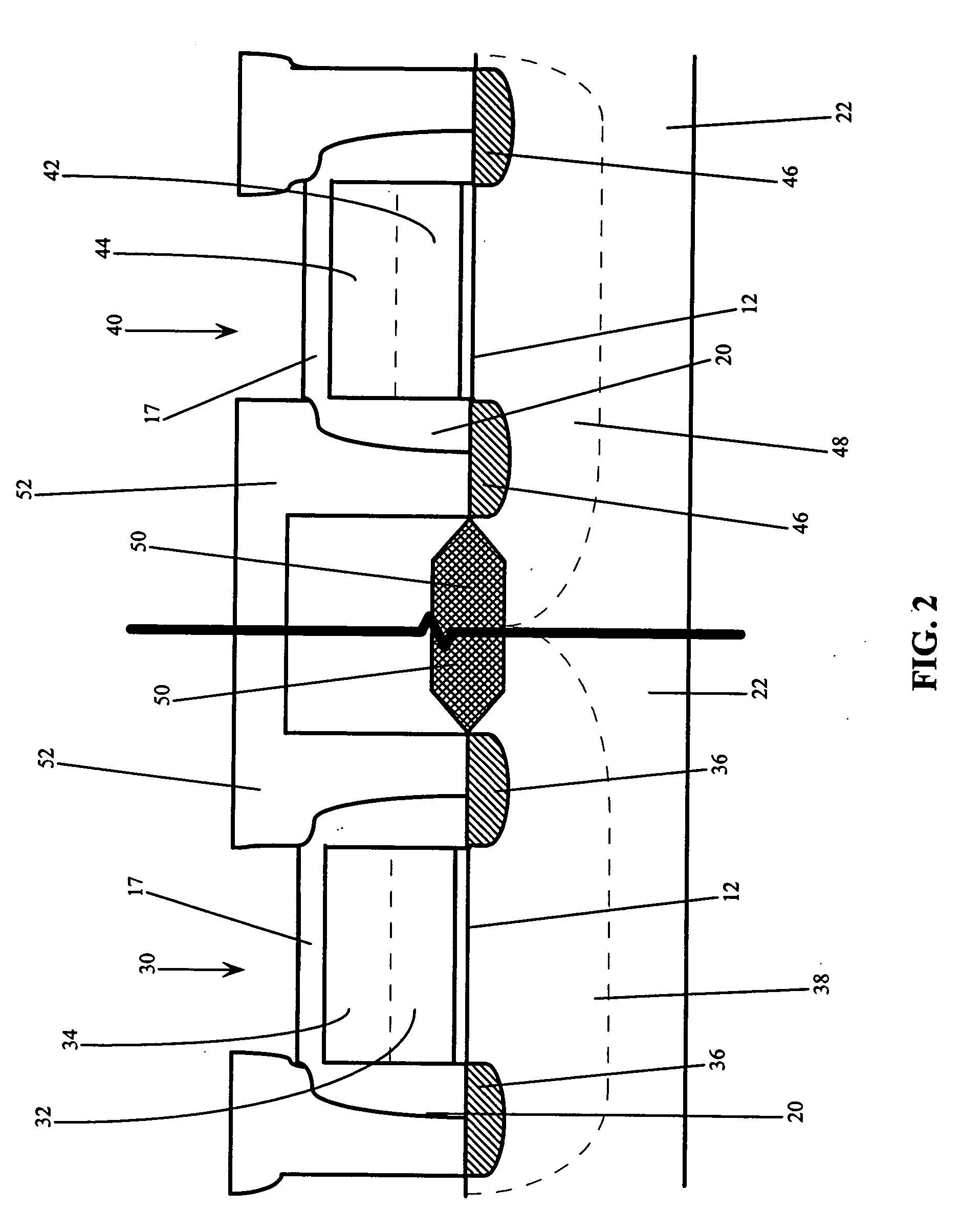

Use of gate electrode workfunction to improve DRAM refresh

InactiveUS6924190B2Reduce decreaseReduced channel region substrate dopingTransistorSolid-state devicesSubstrate dopingEngineering

This invention relates to a method and resulting structure, wherein a DRAM may be fabricated by using silicon midgap materials for transistor gate electrodes, thereby improving refresh characteristics of access transistors. The threshold voltage may be set with reduced substrate doping requirements. Current leakage is improved by this process as well.

Owner:JOHNSON & JOHNSON CONSUMER COPANIES

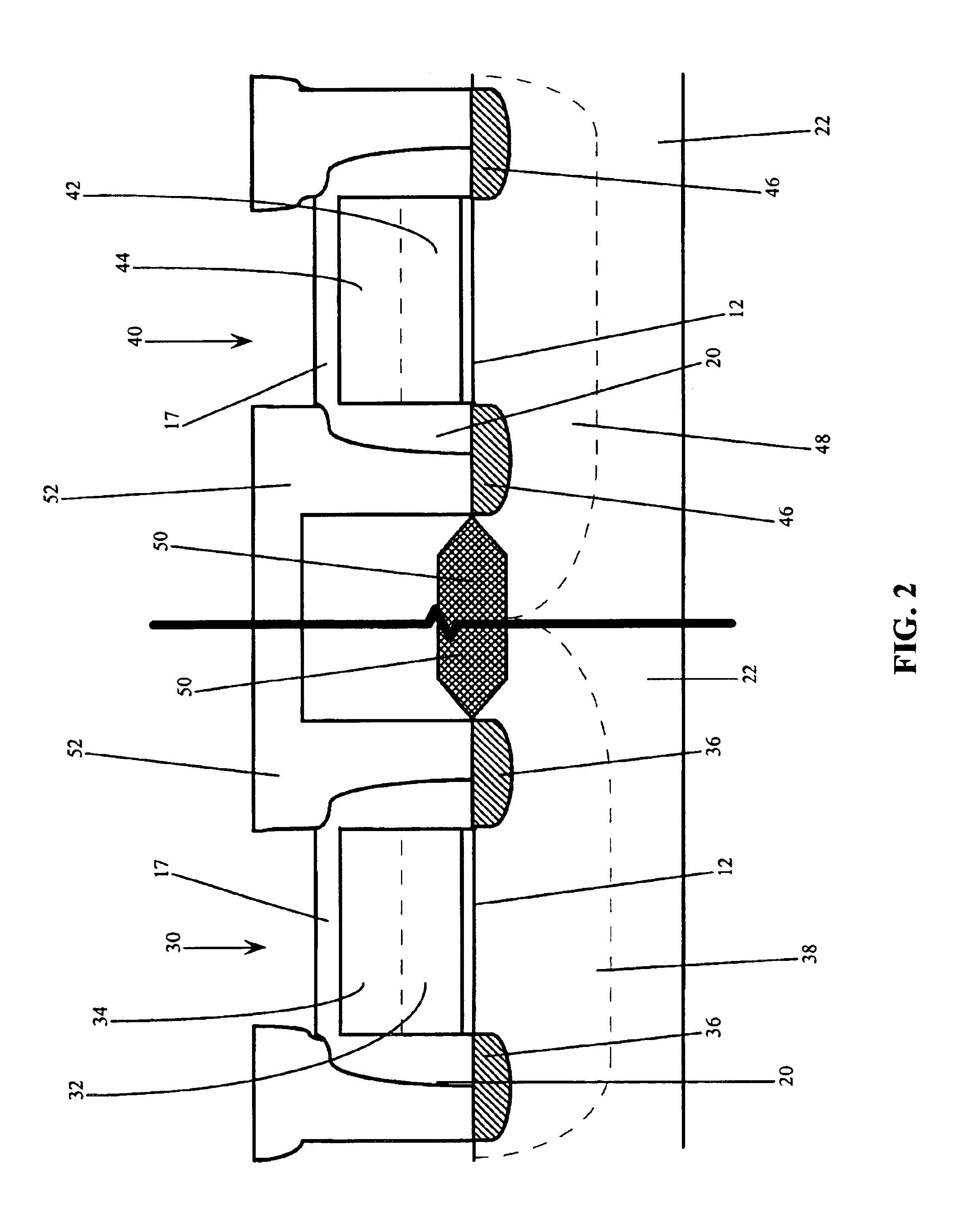

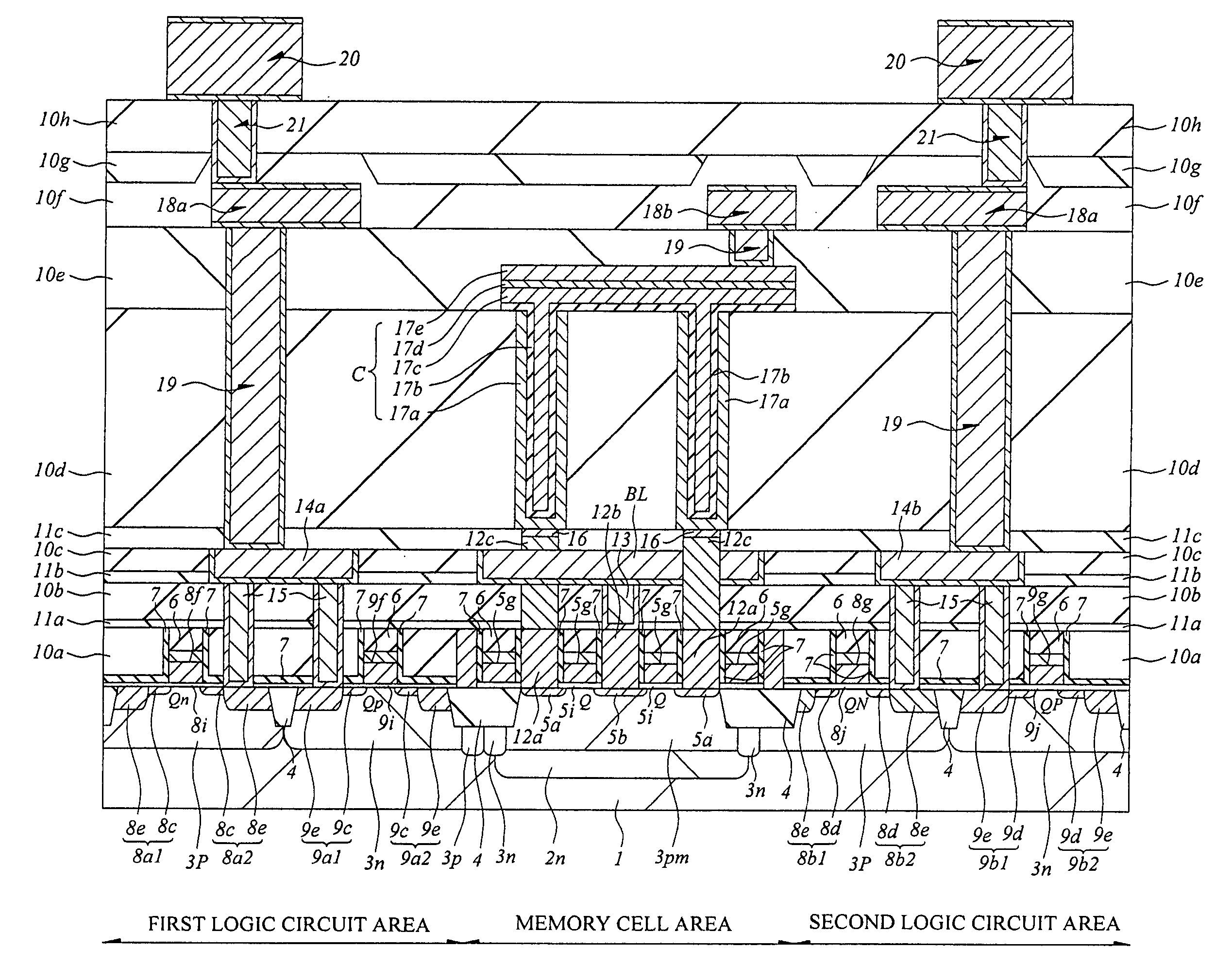

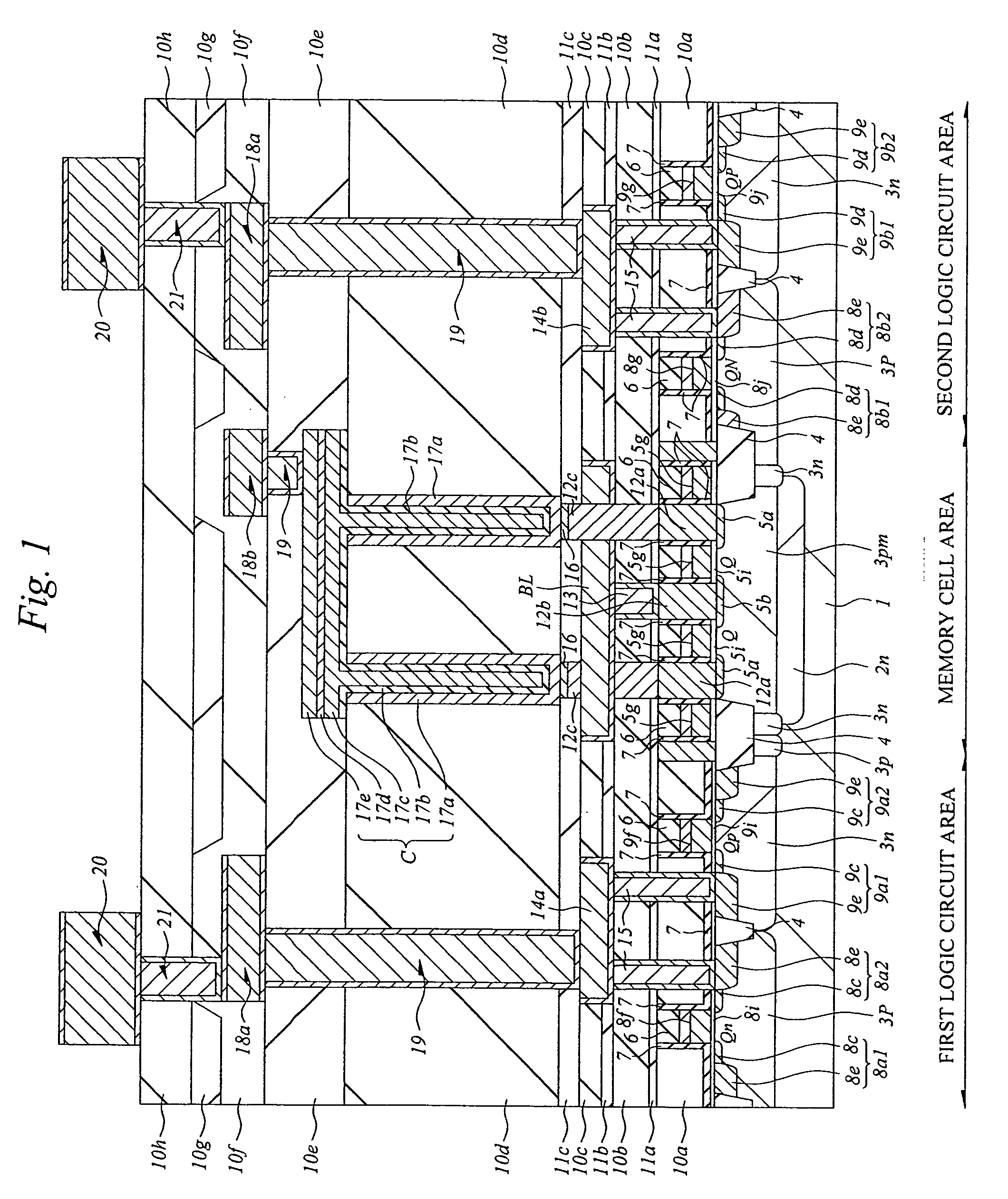

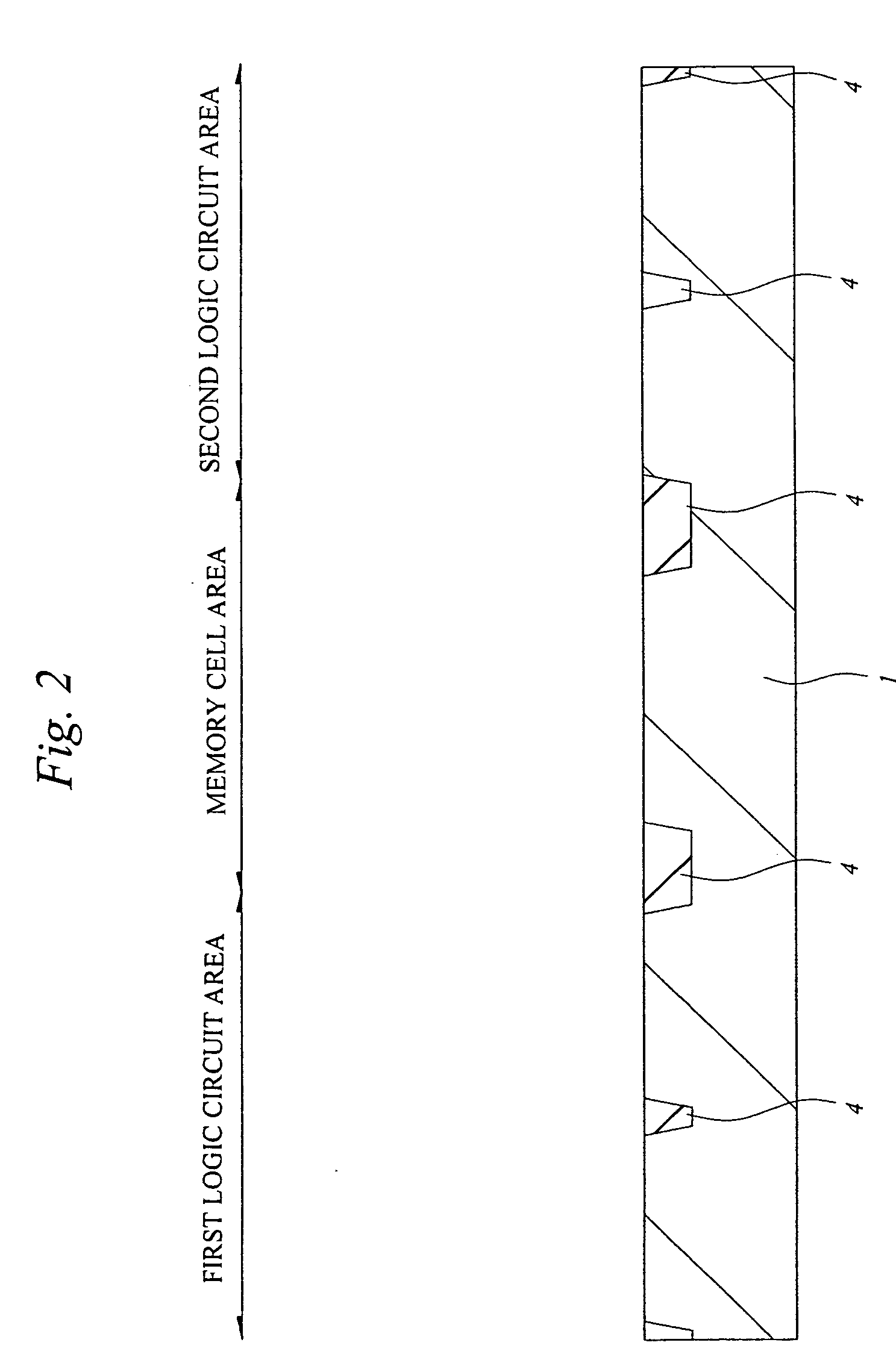

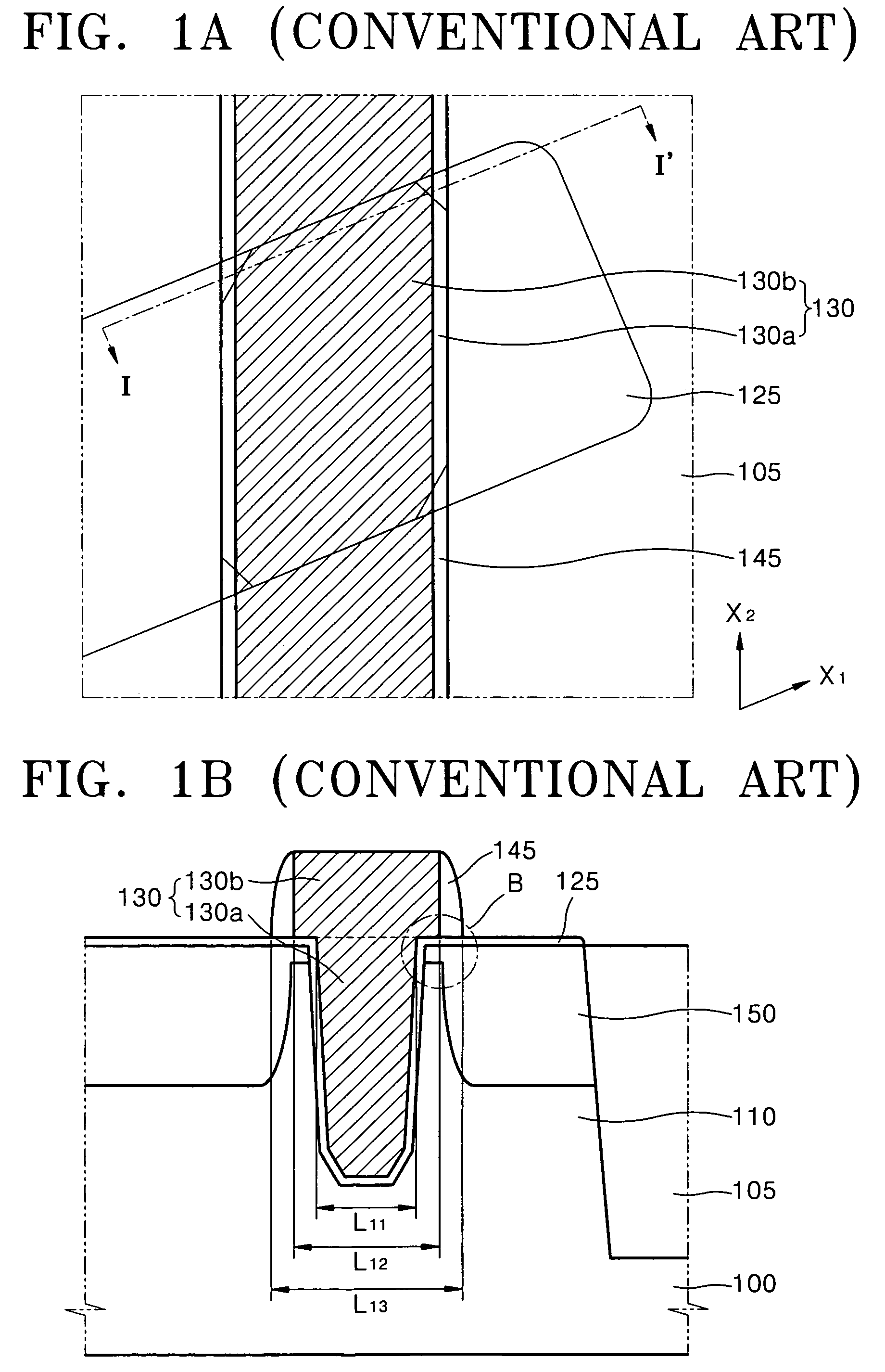

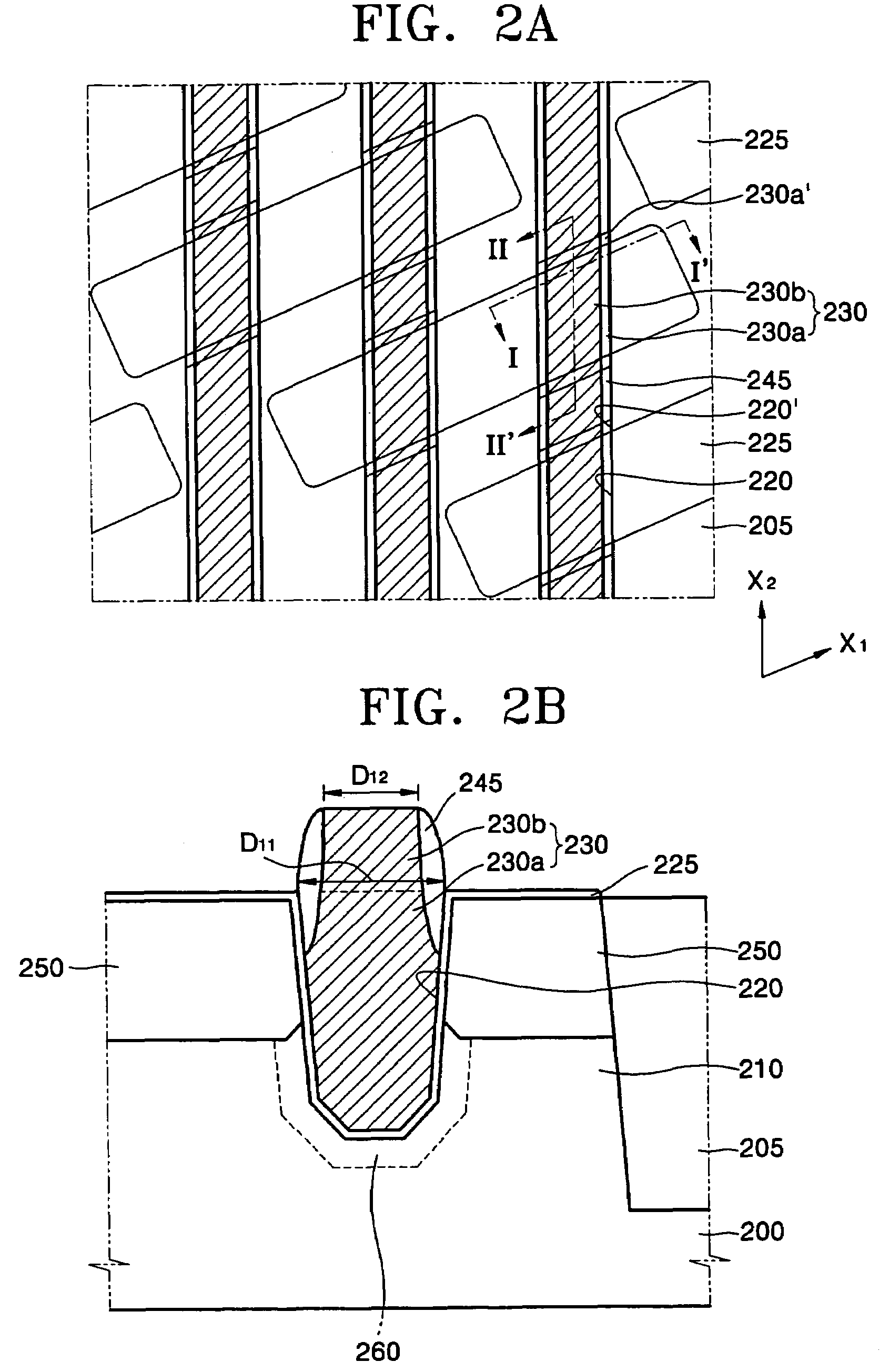

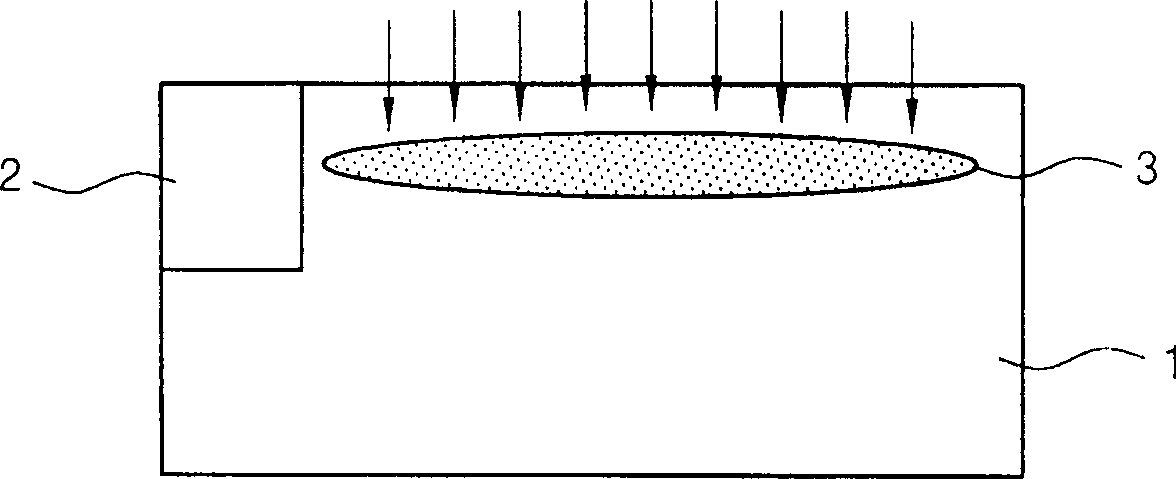

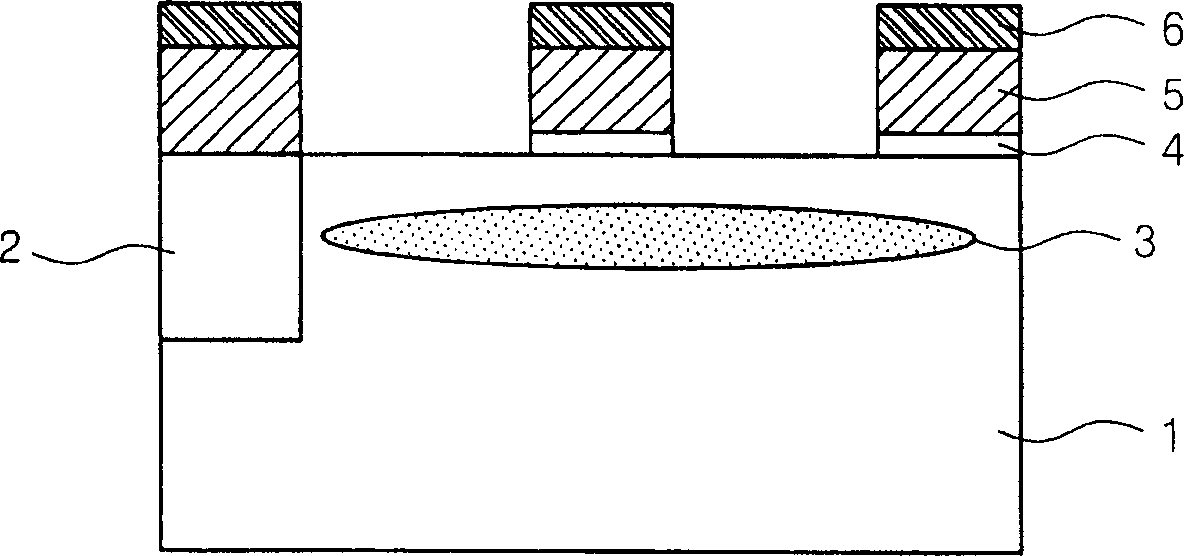

Semiconductor integrated circuit device and production method thereof

InactiveUS20050208716A1Improve refresh featureEasy to integrateTransistorSolid-state devicesDram memoryEngineering

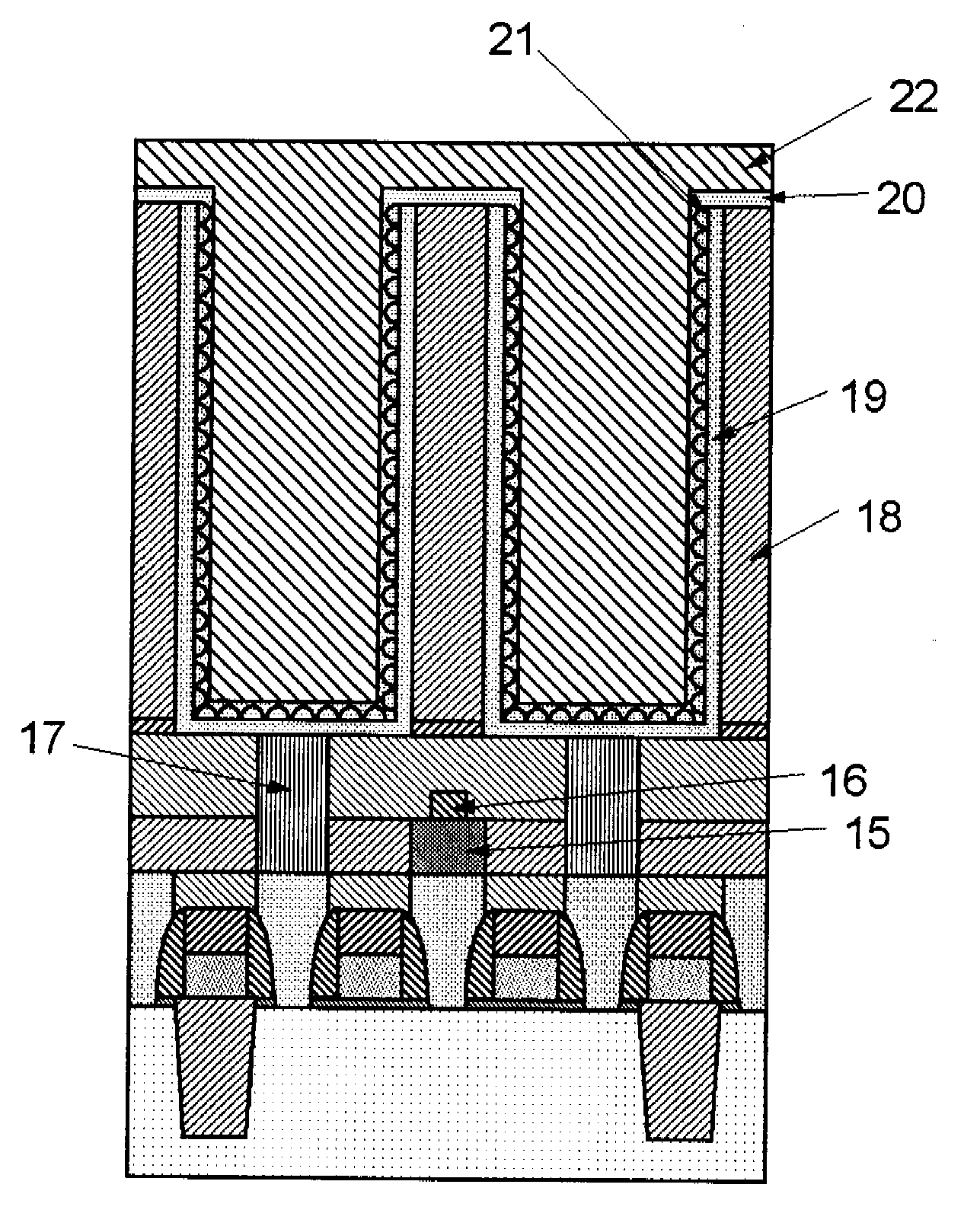

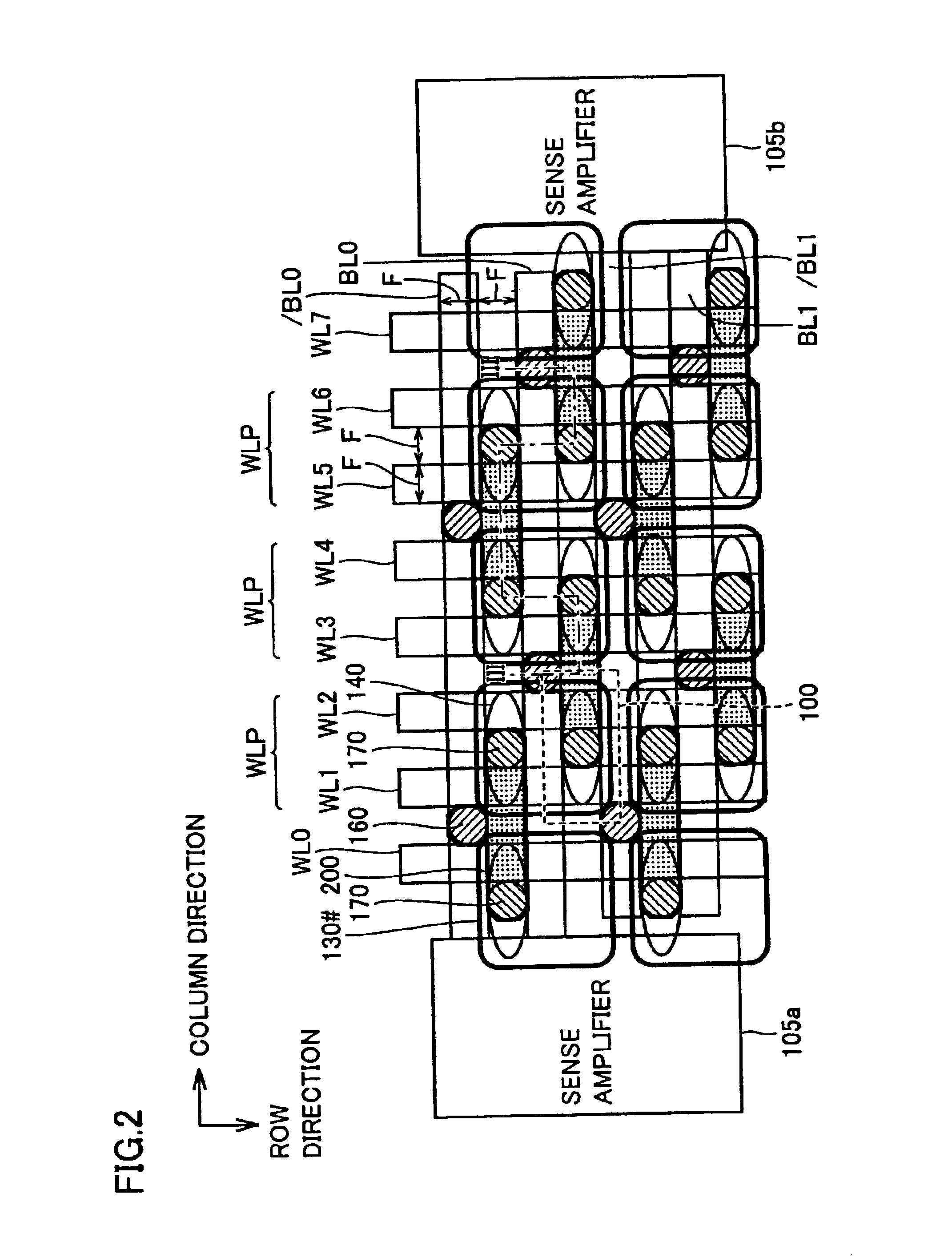

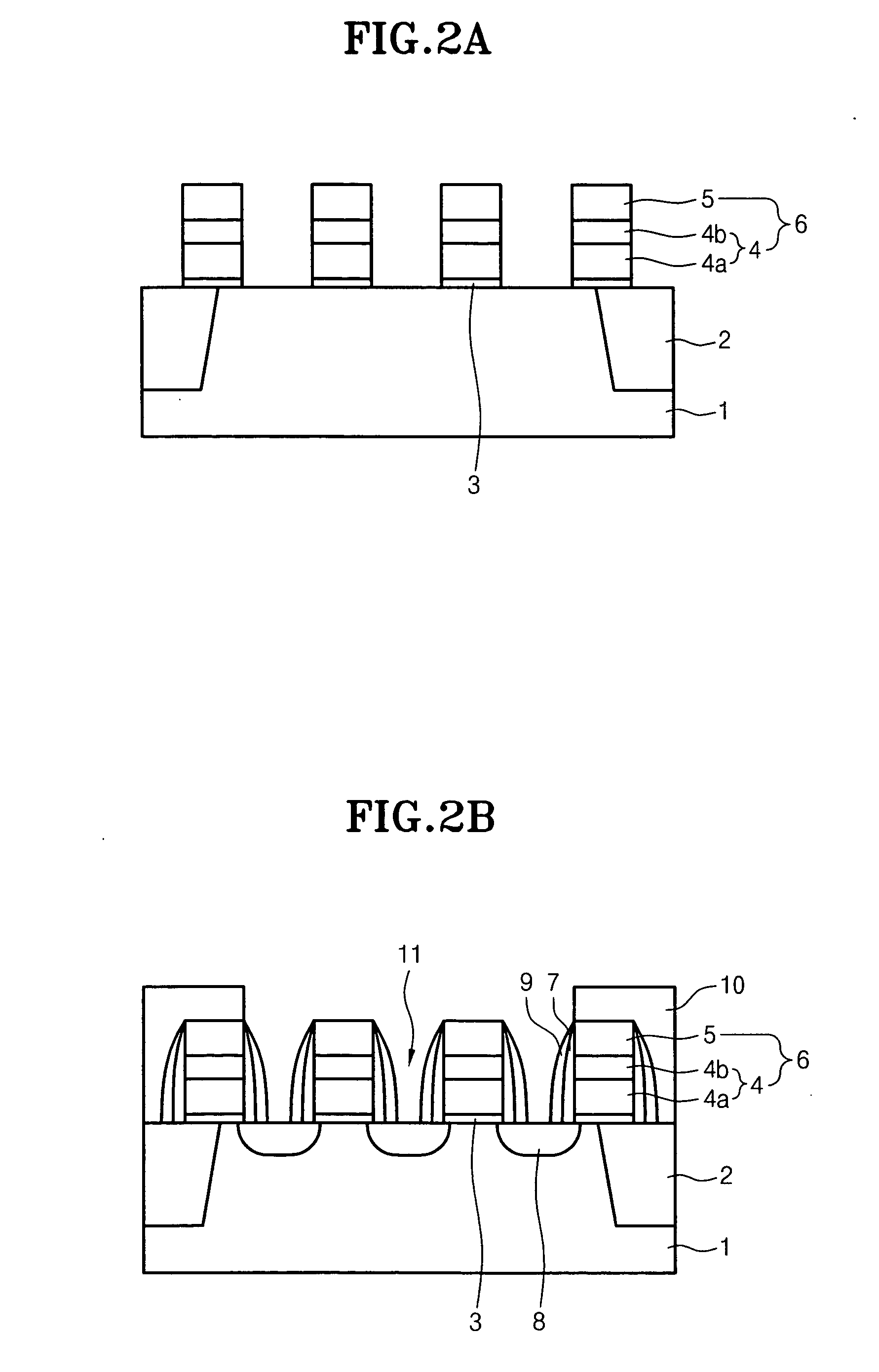

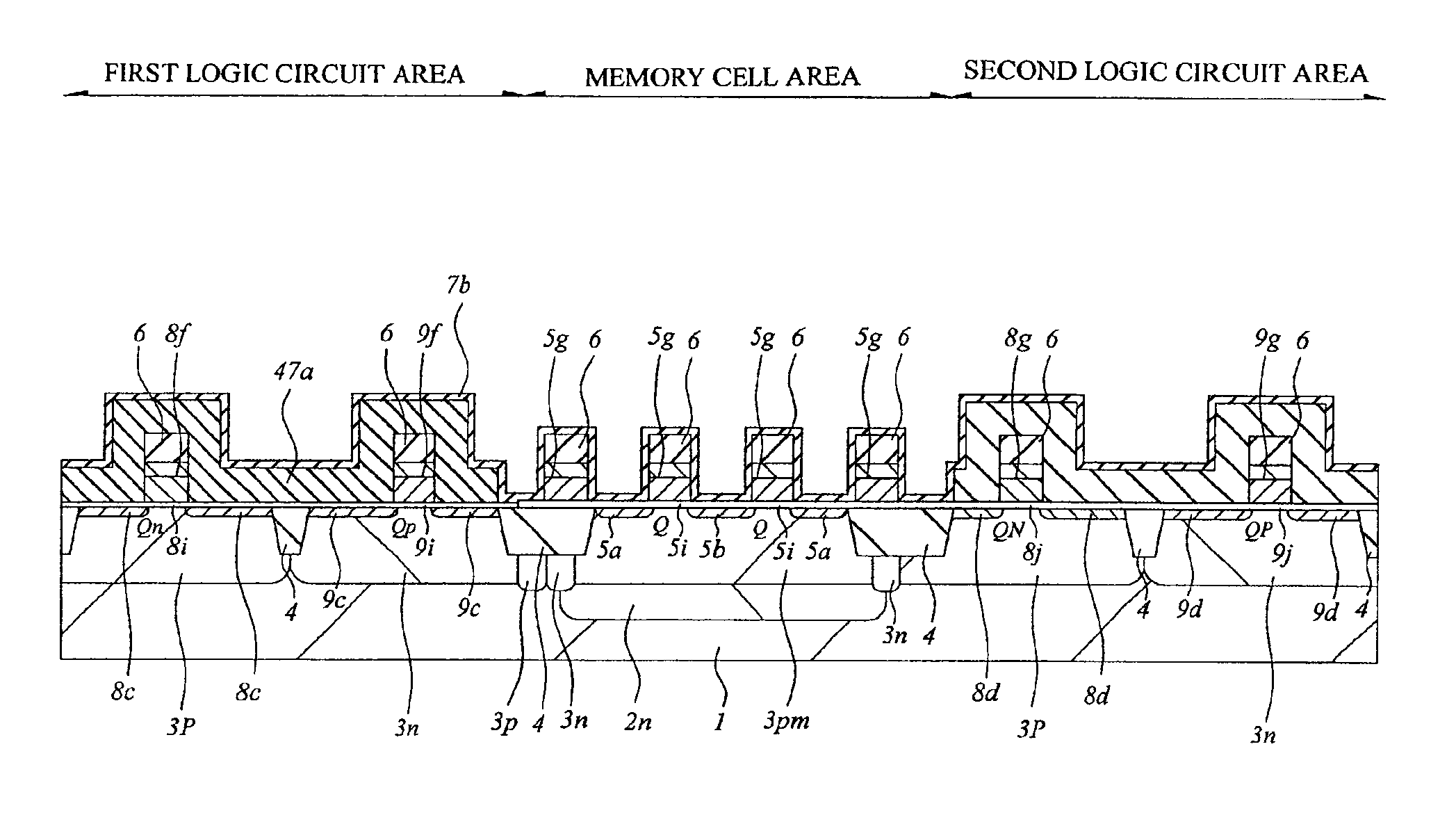

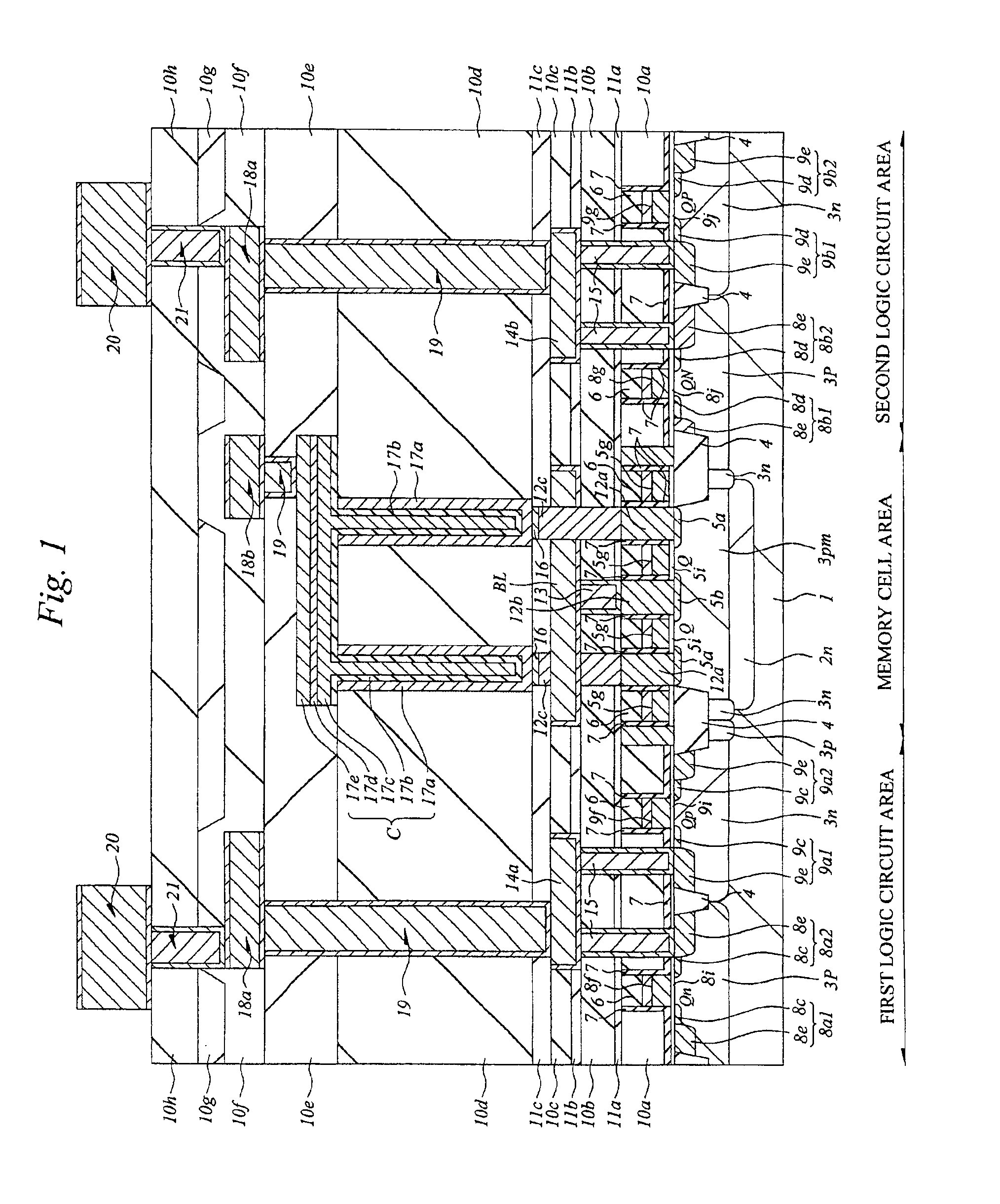

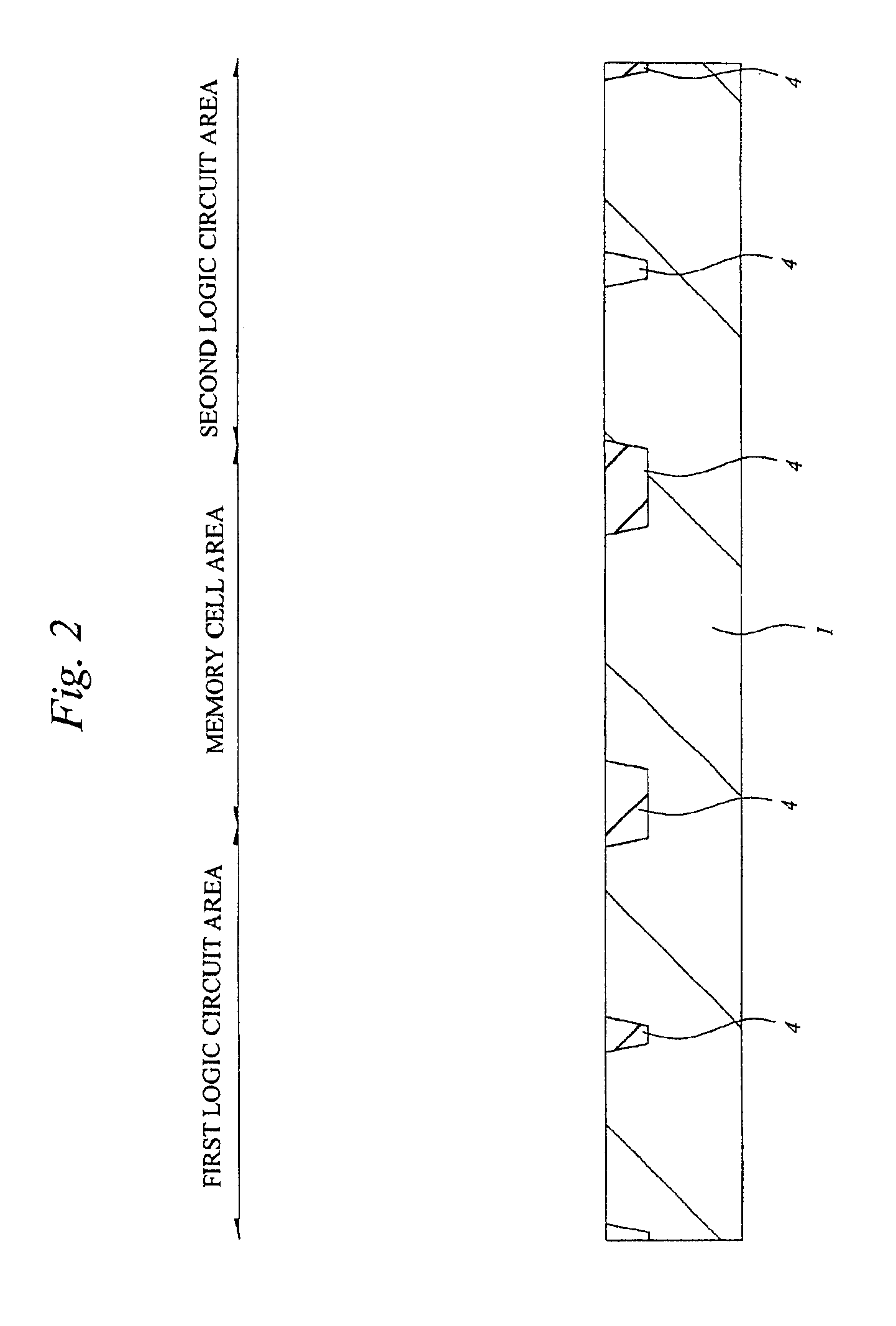

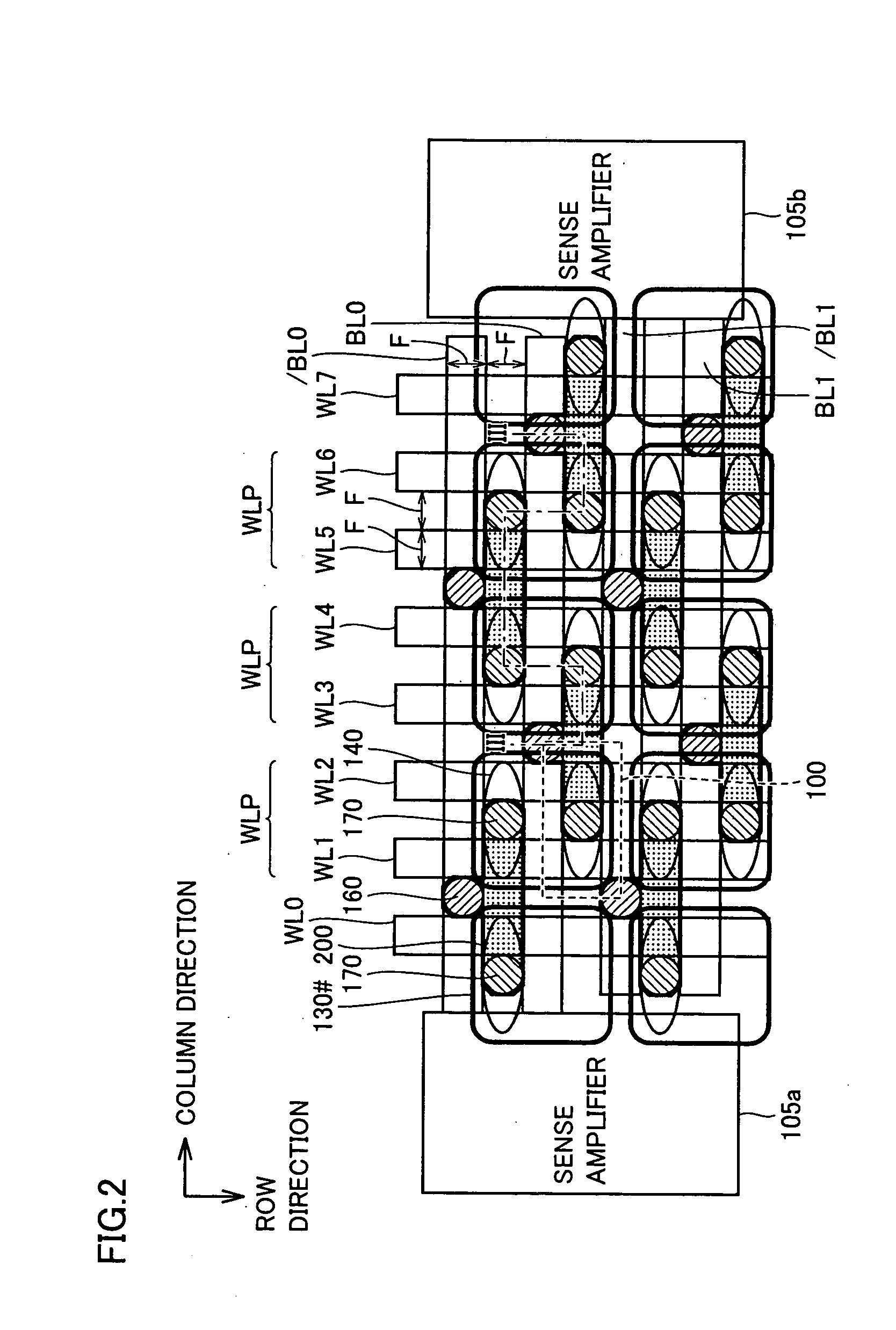

A refresh characteristic of a DRAM memory cell is improved and the performance of a MISFET formed in the periphery thereof and constituting a logic circuit is improved. Each gate electrode in a memory cell area is formed of p type polycrystalline silicon, and a cap insulating film on each gate electrode and a sidewall film on the sidewall thereof are formed of a silicon oxide film. A polycrystalline silicon film formed on the gate electrodes and between the gate electrodes is polished by a CMP method, and thereby contact electrodes are formed. Also, sidewall films each composed of a laminated film of the silicon oxide film and the polycrystalline silicon film are formed on the sidewall of the gate electrodes in the logic circuit area, and these films are used as a mask to form semiconductor areas. As a result, it is possible to reduce the boron penetration and form contact electrodes in a self-alignment manner. In addition, the performance of the MISFET constituting the logic circuit can be improved.

Owner:ELPIDA MEMORY INC

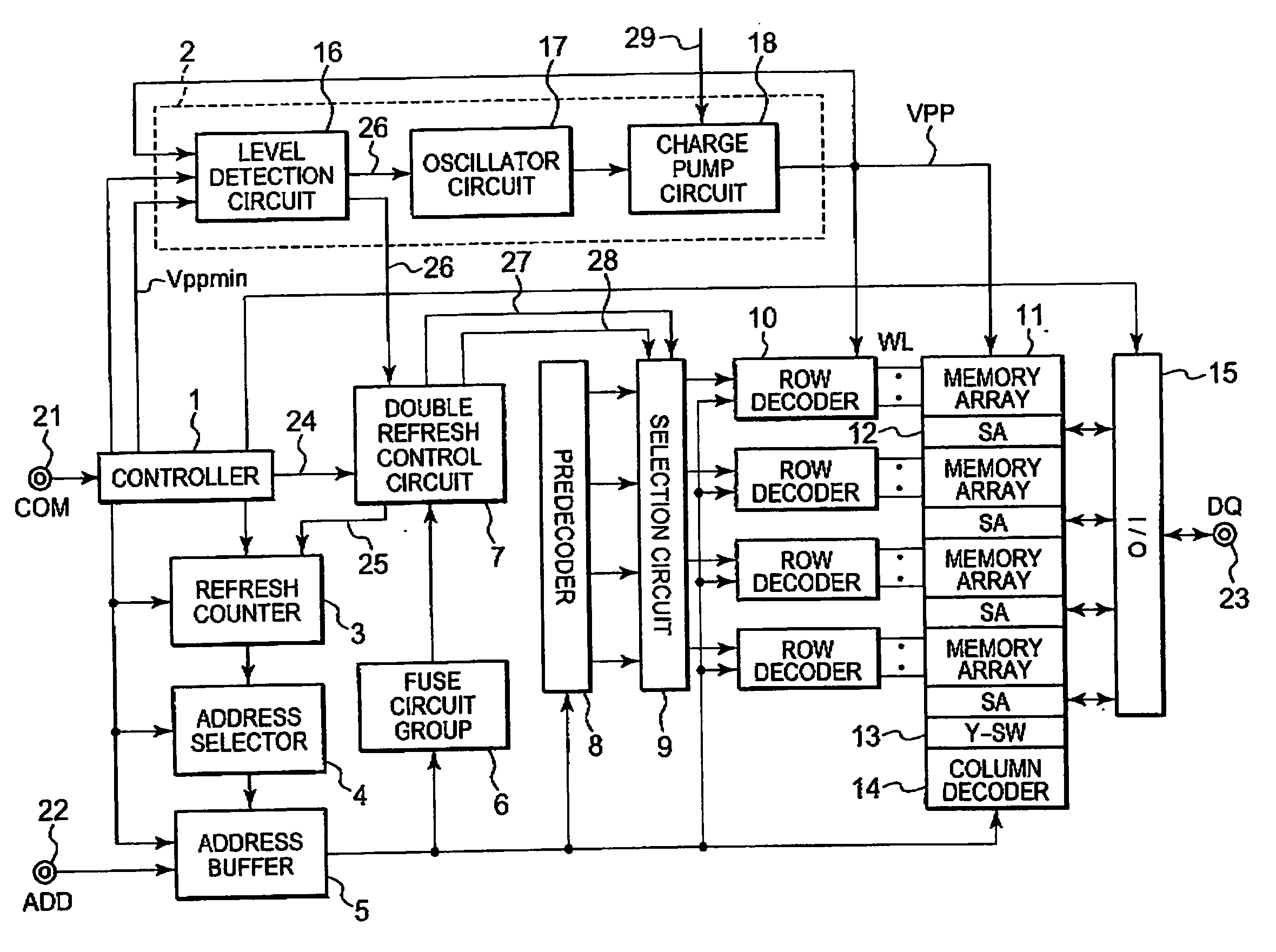

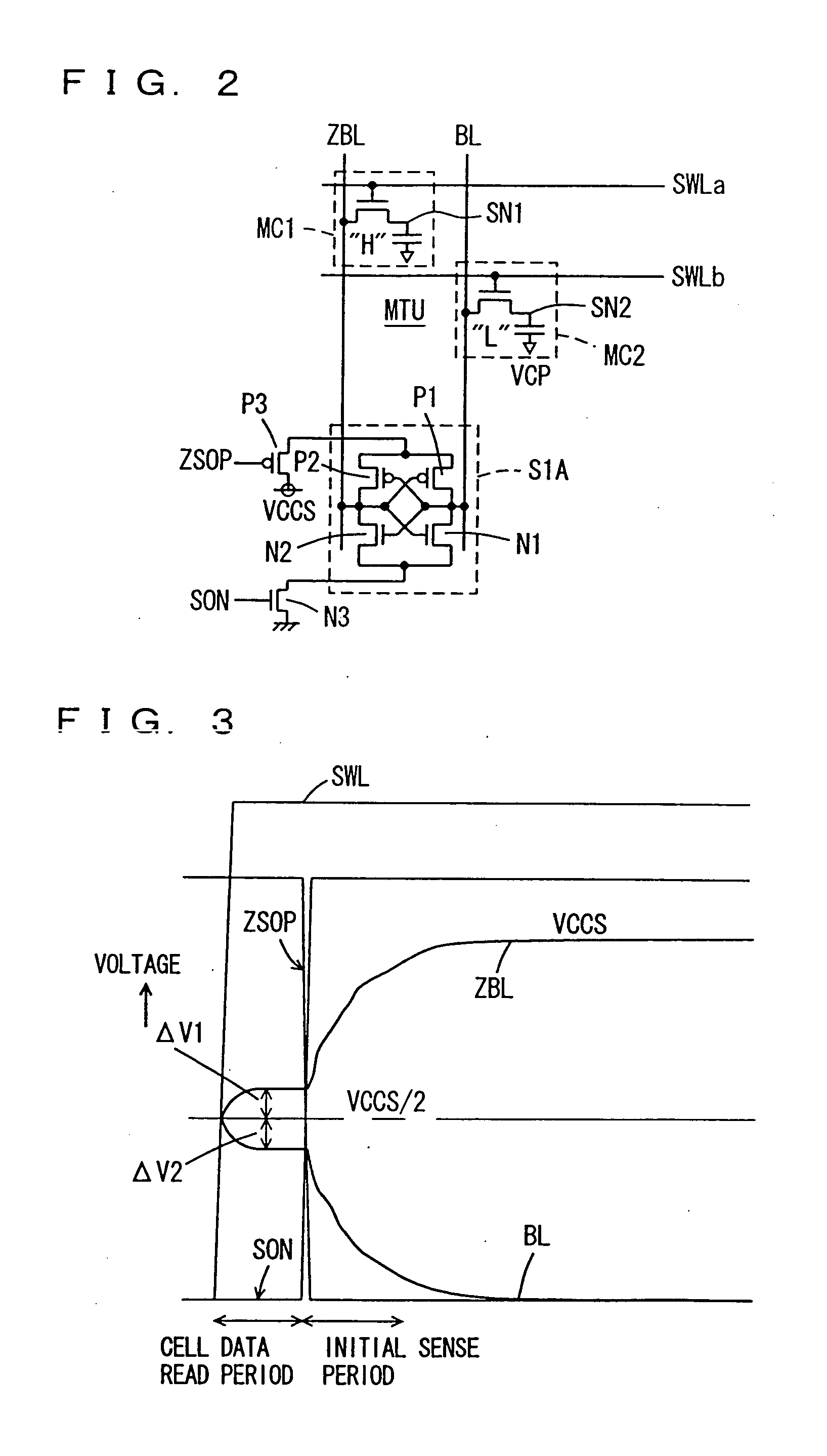

Semiconductor device

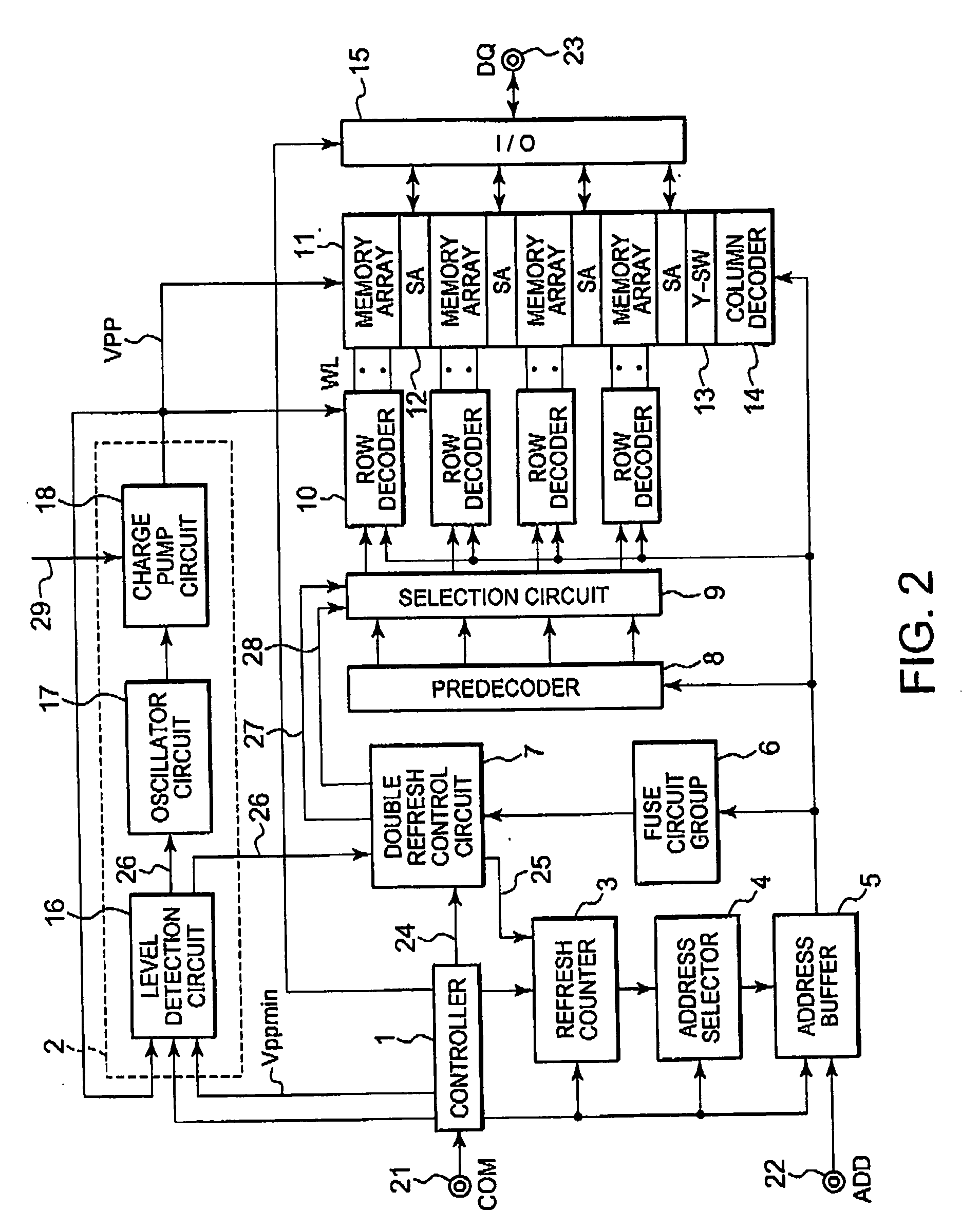

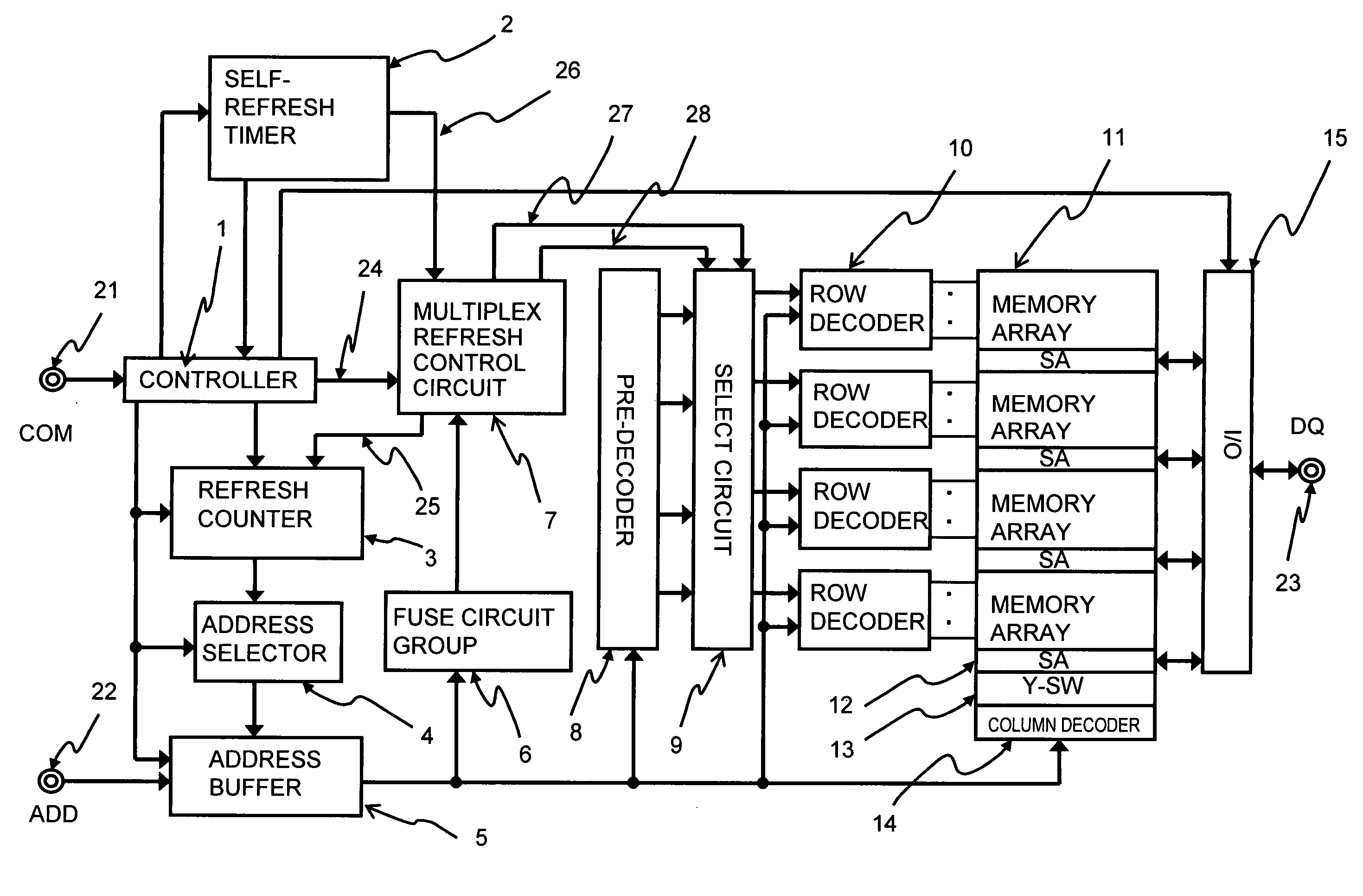

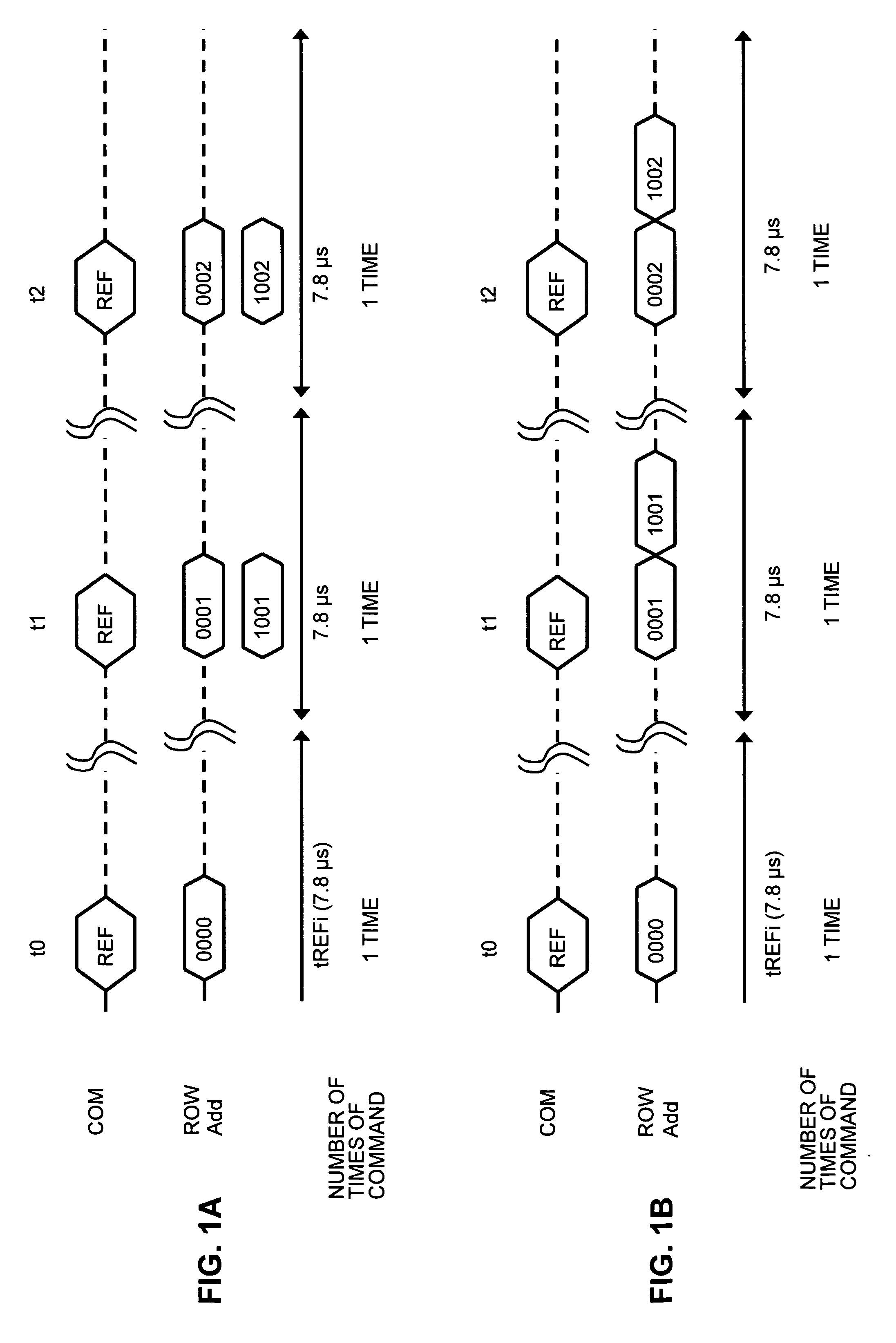

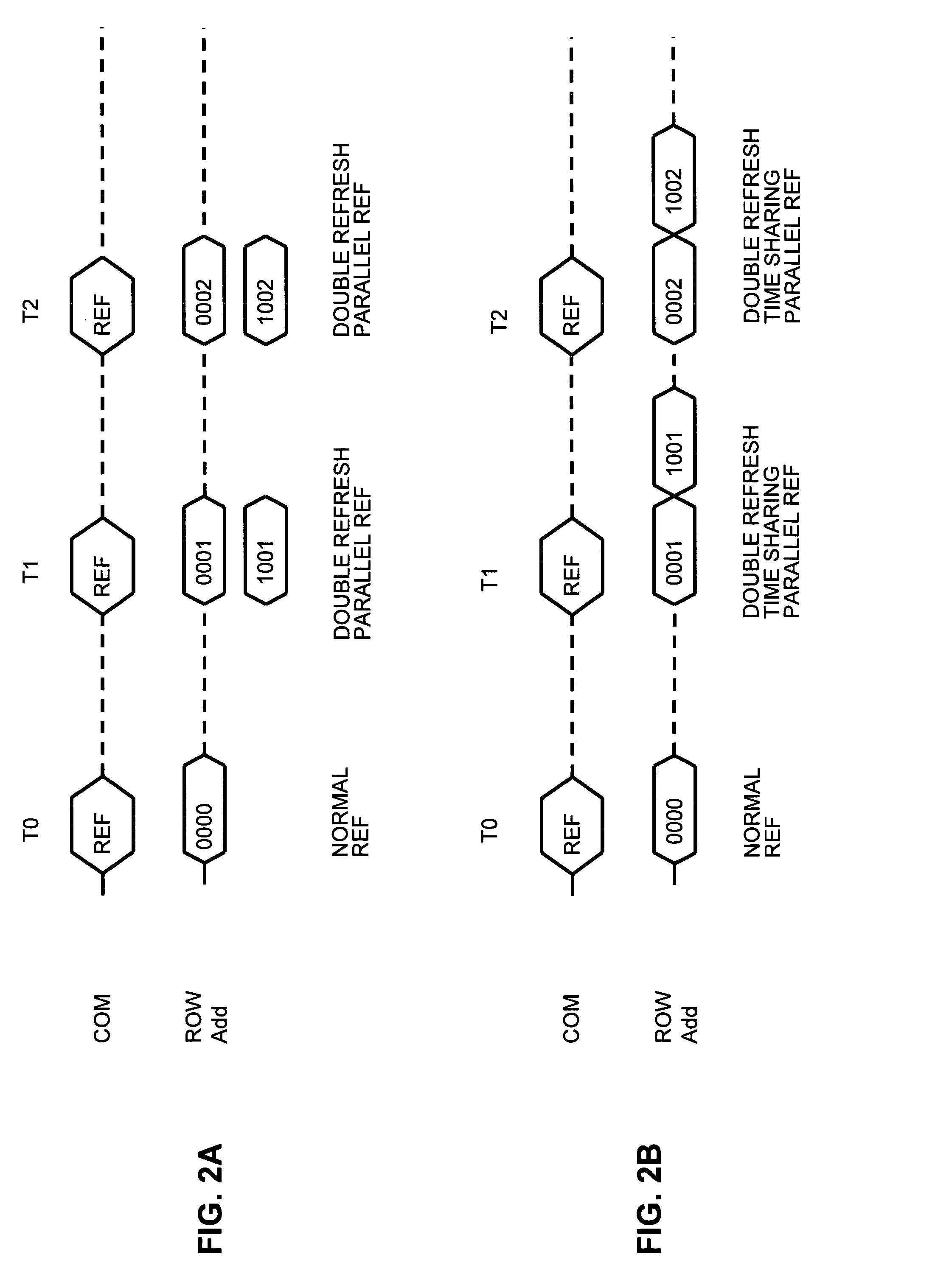

InactiveUS20070008799A1Raise the voltage levelImprove refresh featureDigital storageLower limitRefresh cycle

In a semiconductor device, an internally-generated power supply voltage VPP is monitored. If the internally-generated power supply voltage VPP is lower than a lower limit voltage, serial refresh is selected as a double refresh operation mode. In the serial refresh, double refresh for a pair address is inserted in a next refresh cycle. By the serial refresh, decrease of the internally-generated power supply voltage VPP is suppressed.

Owner:LONGITUDE LICENSING LTD

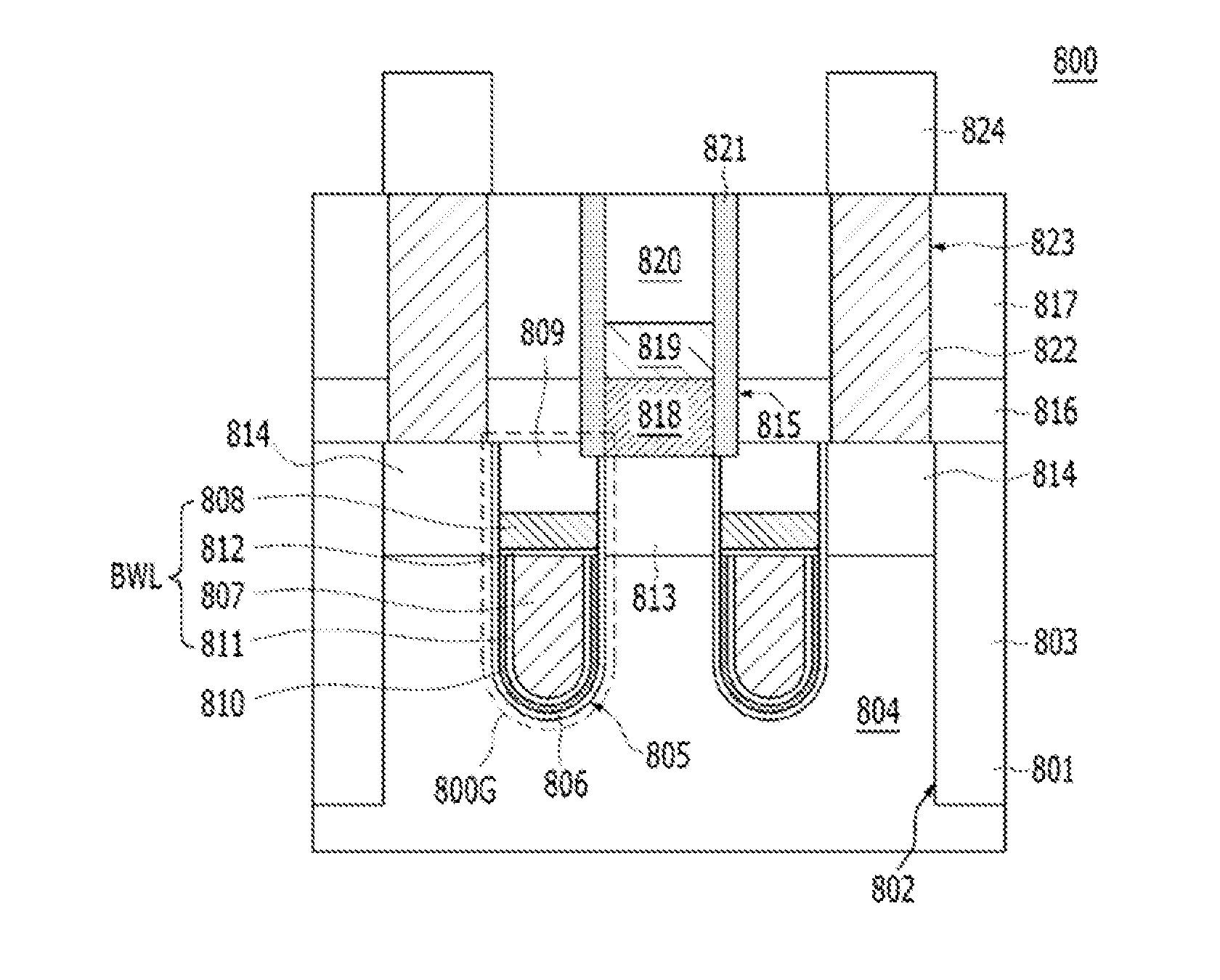

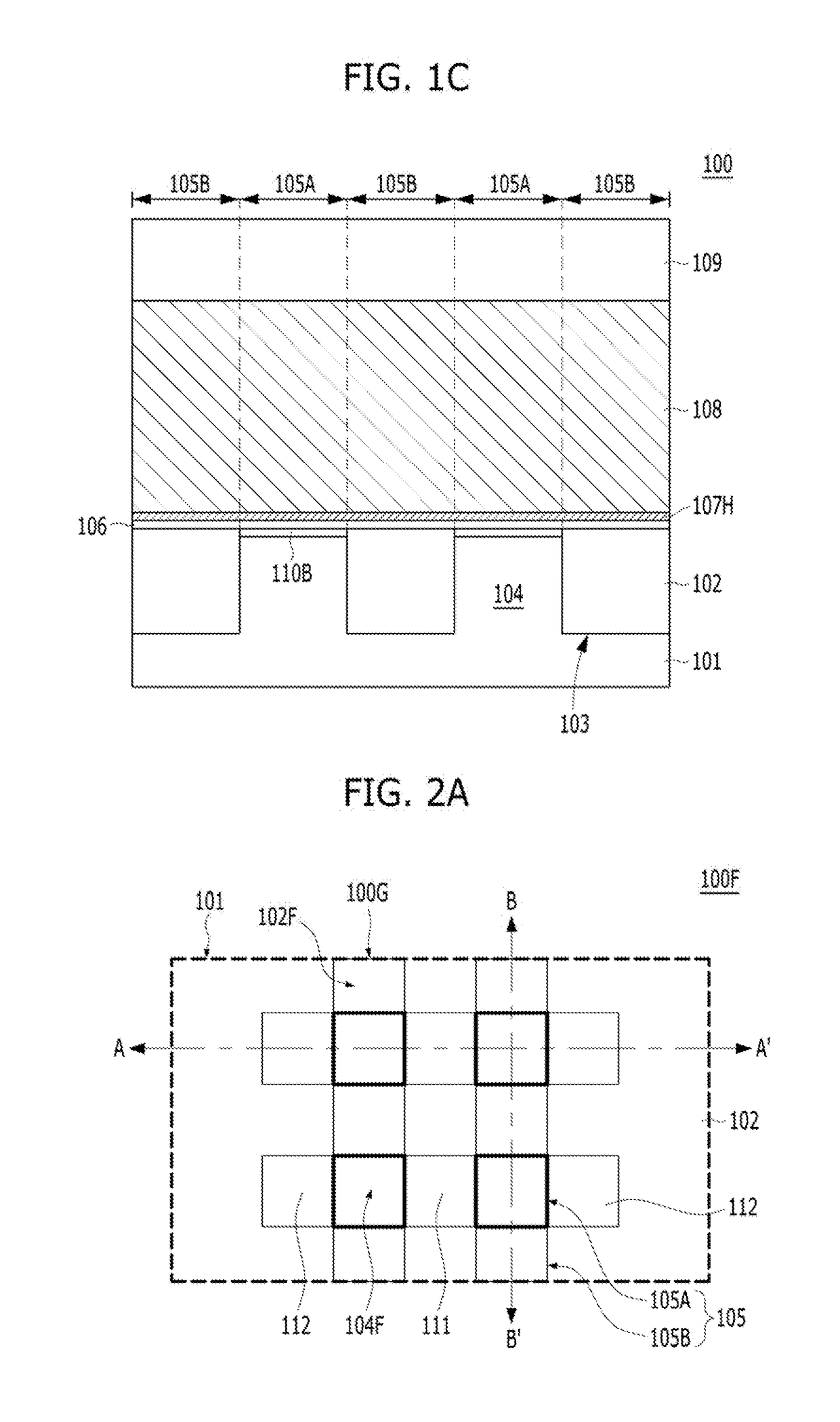

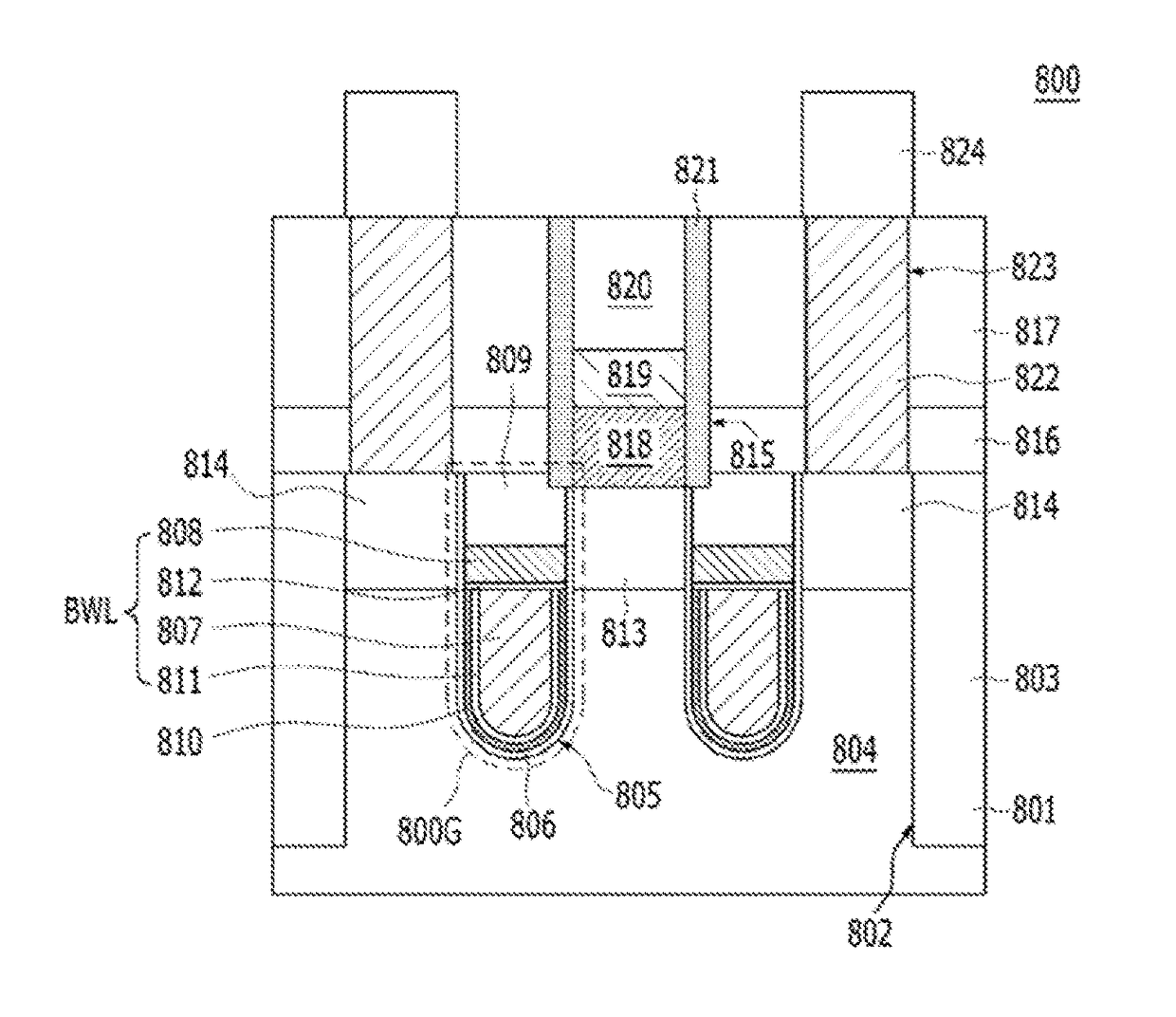

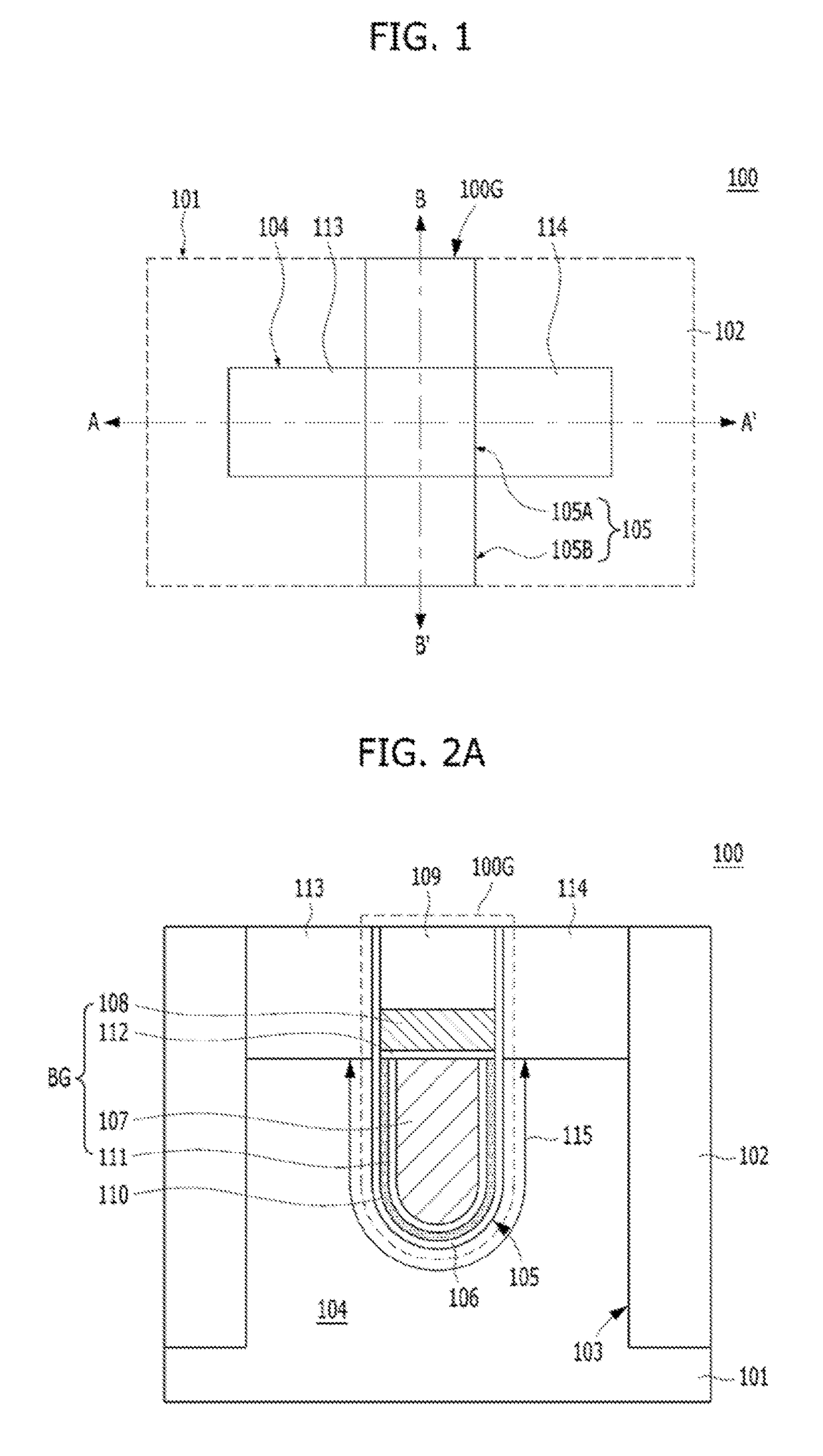

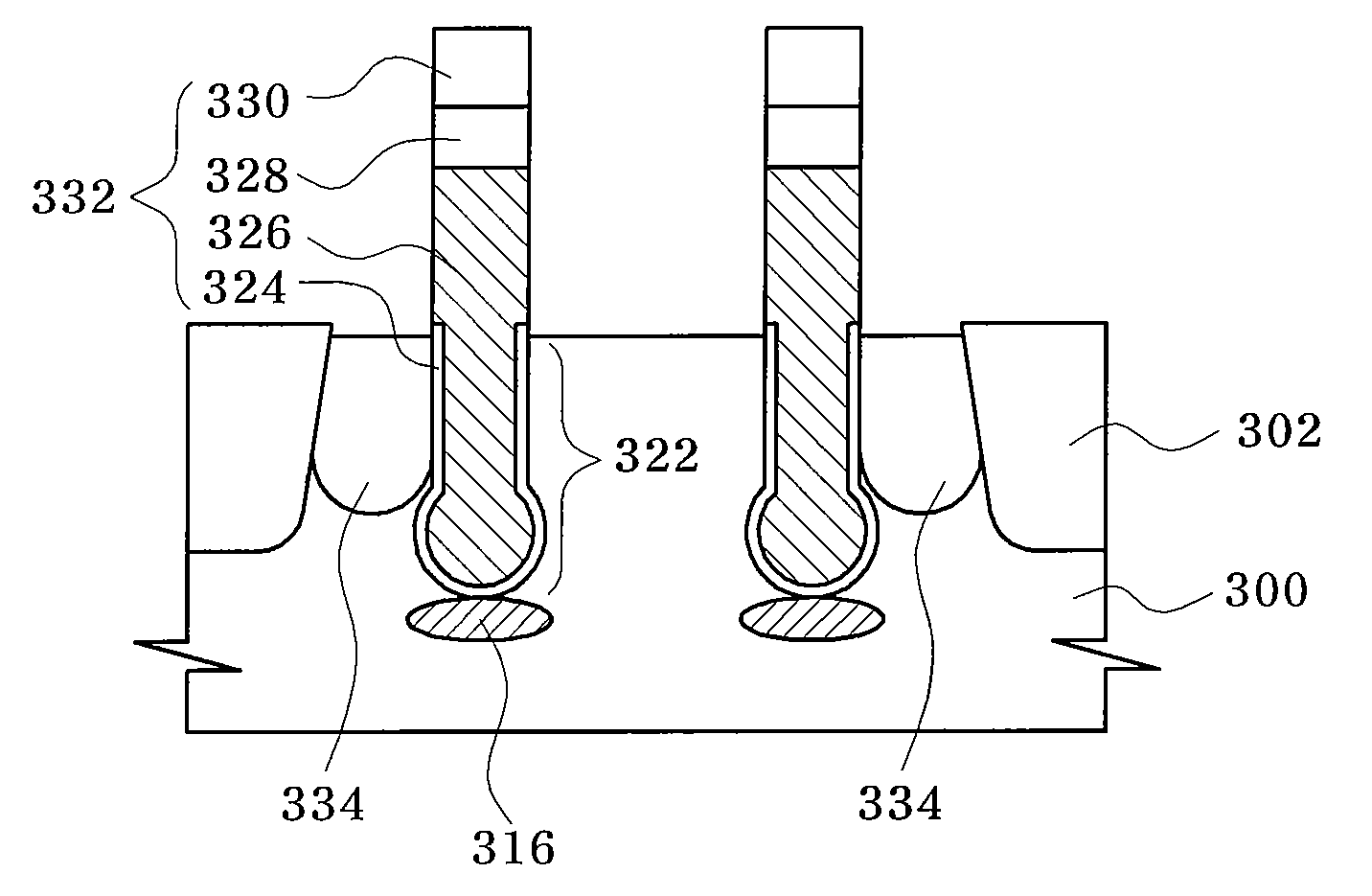

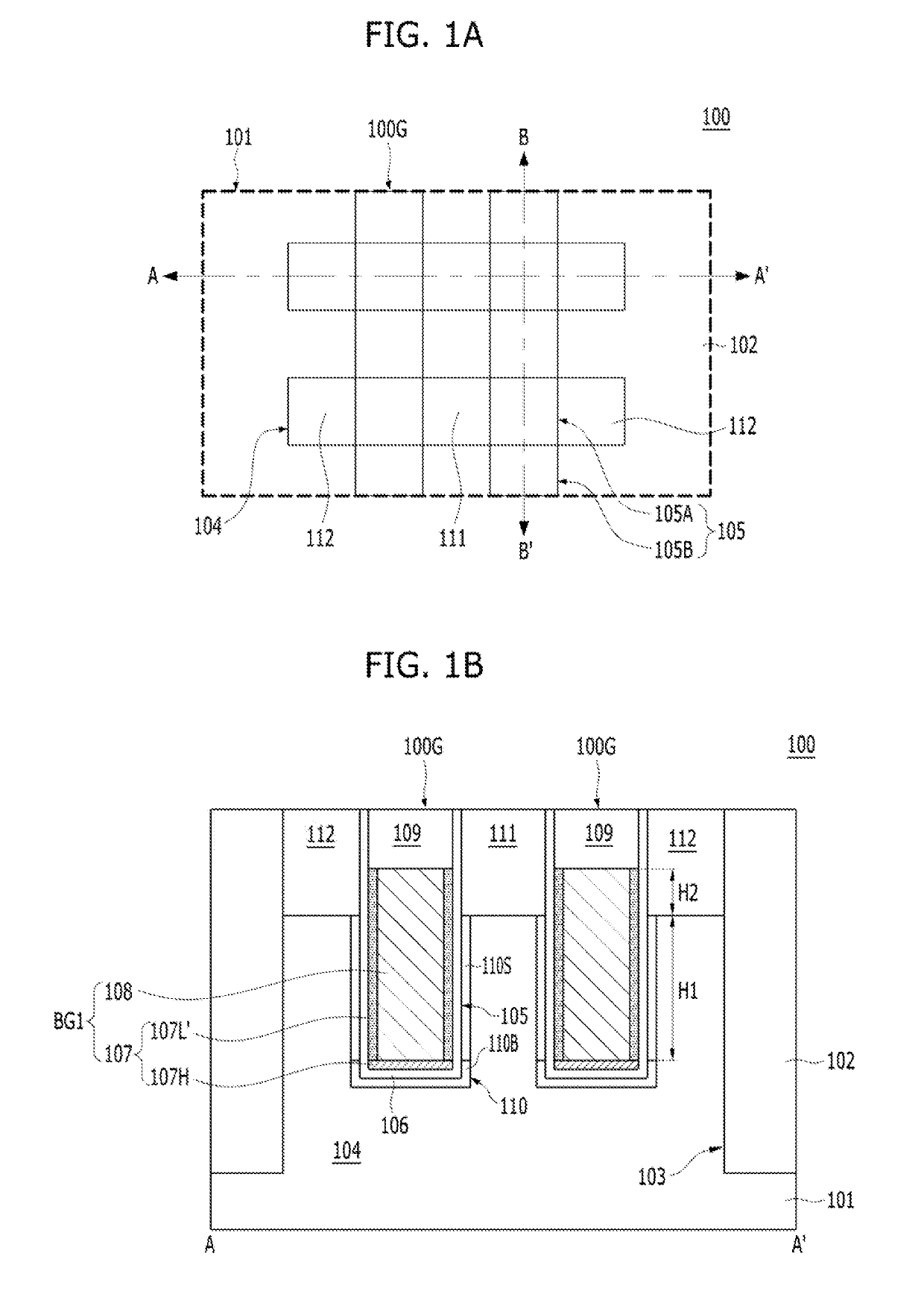

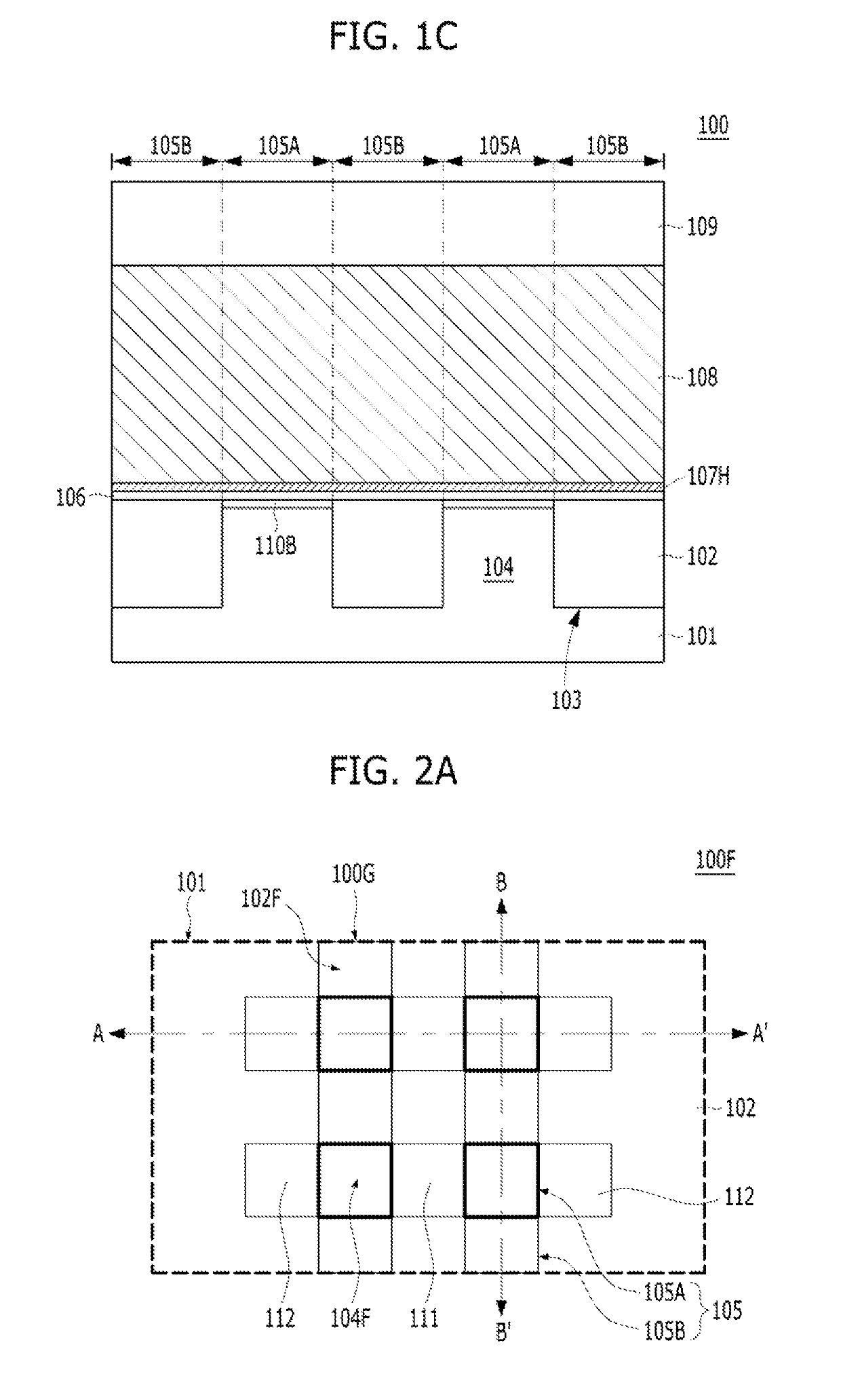

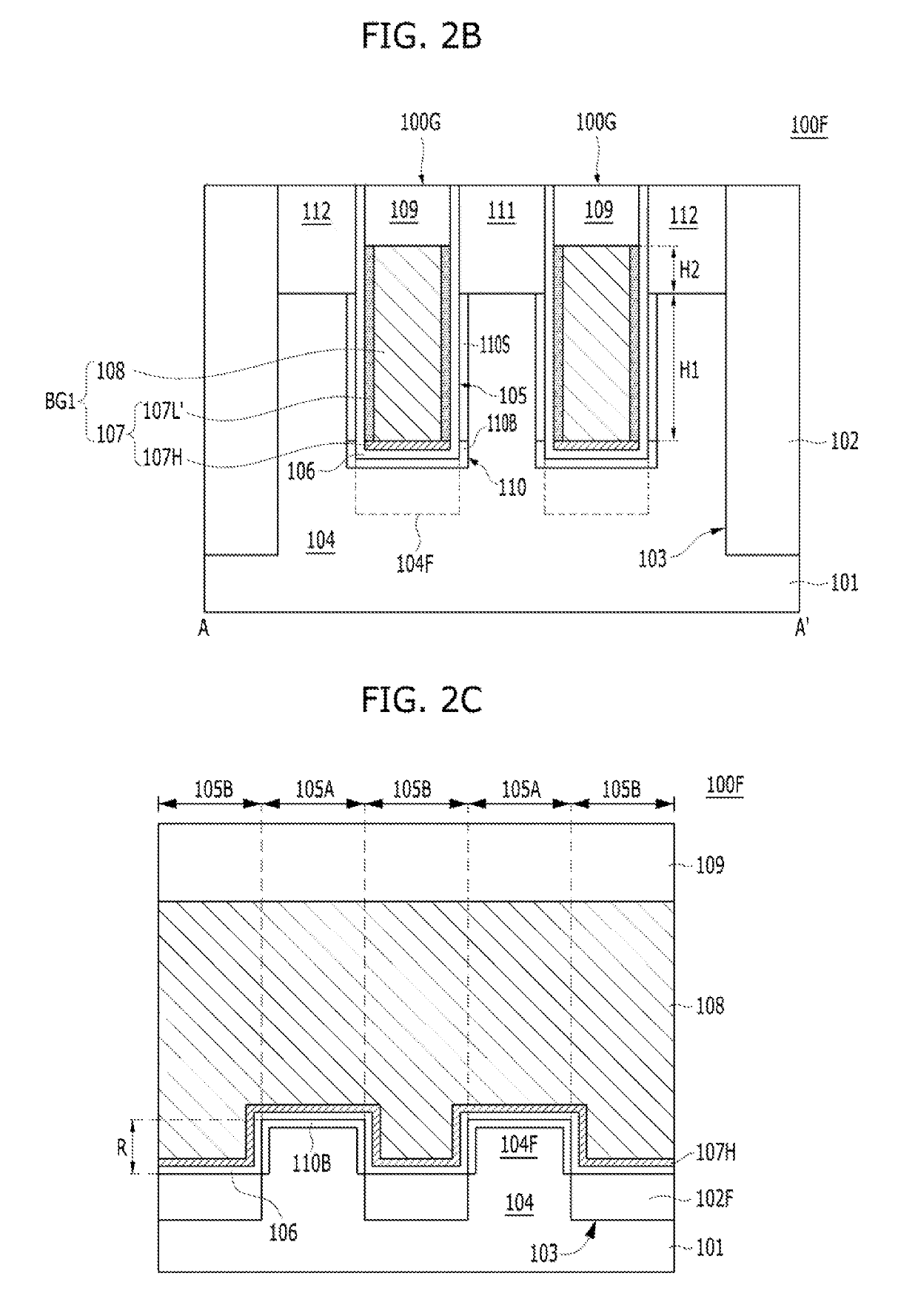

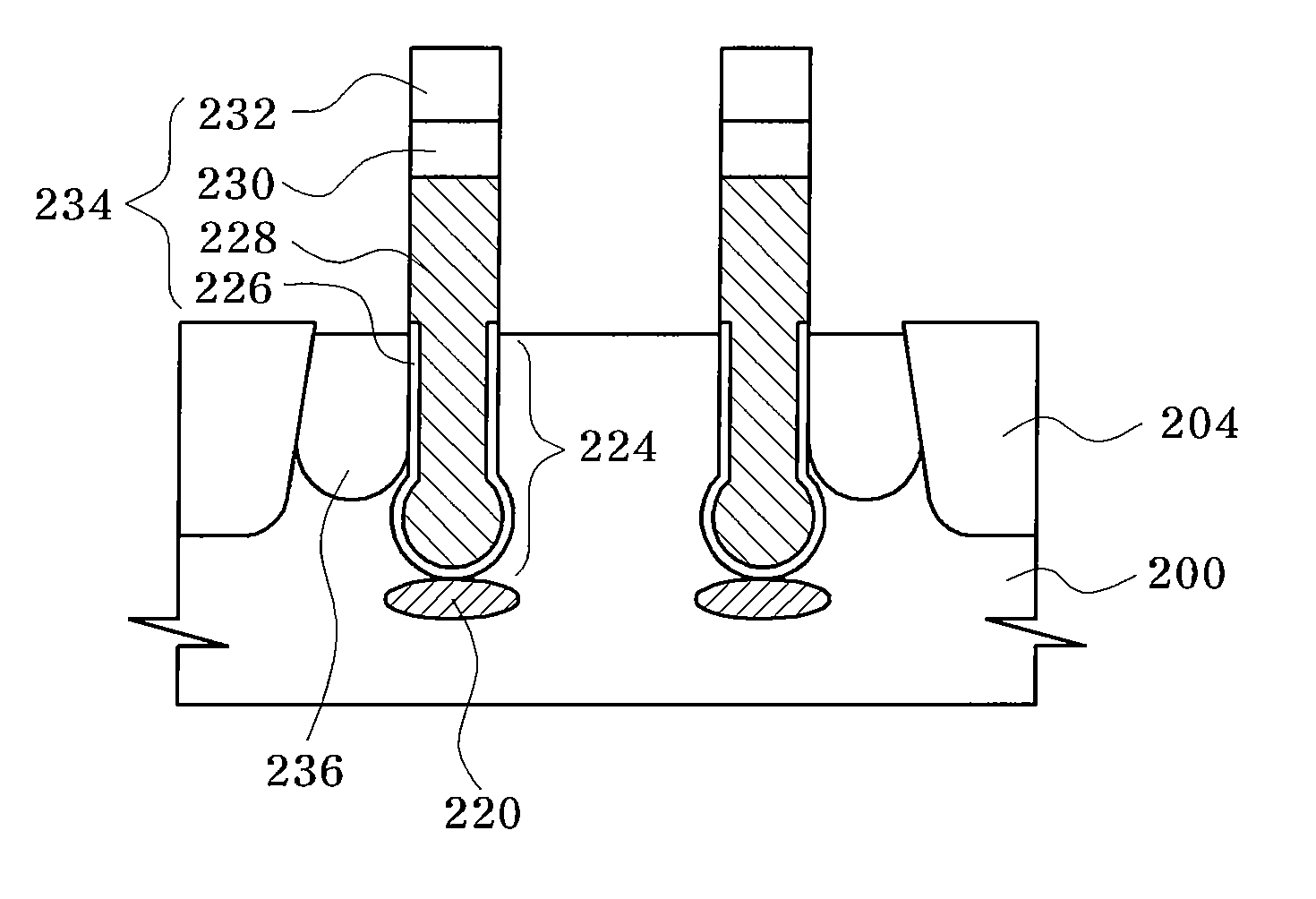

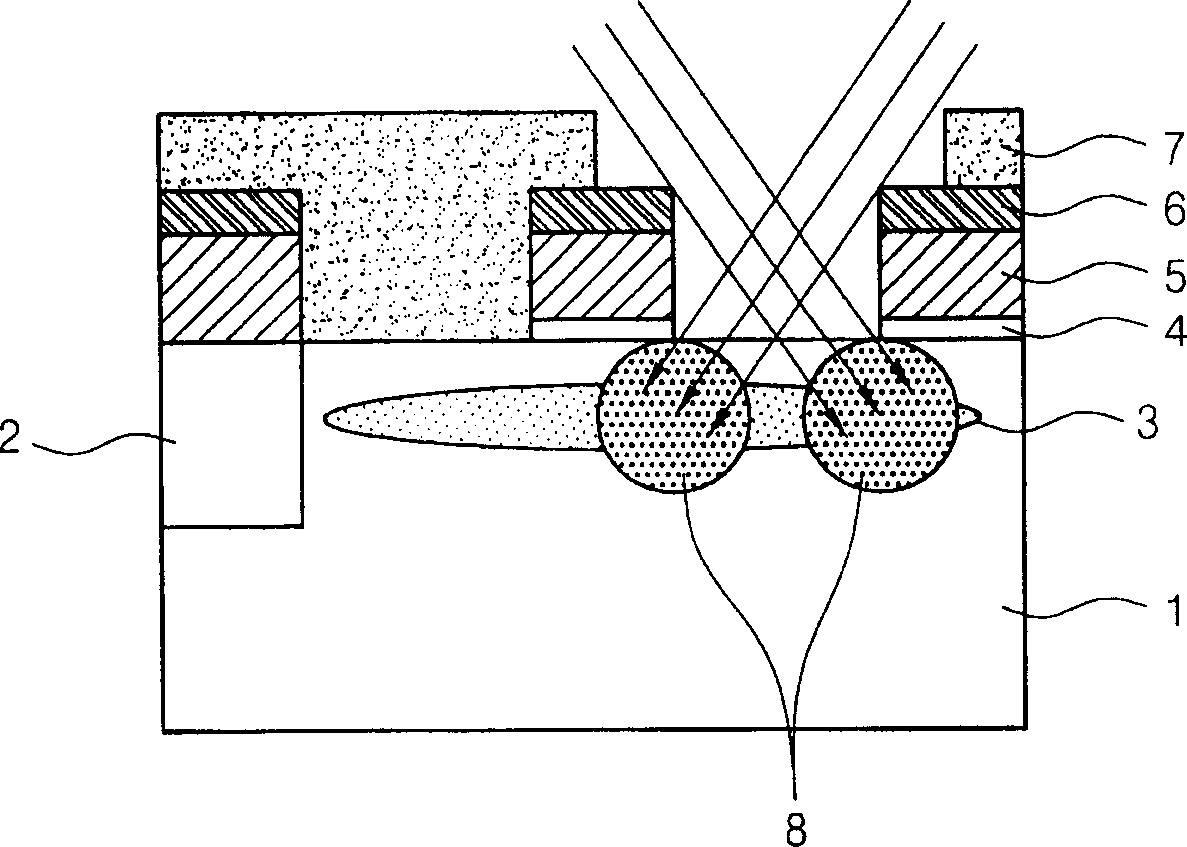

Semiconductor device having buried gate structure and method for manufacturing the same, memory cell having the same and electronic device having the same

ActiveUS20160315088A1Improve refresh featureImprove performanceTransistorSolid-state devicesPower semiconductor deviceGate dielectric

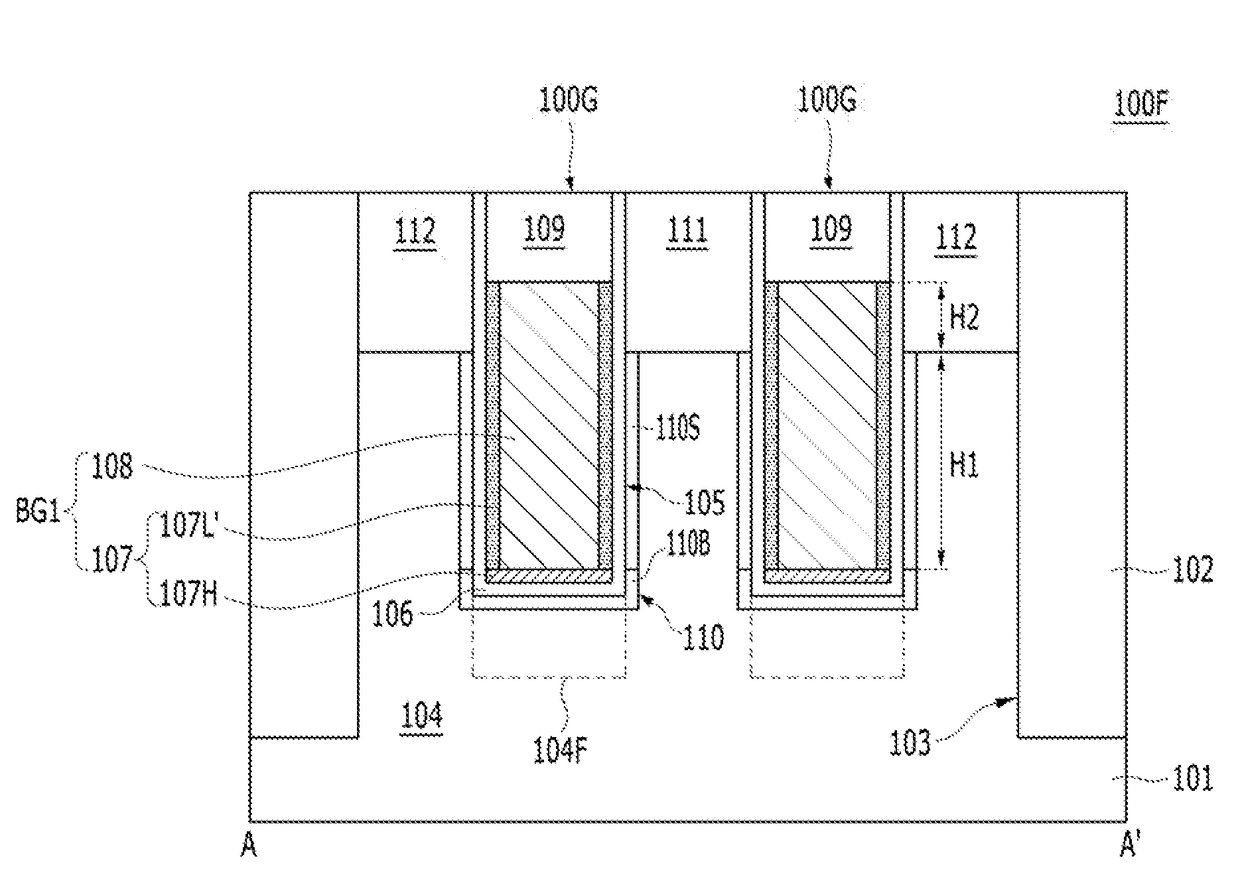

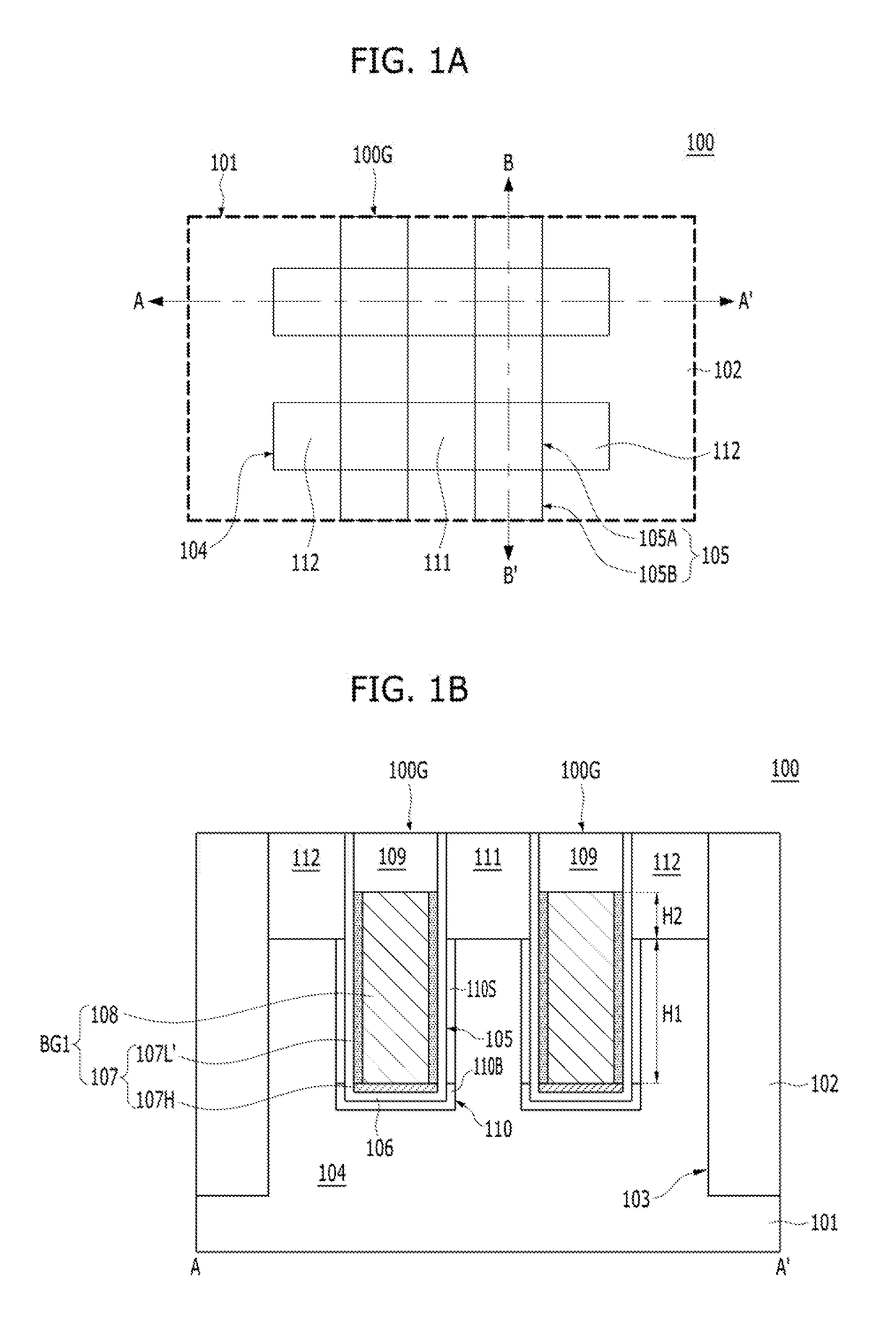

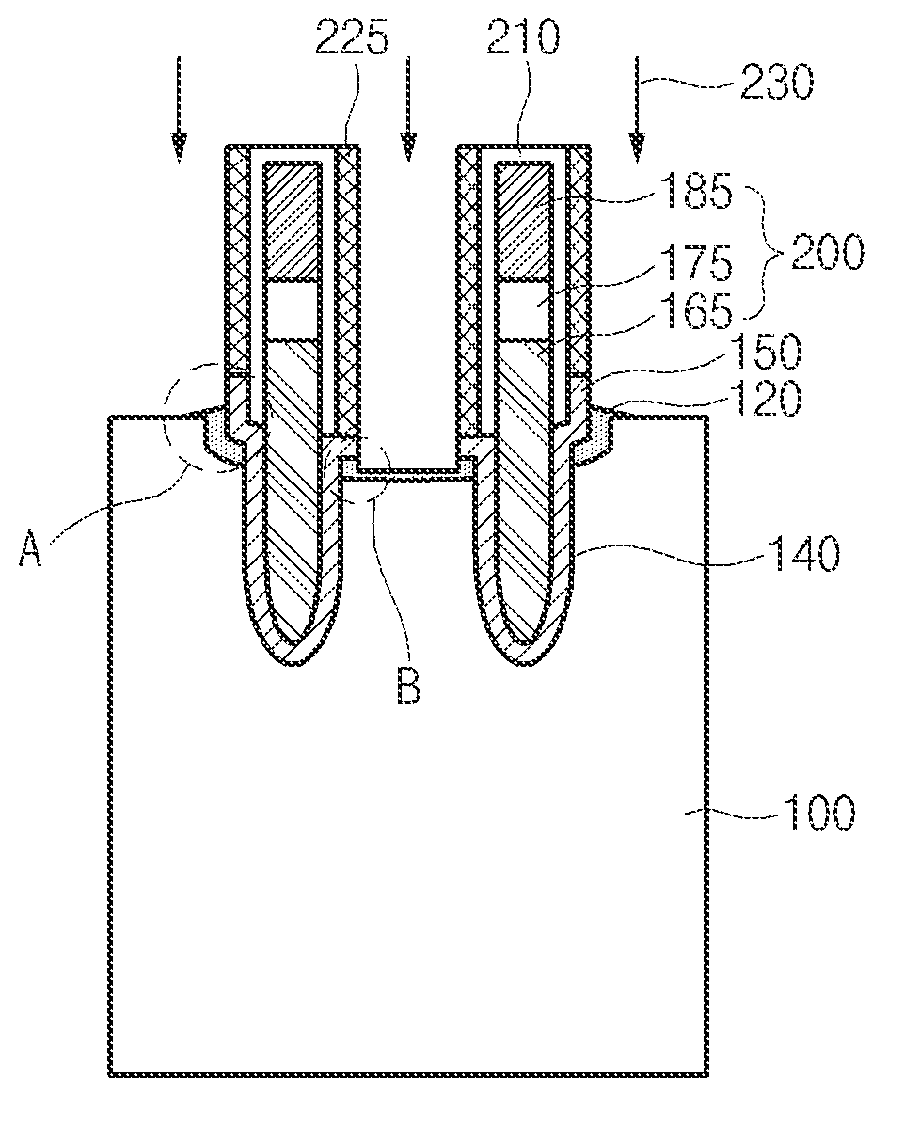

A semiconductor device includes a substrate comprising a trench; a gate dielectric layer formed over a surface of the trench; a gate electrode positioned at a level lower than a top surface of the substrate, and comprising a lower buried portion embedded in a lower portion of the trench over the gate dielectric layer and an upper buried portion positioned over the lower buried portion; and a dielectric work function adjusting liner positioned between the lower buried portion and the gate dielectric layer; and a dipole formed between the dielectric work function adjusting liner and the gate dielectric layer.

Owner:SK HYNIX INC

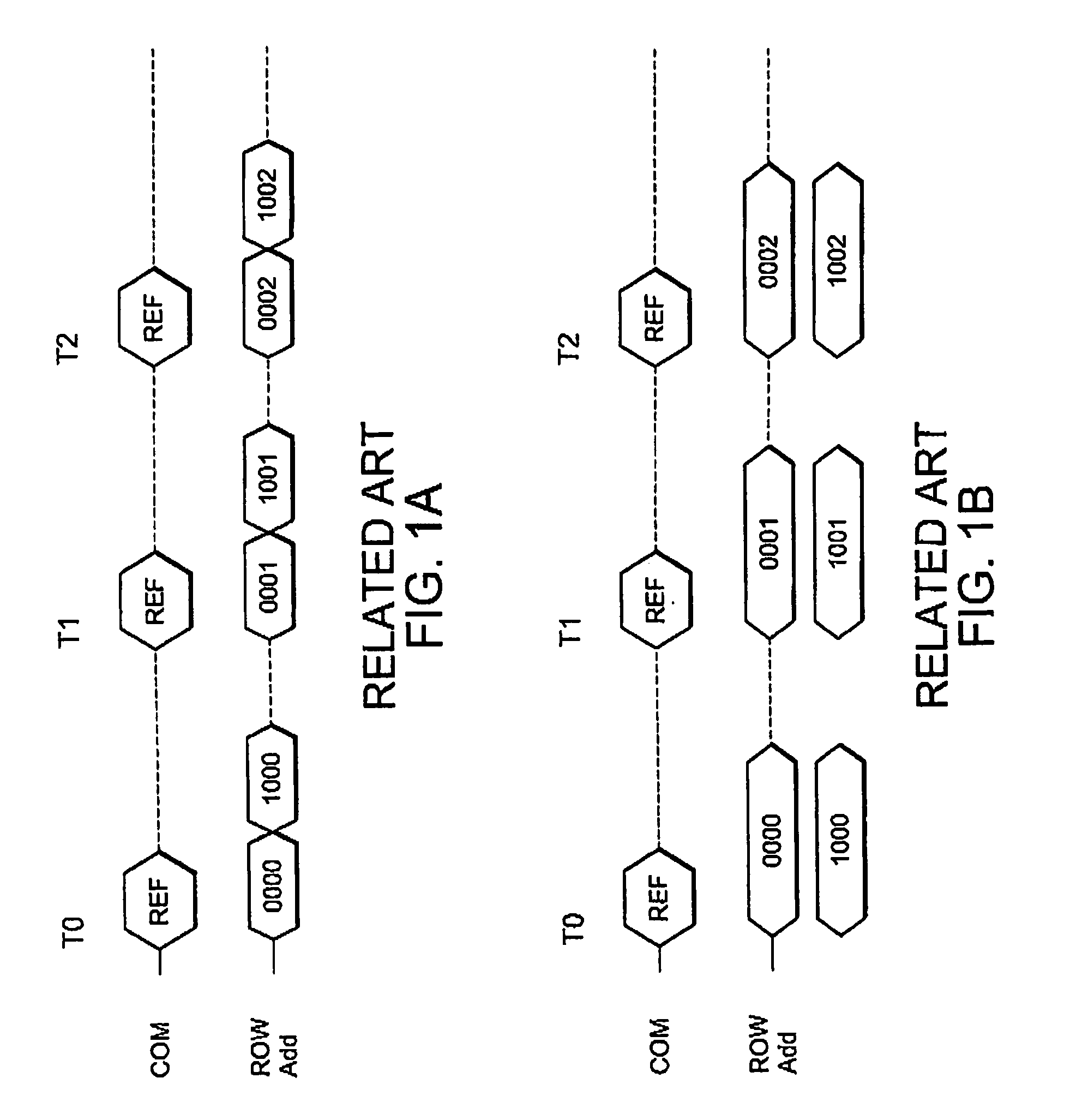

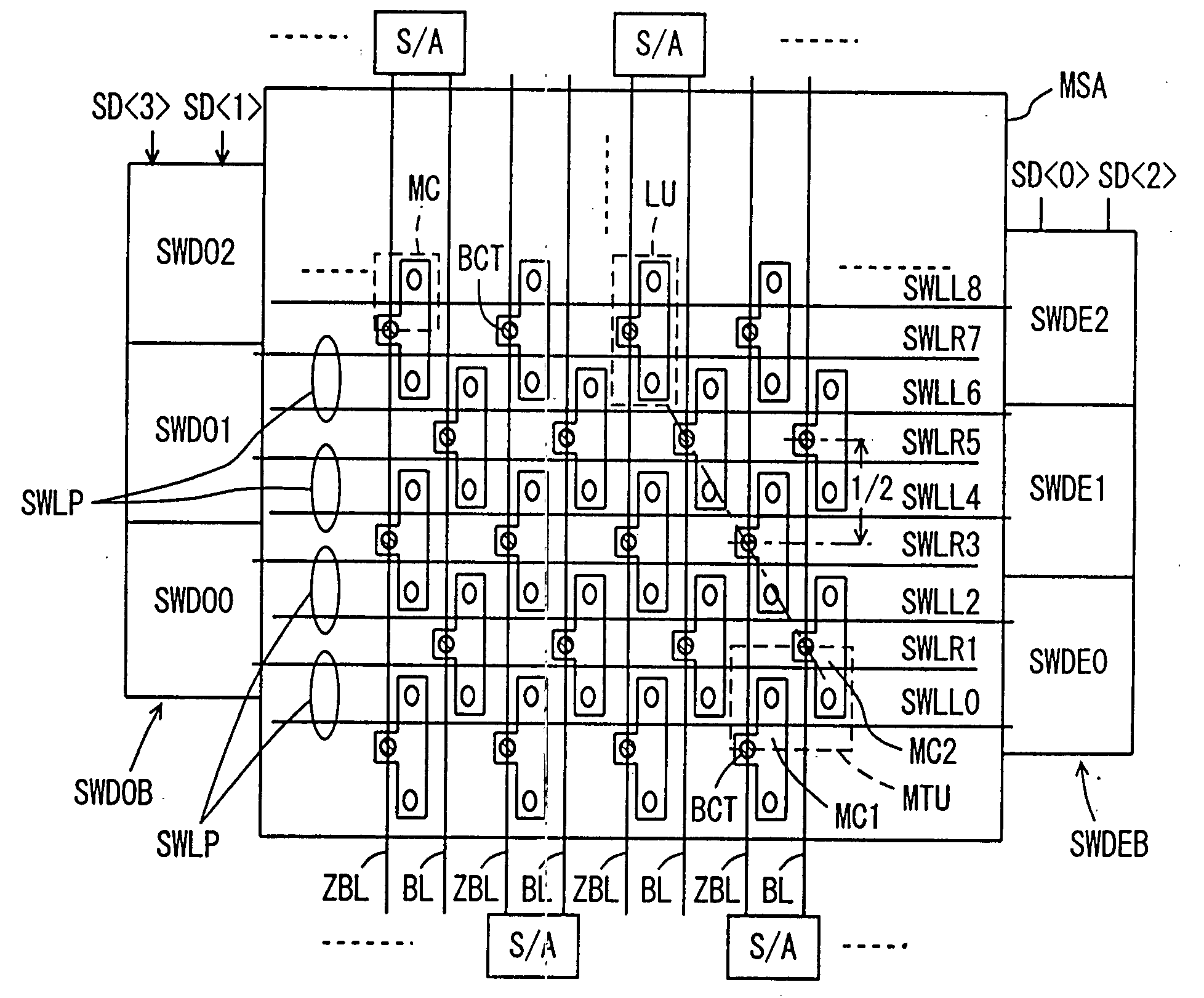

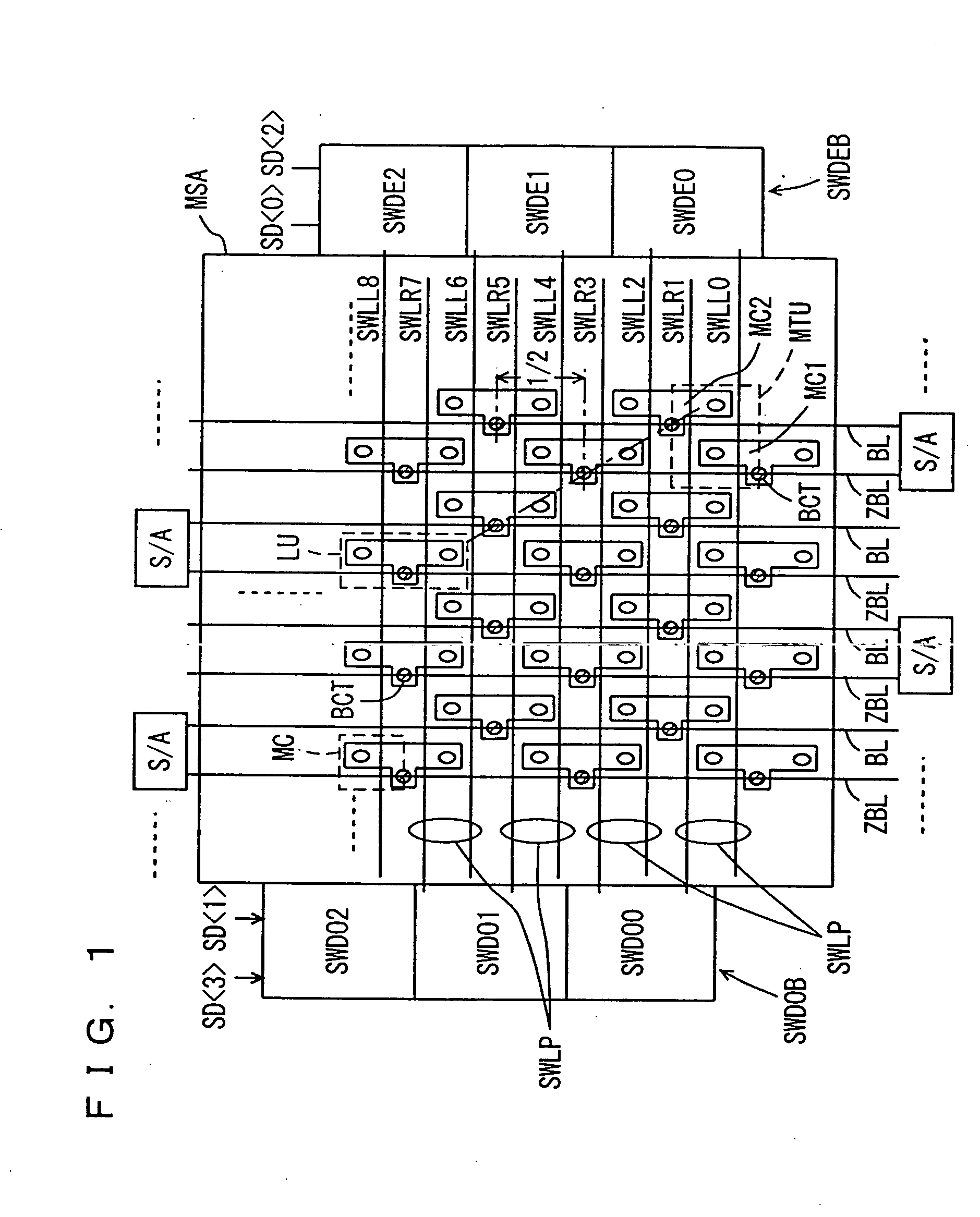

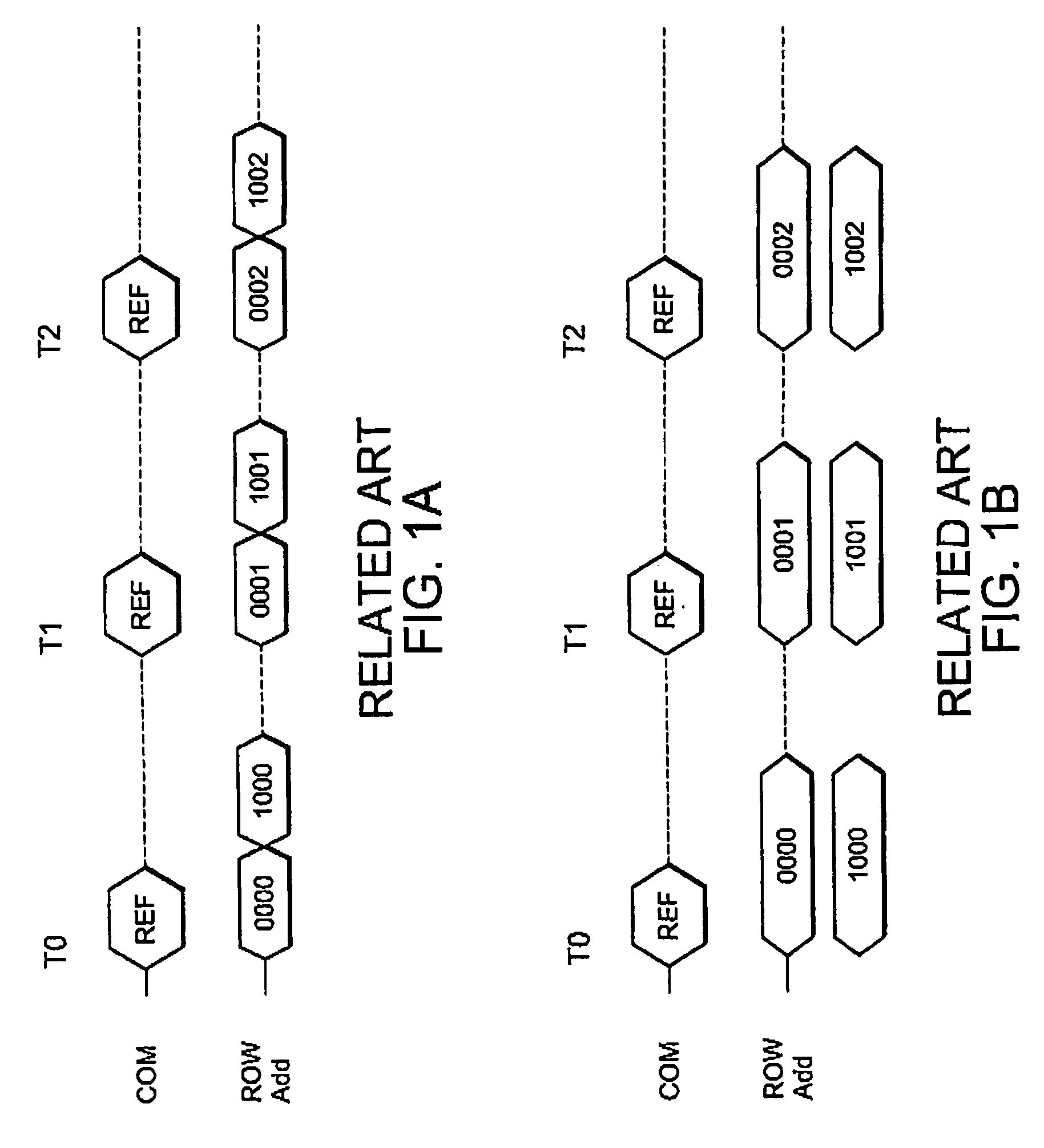

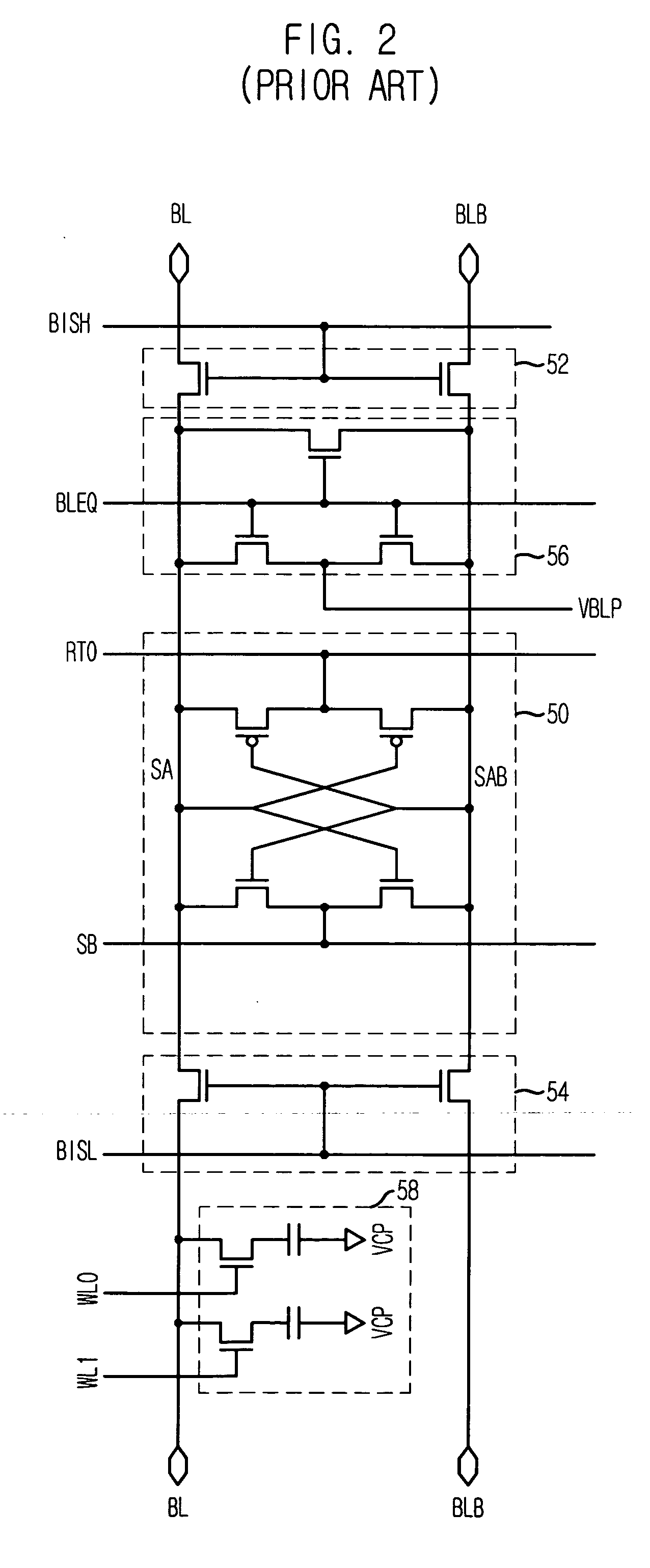

Refresh-free dynamic semiconductor memory device

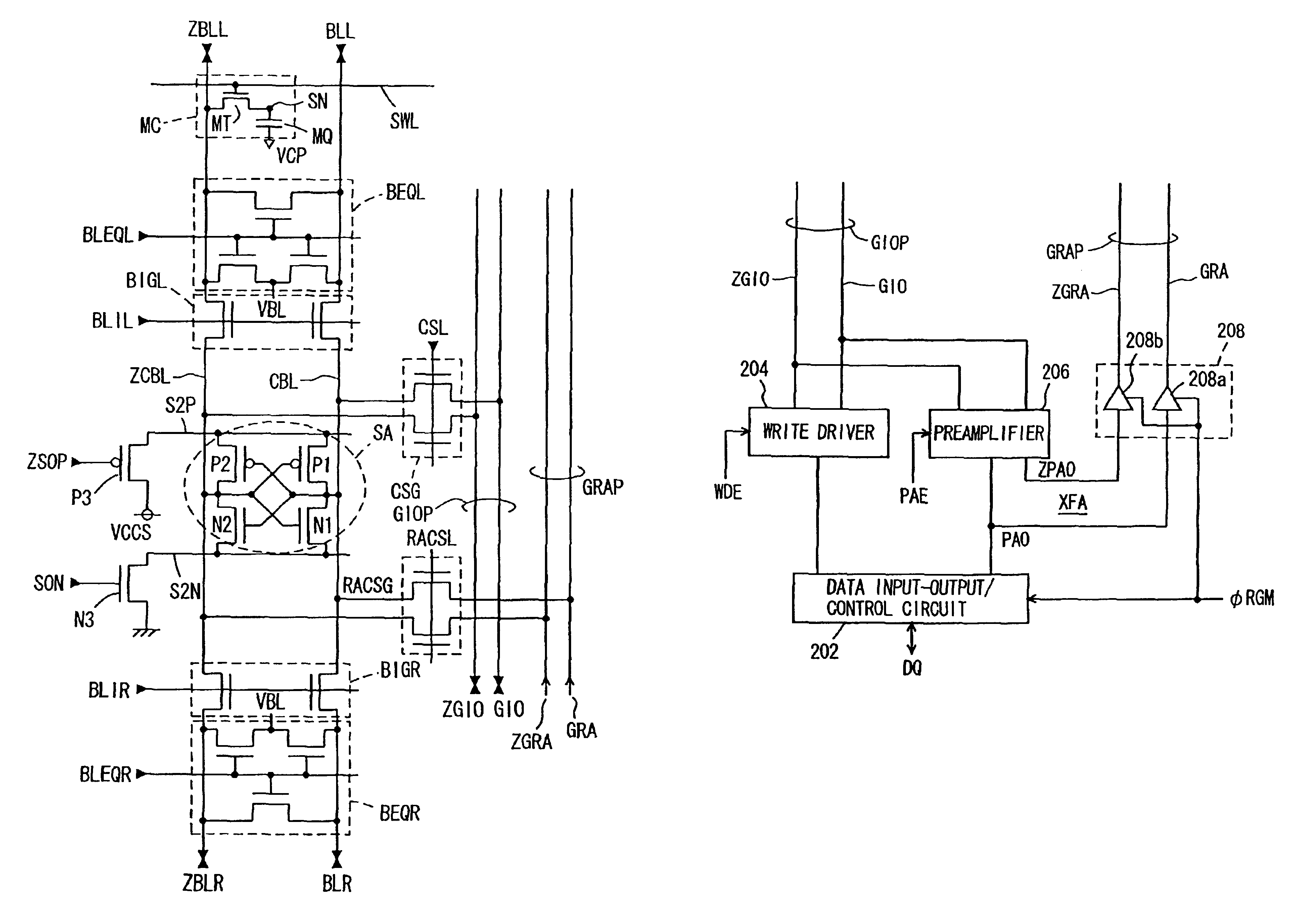

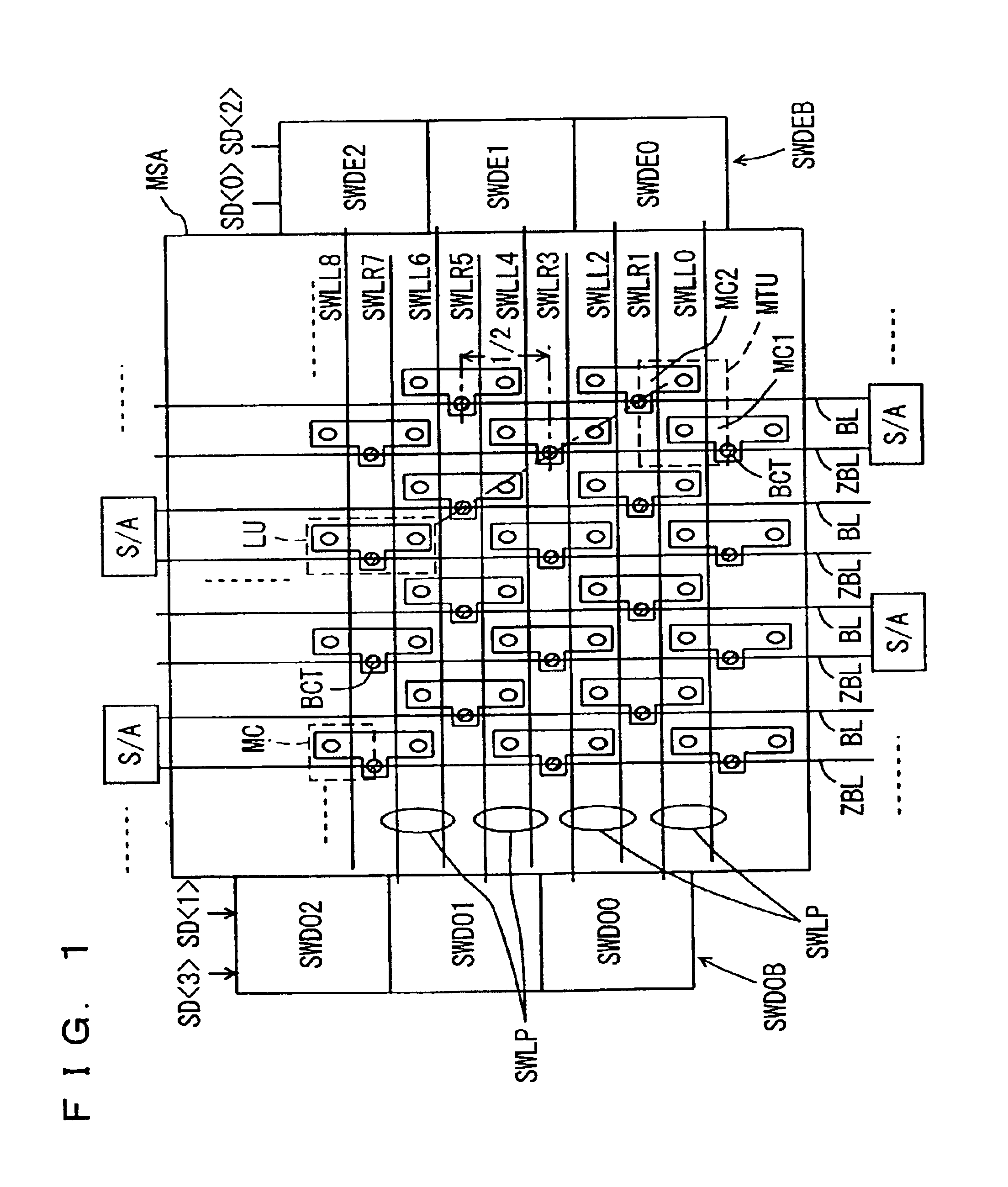

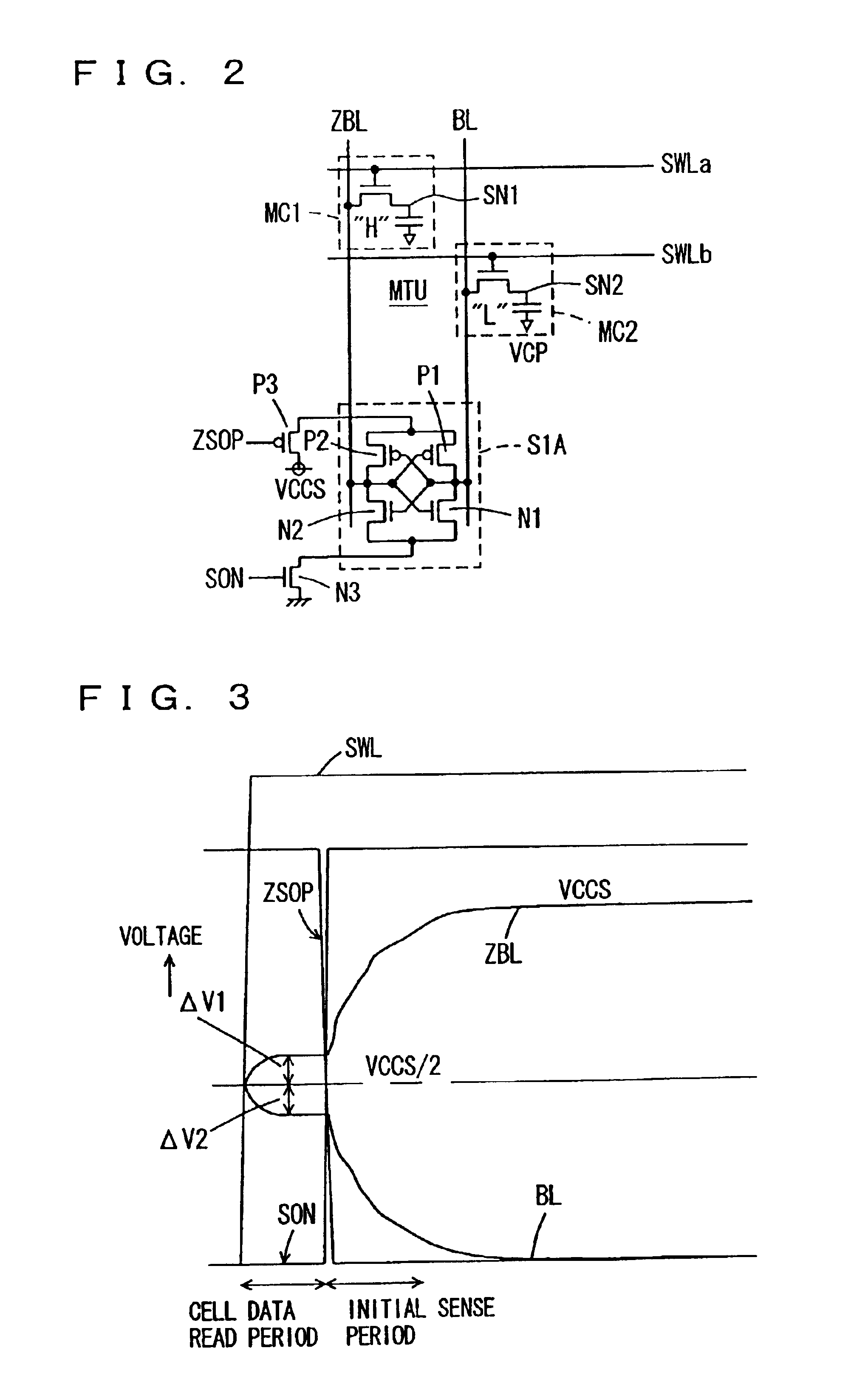

InactiveUS6925022B2Reduce power consumptionImprove refresh featureDigital storageBit lineOperation mode

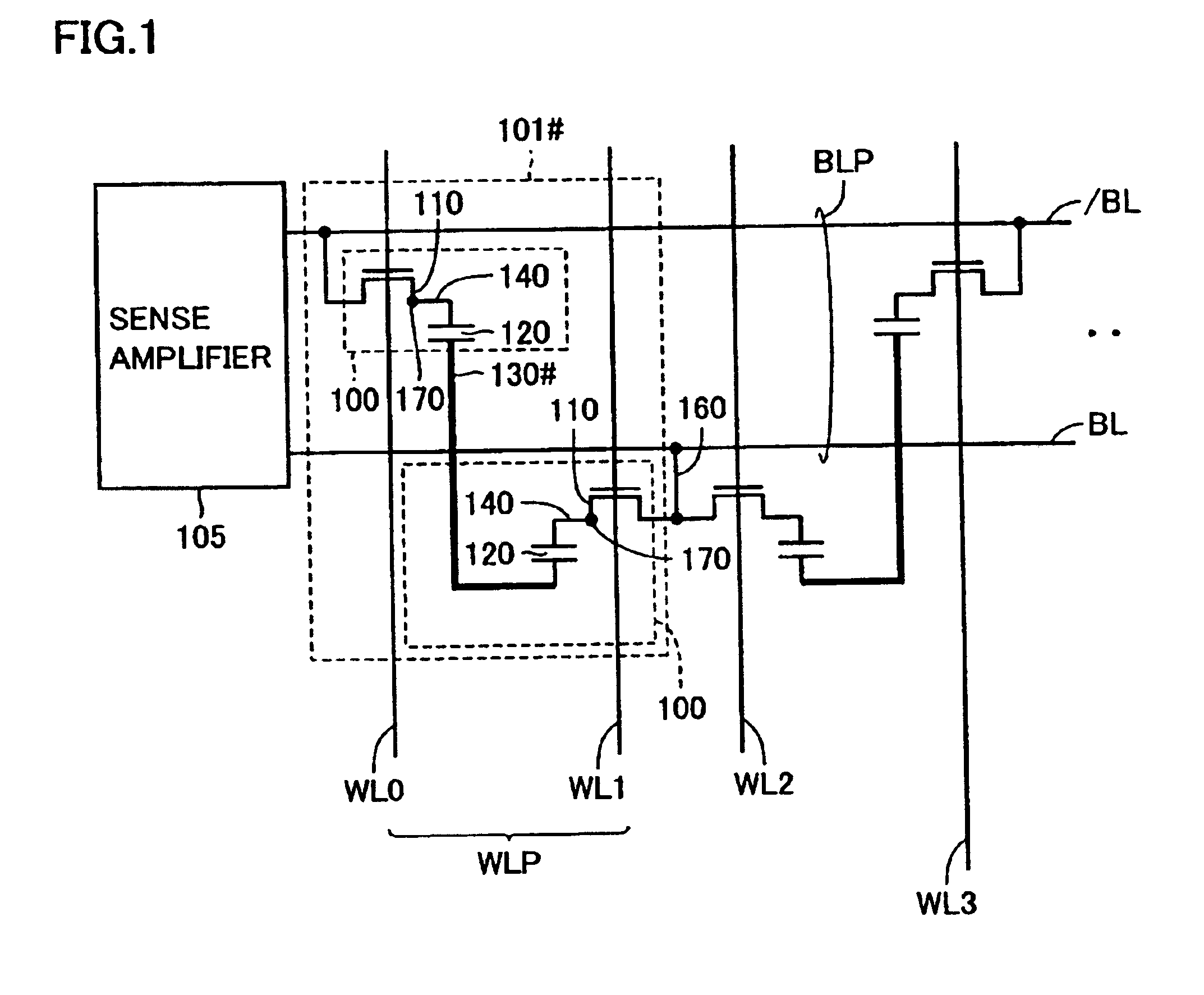

In a data holding mode, data storage in a one bit / one cell scheme in a normal operating mode are rearranged into data storage in a twin-cell mode in which data are stored in a one bit / two cell scheme. In the twin-cell mode, two sub word lines are simultaneously driven into a selected state, and storage data of memory cells are read out on both of bit lines in a pair, to perform a sense operation. Thus, the read-out voltage can be increased to improve the data retention characteristics for lengthening a refresh interval, resulting in a reduced power consumption in the data holding mode.

Owner:RENESAS ELECTRONICS CORP

Method of manufacturing semiconductor device

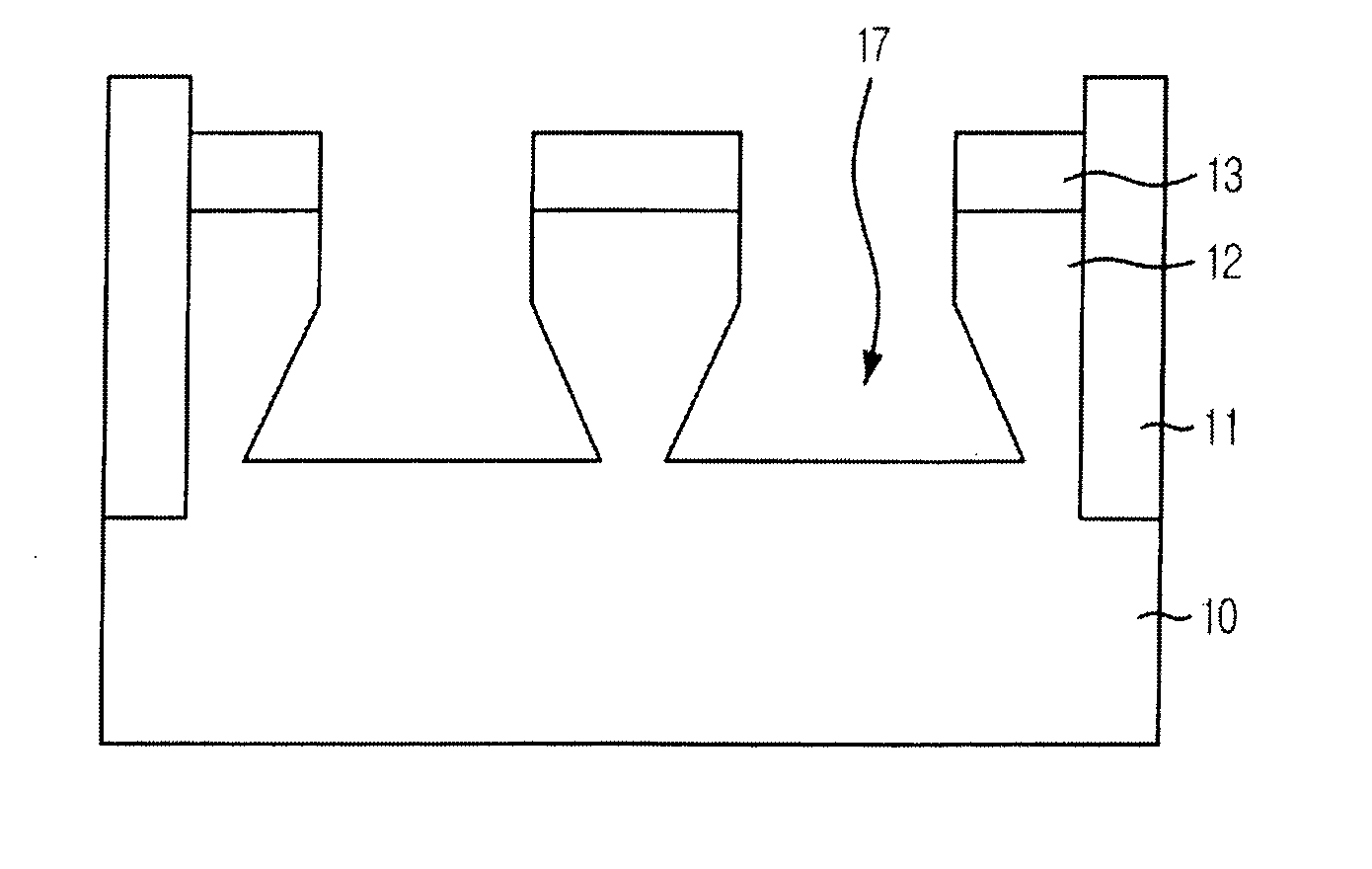

InactiveUS20080242024A1Reduce diffuseImprove refresh featureSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialSemiconductor

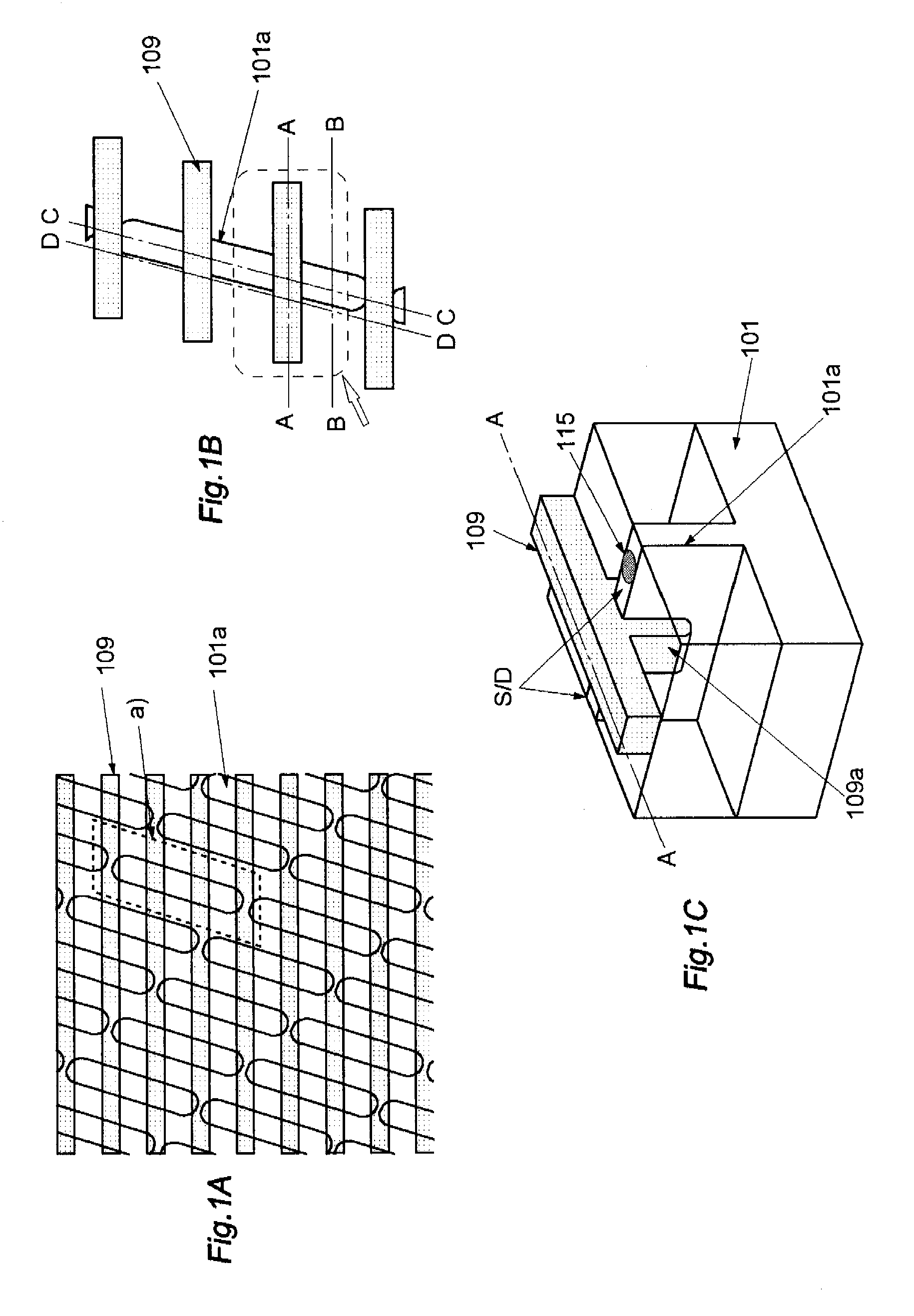

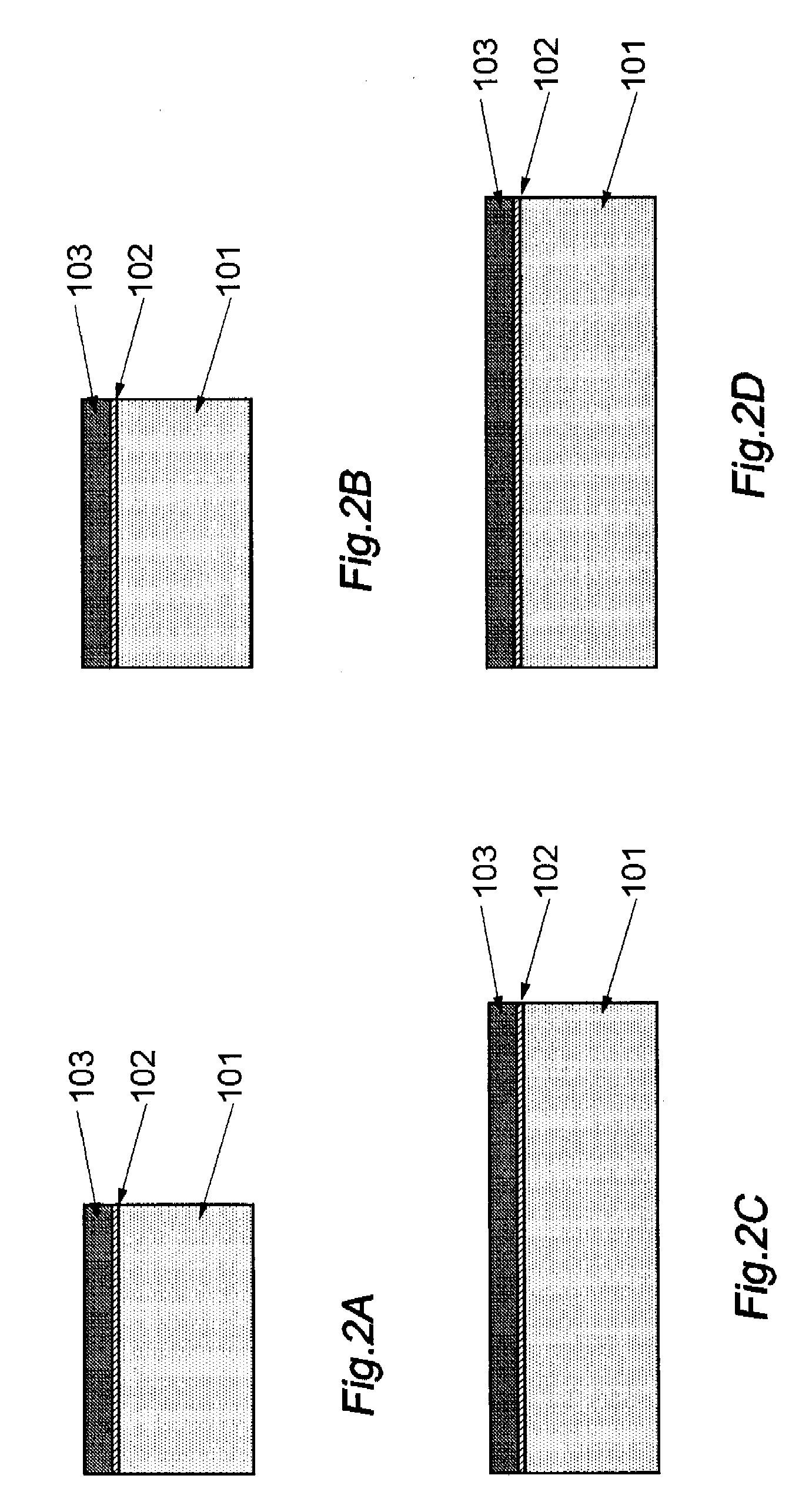

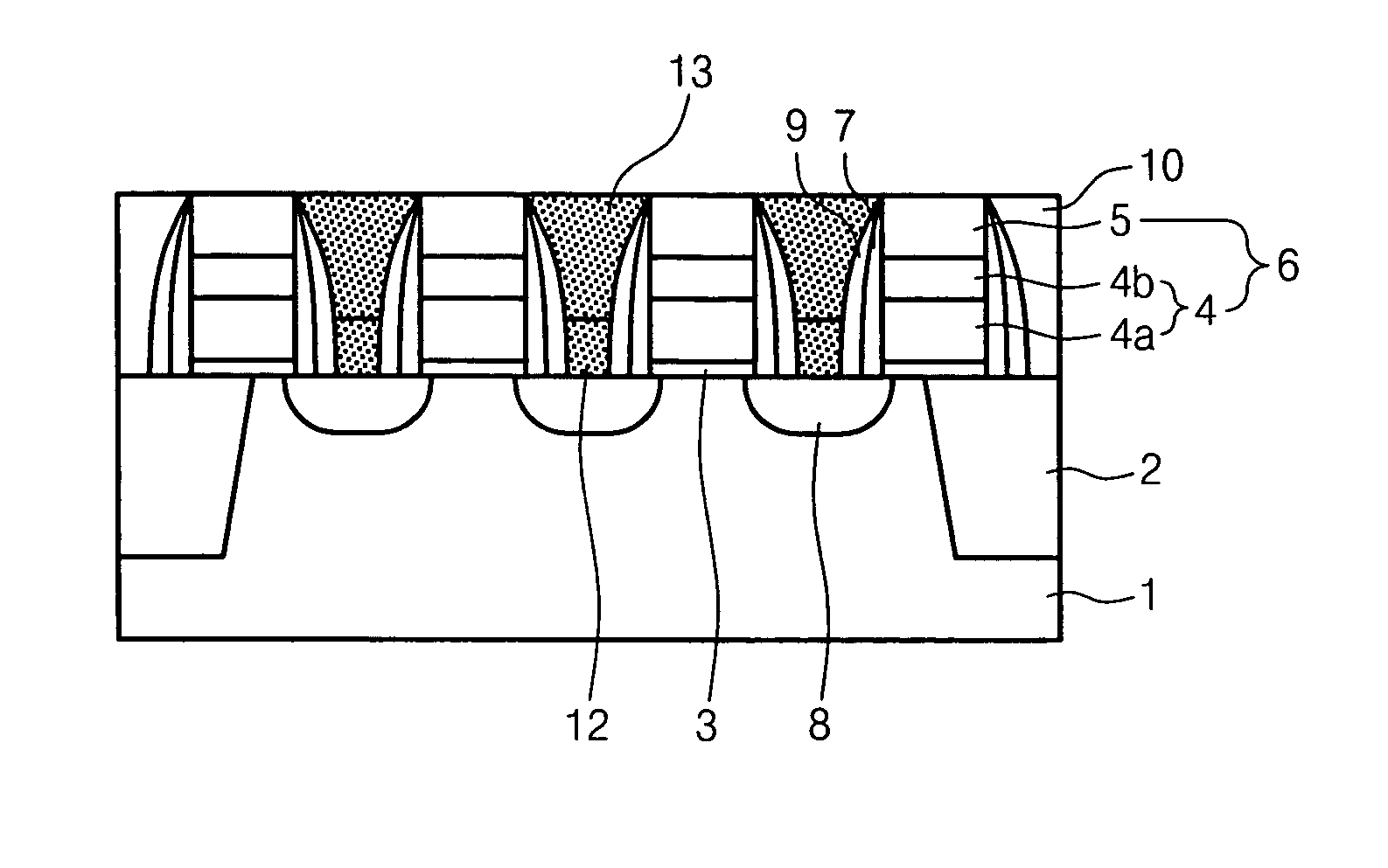

To provide a semiconductor device using a Fin-FET and having a contact configuration such that the GIDL is reduced while limiting an increase in contact resistance, source and drain regions of the Fin-FET are formed by solid-phase diffusion positively utilizing impurity implantation after forming of contact holes 13 and oozing-out of an impurity from polysilicon contact plugs 14. Also, contact plugs 14 are extended to side surfaces of convex semiconductor layers 101a to form side wall portions 14a, thereby increasing the contact area.

Owner:ELPIDA MEMORY INC

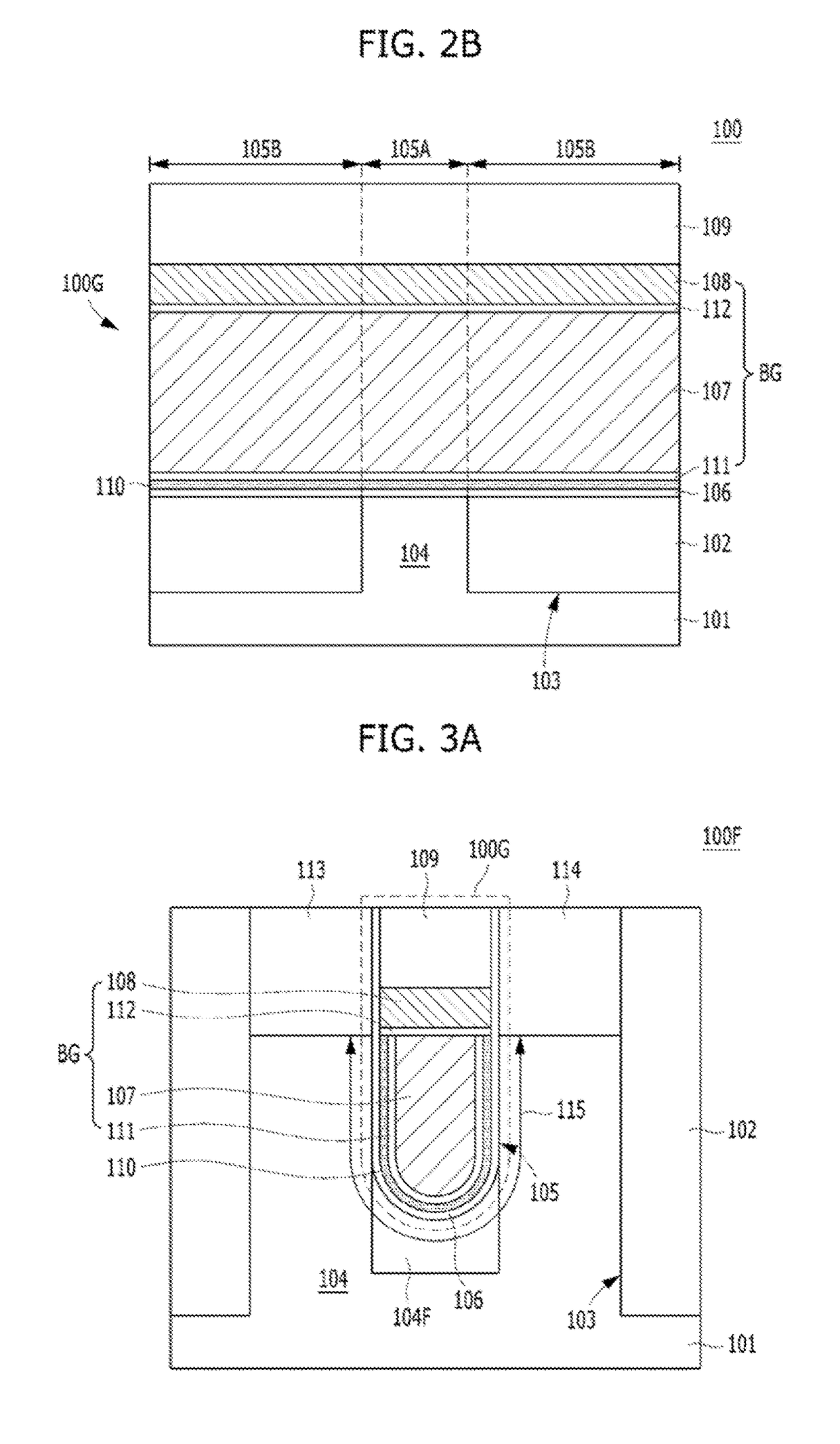

Semiconductor device having buried gate structure and method for fabricating the same

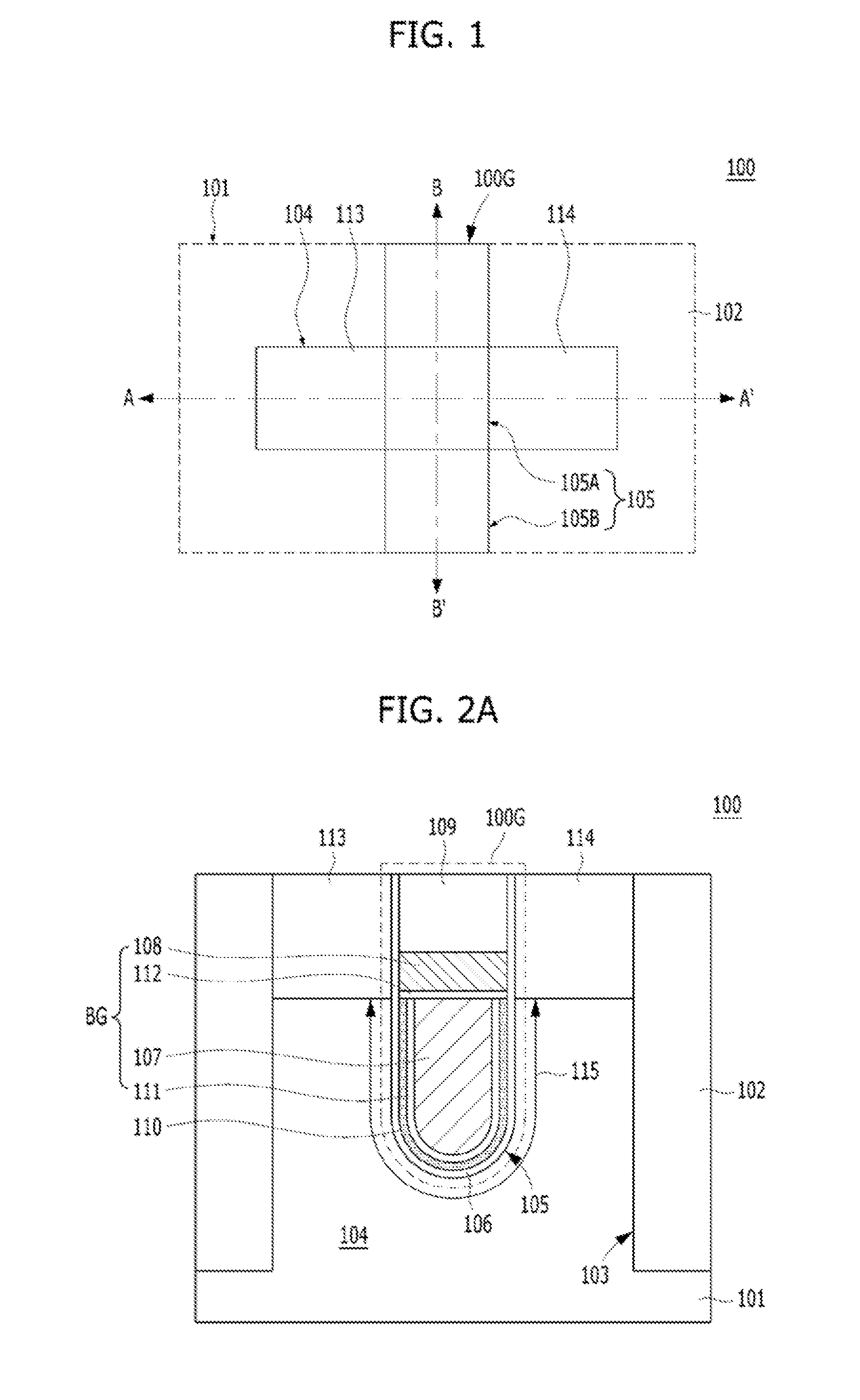

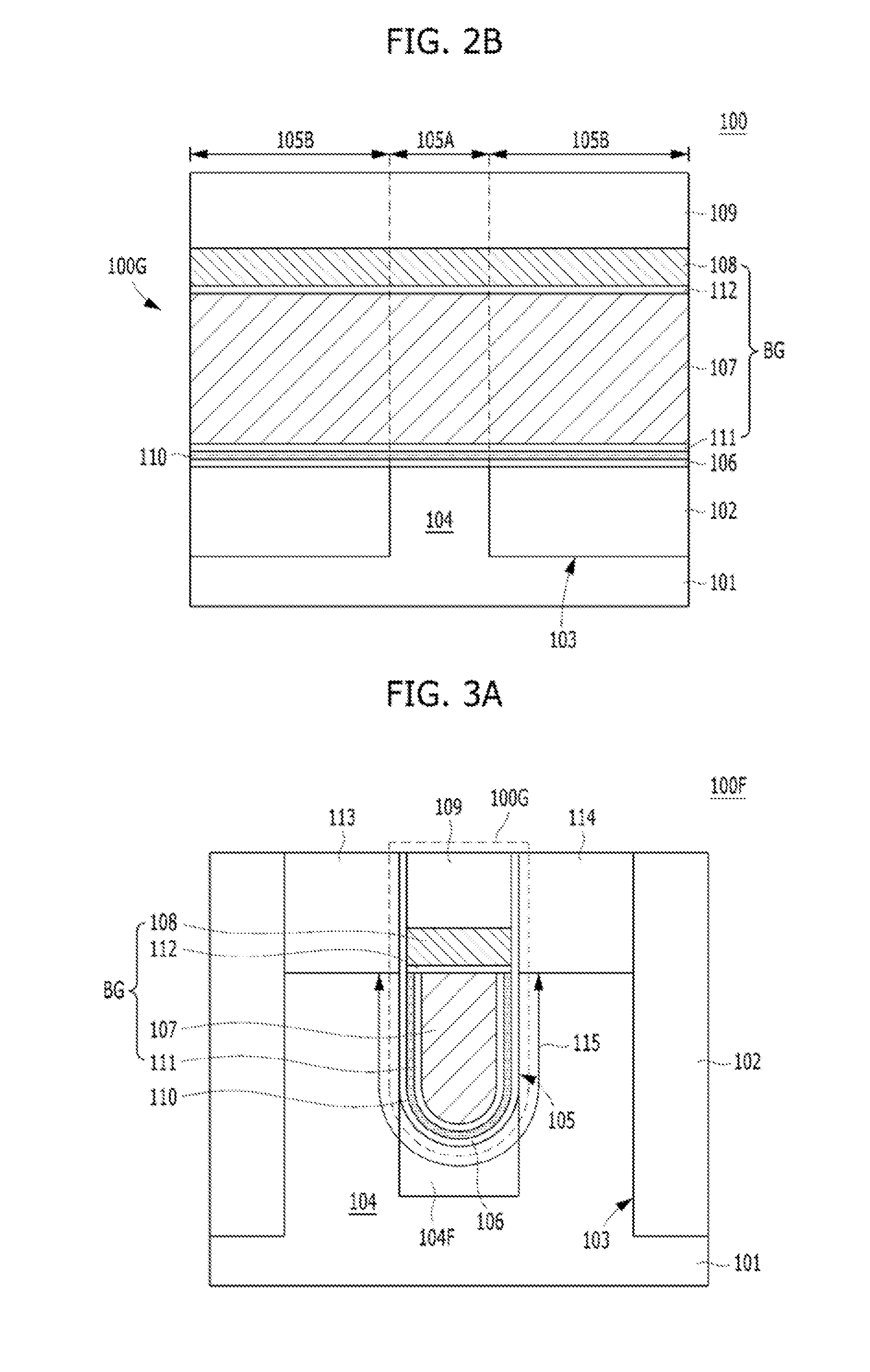

ActiveUS20180174845A1Reducing gate-induced drain leakageImprove refresh featureSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricWork function

A method for fabricating a semiconductor device includes: forming a gate trench in a semiconductor substrate; forming a gate dielectric layer over a bottom surface and sidewalls of the gate trench; forming a first work function layer over the gate dielectric layer; doping a work function adjustment element to form a second work function layer which overlaps with the sidewalls of the gate trench; forming a gate conductive layer that partially fills the gate trench; and forming doped regions inside the semiconductor substrate on both sides of the gate trench.

Owner:SK HYNIX INC

Refresh-free dynamic semiconductor memory device

InactiveUS20060013030A1Reduce power consumptionImprove refresh featureDigital storageBit lineSemiconductor

In a data holding mode, data storage in a one bit / one cell scheme in a normal operating mode are rearranged into data storage in a twin-cell mode in which data are stored in a one bit / two cell scheme. In the twin-cell mode, two sub word lines are simultaneously driven into a selected state, and storage data of memory cells are read out on both of bit lines in a pair, to perform a sense operation. Thus, the read-out voltage can be increased to improve the data retention characteristics for lengthening a refresh interval, resulting in a reduced power consumption in the data holding mode.

Owner:RENESAS ELECTRONICS CORP

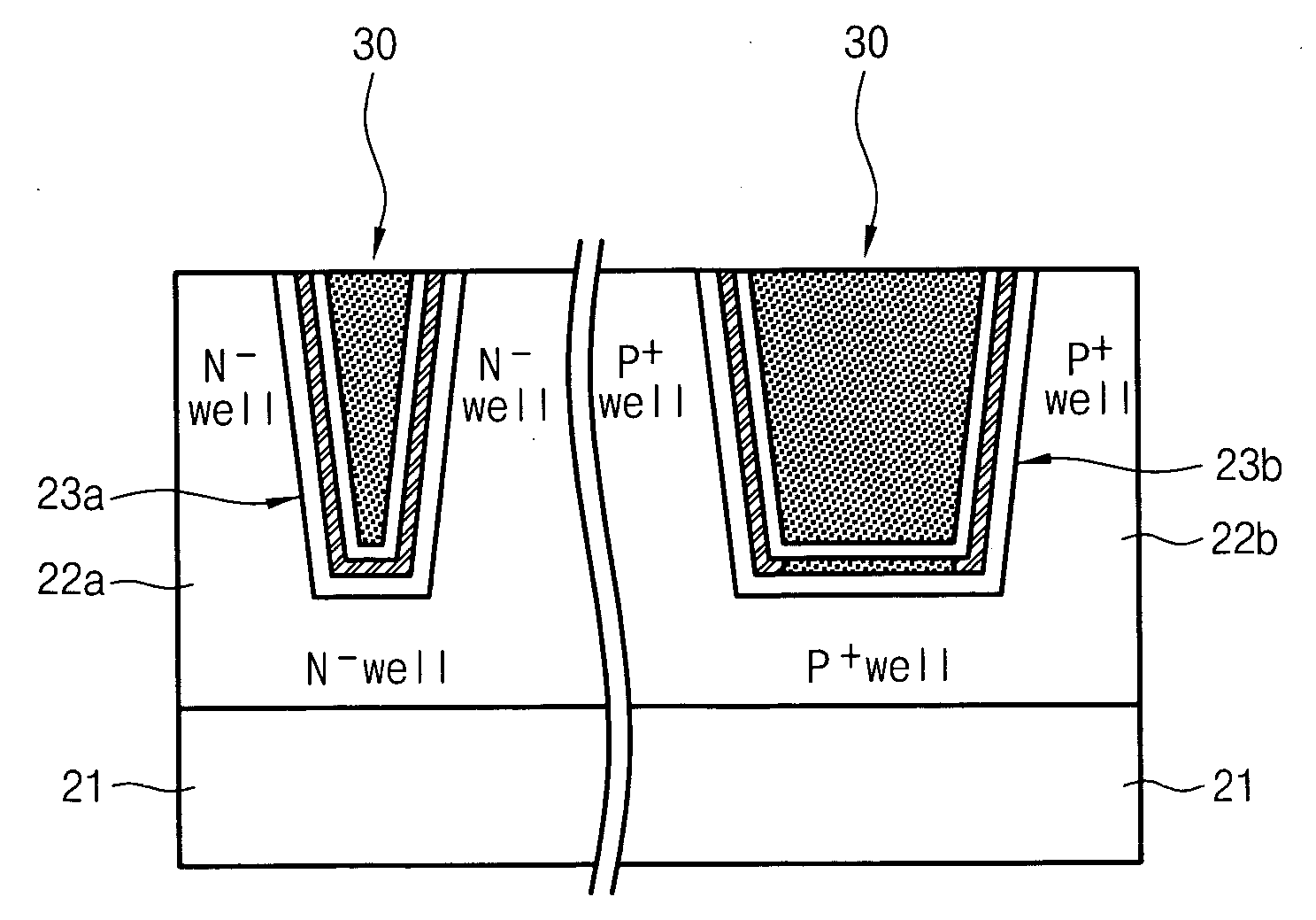

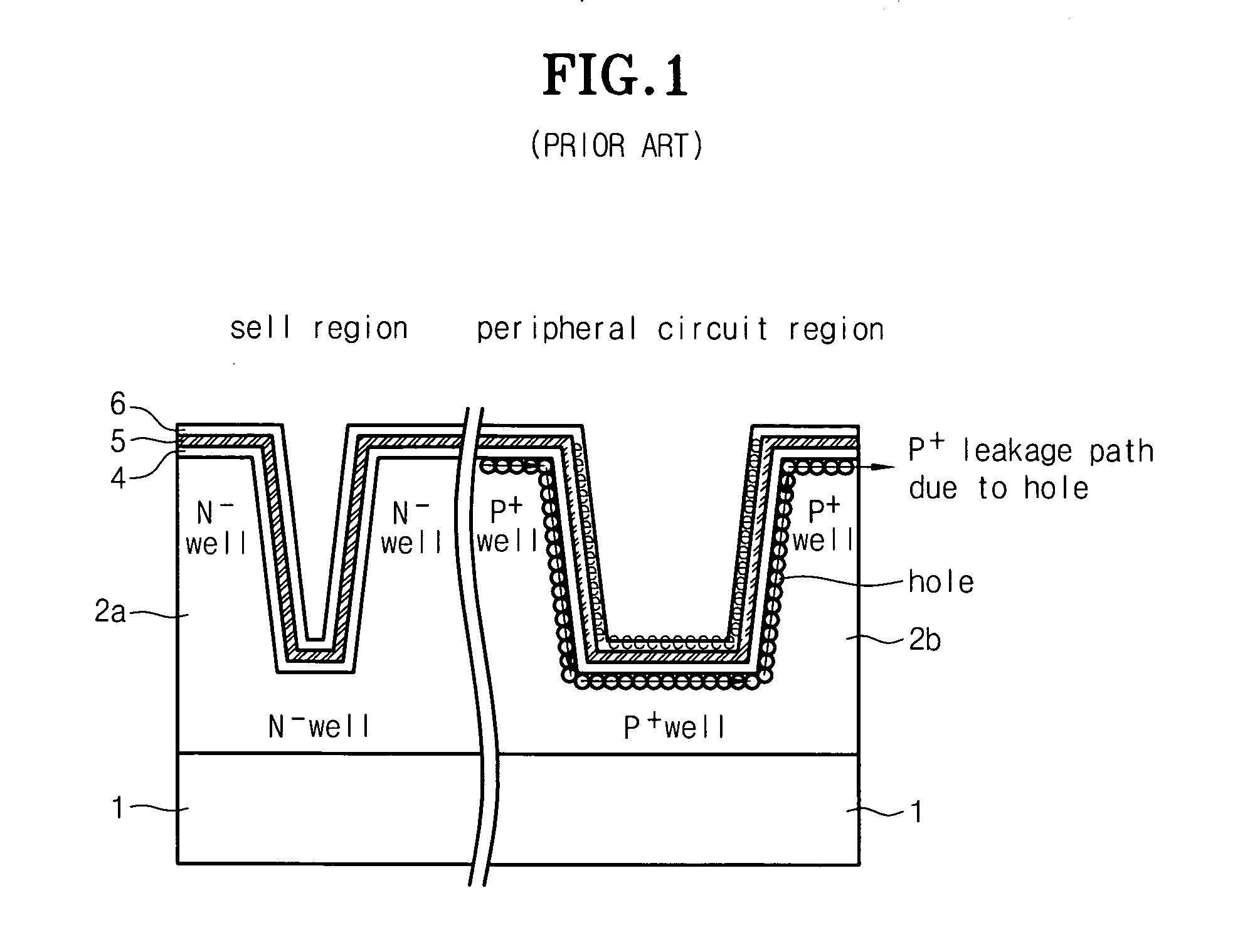

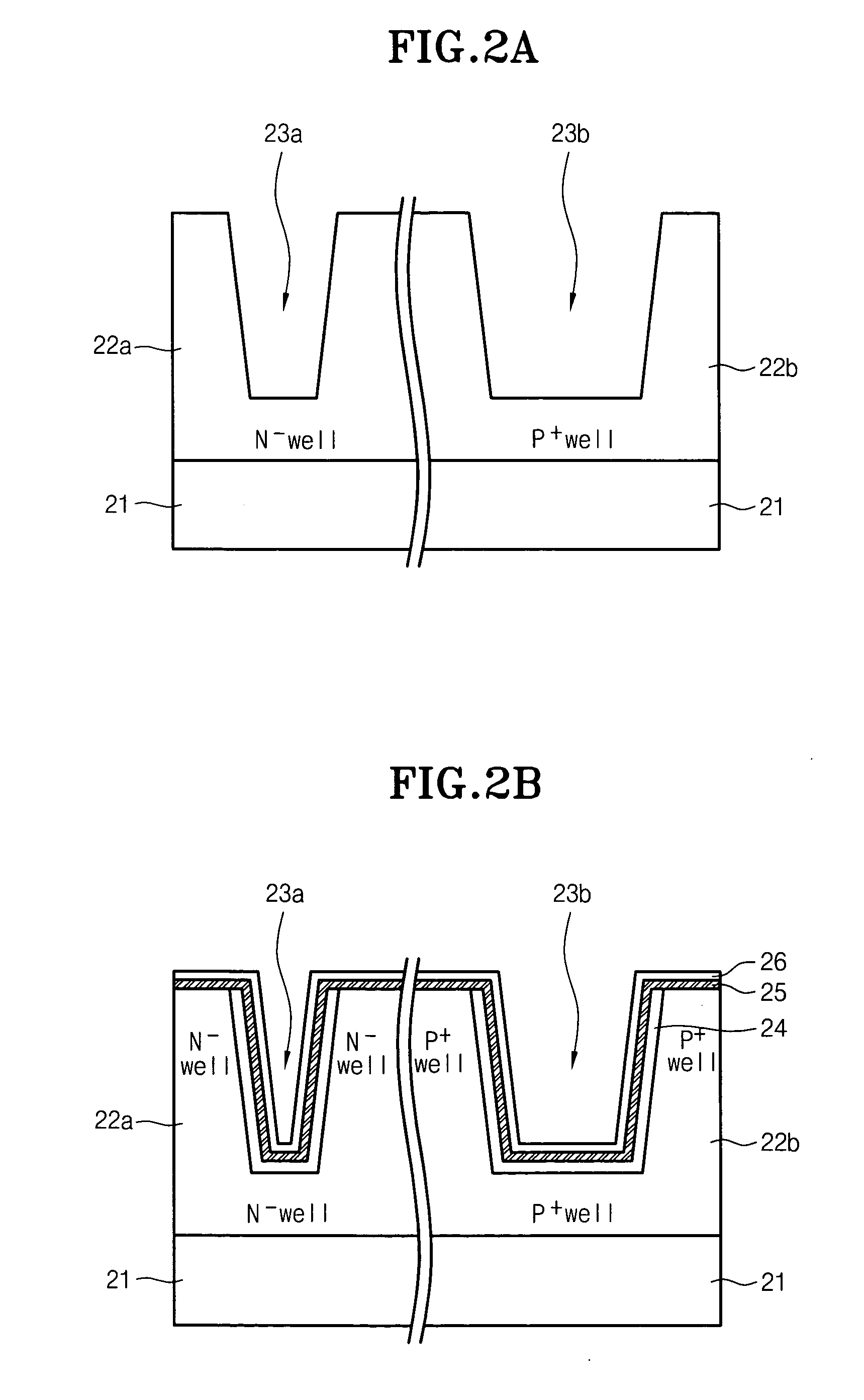

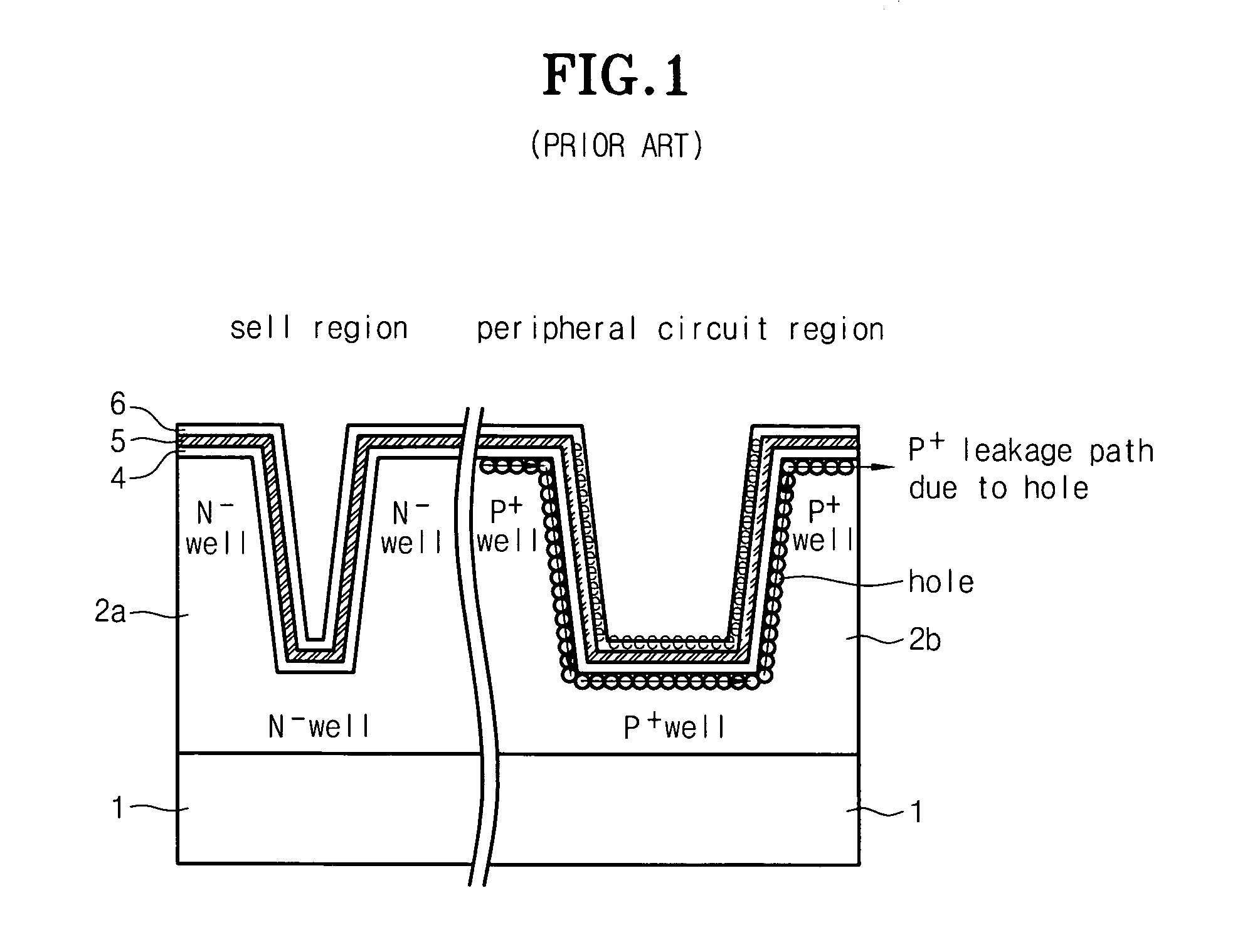

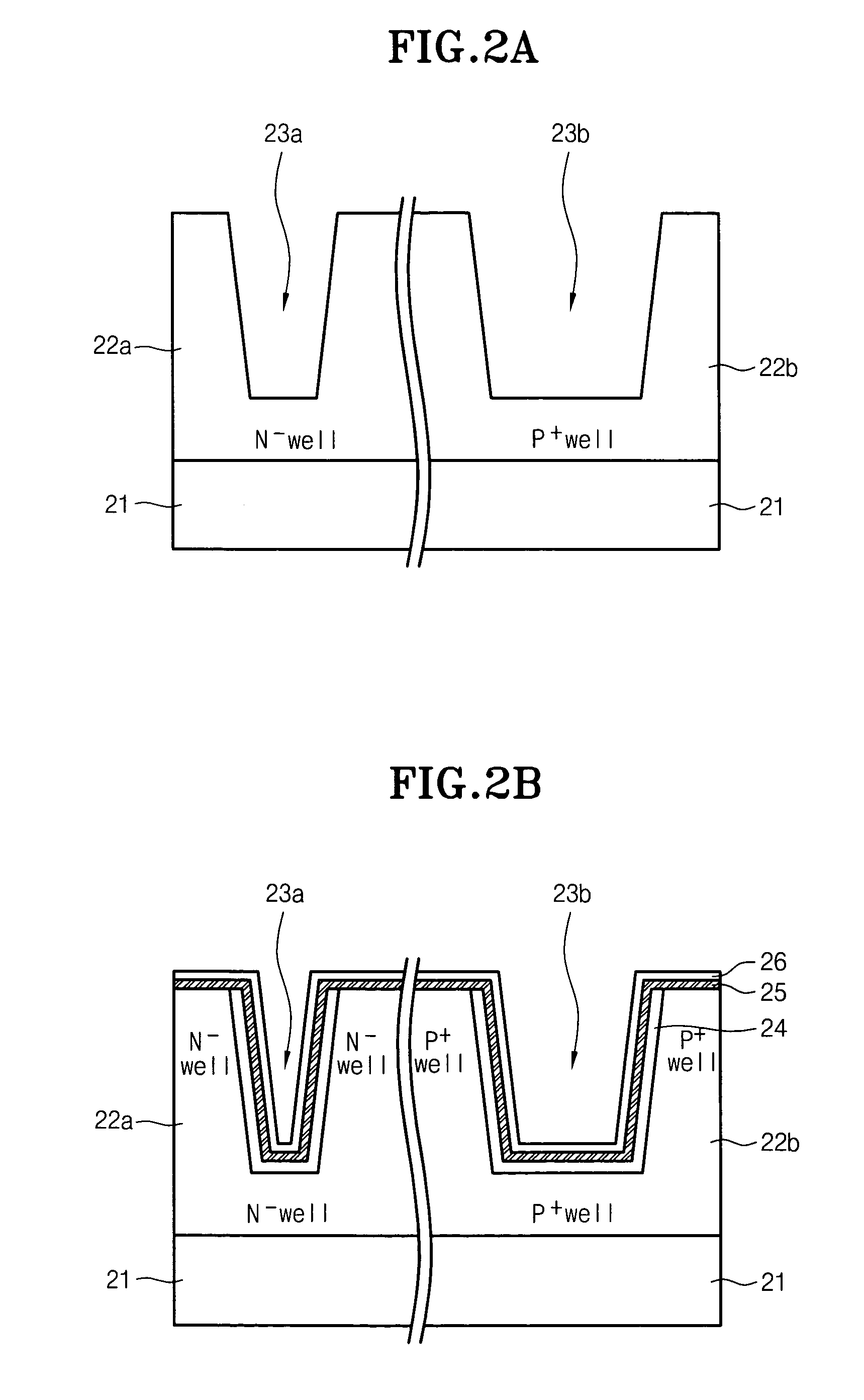

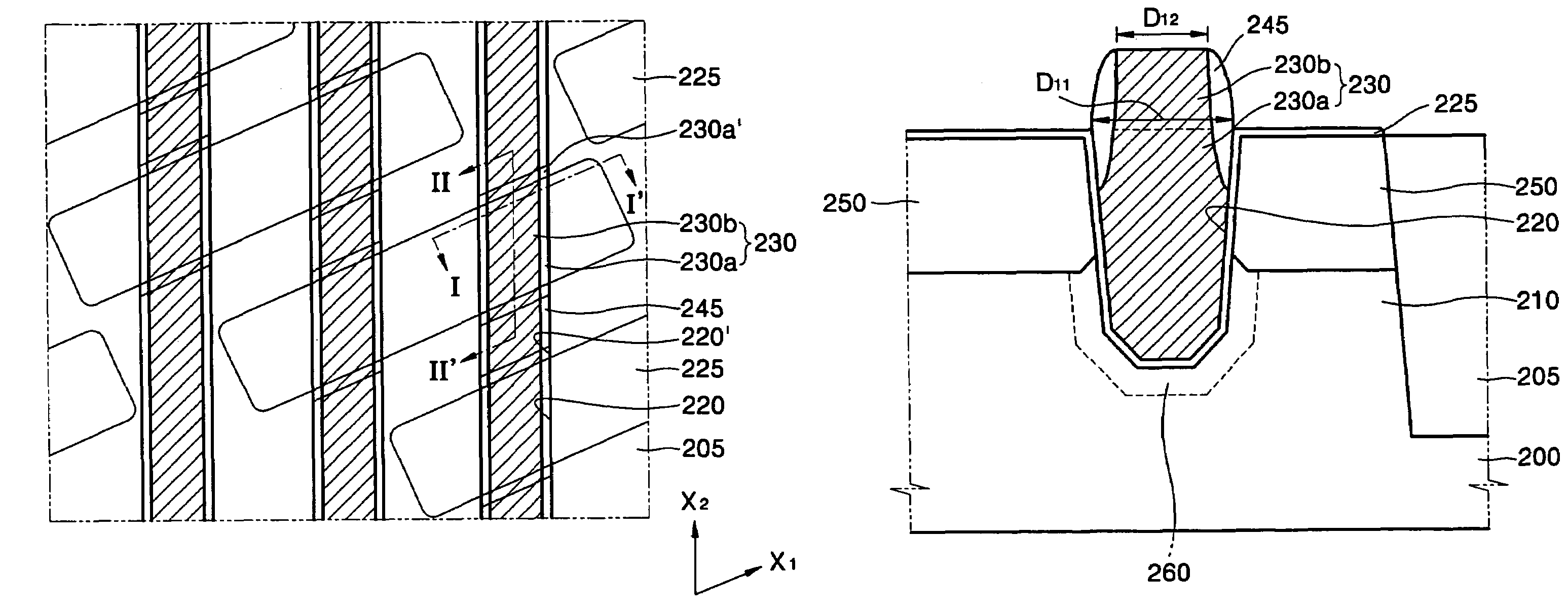

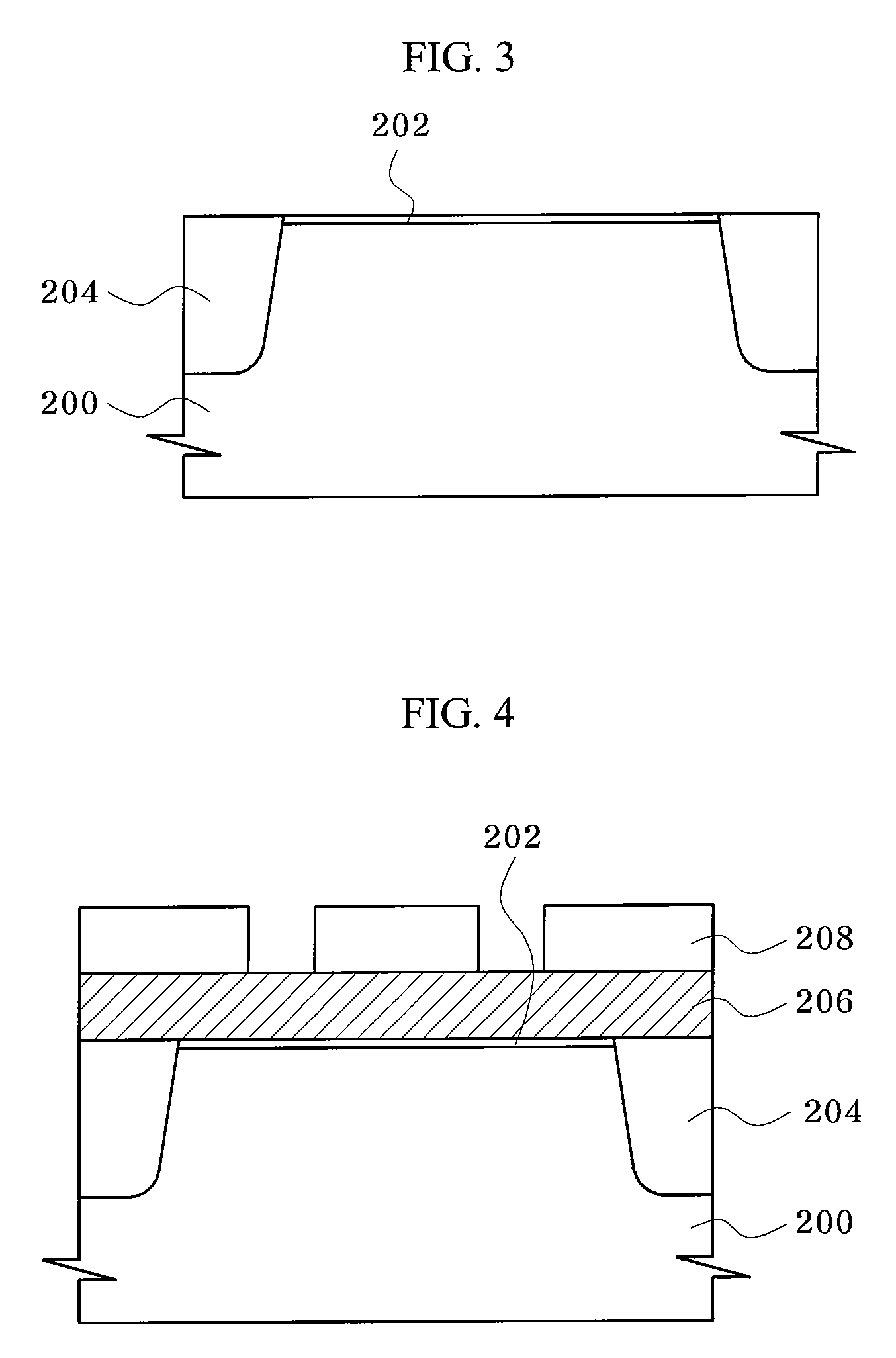

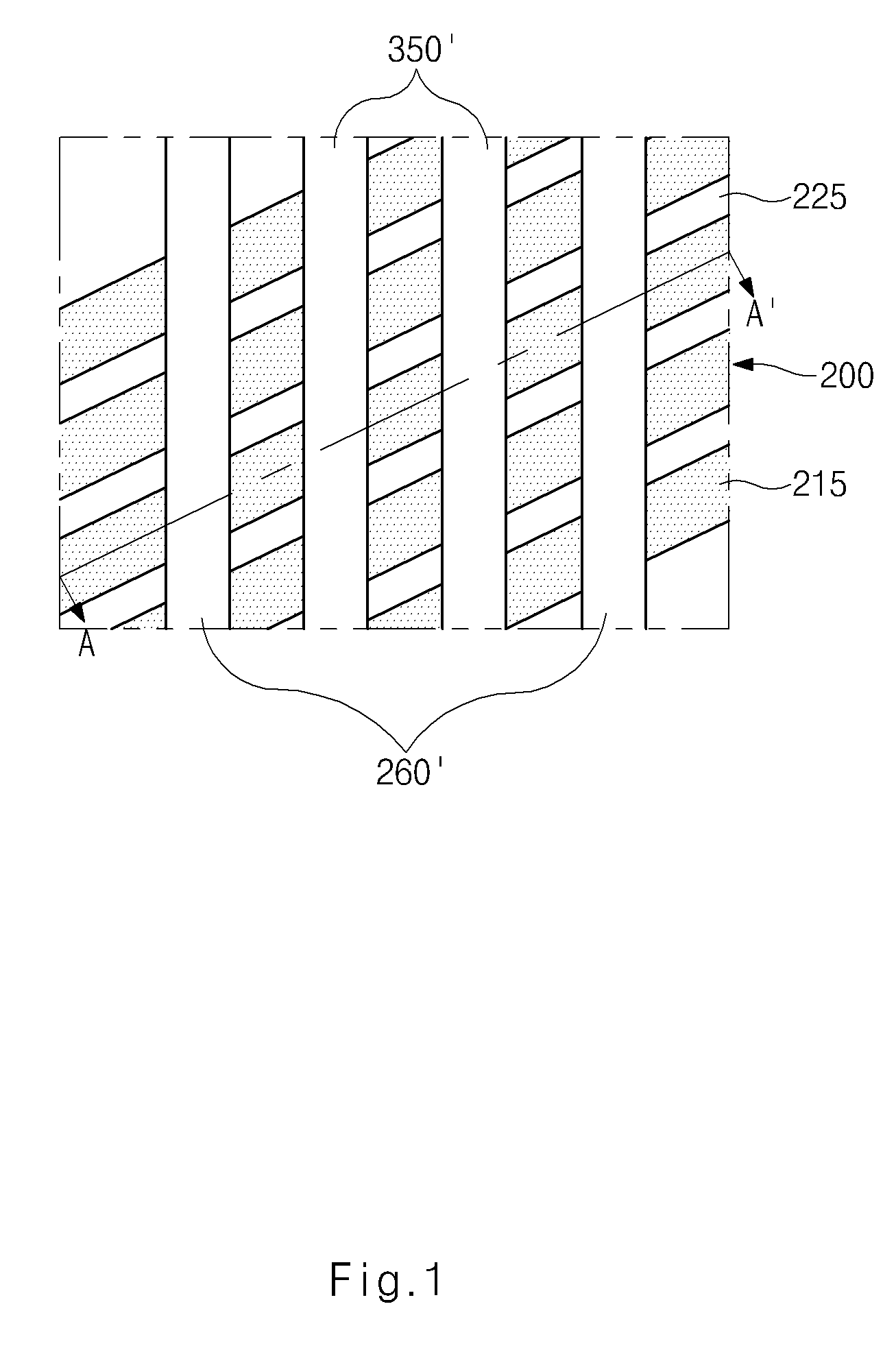

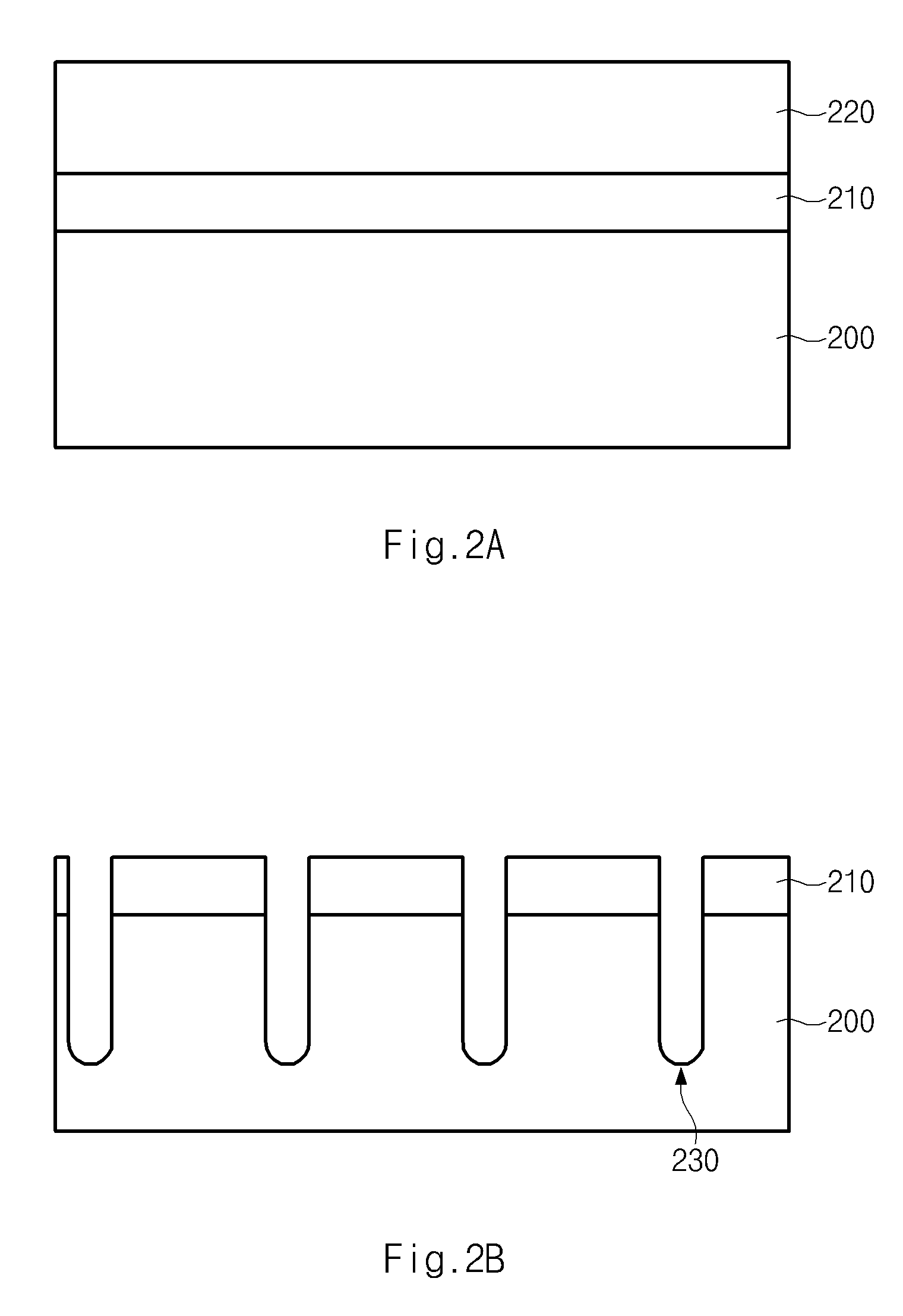

Method for forming isolation layer of semiconductor device

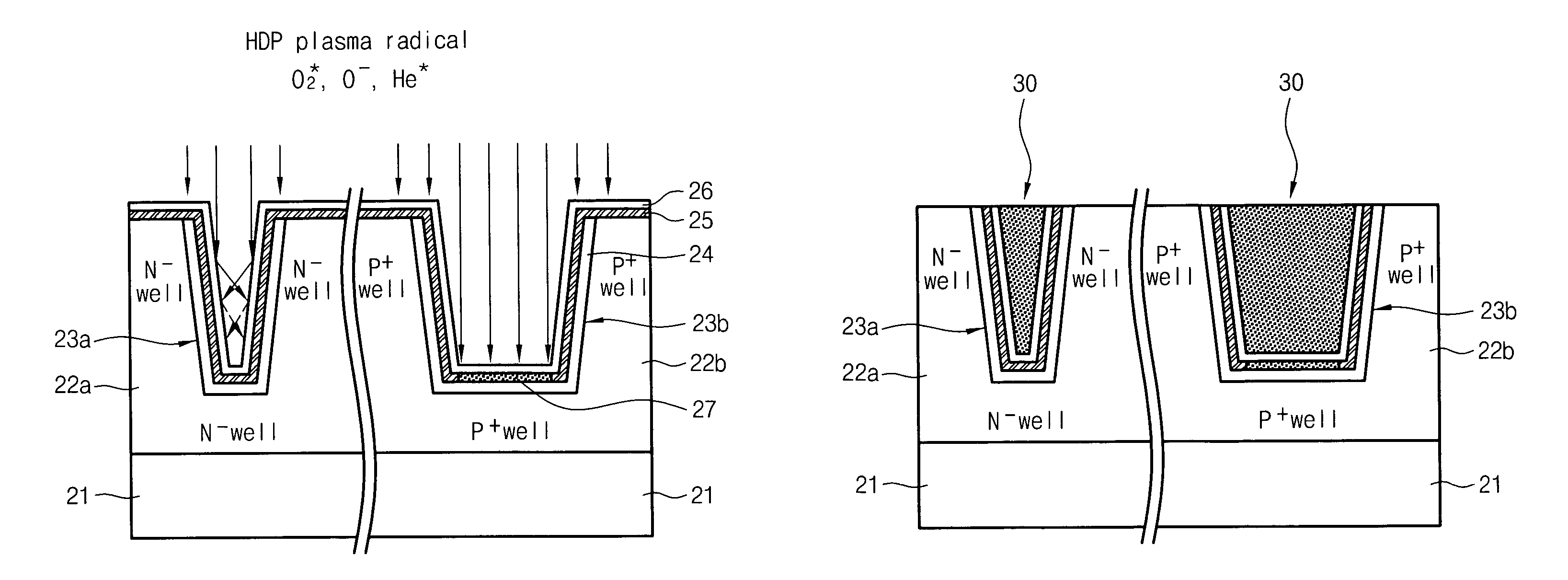

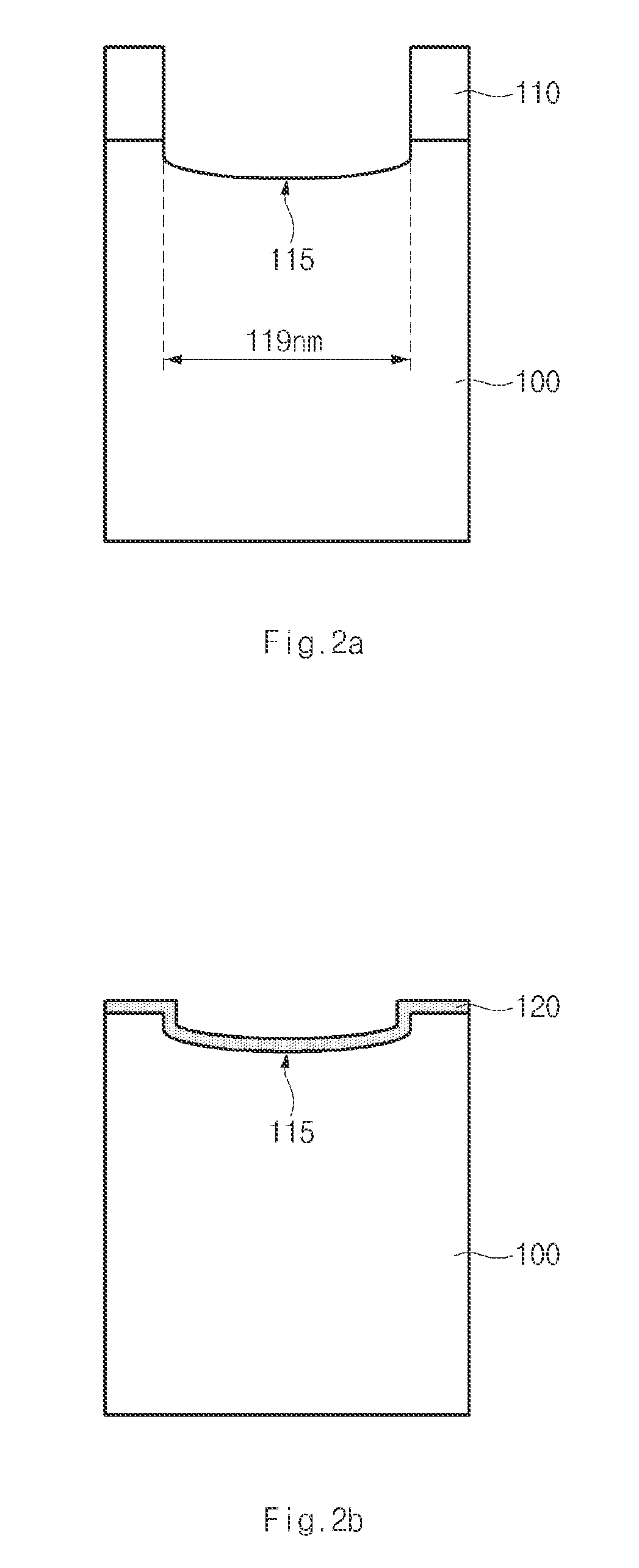

ActiveUS20050118784A1Inhibit deteriorationImprove refresh featureSemiconductor/solid-state device manufacturingDevice materialCell region

A method for forming an isolation layer of a semiconductor device is disclosed, which comprises the steps of: etching a silicon substrate having a cell region and a peripheral circuit region, forming a first trench having a first size in the cell region, and forming a second trench having a second size, which is larger than the first size of the first trench, in the peripheral circuit region; forming a sidewall oxide layer on surfaces of the first trench and the second trench; sequentially depositing a liner nitride layer and a liner oxide layer on a resultant substrate inclusive of the sidewall oxide layer; performing a plasma pre-heating process using O2+He with respect to the resultant substrate in an HDP CVD process chamber and selectively oxidizing a portion of the liner nitride layer remaining on a bottom of the second trench in the peripheral circuit region; continuously depositing an HDP oxide layer on the resultant substrate having been subjected to the plasma pre-heating process, thereby filling the trenches; and performing a chemical mechanical polishing process with respect to the HDP oxide layer.

Owner:SK HYNIX INC

Semiconductor device having buried gate structure and method for manufacturing the same, memory cell having the same and electronic device having the same

ActiveUS9634011B2Improve refresh featureImprove performanceTransistorSolid-state devicesPower semiconductor deviceGate dielectric

A semiconductor device includes a substrate comprising a trench; a gate dielectric layer formed over a surface of the trench; a gate electrode positioned at a level lower than a top surface of the substrate, and comprising a lower buried portion embedded in a lower portion of the trench over the gate dielectric layer and an upper buried portion positioned over the lower buried portion; and a dielectric work function adjusting liner positioned between the lower buried portion and the gate dielectric layer; and a dipole formed between the dielectric work function adjusting liner and the gate dielectric layer.

Owner:SK HYNIX INC

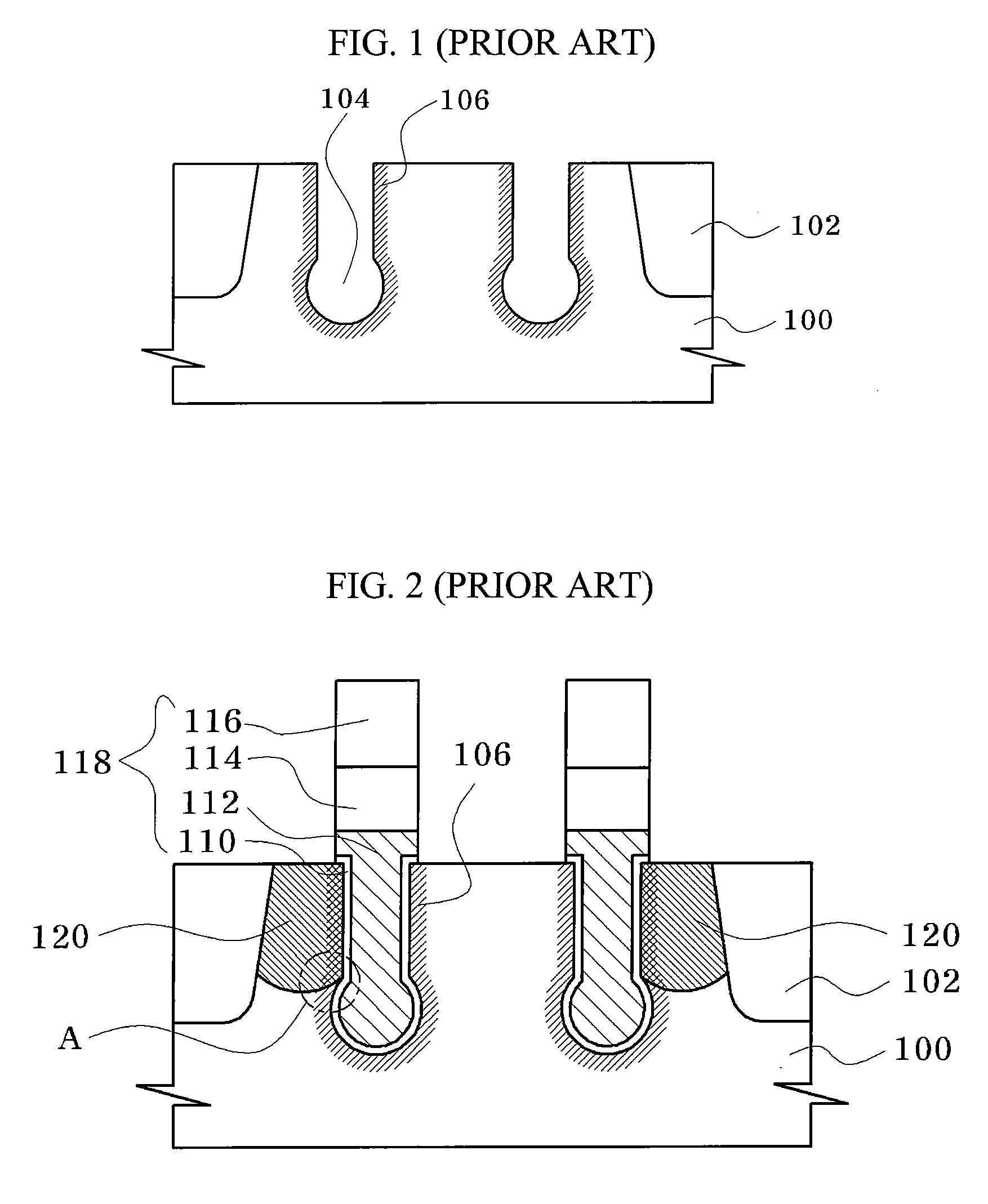

Method for fabricating transistor of semiconductor device

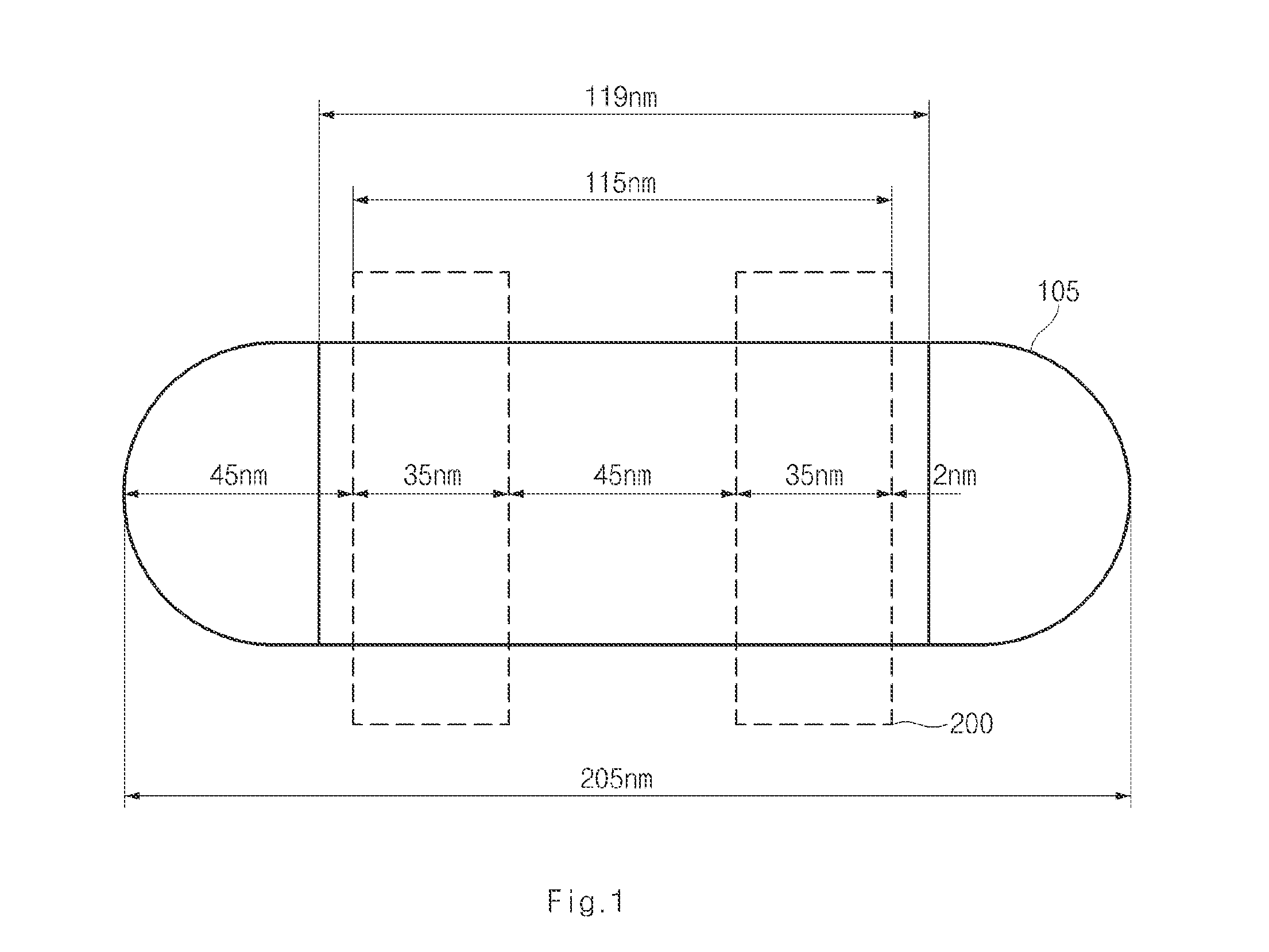

InactiveUS7314792B2Improve refresh featurePerforating toolsSemiconductor/solid-state device manufacturingIsolation layerGate oxide

A method for fabricating a transistor of a semiconductor device is provided. The method includes: forming device isolation layers in a substrate including a bottom structure, thereby defining an active region; etching the active region to a predetermined depth to form a plurality of recess structures each of which has a flat bottom portion with a critical dimension (CD) larger than that of a top portion; and sequentially forming a gate oxide layer and a metal layer on the recess structures; and patterning the gate oxide layer and the metal layer to form a plurality of gate structures.

Owner:SK HYNIX INC

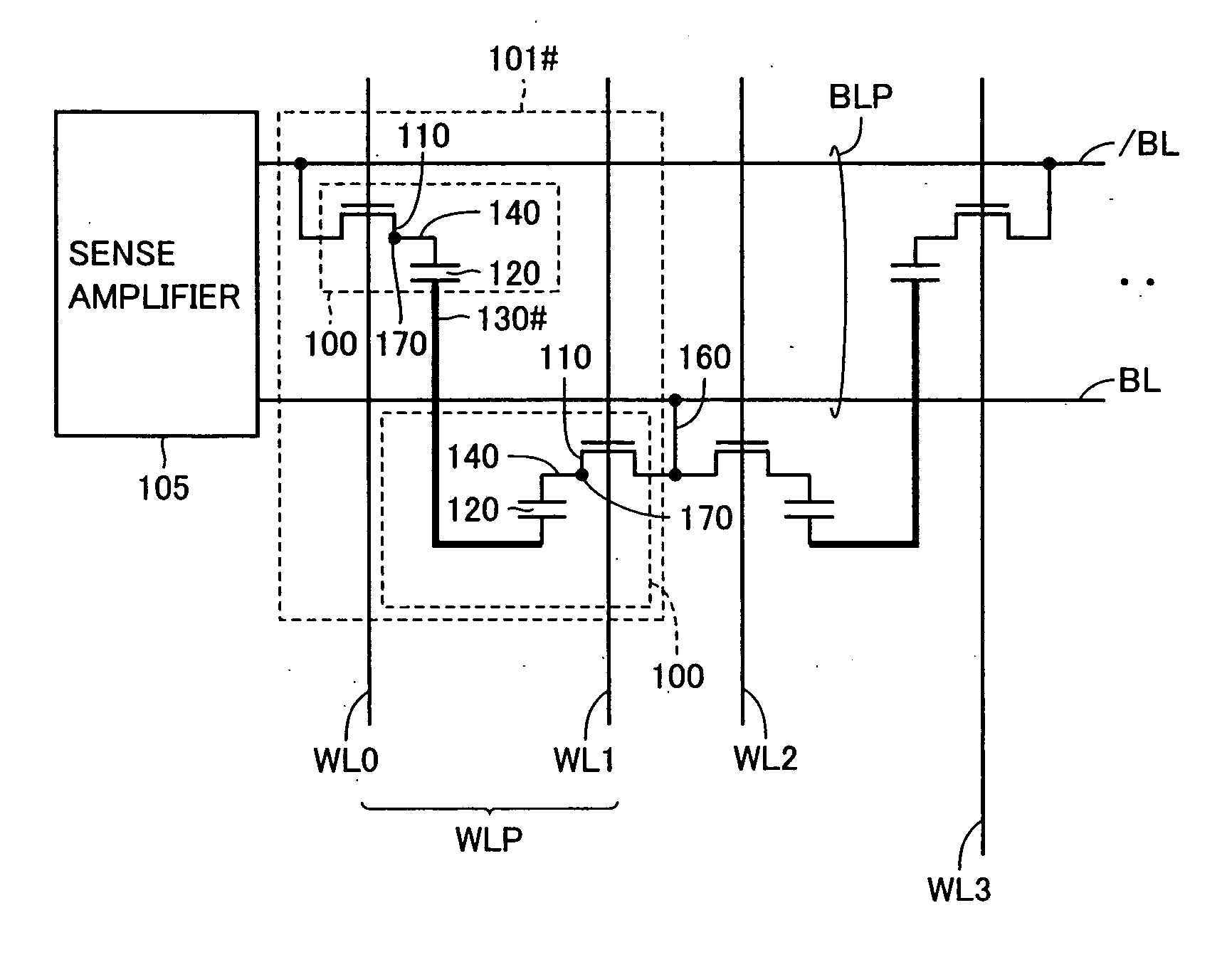

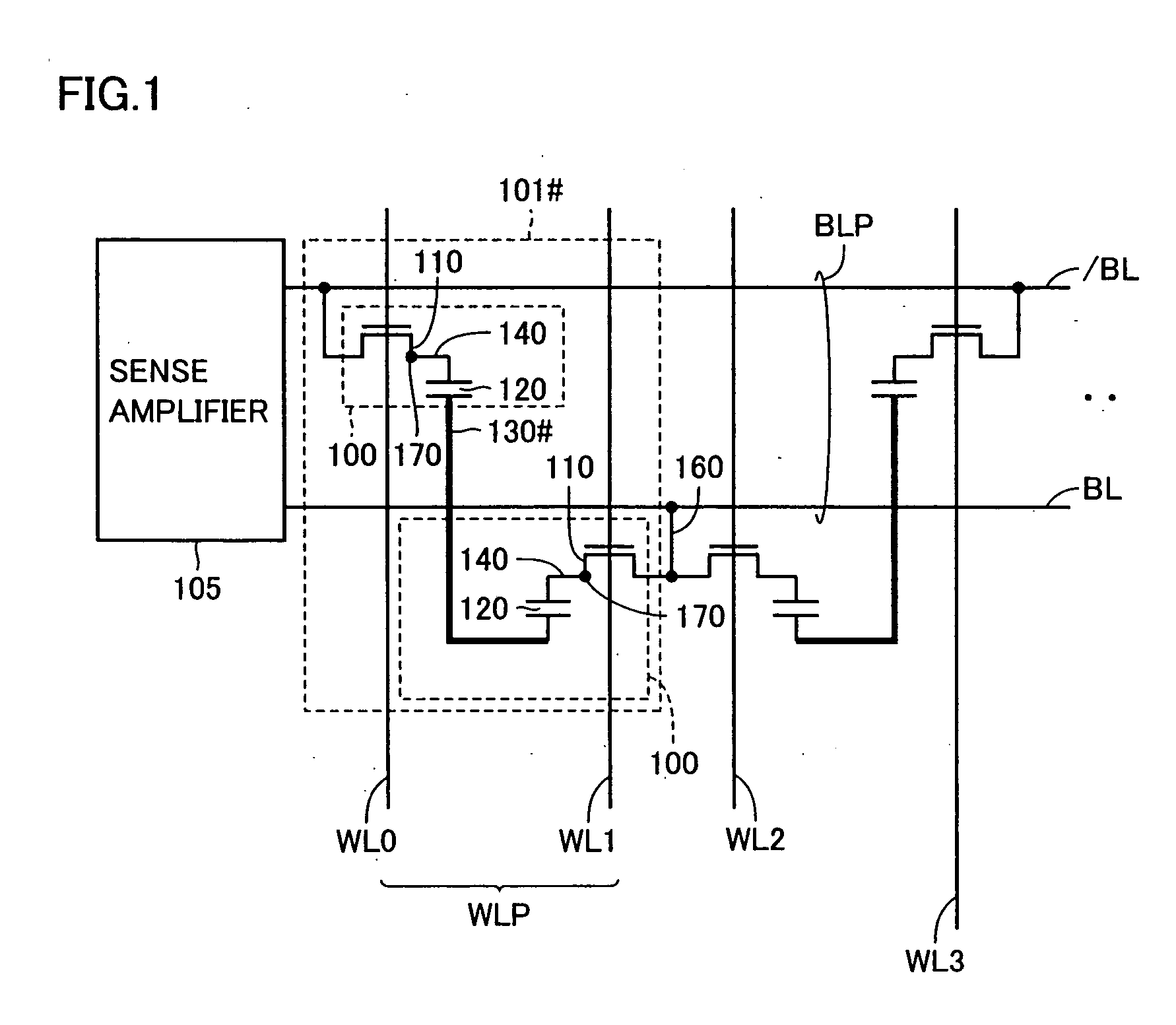

Semiconductor memory device having twin-cell units

InactiveUS6903961B2Improve refresh characteristicImprove manufacturing yieldTransistorSolid-state devicesCapacitanceCapacitive coupling

Each of twin-cell units each formed of two DRAM cells has a cell plate electrically isolated from the cell plates in the other twin-cell units. Thereby, voltages on two storage nodes storing mutually complementary data in the same twin-cell unit change similarly to each other owing to capacitive coupling.

Owner:RENESAS ELECTRONICS CORP

Method for forming contact plug of semiconductor device

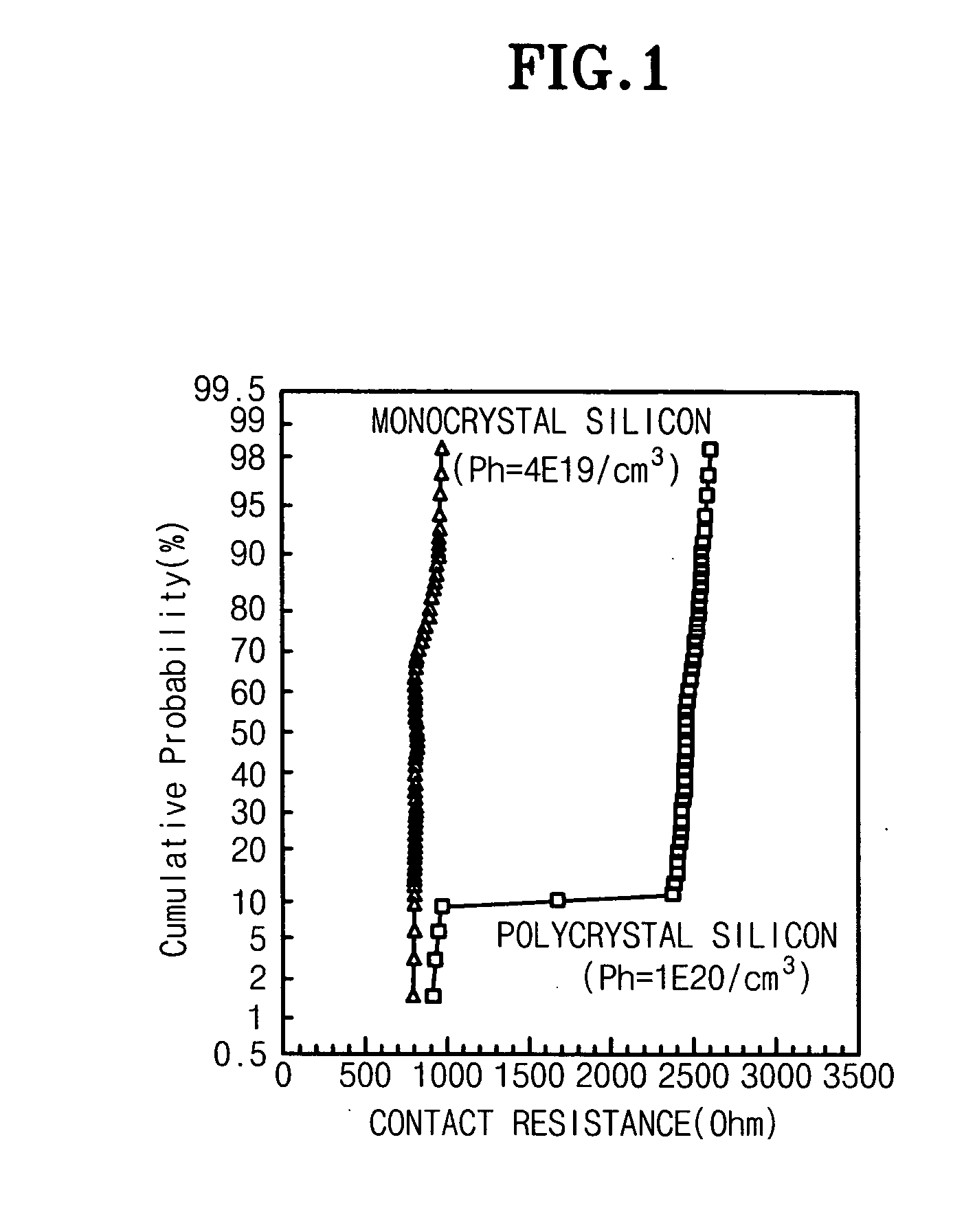

InactiveUS20050245073A1Increase in operationReduced sheet resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesSolid phasesProduction rate

In a method for forming a contact plug of a semiconductor device, epitaxial silicon is formed as contact material using a solid-phase epitaxy method. The method can obtain reduced contact resistance and improved refresh characteristics, compared with prior arts using polysilicon as contact material. Also, the method uses an SPE method, not a conventional SEG method, to form epitaxial silicon so that it can substantially reduce thermal budget through low-temperature processes. The method can also use conventional polysilicon deposition process without modification to form epitaxial silicon with ease and productivity.

Owner:SK HYNIX INC

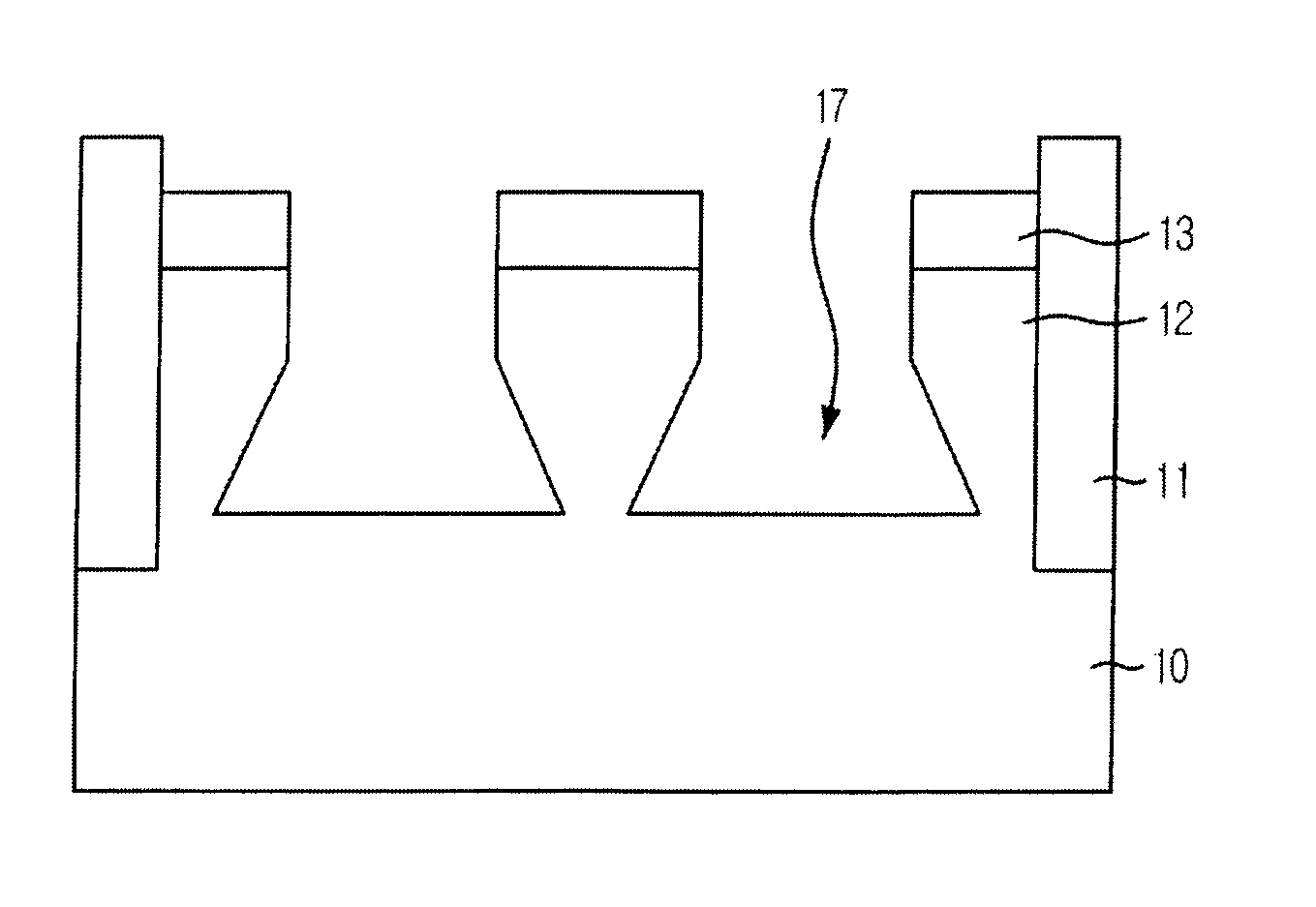

Method for fabricating transistor of semiconductor device

InactiveUS20060246730A1Improve refresh characteristicImprove refresh featurePerforating toolsSemiconductor/solid-state device manufacturingEngineeringSemiconductor

A method for fabricating a transistor of a semiconductor device is provided. The method includes: forming device isolation layers in a substrate including a bottom structure, thereby defining an active region; etching the active region to a predetermined depth to form a plurality of recess structures each of which has a flat bottom portion with a critical dimension (CD) larger than that of a top portion; and sequentially forming a gate oxide layer and a metal layer on the recess structures; and patterning the gate oxide layer and the metal layer to form a plurality of gate structures.

Owner:SK HYNIX INC

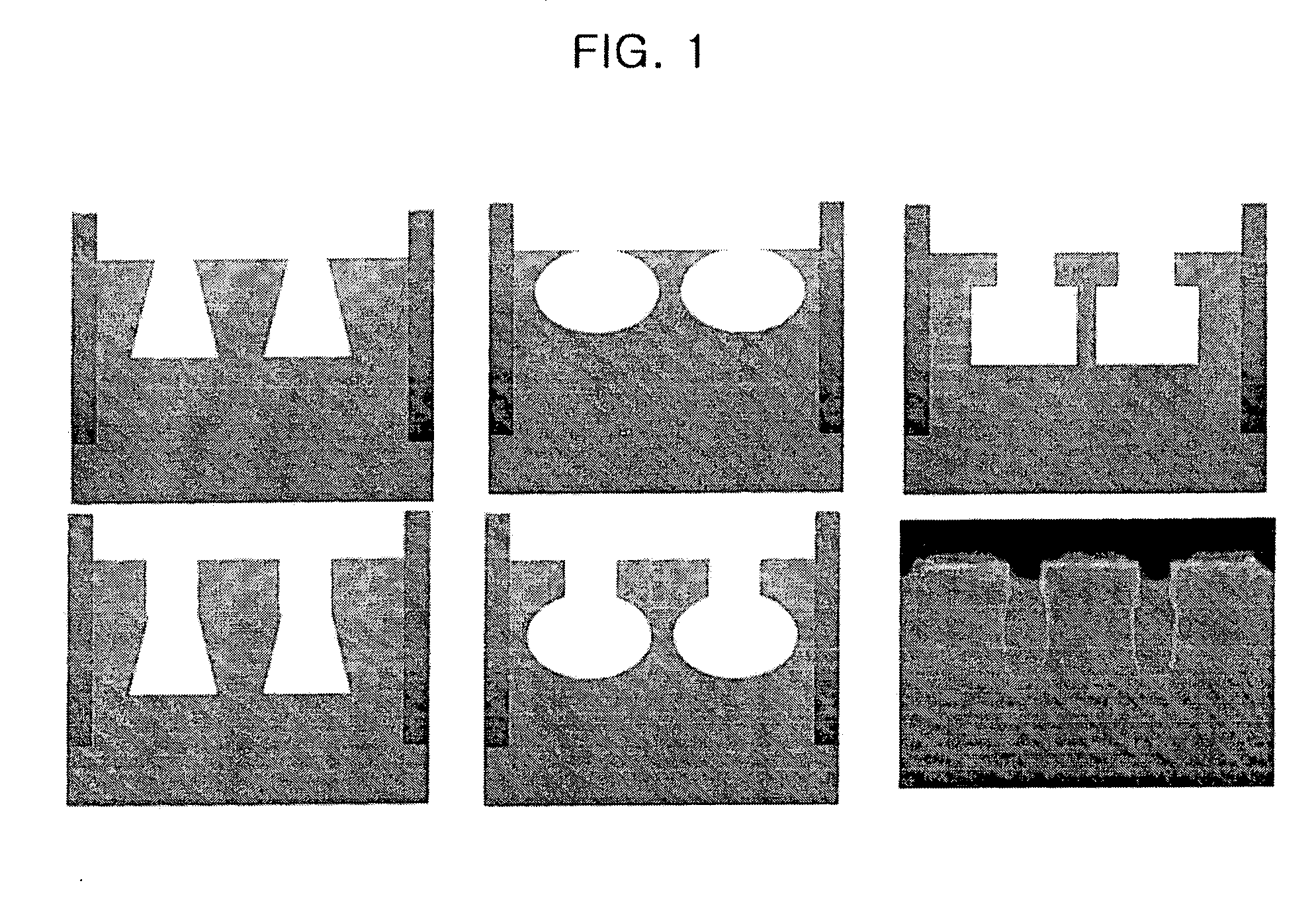

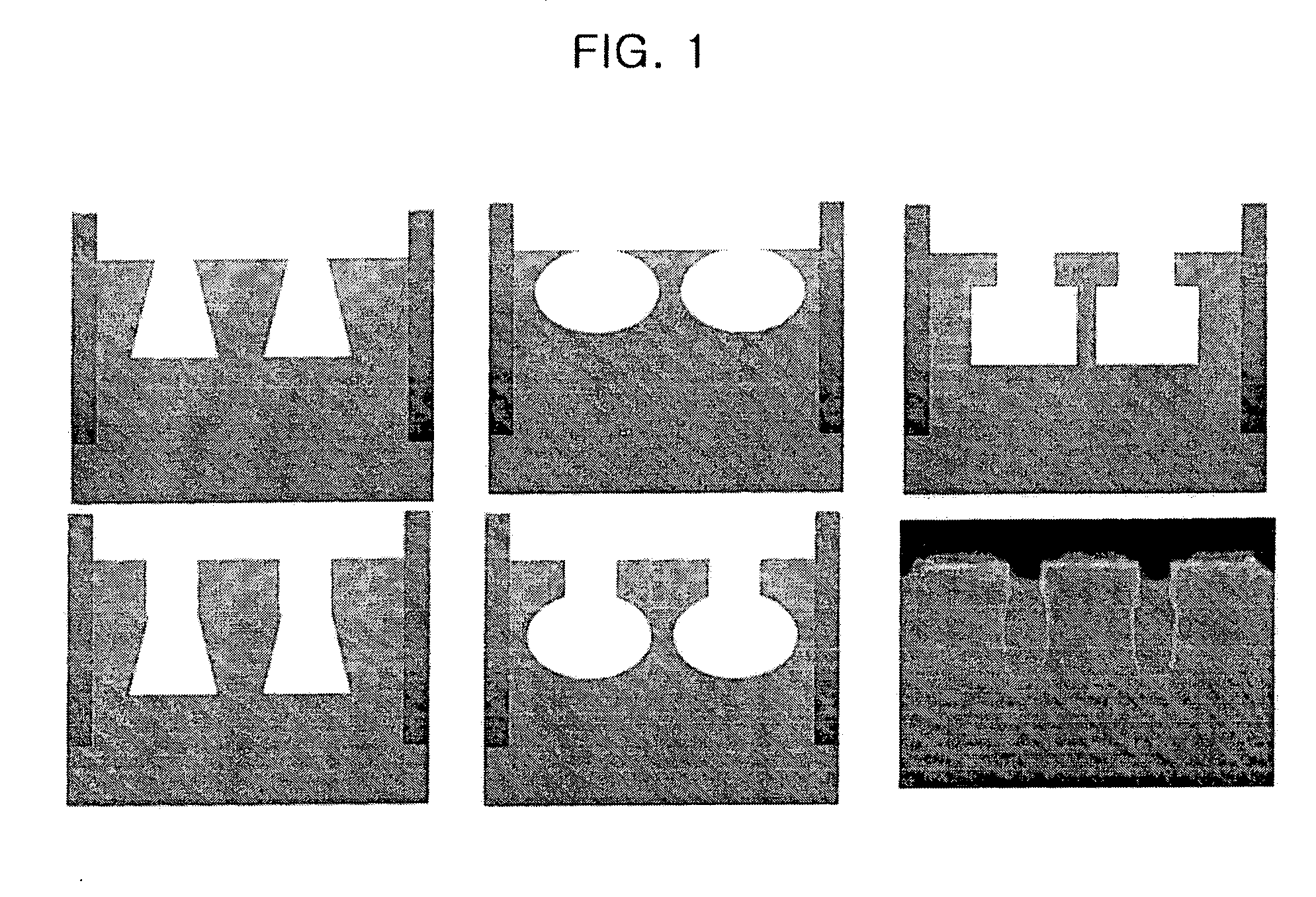

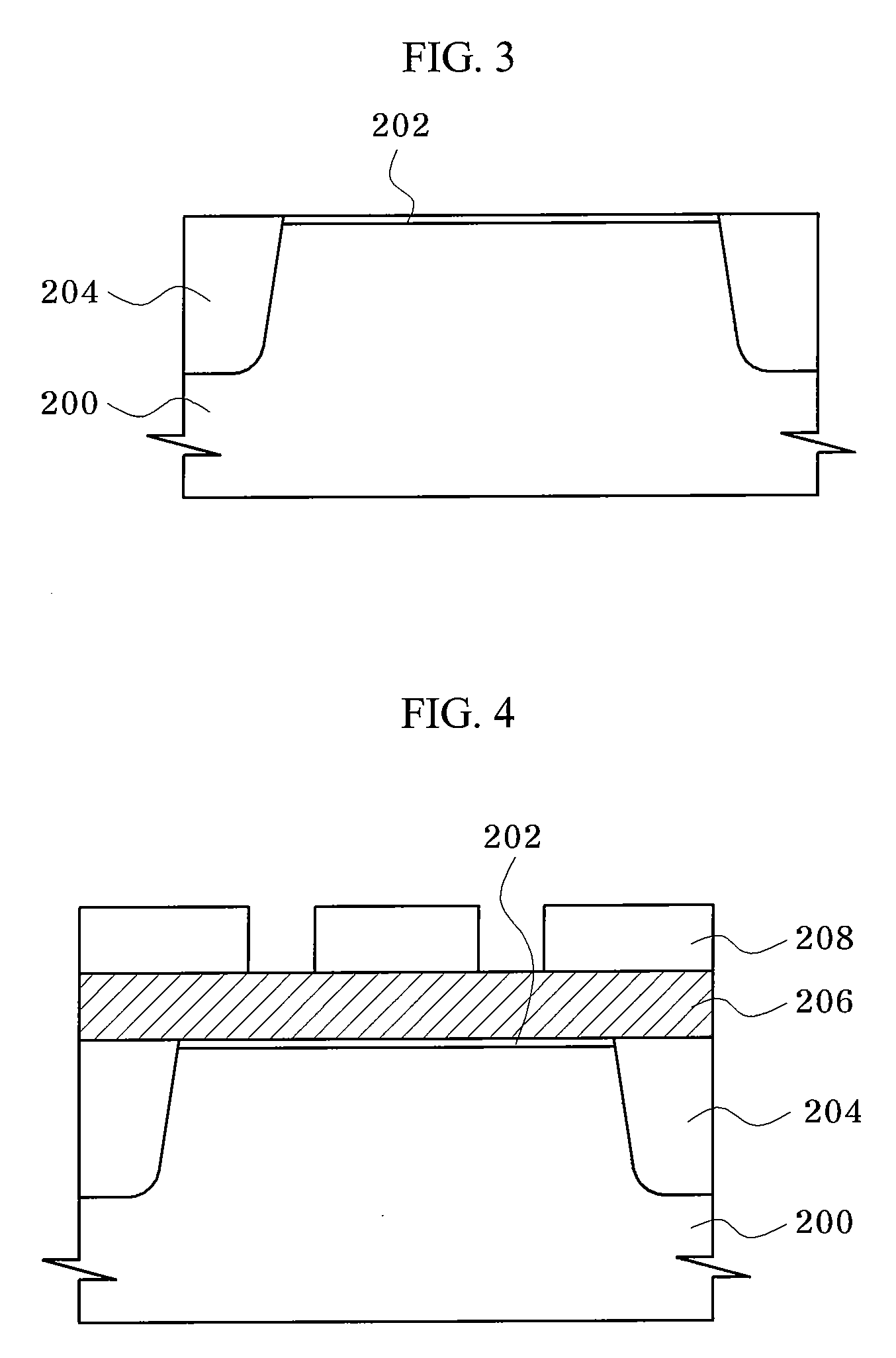

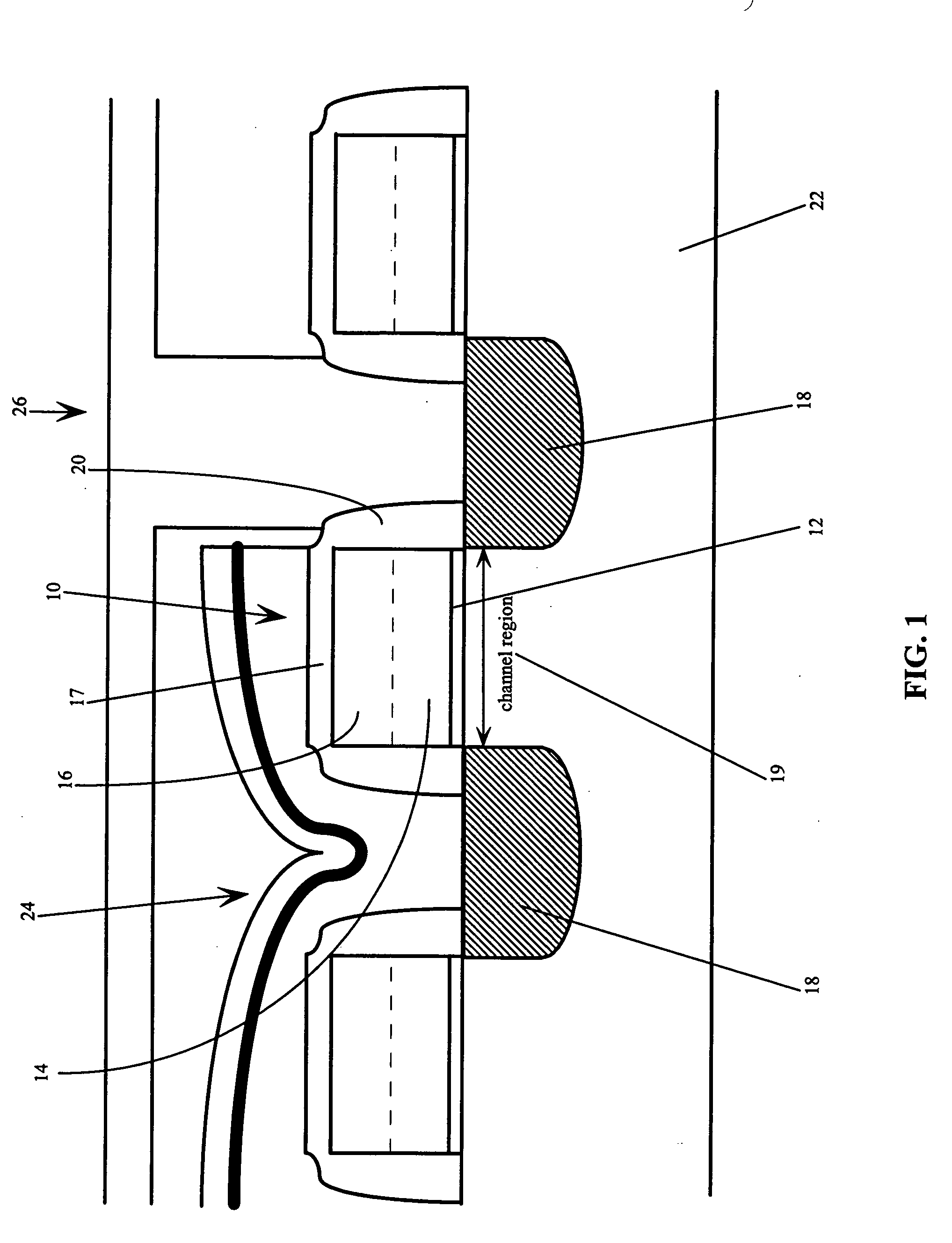

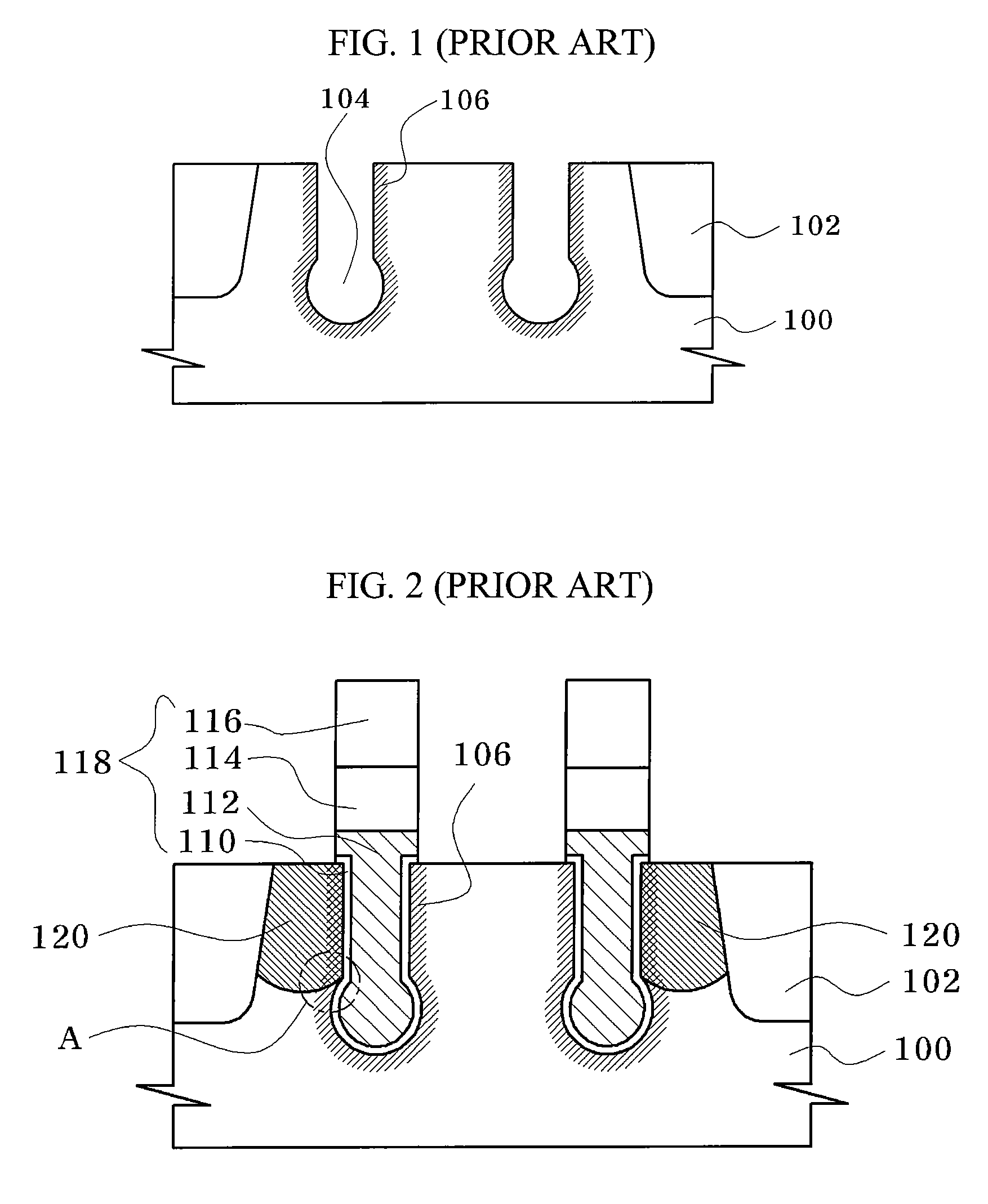

Method for forming a semiconductor device having recess channel

InactiveUS20070155101A1Reduce intensityImprove refresh featureSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

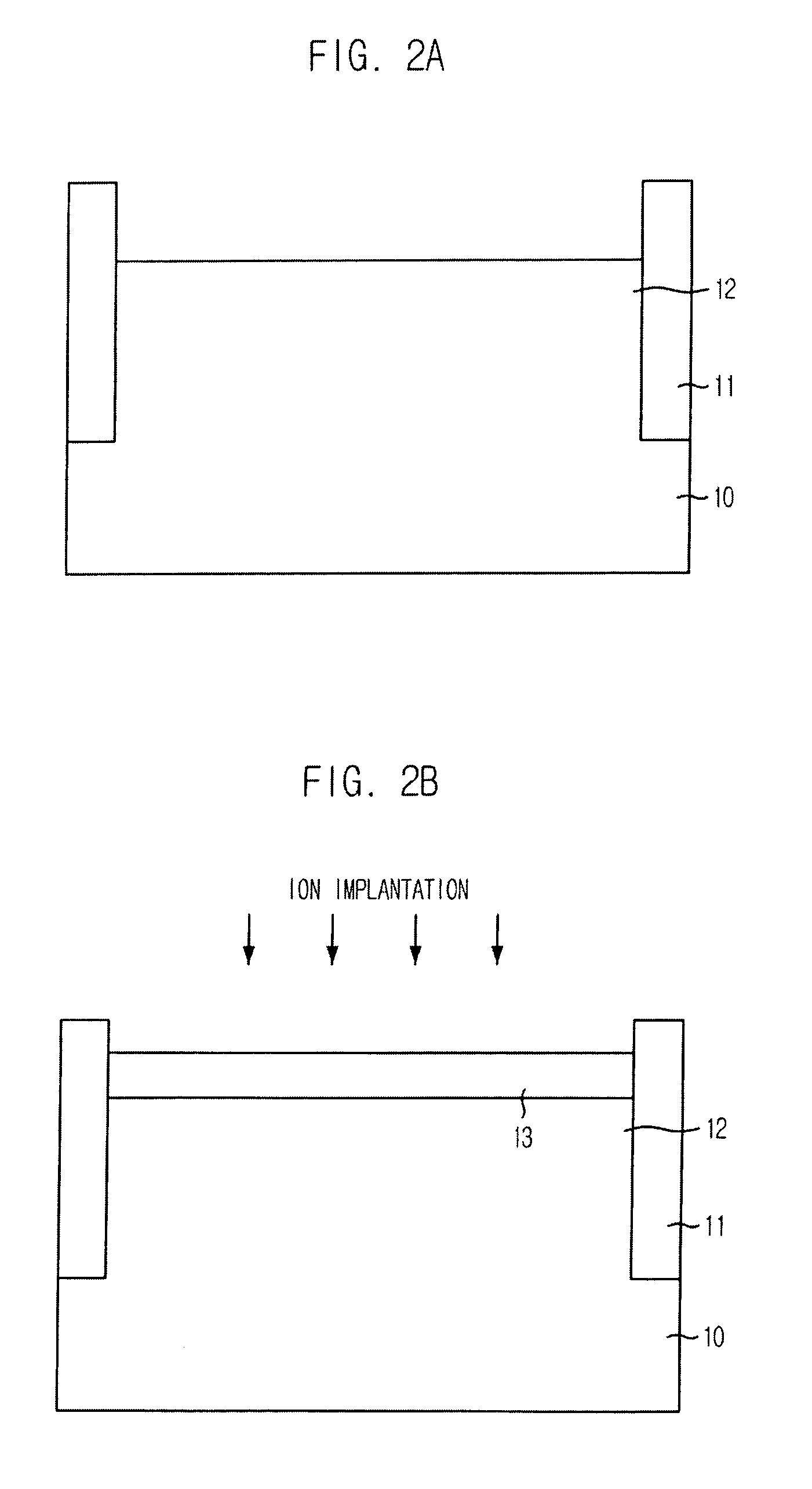

A method for forming a semiconductor device having recess channel includes forming a hard mask film pattern for exposing first regions for forming the trenches on a semiconductor substrate; forming first trenches by a first etching process using the hard mask film pattern as a mask, and removing the hard mask film pattern; forming a barrier film on the semiconductor substrate including the first trenches; forming an ion implantation mask film for exposing the first trenches on the barrier film; forming an ion implantation region in the semiconductor substrate below the first trenches using the ion implantation mask film and the barrier film; forming bulb-shaped second trenches by a second etching process using the ion implantation mask film and the barrier film as a mask, so that bulb-type trenches for recess channels, each including the first trench and the second trench, are formed; and removing the ion implantation mask film and the barrier film.

Owner:SK HYNIX INC

Integrated circuit device with P-type gate memory cell having pedestal contact plug and peripheral circuit

InactiveUS6900492B2Increase heightReduce substrate concentrationTransistorSolid-state devicesDram memorySilicon oxide

A refresh characteristic of a DRAM memory cell is improved and the performance of a MISFET formed in the periphery thereof and constituting a logic circuit is improved.Each gate electrode in a memory cell area is formed of p type polycrystalline silicon, and a cap insulating film on each gate electrode and a sidewall film on the sidewall thereof are formed of a silicon oxide film. A polycrystalline silicon film formed on the gate electrodes and between the gate electrodes is polished by a CMP method, and thereby contact electrodes are formed. Also, sidewall films each composed of a laminated film of the silicon oxide film and the polycrystalline silicon film are formed on the sidewall of the gate electrodes in the logic circuit area, and these films are used as a mask to form semiconductor areas. As a result, it is possible to reduce the boron penetration and form contact electrodes in a self-alignment manner. In addition, the performance of the MISFET constituting the logic circuit can be improved.

Owner:NEC ELECTRONICS CORP +2

Method for forming isolation layer of semiconductor device

ActiveUS7033907B2Inhibit deteriorationImprove refresh featureSemiconductor/solid-state device manufacturingCell regionIsolation layer

A method for forming an isolation layer of a semiconductor device is disclosed, which comprises the steps of: etching a silicon substrate having a cell region and a peripheral circuit region, forming a first trench having a first size in the cell region, and forming a second trench having a second size, which is larger than the first size of the first trench, in the peripheral circuit region; forming a sidewall oxide layer on surfaces of the first trench and the second trench; sequentially depositing a liner nitride layer and a liner oxide layer on a resultant substrate inclusive of the sidewall oxide layer; performing a plasma pre-heating process using O2+He with respect to the resultant substrate in an HDP CVD process chamber and selectively oxidizing a portion of the liner nitride layer remaining on a bottom of the second trench in the peripheral circuit region; continuously depositing an HDP oxide layer on the resultant substrate having been subjected to the plasma pre-heating process, thereby filling the trenches; and performing a chemical mechanical polishing process with respect to the HDP oxide layer.

Owner:SK HYNIX INC

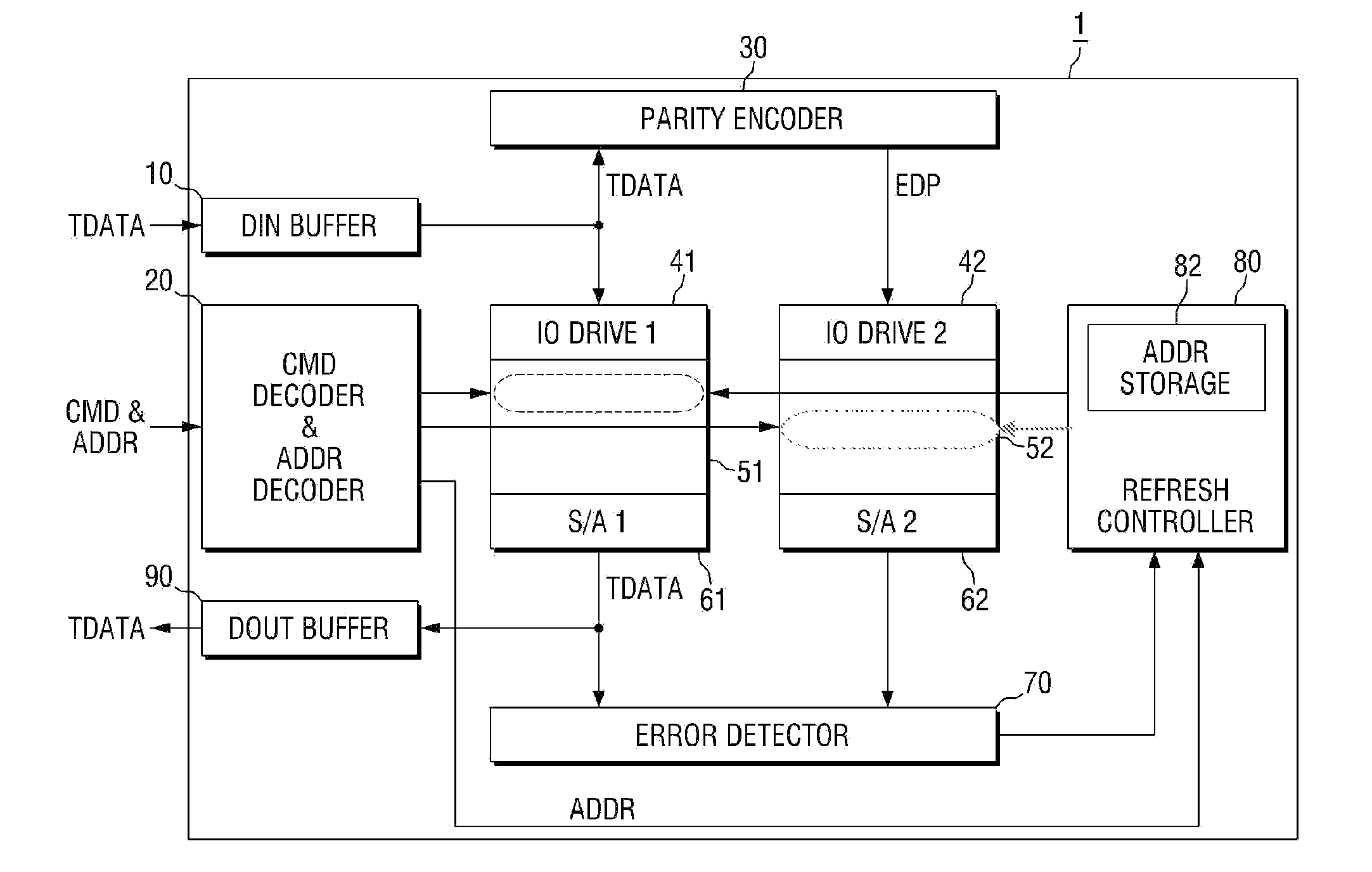

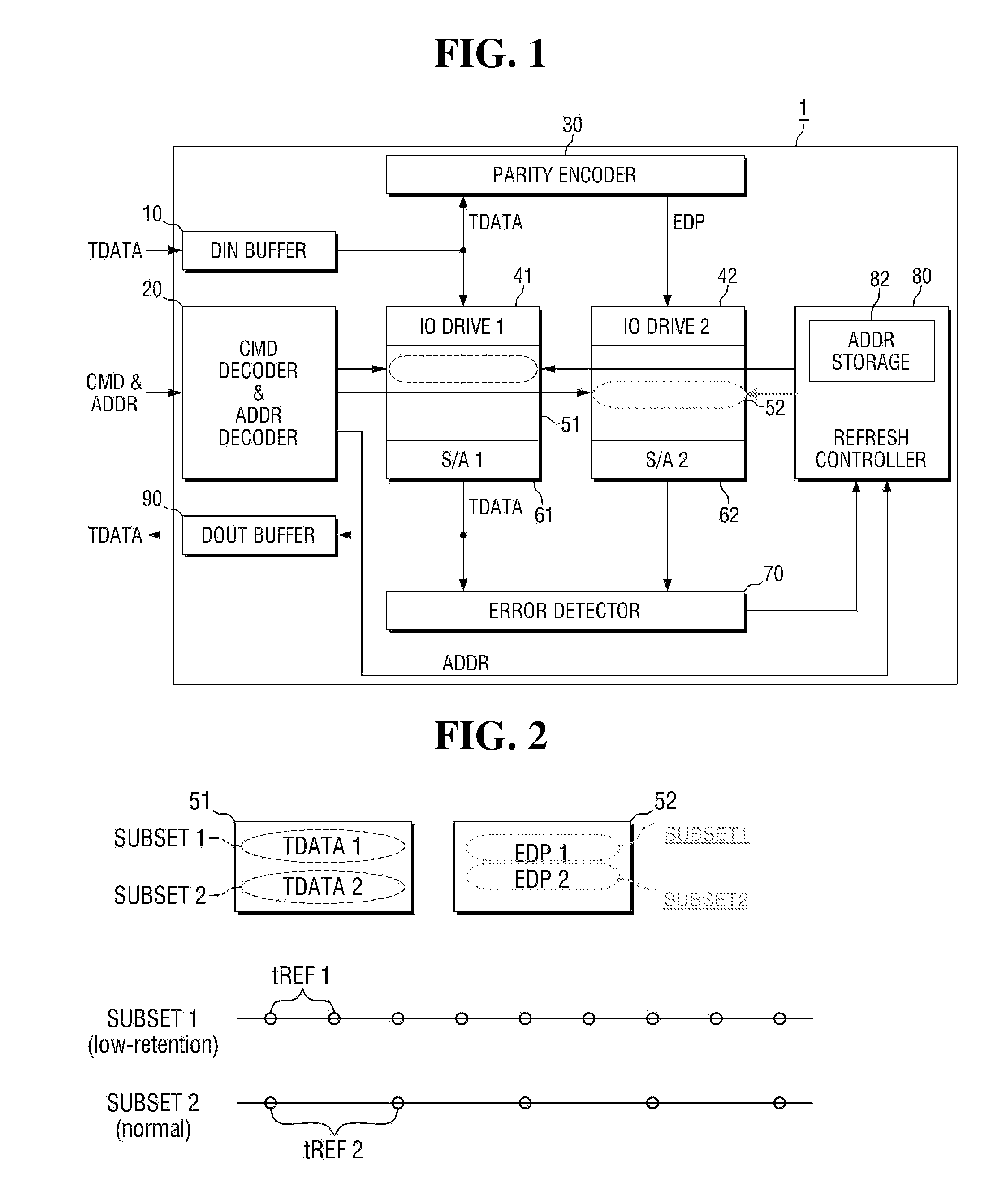

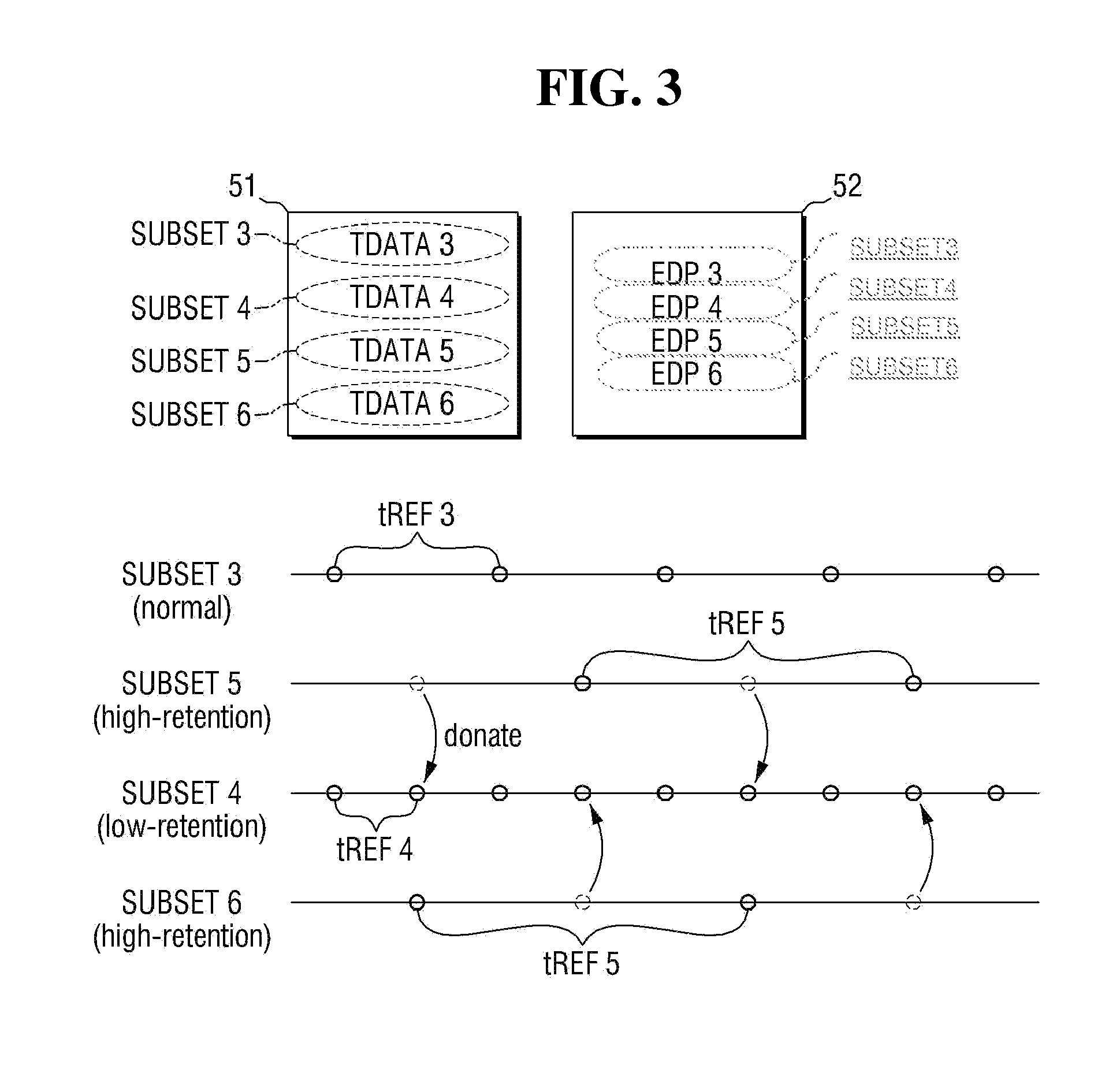

Memory device having reconfigurable refresh timing

ActiveUS20130111296A1Improve refresh featureReduce error rateCode conversionError correction/detection by combining multiple code structuresRefresh cycleStorage area

A memory device comprises a normal storage area comprising first and second subsets configured to store first and second normal data, respectively, an error code storage area configured to store first and second error codes corresponding to the first and second normal data, an error detector configured to receive the first and second normal data and the first and second error codes, and further configured to detect the presence or absence of one or more errors in the first and second normal data or the first and second error codes, and a refresh controller configured to set respective refresh cycle times of the first and second subsets to different values according to the presence or absence of one or more errors in the first and second normal data or error codes.

Owner:SAMSUNG ELECTRONICS CO LTD

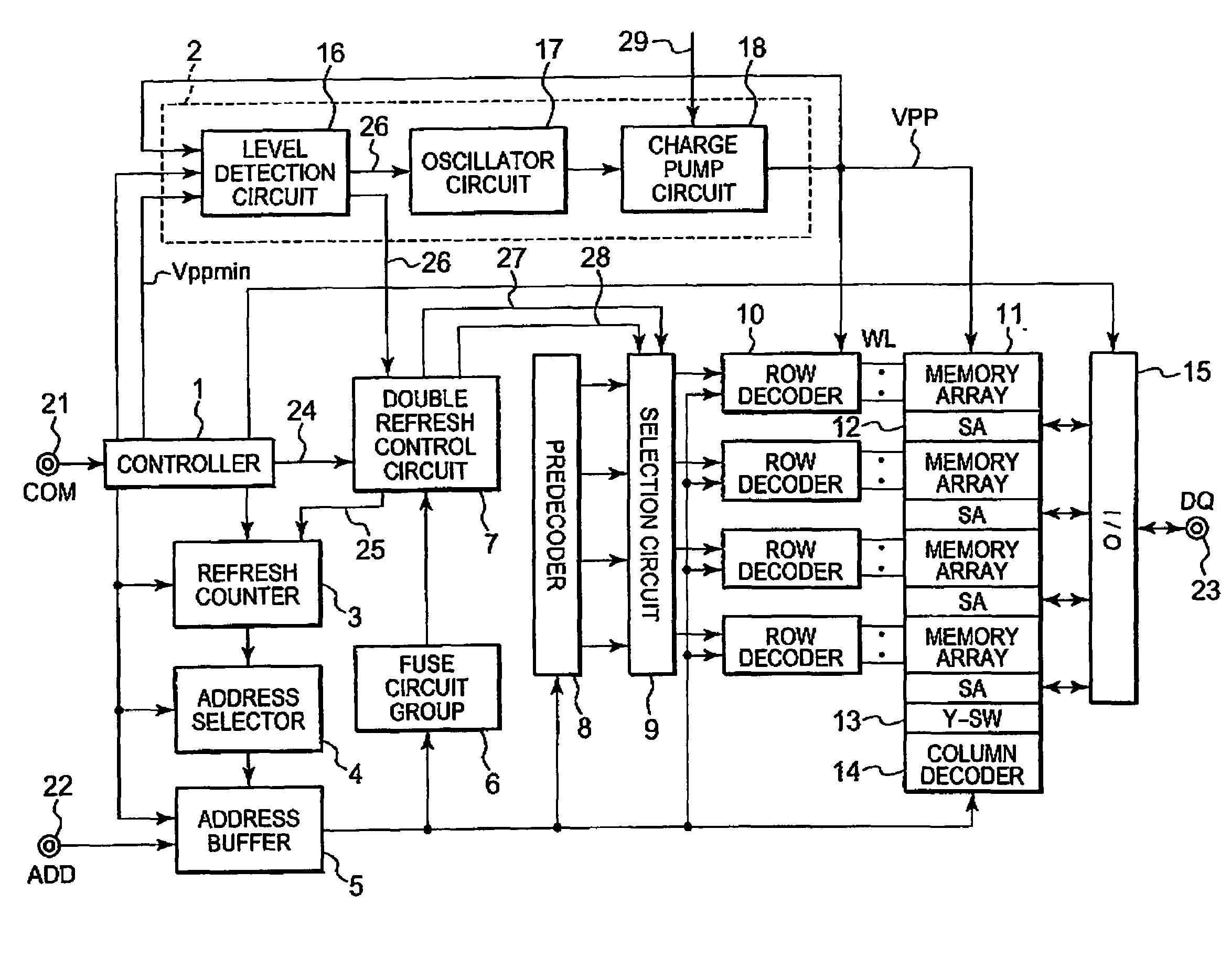

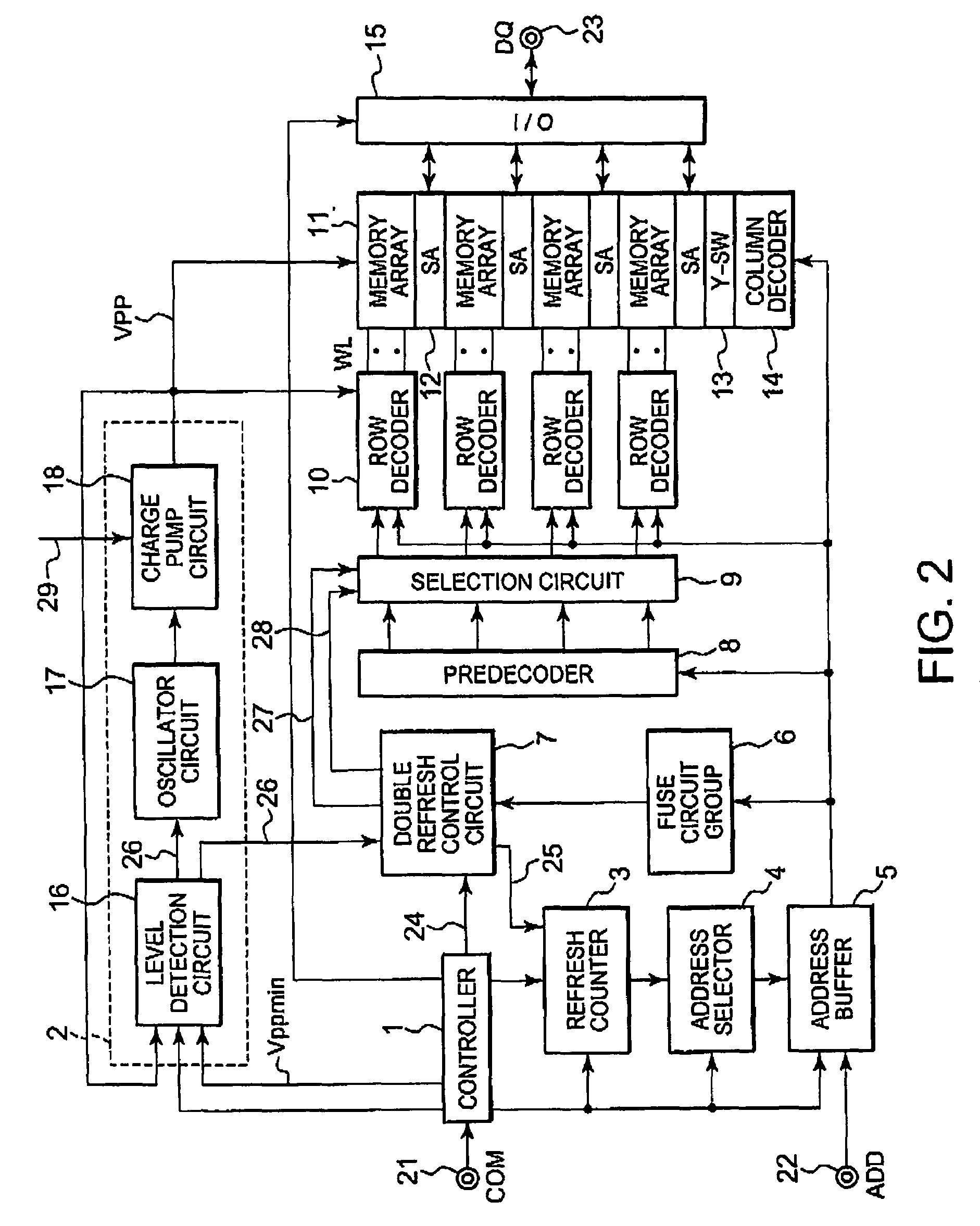

Semiconductor device

In a semiconductor device, an internally-generated power supply voltage VPP is monitored. If the internally-generated power supply voltage VPP is lower than a lower limit voltage, serial refresh is selected as a double refresh operation mode. In the serial refresh, double refresh for a pair address is inserted in a next refresh cycle. By the serial refresh, decrease of the internally-generated power supply voltage VPP is suppressed.

Owner:LONGITUDE LICENSING LTD

Semiconductor device

InactiveUS20060262625A1Improve refresh featureSuppress power supply dropDigital storageEngineeringElectrical and Electronics engineering

Owner:LONGITUDE SEMICON S A R L

Recess gate-type semiconductor device and method of manufacturing the same

InactiveUS7323746B2Improve refresh featureReduce leakage currentTransistorSolid-state devicesJunction leakageDevice material

Owner:SAMSUNG ELECTRONICS CO LTD

Use of gate electrode workfunction to improve DRAM refresh

InactiveUS20050173746A1Improve refresh featureLower requirementTransistorSolid-state devicesSubstrate dopingEngineering

This invention relates to a method and resulting structure, wherein a DRAM may be fabricated by using silicon midgap materials for transistor gate electrodes, thereby improving refresh characteristics of access transistors. The threshold voltage may be set with reduced substrate doping requirements. Current leakage is improved by this process as well.

Owner:MICRON TECH INC

Semiconductor device having buried gate structure and method for fabricating the same

ActiveUS10304684B2Reduce leakageImprove refresh featureTransistorSolid-state devicesGate dielectricWork function

Owner:SK HYNIX INC

Method for forming a semiconductor device having recess channel

InactiveUS7799641B2Reduce intensityImprove refresh featureSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorIon implantation

A method for forming a semiconductor device having recess channel includes forming a hard mask film pattern for exposing first regions for forming the trenches on a semiconductor substrate; forming first trenches by a first etching process using the hard mask film pattern as a mask, and removing the hard mask film pattern; forming a barrier film on the semiconductor substrate including the first trenches; forming an ion implantation mask film for exposing the first trenches on the barrier film; forming an ion implantation region in the semiconductor substrate below the first trenches using the ion implantation mask film and the barrier film; forming bulb-shaped second trenches by a second etching process using the ion implantation mask film and the barrier film as a mask, so that bulb-type trenches for recess channels, each including the first trench and the second trench, are formed; and removing the ion implantation mask film and the barrier film.

Owner:SK HYNIX INC

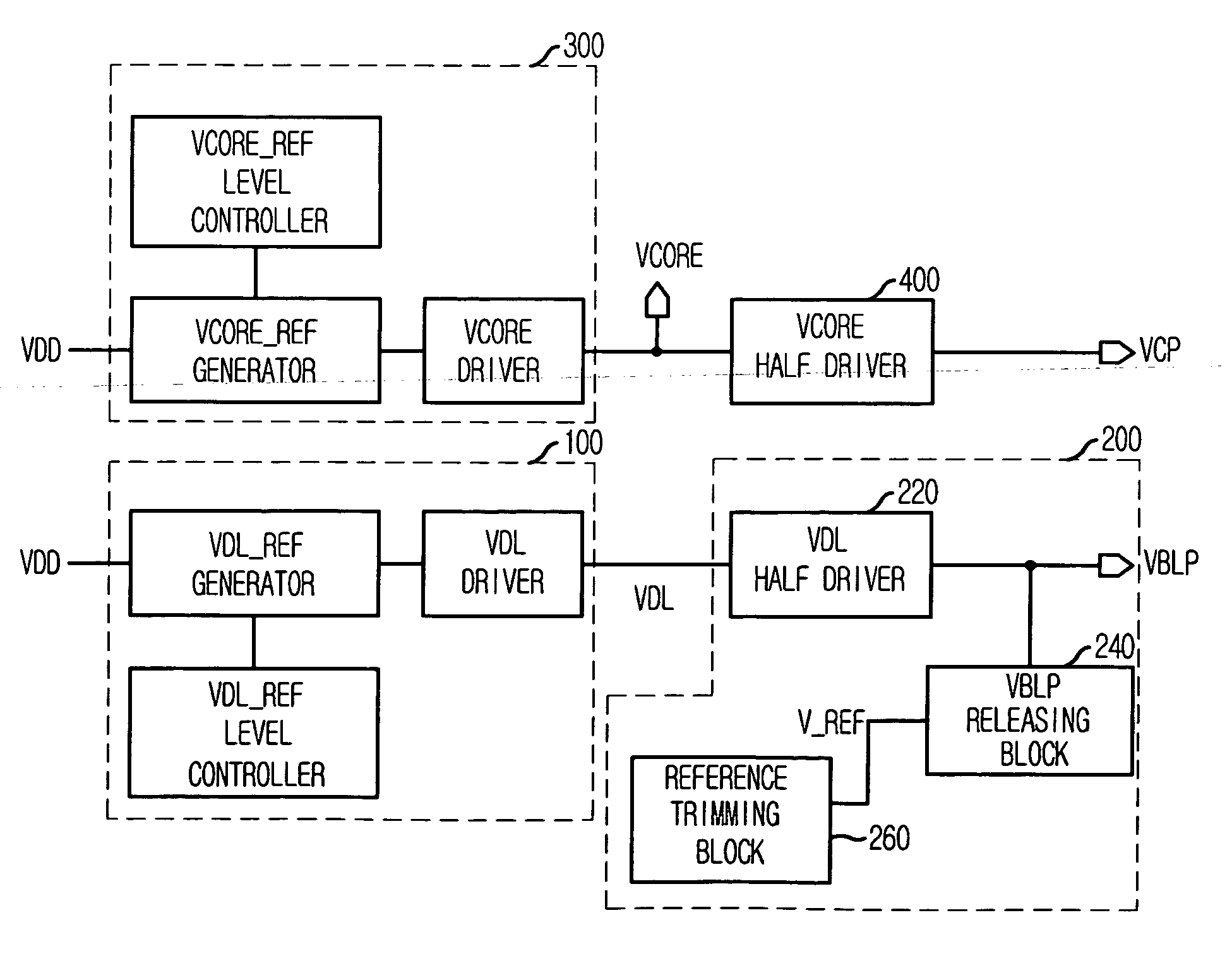

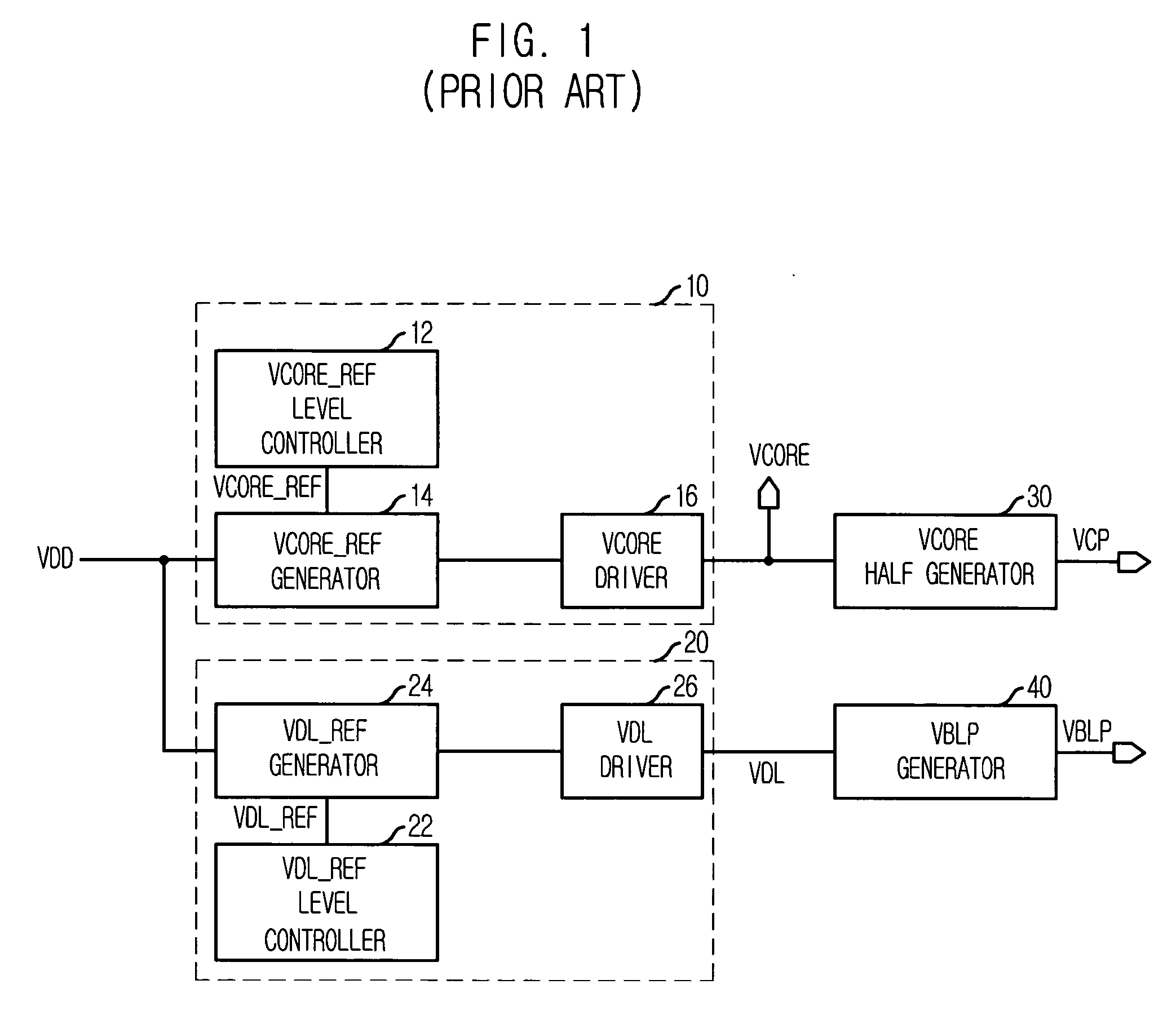

Semiconductor memory device

ActiveUS20060140019A1Improve refresh featureImproving refresh featureDigital storageCharge voltageSemiconductor memory

The present invention is related to a semiconductor memory device improving refresh performance by reliably generating an internal voltage. The internal voltage generator for use in the semiconductor memory device includes a cell plate voltage generator, a driving voltage generator, and a bit line precharge voltage generator. The bit line precharge voltage generator includes a half driving voltage generator for receiving the driving voltage to thereby generate the bit line precharge voltage, a second reference voltage generator for generating the second reference voltage, and a bit line precharge voltage releasing device for discharging a surplus voltage.

Owner:SK HYNIX INC

Semiconductor memory device having dummy word line

InactiveUS20050219893A1Suppression capacitanceAchieve effectTransistorSolid-state devicesEngineeringSemiconductor

Owner:RENESAS ELECTRONICS CORP

Semiconductor device and method for manufacturing the same

ActiveUS20120061750A1Suppress increaseReduce GIDLSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialEngineering

A semiconductor device and a method for manufacturing the same are disclosed. A recess gate structure is formed between an overlapping region between a gate and a source / drain so as to suppress increase in gate induced drain leakage (GIDL), and a gate insulation film is more thickly deposited in a region having weak GIDL, thereby reducing GIDL and thus improving refresh characteristics due to leakage current.

Owner:SK HYNIX INC

Semiconductor memory device and self-refresh method therefor

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor device and method for manufacturing the same

ActiveUS8878289B2Improve refresh featureLower work functionTransistorSolid-state devicesPower semiconductor deviceWork function

In the semiconductor device, a line-type buried gate is formed by burying a non-operating gate (isolation gate) with a polysilicon material to reduce a work function and a Gate Induced Drain Leakage (GIDL) caused by the non-operating gate, resulting in improvement of refresh characteristics of the semiconductor device. Operating gates including a metal conductive material may be formed in a separate step.

Owner:SK HYNIX INC

Manufacturing method for raising new property of semiconductor element

InactiveCN1428847ALower channel boron concentrationImprove refresh featureTransistorSolid-state devicesBit lineVoltage regulation

Disclosed is a method for fabricating a semiconductor device wherein boron-halo ion implantation is performed only to a bit-line contact part while masking a storage node contact part. The method comprises the steps of: performing a first ion implantation into the semiconductor substrate to control the threshold voltage Vt; forming a gate electrode on the semiconductor substrate in which the first ion implantation has been performed; performing a second ion implantation with a tilt of desired degree, using the gate electrode as a mask in order to control the threshold voltage; and performing a third ion implantation to form an LDD region in the substrate region at both sides of the gate electrode. In this method, the first ion implantation is performed at a range of below 90% of the whole doping concentration required to control the threshold voltage, and the second ion implantation is performed with a degree of below 30 DEG and in two directions or four directions vertical to the gate electrode.

Owner:SK HYNIX INC