Patents

Literature

56results about How to "Suppression capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

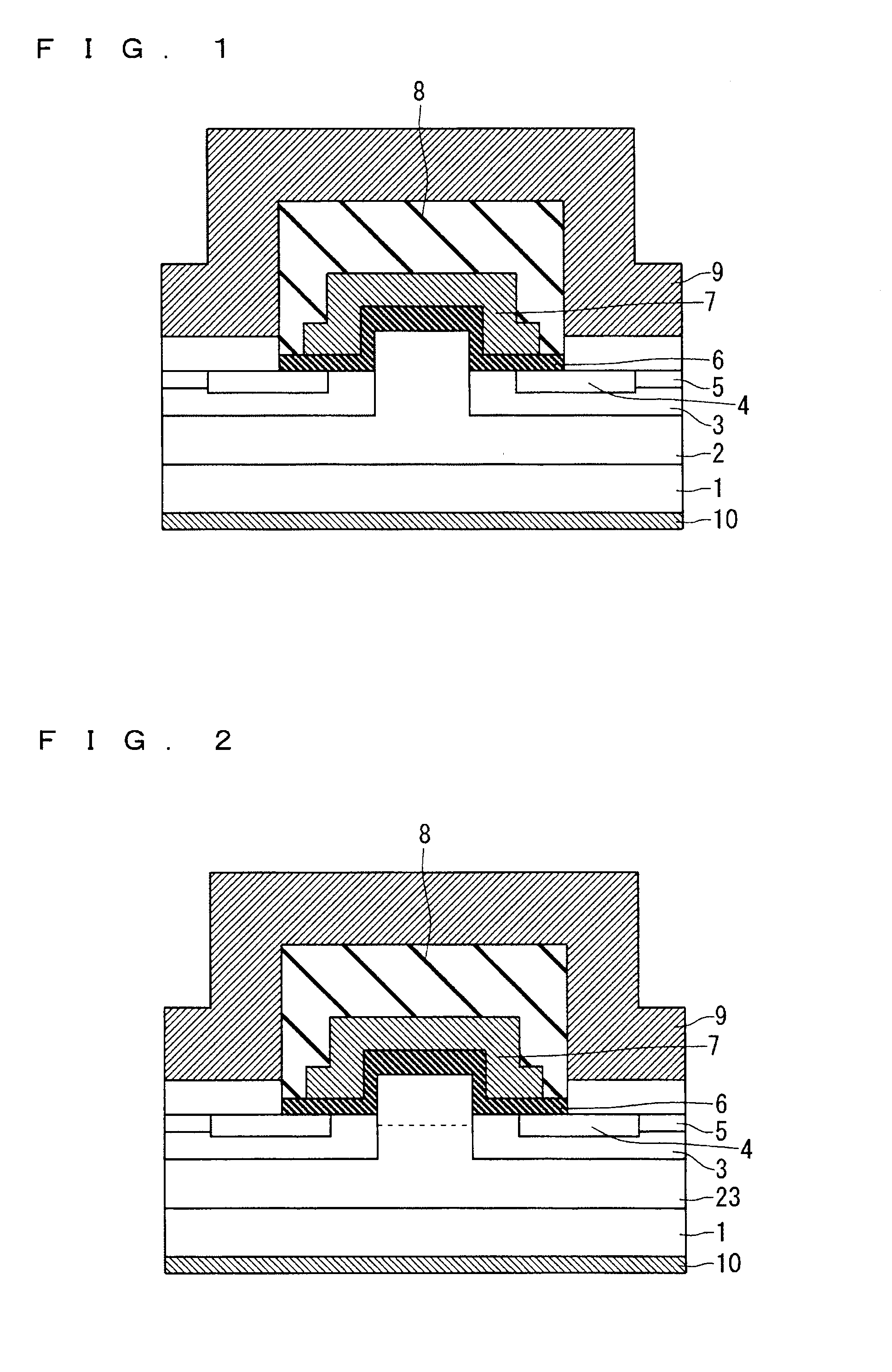

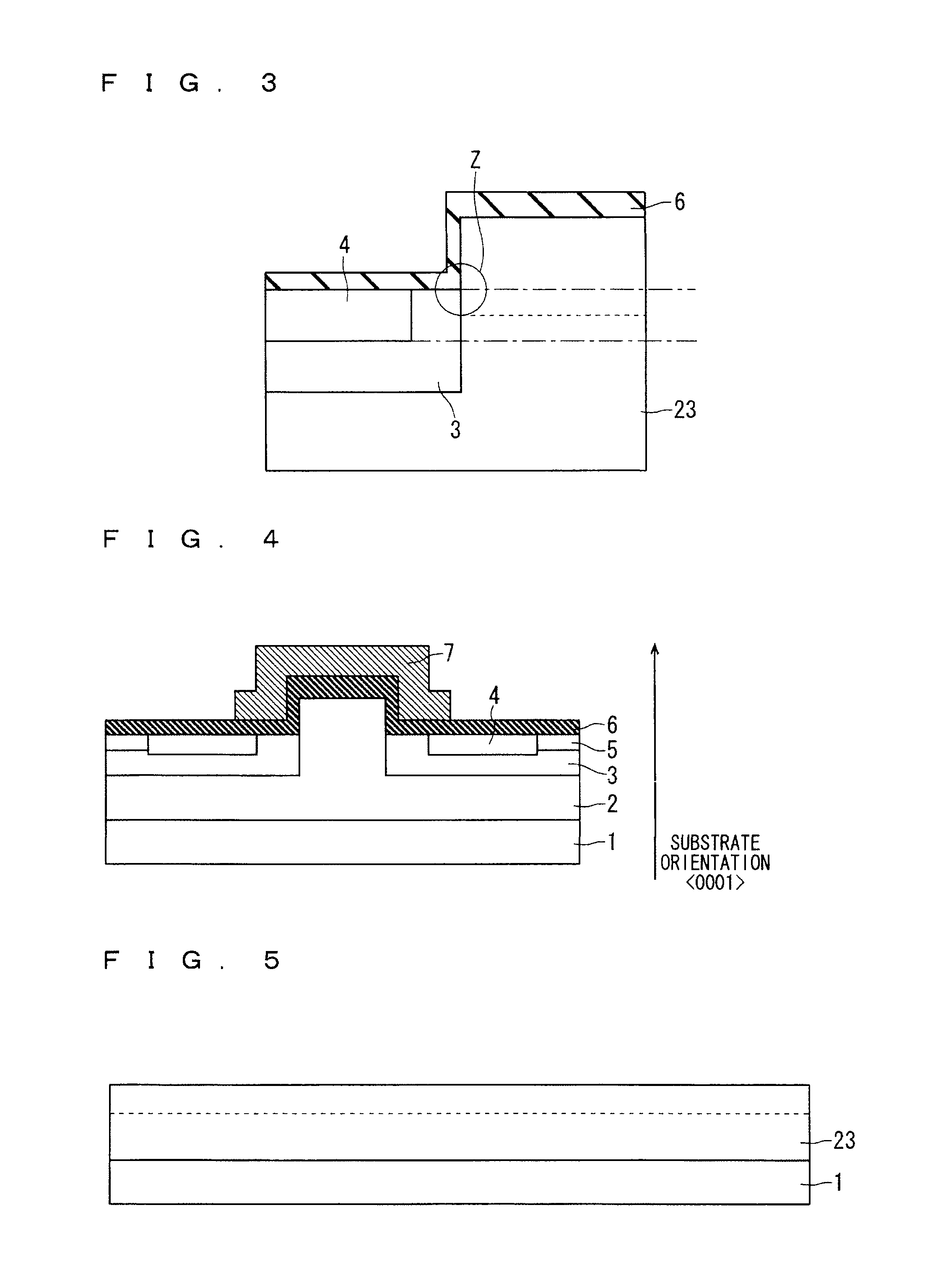

Semiconductor device and method for manufacturing same

InactiveUS20060157798A1Reduce the induction currentMade smallSemiconductor/solid-state device detailsSolid-state devicesMOSFETDevice material

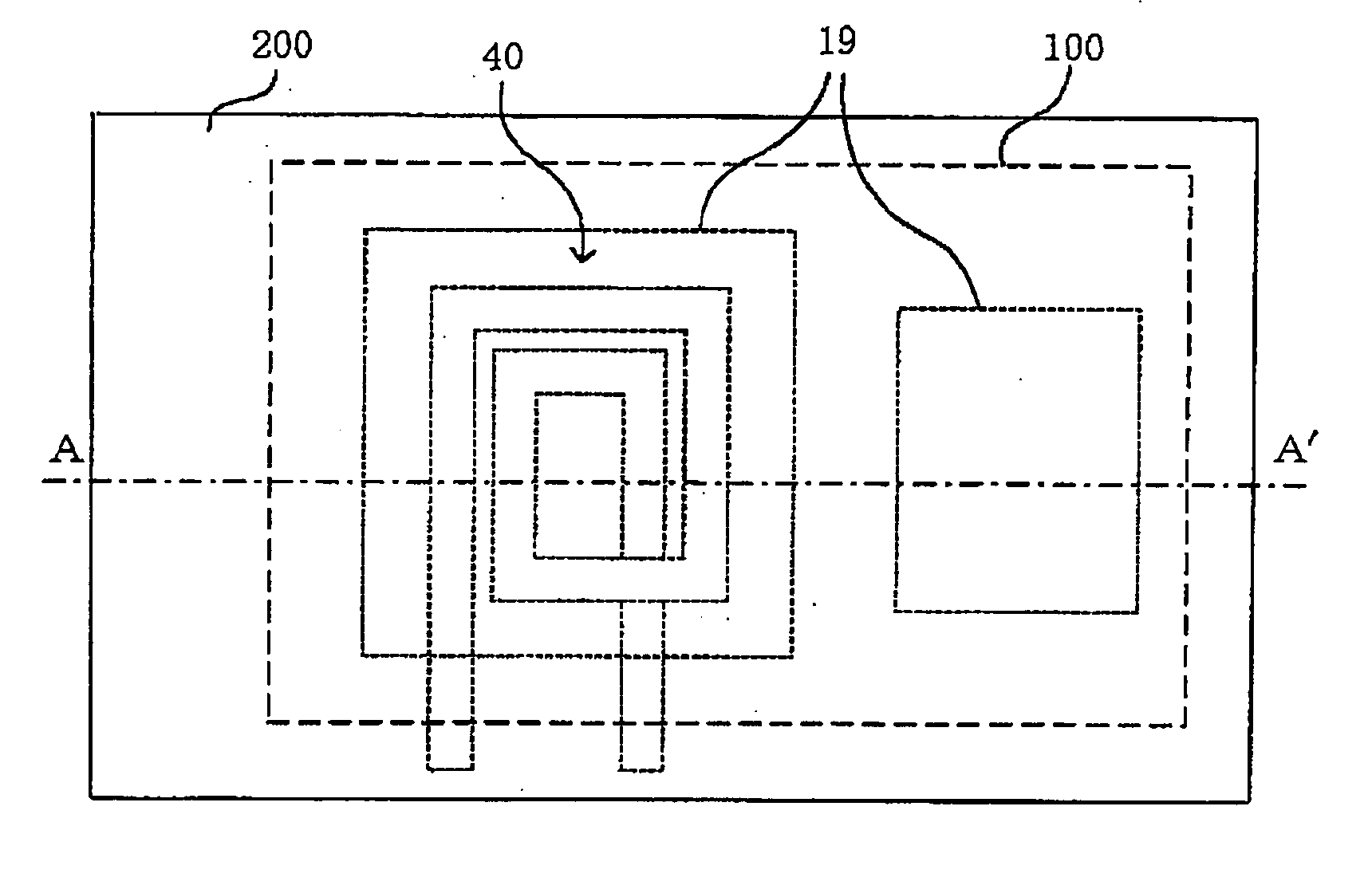

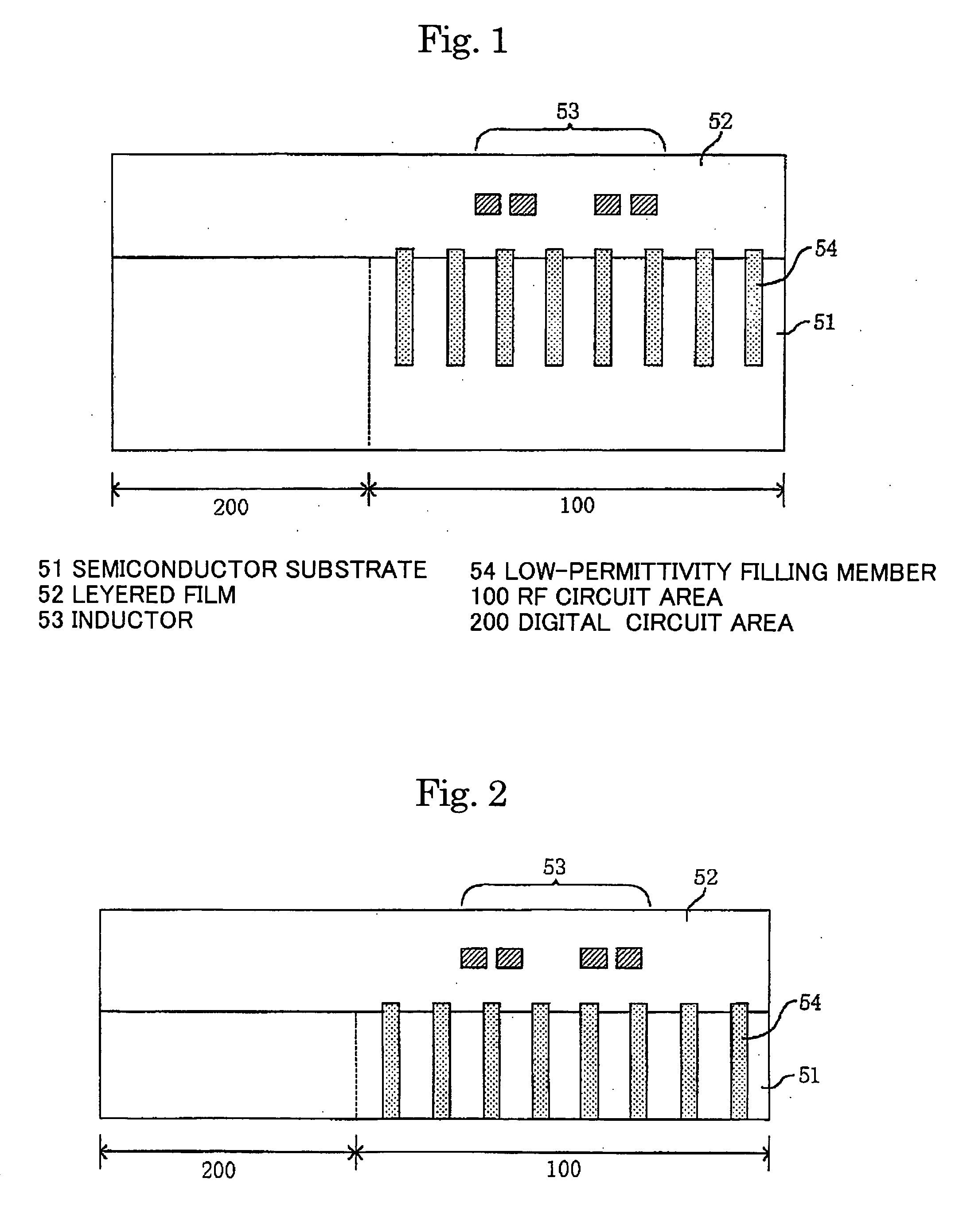

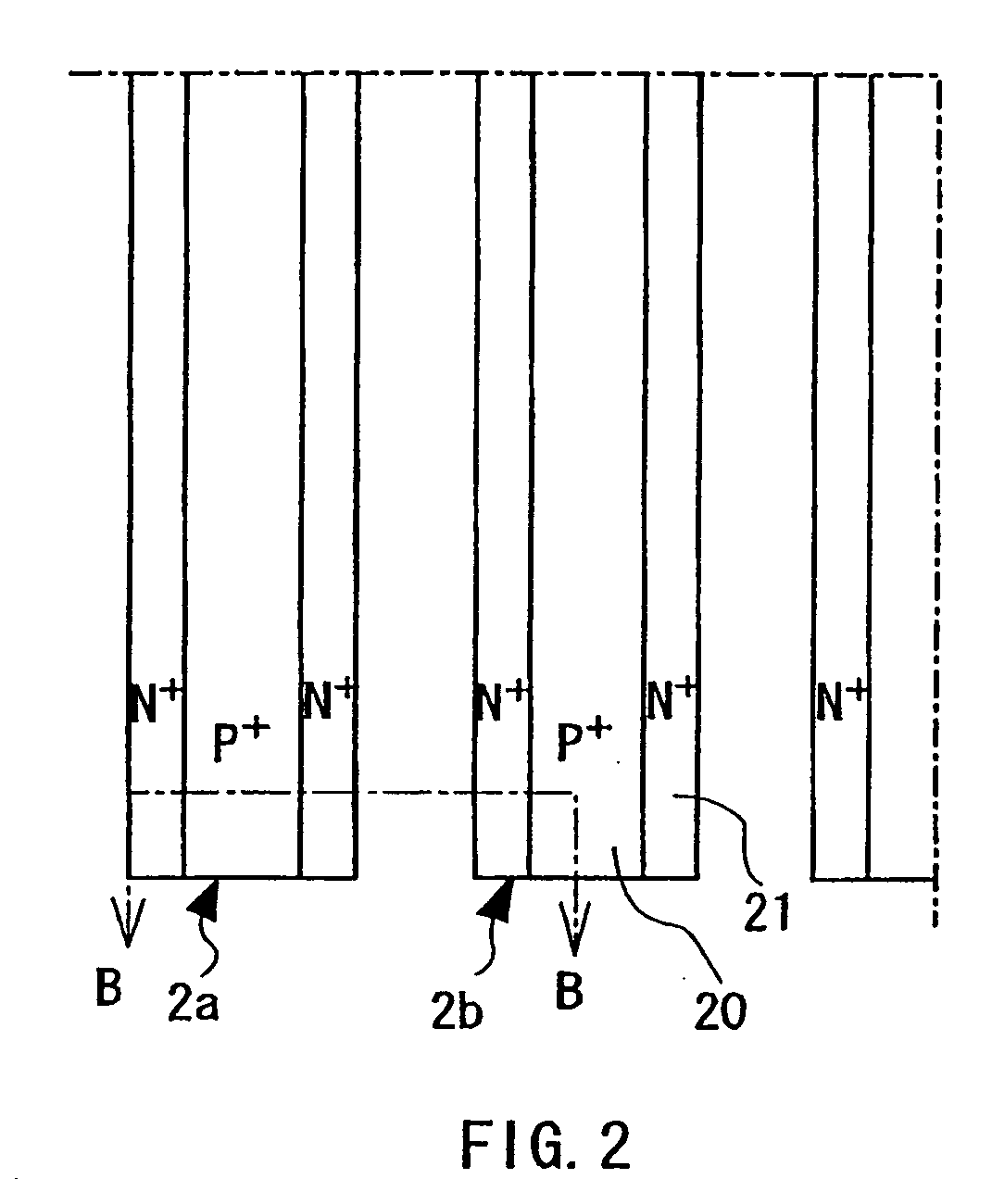

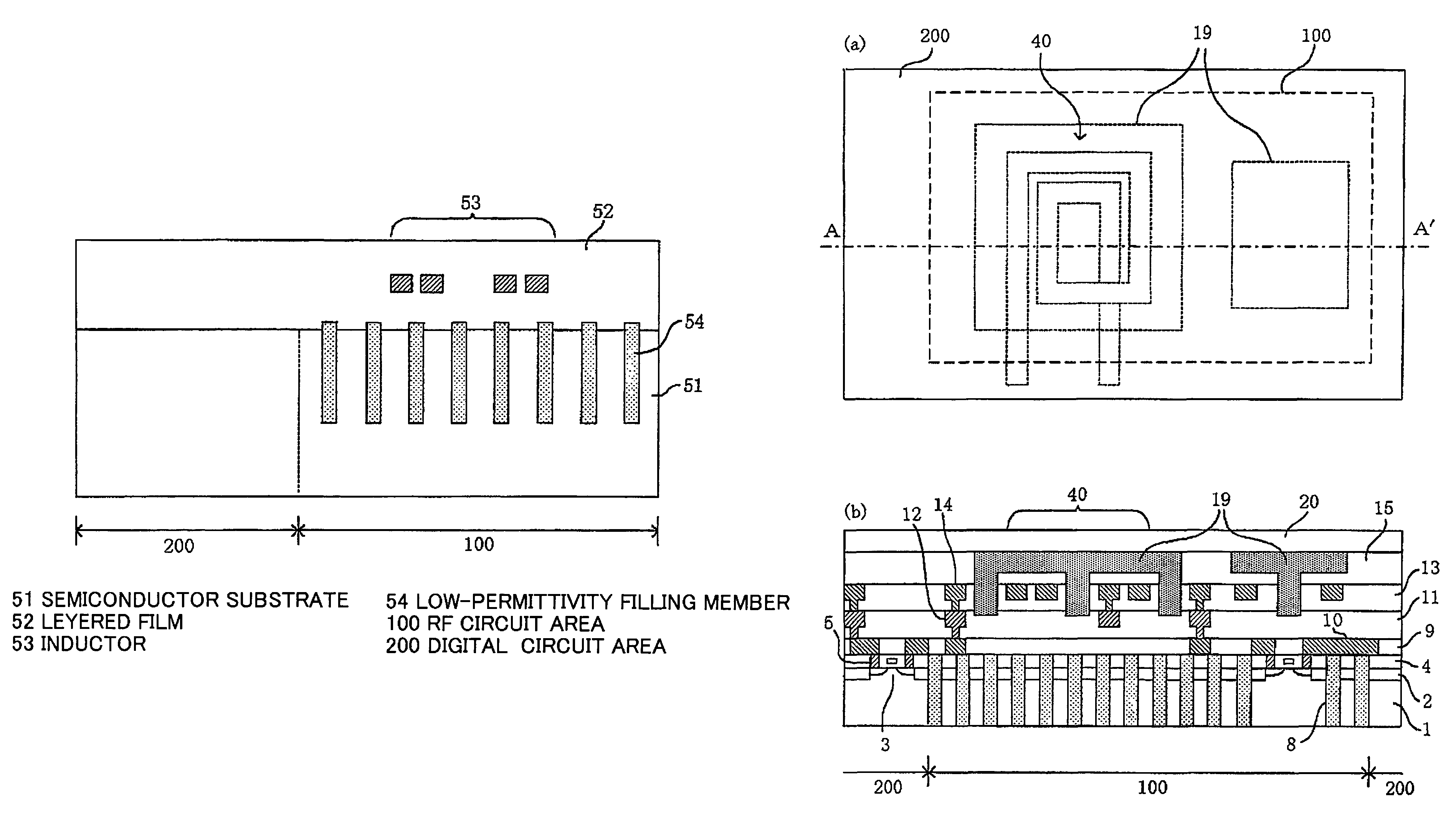

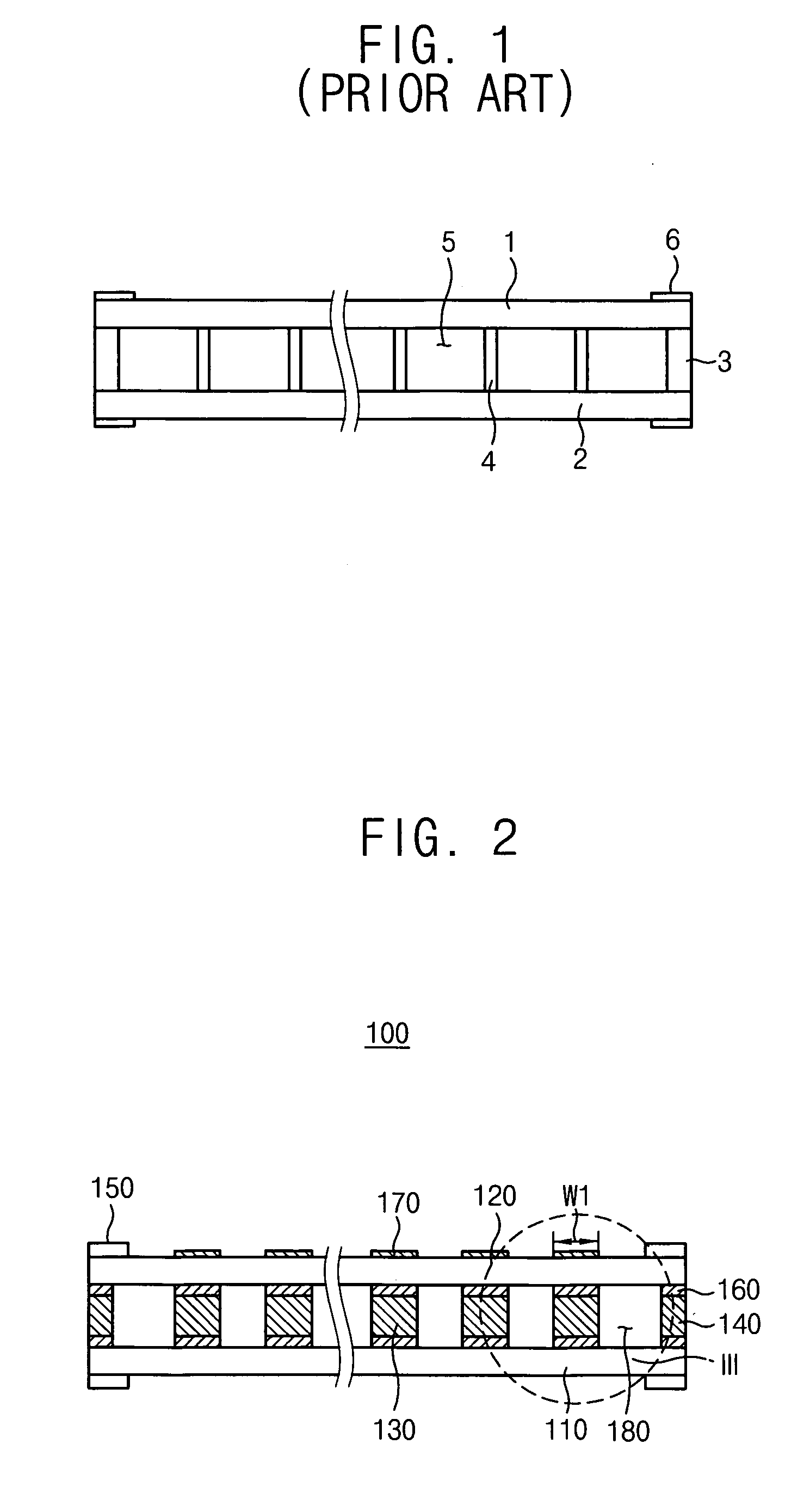

[Object] An object of the present invention is to mount both a RF circuit including an inductor formed therein and a digital circuit on a single chip. [Means for Solving Problems] MOSFETs are formed on a semiconductor substrate 1 in regions isolated by an element isolation film 2. A plurality of low-permittivity insulator rods including a low-permittivity insulator embedded therein and penetrating a first interlevel dielectric film 4 to reach the internal of the silicon substrate are disposed in the RF circuit area 100. An inductor 40 is formed on the interlevel dielectric film in the RF circuit area by using multi-layered interconnects. A high-permeability isolation region in which a composite material including a mixture of high-permeability material and a low-permittivity material is formed in the region of the core of the inductor and periphery thereof.

Owner:NEC CORP

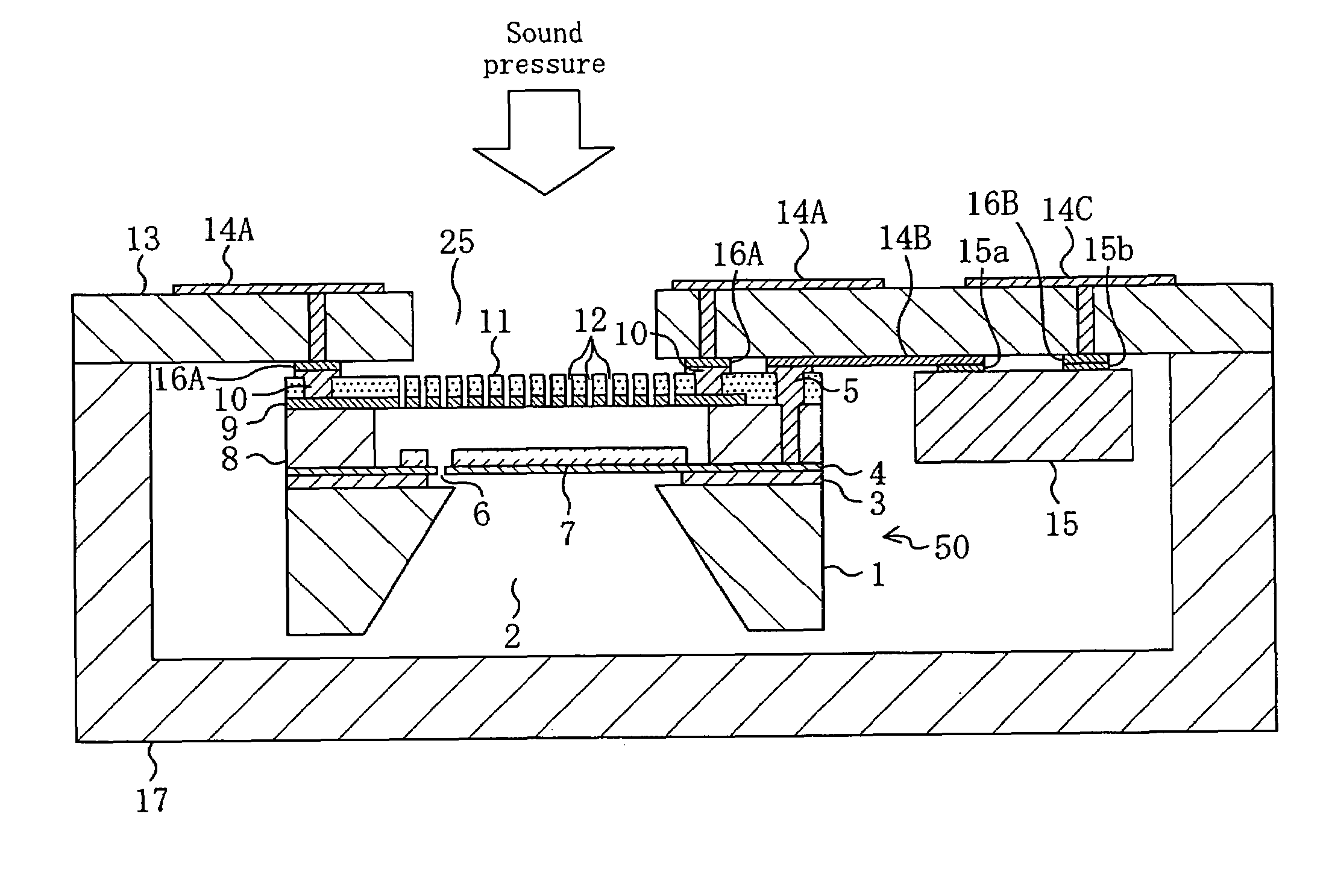

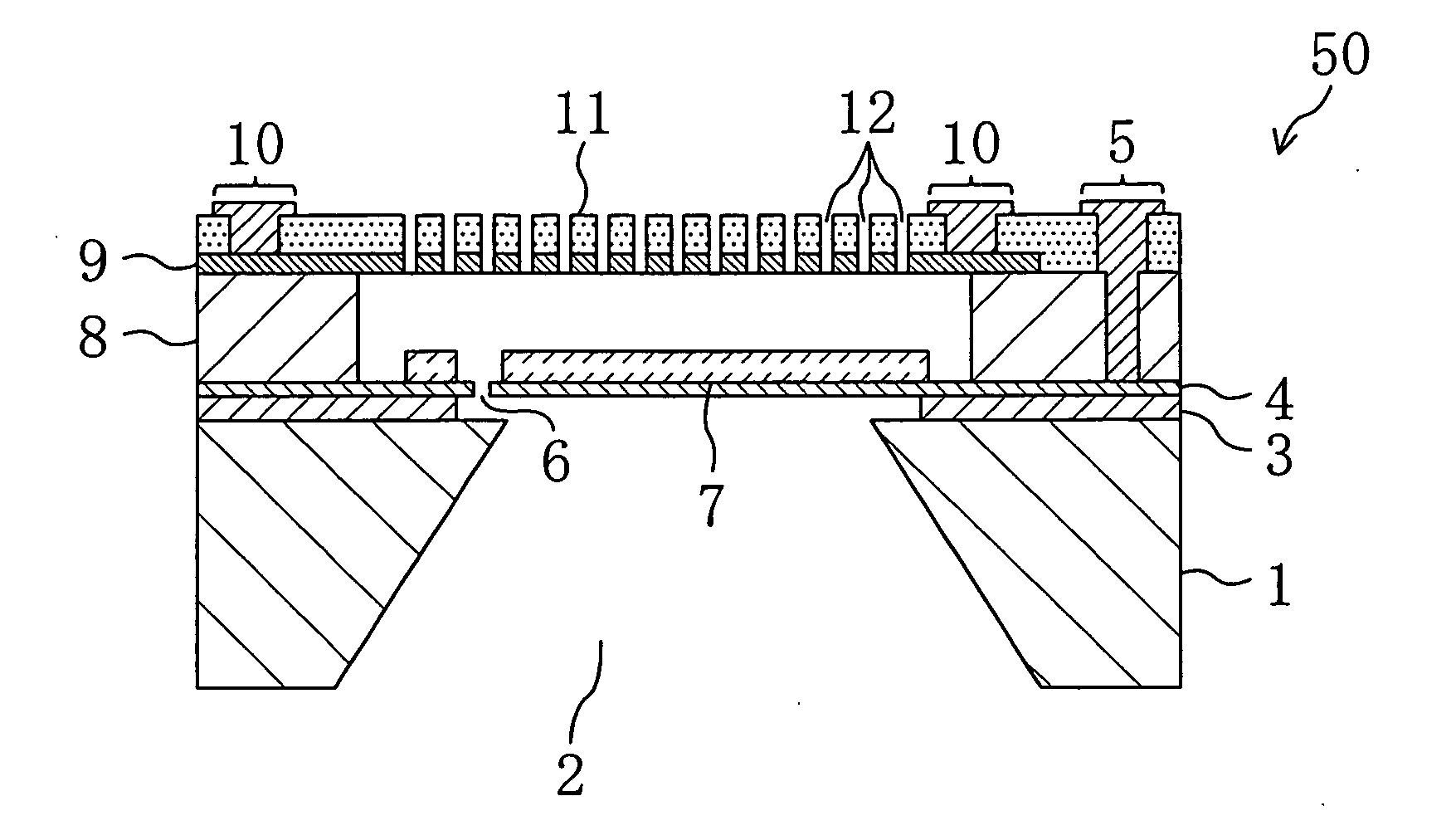

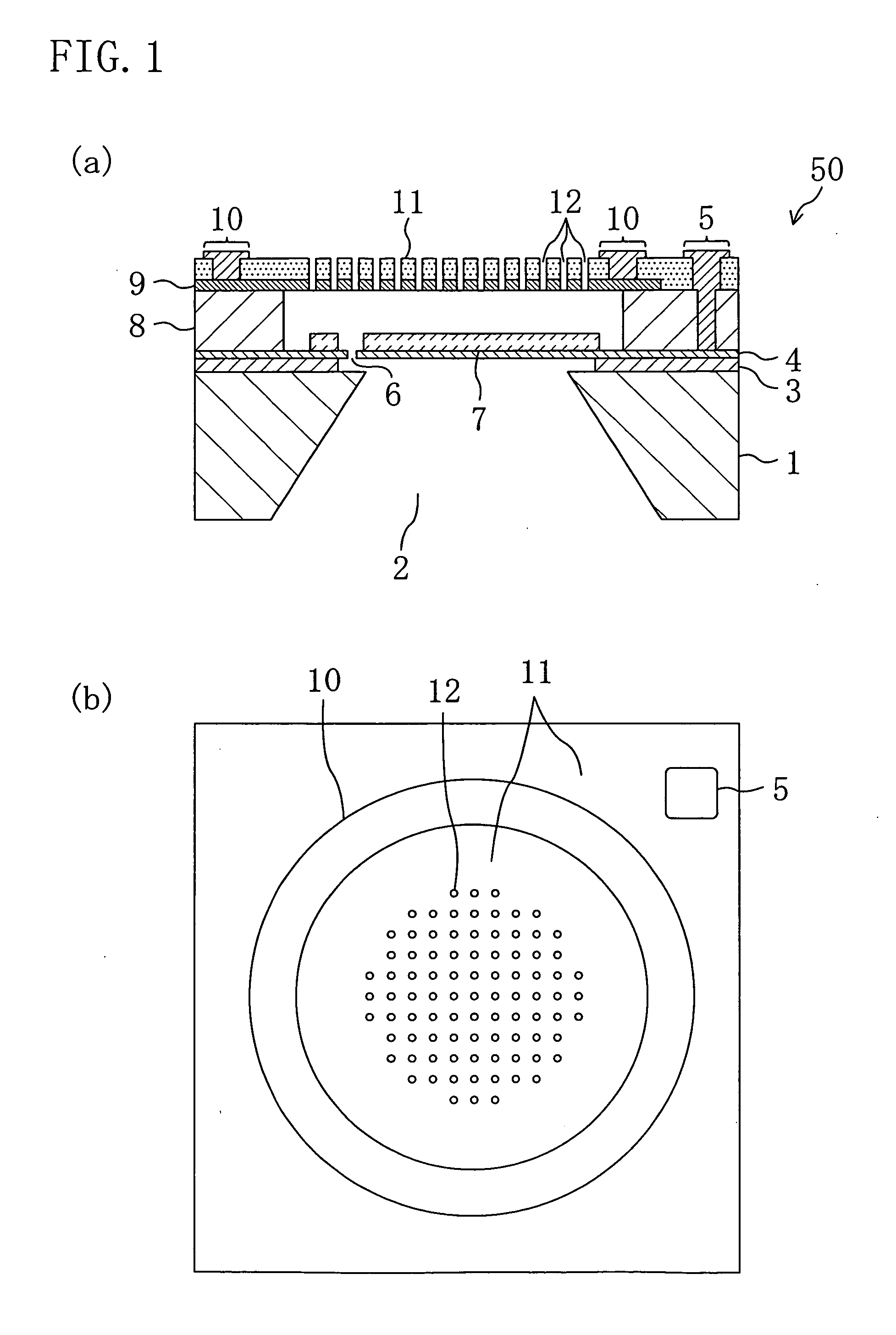

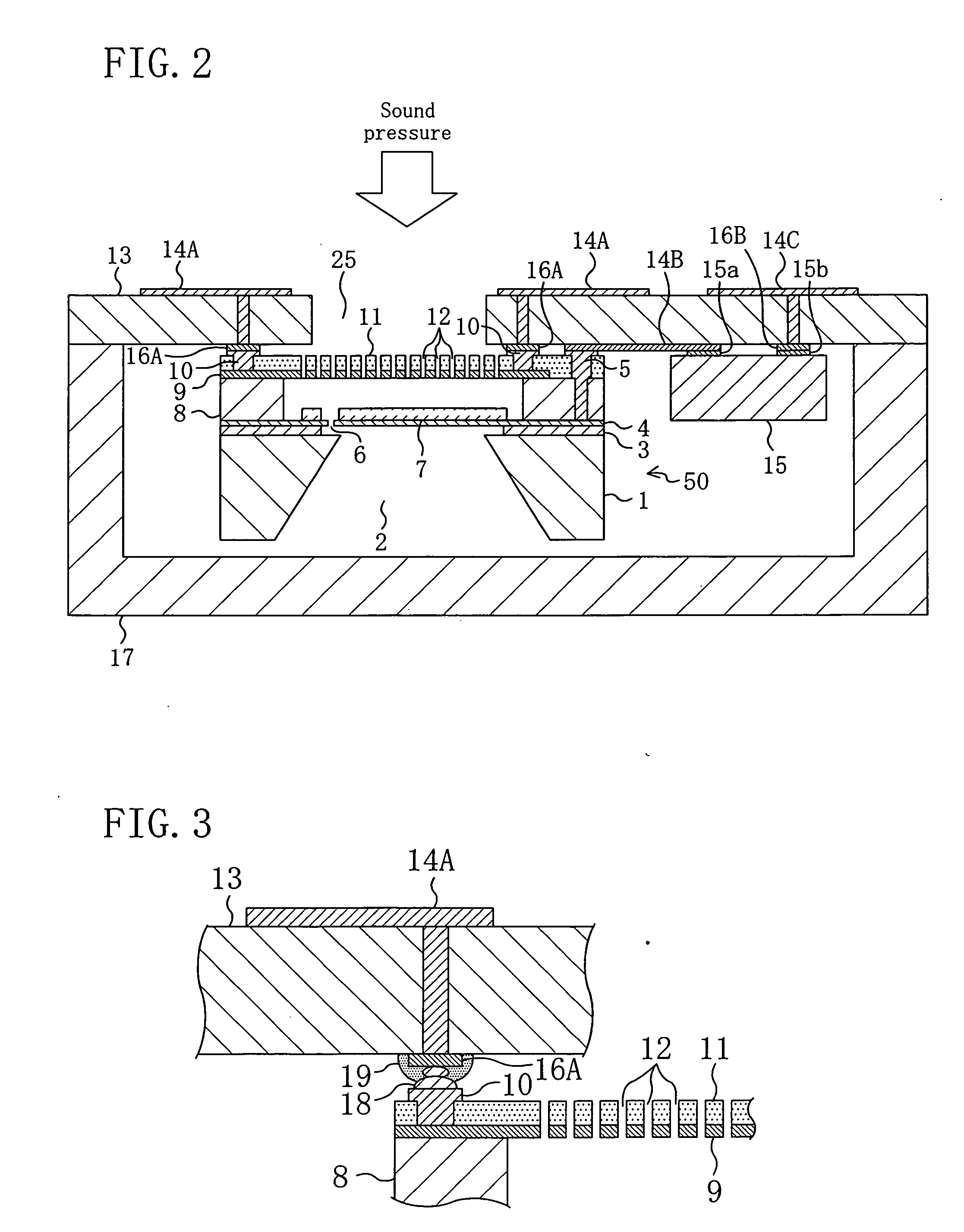

Electret condenser microphone

ActiveUS7466834B2Enhances high-frequency characteristicSuppression capacitanceSemiconductor electrostatic transducersElectrets selectrostatic transducerCapacitanceEngineering

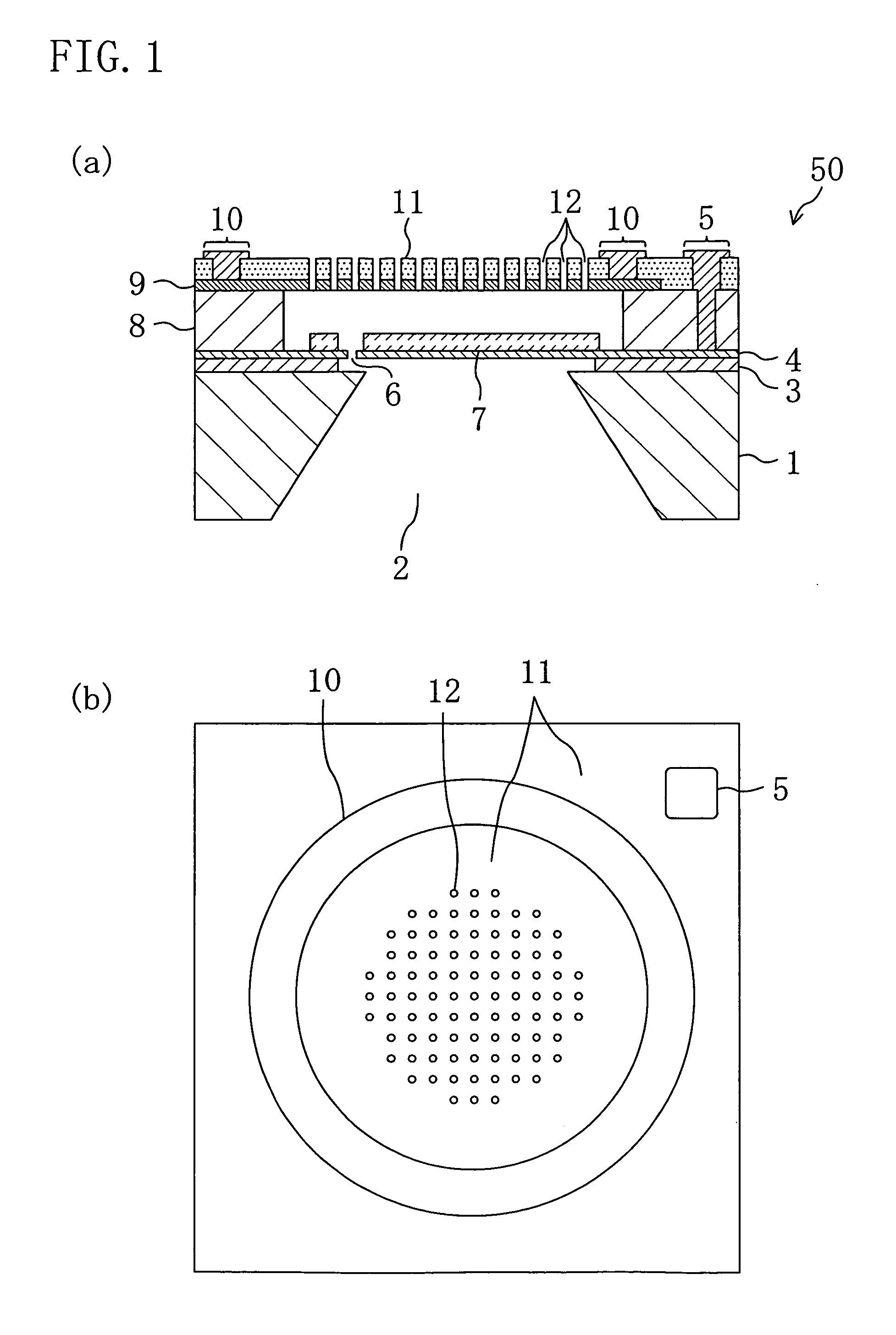

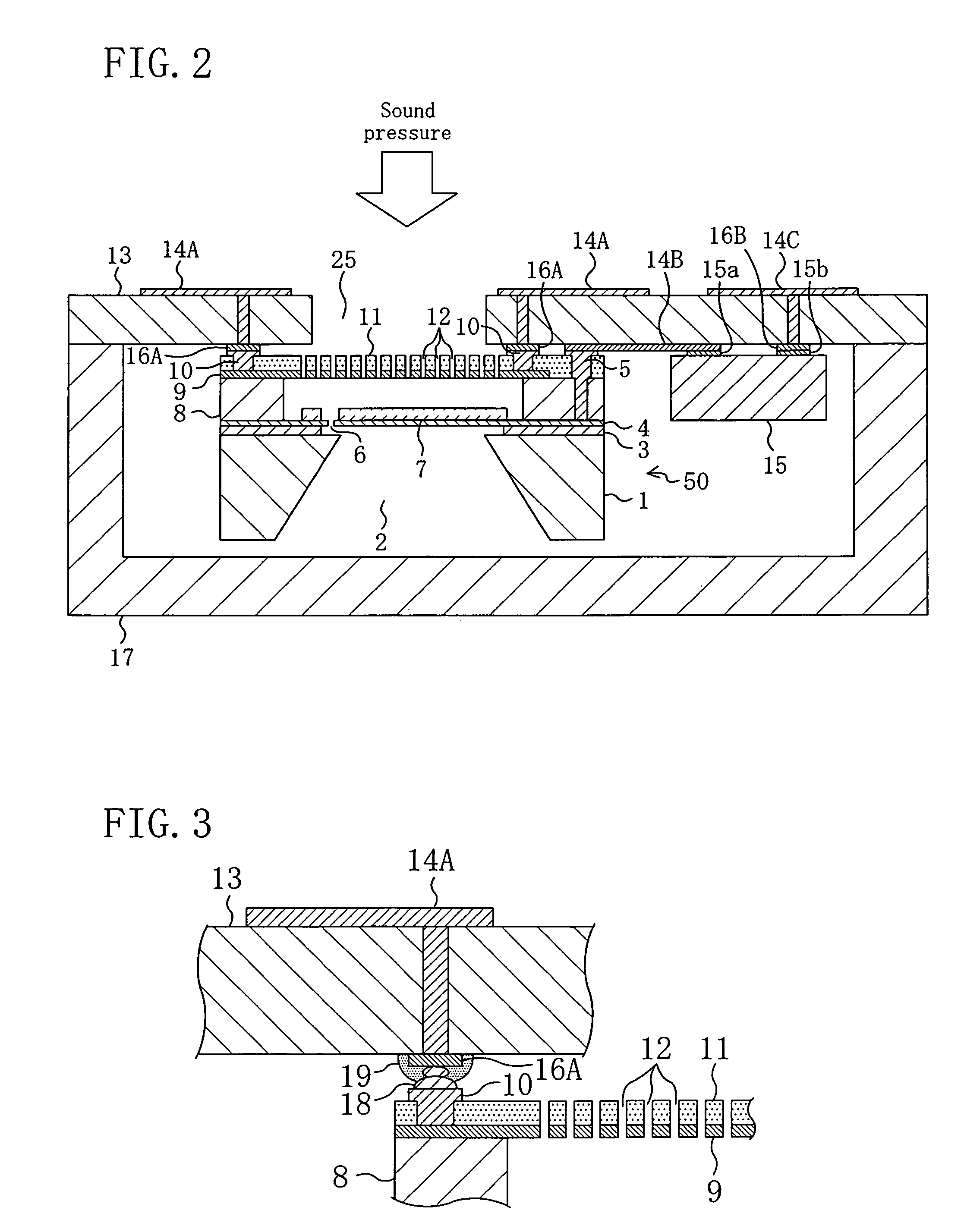

An electret condenser microphone includes: a substrate 13 in which an opening 25 is formed; an electret condenser 50 connected to one face of the substrate 13 so as to close the opening 25 and having an acoustic hole 12 and a cavity 2; a drive circuit element 15 connected to the one face of the substrate 13; and a case 17 mounted over the substrate 13 so as to cover the electret condenser 50 and the drive circuit element 15. Electric contact is established at a joint part between the electret condenser 50 and the substrate 13. The acoustic hole 12 communicates with an external space through the opening 25. The cavity 2 and an internal region of the case 17 serve as a back air chamber for the electret condenser 50.

Owner:TDK CORPARATION

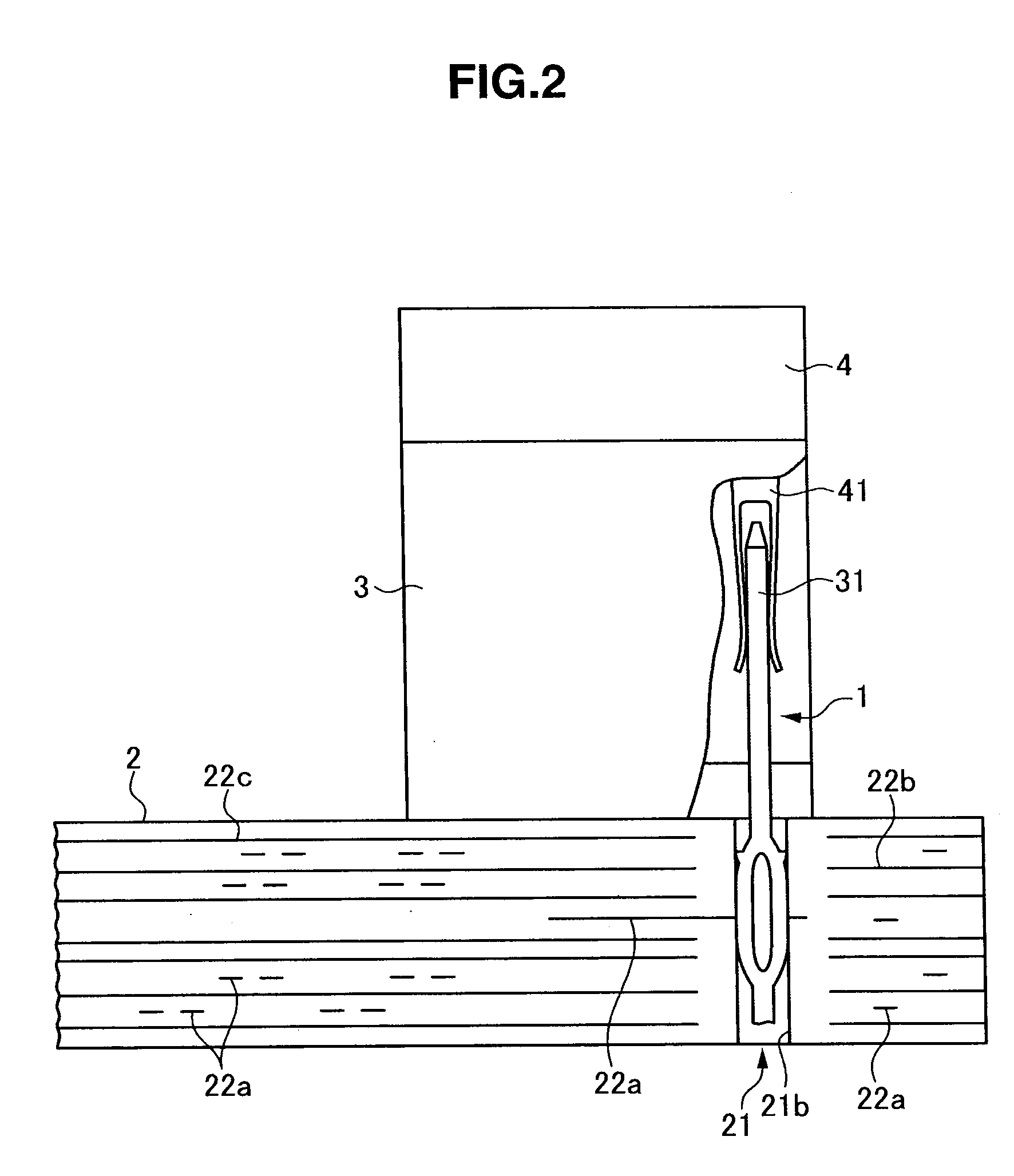

Press-fit pin and board structure

InactiveUS20080207015A1Increase the number ofReduce board costPrinted circuit aspectsPrinted circuit manufactureBoard structureElectrical and Electronics engineering

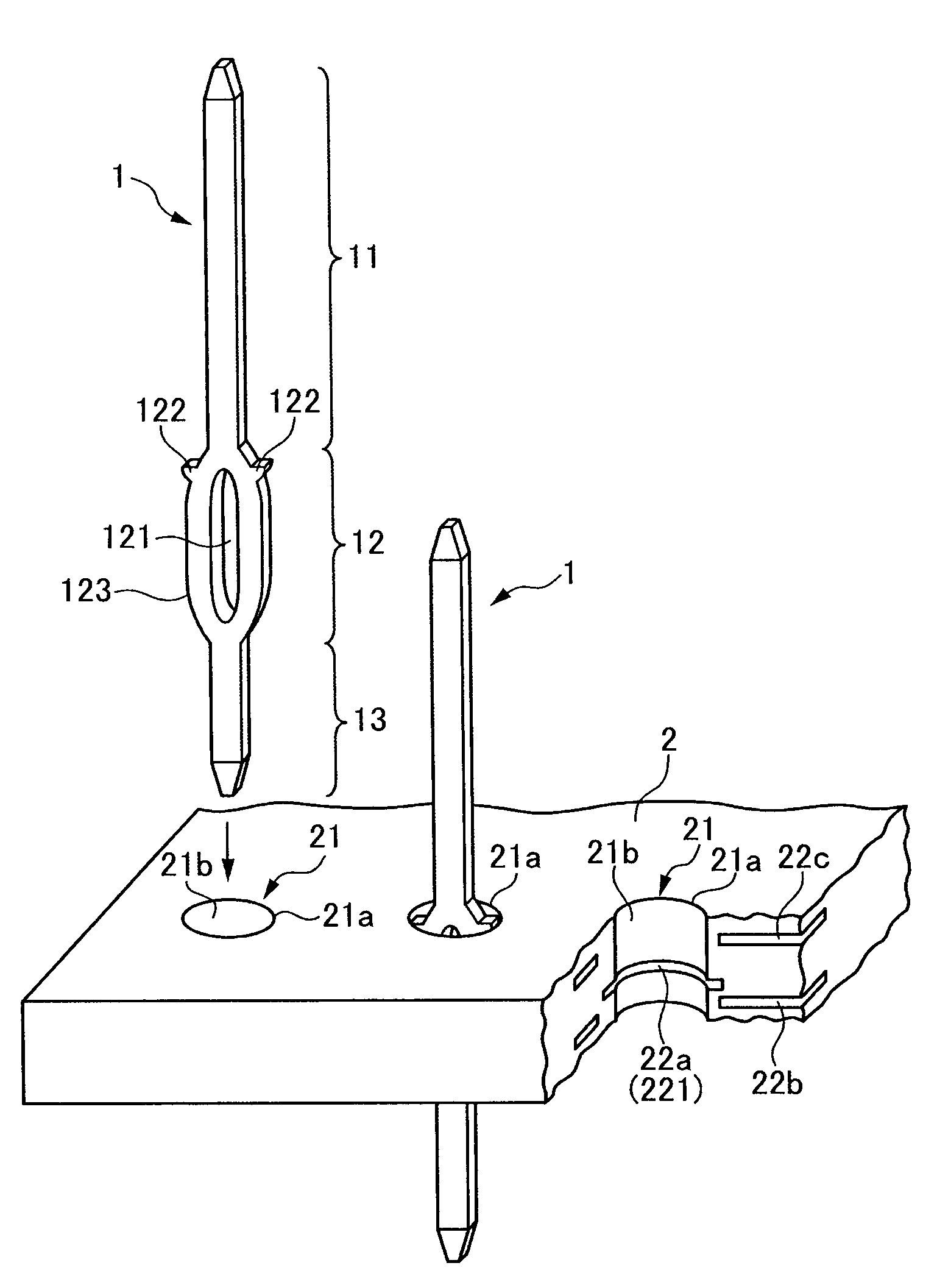

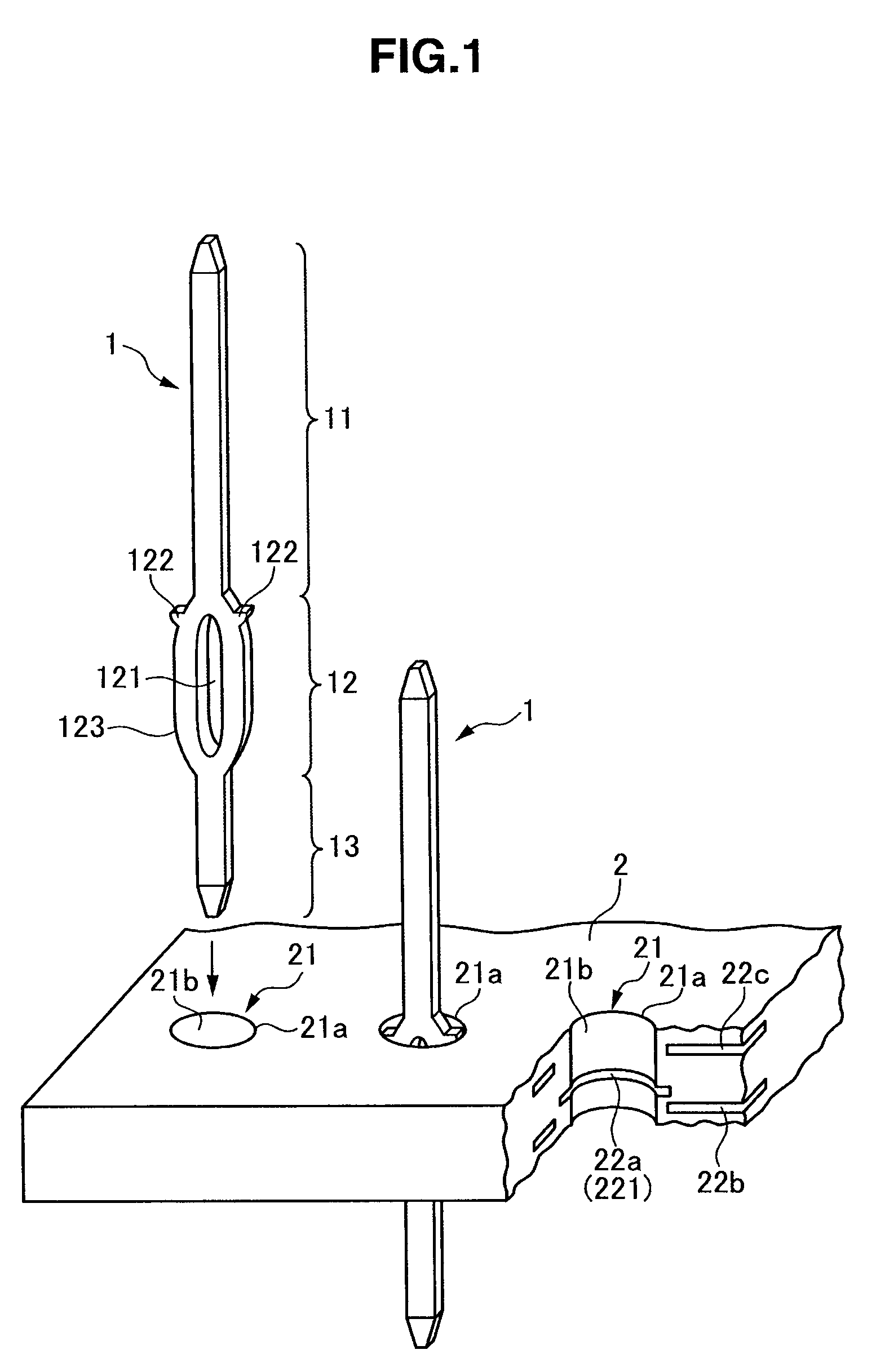

Provided is a printed wiring board formed with a through-hole into which a press-fit pin is press-fitted. The printed wiring board includes at least one signal transmission layer, a signal transmission wiring pattern formed in the signal transmission layer, and an electrode portion of the signal transmission wiring pattern exposed at an inner circumferential surface of the through-hole. The electrode portion is not formed covering the entire inner circumferential surface of the through-hole but at a part of the inner circumferential surface of the through-hole.

Owner:HITACHI LTD

Electret condenser microphone

ActiveUS20070189558A1Suppressing noise occurrenceSuppress parasitic capacitancePiezoelectric/electrostrictive microphonesSemiconductor electrostatic transducersCapacitanceEngineering

An electret condenser microphone includes: a substrate 13 in which an opening 25 is formed; an electret condenser 50 connected to one face of the substrate 13 so as to close the opening 25 and having an acoustic hole 12 and a cavity 2; a drive circuit element 15 connected to the one face of the substrate 13; and a case 17 mounted over the substrate 13 so as to cover the electret condenser 50 and the drive circuit element 15. Electric contact is established at a joint part between the electret condenser 50 and the substrate 13. The acoustic hole 12 communicates with an external space through the opening 25. The cavity 2 and an internal region of the case 17 serve as a back air chamber for the electret condenser 50.

Owner:TDK CORPARATION

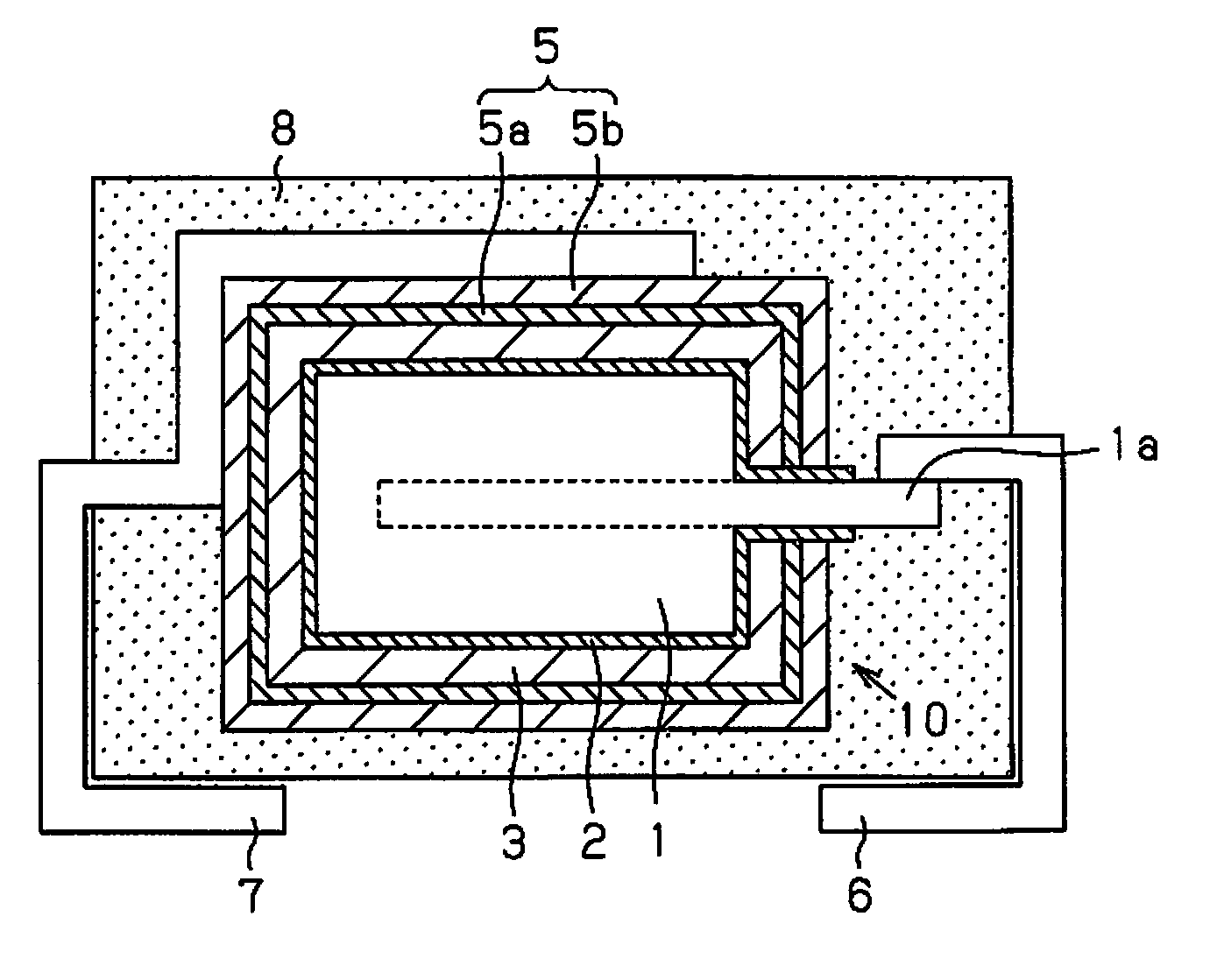

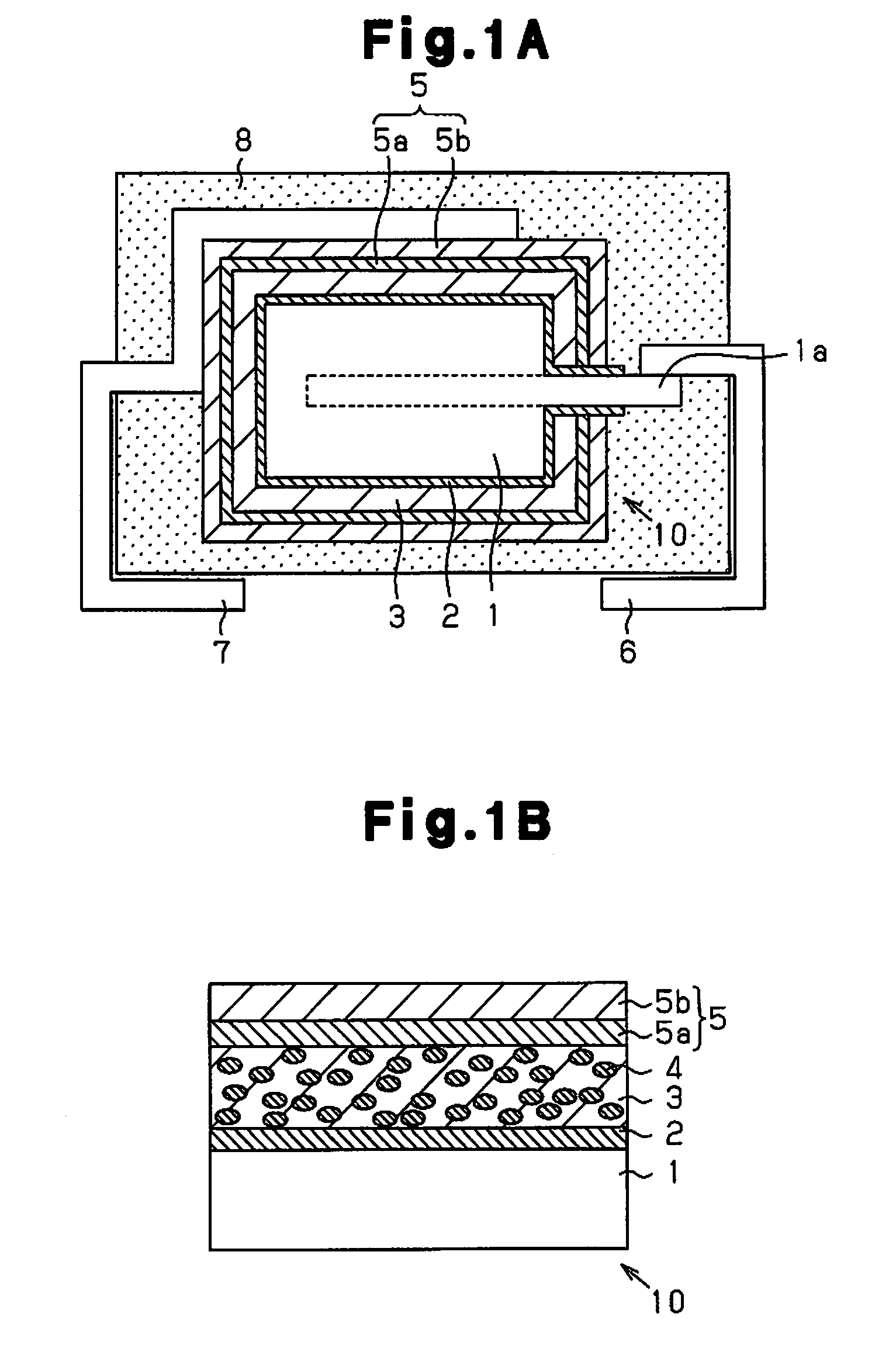

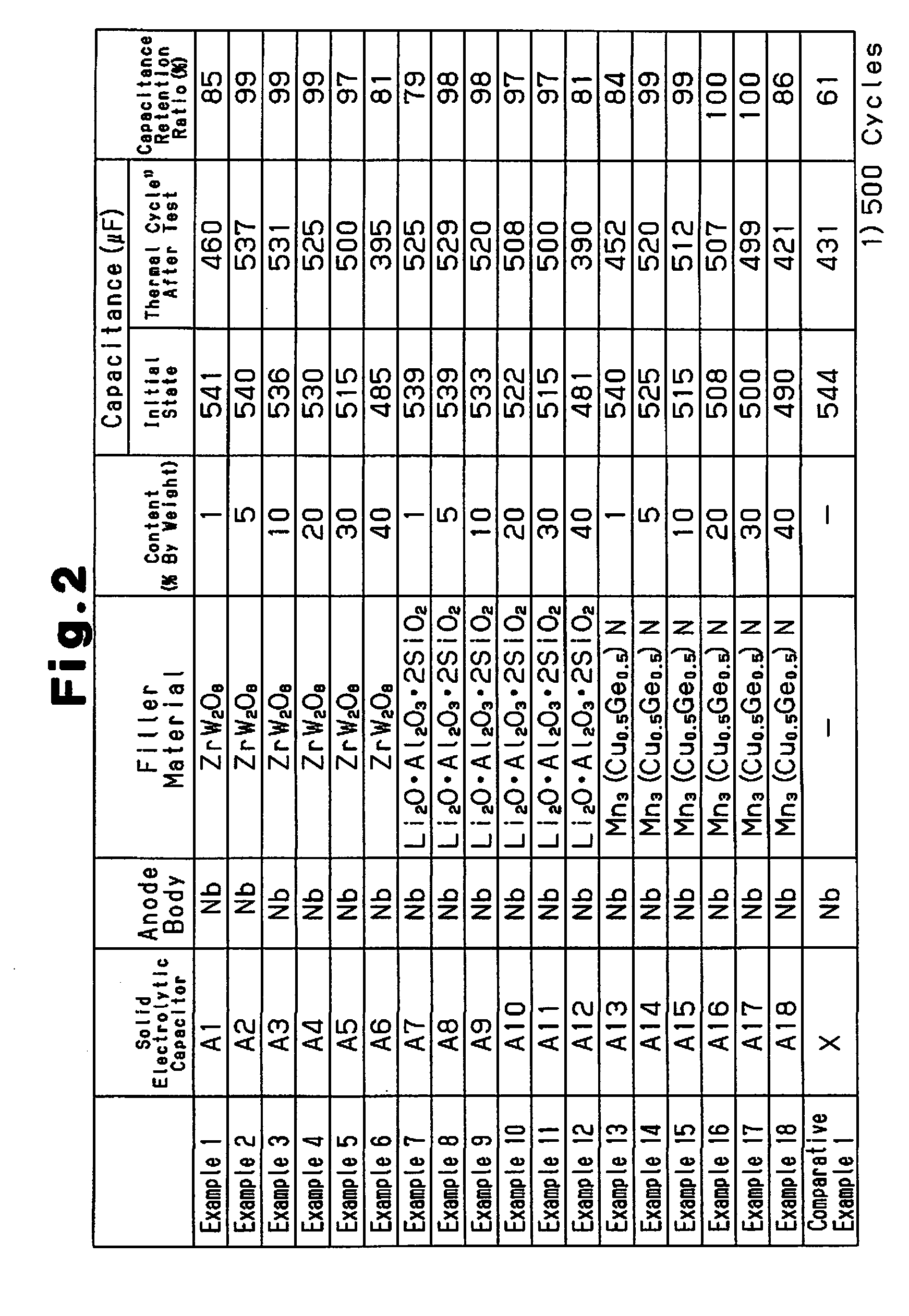

Solid electrolytic capacitor

InactiveUS20090231782A1Suppression capacitanceDuplicating/marking methodsActive material electrodesCapacitanceElectrolysis

A solid electrolytic capacitor that suppresses capacitance decrease caused by thermal loads. The solid electrolytic capacitor includes an anode body, a dielectric layer formed on a surface of the anode body, a conductive polymer layer formed on the dielectric layer, and a cathode layer formed on the conductive polymer layer. The conductive polymer layer contains a filler material having a negative linear expansion coefficient.

Owner:SANYO ELECTRIC CO LTD

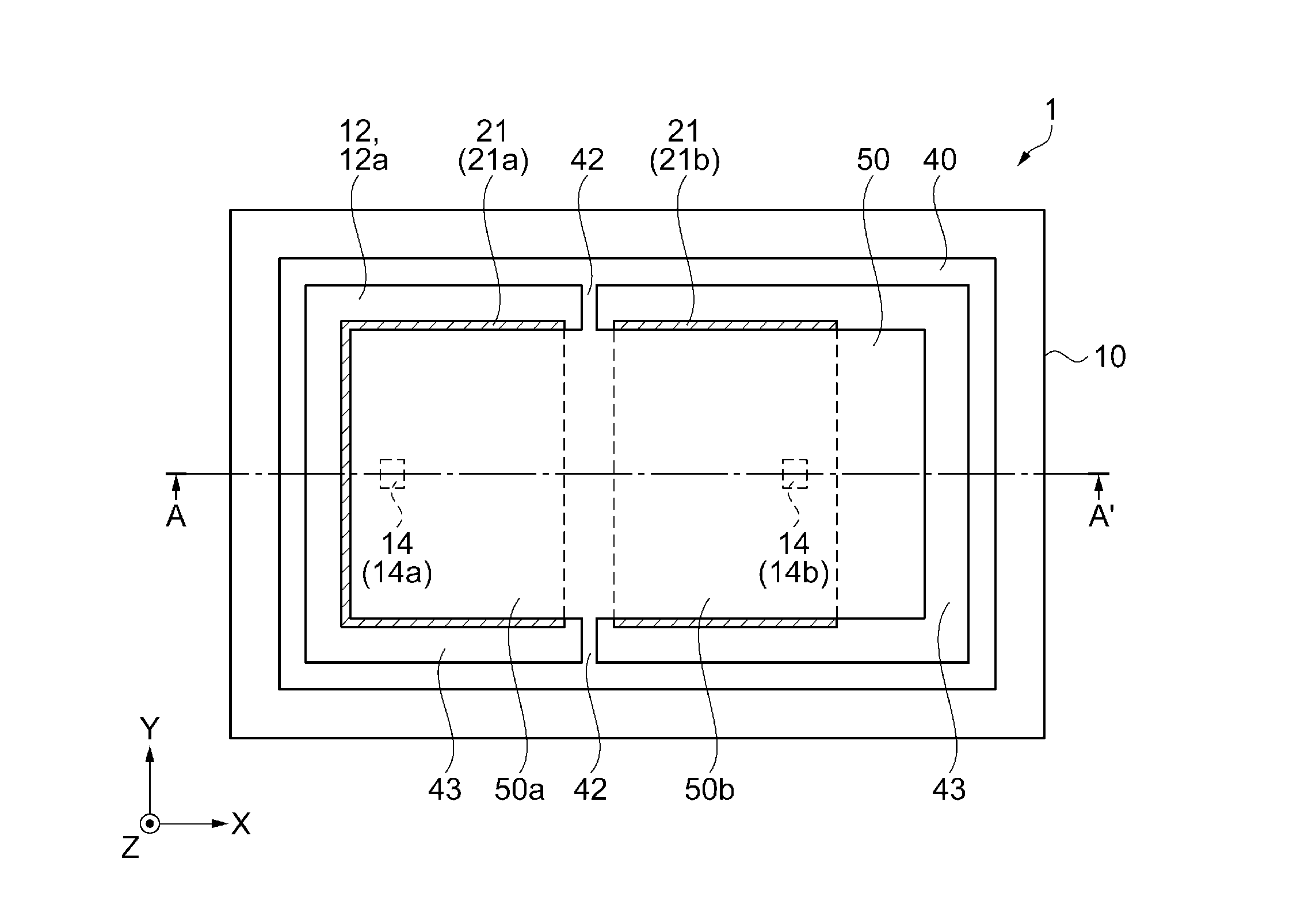

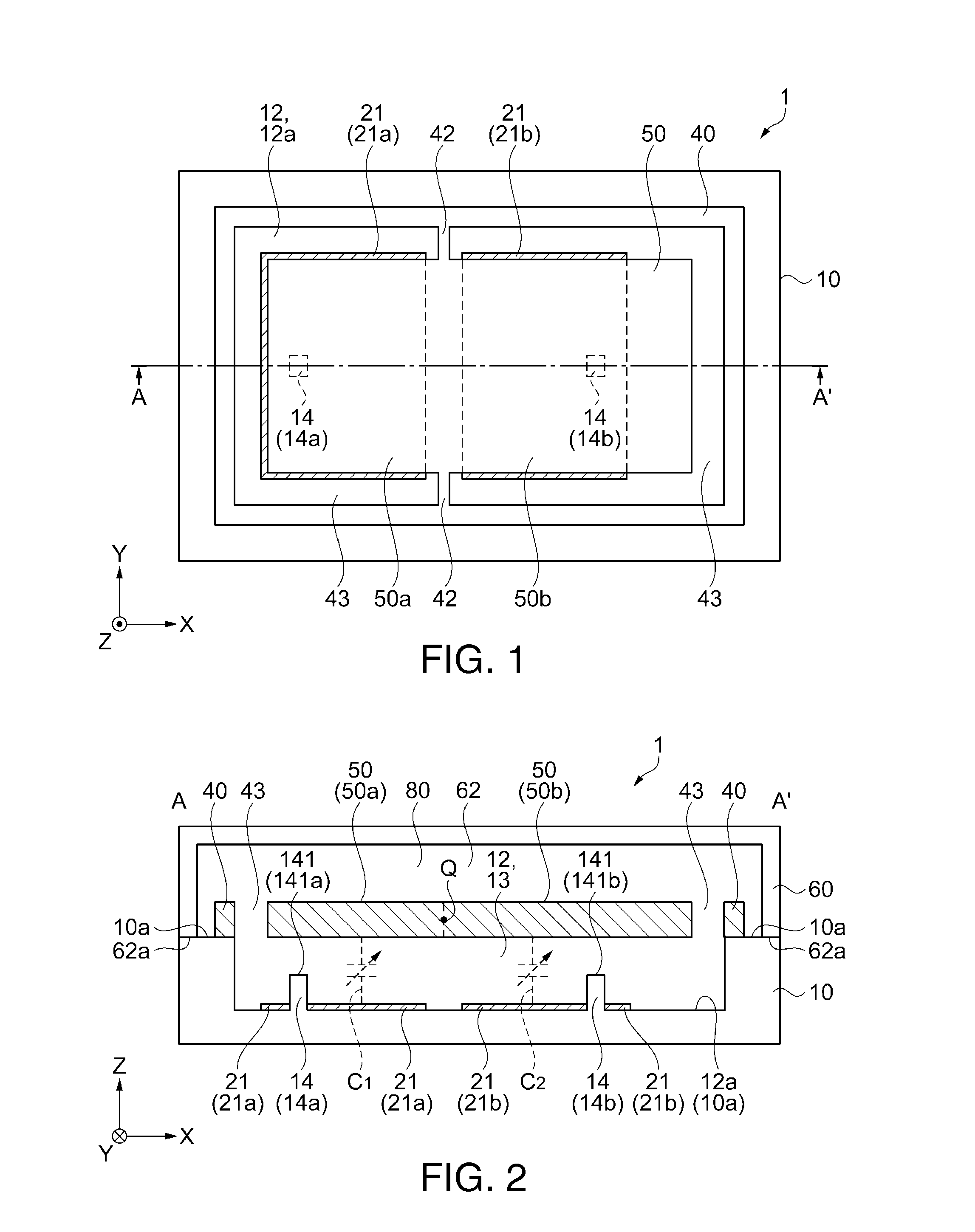

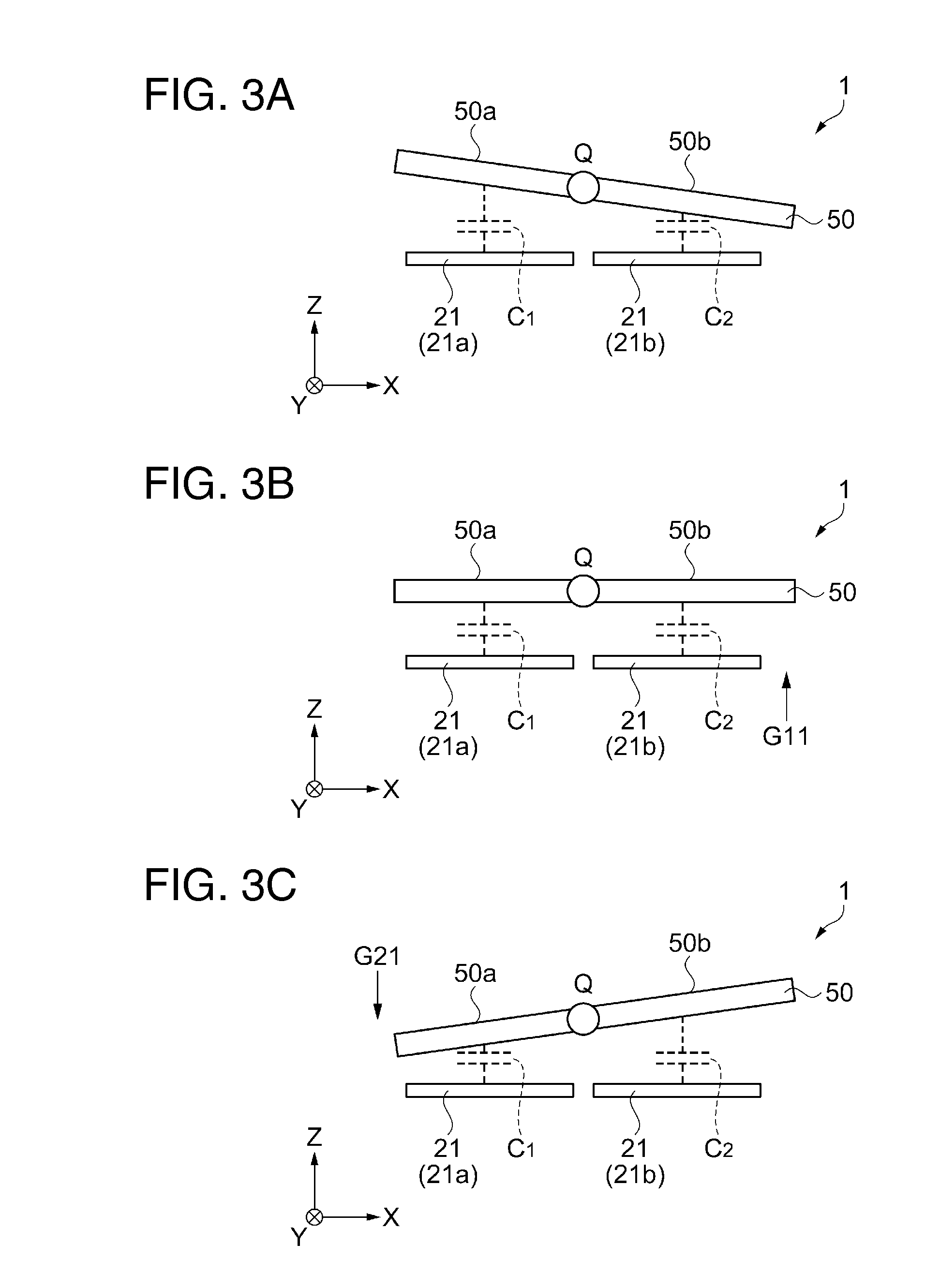

Sensor element, electronic apparatus and moving object

ActiveUS20140338451A1Improve reliabilitySuppression capacitanceAcceleration measurementFlexible microstructural devicesEngineeringElectronic equipment

A sensor element includes: a detection electrode section; a movable body that is provided to face the detection electrode section; and a protruding section that is provided in a region where the detection electrode section is provided in a plan view of the detection electrode section seen in a vertical direction and protrudes toward the movable body. At least a part of a surface of the protruding section is made of an insulating material.

Owner:SEIKO EPSON CORP

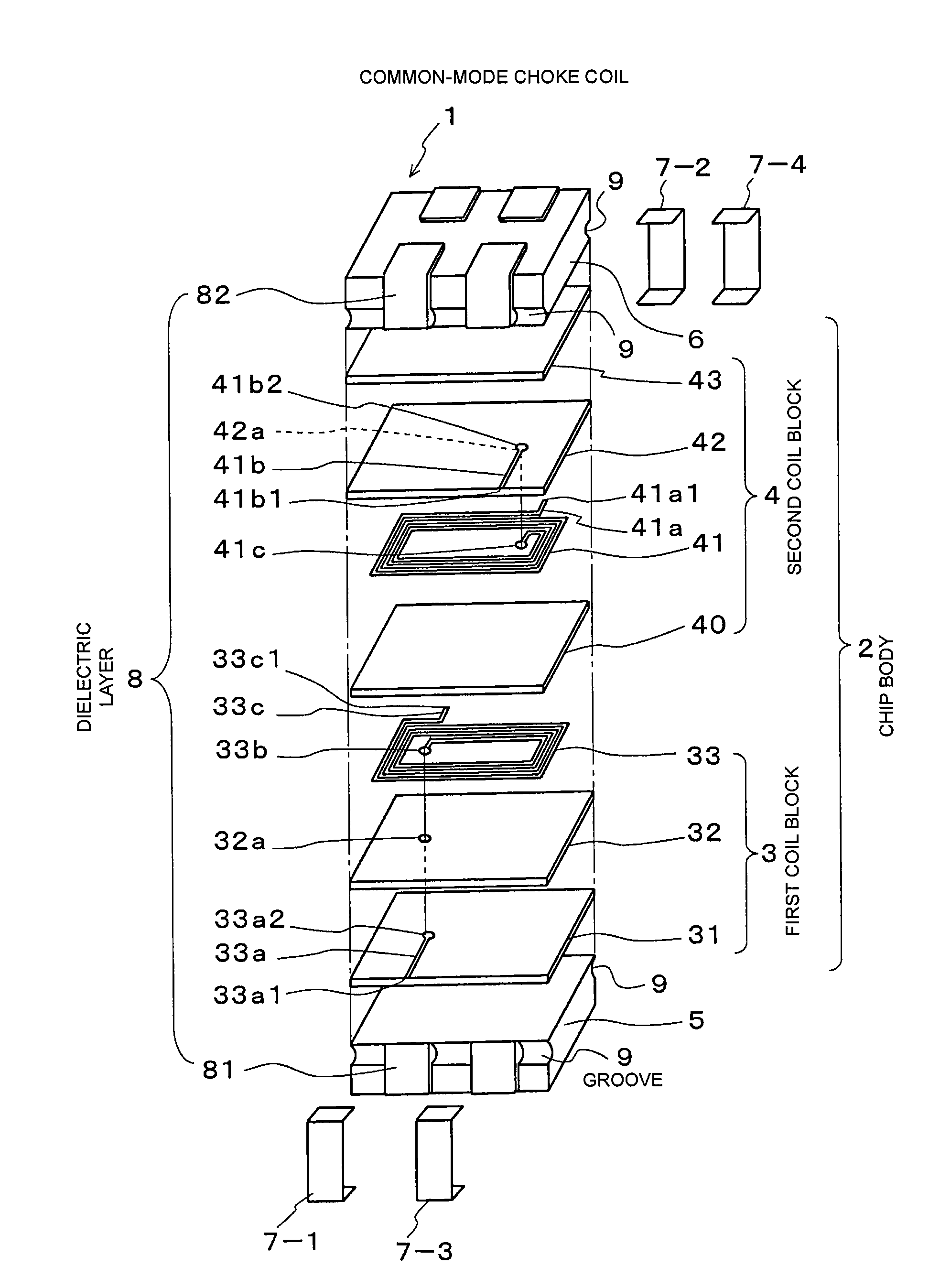

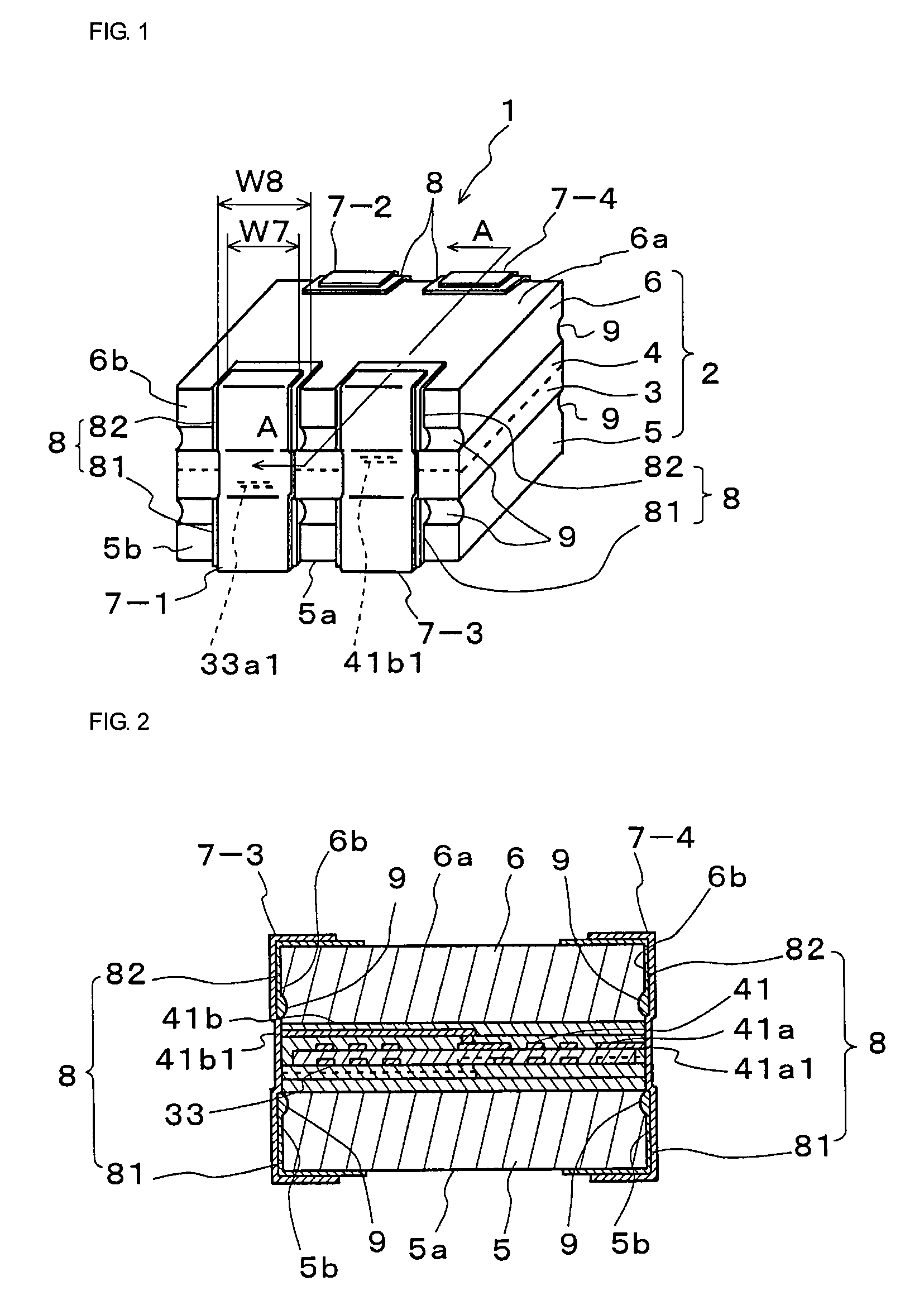

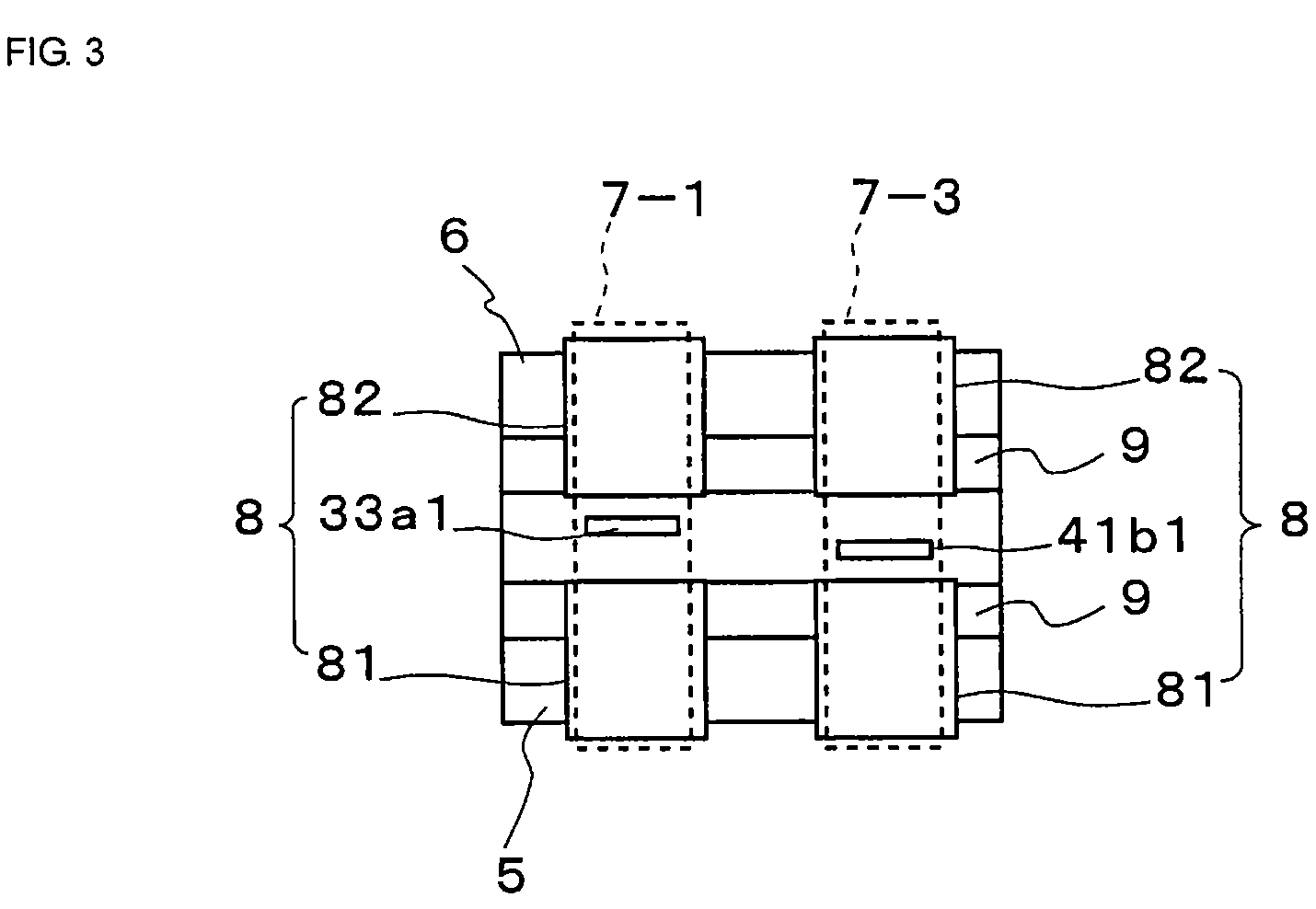

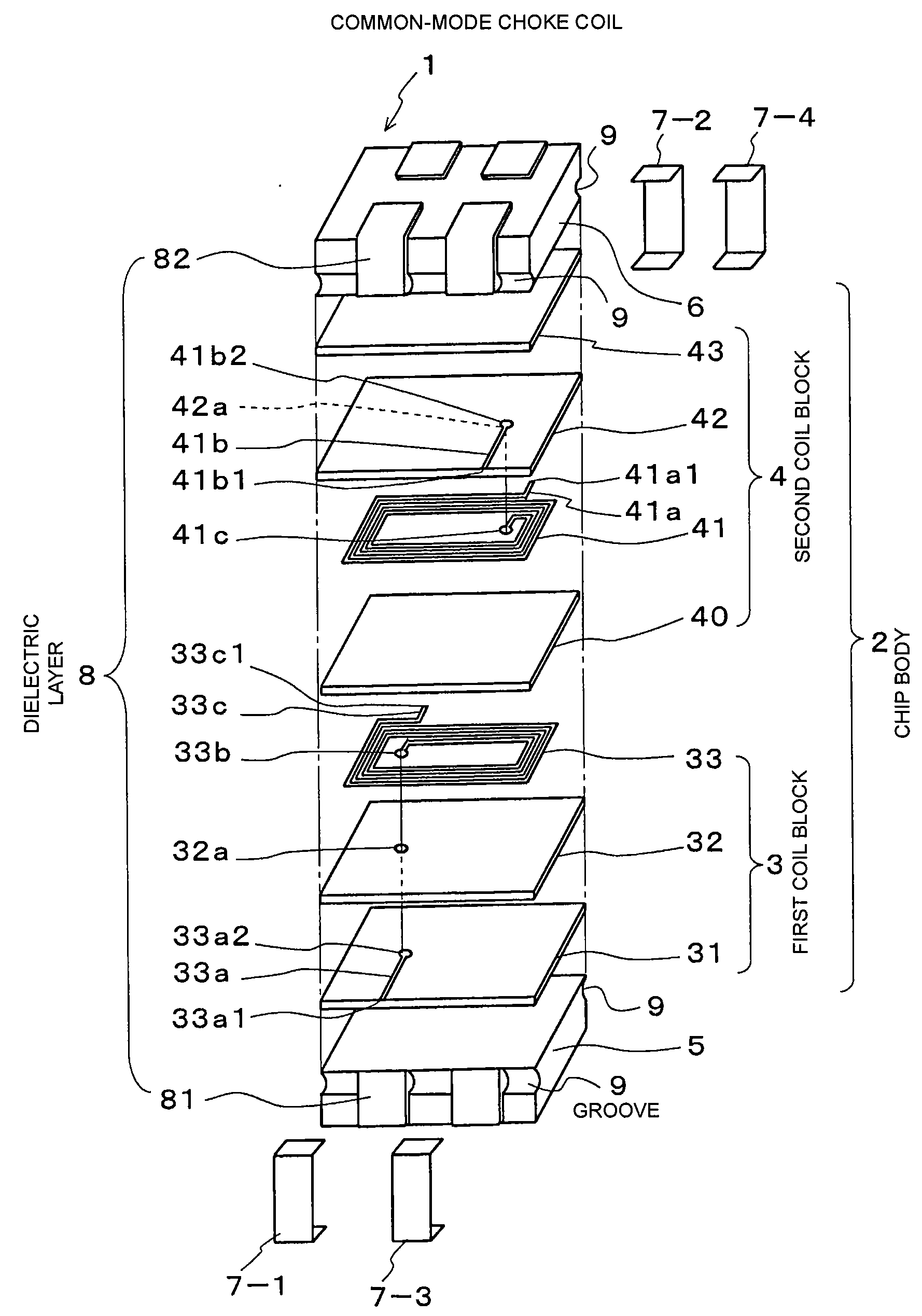

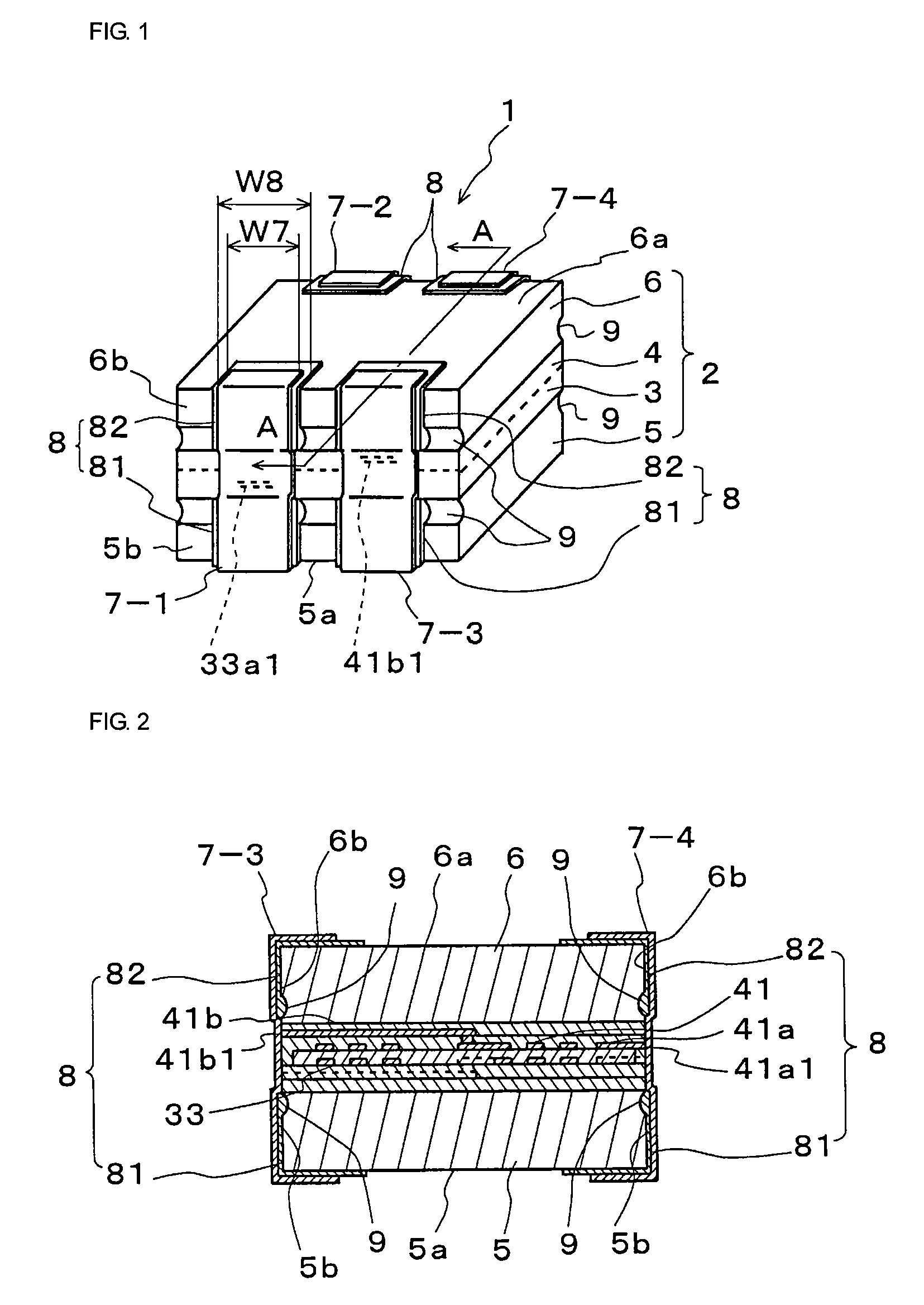

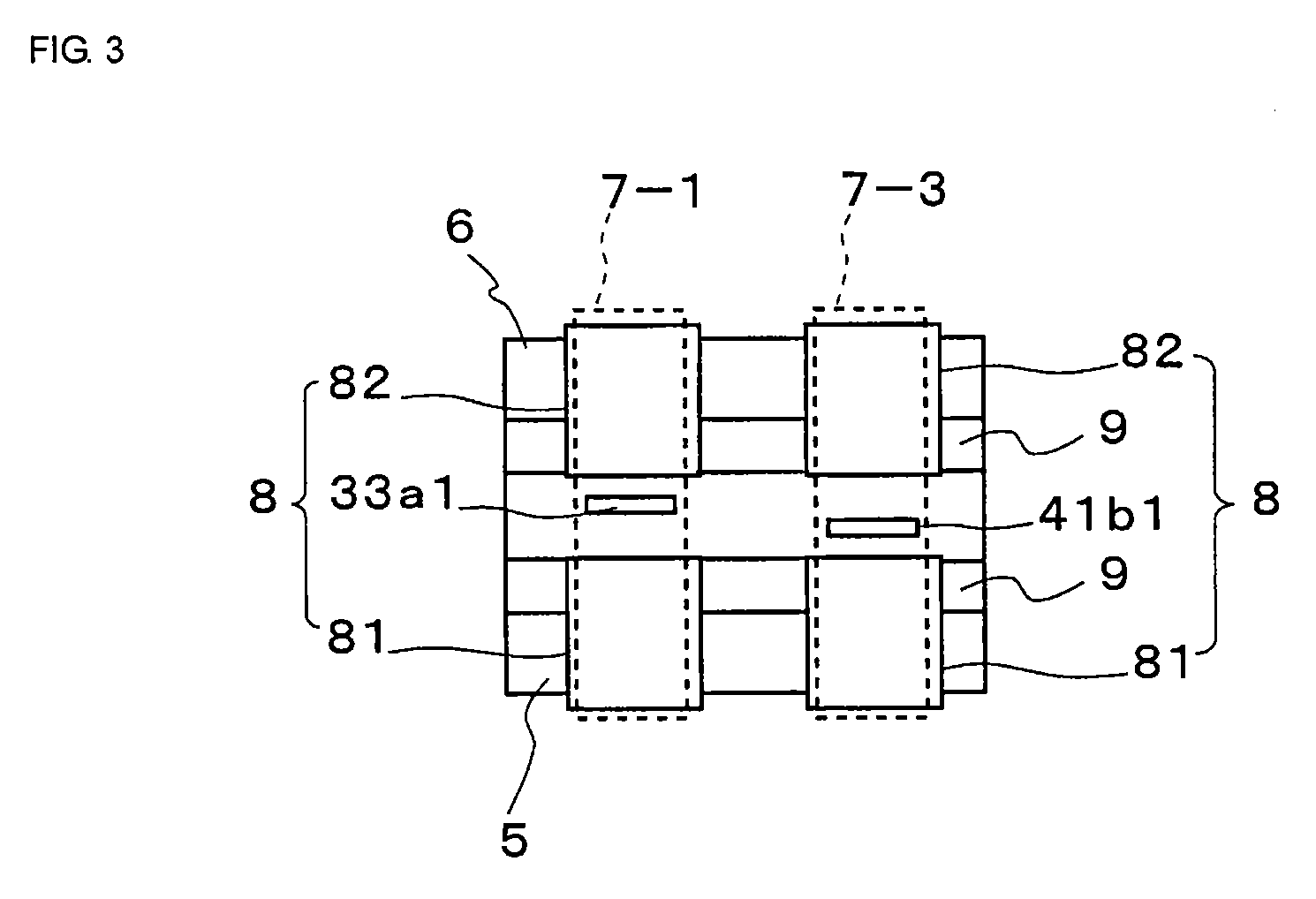

Electronic component and electronic-component production method

InactiveUS7843701B2Suppression capacitanceAvoid impedanceAnti-noise capacitorsFeed-through capacitorsCapacitanceElectronic component

An electronic component and an electronic-component production method in which the magnitude of a stray capacitance produced between adjacent outer electrodes is controllable. The electronic component includes a chip body and first to fourth outer electrodes. In the chip body, first and second coil block are sandwiched between magnetic substrates. Dielectric layers are interposed between the outer electrodes and the chip body such as to be away from exposed portions of coil patterns in the coil blocks. The dielectric layers have a width larger than a width of the outer electrodes, and a dielectric constant of the dielectric layers is set to be lower than the dielectric constant of the magnetic substrates.

Owner:MURATA MFG CO LTD

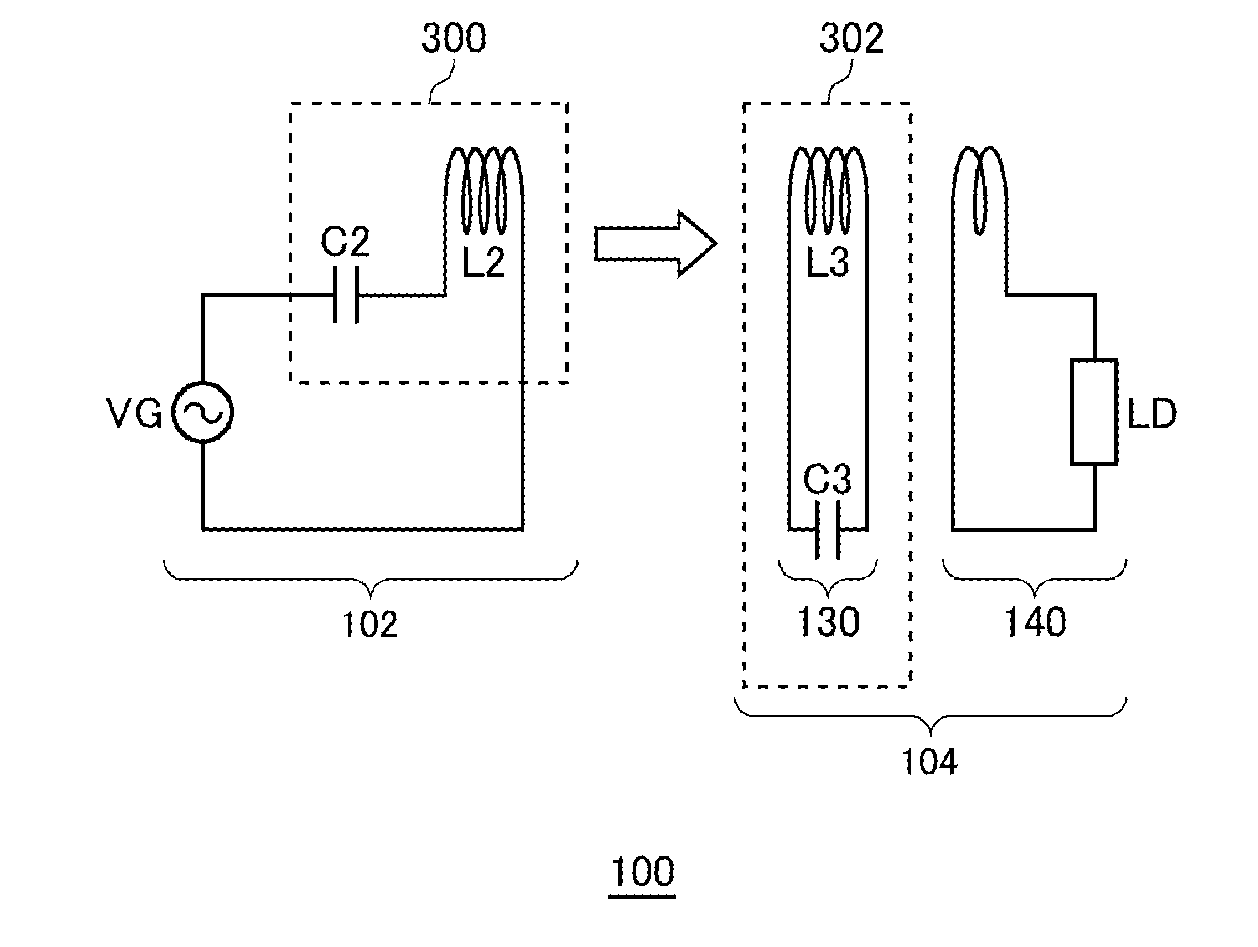

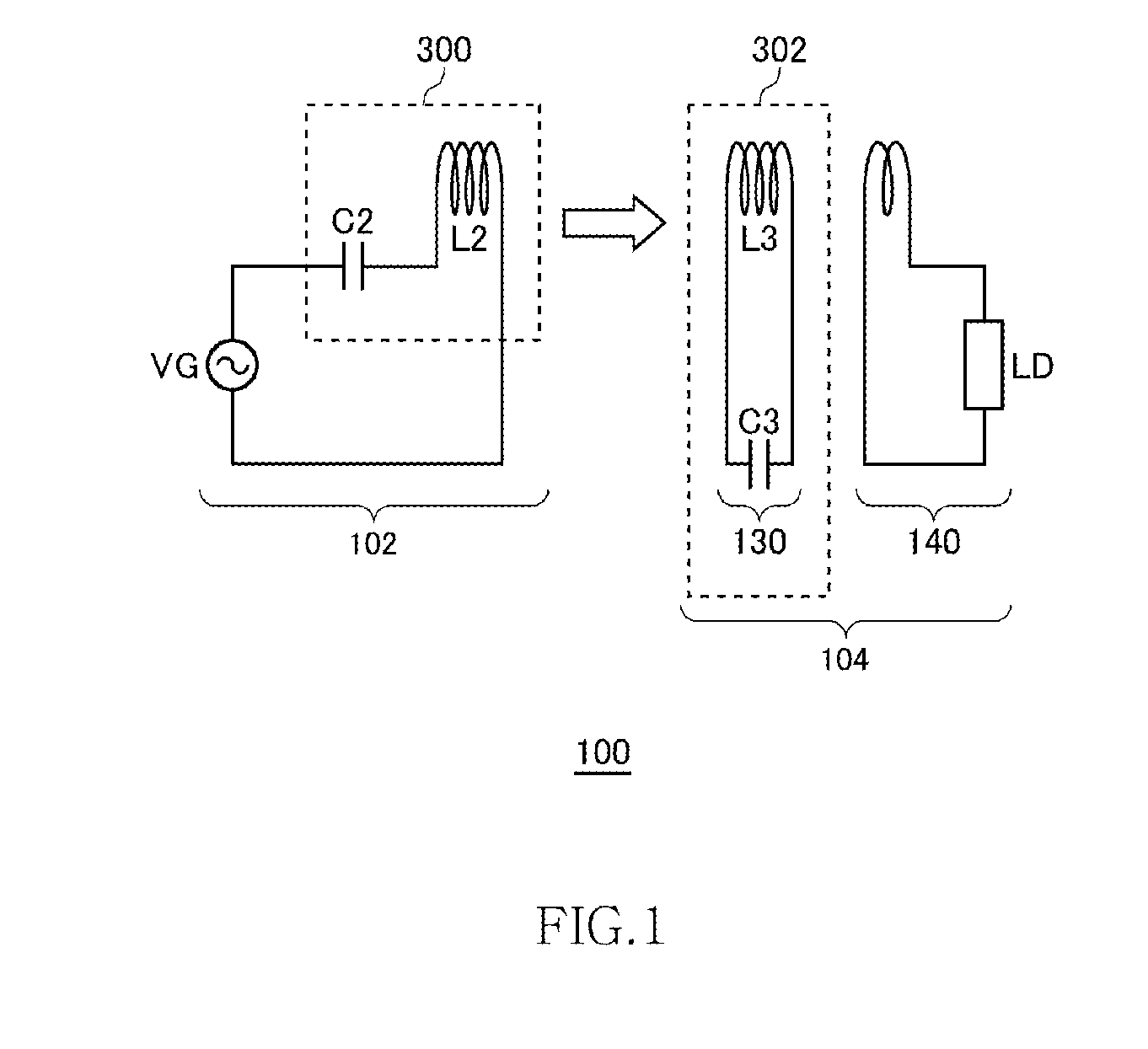

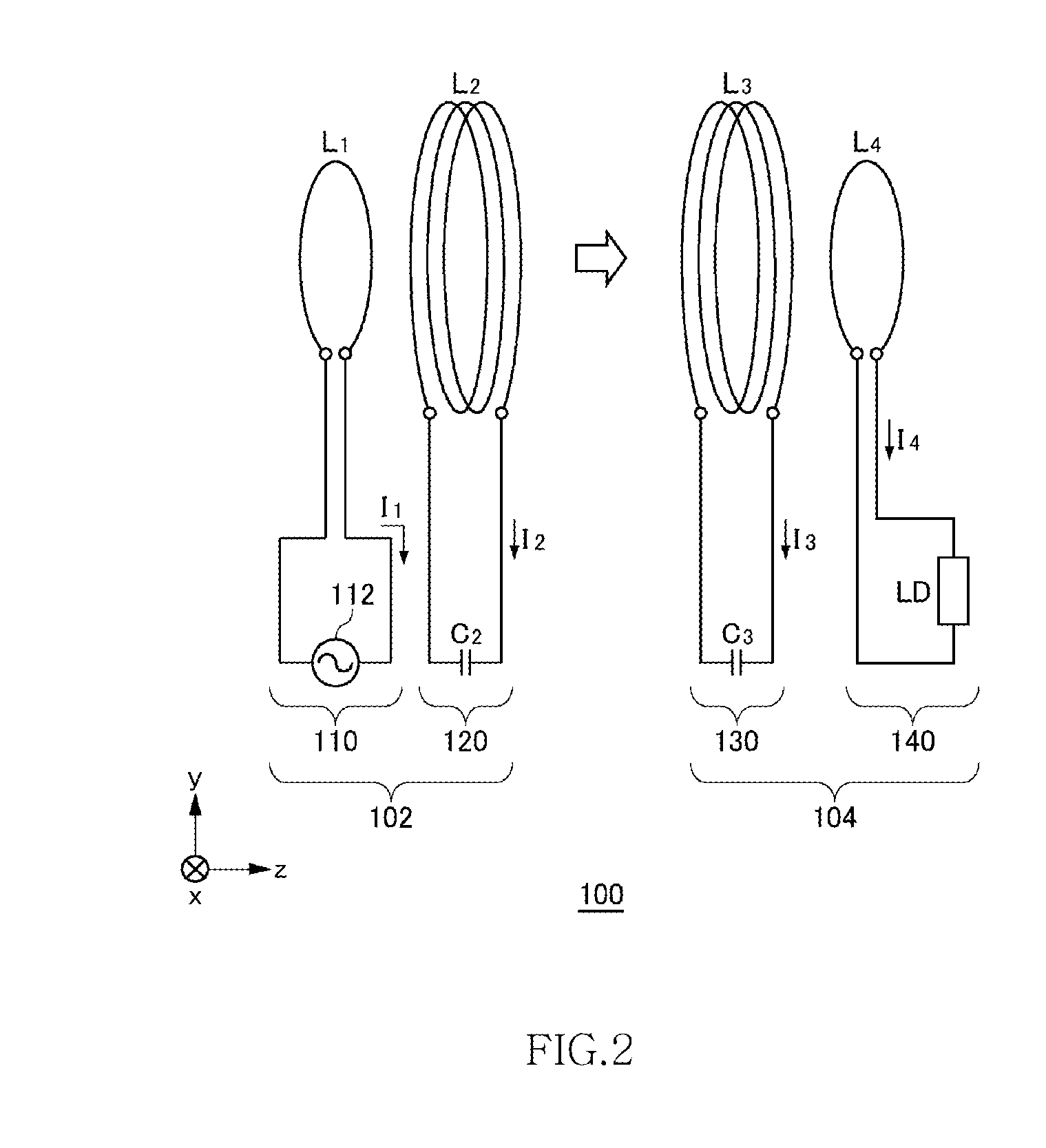

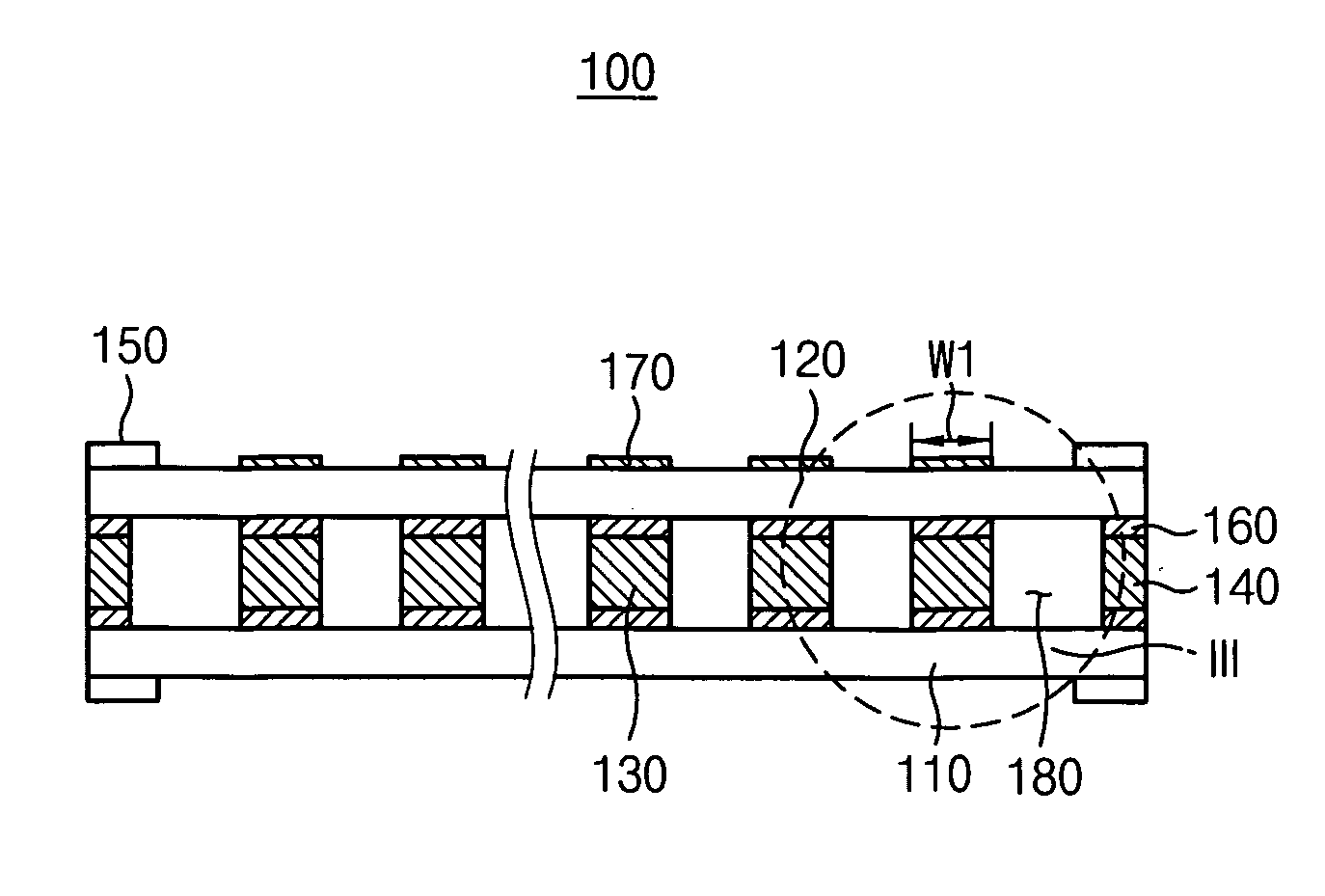

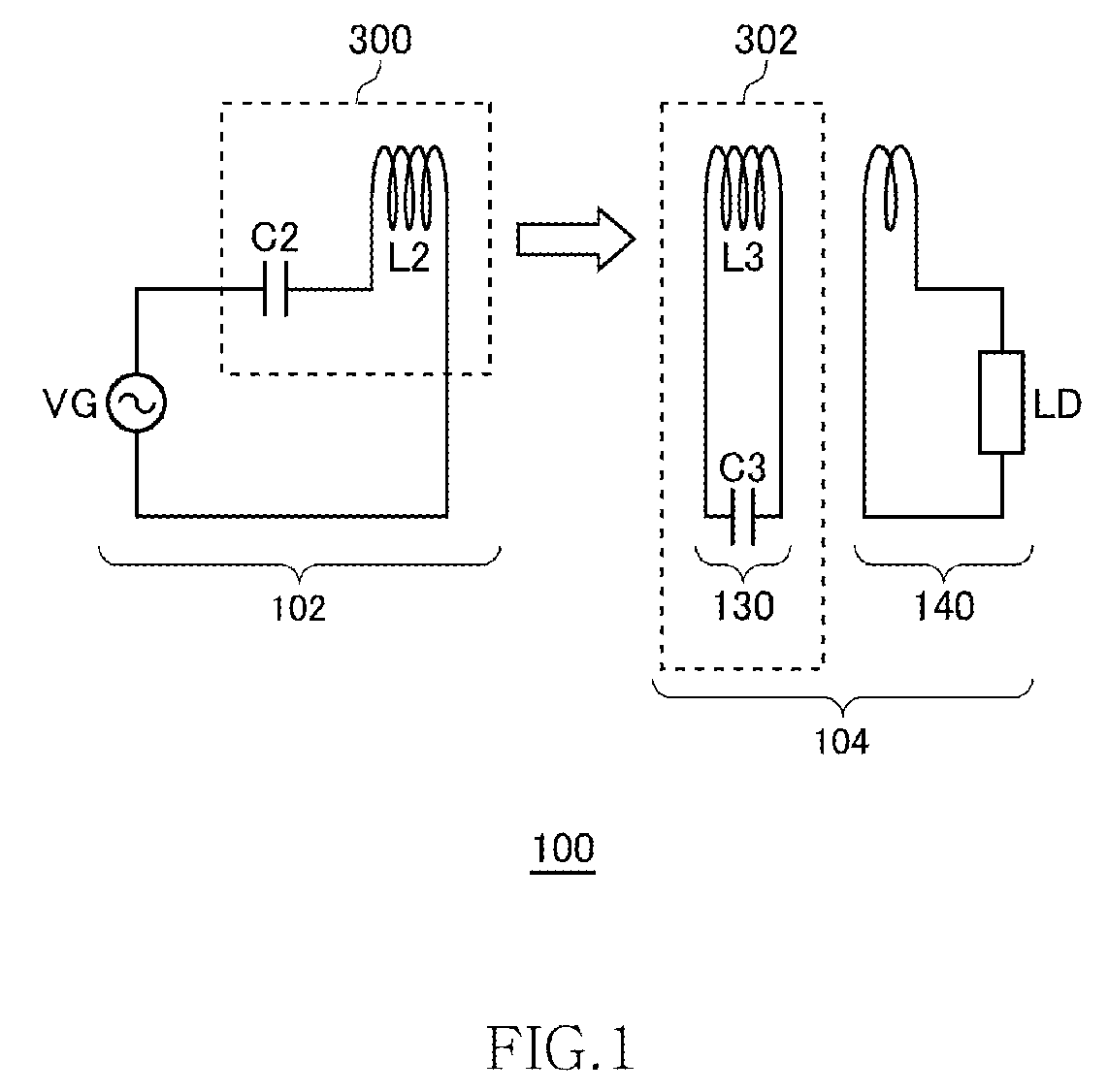

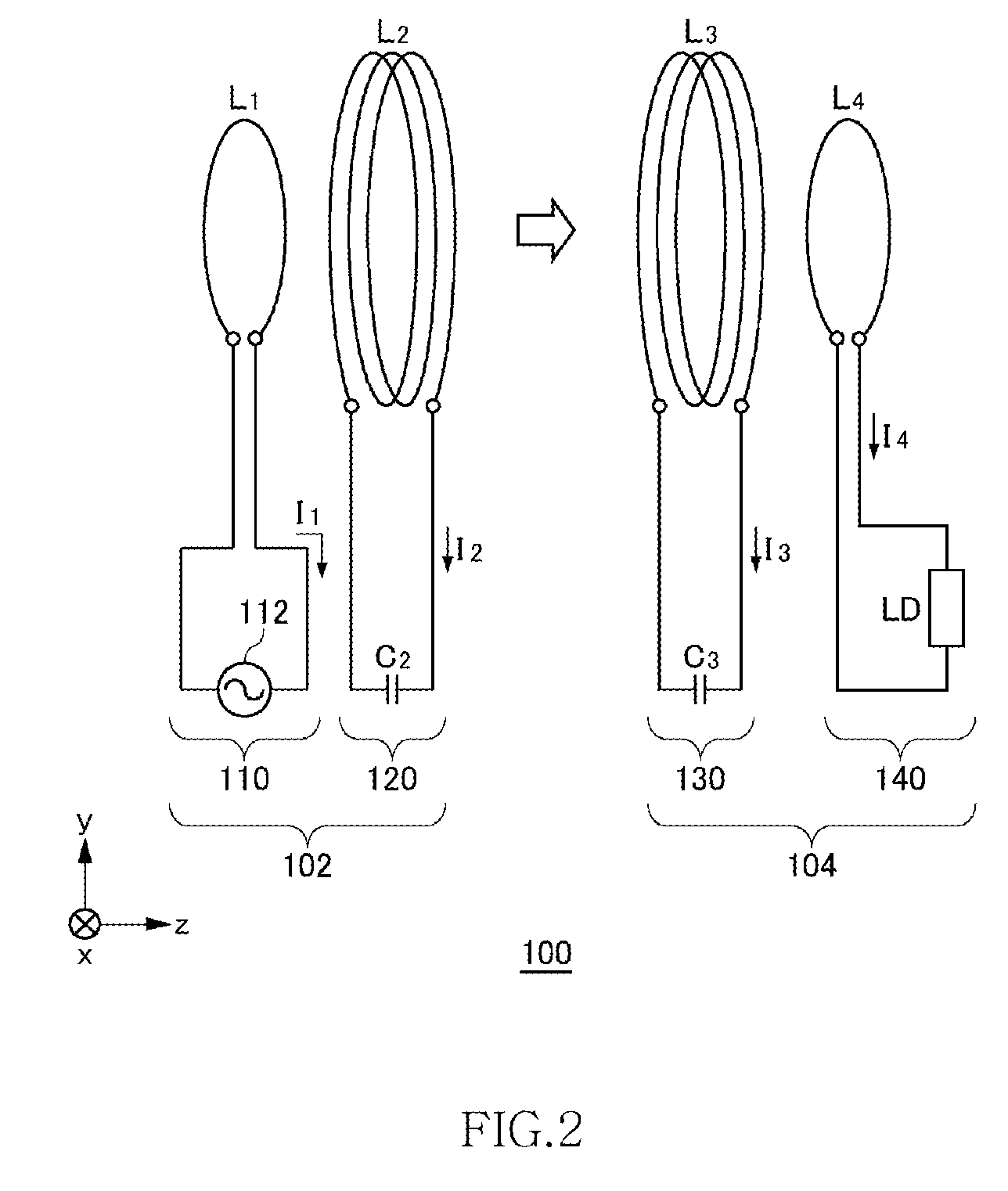

Wireless power feeder, wireless power receiver, and wireless power transmission system

ActiveUS20110198940A1Increase the number of windingsReduce sizeNear-field transmissionTransformersElectrical conductorResonance

Power is fed from a feeding coil to a receiving coil using magnetic resonance. The feeding coil is wound in a first layer substrate 144 of a multilayer substrate 116 with a space provided between the coil conductor thereof and further wound in a second later substrate 146 with a space provided between the coil conductor thereof. The feeding coil is wound such that a coil conductor 106a in the first layer and a coil conductive wire 106b in the second layer do not overlap each other as viewed in the axial direction (z-axis direction).

Owner:TDK CORPARATION

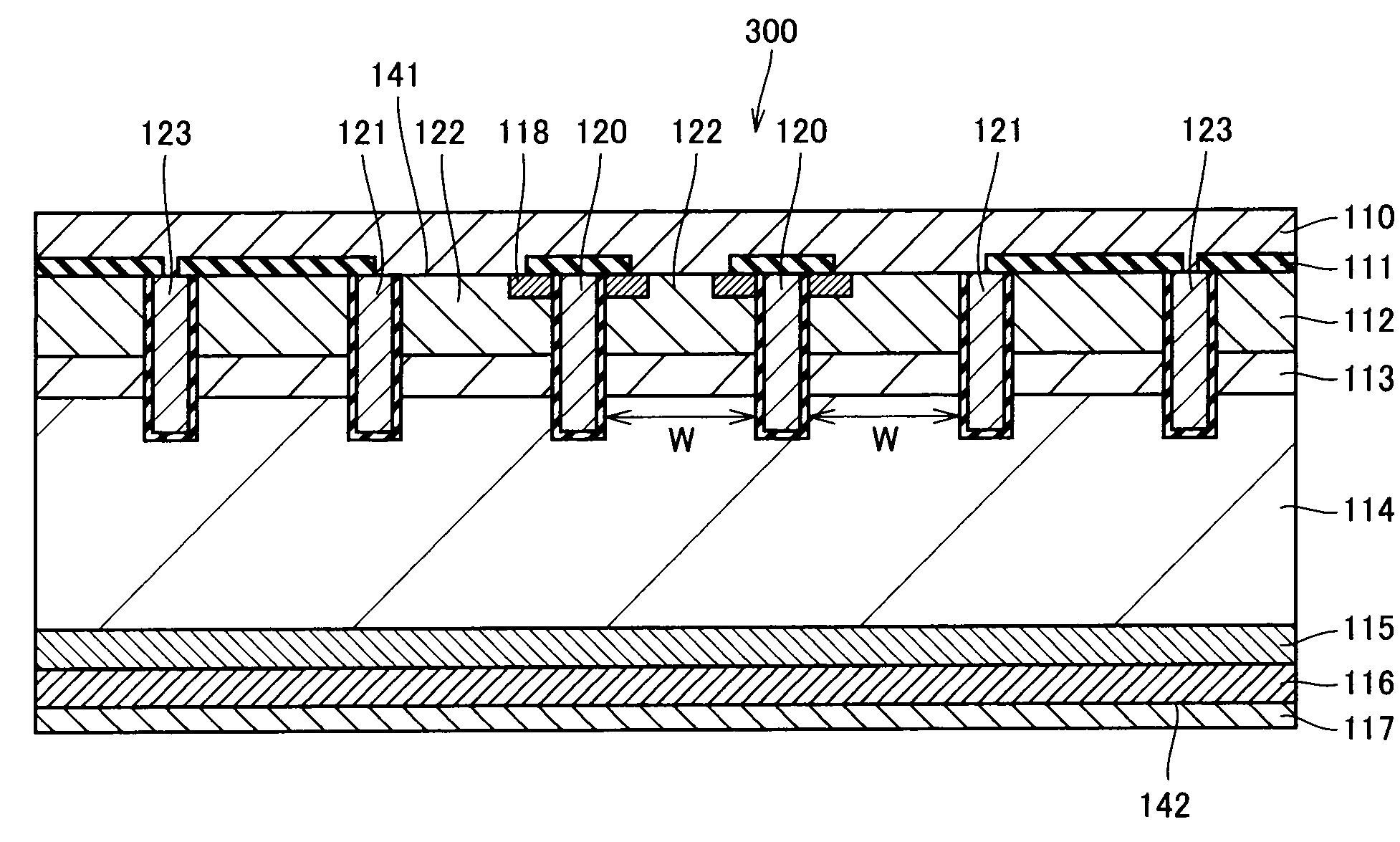

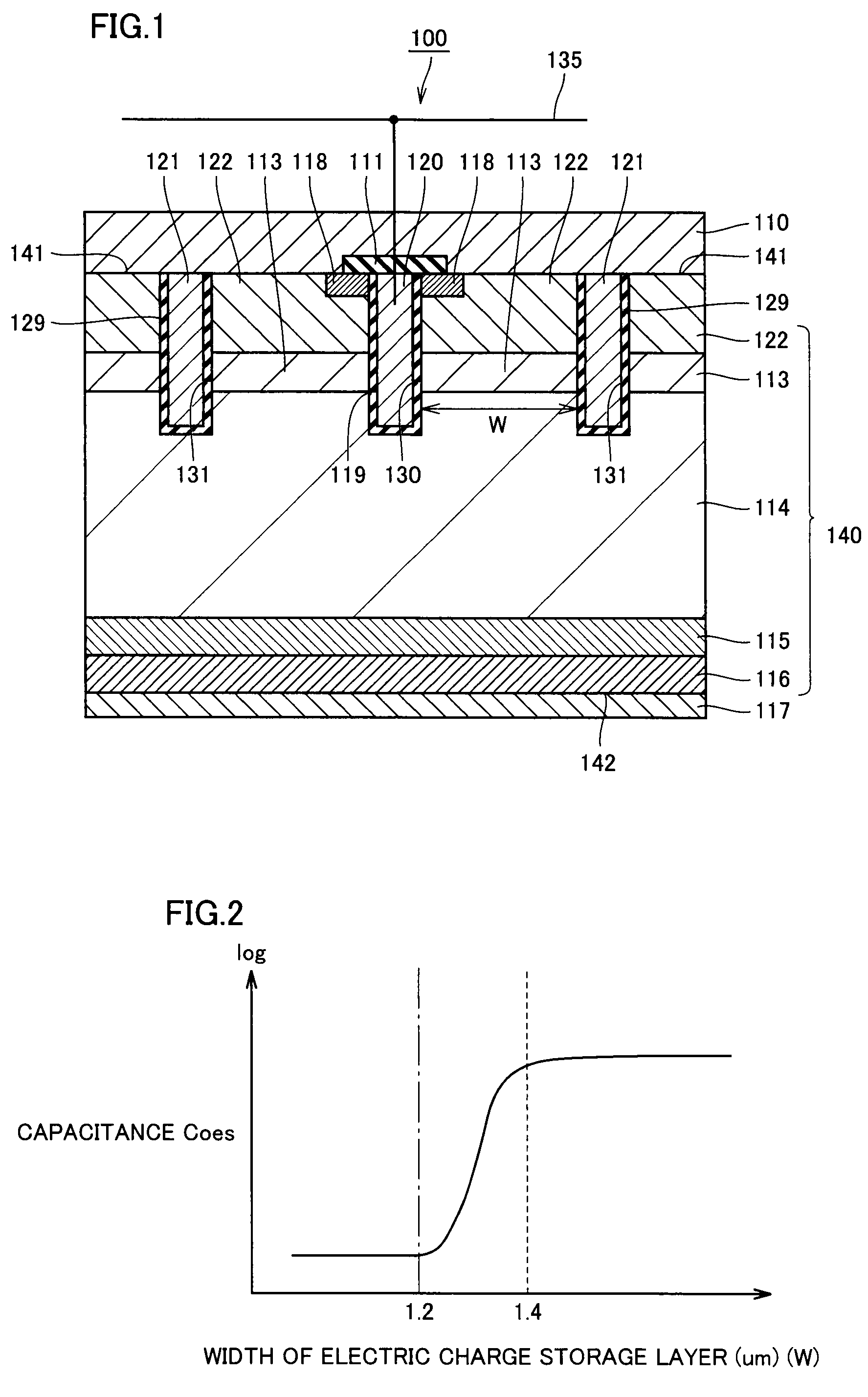

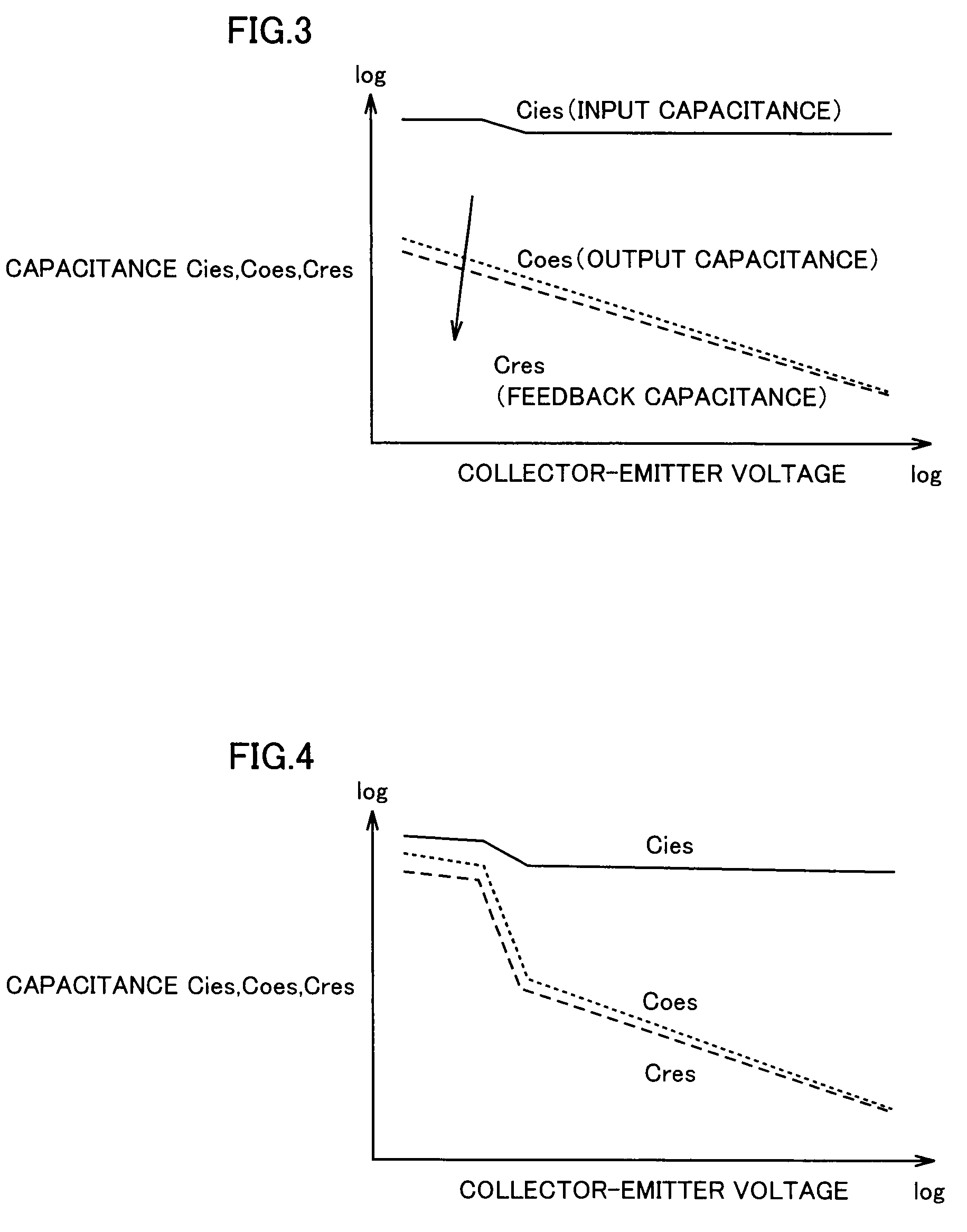

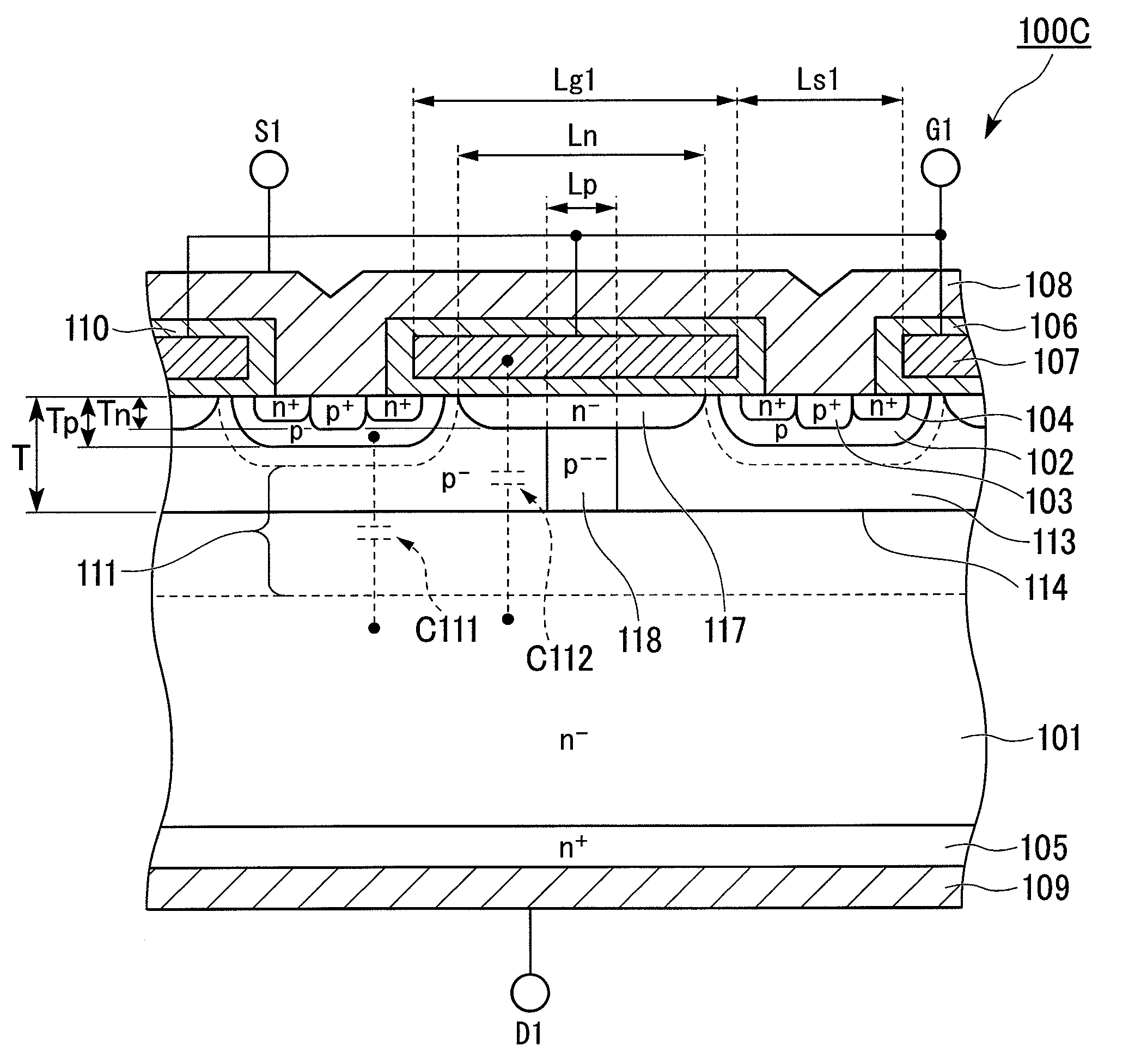

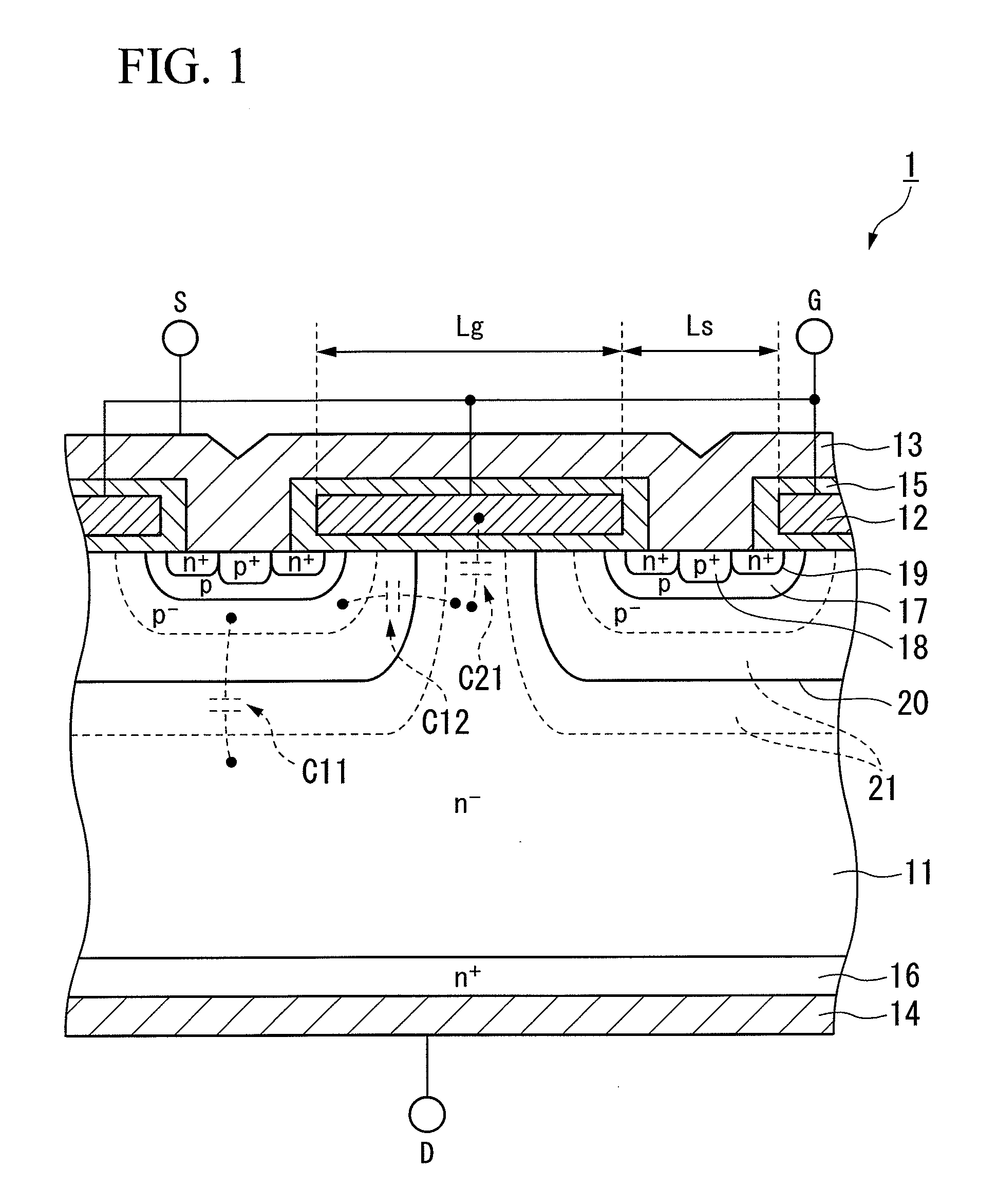

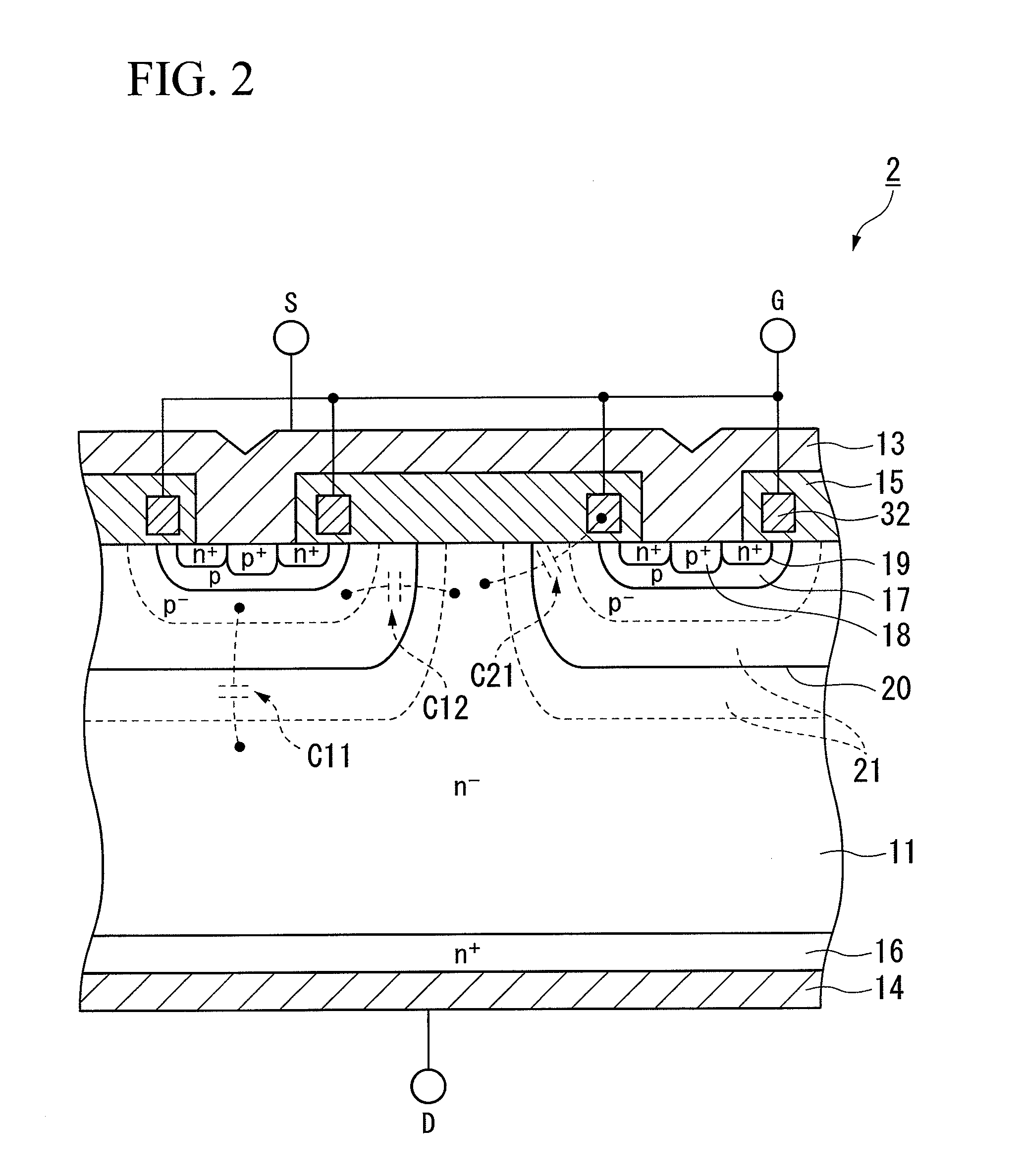

Semiconductor device

ActiveUS8178947B2Reduce fluctuationReduce capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceFeedback capacitance

There is provided a semiconductor device in which an amount of fluctuations in output capacitance and feedback capacitance is reduced. In a trench-type insulated gate semiconductor device, a width of a portion of an electric charge storage layer in a direction along which a gate electrode and a dummy gate are aligned is set to be at most 1.4 μm.

Owner:MITSUBISHI ELECTRIC CORP

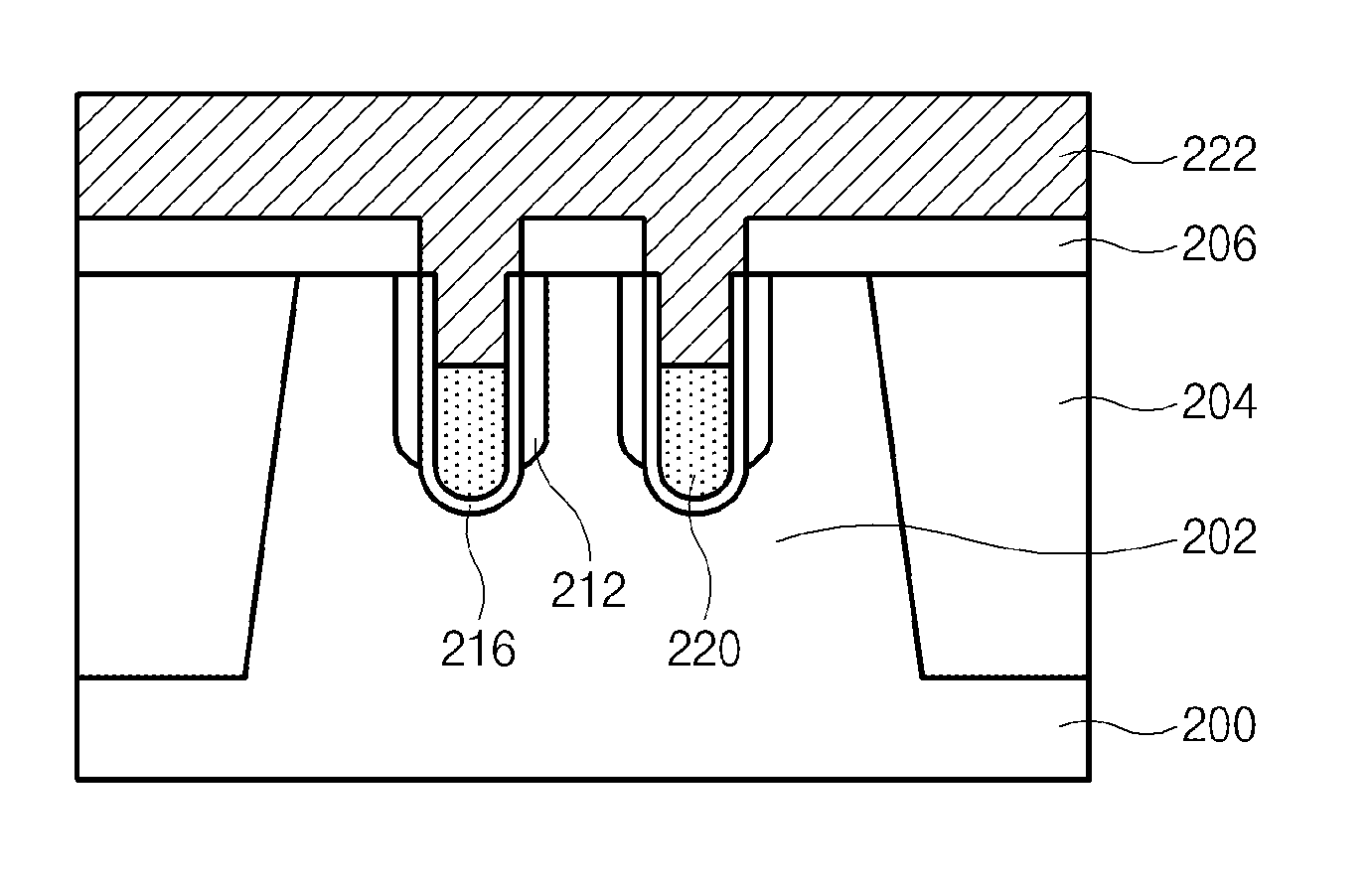

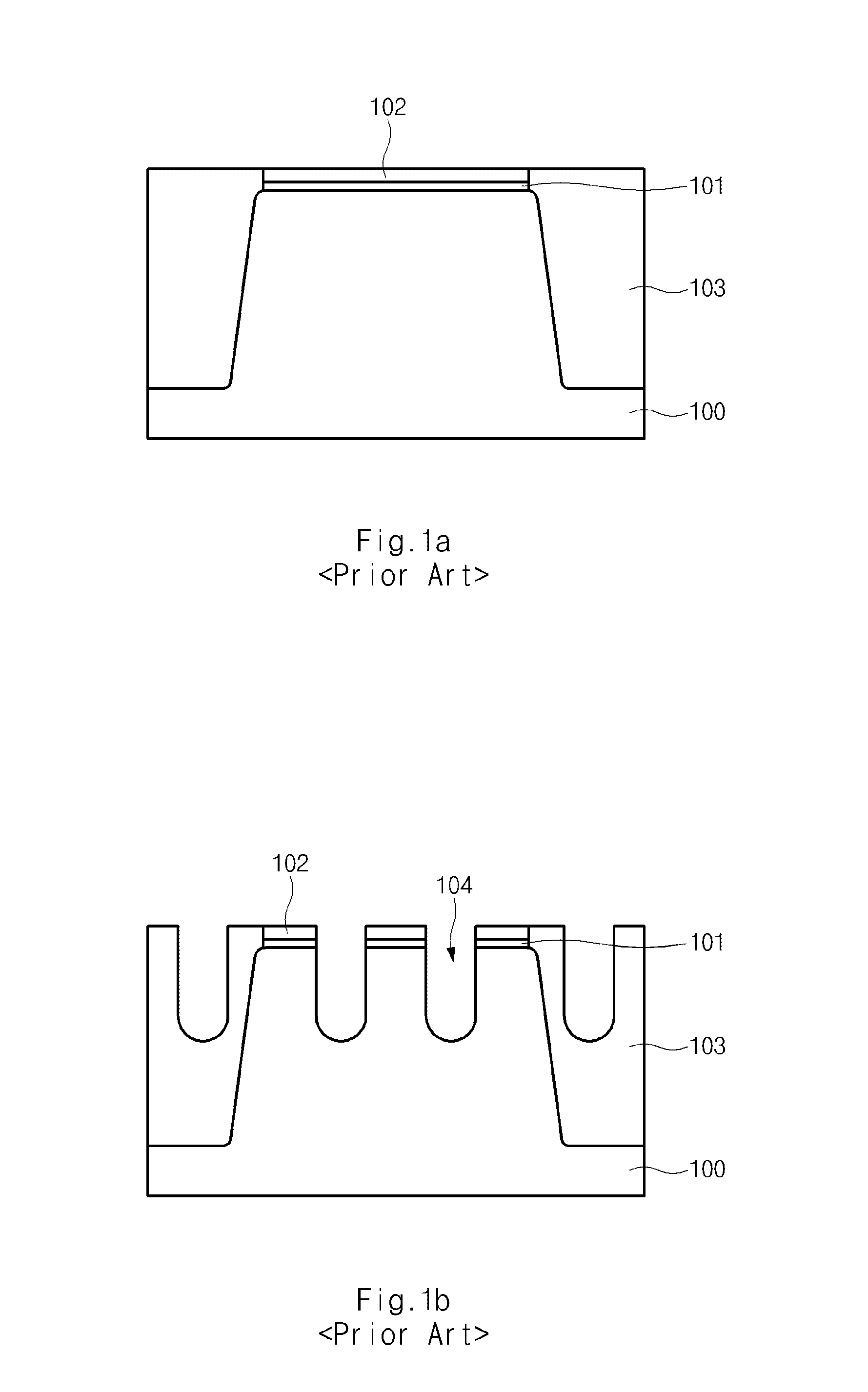

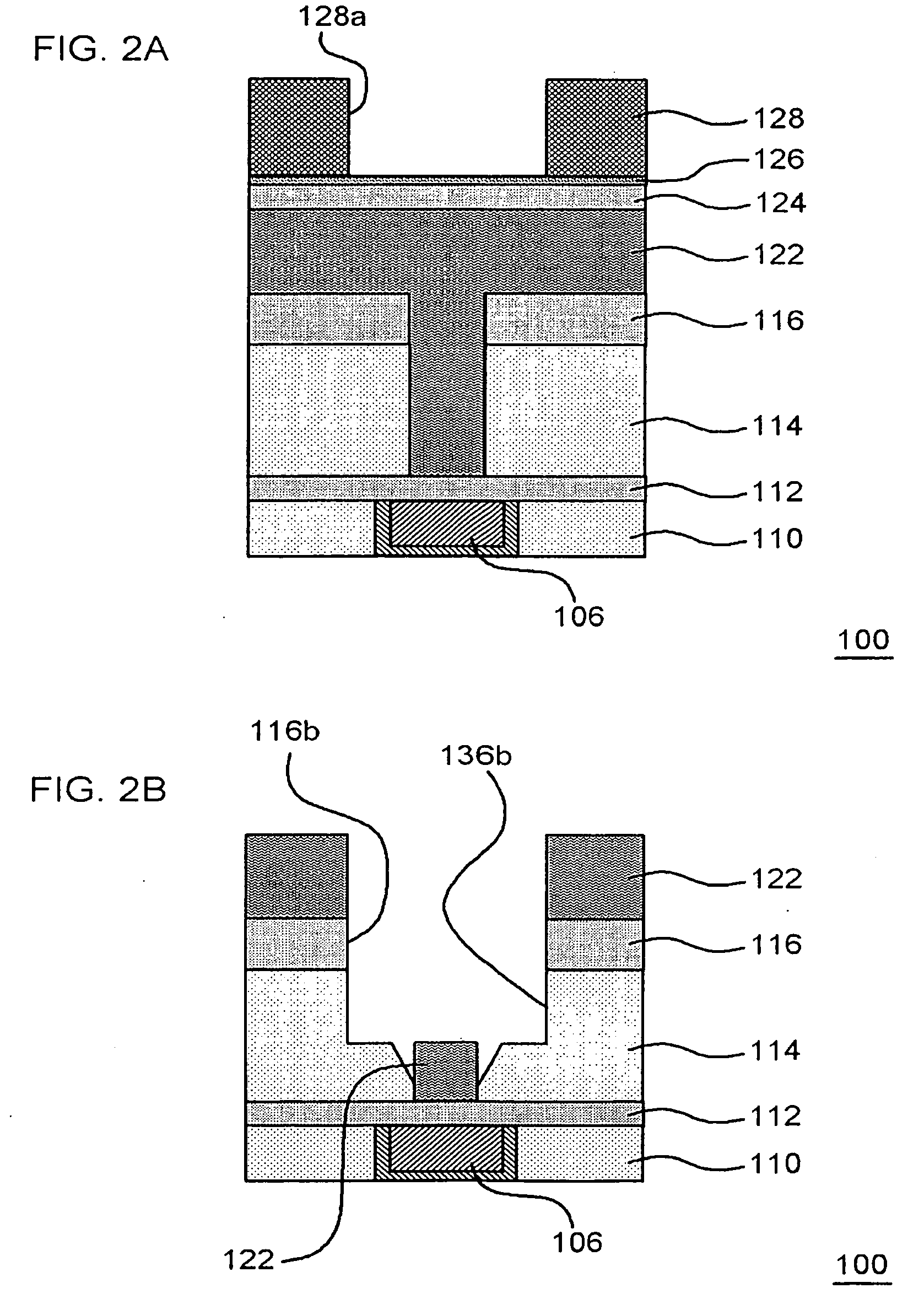

Semiconductor memory device and method for fabricating the same

InactiveUS20110018057A1Reducing GIDL occurrenceSuppress parasitic capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialEngineering

A manufacturing method of a semiconductor device comprises forming a semiconductor substrate including an active region and an element isolation film, forming a first recess on the semiconductor substrate, forming an oxide film on a sidewall of the first recess, forming a second recess by etching a lower part of the first recess, and forming a gate in a lower part of the second recess.

Owner:SK HYNIX INC

Semiconductor device having high frequency wiring and dummy metal layer at multilayer wiring structure

ActiveUS7932578B2Avoid erosionStable manufacturingSemiconductor/solid-state device detailsSolid-state devicesTransformerEngineering

Owner:RENESAS ELECTRONICS CORP

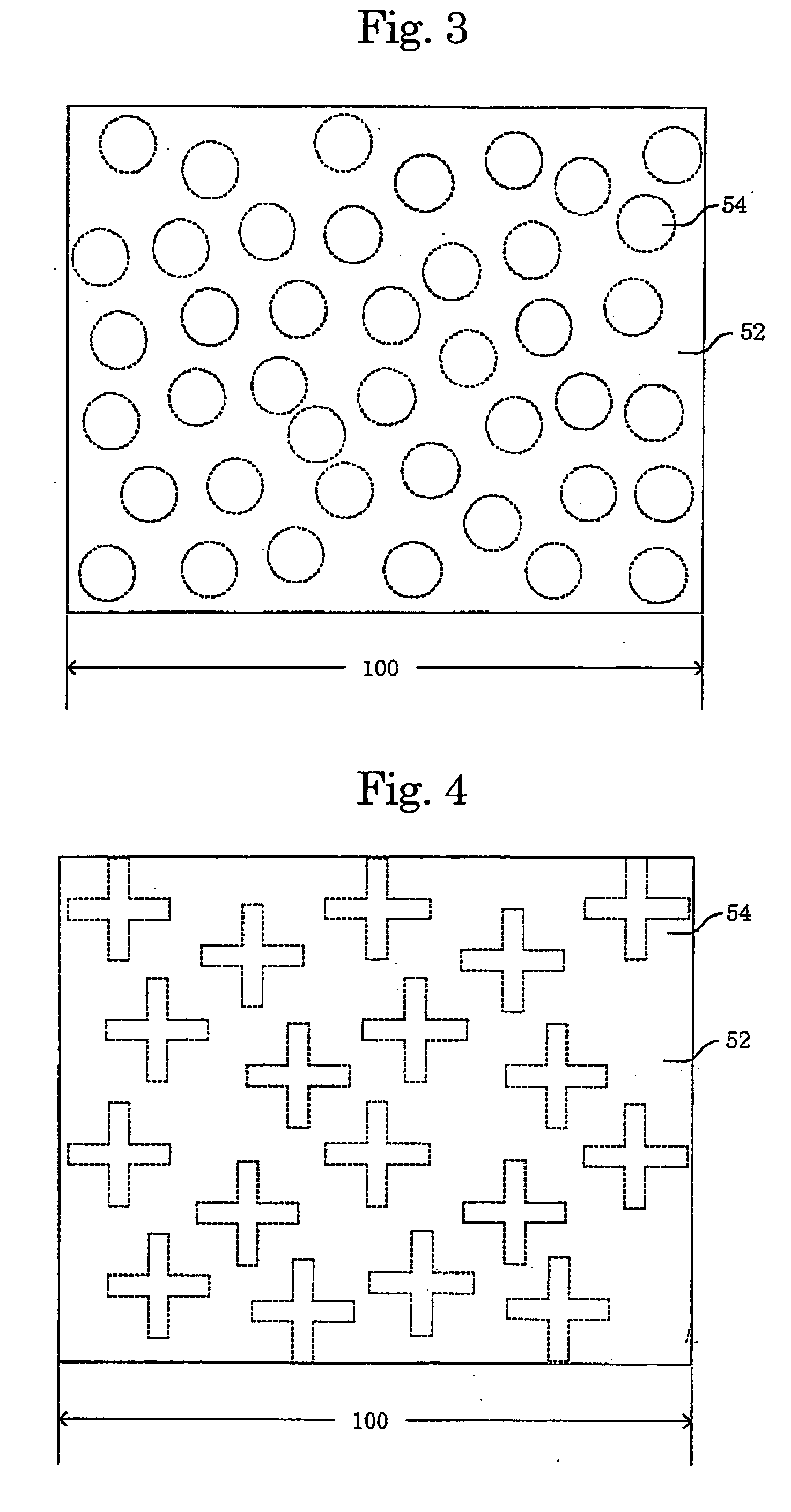

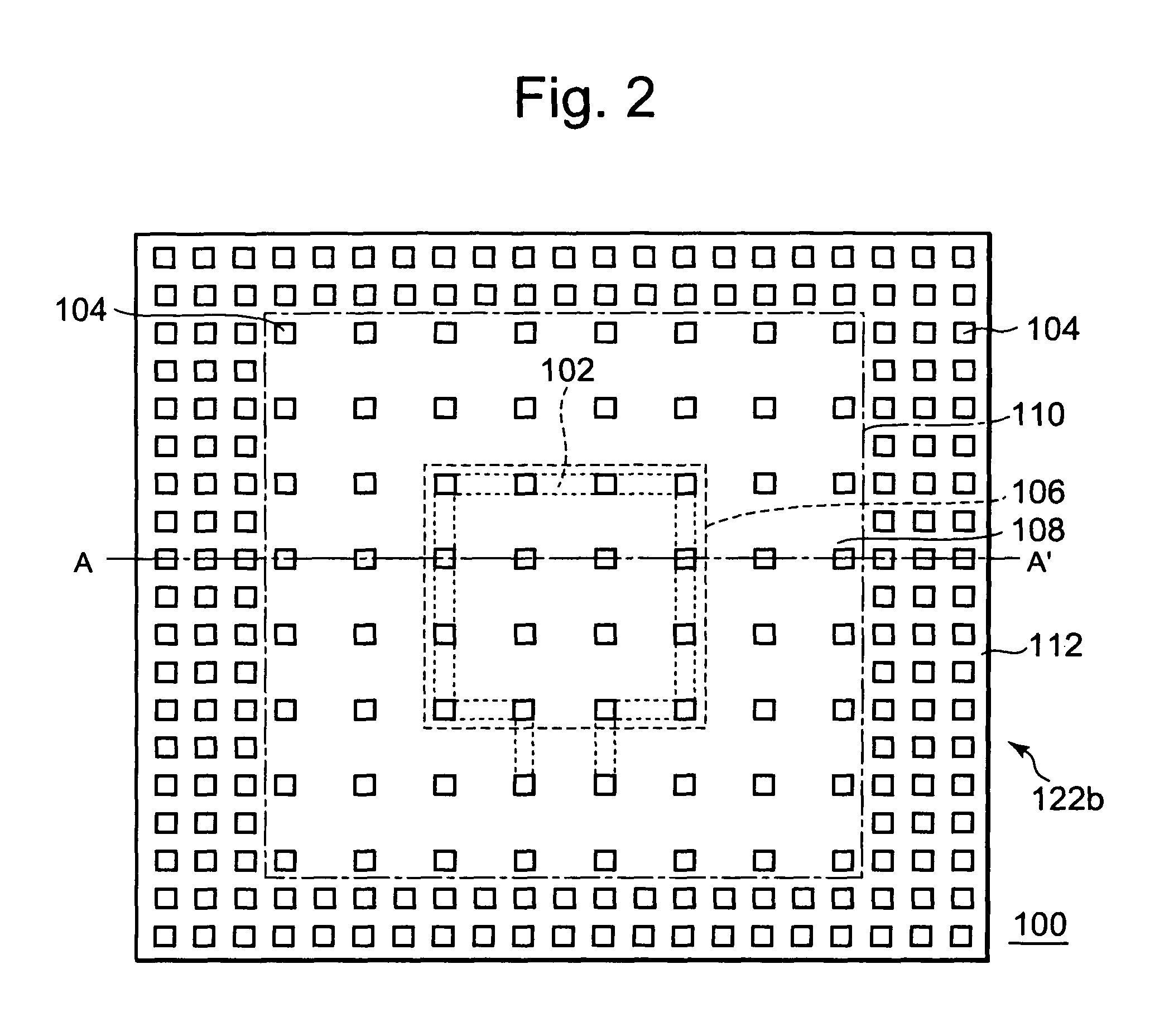

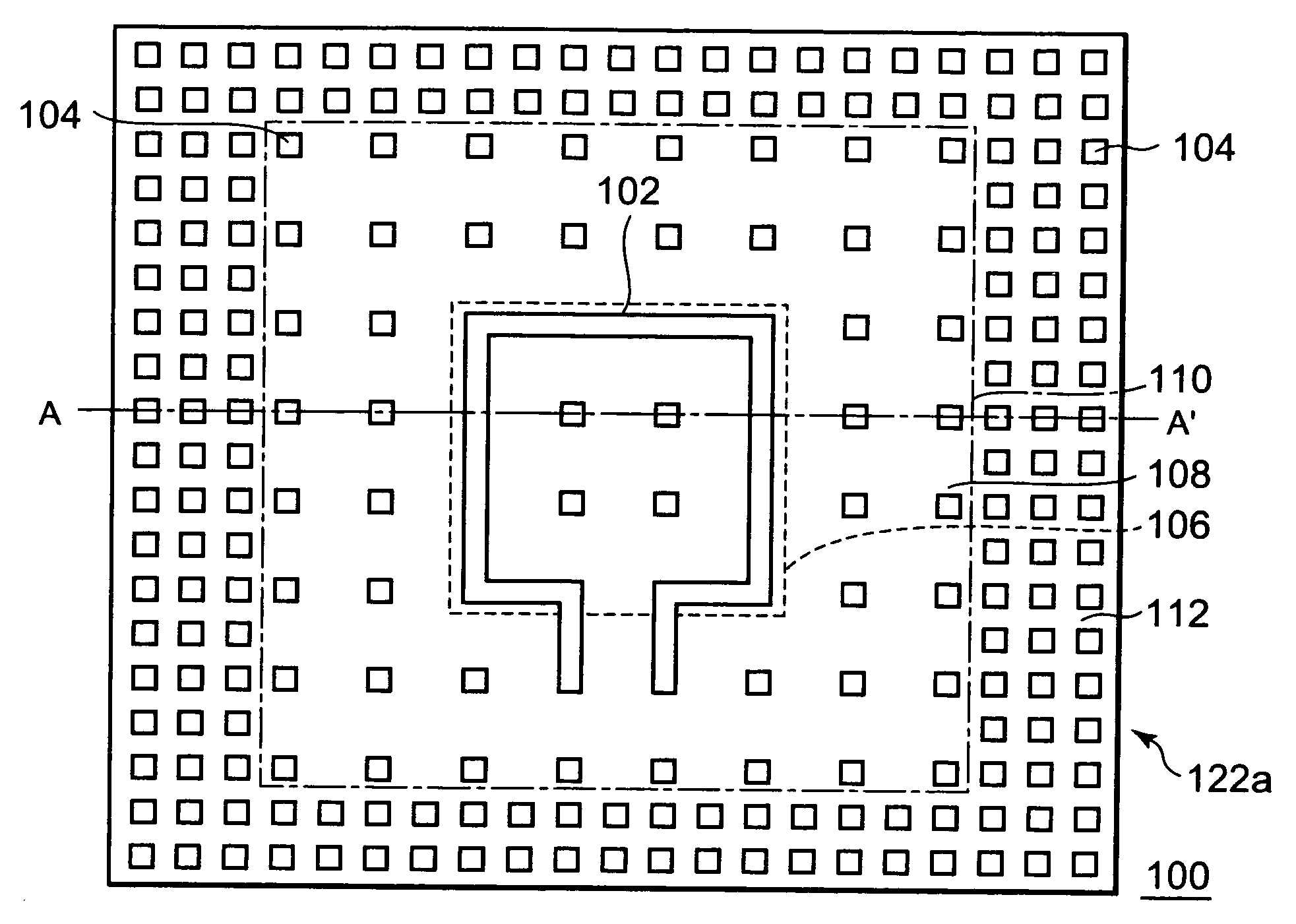

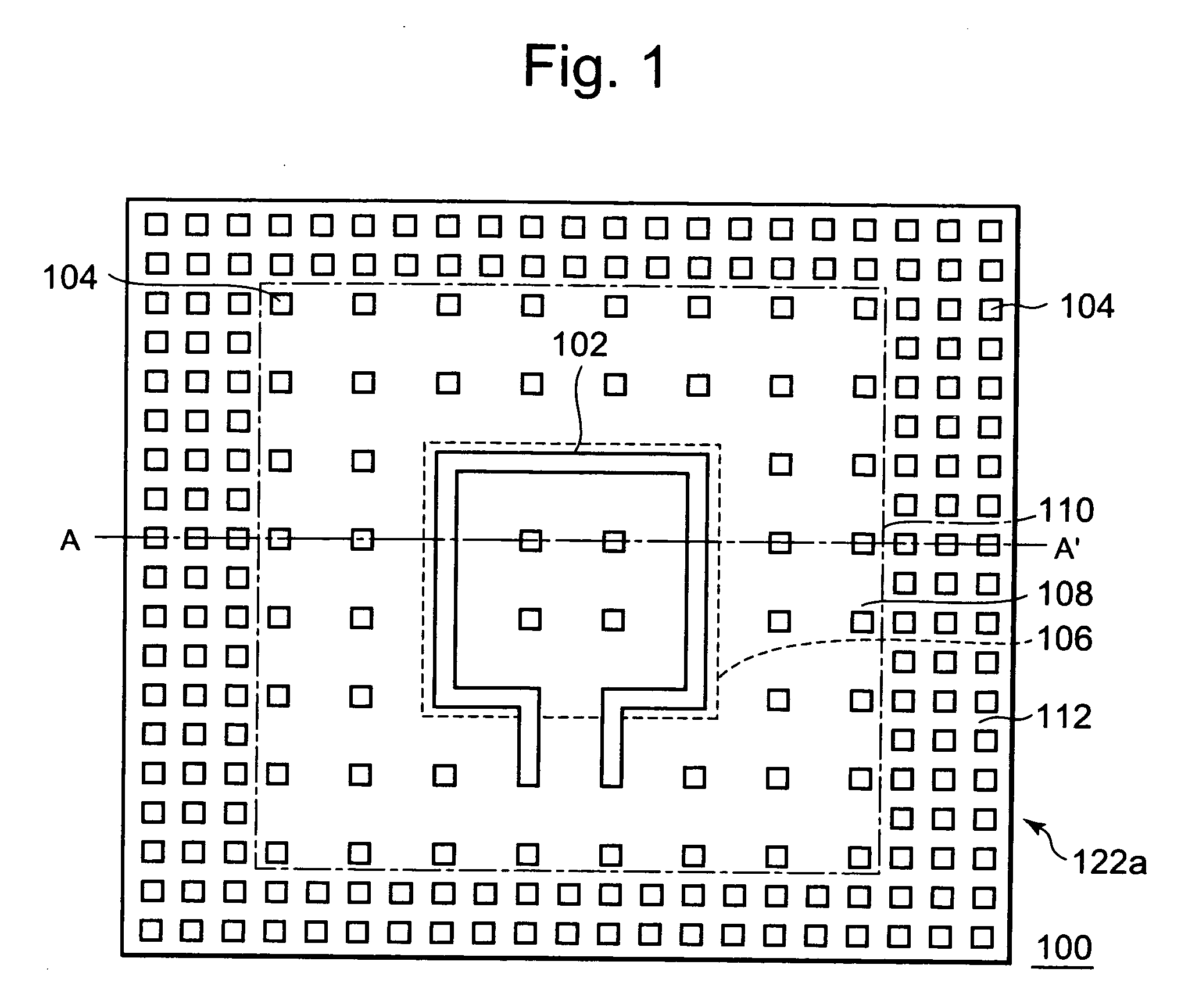

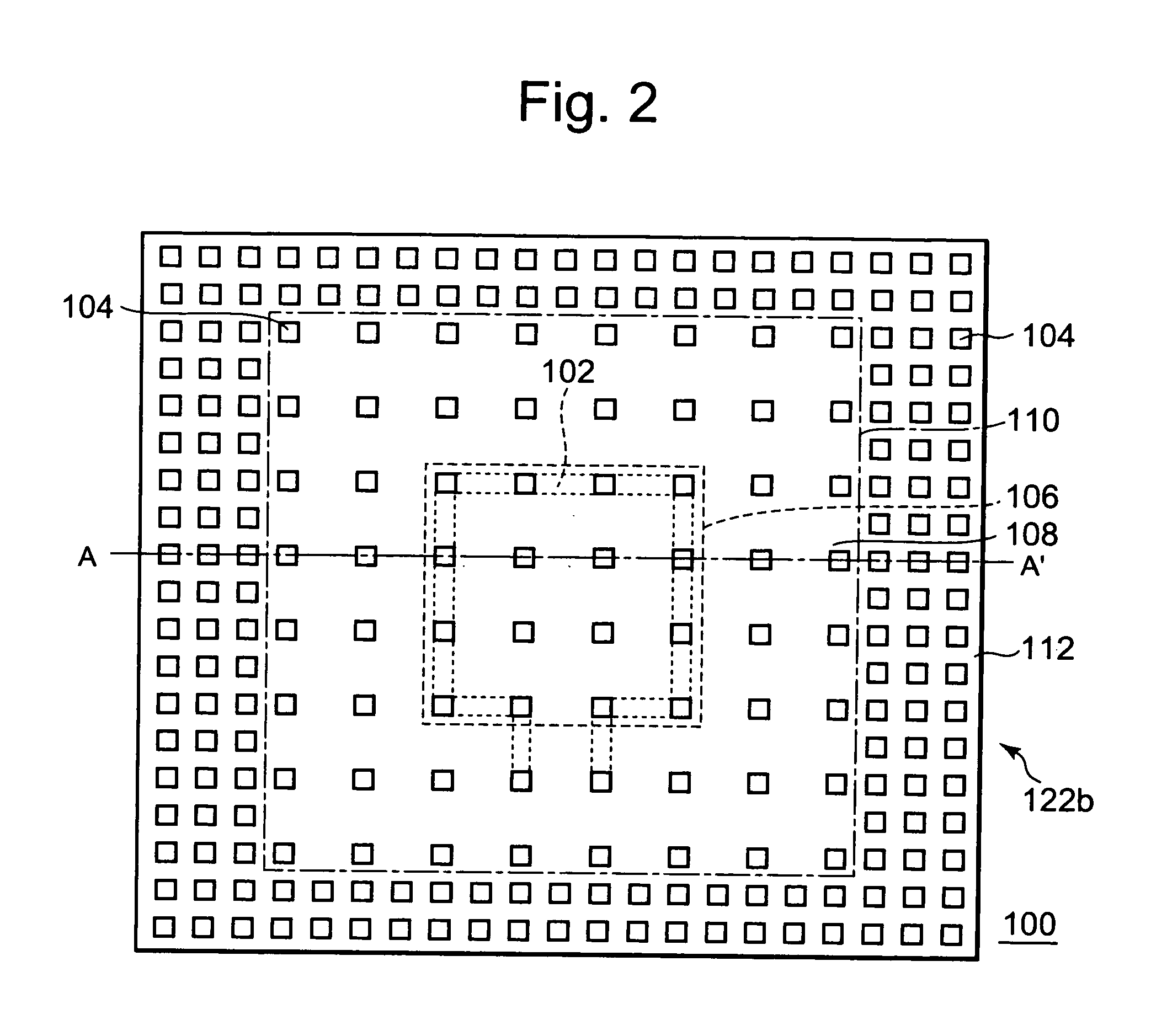

Semiconductor device having high frequency wiring and dummy metal layer at multilayer wiring structure

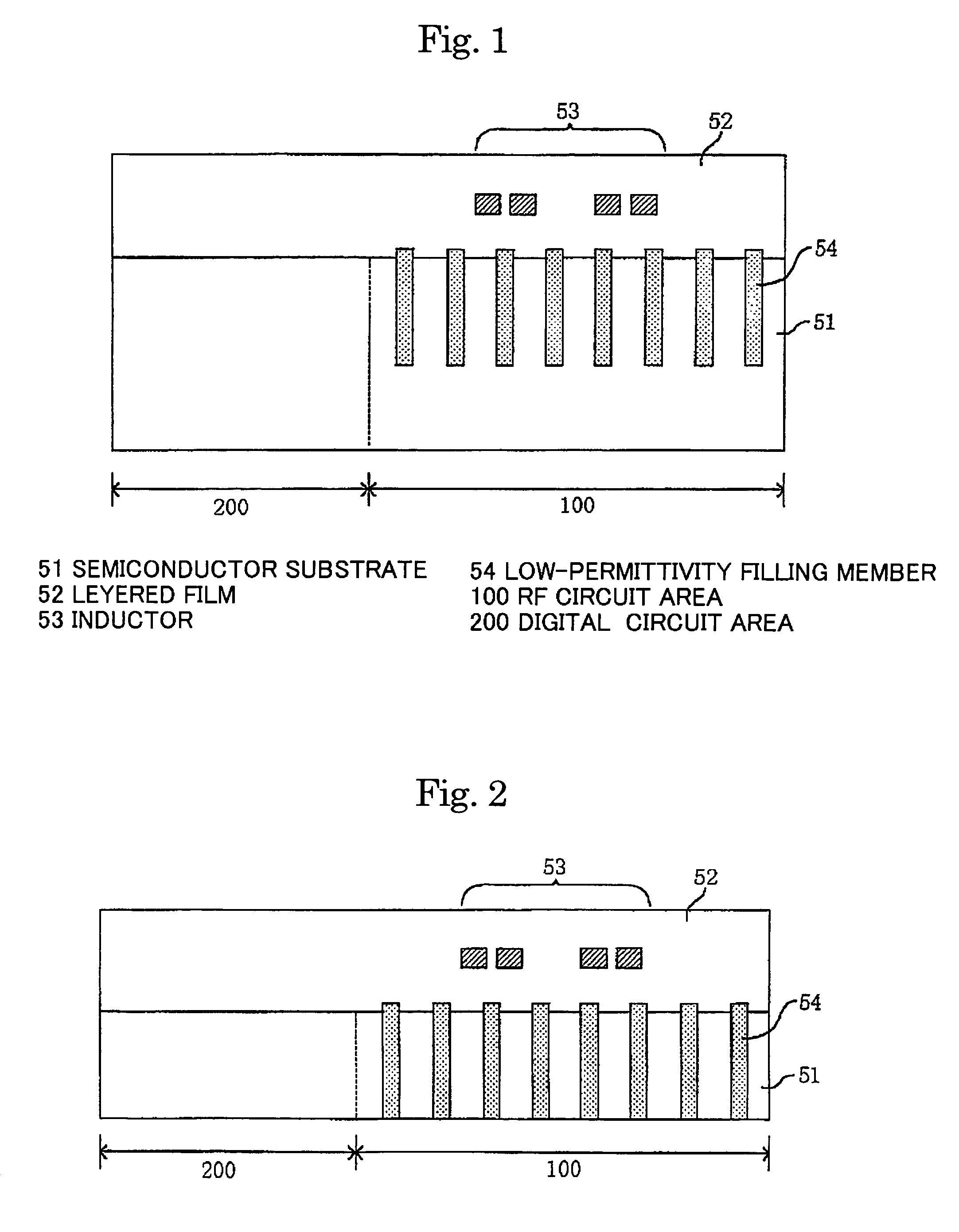

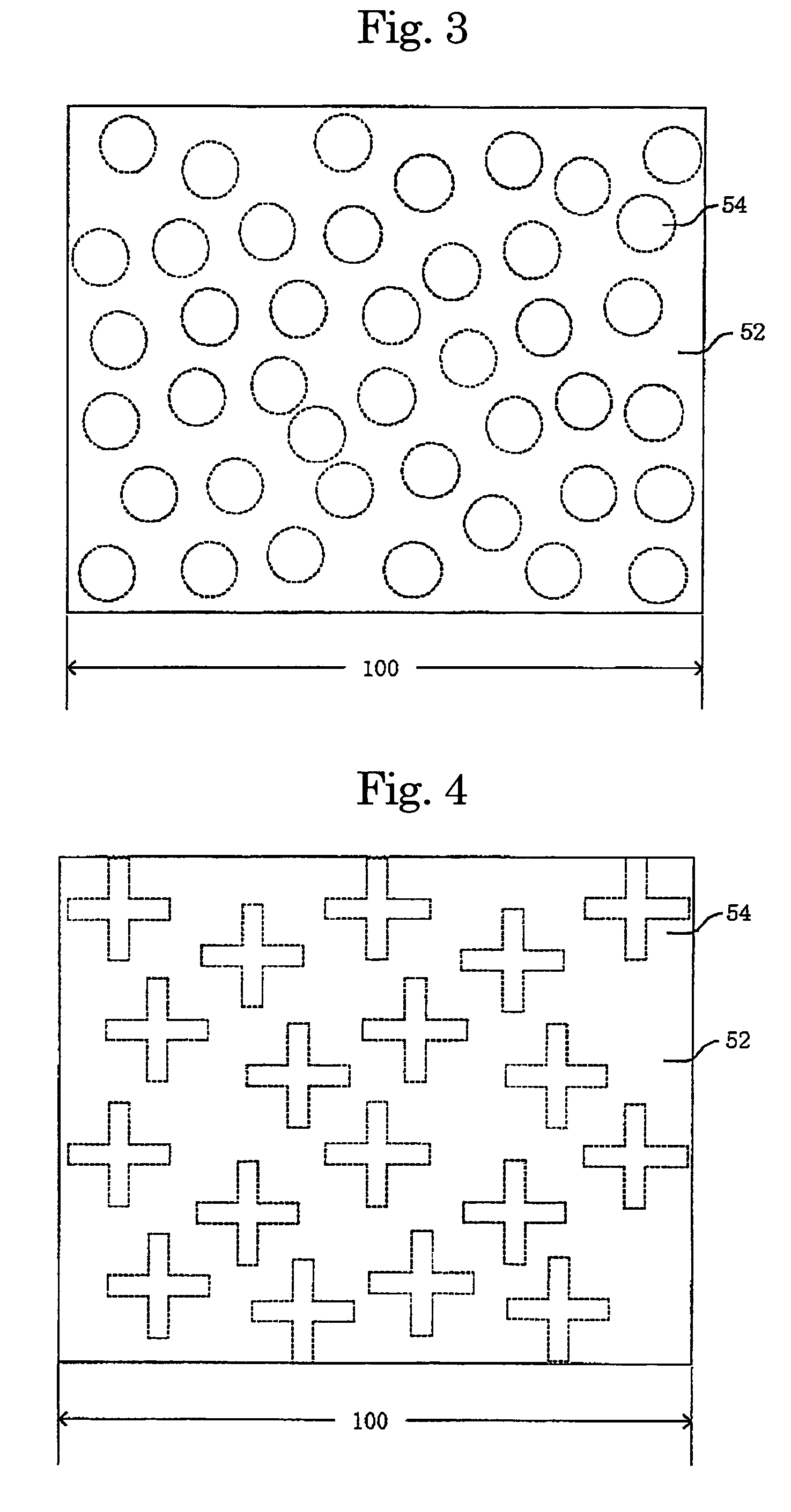

ActiveUS20090096061A1Erosion and dishing can be preventedImprove featuresSemiconductor/solid-state device detailsSolid-state devicesTransformerInductor

A semiconductor device includes, a metal wiring, which functions as an inductor or transformer, formed on a first portion of a semiconductor substrate, a plurality of first dummy layers formed in a first density on the first portion of the semiconductor substrate, a plurality of second dummy layers formed in a second density on a second portion of the semiconductor substrate, the second portion surrounding the first portion, and a plurality of third dummy layers formed in a third density higher than the first and second densities on a third portion of the semiconductor substrate, the third portion surrounding the second portion.

Owner:RENESAS ELECTRONICS CORP

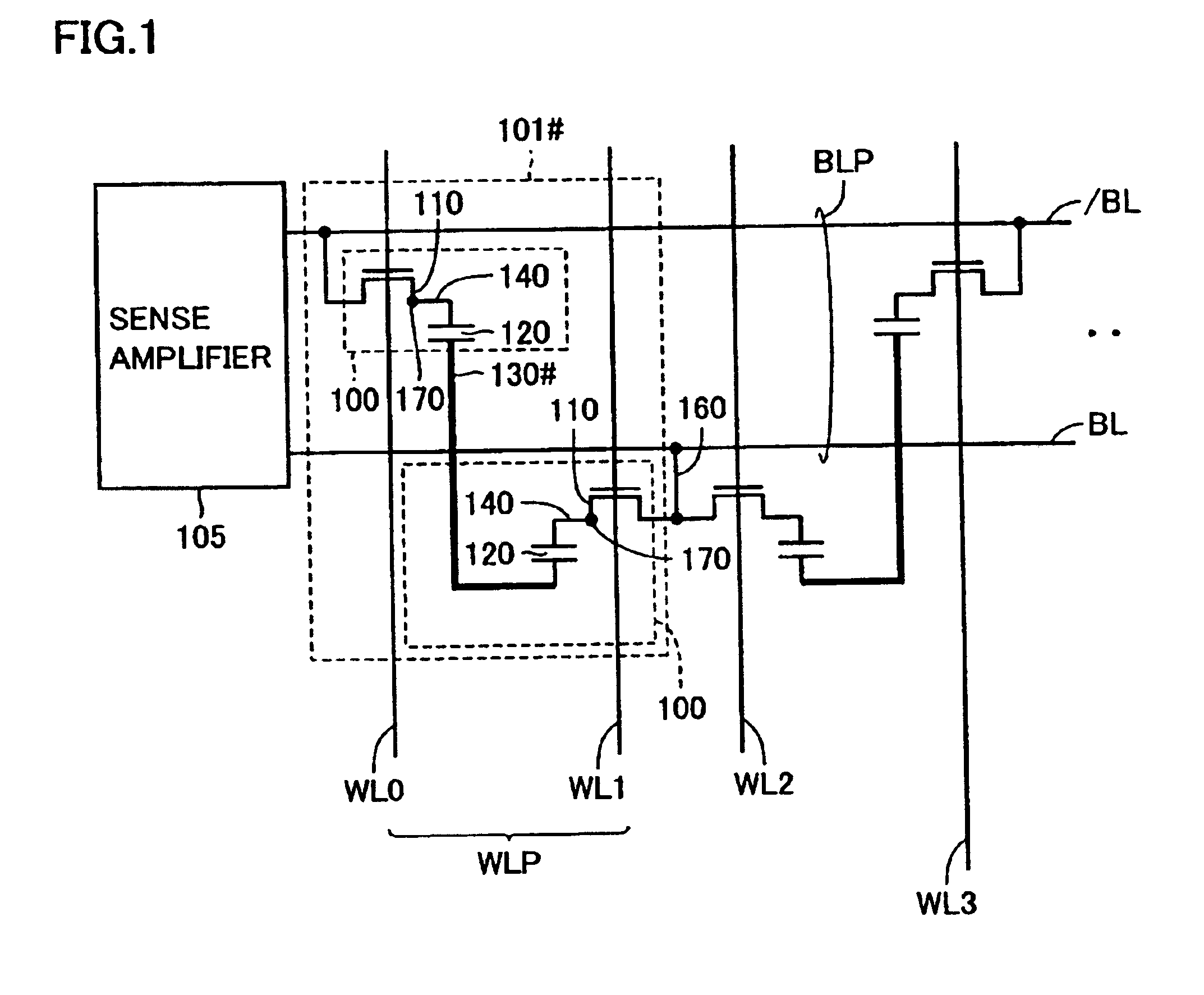

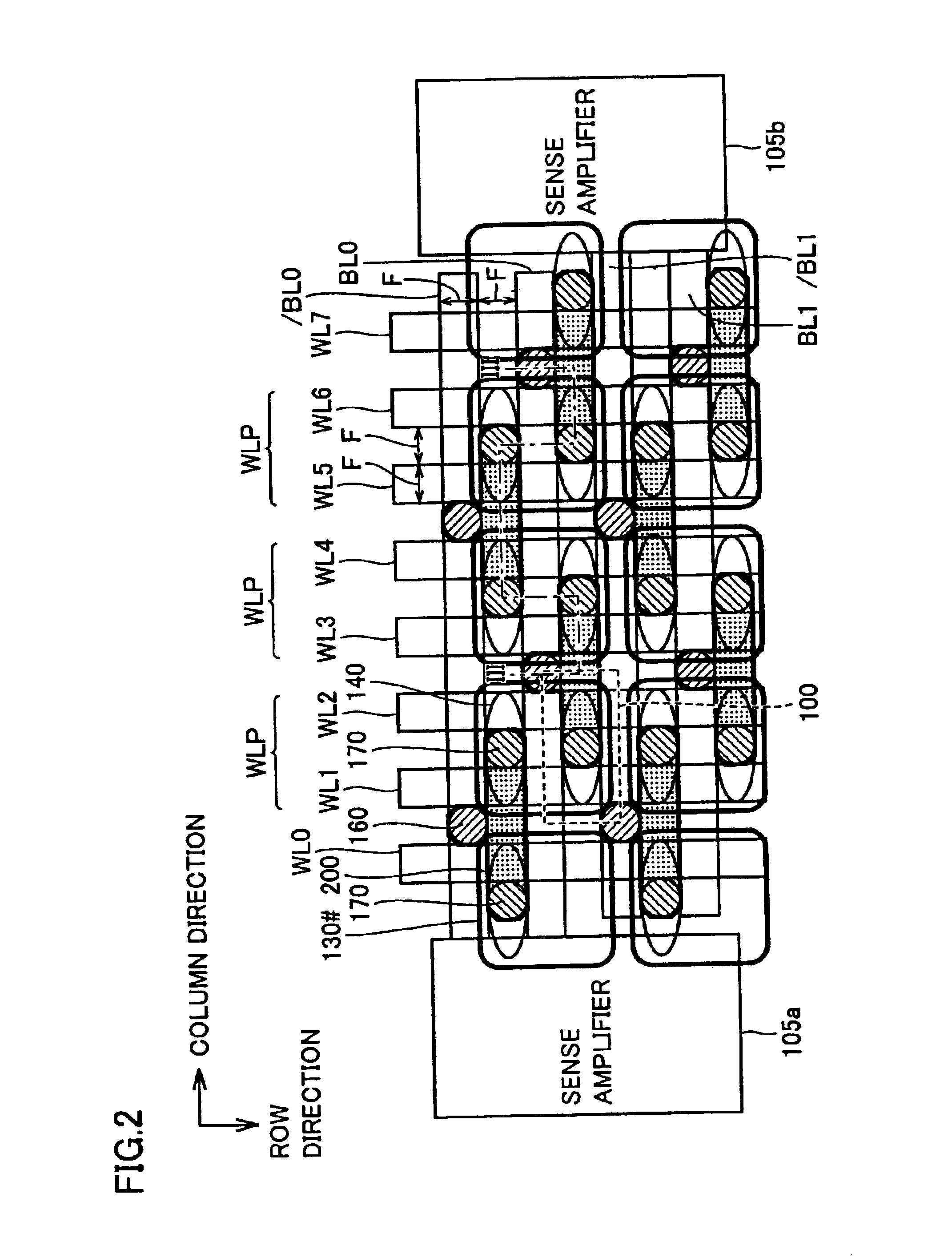

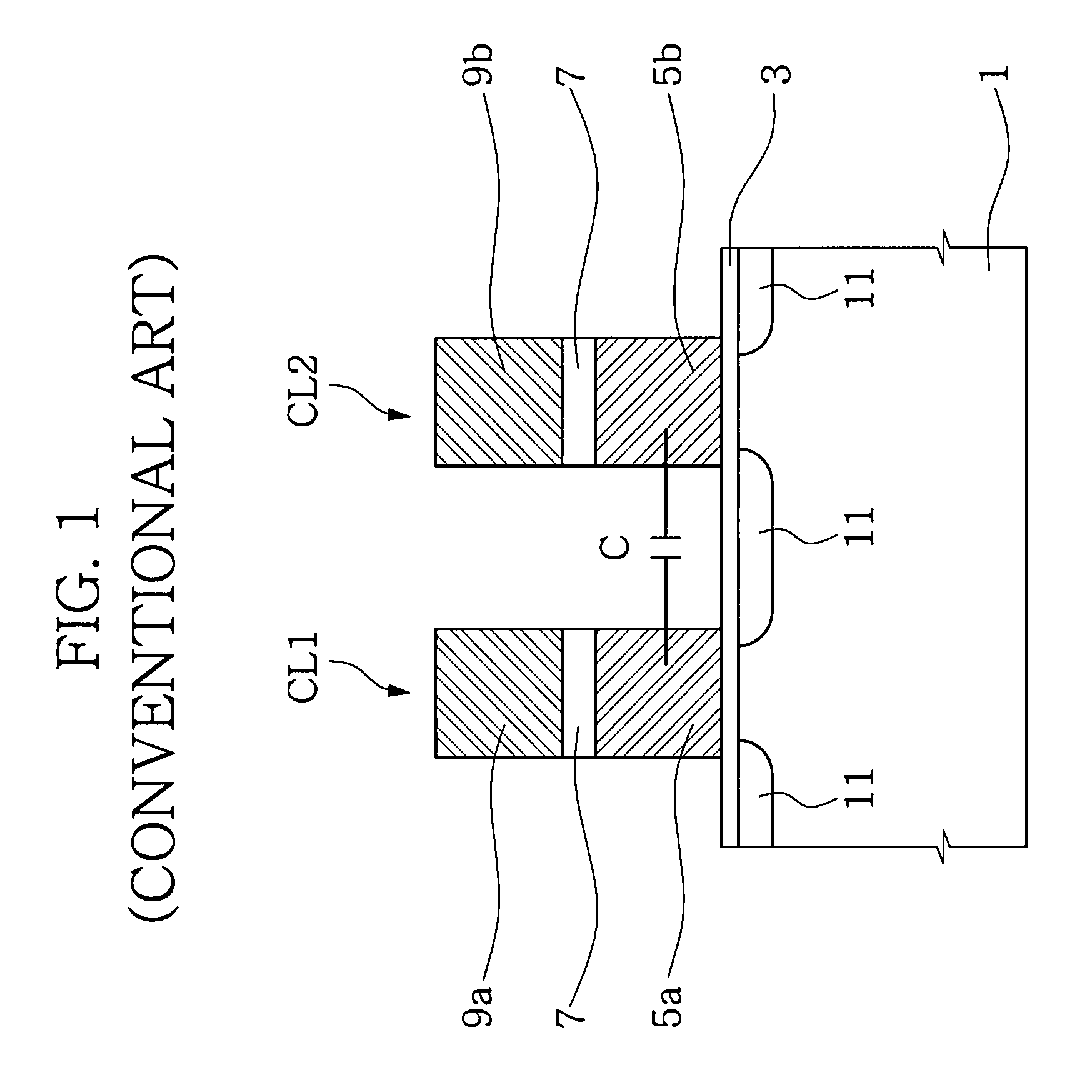

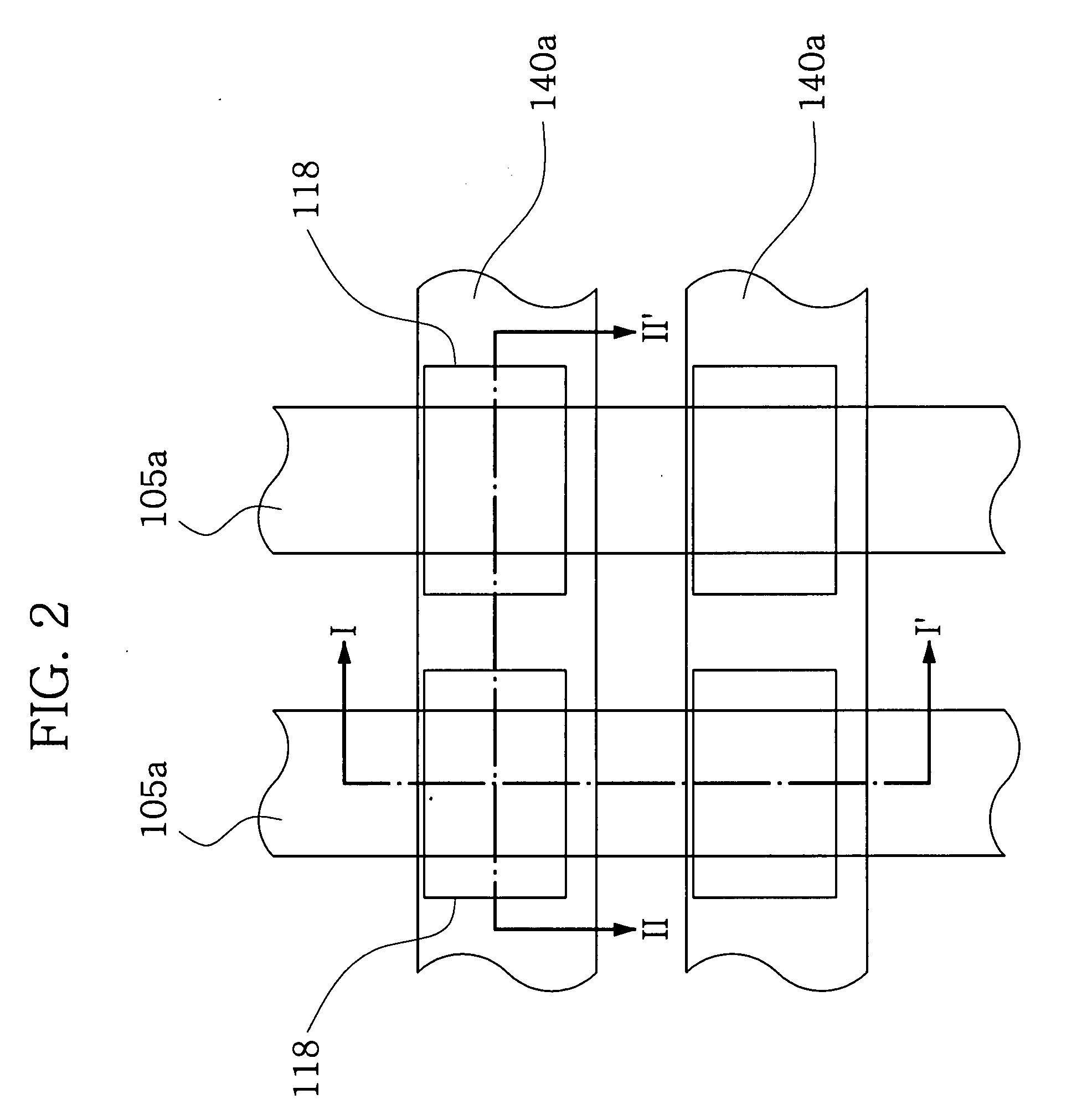

Semiconductor memory device having twin-cell units

InactiveUS6903961B2Improve refresh characteristicImprove manufacturing yieldTransistorSolid-state devicesCapacitanceCapacitive coupling

Each of twin-cell units each formed of two DRAM cells has a cell plate electrically isolated from the cell plates in the other twin-cell units. Thereby, voltages on two storage nodes storing mutually complementary data in the same twin-cell unit change similarly to each other owing to capacitive coupling.

Owner:RENESAS ELECTRONICS CORP

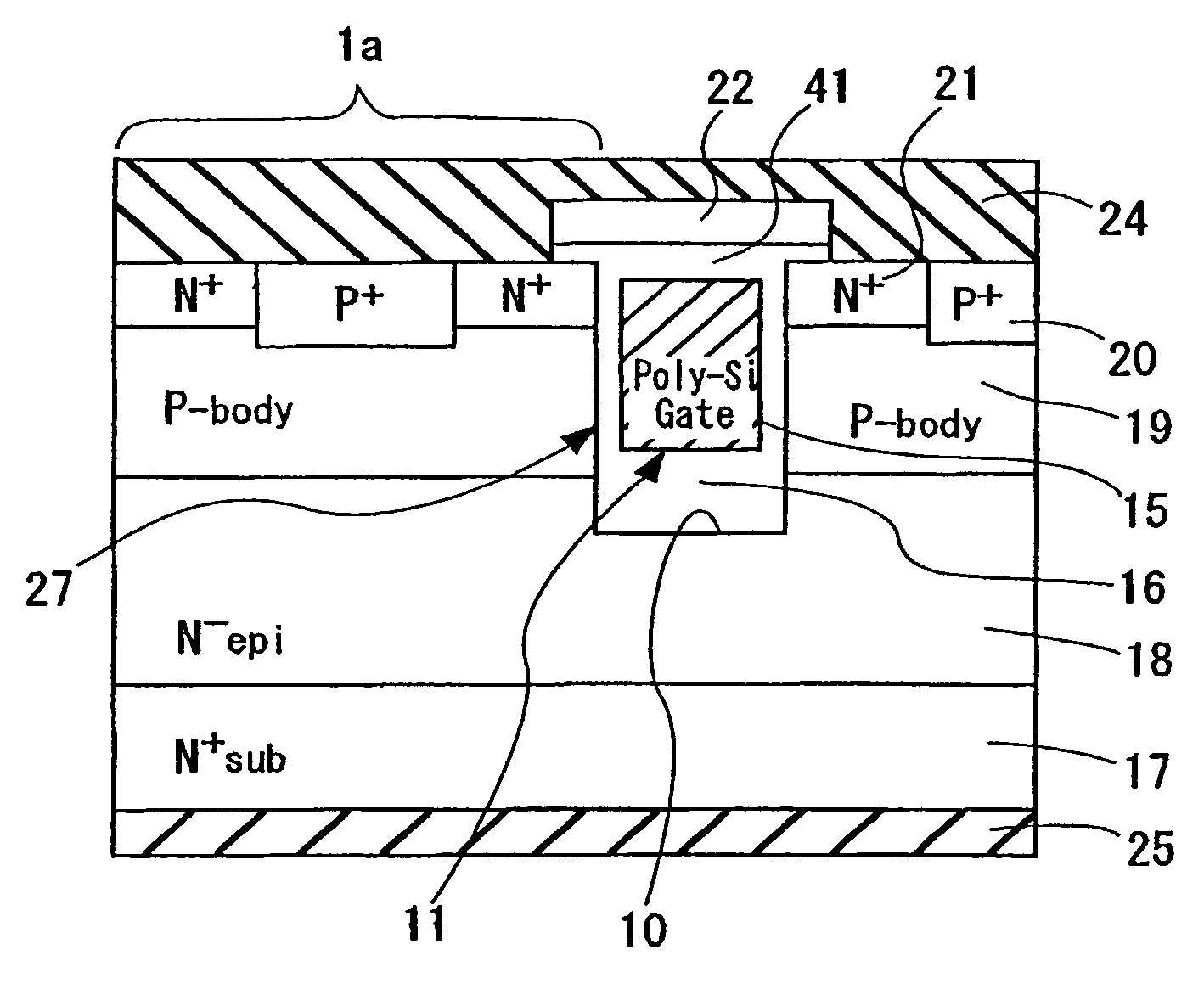

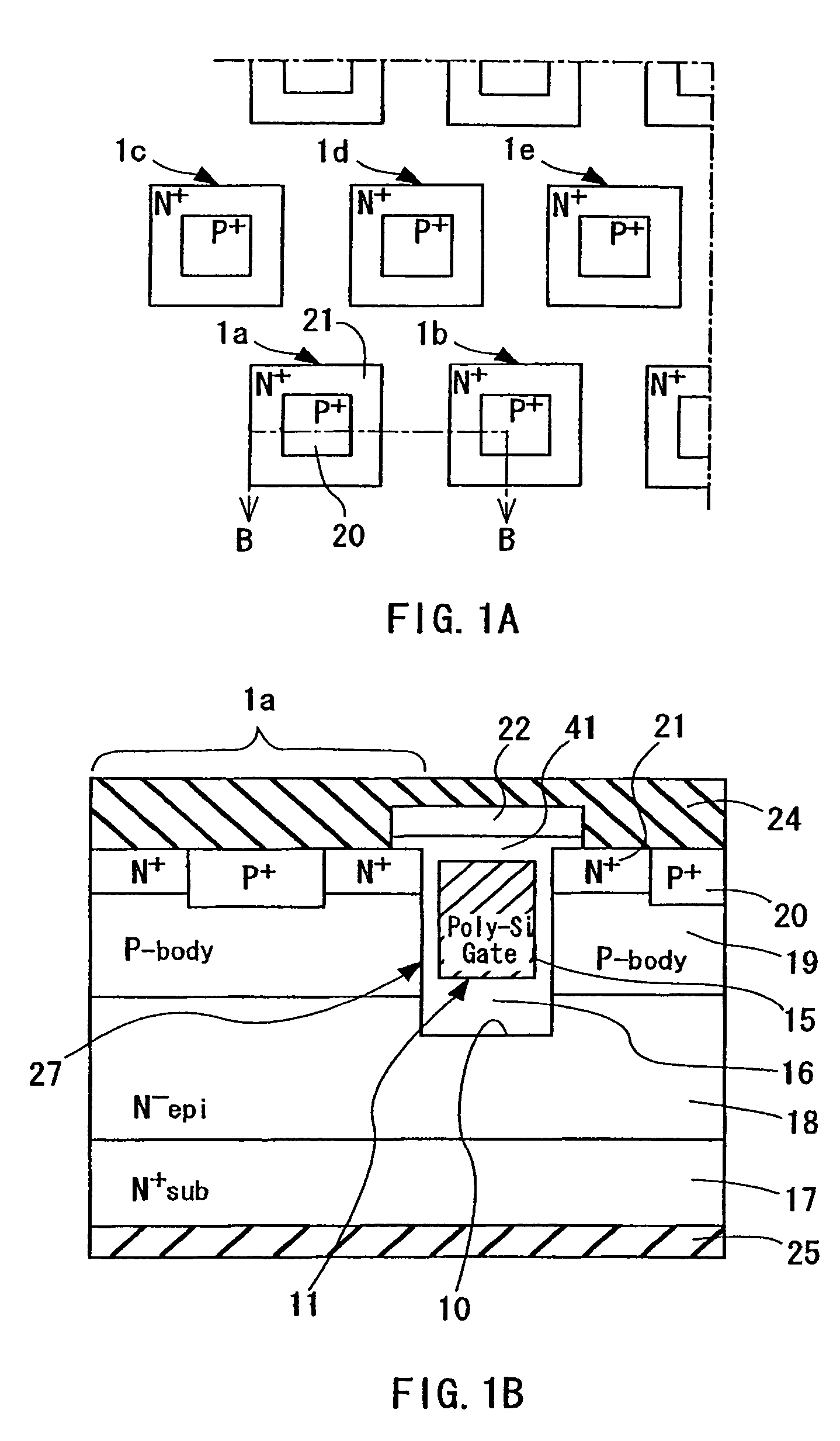

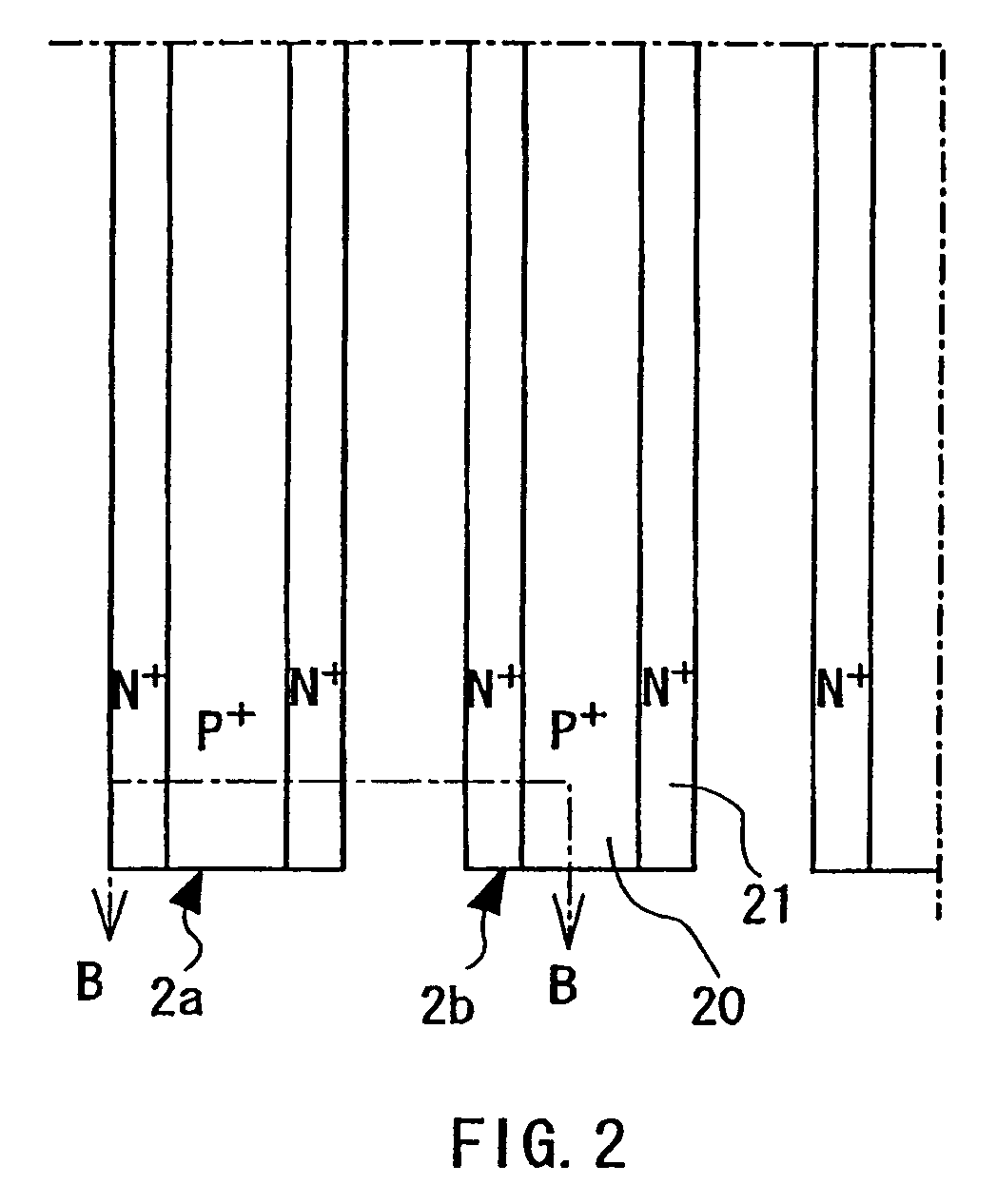

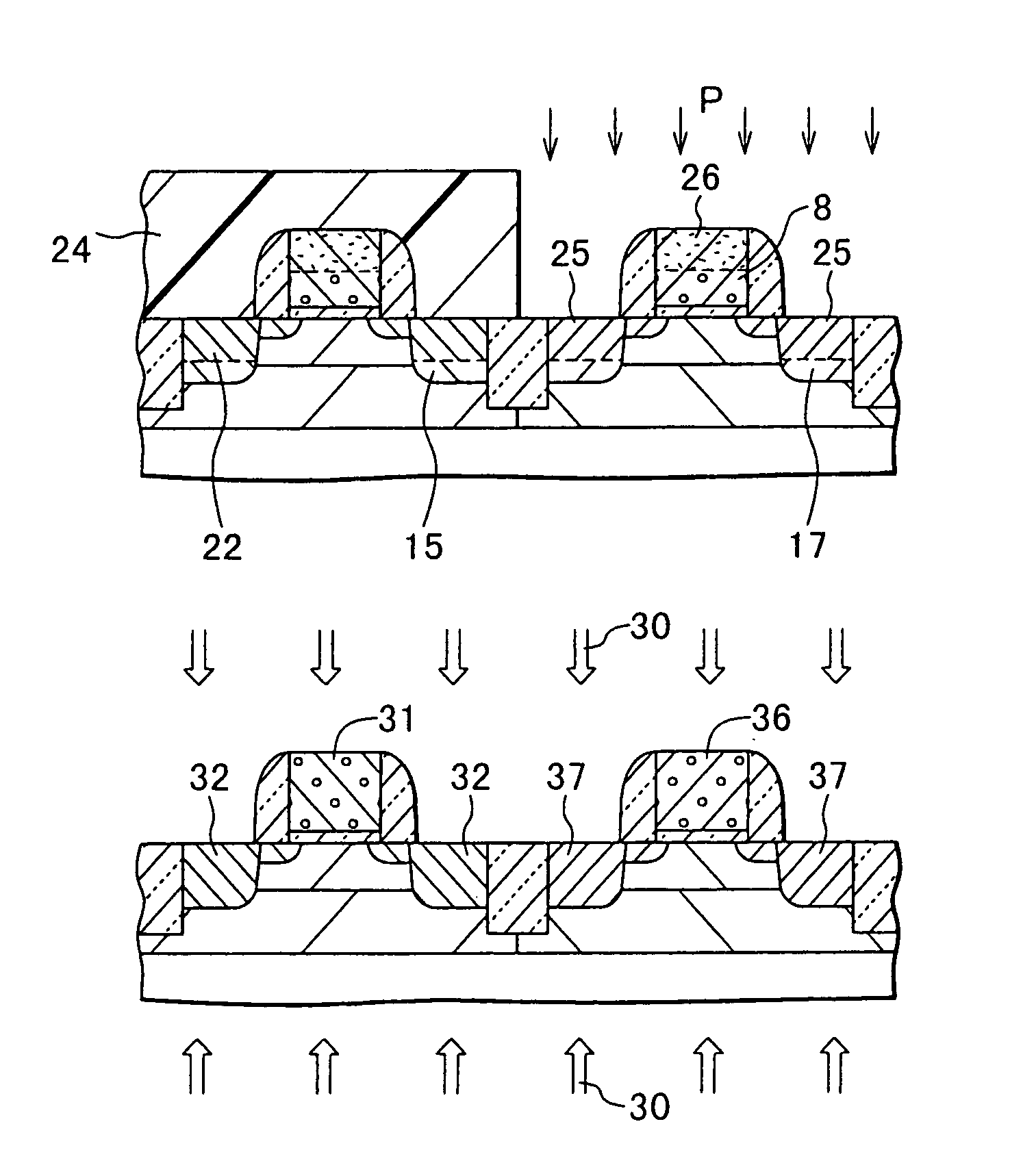

Semiconductor device having shallow trenches and method for manufacturing the same

InactiveUS20050017294A1Reduce capacitanceSufficient breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceSemiconductor

The capacitance between the gate electrode film and the drain layer of semiconductor device is reduced while keeping the resistance low, with the breakdown voltage of the gate insulating film also being maintained at a sufficient level. A trench 10 is formed with the bottom of the trench at a comparatively shallow position in an N-epitaxial layer 18. The thickness of a bottom surface part 16 of a gate electrode film 11 is formed so as to be thicker than other parts of the gate electrode film 11. Also, when a P type body layer 19 is formed, an interface between the P type body layer 19 and an N-epitaxial layer 18 is located at a deeper position than a bottom end of the gate electrode film 11.

Owner:SHINDENGEN ELECTRIC MFG CO LTD

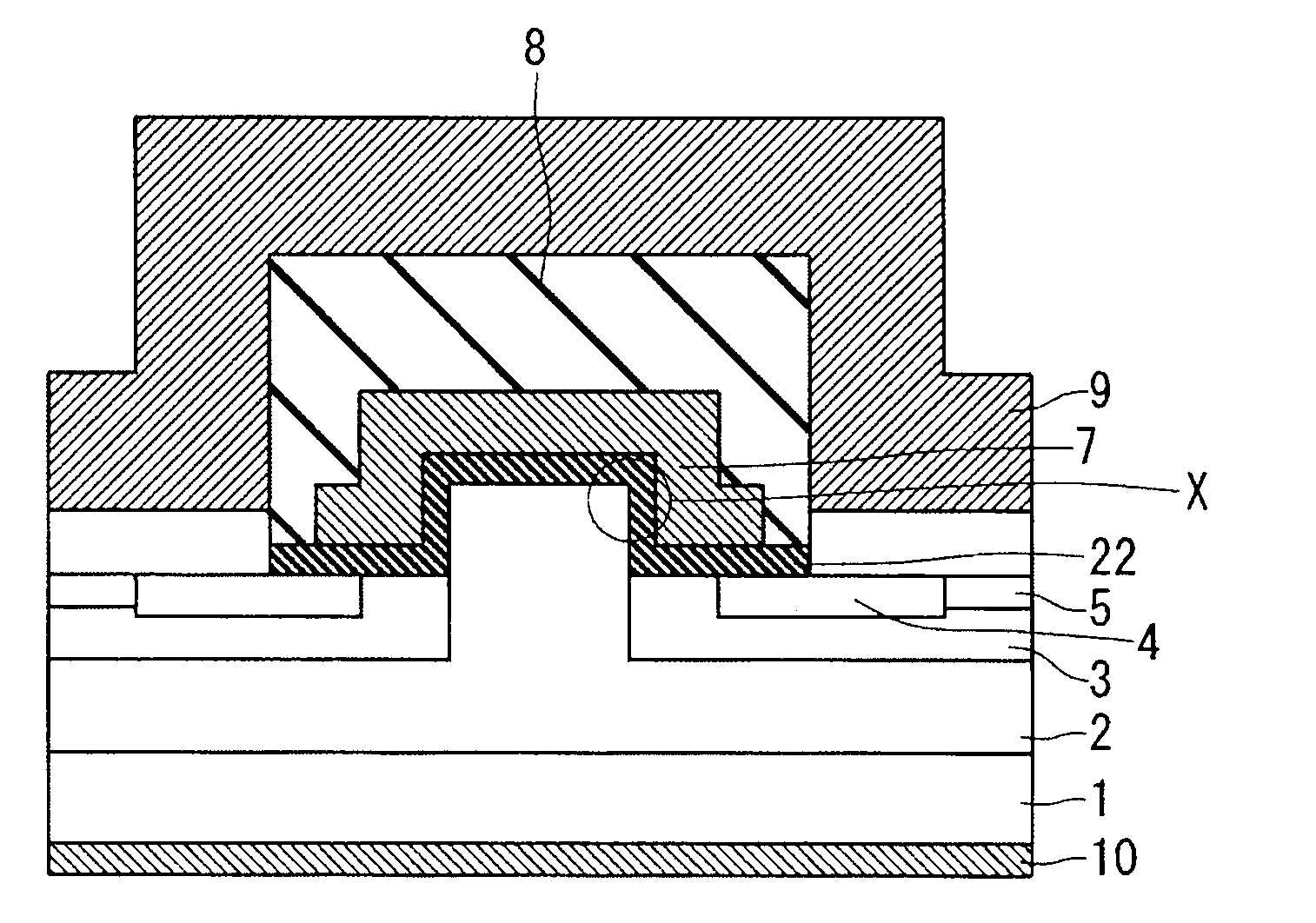

Semiconductor device and method for manufacturing same

InactiveUS7750413B2Reduce the induction currentMade smallSemiconductor/solid-state device detailsSolid-state devicesMOSFETPermittivity

An object of the present invention is to mount both a RF circuit including an inductor formed therein and a digital circuit on a single chip.MOSFETs are formed on a semiconductor substrate 1 in regions isolated by an element isolation film 2. A plurality of low-permittivity insulator rods including a low-permittivity insulator embedded therein and penetrating a first interlevel dielectric film 4 to reach the internal of the silicon substrate are disposed in the RF circuit area 100. An inductor 40 is formed on the interlevel dielectric film in the RF circuit area by using multi-layered interconnects. A high-permeability isolation region in which a composite material including a mixture of high-permeability material and a low-permittivity material is formed in the region of the core of the inductor and periphery thereof.

Owner:NEC CORP

Electronic Component and Electronic-Component Production Method

InactiveUS20080130258A1Improve characteristic impedanceStray capacitanceAnti-noise capacitorsFeed-through capacitorsCapacitanceElectronic component

An electronic component and an electronic-component production method in which the magnitude of a stray capacitance produced between adjacent outer electrodes is controllable. The electronic component includes a chip body and first to fourth outer electrodes. In the chip body, first and second coil block are sandwiched between magnetic substrates. Dielectric layers are interposed between the outer electrodes and the chip body such as to be away from exposed portions of coil patterns in the coil blocks. The dielectric layers have a width larger than a width of the outer electrodes, and a dielectric constant of the dielectric layers is set to be lower than the dielectric constant of the magnetic substrates.

Owner:MURATA MFG CO LTD

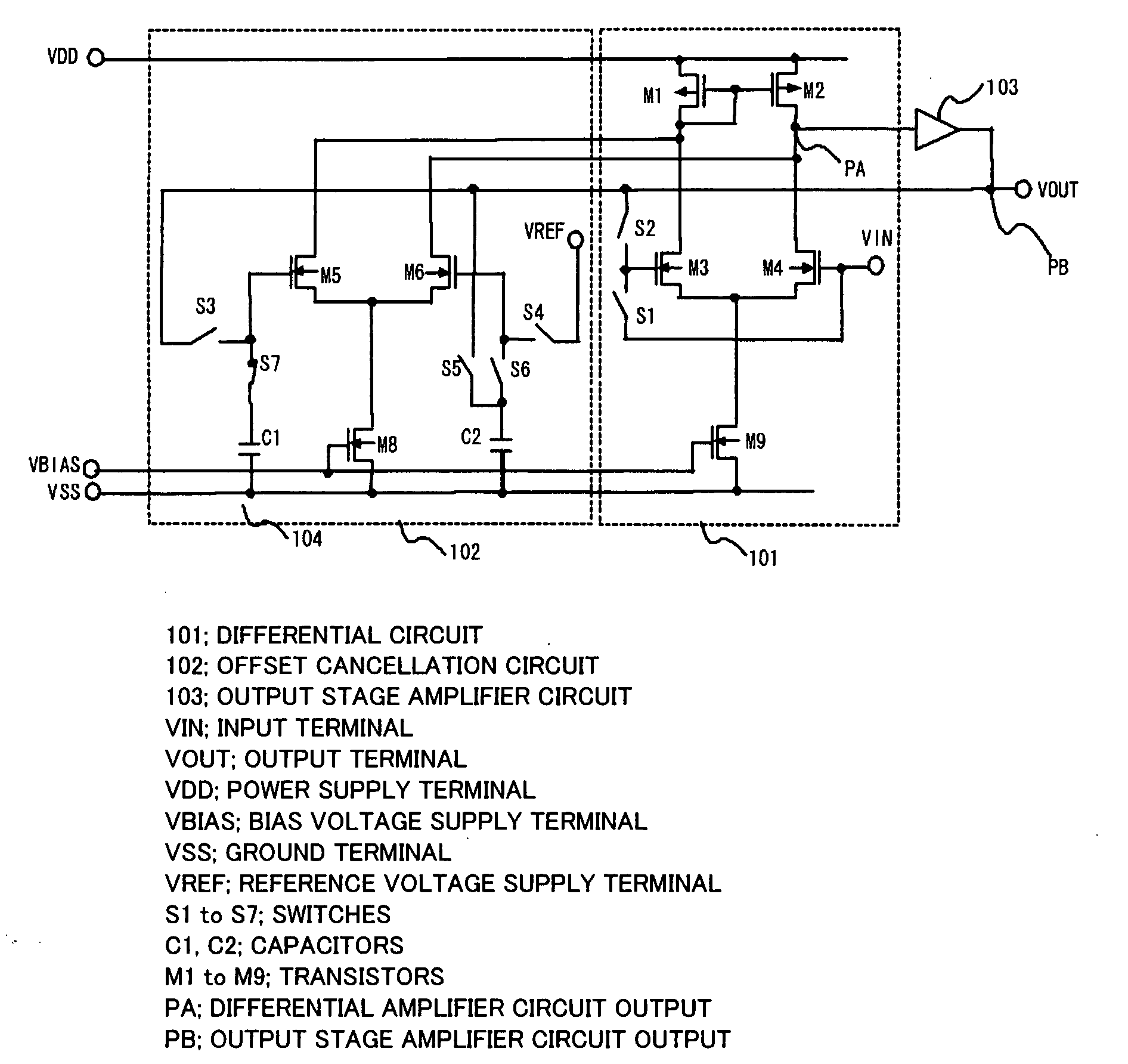

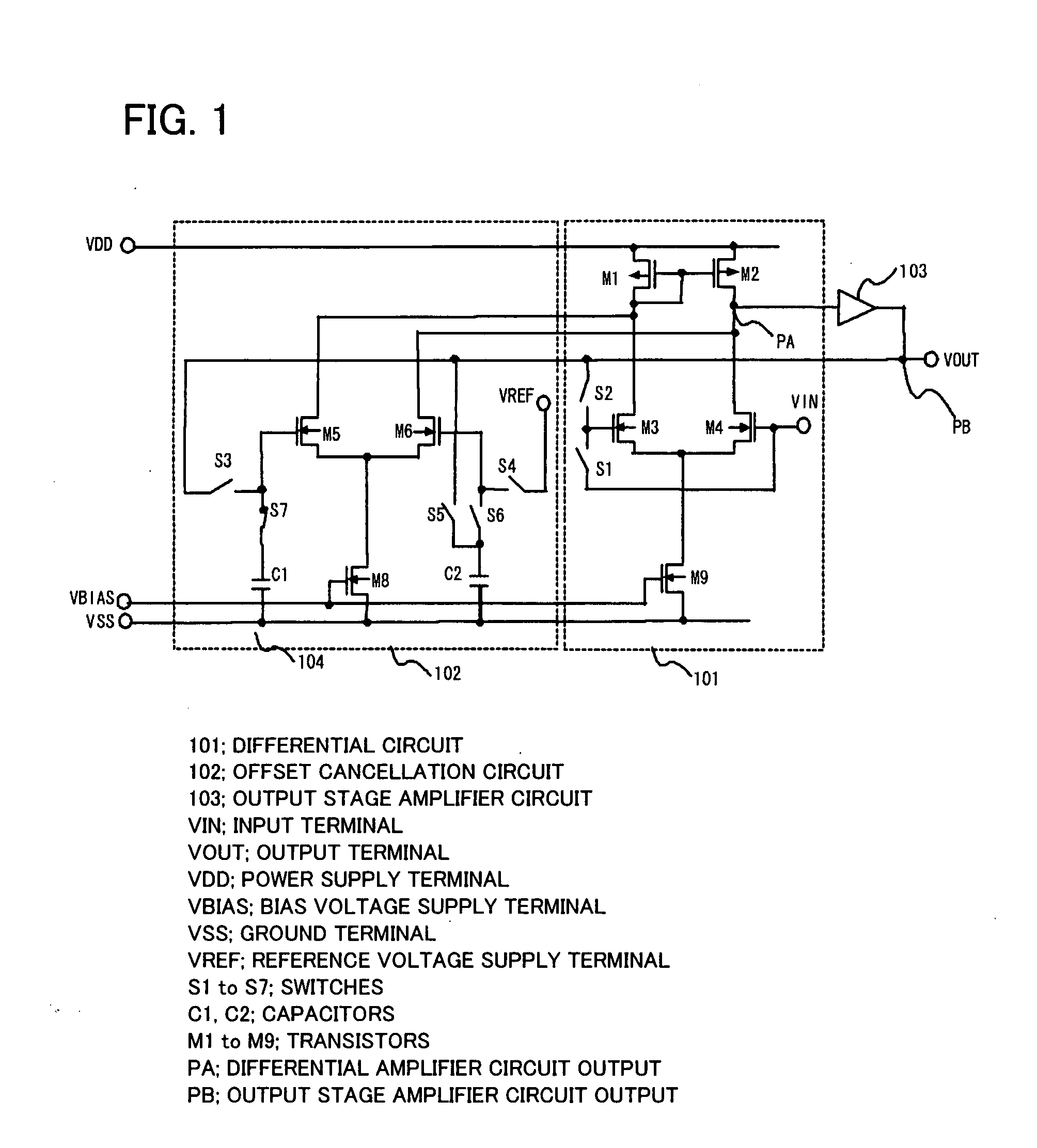

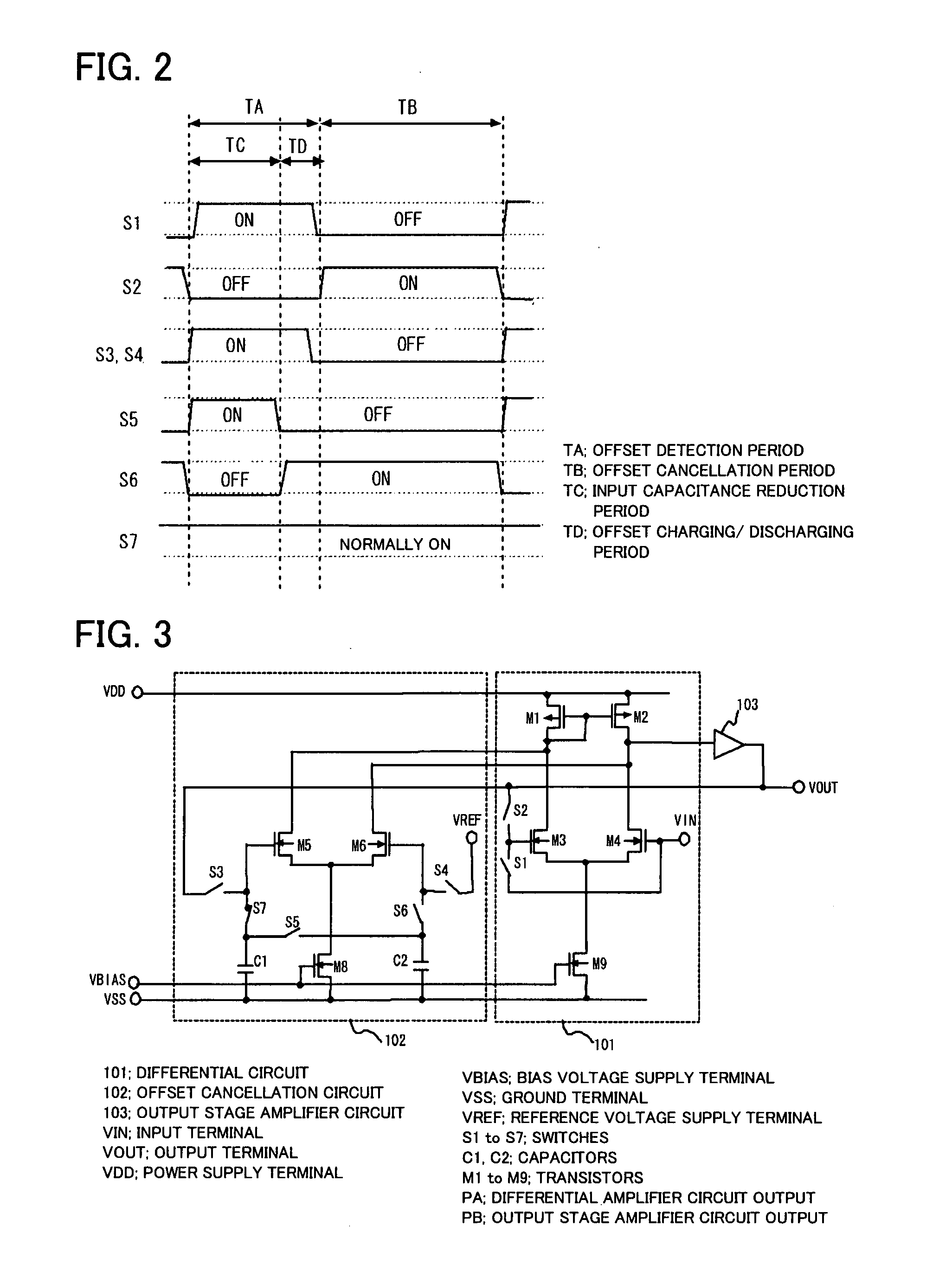

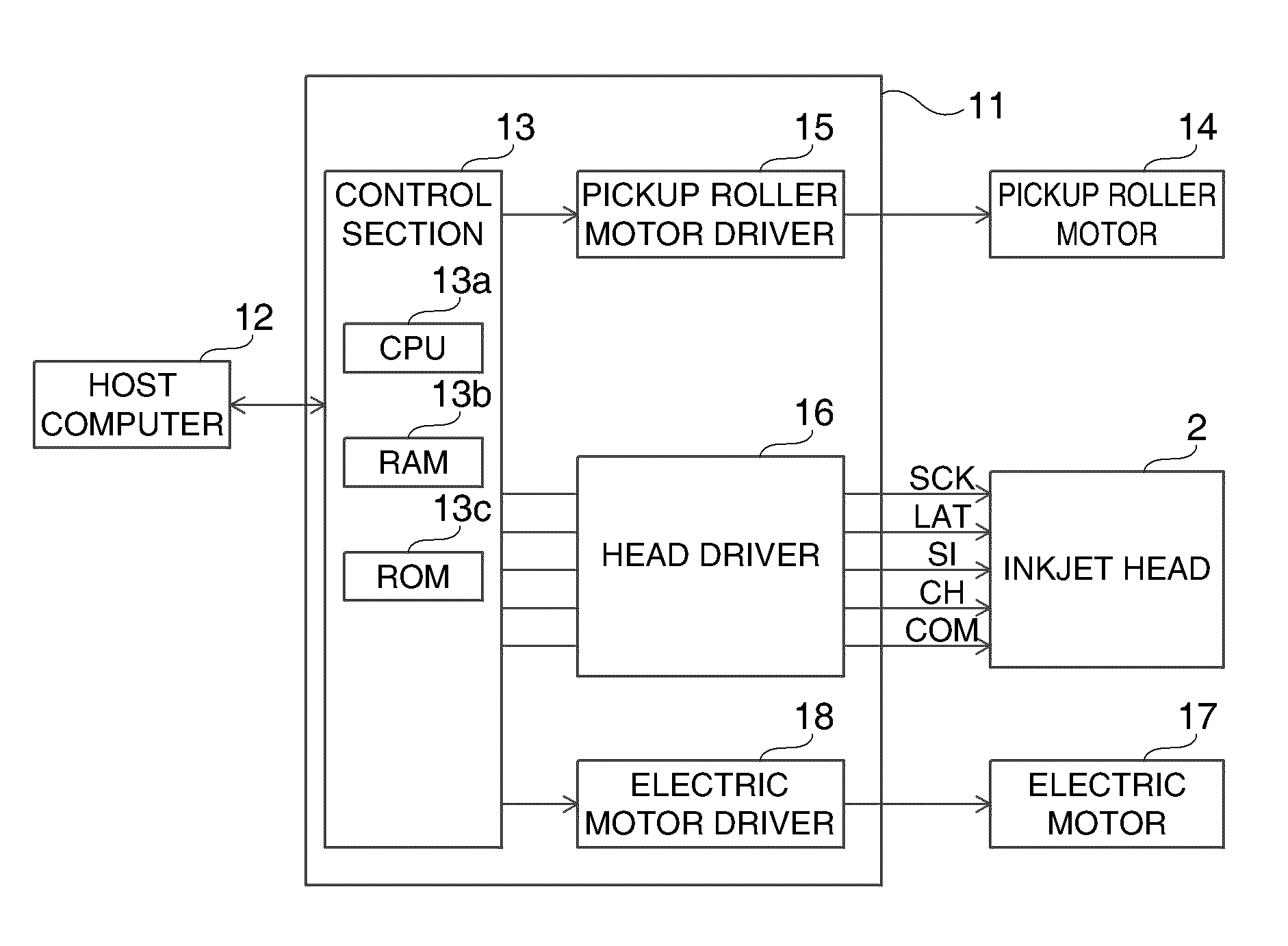

Offset cancellation amplifier, display employing the offset cancellation amplifier and method for controlling the offset cancellation amplifier

InactiveUS20070200620A1Reduction in output accuracyImprove accuracyAmplifier modifications to raise efficiencyAmplifier with semiconductor-devices/discharge-tubesLoad circuitAudio power amplifier

Disclosed is an offset cancellation amplifier which includes a first differential pair, second differential pair, a common load circuit for the two differential pairs, current sources, an amplifier stage, and first and second capacitors. The first capacitor is connected to the gate of one transistor of the first differential pair. During a first period of a data output period, an output voltage and the reference voltage are supplied to the gates of the first differential pair, the second capacitor is disconnected from the gate of the other transistor of the first differential pair. In this state, the output voltage is accumulated in the first and second capacitors. An input voltage is supplied in common to the gates of the second differential pair During the second period, the second capacitor is disconnected from the first capacitor and connected to the gate of the other transistor of the first differential pair. The output voltage is accumulated in the first capacitor, while the reference voltage is accumulated in the second capacitor. During the third period, the gates of the first differential pair cease to be supplied with the output voltage and with the reference voltage, respectively, and are supplied with the voltages accumulated in the first and second capacitors, respectively. The gates of the second differential pair are supplied with the output voltage and with the input voltage, respectively.

Owner:NEC CORP

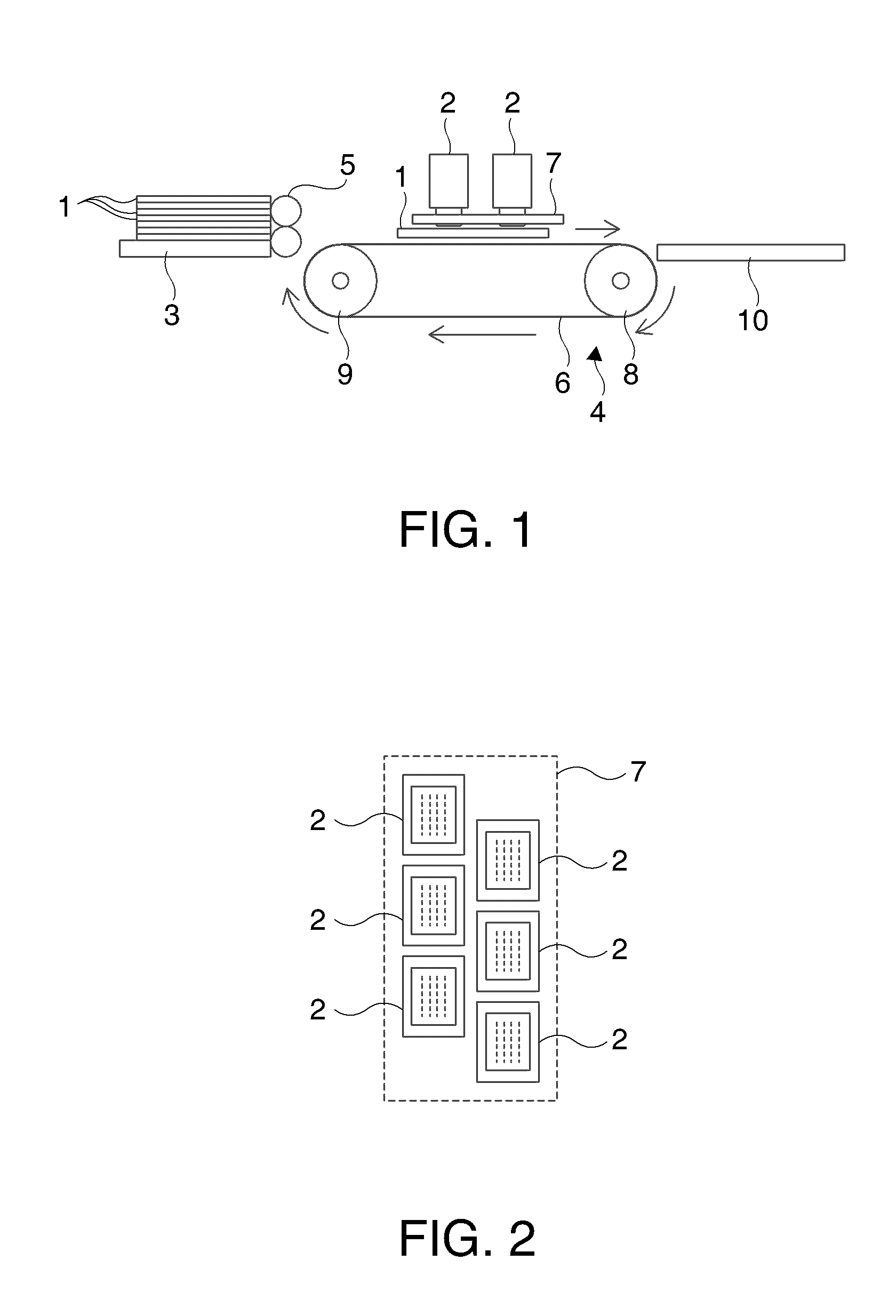

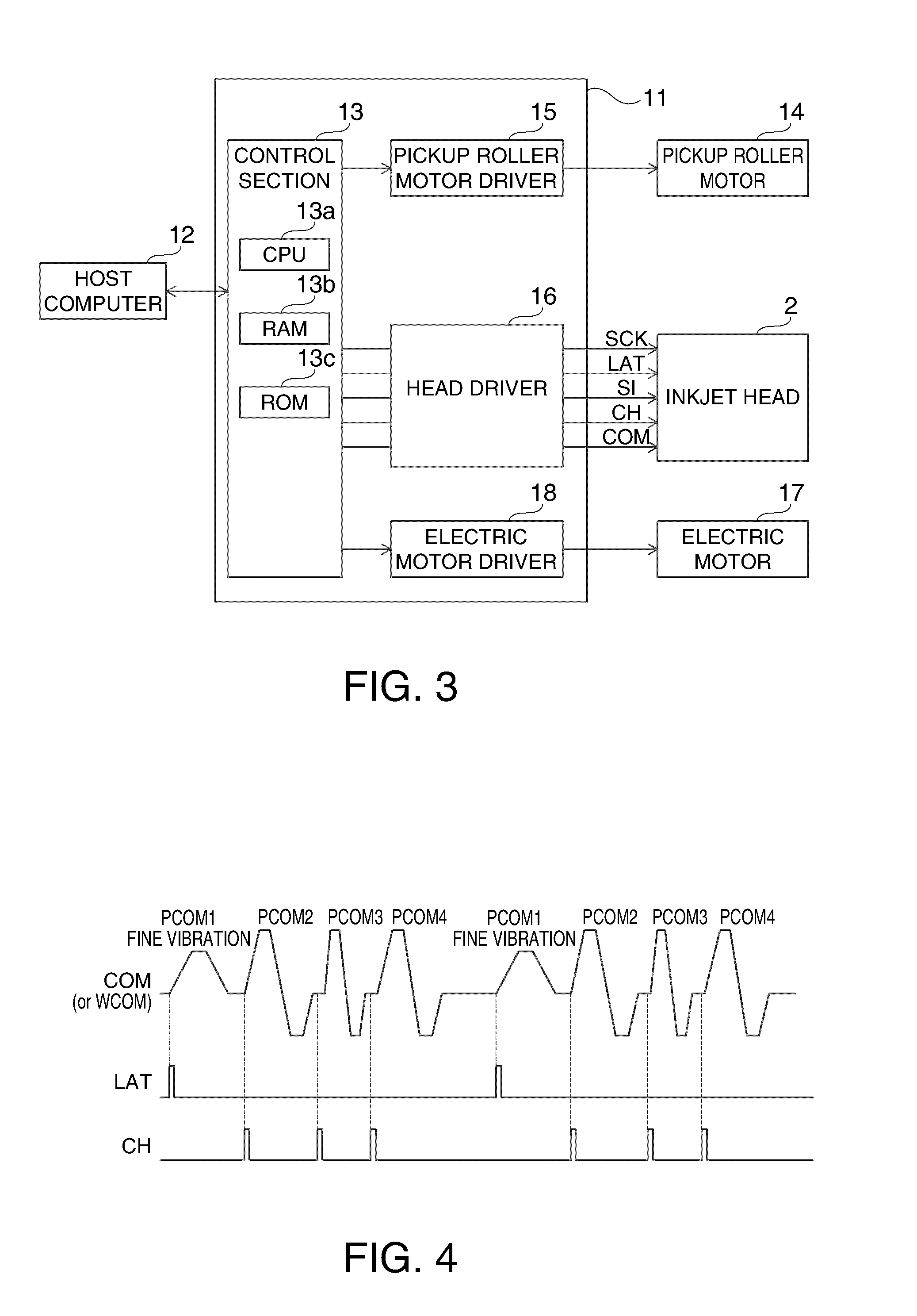

Capacitive load driving device and liquid jet apparatus

InactiveUS20110254887A1Improve accuracySuppression capacitanceElectric pulse generatorOscillations generatorsLiquid jetCapacitance

A capacitive load driving device includes a drive waveform generator that generates a drive waveform signal, a subtractor that outputs a difference signal between the drive waveform signal and a feedback signal, a modulator that pulse-modulates the difference signal to output a modulated signal, a digital power amplifier that amplifies the modulated signal to output an amplified digital signal, a low pass filter that smoothes the amplified digital signal to output a drive signal for a capacitive load, a feedback circuit that outputs the feedback signal obtained from the drive signal, and an adjusting section that adjusts frequency characteristics of the feedback circuit based on capacitance of the capacitive load to be driven.

Owner:SEIKO EPSON CORP

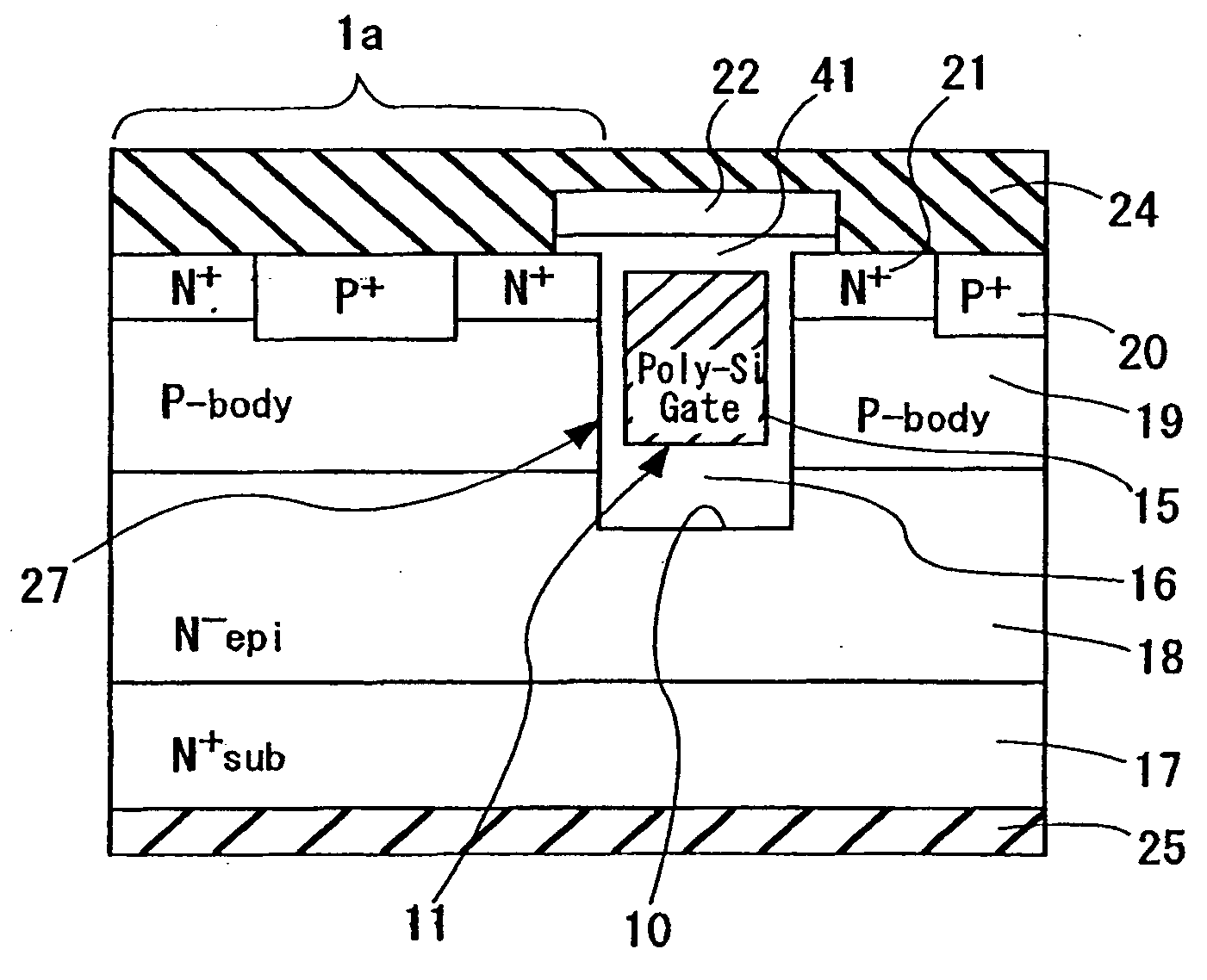

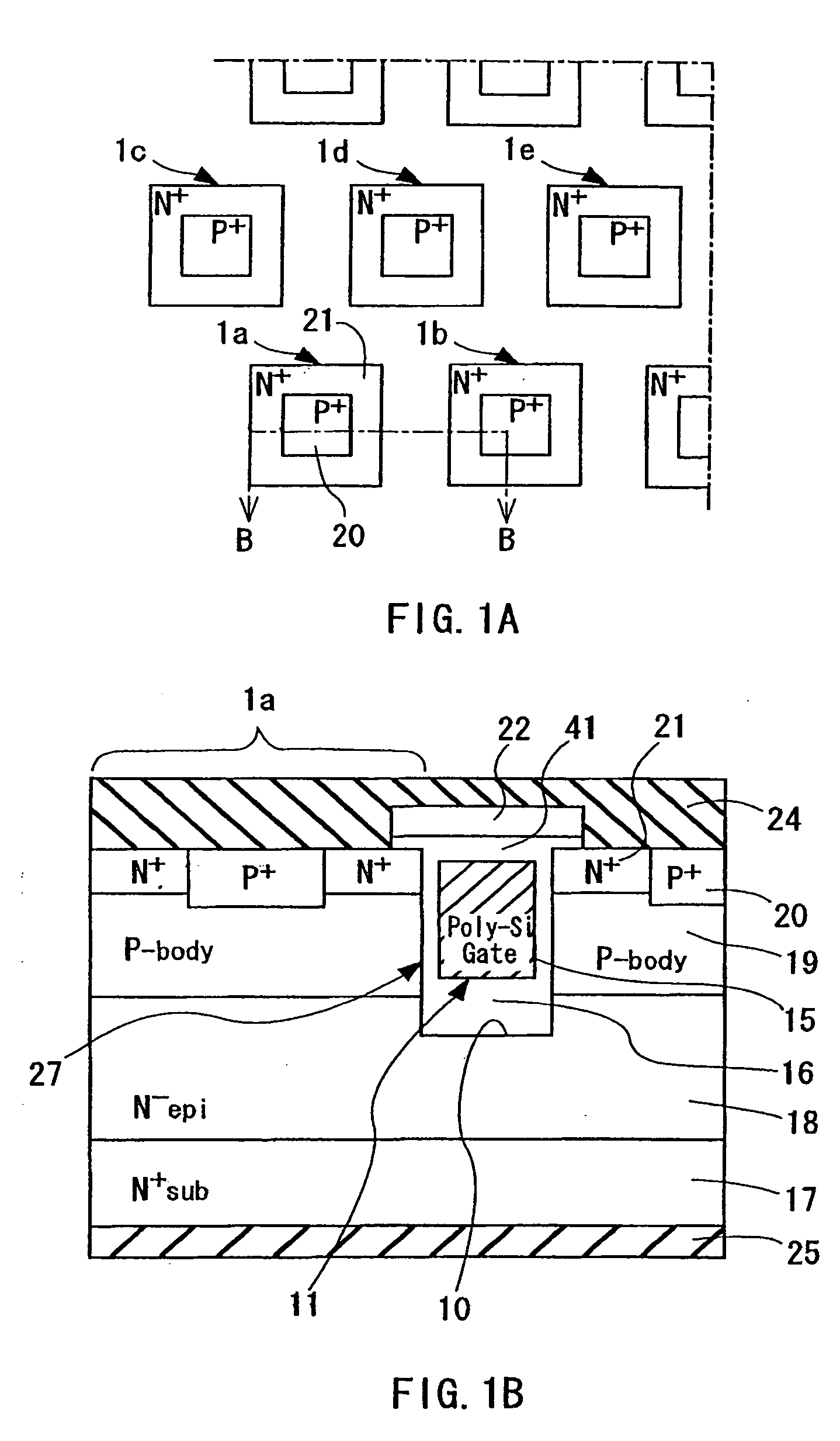

Semiconductor device and method for manufacturing the same

ActiveUS20120112266A1Lowered intensity of electric fieldSuppressing gate capacitanceSemiconductor/solid-state device detailsSolid-state devicesPhysicsSemiconductor

A semiconductor device of the present invention includes: a semiconductor substrate of a first conductive type; an epitaxial layer of the first conductive type formed on the semiconductor substrate and having a protrusion formed on a surface thereof; a well region of a second conductive type formed on the surface of the epitaxial layer at each side of the protrusion; a source region of the first conductive type selectively formed in a surface of the well region; a gate insulating film formed so as to cover at least the protrusion and the surface of the well region; and a gate electrode formed on a part of the gate insulating film corresponding to the protrusion. The gate insulating film is thicker in a region thereof corresponding to an upper surface of the protrusion than the other regions thereof.

Owner:MITSUBISHI ELECTRIC CORP

Semiconductor device having shallow trenches and method for manufacturing the same

InactiveUS7397082B2CapacitanceReduce capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceEngineering

Owner:SHINDENGEN ELECTRIC MFG CO LTD

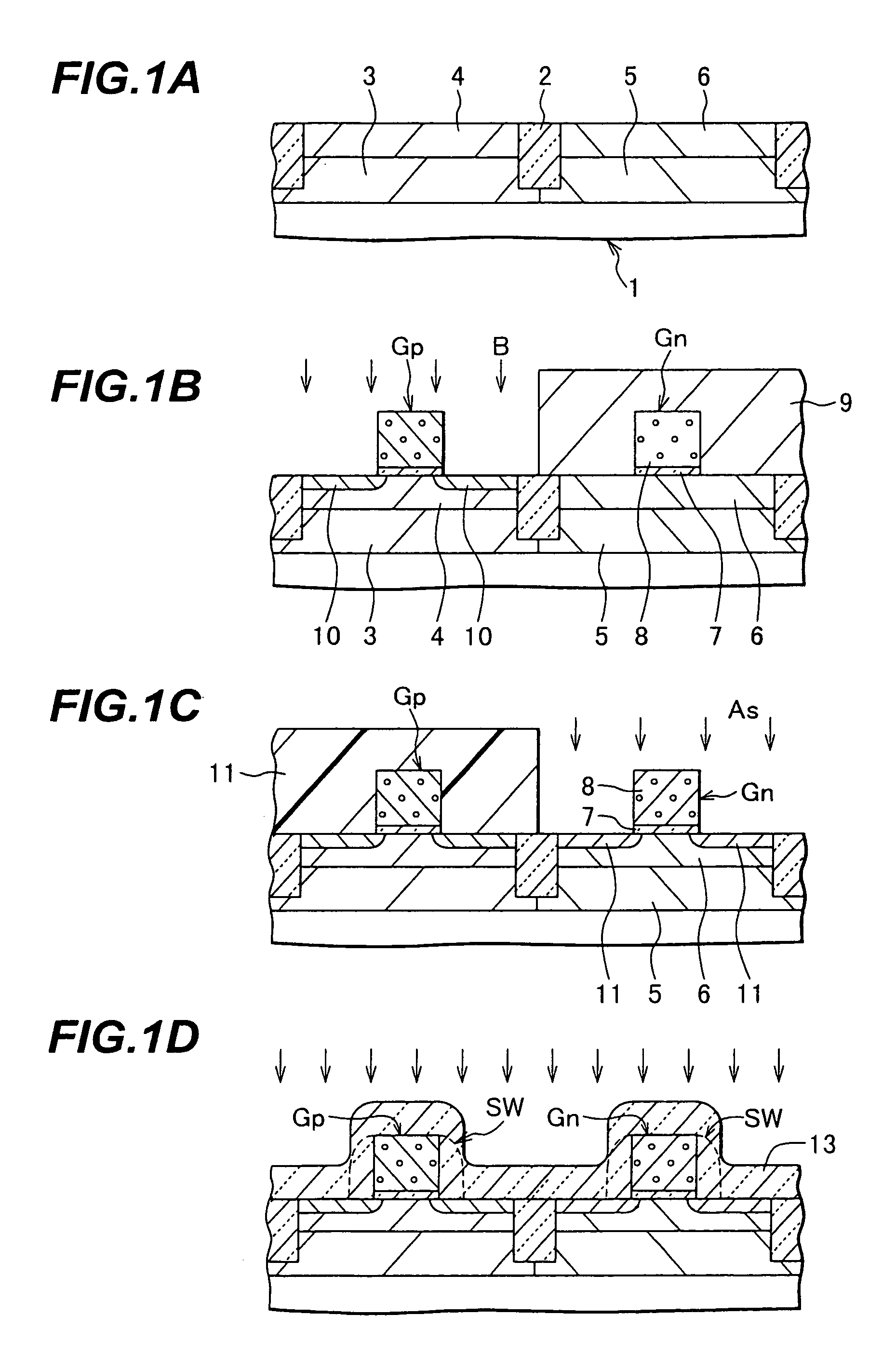

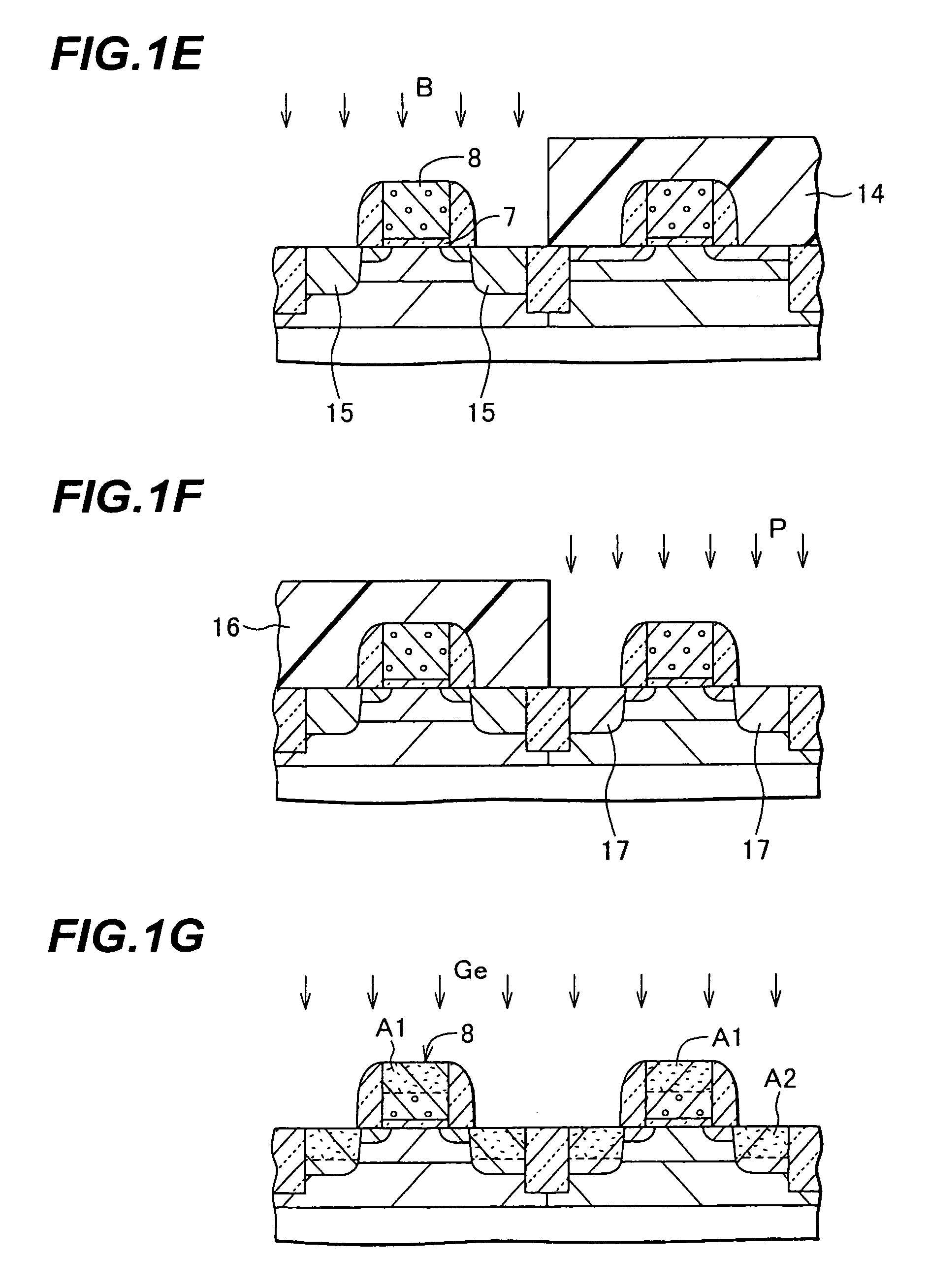

Semiconductor device manufacture method capable of supressing gate impurity penetration into channel

InactiveUS7135393B2Increase capacitanceIncrease currentTransistorSemiconductor/solid-state device manufacturingHigh concentrationDevice material

A gate electrode is formed above an n-type well including an n-type threshold voltage adjustment region, ions of p-type impurity are implanted with a low acceleration energy to form extension regions in the n-type well on both sides of the gate electrode, side wall spacers are formed on the side walls of the gate electrode, ions of p-type impurity are implanted with a small dose causing substantially no abnormal tailing in the gate electrode and with a relatively high acceleration energy to form p-type source / drain regions deeper than the threshold adjustment region, ions of atoms are implanted into the semiconductor substrate to change the upper parts of the gate electrode and the source / drain regions to amorphous state, ions of p-type impurity are implanted with a large dose to form high-concentration parts in the source / drain regions, and the impurities introduced by the ion implantation are activated.

Owner:FUJITSU SEMICON LTD

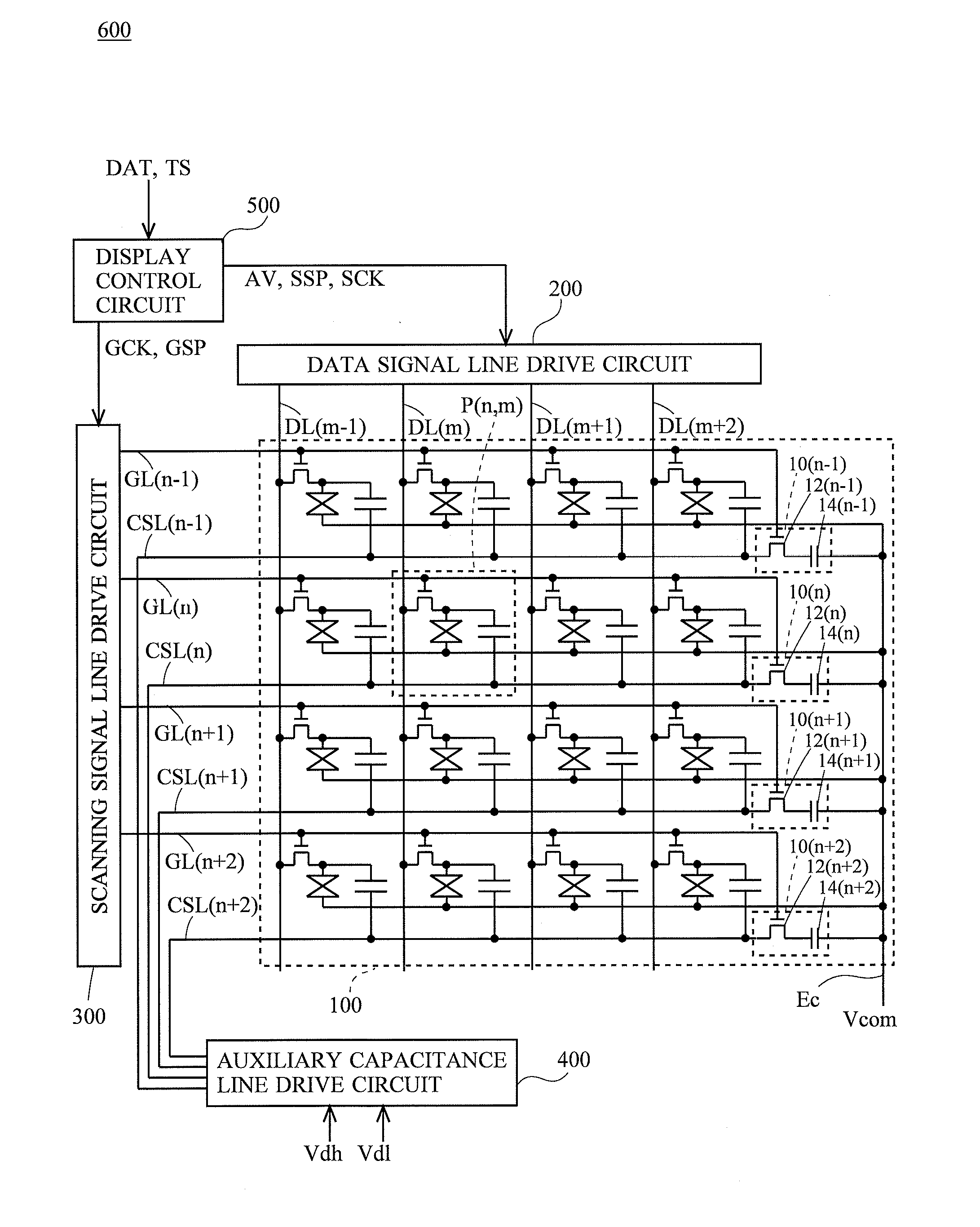

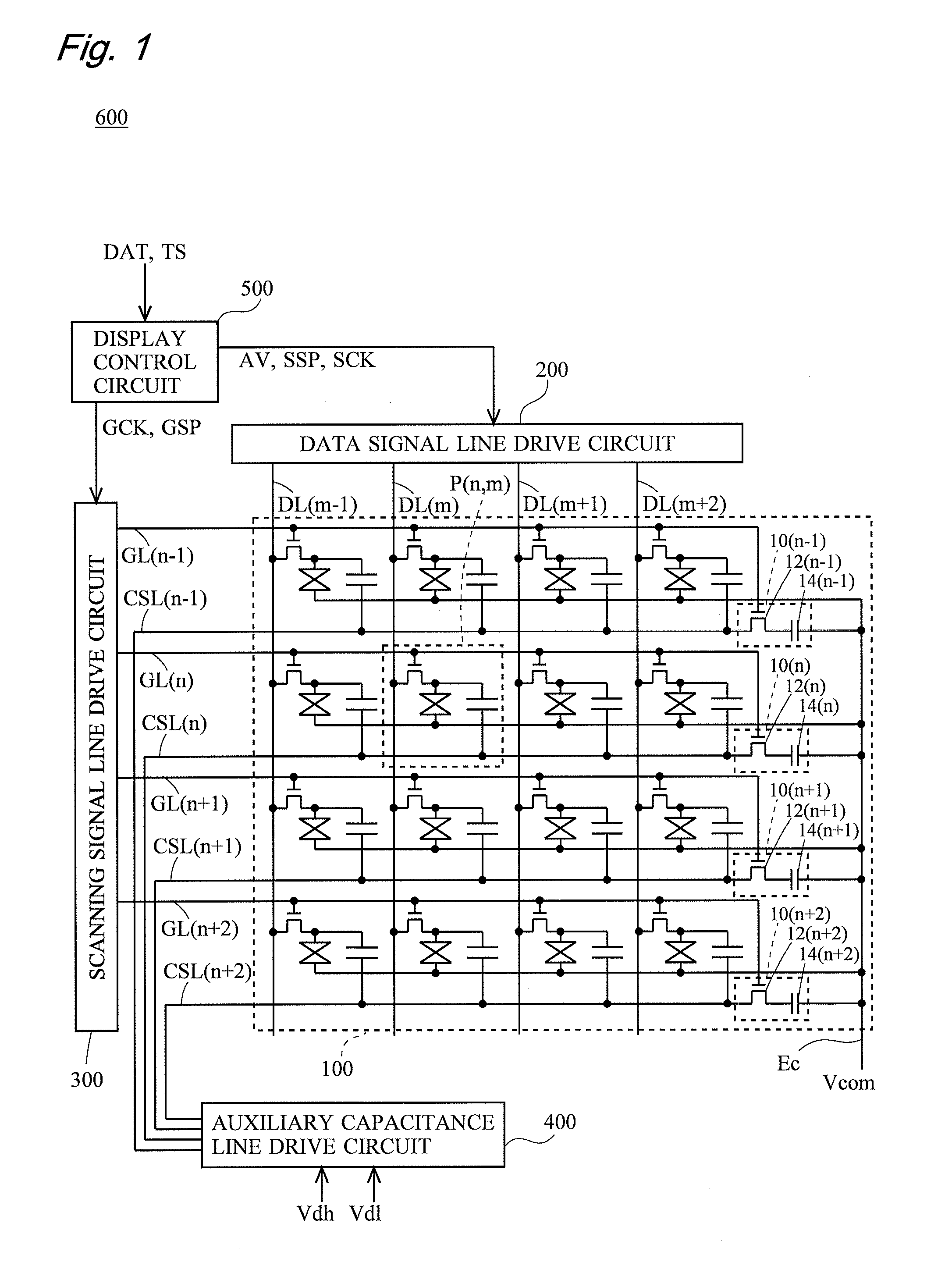

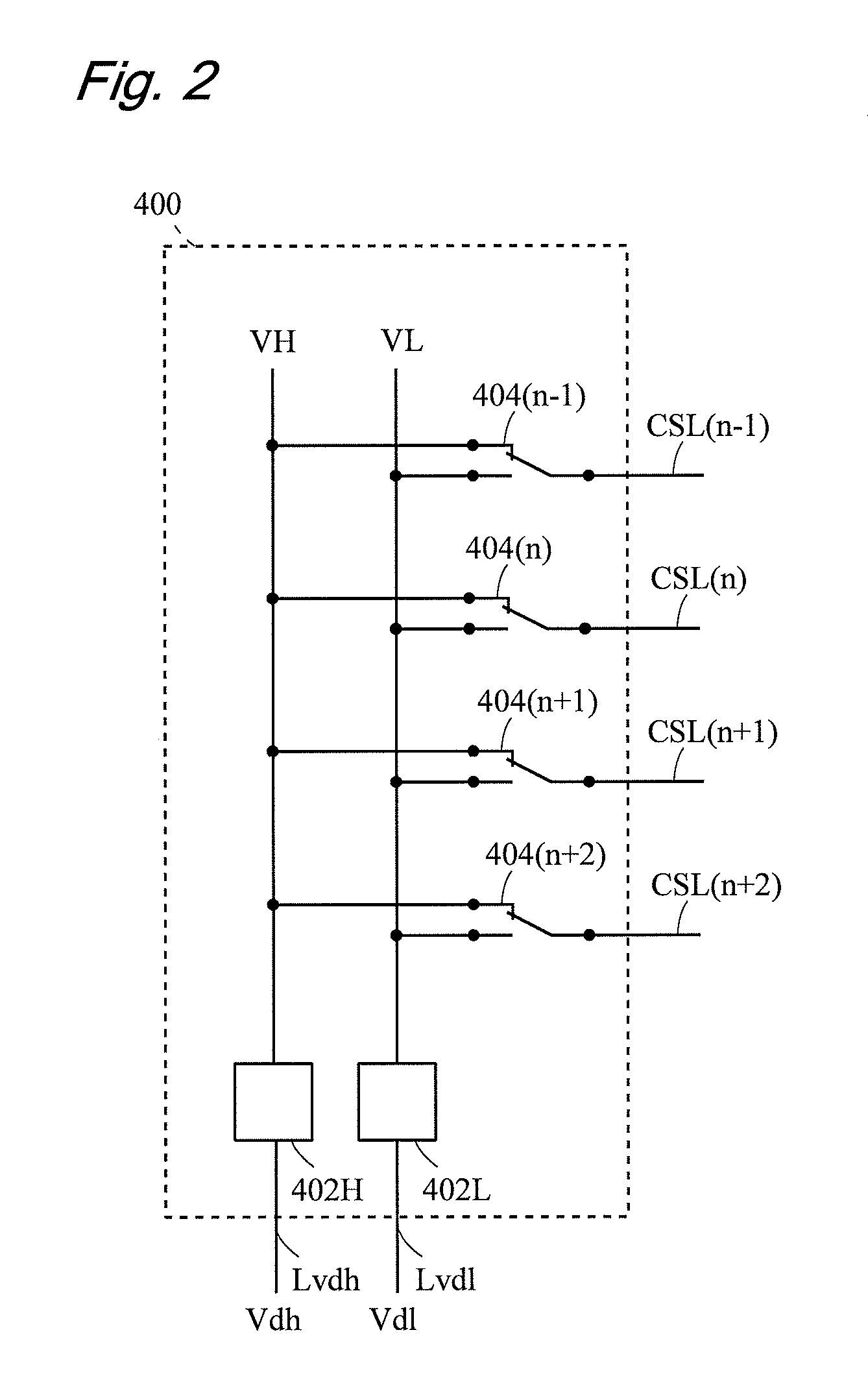

Display device

InactiveUS20130321367A1Avoid volatilityReduce power consumptionCathode-ray tube indicatorsInput/output processes for data processingCapacitanceLiquid-crystal display

A display panel of a liquid crystal display device includes smoothing parts provided on an output end side of auxiliary capacitance lines. Through the smoothing parts, the auxiliary capacitance lines arranged along scanning signal lines and a common electrode are connected to each other. The smoothing parts each have a correction TFT and a capacitor. A source electrode of the correction TFT and each of the auxiliary capacitance lines are connected to each other, and a drain electrode and the common electrode are connected to each other through each of the capacitors. The correction TFT is controlled so as to enter a conductive state when the scanning signal line is in a selected state, and enter a shut state when the scanning signal line is in a non-selected state.

Owner:SHARP KK

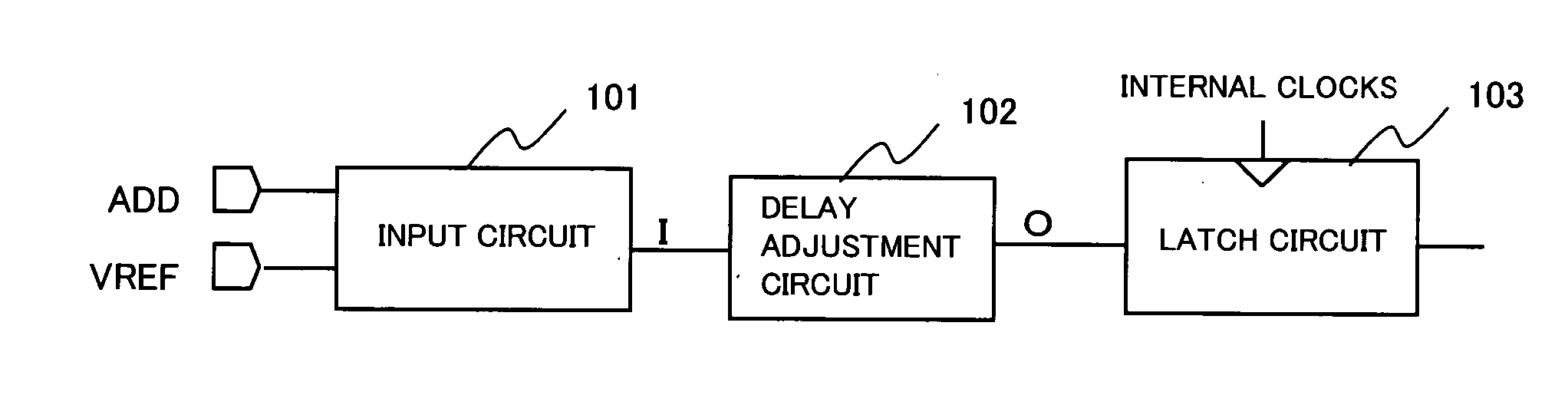

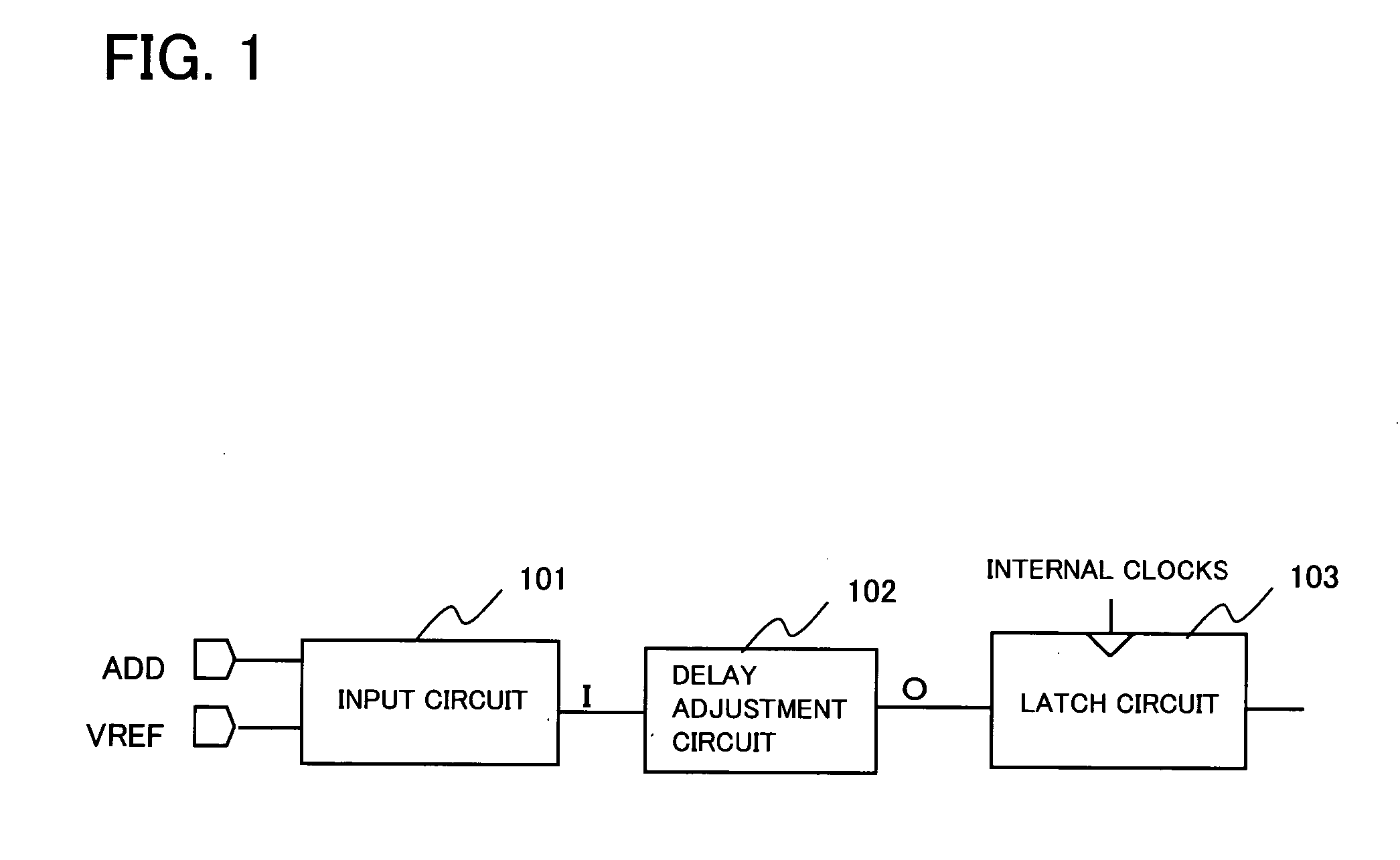

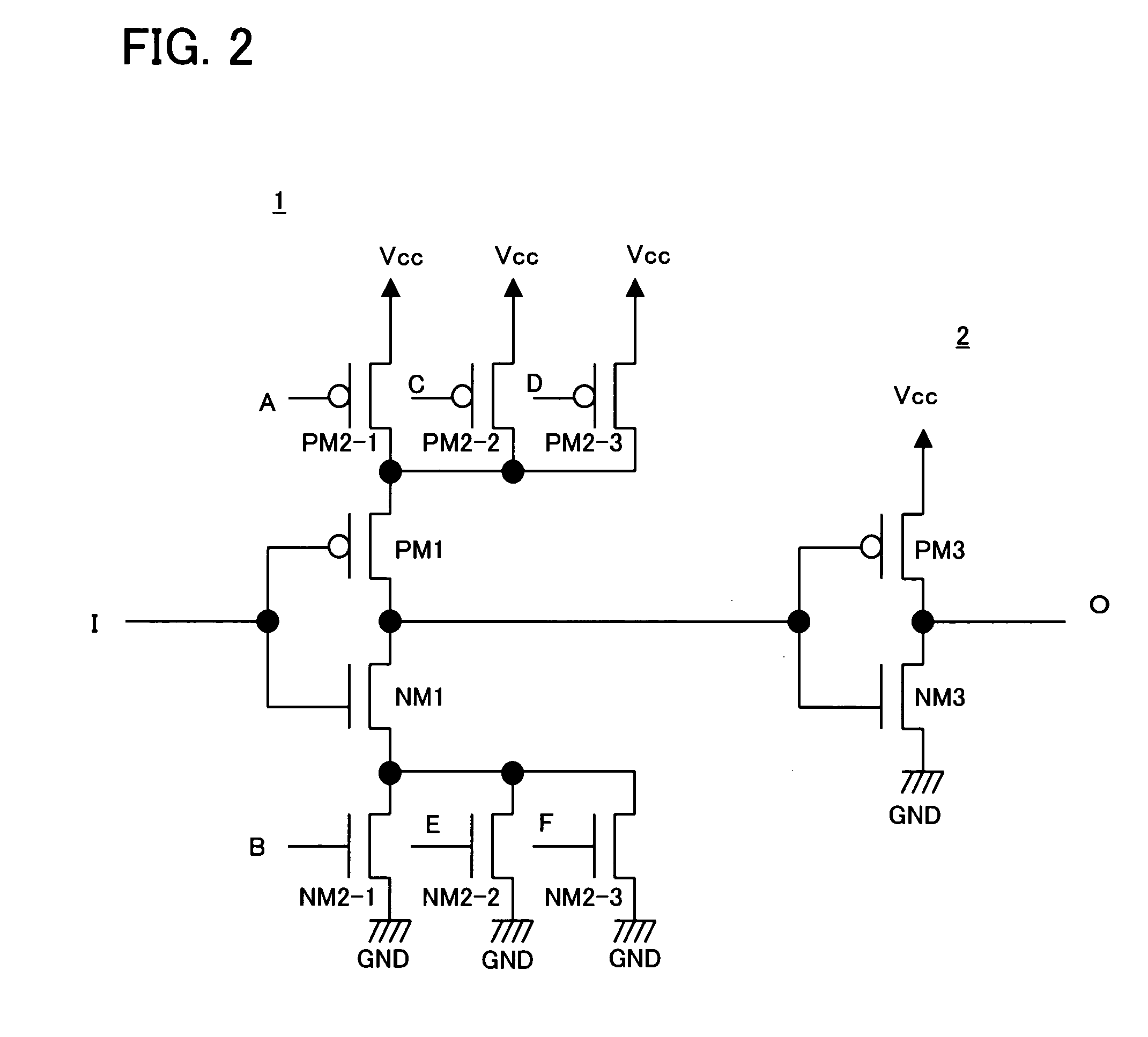

Delay adjustment circuit and synchronous semiconductor device having the delay adjustment circuit

InactiveUS20070046354A1Suppression capacitanceReduce capacitanceSingle output arrangementsTime-delay networksEngineeringSemiconductor

Disclosed is a delay adjustment circuit including a first set of transistors, which are connected between a PMOS transistor forming an inverter and a power supply in parallel and have gates supplied with control signals, respectively, a second set of transistors which are connected between an NMOS transistor forming the inverter, and the ground GND, in parallel and have gates supplied with control signals, respectively, and another inverter receiving an output of the inverter as an input. At least one of the transistors of the first set of transistors and at least one of the transistors of the second set of transistors are set in an on-state.

Owner:ELPIDA MEMORY INC

Semiconductor device

InactiveUS20090179273A1Reduce parasitic capacitanceImprove breakdown voltageSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductorImpurity

A semiconductor device according to the present invention includes: a first region having a first conductive type; a plurality of second regions having a second conductive type that differs from the first conductive type, and formed to be arranged in the first region; a plurality of third regions having the first conductive type and formed in the second regions; an electrode forming a channel between the first region and the third region; and a plurality of extended second regions having the second conductive type, arranged in the first region such as to individually include one of the second regions and having an impurity density that is lower than an impunity density of the second regions.

Owner:YOKOGAWA ELECTRIC CORP

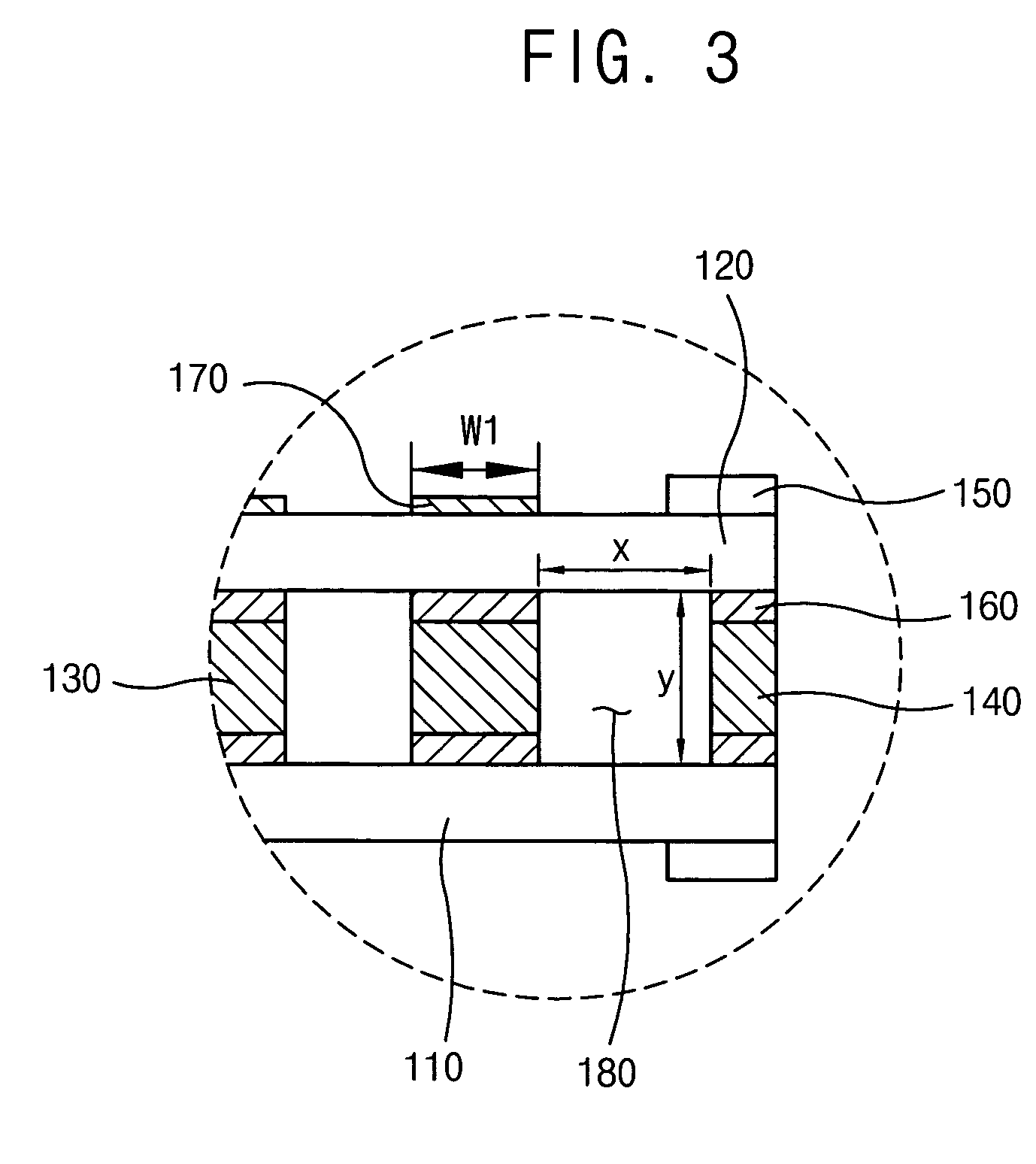

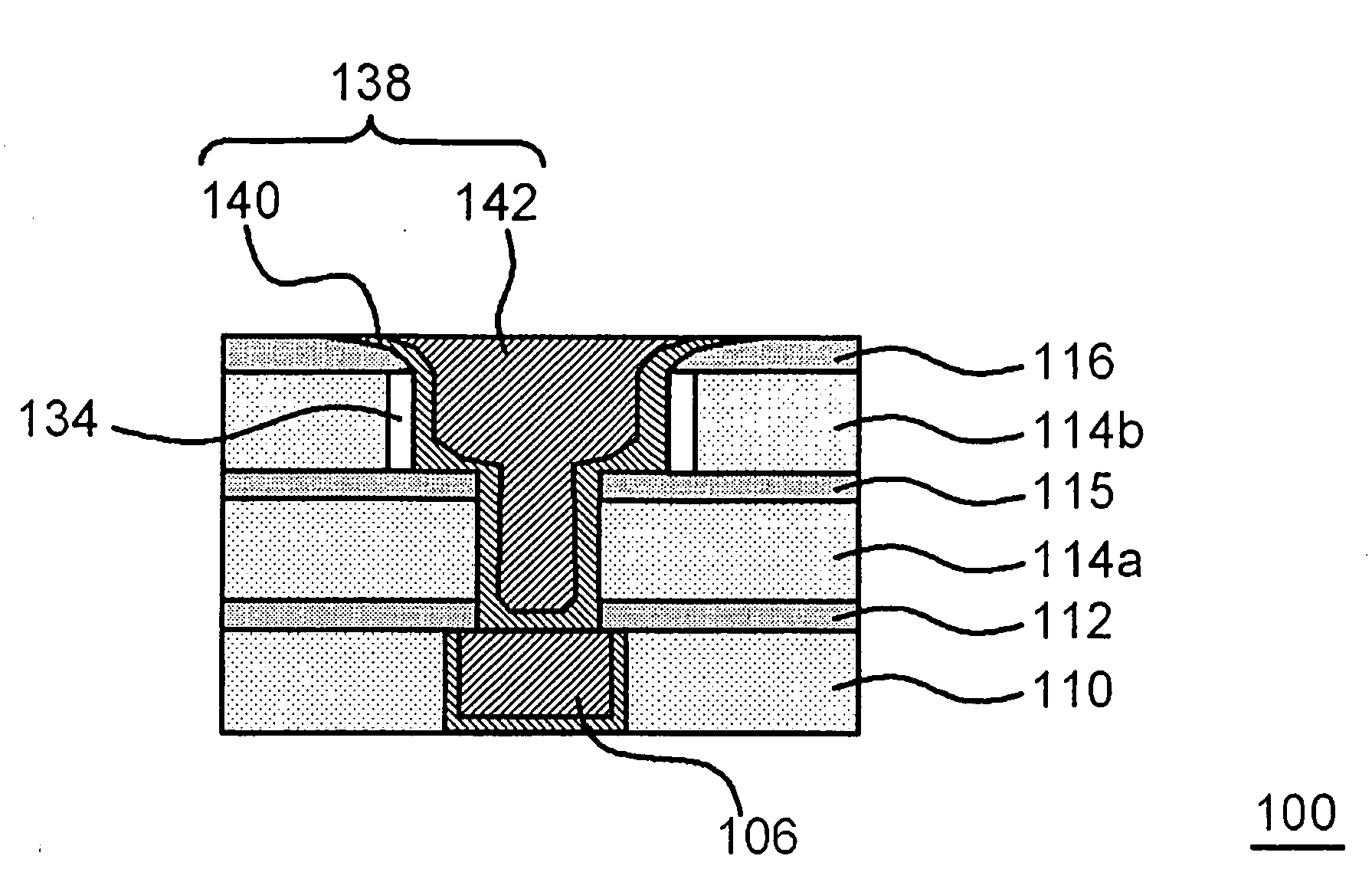

Surface light source device and back light unit having the same

InactiveUS20050200258A1Suppress formationImprove luminanceIncadescent body mountings/supportElectrode assembly support/mounting/spacing/insulationLight sourceParasitic capacitance

A surface light source device includes a light source body having an inner space into which a discharge gas is injected, and an electrode for applying a voltage to the discharge gas. The light source body includes partition walls dividing the inner space into a plurality of discharge spaces. The partition walls have a width for suppressing formation of a parasite capacitance through which a current flows therein.

Owner:SAMSUNG CORNING CO LTD

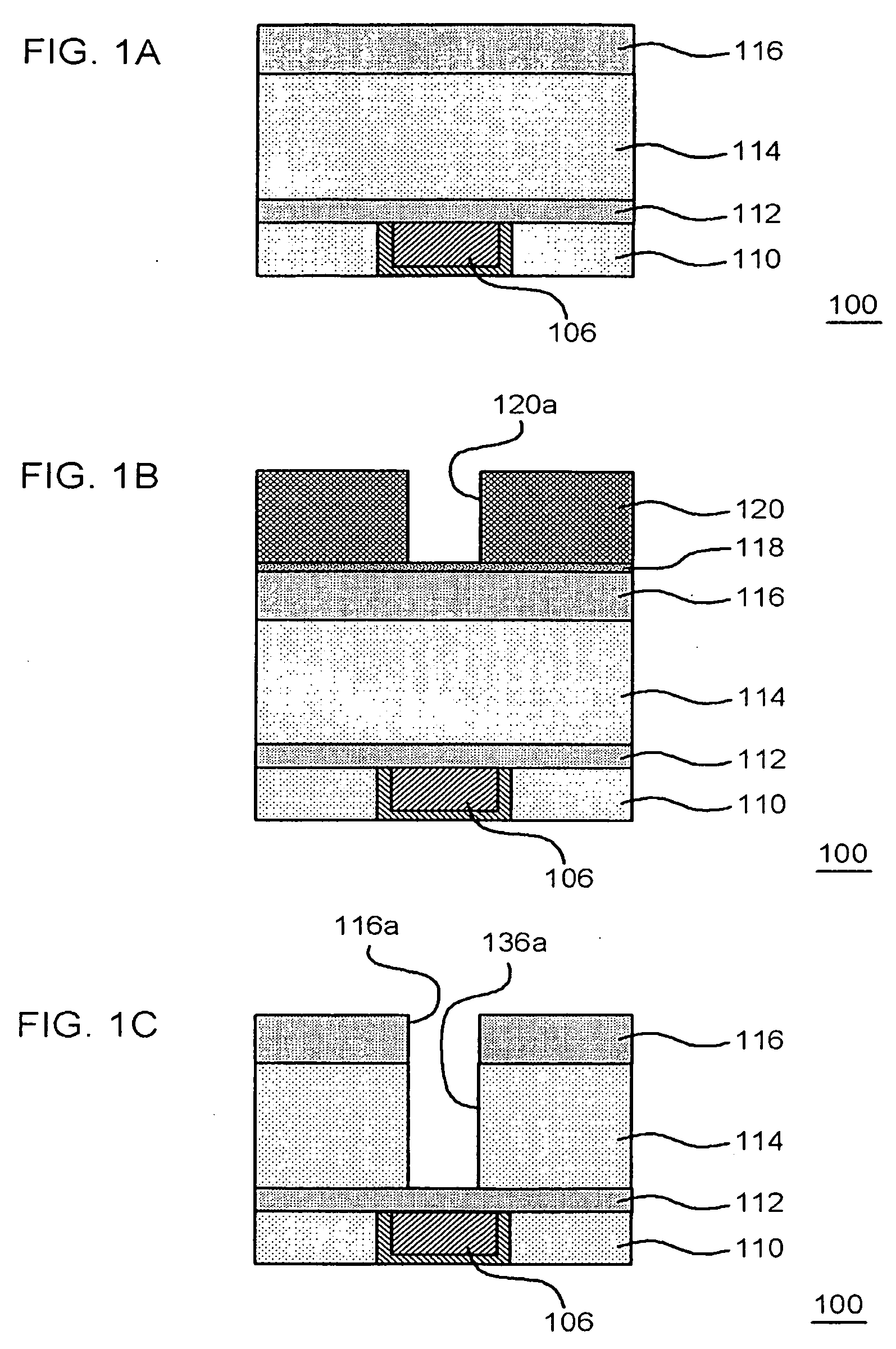

Semiconductor device and method for manufacturing the same

ActiveUS20100102451A1Suppress increment in capacitanceIncrement in capacitanceSemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

A trench is formed by a process which removes a damage layer formed on a sidewall of a low dielectric constant layer, a process which forms a second protection insulating layer by a chemical vapor deposition (CVD) technique and forms a second concave portion by covering a sidewall of the low dielectric constant layer with the second protection insulating layer, and a process which shapes the second protection insulating layer by etch back so that a trench has a sidewall that the second protection insulating layer is selectively formed on a surface of the low dielectric constant layer.

Owner:RENESAS ELECTRONICS CORP

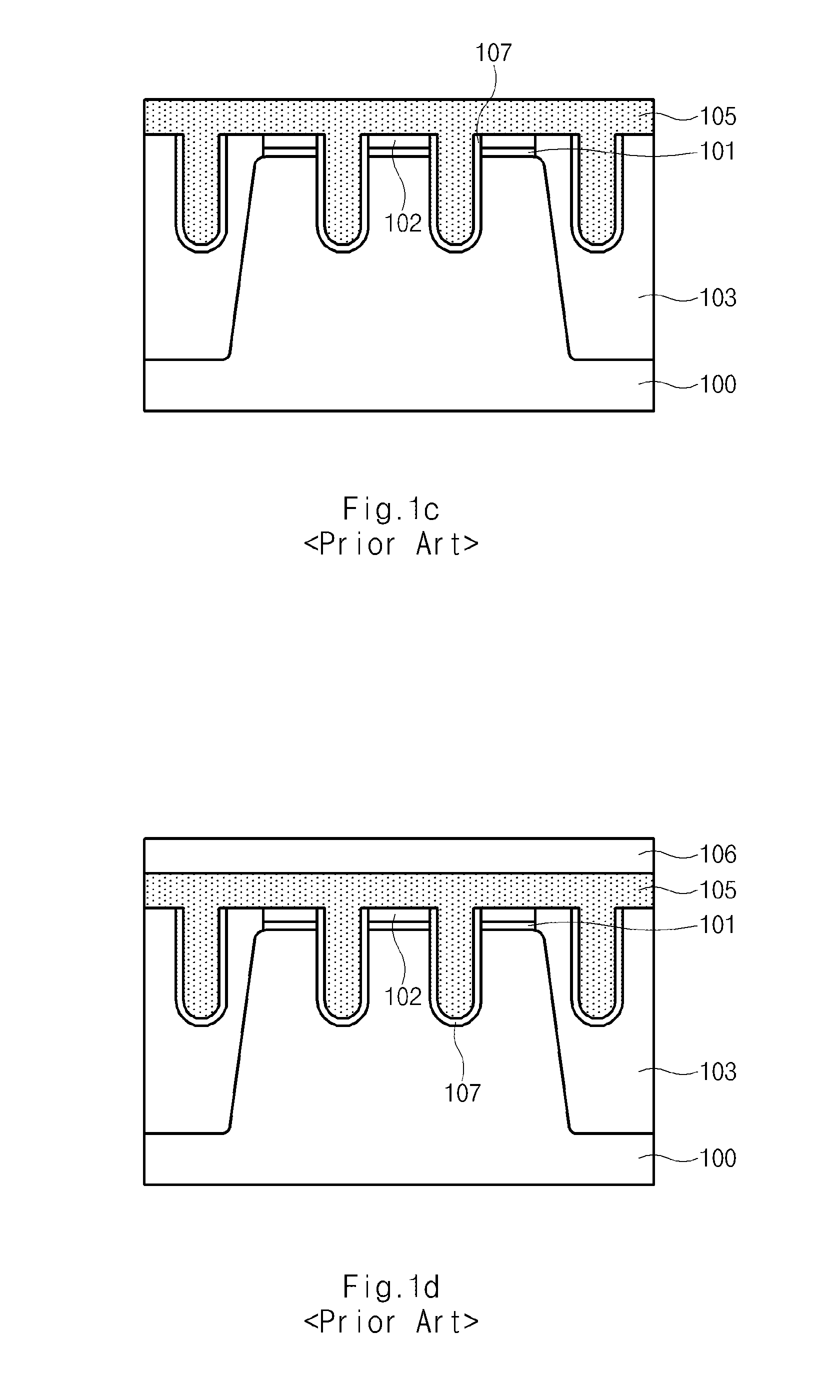

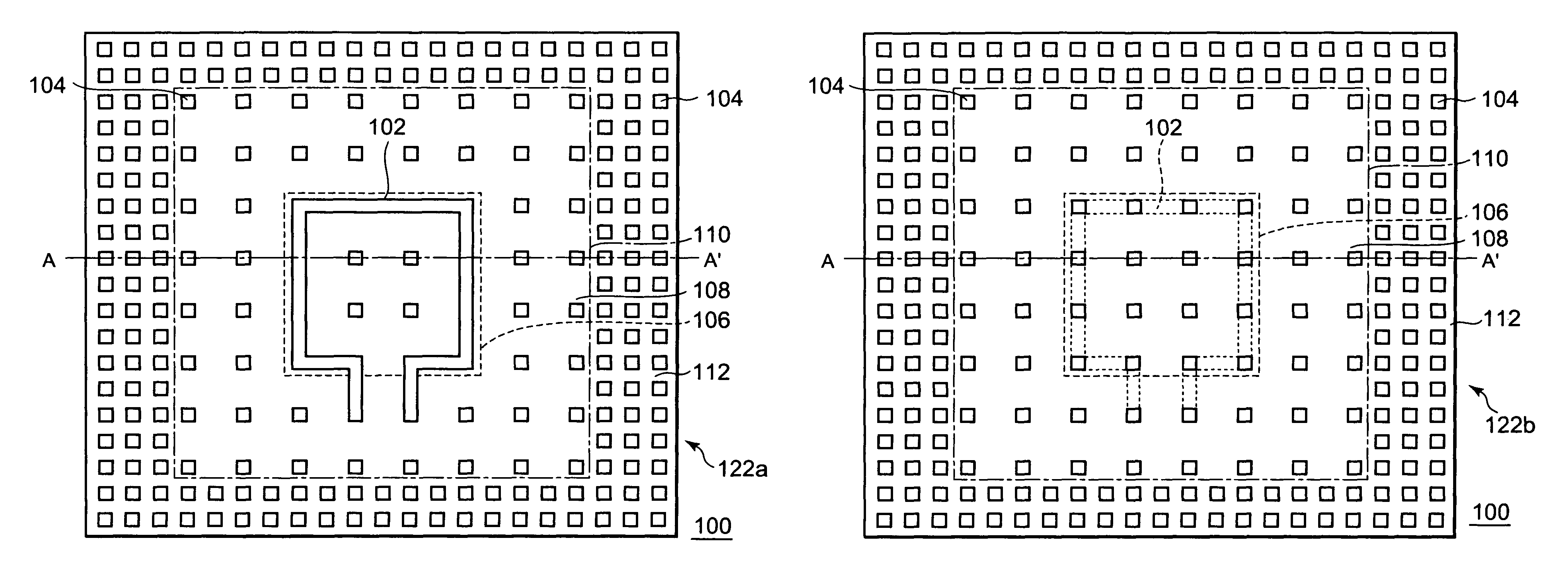

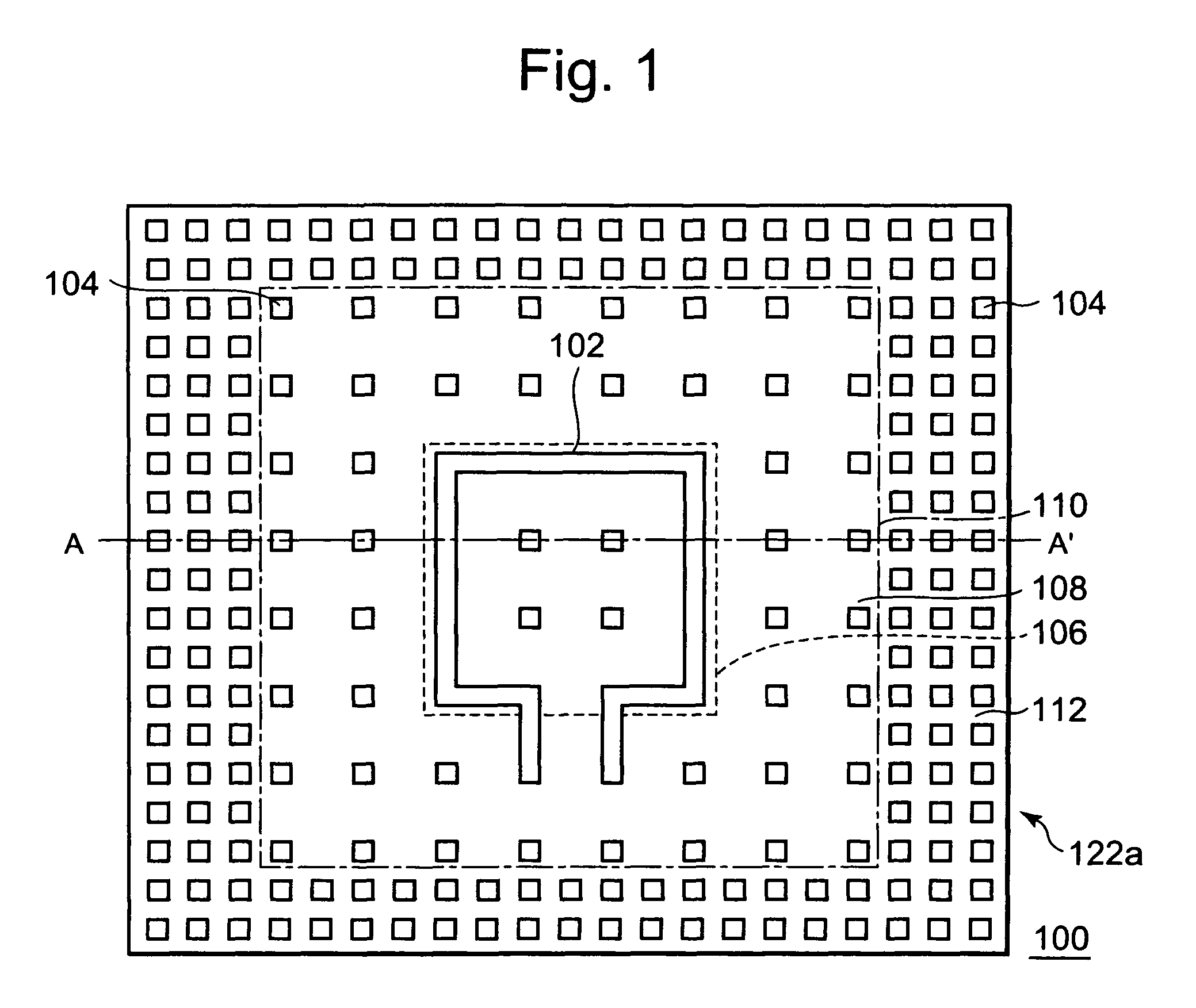

Flash memory device and method of fabricating the same

InactiveUS20080099824A1Improve the coupling ratioSuppression capacitanceTransistorSolid-state devicesIsolation layerSemiconductor

A flash memory device and a method of fabricating the same are provided. The flash memory device may include an isolation layer provided in a semiconductor substrate to define an active region. A floating gate may be provided on the active region. The floating gate may be spaced a first distance apart from the active region. A control gate may be provided, which covers a top surface of the floating gate and one of both sidewalls of the floating gate adjacent to the active region. The portion of the control gate covering one sidewall of the floating gate may be spaced a second distance, which may be greater than the first distance, apart from the active region.

Owner:SAMSUNG ELECTRONICS CO LTD

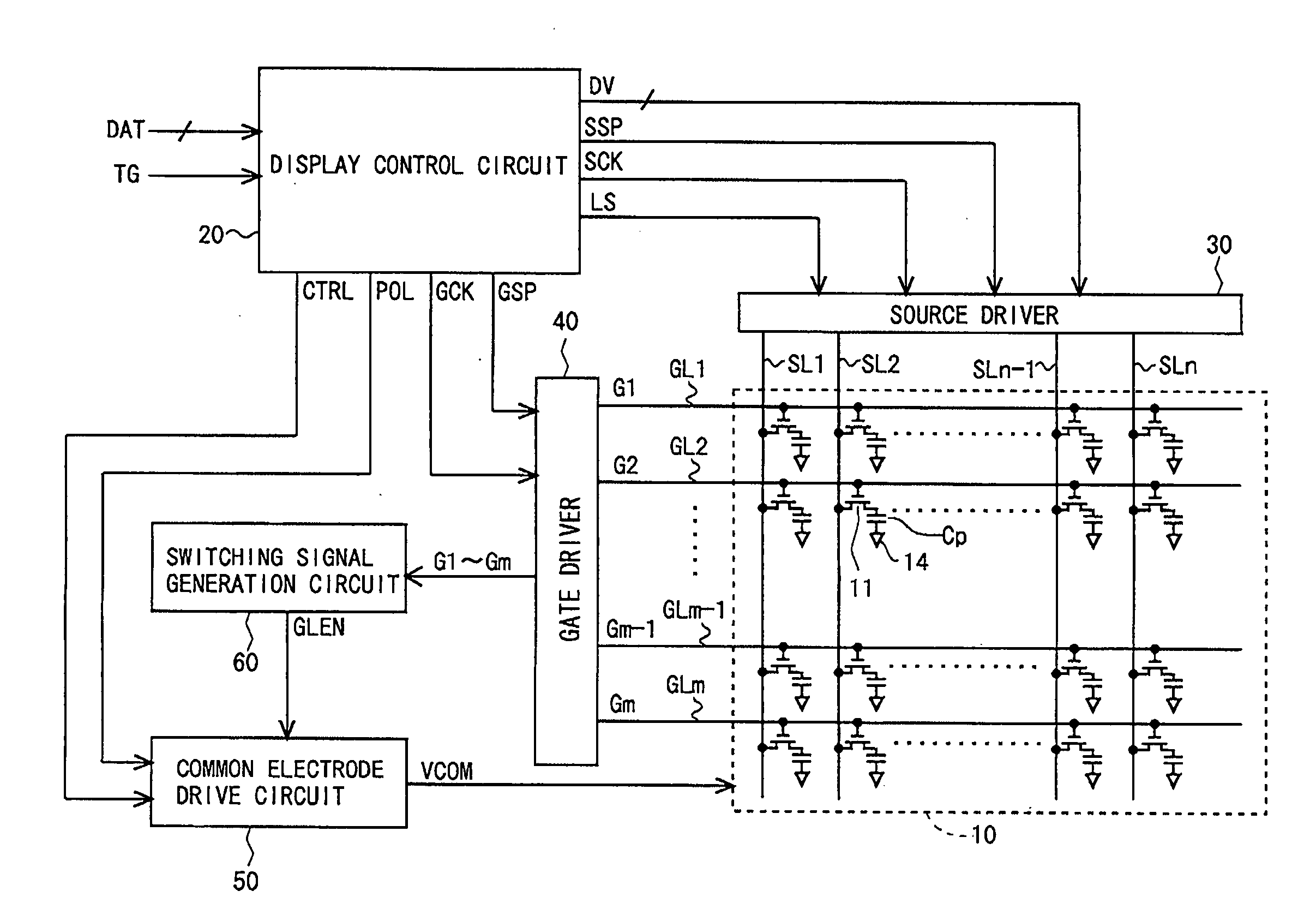

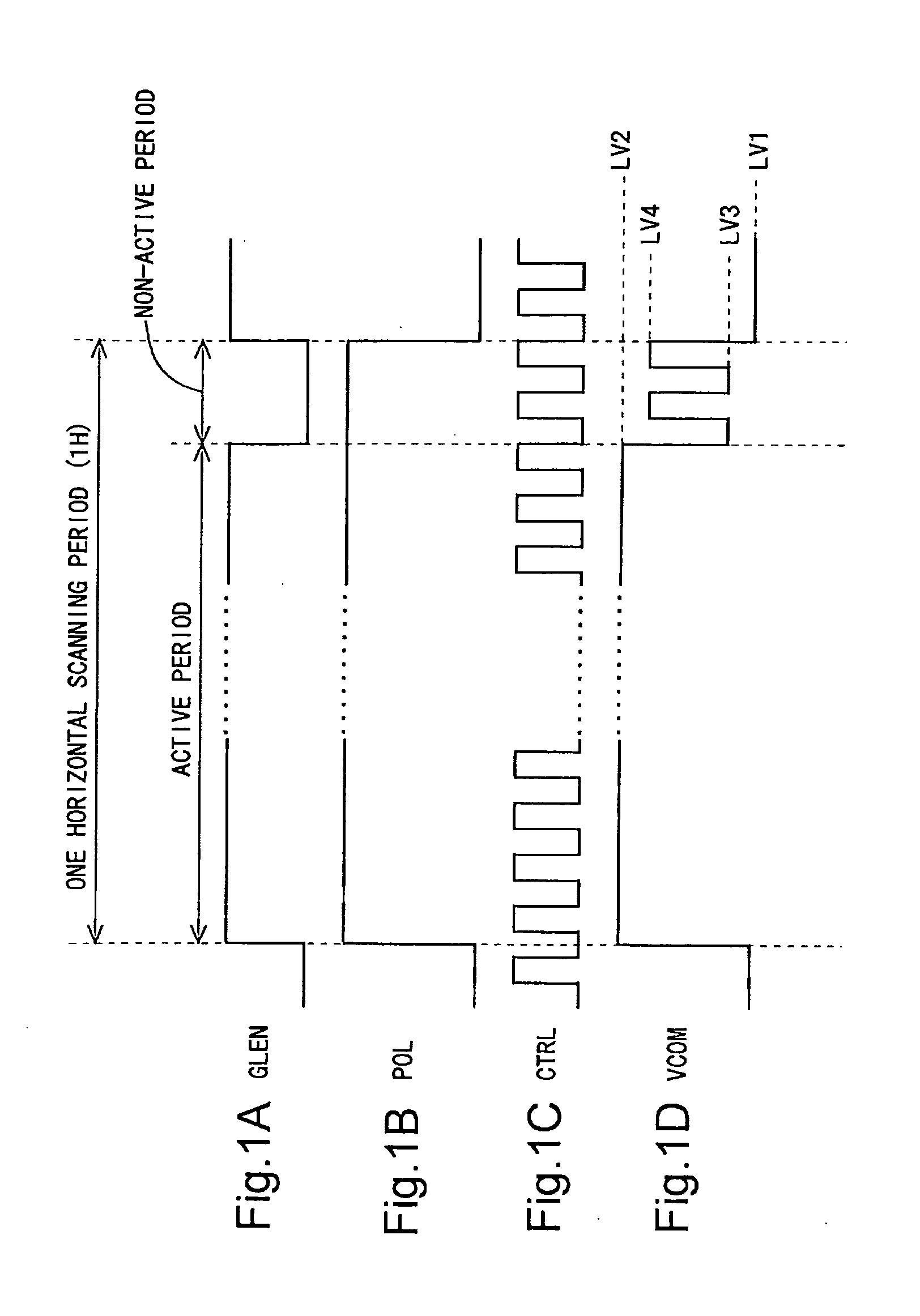

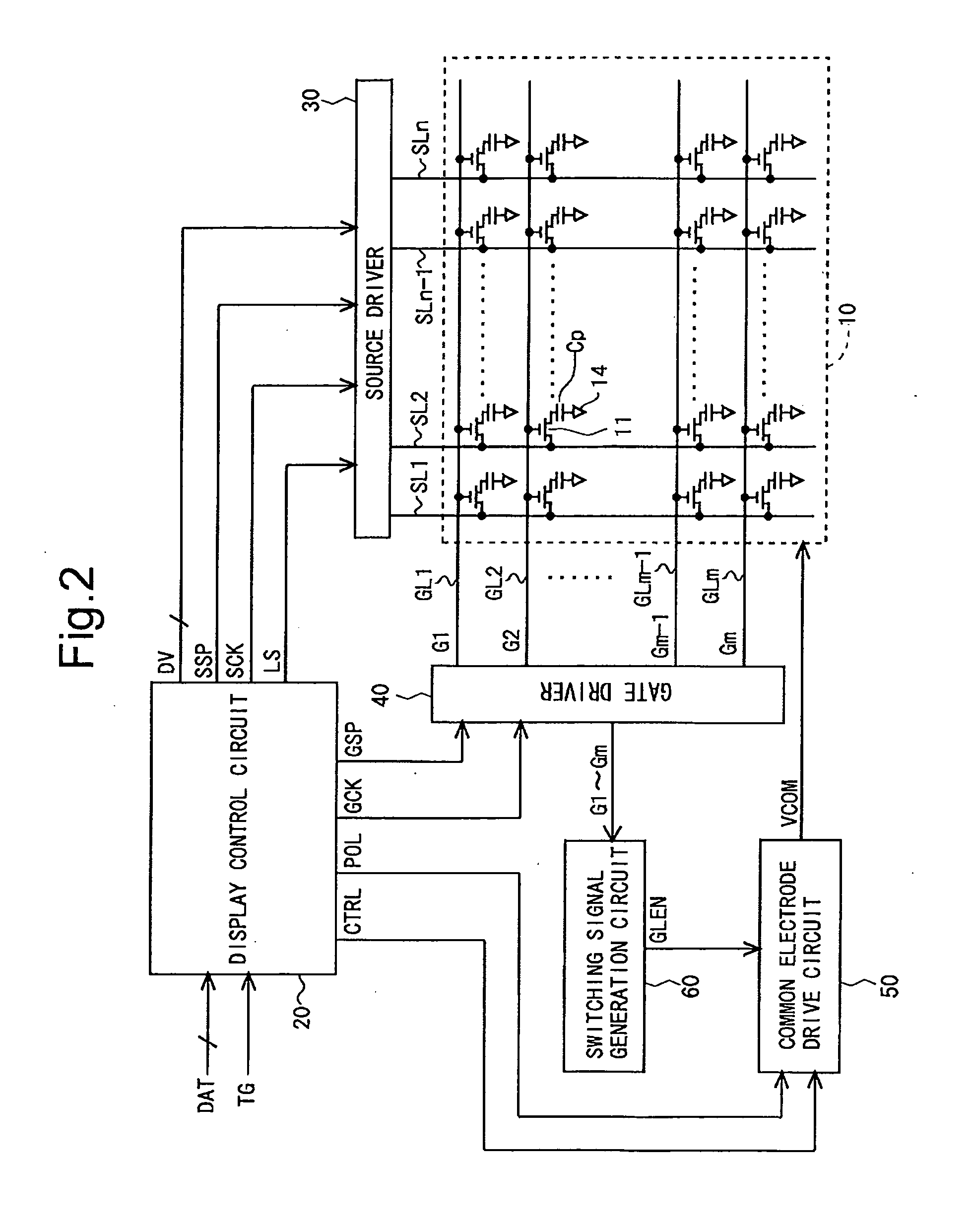

Liquid crystal display apparatus, drive circuit therefor, and drive method therefor

InactiveUS20120062543A1Suppressing sound emissionIncrease currentCathode-ray tube indicatorsInput/output processes for data processingDriver circuitPotential change

A liquid crystal display apparatus is disclosed, which is capable of suppressing sound emission caused by the AC drive of liquid crystal while suppressing an increase in power consumption. A non-active period during which polarity reversal of a common electrode signal (VCOM) is repeated at predetermined intervals is provided in each horizontal scanning period. During an active period, a common electrode drive circuit provides a common electrode signal (VCOM) indicating either one of potentials LV1 and LV2 to a common electrode, based on a polarity instruction signal (POL). During the non-active period, the common electrode drive circuit provides a common electrode signal (VCOM) whose potential changes between LV3 and LV4 to the common electrode, based on a reversal timing control signal (CTRL). Here, the amplitude of the common electrode signal (VCOM) for the non-active period is made smaller than the amplitude of the common electrode signal (VCOM) for the active period.

Owner:SHARP KK

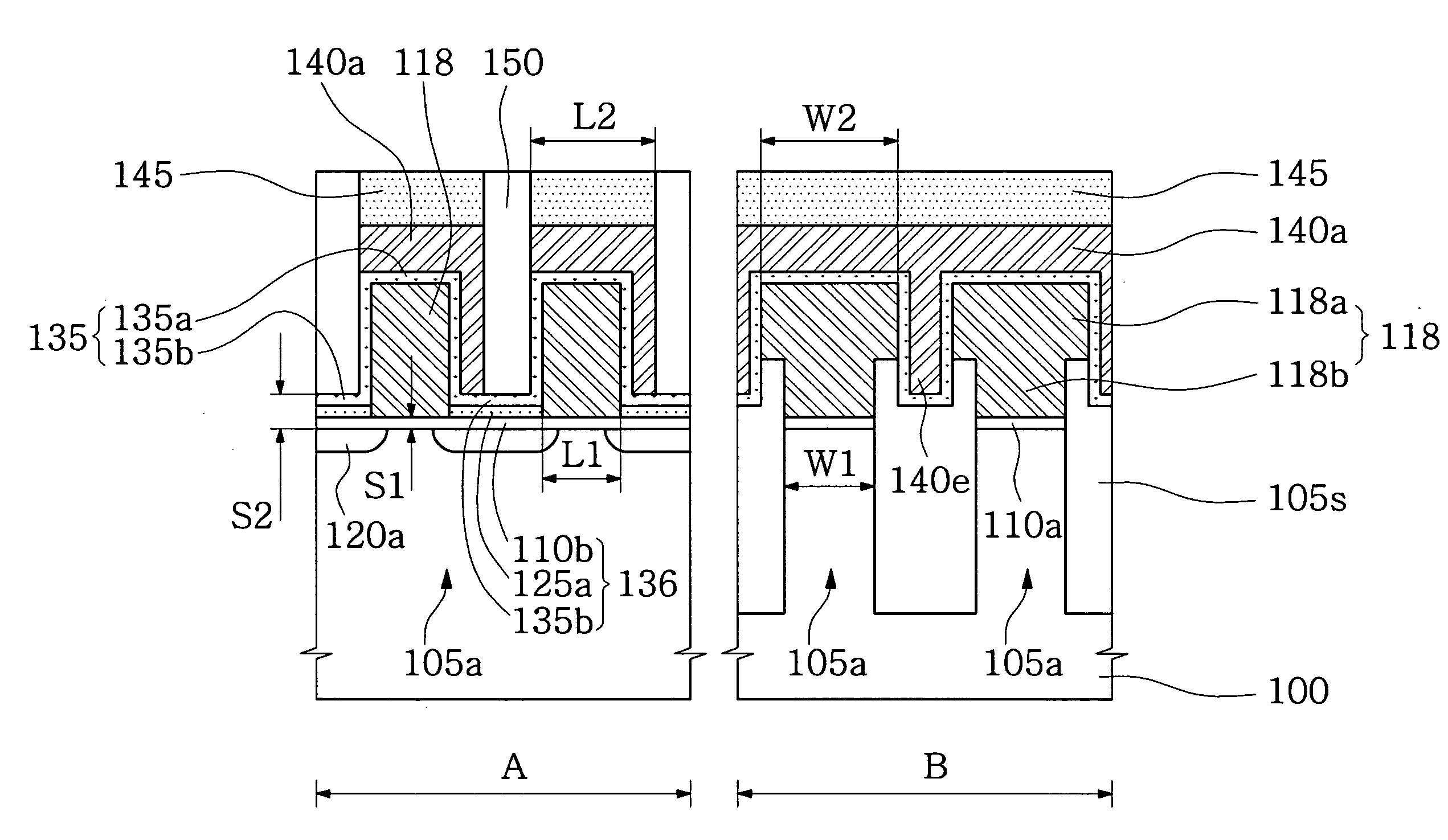

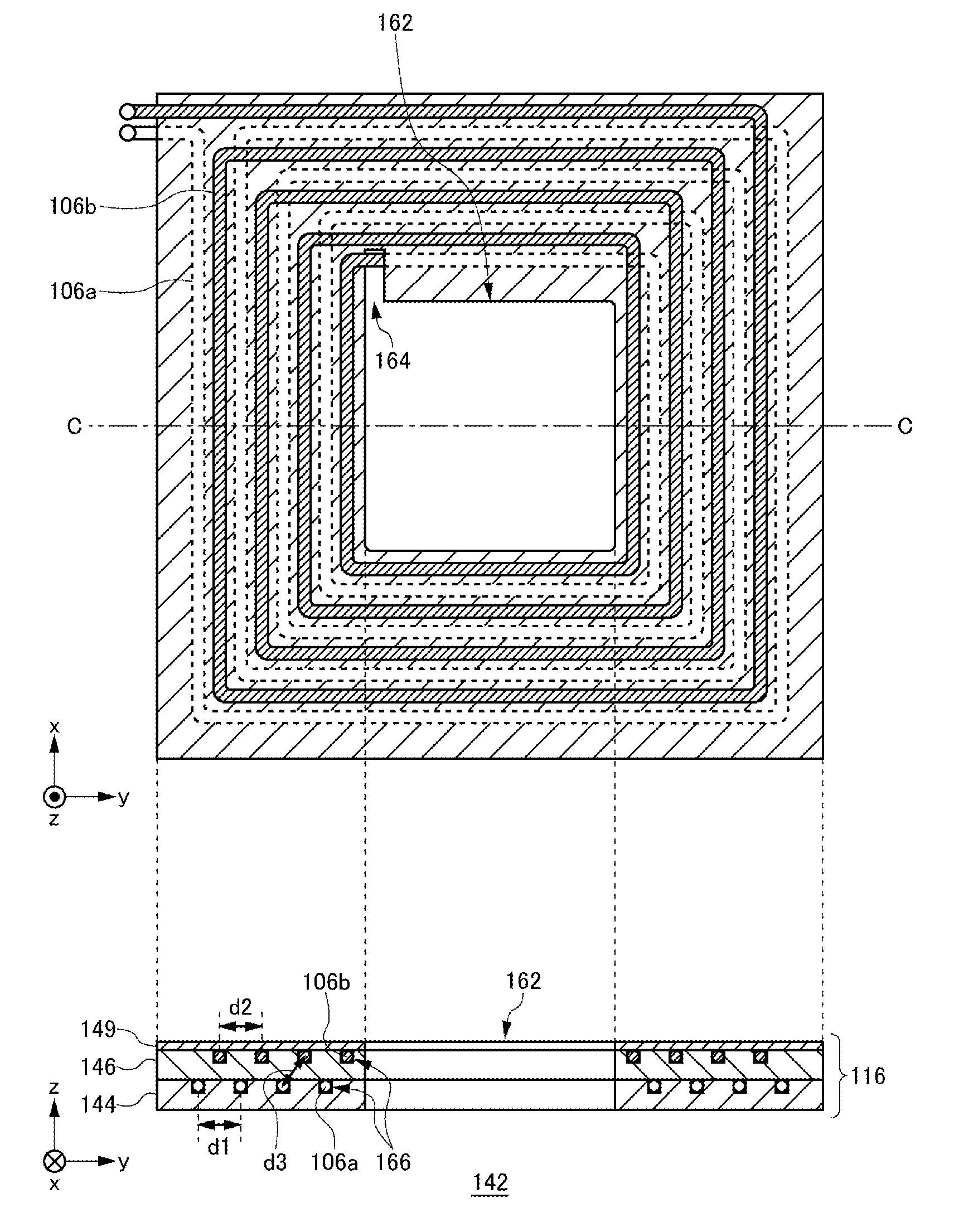

Wireless power feeder, wireless power receiver, and wireless power transmission system

ActiveUS8901776B2Increase the number ofSmall sizeNear-field transmissionTransformersElectric power transmissionElectrical conductor

Power is fed from a feeding coil to a receiving coil using magnetic resonance. The feeding coil is wound in a first layer substrate 144 of a multilayer substrate 116 with a space provided between the coil conductor thereof and further wound in a second later substrate 146 with a space provided between the coil conductor thereof. The feeding coil is wound such that a coil conductor 106a in the first layer and a coil conductive wire 106b in the second layer do not overlap each other as viewed in the axial direction (z-axis direction).

Owner:TDK CORPARATION

Control system for a plug-in hybrid vehicle

InactiveUS20160090080A1Suppress capacitorInhibit progressHybrid vehiclesDigital data processing detailsElectrical batteryCharge and discharge

A hybrid vehicle control device includes a drive system including a starter motor, an engine and a motor / generator, and a power supply system including a high power battery, a capacitor, and a hybrid control module which controls charging and discharging of the capacitor. The hybrid control module performs a starter start-up control, a motor-generator start control and charging and discharging control: during EV mode, when the operating point in accordance with the vehicle speed and required driving force is present in a M / G start-up region, the hybrid control module maintains the capacitor voltage at or below a deterioration free voltage, and when the operating point is deviated from the M / G start-up region, the hybrid control module recharges the capacitor to or above a starter start-up permission voltage.

Owner:NISSAN MOTOR CO LTD