Patents

Literature

146 results about "Feedback capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

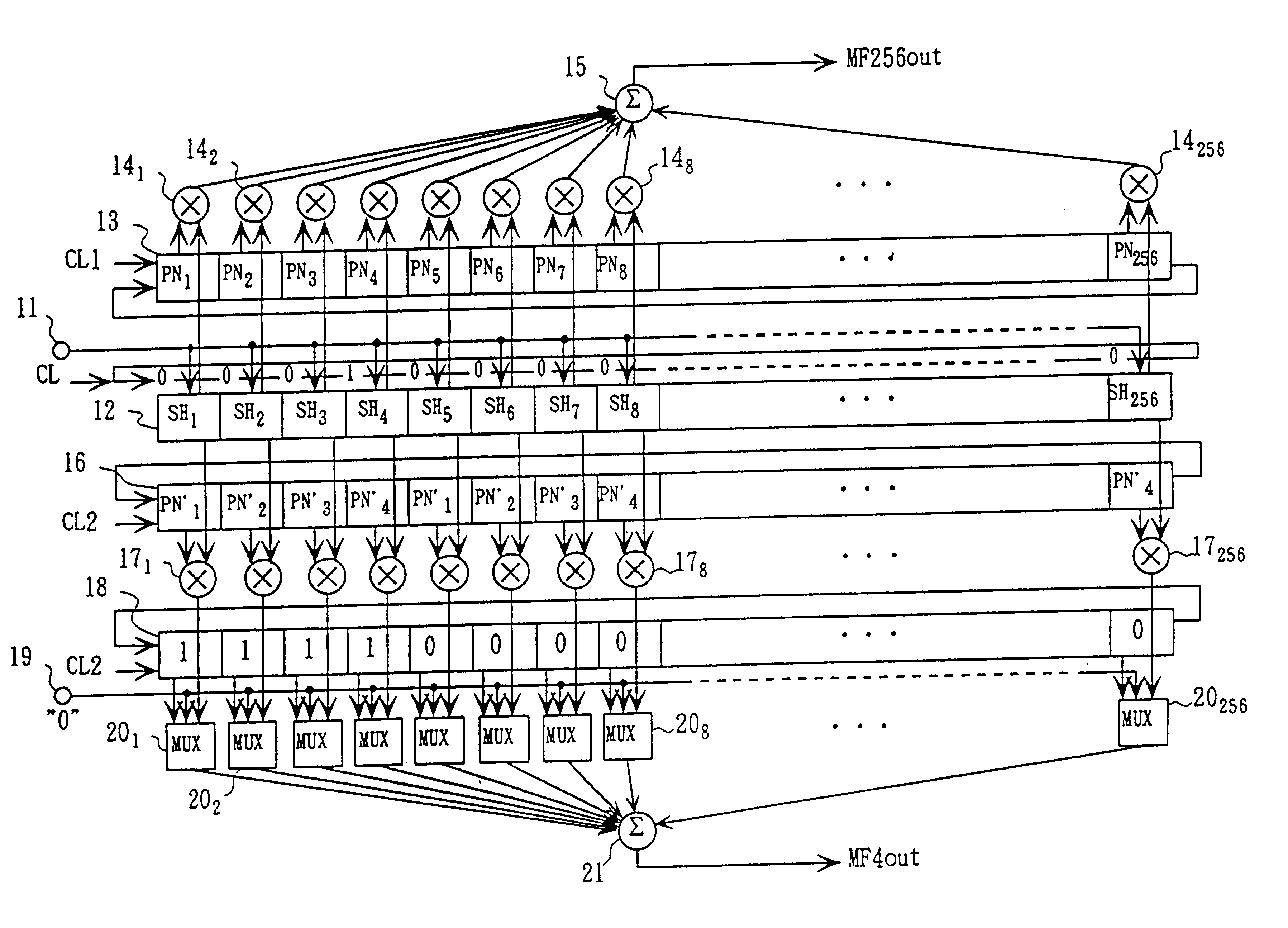

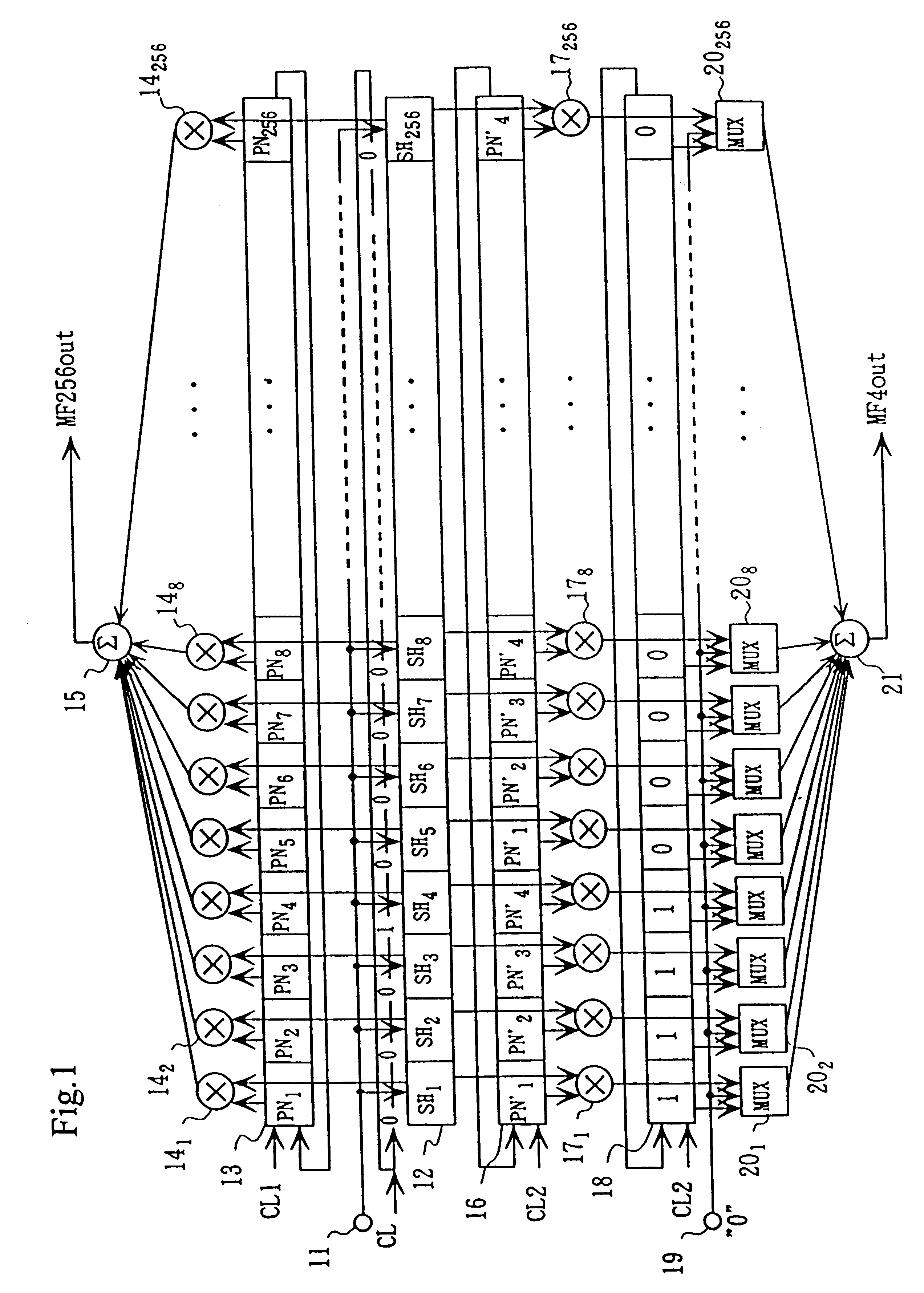

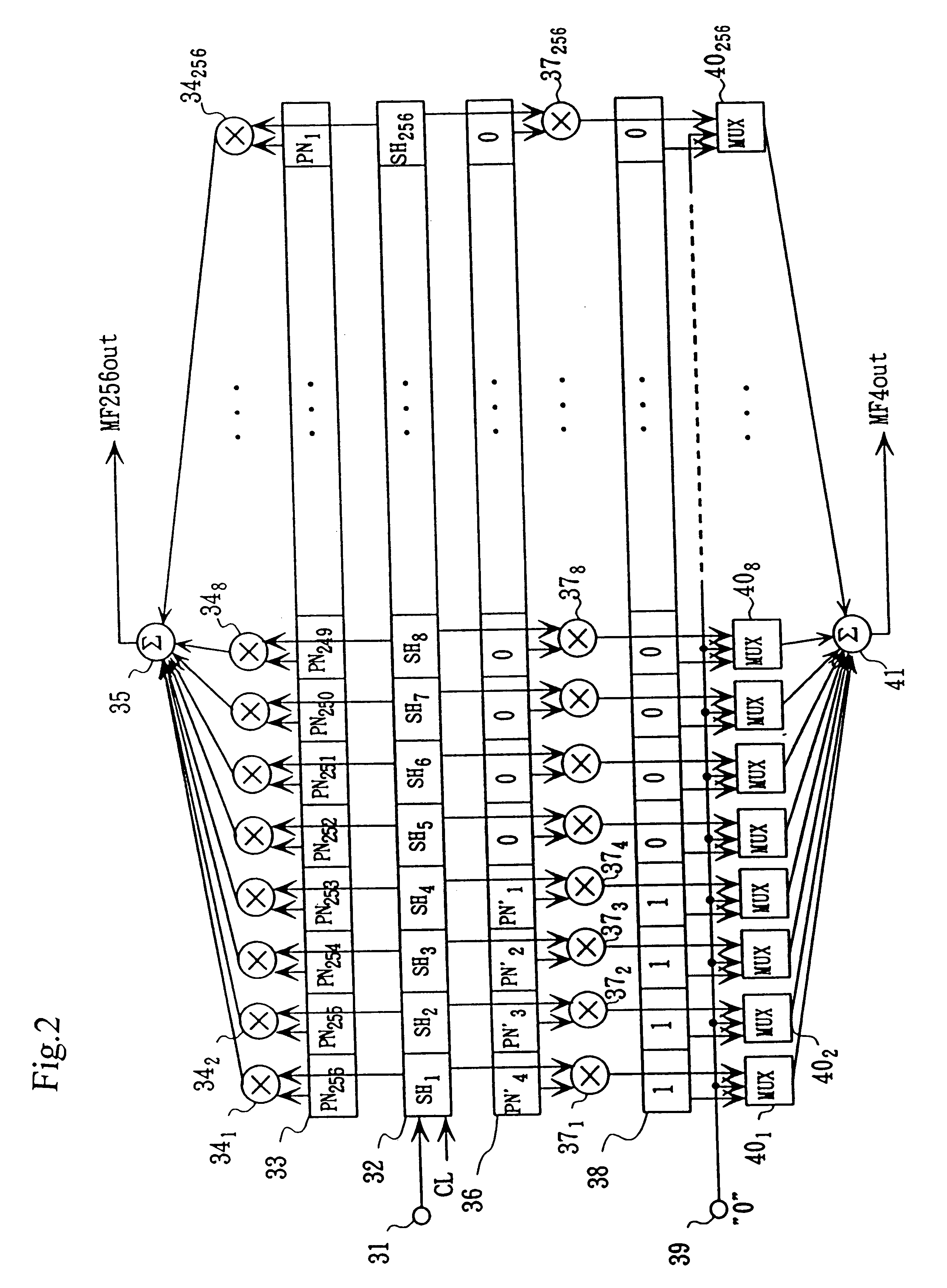

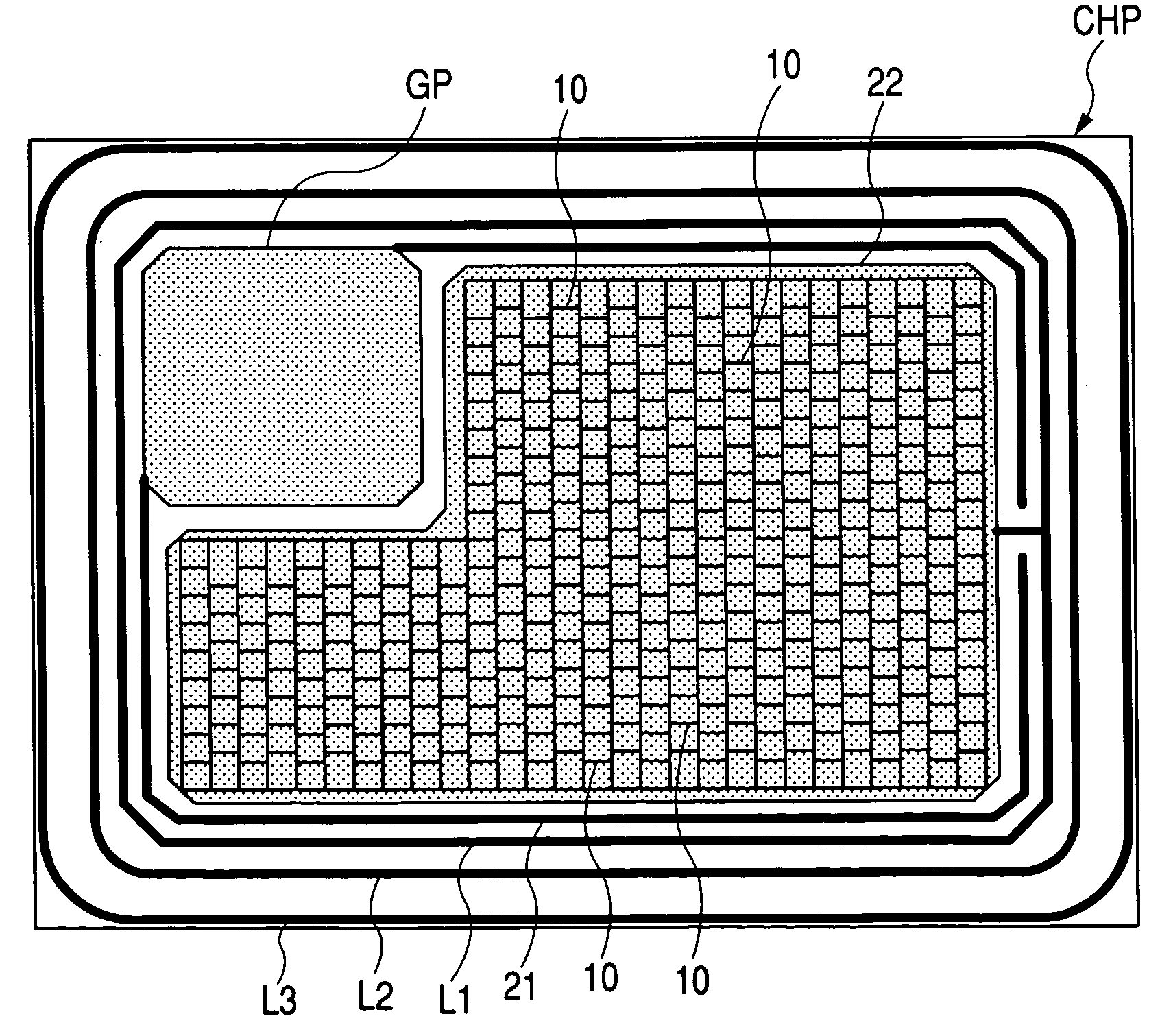

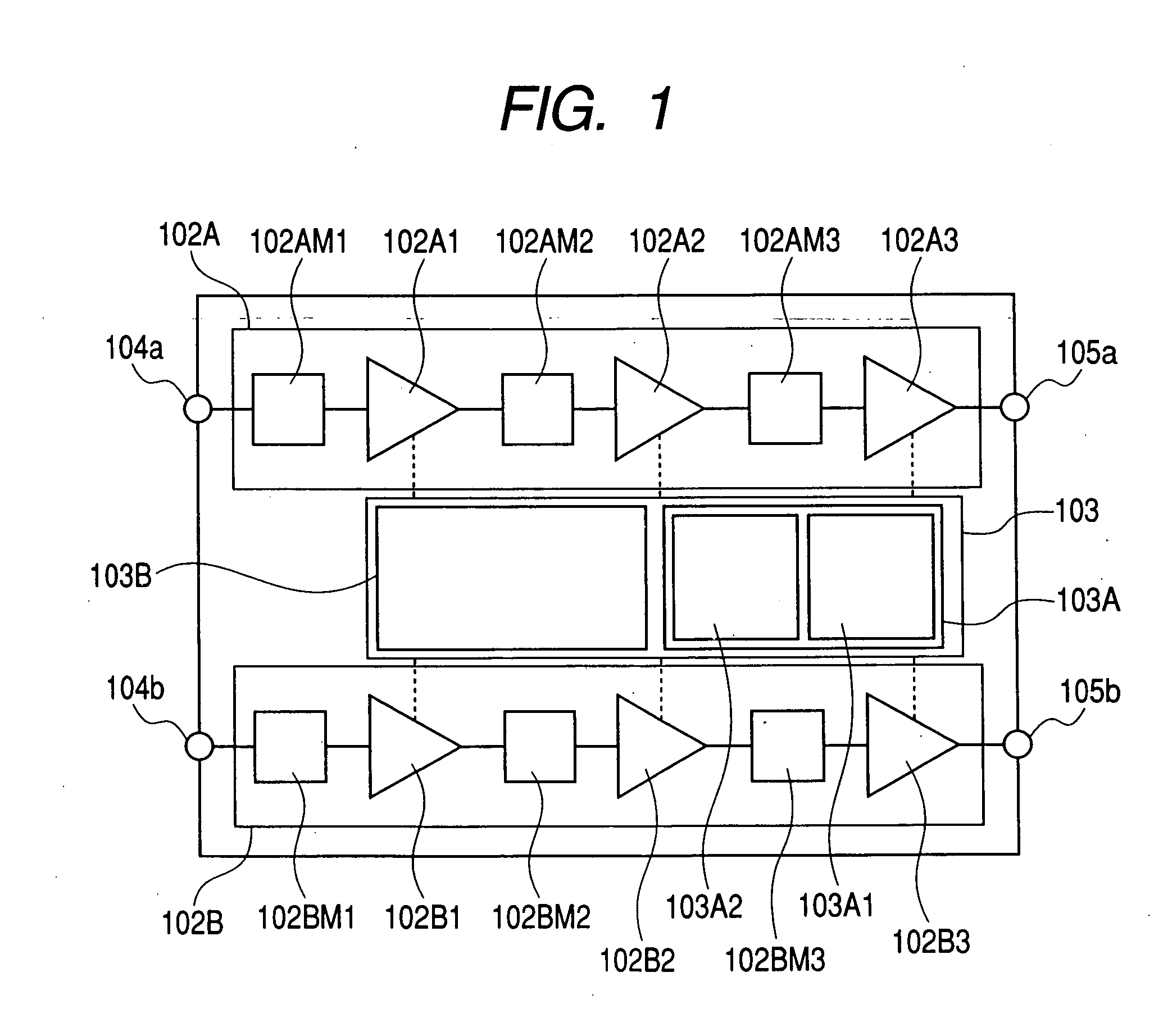

Matched filter bank

InactiveUS6512785B1Amplitude-modulated carrier systemsRadio transmissionCapacitanceAudio power amplifier

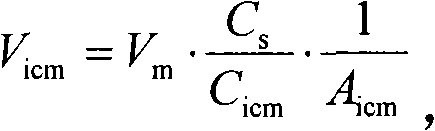

A matched filter bank including a plurality of matched filters and a sampling and holding units commonly used by the total matched filters. Therefore, the circuit size is diminished.An inverting amplifier for the matched filter with a variable gain includes an input capacitance, an inverting amplifier connected to an output of the input capacitance, and a plurality of feedback capacitances connected between an input and output of the inverting amplifier. A plurality of switches are connected to input side of the feedback capacitances for alternatively connecting the feedback capcitanec to the input of the inverting amplifier or a reference voltage. The feedback capacitances connected to the reference voltage are invalid with respect to a composite capacitance of the feedback capacitance and have no influence to the amplifier.

Owner:HANGER SOLUTIONS LLC

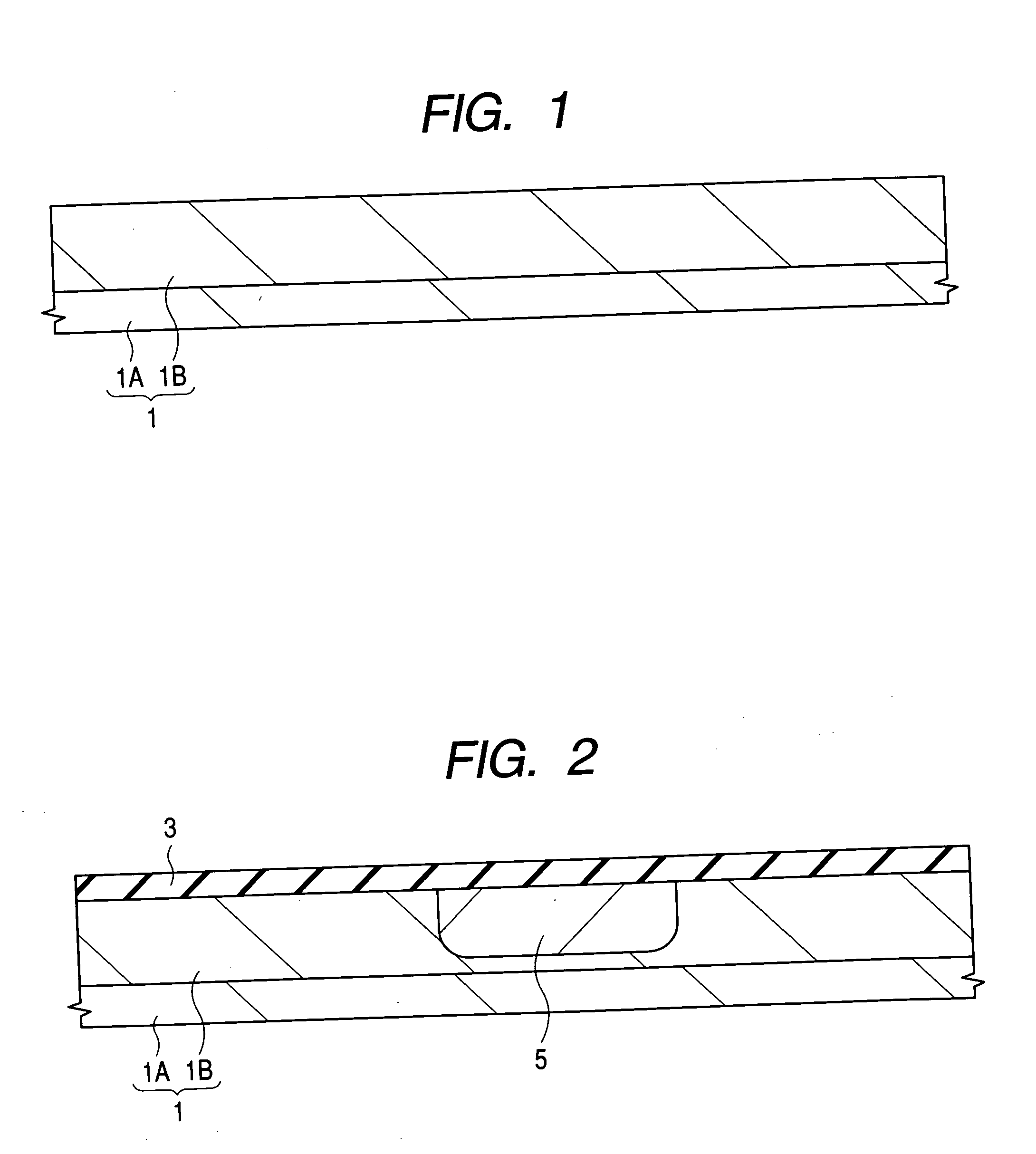

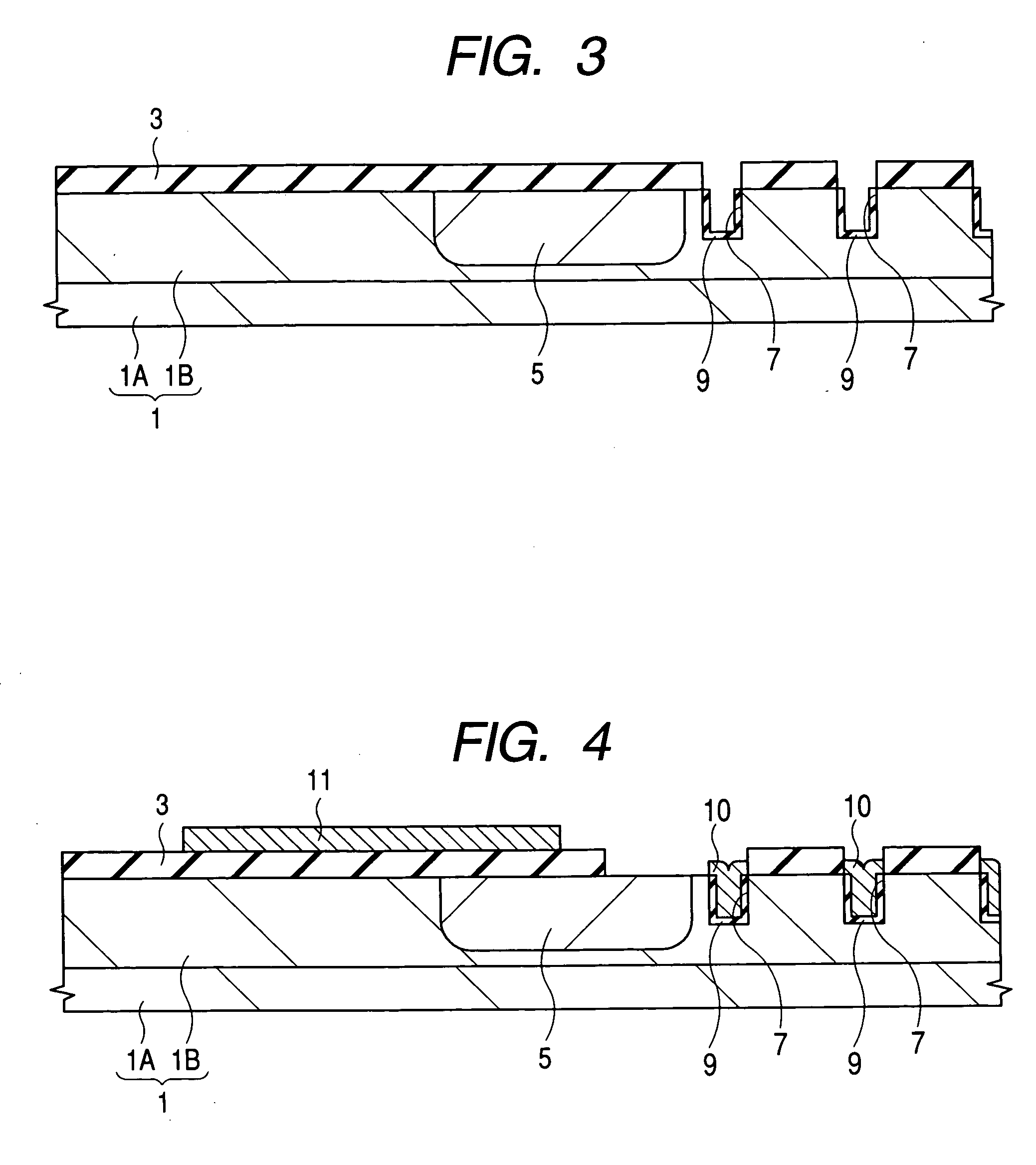

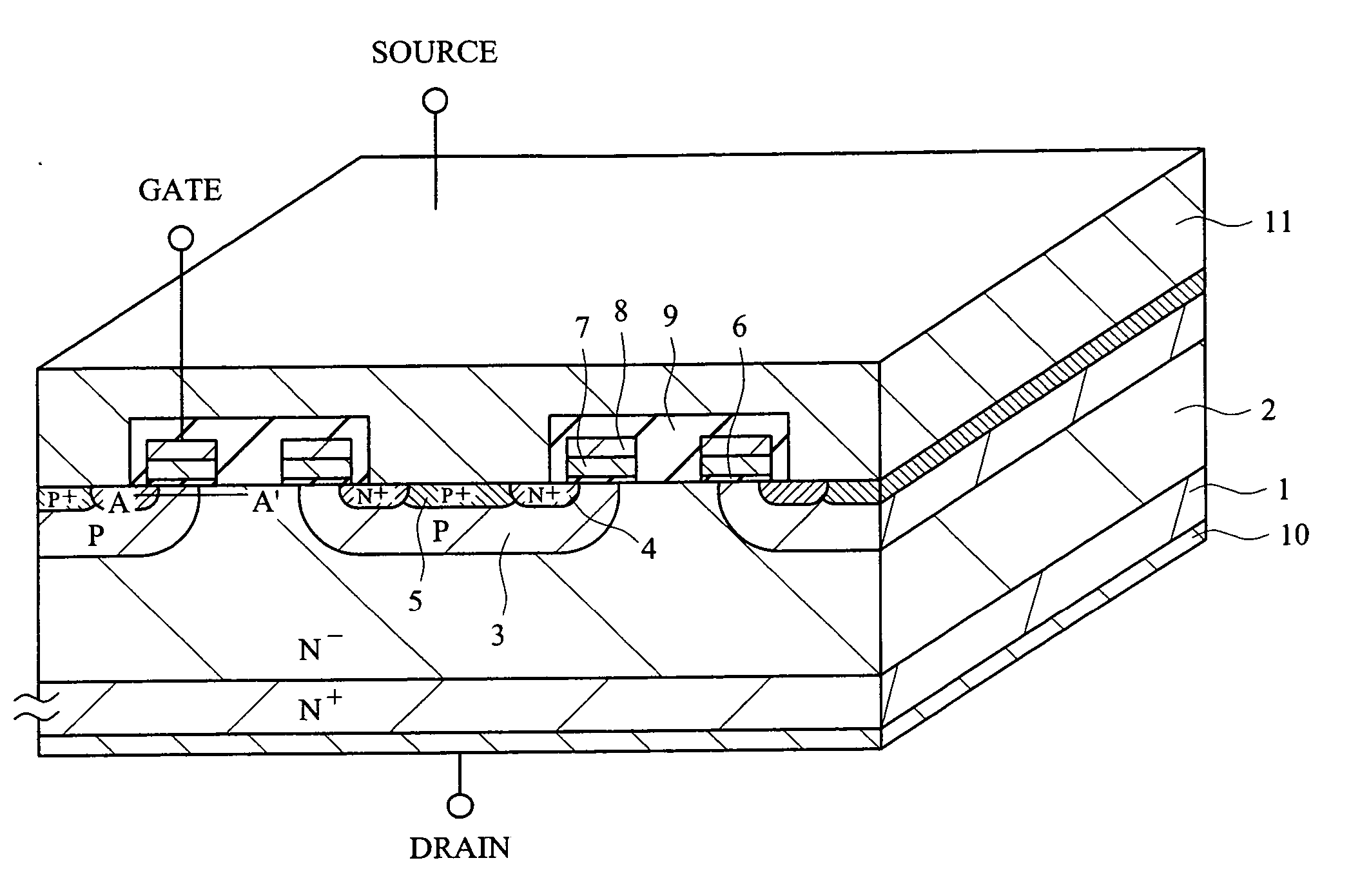

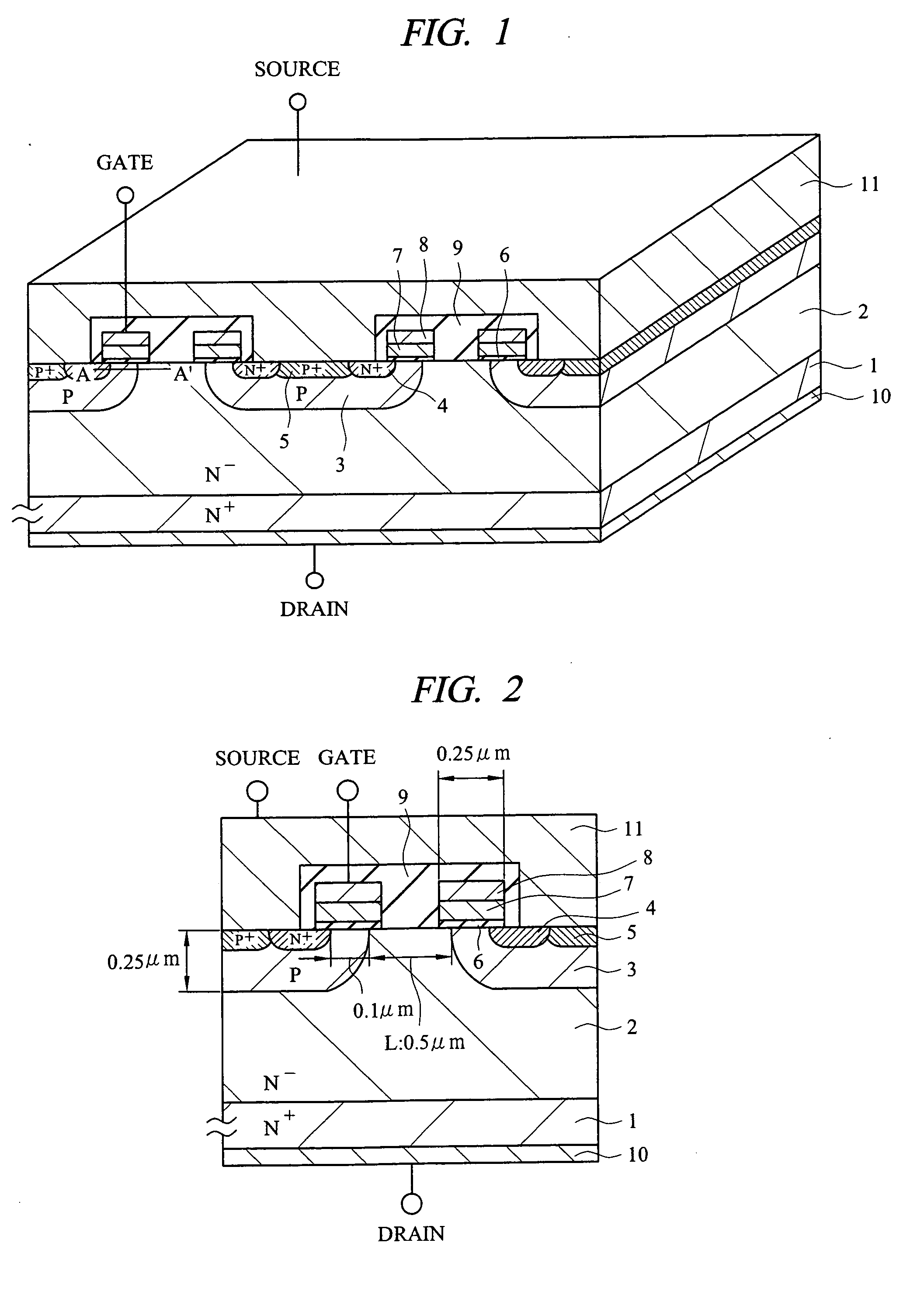

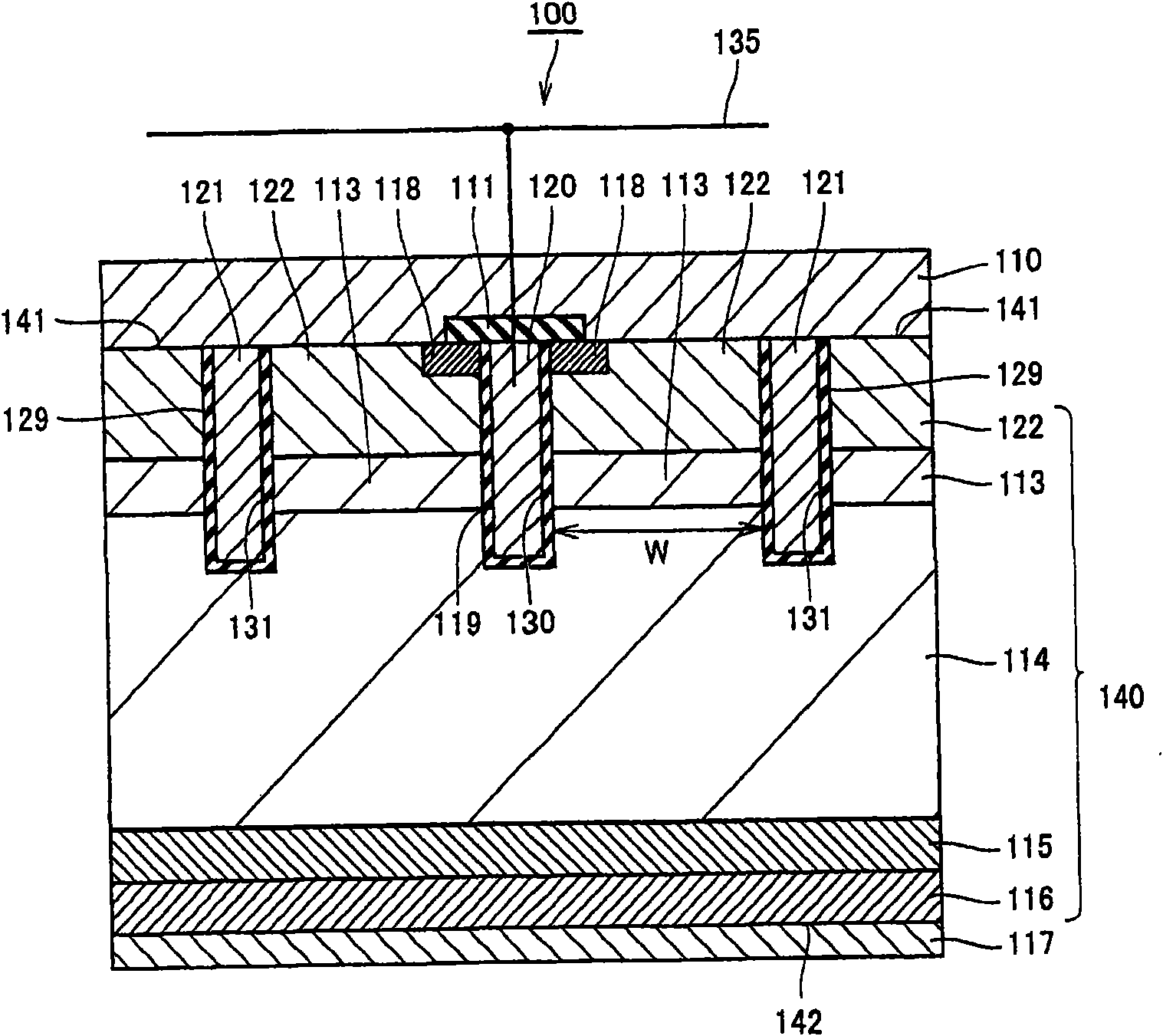

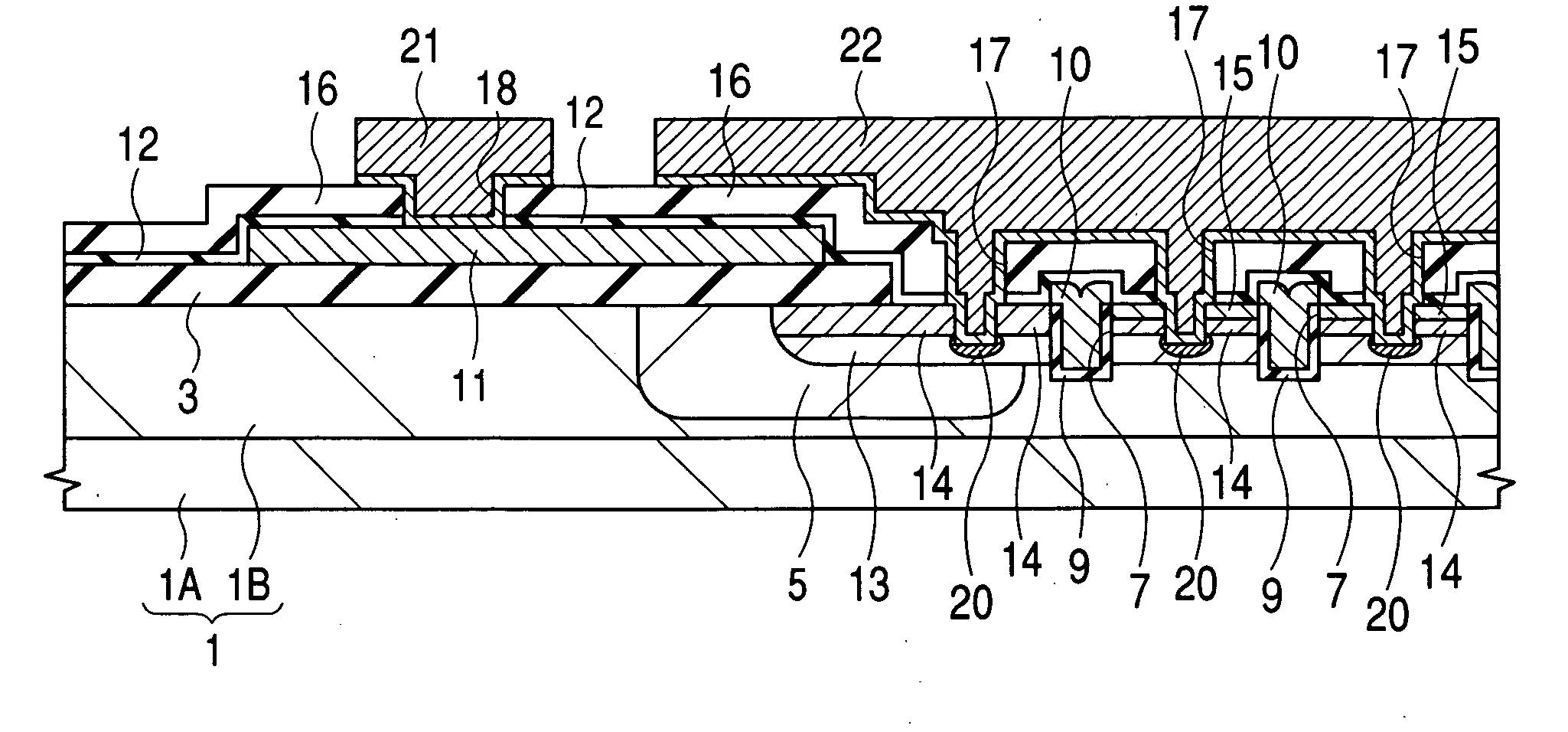

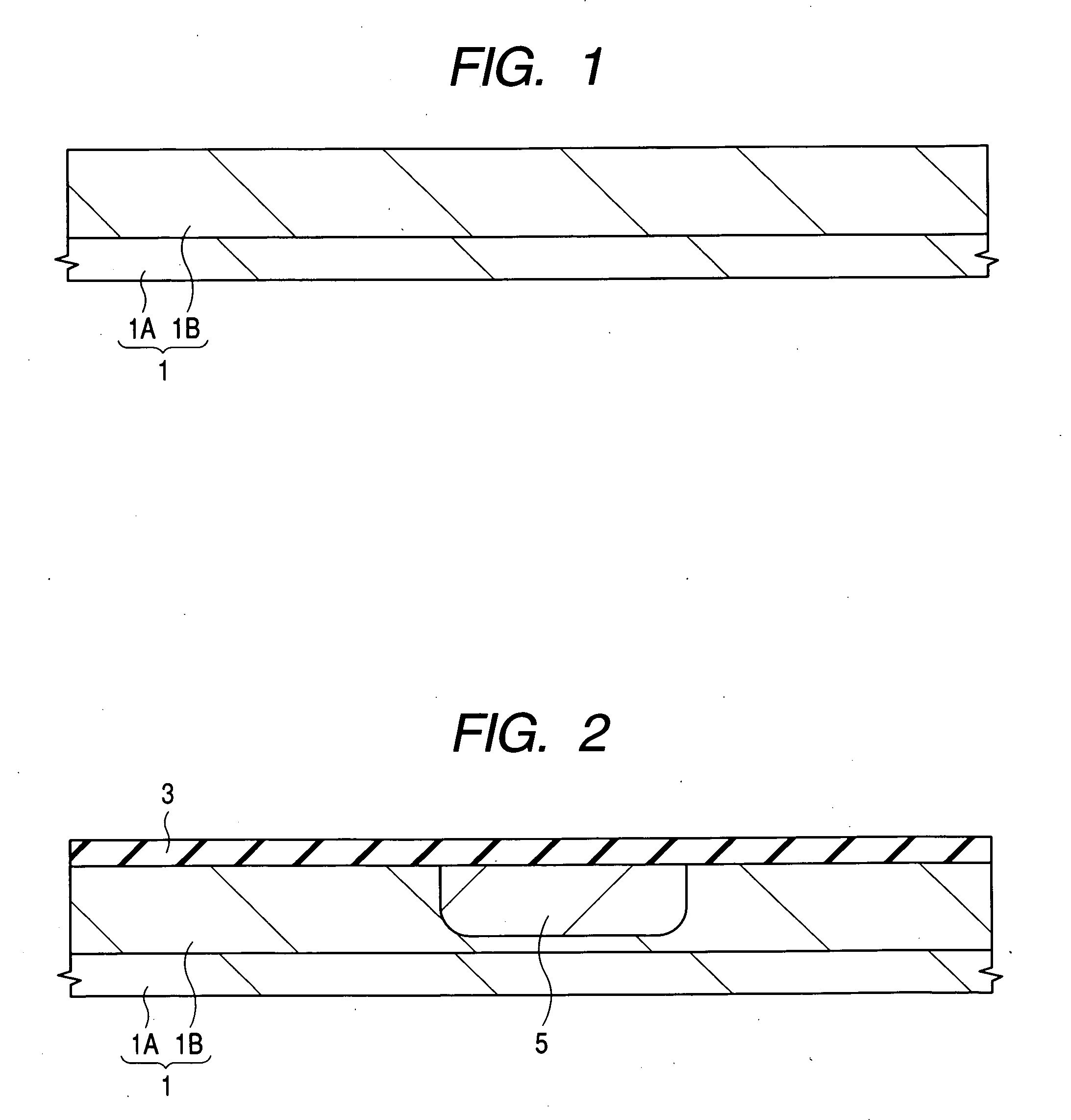

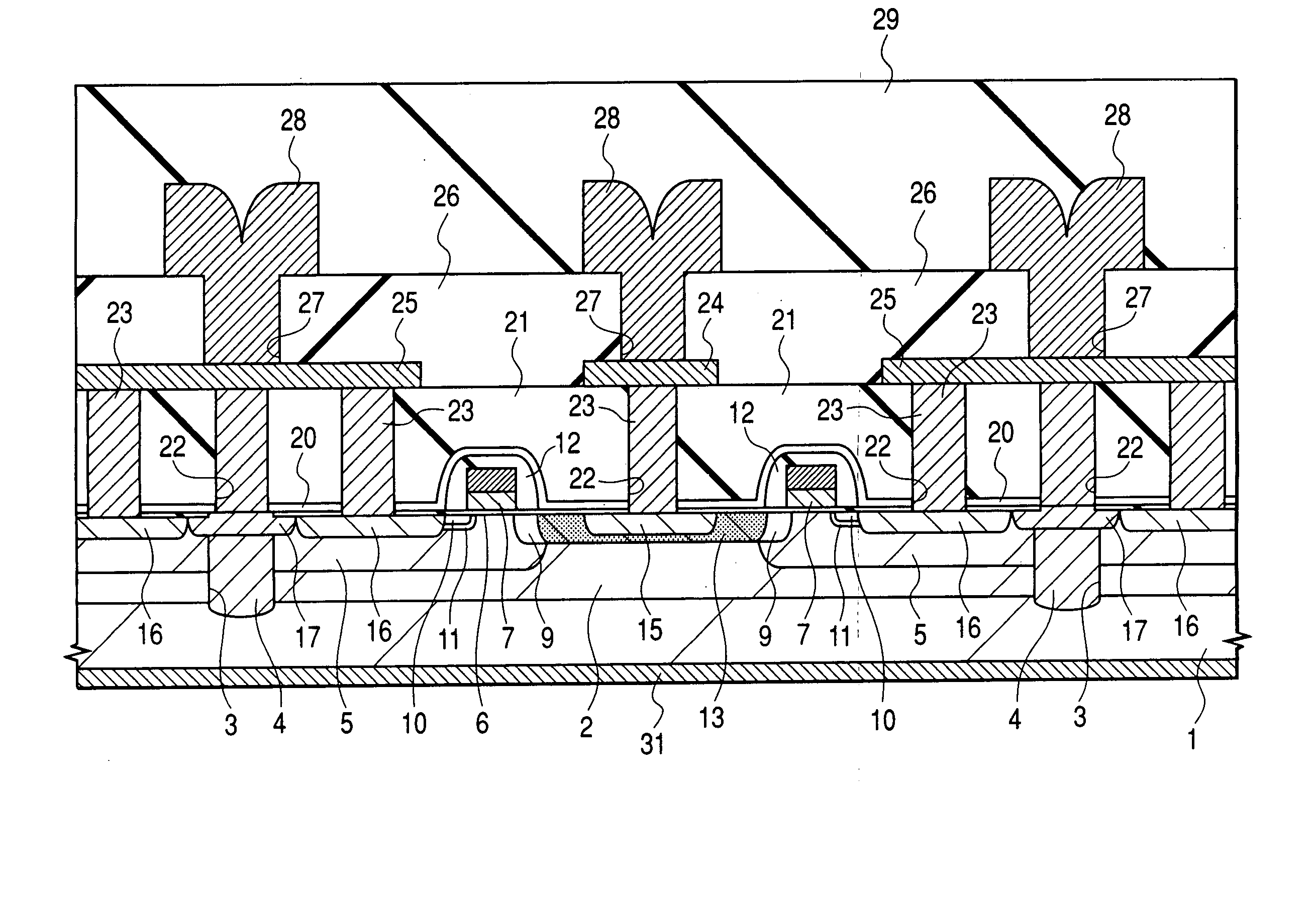

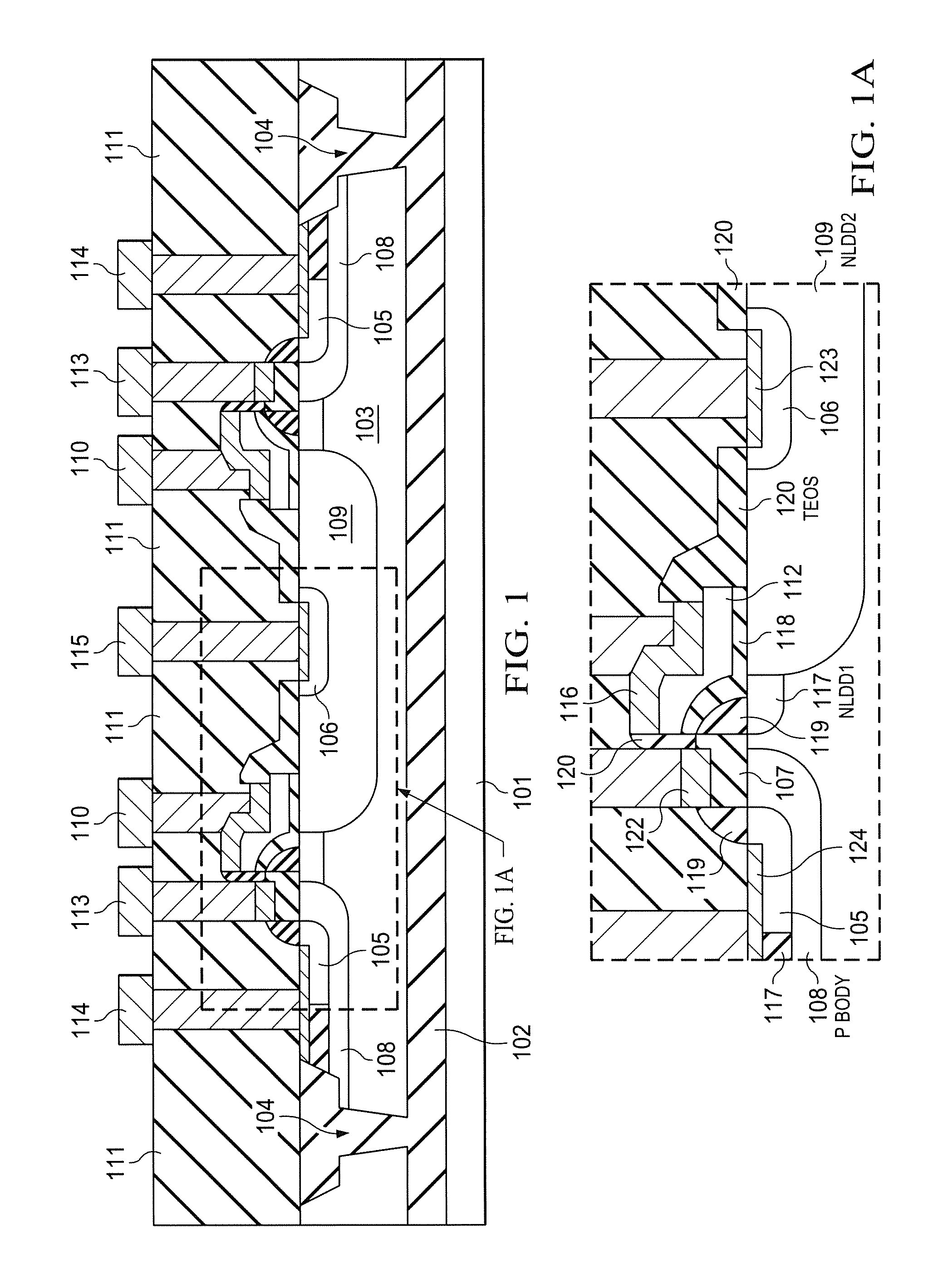

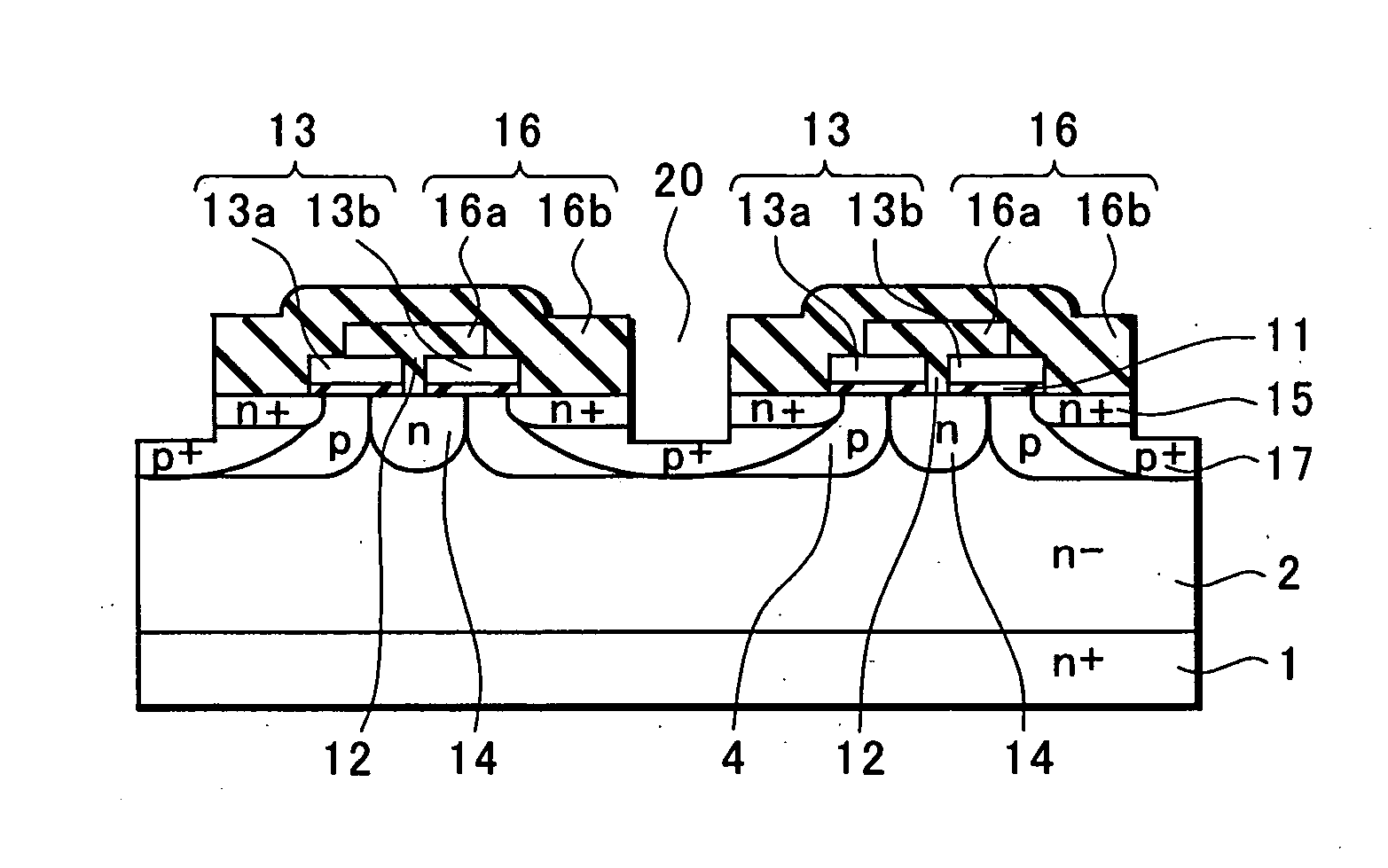

Semiconductor device and a method of manufacturing the same

InactiveUS20050029584A1Easy to integrateReduce resistanceSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceFeedback capacitance

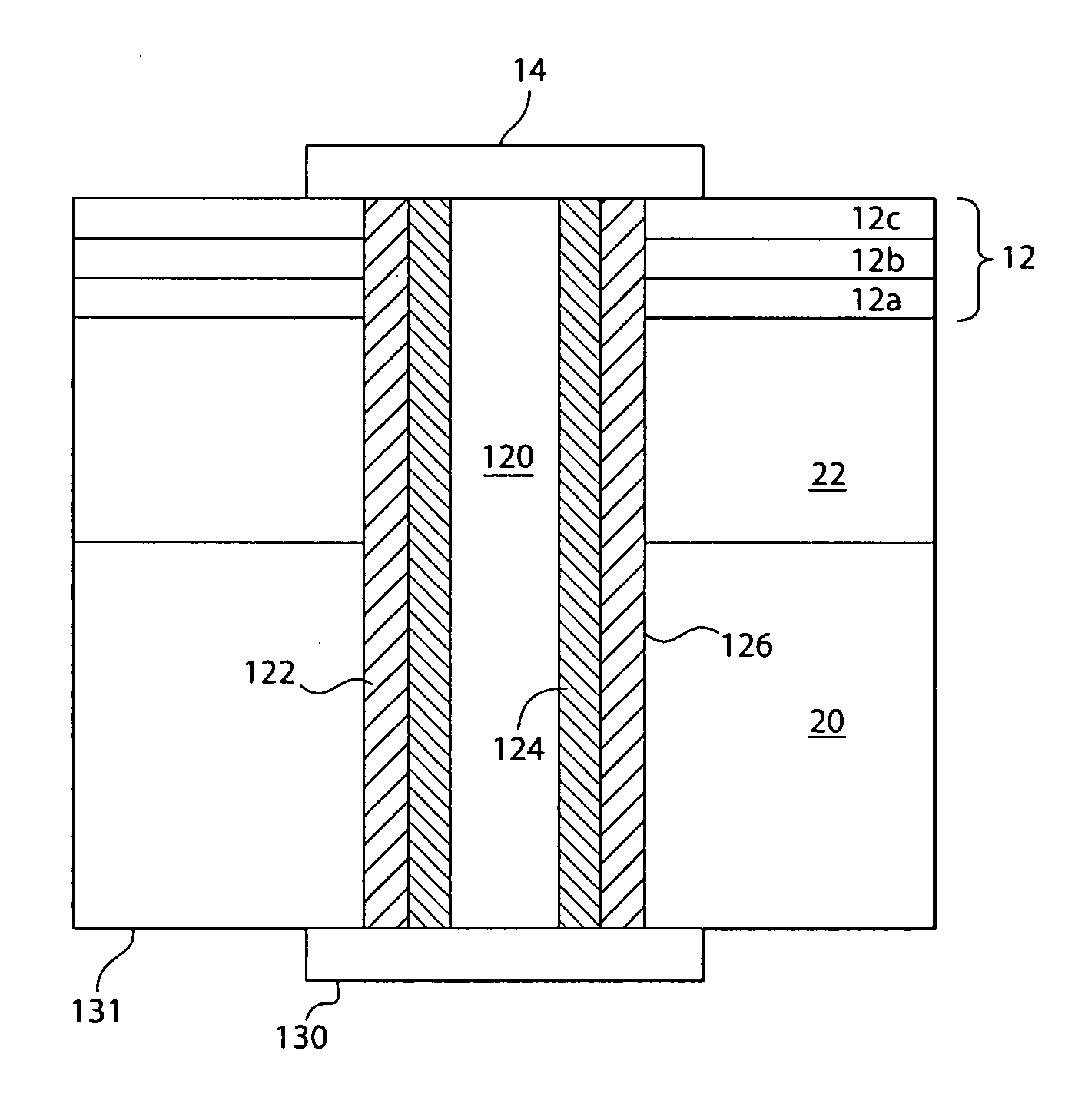

A technology is provided to reduce ON-resistance, and the prevention of punch through is achieved with respect to a trench gate type power MISFET. Input capacitance and a feedback capacitance are reduced by forming a groove in which a gate electrode is formed so as to have a depth as shallow as about 1 μm or less, a p−type semiconductor region is formed to a depth so as not to cover the bottom of the groove, and a p-type semiconductor region higher in impurity concentration than the p−type semiconductor region is formed under a n+type semiconductor region serving as a source region of the trench gate type power MISFET, causing the p-type semiconductor region to serve as a punch-through stopper layer of the trench gate type power MISFET.

Owner:RENESAS TECH CORP

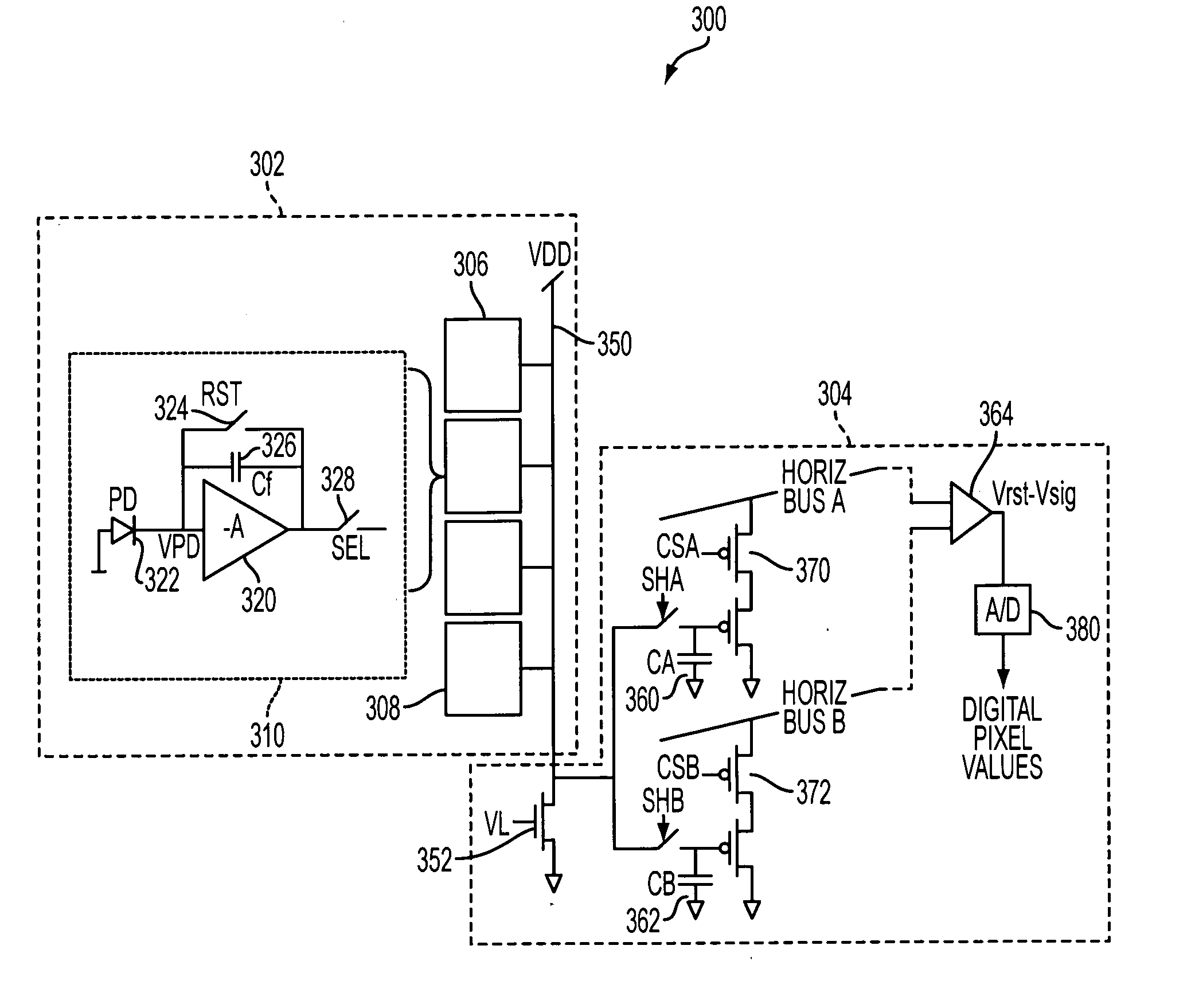

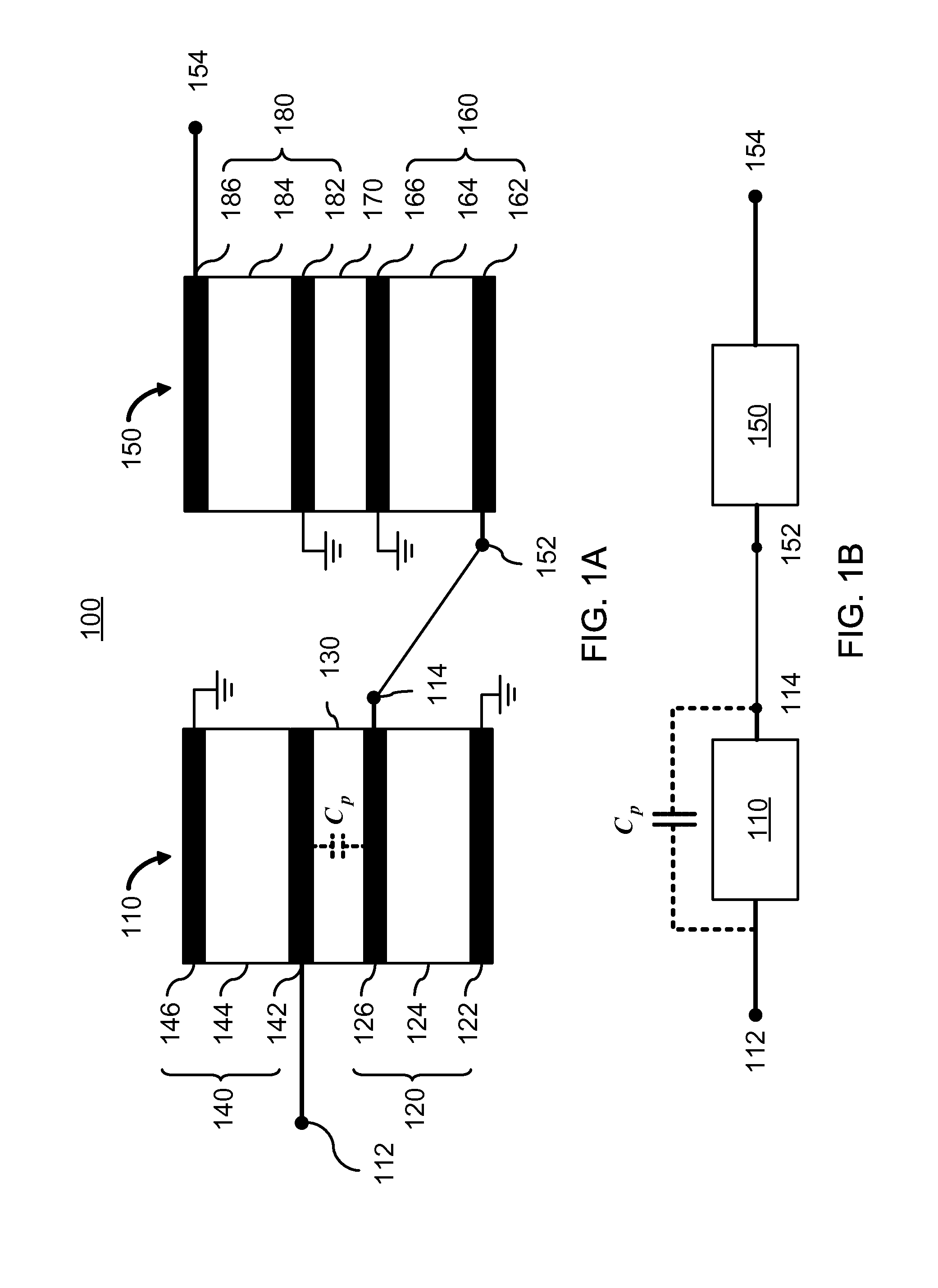

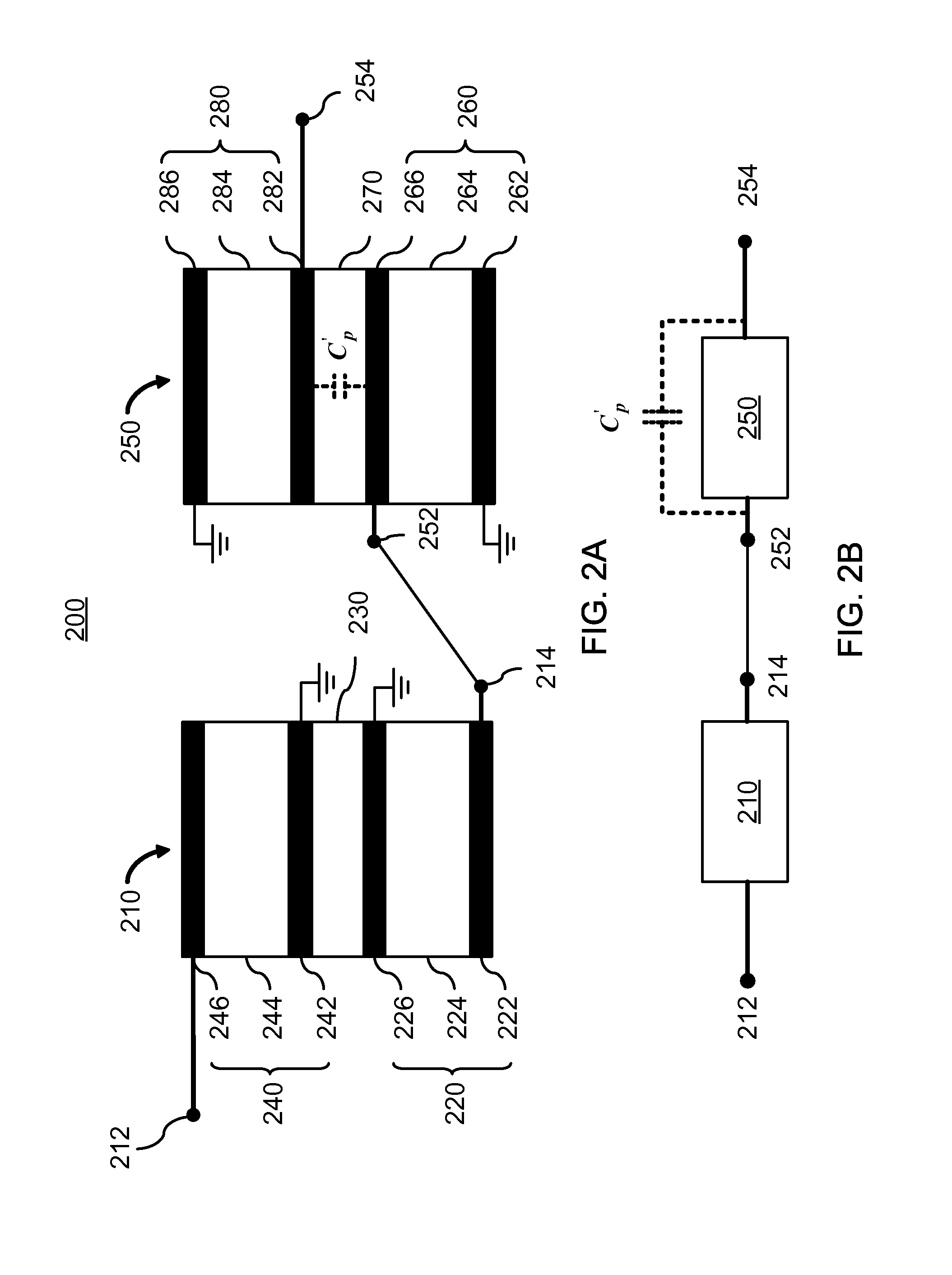

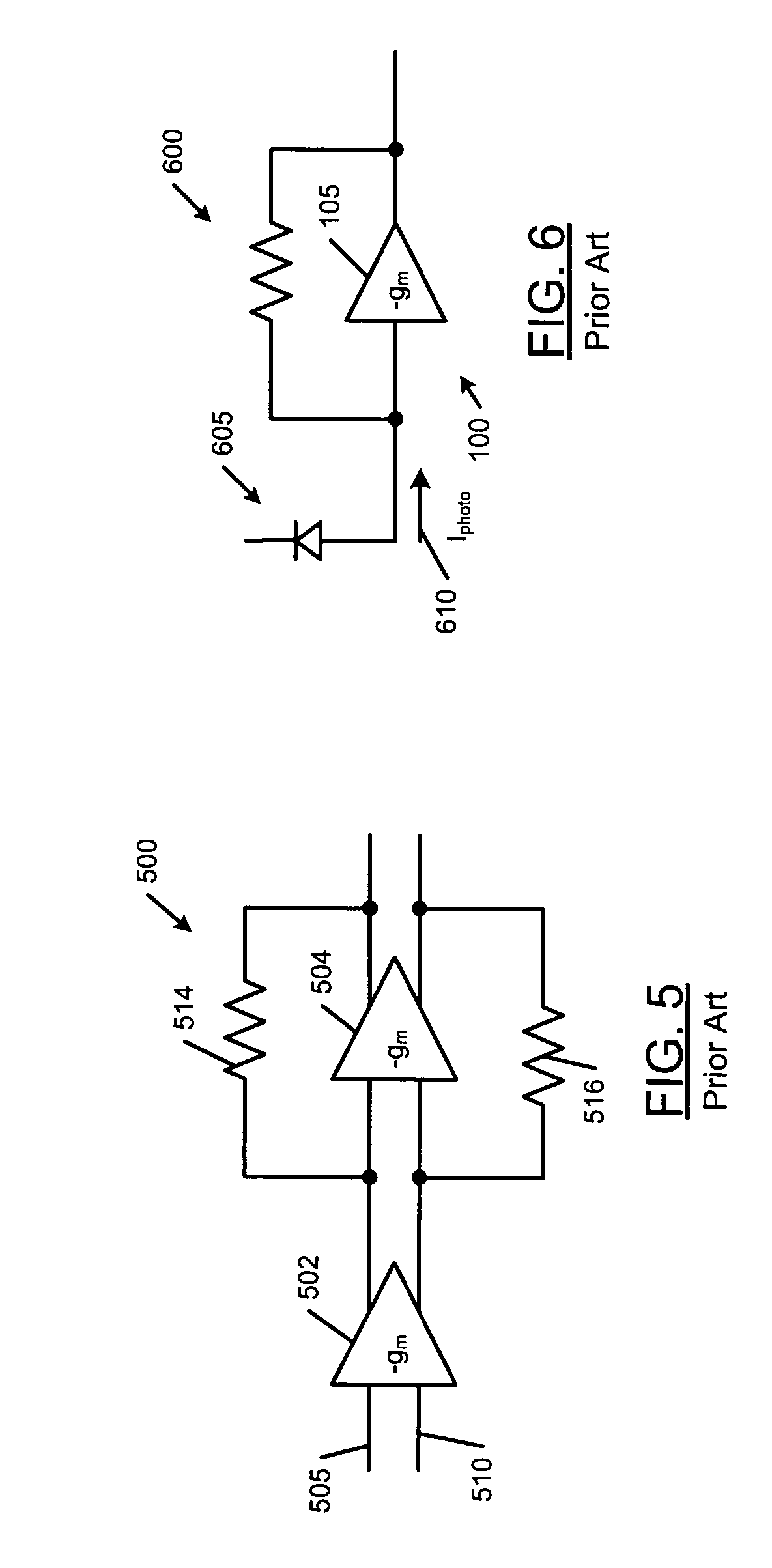

Amplification with feedback capacitance for photodetector signals

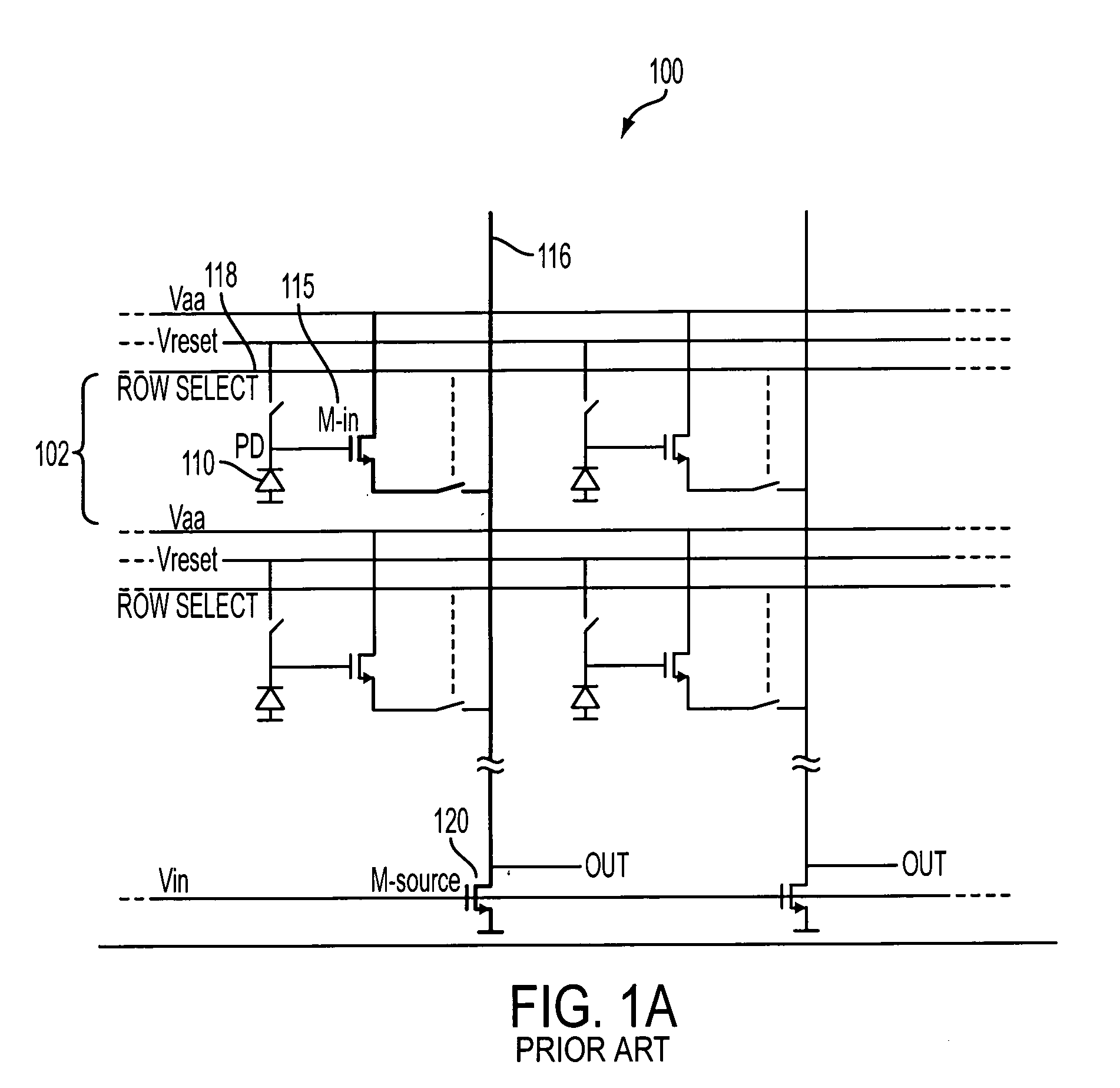

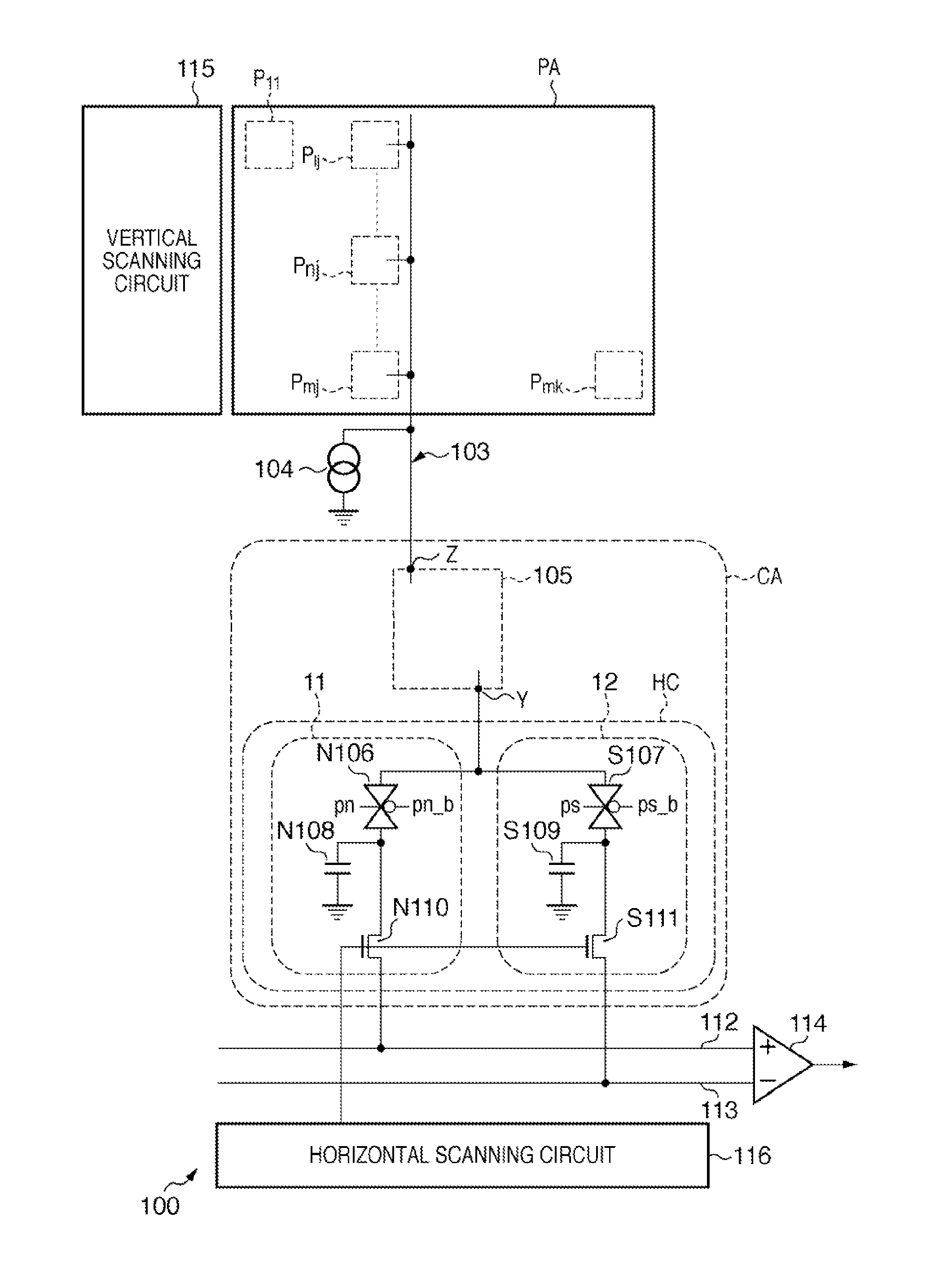

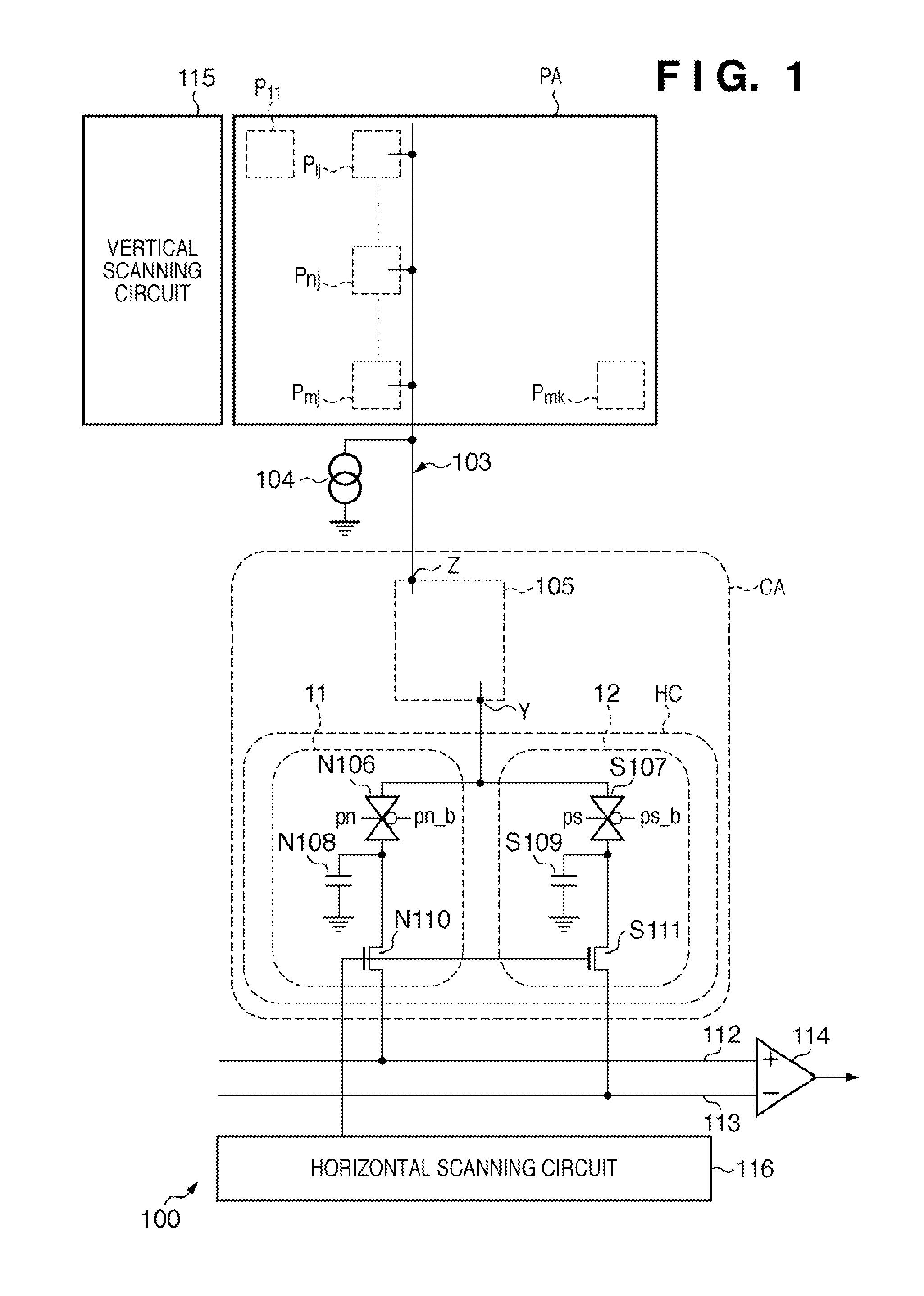

ActiveUS20050218299A1Television system detailsTelevision system scanning detailsCapacitancePhotodetector

Signals from an imager pixel photodetector are received by an amplifier having capacitive feedback, such as a capacitive transimpedance amplifier (CTIA). The amplifier can be operated at a low or no power level during an integration period of a photodetector to reduce power dissipation. The amplifier can be distributed, with an amplifier element within each pixel of an array and with amplifier output circuitry outside the pixel array. The amplifier can be a single ended cascode amplifier, a folded cascode amplifier, a differential input telescopic cascode amplifier, or other configuration. The amplifier can be used in pixel configurations where the amplifier is directly connected to the photodetector, or in configurations which use a transfer transistor to couple signal charges to a floating diffusion node with the amplifier being coupled to the floating diffusion node.

Owner:APTINA IMAGING CORP

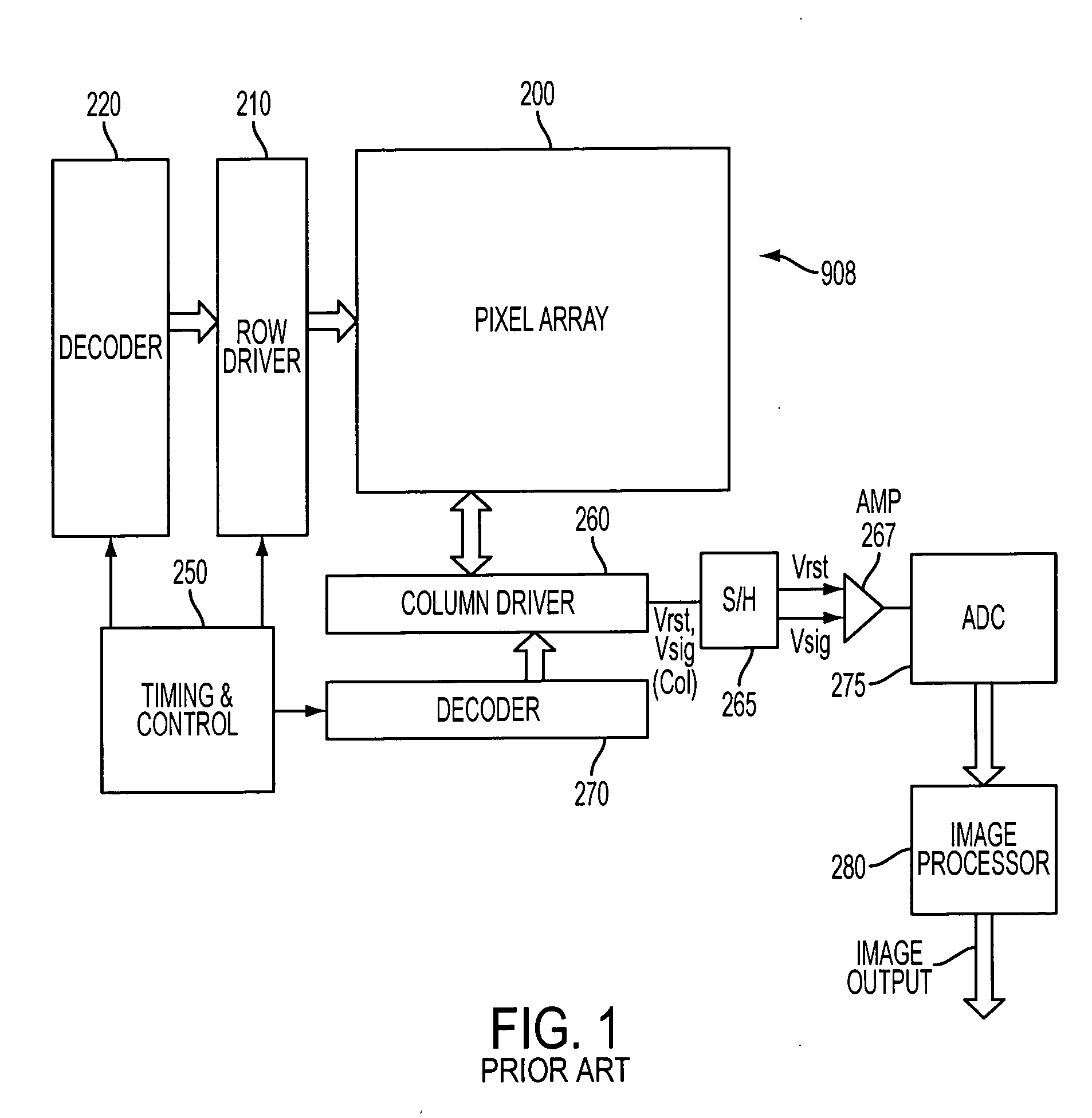

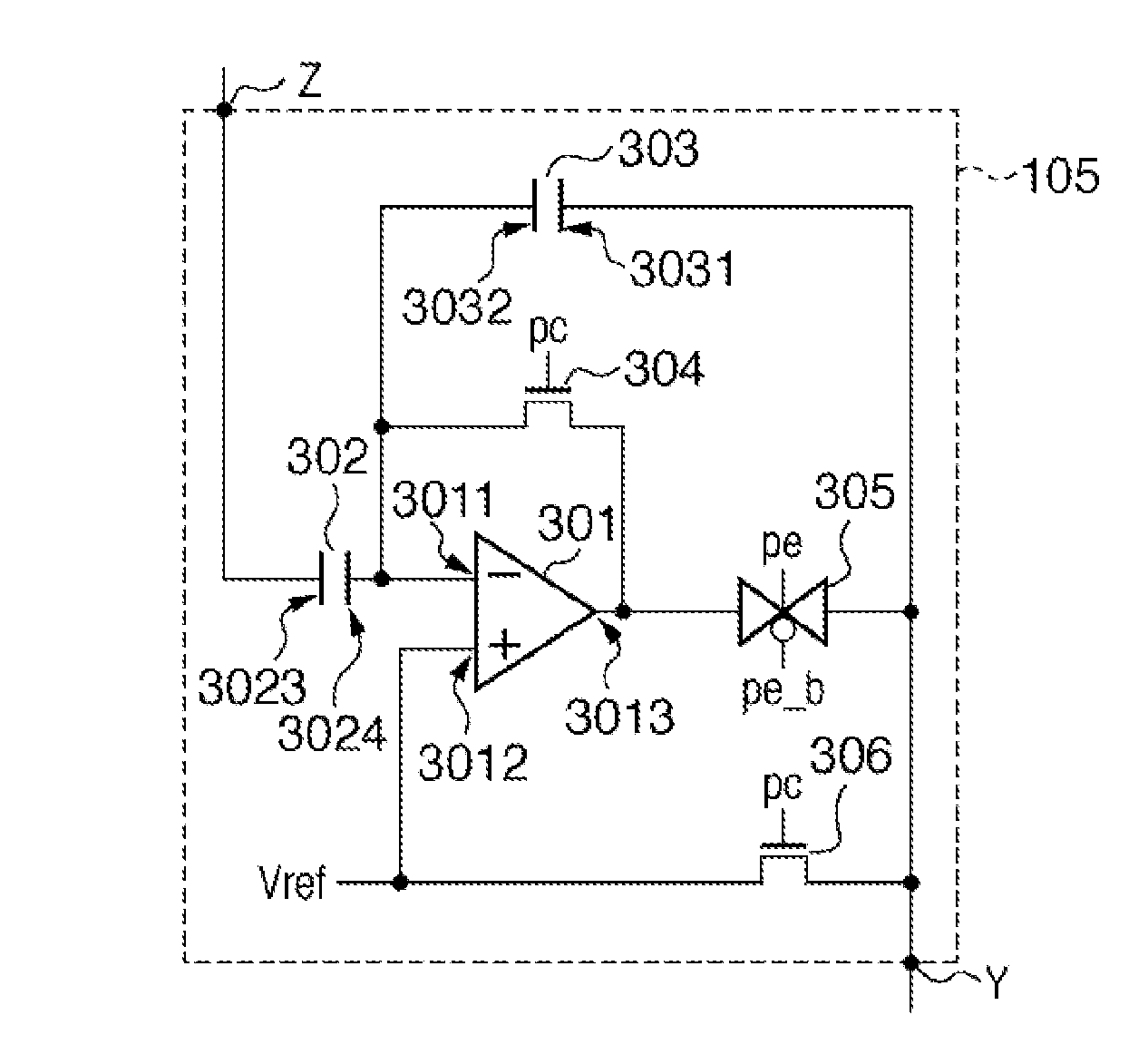

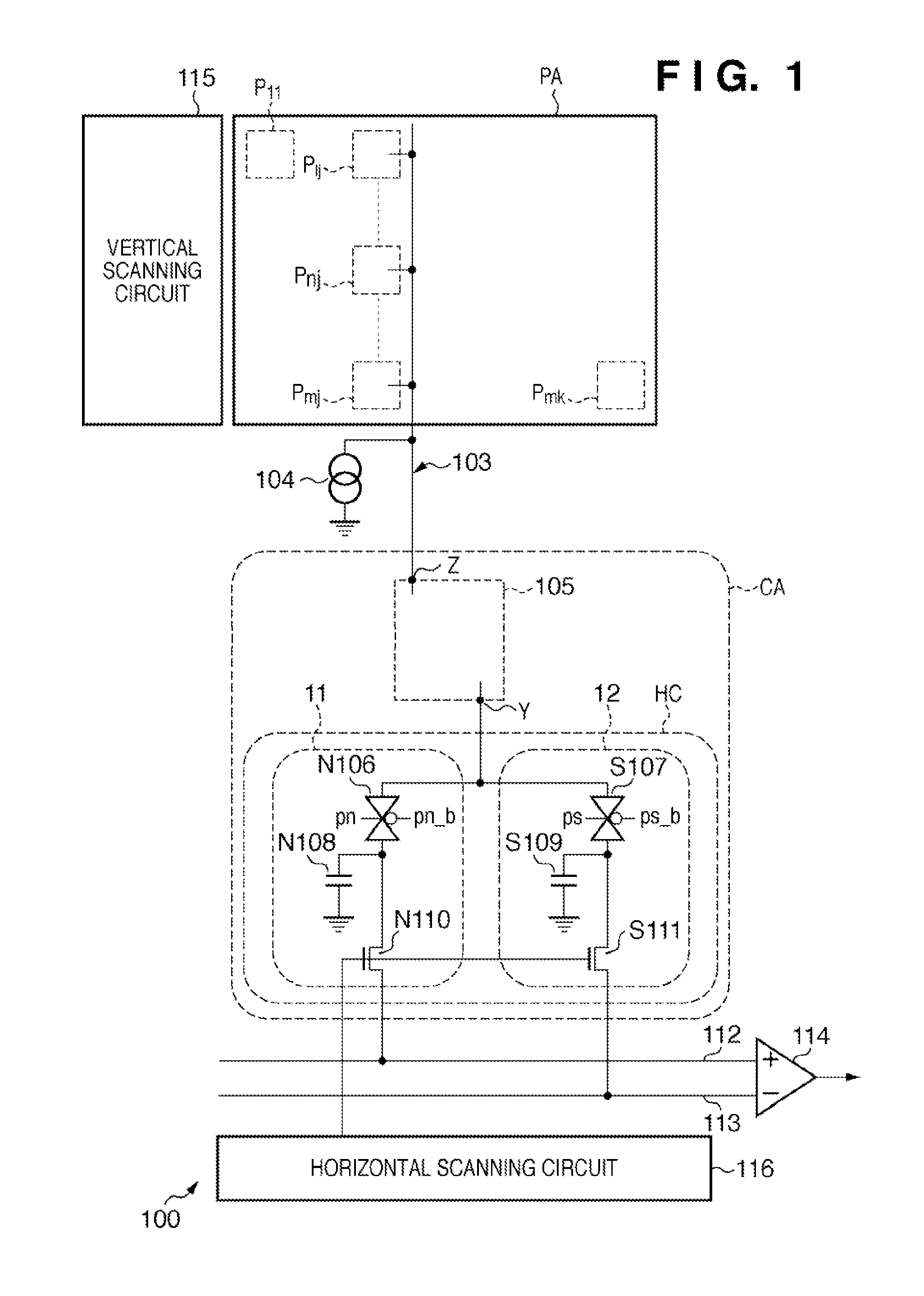

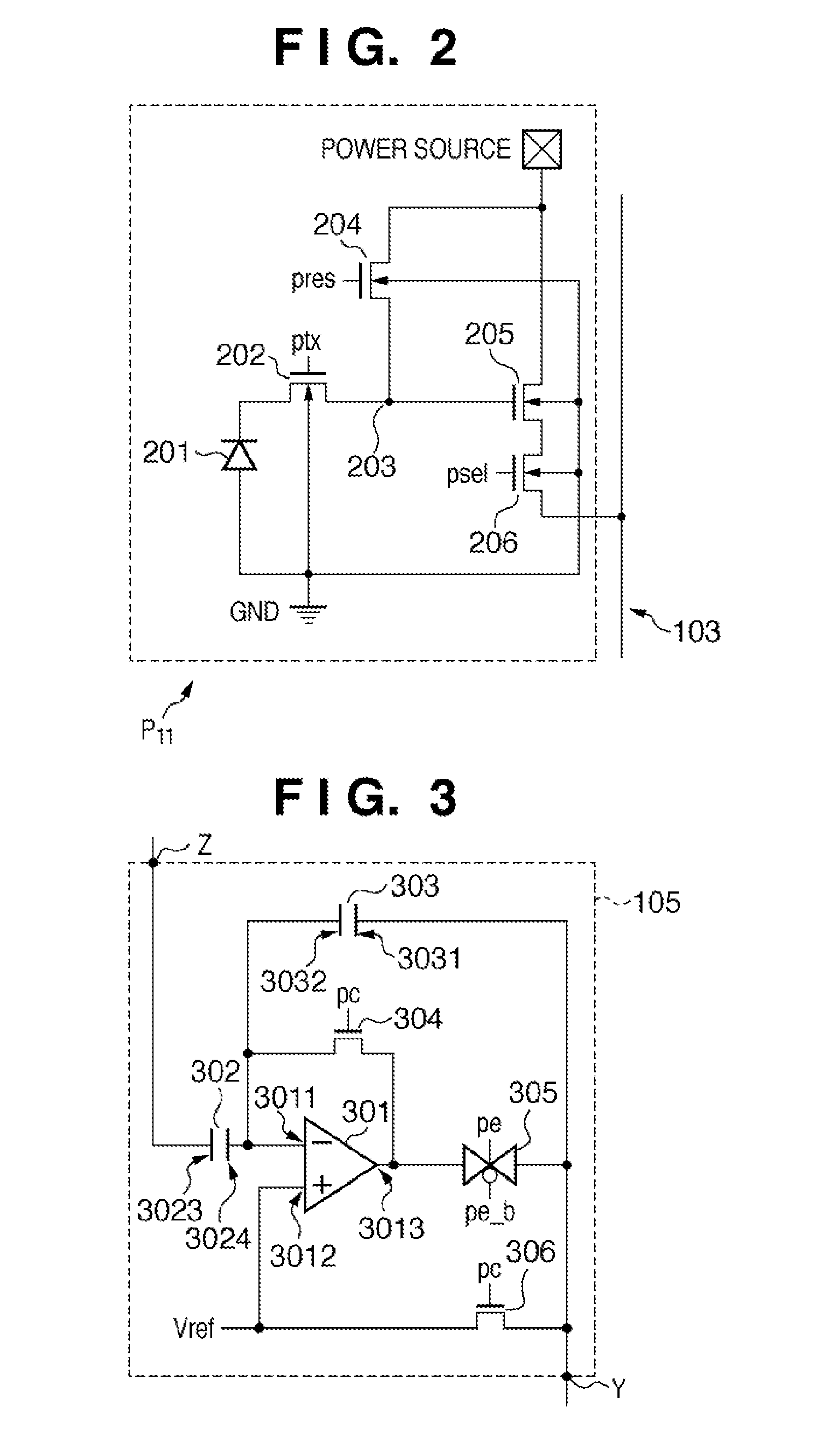

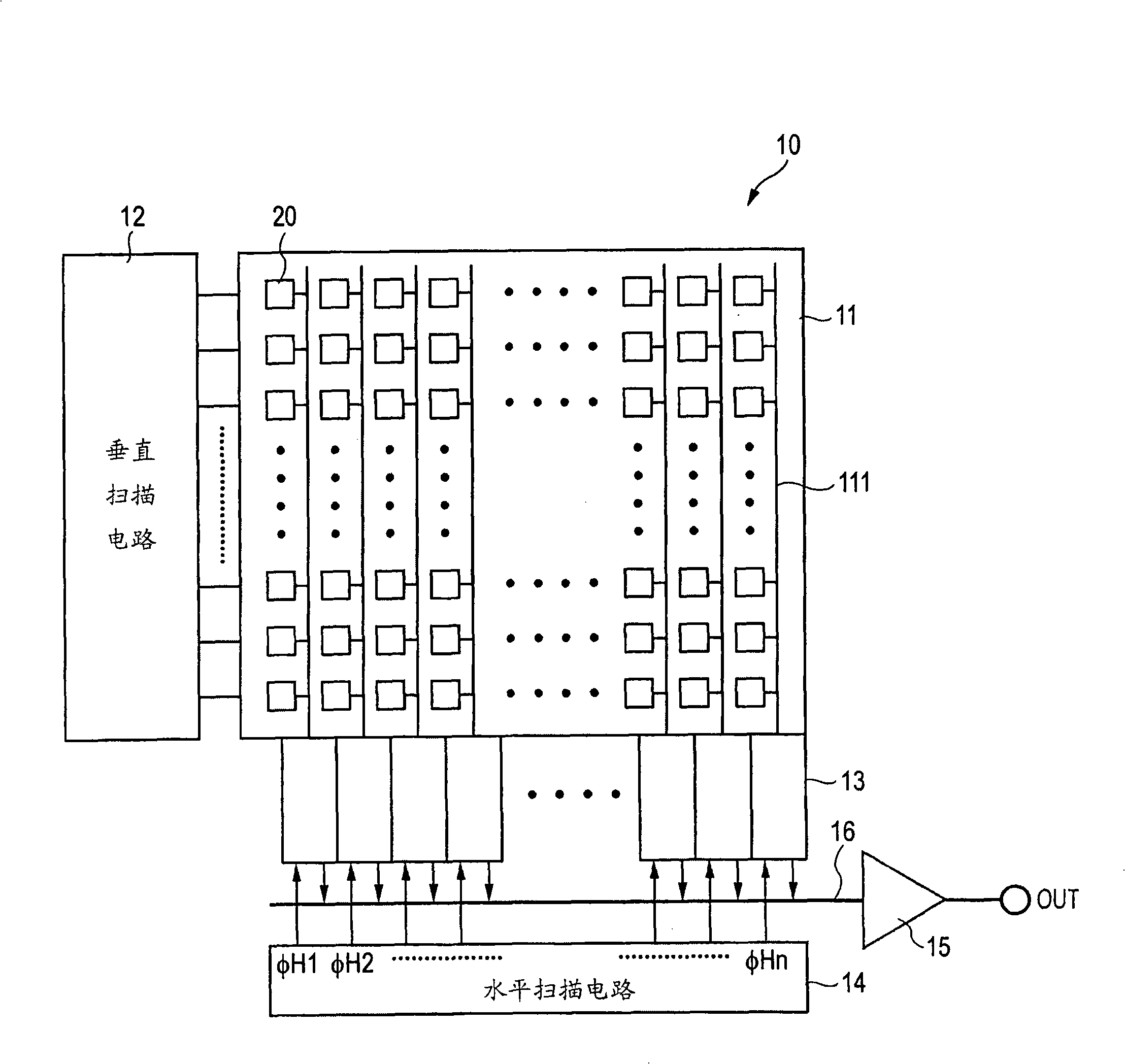

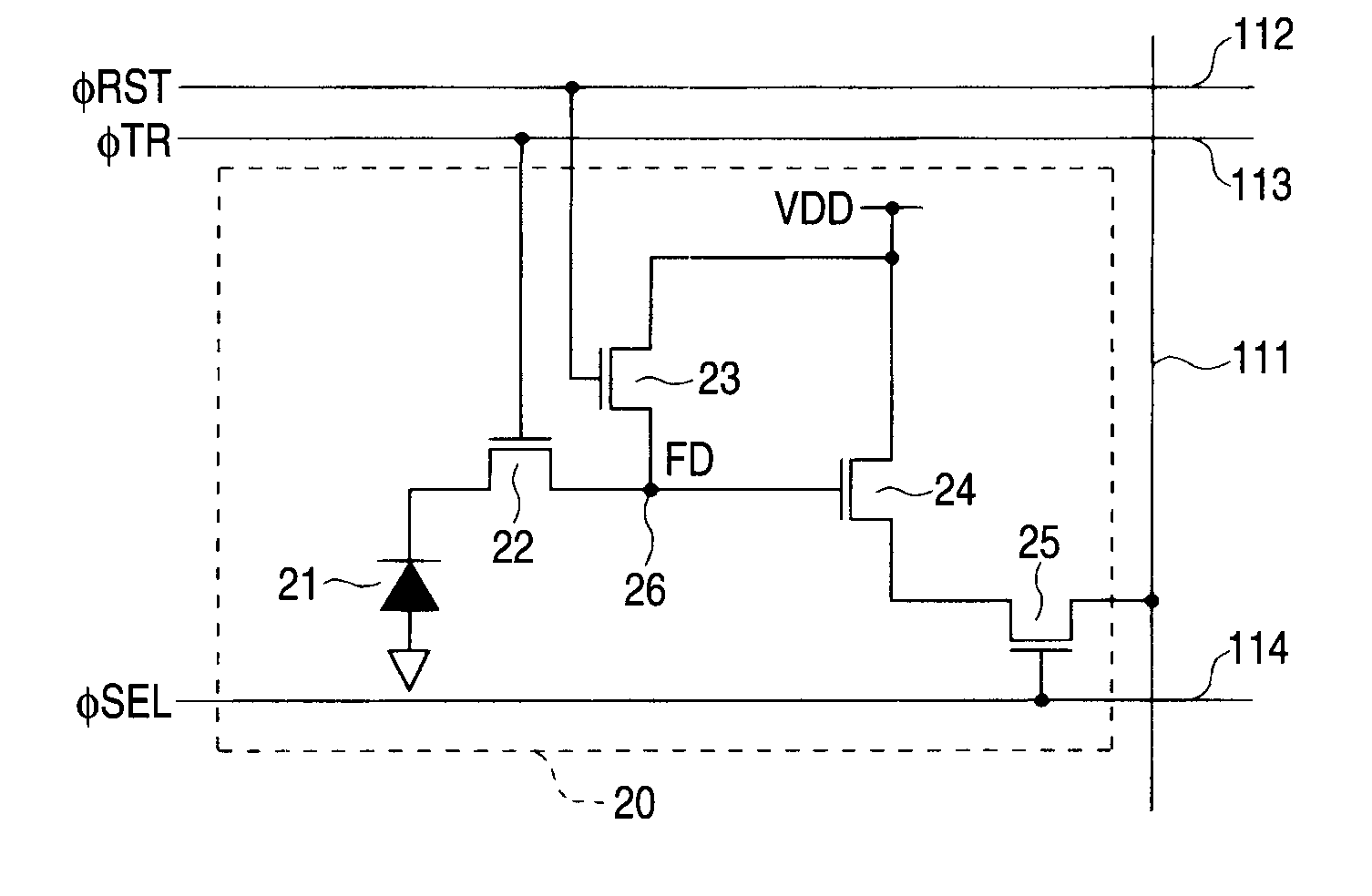

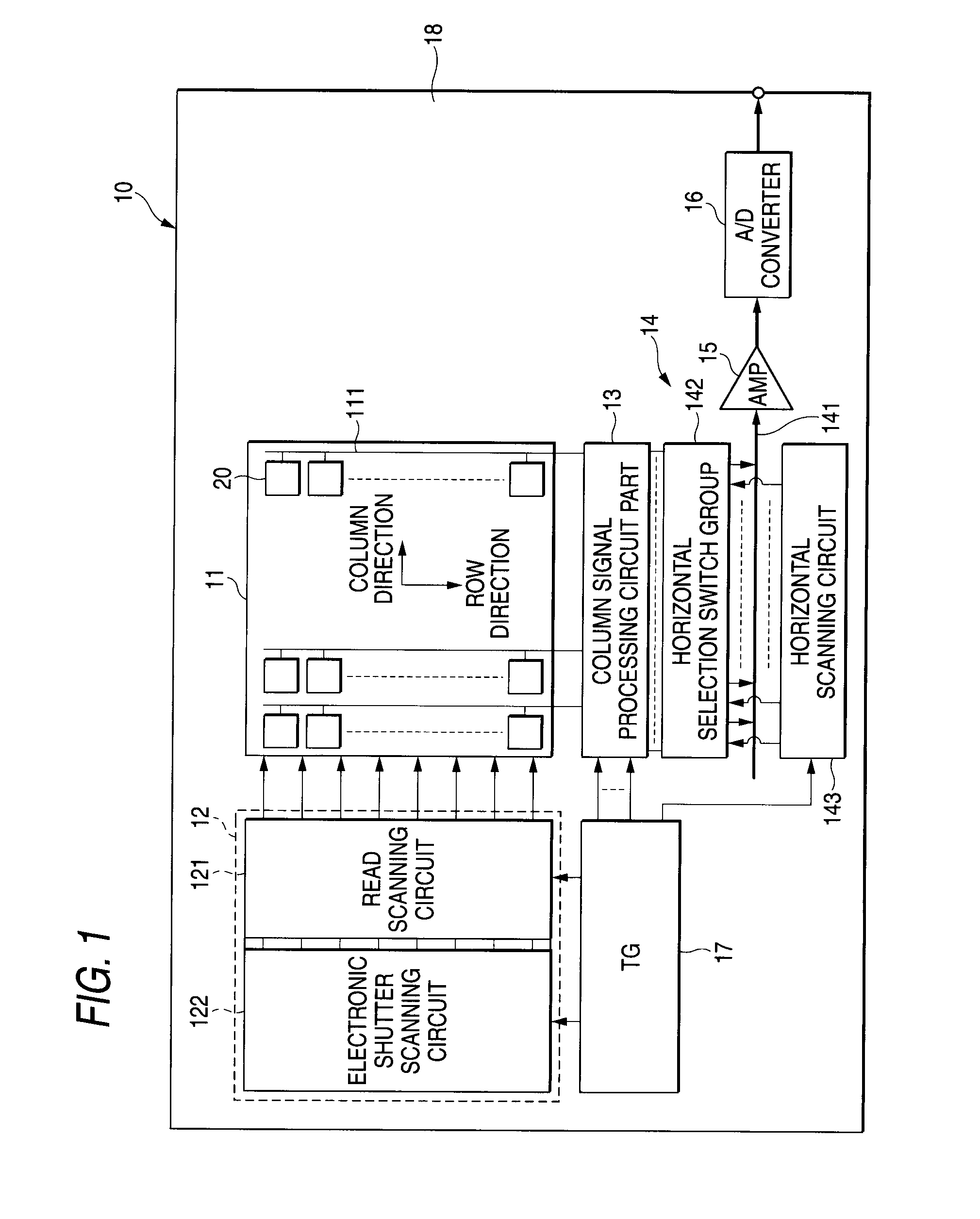

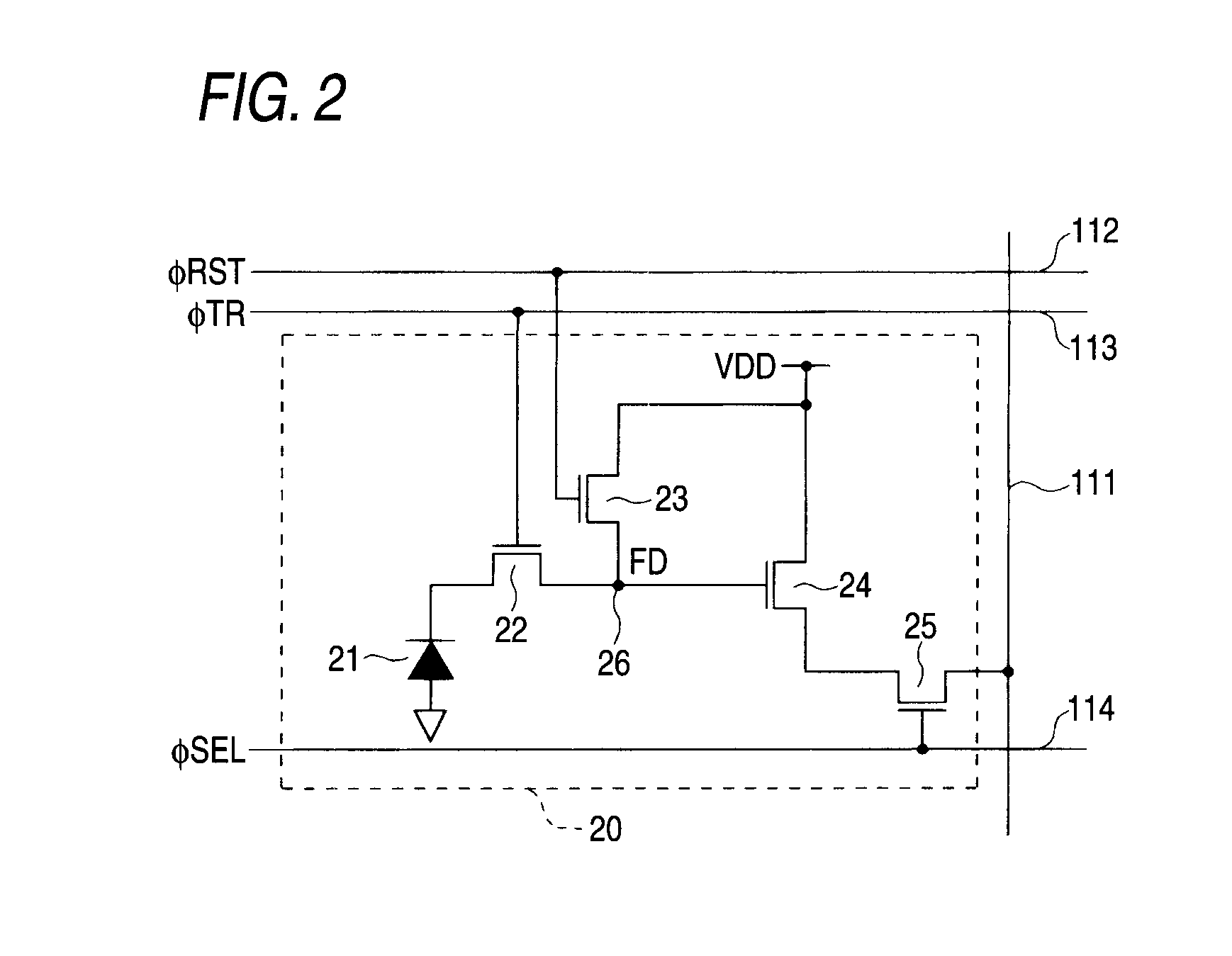

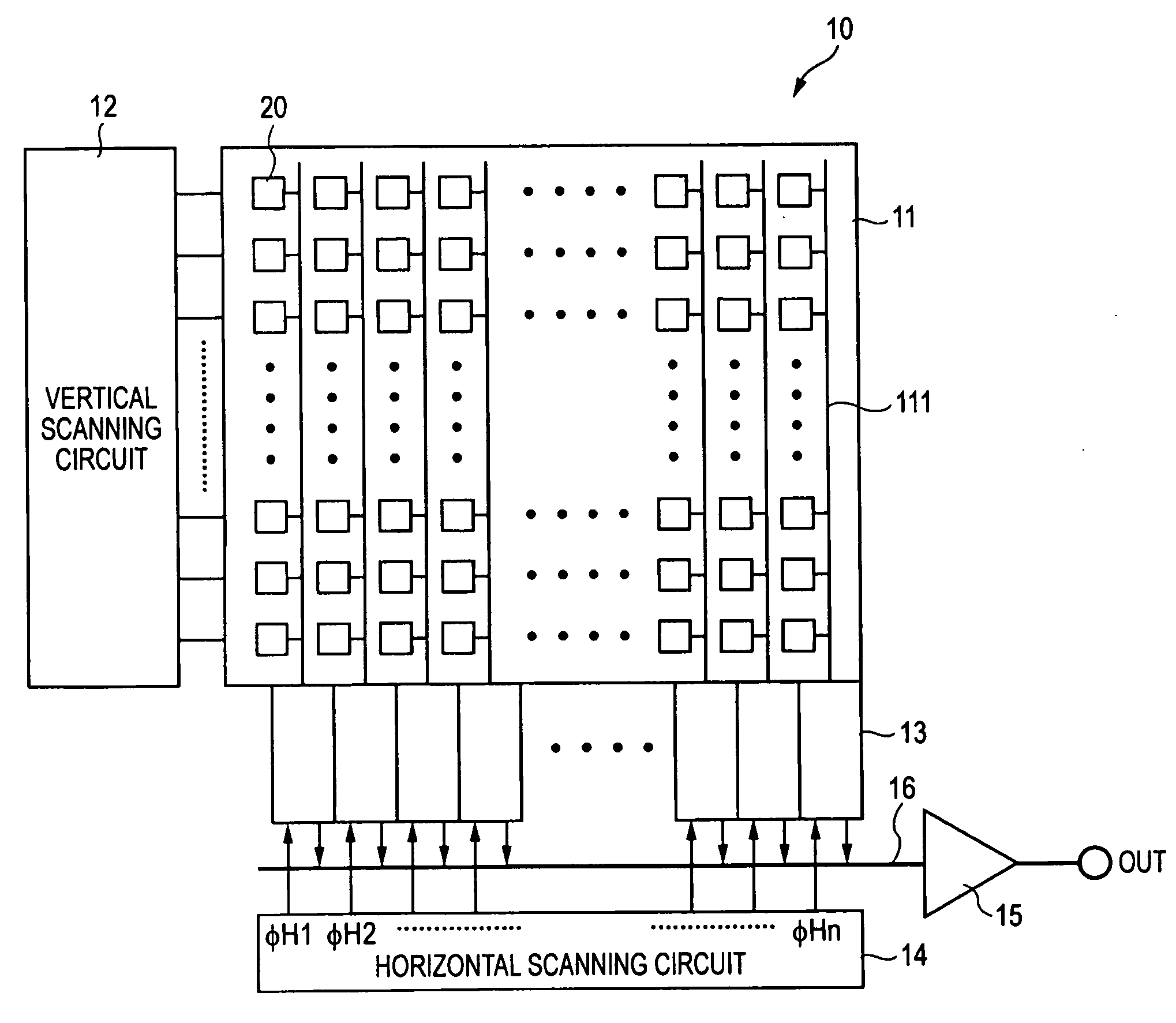

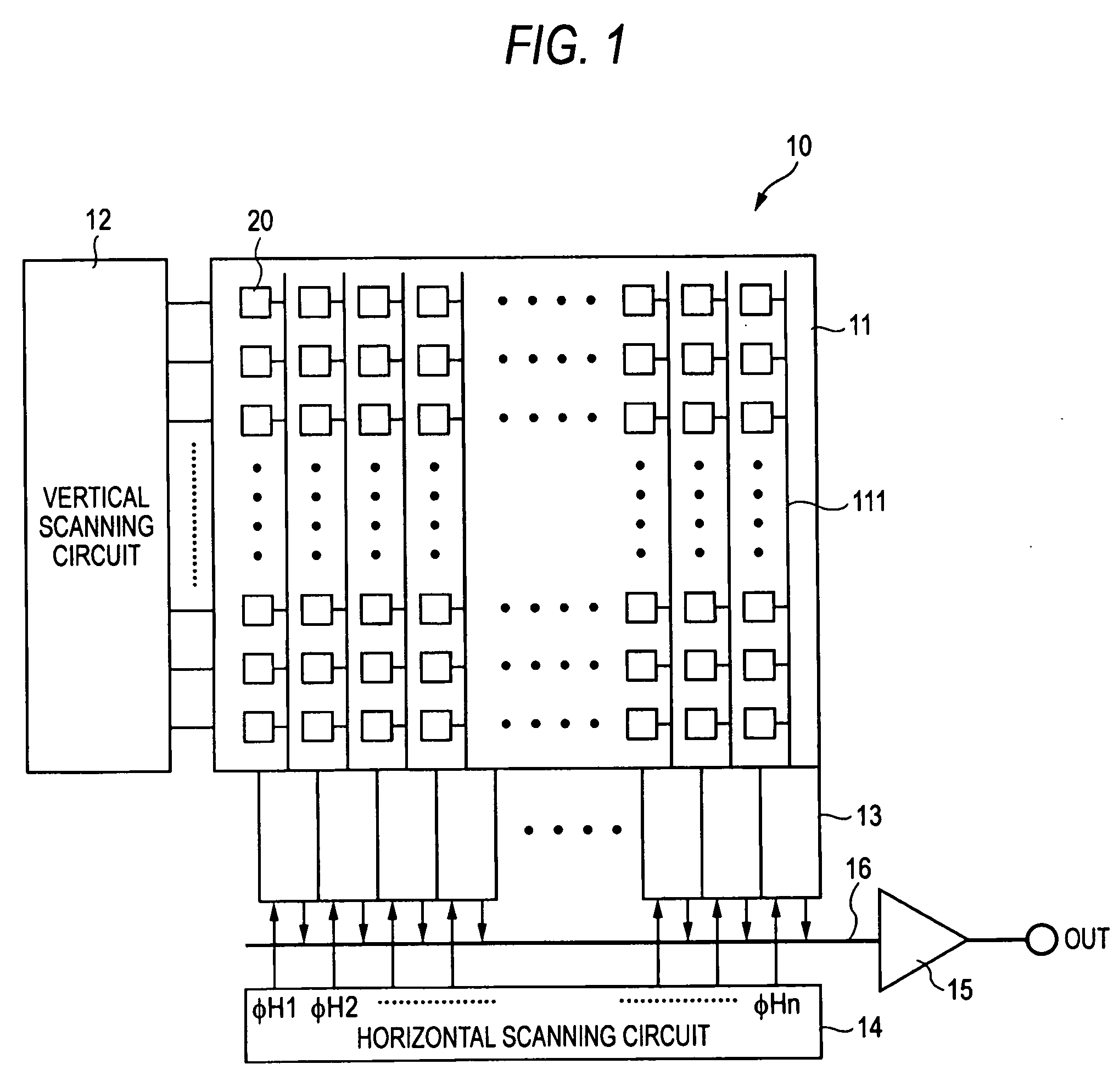

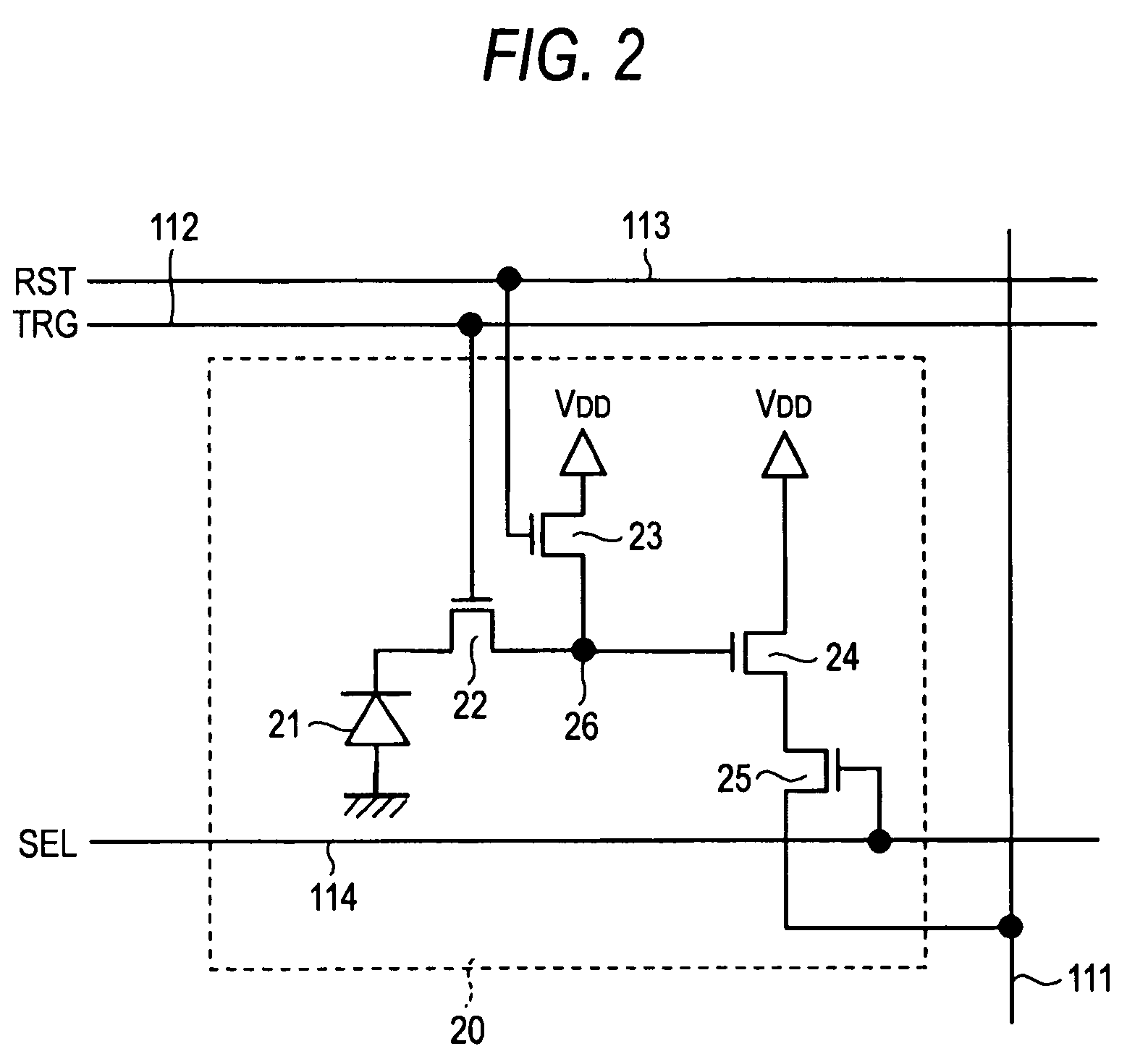

Image capturing device, image capturing system, and method of driving image capturing device

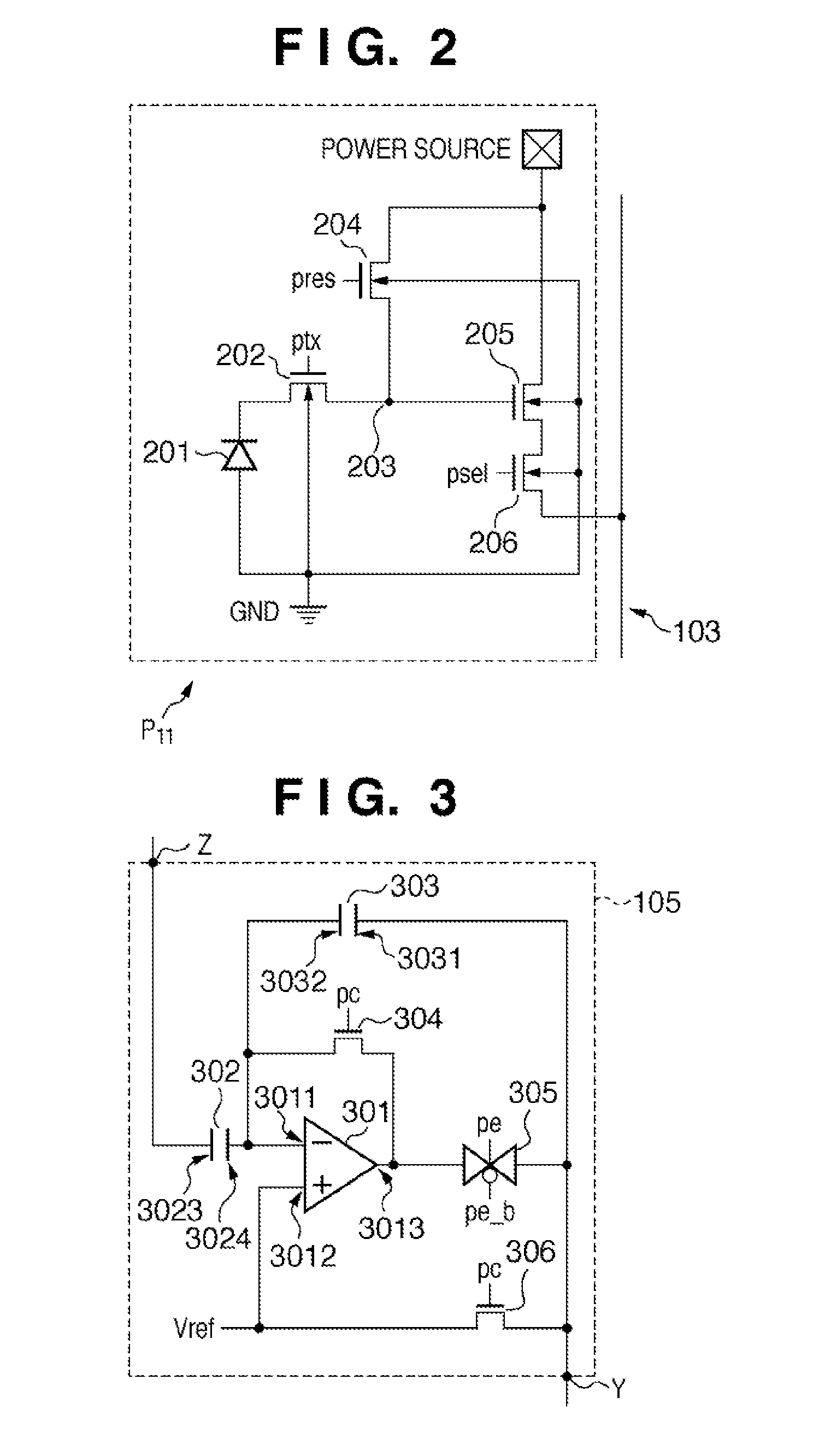

InactiveUS8400546B2Remove noiseTelevision system detailsTelevision system scanning detailsCapacitanceAudio power amplifier

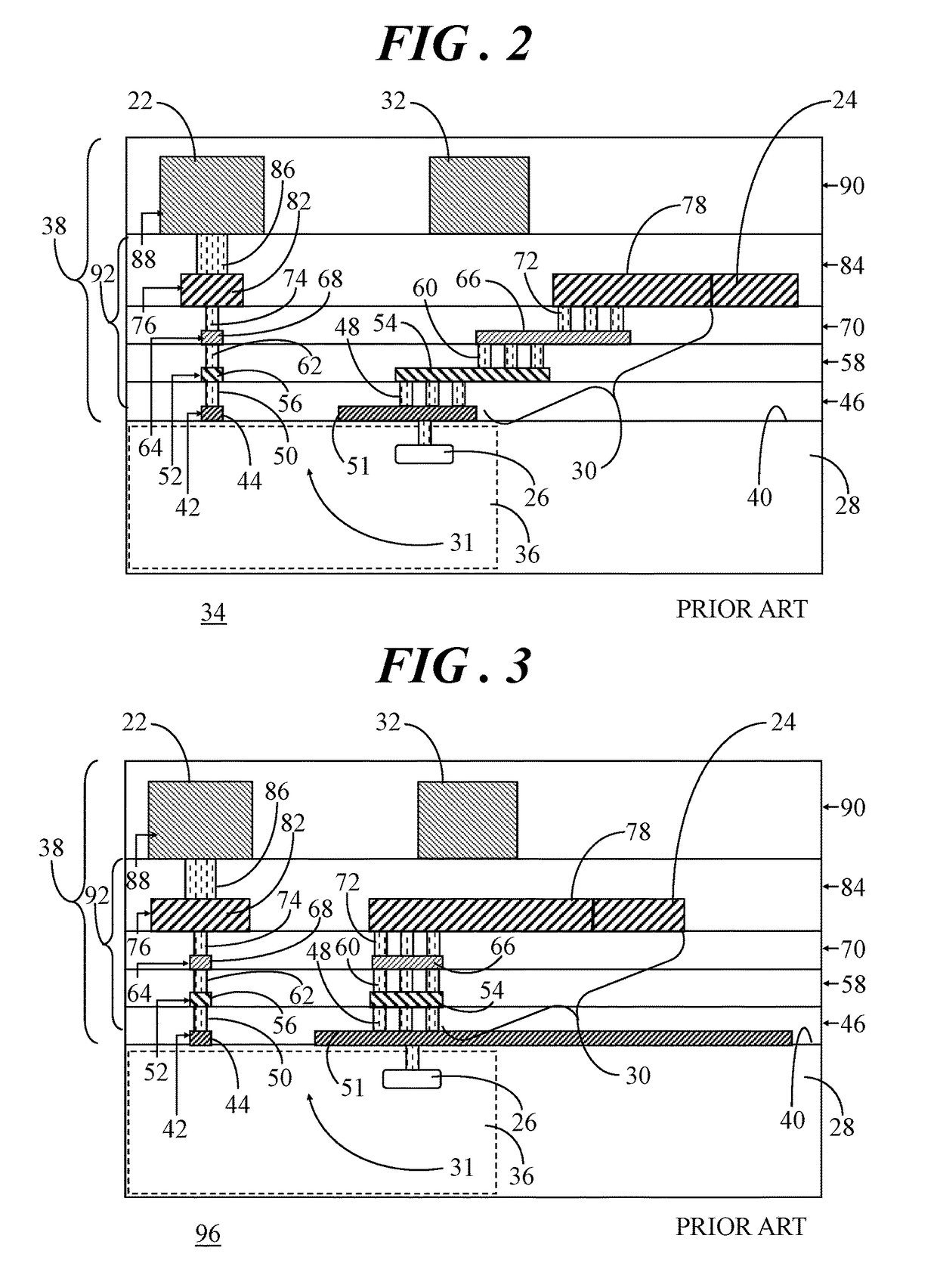

An image capturing device comprises a pixel array having a plurality of pixels each including a photoelectric conversion portion, a plurality of signal lines connected to the pixel array, a plurality of column amplifiers configured to respectively amplify signals transferred from the pixel array via the signal lines, the column amplifier comprising a first input terminal, a first output terminal, an amplifier having a second input terminal and a second output terminal, a feedback capacitance arranged between the second input terminal and the first output terminal, an input capacitance having an electrode connected to the first input terminal, and an electrode connected to the second input terminal, a first switch arranged between the second input terminal and the second output terminal, a second switch arranged between the first output terminal and the second output terminal, and a third switch arranged between a reference voltage terminal and the first output terminal.

Owner:CANON KK

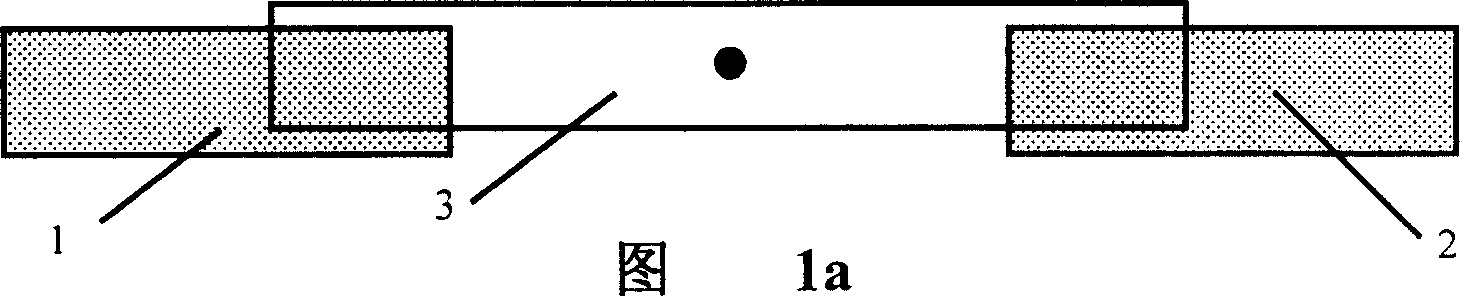

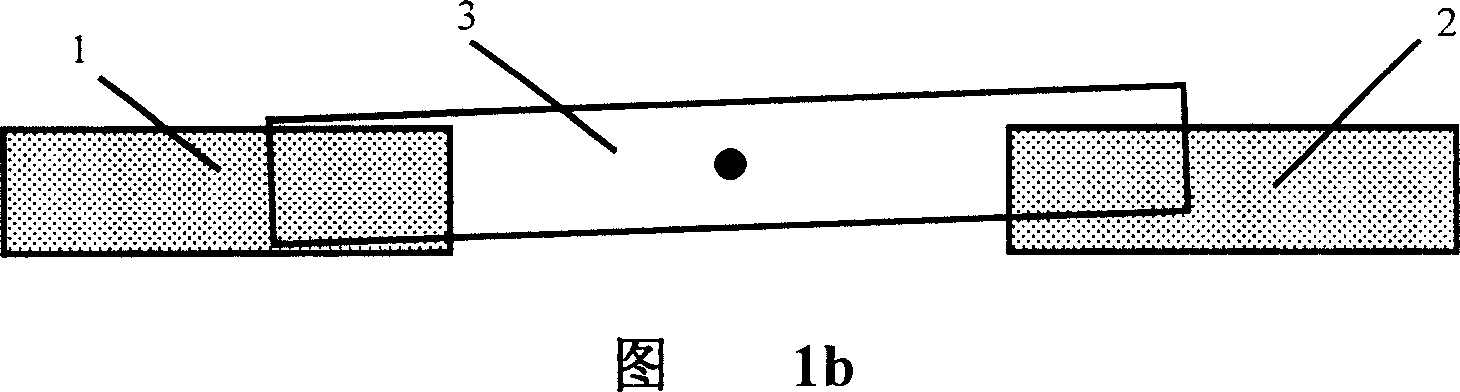

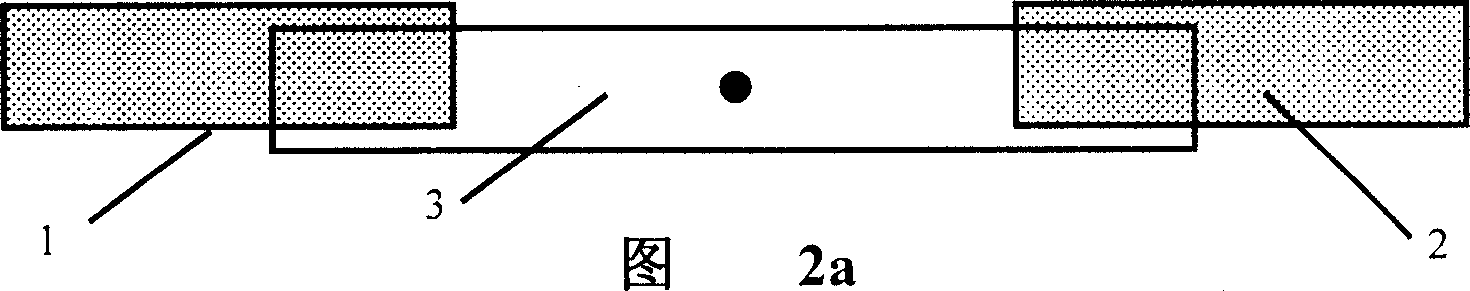

Capacitive type complete decoupling horizontal axis miniature mechanical gyro

InactiveCN1948906AExercise does not affectTwisting motion does not occurSpeed measurement using gyroscopic effectsTurn-sensitive devicesCapacitanceHorizontal axis

The invention relates to capacitance complete decoupling horizontal axis micro mechanical gyro. Its features are that it includes glass substrate, drive capacitance, drive feedback capacitance, test capacitance, drive mass block, asymmetry mass block, and test mass block. The drive mass block is set on the center of which two ends are respectively connected with the glass substrate. The mobile electrode of the drive capacitance and drive feed back capacitance are connected with the drive block. And their fixed electrodes are connected with glass substrate. The outside two ends of the asymmetry mass block are connected with the test mass block. And the inside two ends are connected with the drive mass block. The mobile electrode of the test capacitance is fixed on the test mass block. And its fixed electrode is fixed on the glass substrate. The two ends of the test mass block are fixed on the glass substrate. The invention has double-decoupling structure which can restrain ghost effect, reduce excursion, and good linearity and offset axis sensitivity.

Owner:PEKING UNIV

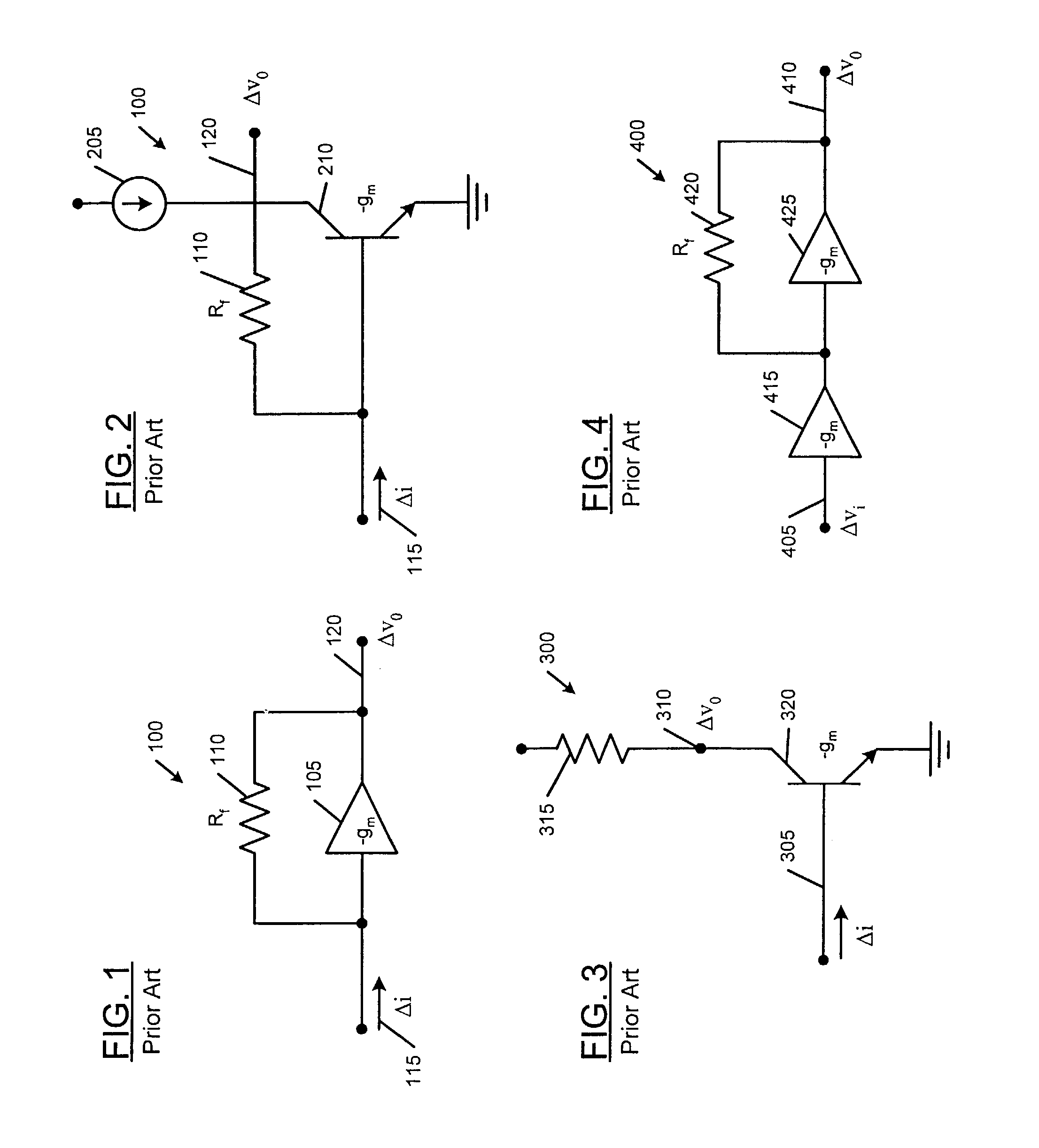

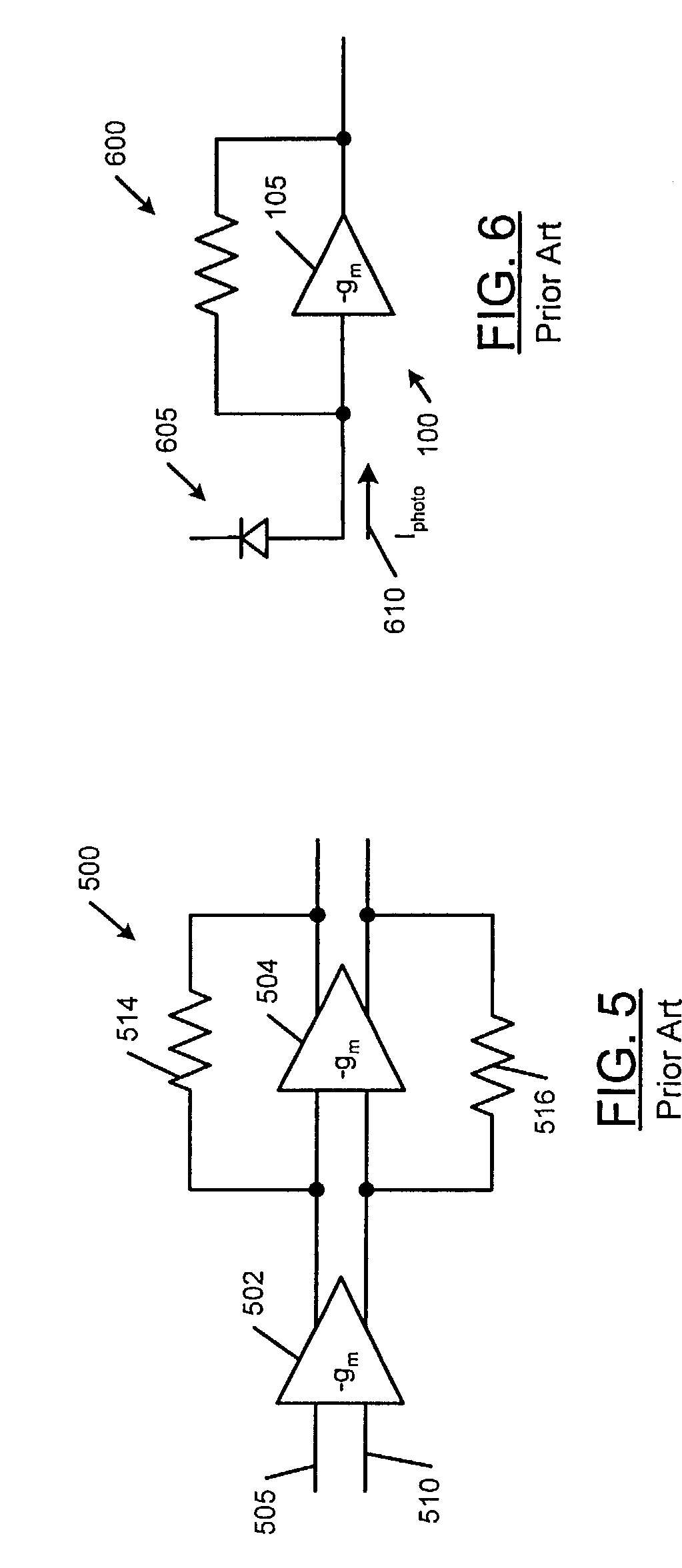

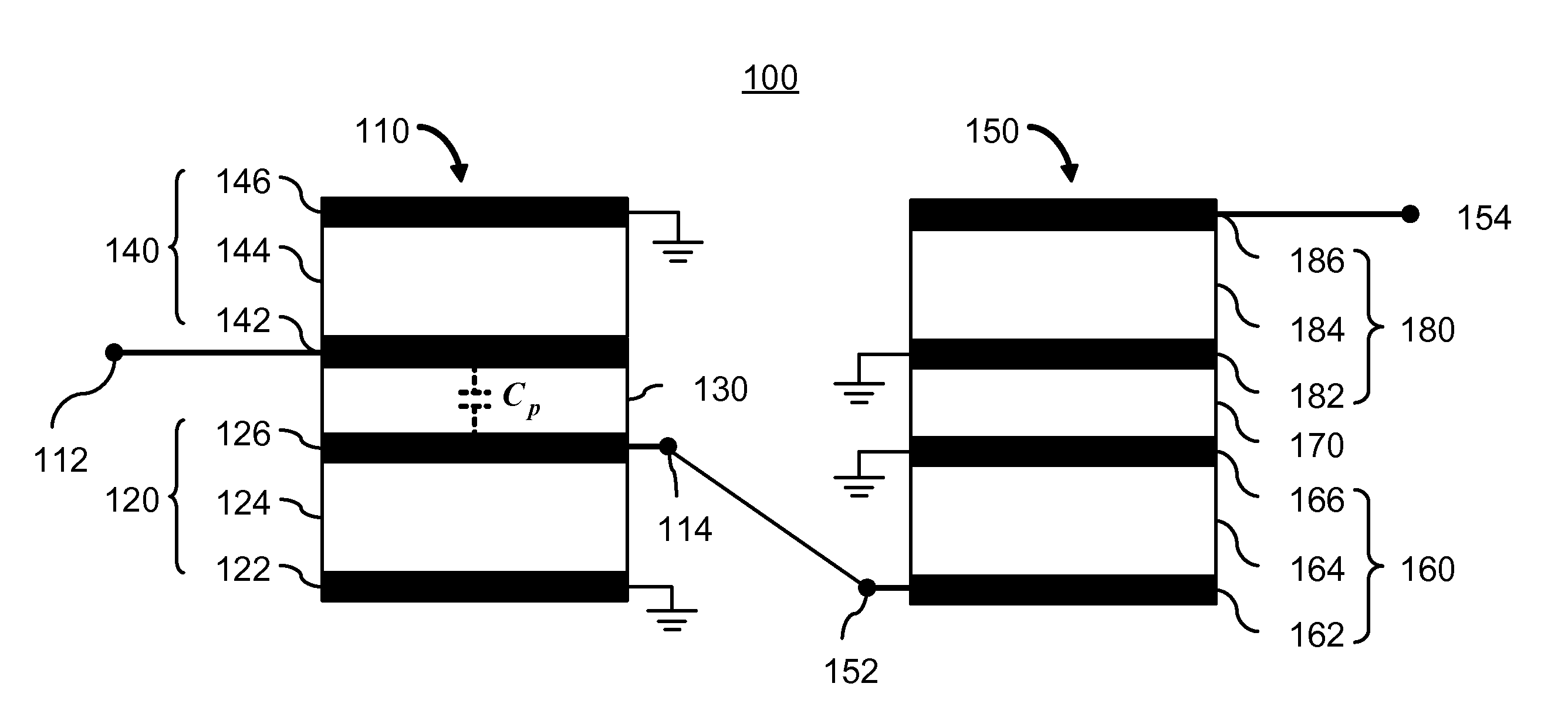

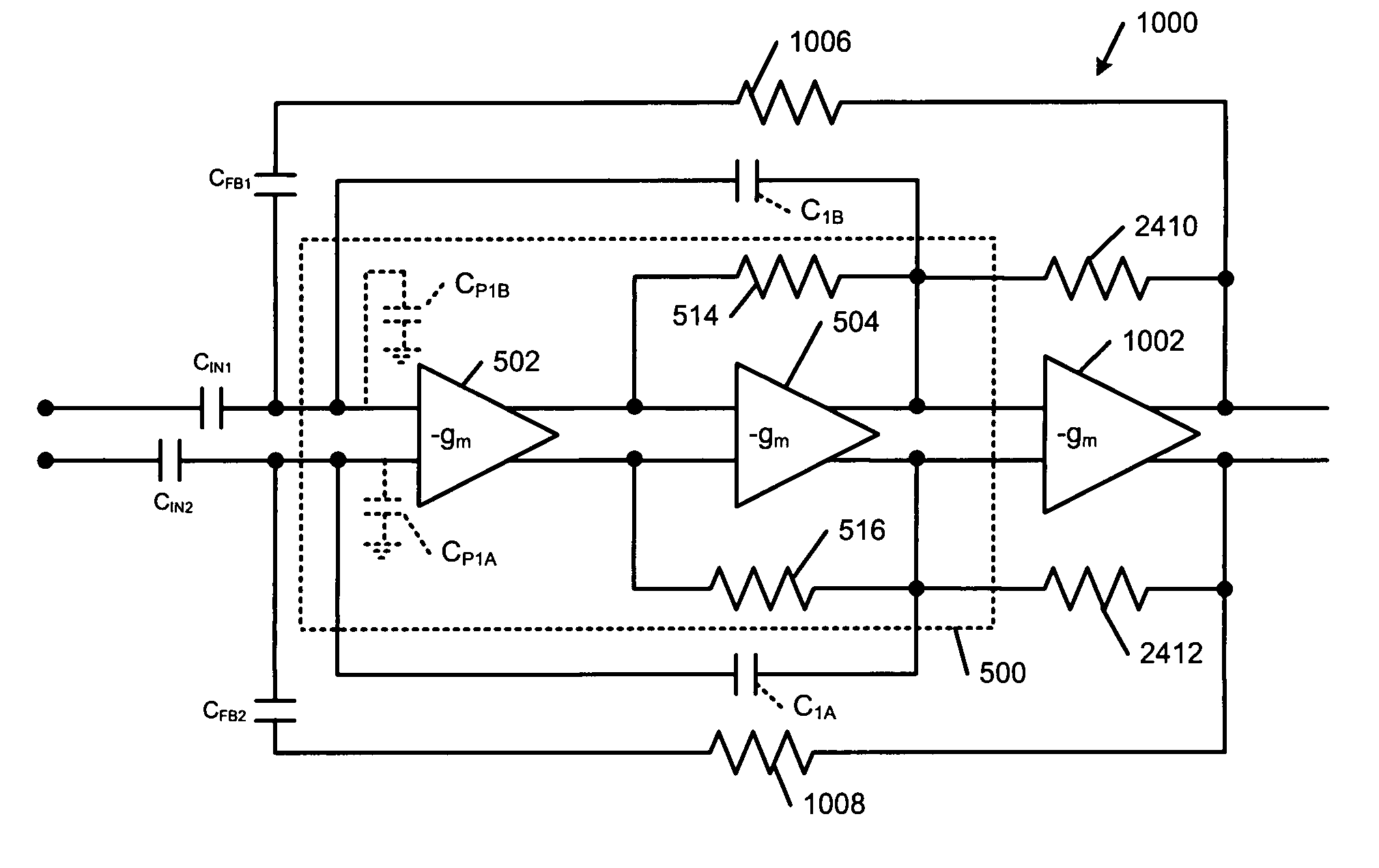

Nested transimpedance amplifier

InactiveUS7276965B1Negative-feedback-circuit arrangementsHigh frequency amplifiersCapacitanceAudio power amplifier

A nested transimpedance amplifier (TIA) circuit includes a zero-order TIA having an input and an output. A first operational amplifier (opamp) has an input that communicates with the output of the zero-order TIA and an output. A first feedback resistance has one end that communicates with the input of the zero-order TIA and an opposite end that communicates with the output of the first opamp. A first feedback capacitance has a first end that communicates with the input of the zero-order TIA and a second end that communicates with the output of the zero-order TIA. A capacitor has one end that communicates with the input of the zero-order TIA.

Owner:MARVELL ASIA PTE LTD

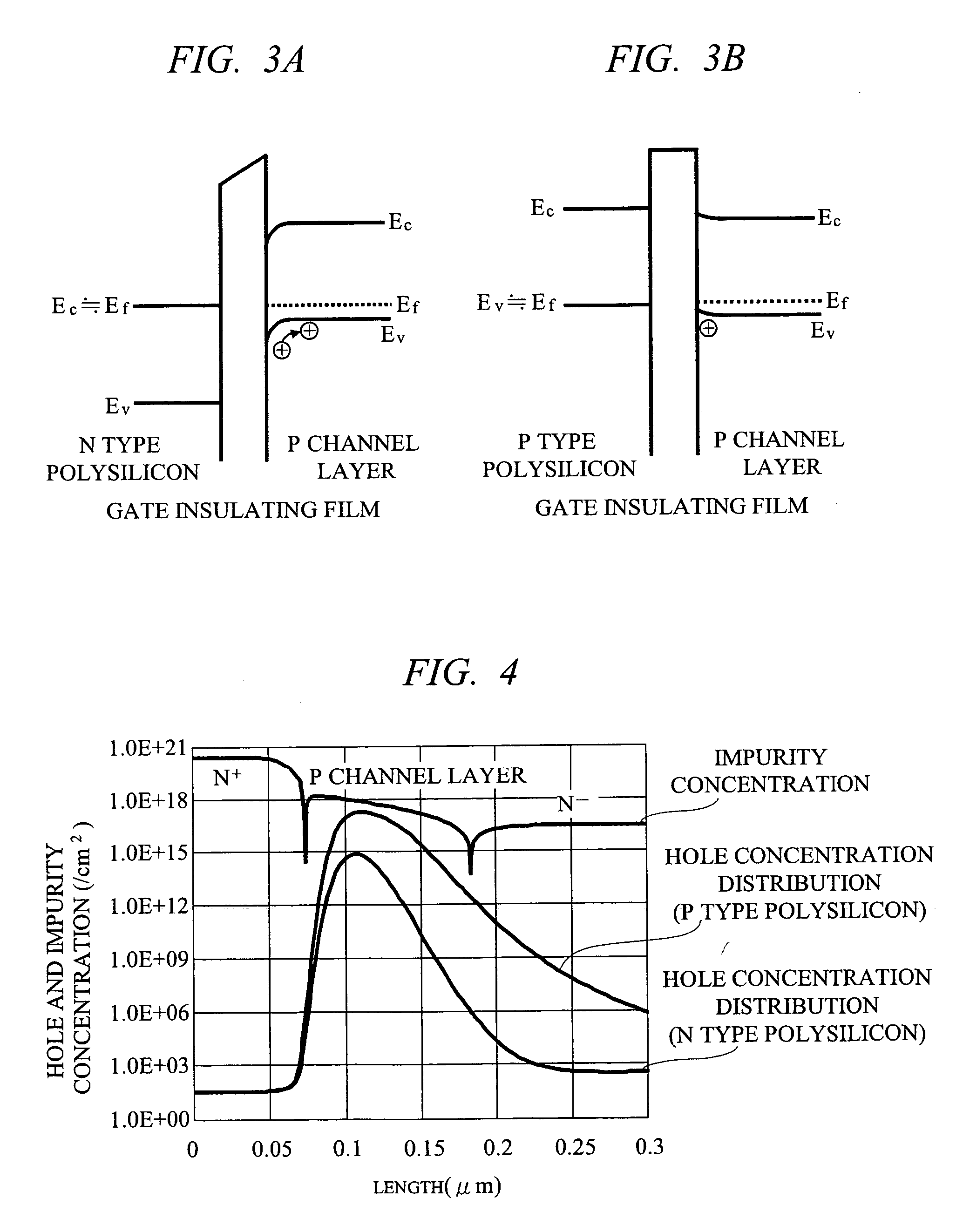

DMOSFET and planar type MOSFET

A technology capable of realizing a MOSFET with low ON-resistance and low feedback capacitance, in which the punch through of a channel layer can be prevented even when the shallow junction of the channel layer is formed in a planar type MOSFET is provided. A P type polysilicon is used for a gate electrode in a planar type MOSFET, in particular, in an N channel DMOSFET.

Owner:RENESAS TECH CORP

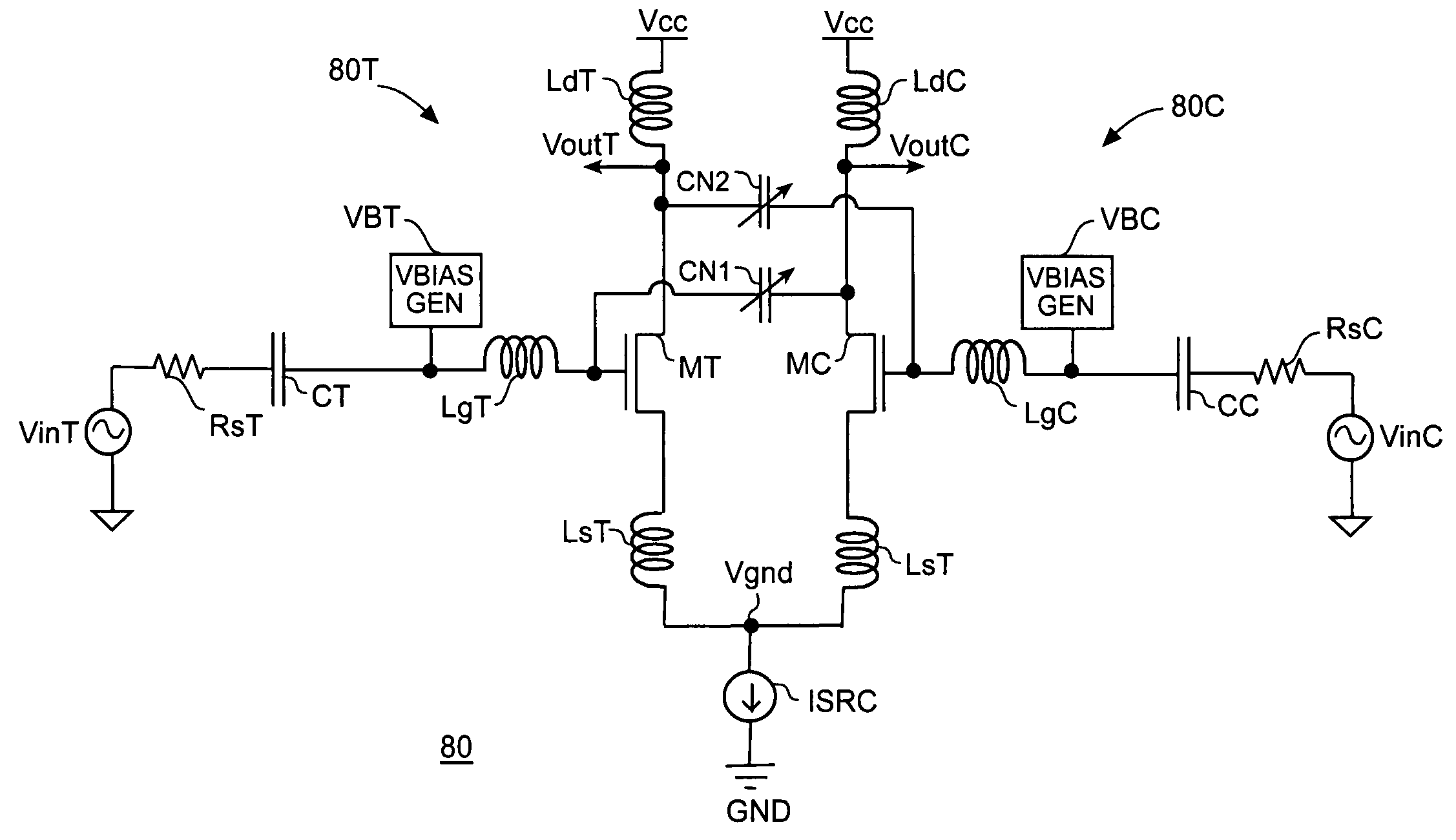

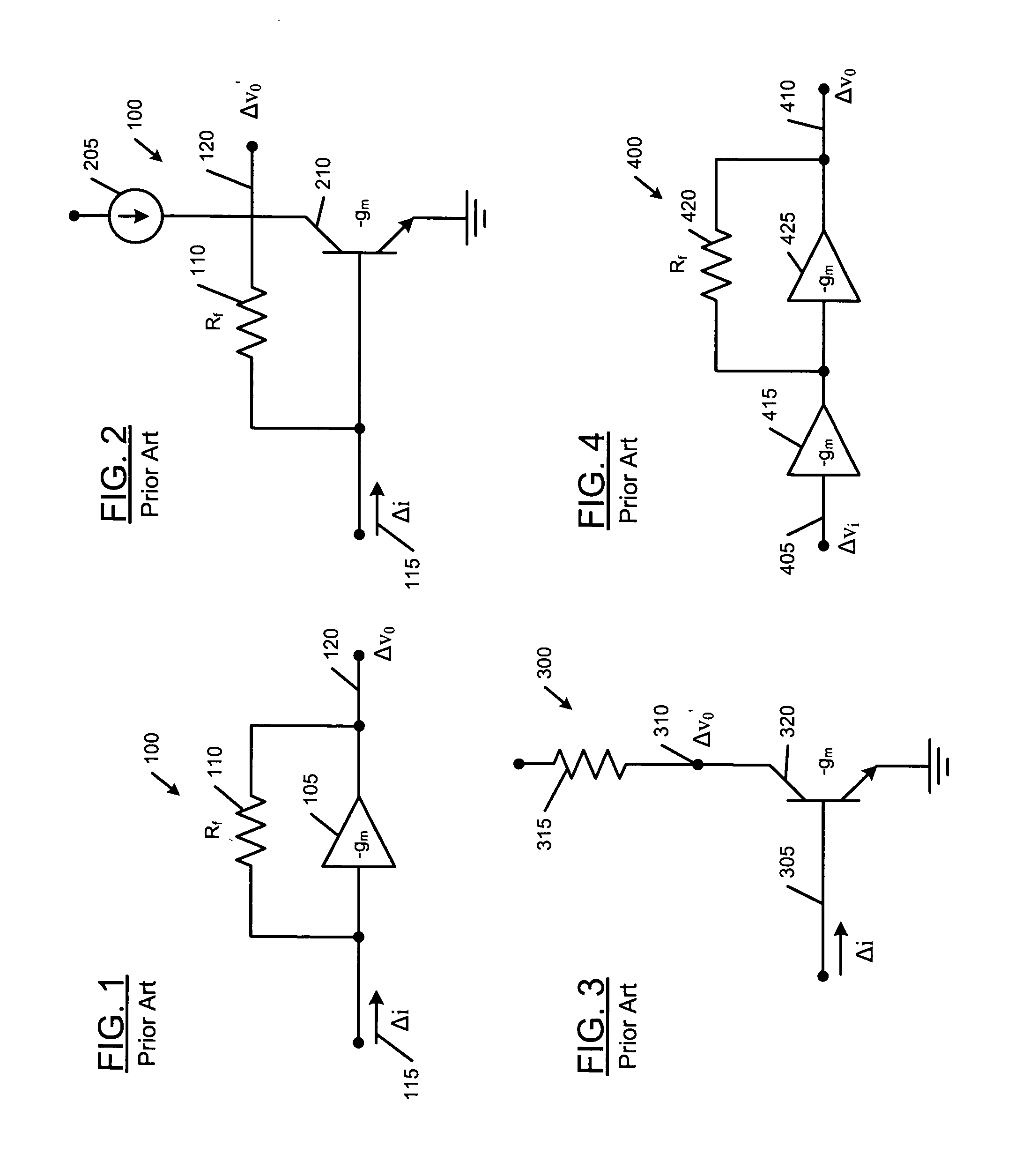

Neutralization techniques for differential low noise amplifiers

InactiveUS7256646B2Reducing available voltage headroomImprove isolationMultiple input and output pulse circuitsAmplifier modifications to reduce noise influenceCapacitanceLow noise

Owner:SEIKO EPSON CORP

Semiconductor device

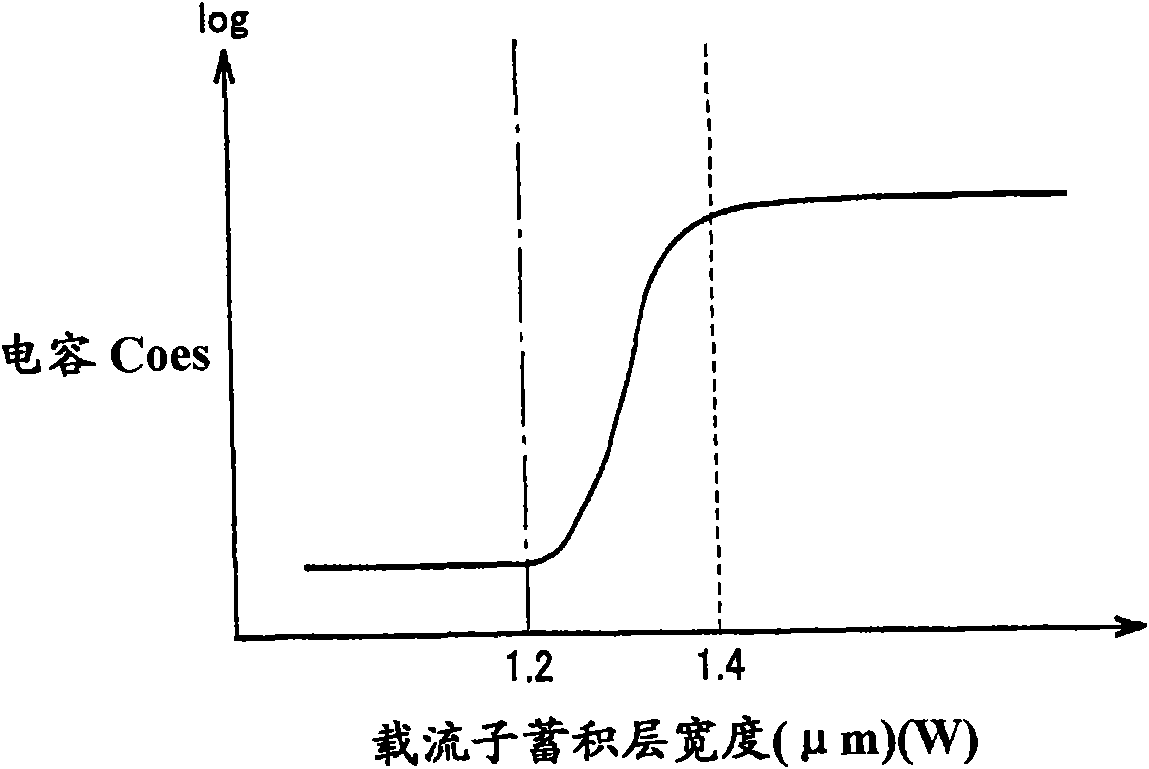

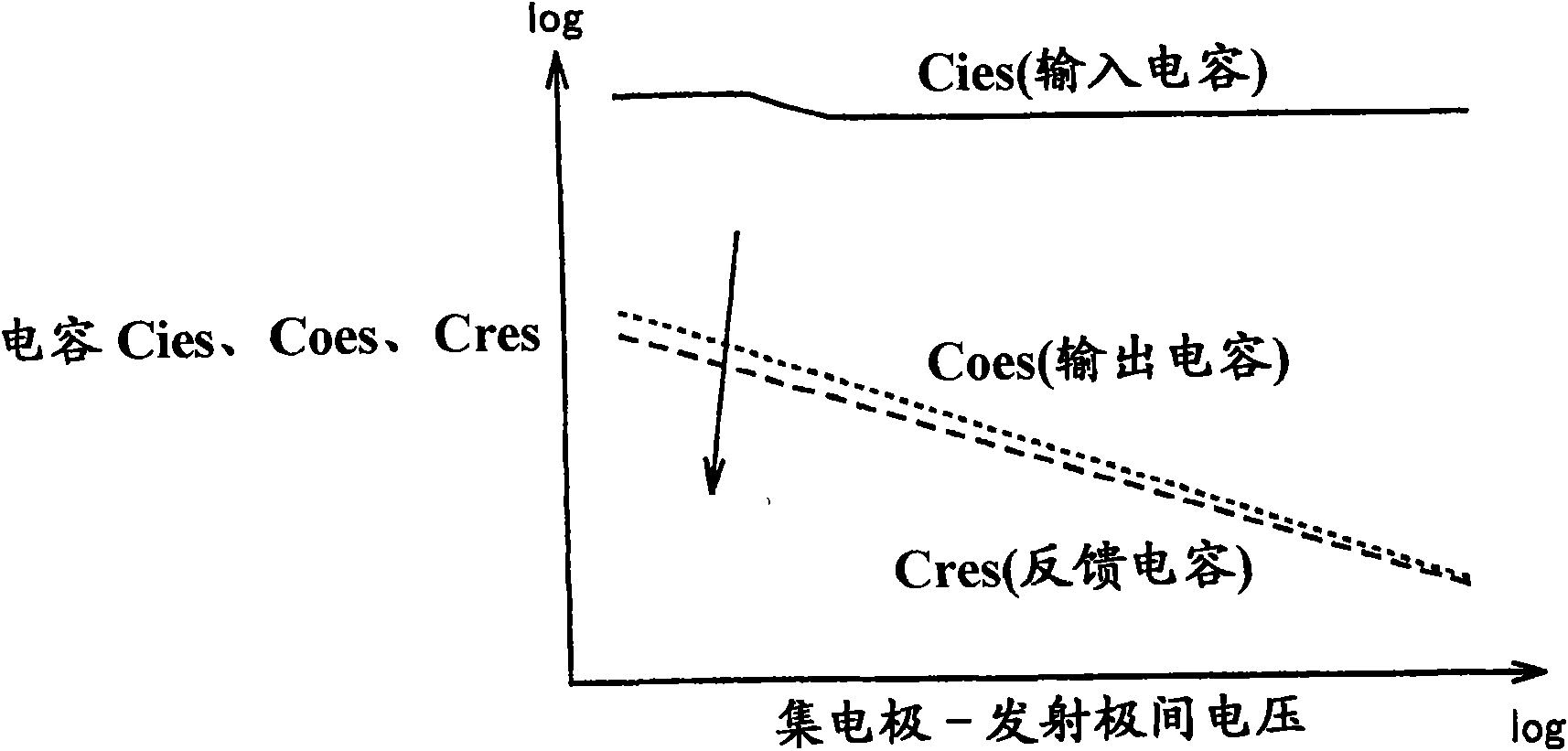

ActiveCN101582443ASuppress changesSuppress electromagnetic noiseSemiconductor devicesCapacitanceEngineering

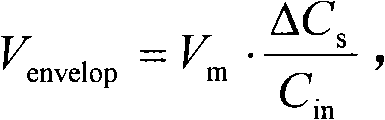

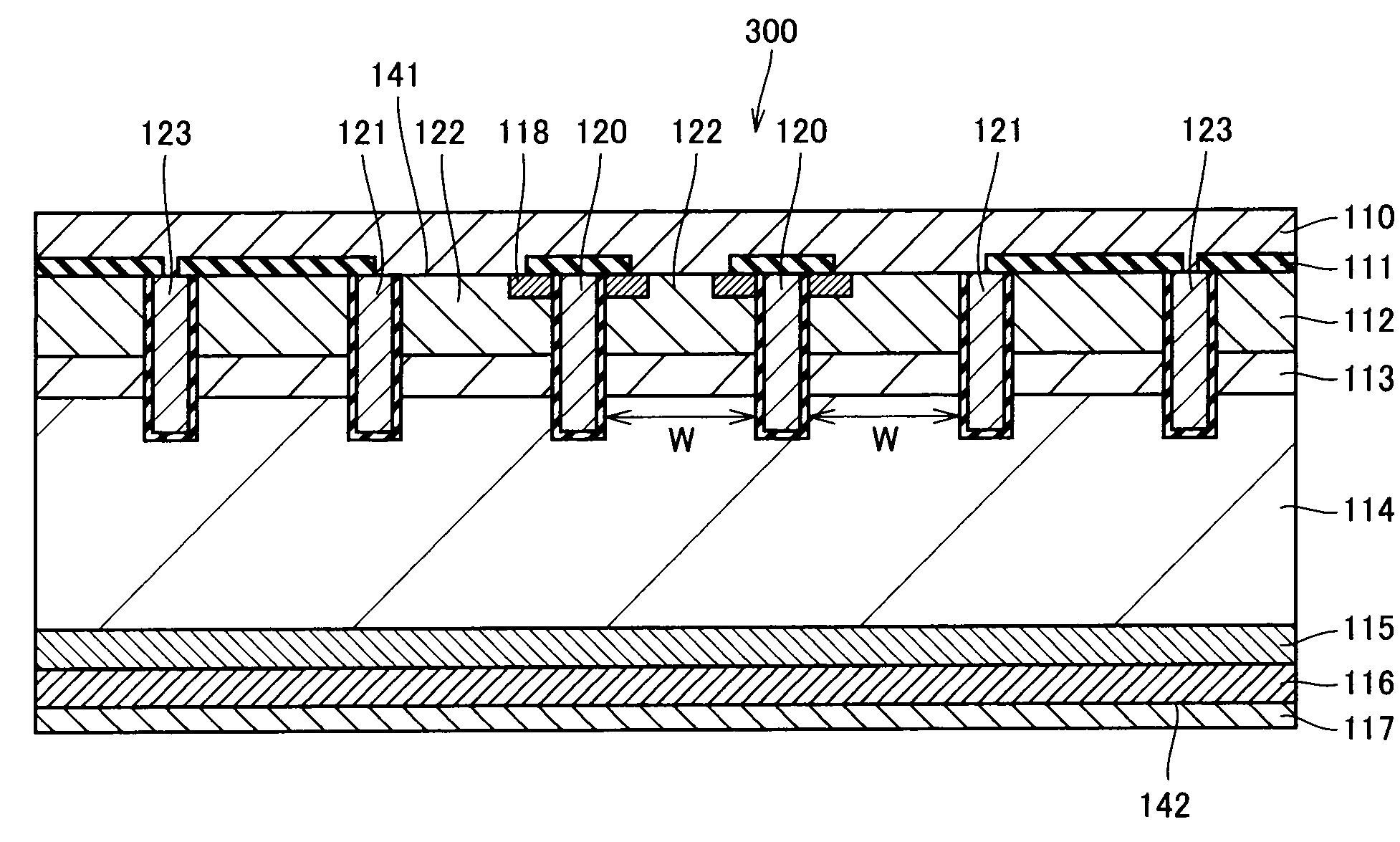

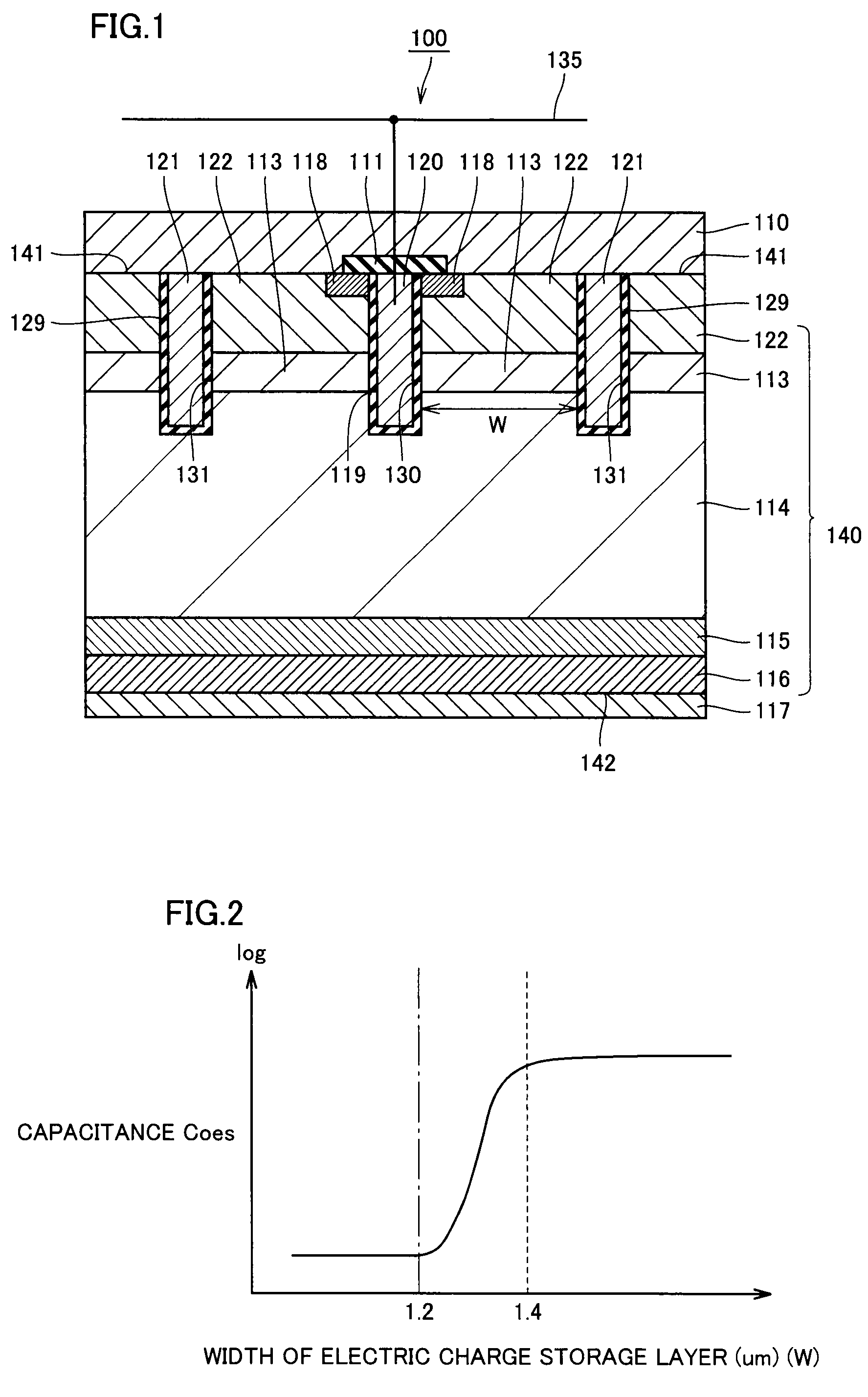

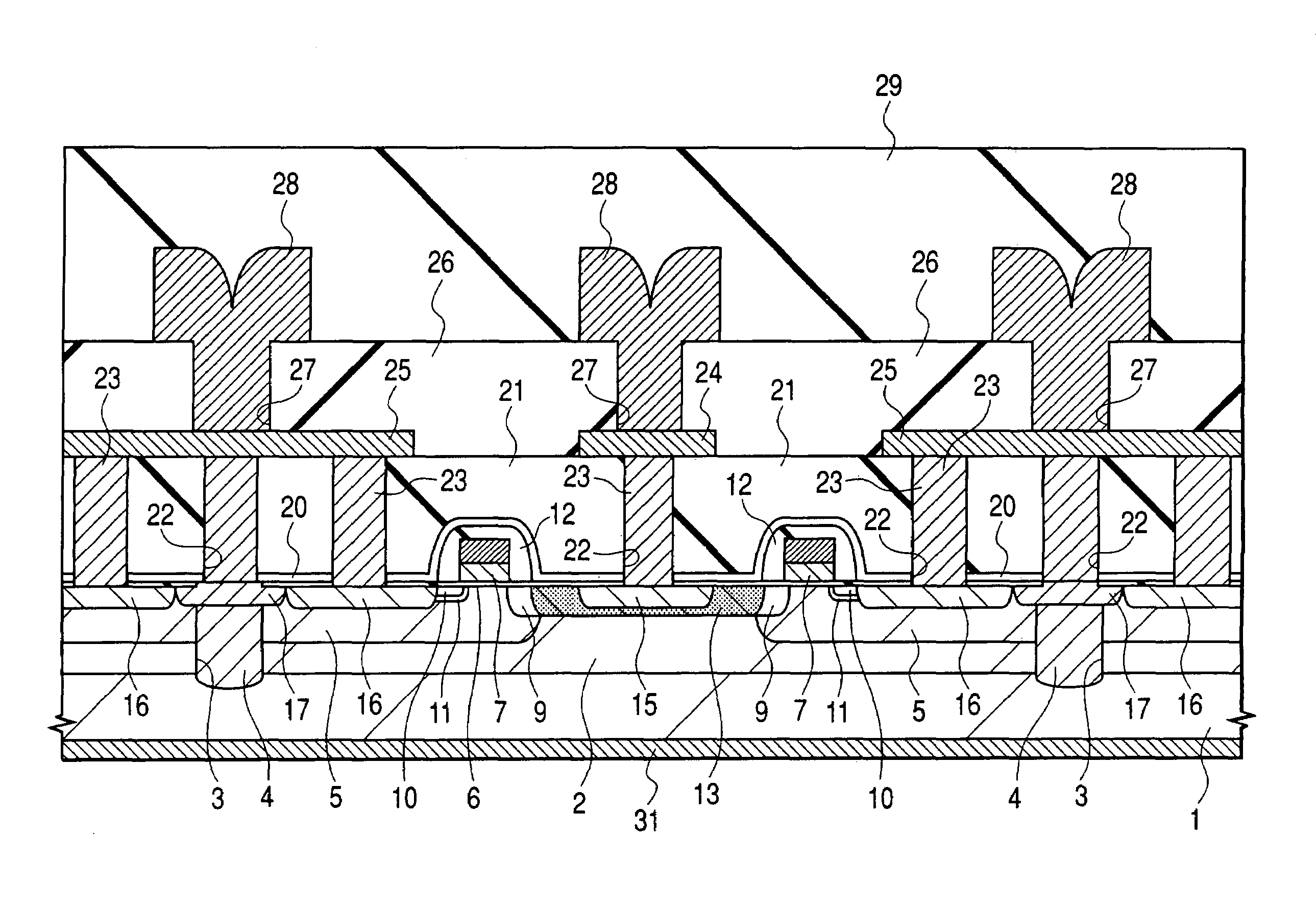

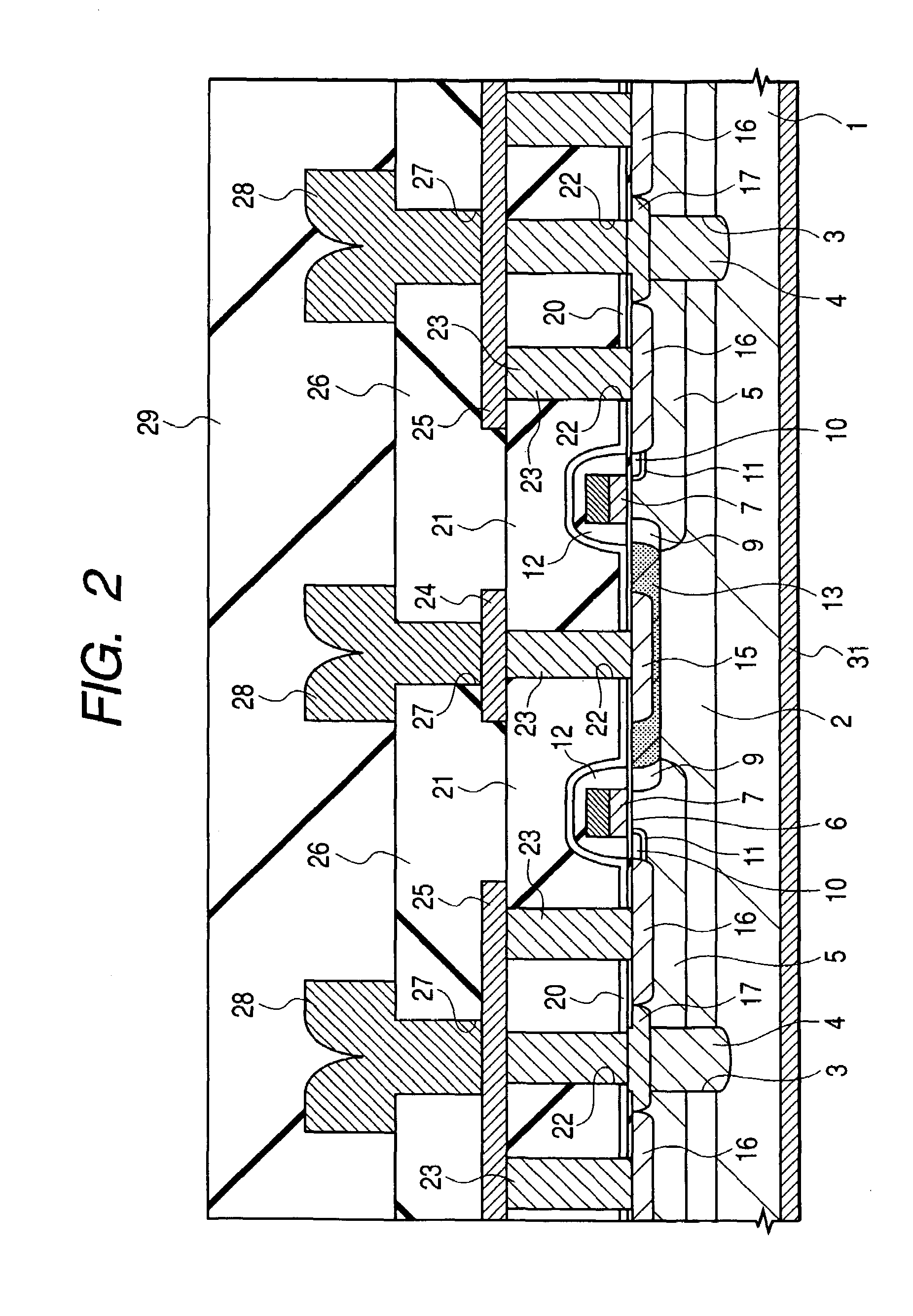

There is provided a semiconductor device in which an amount of fluctuations in output capacitance and feedback capacitance is reduced. In a trench-type insulated gate semiconductor device, a width of a portion of an electric charge storage layer in a direction along which a gate electrode and a dummy gate are aligned is set to be at most 1.4 mum.

Owner:MITSUBISHI ELECTRIC CORP

Image capturing device, image capturing system, and method of driving image capturing device

InactiveUS20120026371A1Remove noiseTelevision system detailsTelevision system scanning detailsCapacitanceAudio power amplifier

An image capturing device comprises a pixel array having a plurality of pixels each including a photoelectric conversion portion, a plurality of signal lines connected to the pixel array, a plurality of column amplifiers configured to respectively amplify signals transferred from the pixel array via the signal lines, the column amplifier comprising a first input terminal, a first output terminal, an amplifier having a second input terminal and a second output terminal, a feedback capacitance arranged between the second input terminal and the first output terminal, an input capacitance having an electrode connected to the first input terminal, and an electrode connected to the second input terminal, a first switch arranged between the second input terminal and the second output terminal, a second switch arranged between the first output terminal and the second output terminal, and a third switch arranged between a reference voltage terminal and the first output terminal.

Owner:CANON KK

Transistor with shield structure, packaged device, and method of manufacture

A transistor includes a semiconductor substrate having an intrinsic active device, a first terminal, and a second terminal. The transistor also includes an interconnect structure formed of multiple layers of dielectric material and electrically conductive material on an upper surface of the semiconductor substrate. The interconnect structure includes a pillar, a tap interconnect, and a shield structure formed from the electrically conductive material. The pillar electrically contacts the first terminal, extends through the dielectric material, and connects to a first runner. The tap interconnect electrically contacts the second terminal, extends through the dielectric material, and connects to a second runner. The shield structure extends from a shield runner through the dielectric material toward the semiconductor substrate. The shield structure is positioned between the pillar and the tap interconnect to limit feedback capacitance between the tap interconnect and the pillar.

Owner:NXP USA INC

Gallium nitride material devices and associated methods

ActiveUS20070272957A1Semiconductor/solid-state device manufacturingSemiconductor devicesCapacitancePower application

Gallium nitride material devices and methods associated with the same. In some embodiments, the devices may be transistors which include a conductive structure connected to a source electrode. The conductive structure may form a source field plate which can be formed over a dielectric material and can extend in the direction of the gate electrode of the transistor. The source field plate may reduce the electrical field (e.g., peak electrical field and / or integrated electrical field) in the region of the device between the gate electrode and the drain electrode which can lead to a number of advantages including reduced gate-drain feedback capacitance, reduced surface electron concentration, increased breakdown voltage, and improved device reliability. These advantages enable the gallium nitride material transistors to operate at high drain efficiencies and / or high output powers. The devices can be used in RF power applications, amongst others.

Owner:MACOM TECH SOLUTIONS HLDG INC

Semiconductor device and a method of manufacturing the same

InactiveUS20070120194A1Easy to integrateReduce resistanceSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceDevice material

A technology is provided to reduce ON-resistance, and the prevention of punch through is achieved with respect to a trench gate type power MISFET. Input capacitance and a feedback capacitance are reduced by forming a groove in which a gate electrode is formed so as to have a depth as shallow as about 1 μm or less, a p− type semiconductor region is formed to a depth so as not to cover the bottom of the groove, and a p-type semiconductor region higher in impurity concentration than the p− type semiconductor region is formed under a n+ type semiconductor region serving as a source region of the trench gate type power MISFET, causing the p-type semiconductor region to serve as a punch-through stopper layer of the trench gate type power MISFET.

Owner:RENESAS TECH CORP

Coupled acoustic devices

Owner:PANG WEI +1

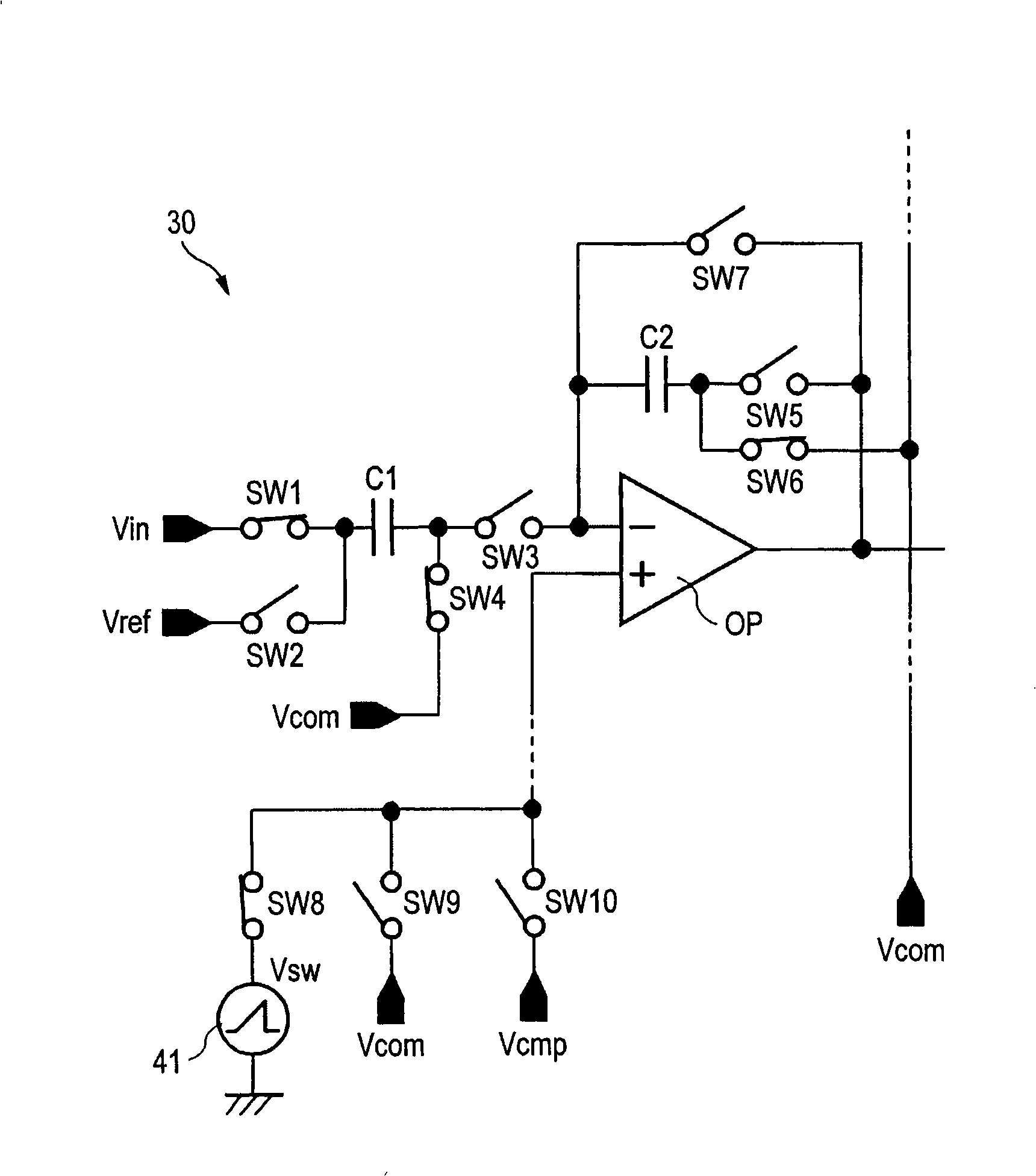

A/d conversion circuit, control method thereof, solid-state imaging device, and imaging apparatus

InactiveCN101320974ASmall footprintTelevision system detailsElectric signal transmission systemsCapacitanceAudio power amplifier

An A / D conversion circuit includes: an input capacitance to which an input signal and a reference signal are sequentially applied; an operational amplifier; a first switch connected between the other end of the input capacitance and a first input end of the operational amplifier; a feedback capacitance connected to the first input end of the operational amplifier; a second switch connected between the other end of the feedback capacitance and an output end of the operational amplifier; a third switch selectively applying a predetermined voltage to the other end of the feedback capacitance; a fourth switch selectively causing a short circuit between the first input end and the output end of the operational amplifier; a fifth switch applying the predetermined voltage to a second input end of the operational amplifier; and a sixth switch applying a ramp reference voltage to the second input end of the operational amplifier.

Owner:SONY CORP

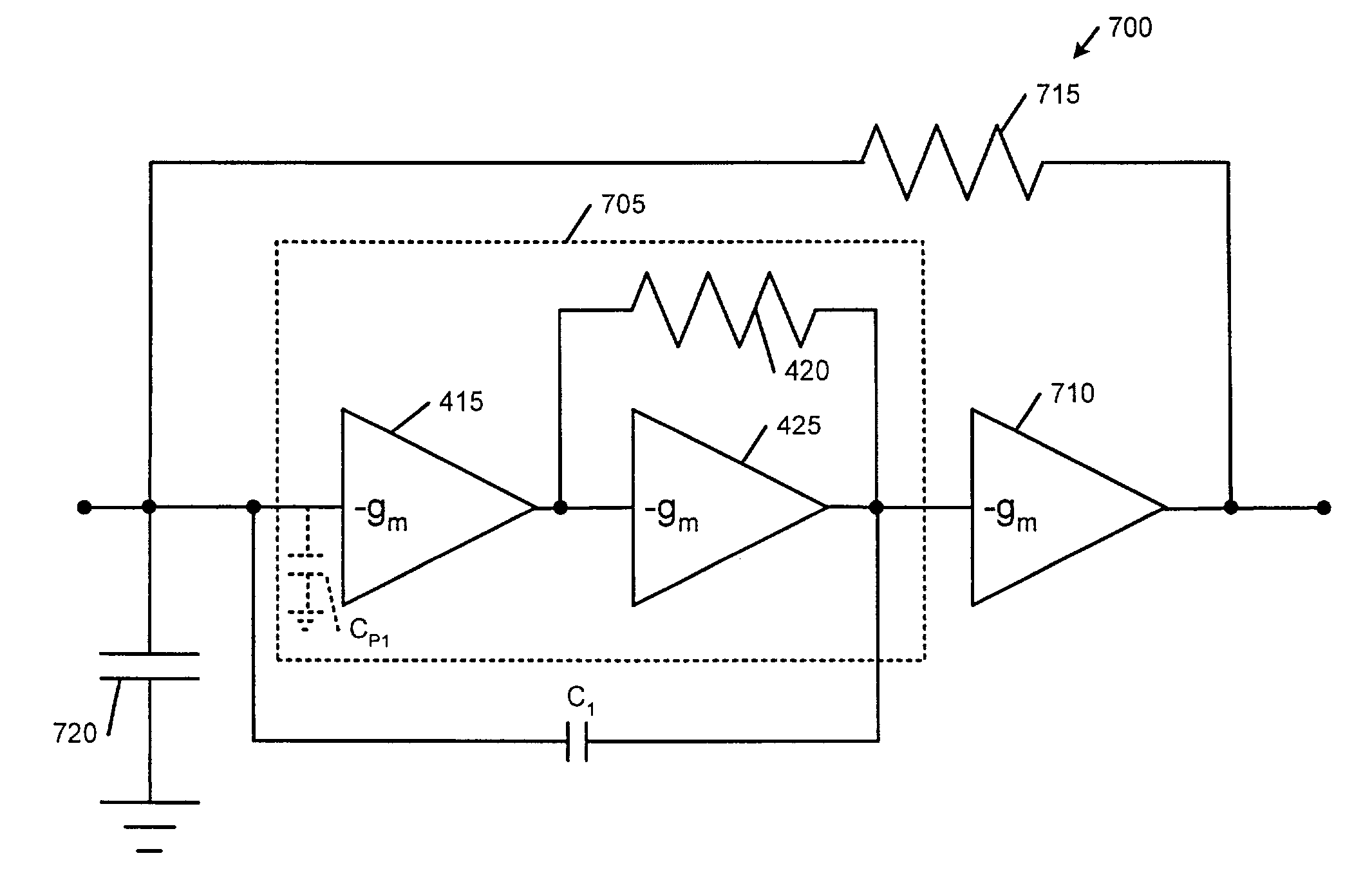

Nested transimpedance amplifier with capacitive cancellation of input parasitic capacitance

InactiveUS7173486B1Negative-feedback-circuit arrangementsHigh frequency amplifiersAudio power amplifierParasitic capacitance

A nested transimpedance amplifier (TIA) circuit comprises a zero-order TIA having an input and an output. A first transconductance amplifier has an input that communicates with said output of said zero-order TIA and an output. A first feedback resistance has one end that communicates with said input of said zero-order TIA and an opposite end that communicates with said output of said first transconductance amplifier. A first feedback capacitance has a first end that communicates with said input of said zero-order TIA and a second end that communicates with said output of said zero-order TIA. A capacitance has one end that communicates with said input of said zero-order TIA.

Owner:MARVELL ASIA PTE LTD

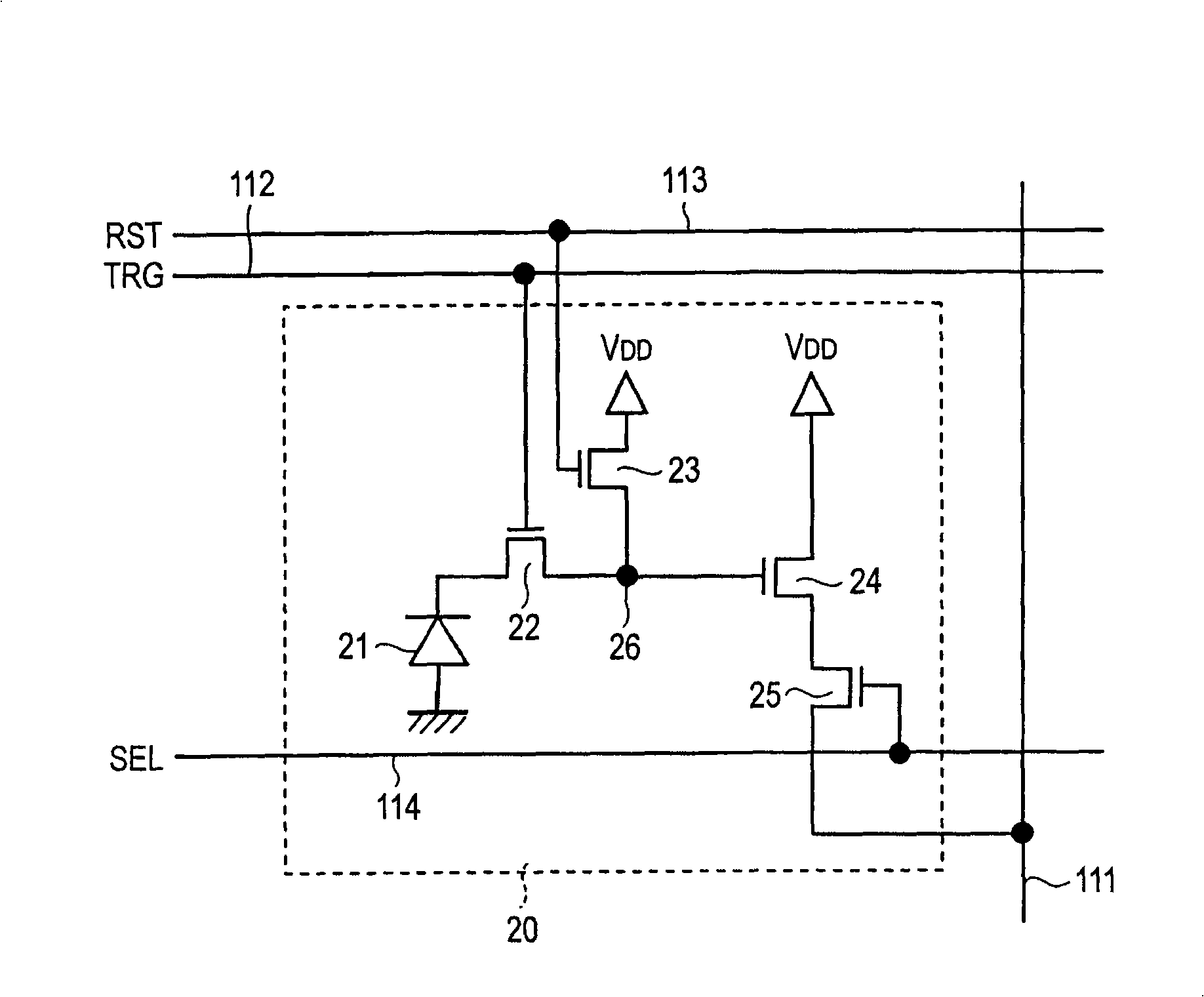

Solid state imaging device, method of driving solid state imaging device and image pickup apparatus

ActiveUS20060243883A1Better signal to noise ratioEnhanced signalTelevision system detailsTelevision system scanning detailsCapacitanceSignal processing circuits

When an addition / averaging process is done for pixels in the same color in a unit pixel block in a stage reading pixel information to a horizontal signal line, the addition / averaging process is also done for a noise component added in a signal process from the pixels to the horizontal signal line. Thus, a problem arises in the signal-to-noise ratio. Each of signal processing circuits of a column signal processing circuit part is provided with reverse amplifiers which output signals of pixels transmitted by a vertical signal line at a low impedance, and with feedback capacitances which are adjustably connected in parallel to these reverse amplifiers, the signal processing circuit being disposed at every column. These feedback capacitances are used to do row wise and column wise pixel addition for the pixels in the same color in the unit pixel block to take out pixel signals for a single pixel in simulation.

Owner:SONY SEMICON SOLUTIONS CORP

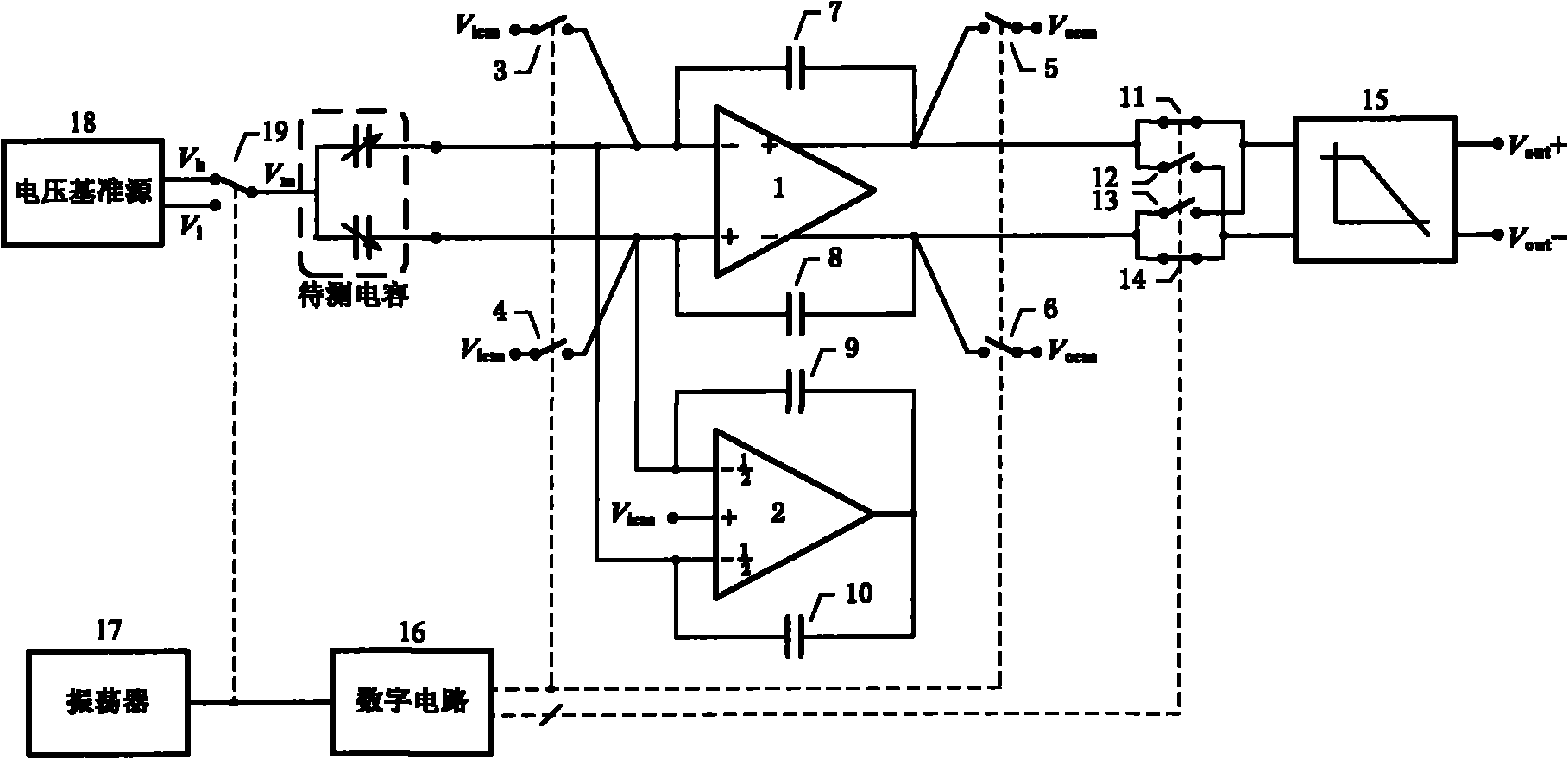

High accuracy capacitive readout circuit with temperature compensation

ActiveCN102072737ASolving high impedance node biasing issuesHigh precisionMitigation of undesired influencesIntegratorSwitching cycle

The invention discloses a high accuracy capacitive readout circuit with temperature compensation, belonging to the design field of integrated circuits. The circuit realizes high accuracy capacitive readout owing to the adoption of a chopping modulation technology, and can simultaneously realize temperature compensation by adjusting temperature characteristics of internal voltage reference. The circuit comprises an oscillator, a voltage reference source, a full-differential operational amplification unit, a common-mode operational amplification unit, a low pass filter, a switch device and a digital circuit. The voltage reference source generates a square wave in cooperation with a single-pole double throw switch, and the square wave is applied to an intermediate polar plate of a differential capacitance to be detected in order to implement modulation. The full-differential operational amplification unit and a feedback capacitance constitute a charge integrator to detect a transfer charge formed by the variation of the capacitance to be detected. Demodulation is realized by the switch device and the low pass filter. Both an input end and an output end of the full-differential operational amplification unit are set through a switch cycle. The common-mode operational amplification unit and the feedback capacitance constitute a common-mode feedback loop which is connected with the input end of the full-differential operational amplification unit to play the role of inputting common-mode voltage stably.

Owner:INST OF ELECTRONICS CHINESE ACAD OF SCI

Semiconductor device

ActiveUS8178947B2Reduce fluctuationReduce capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceFeedback capacitance

There is provided a semiconductor device in which an amount of fluctuations in output capacitance and feedback capacitance is reduced. In a trench-type insulated gate semiconductor device, a width of a portion of an electric charge storage layer in a direction along which a gate electrode and a dummy gate are aligned is set to be at most 1.4 μm.

Owner:MITSUBISHI ELECTRIC CORP

A/D conversion circuit, control method thereof, solid-state imaging device, and imaging apparatus

ActiveUS20080303705A1Reduced footprintTelevision system detailsElectric signal transmission systemsCapacitanceAudio power amplifier

An A / D conversion circuit includes: an input capacitance to which an input signal and a reference signal are sequentially applied; an operational amplifier; a first switch connected between the other end of the input capacitance and a first input end of the operational amplifier; a feedback capacitance connected to the first input end of the operational amplifier; a second switch connected between the other end of the feedback capacitance and an output end of the operational amplifier; a third switch selectively applying a predetermined voltage to the other end of the feedback capacitance; a fourth switch selectively causing a short circuit between the first input end and the output end of the operational amplifier; a fifth switch applying the predetermined voltage to a second input end of the operational amplifier; and a sixth switch applying a ramp reference voltage to the second input end of the operational amplifier.

Owner:SONY CORP

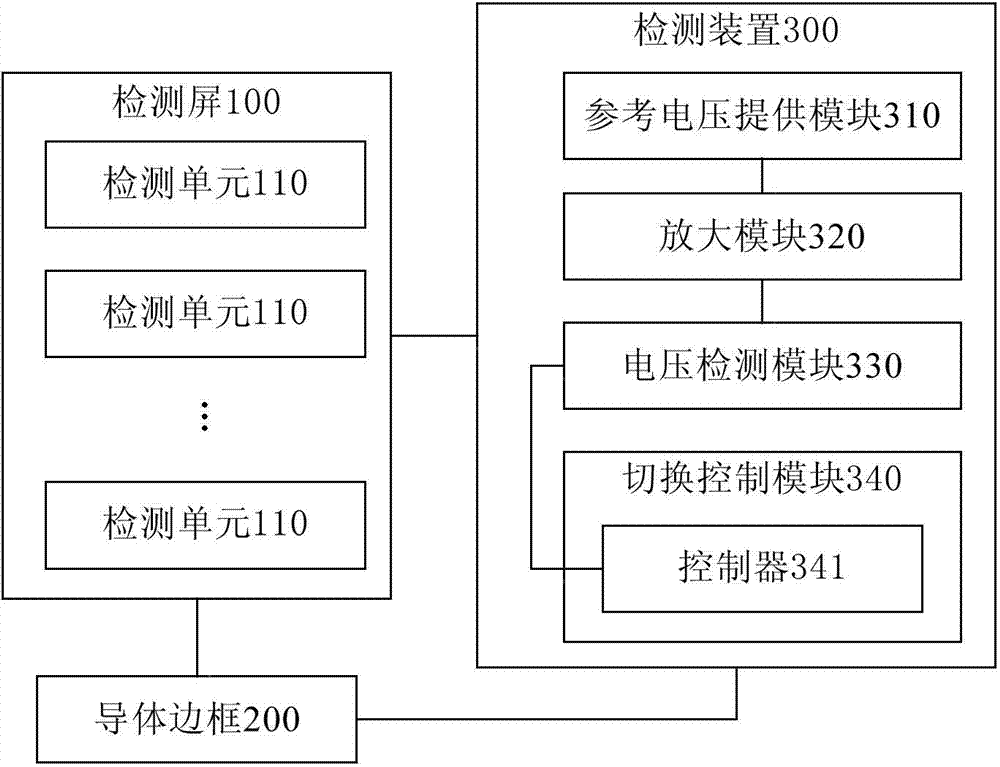

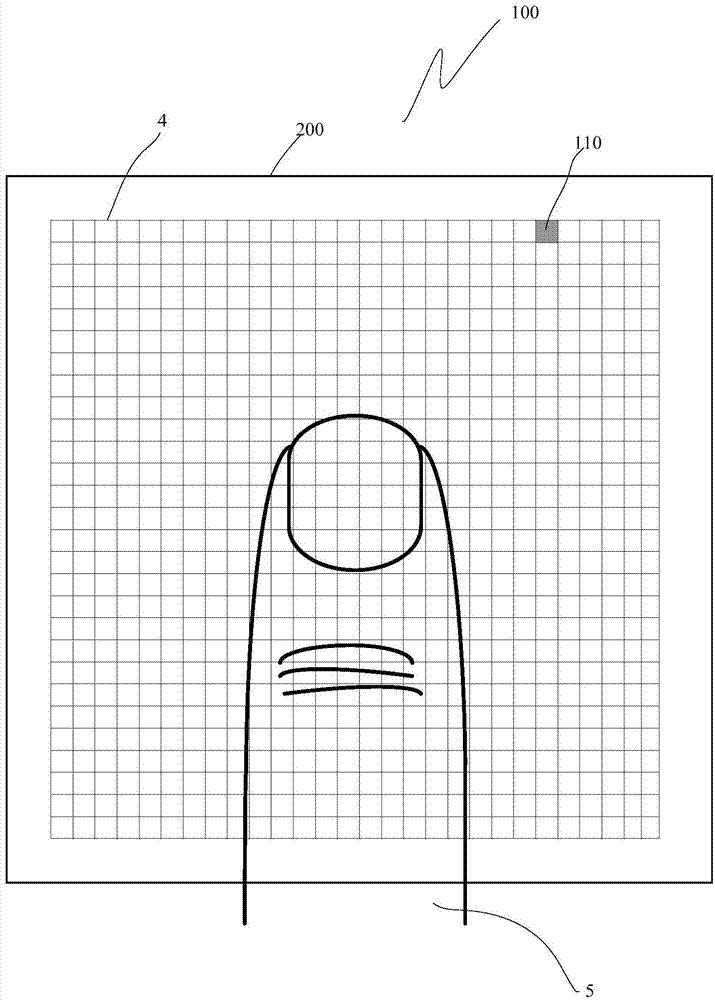

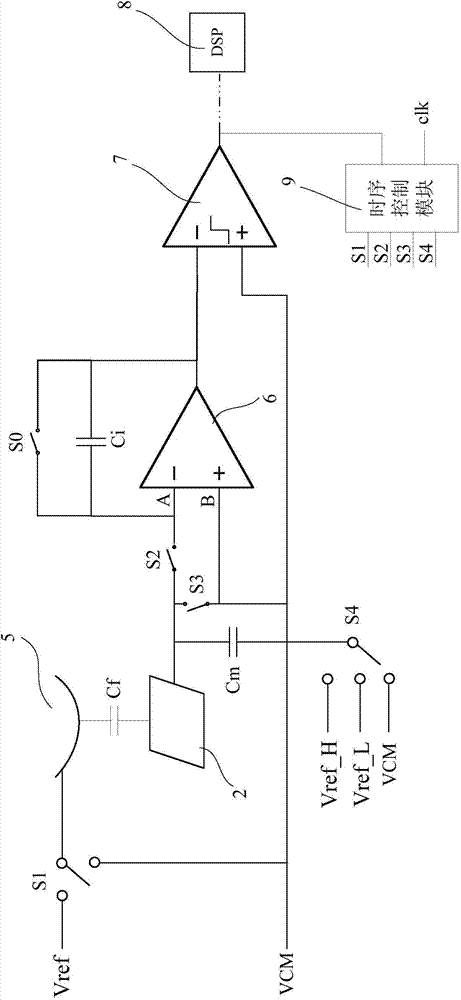

Capacitance detection device used for fingerprint identification and fingerprint identification device provided with same

ActiveCN104748770ARealize identificationSmall scaleCharacter and pattern recognitionConverting sensor output electrically/magneticallyCapacitanceElectricity

The invention discloses a capacitance detection device used for fingerprint identification, comprising a detection screen, a conductor frame and a detection device. The detection screen comprises a plurality of detection units, and each detection unit comprises a first conductor layer, a second conductor layer, a third conductor layer, and a fourth conductor layer. The induction capacitance can be generated by the first conductor layer and a finger touching the detection screen. The feedback capacitance can be generated between the first conductor layer and the second conductor layer, and the integral capacitance can be generated between the third conductor layer and the fourth conductor layer. When the finger contacts the detection screen, the finger is electrically connected with the conductor frame. The detection device is used to charge the induction capacitance and the feedback capacitance in the sampling phase, and can be used to measure and control the transfer of the charges of the induction capacitance and the feedback capacitance to the integral capacitance in the integral phase, and at the same time, can be used to measure the voltage variable quantity of the integral capacitance in the integral phase, and can be used to calculate the induction capacitance according to the voltage variable quantity. The capacitance detection device is advantageous in that the fingerprint detection accuracy can be improved, and at the same time, the circuit noises can be effectively reduced, and the power consumption and the area of the circuit can be reduced. The invention also discloses a fingerprint identification device.

Owner:BYD SEMICON CO LTD

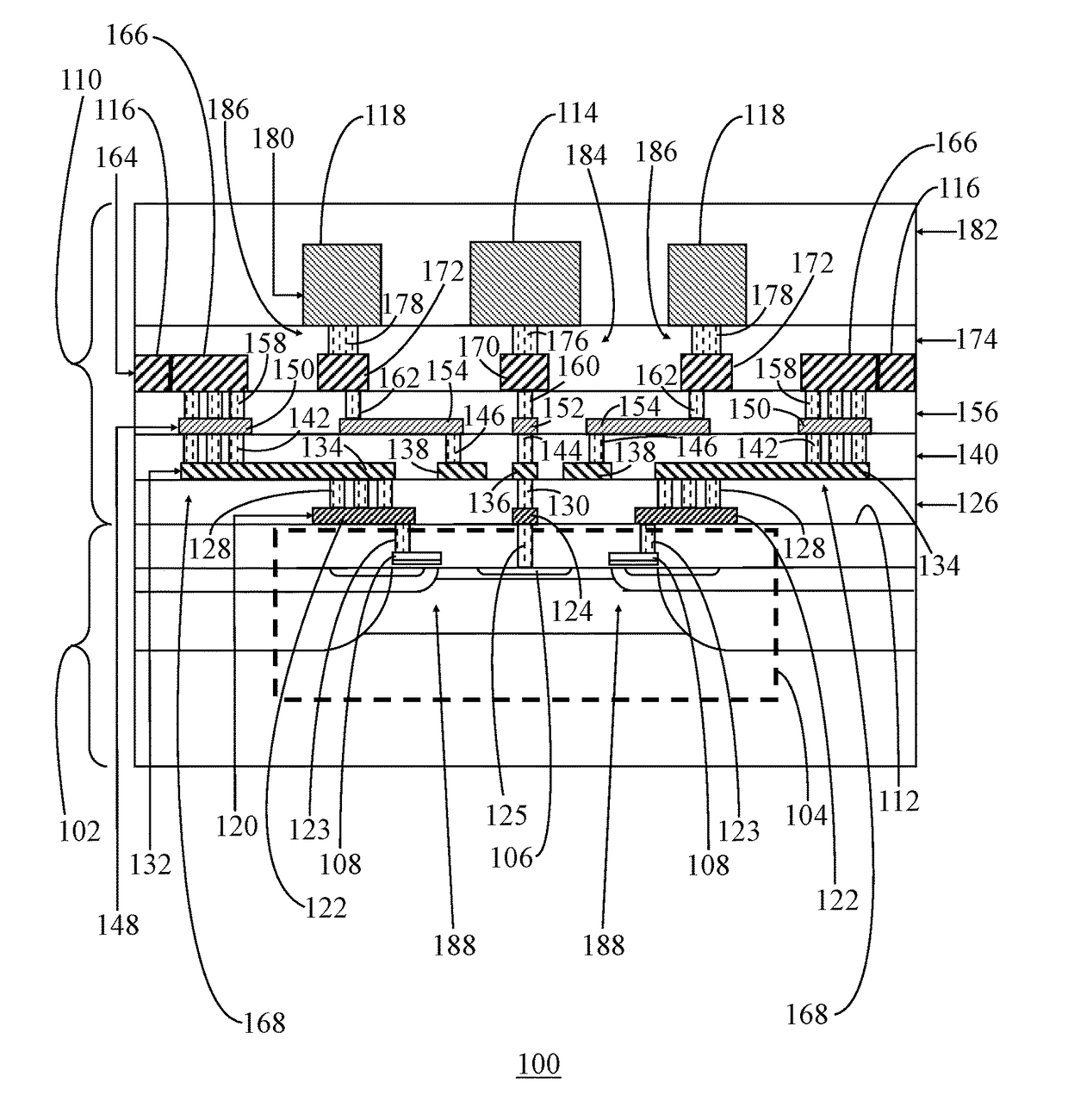

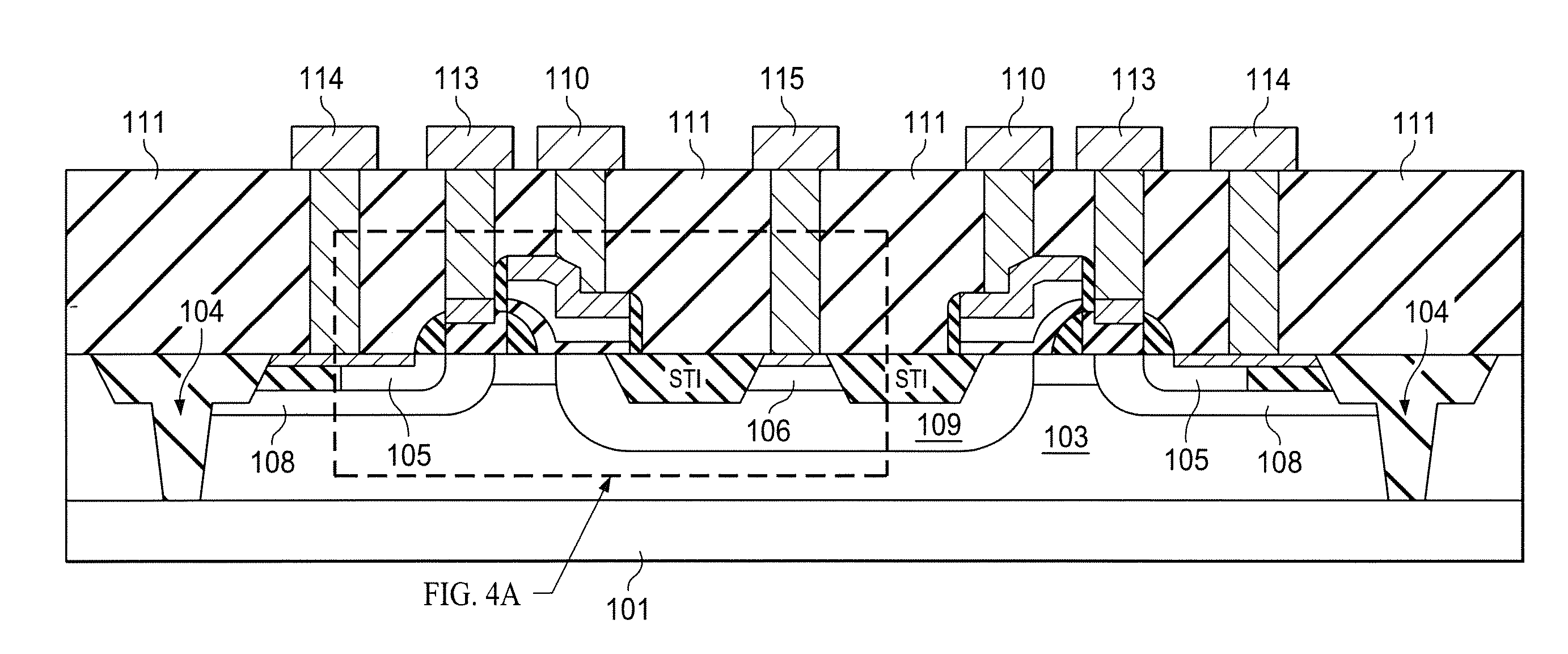

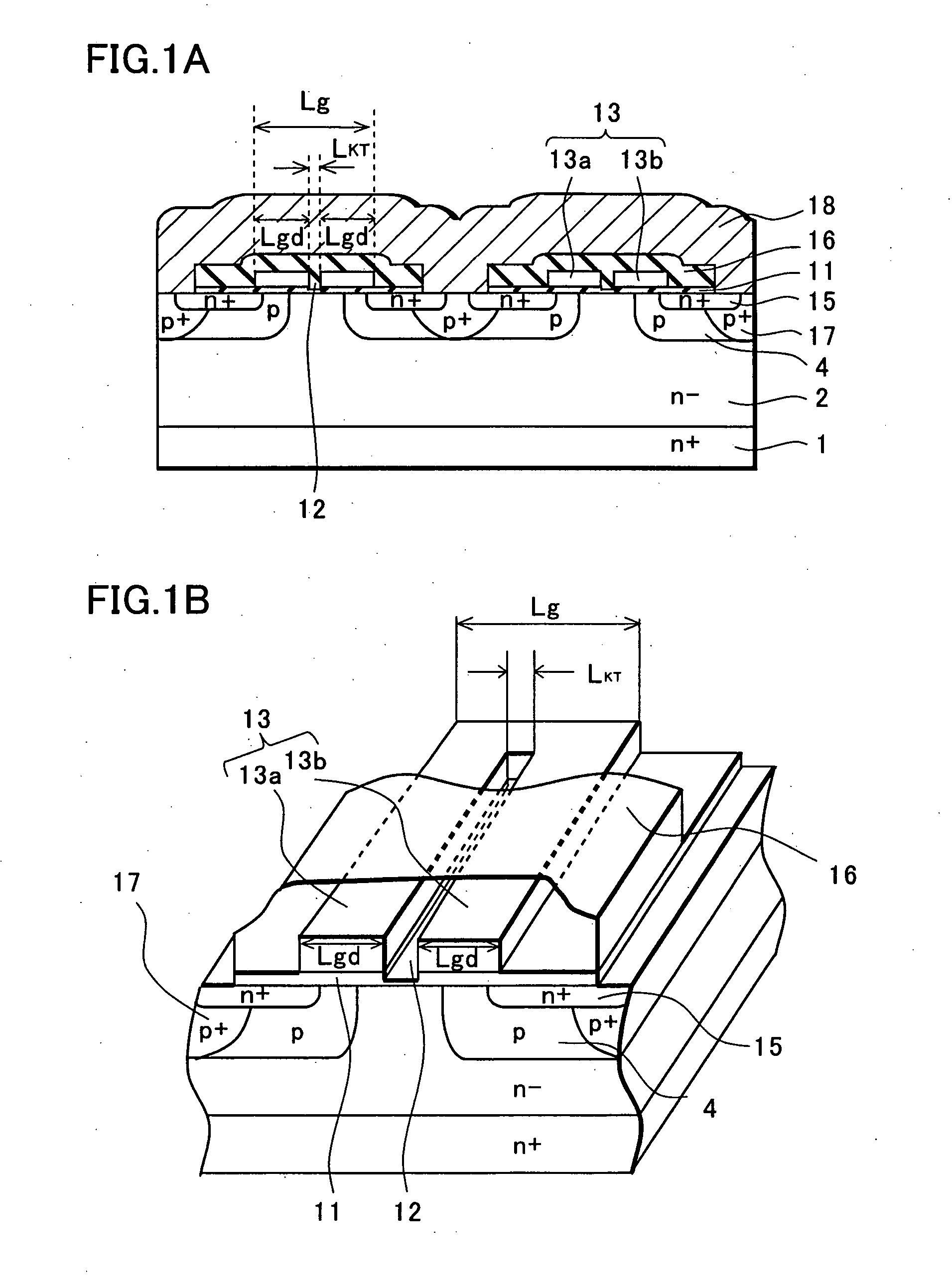

Semiconductor device and a method of manufacturing the same

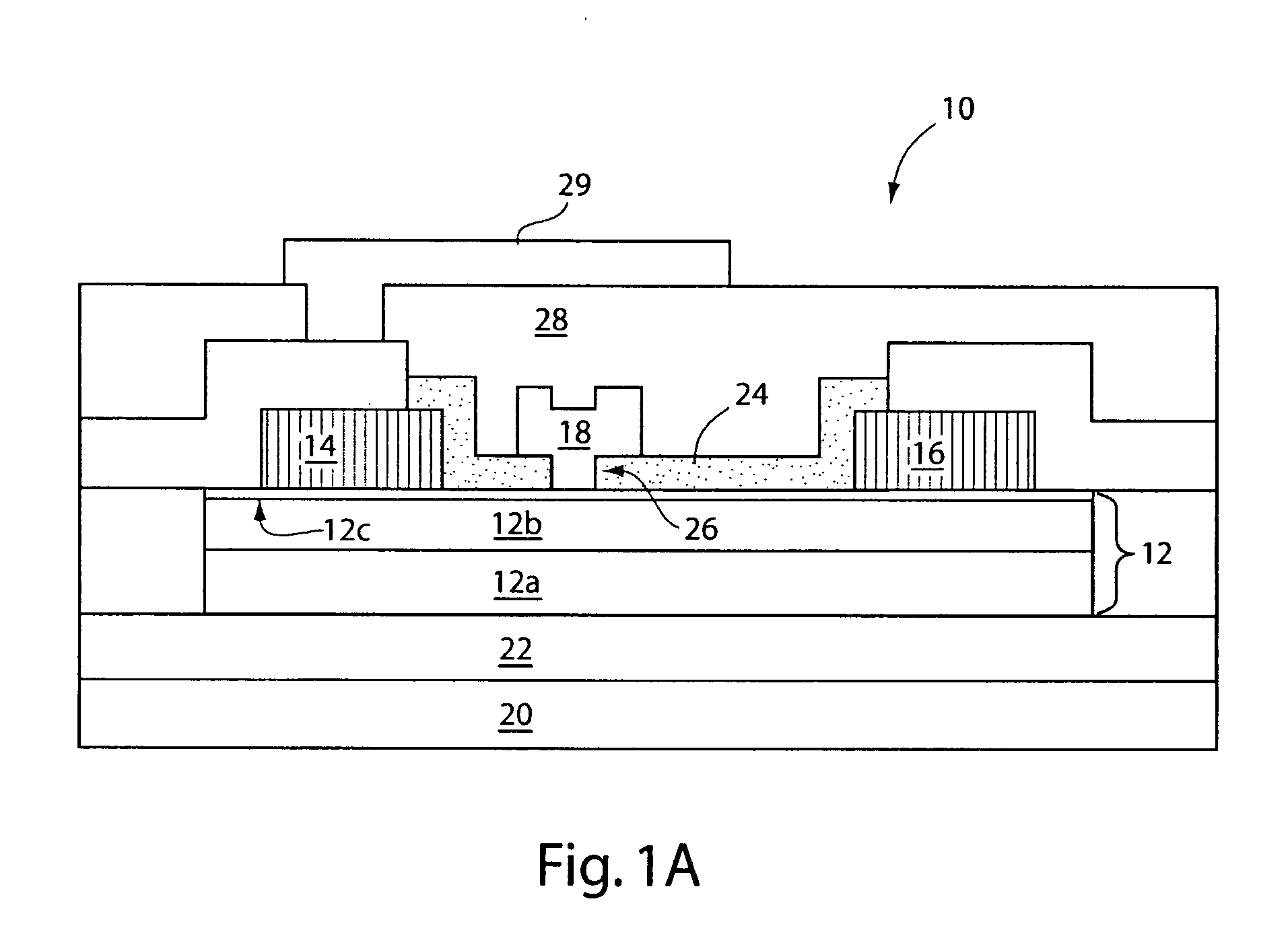

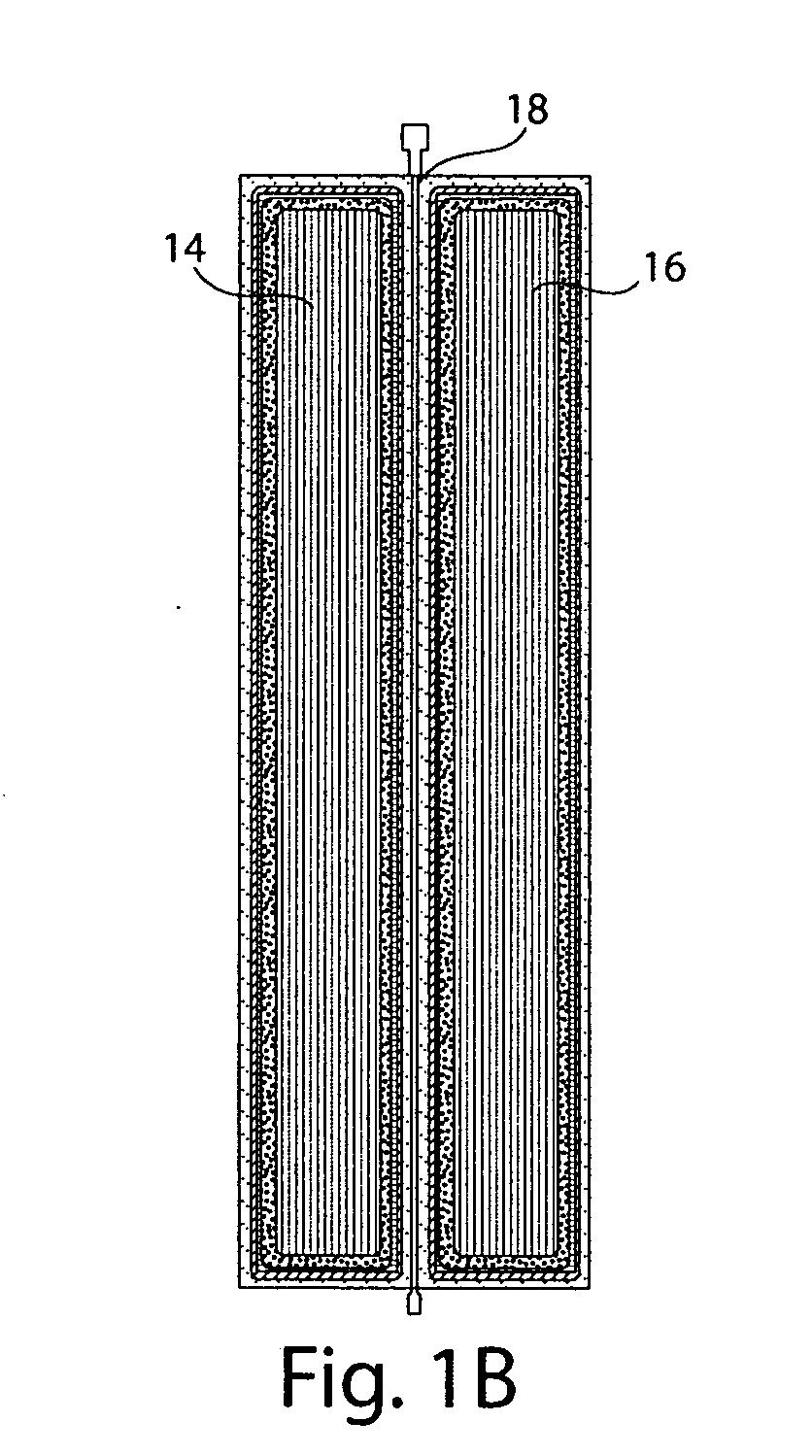

ActiveUS20050051814A1Easy to controlImprove batch productivityTransistorEnergy efficient ICTCapacitanceDevice material

To reduce the size and improve the power added efficiency of an RF power module having an amplifier element composed of a silicon power MOSFET, the on resistance and feedback capacitance, which were conventionally in a trade-off relationship, are reduced simultaneously by forming the structure of an offset drain region existing between a gate electrode and an n+ type drain region of the power MOSFET into a double offset one. More specifically, this is accomplished by adjusting the impurity concentration of an n− type offset drain region, which is closest to the gate electrode, to be relatively low and adjusting the impurity concentration of an n type offset drain region, which is distant from the gate electrode, to be relatively high.

Owner:RENESAS ELECTRONICS CORP

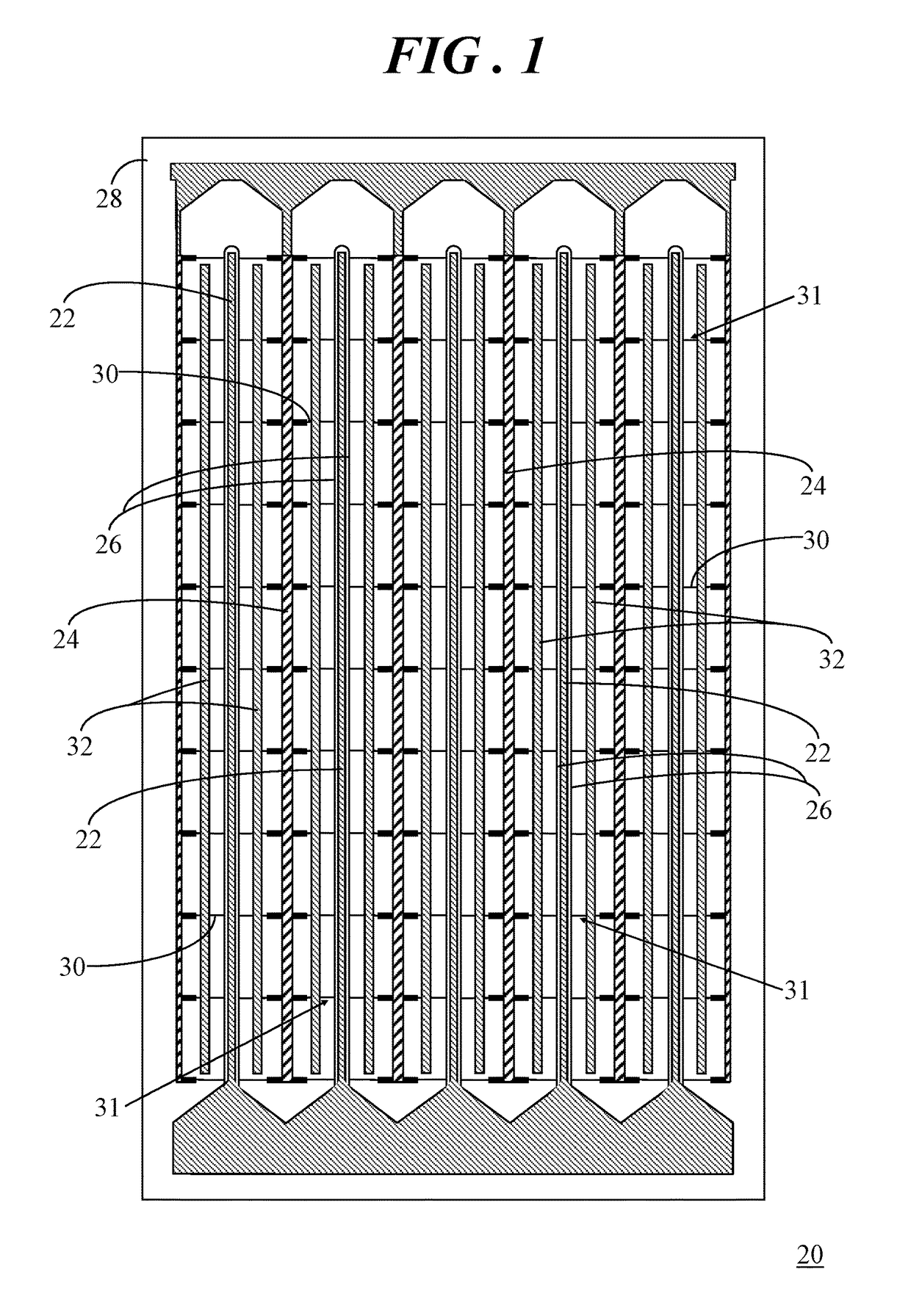

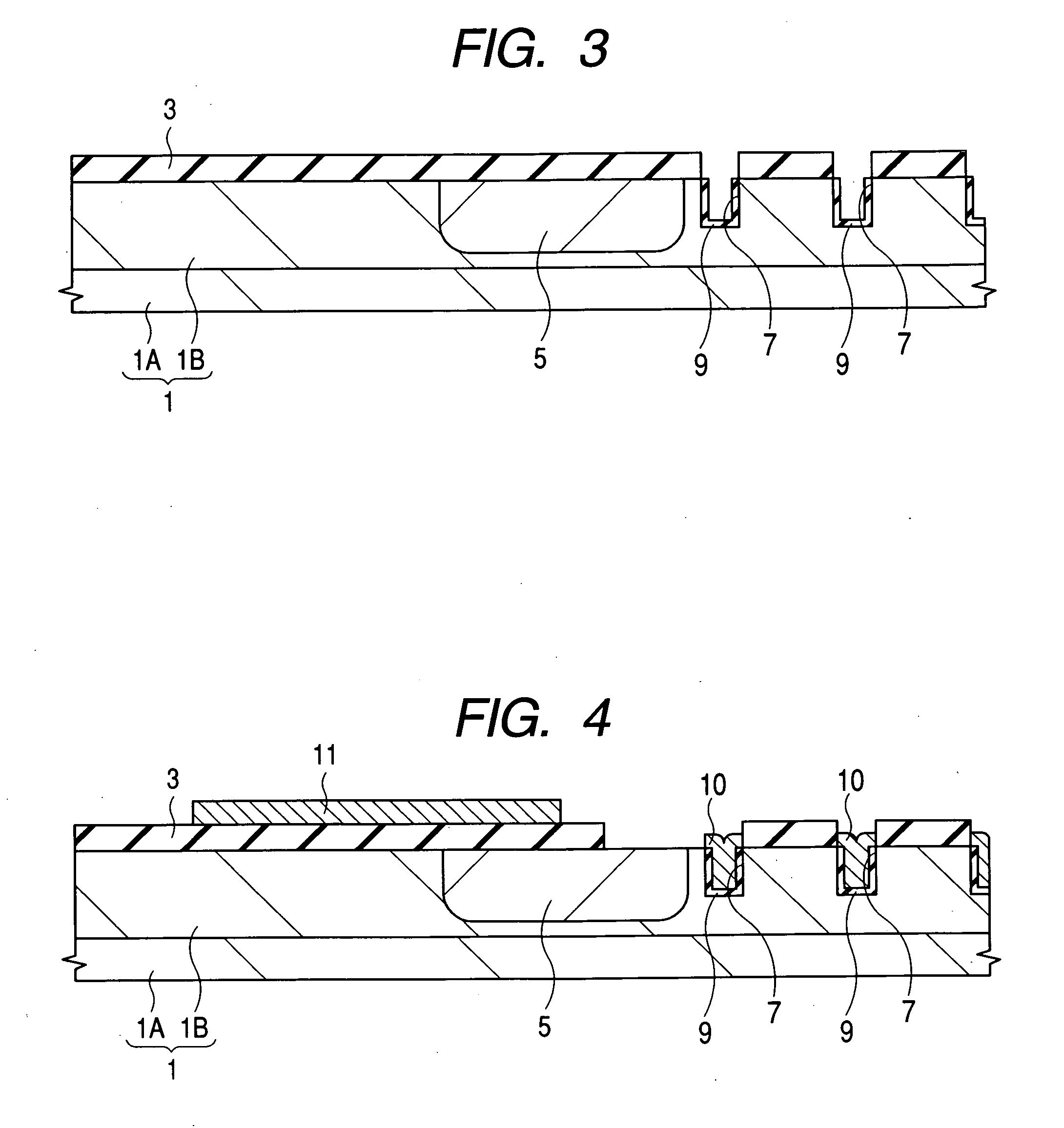

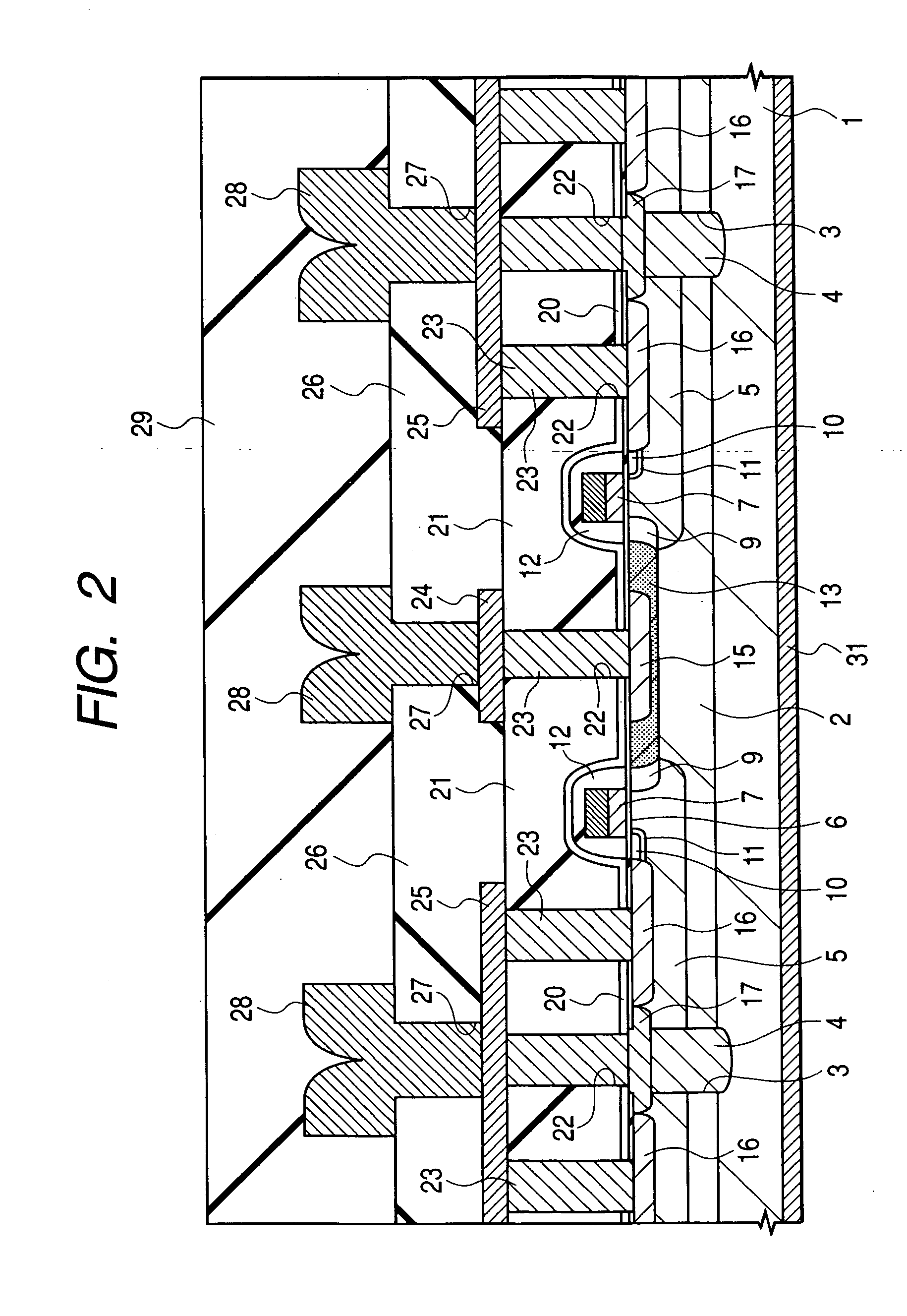

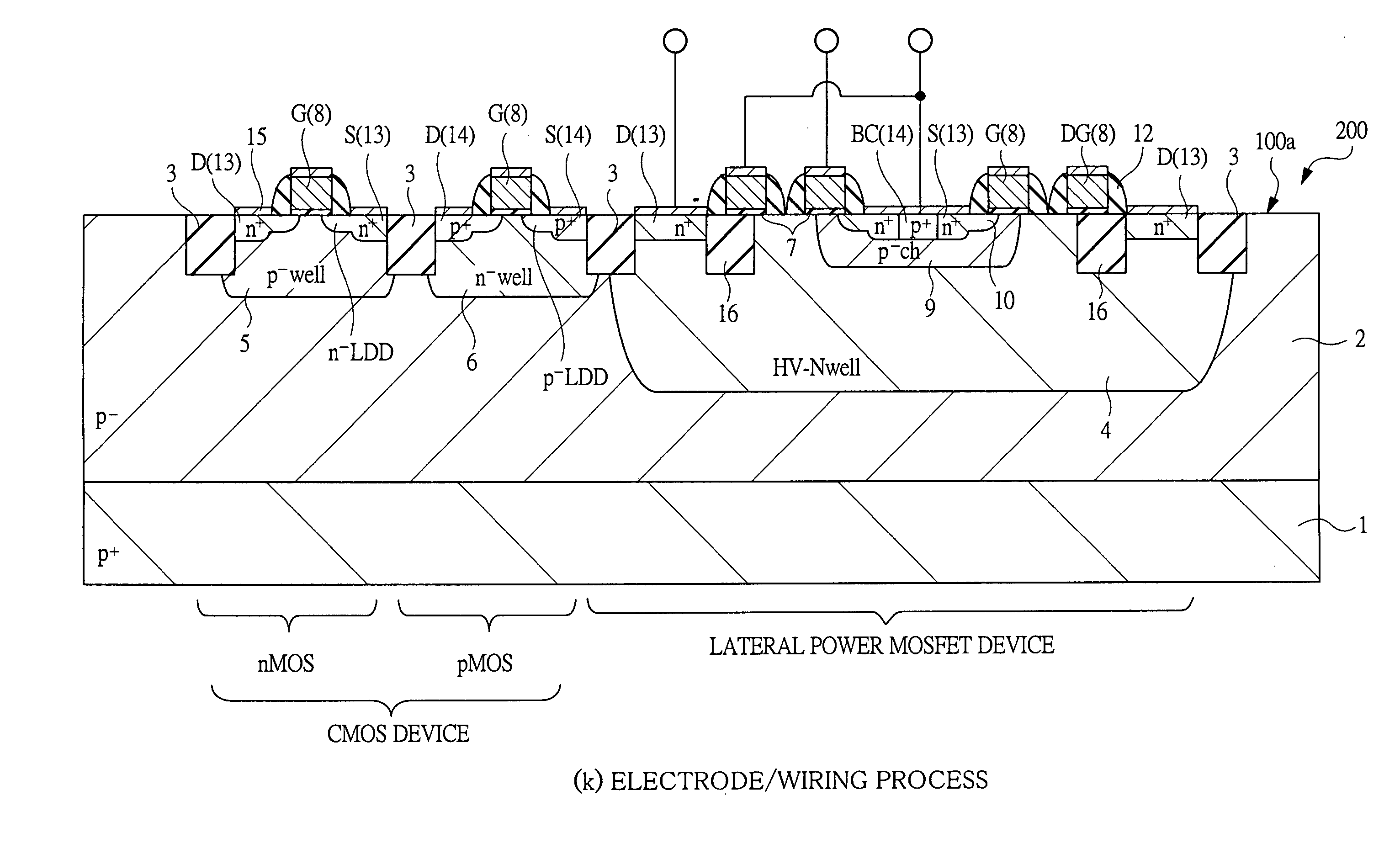

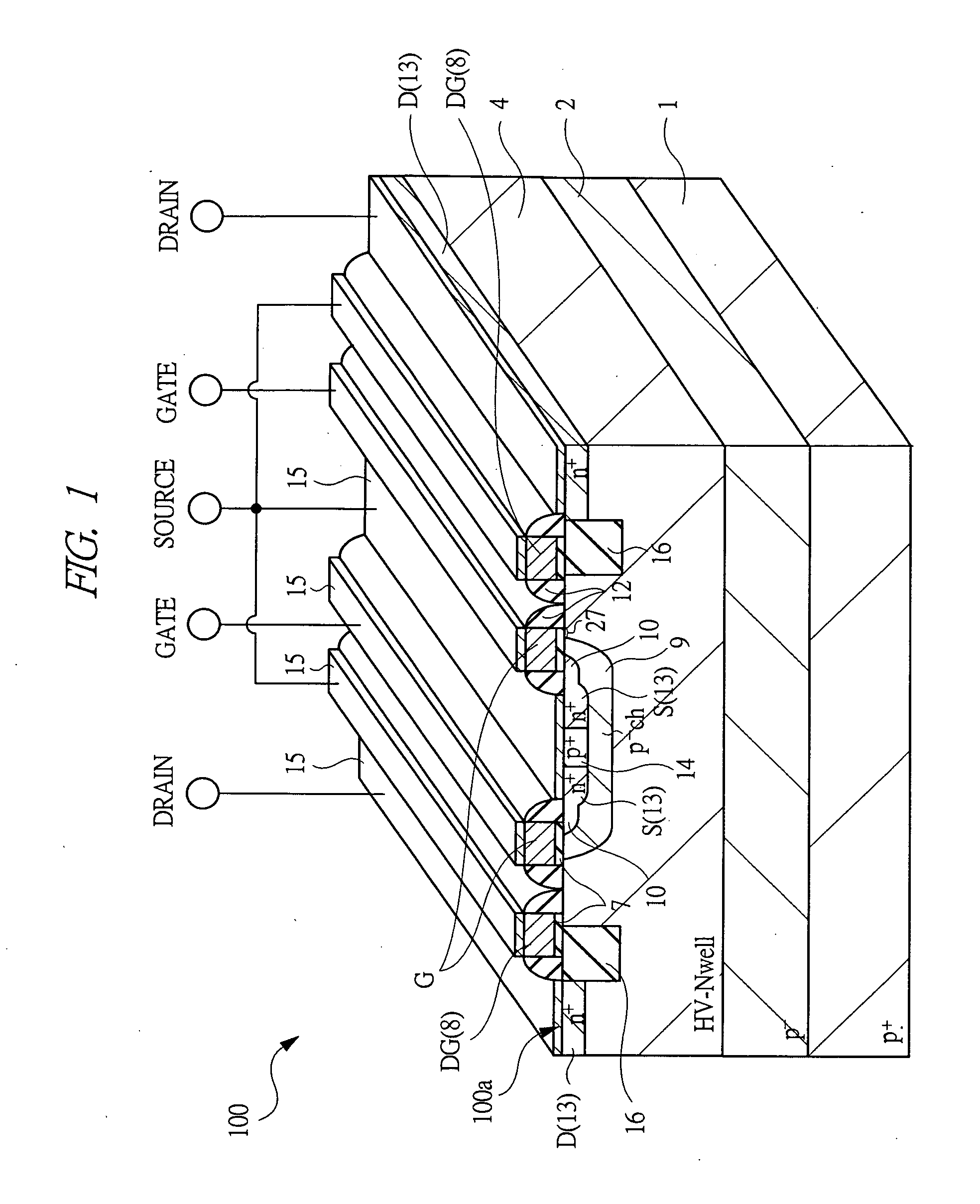

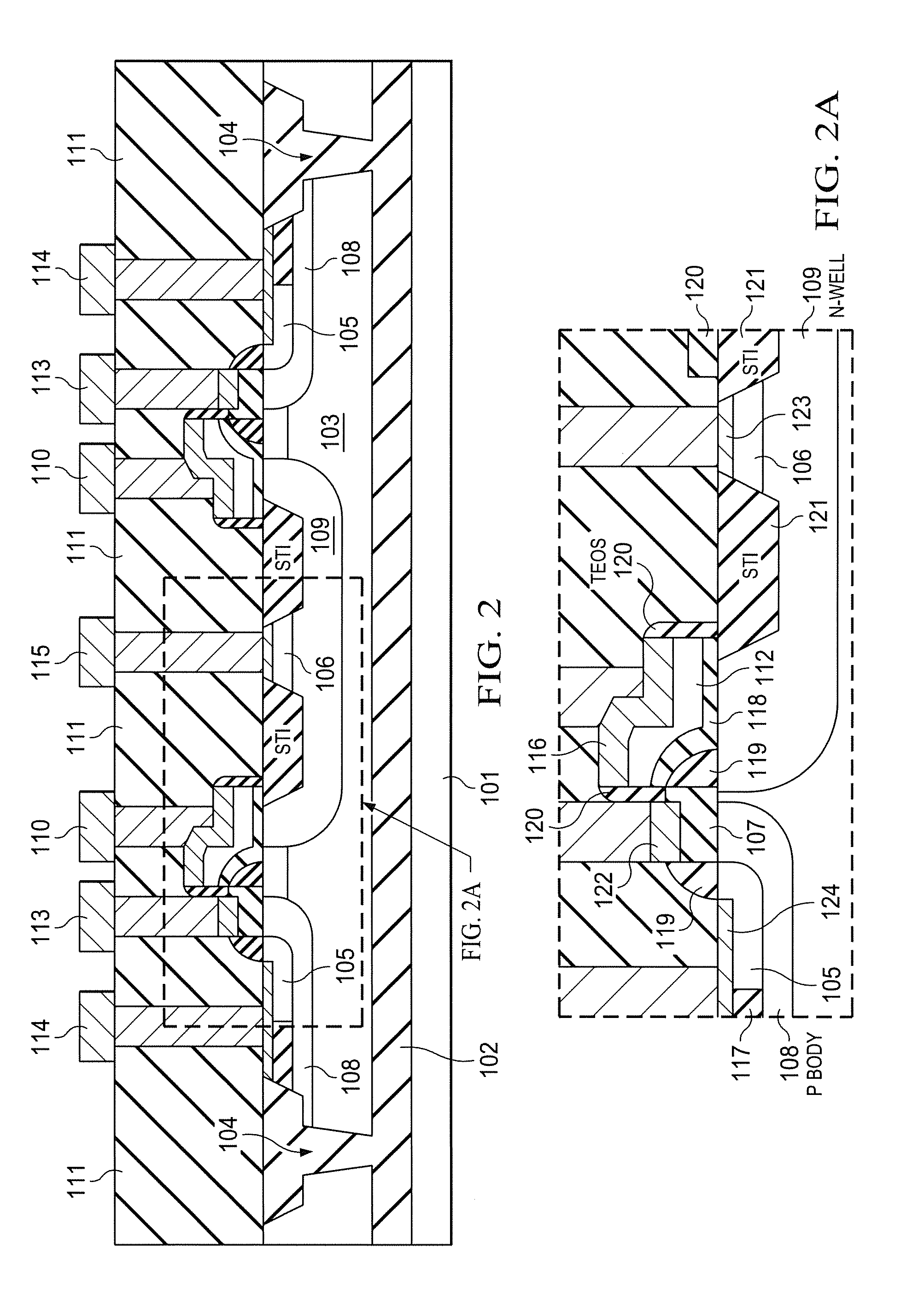

Power MISFET, semiconductor device and DC/DC converter

ActiveUS20080180974A1High trafficLow conversion efficiencyTransistorDc-dc conversionPower semiconductor deviceCapacitance

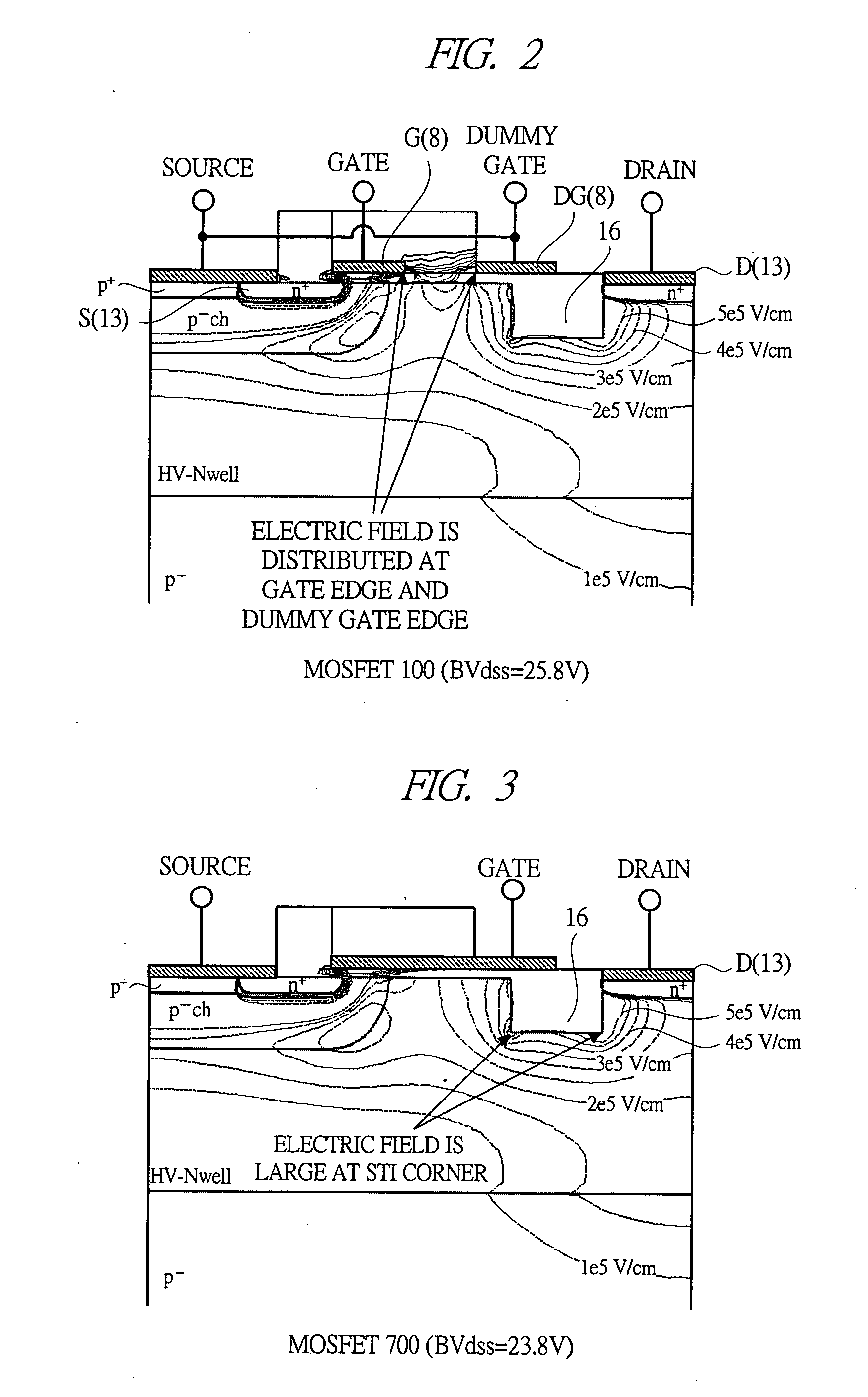

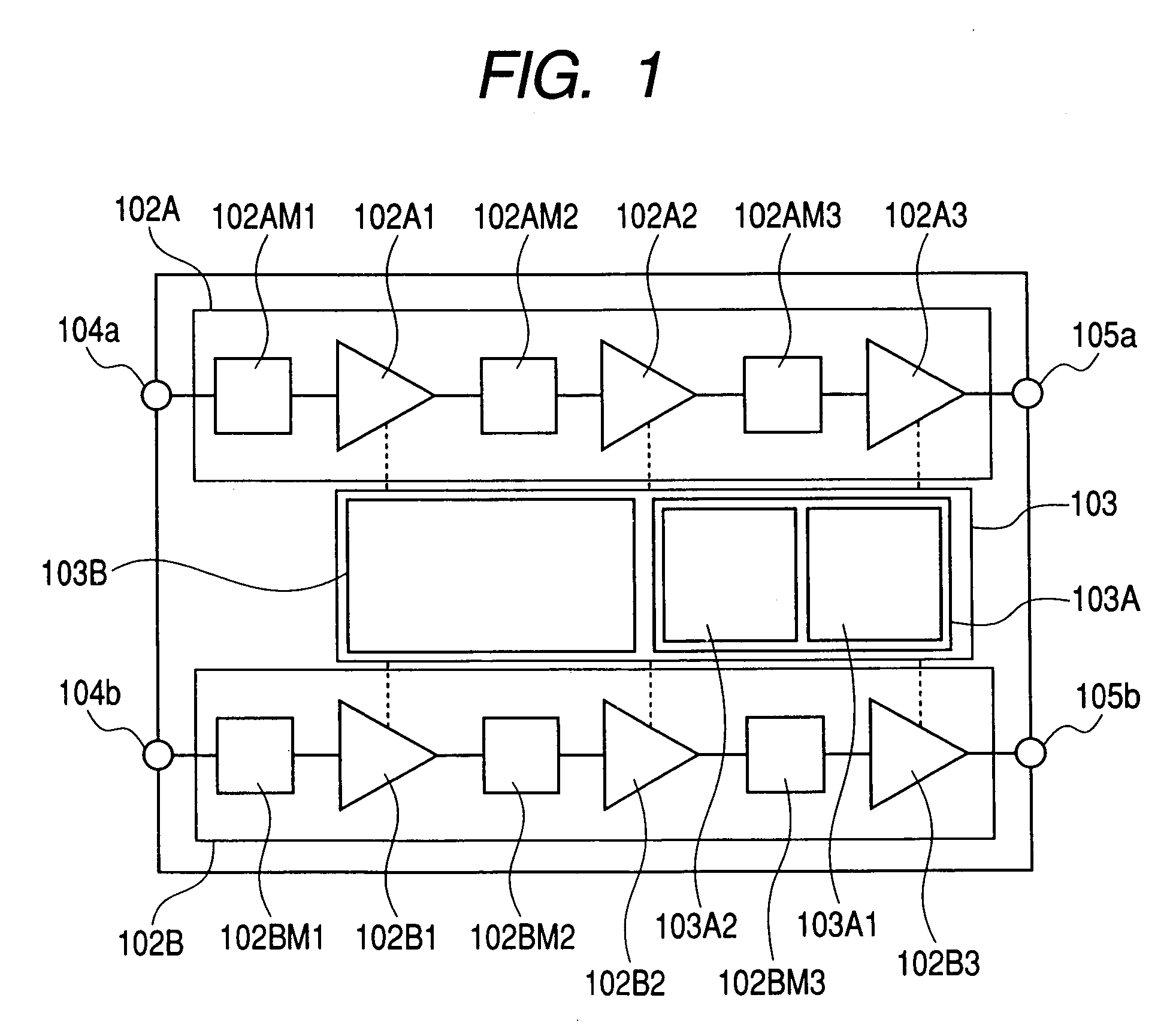

A technique for suppressing lowering of withstand voltage and lowering of breakdown resistance and reducing a feedback capacitance of a power MISFET is provided. A lateral power MISFET that comprises a trench region whose insulating layer is formed shallower than an HV-Nwell layer is provided in the HV-Nwell layer (drift region) formed on a main surface of a semiconductor substrate in a direction from the main surface to the inside. The lateral power MISFET has an arrangement on a plane of the main surface including a source layer (source region) and a drain layer (drain region) arranged at opposite sides to each other across a gate electrode (first conducting layer), and a dummy gate electrode (second conducting layer) that is different from the gate electrode is arranged between the gate electrode and the drain layer.

Owner:RENESAS ELECTRONICS CORP

Semiconductor device and a method of manufacturing the same

ActiveUS7176520B2Easy to controlImprove batch productivityTransistorEnergy efficient ICTCapacitanceFeedback capacitance

To reduce the size and improve the power added efficiency of an RF power module having an amplifier element composed of a silicon power MOSFET, the on resistance and feedback capacitance, which were conventionally in a trade-off relationship, are reduced simultaneously by forming the structure of an offset drain region existing between a gate electrode and an n+ type drain region of the power MOSFET into a double offset one. More specifically, this is accomplished by adjusting the impurity concentration of an n− type offset drain region, which is closest to the gate electrode, to be relatively low and adjusting the impurity concentration of an n type offset drain region, which is distant from the gate electrode, to be relatively high.

Owner:RENESAS ELECTRONICS CORP

Semiconductor device

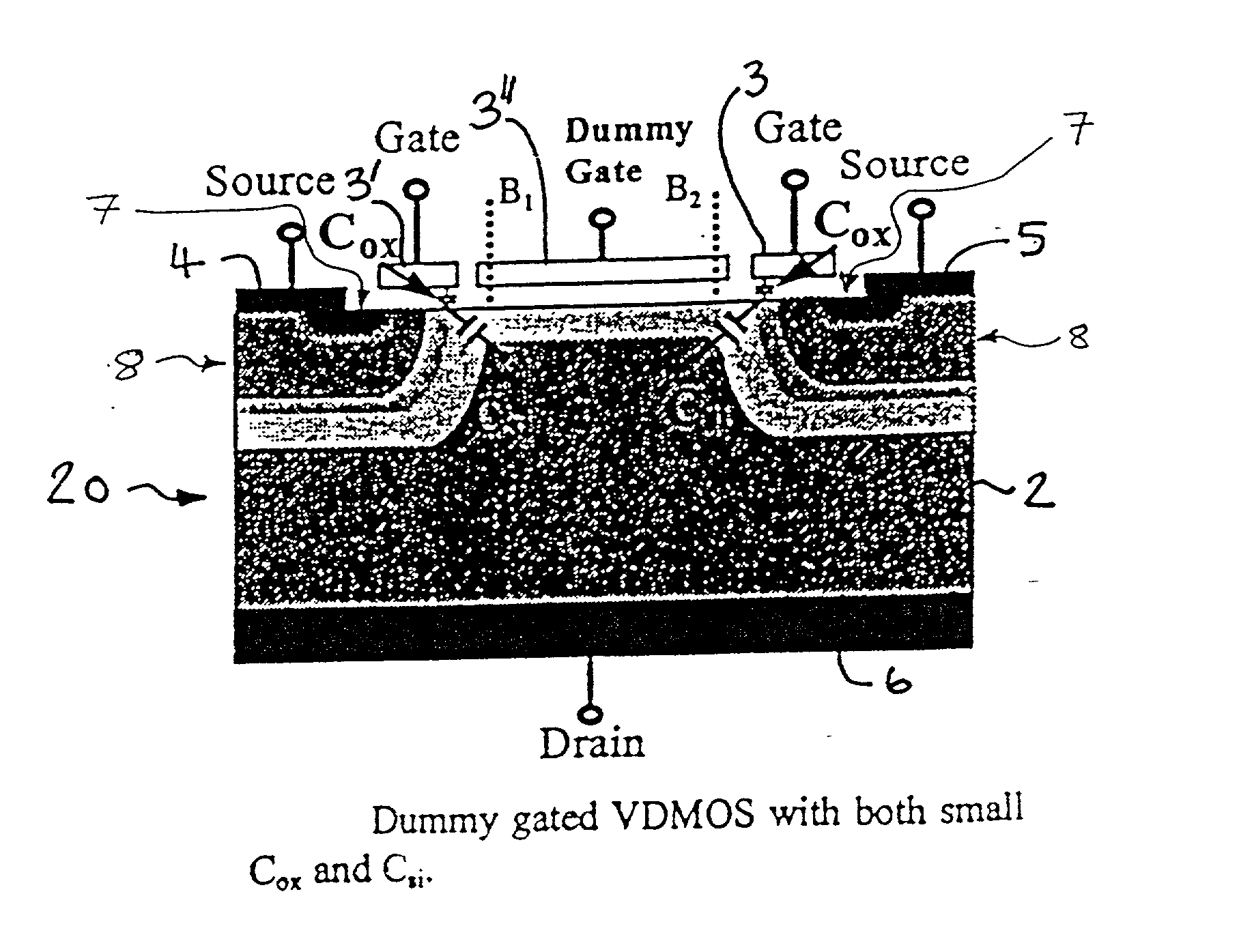

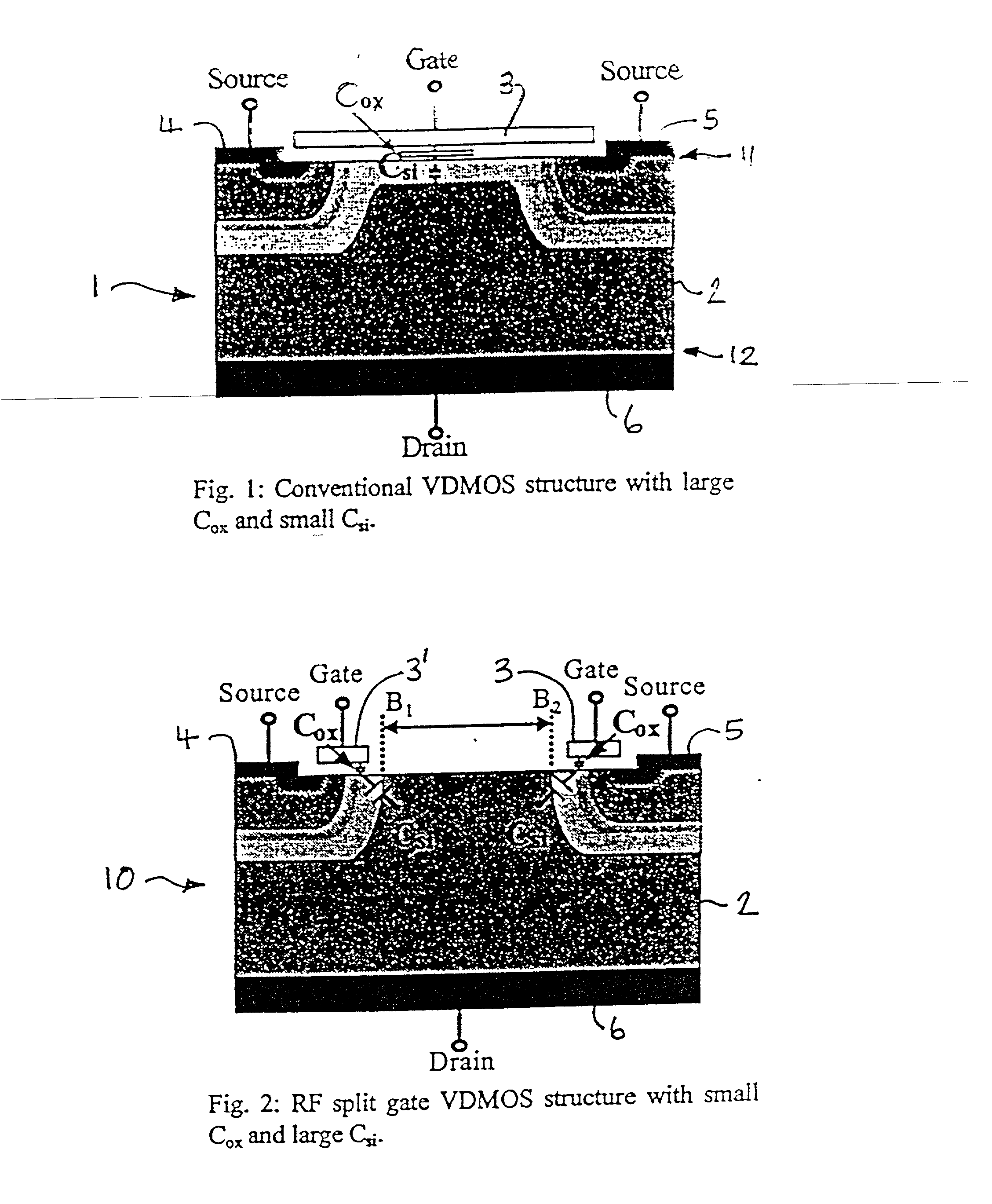

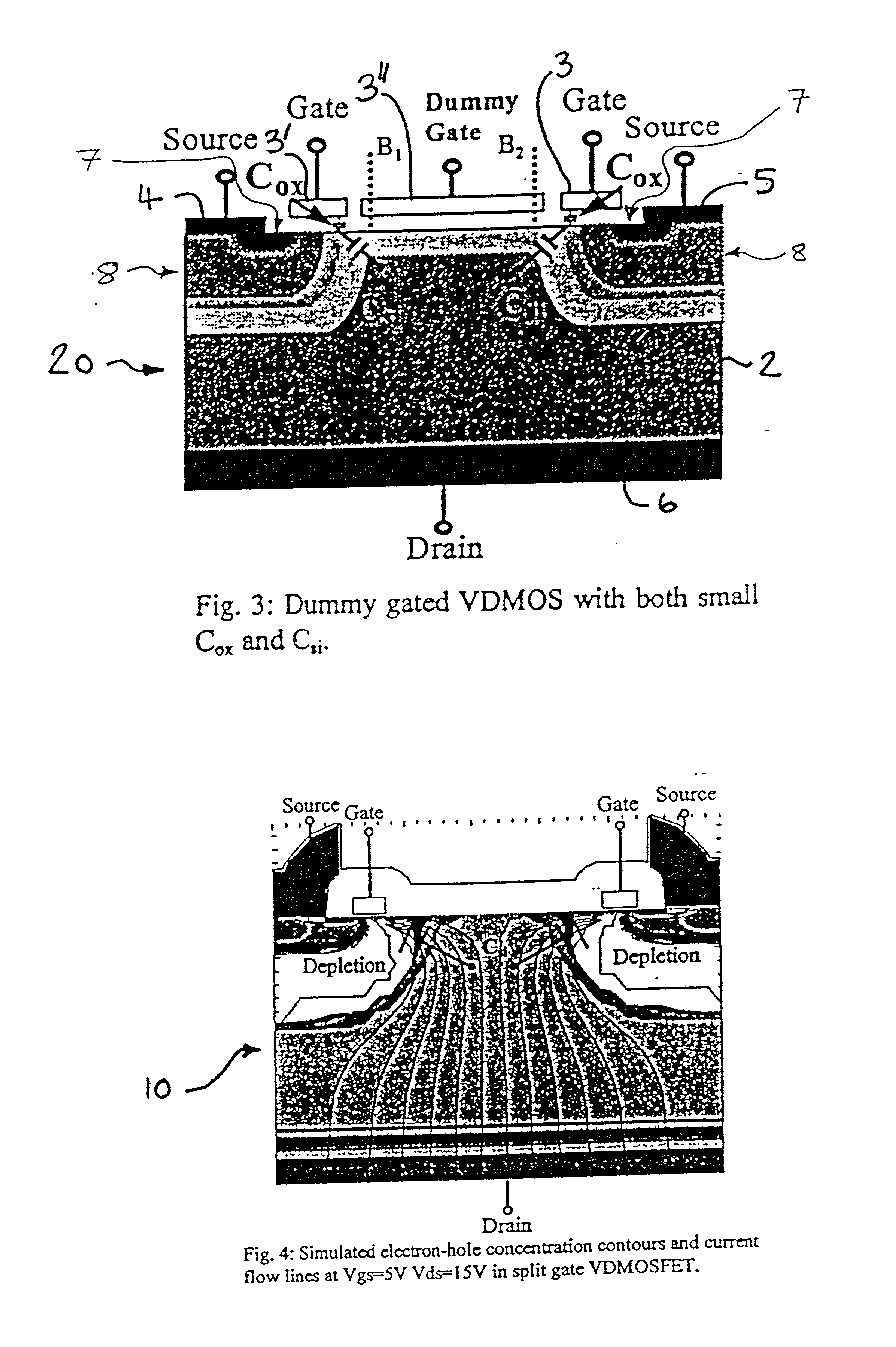

InactiveUS20020017682A1Efficient and reliable for applicationImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETPower application

A VD (vertical diffusion) MOSFET device for use in RF power applications has a split gate structure and an additional, dummy gate is provided between the spaced apart gates and, in operation of the device, is electrically coupled to source electrodes provided outside of the gates. The split gate structure reduces gate overlap capacitance and the dummy gate induces depletion in the semiconductor body of the device and reduces the substrate capacitance. The gate overlap capacitance and the substrate capacitance both contribute to the feedback capacitance of the device which has to be as low as possible for high frequency operation. By reducing both of these components, the invention provides advantageous high frequency operation.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

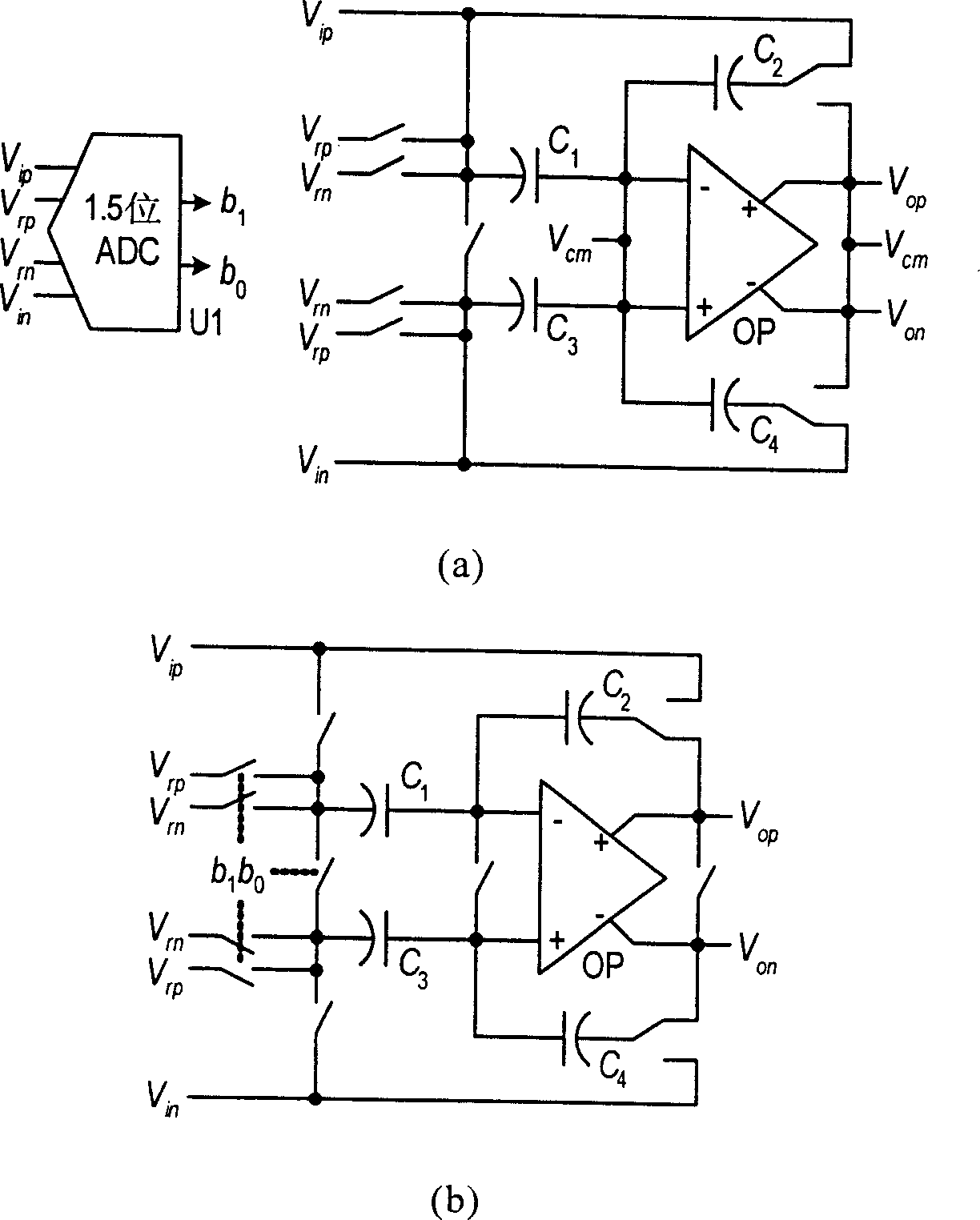

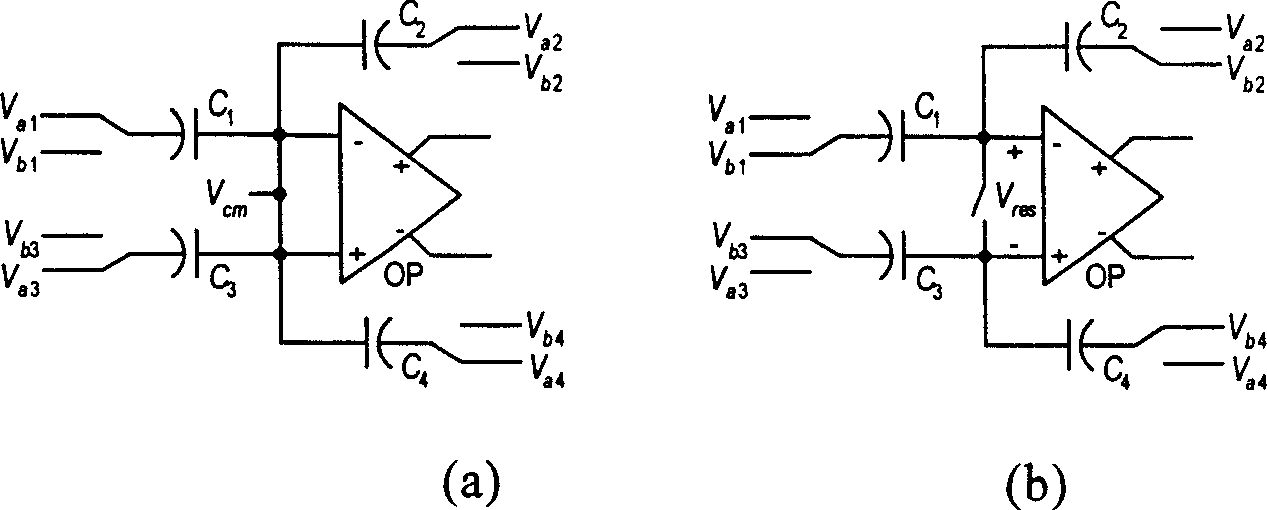

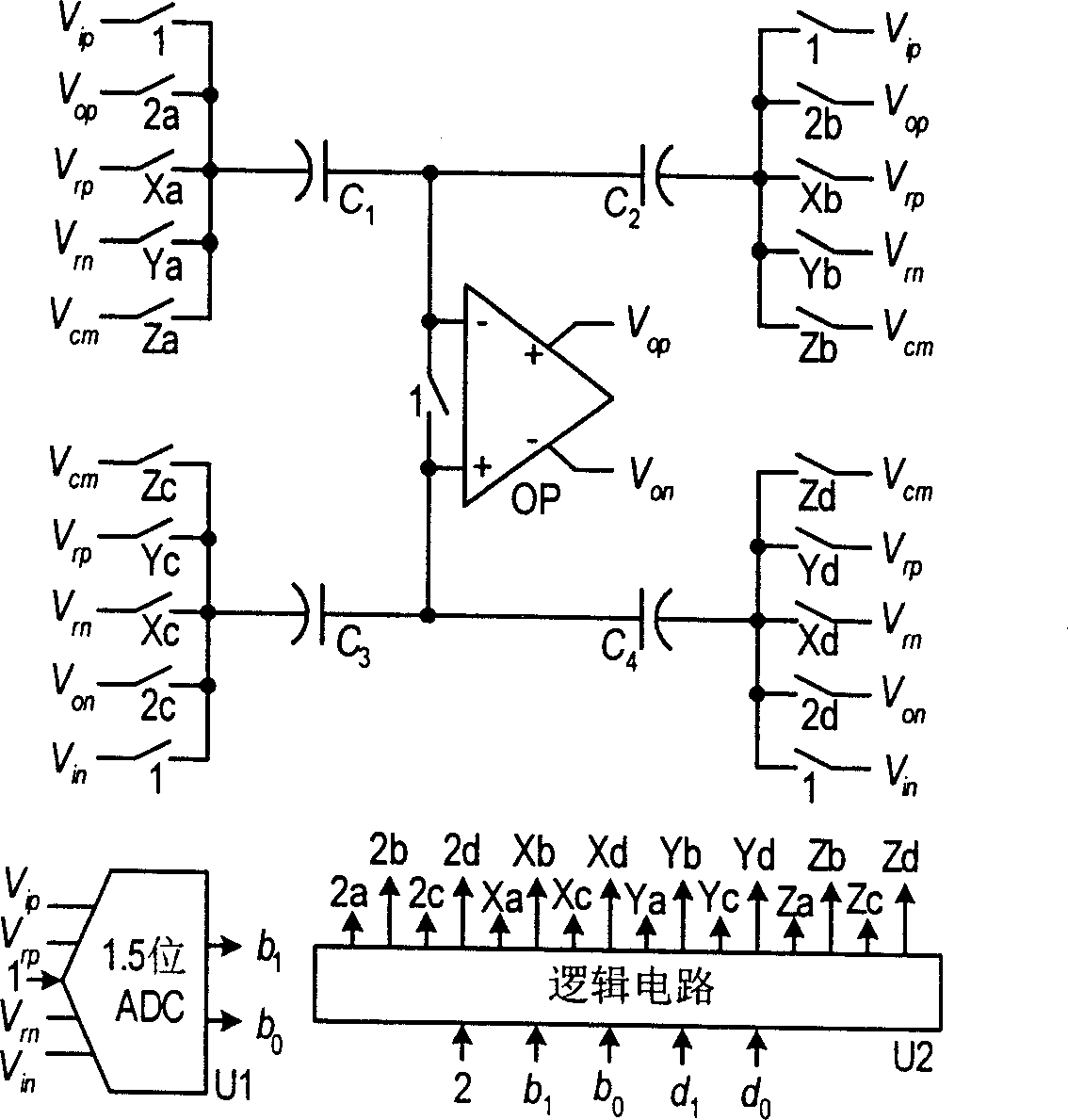

Method for reducing analog-digital converter capacitance mismatch error based on capacitance match

InactiveCN1866749AReduce power consumptionDoes not slow down workAnalogue-digital convertersAnalogue/digital conversion calibration/testingFeedback capacitanceIntegrated circuit

The invention discloses a reducing analogue digital converter capacitance dismatch error method in the integrated circuit design technique domain, which is characterized by the following: four work capacitances of analogue-digital converter are defined; the two capacitances which two roofs connects to input amplifier positive carry-in terminal are C1and C2; the capacitances which two roofs connects to input amplifier negative carry-in terminal are C3 and C4; C1 and C3 are the first pair of difference displacement volume; C2 and C4 are the second pair of difference displacement volume; the two pairs of difference displacement volumes are the difference sampling capacitance or difference feedback capacitance of grade circuit; comparing four work capacitances forms two pairs of new difference work capacitances; one pair of difference work capacitance with the smaller capacitance value is used for grade circuit difference feedback capacitance. The invention doesn't improve the circuit power consumption and doesn't reduce the load speed.

Owner:TSINGHUA UNIV

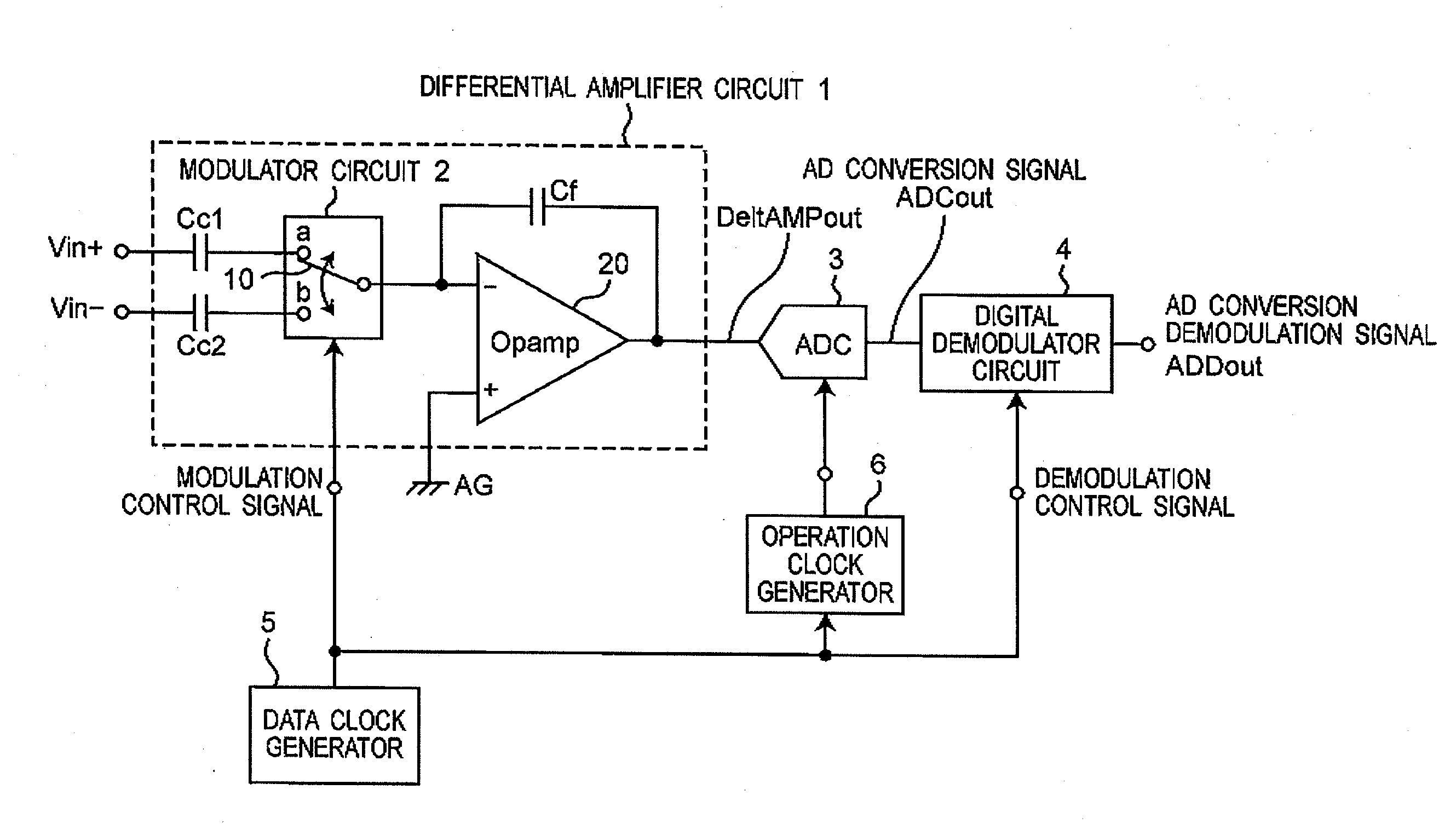

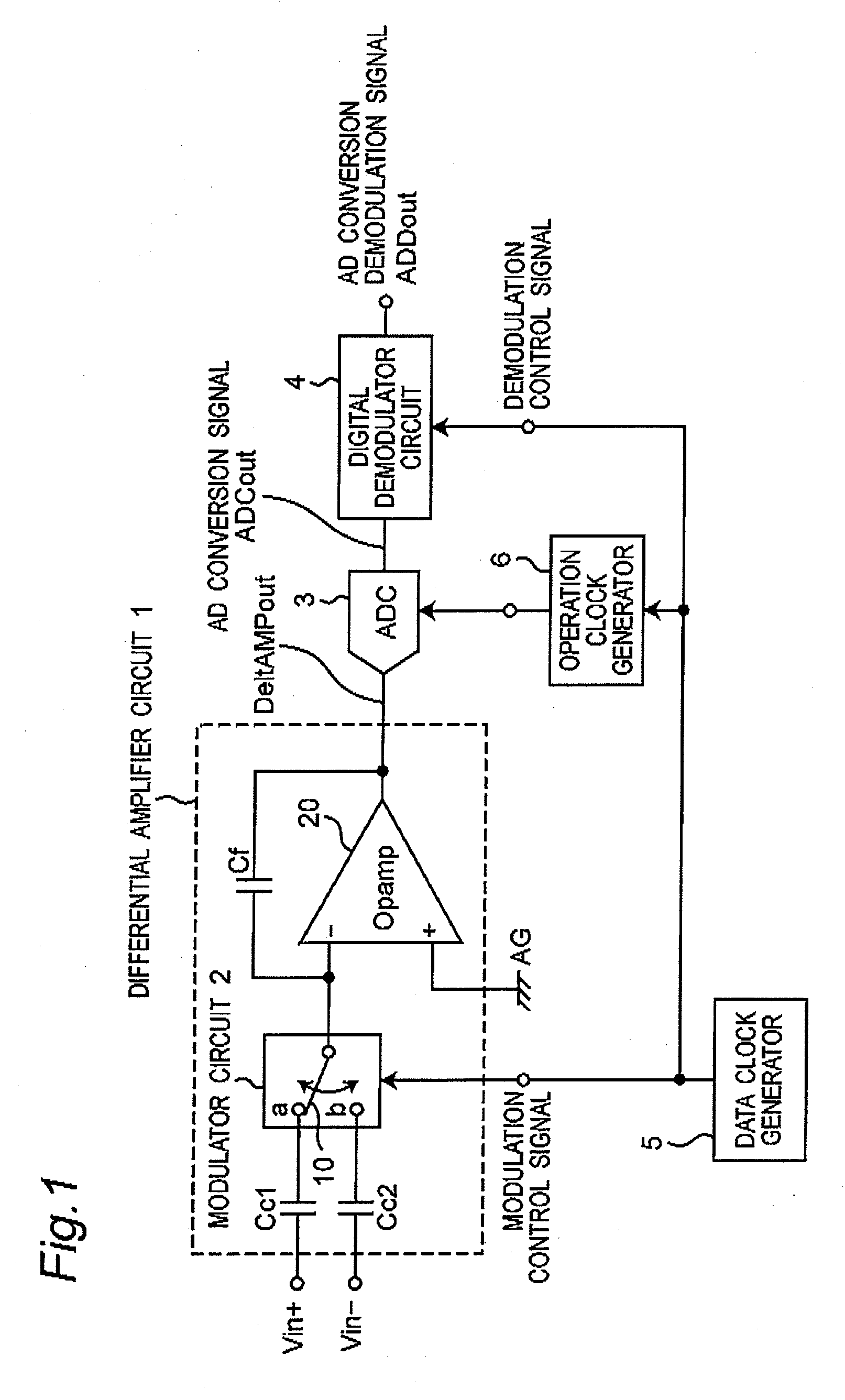

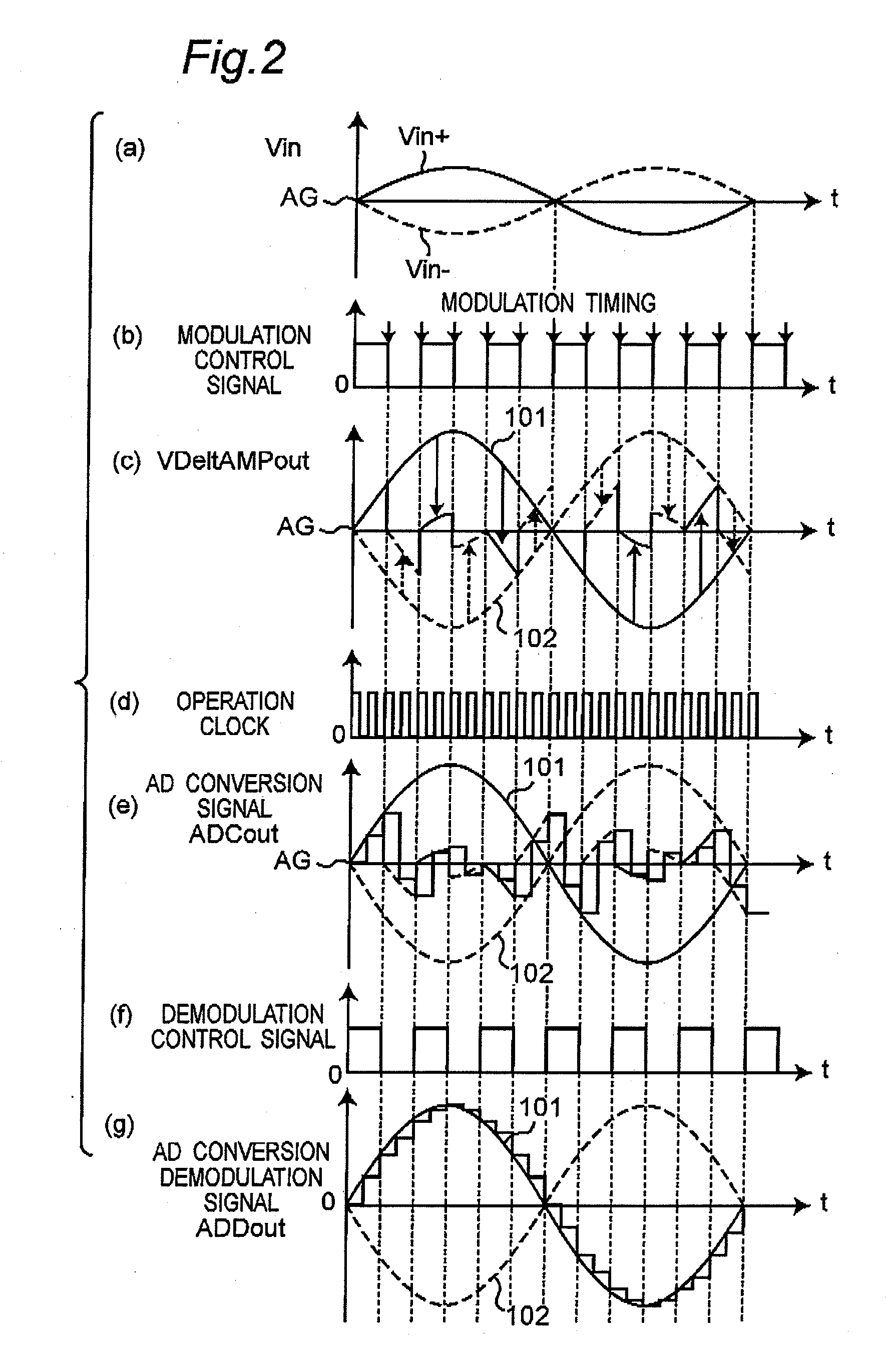

Differential amplifier circuit amplifying differential signals with selectively switching between differential signals and ad converter apparatus

InactiveUS20100103015A1Reduce voltageImproved voltage resolutionElectric signal transmission systemsDelta modulationAudio power amplifierControl signal

A differential amplifier circuit is provided with an operational amplifier and a modulator. The operational amplifier includes a feedback capacitance, and amplifies an analog input signal and outputs an amplified analog output signal. The modulator is connected to a virtual ground point of an input terminal of the operational amplifier, and the modulator switches between a pair of inputted analog differential signals to alternately select one of the analog differential signals based on a predetermined modulation control signal, and outputs a selected analog differential signal. The differential amplifier circuit alternately folds and amplifies the analog input signal within a predetermined input level limit range to generate a signal having different polarities sequentially so as to start from a voltage potential of the virtual ground point at a timing of the modulation control signal. In addition, an converter apparatus is provided with the differential amplifier circuit.

Owner:SEMICON TECH ACADEMIC RES CENT

Method for creation of the gate shield in analog/rf power ed-cmos in sige bicmos technologies

A method of fabricating a MOSFET transistor in a SiGe BICMOS technology and resulting structure having a drain-gate feedback capacitance shield formed between a gate electrode and the drain region. The shield does not overlap the gate and thereby minimizes effect on the input capacitance of the transistor. The process does not require complex or costly processing since the shield is composed of bipolar base material commonly used in SiGe BICMOS technologies.

Owner:TEXAS INSTR INC

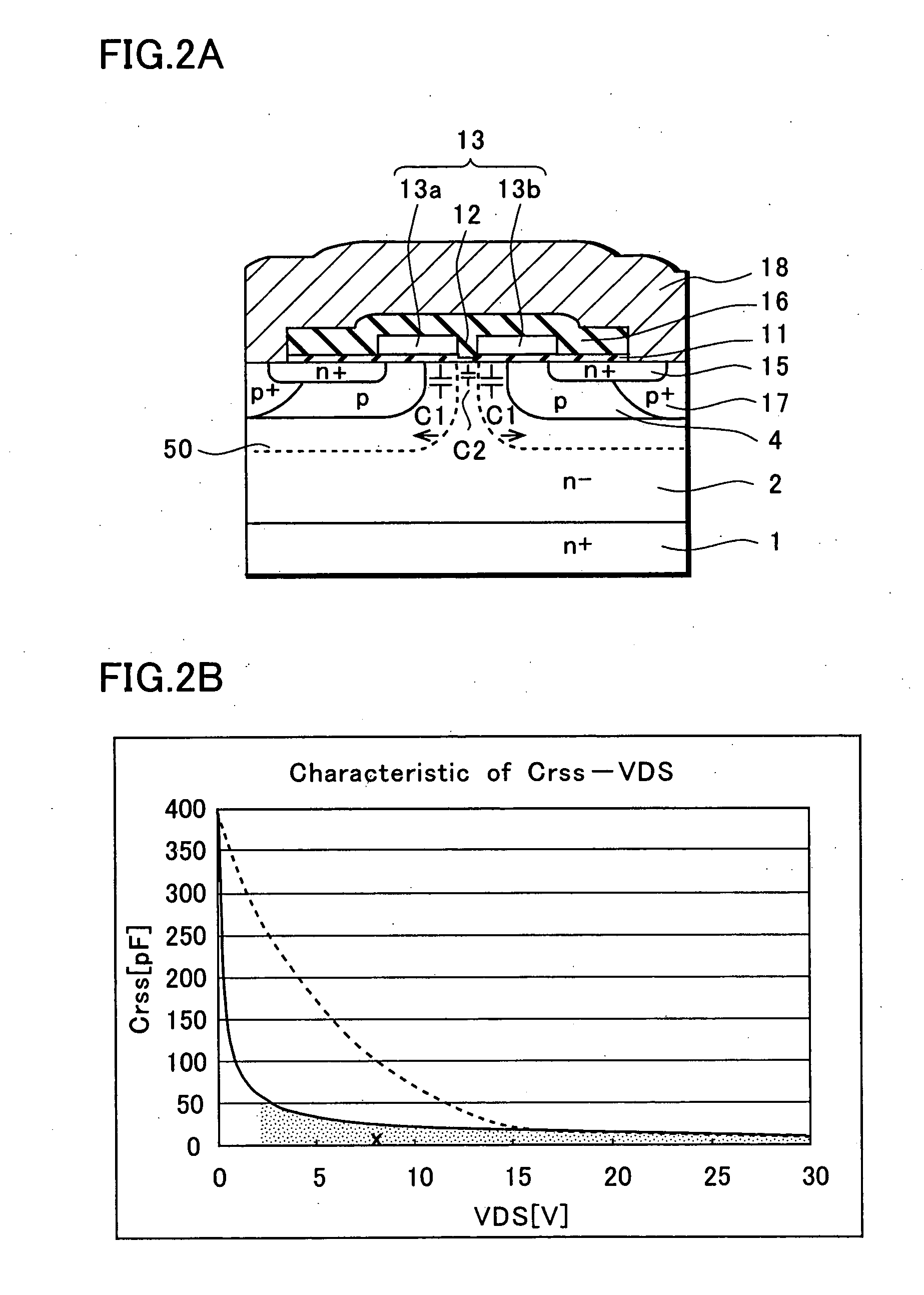

Insulated gate field effect transistor and manufacturing method thereof

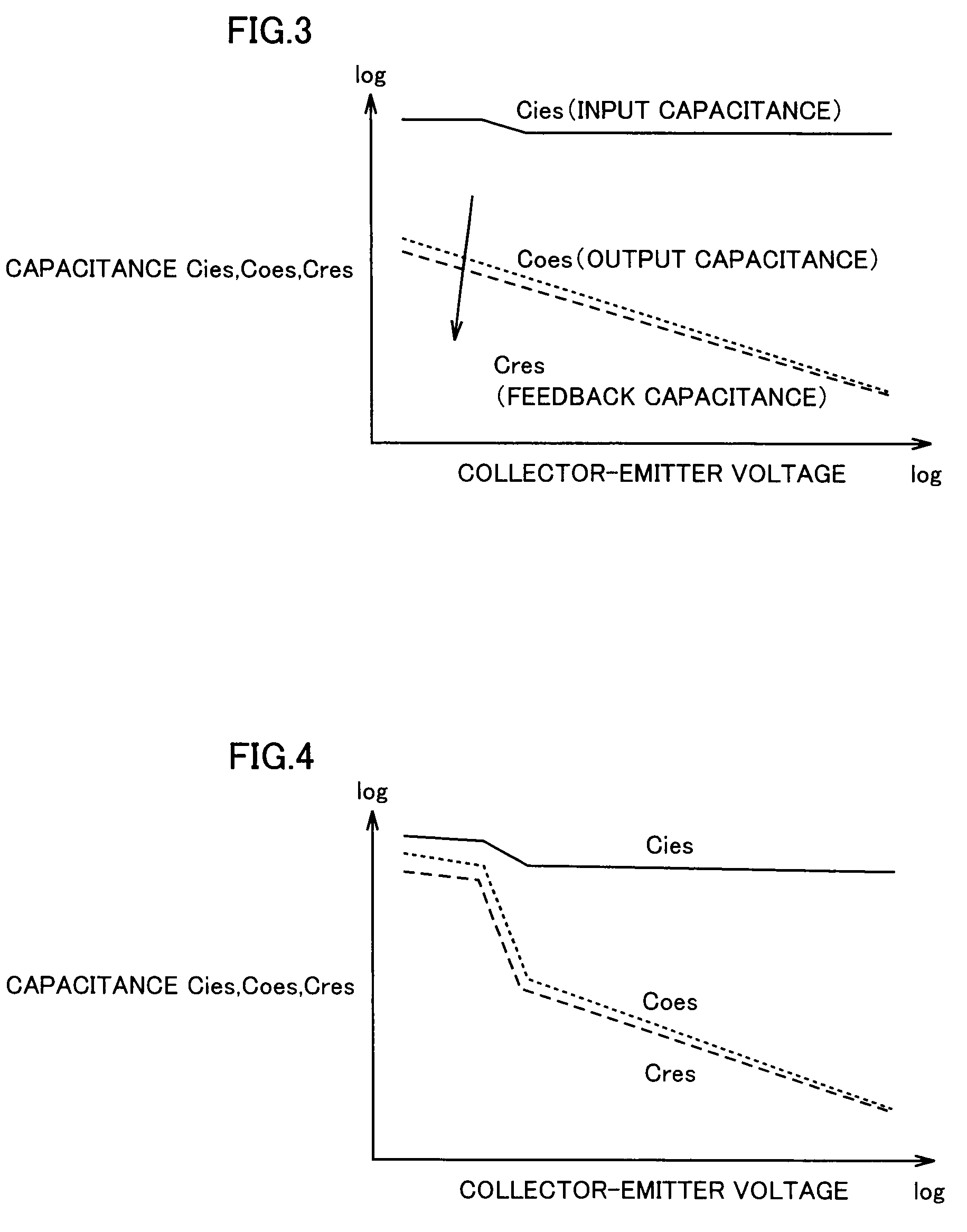

InactiveUS20070072352A1Reduce resistanceOn-resistance can be reducedSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceElectrical resistance and conductance

A separation hole is provided in the center of the gate electrode. Accordingly, it is possible to suppress a drastic increase in feedback capacitance Crss in the case where drain-source voltage VDS is decreased and the width of the depletion layer is narrowed. Thus, high-frequency switching characteristics are improved. Moreover, n type impurities are implanted from the separation hole to form an n type impurity region between channel regions. Since a resistance in a portion below the gate electrode can be reduced, an on-resistance can be reduced. The n type impurity region can be formed in a self-aligning manner.

Owner:SANYO ELECTRIC CO LTD

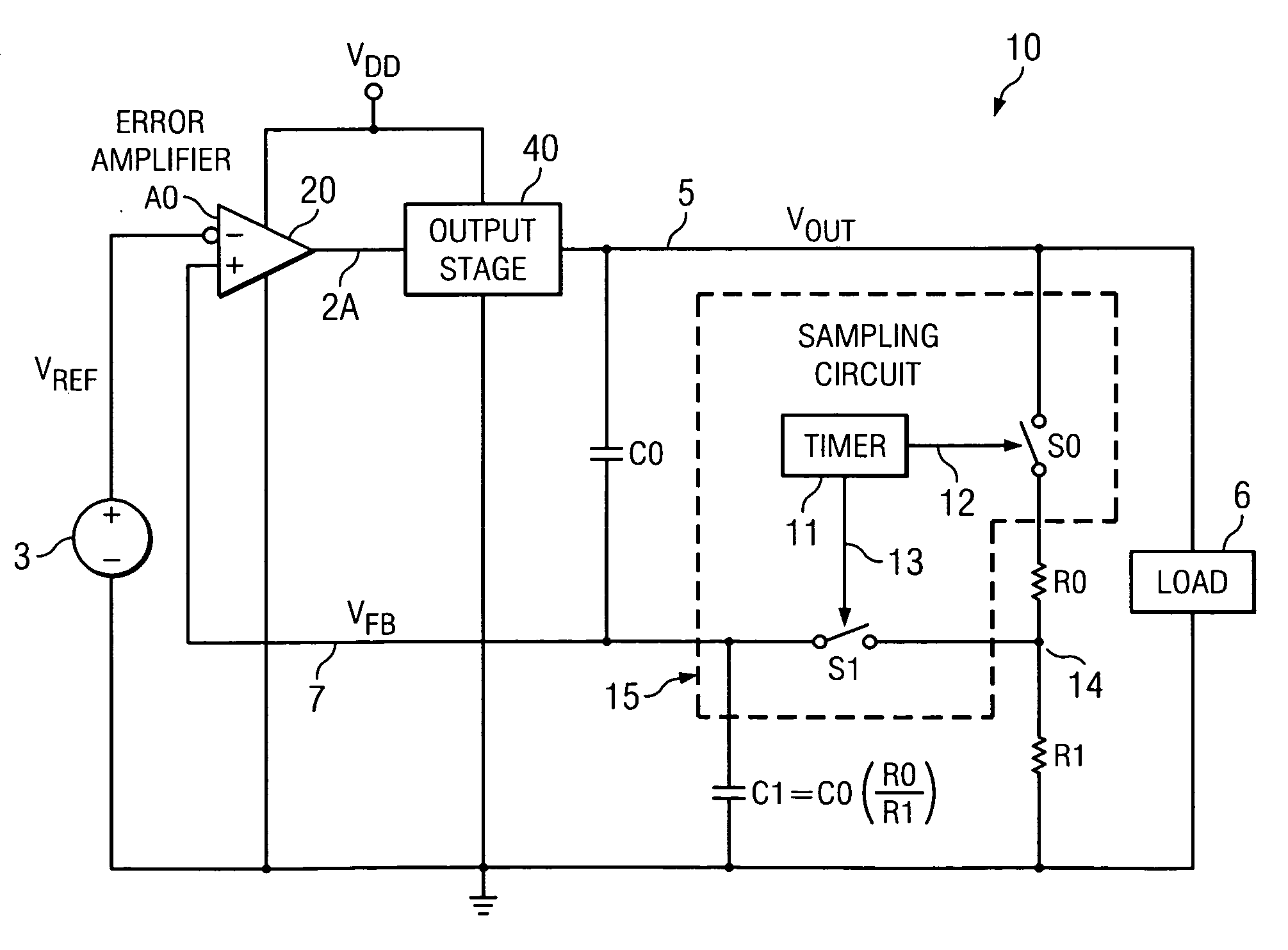

Low-power feedback and method for DC-DC converters and voltage regulators for energy harvesters

ActiveUS20110181258A1Total current dropReduce power consumptionAc network voltage adjustmentElectric variable regulationElectrical conductorEnergy harvester

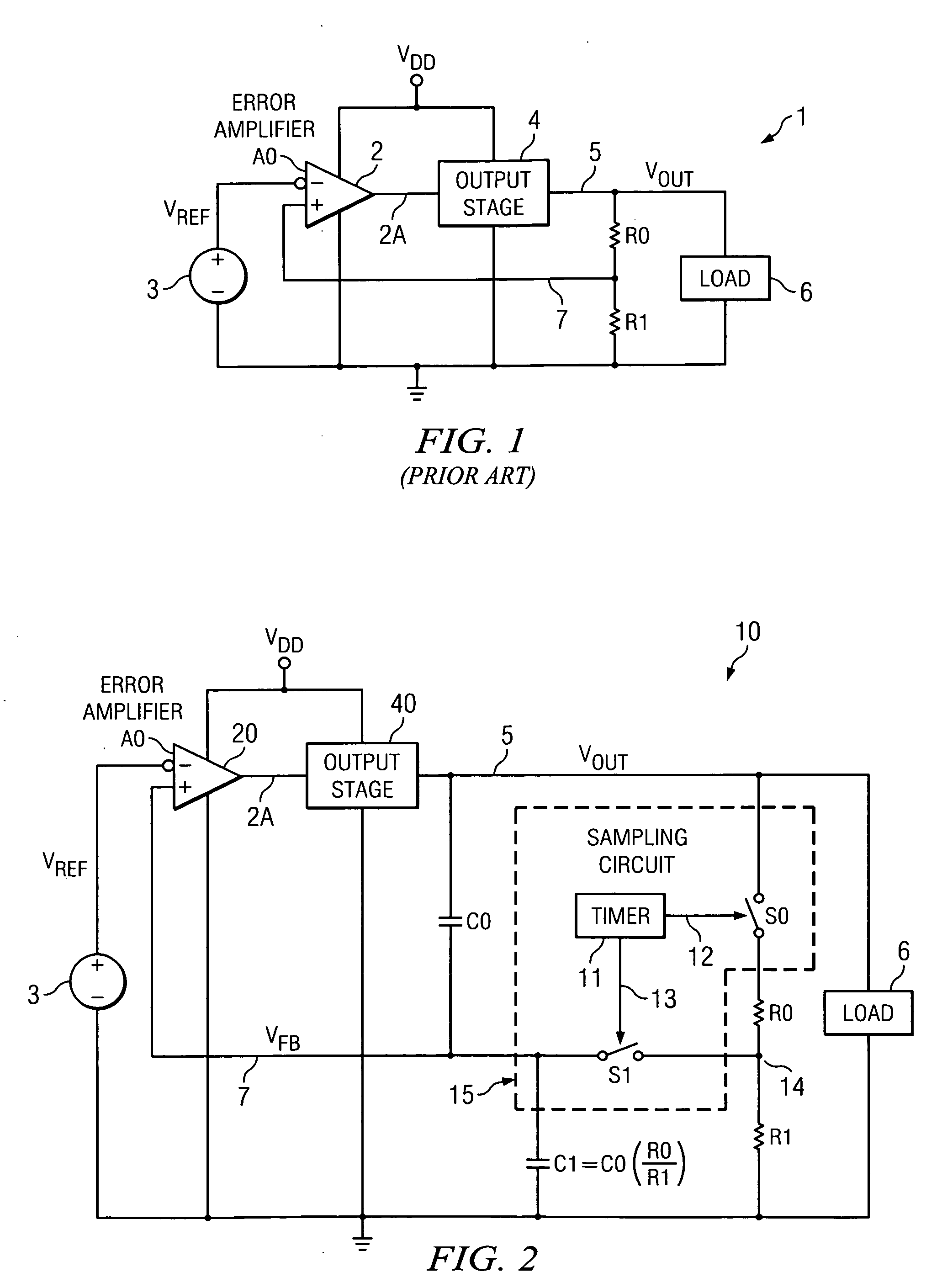

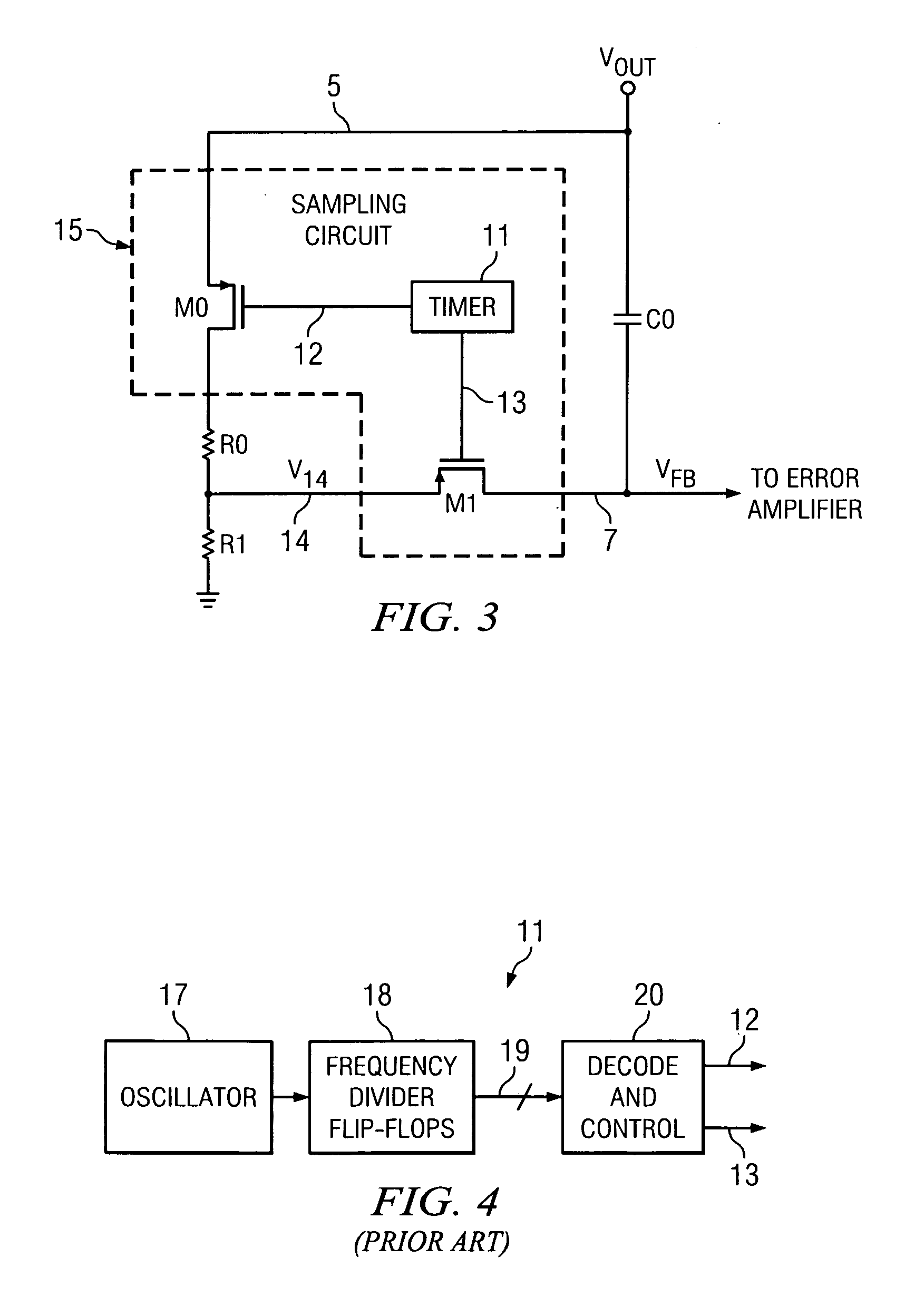

A converter (10) for converting a first DC voltage (VDD) to a second DC voltage (VOUT) includes an output stage (40) for producing the second DC voltage (VOUT) in response to both the first DC voltage (VDD) and an output of an error amplifier (20). A sampling circuit (15) periodically energizes a voltage divider (R0,R1) by periodically coupling a first terminal thereof to the second DC voltage and periodically coupling an output (14) of the energized voltage divider to a feedback conductor (7) to refresh a feed back capacitor (C0) coupled between the second DC voltage and the feedback conductor. The feedback conductor is coupled to an input of the error amplifier.

Owner:TEXAS INSTR INC