Patents

Literature

9327results about "Analogue-digital converters" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Coding method and apparatus for multiple channels of audio information representing three-dimensional sound fields

InactiveUS6021386AConserve substantial bandwidthConveniently implementedBroadcast information characterisationSpeech analysisFrequency spectrumBit allocation

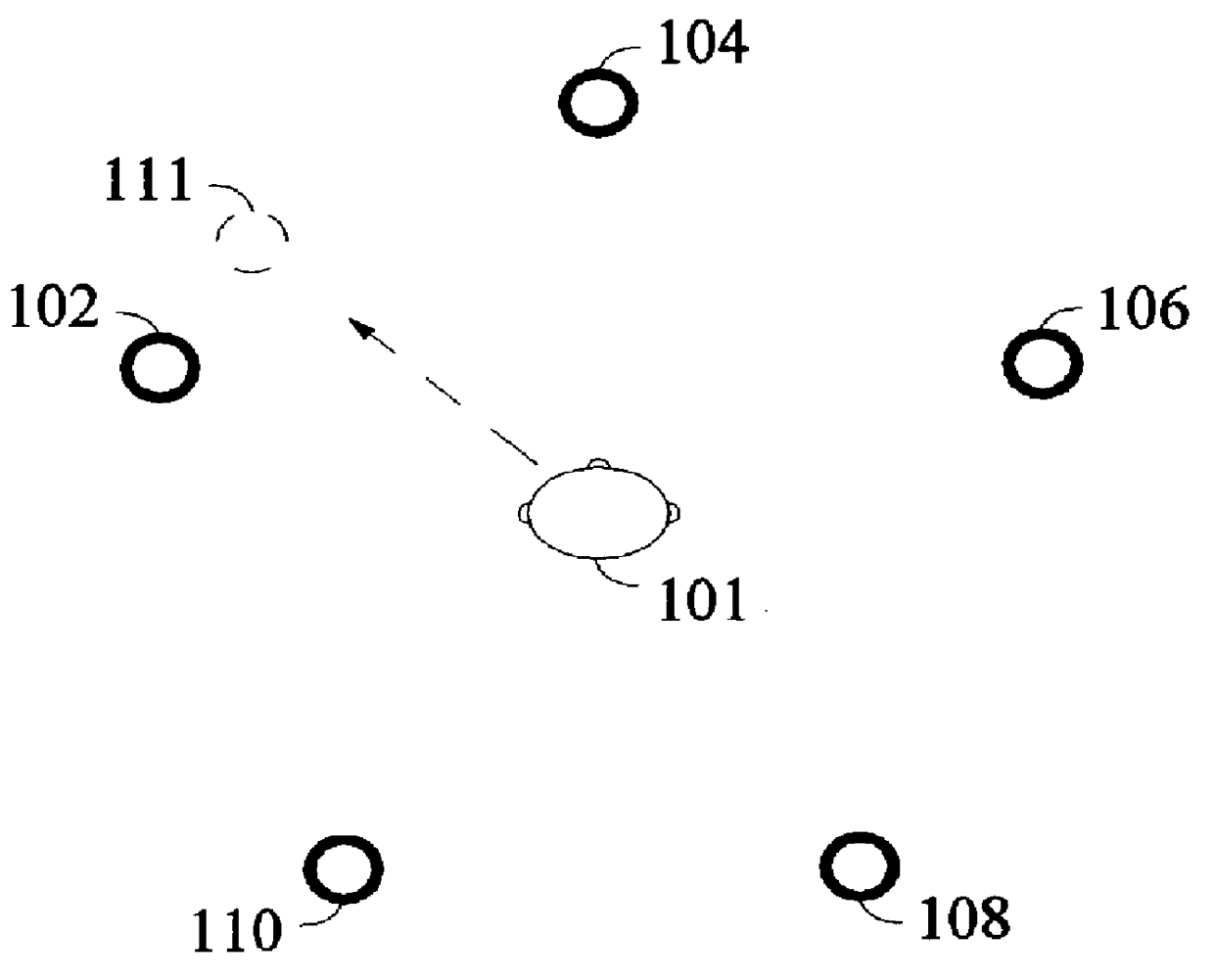

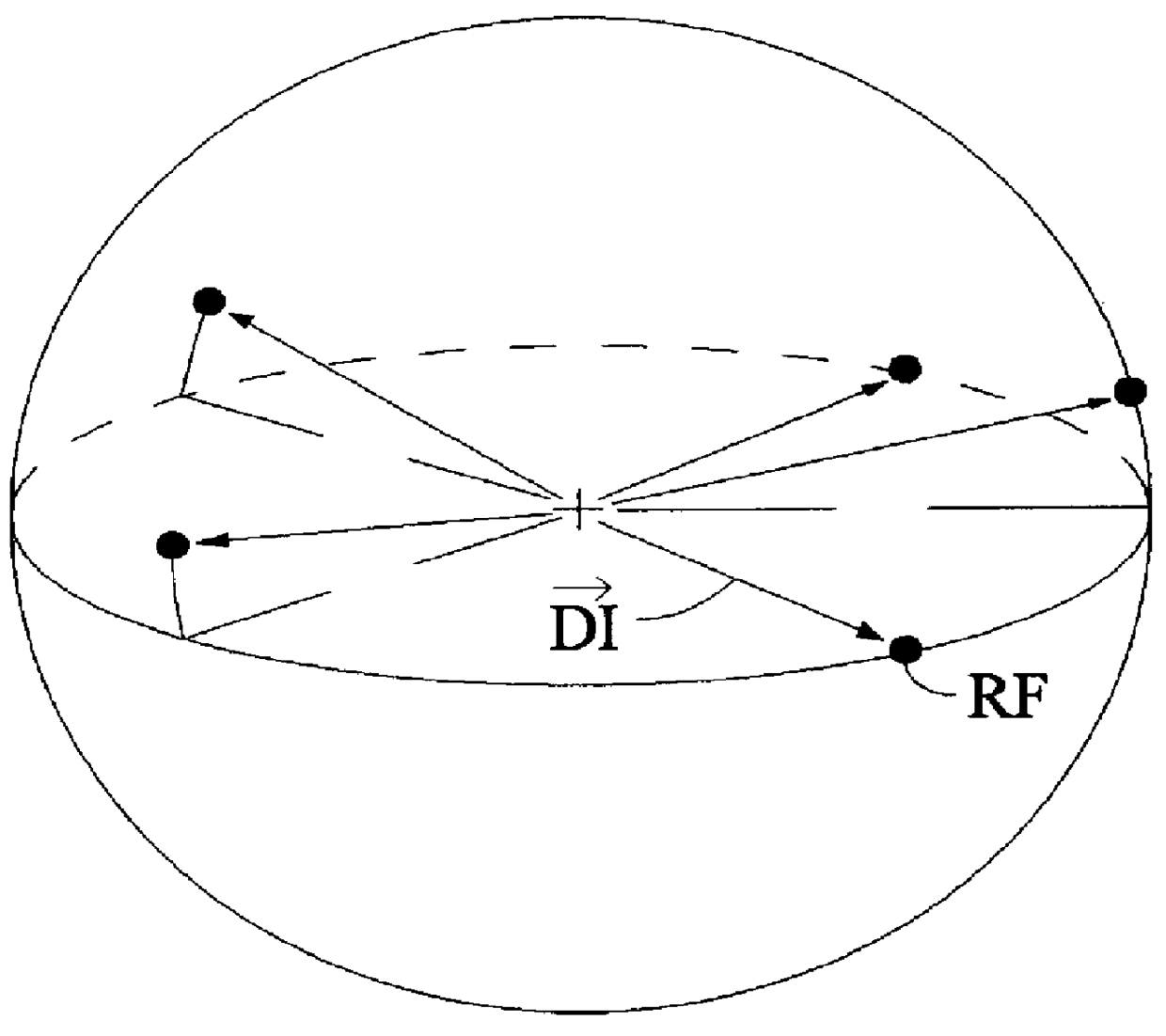

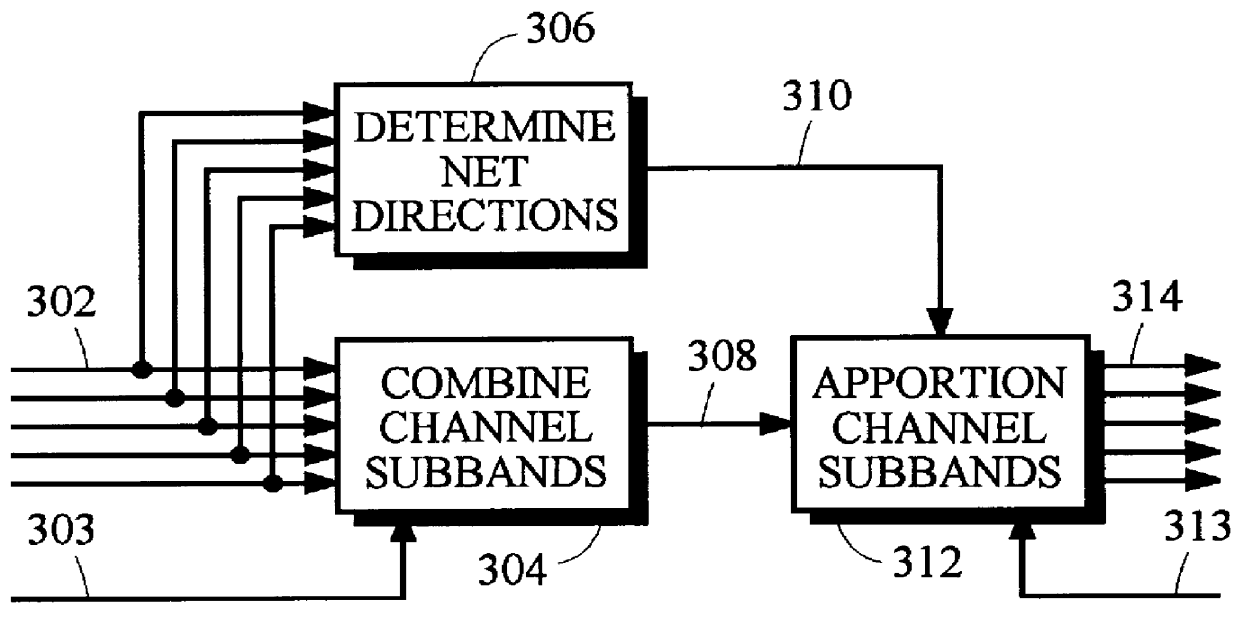

In an encoder, multiple channels of audio information representing multidimensional sound fields are split into subband signals and the subband signals in one or more subbands are combined to form composite signals. The composite signals, the subband signals not combined into a composite signal and information describing the spectral levels of subband signals combined into composite signals are assembled into an encoded output signal. The spectral level information conveys either the amplitude or power of the combined subband signals or the apparent direction of the sound field represented by the combined subband signals. In digital implementations, adaptive bit allocation may be used to reduce the informational requirements of the encoded signal.

Owner:DOLBY LAB LICENSING CORP

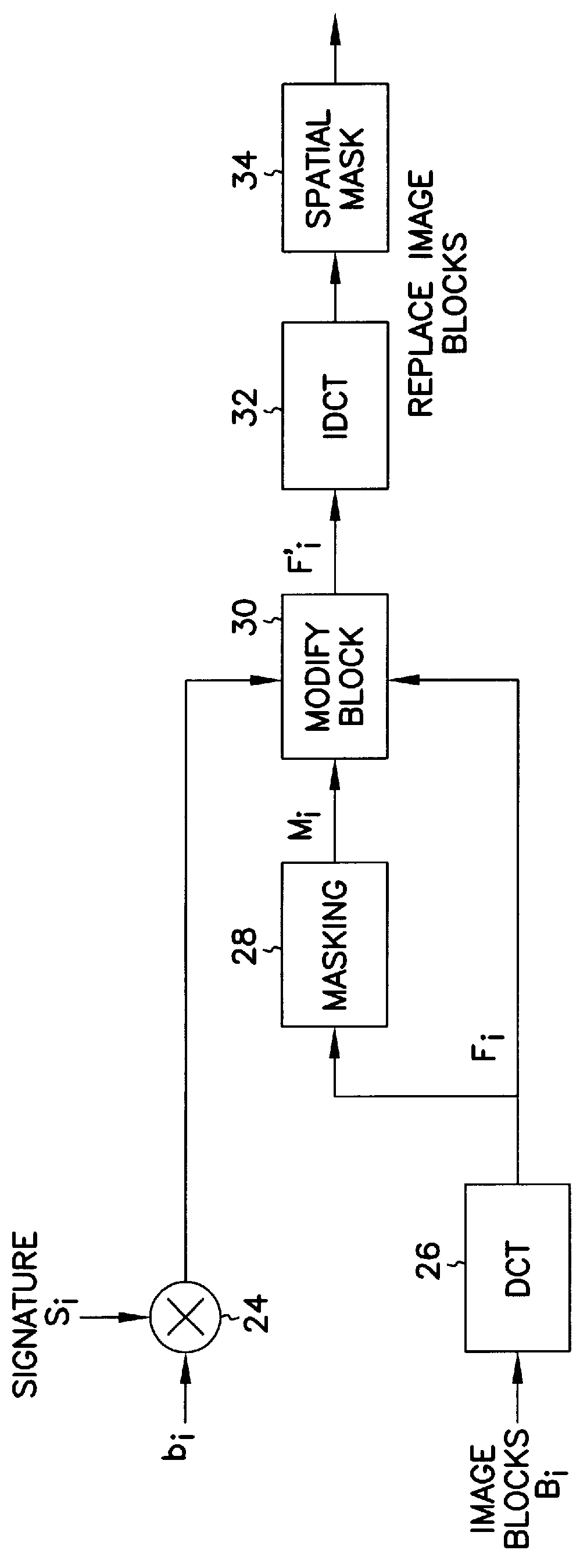

Method and apparatus for embedding data, including watermarks, in human perceptible images

InactiveUS6031914AGood autocorrelationPromote generationElectric signal transmission systemsCharacter and pattern recognitionPattern recognitionFrequency spectrum

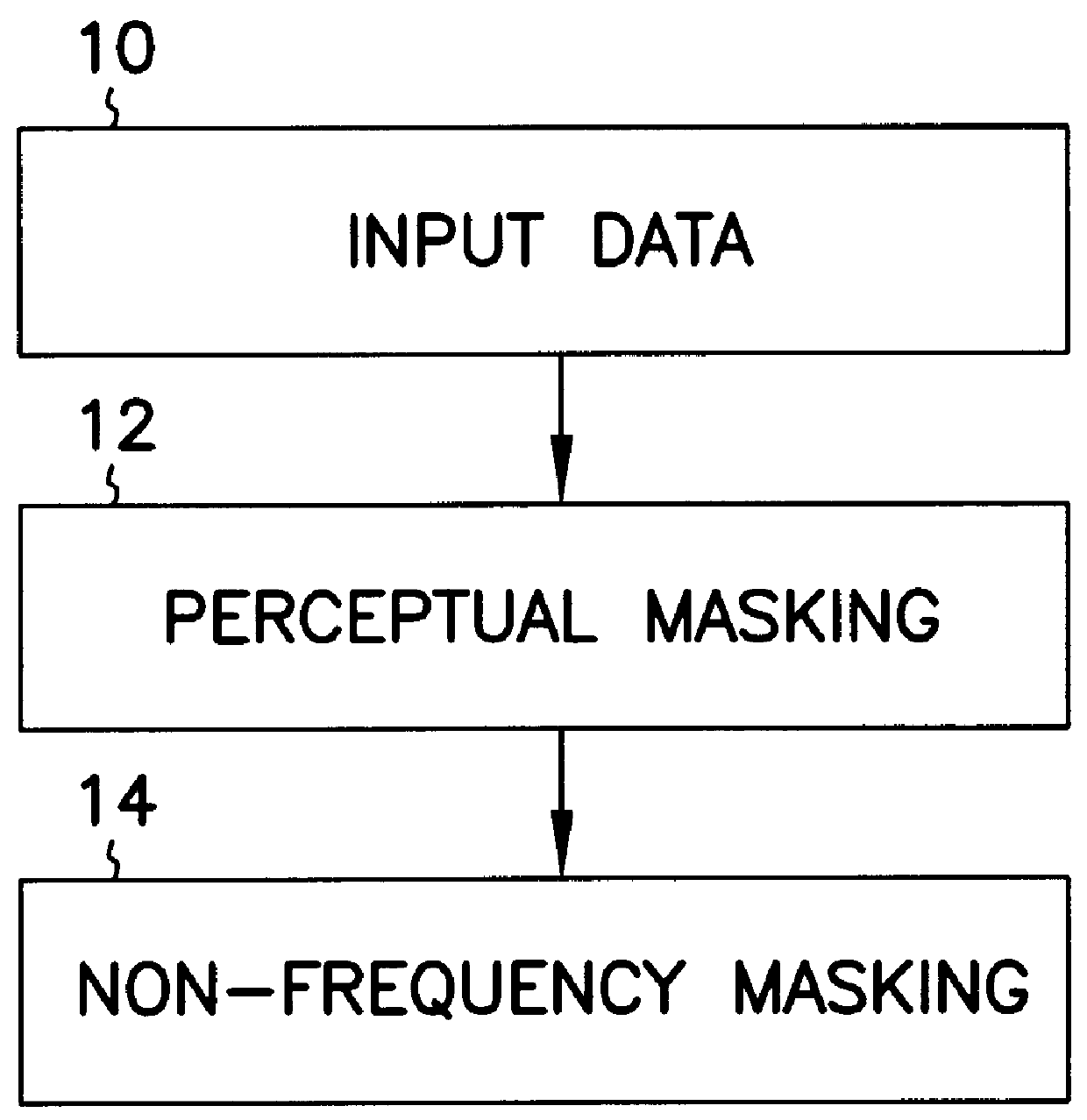

A technique for hiding of data, including watermarks, in human-perceptible images, that is, image host data, is disclosed. In one embodiment a method comprises three steps. In the first step, data to be embedded is inputted. In the case of a watermark, this data is a unique signature, and may be a pseudo-noise (PN) code. In the case of hidden data to be embedded in the host data, this data is the hidden data itself, or the hidden data as spread against the frequency spectrum by a pseudo-noise (PN) code. In the second step, the inputted data is embedded within the host data, in accordance with a perceptual mask of the host data. The perceptual mask determines the optimal locations within the host data to insert the inputted data. In the case of images, these optimal locations are determined by reference to the human visual system. In the third step, the host data, with the embedded data, is further masked by a non-frequency mask. In the case of image data, the non-frequency mask is a spatial mask.

Owner:MINNESOTA RGT UNIV OF A CORP OF MN

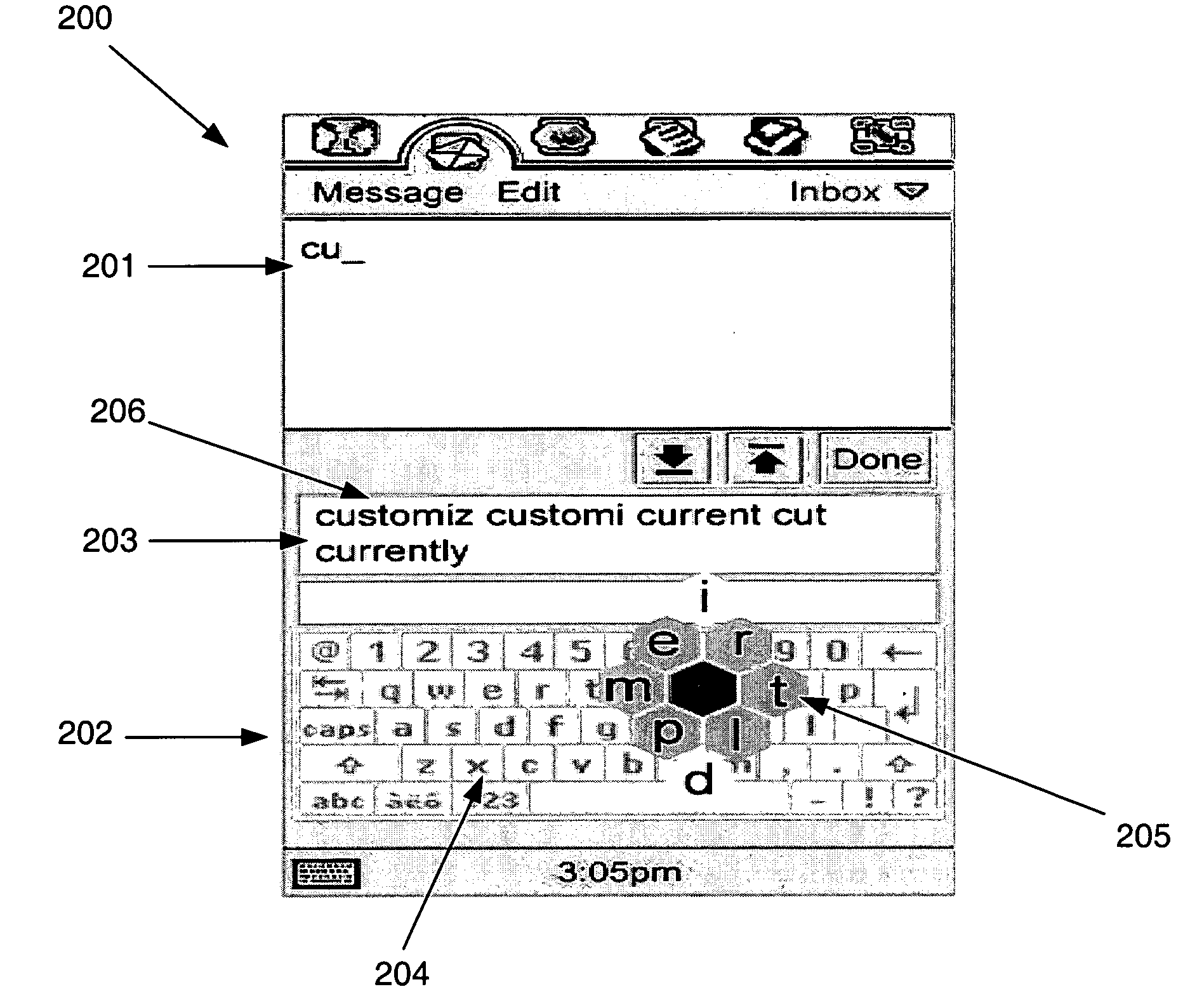

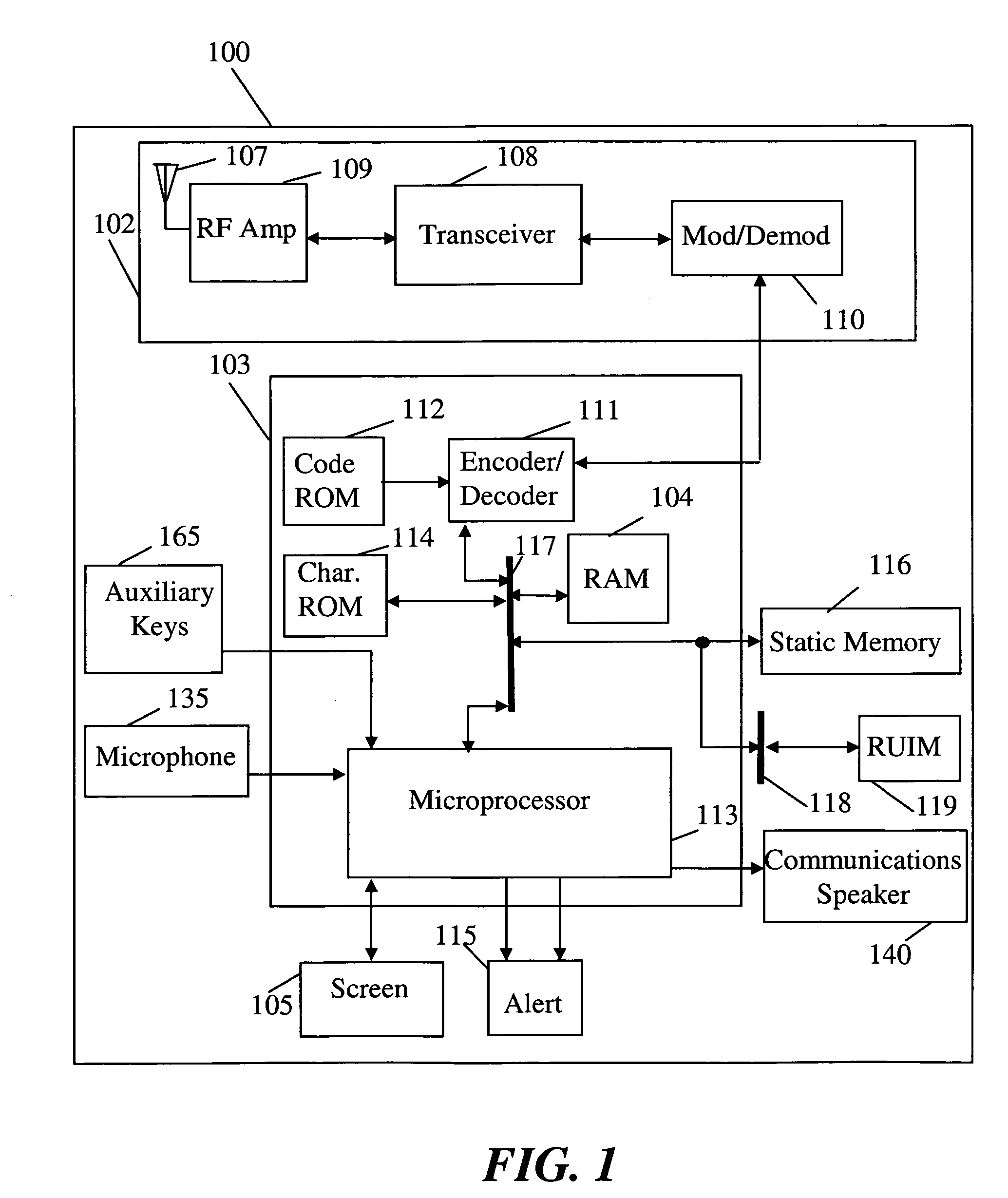

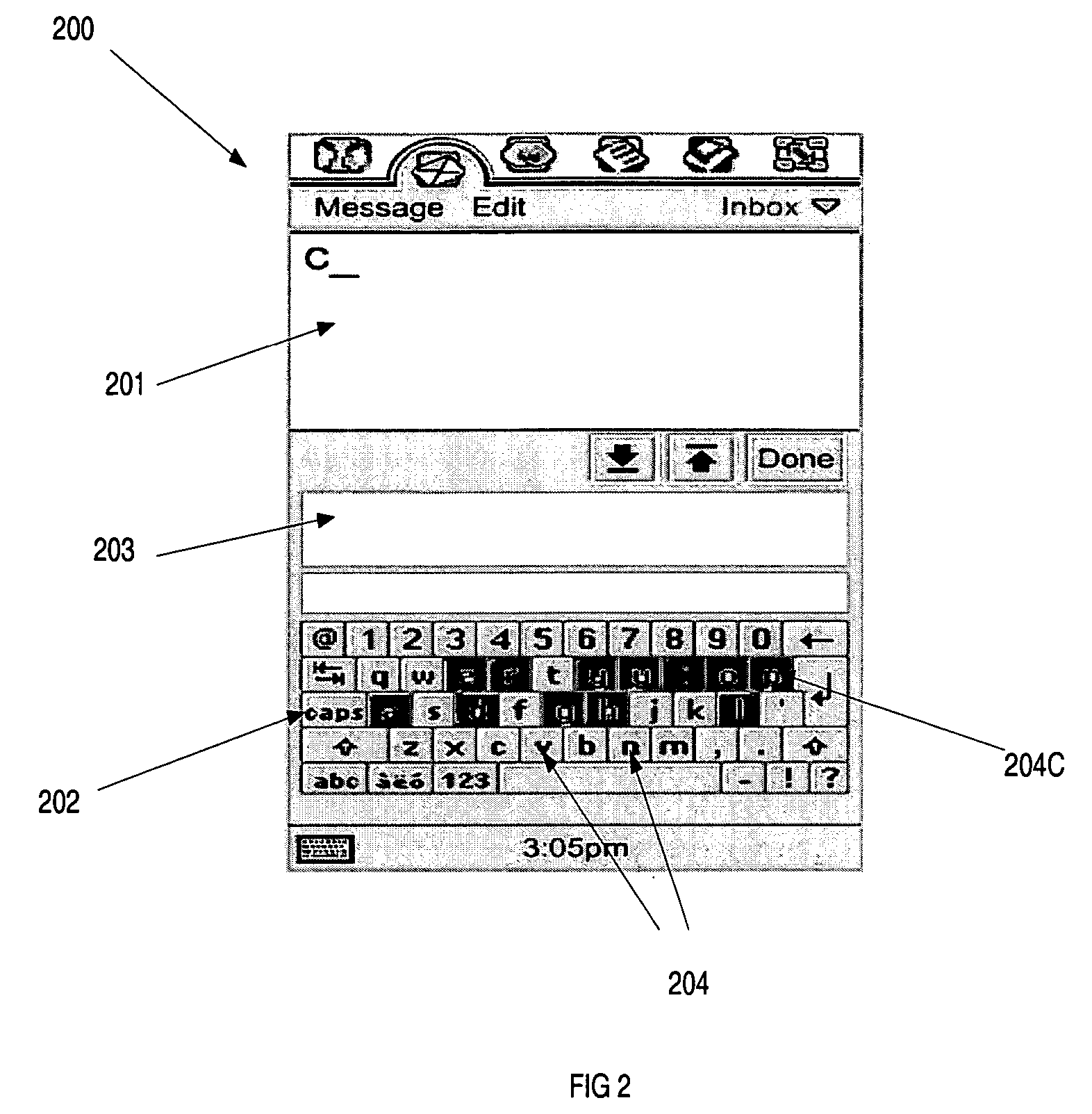

Entering a character into an electronic device

ActiveUS7443316B2Easy for to identify wantedEasy for to see and also to selectInput/output for user-computer interactionCharacter and pattern recognitionAlgorithmEngineering

Owner:GOOGLE TECH HLDG LLC

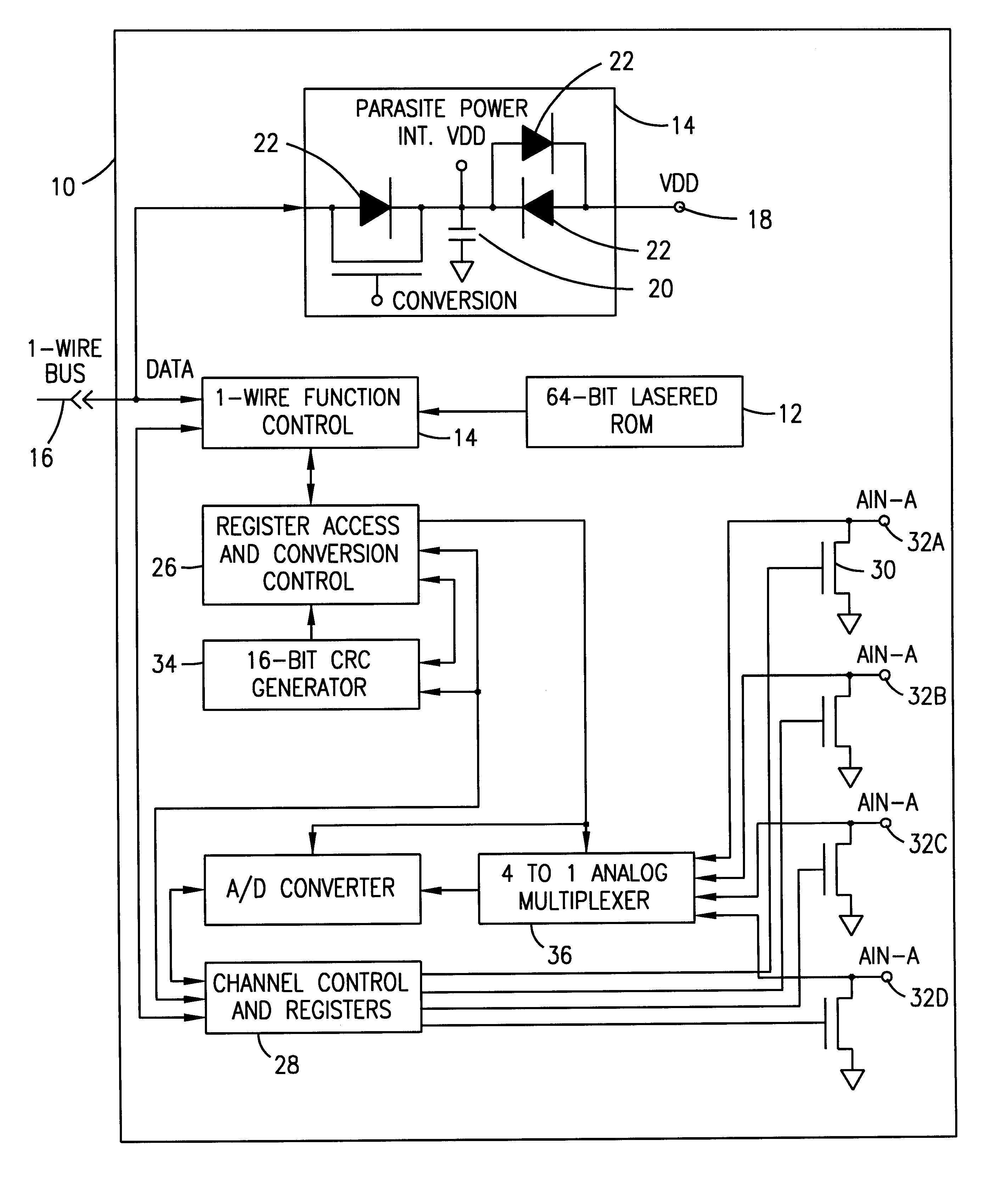

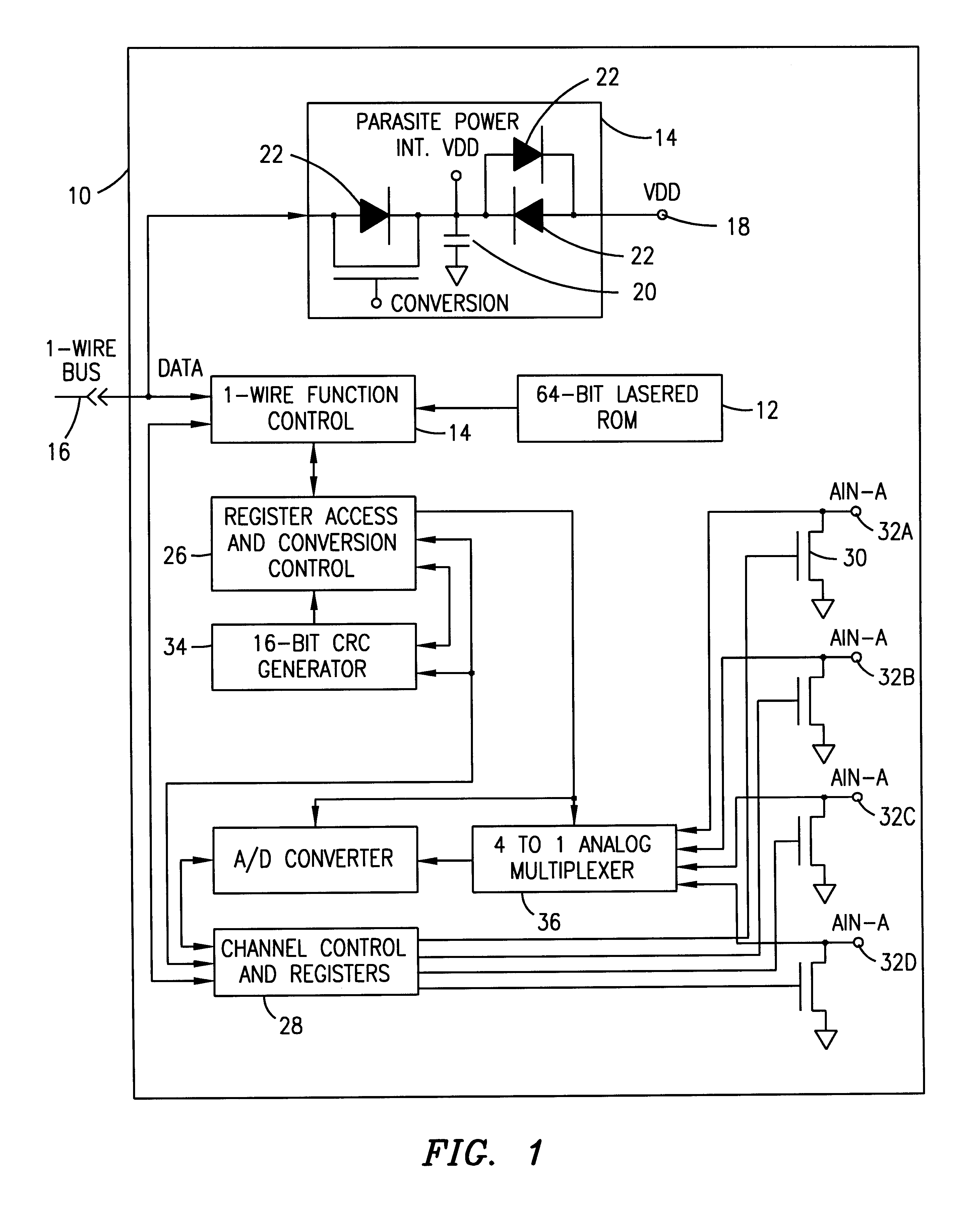

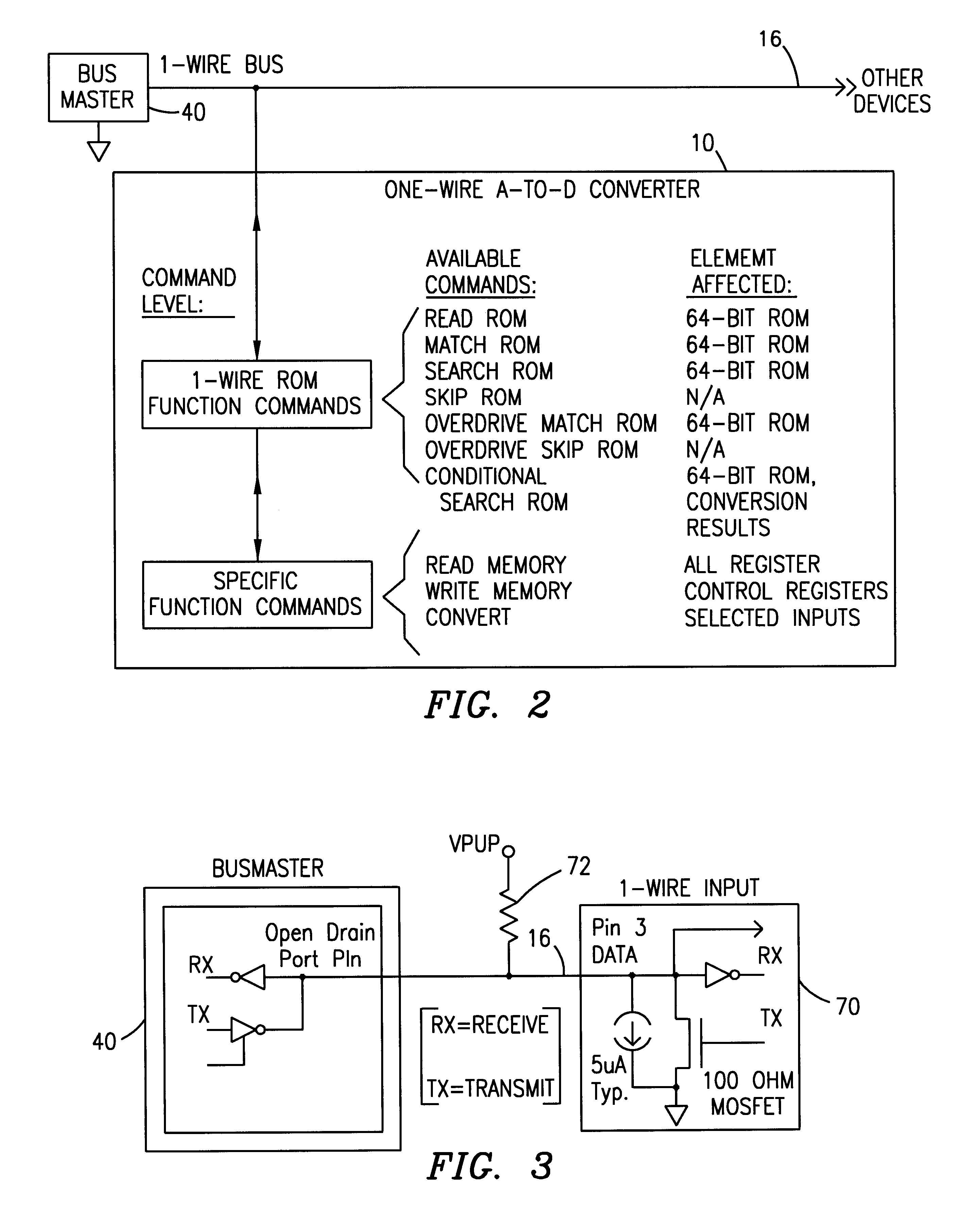

One-wire device with A-to-D converter

InactiveUS6239732B1Electric signal transmission systemsAnalogue-digital convertersĆuk converterAnalog signal

A low power integrated circuit having analog to digital conversion circuitry capable of receiving a plurality of analog signals and converting them to a digital value. The digital value is then transmitted, upon request, over a single wire bus. The accuracy of the analog to digital conversion circuitry can be calibrated via trim codes stored in an onboard EPROM.

Owner:MAXIM INTEGRATED PROD INC

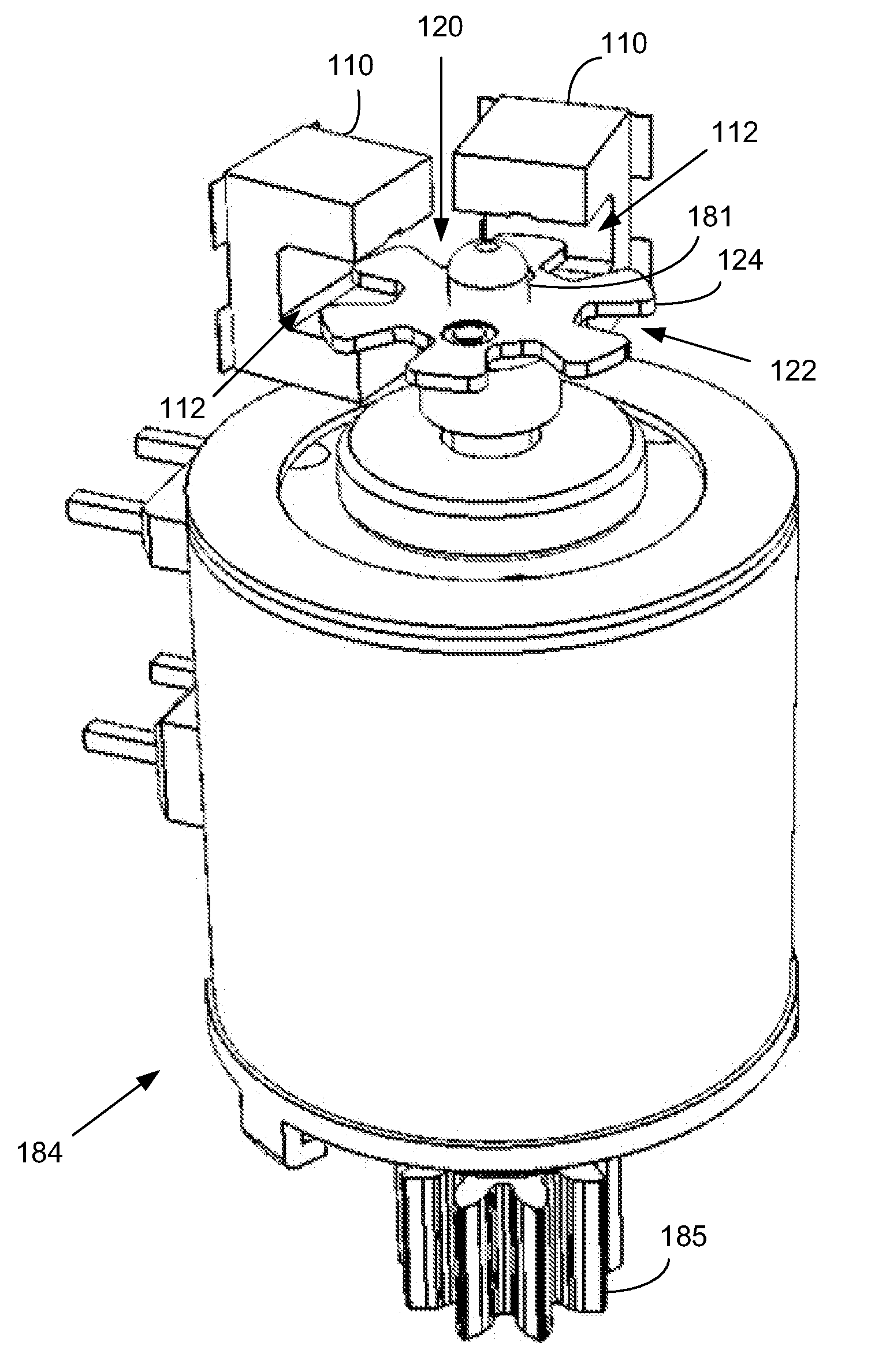

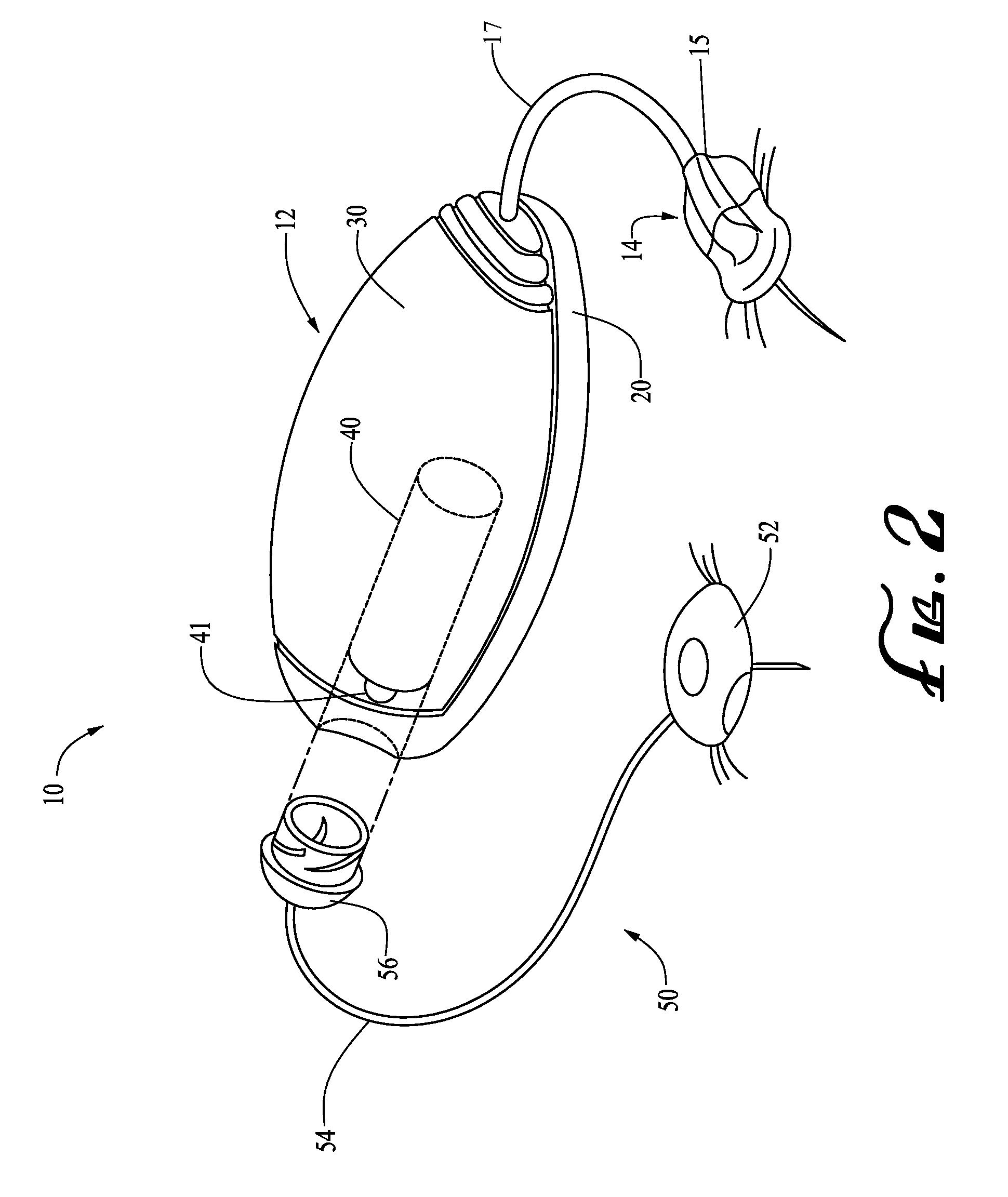

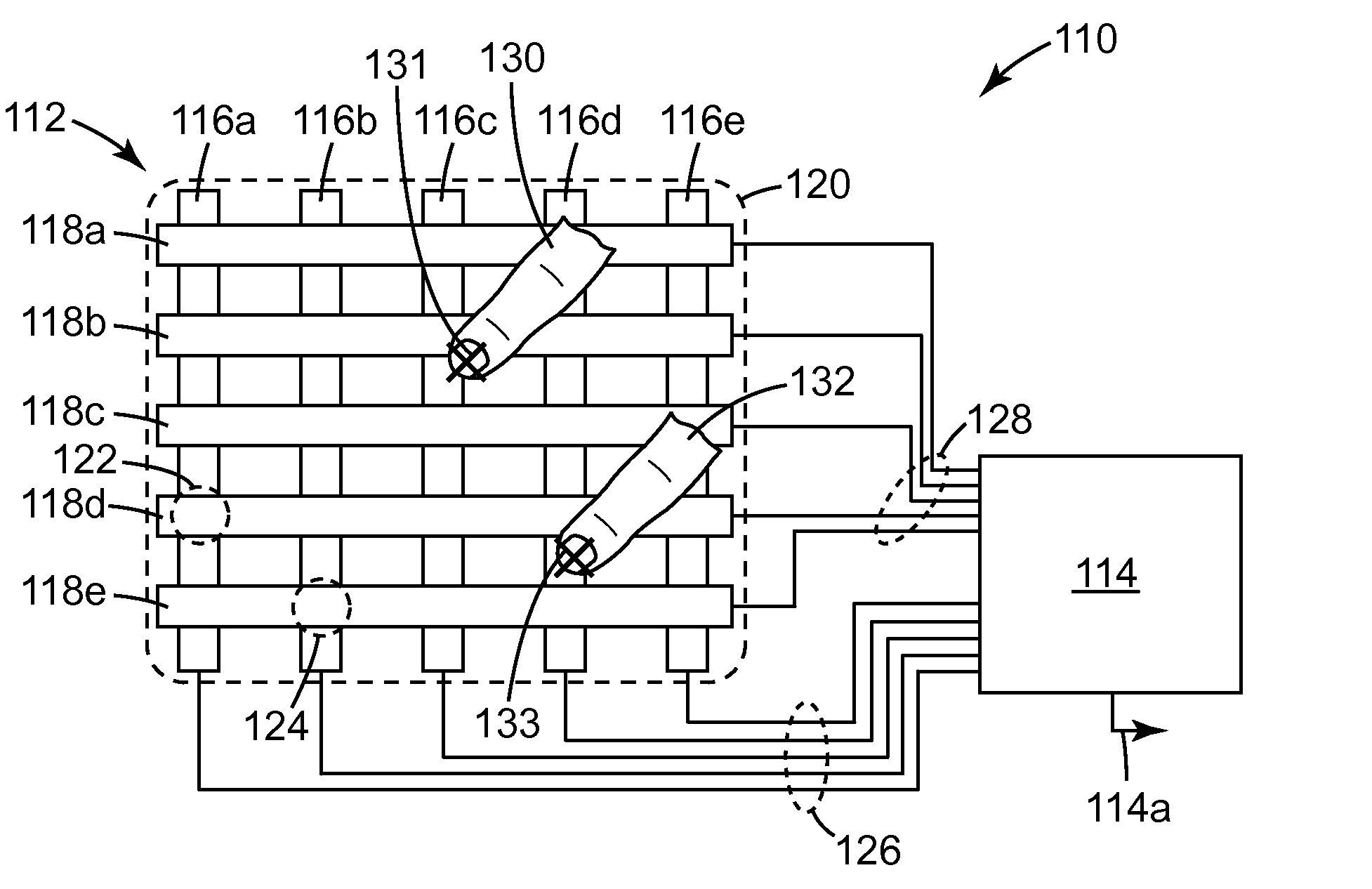

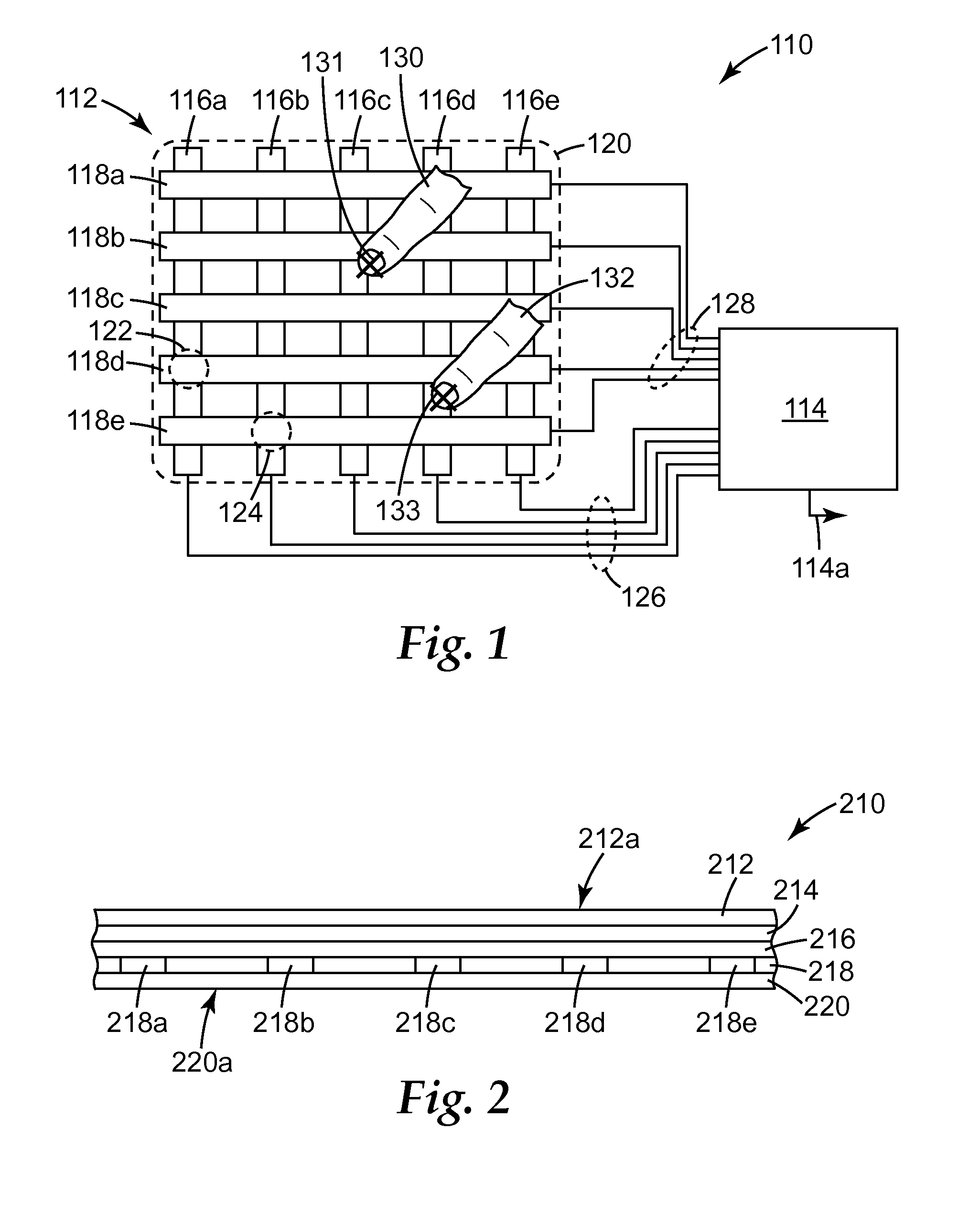

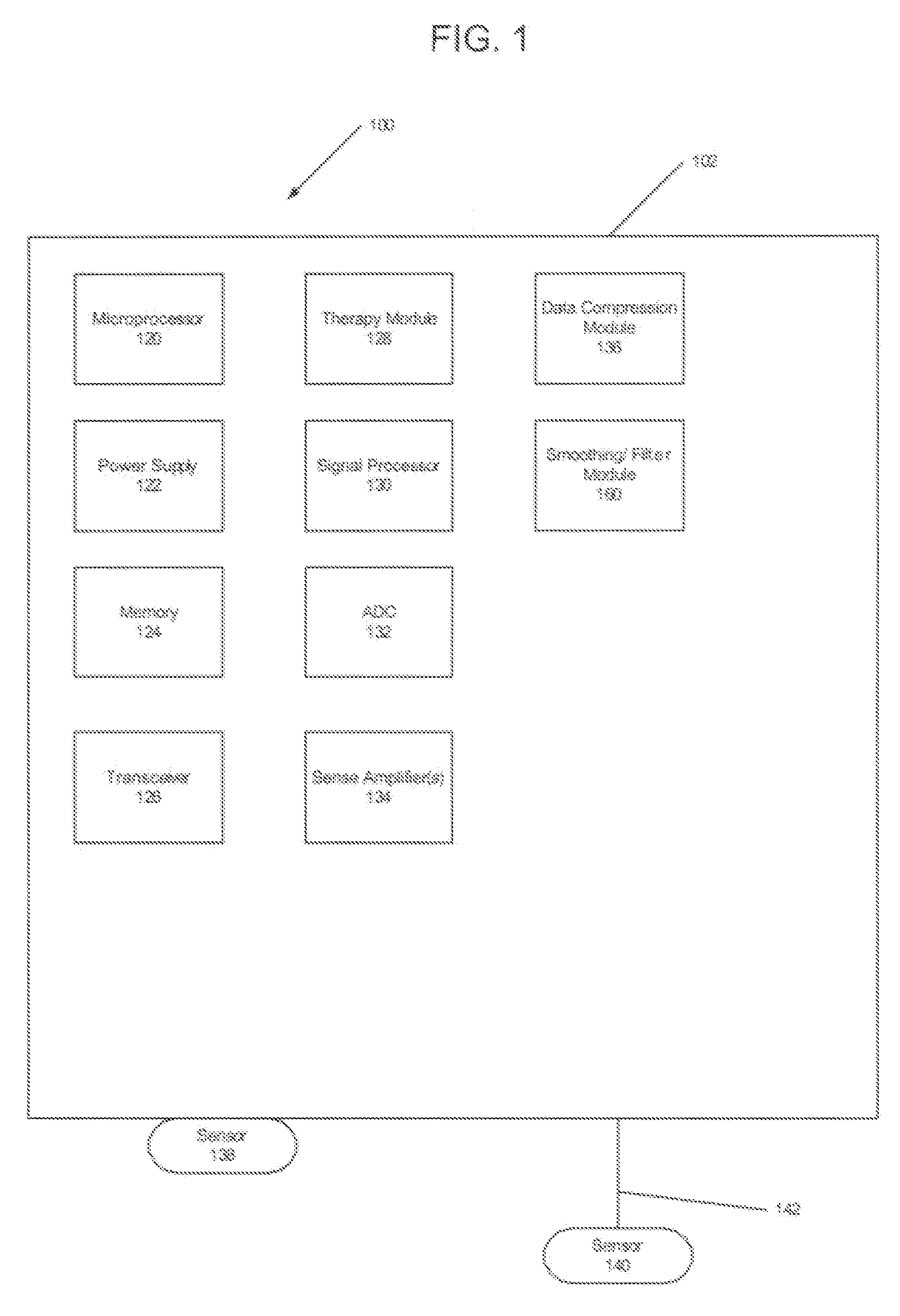

Motor assembly sensor capture systems and methods

A motor may be configured to drive a drive shaft and an engagement member supported on the drive shaft. A detectable feature comprising a rotary member may be supported on the drive shaft such that movement of the drive shaft by the motor changes a state of the detectable feature. At least one sensor may be arranged to detect the state of the detectable feature. Circuitry may be configured to provide a signal in response to a change in the state of the detectable feature detected by the at least one sensor.

Owner:MEDTRONIC MIMIMED INC

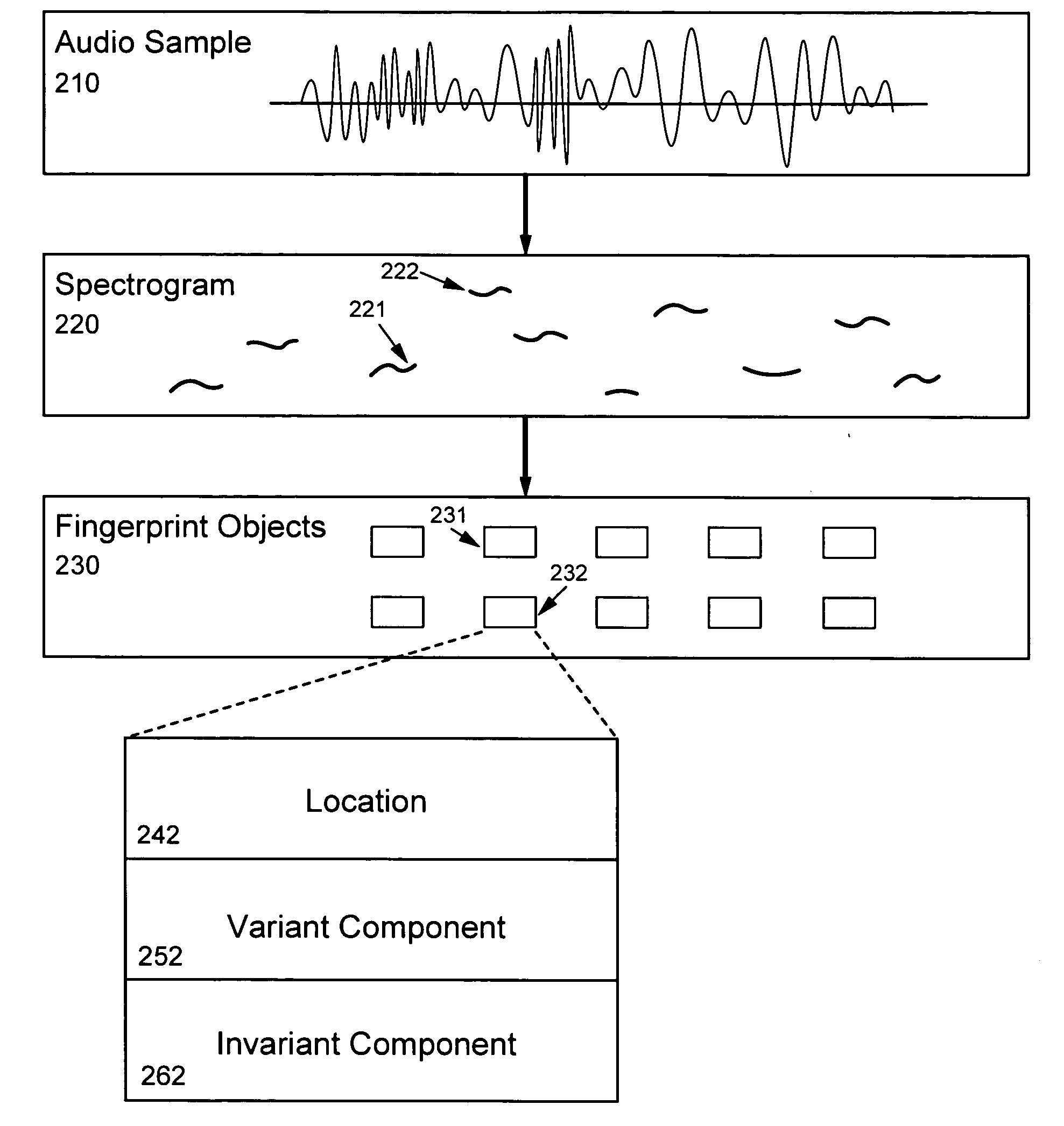

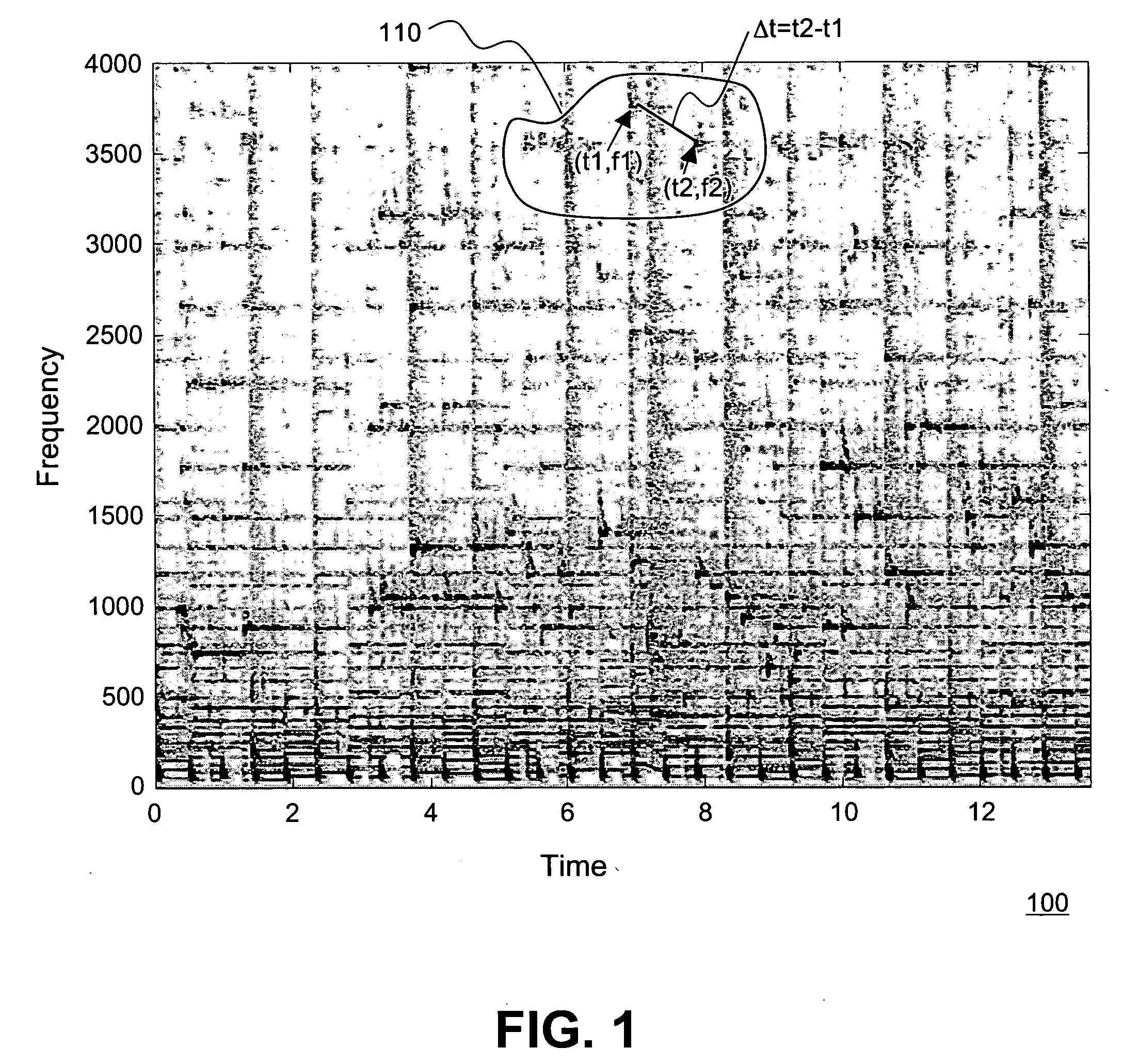

Robust and invariant audio pattern matching

ActiveUS20050177372A1Improve accuracyMethod is fastTelevision system detailsElectrophonic musical instrumentsPattern matchingAudio frequency

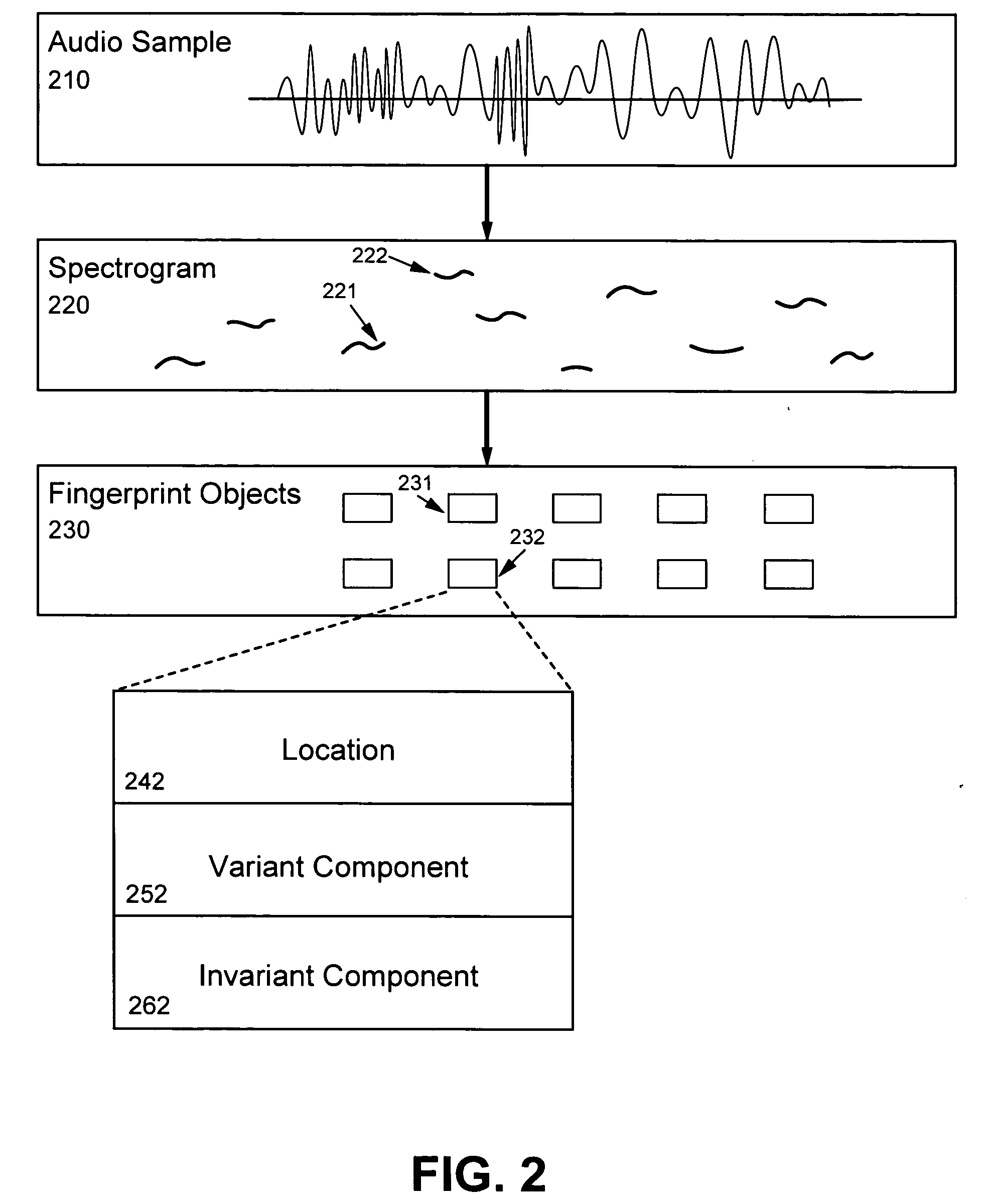

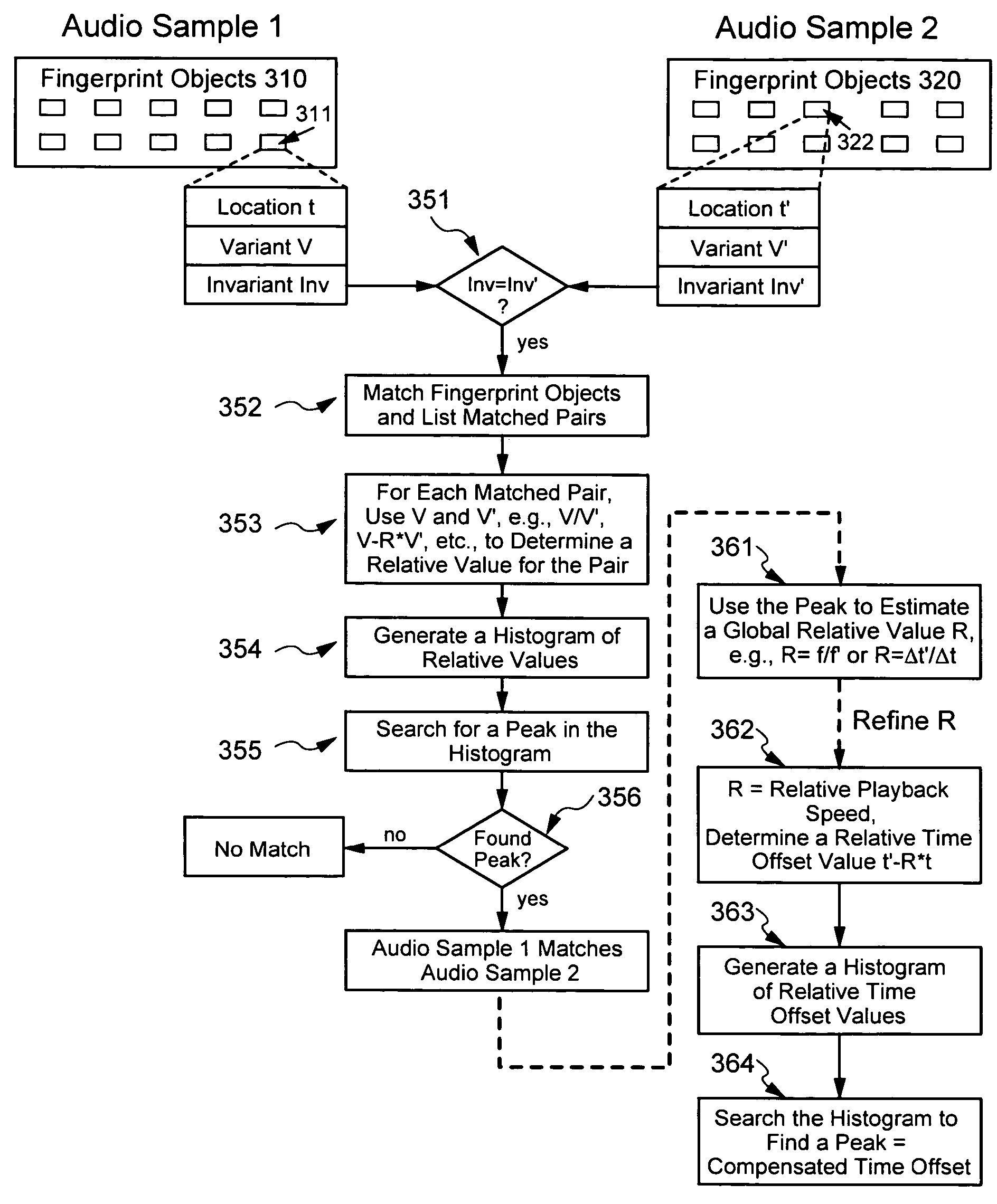

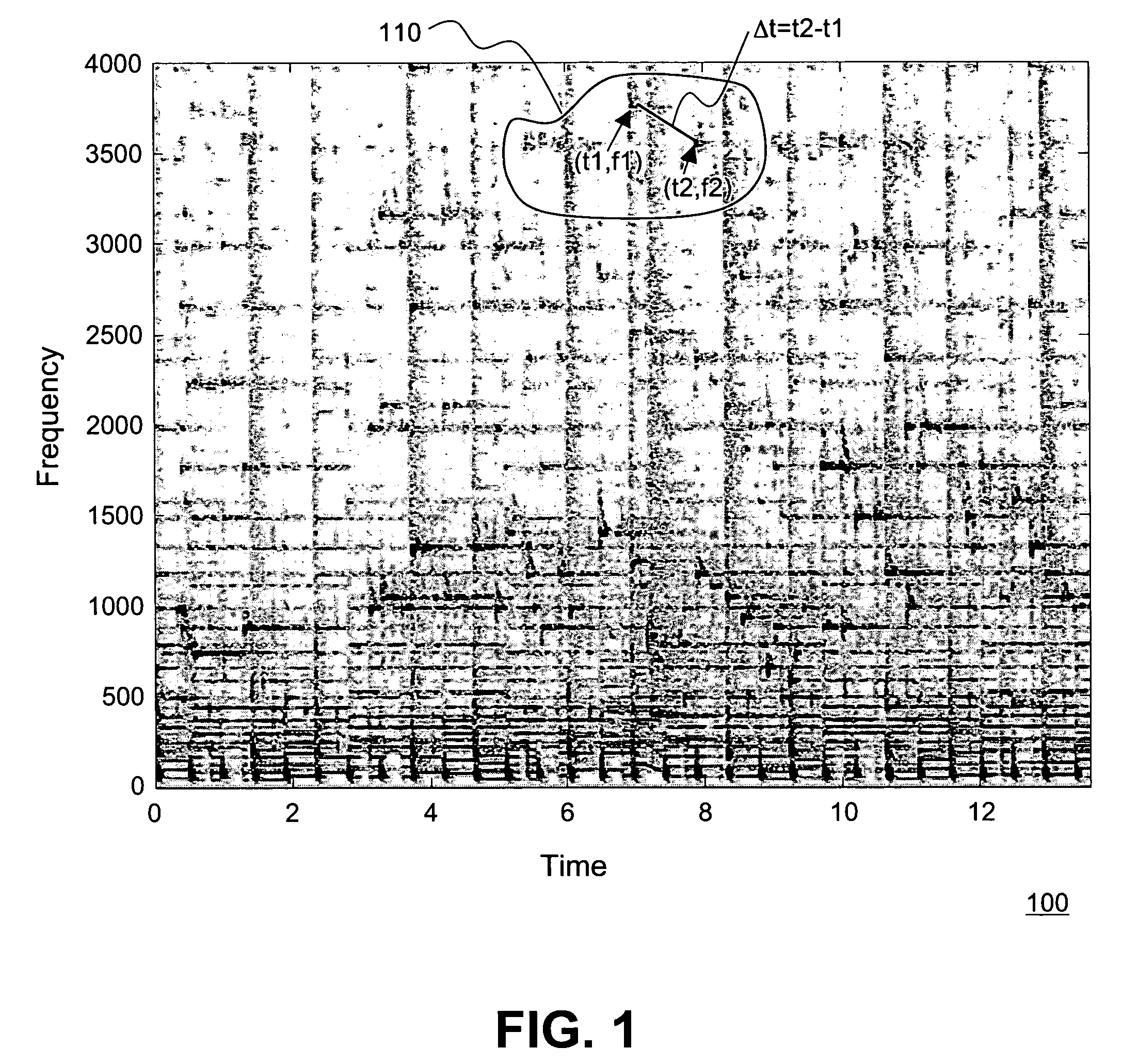

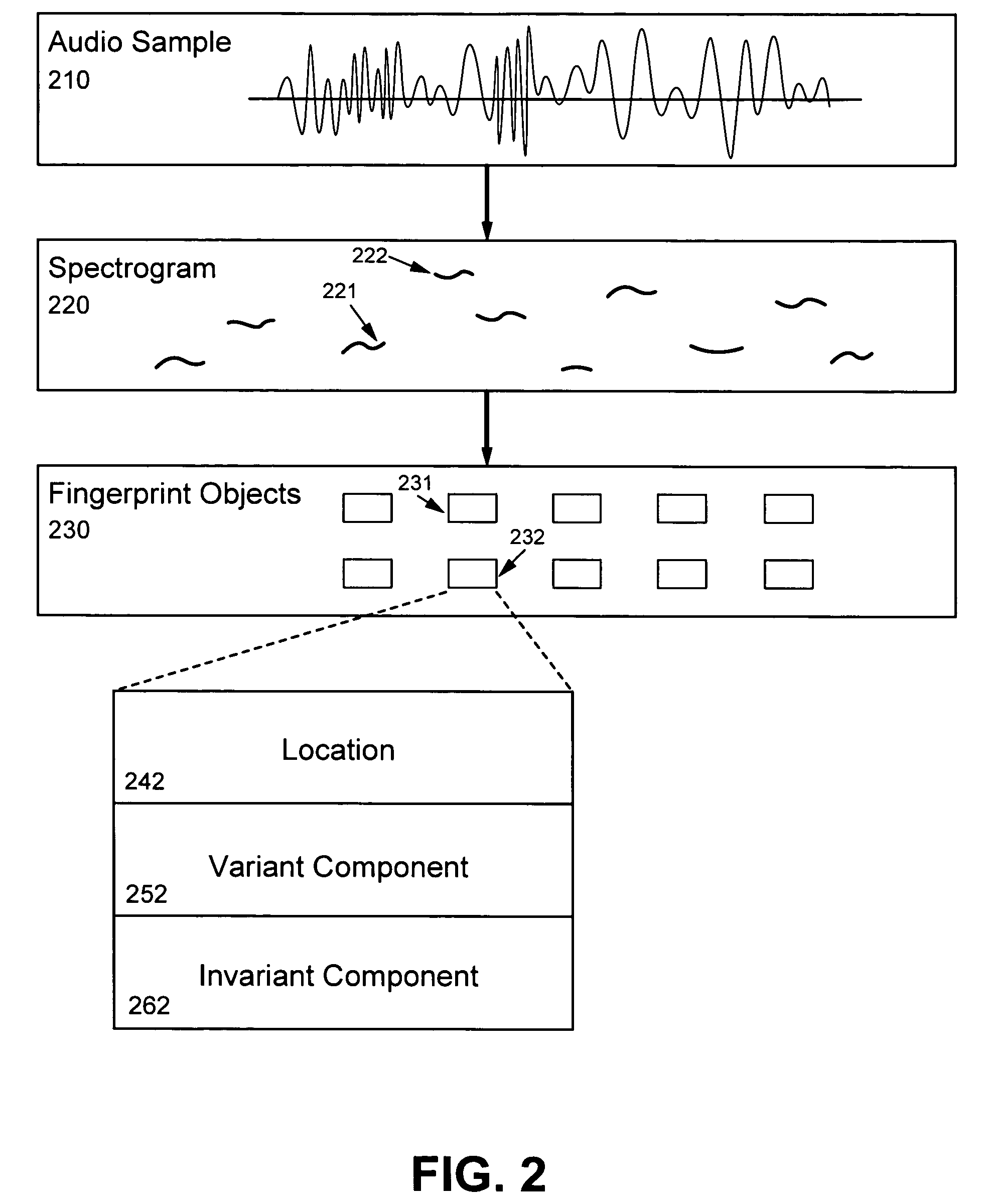

The present invention provides an innovative technique for rapidly and accurately determining whether two audio samples match, as well as being immune to various kinds of transformations, such as playback speed variation. The relationship between the two audio samples is characterized by first matching certain fingerprint objects derived from the respective samples. A set (230) of fingerprint objects (231,232), each occurring at a particular location (242), is generated for each audio sample (210). Each location (242) is determined in dependence upon the content of the respective audio sample (210) and each fingerprint object (232) characterizes one or more local features (222) at or near the respective particular location (242). A relative value is next determined for each pair of matched fingerprint objects. A histogram of the relative values is then generated. If a statistically significant peak is found, the two audio samples can be characterized as substantially matching.

Owner:SHAZAM INVESTMENTS +1

Robust and invariant audio pattern matching

ActiveUS7627477B2Method is fastImprove accuracyTelevision system detailsElectrophonic musical instrumentsMedicineAudio frequency

The present invention provides an innovative technique for rapidly and accurately determining whether two audio samples match, as well as being immune to various kinds of transformations, such as playback speed variation. The relationship between the two audio samples is characterized by first matching certain fingerprint objects derived from the respective samples. A set (230) of fingerprint objects (231,232), each occurring at a particular location (242), is generated for each audio sample (210). Each location (242) is determined in dependence upon the content of the respective audio sample (210) and each fingerprint object (232) characterizes one or more local features (222) at or near the respective particular location (242). A relative value is next determined for each pair of matched fingerprint objects. A histogram of the relative values is then generated. If a statistically significant peak is found, the two audio samples can be characterized as substantially matching.

Owner:SHAZAM INVESTMENTS +1

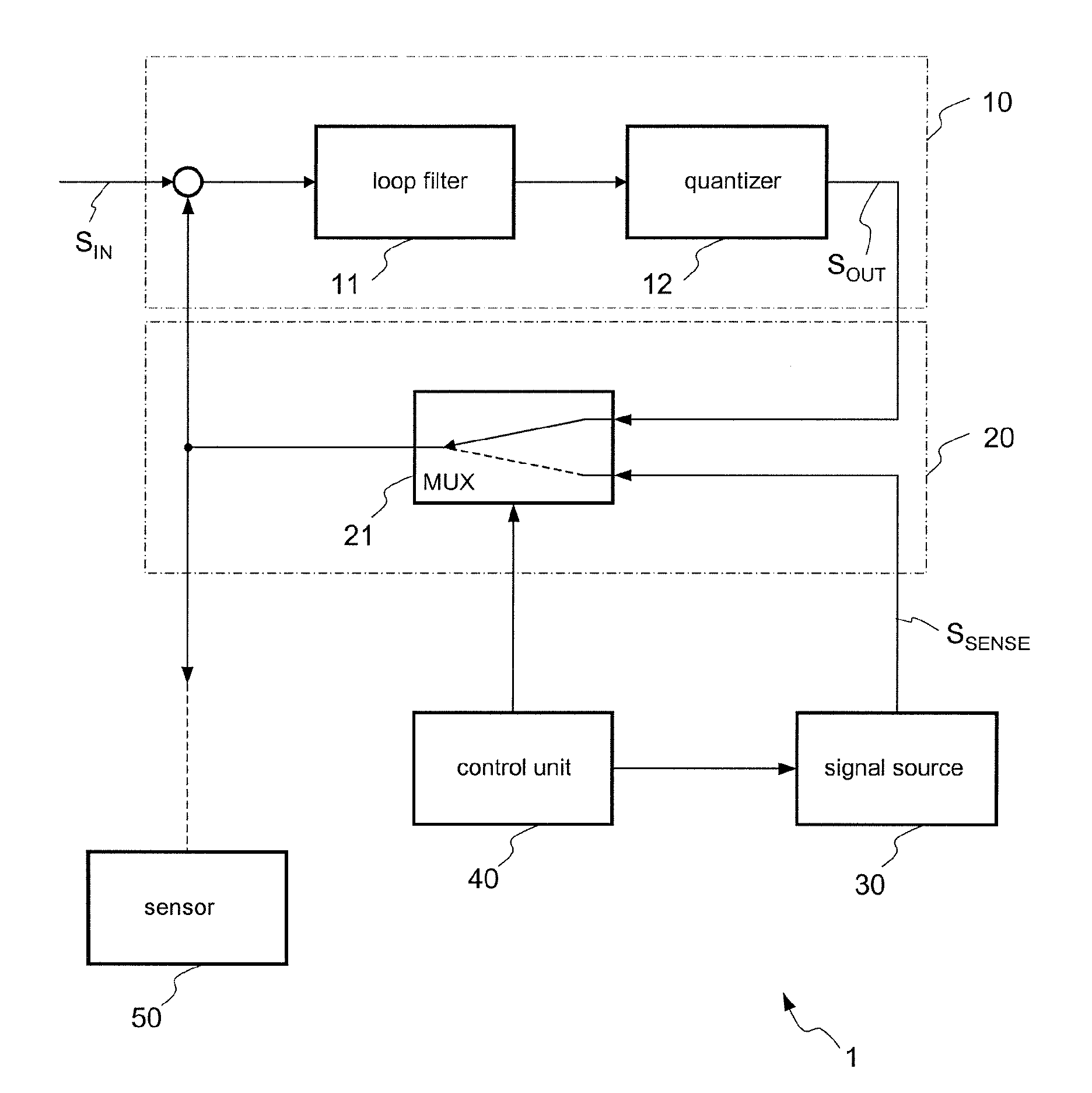

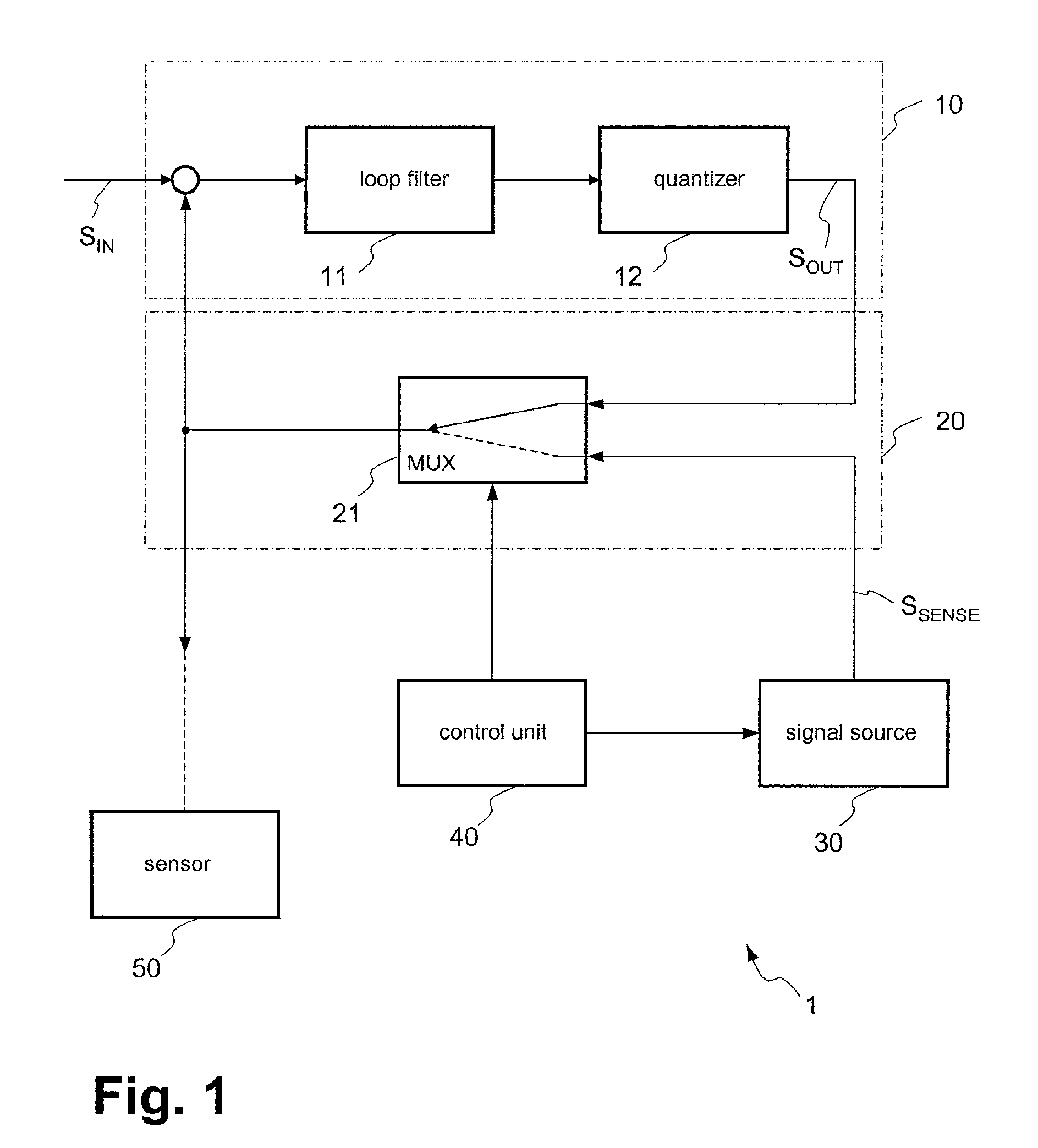

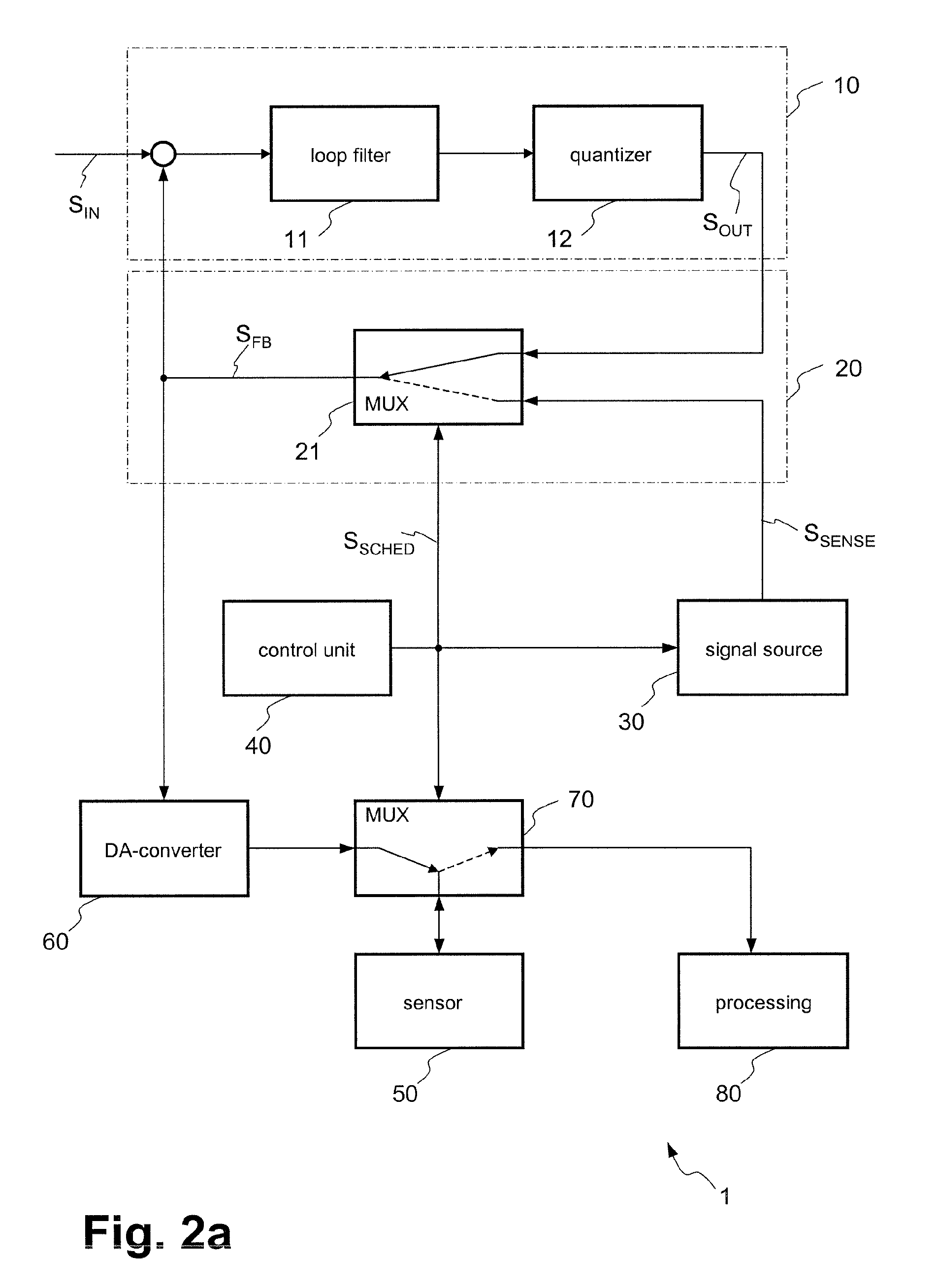

Sigma-delta modulator for operating sensors

InactiveUS7528755B2Electric signal transmission systemsAcceleration measurement using interia forcesLoop filterControl signal

A sigma-delta modulator can be used for actuating a sensor element. The sigma delta modulator includes: a forward branch to which an input signal is fed at an input and which includes a loop filter, a quantizer and an output for providing an output signal. A feedback branch is configured to feed back the output signal of the forward branch at least temporarily to the input of the forward branch. A signal source is configured to generate a readout signal which corresponds to the voltage profile at the sensor element during a measuring process. A control unit is configured to generate a control signal dependent on which either the output signal of the forward branch or the readout signal of the signal source is fed back to the input of the forward branch.

Owner:INFINEON TECH AG

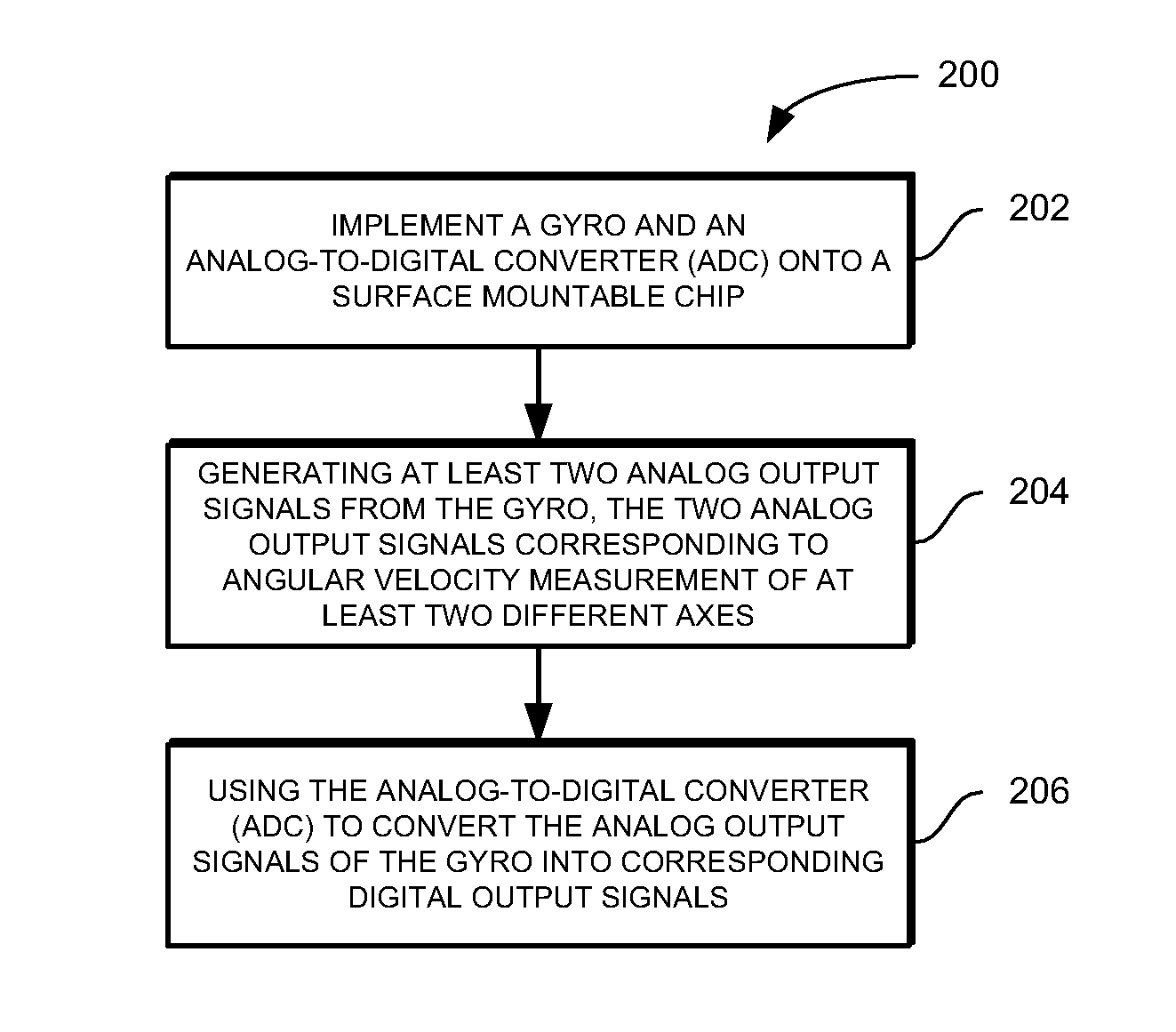

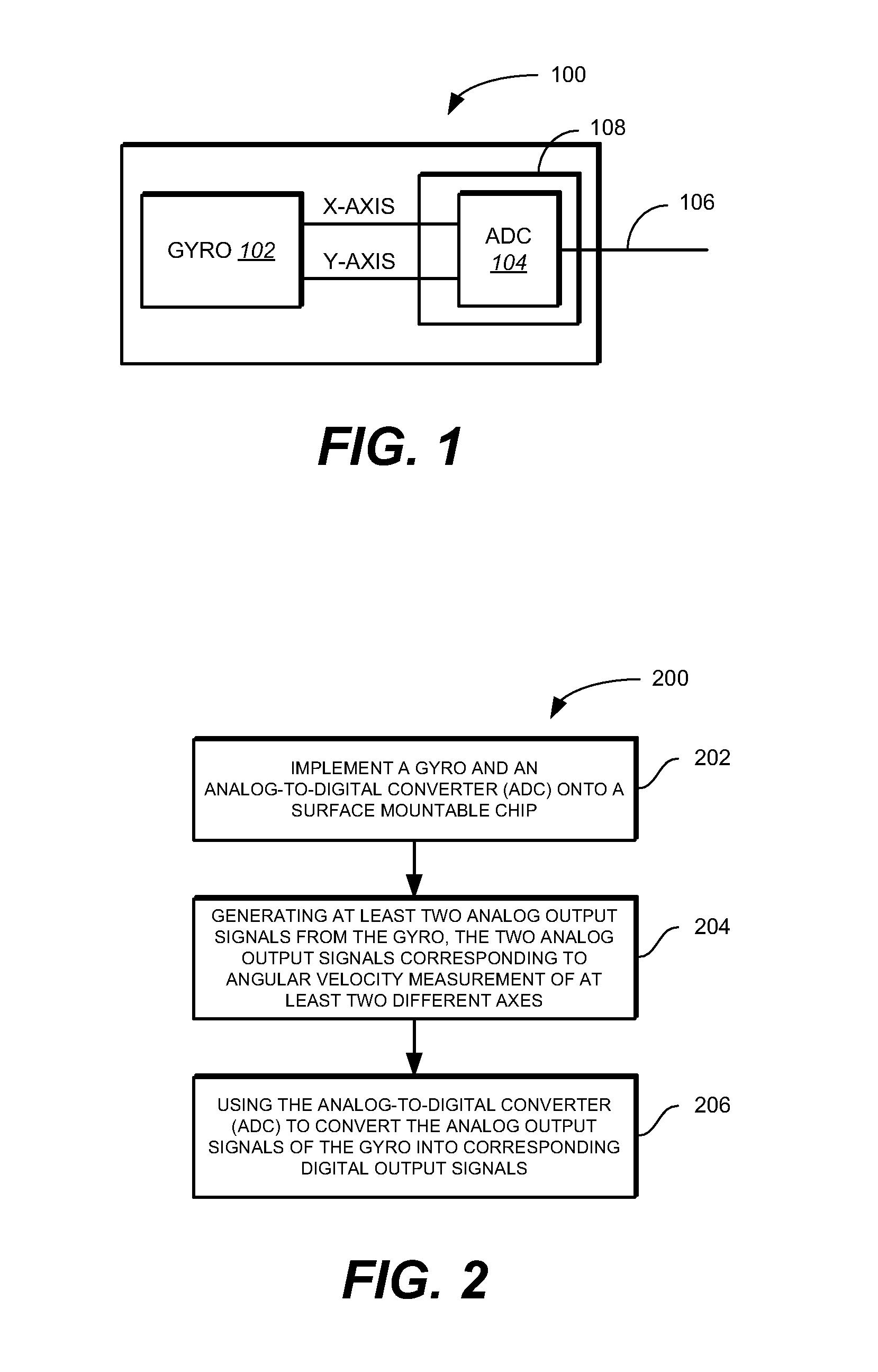

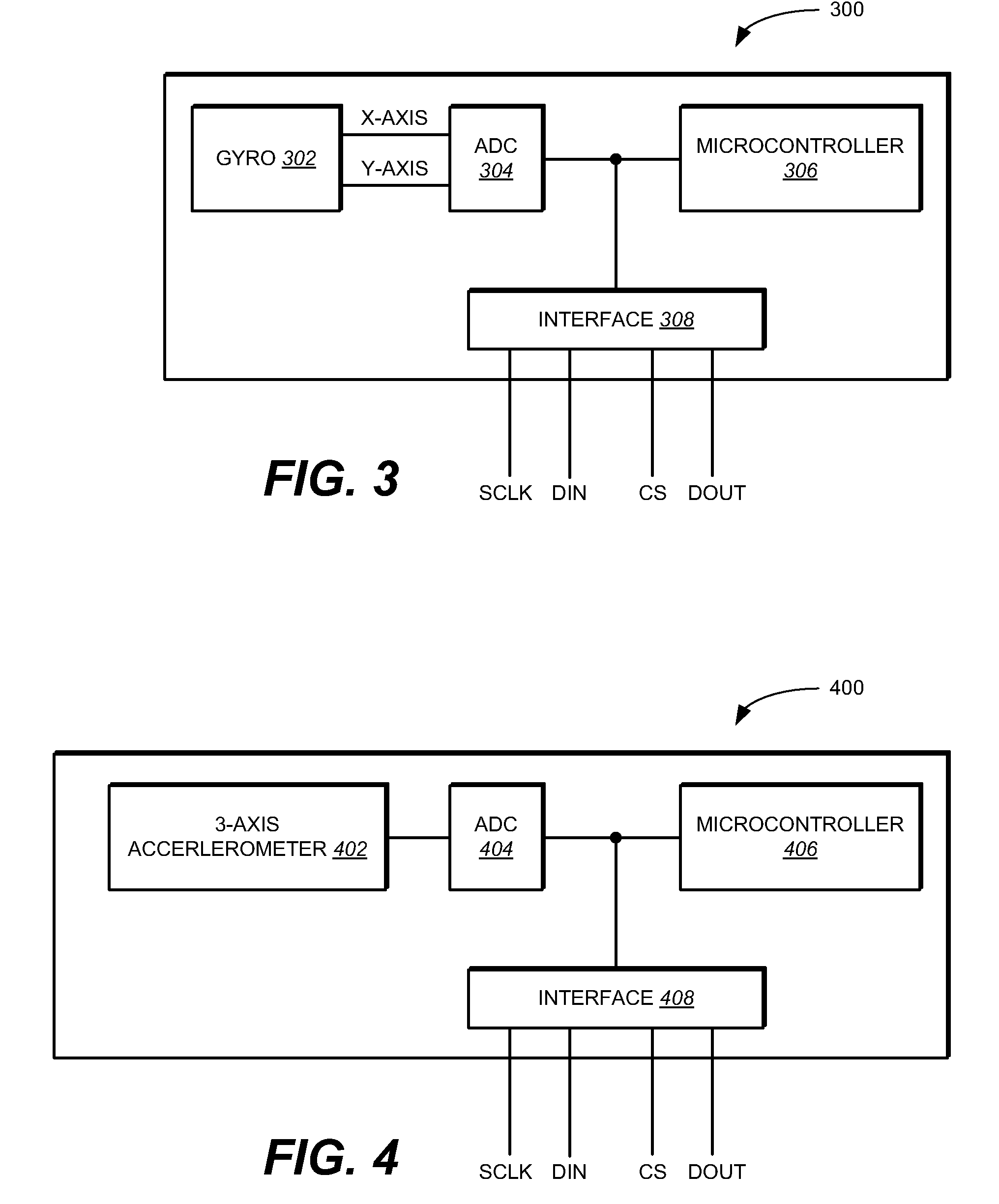

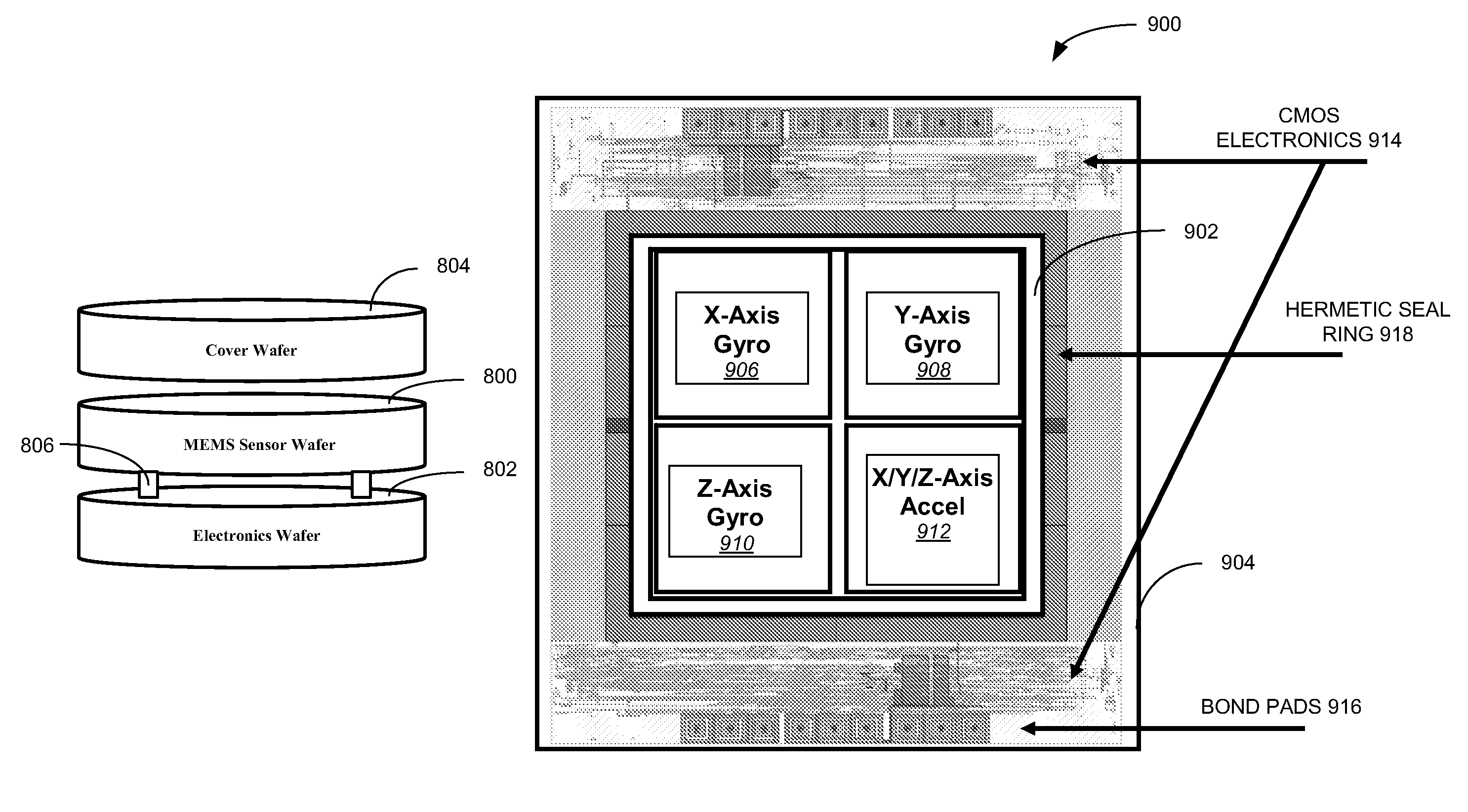

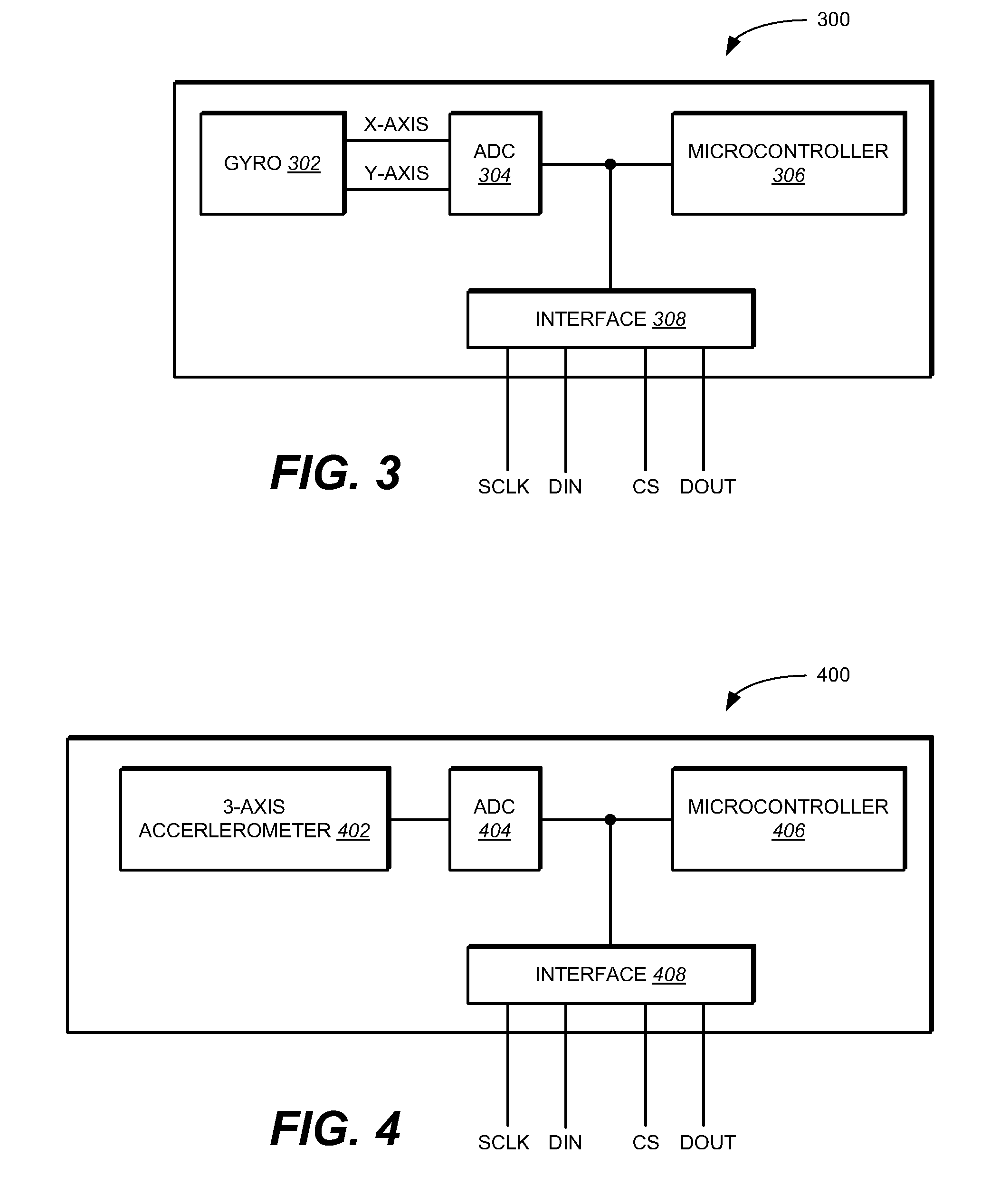

Integrated Motion Processing Unit (MPU) With MEMS Inertial Sensing And Embedded Digital Electronics

ActiveUS20090007661A1Small packageLower performance requirementsElectric signal transmission systemsAcceleration measurement using interia forcesMotion processingAccelerometer

A module operable to be mounted onto a surface of a board. The module includes a linear accelerometer to provide a first measurement output corresponding to a measurement of linear acceleration in at least one axis, and a first rotation sensor operable to provide a second measurement output corresponding to a measurement of rotation about at least one axis. The accelerometer and the first rotation sensor are formed on a first substrate. The module further includes an application specific integrated circuit (ASIC) to receive both the first measurement output from the linear accelerometer and the second measurement output from the first rotation sensor. The ASIC includes an analog-to-digital converter and is implemented on a second substrate. The first substrate is vertically bonded to the second substrate.

Owner:INVENSENSE

Integrated motion processing unit (MPU) with MEMS inertial sensing and embedded digital electronics

ActiveUS8250921B2Low costSmall packageElectric signal transmission systemsSpeed/acceleration/shock instrument detailsMotion processingAccelerometer

Owner:INVENSENSE

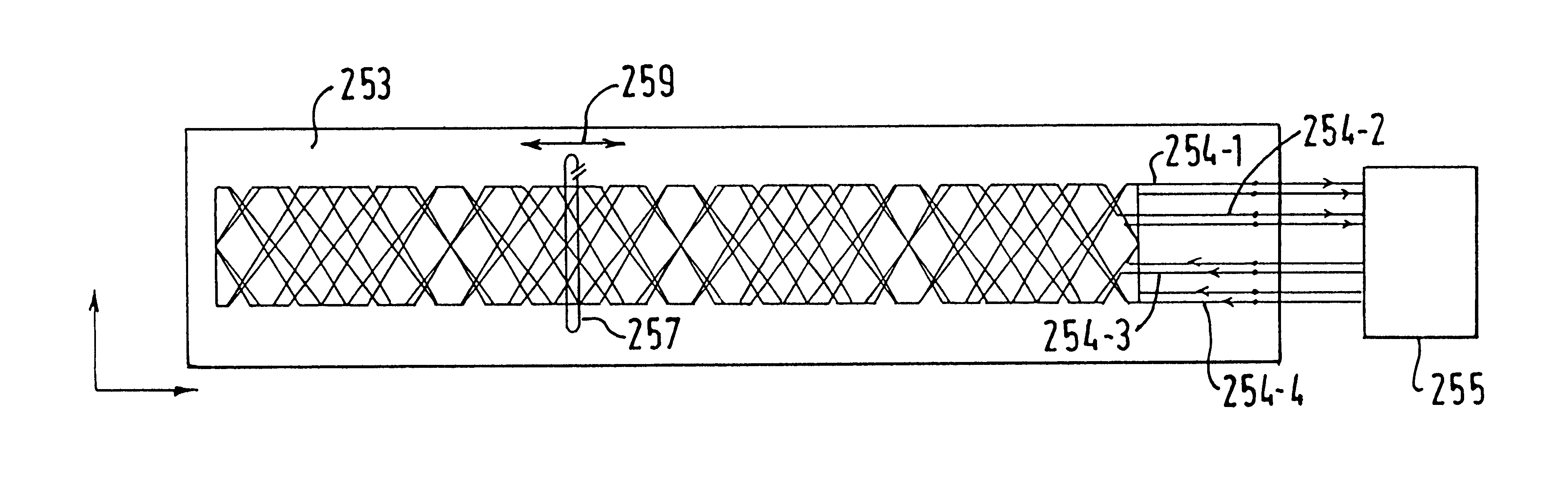

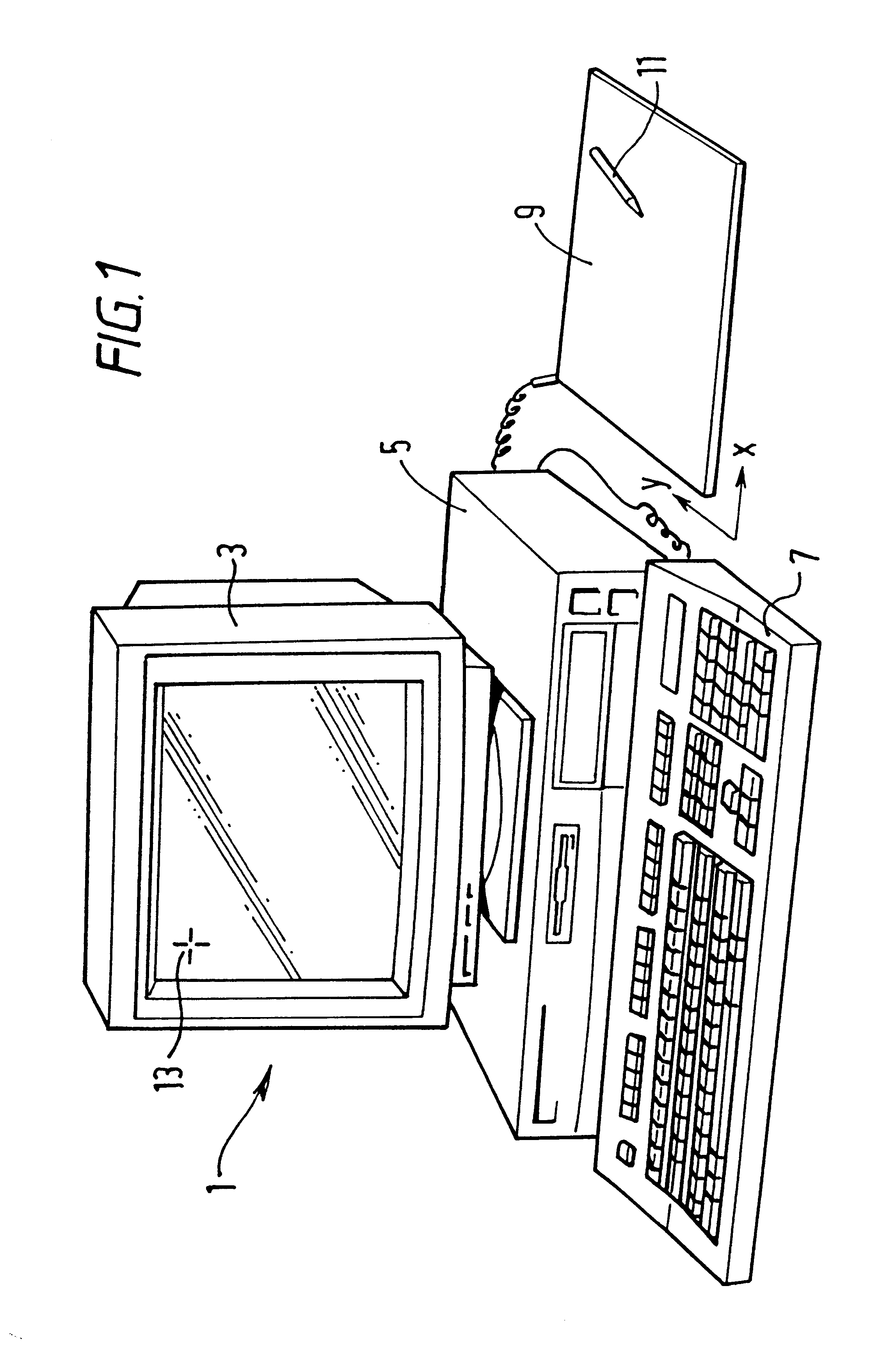

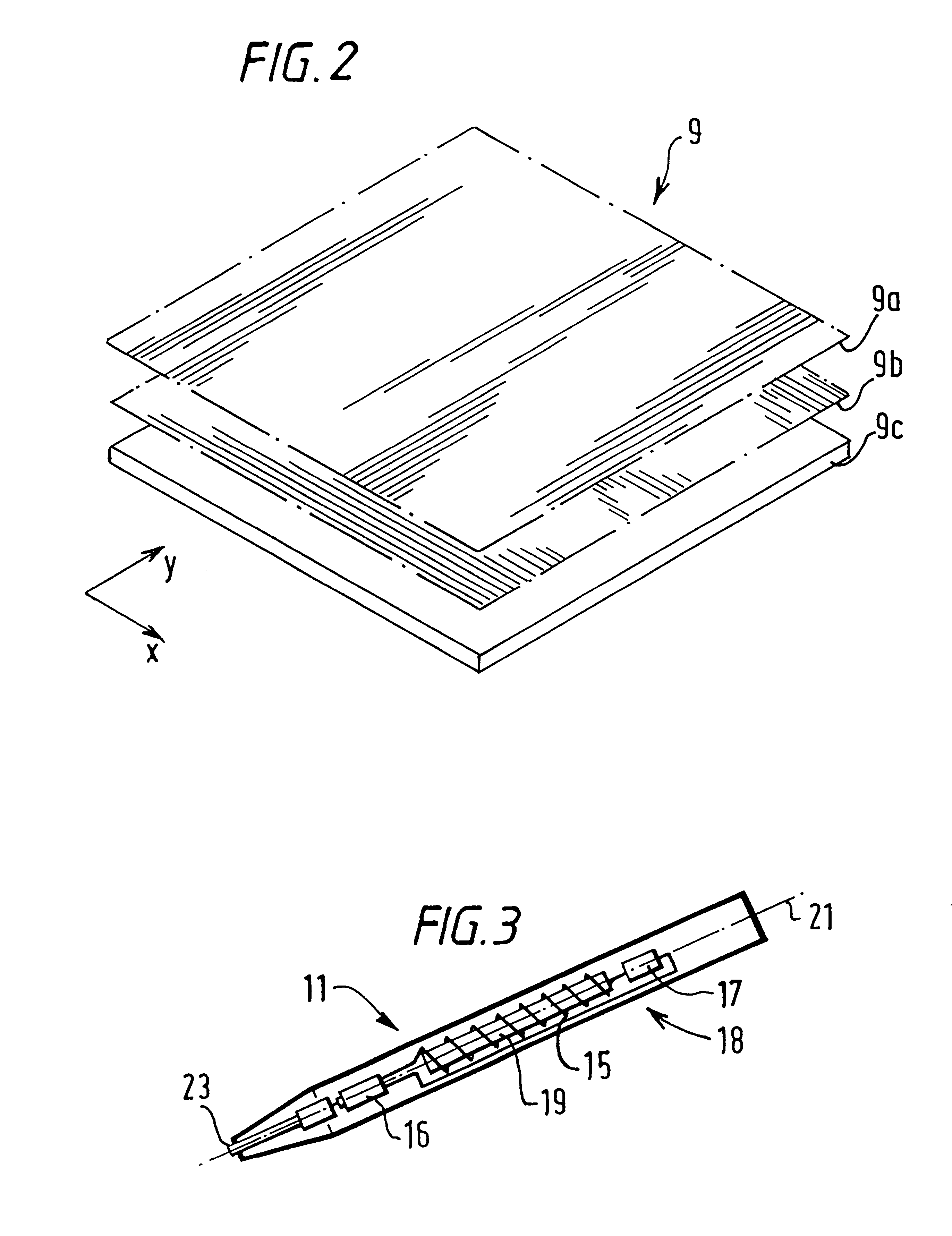

Position detector

InactiveUS6249234B1Avoid the needSuitable and convenientElectric signal transmission systemsUsing electrical meansElectrical conductorFull Relative

A position detector is provided for detecting the relative movement of first and second members which are mounted for relative movement along a measuring path. One of the members comprises a magnetic field generator for generating a magnetic field and the other member comprises first and second conductors which are inductively coupled to said magnetic field generator. The arrangement of the first and second conductors and the magnetic field generator is such that output signals are generated in a first and second receive circuits whose position varies with the relative movement between the two members. In addition to carrying information relating to the relative position between the two members, the signals induced in the receive circuits also comprise information defining the relative orientation of the two movable members, and by suitable processing of the received signals the relative orientation of the two members can also be determined. In a preferred form of the invention, the system operates to define the relative position and orientation of the two movable members in first and second directions from which the relative orientation of the two members in a plane containing the two directions can be determined. The signals induced in the receive circuits can also be processed to give an indication of the gap between the two circuits and to provide an indication of the full relative orientation of the two members.

Owner:SINNAPTIX

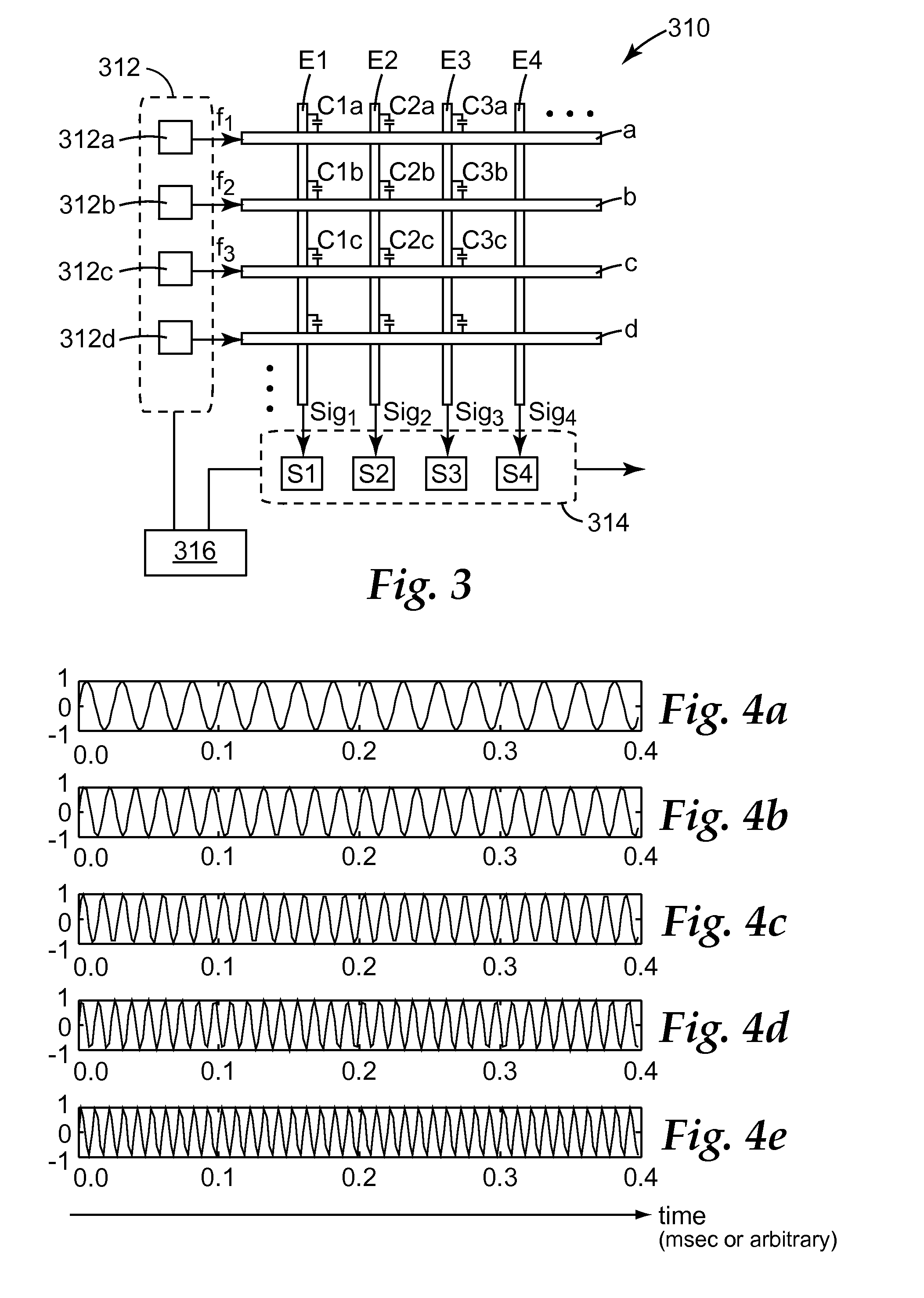

Multi-touch touch device with multiple drive frequencies and maximum likelihood estimation

InactiveUS20110084857A1Reduce eliminateMeasurement technique can be simplifiedElectric signal transmission systemsAnalogue-digital convertersCapacitanceCapacitive coupling

A touch-sensitive device includes a touch panel, drive unit, and measurement unit. A touch applied to a given node of the panel changes a capacitive coupling between a given drive and sense electrode of the touch panel. The drive unit delivers first and second drive signals, having different first and second frequencies, to first and second drive electrodes respectively at the same or overlapping times. The measurement unit receives a first response signal from a sense electrode, and analyzes the signal using maximum likelihood estimation to determine the coupling capacitance between the first drive electrode and the sense electrode, and between the second drive electrode and the sense electrode. More drive electrodes, including in some cases all the drive electrodes, can be driven with unique drive frequencies, and more sense electrodes, including in some cases all the sense electrodes, can be sensed by the measurement unit.

Owner:3M INNOVATIVE PROPERTIES CO

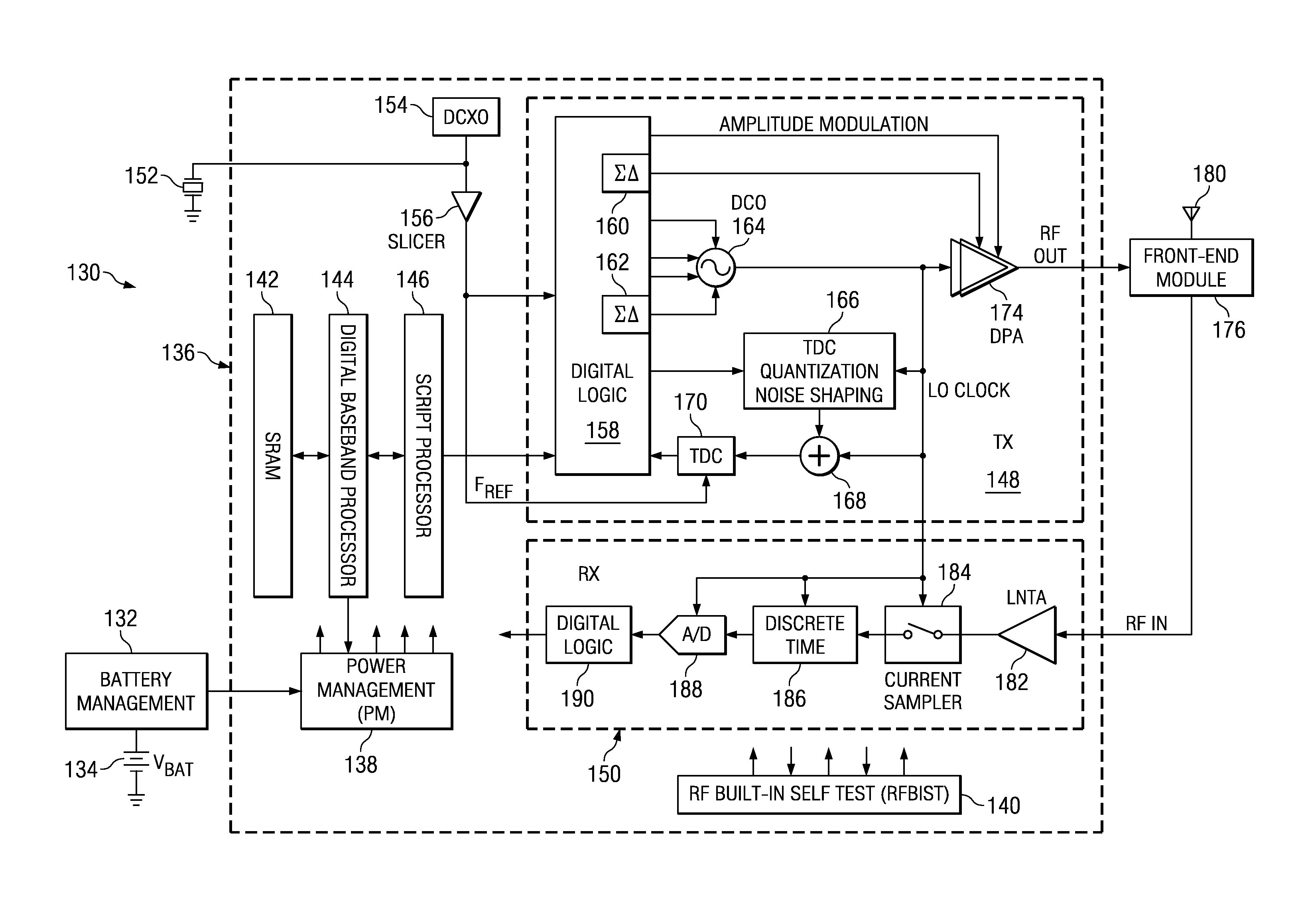

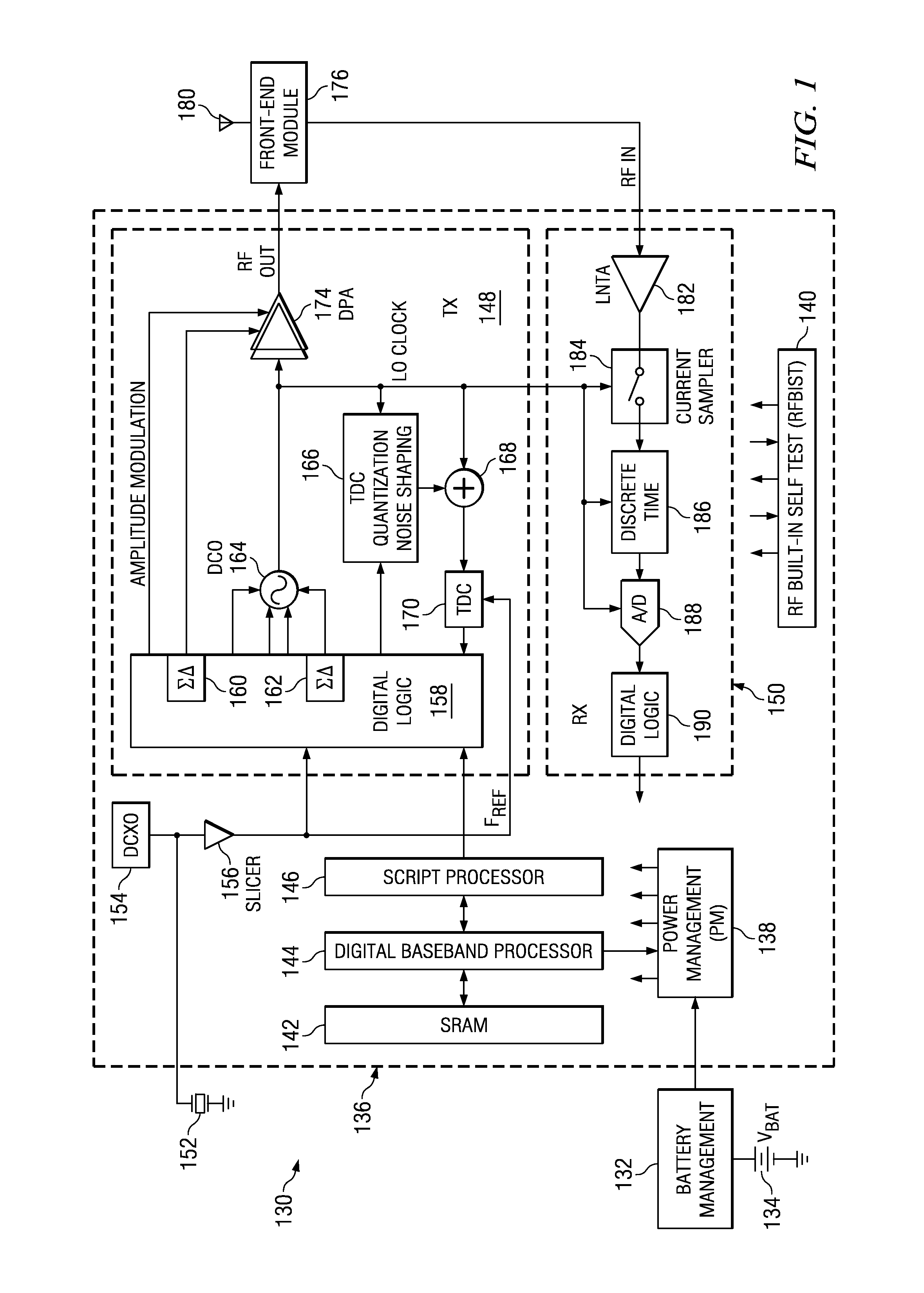

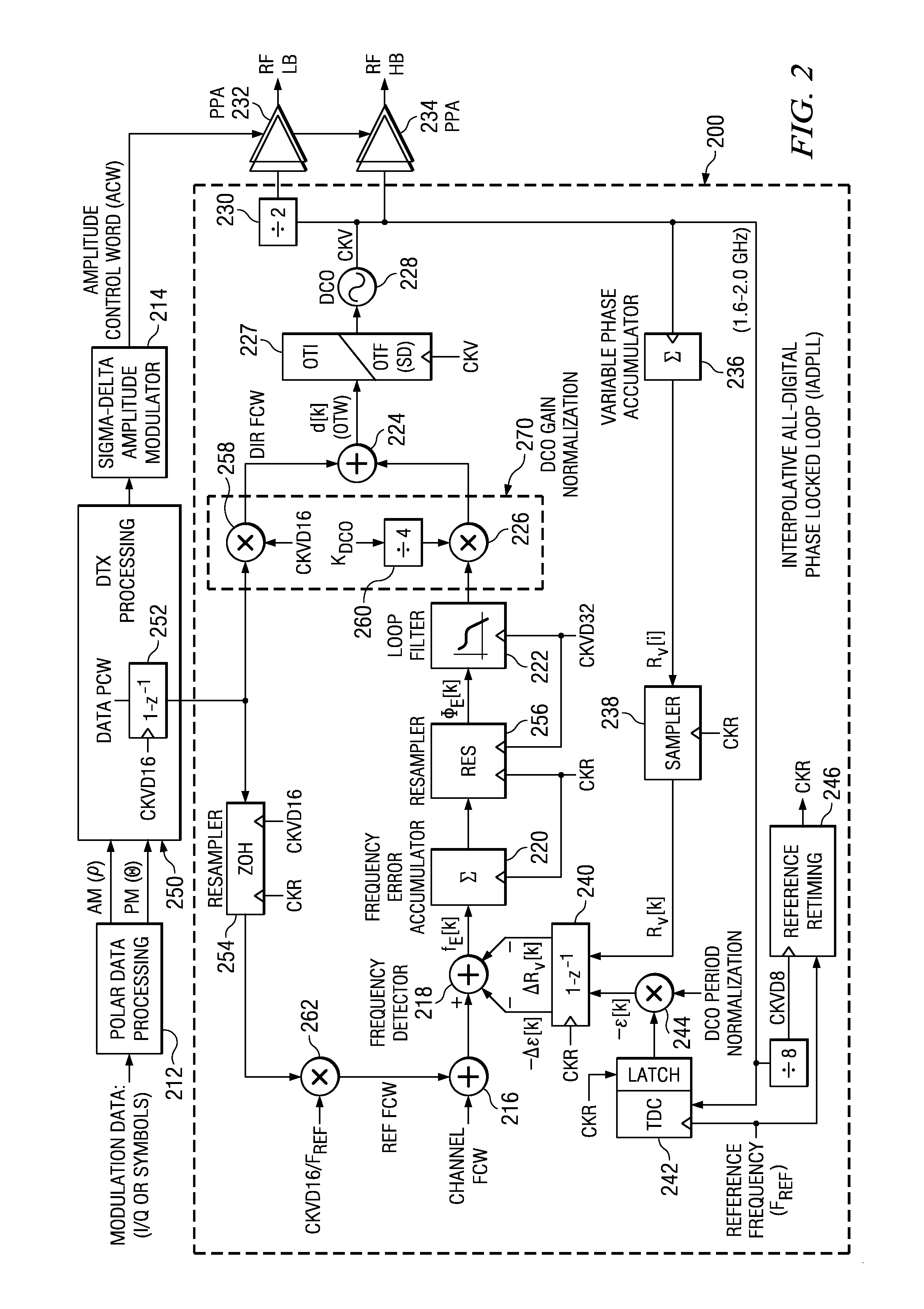

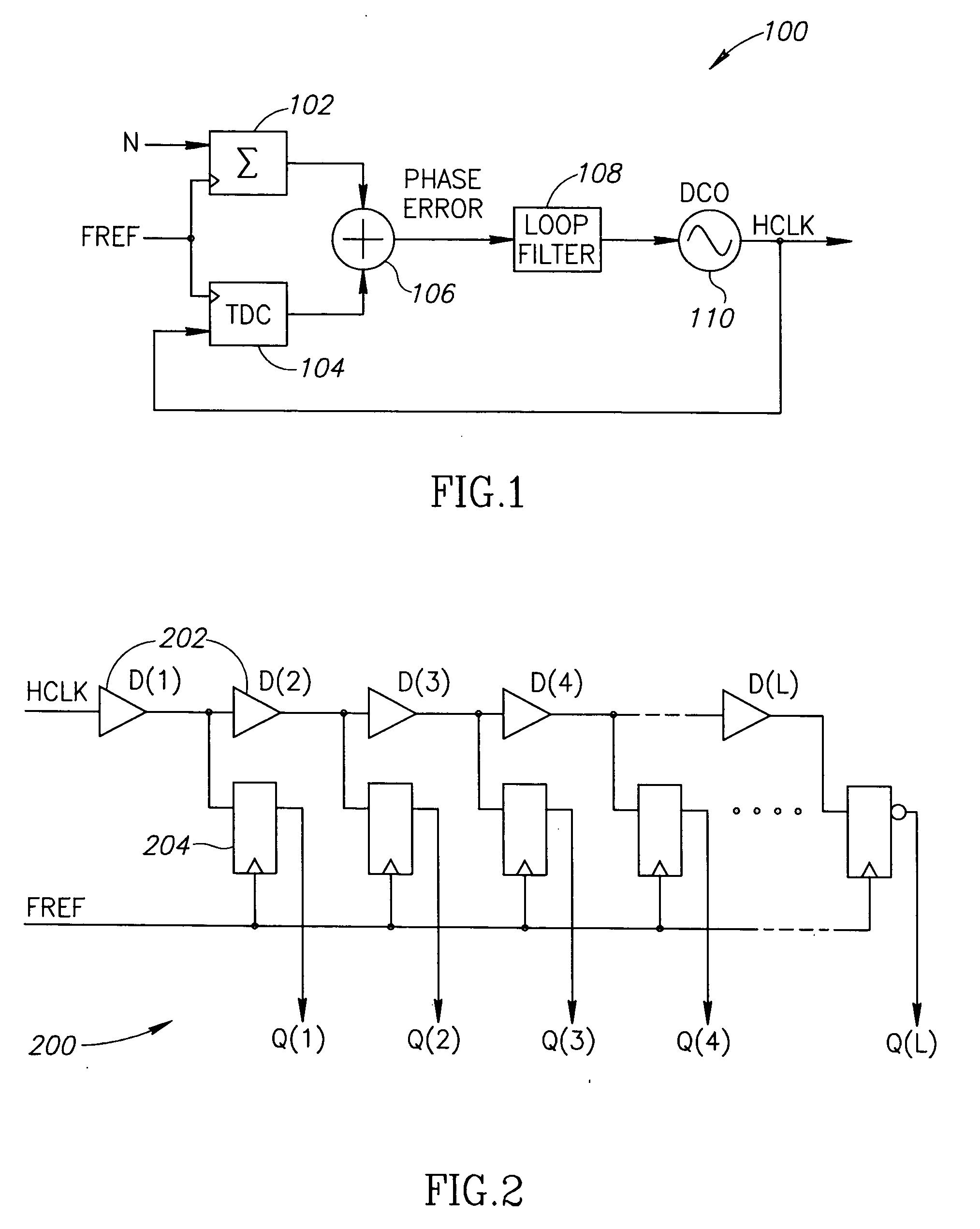

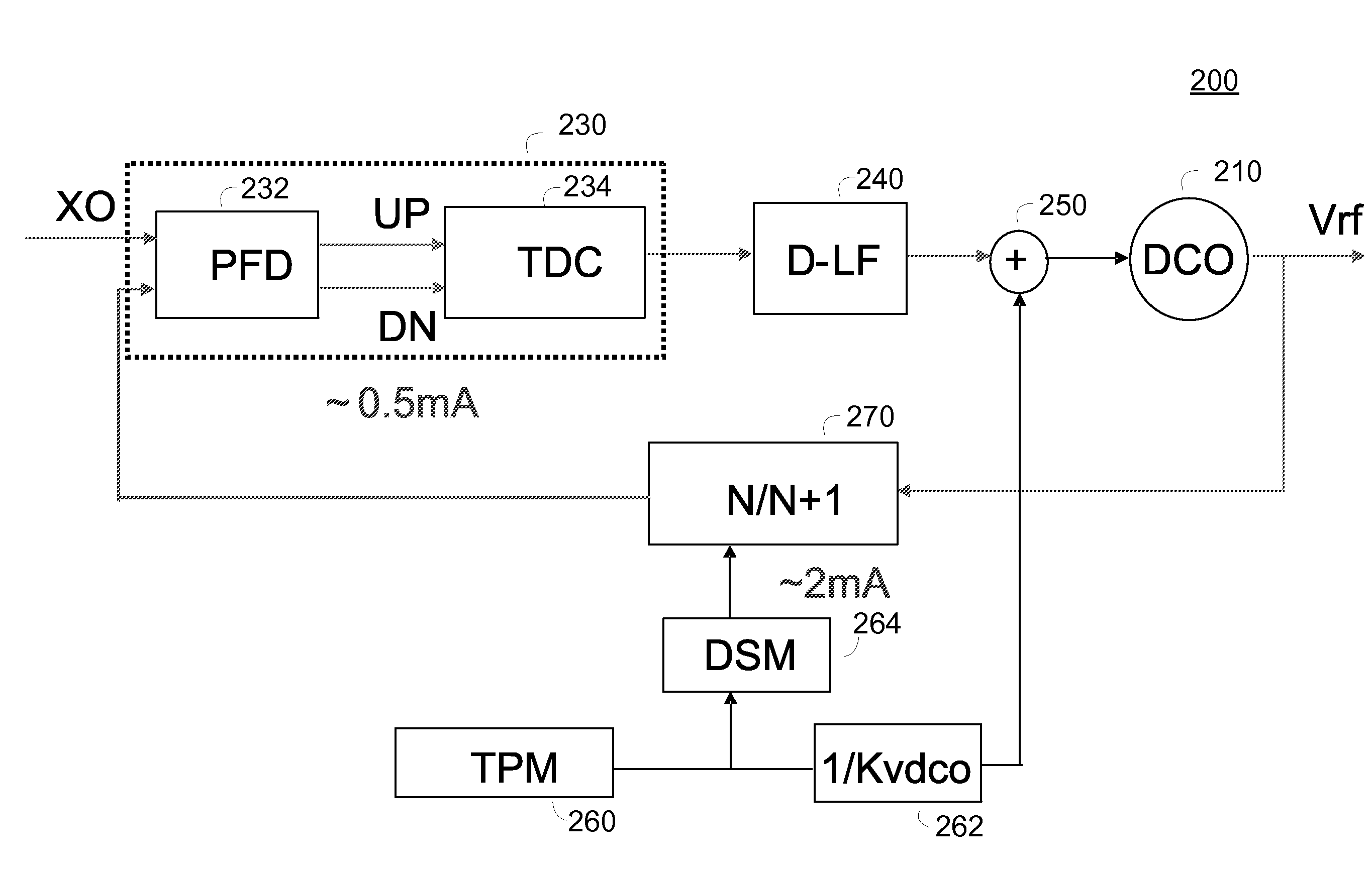

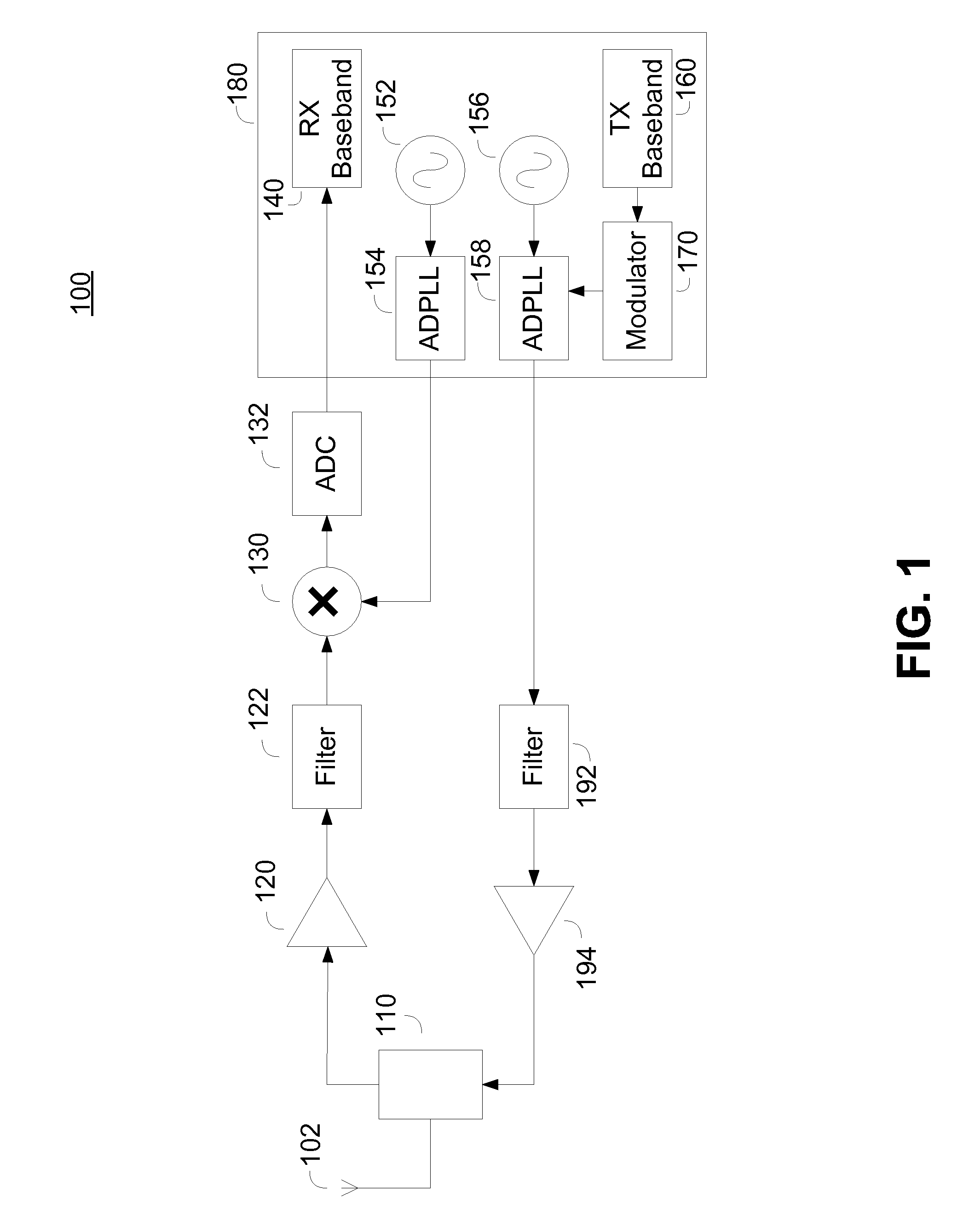

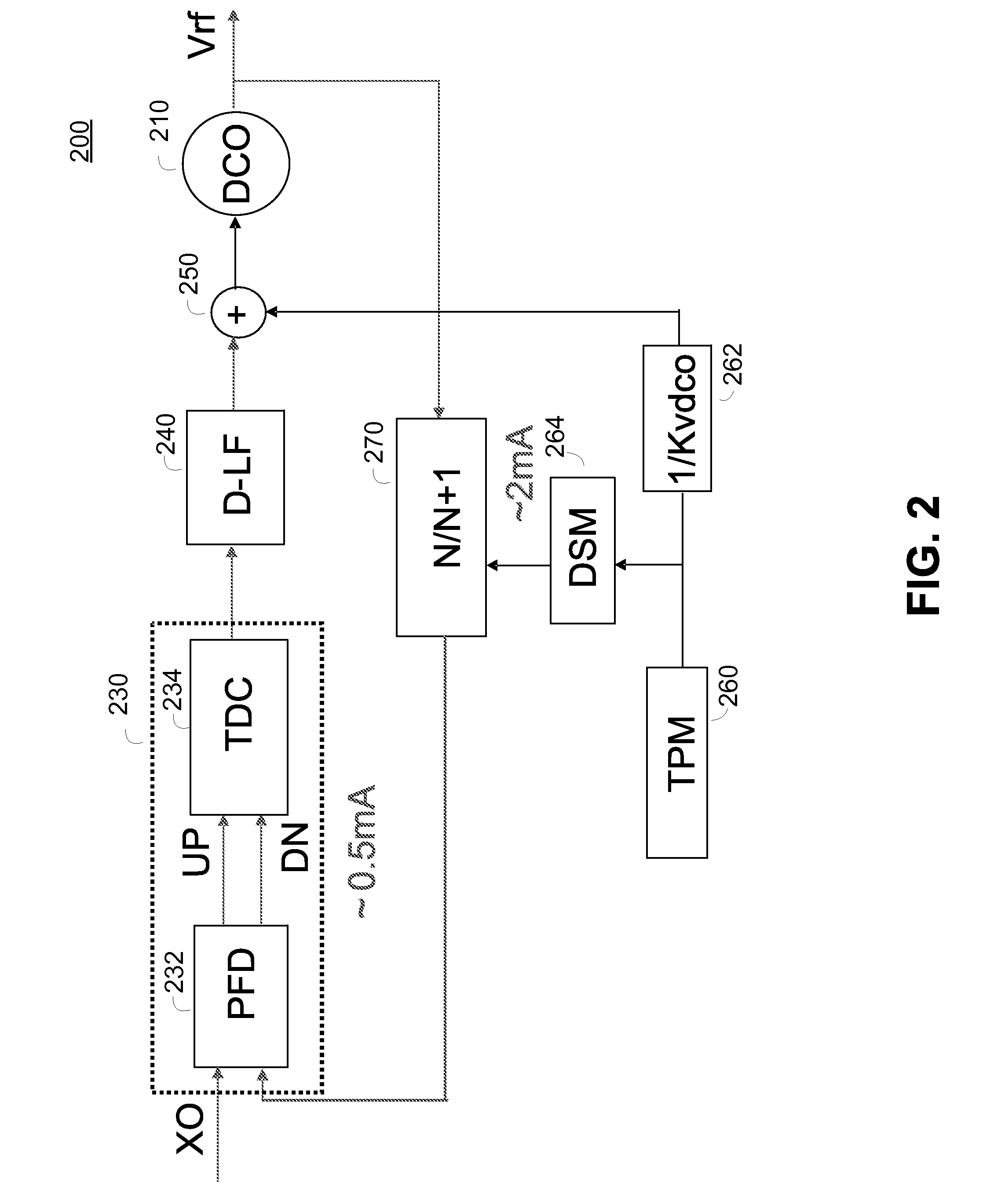

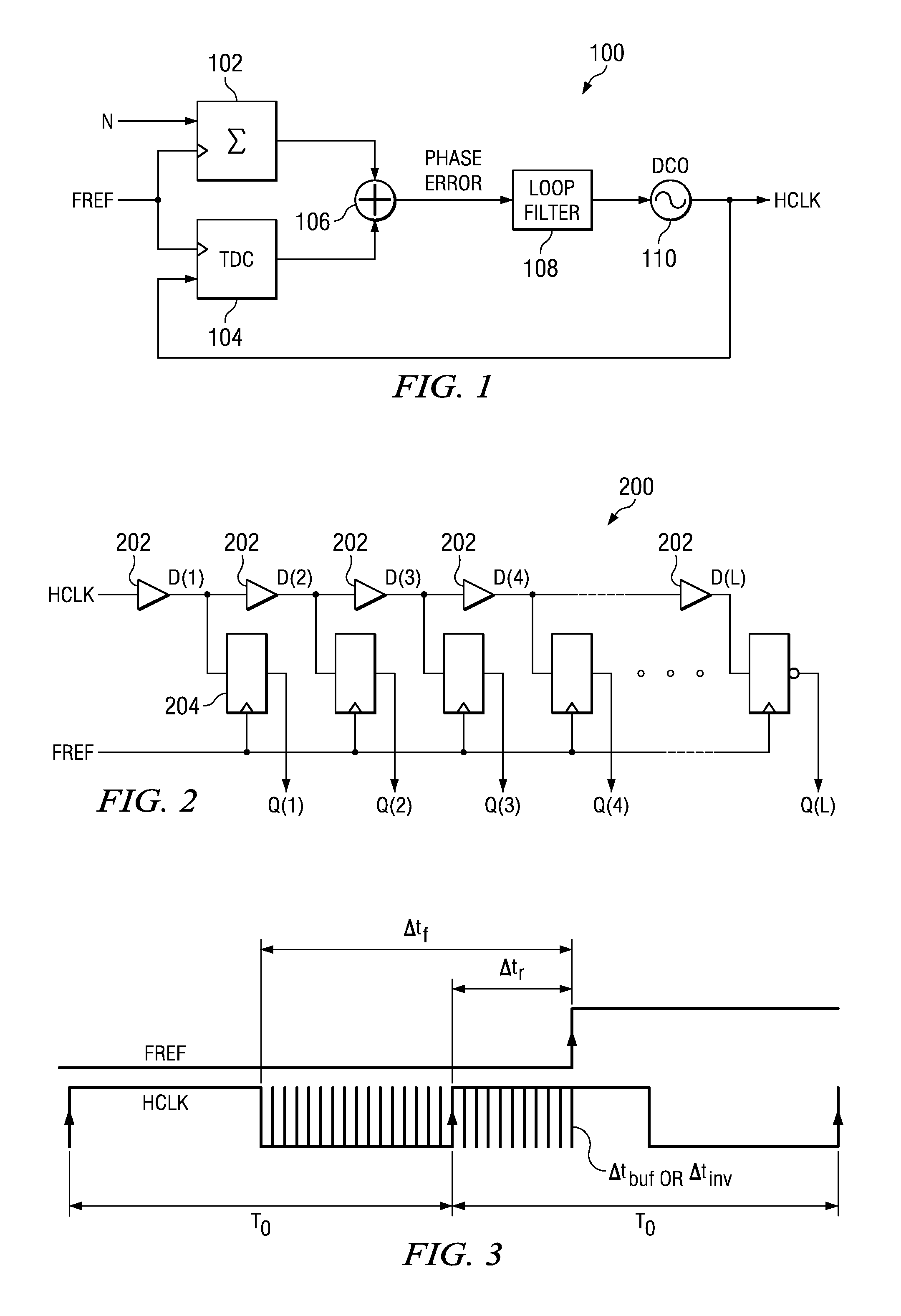

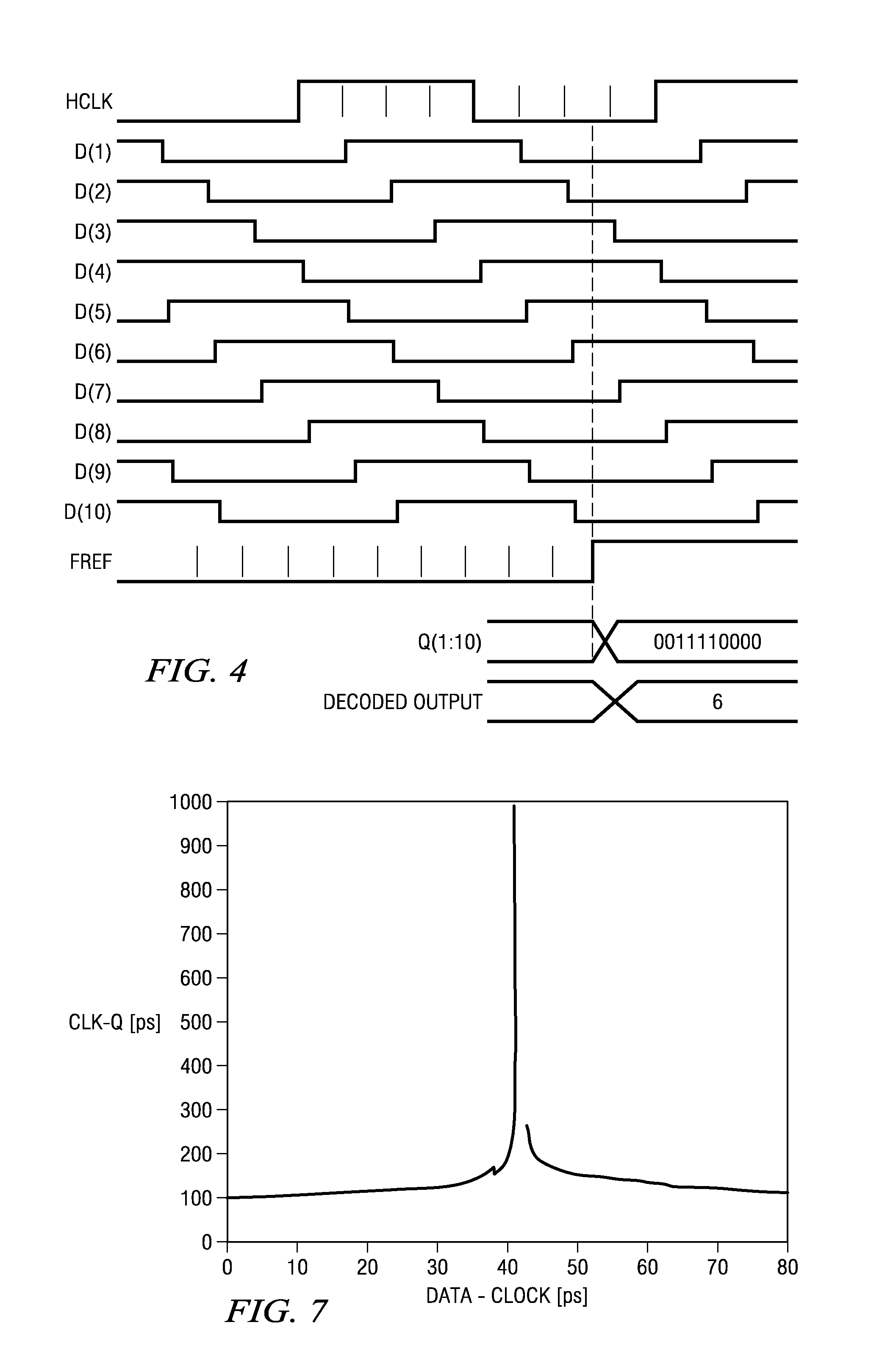

Digital Phase Locked Loop with Integer Channel Mitigation

An embodiment of the present invention provides a phase locked loop that operates on clock signals derived from an RF clock signal generated by the phase locked loop. A frequency reference input provides a reference clock. A controllable oscillator generates the RF clock signal with a plurality of phases. A switch is coupled to receive the RF clock, and is operative to select one of the plurality of phases. A phase detection circuit is coupled to the switch and is operable to receive a selected phase and to provide digital phase error samples indicative of a time difference between the reference clock and the selected phase.

Owner:TEXAS INSTR INC

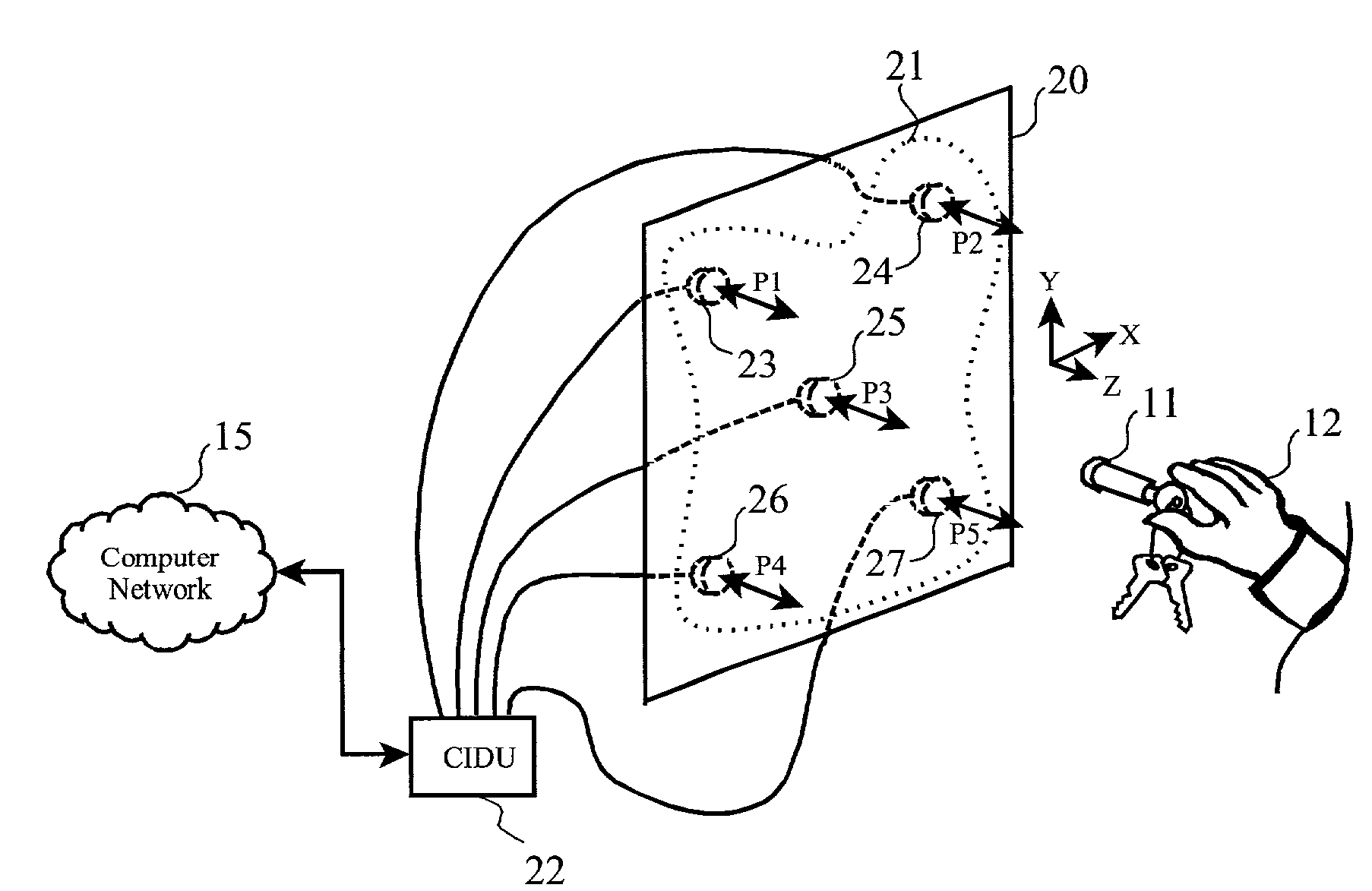

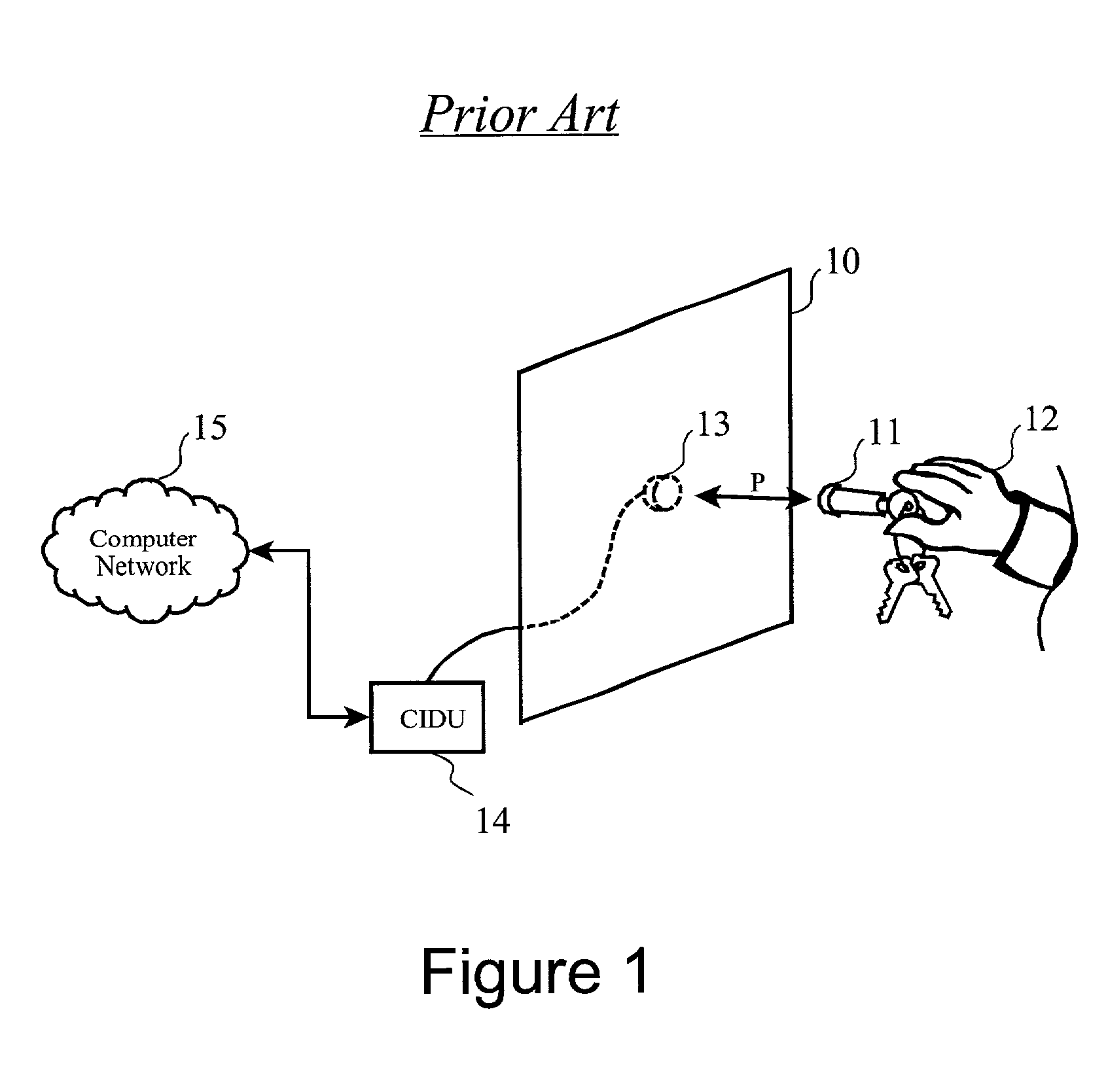

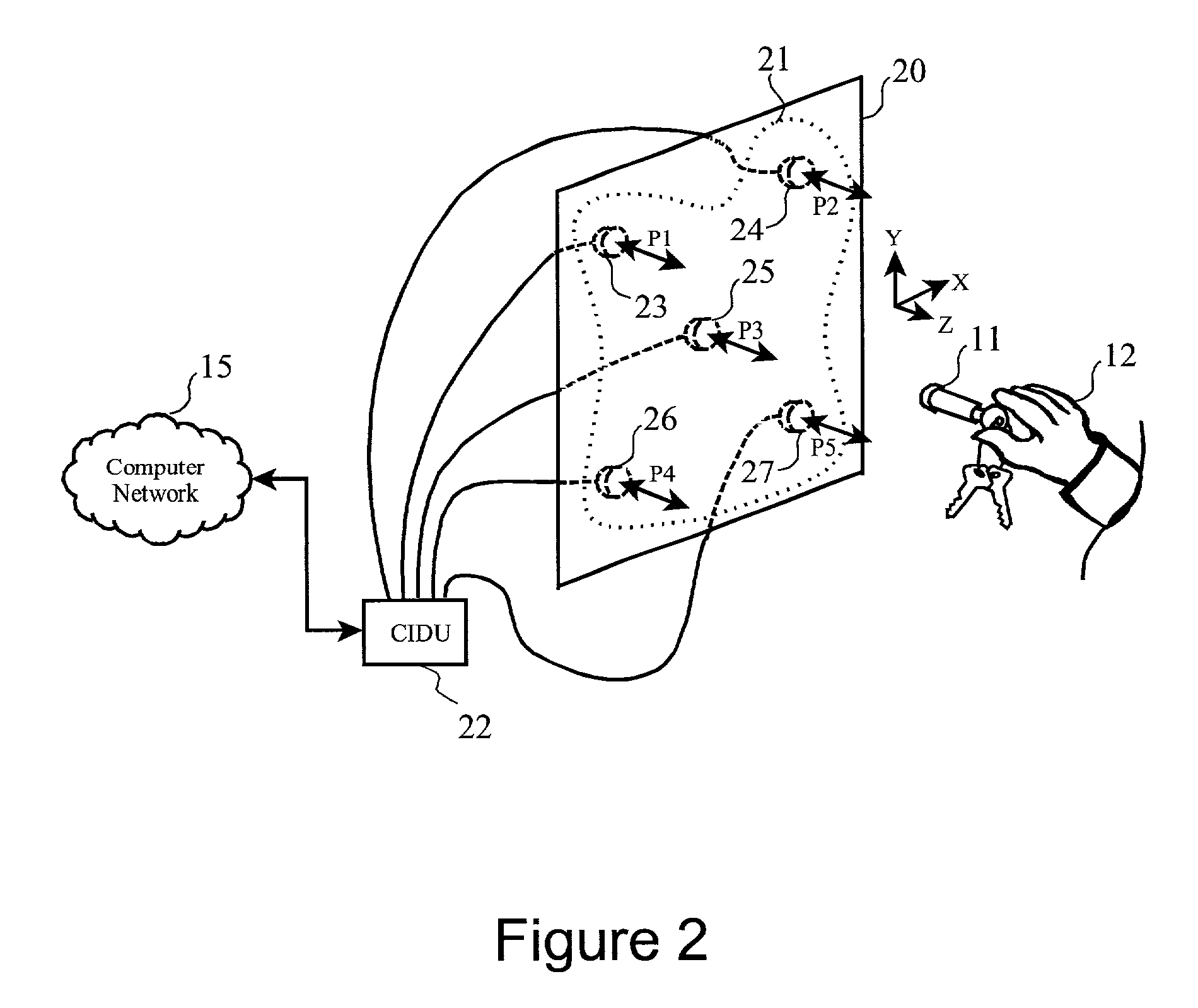

Free-space gesture recognition for transaction security and command processing

InactiveUS7394346B2Quick and efficient in handlingImprove securityInput/output for user-computer interactionElectric signal transmission systemsAuthorizationComputer science

A sensor panel having a matrix of independently decoded sensors, arranged in a two-dimensional pattern allows a consumer identification unit (CIDU) to detect a user-specific gesture made with a gesturing instrument such as an RF ID device. The CIDU monitors on a timed basis which of the sensors in the panel are receiving a signal from an RF ID device which has entered the proximity of one or more of the sensors. The user moves the sensor in a two-dimensional pattern to perform a “gesture signature” in free space near the panel, and the CIDU records the sequence of receiving sensors. This sequence can then be quickly and efficiently handled as a number to be looked up to identify and authenticate the user. Preferably, the user is allowed to define multiple signature gestures, each having the possibility of being associated with a transaction or authorization level.

Owner:SNAP INC

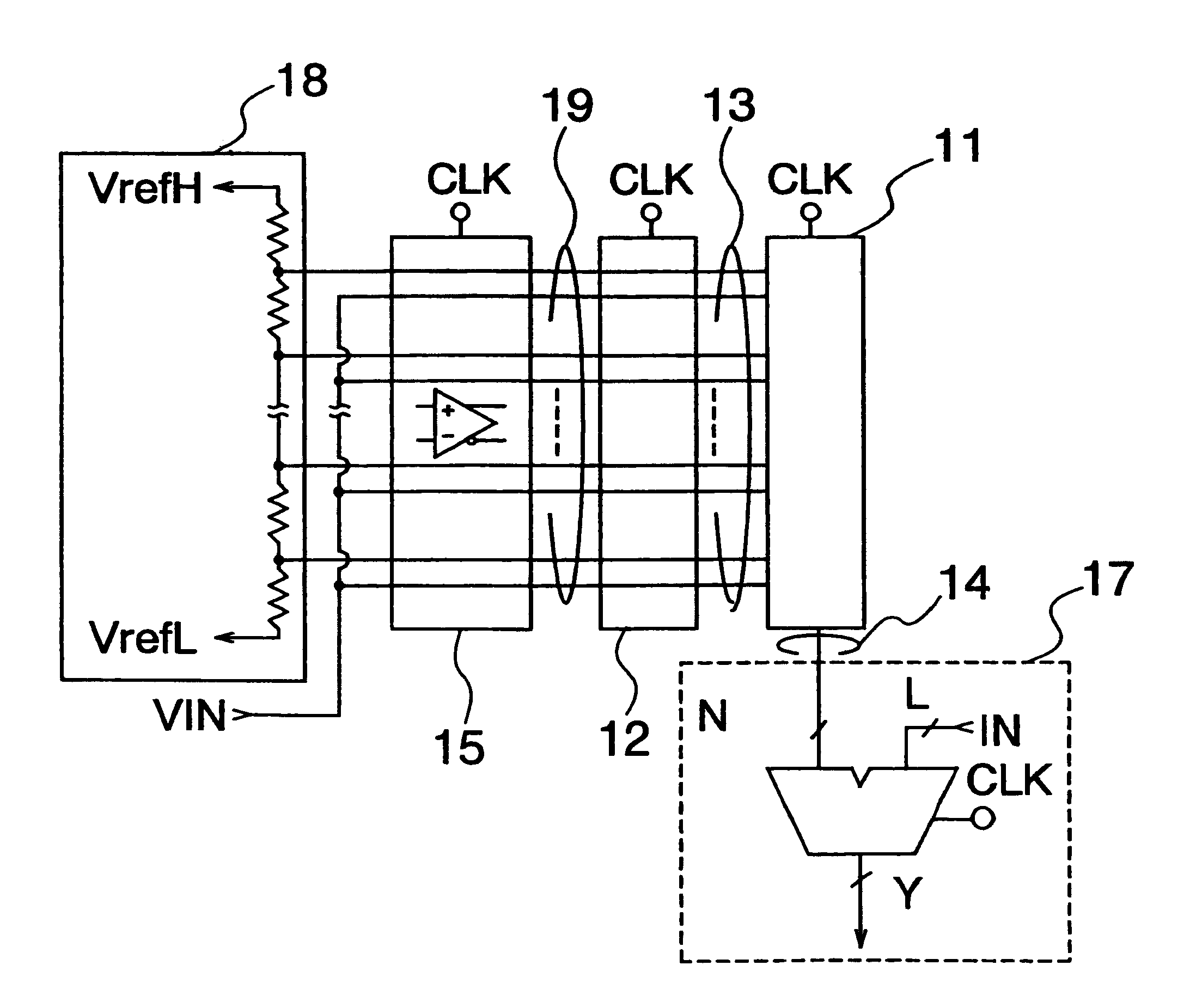

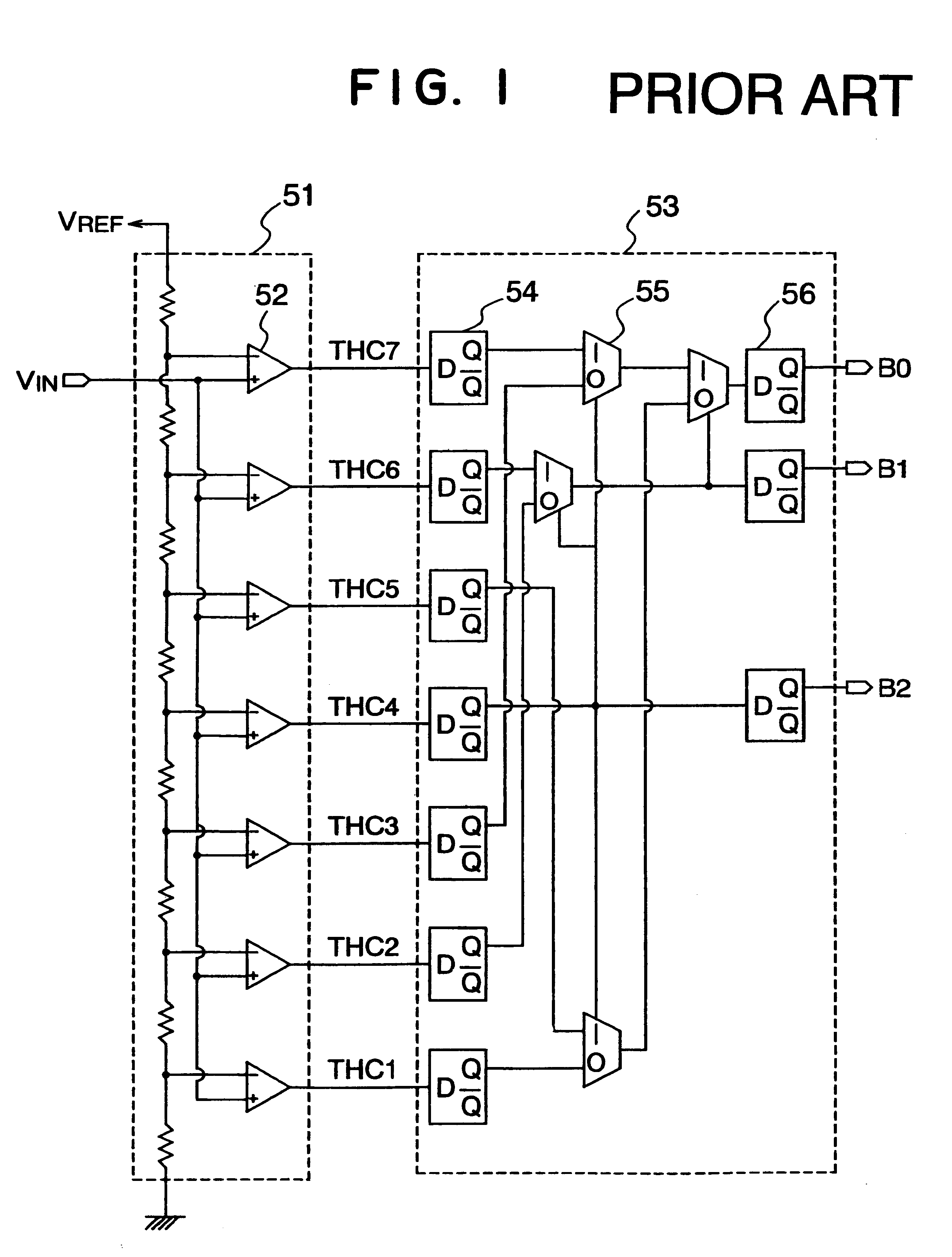

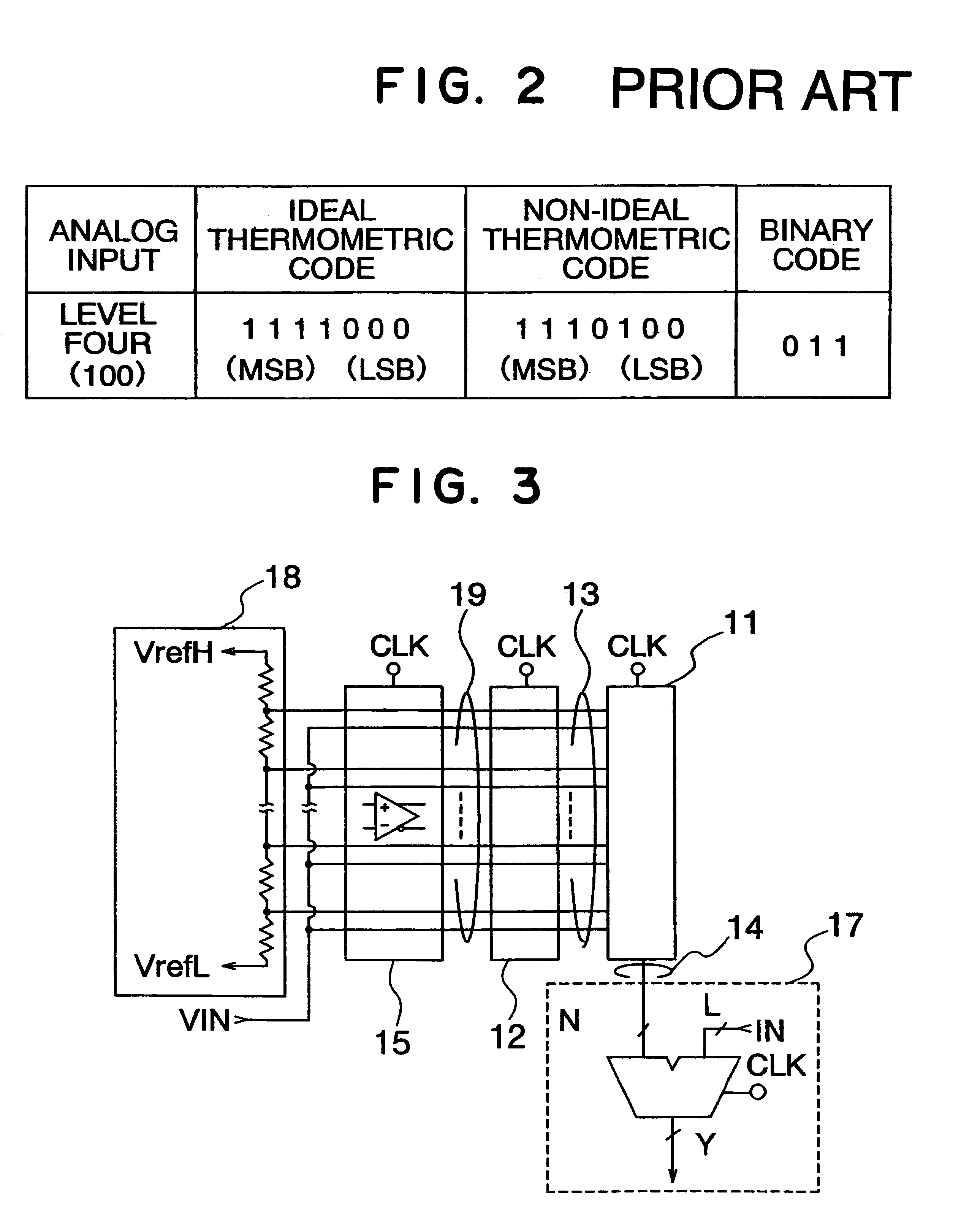

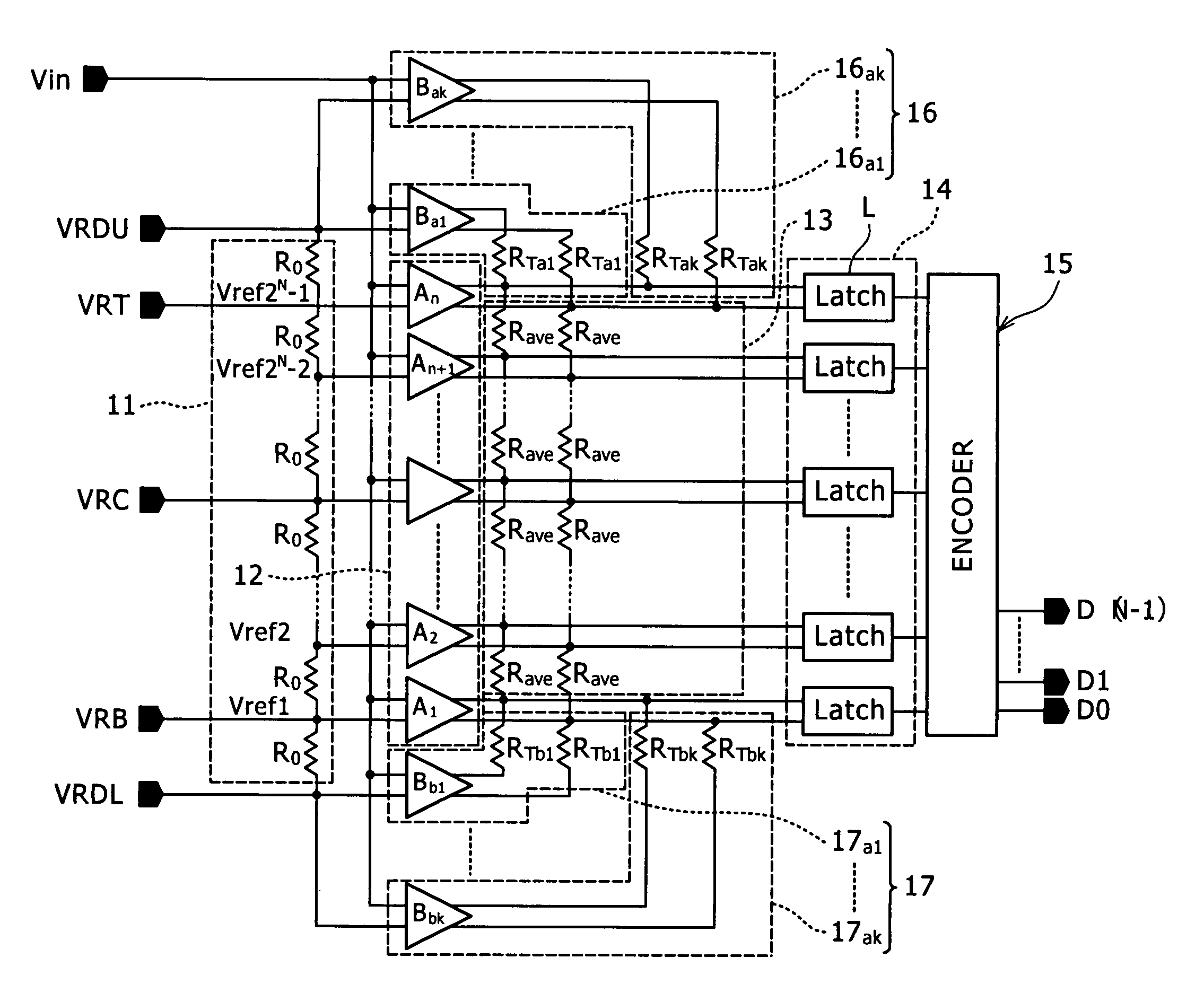

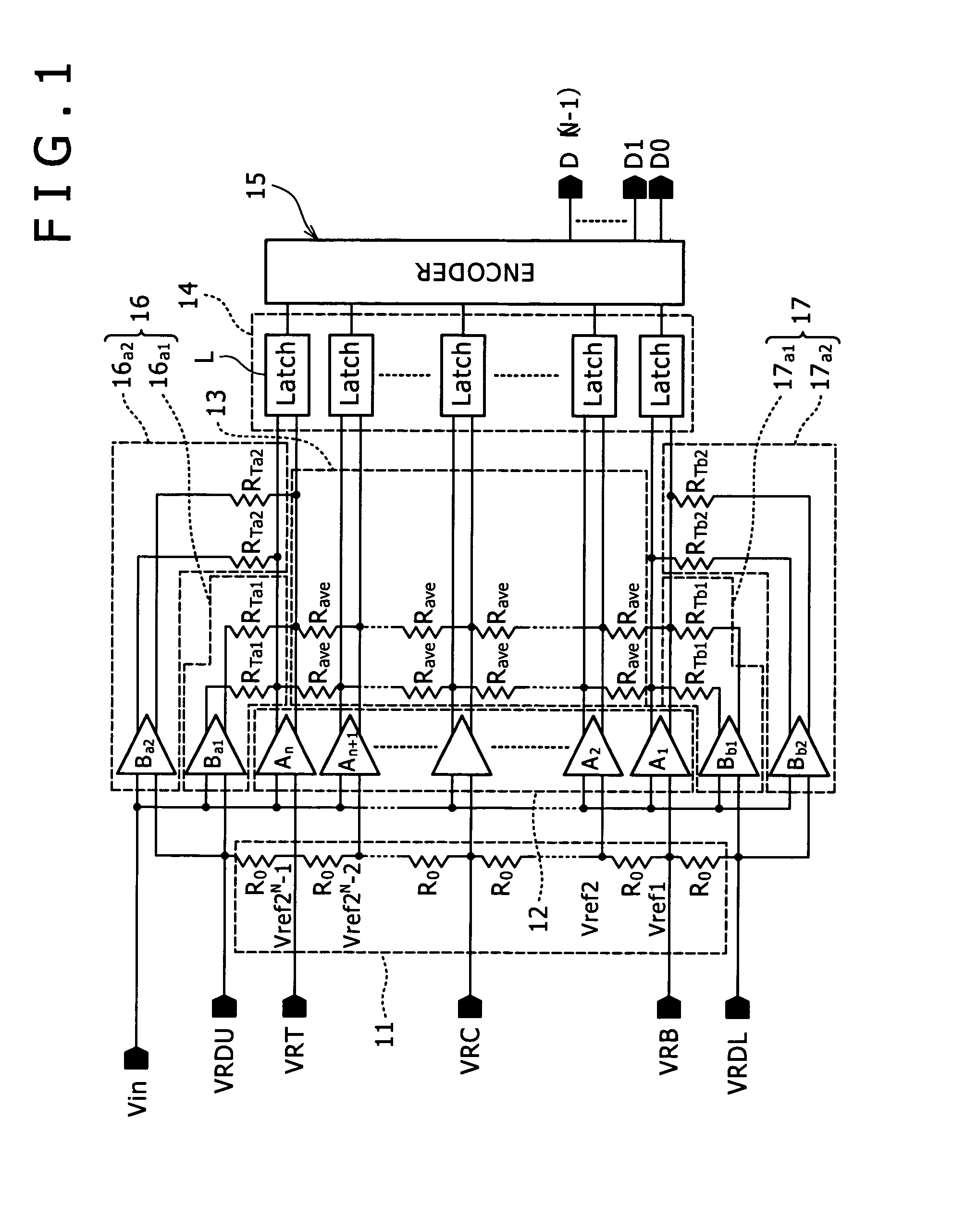

A/D converter having a dynamic encoder

InactiveUS6232908B1Increase speedReduce circuit sizeElectric signal transmission systemsAnalogue-digital convertersBuck converterA d converter

An A / D converter includes a resistor ladder for generating a plurality of reference potentials, a comparing section for comparing each of the reference potentials against an input analog signal to output a thermometric code, and a dynamic encoder composed of a combinational circuit to encode the thermometric code to a binary code by responding a clock signal. The A / D conversion is finished in a single clock cycle at a high speed, with a reduced number of elements and reduced power dissipation.

Owner:NEC ELECTRONICS CORP

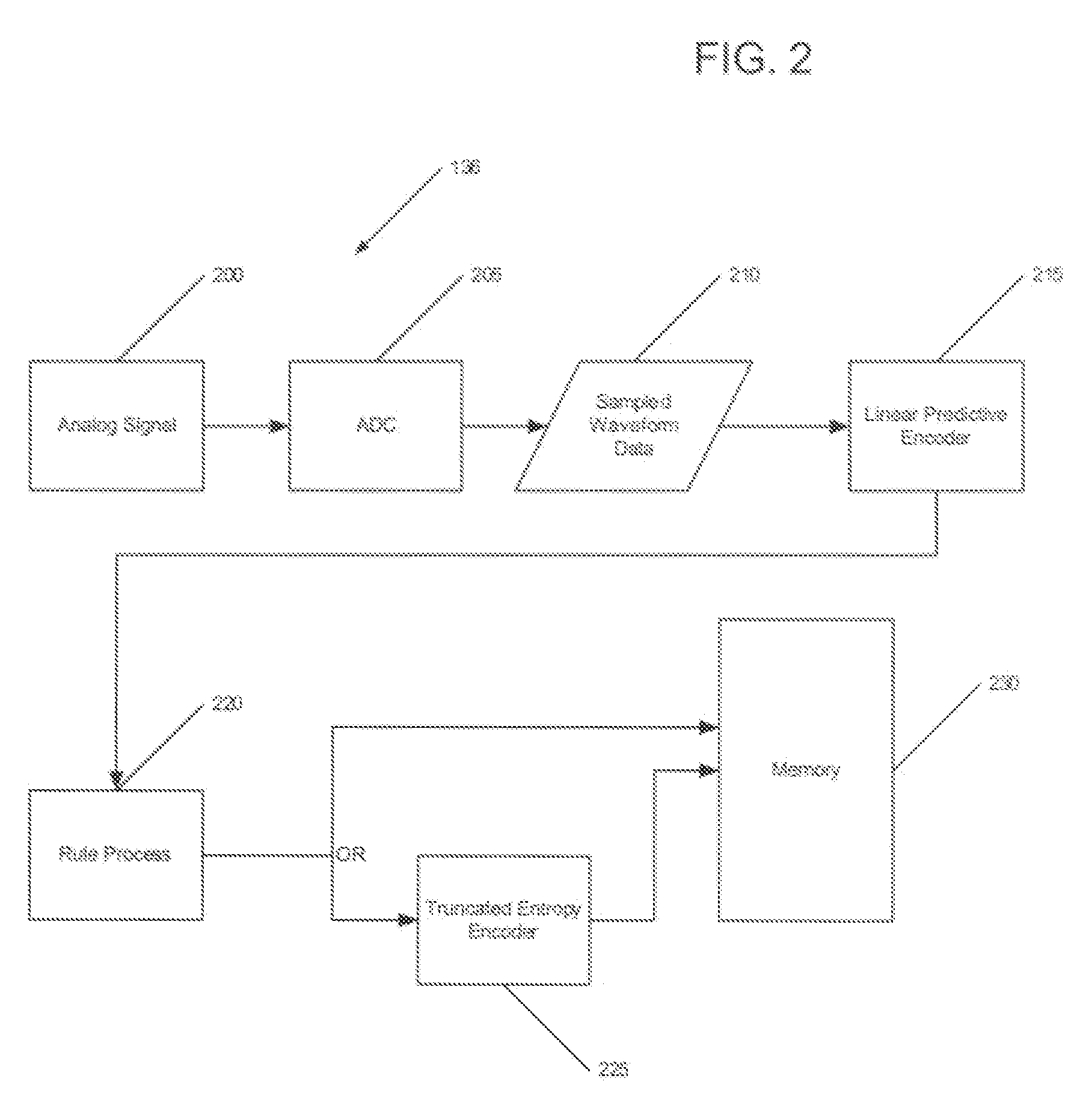

Method of compressing waveform data with differential entropy based compression

Waveforms are digitally sampled and compressed for storage in memory. The compression of the data includes generating a truncated entropy encoding map and using the values within the map to obtain good compression. An encoder further sub-selects values to be encoded and values to remain unencoded to provide an overall compression of the data.

Owner:MEDTRONIC INC

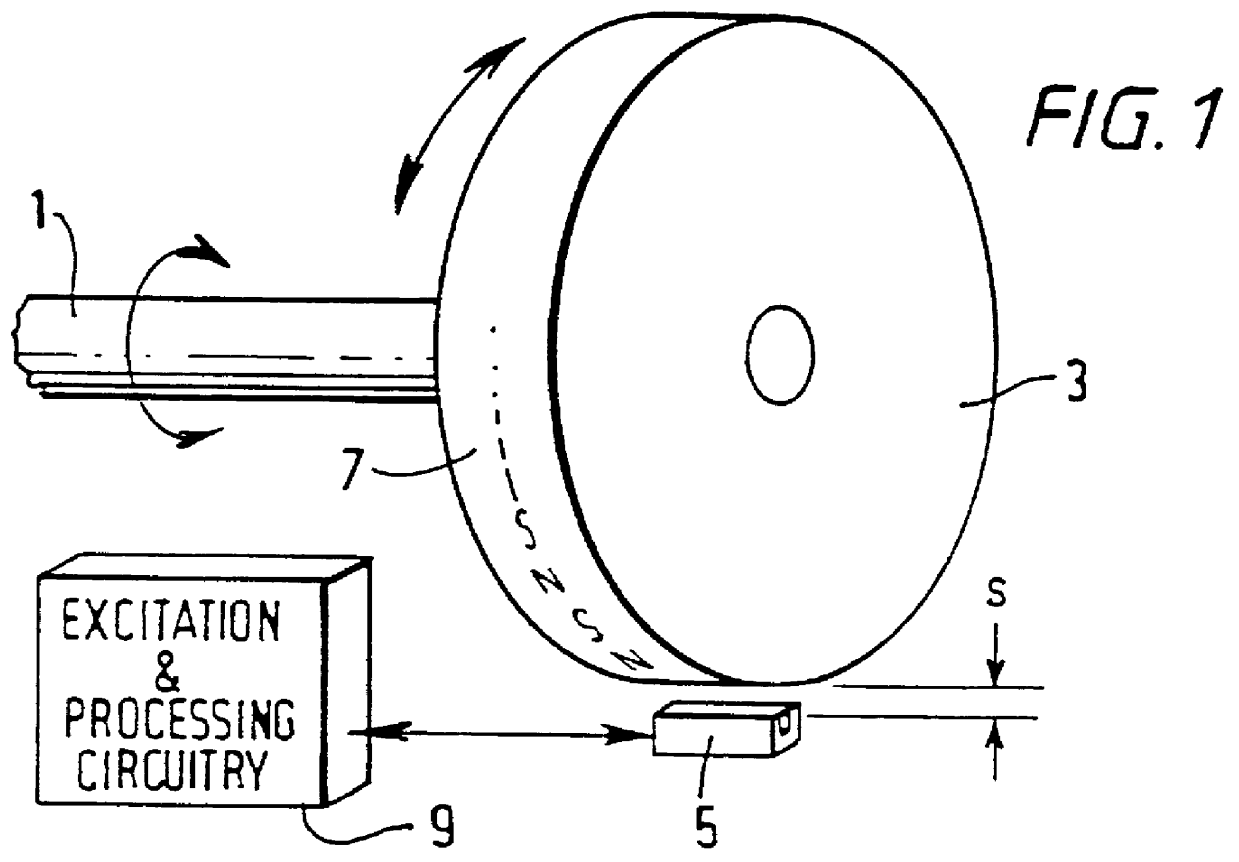

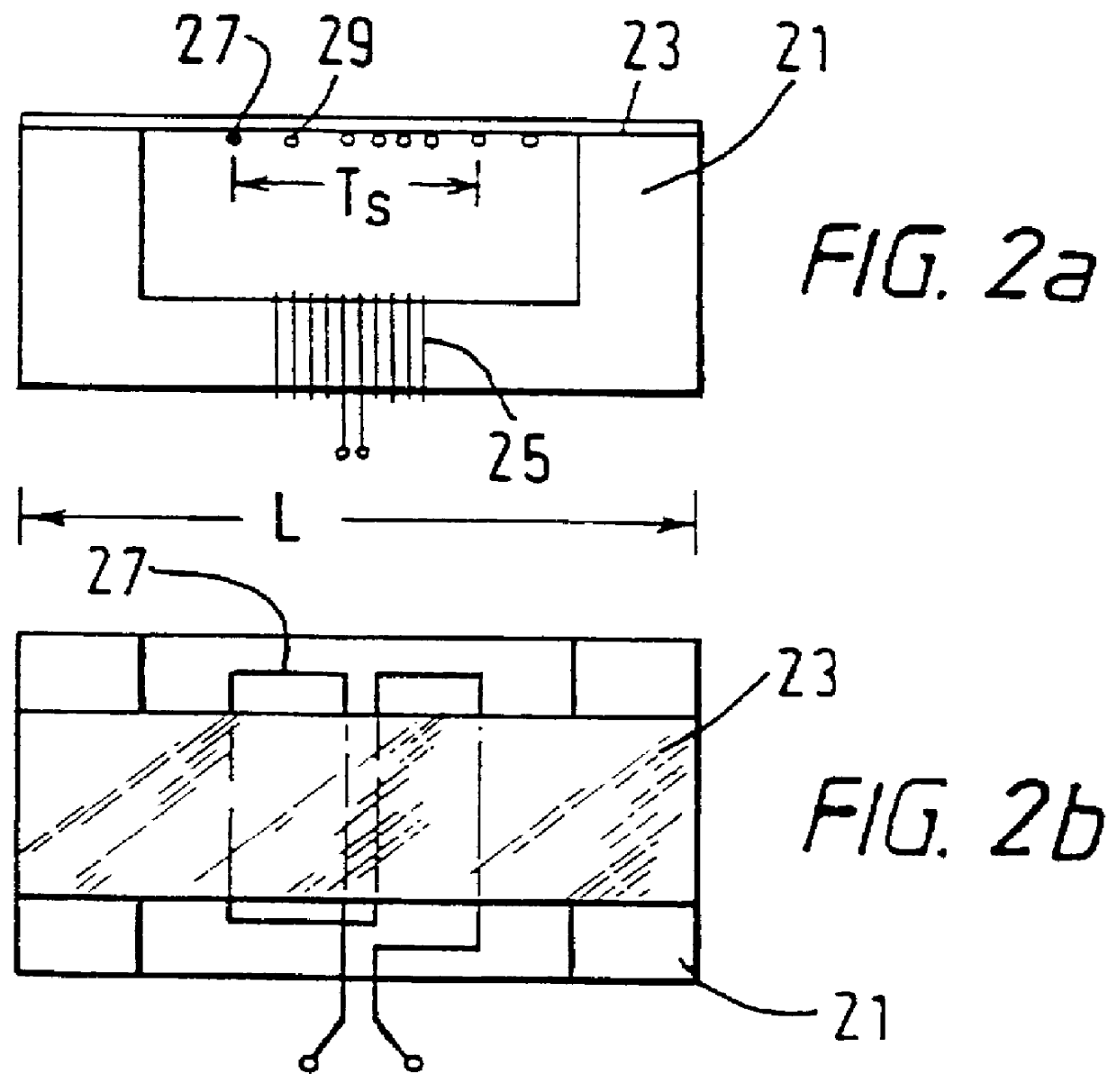

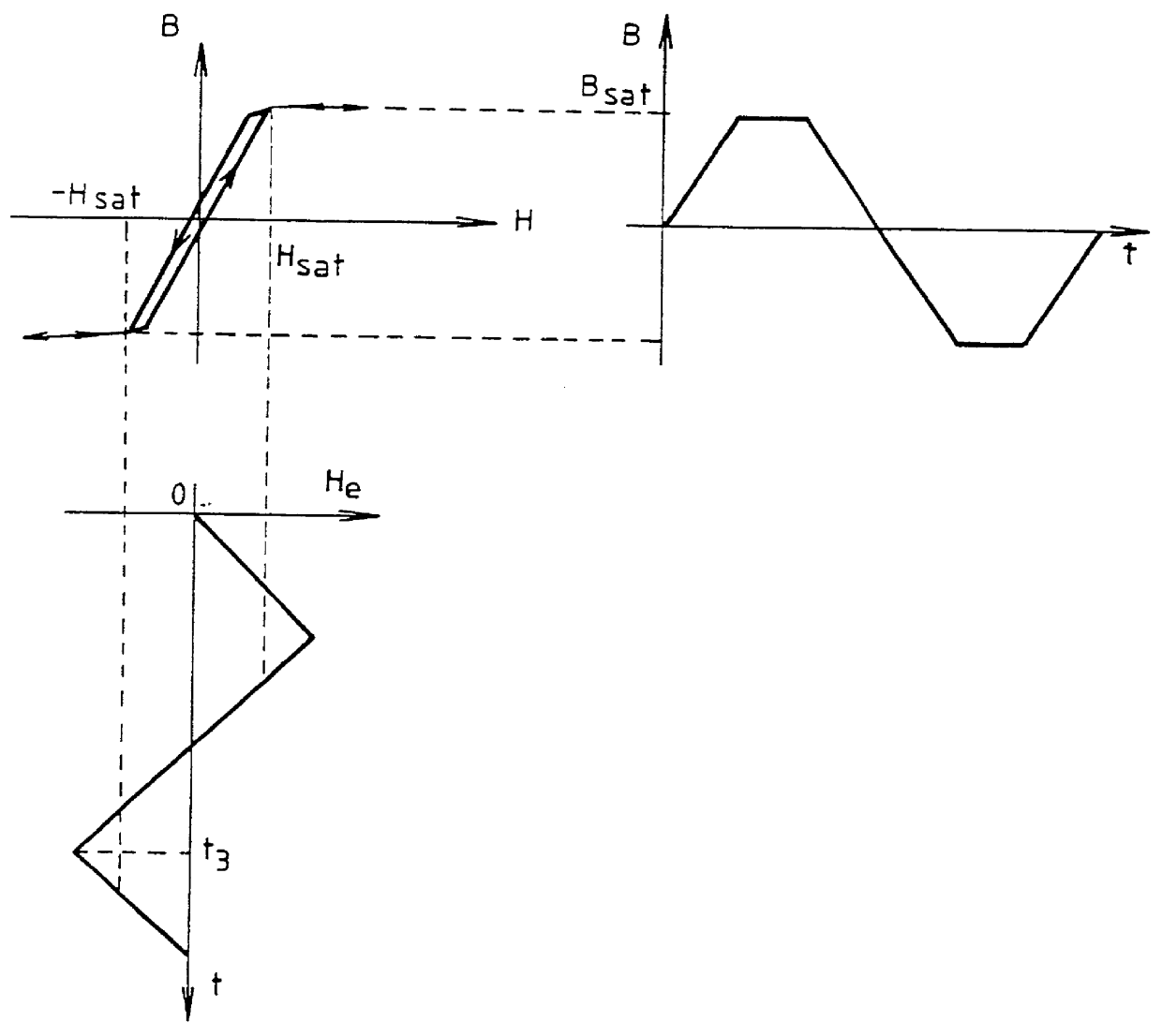

Position encoder using saturable reactor interacting with magnetic fields varying with time and with position

InactiveUS6118271AElectric signal transmission systemsMagnetic bodiesElectrical conductorConductor Coil

PCT No. PCT / GB96 / 02560 Sec. 371 Date Apr. 17, 1998 Sec. 102(e) Date Apr. 17, 1998 PCT Filed Oct. 17, 1996 PCT Pub. No. WO97 / 14935 PCT Pub. Date Apr. 24, 1997A position encoder is provided for indicating the relative position between first and second relatively movable members. One of the members carries a multi-pole magnetic scale which generates a magnetic field whose magnitude and direction vary with position and the other member carries at least one sense conductor. A saturable magnetic element is located in the positionally varying magnetic field of the magnetic scale and an excitation winding is provided which, when energized, generates a magnetic filed which interacts with the positionally varying magnetic field to cause different portions of the saturable magnetic element to saturate and desaturate at different times. The arrangement of the sense conductor is such that as the magnetic element is driven into and out of saturation, it outputs a signal which is indicative of the position of the magnetic scale relative to the sense conductor.

Owner:SCI GENERICS LTD

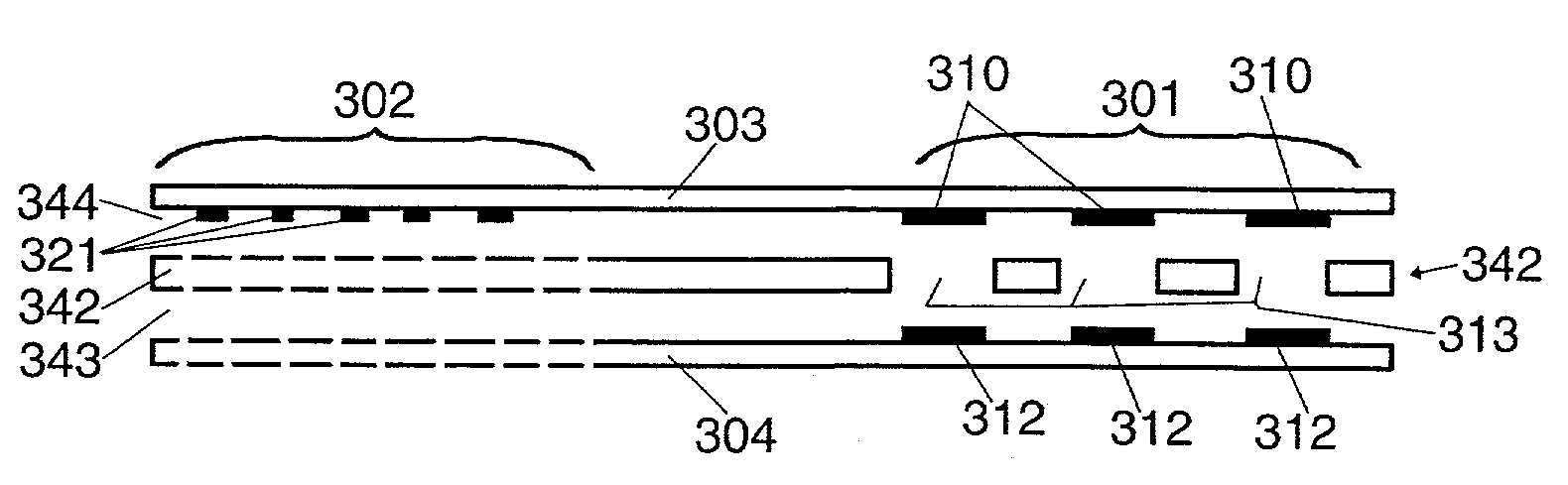

Method and apparatus for providing an integrated membrane switch and capacitive sensor

InactiveUS6943705B1Easy to installReduce the amount requiredElectric signal transmission systemsElectronic switchingCapacitive couplingMembrane switch

A circuit assembly for providing a switch sensor and a capacitive sensor. The circuit assembly has a first pattern of conductive material in a first plane and a second pattern of conductive material in a second plane. An insulating member in an intermediate plane separates the first and second patterns. In a switch sensor area, the insulating member has openings to allow a first conductive element in the first pattern to contact a second conductive element in the second pattern responsive a force being applied to the first conductive element. In the capacitive sensor area, the insulating member maintains spacing between conductive material in the first and second patterns. The circuit assembly also includes a preventative capacitance configuration that limits non-intentional capacitive coupling in the capacitive sensor area.

Owner:SYNAPTICS INC

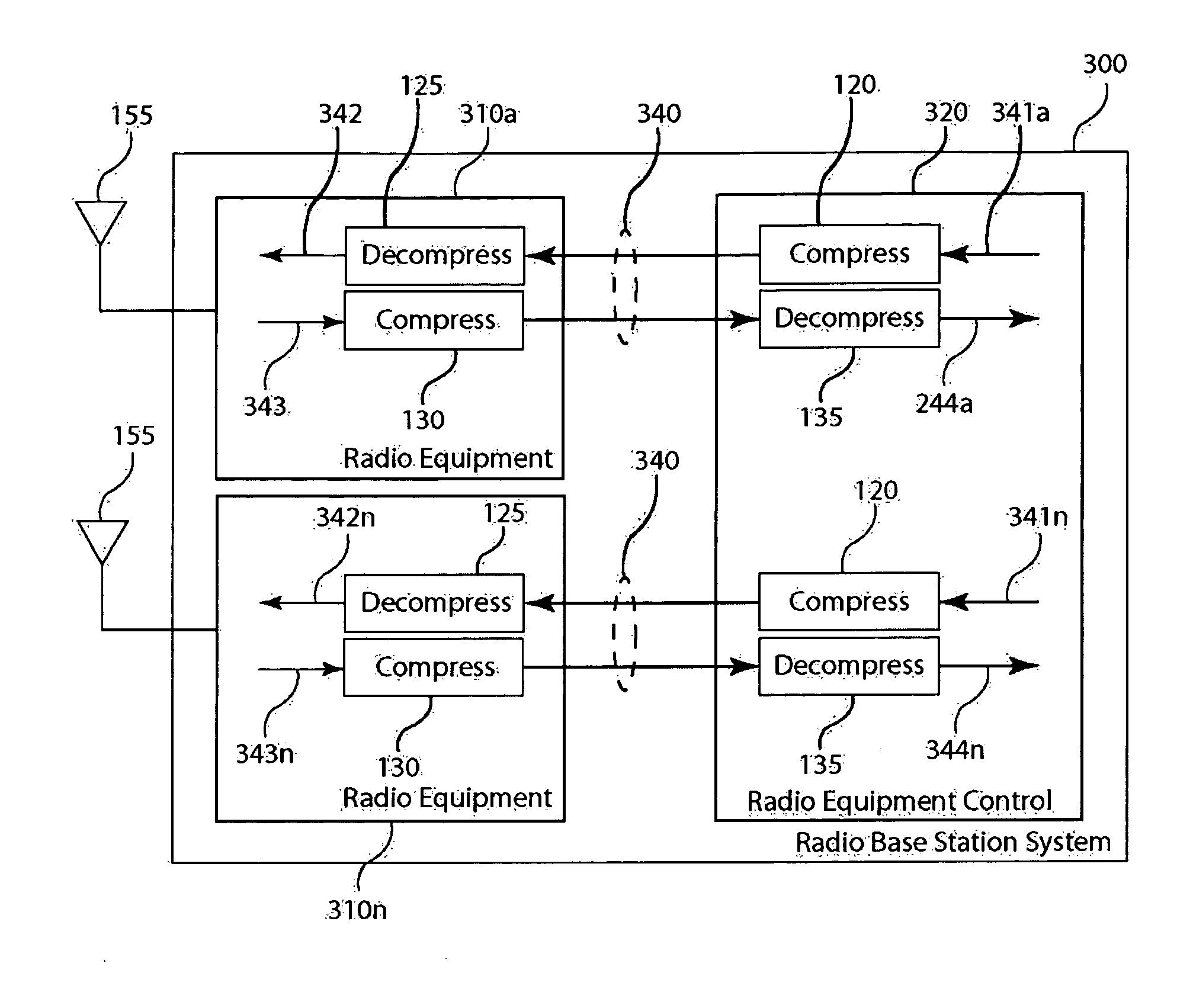

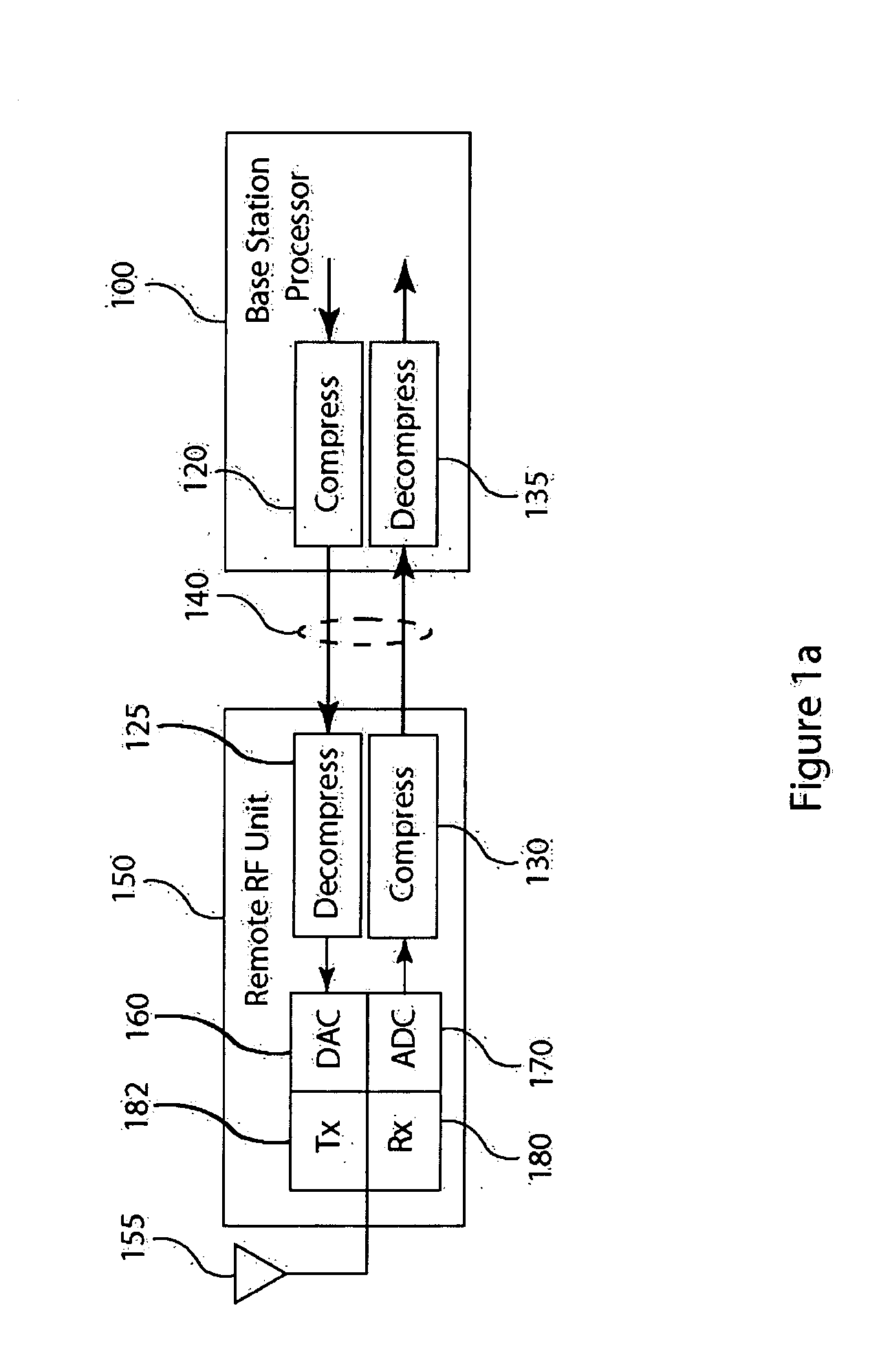

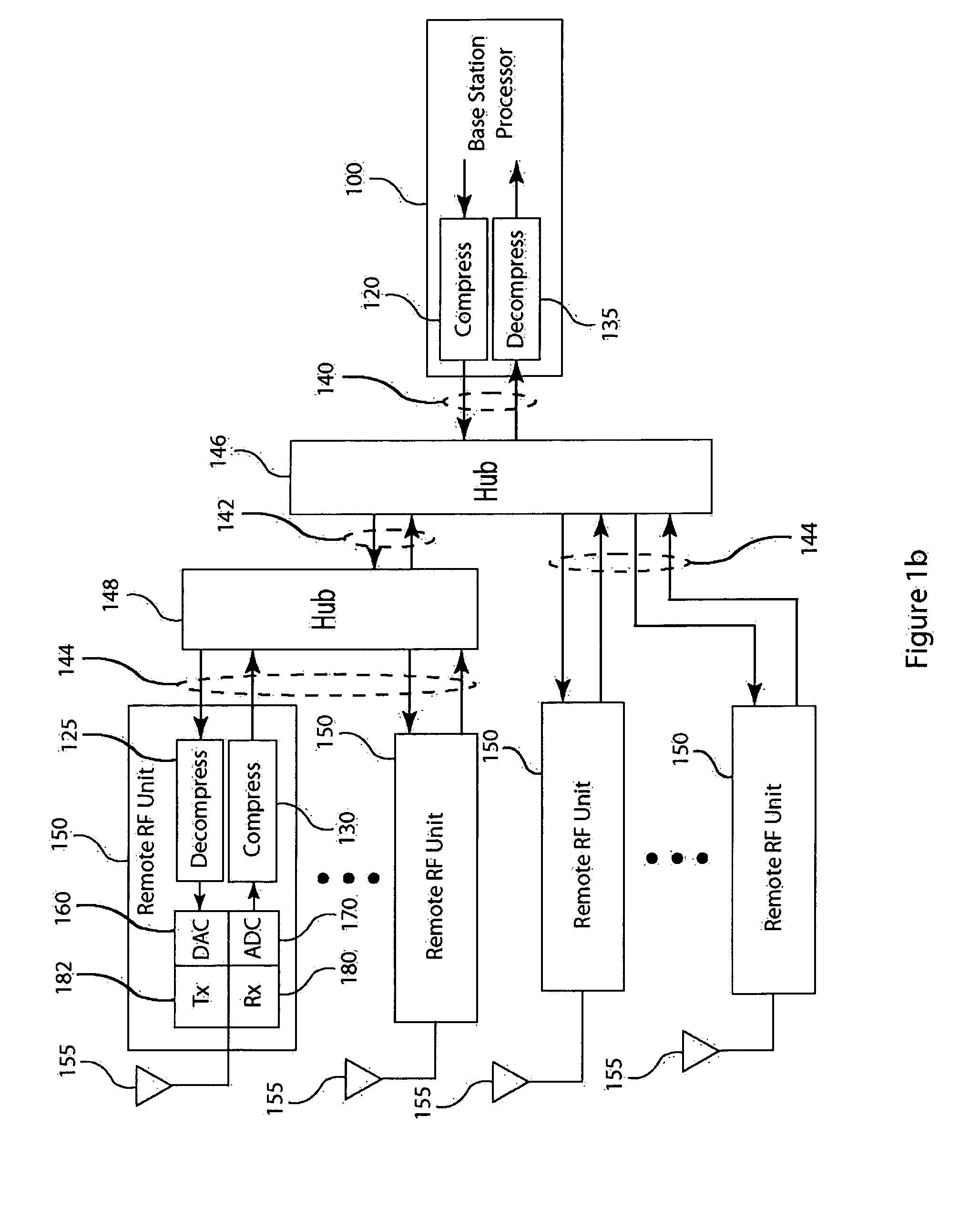

Compression of signals in base transceiver systems

ActiveUS20090290632A1Increase capacityElectric signal transmission systemsEqual length code transmitterTransceiverDistributed antenna system

A signal compression method and apparatus for a base transceiver system (BTS) in a wireless communication network provides efficient transfer of compressed signal samples over serial data links in the system. For the uplink, an RF unit of the BTS compresses signal samples resulting from analog to digital conversion of an analog signal received via an antenna. The RF unit transfers the compressed signal samples over the serial data link to the base station processor where they are decompressed prior to the normal signal processing operations. For the downlink, the base station processor compresses signal samples and transfers the compressed signal samples over the serial data link to the RF unit. The RF unit decompresses the compressed samples and converts the decompressed samples to an analog signal for transmission over an antenna. Compression and decompression can be incorporated into operations of conventional base stations and distributed antenna systems.

Owner:INTEGRATED DEVICE TECH INC

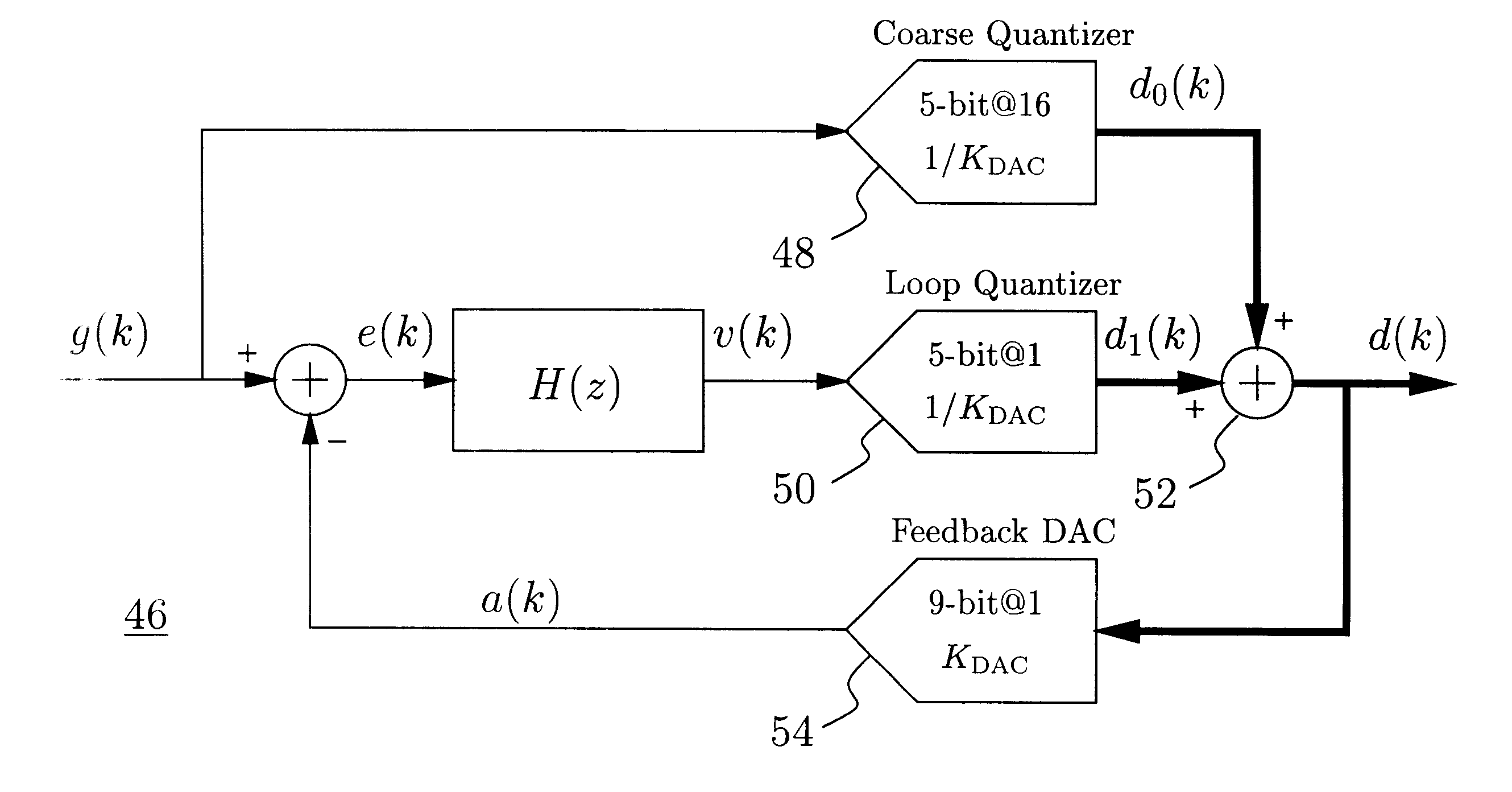

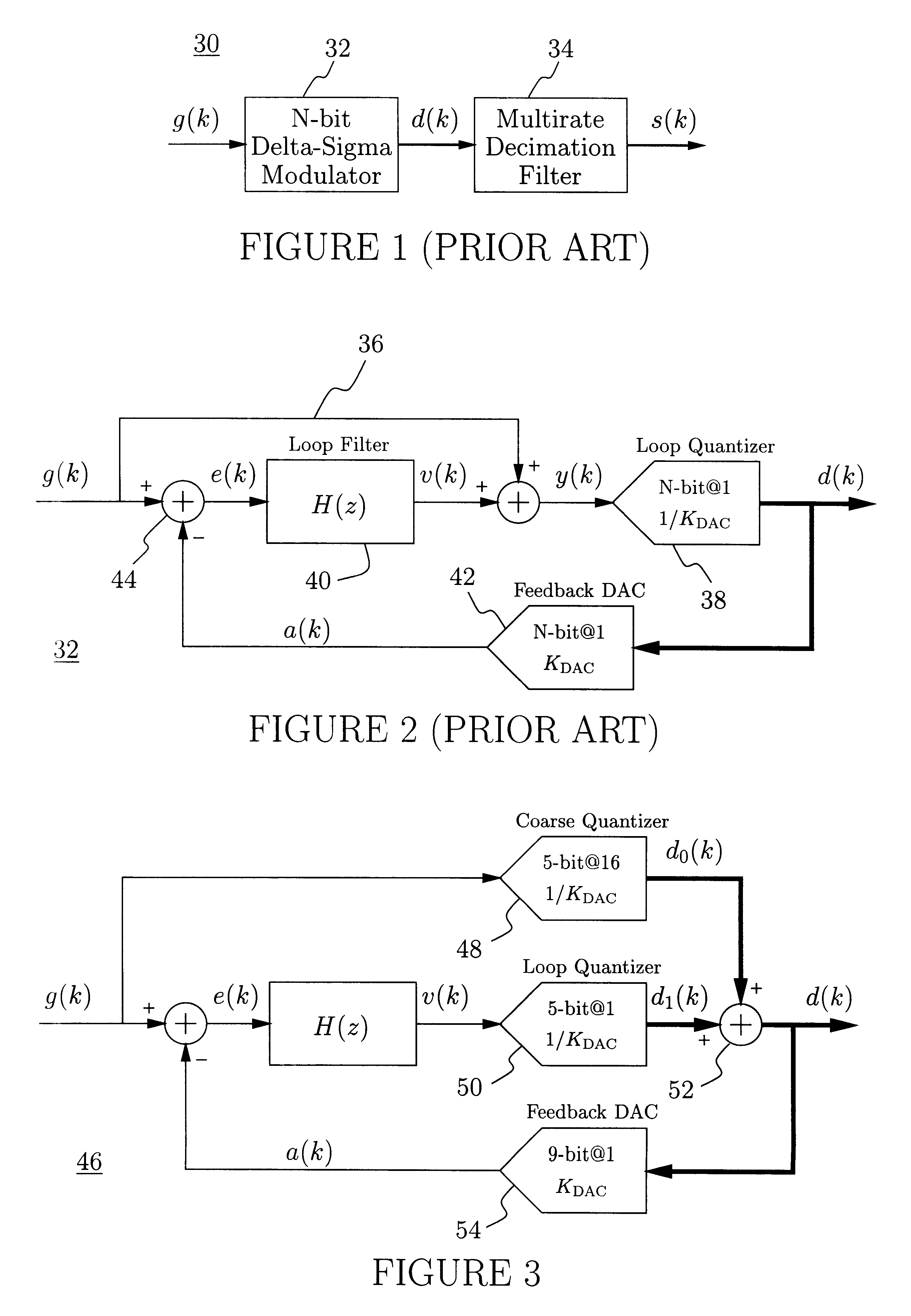

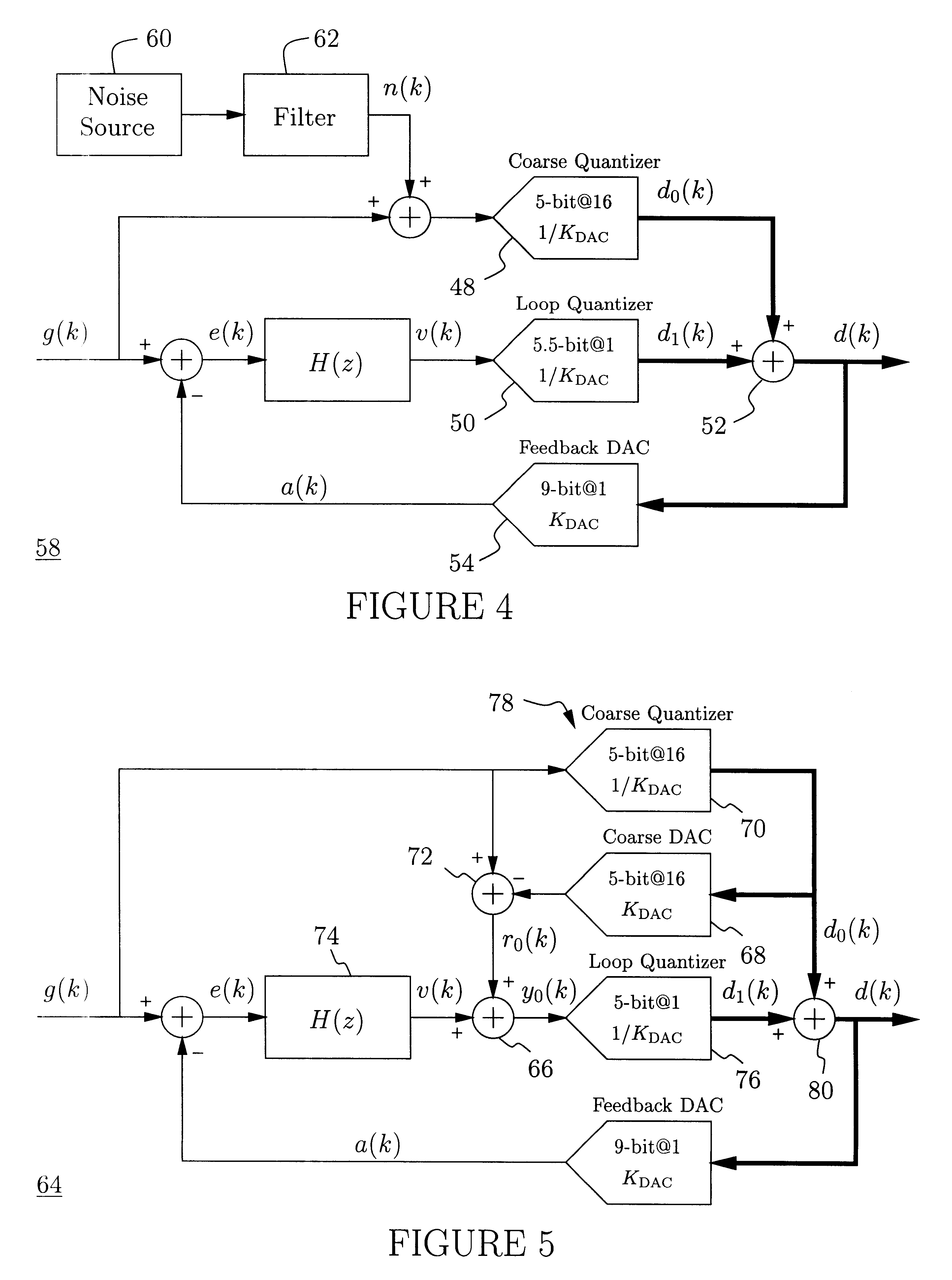

Delta-sigma A/D converter

InactiveUS6271782B1Without compromising the modulator's stabilityTo overcome the large delayElectric signal transmission systemsDifferential modulationLoop filterAnalog feedback

A delta-sigma modulator comprising a first quantizer providing a first digital signal d0(k) representing the input signal g(t); a loop filter with input signal paths; a loop quantizer providing a corrective digital signal d1(k) representing the loop filter's output signal y(t); an array of feedback DACs D / A converting the sum d(k)=df(k)=d0(k)+d1(k) of the first and the corrective digital signals and injecting feedback signals into the loop filter.The loop filter's input node is applied the difference of the input signal g(t) and the global analog feedback signal a3(t). The global feedback signal a3(t) is delayed several clock cycles with respect to the digital output signal d(k). The delay is used to carry out mismatch-shaping and deglitching algorithms in the feedback DACs. The feedback DACs' different delays and gain coefficients are designed such that the modulator is stable. The filter's input signal paths and the compensating DAC are designed such that the gain from the input signal g(t) to the loop quantizer is small, ideally zero. Thus, the loop quantizer's resolving range can be a fraction of the first quantizer's resolving range, whereby the output signal's d(k) resolution can be much higher than the individual resolutions of d0(k) and d1(k).The delta-sigma modulator is well suited for the implementation of high-resolution wide-bandwidth A / D converters. Important applications include digital communication systems.

Owner:ANALOG DEVICES BV

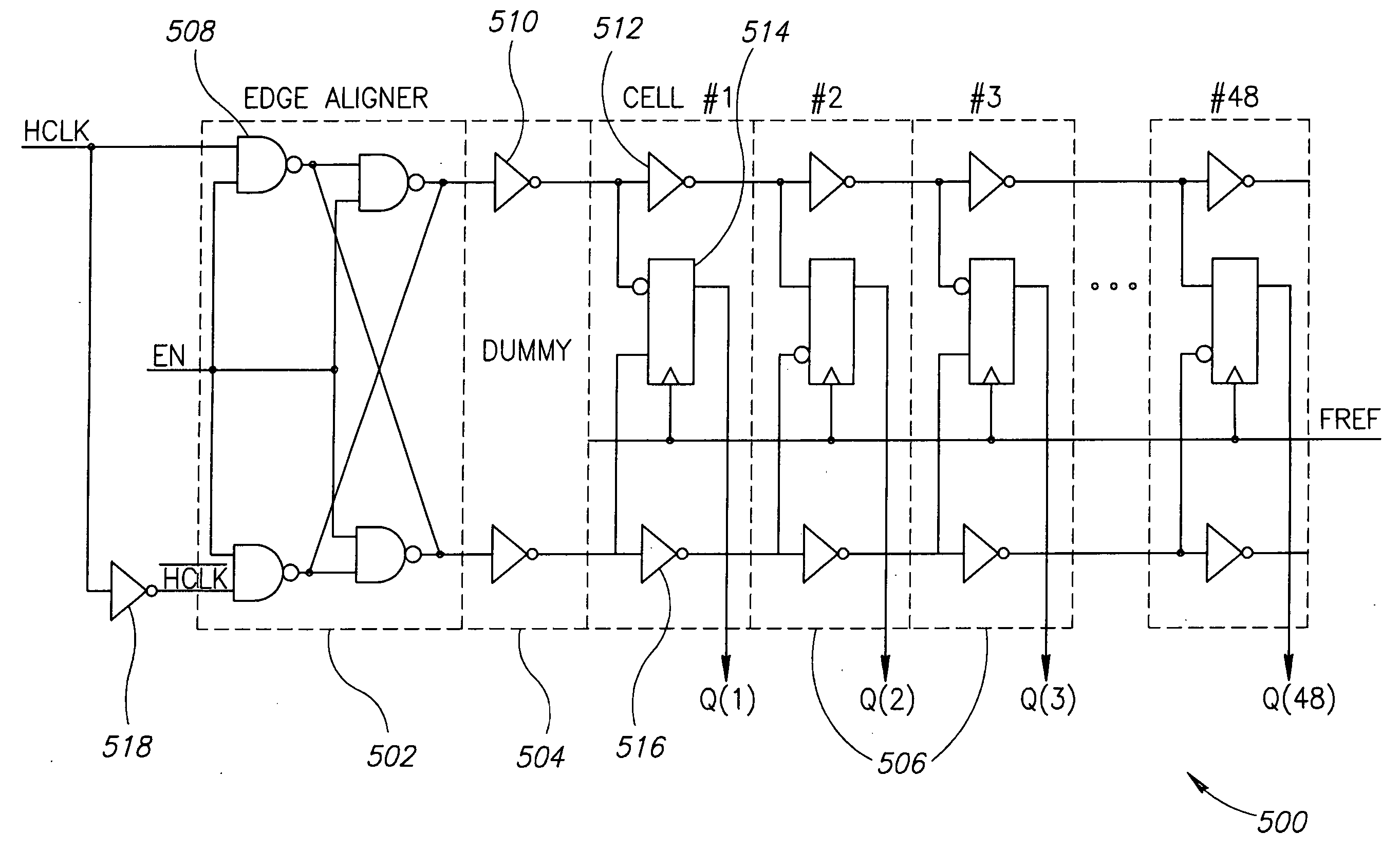

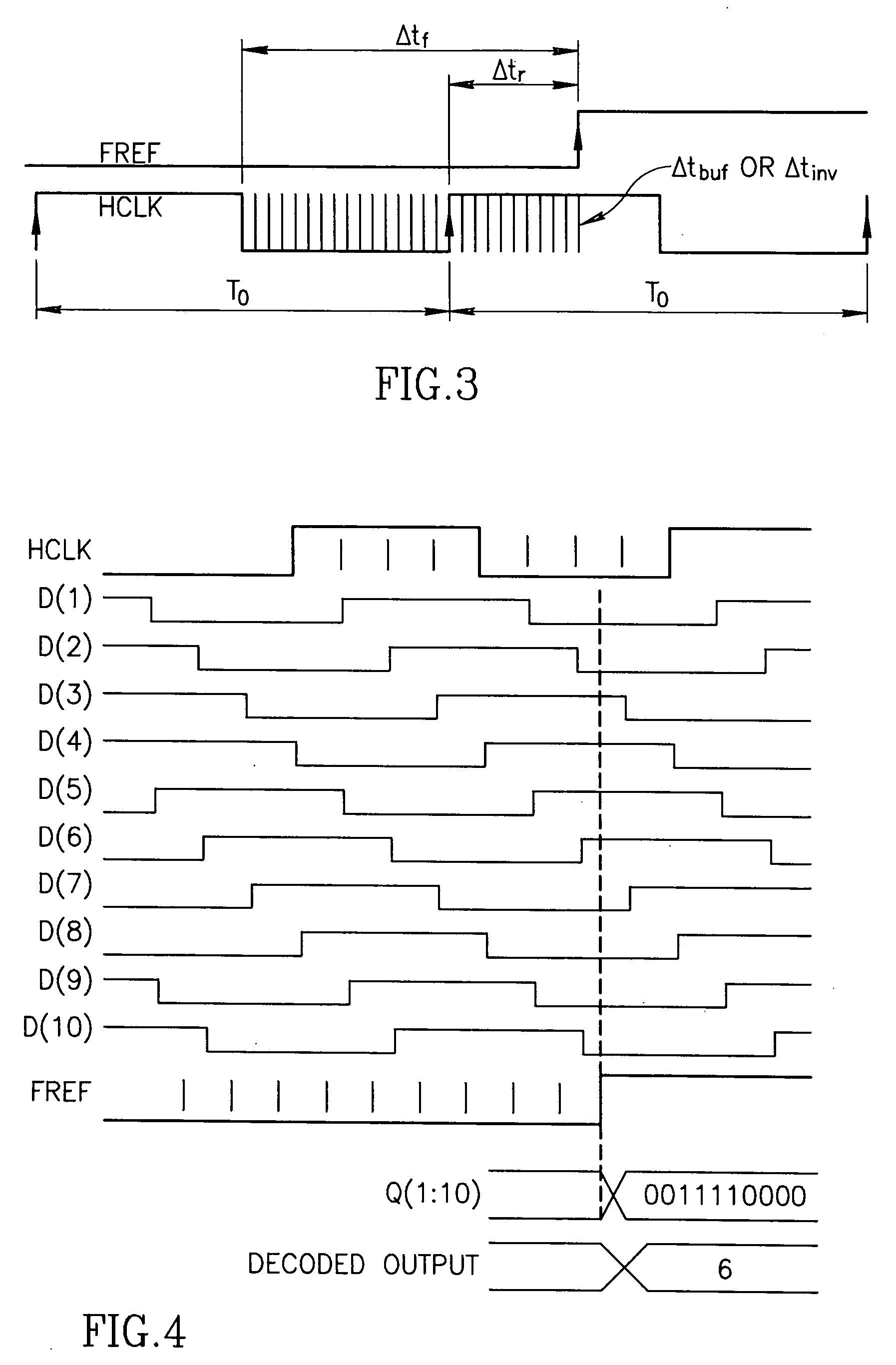

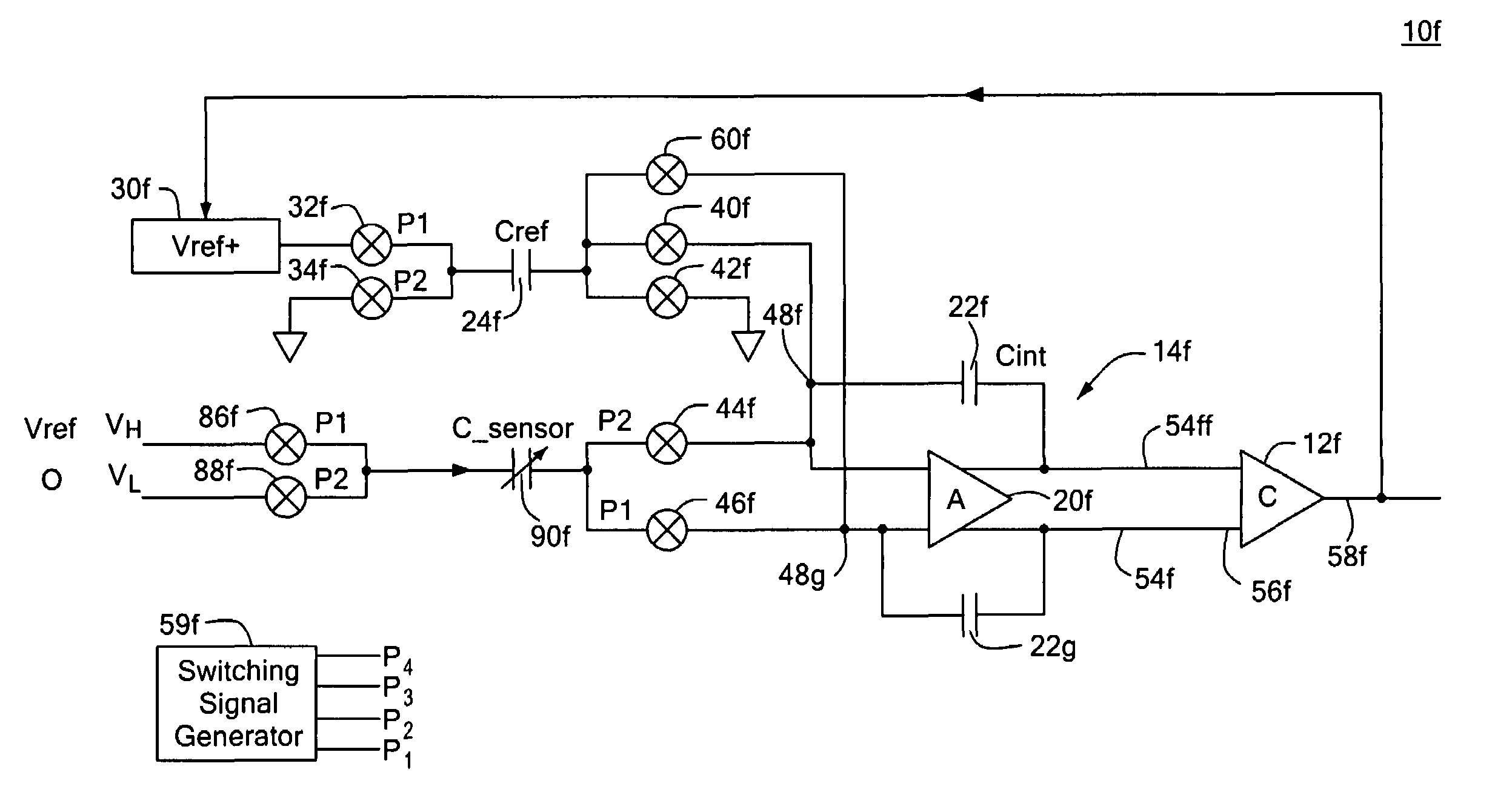

Circuit for high-resolution phase detection in a digital RF processor

ActiveUS20060103566A1Less sensitiveReduce power consumptionElectric signal transmission systemsPulse automatic controlEngineeringDigital converter

A novel time-to-digital converter (TDC) used as a phase / frequency detector and charge pump replacement in an all-digital PLL within a digital radio processor. The TDC core is based on a pseudo-differential digital architecture making it insensitive to NMOS and PMOS transistor mismatches. The time conversion resolution is equal to an inverter propagation delay, e.g., 20 ps, which is the finest logic-level regenerative timing in CMOS. The TDC is self calibrating with the estimation accuracy better than 1%. The TDC circuit can also serve as a CMOS process strength estimator for analog circuits in large SoC dies. The circuit also employs power management circuitry to reduce power consumption to a very low level.

Owner:TEXAS INSTR INC

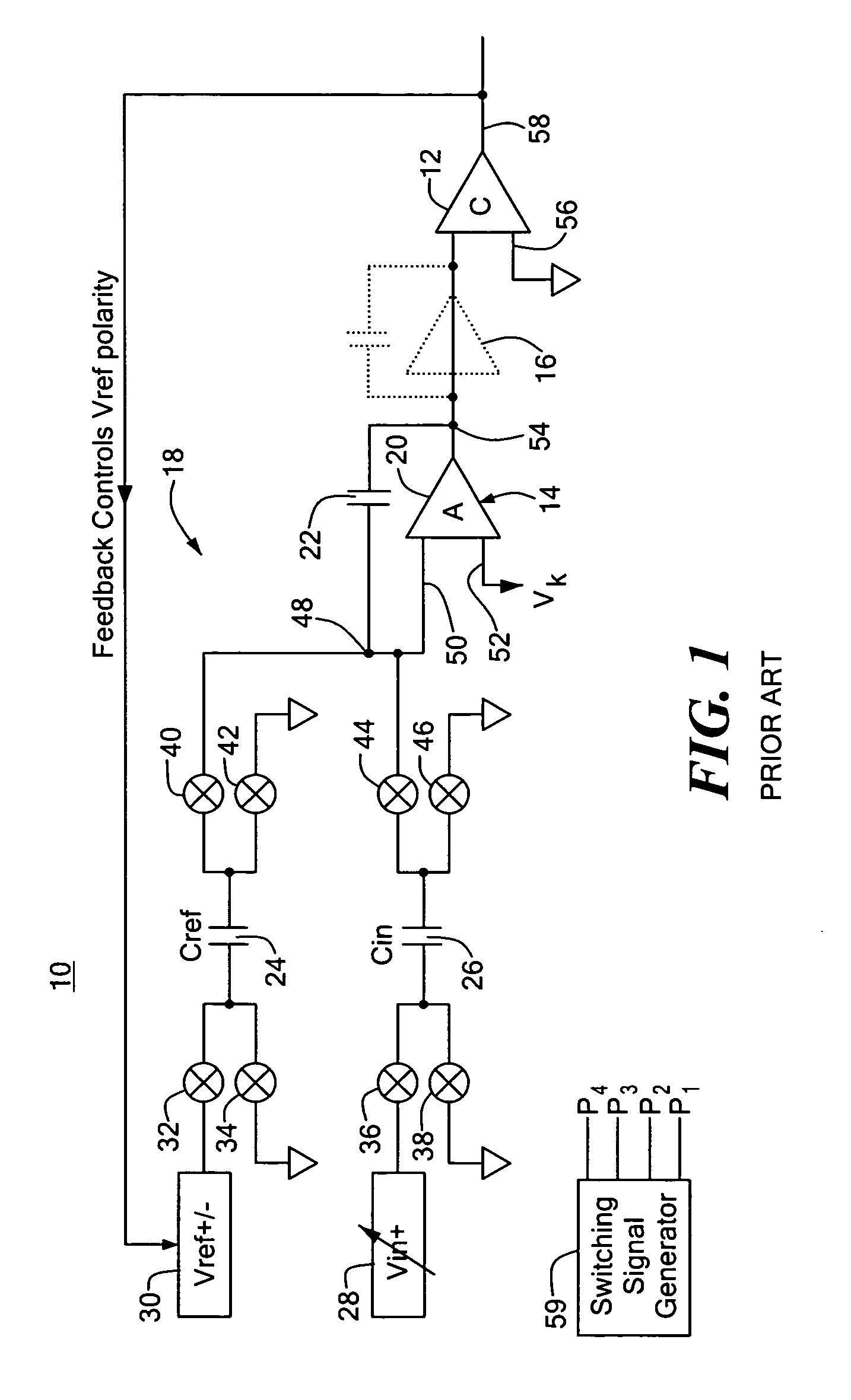

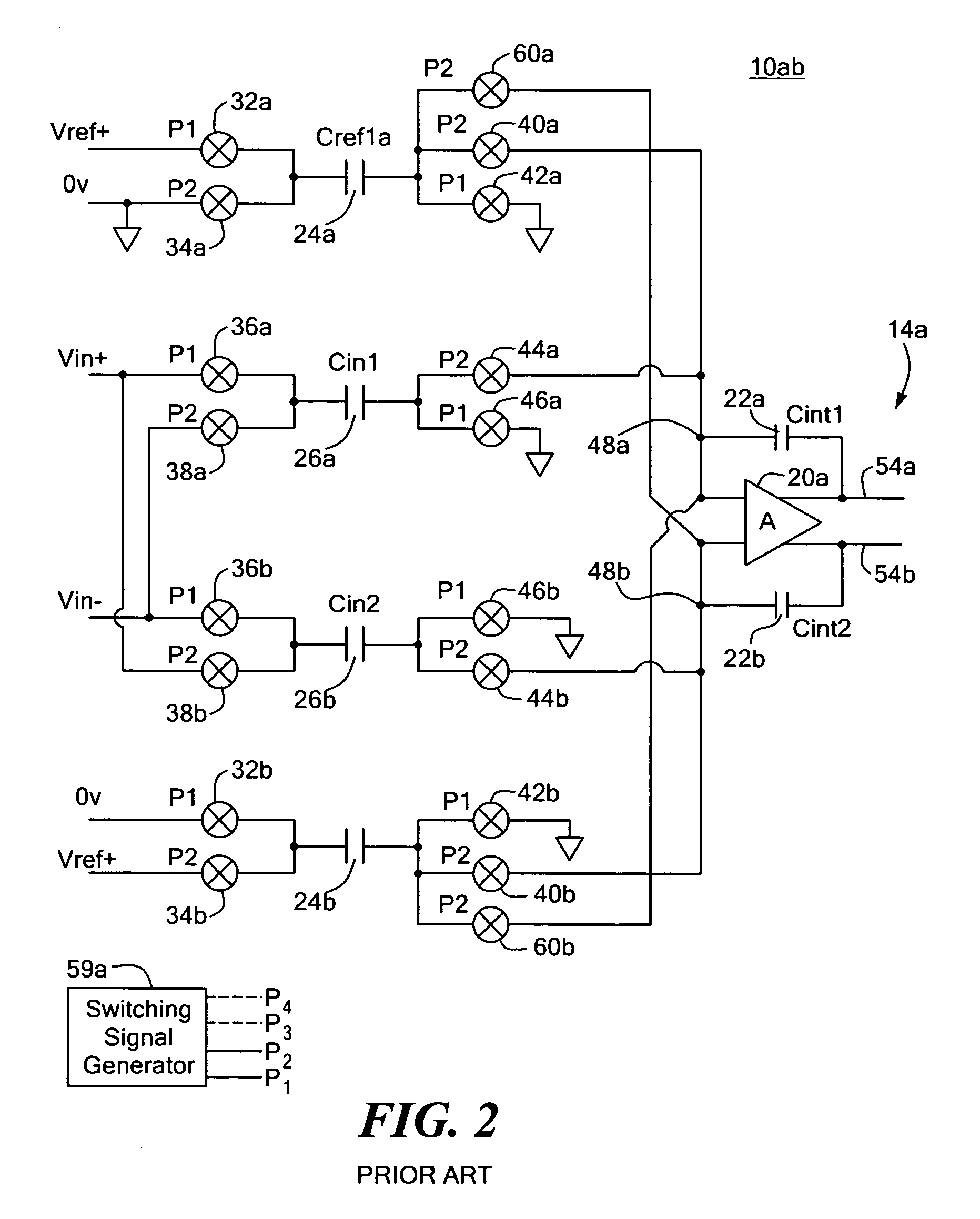

Variable capacitance switched capacitor input system and method

ActiveUS6970126B1Current errorElectric signal transmission systemsDelta modulationCapacitanceIntegrator

A variable capacitance switched capacitor input system and method includes a differential integrator circuit having first and second input summing nodes and a variable sensing capacitor; one terminal of the variable sensing capacitor is connected to one of the nodes in the first phase and to the other of the nodes in the second phase; an input terminal connected to a second terminal of the variable sensing capacitor receives a first voltage level in the first phase and a second voltage level in the second phase for delivering the charge on the variable sensing capacitor to the first summing node in the first phase and to the second summing node in the second phase and canceling errors in a differential integrator circuit output caused by leakage current.

Owner:ANALOG DEVICES INC

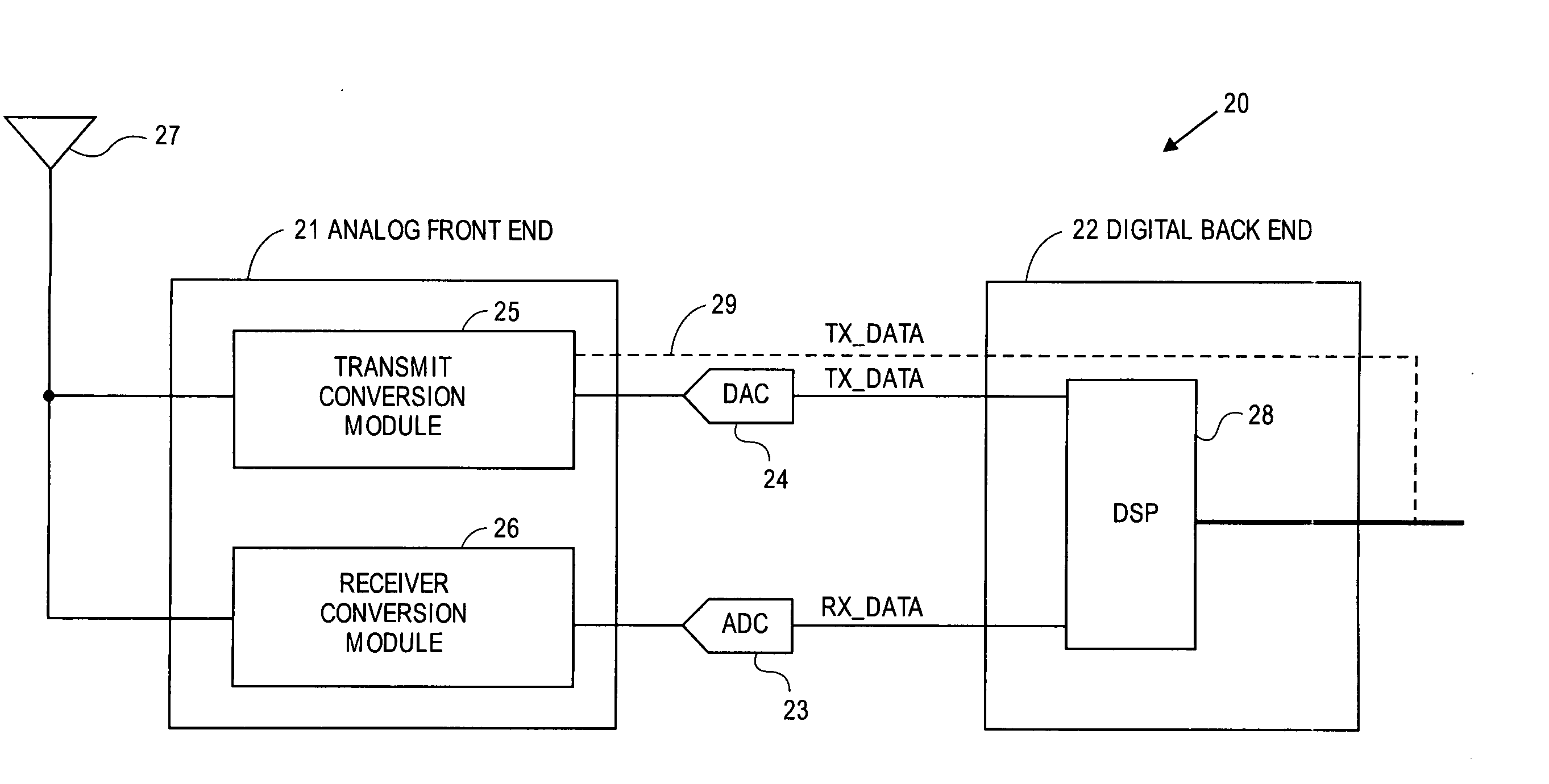

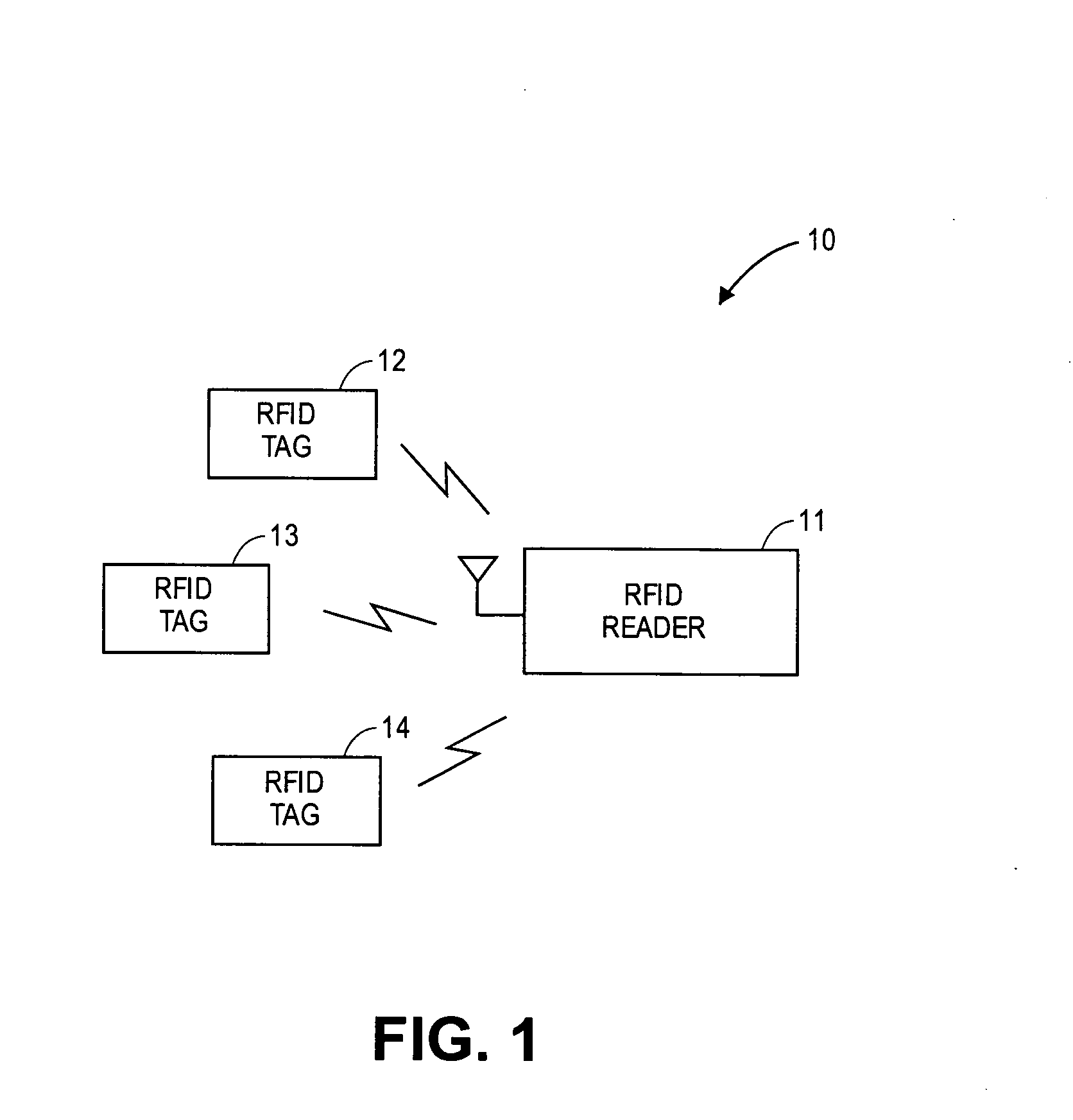

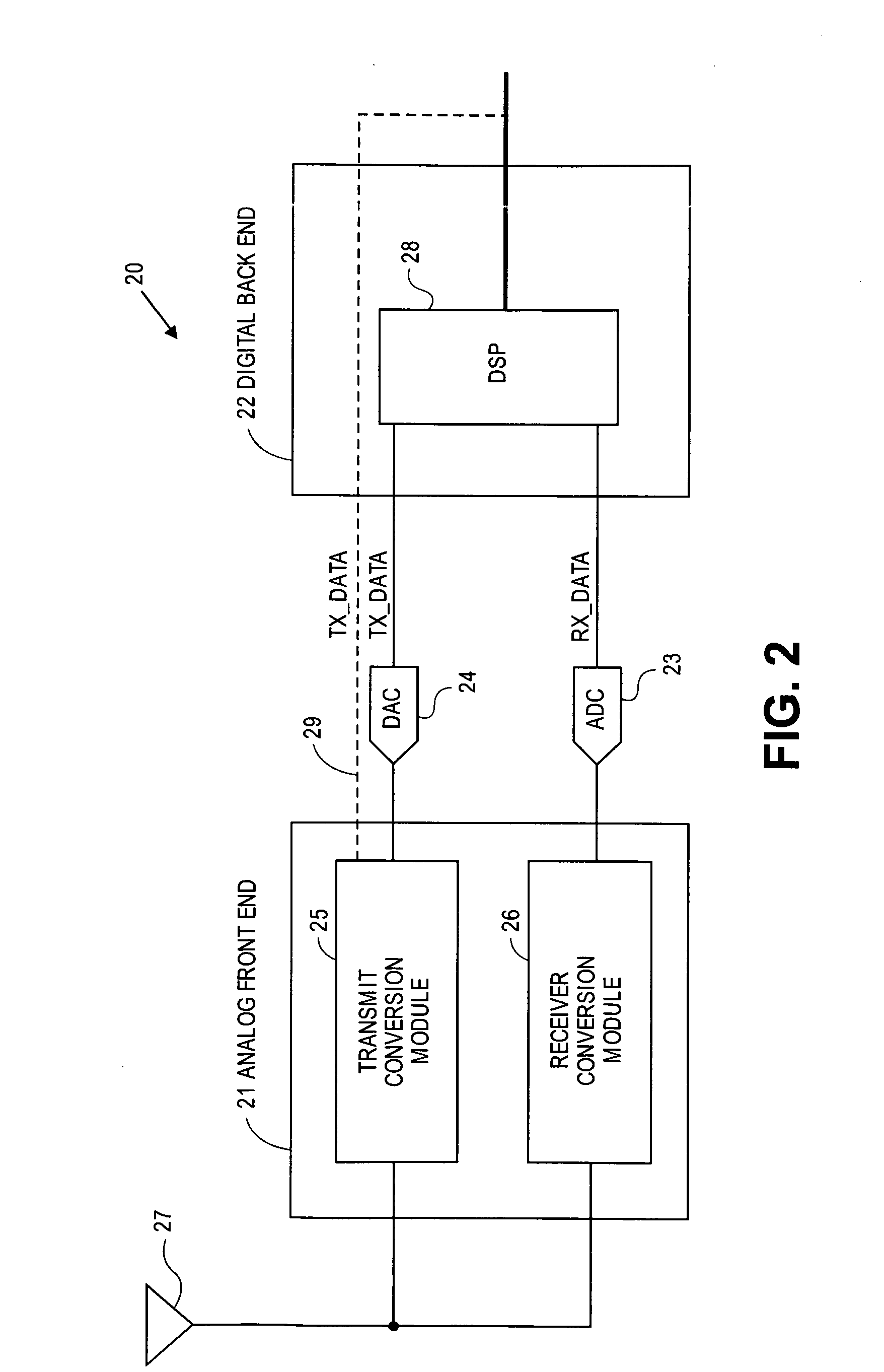

Multi-protocol radio frequency identification reader transceiver

ActiveUS20060186995A1Electric signal transmission systemsError preventionTransceiverDown conversion mixer

A transceiver for a RFID reader and a transceiver for a RFID transponder (tag) allow communication between the two devices. The RFID reader utilizes an analog front end and a digital backend. In the receiver portion of the transceiver, the front end of the RFID reader uses a pair of down-conversion mixers to demodulate a received signal into in-phase (I) and quadrature (Q) components and analog-to-digital converters (ADC) digitize the signal. A digital signal processor (DSP) in the back end processes the digital signal and uses a matched filter for data detection. The RFID tag receives an inductively coupled signal from the reader and the receiver portion of the tag uses a pulse / level detector that employs an analog comparator and a sample and hold circuit to detect the received signal. A digital decoder / controller is used to decode the incoming data and to establish a sampling clock for the pulse / level detector. An automatic gain control (AGC) circuit adjusts a receiver gain according to the received signal strength and controls tuning of magnetic coupling circuitry.

Owner:NXP USA INC

Phase to digital converter in all digital phase locked loop

ActiveUS20090256601A1Low power operationLower requirementElectric signal transmission systemsPulse automatic controlDigital down converterReference Period

A phase to digital converter, all digital phase locked loop, and apparatus having an all digital phase locked loop are described herein. The phase to digital converter includes a phase to frequency converter driving a time to digital converter. The time to digital converter determines a magnitude and sign of the phase differences output by the phase to frequency converter. The time to digital converter utilizes tapped delay lines and looped feedback counters to enable measurement of small timing differences typical of a loop tracking process and large timing differences typical of an loop acquisition process. The tapped delay lines permit the measurement of fractions of a reference period and enable lower power operation of the phase to digital converter by reducing requirements on the speed of the reference clock.

Owner:QUALCOMM INC

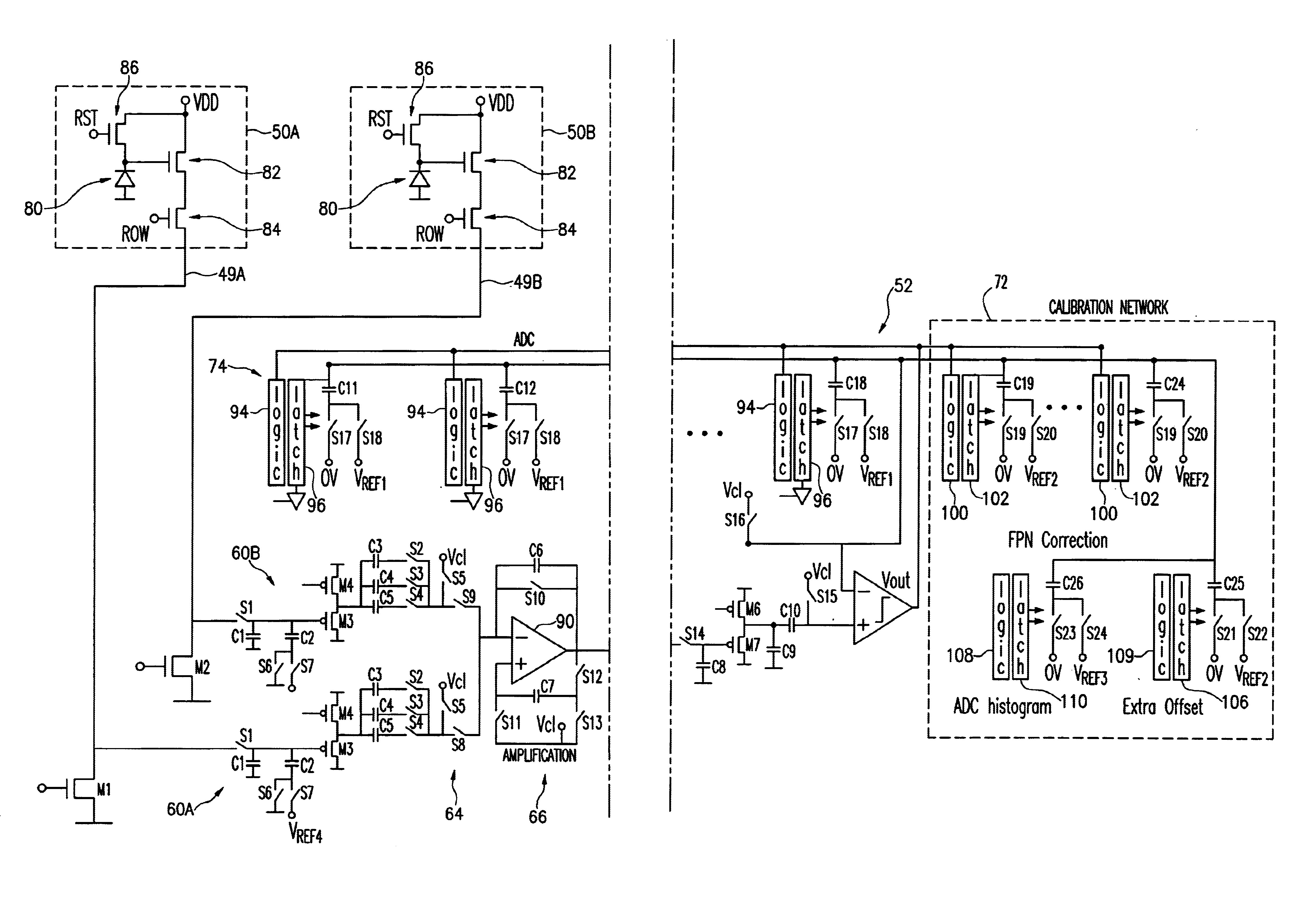

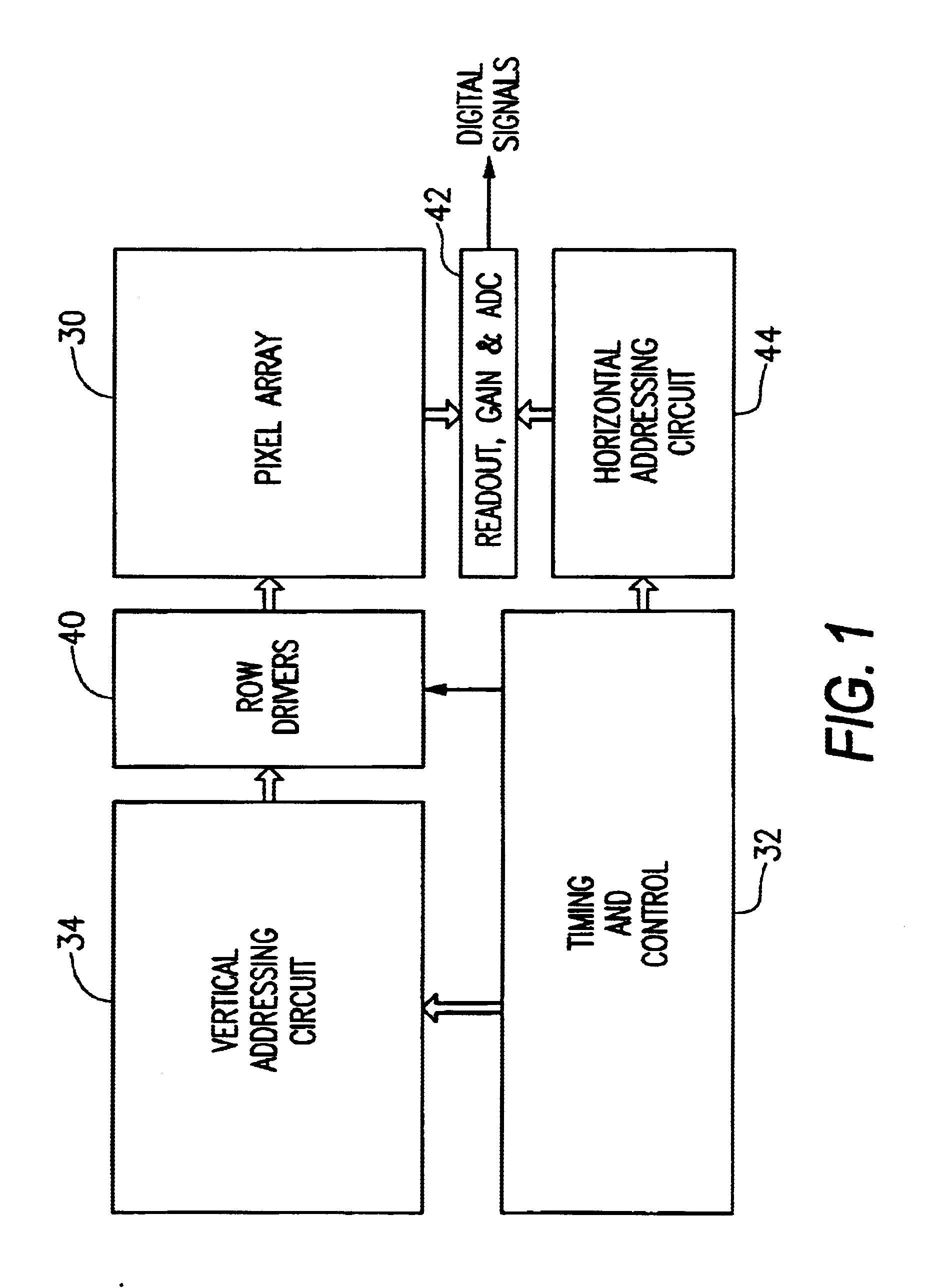

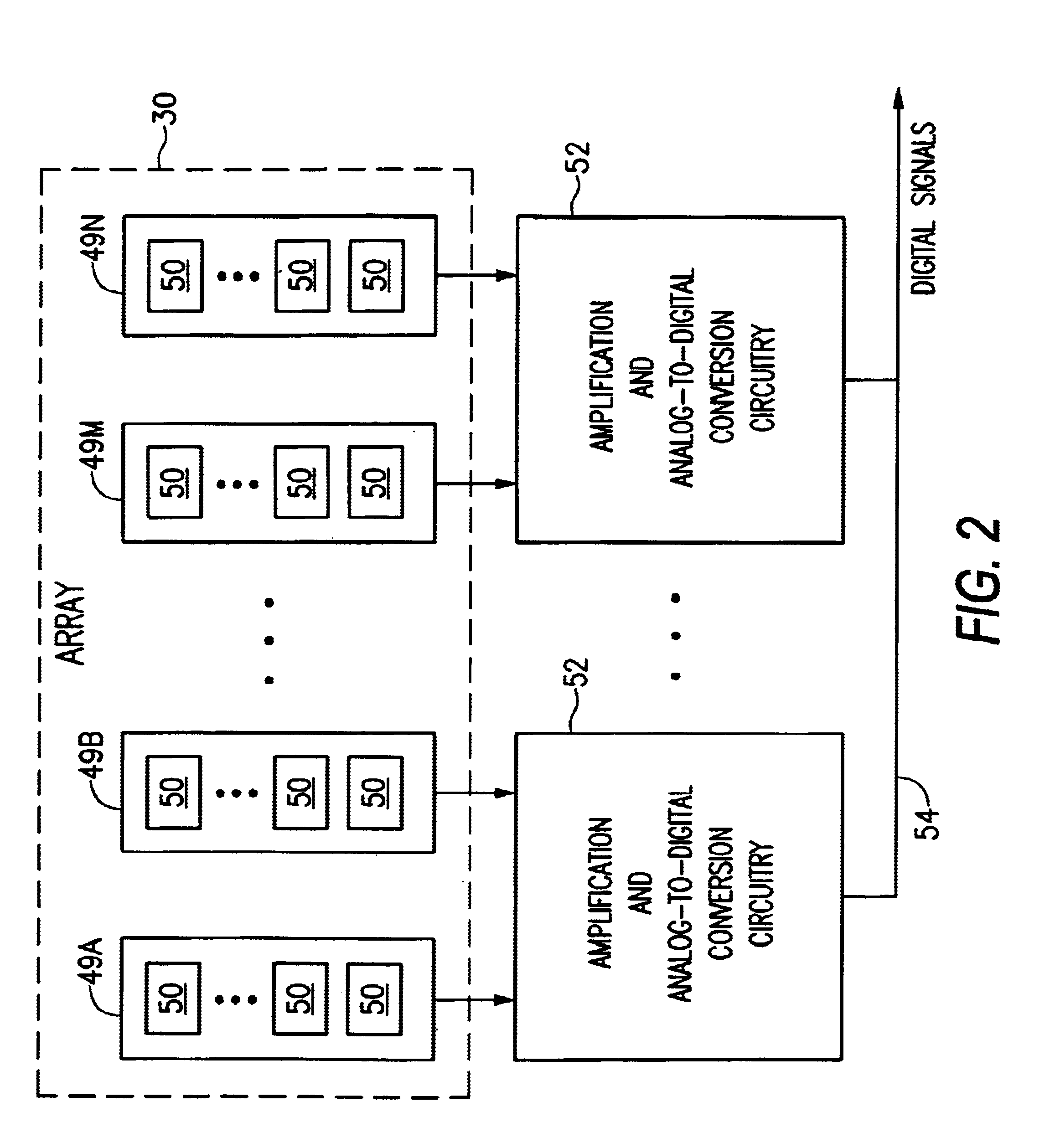

Readout circuit with gain and analog-to-digital a conversion for image sensor

InactiveUS6885396B1Increase parallel structureAttenuation bandwidthTelevision system detailsElectric signal transmission systemsSensor arrayCMOS sensor

A CMOS imager includes an array of active pixel sensors, wherein each pixel is associated with a respective column in the array. The imager also includes multiple circuits for reading out values of pixels from the active sensor array. Each readout circuit can be associated with a respective pair of columns in the array and can include first and second sample-and-hold circuits. The first and second sample-and-hold circuits are associated, respectively, with first and second columns of pixels in the array. Each readout circuit also includes an operational amplifier-based charge sensing circuit that selectively provides an amplified differential output signal based on signals sampled either by the first sample-and-hold circuit or the second sample-and-hold circuit. The readout circuit also has an analog-to-digital converter for converting the differential output to a corresponding digital signal using a successive approximation technique. Use of the readout circuit can increase the parallel structure of the overall chip, thereby reducing the bandwidth which each readout circuit must be capable of handling.

Owner:APTINA IMAGING CORP

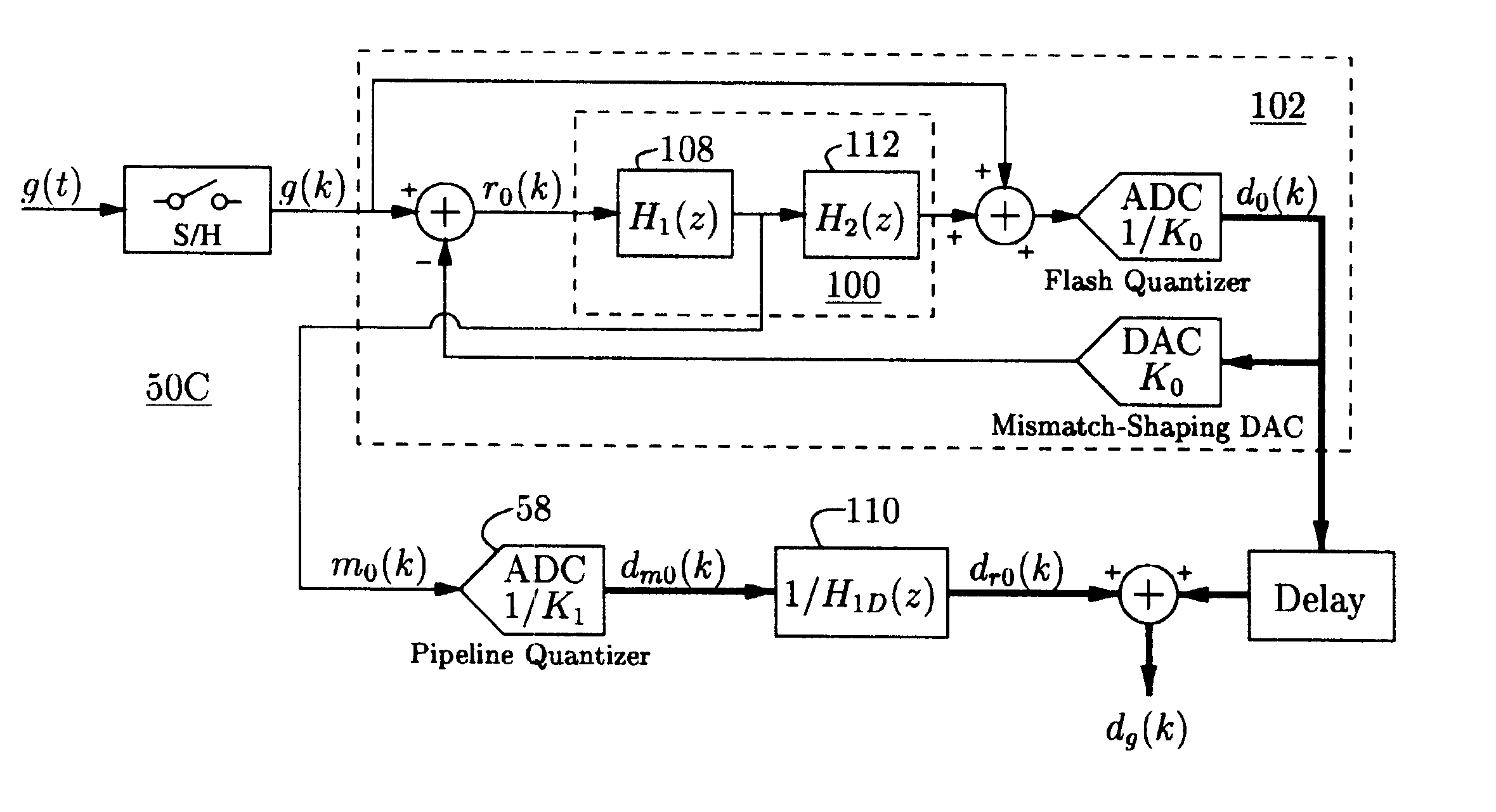

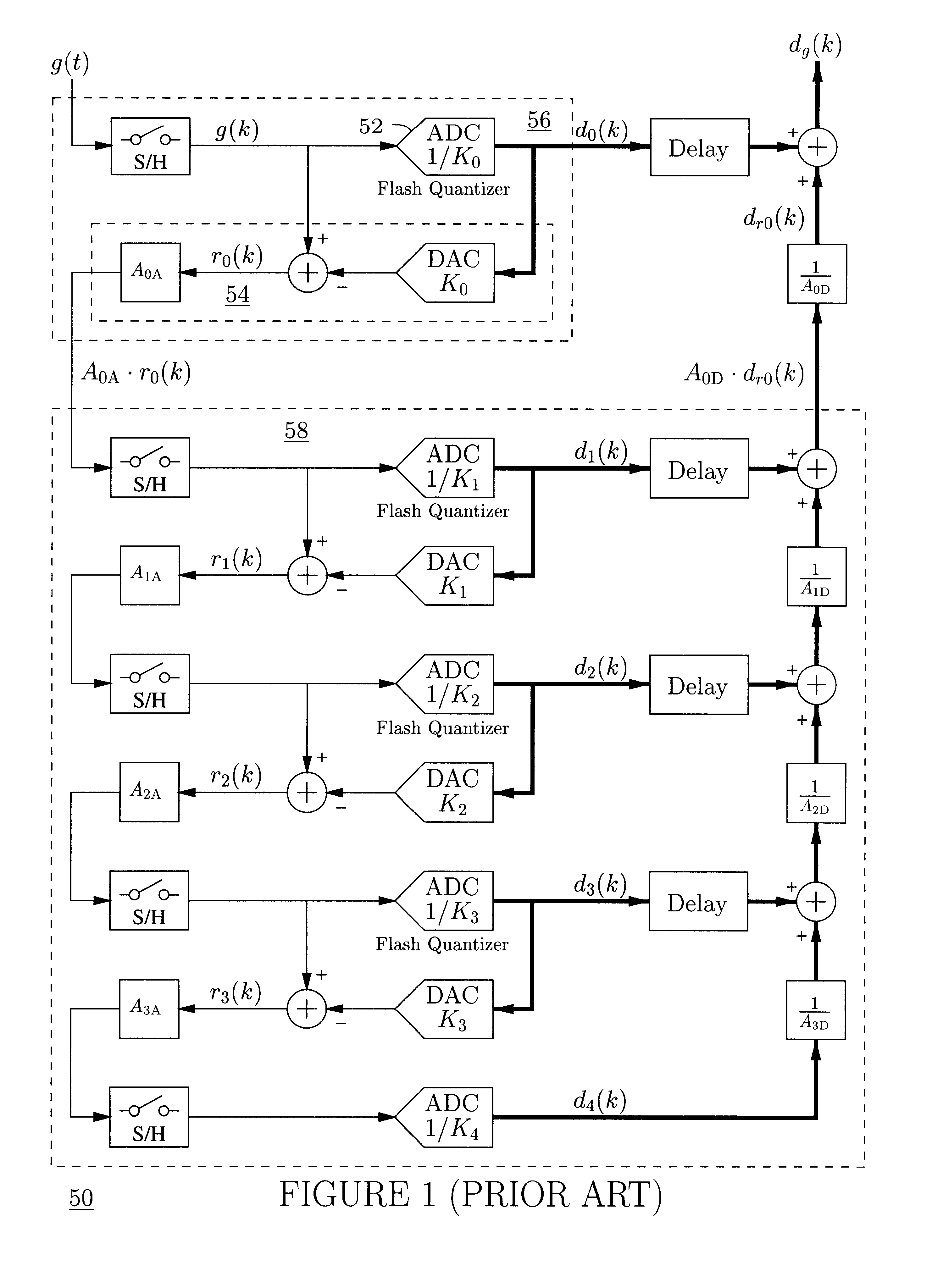

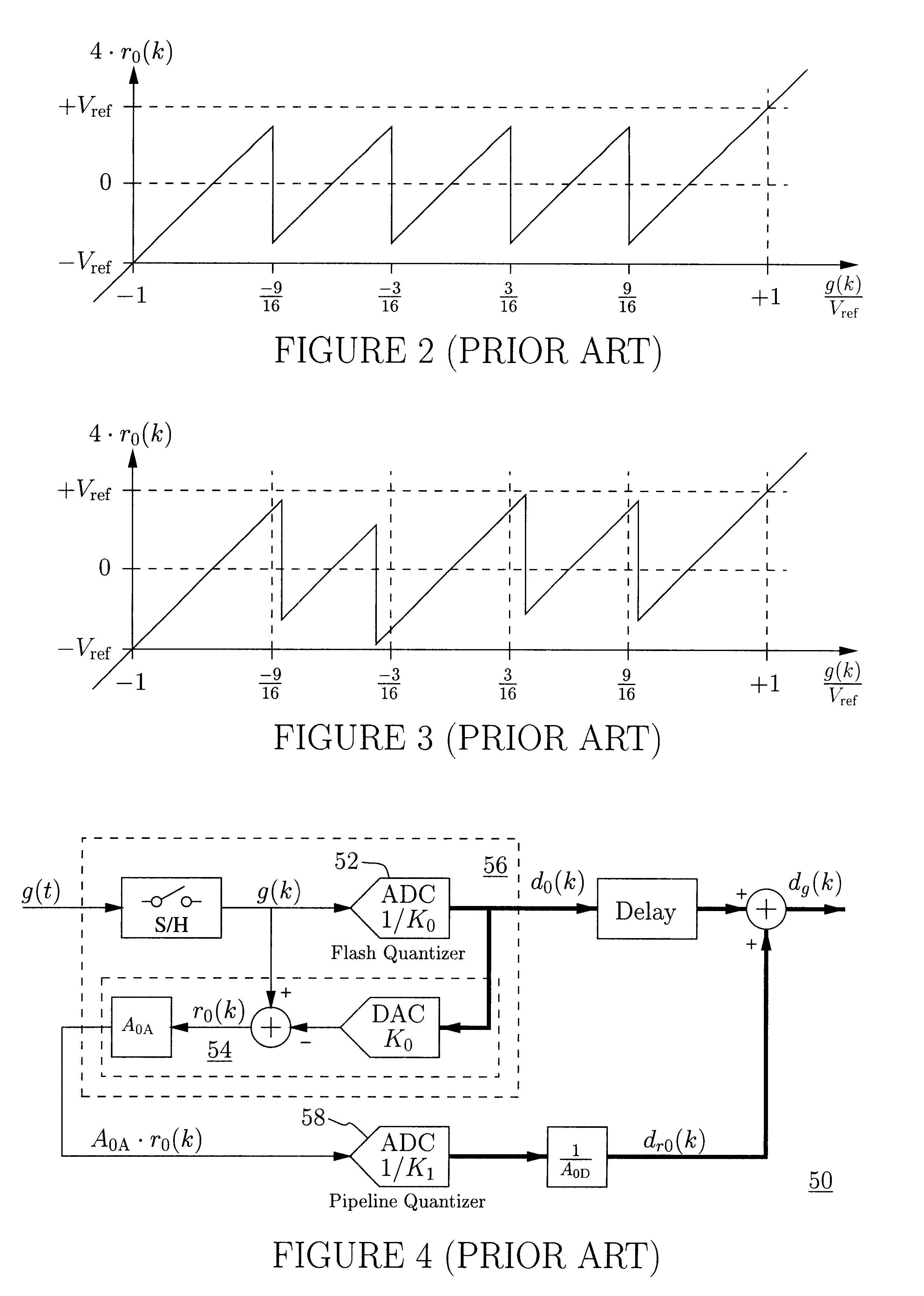

Residue-compensating A/D converter

InactiveUS6556158B2Low-cost highly-linearSuitable for useElectric signal transmission systemsDifferential modulationModem deviceFrequency spectrum

An analog-to-digital converter system [50D] processing an input signal, g, which can be either a discrete-time or a continuous-time signal. A first quantizer [154] generates a first digital signal, d0(k), representing the sum of the input signal, g, and a dithering signal, y0. A digital-to-analog converter [156] generates an analog feedback signal, alpha, representing accurately the first digital signal, d0(k). The DAC [156] may be linearized by the use of mismatch-shaping techniques. A filter [158] generates the dithering signal, y0, by selectively amplifying in the signal band the residue signal, r0, defined as the difference of the input signal, g, and the analog feedback signal, alpha. Optional signal paths [166][168] are used to minimize the closed-loop signal transfer function from g to y0, which ideally will be zero. An analog compensation signal, m0, which is described by a well-controlled relationship to the residue signal, r0, is extracted from the filter [158]. Ideally, the closed-loop signal transfer function from g to m0 will be zero, or at least small in the signal band. A second quantizer [160] converts the analog compensation signal, m0, into a second digital signal, dm0(k). The two digital signals, d0(k) and dm0(k), are filtered individually and then added to form the overall output signal, dg(k). The second digital filter [164] has a low signal-band gain, which implies that the sensitivity to signal-band errors caused by the second quantizer [160] will be low. The output signal, dg(k), is a highly-accurate high-resolution representation of the input signal, g. Circuit imperfections, such as mismatch, gain errors, and nonlinearities, will cause only noise-like errors having a very low spectral power density in the signal band.The invention facilitates the implementation of uncalibrated highly-linear high-resolution wide-bandwidth A / D converters [50D], e.g., for use in digital communication systems, such as xDSL modems and other demanding consumer-market products for which low cost is of the essence.

Owner:ANALOG DEVICES BV

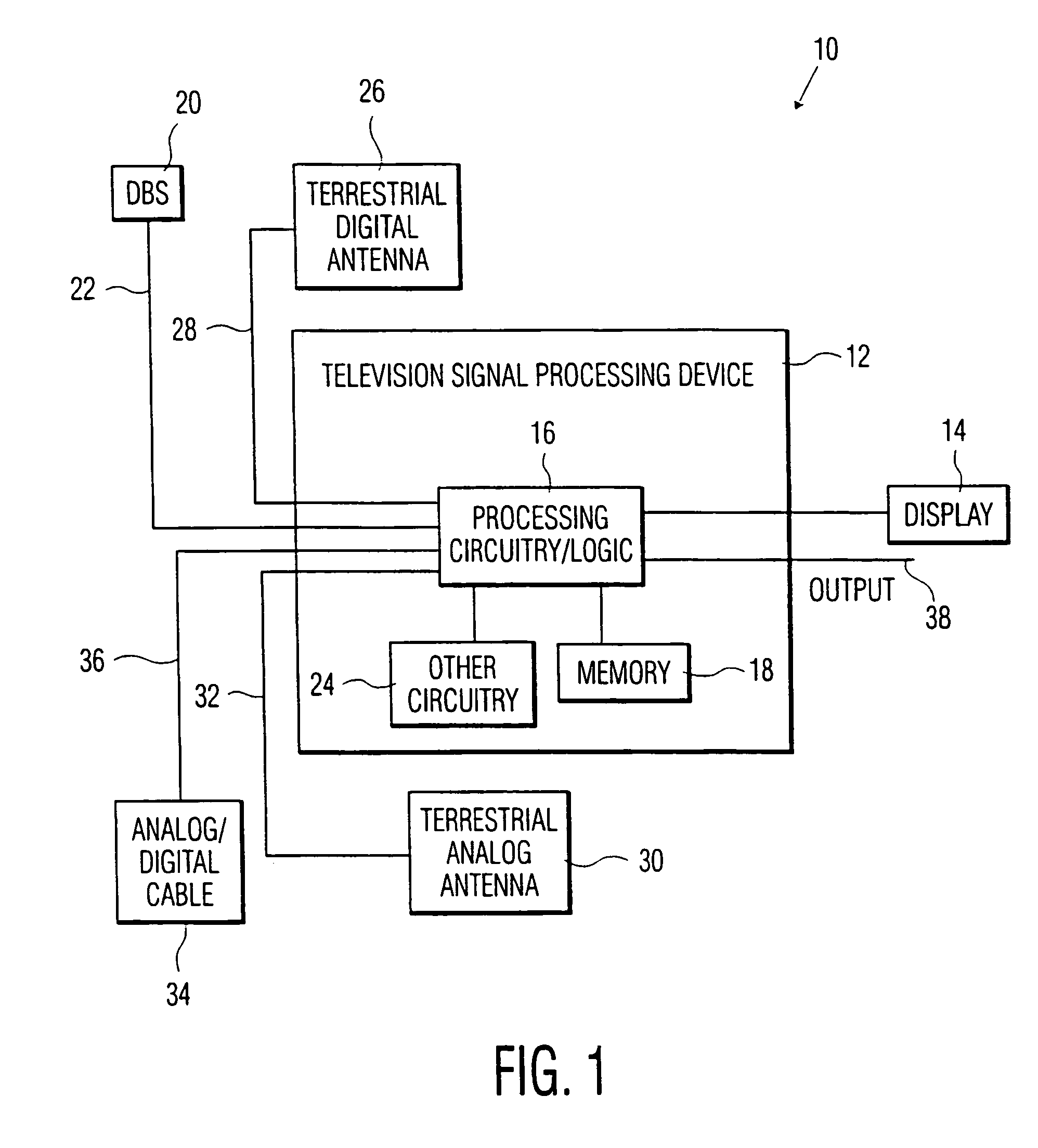

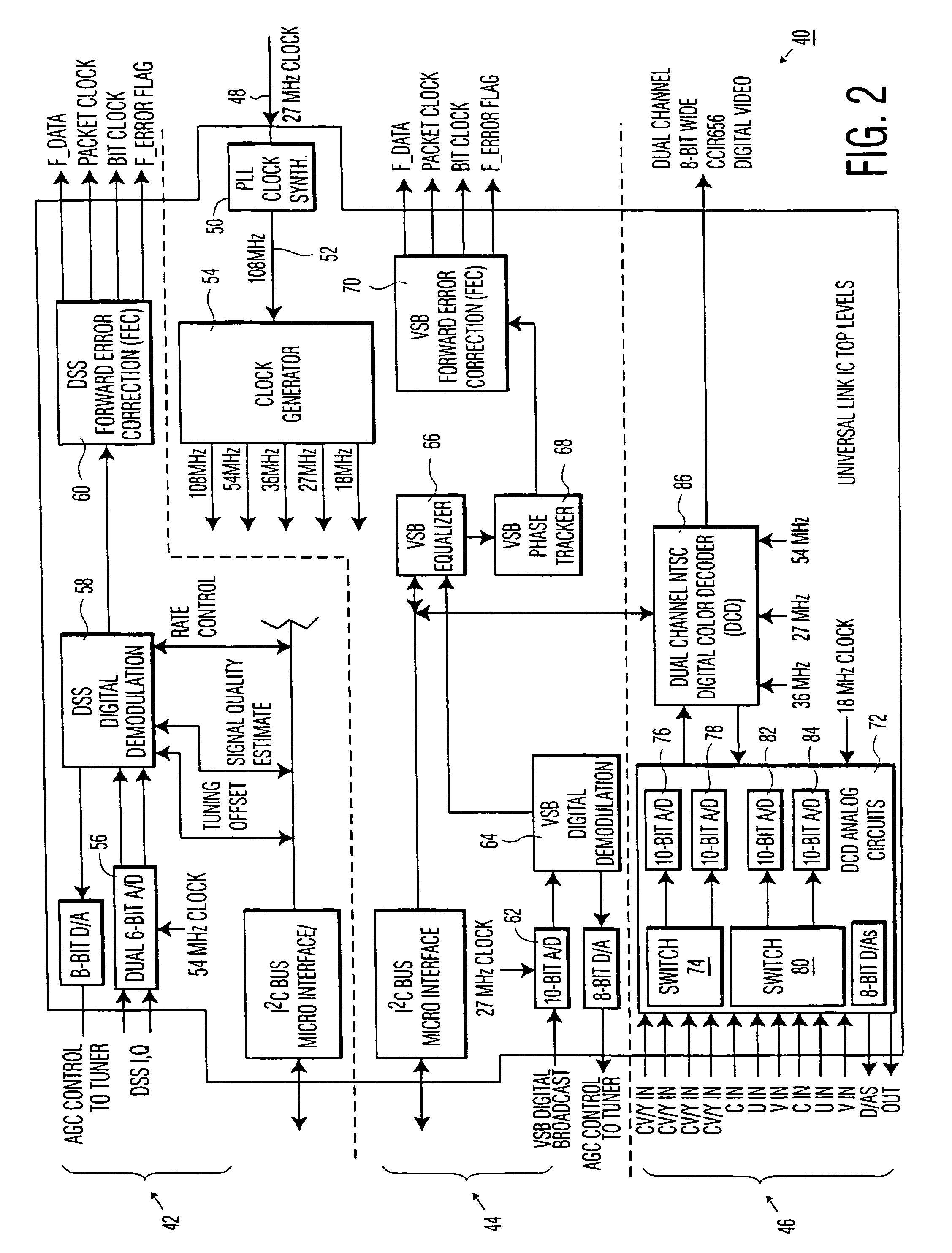

Digital and analog television signal digitization and processing device

InactiveUS7102692B1Easy to processImprove sampling performanceTelevision system detailsElectric signal transmission systemsFrequency generationAnalog signal processing

A digital and analog television signal digitization and processing device that performs the digitization and processing functions using a common reference frequency source that is used to generate multiple subclock signals, wherein the reference frequency source is independent of any synchronizing characteristic of the input signal. For dual channel analog signal processing, the common frequency source is not locked to either channel / input signal. Digital signal processing is accomplished based on the same common reference frequency source. Advantageously, the present invention allows all of the analog-to-digital converters and decoder circuitry / logic necessary for simultaneously digitizing and processing several analog and digital television signals to be integrated on a single integrated circuit as well as eliminating duplicate frequency generation circuits.

Owner:MAGNOLIA LICENSING LLC

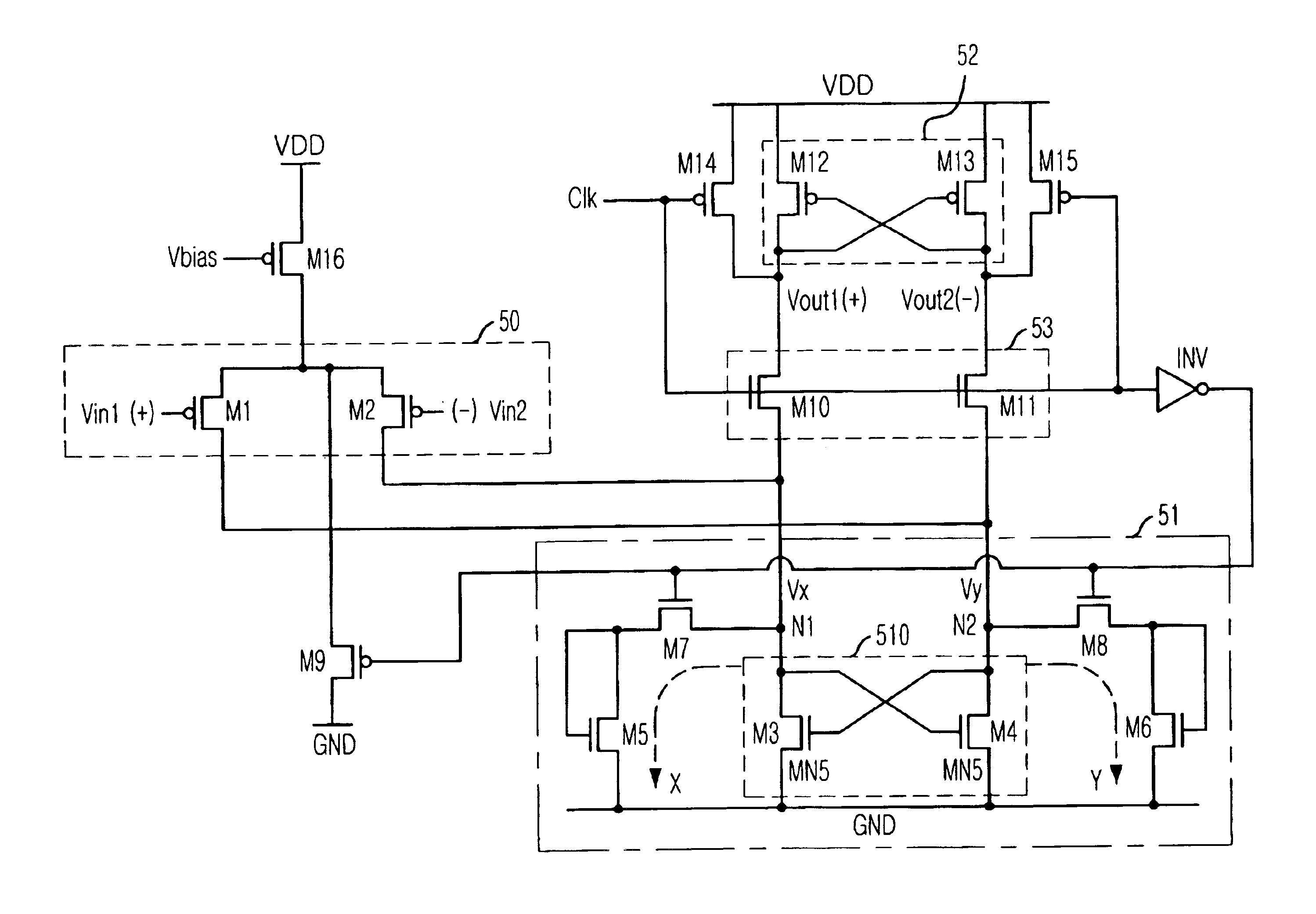

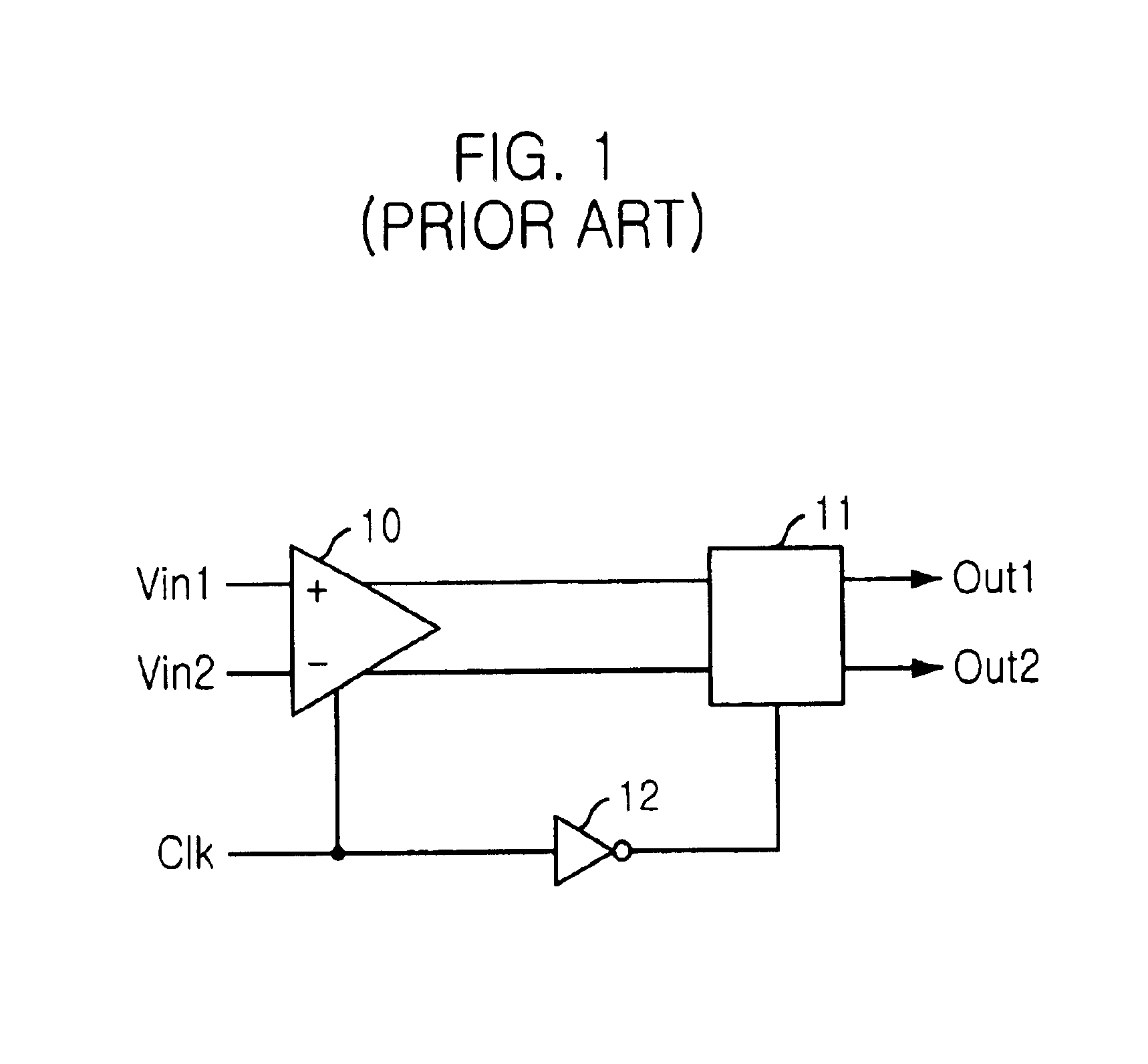

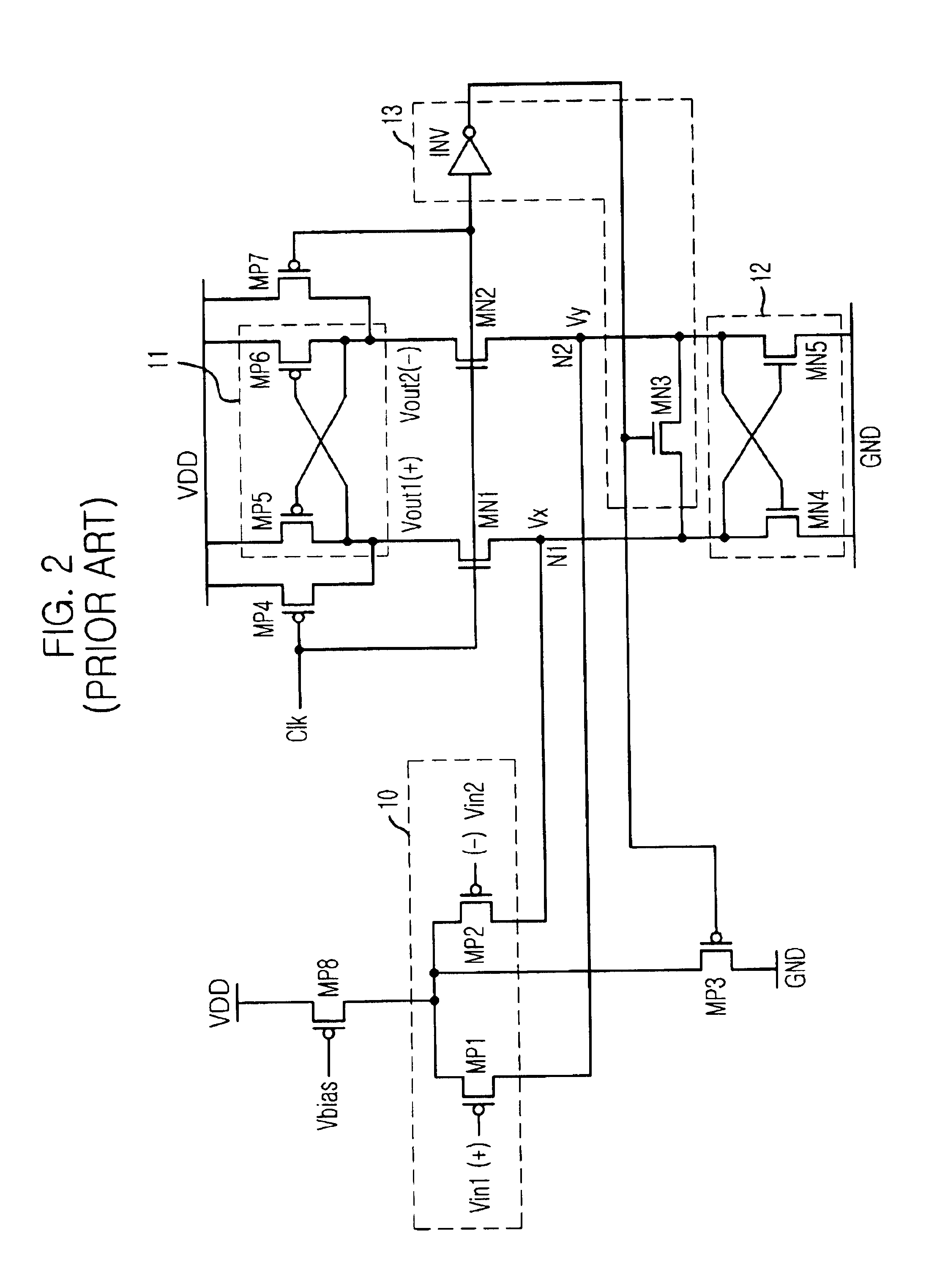

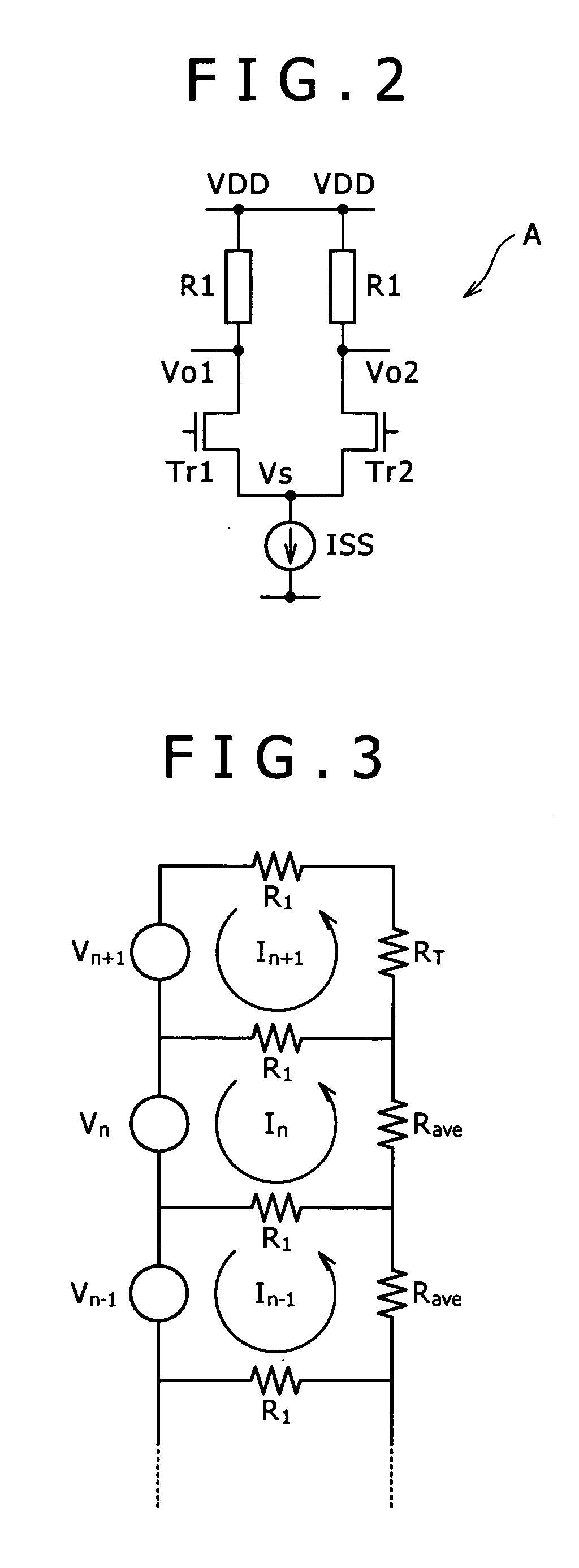

Comparison apparatus operated at a low voltage

InactiveUS6847234B2Inhibition of changes in propertiesGuaranteed uptimeElectric signal transmission systemsMultiple input and output pulse circuitsCmos comparatorLow voltage

The present invention provide an CMOS comparator outputting one bit digital signal after comparing two analog input signals through alternately performing a track mode operation and latch mode operation decided by a clock signal having a constant period, including: a latching unit having the main / sub input terminal; a first switching transistor having the clock signal as a gate input and having one end coupled to main input terminal; a first load transistor diode-connected to the other end of the first switching transistor and a ground end; a second switching transistor having a gate receiving the clock signal as a gate input and one end coupled to the sub input terminal; and a second load transistor diode-connected to the second switching transistor and to the other end of the ground terminal.

Owner:KEY FOUNDRY CO LTD

AD converter

InactiveUS8106806B2Reduce power consumptionReduce areaElectric signal transmission systemsAnalogue-digital convertersVoltage generatorAudio power amplifier

Owner:SONY CORP

Circuit for high-resolution phase detection in a digital RF processor

ActiveUS7205924B2Less sensitiveReduce power consumptionElectric signal transmission systemsModulated-carrier systemsDigital converterCmos process

A novel time-to-digital converter (TDC) used as a phase / frequency detector and charge pump replacement in an all-digital PLL within a digital radio processor. The TDC core is based on a pseudo-differential digital architecture making it insensitive to NMOS and PMOS transistor mismatches. The time conversion resolution is equal to an inverter propagation delay, e.g., 20 ps, which is the finest logic-level regenerative timing in CMOS. The TDC is self calibrating with the estimation accuracy better than 1%. The TDC circuit can also serve as a CMOS process strength estimator for analog circuits in large SoC dies. The circuit also employs power management circuitry to reduce power consumption to a very low level.

Owner:TEXAS INSTR INC