Patents

Literature

8206 results about "Analog to digital conversion" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

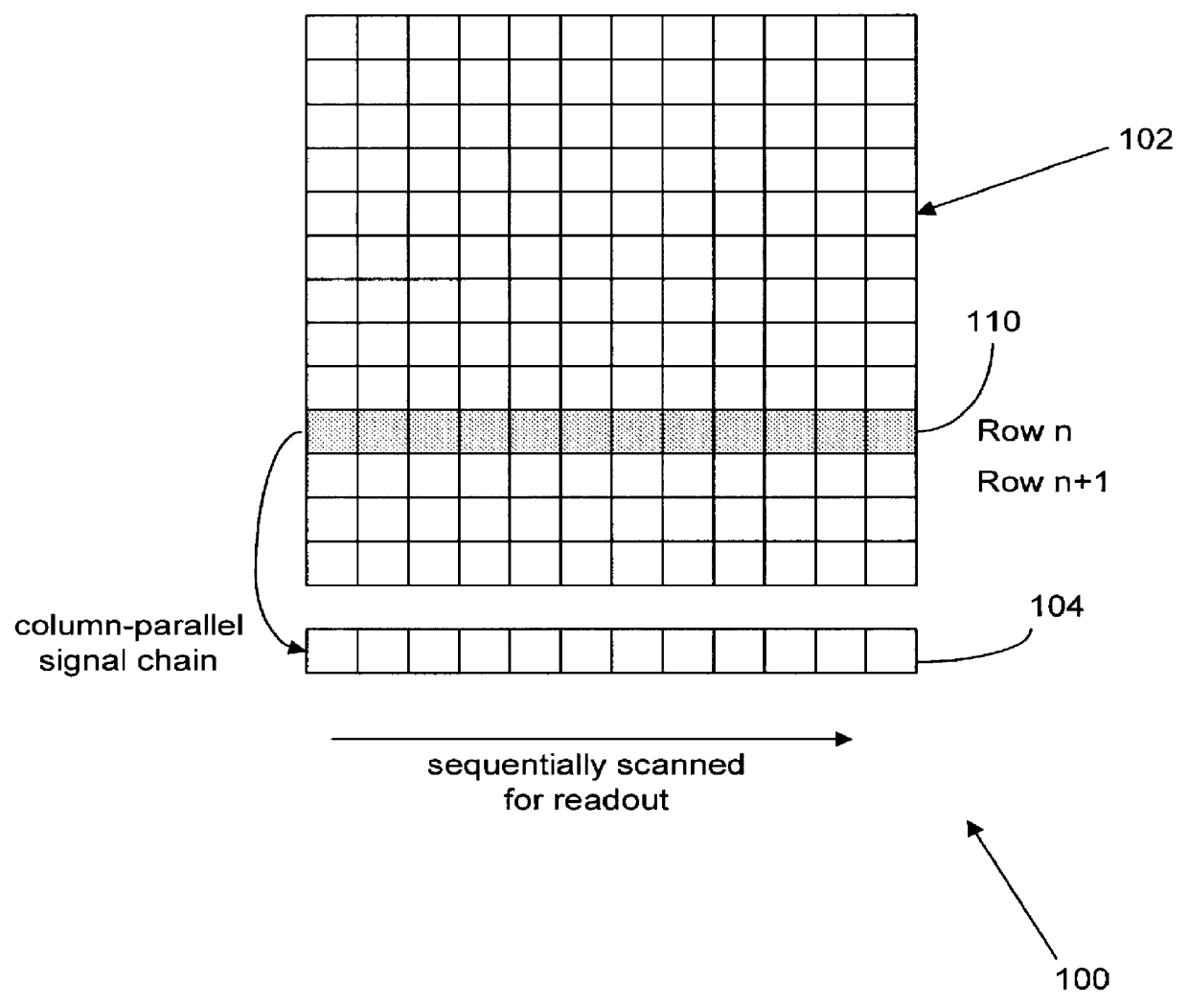

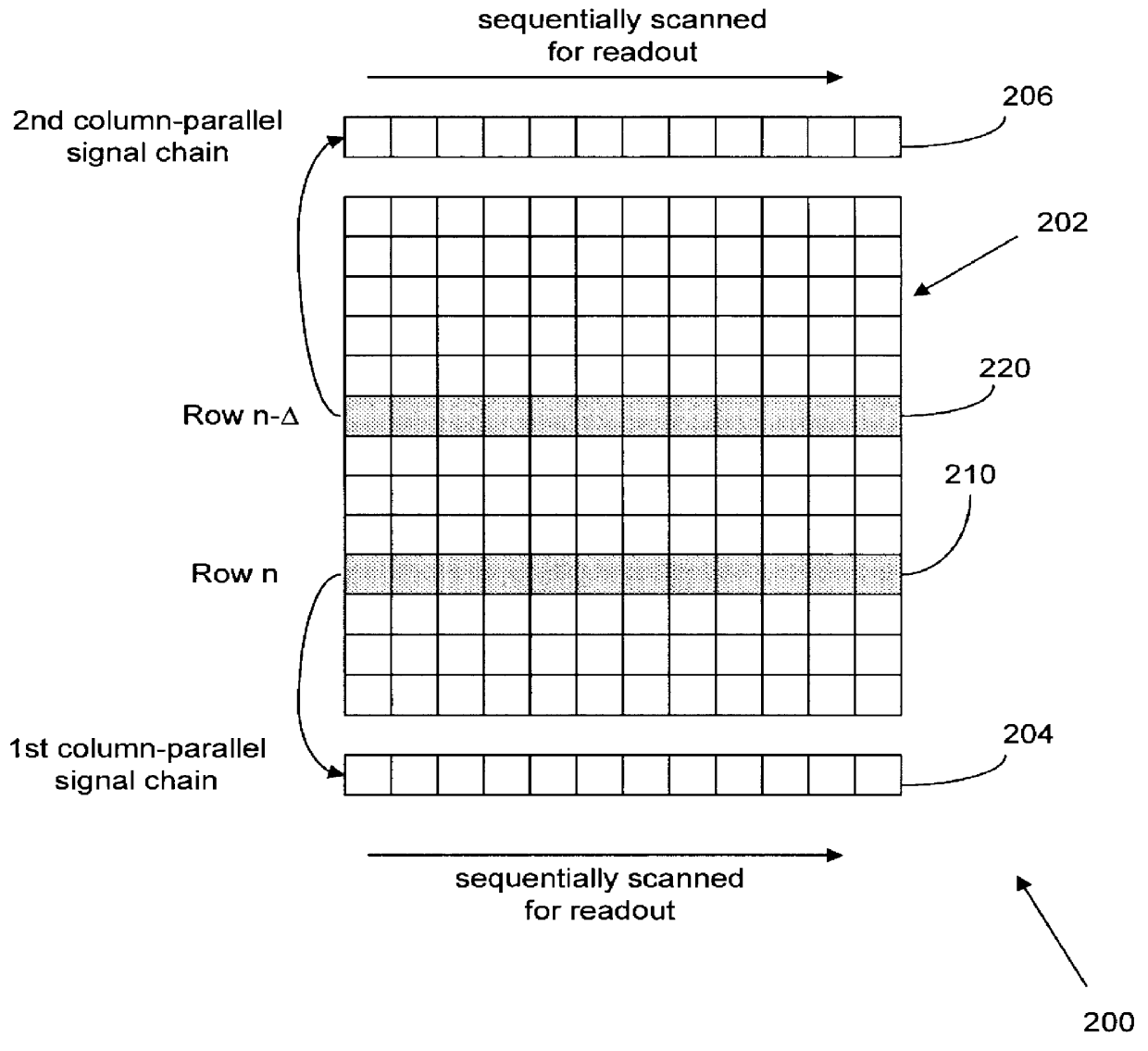

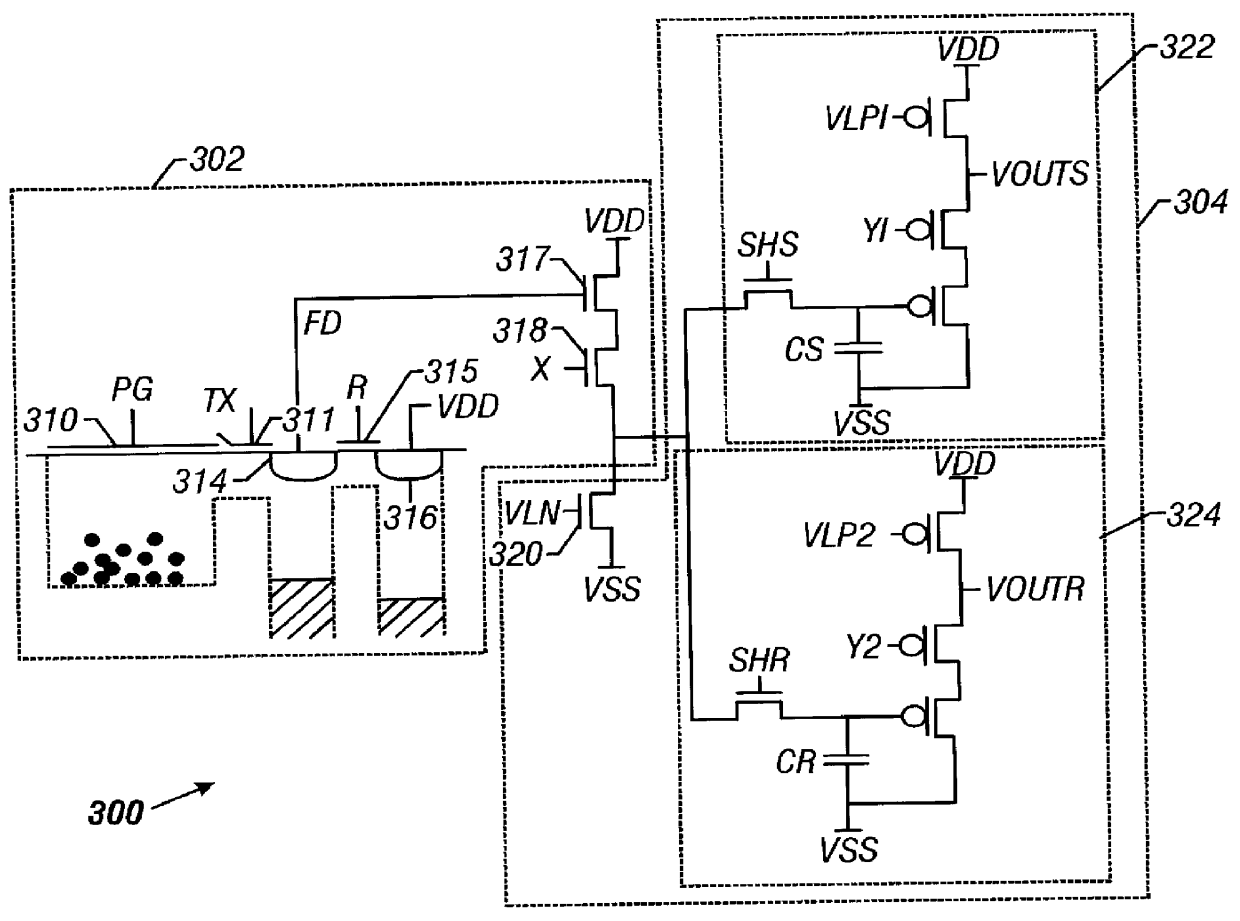

Image sensor producing at least two integration times from each sensing pixel

InactiveUS6115065AIncrease flexibilityImprove performanceTelevision system detailsTelevision system scanning detailsHigh frame rateComputer science

Designs and operational methods to increase the dynamic range of image sensors and APS devices in particular by achieving more than one integration times for each pixel thereof. An APS system with more than one column-parallel signal chains for readout are described for maintaining a high frame rate in readout. Each active pixel is sampled for multiple times during a single frame readout, thus resulting in multiple integration times. The operation methods can also be used to obtain multiple integration times for each pixel with an APS design having a single column-parallel signal chain for readout. Furthermore, analog-to-digital conversion of high speed and high resolution can be implemented.

Owner:CALIFORNIA INST OF TECH

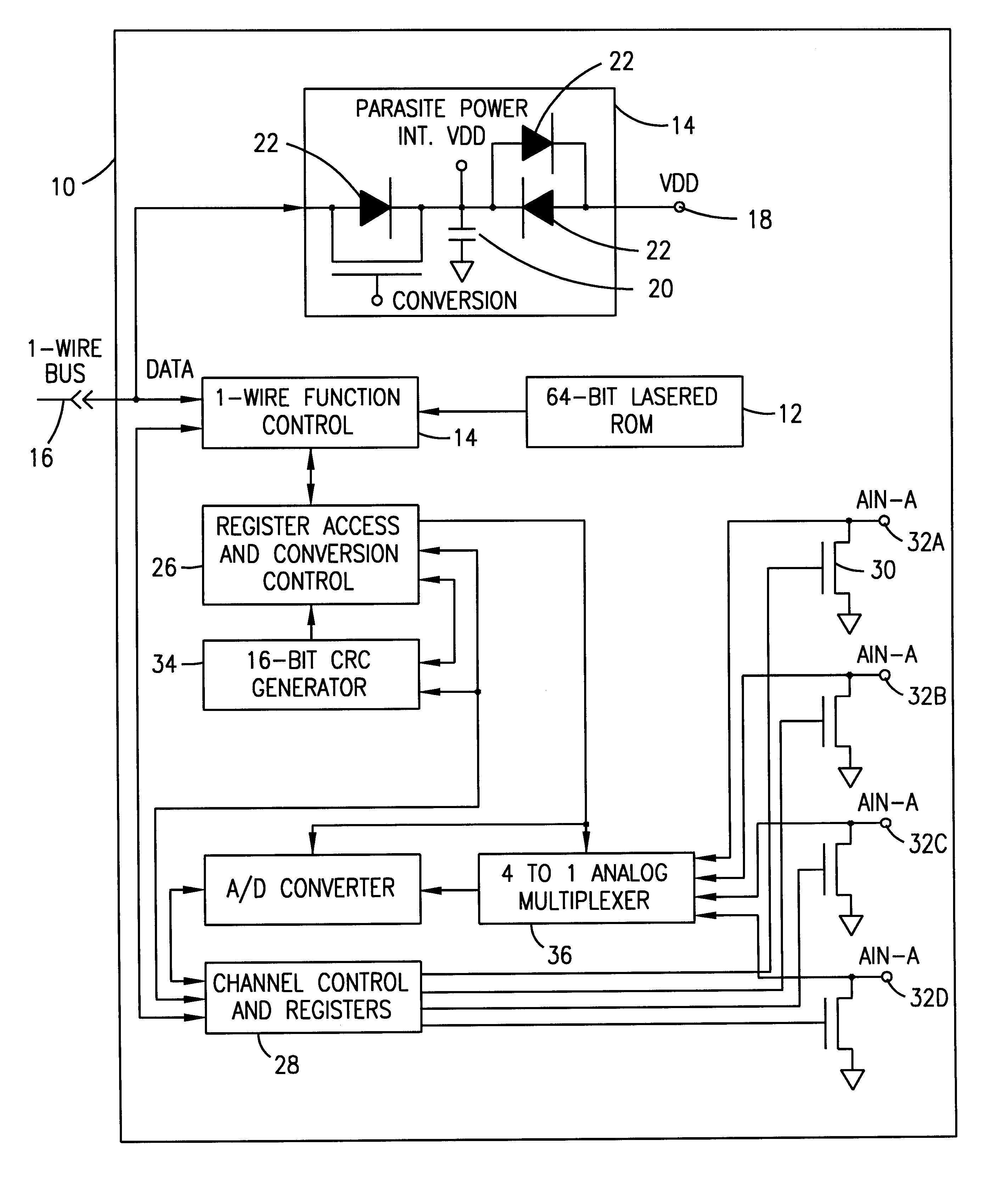

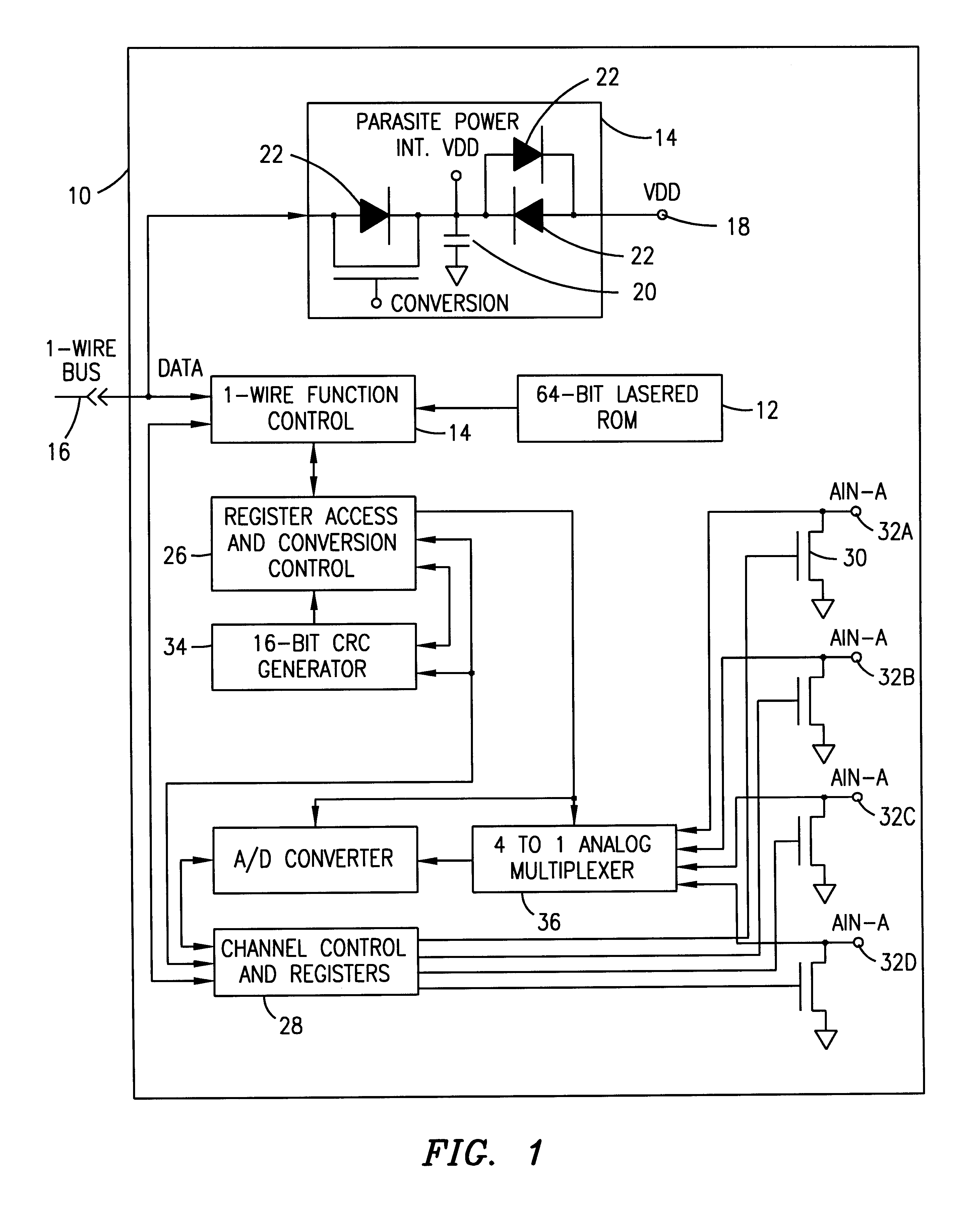

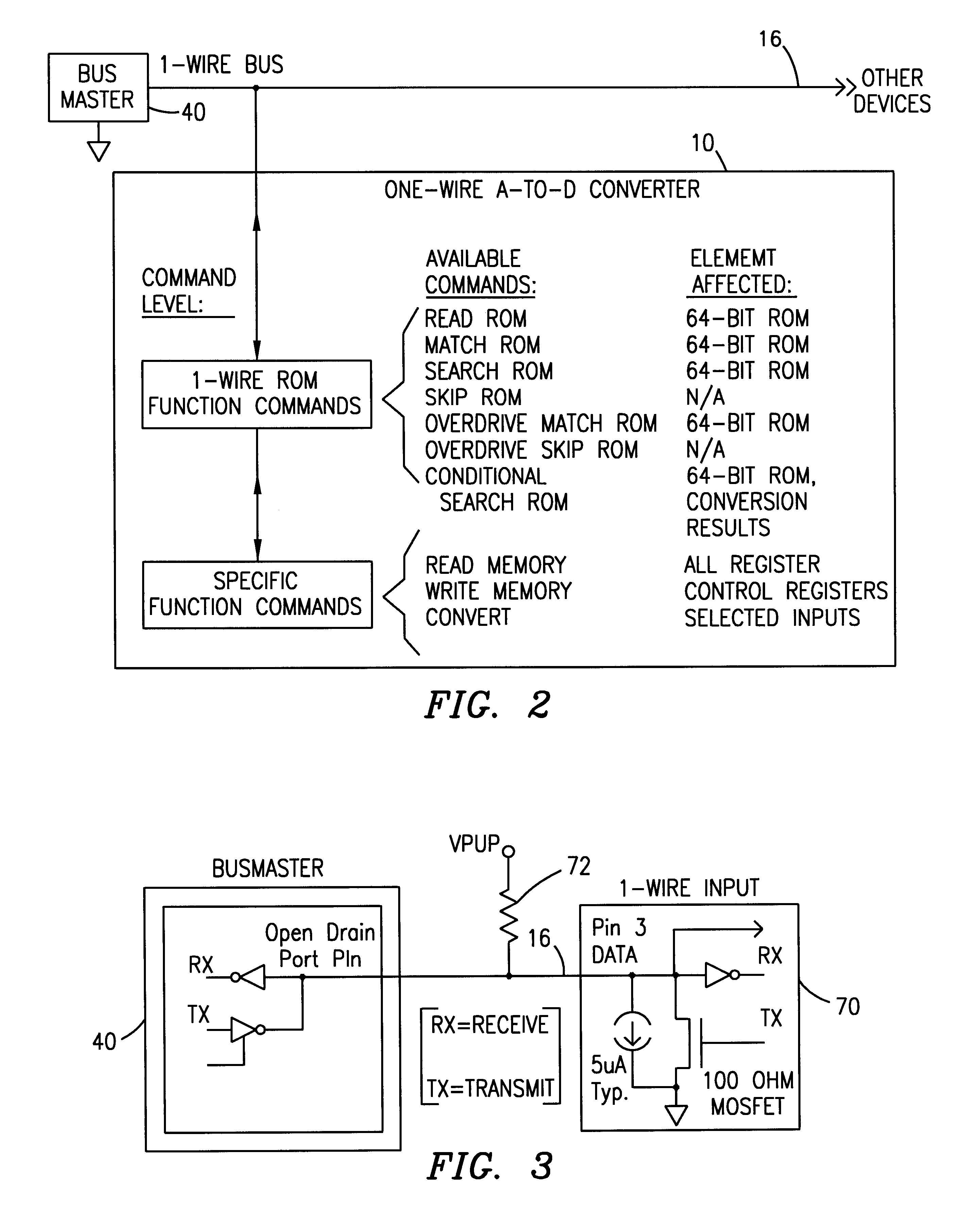

One-wire device with A-to-D converter

InactiveUS6239732B1Electric signal transmission systemsAnalogue-digital convertersĆuk converterAnalog signal

A low power integrated circuit having analog to digital conversion circuitry capable of receiving a plurality of analog signals and converting them to a digital value. The digital value is then transmitted, upon request, over a single wire bus. The accuracy of the analog to digital conversion circuitry can be calibrated via trim codes stored in an onboard EPROM.

Owner:MAXIM INTEGRATED PROD INC

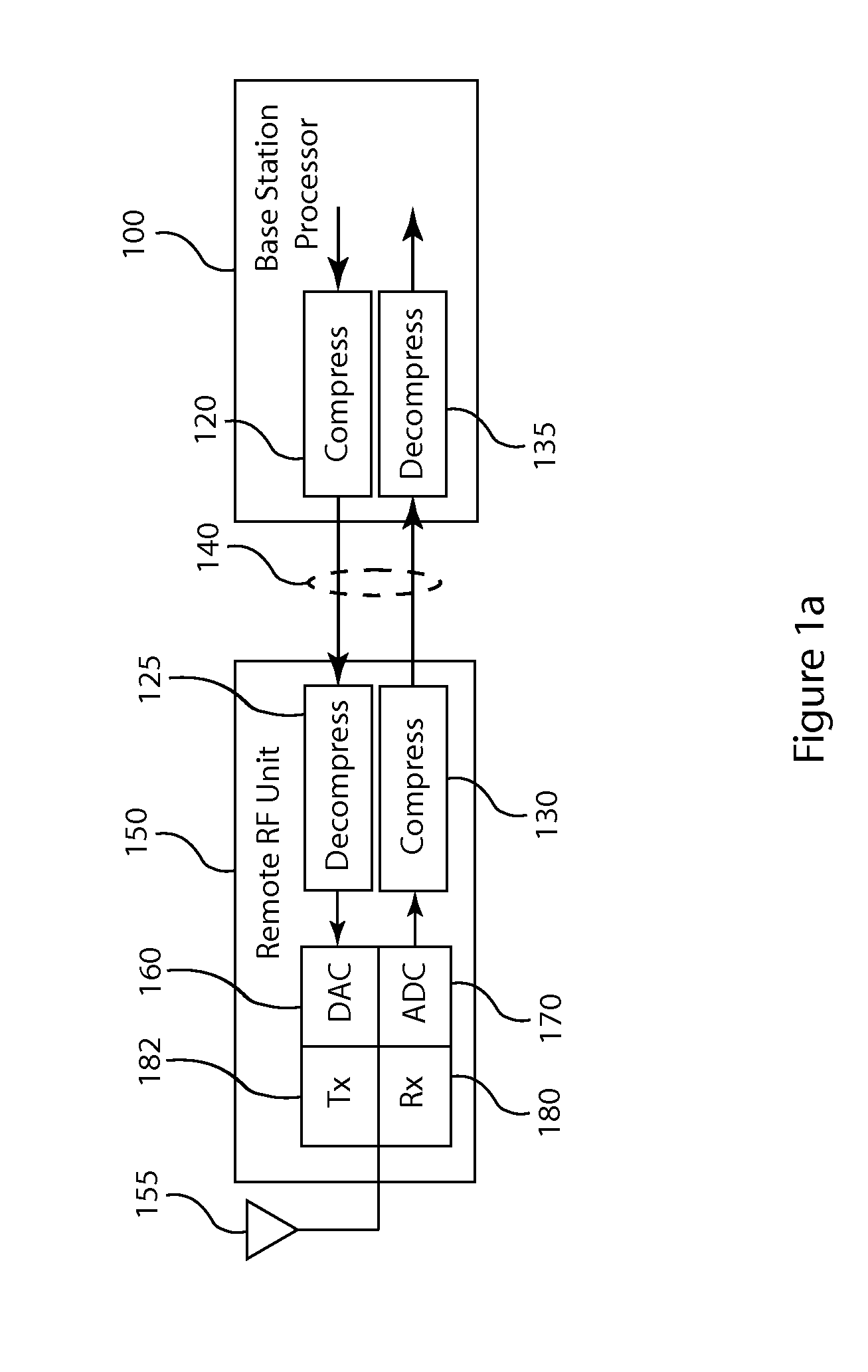

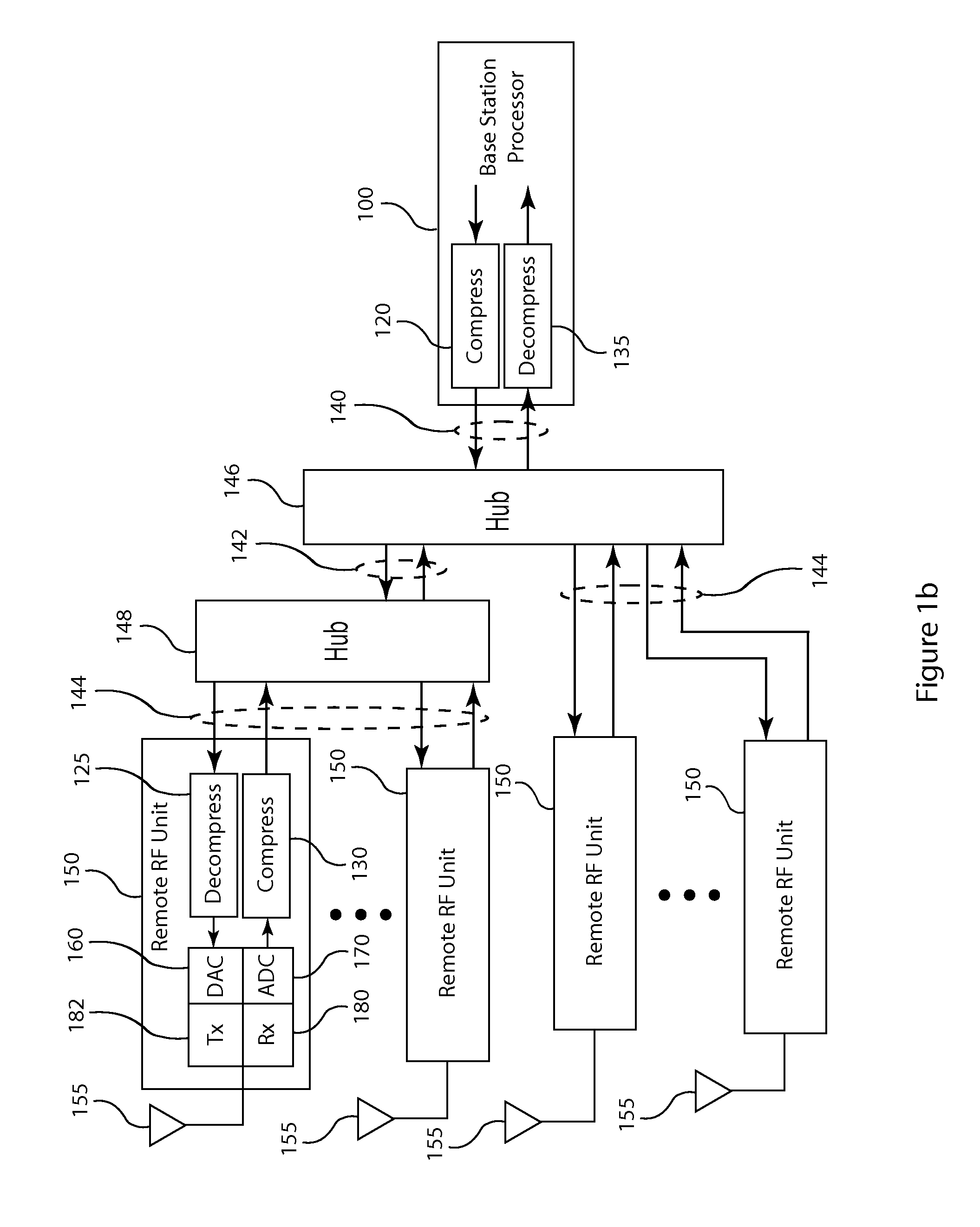

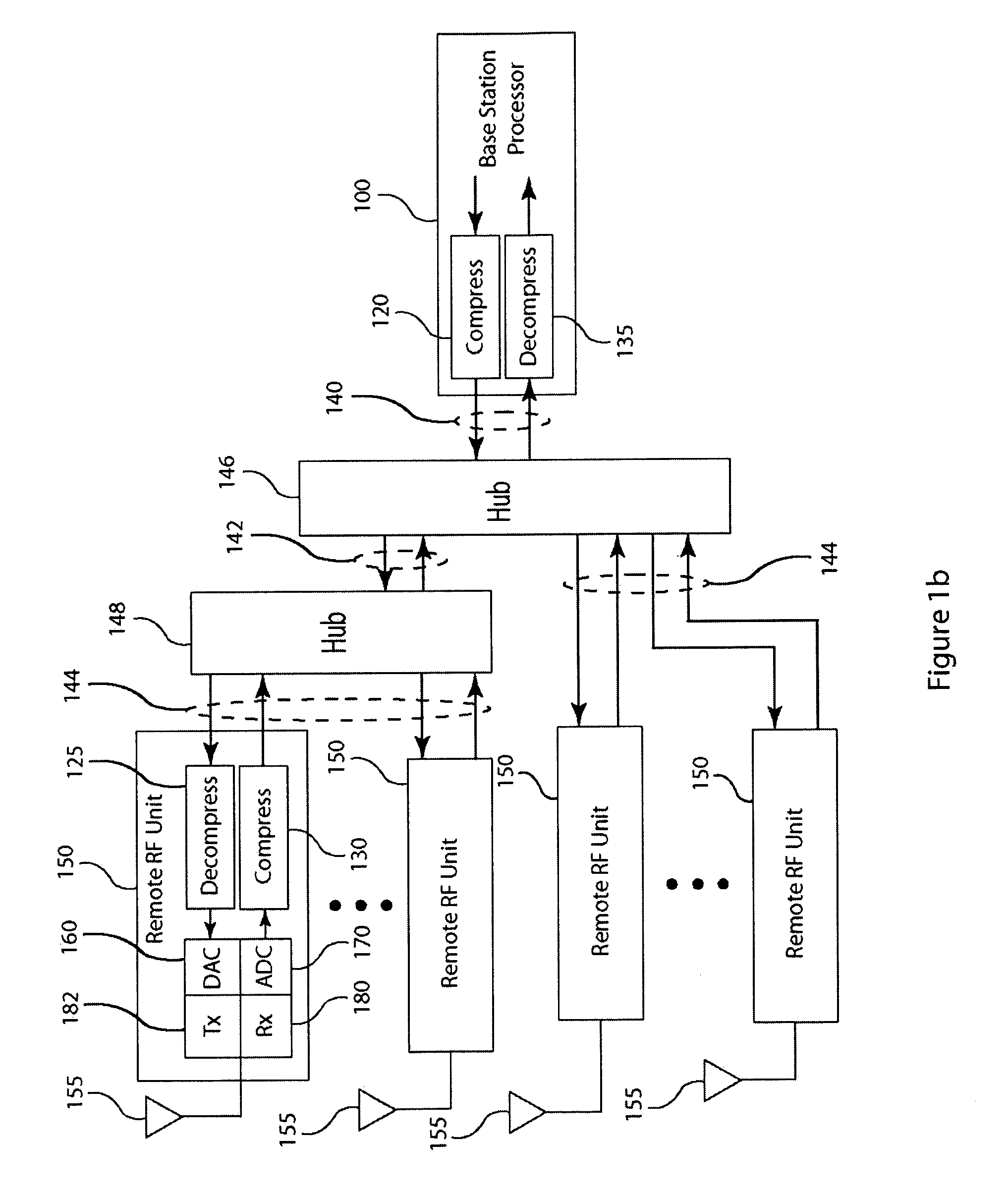

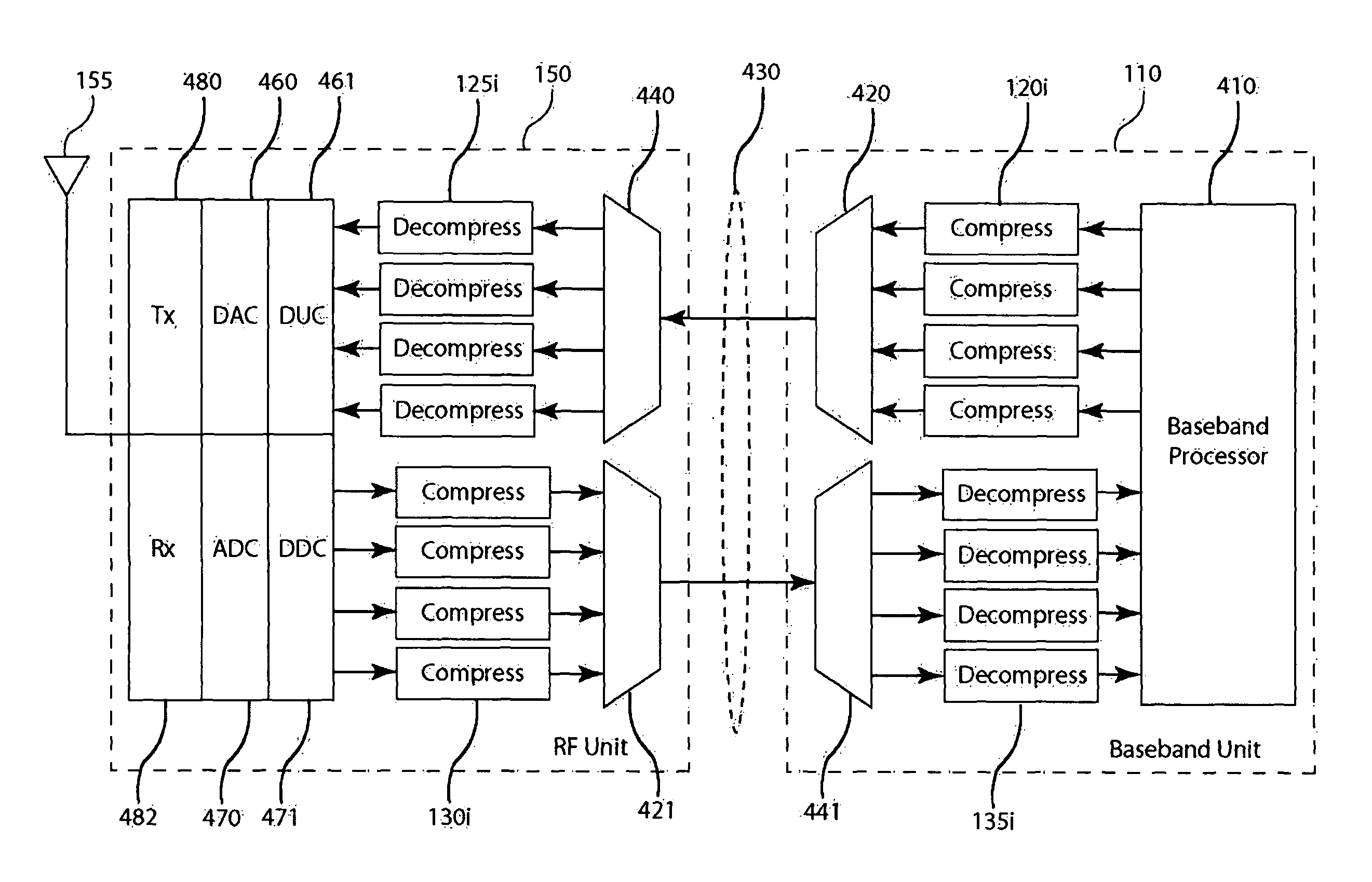

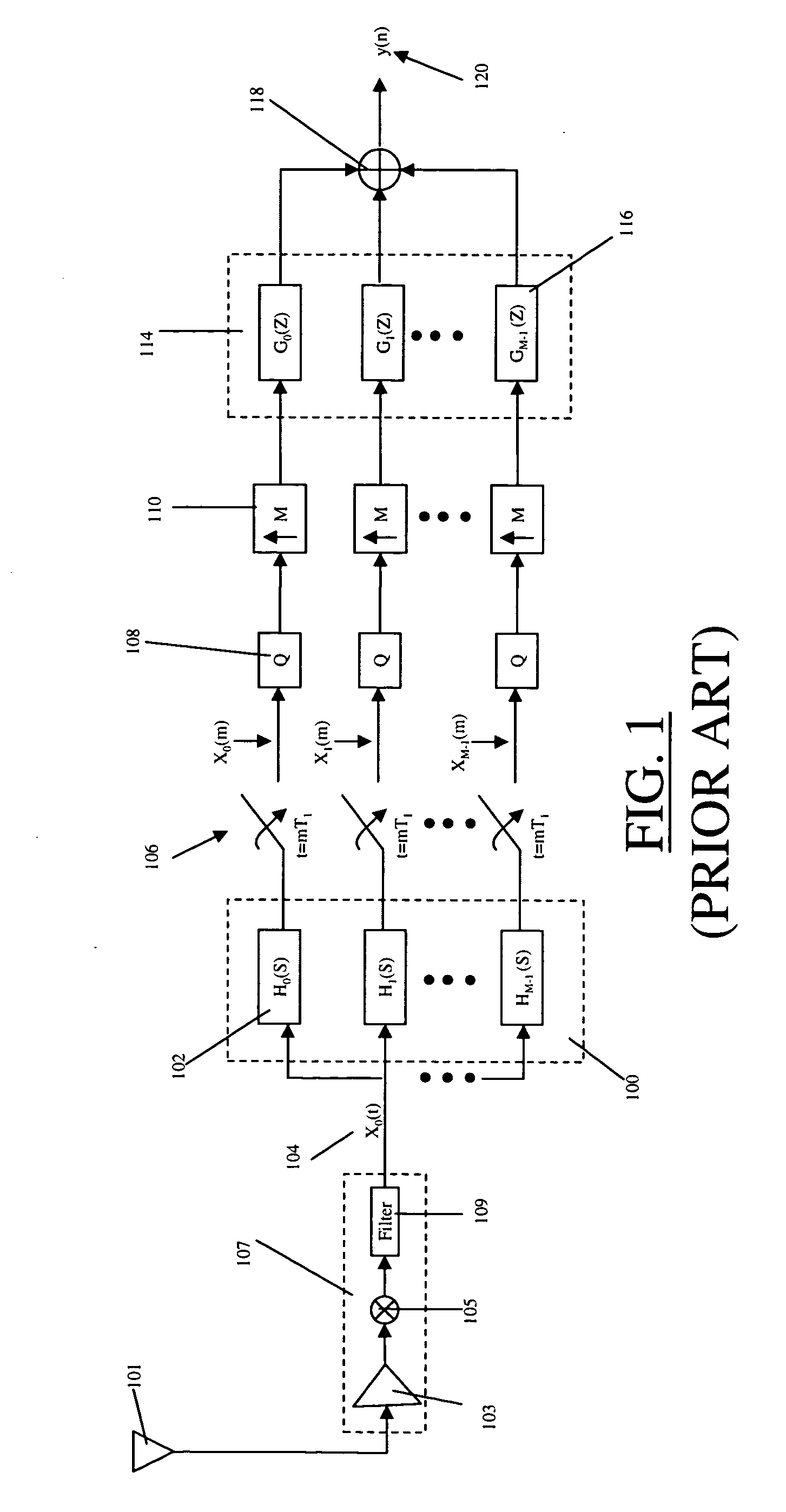

OFDM signal processing in a base transceiver system

ActiveUS20120250740A1Removing unnecessary processing stepSimple designModulated-carrier systemsCode conversionTransceiverDigital down conversion

A method and apparatus provides OFDM signal compression for transfer over serial data links in a base transceiver system (BTS) of a wireless communication network. For the uplink, an RF unit of the BTS applies OFDM cyclic prefix removal and OFDM frequency transformation of the baseband signal samples followed by frequency domain compression of the baseband signal samples, resulting from analog to digital conversion of received analog signals followed by digital downconversion, forming compressed coefficients. After transfer over the serial data link, the baseband processor applies frequency domain decompression to the compressed coefficients prior to further signal processing. For the downlink, the RF unit performs frequency domain decompression of the compressed coefficients and applies OFDM inverse frequency transformation of the decompressed coefficients and OFDM cyclic prefix insertion prior to digital upconversion and digital to analog conversion, generating the analog signal for transmission over the antenna.

Owner:INTEGRATED DEVICE TECH INC

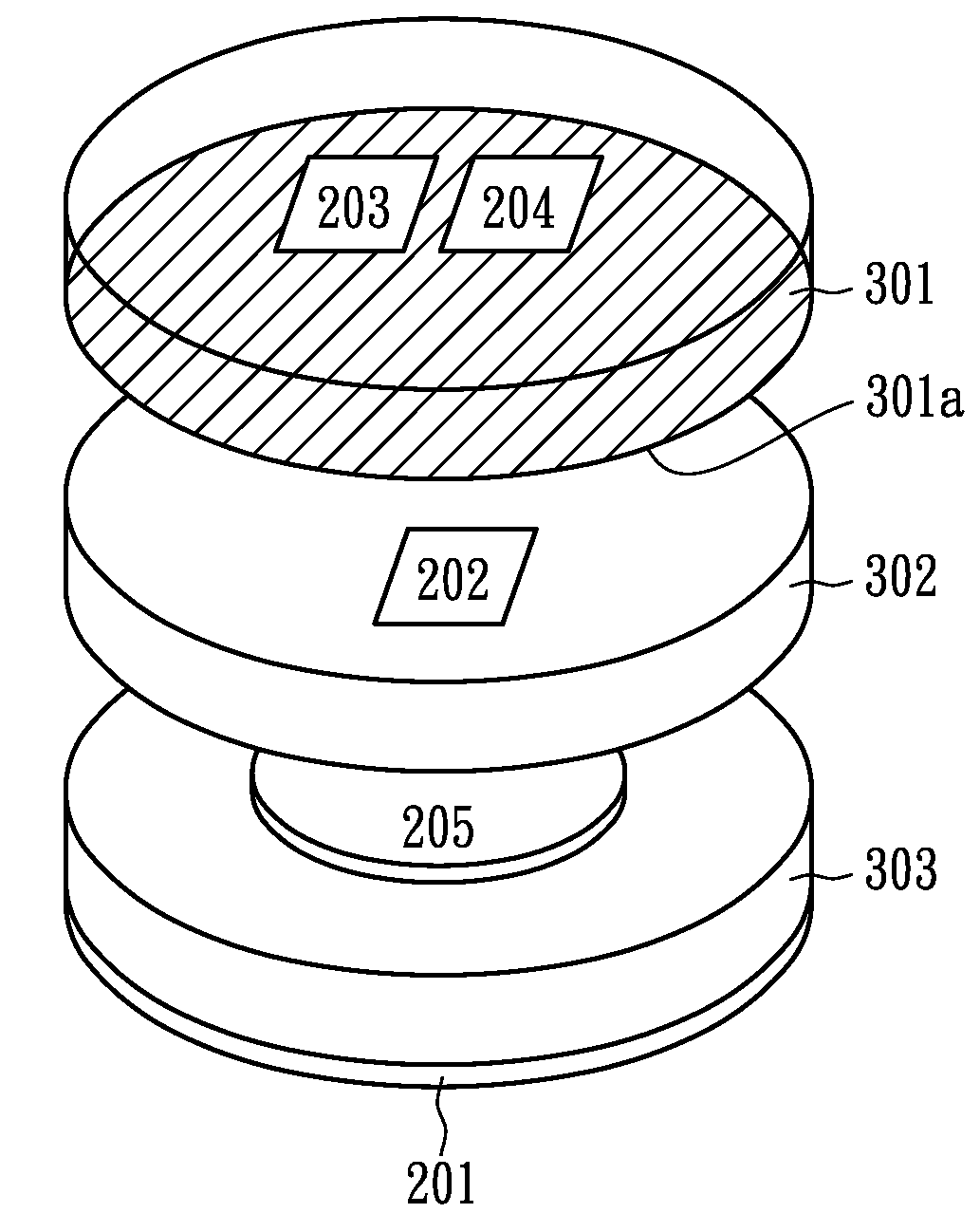

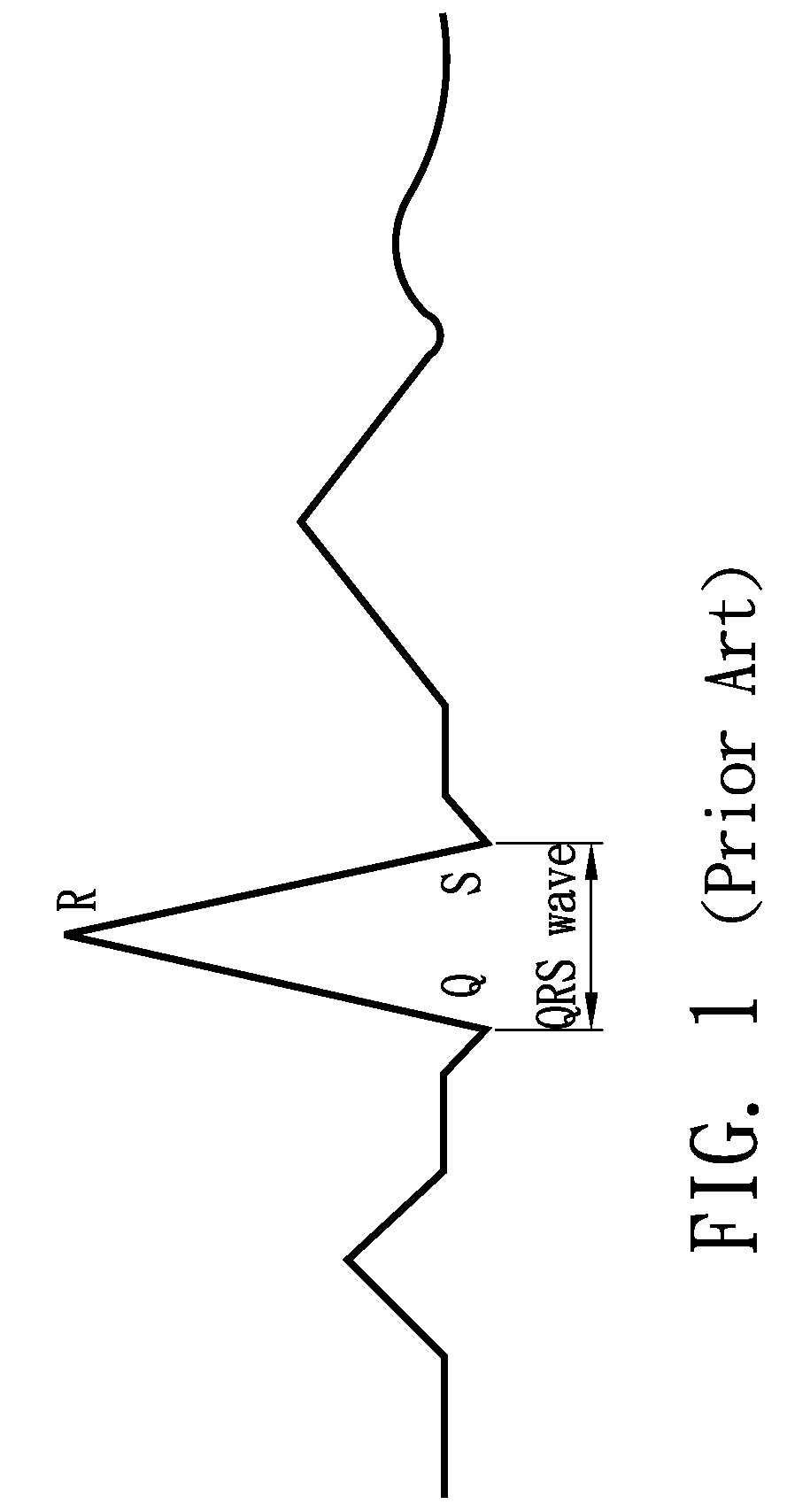

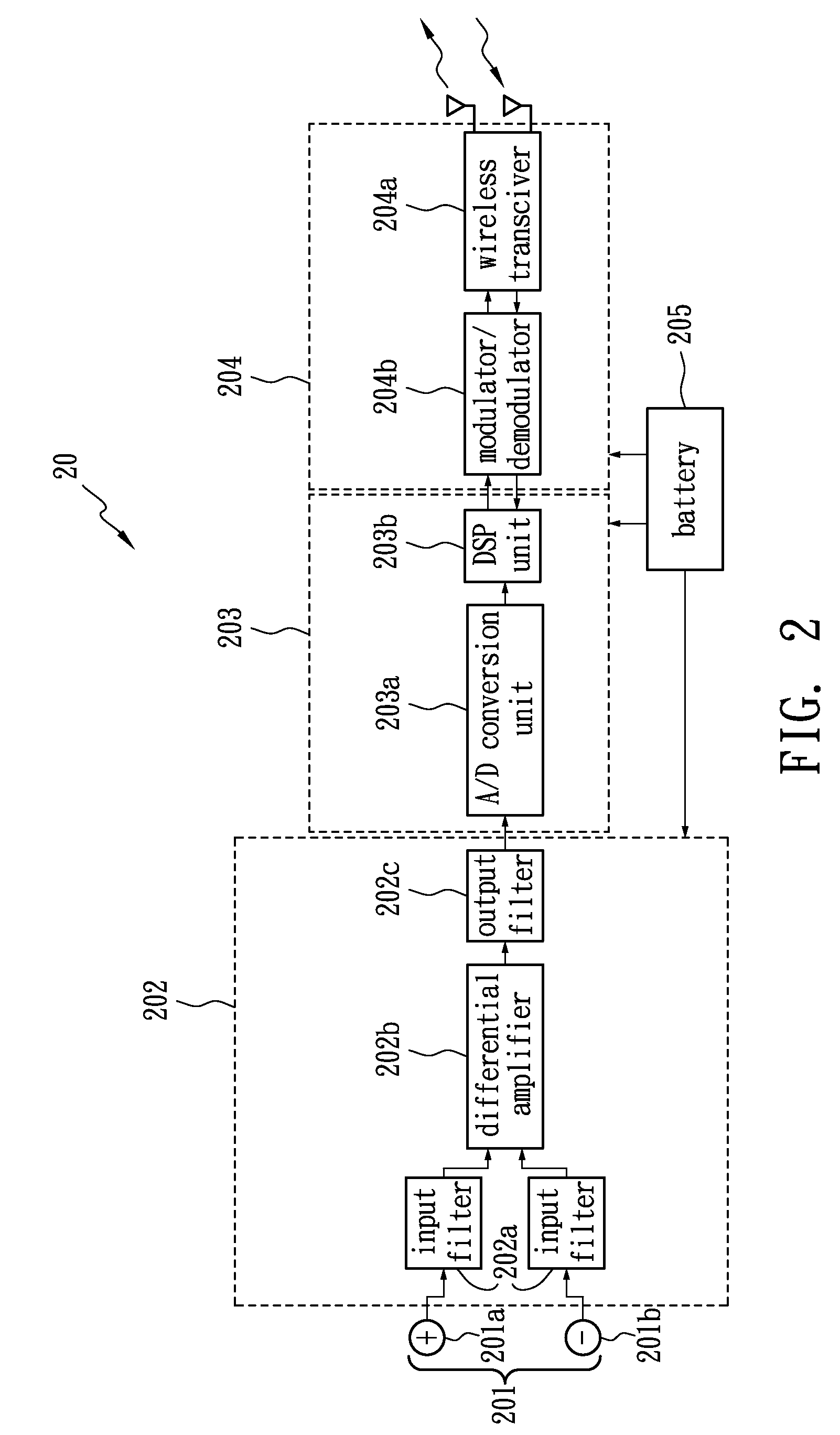

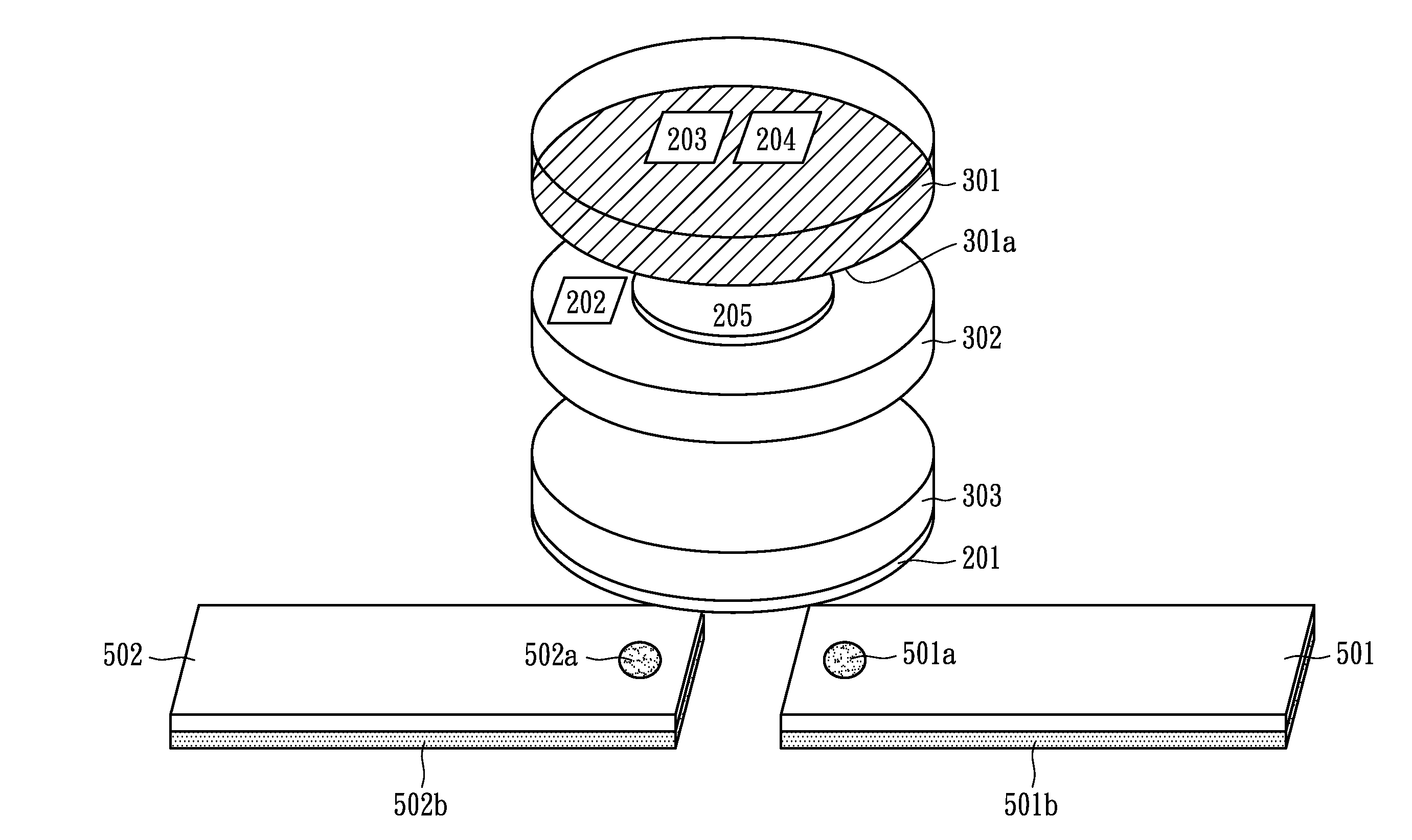

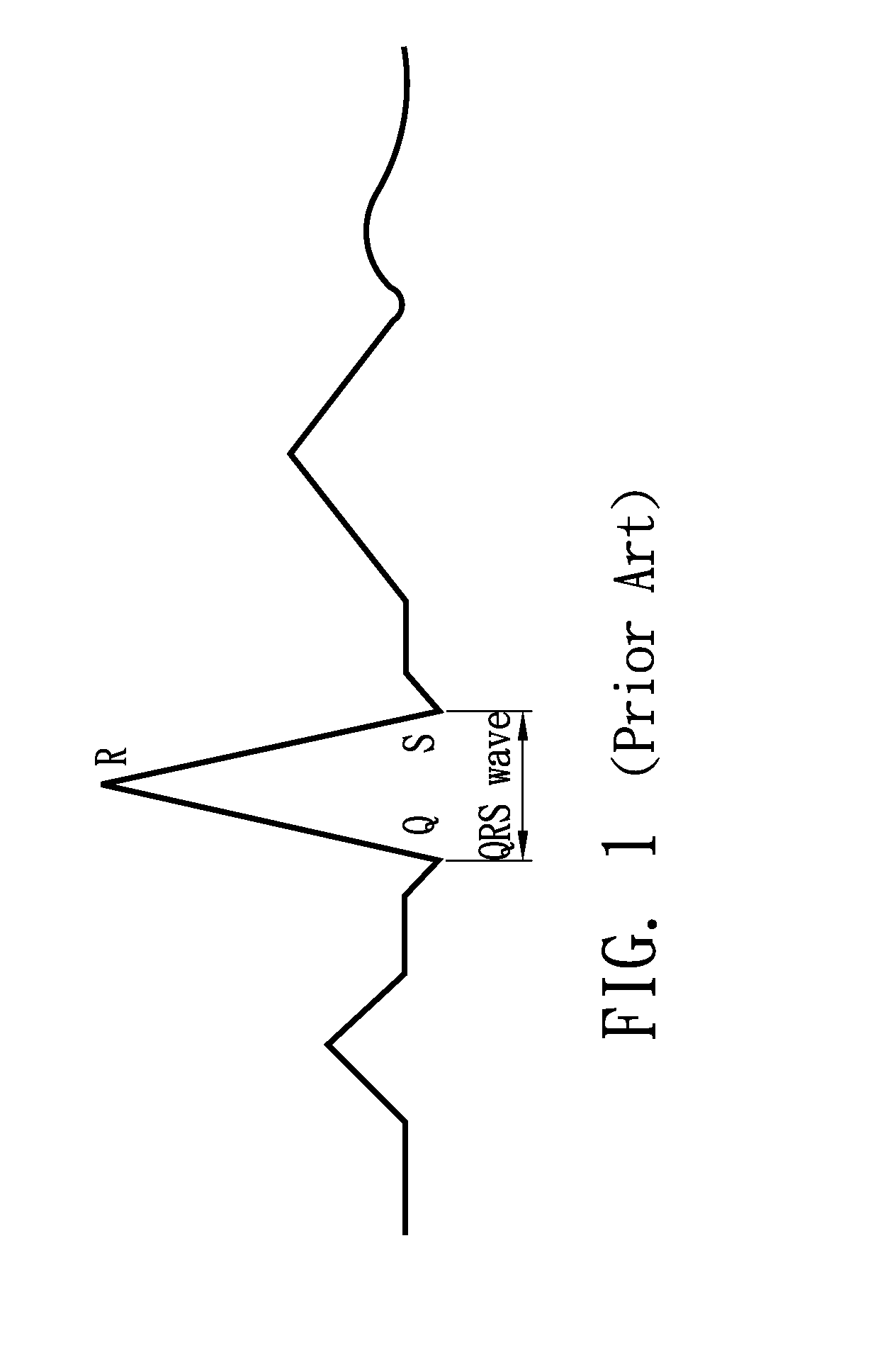

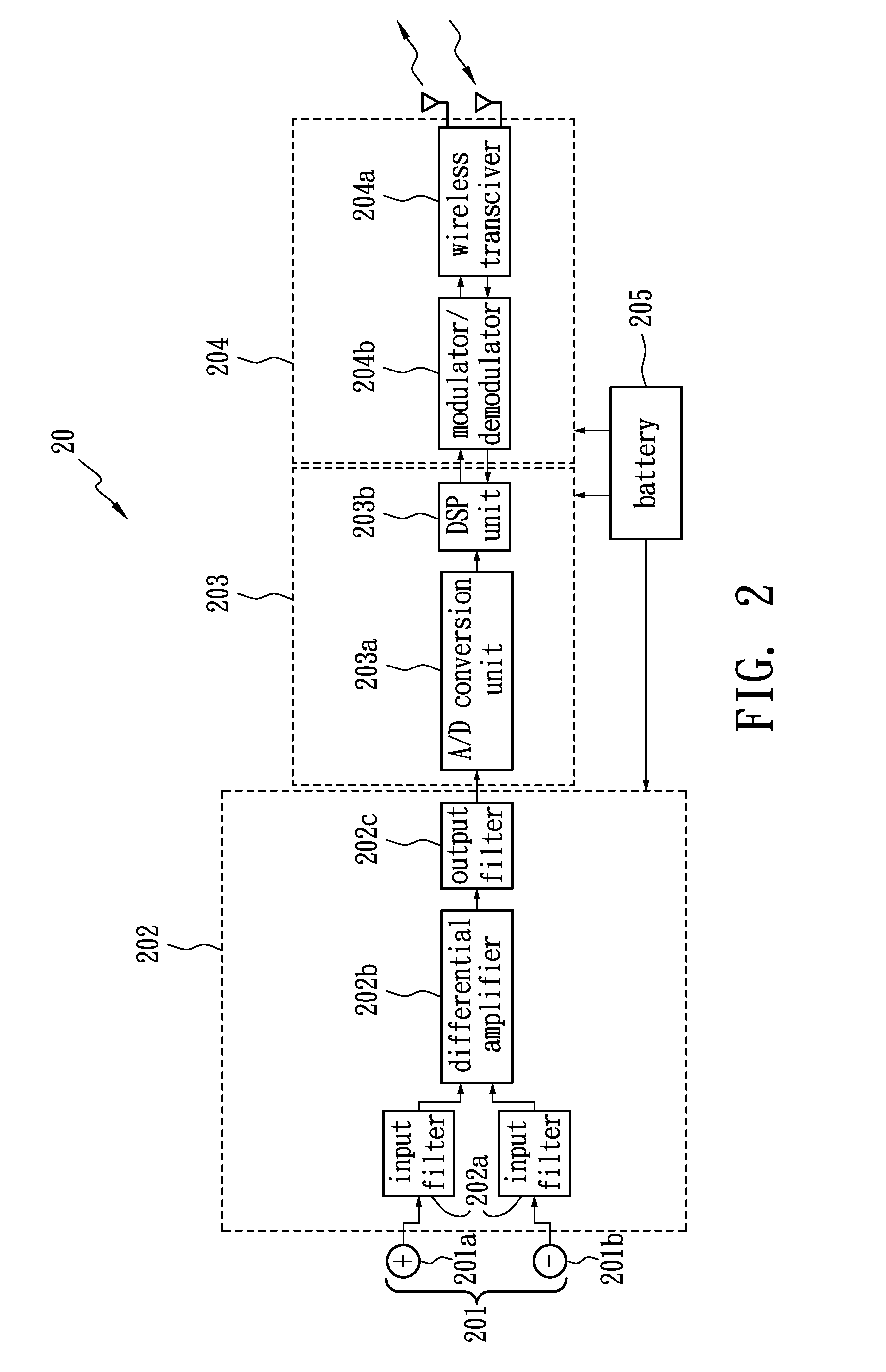

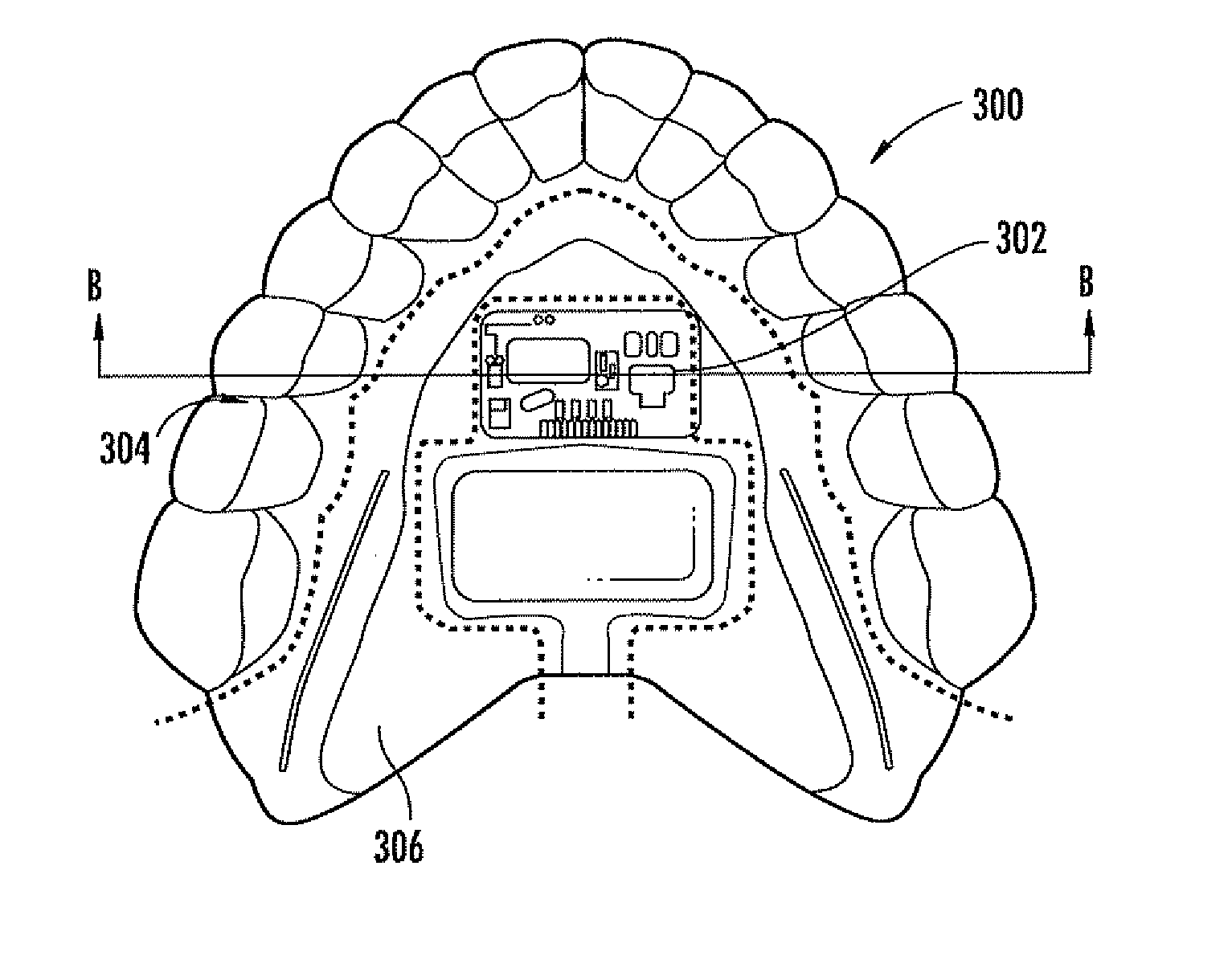

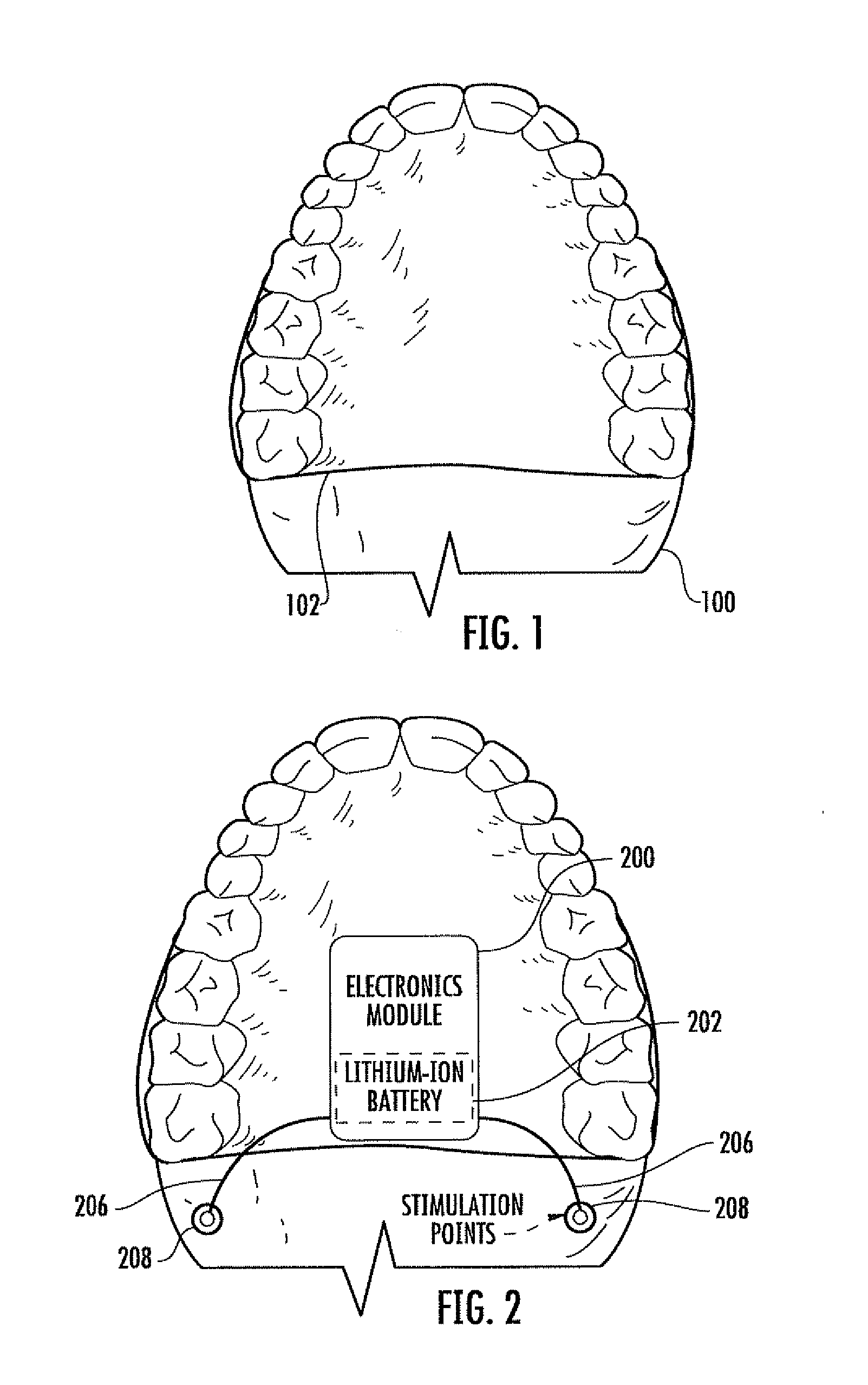

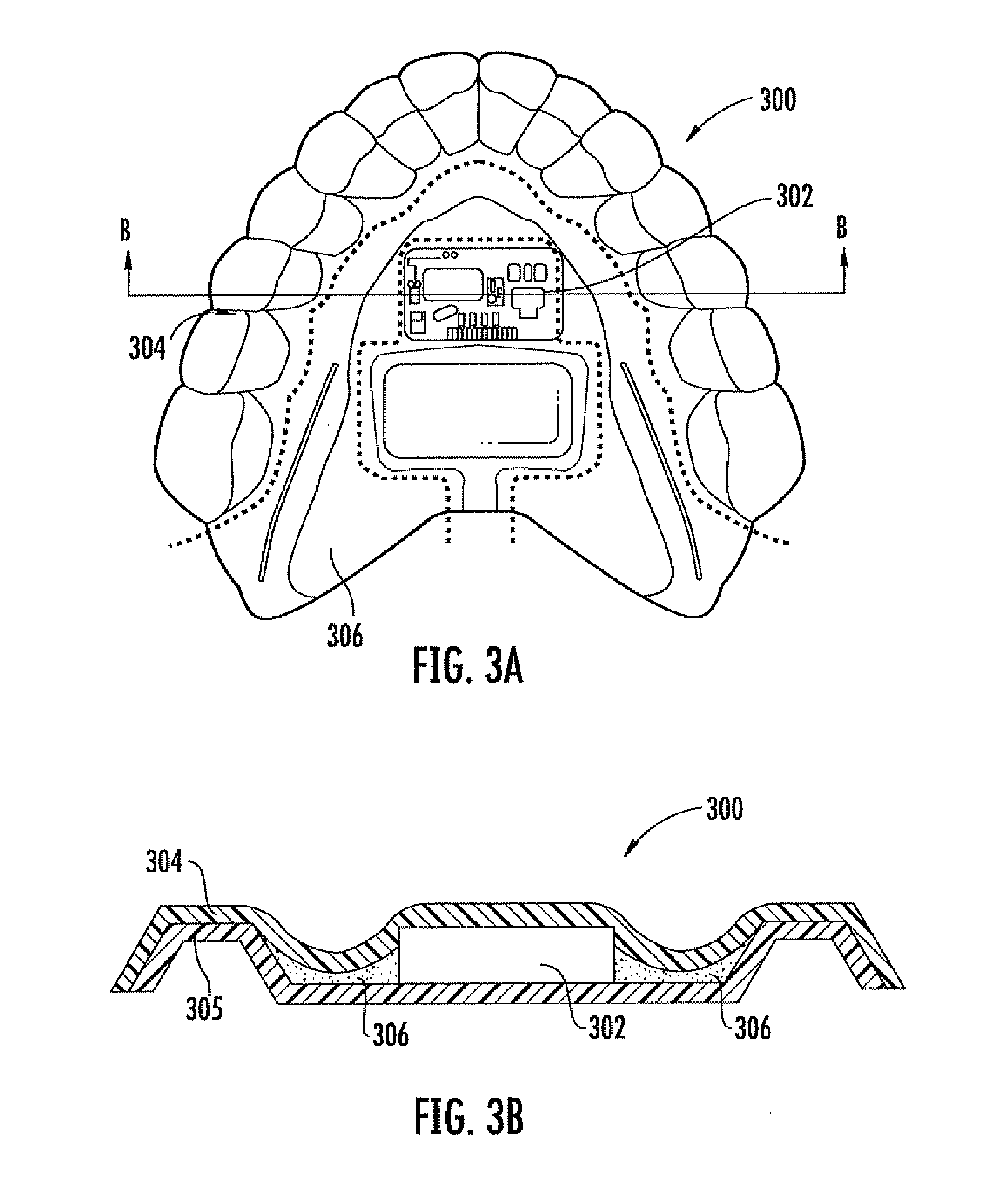

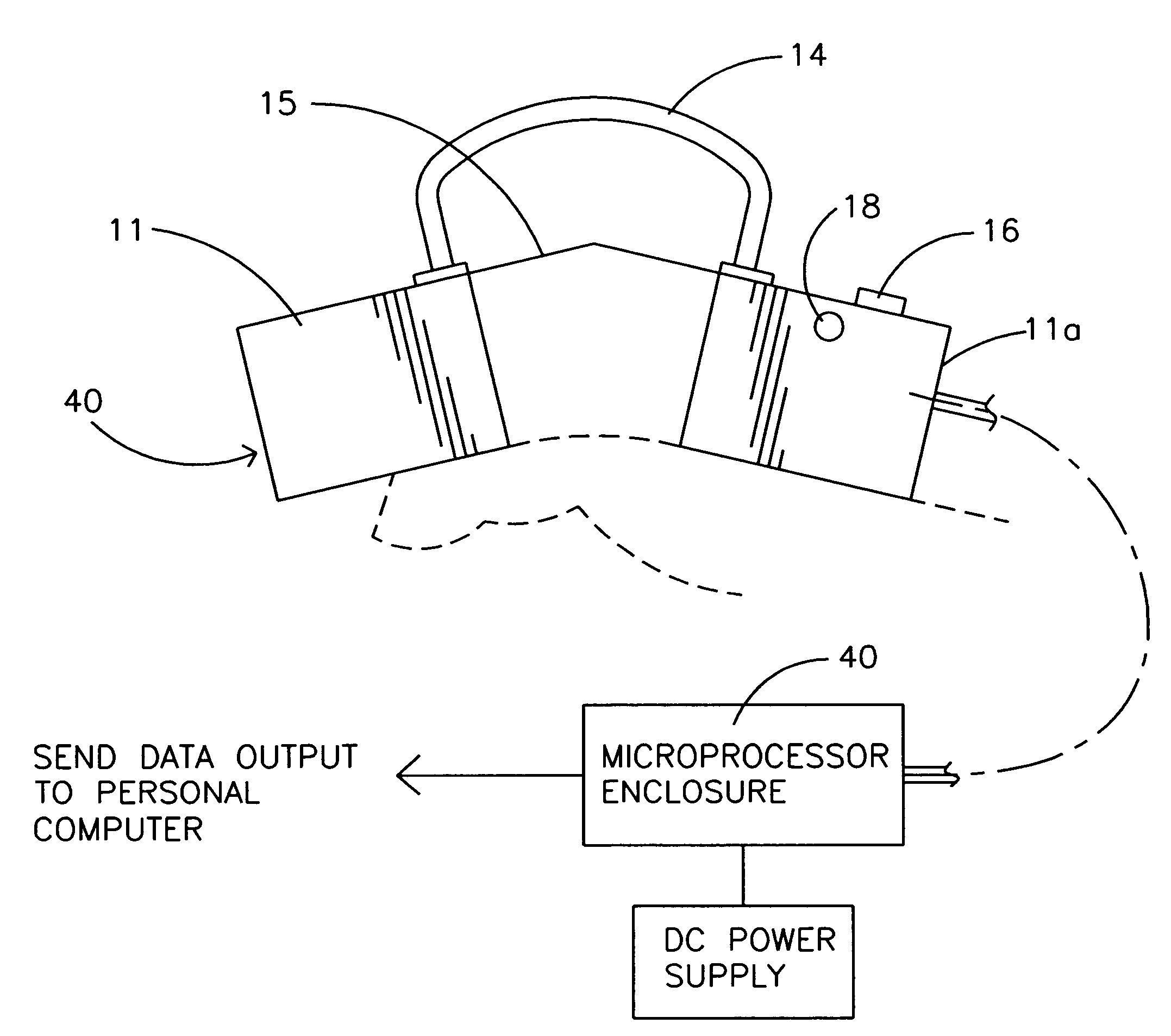

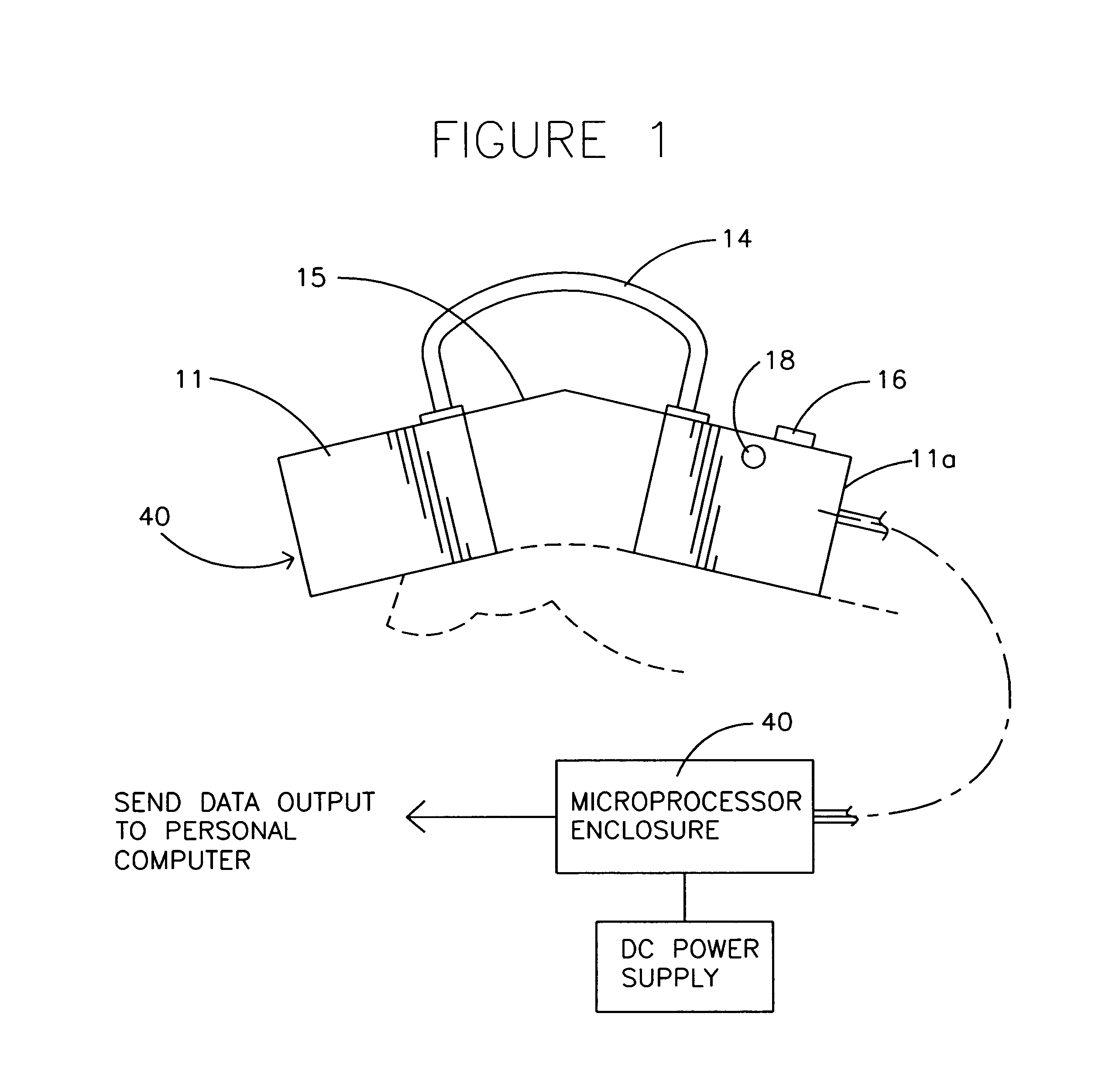

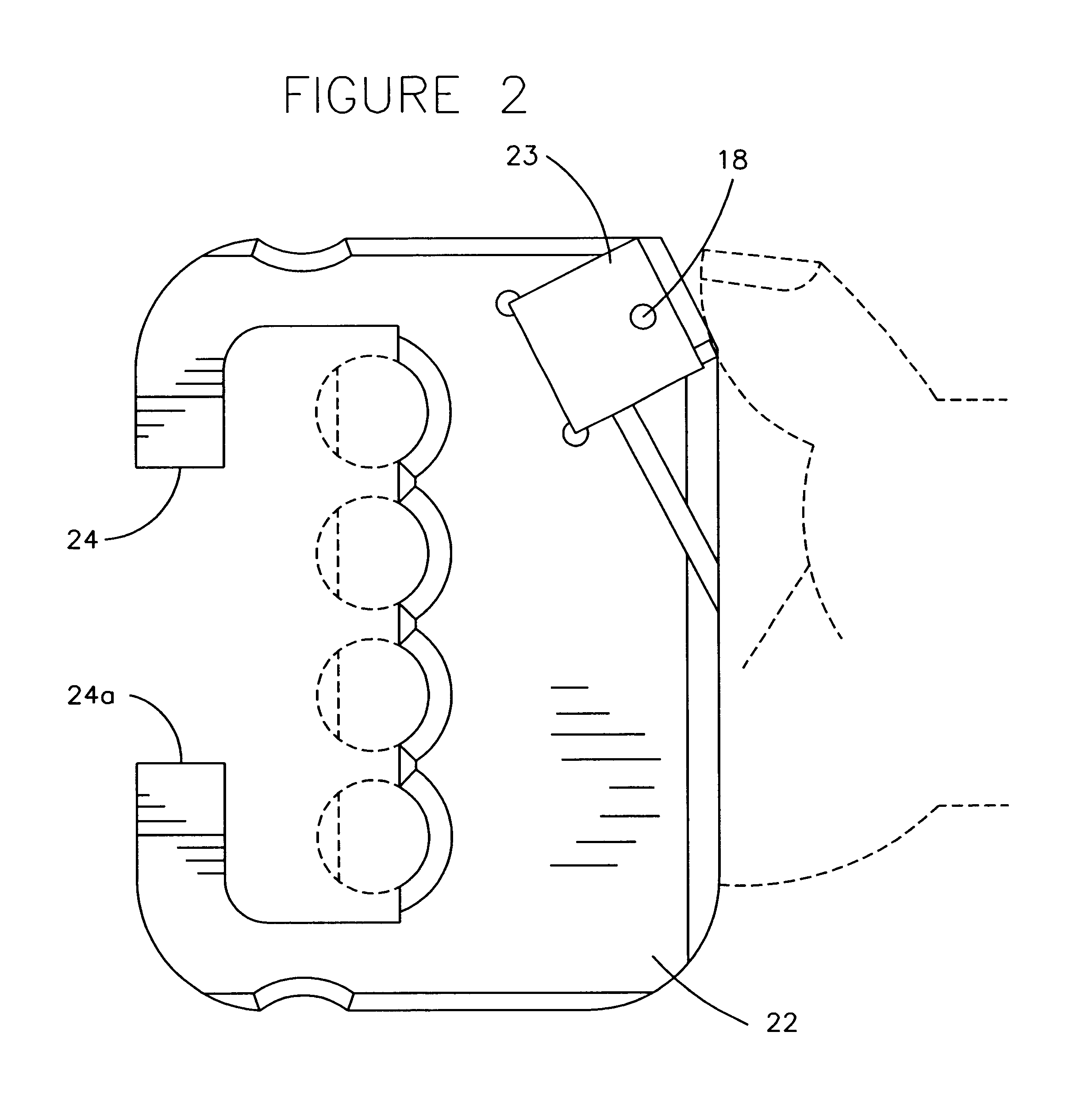

Miniature wireless apparatus for collecting physiological signals

InactiveUS7672714B2Simple materialLow costControlling membersElectrocardiographyMicrocontrollerData compression

Owner:KUO TERRY B J +2

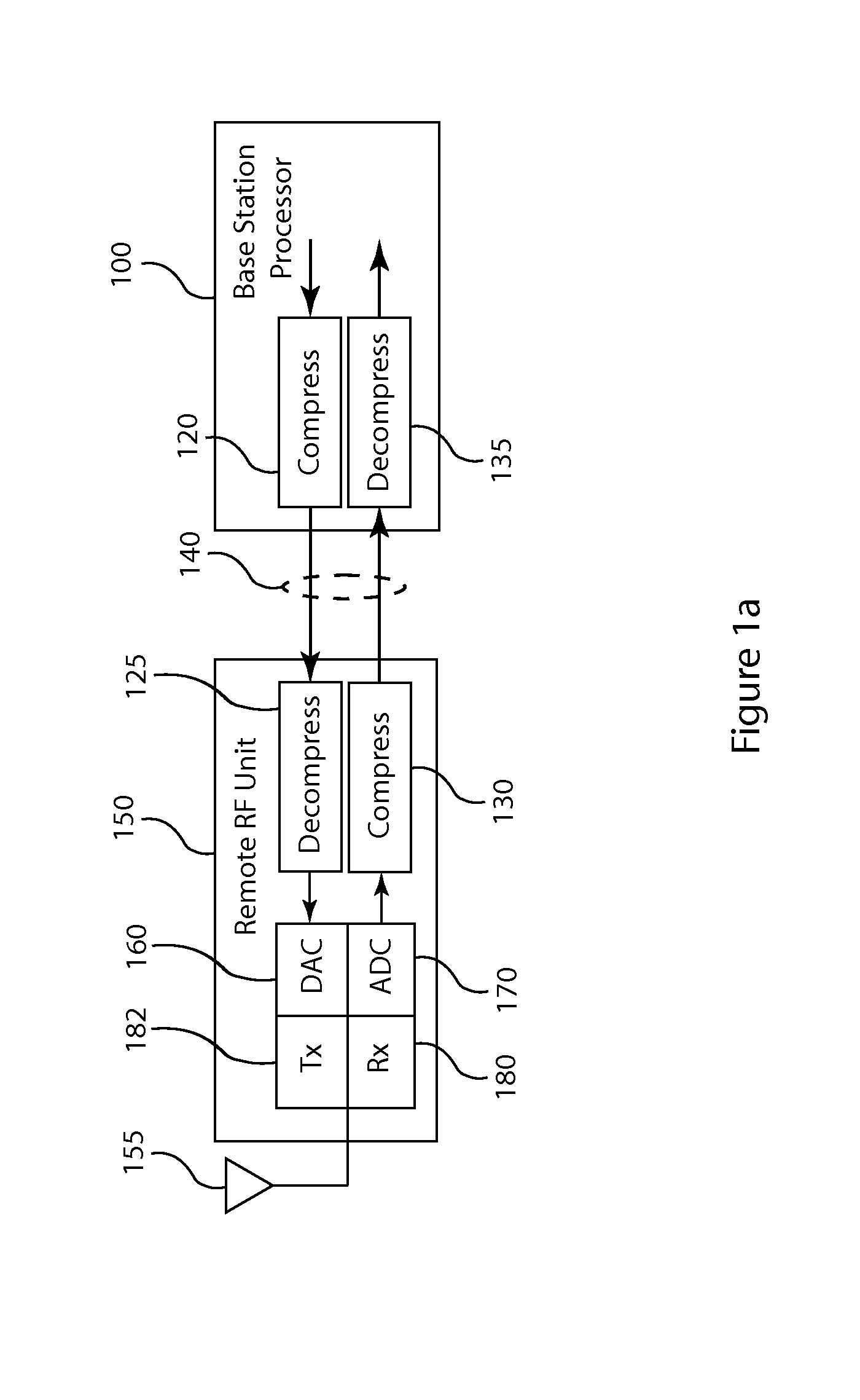

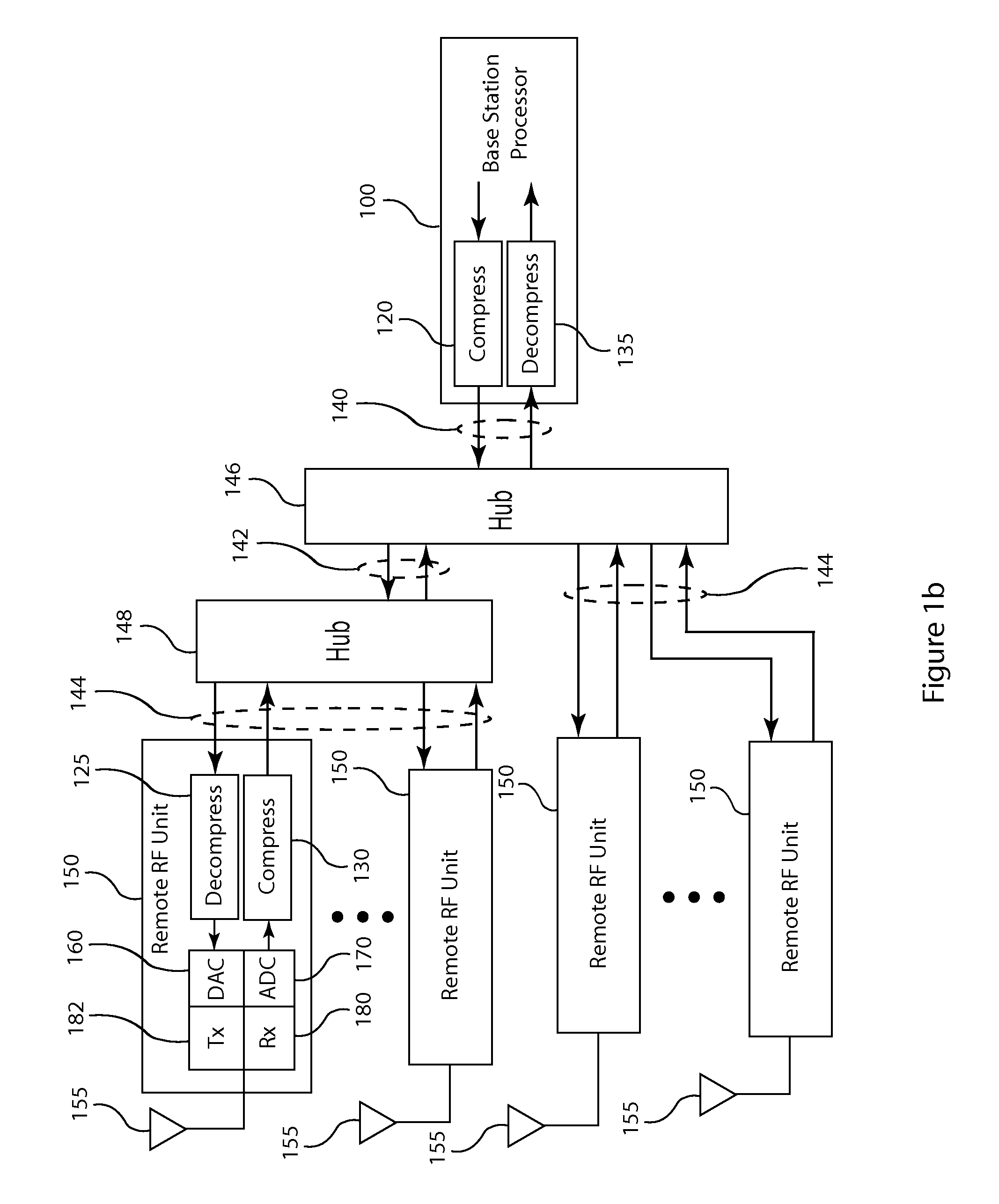

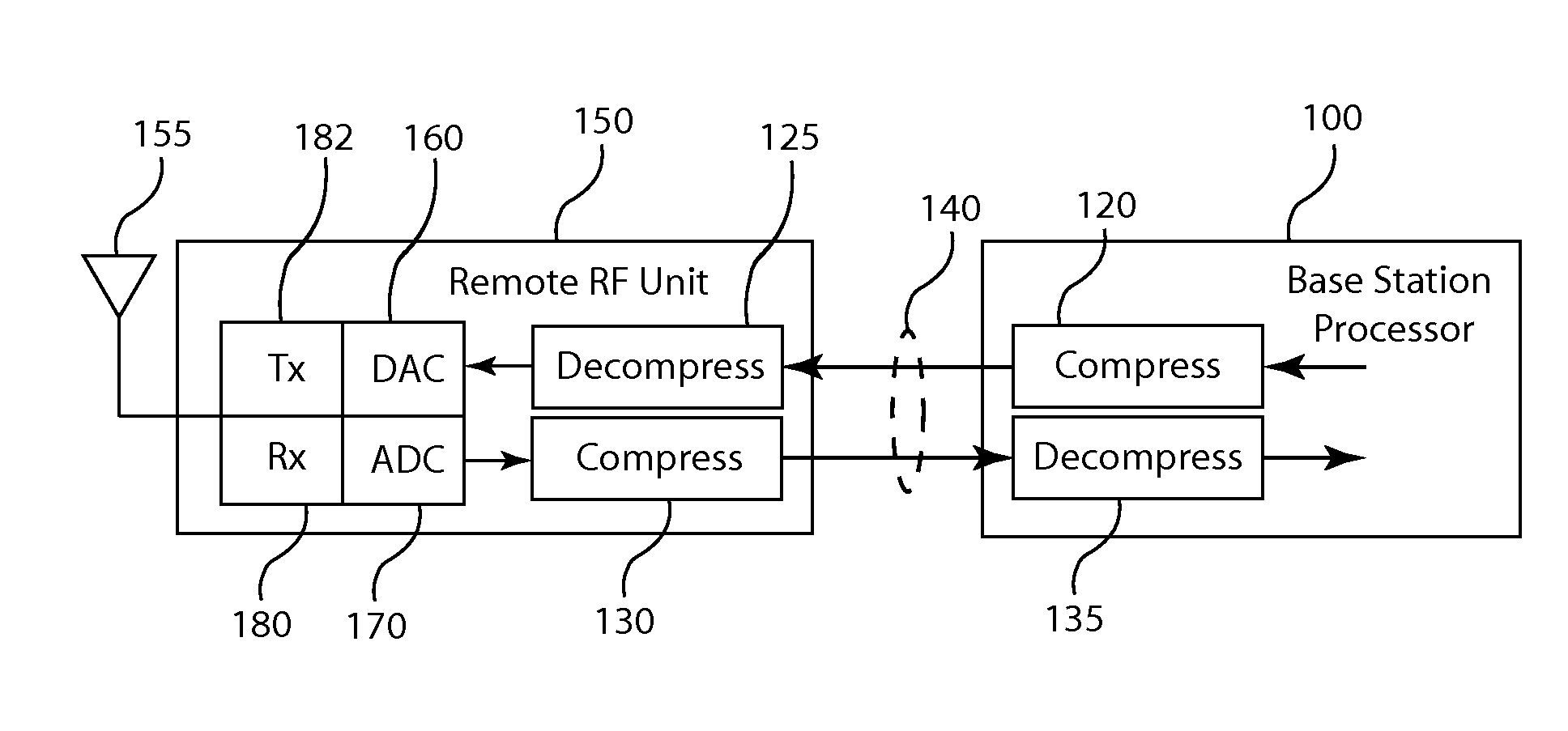

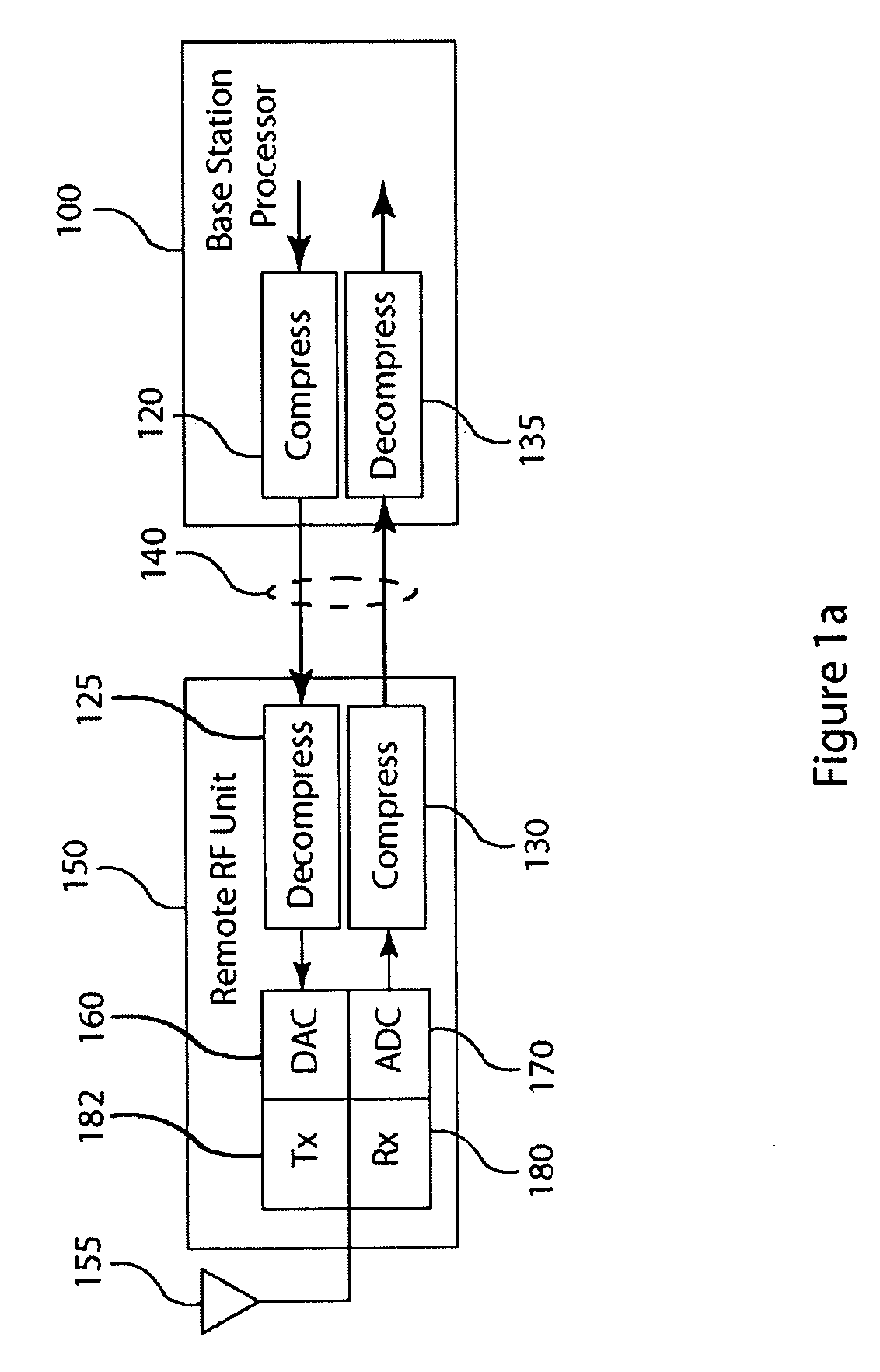

Frequency domain compression in a base transceiver system

ActiveUS20120176966A1Significant compressionReduce processing overheadModulated-carrier systemsTransmitter/receiver shaping networksTransceiverImage compression

A method and apparatus provide signal compression for transfer over serial data links in a base transceiver system (BTS) of a wireless communication network. For the uplink, an RF unit of the BTS applies frequency domain compression of baseband signal samples, resulting from analog to digital conversion of received analog signals followed by digital downconversion, forming compressed coefficients. After transfer over the serial data link, the baseband processor then applies frequency domain decompression to the compressed coefficients prior to normal signal processing. For the downlink, the baseband processor applies frequency domain compression of baseband signal samples and transfers the compressed coefficients to the RF unit. The RF unit applies frequency domain decompression to the compressed coefficients prior to digital upconversion and digital to analog conversion, generating the analog signal for transmission over the antenna. This abstract does not limit the scope of the invention as described in the claims.

Owner:INTEGRATED DEVICE TECH INC

Miniature wireless apparatus for collecting physiological signals

InactiveUS20070167848A1Simple materialLow costControlling membersElectrocardiographyMicrocontrollerData compression

Owner:KUO TERRY B J +2

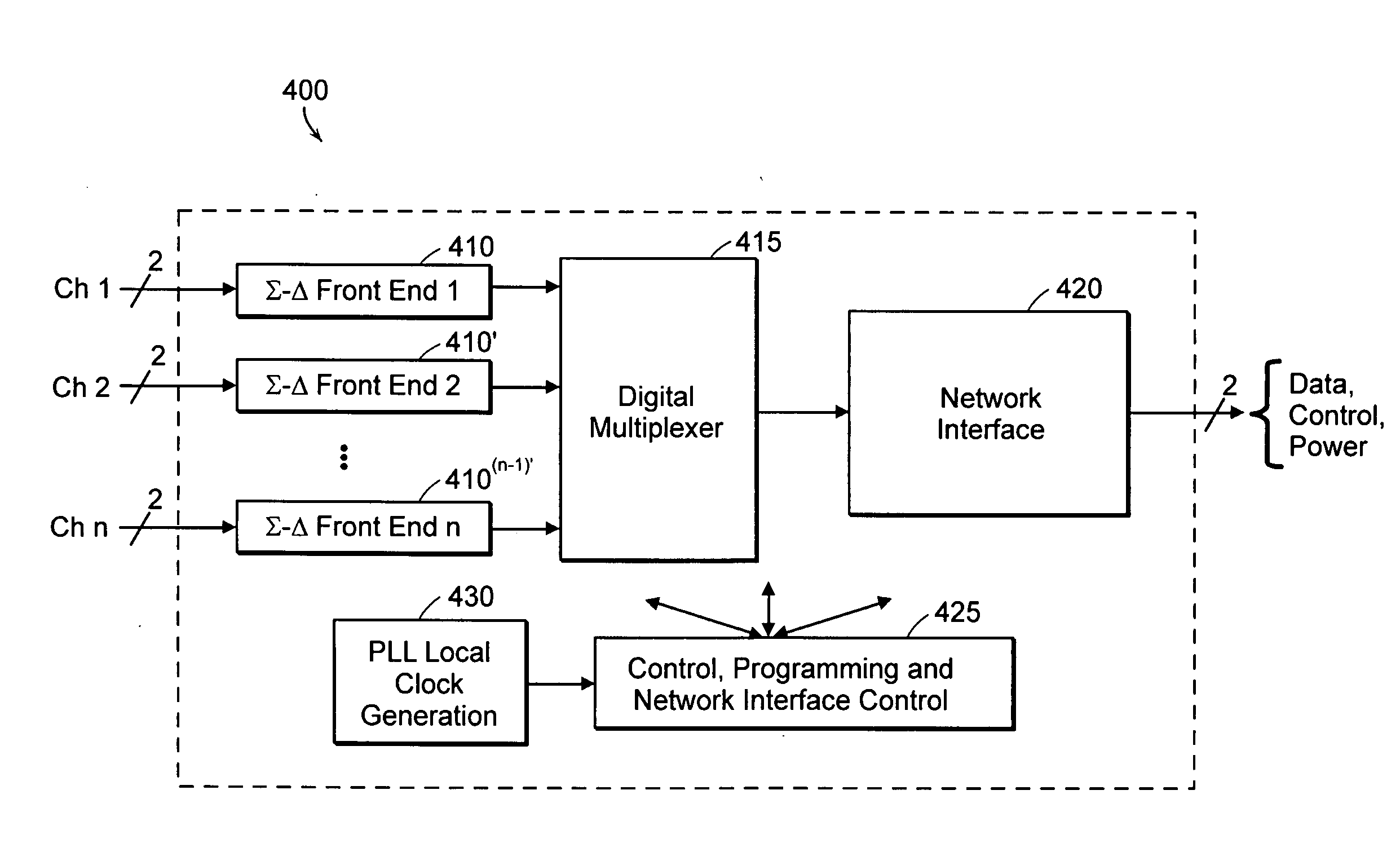

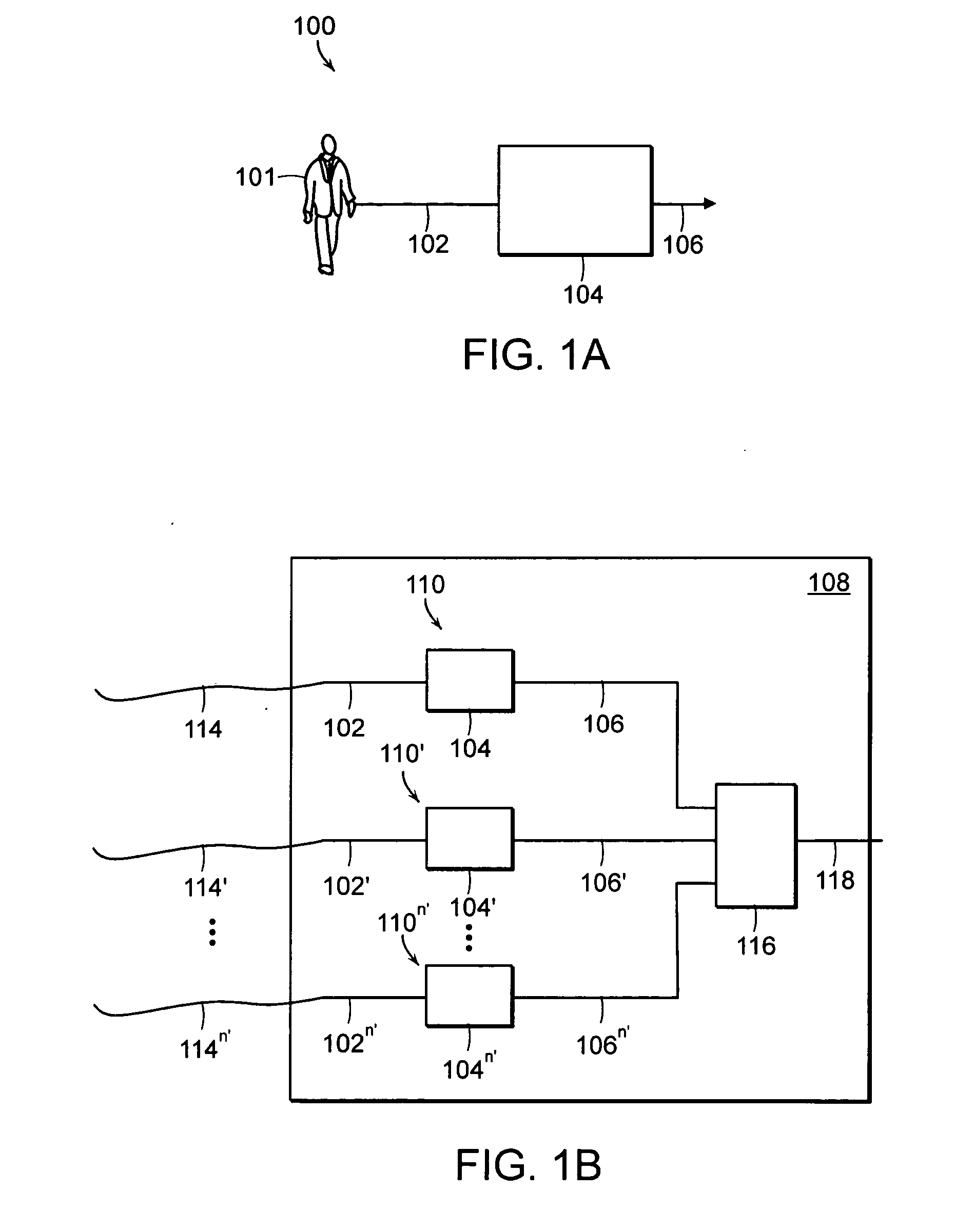

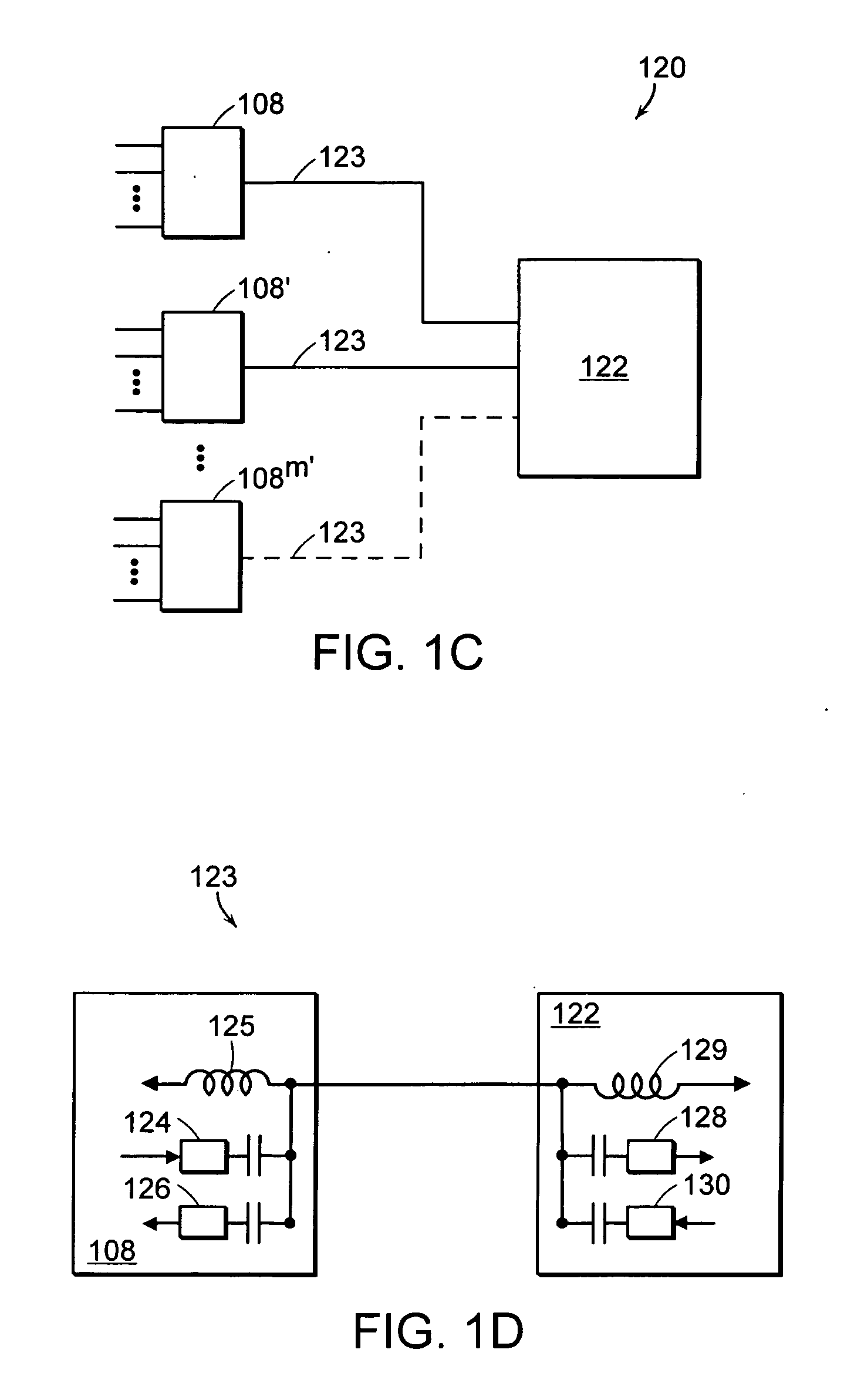

Multi-channel electrophysiologic signal data acquisition system on an integrated circuit

InactiveUS20060173364A1Reduce complexitySmall sizeElectroencephalographyElectrocardiographyControl signalData acquisition

A physiologic data acquisition system includes an analog input, a sigma-delta front end signal conditioning circuit adapted to subtract out DC and low frequency interfering signals from and amplify the analog input before analog to digital conversion. The system can be programmed to acquire a selected physiologic signal, e.g., a physiologic signal characteristic of or originating from a particular biological tissue. The physiologic data acquisition system may include a network interface modulating a plurality of subcarriers with respective portions of an acquired physiologic signal. A receiver coupled to the network interface can receive physiologic data from, and send control signals and provide power to the physiologic data acquisition system over a single pair of wires. The network interface can modulate an RF carrier with the plurality of modulated subcarriers and transmit the resulting signal to the receiver across a wireless network. An integrated circuit may include the physiologic data acquisition system. Also included are methods for acquiring physiologic data comprising the step of selectively controlling an acquisition circuit to acquire the physiologic signal.

Owner:WORCESTER POLYTECHNIC INSTITUTE

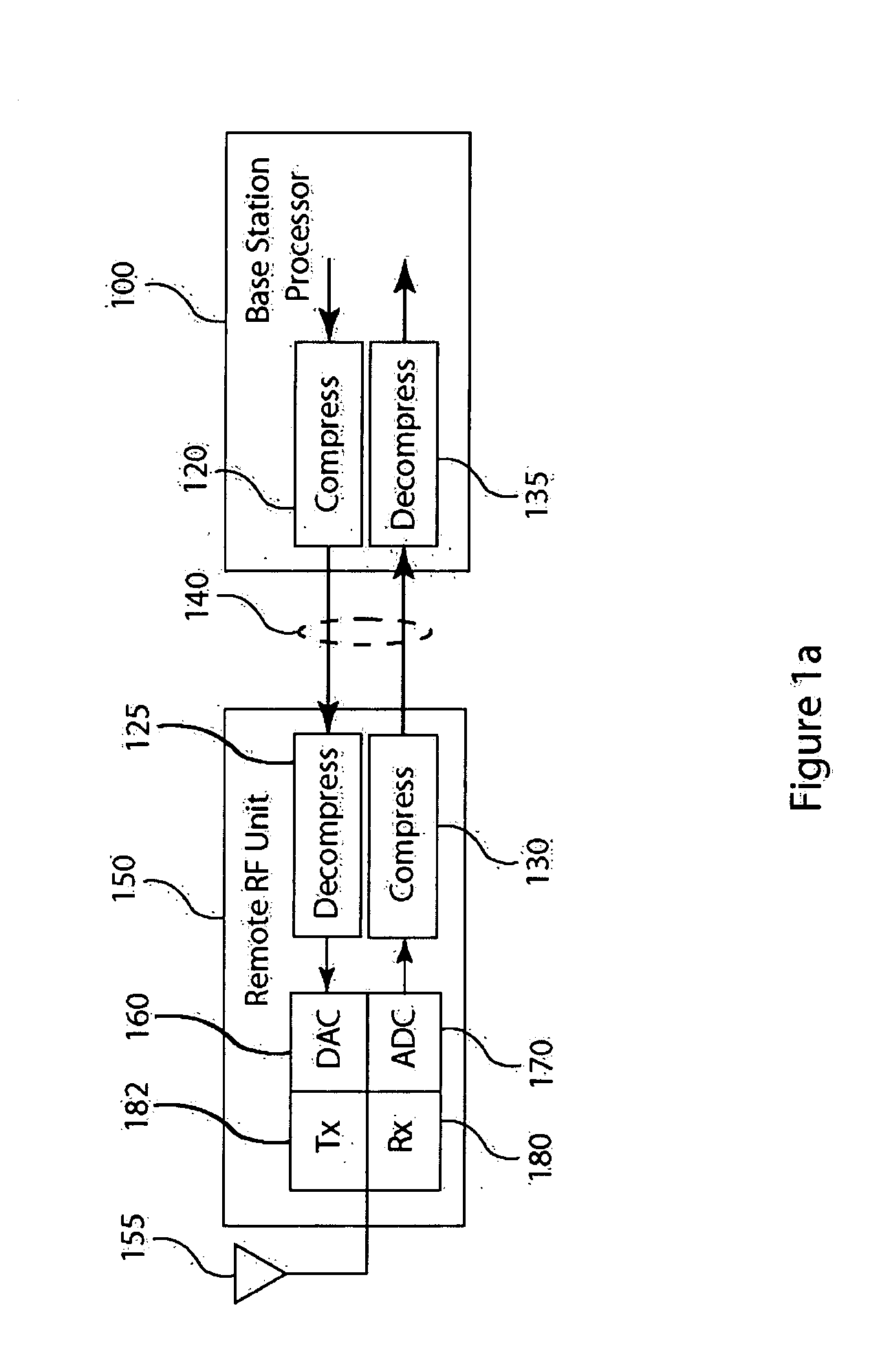

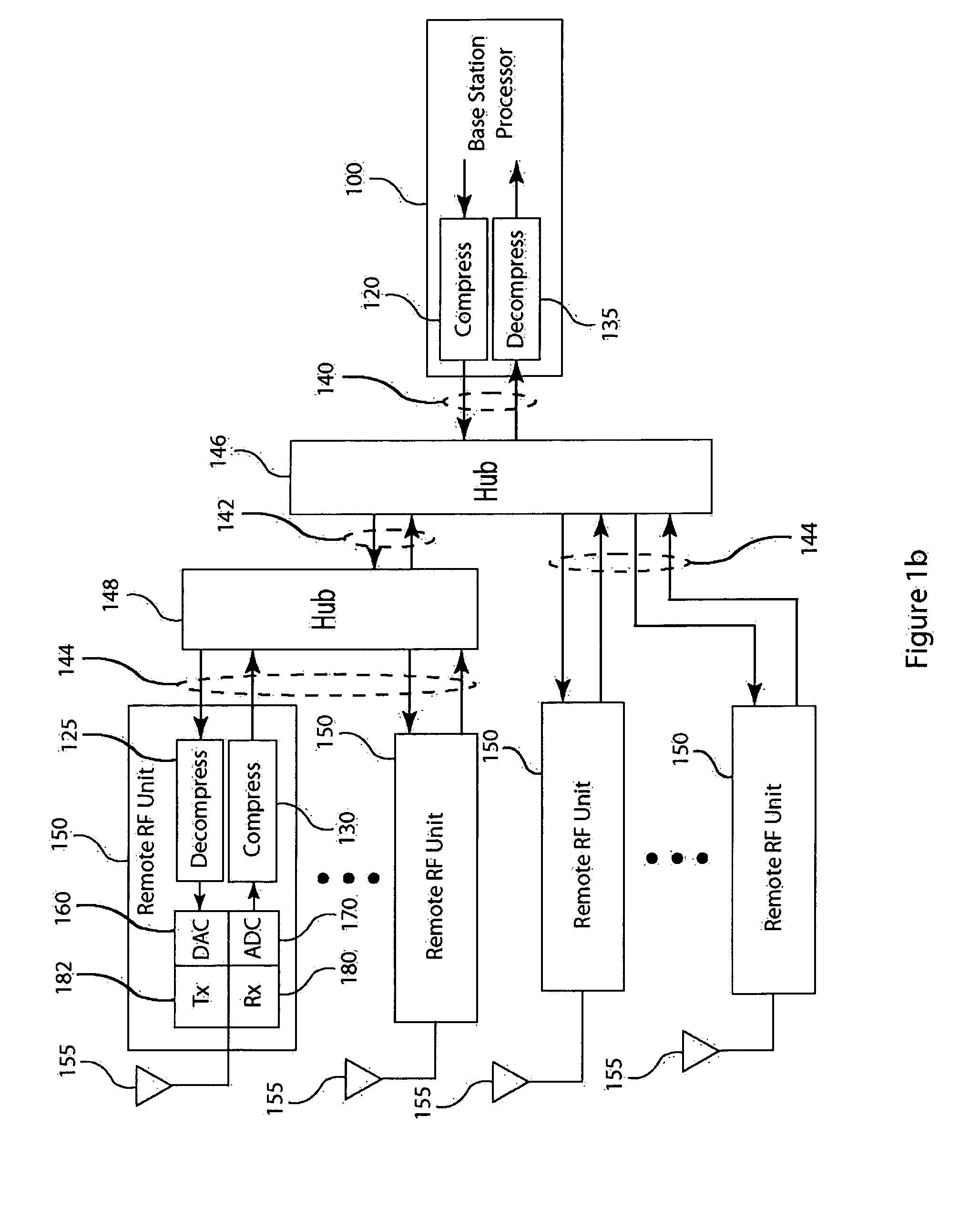

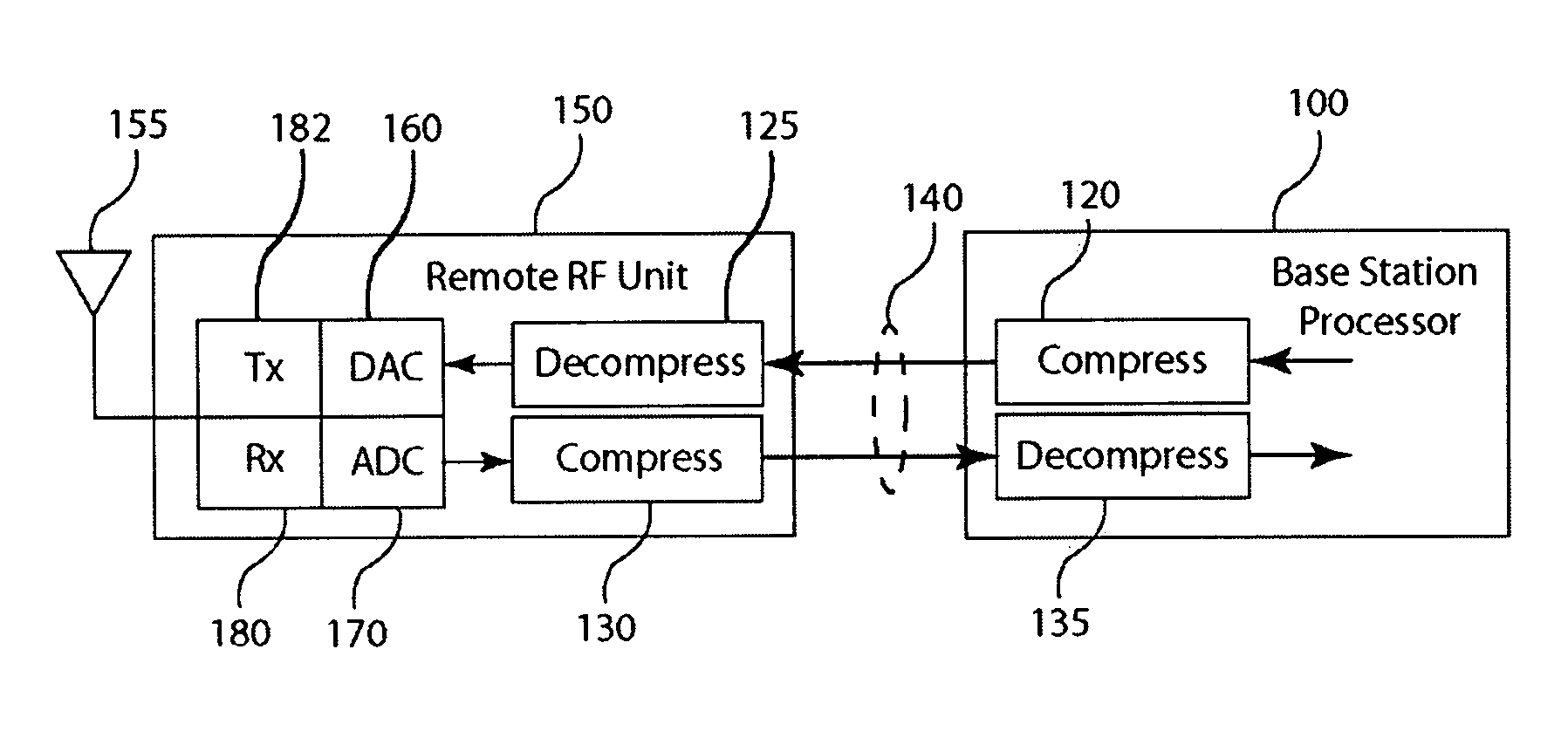

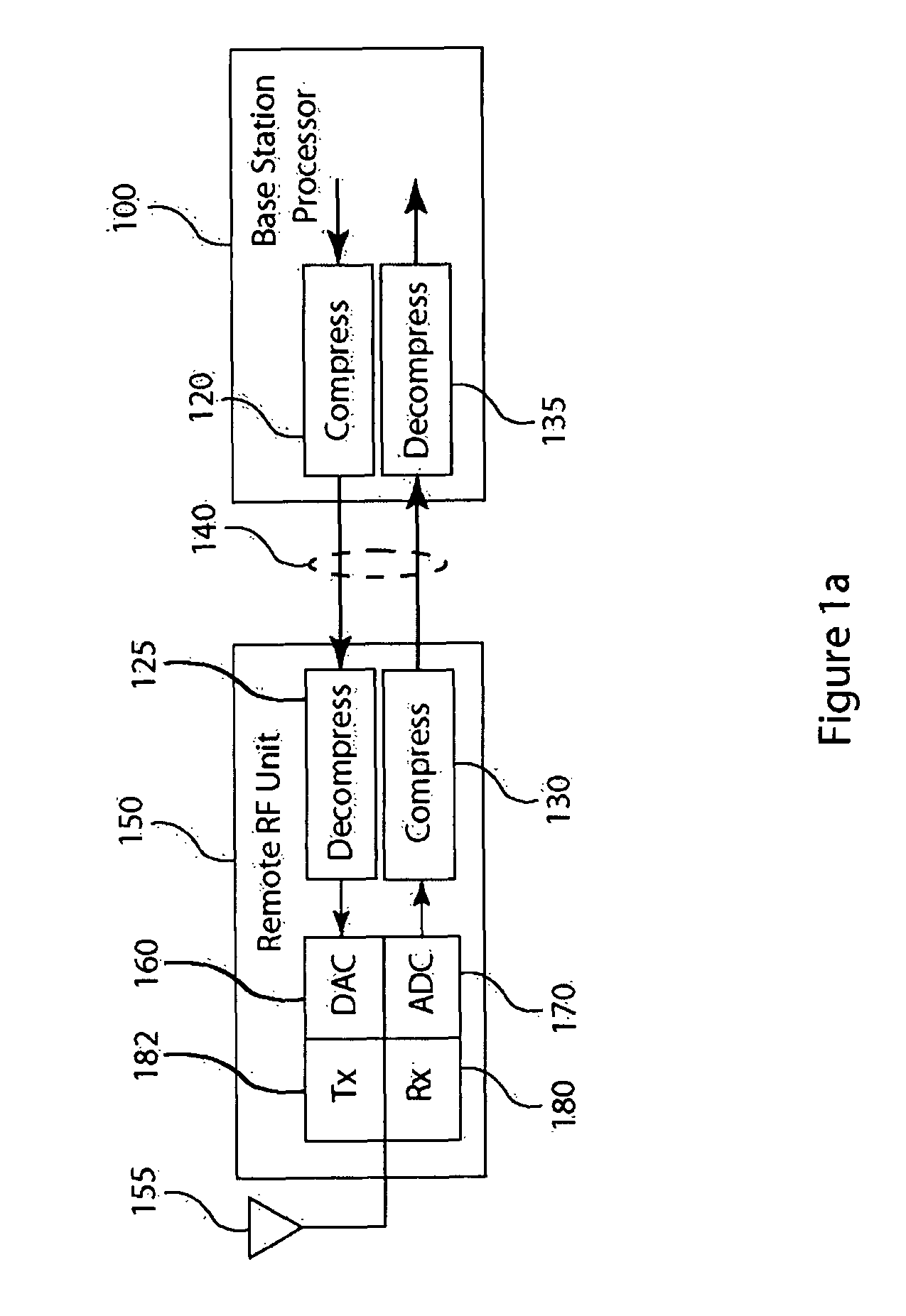

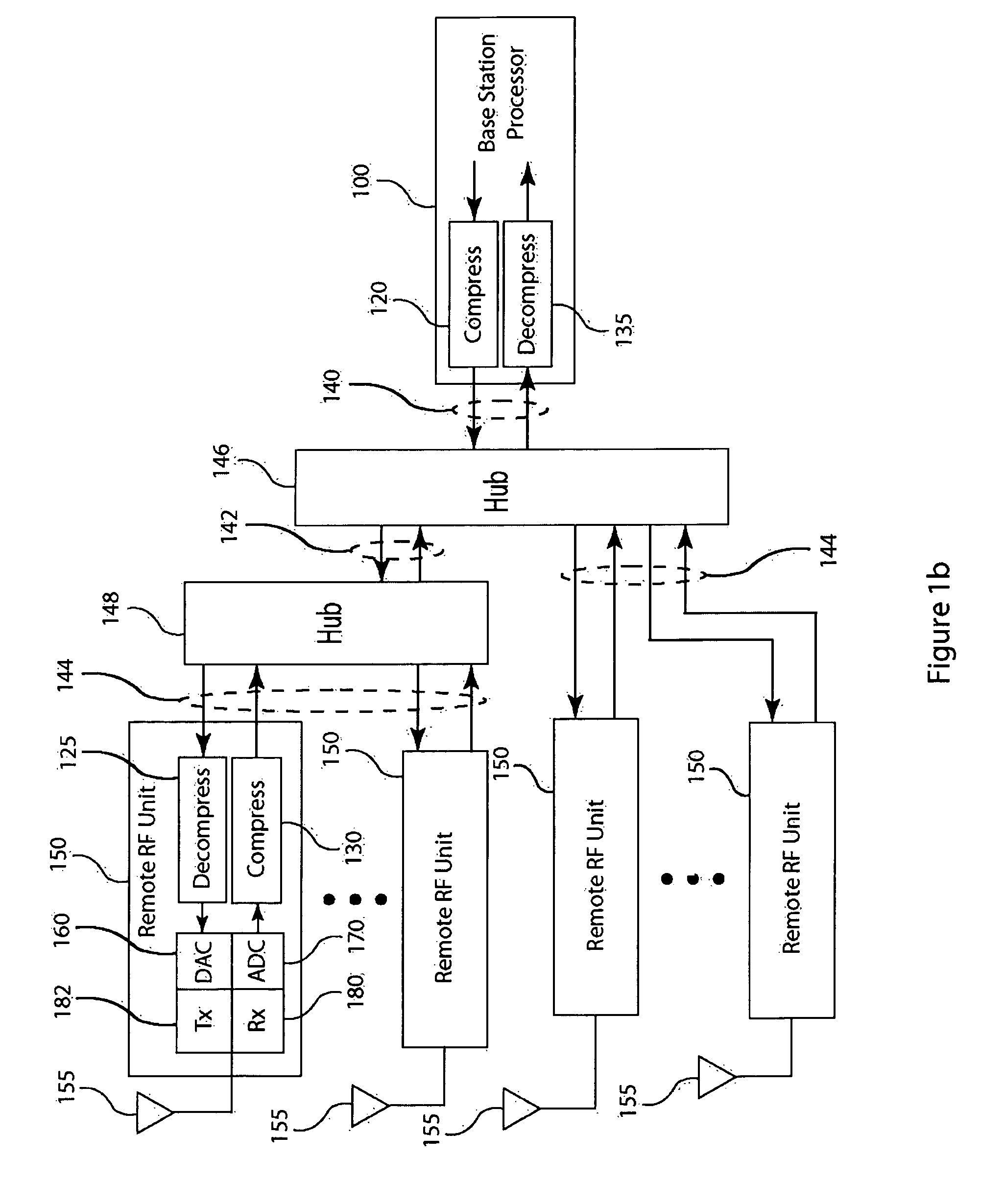

Compression of signals in base transceiver systems

ActiveUS20090290632A1Increase capacityElectric signal transmission systemsEqual length code transmitterTransceiverDistributed antenna system

A signal compression method and apparatus for a base transceiver system (BTS) in a wireless communication network provides efficient transfer of compressed signal samples over serial data links in the system. For the uplink, an RF unit of the BTS compresses signal samples resulting from analog to digital conversion of an analog signal received via an antenna. The RF unit transfers the compressed signal samples over the serial data link to the base station processor where they are decompressed prior to the normal signal processing operations. For the downlink, the base station processor compresses signal samples and transfers the compressed signal samples over the serial data link to the RF unit. The RF unit decompresses the compressed samples and converts the decompressed samples to an analog signal for transmission over an antenna. Compression and decompression can be incorporated into operations of conventional base stations and distributed antenna systems.

Owner:INTEGRATED DEVICE TECH INC

Compression of baseband signals in base transceiver systems

ActiveUS20110135013A1Increase data transfer capacity of dataIncrease capacityCode conversionAmplitude-modulated carrier systemsTransceiverDistributed antenna system

A signal compression method and apparatus for a base transceiver system (BTS) in a wireless communication network provides efficient transfer of compressed signal samples over serial data links in the system. For the uplink, an RF unit of the BTS compresses baseband signal samples resulting from analog to digital conversion of a received analog signal followed by digital downconversion. The compressed signal samples are transferred over the serial data link to the baseband processor then decompressed prior to normal signal processing. For the downlink, the baseband processor compresses baseband signal samples and transfers the compressed signal samples to the RF unit. The RF unit decompresses the compressed samples prior to digital upconversion and digital to analog conversion to form an analog signal for transmission over an antenna. Compression and decompression can be incorporated into operations of conventional base stations and distributed antenna systems, including OBSAI or CPRI compliant systems.

Owner:INTEGRATED DEVICE TECH INC

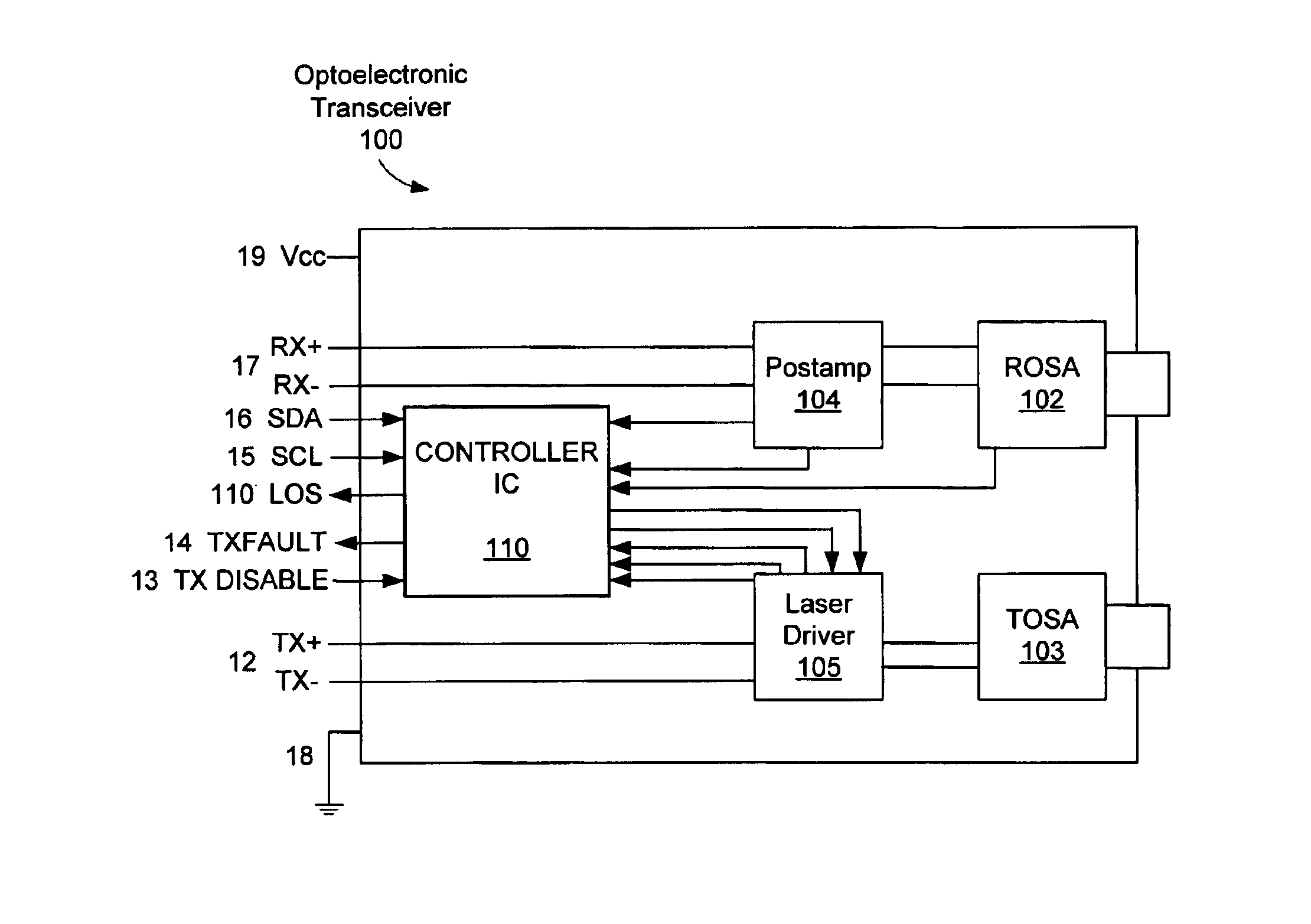

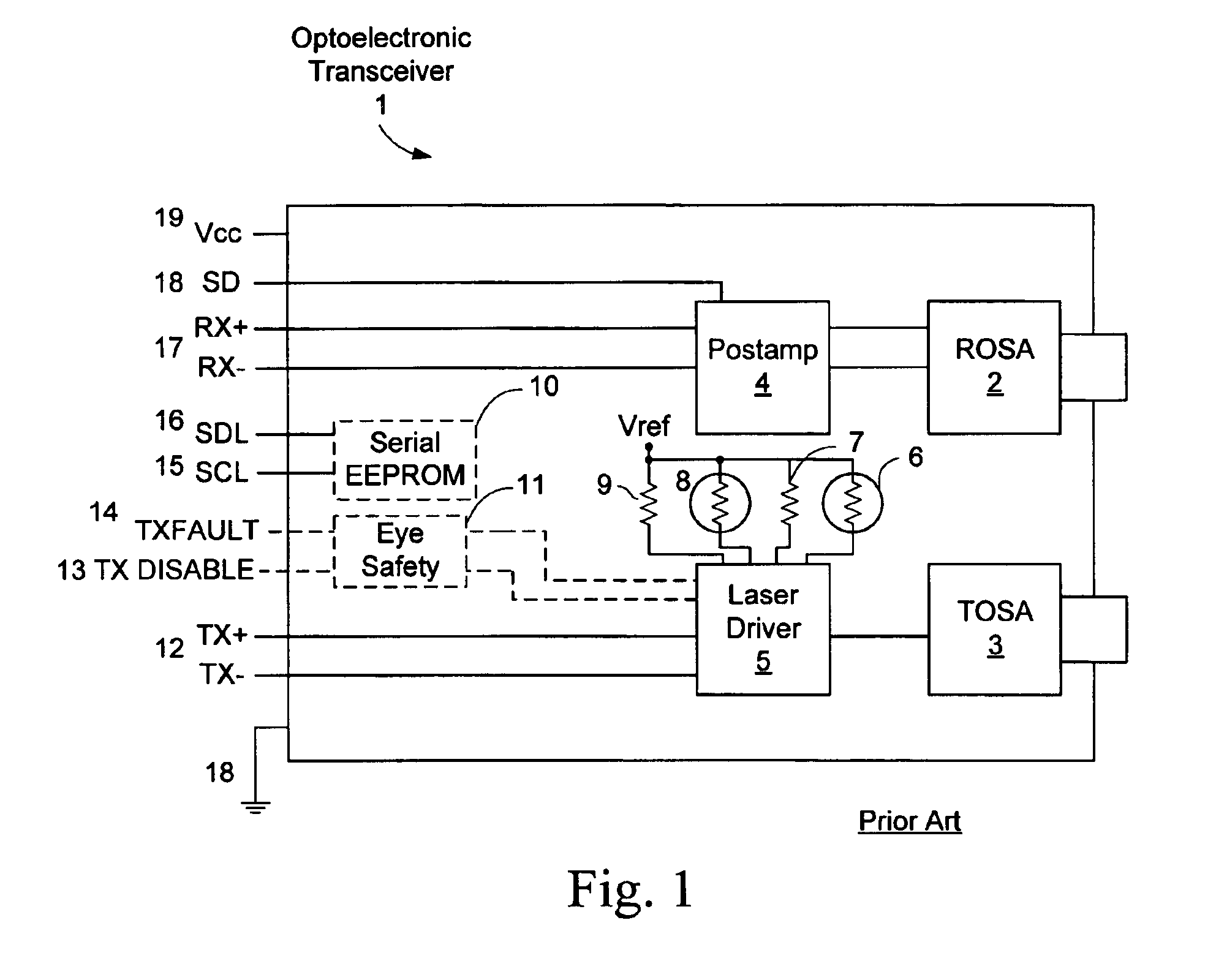

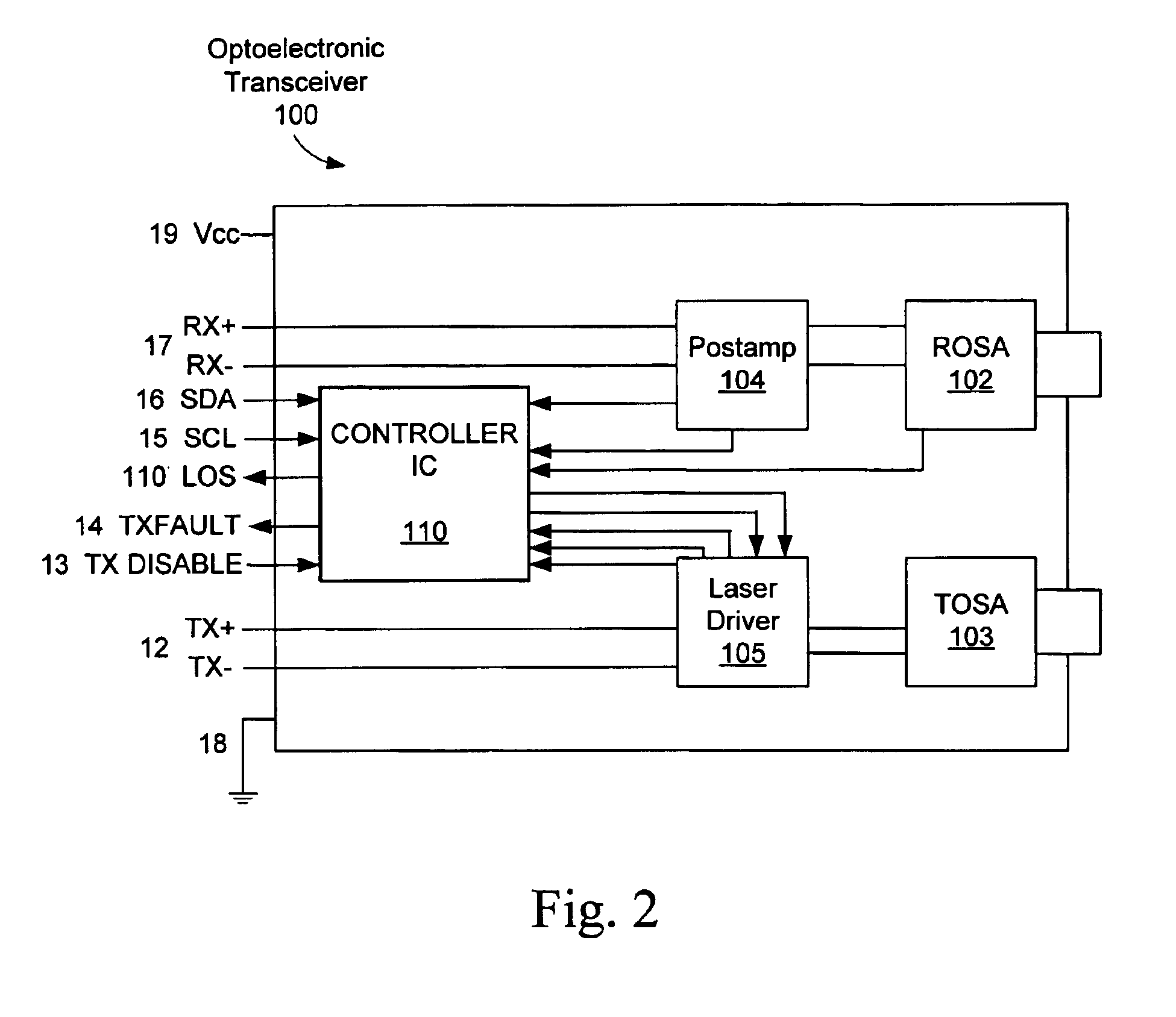

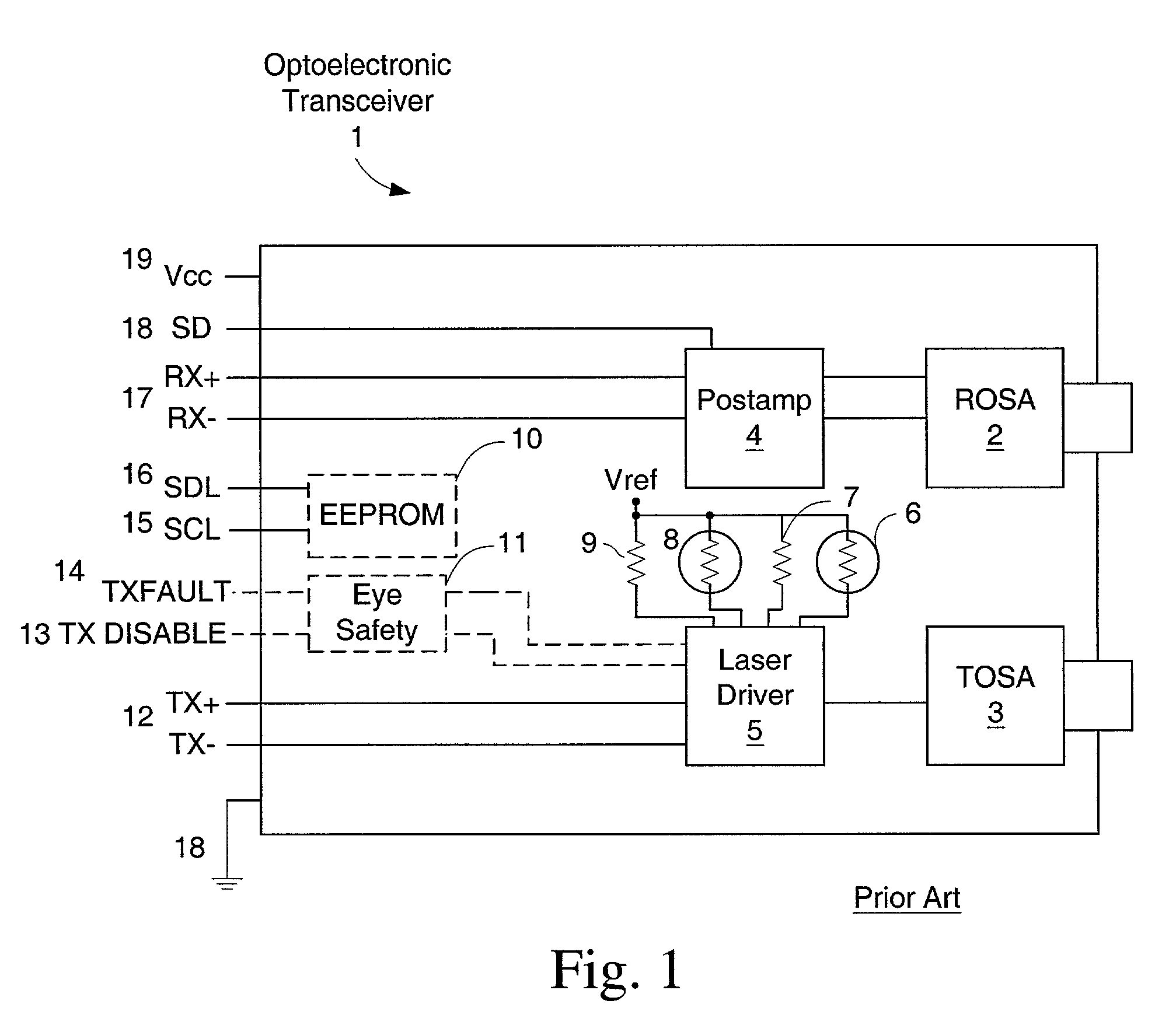

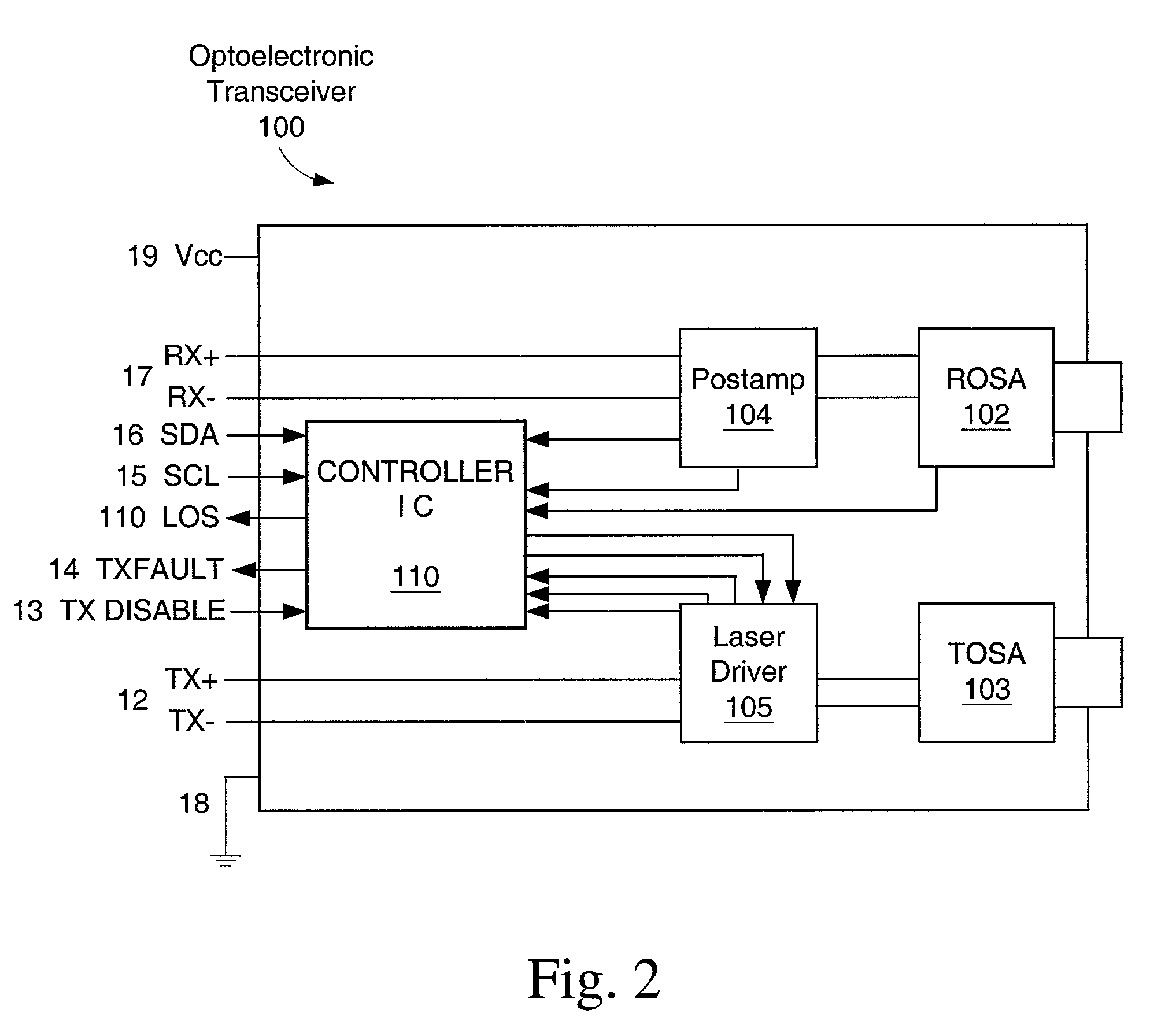

Memory mapped monitoring circuitry for optoelectronic device

InactiveUS6941077B2Laser detailsTransmission monitoring/testing/fault-measurement systemsLaser transmitterAnalog signal

Circuitry for monitoring operation of an optoelectronic device having a laser transmitter and a photodiode receiver includes analog to digital conversion circuitry for receiving a plurality of analog signals from the laser transmitter and photodiode receiver, converting the received analog signals into digital values, and storing the digital values in predefined memory-mapped locations within the optoelectronic device. Comparison logic compares one or more of these digital values with limit values, generates flag values based on the comparisons, and stores the flag values in predefined locations within the optoelectronic device. An interface enables a host device to read from and write to host-specified memory mapped locations within the optoelectronic device.

Owner:II VI DELAWARE INC

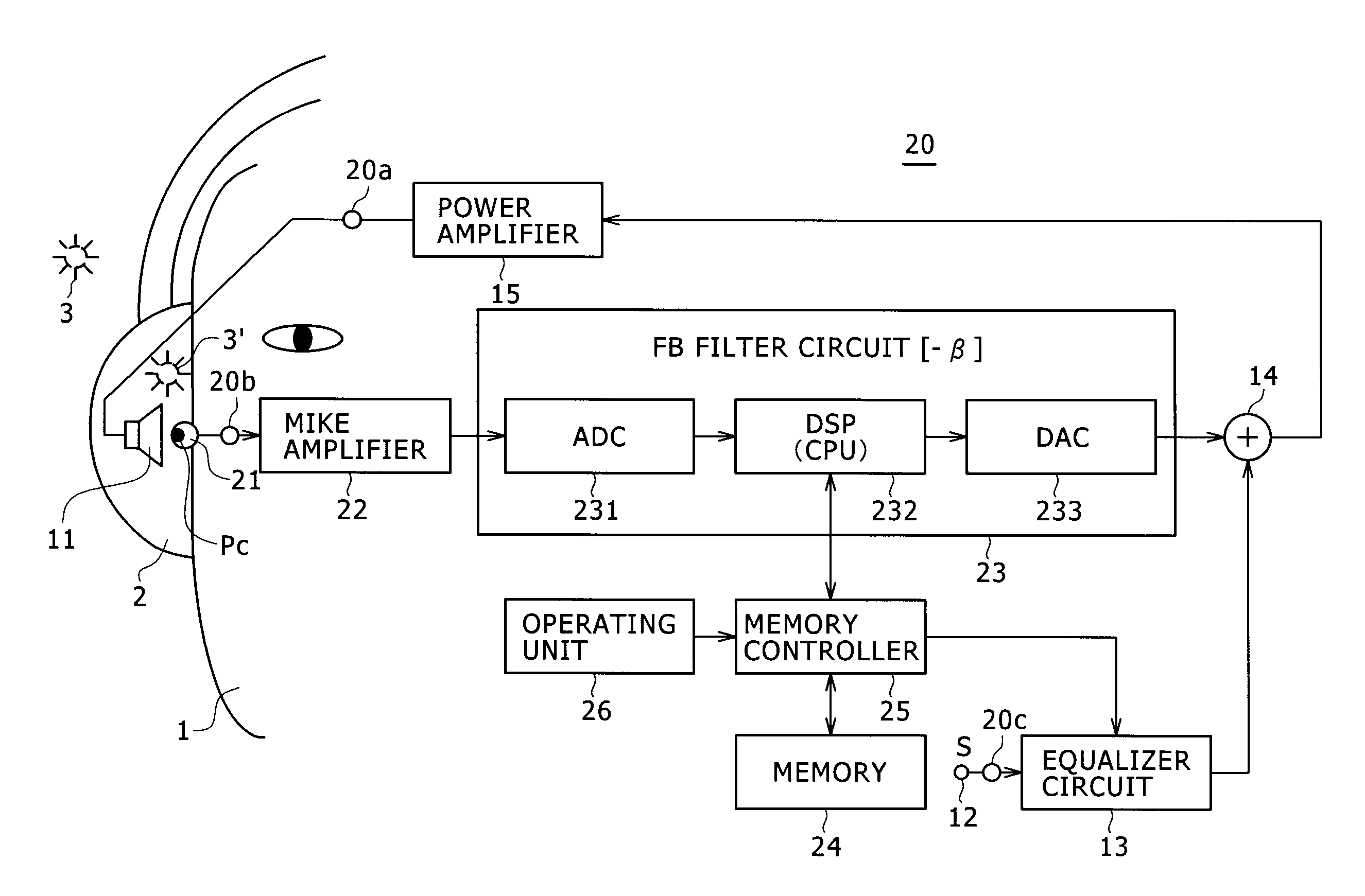

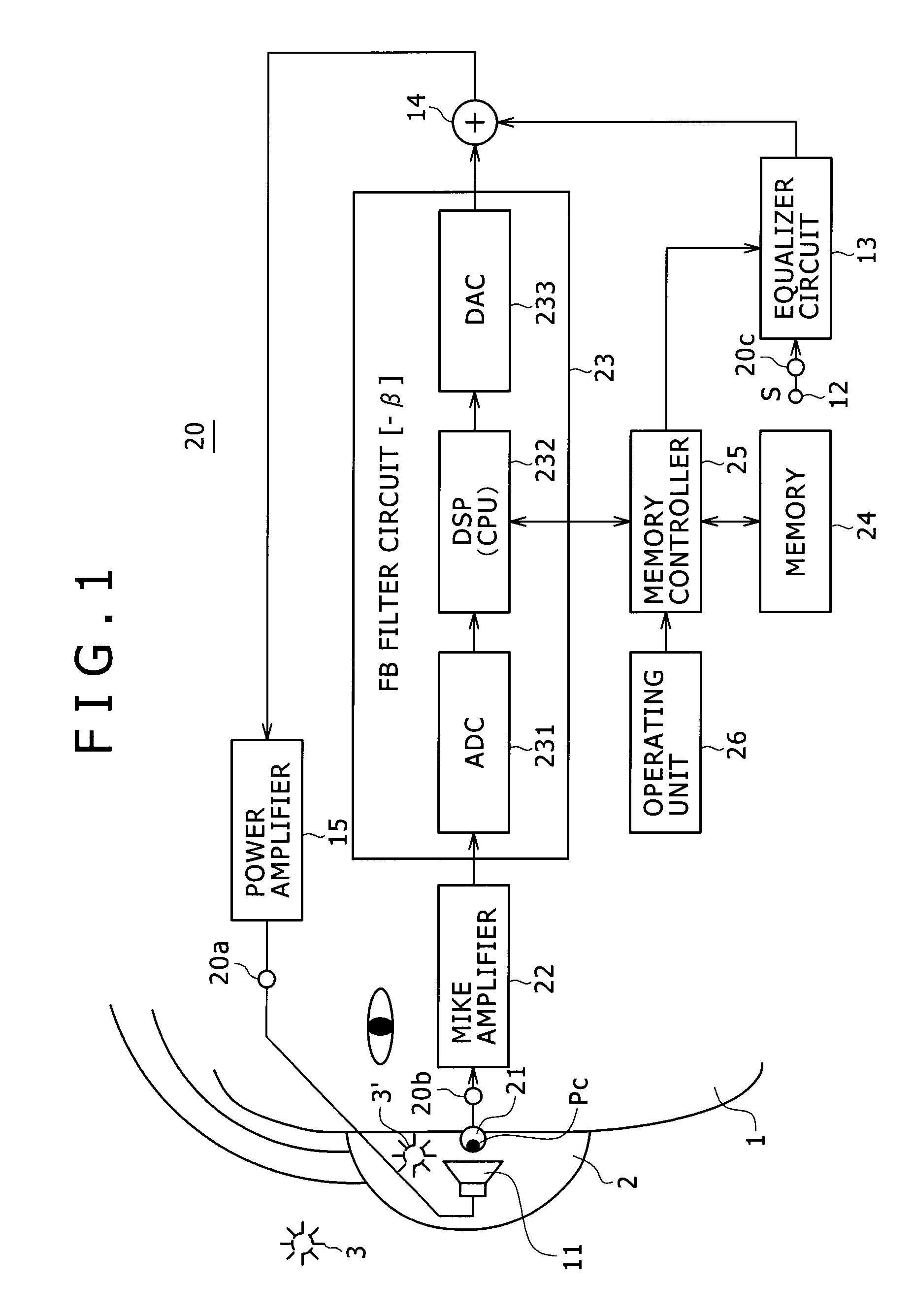

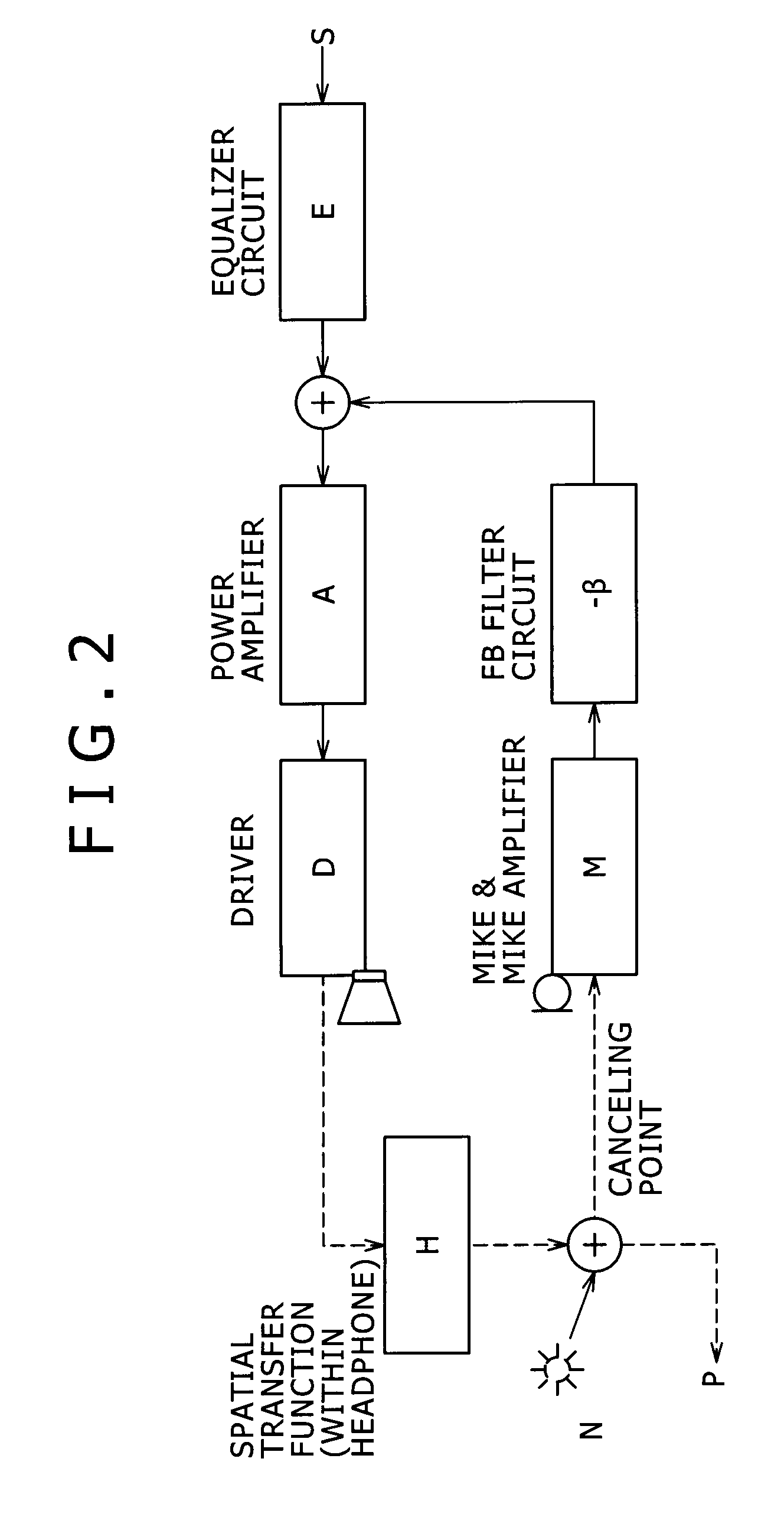

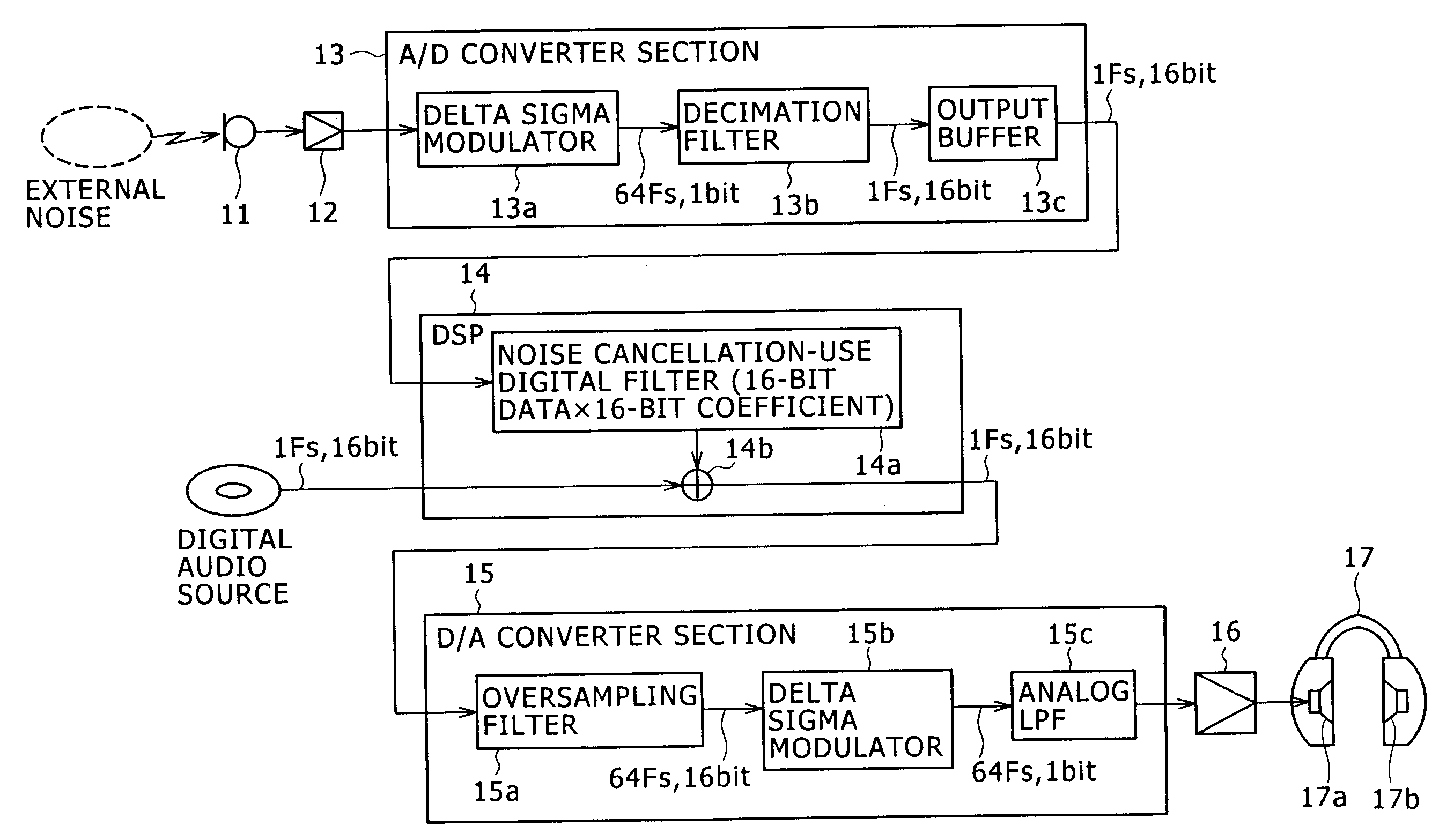

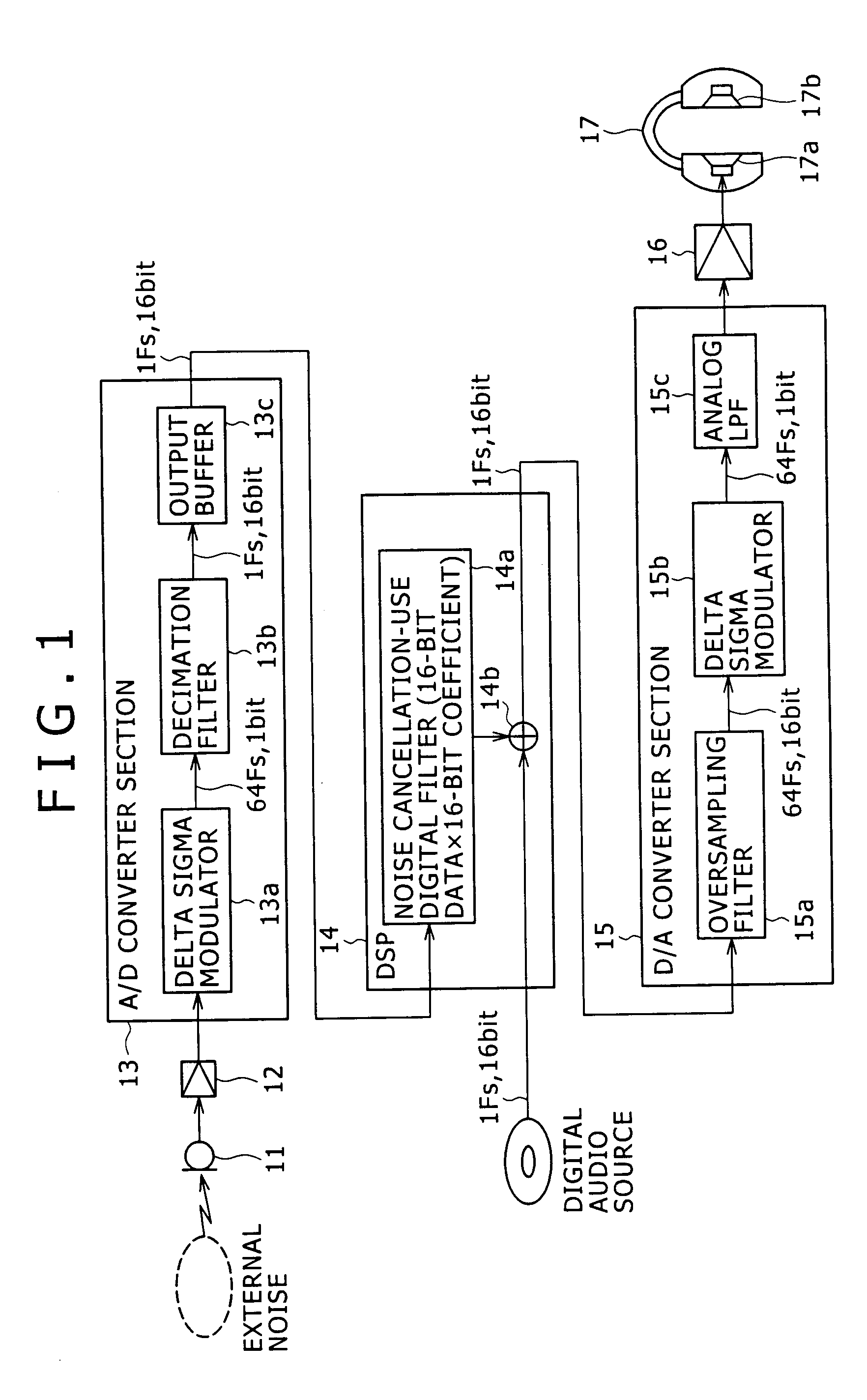

Noise reducing device, noise reducing method, noise reducing program, and noise reducing audio outputting device

InactiveUS20080112569A1Configuration simple and advantageousSimple and advantageous in of costEar treatmentHearing device active noise cancellationSignal onOutput device

A noise reducing device includes: an acoustic-to-electric conversion section for collecting noise and outputting an analog noise signal; an analog-to-digital conversion section for converting the analog noise signal into a digital noise signal; and a digital processing section for generating a digital noise reducing signal on a basis of the digital noise signal and a desired parameter. The device further includes: a retaining section for retaining a plurality of parameters corresponding to a plurality of kinds of noise characteristics; a setting section for setting one of the plurality of parameters as the desired parameter of the digital processing section; a digital-to-analog conversion section for converting the digital noise reducing signal into an analog noise reducing signal; and an electric-to-acoustic conversion section for outputting noise reducing sound on a basis of the analog noise reducing signal.

Owner:SONY CORP

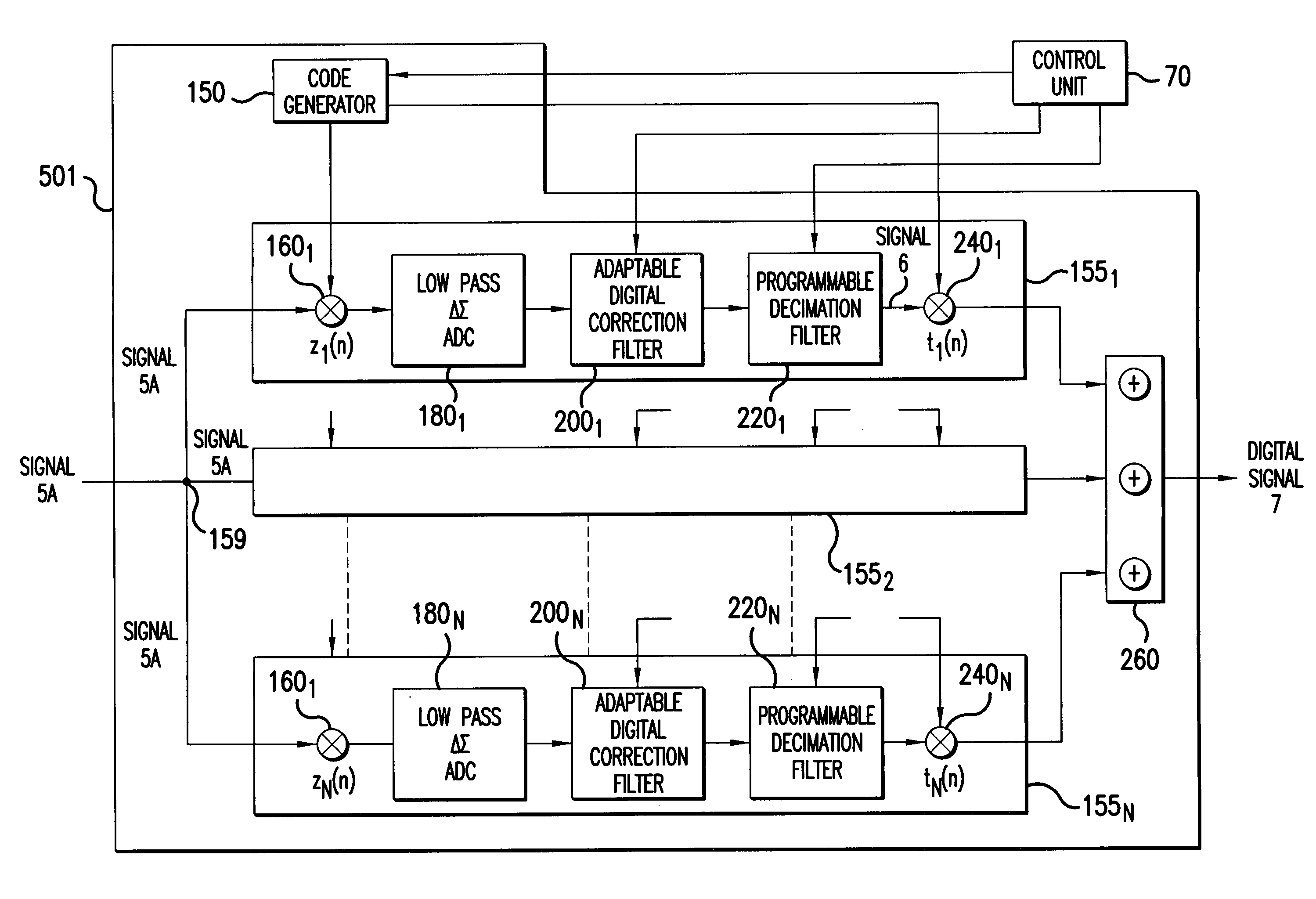

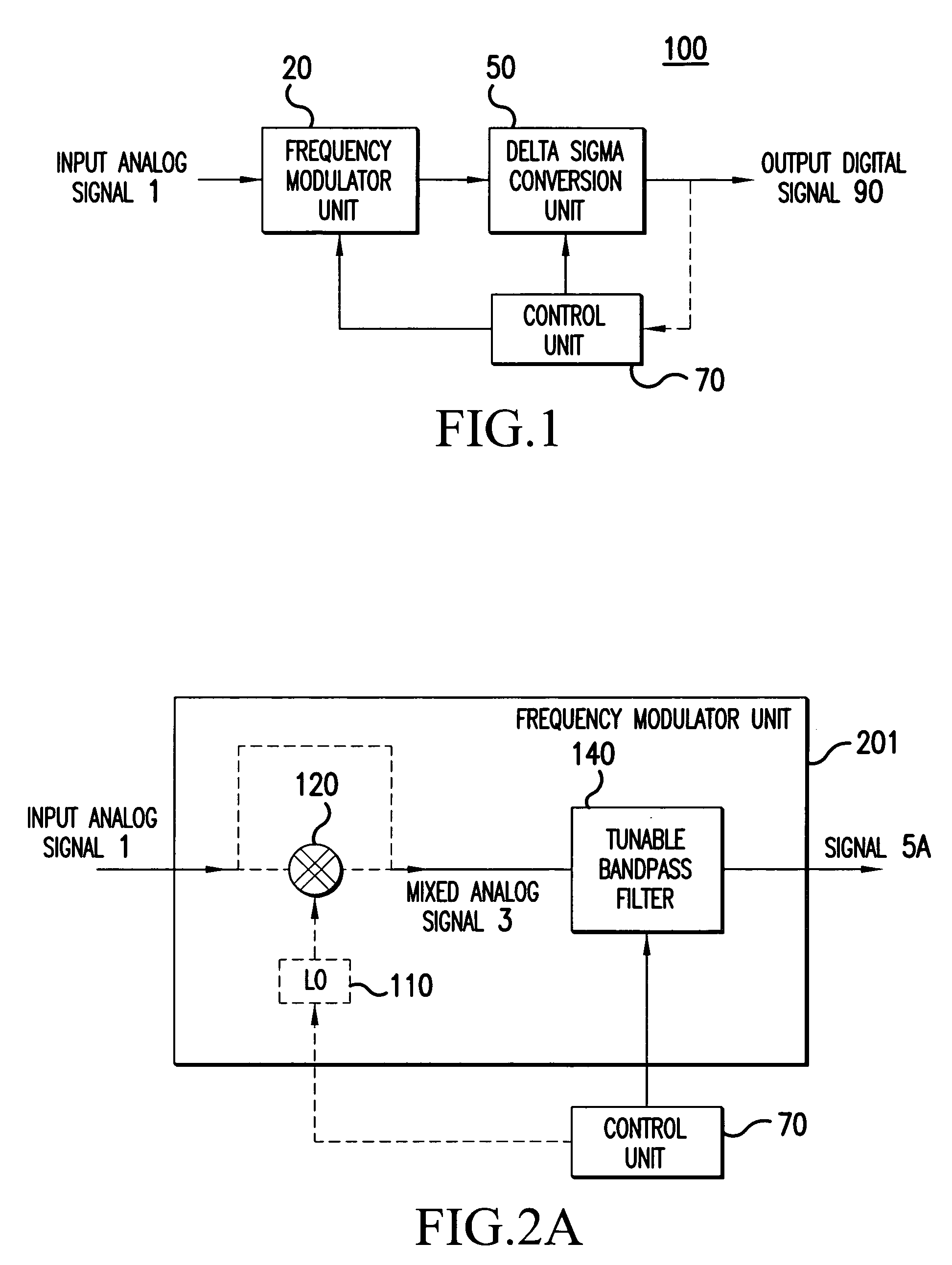

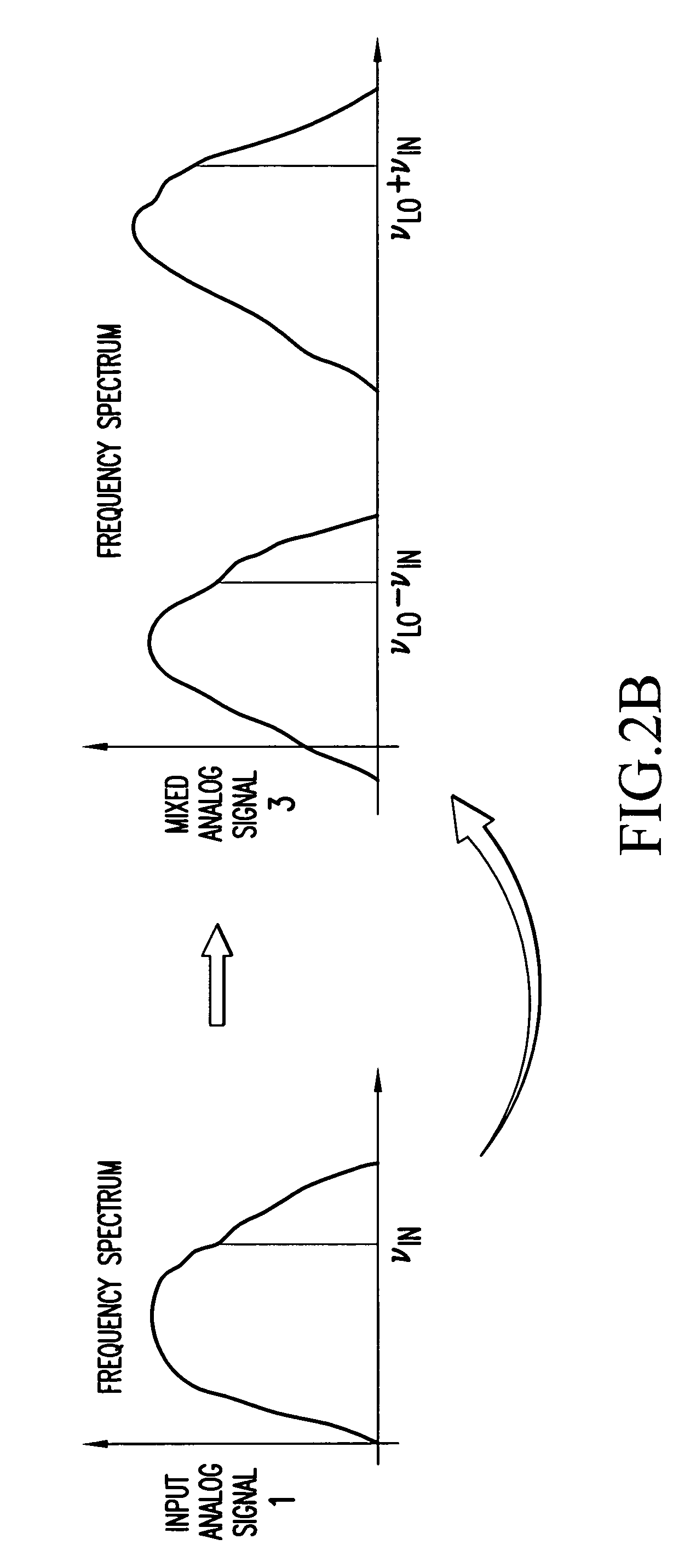

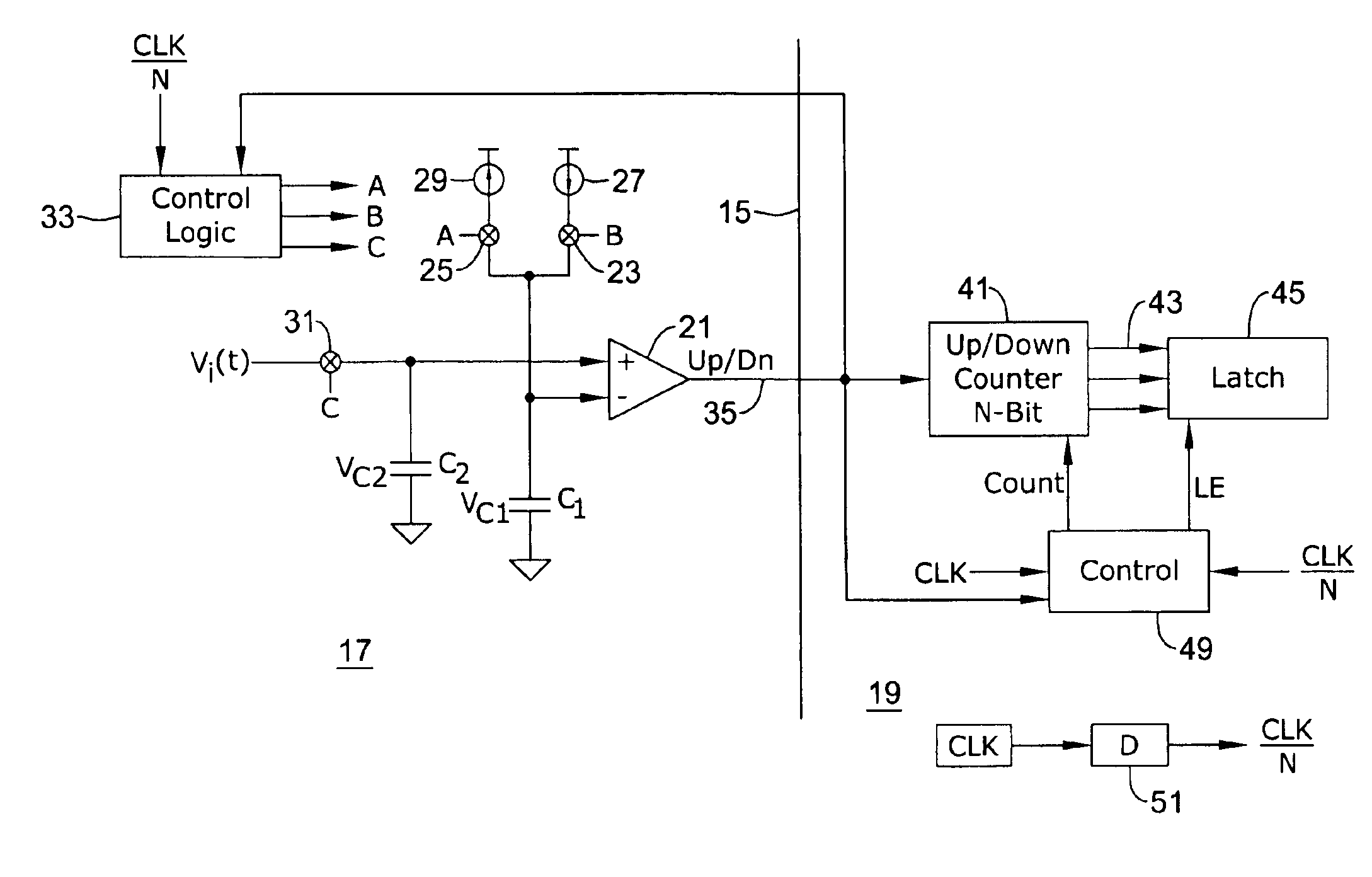

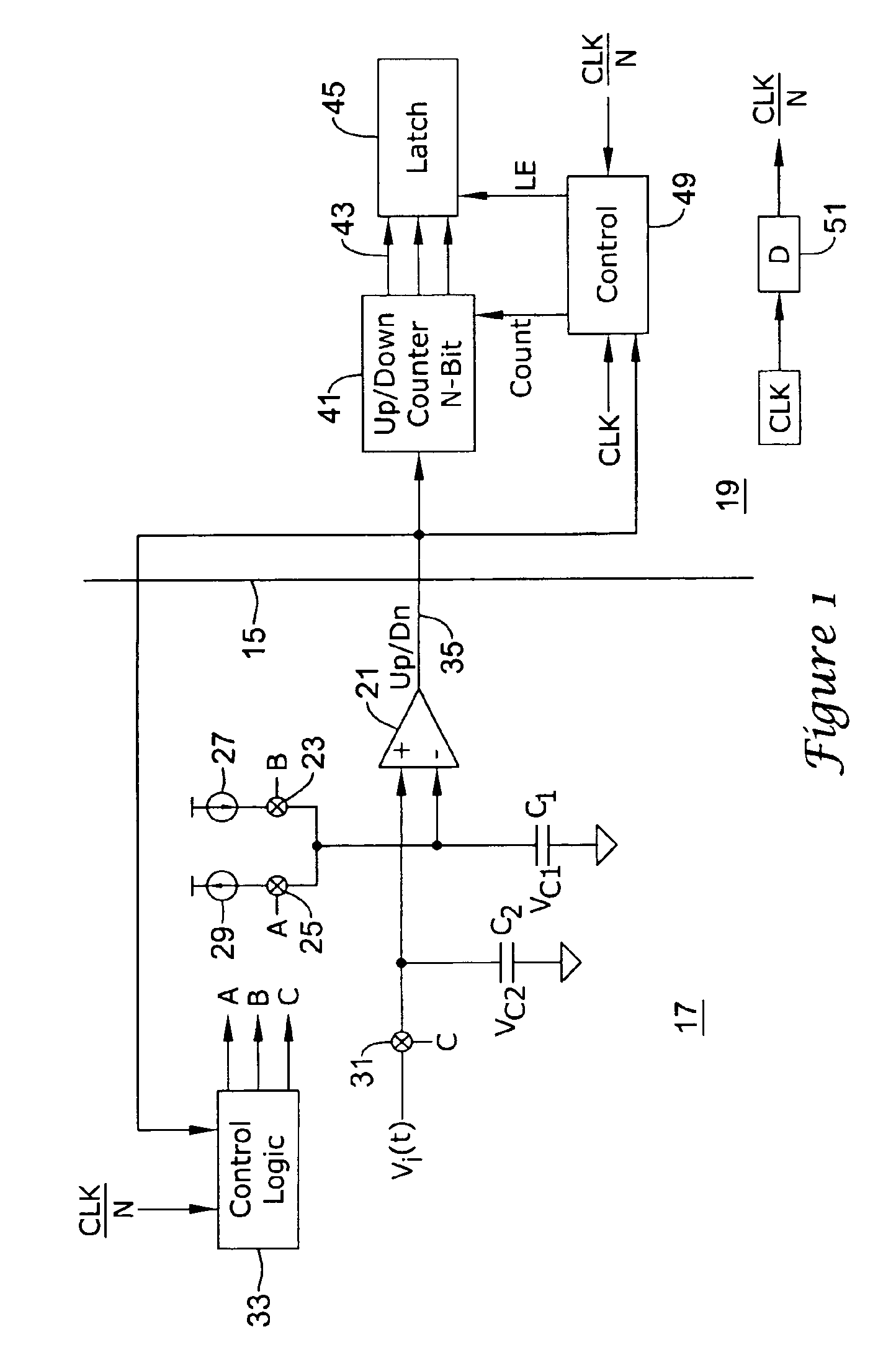

Parallel, adaptive delta sigma ADC

InactiveUS7193544B1Electric signal transmission systemsAnalogue conversionFrequency spectrumAnalog signal

An apparatus performs adaptive analog-to-digital conversion. The apparatus according to one embodiment comprises a frequency modulator unit for changing an input analog signal into a modulated analog signal with a frequency spectrum in a bandwidth of interest, a parallel delta sigma conversion unit operatively connected to the frequency modulator unit, the parallel delta sigma conversion unit converting the modulated analog signal into a digital signal, and a controller operatively connected to the frequency modulator unit and the parallel delta sigma conversion unit, the controller adjusting at least one parameter relating to a frequency characteristic of the frequency modulator unit and / or the parallel delta sigma conversion unit.

Owner:NORTHROP GRUMAN CORP

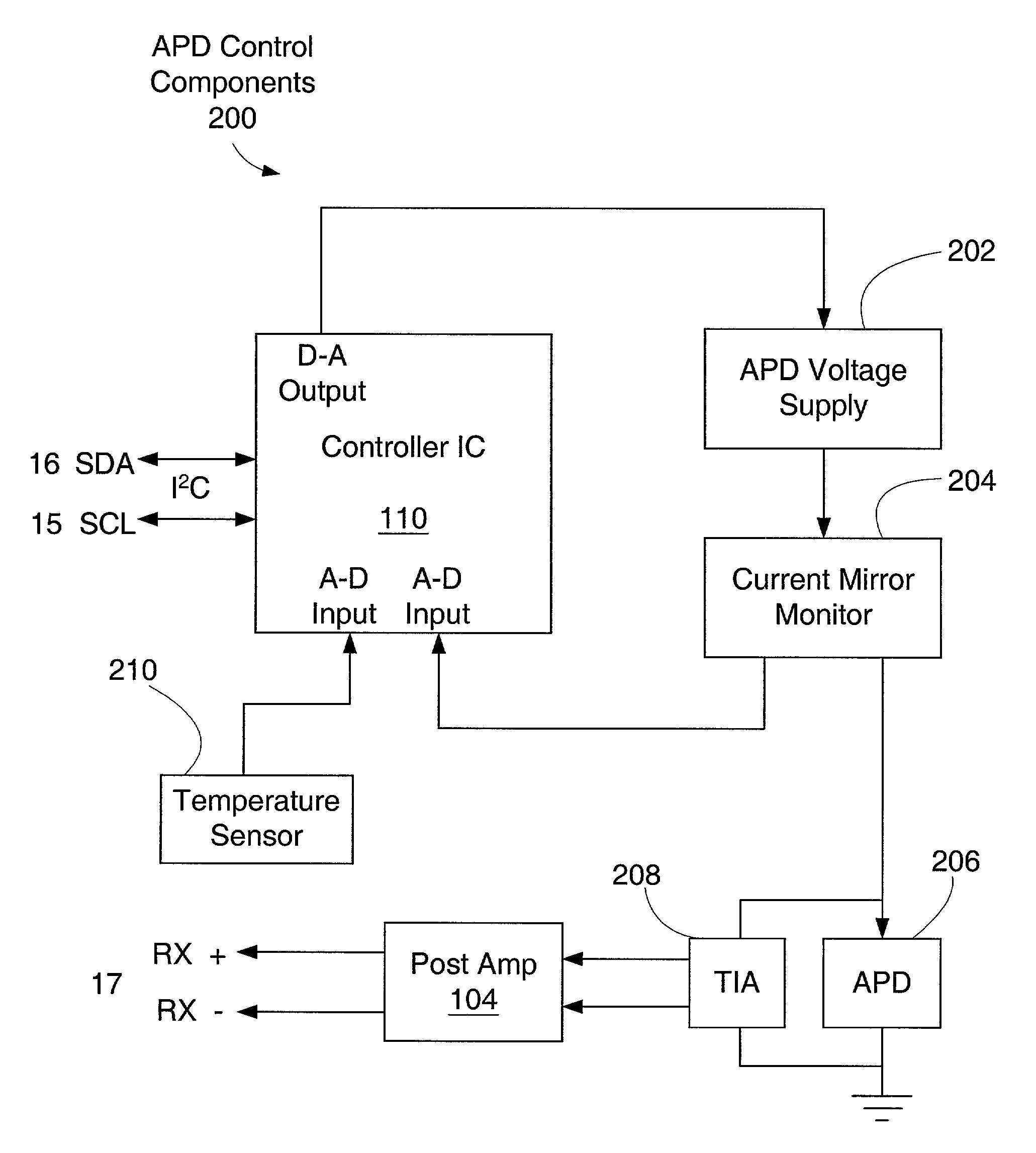

Avalanche photodiode controller circuit for fiber optics transceiver

A controller for controlling the reverse-bias voltage of an avalanche photodiode in a transceiver or receiver. The controller includes memory for storing information related to the avalanche photodiode, and analog to digital conversion circuitry for receiving an analog signal corresponding to the temperature of the avalanche photodiode, converting the received analog signal into a digital value, and storing the digital value in a predefined location within the memory. Control circuitry in the controller controls the operation of the avalanche photodiode in accordance with the digital value corresponding to the temperature of the avalanche photodiode and a temperature lookup table stored in the memory. A serial interface is provided to enable a host device to read from and write to locations within the memory. The invention is also implemented as a method for controlling the reverse-bias voltage of an avalanche photodiode in a transceiver or receiver and a method for calibrating a transceiver or receiver having an avalanche photodiode.

Owner:II VI DELAWARE INC

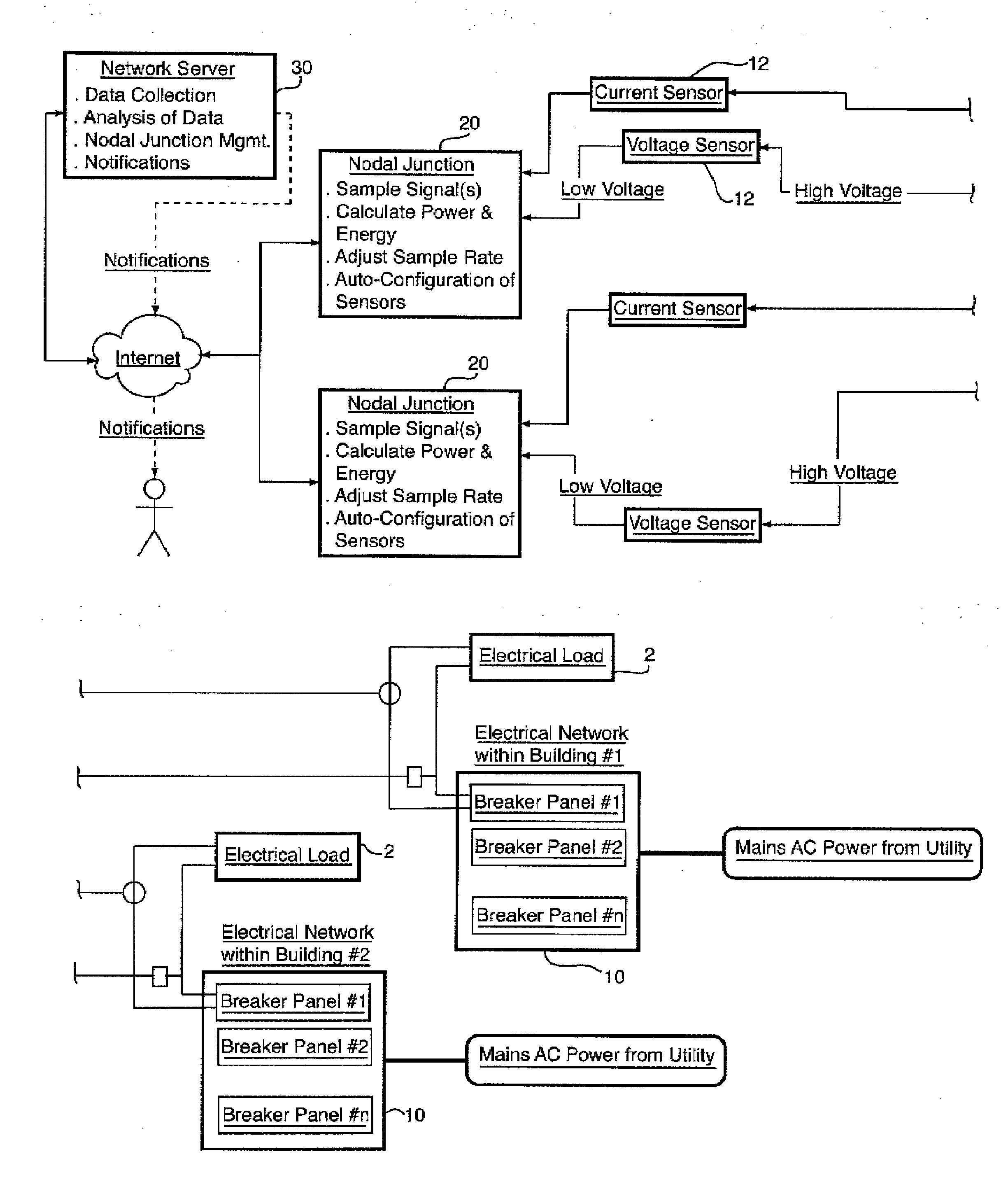

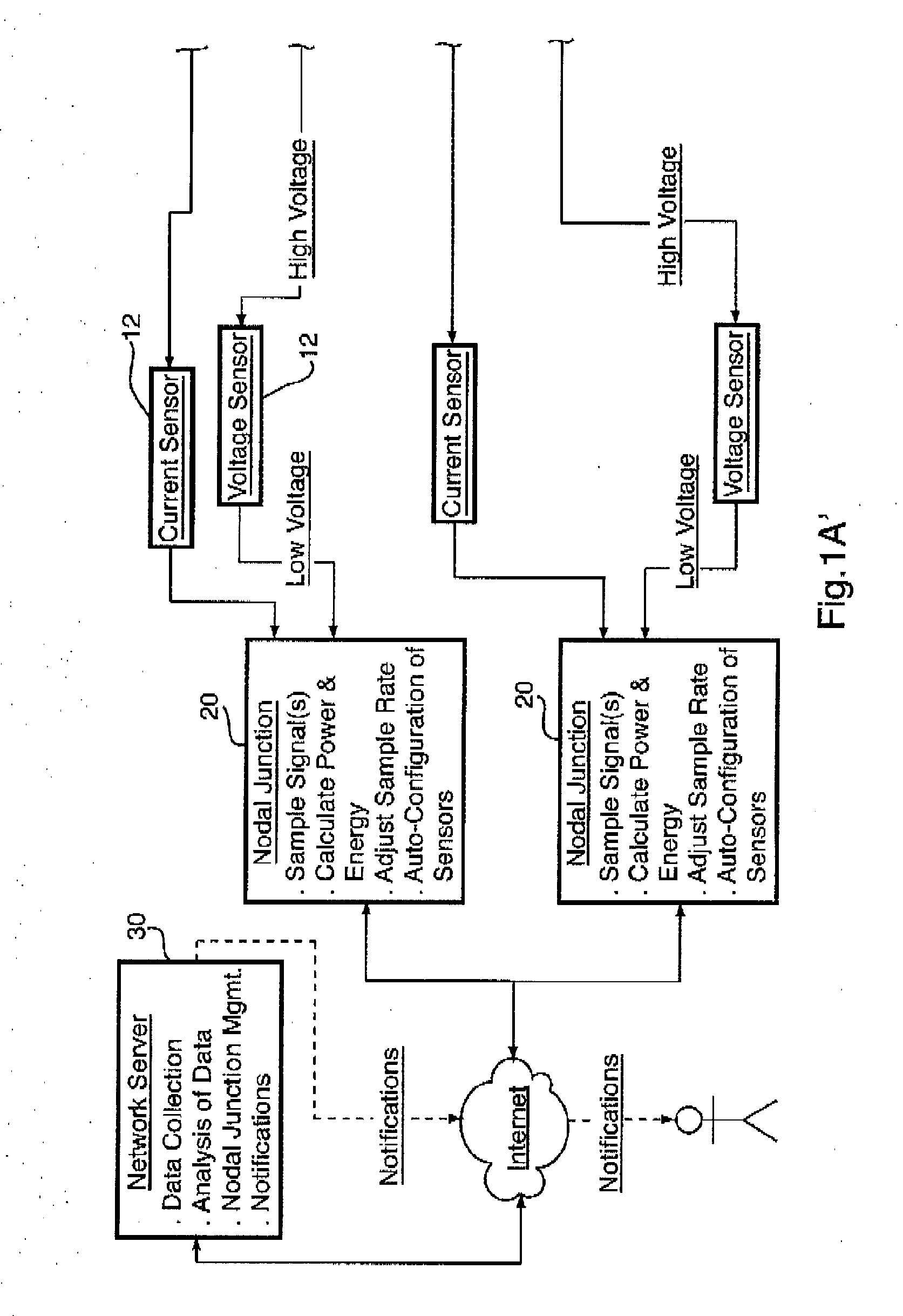

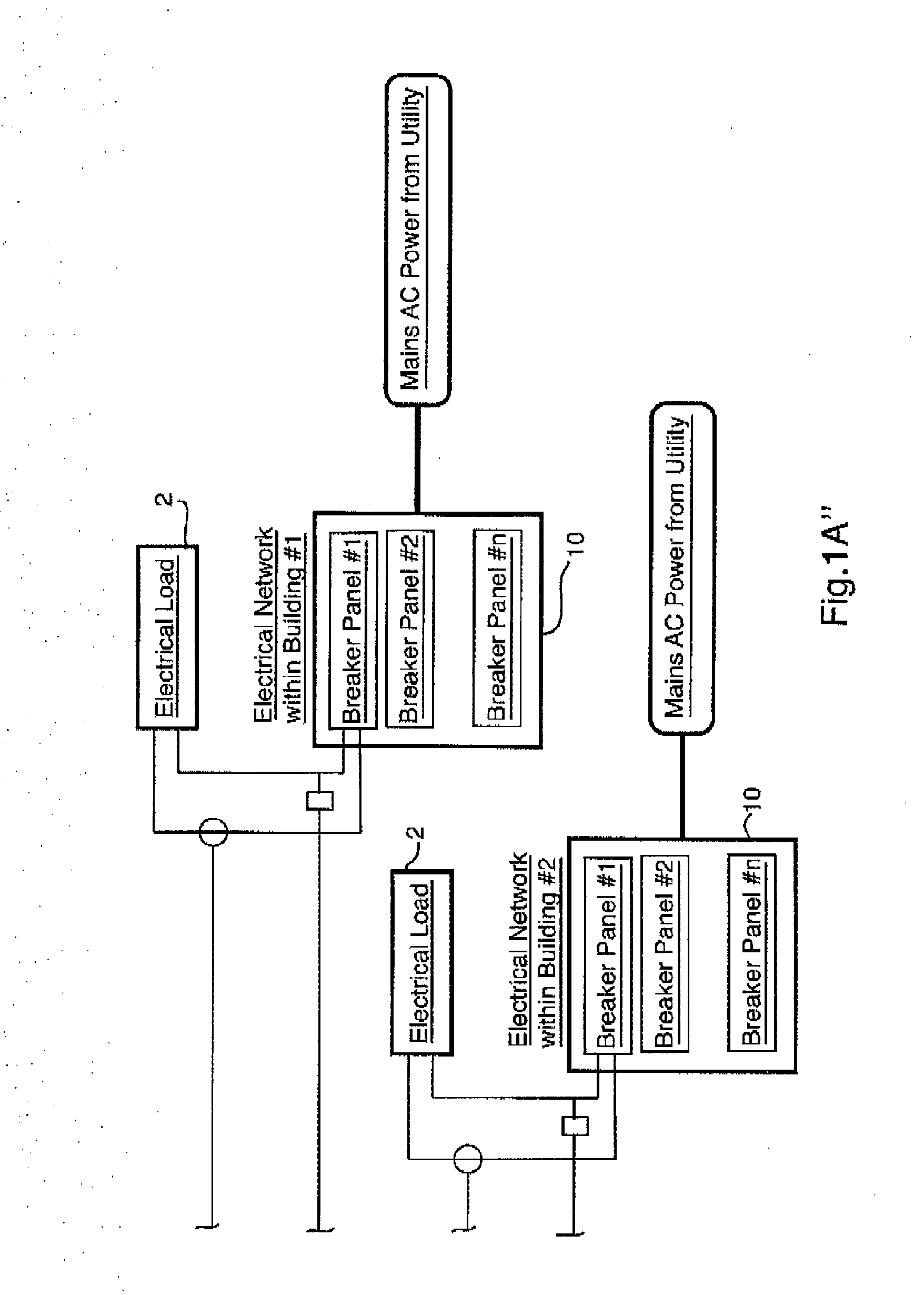

System and method for monitoring an electrical network

An energy monitoring system which in preferred embodiments employs at least one nodal junction receiving and creating data by analog to digital conversion from a plurality of local node sensors. Data accumulated by the nodal junction is used for analysis of wave patterns to detect anomalies in the local electrical network and / or loads connected to the local electrical network. Anomalies can be detected in various ways, including: comparison of data with historical data acquired from the local node sensors; comparison of data with known wave pattern profiles for similar loads; and comparison of data with data acquired from local node sensors at other locations. Thus, the accumulation of data in the system of the invention provides the ability to perform comparative analysis to a baseline or standard, and also the ability to perform comparative analysis at an enterprise level across different target locations.

Owner:CIRCUITMETER

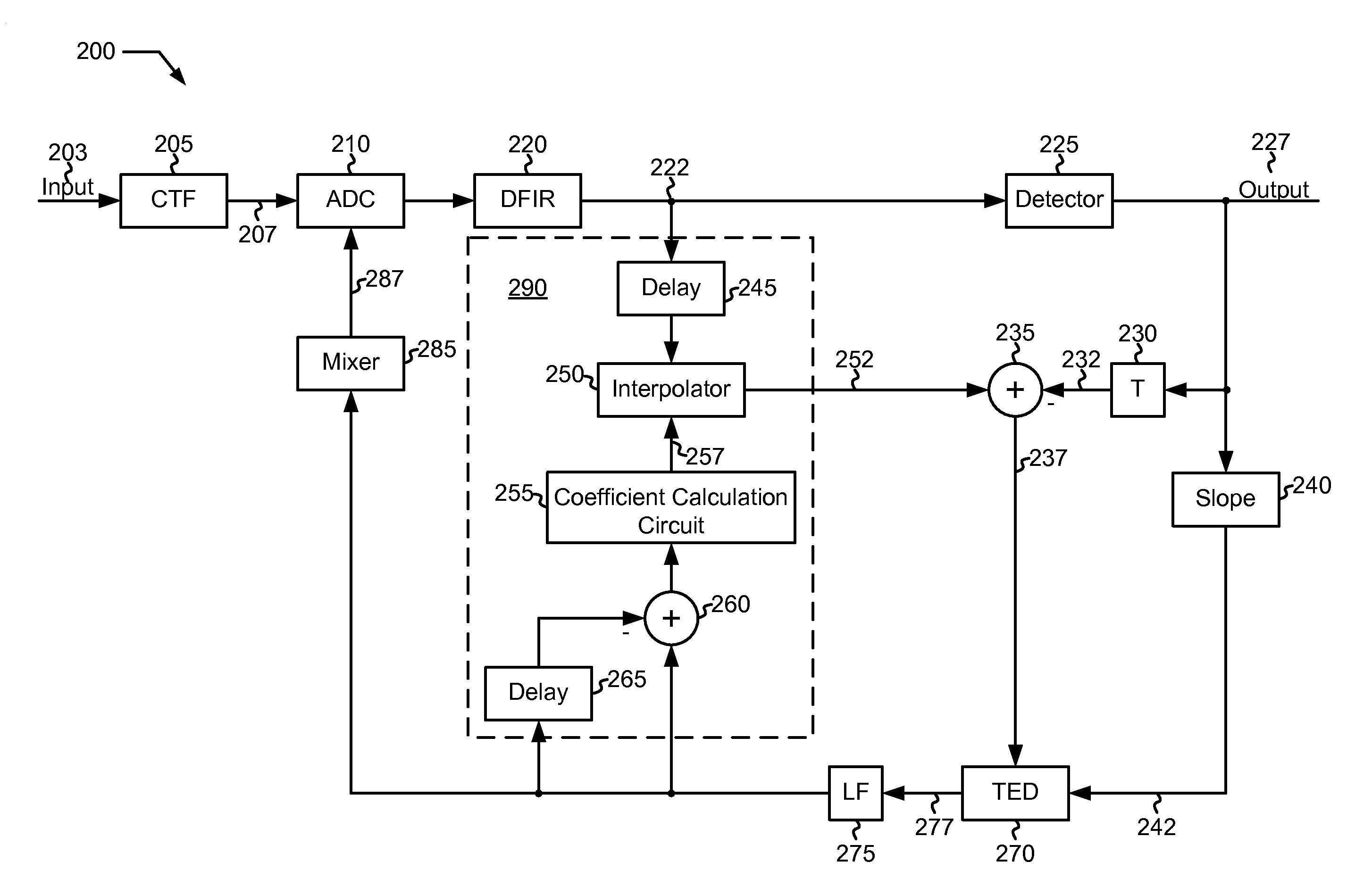

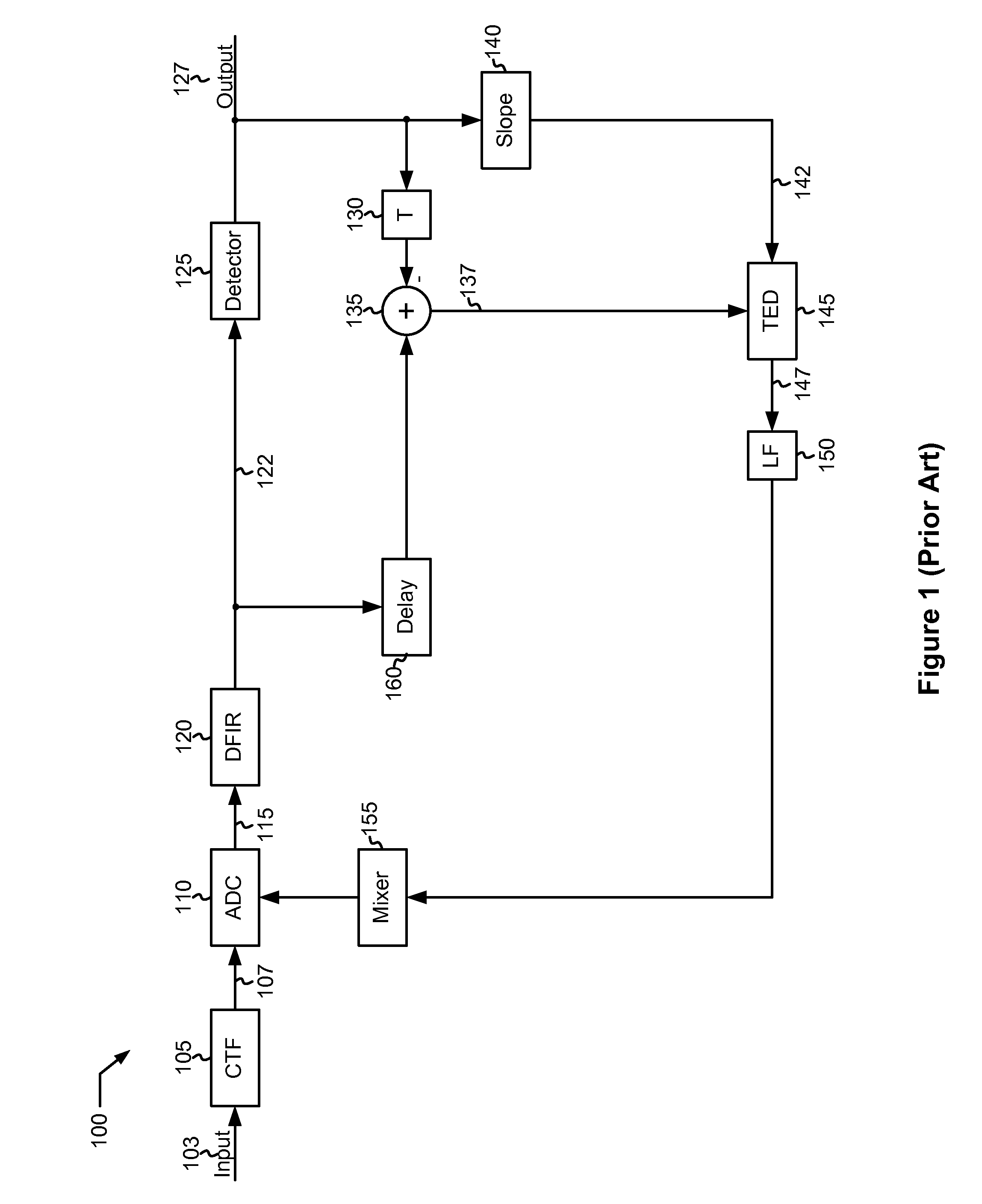

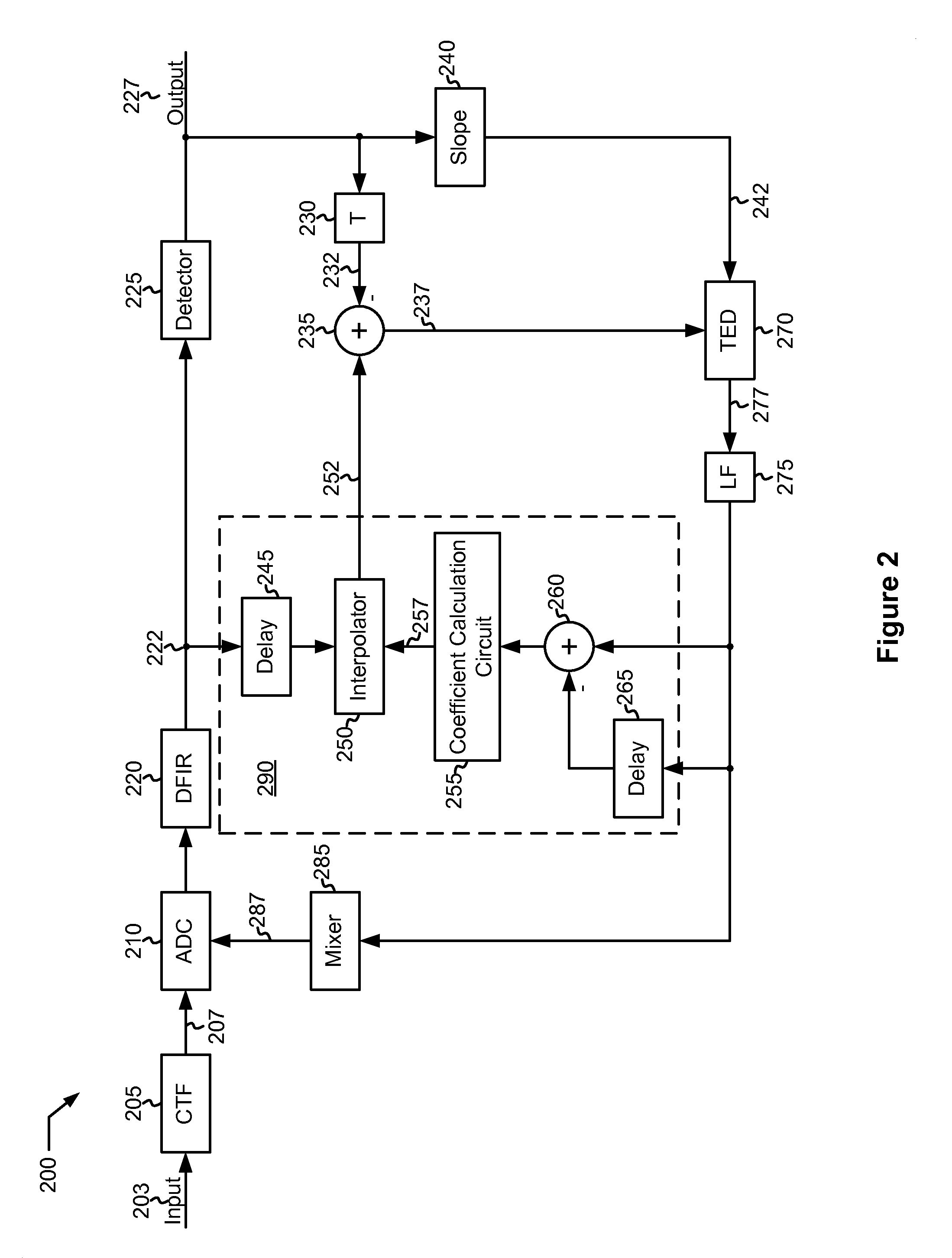

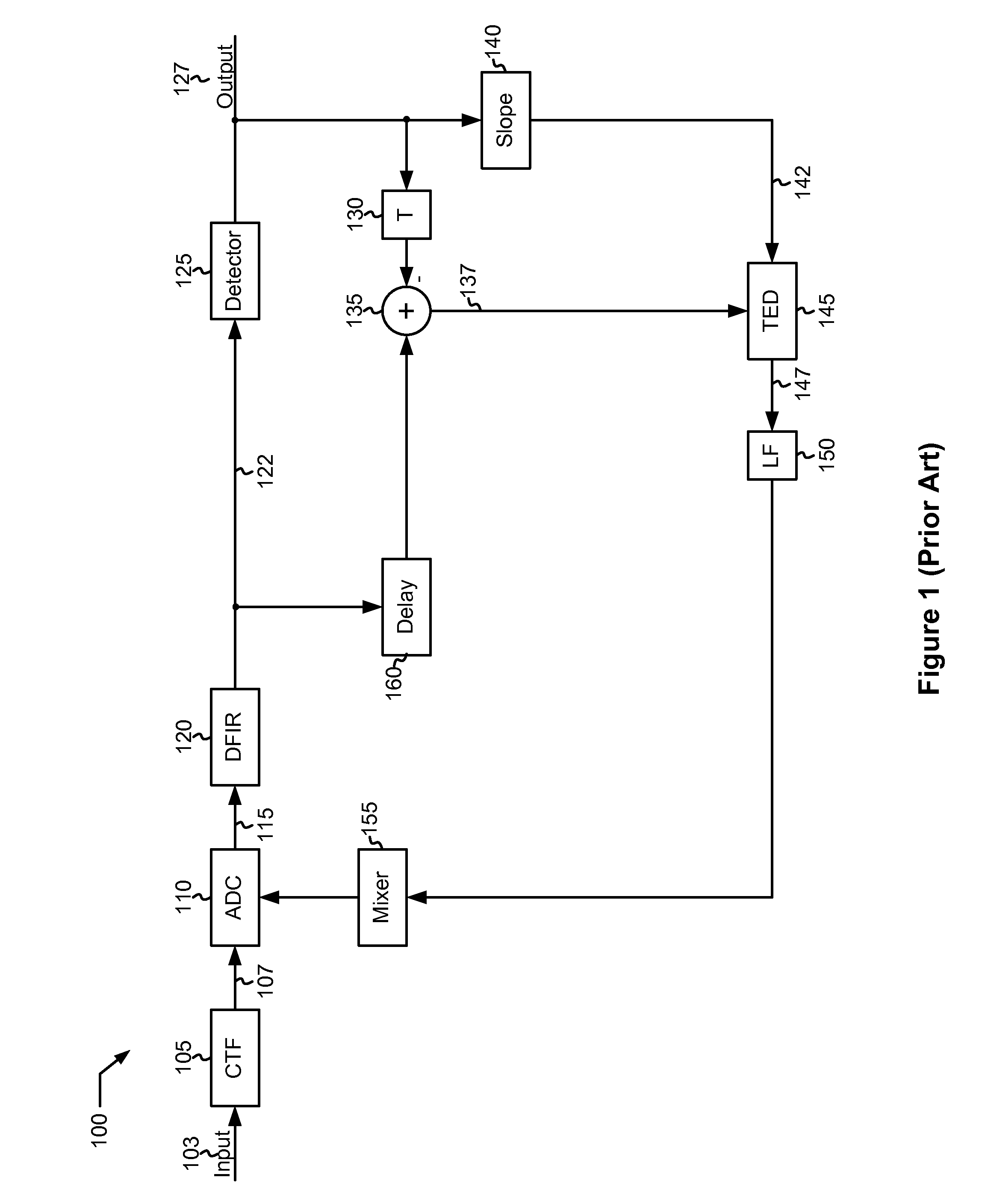

Systems and methods for mitigating latency in a data detector feedback loop

InactiveUS8018360B2Reduce latency impactLower latencyModification of read/write signalsElectric signal transmission systemsSampling instantData retrieval

Methods and systems for mitigating latency in a data detector feedback loop are included. For example, a method for reducing latency in an error corrected data retrieval system is included. The method includes performing an analog to digital conversion at a sampling instant to create a digital sample, and performing a data detection on the digital sample to create a detected output. The detected output is compared with the digital sample to determine a phase error. During an interim period, the digital sample is adjusted to reflect the phase error to create an adjusted digital sample. After the interim period, the sampling instant is adjusted to reflect the phase error.

Owner:LSI CORP +1

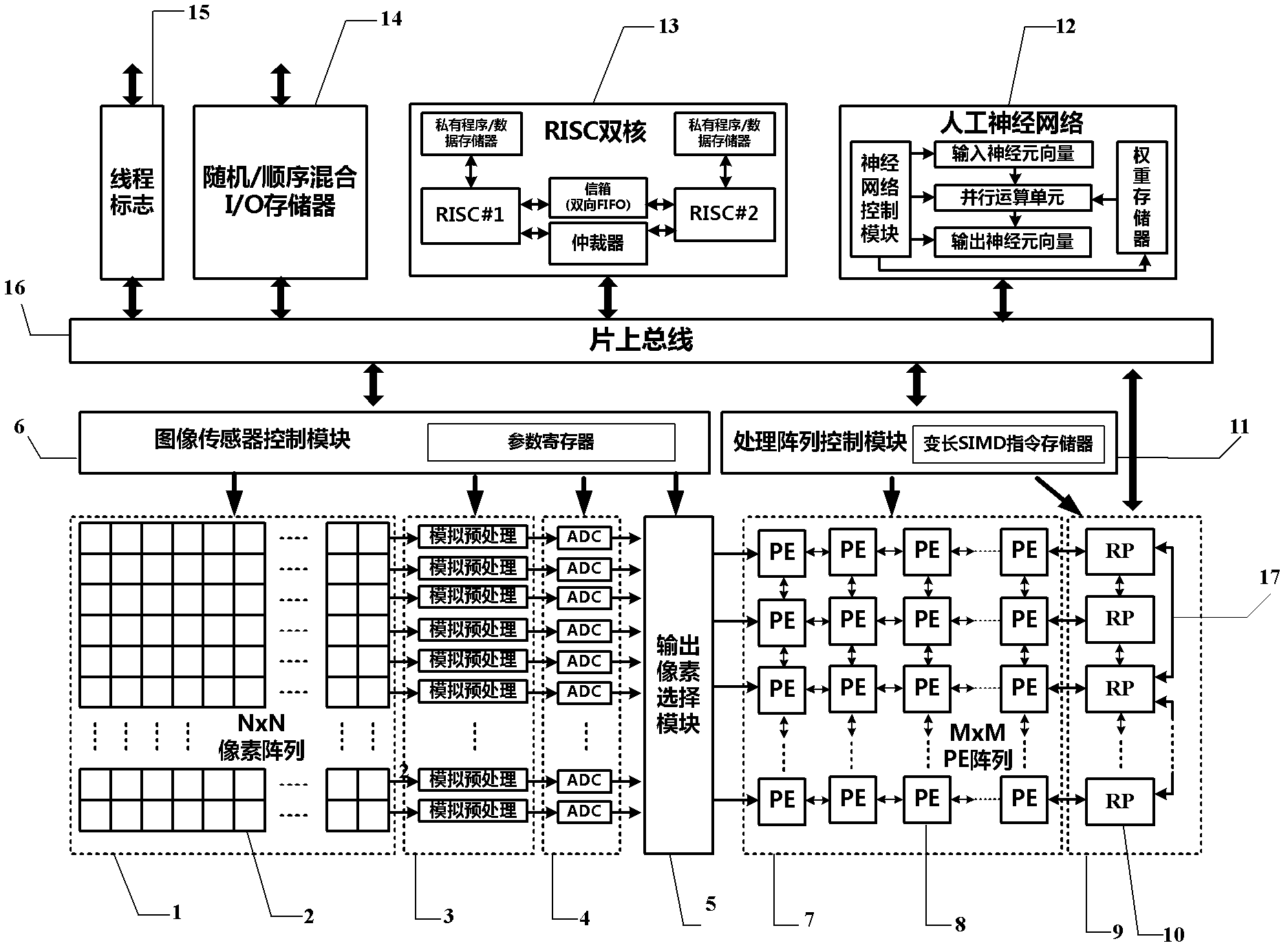

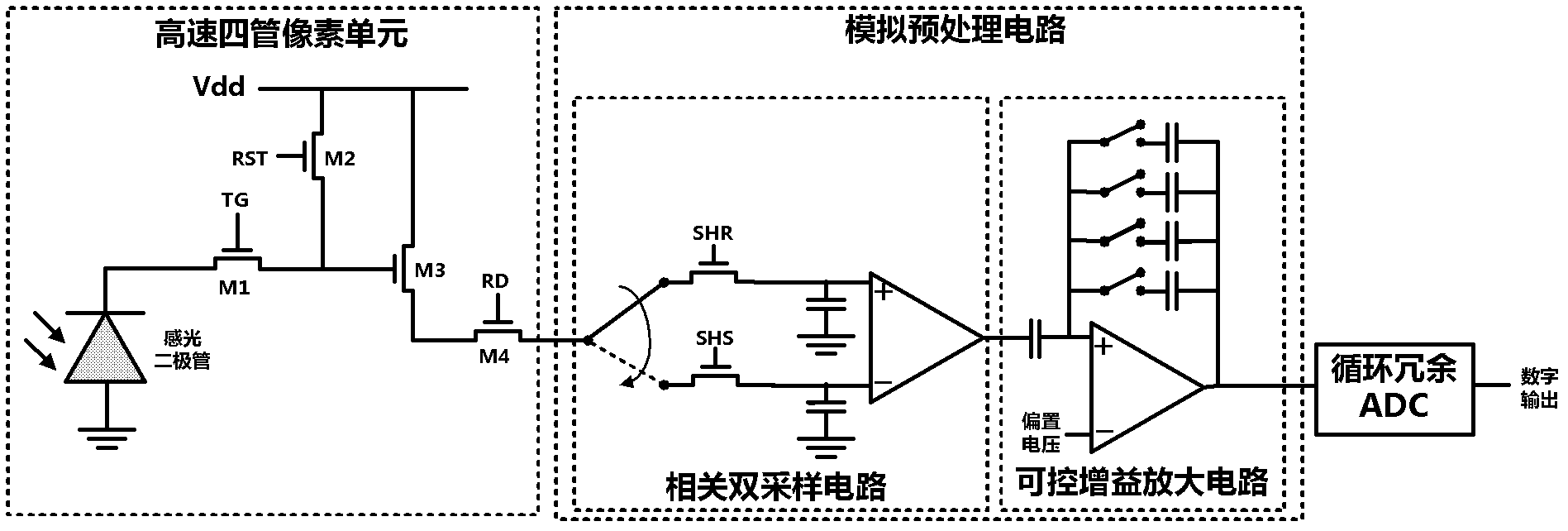

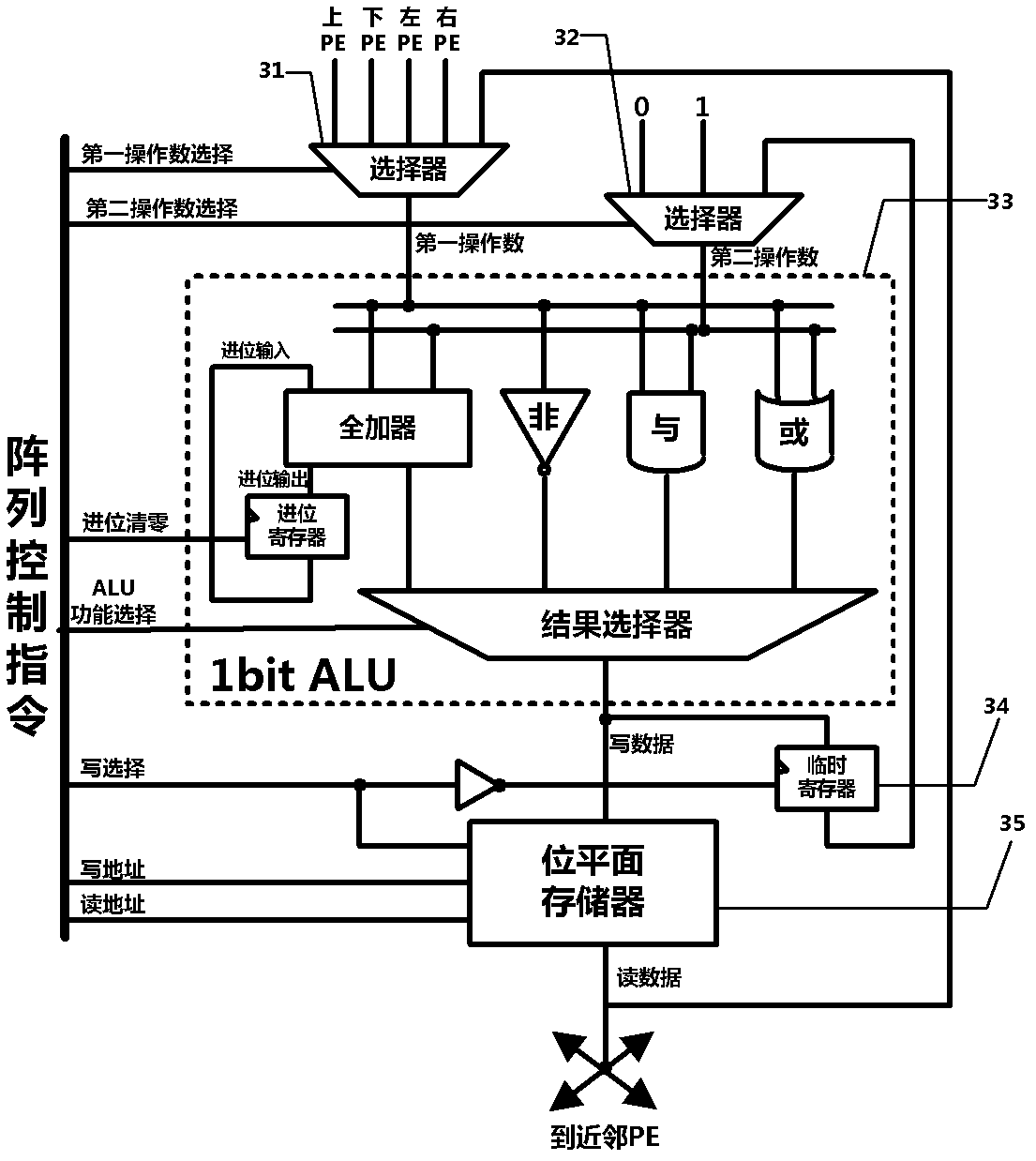

Programmable visual chip-based visual image processing system

ActiveCN102665049AFlexible handlingFlexible multi-resolution processingTelevision system detailsColor television detailsFace detectionDual core

Disclosed in the invention is a programmable visual chip-based visual image processing system, comprising an image sensor and a multilevel parallel digital processing circuit. The image sensor mainly includes a pixel array, an analog preprocessing circuit array and an analog-to-digital conversion circuit array; and the digital processing circuit consists of a parallel processing unit array with an M*M pixel level, a parallel processing unit array with M*1 rows, an on-chip artificial neural network and a reduced instruction processor dual-core subsystem. According to the provided system, high quality image collection with high speed and multilevel parallel image processing are realized and several high-speed intelligent visual application can be realized by programming; and compared with a traditional image system, the provided system has advantages of high speed, high integration, low power consumption and low cost. Moreover, the invention brings forward an embodiment for realizing the above-mentioned system as well as several high-speed intelligent visual image processing algorithms based on the embodiment. High-speed motion detection, high-speed gesture identification and rapid face detection are included; and the processing speed can reach 1000 frames per second. Therefore, a requirement of high-speed real-time processing can be met.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

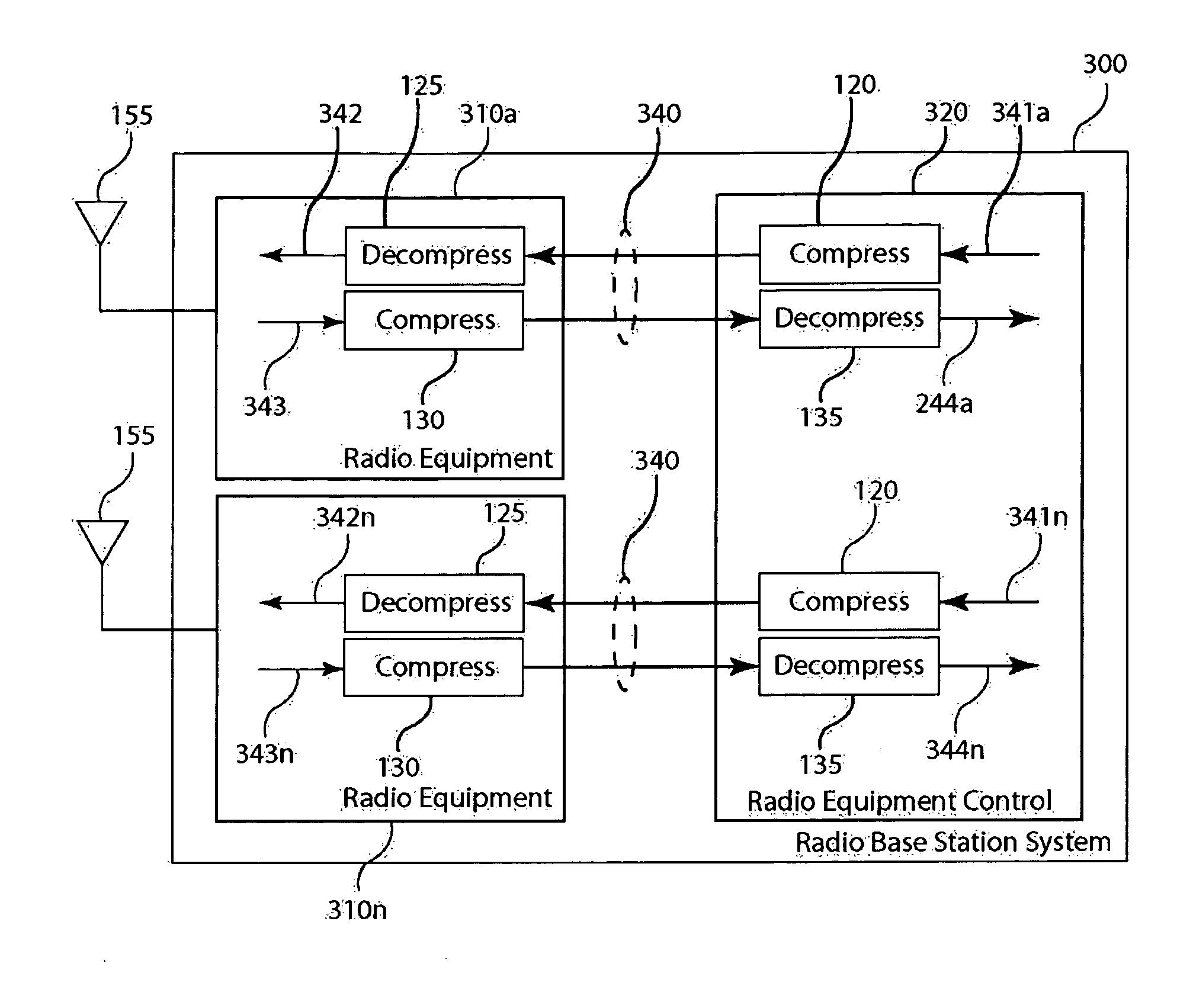

Compression of signals in base transceiver systems

ActiveUS8174428B2Increase capacityElectric signal transmission systemsEqual length code transmitterTransceiverDistributed antenna system

A signal compression method and apparatus for a base transceiver system (BTS) in a wireless communication network provides efficient transfer of compressed signal samples over serial data links in the system. For the uplink, an RF unit of the BTS compresses signal samples resulting from analog to digital conversion of an analog signal received via an antenna. The RF unit transfers the compressed signal samples over the serial data link to the base station processor where they are decompressed prior to the normal signal processing operations. For the downlink, the base station processor compresses signal samples and transfers the compressed signal samples over the serial data link to the RF unit. The RF unit decompresses the compressed samples and converts the decompressed samples to an analog signal for transmission over an antenna. Compression and decompression can be incorporated into operations of conventional base stations and distributed antenna systems.

Owner:INTEGRATED DEVICE TECH INC

Low power A/D converter

InactiveUS6927721B2Analogue/digital conversionElectric signal transmission systemsBuck converterĆuk converter

A comparator is arranged to compare a series of analog voltage signal samples on a first capacitor with a voltage on a second capacitor which is linearly increased or decreased to equal the sample value. The comparator's single output freezes the count of the counter at counts which are proportional to the voltage of the respective samples. In this manner, analog to digital conversion can be accomplished using a single line between the analog and digital sides of a circuit, thereby reducing parasitic capacitance.

Owner:CAMERON HEALTH

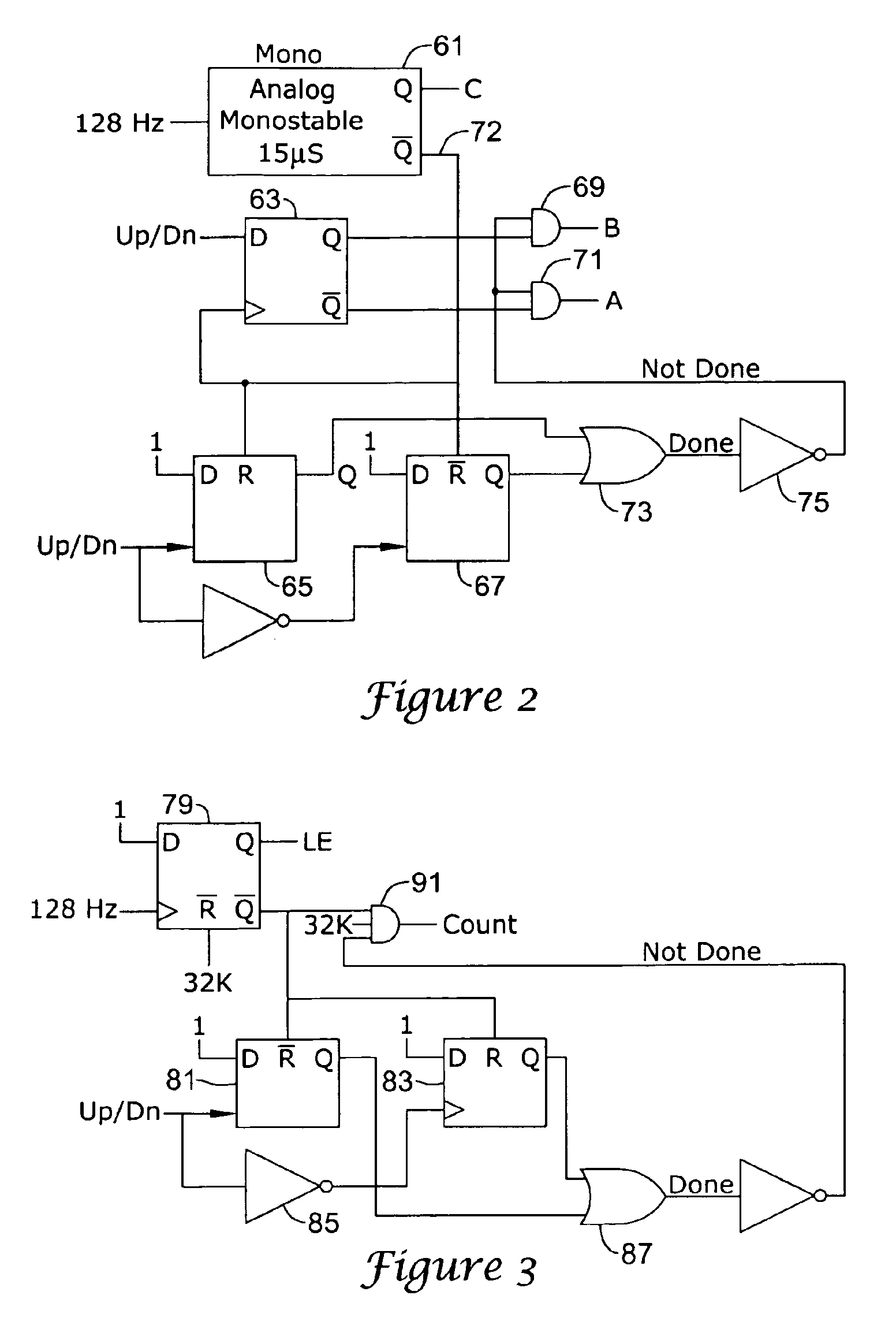

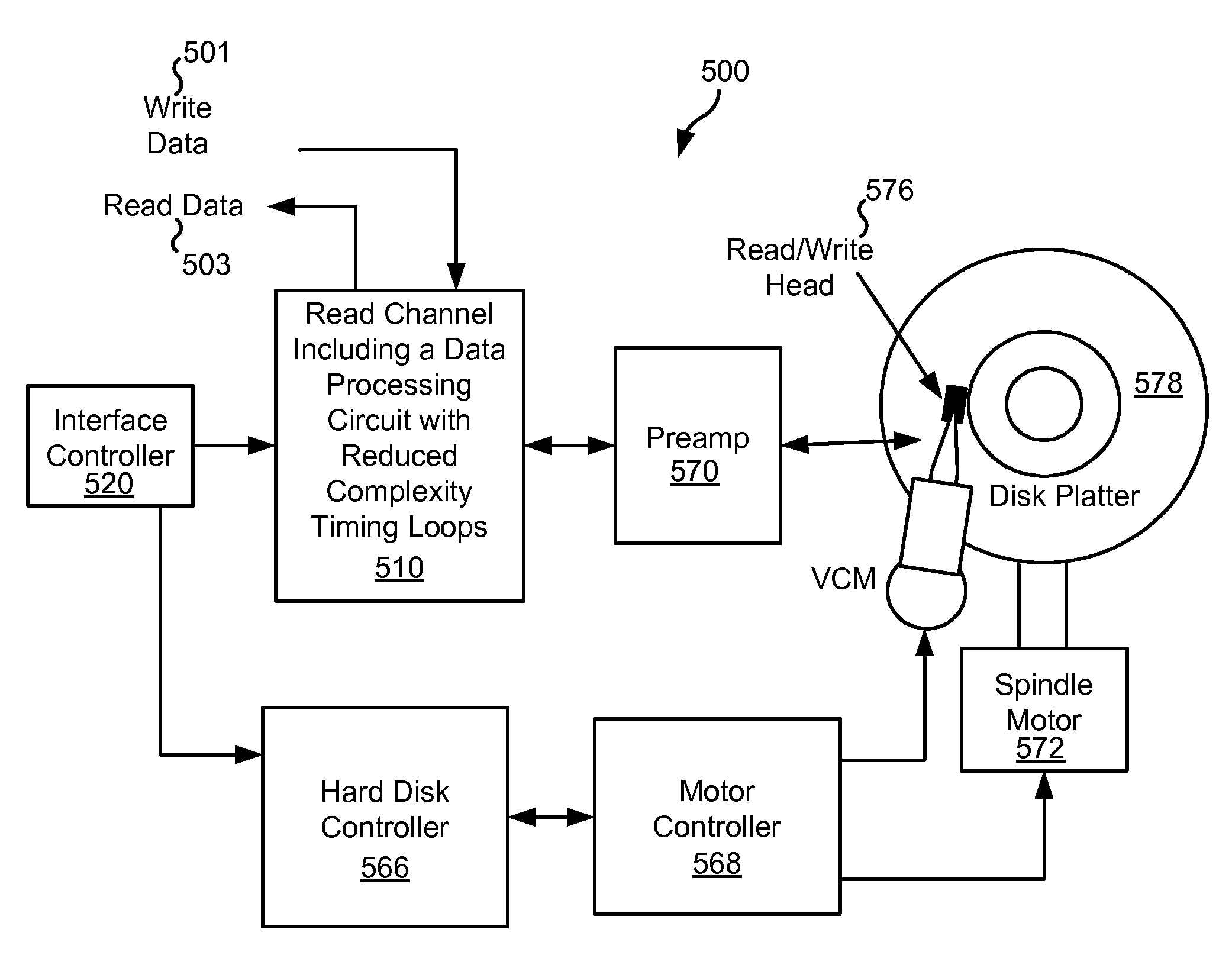

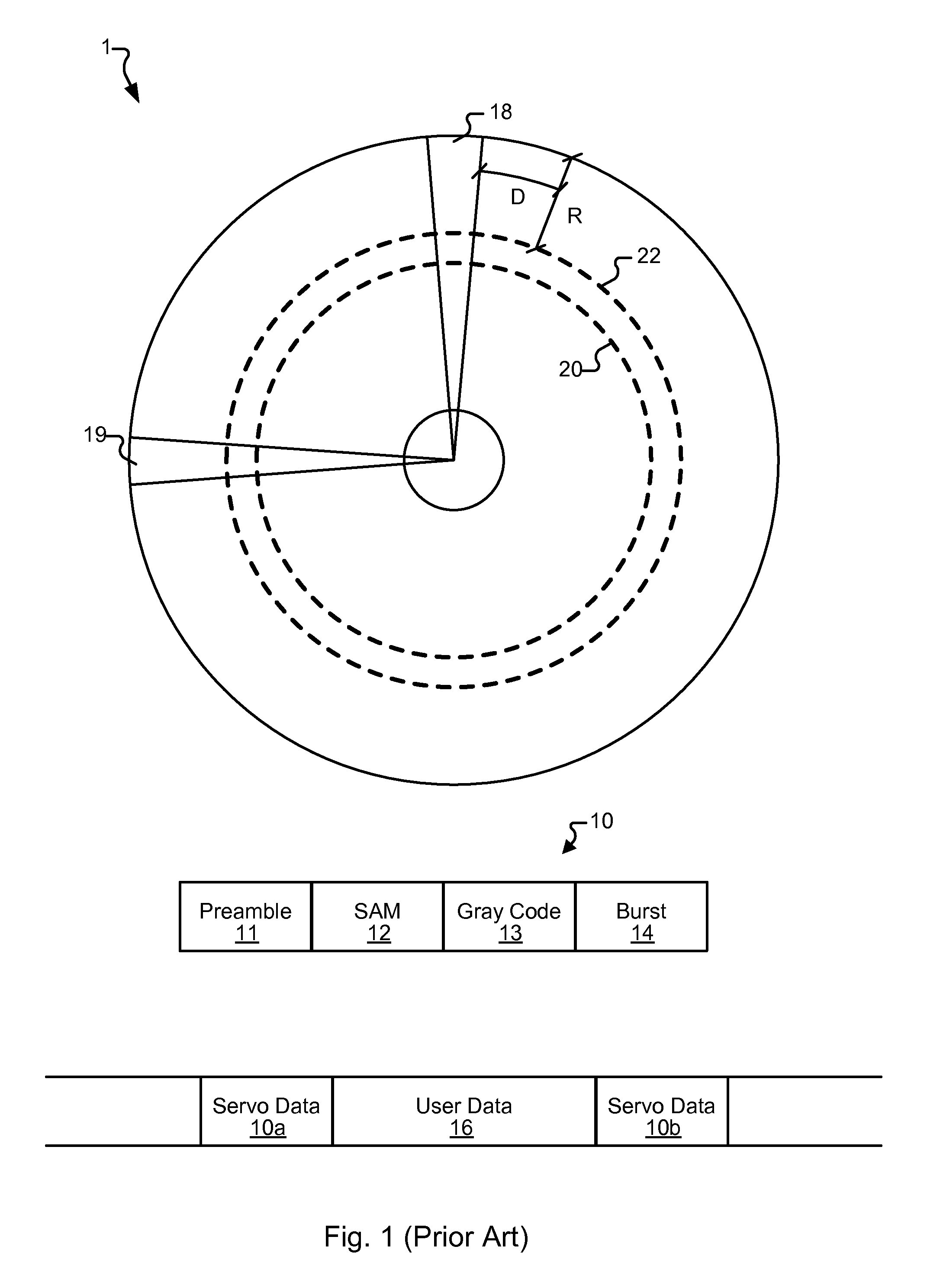

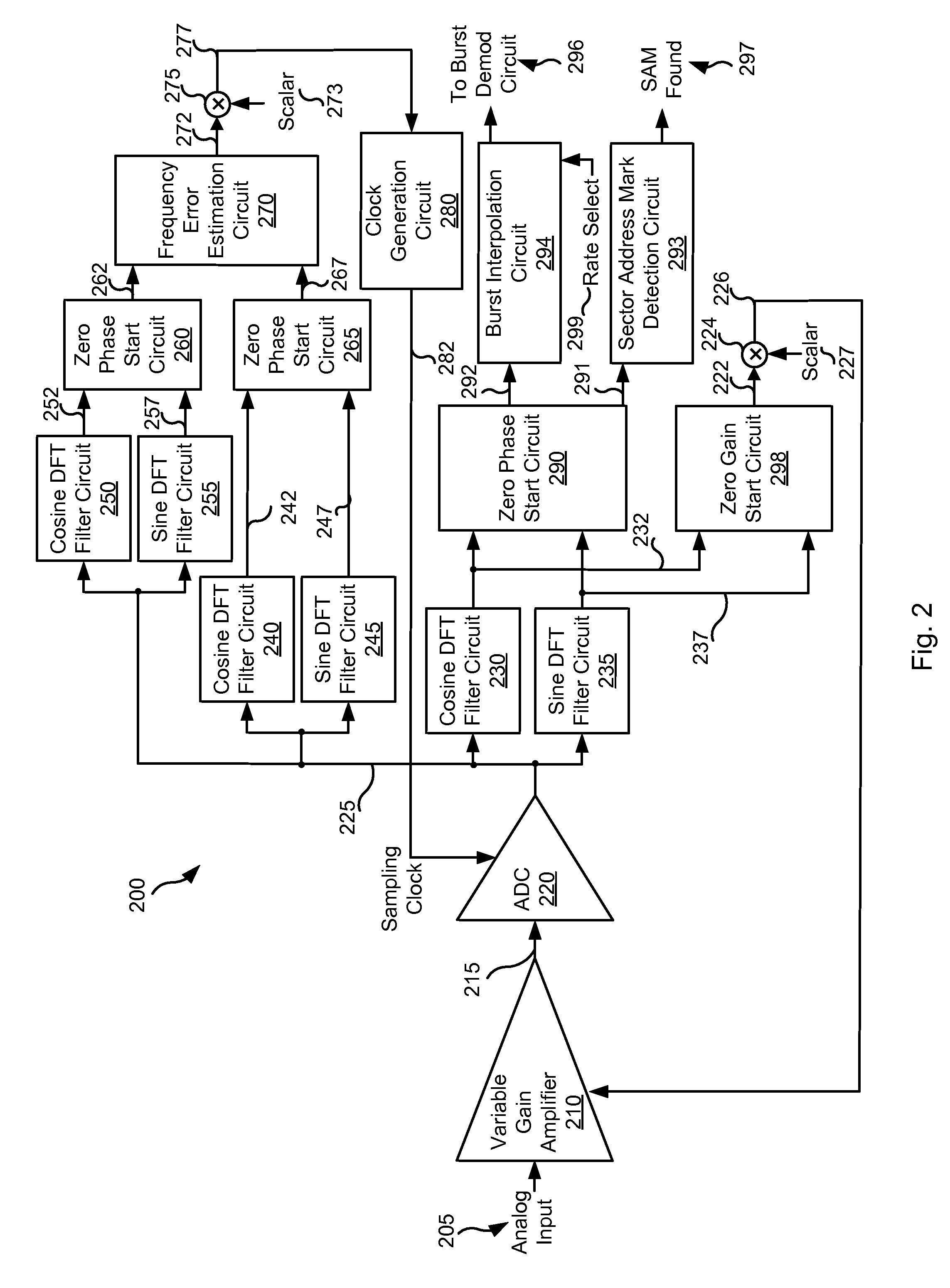

Systems and Methods for Reduced Format Data Processing

InactiveUS20120182643A1Record information storageAlignment for track following on disksAudio power amplifierVariable-gain amplifier

Various embodiments of the present invention provide systems and methods for data processing. For example, some embodiments of the present invention provide data processing circuits that include a variable gain amplifier circuit, an analog to digital conversion circuit, a cosine component calculation circuit, a sine calculation circuit, and a zero gain start calculation circuit. The variable gain amplifier circuit is operable to apply a gain to a data input corresponding to a gain feedback value and providing an amplified output. The analog to digital conversion circuit is operable to convert the amplified output to a corresponding series of digital samples. The cosine component calculation circuit is operable to calculate a cosine component from the series of digital samples, and the sine component calculation circuit operable to calculate a sine component from the series of digital samples. The zero gain start calculation circuit is operable to calculate a raw gain error value based on the cosine component and the sine component, where the gain feedback value is derived from the raw gain error value.

Owner:BROADCOM INT PTE LTD

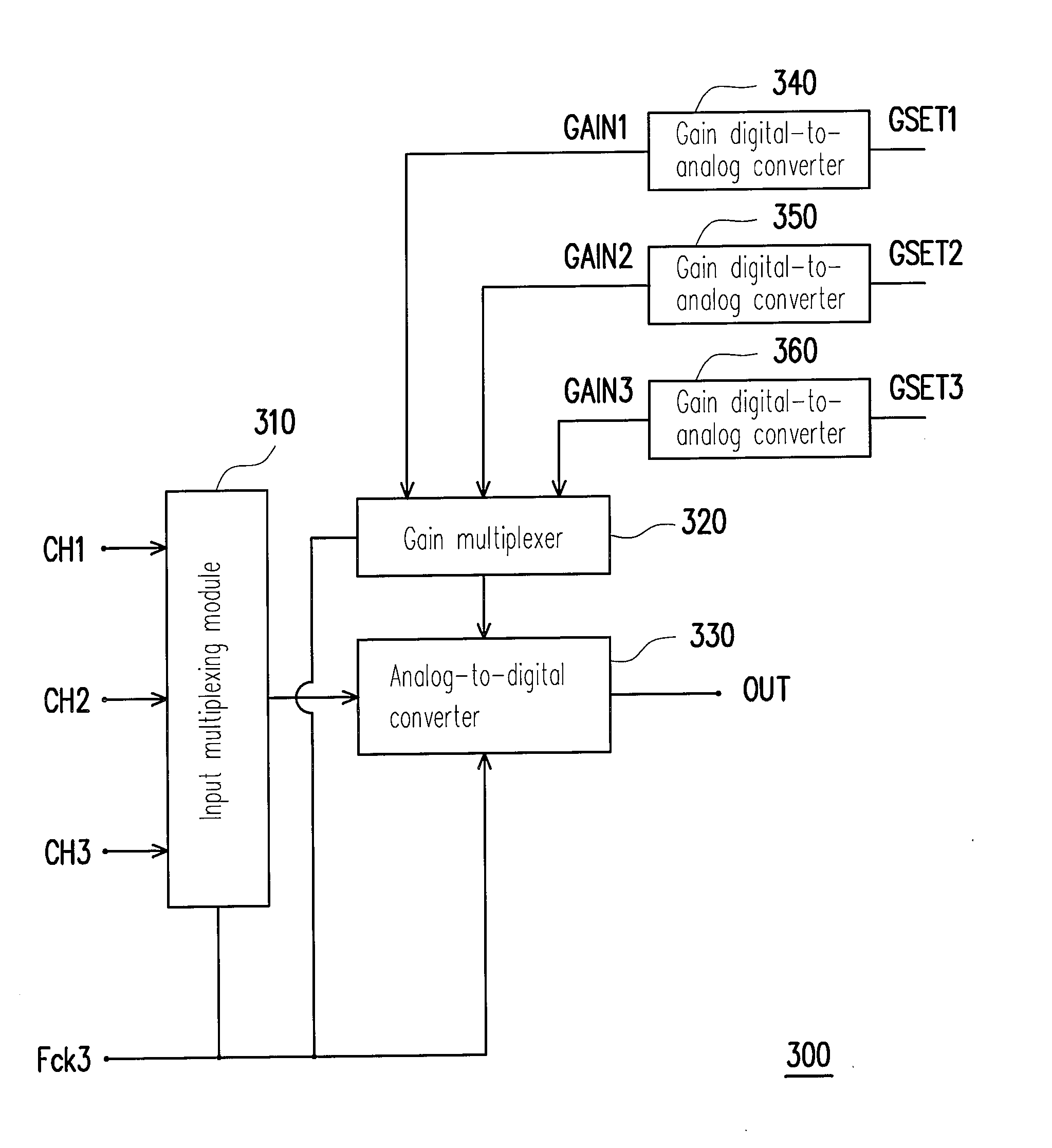

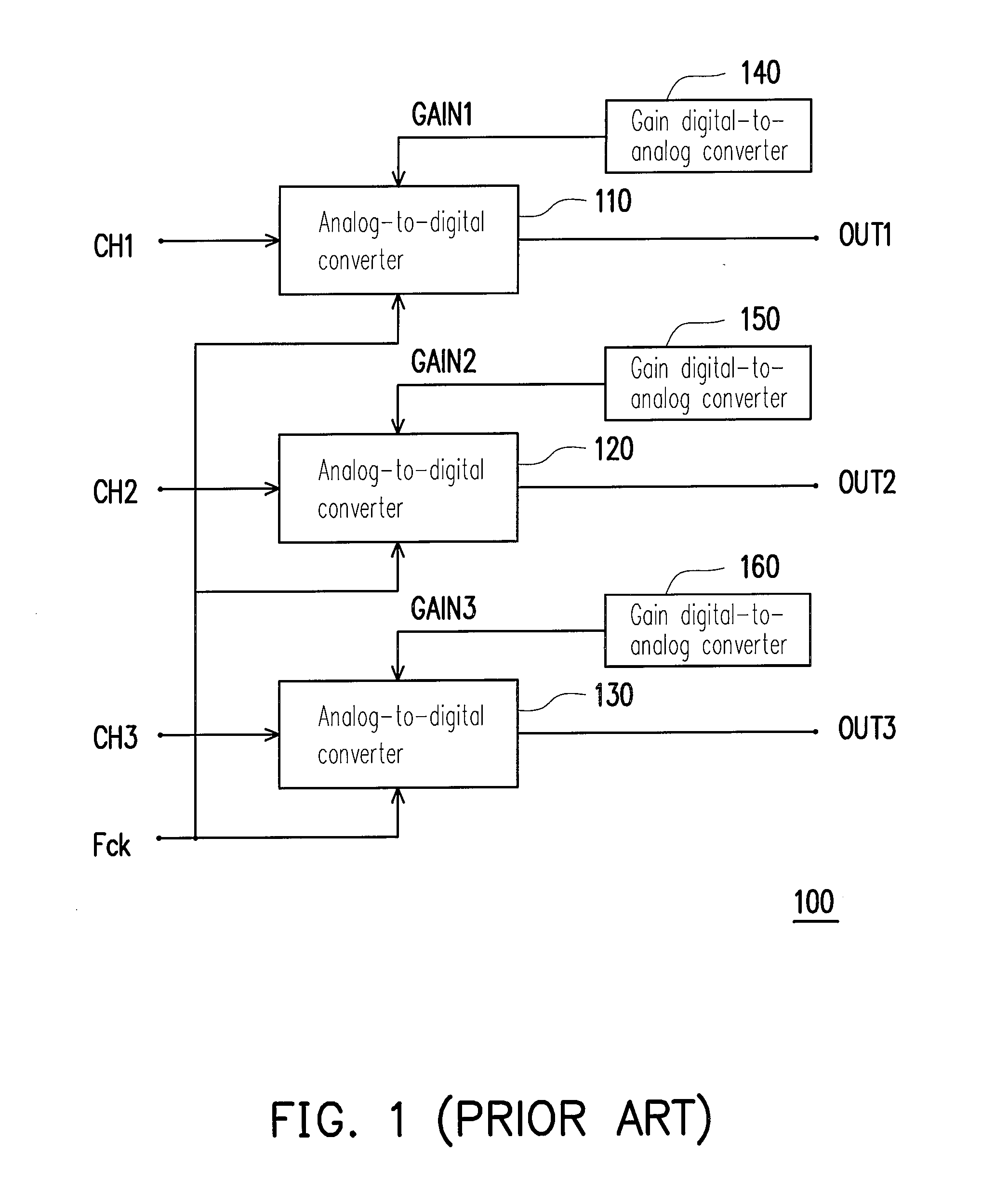

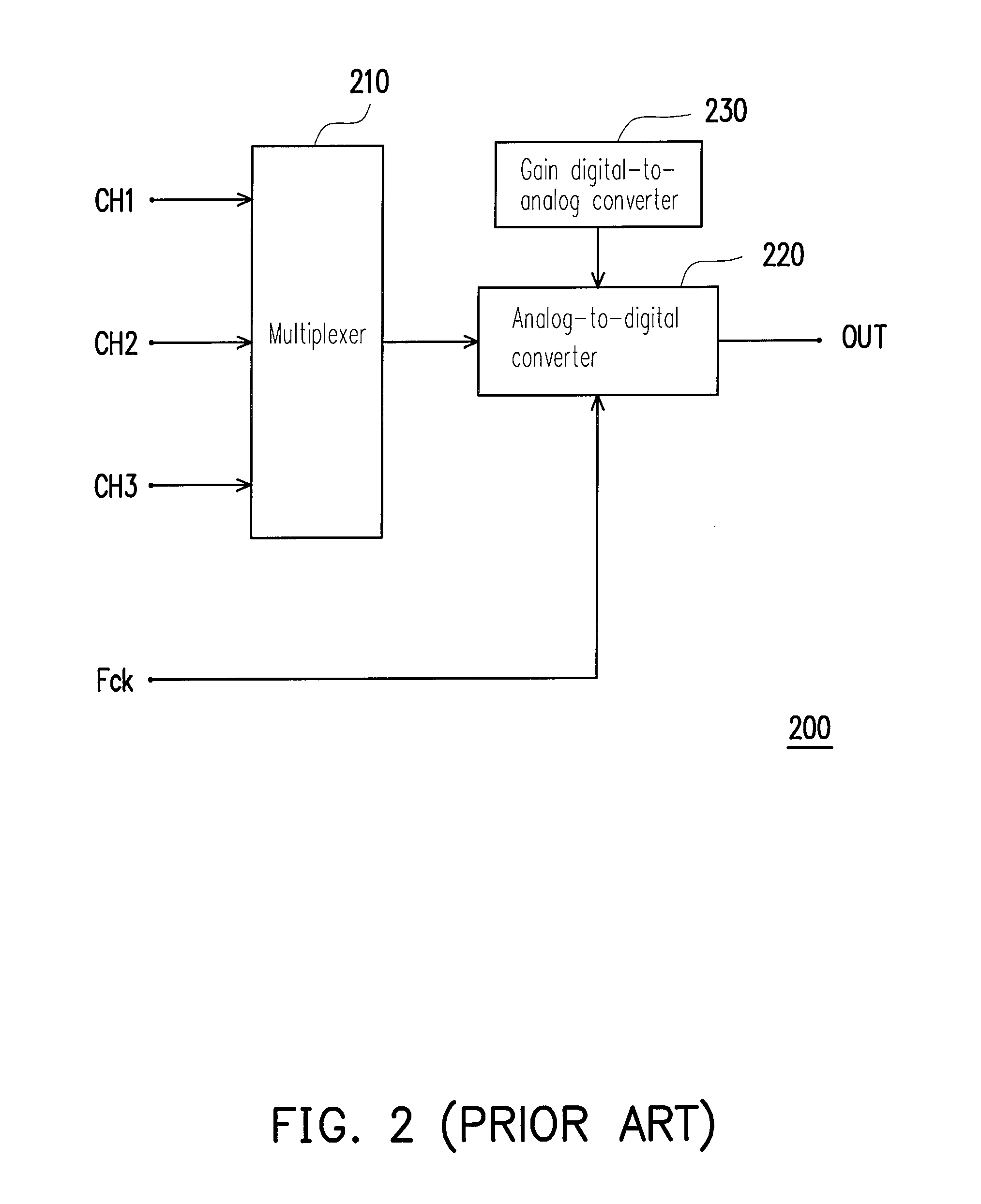

Time-interleaved analog-to-digital conversion apparatus

InactiveUS20090256734A1Improve signal-to-noise ratioIncrease each SNR thereofElectric signal transmission systemsAnalogue-digital convertersA d converterAnalog to digital conversion

A time-interleaved analog-to-digital conversion apparatus is disclosed. The time-interleaved analog-to-digital conversion apparatus is applied for a television system and includes an input multiplexing module, a gain multiplexer and an analog-to-digital converter. The input multiplexing module receives a plurality of image signals, and samples the image signals according to a clock signal to generate a sample multiplexing signal. The gain multiplexer receives a plurality of gain signals and selectively transmits one of the gain signals corresponding to the sample multiplexing signal according to the clock signal, so as to generate a gain multiplexing signal. The analog-to-digital converter receives the sample multiplexing signal, the gain multiplexing signal and the clock signal. The analog-to-digital converter amplifies and converts the sample multiplexing signal to a digital signal according to the gain multiplexing signal and the clock signal.

Owner:NOVATEK MICROELECTRONICS CORP

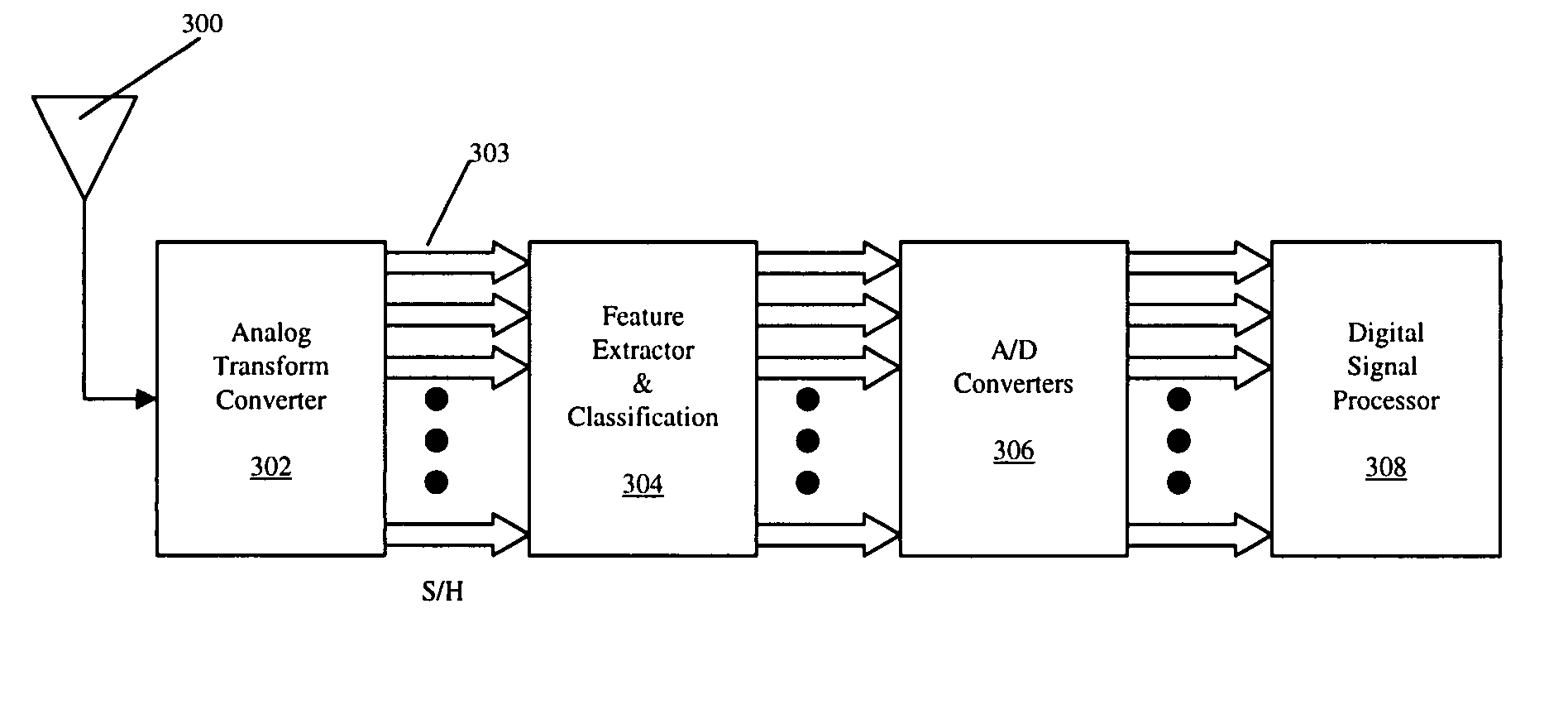

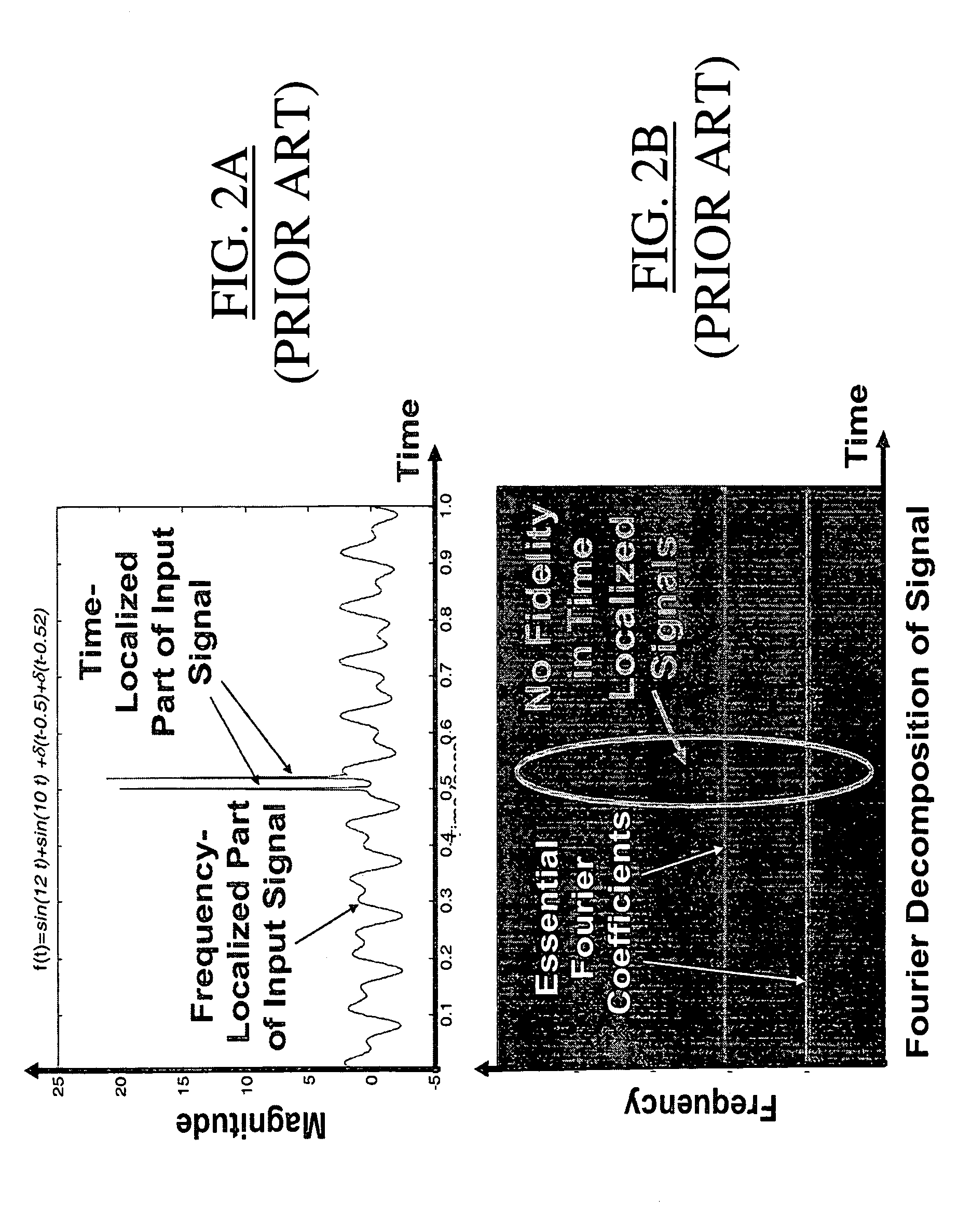

Adaptive, intelligent transform-based analog to information converter method and system

InactiveUS20050156775A1Made preciselyImprove detection rateElectric signal transmission systemsAnalogue conversionFeature extractionAnalog signal

The present invention provides an adaptive, intelligent transform based Analog to Information Converter (AIC) for wideband signals by directly converting an analog signal to information (e.g., features, decisions). This direct conversion is achieved by (i) capturing most of the information of a wideband signal via hardware / software implemented mathematical transformations, (ii) effectively removing unwanted signals such as jammer and interfere from the input signal, and (iii) using novel algorithms for highly accurate decision making and feature extraction (e.g., high probability of detection with low probability of false alarm). The jump in the improvement over today's state-of-the-art is in terms of effective and optimum signal information extraction at high-speed.

Owner:HRL LAB

Electronic snore recording device and associated methods

The snore recording device includes a portable housing, a microphone carried by the housing for capturing an audio input signal including snoring, a memory, such as a removable memory, carried by the housing, and processing circuitry carried by the housing and coupled to the microphone and the memory. The processing circuitry is for low pass filtering the audio input signal from the microphone to generate a low pass filtered analog signal, performing analog-to-digital conversion (ADC) on the low pass filtered analog signal to generate an intermediate digital signal, performing a moving average filtering of the intermediate digital signal to generate moving average intensity data, performing a Fast Fourier Transform (FFT) on the intermediate digital signal to generate frequency component data, and storing at least the moving average intensity data and frequency component data in the memory.

Owner:ZURLIN TECH HLDG

Miniaturized inclinometer for angle measurement with accurate measurement indicator

InactiveUS6871413B1Accurate measurementUnlimited 360 degree resolutionAngles/taper measurementsUsing electrical meansMultiplexerSignal conditioning

The novel miniaturized inclinometer for angle measurement with accurate measurement indicator is designed to monitor the angular motion of limbs. The device contains at least one inclinometer with signal conditioning electronics, including a microprocessor, placed within a miniature housing. A number of different sensors can be used and positioned in their housings so that their outputs vary as a function of their angle with respect to the gravity sector. The microprocessor controls a multiplexer, which controls the activities of the sensors; performs analog to digital conversions and measures the output curves from the sensor pairs to perform a conversion which results in a three hundred and sixty degree range with respect to gravity. Calibration data is stored in a read only memory and the microprocessor corrects variables to ensure accuracy and measures the difference in angle between the pairs of sensors.

Owner:LORD CORP

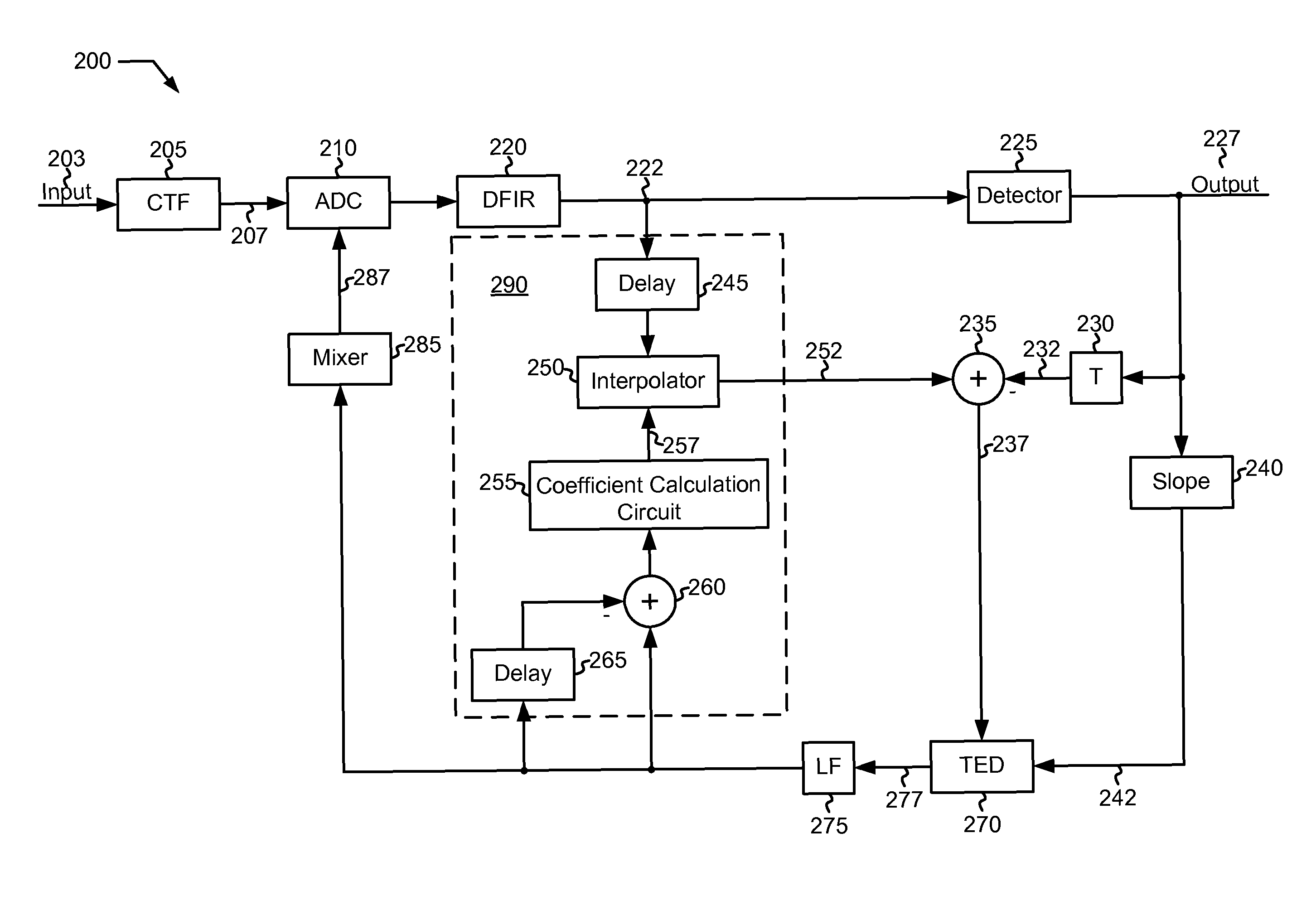

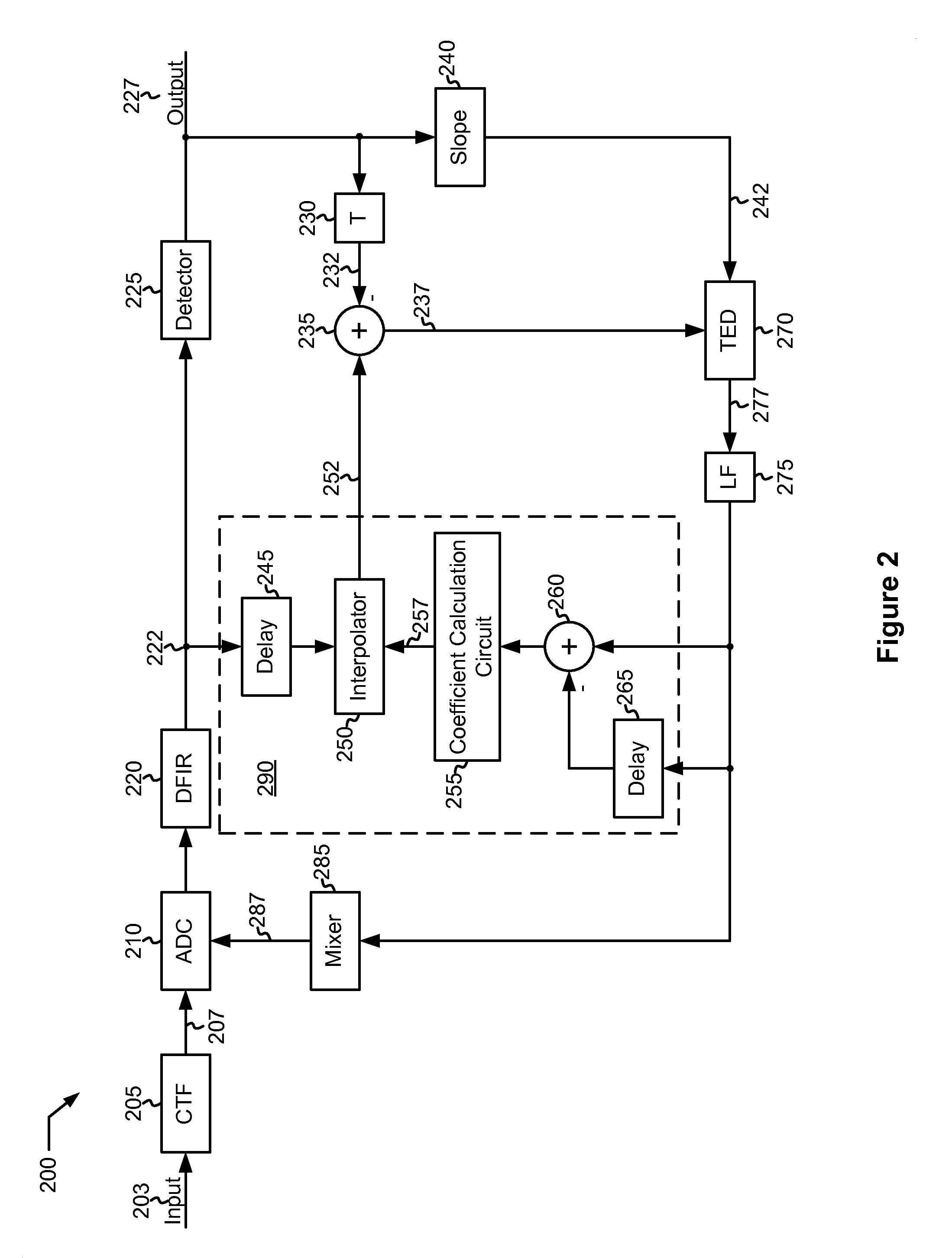

Systems and Methods for Mitigating Latency in a Data Detector Feedback Loop

ActiveUS20100164764A1Reduce latency impactLower latencyModification of read/write signalsElectric signal transmission systemsSampling instantData retrieval

Various embodiments of the present invention provide systems and methods for mitigating latency in a data detector feedback loop. For example, a method for reducing latency in an error corrected data retrieval system is disclosed. The method includes performing an analog to digital conversion at a sampling instant to create a digital sample, and performing a data detection on the digital sample to create a detected output. The detected output is compared with the digital sample to determine a phase error. During an interim period, the digital sample is adjusted to reflect the phase error to create an adjusted digital sample. After the interim period, the sampling instant is adjusted to reflect the phase error.

Owner:LSI CORPORATION +1

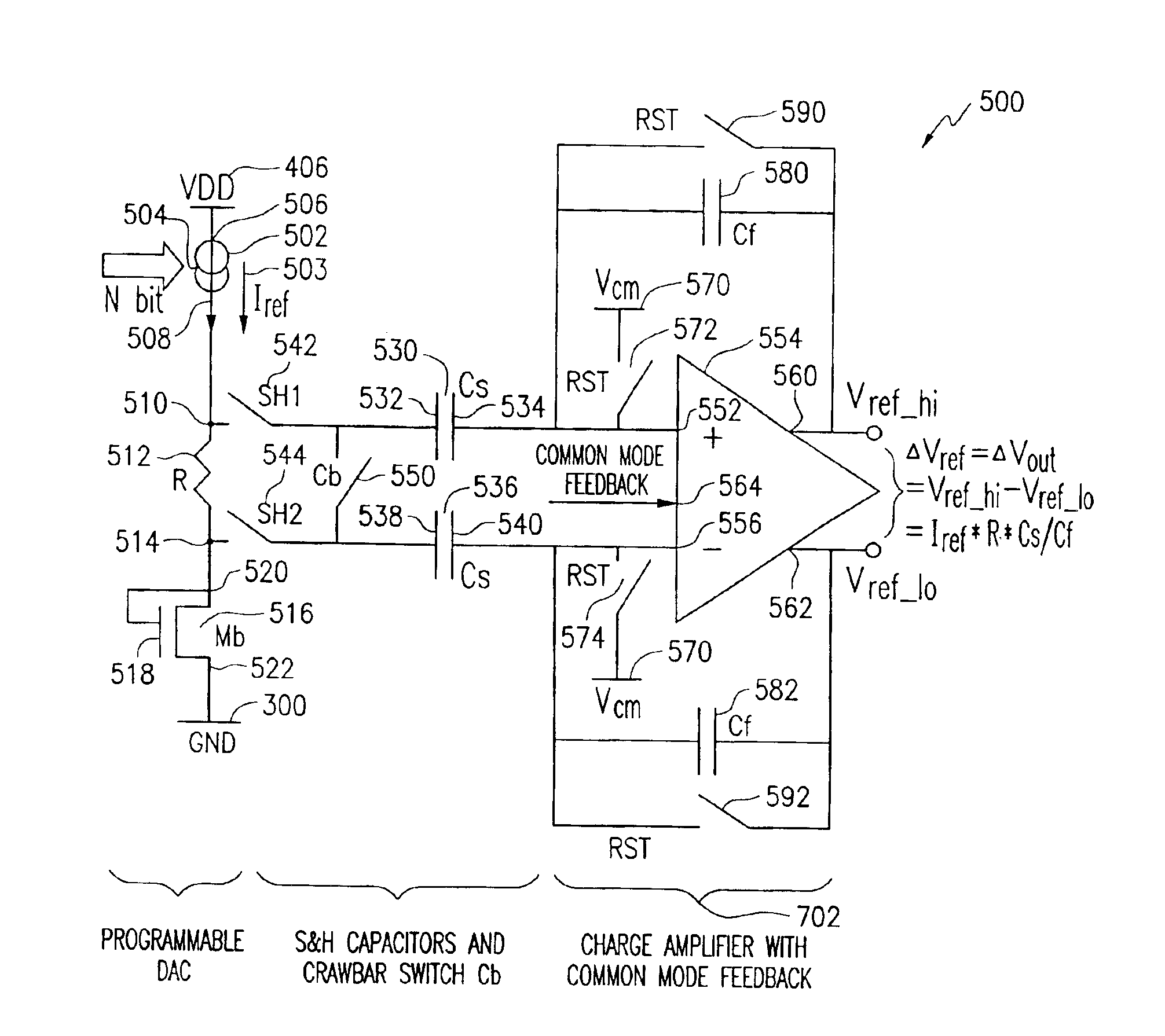

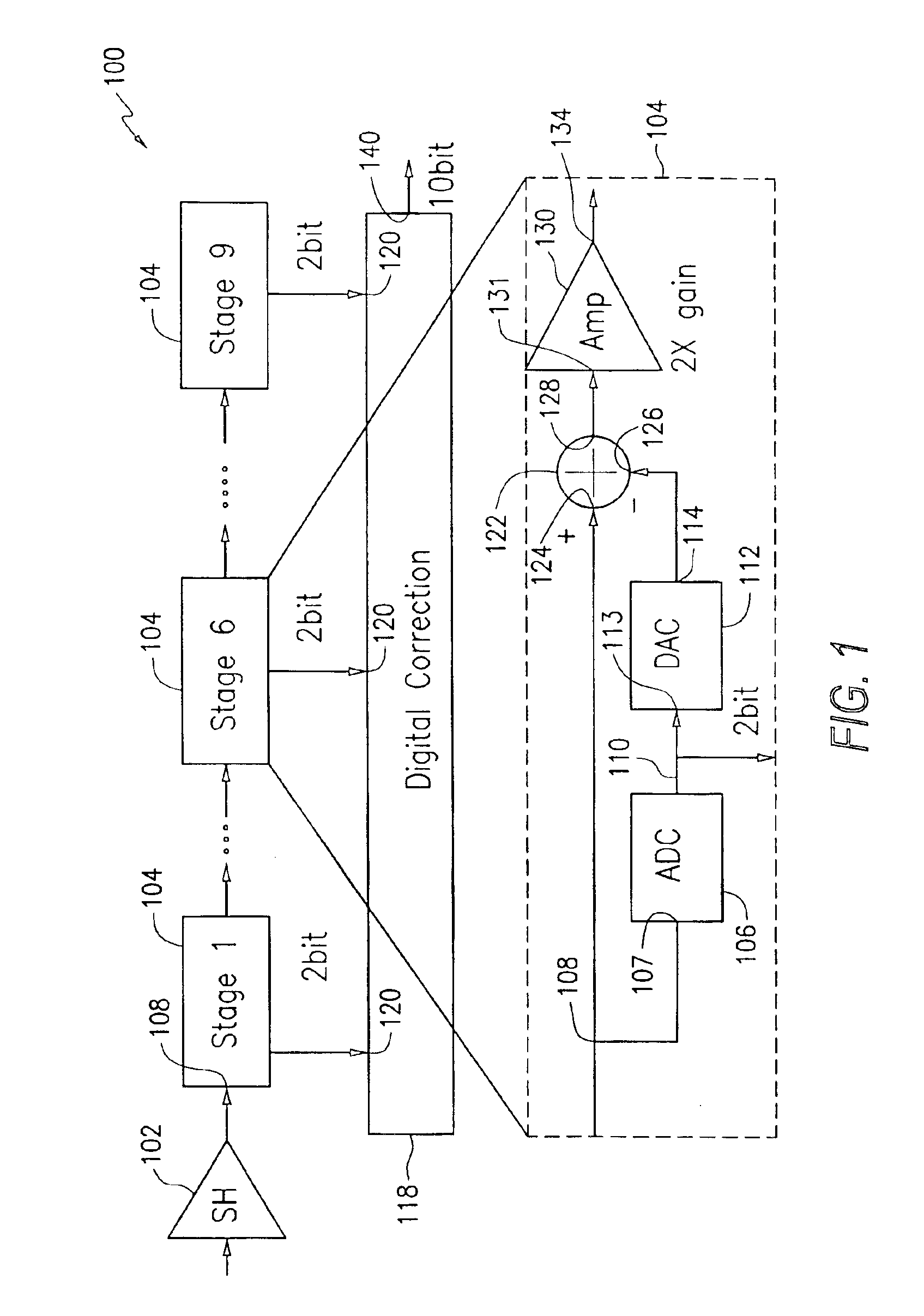

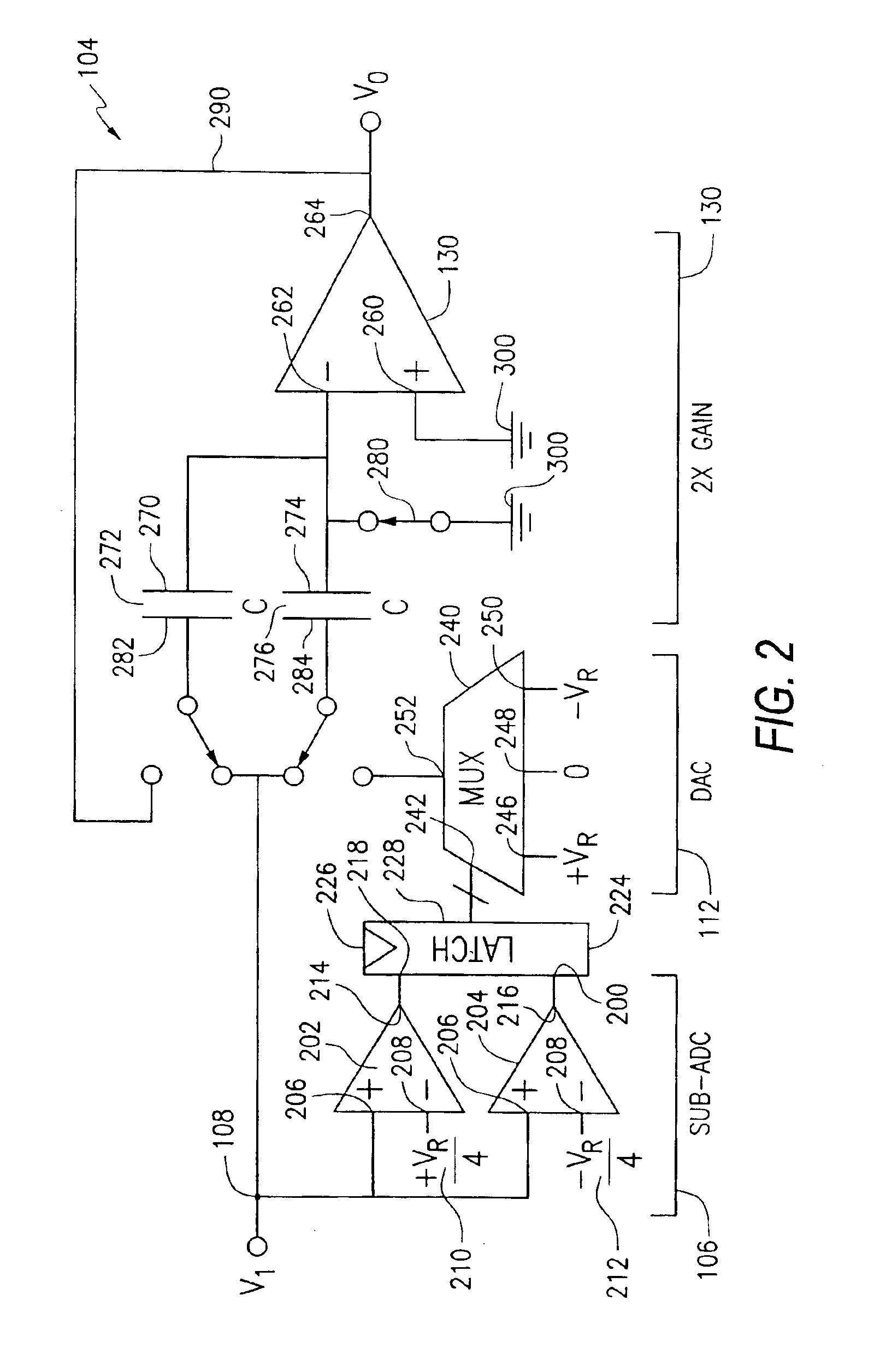

Fully differential reference driver for pipeline analog to digital converter

InactiveUS6909391B2Electric signal transmission systemsAnalogue-digital convertersCapacitanceVoltage reference

An analog to digital conversion (ADC) circuit is disclosed including a fully differential reference voltage source. The reference voltage source includes a programmable current supply adapted to drive a programmed current through a resistor so as to establish an initial reference voltage. The initial reference voltage is sampled onto a capacitive network during a first sampling time interval. The capacitive network is coupled to a differential input of a fully differential amplifier, and maintained at a differential output of the differential amplifier during a second output time interval. An output coupling between the differential output and differential input of the differential amplifier acts to maintain stability of the output voltage during the output time interval.

Owner:APTINA IMAGING CORP

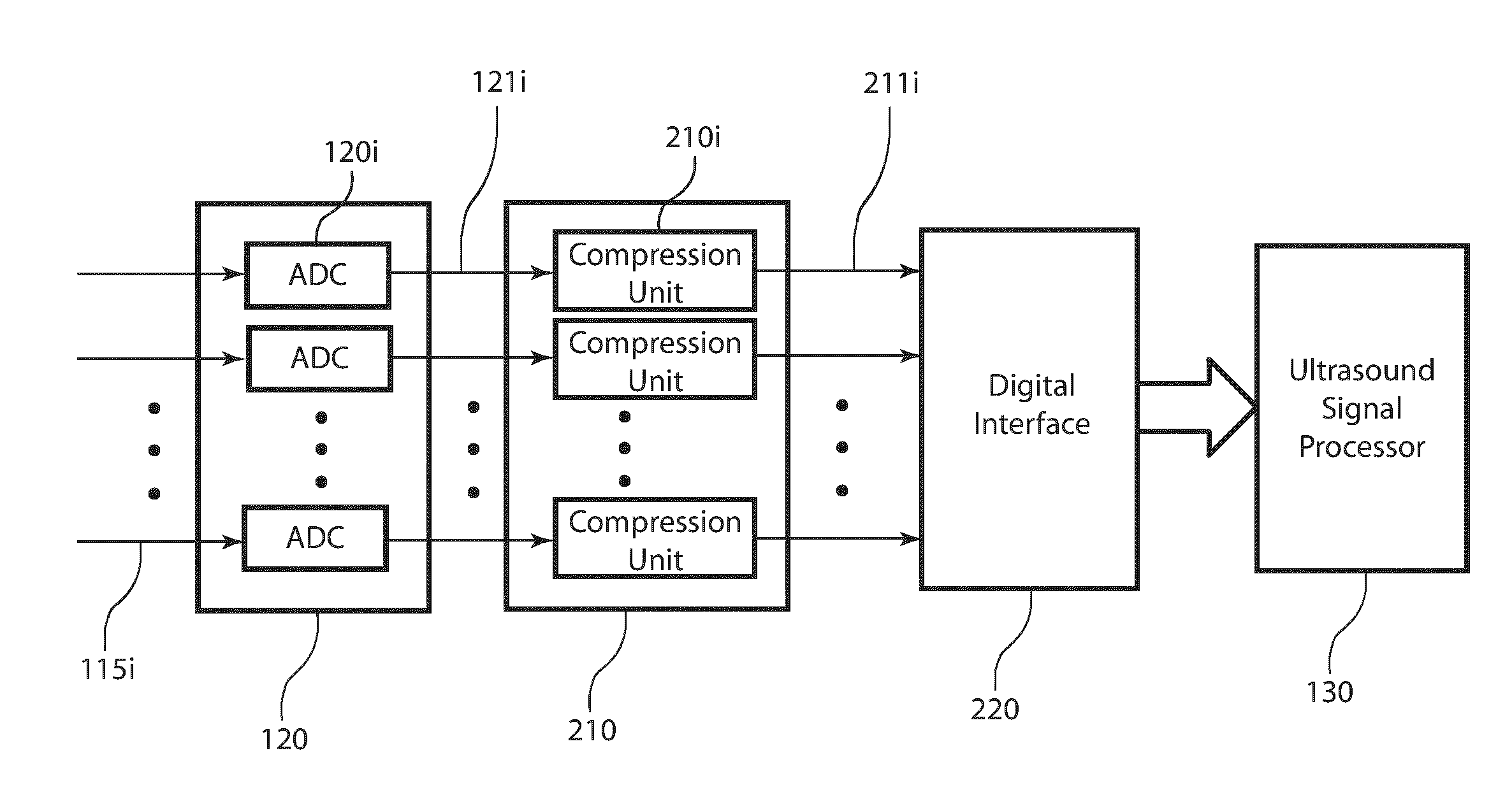

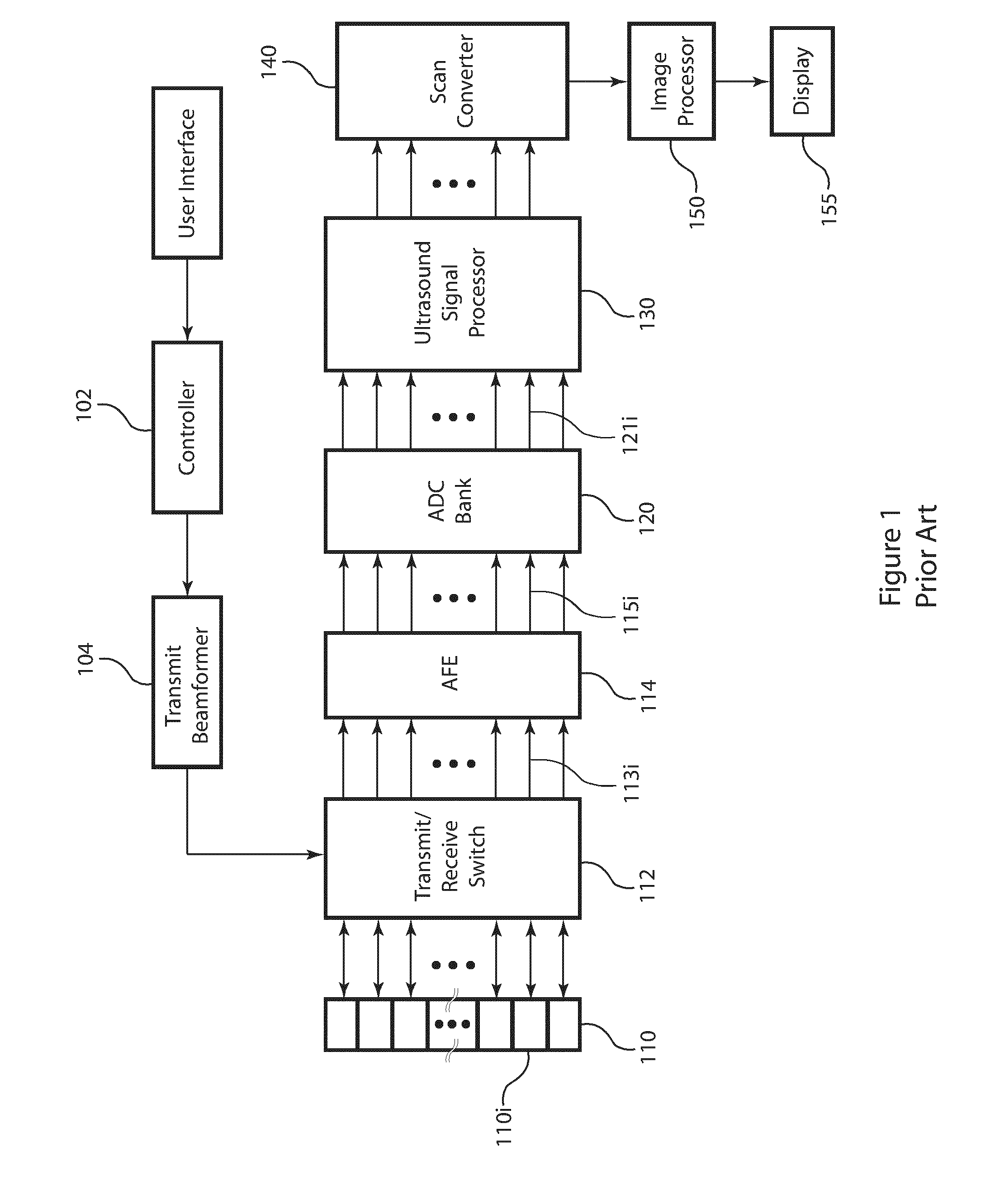

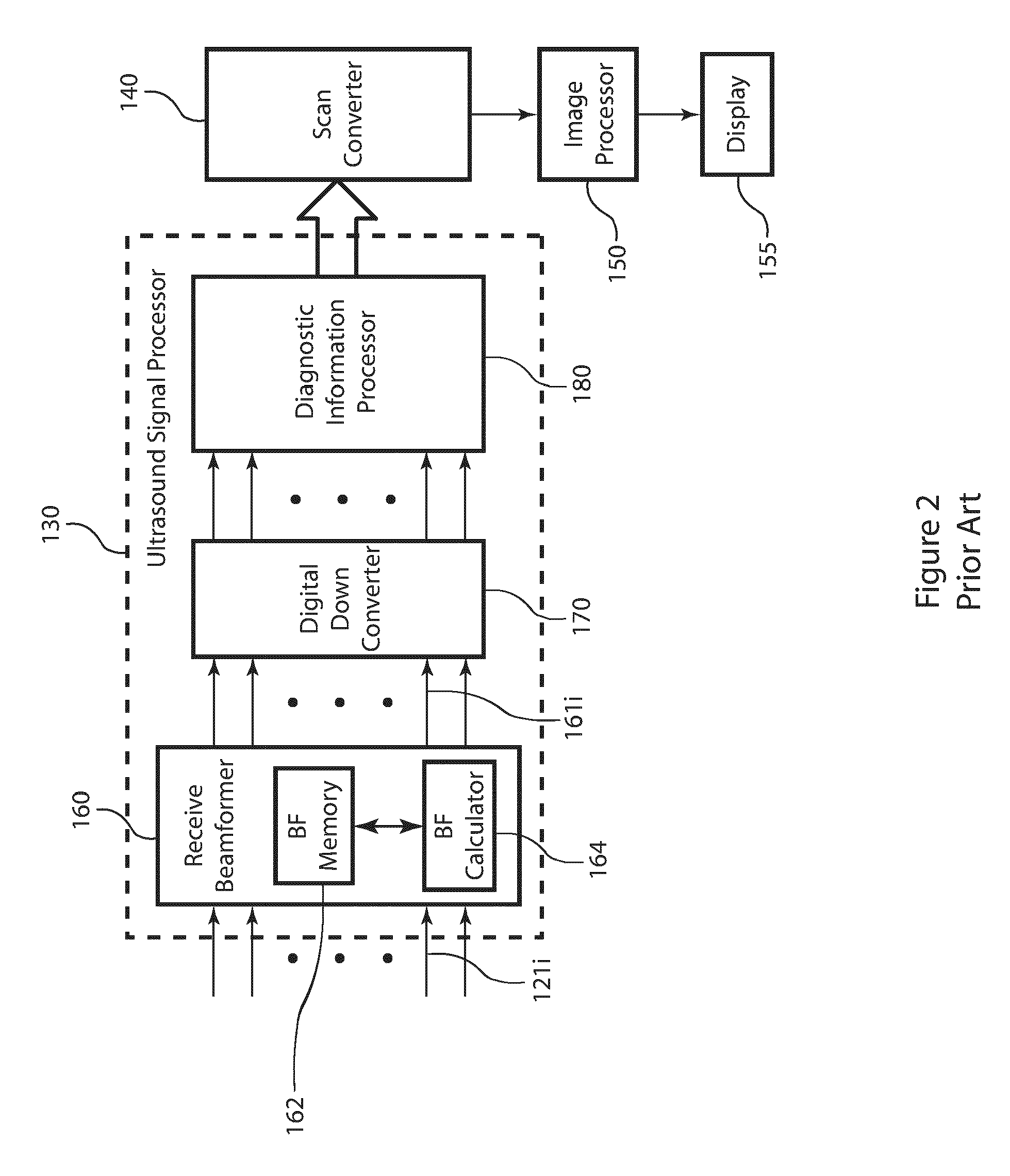

Ultrasound signal compression

ActiveUS20100305449A1More data bandwidthUltrasonic/sonic/infrasonic diagnosticsElectric signal transmission systemsSonificationUltrasonic sensor

A method and an apparatus for an ultrasound system provide compression of ultrasound signal samples after analog to digital conversion and before beamforming. The analog ultrasound signals received from an array of ultrasound transducer elements are digitally sampled by a plurality of analog to digital converters (ADCs) to produce a plurality of sequences of signal samples. Each sequence of signal samples is compressed to form a corresponding sequence of compressed samples. The resulting sequences of compressed samples are transferred via a digital interface to an ultrasound signal processor. At the ultrasound signal processor, the received sequences of compressed samples are decompressed. The typical processing operations, such as beamforming, downconversion and detection, are applied to decompressed samples. This abstract does not limit the scope of the invention as described in the claims.

Owner:ALTERA CORP

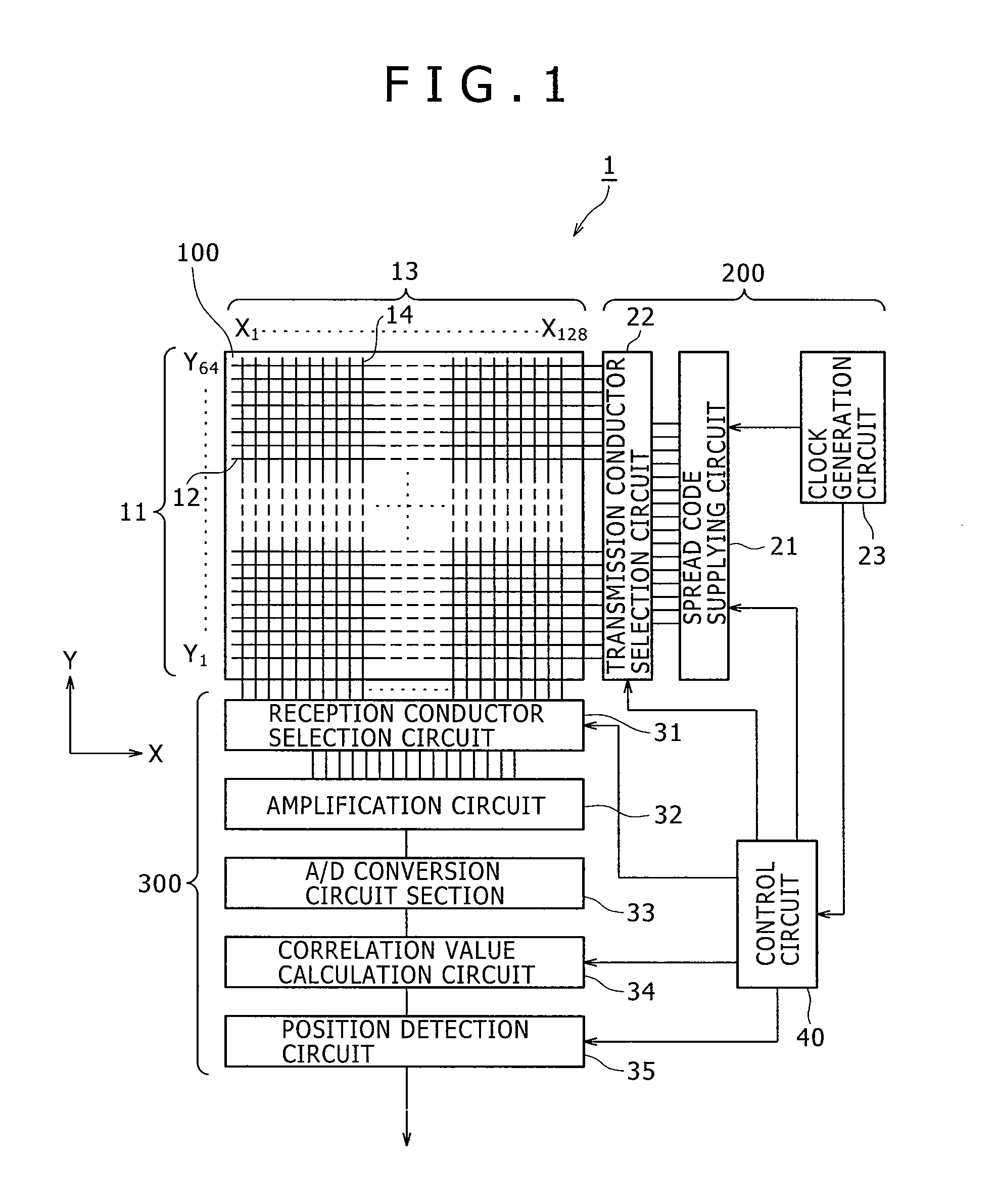

Pointer detection apparatus and pointer detection method

ActiveUS20110153263A1Detect presenceDigital computer detailsSpeed measurement using gyroscopic effectsElectrical conductorElectrostatic coupling

Owner:WACOM CO LTD

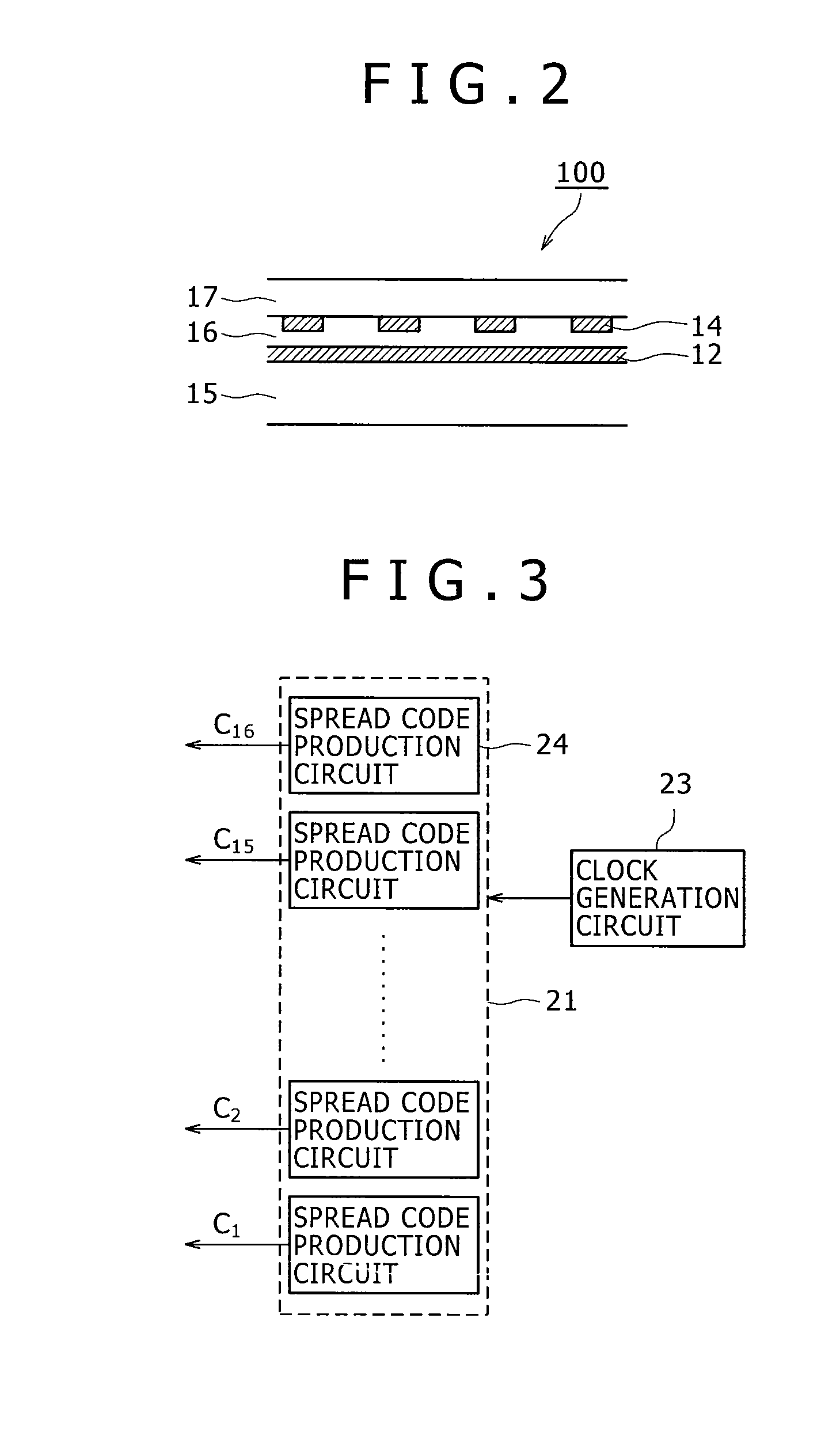

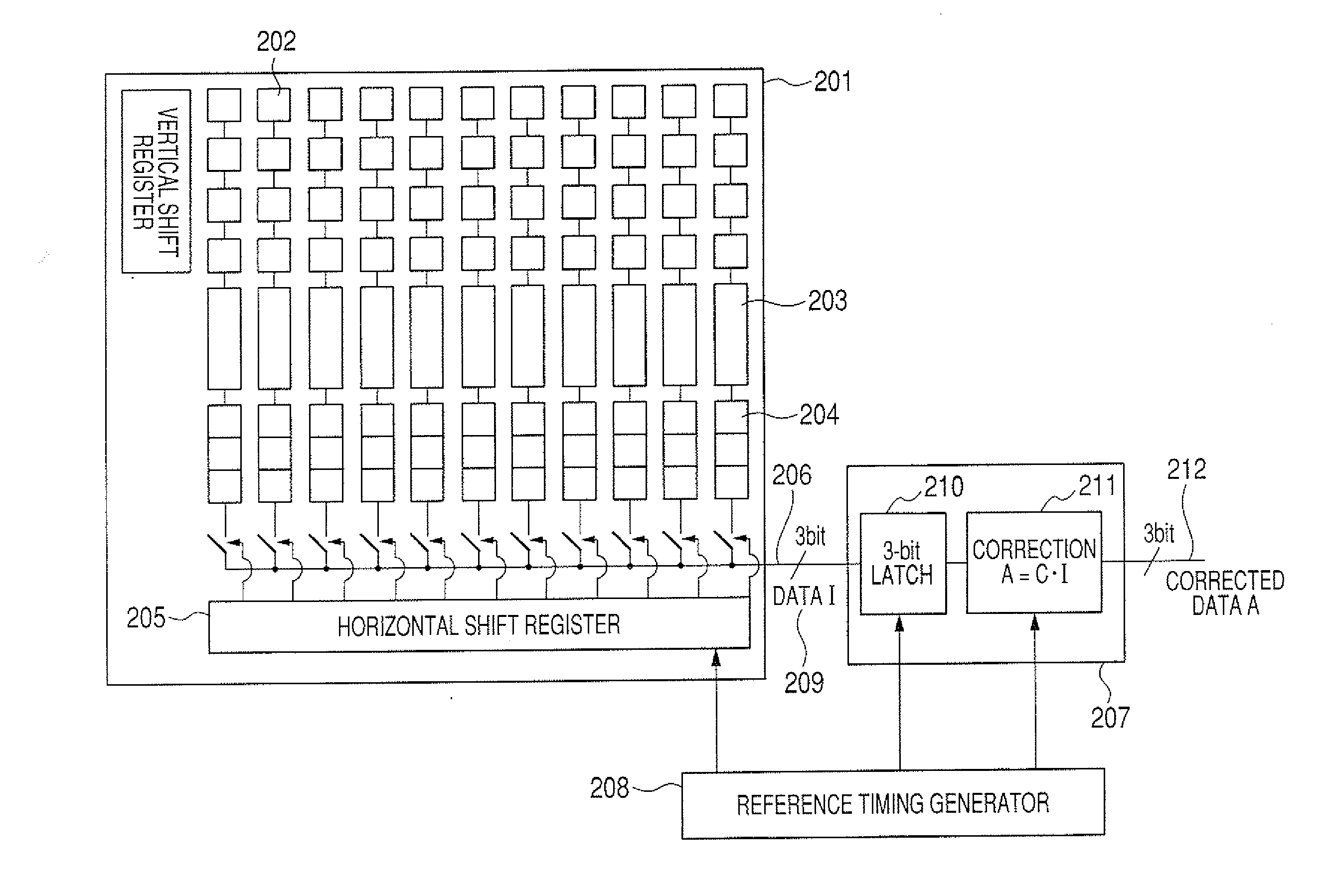

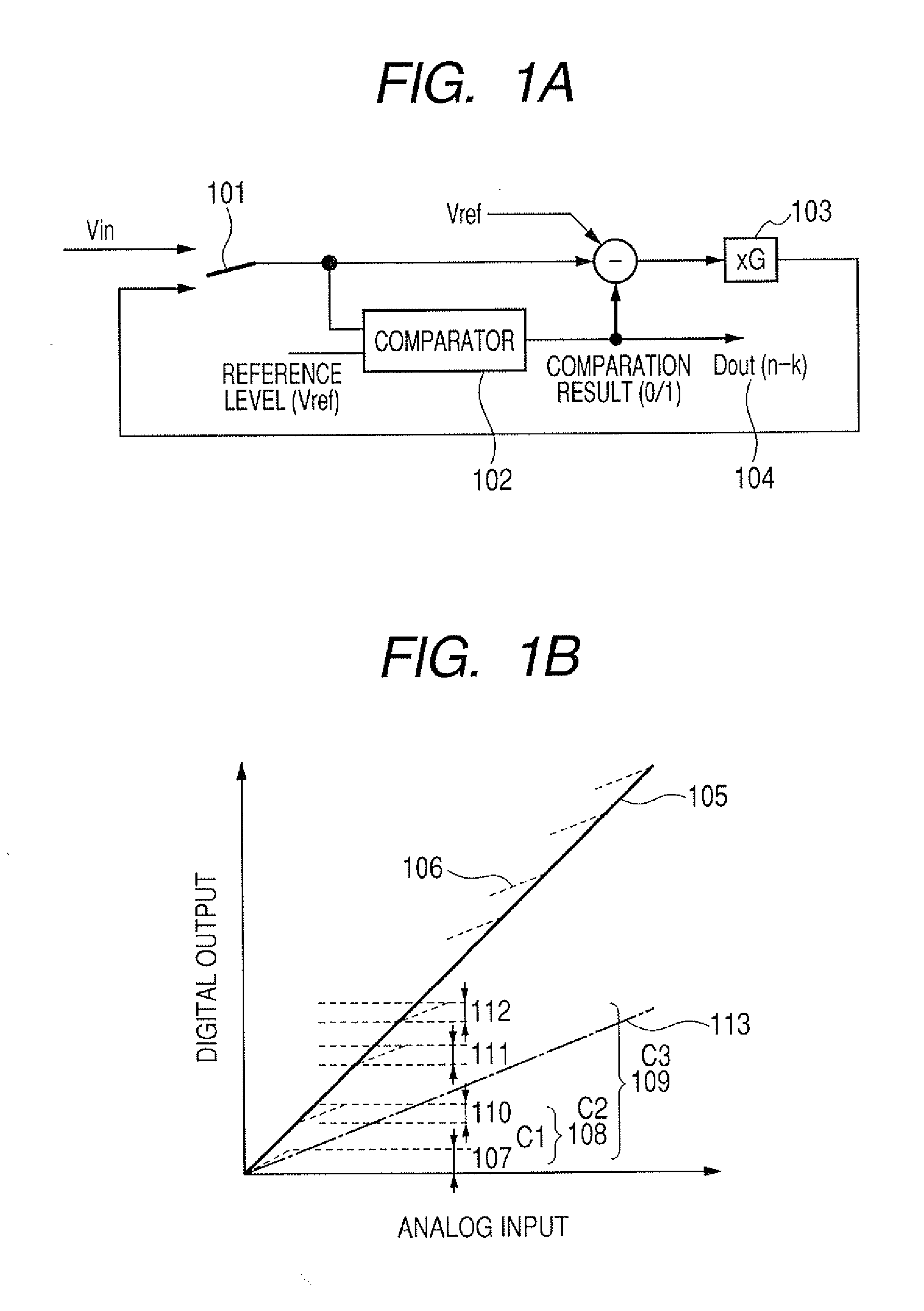

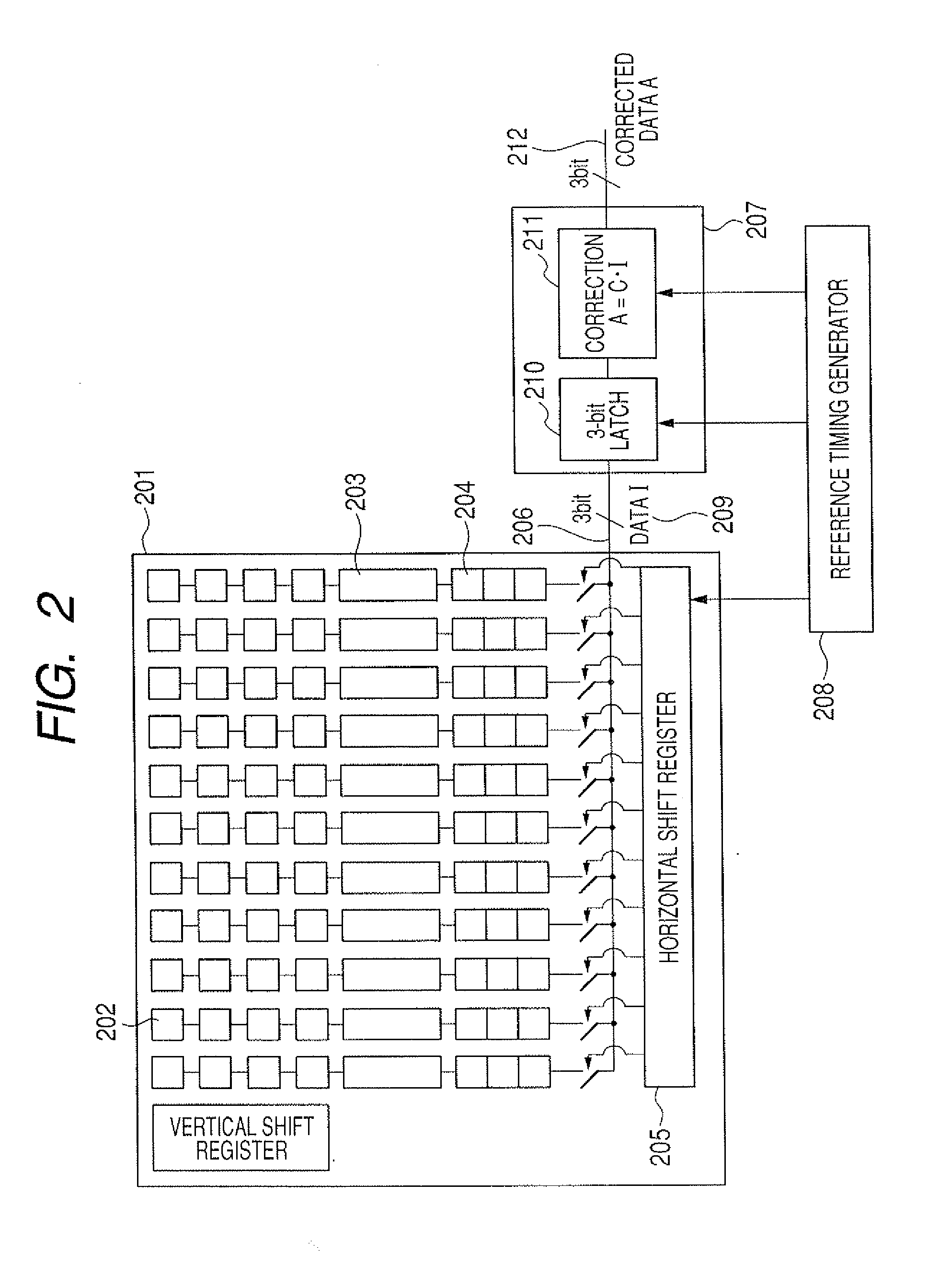

Image pickup device and signal processing method thereof

InactiveUS20090244328A1Television system detailsElectric signal transmission systemsDigital down converterDigital converter

Owner:CANON KK

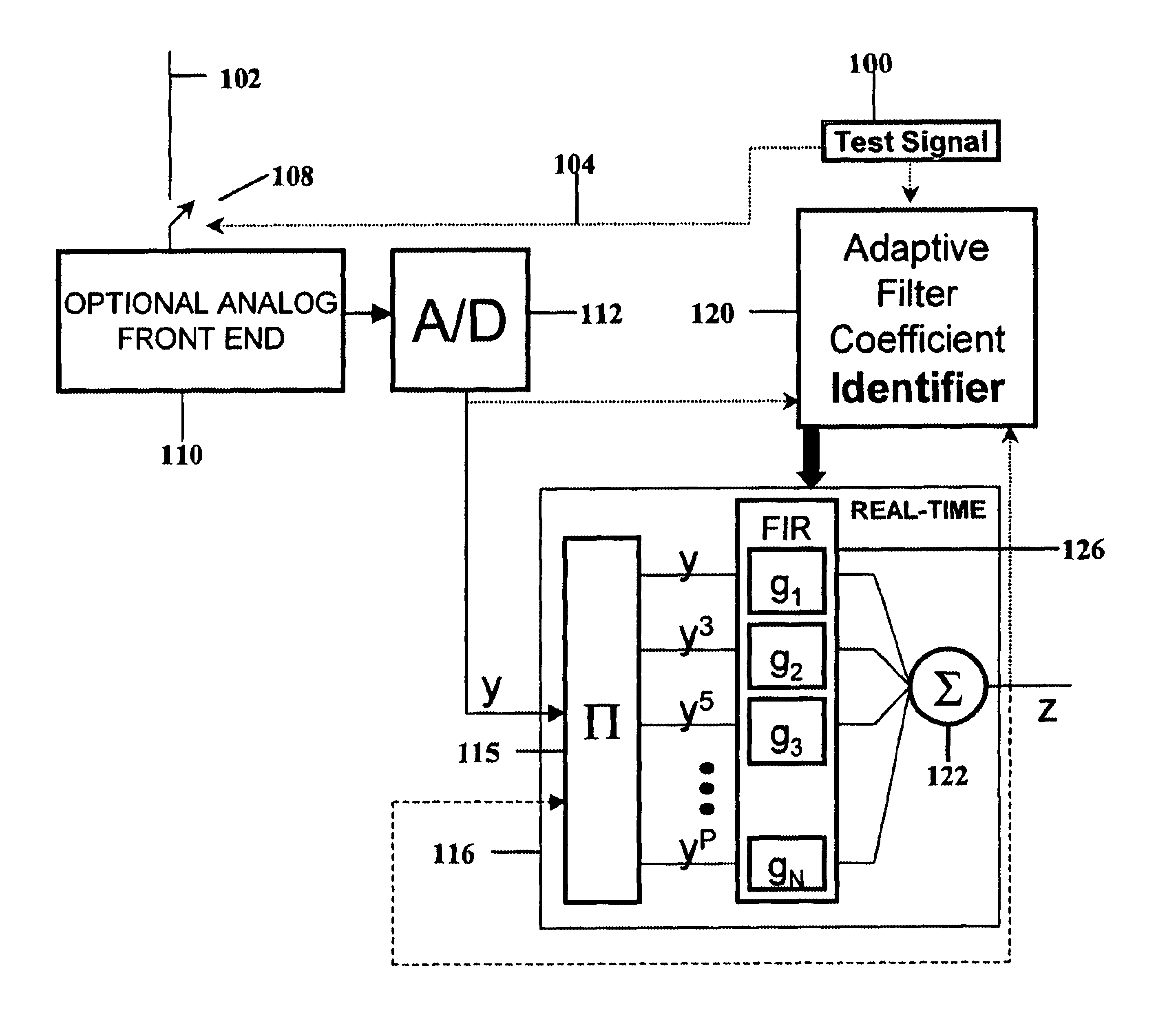

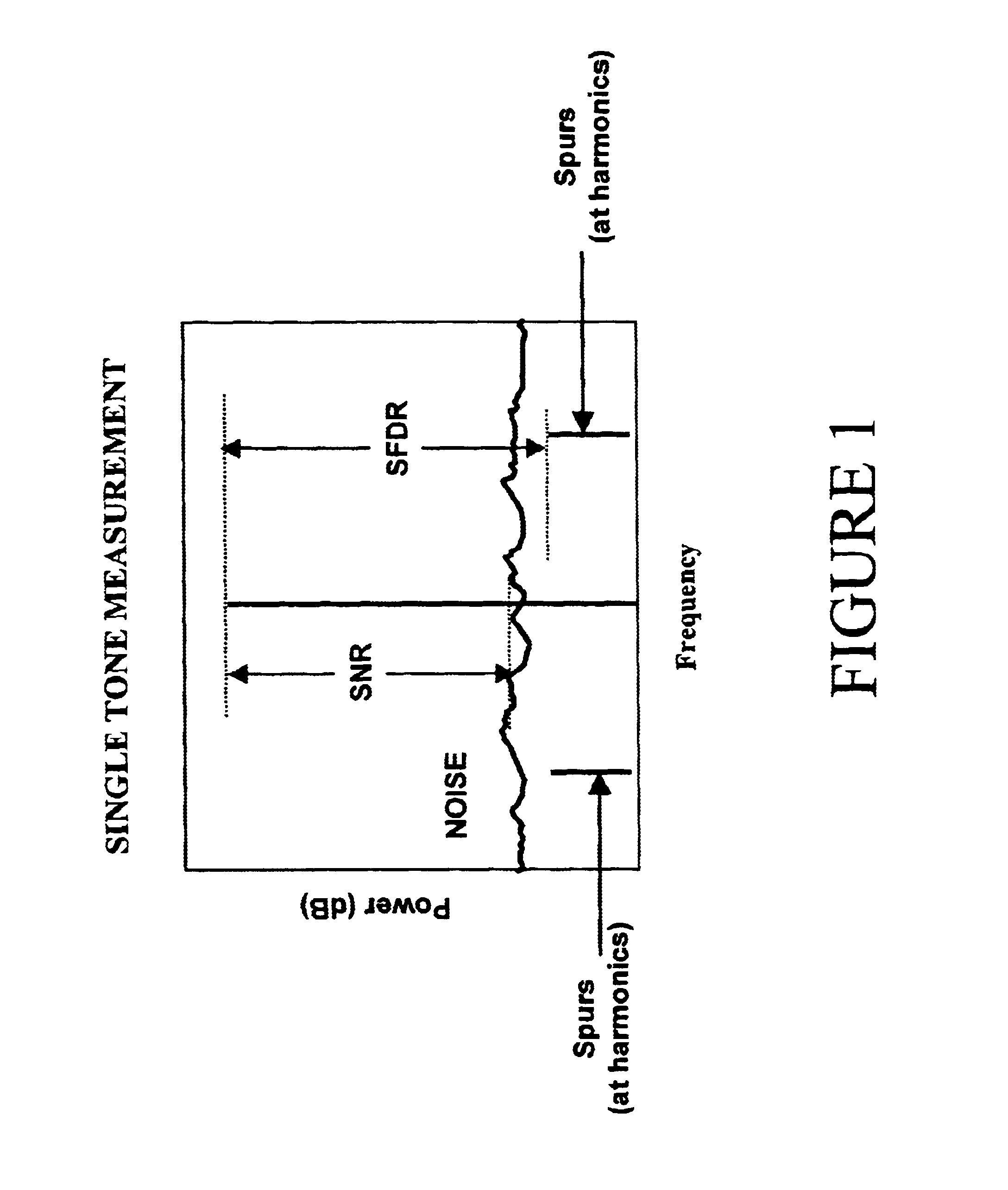

Highly linear analog-to-digital conversion system and method thereof

InactiveUS6639537B1Reduce nonlinear distortionMinimizes non-linear distortionElectric signal transmission systemsAnalogue conversionFinite impulse responseNonlinear distortion

A highly linear analog-to-digital (ADC) conversion system has an analog front-end device in cascade with a standard ADC converter, and a tunable digital non-linear equalizer. The equalizer corrects the quantization distortion, deviations from ideal response, and additive noises generated by the analog front-end device and ADC converter. The equalizer is formed by three main parts: Generate Function Streams Unit, Finite Impulse Response FIR filters and a summer. The equalizer receives the unequalized output from the ADC converter and generates a plurality of monomial streams in a systolic fashion. Each of the monomial streams is passed through a corresponding linear finite impulse response FIR filter. A convolution sum of all outputs from the FIR filters produces a unique equalized output with the non-linear distortion reduced to a satisfactory level. The FIR filter coefficients are determined by an Identity Equalizer Coefficient Unit, and a Test Signal Generator with different types of test signals. The FIR filter coefficients are set to minimize an error function.

Owner:MASSACHUSETTS INST OF TECH

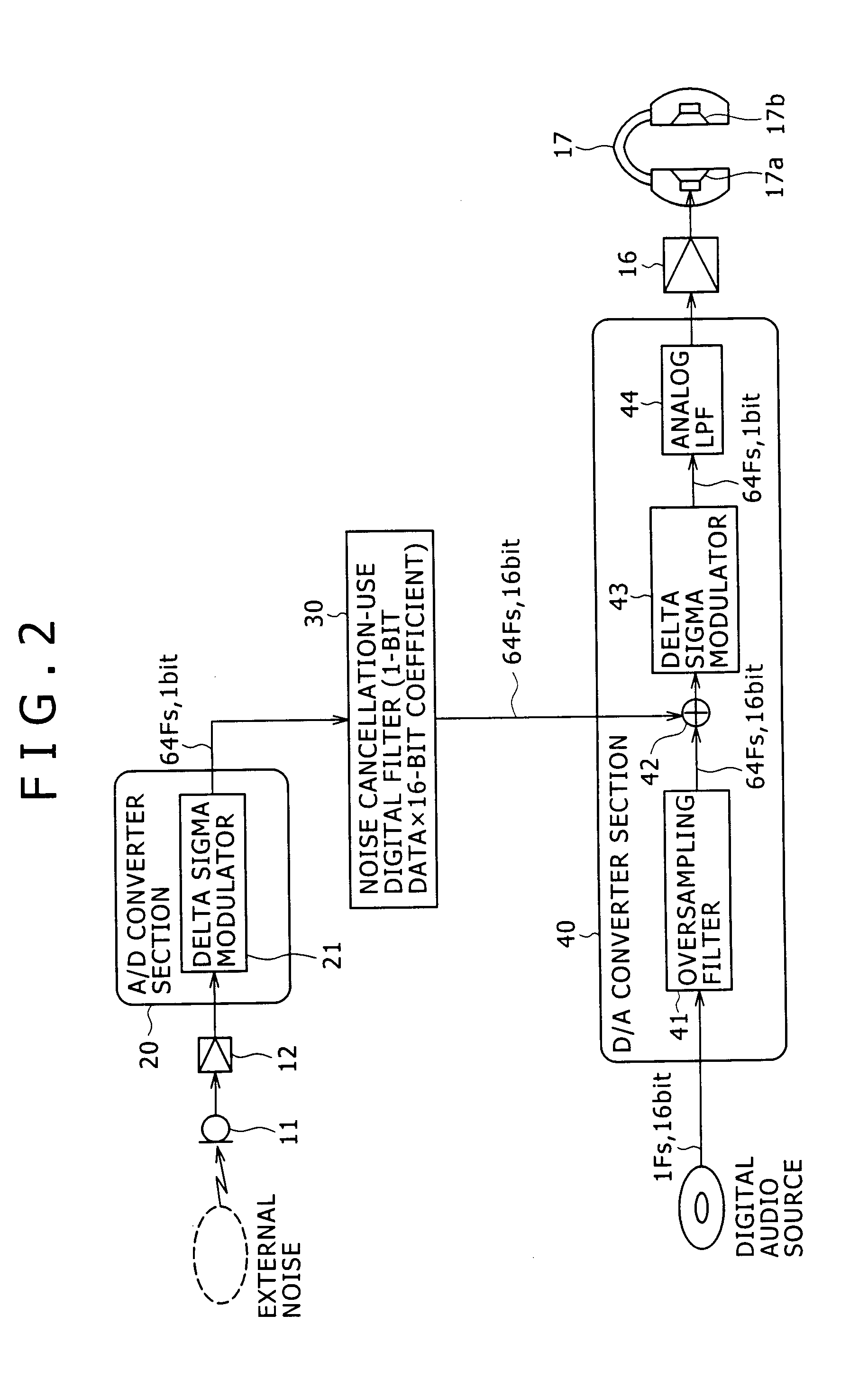

Signal processing apparatus and signal processing method

ActiveUS20080186218A1Improve sound qualityImprove practicalityElectric signal transmission systemsAnalogue conversionDigital filterAnalog signal

Disclosed herein is a signal processing apparatus including: analog-to-digital conversion means for performing delta sigma modulation of generating a digital signal having a predetermined sampling frequency and a predetermined quantization bit rate of one or more bits based on an input analog signal; signal processing means including a digital filter having a characteristic for outputting a digital signal having a sampling frequency n×Fs (Fs is a reference sampling frequency) and a quantization bit rate of a bits (a is a natural number greater than one) based on the above digital signal; and digital-to-analog conversion means including a part for performing delta sigma modulation for outputting a digital signal having a sampling frequency n×Fs and a quantization bit rate of b bits (b is a natural number greater than zero and less than a) based on a digital signal outputted from the signal processing means.

Owner:SONY CORP