Patents

Literature

675 results about "Analog to information converter" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

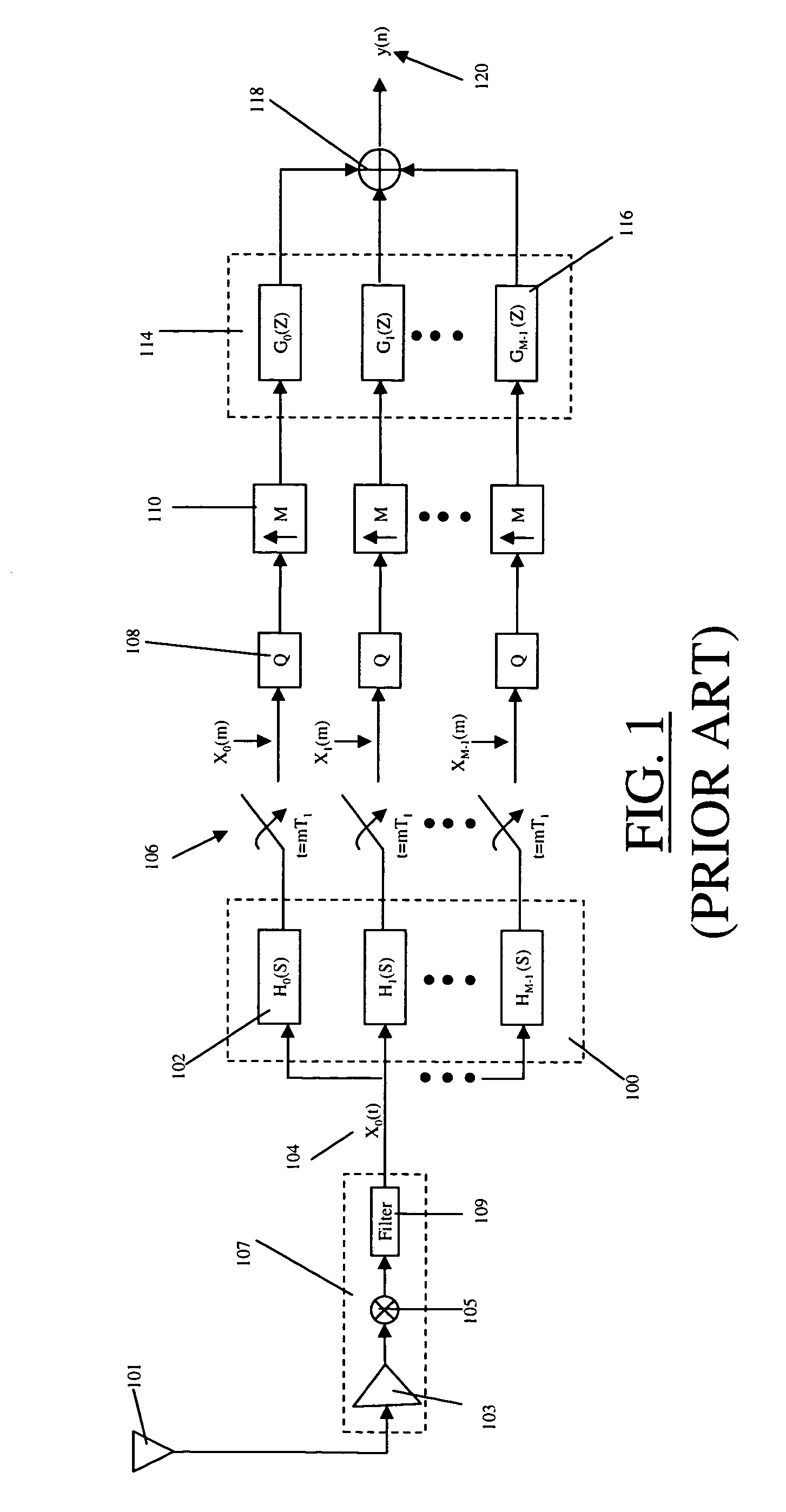

Method and Apparatus for On-Line Compressed Sensing

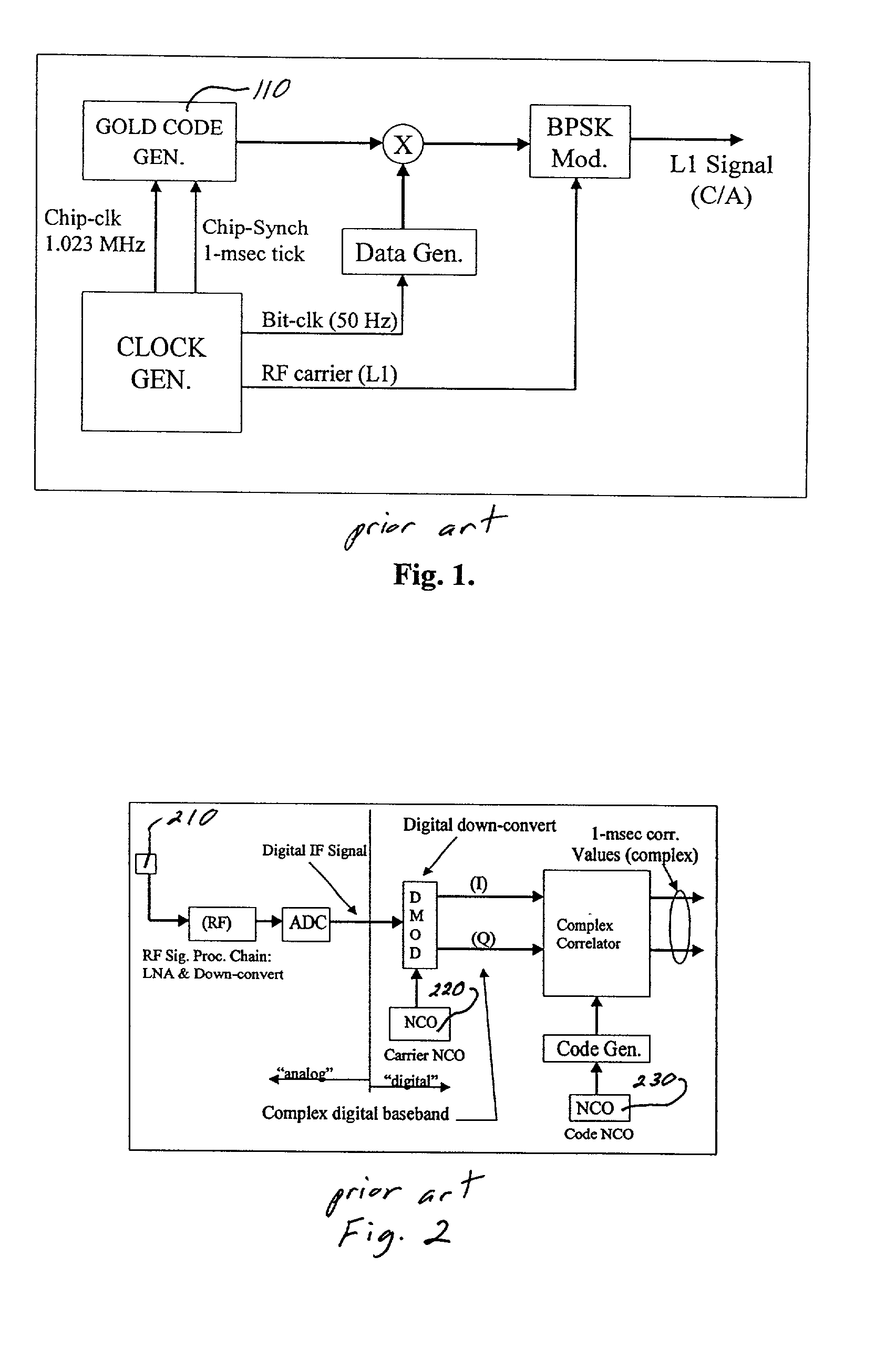

ActiveUS20090222226A1Improve system performanceAnalogue/digital conversionError correction/detection using multiple parity bitsHigh rateDiscrete-time signal

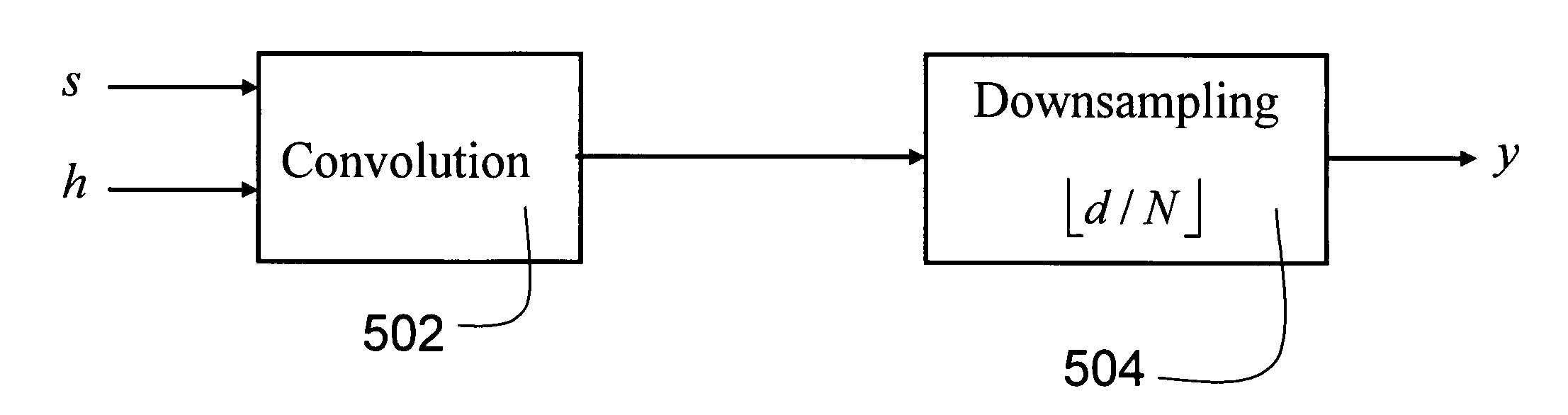

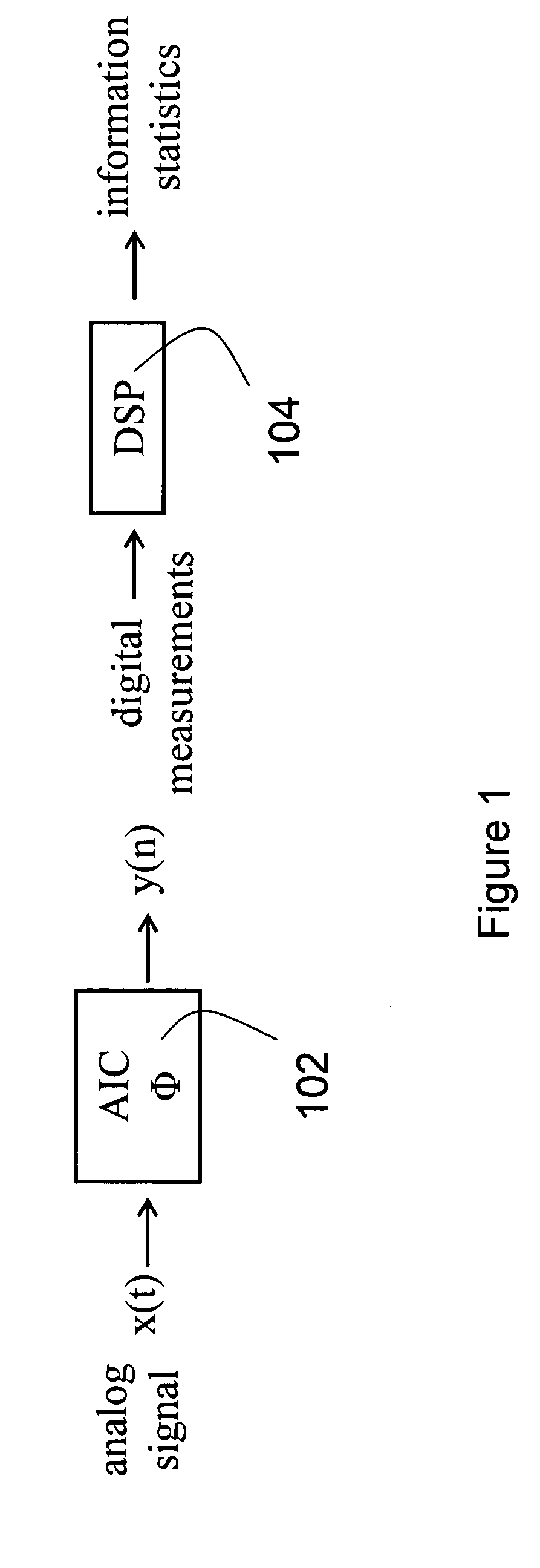

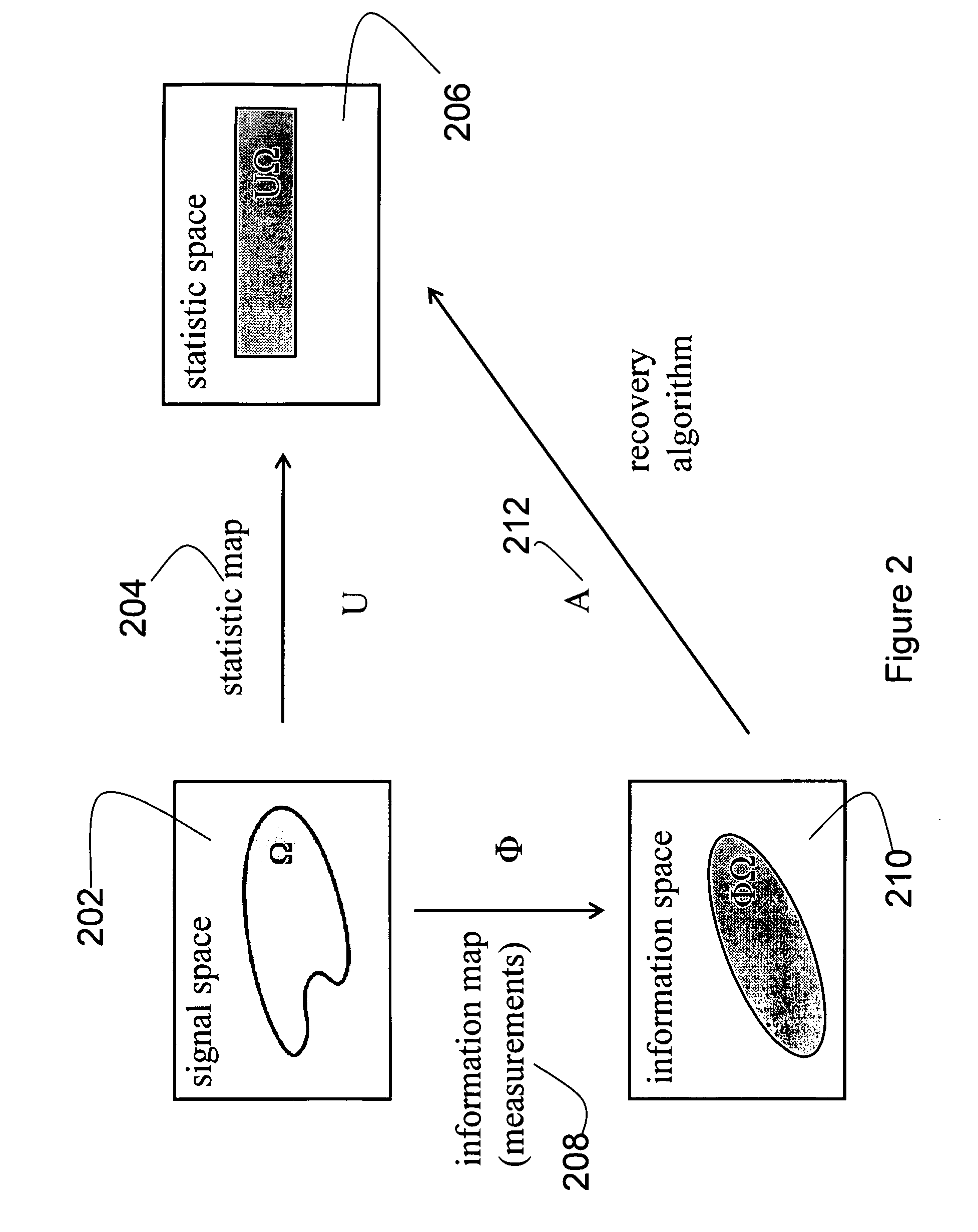

A typical data acquisition system takes periodic samples of a signal, image, or other data, often at the so-called Nyquist / Shannon sampling rate of two times the data bandwidth in order to ensure that no information is lost. In applications involving wideband signals, the Nyquist / Shannon sampling rate is very high, even though the signals may have a simple underlying structure. Recent developments in mathematics and signal processing have uncovered a solution to this Nyquist / Shannon sampling rate bottlenck for signals that are sparse or compressible in some representation. We demonstrate and reduce to practice methods to extract information directly from an analog or digital signal based on altering our notion of sampling to replace uniform time samples with more general linear functionals. One embodiment of our invention is a low-rate analog-to-information converter that can replace the high-rate analog-to-digital converter in certain applications involving wideband signals. Another embodiment is an encoding scheme for wideband discrete-time signals that condenses their information content.

Owner:RGT UNIV OF MICHIGAN +1

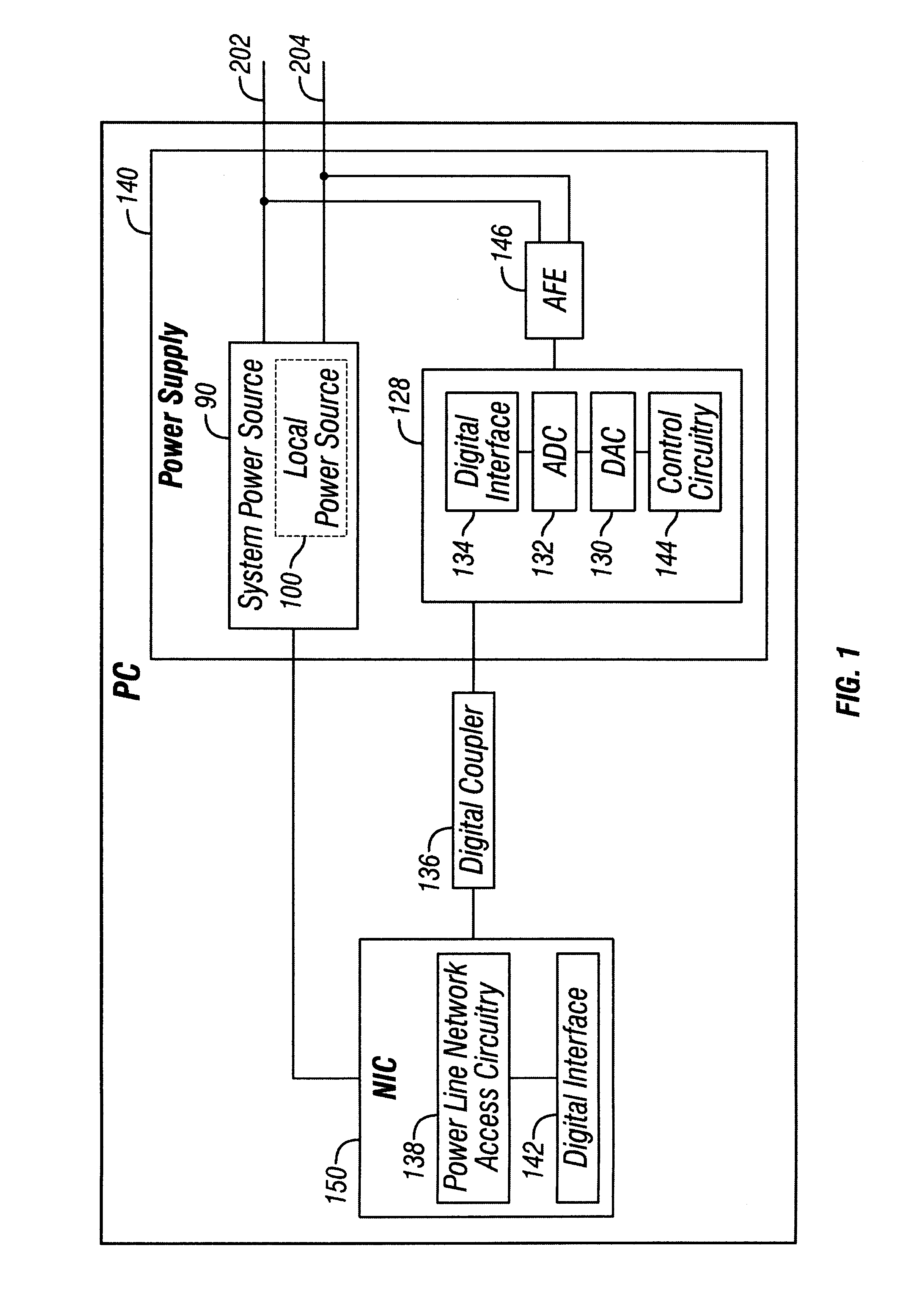

Power supply with digital data coupling for power-line networking

InactiveUS6373377B1Electric signal transmission systemsPower distribution line transmissionDigital dataPower line network

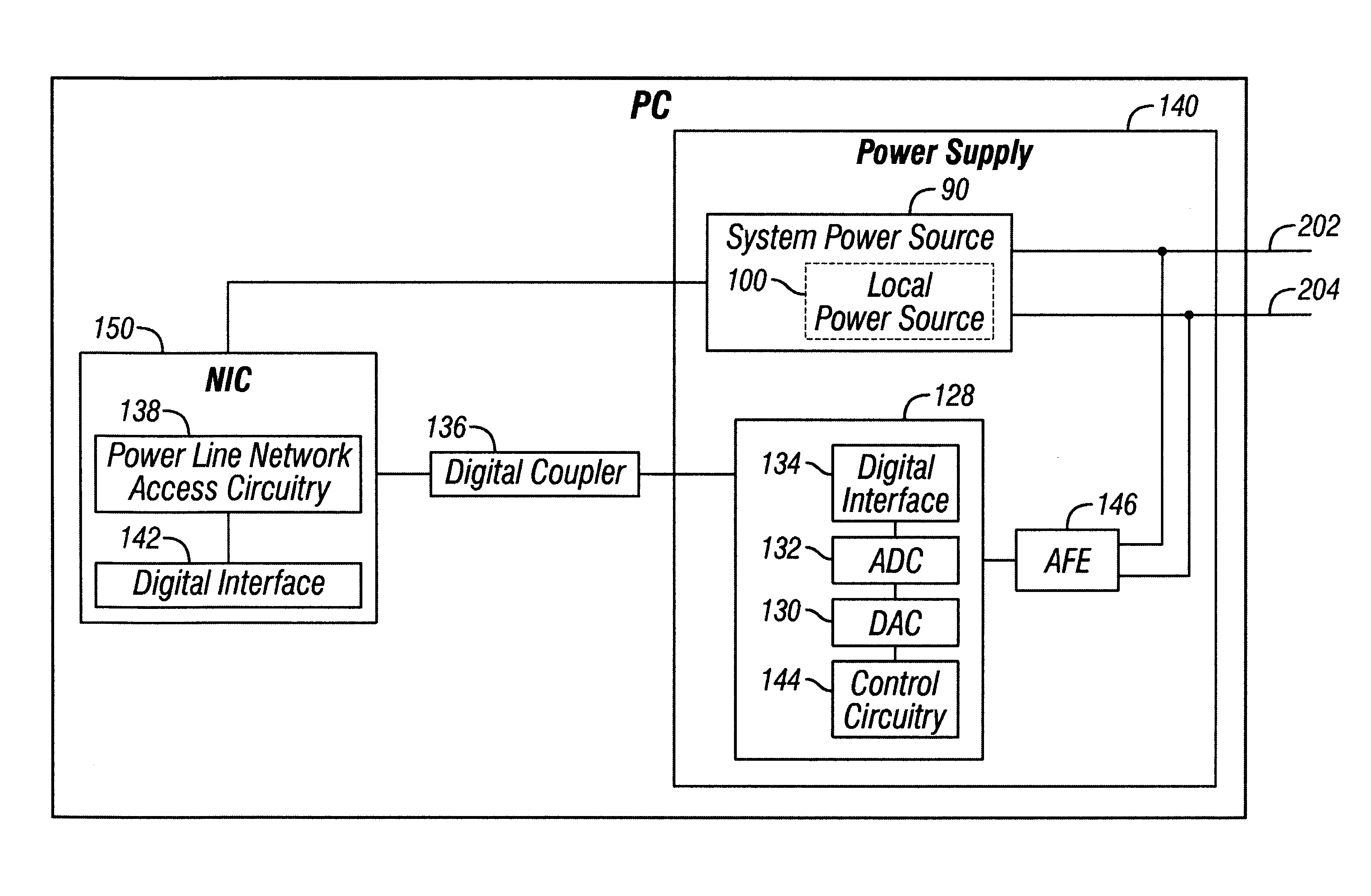

A power supply provides digital data coupling for power-line networking. The power supply includes a power supply side digital interface to transmit and receive a digital data passed through a digital coupler to and from a power-line network access circuitry side digital interface of power-line network access circuitry. The power supply further includes a digital-to-analog converter to process digital data into a high-frequency analog data carrier to provide to a power line of a power-line network. An analog-to-digital converter of the power supply converts a high-frequency analog data carrier from the power line into digital data for the power-line network access circuitry. A power-line analog front end of the power supply transmits and receives the high-frequency analog data carrier to and from the power line. Digital data exchanged between the power supply and the network access circuitry may include control signals for a control circuitry of the power supply. Control circuitry of the power supply may handle control of the digital-to-analog converter, the analog-to-digital converter and the analog front end.

Owner:SYNAPTICS INC

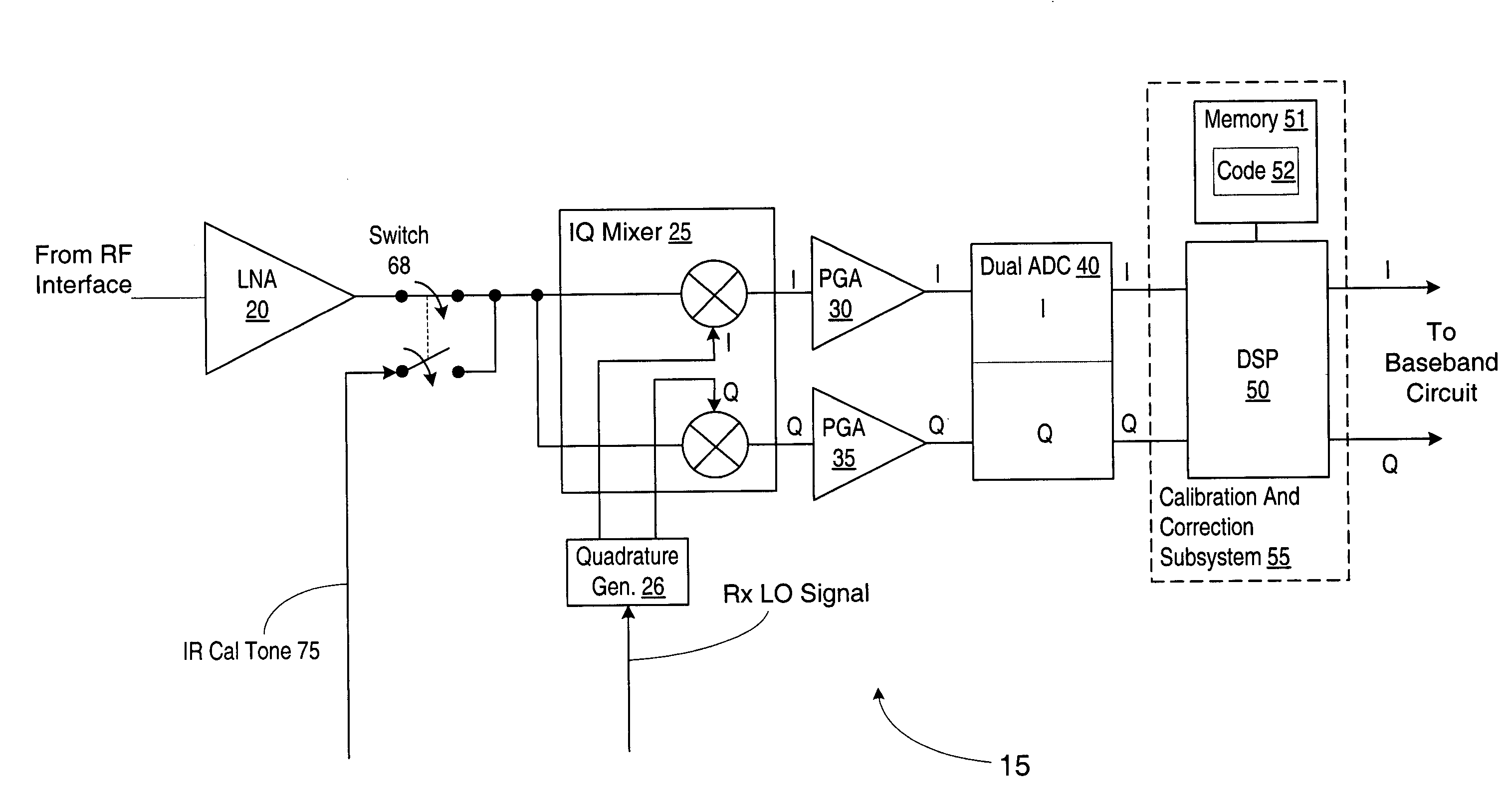

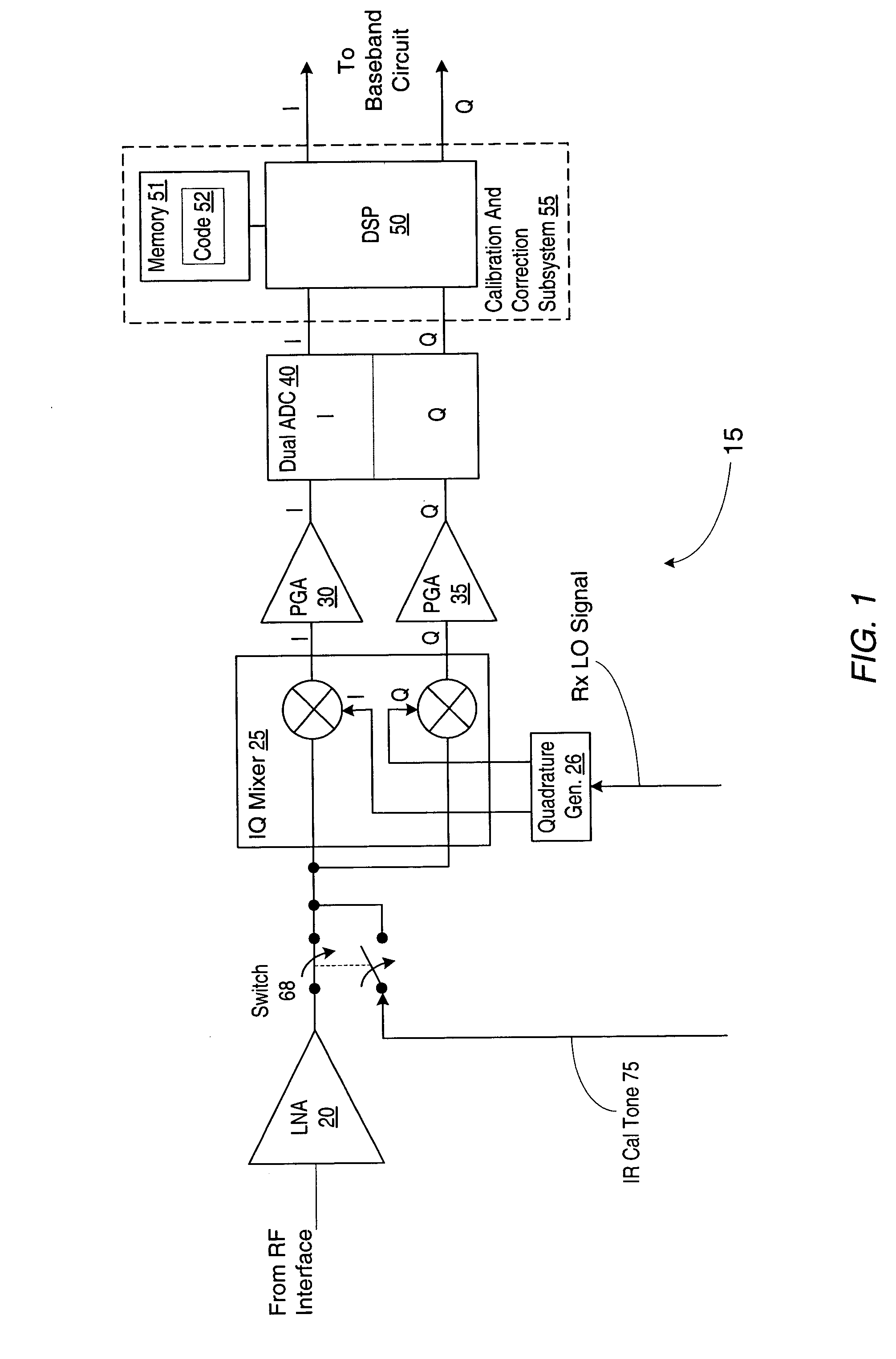

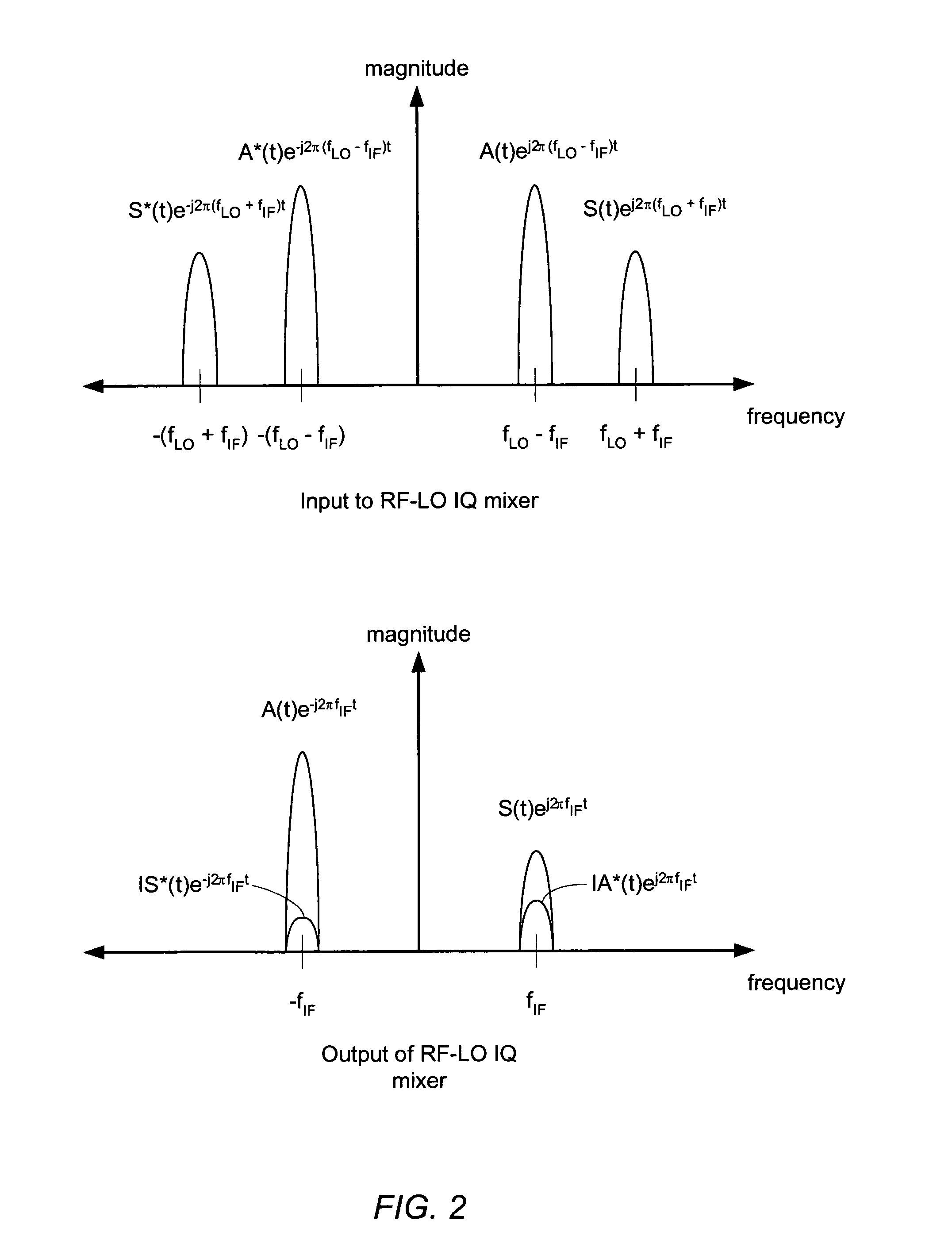

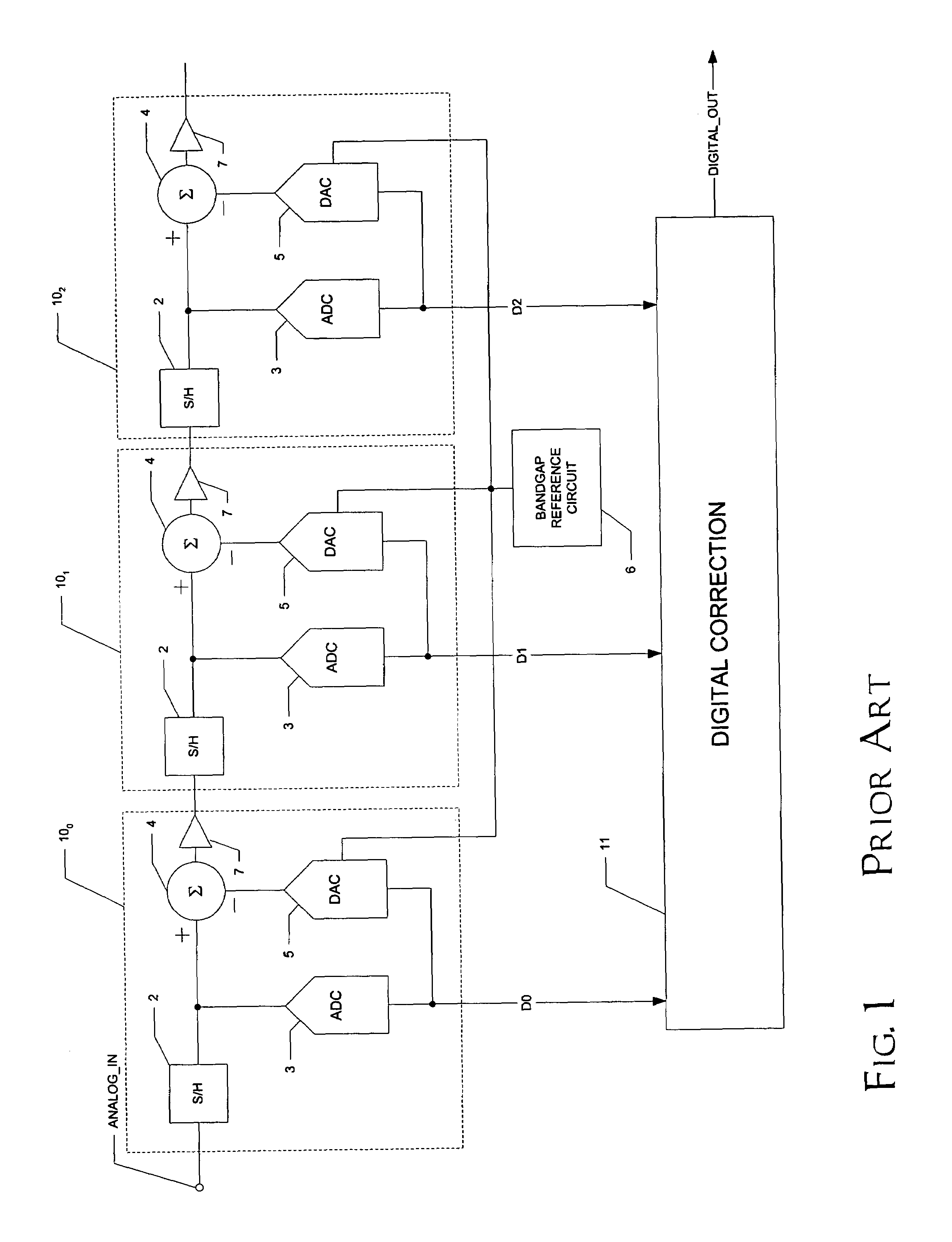

Apparatus and method for digital image correction in a receiver

ActiveUS7142835B2Angle demodulation by oscillations conversionRelay systems monitoringProgram instructionImage correction

An apparatus and method for performing digital image correction in a receiver. In one embodiment, a receiver circuit may include an IQ signal source configured to provide a digital signal comprising in-phase (I) and quadrature (Q) components, such as an IQ mixer in combination with an analog to digital converter, for example. The receiver circuit may also include an image correction unit coupled to the IQ signal source and configured to combine the digital signal with a complex image correction factor. The image correction unit may be implemented using a digital signal processor under the control of associated program instructions, for example. In one specific implementation of the receiver circuit, the image correction unit may be configured to combine the digital signal with the complex image correction factor using a cross-accumulation operation.

Owner:SILICON LAB INC

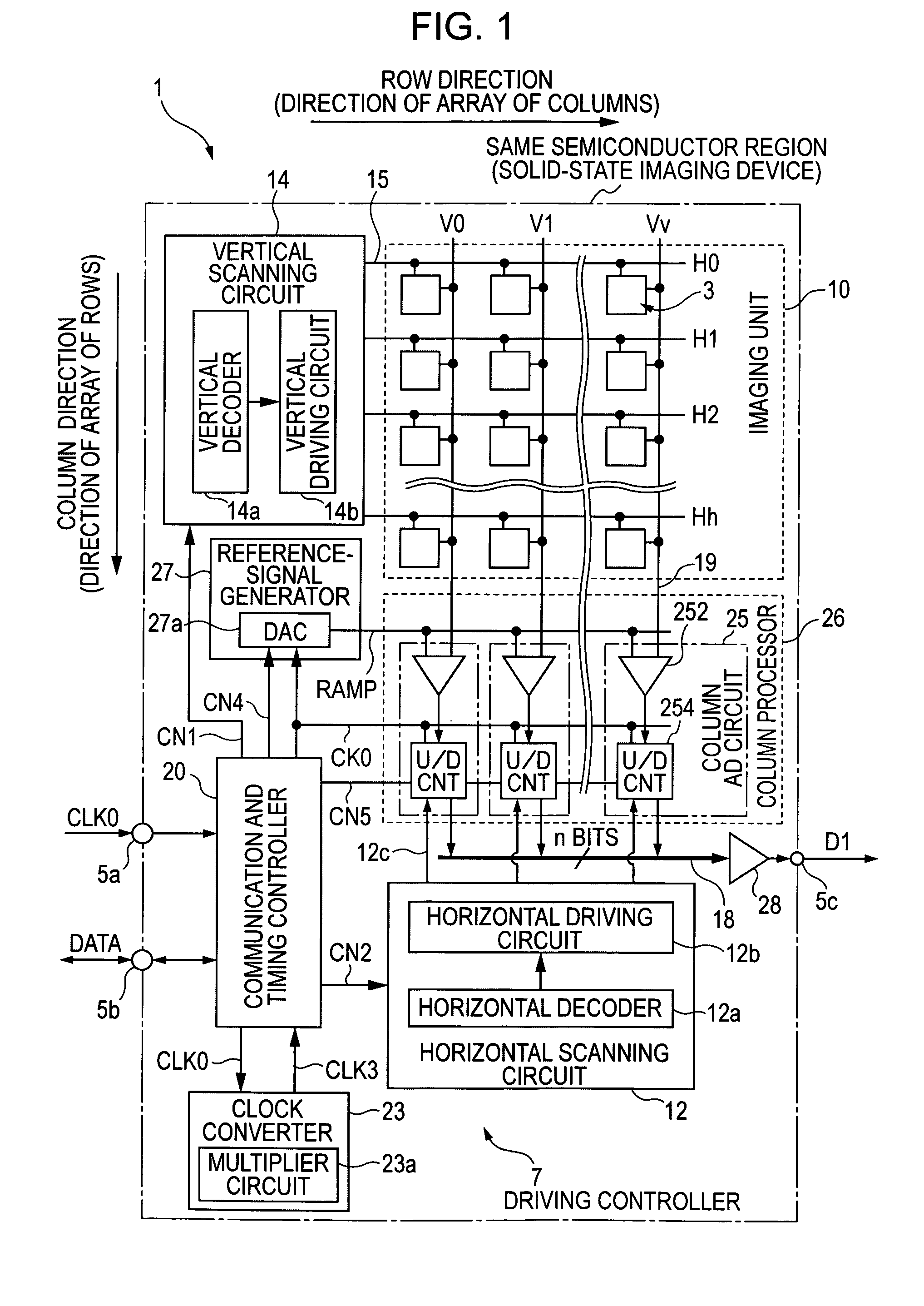

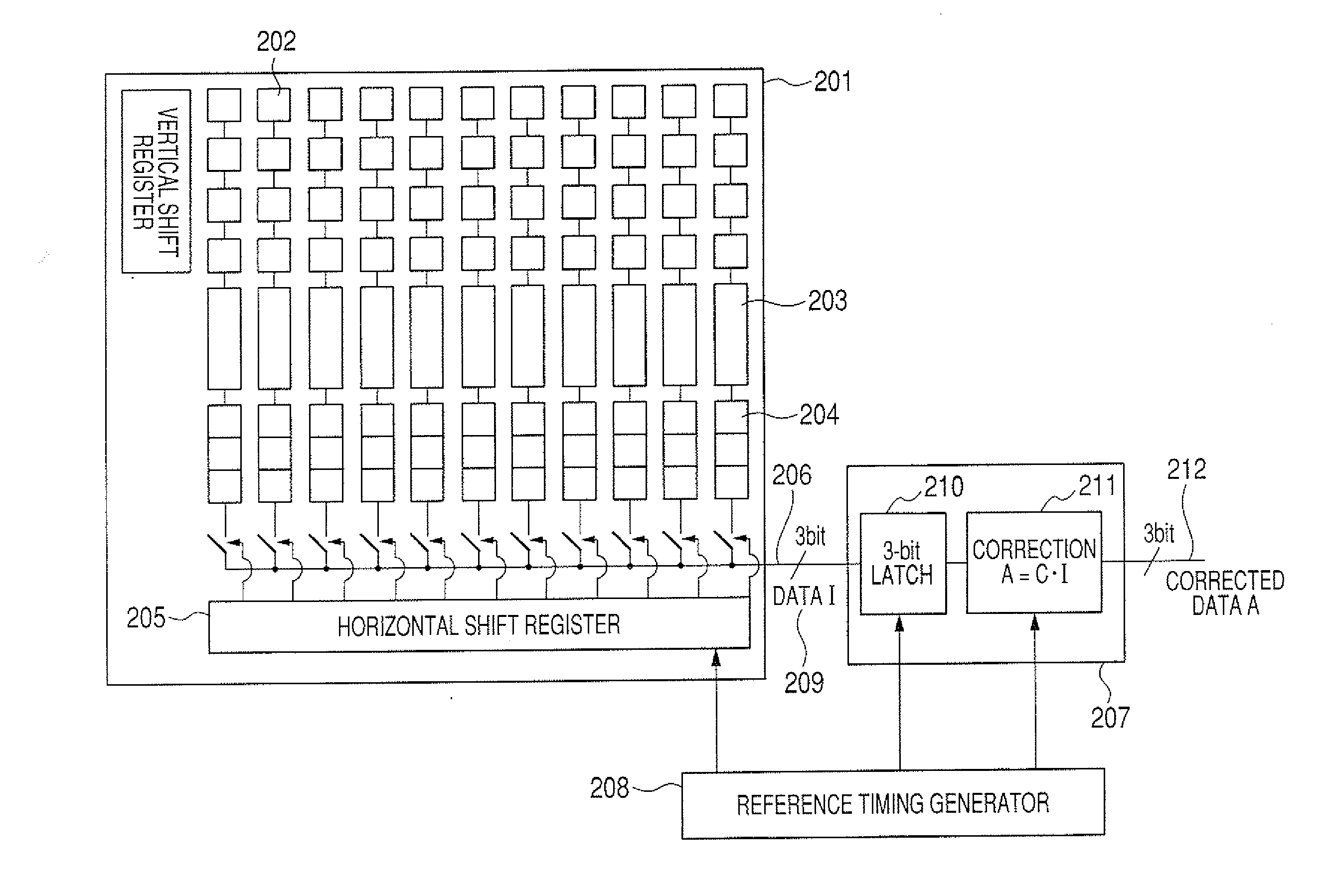

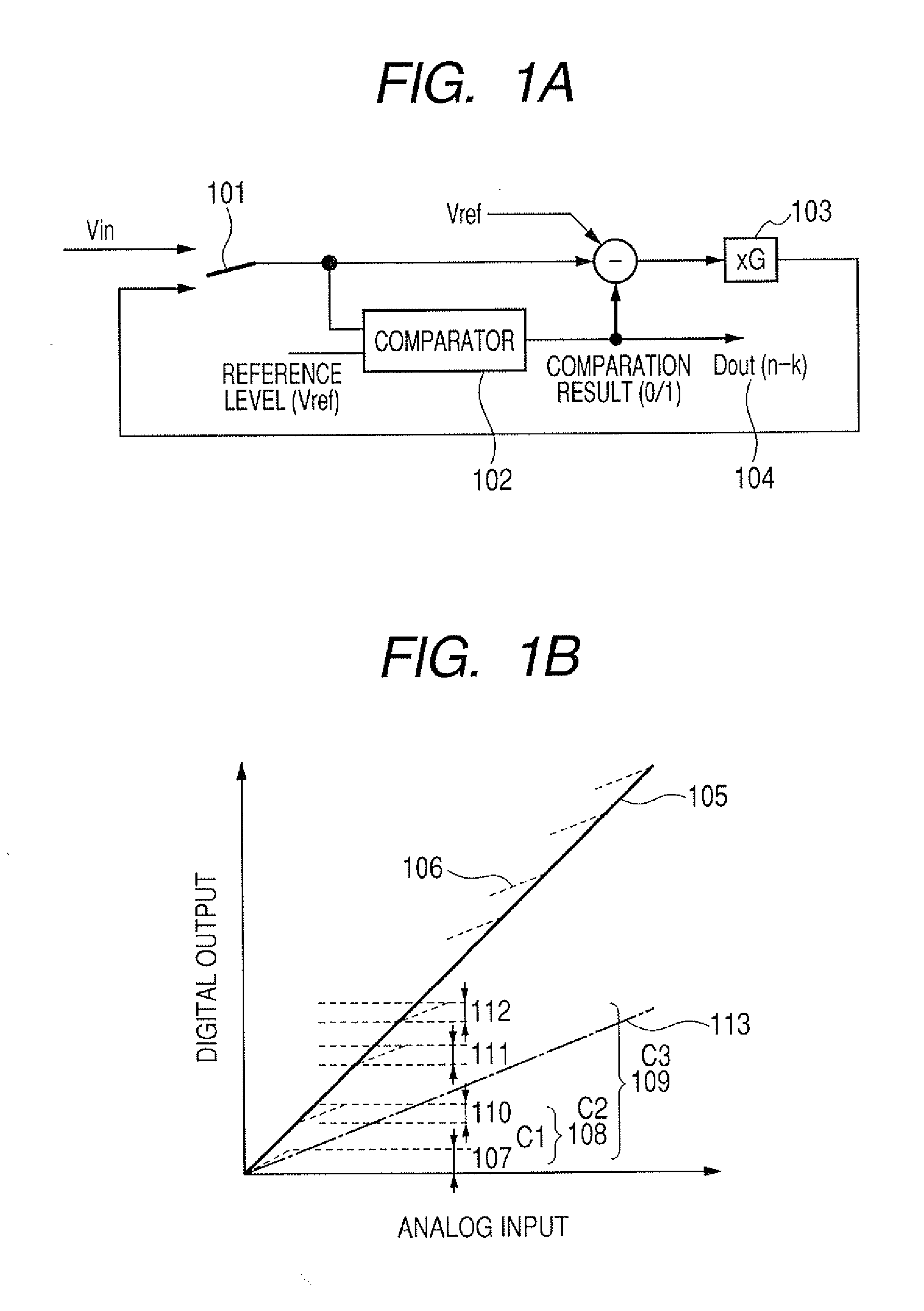

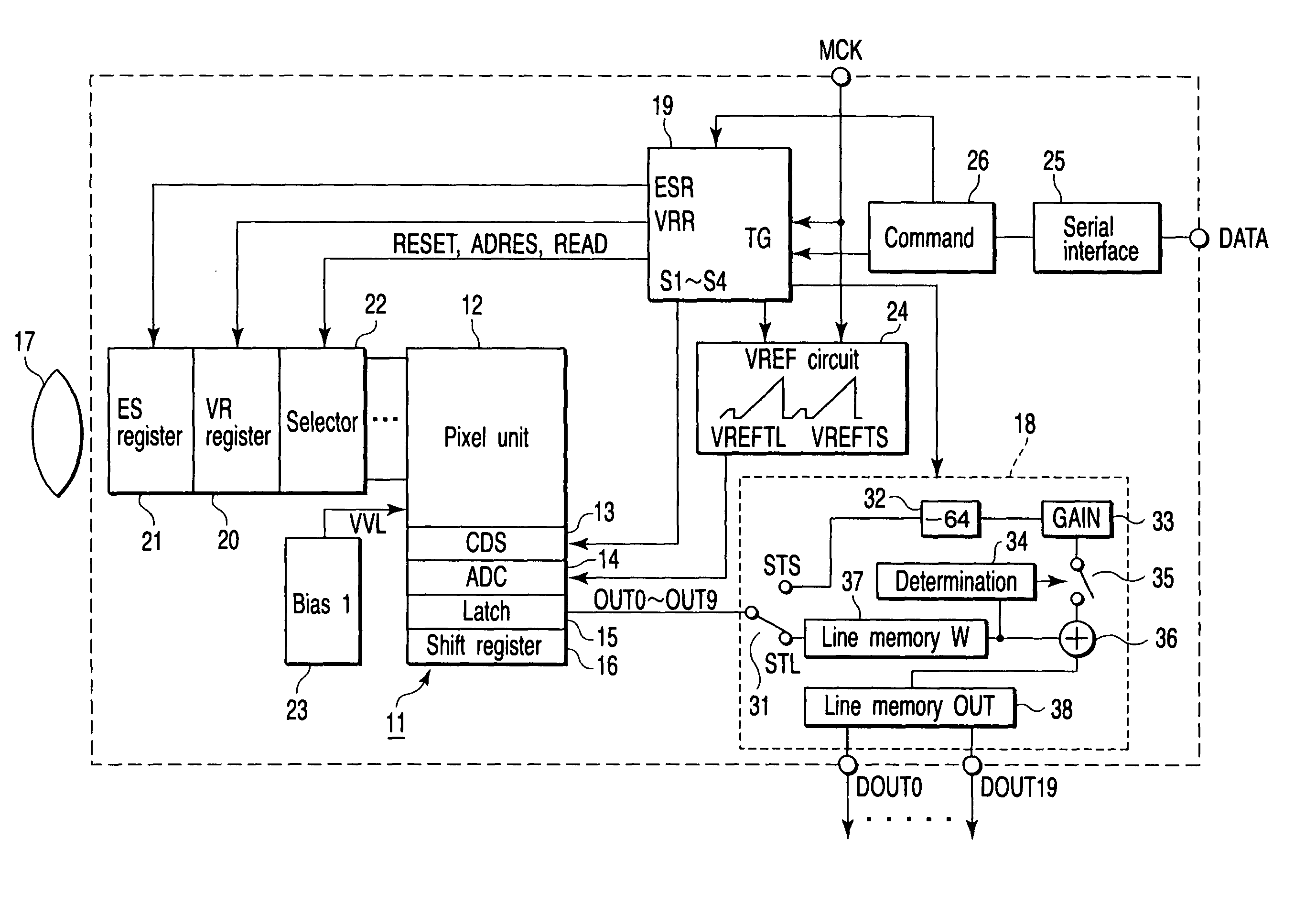

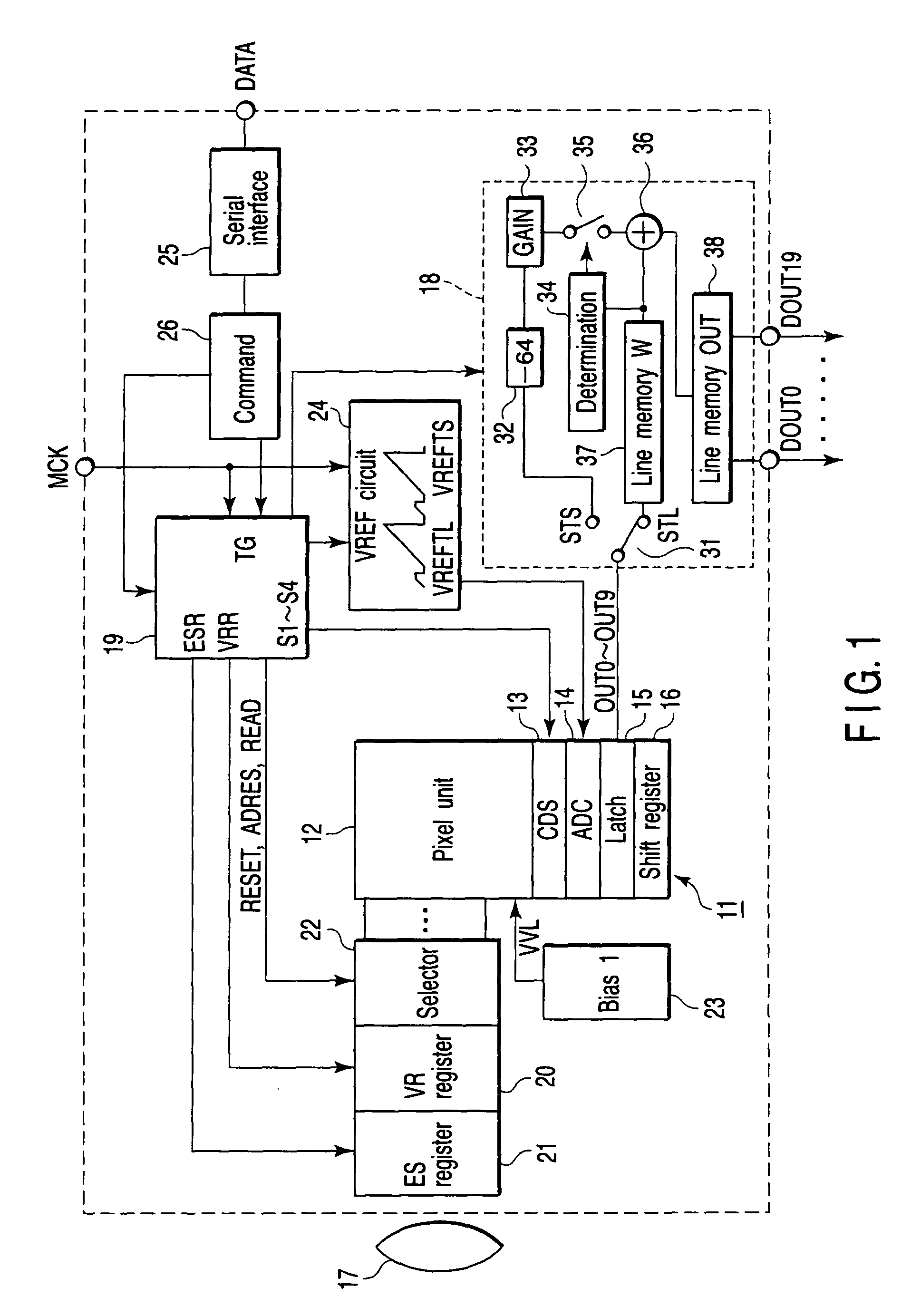

Analog-to-digital converter and semiconductor device

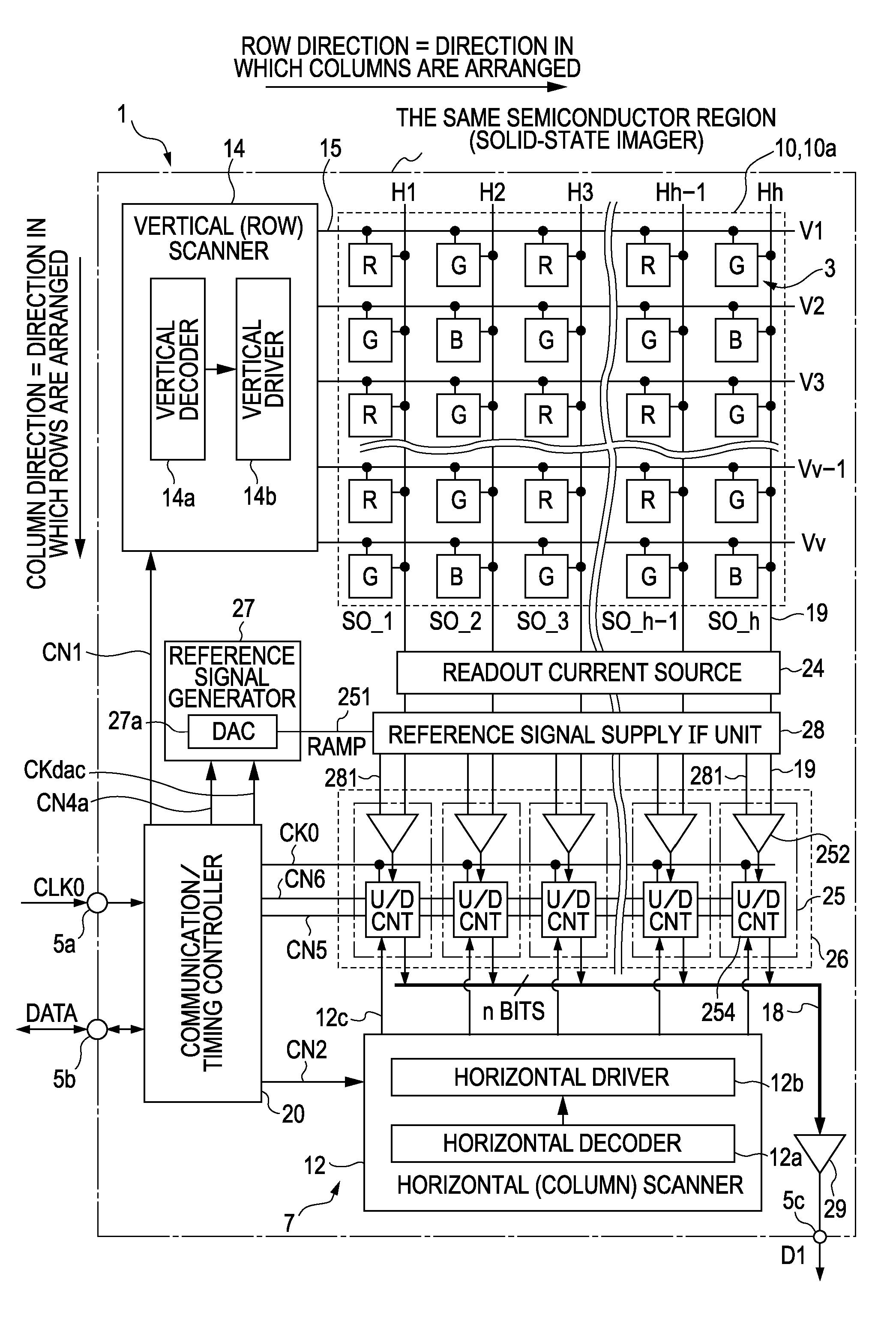

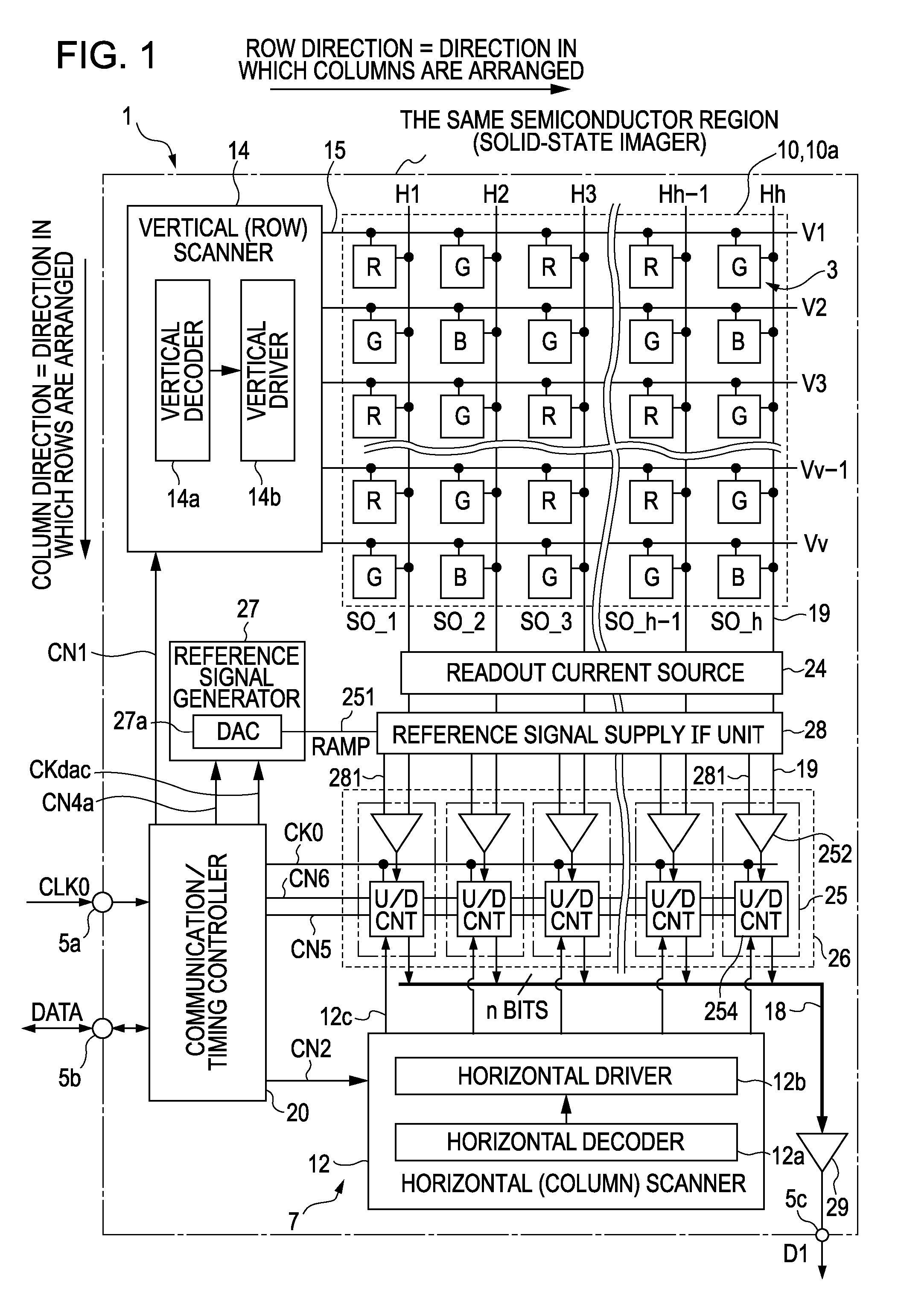

ActiveUS7321329B2Reduce adverse effectsTelevision system detailsElectric signal transmission systemsCMOSDigital down converter

An electronic apparatus includes a CMOS image sensor and a signal processor operable to process an output signal from the CMOS image sensor. The CMOS image sensor includes the following elements: an imaging region; a reference signal generator operable to generate a reference signal; a comparator operable to compare the reference signal generated by the reference signal generator with a signal transmitted from the imaging region; a counter operable to count, in parallel with comparison performed by the comparator, a predetermined count clock and to hold a count value at the time of completion of comparison performed by the comparator; and a reference signal supply interface unit operable to supply the reference signal generated by the reference signal generator to a plurality of comparators via different signal lines, respectively.

Owner:SONY CORP

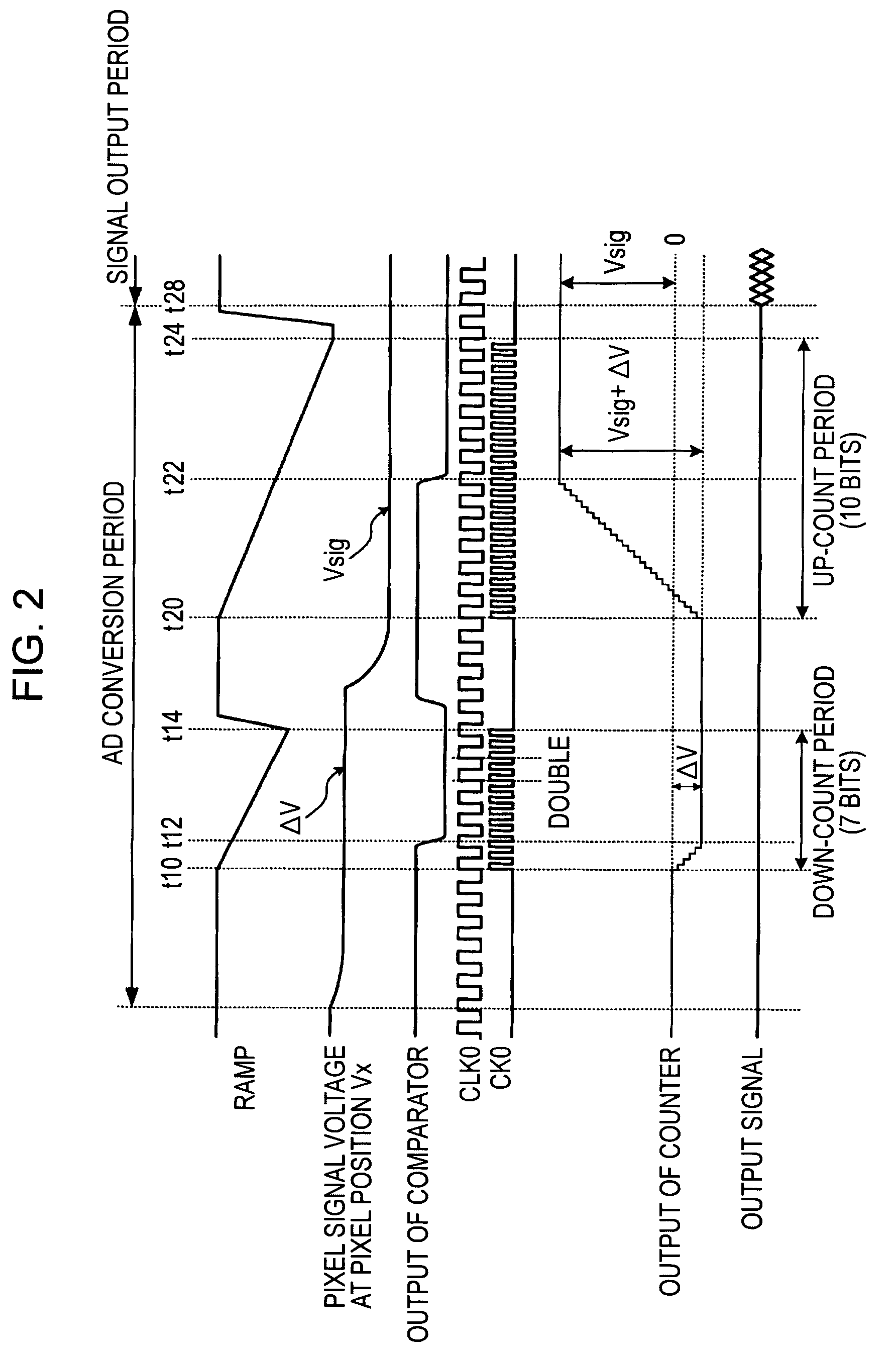

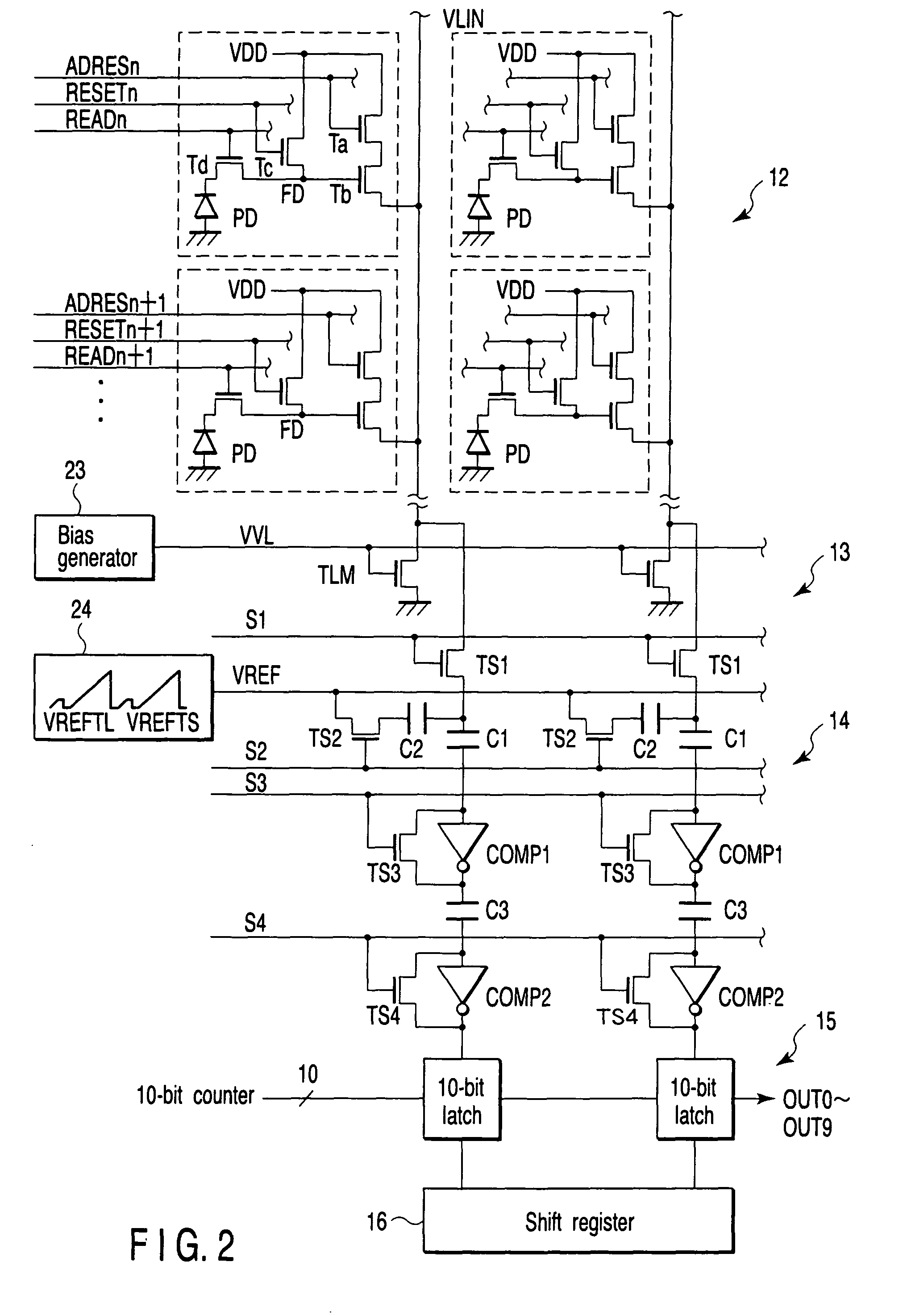

AD conversion method, AD converter, semiconductor device for detecting distribution of physical quantities, and electronic apparatus

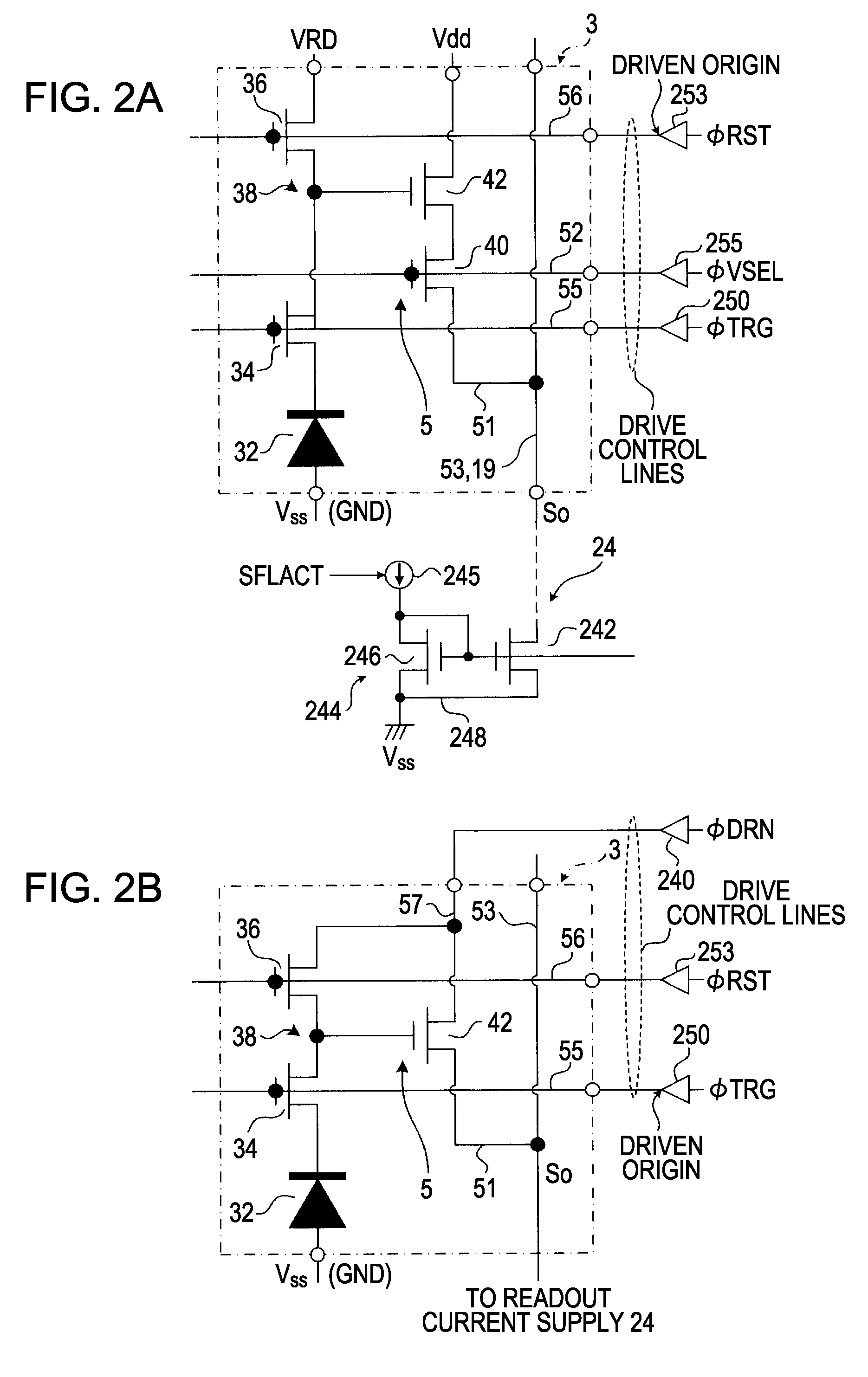

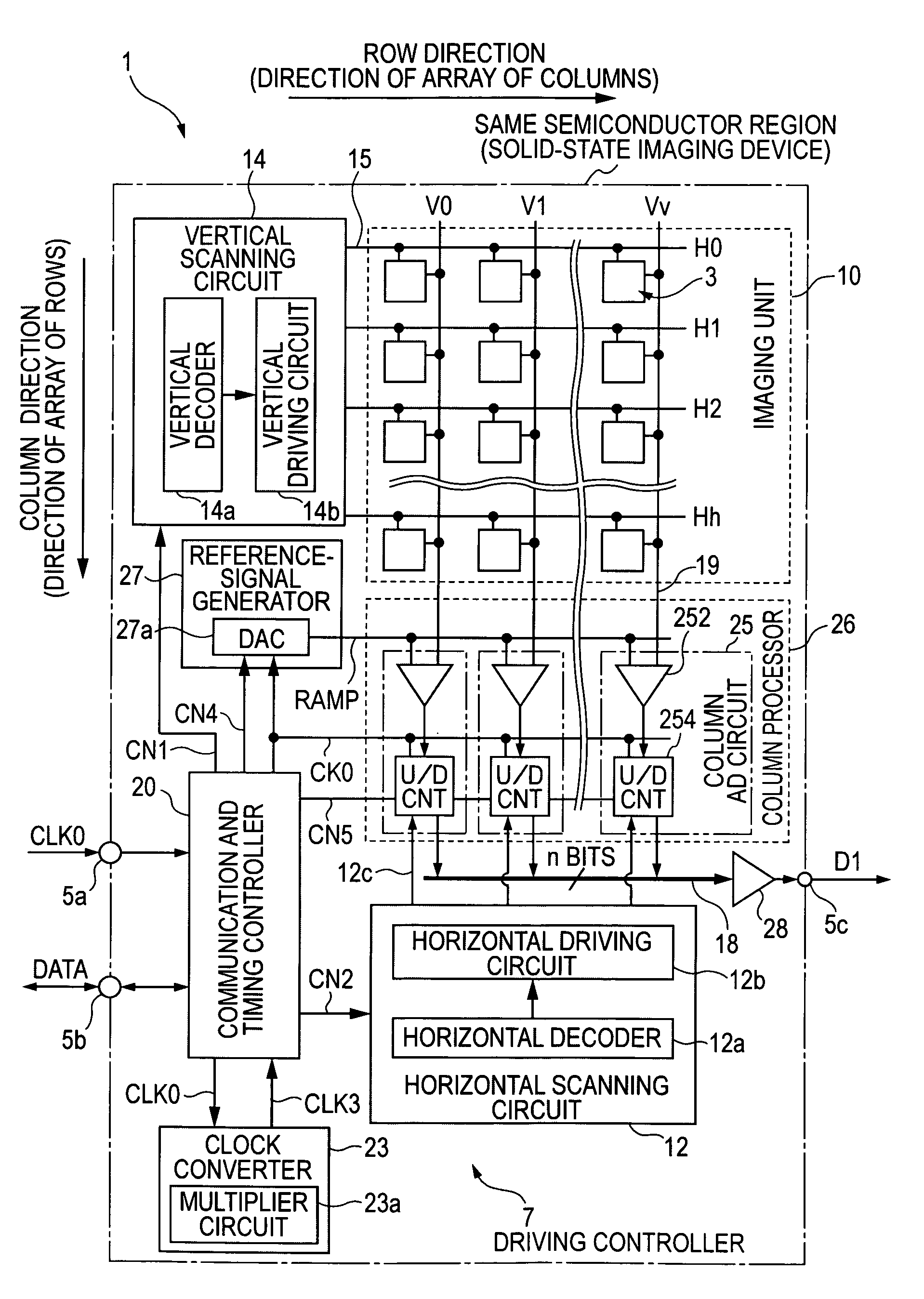

ActiveUS7088279B2Television system detailsElectric signal transmission systemsControl lineĆuk converter

In a solid-state imaging device including an analog-to-digital converter, a clock converter that generates a high-speed clock that is faster than a master clock is provided. A voltage comparator compares a pixel signal input from a vertical signal line for each row control line with a reference voltage, generating pulses having magnitudes corresponding to a reset component or a signal component in a temporal direction. A counter counts the width of pulse signals until completion of the comparison in the voltage comparator based on a clock that is generated based on the high-speed clock, holding a count value at a time of completion of the comparison. A communication and timing controller exercises control so that the voltage comparator performs comparison for the reset component and the counter performs down-counting in a first processing iteration and so that the voltage comparator performs comparison for the signal component and the counter performs up-counting in a second processing iteration.

Owner:SONY CORP

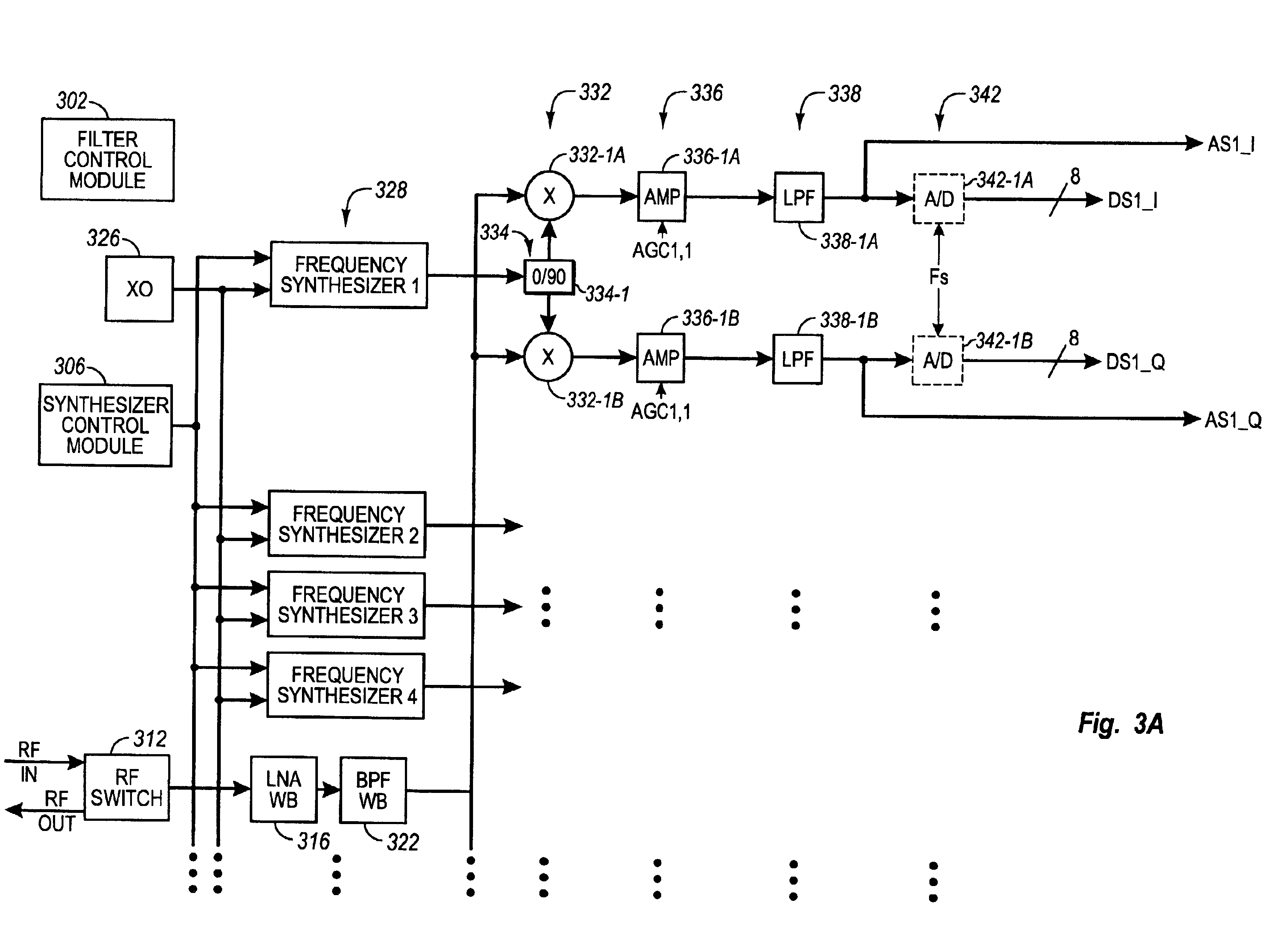

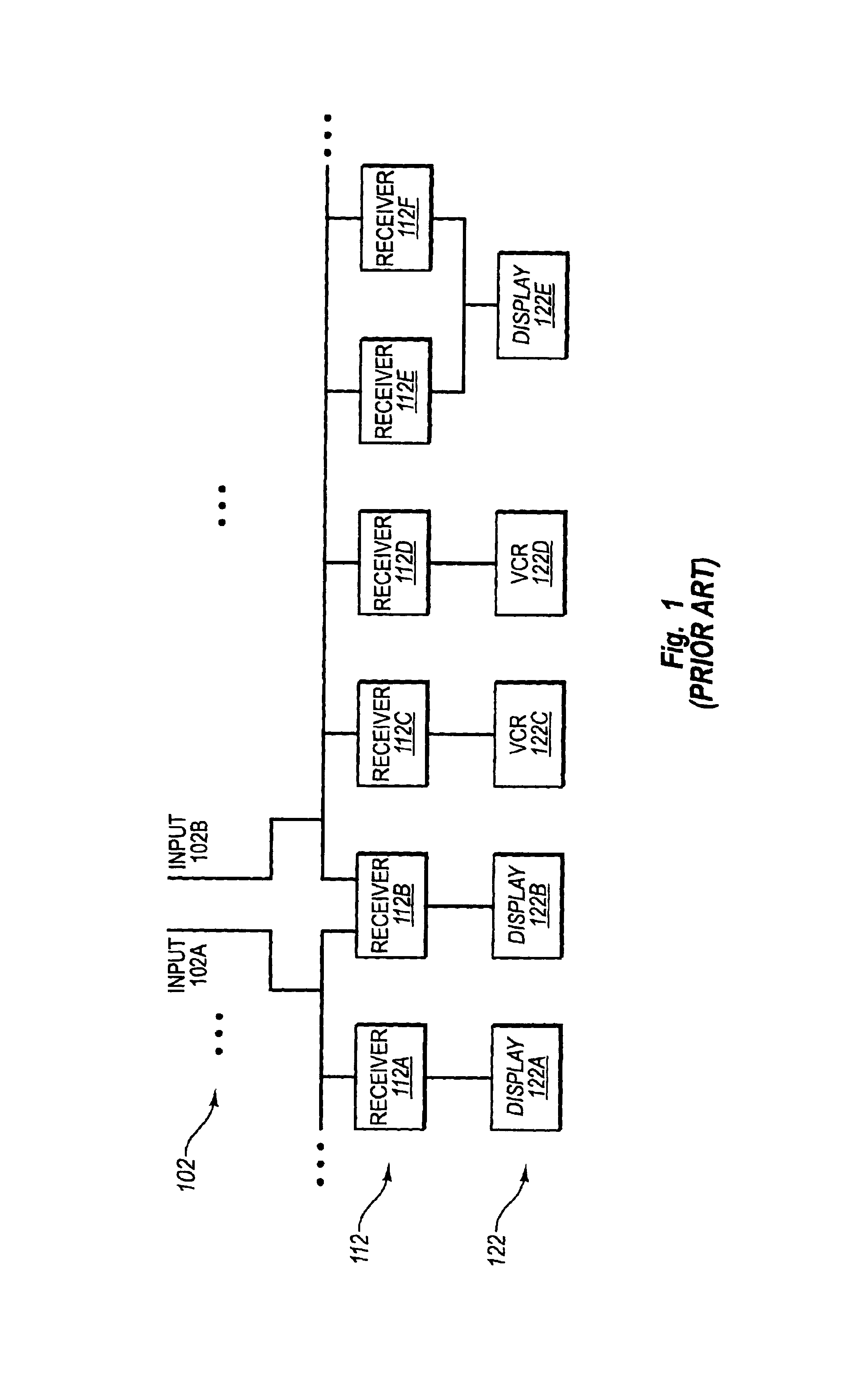

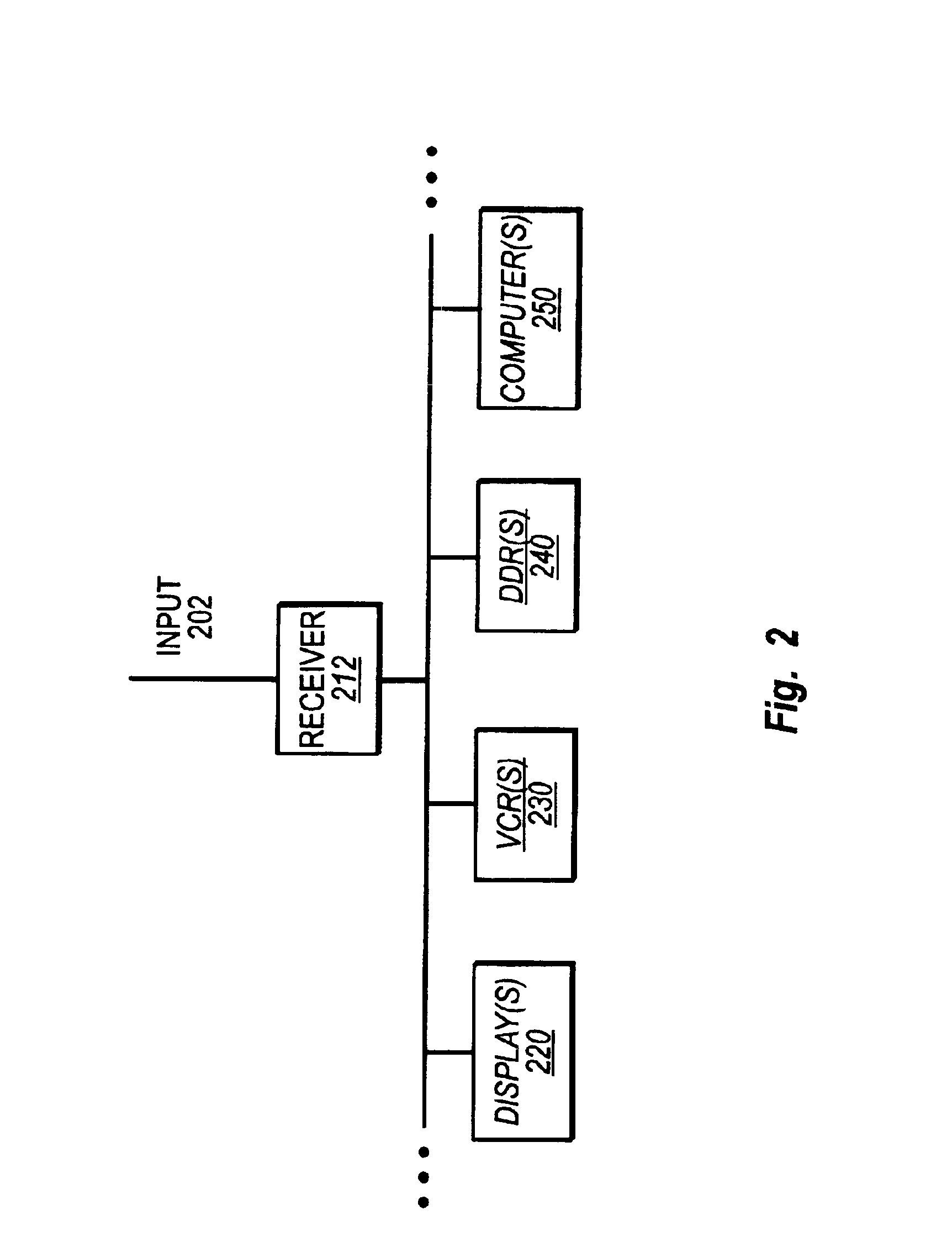

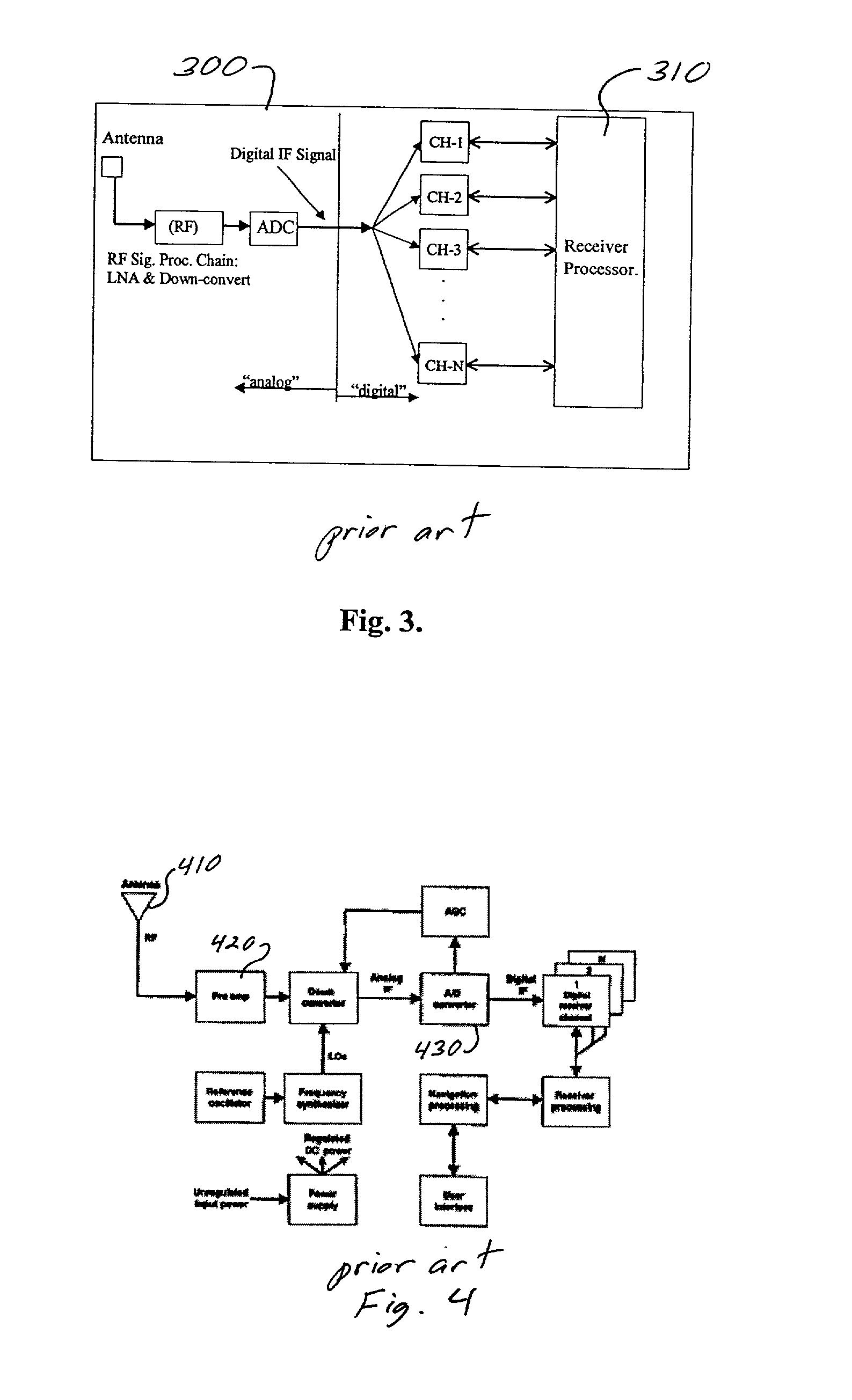

Simultaneous tuning of multiple channels using intermediate frequency sub-sampling

ActiveUS6888888B1Improve cooling effectImprove reliabilityTelevision system detailsPicture reproducers using cathode ray tubesAudio power amplifierIntermediate frequency

Owner:MICROSOFT TECH LICENSING LLC

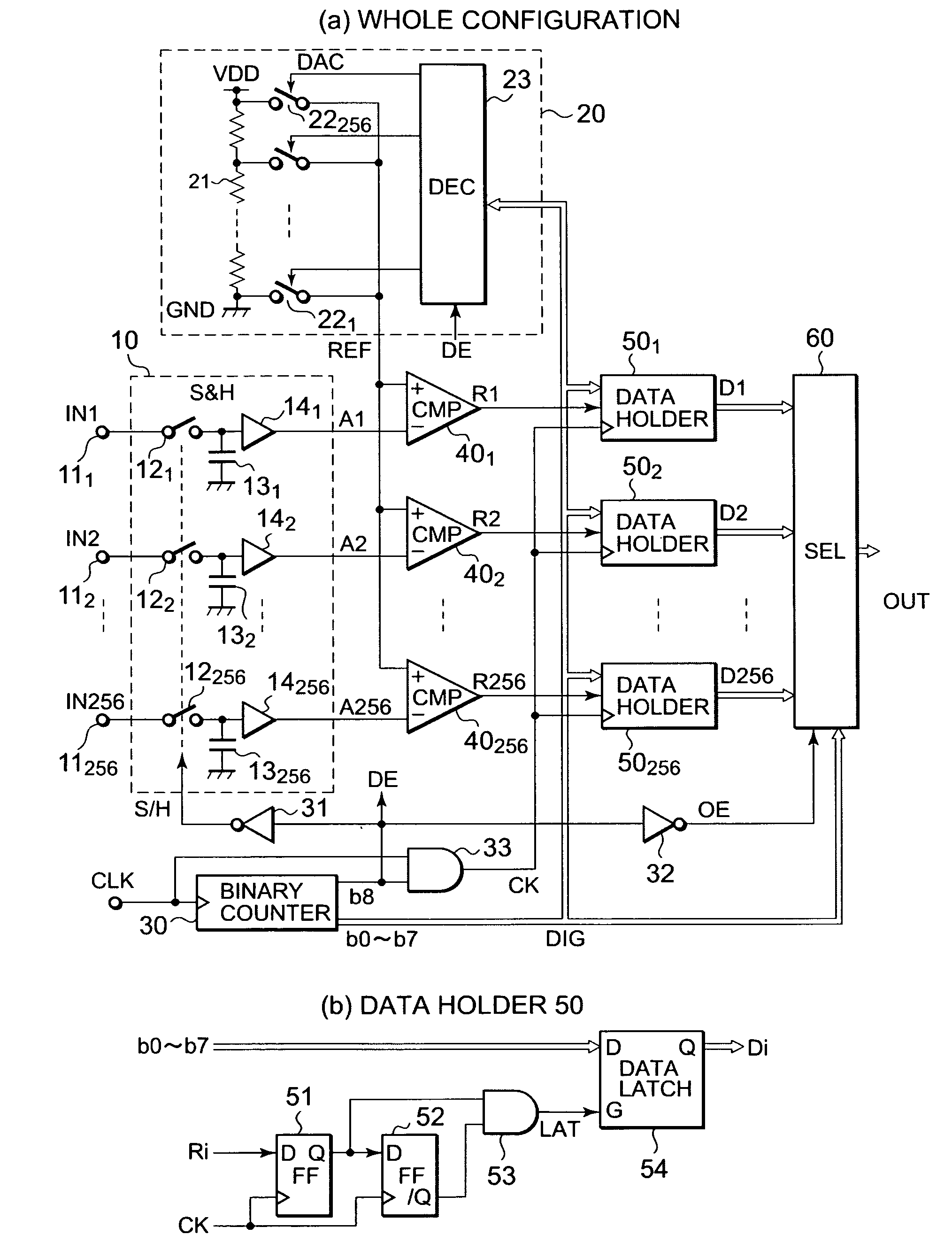

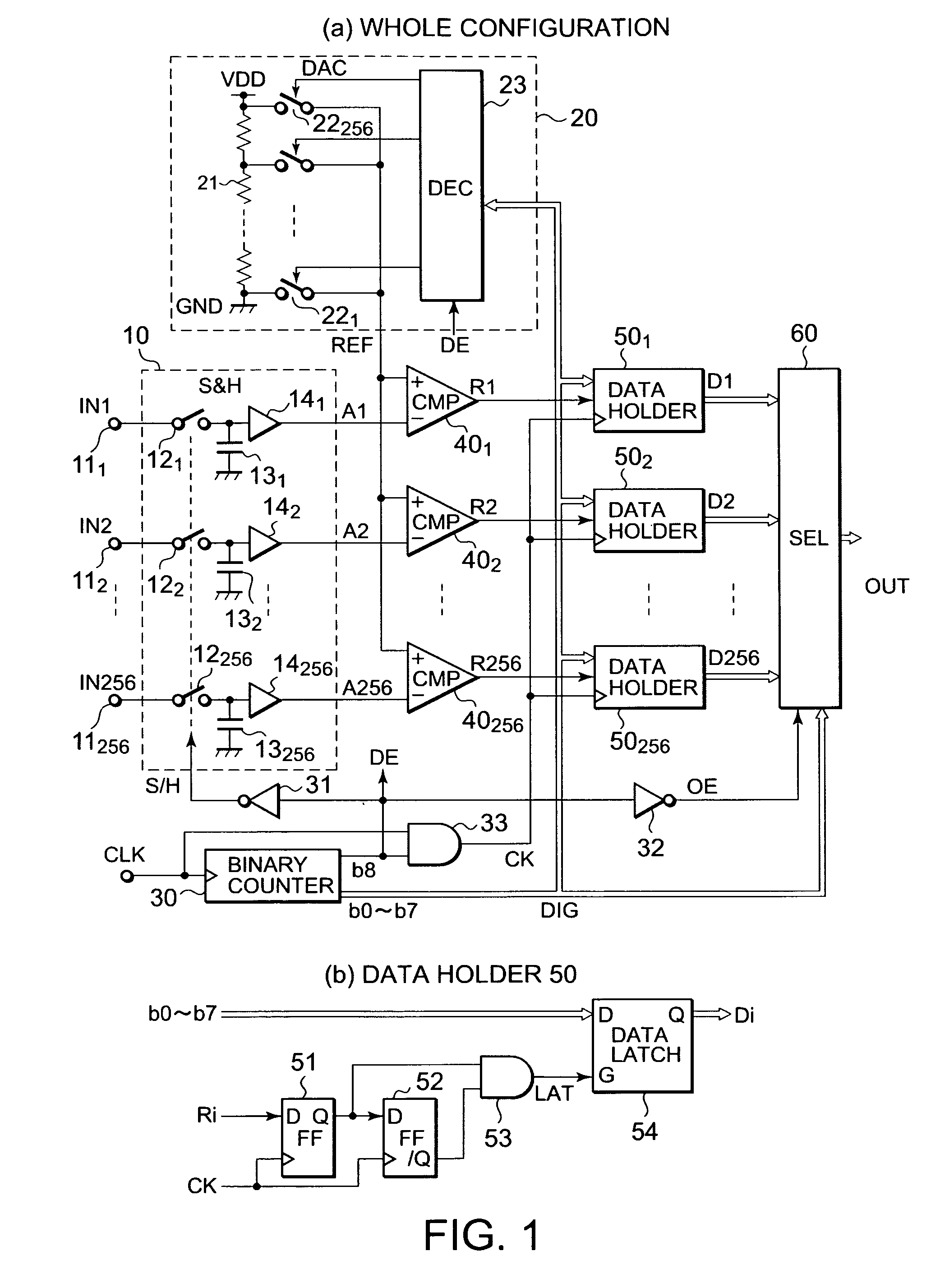

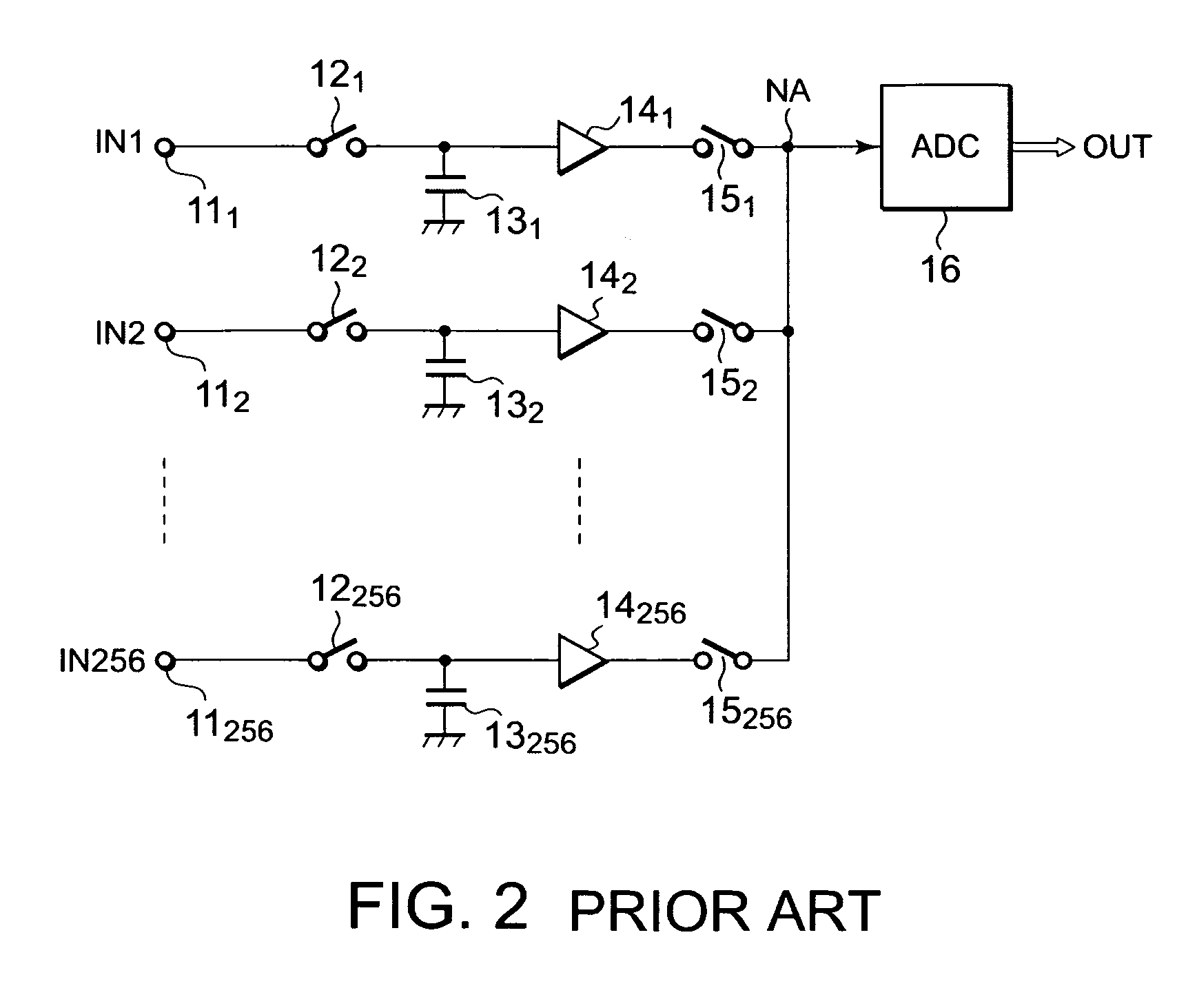

Analog-digital converter circuit

ActiveUS7372390B2Reduced conversion timeSimple circuit configurationElectric signal transmission systemsAnalogue-digital convertersMulti inputCurrent consumption

The present invention provides a multi-input A / D converter circuit capable of shorting a conversion time without increasing its layout area and current consumption. When a most significant bit of a binary counter is “L”, individual input signals are sampled by a sample and hold unit, and digital signals held in respective data holders are sequentially selected by a selector. When the most significant bit is brought to “H”, the respective input signals are held as analog signals and compared with each of reference voltages produced corresponding to a digital signal by a DAC. When decision signals outputted from comparators are changed from “L” to “H”, the digital signal at that time is held in the individual data holders as digital signals.

Owner:LAPIS SEMICON CO LTD

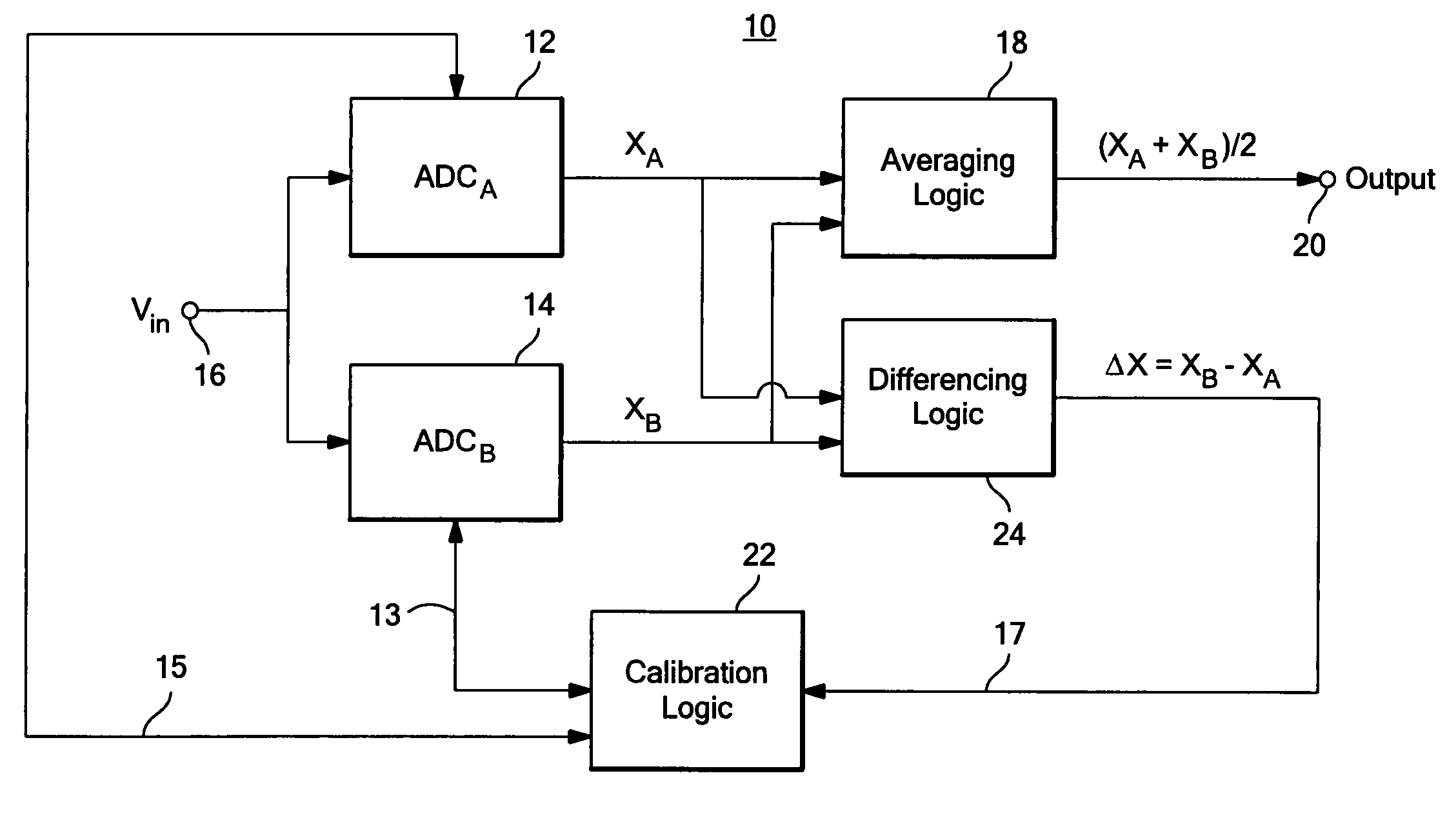

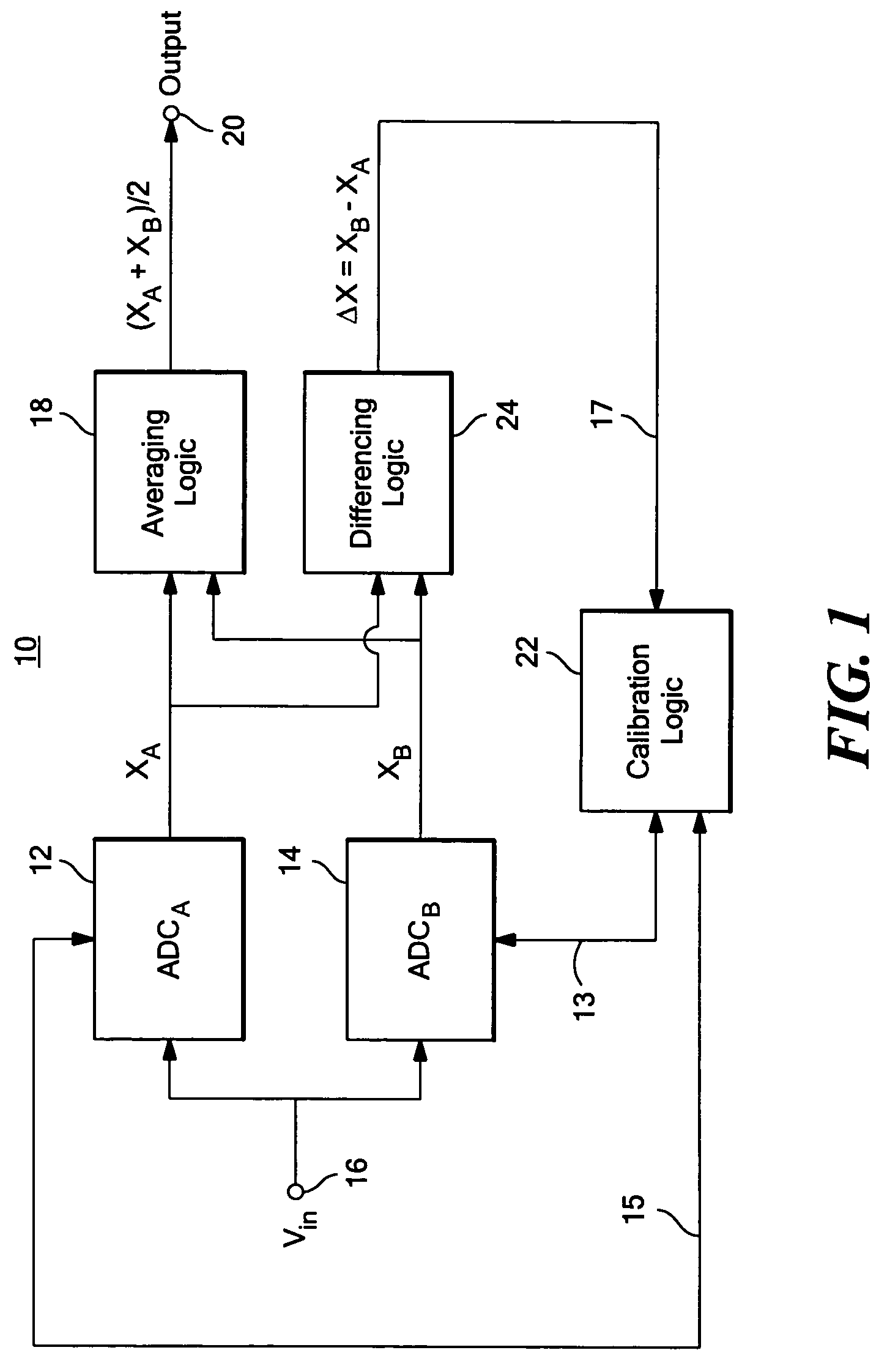

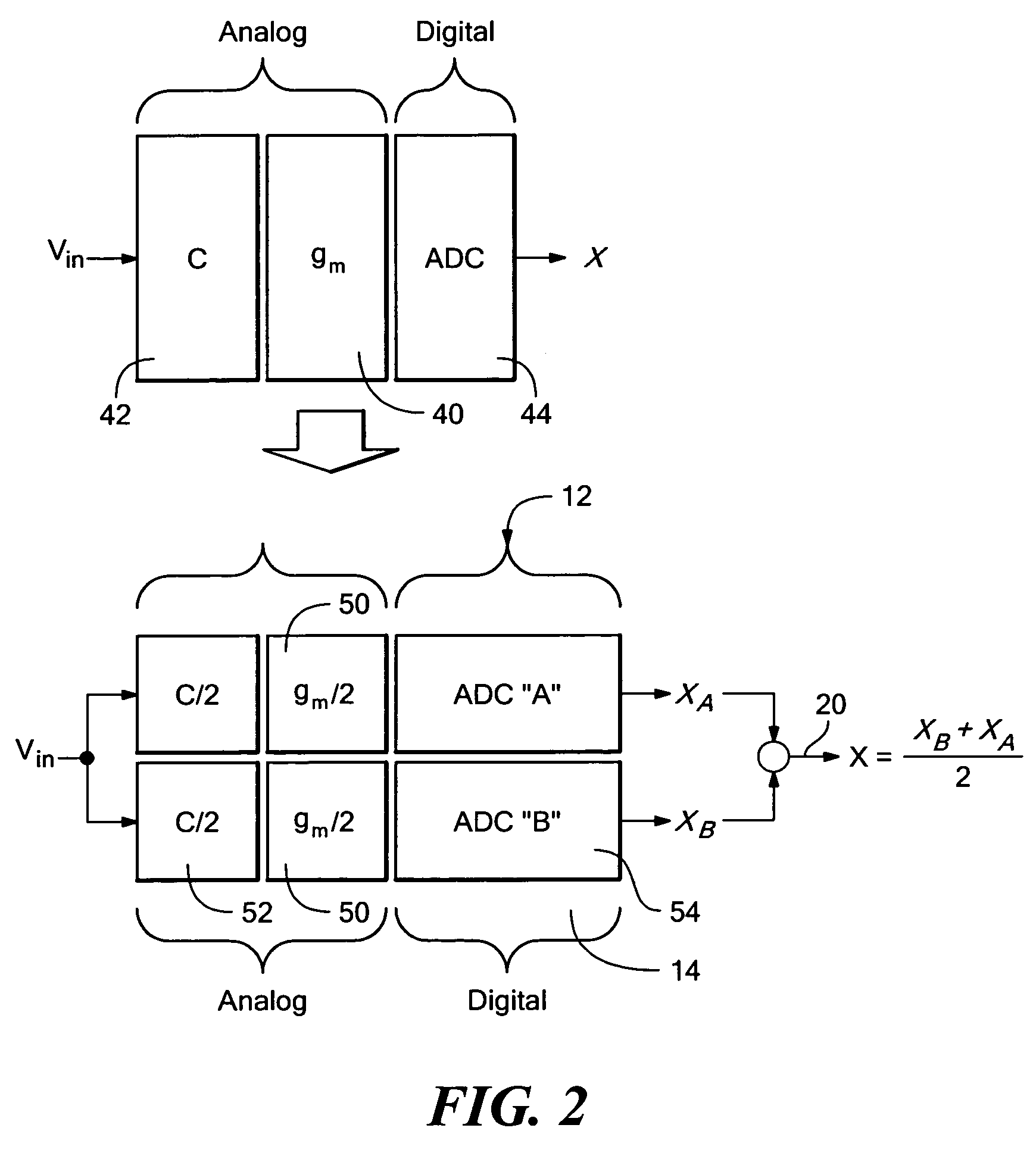

Calibratable analog-to-digital converter system

ActiveUS7312734B2Control areaLimited powerElectric signal transmission systemsAnalogue-digital convertersAnalog signalEngineering

A calibratable analog-to-digital converter system with a split analog-to-digital converter architecture including N Analog-to-Digital Converters (ADCs) each configured to convert the same analog input signal into a digital signal. Calibration logic is responsive to the digital signals output by the N ADCs and is configured to calibrate each of the ADCs based on the digital signals output by each ADC.

Owner:ANALOG DEVICES INC

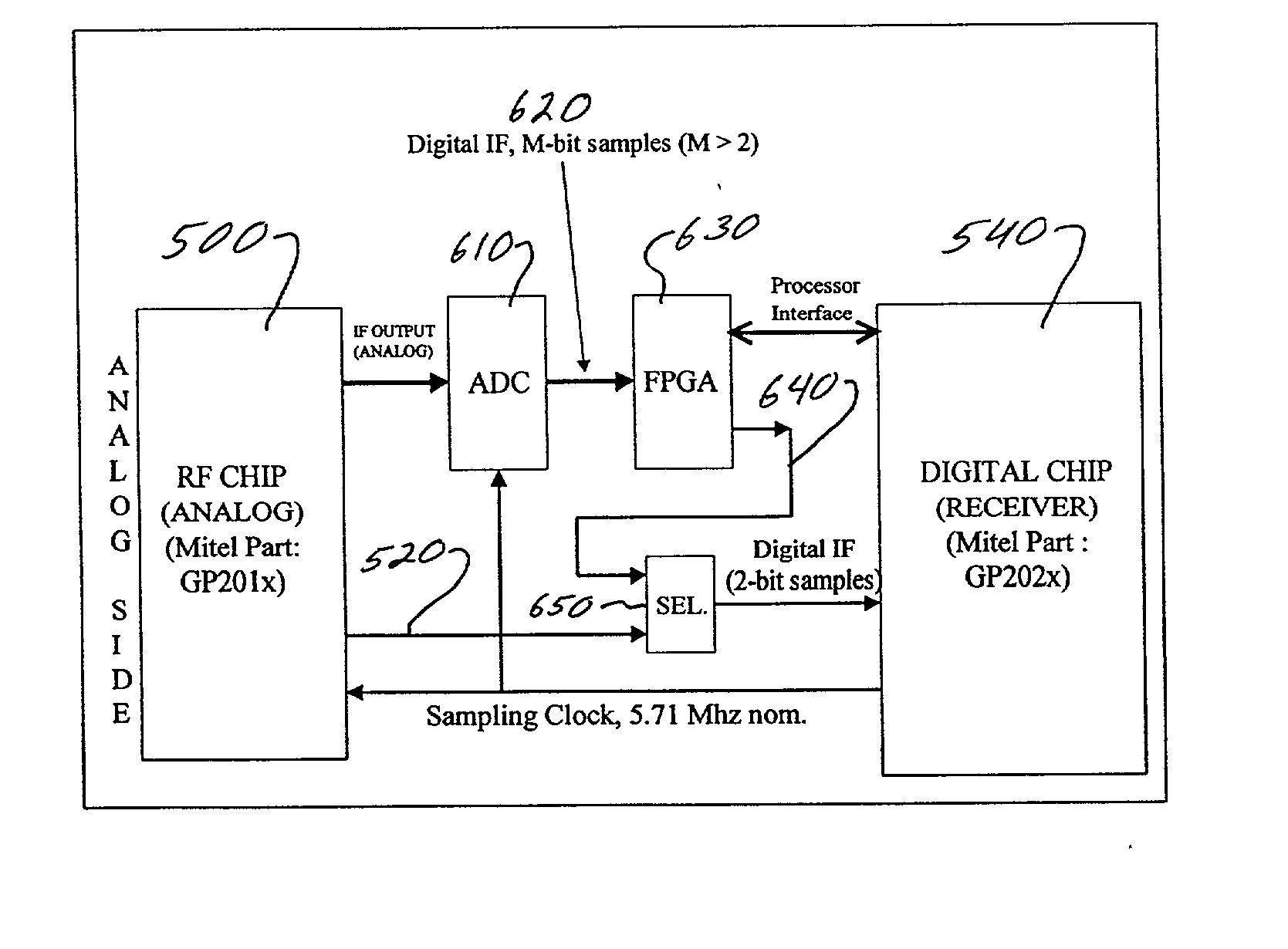

Global positioning system receiver capable of functioning in the presence of interference

Systems and methods are described for a GPS receiver capable of functioning in the presence of interference. A method includes detecting an interfering signal including: tuning a band pass filter over a frequency range; and at each of a plurality of incremental frequencies: computing a set of band pass filter coefficients; sending the set of band pass filter coefficients to a digital filter; repeatedly transforming an analog-to-digital converter output having a quantization level in excess of 2 bits into a band pass filter output with the digital filter to obtain a plurality of samples; computing an average of the plurality of samples; and comparing the average to a threshold to detect peaks that exceed a threshold. An apparatus, comprising: an analog radio frequency circuit; an analog-to-digital converter coupled to the analog radio frequency circuit, the analog-to-digital converter providing a quantization level in excess of 2 bits; a digital filter coupled to the analog-to-digital converter; and a digital circuit coupled to the digital filter.

Owner:IP GEM GRP LLC

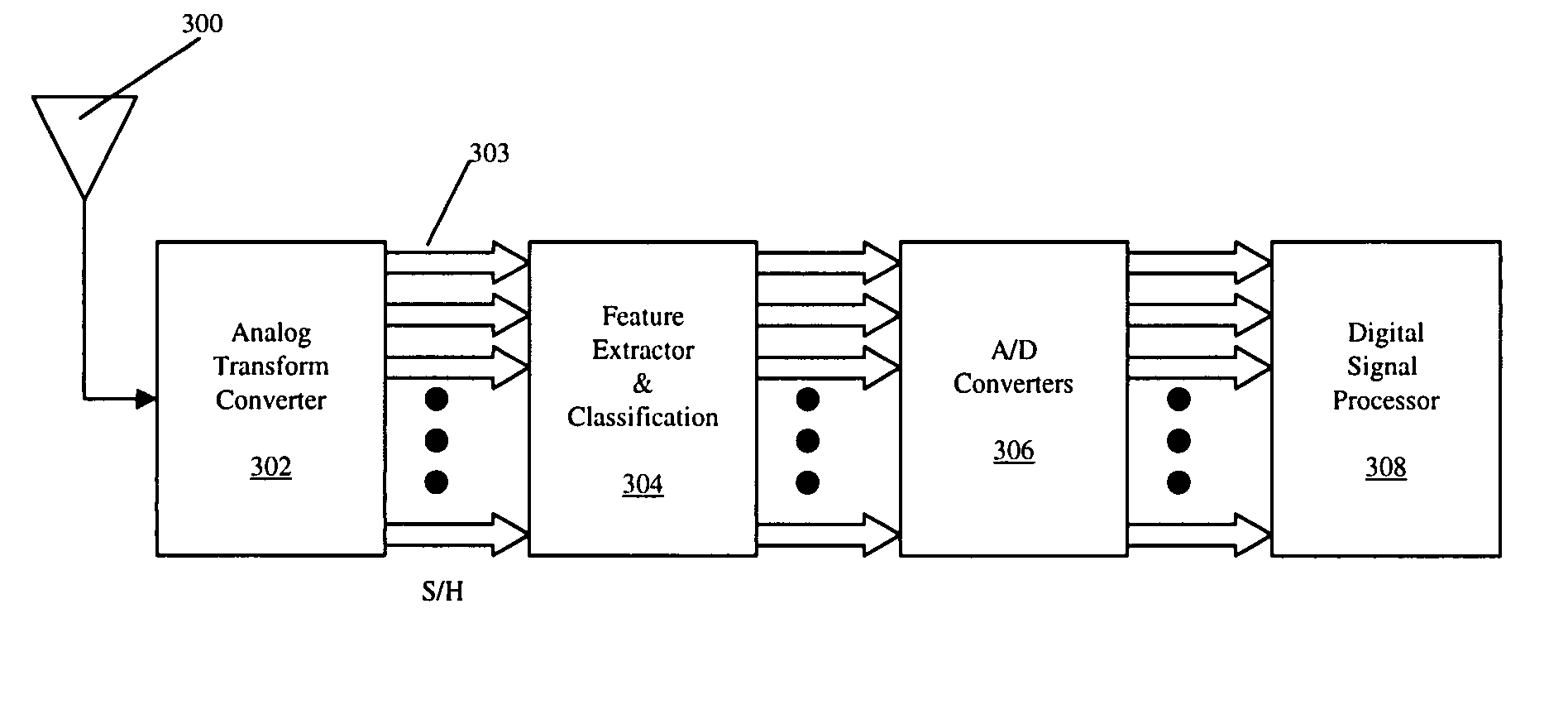

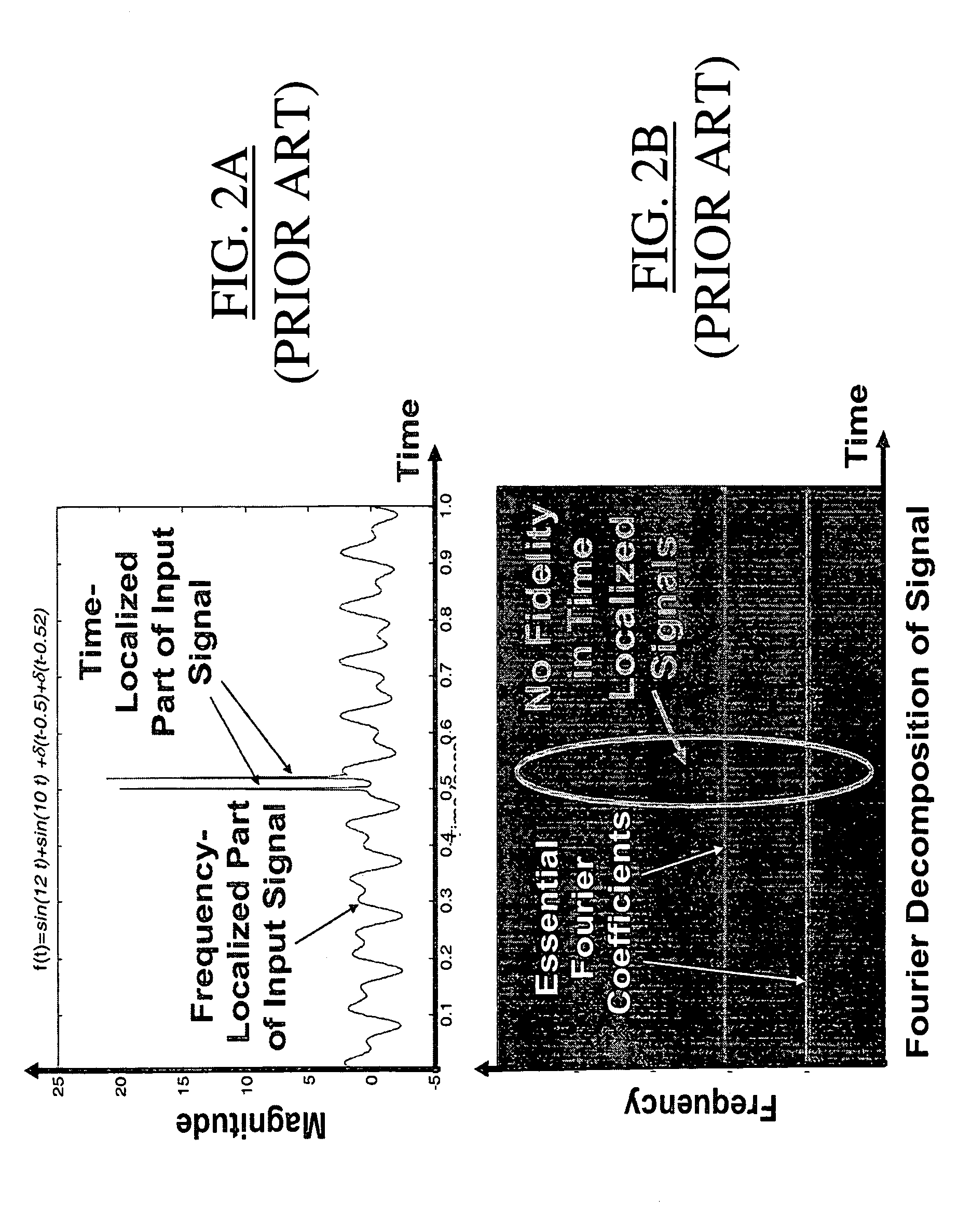

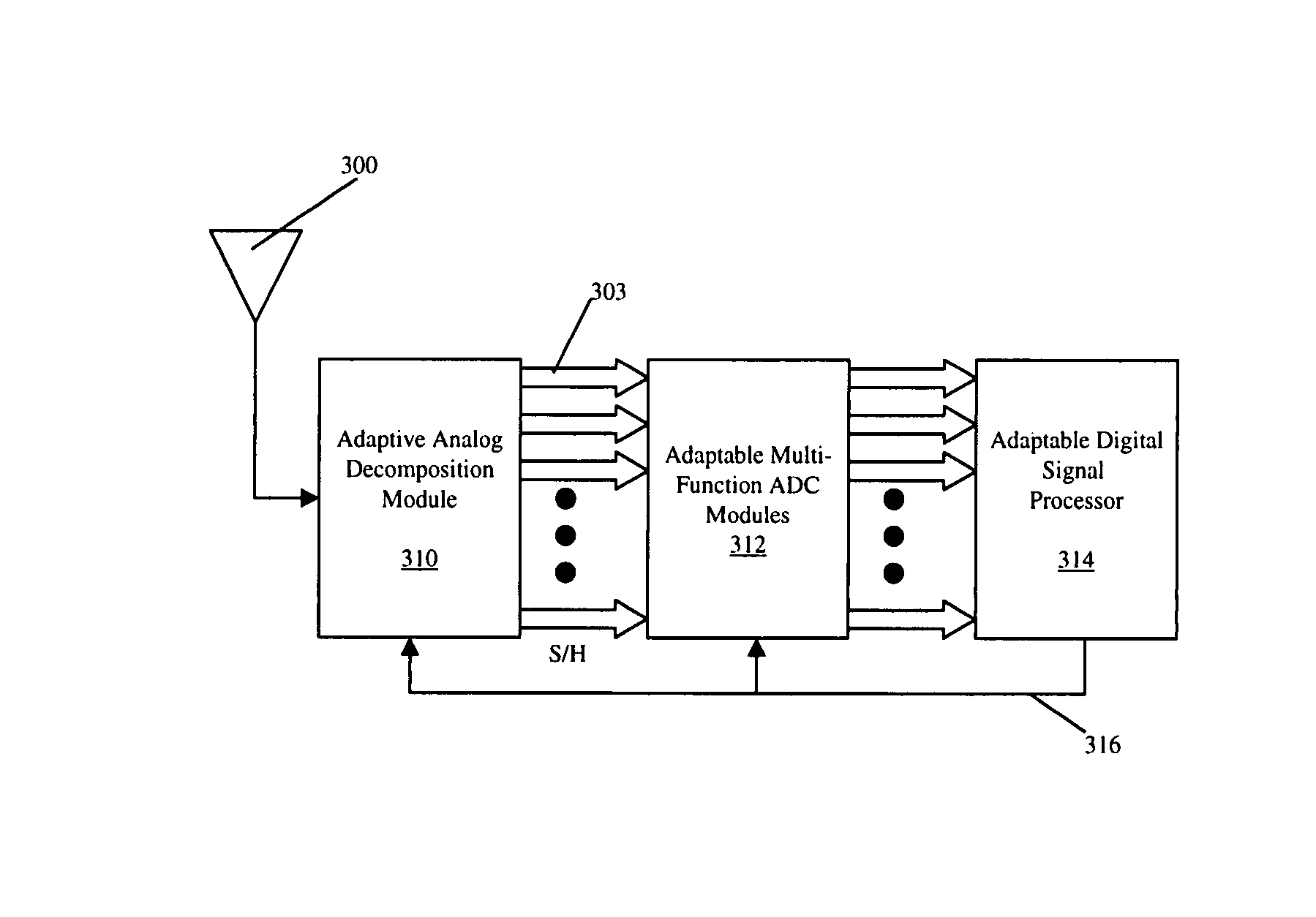

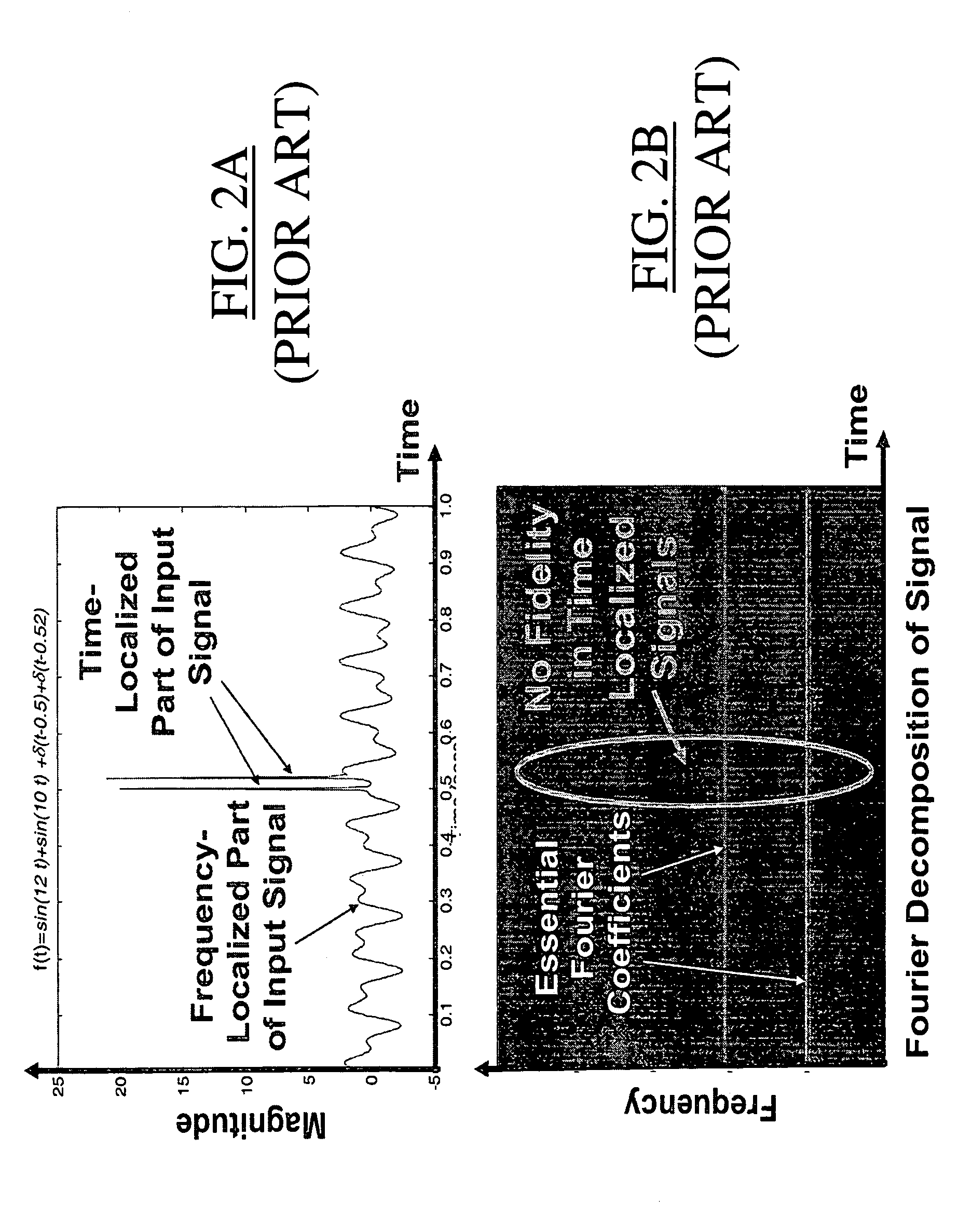

Adaptive, intelligent transform-based analog to information converter method and system

InactiveUS20050156775A1Made preciselyImprove detection rateElectric signal transmission systemsAnalogue conversionFeature extractionAnalog signal

The present invention provides an adaptive, intelligent transform based Analog to Information Converter (AIC) for wideband signals by directly converting an analog signal to information (e.g., features, decisions). This direct conversion is achieved by (i) capturing most of the information of a wideband signal via hardware / software implemented mathematical transformations, (ii) effectively removing unwanted signals such as jammer and interfere from the input signal, and (iii) using novel algorithms for highly accurate decision making and feature extraction (e.g., high probability of detection with low probability of false alarm). The jump in the improvement over today's state-of-the-art is in terms of effective and optimum signal information extraction at high-speed.

Owner:HRL LAB

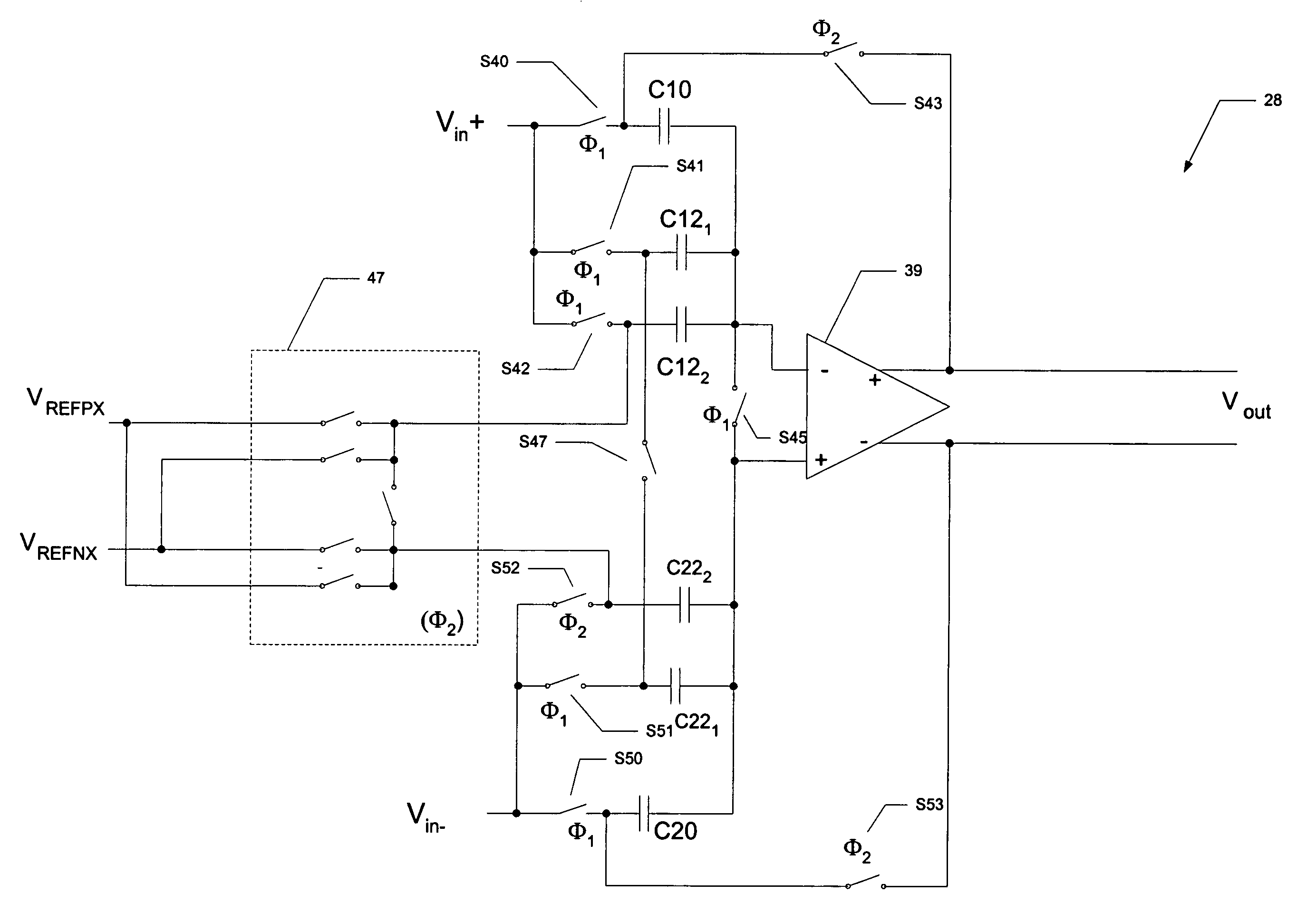

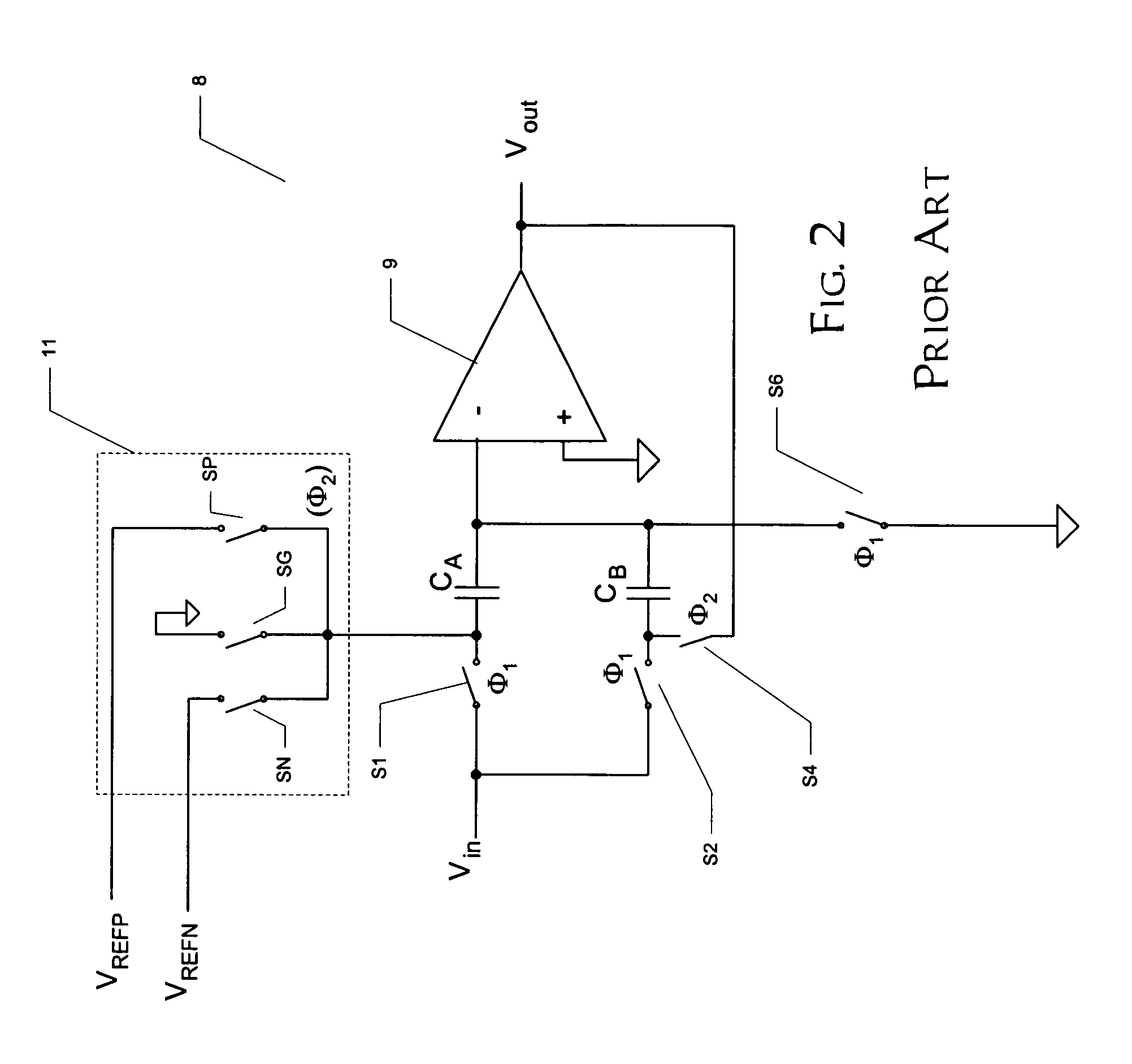

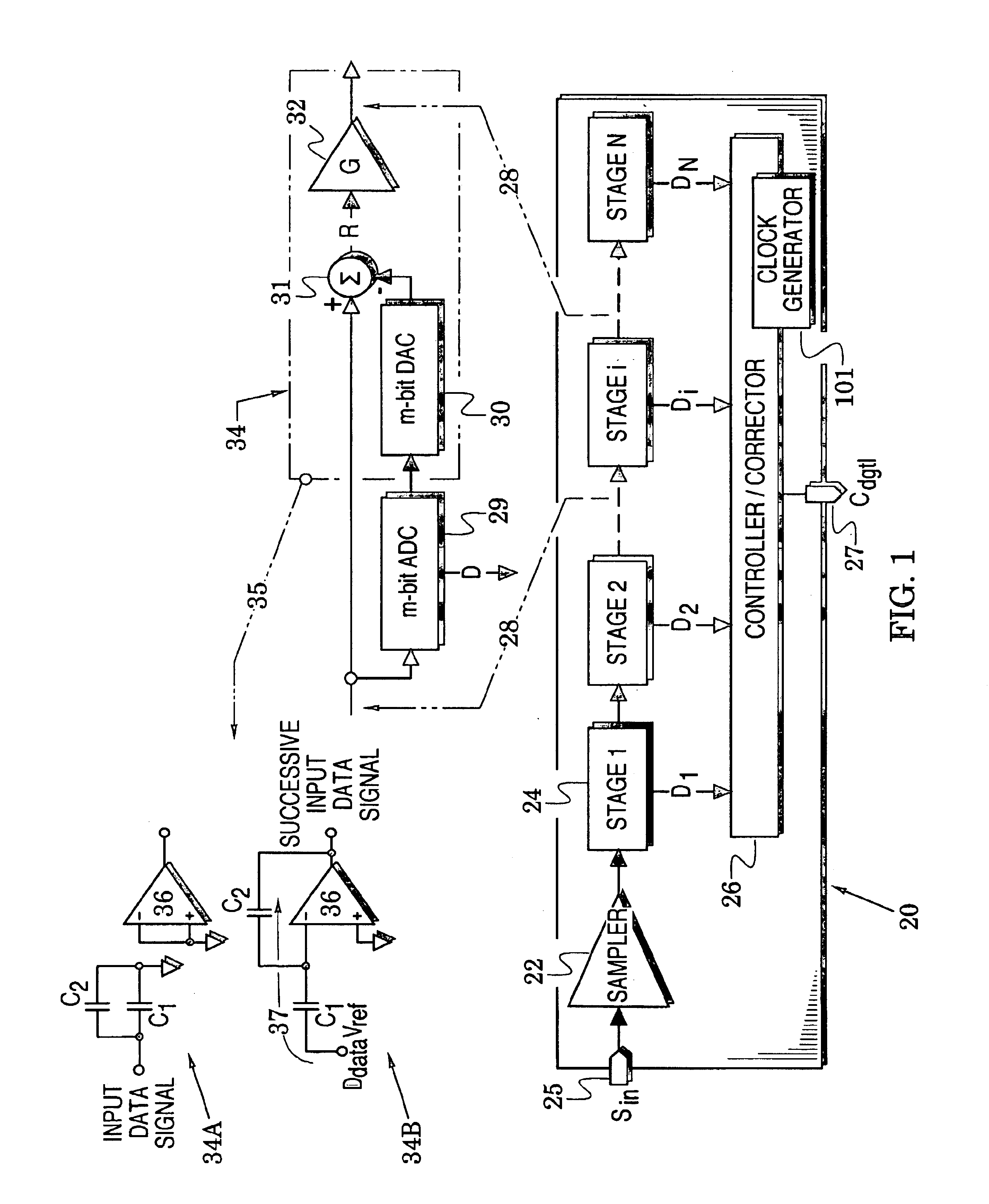

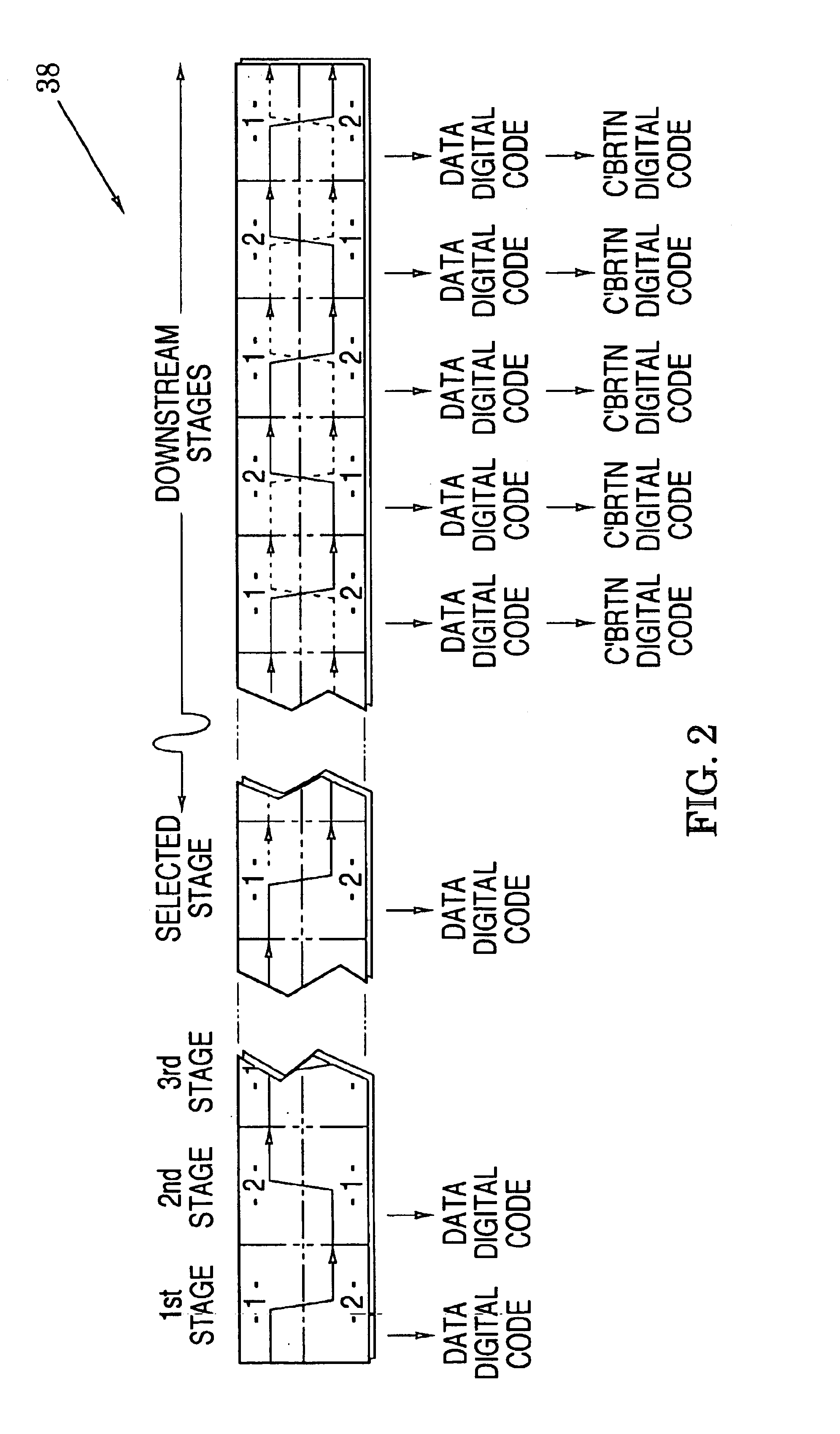

Switched-capacitor circuit with scaled reference voltage

ActiveUS7009549B1Improve precisionImprove stabilityElectric signal transmission systemsAnalogue-digital convertersCapacitanceAudio power amplifier

A pipelined analog-to-digital converter (ADC) (30) with improved precision is disclosed. The pipelined ADC (30) includes a sequence of stages (20), each of which includes a sample-and-hold circuit (22), an analog-to-digital converter (23), and the functions of a digital-to-analog converter (DAC) (25), an adder (24), and a gain stage (27) at which a residue signal (RES) is generated for application to the next stage (20) in the sequence. A multiplying DAC (28) performs the functions of the DAC (25), adder (24), and gain stage (27) in the stage (20), and is based on an operational amplifier (29). Sample capacitors (C10, C20) and reference capacitors (C122, C222) receive the analog input from the sample-and-hold circuit (22) in a sample phase; parallel capacitors (C121, C221) are provided to maintain constant circuit gain. Extended reference voltages (VREFPX, VREFNX) at levels that exceed the output range (V0+, V0−) of the operational amplifier (29) are applied to the reference capacitors, in response to the digital output of the analog-to-digital converter (23) in its stage (20). The reference capacitors (C12, C22) are scaled according to the extent to which the extended reference voltages (VREFPX, VREFNX) exceed the op amp output levels (V0+, V0−). The effects of noise on the reference voltages (VREFPX, VREFNX) on the residue signal (RES) are thus greatly reduced.

Owner:TEXAS INSTR INC

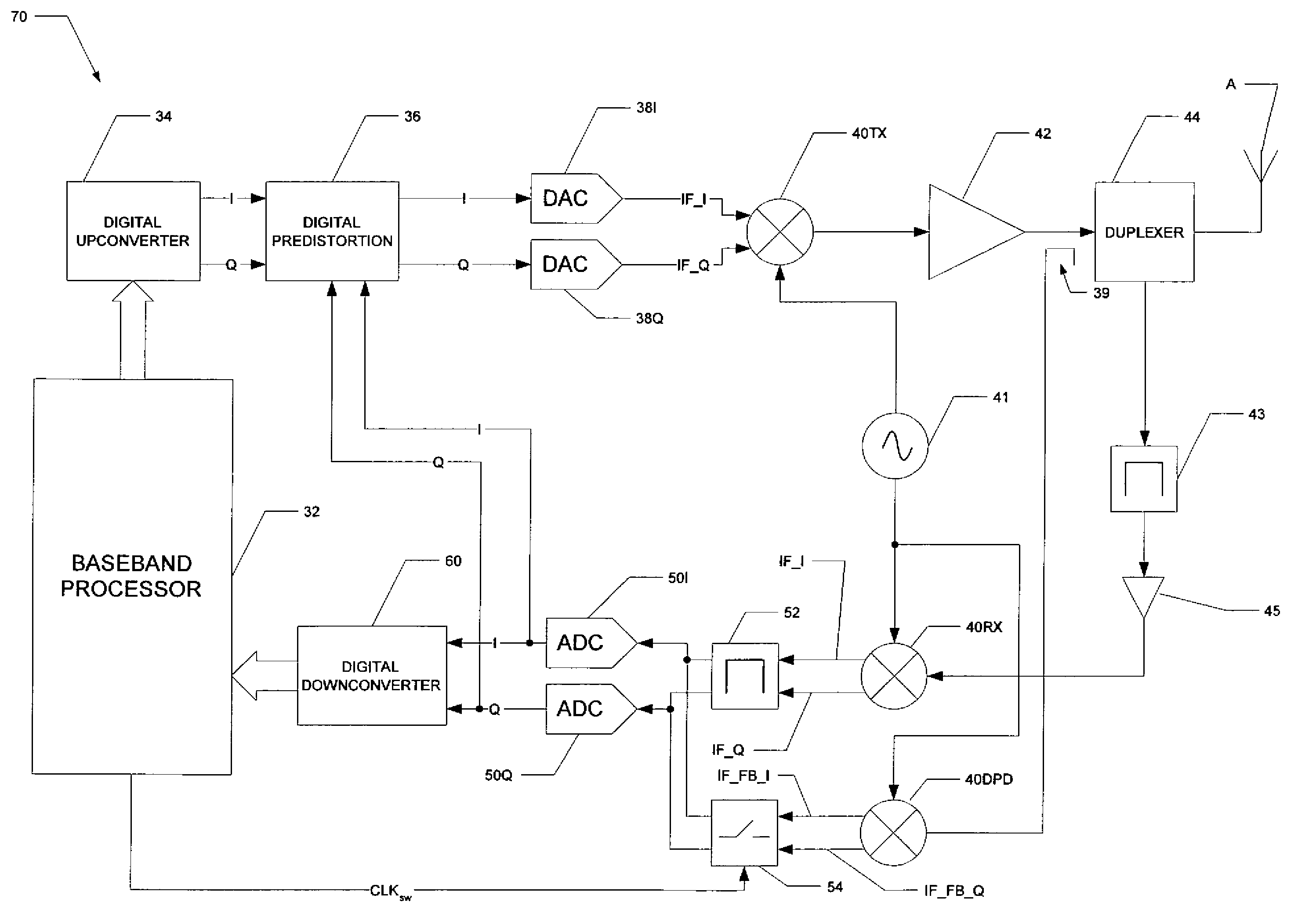

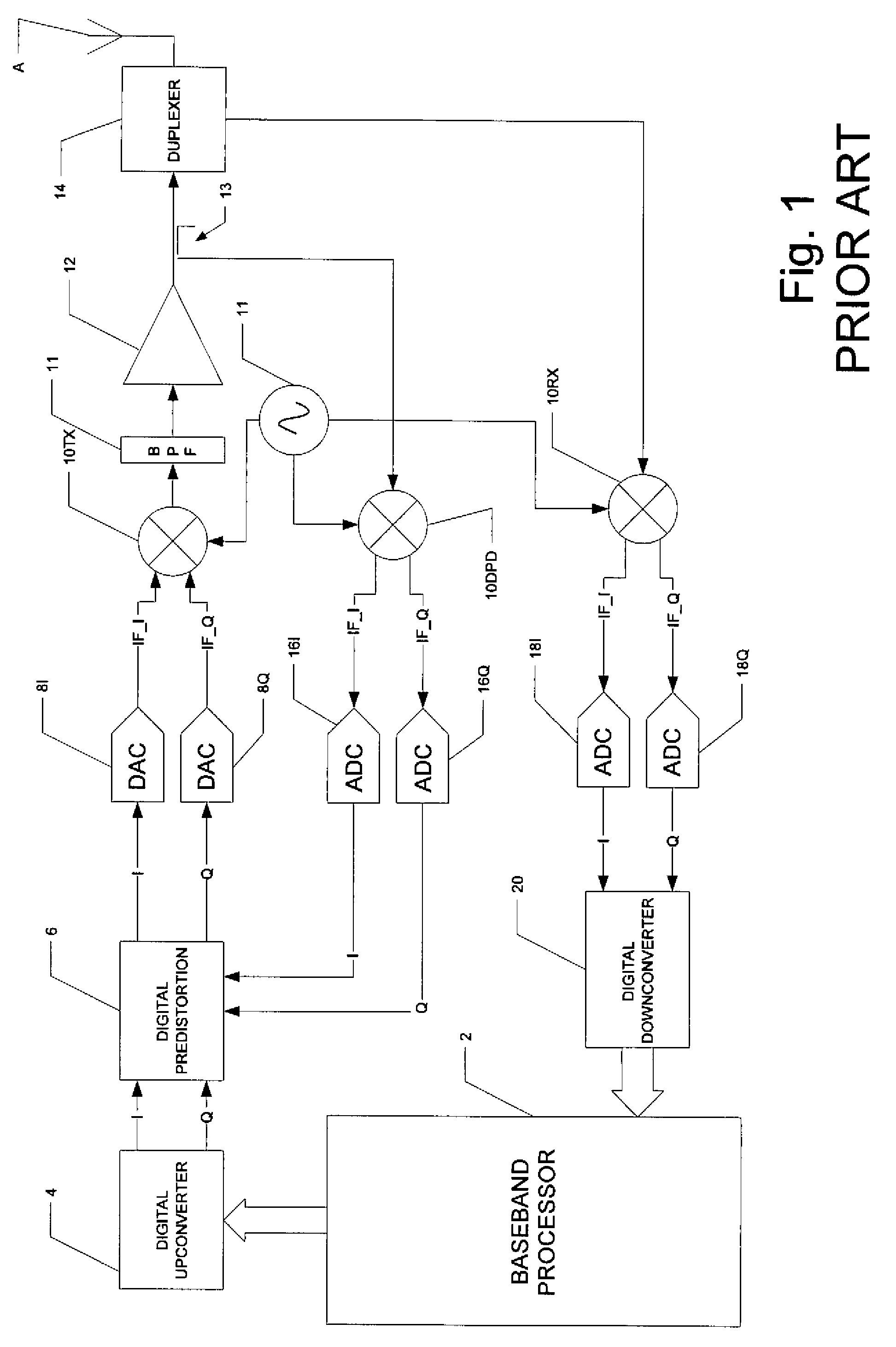

Simplified Digital Predistortion in a Time-Domain Duplexed Transceiver

ActiveUS20080144539A1Efficient implementationReduce in quantityModulated-carrier systemsTransmission control/equalisingTime domainAudio power amplifier

A transceiver for time-domain duplexed (TDD) communications, for example in connection with wireless broadband data communications, is disclosed. The transceiver includes digital predistortion compensation circuitry, which compensates the digital signals to be transmitted based on feedback signals from the output of the power amplifier, in order to linearize the output from the power amplifier. The feedback signals from the power amplifier are coupled back to the digital predistortion circuitry over part of the same receive path as the received signals from the wireless communications channel. The shared path includes analog-to-digital converters that are used both in the transmit period of the TDD cycle to convert the feedback signals from the power amplifier output, and in the receive period of the TDD cycle to convert the analog received signals.

Owner:TEXAS INSTR INC

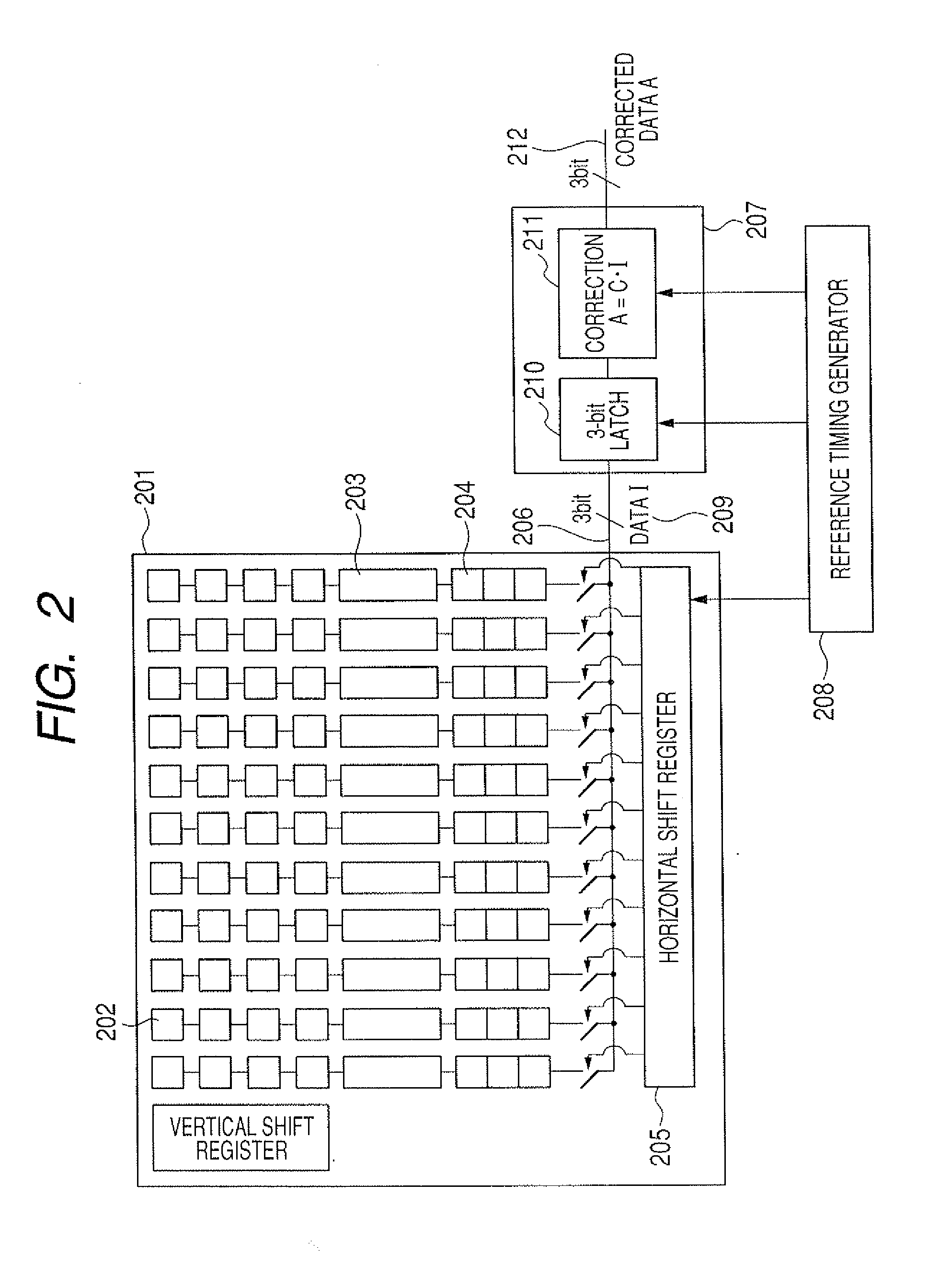

Image pickup device and signal processing method thereof

InactiveUS20090244328A1Television system detailsElectric signal transmission systemsDigital down converterDigital converter

Owner:CANON KK

Adaptive, intelligent transform-based analog to information converter method and system

InactiveUS7324036B2Effectively removing unwanted signalsMade preciselyElectric signal transmission systemsAnalogue conversionFeature extractionAnalog signal

The present invention provides an adaptive, intelligent transform based Analog to Information Converter (AIC) for wideband signals by directly converting an analog signal to information (e.g., features, decisions). This direct conversion is achieved by (i) capturing most of the information of a wideband signal via hardware / software implemented mathematical transformations, (ii) effectively removing unwanted signals such as jammer and interfere from the input signal, and (iii) using novel algorithms for highly accurate decision making and feature extraction (e.g., high probability of detection with low probability of false alarm). The jump in the improvement over today's state-of-the-art is in terms of effective and optimum signal information extraction at high-speed.

Owner:HRL LAB

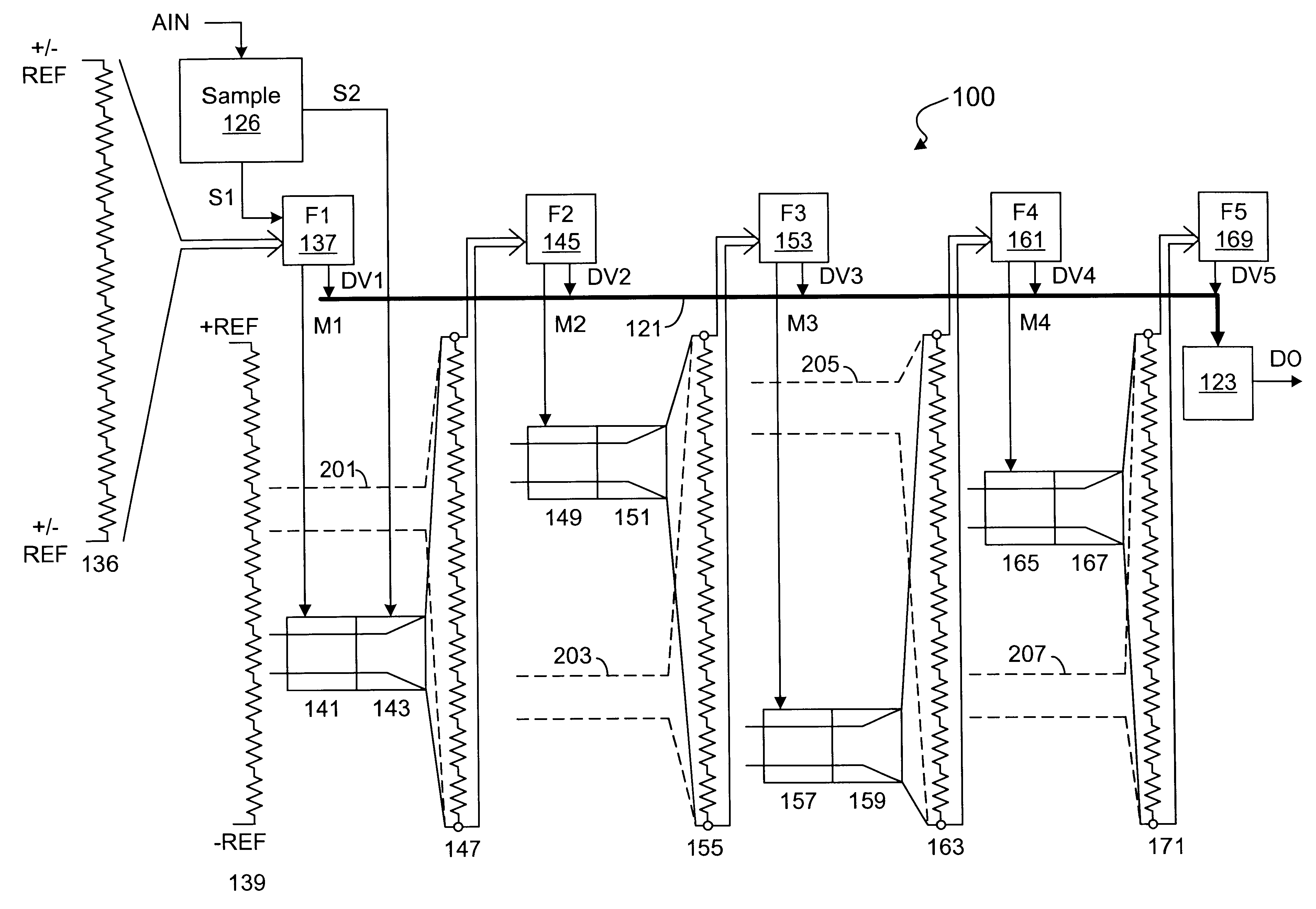

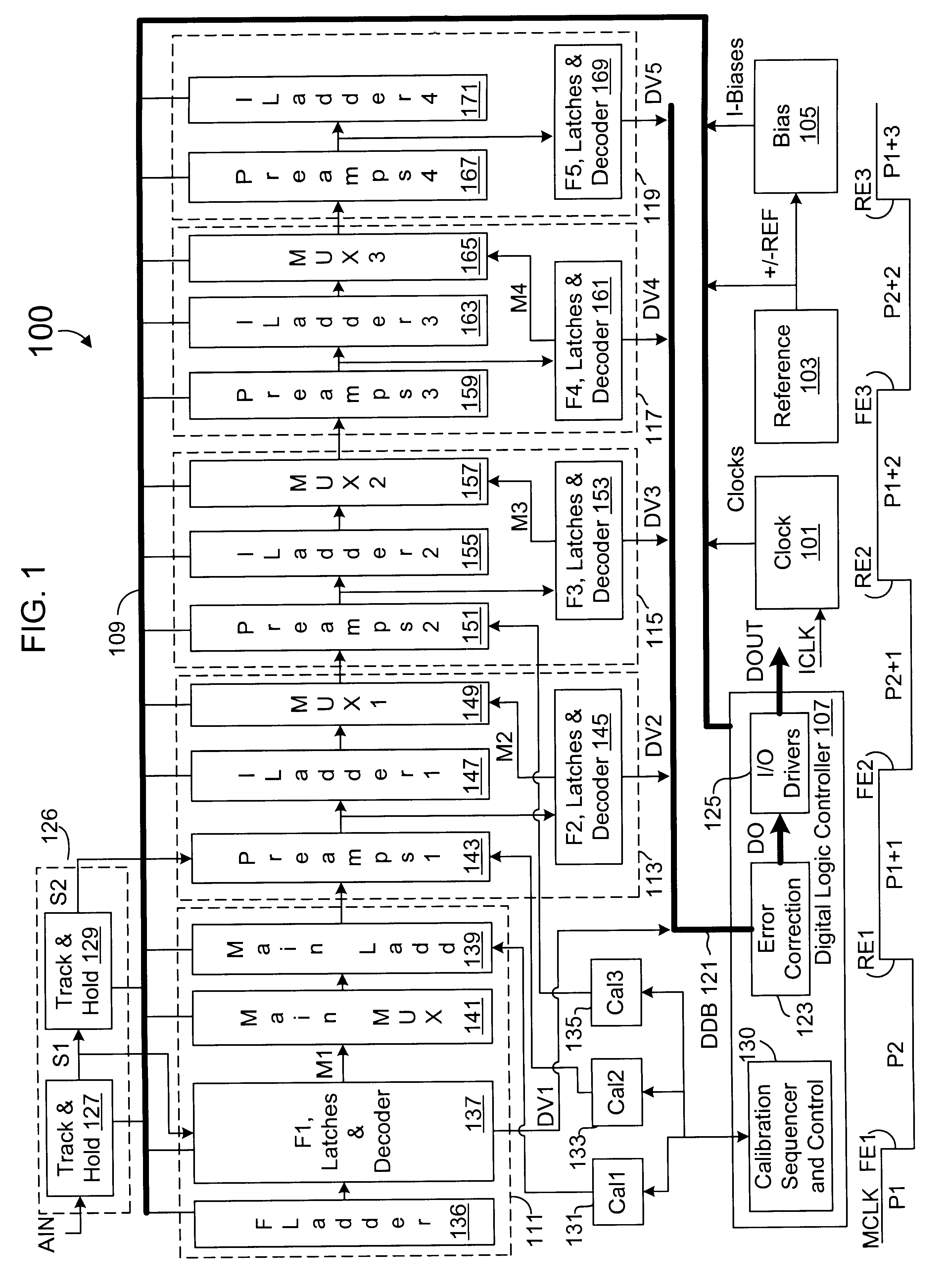

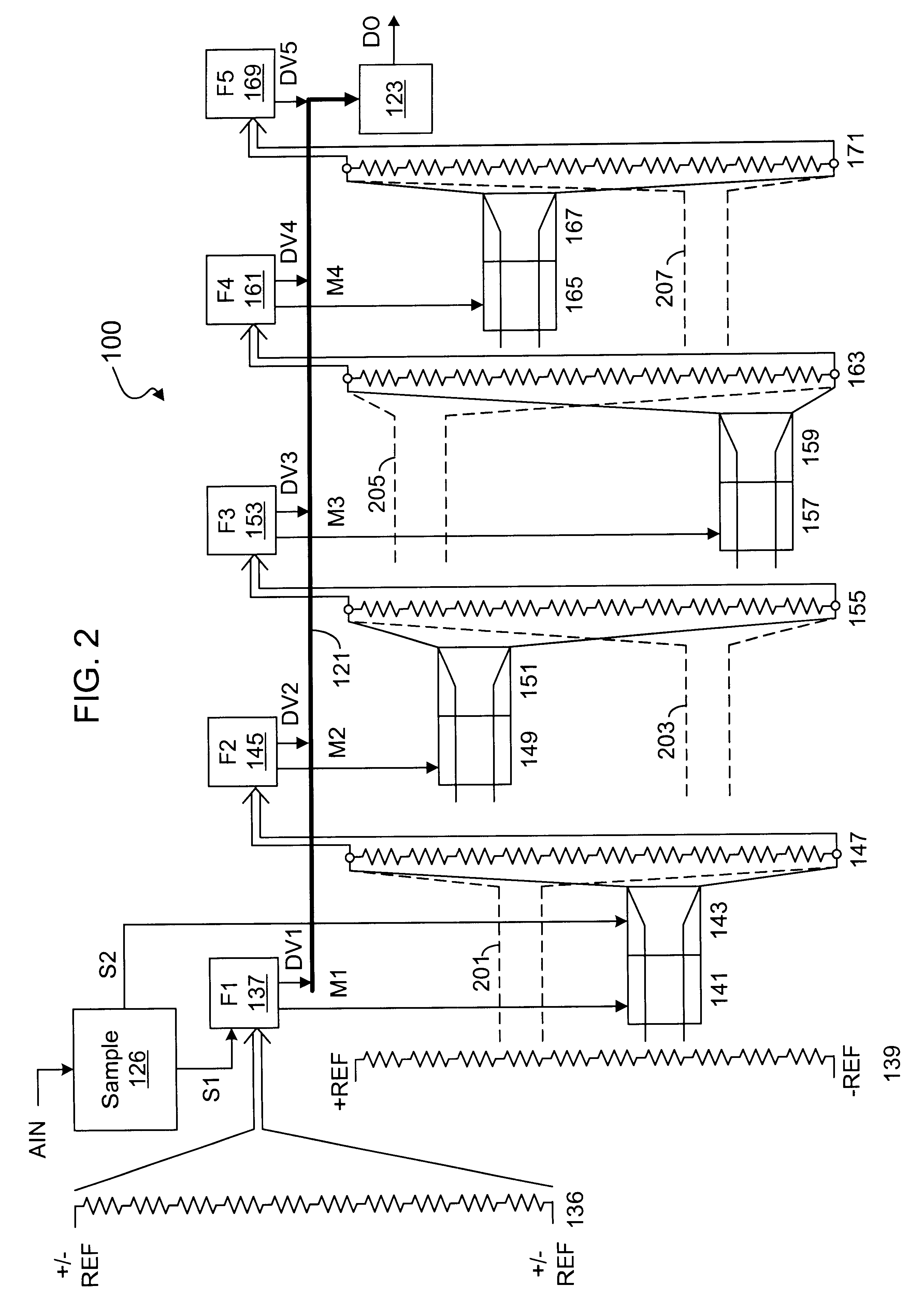

Analog to digital converter using subranging and interpolation

InactiveUS6570523B1Improve signal-to-noise ratioAccurate representationElectric signal transmission systemsAnalogue-digital convertersDigital down converterEngineering

A multistage ADC that subranges and interpolates, and that amplifies selected subranges to convert an analog signal to a stream of digital values. The ADC samples the analog signal and provides a stream of sample signals. A first stage flash converts each sample signal into a first multiple bit value and subranges a reference ladder according to the first multiple bit value into selected reference signals. Each additional secondary stage amplifies a selected subrange of signals from a prior stage, flash converts the amplified residual signals to provide an additional multiple bit value, interpolates each set of amplified residual signals and subranges the interpolated signals according to the corresponding multiple bit value. A final stage amplifies and flash converts to determine a final multiple bit value. An error corrector combines each set of multiple bit values into a digital value.

Owner:INTERSIL INC

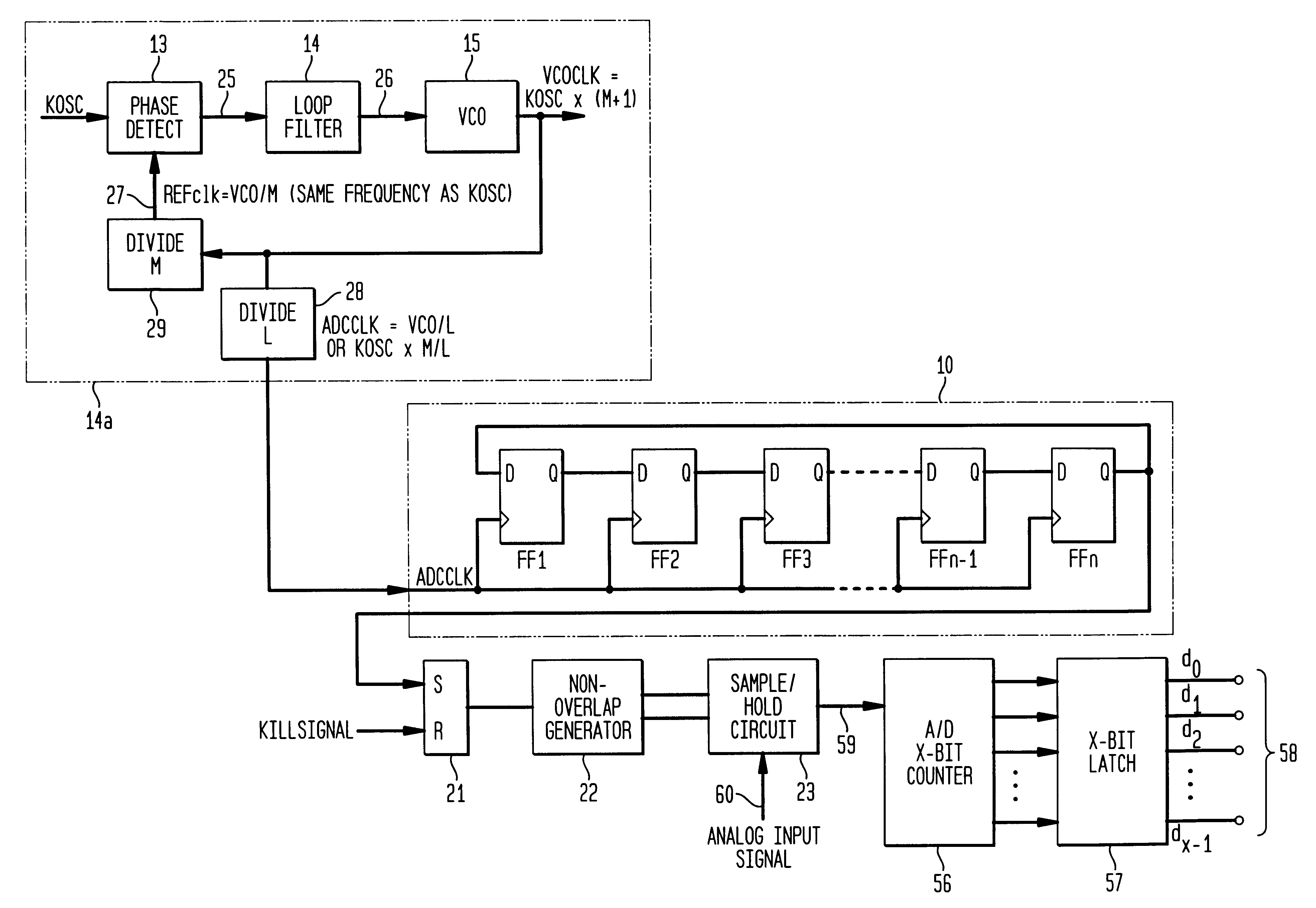

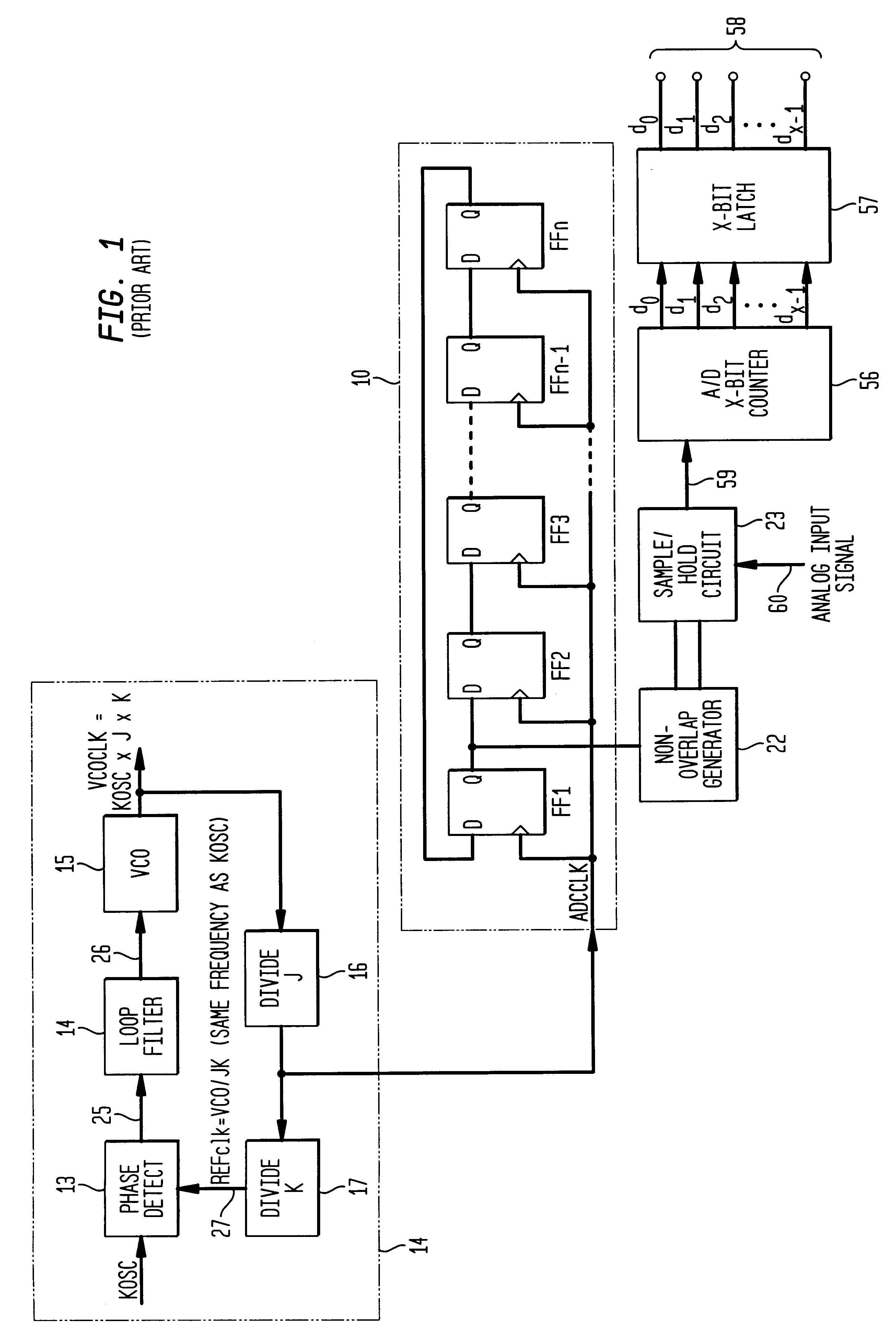

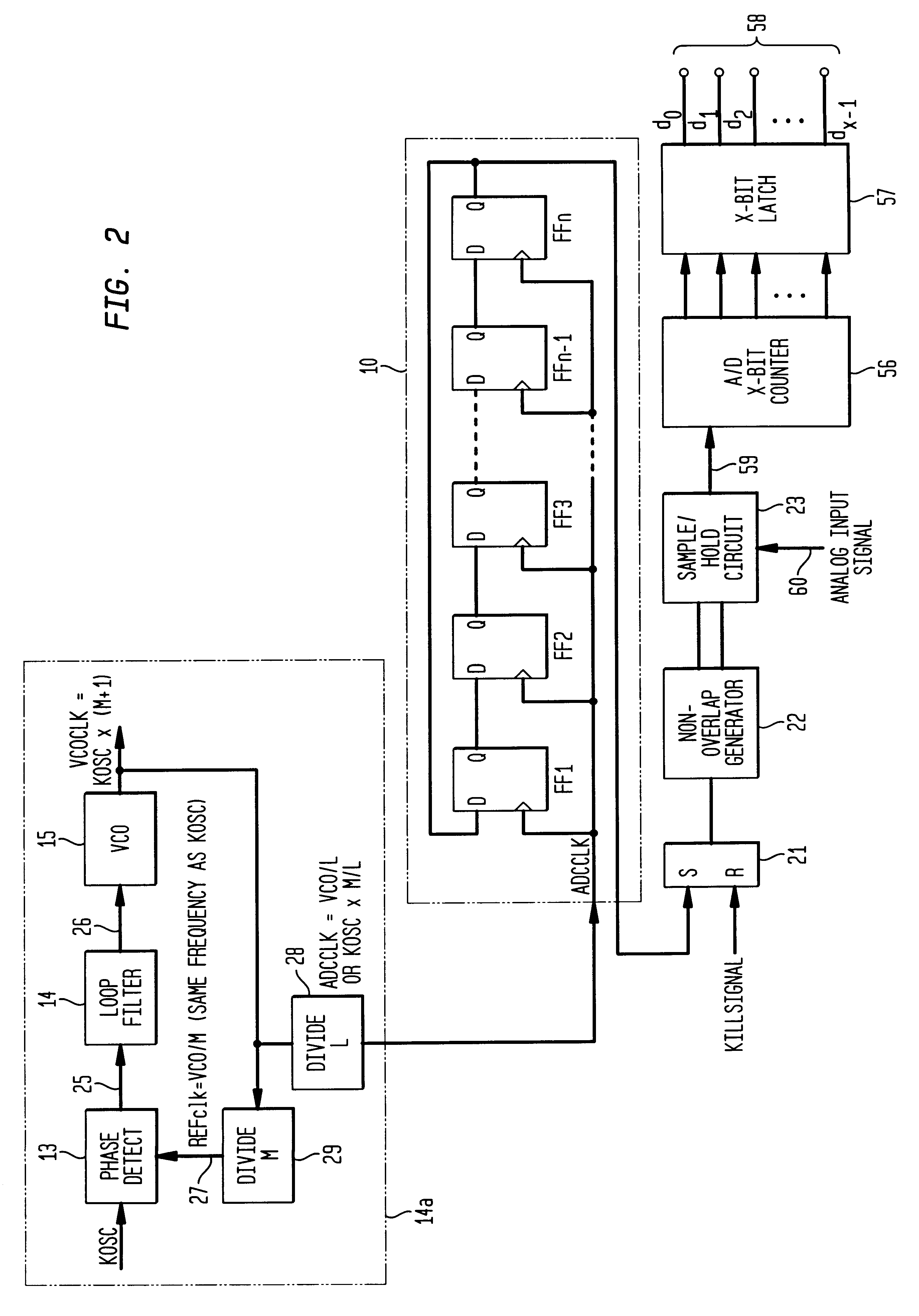

Clocking technique for reducing sampling noise in an analog-to-digital converter

InactiveUS6232905B1Low costHigh resolutionElectric signal transmission systemsAnalogue-digital convertersLeading edgeDigital down converter

A method and apparatus are disclosed for improving the operation of an analog-to-digital converter ("ADC"). A separate "clean" oscillator clock is to be used in combination with a "noisy" ADC clock being regulated by a phase-locked-loop (PLL) circuit. The "noisy" ADC clock drives the digital control logic and also turns on the sample signal for the purpose of sampling. The second clock, which has a substantially fixed (i.e., "clean") frequency is used to generate a short pulse, the leading edge of which turns off the sample signal, thereby providing an improved sampling process with greater resolution. The interaction of the two clocks is controlled with digital logic circuitry.

Owner:LUCENT TECH INC

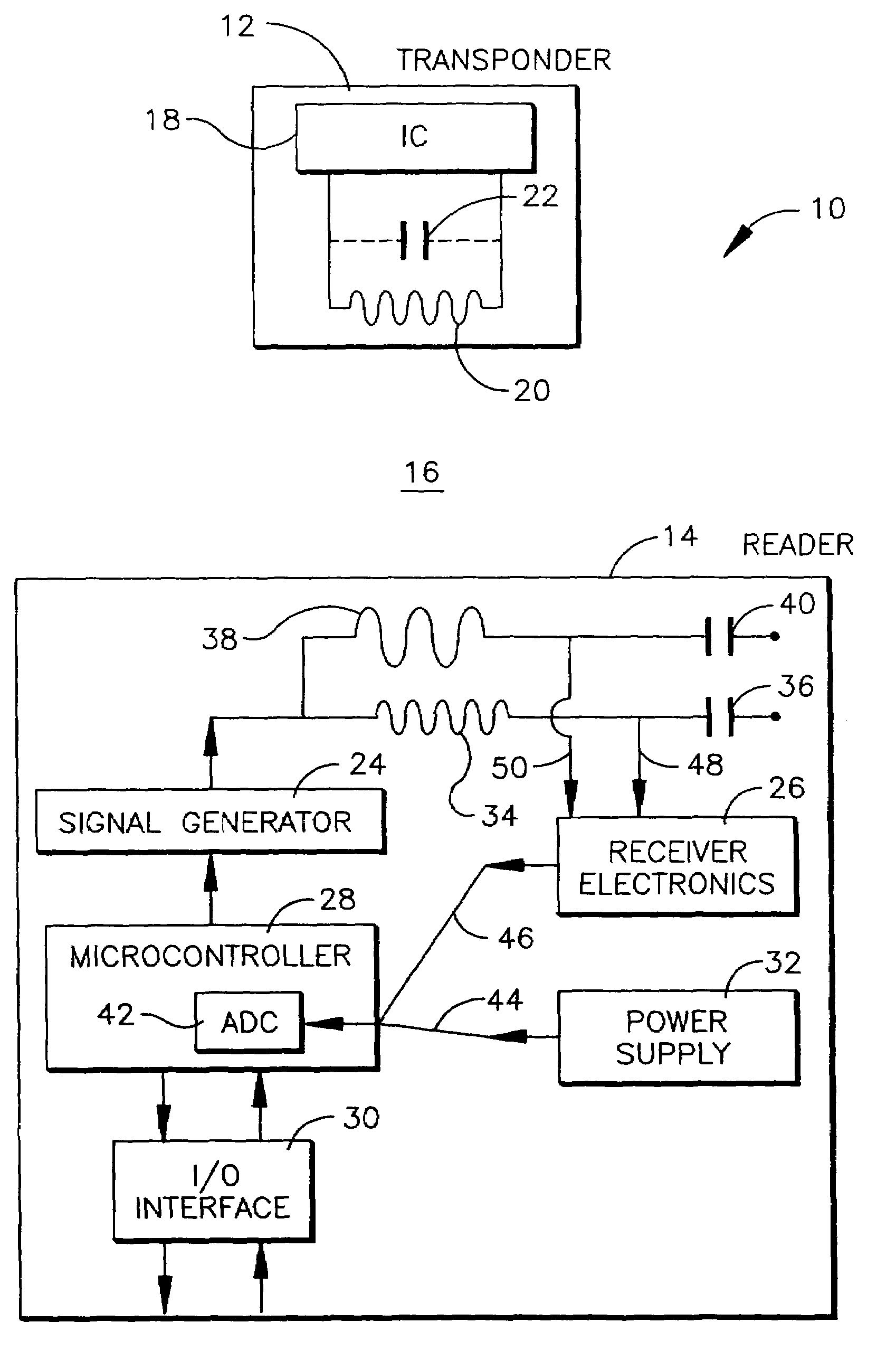

RFID reader utilizing an analog to digital converter for data acquisition and power monitoring functions

ActiveUS7180403B2Reduce the voltage valueMaintaining voltage rangeMemory record carrier reading problemsTyre measurementsDigital dataMicrocontroller

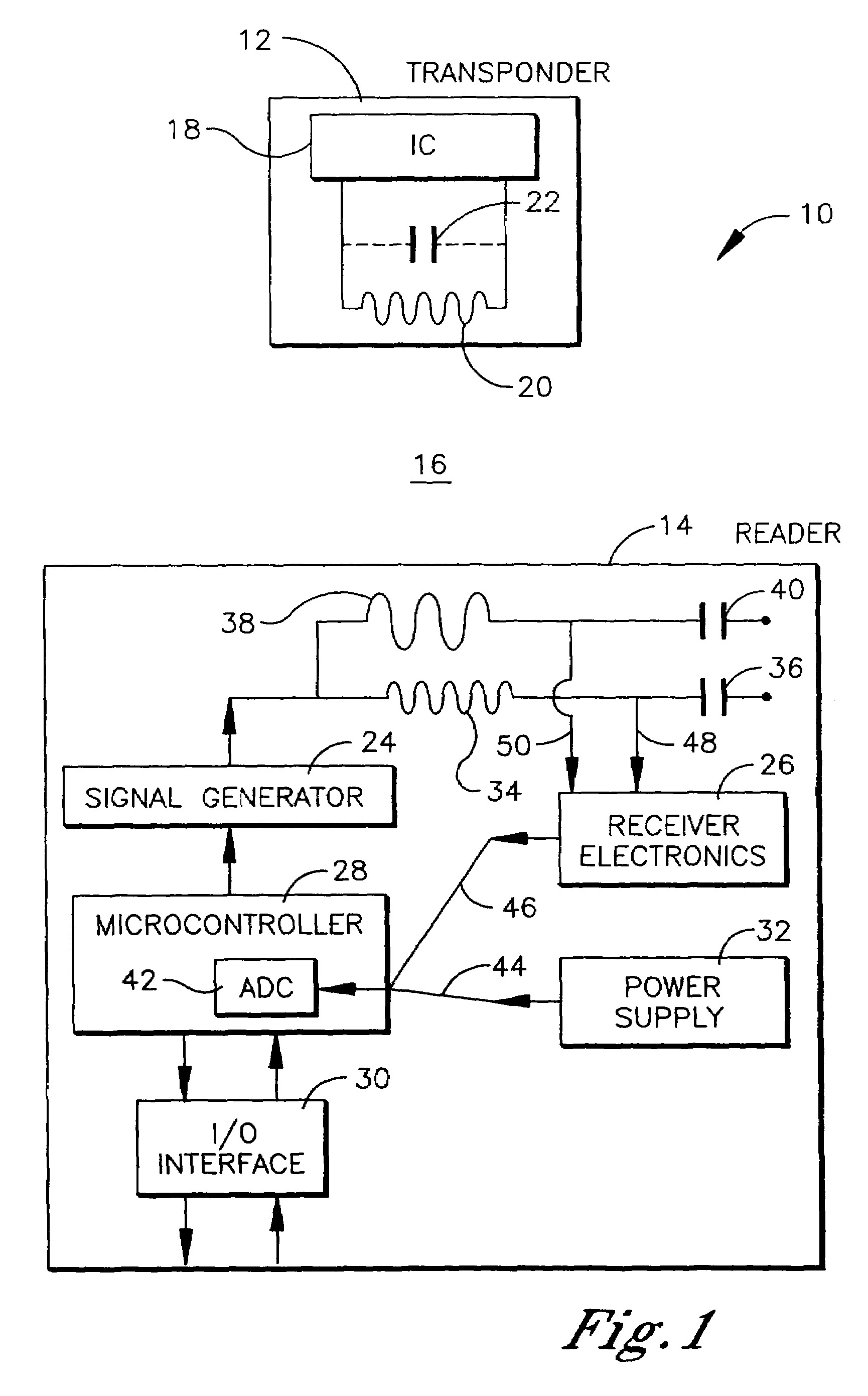

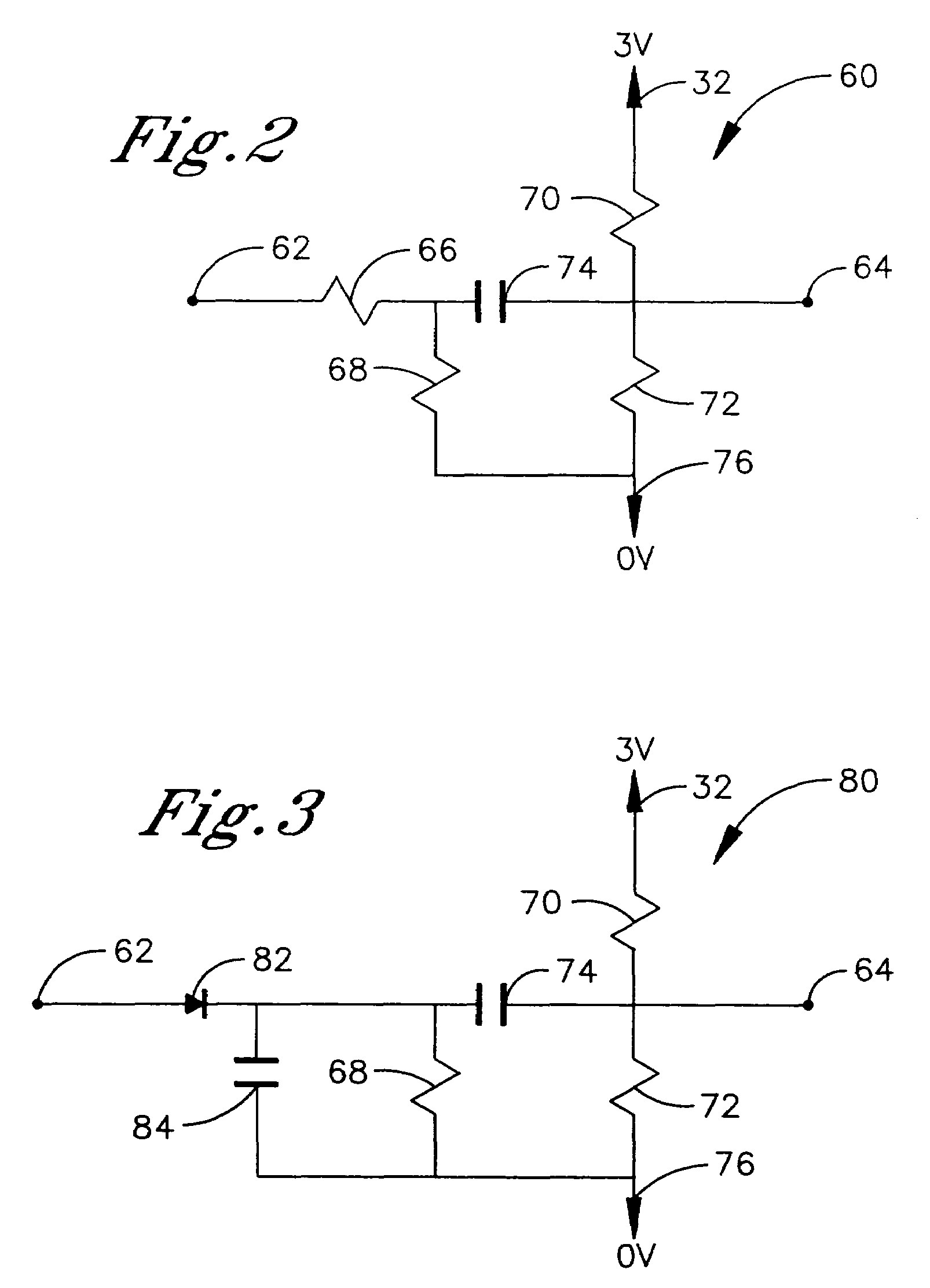

A reader for an RFID system includes an internal power source, a signal generator for generating a detection signal containing analog data and an excitation signal, a transmitting antenna for transmitting the detection and excitation signals, and a receiving antenna for receiving a transponder data signal from a transponder containing digital data. Receiver electronics are coupled with the receiving antenna for conditioning the transponder data signal before reading the digital data. The reader further includes a single-chip microcontroller coupled with the internal power source and the receiver electronics. The single-chip microcontroller has an analog to digital converter to measure the declining power level of the internal power source and to acquire the analog data from the detection signal and the digital data from the transponder data signal. The single-chip microcontroller also includes a firmware and / or software-based demodulator for demodulating the transponder data signal to read the digital data.

Owner:ASSA ABLOY AB

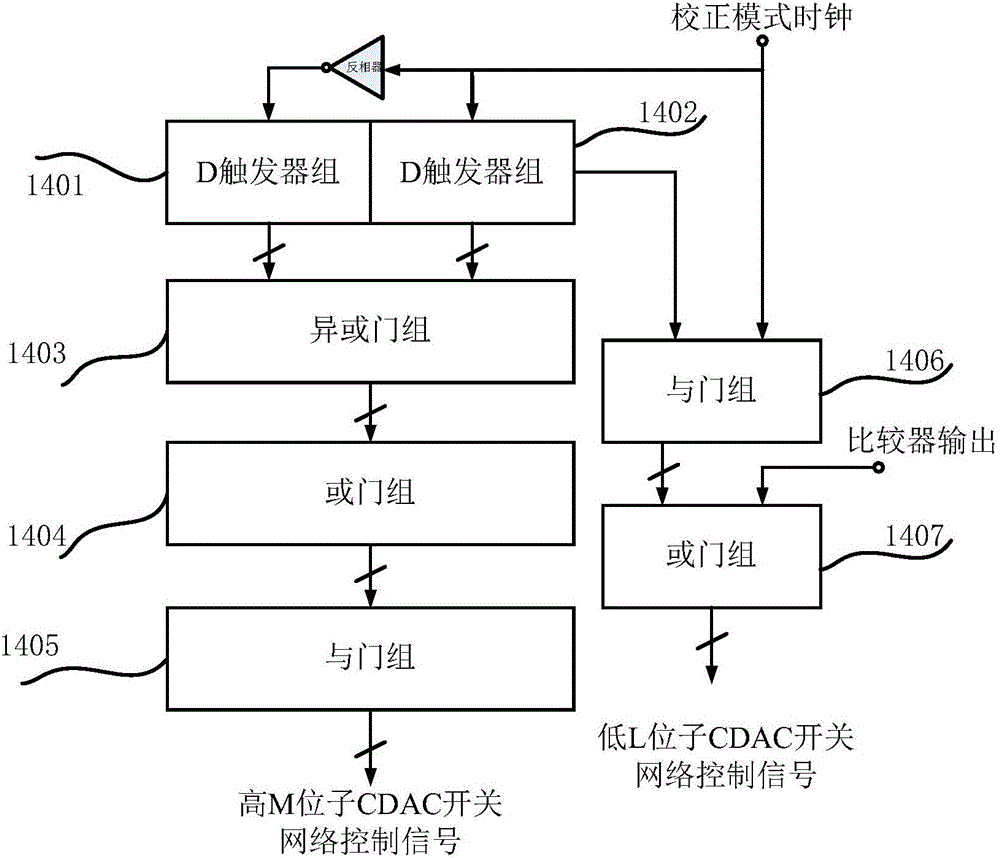

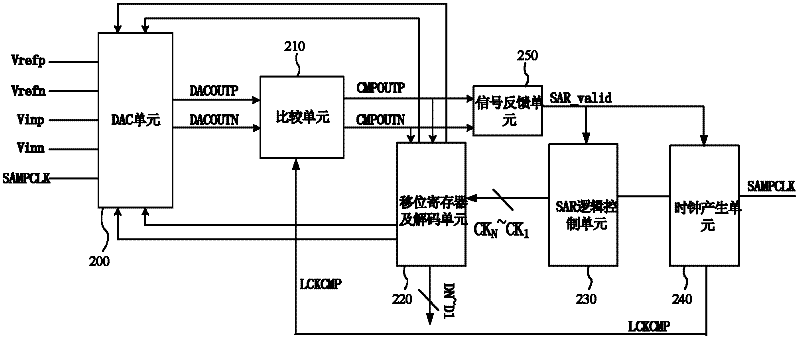

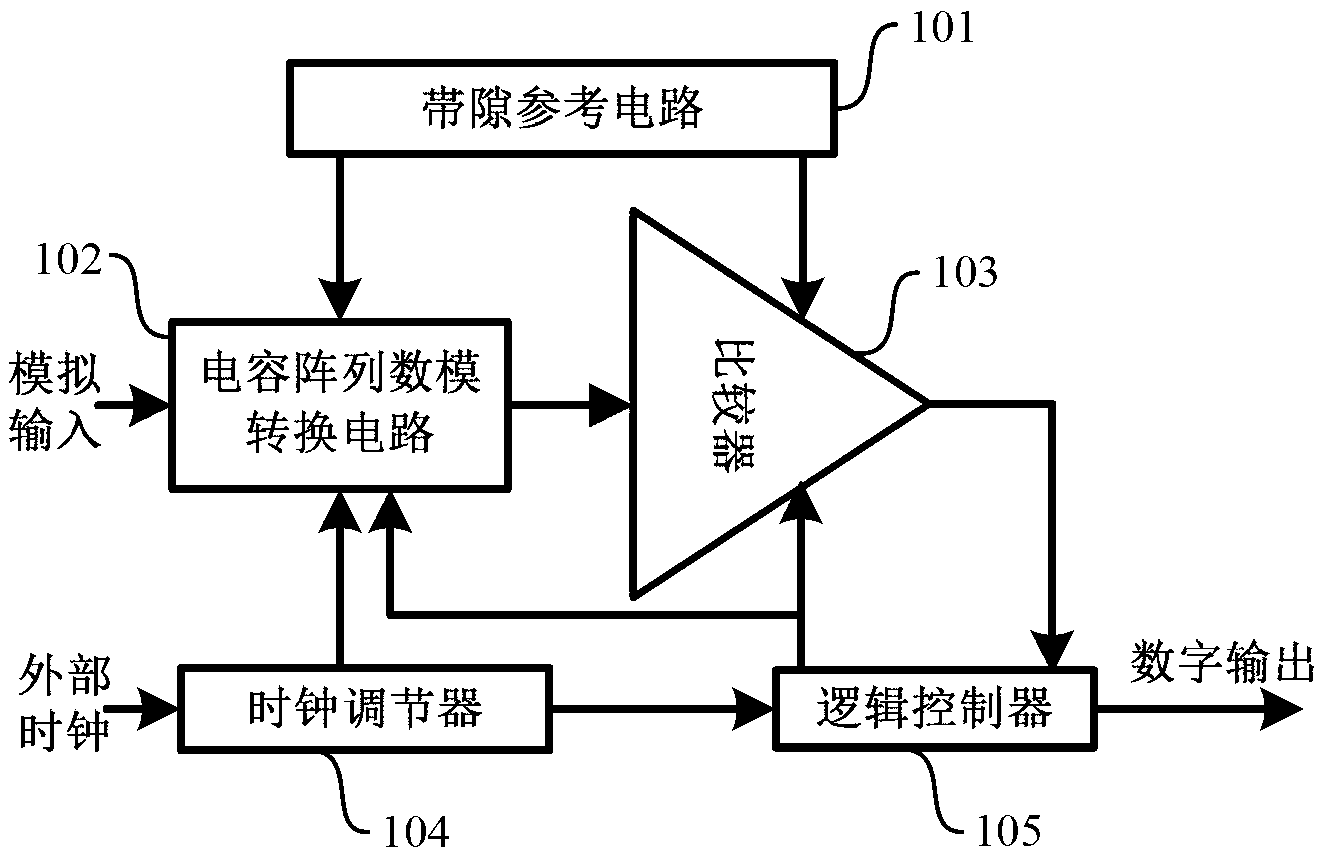

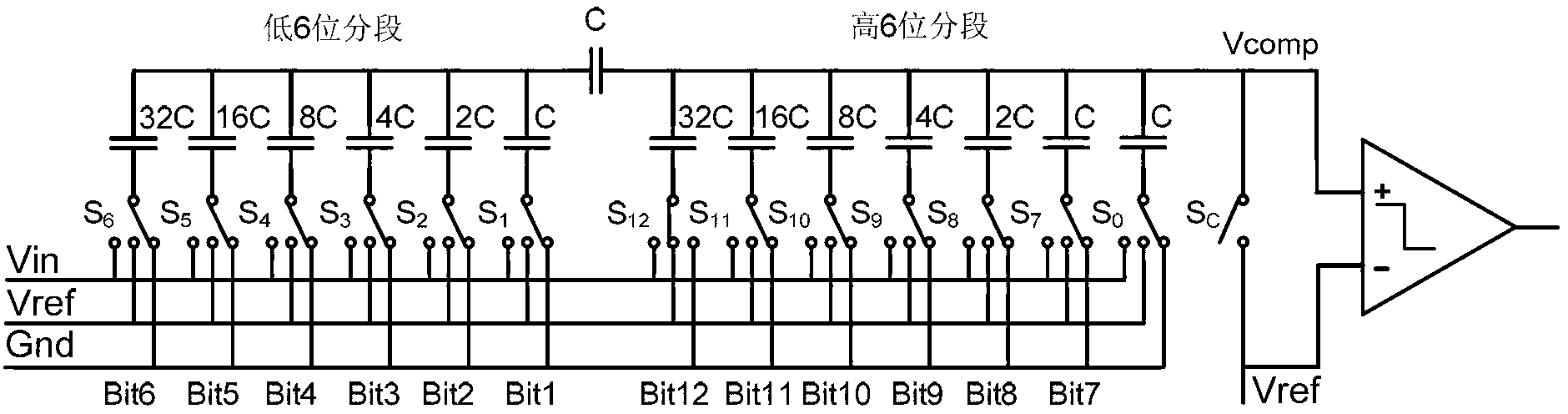

Successive approximation analog-digital converter and analog-digital conversion method based on digital domain self-correcting

ActiveCN106374930AReduce non-linearityHigh precisionElectric signal transmission systemsAnalogue/digital conversion calibration/testingCapacitanceDigital down converter

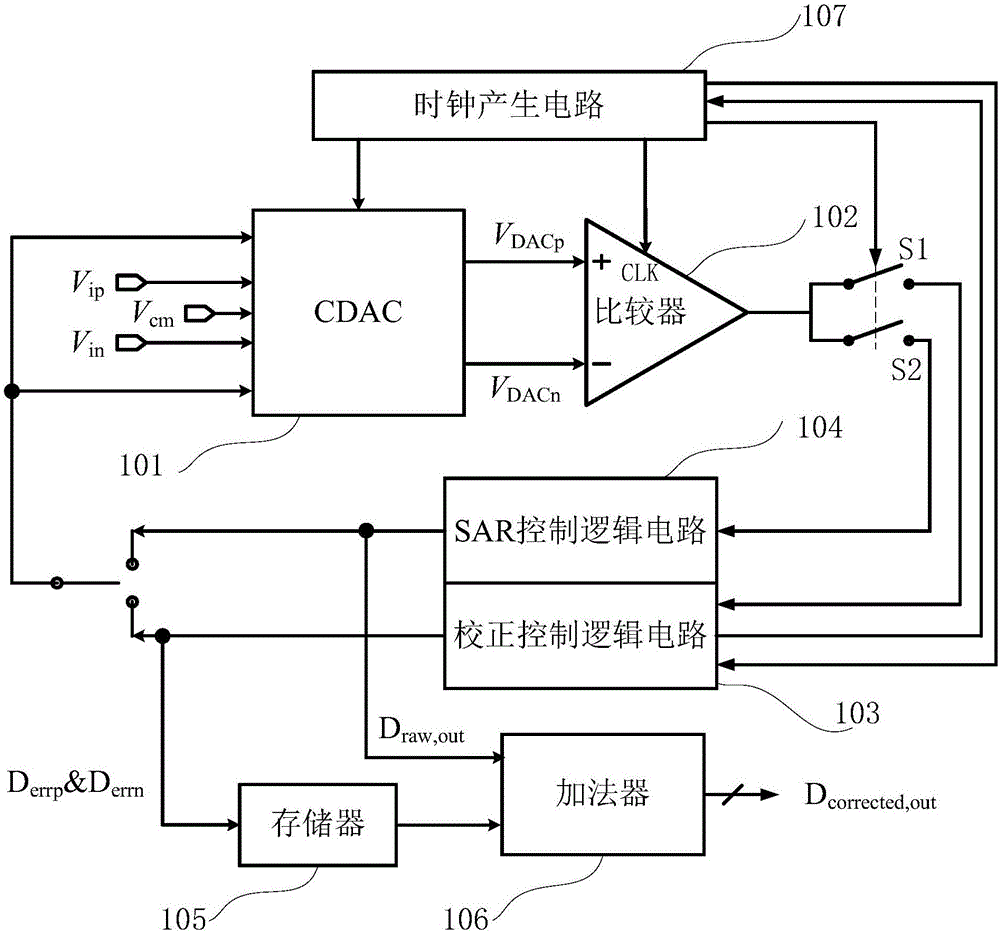

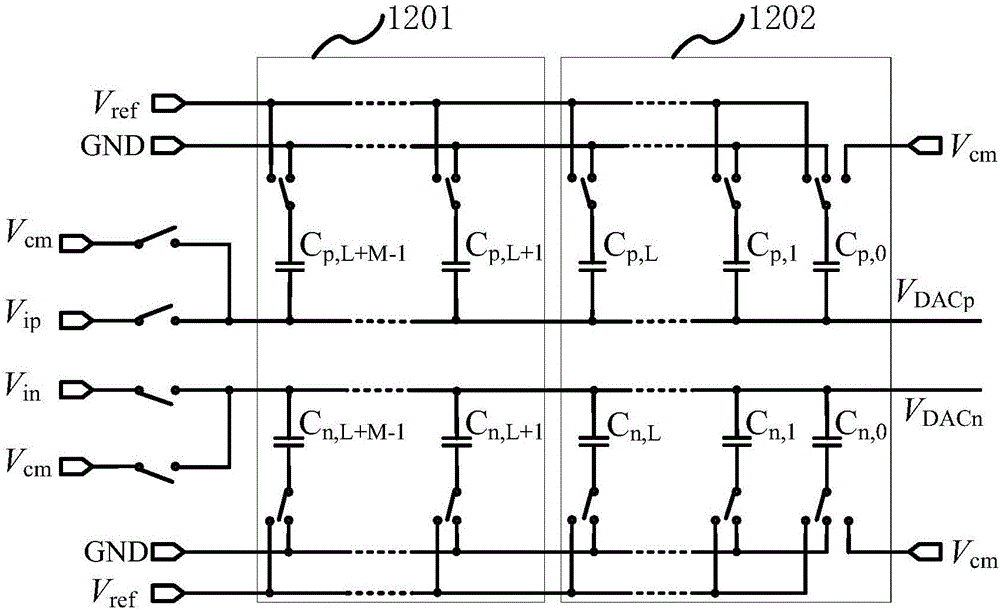

The invention provides a successive approximation analog-digital converter and an analog-digital conversion method based on digital domain self-correcting. The successive approximation analog-digital converter comprises a CDAC, a comparator, an SAR control logic circuit, a correction control logic circuit, a storage, an adder and a clock circuit; a differential structure is adopted in the CDAC; capacitor arrays of the CDAC respectively form a high-M-level CDAC and a low-L-level CDAC; on the basis of a capacitor array reusing thought, mismatching errors of various capacitors in the high-M-level CDAC capacitor array are detected by reusing the low-L-level CDAC in a self-correcting stage; detected error values are quantized; error voltage is converted into an error code to output; the output error code is output into the storage; after mismatching error detection and quantization are completed, digital conversion of an input analog signal begins to perform; an original code is output, and operated with the error code at the corresponding bit called from the storage; therefore, the final output codeword after being corrected is obtained; and thus, the linearity of the SAR ADC is increased.

Owner:SOUTHEAST UNIV

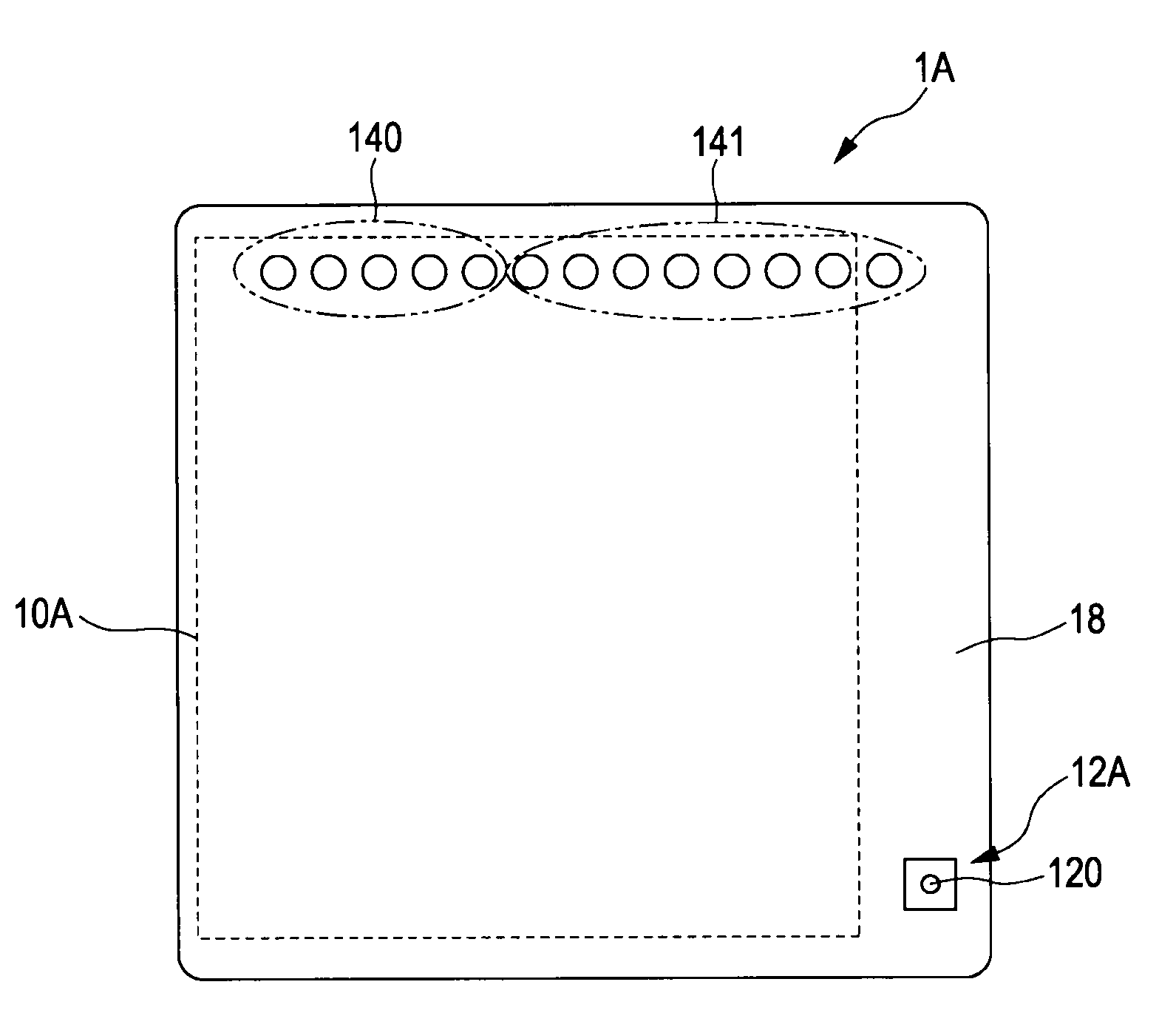

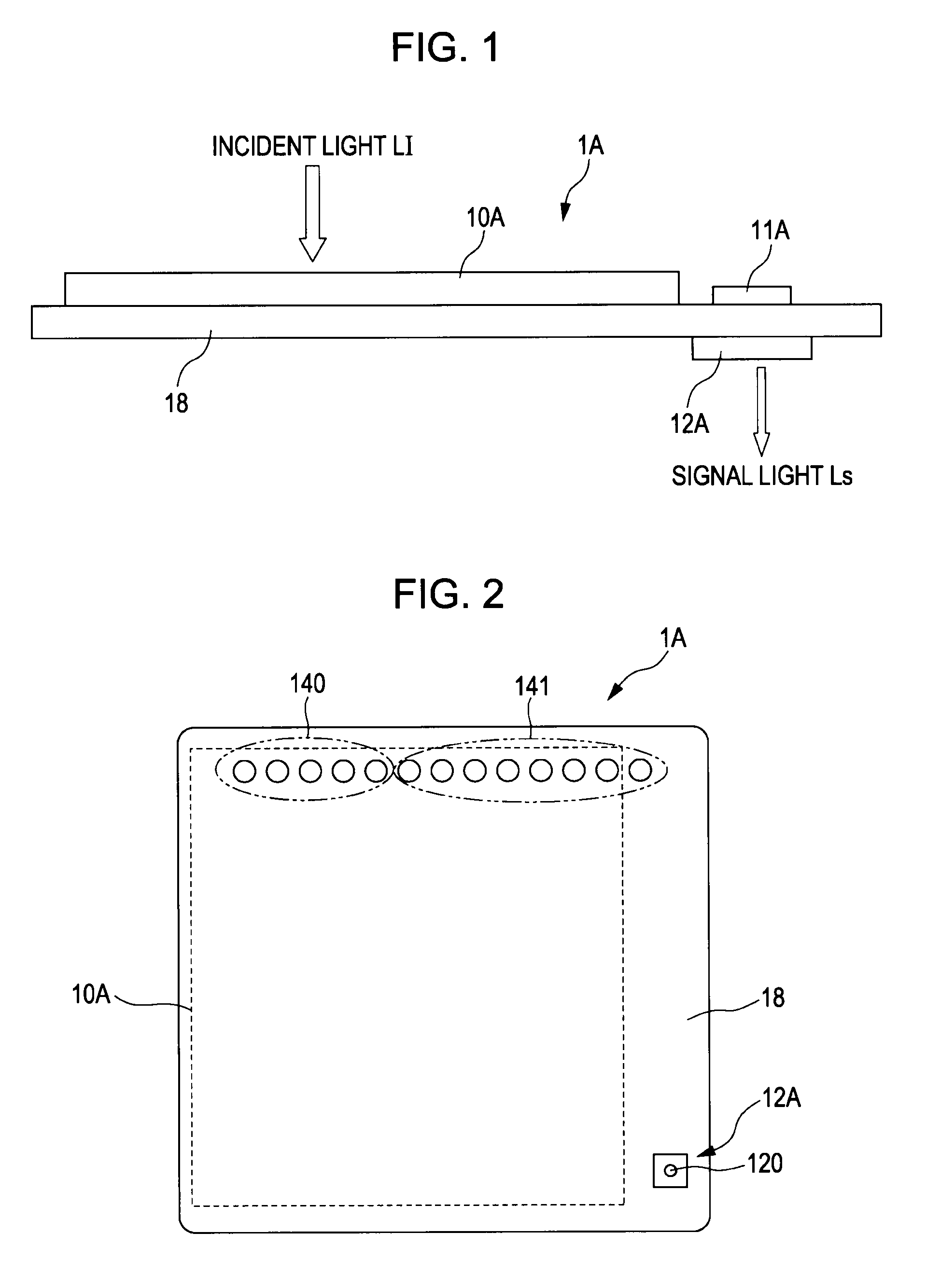

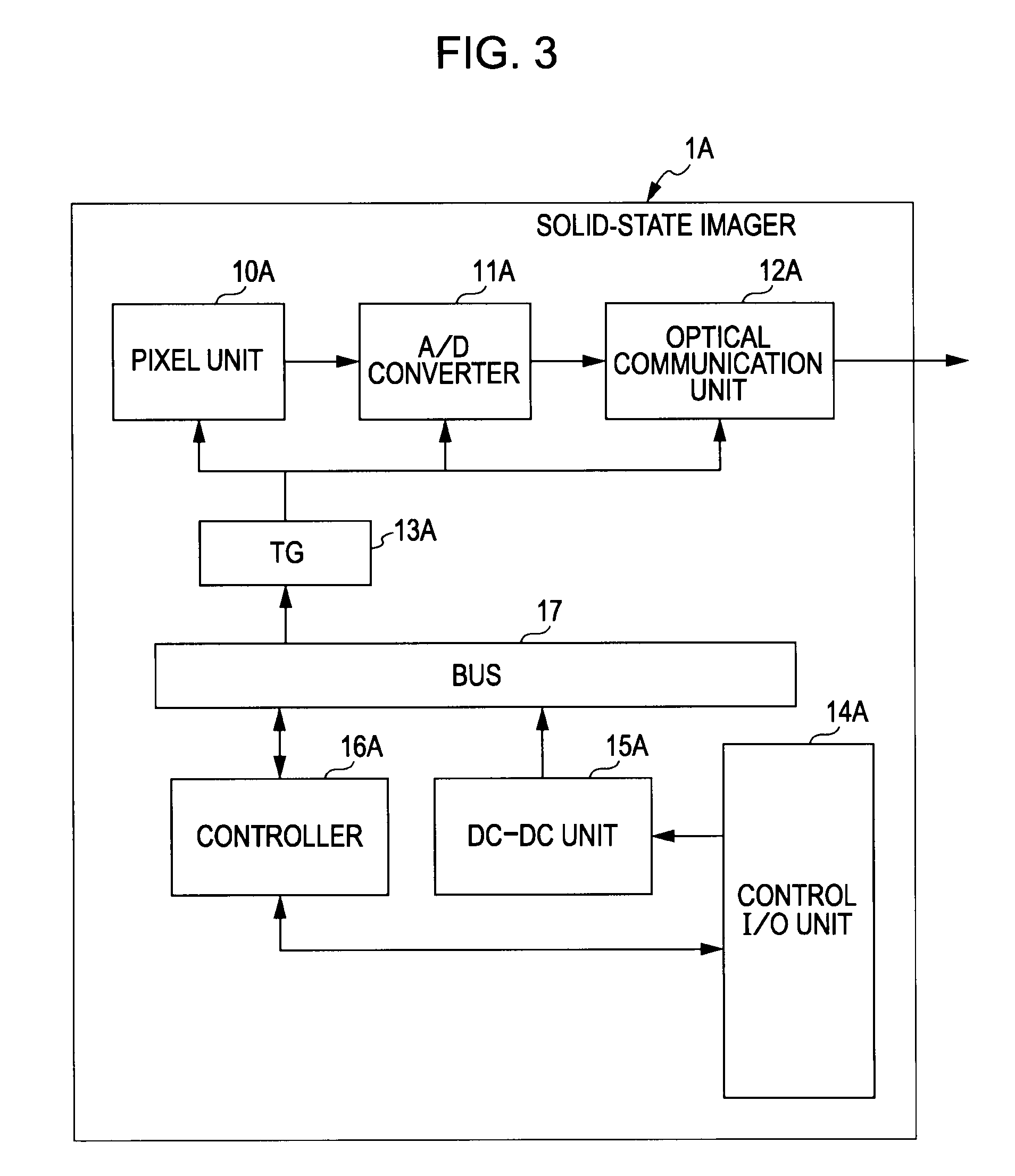

Solid-state imager and signal processing system

InactiveUS20100091128A1Improve layout freedomReduce thermal effectsTelevision system detailsTelevision system scanning detailsEngineeringLight signal

A solid-state imager includes a pixel unit for converting incident light into an electrical signal, a substrate bearing the pixel unit formed thereon, an analog-to-digital converter, formed on the substrate, for converting a signal read from the pixel unit into a digital signal, an optical communication unit, arranged on the bottom surface of the substrate opposite the surface of the substrate bearing opposite the top surface of the substrate bearing the pixel unit receiving the incident light, for converting the digital signal converted by the analog-to-digital converter into a light signal and outputting the light signal, and a signal line for transferring the digital signal, converted by the analog-to-digital converter, to the optical communication unit arranged on the bottom surface of the substrate.

Owner:SONY CORP

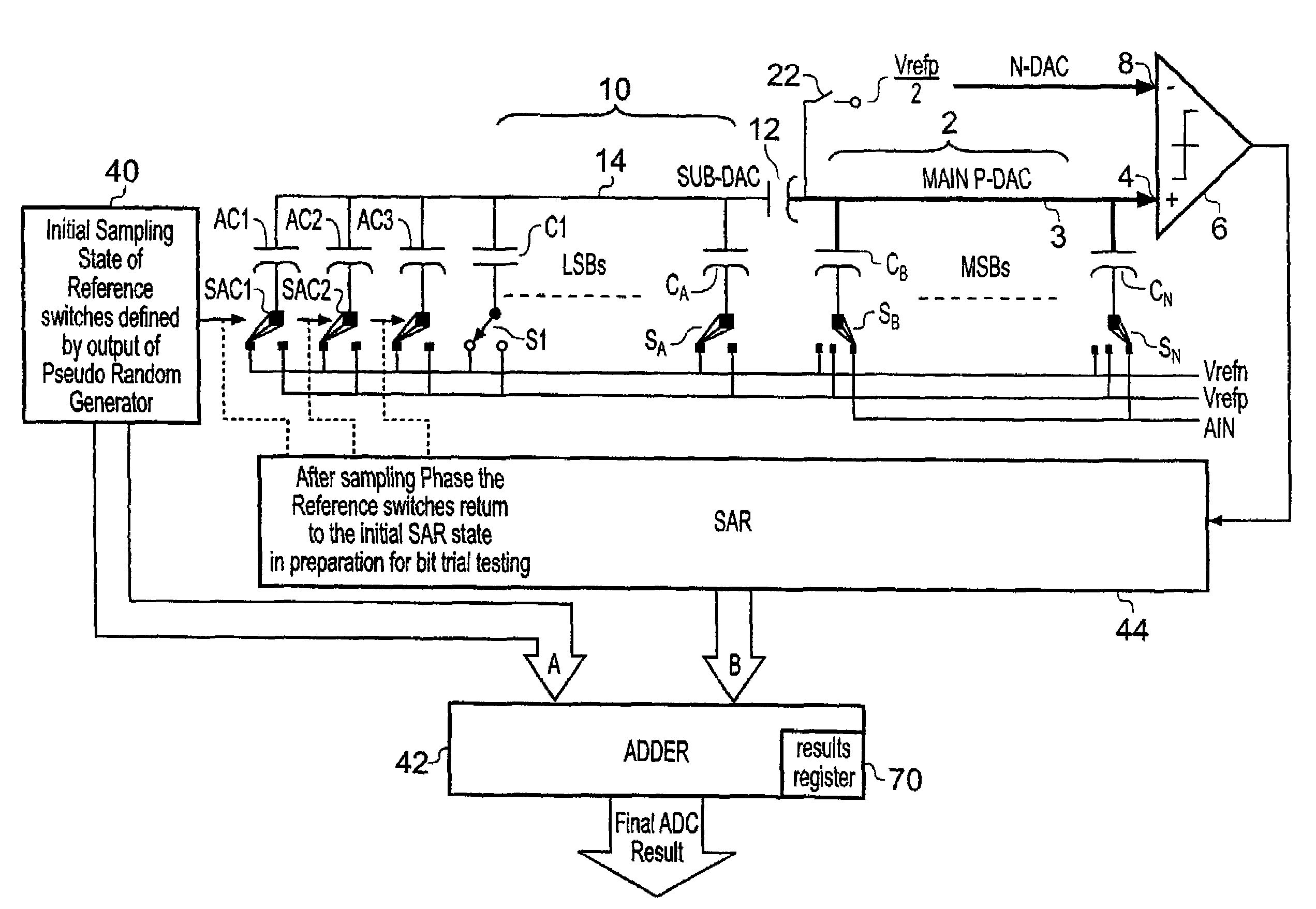

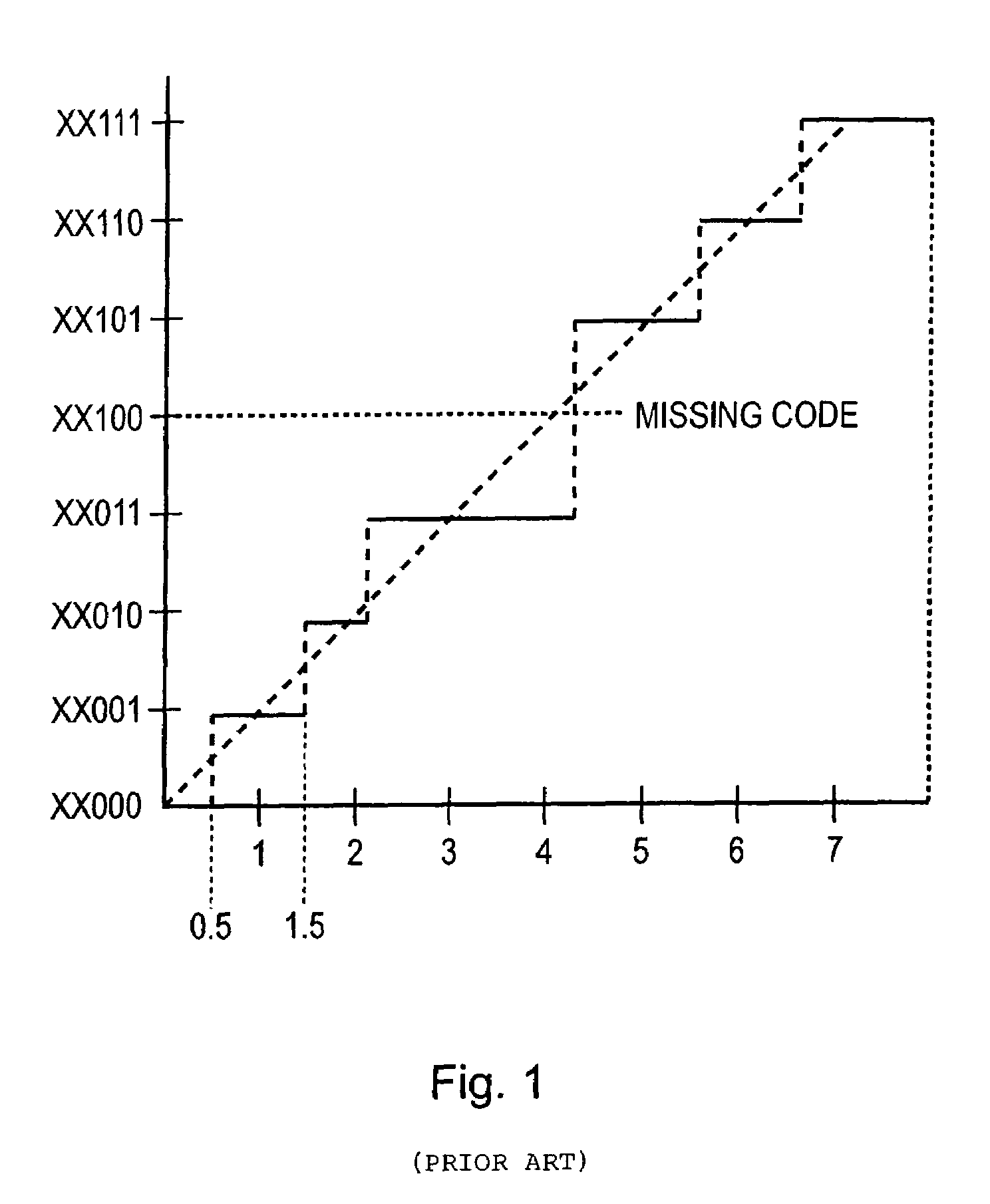

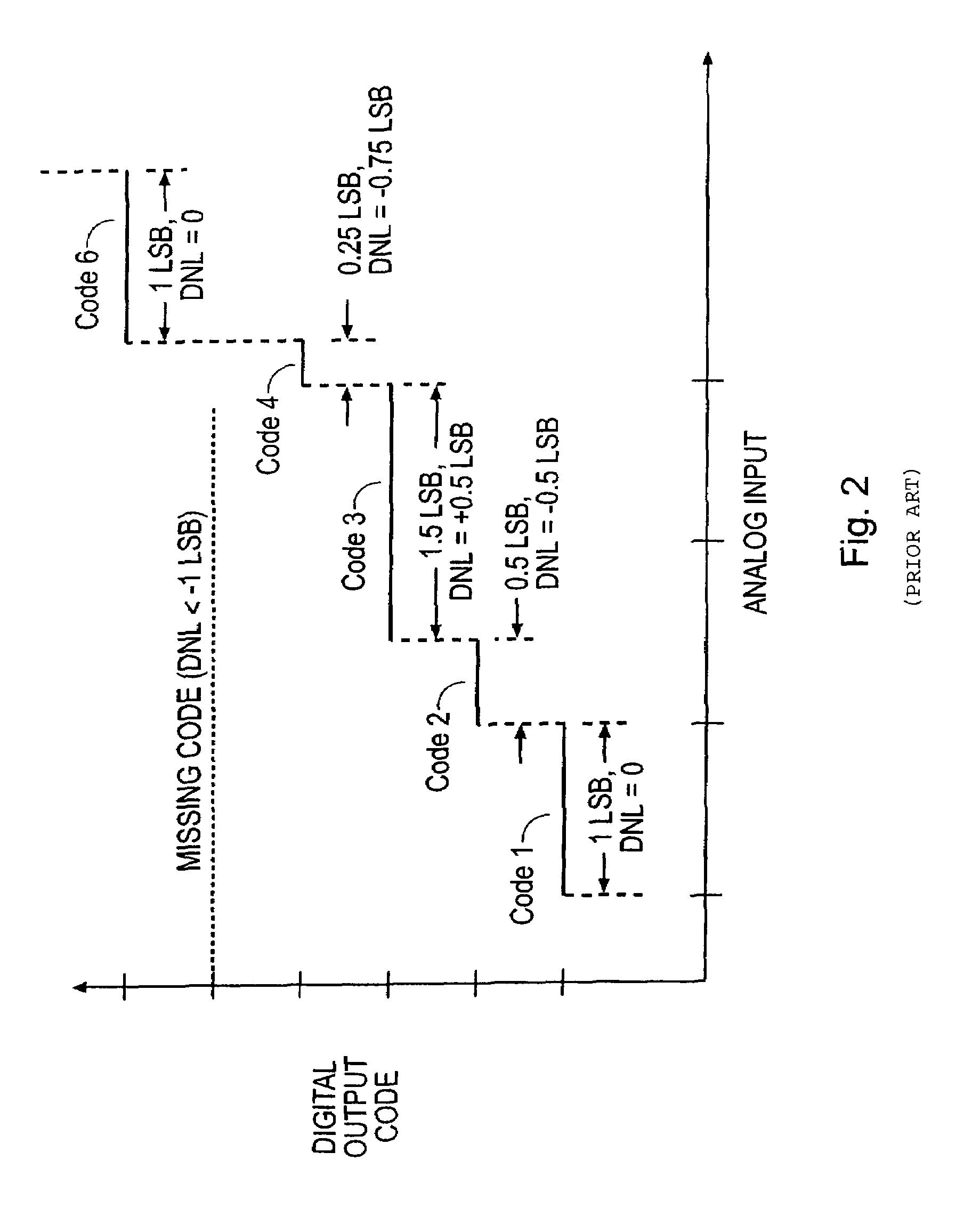

Analog to digital converter with dither

ActiveUS7286075B2Reduce the possibilityImprove errorElectric signal transmission systemsAnalogue-digital convertersVoltage referenceEngineering

An analog to digital converter is provided comprising an array of capacitors for sampling an input, each capacitor having at least one associated switch for controllably connecting a terminal of the capacitor to a first reference voltage or to a second reference voltage; and a sequence generator for generating a sequence of bits, wherein during sampling of the input onto the array of capacitors an output of the sequence generator is supplied to the switches of a first group of capacitors to control whether a given capacitor within the first group is connected by its associated switch to the first reference voltage or to the second reference voltage.

Owner:ANALOG DEVICES INC

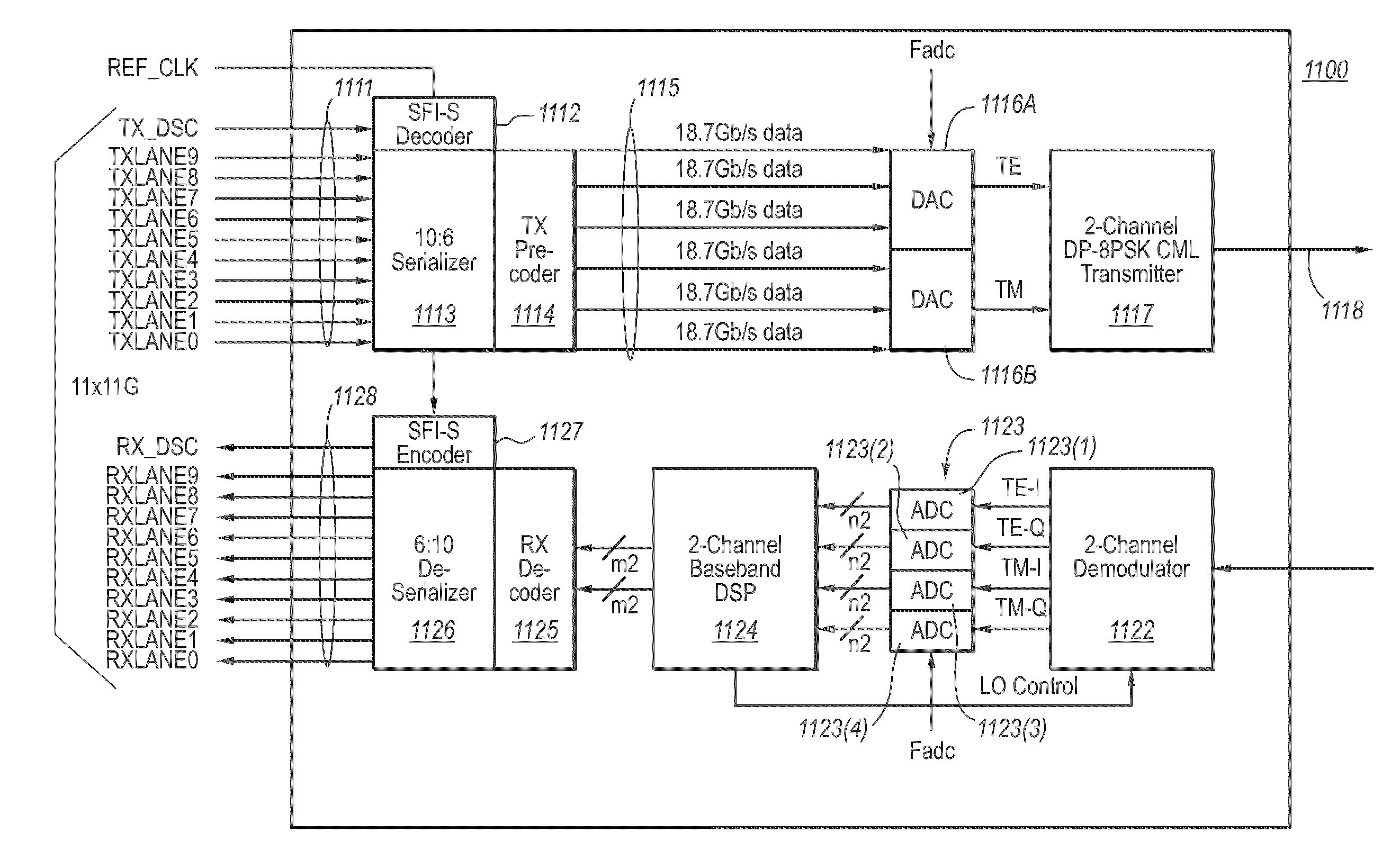

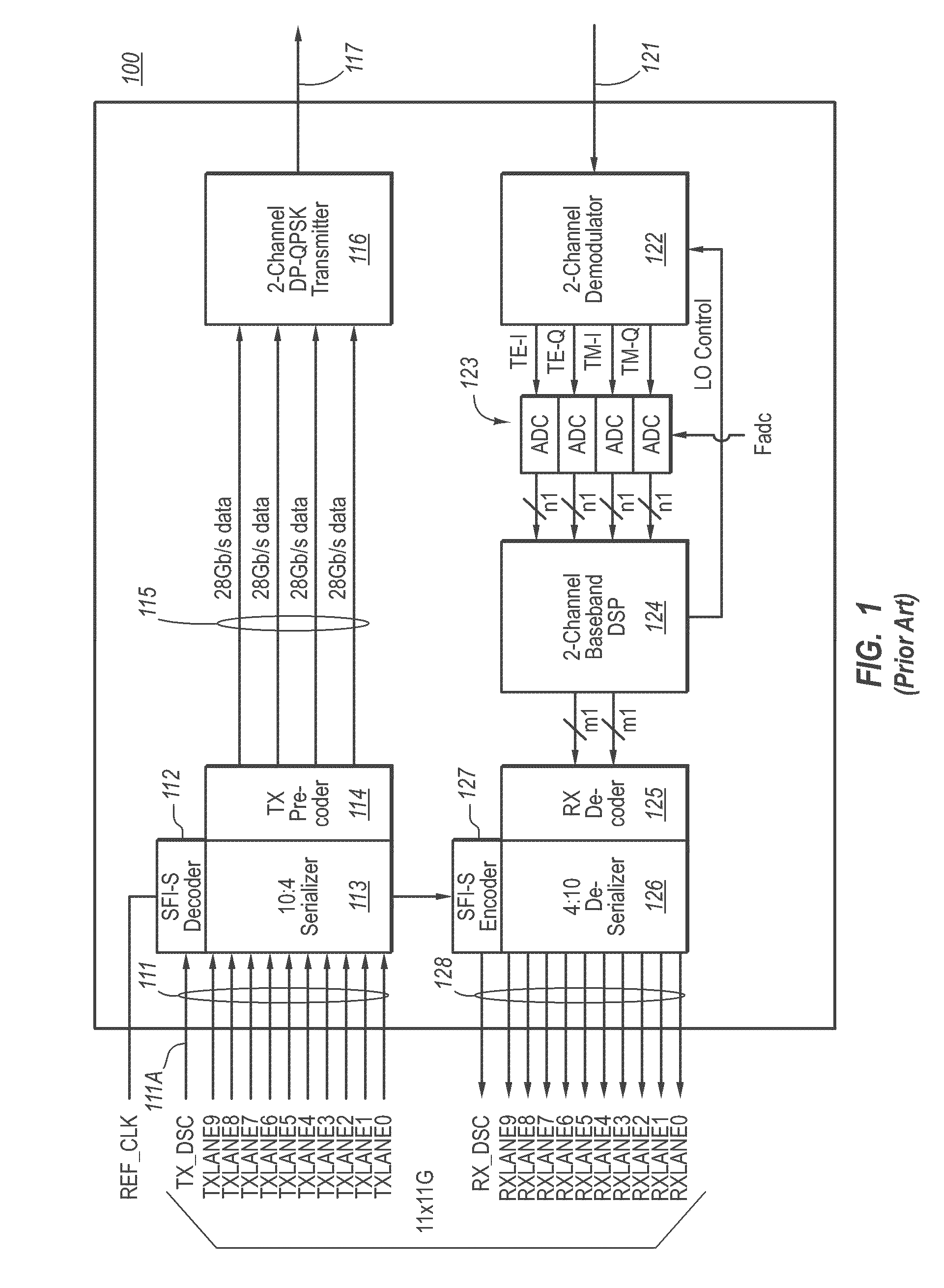

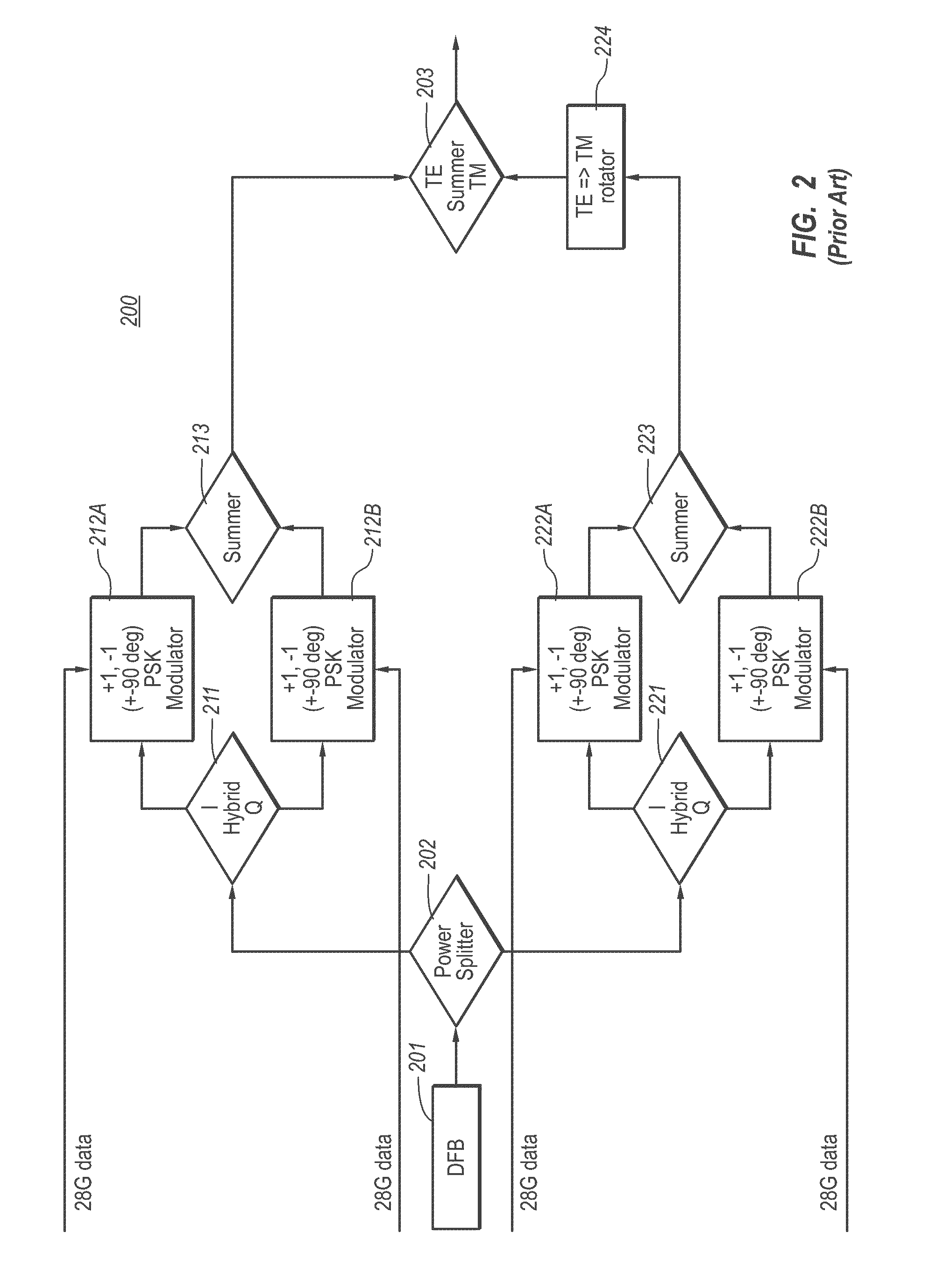

Phase shift keyed modulation of optical signal using chirp managed laser

ActiveUS8068742B2Reduce difficultyReduce complexityElectromagnetic transmittersElectromagnetic receiversEngineeringAnalog-to-digital converter

A high-speed optical transmitter comprises multiple digital lanes that are provided to a bank of digital-to-analog converters. The analog signals are then used to Phase Shift Keyed (PSK) modulation using a Chirp Managed Laser (CML)-based transmitter, and potentially using dual polarization. A corresponding optical receiver receives the sequence of optical signals at a demodulator. For each polarization, the demodulator includes a corresponding demodulation channel that is configured to demodulate that polarization component of the optical signal into one or more signal components. Each of these signal components is converted into a corresponding digital signal using a corresponding analog-to-digital converter. In the case of higher-order PSK modulation (e.g., 8PSK or higher), for each polarization, the analog converter has a lower sampling rate than for QPSK modulation.

Owner:II VI DELAWARE INC

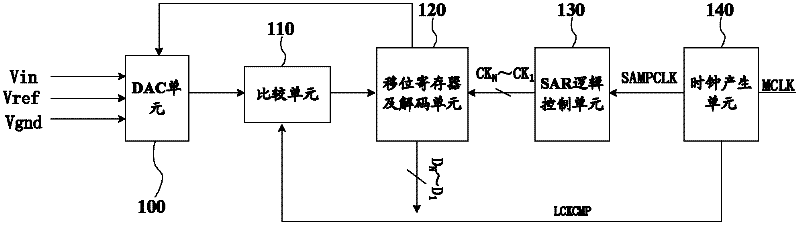

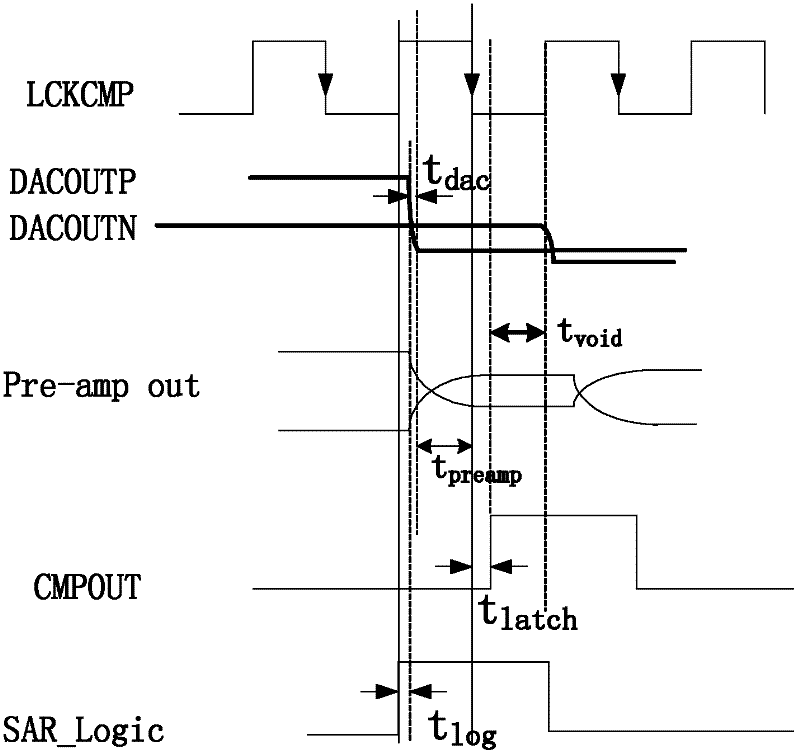

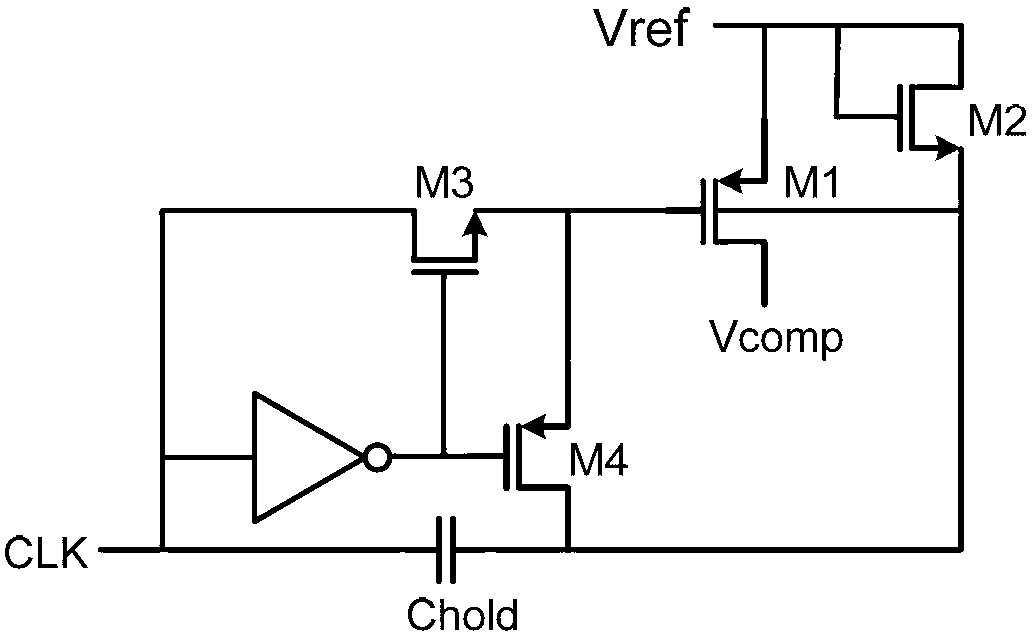

Successive approximation register analog-digital converter

ActiveCN102355266AWork fasterAnalogue/digital conversionElectric signal transmission systemsShift registerIdle time

The invention provides a successive approximation register analog-digital converter which comprises a digital-analog conversion unit, a comparison unit, a successive approximation logic control unit, a shift register and decoding unit and a clock generation unit. The successive approximation register analog-digital converter also comprises a signal feedback unit. An input terminal of the signal feedback unit connects with an output terminal of the comparison unit. An output terminal of the signal feedback unit connects with an input terminal of the successive approximation logic control unit. The signal feedback unit receives a comparison result outputted by the comparison unit, generates a feedback signal, outputs the feedback signal to the successive approximation logic control unit to trigger the successive approximation logic control unit to control the shift register and decoding unit to carry out shift motion, a problem that a whole analog-digital converter has a segment of idle time after a traditional successive approximation analog-digital converter compares unit latch difference signals is avoided, and a work speed of the successive approximation analog-digital converter is effective raised.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

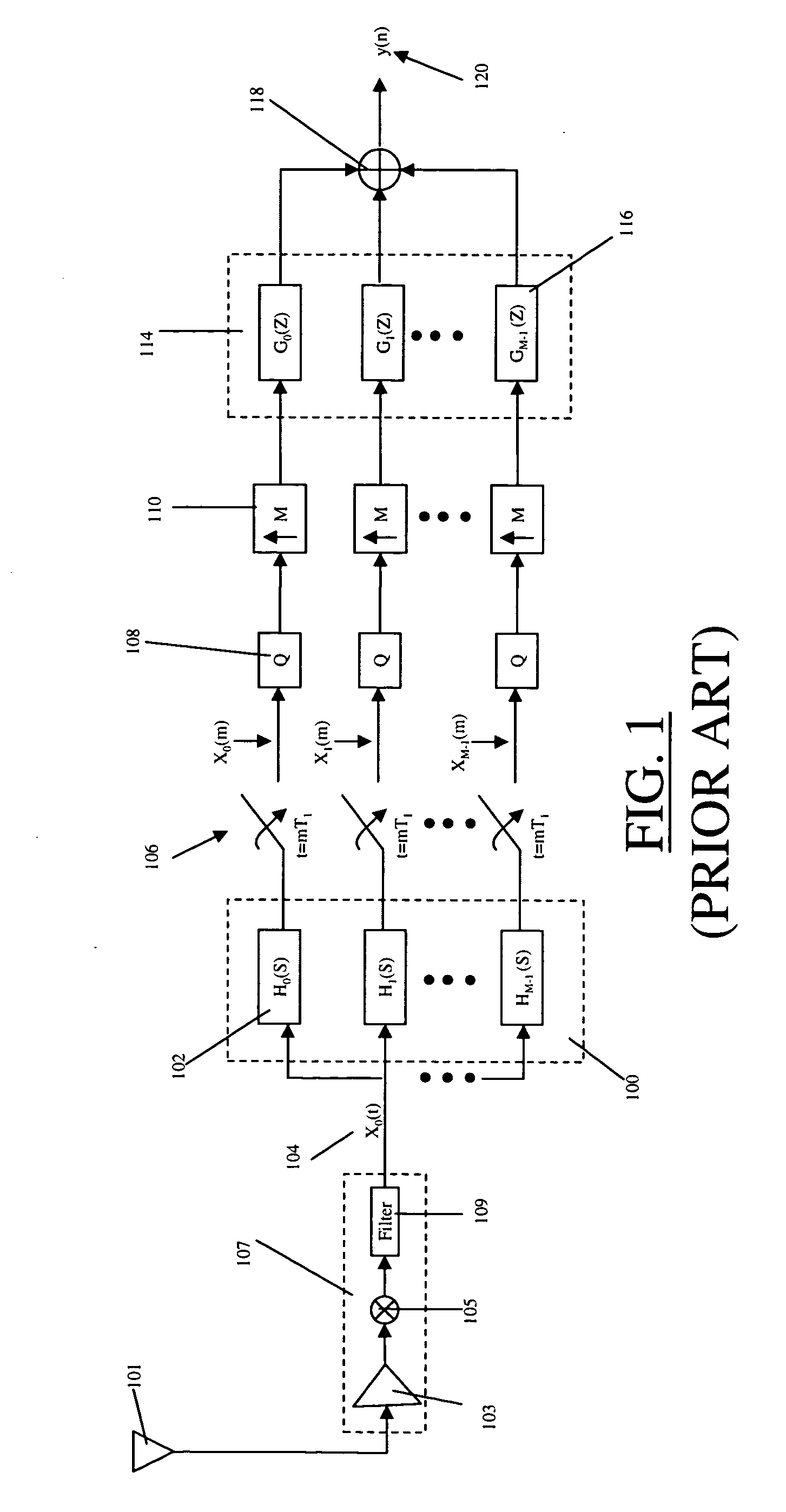

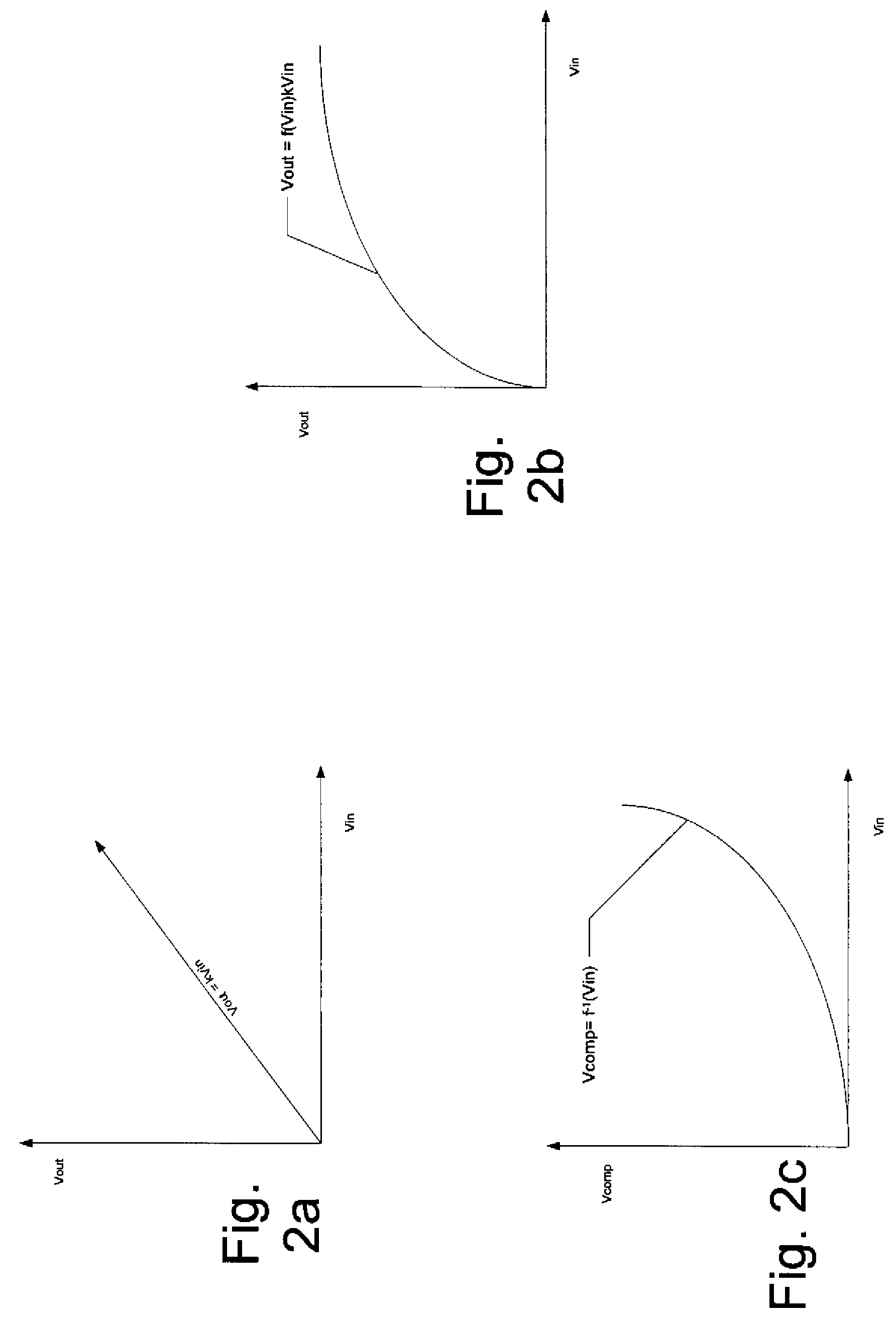

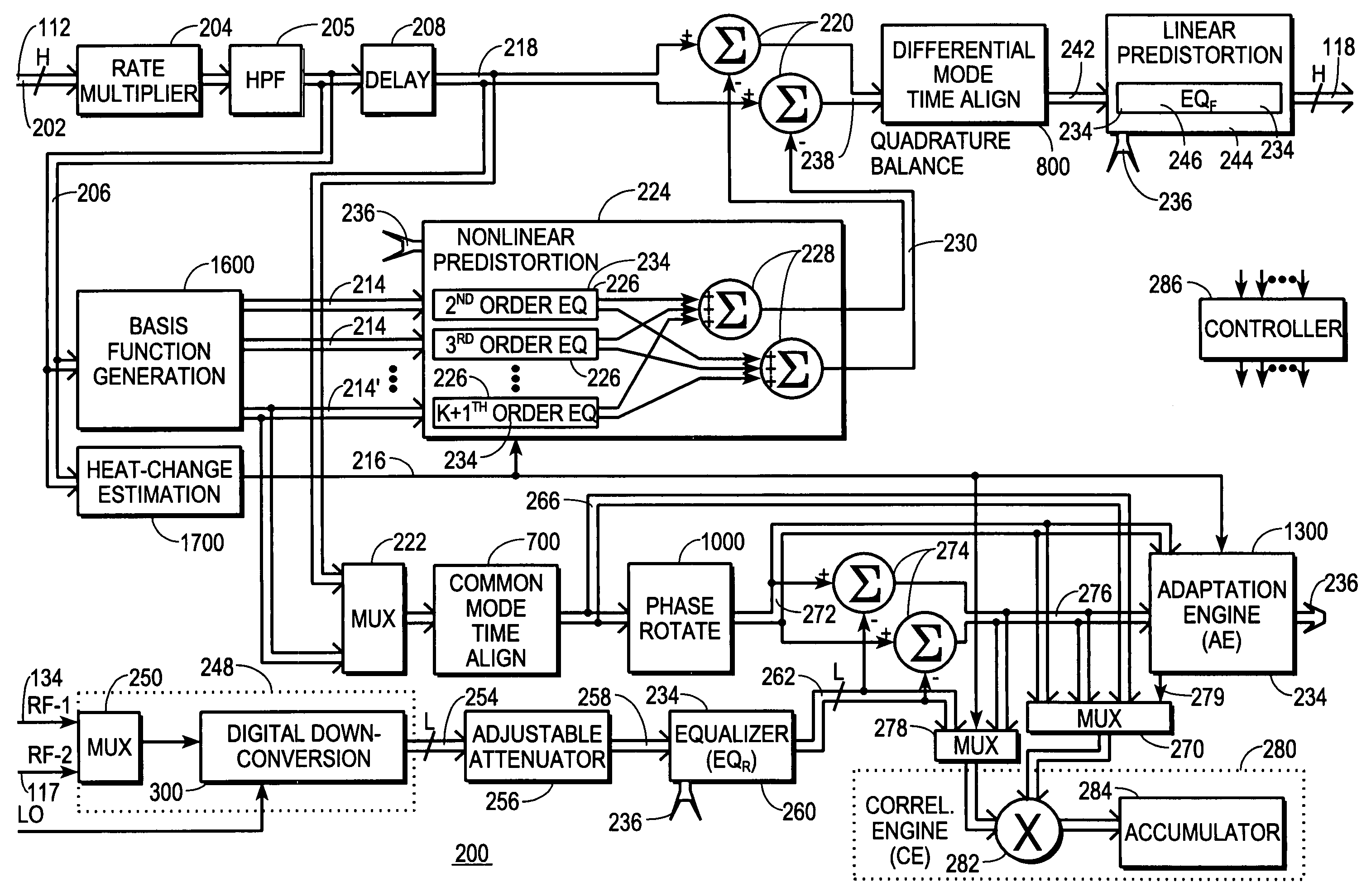

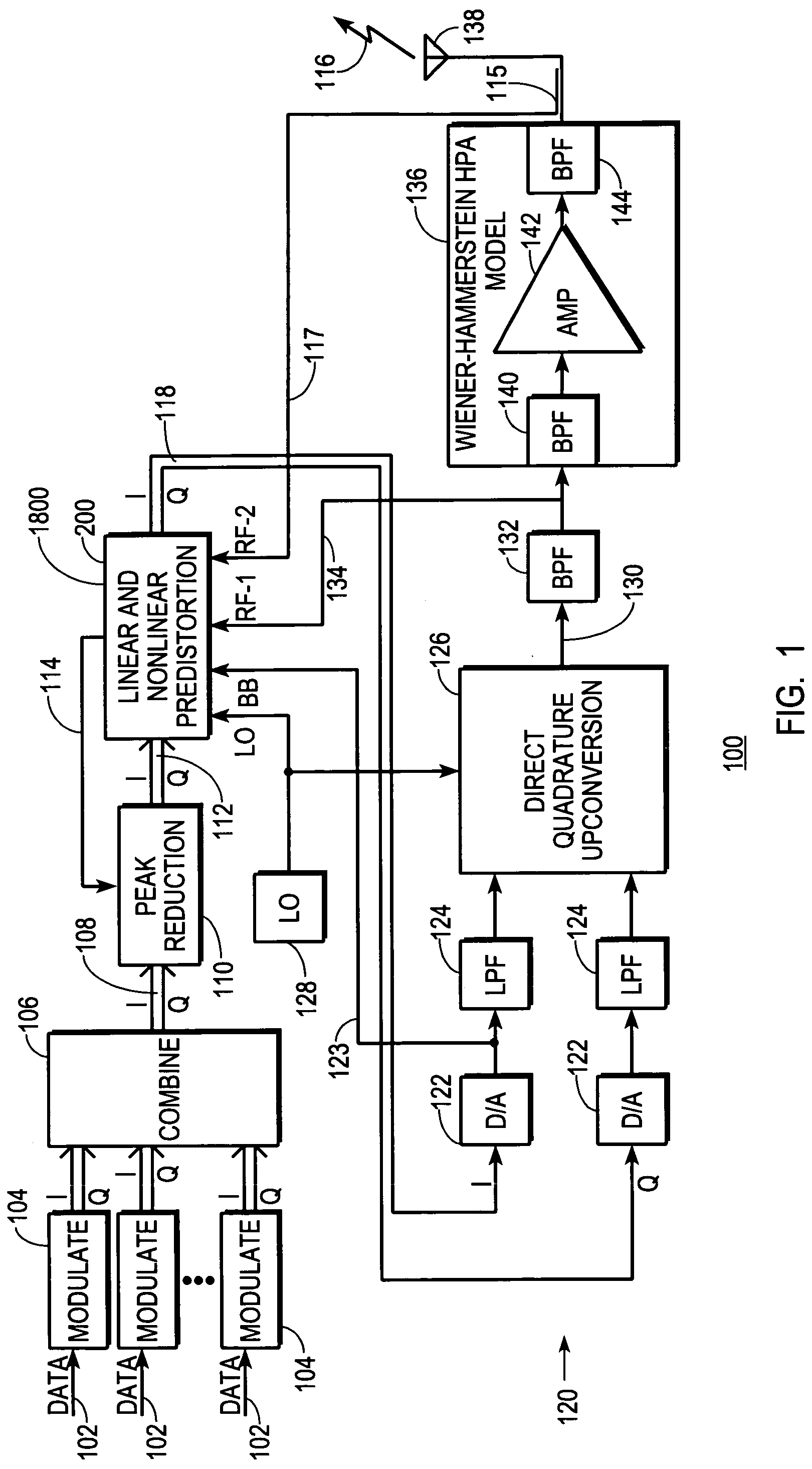

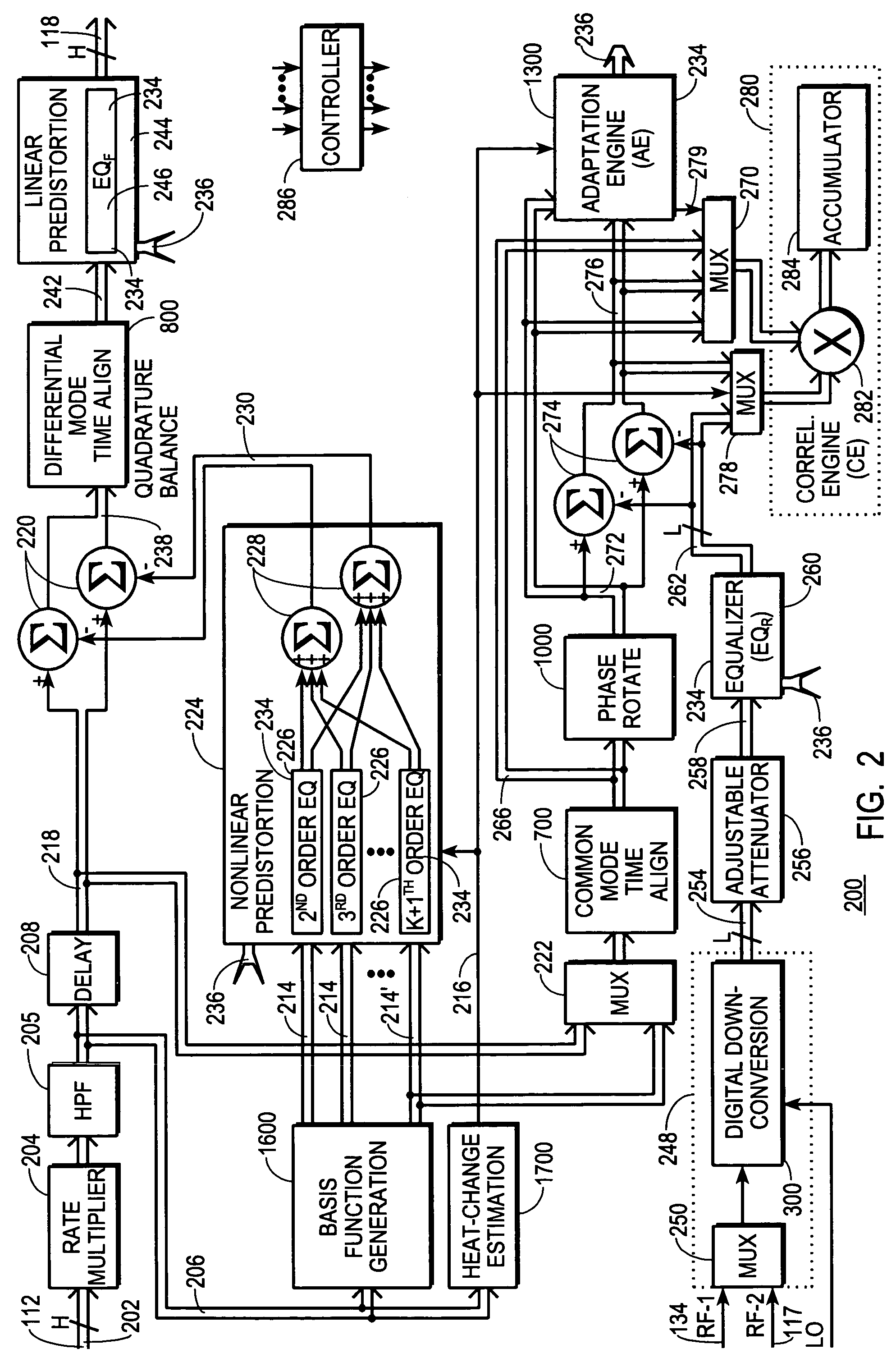

Predistortion circuit and method for compensating A/D and other distortion in a digital RF communications transmitter

InactiveUS7342976B2Compensation DistortionReduce errorsPower amplifiersCombined modulated pulse demodulationNonlinear distortionData stream

A digital communications transmitter (100) includes a digital linear-and-nonlinear predistortion section (200, 1800) to compensate for linear and nonlinear distortion introduced by transmitter-analog components (120). A direct-digital-downconversion section (300) generates a complex digital return-data stream (254) from the analog components (120) without introducing quadrature imbalance. A relatively low resolution exhibited by the return-data stream (254) is effectively increased through arithmetic processing. Distortion introduced by an analog-to-digital converter (304) may be compensated using a variety of adaptive techniques. Linear distortion is compensated using adaptive techniques with an equalizer (246) positioned in the forward-data stream (112). Nonlinear distortion is then compensated using adaptive techniques with a plurality of equalizers (226) that filter a plurality of orthogonal, higher-ordered-basis functions (214) generated from the forward-data stream (112). The filtered-basis functions are combined together and subtracted from the forward-data stream (112).

Owner:CRESTCOM INC

CMOS image sensor having wide dynamic range

InactiveUS7733402B2Television system detailsTelevision system scanning detailsEngineeringAnalog-to-digital converter

A solid-state image sensing device includes a pixel unit, analog-to-digital converter, controller, and adder. In the pixel unit, cells are two-dimensionally arranged on a semiconductor substrate. An output analog signal from the pixel unit is converted into a digital signal by the analog-to-digital converter and output. The controller controls the pixel unit and analog-to-digital converter, and causes the analog-to-digital converter to digitize a plurality of analog signals different in storage time in the pixel unit during the storage period of the electric charge of one frame. The adder adds digital signals corresponding to the analog signals different in storage time and output from the analog-to-digital converter.

Owner:KK TOSHIBA

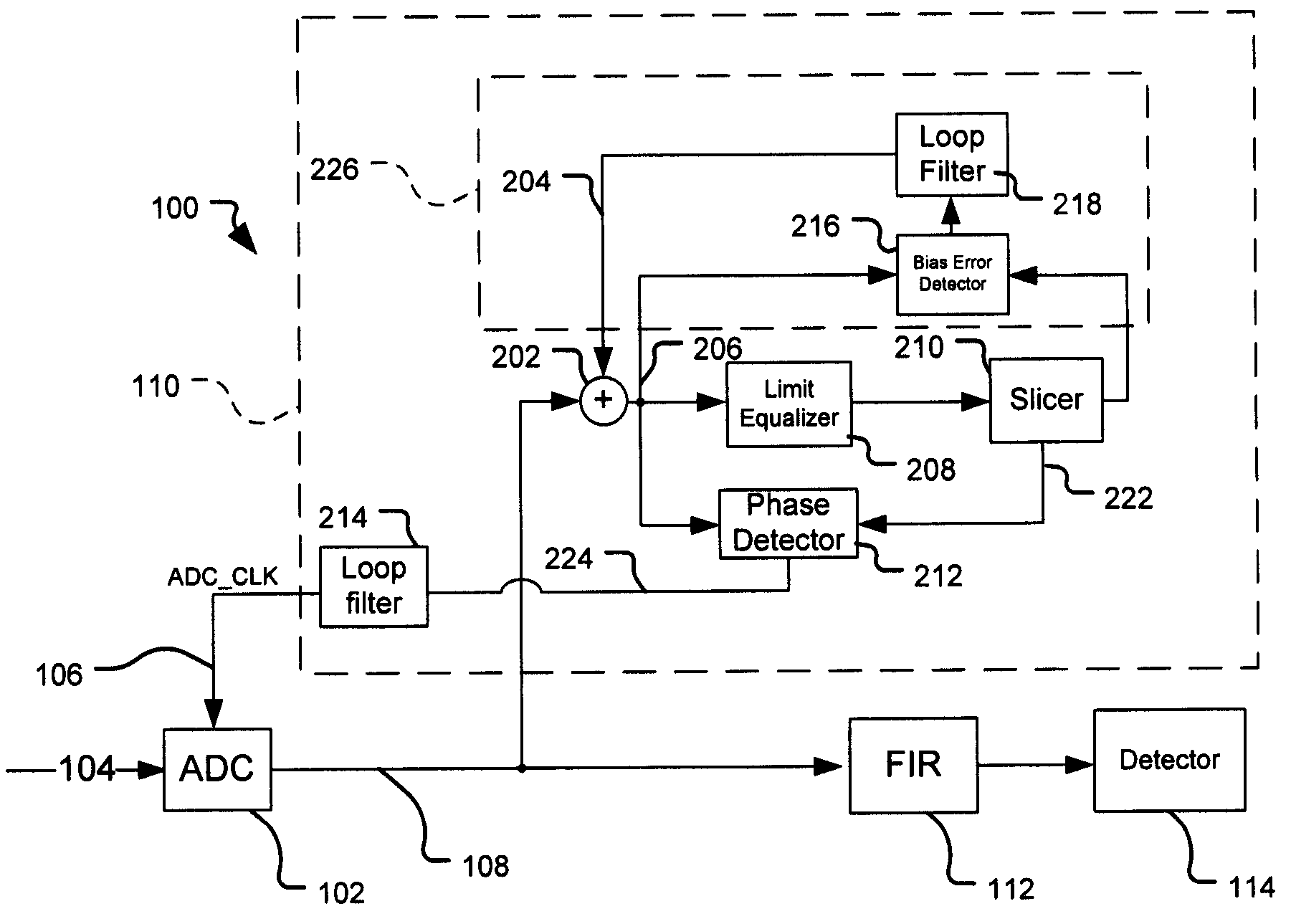

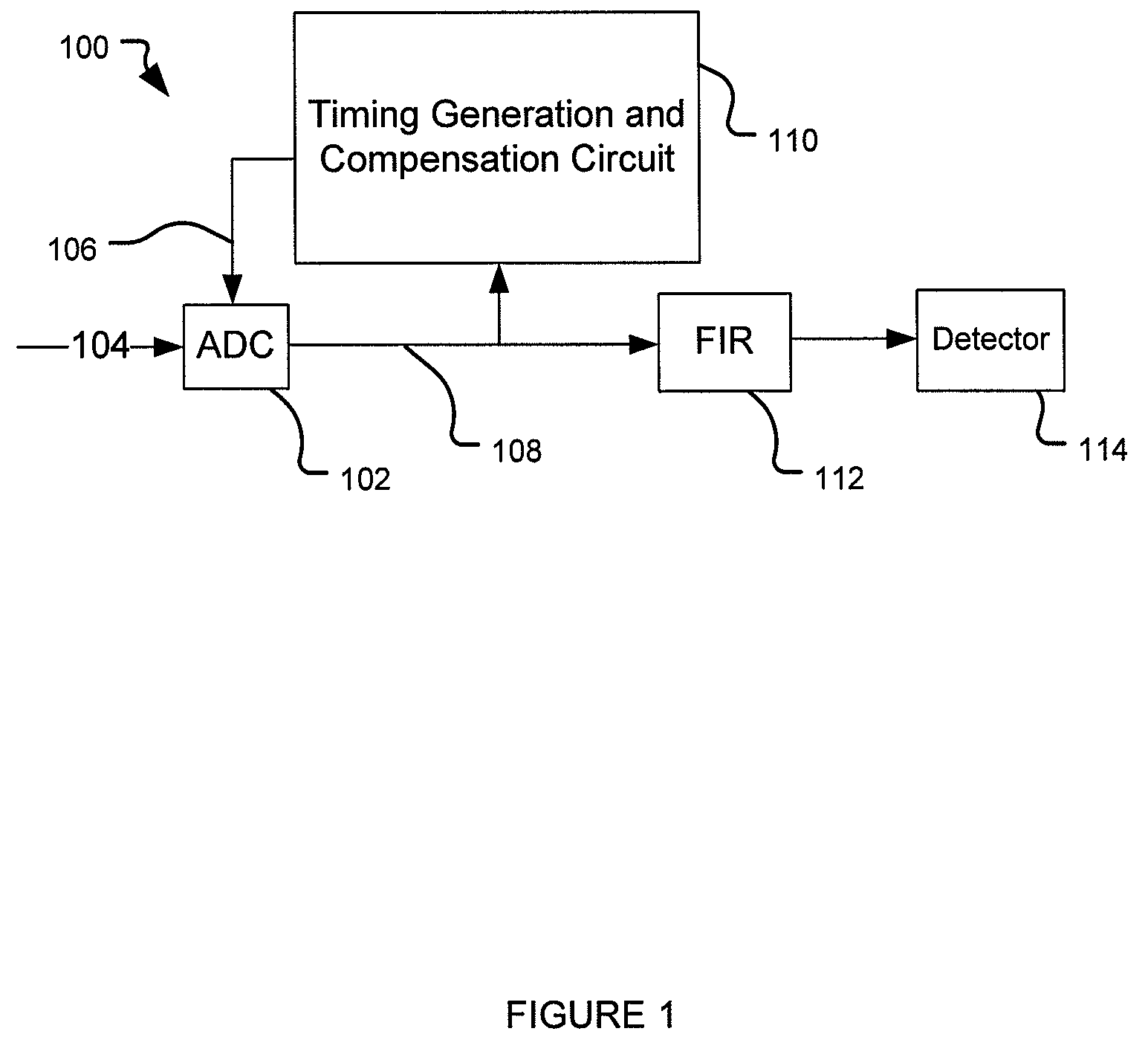

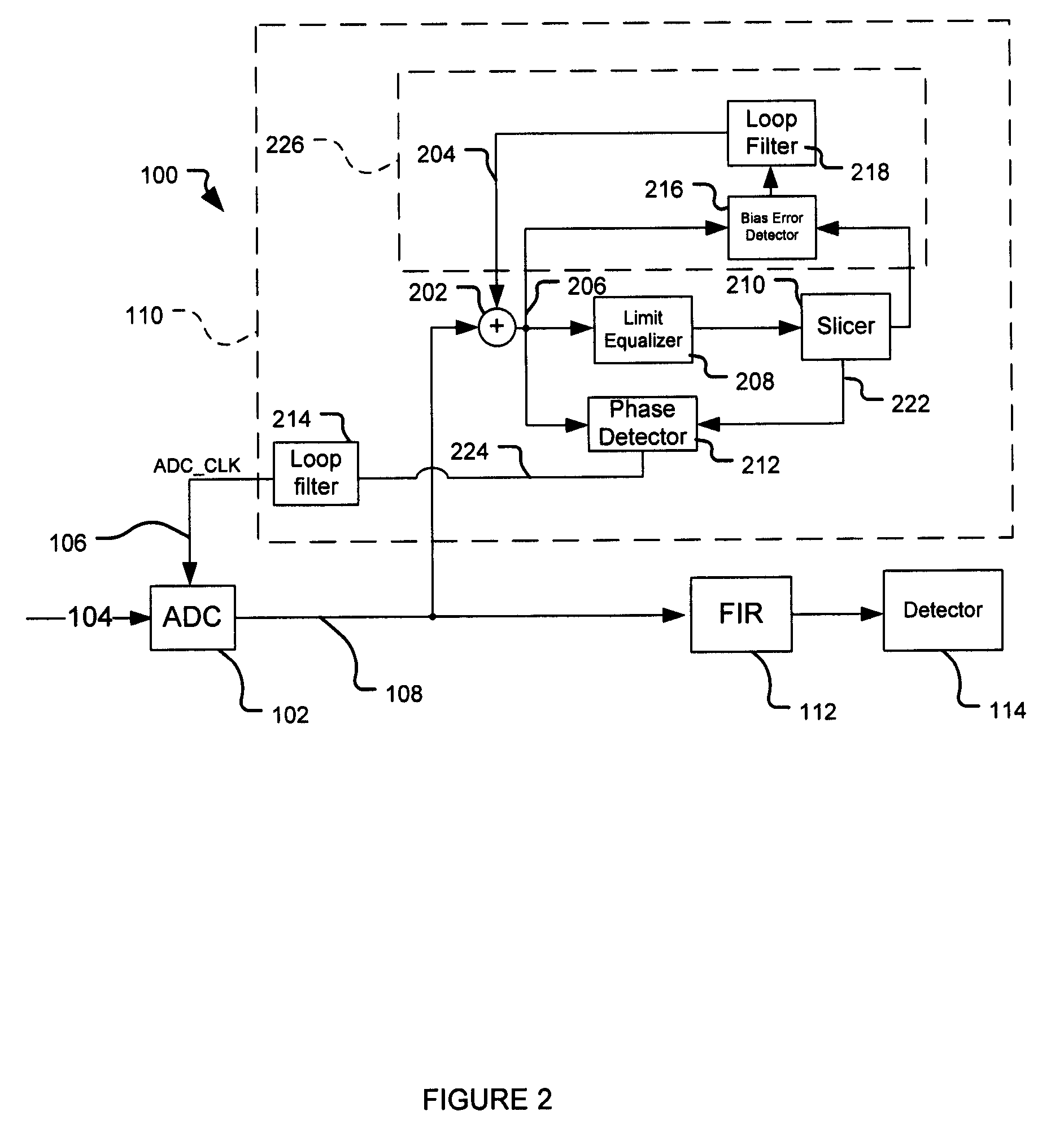

Timing loop based on analog to digital converter output and method of use

ActiveUS7525460B1Innovative designElectric signal transmission systemsModification of read/write signalsEngineeringAnalog-to-digital converter

A device and process to compensate for asymmetrical qualities of an analog input signal, if present, and generate a timing signal. The timing signal is then used for analog to digital conversion.

Owner:MARVELL ASIA PTE LTD

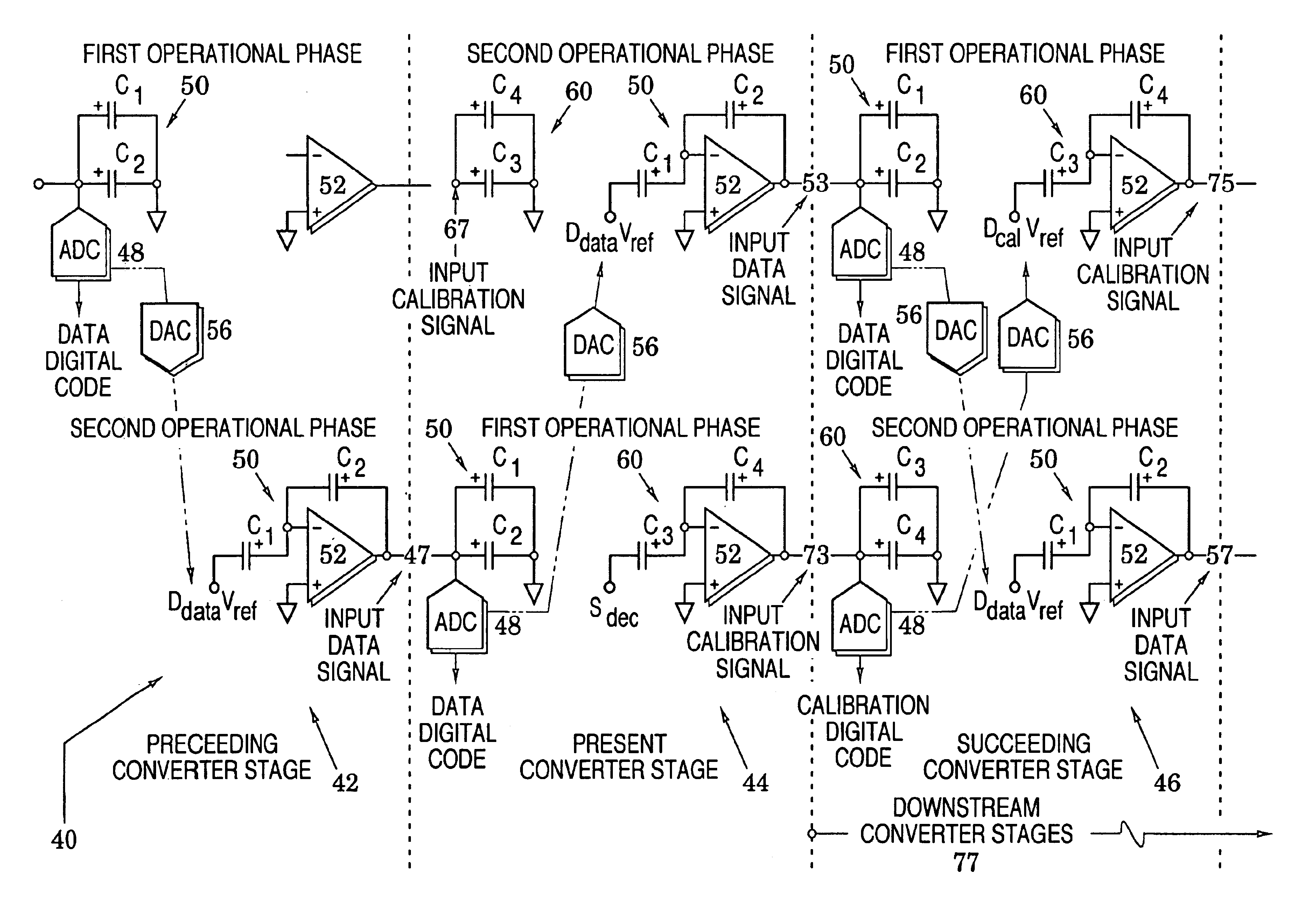

Analog-to-digital converter methods and structures for interleavably processing data signals and calibration signals

InactiveUS6839009B1Minimal increase in circuit spaceMinimal increase in power consumptionElectric signal transmission systemsAnalogue-digital convertersData signalEngineering

Methods and structures are provided for the interleaved calibration and subsequent correction of errors in switched-capacitor converter stages of pipelined analog-to-digital converters. The interleaved calibration can be run continuously or at selected times without disturbing the ongoing processing of input data signals. With first and second sets of capacitors, converter stages interleavably process input data signals and input calibration signals. Once these stages have been calibrated with their second sets of capacitors, the first and second sets are exchanged and the converter stages subsequently process input data signals with their second sets of capacitors.

Owner:ANALOG DEVICES INC

Successive approximation type analog/digital converter

ActiveCN102801422AReduce application complexitySolve the problem of voltage overshootAnalogue/digital conversionElectric signal transmission systemsCapacitanceVoltage overshoot

The invention discloses a successive approximation type analog / digital converter, wherein a capacitor array digital / analog conversion circuit comprises a capacitor array, an auxiliary capacitor is connected between the capacitor array and the output end of a comparer, and the oscillation amplitude between the capacitor array and the output end of the comparer ranges from 0V to power voltage when the capacitance value of the auxiliary capacitor is selected in a range enabling the oscillation amplitude of the input voltage to be from 0V to the power voltage. A measure of carrying out limiting and compression on a quantification range or increasing complicated circuits, which is adopted for preventing voltage overshoot in the traditional scheme, is avoided. According to the circuit structure provided by the invention, the requirements on input offset of the comparer in the ADC (analog / digital converter) and performance of other internal circuits are reduced, so that higher resolution ratio can be achieved under the condition of not increasing power consumption of the ADC using the circuit structure.

Owner:SOI MICRO CO LTD

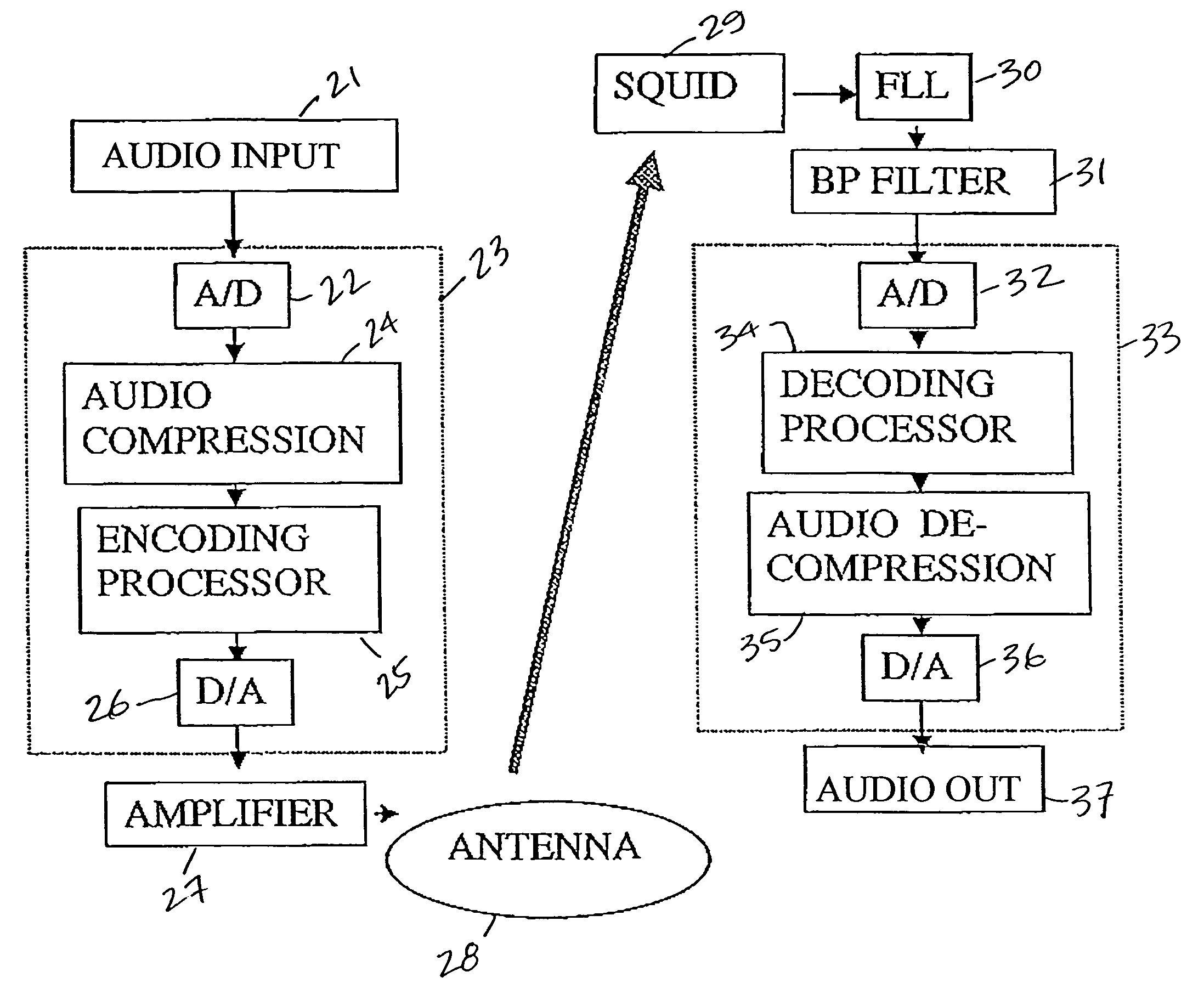

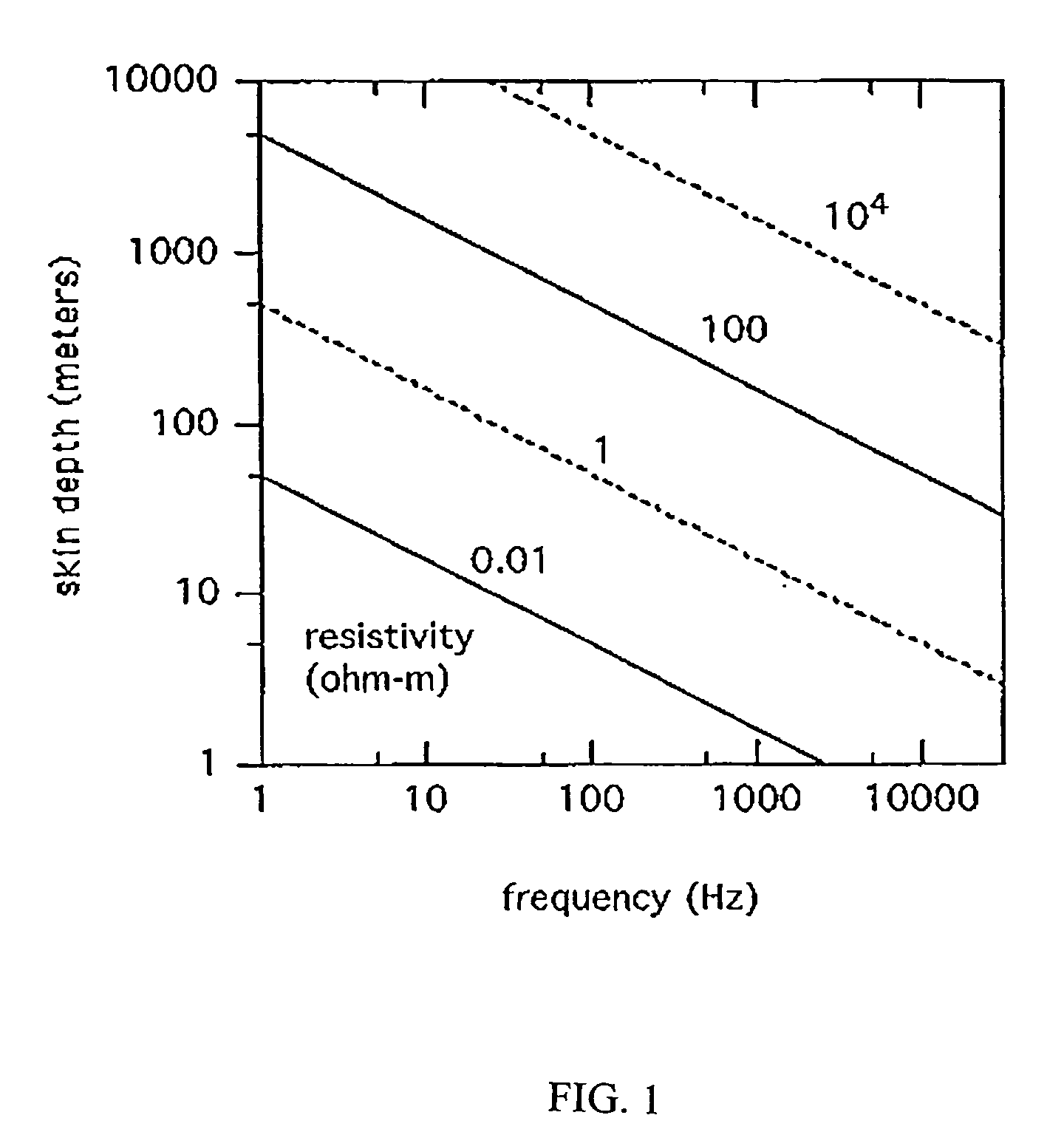

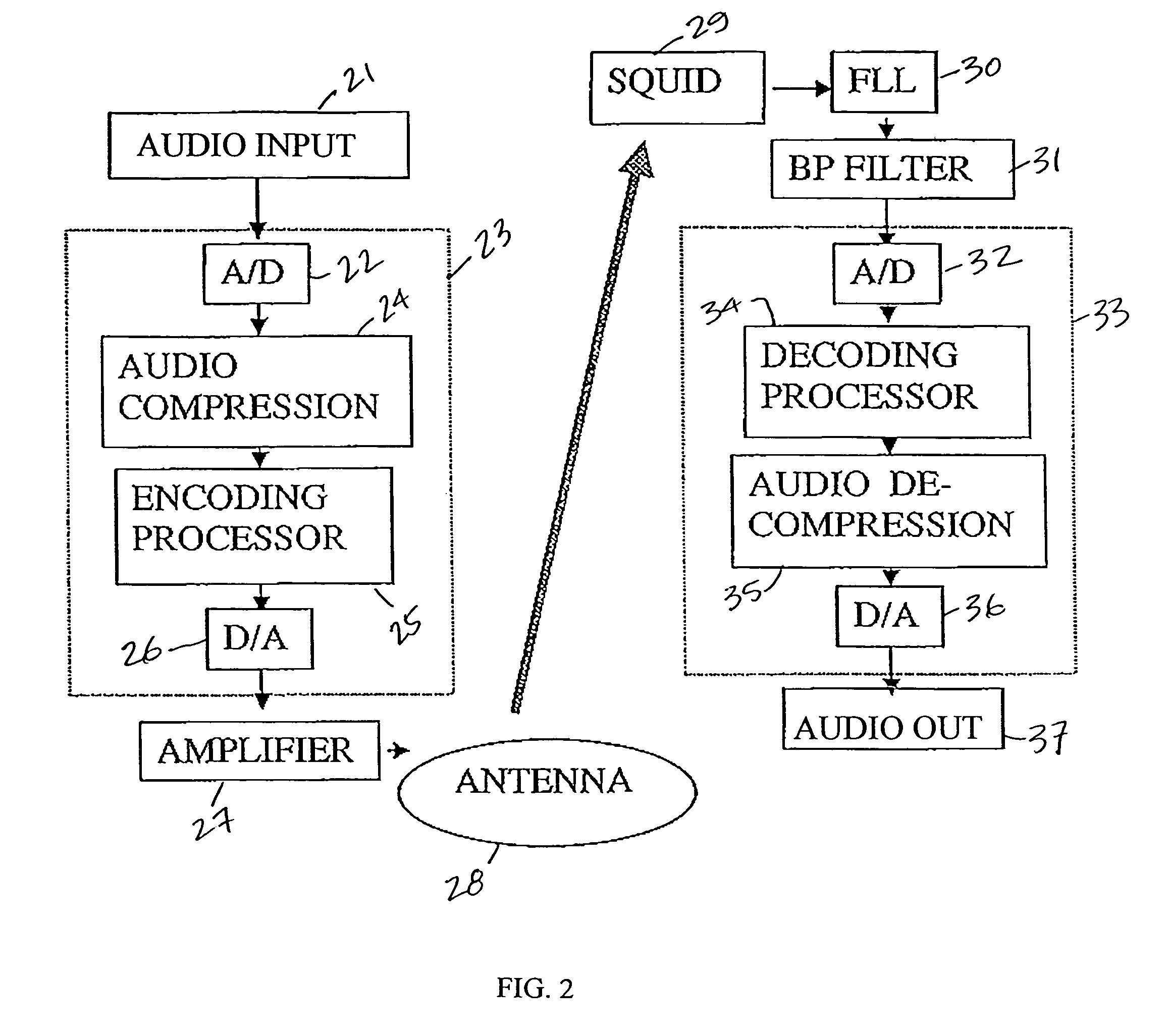

Through-the-earth radio

InactiveUS7043204B2Effective penetrationEffective distanceModulated-carrier systemsSubstation equipmentDigital-to-analog converterAnalog to information converter

A method and apparatus for effective through-the-earth communication involves a signal input device connected to a transmitter operating at a predetermined frequency sufficiently low to effectively penetrate useful distances through-the earth, and having an analog to digital converter receiving the signal input and passing the signal input to a data compression circuit that is connected to an encoding processor, the encoding processor output being provided to a digital to analog converter. An amplifier receives the analog output from the digital to analog converter for amplifying said analog output and outputting said analog output to an antenna. A receiver having an antenna receives the analog output passes the analog signal to a band pass filter whose output is connected to an analog to digital converter that provides a digital signal to a decoding processor whose output is connected to an data decompressor, the data decompressor providing a decompressed digital signal to a digital to analog converter. An audio output device receives the analog output form the digital to analog converter for producing audible output.

Owner:LOS ALAMOS NATIONAL SECURITY

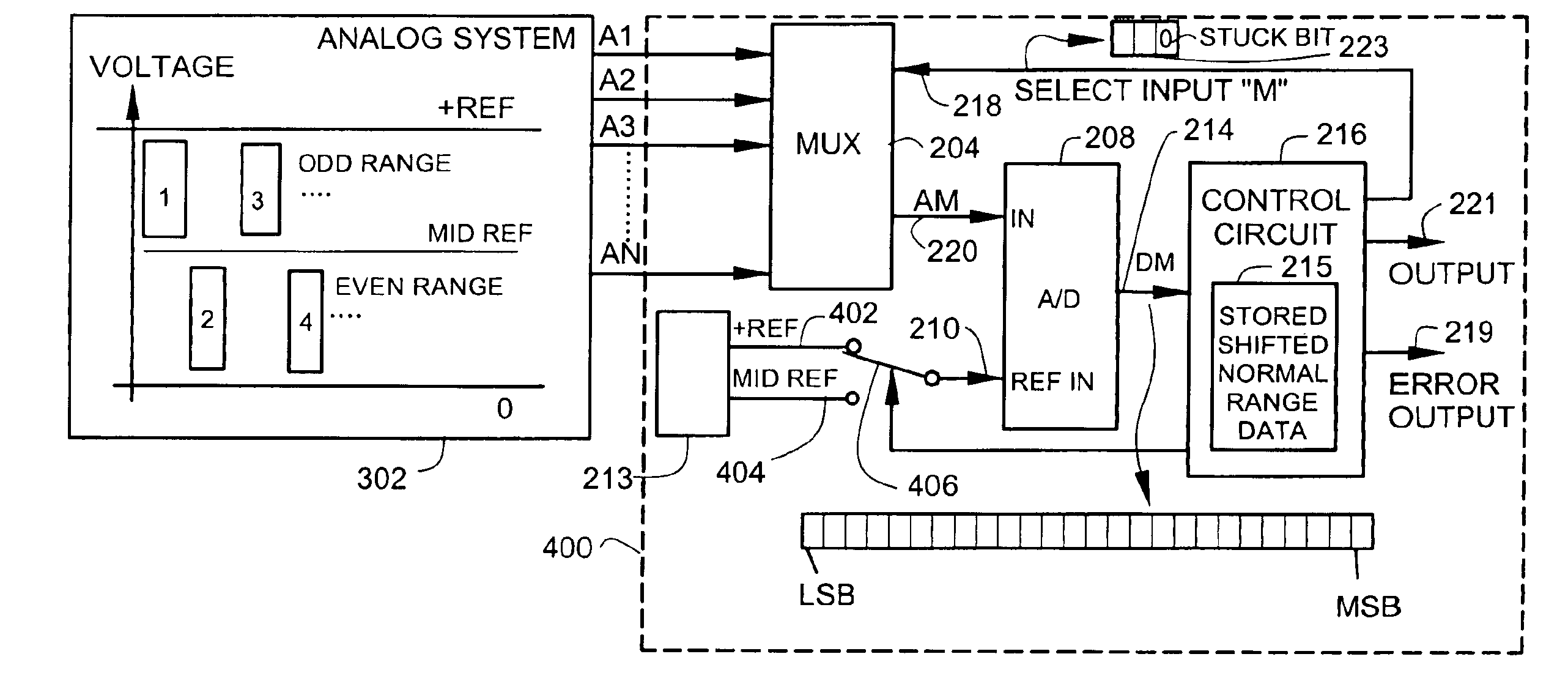

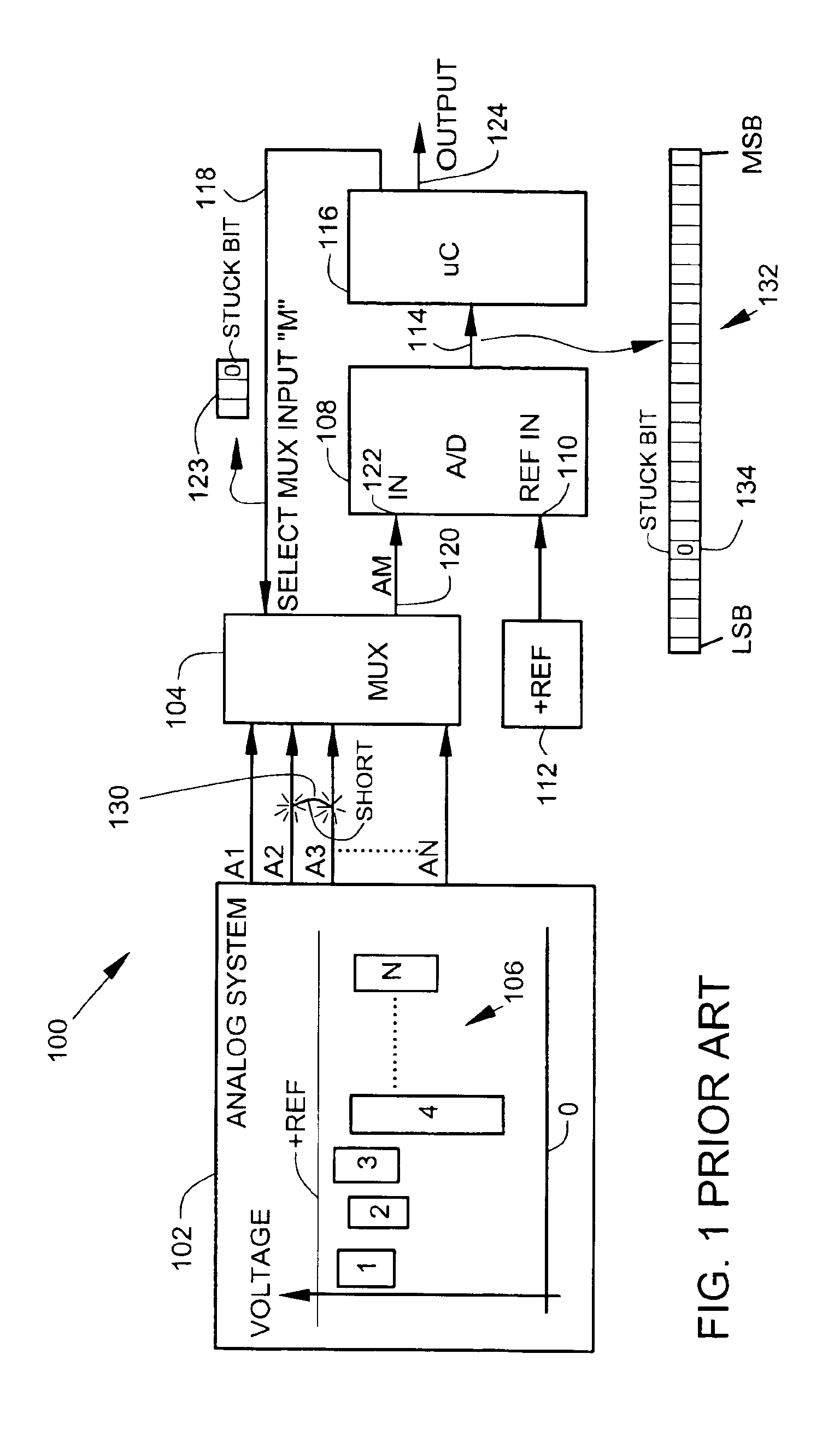

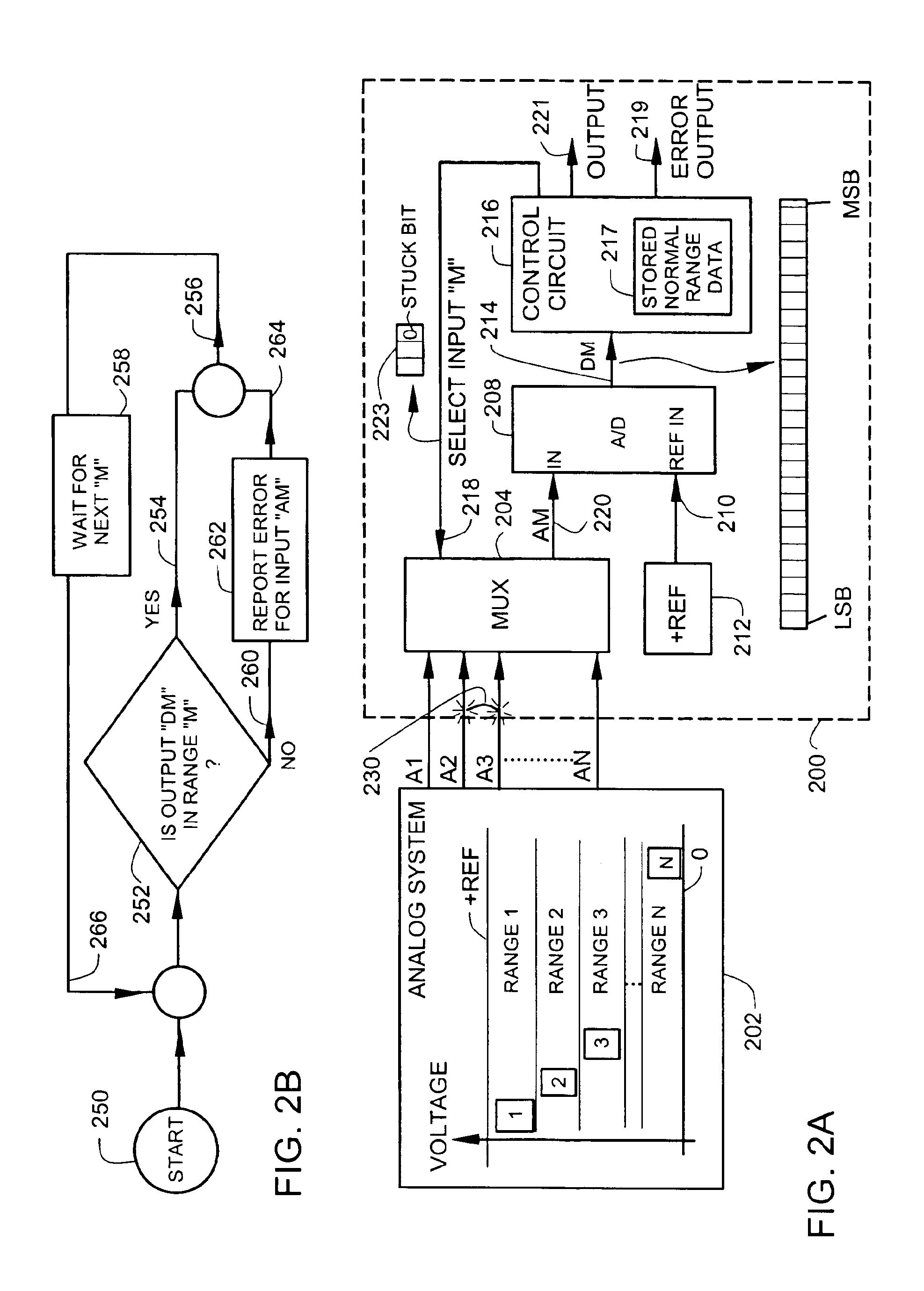

Analog-to-digital converter with range error detection

ActiveUS7046180B2Electric signal transmission systemsAnalogue-digital convertersDigital down converterMultiplexer

Owner:ROSEMOUNT INC

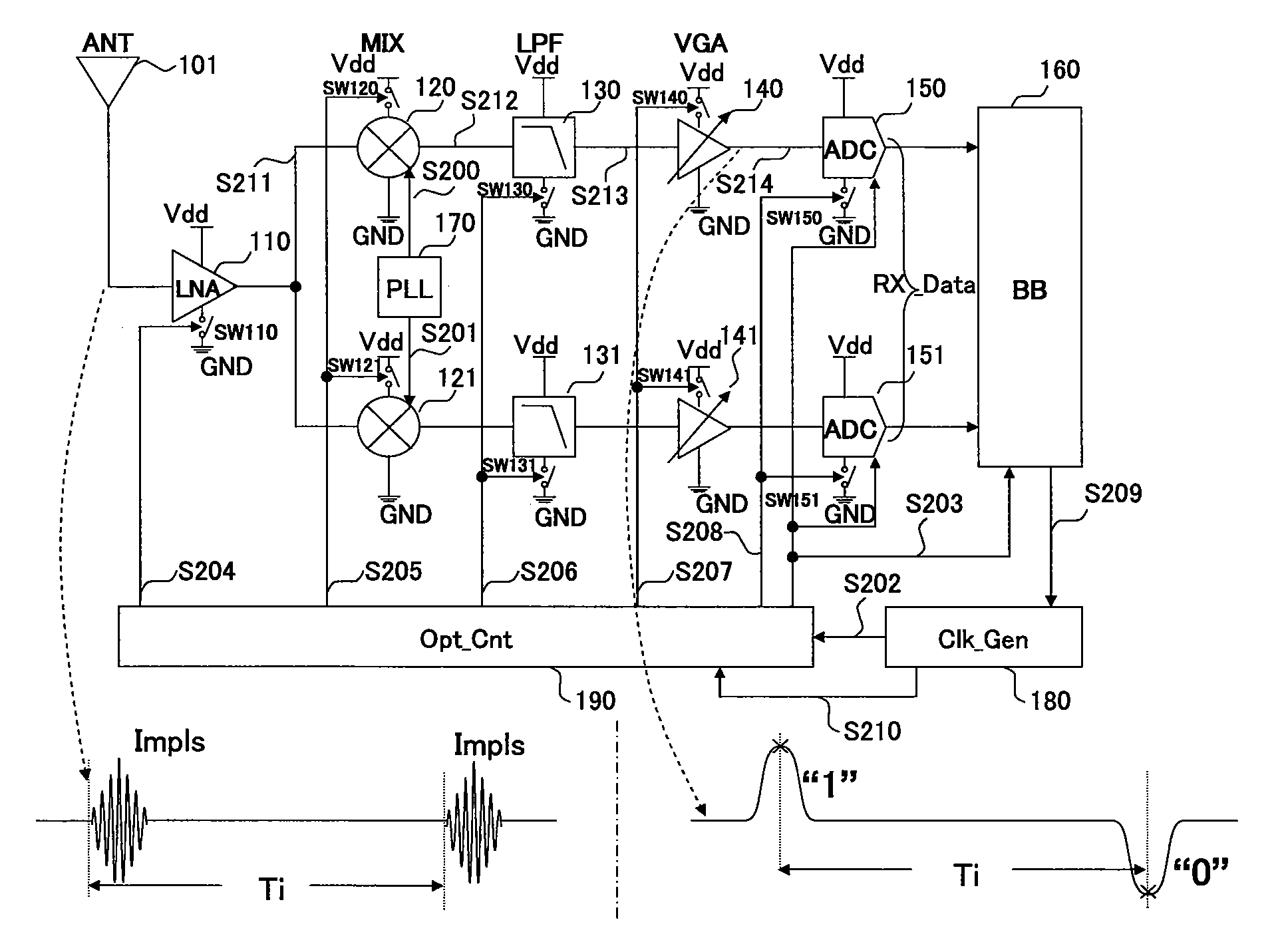

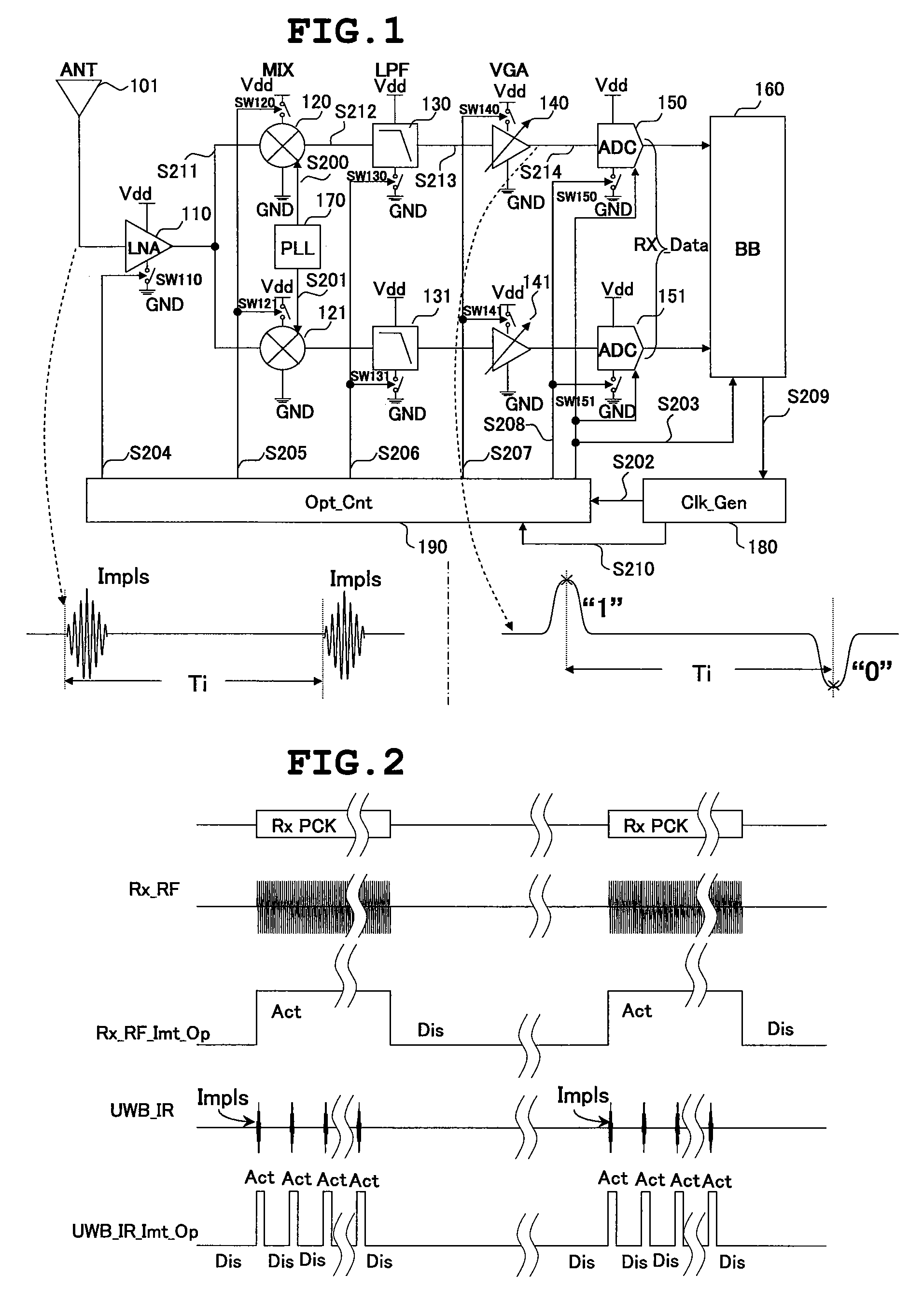

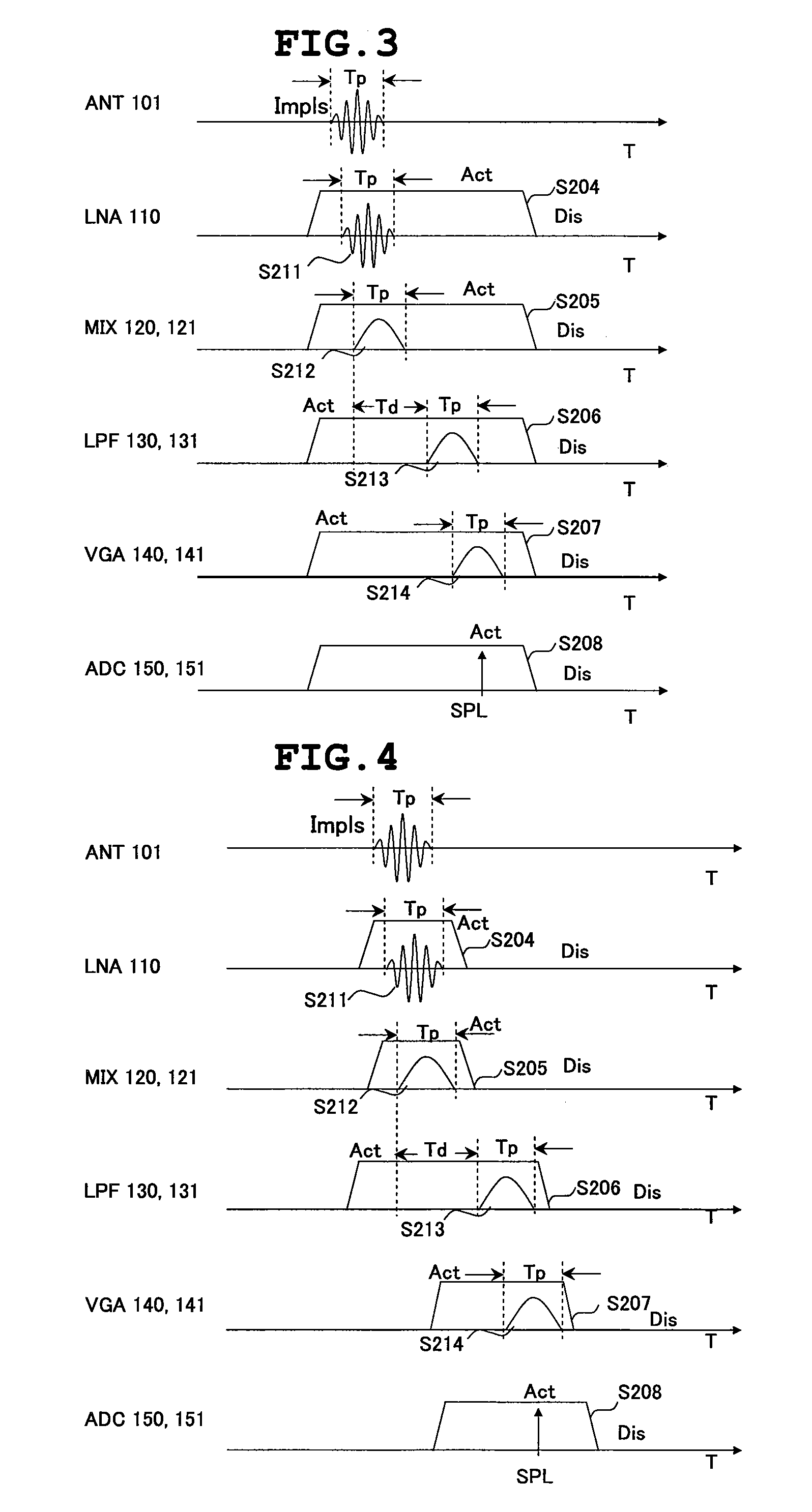

Receiver

ActiveUS20080069183A1Reduce power consumptionIncreased power consumptionModulated-carrier systemsPulse demodulatorVariable-gain amplifierAudio power amplifier

Power switches of circuits at respective stages of a low noise amplifier, demodulators, low-pass filers, variable gain amplifiers, and analog-to-digital converters are controlled to be off by an operation control unit in a non-reception period of an impulse signal. An increase in power consumption due to the adoption of an active filter or a variable gain amplifier is compensated for by a reduction in power consumption through intermittent operations of the circuits at the respective stages according to on and off control of the power switches.

Owner:RENESAS ELECTRONICS CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com