Patents

Literature

323results about "Continuous tuning details" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

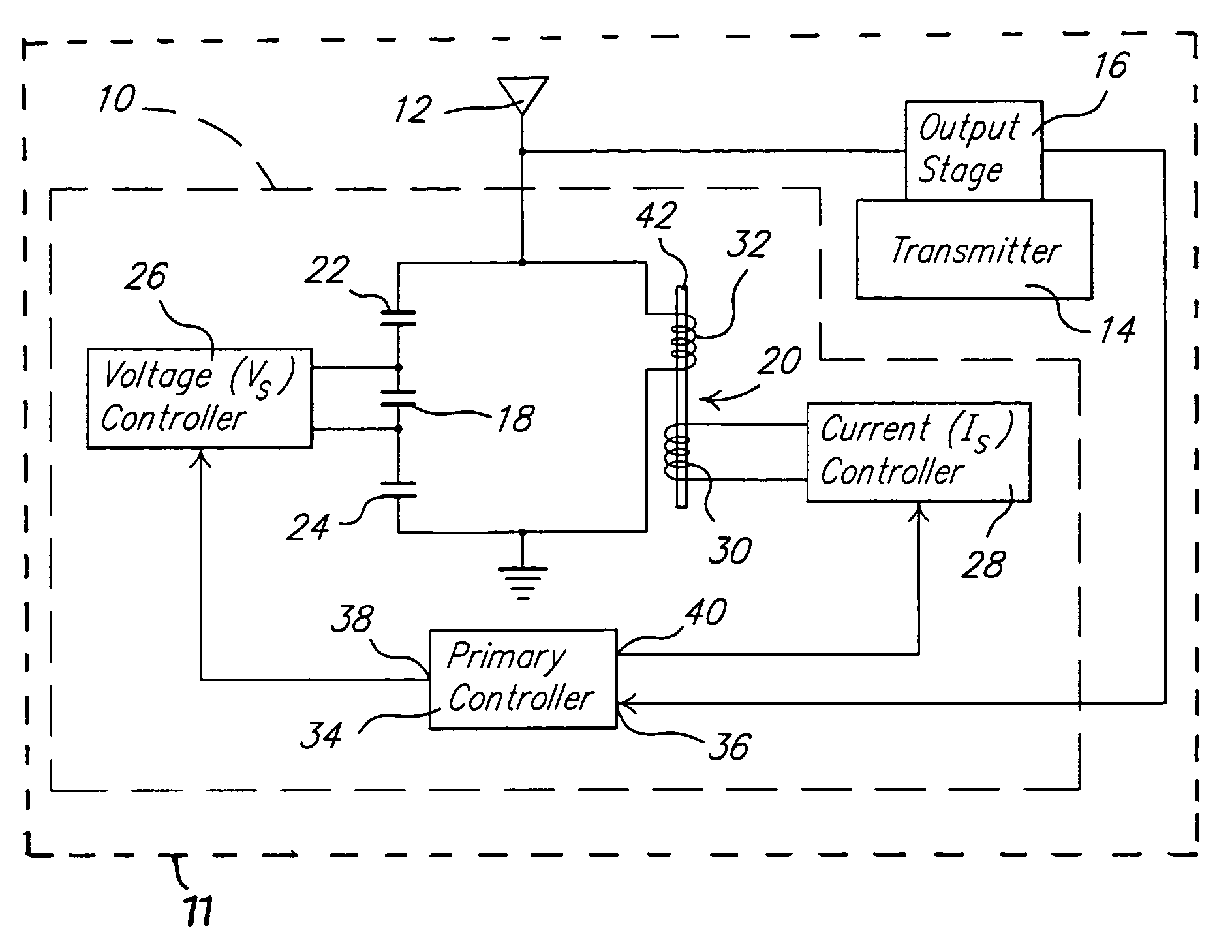

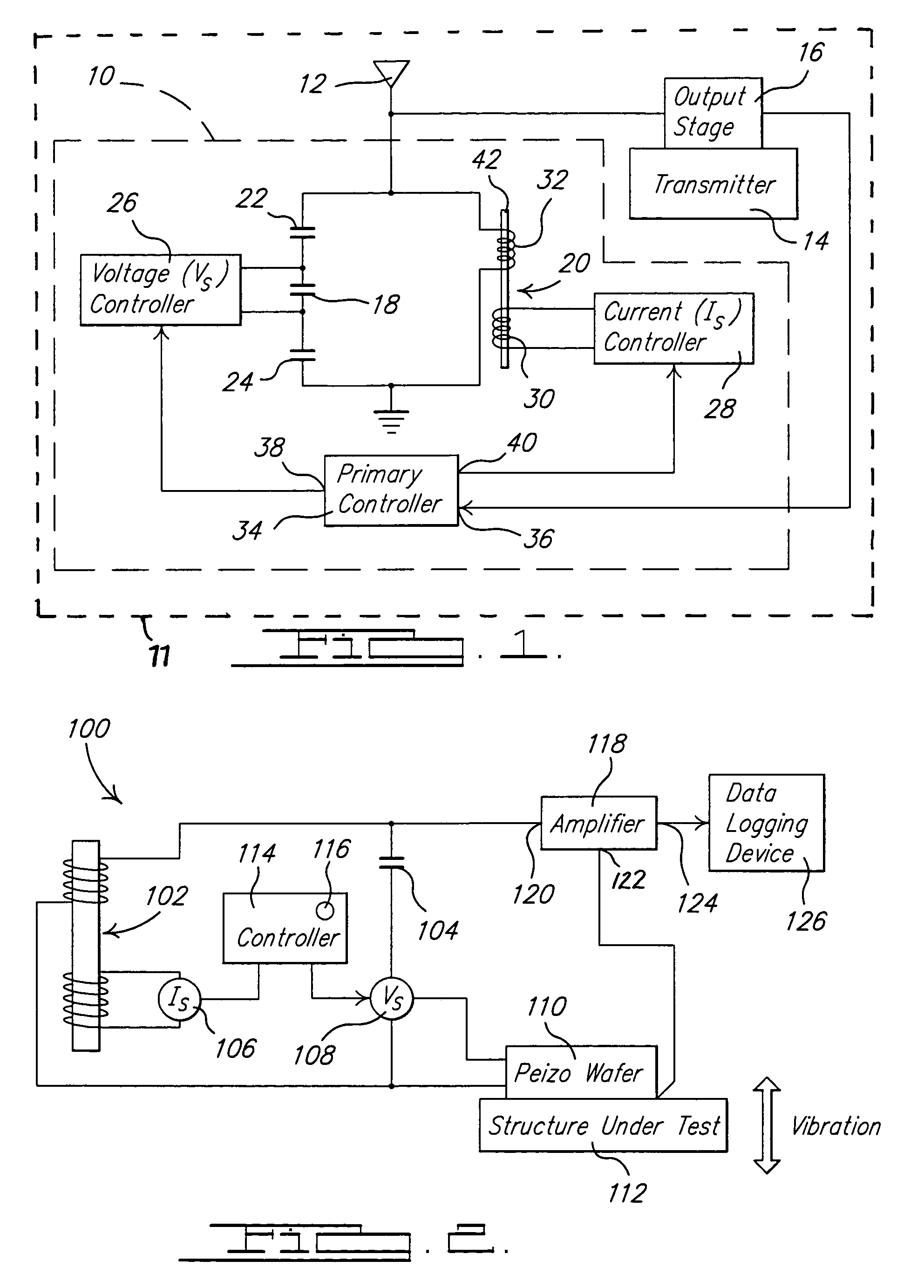

Electrically tuned resonance circuit using piezo and magnetostrictive materials

An impedance tuning system, especially for a cellular telephone system. The system can be used to match the impedance of an antenna element with that of an output stage of a transmitter driving the antenna element. The system includes a piezo capacitor in parallel with the magnetostrictive inductor to form an LC circuit. A voltage controller applies a voltage bias signal to the piezo capacitor and a current controller applies a current bias signal to the inductor. A primary controller monitors the frequency of the output signal from the transmitter and controls the voltage and current controllers as needed to alter the impedance of the system as needed to match the impedance of the antenna element with that of the output stage of the transmitter. In an alternative form an ultrasonic sensor is provided.

Owner:THE BOEING CO

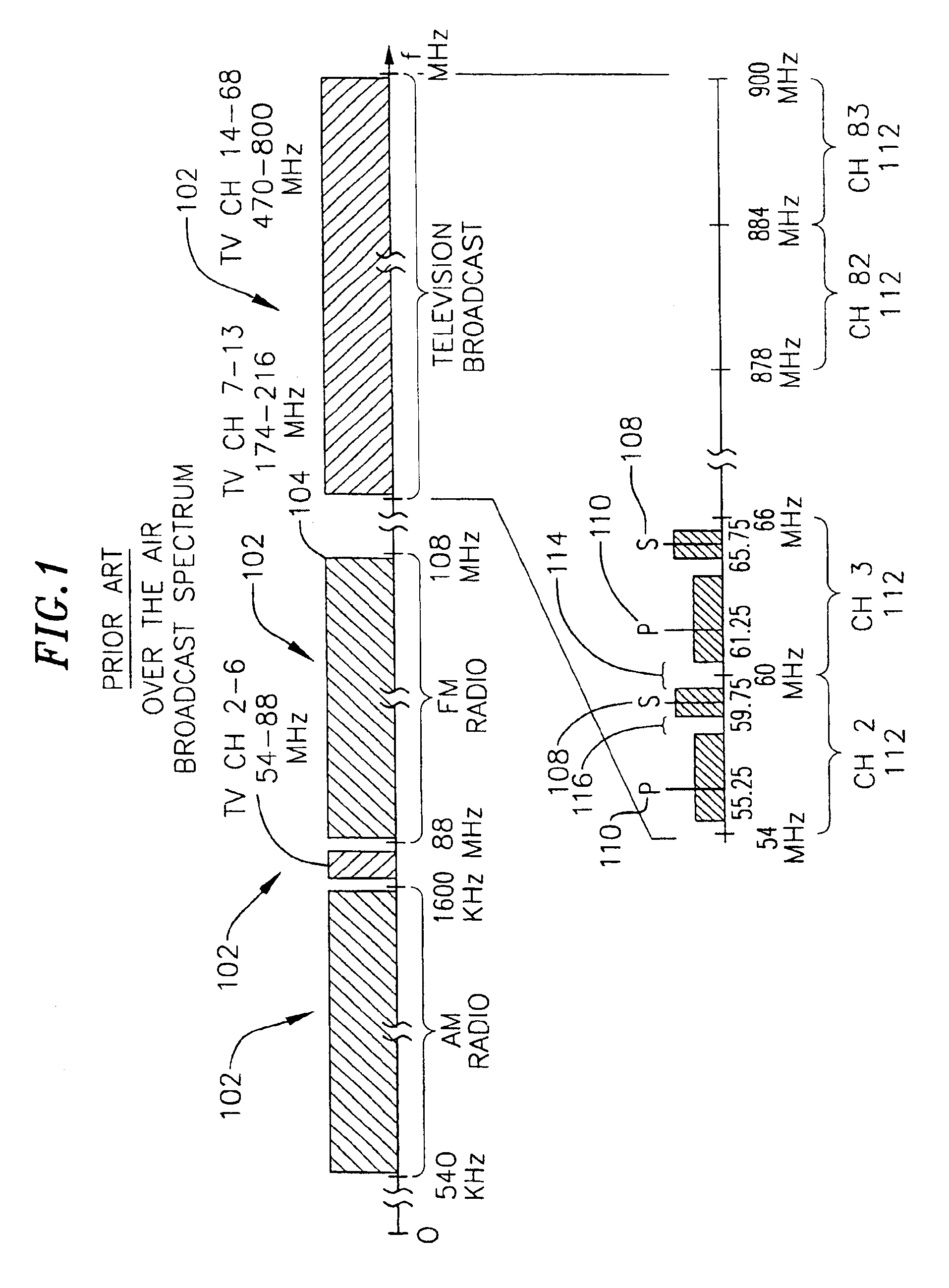

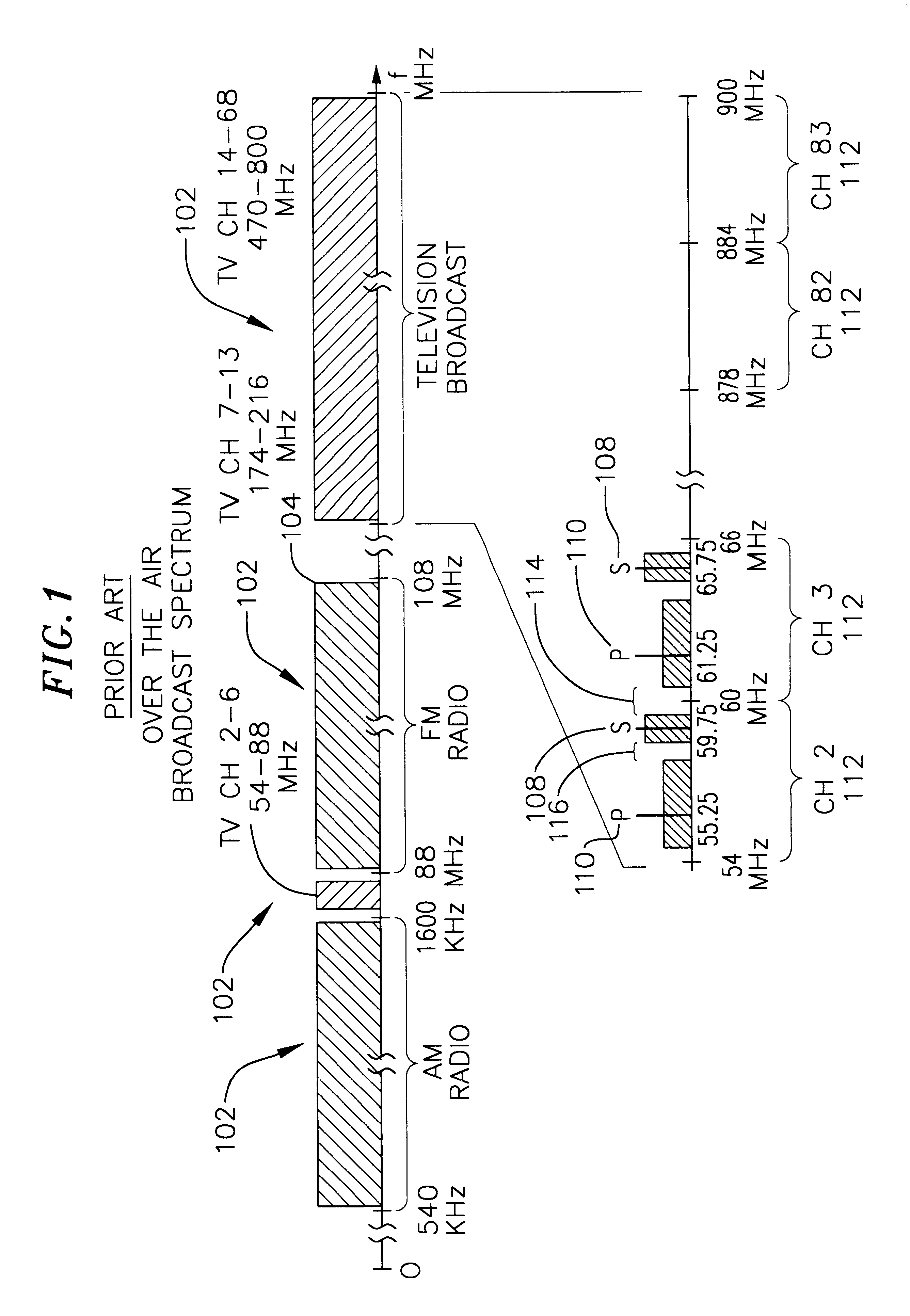

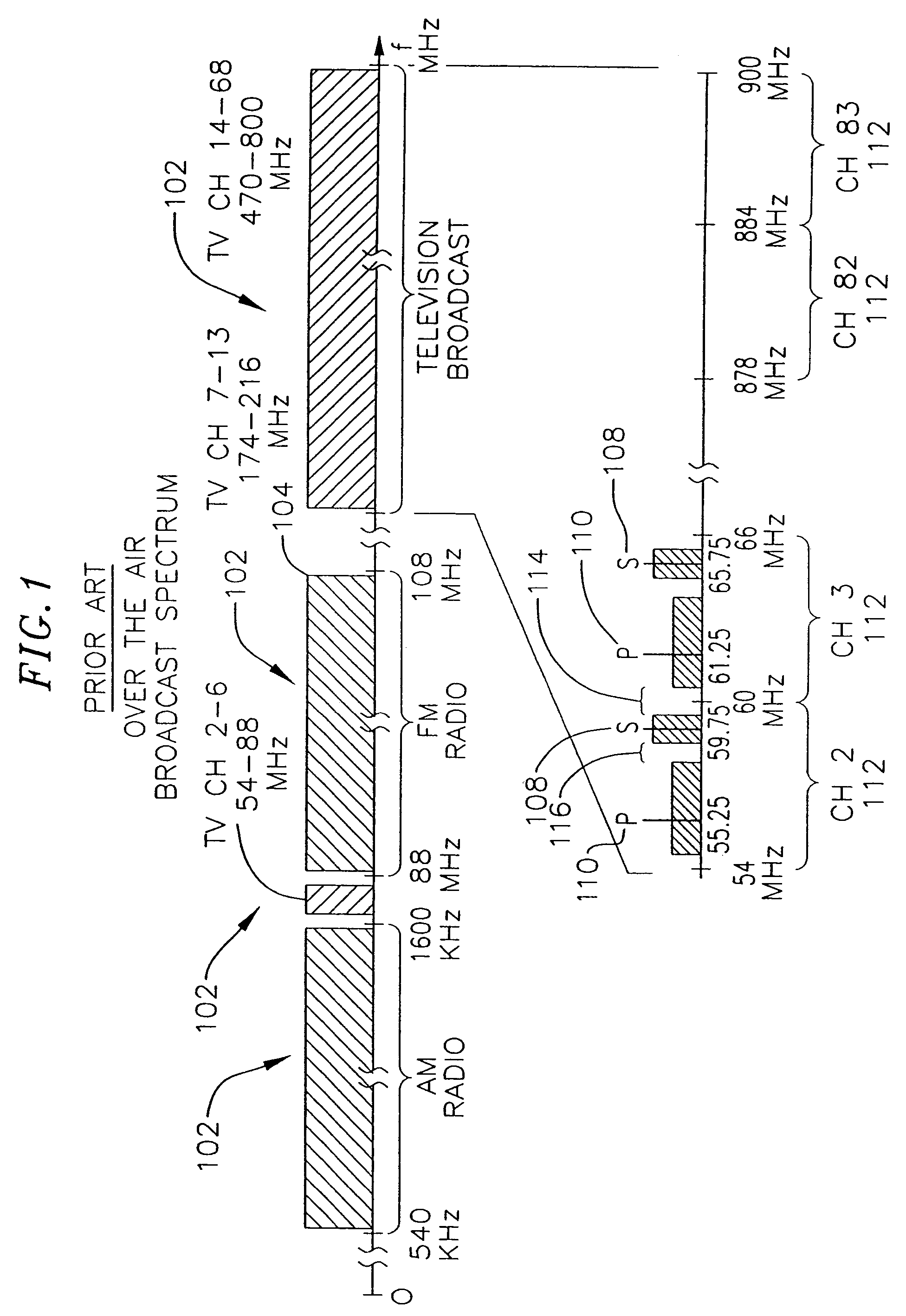

Tuner and broadcasting signal receiver including the same

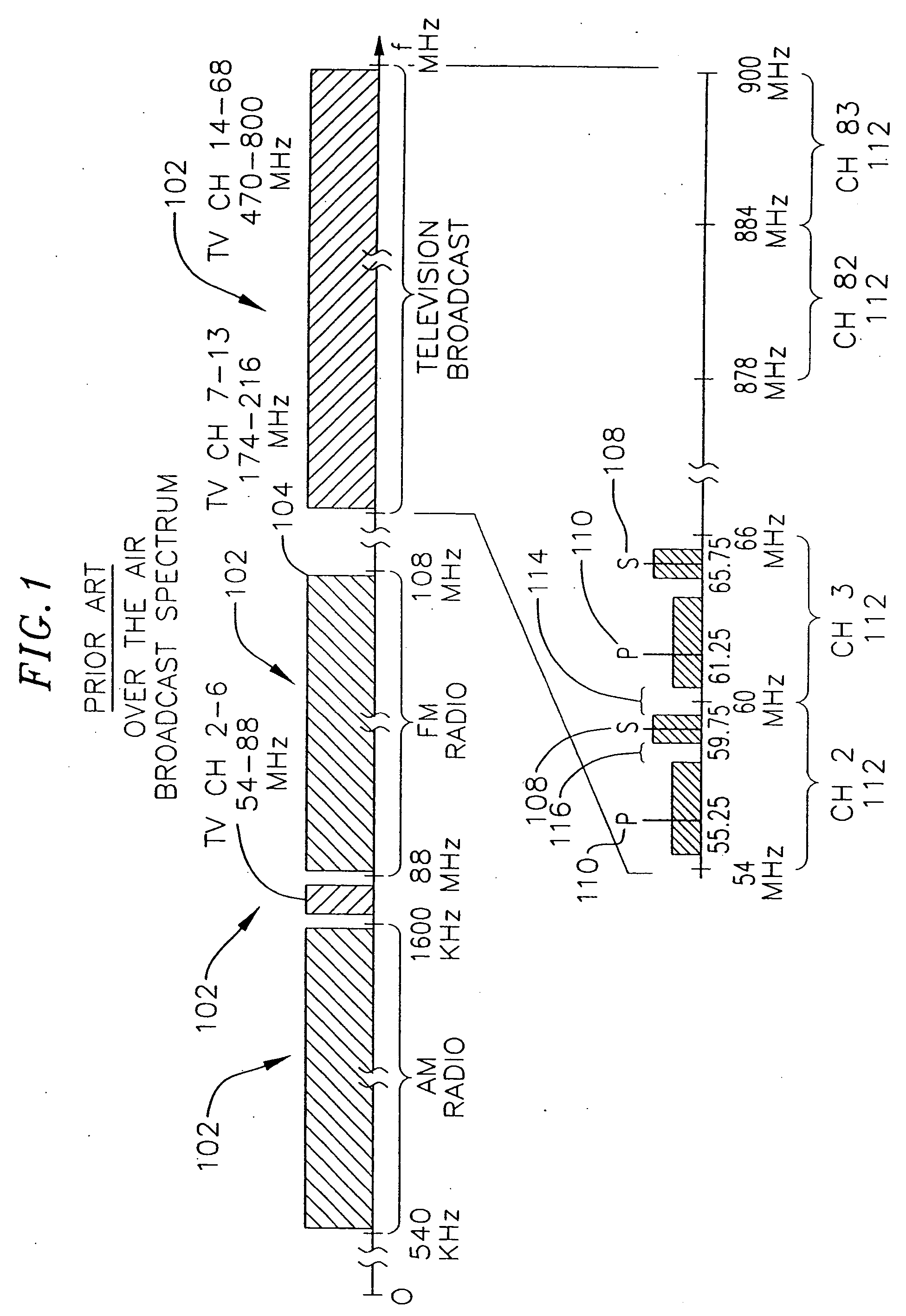

InactiveUS20070042734A1Improve featuresImprove performanceTelevision system detailsContinuous tuning detailsReceived signal strength indicationEngineering

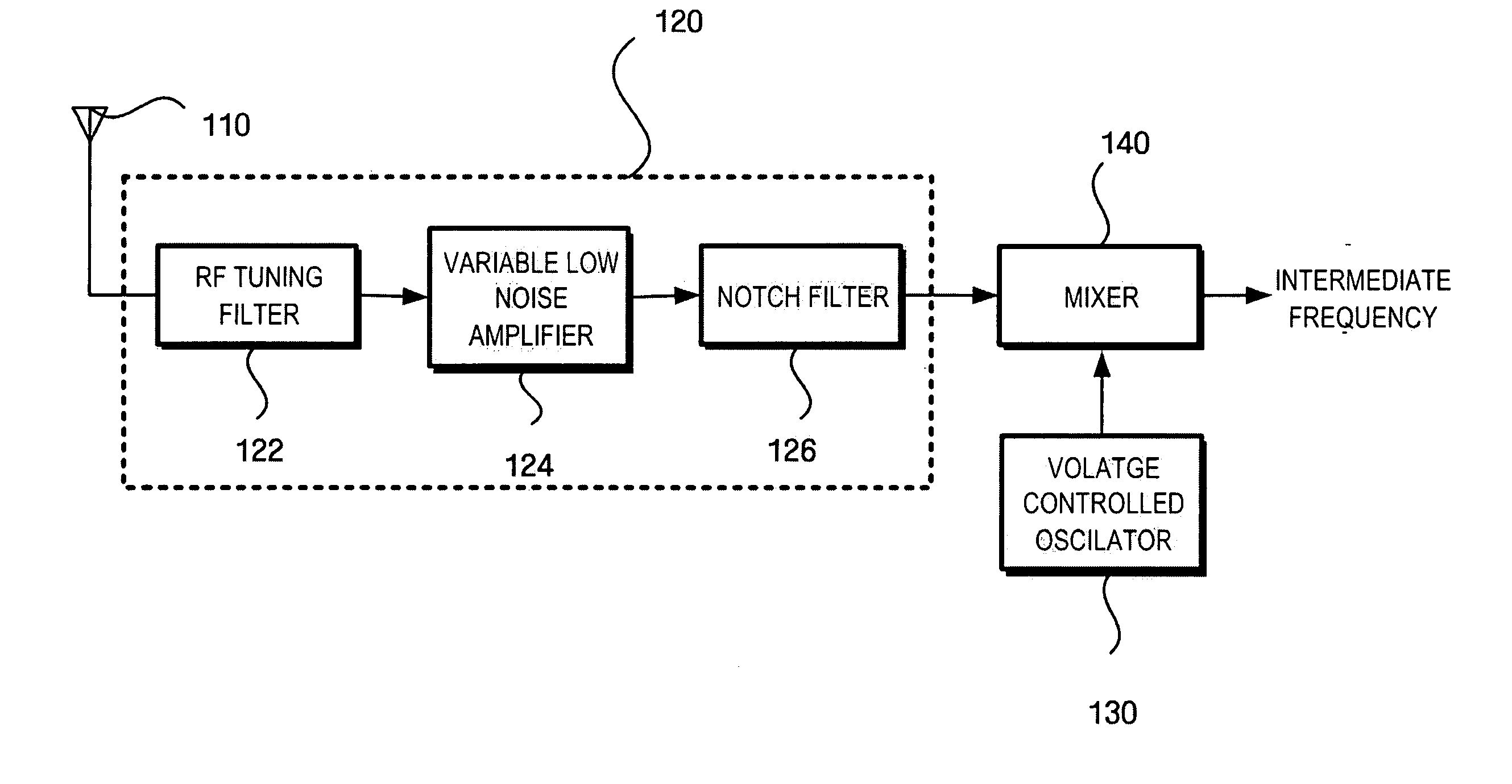

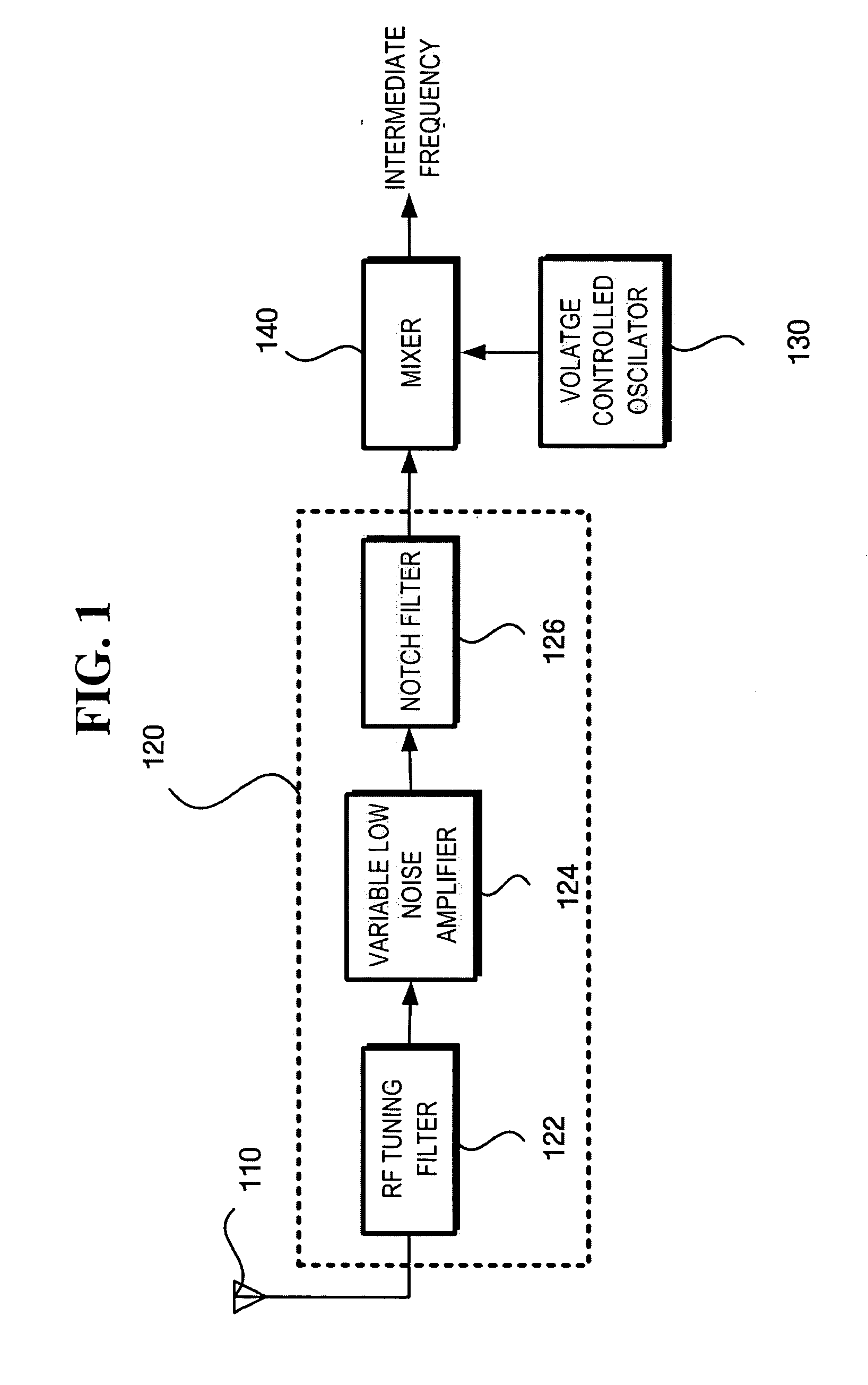

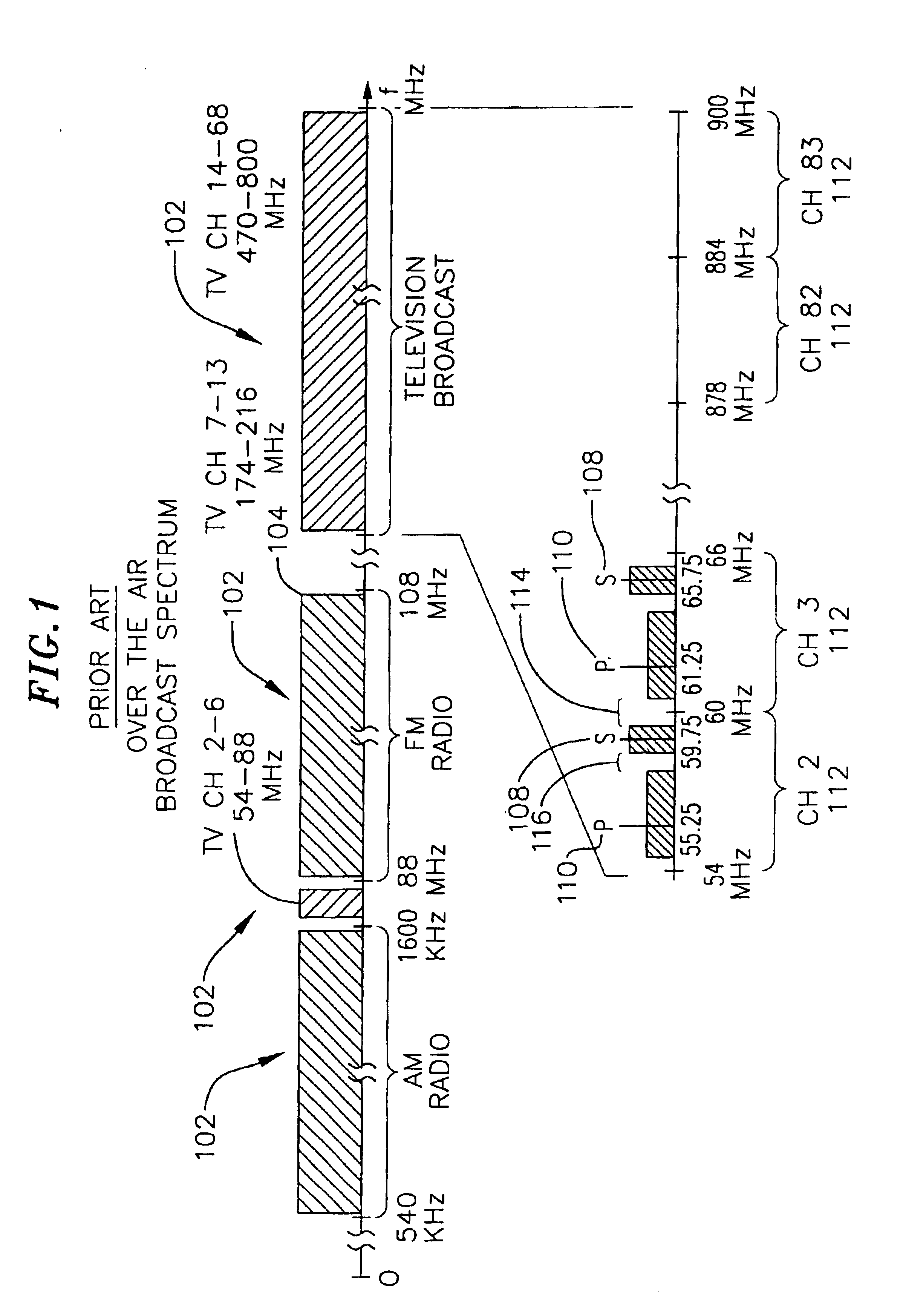

A tuner and a broadcasting signal receiver including the tuner. The tuner includes a band selection module that selects an RF broadcasting signal within the frequency band corresponding to a selected channel, and a low noise amplifier module that amplifies the signal with a specific received signal strength indicator (RSSI) to produce an RF broadcasting signal with a specific gain.

Owner:SAMSUNG ELECTRONICS CO LTD

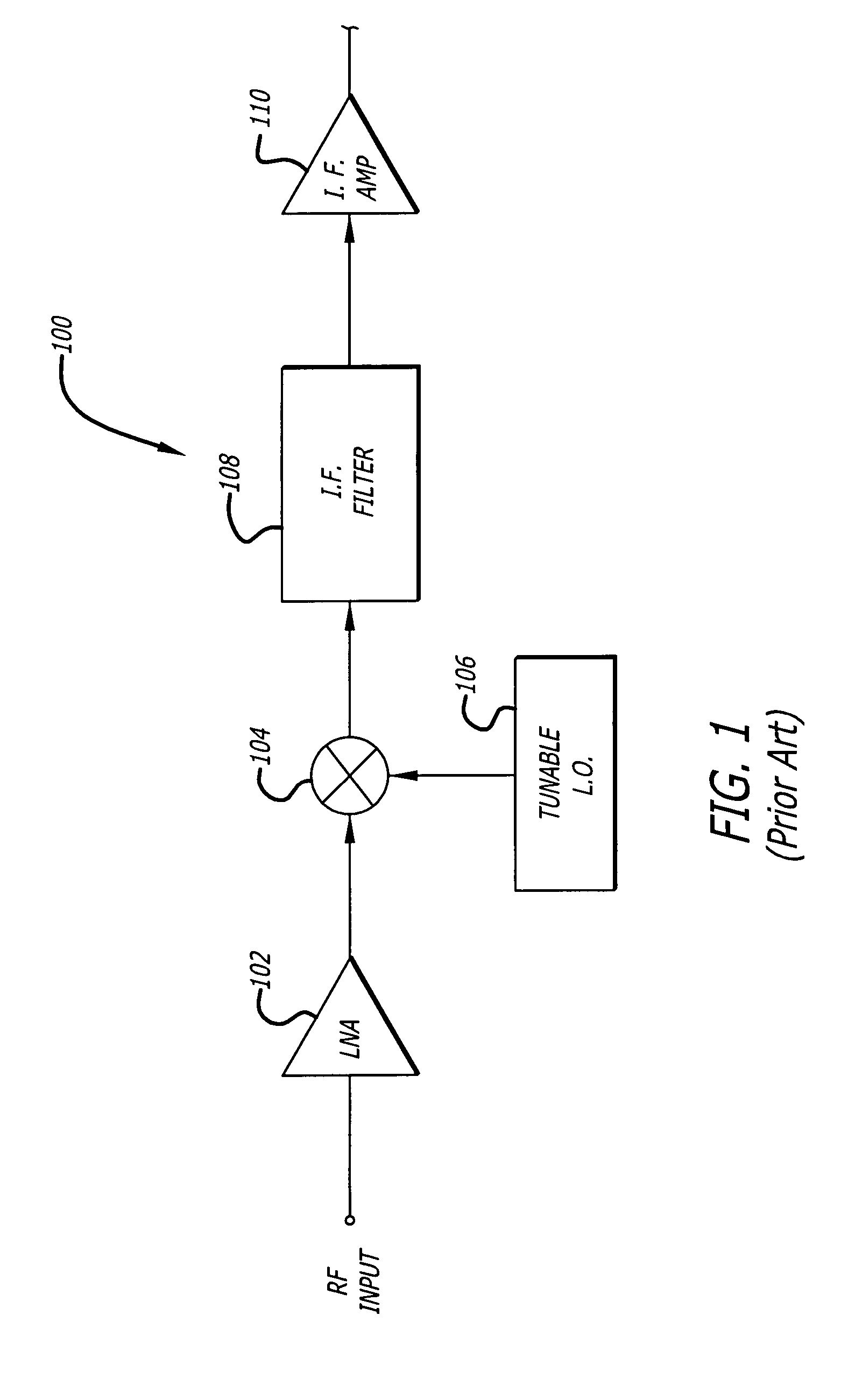

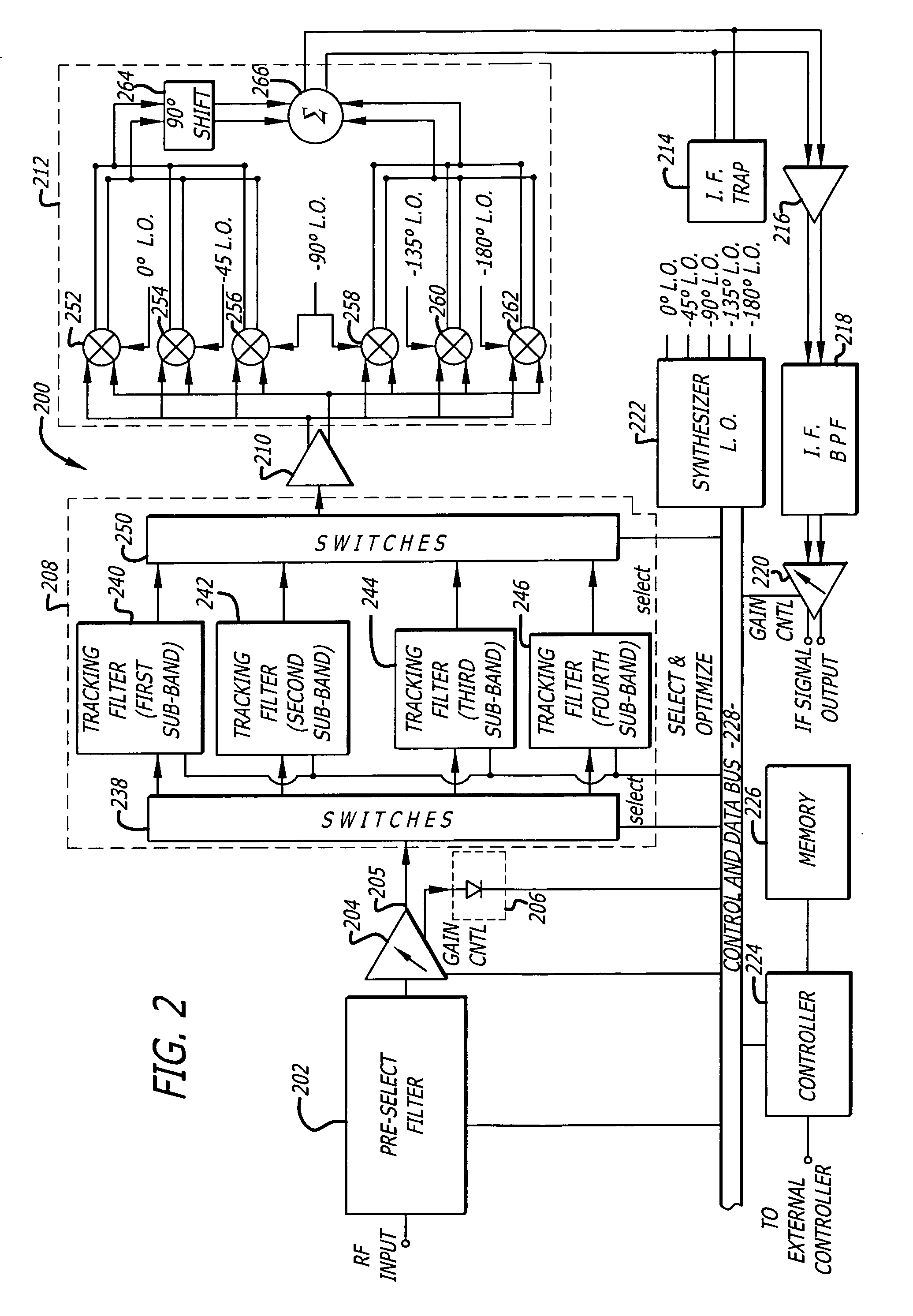

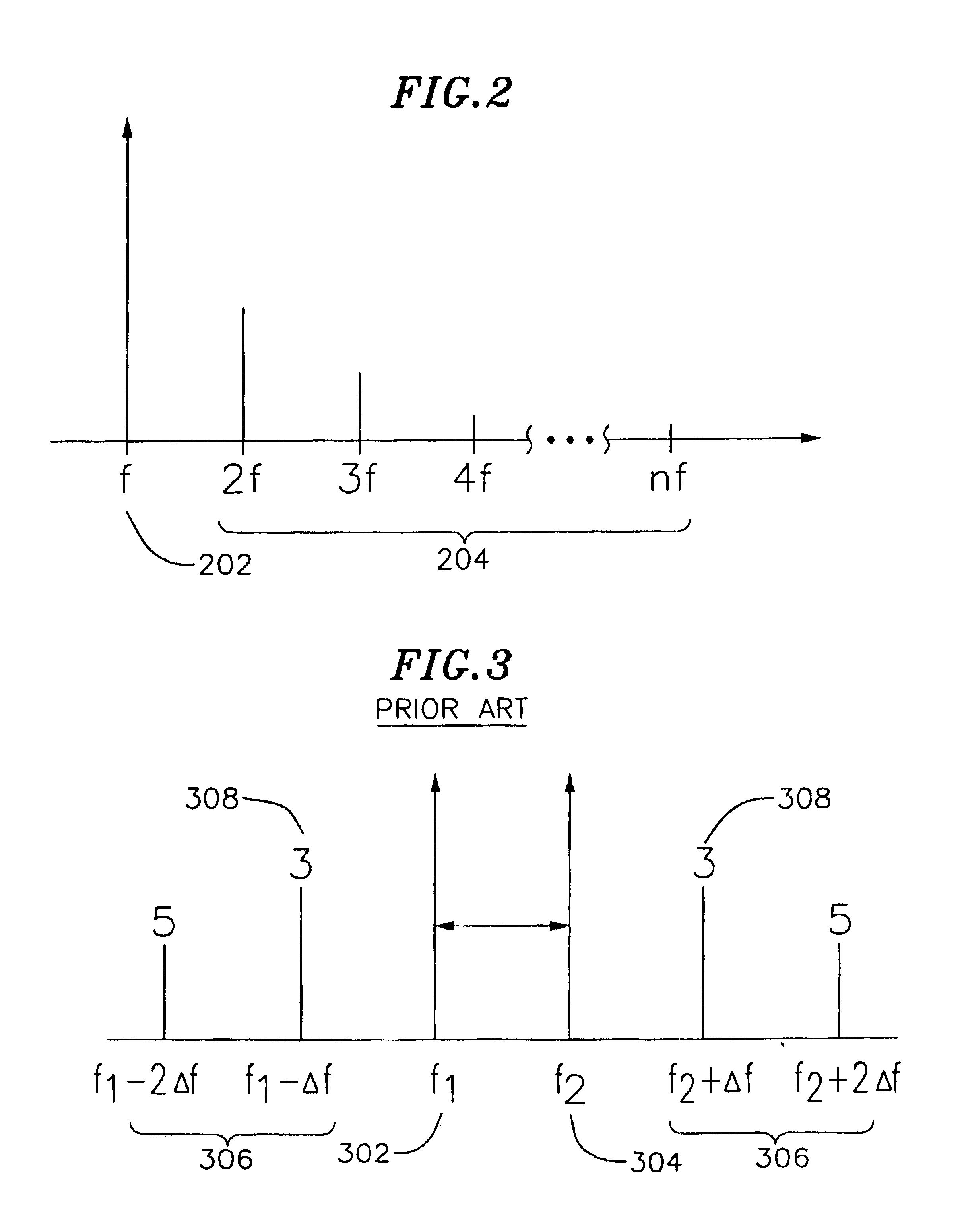

Broadband integrated digitally tunable filters

InactiveUS20050040909A1Multiple-port networksTransmission control/equlisationAudio power amplifierBroadband

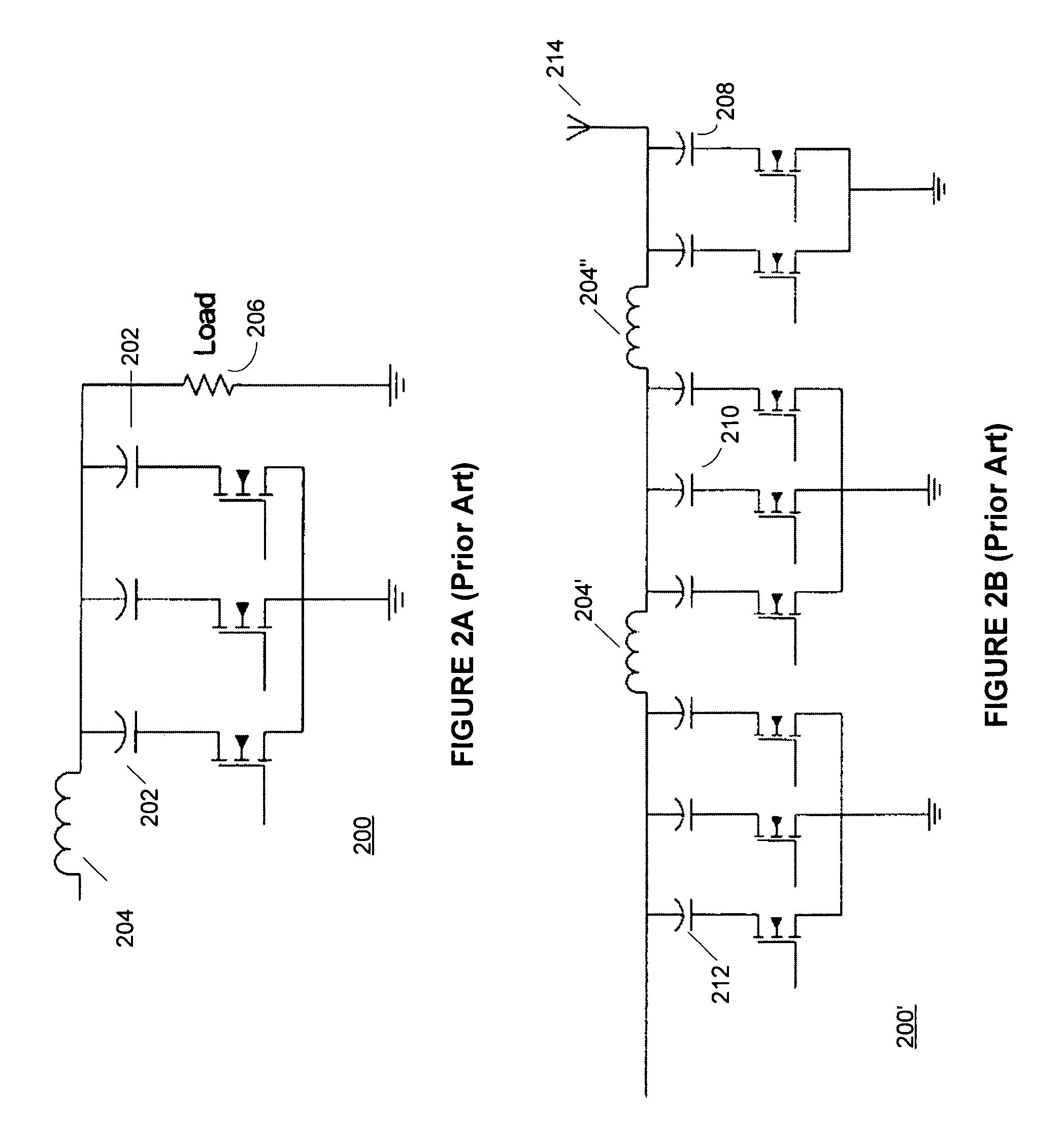

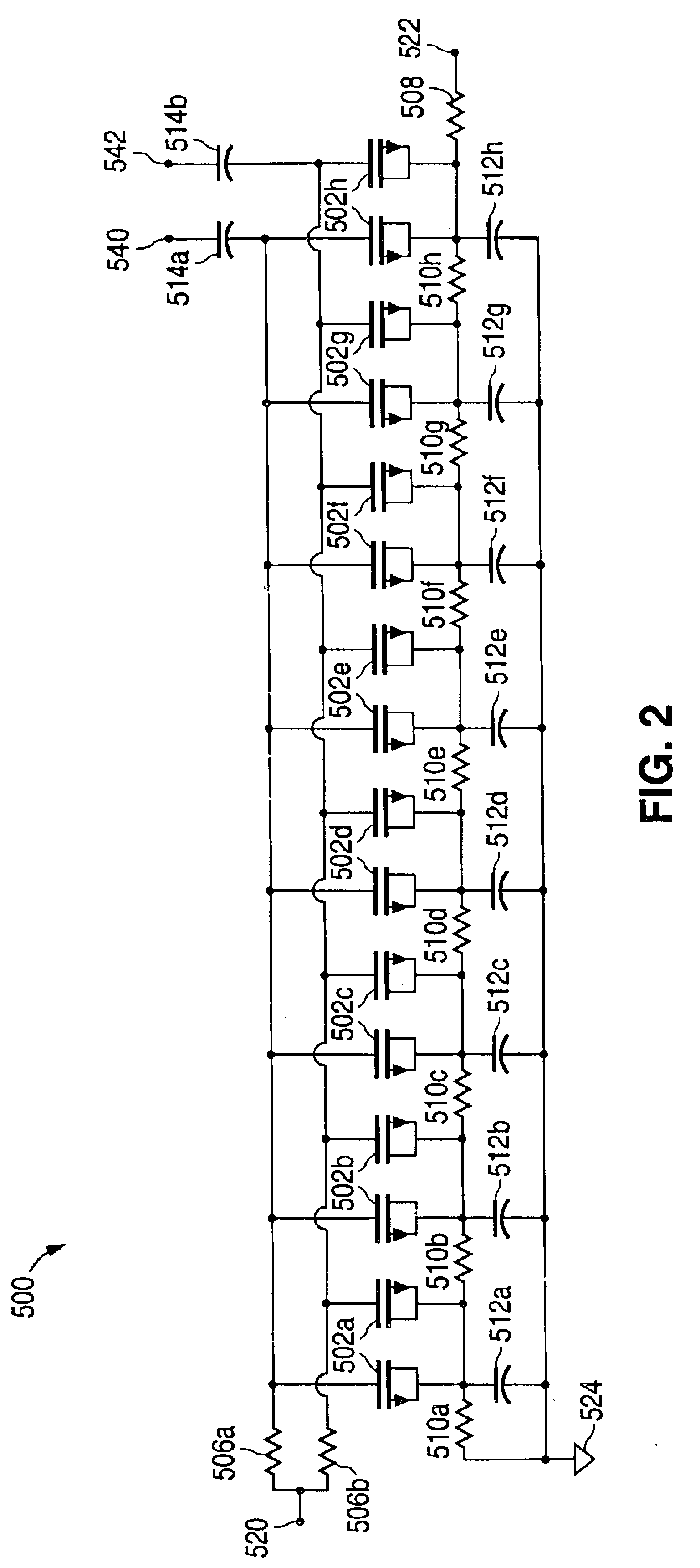

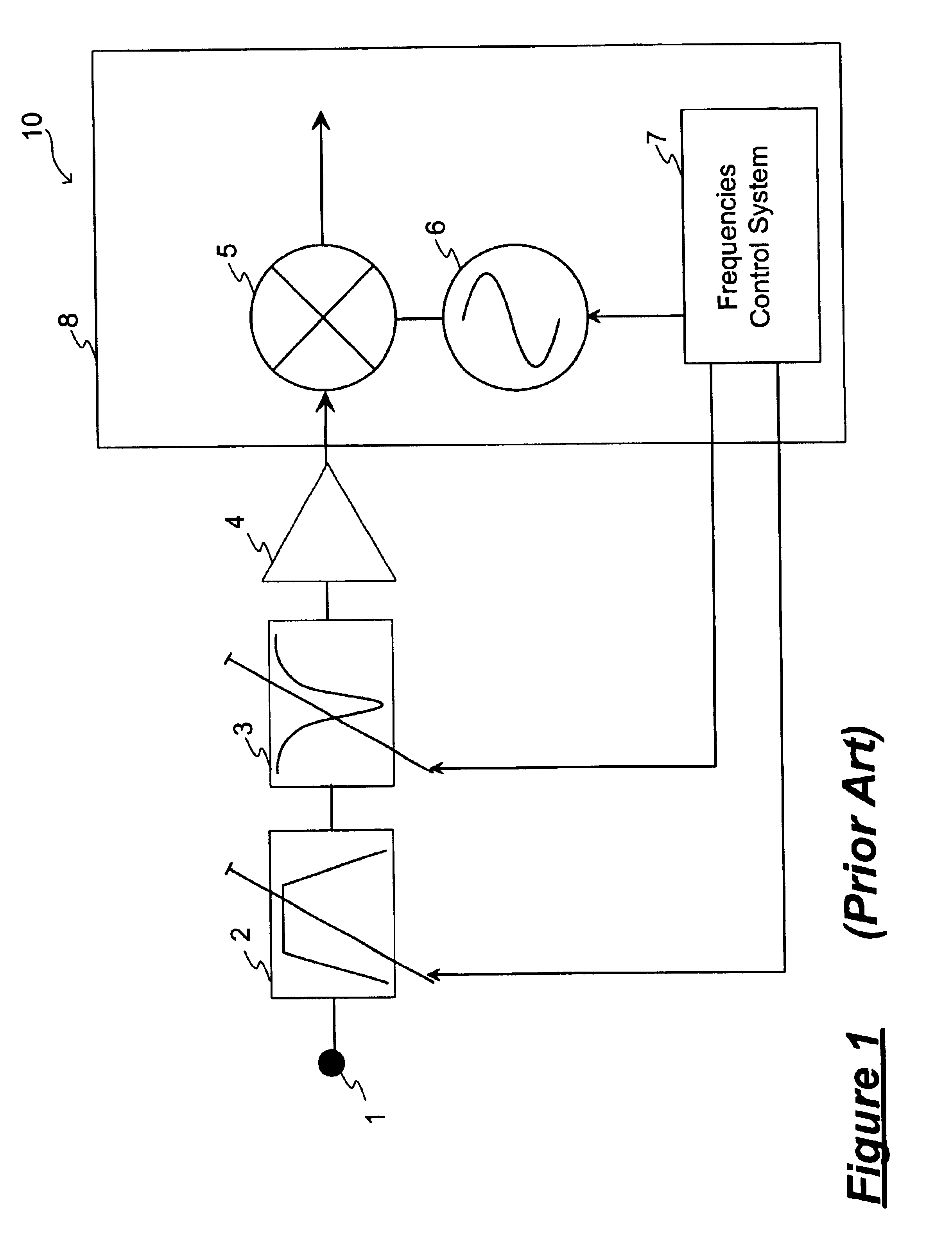

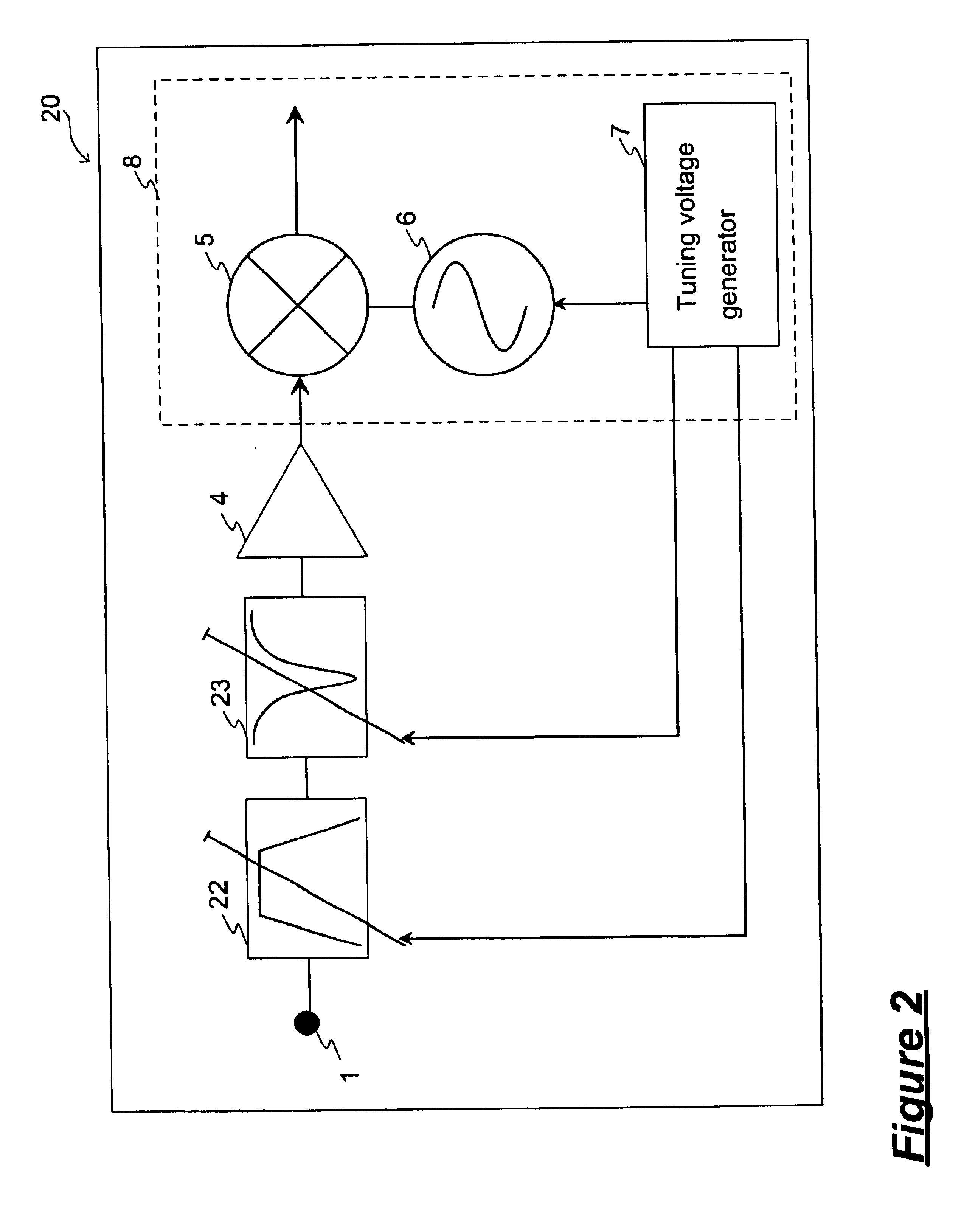

A tunable receiver is disclosed including a plurality of select filters to perform an initial band selection, a variable-gain low noise amplifier (LNA) whose gain is controlled to prevent its output power level to exceed a predetermined power threshold, a plurality of digitally-tunable tracking filters to pass signals within a selected channel and to reject signals in a corresponding image band, a second LNA to further amplify the received RF signal and to generate differential signal outputs, a down converting stage which converts the received RF signal to an IF signal while rejecting signals in the image band, an IF trap to further reject undesired signals present at the output of the down converting stage, an IF amplifier to amplify the IF signal to compensate for losses, an IF filter to provide channel select and reject undesirable signals, and a variable-gain IF amplifier to amplify the IF signal and maintain its power level within specification.

Owner:MAXIM INTEGRATED PROD INC

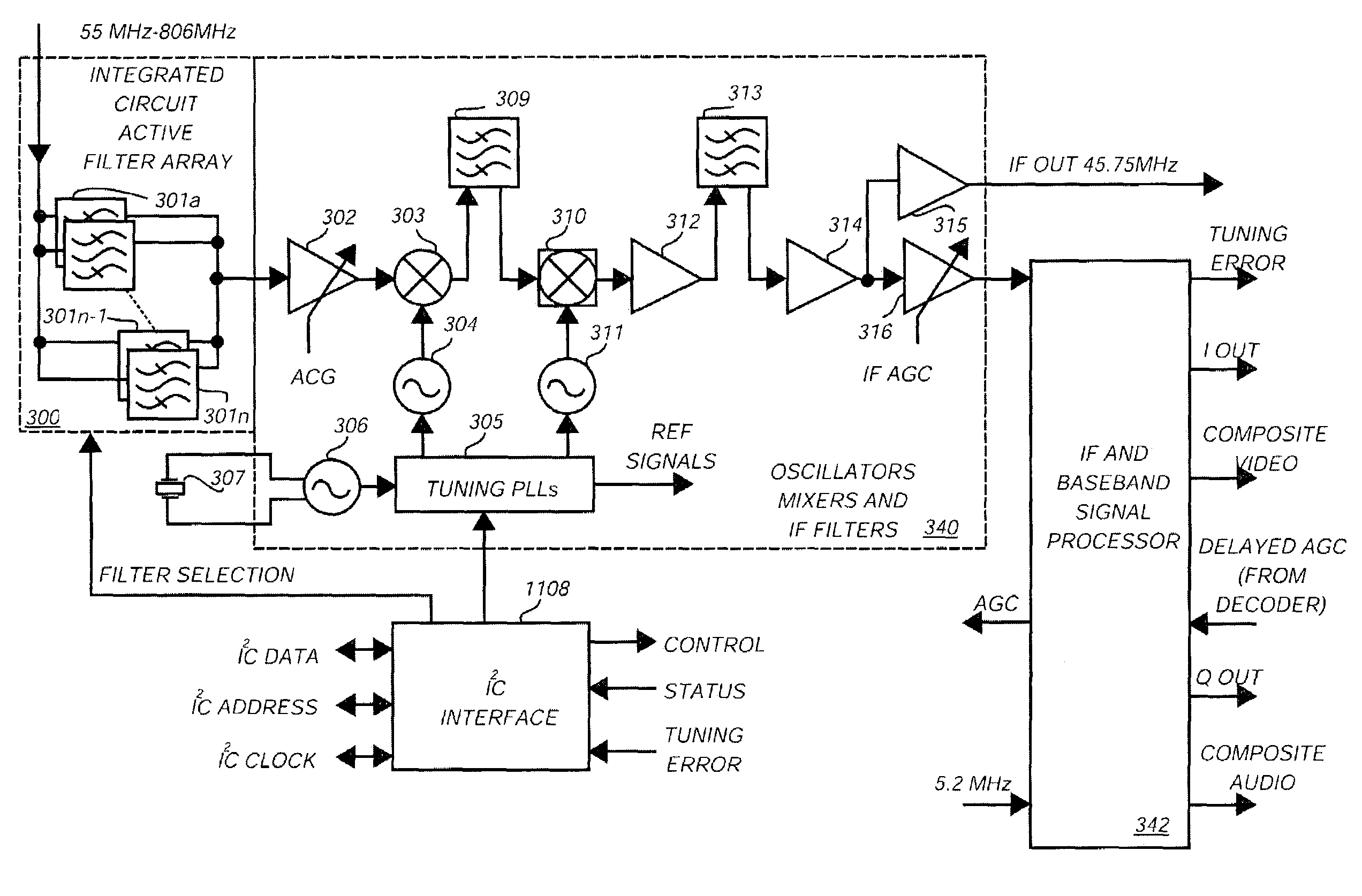

Integrated circuit tuner with broad tuning range

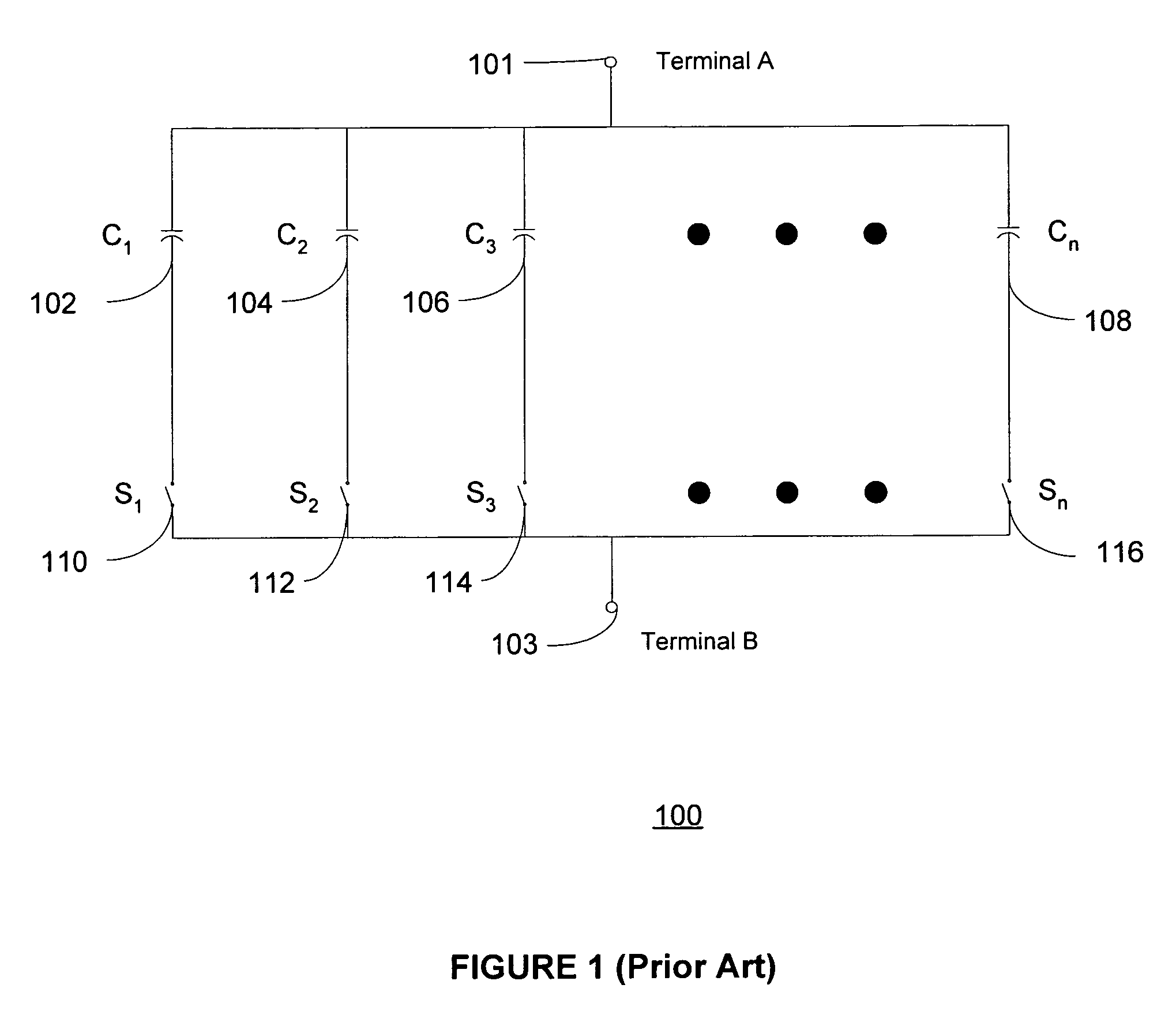

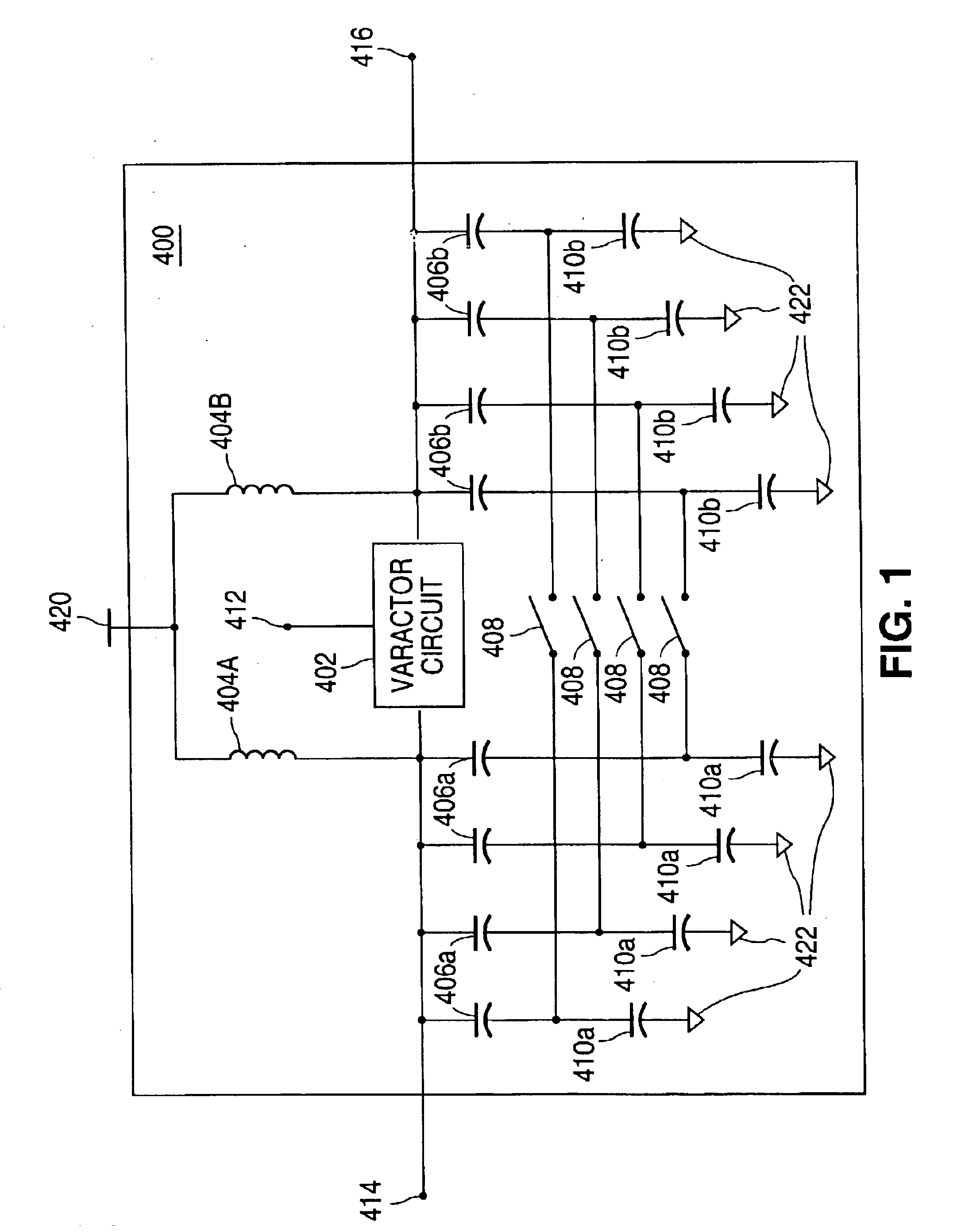

An integrated front end filter for a tuner provides an array of from several to a multitude of passbands, each for passing at least one but less than all channels designated in a band of frequencies. Each passband is exclusively selectable. The integrated front end filter can include at least one active filter unit with an active reactance element in either of fixed and variable filter configurations and a decoder coupled to said at least one active filter unit and being responsive to a control signal for selecting a one of the passbands. In one example, a multitude of active filter units of fixed filter configuration provide the multitude of passbands. In another example, a plurality of data corresponds to a like plurality of selectable passbands in combination with a filter element of the variable filter configuration. Each data is stored at a predetermined location and reproduced in response to a corresponding control data signal from a tuner controller. Each data characterizes one of the plurality of passbands. The filter element is switchable from one passband to another in response to the control data signal. Lower power dissipation and lesser requirements of an on-following integrated circuitry tuner permit a reduction of “off chip” connections and cost.

Owner:INTELLECTUAL VENTURES HLDG 75

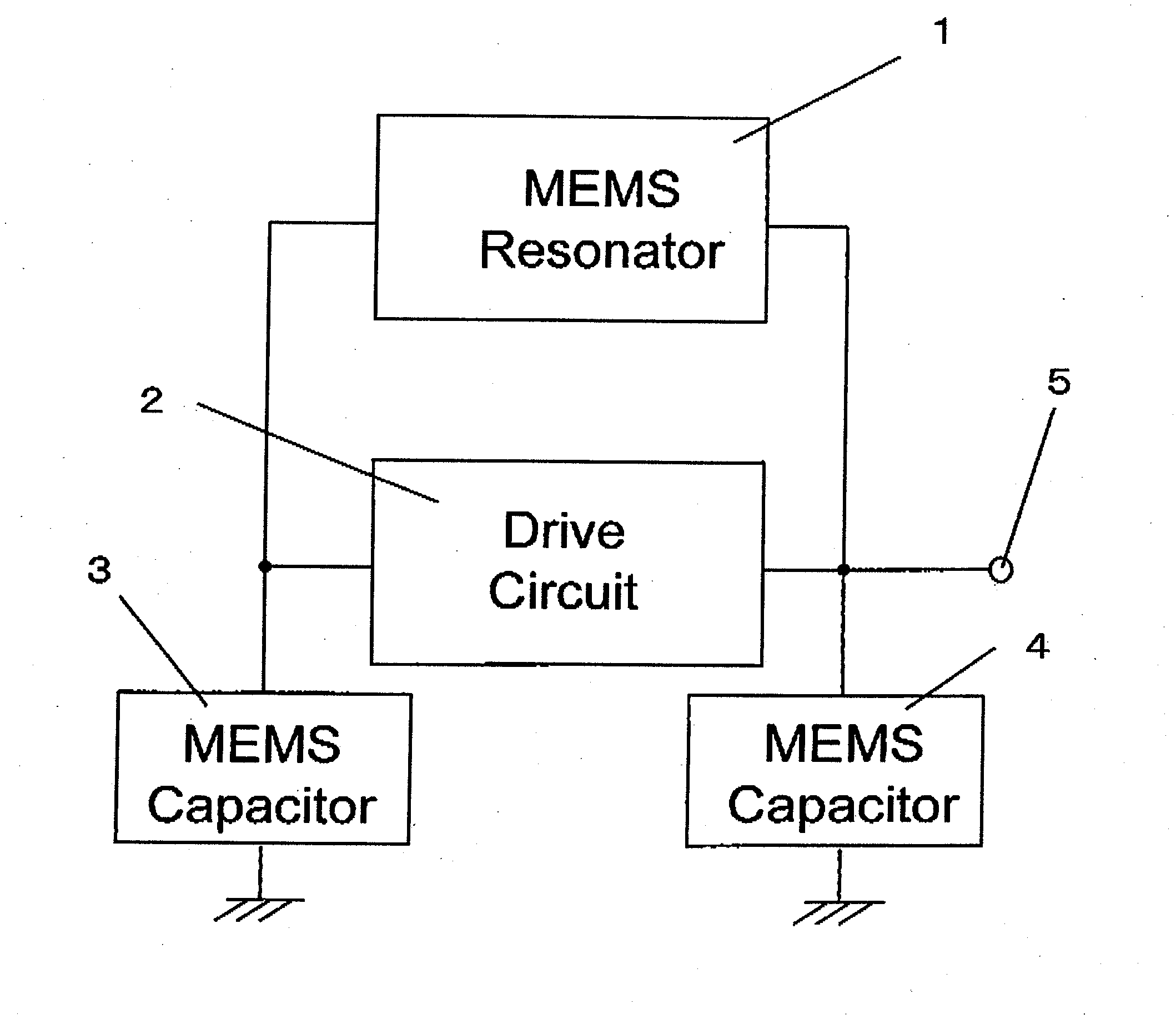

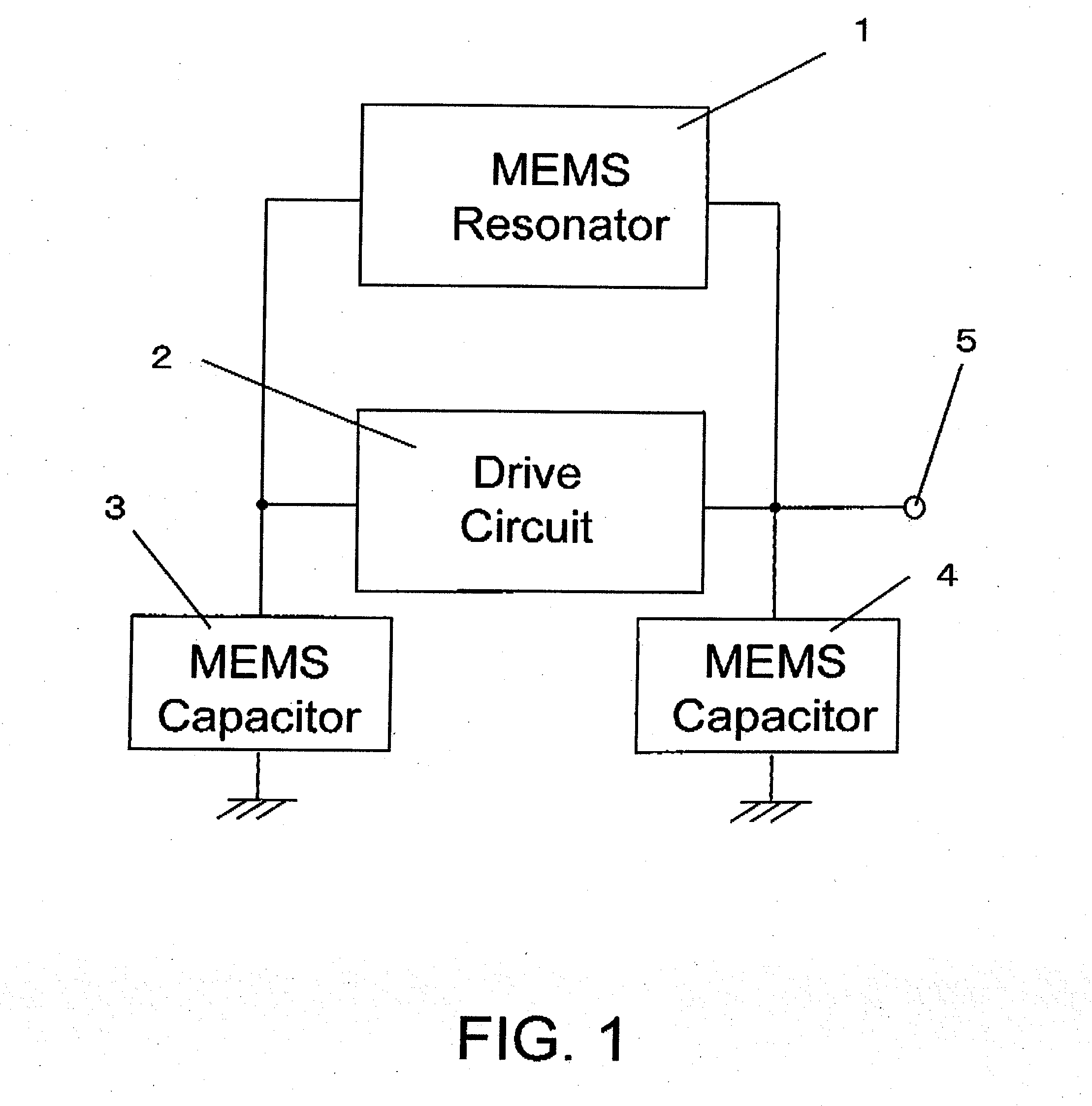

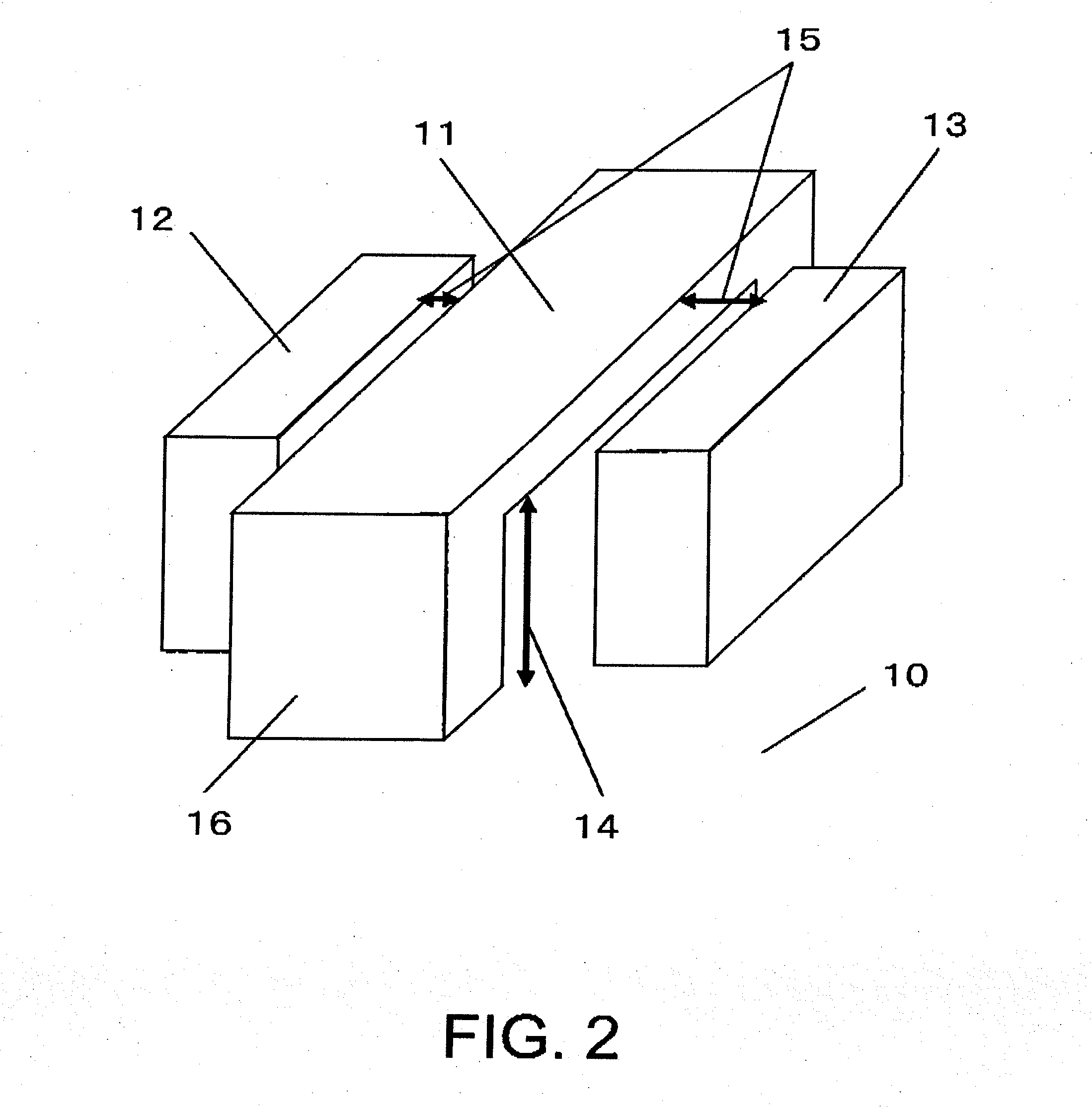

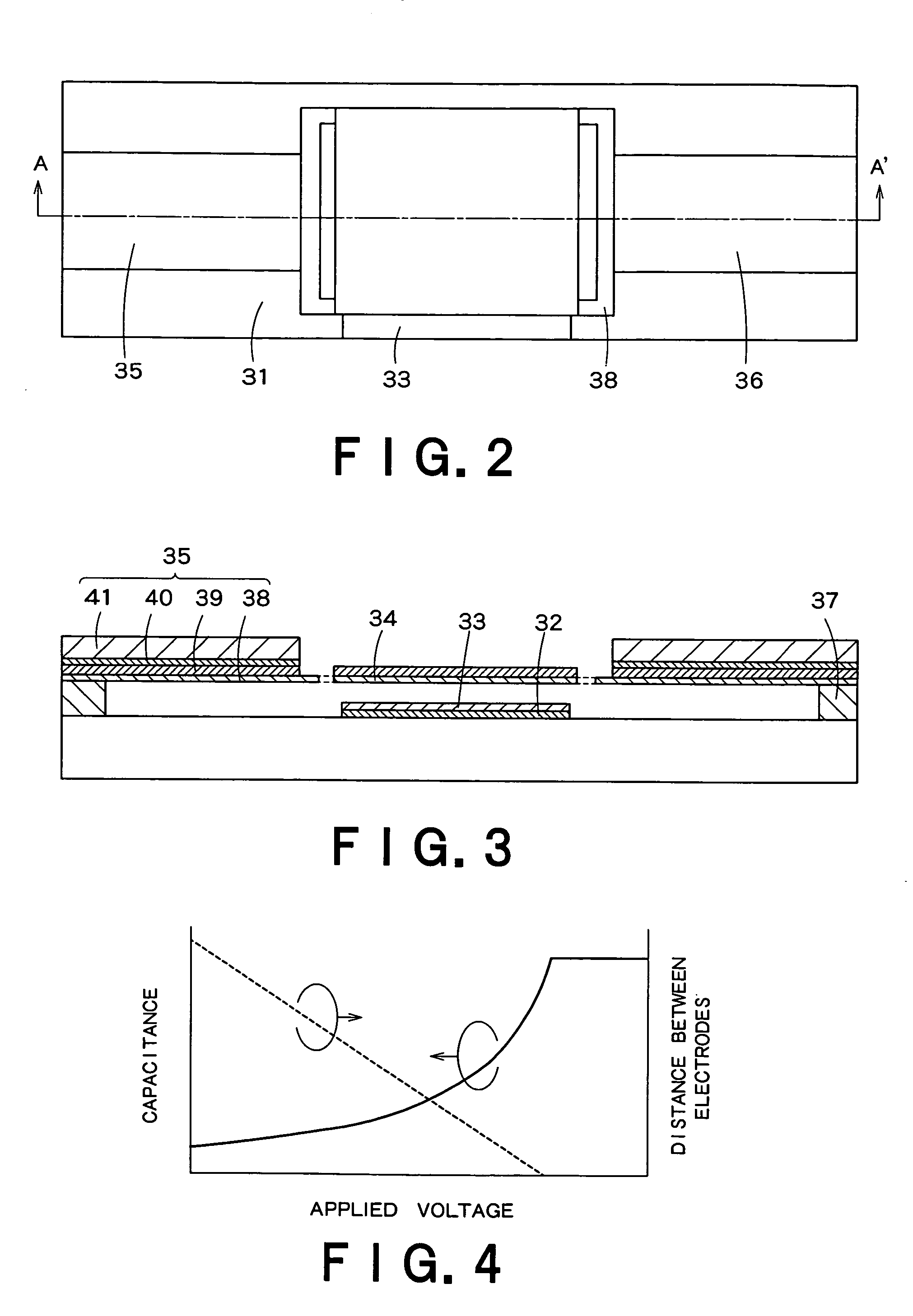

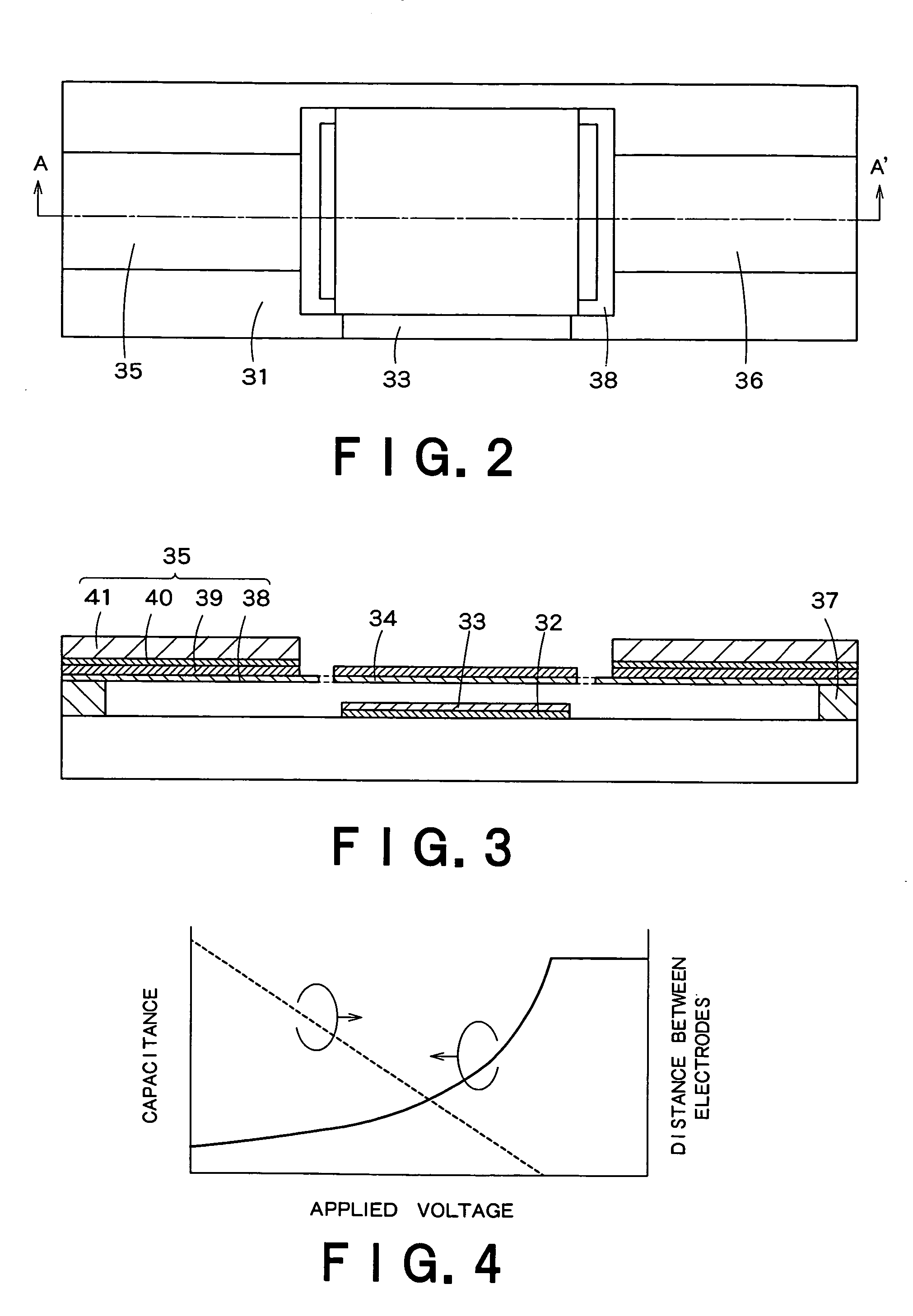

Oscillator

InactiveUS20080204153A1Small sizeChange frequencyResonant circuit auxillary power controlRadiation pyrometryMems capacitorsCapacitance

Provided is an oscillator including: a MEMS resonator for mechanically vibrating; an output oscillator circuit for oscillating at a resonance frequency of the MEMS resonator to output an oscillation signal; and a MEMS capacitor for changing a capacitance thereof caused by a change in a distance between an anode electrode and a cathode beam according to an environmental temperature.

Owner:SEIKO INSTR INC

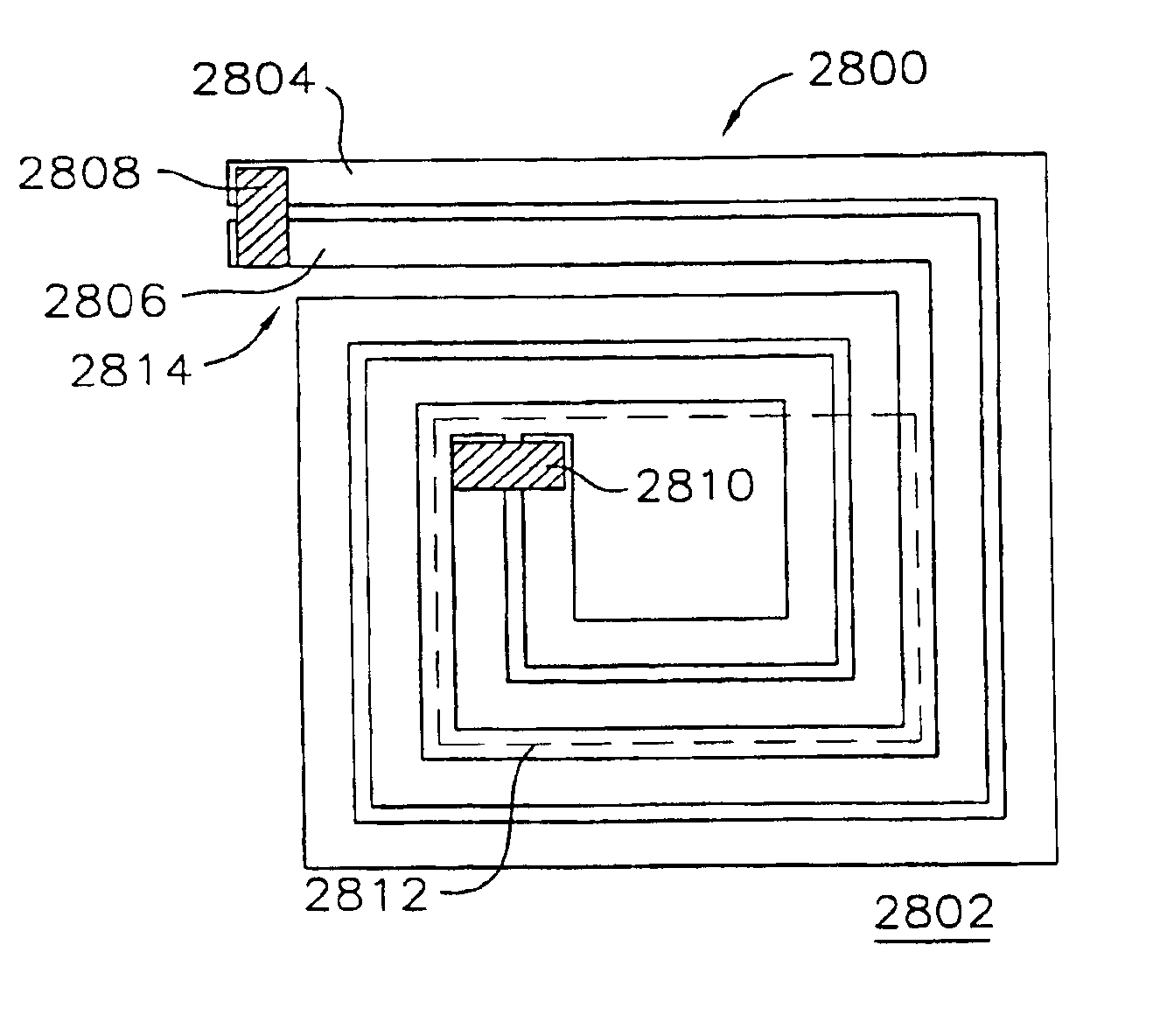

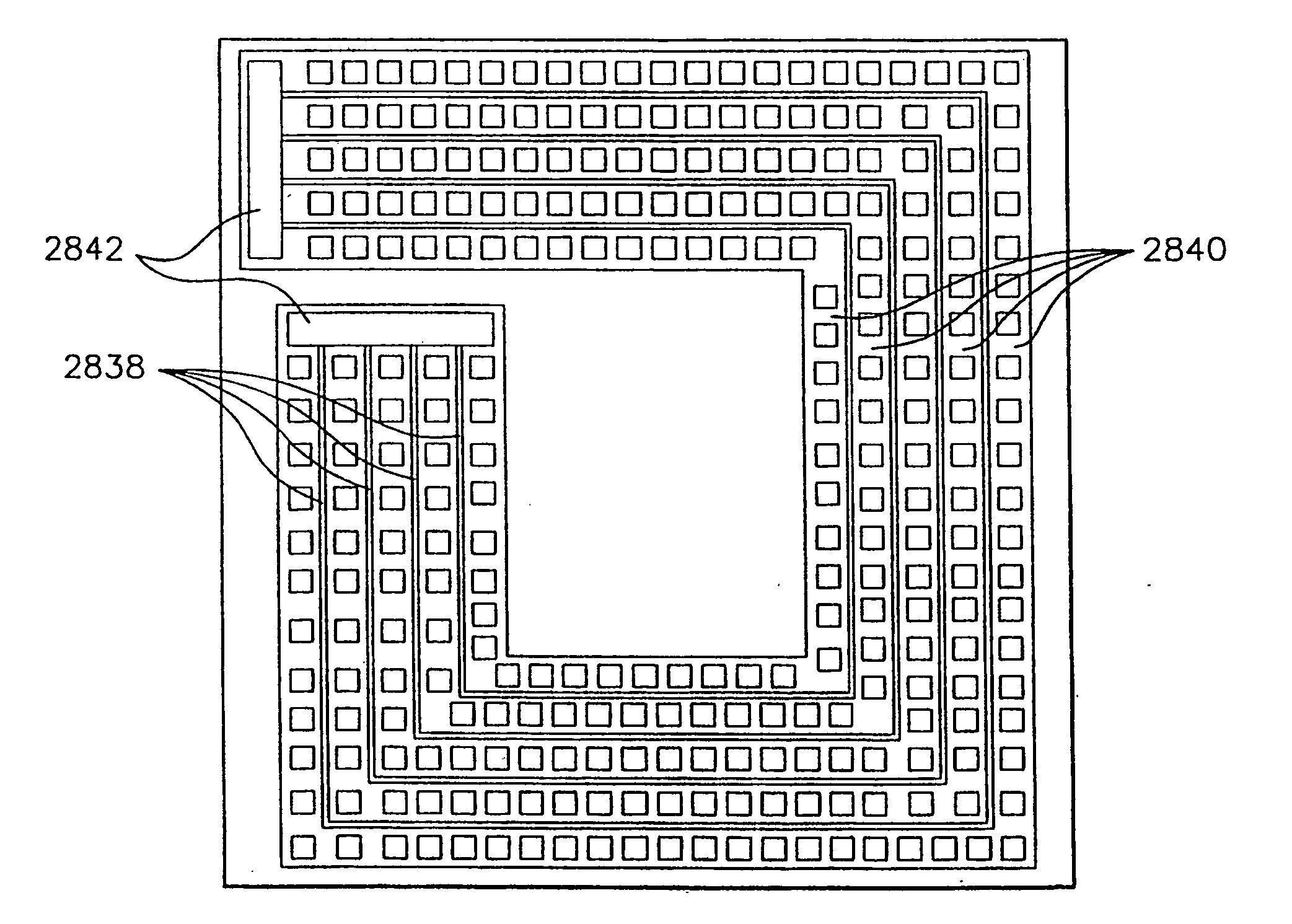

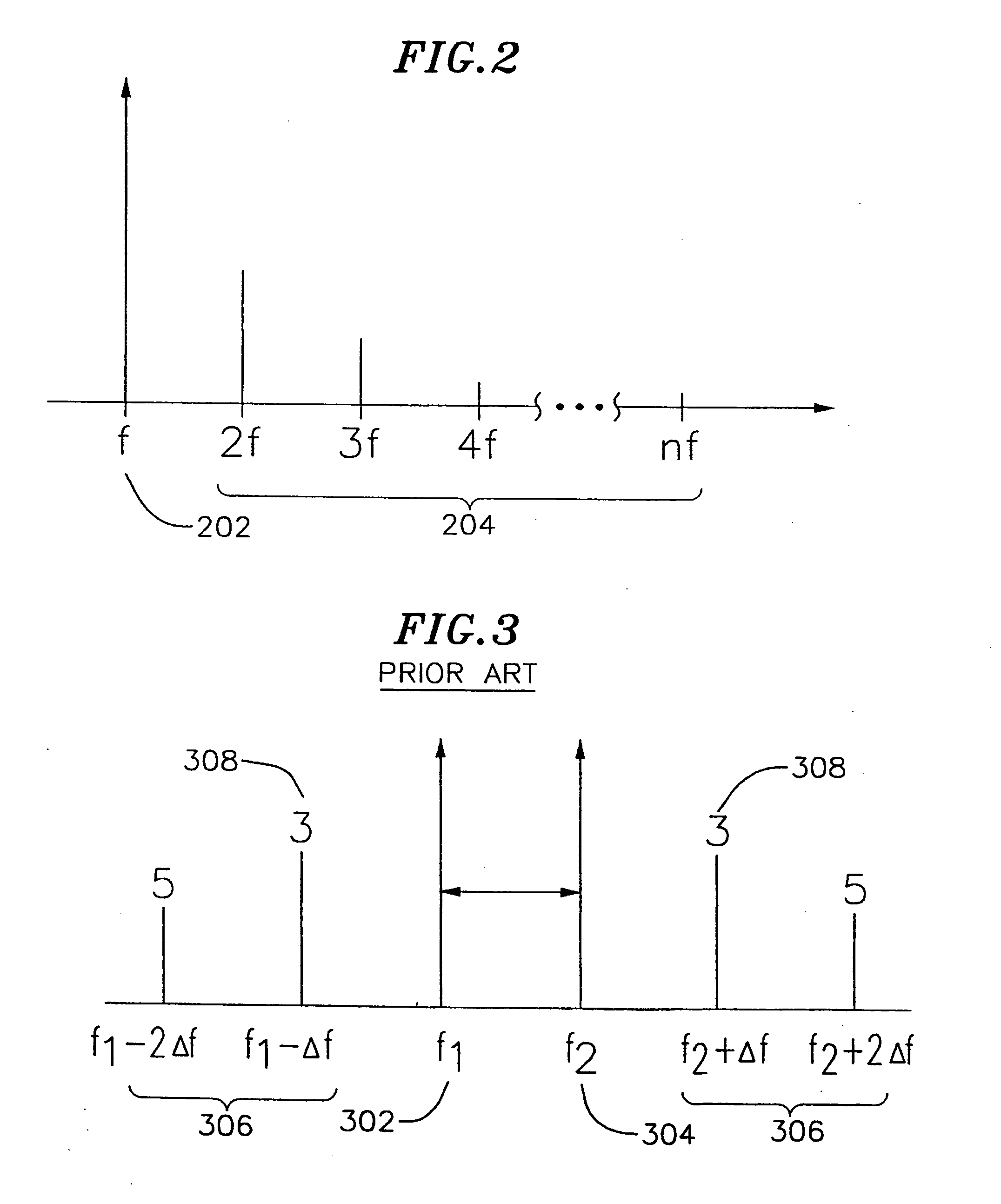

Multi-track integrated spiral inductor

InactiveUS6885275B1Resonant circuit detailsSemiconductor/solid-state device detailsSpiral inductorEngineering

An integrated circuit inductor includes a spiral pattern disposed upon a substrate. The track of the spiral is divided into multiple tracks to form a multi-track inductor. The individual tracks are disposed side by side and in different layers. Tracks that are aligned vertically are coupled by feed throughs, or vias. Multiple vias are used along the length of each of the multiple tracks. Tracks disposed in the same layer are joined together at their beginning, and at their termination. A patterned shield is fabricated from conductive fingers of n+ salicided material that is separated by non conducting polysilicon that fills the gaps between the fingers. The conductive fingers are coupled together in groups, which are in turn tied to a single point ground. In tying the groups together, a gap in the conducting path is provided to prevent ground loop currents. The shield is disposed between the multi-track inductor and the substrate.

Owner:AVAGO TECH INT SALES PTE LTD

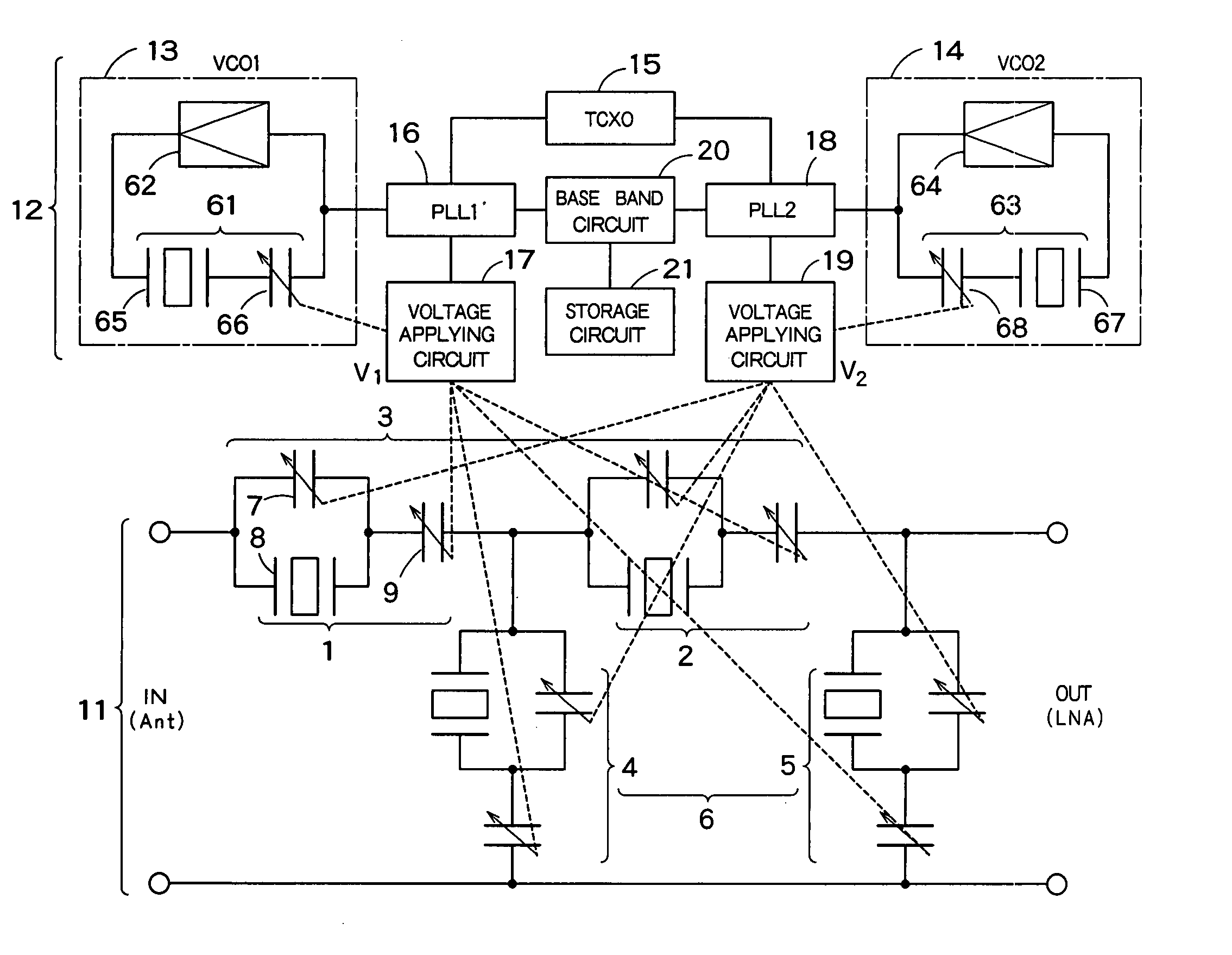

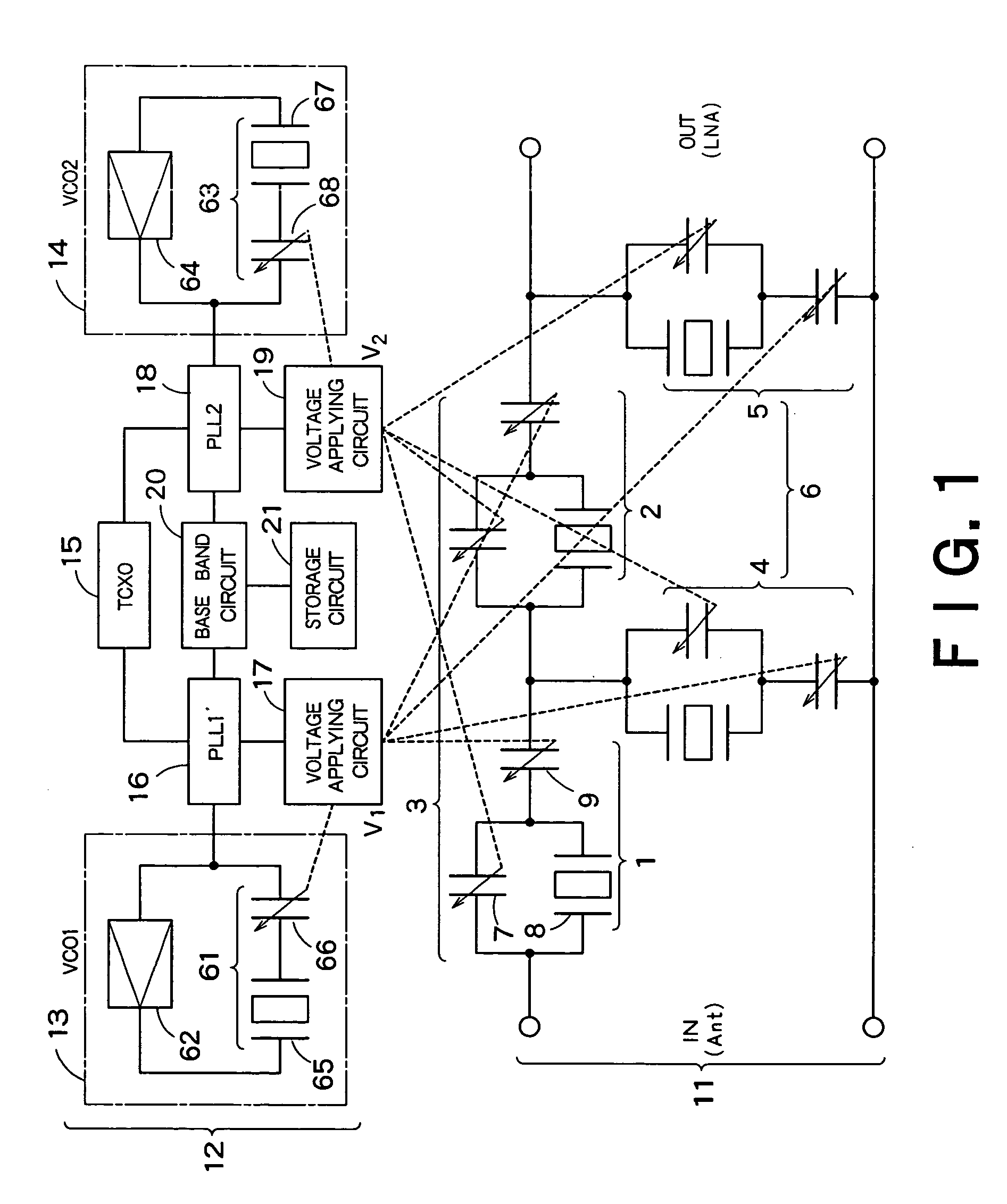

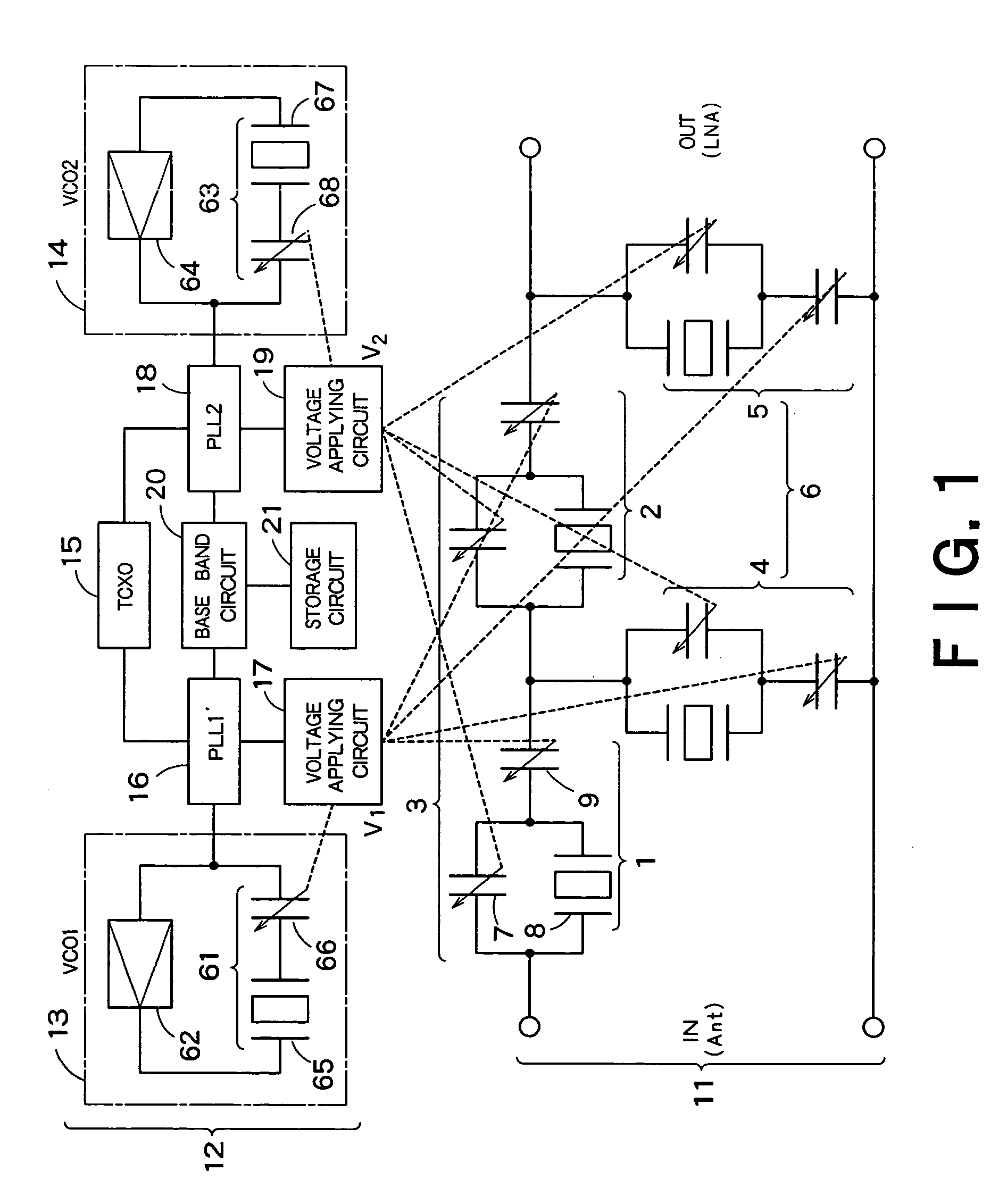

Tunable filter and portable telephone

InactiveUS20050212612A1Low insertion lossImprove reliabilityMultiple-port networksTransmission control/equlisationCapacitanceEngineering

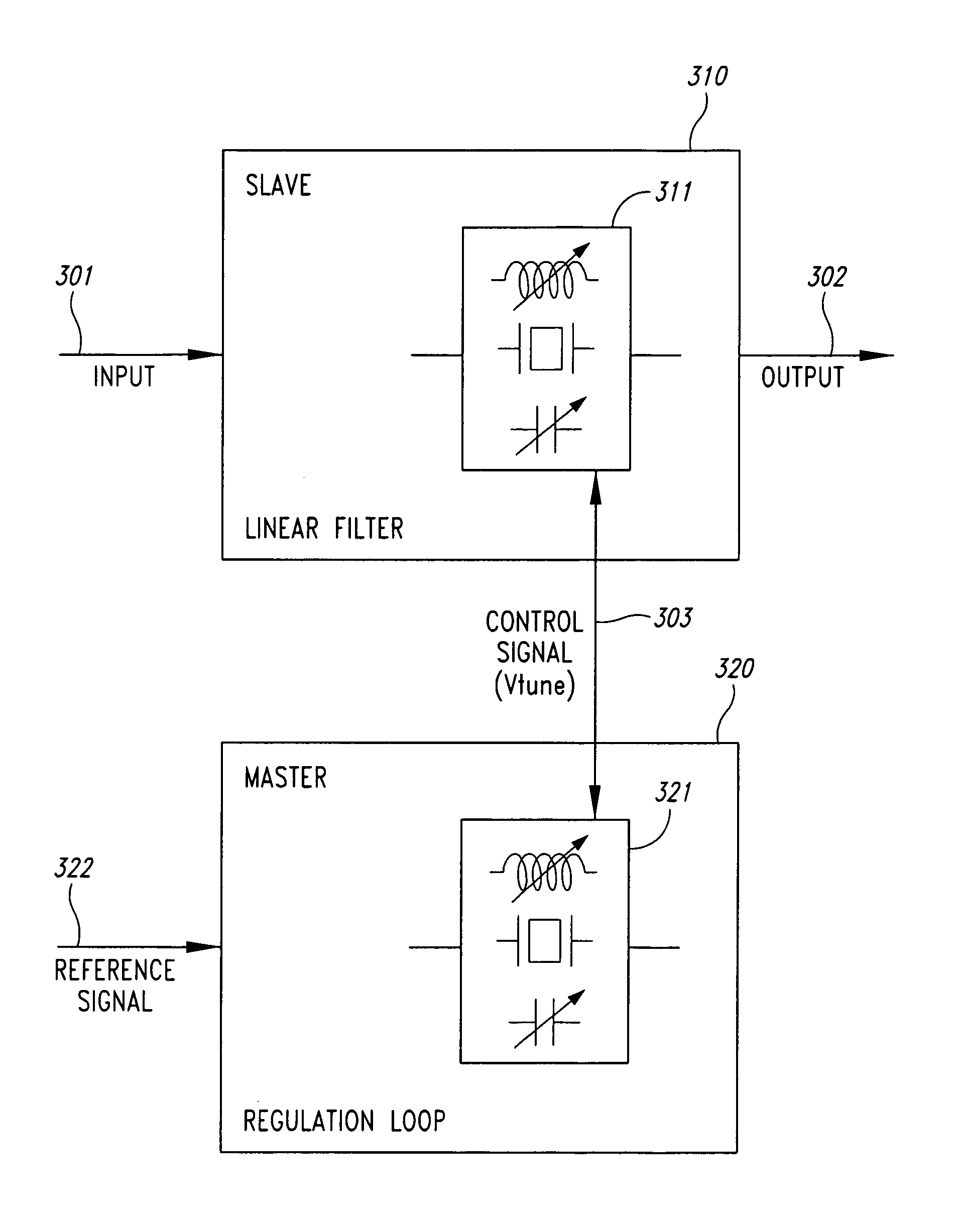

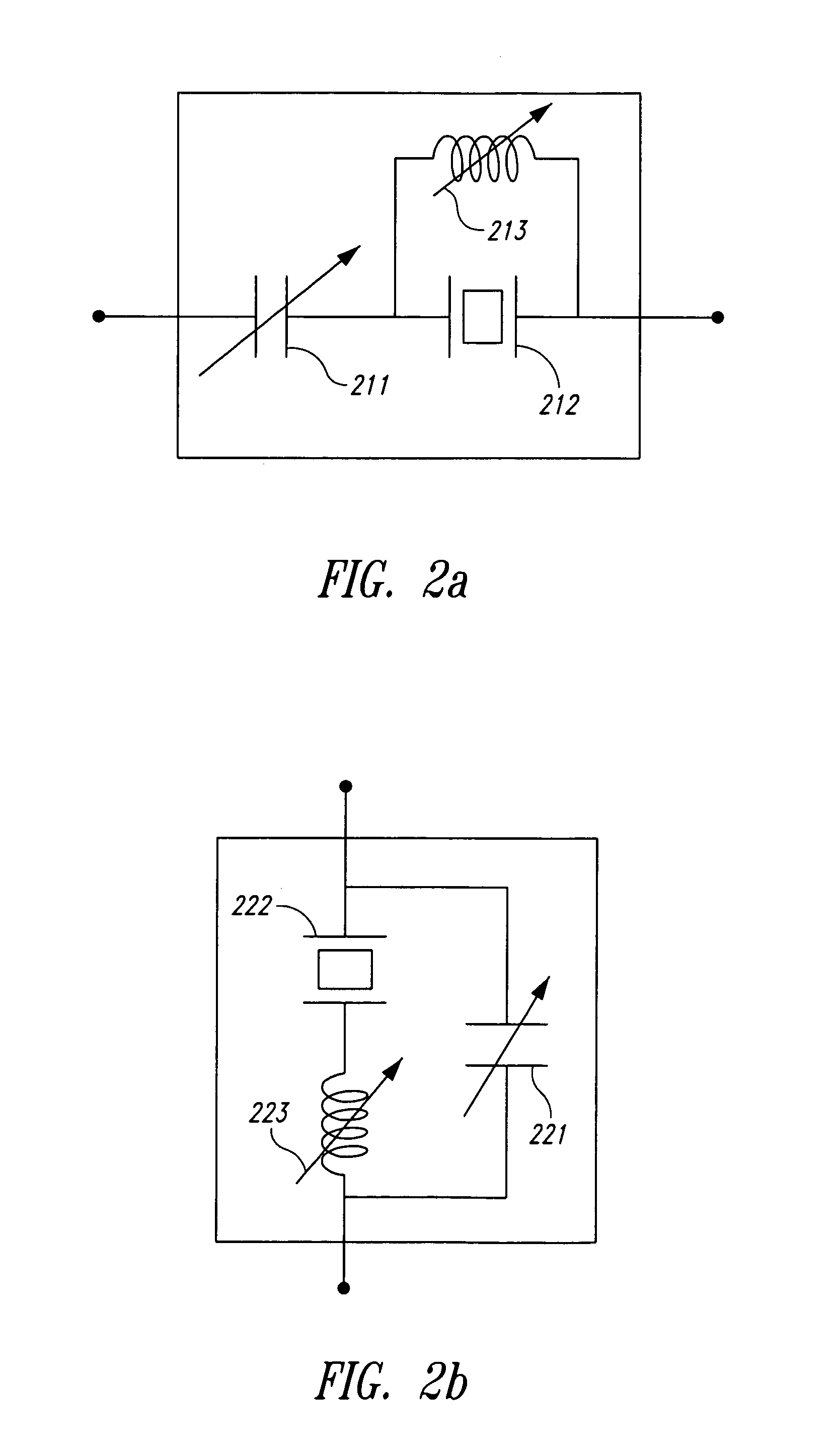

A tunable filter has a plurality of variable capacitors and a plurality of inductor elements, each being formed on a common substrate, a filter circuit formed by using at least a portion of the plurality of variable capacitors and a portion of the plurality of inductor elements, a monitor circuit formed by using at least a portion of the plurality of variable capacitors and a portion of the plurality of inductor elements, a detecting circuit which detects a prescribed circuit constant of the monitor circuit, a storage which stores information relating to a reference circuit constant of the monitor circuit, and a capacitance control circuit which controls capacitance of the variable capacitors in the monitor circuit and capacitance of the variable capacitors in the filter circuit, based on a result detected by the detecting circuit and information stored in the storage.

Owner:KK TOSHIBA

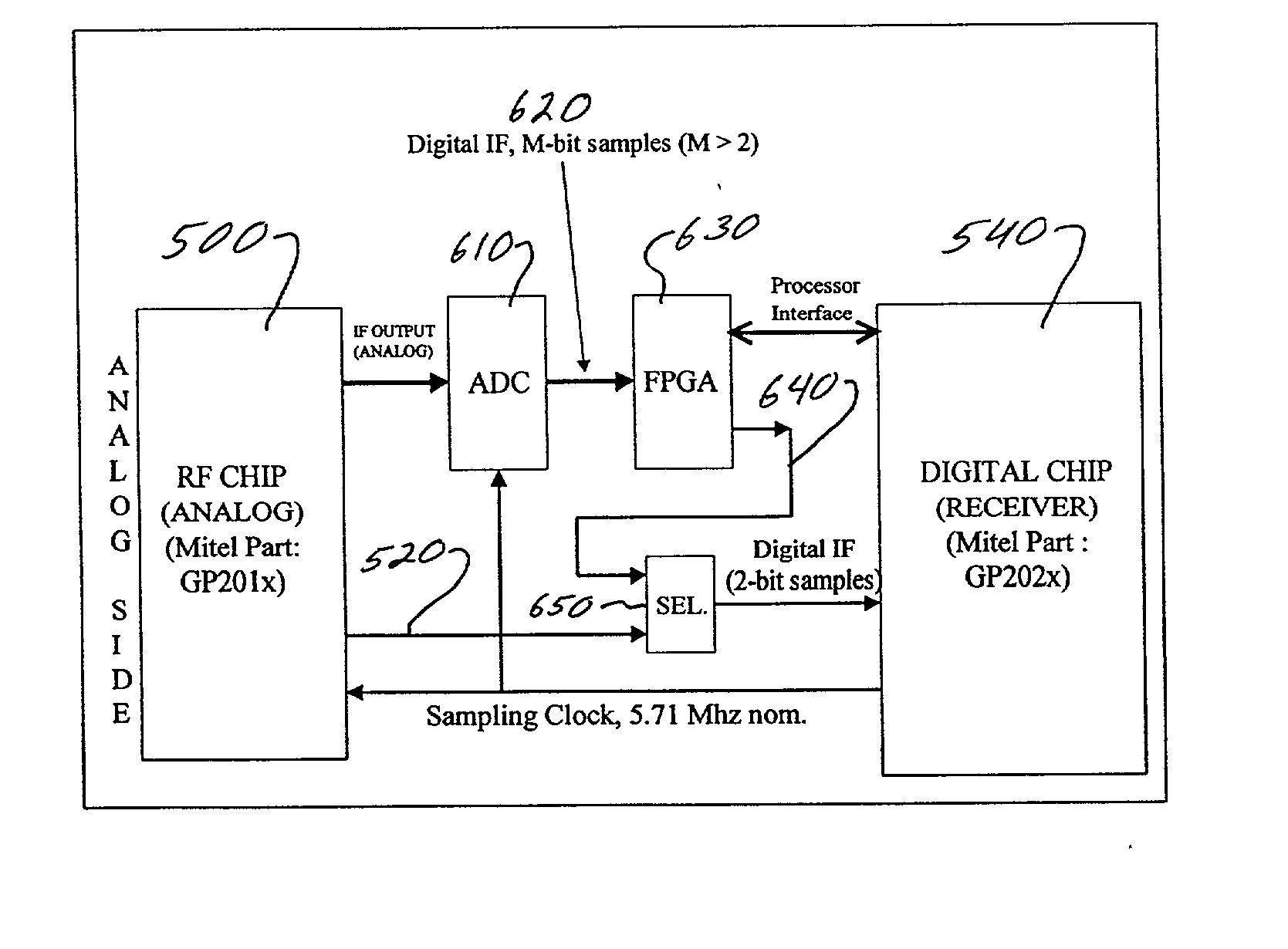

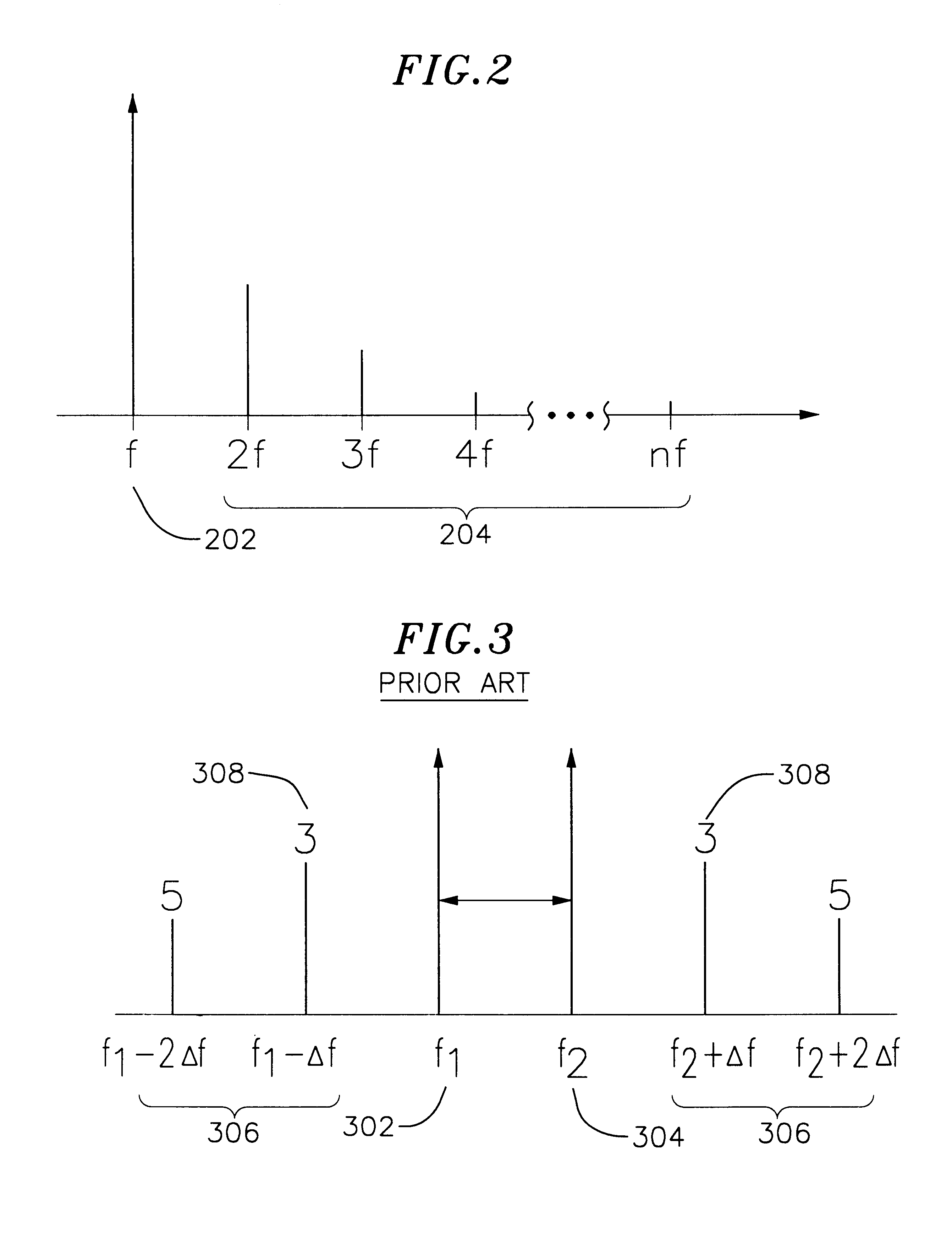

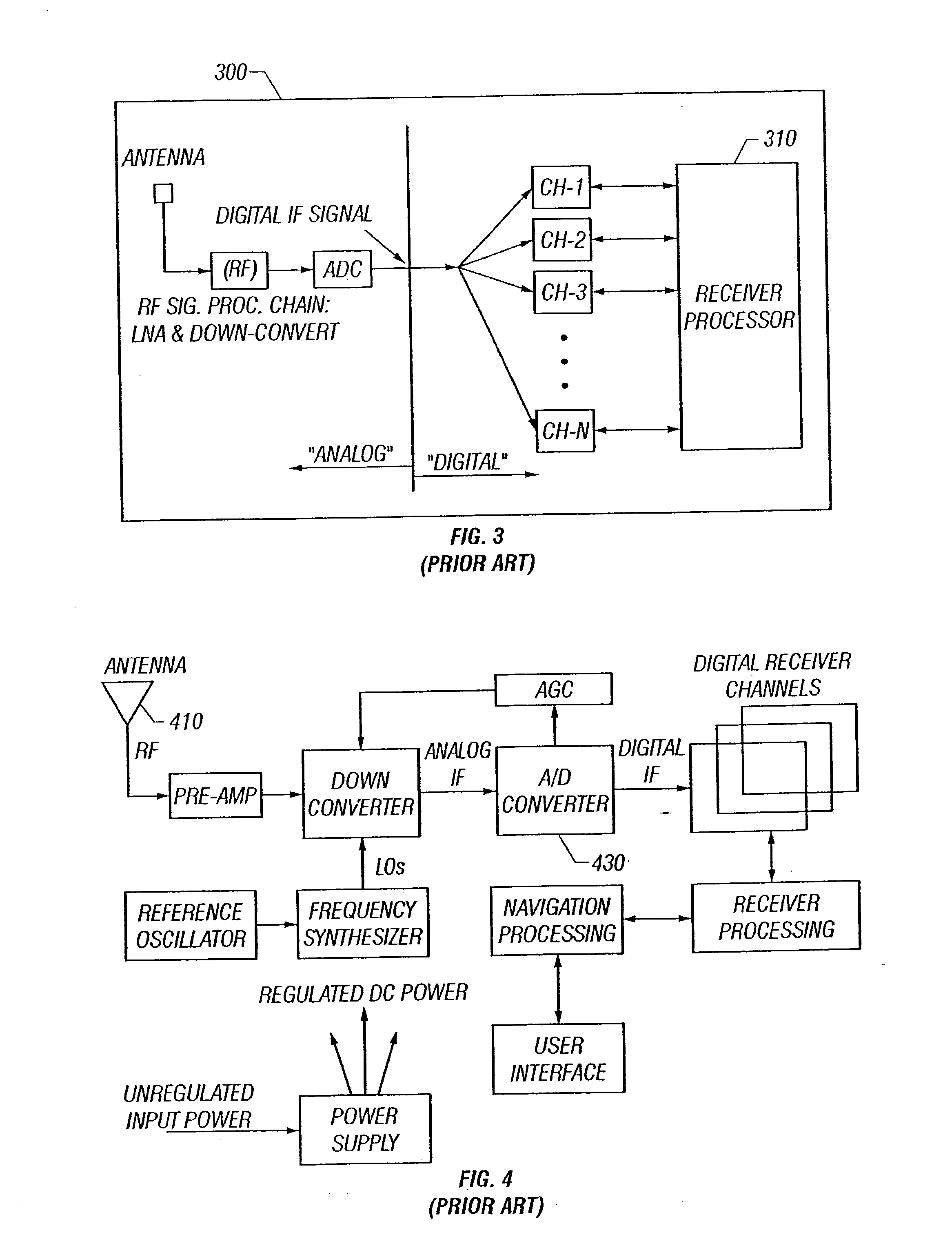

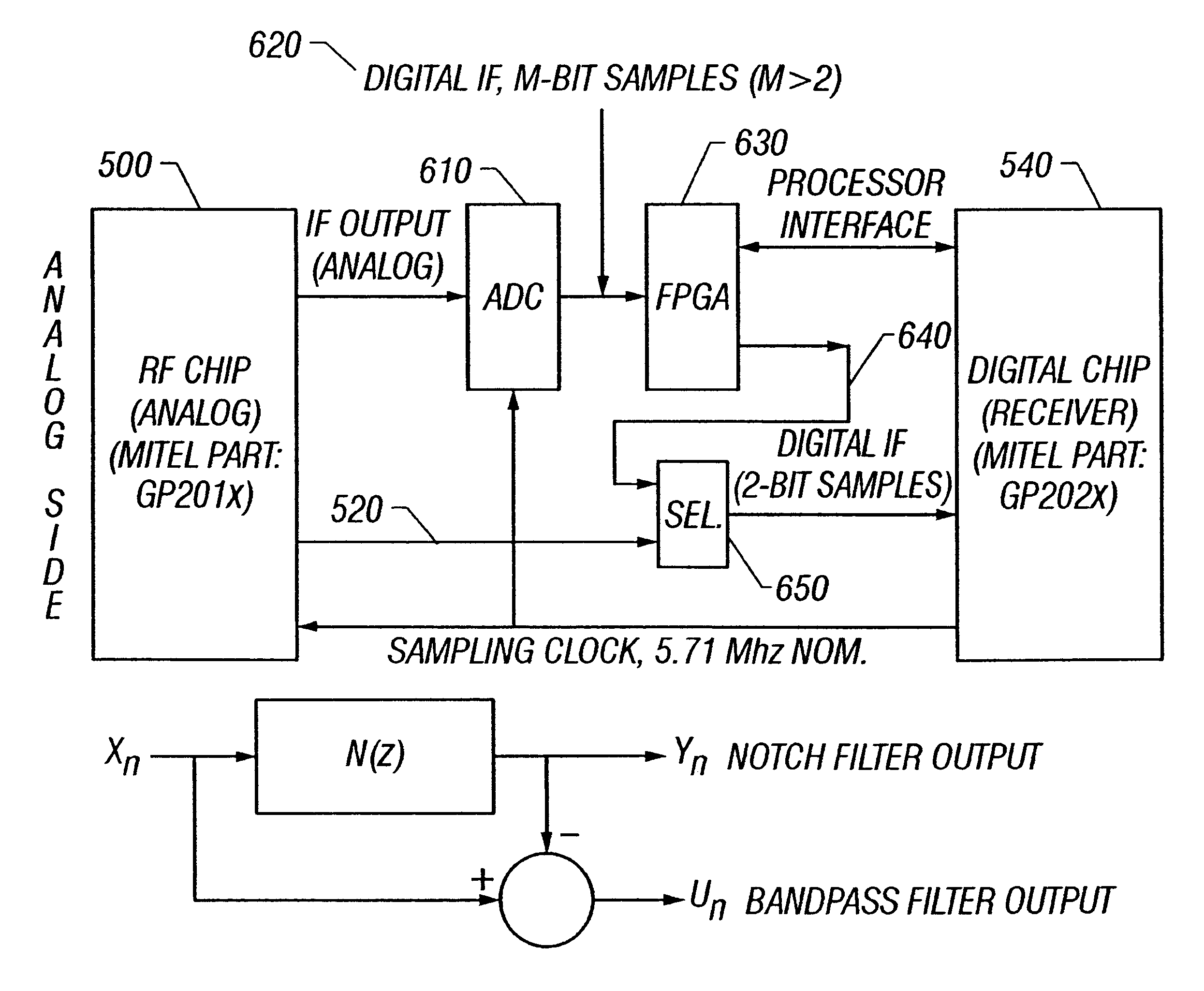

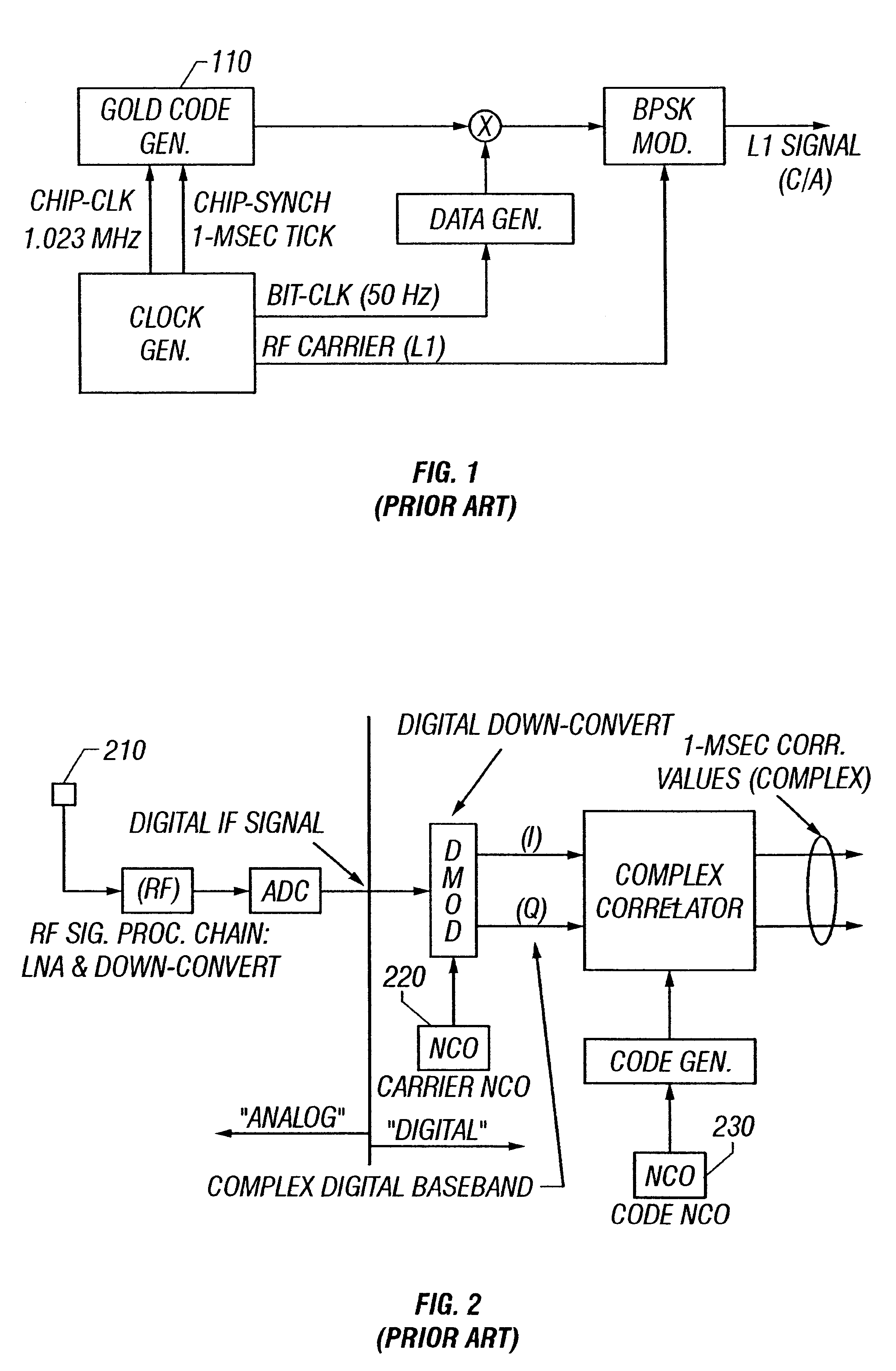

Global positioning system receiver capable of functioning in the presence of interference

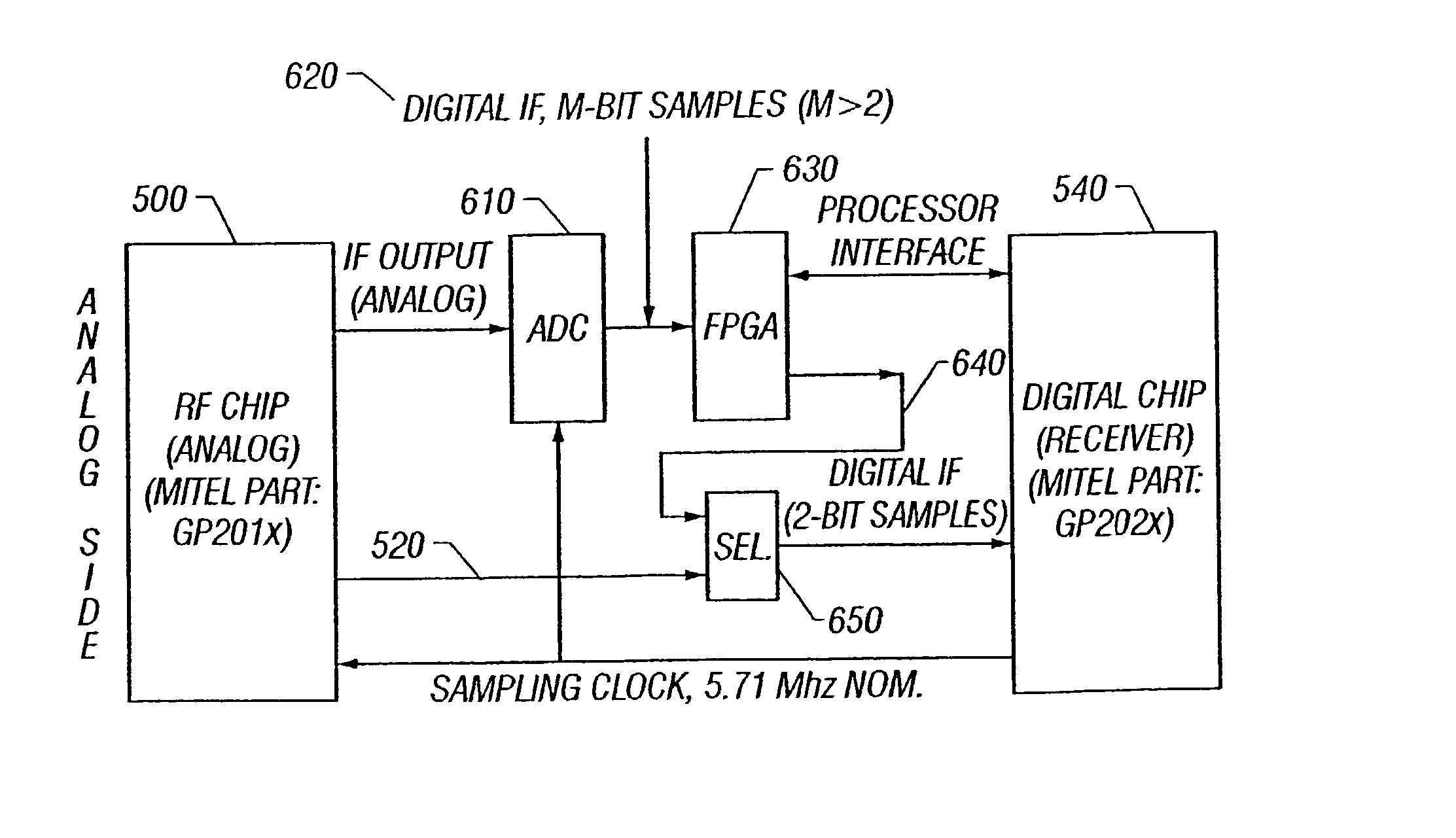

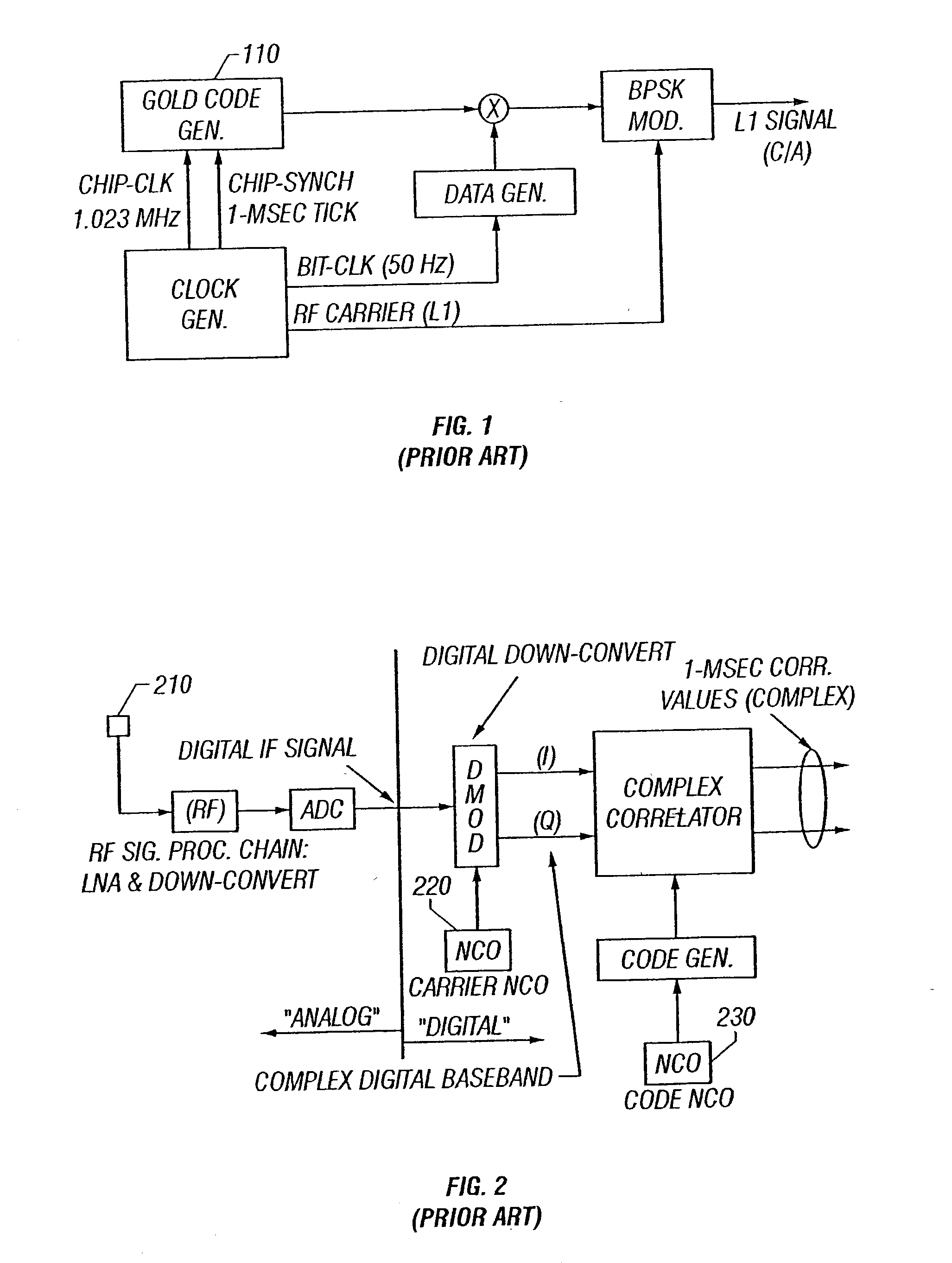

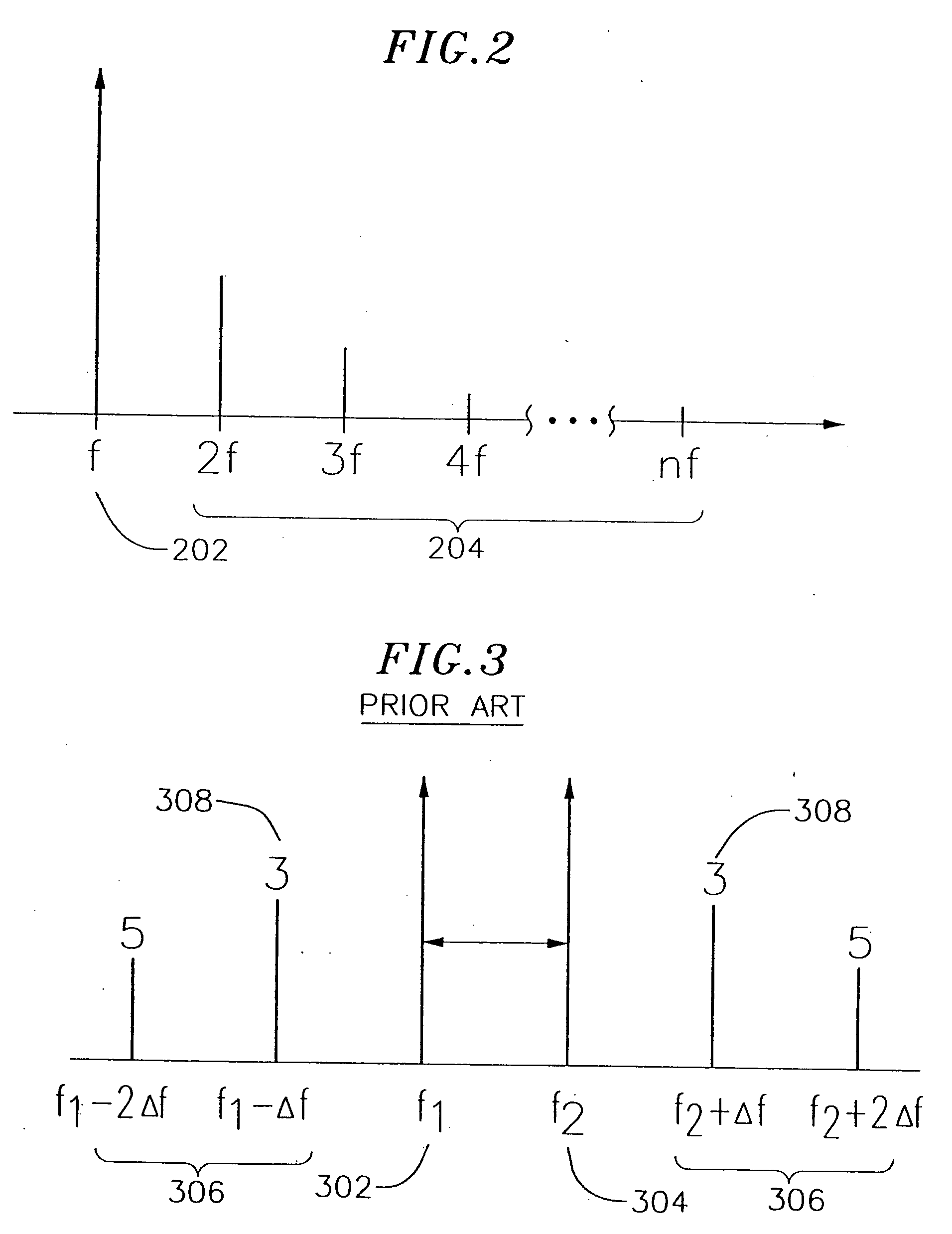

Systems and methods are described for a GPS receiver capable of functioning in the presence of interference. A method includes detecting an interfering signal including: tuning a band pass filter over a frequency range; and at each of a plurality of incremental frequencies: computing a set of band pass filter coefficients; sending the set of band pass filter coefficients to a digital filter; repeatedly transforming an analog-to-digital converter output having a quantization level in excess of 2 bits into a band pass filter output with the digital filter to obtain a plurality of samples; computing an average of the plurality of samples; and comparing the average to a threshold to detect peaks that exceed a threshold. An apparatus, comprising: an analog radio frequency circuit; an analog-to-digital converter coupled to the analog radio frequency circuit, the analog-to-digital converter providing a quantization level in excess of 2 bits; a digital filter coupled to the analog-to-digital converter; and a digital circuit coupled to the digital filter.

Owner:IP GEM GRP LLC

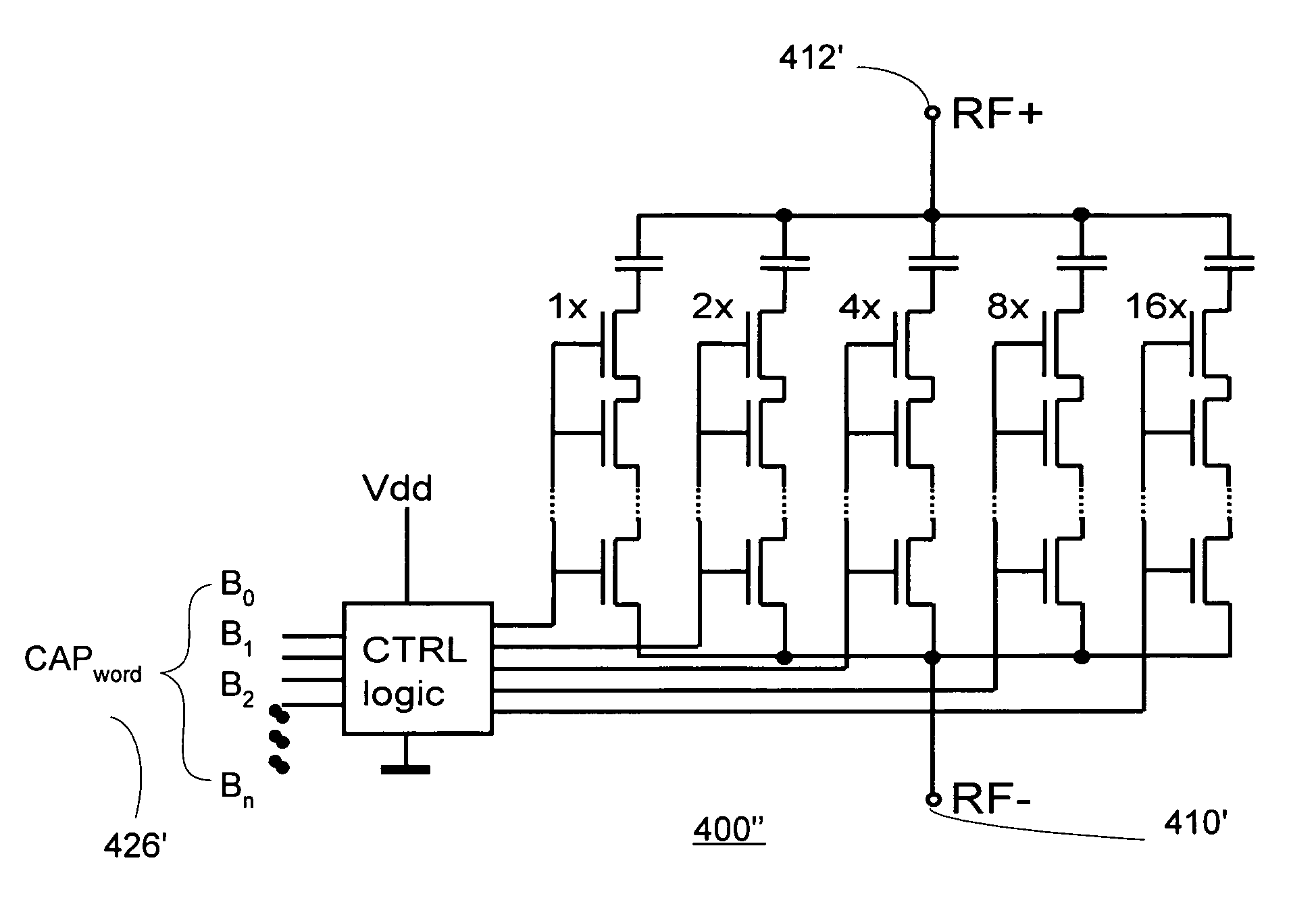

Method and apparatus for use in digitally tuning a capacitor in an integrated circuit device

ActiveUS9024700B2Easy to controlHigh Power Handling CapabilityMultiple-port networksImpedence matching networksCapacitanceLeast significant bit

Owner:PSEMI CORP

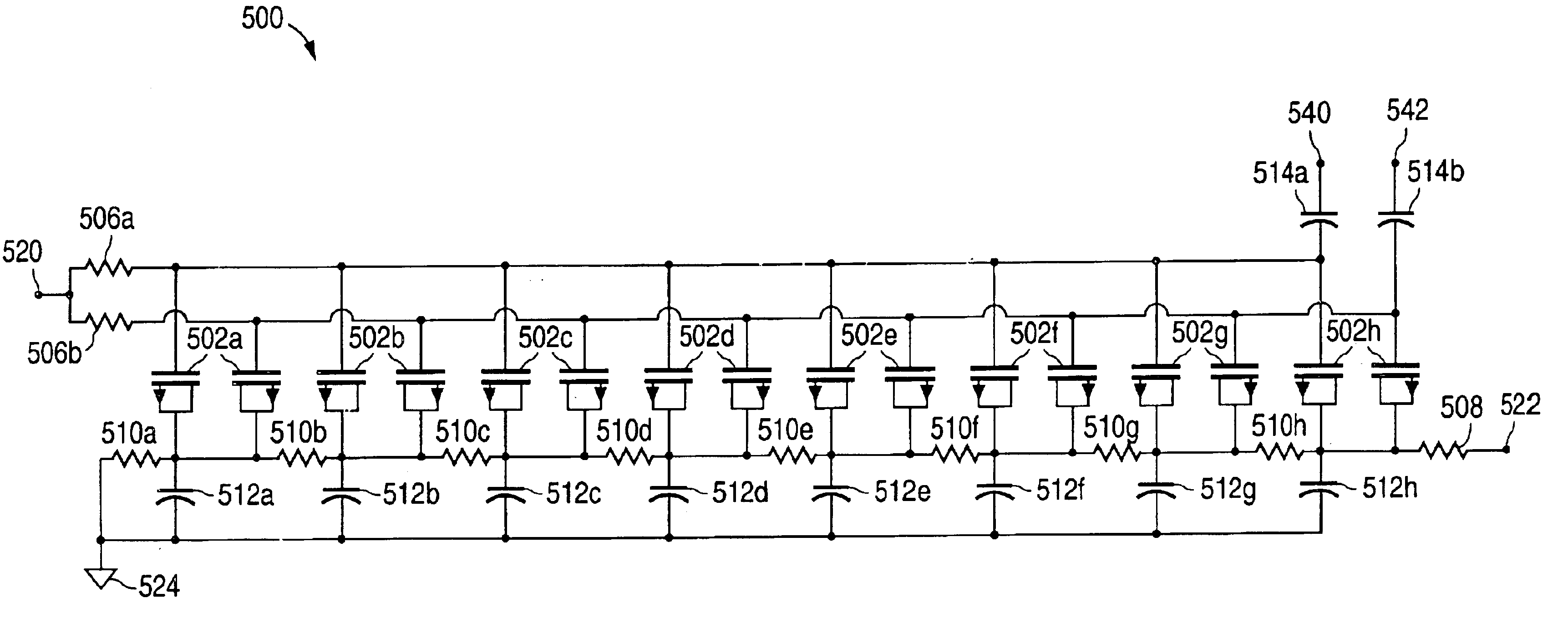

Integrated switchless programmable attenuator and low noise amplifier

InactiveUS6879816B2Multiple-port active networksSwitched capacitor networksCapacitanceLocal oscillator signal

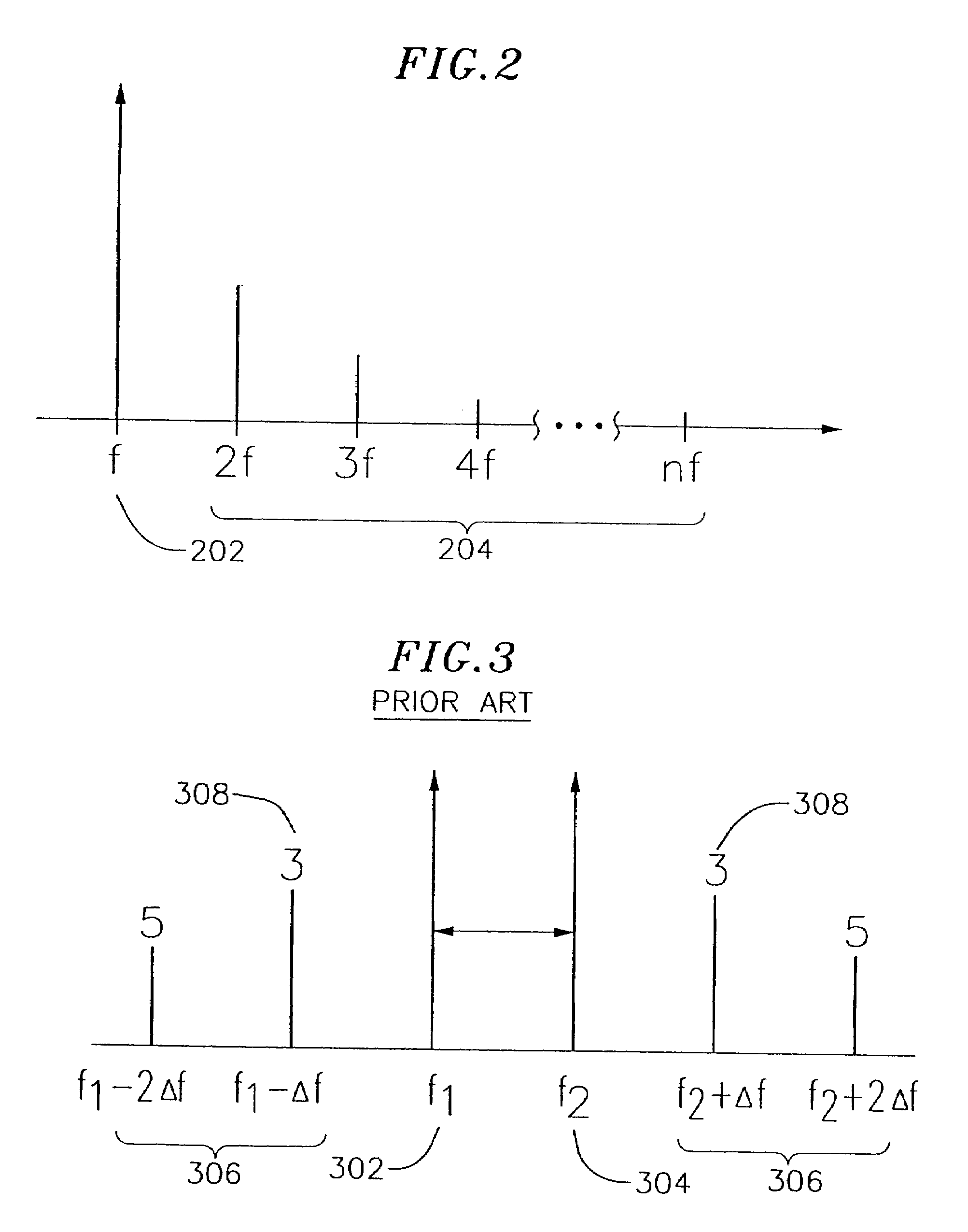

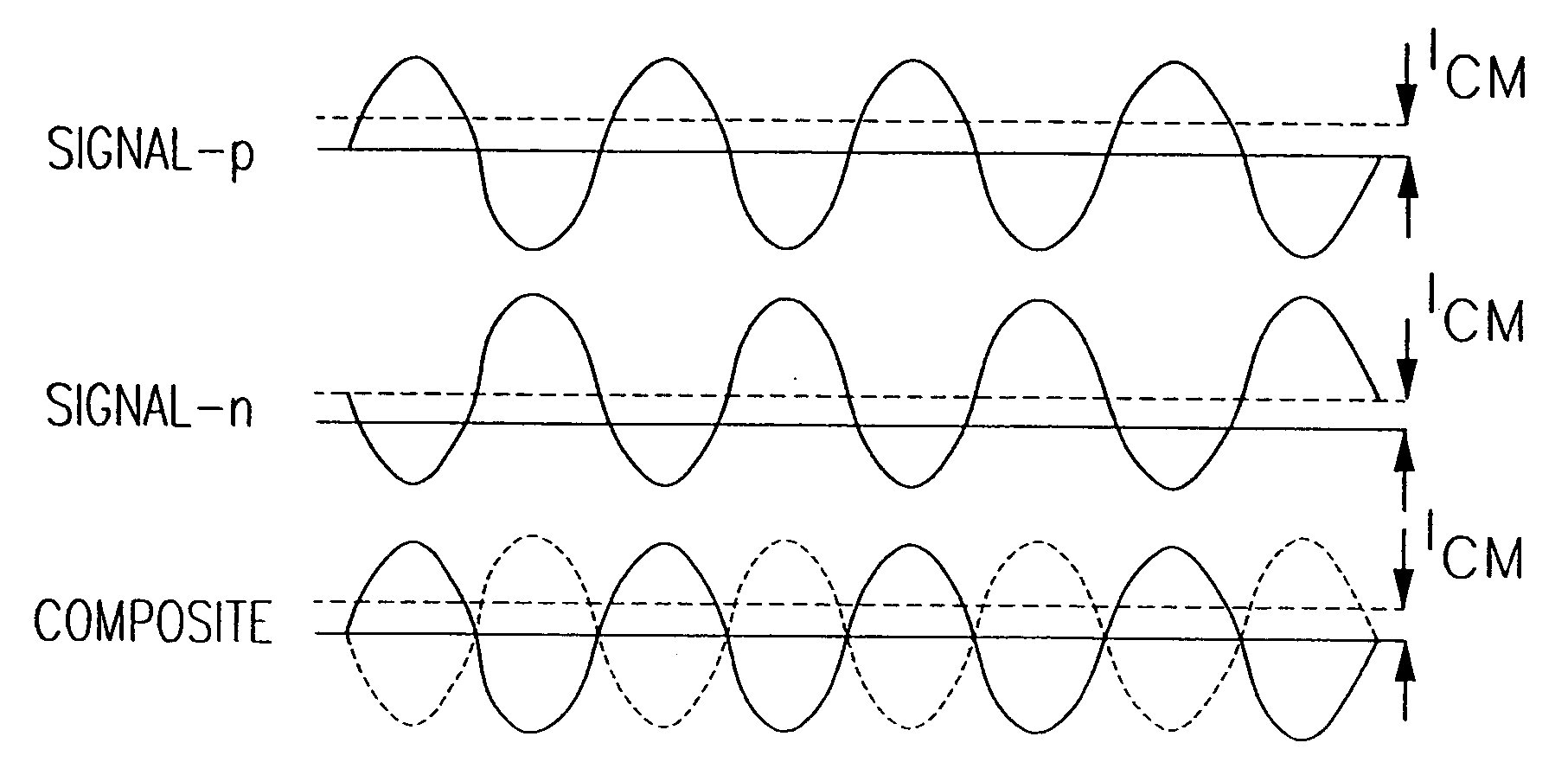

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides programmable attenuation and a programmable gain low noise amplifier. Frequency conversion circuitry advantageously uses LC filters integrated onto the substrate in conjunction with image reject mixers to provide sufficient image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. The filters utilize multi track spiral inductors. The filters are tuned using local oscillators to tune a substitute filter, and frequency scaling during filter component values to those of the filter being tuned. In conjunction with filtering, frequency planning provides additional image rejection. The advantageous choice of local oscillator signal generation methods on chip is by PLL out of band local oscillation and by direct synthesis for in band local oscillator. The VCOs in the PLLs are centered using a control circuit to center the tuning capacitance range. A differential crystal oscillator is advantageously used as a frequency reference. Differential signal transmission is advantageously used throughout the receiver.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

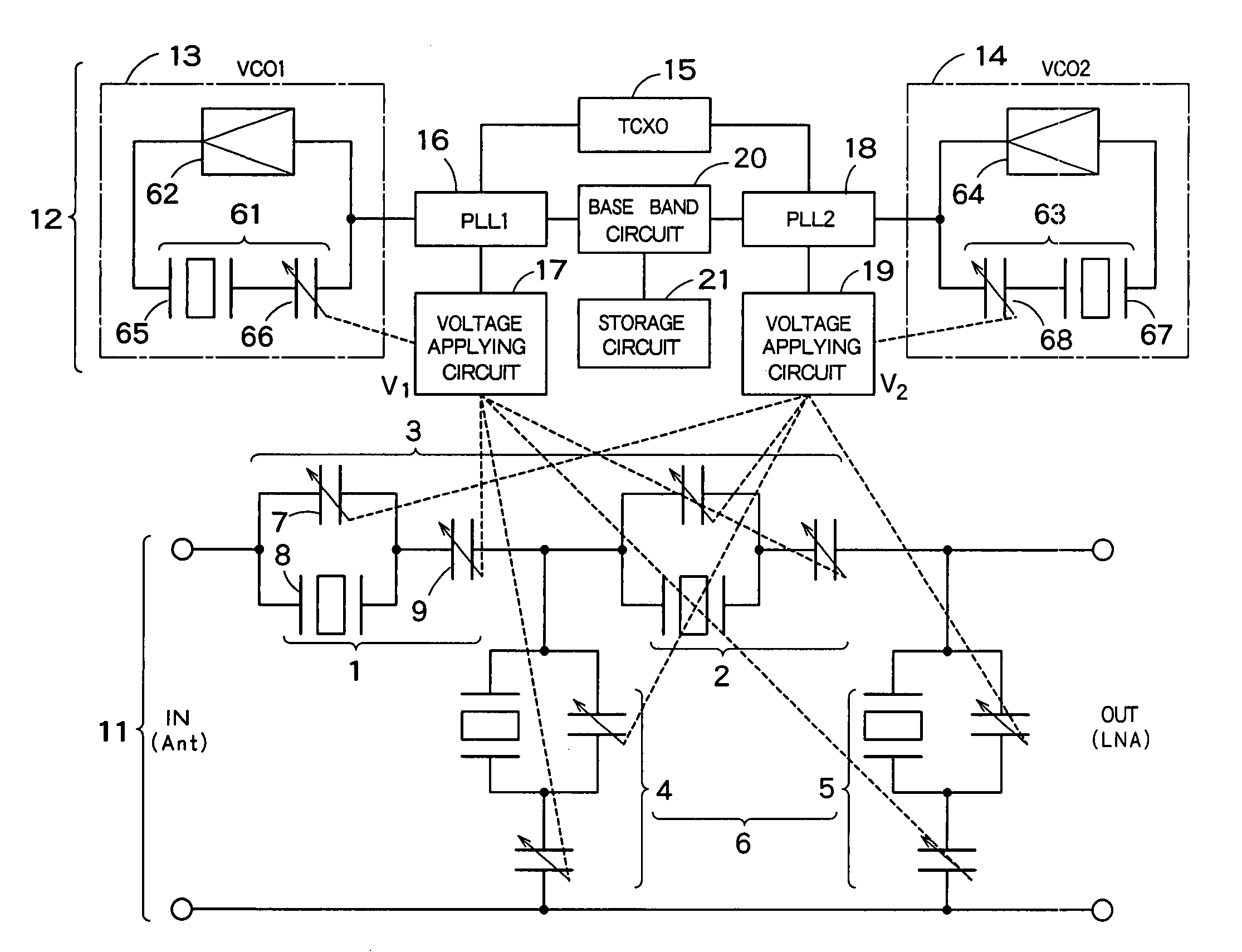

Tunable filter and portable telephone

InactiveUS7135940B2Good reproducibility and reliabilityLow insertion lossMultiple-port networksTransmission control/equlisationCapacitanceInductor

A tunable filter has a plurality of variable capacitors and a plurality of inductor elements, each being formed on a common substrate, a filter circuit formed by using at least a portion of the plurality of variable capacitors and a portion of the plurality of inductor elements, a monitor circuit formed by using at least a portion of the plurality of variable capacitors and a portion of the plurality of inductor elements, a detecting circuit which detects a prescribed circuit constant of the monitor circuit, a storage which stores information relating to a reference circuit constant of the monitor circuit, and a capacitance control circuit which controls capacitance of the variable capacitors in the monitor circuit and capacitance of the variable capacitors in the filter circuit, based on a result detected by the detecting circuit and information stored in the storage.

Owner:KK TOSHIBA

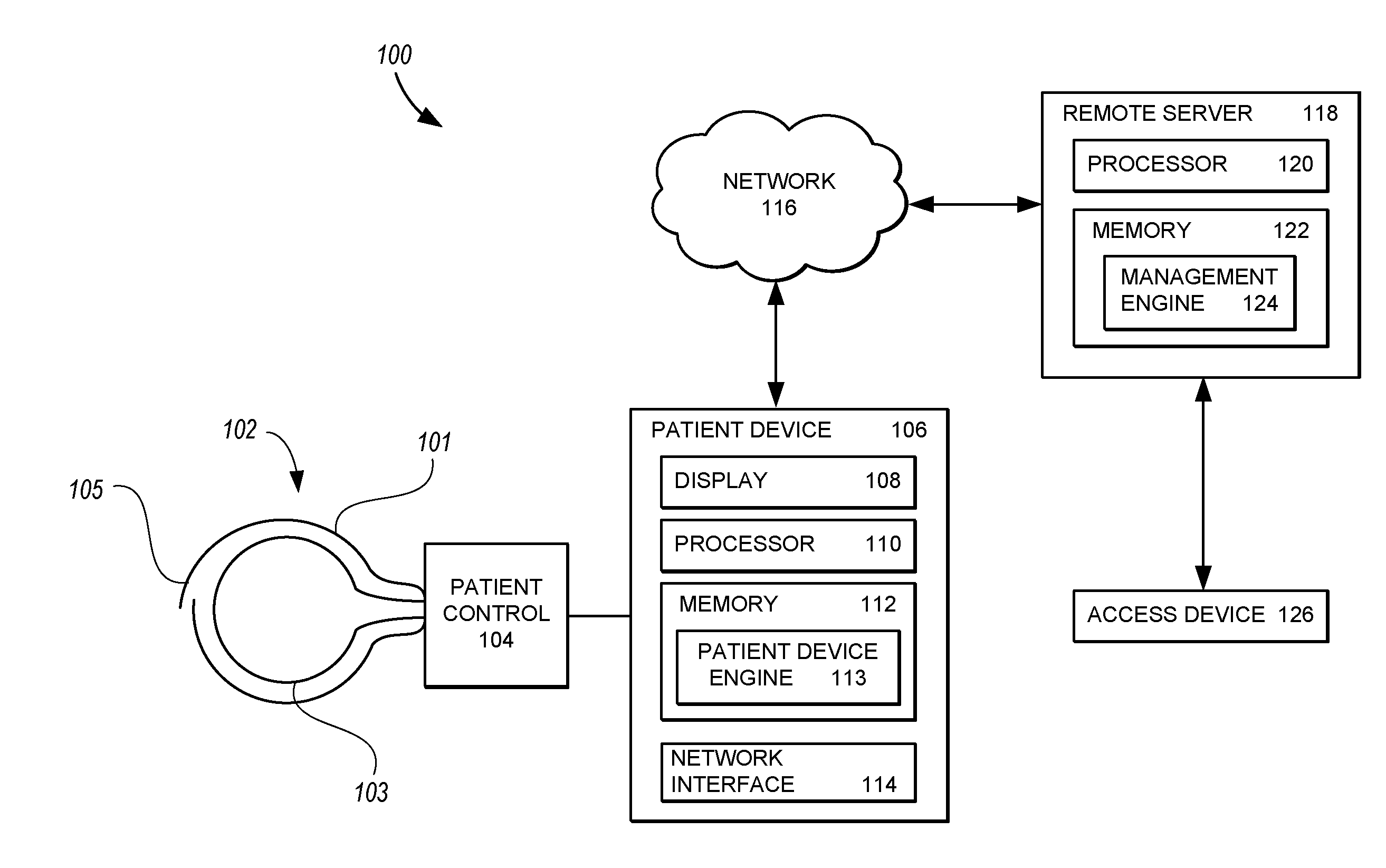

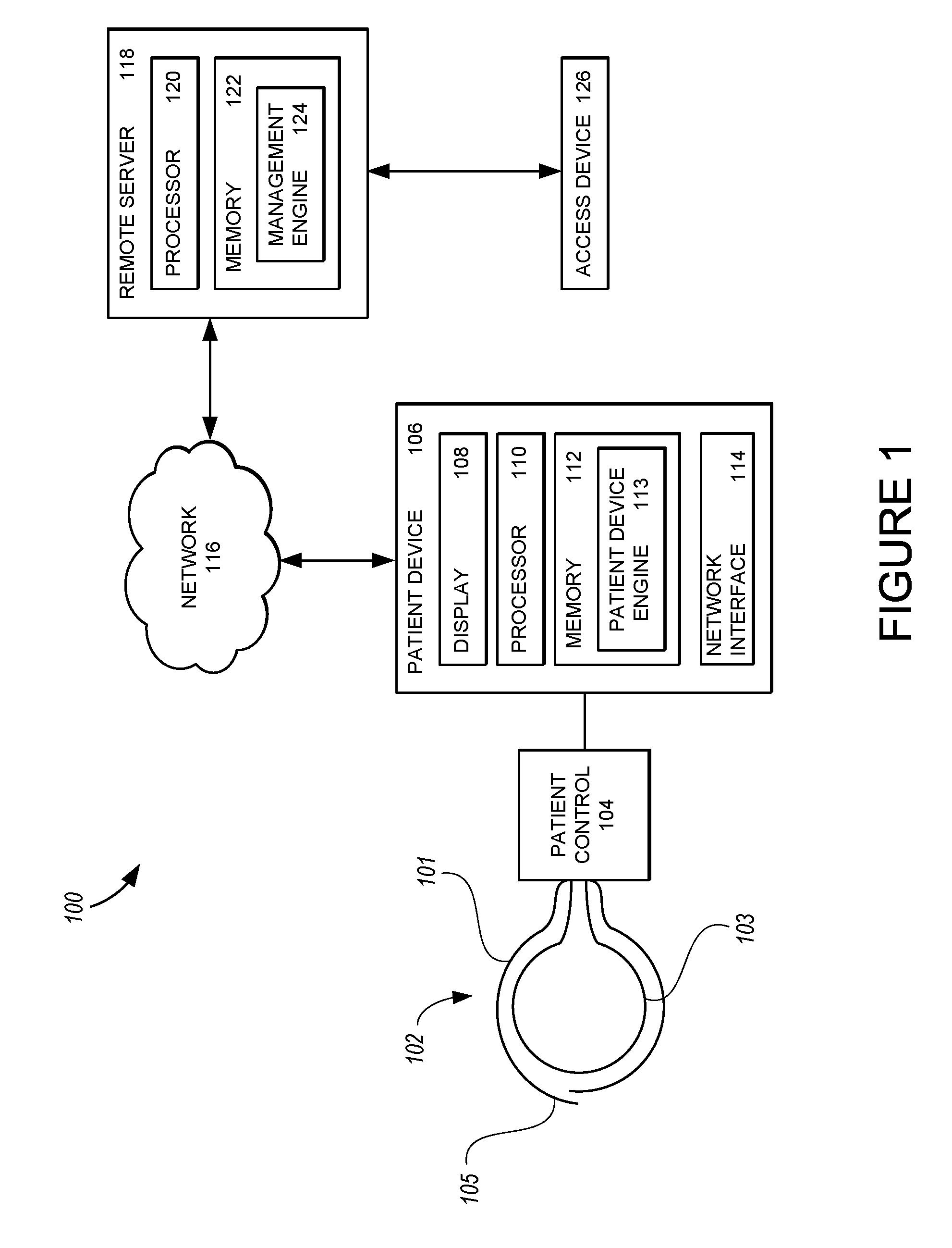

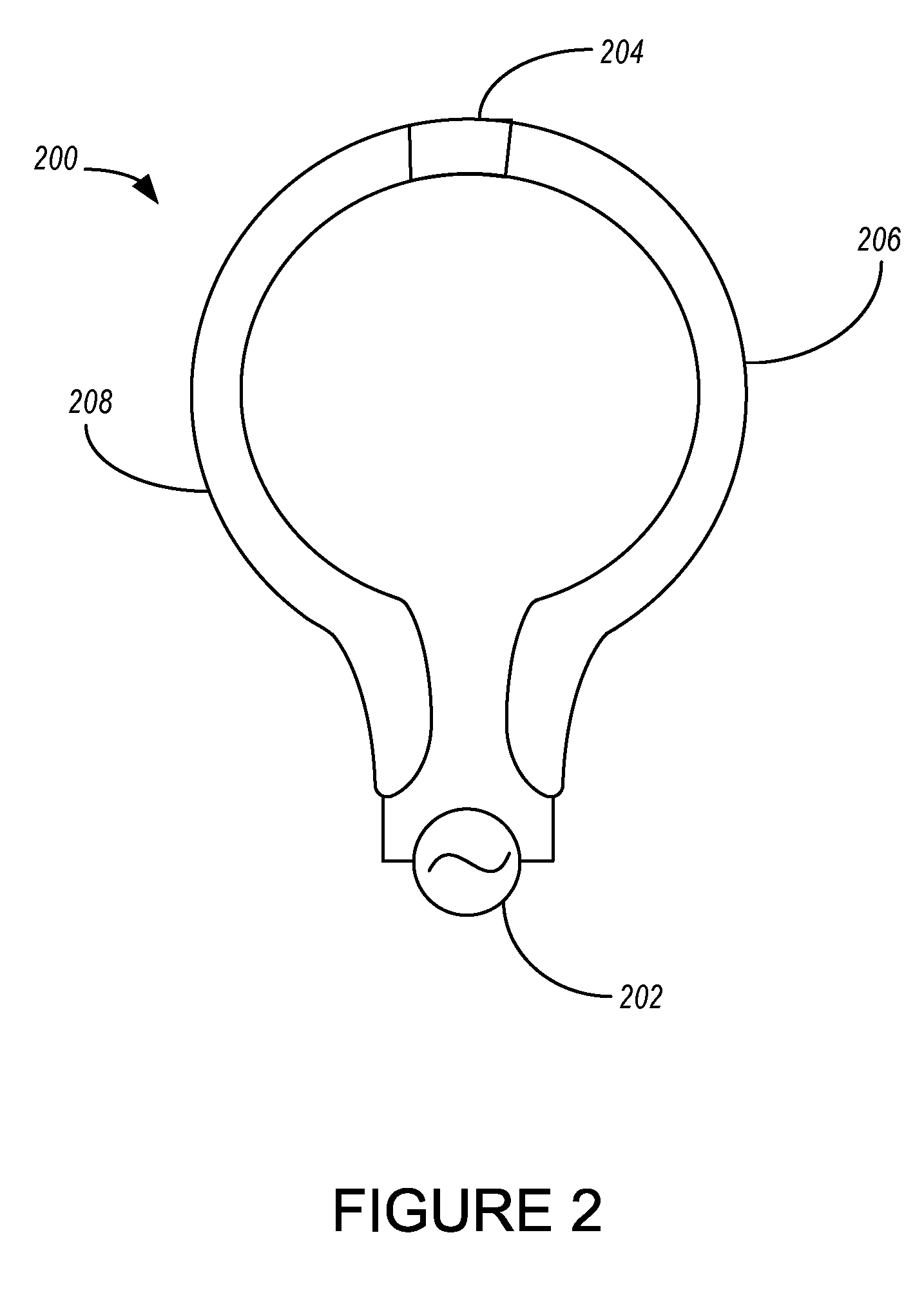

Physiological data acquisition and management system for use with an implanted wireless sensor

ActiveUS20080081962A1Allow useReduce environmental impactResonant circuit auxillary power controlContinuous tuning detailsLine sensorData acquisition

Aspects and embodiments of the present invention provide a system for obtaining, processing and managing data from an implanted sensor. In some embodiments, a patient or other persons can use a flexible antenna to obtain data from the implanted sensor. The flexible antenna includes at least one transmit loop and at least one receive loop. The transmit loop is adapted to propagate energizing signals to the implanted sensor. The receive loop is adapted to detect a response signal from the implanted sensor. The transmit loop includes a capacitor formed by a discontinuous area. The capacitor is adapted to allow the loop to be tuned. The flexible antenna can communicate with a patient device that collects the data from the implanted sensor, creates a data file and transmits the data file to a remote server over a network. A physician or other authorized person may access the remote server using an access device.

Owner:ST JUDE MEDICAL LUXEMBOURG HLDG II S A R L SJM LUX II

Integrated VCO having an improved tuning range over process and temperature variations

InactiveUS7019598B2Angle modulation by variable impedenceResonant circuit detailsState variableControl circuit

An integrated VCO having an improved tuning range over process and temperature variations. There is therefore provided in a present embodiment of the invention an integrated VCO. The VCO comprises, a substrate, a VCO tuning control circuit responsive to a VCO state variable that is disposed upon the substrate, and a VCO disposed upon the substrate, having a tuning control voltage input falling within a VCO tuning range for adjusting a VCO frequency output, and having its tuning range adjusted by the tuning control circuit in response to the VCO state variable.

Owner:AVAGO TECH INT SALES PTE LTD

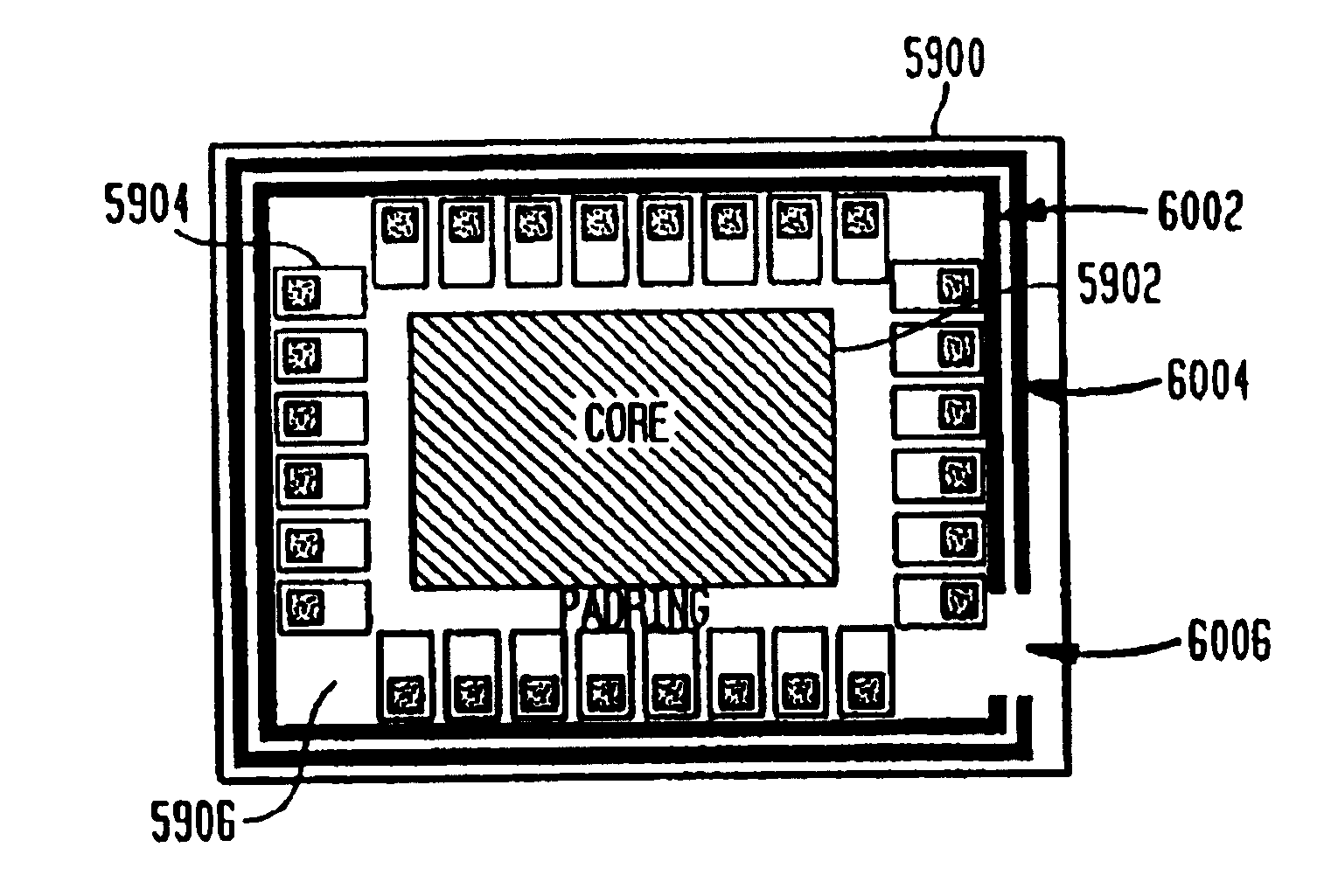

Integrated spiral inductor

InactiveUS20050156700A1Resonant circuit detailsSemiconductor/solid-state device detailsCapacitanceShunt Device

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides programable attenuation and a programable gain low noise amplifier. Frequency conversion circuitry advantageously uses LC filters integrated onto the substrate in conjunction with image reject mixers to provide sufficient image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. The filters utilize multi track spiral inductors with shields to increase circuit Q. The filters are tuned using local oscillators to tune a substitute filter, and frequency scaling during filter component values to those of the filter being tuned. In conjunction with filtering, frequency planning provides additional image rejection. The advantageous choice of local oscillator signal generation methods on chip is by PLL out of band local oscillation and by direct synthesis for in band local oscillator. The VCOs in the PLLs are centered using a control circuit to center the tuning capacitance range. A differential crystal oscillator is advantageously used as a frequency reference. Differential signal transmission is advantageously used throughout the receiver. ESD protection is provided by a pad ring and ESD clamping structure that maintains signal integrity. Also provided are shunts at each pin to discharge ESD build up. The shunts utilize a gate boosting structure to provide sufficient small signal RF performance, and minimal parasitic loading.

Owner:AVAGO TECH INT SALES PTE LTD

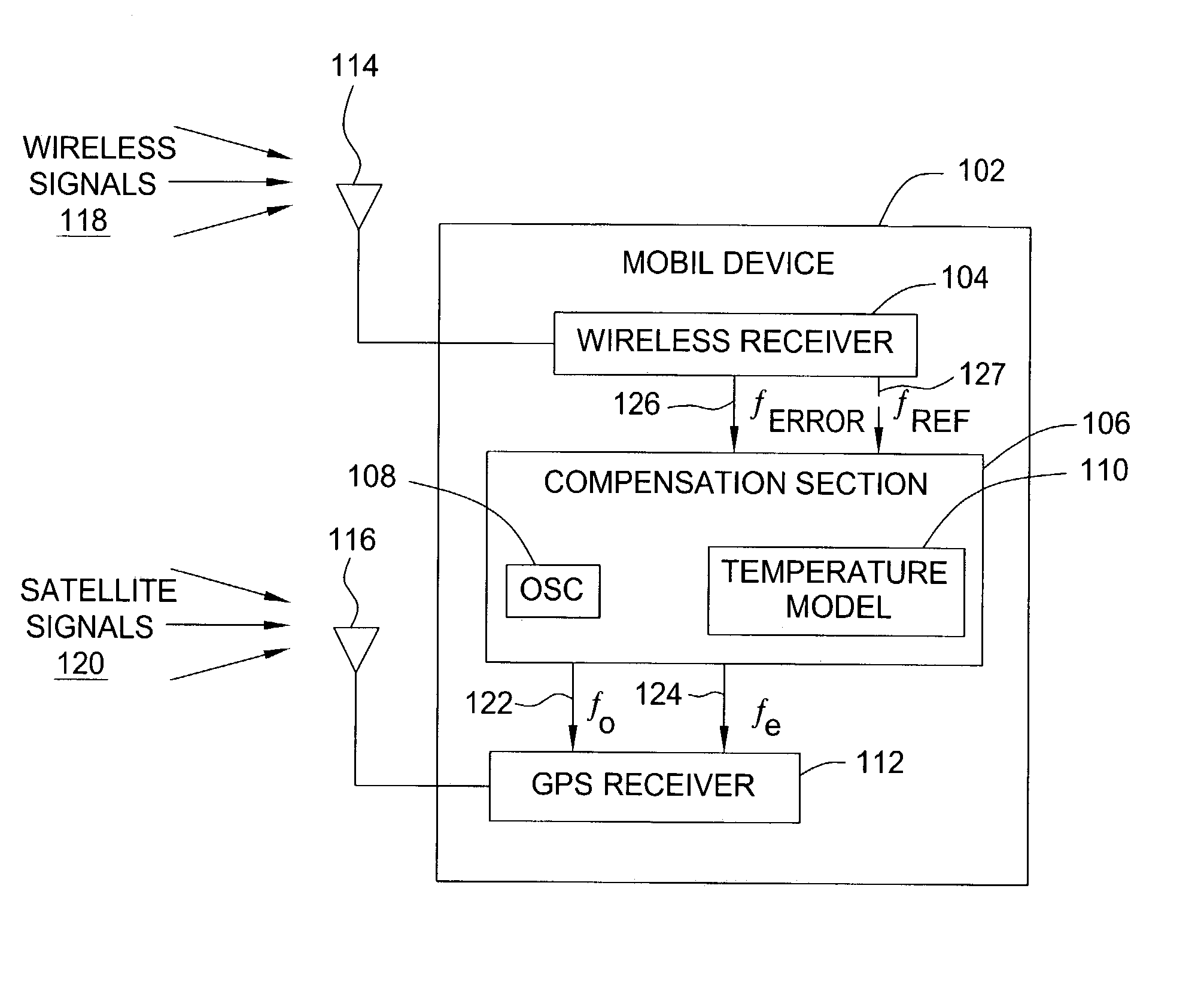

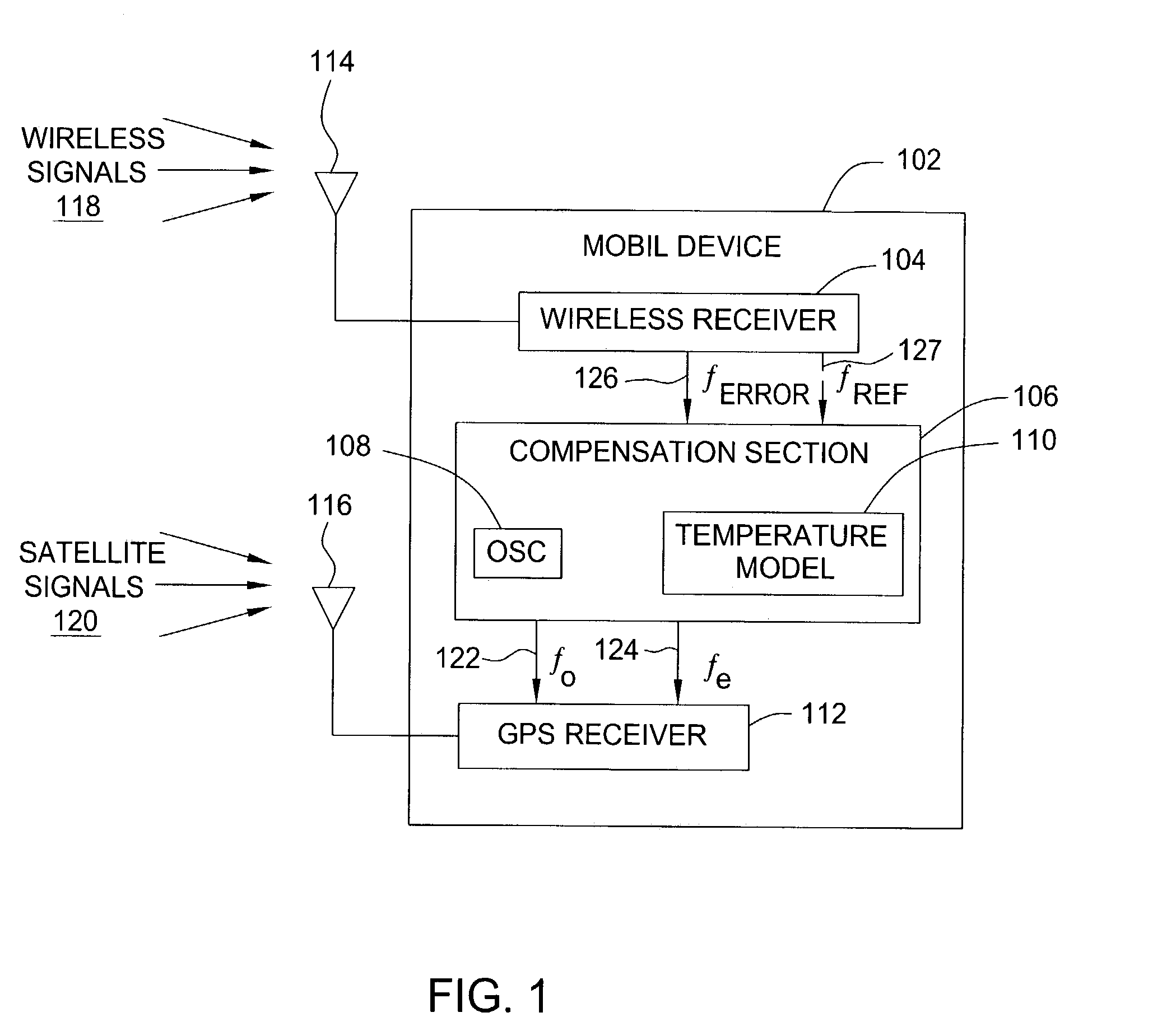

Method and apparatus for compensating an oscillator in a location-enabled wireless device

A method and apparatus for compensating an oscillator in a location-enabled wireless device is described. In an example, a mobile device includes a wireless receiver for receiving wireless signals and a GPS receiver for receiving GPS signals. The mobile device also includes an oscillator having an associated temperature model. A frequency error is derived from a wireless signal. The temperature model is adjusted in response to the frequency error and a temperature proximate the oscillator. Frequency error of the oscillator is compensated using the adjusted temperature model. In another example, a frequency error is derived using a second oscillator within the wireless receiver.

Owner:AVAGO TECH INT SALES PTE LTD

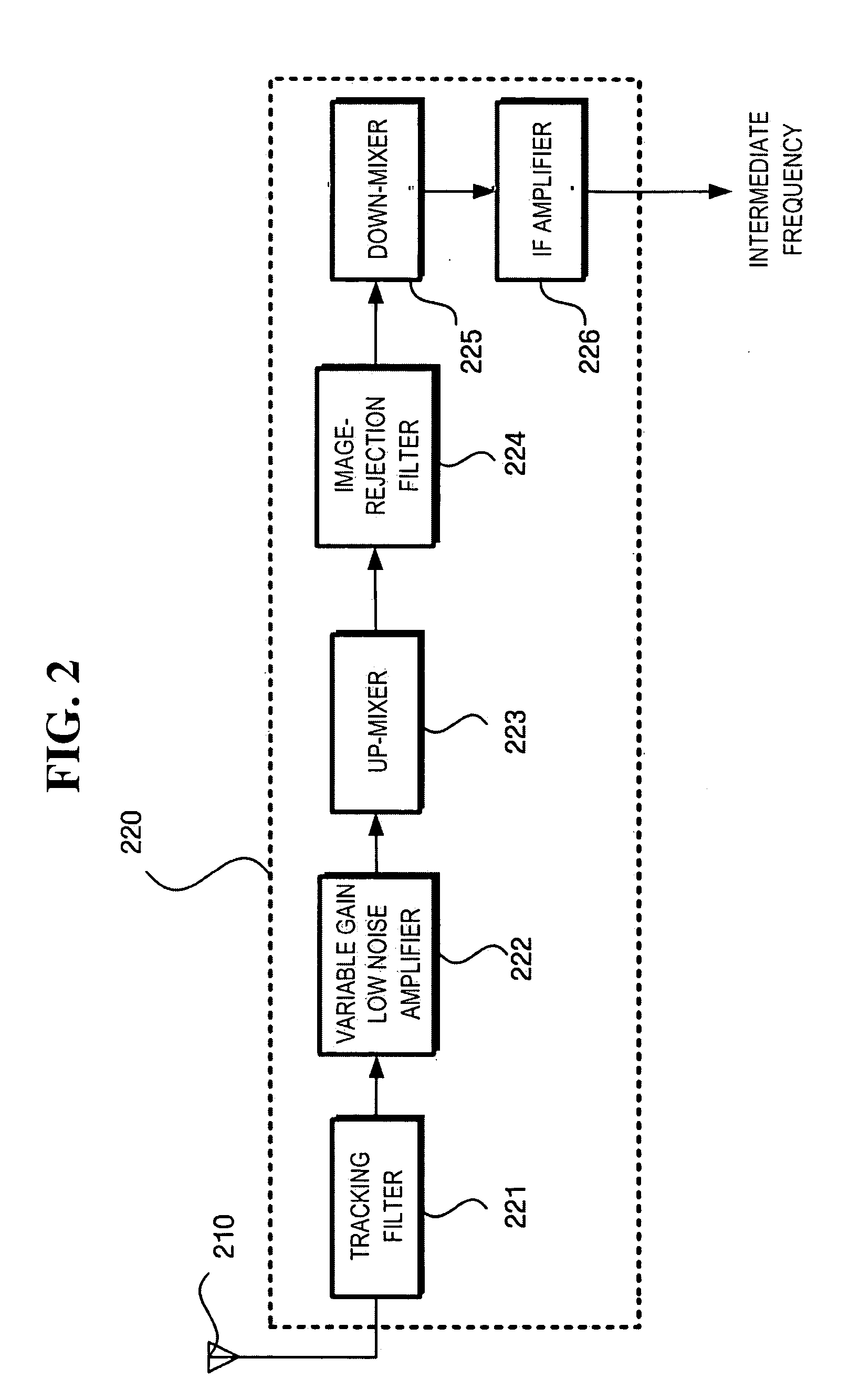

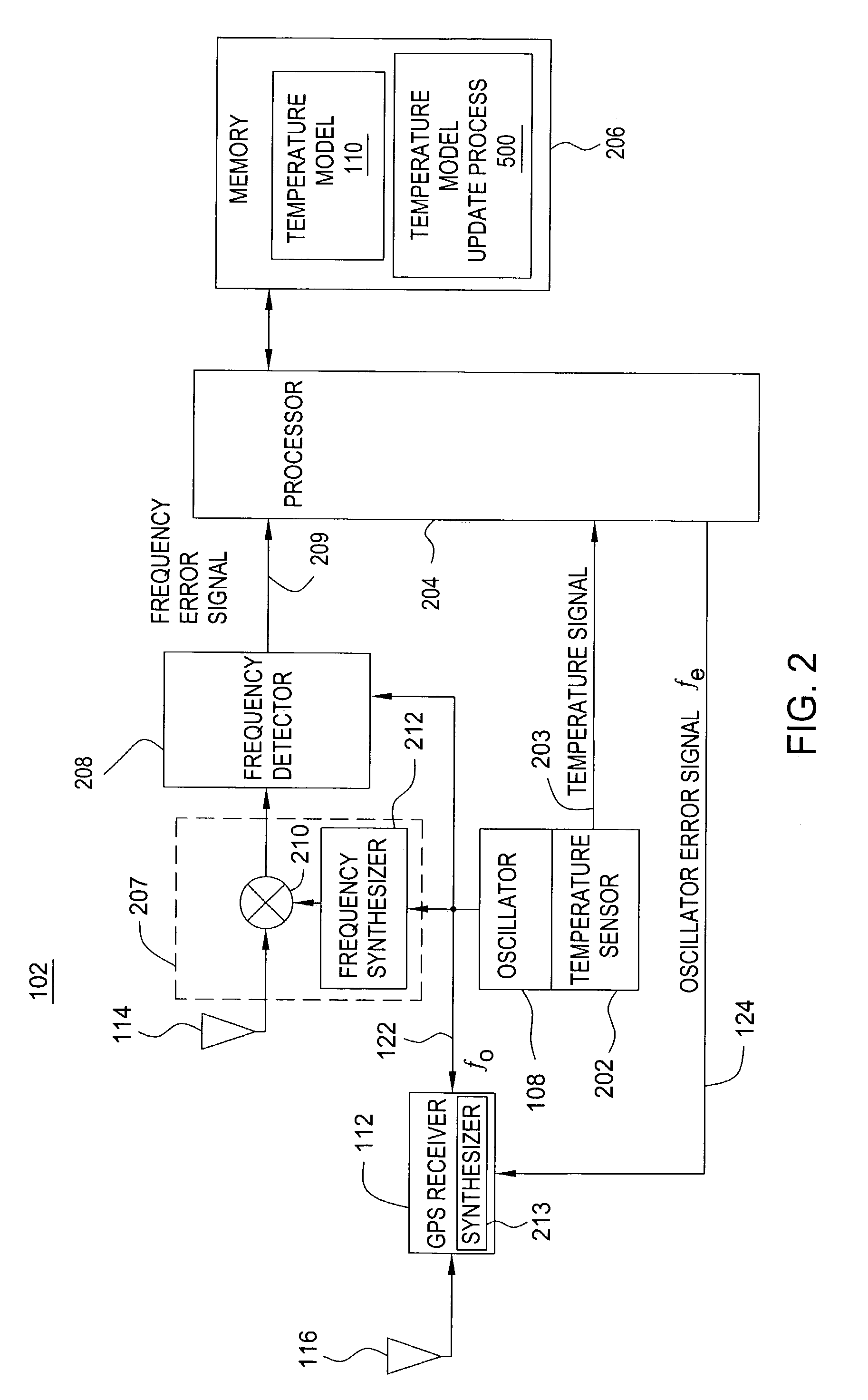

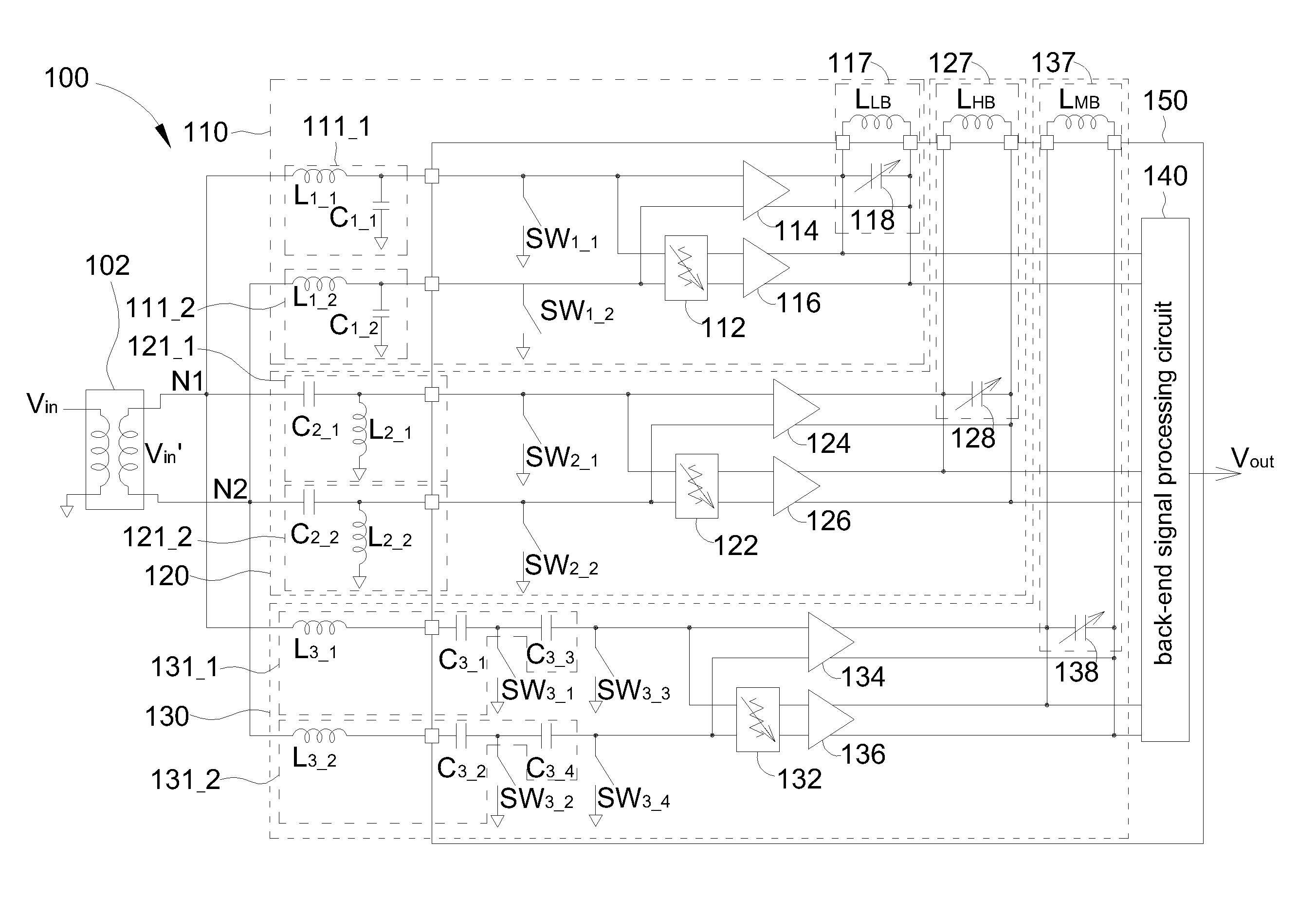

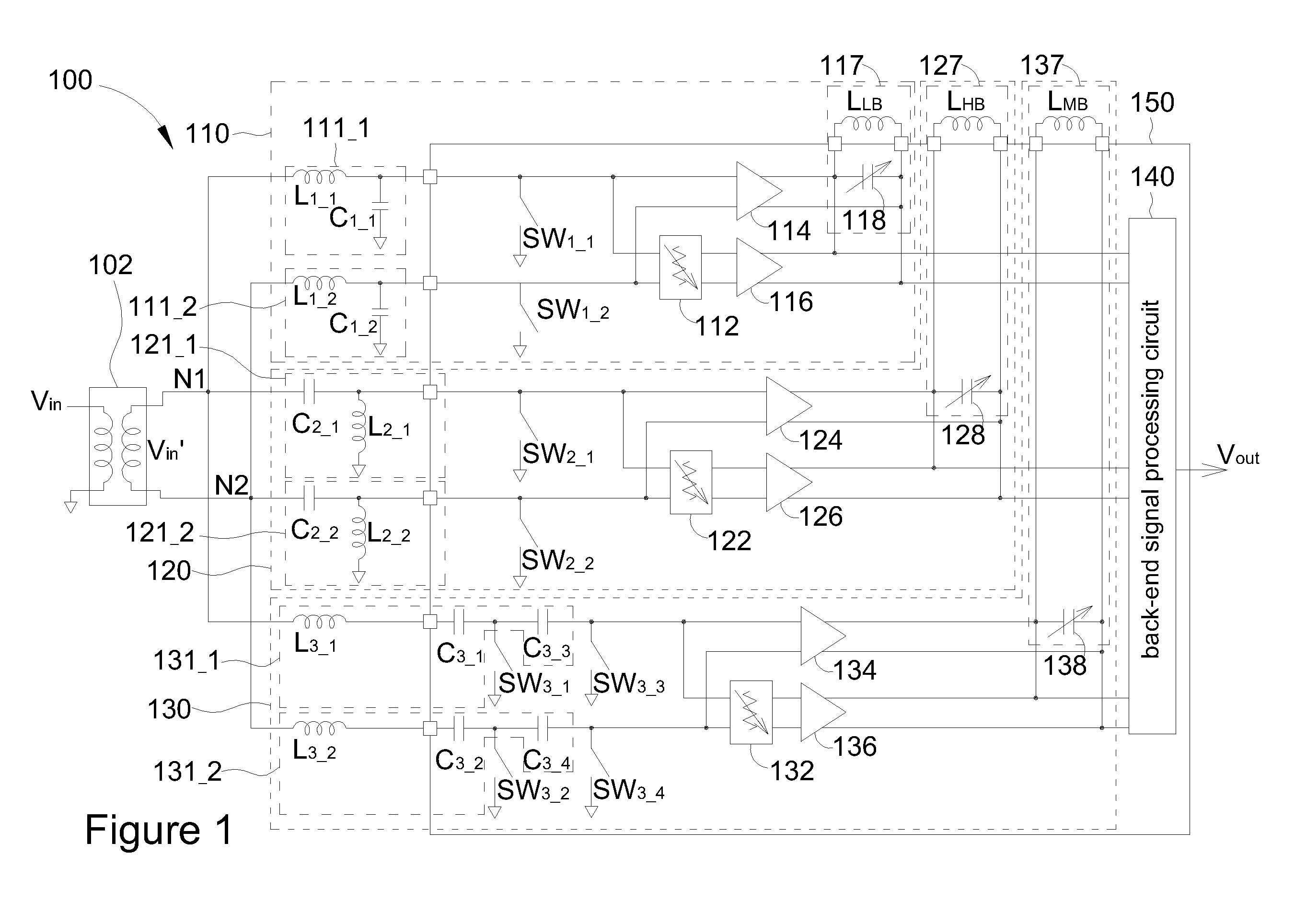

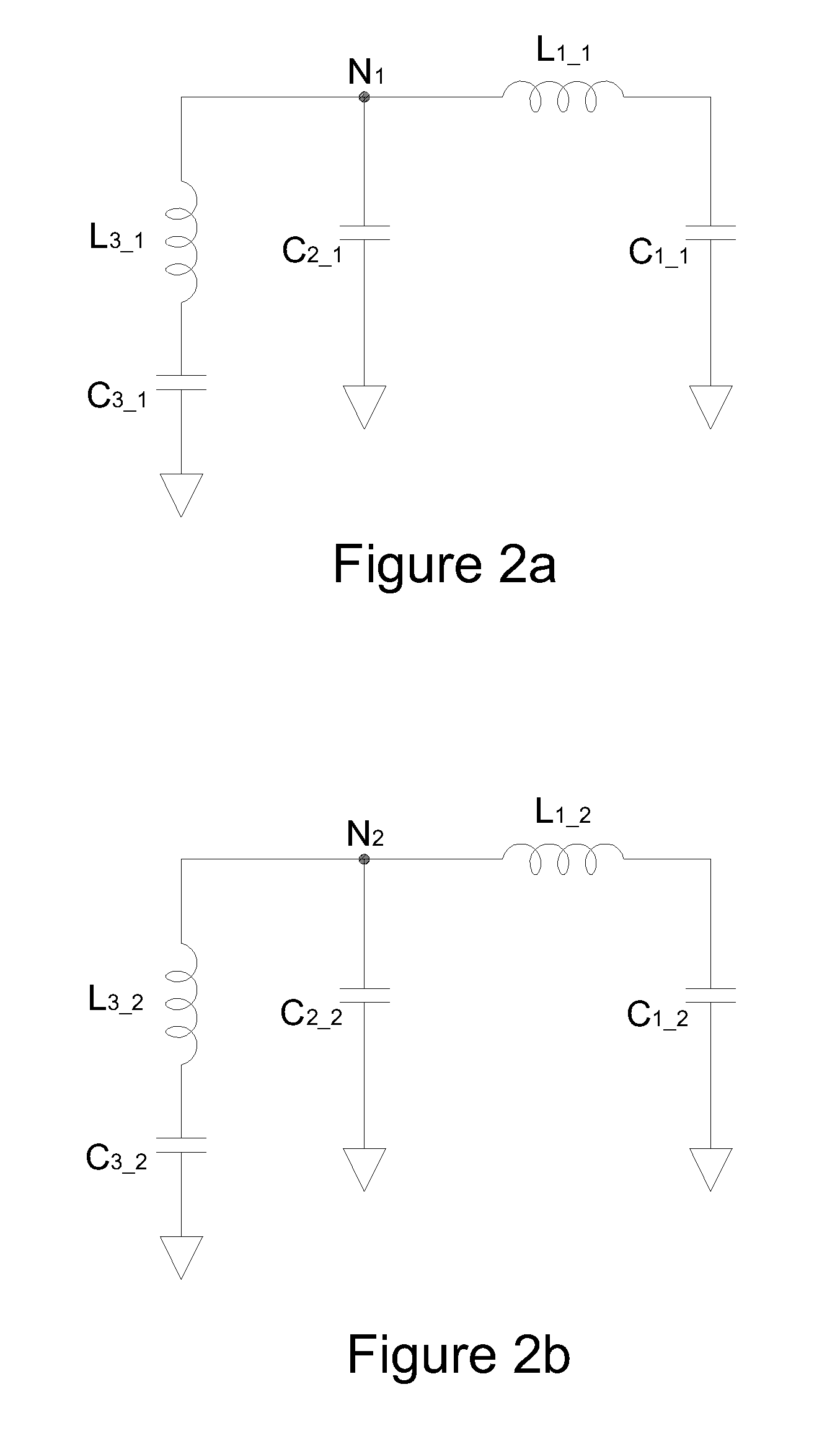

Tuner and Front-end Circuit Thereof

ActiveUS20110051014A1Low production costPreferable filtering qualityTelevision system detailsContinuous tuning detailsCMOSAudio power amplifier

A tuner includes a plurality of paths, and at least one of the paths includes a front-end filter circuit, an amplifier, and a trace filter. The trace filter includes a varactor and an inductor, which are coupled to an output end of the amplifier. Further, the amplifier and the varactor of the tuner are packed in a complementary metal-oxide semiconductor (CMOS) chip.

Owner:MEDIATEK INC

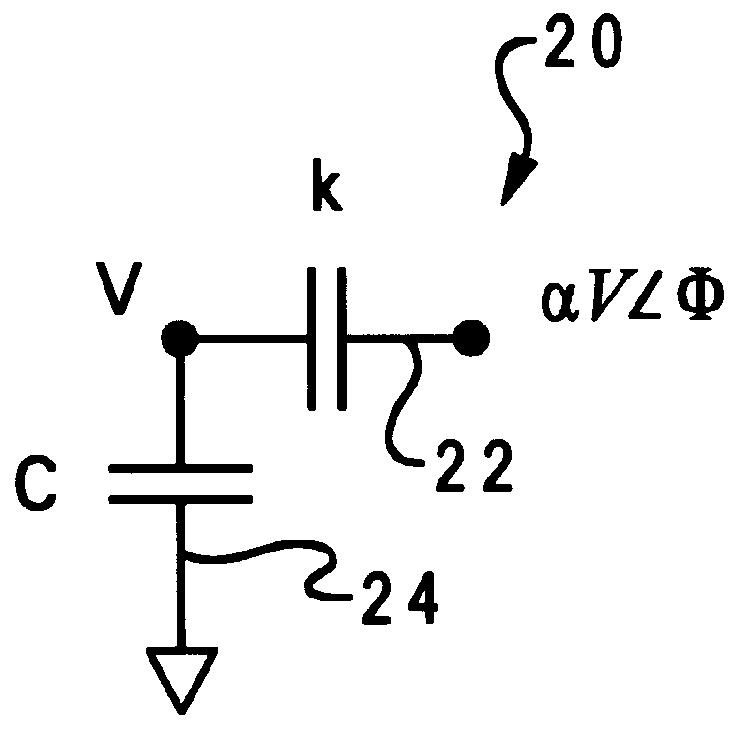

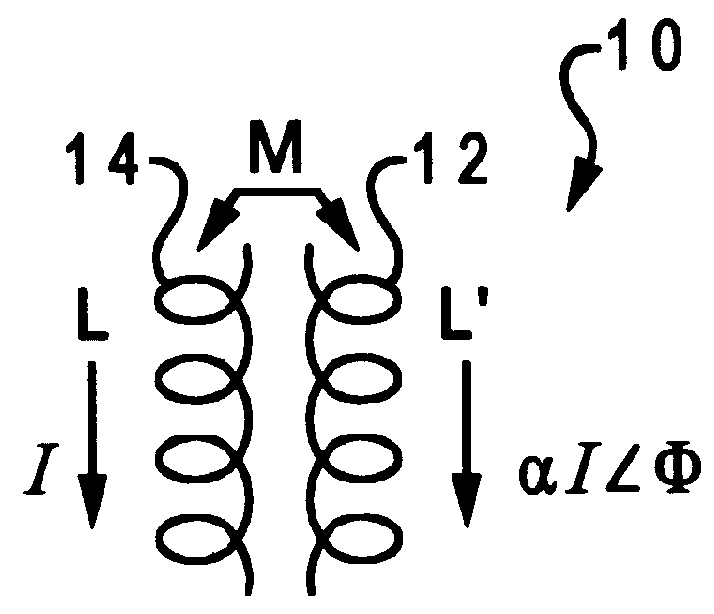

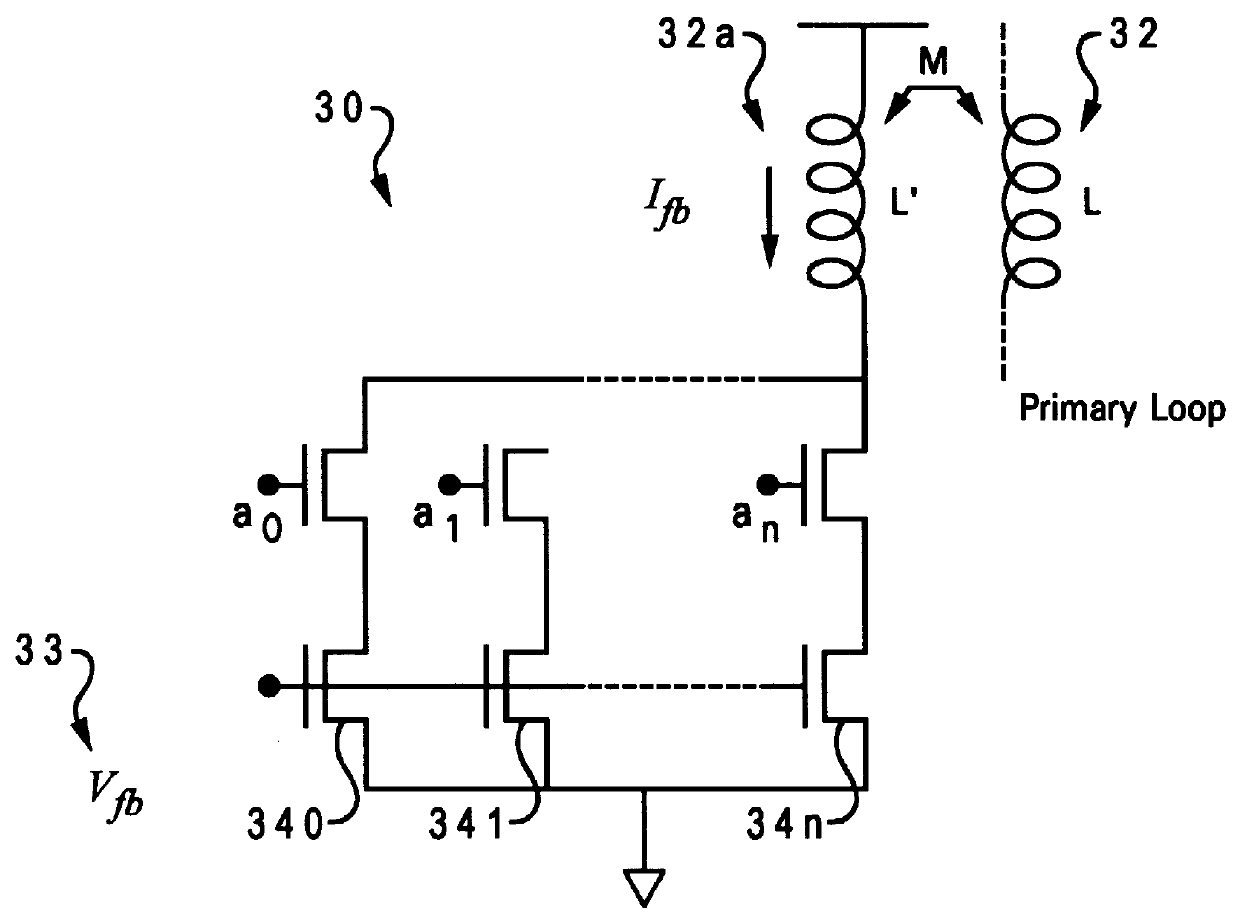

Digitally adjustable inductive element adaptable to frequency tune an LC oscillator

A digitally adjustable inductive element which can be implemented in an integrated circuit. The digitally adjustable inductive element can include a first inductor, and a digital inductance controller operatively coupled to the first inductor which can be utilized to vary the effective inductance of the first inductor. The digitally adjustable inductive element can include a second inductor operatively coupled to the first inductor, and a digital current controller operatively coupled to the second inductor. The digital current controller can include a number of transistors operatively coupled to the second inductor. The digitally adjustable inductive element can be utilized to create a tunable oscillator. The tunable oscillator can include a first inductor, a digital inductance controller operatively coupled to the first inductor which can be utilized to vary the effective inductance of the first inductor, and an oscillator circuit which generates an oscillating signal utilizing the effective inductance of the first inductor. The tunable oscillator can include a second inductor operatively coupled to the first inductor, and a digital current controller operatively coupled to the second inductor. The digital current controller can include a number of transistors operatively coupled to the second inductor.

Owner:IBM CORP

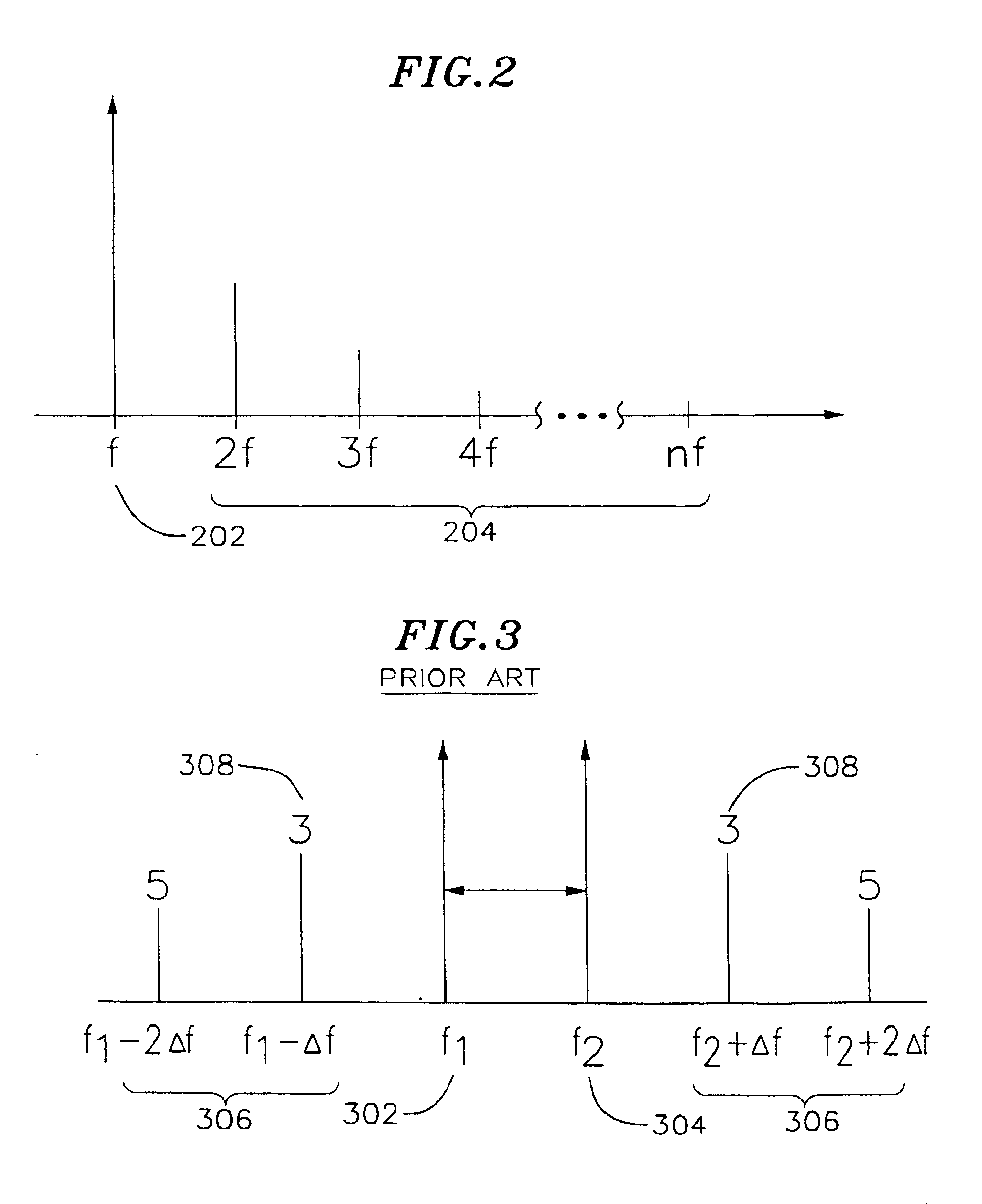

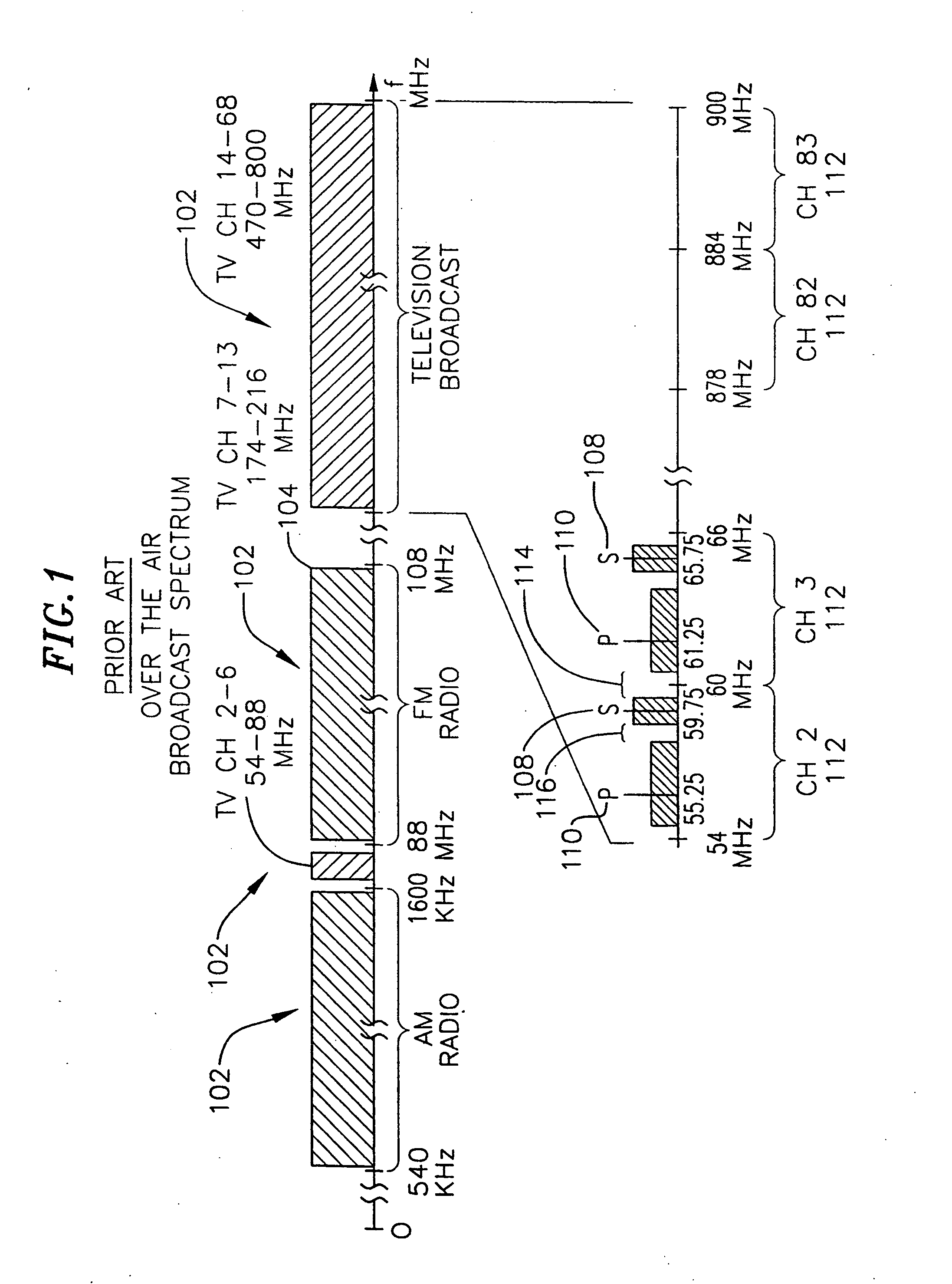

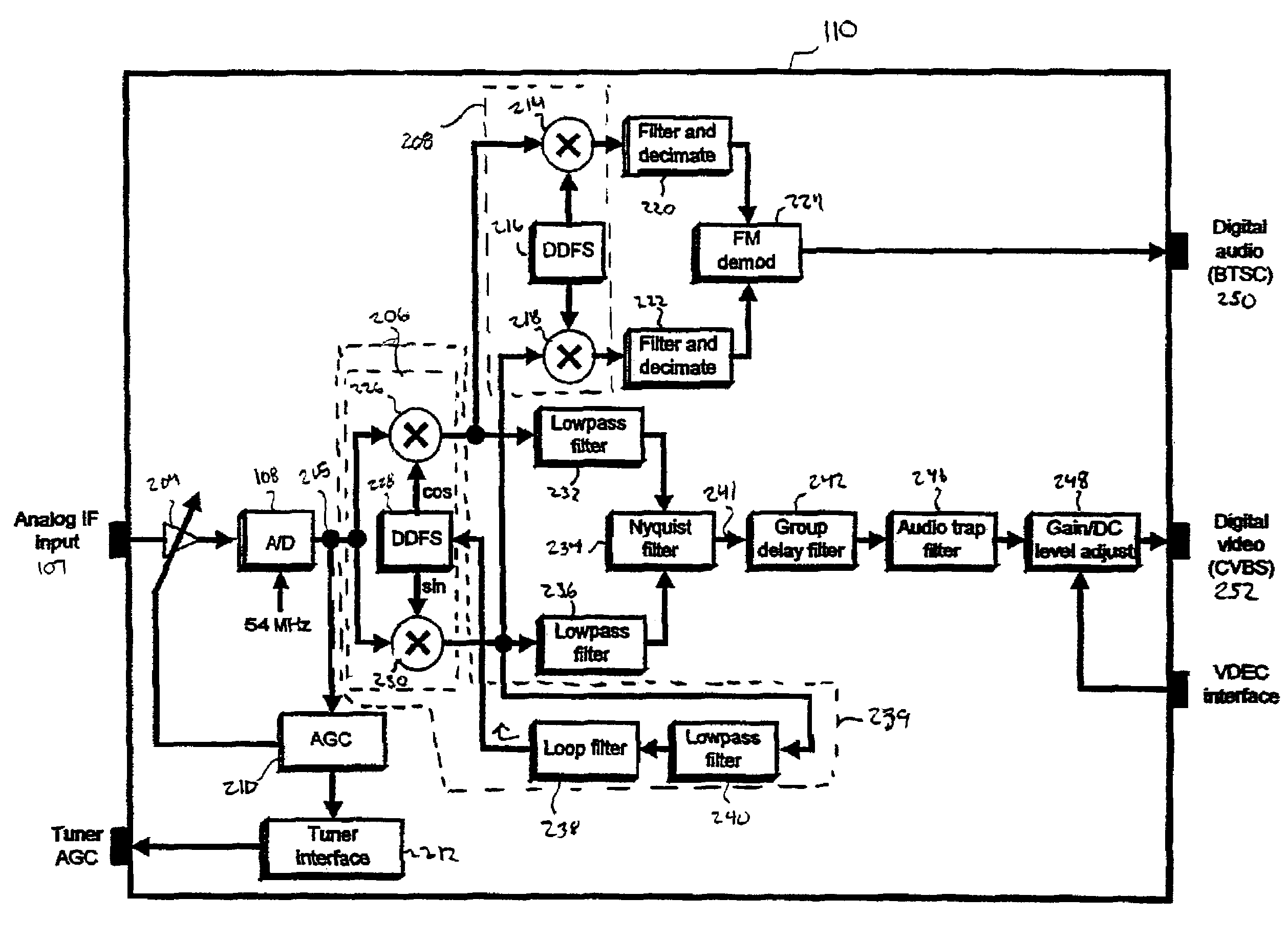

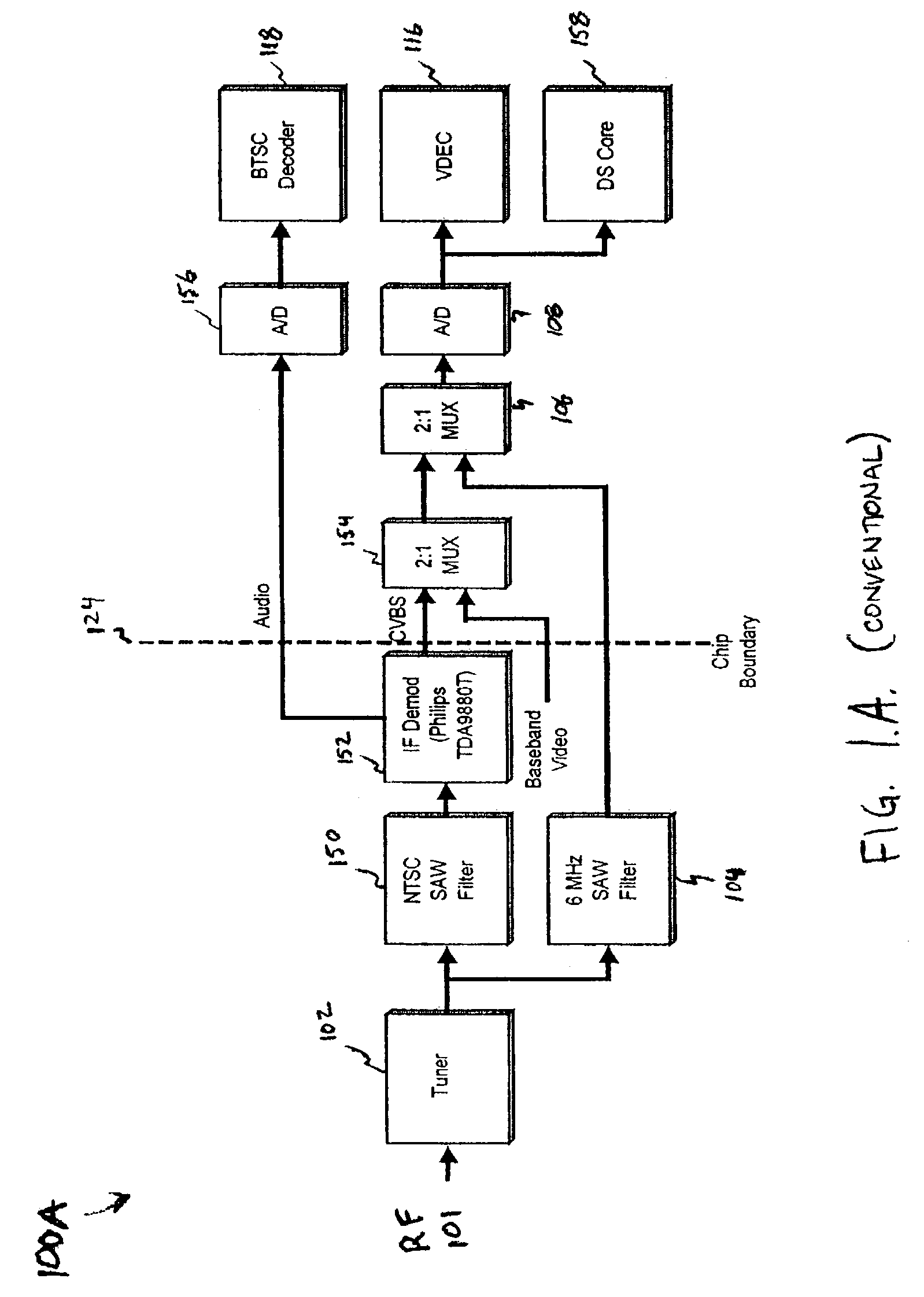

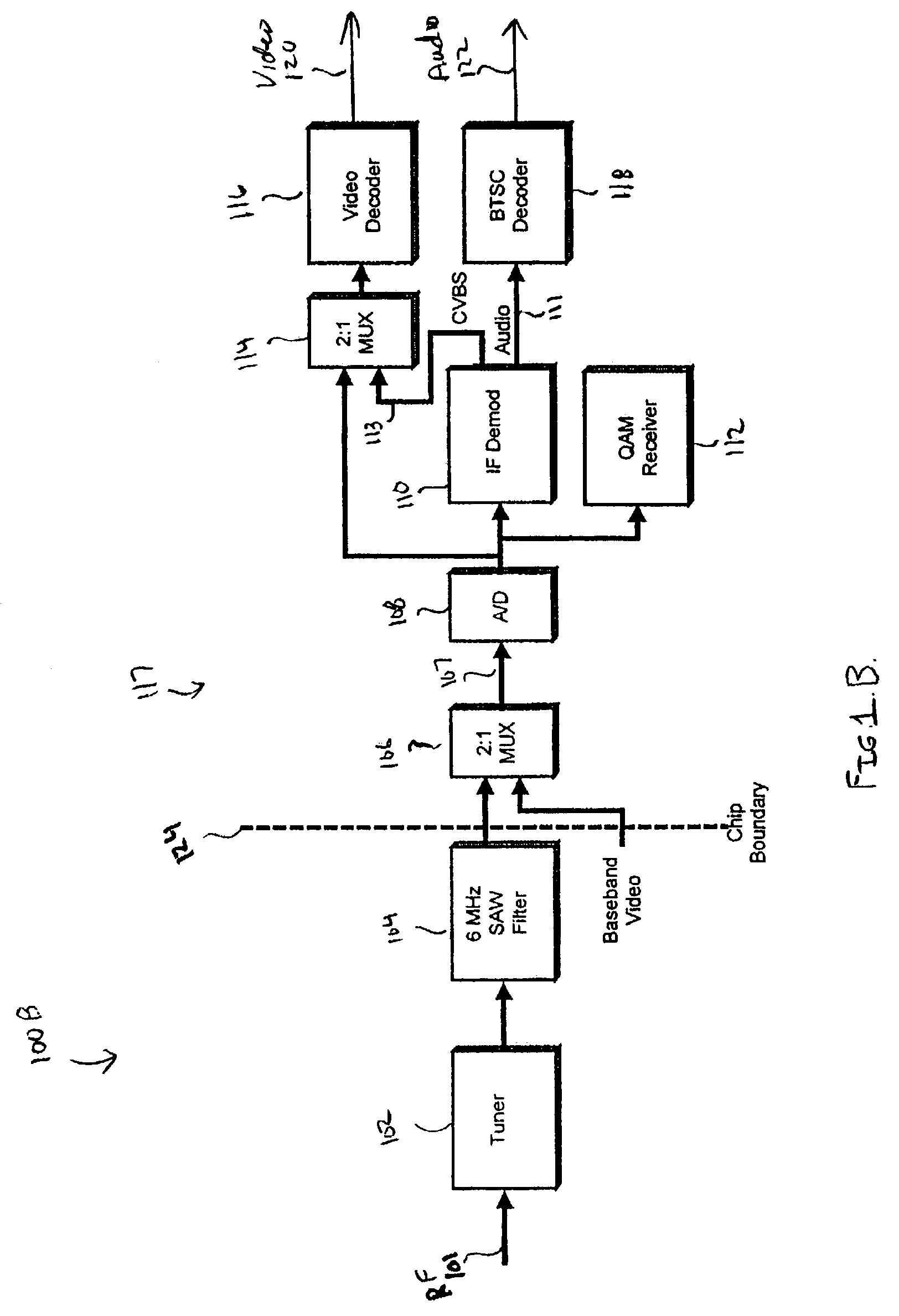

Digital IF demodulator with carrier recovery

A digital IF demodulator receives and demodulates an analog IF input signal to produce a digital audio signal and a digital video signal. The digital IF demodulator includes an A / D converter, a first digital complex mixer, a second digital complex mixer, and various digital filters. The first digital complex mixer receives the output of the A / D converter and down-converts the output of the A / D converter to baseband. Additionally, the picture carrier is recovered from the output of the first digital complex mixer, and fed back to a direct digital synthesizer to control the tuning accuracy of the first digital complex mixer. More specifically, a feedback loop is formed to so that the picture carrier is down-converted to DC so as to control the tuning accuracy of the first digital complex mixer. The complex output of the first complex mixer is further processed using Nyquist filtering and other filtering to recover the digital video signal. The digital audio signal is recovered by further processing the output of the first digital complex mixer. With the picture carrier located at DC, the audio signal is shifted off DC by approximately 4.5 Mhz. A second complex mixer down-converts the output of the first digital complex mixer so that the audio signal at 4.5 MHz is down-converted to baseband. After filtering and demodulation, the digital audio signal is recovered.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

System and method for ESD protection

InactiveUS6963110B2Reduce areaReduce capacitanceResonant circuit detailsSemiconductor/solid-state device detailsShunt DeviceCapacitance

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides programable attenuation and a programable gain low noise amplifier. Frequency conversion circuitry advantageously uses LC filters integrated onto the substrate in conjunction with image reject mixers to provide sufficient image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. The filters utilize multi track spiral inductors. The filters are tuned using local oscillators to tune a substitute filter, and frequency scaling during filter component values to those of the filter being tuned. In conjunction with filtering, frequency planning provides additional image rejection. The advantageous choice of local oscillator signal generation methods on chip is by PLL out of band local oscillation and by direct synthesis for in band local oscillator. The VCOs in the PLLs are centered using a control circuit to center the tuning capacitance range. A differential crystal oscillator is advantageously used as a frequency reference. Differential signal transmission is advantageously used throughout the receiver. ESD protection is provided by a pad ring and ESD clamping structure that maintains signal integrity. Also provided are shunts at each pin to discharge ESD build up. The shunts utilize a gate boosting structure to provide sufficient small signal RF performance, and minimal parasitic loading.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

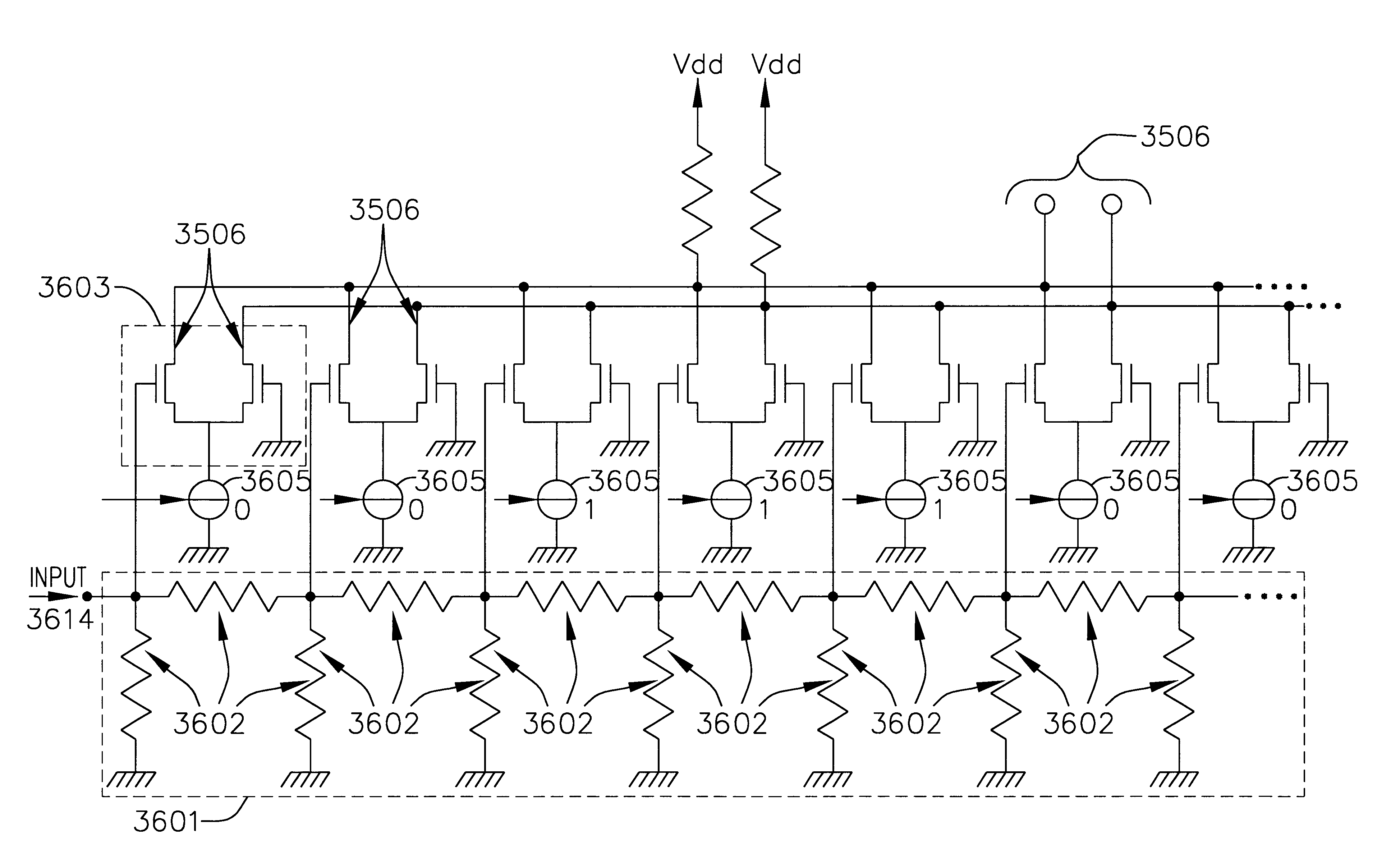

Linear voltage controlled capacitance circuit

InactiveUS6853272B1Eliminate and reduce disadvantageEliminate and reduce and problemContinuous tuning detailsOne-port networksCapacitanceEngineering

A linear voltage controlled capacitance circuit is provided that includes a plurality of MOS varactor pairs. Each MOS varactor pair is operable to receive a first tuning voltage, a second tuning voltage, and a bias voltage unique to the MOS varactor pair. The capacitance circuit is operable to generate a positive tank node signal and a negative tank node signal based on the first and second tuning voltages and the bias voltages. A means to control voltage-to-capacitance gain is also provided to compensate for coarse tuning capacitance change.

Owner:NAT SEMICON CORP

Global positioning system receiver capable of functioning in the presence of interference

Systems and methods are described for a GPS receiver capable of functioning in the presence of interference. A method includes detecting an interfering signal including: tuning a band pass filter over a frequency range; and at each of a plurality of incremental frequencies: computing a set of band pass filter coefficients; sending the set of band pass filter coefficients to a digital filter; repeatedly transforming an analog-to-digital converter output having a quantization level in excess of 2 bits into a band pass filter output with the digital filter to obtain a plurality of samples; computing an average of the plurality of samples; and comparing the average to a threshold to detect peaks that exceed a threshold. An apparatus, comprising: an analog radio frequency circuit; an analog-to-digital converter coupled to the analog radio frequency circuit, the analog-to-digital converter providing a quantization level in excess of 2 bits; a digital filter coupled to the analog-to-digital converter; and a digital circuit coupled to the digital filter.

Owner:IP GEM GRP LLC

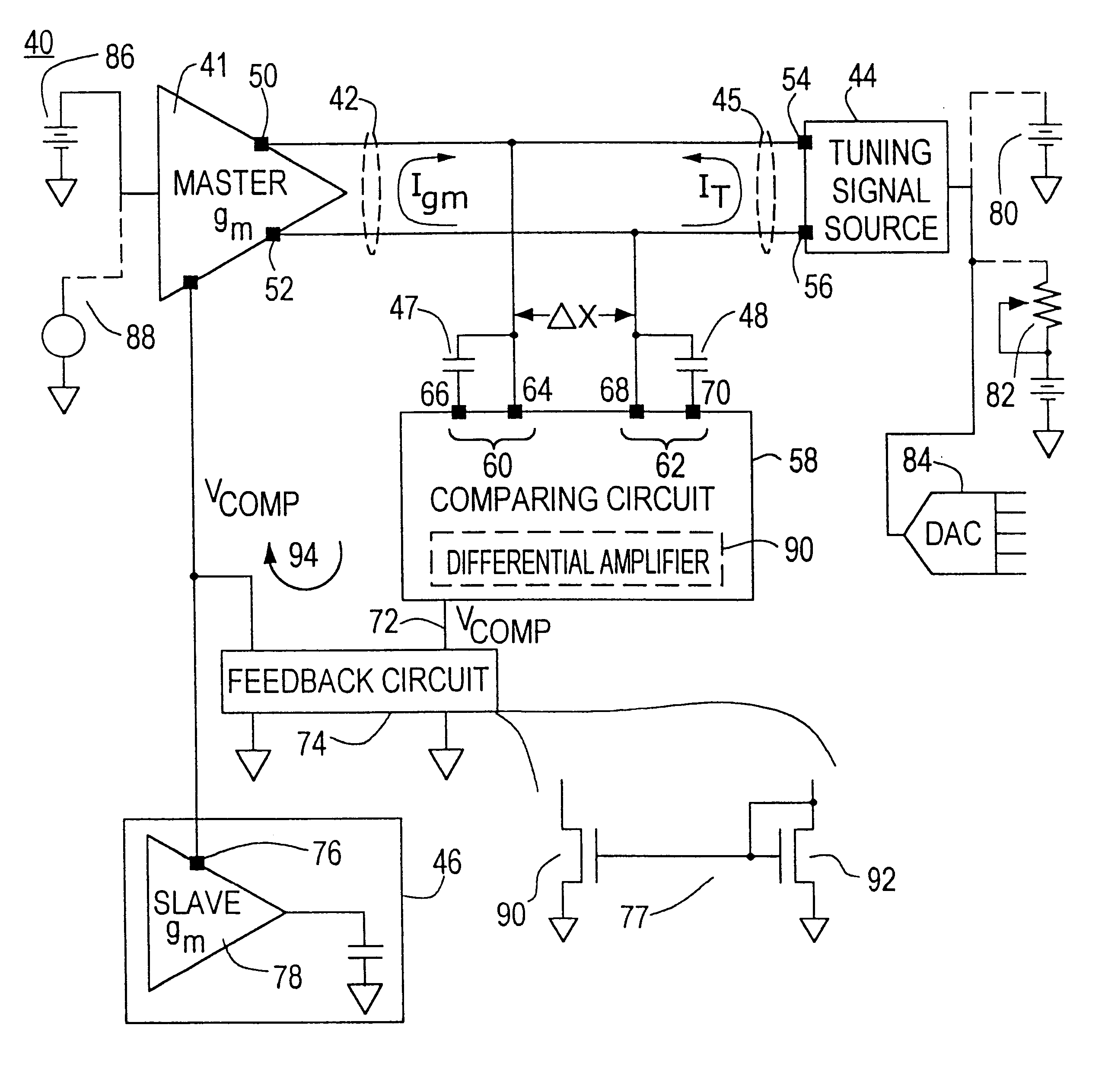

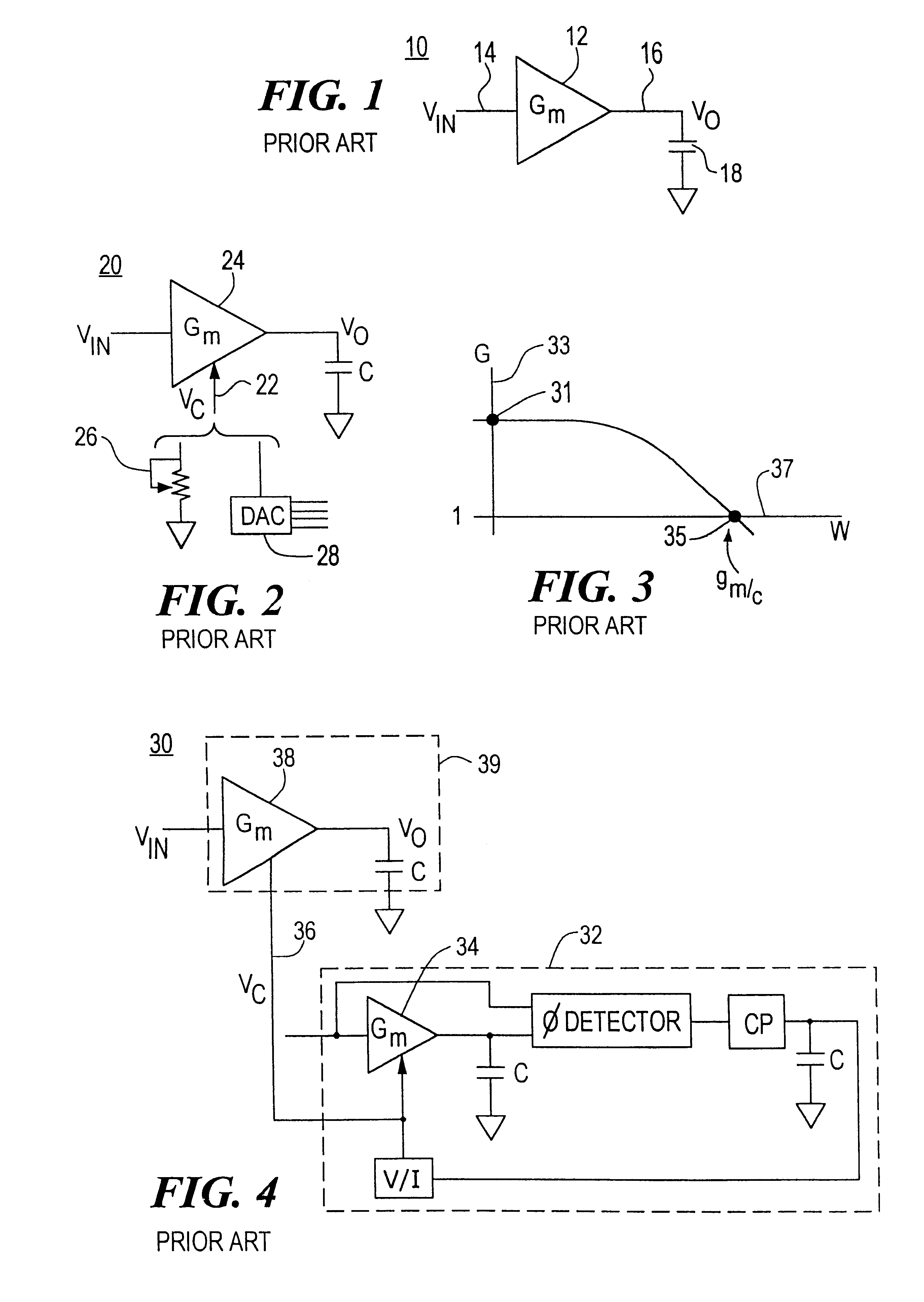

Transconductance filter control system

InactiveUS6172569B1Increase power consumptionIncrease in sizeContinuous tuning detailsGain controlAudio power amplifierControl system

A transconductance filter control system for compensating for drift in transconductance of a slave transconductance amplifier in a continuous time transconductance filter including: a master transconductance amplifier having an output which is a function of its transconductance and a control input for controlling the transconductance of the master transconductance amplifier; a tuning signal source for providing a tuning signal representative of a preselected characteristic of the transconductance filter; a comparing circuit, responsive to any deviation from a predetermined difference between the tuning signal and the output of the master transconductance amplifier, representative of a deviation of the transconductance of the master transconductance amplifier, for providing a compensation signal; and a circuit for applying the compensation signal to the control input of the master transconductance amplifier and to the control input of the slave transconductance amplifier in the transconductance filter to adjust the transconductance of both the master and slave transconductance amplifiers and restore the predetermined difference between the tuning signal and the output of the master transconductance amplifier.

Owner:ANALOG DEVICES INC +1

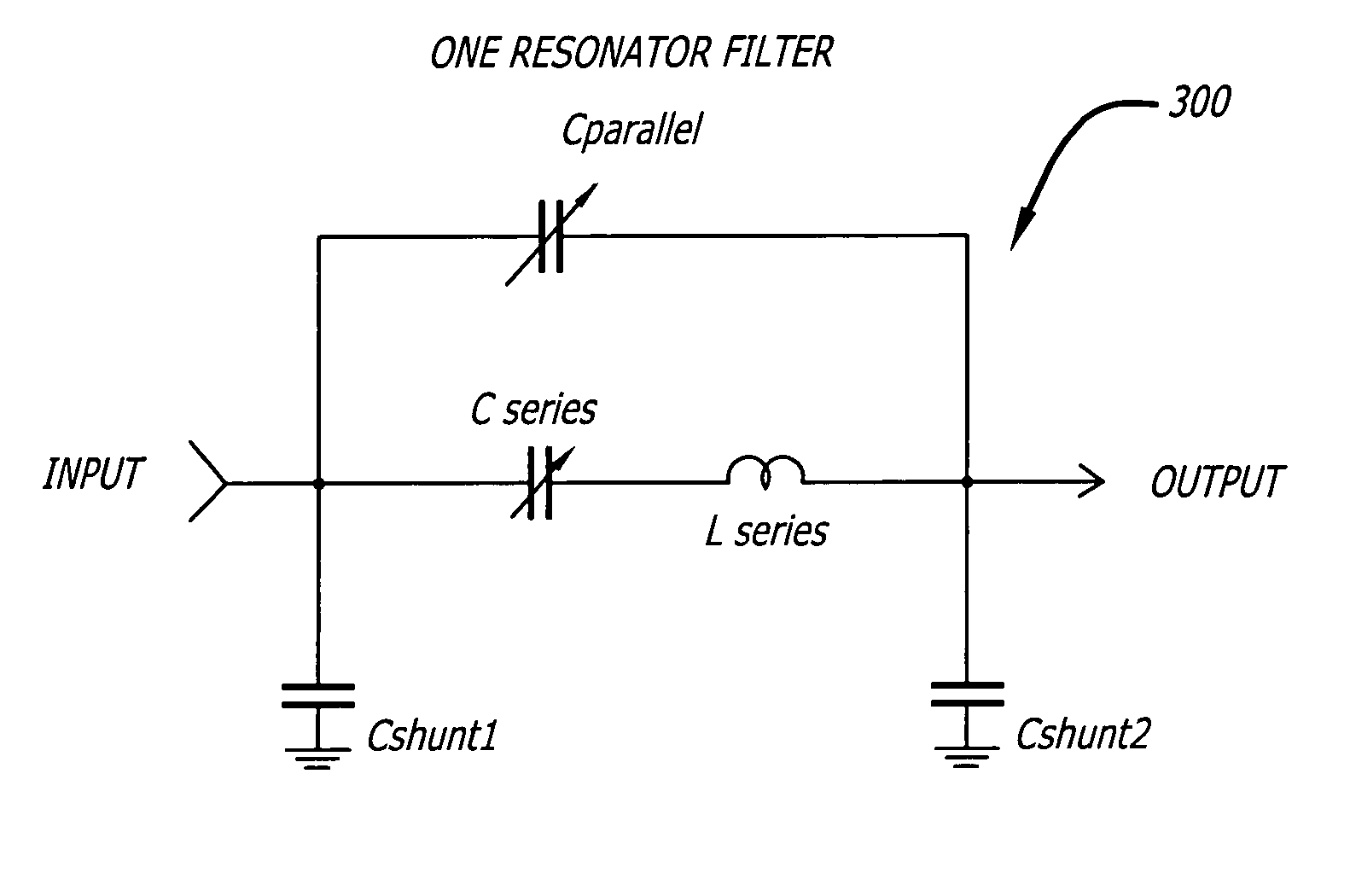

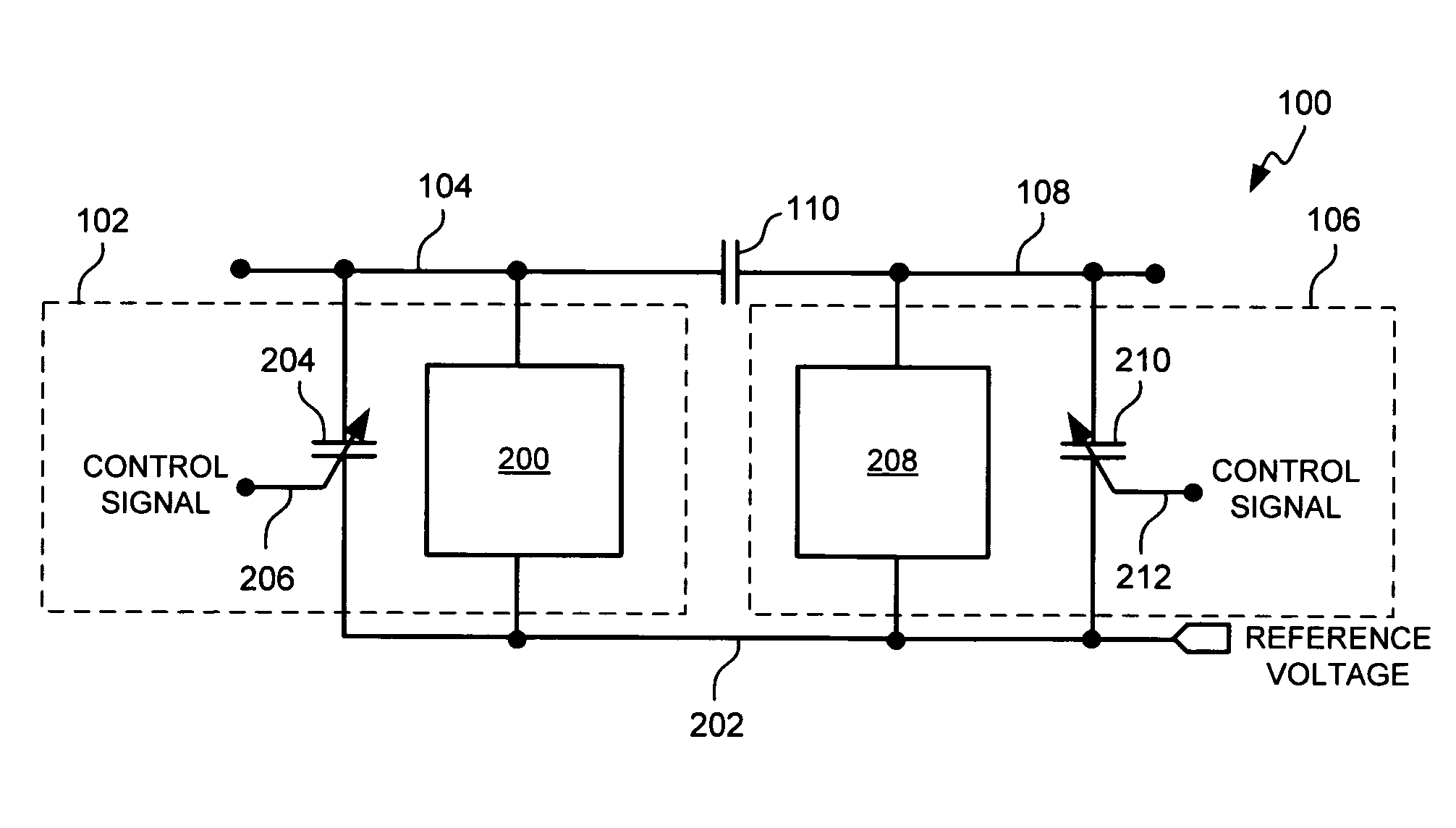

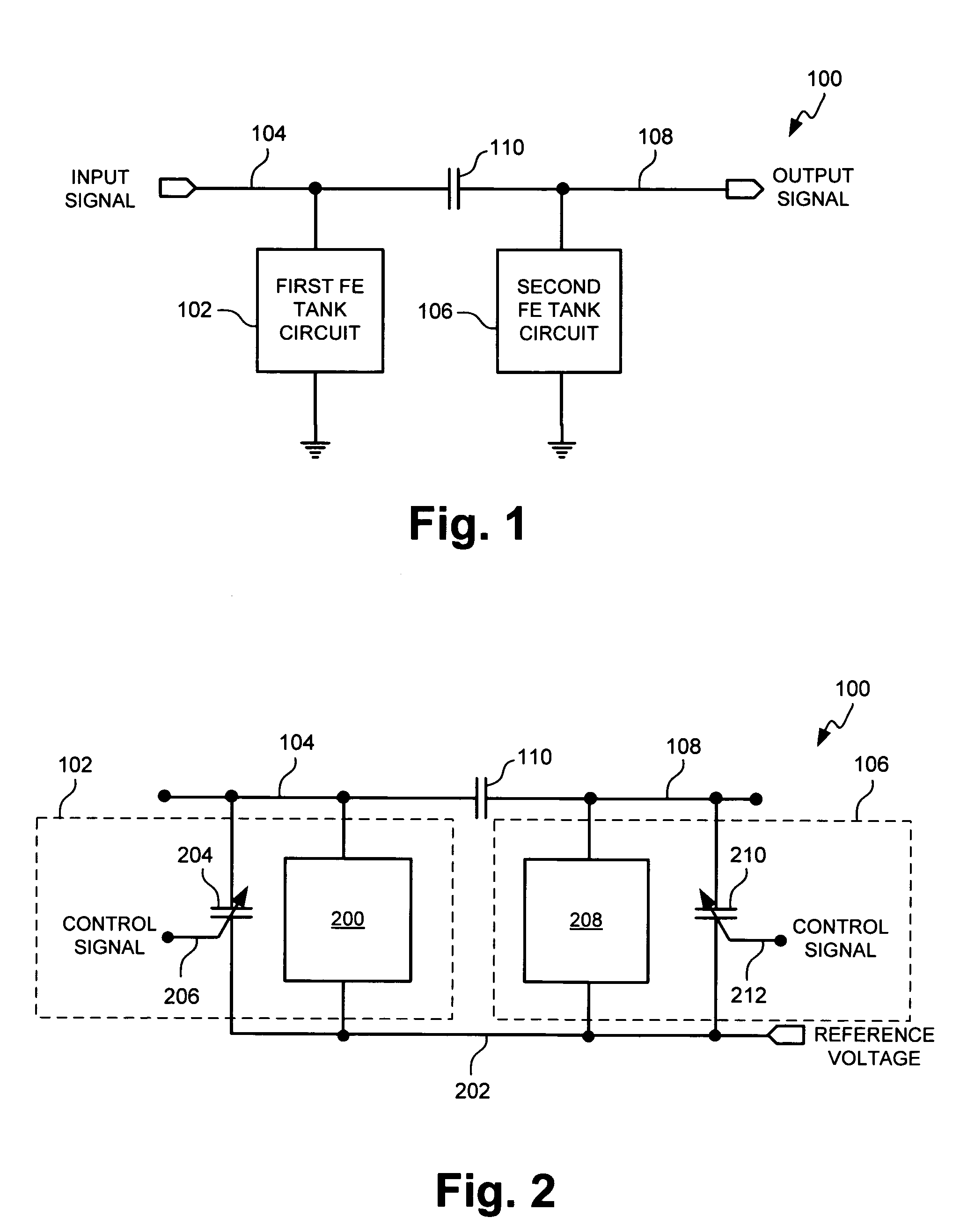

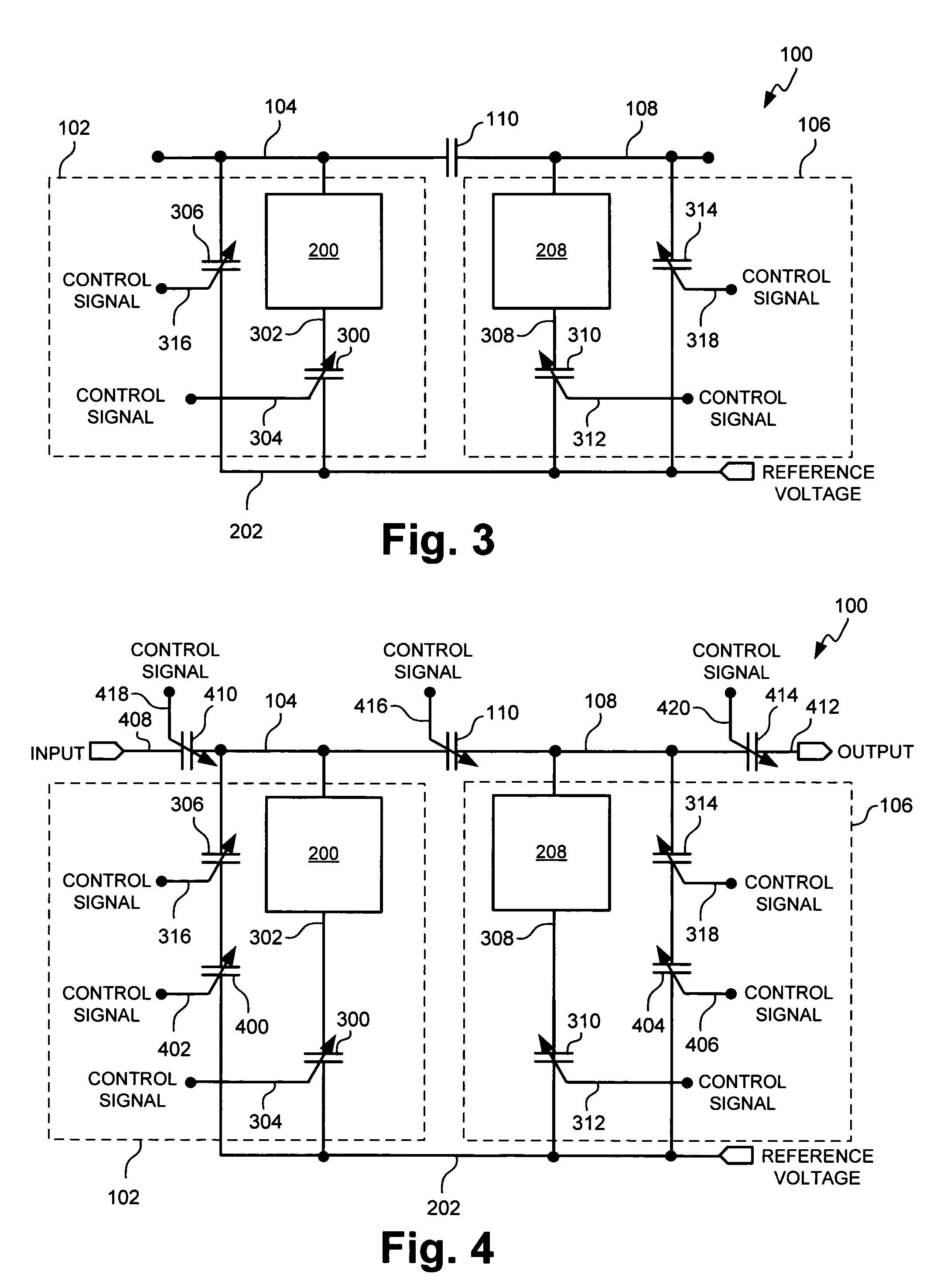

Bandpass filter with tunable resonator

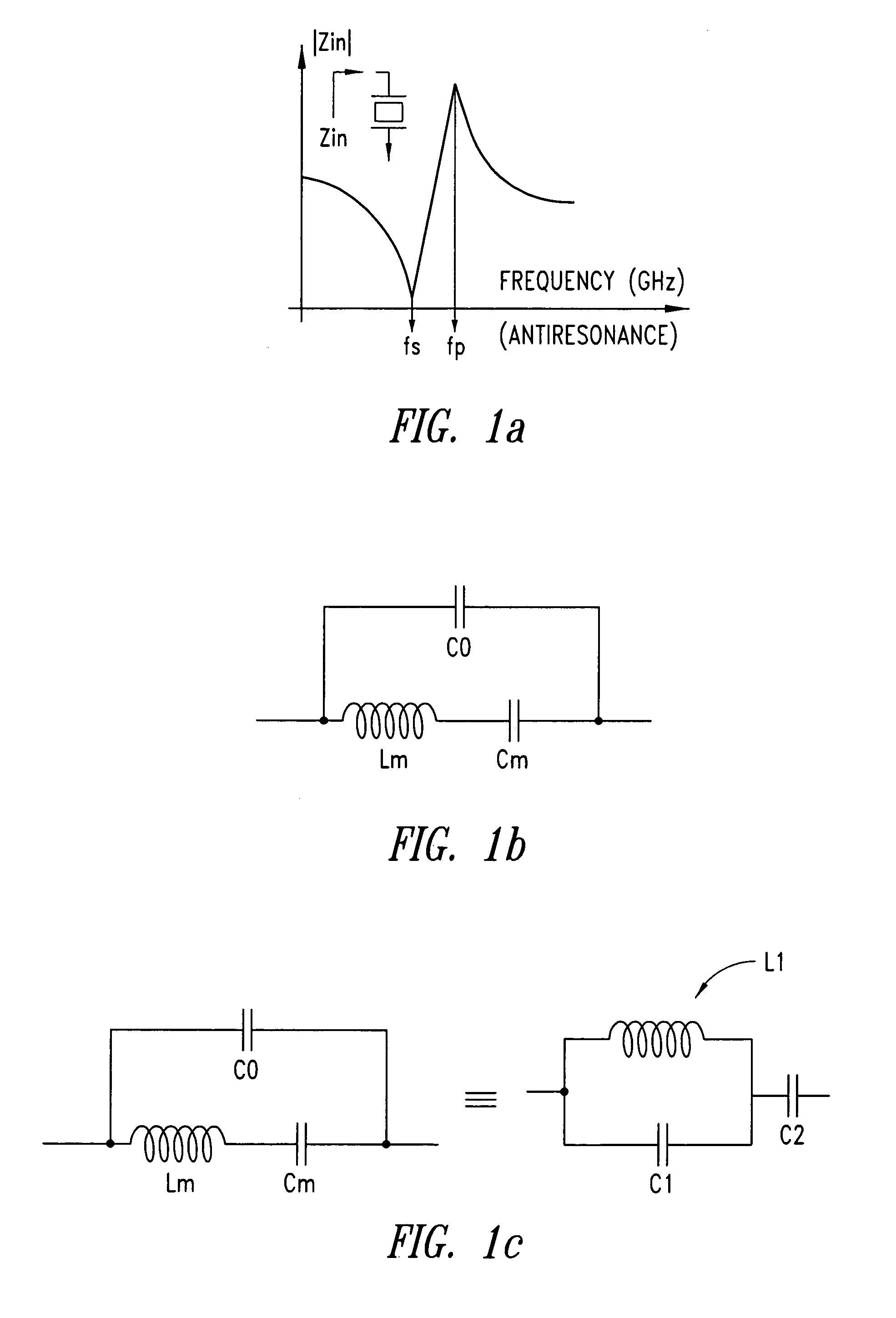

InactiveUS7174147B2Low insertion lossLess insertion lossMultiple-port networksResonant long antennasBandpass filteringVoltage reference

A tunable bandpass filter is provided that comprises a first shunt-connected ferroelectric (FE) tunable tank circuit having a first node to accept an input signal. A second shunt-connected FE tunable tank circuit has a second node to supply a bandpass filtered signal. A first capacitor is connected in series between the first and second nodes. In one aspect, the first tank circuit comprises a first resonator connected to the first node, and a fourth capacitor connected between the first resonator and a reference voltage. The fourth capacitor is a tunable FE capacitor. Typically, a fifth capacitor is connected between the first node and the reference voltage. Likewise, the second tank circuit comprises a second resonator connected to the second node, and a sixth (FE) capacitor connected between the second resonator and the reference voltage. A seventh capacitor is connected between the second node and the reference voltage.

Owner:KYOCERA CORP

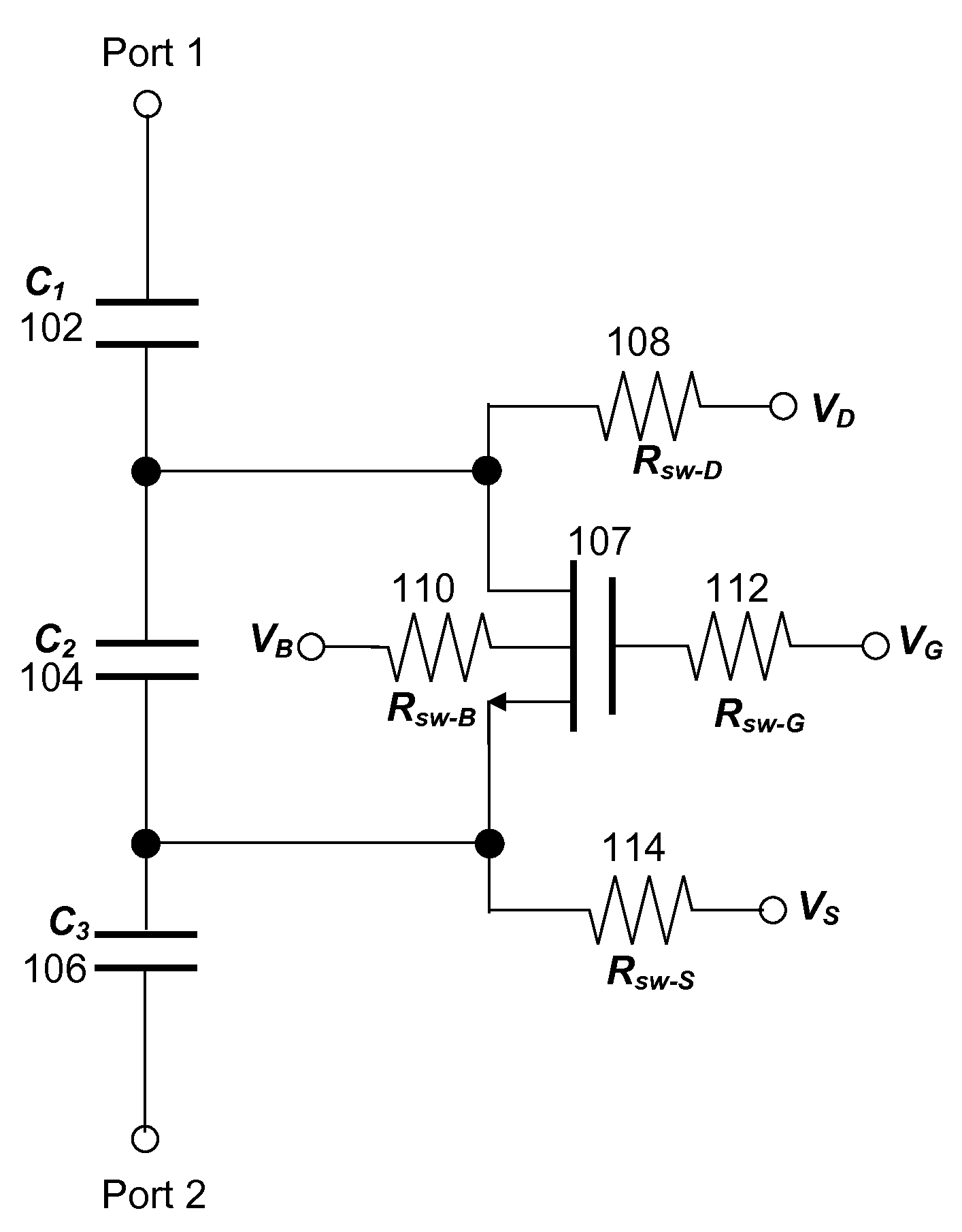

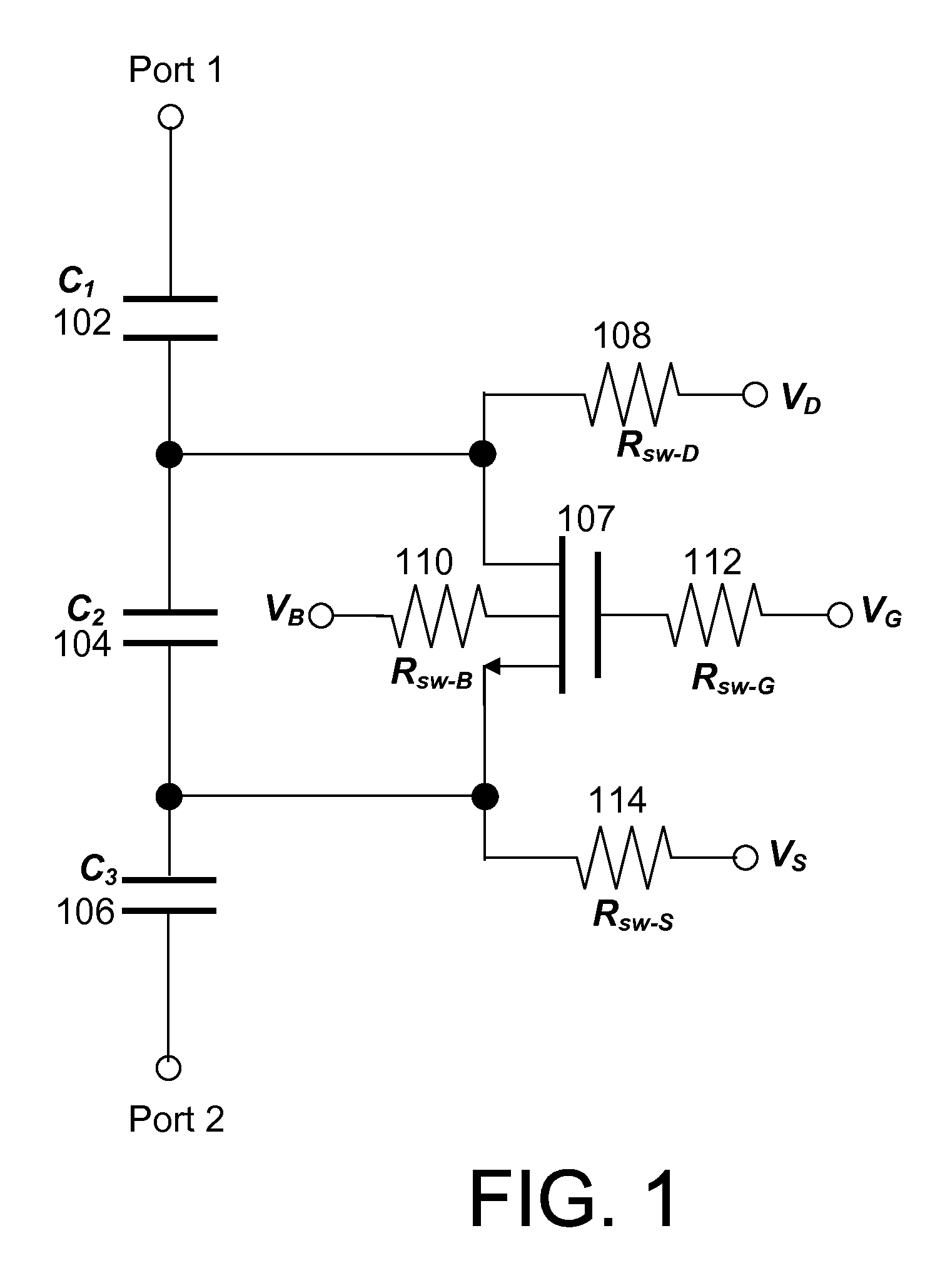

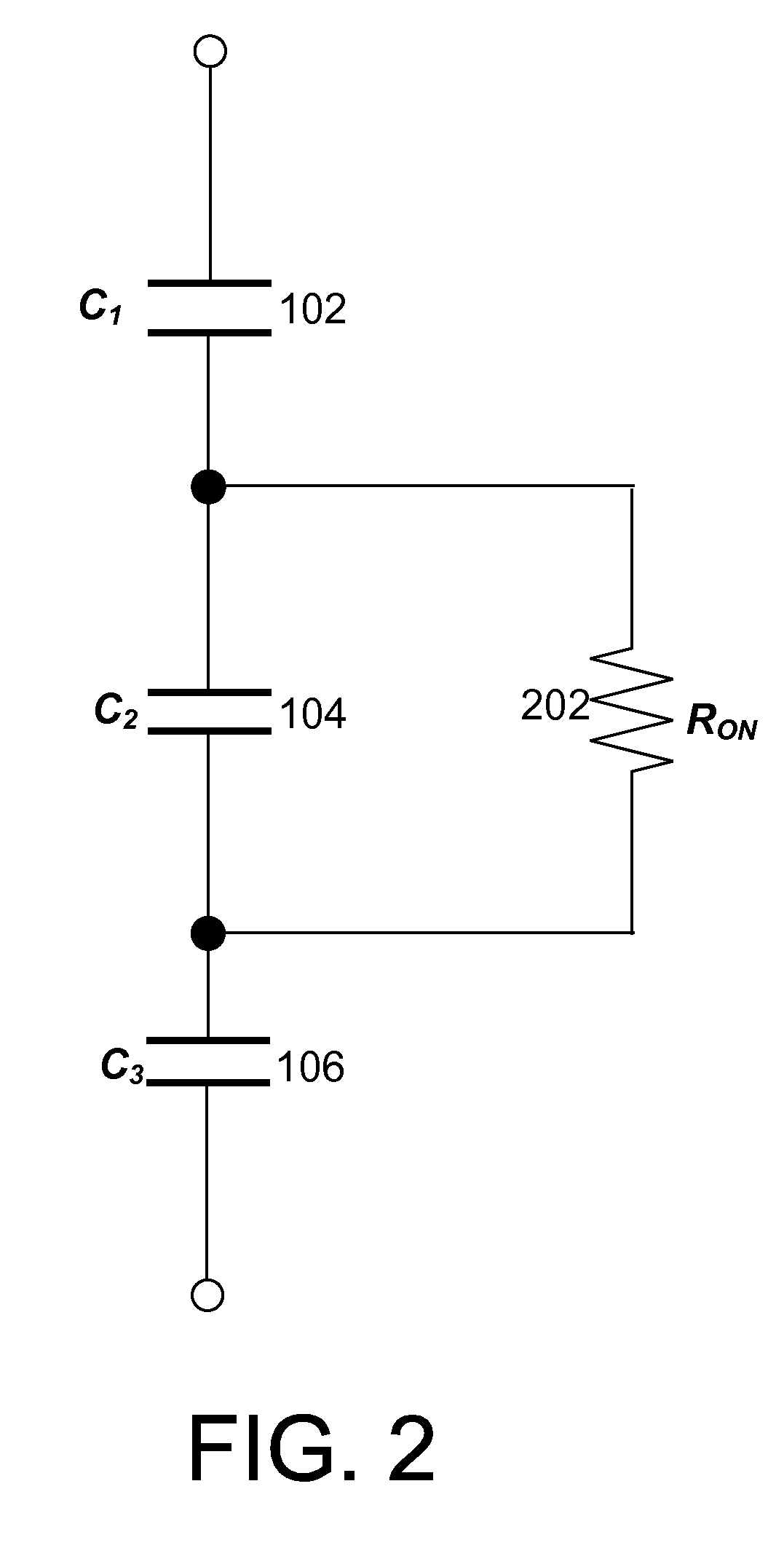

High-power tunable capacitor

ActiveUS20110127849A1Increased power capacityMaximize the allowed voltage-swingContinuous tuning detailsApparatus without intermediate ac conversionEngineeringCapacitor

A tunable capacitor device may be provided in accordance with example embodiments of the invention. The tunable capacitor device may include a first capacitor; a second capacitor; a third capacitor, where the first, second, and third capacitors are connected in series, wherein the second capacitor is positioned between the first capacitor and the second capacitor; and at least one switch transistor, where the at least one switch transistor is connected in parallel with the second capacitor.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD +1

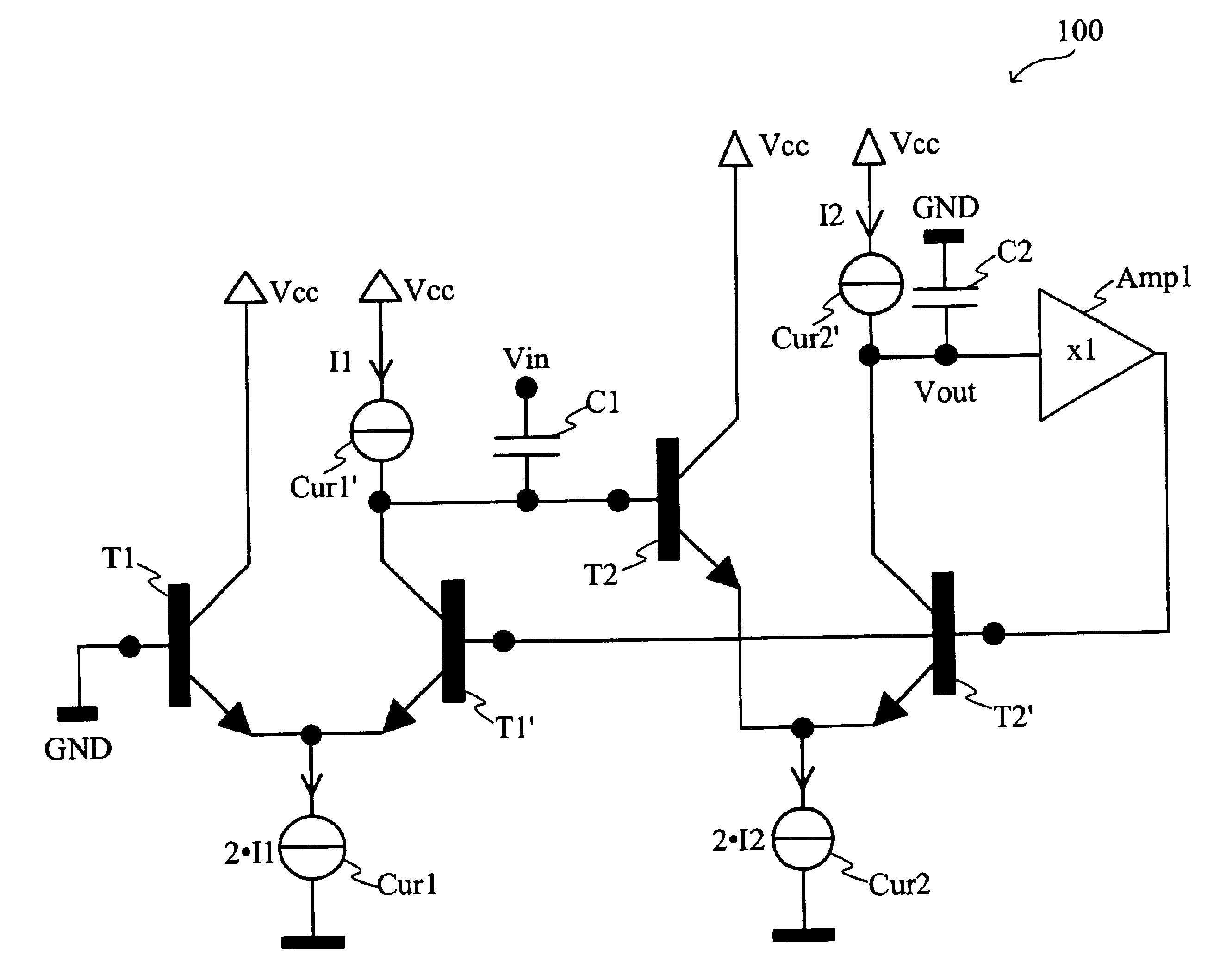

Integrated tunable filter for broadband tuner

ActiveUS6915121B2Precise changeVariation in resistanceContinuous tuning detailsRadio transmissionBandpass filteringEngineering

A tunable filter circuit includes a first differential pair biased by a first current, a second differential pair biased by a second current, a first capacitor and a second capacitor. The tunable filter circuit of the present invention can be configured as a bandpass filter or a bandstop filter by connecting the input voltage signal to different input nodes of the tunable filter circuit. The tunable filter circuit can be tuned by adjusting the values of the first current and the second current. In an alternate embodiment, frequency tuning is achieved either by switching capacitive loads or changing resistive impedances introduced at the emitter of the differential pairs, which also extends the input voltage range of the filter. This emitter resistance is implemented using MOS switches whose on-resistance can be controlled for a precise tuning within a large frequency range.

Owner:CF CRESPE LLC

Integrated electronic circuit comprising a tunable resonator

ActiveUS7187240B2Improve performanceEasy to adjustAngle modulation detailsSemiconductor/solid-state device detailsEngineeringInductor

Owner:STMICROELECTRONICS SRL

Integrated VCO having an improved tuning range over process and temperature variations

InactiveUS20050030108A1Resonant circuit detailsSemiconductor/solid-state device detailsState variableControl circuit

An integrated VCO having an improved tuning range over process and temperature variations. There is therefore provided in a present embodiment of the invention an integrated VCO. The VCO comprises, a substrate, a VCO tuning control circuit responsive to a VCO state variable that is disposed upon the substrate, and a VCO disposed upon the substrate, having a tuning control voltage input falling within a VCO tuning range for adjusting a VCO frequency output, and having its tuning range adjusted by the tuning control circuit in response to the VCO state variable.

Owner:AVAGO TECH INT SALES PTE LTD

Global positioning system receiver capable of functioning in the presence of interference

Owner:IP GEM GRP LLC

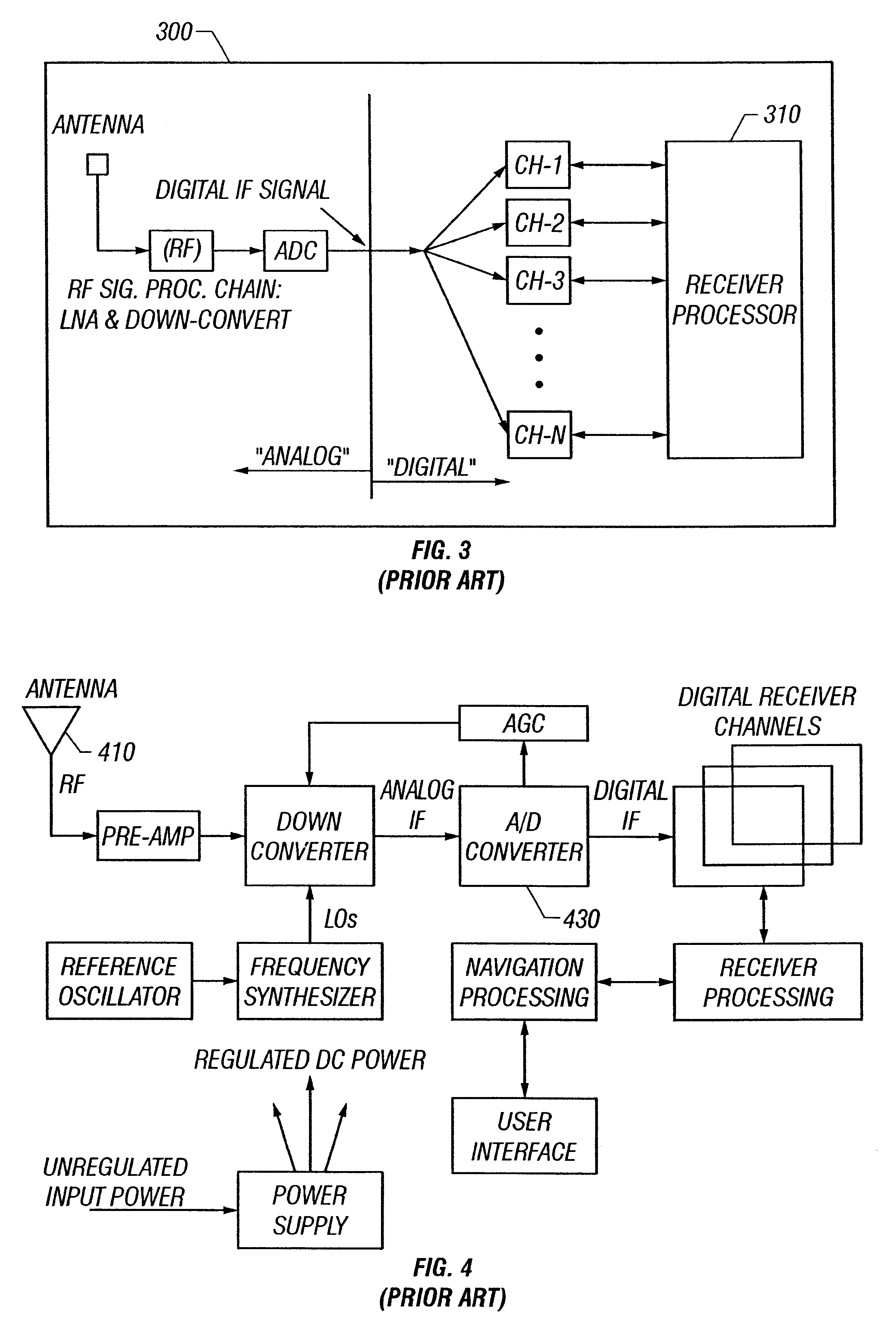

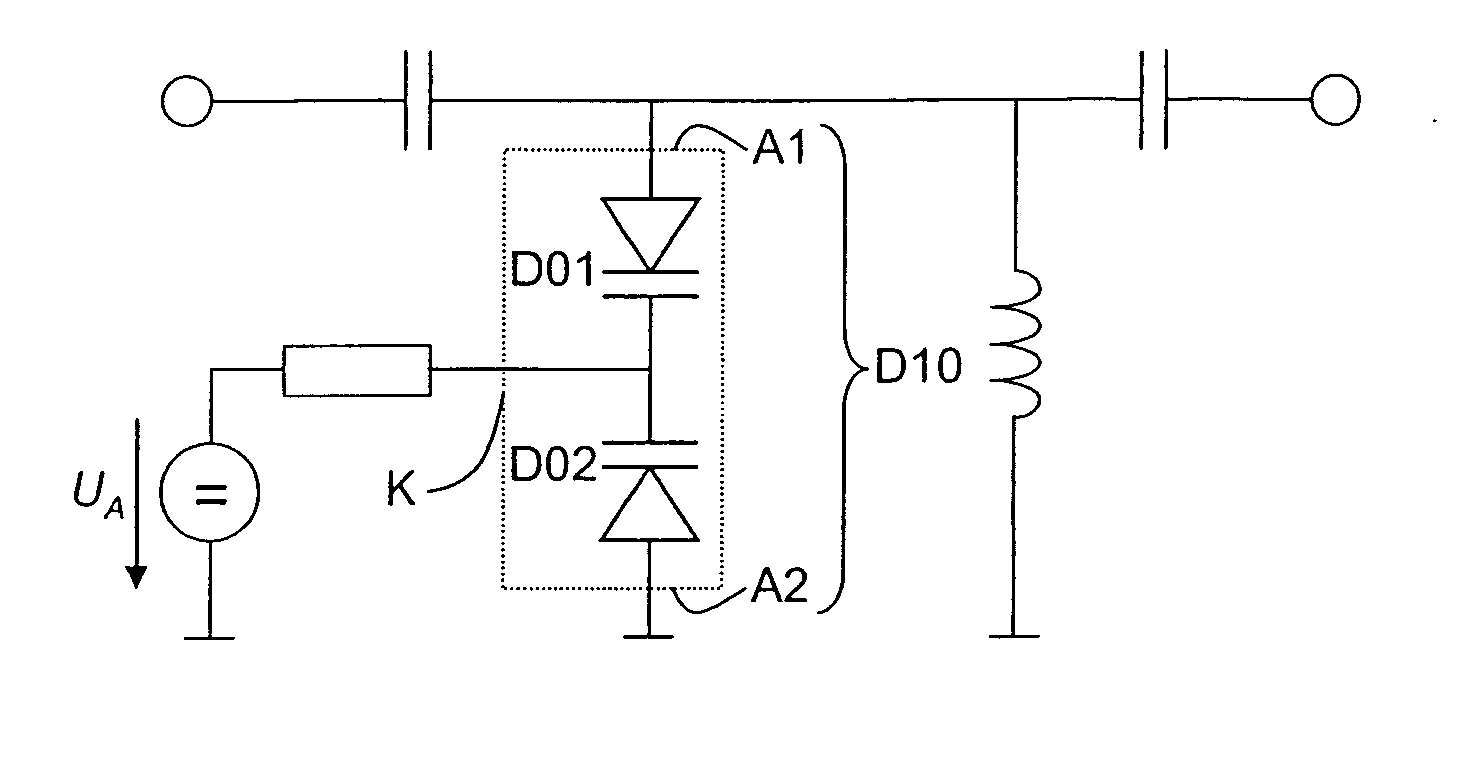

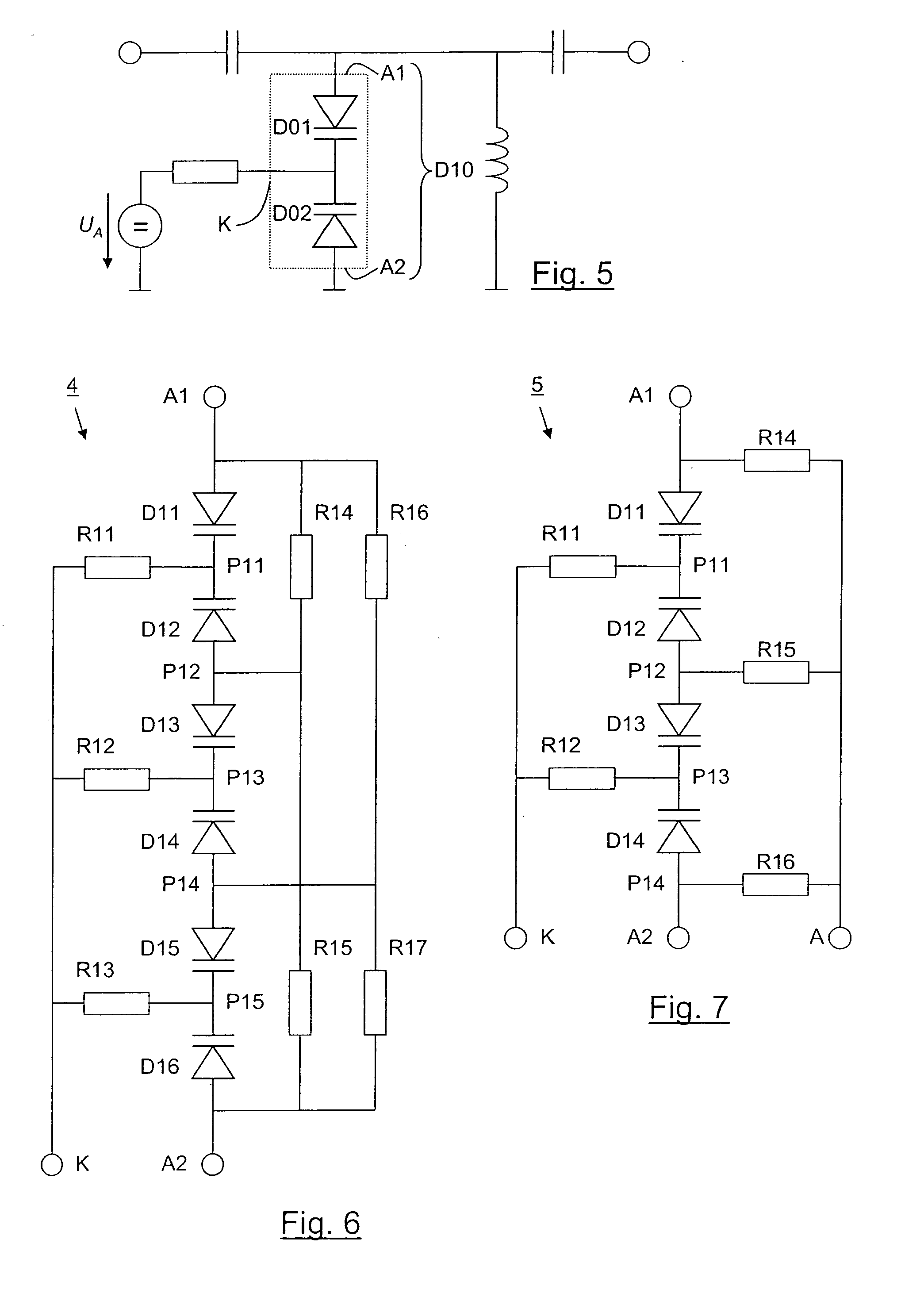

Varactor diode alternative circuit

InactiveUS20070164833A1Avoid interferenceIncrease capacitanceAngle modulation by variable impedenceContinuous tuning detailsElectrical resistance and conductanceInductor

A varactor diode alternative circuit having at least three varactor diodes that are in each case connected in series alternatingly opposite to one another and a resistor network and / or inductor network, which has the effect that at each of the varactor diodes, a control voltage supplied to the circuit for adjusting the capacitance is present at least approximately at full extent, and an alternating voltage that is applied at the series connection of the varactor diodes, which is at a higher frequency compared to the control voltage, is distributed preferably at least approximately uniformly to the varacter diodes. A varactor diode alternative circuit has the advantage that even for a smaller, or not larger, or not substantially larger tuning voltage compared to the amplitude of a signal voltage that is to be processed in the oscillator circuit that has the alternative circuit, the reactions of the signal voltage on the set capacitance of the varactor diode alternative circuit remain negligible, or at least low. Thus, intermodulation interferences are effectively avoided. In addition, the circuit may be advantageously used in an electrical unit in which only one small operating voltage is available, for instance, in a battery-operated unit.

Owner:ROBERT BOSCH GMBH

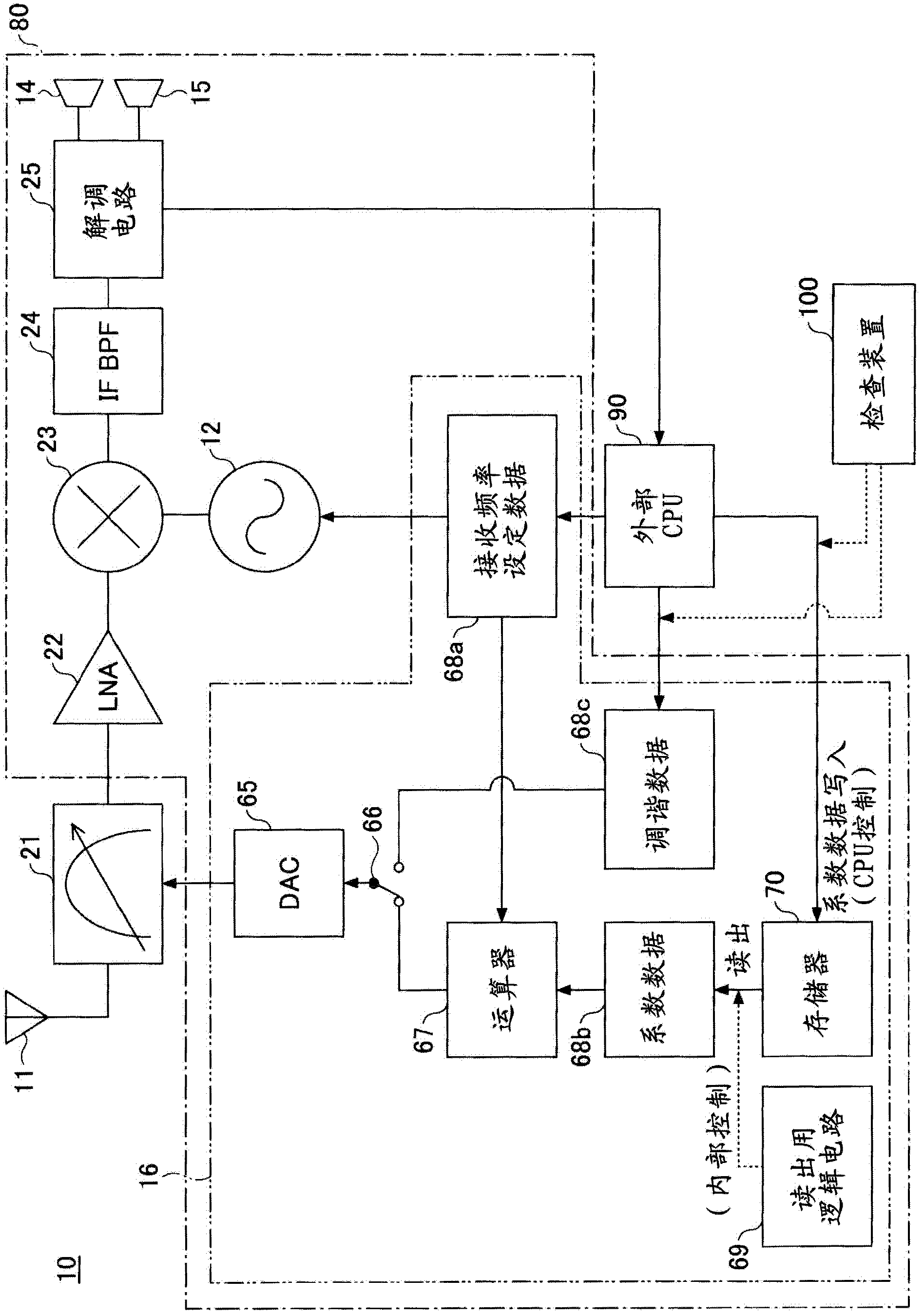

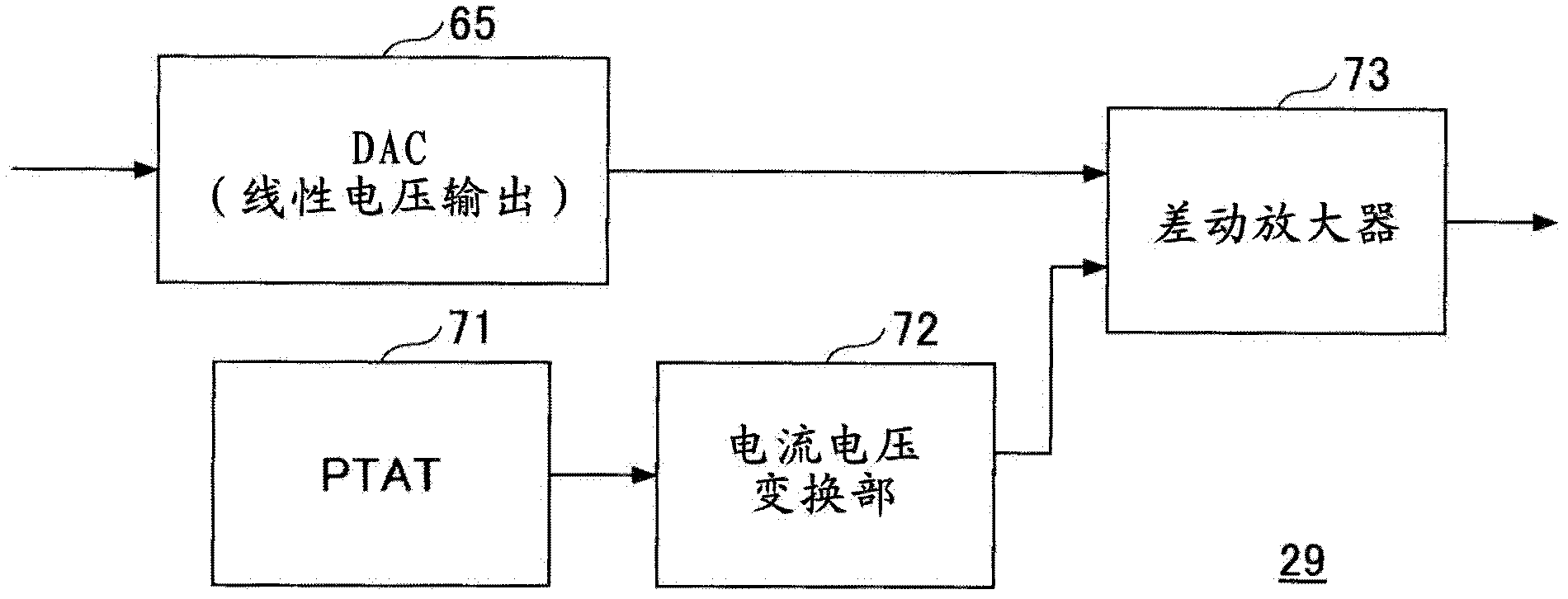

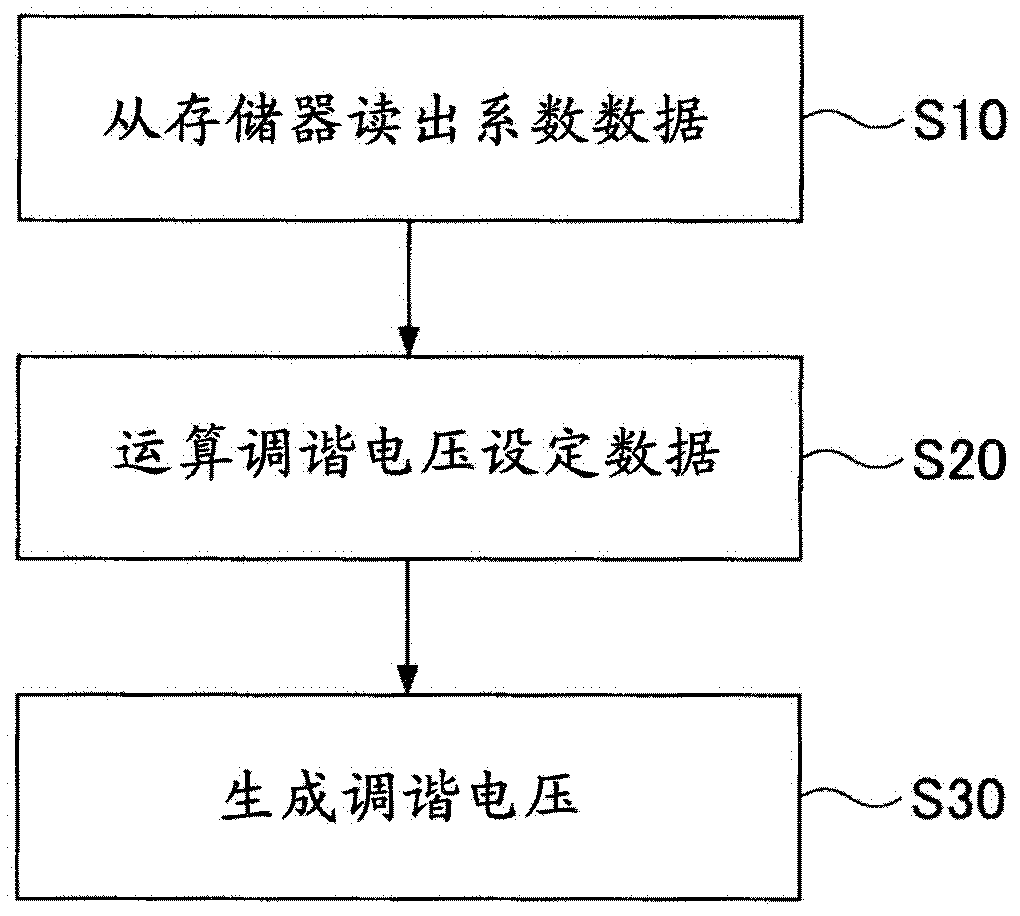

Superheterodyne receiver apparatus and reception method, and semiconductor integrated circuit for receiver apparatus

InactiveCN102484492AEasy to tuneContinuous tuning detailsResonant circuit detailsCapacitanceIntermediate frequency

A superheterodyne receiver apparatus comprises: a tuning circuit for selecting and receiving a high frequency signal, said circuit being composed of a voltage-variable capacitance element and an inductance element; and a frequency converting unit for frequency converting the high frequency signal to an intermediate frequency signal. The superheterodyne receiver apparatus further comprises: an electrically rewritable read only memory; a calculation unit for calculating tuning voltage setting data, which used to set the tuning circuit to a tuning voltage corresponding to a desired reception frequency, in accordance with a mathematical expression that uses the data stored in the memory as coefficients; and a D / A conversion unit for D / A converting the tuning voltage setting data to the tuning voltage.

Owner:MITSUMI ELECTRIC CO LTD

Popular searches

Oscillations generators Transmission Single resonant circuit with varying inductance and capacitance simultaneously Resonant circuits using central processing units Signal/carrier strength dependant limiting amplitude Color television details Selective content distribution Temperatue control Thermometers using electric/magnetic elements Material analysis by electric/magnetic means