Patents

Literature

575results about "Impedence matching networks" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

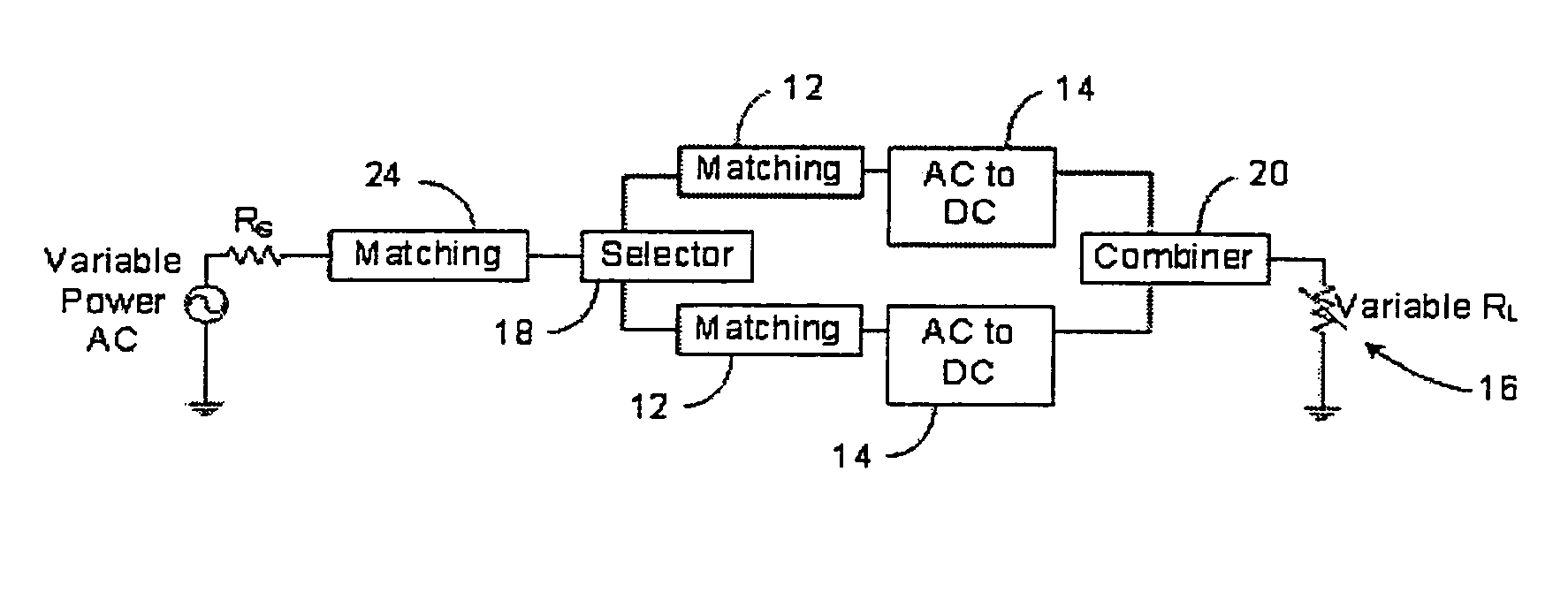

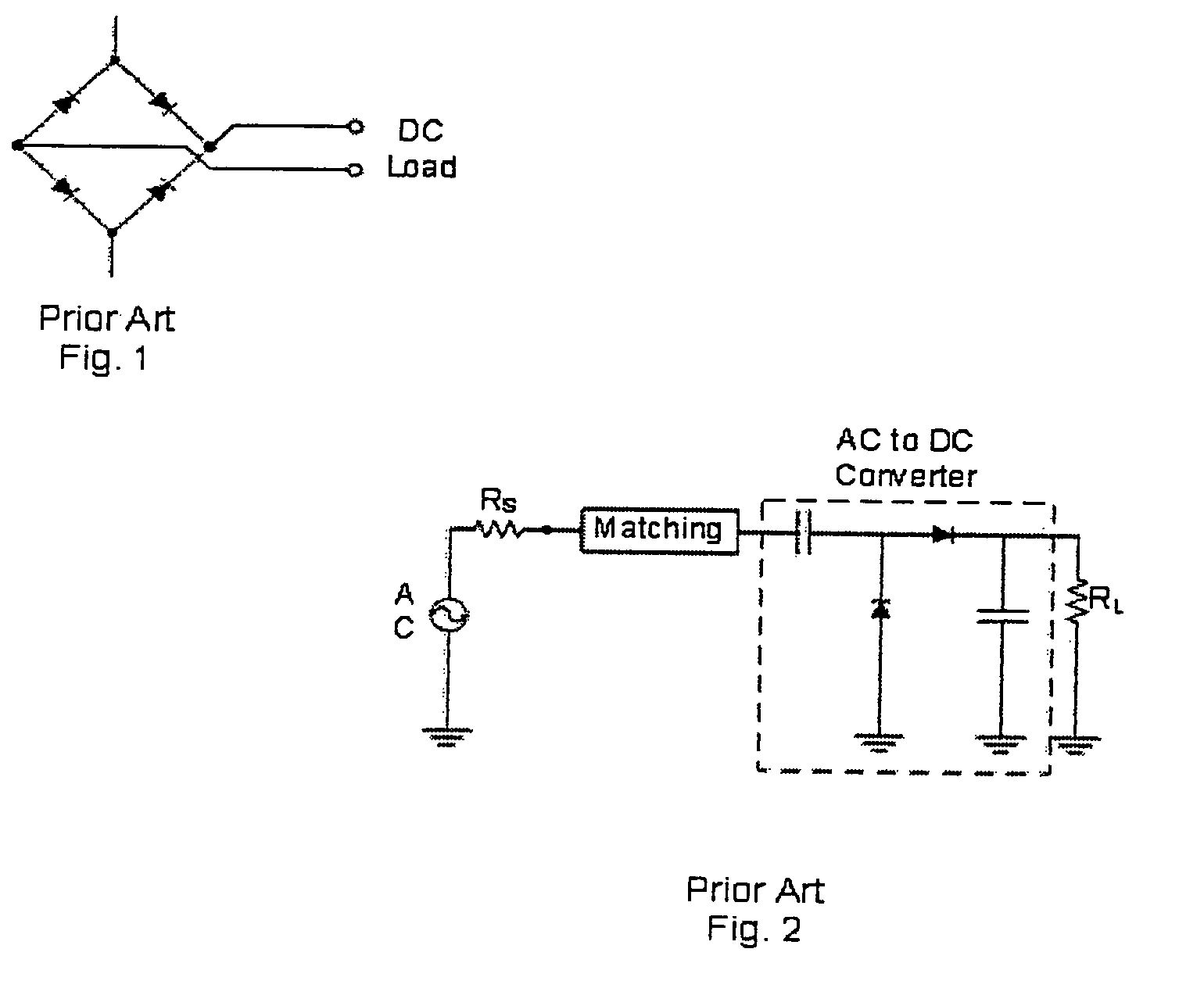

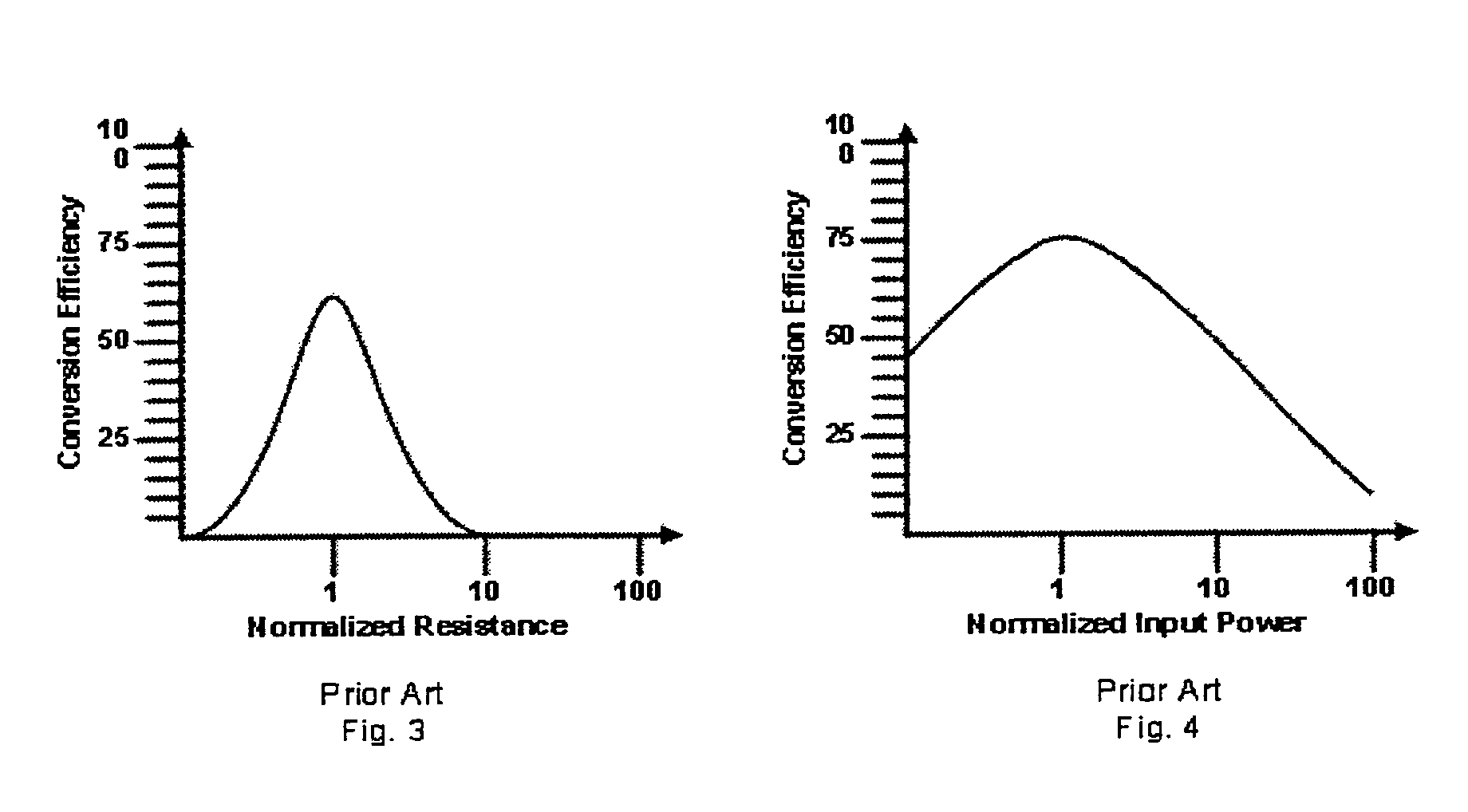

Method and apparatus for high efficiency rectification for various loads

An apparatus for converting power includes at least one impedance matching network which receives an electrical signal. The apparatus includes at least one AC to DC converter in communication with the impedance matching network. Also disclosed is a method for powering a load and an apparatus for converting power and additional embodiments of an apparatus for converting power.

Owner:POWERCAST

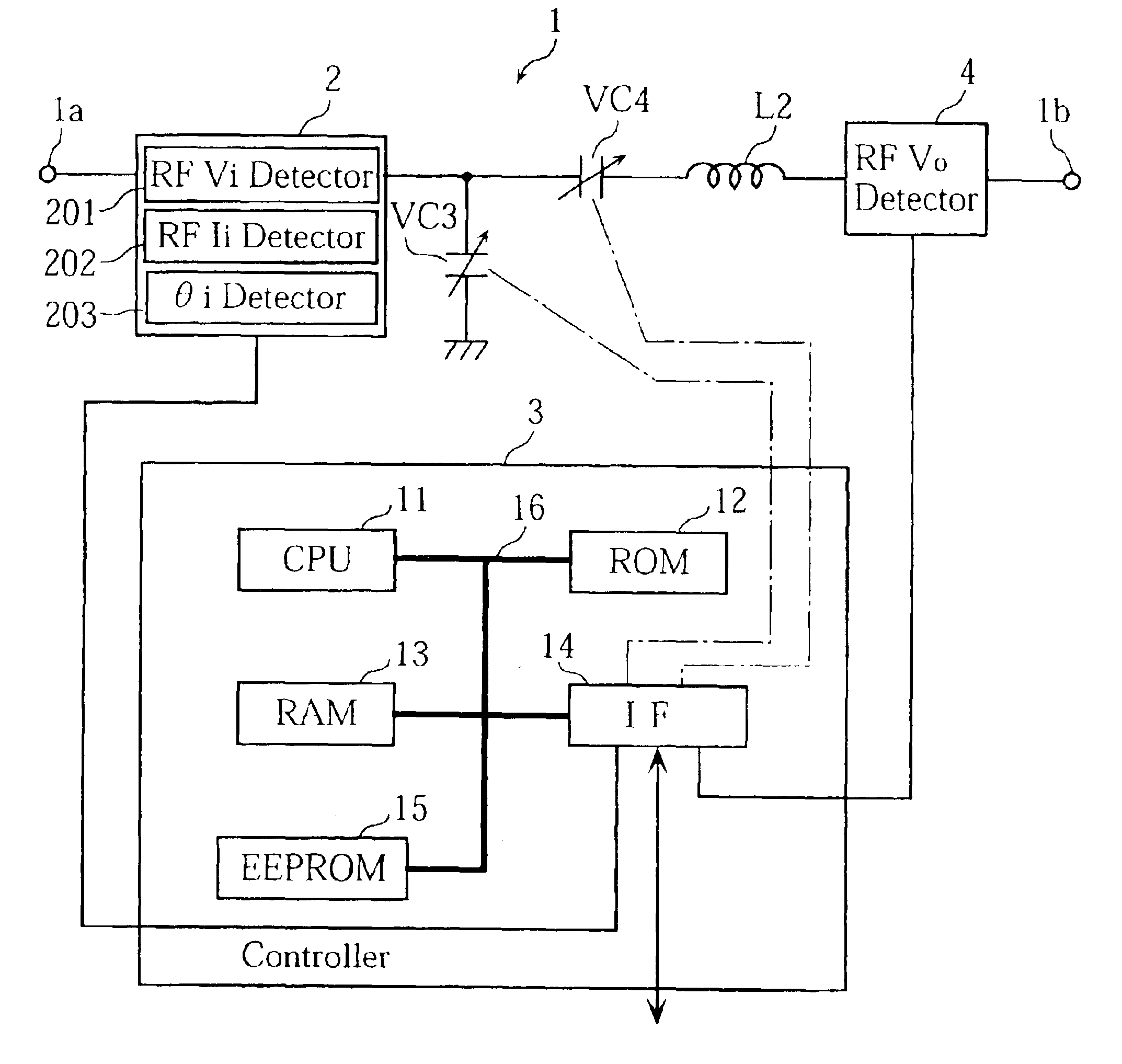

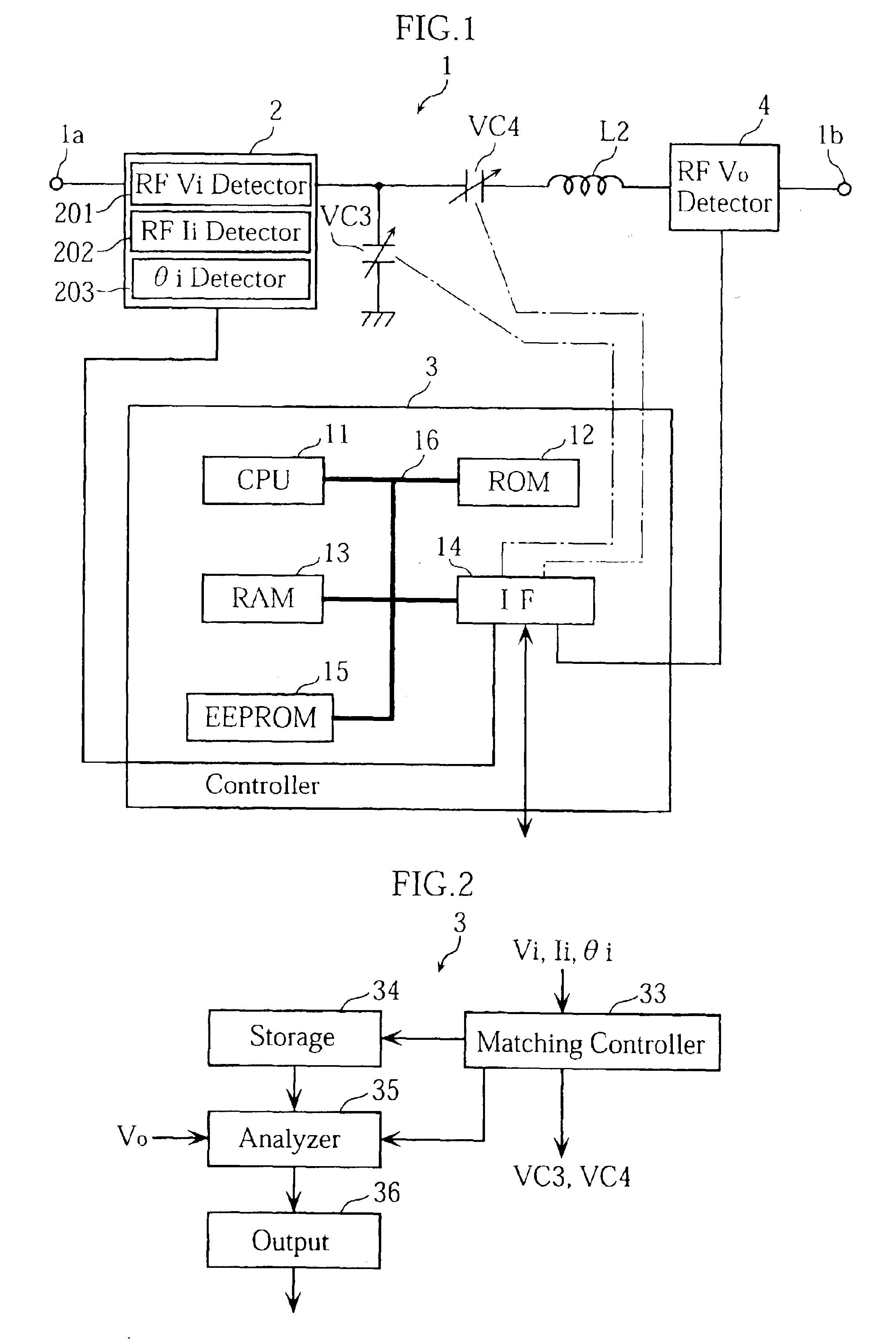

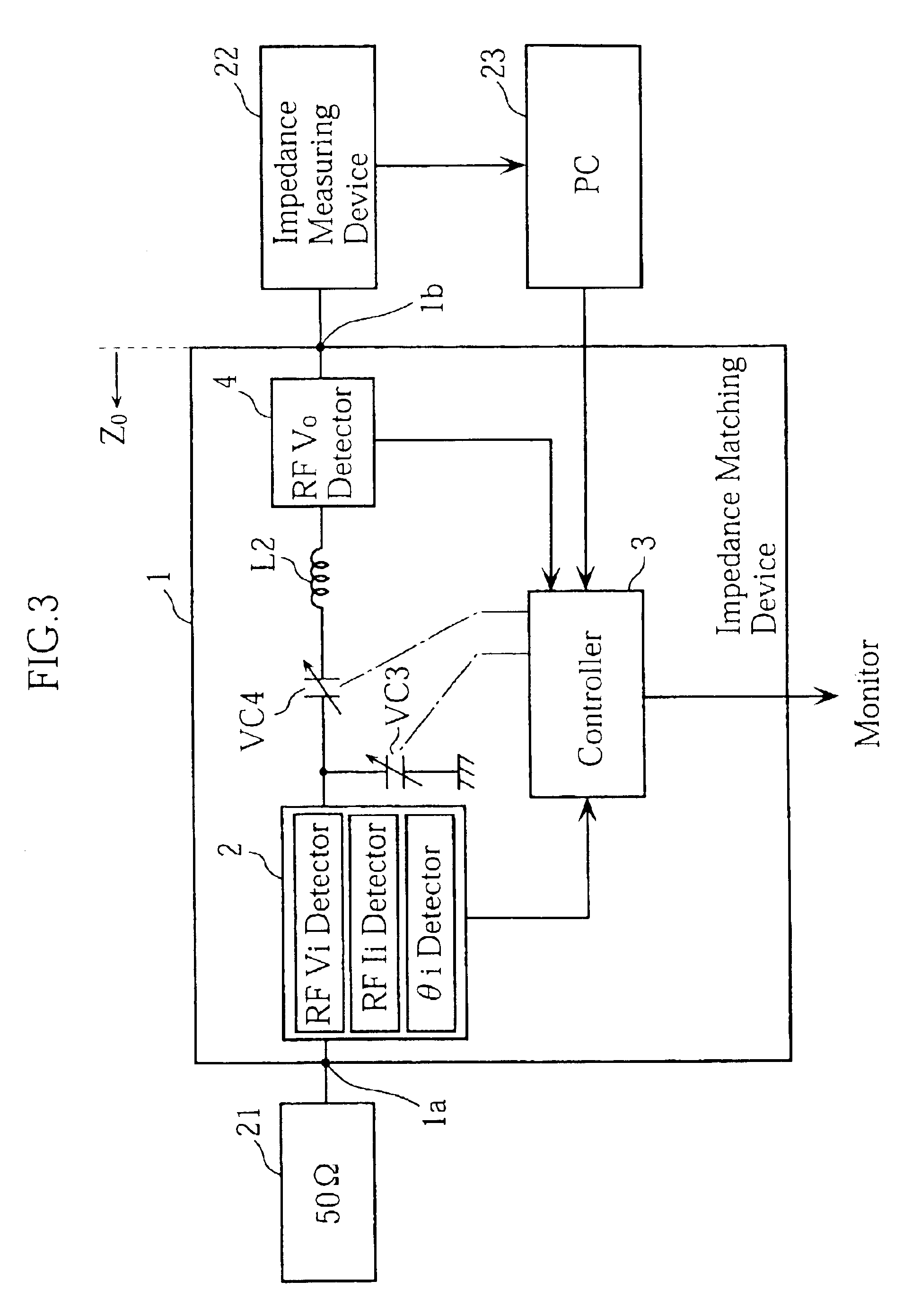

Impedance matching device provided with reactance-impedance table

InactiveUS6946847B2Accurate analysisImpedence matching networksMultiple-port networksCapacitanceElectricity

An impedance matching device is provided, for which the electric characteristics at an output terminal are accurately analyzed. The matching device is provided with an input detector for detecting RF voltage and current at the input terminal, and an output detector for detecting RF voltage outputted from the output terminal. The matching device also includes a controller for achieving impedance matching between a high frequency power source connected to the input terminal and a load connected to the output terminal. The impedance matching is performed by adjusting variable capacitors based on the detection data supplied from the input detector. When the impedance of the power source is matched to that of the load, the controller calculates the output impedance, RF voltage and RF current at the output terminal, based on the adjusted capacitances of the capacitors, a pre-obtained reactance-impedance data and the detection data supplied from the output detector.

Owner:DAIHEN CORP

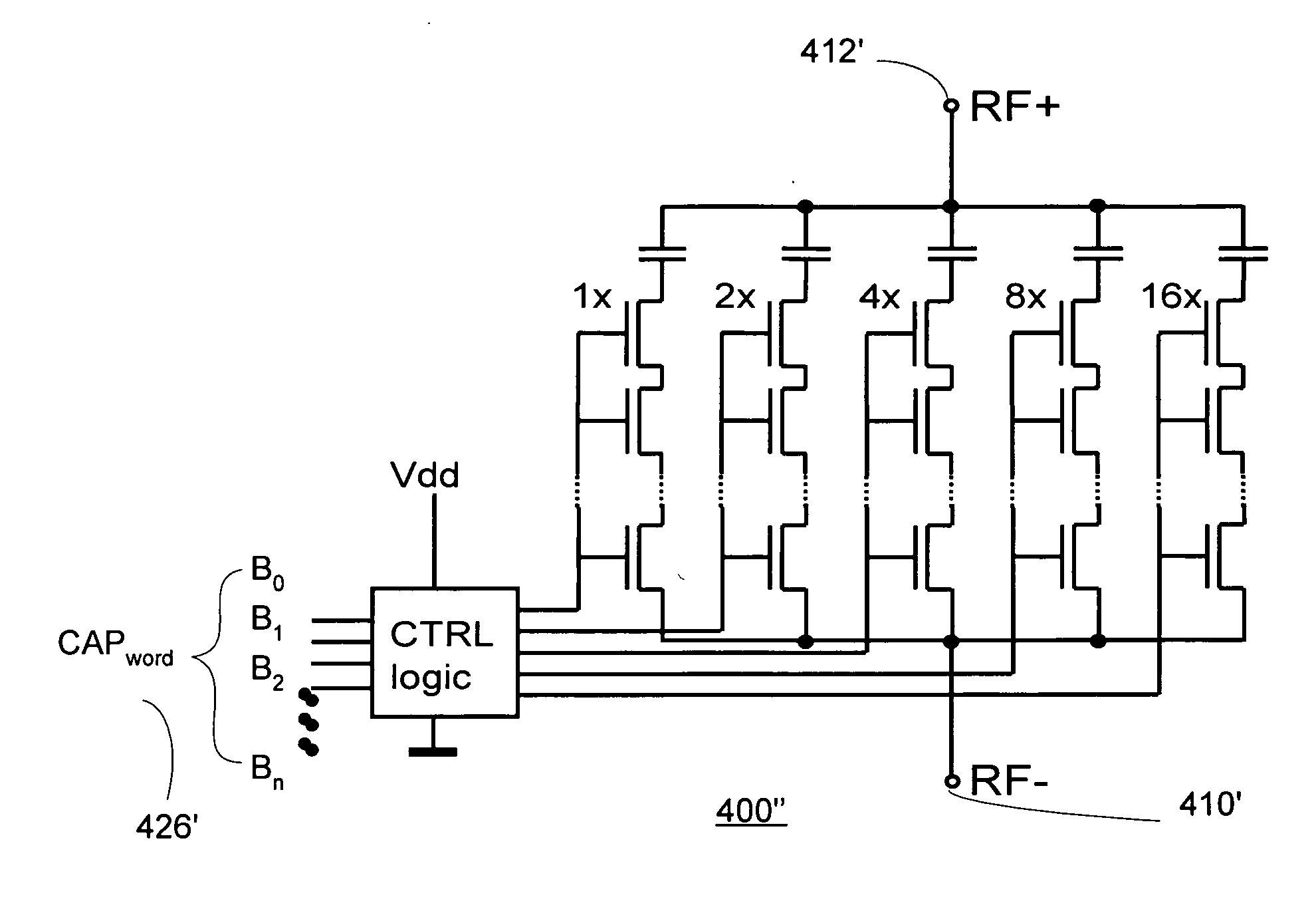

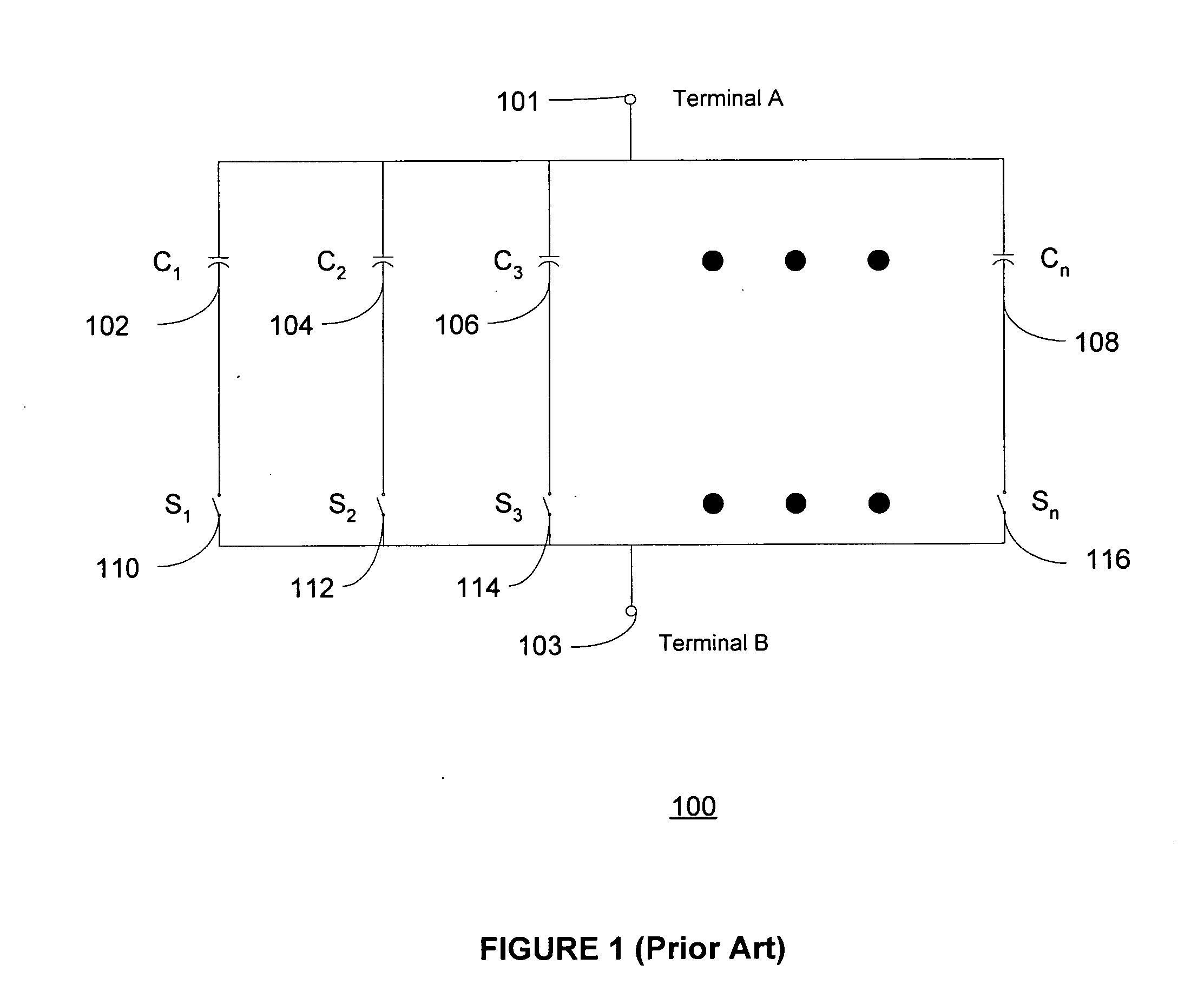

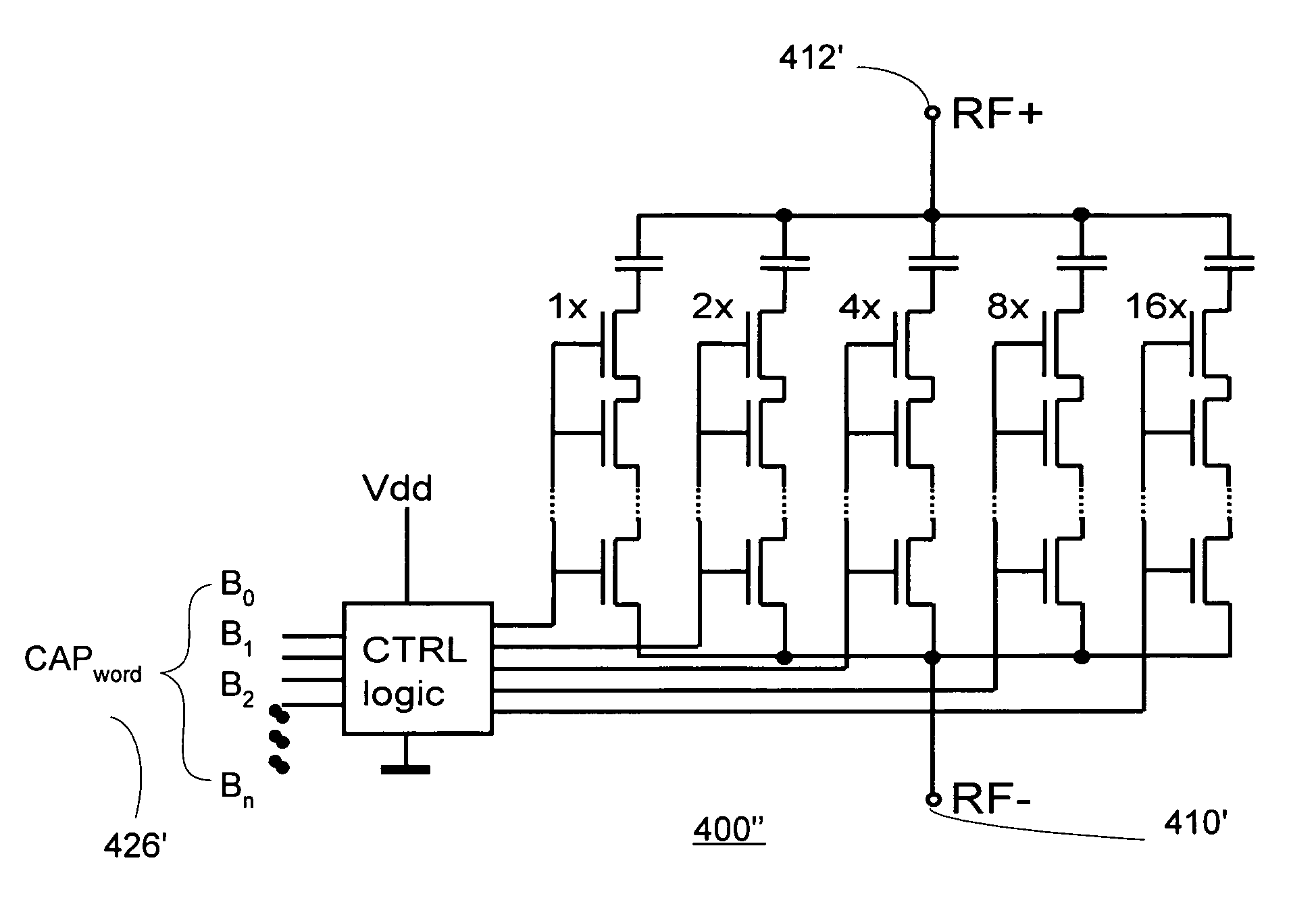

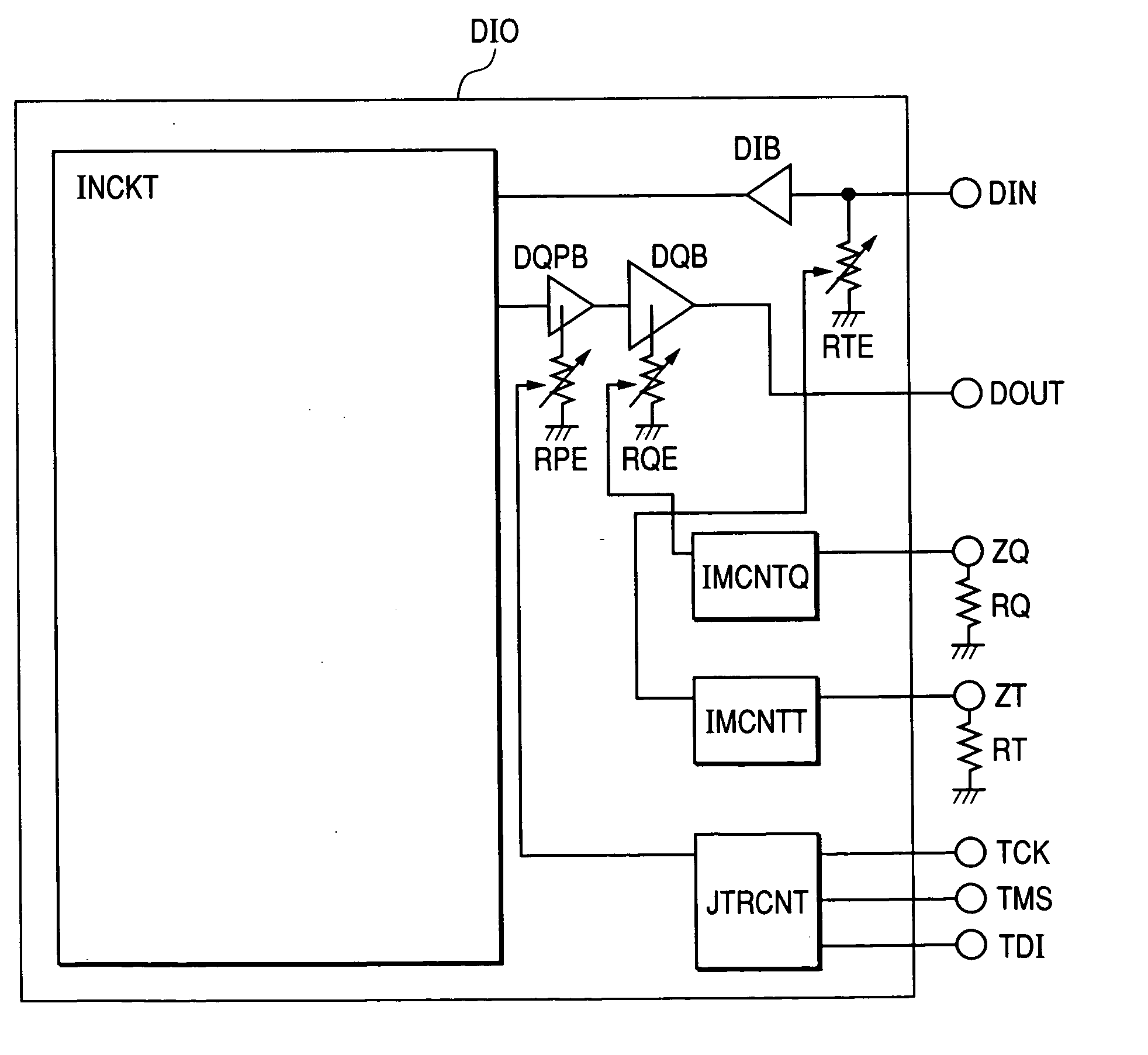

Method and apparatus for use in digitally tuning a capacitor in an integrated circuit device

ActiveUS20110002080A1Easy to controlHigh Power Handling CapabilityAnalogue/digital conversionImpedence matching networksCapacitanceLeast significant bit

A method and apparatus for use in a digitally tuning a capacitor in an integrated circuit device is described. A Digitally Tuned Capacitor DTC is described which facilitates digitally controlling capacitance applied between a first and second terminal. In some embodiments, the first terminal comprises an FW+ terminal and the second terminal comprises an RF terminal. In accordance with some embodiments, the DTCs comprises a plurality of sub-circuits ordered in significance from least significant bit (LSB) to most significant bit (MSB) sub-circuits, wherein the plurality of significant bit sub-circuits are coupled together in parallel, and wherein each sub-circuit has a first node coupled to the first RF terminal, and a second node coupled to the second FW terminal. The DTCs further include an input means for receiving a digital control word, wherein the digital control word comprises bits that are similarly ordered in significance from an LSB to an MSB.

Owner:PSEMI CORP

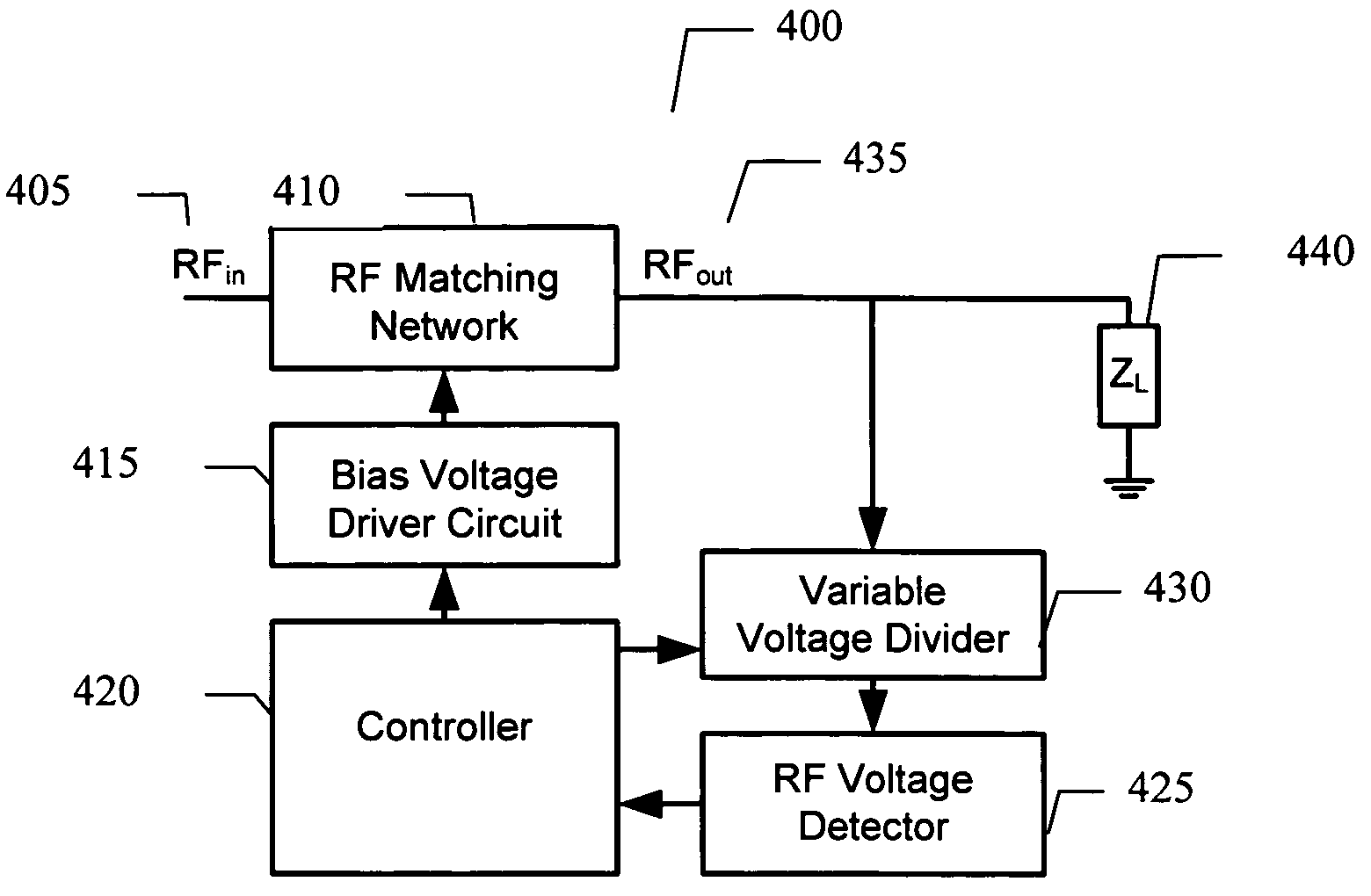

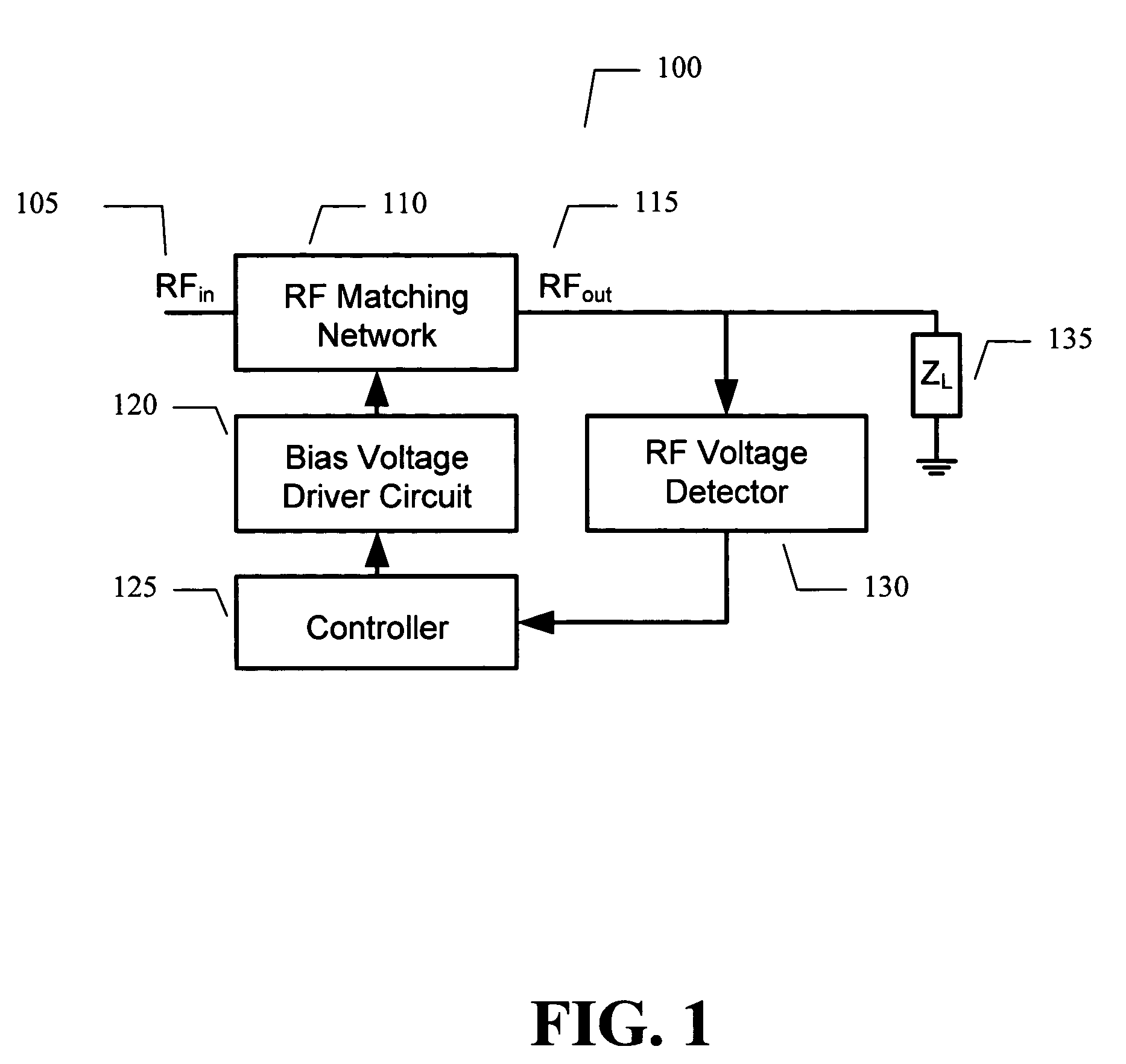

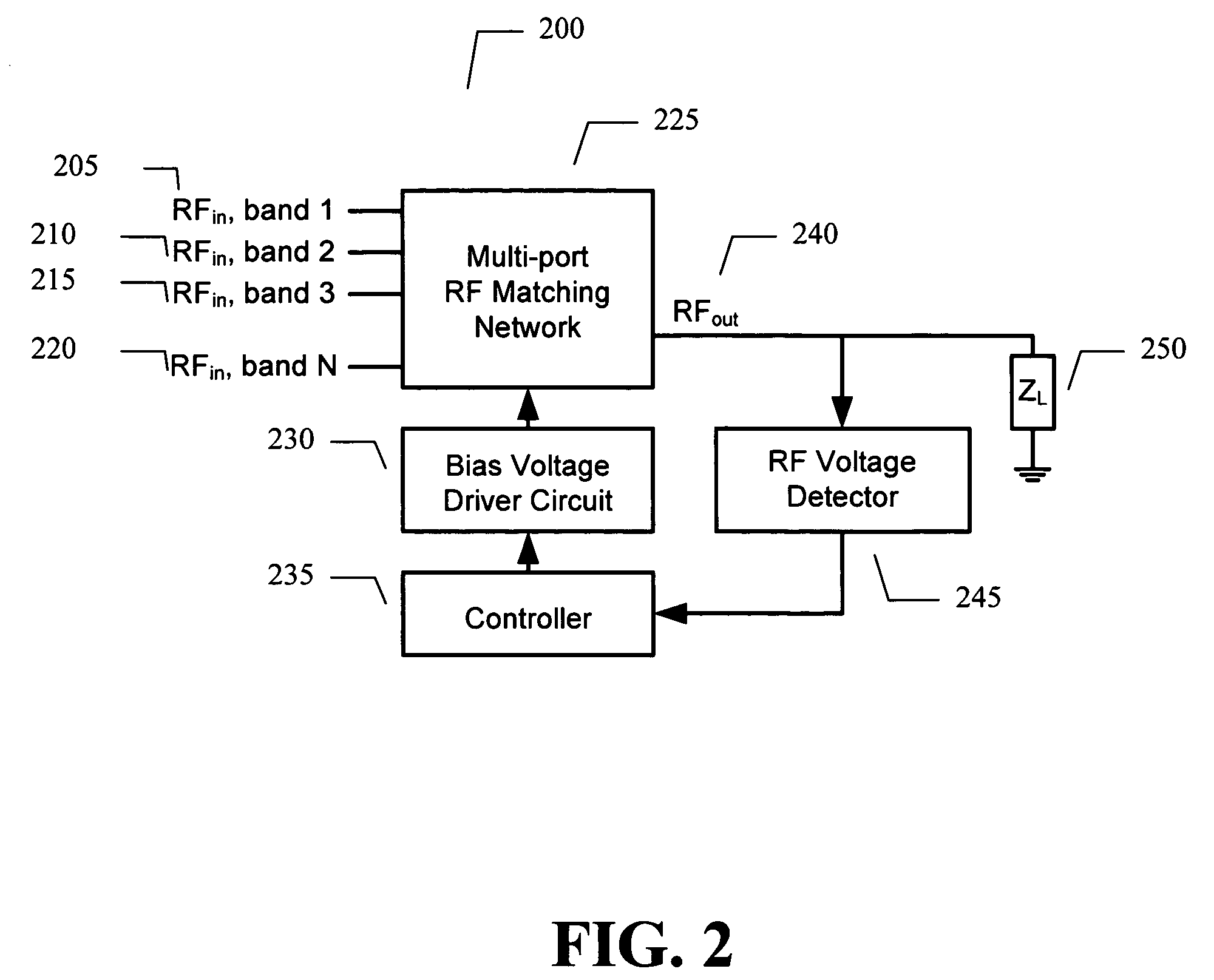

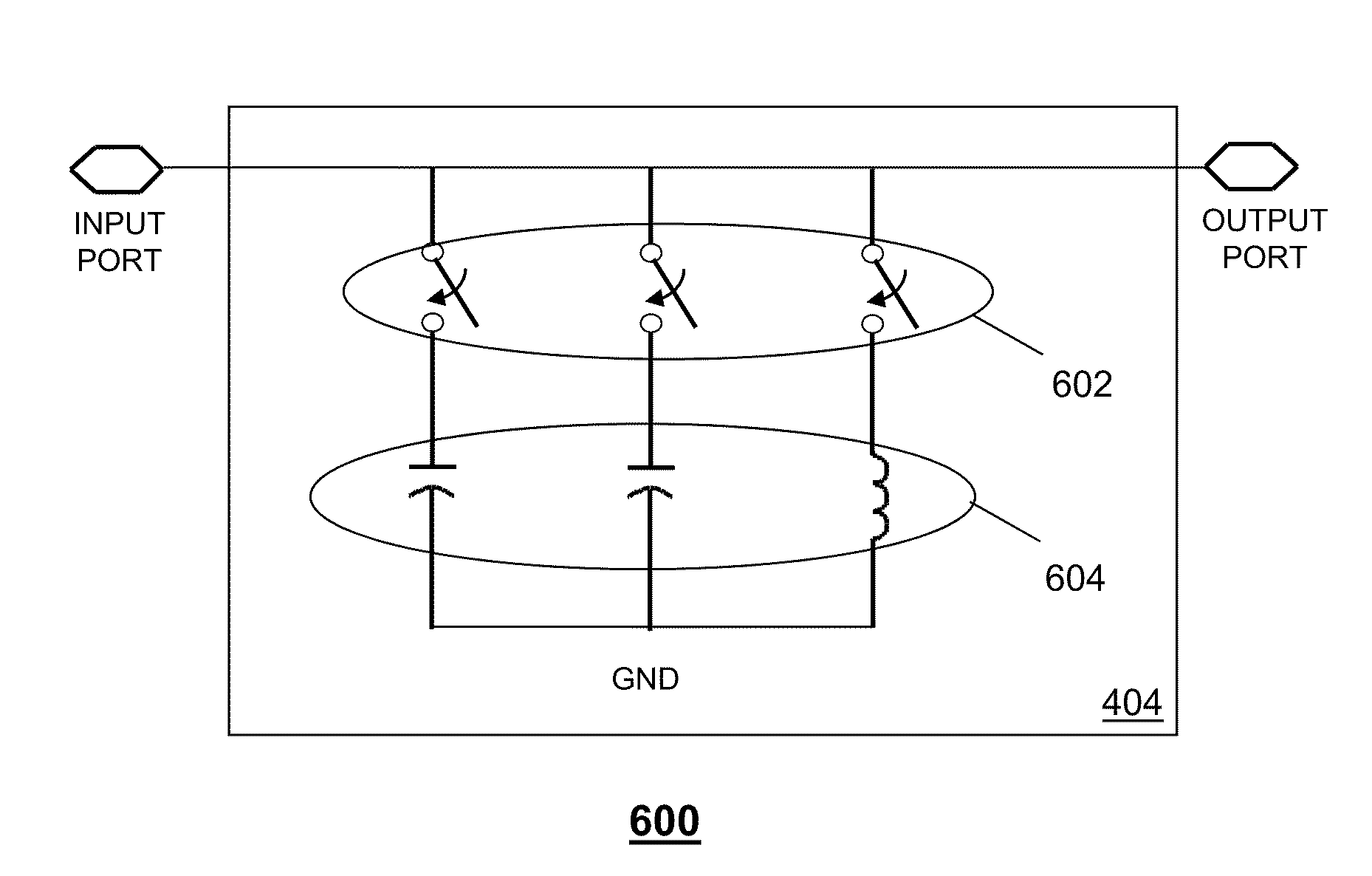

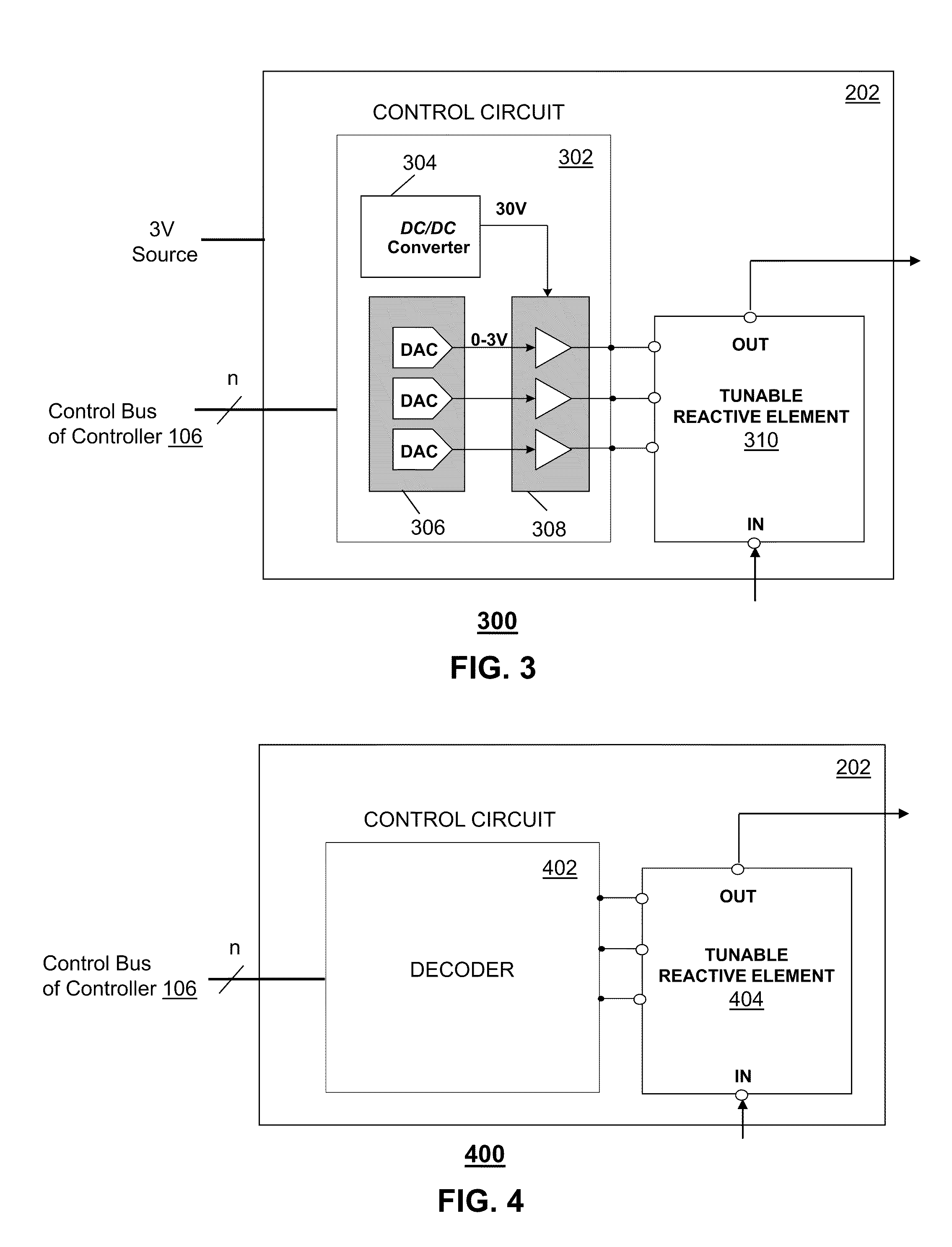

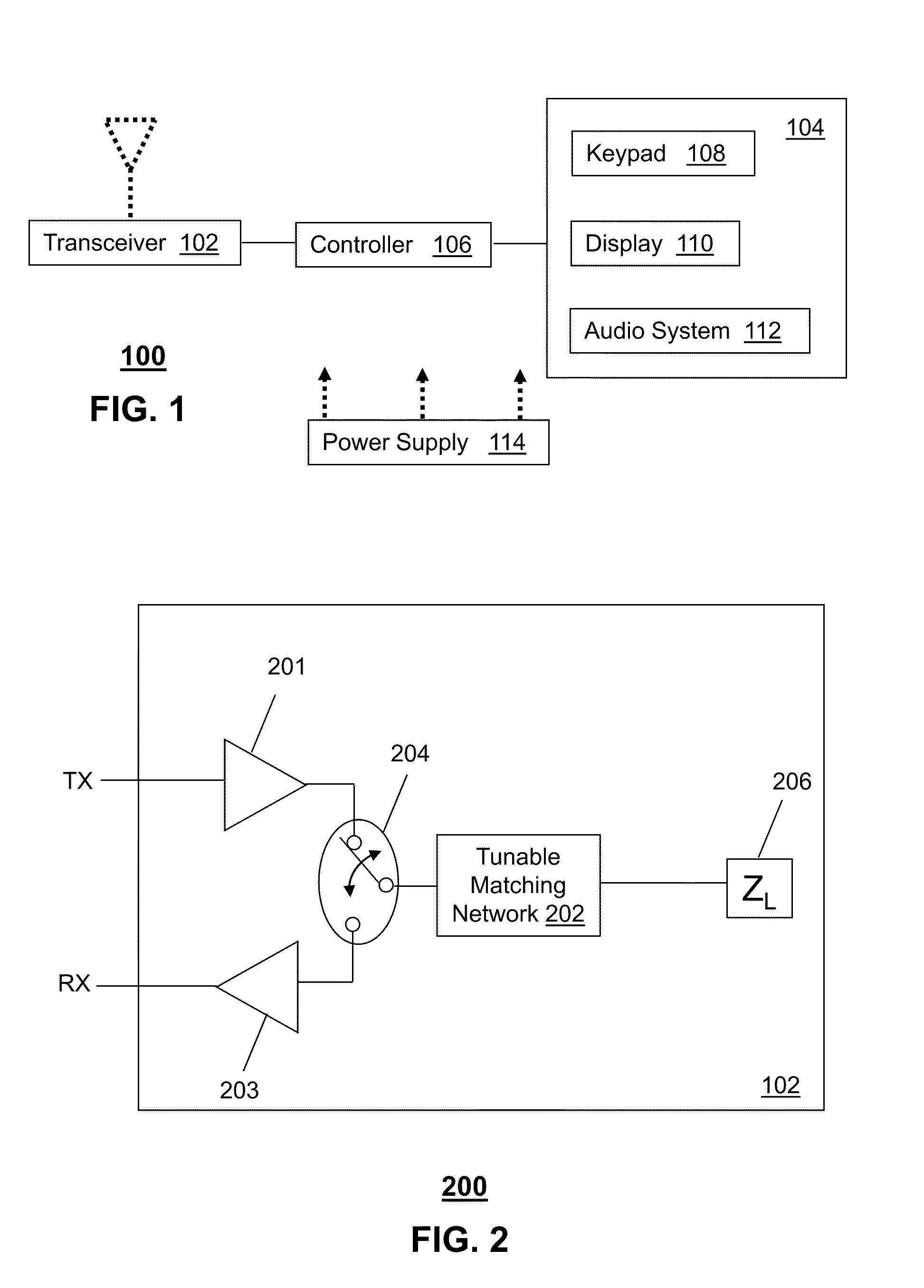

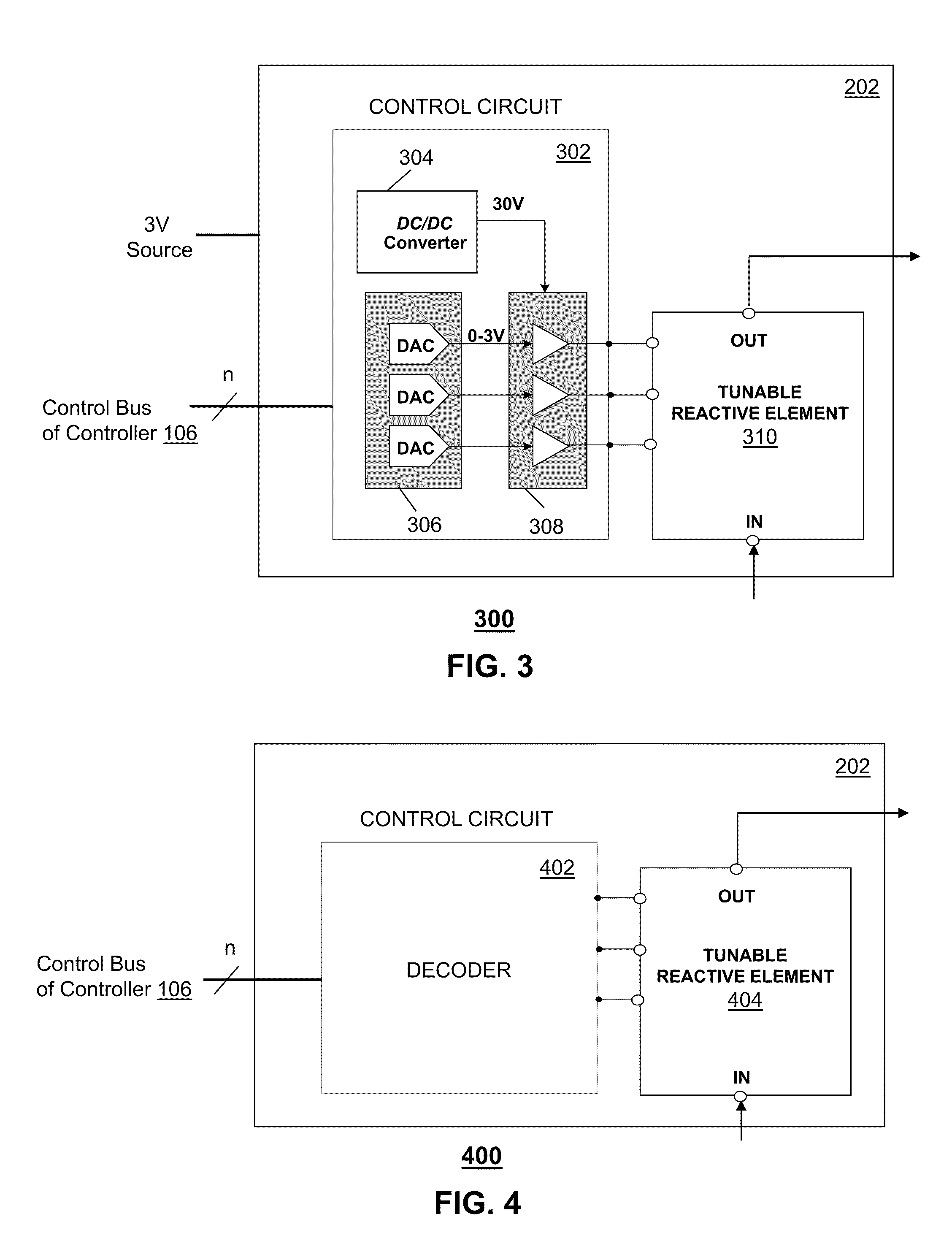

Adaptive impedance matching apparatus, system and method

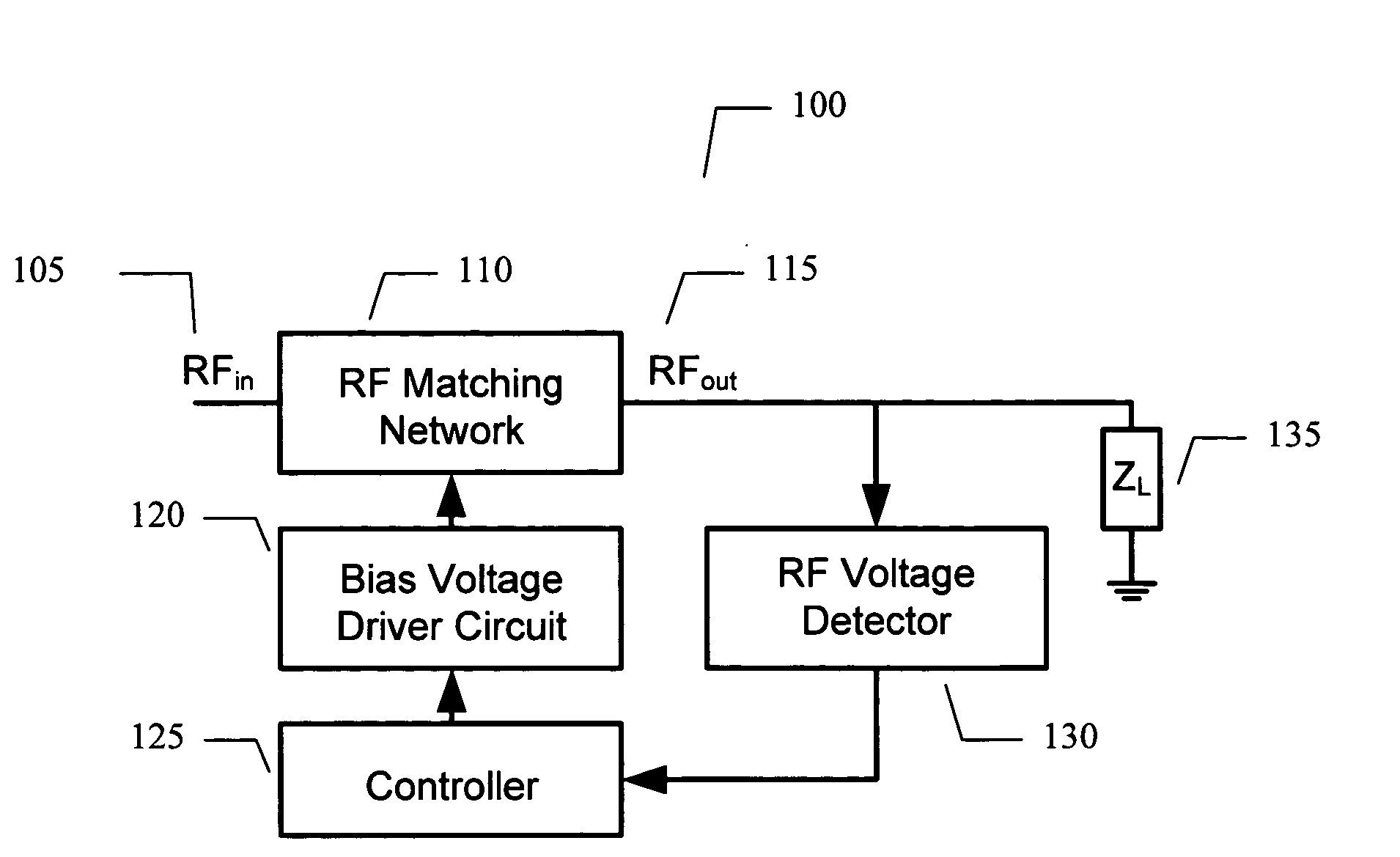

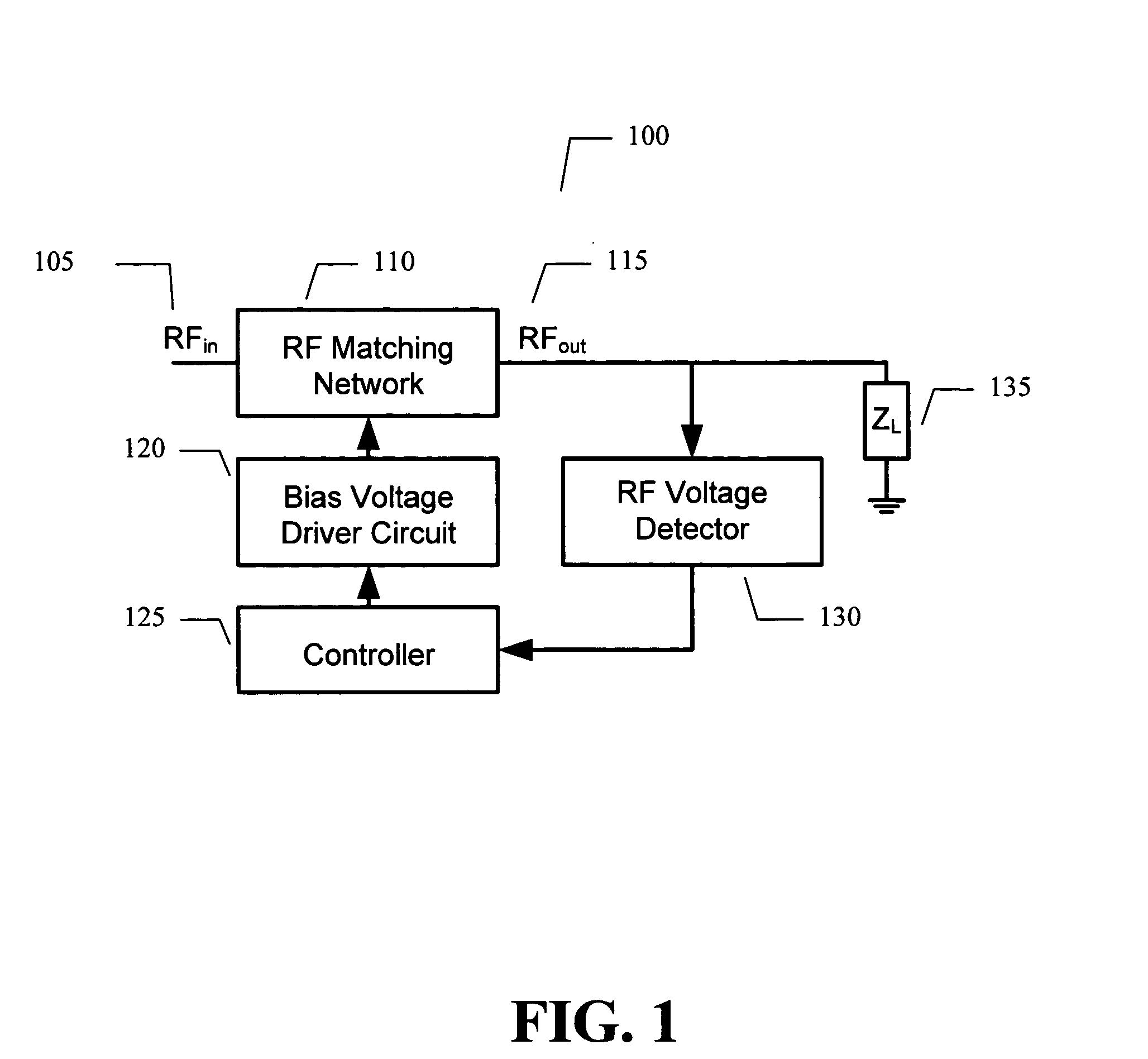

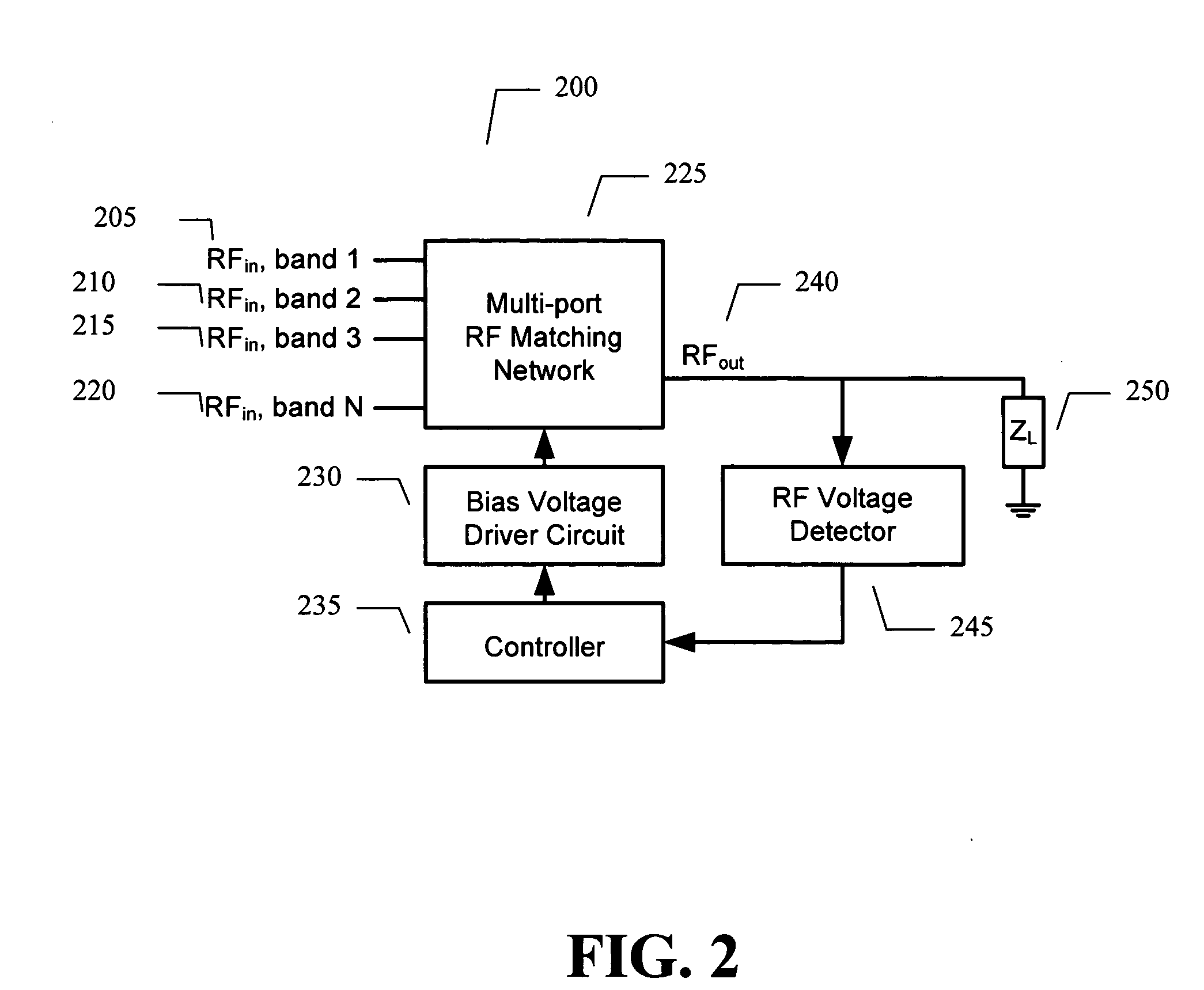

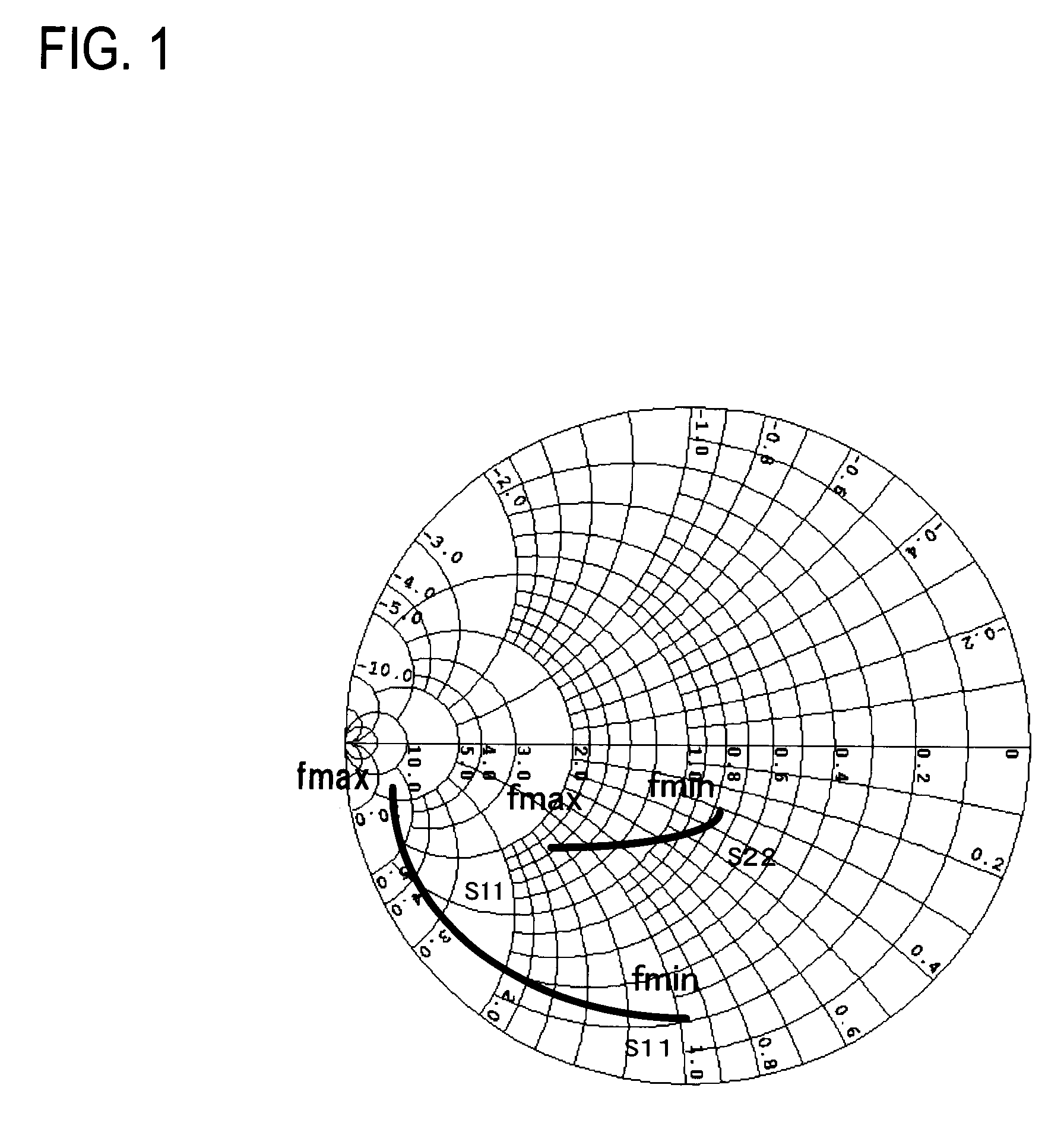

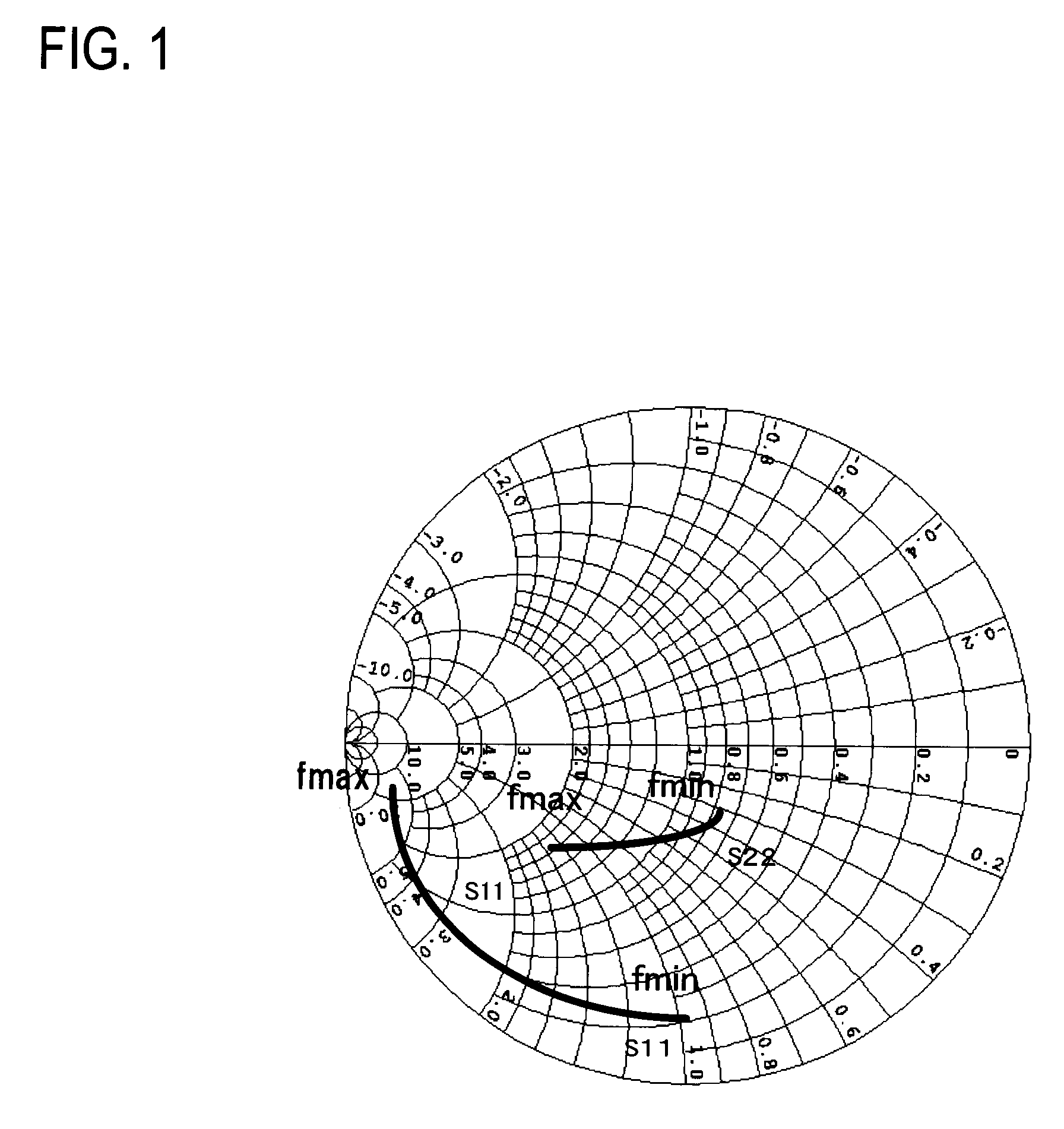

ActiveUS7714676B2Power maximizationMaximize RF voltagePower managementMultiple-port networksCapacitanceImpedance matching

An embodiment of the present invention provides an apparatus, comprising an RF matching network connected to at least one RF input port and at least one RF output port and including one or more voltage or current controlled variable reactive elements and wherein the RF matching network is adapted to maximize RF power transferred from the at least one RF input port to the at least one RF output port by varying the voltage or current to the voltage or current controlled variable reactive elements to maximize the RF voltage at the at least one RF output port. The variable reactive elements may be variable capacitances, variable inductances, or both.

Owner:NXP USA INC

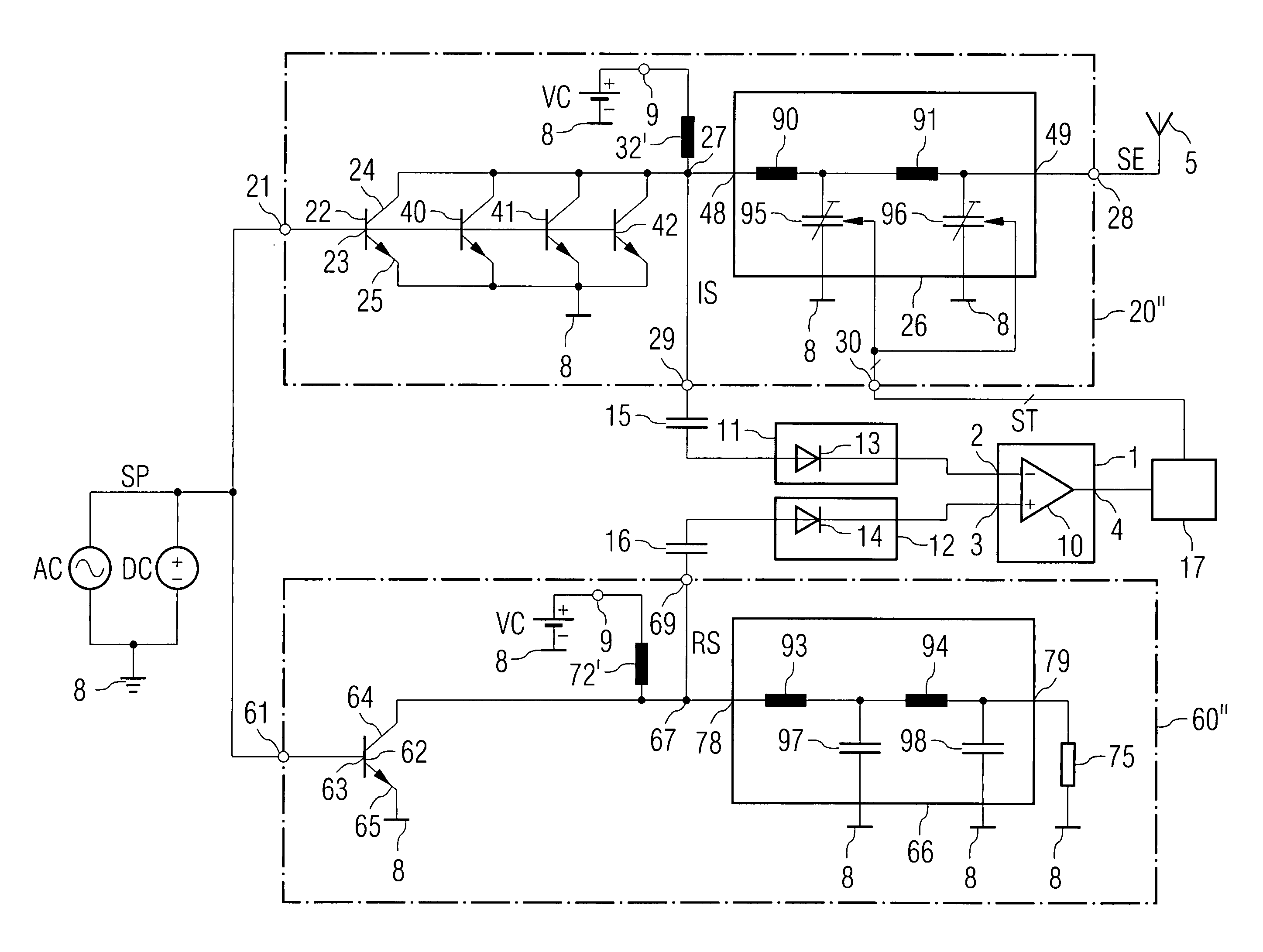

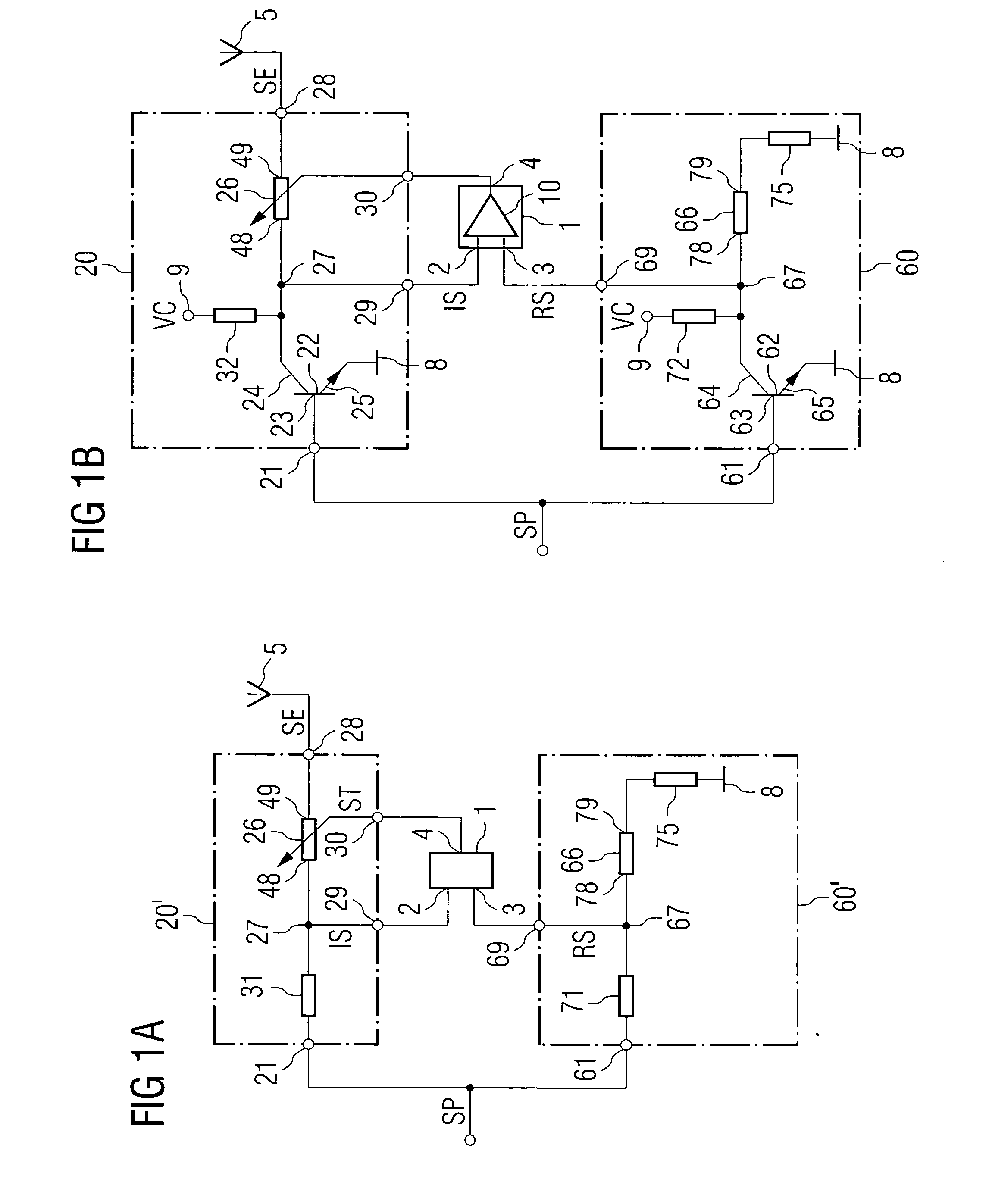

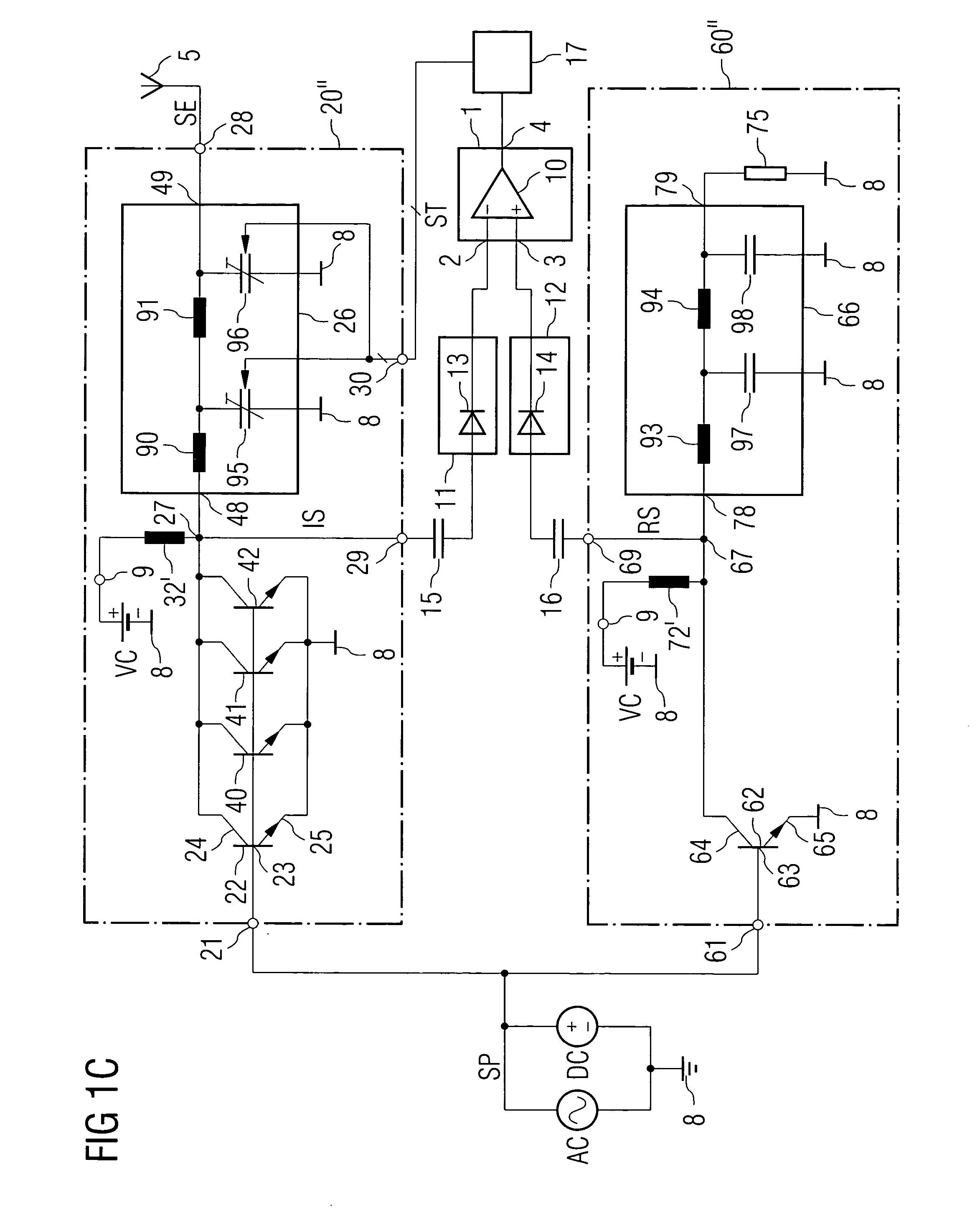

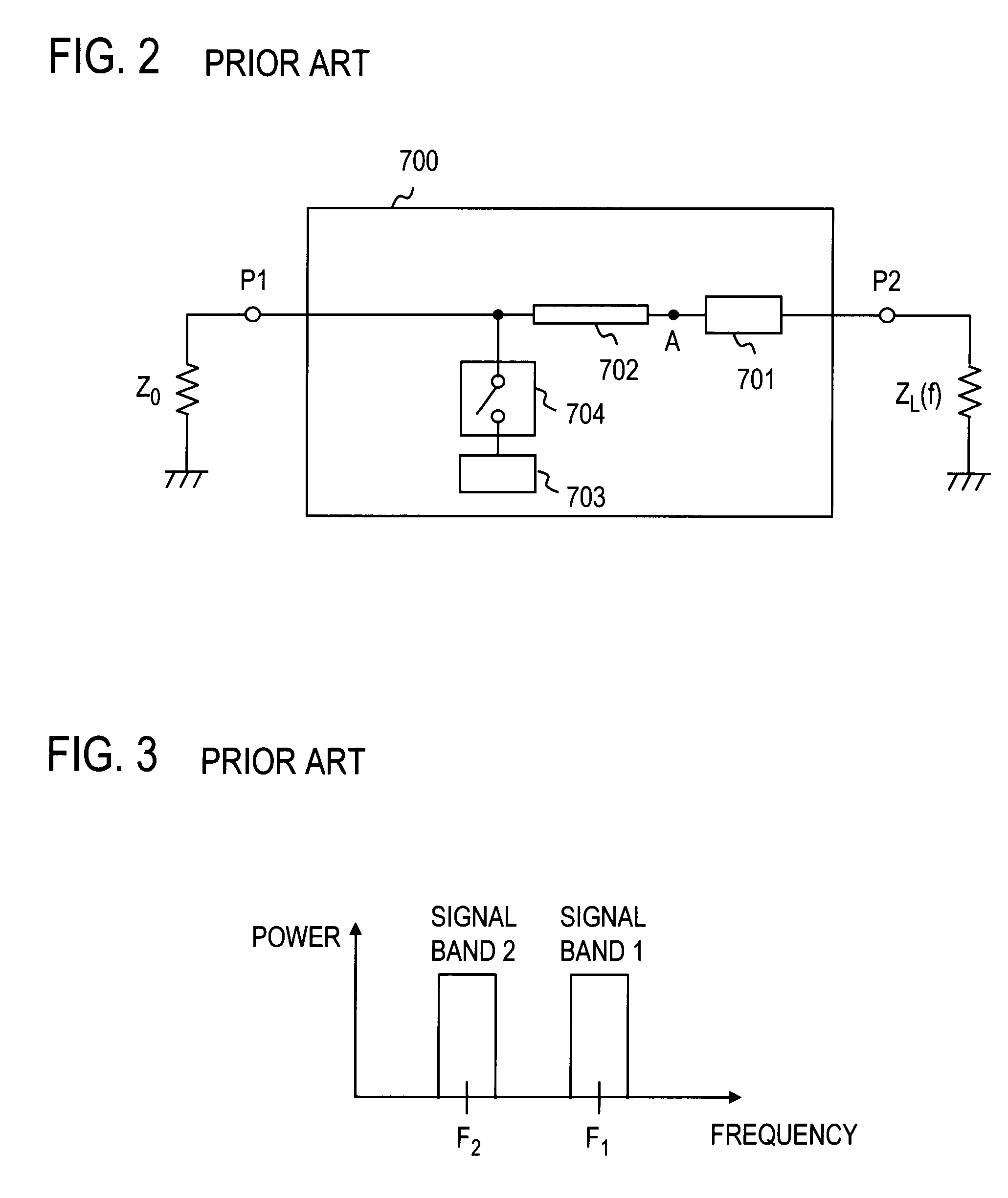

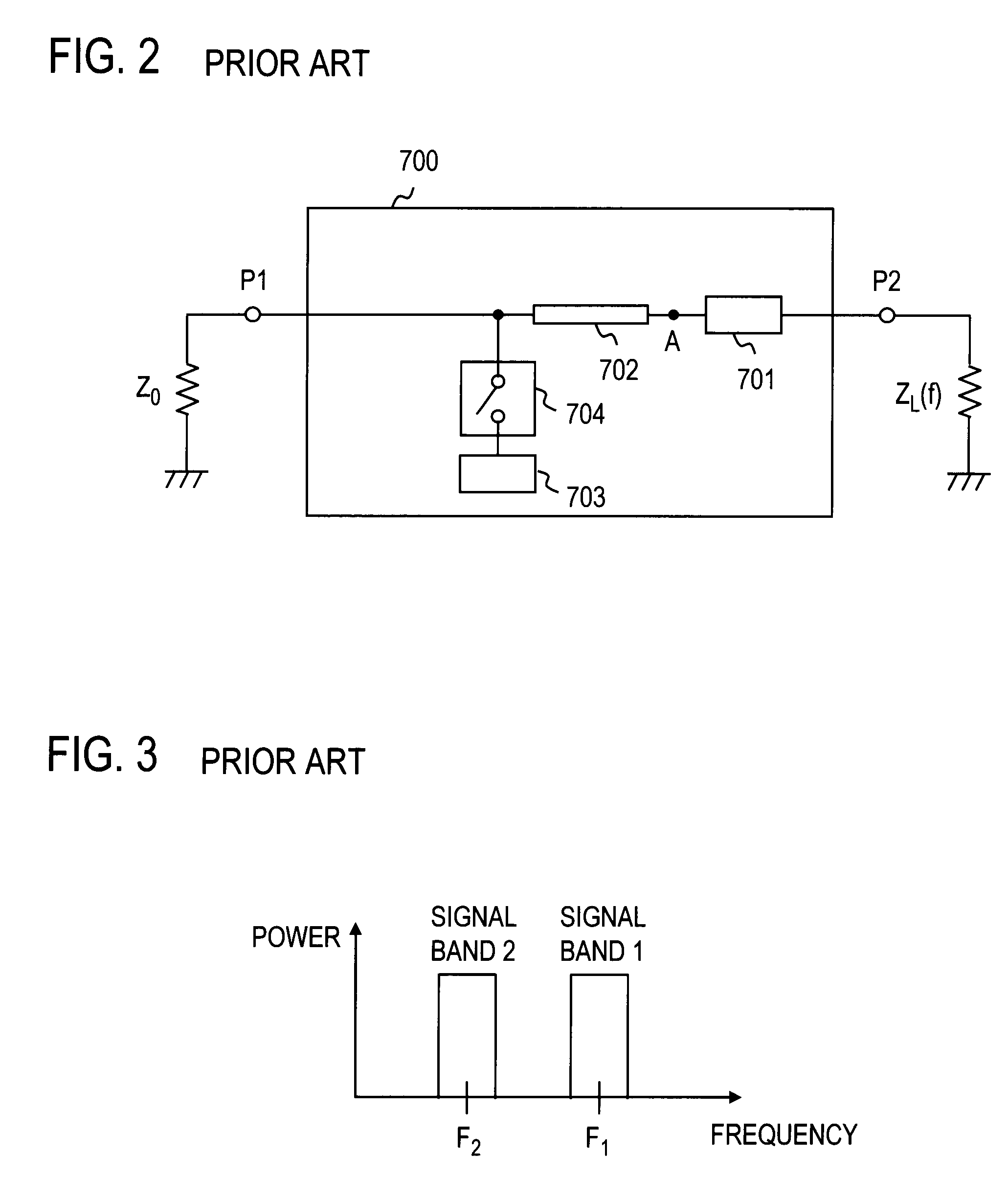

Transmitting arrangement and method for impedance matching

ActiveUS20070085609A1Impedence matching networksModulation with suppressed carrierImpedance matchingReference circuit

A transmitting arrangement includes a matching circuit, a reference circuit and a comparator. The output of the matching circuit can be coupled to an antenna and comprises an adjustable impedance. The reference circuit is connected to an input of the matching circuit and comprises a reference impedance. Inputs of the comparator are coupled to the matching circuit and the reference circuit and its output is coupled to the adjustable impedance via a control input of the matching circuit.

Owner:INTEL CORP

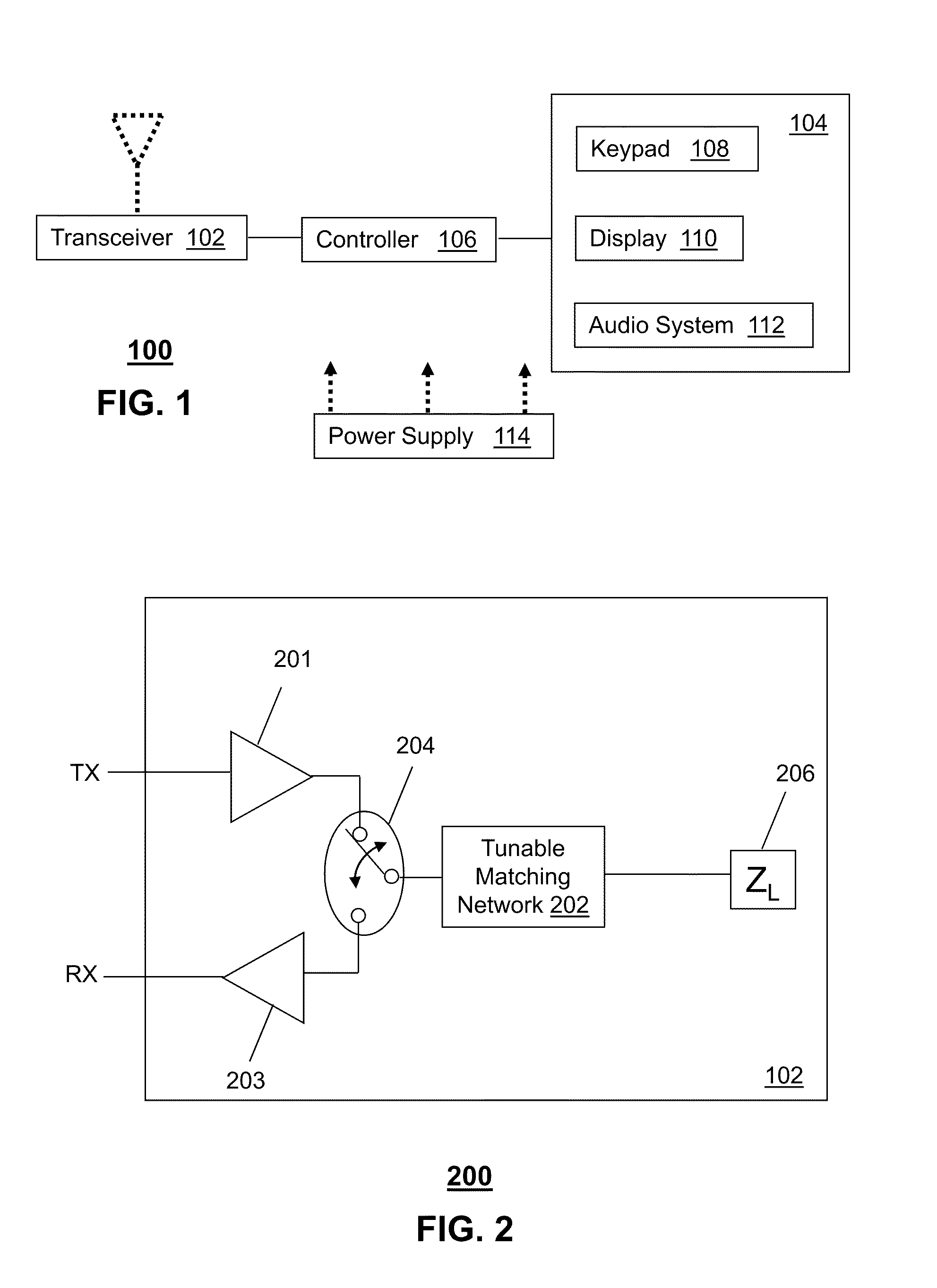

Balanced high-frequency device and balance-characteristics improving method and balanced high-frequency circuit using the same

InactiveUS6900705B2Reduce componentsImpedence matching networksMultiple-port networksHemt circuitsEngineering

Owner:SKYWORKS PANASONIC FILTER SOLUTIONS JAPAN

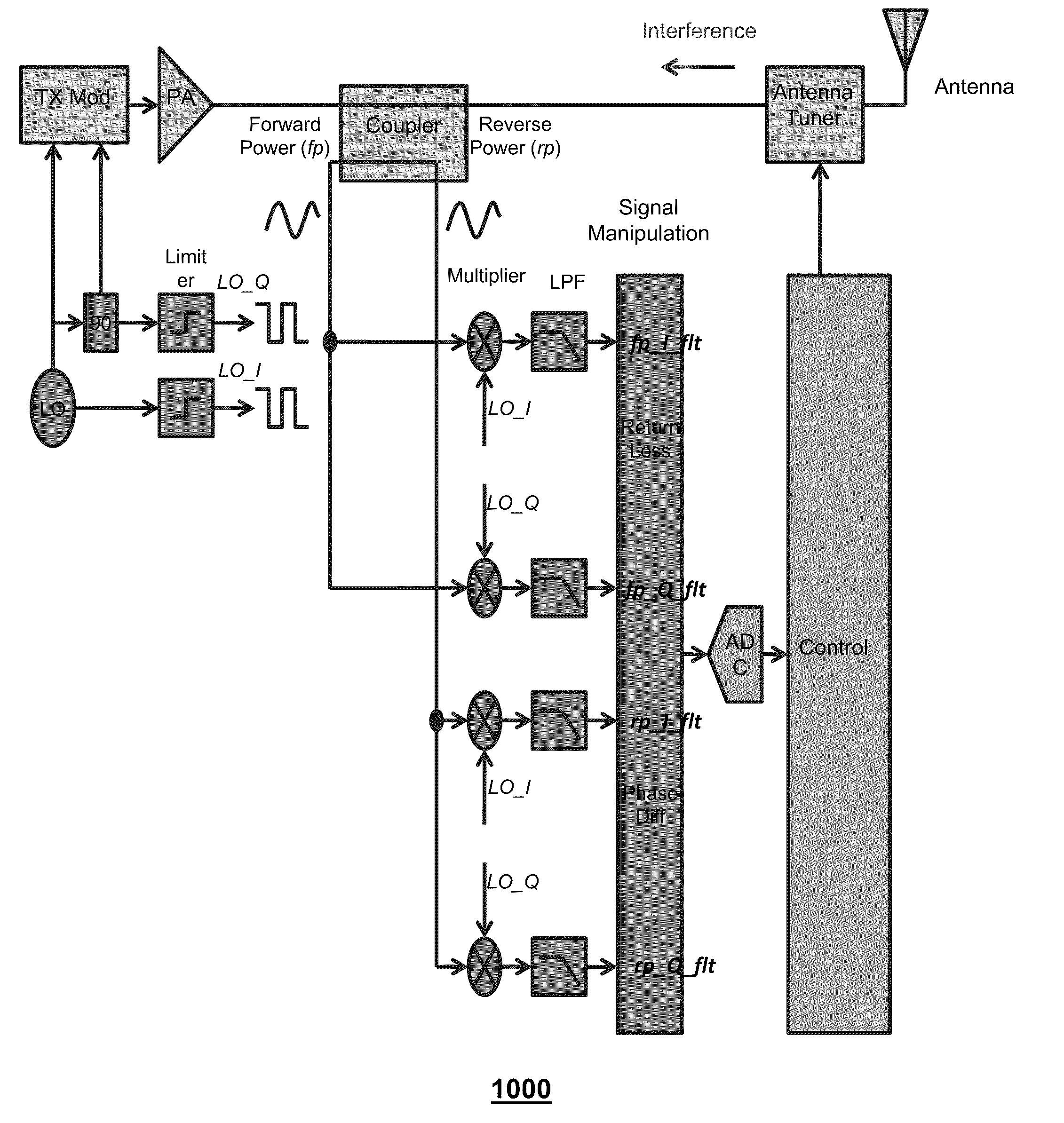

Method and apparatus for managing interference in a communication device

A system that incorporates teachings of the present disclosure may include, for example, a matching network including a tunable reactance circuit configured to be coupled to at least one of a transmitter portion and a receiver portion of a communication device, wherein the tunable reactance circuit is adjustable to a plurality of tuning states, and wherein the determination of a tuning state is based on parameters associated with a detected interference. Additional embodiments are disclosed.

Owner:NXP USA INC

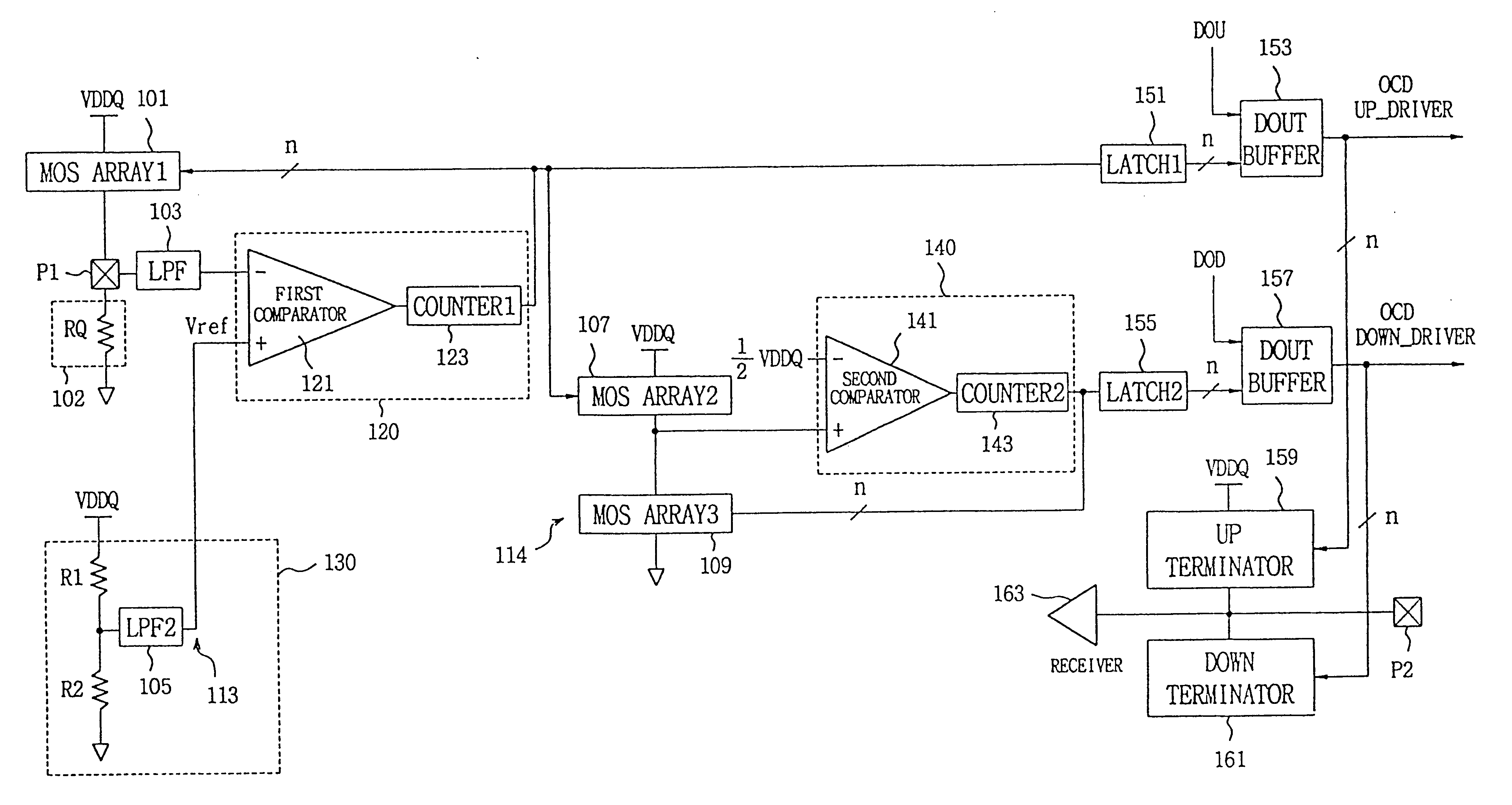

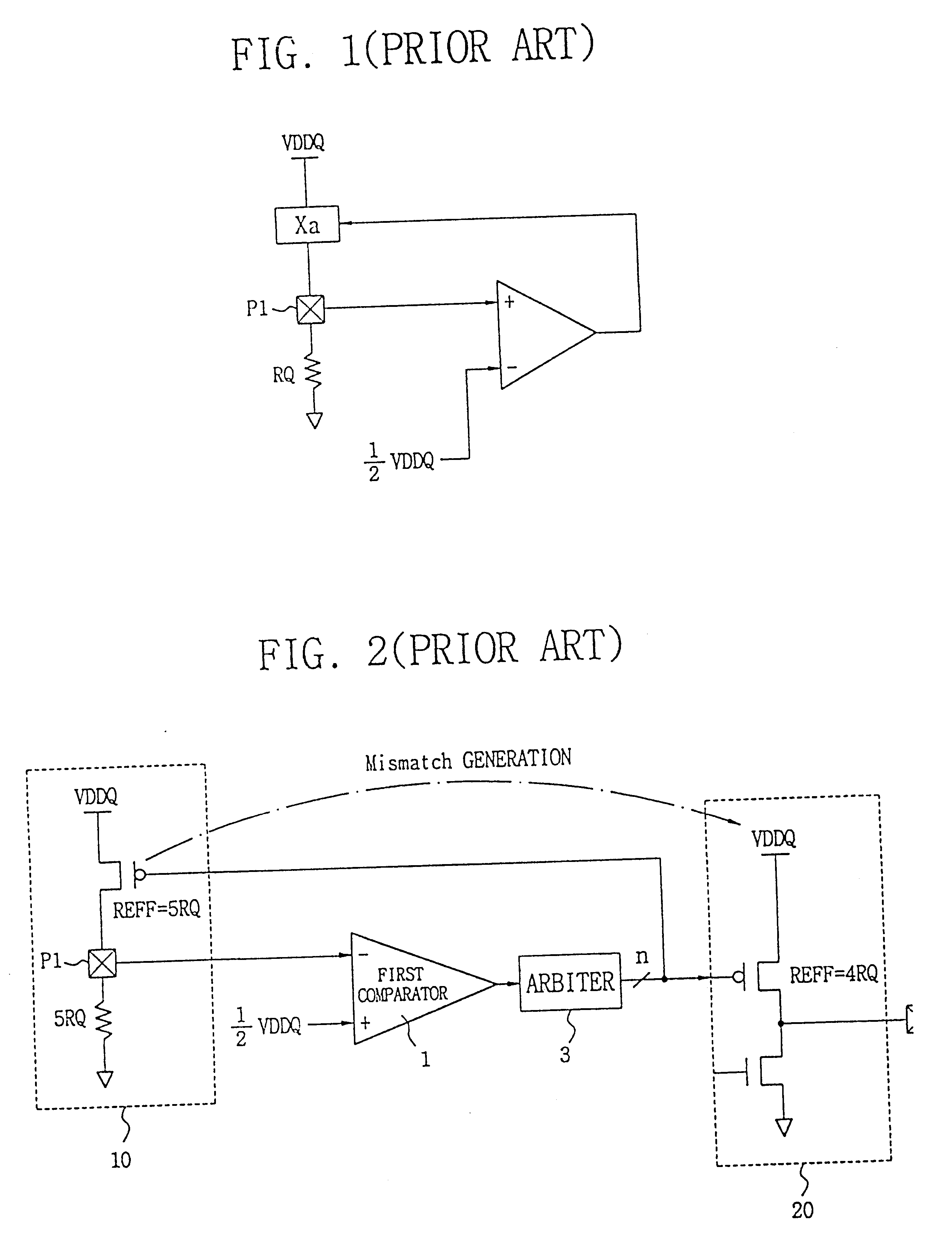

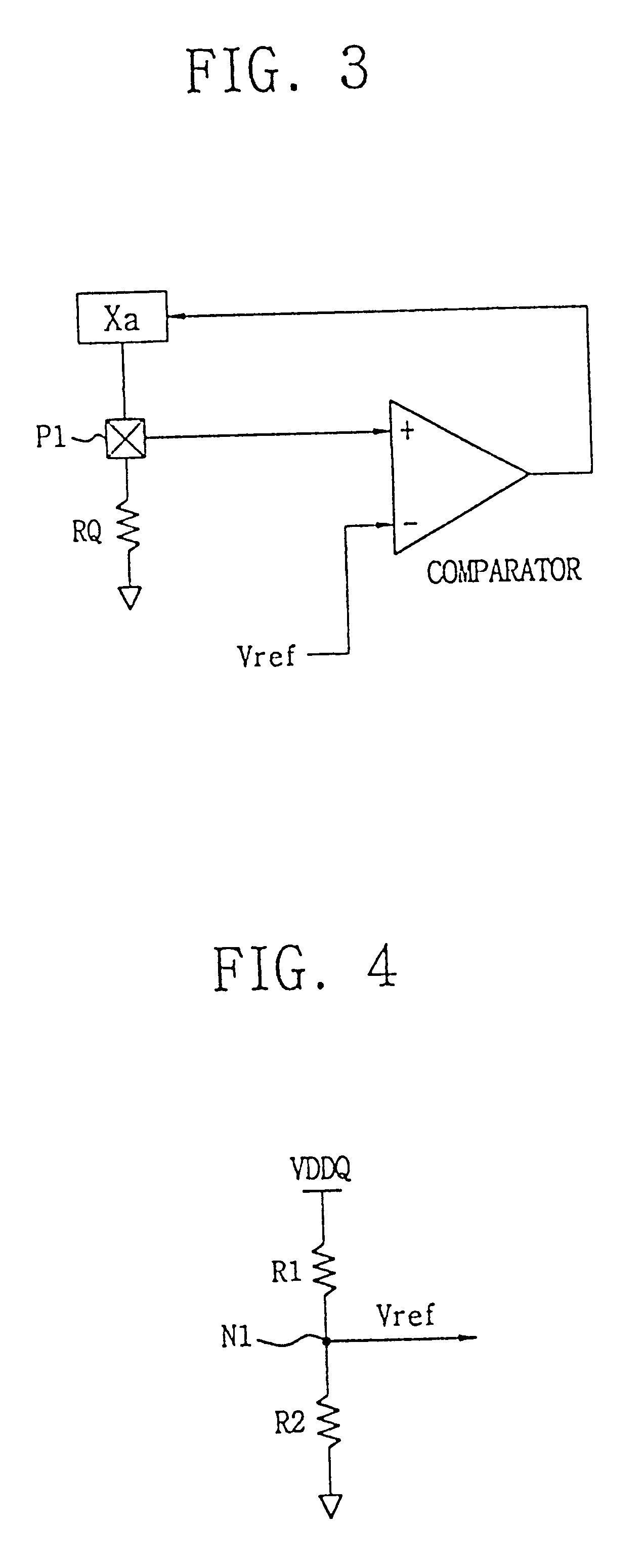

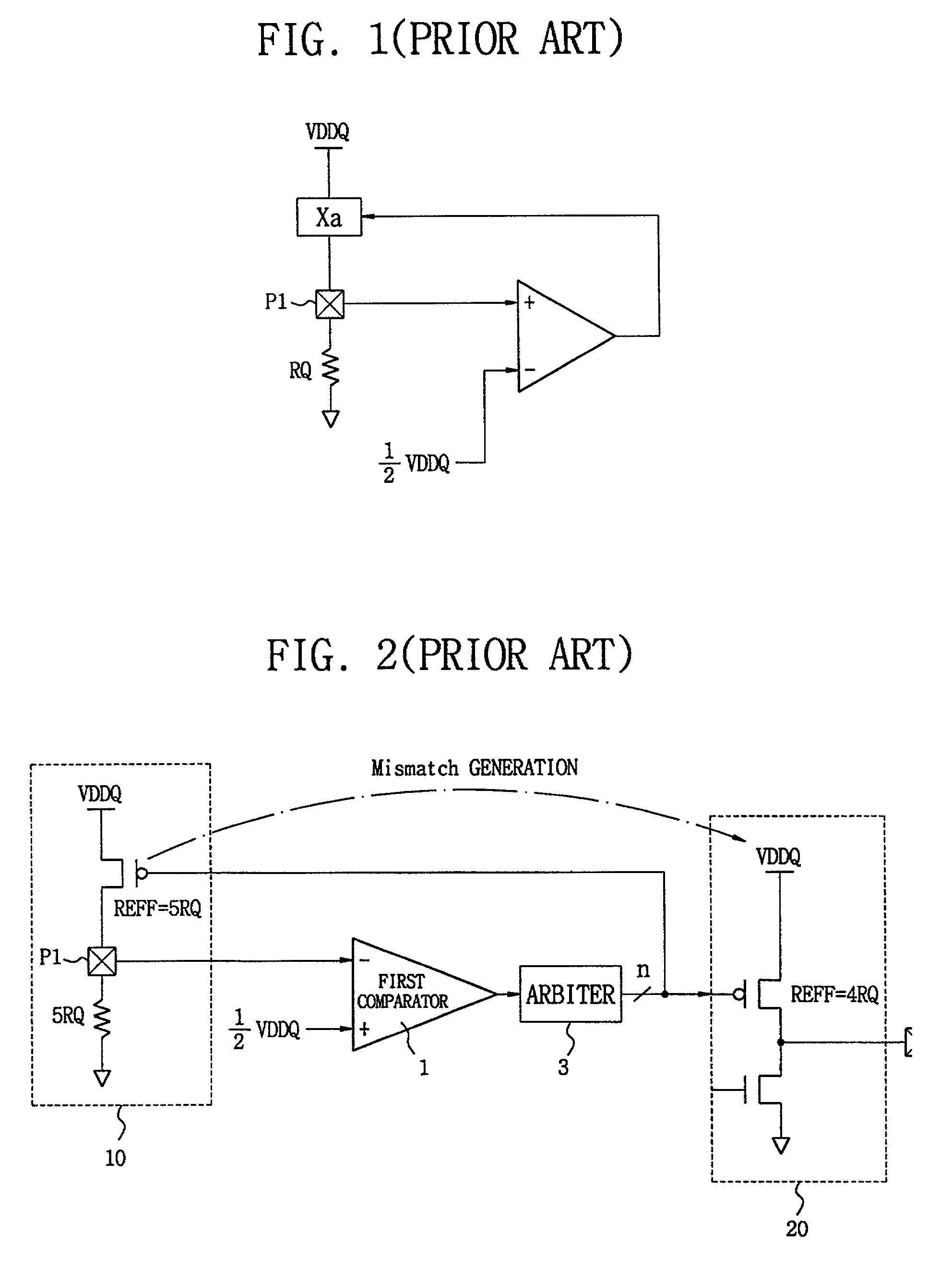

Programmable impedance control circuit

InactiveUS6525558B2Multiple-port networksImpedence matching networksElectrical resistance and conductanceVoltage generator

Disclosed is a programmable impedance control circuit, comprising a voltage divider, the voltage divider comprising an MOS array supplied with a first voltage and an external resistance having an external impedance equal to N times said external resistance. The voltage divider outputs a second voltage. A reference voltage generator is provided for generating a third voltage corresponding to N / (N+M) times said first voltage as a reference voltage for said second voltage, and wherein M times internal impedance is used for N times external impedance (N=M or N<> M).

Owner:SAMSUNG ELECTRONICS CO LTD

Method and apparatus for use in digitally tuning a capacitor in an integrated circuit device

ActiveUS9024700B2Easy to controlHigh Power Handling CapabilityMultiple-port networksImpedence matching networksCapacitanceLeast significant bit

Owner:PSEMI CORP

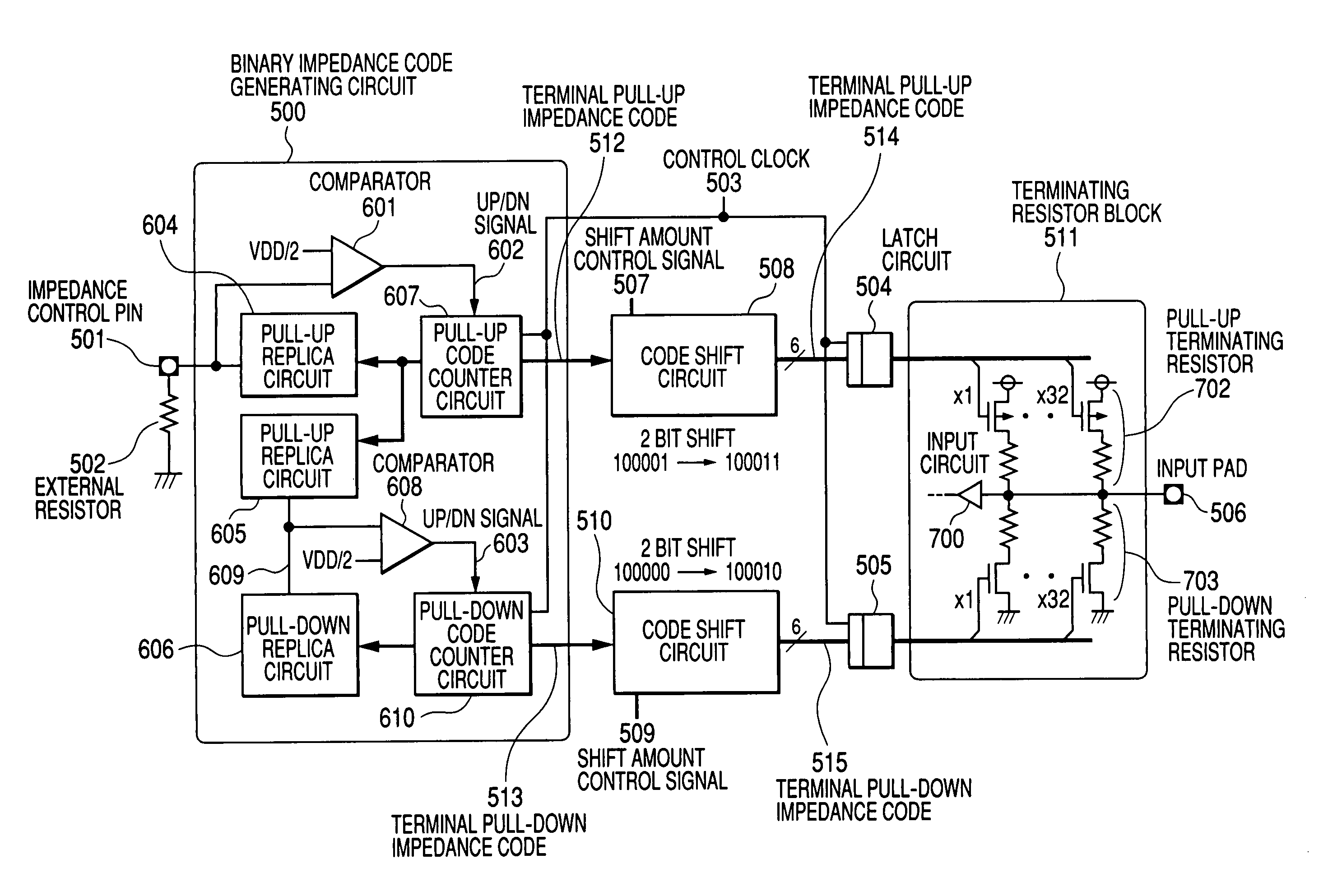

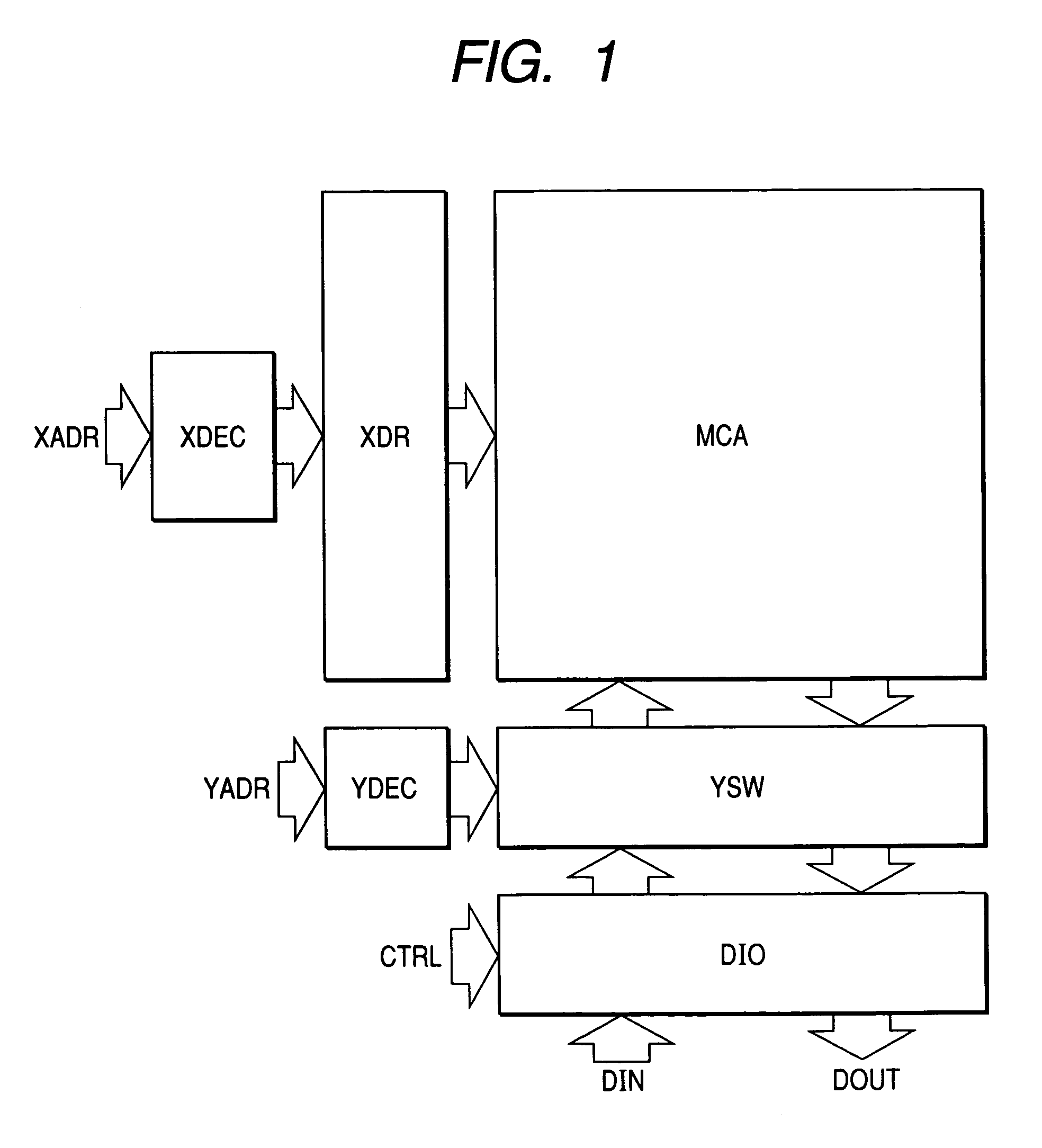

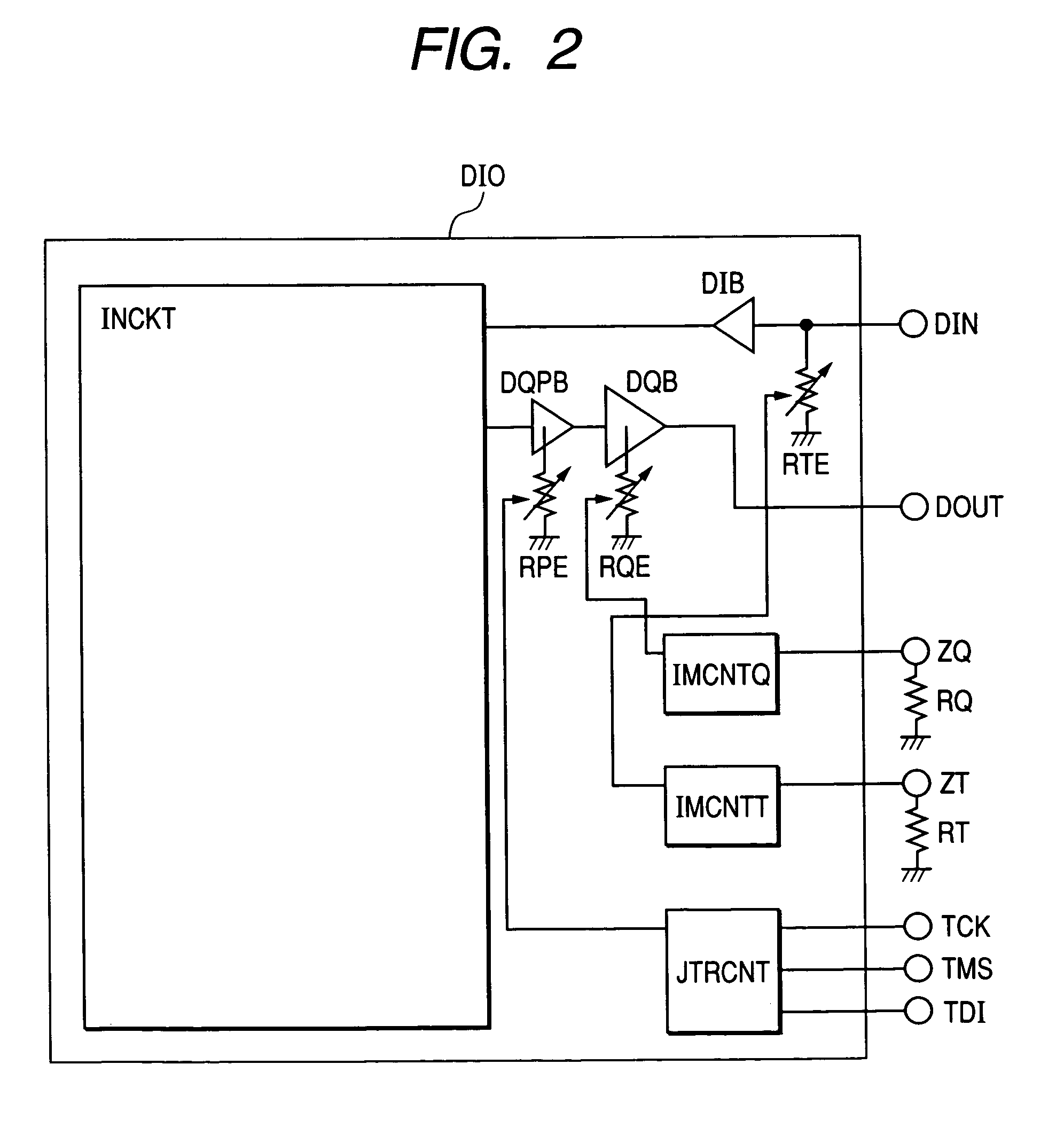

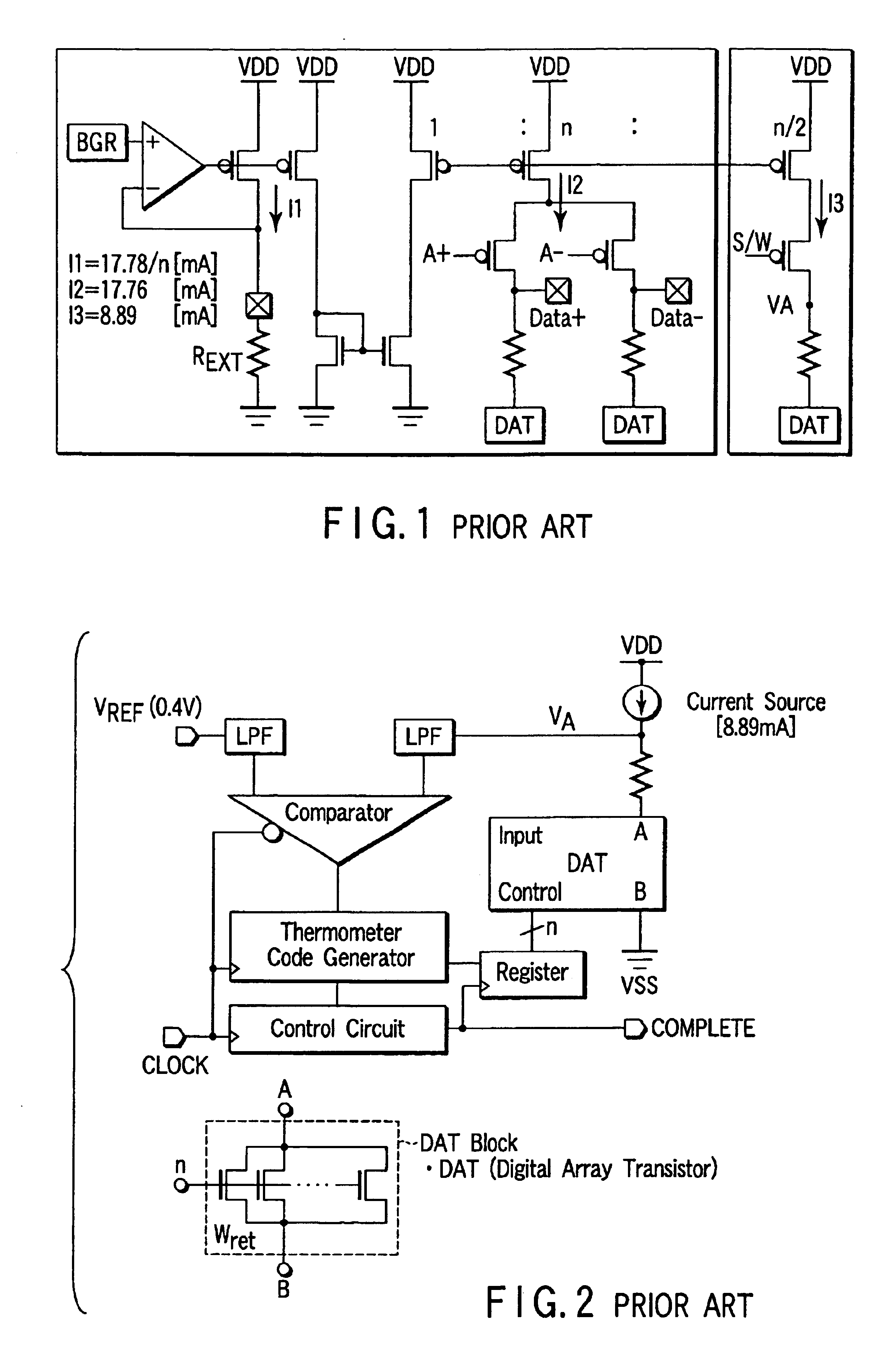

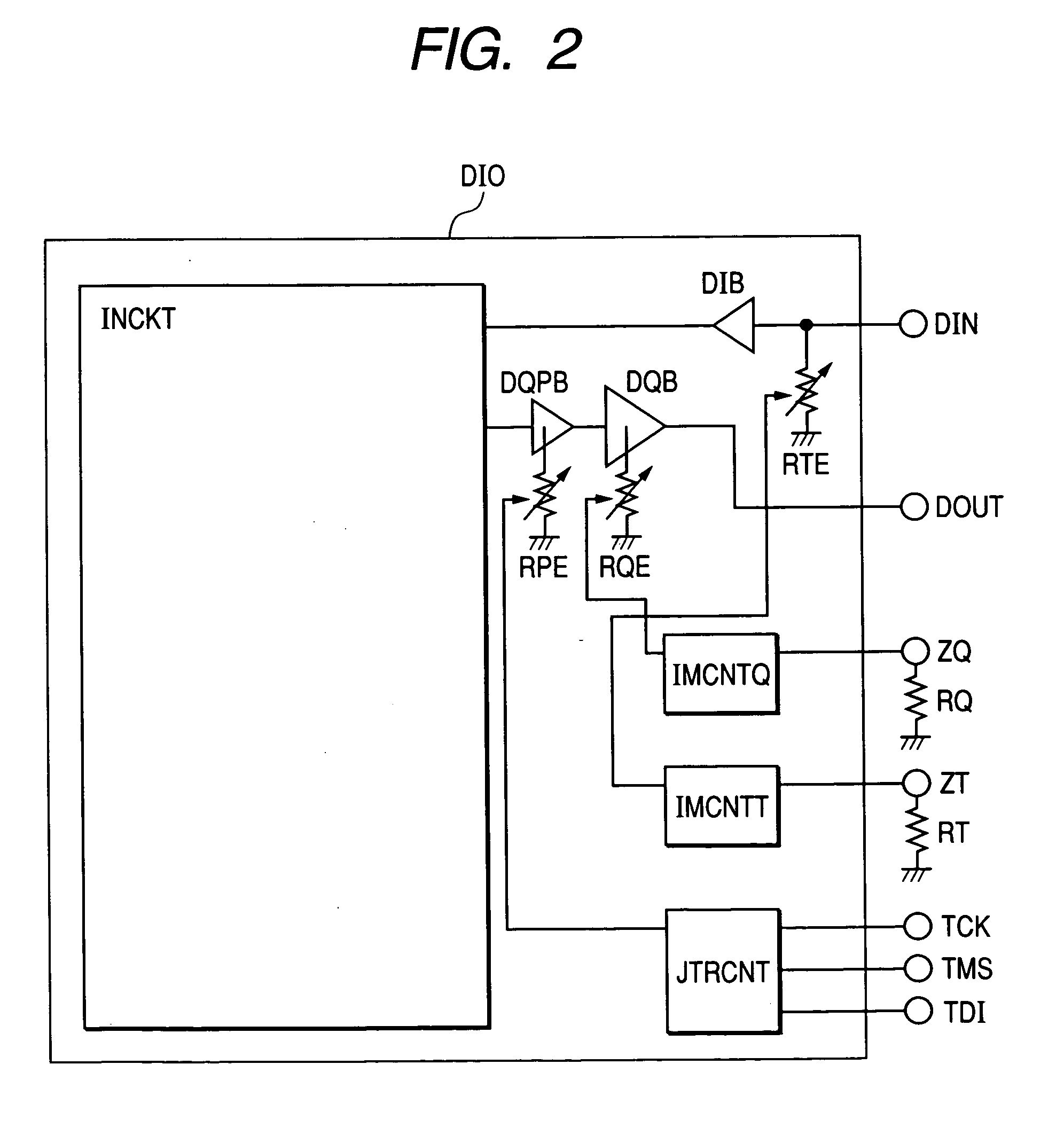

Semiconductor integrated circuit device

InactiveUS7038486B2Improve accuracyReduce yieldInput/output impedence modificationReliability increasing modificationsElectrical resistance and conductanceEngineering

A plurality of sets of circuits are provided, each of which generates an impedance code through the use of an impedance control circuit in association with a resistive element connected to an external terminal, and each of which varies the impedance in accordance with such an impedance code. The impedance control circuit includes an impedance comparator which is formed equivalently to the resistive element and the plurality of sets of circuits, and which performs an impedance comparison with each of a plurality of replica circuits to form an up signal that increases the impedance and a down signal that decreases the impedance. Counters are provided adjacent to the individuals of the plurality of sets of circuits to thereby generate the impedance codes in response to the up signal and the down signal.

Owner:RENESAS ELECTRONICS CORP

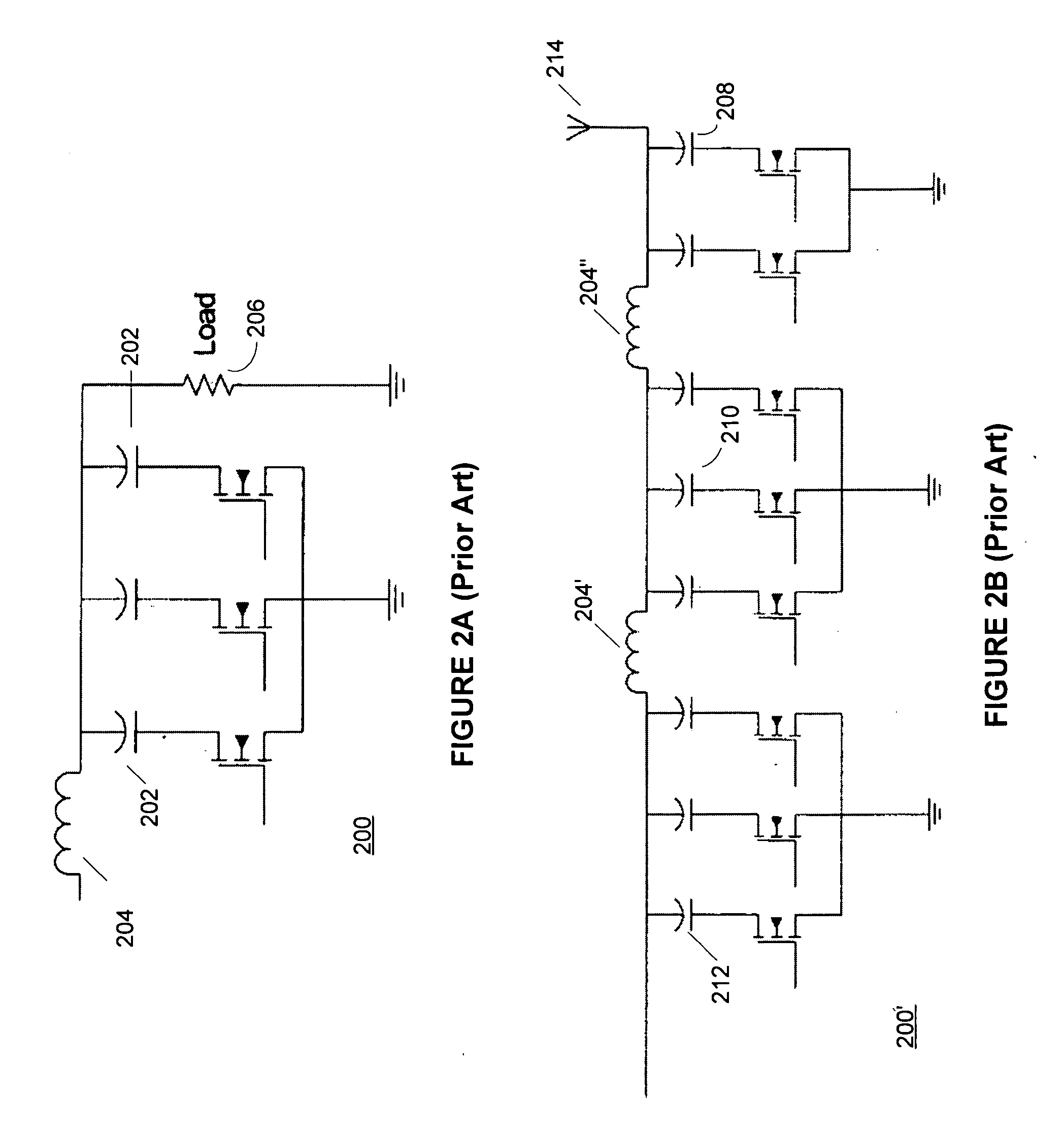

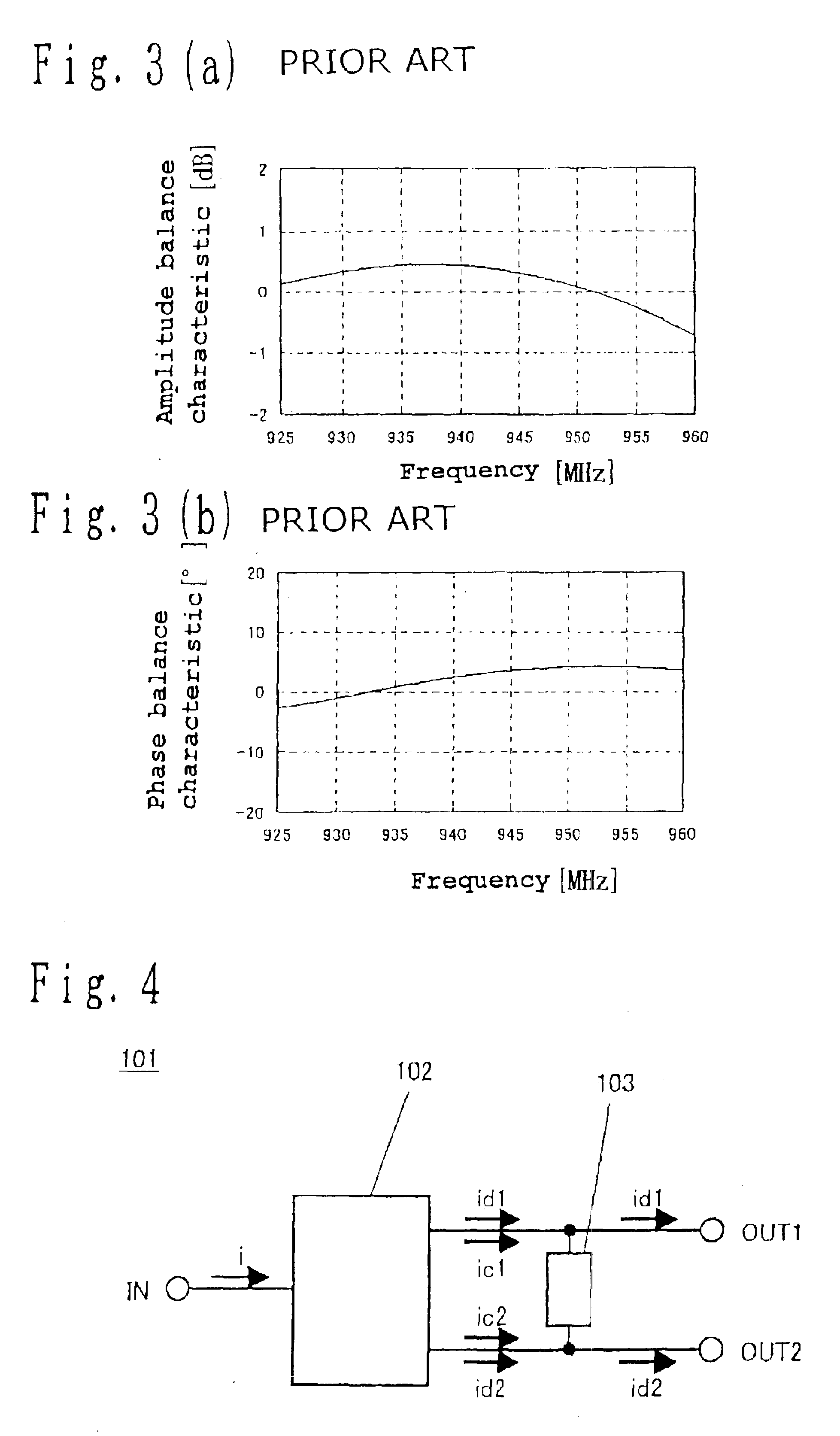

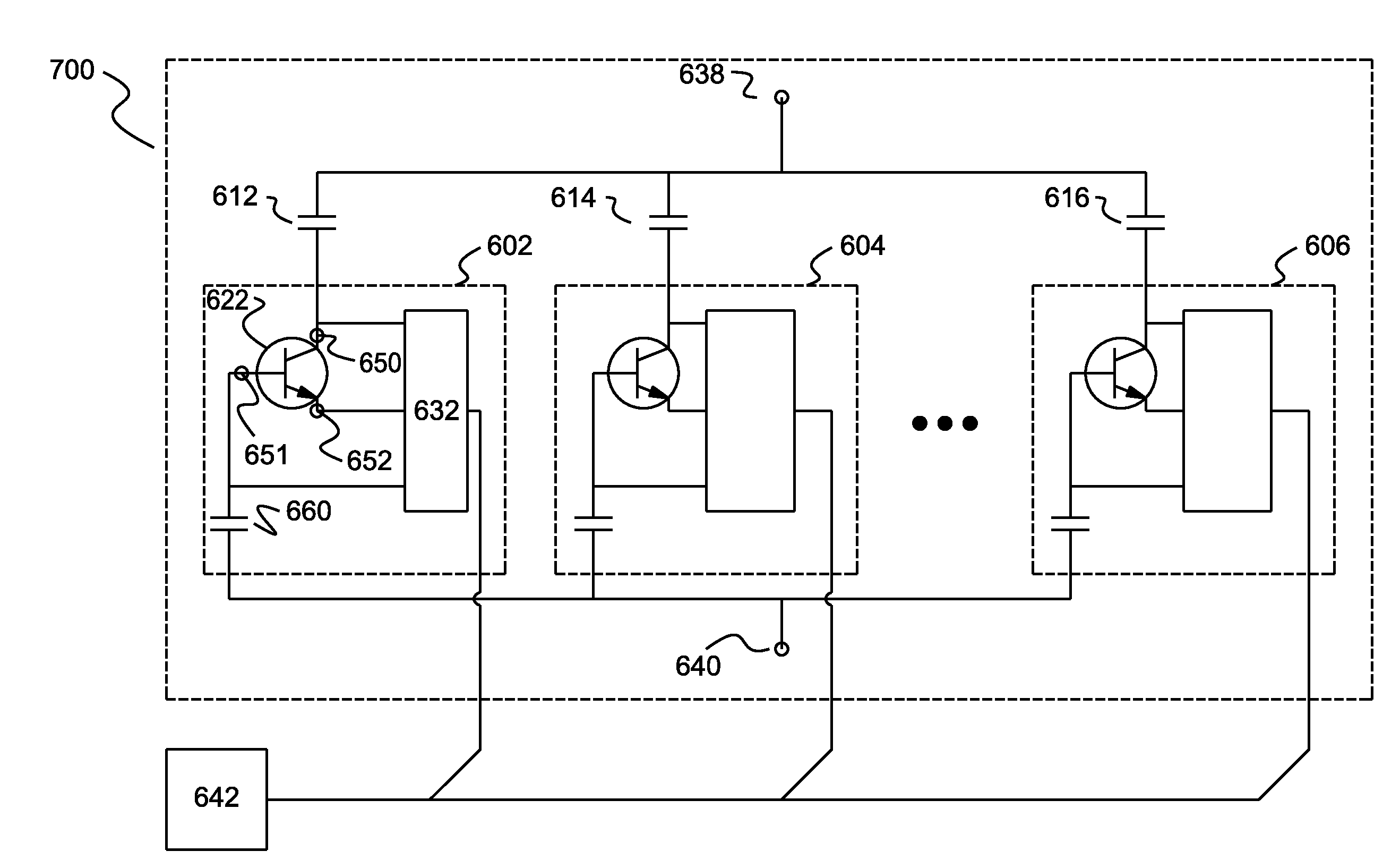

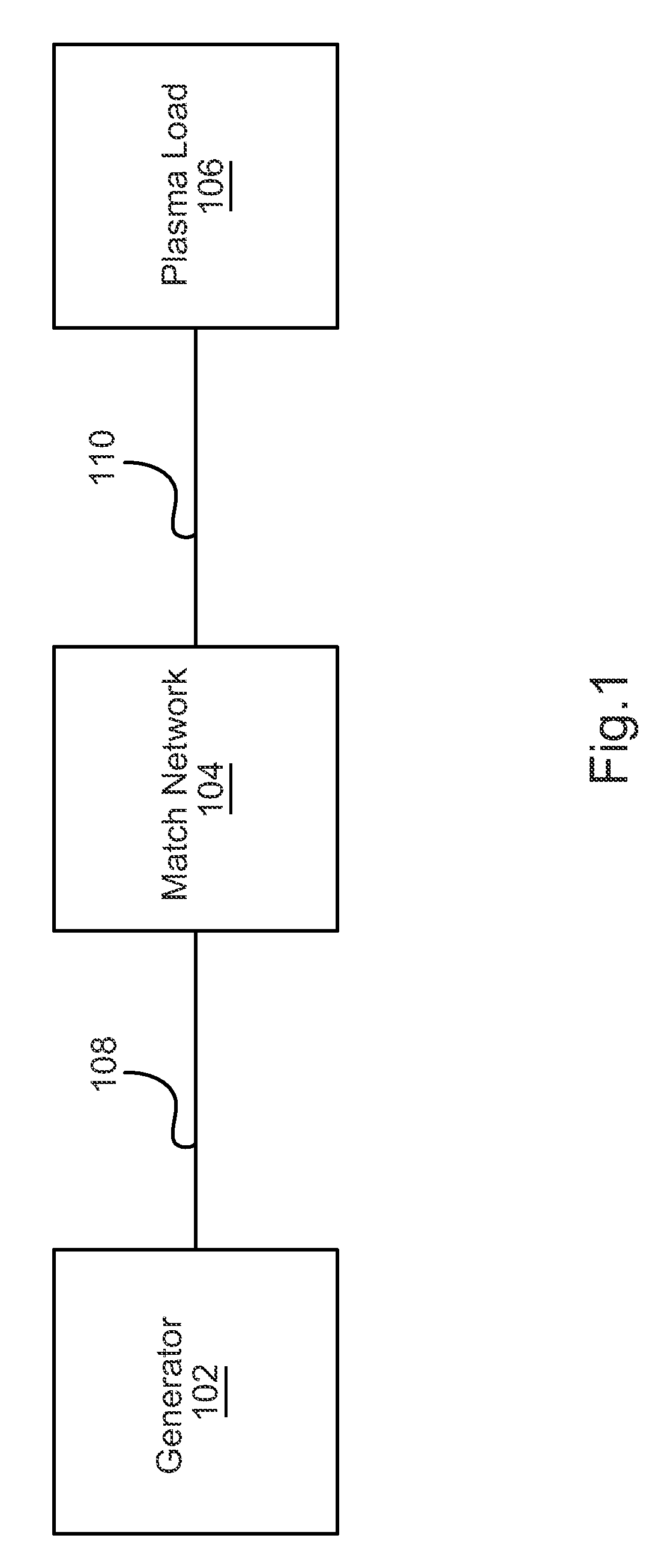

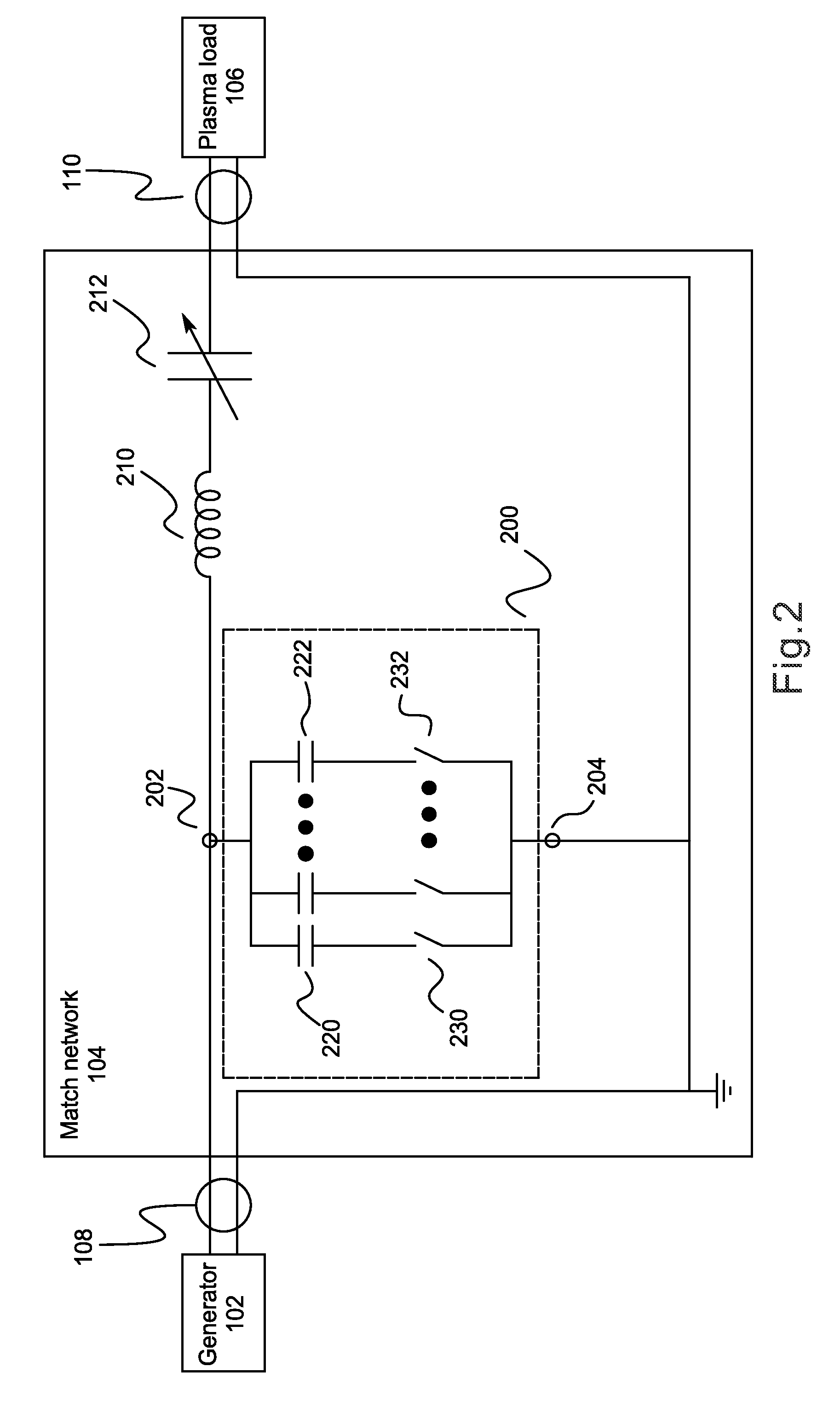

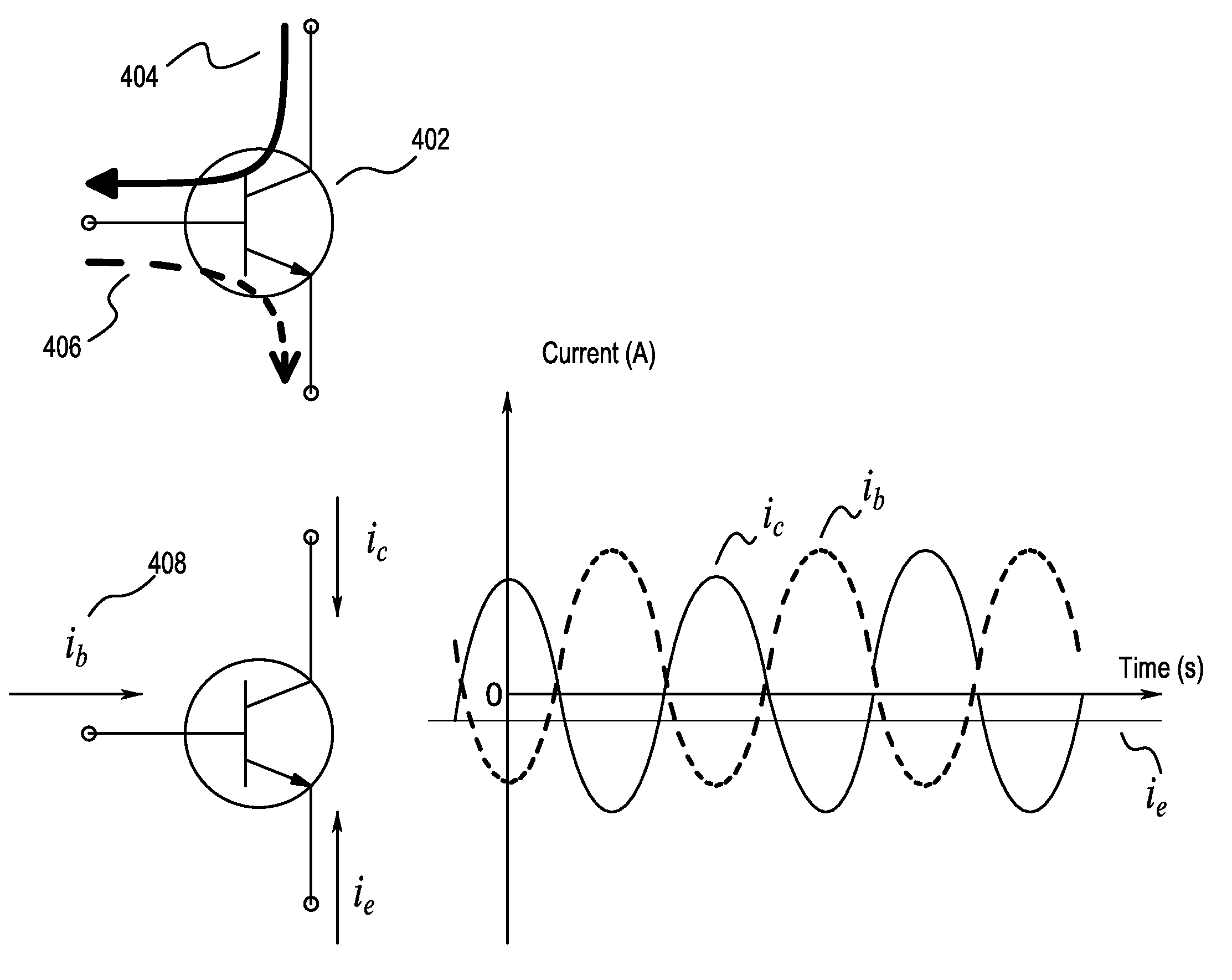

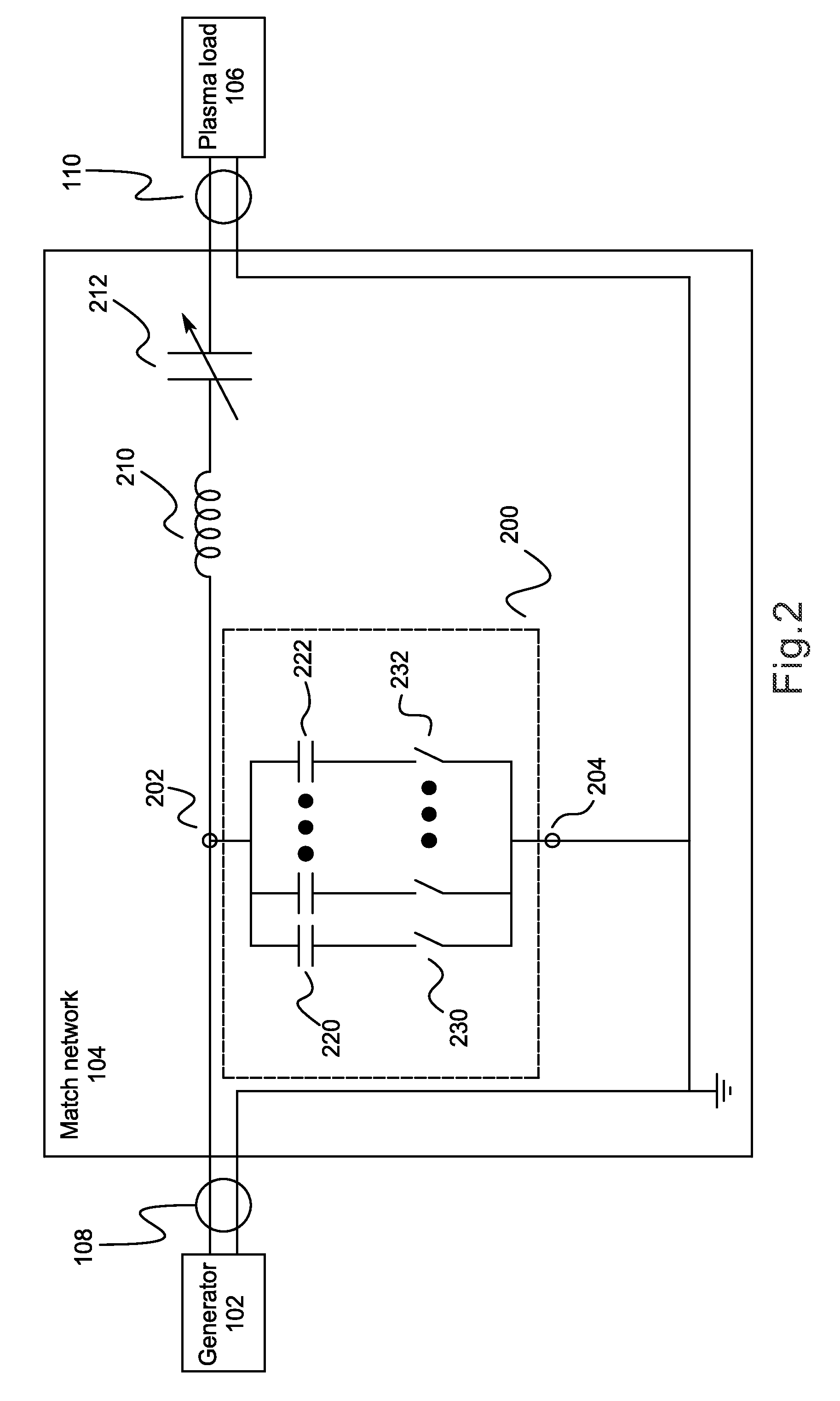

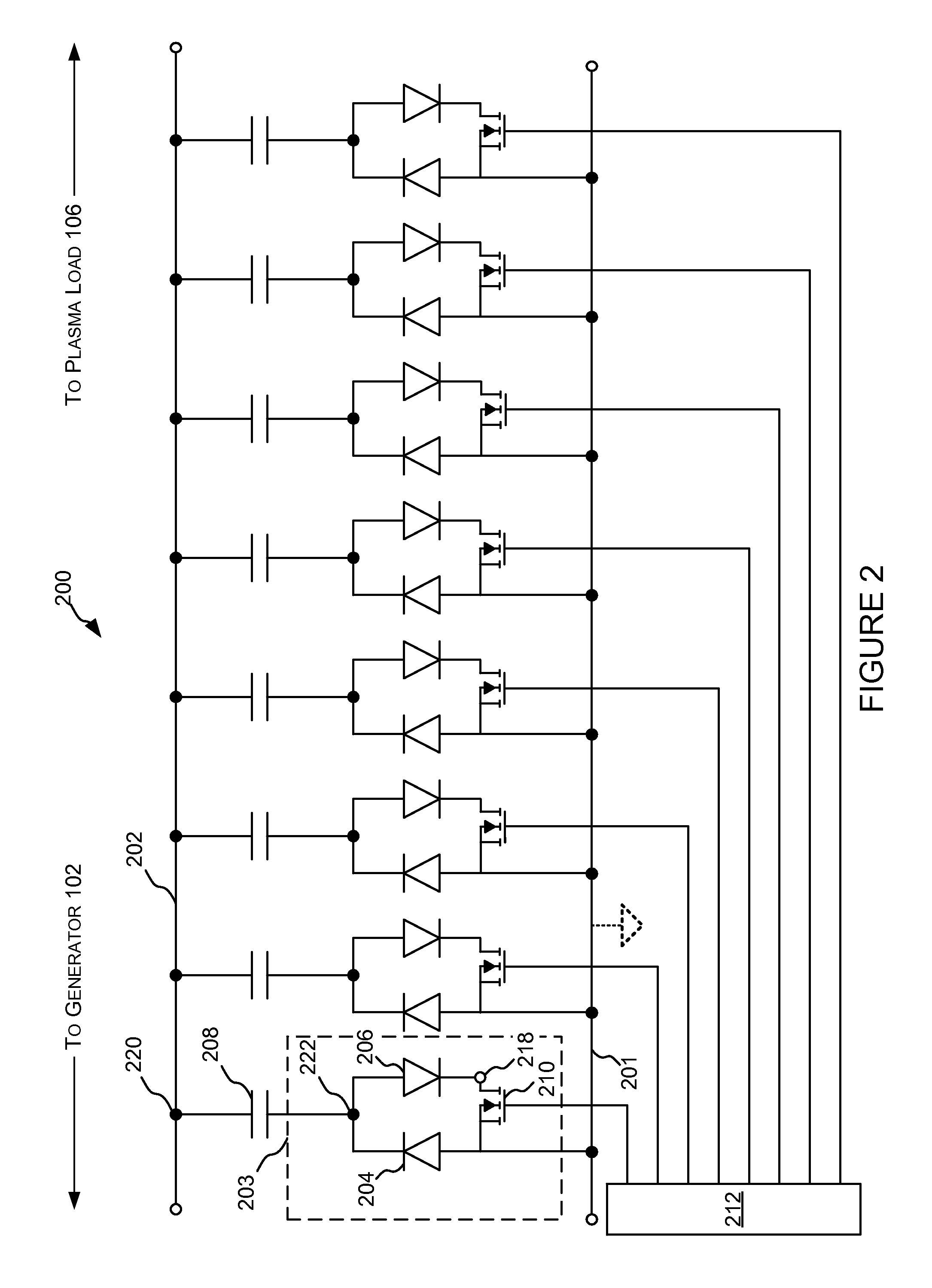

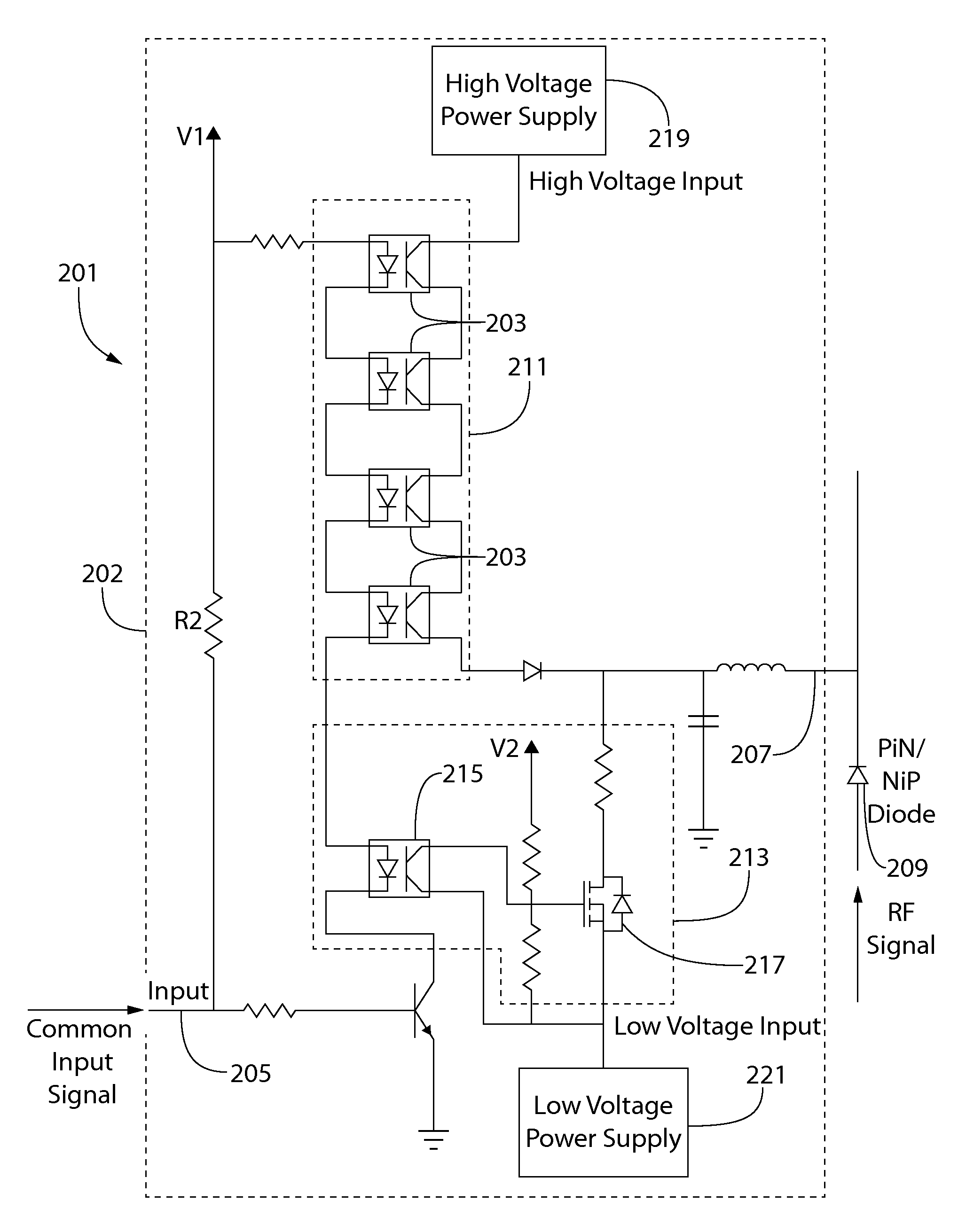

Impedance-Matching Network Using BJT Switches in Variable-Reactance Circuits

ActiveUS20120188007A1Reduce voltageTransistorMultiple-port networksVacuum variable capacitorImpedance matching

This disclosure describes systems, methods, and apparatuses for impedance-matching radio frequency power transmitted from a radio frequency generator to a plasma load in a semiconductor processing chamber. Impedance-matching can be performed via a match network having a variable-reactance circuit. The variable-reactance circuit can comprise one or more reactive elements all connected to a first terminal and selectively shorted to a second terminal via a switch. The switch can comprise a bipolar junction transistor (BJT) or insulated gate bipolar transistor (IGBT) controlled via bias circuitry. In an on-state, the BJT base-emitter junction is forward biased, and AC is conducted between a collector terminal and a base terminal. Thus, AC passes through the BJT primarily from collector to base rather than from collector to emitter. Furthermore, the classic match network topology used with vacuum variable capacitors can be modified such that voltages do not overload the BJT's in the modified topology.

Owner:AES GLOBAL HLDG PTE LTD

Impedance-matching network using BJT switches in variable-reactance circuits

ActiveUS8416008B2Reduce voltageTransistorMultiple-port networksVacuum variable capacitorImpedance matching

Owner:AES GLOBAL HLDG PTE LTD

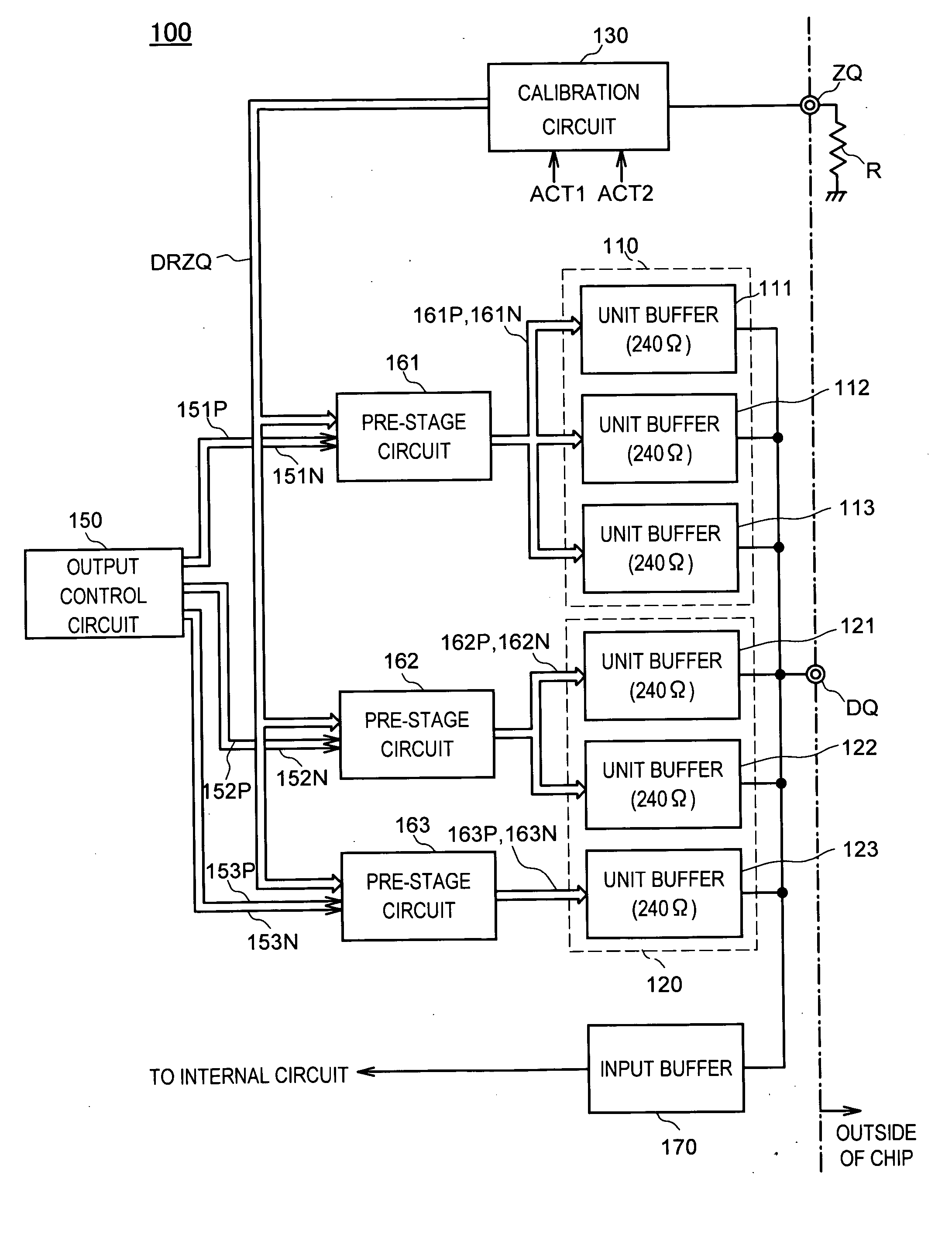

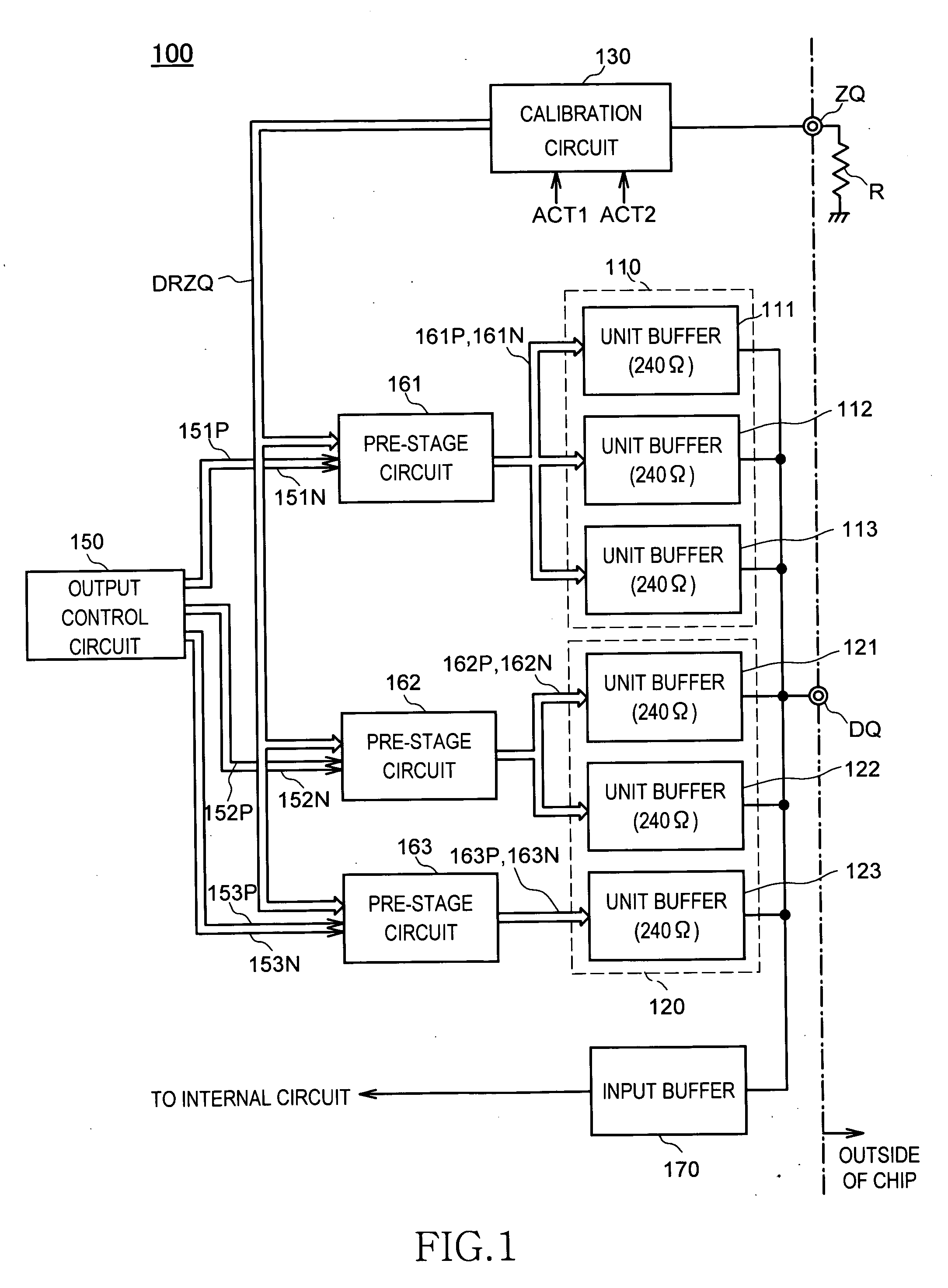

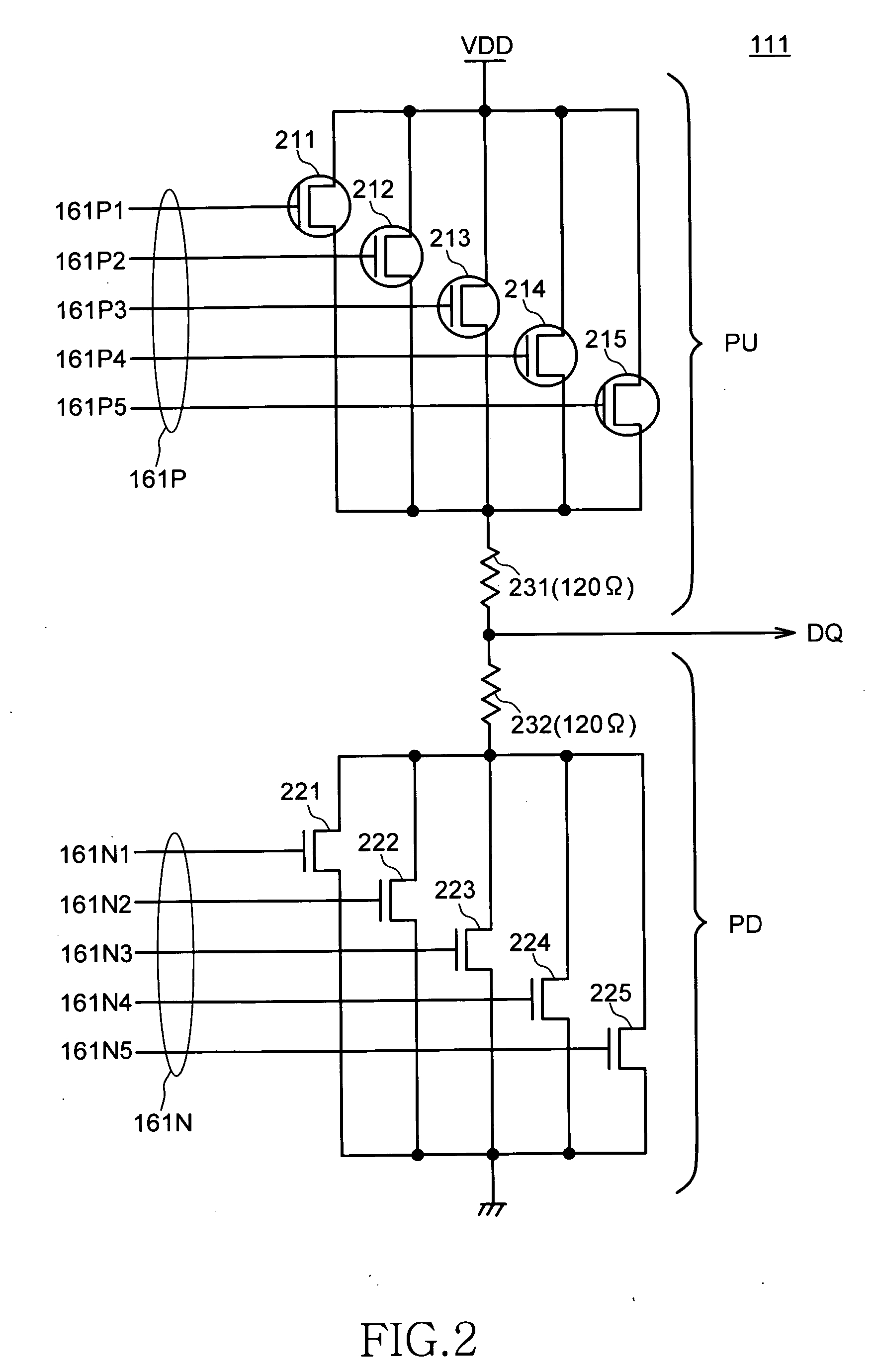

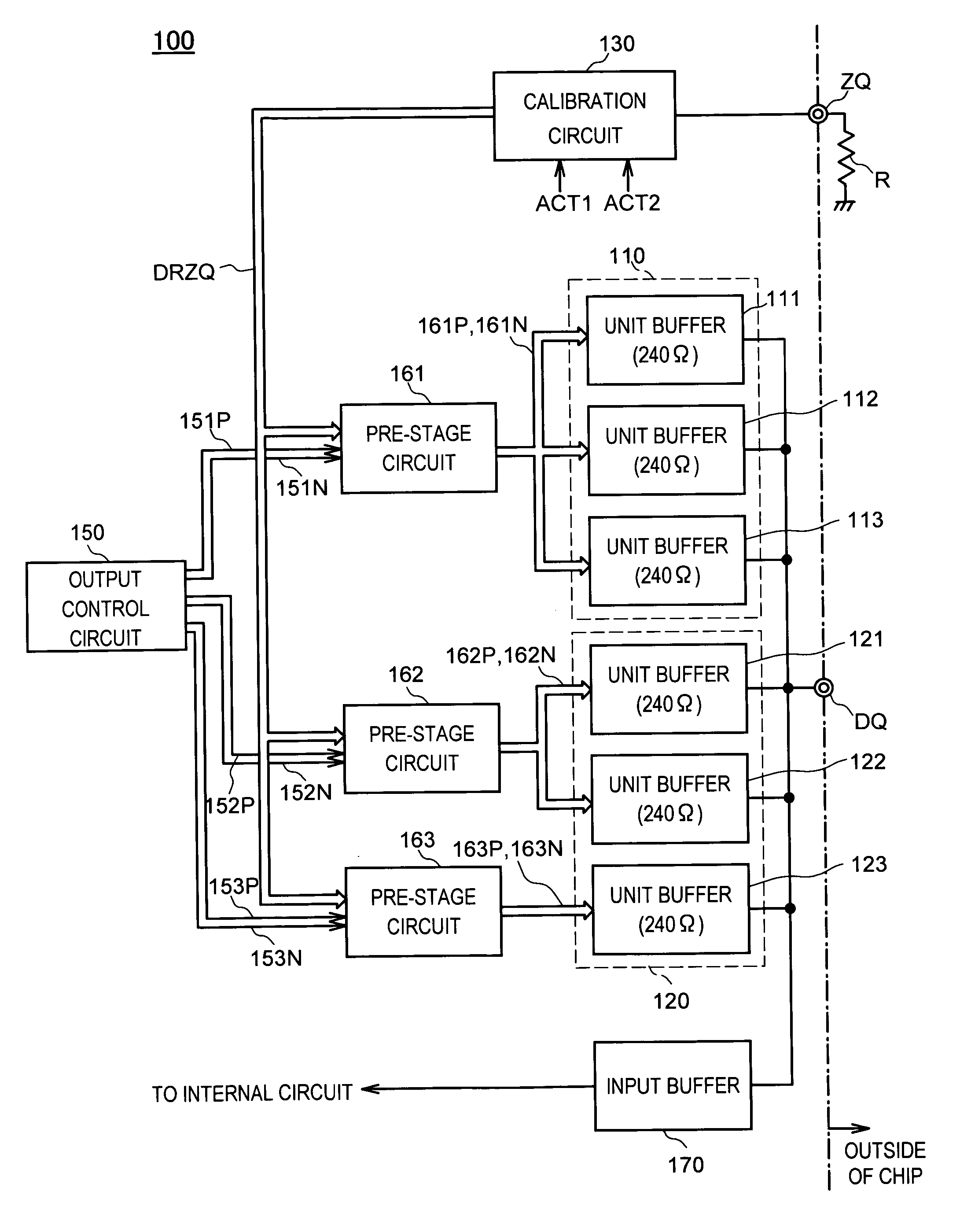

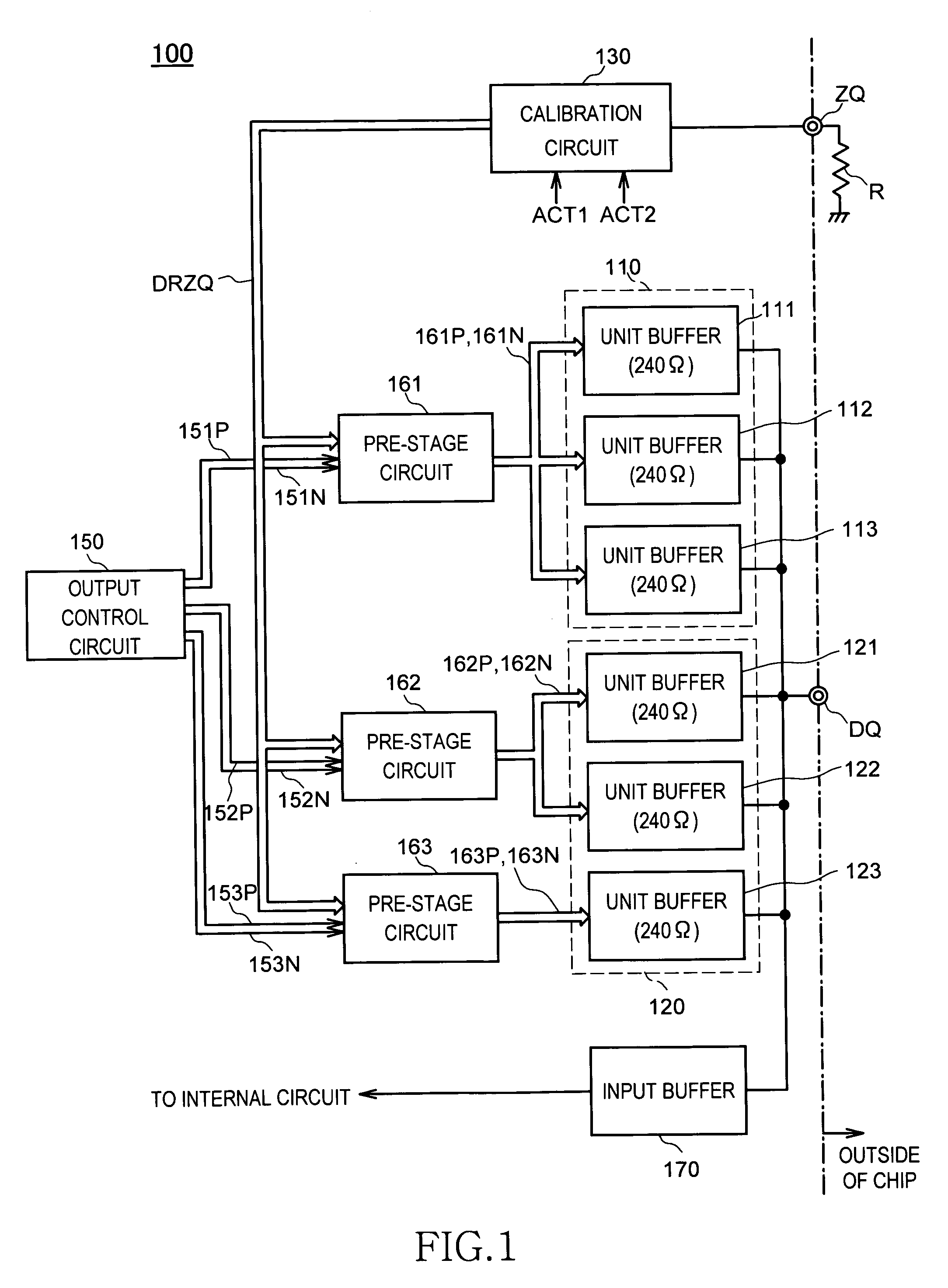

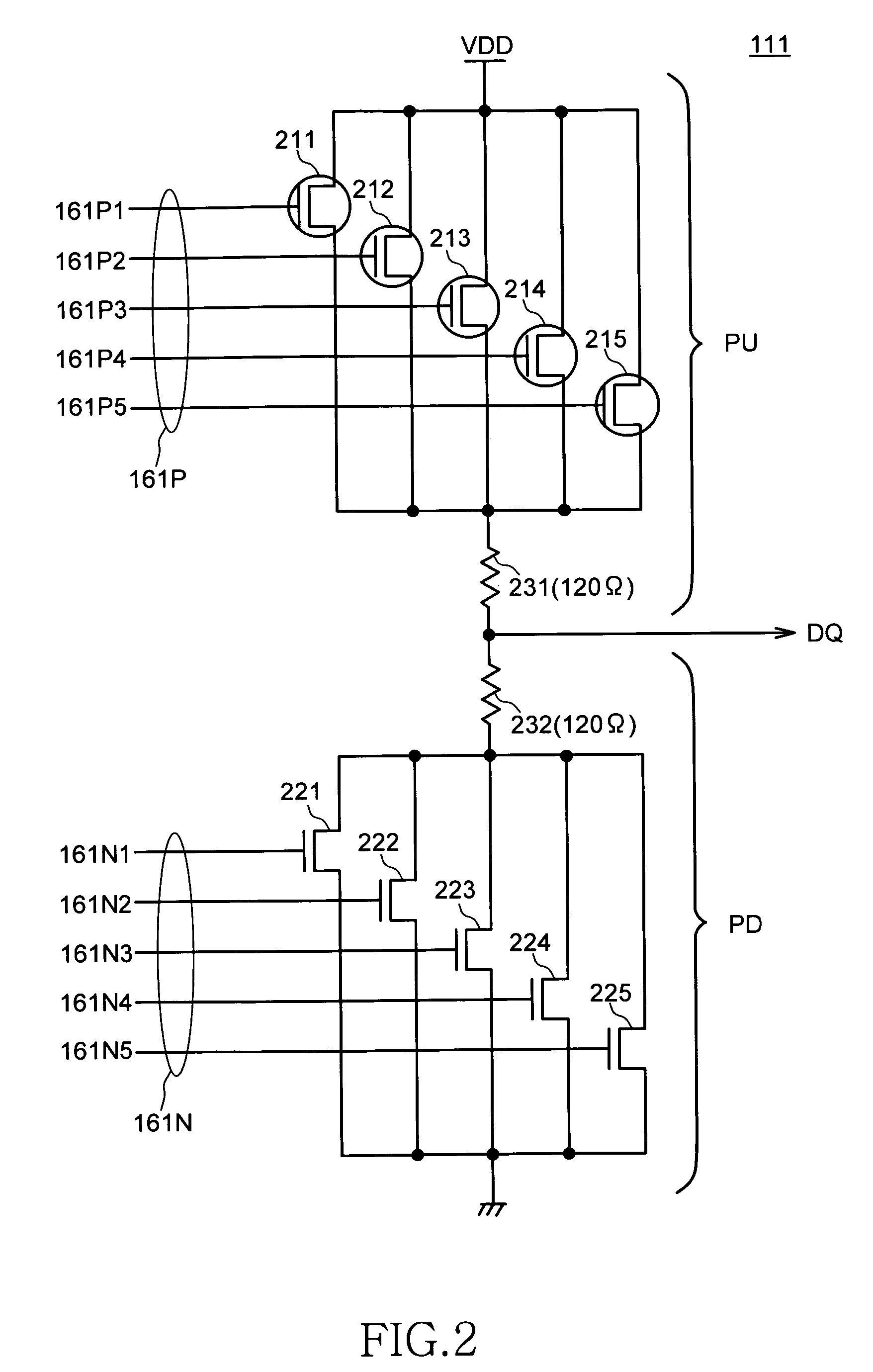

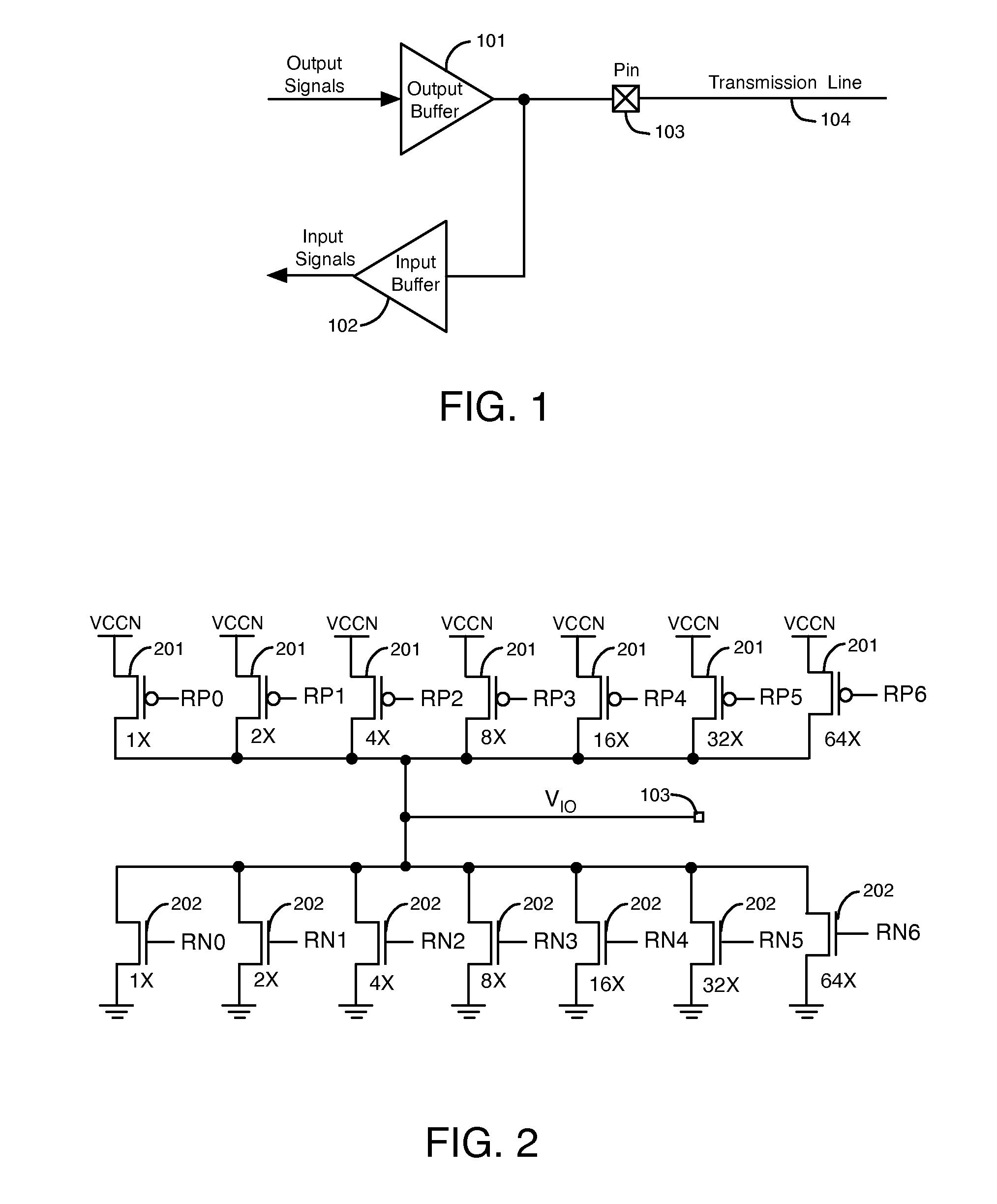

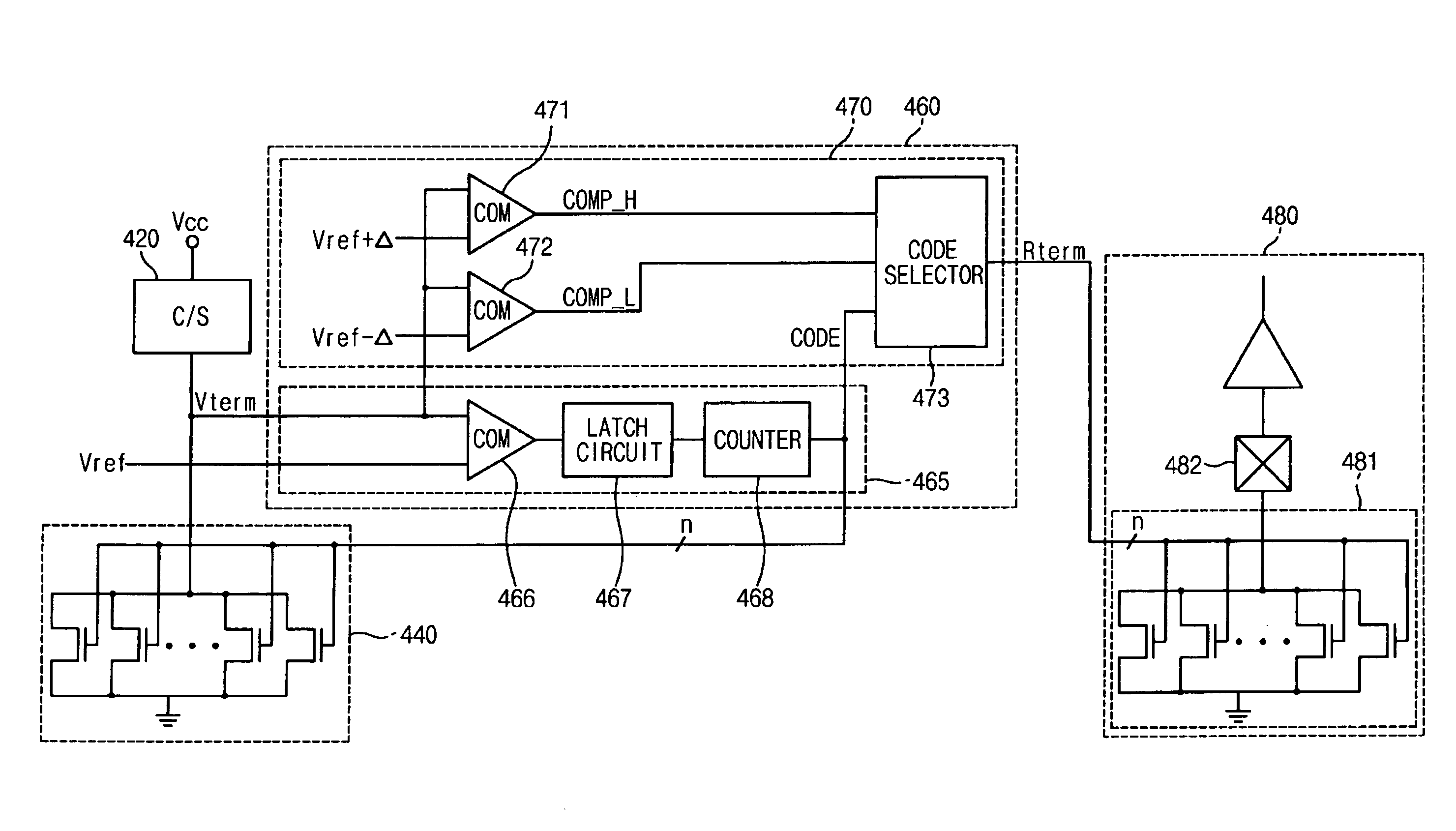

Output circuit for semiconductor device, semiconductor device having output circuit, and method of adjusting characteristics of output circuit

ActiveUS20060158198A1Reduce calibration timeReduce circuit sizeInput/output impedence modificationImpedence matching networksEngineeringSemiconductor

Owner:LONGITUDE LICENSING LTD

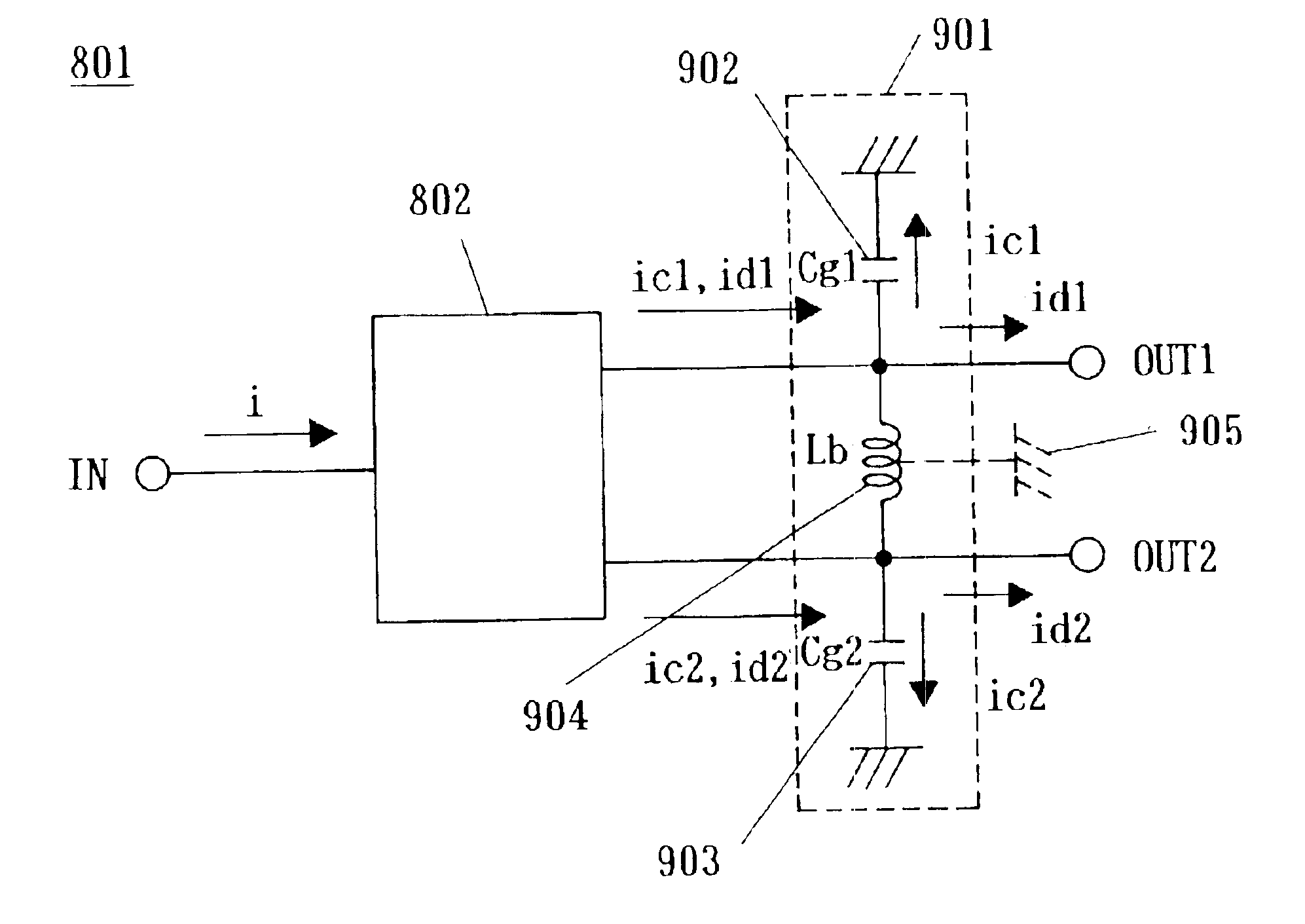

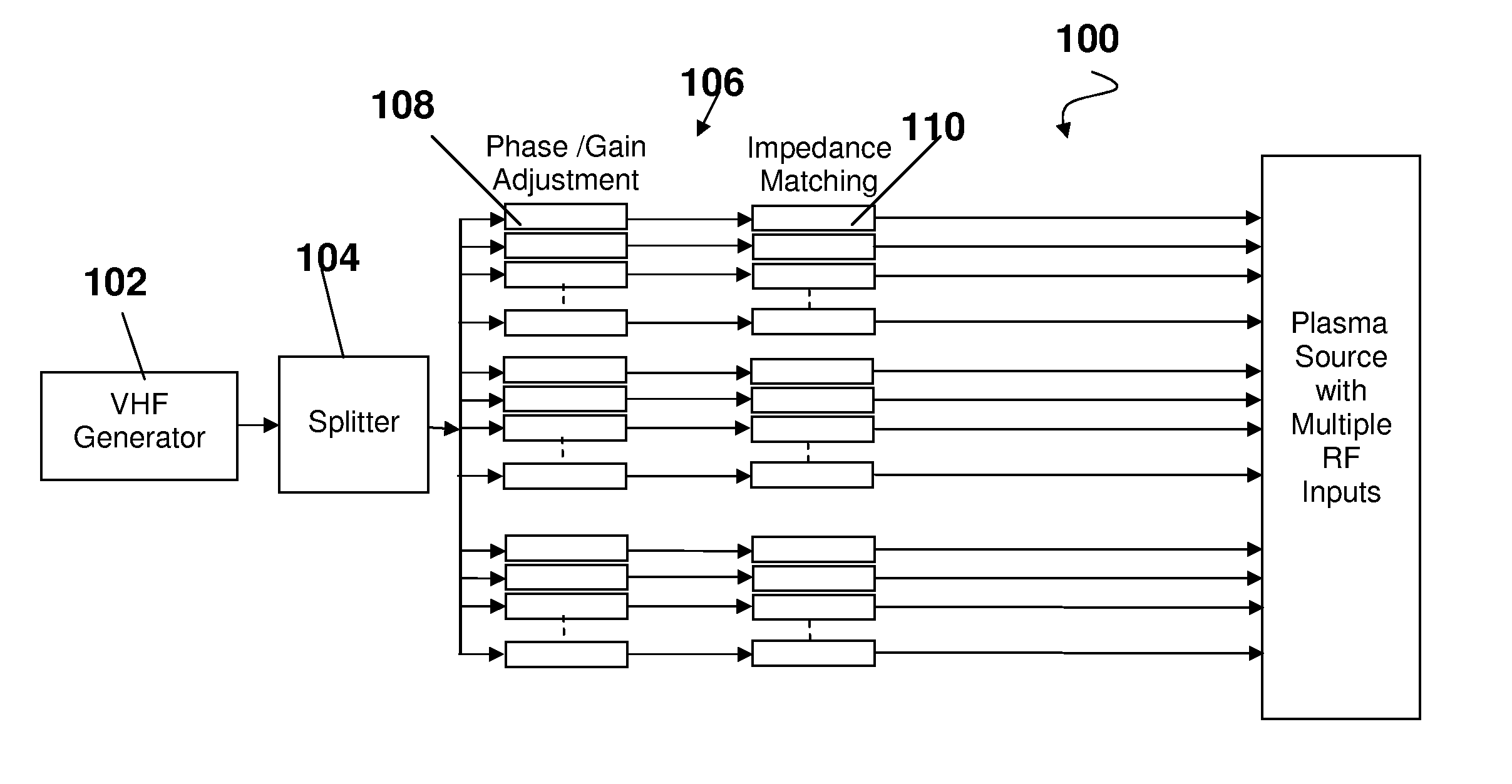

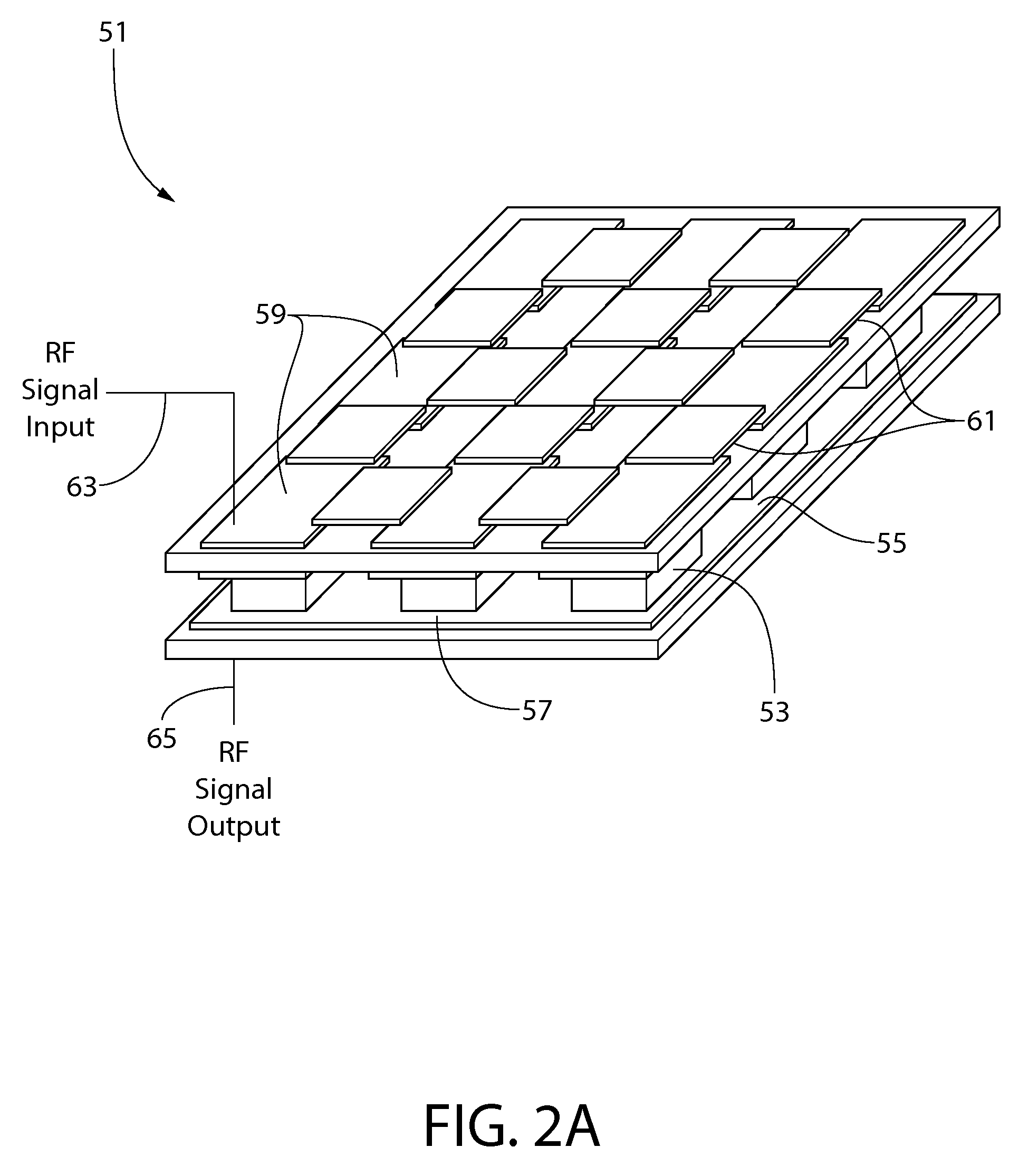

System for providing a substantially uniform potential profile

InactiveUS20100123502A1Uniform potential distributionImpedence matching networksMultiple-port networksEngineeringSignal generator

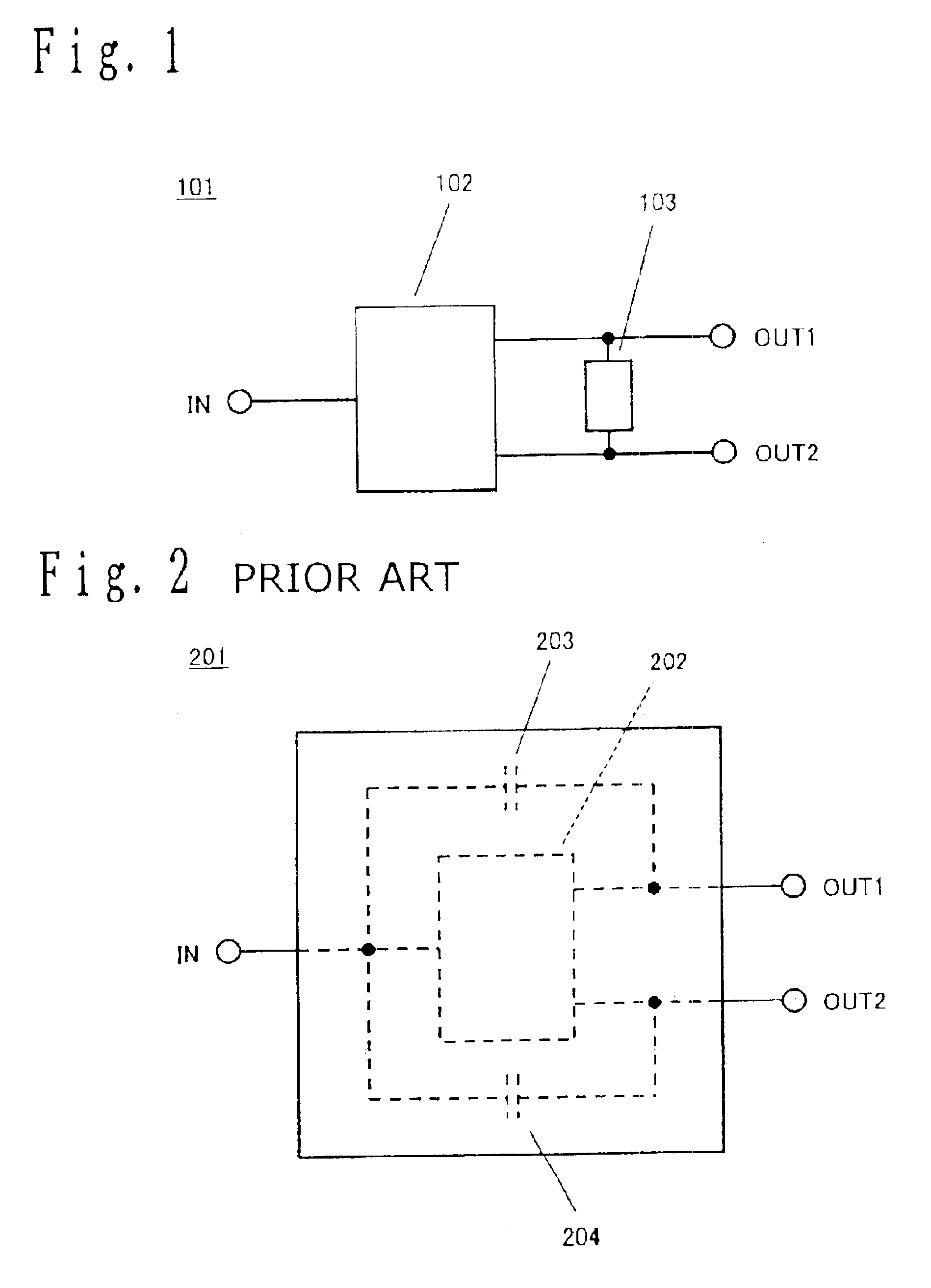

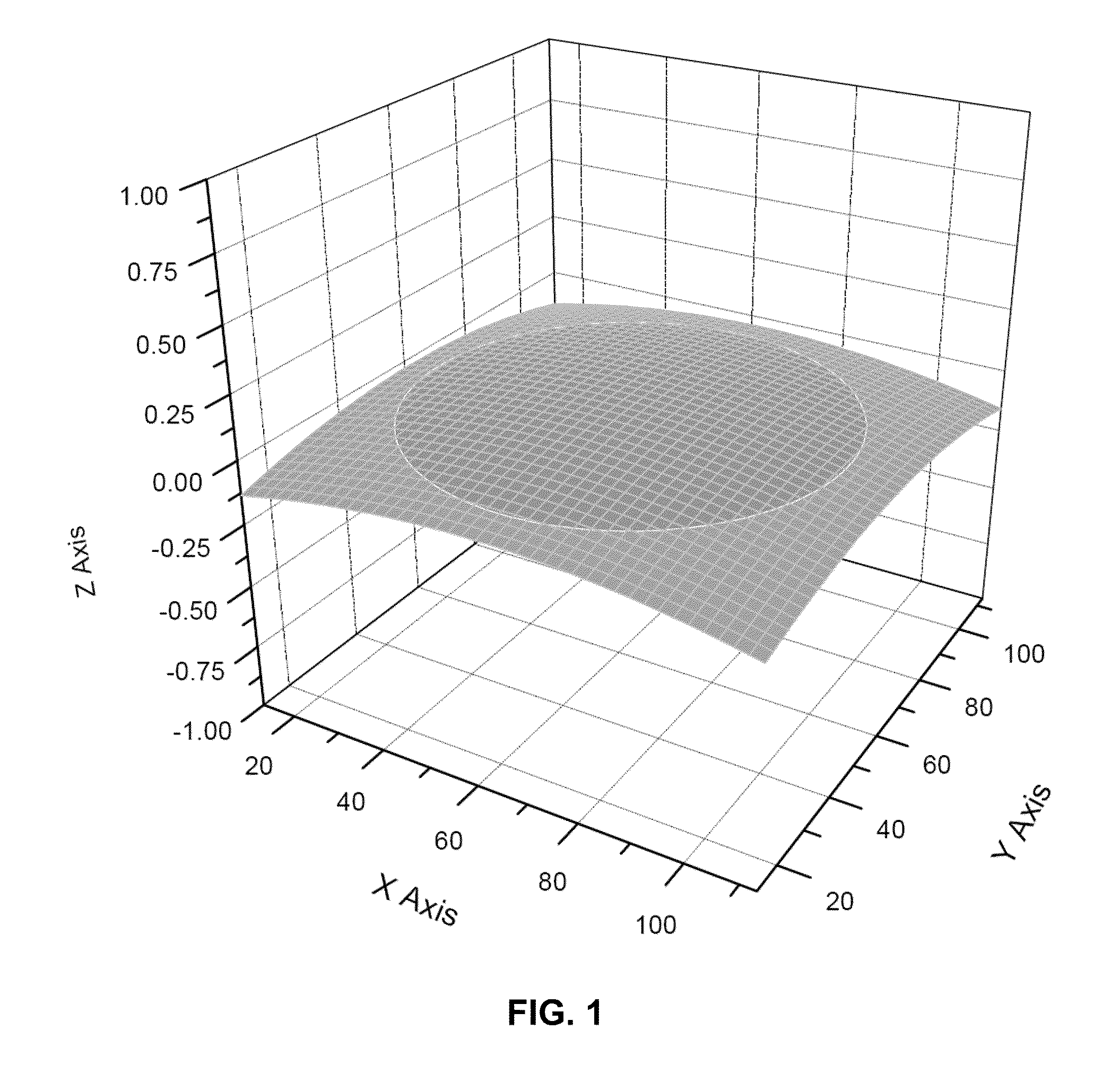

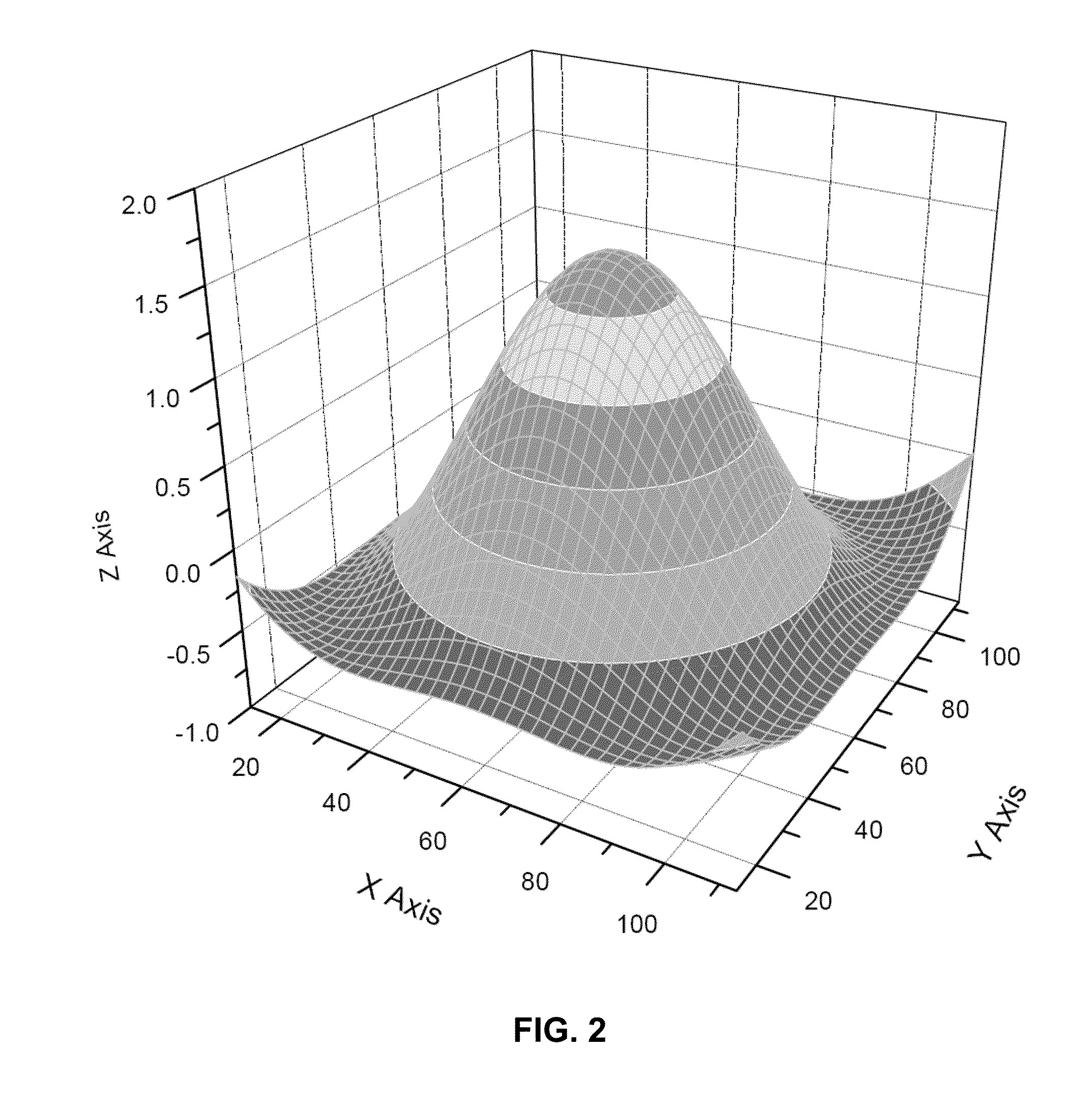

A system for providing at least two output signals to produce a substantially uniform potential profile includes a signal generator adapted to emit a frequency at least about 30 megahertz, a splitter in communication with the signal generator, and a signal manipulator in communication with the splitter. The splitter is adapted to split the signal of the signal generator into the two output signals, and the signal manipulator is adapted to manipulate a phase, a gain, or an impedance of the two output signals. The signal manipulator manipulates the two output signals so that the two output signals produce the substantially uniform potential profile.

Owner:RENO SUB-SYST INC

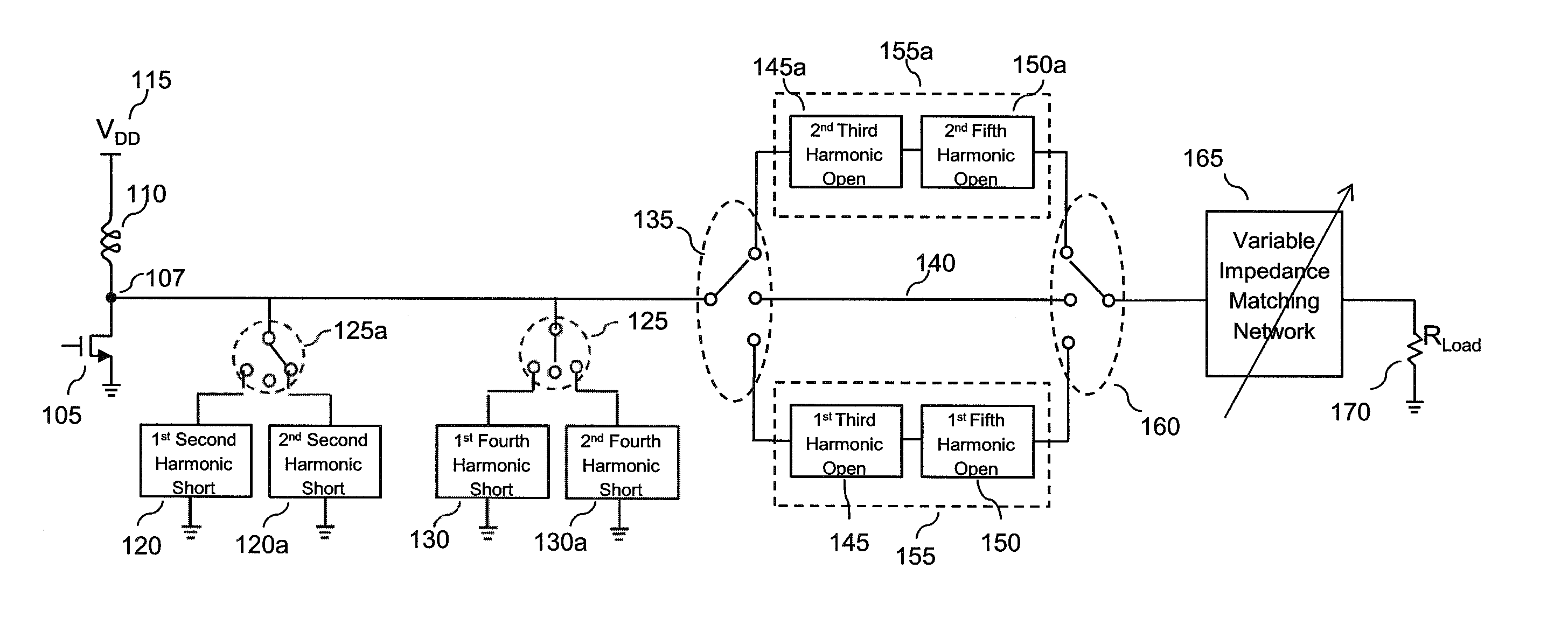

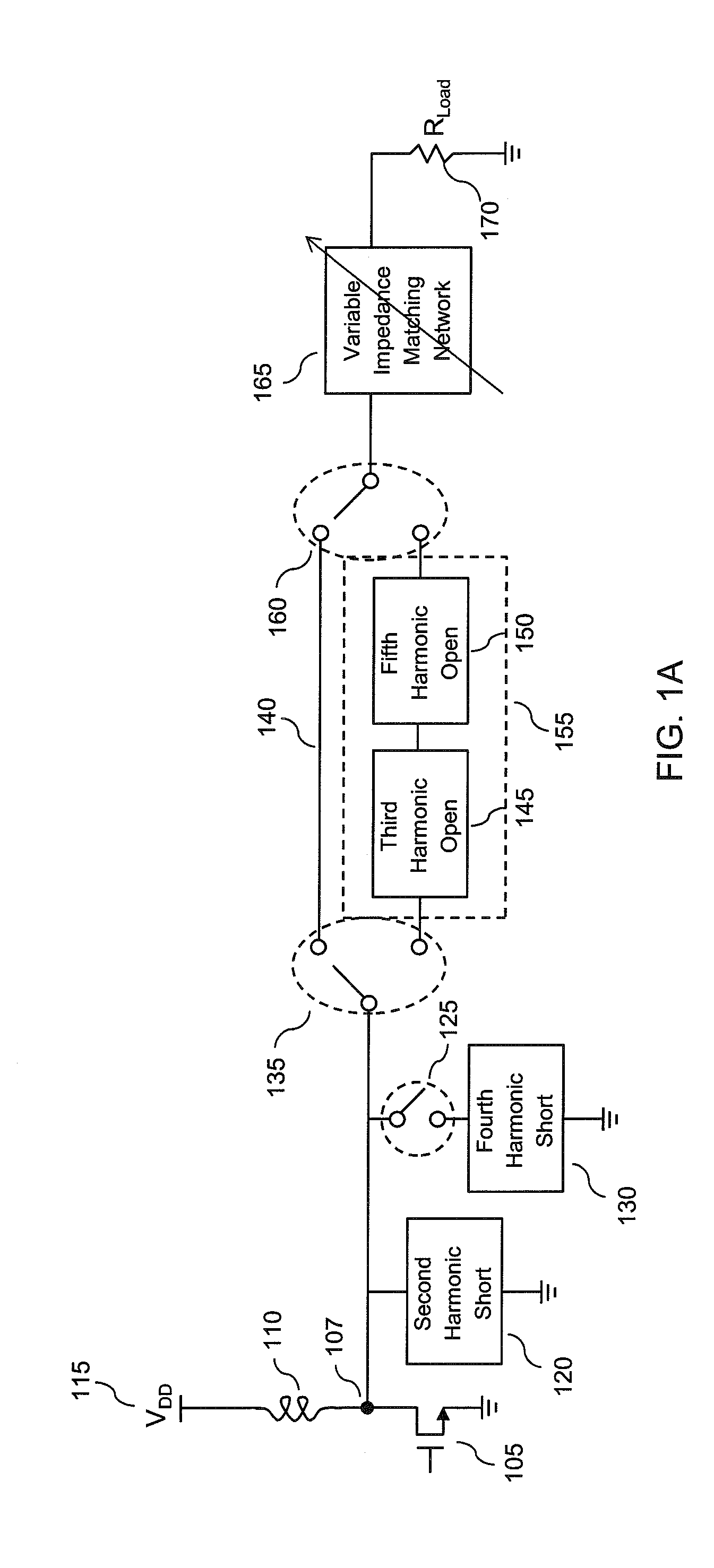

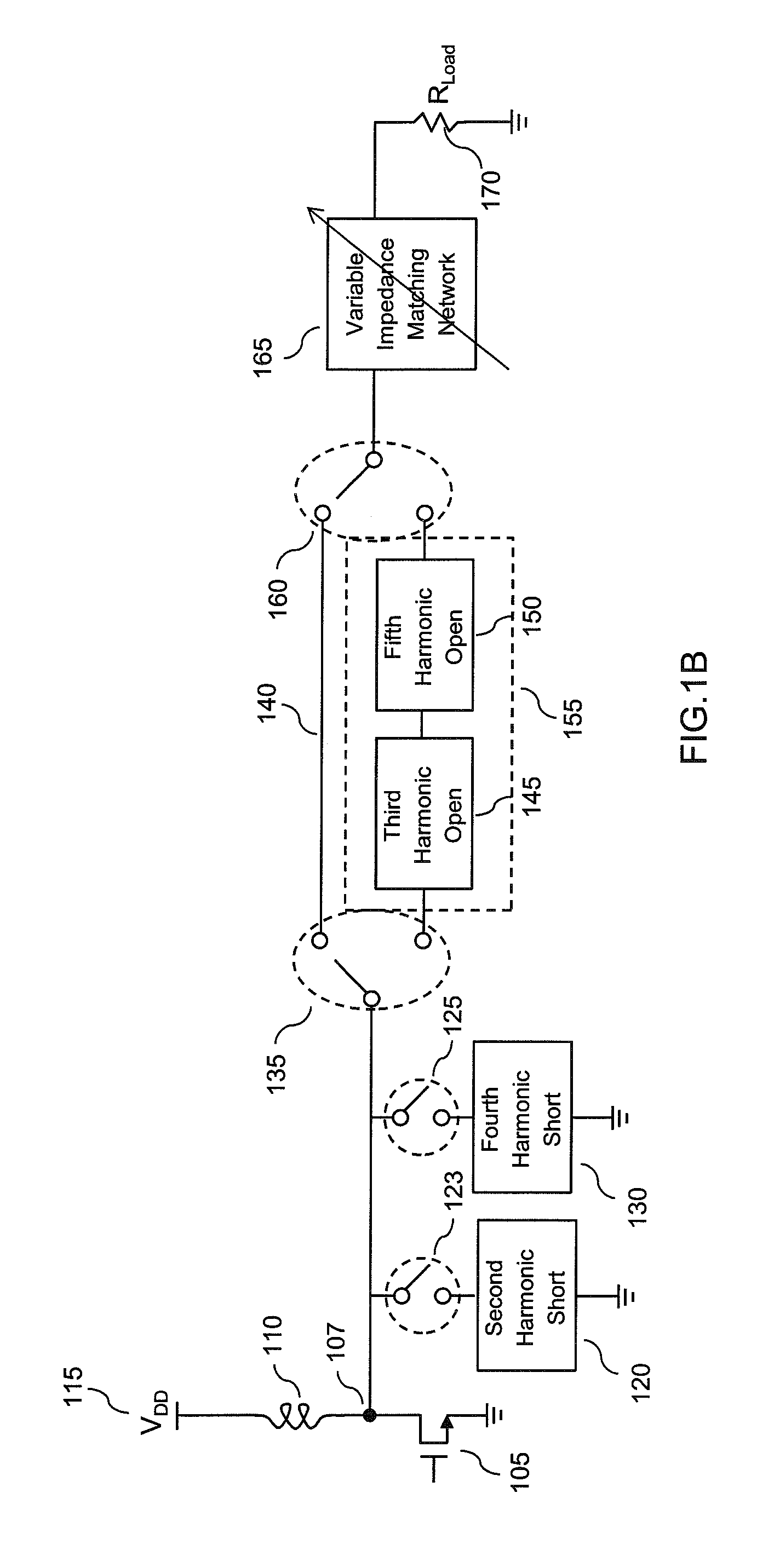

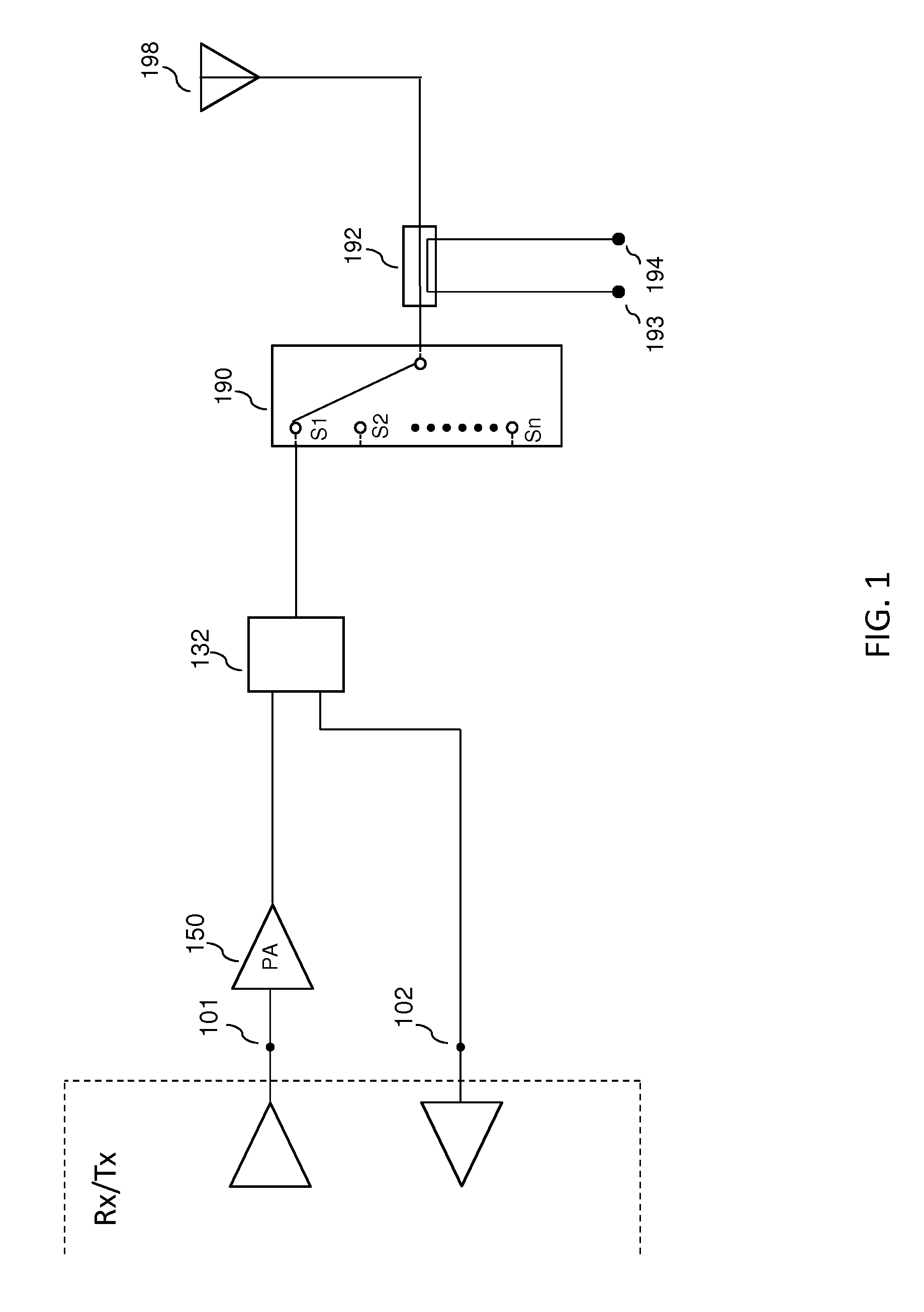

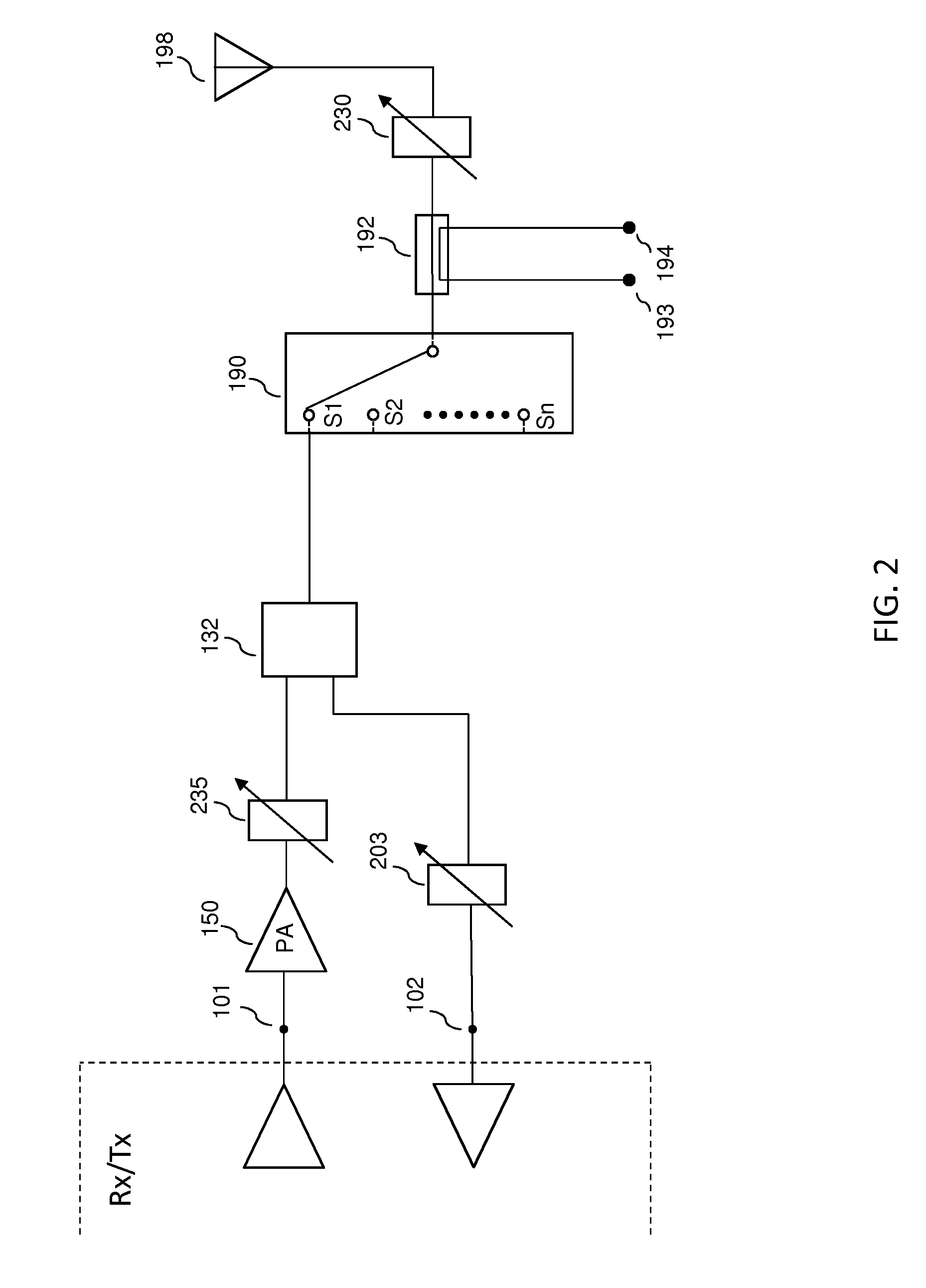

Variable impedance match and variable harmonic terminations for different modes and frequency bands

ActiveUS20140266455A1Multiple-port networksImpedence matching networksAudio power amplifierSoftware engineering

An amplifier with switchable and tunable harmonic terminations and a variable impedance matching network is presented. The amplifier can adapt to different modes and different frequency bands of operation by appropriate switching and / or tuning of the harmonic terminations and / or the variable impedance matching network.

Owner:PSEMI CORP

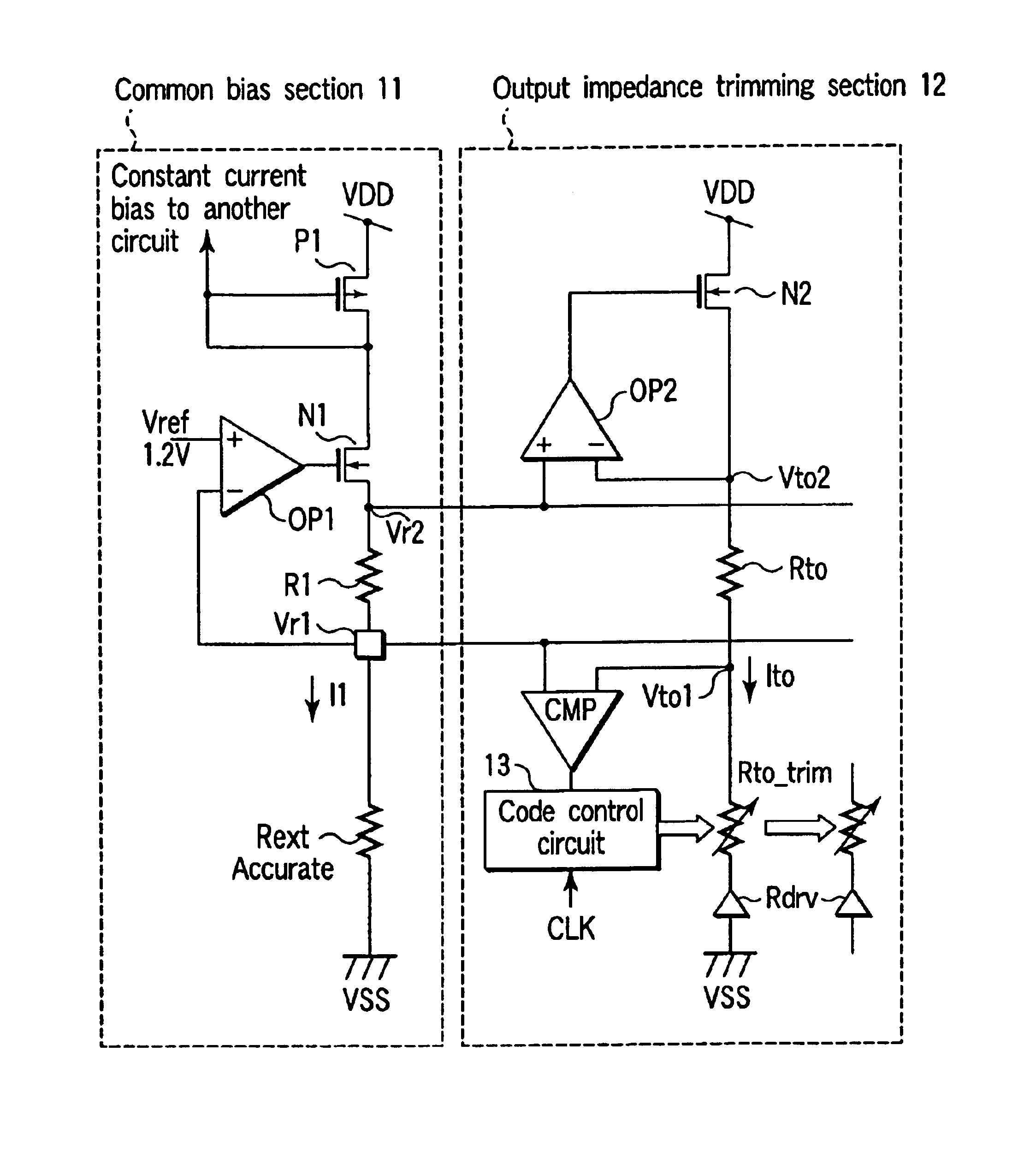

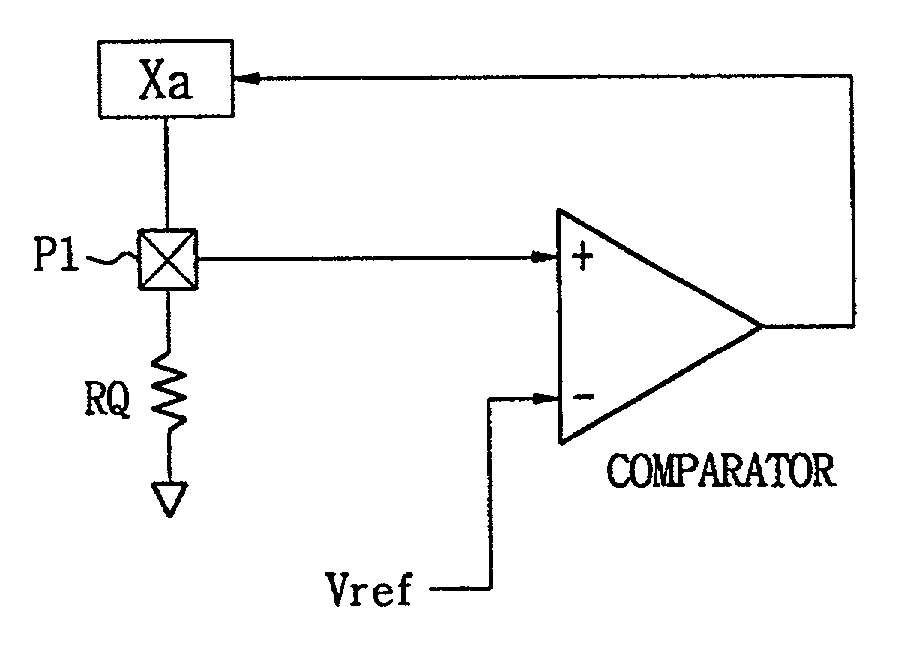

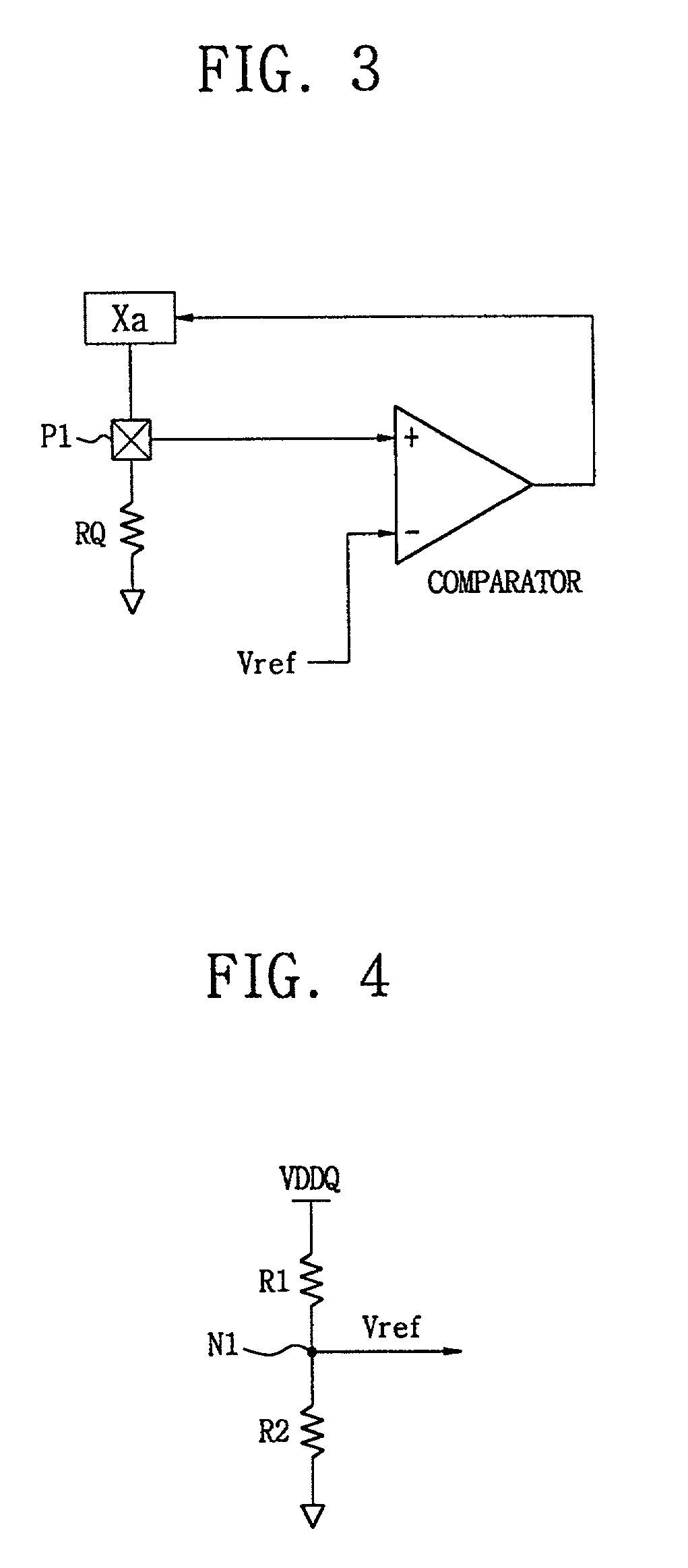

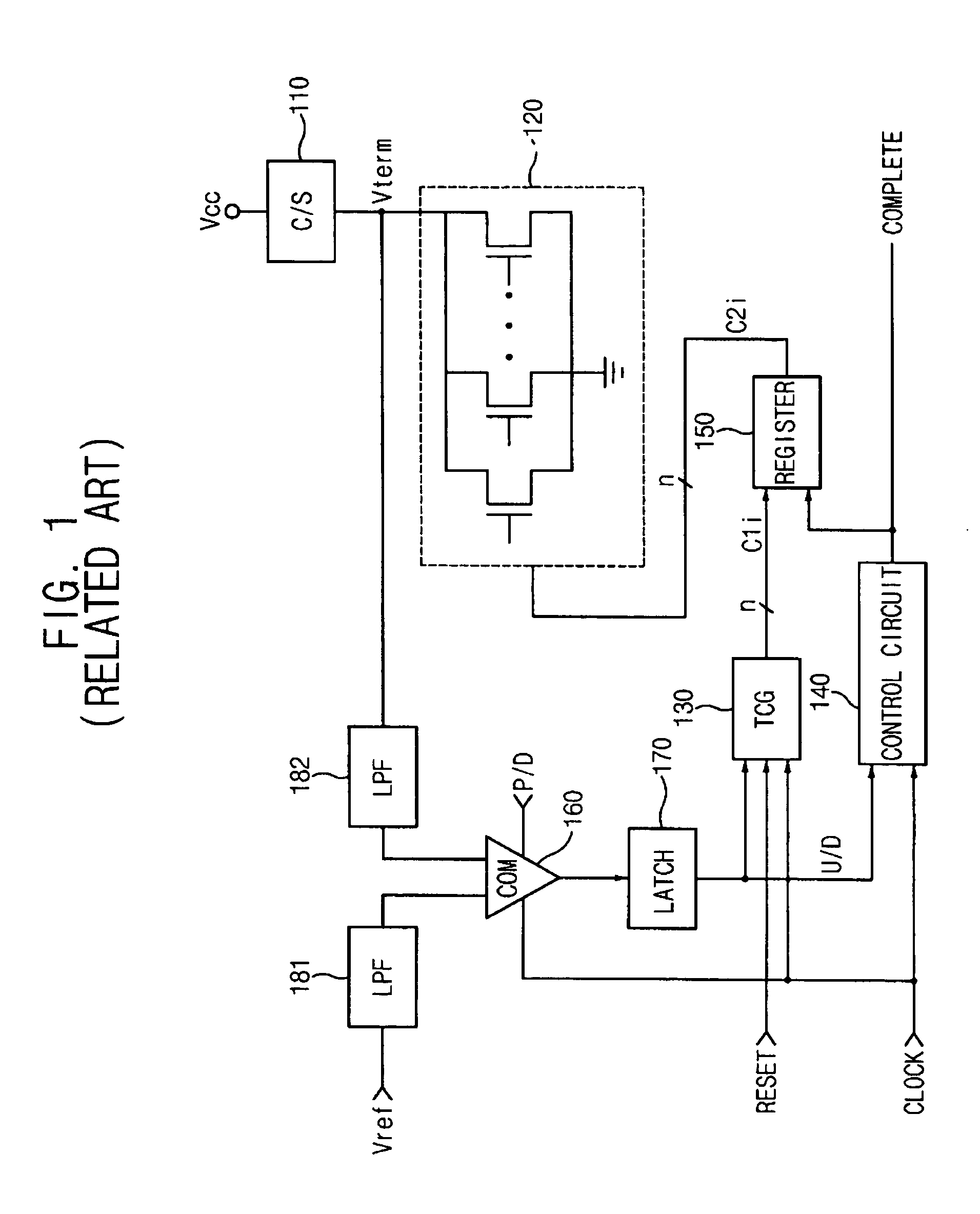

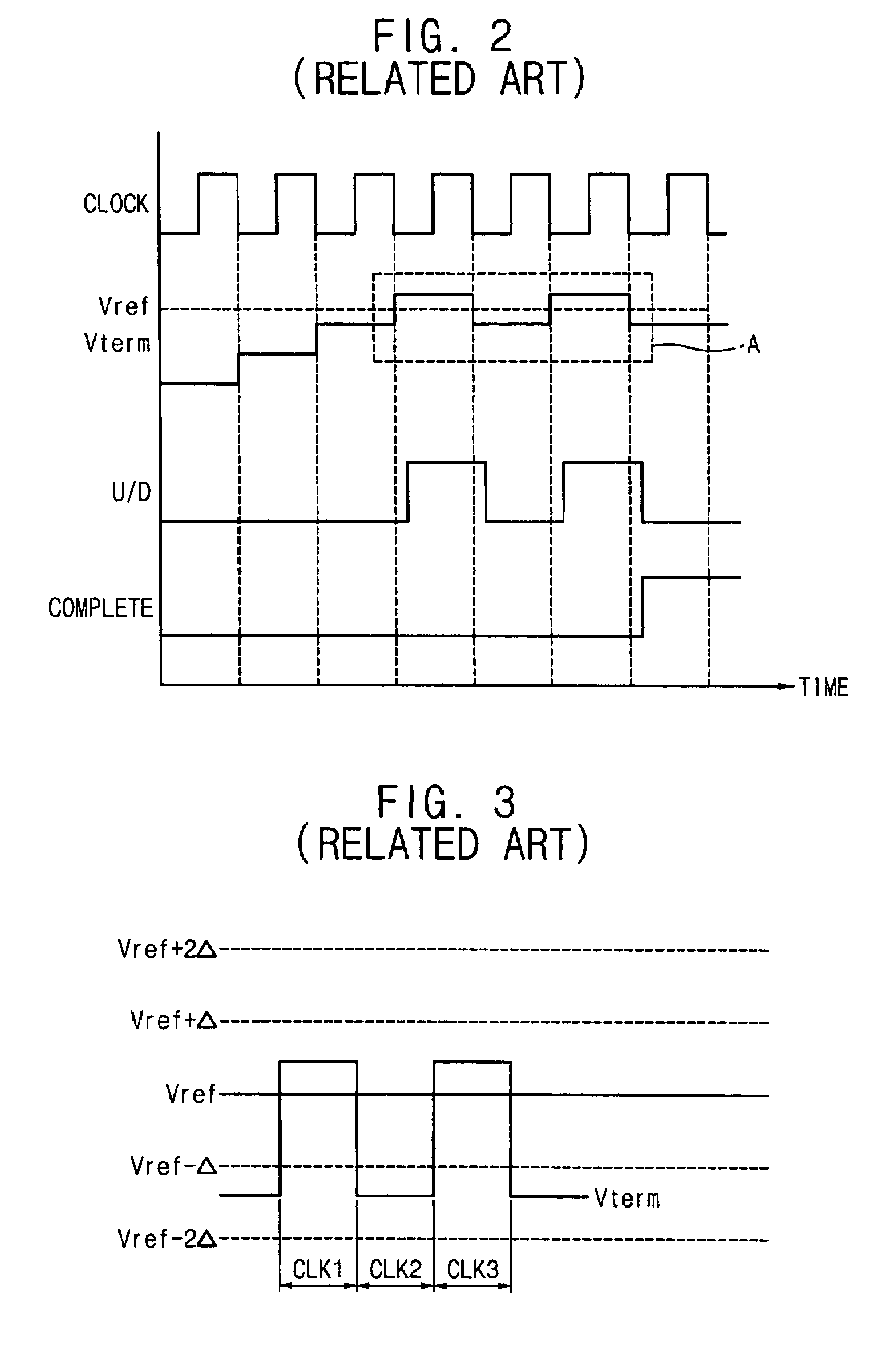

Impedance trimming circuit

InactiveUS6836170B2Reliability increasing modificationsImpedence matching networksExternal resistanceVoltage reference

A common bias section is composed of a first series circuit having an internal resistor and an external resistor connected in series and an operational amplifier having a first input terminal connected to a reference voltage, a second input terminal connected to a Vr1 node, and an output terminal connected to the series circuit. An impedance trimming section is composed of a series circuit having an internal resistor and an impedance dummy resistor connected in series, a comparator CMP having a first input terminal connected to the Vr1 node and a second input terminal connected to a Vto1 node, a code control circuit which uses a clock signal to latch an output signal from the comparator to generate a plurality of switching codes, and a switching circuit which switch a resistance value of the impedance dummy resistor.

Owner:KK TOSHIBA

Programmable impedance control circuit

InactiveUS20020063576A1Multiple-port networksReliability increasing modificationsVoltage generatorElectrical resistance and conductance

Disclosed is a programmable impedance control circuit, comprising a voltage divider, the voltage divider comprising an MOS array supplied with a first voltage and an external resistance having an external impedance equal to N times said external resistance. The voltage divider outputs a second voltage. A reference voltage generator is provided for generating a third voltage corresponding to N / (N+M) times said first voltage as a reference voltage for said second voltage, and wherein M times internal impedance is used for N times external impedance (N=M or N<> M).

Owner:SAMSUNG ELECTRONICS CO LTD

Output circuit for semiconductor device, semiconductor device having output circuit, and method of adjusting characteristics of output circuit

ActiveUS7215128B2Reduce calibration timeReduce circuit sizeInput/output impedence modificationImpedence matching networksEngineeringSemiconductor

Owner:LONGITUDE LICENSING LTD

High frequency solid state switching for impedance matching

ActiveUS20130207738A1Total current dropReduce partImpedence matching networksMultiple-port networksImpedance matchingPower MOSFET

In accordance with this invention the above and other problems are solved by a switching apparatus and method that uses a switching circuit having a pair of parallel solid-state diodes (e.g., PN or PIN diodes), one of which is connected to a transistor (e.g., power MOSFET or IGBT), to switch a capacitor (or reactance element) in or out of a variable capacitance element (or variable reactance element) of an impedance matching network. Charging a body capacitance of the transistor reverse biases one of the two diodes so as to isolate the transistor from the RF signal enabling a low-cost high capacitance transistor to be used. Multiple such switching circuits and capacitors (or reactance elements) are connected in parallel to provide variable impedance for the purpose of impedance matching.

Owner:AES GLOBAL HLDG PTE LTD

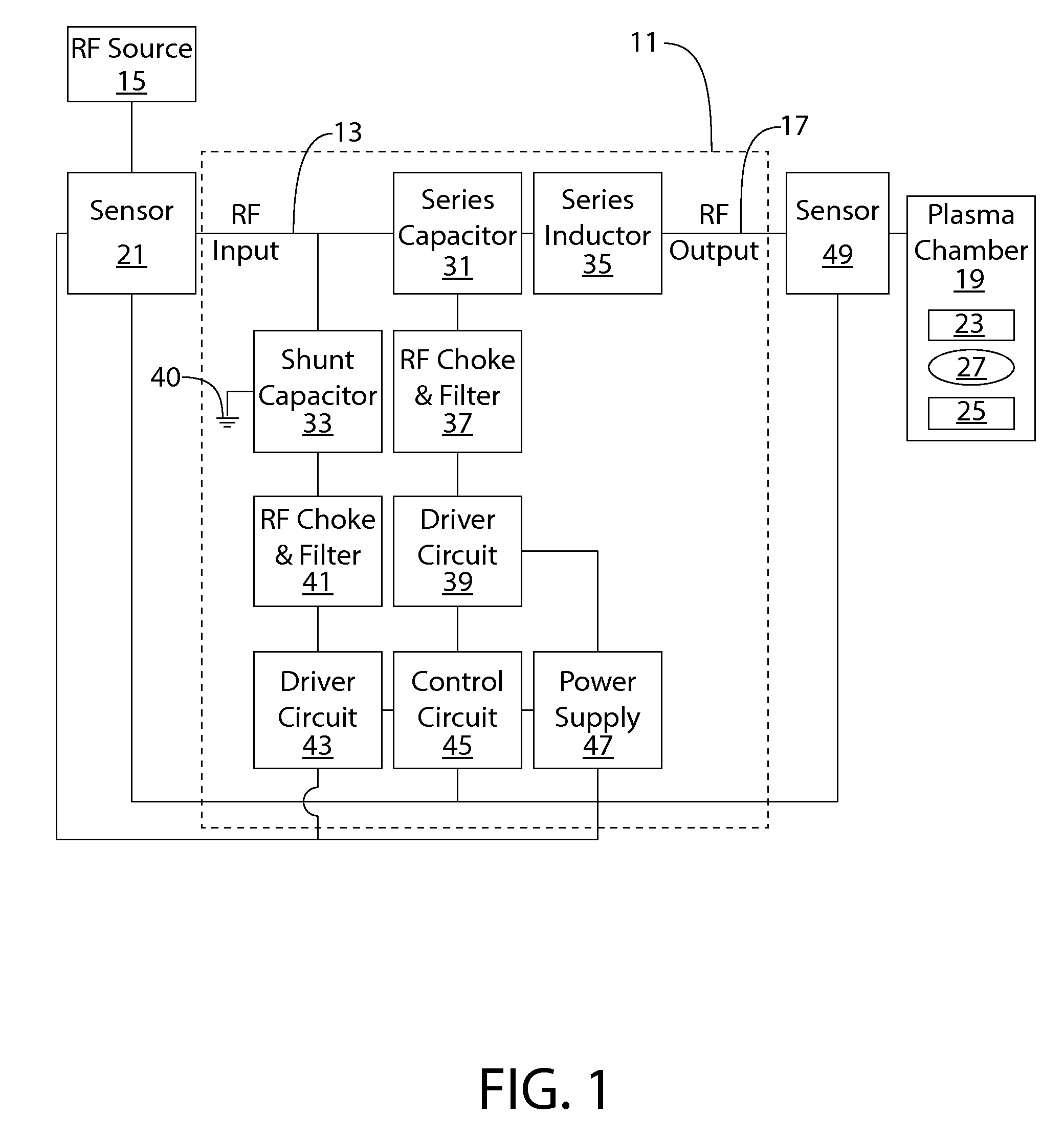

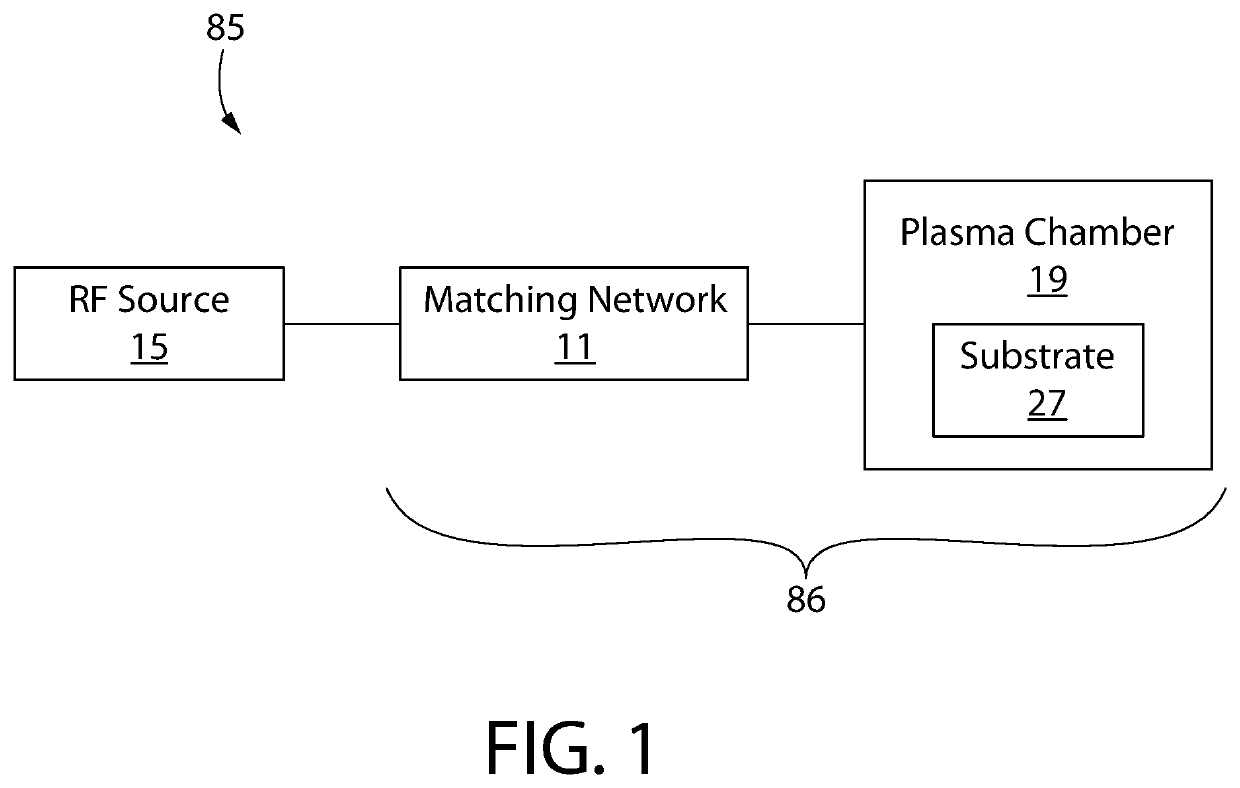

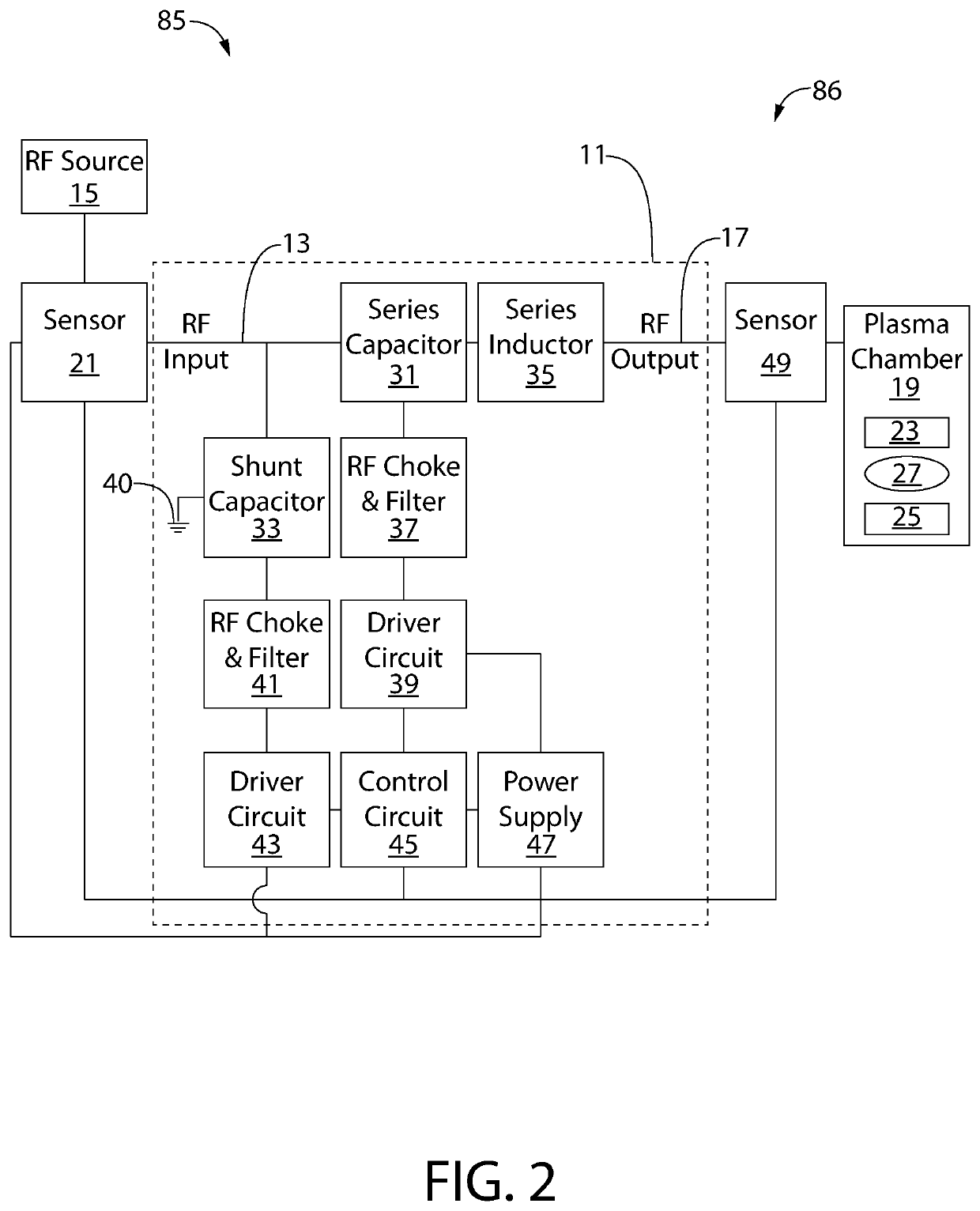

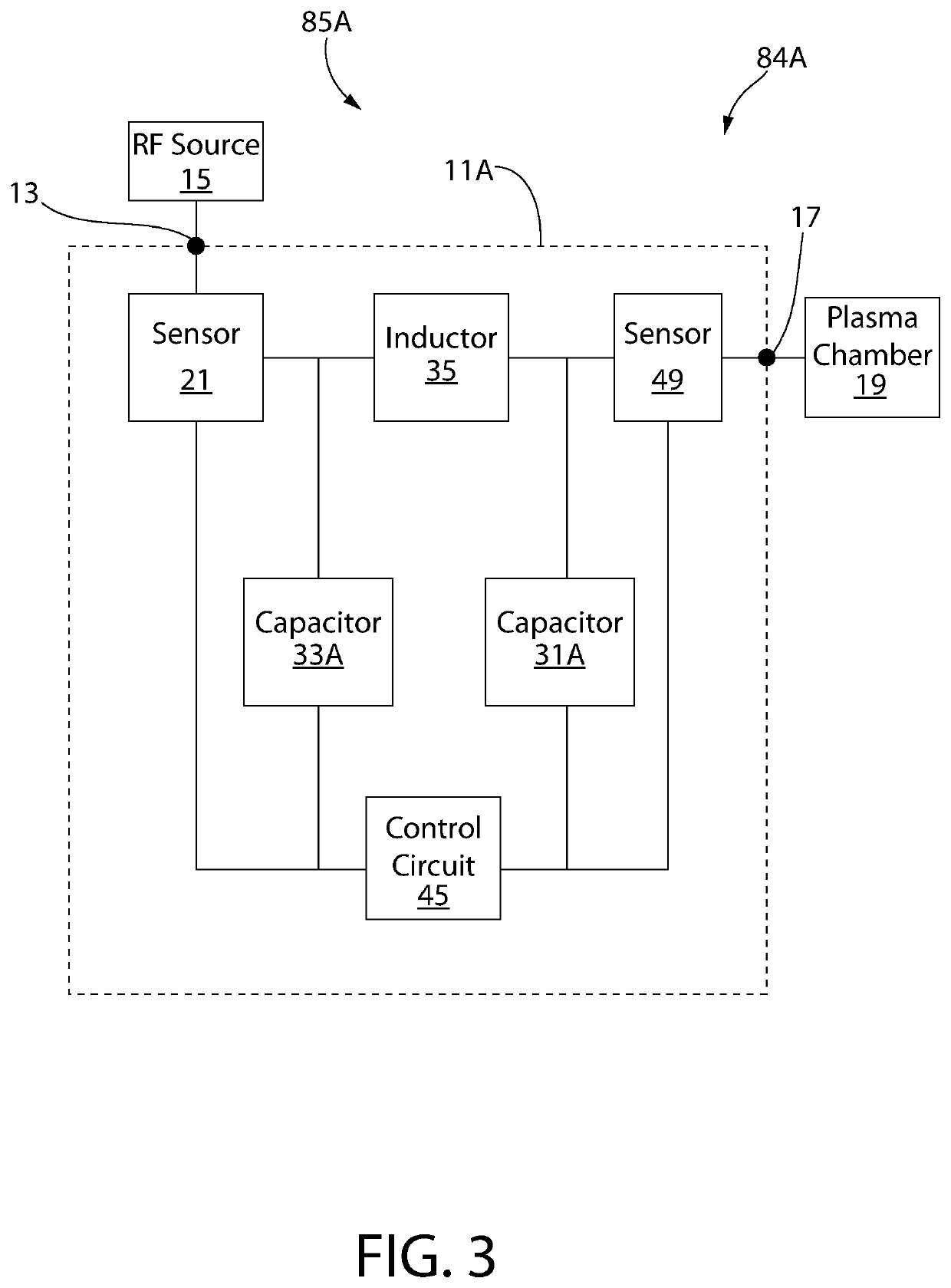

RF impedance matching network

ActiveUS9196459B2Shorten the timeImpedence matching networksMultiple-port networksPlasma impedanceControl signal

An RF impedance matching network includes an RF input; an RF output configured to operably couple to a plasma chamber; a series electronically variable capacitor (“series EVC”), the series EVC electrically coupled in series between the RF input and the RF output; and a shunt electronically variable capacitor (“shunt EVC”), the shunt EVC electrically coupled in parallel between a ground and one of the RF input and the RF output; a control circuit to control the series variable capacitance and the shunt variable capacitance, wherein the control circuit is configured to determine the variable plasma impedance of the plasma chamber, determine a series capacitance value and a shunt capacitance value, and generate a control signal to alter at least one of the series variable capacitance and the shunt variable capacitance; wherein the alteration is caused by at least one of a plurality of switching circuits.

Owner:ASM AMERICA INC

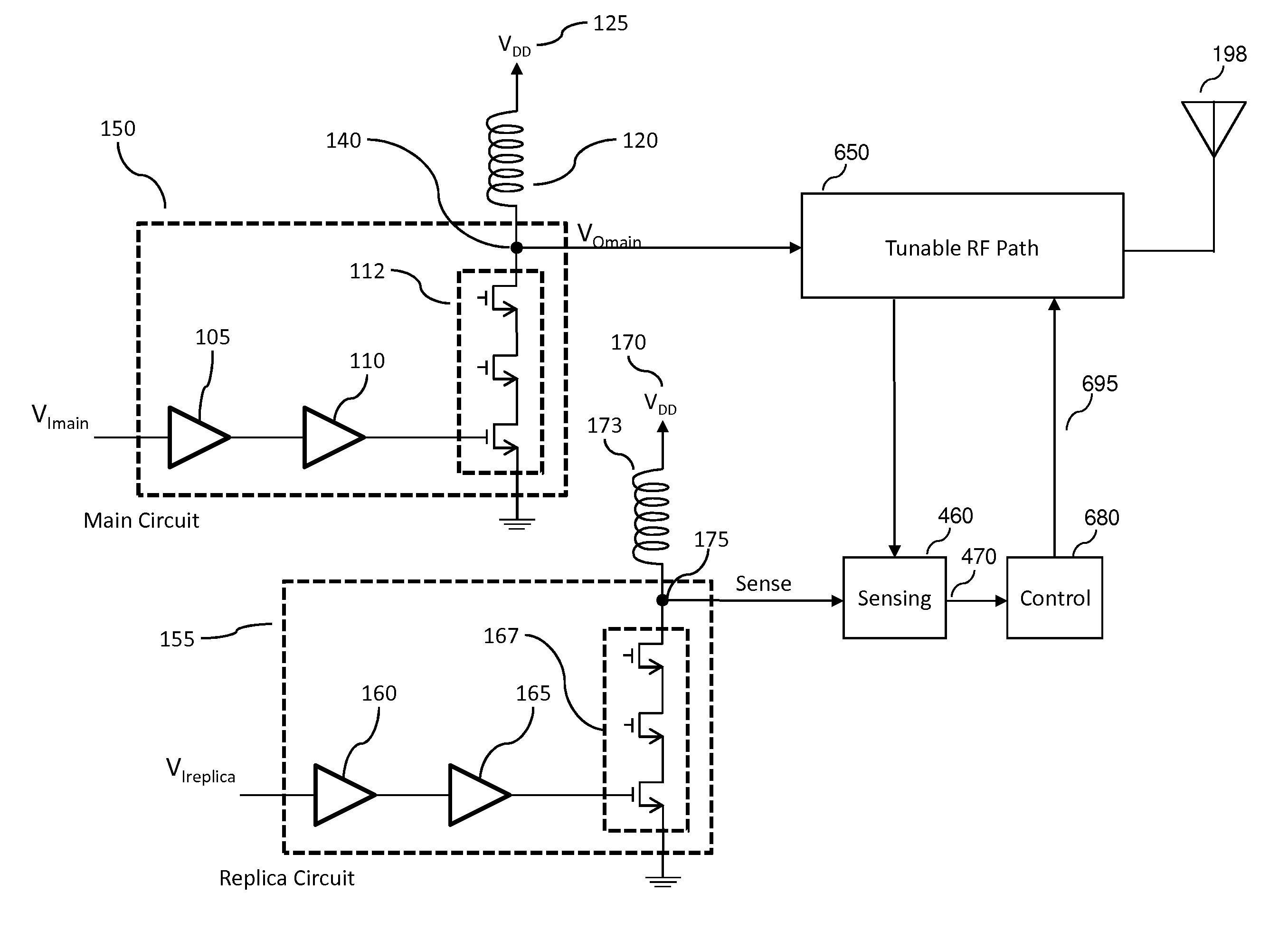

Mismatch detection using replica circuit

An apparatus for detecting an operating characteristic mismatch at an output of an amplifier by using a replica circuit is presented. In one exemplary case, a detected voltage difference at the output of the two circuits is used to drive a tuning control loop to minimize an impedance mismatch at the output of the amplifier. In another exemplary case, the replica circuit is used to detect a fault in operation in a corresponding main circuit. A method for detecting a load mismatch in a main RF circuit using the replica circuit is also presented.

Owner:PSEMI CORP

Restricted capacitor switching

In one embodiment, the present disclosure is directed to a method for matching an impedance. The method can include determining or receiving a reflection parameter value at an RF input or output; stopping the altering of a first capacitance and a second capacitance when the reflection parameter value is at or below a first reflection value; causing a limited altering of the first capacitance and the second capacitance to pursue an impedance match when the reflection parameter value is at or above a second reflection value and at or below the third reflection value; and causing an unlimited altering of the first capacitance and the second capacitance to pursue an impedance match when the reflection parameter value is at or above a third reflection value.

Owner:ASM AMERICA INC

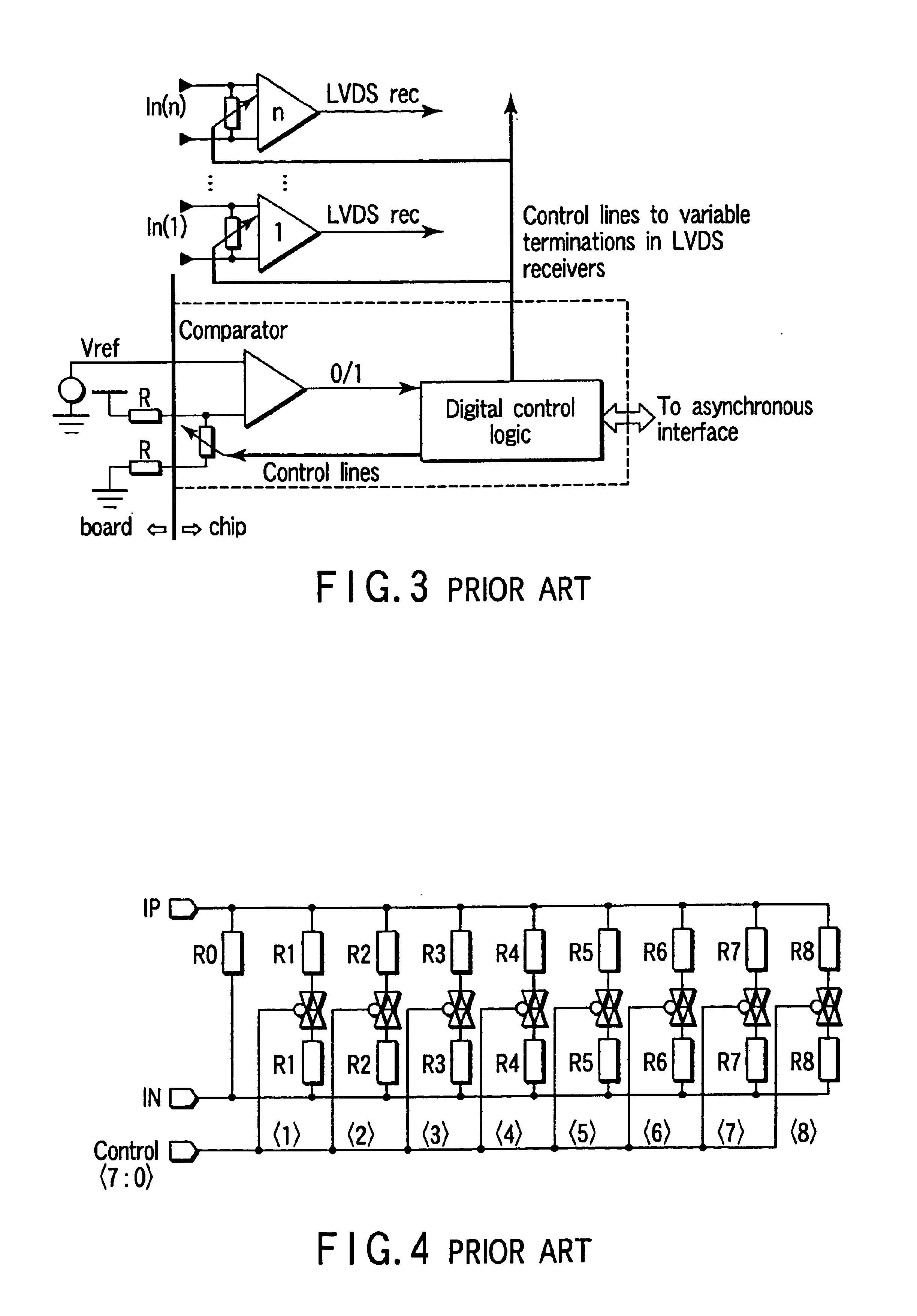

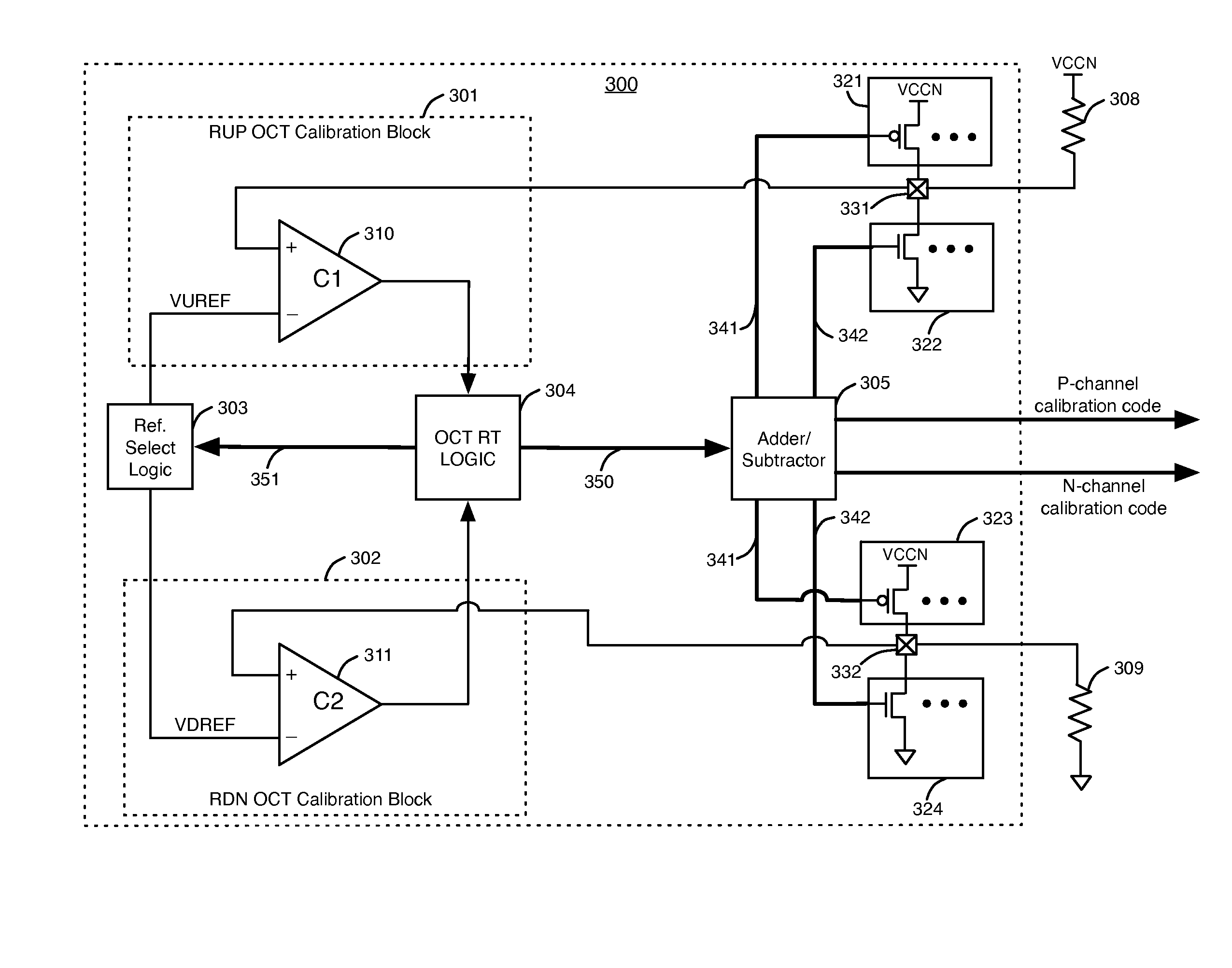

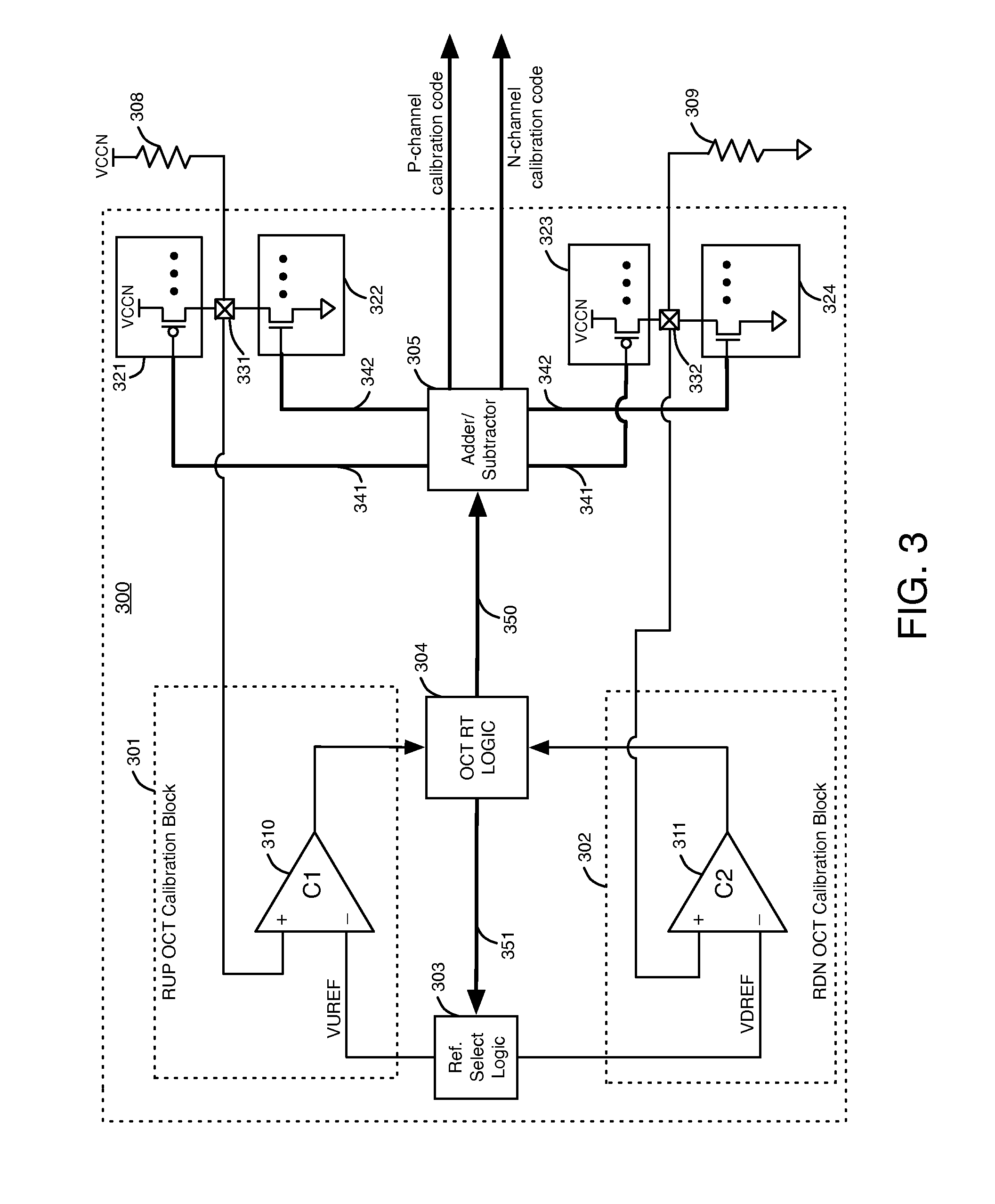

Techniques for providing calibrated parallel on-chip termination impedance

InactiveUS7443193B1Reliability increasing modificationsImpedence matching networksEngineeringElectrical impedance

Techniques are provided for calibrating parallel on-chip termination (OCT) impedance circuits. An on-chip termination (OCT) calibration circuit generates first calibration codes and second calibration codes. The first calibration codes control the conductive states of first transistors that are coupled in parallel between a supply voltage and a first terminal. The second calibration codes control the conductive states of second transistors that are coupled in parallel between the first terminal and ground. The OCT calibration circuit selects a first calibration code and a second calibration code and transmits the selected calibration codes to third and fourth transistors to control a parallel on-chip termination impedance at a pin.

Owner:ALTERA CORP

Adaptive impedance matching apparatus, system and method

ActiveUS20080106349A1Maximize RF voltageMaximize RF powerPower managementImpedence matching networksCapacitanceEngineering

An embodiment of the present invention provides an apparatus, comprising an RF matching network connected to at least one RF input port and at least one RF output port and including one or more voltage or current controlled variable reactive elements and wherein the RF matching network is adapted to maximize RF power transferred from the at least one RF input port to the at least one RF output port by varying the voltage or current to the voltage or current controlled variable reactive elements to maximize the RF voltage at the at least one RF output port. The variable reactive elements may be variable capacitances, variable inductances, or both.

Owner:NXP USA INC

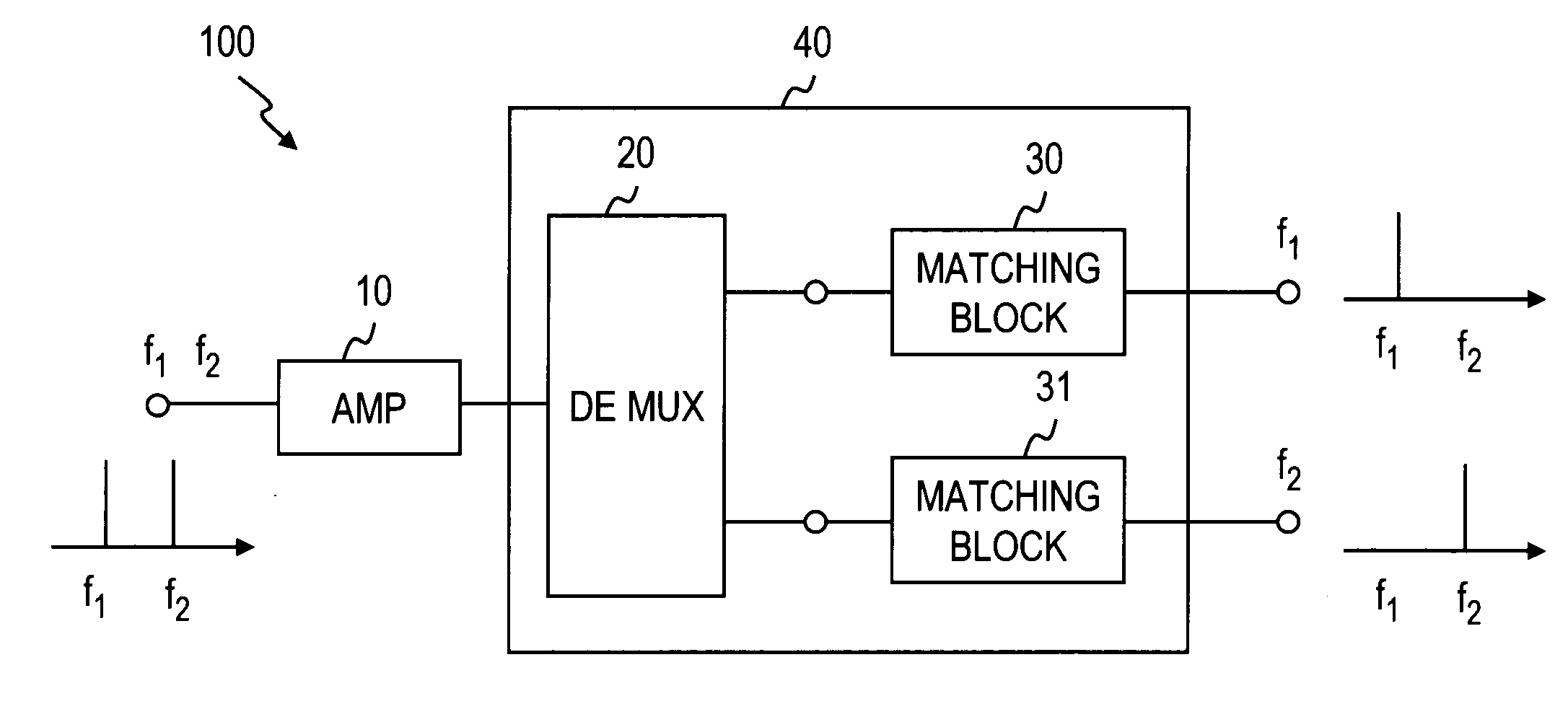

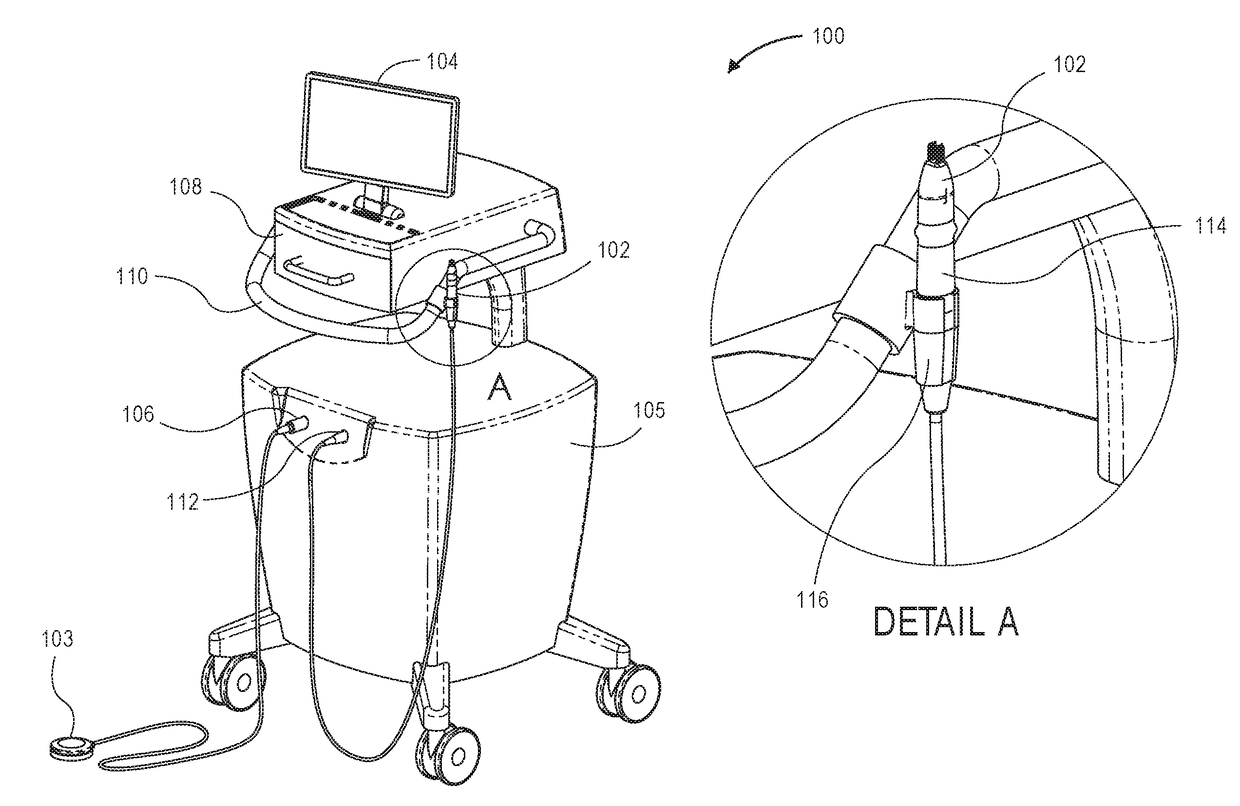

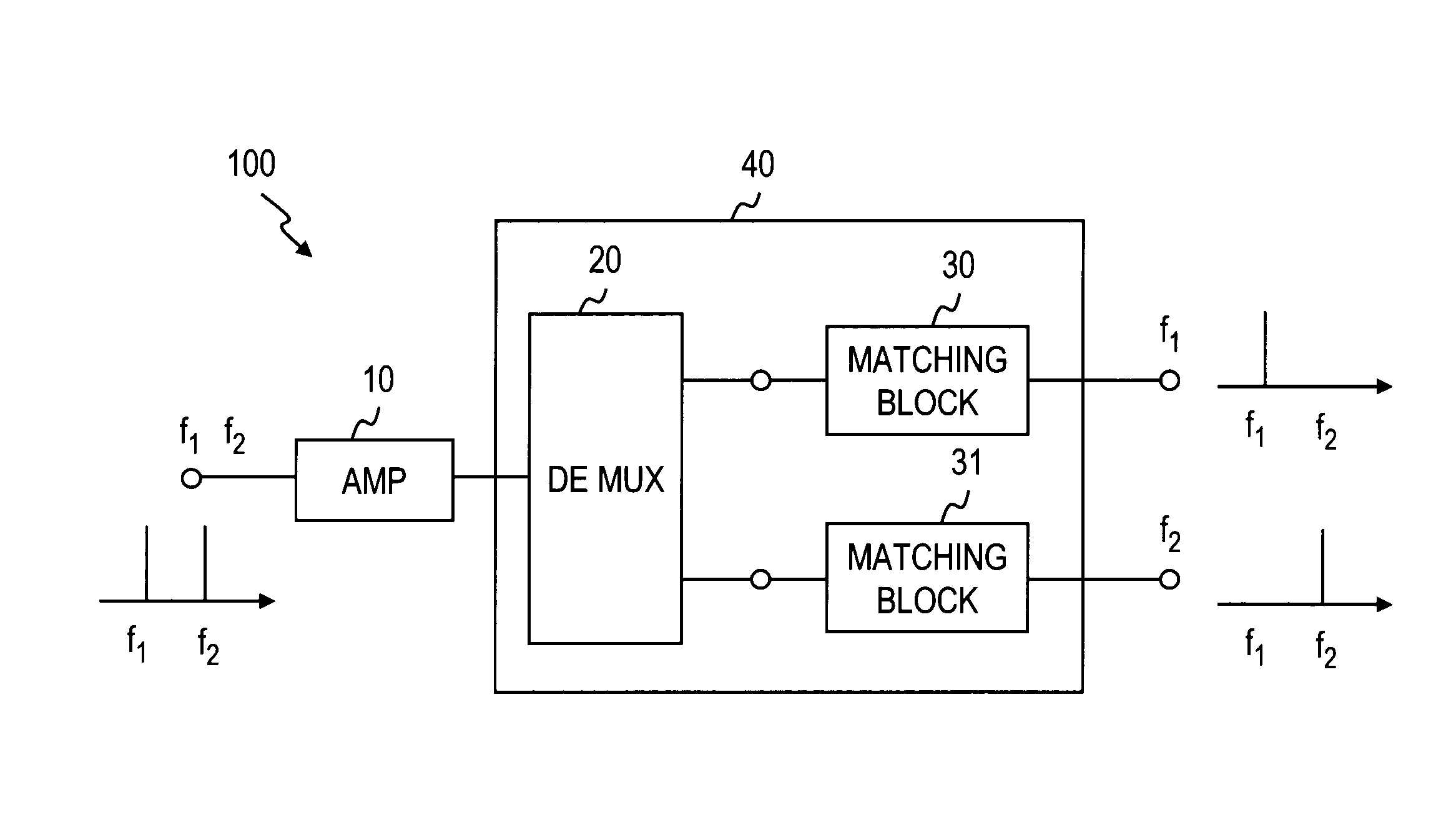

Matching circuit and multi-band amplifier

InactiveUS20080129410A1Easy to operateEnhanced signalMultiple-port networksImpedence matching networksFrequency bandMultiple frequency

A matching circuit includes a demultiplexer for demultiplexing a signal outputted from an amplification device into signals of respective frequency bands, and at least two matching blocks which are connected to the demultiplexer, are respectively fed with the signals of the respective frequency bands, and perform impedance matching in the respective frequency bands of the inputted signals. Impedance matching is performed on each of the demultiplexed signals of the respective frequency bands, thereby achieving a matching circuit capable of efficiently performing impedance matching in the respective frequency bands. With this matching circuit, it is possible to achieve a multi-band amplifier capable of simultaneously amplifying signals of multiple frequency bands with high efficiency and low noise.

Owner:NTT DOCOMO INC

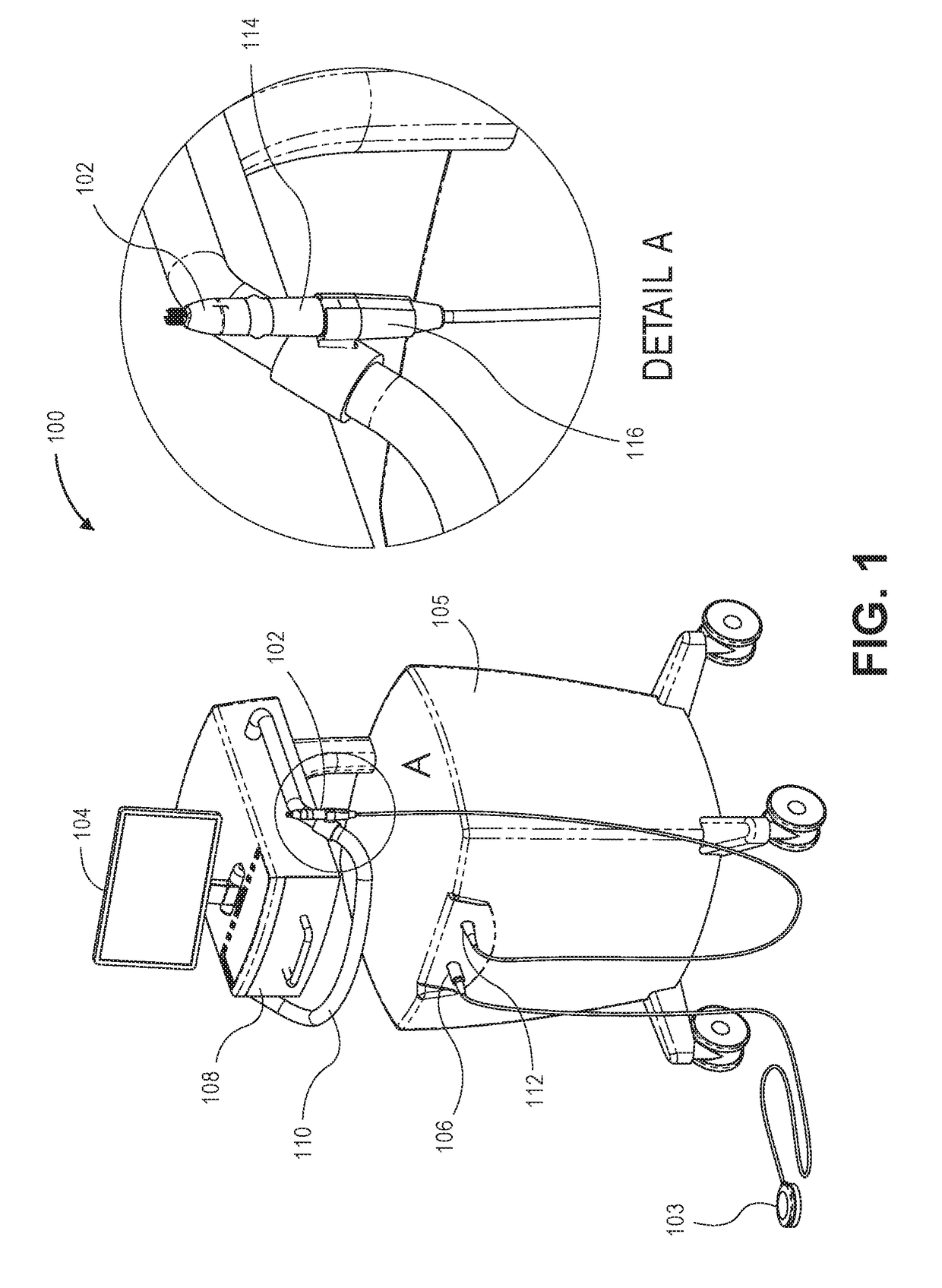

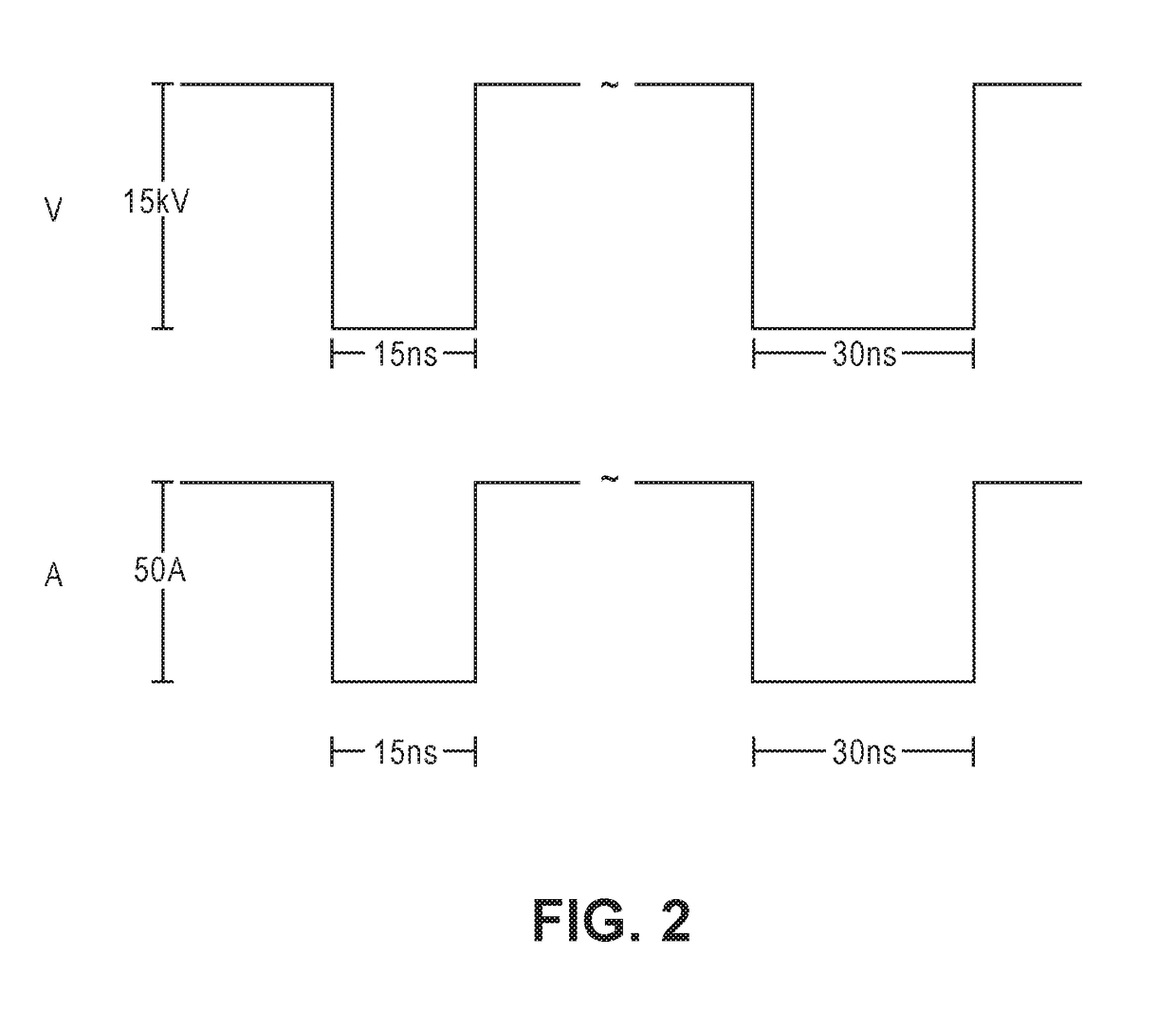

Low-voltage impedance check pulse generator

A method of testing a therapeutic pulse generator circuit is disclosed. The method includes charging the pulse generator circuit to a first charge voltage, with the pulse generator circuit, delivering a first voltage pulse to a load through an electrode, and determining an impedance of the load with the first voltage pulse. The method also includes comparing the impedance with an expected impedance, as a result of the comparison, determining to deliver a second voltage pulse to the load based, and delivering the second voltage pulse to the load, where at least one of the first and second voltage pulses is therapeutic to the load.

Owner:PULSE BIOSCI INC

Impedance control circuits and methods of controlling impedance

ActiveUS7285977B2Reduced board sizeLess complicatedReliability increasing modificationsMultiple-port networksControl signalEngineering

A circuit for controlling impedance may include an impedance adjustment circuit and a control signal generation circuit. The impedance adjustment circuit may adjust an impedance value based on a control signal. The control signal generation circuit may provide the impedance adjustment circuit with a control signal that corresponds to one of an impedance value at a first clock cycle and an impedance value at a second clock cycle that approaches a target impedance.

Owner:SAMSUNG ELECTRONICS CO LTD

Matching circuit and multi-band amplifier

InactiveUS7656228B2Easy to operateEnhanced signalImpedence matching networksMultiple-port networksLow noiseMulti band

A matching circuit includes a demultiplexer for demultiplexing a signal outputted from an amplification device into signals of respective frequency bands, and at least two matching blocks which are connected to the demultiplexer, are respectively fed with the signals of the respective frequency bands, and perform impedance matching in the respective frequency bands of the inputted signals. Impedance matching is performed on each of the demultiplexed signals of the respective frequency bands, thereby achieving a matching circuit capable of efficiently performing impedance matching in the respective frequency bands. With this matching circuit, it is possible to achieve a multi-band amplifier capable of simultaneously amplifying signals of multiple frequency bands with high efficiency and low noise.

Owner:NTT DOCOMO INC

Semiconductor integrated circuit device

InactiveUS20050012533A1Improve data transfer rateReduce in quantityInput/output impedence modificationImpedence matching networksElectrical resistance and conductanceComparator

A plurality of sets of circuits are provided, each of which generates an impedance code through the use of an impedance control circuit in association with a resistive element connected to an external terminal, and each of which varies the impedance in accordance with such an impedance code. The impedance control circuit includes an impedance comparator which is formed equivalently to the resistive element and the plurality of sets of circuits, and which performs an impedance comparison with each of a plurality of replica circuits to form an up signal that increases the impedance and a down signal that decreases the impedance. Counters are provided adjacent to the individuals of the plurality of sets of circuits to thereby generate the impedance codes in response to the up signal and the down signal.

Owner:RENESAS ELECTRONICS CORP