Patents

Literature

1145 results about "Power MOSFET" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A power MOSFET is a specific type of MOSFET (metal-oxide-semiconductor field-effect transistor) designed to handle significant power levels. Compared to the other power semiconductor devices, for example an insulated-gate bipolar transistor (IGBT) or a thyristor, its main advantages are high switching speed and good efficiency at low voltages. It shares with the IGBT an isolated gate that makes it easy to drive. They can be subject to low gain, sometimes to a degree that the gate voltage needs to be higher than the voltage under control.

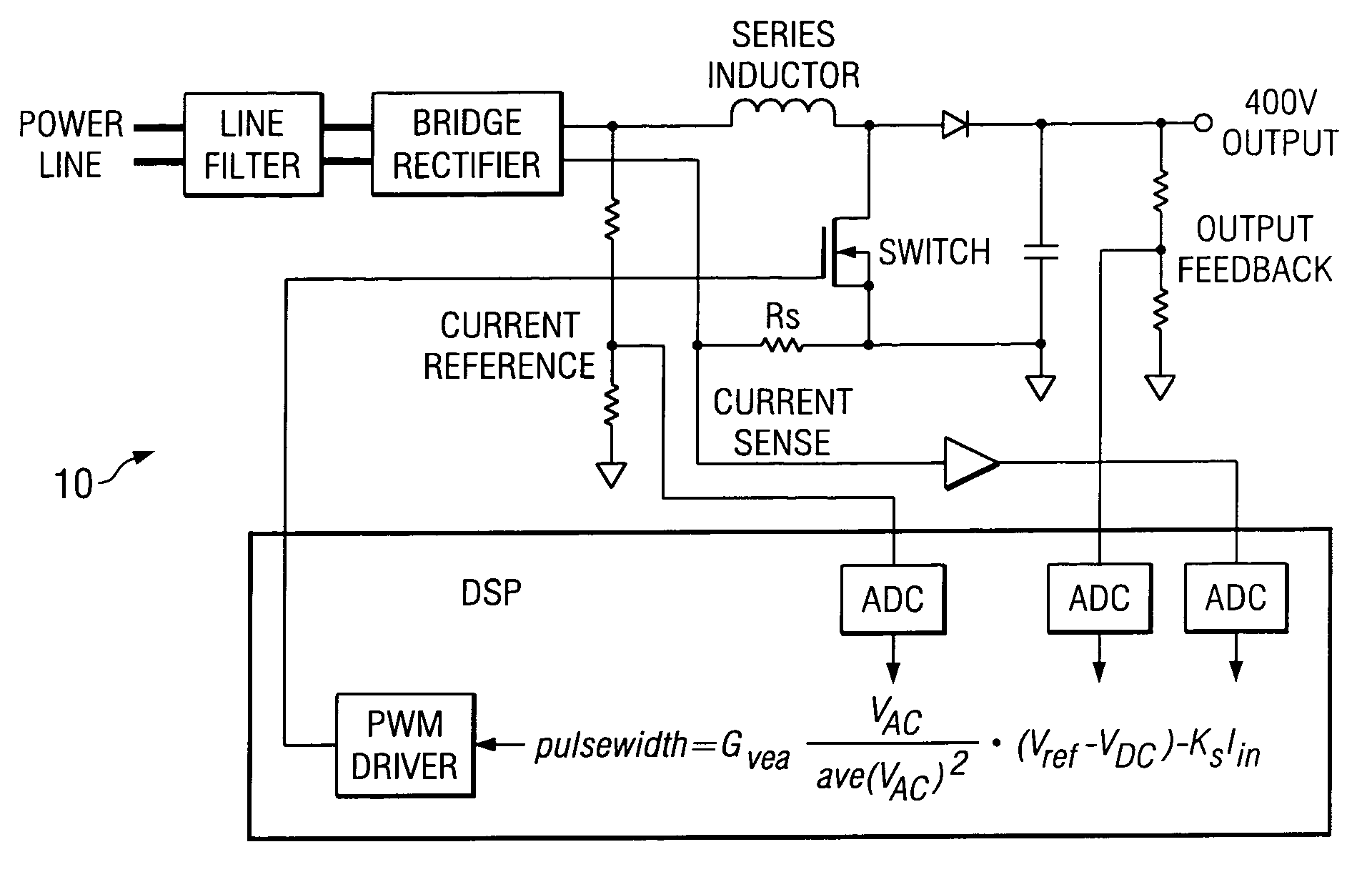

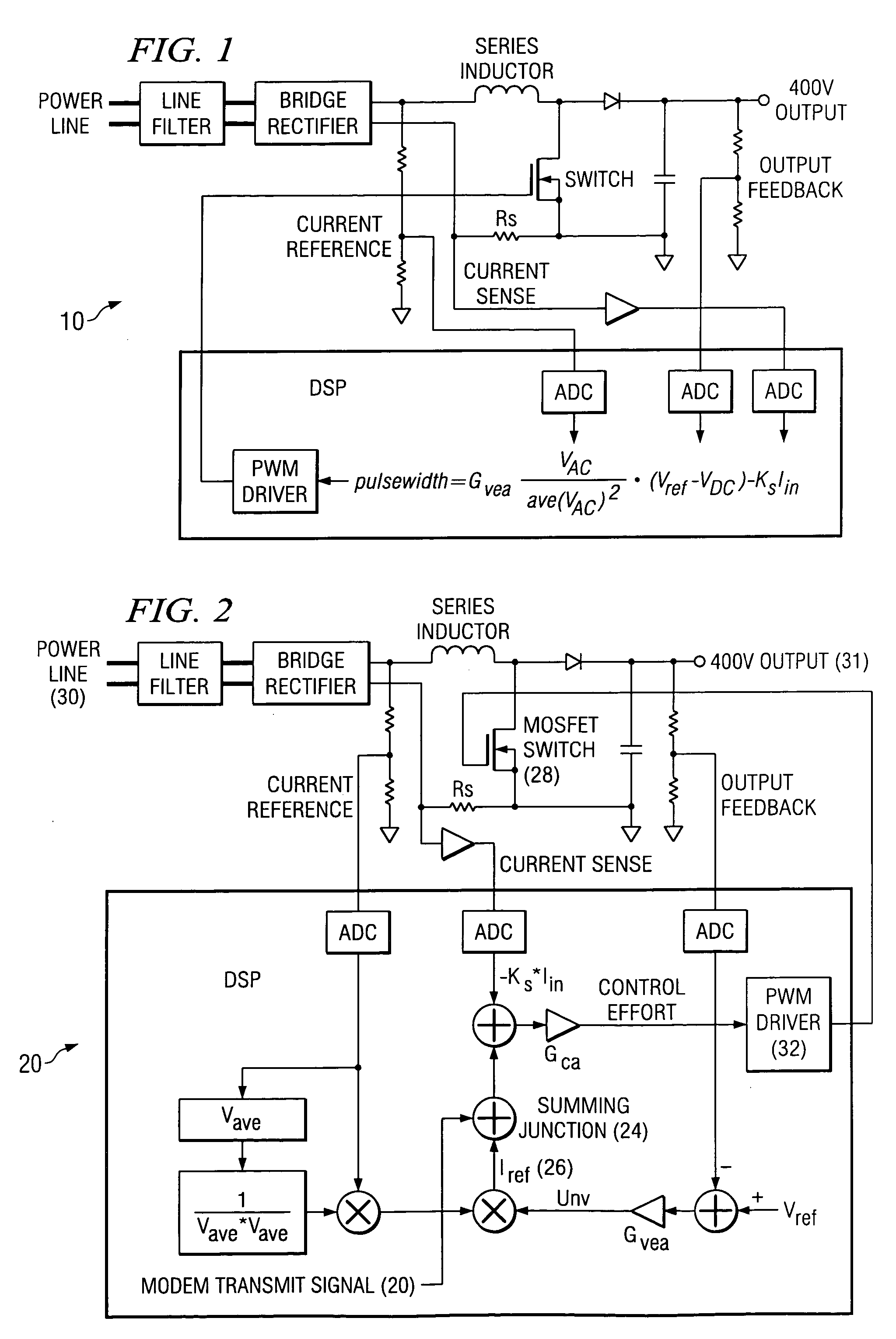

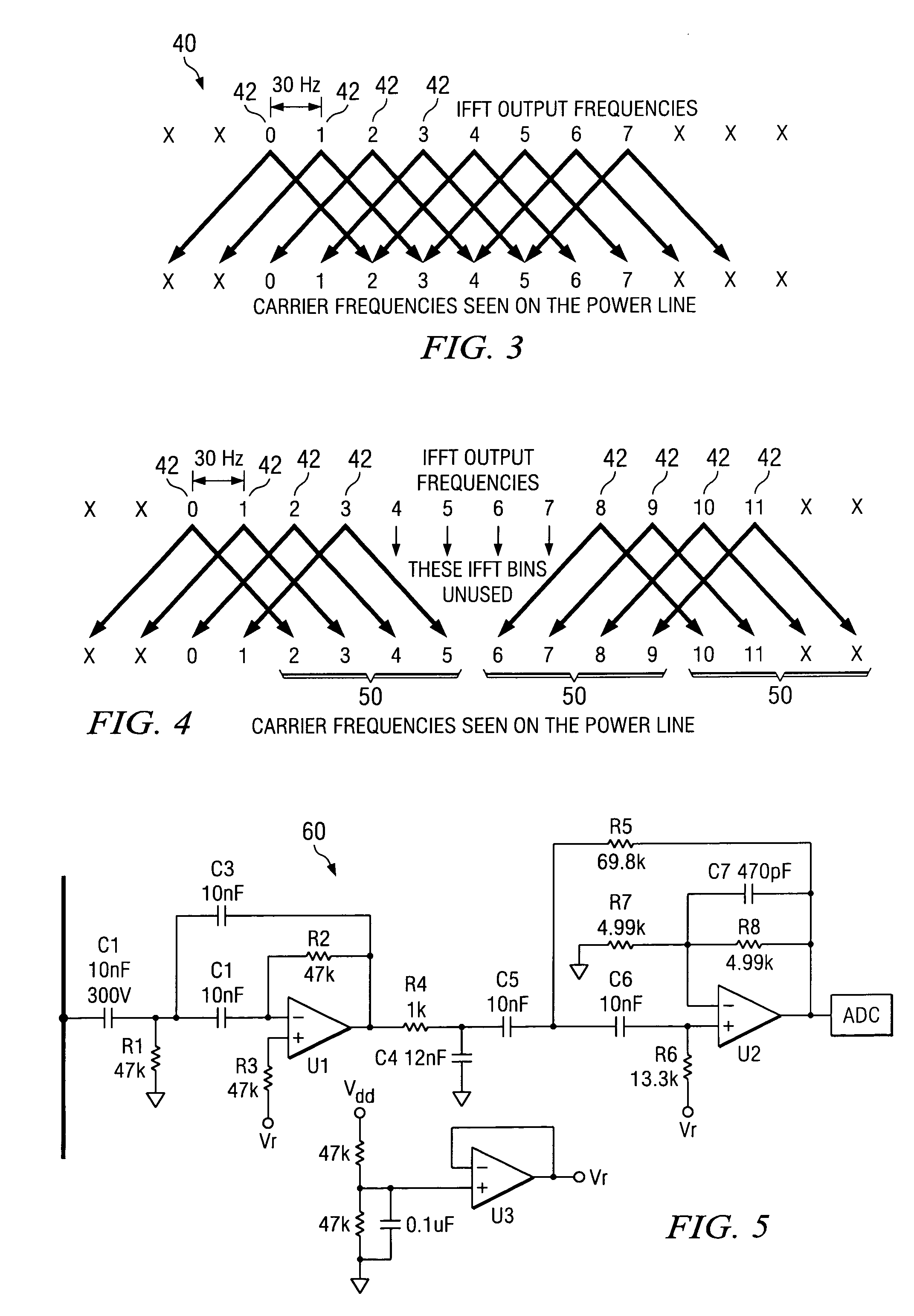

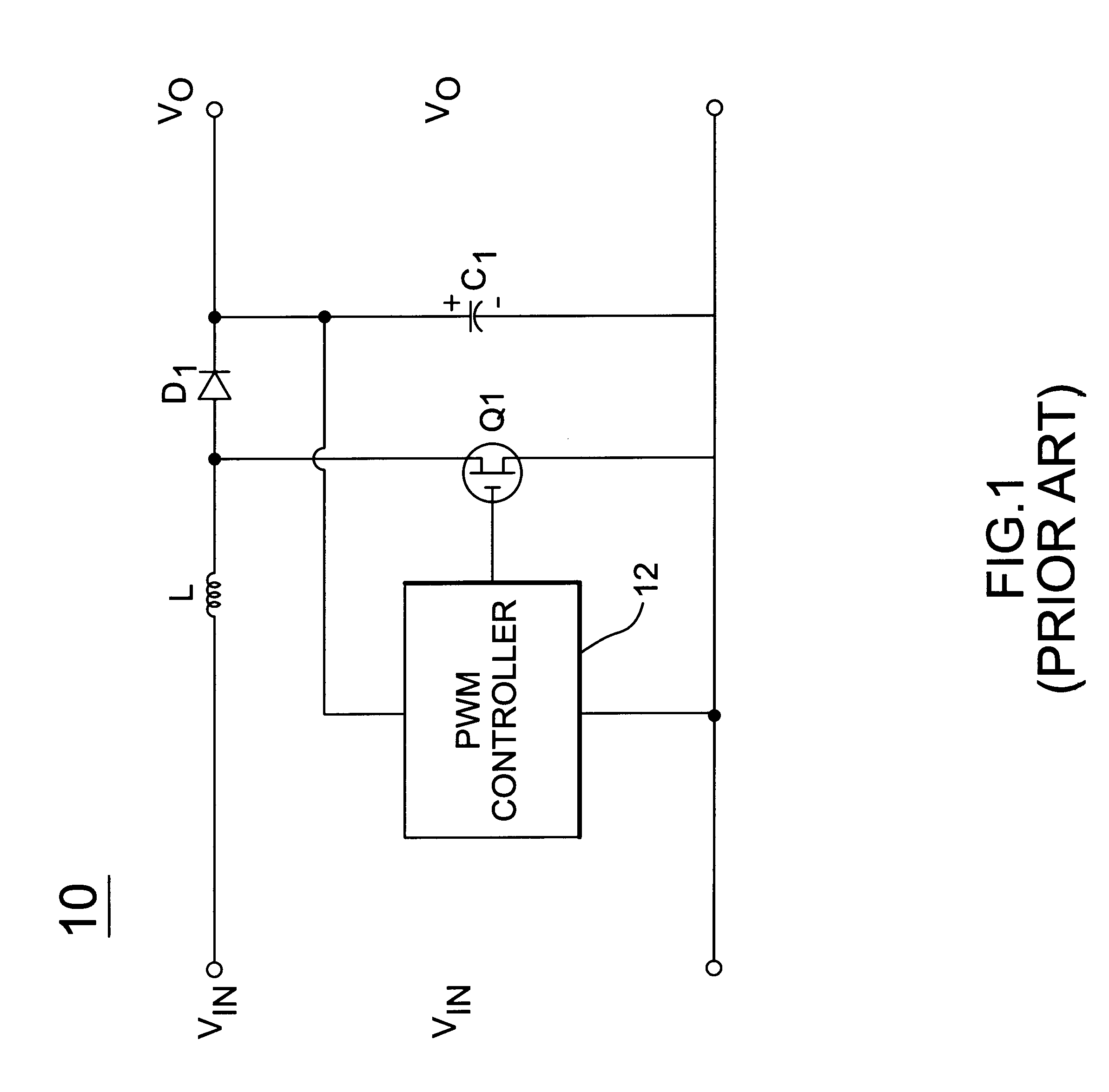

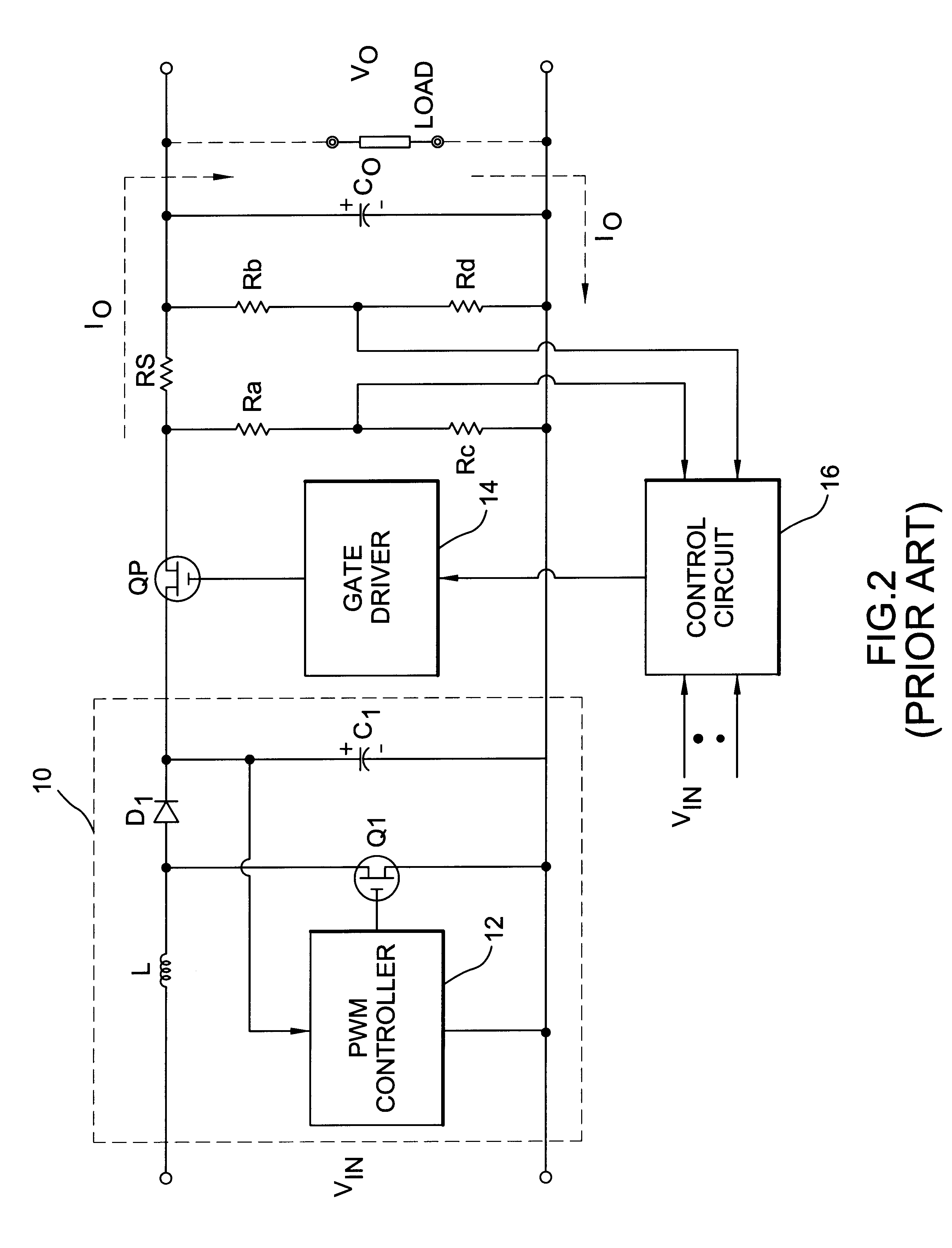

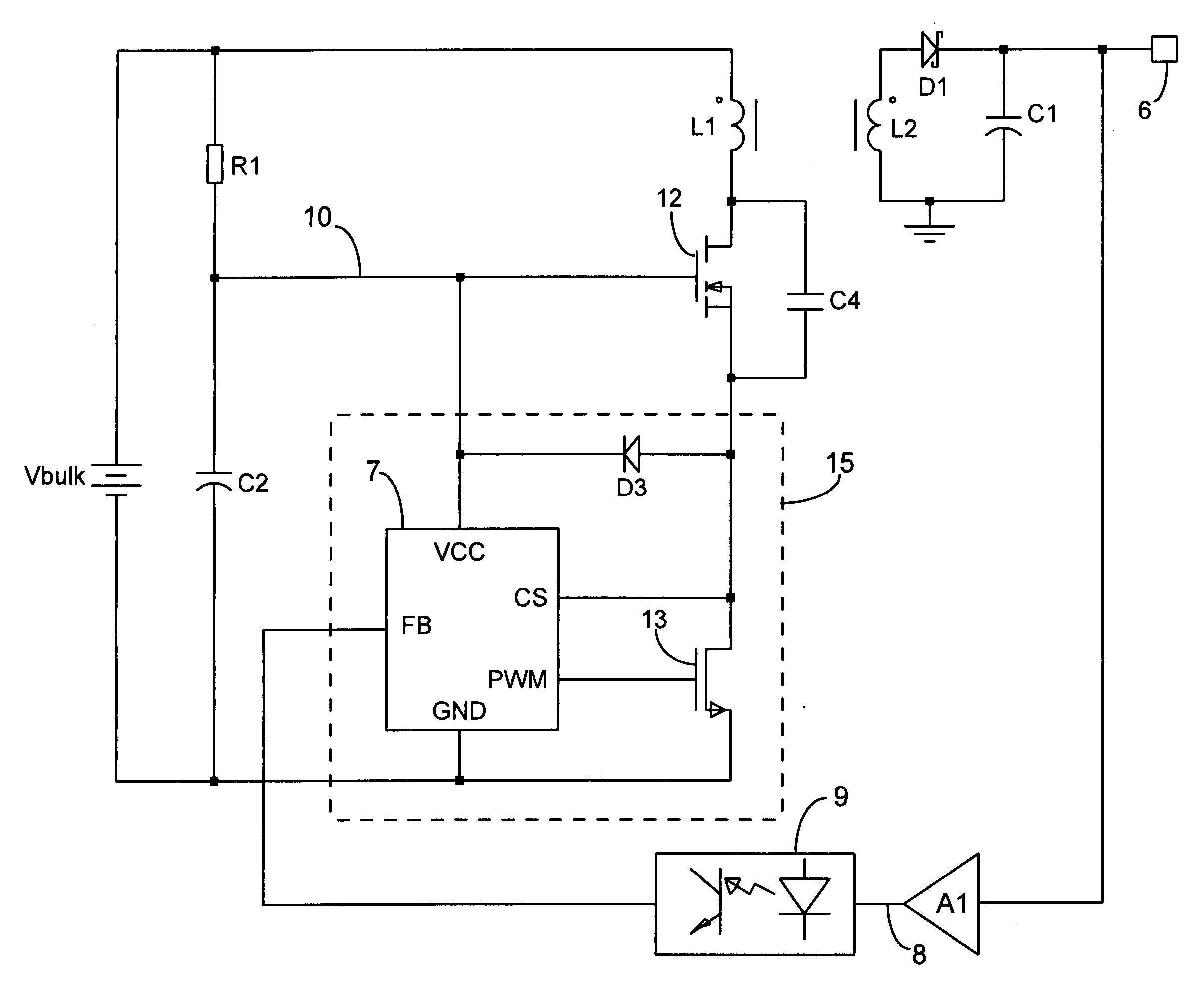

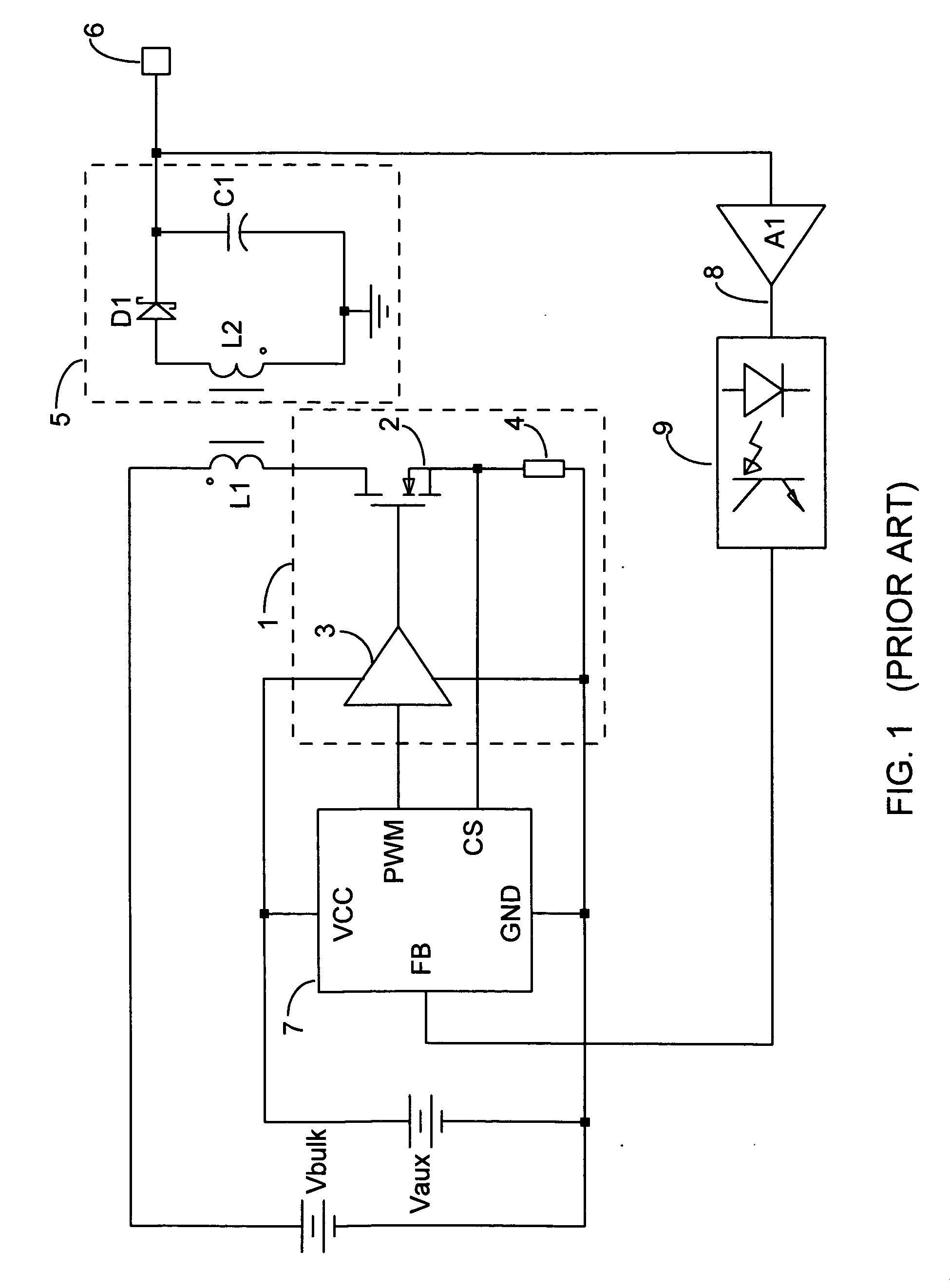

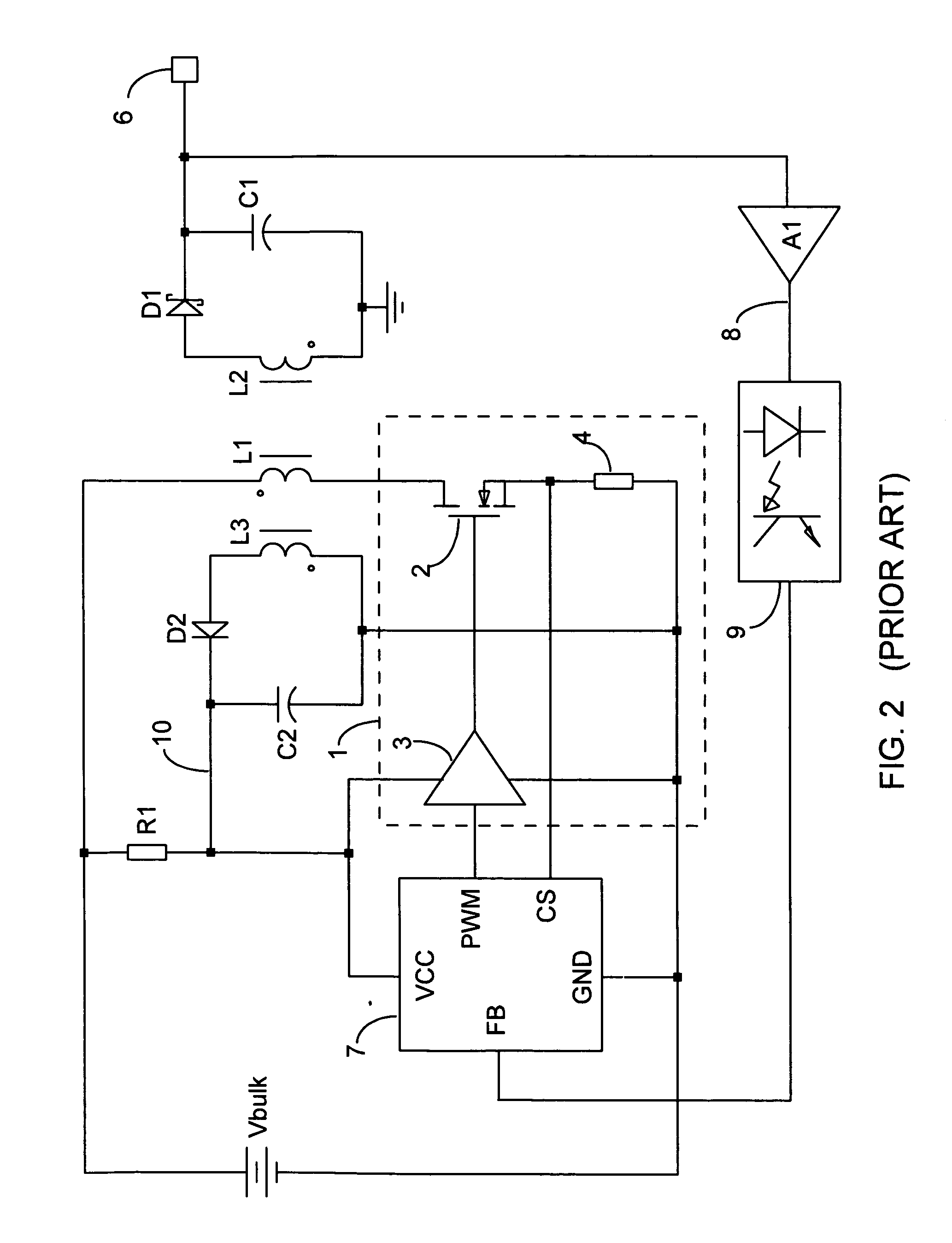

Power line communication using power factor correction circuits

ActiveUS7205749B2Systems using filtering and bypassingAc-dc conversion without reversalElectronic systemsPower MOSFET

A PFC circuit modulating a power line using pulse width modulation (PWM) to drive a power MOSFET and series inductor across the power line. Since many modern electronic systems include a power factor correction circuit (PFC) that already includes a series inductor and power MOSFET, a PLC is incorporated into a controller to inject a PLC transmit signal into a control loop for the PFC circuit. This can be done using either an analog PFC controller, such as the UCC28517, the UCC2819A, or a digital PFC controller such as based on a TMS320C24xx DSP.

Owner:TEXAS INSTR INC

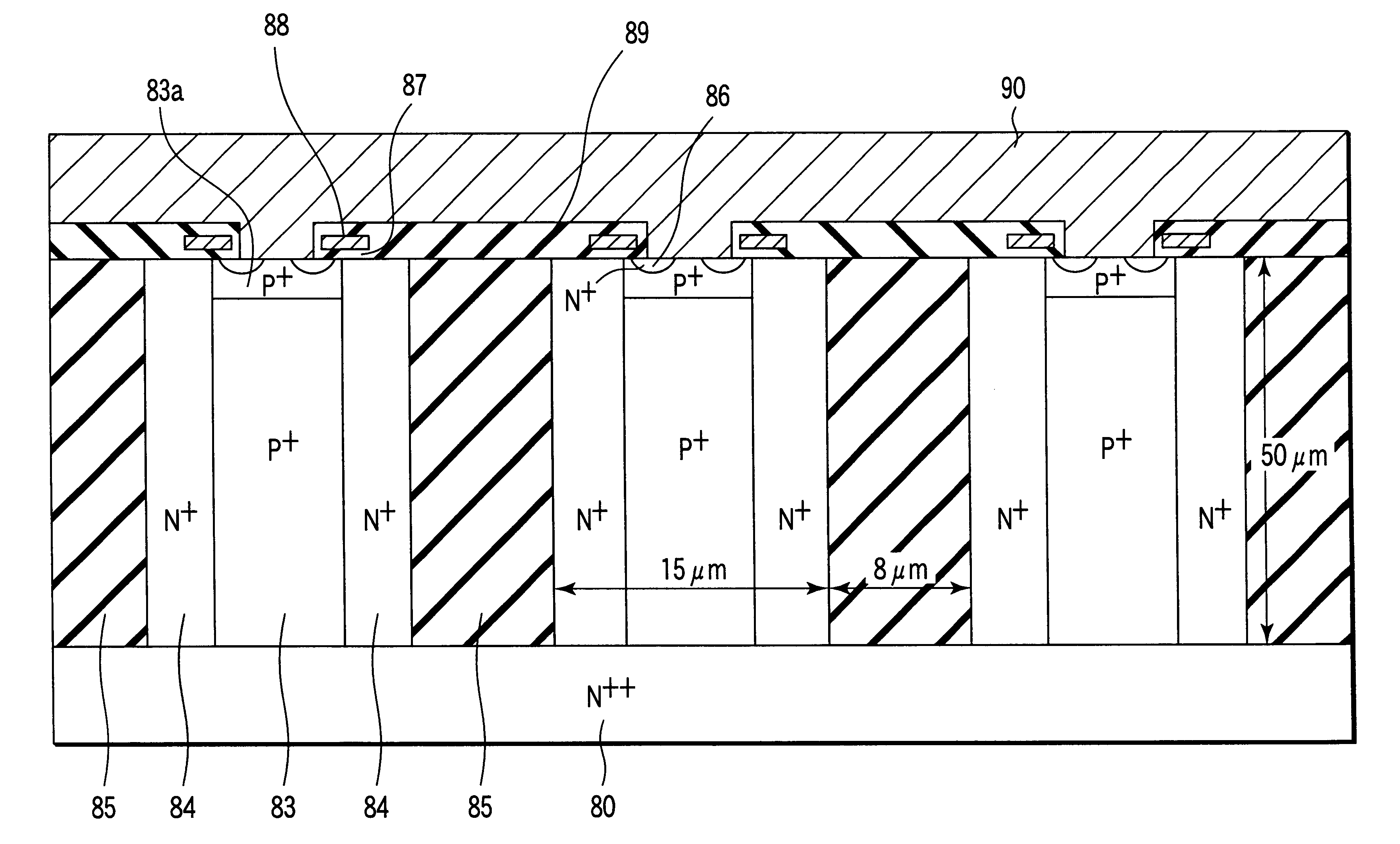

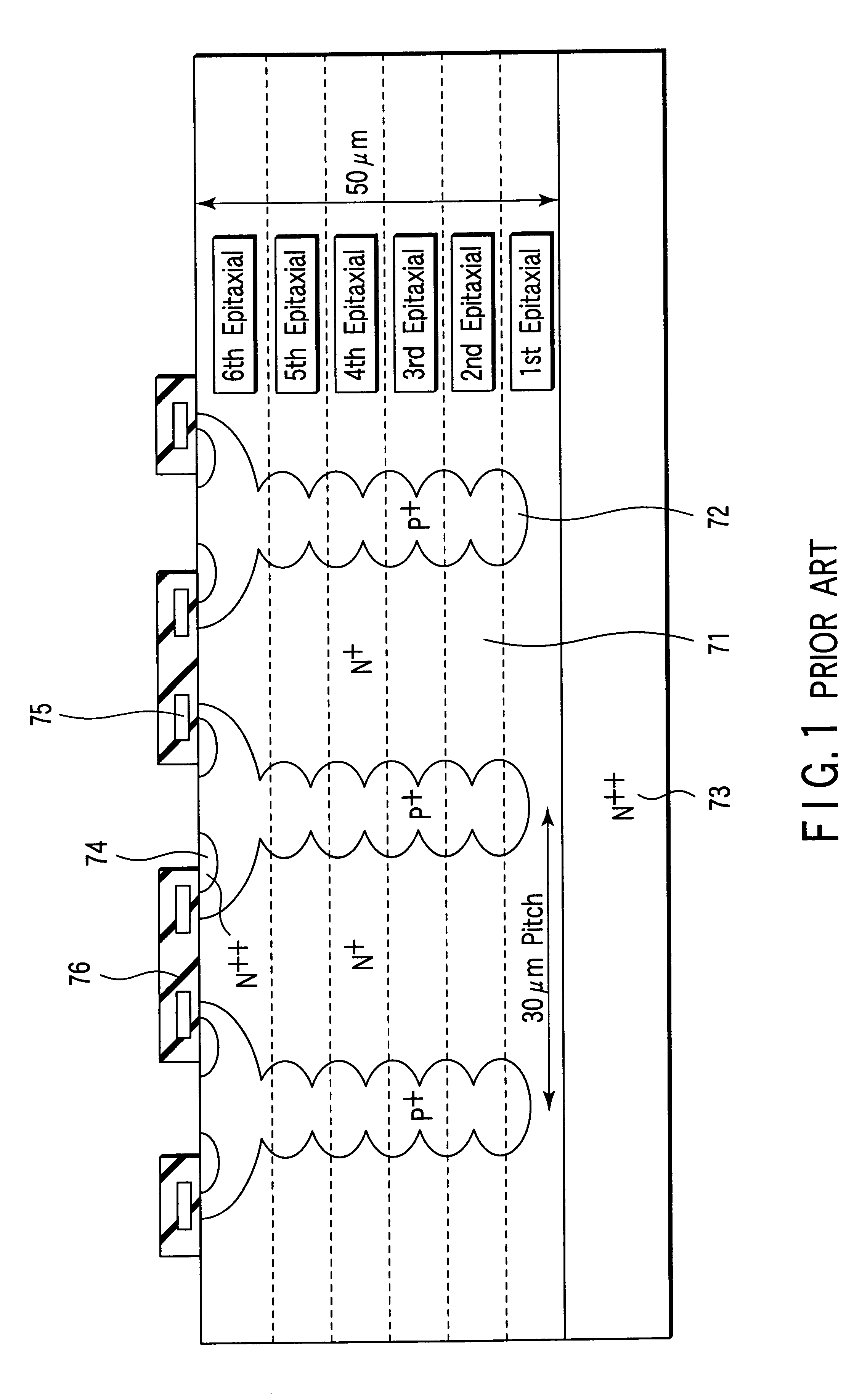

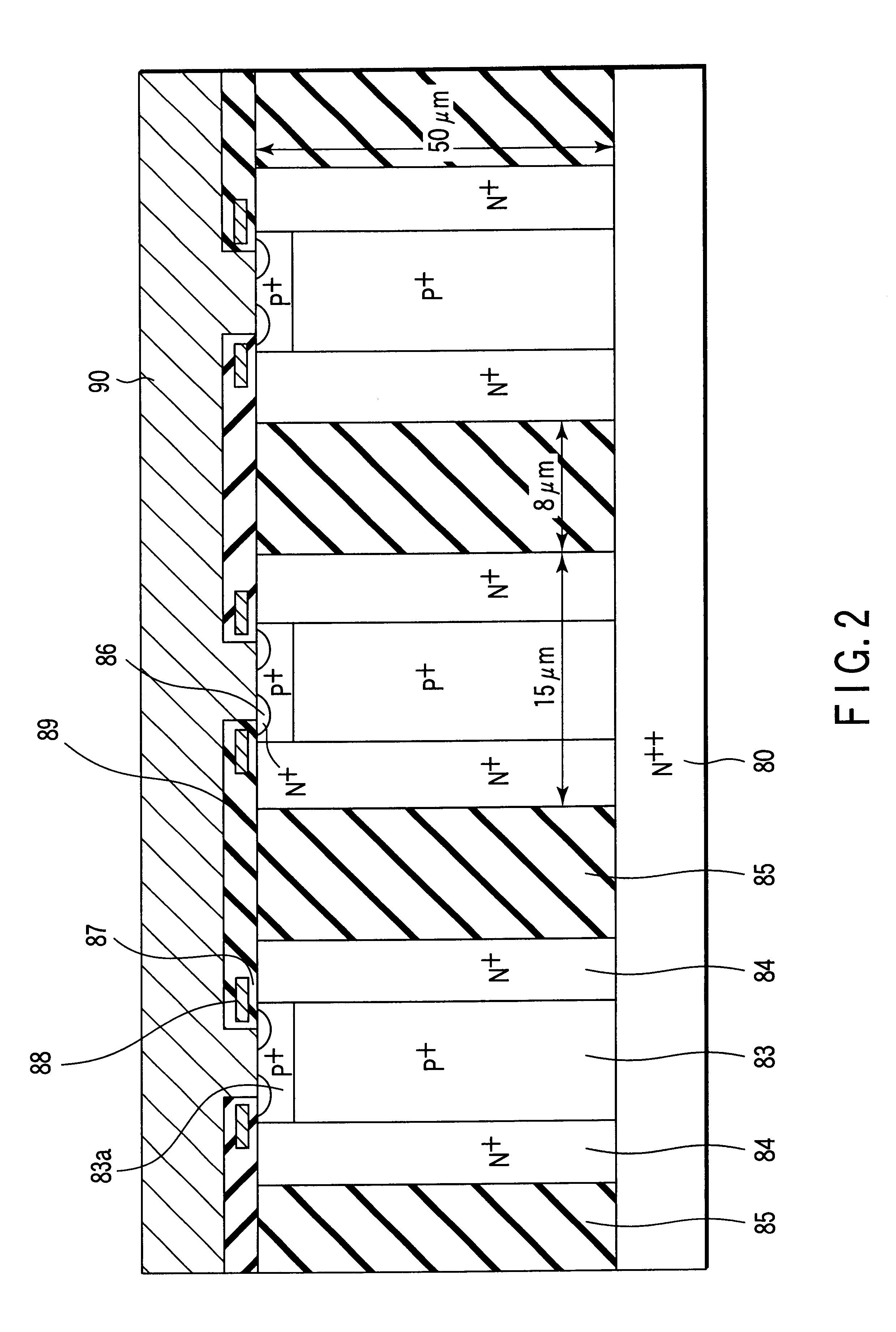

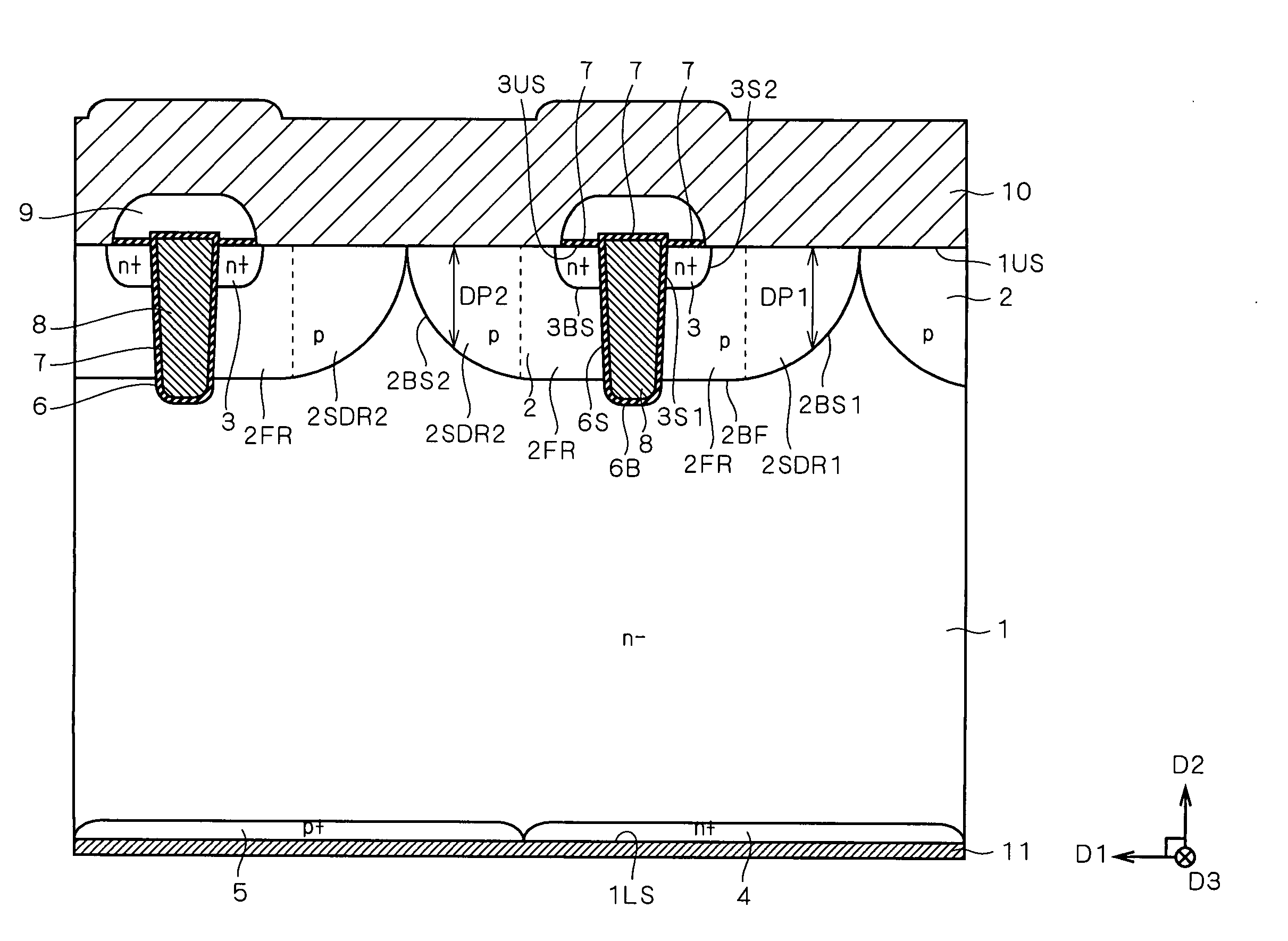

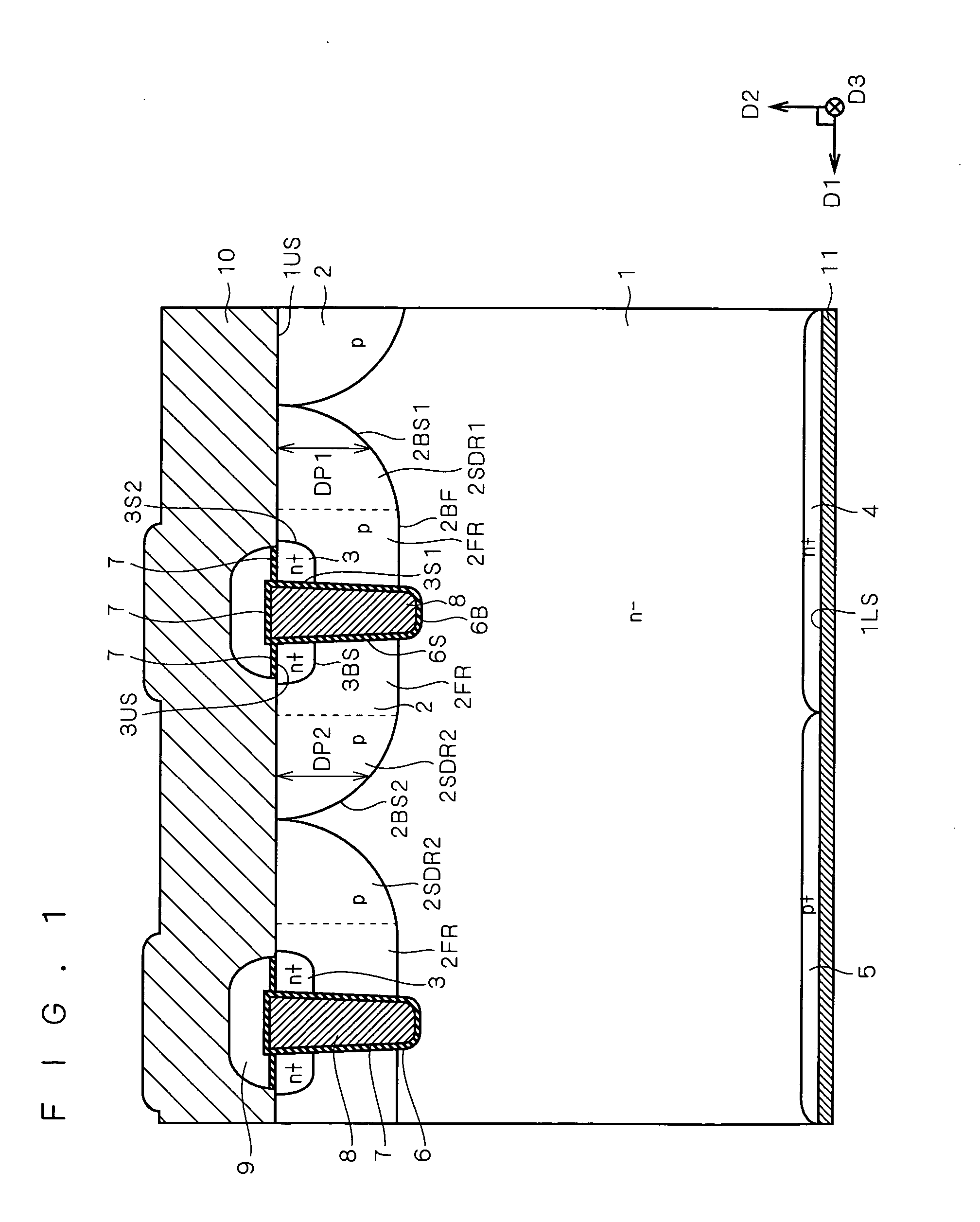

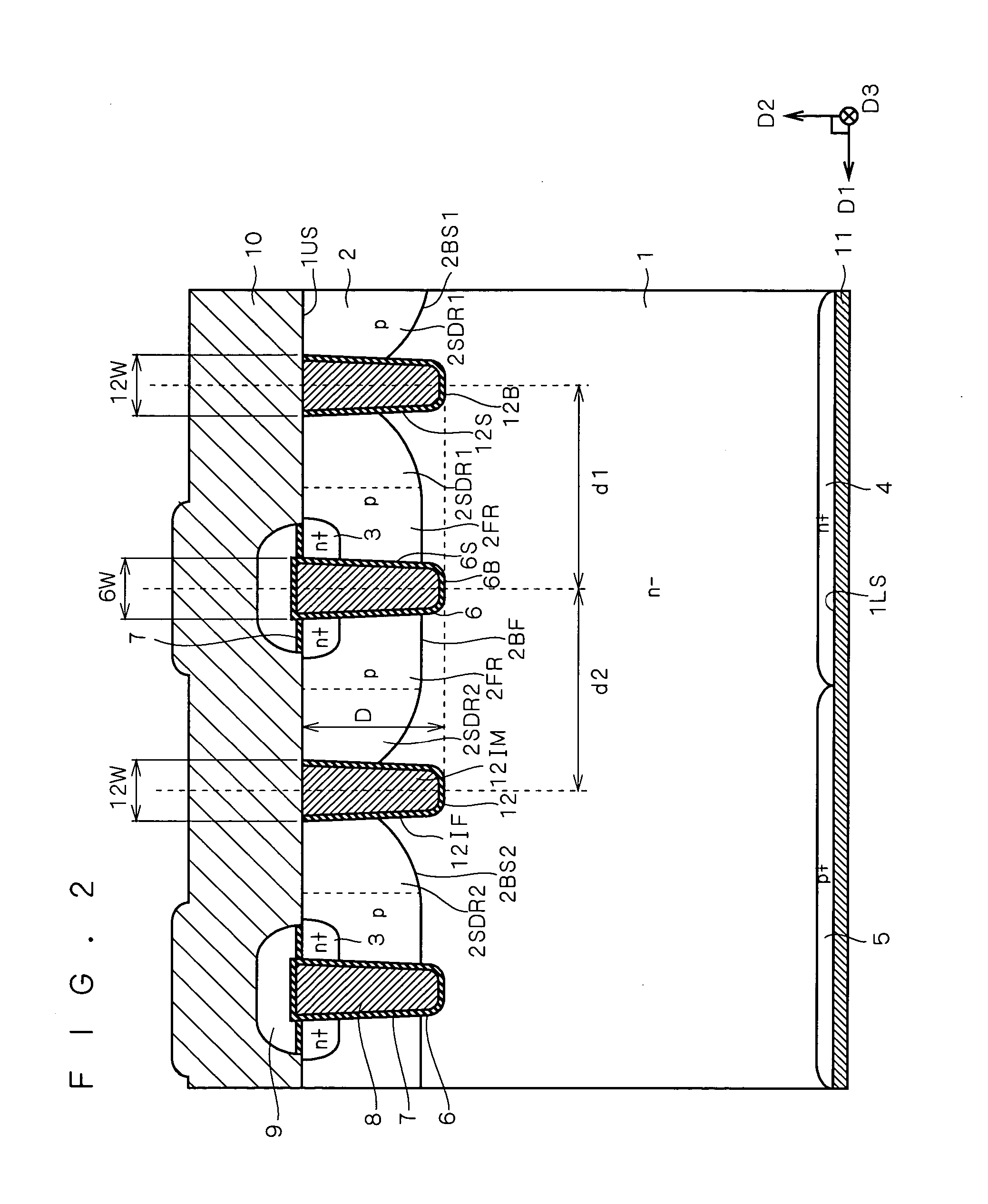

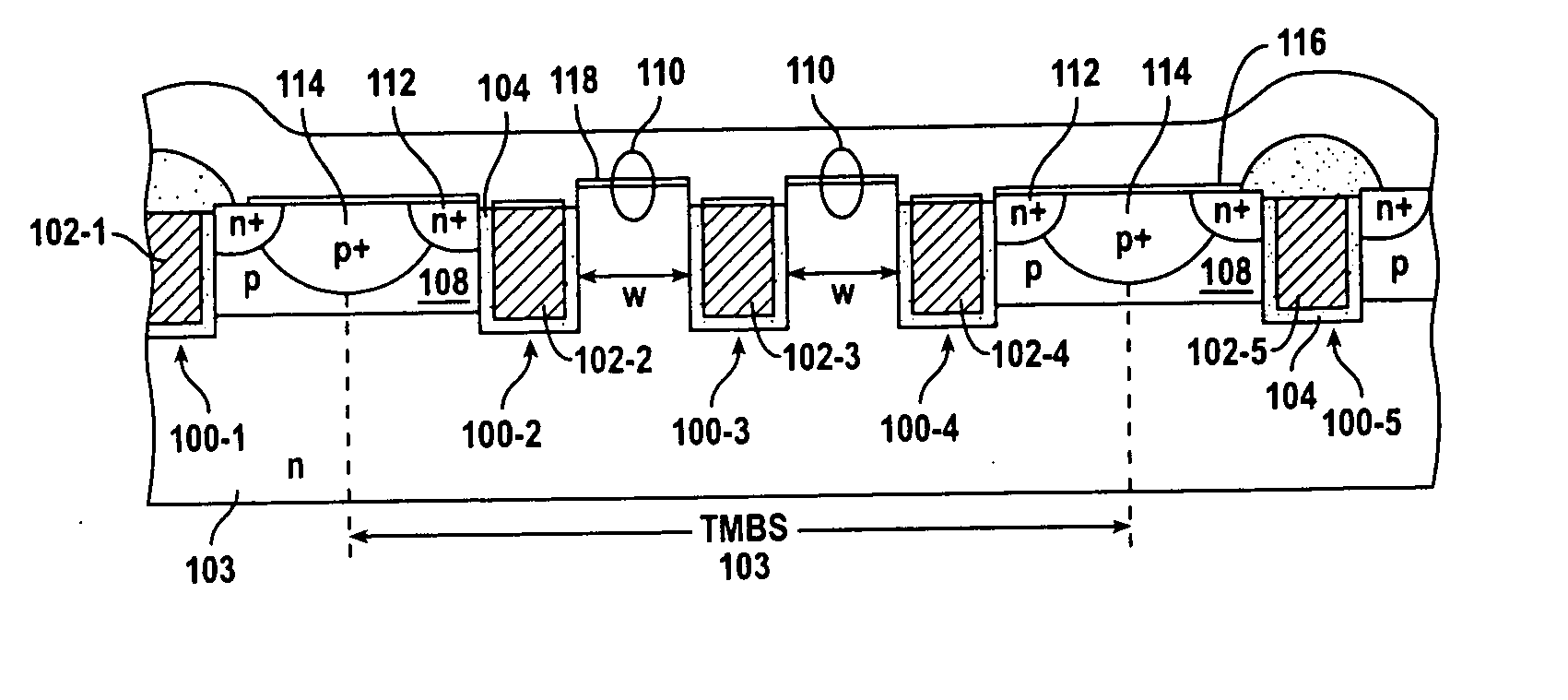

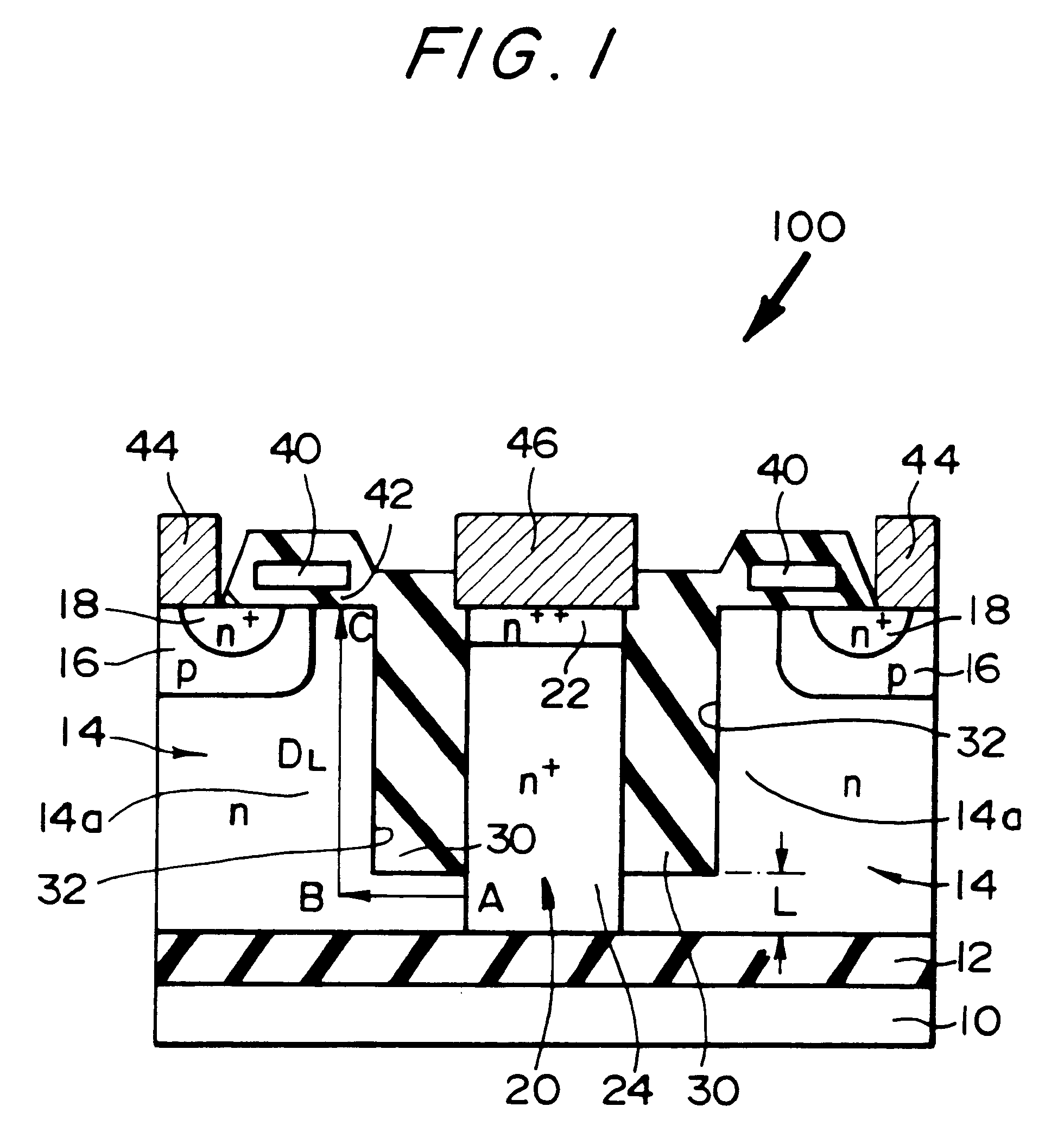

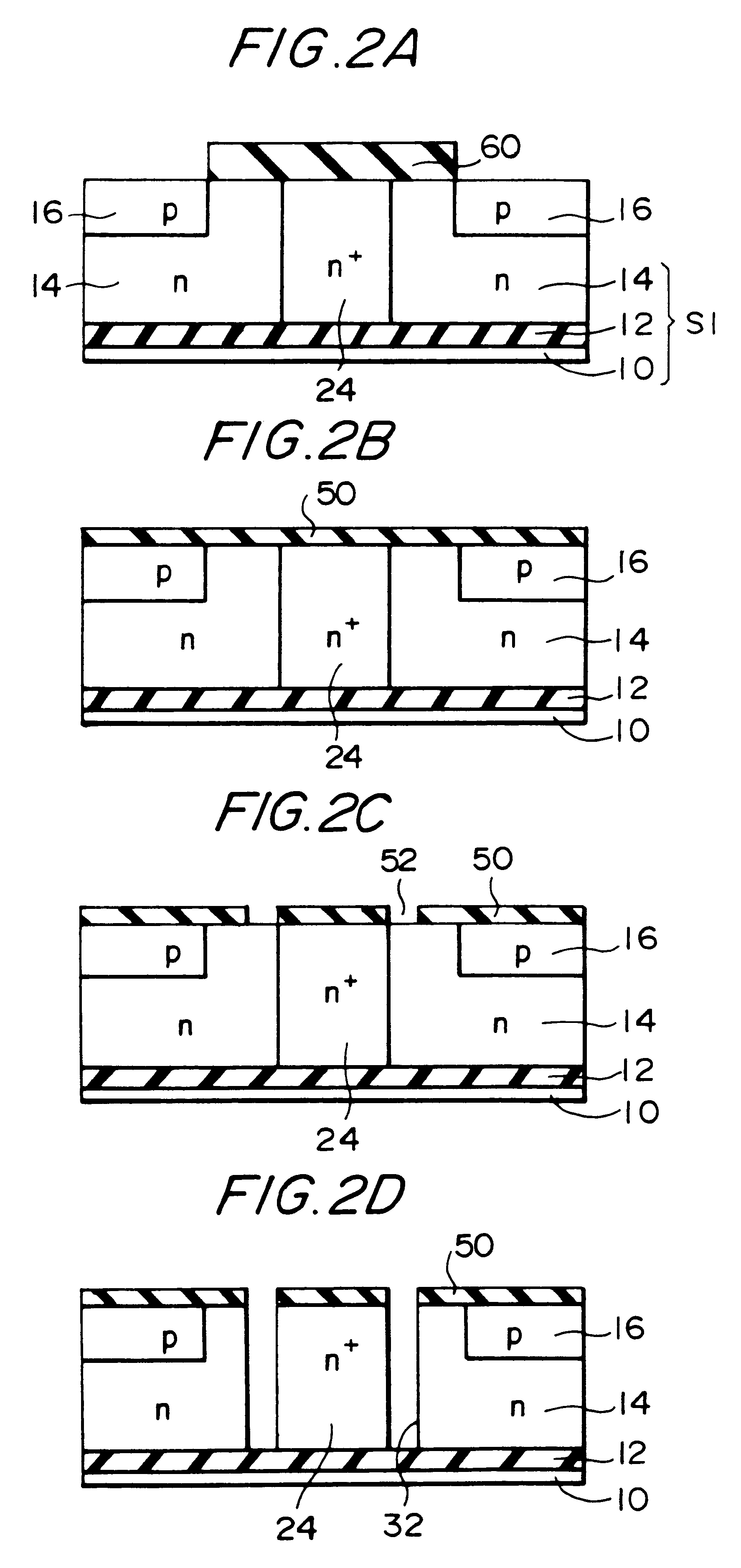

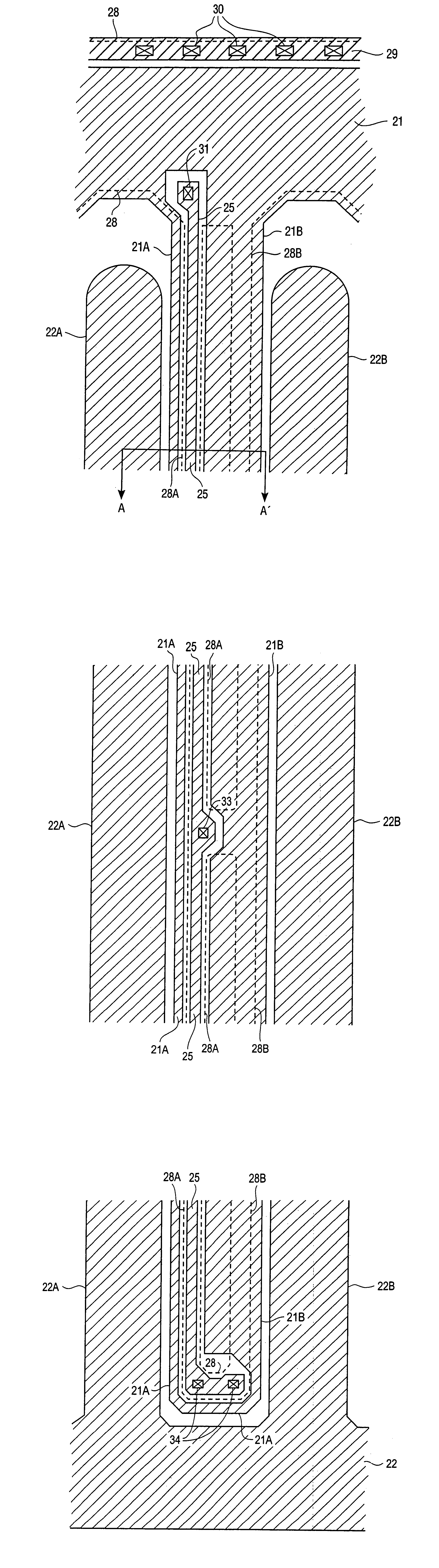

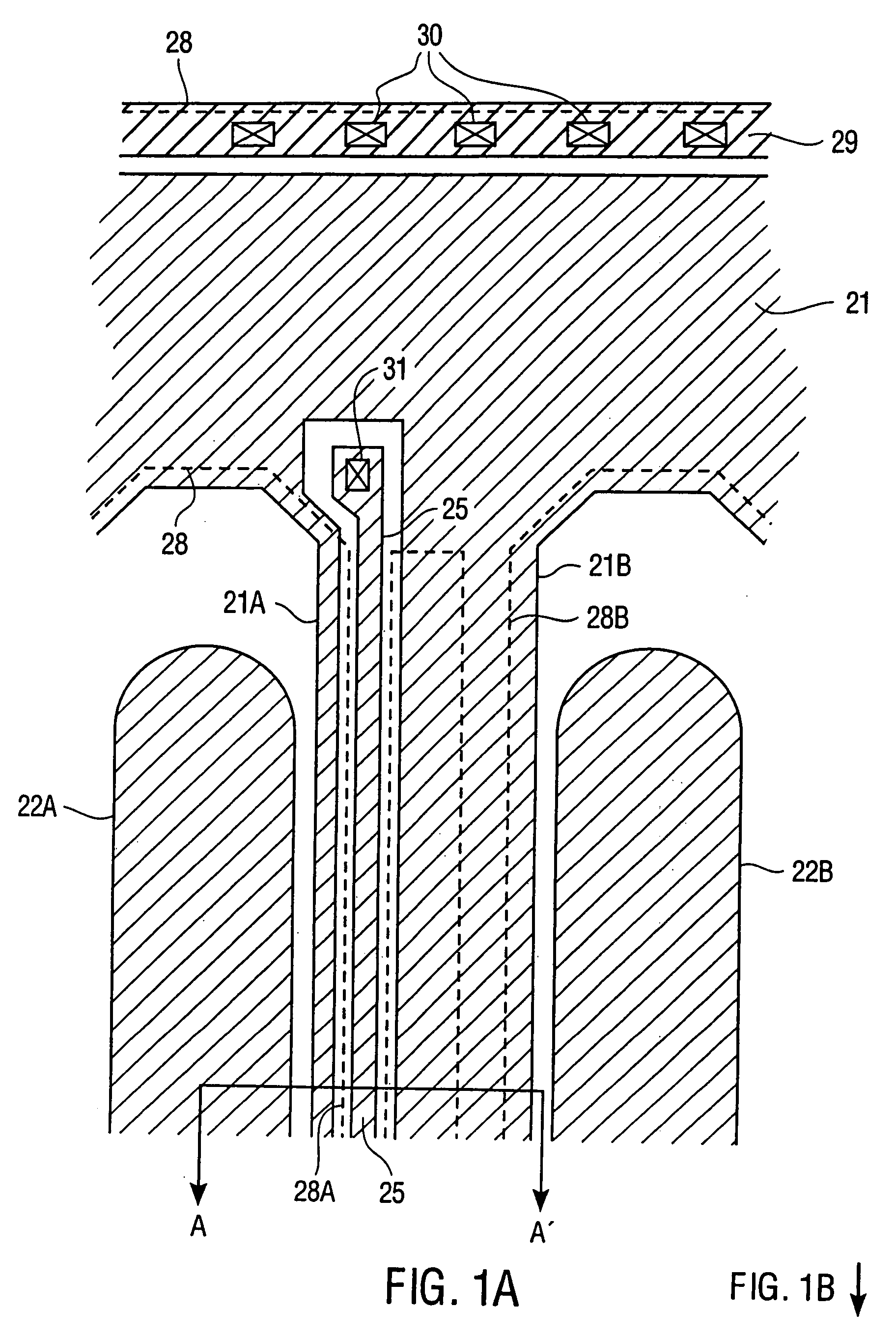

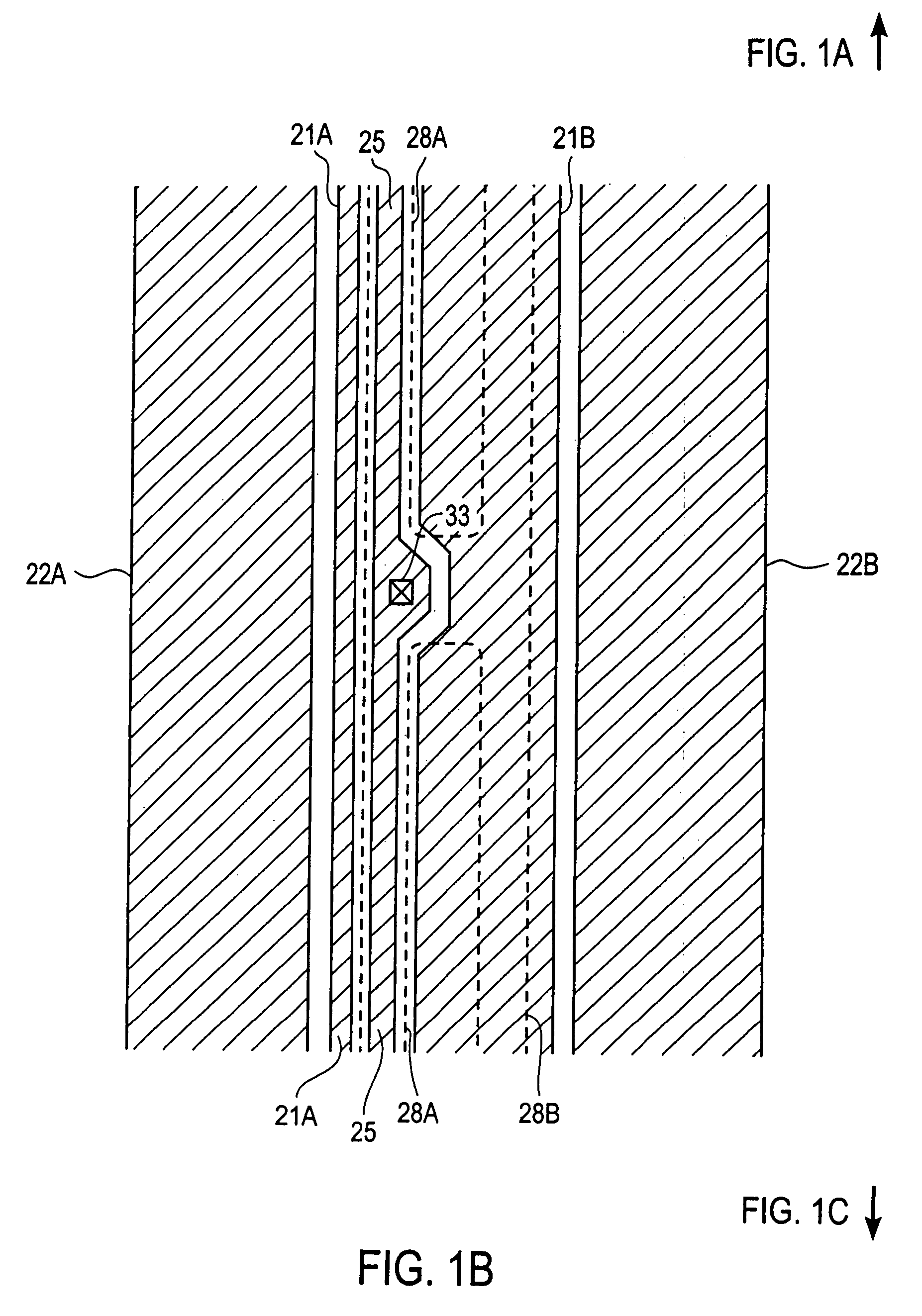

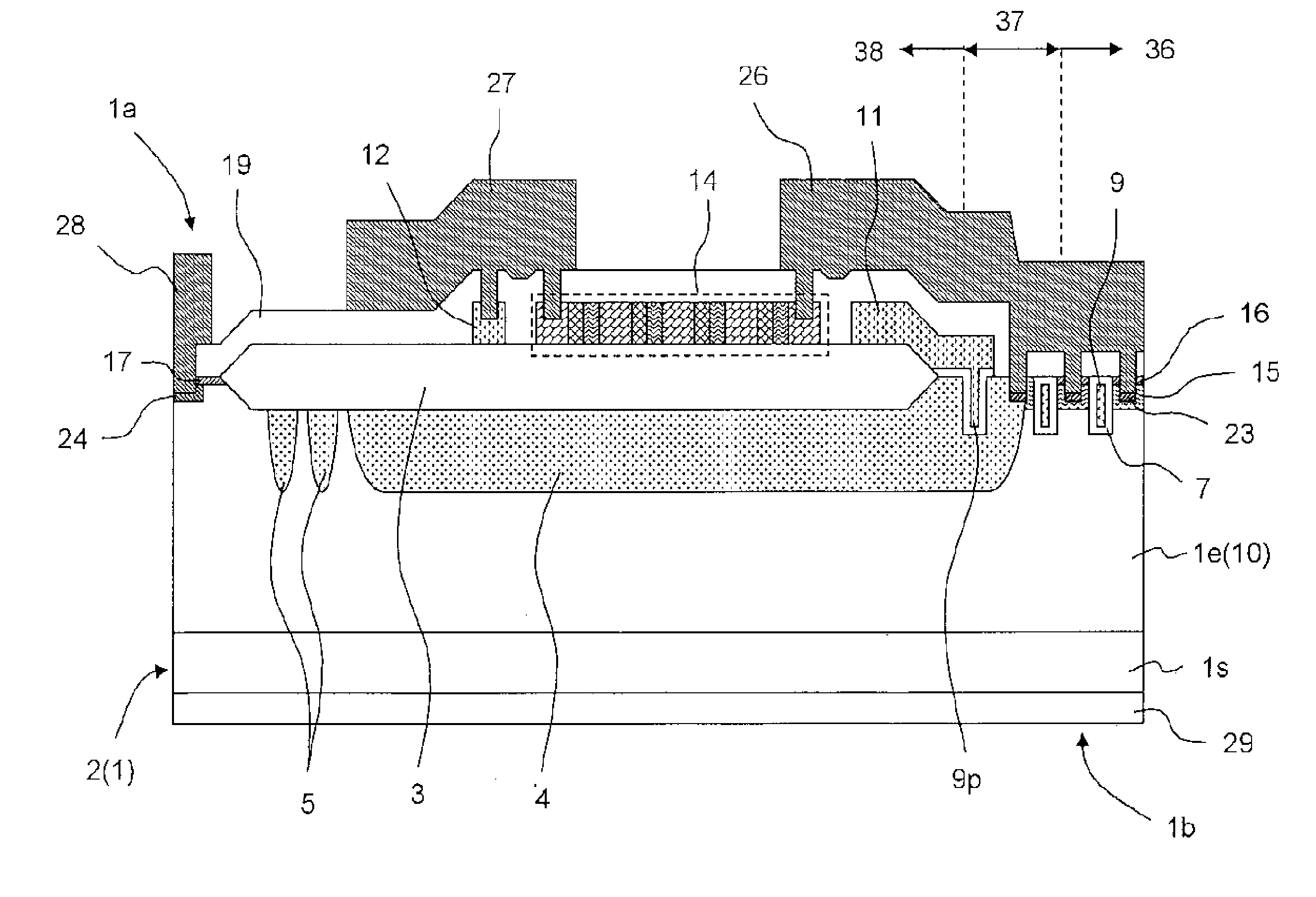

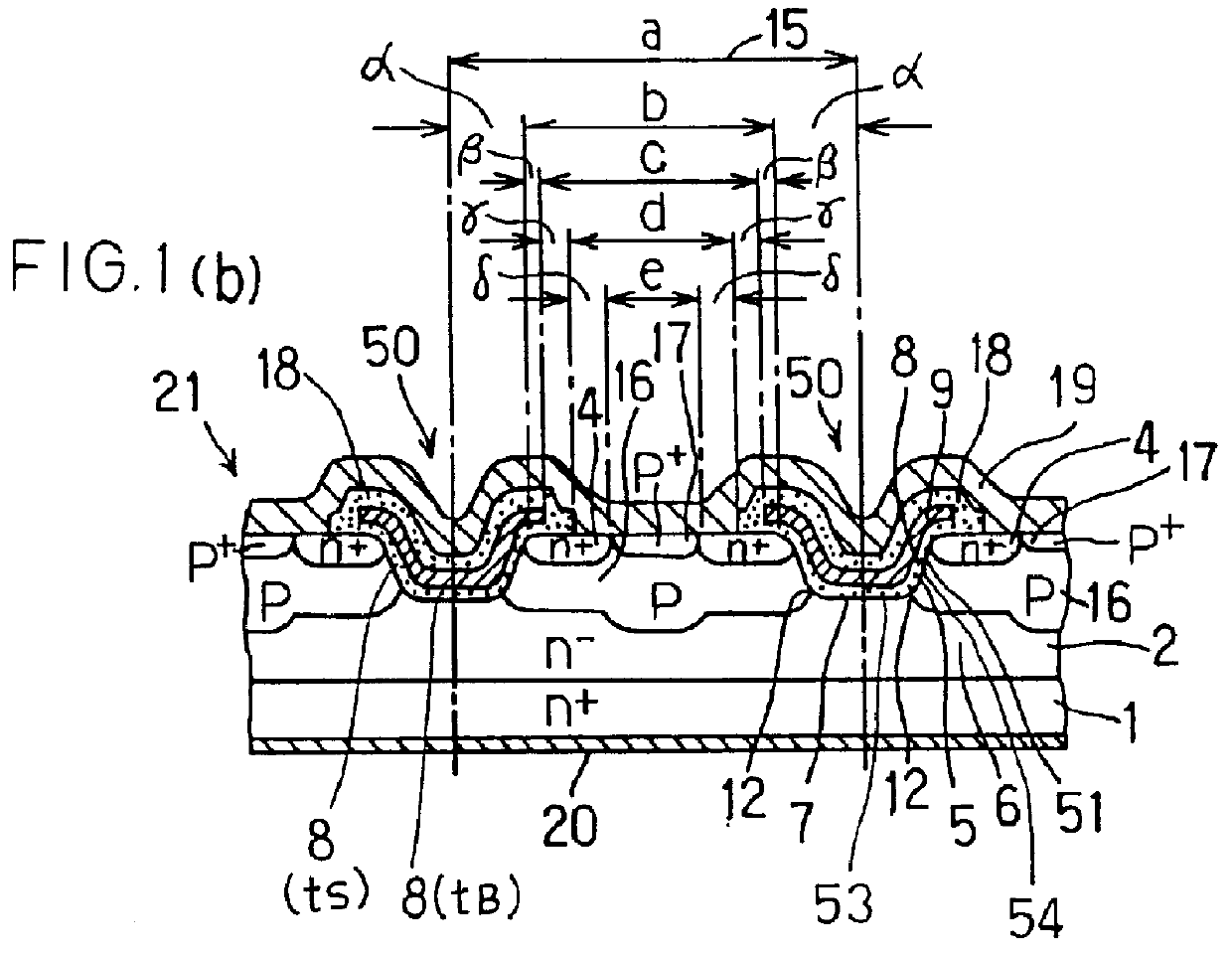

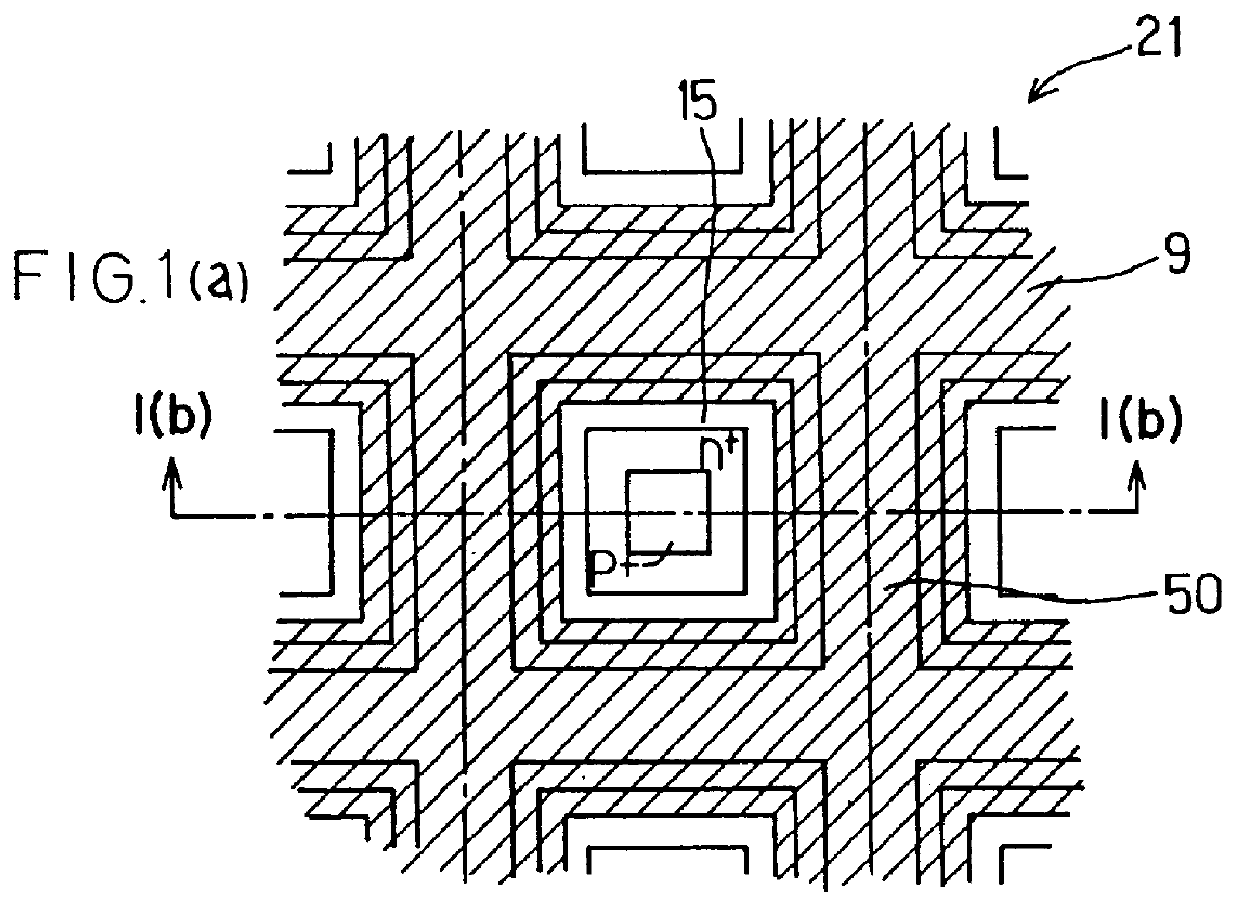

Power MOSFET having laterally three-layered structure formed among element isolation regions

A semiconductor apparatus has an NPN (or PNP) laterally three-layered pillar formed in a mesh form among a plurality of trench type element isolation regions, and having a source and gate on an upper surface of the three-layered pillar, and a drain on a lower surface thereof. A depth DT and minimum planar width WTmin of the element isolation region and a width WP of the three-layered pillar are configured to satisfy a relation of 3.75<=DT / WP<=60 or 5.5<=DT / WTmin<=14.3. The above configuration realizes a high breakdown voltage and low on-resistance are realized.

Owner:KK TOSHIBA

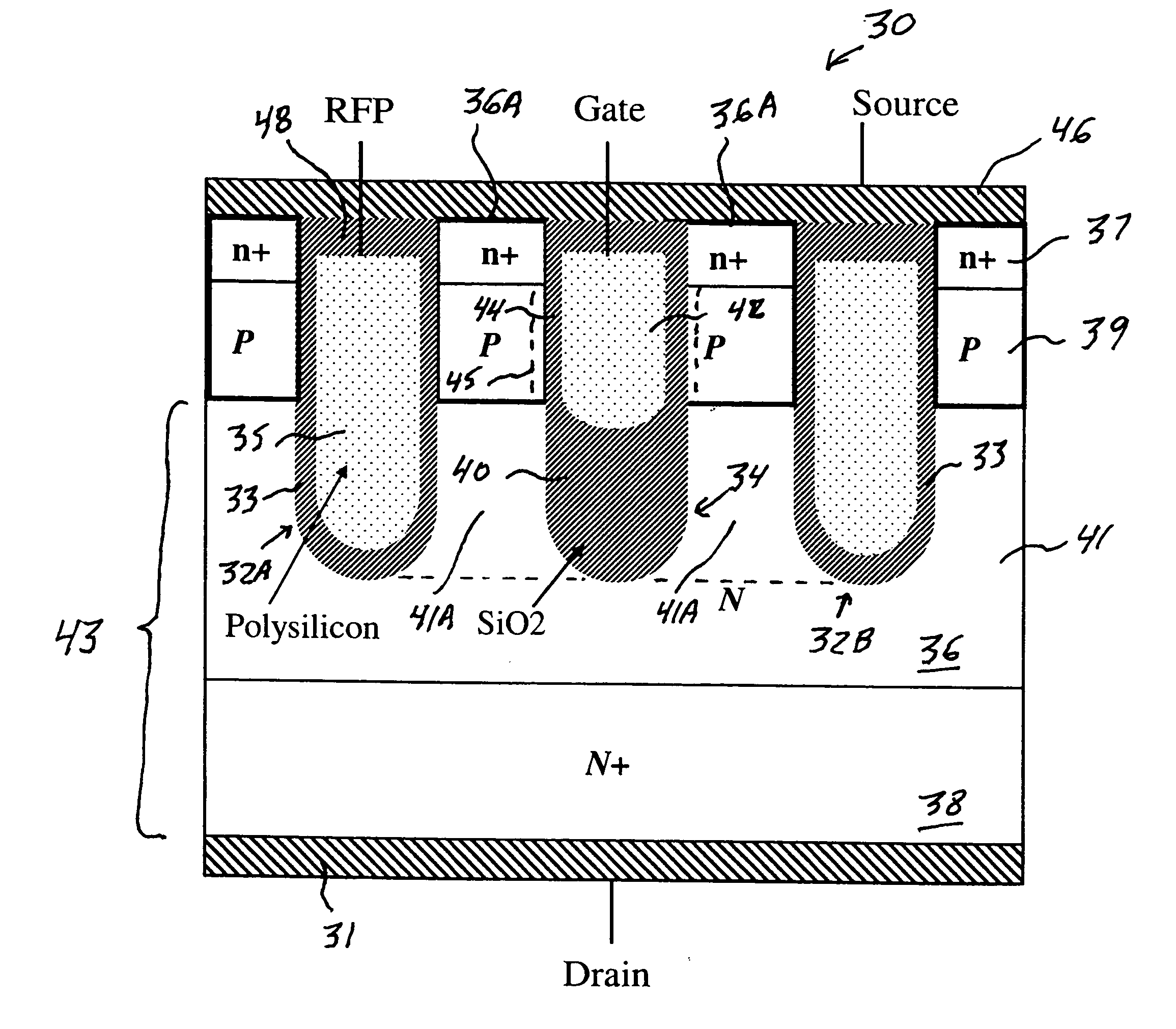

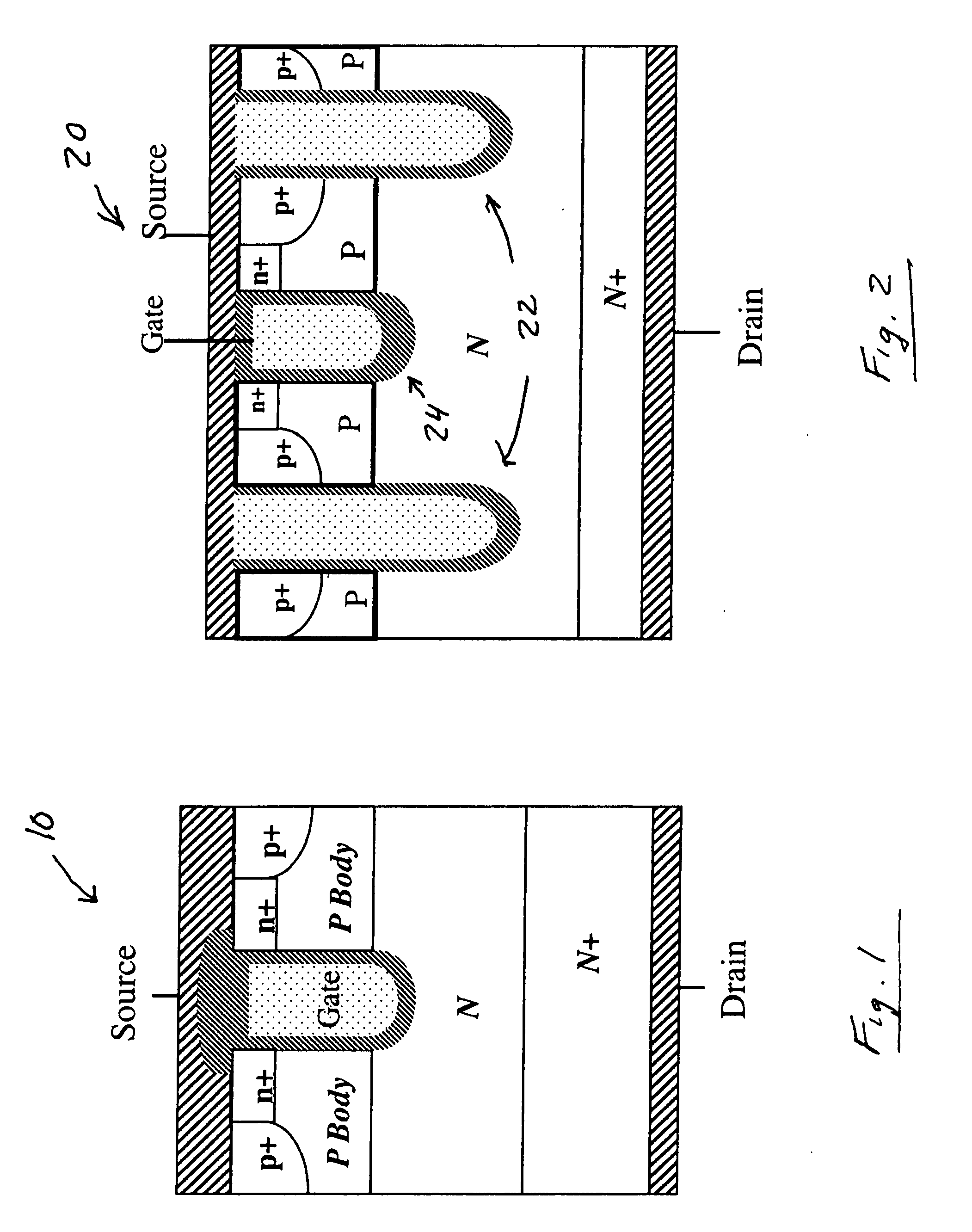

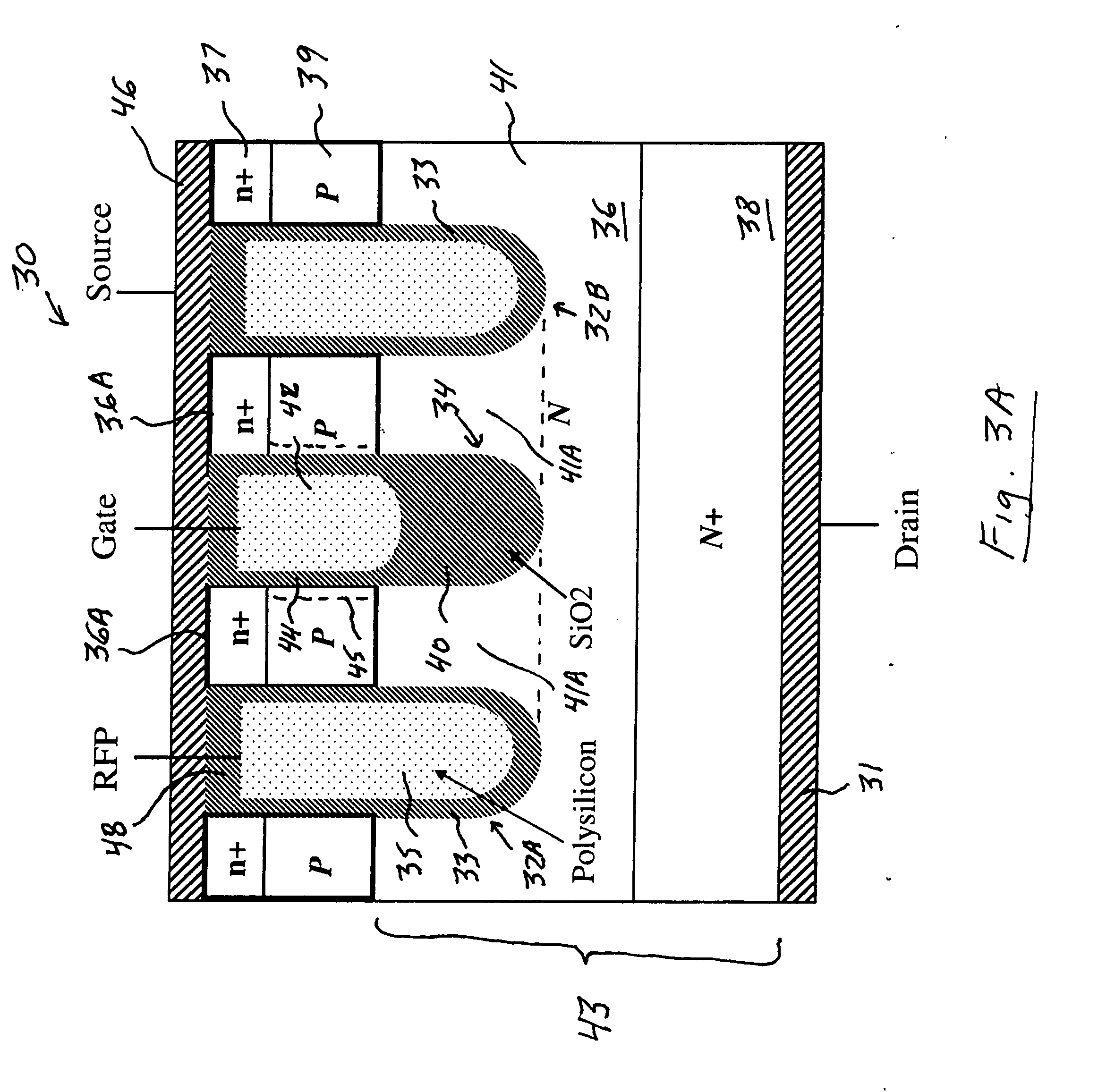

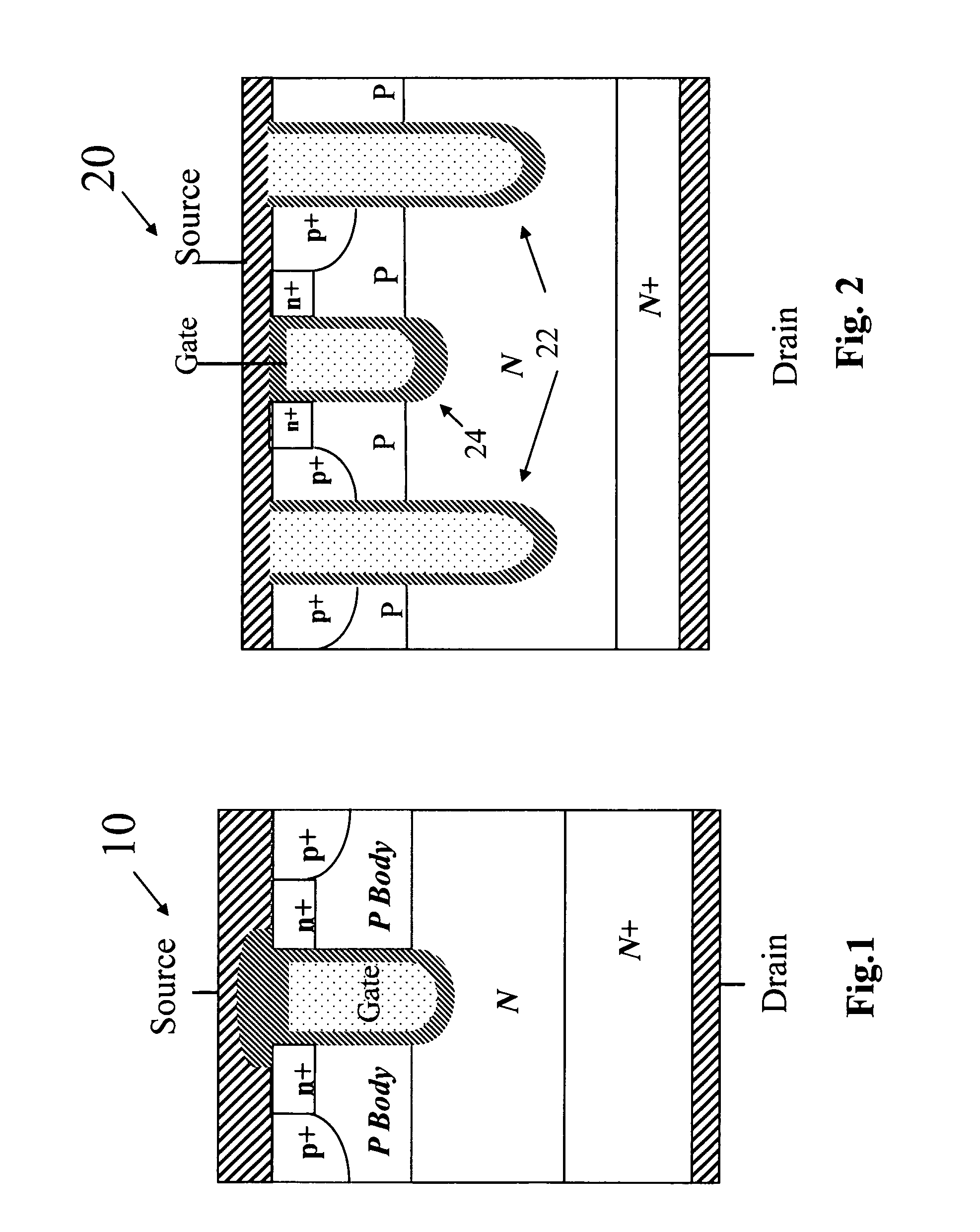

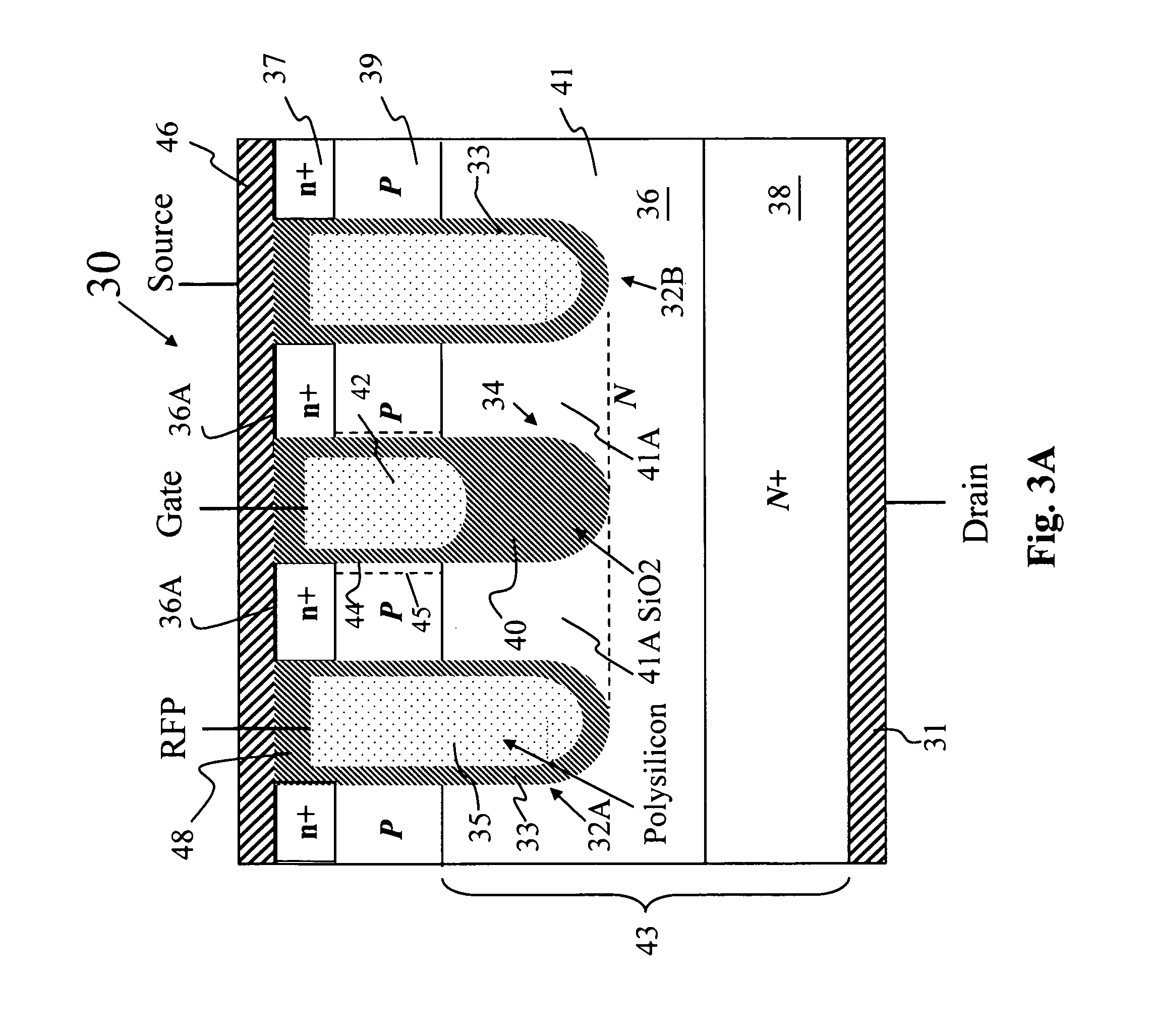

Power MOSFET with recessed field plate

ActiveUS20080073707A1Solid-state devicesSemiconductor/solid-state device manufacturingTrench mosfetReverse recovery

A trench MOSFET contains a recessed field plate (RFP) trench adjacent the gate trench. The RFP trench contains an RFP electrode insulated from the die by a dielectric layer along the walls of the RFP trench. The gate trench has a thick bottom oxide layer, and the gate and RFP trenches are preferably formed in the same processing step and are of substantially the same depth. When the MOSFET operates in the third quadrant (with the source / body-to-drain junction forward-biased), the combined effect of the RFP and gate electrodes significantly reduces in the minority carrier diffusion current and reverse-recovery charge. The RFP electrode also functions as a recessed field plates to reduce the electric field in the channel regions when the MOSFET source / body to-drain junction reverse-biased.

Owner:MAXPOWER SEMICON INC

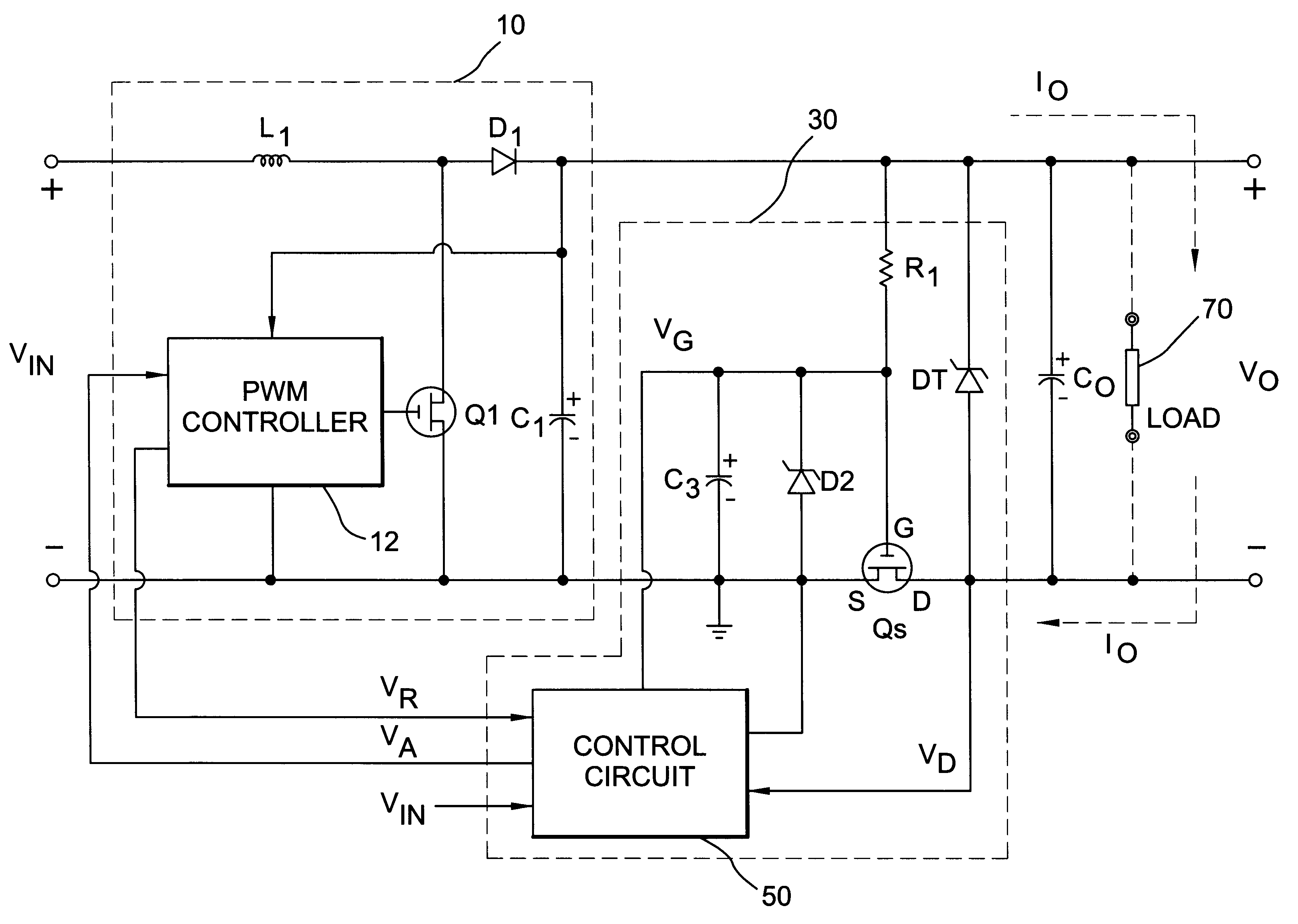

Protection circuit for a boost power converter

InactiveUS6185082B1Apparatus without intermediate ac conversionArrangements responsive to excess currentCurrent limitingTime delays

A protection circuit for a boost power converter provides input under-voltage protection and output over-voltage and over-current protection. The protection circuit includes a control power MOSFET connected in series between the ground of the boost power converter and the ground of the load. The arrangement of the circuit makes it easy to drive the gate of an N-channel power MOSFET and is ideal for current-limiting control, which utilizes the Rds-on of the MOSFET as a current sensing element. Neither a specific gate-driver nor a current sensing resistor is required, and thus high efficiency can be achieved. Furthermore, the slow slew-rate at the gate of the MOSFET provides a soft-start to the load. The protection circuit includes a temperature compensation circuitry to offset the variation of the Rds-on. A time delay circuit prevents the switching elements and protection elements from overload damage.

Owner:SEMICON COMPONENTS IND LLC

Insulated gate transistor incorporating diode

ActiveUS20050045960A1Effectively improve characteristicPromote recoveryAc-dc conversionSolid-state devicesPower MOSFETTransistor

A p-type base layer shaped like a well is formed for each of IGBT cells, and a p+-type collector layer and an n+-type cathode layer are formed on a surface opposite to a surface on which the p-type base layer is formed so as to be situated just below the p-type base layer. The p-type base layer of each of the IGBT cells includes a flat region including an emitter region and a bottom surface penetrated by a main trench, and first and second side diffusion regions between which the flat region is interposed. The first side diffusion region is situated just above the n+-type cathode layer and each of the bottom surfaces of the side diffusion regions forms a parabola-shaped smooth curve in longitudinal section. By replacing the p+-type collector layer with the n+-type cathode layer, it is possible to apply features of the above structure to a power MOSFET.

Owner:MITSUBISHI ELECTRIC CORP

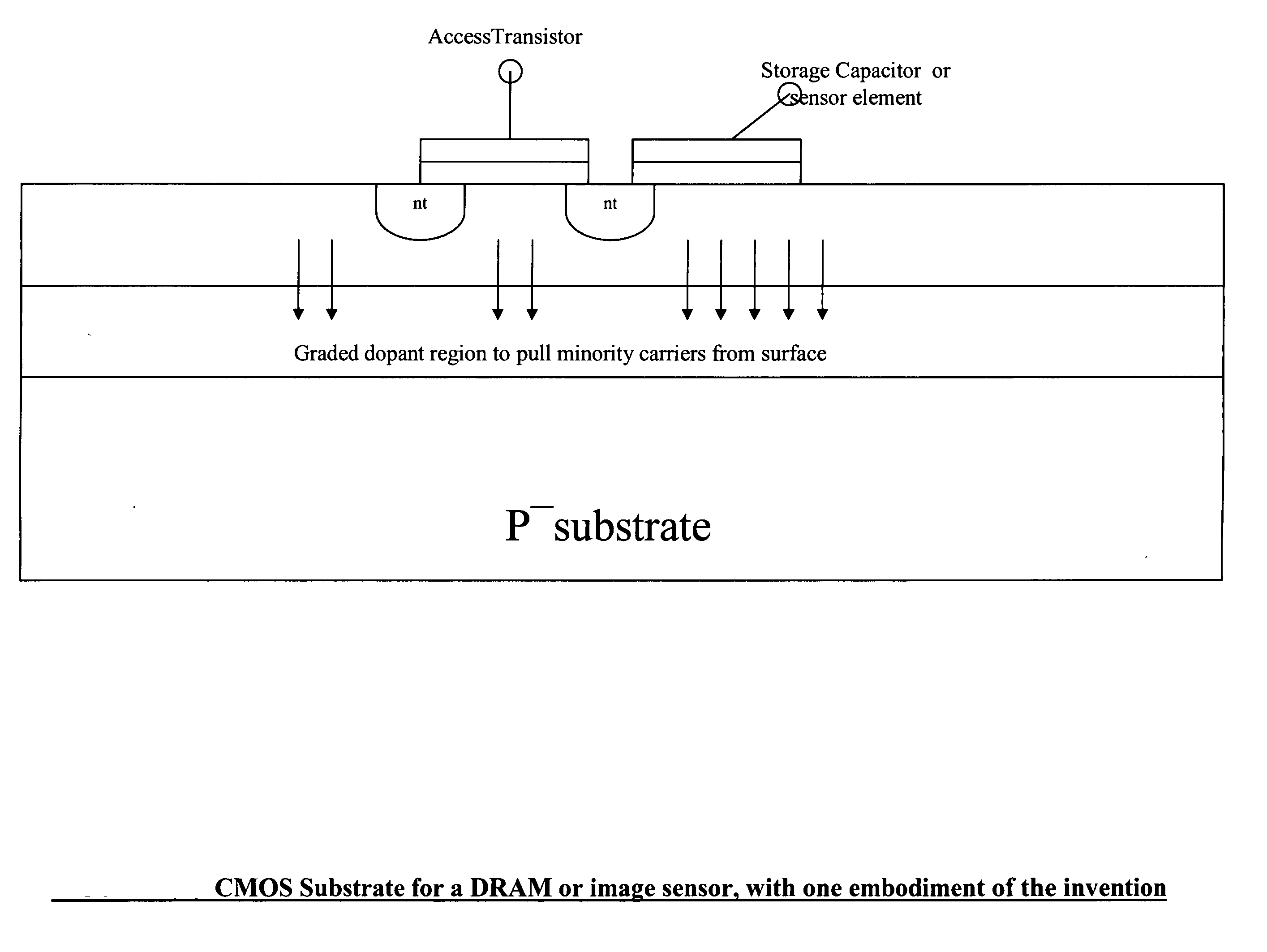

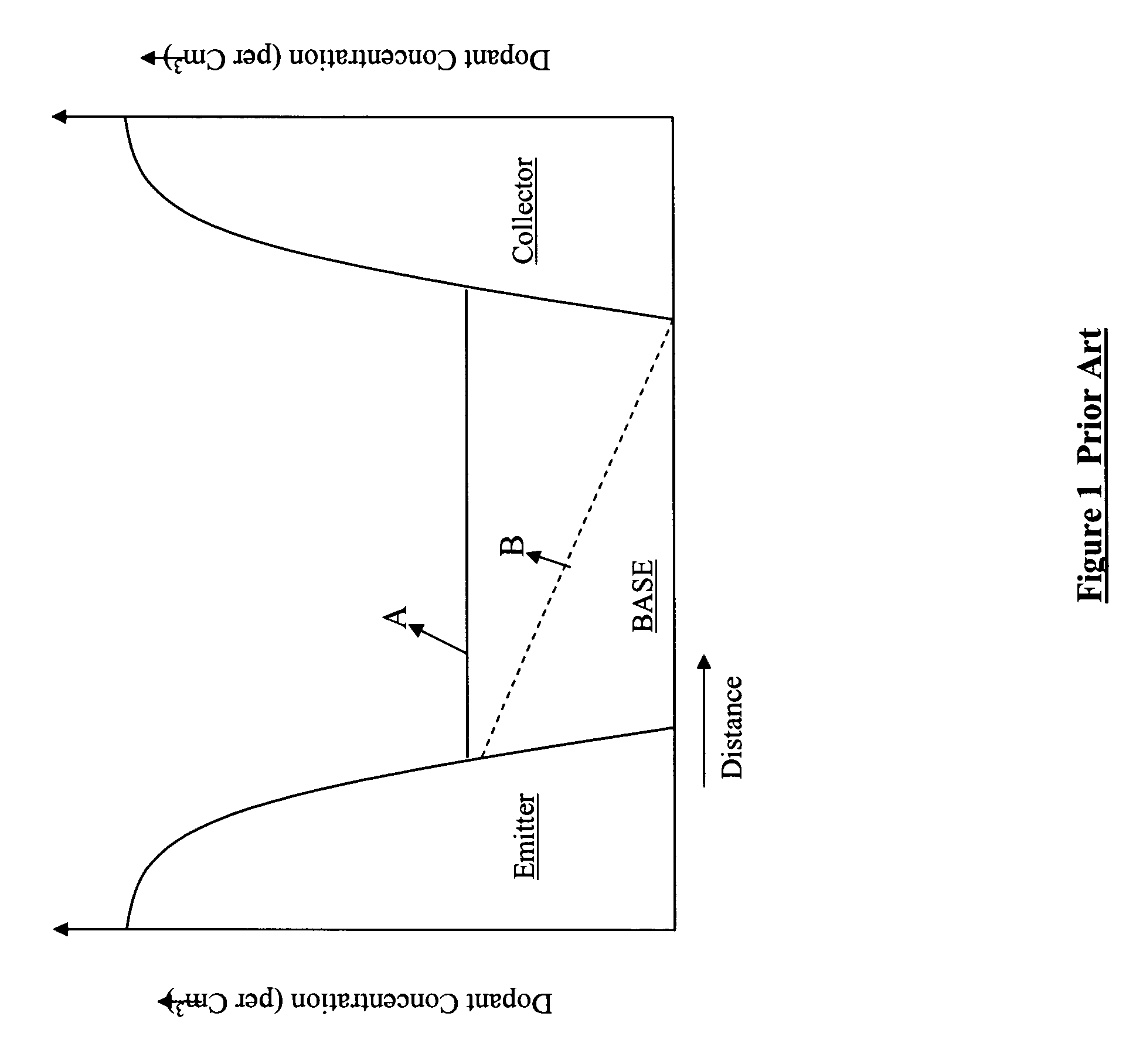

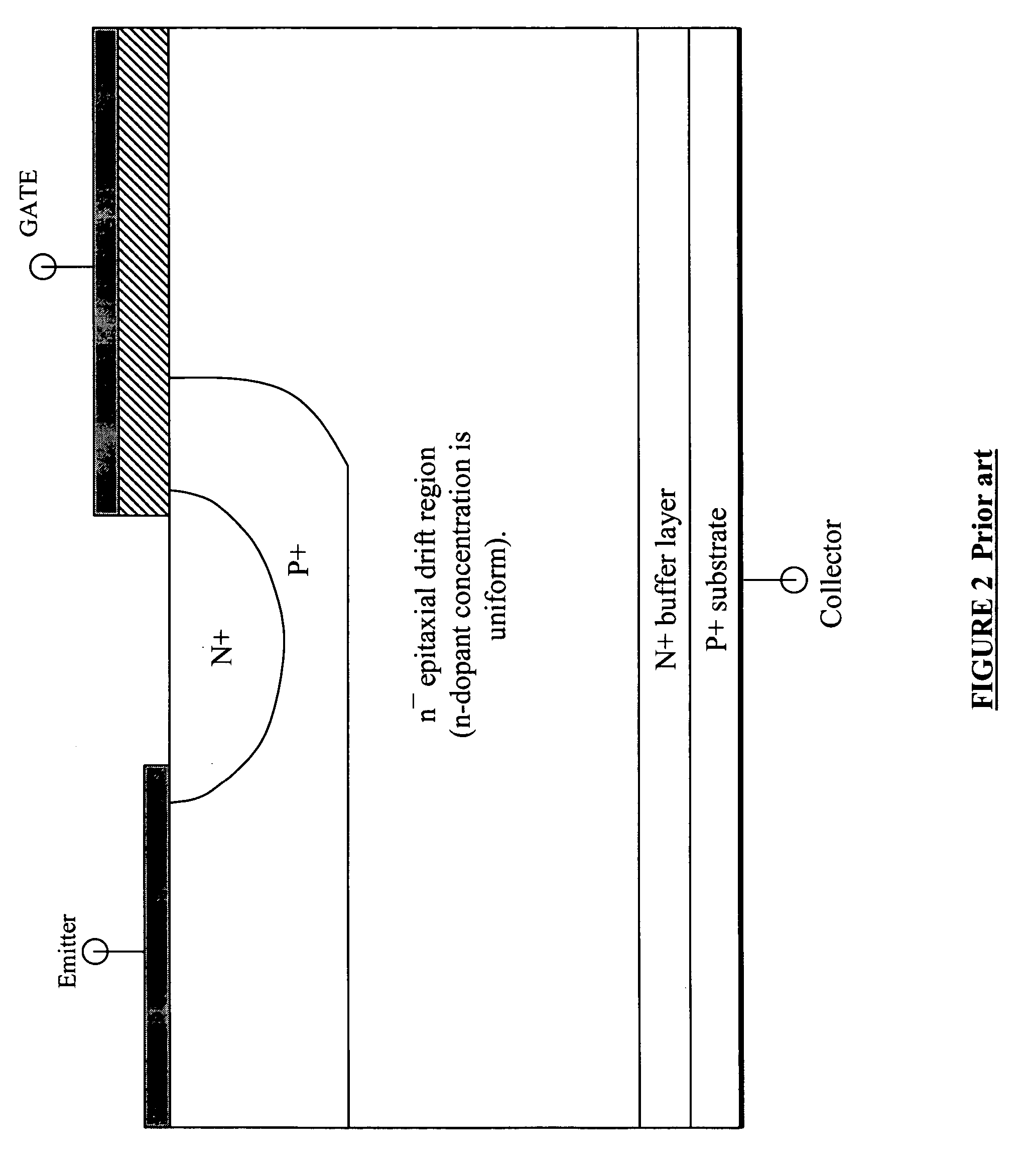

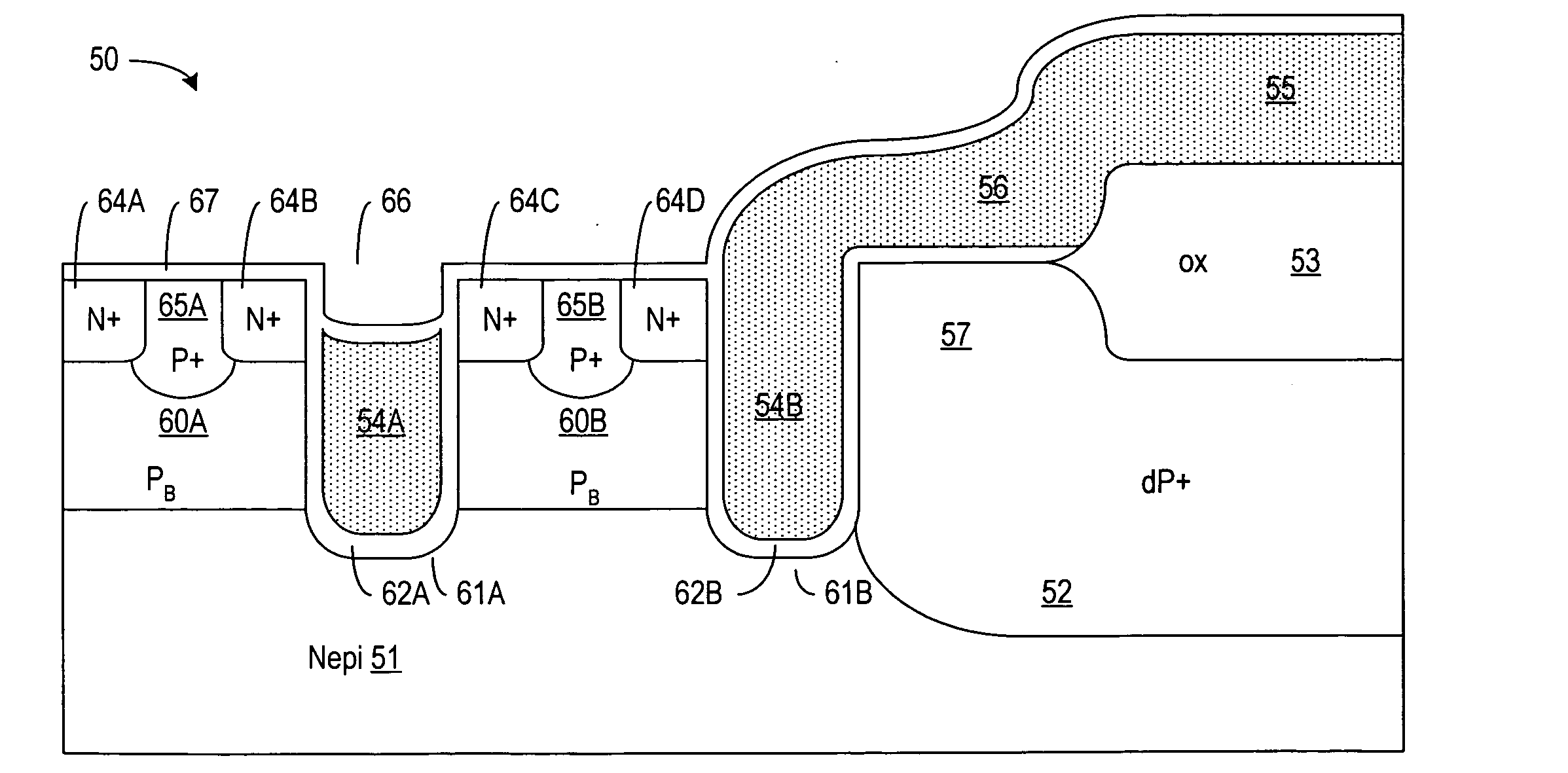

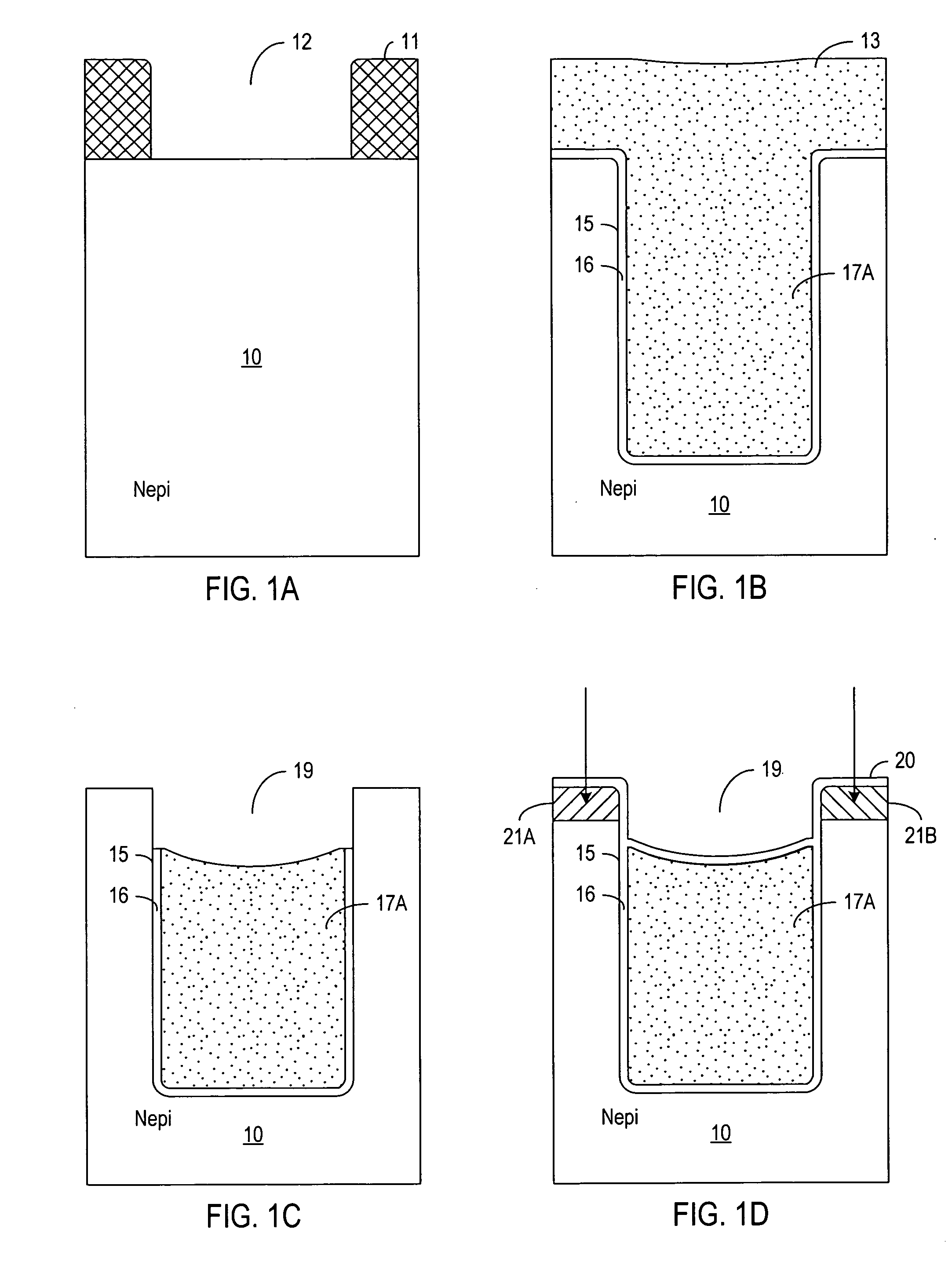

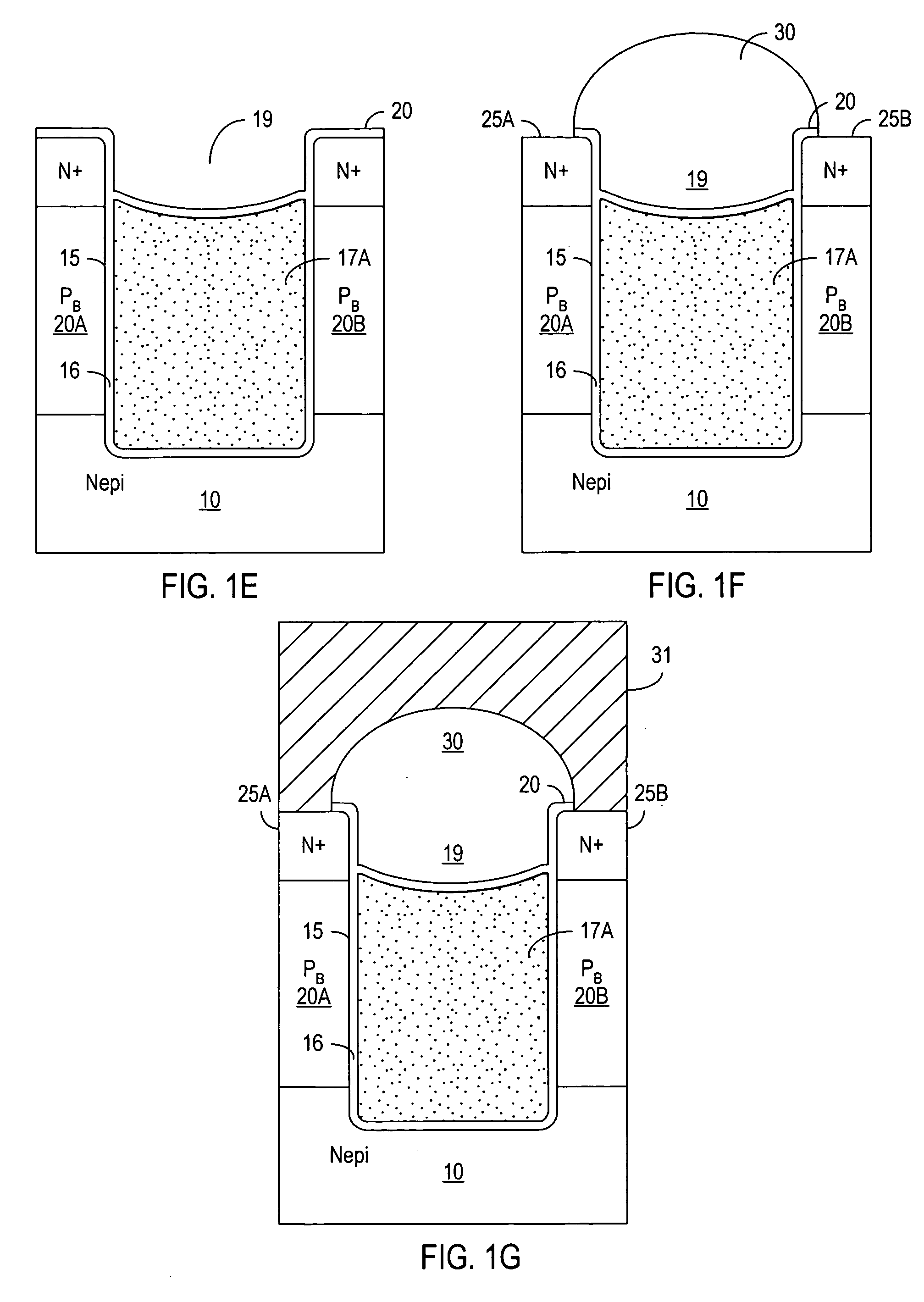

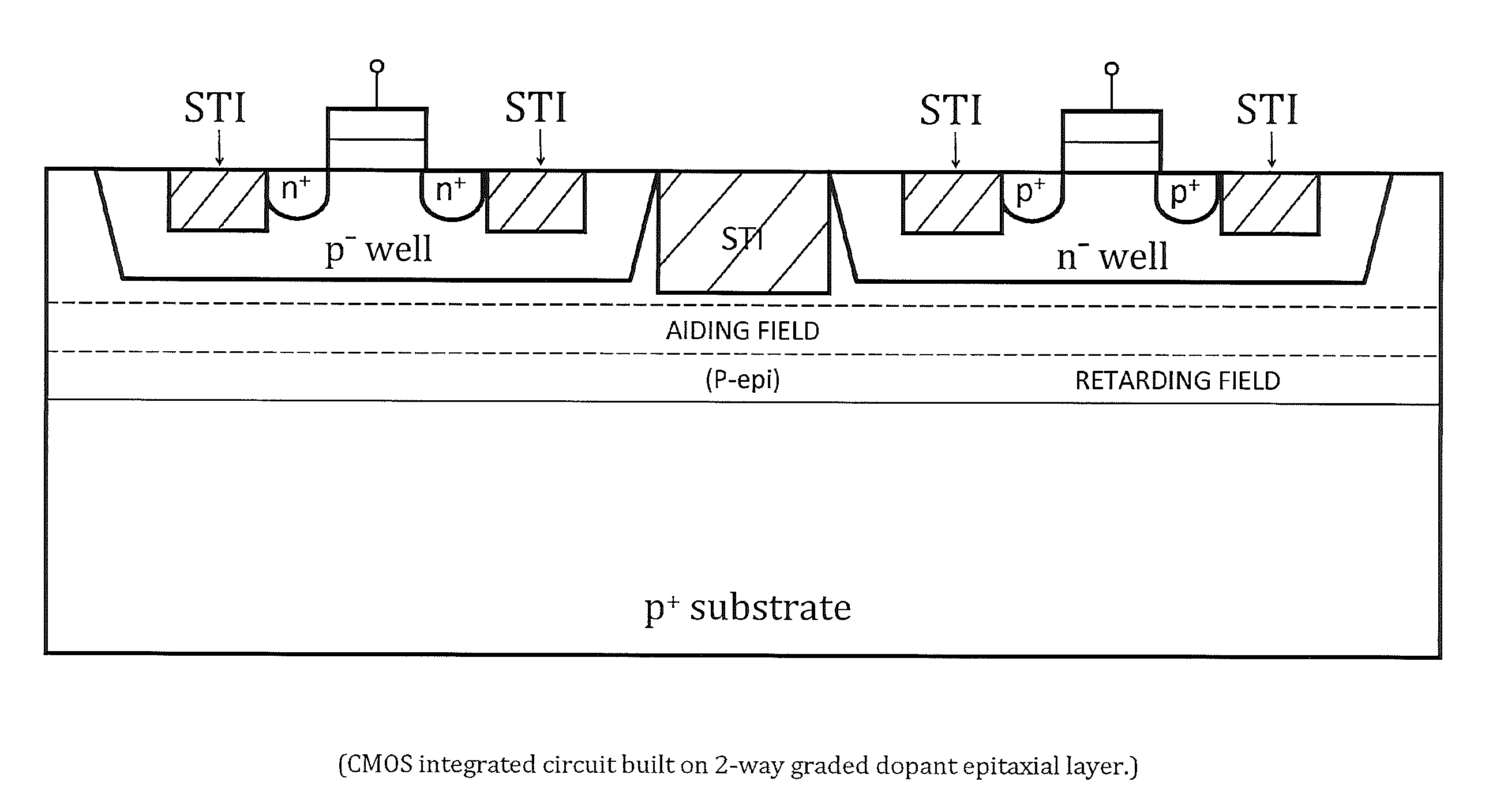

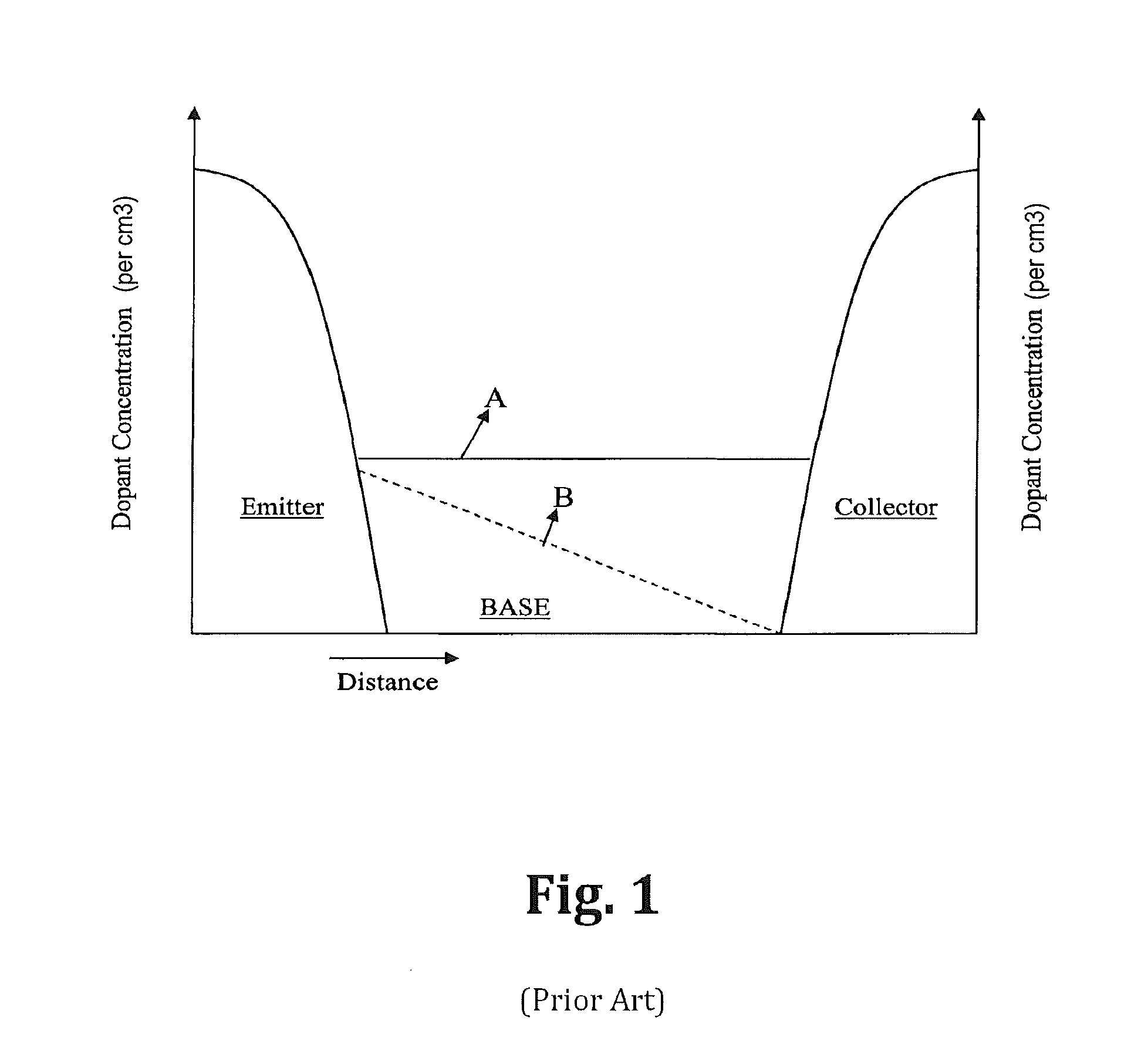

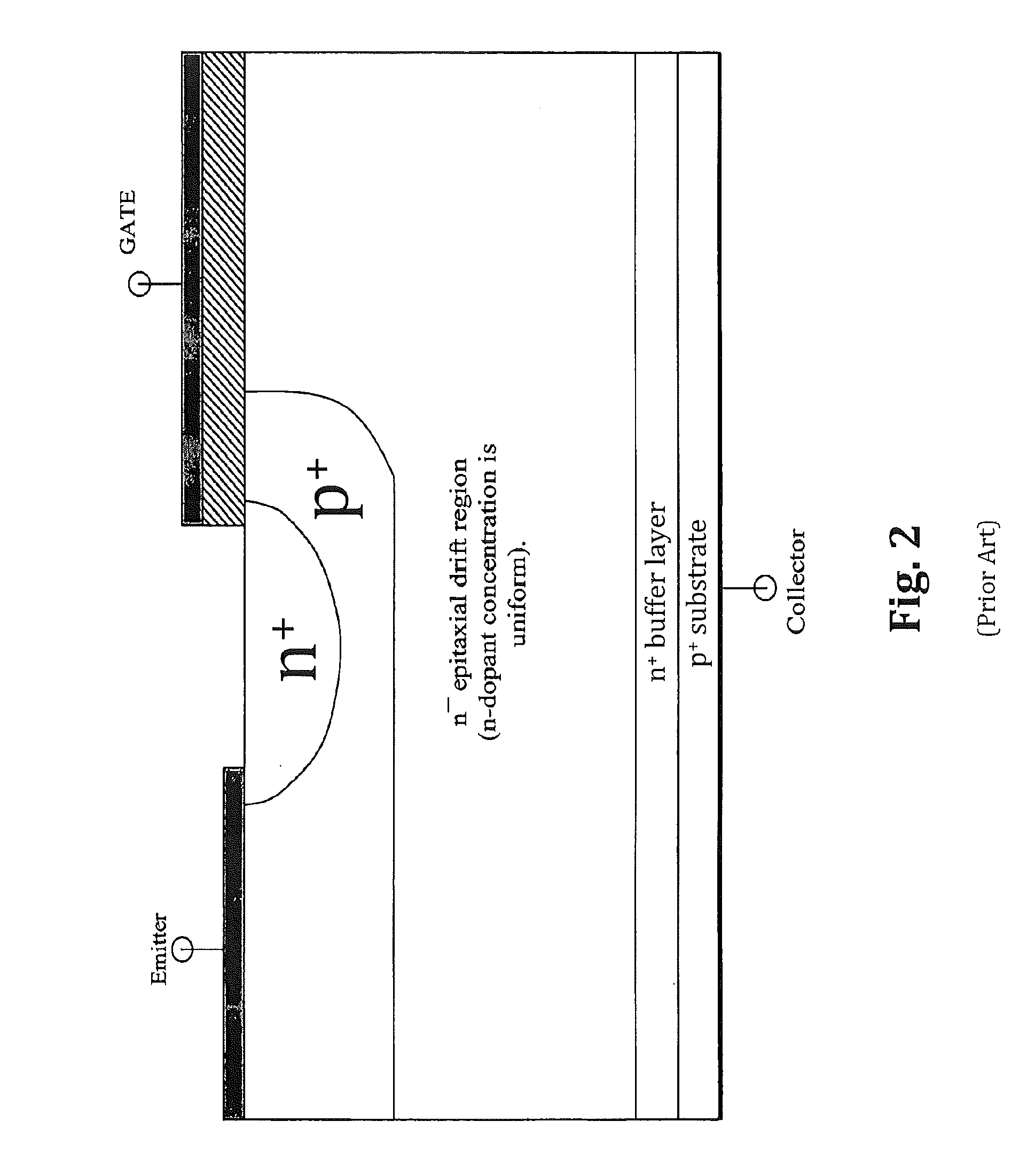

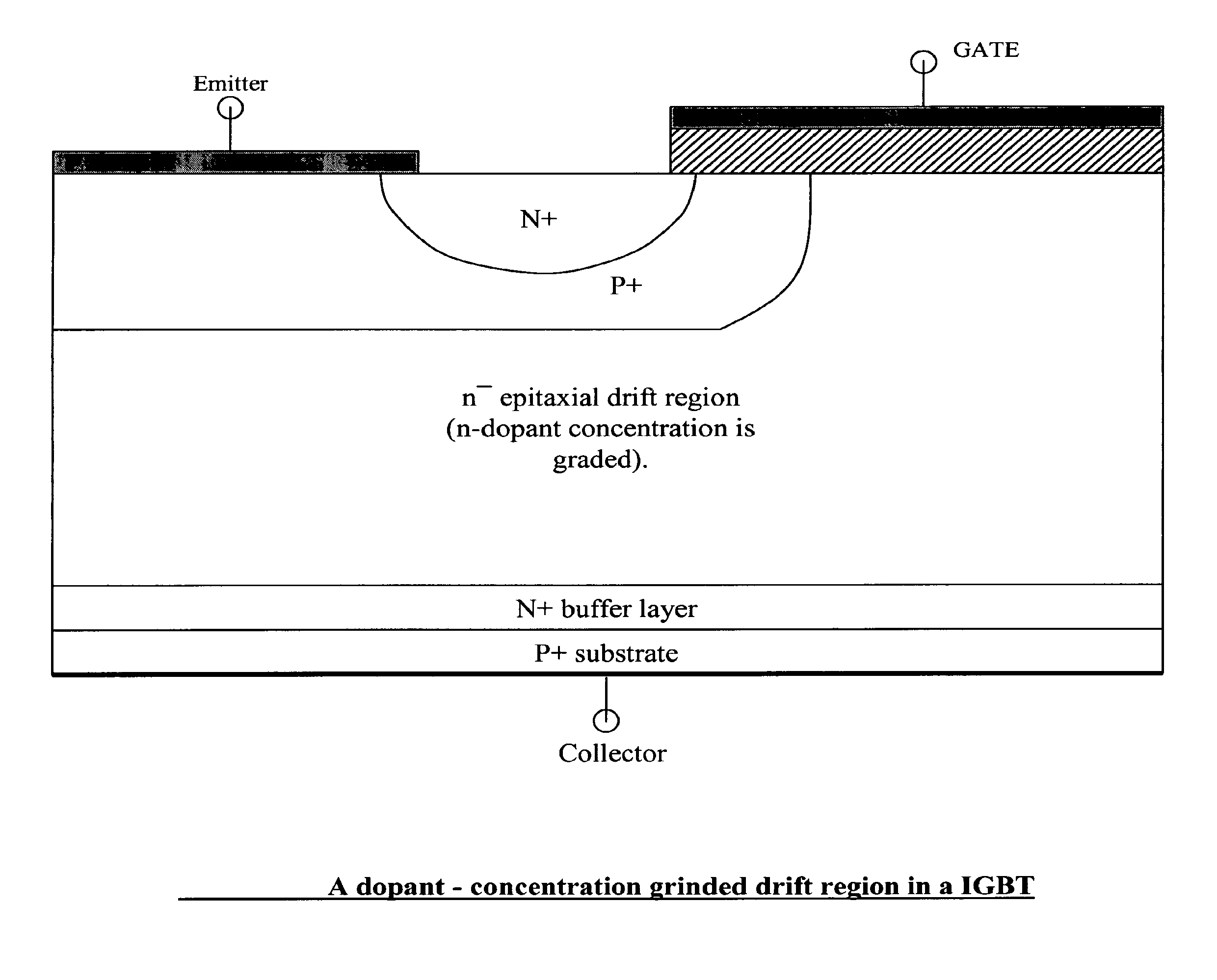

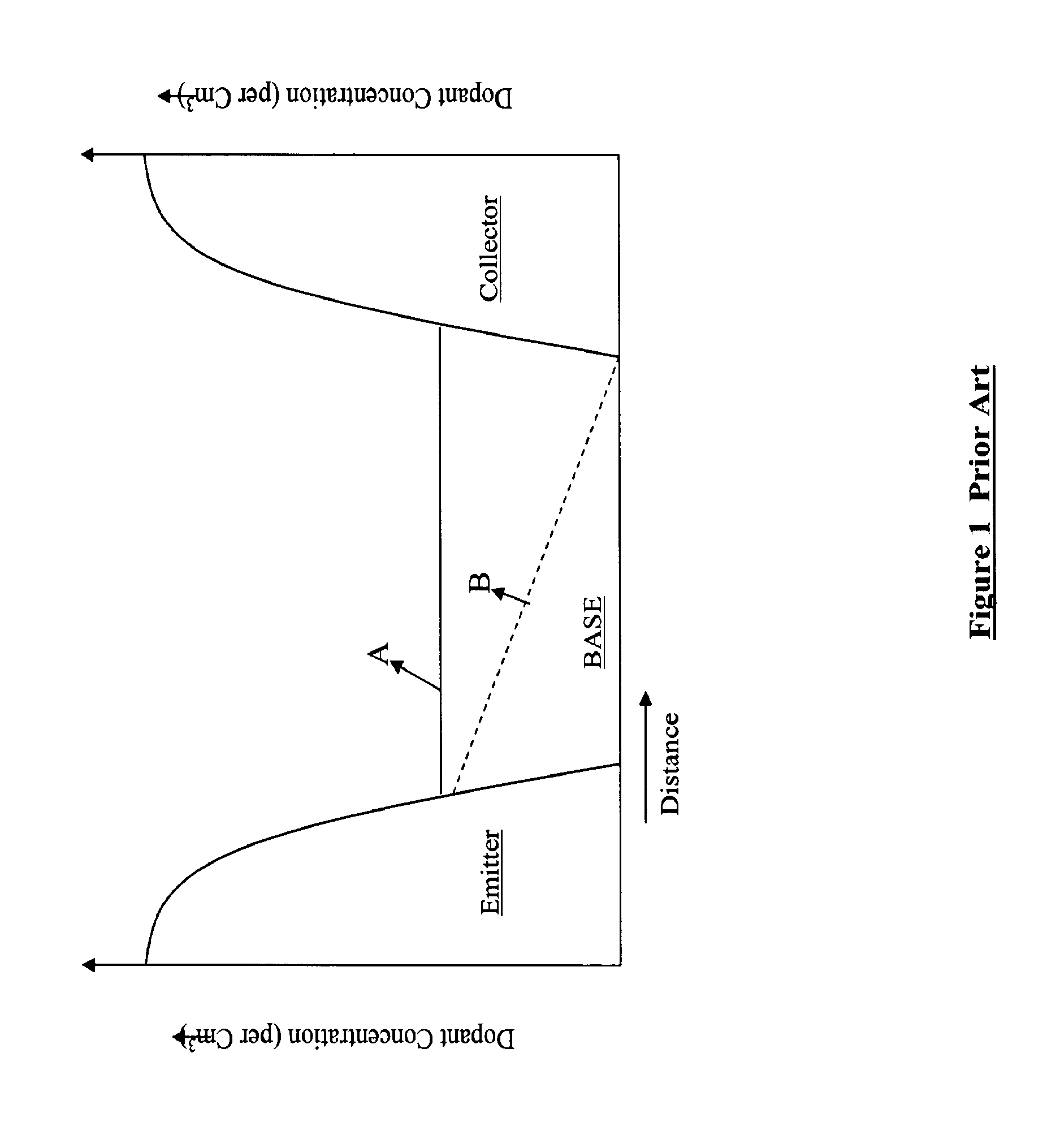

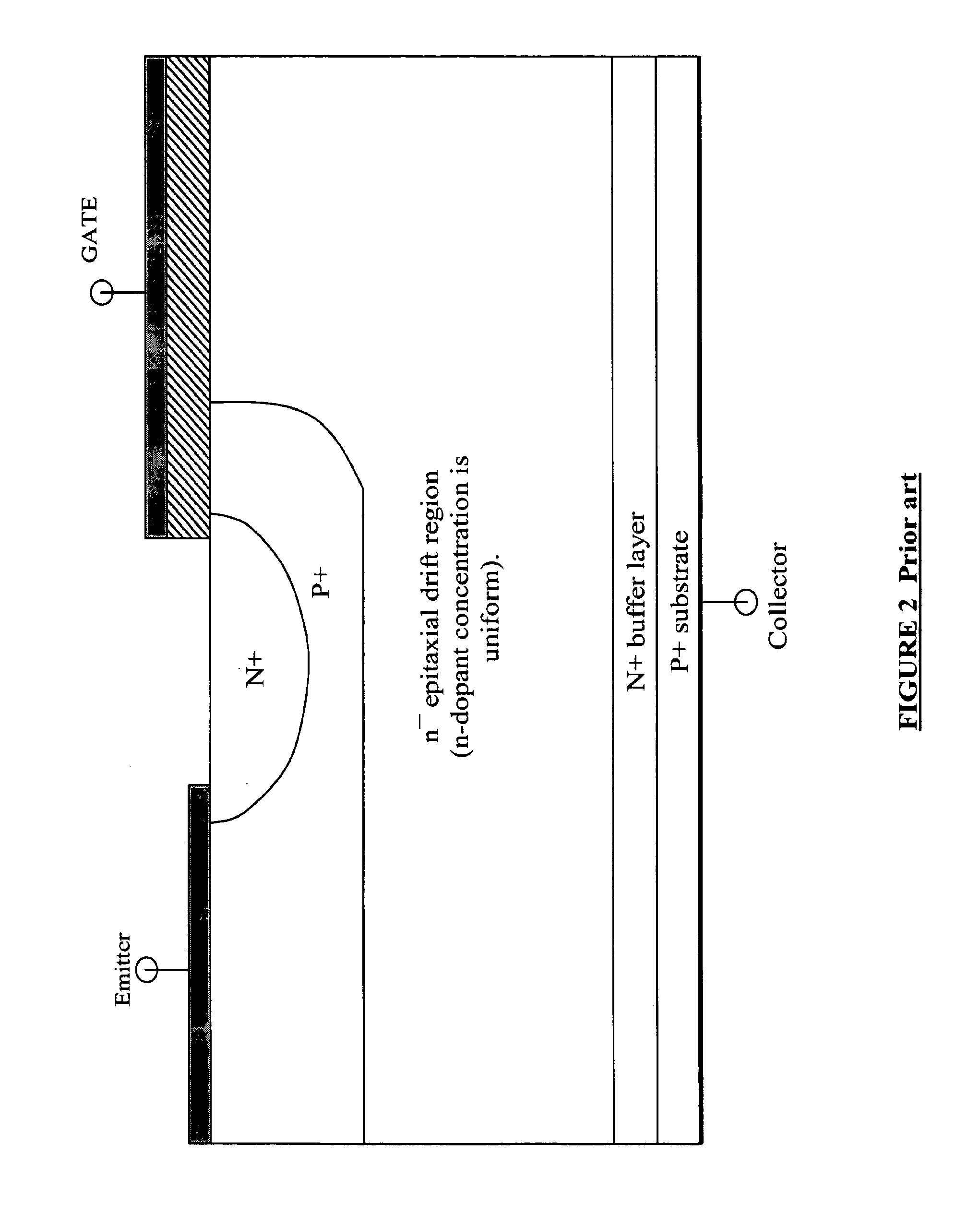

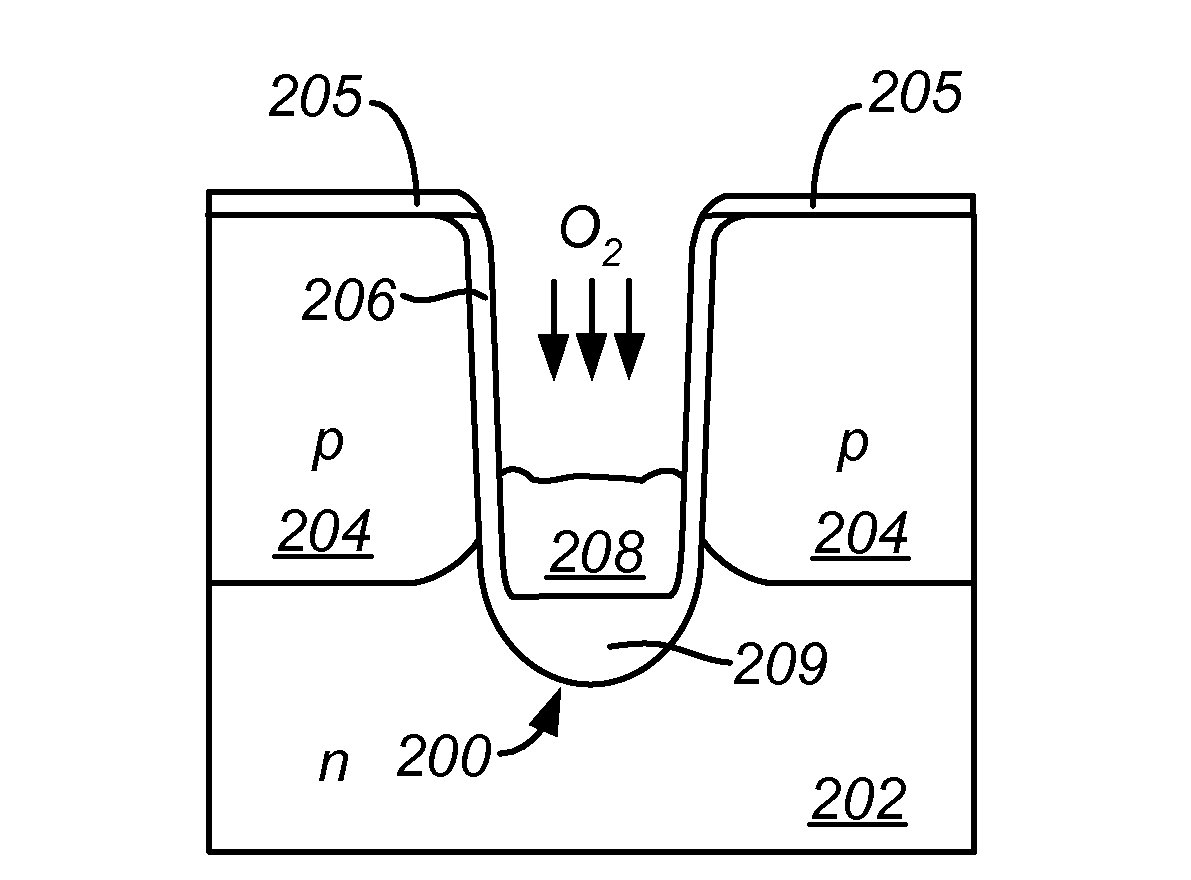

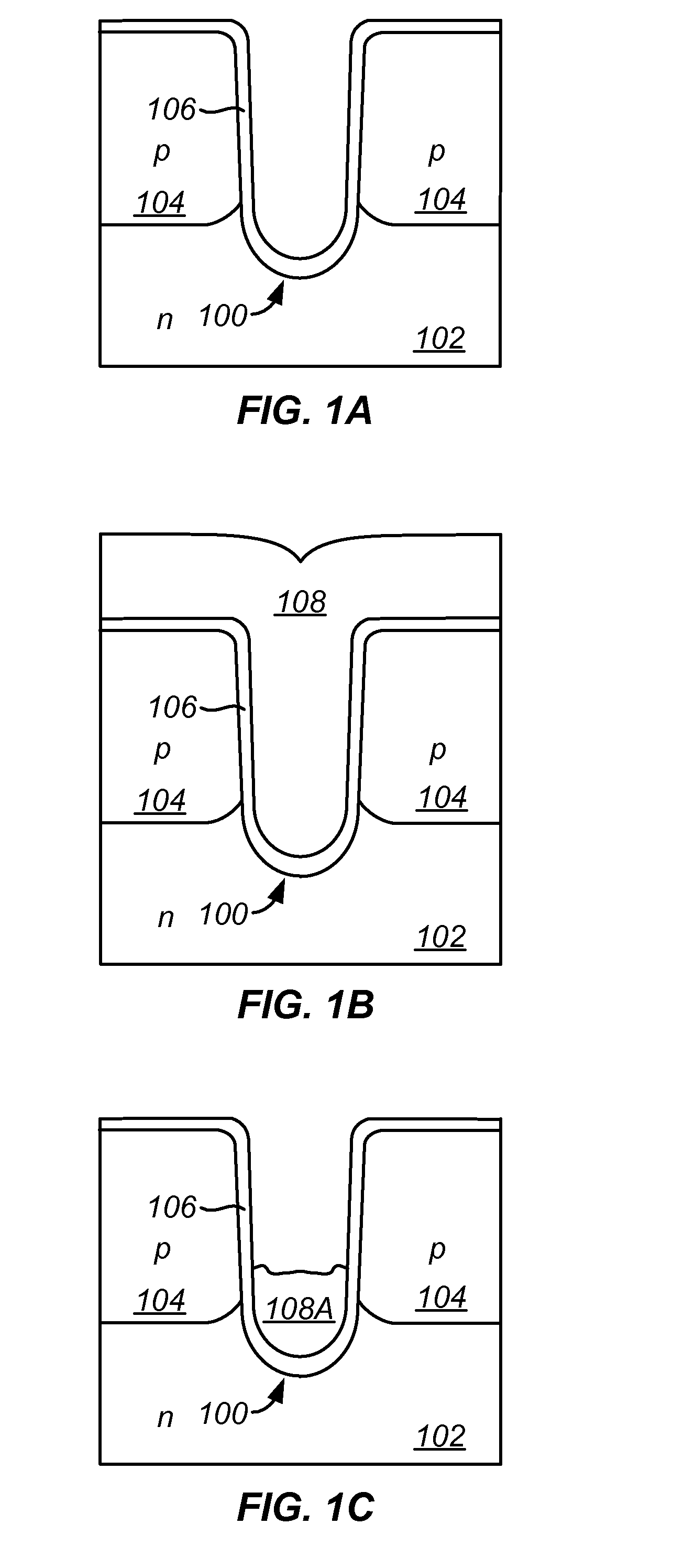

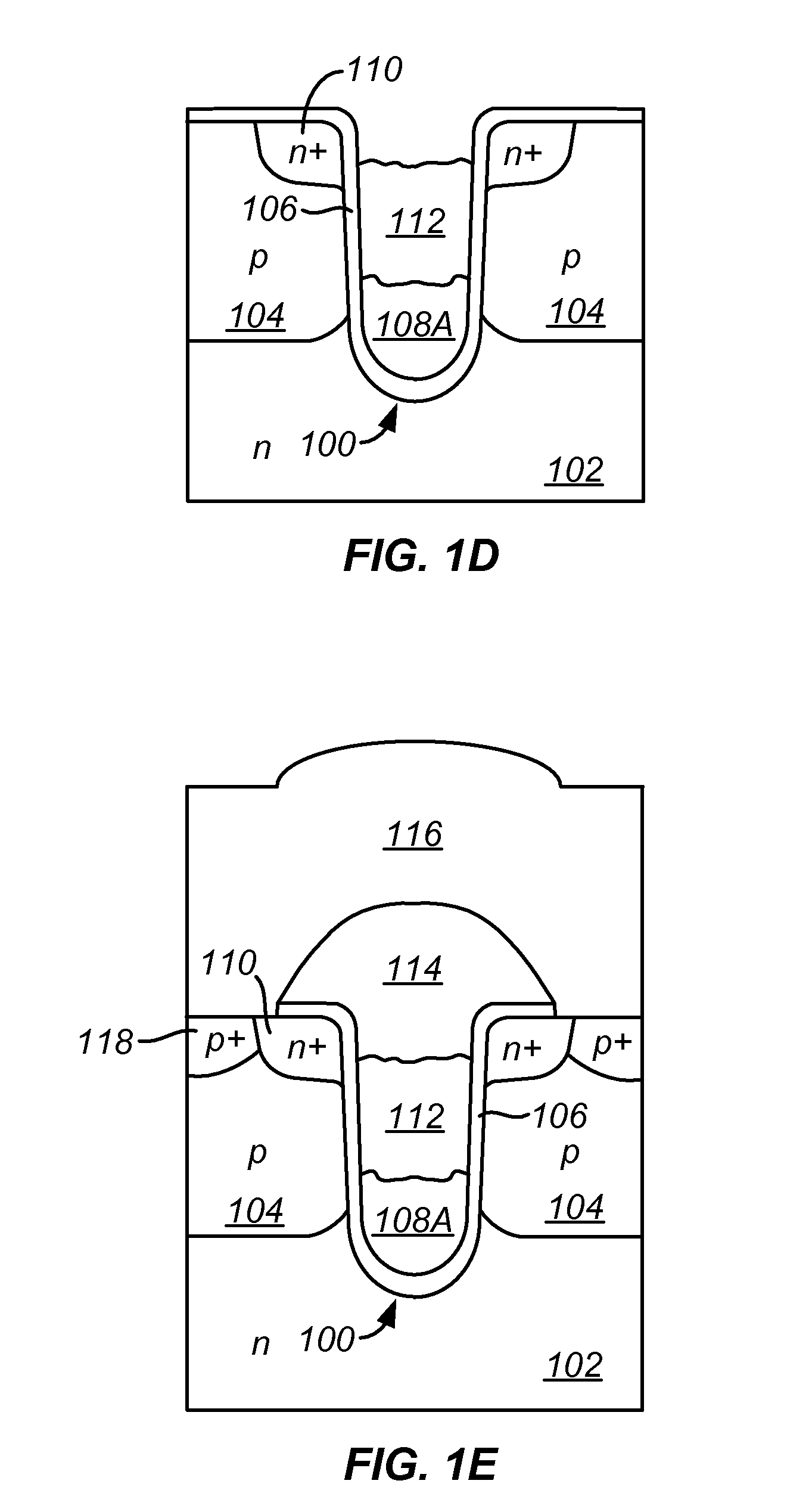

Semiconductor devices with graded dopant regions

Most semiconductor devices manufactured today, have uniform dopant concentration, either in the lateral or vertical device active (and isolation) regions. By grading the dopant concentration, the performance in various semiconductor devices can be significantly improved. Performance improvements can be obtained in application specific areas like increase in frequency of operation for digital logic, various power MOSFET and IGBT ICS, improvement in refresh time for DRAM's, decrease in programming time for nonvolatile memory, better visual quality including pixel resolution and color sensitivity for imaging ICs, better sensitivity for varactors in tunable filters, higher drive capabilities for JFET's, and a host of other applications.

Owner:GREENTHREAD

Trench power MOSFET with planarized gate bus

InactiveUS20040173844A1Increase contactMaximize device densitySemiconductor/solid-state device manufacturingSemiconductor devicesPower MOSFETSubstrate surface

Power MOSFETs and fabrication processes for power MOSFETs use a continuous conductive gate structure within trenches to avoid problems arising from device topology caused when a gate bus extends above a substrate surface. The conductive gate structure forms gates in device trenches in an active device region and forms a gate bus in a gate bus trench. The gate bus trench that connects to the device trenches can be wide to facilitate forming a gate contact to the gate bus, while the device trenches can be narrow to maximize device density. CMP process can be used to planarize the conductive gate structure and / or overlying insulating layers. The processes are compatible with processes forming self-aligned or conventional contacts in the active device region.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED +1

Semiconductor devices with graded dopant regions

ActiveUS8106481B2Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringPower MOSFET

Most semiconductor devices manufactured today, have uniform dopant concentration, either in the lateral or vertical device active (and isolation) regions. By grading the dopant concentration, the performance in various semiconductor devices can be significantly improved. Performance improvements can be obtained in application specific areas like increase in frequency of operation for digital logic, various power MOSFET and IGBT ICS, improvement in refresh time for DRAM's, decrease in programming time for nonvolatile memory, better visual quality including pixel resolution and color sensitivity for imaging ICs, better sensitivity for varactors in tunable filters, higher drive capabilities for JFET's, and a host of other applications.

Owner:GREENTHREAD

Semiconductor devices with graded dopant regions

Most semiconductor devices manufactured today, have uniform dopant concentration, either in the lateral or vertical device active (and isolation) regions. By grading the dopant concentration, the performance in various semiconductor devices can be significantly improved. Performance improvements can be obtained in application specific areas like increase in frequency of operation for digital logic, various power MOSFET and IGBT ICS, improvement in refresh time for DRAM's, decrease in programming time for nonvolatile memory, better visual quality including pixel resolution and color sensitivity for imaging ICs, better sensitivity for varactors in tunable filters, higher drive capabilities for JFET's, and a host of other applications.

Owner:GREENTHREAD

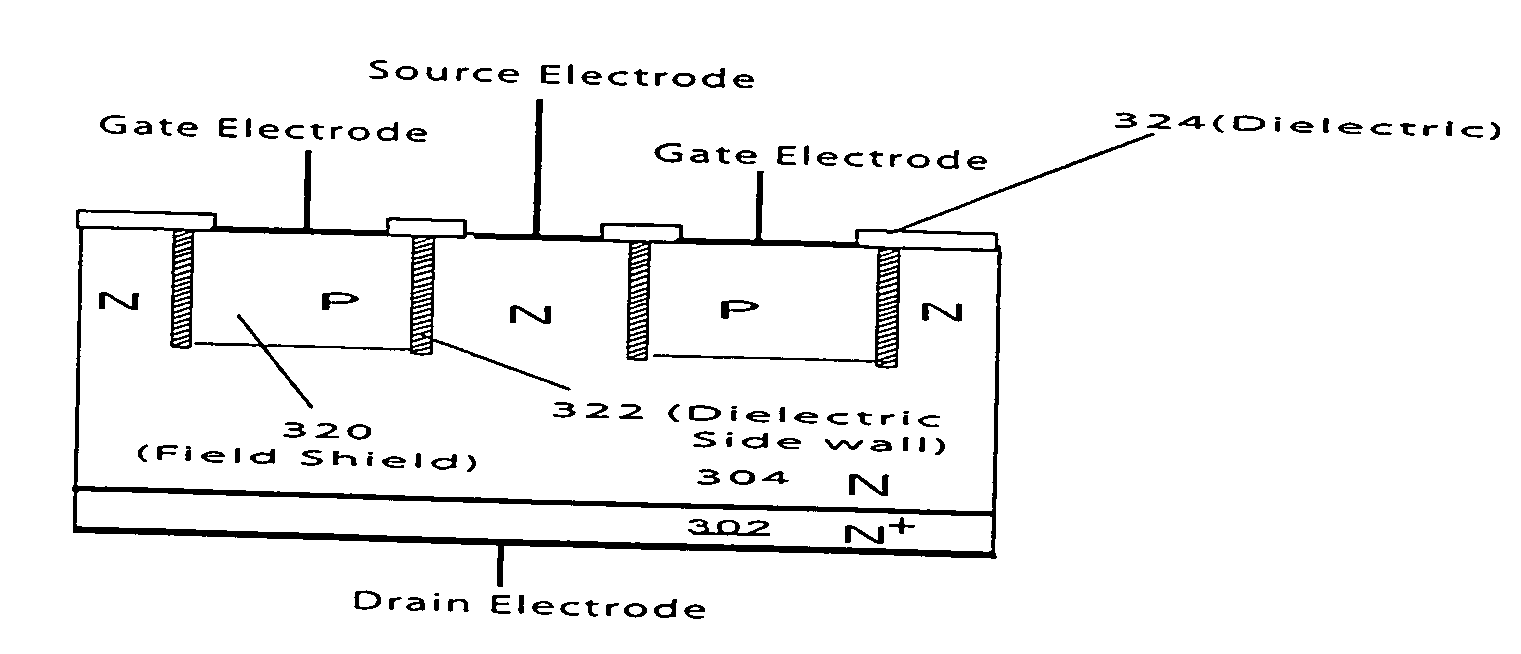

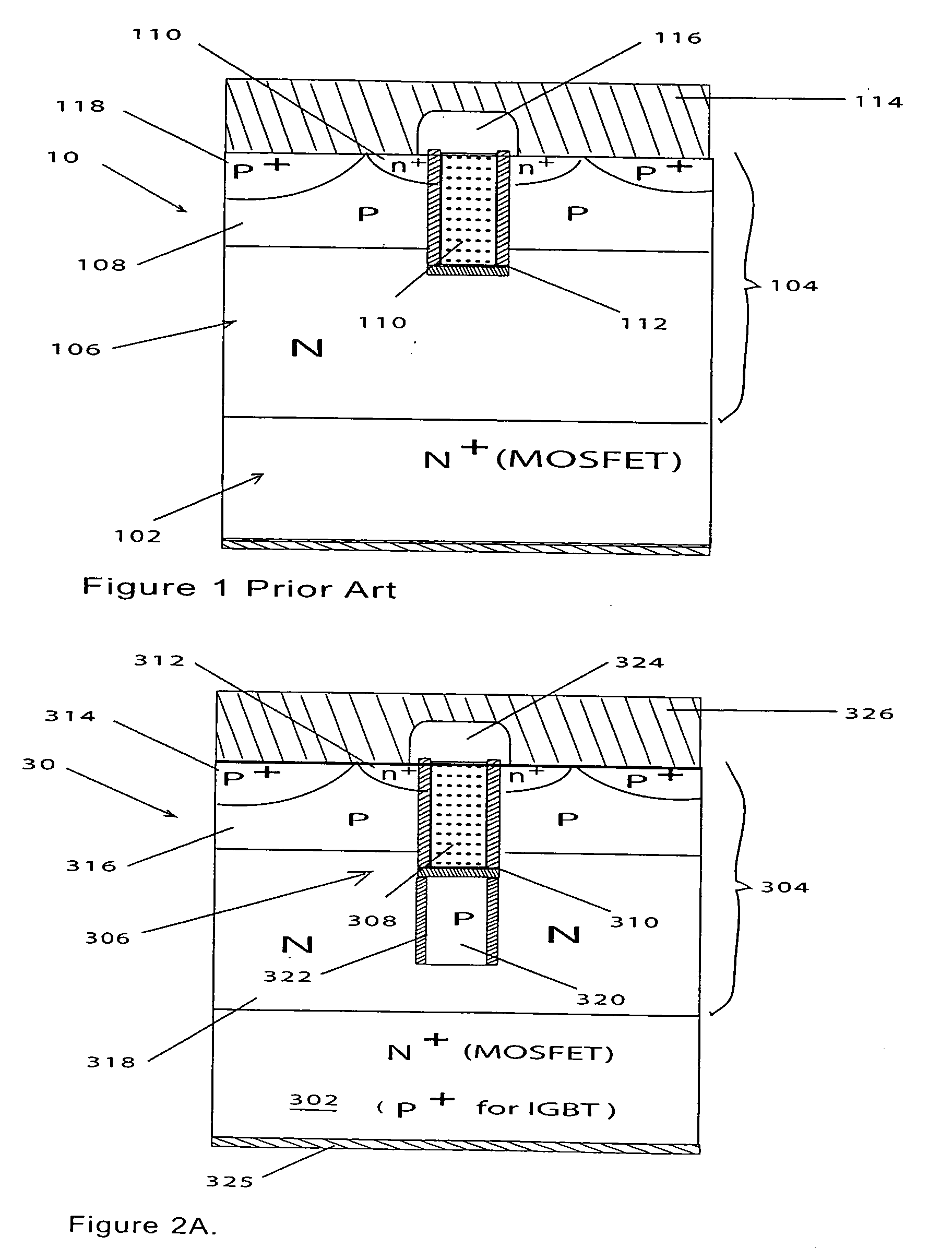

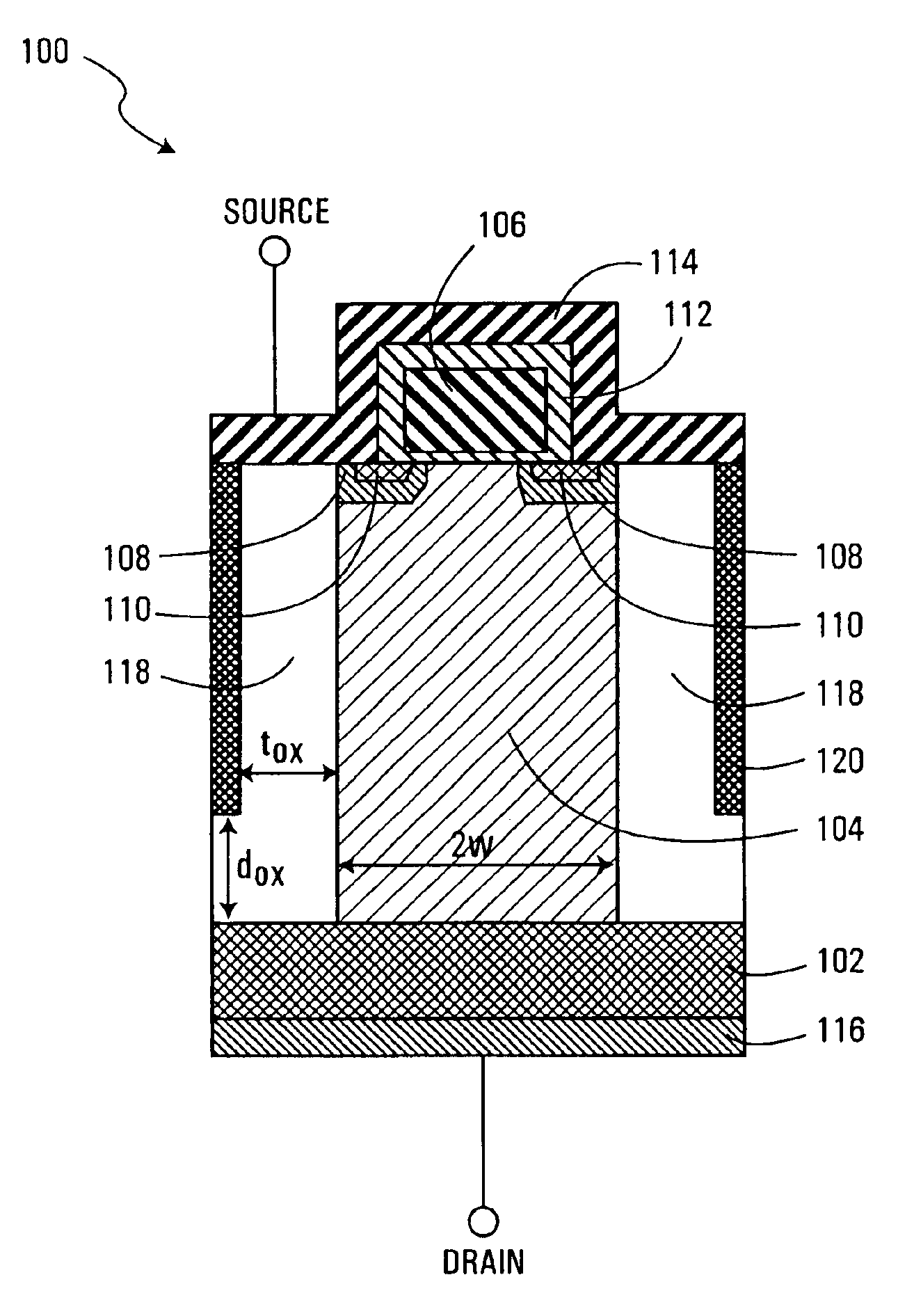

Semiconductor device containing dielectrically isolated pn junction for enhanced breakdown characteristics

InactiveUS20050167695A1Increased avalanche breakdown voltageLower on-resistanceThyristorSemiconductor/solid-state device manufacturingDevice materialPower MOSFET

A semiconductor device includes a field shield region that is doped opposite to the conductivity of the substrate and is bounded laterally by dielectric sidewall spacers and from below by a PN junction. For example, in a trench-gated MOSFET the field shield region may be located beneath the trench and may be electrically connected to the source region. When the MOSFET is reverse-biased, depletion regions extend from the dielectric sidewall spacers into the “drift” region, shielding the gate oxide from high electric fields and increasing the avalanche breakdown voltage of the device. This permits the drift region to be more heavily doped and reduces the on-resistance of the device. It also allows the use of a thin, 20 Å gate oxide for a power MOSFET that is to be switched with a 1V signal applied to its gate while being able to block over 30V applied across its drain and source electrodes, for example.

Owner:ALPHA & OMEGA SEMICON INC

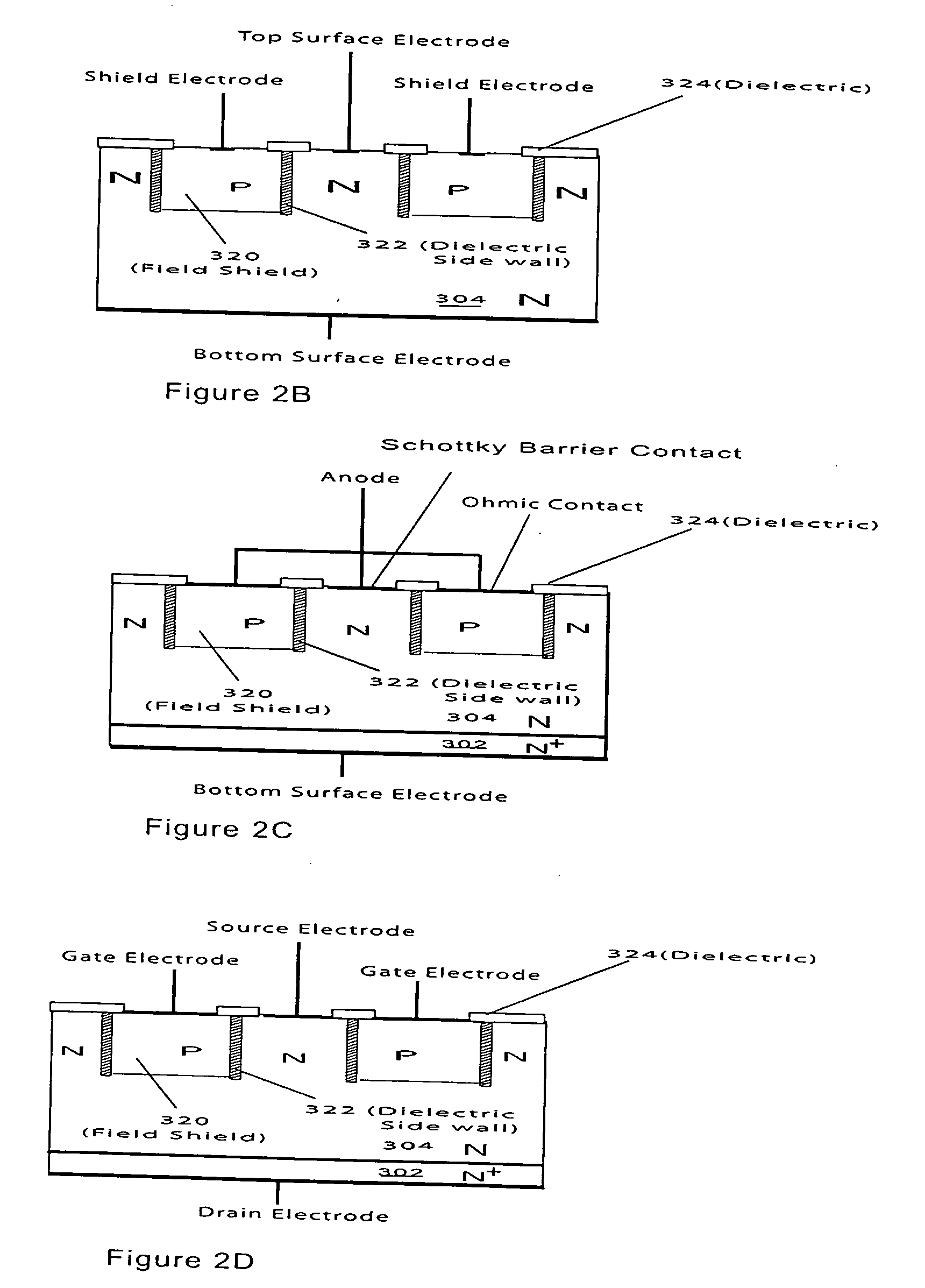

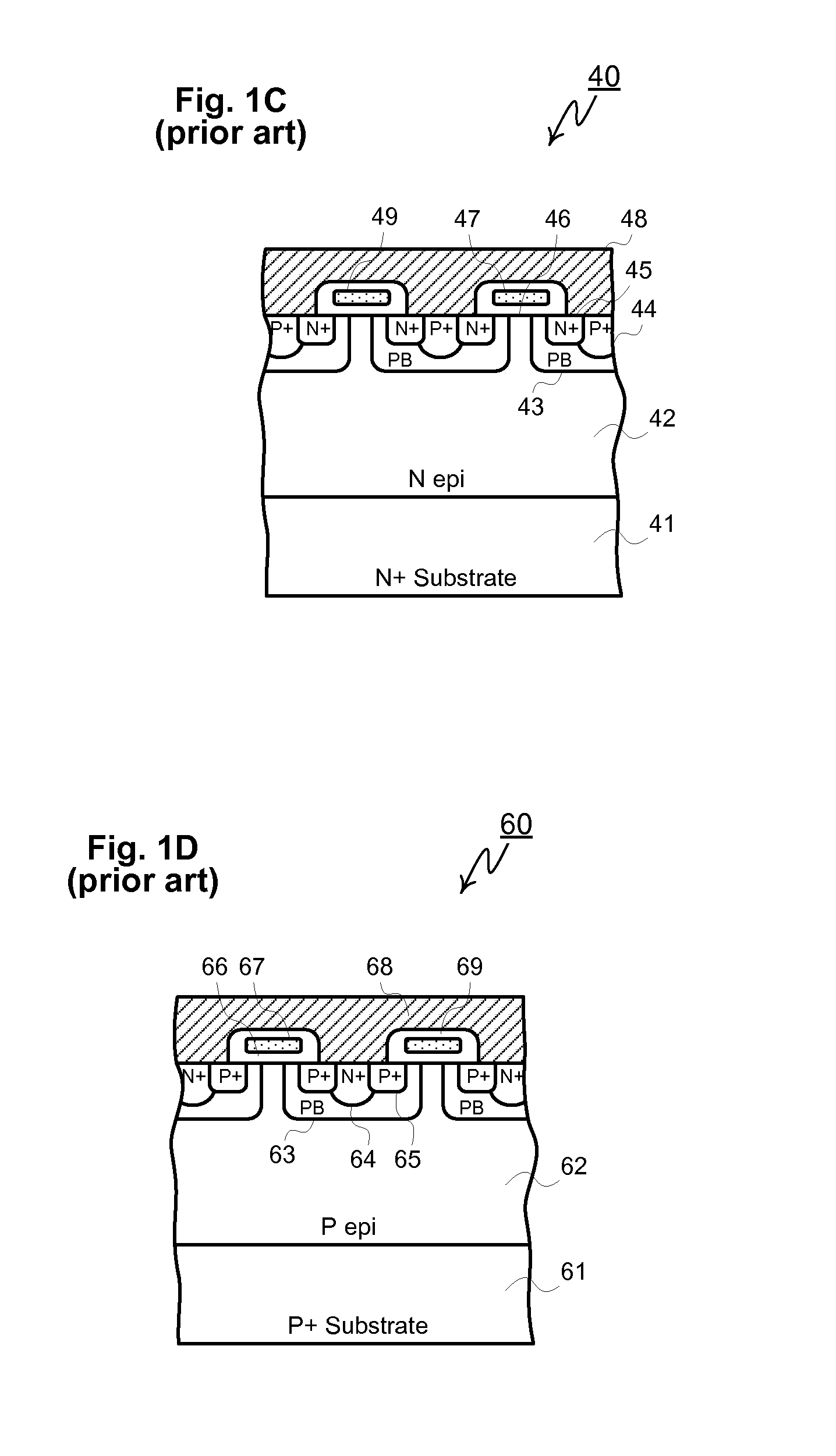

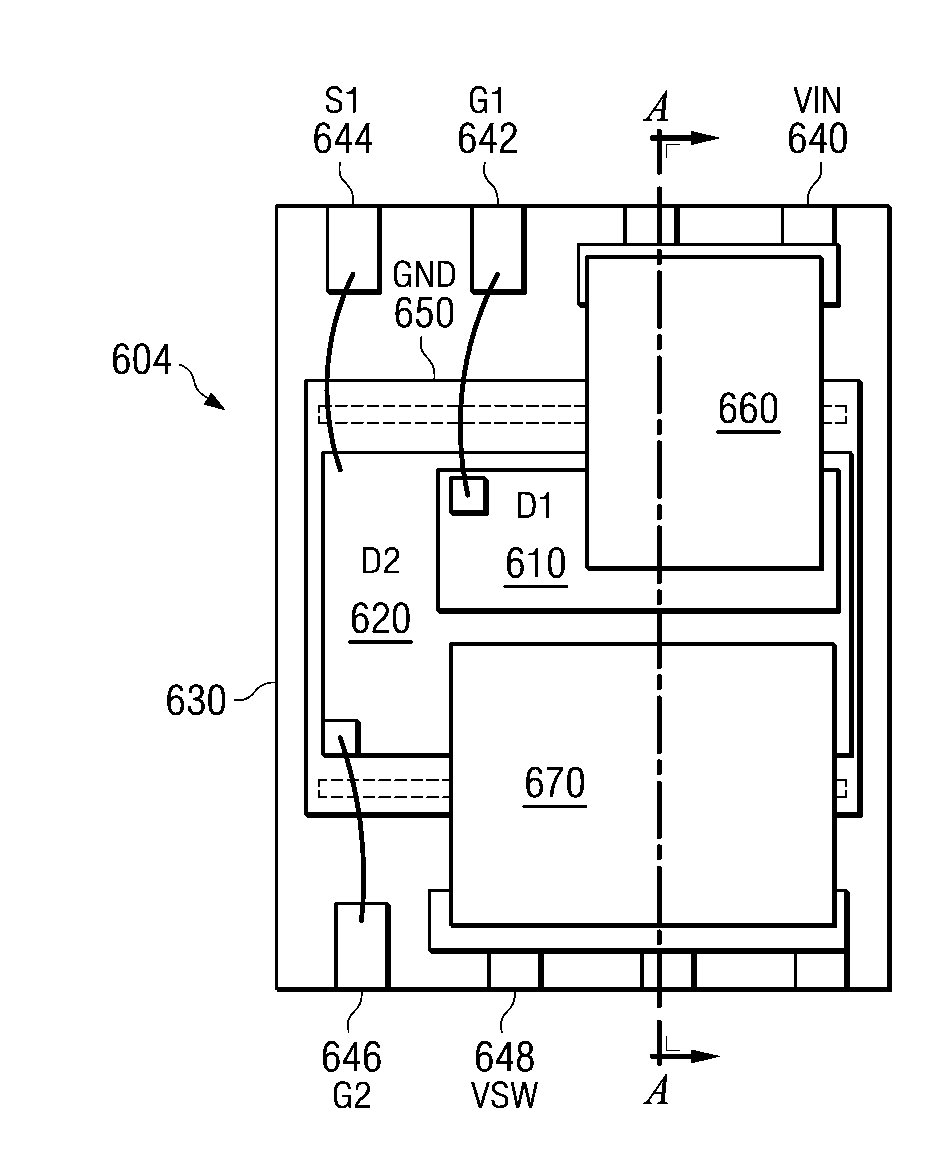

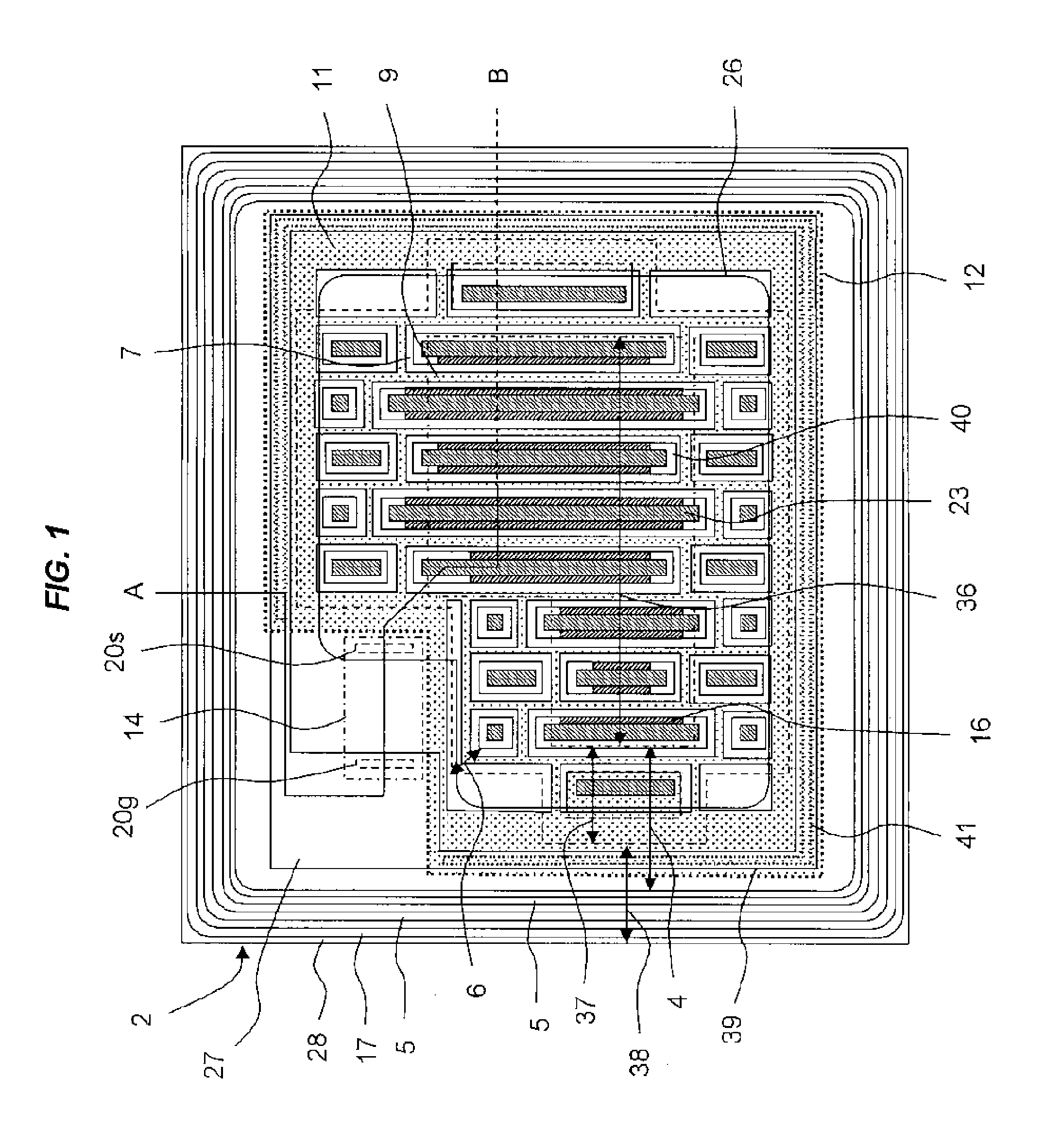

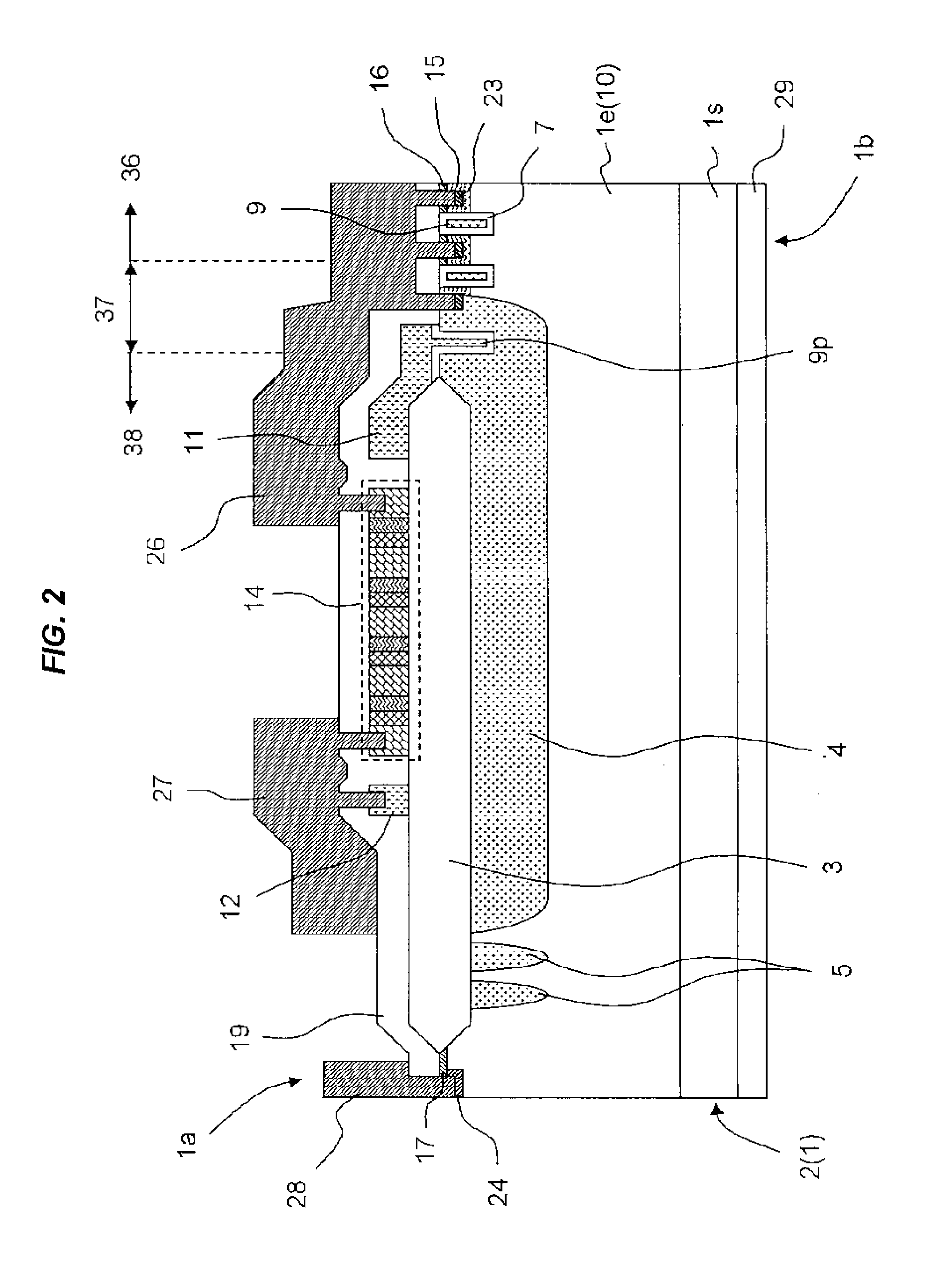

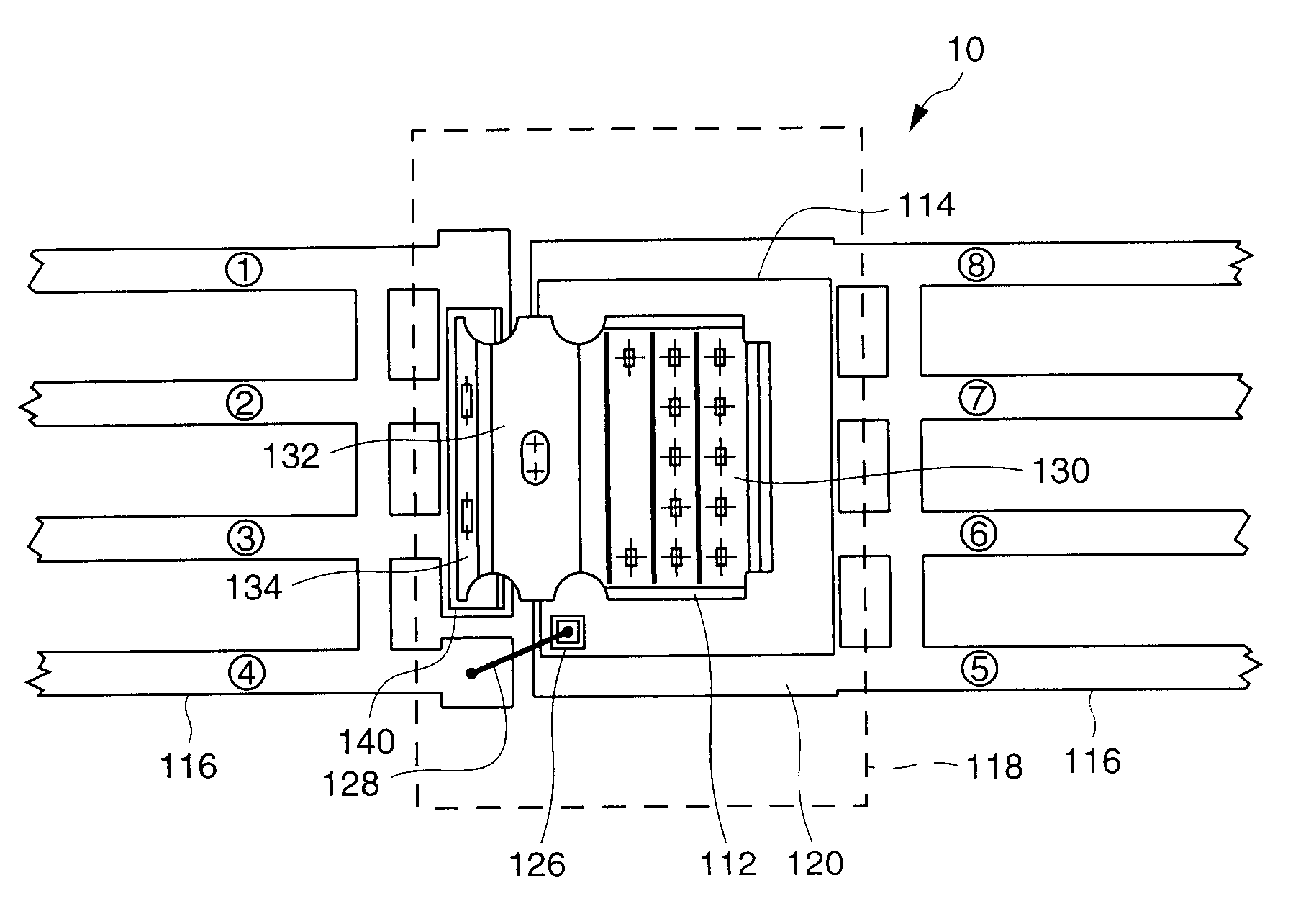

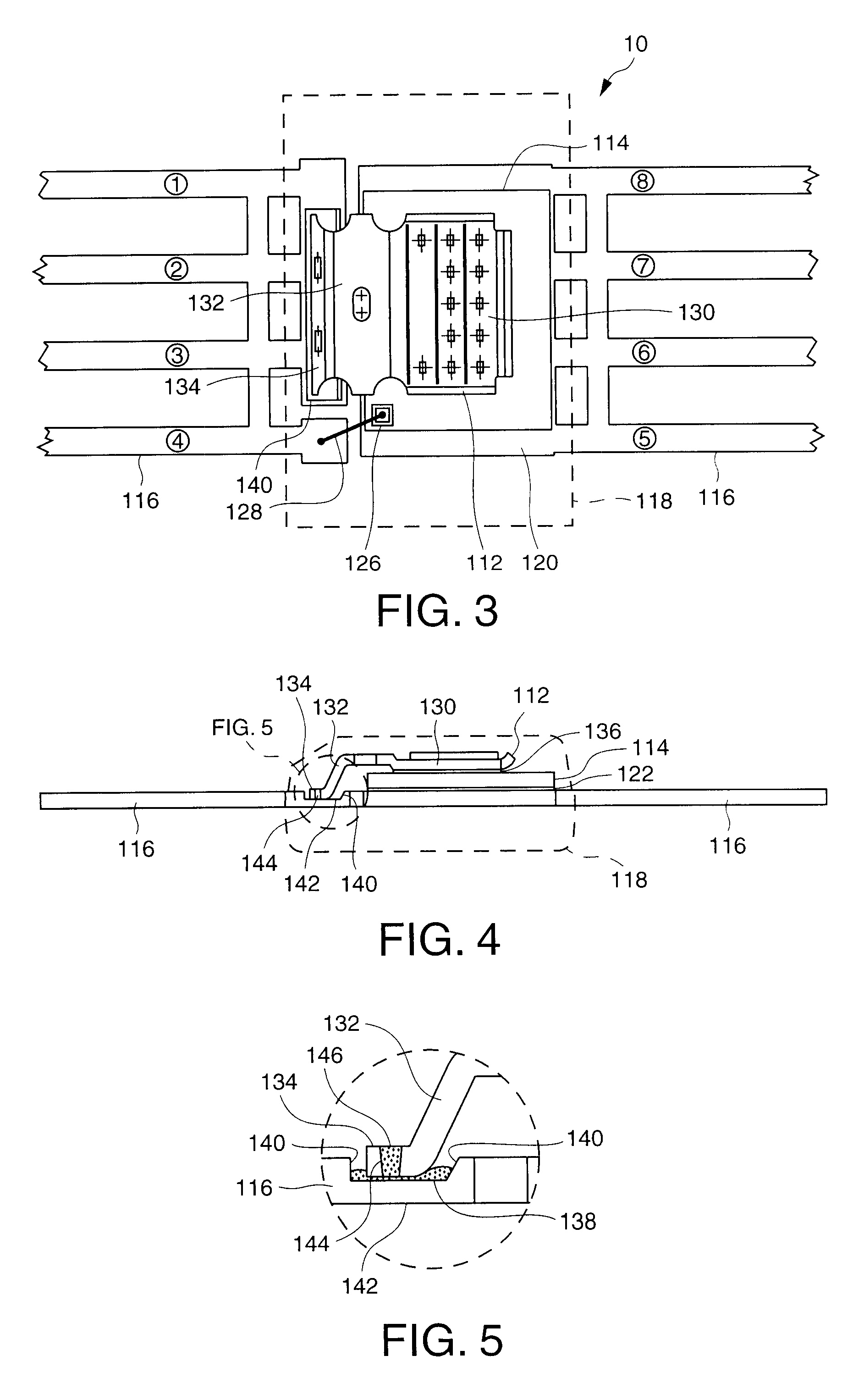

Power-MOSFETs with Improved Efficiency for Multi-channel Class-D Audio Amplifiers and Packaging Thereof

InactiveUS20080252372A1Lower on-resistanceSimple preparation techniqueTransistorSemiconductor/solid-state device detailsGround contactAudio power amplifier

A stereo class-D audio system includes a first die including four monolithically integrated NMOS high-side devices and a second a second die including four monolithically integrated PMOS low-side devices. The audio system also includes a set of electrical contacts for connecting the high and low-side devices to components within the a stereo class-D audio system, the set of electrical contacts including at least one supply contact for connecting the drains of the high-side devices to a supply voltage (Vcc) and at least one ground contact for connecting the drains of the low-side devices to ground, the electrical contacts also including respective contacts for each source of the high and low-side devices allowing the source of each high-side device to be connected to the source of a respective low-side device to form two H-bridge circuits.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

Low resistance gate for power mosfet applications and method of manufacture

ActiveUS20070190728A1Semiconductor/solid-state device manufacturingSemiconductor devicesPower MOSFETField-effect transistor

A trench gate field effect transistor is formed as follows. A trench is formed in a semiconductor region, followed by a dielectric layer lining sidewalls and bottom of the trench and extending over mesa regions adjacent the trench. A conductive seed layer is formed in a bottom portion of the trench over the dielectric layer. A low resistance material is grown over the conductive seed layer, wherein the low resistance material is selective to the conductive seed layer.

Owner:SEMICON COMPONENTS IND LLC +1

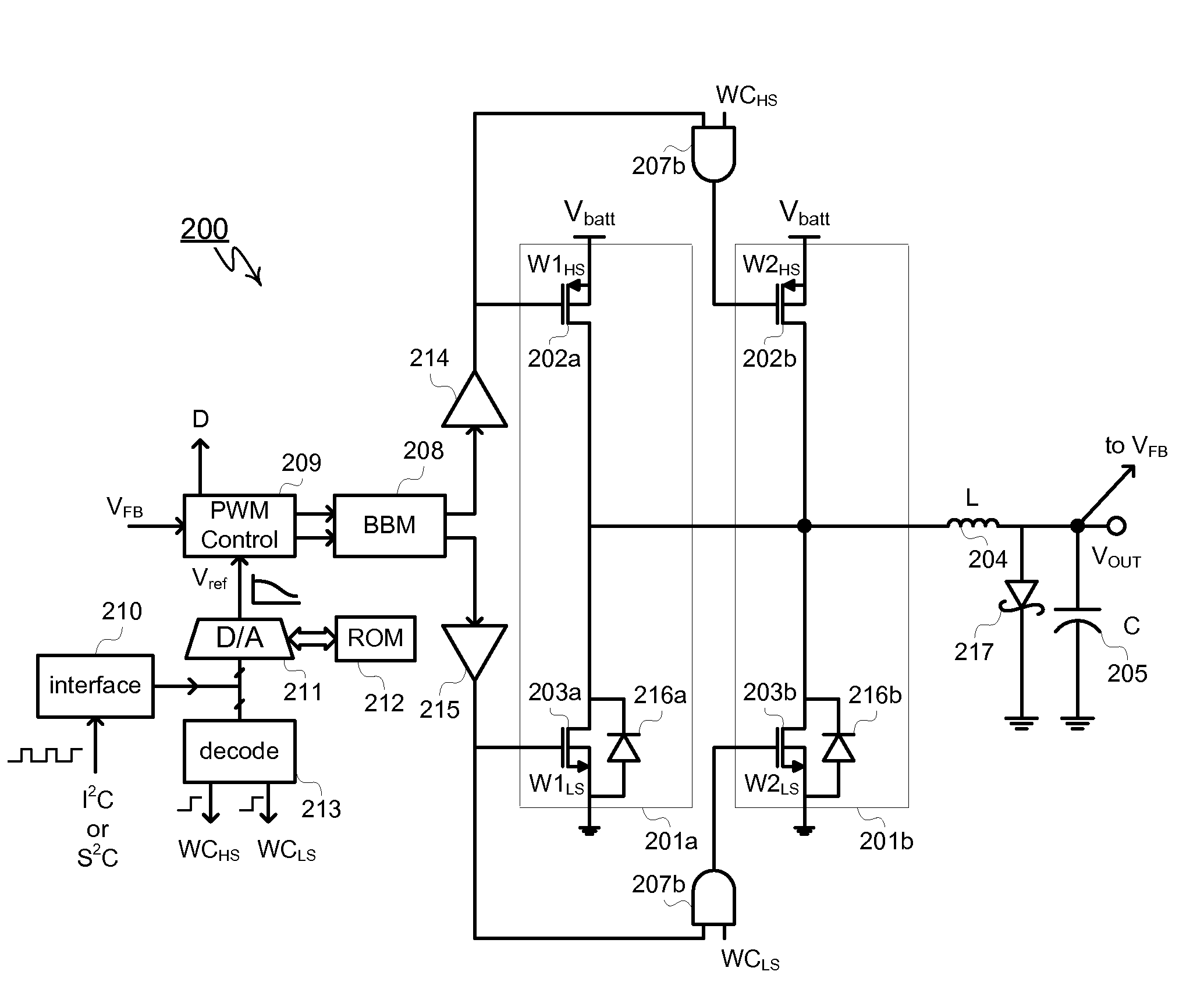

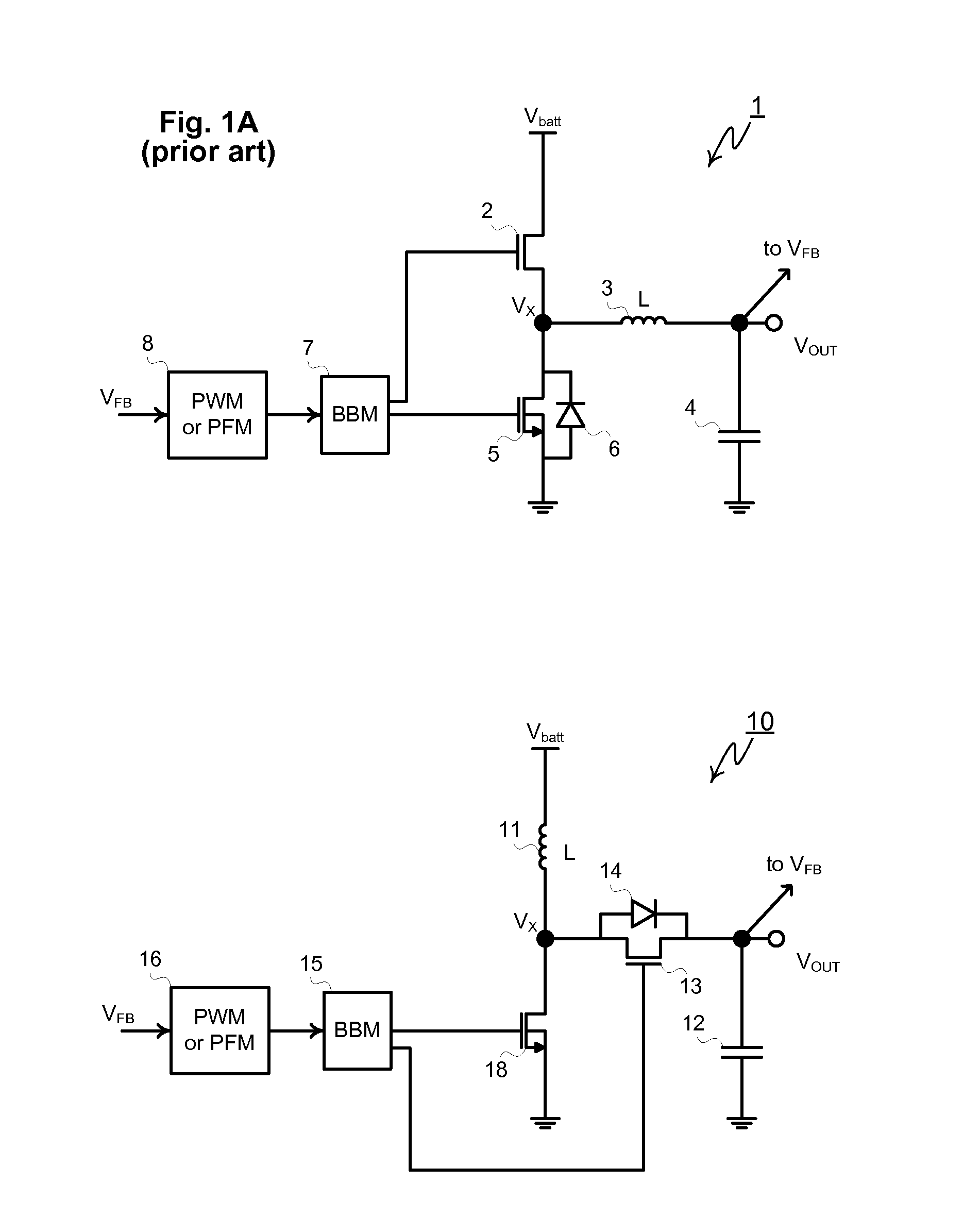

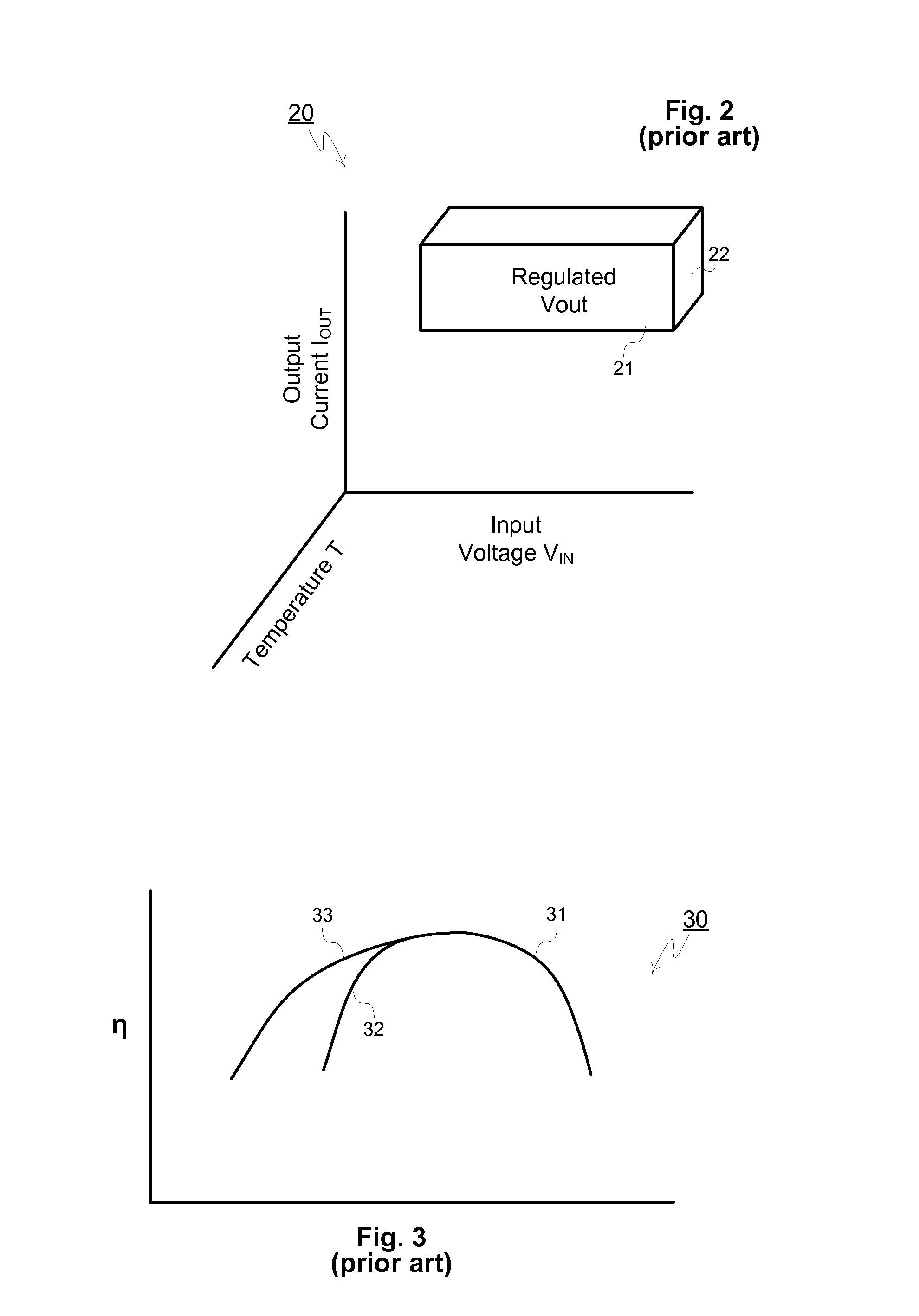

Programmable Step-Down Switching Voltage Regulators with Adaptive Power MOSFETs

InactiveUS20100001704A1Tight regulationPeak efficiencyDc-dc conversionElectric variable regulationControl signalVoltage regulation

A step-down switching voltage regulator includes M high-side switches connected between an input voltage and a node; N synchronous rectifiers connected between the node Vx and a ground voltage and an inductor connected between an input voltage and a node Vx and an inductor connected between the node Vx and an output node. An interface circuit decodes a control signal to identify: 1) a subset (m) of the high-side switches, 2) a subset (n) of the synchronous rectifiers. A control circuit drives the high-side switches and synchronous rectifiers in a repeating sequence that includes an inductor charging phase where the high-side switches in the subset m are activated to connect the node Vx to the input voltage; and an inductor discharging phase where the synchronous rectifiers in the subset n are activated to connect the node Vx to the ground voltage.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

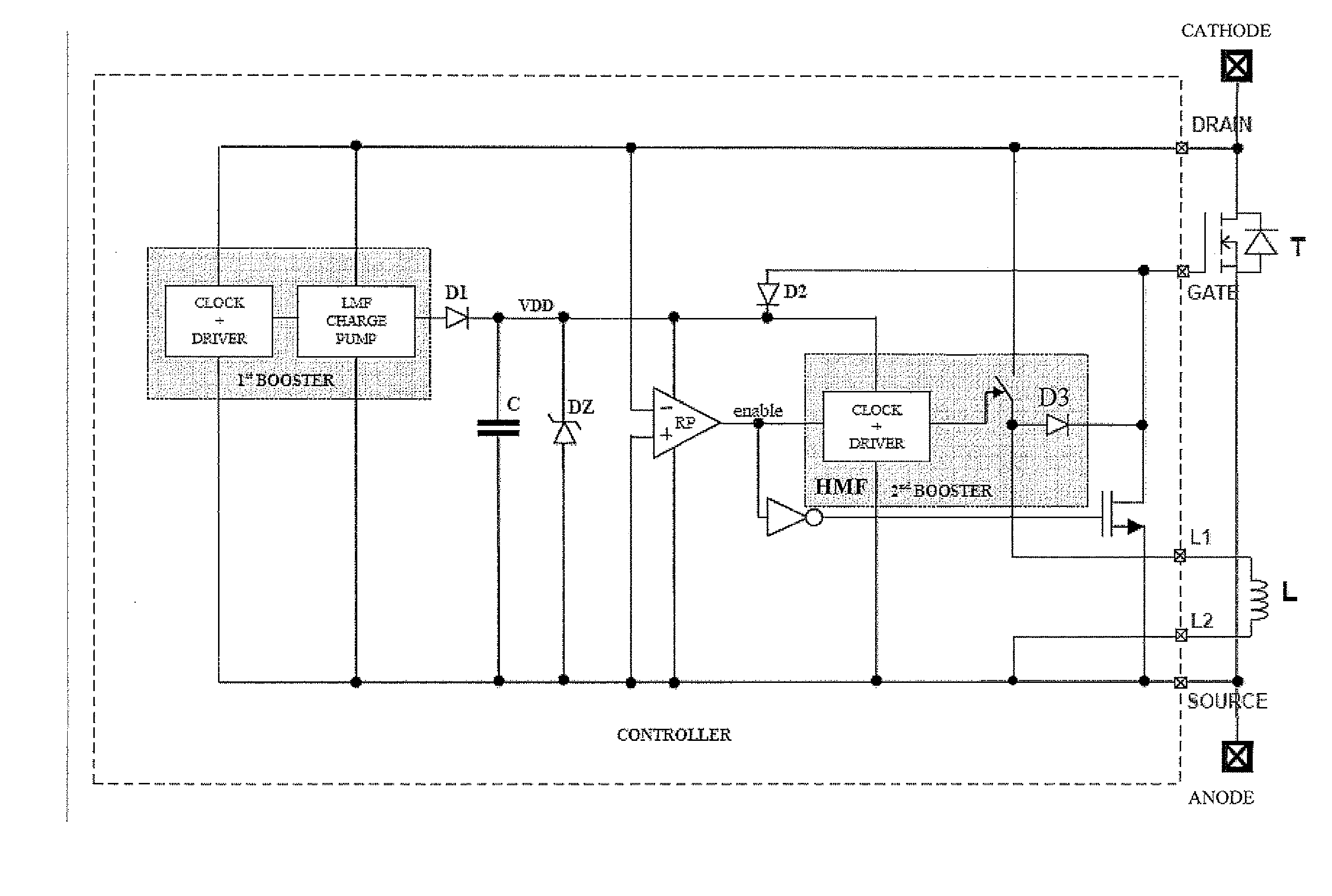

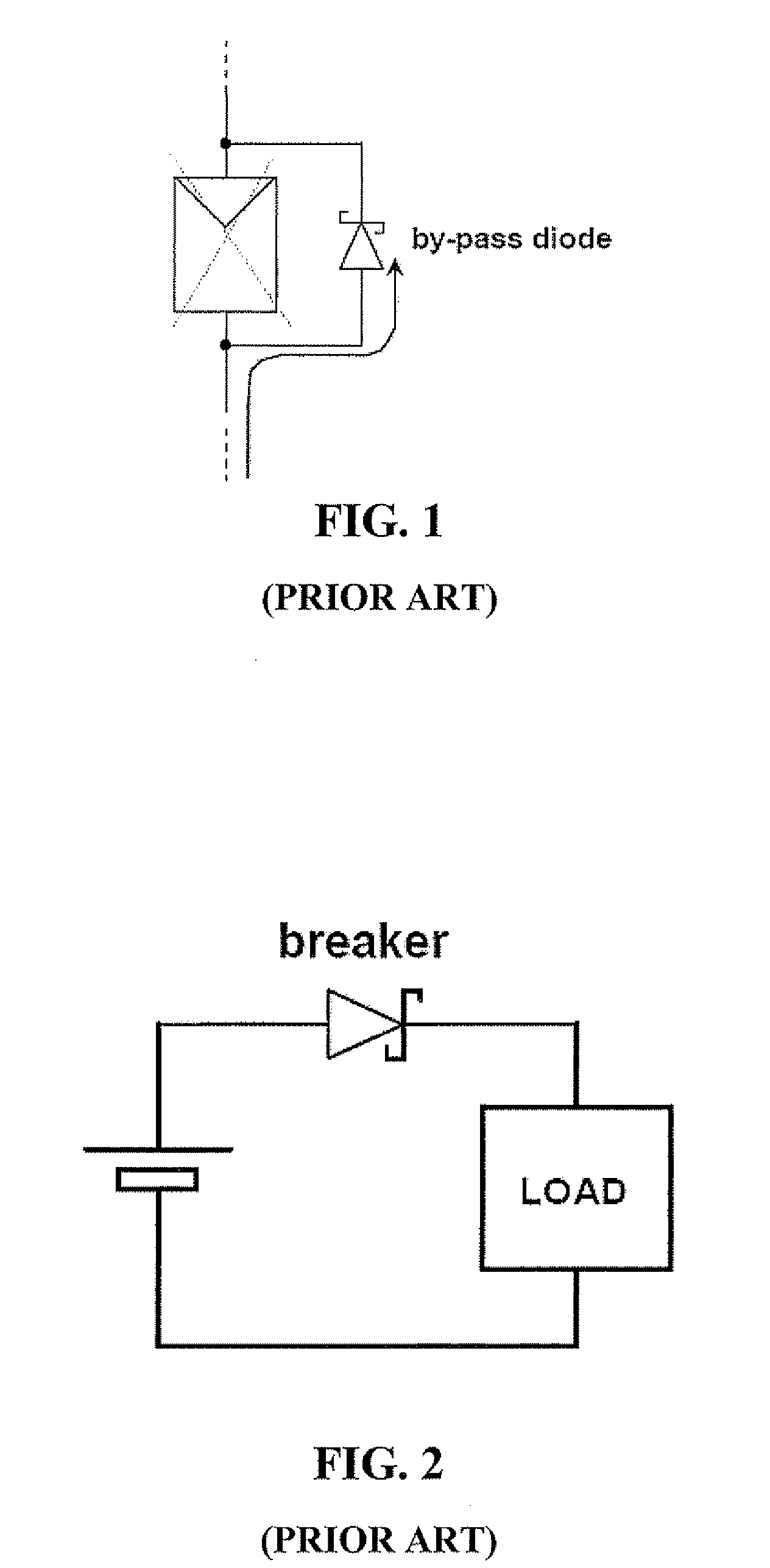

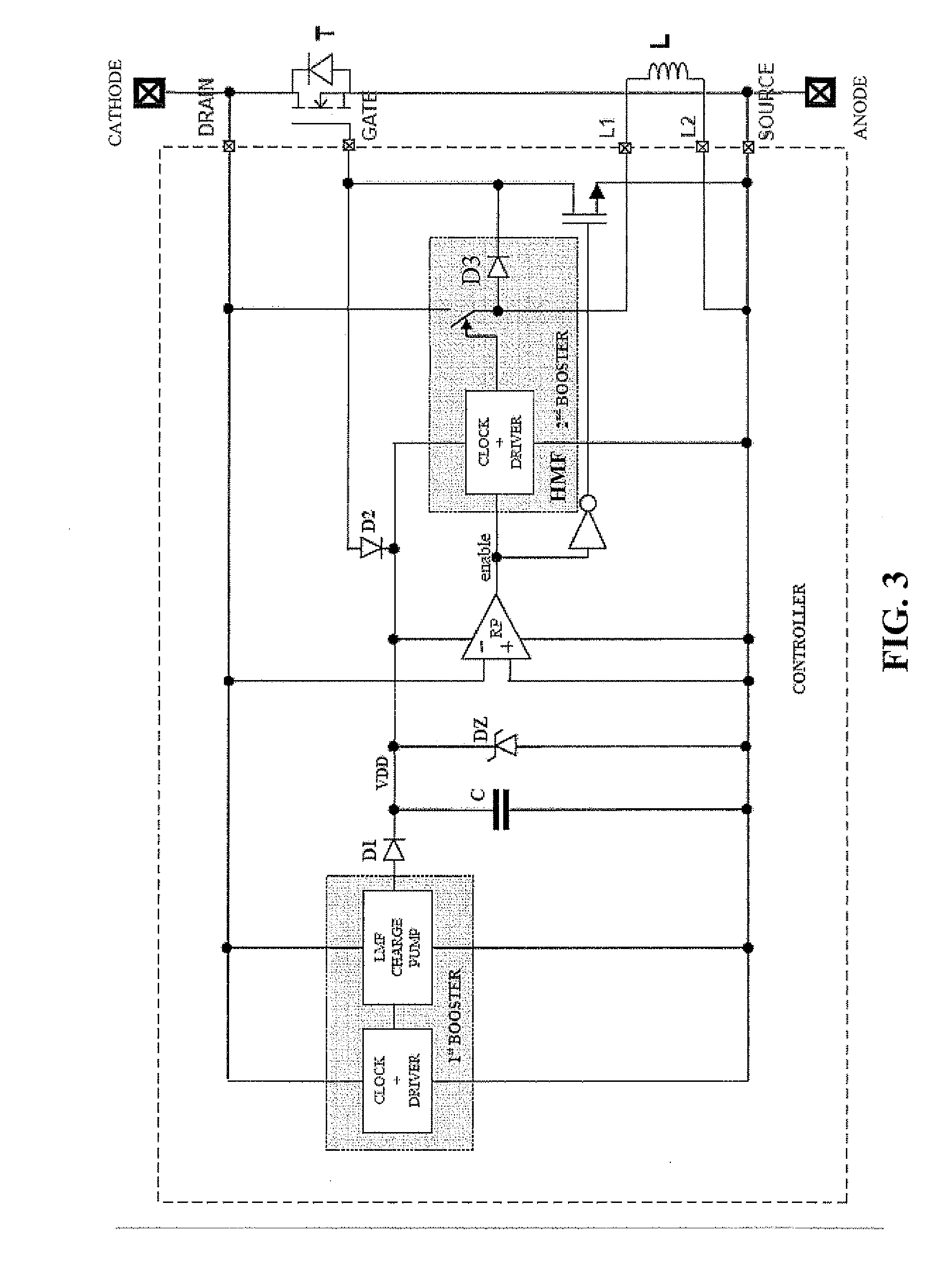

Low on-resistance mosfet implemented, by-pass diode or circuit breaker and related self-powering and control circuit

A MOSFET implemented self-powered current by-pass or circuit breaker device is based on the use of a high multiplication factor (HMF) inductive voltage booster, adapted to boost a voltage as low as few tens of mV up to several Volts, assisted by a start-up low multiplication factor (LMF) charge pump made with low threshold transistors for providing a supply voltage to a polarity inversion detecting comparator of the drain-to-source voltage difference of a power MOSFET connected in parallel to a DC source or string of series connected DC sources or battery, in series to other DC sources during normal operation of the parallel connected DC source or string of series connected DC sources or battery. The inductance for the high multiplication factor, inductive voltage booster for most of the considered power applications is on the order of a few pH and such a relatively send inductor may be included as a discrete component in a compact package or “system-in-package” of monolithically integrated circuits.

Owner:STMICROELECTRONICS SRL

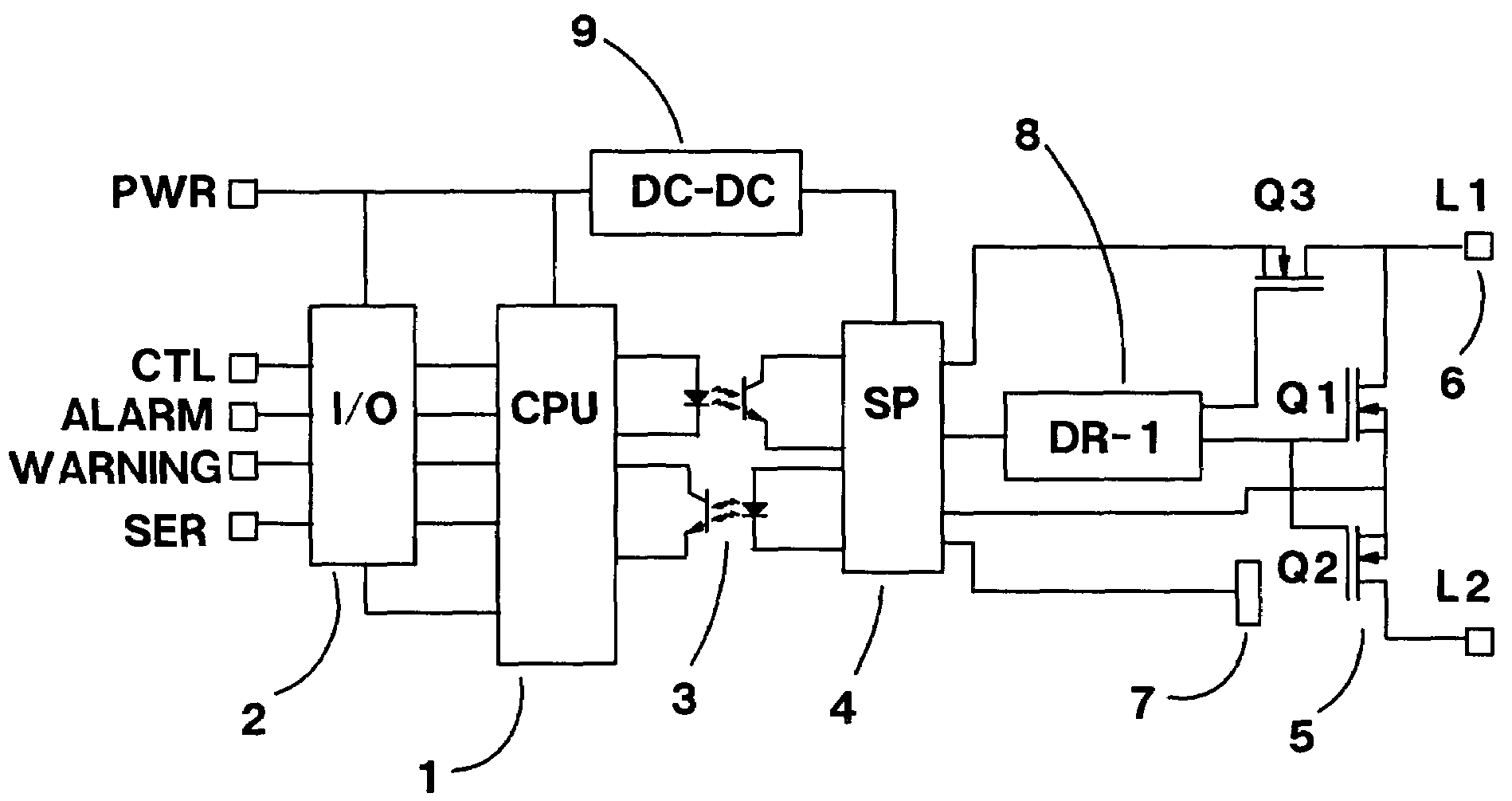

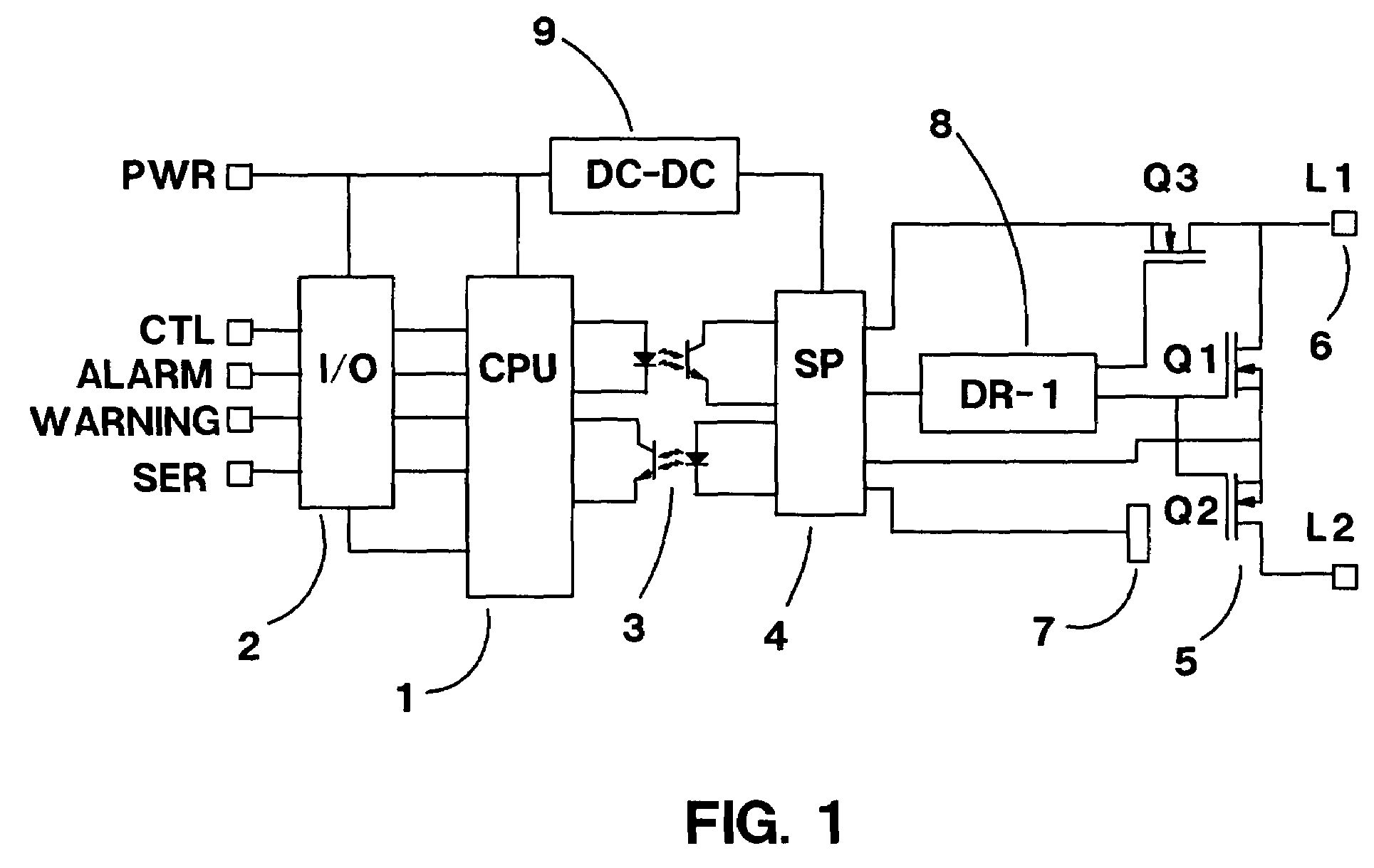

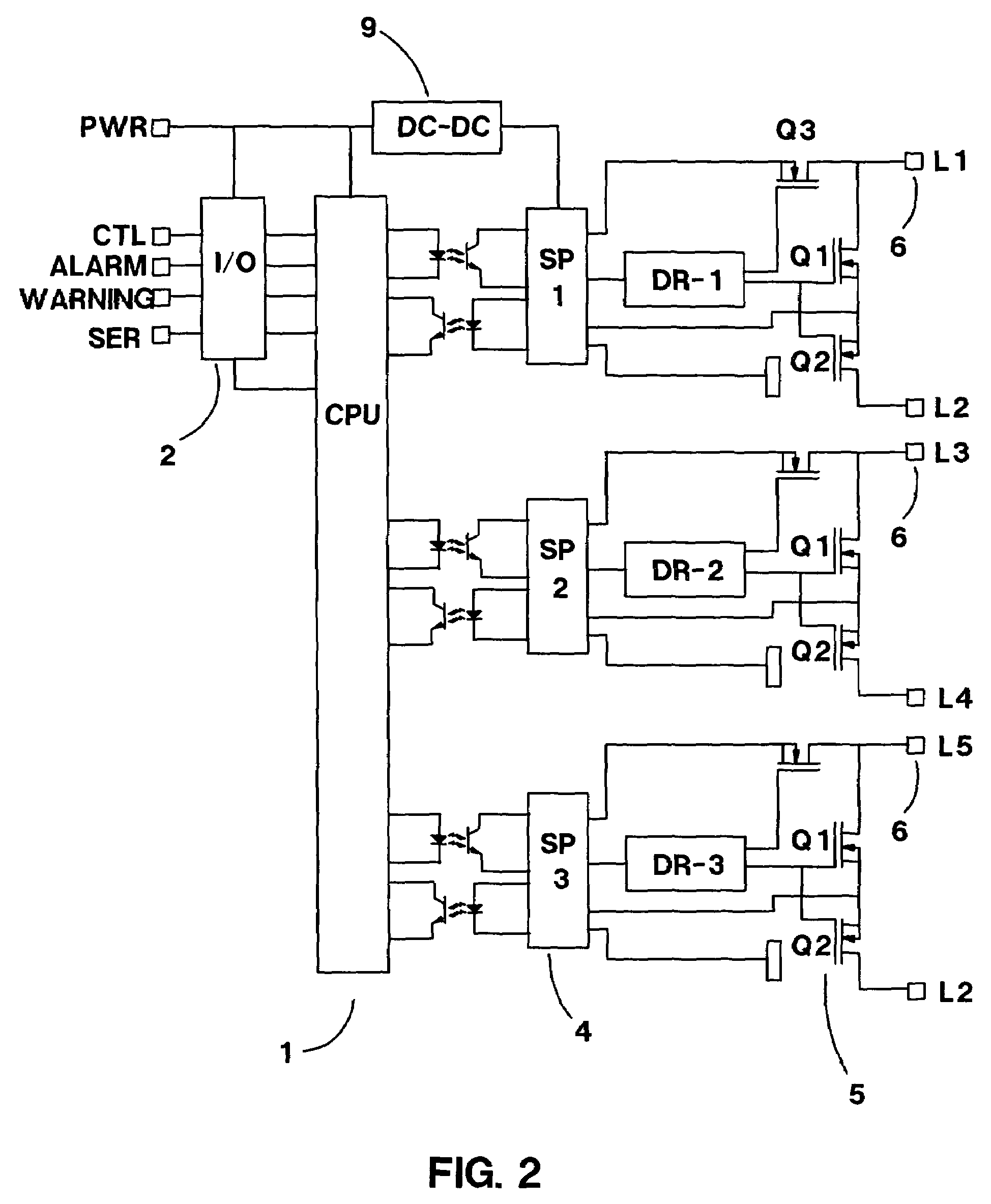

Intelligent solid state relay/breaker

InactiveUS7304828B1High currentImprove survivabilityArrangements responsive to excess currentEmergency protective arrangements for limiting excess voltage/currentHysteresisSlew rate

A solid-state relay / breaker that can replace mechanical units to control any type of AC or DC load. Power MOSFETs or other transistors control a load current. A bypass current sensing path monitors MOSFET current and causes a shutdown through signal processing in the event of an over-current condition. This shutdown resembles that of a slow-blow fuse where the rate of shutdown is proportional to the value of the current. This prevents shutdown on momentary spikes or in-rush. In addition, temperature and internal power supply voltages are monitored to determine additional operational conditions where over-temperature or voltages out of range can also cause shutdown. The MOSFET and current sensing path are turned on and off in staggered timing with different slew rates to provide built-in hysteresis. The device can be manufactured in any type of package to match any type of environment or existing replacement requirement.

Owner:SHVARTSMAN VLADIMIR A

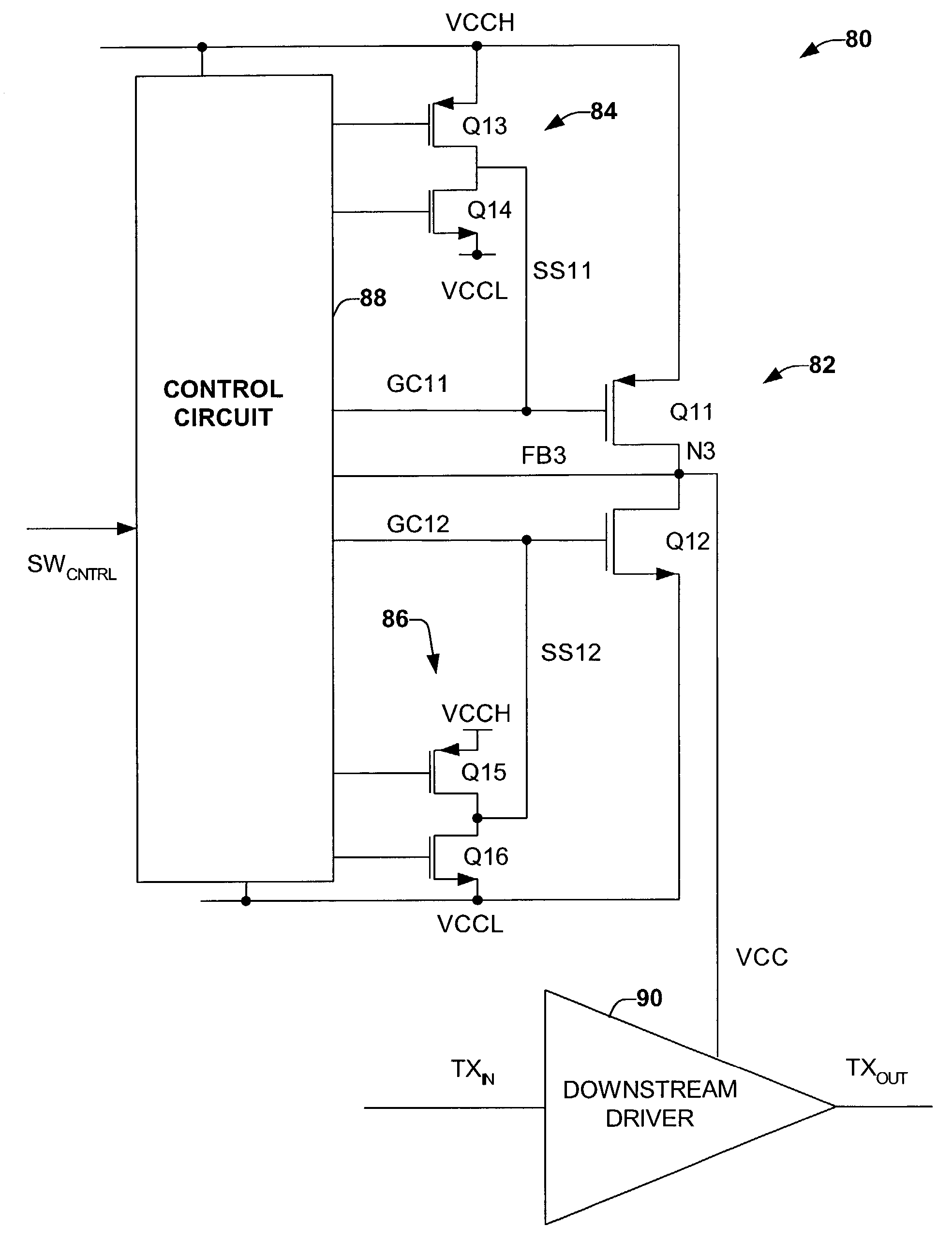

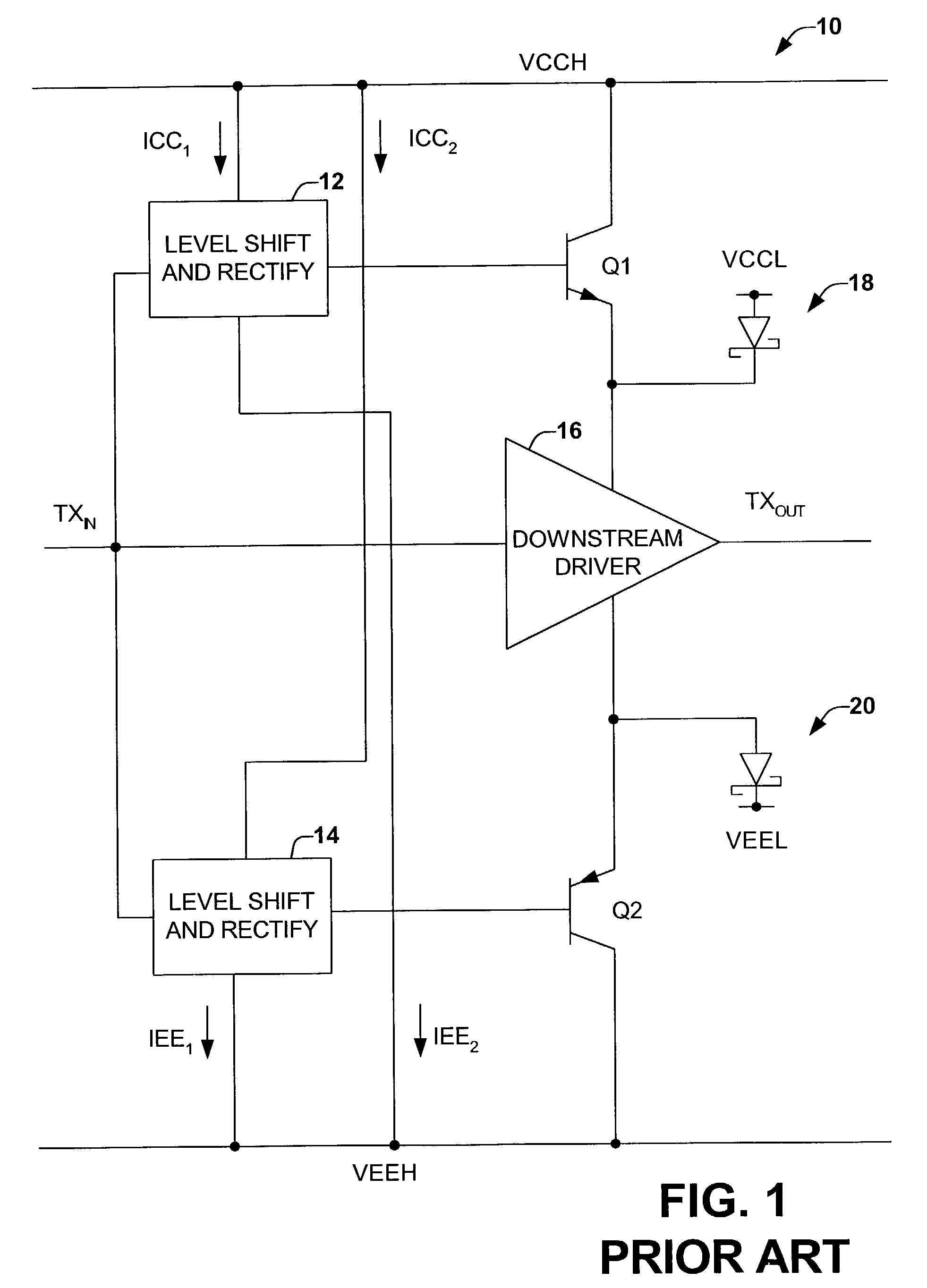

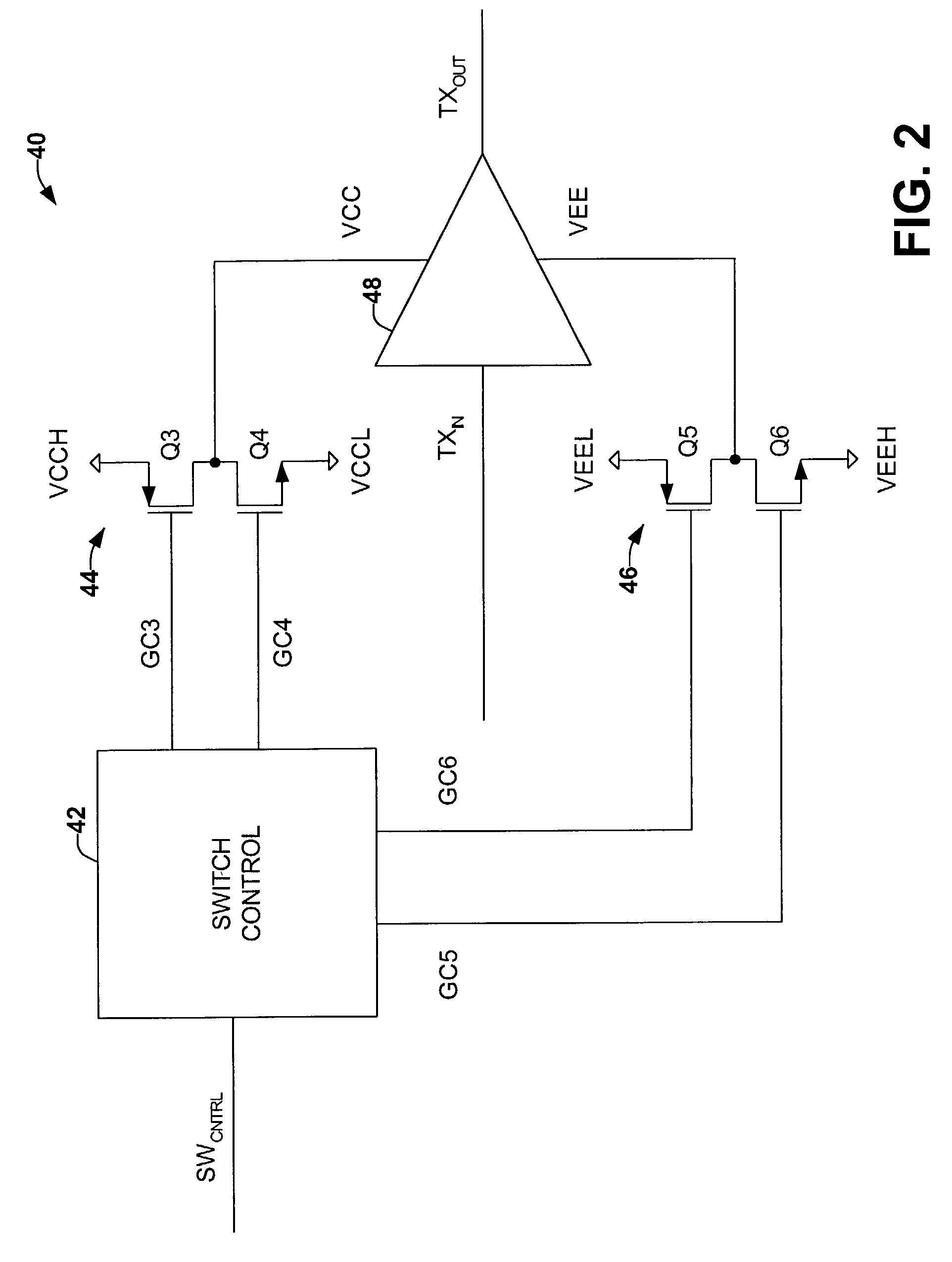

Power efficient ADSL central office downstream class G power switch

ActiveUS7177418B2Reduce noiseReduce spikesInterconnection arrangementsCurrent supply arrangementsAudio power amplifierEngineering

Systems and methods are provided for switching between power supply rail voltages for a differential driver device of a class G amplifier device. The amplifier device employs power MOSFETs to switch between supplying high supply voltages and low supply voltages to the power rails of the differential driver. The class G amplifier can be employed in driving an ADSL signal over a telephone line. A control device ramps the power supply rail voltage between low power supply states and high power supply states to mitigate noise and spikes that can be coupled to the output signal.

Owner:TEXAS INSTR INC

Cascode switch power supply

ActiveUS20070070659A1Reduce power lossMinimum of componentDc-dc conversionElectric variable regulationLow voltageCascode

A switching power supply is disclosed for improving the no-load power drain of low-power mains operated supplies. The power converter utilizes a cascoded switch arrangement with a conventional high voltage power MOSFET and a low voltage, low gate charge MOSFET. Driving only the small low voltage device reduces the power required for gate drive. The disclosed configuration is also capable of generating a non-isolated auxiliary rail for powering its control circuitry utilizing the parasitic capacitance of the high voltage power devices as an element in a charge pump. The resulting power supply requires significantly fewer components.

Owner:DIALOG SEMICONDUCTOR GMBH

Packaged power switching device

InactiveUS20100171543A1Semiconductor/solid-state device detailsSolid-state devicesPower applicationPower switching

A packaged switching device for power applications includes at least one pair of power MOSFET transistor dies connected between upper and lower power source rail leads, a high side one of the pair of MOSFET transistor dies being connected to the upper power source rail lead and a low side one of the pair of MOSFET transistor dies being connected to the lower power source rail lead. At least one of the MOSFET transistor dies is configured for vertical current flow therethrough and has a source electrode at a backside thereof.

Owner:CICLON SEMICON DEVICE

MOSFET gate drive with reduced power loss

InactiveUS20080290911A1Reduce the total amount of chargingReduce the required powerTransistorElectronic switchingDc dc converterEngineering

A gate driver for a power MOSFET in, for example, a DC-DC converter switches the MOSFET between a fully-on condition and a low-current condition instead of switching the MOSFET between fully-on and fully-off conditions. The amount of charge that must be transferred to charge and discharge the gate of the MOSFET is thereby reduced, and the efficiency of the MOSFET is improved. A feedback circuit may be used to assure that the magnitude of current in the power MOSFET in its low-current condition is correct. Alternatively, a trimming process may be used to correct the magnitude of the voltage supplied by the gate driver to the gate of the power MOSFET in the low-current condition.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

Progressive start-up circuit for activating a charge pump

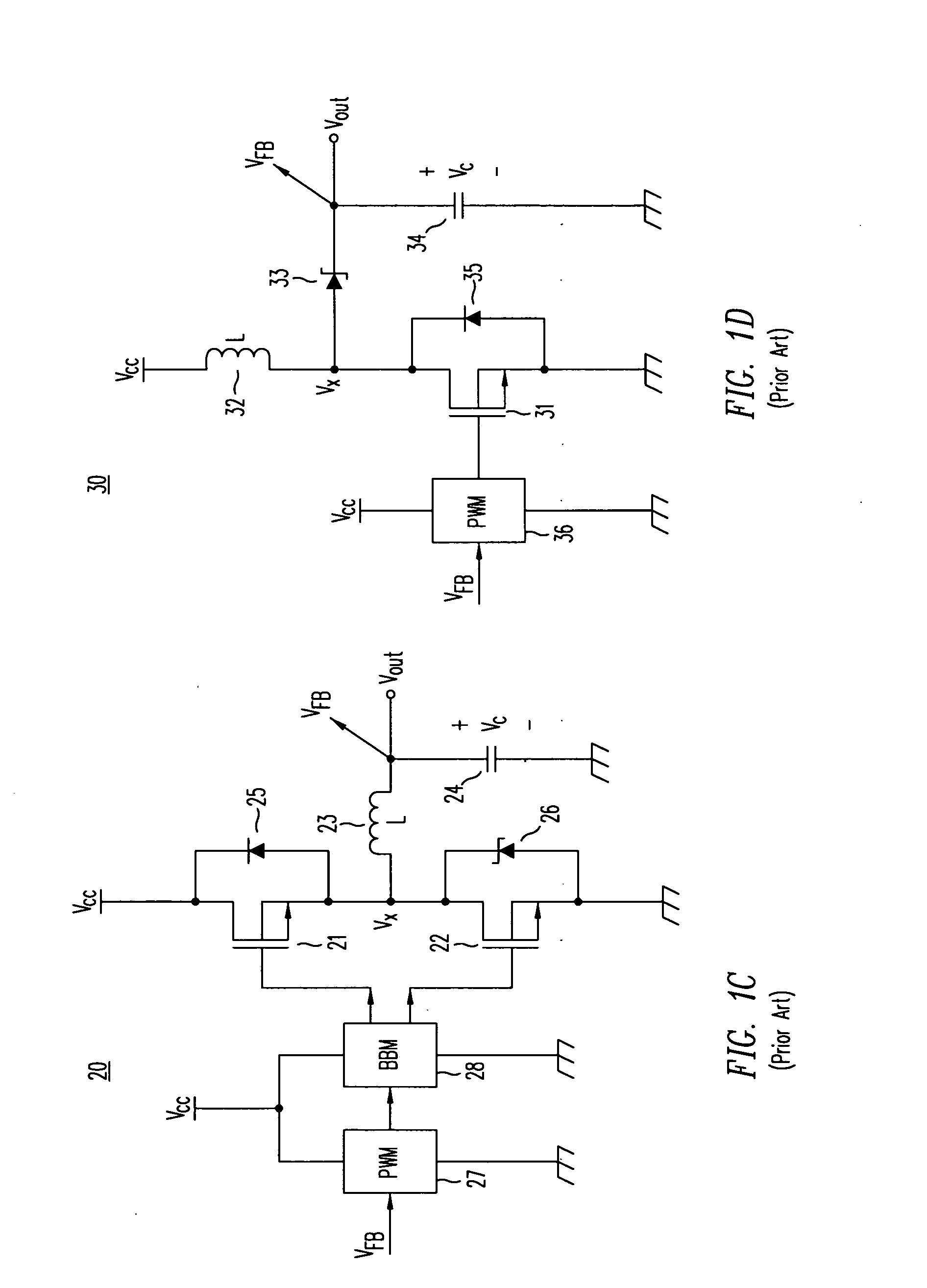

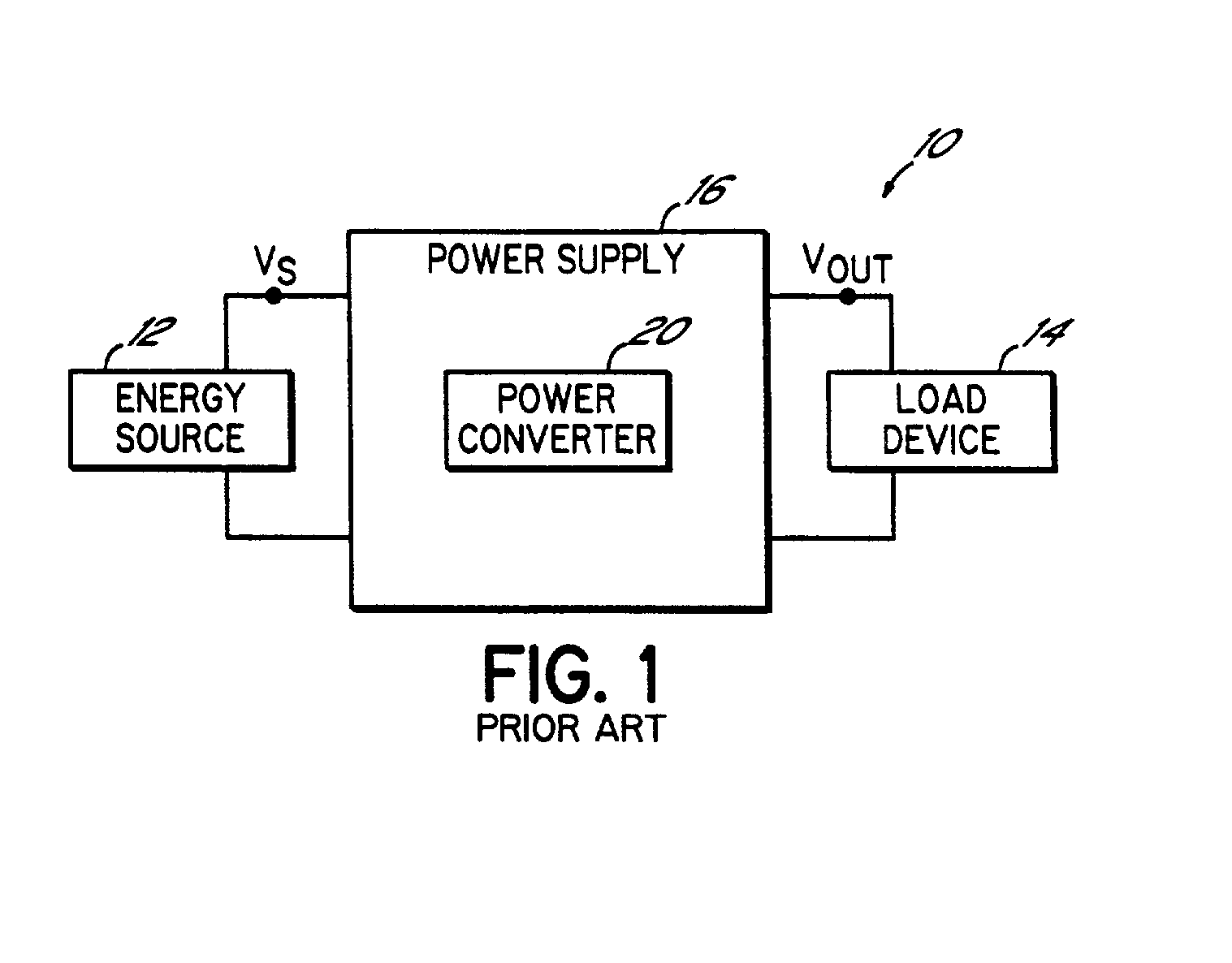

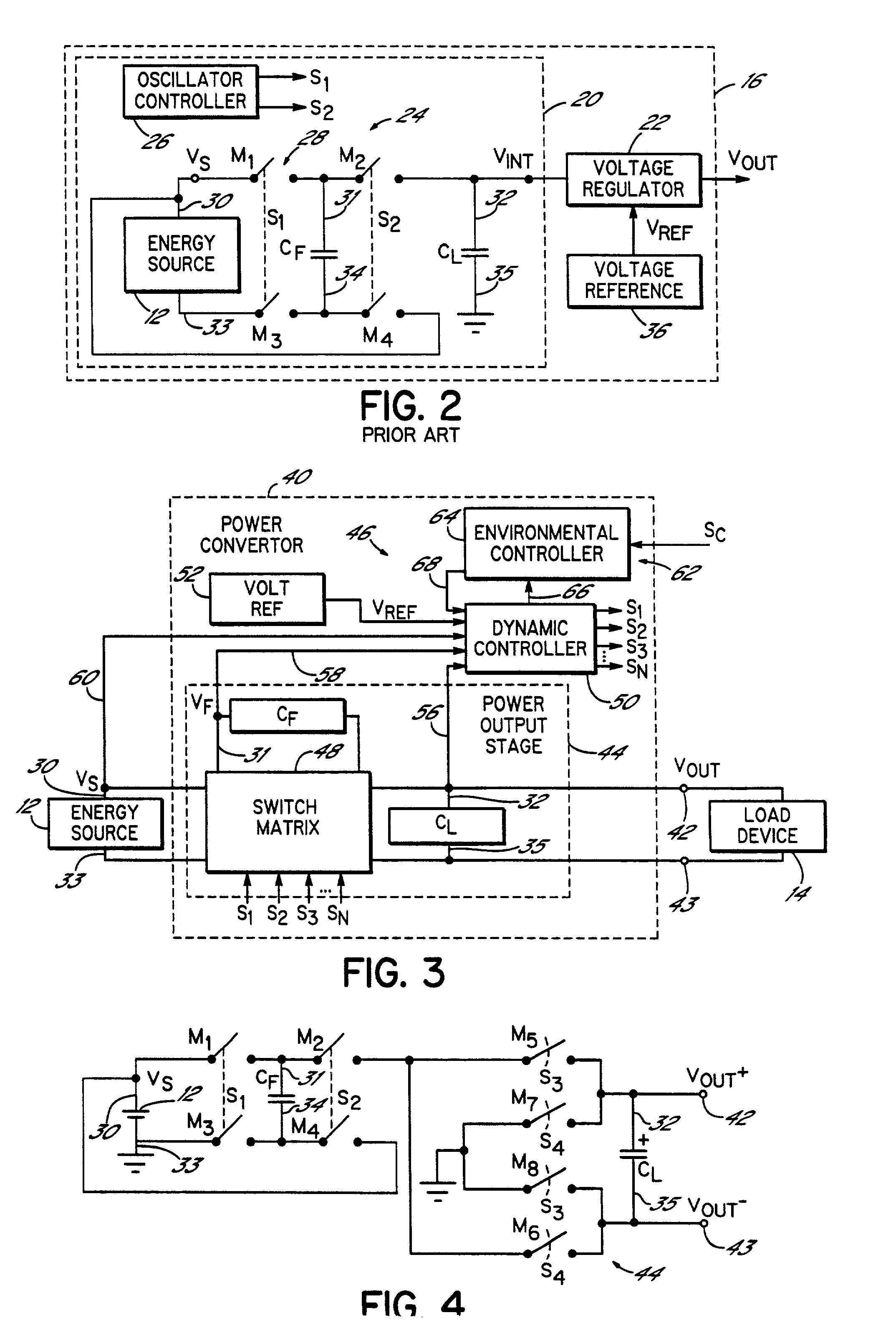

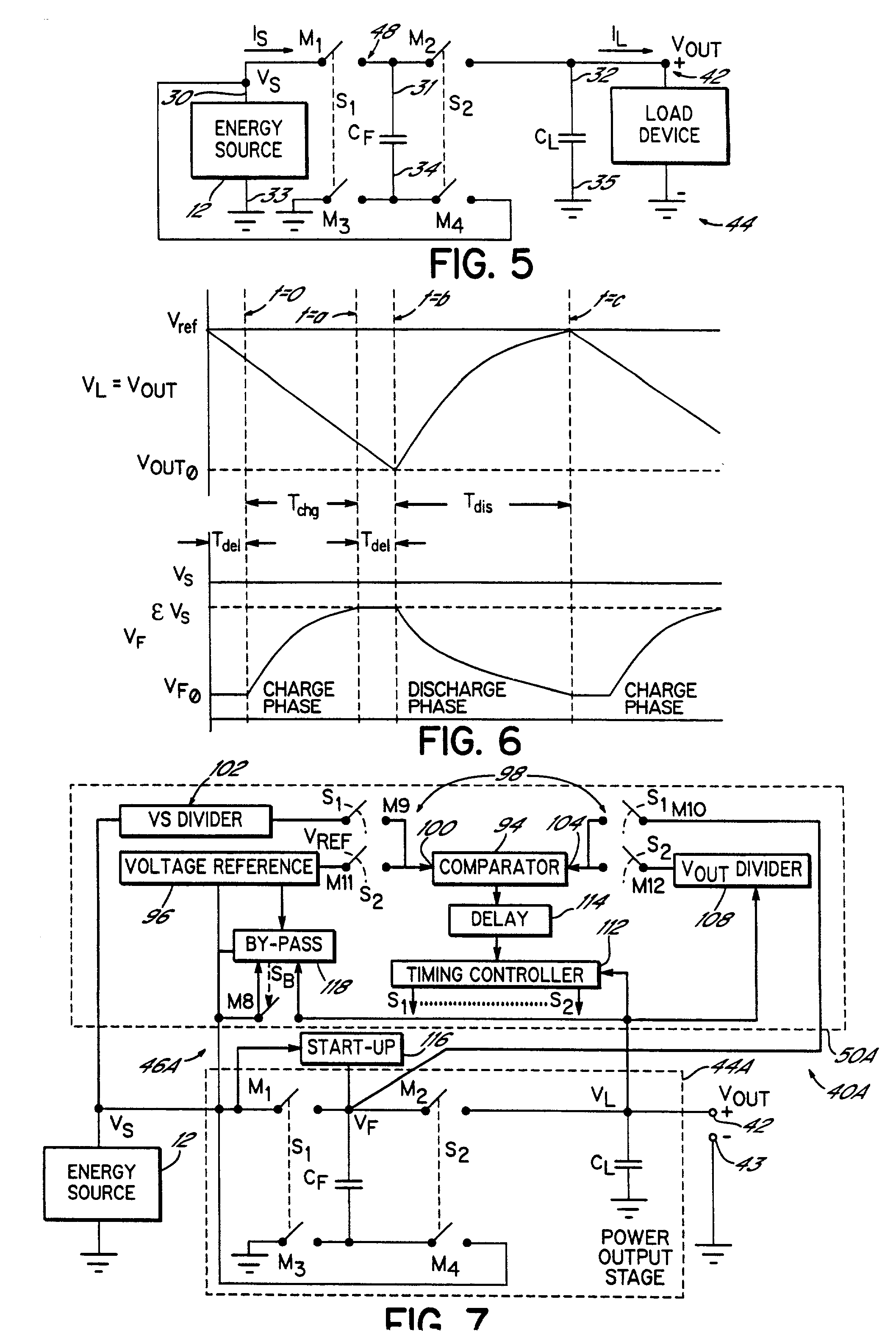

InactiveUS20010033501A1Enhance battery service lifeHigh energyBatteries circuit arrangementsEfficient power electronics conversionClosed loopPower MOSFET

A charge pump power converter efficiently provides electrical power by dynamically controlling a switch matrix of the charge pump. Instead of open-loop oscillator-based control, a dynamic controller provides power upon demand by sensing the output voltage and changing the operating frequency of the charge pump in response. Moreover, this closed-loop dynamic control intrinsically voltage regulates the output voltage of the charge pump power converter without the inefficient addition of a step-down voltage regulator, downstream of the power converter. In addition, this closed-loop dynamic control allows for maintaining a desired output voltage even with variations in the input voltage. Also, the dynamic control accommodates the advantages of using ultra-capacitors in the charge pump. The power converter is capable of operating with a sub-one volt input voltage incorporating low-threshold, low on-resistance power MOSFET switches in the switch matrix of the charge pump. A progressive start-up circuit further allows the power converter to start from a discharged state even with a sub-one volt input voltage.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

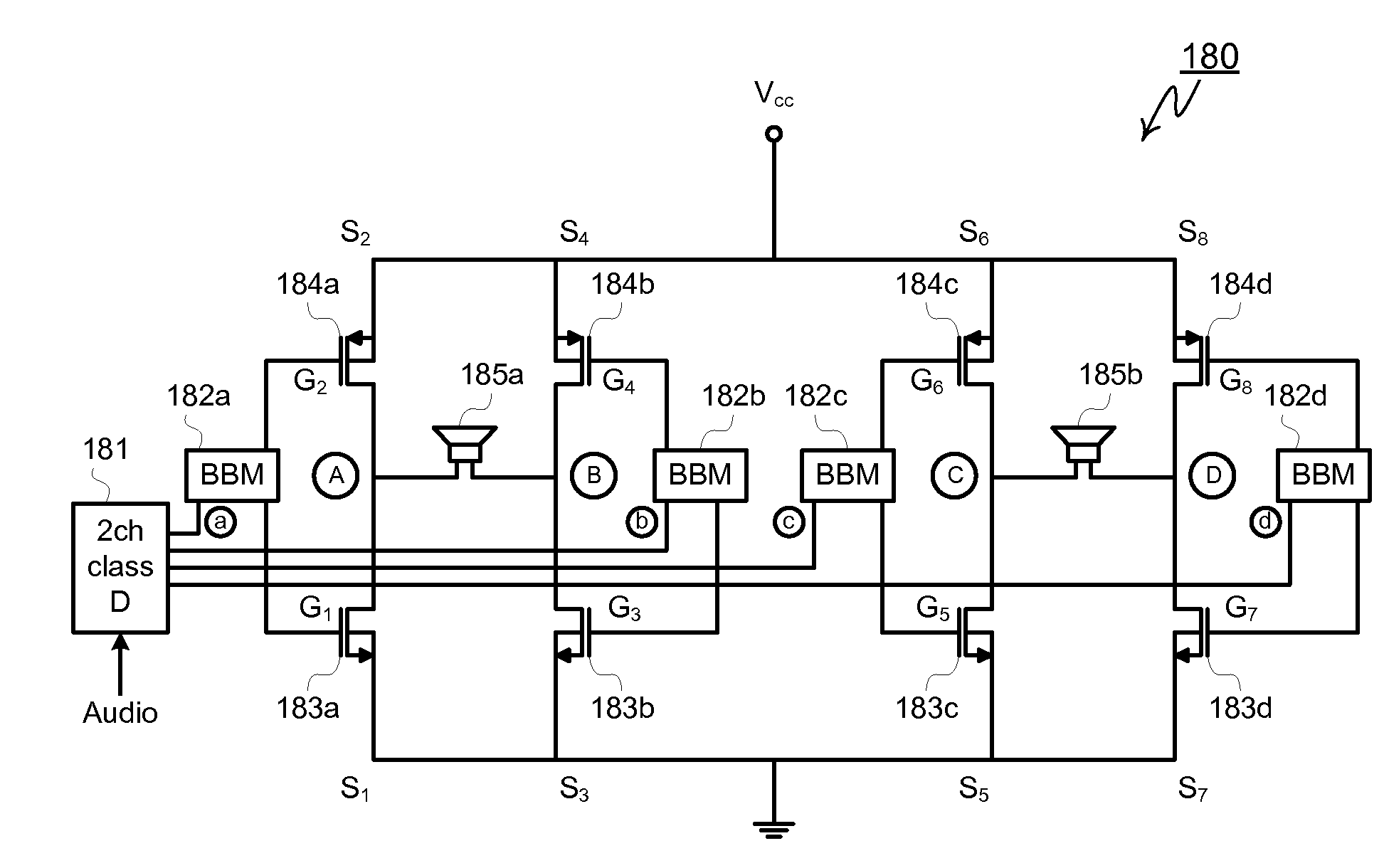

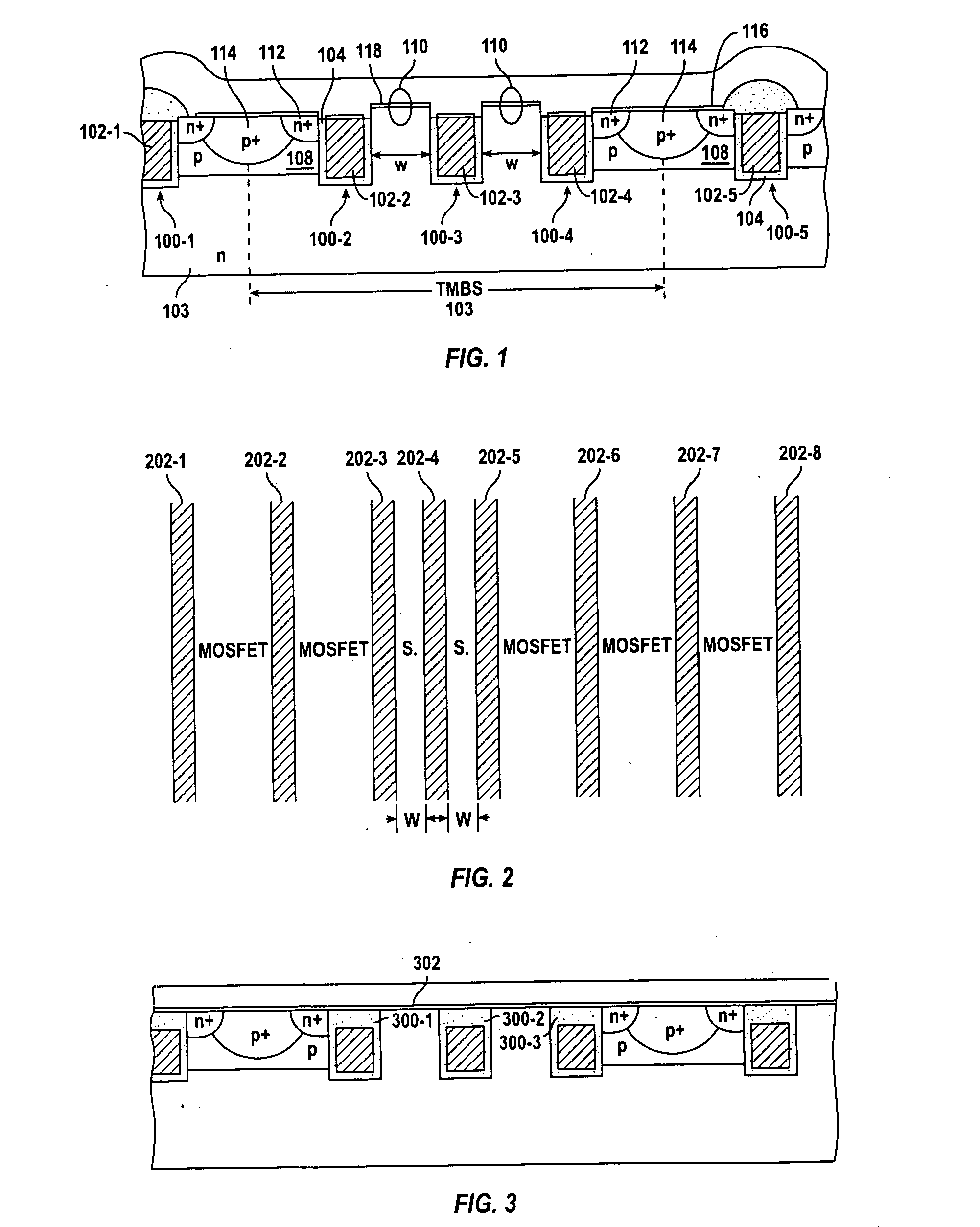

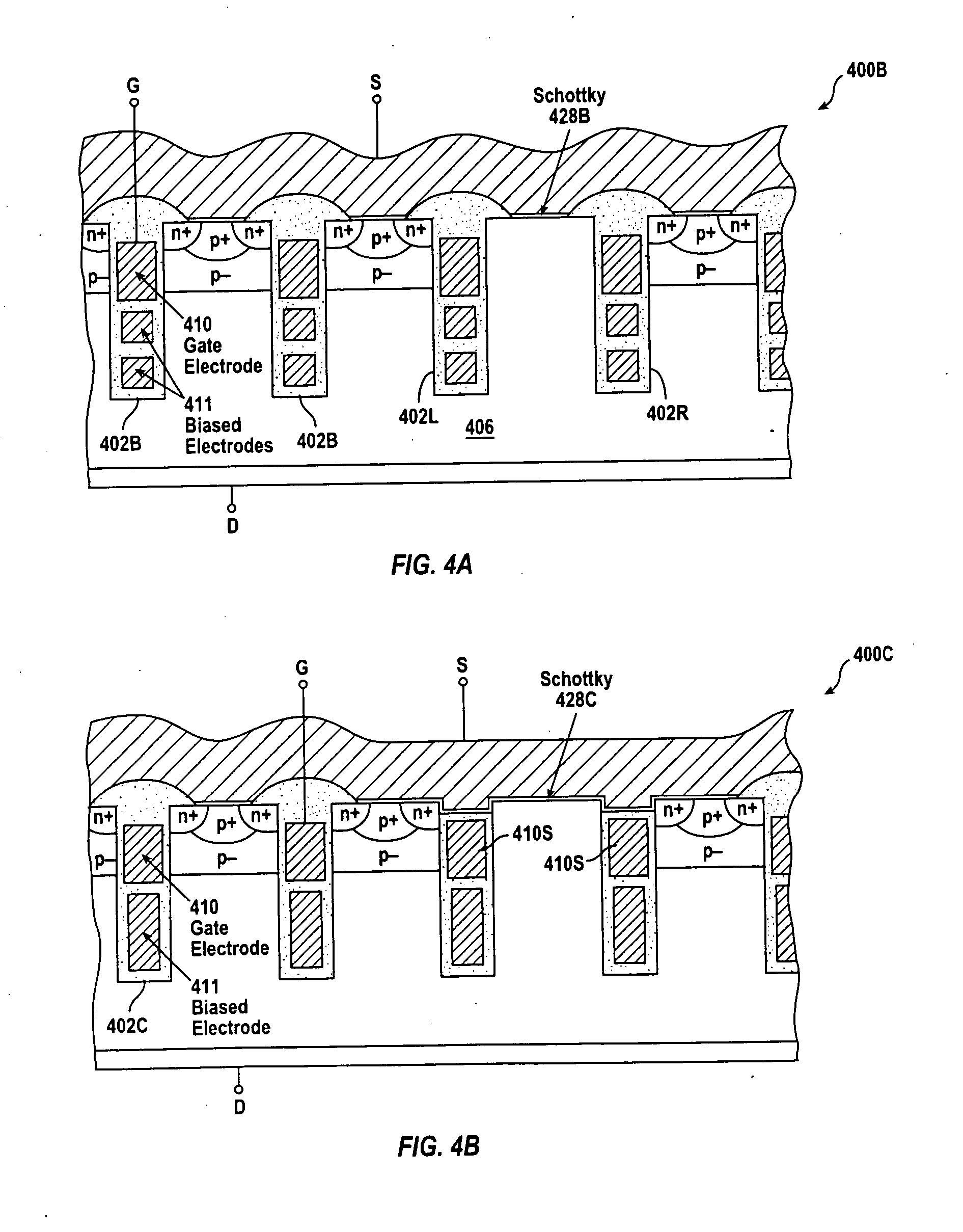

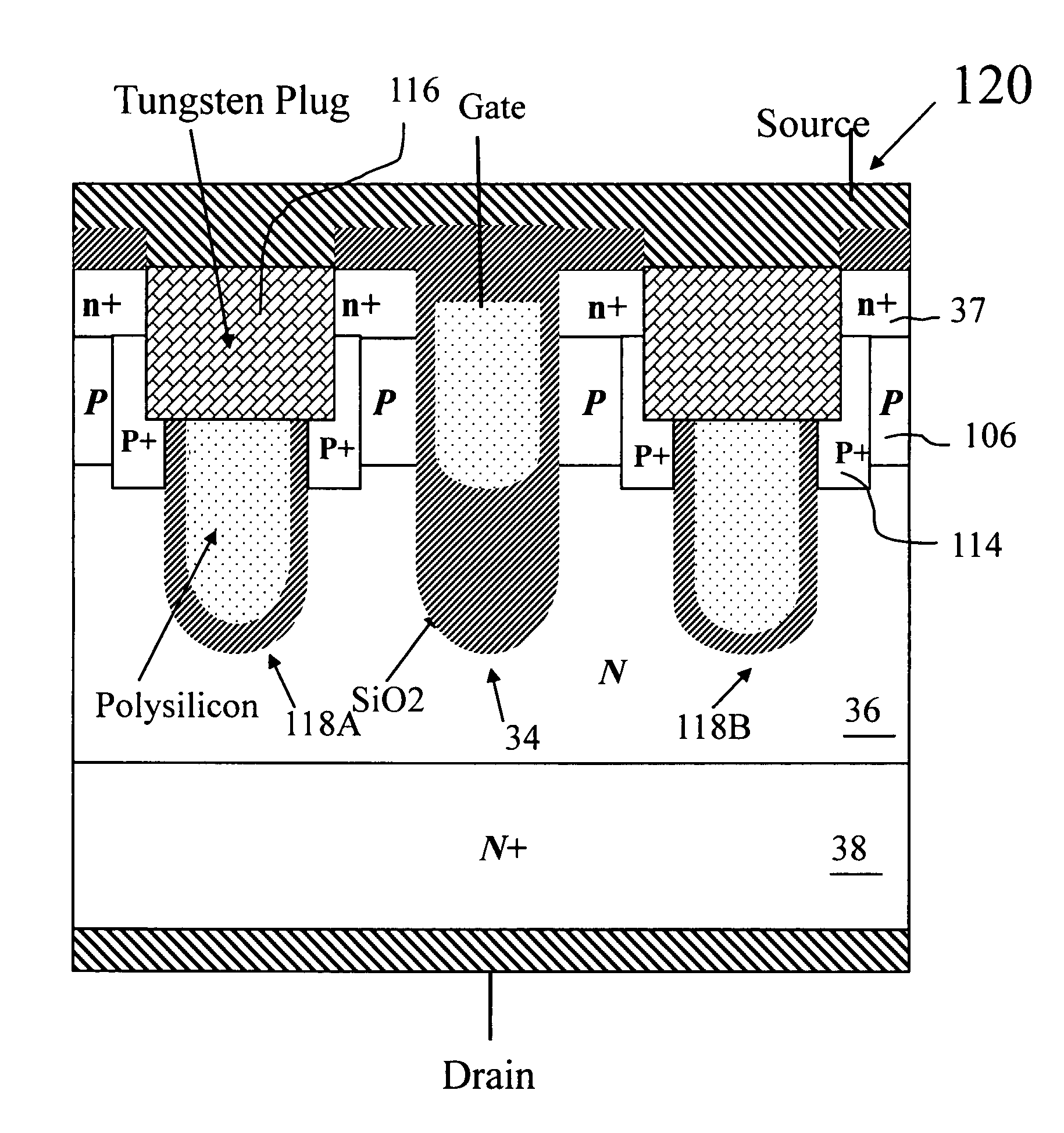

Optimized trench power MOSFET with integrated schottky diode

In accordance with the present invention, a monolithically integrated structure combines a field effect transistor and a Schottky structure in an active area of a semiconductor substrate. The field effect transistor includes a first trench extending into the substrate and substantially filled by conductive material forming a gate electrode of the field effect transistor. A pair of doped source regions are positioned adjacent to and on opposite sides of the trench and inside a doped body region. The Schottky structure includes a pair of adjacent trenches extending into the substrate. Each of the pair of adjacent trenches is substantially filled by a conductive material which is separated from trench side-walls by a thin layer of dielectric. The Schottky structure consumes 2.5% to 5.0% of the active area, and the field effect transistor consumes the remaining portion of the active area.

Owner:SEMICON COMPONENTS IND LLC

Semiconductor device with a high breakdown voltage,low on-resistance,lateral power mosfet

InactiveUS6177704B1Shorten the lengthSufficient level of breakdown voltageTransistorSolid-state devicesElectrical conductorInsulation layer

A semiconductor device containing a lateral MOS transistor comprising a silicon substrate, an n-type first semiconductor layer constituting a drain drift region, a p-type second semiconductor layer prepared within the first semiconductor layer to constitute a body region and with a channel region formed within a portion of said body region, an n-type third semiconductor layer prepared on the surface of the second semiconductor layer to constitute a source region, an n-type fourth semiconductor layer constituting a drain region, and an insulation layer that is constituted of insulating material filled into a trench prepared in the first semiconductor layer and arranged along the two sides of the drain region. The drain region is formed into a region deeper than the insulation layer and in contact with the drain drift region at a portion beneath the insulation layer. The semiconductor device provides a high breakdown voltage and a low on-resistance, and can be fabricated with a reduced cell pitch.

Owner:TOYOTA CENT RES & DEV LAB INC

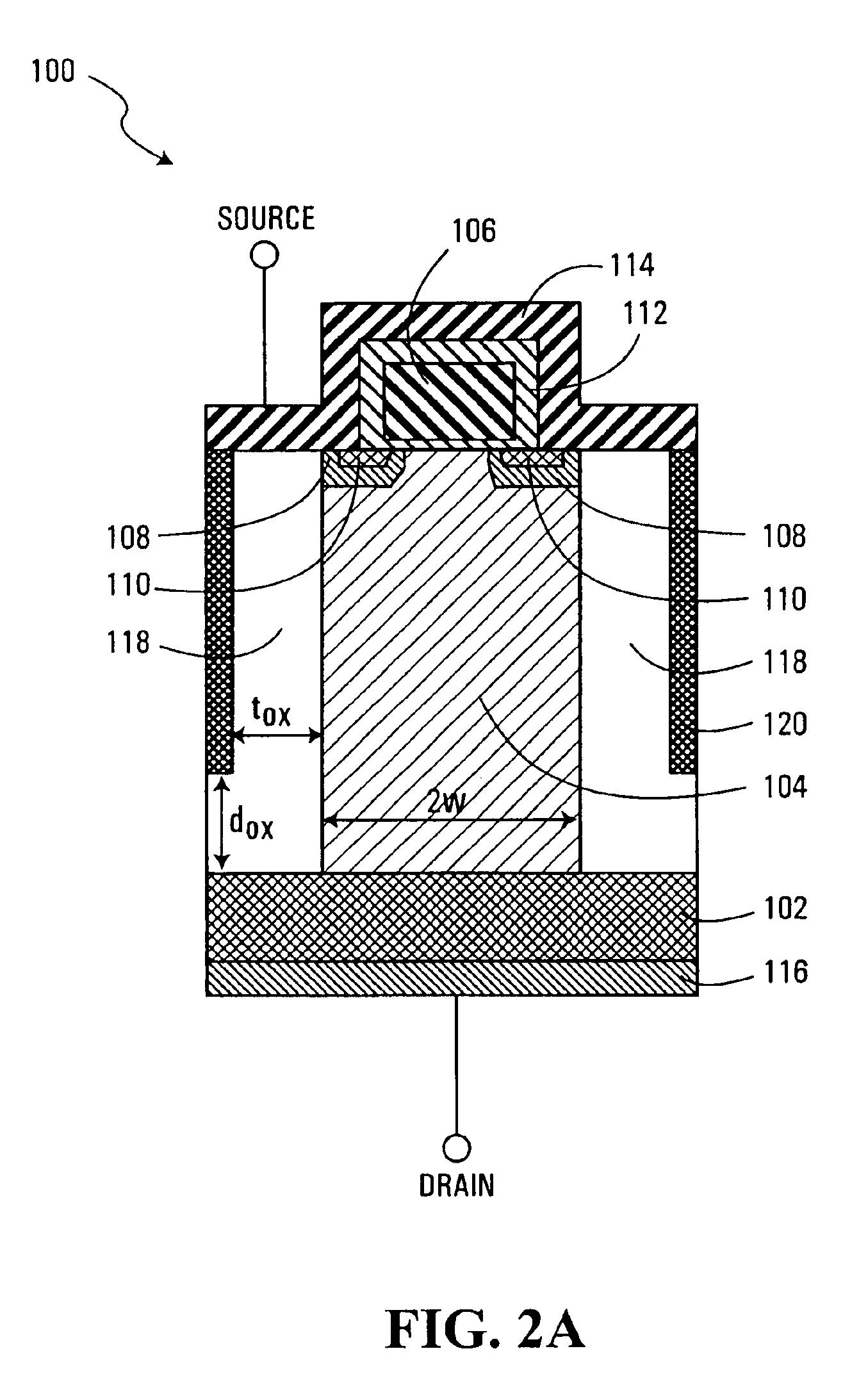

Power MOSFET having enhanced breakdown voltage

InactiveUS6853033B2Improve breakdown voltageHigh dopingSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricPower MOSFET

A MOSFET includes a dielectric, preferably in the form of a metal thick oxide that extends alongside the MOSFET's drift region. A voltage across this dielectric between its opposing sides exerts an electric field into the drift region to modulate the drift region electric field distribution so as to increase the breakdown voltage of a reverse biased semiconductor junction between the drift region and body region. This allows for higher doping of the drift region, for a given breakdown voltage when compared to conventional MOSFETs.

Owner:NAT UNIV OF SINGAPORE

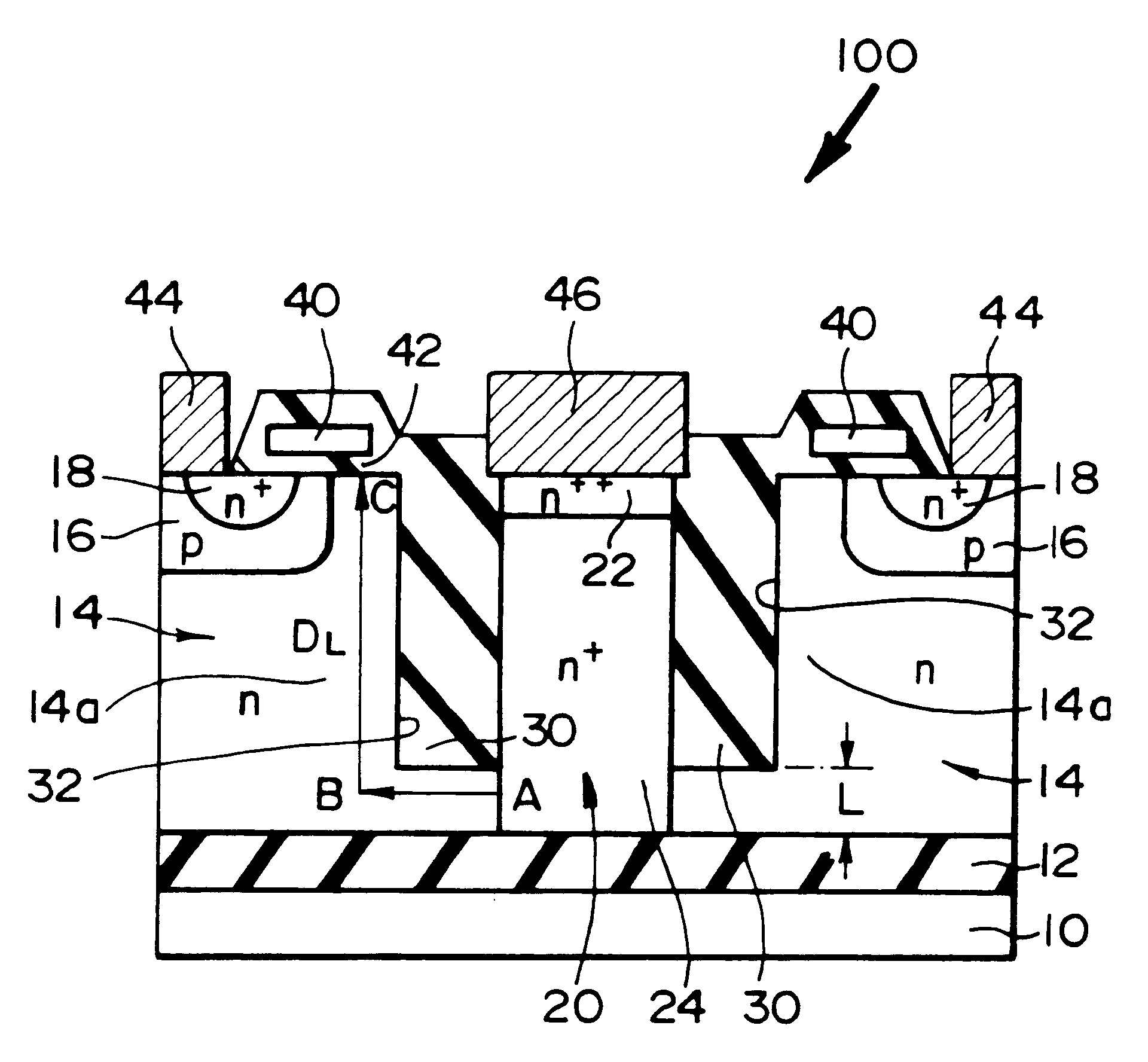

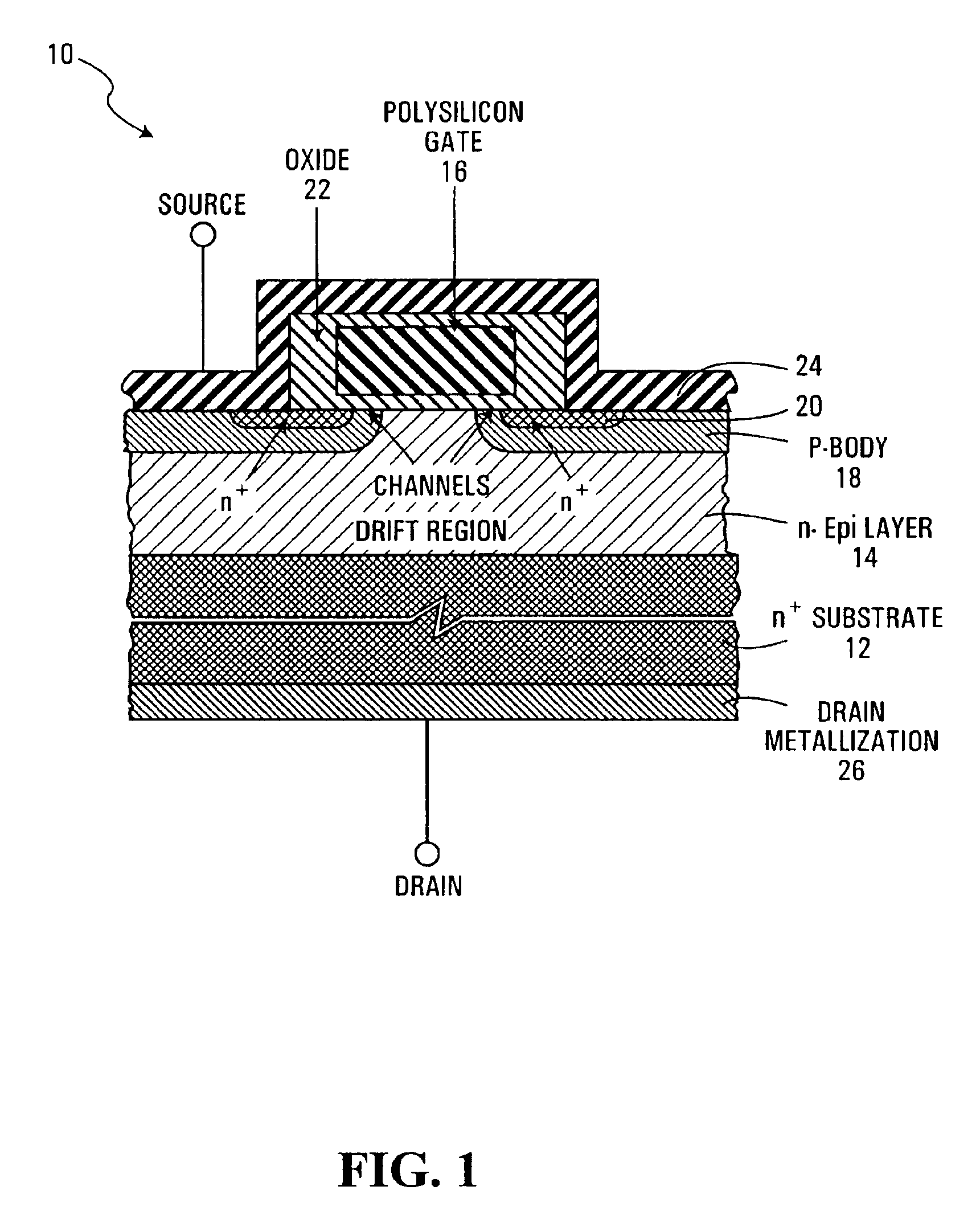

Lateral power MOSFET for high switching speeds

A lateral power metal-oxide-semiconductor field effect transistor (MOSFET) having a gate structure in which the insulated gate is coupled to the gate electrode through contacts at a plurality of locations. The source electrode includes first and second segments. The first segment is interposed between the drain electrode and the gate electrode and acts as a field plate.

Owner:POWER INTEGRATIONS INC

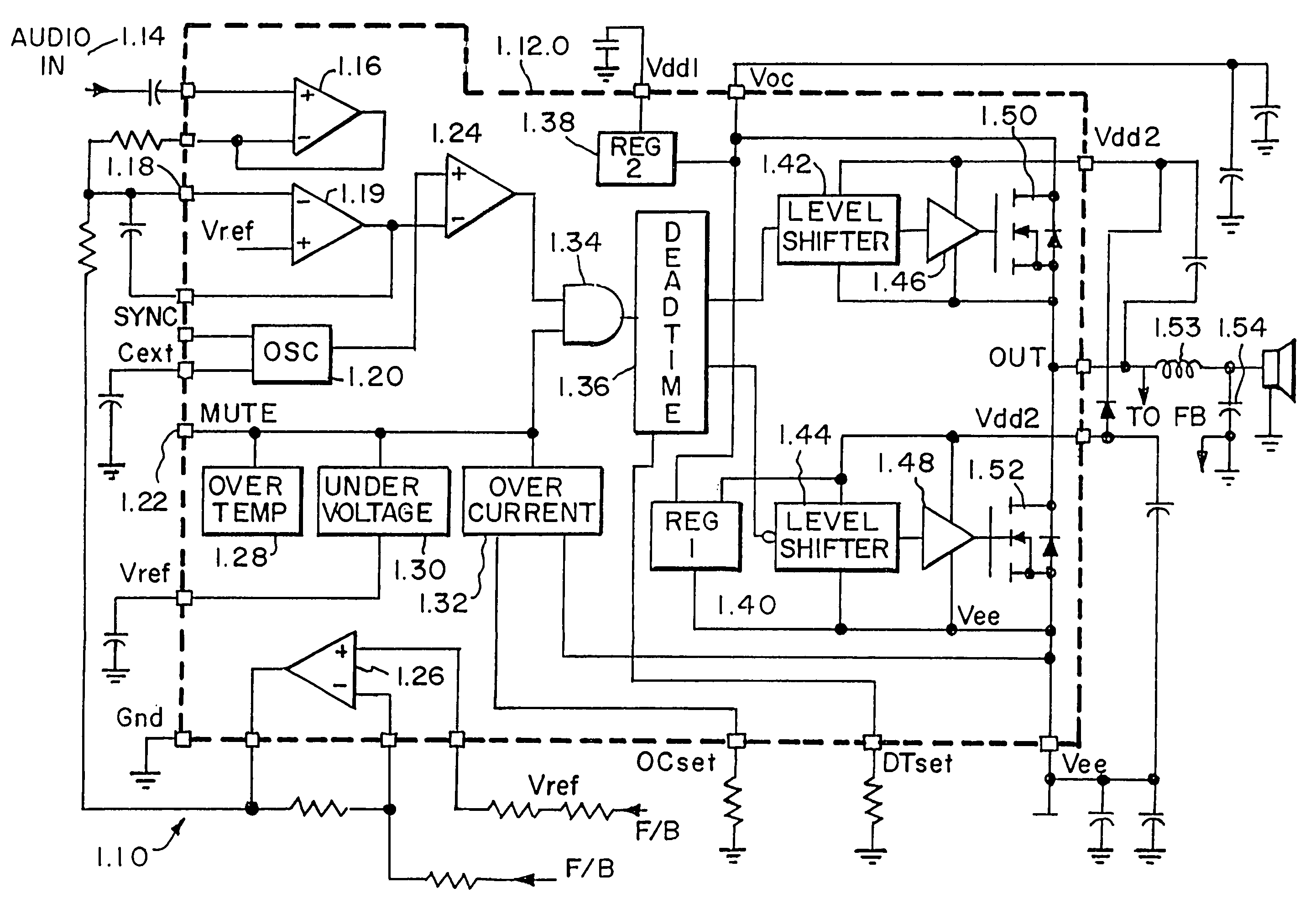

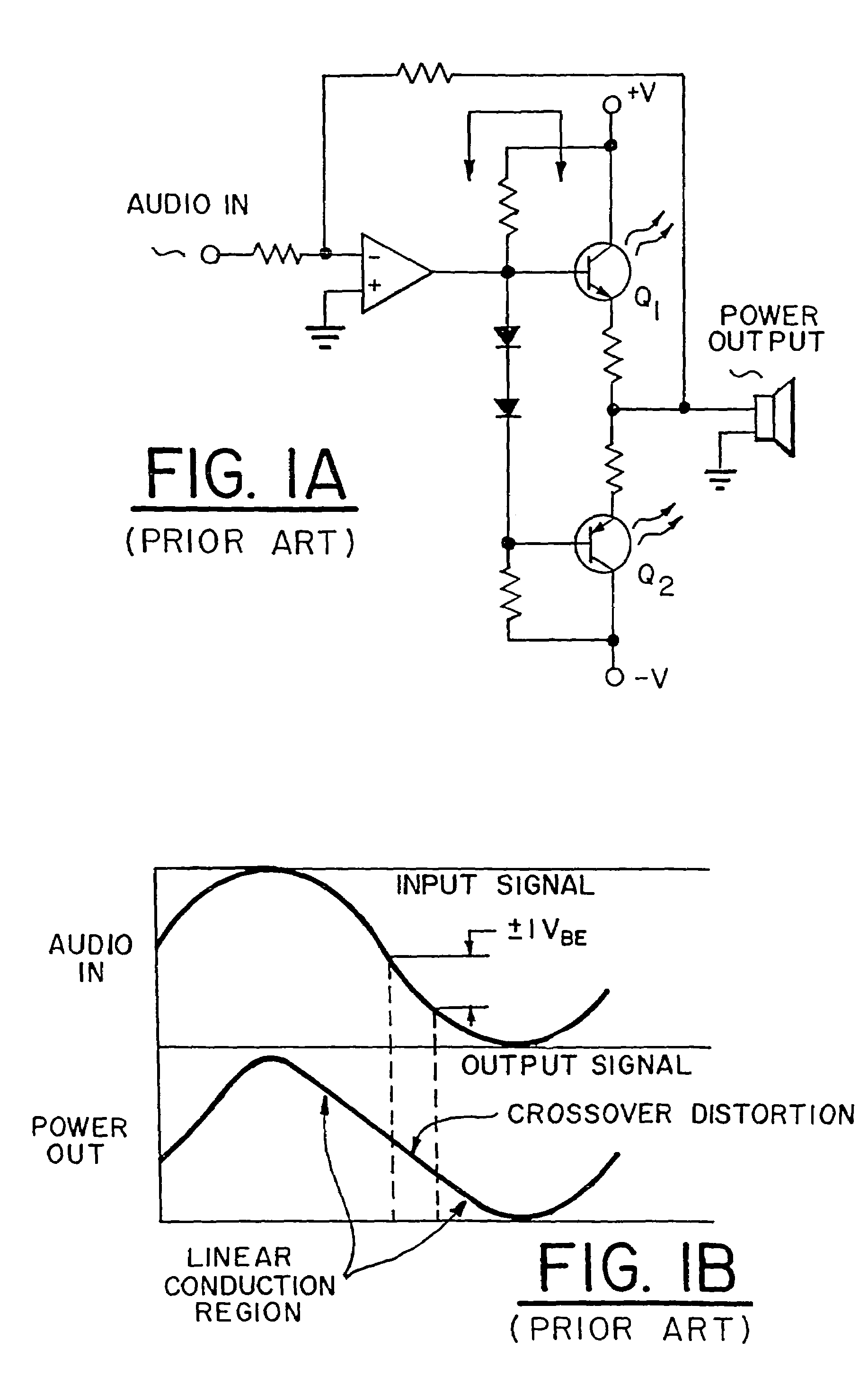

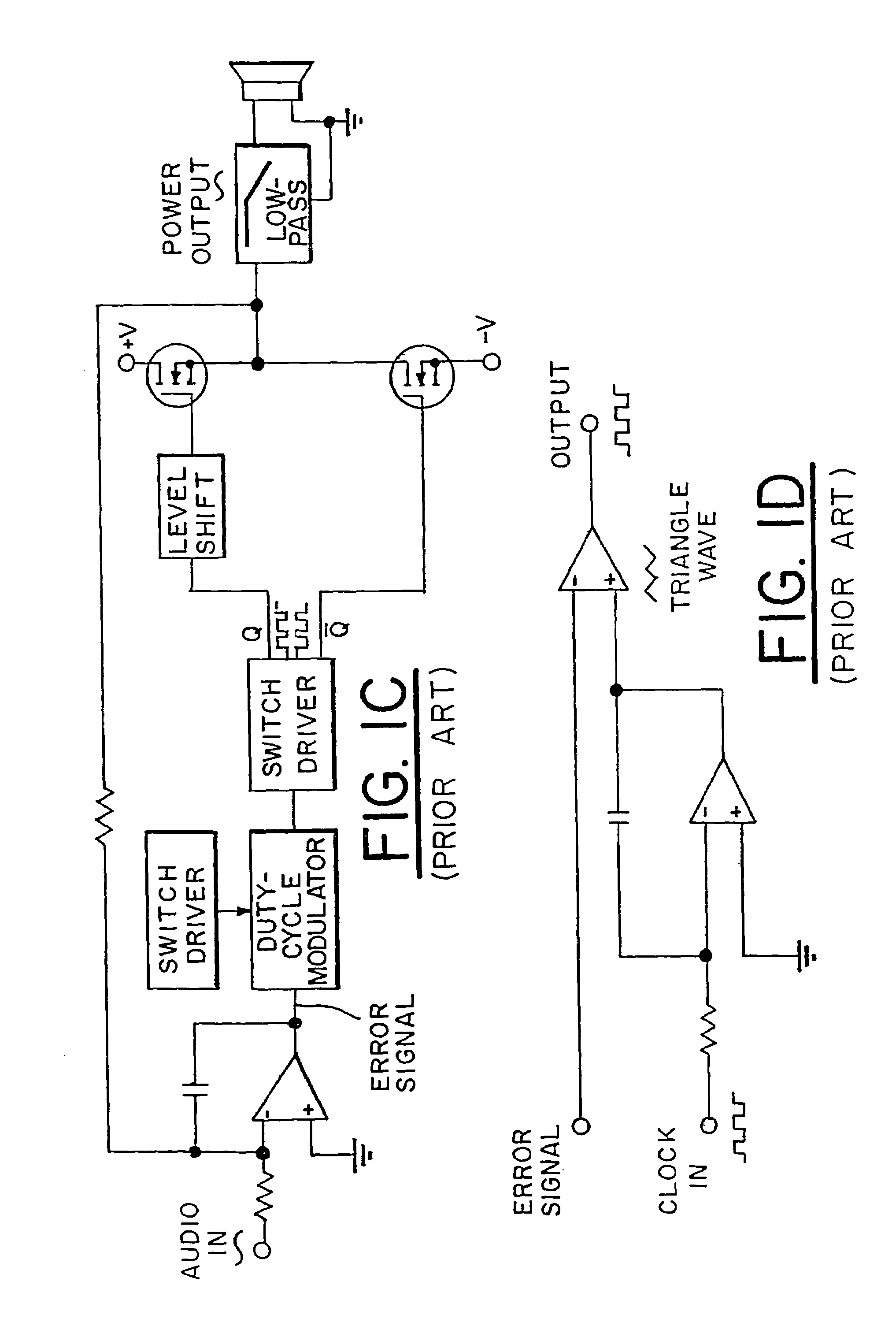

Monolithic class D amplifier

InactiveUS7076070B2Minimized cell areaMaximizing specific channel widthTransistorGated amplifiersDriver circuitAudio power amplifier

A monolithic 1.75 is mounted in a speaker cabinet 1.71 to drive the voice coil 1.74 of the speaker 1.70. The monolithic integrated circuit may be a class D amplifier 1.10, and is at least a half-bridge or full bridge power MOSFET device. Structures and process for forming the mos switching devices 2.20 of the bridge driver circuits are disclosed. Also disclosed is the N+ buried layer 4.14 of the QVDMOS transistors 4.43 of the bridge circuits.

Owner:INTERSIL INC

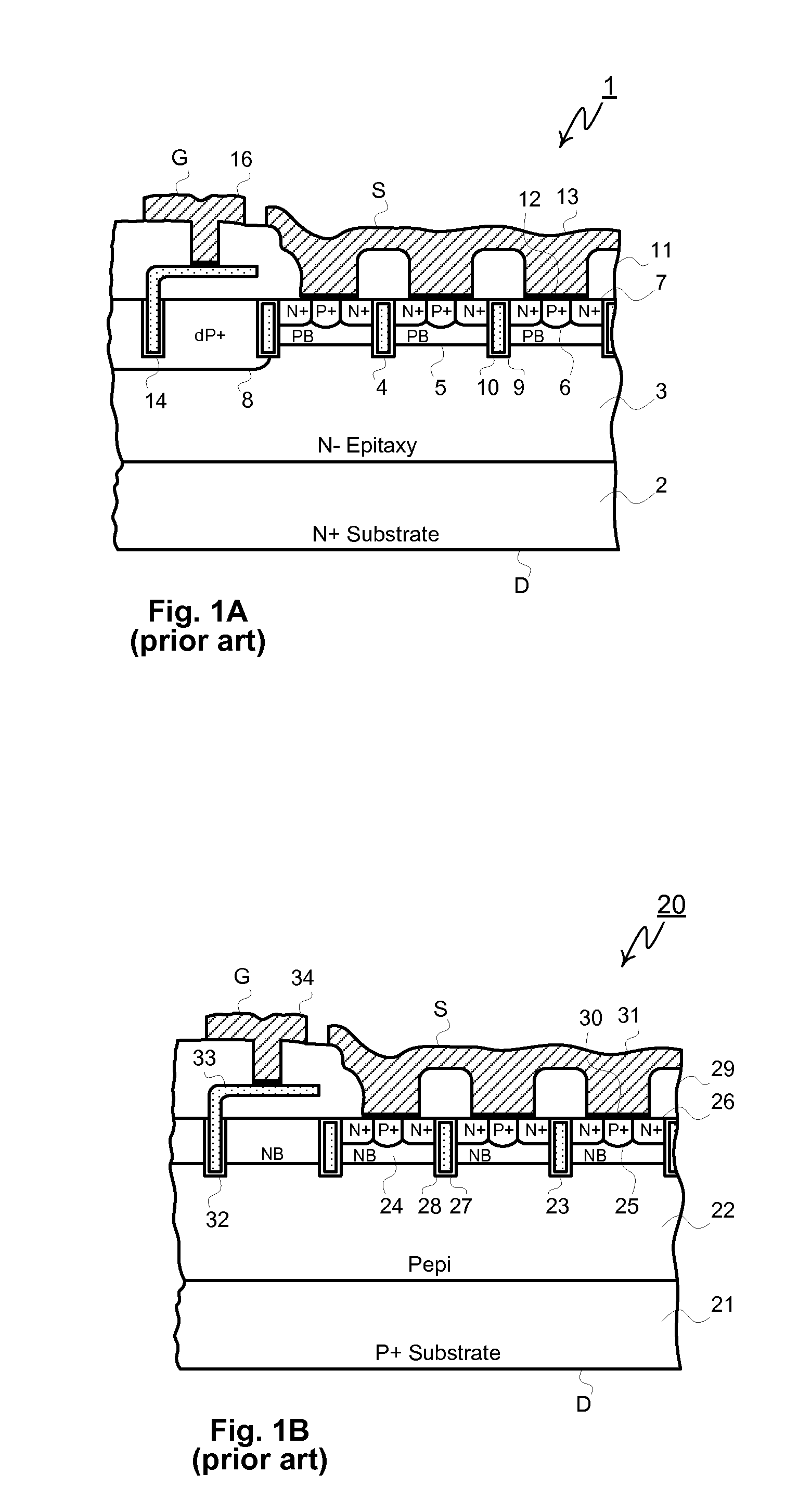

Semiconductor device

InactiveUS20120049187A1Reliable manufacturingEffectively prevent deteriorationSolid-state devicesDiodeZener diodeMiniaturization

Accompanying the miniaturization of a gate electrode of a trench gate power MOSFET, the curvature of the bottom part of the trench increases, and thereby, electric fields concentrate on the part and deterioration of a gate oxide film (insulating film) occurs. The deterioration of the gate insulating film is more likely to occur when the gate side bias is negative in the case of an N-channel type power MOSFET and when the gate side bias is positive in the case of a P-channel type power MOSFET.The present invention is a semiconductor device including an insulating gate power transistor etc. in a chip, wherein a gate protection element includes a bidirectional Zener diode and the bidirectional Zener diode has a plurality of P-type impurity regions (or a P-type impurity region) having different concentrations so that the withstand voltage with its gate side negatively biased and the withstand voltage with the gate side positively biased are different from each other.

Owner:RENESAS ELECTRONICS CORP

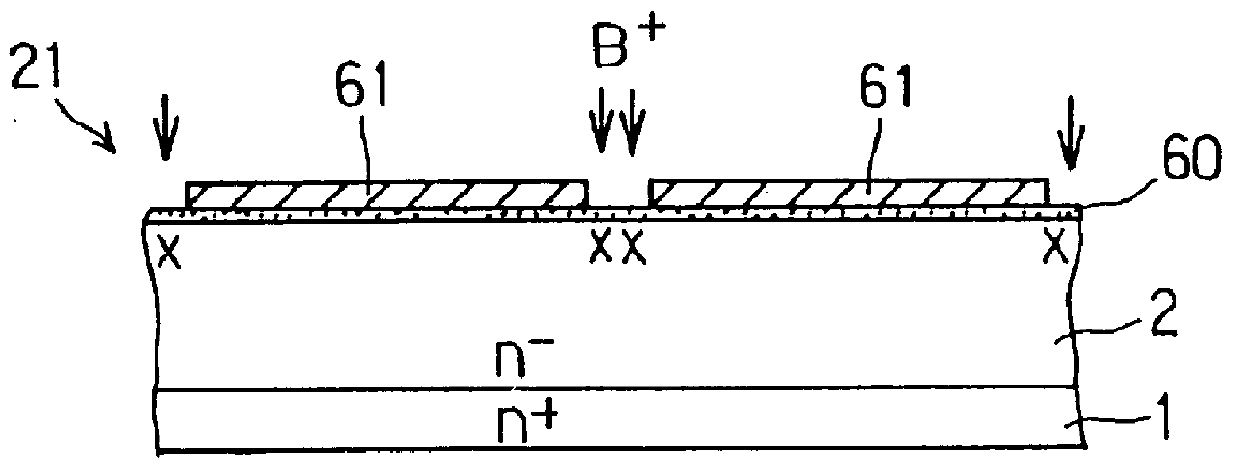

Production method of a vertical type MOSFET

InactiveUS6015737AMade smallSmall on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesDouble diffusionLOCOS

A vertical type power MOSFET remarkably reduces its ON-resistance per area. A substantial groove formation in which a gate structure is constituted is performed beforehand utilizing the LOCOS method before the formation of a p-type base layer and an n+-type source layer. The p-type base layer and the n+-type source layer are then formed by double diffusion in a manner of self-alignment with respect to a LOCOS oxide film, simultaneously with which channels are set at sidewall portions of the LOCOS oxide film. Thereafter the LOCOS oxide film is removed to provide a U-groove so as to constitute the gate structure. Namely, the channels are set by the double diffusion of the manner of self-alignment with respect to the LOCOS oxide film, so that the channels, which are set at the sidewall portions at both sides of the groove, provide a structure of exact bilateral symmetry, there is no positional deviation of the U-groove with respect to the base layer end, and the length of the bottom face of the U-groove can be made minimally short. Therefore, the unit cell size is greatly reduced, and the ON-resistance per area is greatly decreased.

Owner:DENSO CORP

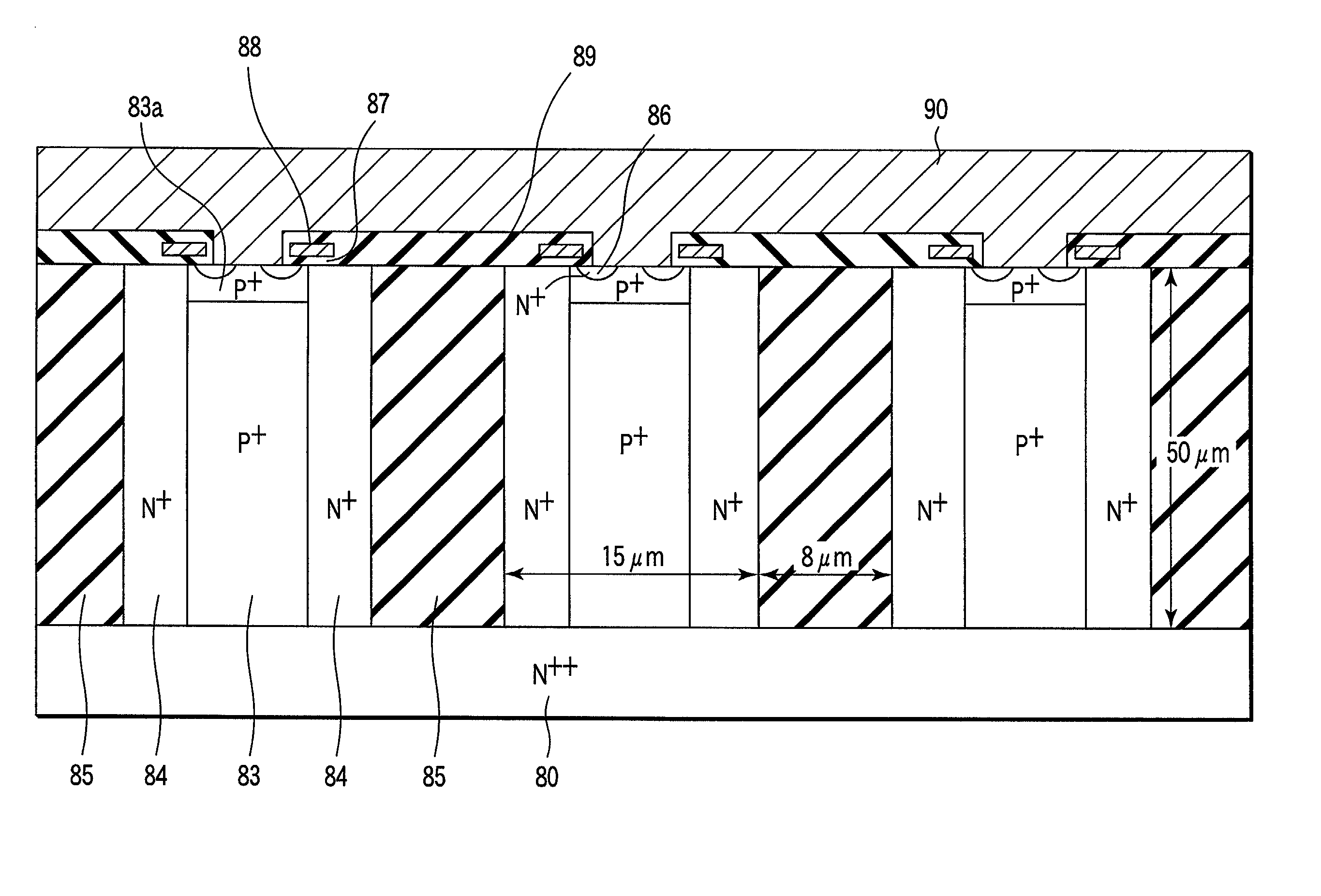

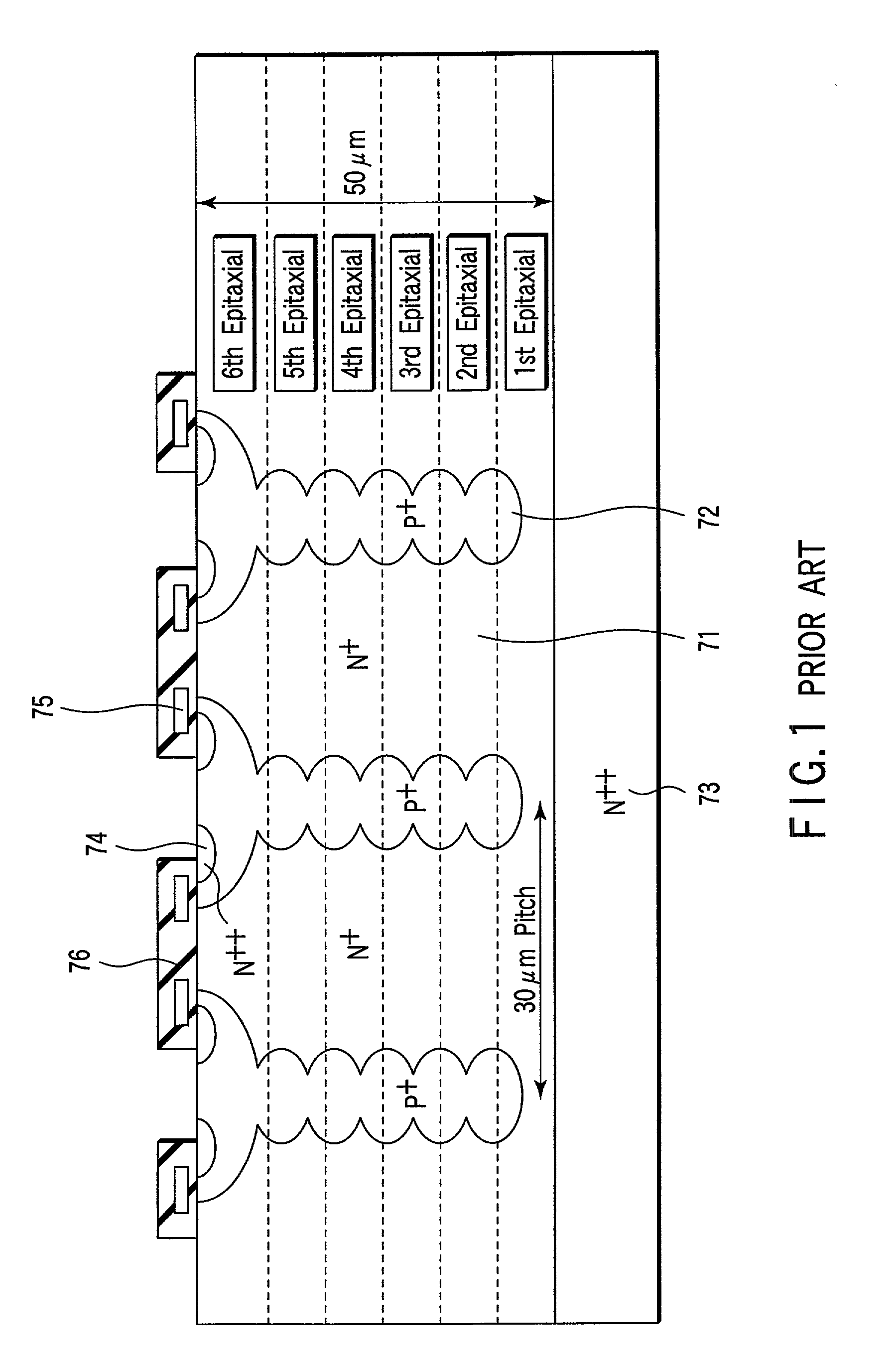

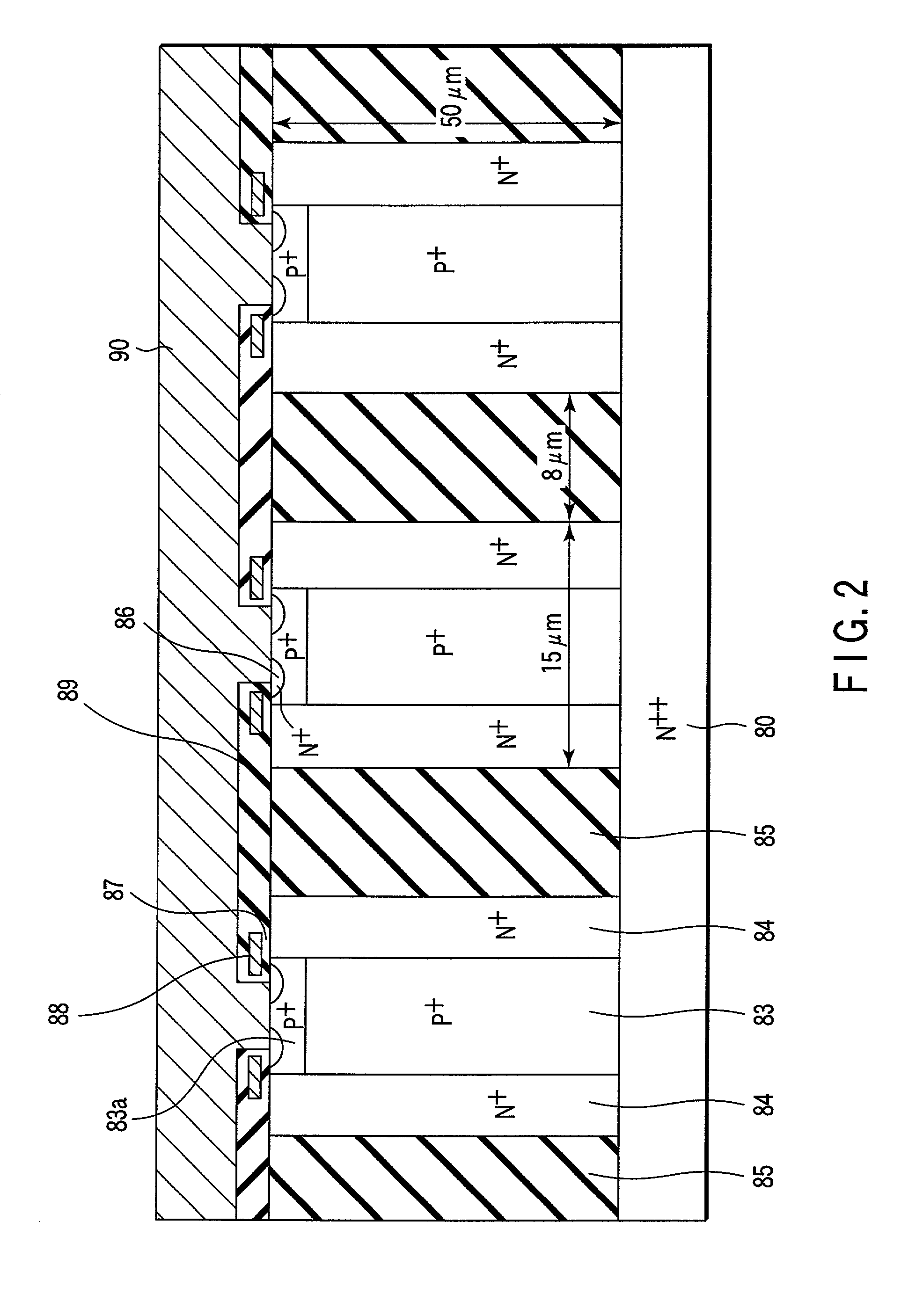

A power mosfet having laterally three-layered structure formed among element isolation regions

A semiconductor apparatus has an NPN (or PNP) laterally three-layered pillar formed in a mesh form among a plurality of trench type element isolation regions, and having a source and gate on an upper surface of the three-layered pillar, and a drain on a lower surface thereof. A depth DT and minimum planar width WTmin of the element isolation region and a width WP of the three-layered pillar are configured to satisfy a relation of 3.75<=DT / WP<=60 or 5.5<=DT / WTmin<=14.3. The above configuration realizes a high breakdown voltage and low on-resistance are realized.

Owner:KK TOSHIBA

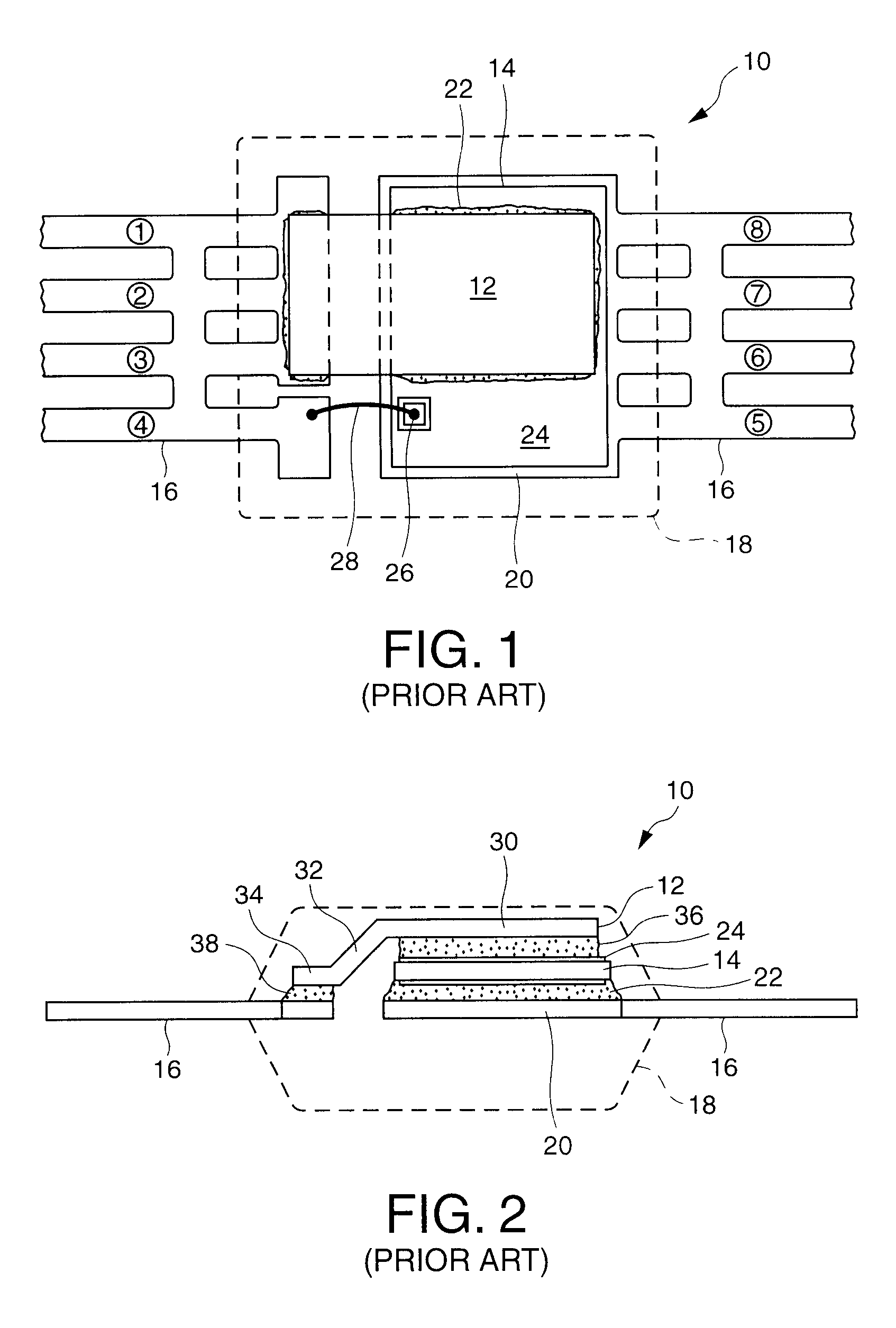

Attaching semiconductor dies to substrates with conductive straps

InactiveUS6459147B1Prevent lateral movementFreedom of movementElectrically conductive connectionsSemiconductor/solid-state device detailsElastomerShear stress

This invention provides a method apparatus for electrically connecting a semiconductor die, such as a power MOSFET, to a substrate on which the die is mounted, e.g., a lead frame, with a conductive strap, such that the connection is resistant to the shear stresses incident upon it with changes in temperature of the device. The method includes providing a conductive strap, and in one embodiment thereof, forming a recess in the top surface of the substrate. The bottom surface of a flange portion of the strap is attached to the floor of the recess such that the recess captures the flange and prevents relative horizontal movement of the flange and substrate with variations in the temperature of the device.Other embodiments include attaching the strap to the die and substrate with joints of a resilient conductive elastomer, and forming apertures in the strap and substrate that cooperate with a conductive joint material to reinforce the connection against temperature-induced shear forces.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

Power MOSFET with recessed field plate

ActiveUS7843004B2Solid-state devicesSemiconductor/solid-state device manufacturingTrench mosfetReverse recovery

A trench MOSFET contains a recessed field plate (RFP) trench adjacent the gate trench. The RFP trench contains an RFP electrode insulated from the die by a dielectric layer along the walls of the RFP trench. The gate trench has a thick bottom oxide layer, and the gate and RFP trenches are preferably formed in the same processing step and are of substantially the same depth. When the MOSFET operates in the third quadrant (with the source / body-to-drain junction forward-biased), the combined effect of the RFP and gate electrodes significantly reduces in the minority carrier diffusion current and reverse-recovery charge. The RFP electrode also functions as a recessed field plates to reduce the electric field in the channel regions when the MOSFET source / body to-drain junction reverse-biased.

Owner:MAXPOWER SEMICON INC