Patents

Literature

341results about How to "High doping" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

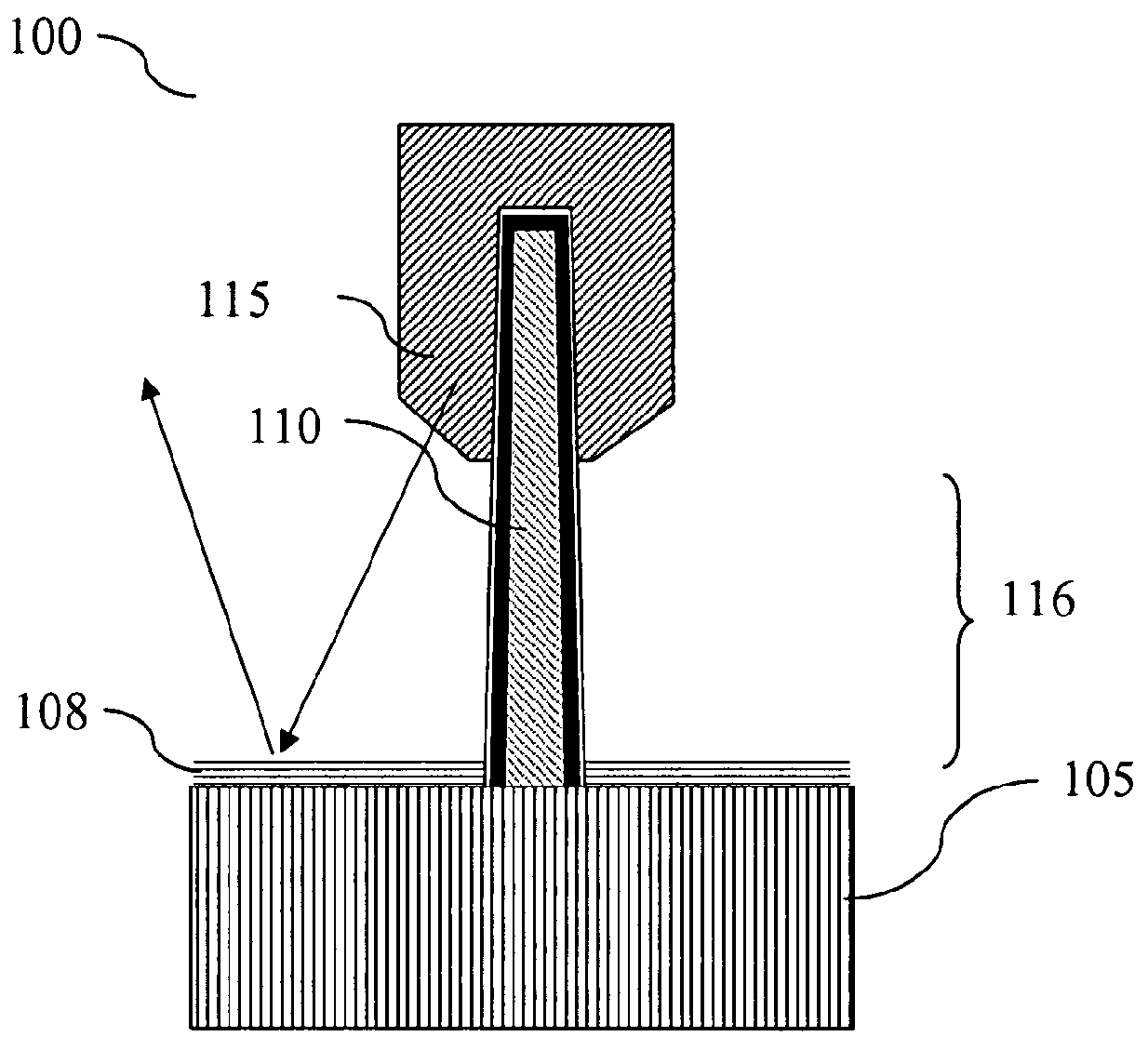

Led with upstanding nanowire structure and method of producing such

ActiveUS20080149944A1High dopingGood wave-guiding propertyNanoinformaticsSolid-state devicesNanowireActive component

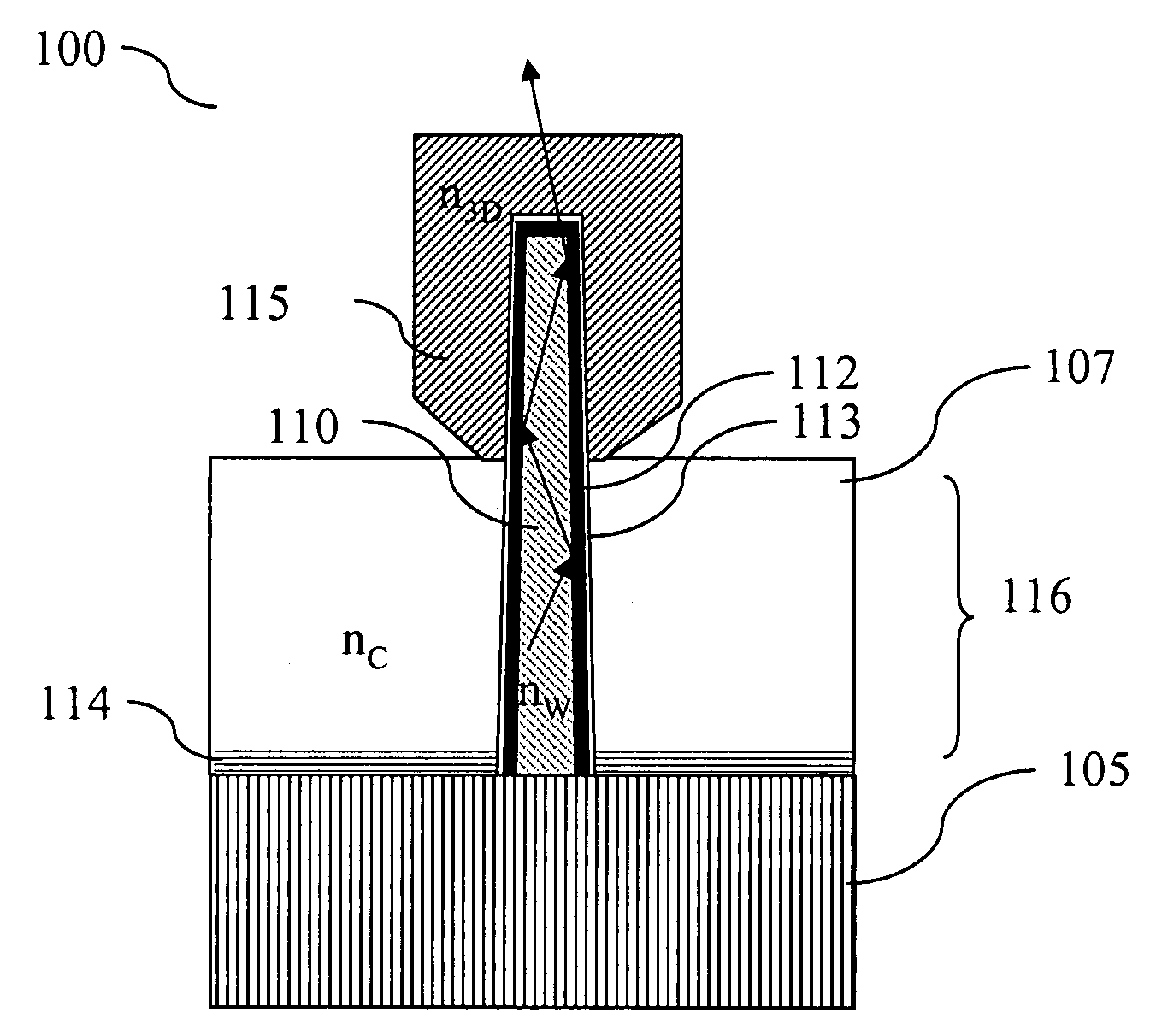

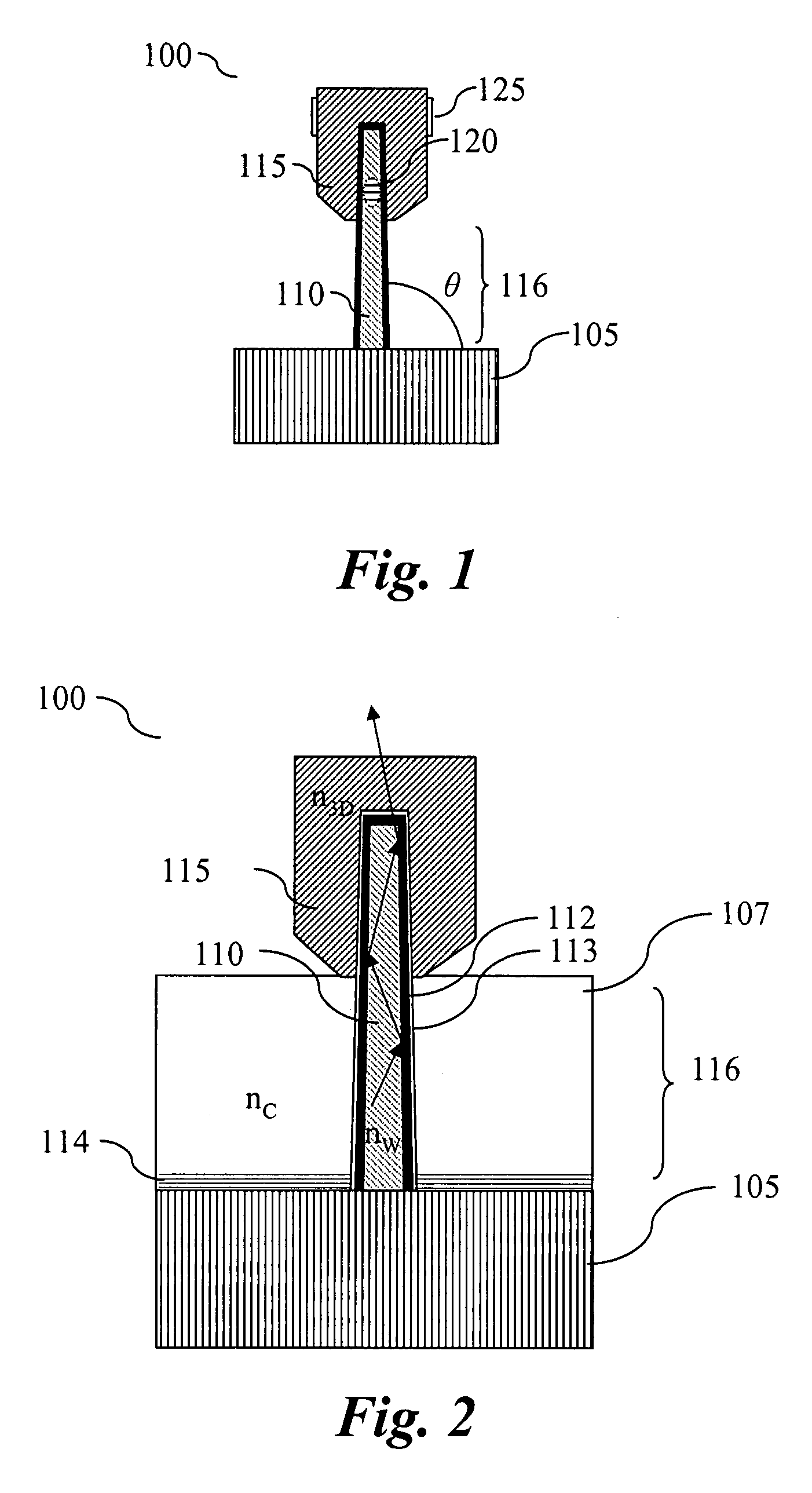

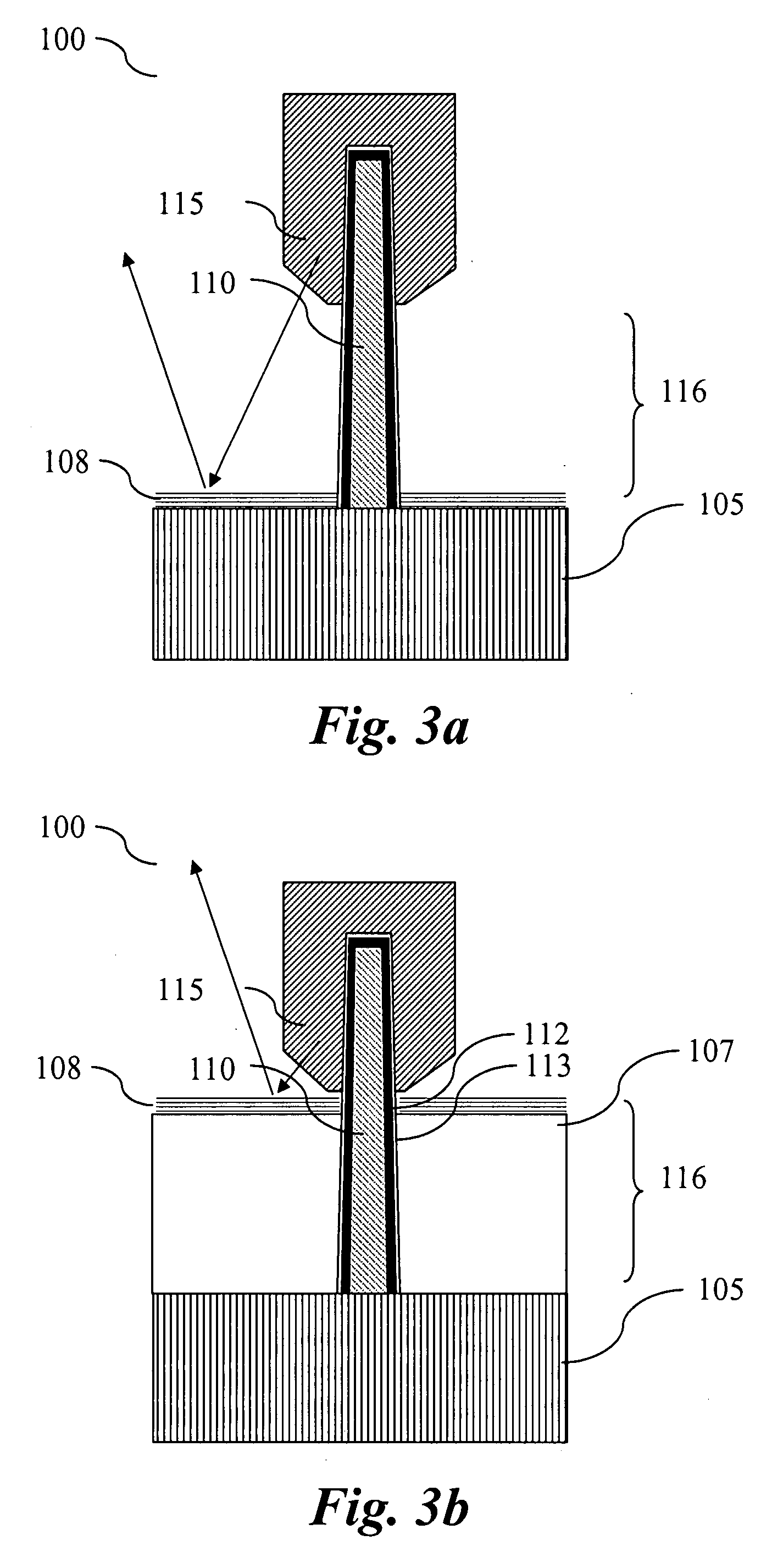

The present invention relates to light emitting diodes, LEDs. In particular the invention relates to a LED comprising a nanowire as an active component. The nanostructured LED according to the embodiments of the invention comprises a substrate and at an upstanding nanowire protruding from the substrate. A pn-junction giving an active region to produce light is present within the structure. The nanowire, or at least a part of the nanowire, forms a wave-guiding section directing at least a portion of the light produced in the active region in a direction given by the nanowire.

Owner:QUNANO

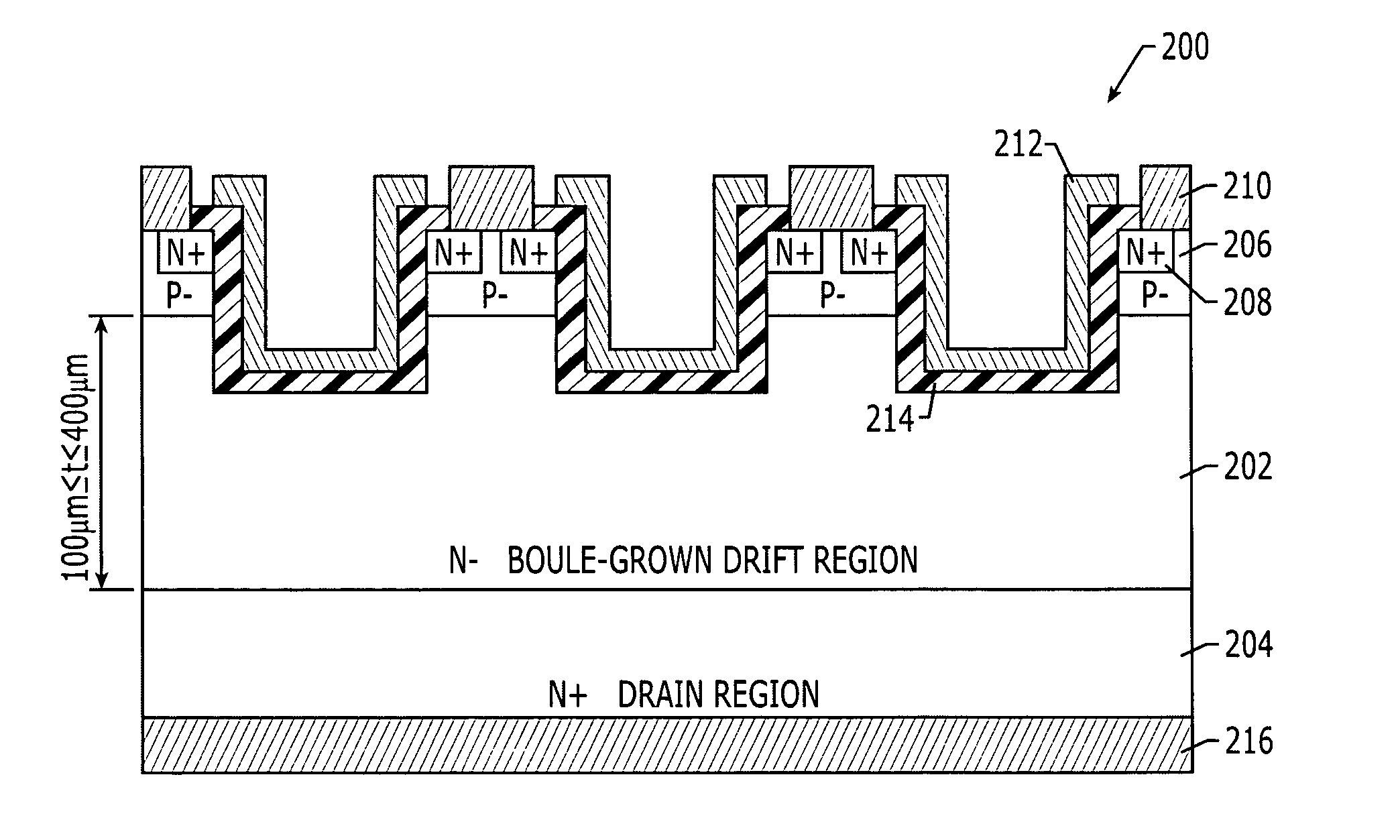

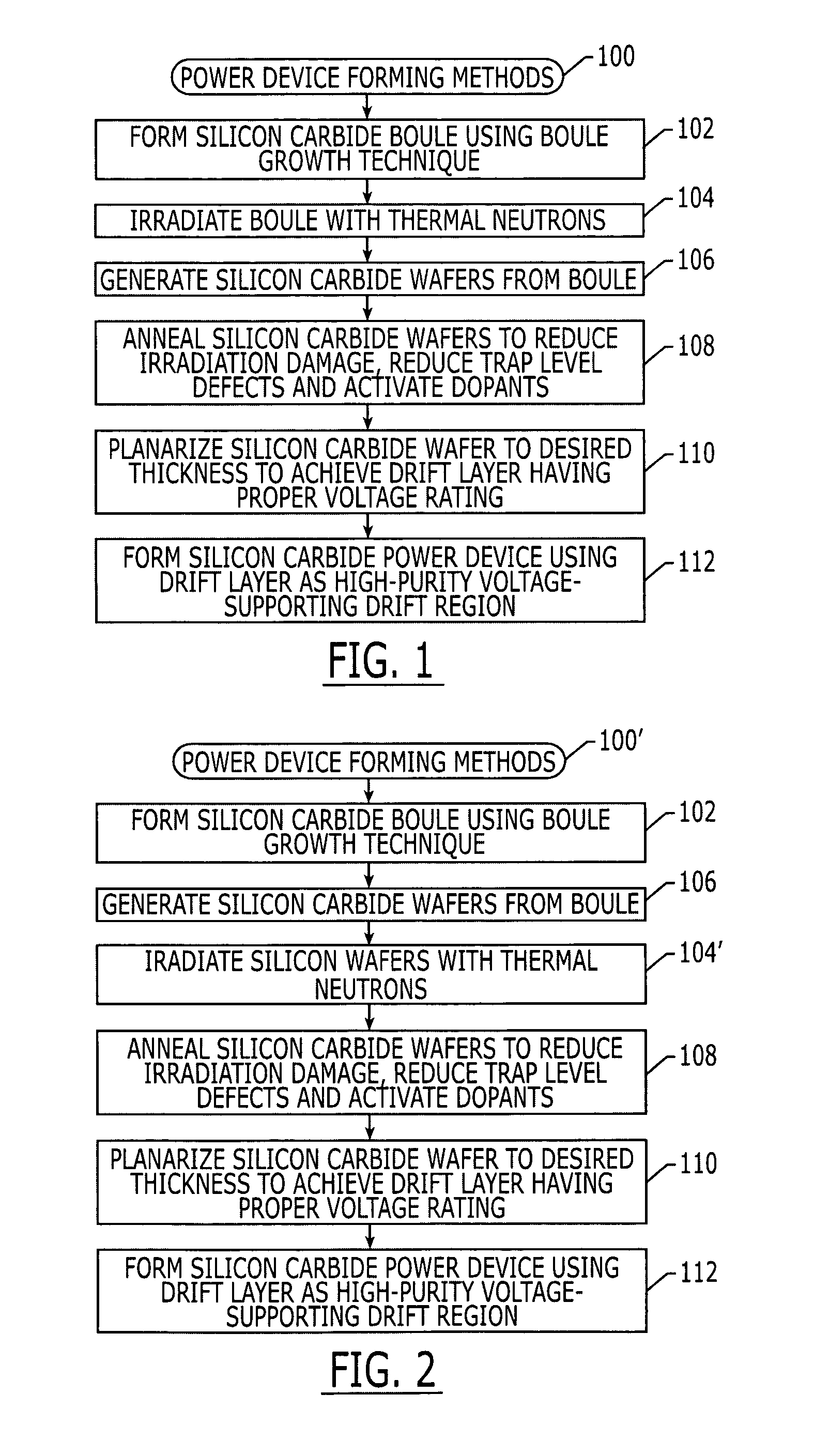

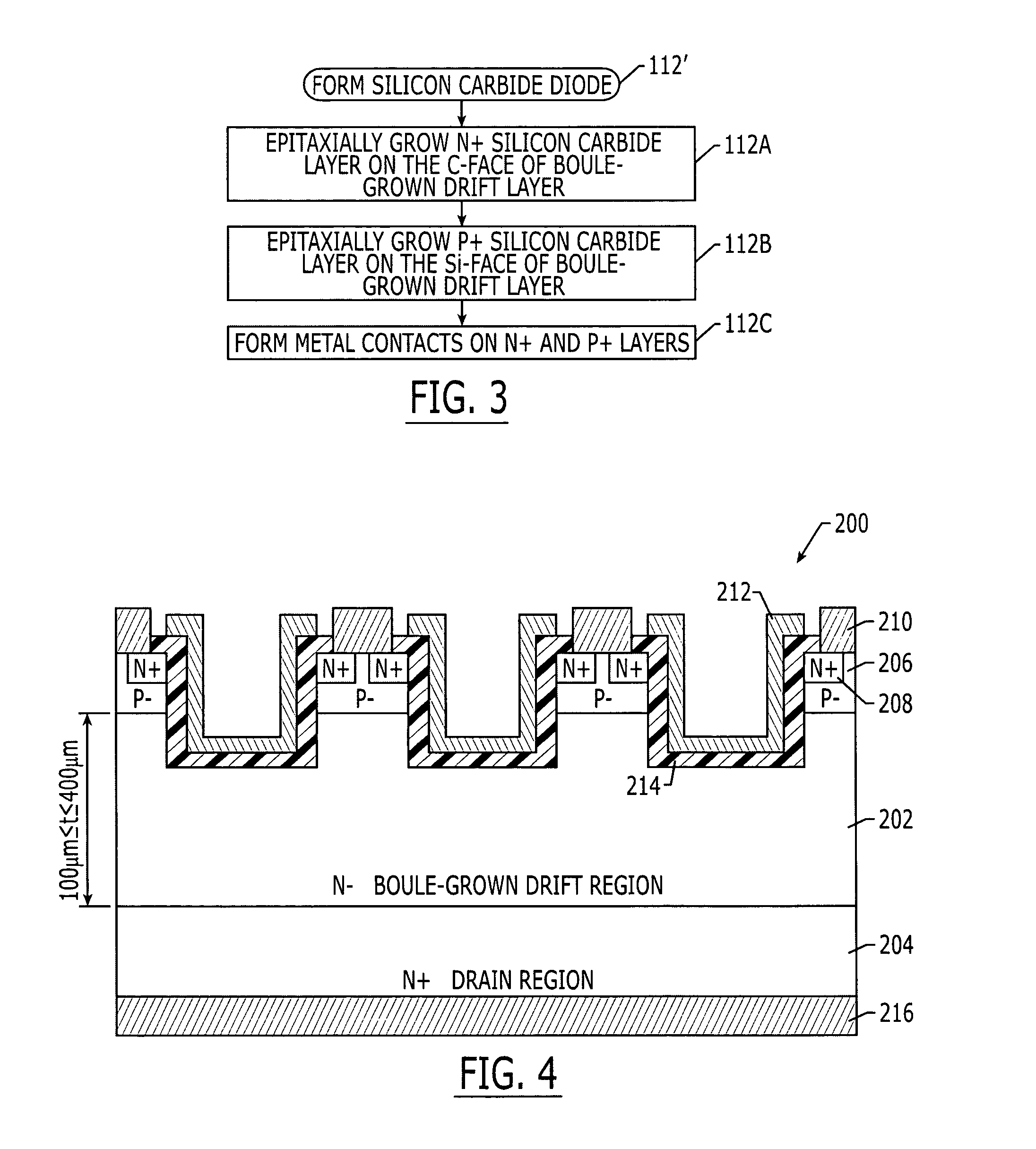

Methods of forming power semiconductor devices using boule-grown silicon carbide drift layers and power semiconductor devices formed thereby

ActiveUS20050082542A1High dopingPolycrystalline material growthDiffusion/dopingPower semiconductor deviceDopant

Methods of forming high voltage silicon carbide power devices utilize high purity silicon carbide drift layers that are derived from high purity silicon carbide wafer material, instead of prohibitively costly epitaxially grown silicon carbide layers. The methods include forming both minority carrier and majority carrier power devices that can support greater than 10 kV blocking voltages, using drift layers having thicknesses greater than about 100 um. The drift layers are formed as boule-grown silicon carbide drift layers having a net n-type dopant concentration therein that is less than about 2×1015 cm−3. These n-type dopant concentrations can be achieved using neutron transmutation doping (NTD) techniques.

Owner:CREE INC

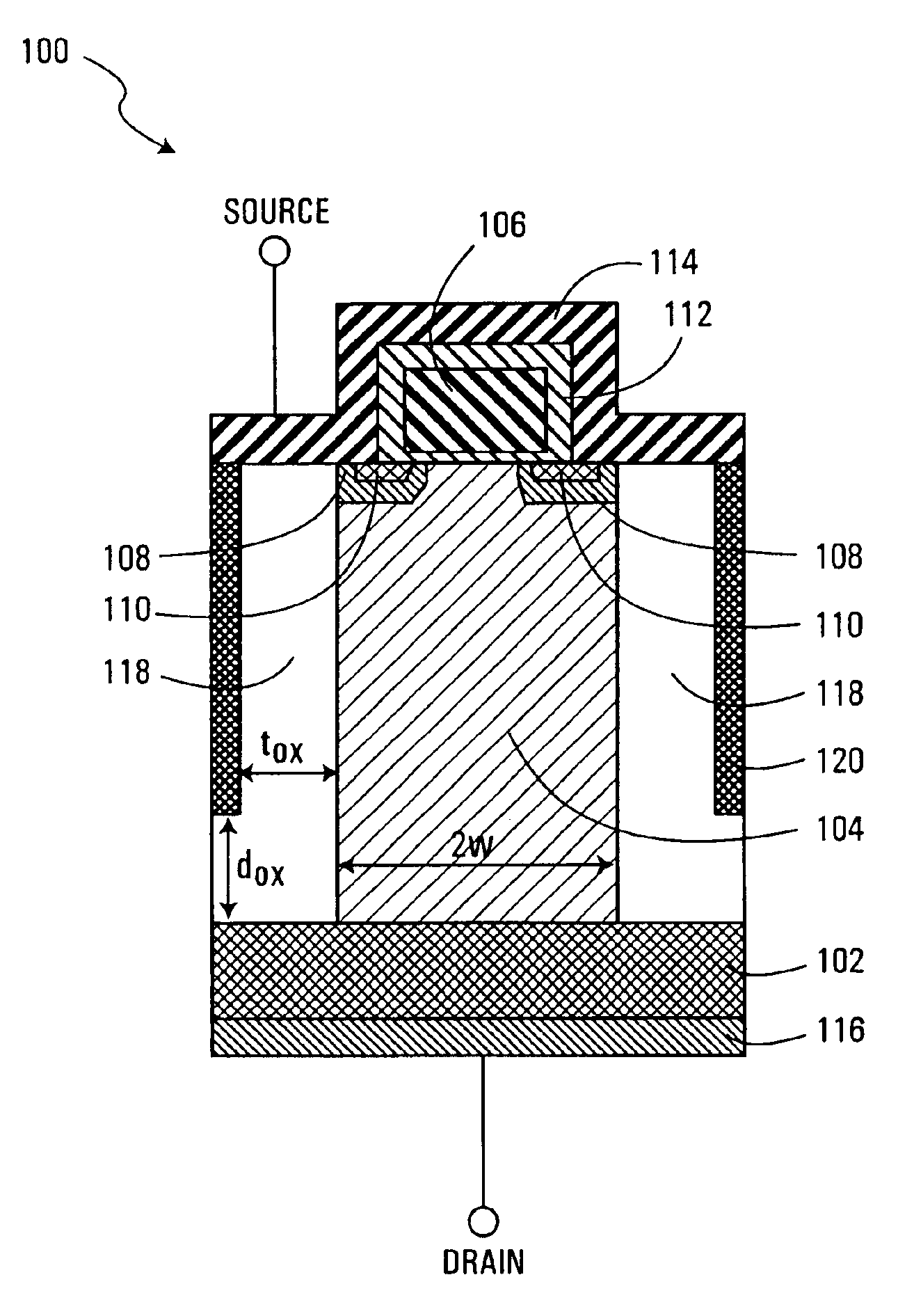

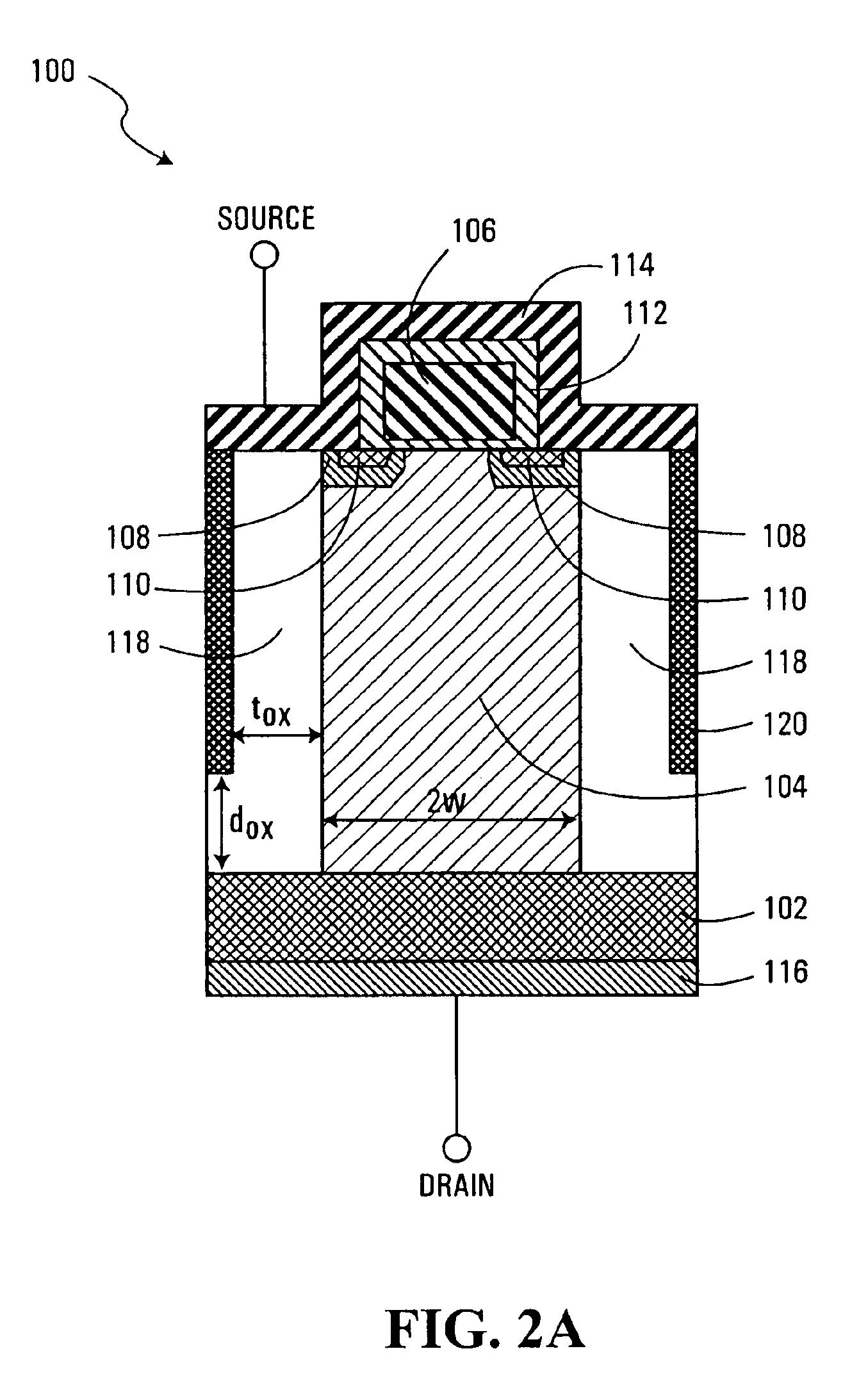

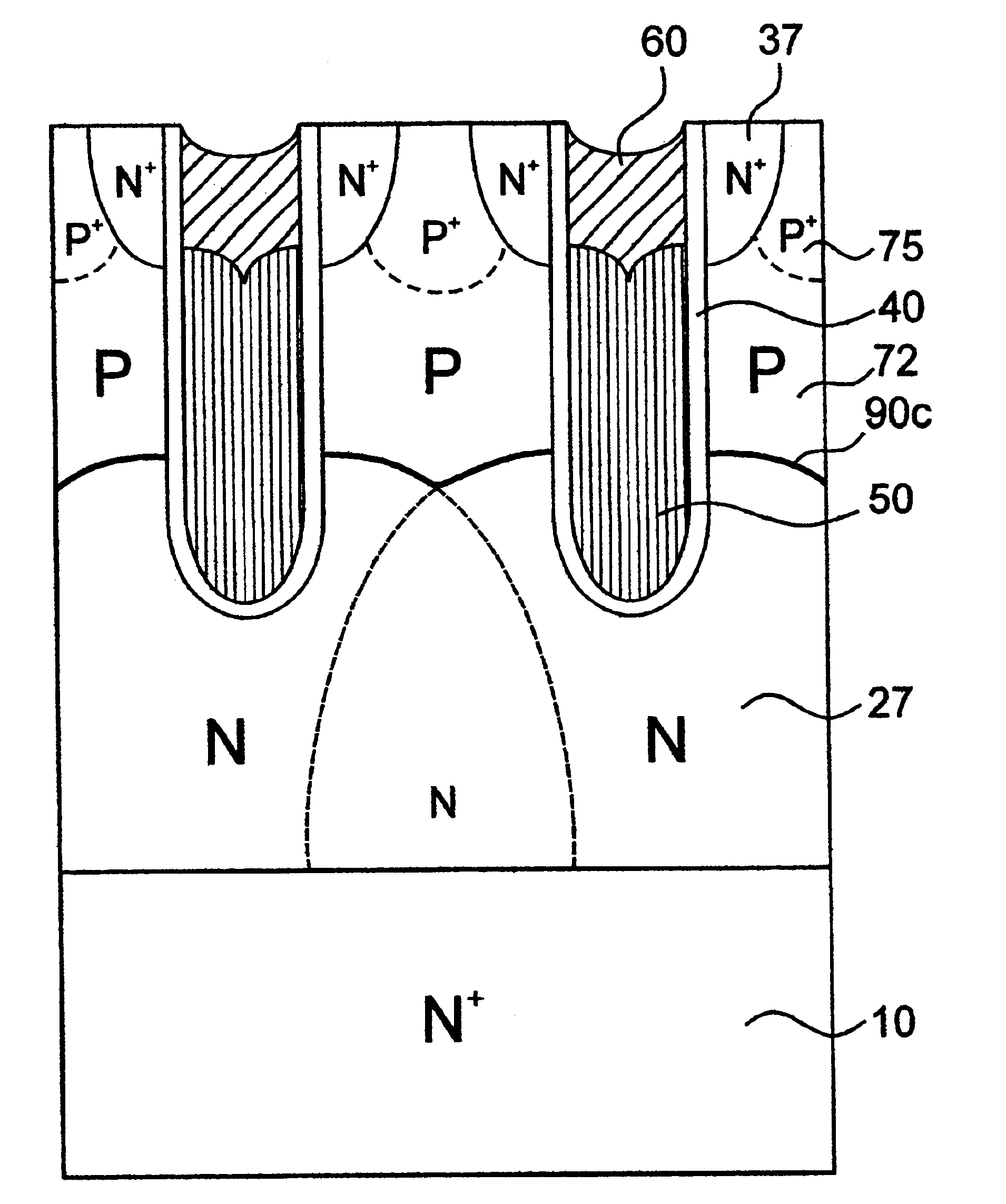

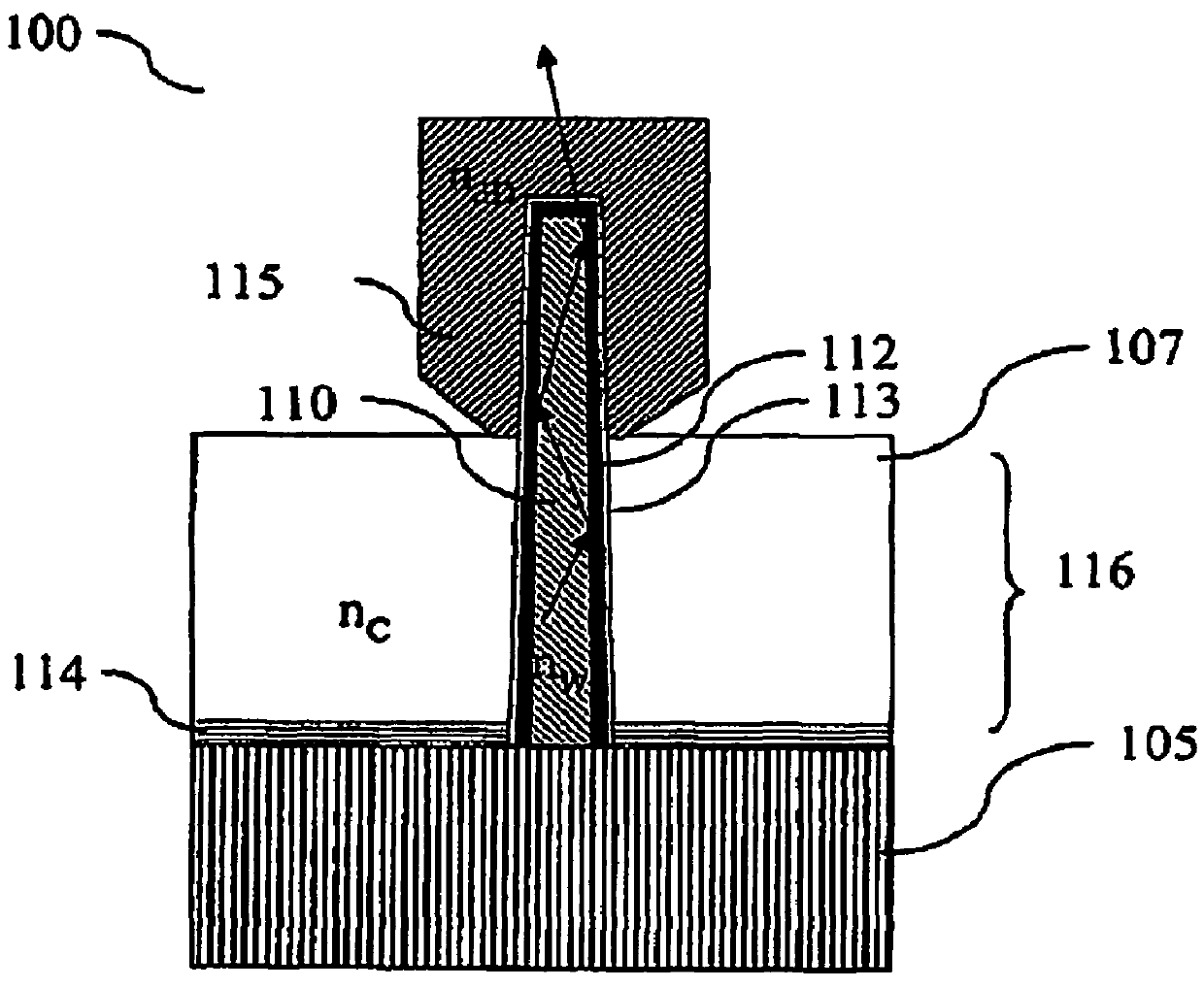

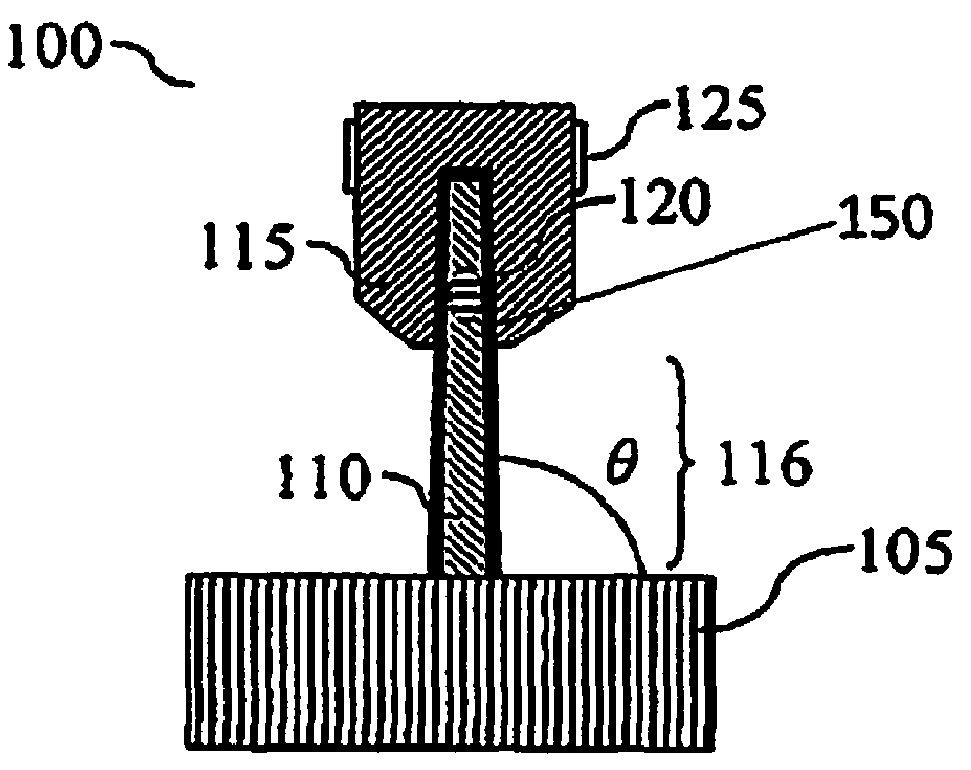

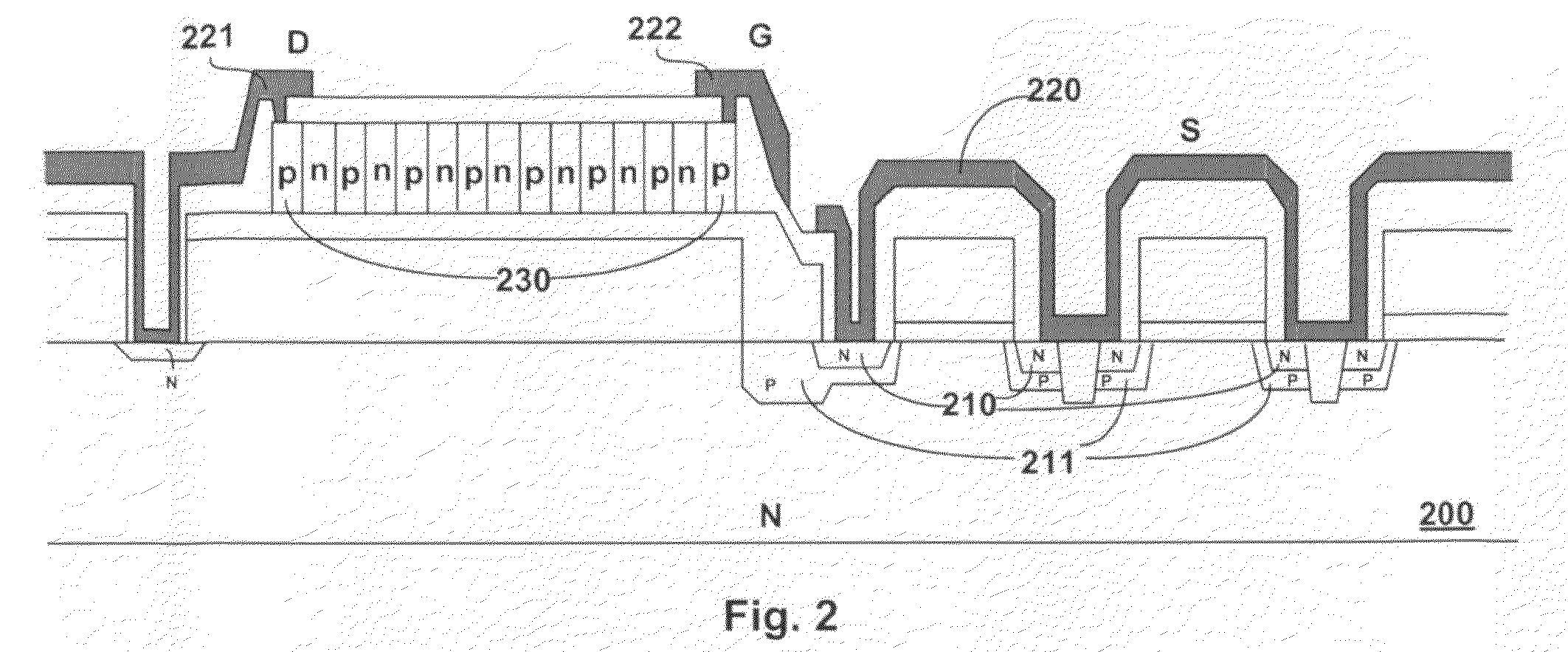

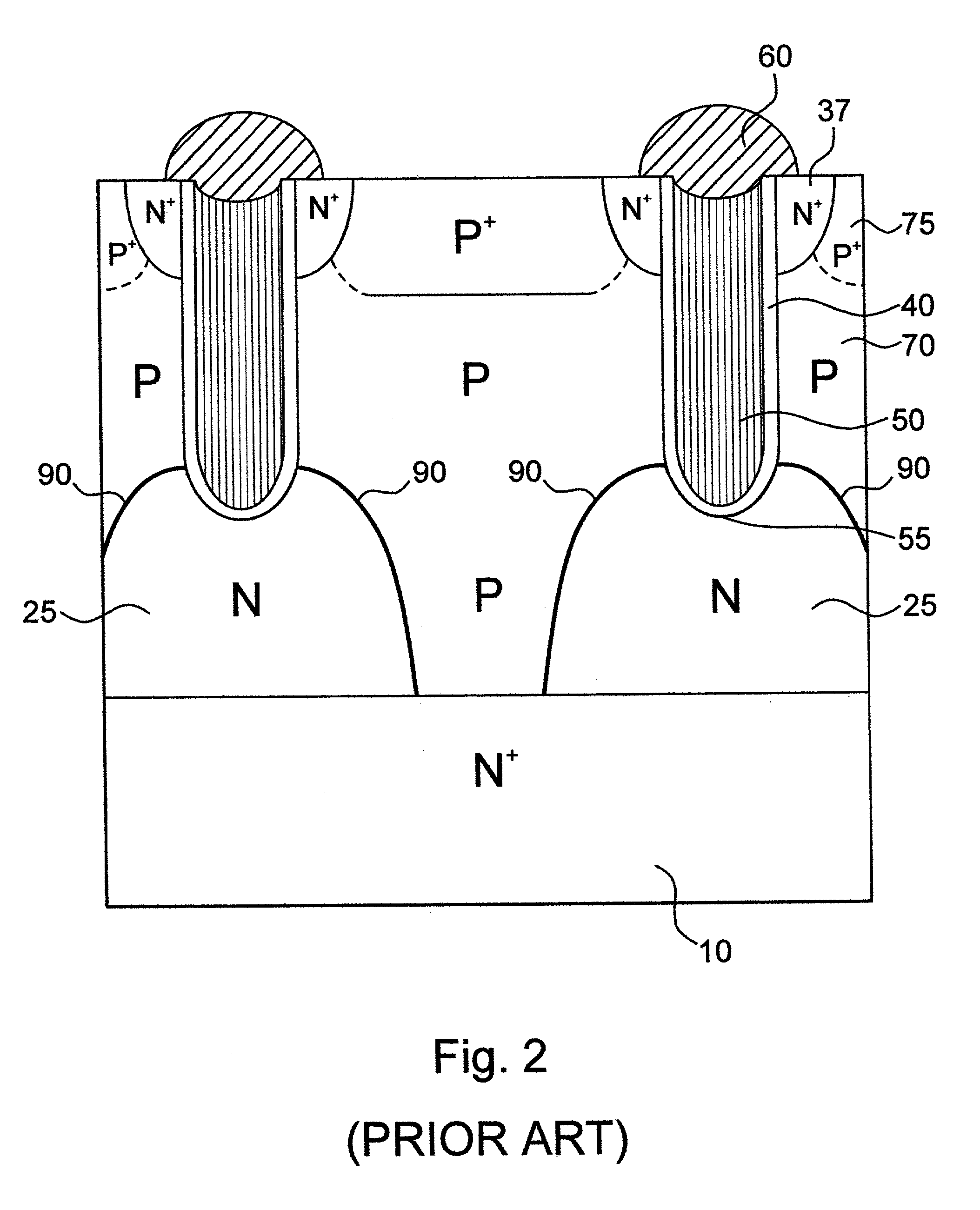

Power MOSFET having enhanced breakdown voltage

InactiveUS6853033B2Improve breakdown voltageHigh dopingSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricPower MOSFET

A MOSFET includes a dielectric, preferably in the form of a metal thick oxide that extends alongside the MOSFET's drift region. A voltage across this dielectric between its opposing sides exerts an electric field into the drift region to modulate the drift region electric field distribution so as to increase the breakdown voltage of a reverse biased semiconductor junction between the drift region and body region. This allows for higher doping of the drift region, for a given breakdown voltage when compared to conventional MOSFETs.

Owner:NAT UNIV OF SINGAPORE

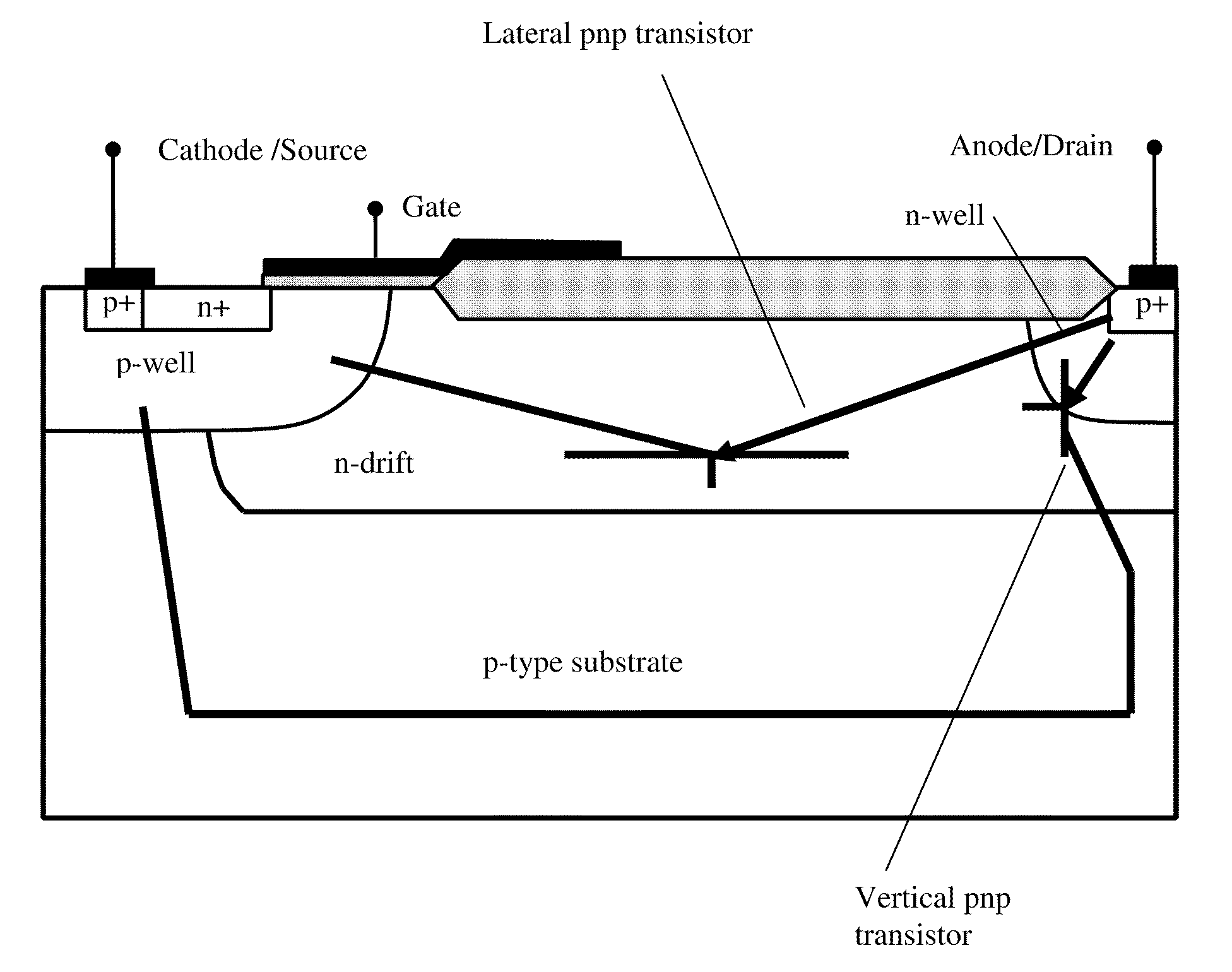

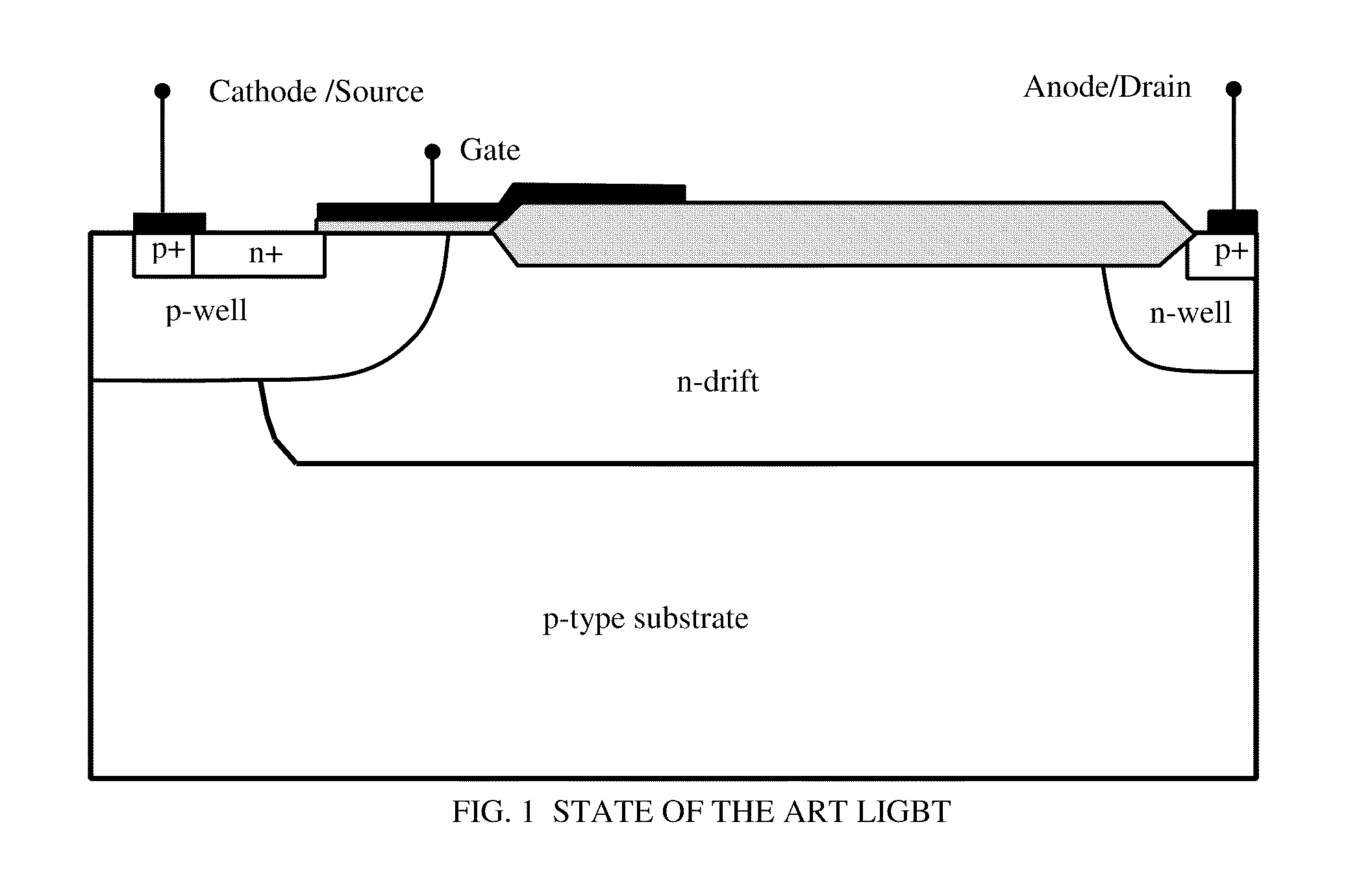

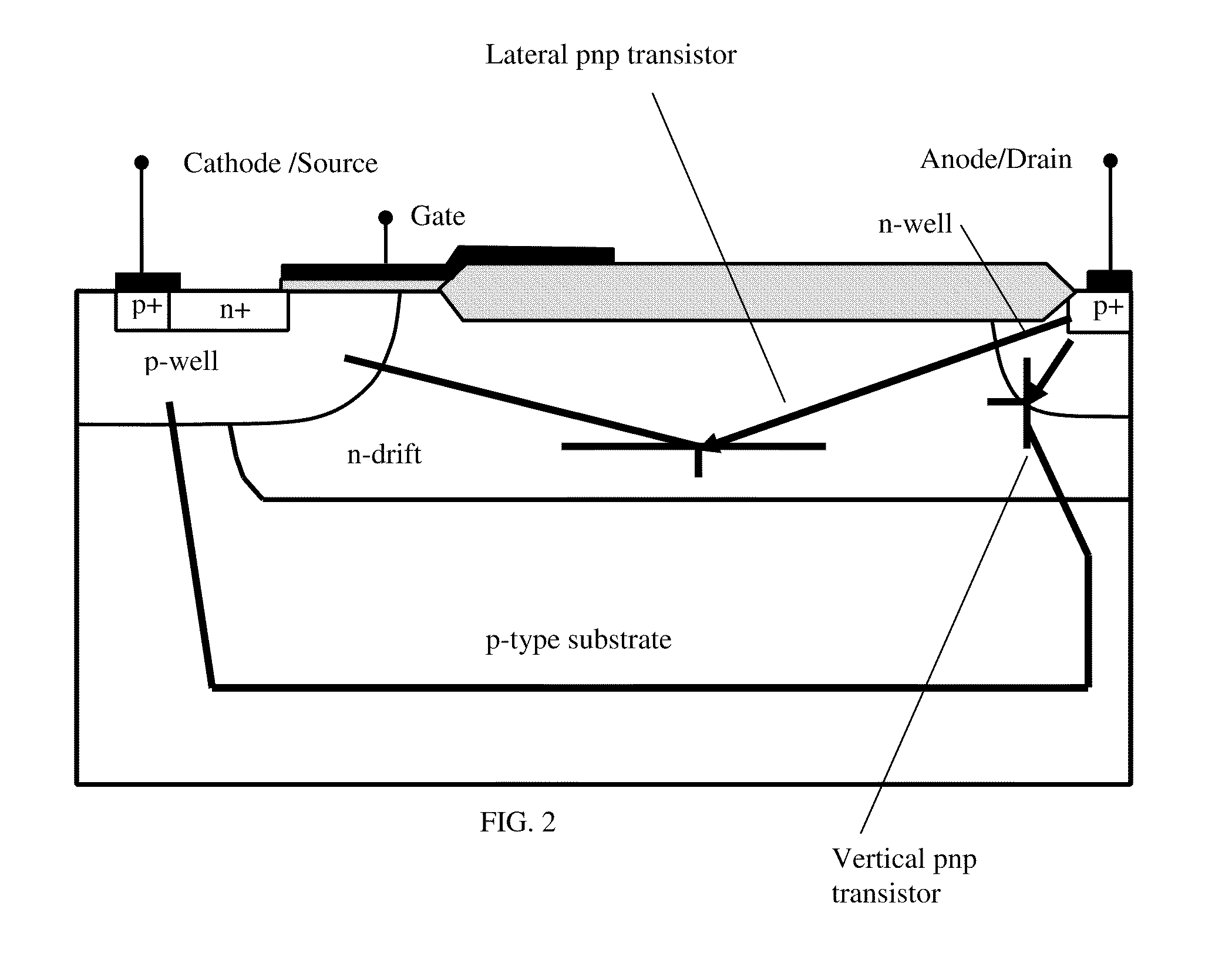

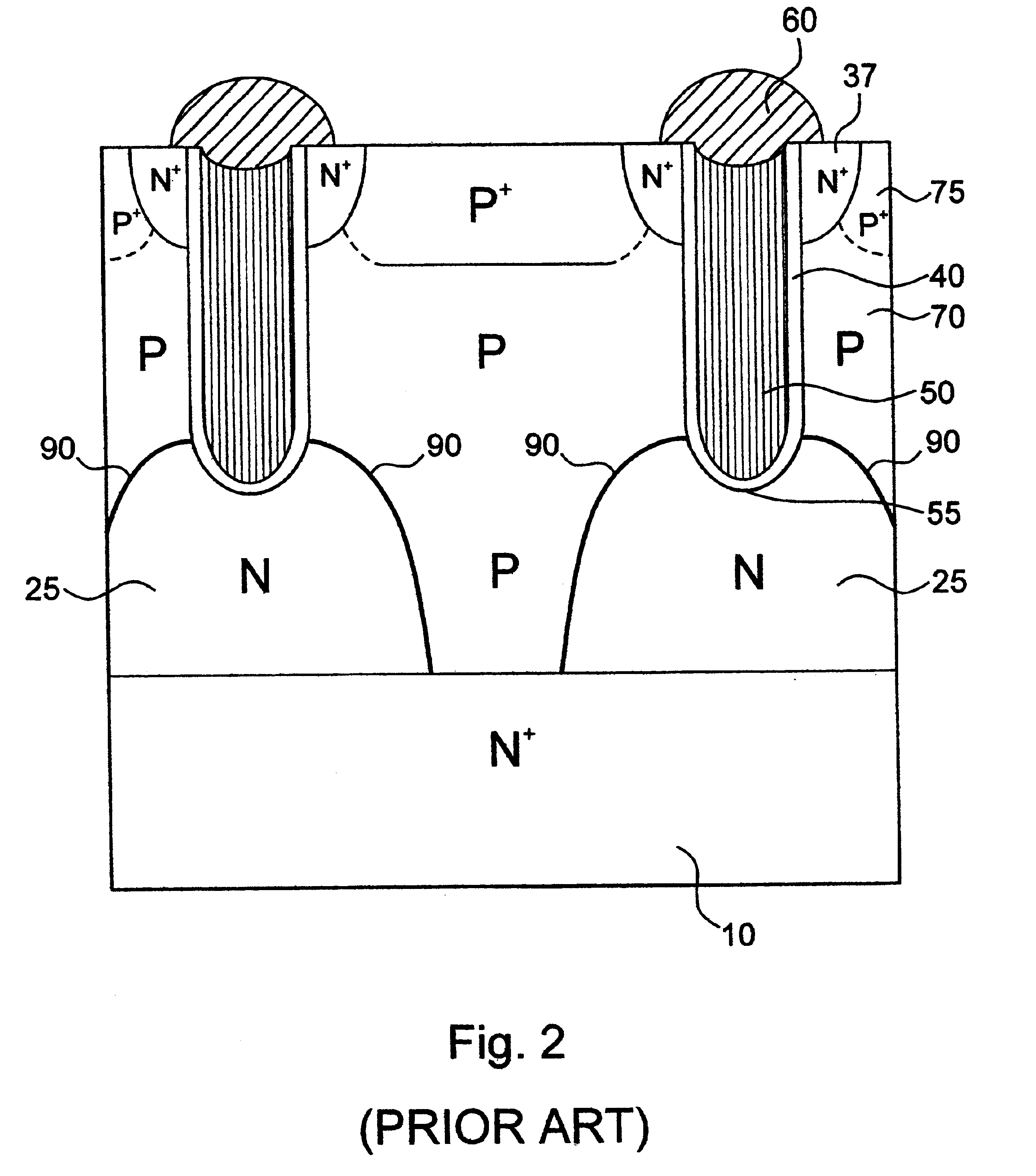

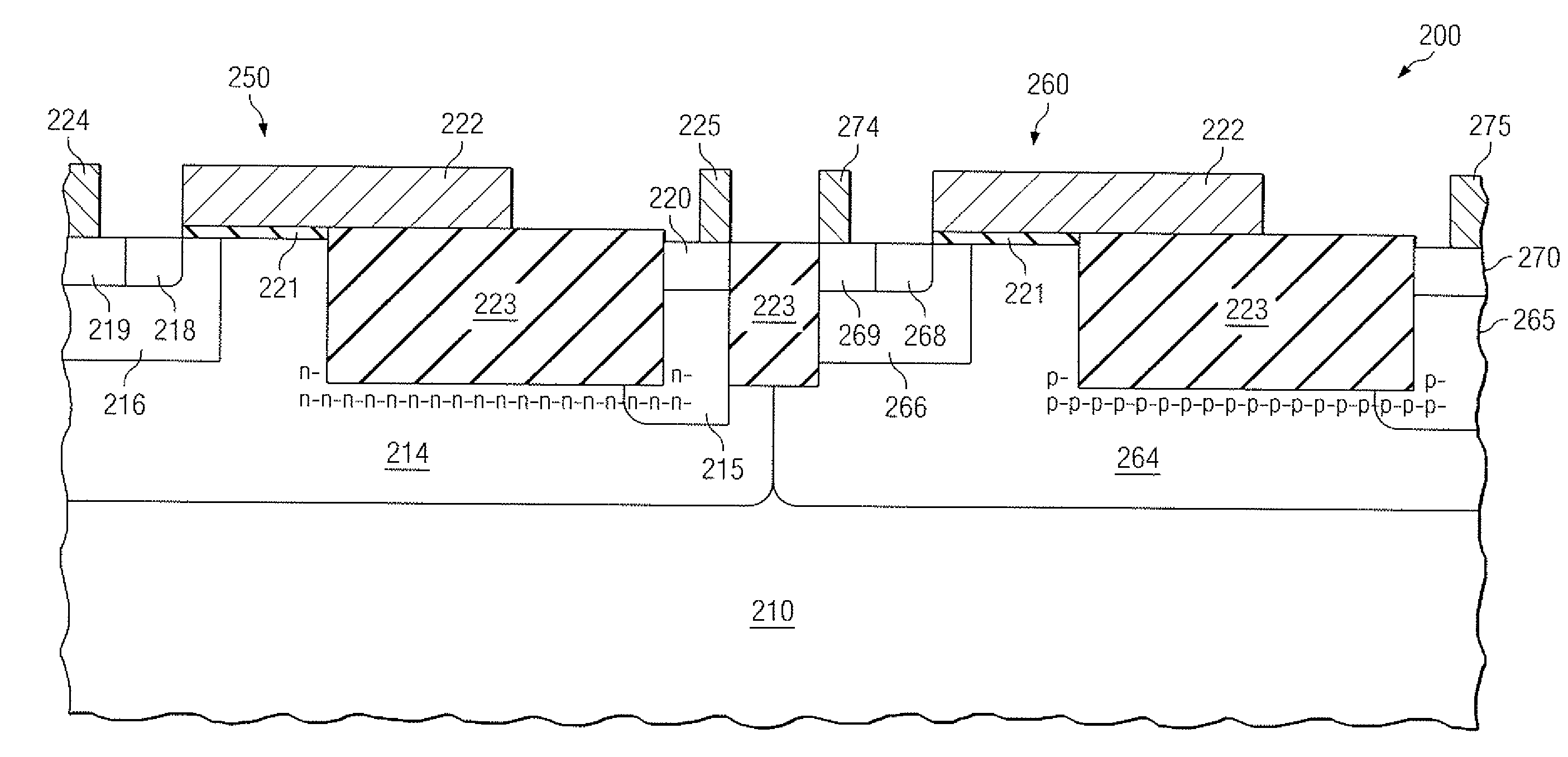

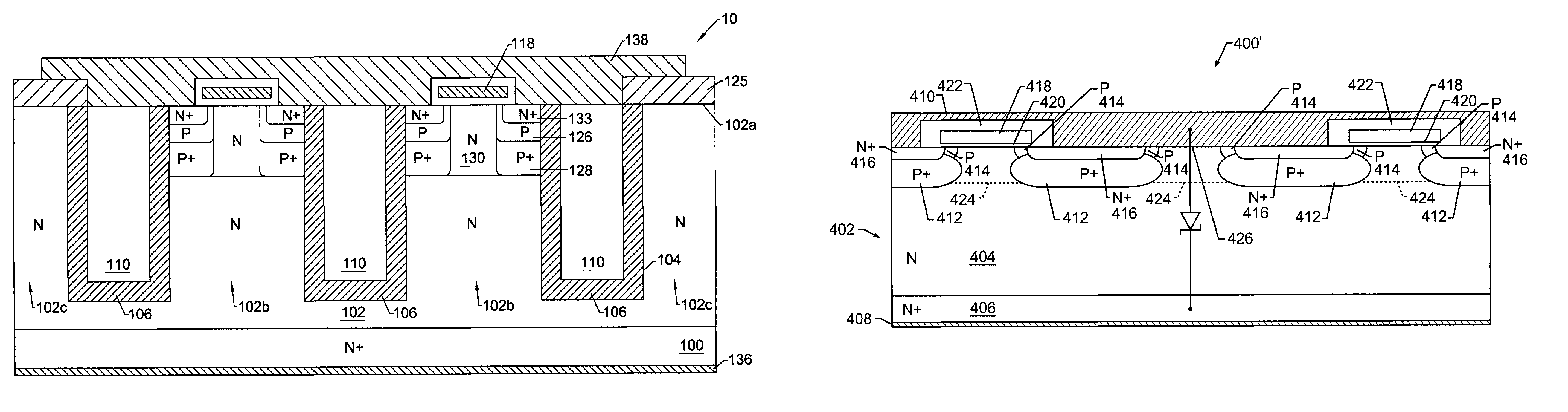

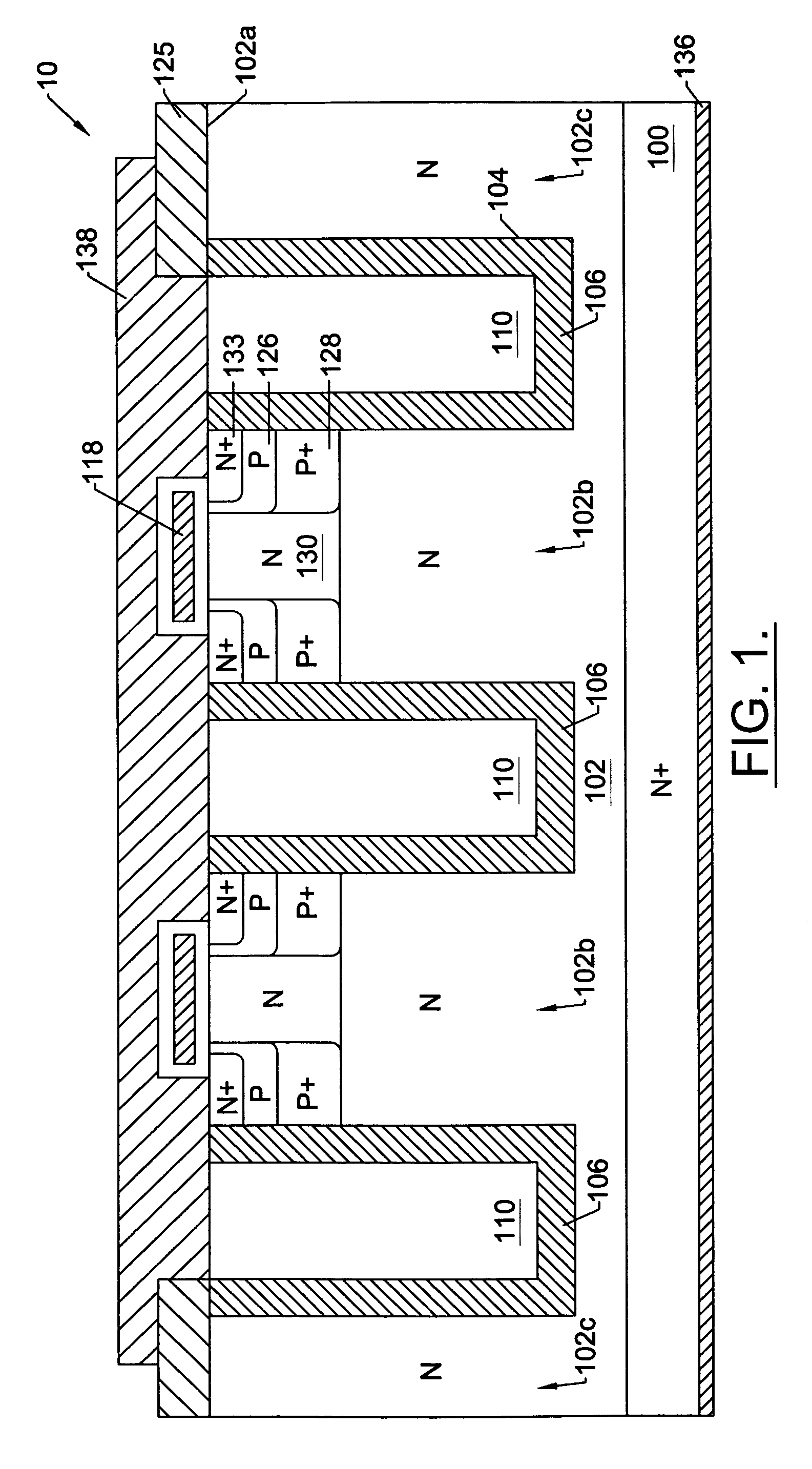

Lateral Insulated Gate Bipolar Transistors (LIGBTS)

InactiveUS20110057230A1Reduce gainReduction in current gainSemiconductor/solid-state device manufacturingSemiconductor devicesEpoxyParasitic bipolar transistor

This invention generally relates to lateral insulated gate bipolar transistors (LIGBTs), for example in integrated circuits, methods of increasing switching speed of an LIGBT, a method of suppressing parasitic thyristor latch-up in a bulk silicon LIGBT, and methods of fabricating an LIGBT. In particular, a method of suppressing parasitic thyristor latch-up in a bulk silicon LIGBT comprises selecting a current gain αv for a vertical transistor of a parasitic thyristor of the LIGBT such that in at least one predetermined mode of operation of the LIGBT αv<1−αp where αp is a current gain of a parasitic bipolar transistor having a base-emitter junction formed by a Schottky contact between the a semiconductor surface and a metal enriched epoxy die attach.

Owner:POWER INTEGRATIONS INC

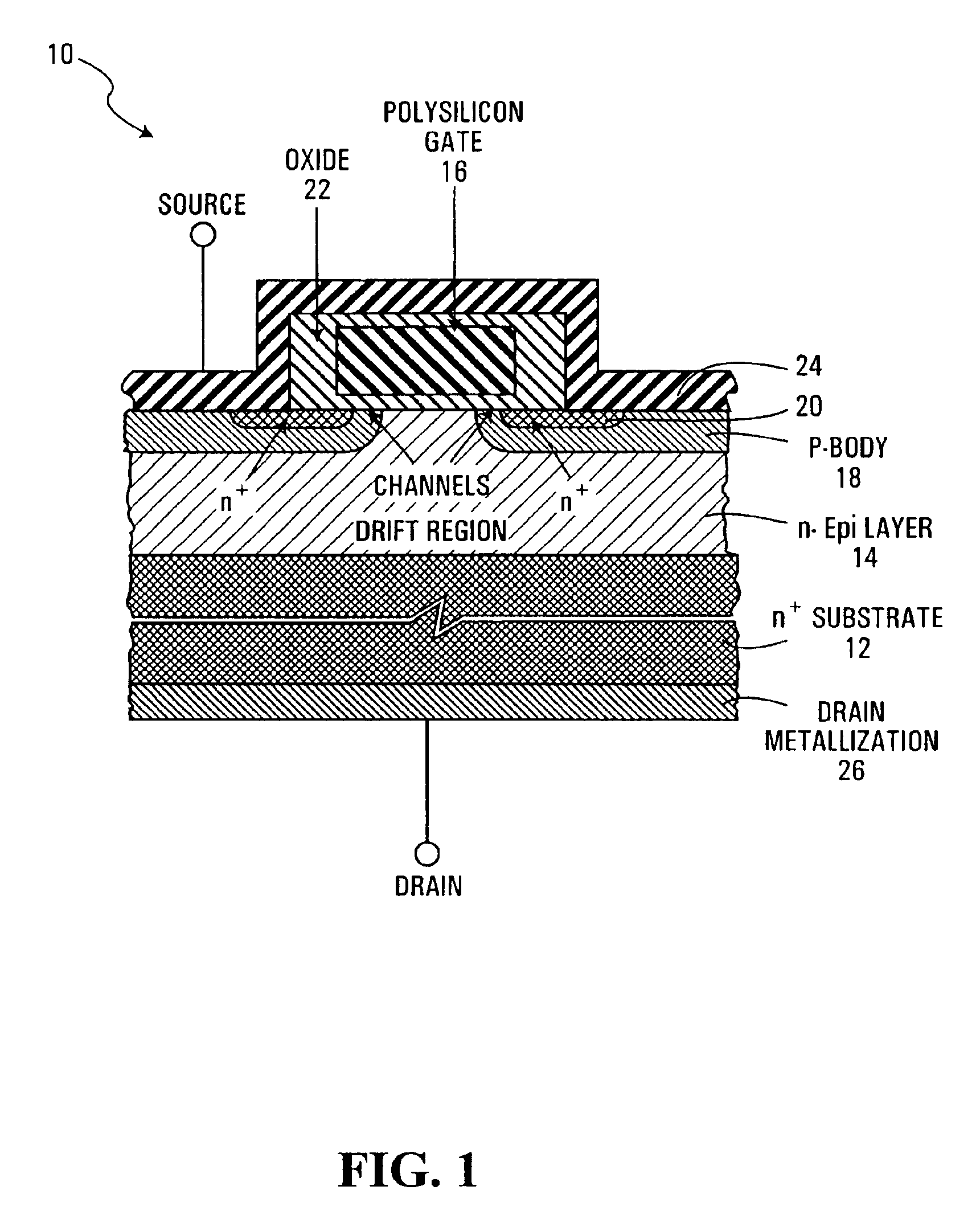

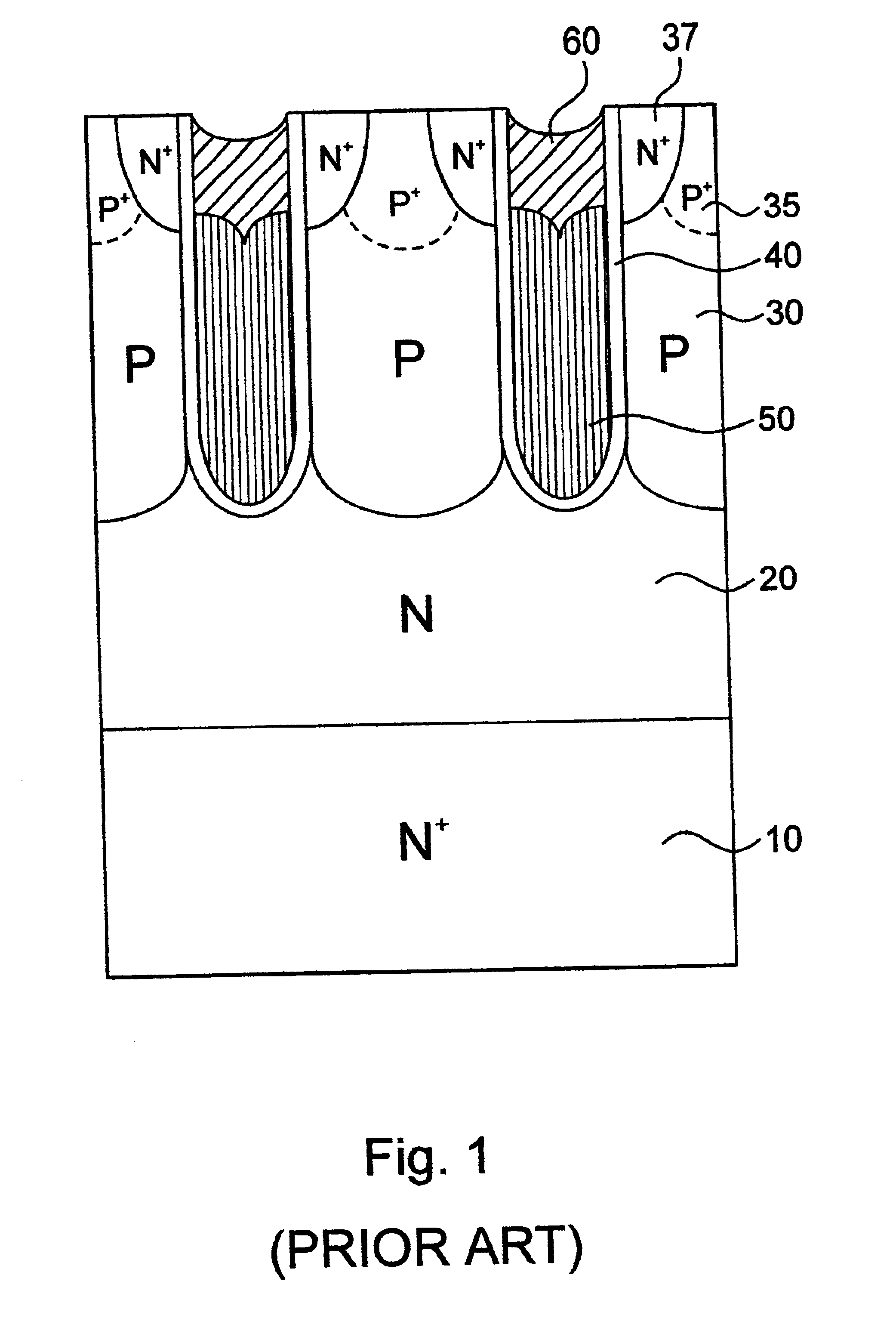

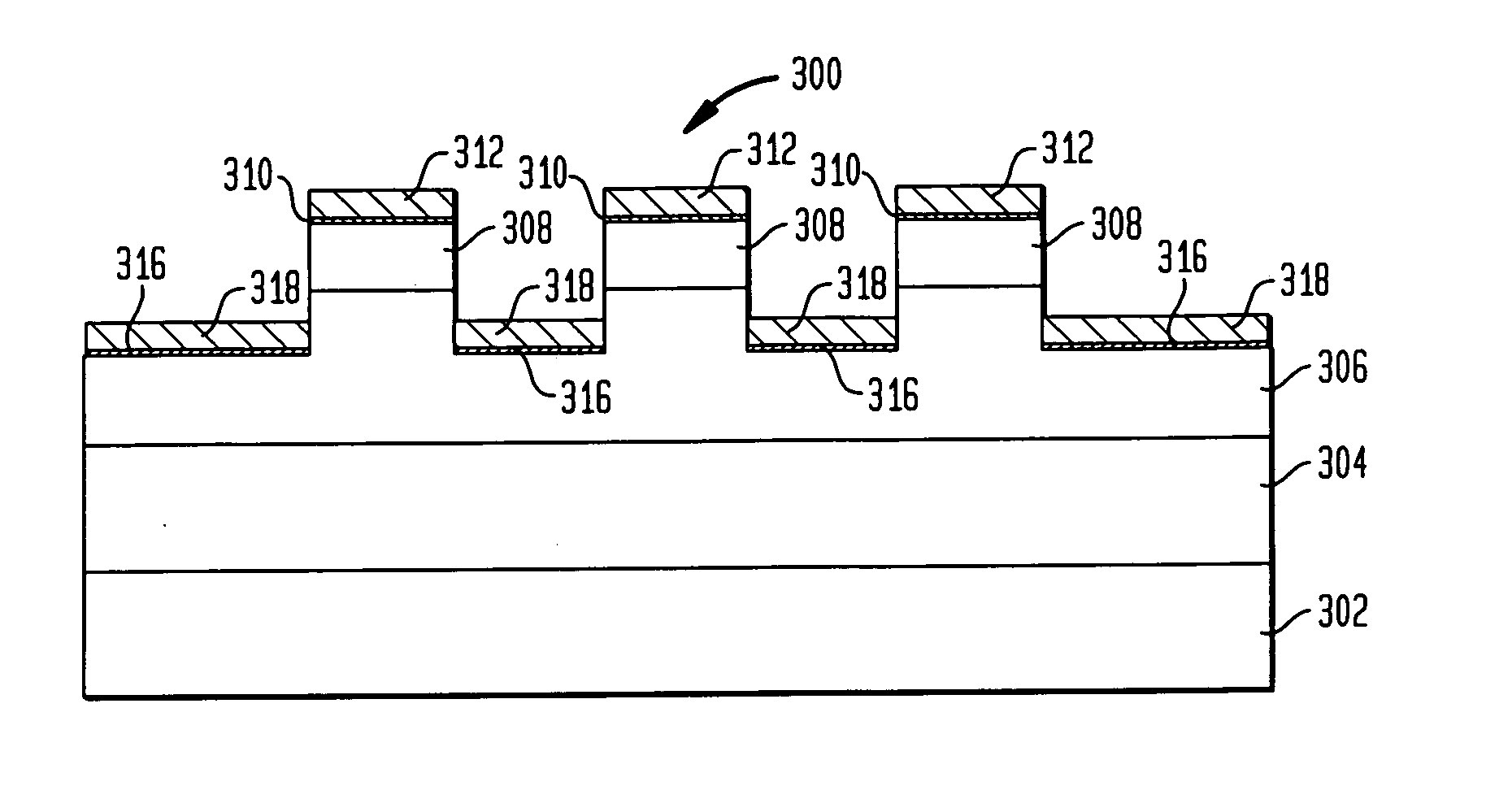

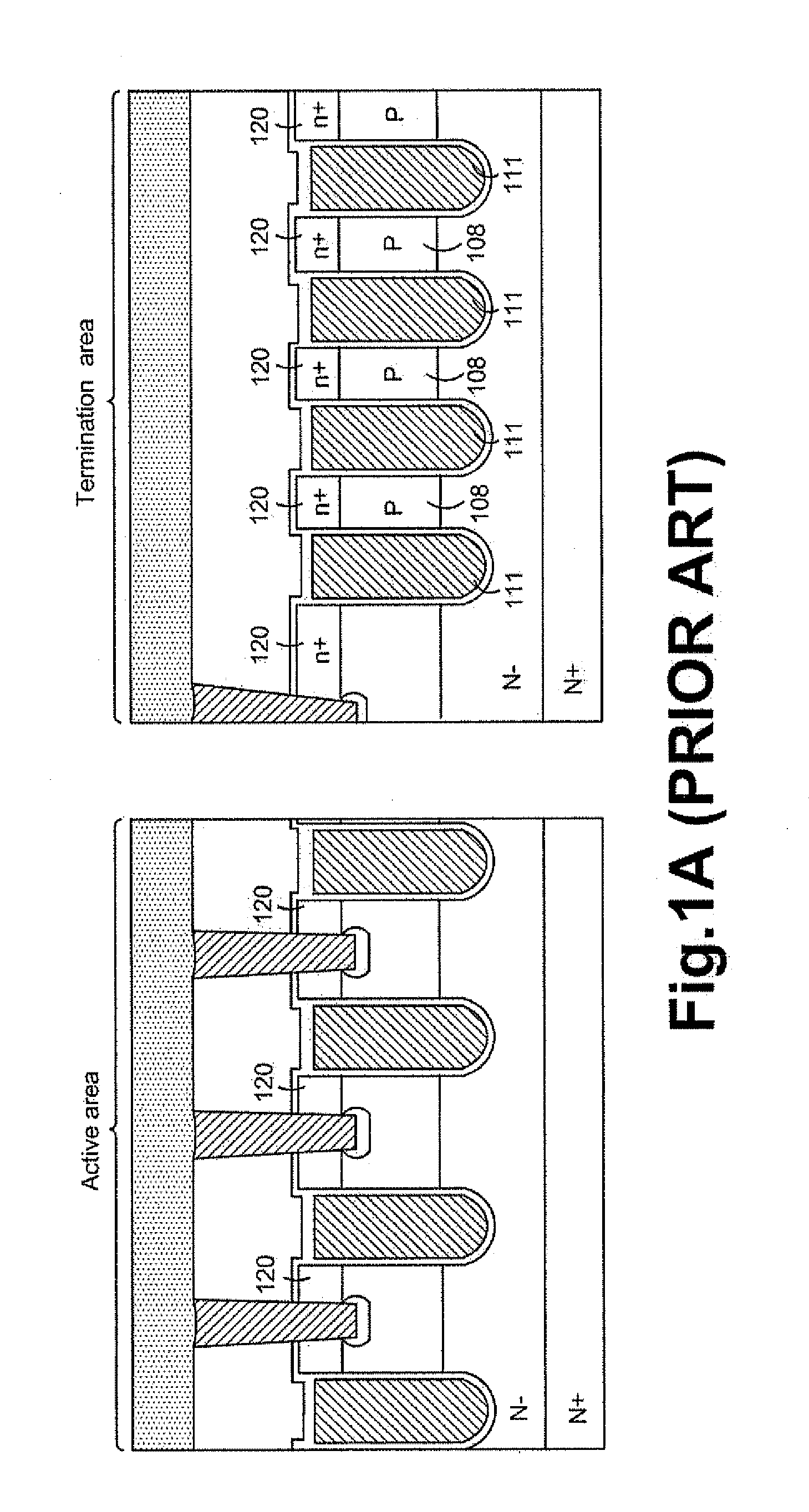

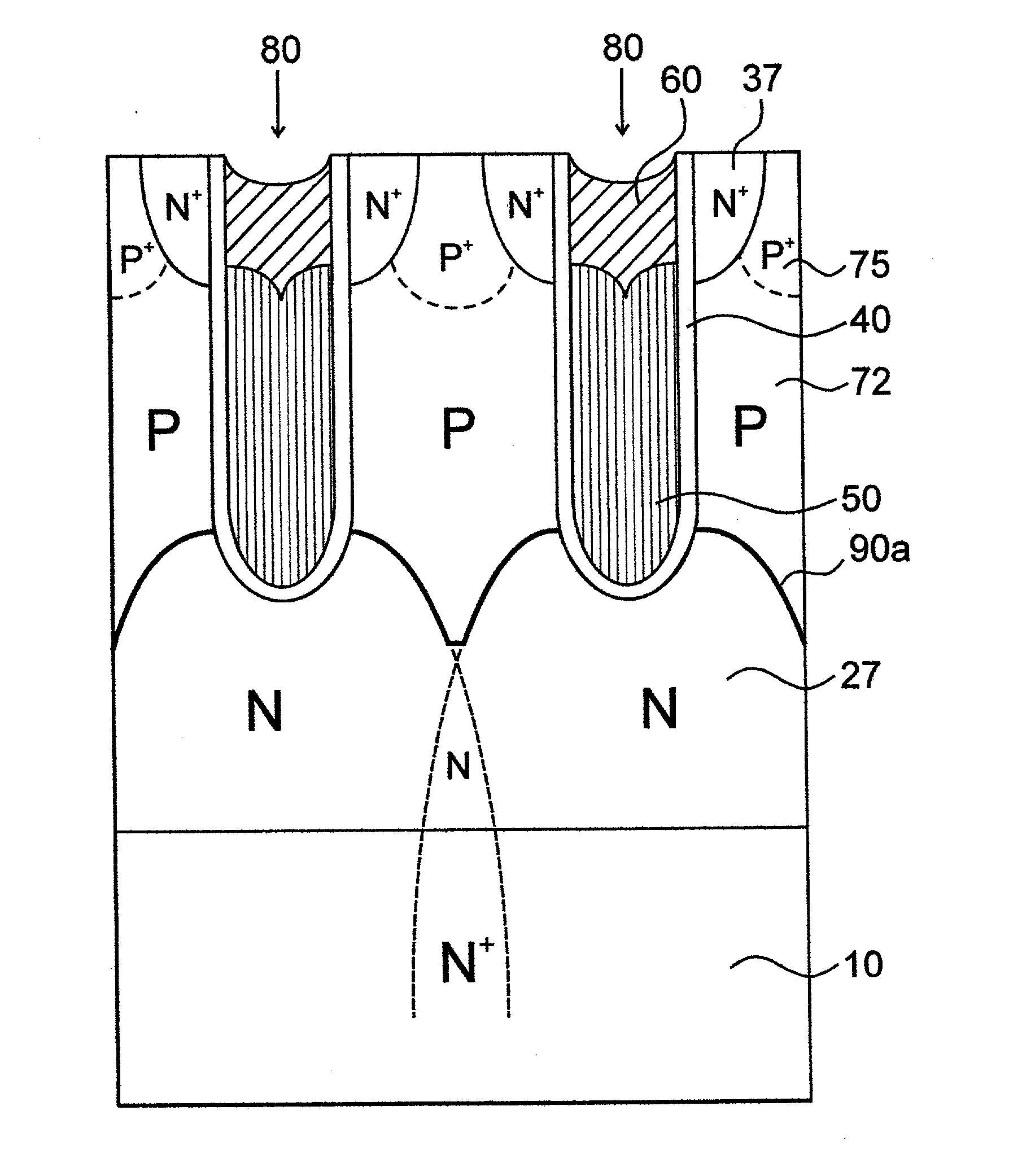

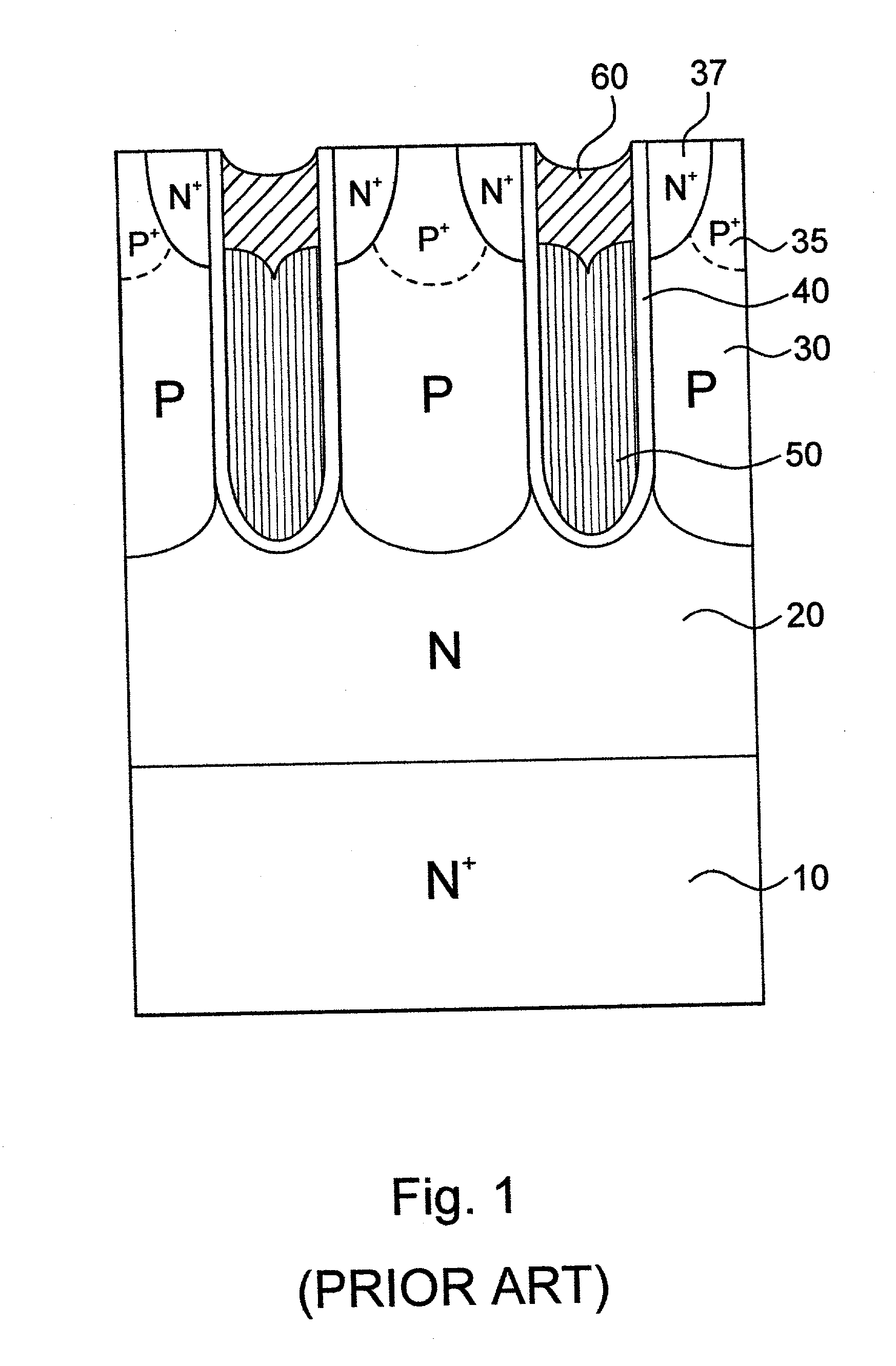

Low voltage high density trench-gated power device with uniformly doped channel and its edge termination technique

InactiveUS6784505B2Increase reverse voltageLow densityTransistorSolid-state devicesDopantChannel density

Merging together the drift regions in a low-power trench MOSFET device via a dopant implant through the bottom of the trench permits use of a very small cell pitch, resulting in a very high channel density and a uniformly doped channel and a consequent significant reduction in the channel resistance. By properly choosing the implant dose and the annealing parameters of the drift region, the channel length of the device can be closely controlled, and the channel doping may be made highly uniform. In comparison with a conventional device, the threshold voltage is reduced, the channel resistance is lowered, and the drift region on-resistance is also lowered. Implementing the merged drift regions requires incorporation of a new edge termination design, so that the PN junction formed by the P epi-layer and the N<+> substrate can be terminated at the edge of the die.

Owner:SEMICON COMPONENTS IND LLC

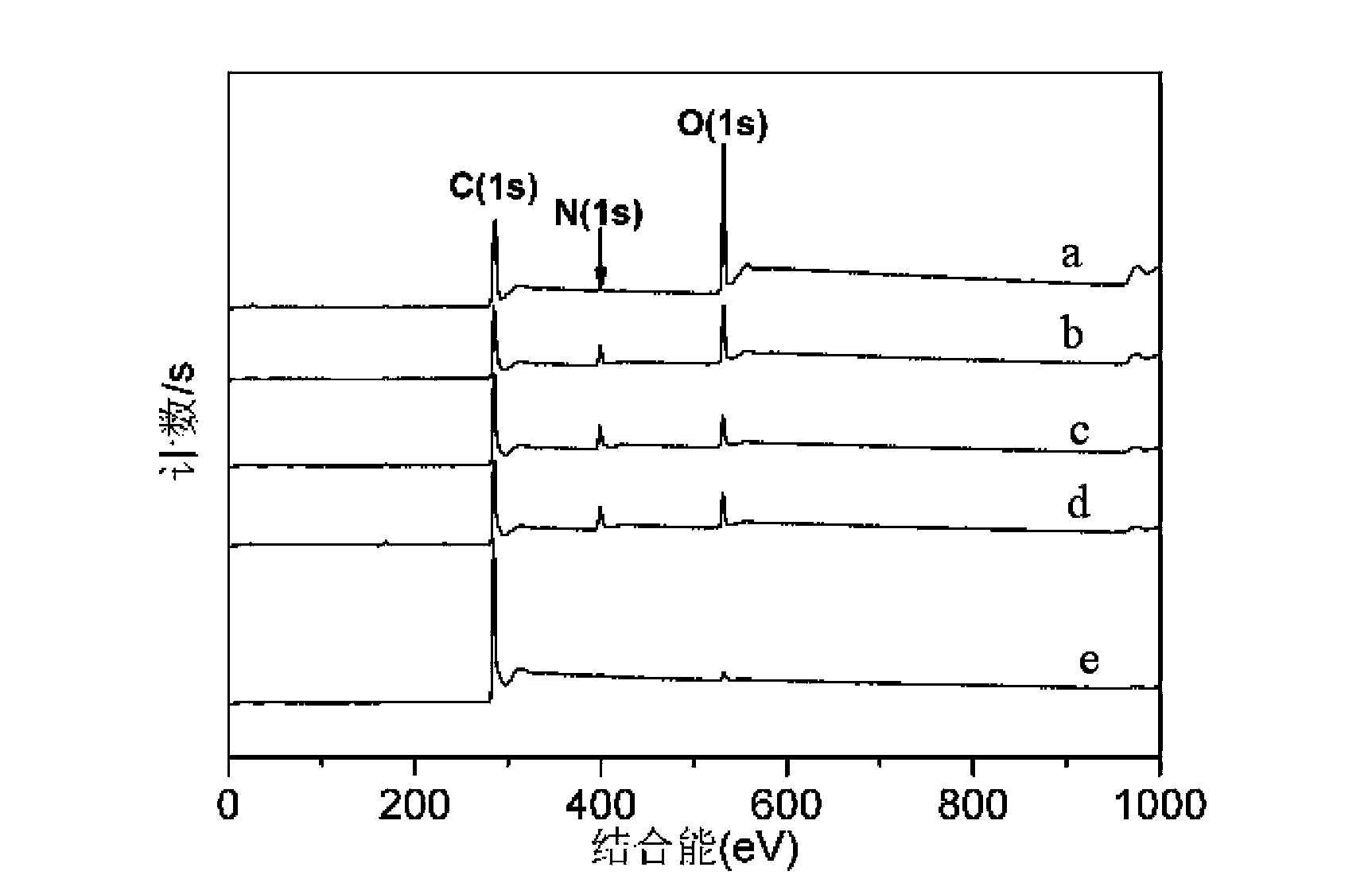

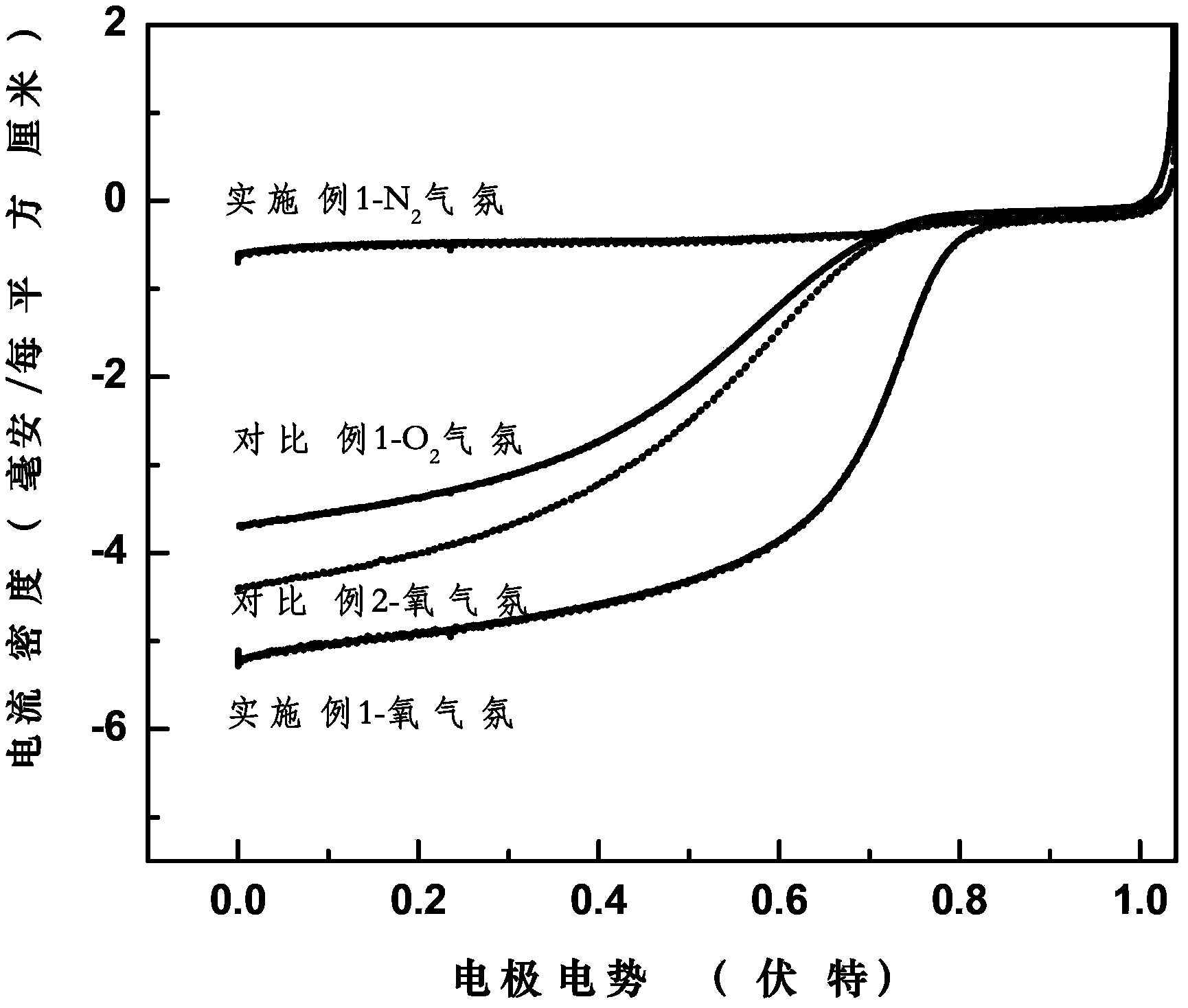

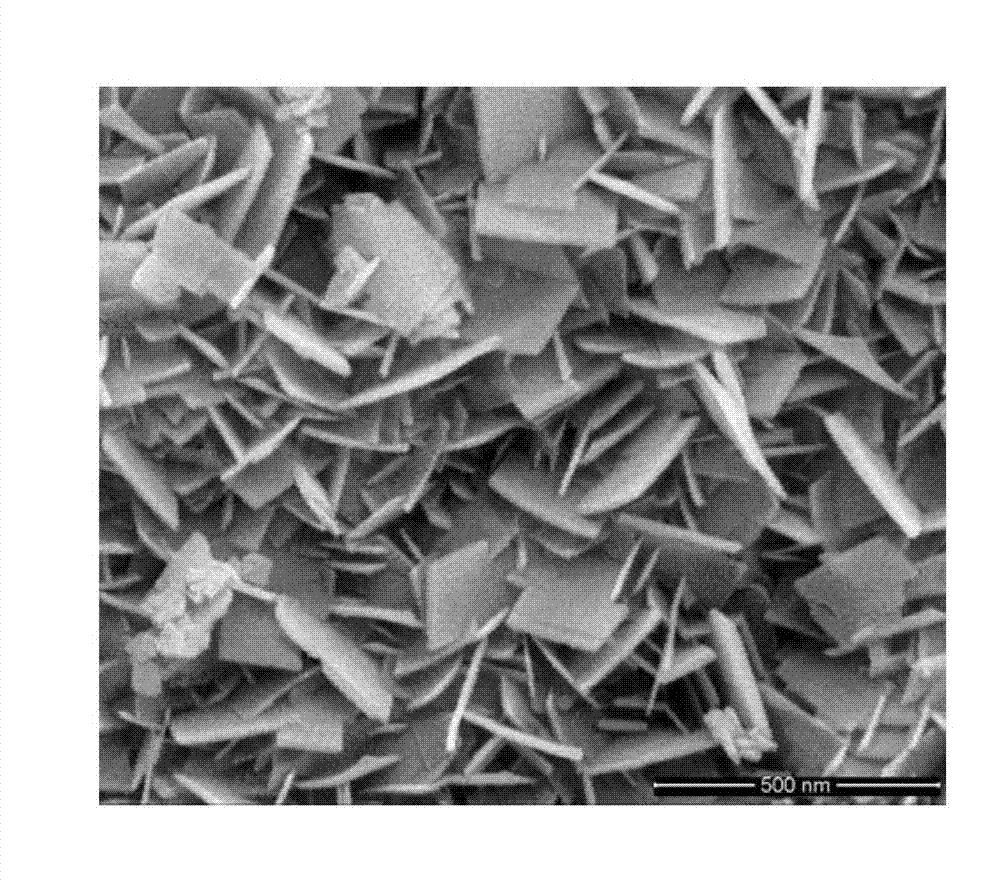

Preparation method of nitrogen doped graphene and application of nitrogen doped graphene

ActiveCN103626158AHighly dopedIncrease pressureHybrid capacitor electrodesGrapheneReaction temperatureSupercapacitor

The invention provides a preparation method of nitrogen doped graphene and an application of the nitrogen doped graphene in super capacitors. The preparation method of the nitrogen doped graphene specifically comprises the following steps: putting a carbon material and a compound containing active nitrogen elements in an enclosed container, and heating to a temperature of 100 to 300 DEG C so as to obtain the nitrogen doped graphene. In the preparation process of the nitrogen doped graphene, under a heating condition, nitrogen elements in the compound containing active nitrogen elements are mixed into the carbon material so as to obtain the nitrogen doped graphene. The nitrogen doped graphene preparation method mentioned above avoids adopting a high reaction temperature, and has the advantages of mild preparation conditions and low production cost. The prepared nitrogen doped graphene is used as an electrode material of a super capacitor, and the specific capacity of the super capacitor can reach 190 F / g, when the electric current density is 5 A / g. The capacity retention ratio is 96.3% after 10000 times of circulation.

Owner:NINGBO GRAPHENE INNOVATION CENT CO LTD

LED with upstanding nanowire structure and method of producing such

ActiveUS8183587B2High dopingGood wave-guiding propertyNanoinformaticsSolid-state devicesNanowireActive component

The present invention relates to light emitting diodes, LEDs. In particular the invention relates to a LED comprising a nanowire as an active component. The nanostructured LED according to the embodiments of the invention comprises a substrate and at an upstanding nanowire protruding from the substrate. A pn-junction giving an active region to produce light is present within the structure. The nanowire, or at least a part of the nanowire, forms a wave-guiding section directing at least a portion of the light produced in the active region in a direction given by the nanowire.

Owner:QUNANO

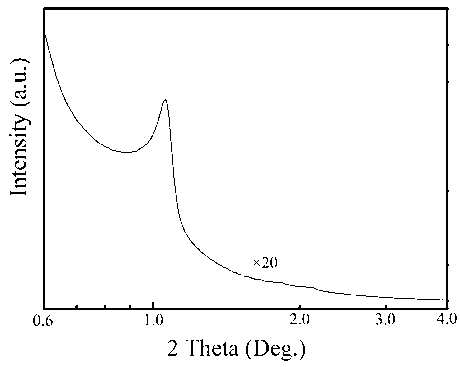

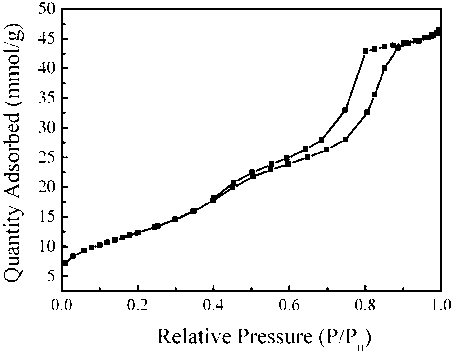

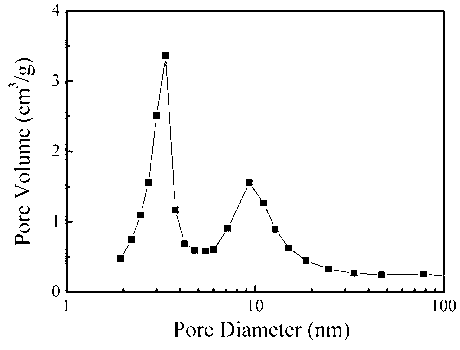

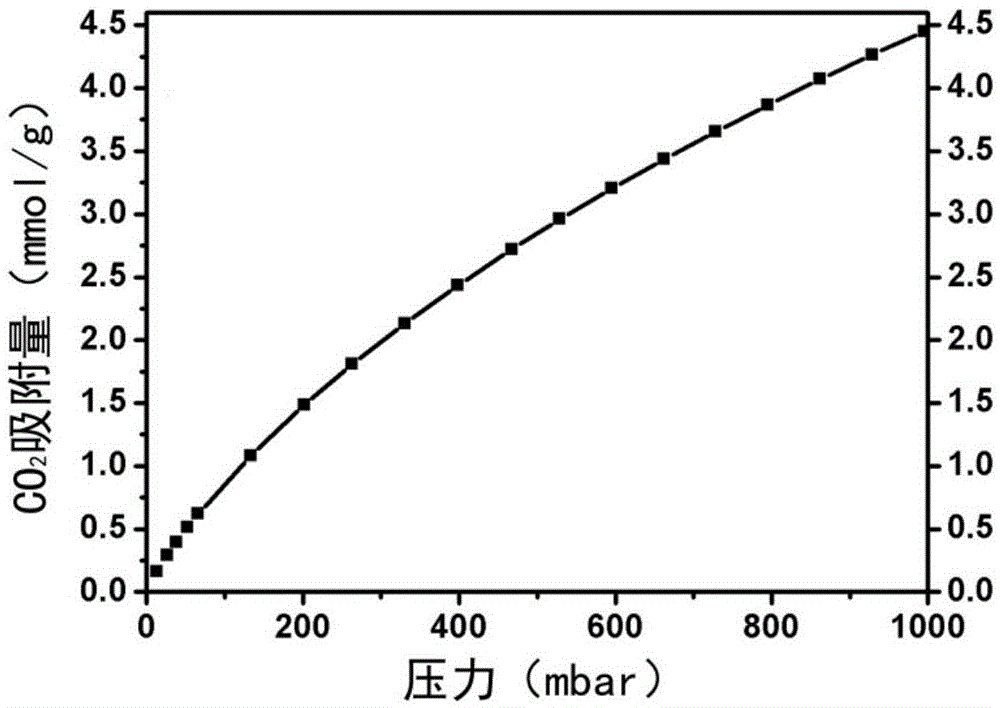

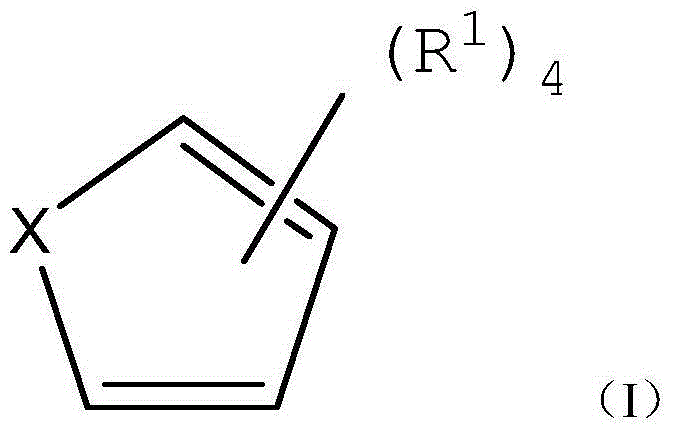

Preparation method of nitrogen-doping ordered mesoporous carbon materials

InactiveCN103072973AWell-ordered pore structureHigh dopingCarbon preparation/purificationMolecular sieveSpace group

The invention provides a preparation method of nitrogen-doping ordered mesoporous carbon materials. According to the method, rich-hydroxyl saccharide carbohydrate is used as carbon sources, ammonia water is used as nitrogen sources, amination reaction under the hydrothermal condition is adopted for preparing rich-nitrogen precursors, mesoporous silica molecular sieves SBA-15 (space group P6mm) are used as templates, and the nitrogen-doping ordered mesoporous carbon materials in two-dimensional orthohexagonal ordered mesostructures are prepared through multi-time wetting combined with the high-temperature themolysis technology.

Owner:LANZHOU UNIVERSITY OF TECHNOLOGY

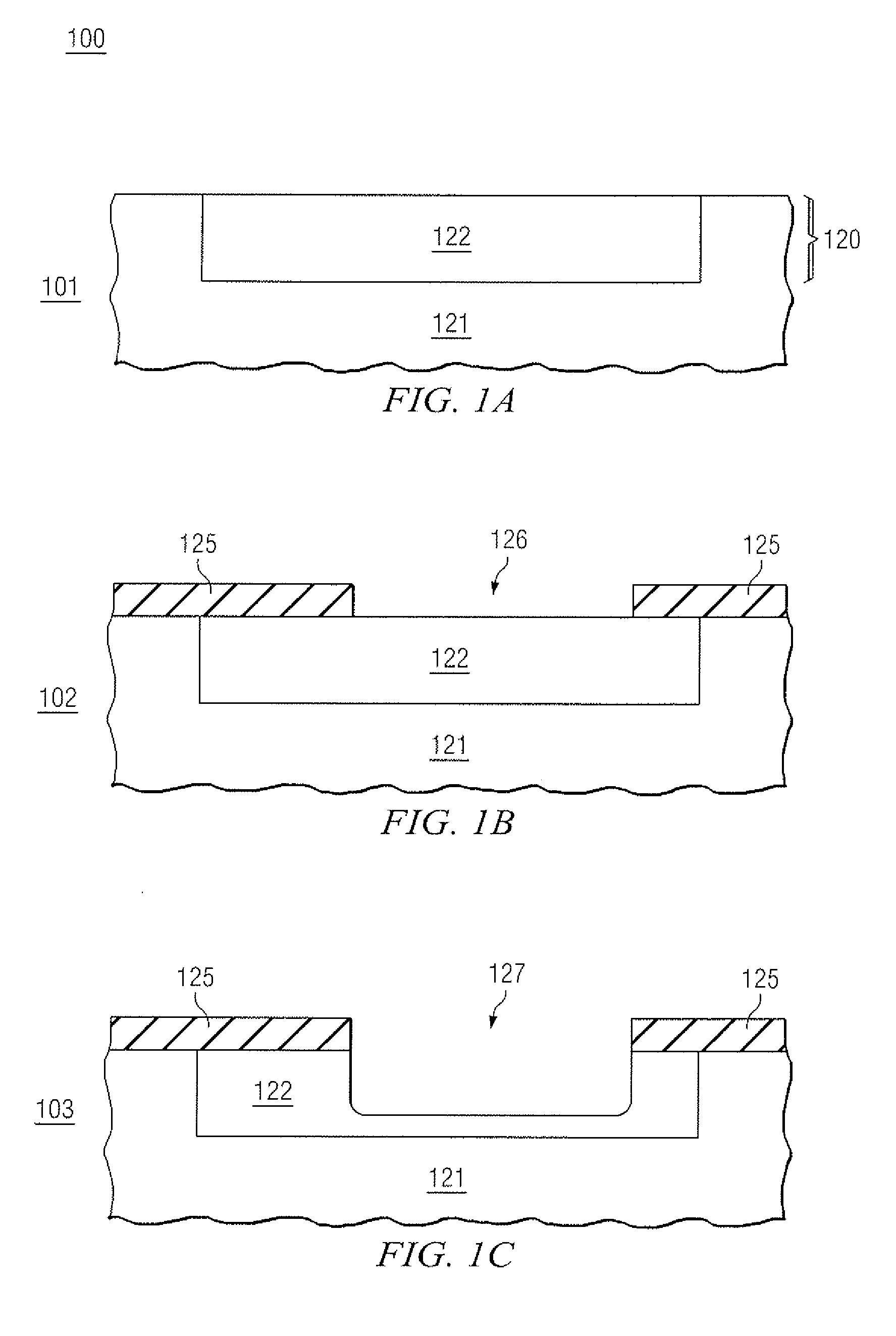

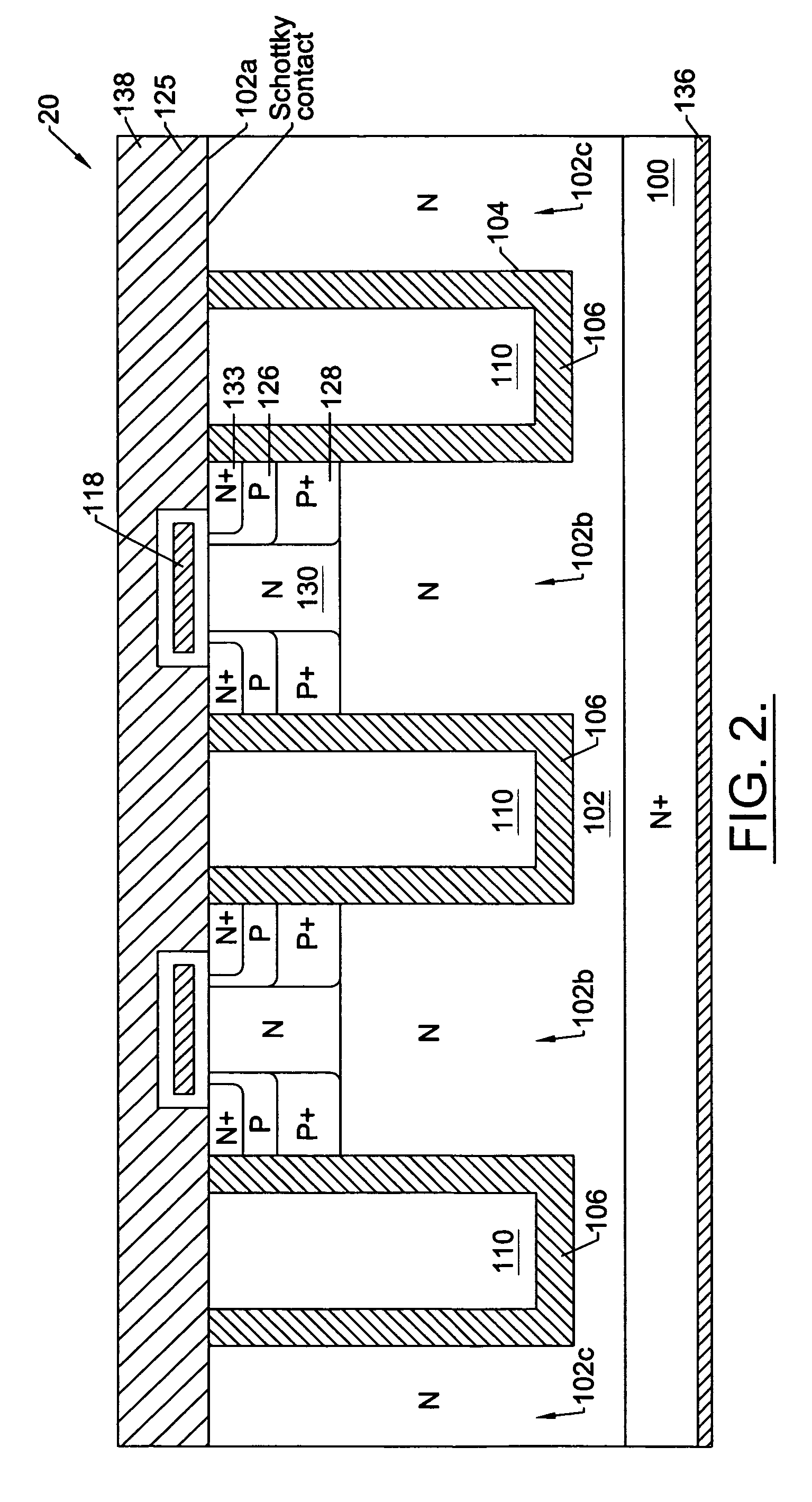

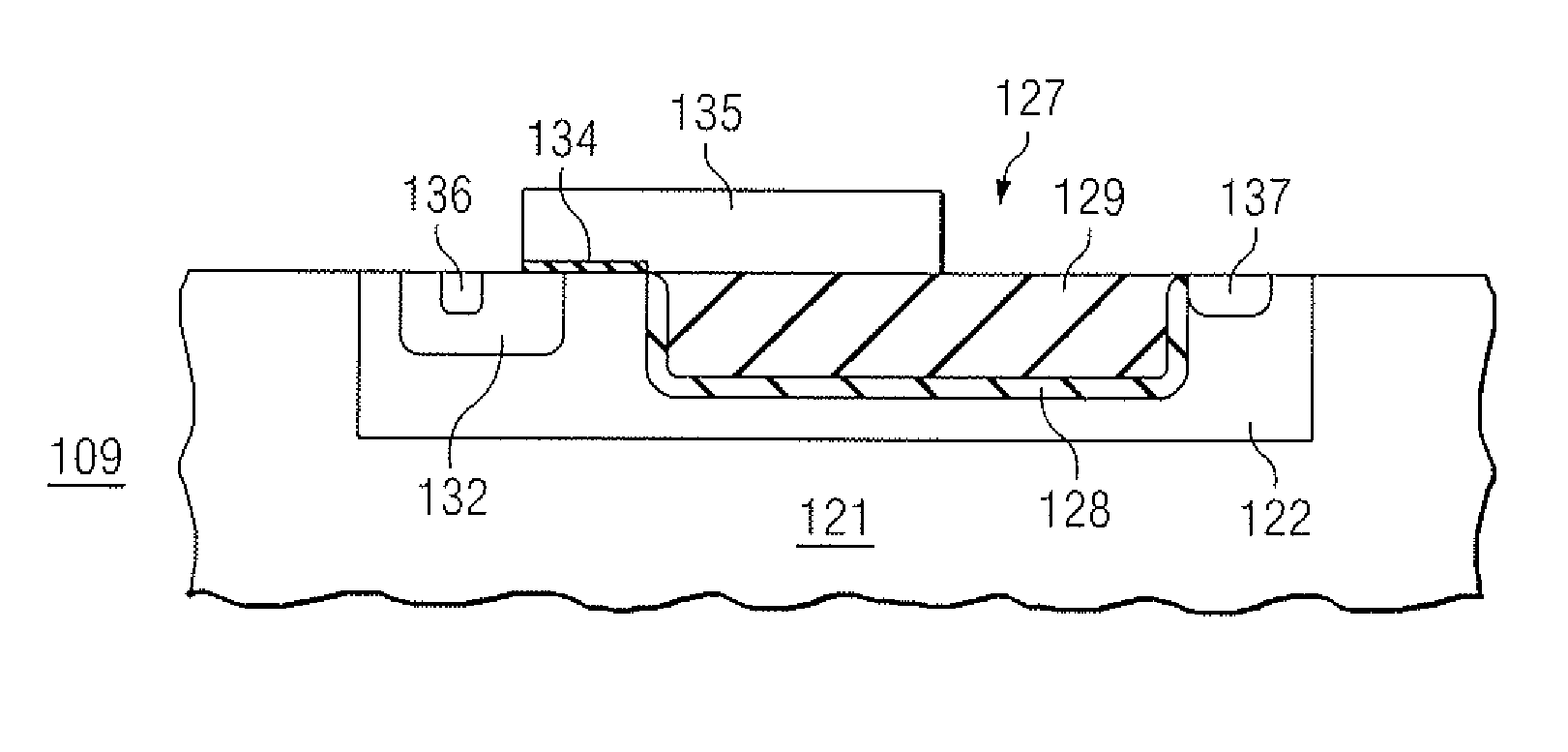

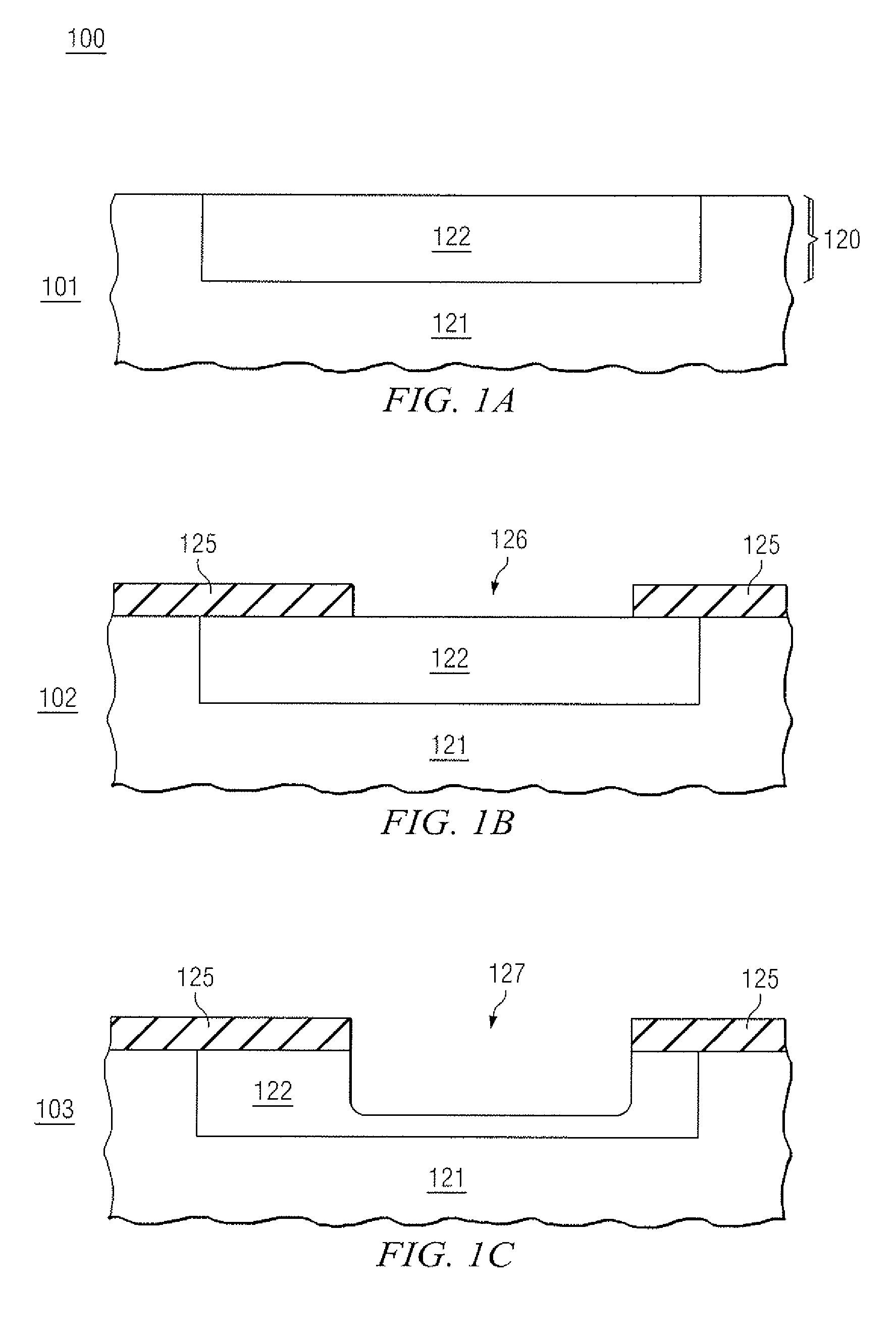

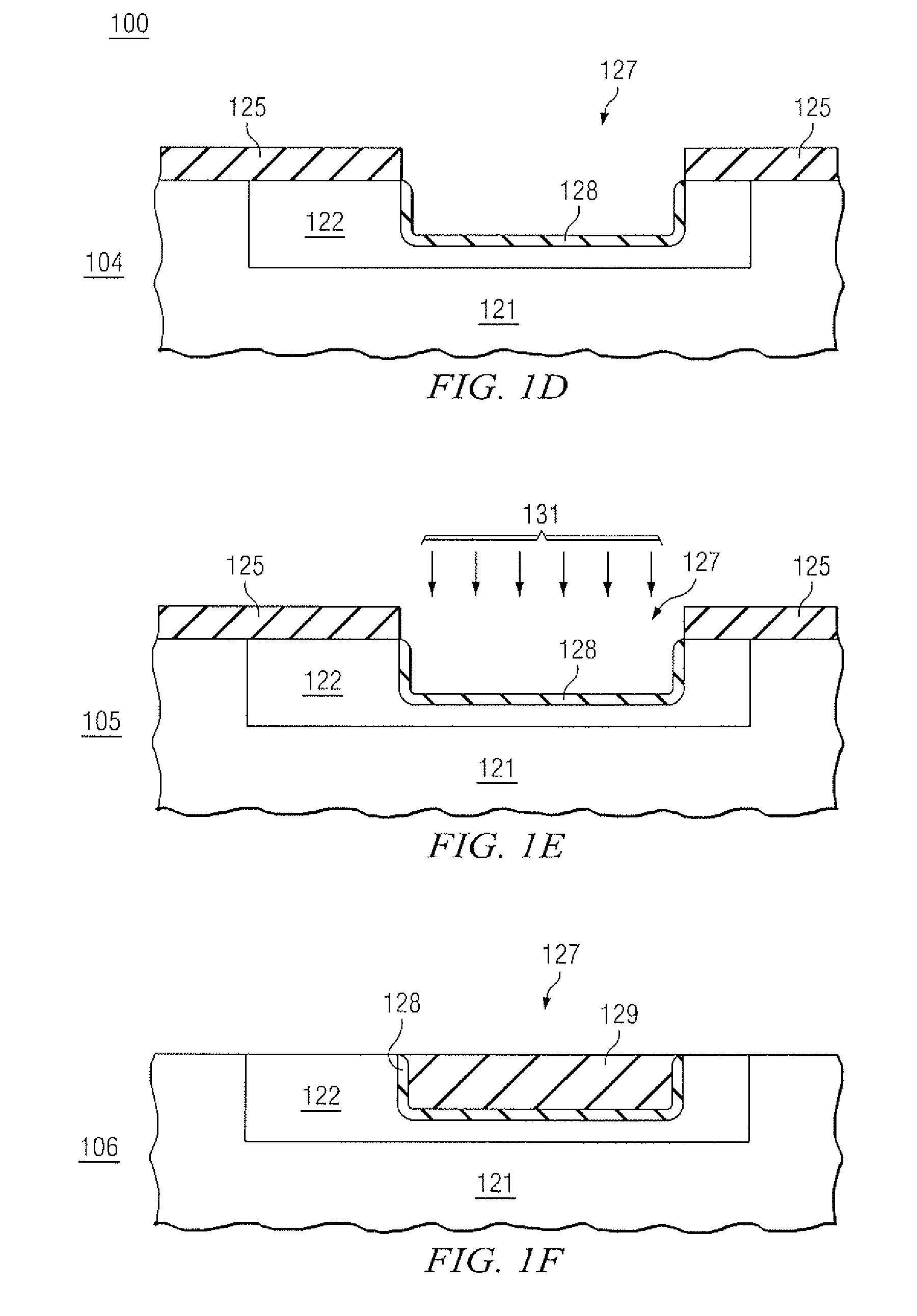

Methods of manufacturing trench isolated drain extended mos (DEMOS) transistors and integrated circuits therefrom

ActiveUS20100117150A1Reduce conductionReduce dopant sensitivitySolid-state devicesSemiconductor/solid-state device manufacturingDopantGate dielectric

A method of fabricating an integrated circuit (IC) including at least one drain extended MOS (DEMOS) transistor and ICs therefrom includes providing a substrate having a semiconductor surface, the semiconductor surface including at least a first surface region that provides a first dopant type. A patterned masking layer is formed on the first surface region, wherein at least one aperture in the masking layer is defined. The first surface region is etched to form at least one trench region corresponding to a position of the aperture. A dopant of a first dopant type is implanted to raise a concentration of the first dopant type in a first dopant type drift region located below the trench region. After the implanting, the trench region is filled with a dielectric fill material. A body region is then formed having a second dopant type in a portion of the first surface region. A gate dielectric is then formed over a surface of the body region and the first surface region. A patterned gate electrode layer is formed over the gate dielectric, a source region in the body region and a drain region in the first surface region on a side of the trench region opposite to the source are formed, and fabrication of the IC is completed.

Owner:TEXAS INSTR INC

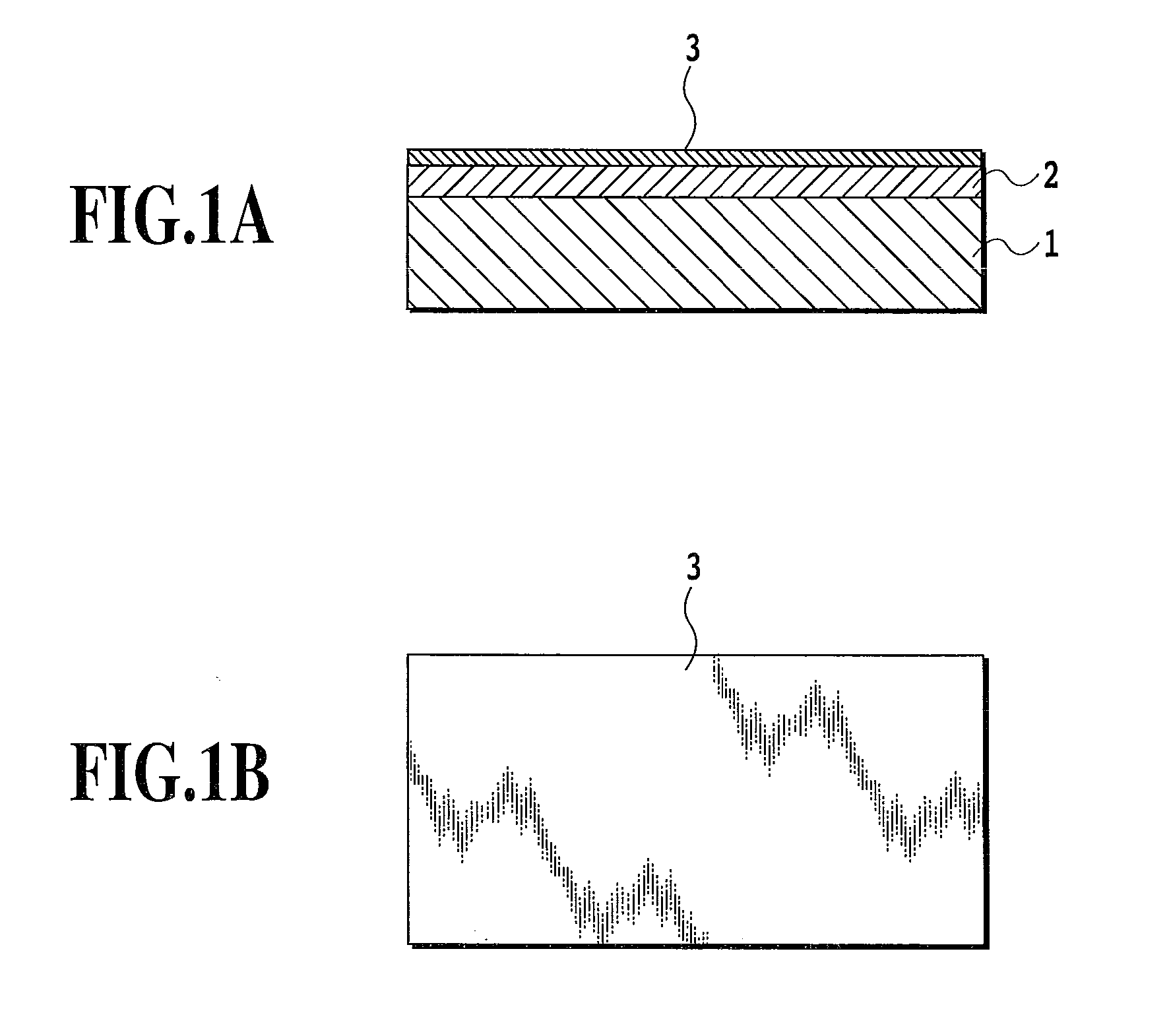

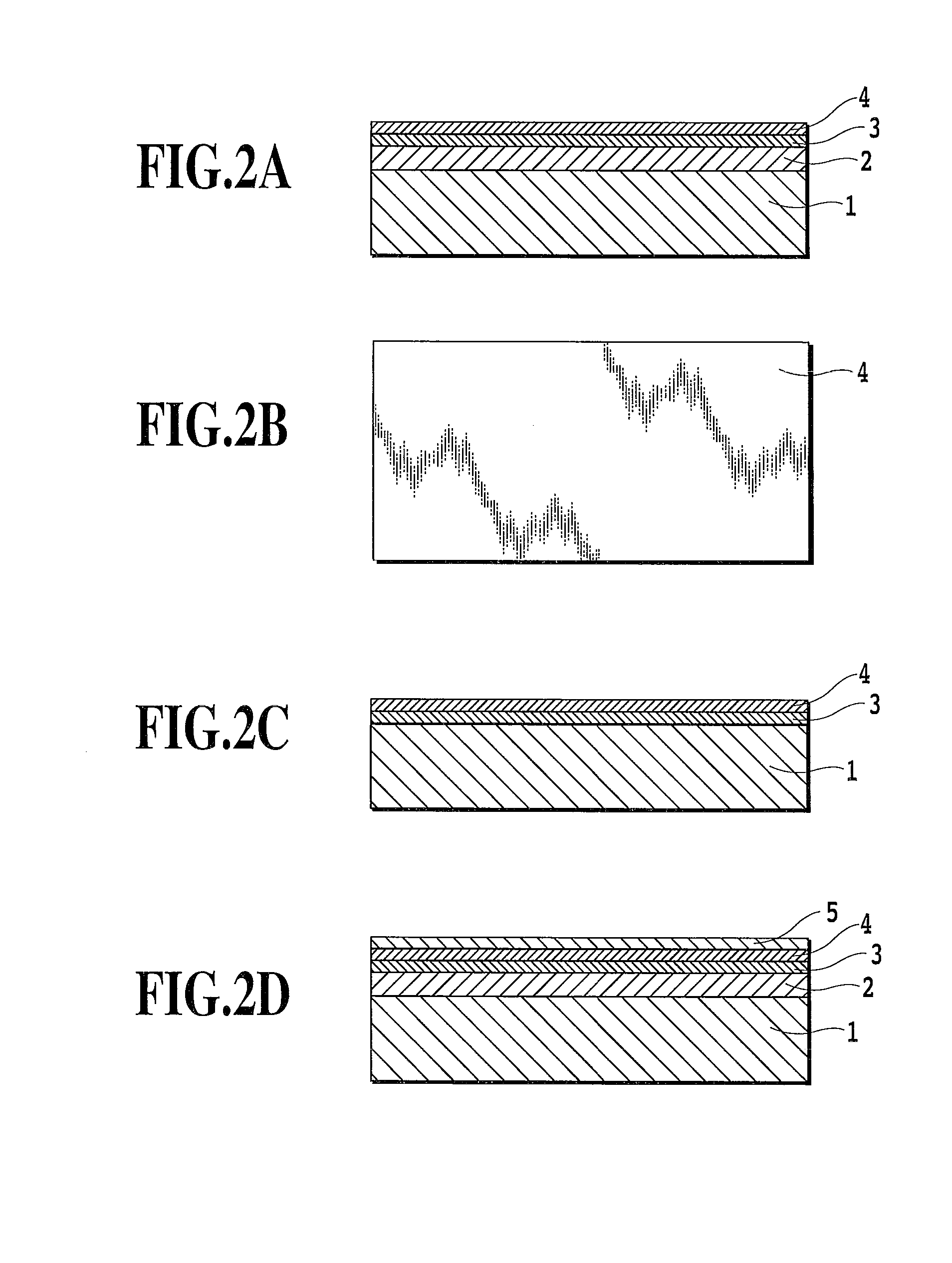

Thin film lamination, thin film magnetic sensor using the thin film lamination and method for manufacturing the thin film lamination

InactiveUS20100045282A1Reduce componentsImprove buffering effectMagnetic-field-controlled resistorsSolid-state devicesElectrical resistance and conductanceHigh resistance

Relating to a thin film lamination and a thin film magnetic sensor using the thin film lamination and a method for manufacturing the thin film lamination that realizes a thin film conducting layer having high electron mobility and sheet resistance as an InAsSb operating layer. A thin film lamination is provided which is characterized by having an AlxIn1-xSb mixed crystal layer formed on a substrate, and an InAsxSb1-x (0<x≦1) thin film conducting layer directly formed on the AlxIn1-xSb layer, in which the AlxIn1-xSb mixed crystal layer is a layer that exhibits higher resistance than the InAsxSb1-x thin film conducting layer or exhibits insulation or p-type conductivity, and its band gap is greater than the InAsxSb1-x thin film conducting layer, and the a lattice mismatch is +1.3% to −0.8%.

Owner:ASAHI KASEI KK

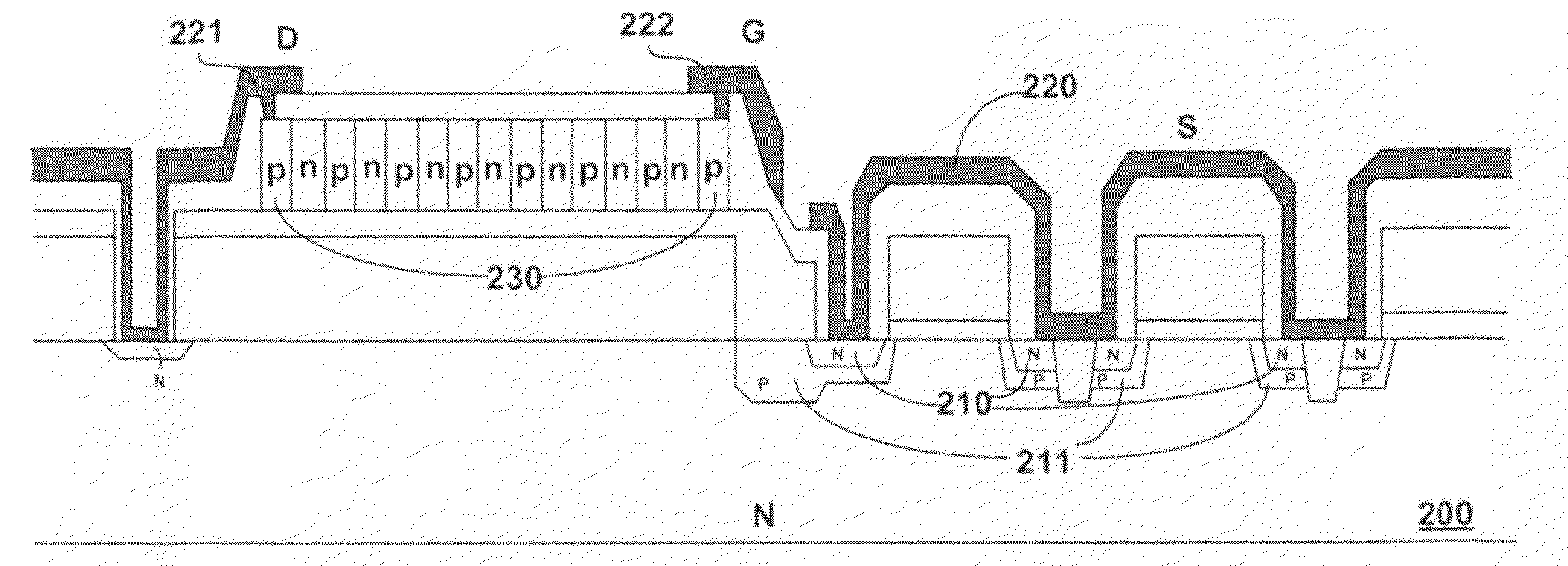

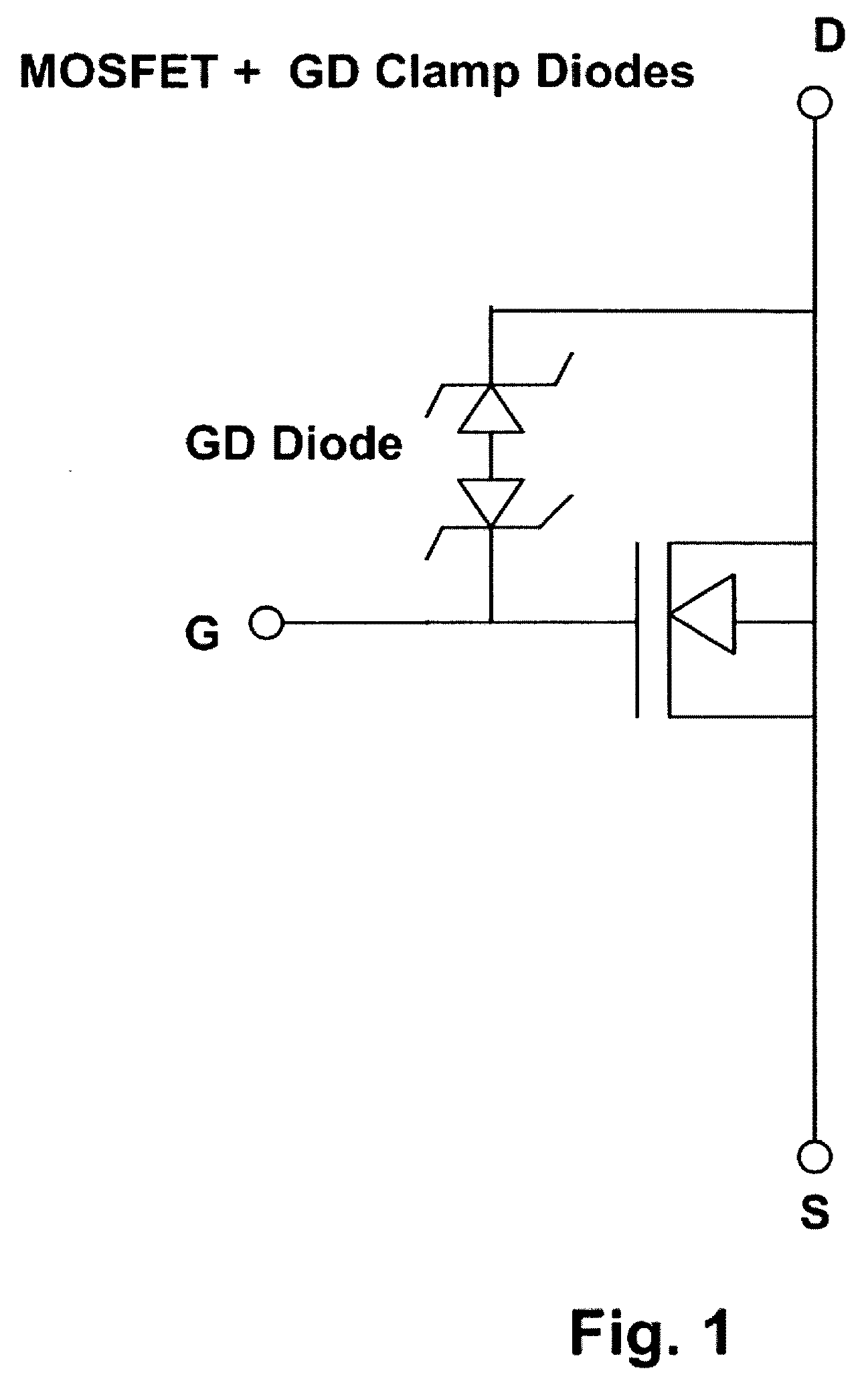

Power semiconductor devices integrated with clamp diodes sharing same gate metal pad

InactiveUS20100314681A1Reduce contact resistanceAvoid shortageTransistorSolid-state devicesPower semiconductor deviceSemiconductor

A structure of power semiconductor device integrated with clamp diodes sharing same gate metal pad is disclosed. This improved structure can prevent the degradation of breakdown voltage due to electric field in termination region blocked by polysilicon.

Owner:FORCE MOS TECH CO LTD

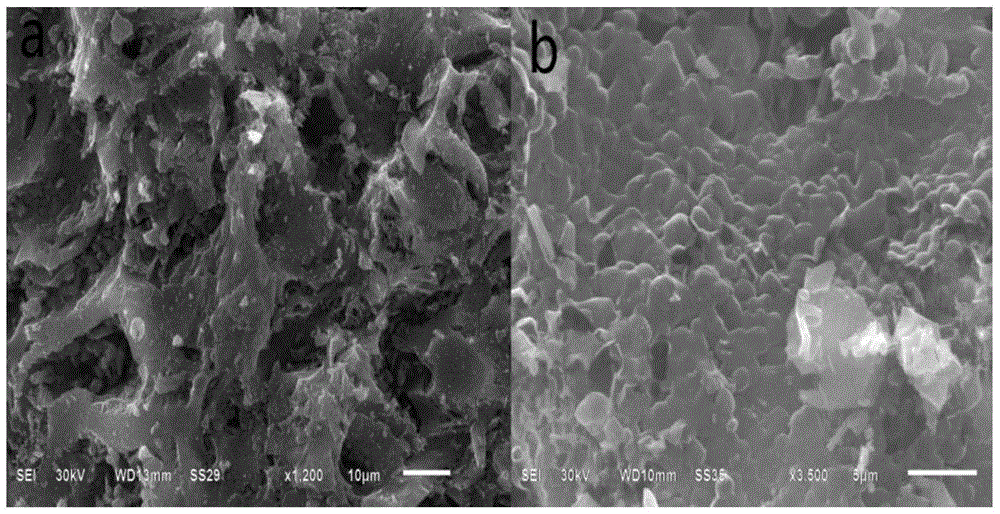

Process using date pits to prepare nitrogen-doped porous carbon material and preparation method of super-capacitor electrode

ActiveCN105645408AHigh cycle efficiency ratioImprove electrochemical performanceCarbon compoundsHybrid capacitor electrodesCapacitancePorous carbon

The invention belongs to the field of biomass carbon material preparation and particularly discloses a process using date pits to prepare nitrogen-doped porous carbon material and a preparation method of a super-capacitor electrode. The process includes the steps of firstly, preprocessing the date pits; secondly, preparing nitrogen-doped carbon material; thirdly, preparing the nitrogen-doped porous carbon material. The process is characterized in that the date pits are used as the carbon source and mixed with ammonia gas and steam in inert protecting gas, the nitrogen doping reaction is performed during the carbonization process, activated perforation is performed under the effect of activating agent, and the nitrogen-doped porous carbon material with high specific surface area and pore volume is prepared. The preparation method is simple, low in cost, high in preparation efficiency and energy saving. Experiments show that the super-capacitor electrode prepared by the nitrogen-doped porous carbon material has high specific capacitance, ideal pseudo-capacitance and high circulation stability, the performance of the super-capacitor electrode is better than the performance of commercial activated-carbon super-capacitors, and the performance of the nitrogen-doped porous carbon material is better than that of most nitrogen-doped porous carbon materials.

Owner:XIANGTAN UNIV

Technique for preparing phase-change temperature controllable tungsten doping nano vanadium dioxide powder

InactiveCN101164900AHigh chemical activityHigh dopingHeat-exchange elementsVanadium oxidesVanadium dioxideNanometre

This invention discloses a method for preparing controllable phase-transformation and tungsten-doped vanadium dioxide powder. In this invention, controlled, strictly, is the pH value (being at 7-9) of the solution for preparing prodecessor; selected is combined reductant containing organic amine and formic acid; protected by inert gas during whole process. By using this inventive method, obtained is high pureness single-phase VO2 nanometer powder. Due to the activity of white tungstic acid is far higher than that of other tungsten compounds, the adulteration of W6+ in VO2 crystal lattice is increased greatly, to achieve the effective adulteration, and then to realize controllable phase transformation temperature.

Owner:SHANGHAI NORMAL UNIVERSITY

Methods of forming power semiconductor devices having laterally extending base shielding regions

InactiveUS7041559B2Avoiding characteristicHigh dopingSemiconductor/solid-state device manufacturingDiodePower semiconductor deviceDopant

Methods of forming power semiconductor devices include forming a semiconductor substrate having a drift region of first conductivity type therein and a transition region of first conductivity type that extends between the drift region and a first surface of the semiconductor substrate. A gate electrode is formed on the first surface. Base and base shielding region dopants are implanted into the transition region using the gate electrode as an implant mask. A plurality of annealing steps are performed so that the base shielding region dopants are driven in laterally and vertically to substantially their full and final depth within the substrate and thereby define first and second base shielding regions that constrict a neck of the transition region to a minimum width.

Owner:SEMICON COMPONENTS IND LLC

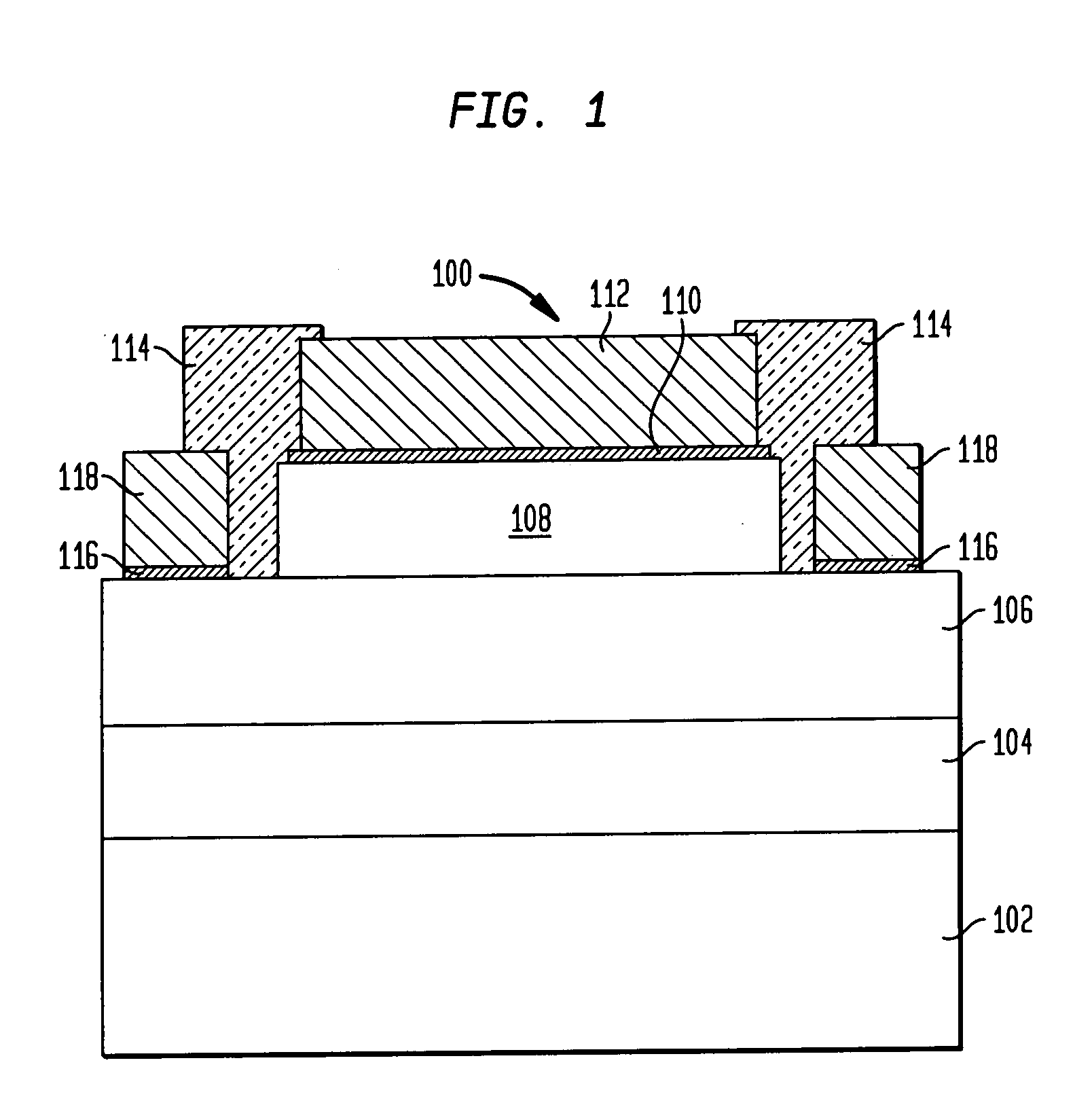

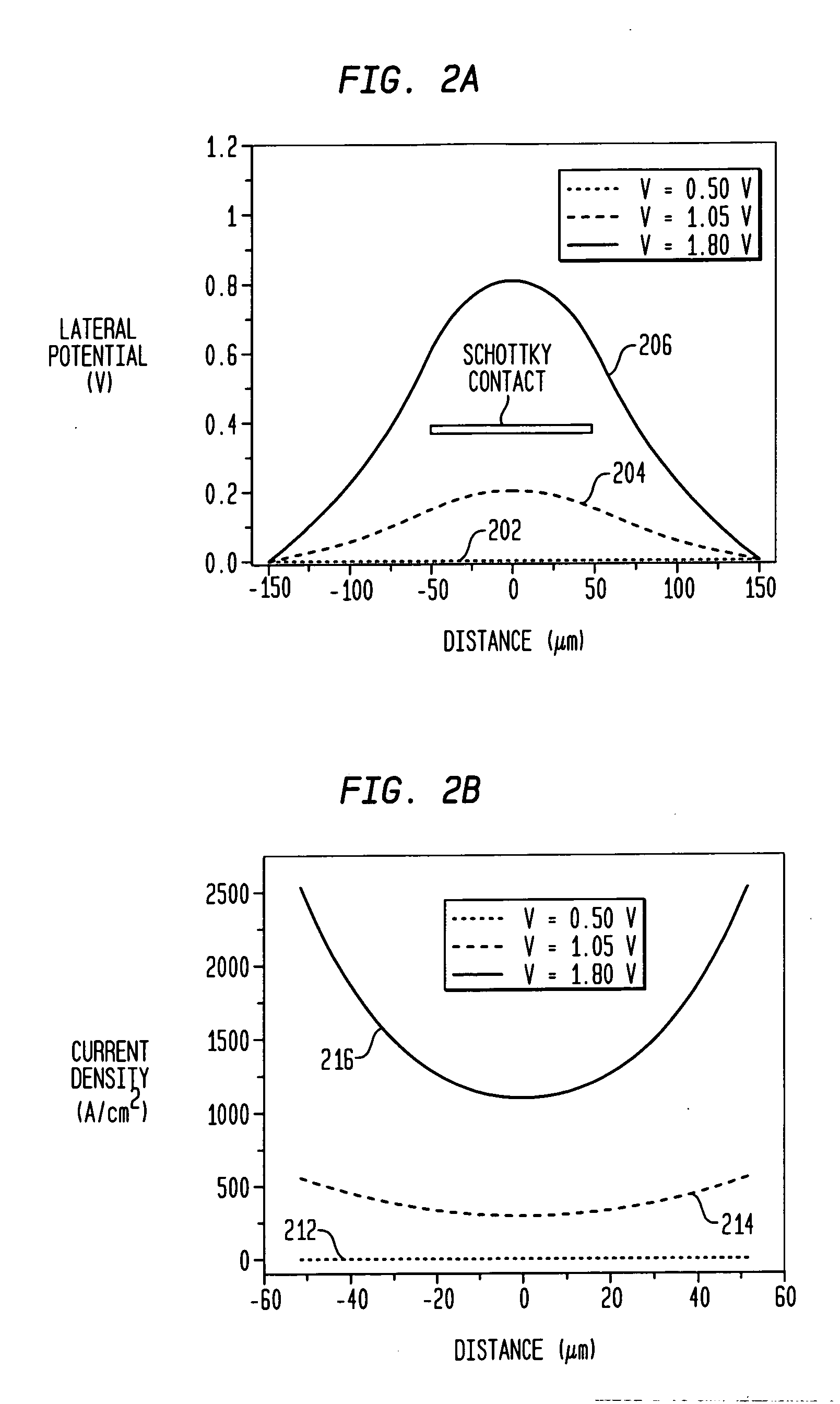

Lateral conduction schottky diode with plural mesas

ActiveUS20050179104A1High dopingReduce heat buildupSolid-state devicesSemiconductor/solid-state device manufacturingElectrical resistance and conductancePath length

A lateral conduction Schottky diode includes multiple mesa regions upon which Schottky contacts are formed and which are at least separated by ohmic contacts to reduce the current path length and reduce current crowding in the Schottky contact, thereby reducing the forward resistance of a device. The multiple mesas may be isolated from one another and have sizes and shapes optimized for reducing the forward resistance. Alternatively, some of the mesas may be finger-shaped and intersect with a central mesa or a bridge mesa, and some or all of the ohmic contacts are interdigitated with the finger-shaped mesas. The dimensions of the finger-shaped mesas and the perimeter of the intersecting structure may be optimized to reduce the forward resistance. The Schottky diodes may be mounted to a submount in a flip chip arrangement that further reduces the forward voltage as well as improves power dissertation and reduces heat generation.

Owner:POWER INTEGRATIONS INC

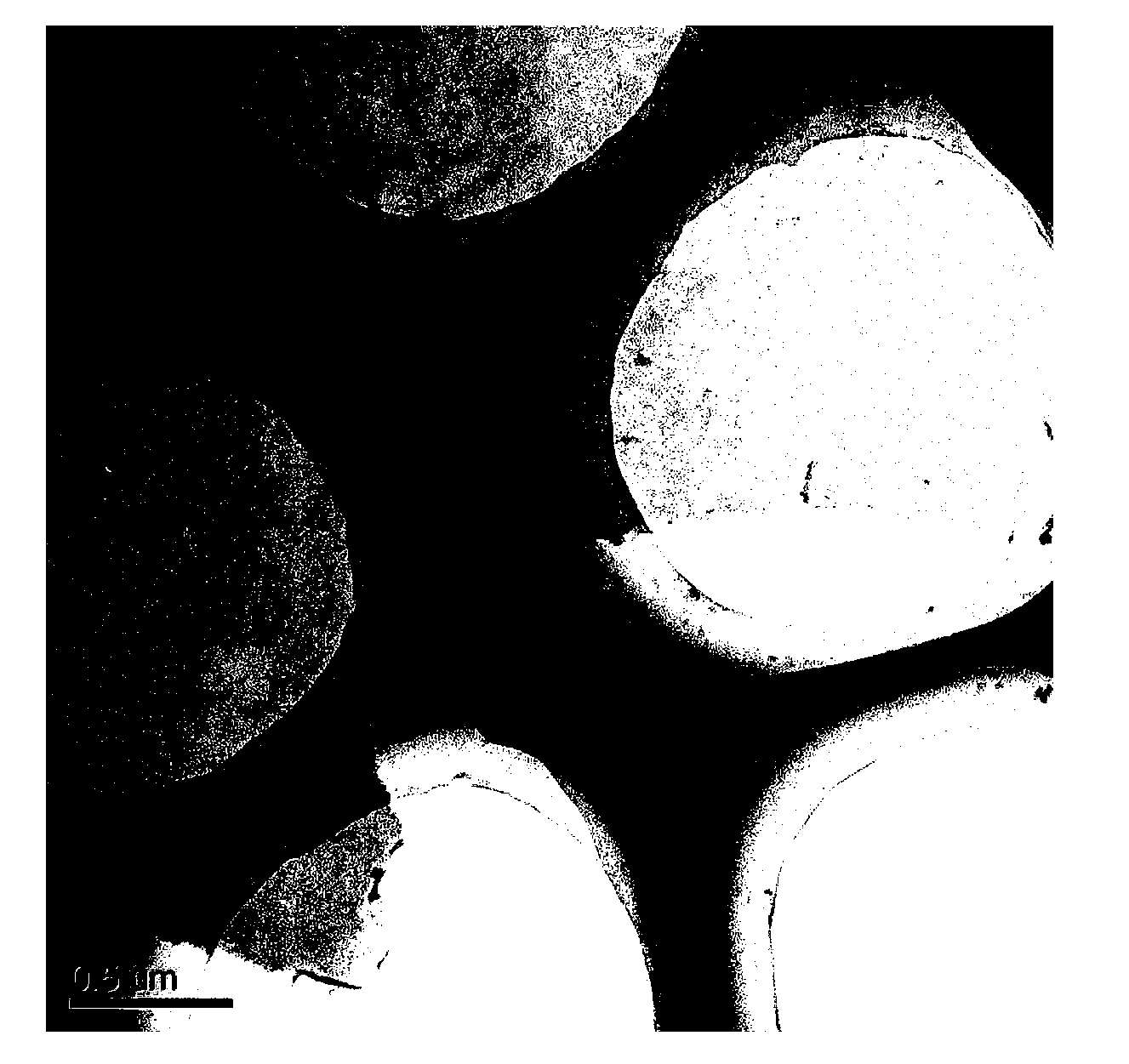

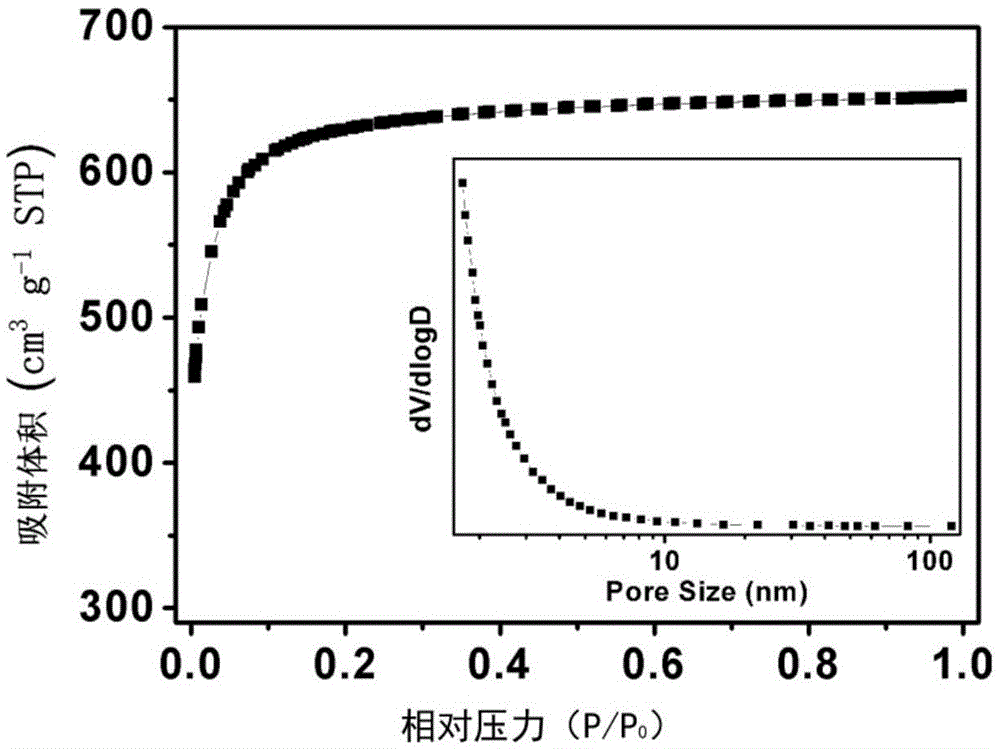

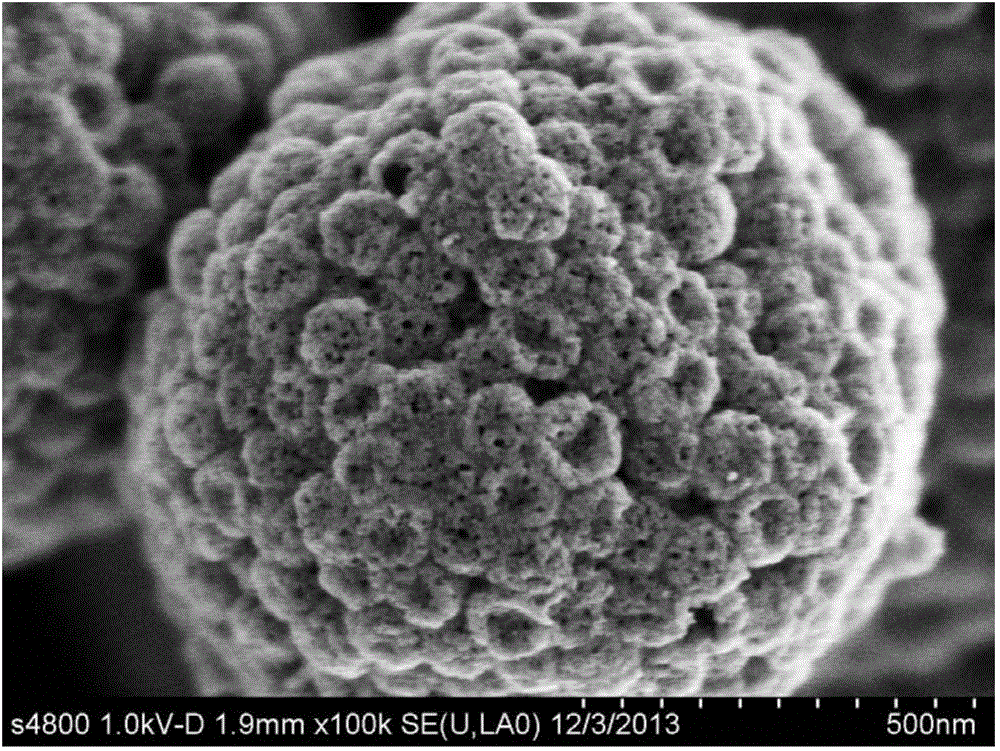

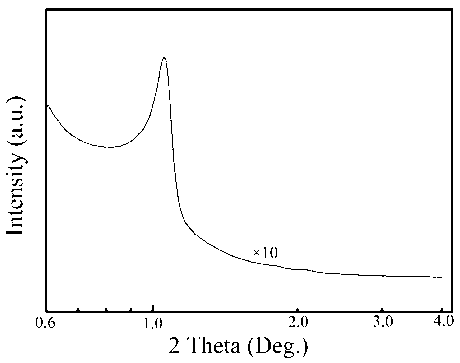

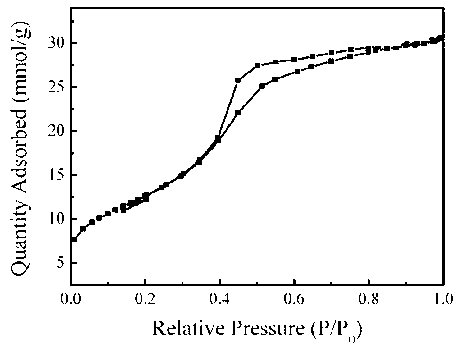

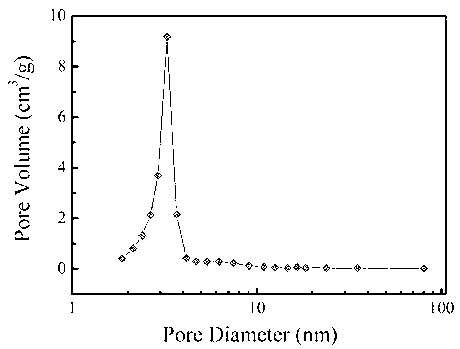

Heteroatom-doped carbon microsphere and preparation method thereof

The invention relates to a heteroatom-doped carbon microsphere. The carbon microsphere is composed of a carbon nanoparticle with a hierarchical pore structure. The carbon nanoparticle has micropores with pore sizes of 2 nm, mesopores with pore sizes of 2 to 50 nm and large pores with pore sizes of more than 50 nm; the BET specific surface area of the carbon nanoparticle is 300 to 1000 m2 / g; the content of heteroatoms in the carbon nanoparticle is 2 to 25 wt%; and the heteroatoms are at least one selected from the group consisting of nitrogen, phosphorus, sulfur and boron. The invention also discloses a preparation method for the carbon microsphere.

Owner:CHINA PETROLEUM & CHEM CORP +1

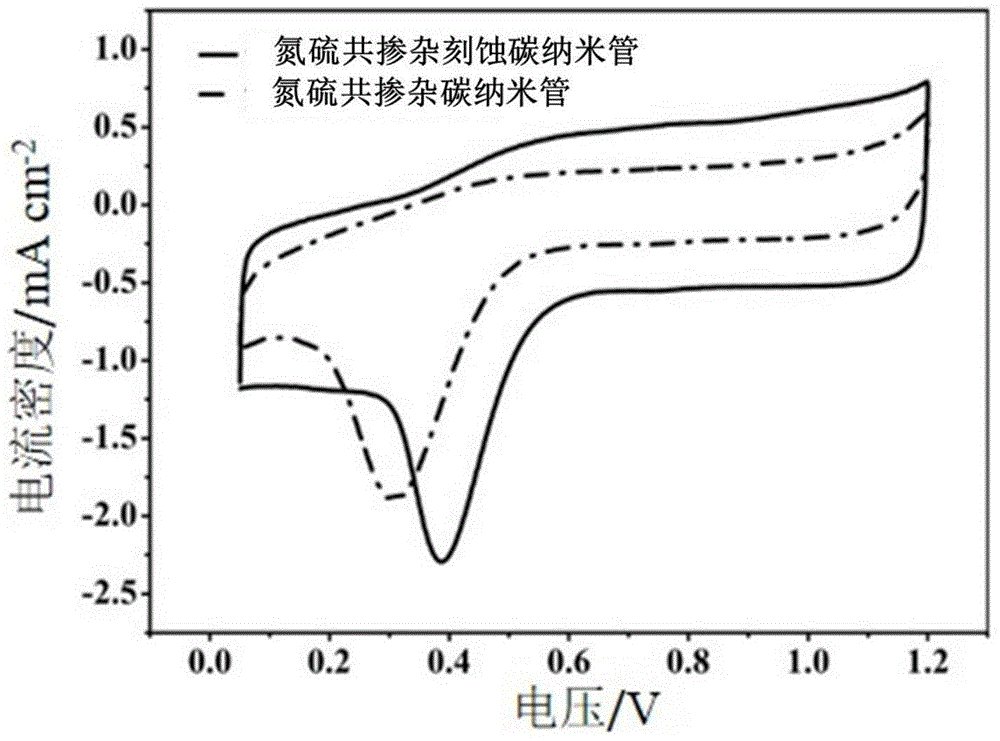

Preparation method of nitrogen and sulfur co-doping ordered mesoporous carbon materials

InactiveCN103072972AHigh dopingImprove physicsCarbon preparation/purificationPtru catalystIncipient wetness impregnation

The invention relates to a preparation method of nitrogen and sulfur co-doping ordered mesoporous carbon materials. According to the method, pyrrole is used as carbon sources and nitrogen sources, sulfuric acid is used as acid catalysts and sulfur sources, pyrrole oligomers are used as precursors, mesoporous silica molecular sieves SBA-15 (space group P6mm) and KIT-6 (space group Ia3d) are used as templates, a primary wet impregnation method is combined with the high-temperature themolysis technology for preparing the nitrogen and sulfur co-doping ordered mesoporous carbon materials in two-dimensional orthohexagonal and three-dimensional cubic ordered mesostructures.

Owner:LANZHOU UNIVERSITY OF TECHNOLOGY

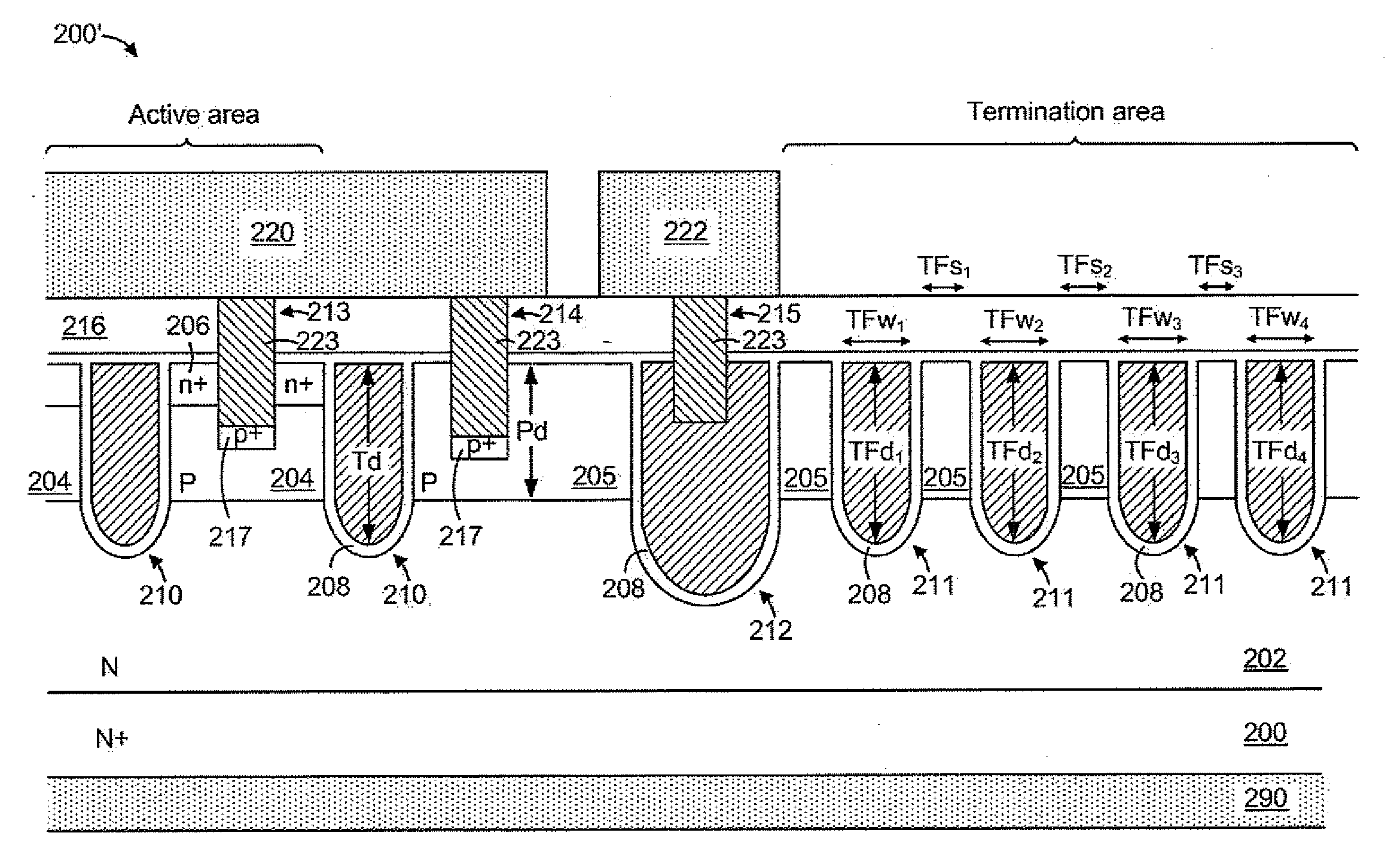

Trench mosfet with trenched floating gates in termination

ActiveUS20120211831A1High dopingReduce contact resistanceTransistorSemiconductor/solid-state device manufacturingTrench mosfetBody region

A trench MOSFET comprising multiple trenched floating gates in termination area is disclosed. The trenched floating gates have trench depth equal to or deeper than body junction of body regions in active area. The trench MOSFET further comprise an EPR surrounding outside the multiple trenched floating gates in the termination area.

Owner:FORCE MOS TECH CO LTD

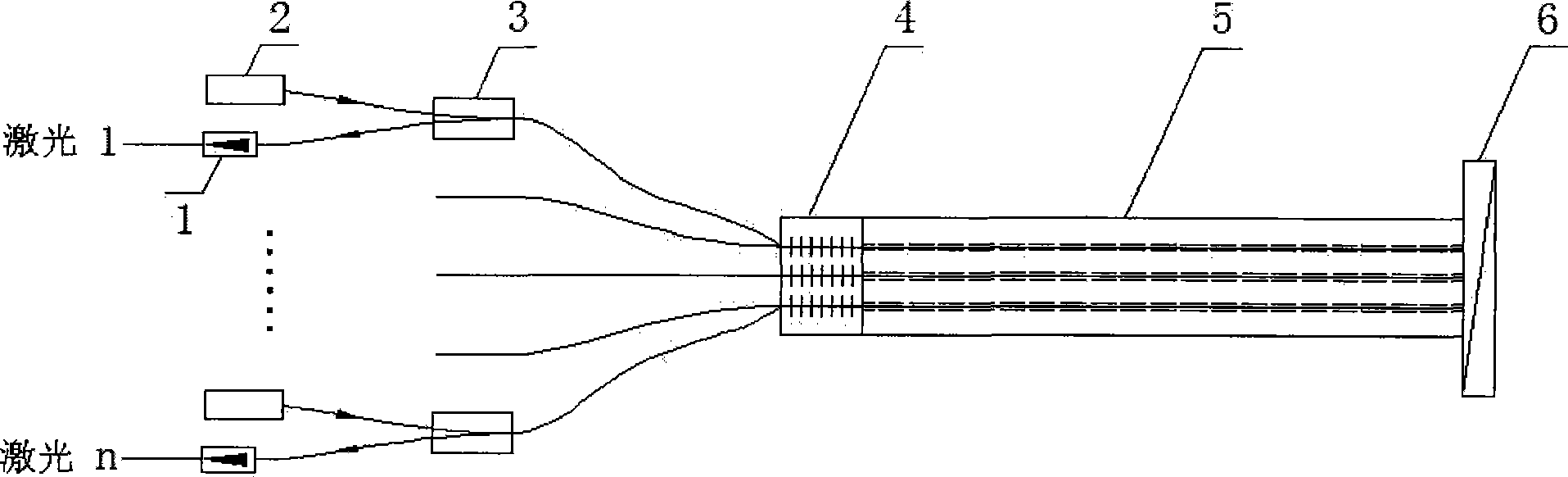

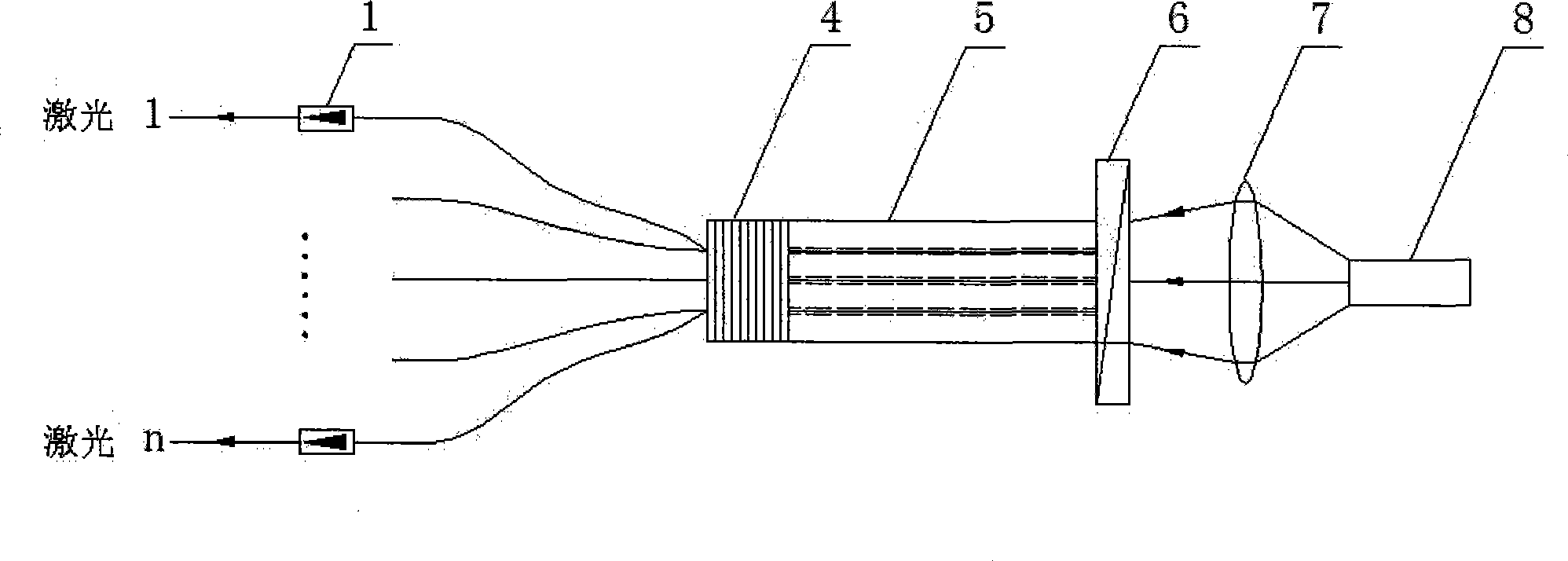

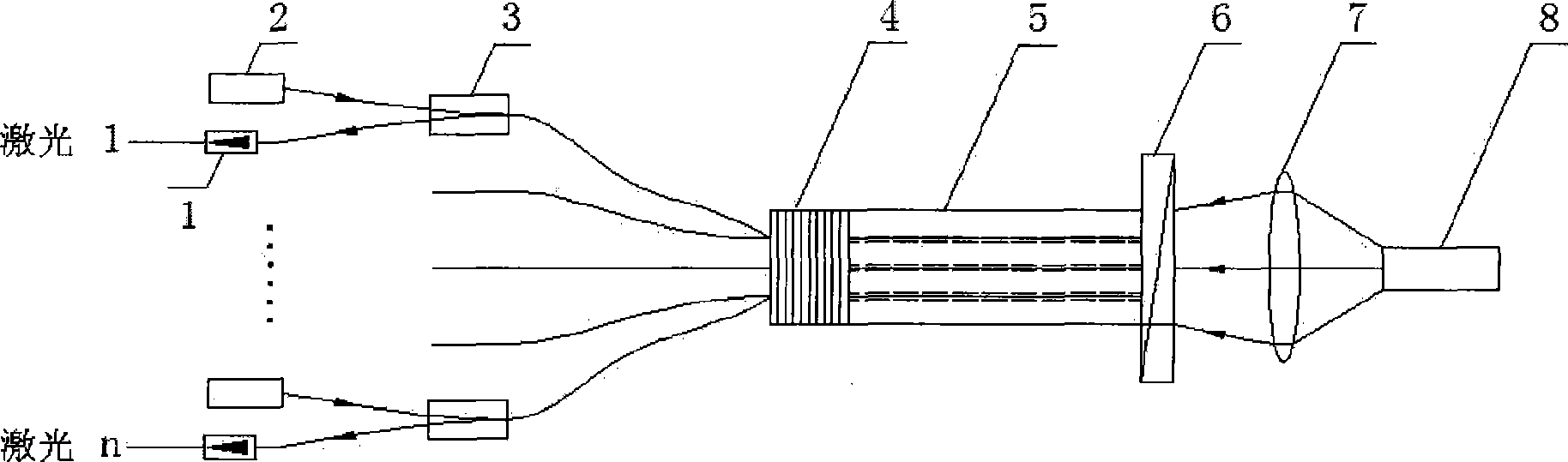

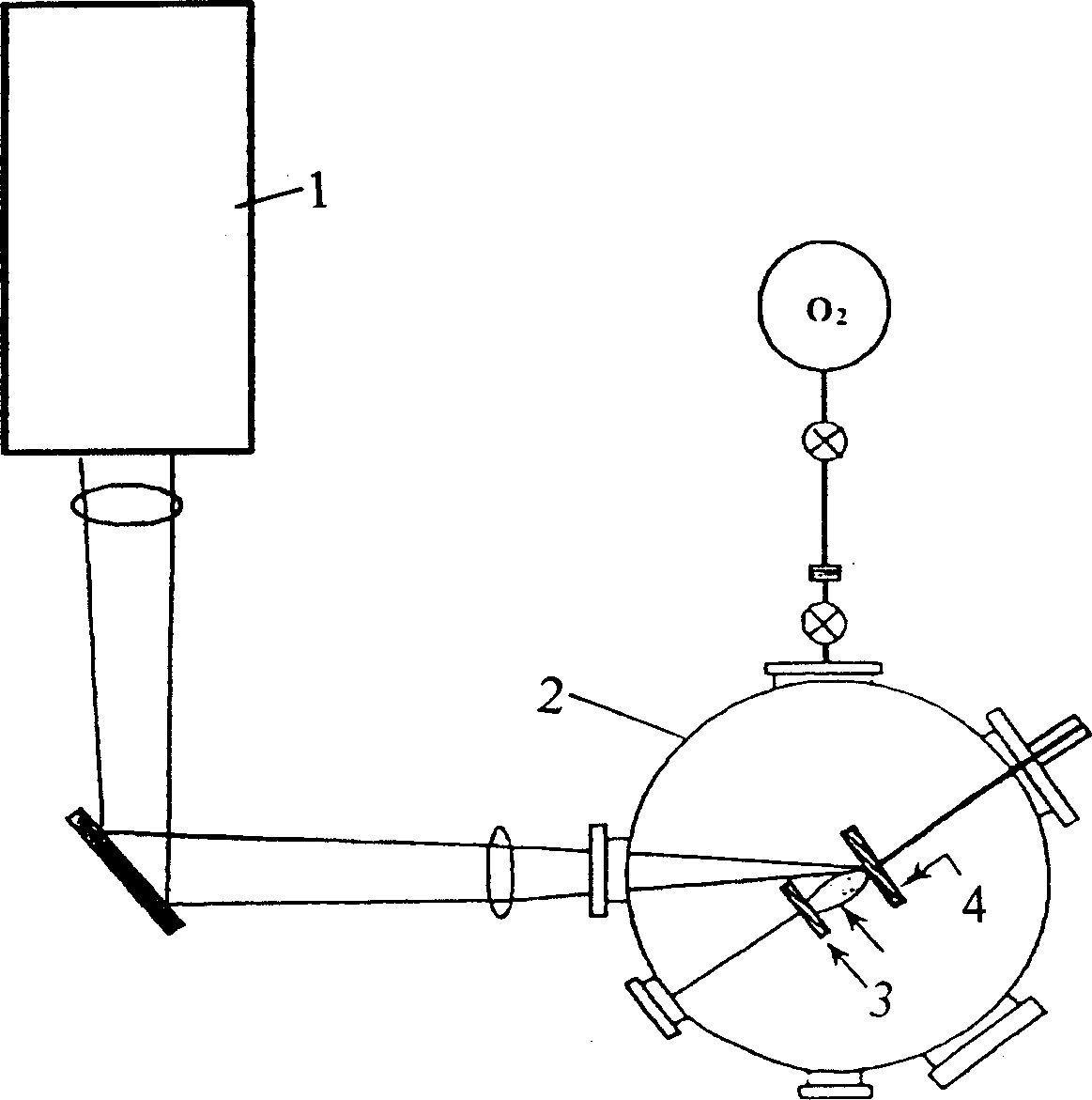

Multiple wavelength outputting ultra-narrow wire single frequency optical fiber laser

ActiveCN101459313AHigh dopingHigh gain characteristicActive medium shape and constructionWavelength-division multiplexingLine width

The invention provides a multiple wavelength output single-frequency optical fiber laser with ultra-narrow line width, which comprises high-gain dual-cladding two-dimensional array optical fiber, narrow-band optical fiber grating arrays, a dichroscope or wide-band optical fiber grating arrays, a pump light source (single mode LD or multiple mode LD or both together), an optical fiber isolator, a coupling lens and a wavelength-division multiplexer. The single-frequency optical fiber laser can realize simultaneously output multi-path high-power (>100mW) and ultra-narrow line width (KHz level) single-frequency laser of a single-transverse mode with identical wavelength or different wavelength, and the outputted multi-path single-frequency lasers do not interfere each other. The multiple wavelength output single-frequency optical fiber laser can be applied to the military or space filed which requires high accurate sensing, detection and indication to multiple targets.

Owner:SOUTH CHINA UNIV OF TECH

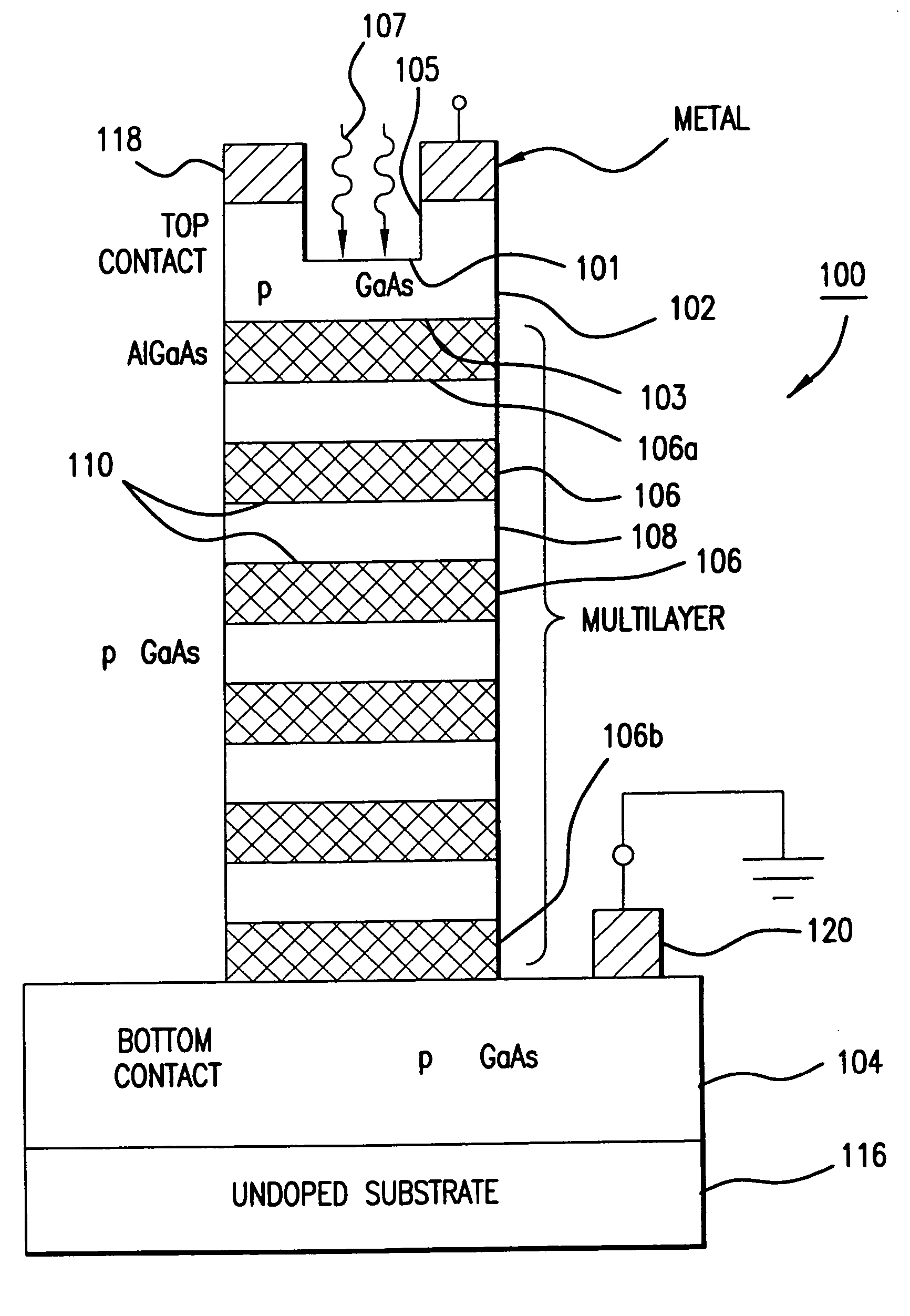

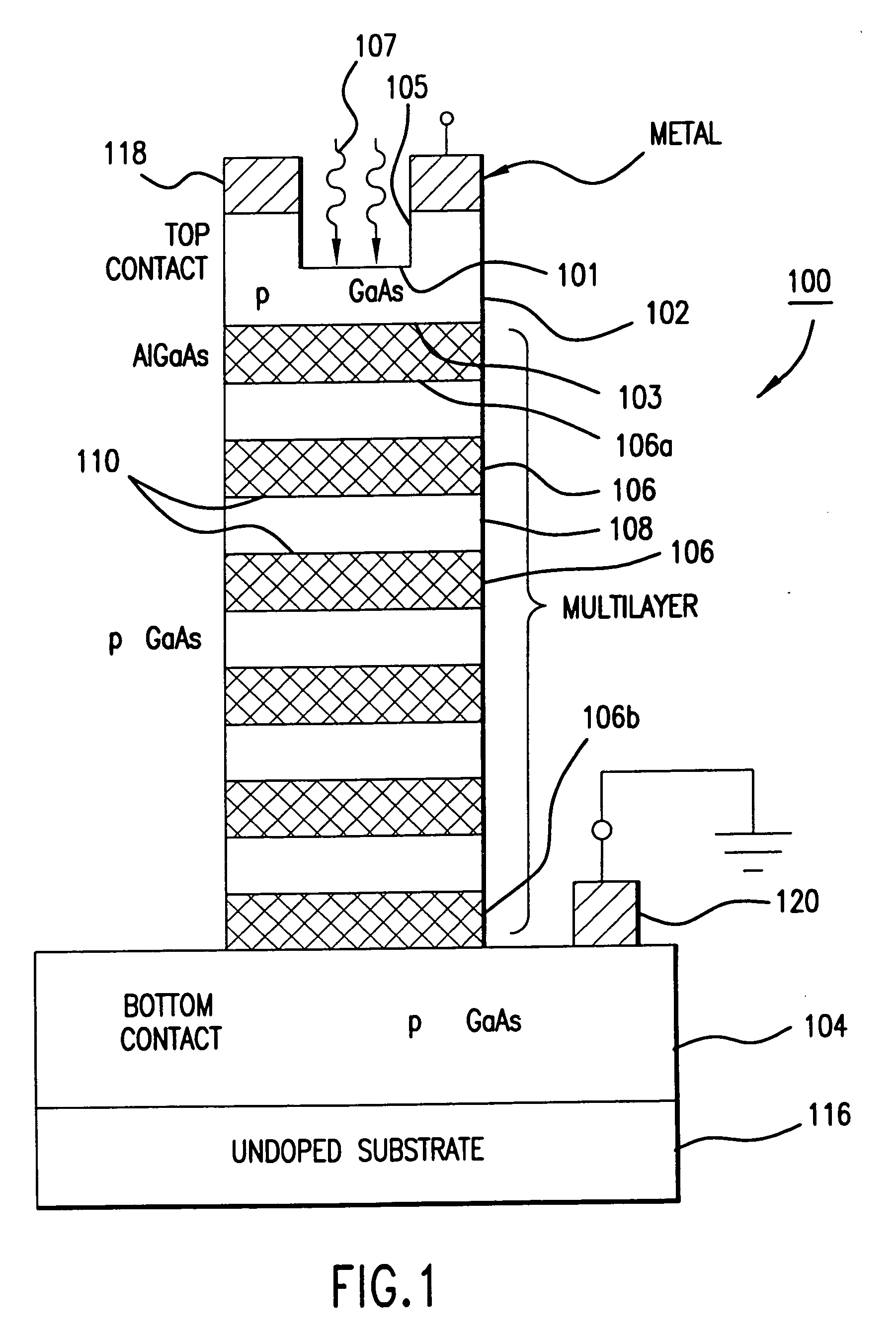

Heterojunction far infrared photodetector

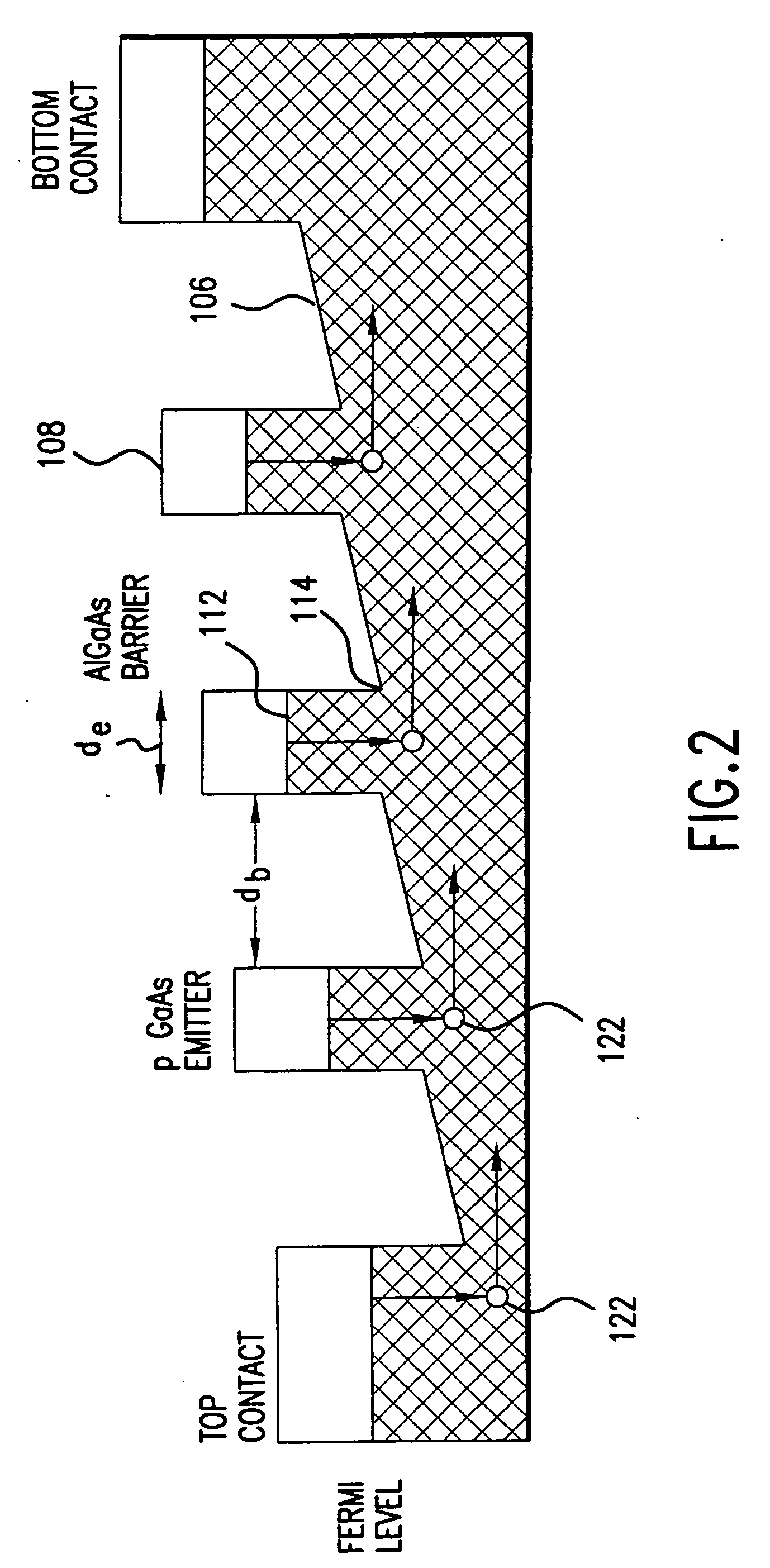

A photodetector and method of detecting far infrared optical signals. In one embodiment of the present invention, the photodetctor has a plurality of N barriers, N being an integer greater than 1, each barrier being a layer of a material made from a first and a second group III elements and a first group V element and characterized by a bandgap. The photodetector further has a plurality of N−1 emitters, each emitter being a layer of material made from a third group III element and a second group V element and characterized by a bandgap different from that of the barriers and having at least one free carrier responsive to optical signals, wherein each emitter is located between two barriers so as to form a heterojunction at each interface between an emitter and a barrier. Moreover, each emitter is doped with a first group II, IV or VI element to cause free carriers in the emitter, wherein at least one construction parameter of each emitter causes at least one free carrier to occupy a range of substantially continuously distributed energies characterized by a three dimensional Fermi level and respond to optical signals having wavelength in the range of 3 to 100 μm with significant absorption.

Owner:GEORGIA STATE UNIV RES FOUND INC

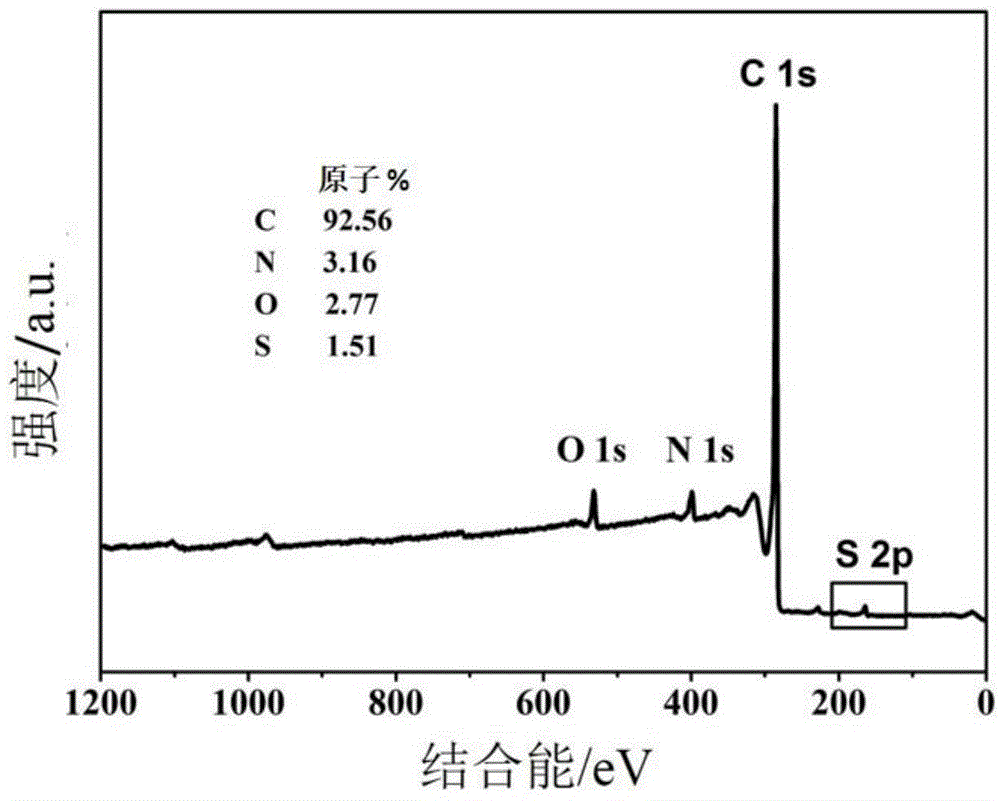

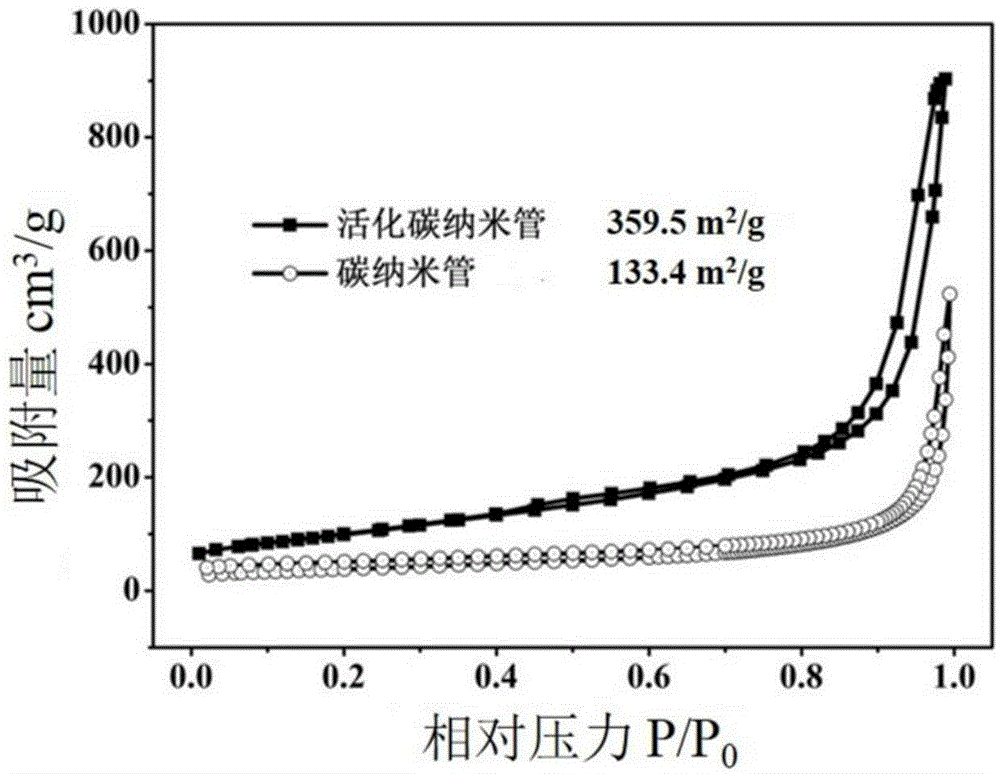

Carbon nanotube, and preparation method and application thereof

InactiveCN104370279AIncrease power storageHigh specific surface areaMaterial nanotechnologyPhysical/chemical process catalystsHeteroatomOxygen

The invention discloses a carbon nanotube, and a preparation method and an application thereof. The carbon nanotube is a heteroatom-doped carbon nanotube, the mass ratio of heteroatoms is 3%-6%, the surface of the carbon nanotube has a mesoporous structure, the mesoporous average pore size is 2 nm-9 nm, and the specific surface area of the carbon nanotube is 150 m<2> / g-1200 m<2> / g. The preparation method comprises the following steps: (1) evenly mixing the carbon nanotube with an etching agent, and making the mass ratio be 1:3 to 1:5; (2) under an oxygen isolated condition, heating up to 500 DEG C-900 DEG C, and calcining for 1 h-3 h; (3) washing and drying; and (4) carrying out heteroatom doping. The specific surface area of the carbon nanotube can be improved, the catalytic activity of the carbon nanotube is increased, and the carbon nanotube has the advantages of simple process and low cost, and is applied to preparation of electrocatalysts having good performance.

Owner:HUAZHONG UNIV OF SCI & TECH

Perforated foil used for current collector and its making method

ActiveCN103531815AHighly dopedEvenly dopedElectrode carriers/collectorsHybrid/EDL manufactureMetal foilSupercapacitor

The invention relates to a making method of a perforated foil used for a current collector. The method includes: firstly employing a printing technology to print a figure on the surface of a metal foil used for a current collector, and then adopting a wet etching technology to etch the foil so as to make the perforated foil. With the characteristics of simplicity and low production cost, the making method is suitable for commercial batch production. The made perforated foil not only can be used for lithium ion capacitors, and also can be used in lithium ion batteries, super capacitors and other fields. In addition, the invention also relates to the perforated foil used for a current collector made by the method.

Owner:RESEARCH INSTITUTE OF TSINGHUA UNIVERSITY IN SHENZHEN

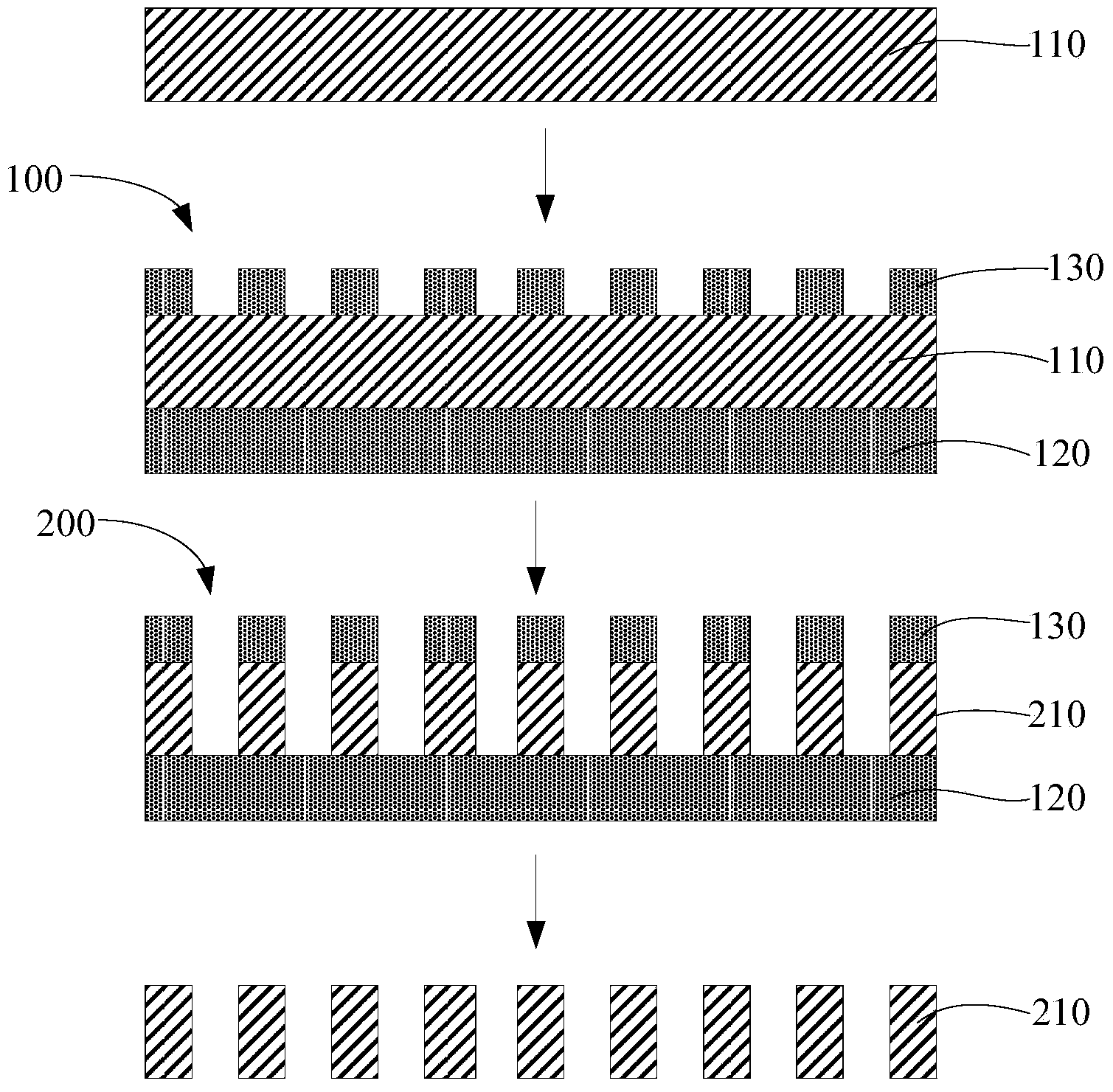

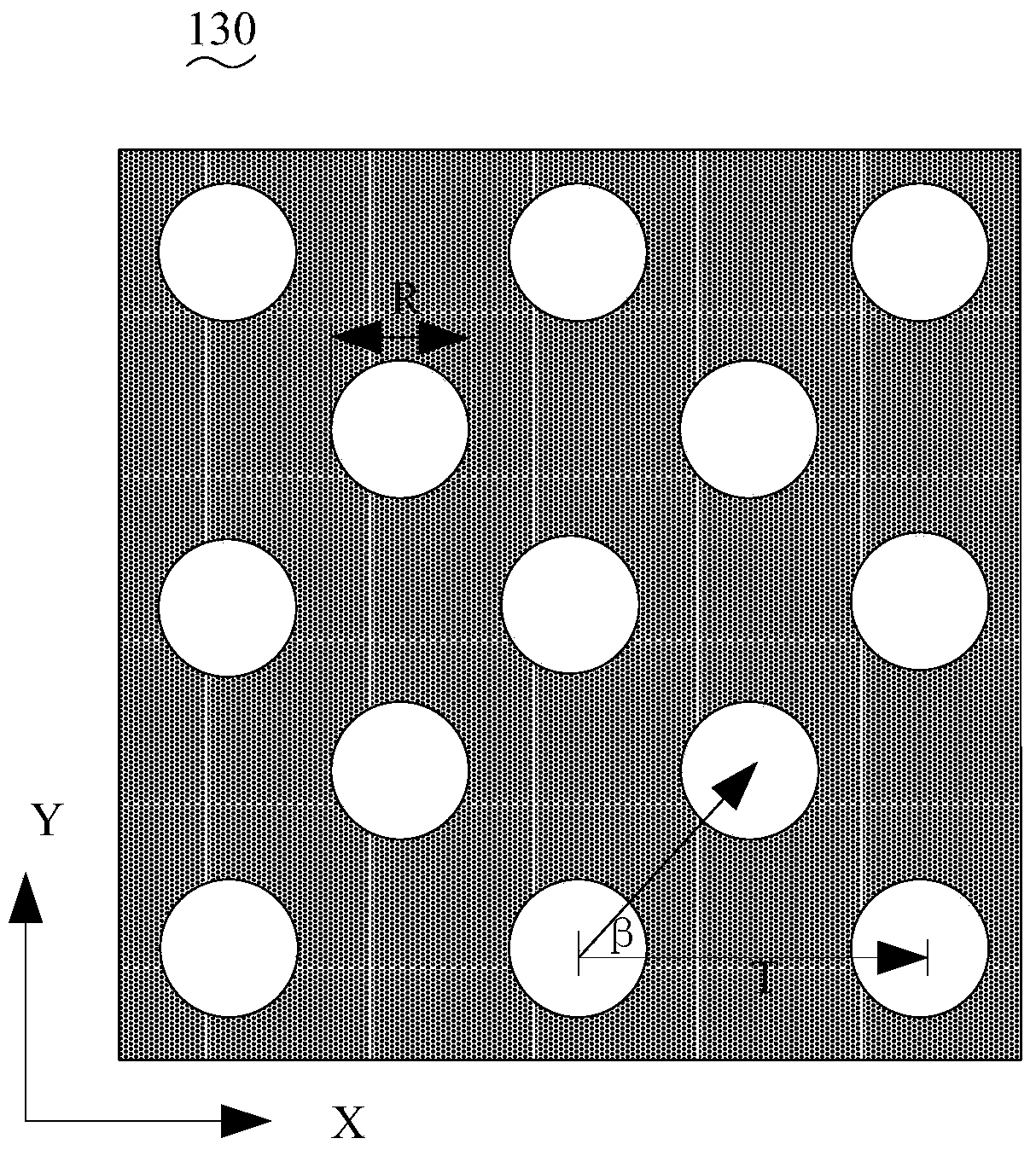

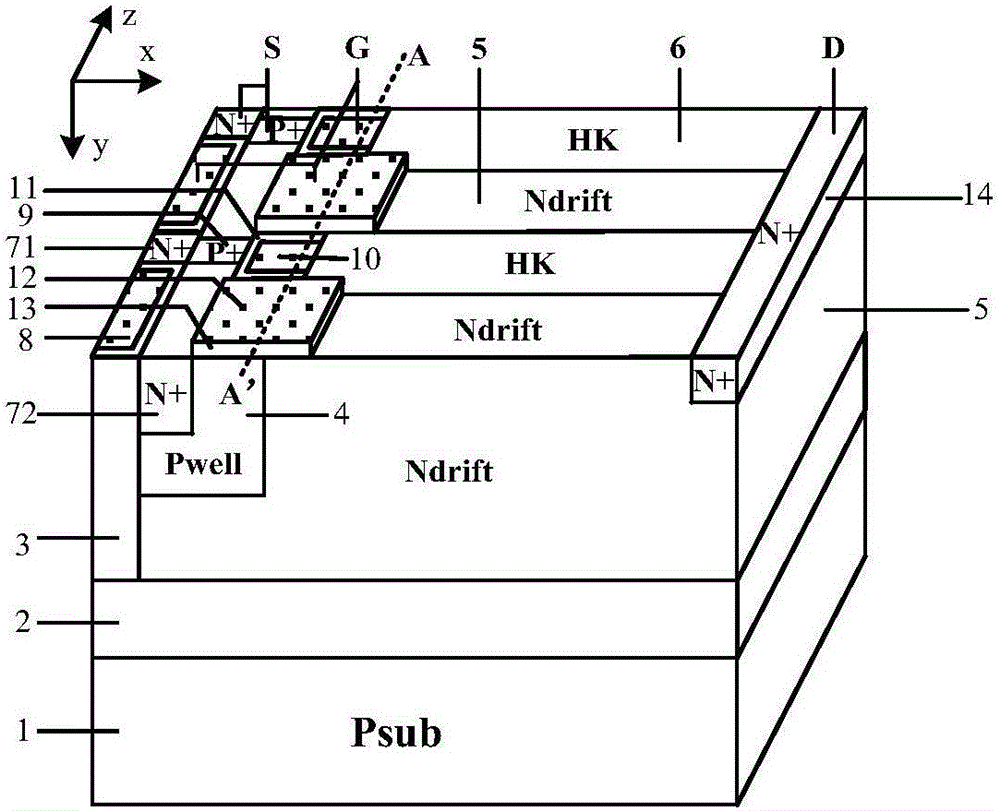

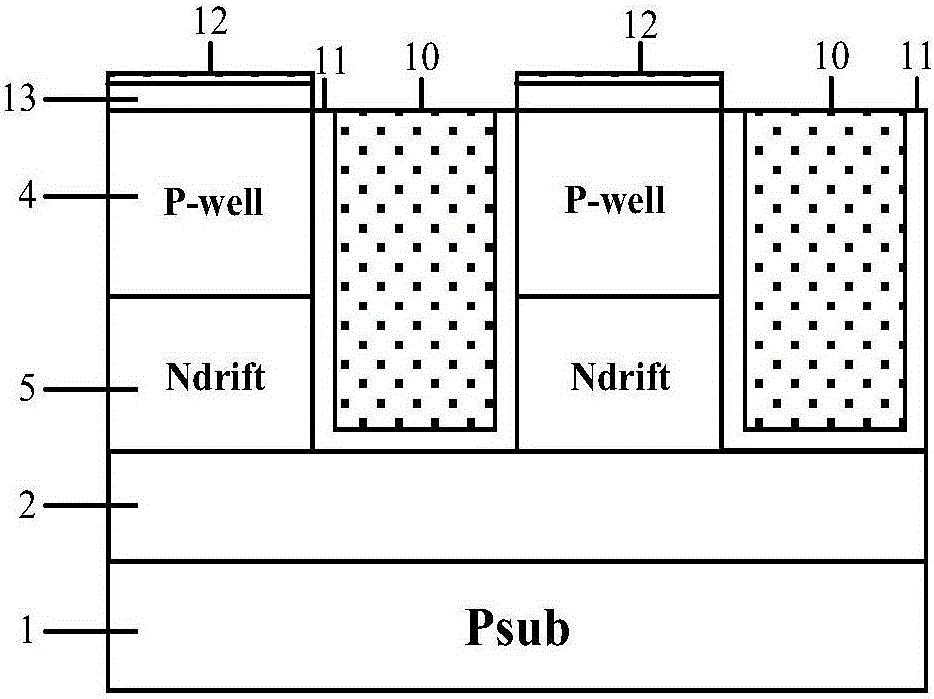

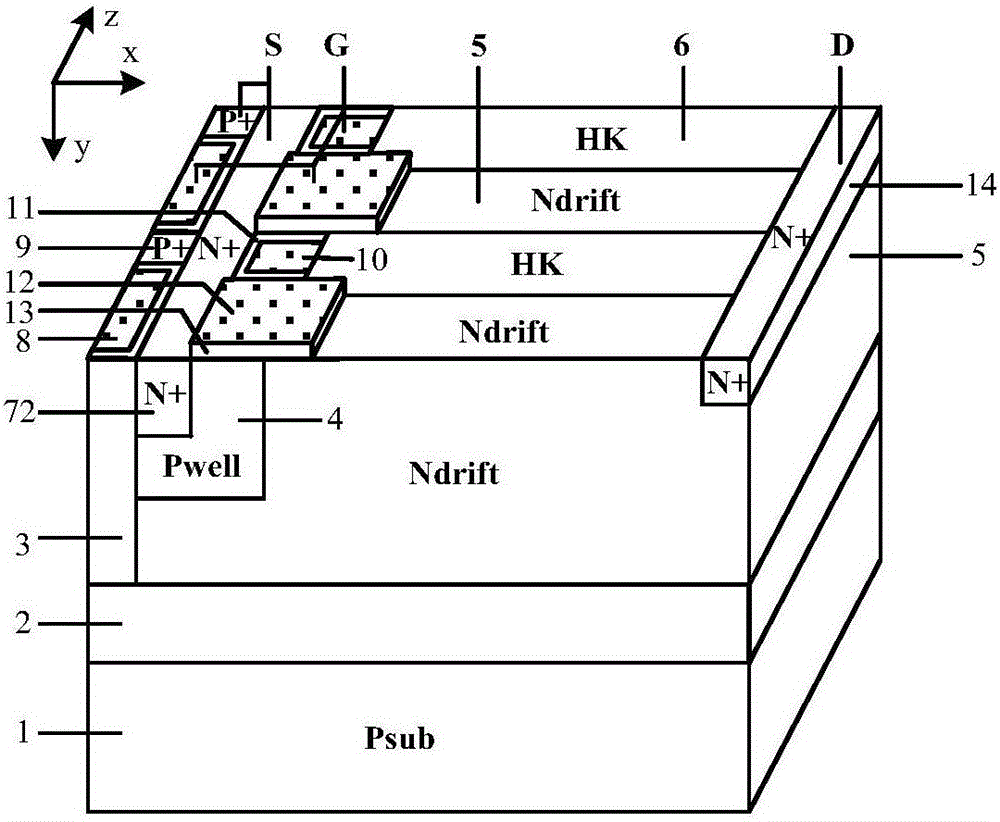

HK SOI LDMOSdevice having three-grating structure

The invention belongs to a field of semiconductor technology and specifically relates to an HK SOI LDMOS (Lateral Double-Diffusion Metal Oxide Semiconductor) device. The device has the following characteristics. First, the device has three separated grating structures including a plane grate and two channel grates. In an open state, the three-grating structure an form a plurality of crosswise and longitudinal channels, thus increasing channel density, increasing current and reducing specific on-resistance. Second, high K mediums are embedded into drifting zones adjacent to a semiconductor zone and are arranged in alternation with the drifting zones. In the open state, electron accumulation layers are formed on side walls of the drifting zones adjacent to the high K mediums, so that low resistance channels are provided and the specific on-resistance is reduced. In a closed state, the high K mediums assist to drain the drifting zones, so that the drifting zone doping is improved, the electric field is improved and the specific on-resistance is reduced and the voltage holding performance is improved further. Third, an SOI structure is adopted, so that longitudinal voltage holding performance is improved, leakage current is reduced and a latch-up effect is eliminated.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

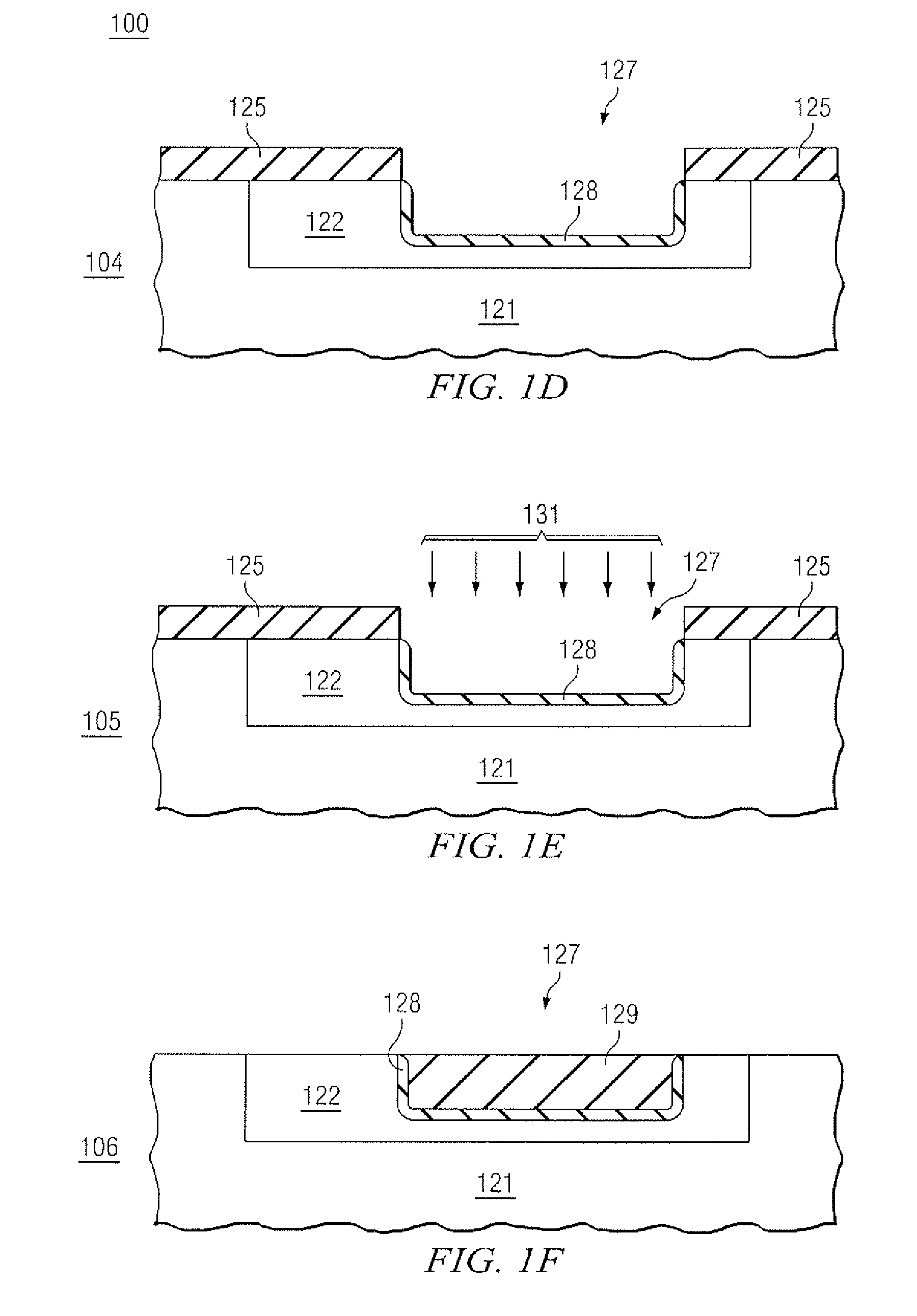

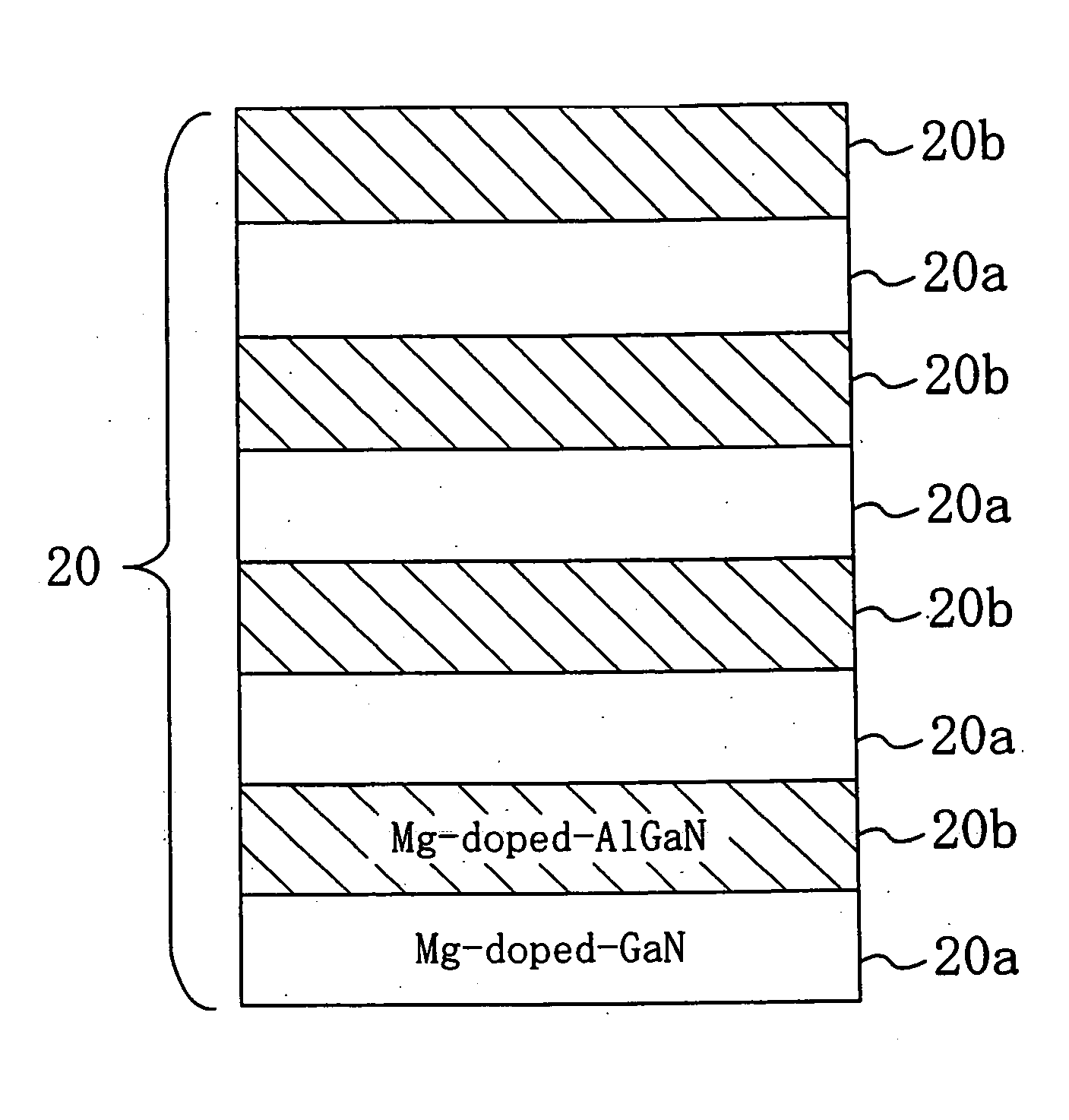

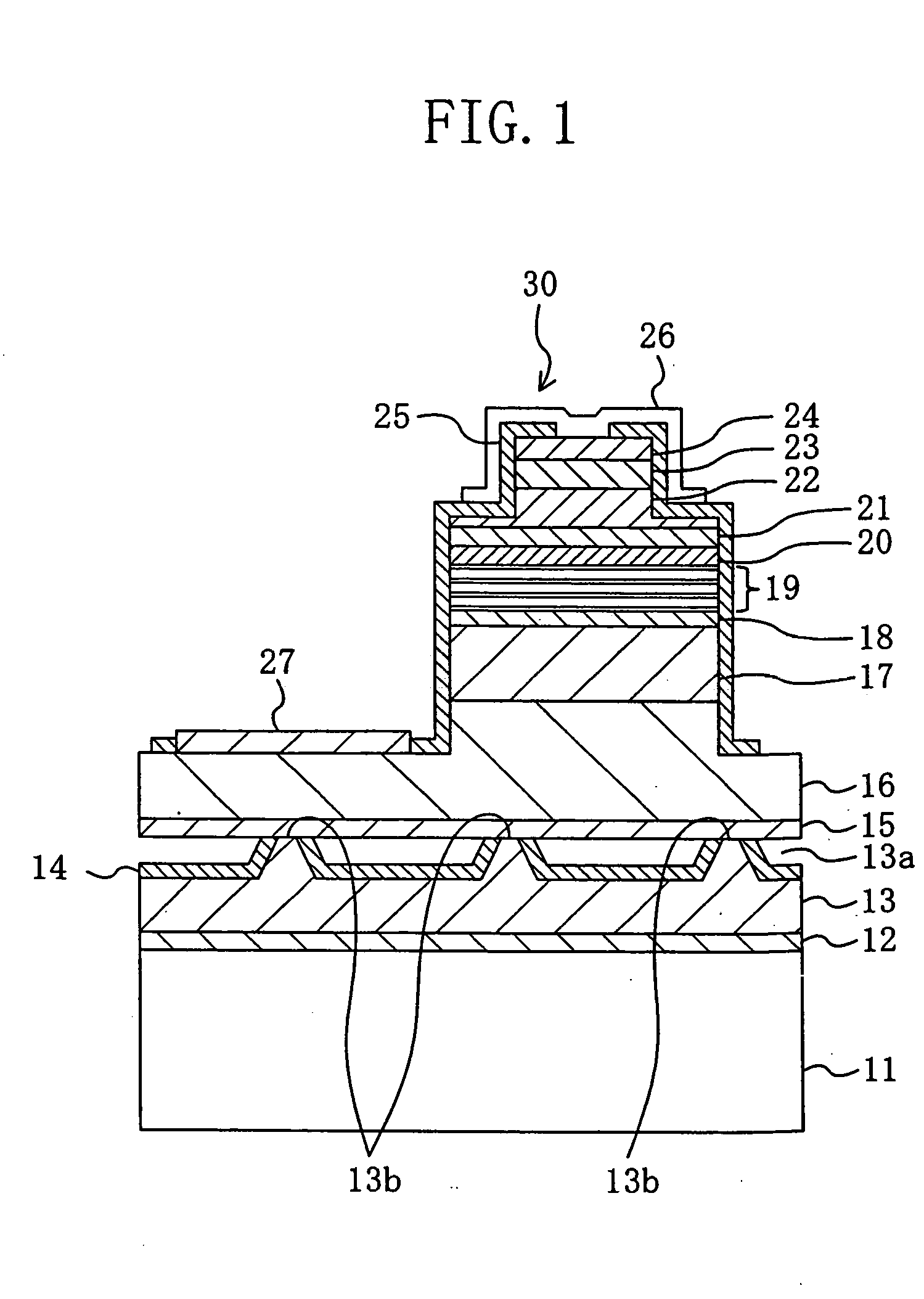

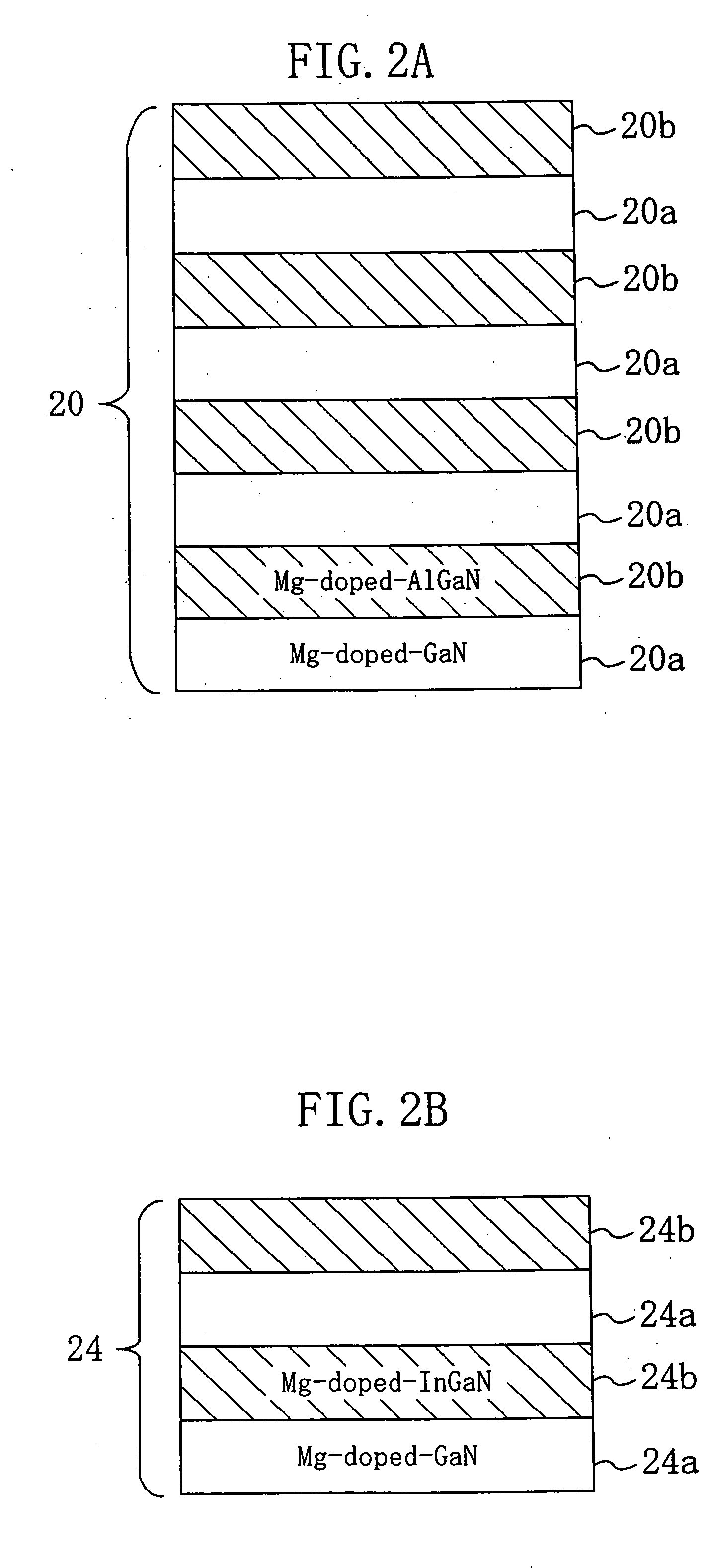

Method for fabricating nitride semiconductor, method for fabricating nitride semiconductor device, and nitride semiconductor device

InactiveUS20050142682A1Lower resistanceSteep p-type impurity profileOptical wave guidanceLaser detailsDopantElectrical conductor

The method for fabricating a nitride semiconductor of the present invention includes the steps of: (1) growing a first semiconductor layer made of a first group III nitride over a substrate by supplying a first group III source and a group V source containing nitrogen; and (2) growing a second semiconductor layer made of a second group III nitride on the first semiconductor layer by supplying a second group III source and a group V source containing nitrogen. At least one of the steps (1) and (2) includes the step of supplying a p-type dopant over the substrate, and an area near the interface between the first semiconductor layer and the second semiconductor layer is grown so that the density of the p-type dopant locally increases.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

Preparation method of carbon based catalyst with high graphitization degree and used for fuel cell cathode

ActiveCN104289242AChange the microstructureHigh catalytic activity for oxygen reductionPhysical/chemical process catalystsCell electrodesProtonNitrogen doped

The invention relates to a preparation method of a carbon based catalyst with high graphitization degree and used for a fuel cell cathode. The method is as below: using pitch as a carbon precursor, heating and melting the precursor by high temperature, and immersing the precursor in a template agent; mixing evenly, adding a nitrogen-containing precursor, and adding metal salt; then carrying out drying, high temperature treatment and two times of nitridation; then washing in an acidic solution and removing the template; and finally filtering, washing and drying to obtain the nitrogen doped carbon based catalyst material with high degree of graphitization. The catalyst has high graphitization degree, high specific surface area and ordered pore structure. The catalyst used as the cathode catalyst for a proton exchange membrane fuel cell shows good oxygen reduction activity, and the catalyst is environment-friendly, low in cost, microscopic controllable, and rich in resources, and is expected to become electric catalyst for proton exchange membrane fuel cells.

Owner:DALIAN INST OF CHEM PHYSICS CHINESE ACAD OF SCI

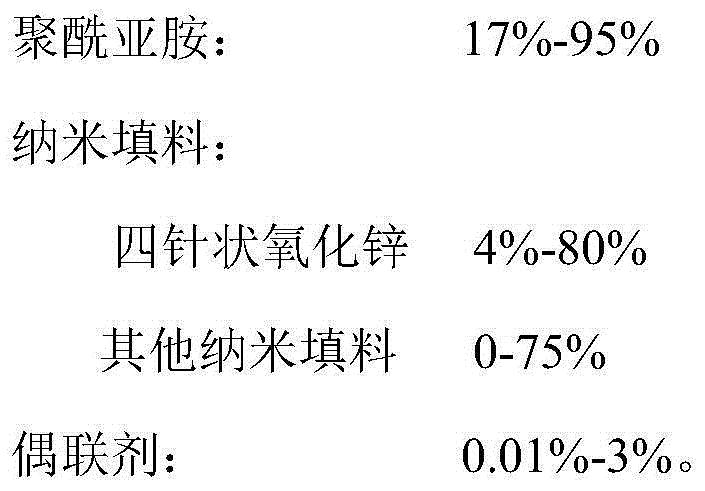

Polyimide composite film with electromagnetic shielding function and preparation method thereof

InactiveCN105037759AUniform performanceThe experimental operation process is controllableComposite filmIn situ polymerization

The invention relates to a polyimide film with an electromagnetic shielding function and a preparation method thereof. The polyimide composite film is characterized by being composed of the following components in percentage by weight: 17 to 95% of polyimide, 4 to 80% of nano filler (tetrapod-like zinc oxide), 0 to 75% of other nano filler, and 0.01 to 3% of coupling agent. The target product is obtained through an in-situ polymerization method and thermal imidization. The reaction raw materials comprise diamine, dianhydride, nano filler dispersed in polymer, and a coupling agent for improving the dispersibility. The reaction process is controller, the doping amount of nano filler is high, the components in the composite material are evenly mixed, the structure and property of the film are stable, moreover, the film has an electromagnetic shielding function, and thus the film has a high application value in the fields of electronic / electromagnetic shielding and electrochemistry.

Owner:NANJING UNIV OF TECH

Methods of manufacturing trench isolated drain extended MOS (demos) transistors and integrated circuits therefrom

ActiveUS7745294B2Improve bindingLower levelSemiconductor/solid-state device manufacturingSemiconductor devicesDopantGate dielectric

A method of fabricating an integrated circuit (IC) including at least one drain extended MOS (DEMOS) transistor and ICs therefrom includes providing a substrate having a semiconductor surface, the semiconductor surface including at least a first surface region that provides a first dopant type. A patterned masking layer is formed on the first surface region, wherein at least one aperture in the masking layer is defined. The first surface region is etched to form at least one trench region corresponding to a position of the aperture. A dopant of a first dopant type is implanted to raise a concentration of the first dopant type in a first dopant type drift region located below the trench region. After the implanting, the trench region is filled with a dielectric fill material. A body region is then formed having a second dopant type in a portion of the first surface region. A gate dielectric is then formed over a surface of the body region and the first surface region. A patterned gate electrode layer is formed over the gate dielectric, a source region in the body region and a drain region in the first surface region on a side of the trench region opposite to the source are formed, and fabrication of the IC is completed.

Owner:TEXAS INSTR INC

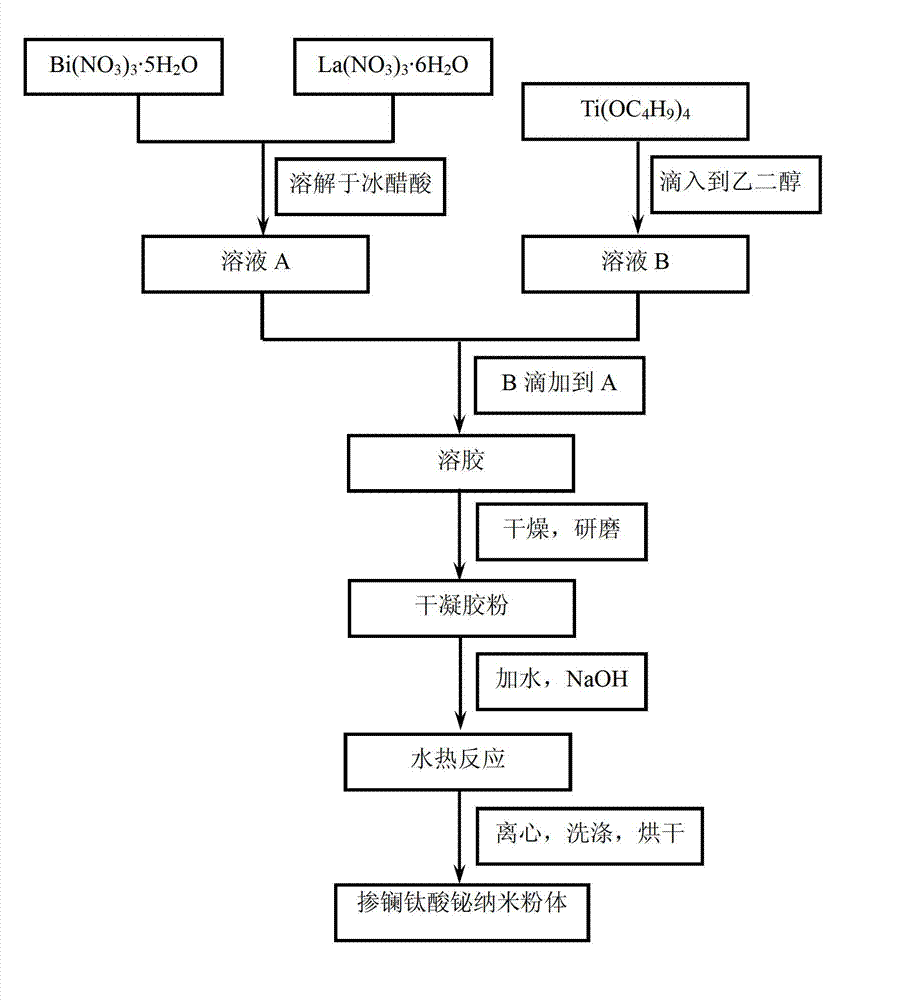

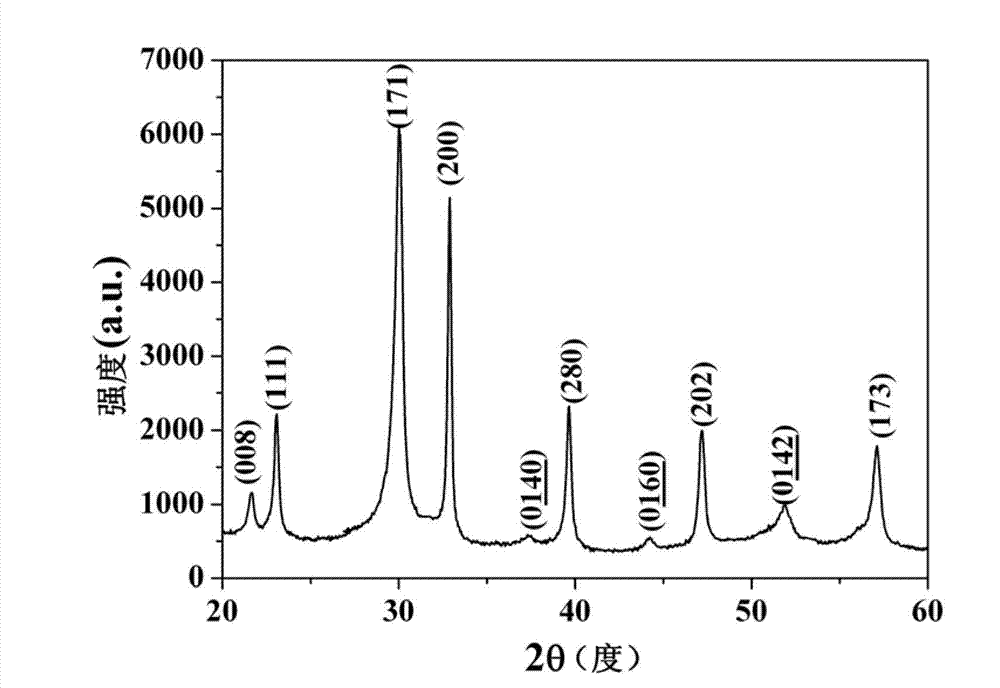

Method for preparing lanthanum-doped bismuth titanate nano powder by sol-gel hydrothermal method

ActiveCN102963929ASave energySimple equipmentMaterial nanotechnologyChemical industryOrganic solventAcetic acid solution

The invention discloses a method for preparing lanthanum-doped bismuth titanate nano powder by a sol-gel hydrothermal method, which comprises the following steps of: dissolving Bi (NO3) 3.5H2O and La (NO3) 3.6H2O into glacial acetic acid solution to obtain solution A; dropwise adding Ti (OC4H9) 4 into organic solvent to obtain solution B; dropwise adding the solution B into the solution A, and preparing even sol by magnetic stirring; putting the sol into a drying oven, and drying to obtain xerogel; grinding to obtain powdered hydrothermal reaction precursor; putting the hydrothermal reaction precursor into a hydrothermal kettle, and adding pure water taken as solvent and NaOH taken as mineralizer into the hydrothermal kettle; sealing the reaction kettle, and putting the reaction kettle into the drying oven at 160-170 DEG C; taking out products after reaction, and filtering to obtain precipitate; and finally, washing and drying the precipitate to obtain the lanthanum-doped bismuth titanate nano powder. The method can be used for preparing the lanthanum-doped bismuth titanate nano powder under the condition of low temperature, so that the energy is saved, and lanthanum-doped bismuth titanate is perfect in crystallization.

Owner:SOUTH CHINA UNIV OF TECH

Low voltage high density trench-gated power device with uniformly doped channel and its edge termination technique

InactiveUS20030205758A1Increase reverse voltageLow densityTransistorSolid-state devicesChannel densityLow voltage

Merging together the drift regions in a low-power trench MOSFET device via a dopant implant through the bottom of the trench permits use of a very small cell pitch, resulting in a very high channel density and a uniformly doped channel and a consequent significant reduction in the channel resistance. By properly choosing the implant dose and the annealing parameters of the drift region, the channel length of the device can be closely controlled, and the channel doping may be made highly uniform. In comparison with a conventional device, the threshold voltage is reduced, the channel resistance is lowered, and the drift region on-resistance is also lowered. Implementing the merged drift regions requires incorporation of a new edge termination design, so that the PN junction formed by the P epi-layer and the N<+> substrate can be terminated at the edge of the die.

Owner:SEMICON COMPONENTS IND LLC

P-zn1-xmgxo crystal film and method for making same

InactiveCN1542915ABand gap adjustableQuality improvementLaser detailsSemiconductor/solid-state device manufacturingDopantMetallurgy

This invented P-Zn1-xMgxO crystal film is one doped by one or several in B, Al, Ga and In as the donor and one or several of N, P, AS gases as the acceptor, the molar content of X is larger than 0 smaller than 40%, and the doped density is 1015~1019cm[-3]. The film is prepared by pulse laser deposition, the target is a ceramic one sintered with pure ZnO, MgO and donor doping agent powder, among which, the molar content of MgO is larger than 0 but smaller than 40%, that of the donor doping agent is larger than 0 but smaller than 3%, the grown temperature is 400~700deg.C, the grown atmosphere is a mixed gas containing the acceptor activated by plasma and pure O2, the doped density can be controlled by adjusting different intrinsic stand-off ratios of the input gas with acceptor and O2 and molar content of the donor doping agents in the target material and the successive annealing temperature.

Owner:ZHEJIANG UNIV