Patents

Literature

365 results about "Fermi level" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

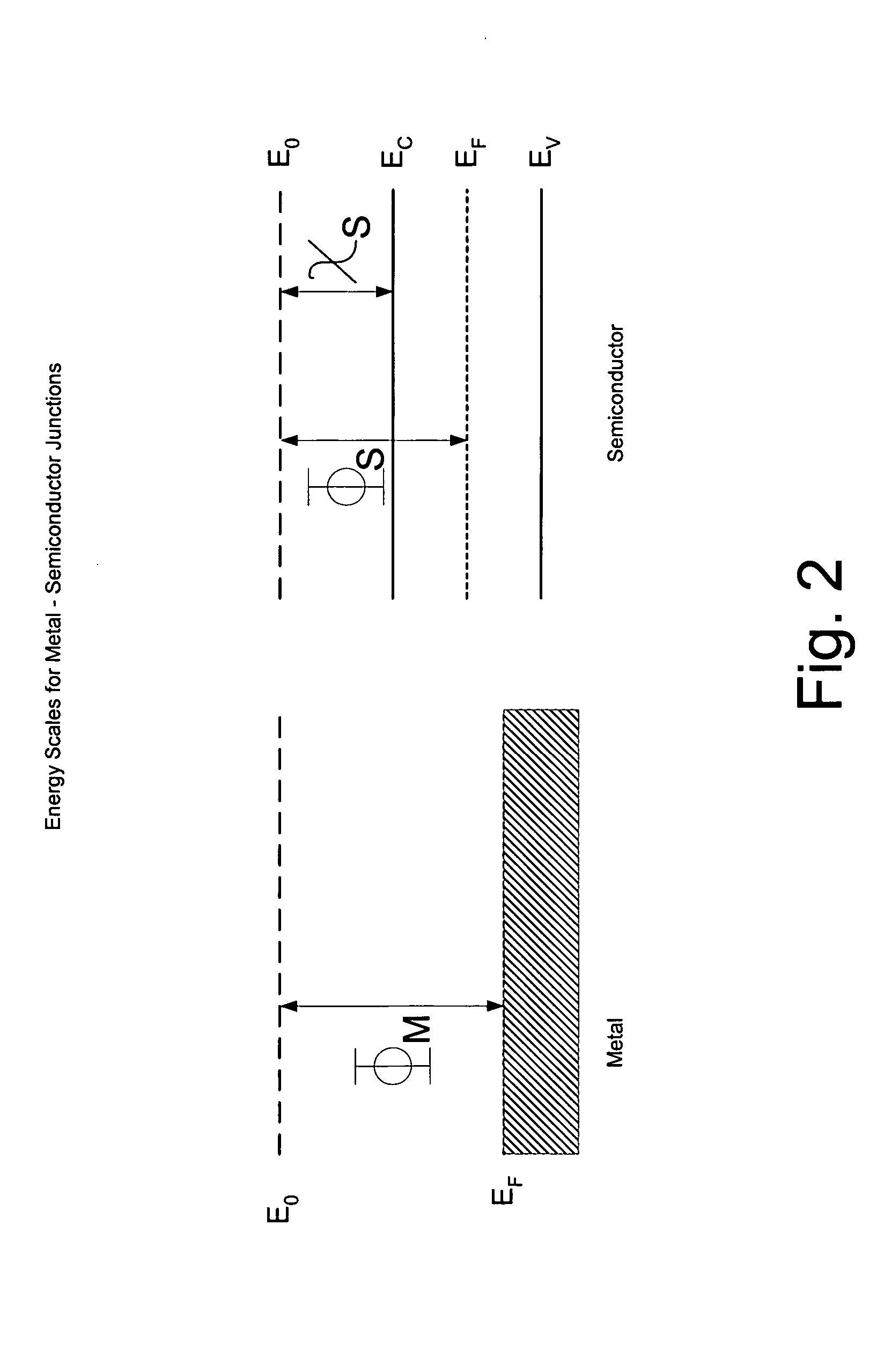

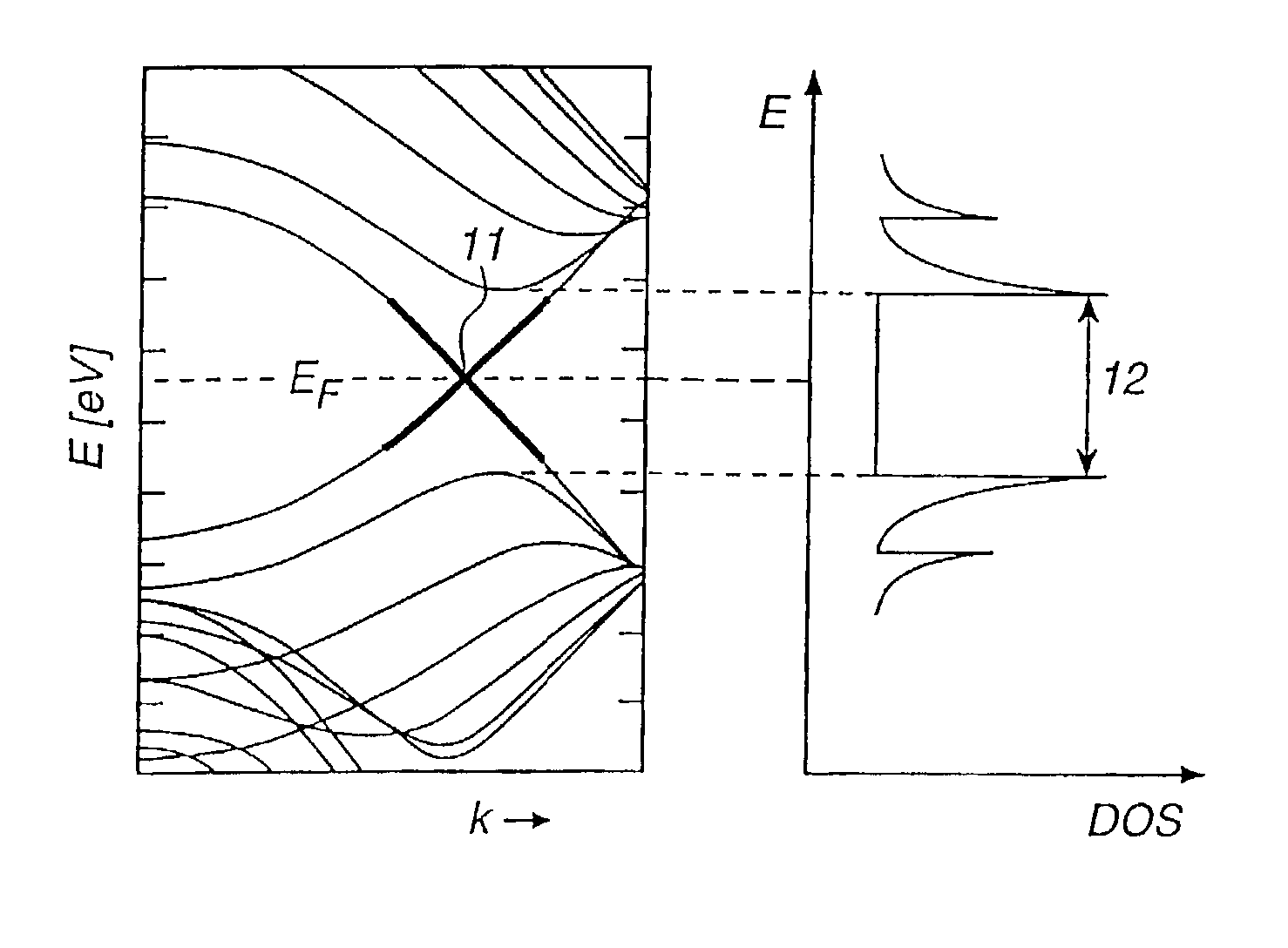

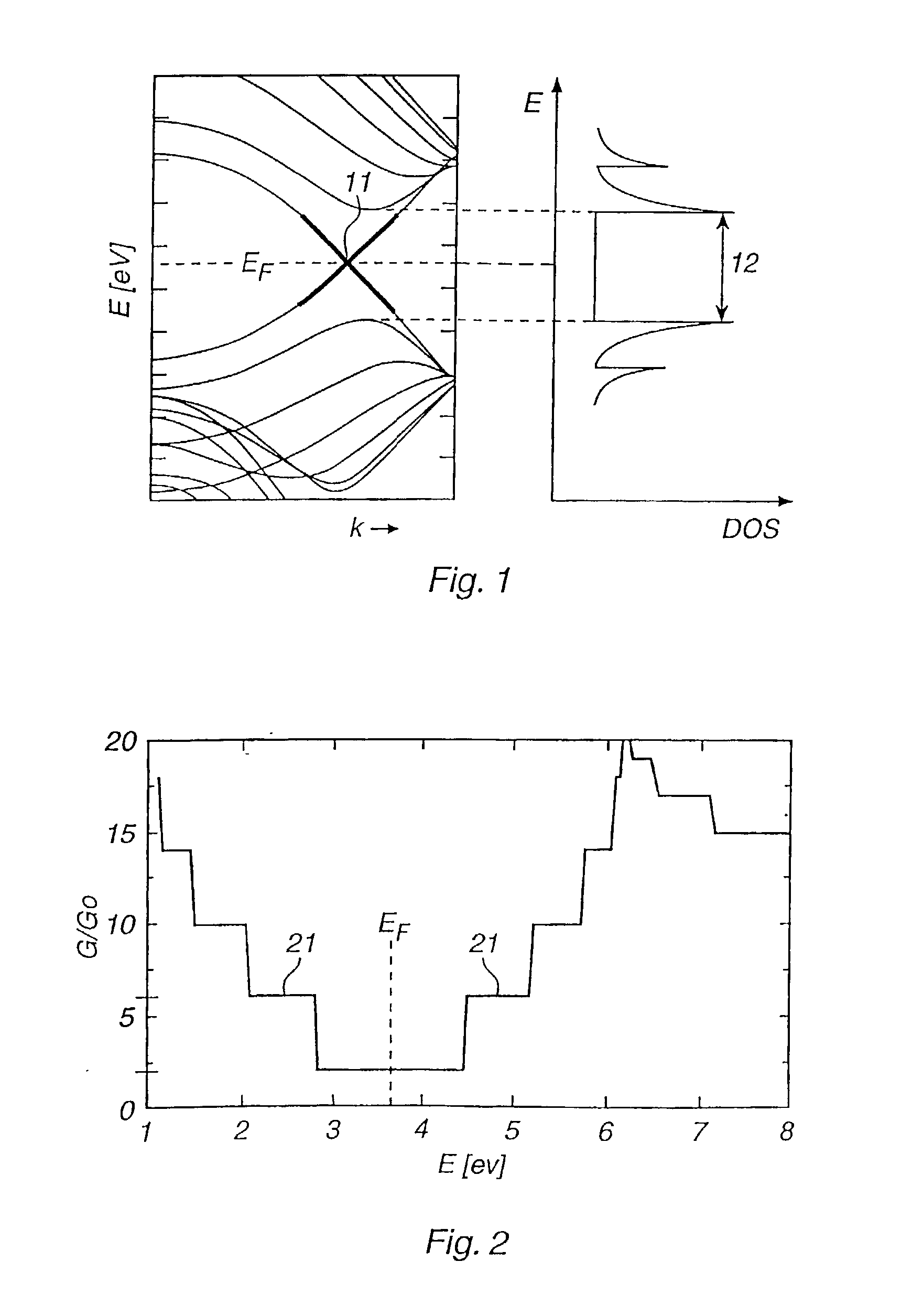

The Fermi level of a solid-state body is the thermodynamic work required to add one electron to the body. It is a thermodynamic quantity usually denoted by µ or EF for brevity. The Fermi level does not include the work required to remove the electron from wherever it came from. A precise understanding of the Fermi level—how it relates to electronic band structure in determining electronic properties, how it relates to the voltage and flow of charge in an electronic circuit—is essential to an understanding of solid-state physics.

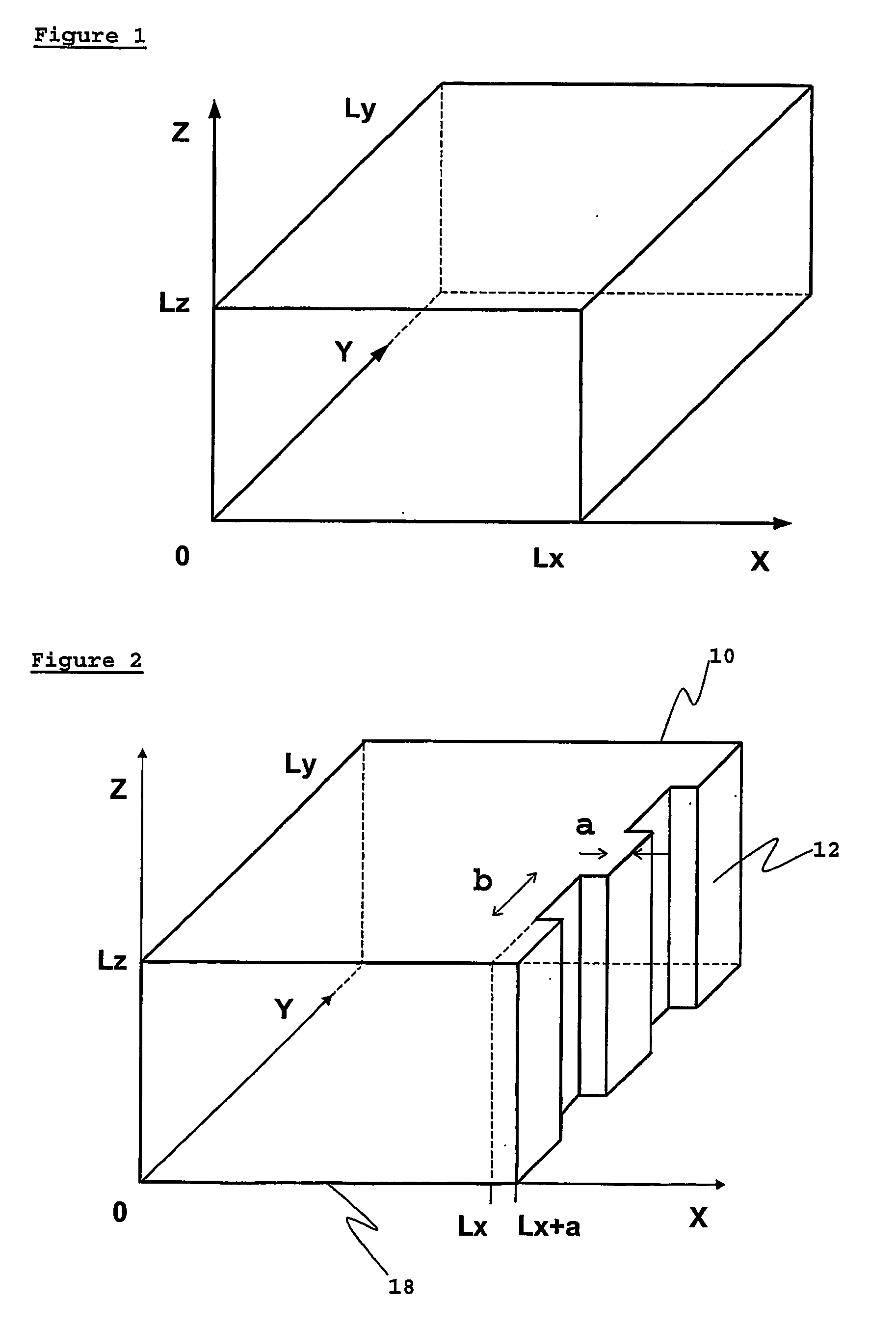

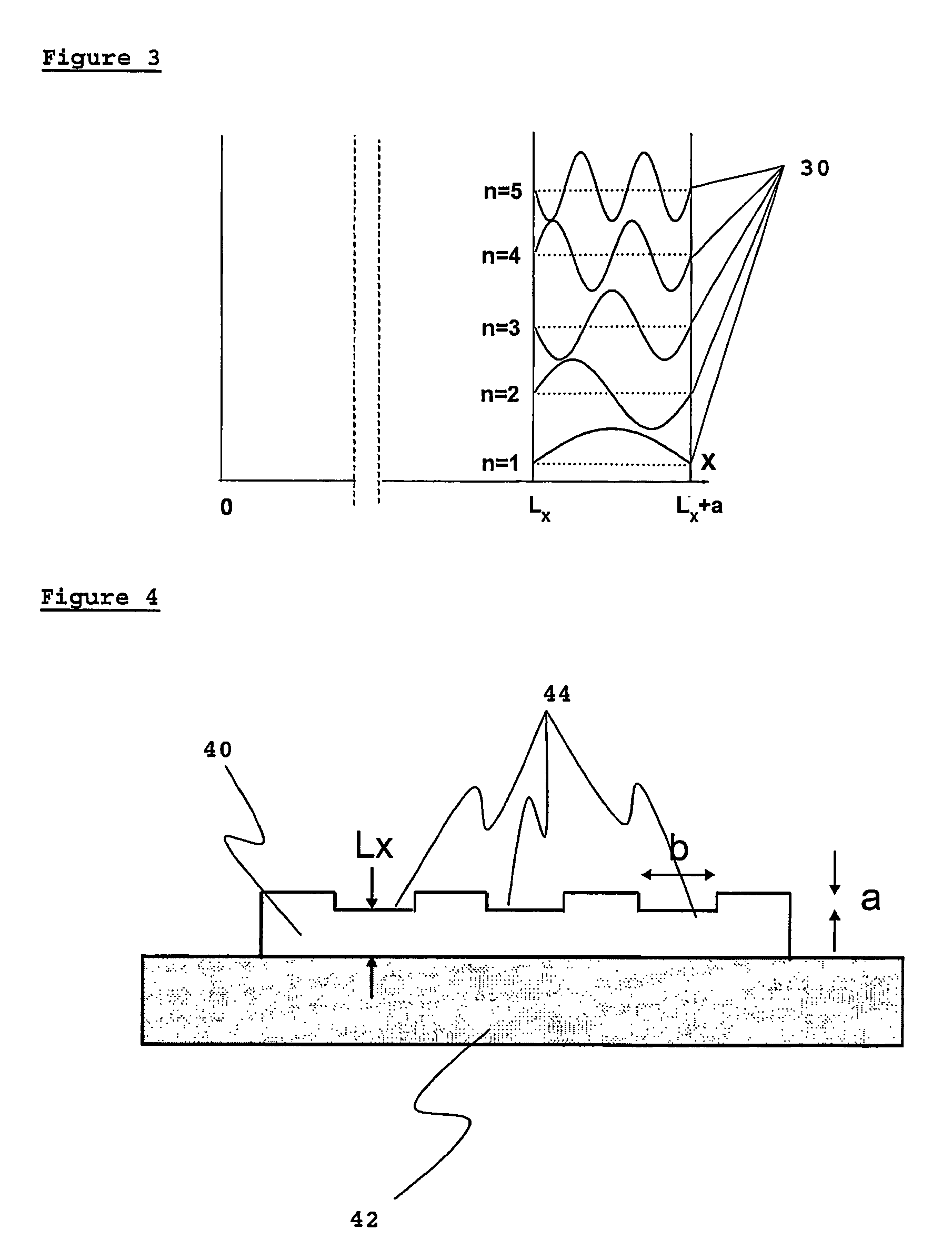

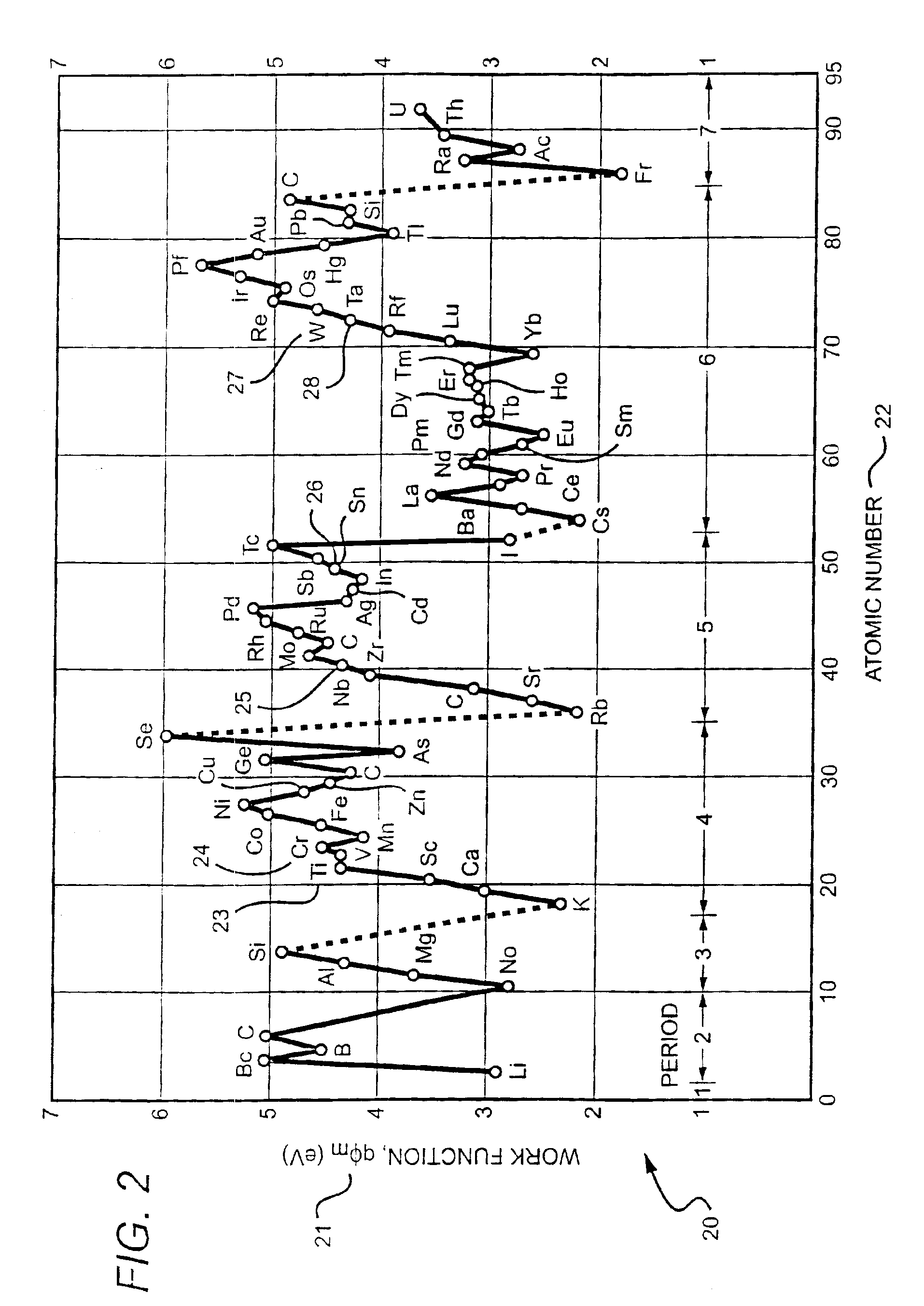

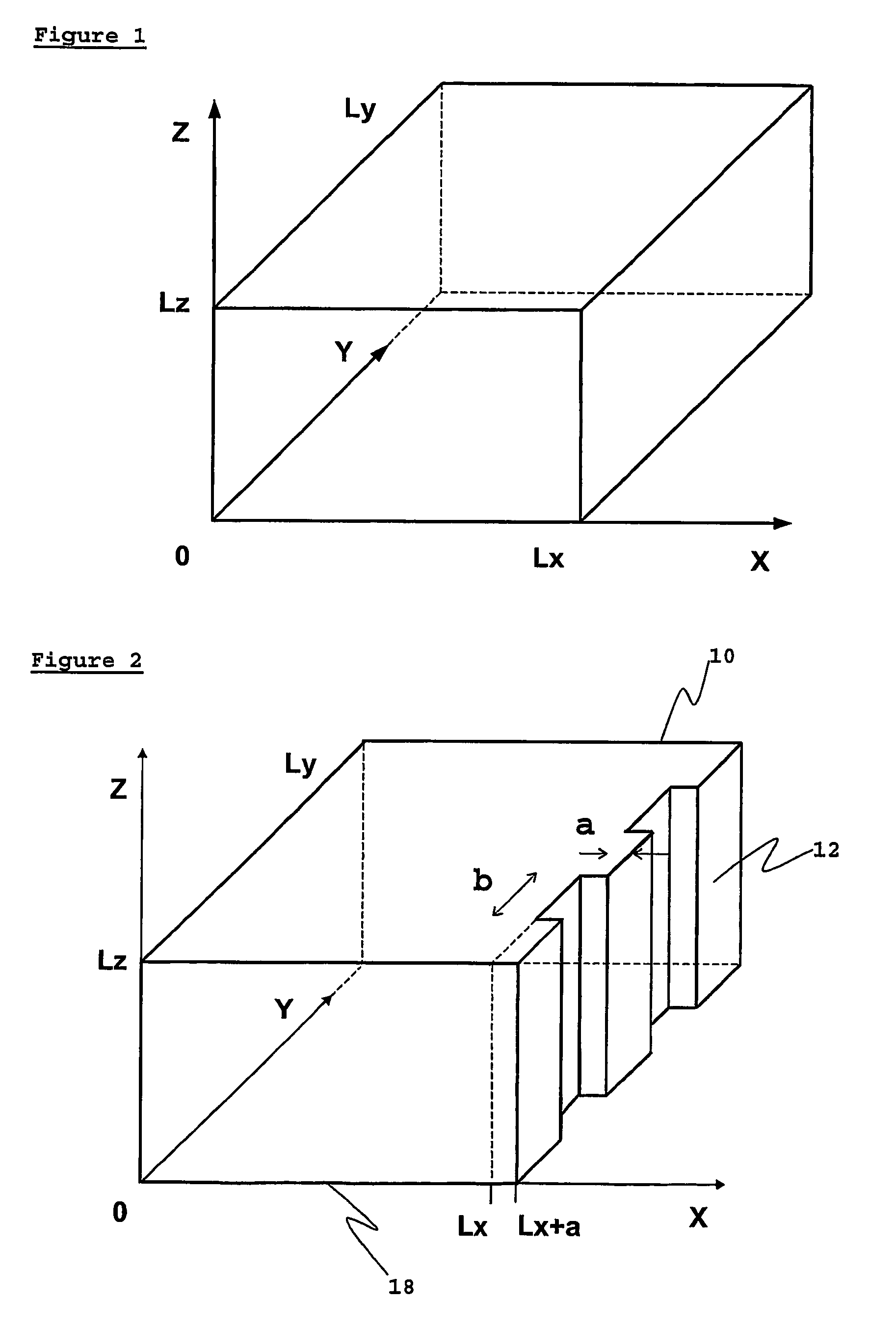

Influence of surface geometry on metal properties

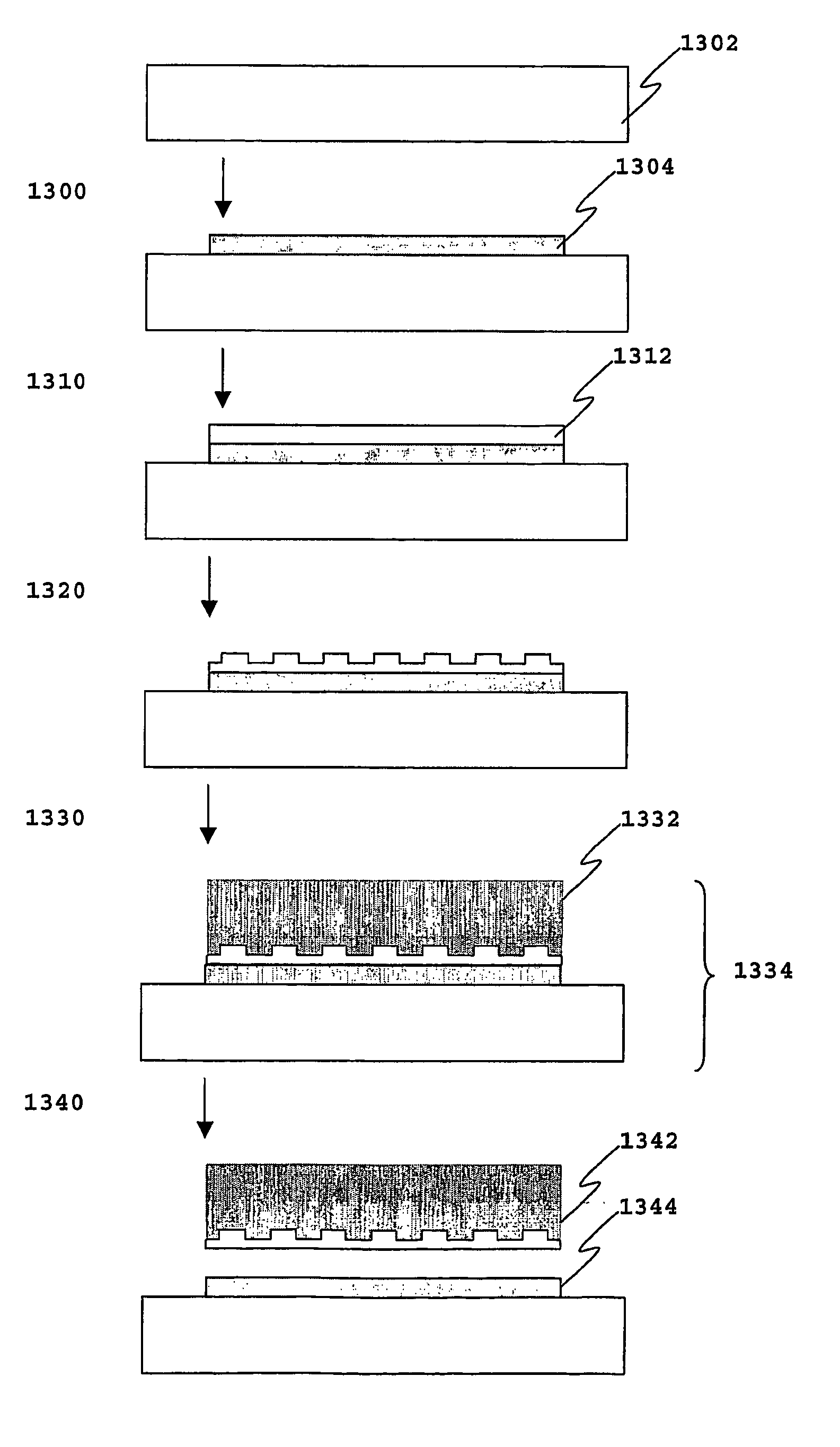

InactiveUS20050147841A1Easy transferIncreased particle emissionLine/current collector detailsPolycrystalline material growthWork functionFermi energy

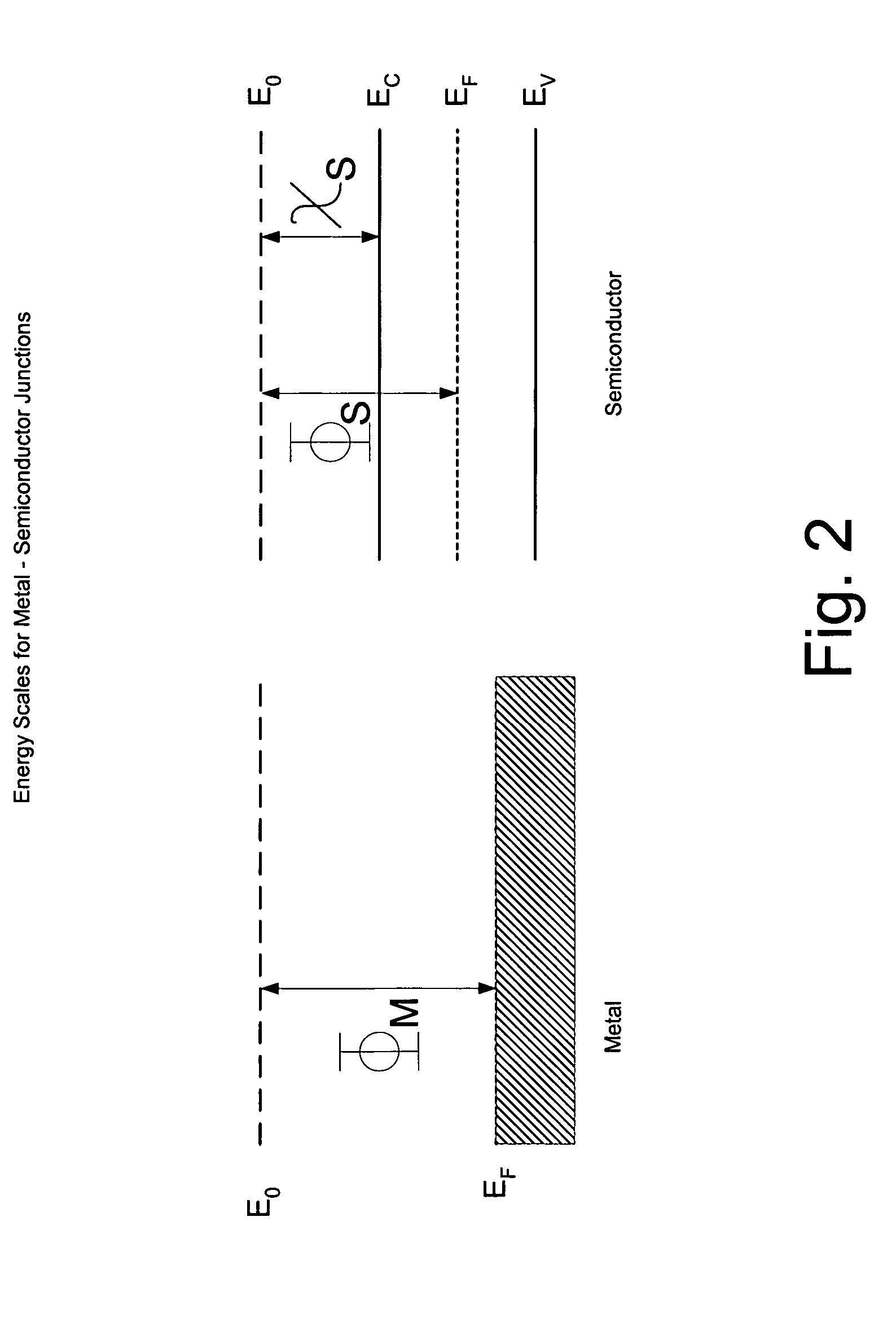

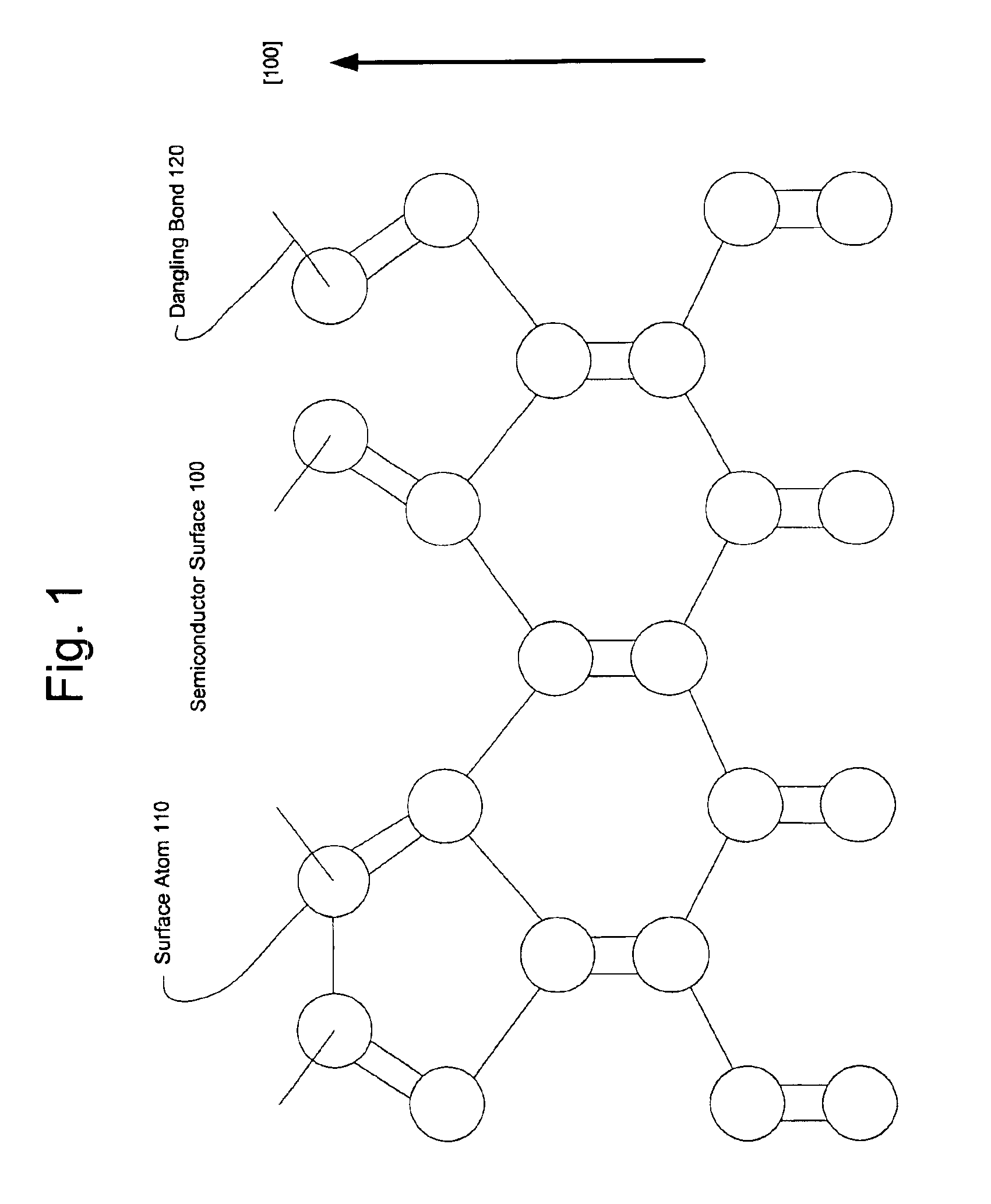

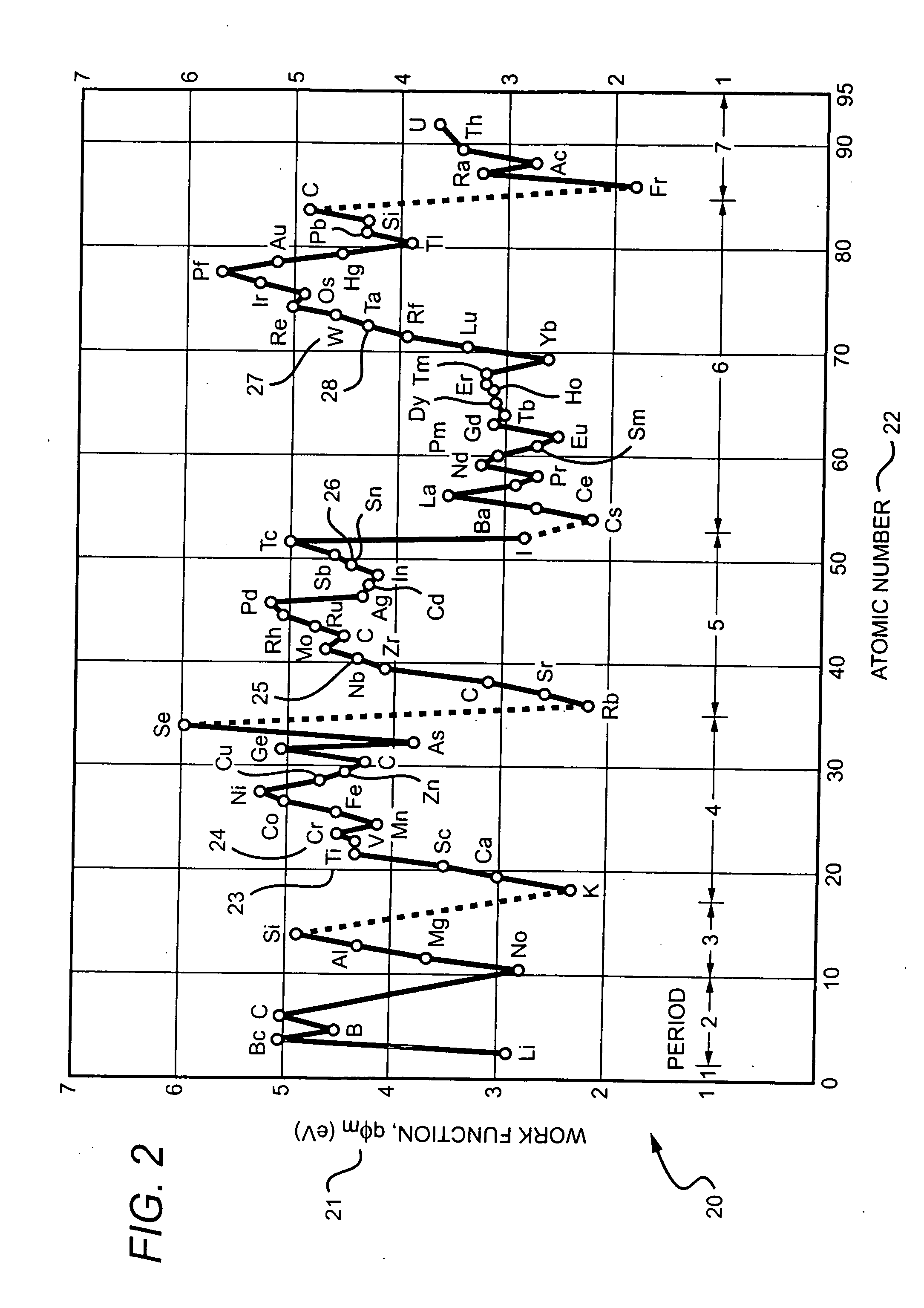

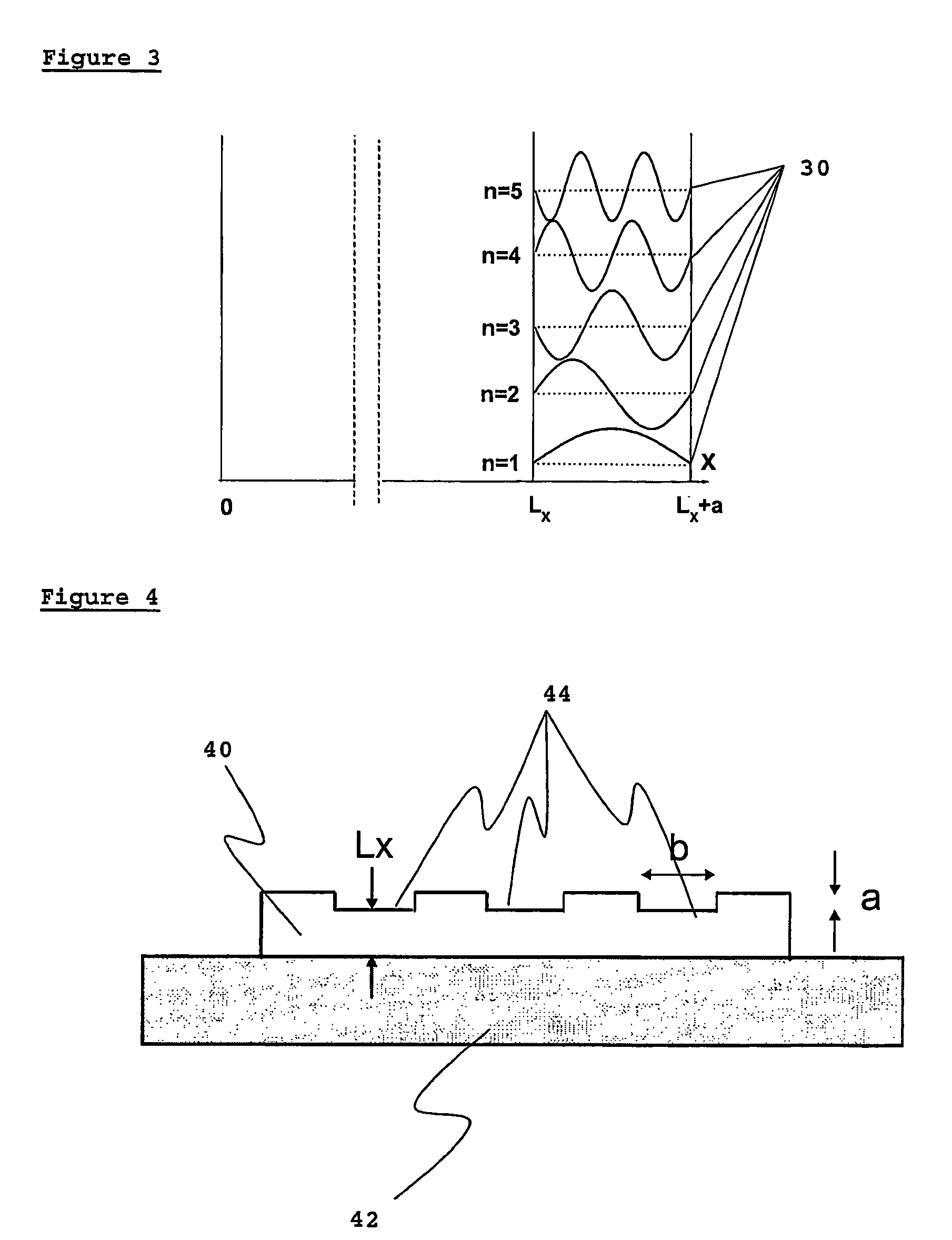

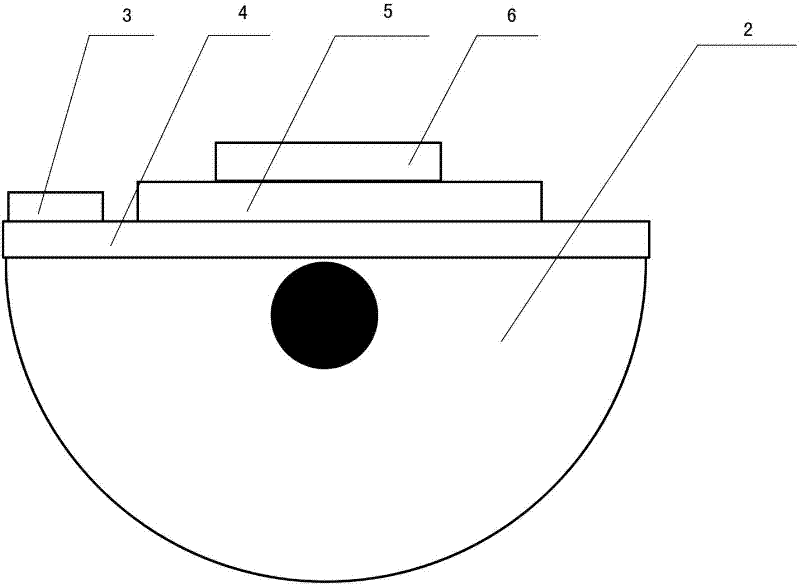

The influence of surface geometry on metal properties is studied within the limit of the quantum theory of free electrons. It is shown that a metal surface can be modified with patterned indents to increase the Fermi energy level inside the metal, leading to decrease in electron work function. This effect would exist in any quantum system comprising fermions inside a potential energy box. Also disclosed is a method for making nanostructured surfaces having perpendicular features with sharp edges.

Owner:BOREALIS TECH LTD

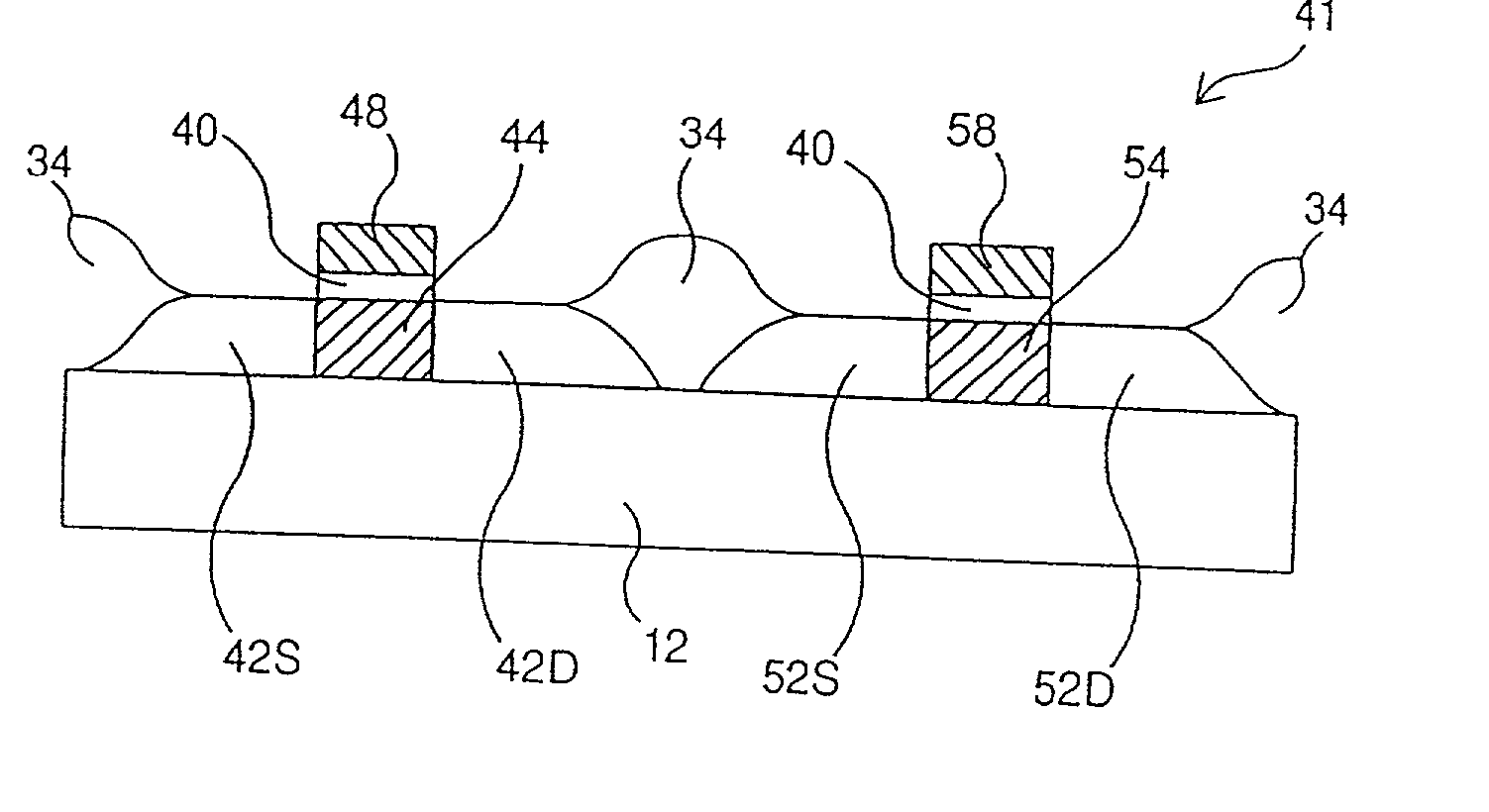

Field effect transistor

ActiveUS20110309411A1Reduce FET characteristicReduce the impactTransistorSemiconductor/solid-state device manufacturingElectrical conductorIndium

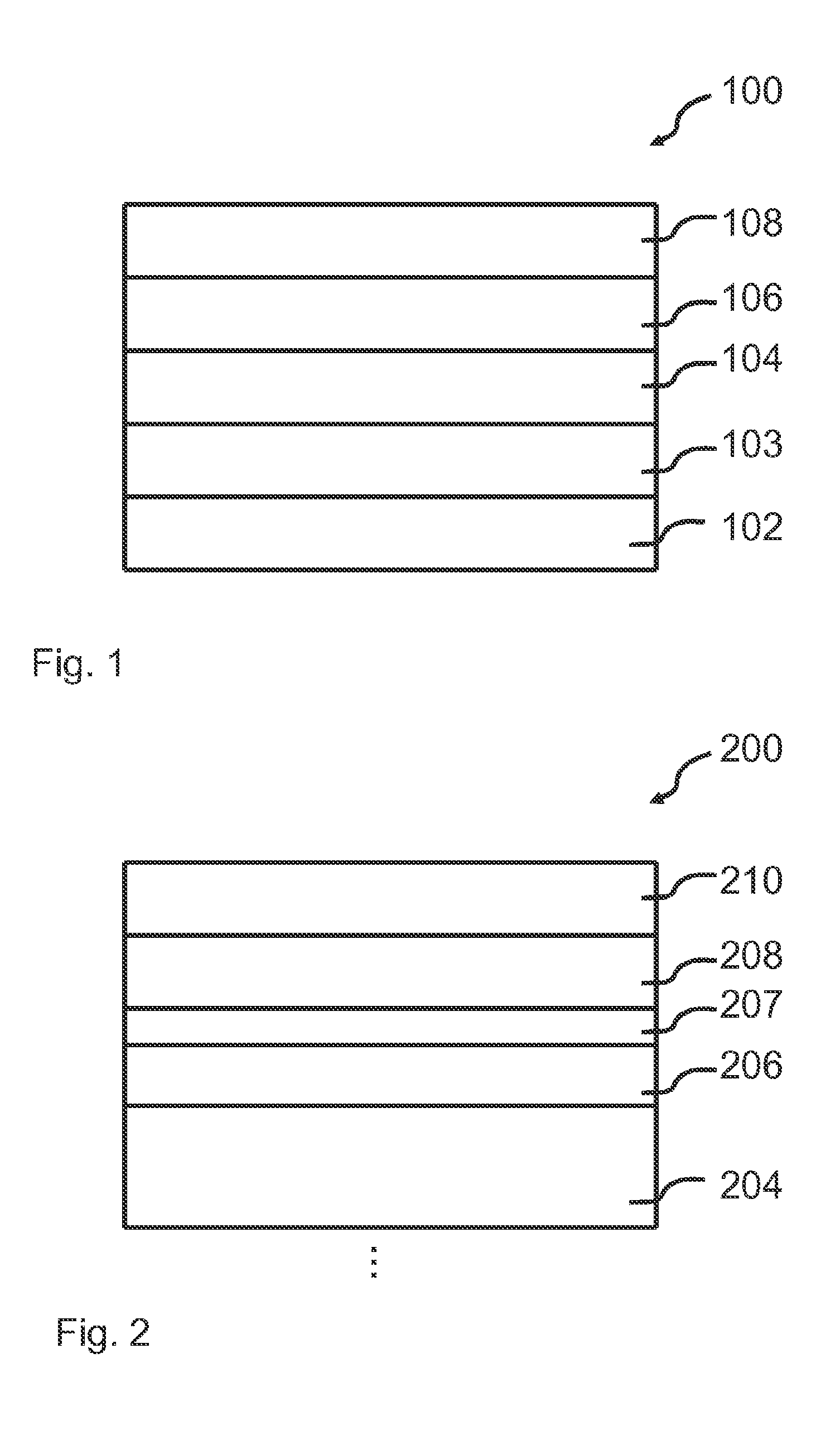

An insulating film is provided over one surface of a first semiconductor layer including a first oxide semiconductor including indium as a main component, and a second semiconductor layer including an i-type second oxide semiconductor is provided in contact with the other surface. The energy difference between a vacuum level and a Fermi level in the second oxide semiconductor is larger than that in the first oxide semiconductor. In the first semiconductor layer, a region in the vicinity of the junction surface with the second oxide semiconductor which satisfies the above condition is a region having an extremely low carrier concentration (a quasi-i-type region). By using the region as a channel, the off-state current can be reduced. Further, a drain current of the FET flows through the first oxide semiconductor having a high mobility; accordingly, a large amount of current can be extracted.

Owner:SEMICON ENERGY LAB CO LTD

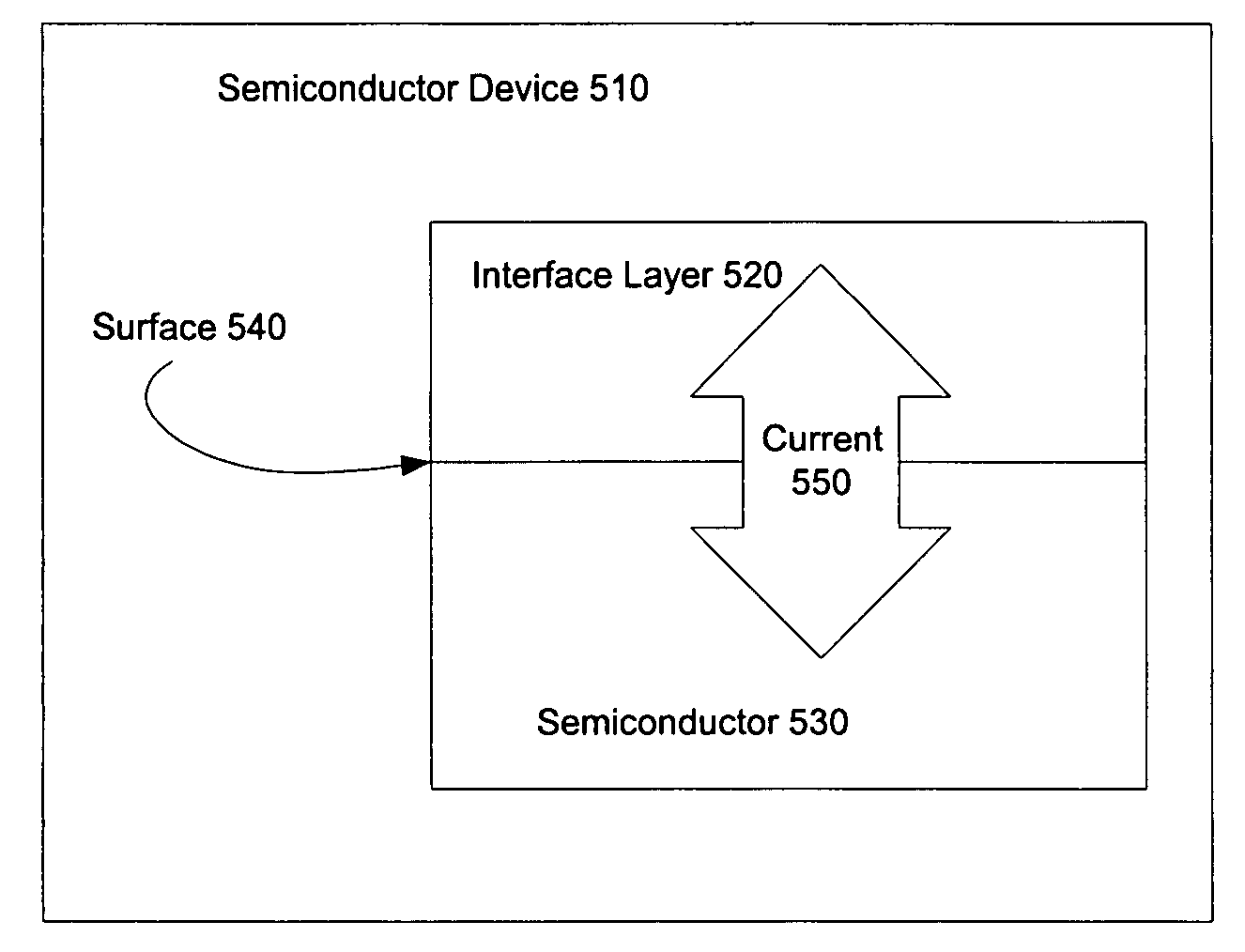

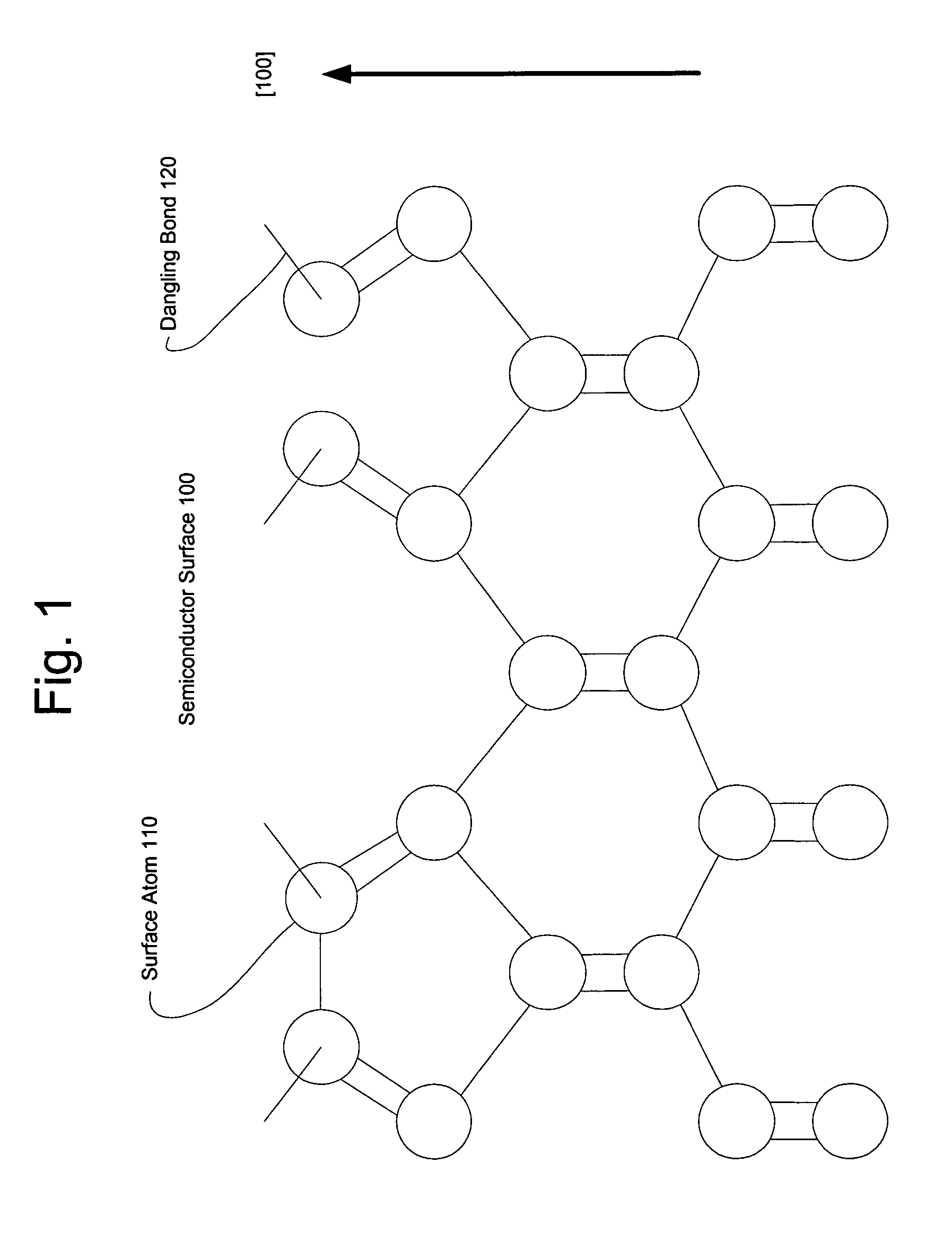

Method for depinning the Fermi level of a semiconductor at an electrical junction and devices incorporating such junctions

InactiveUS7176483B2Reduce impactHigh currentTransistorSolid-state devicesElectrical junctionElectrical resistance and conductance

Owner:ACORN SEMI LLC

Method for depinning the Fermi level of a semiconductor at an electrical junction and devices incorporating such junctions

InactiveUS7084423B2Reduce impactHigh currentTransistorSemiconductor/solid-state device manufacturingElectrical junctionEngineering

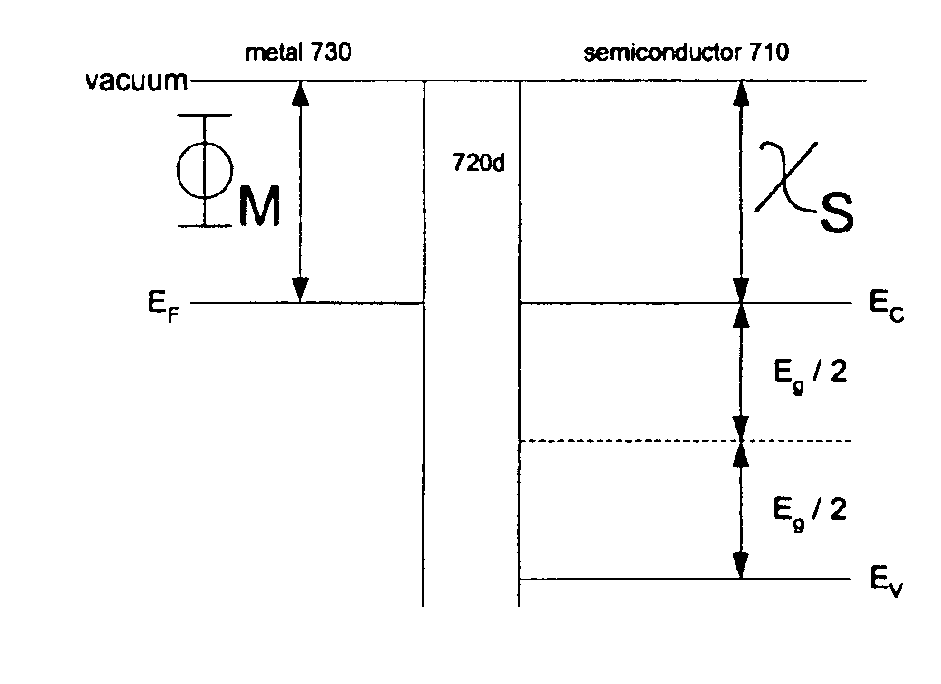

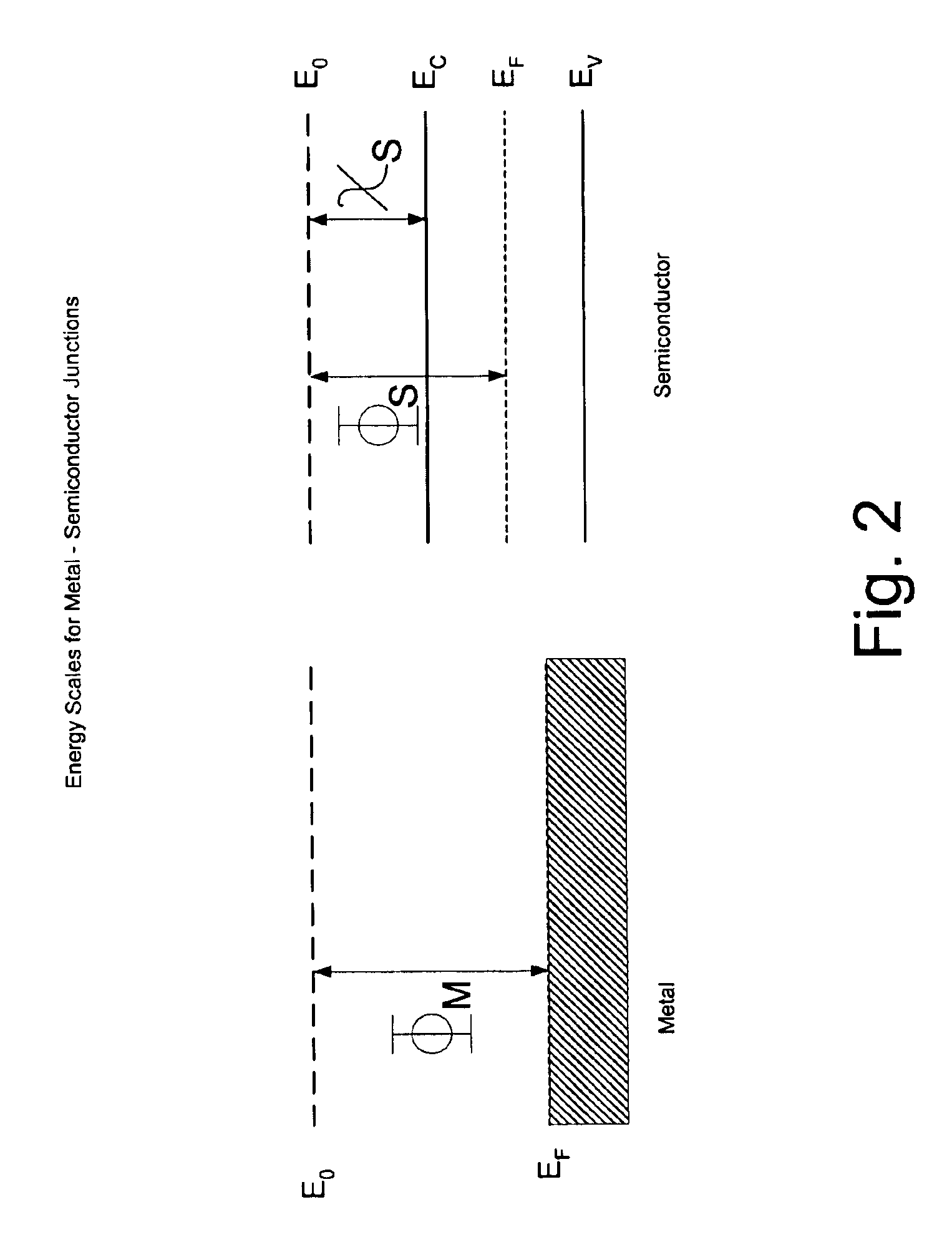

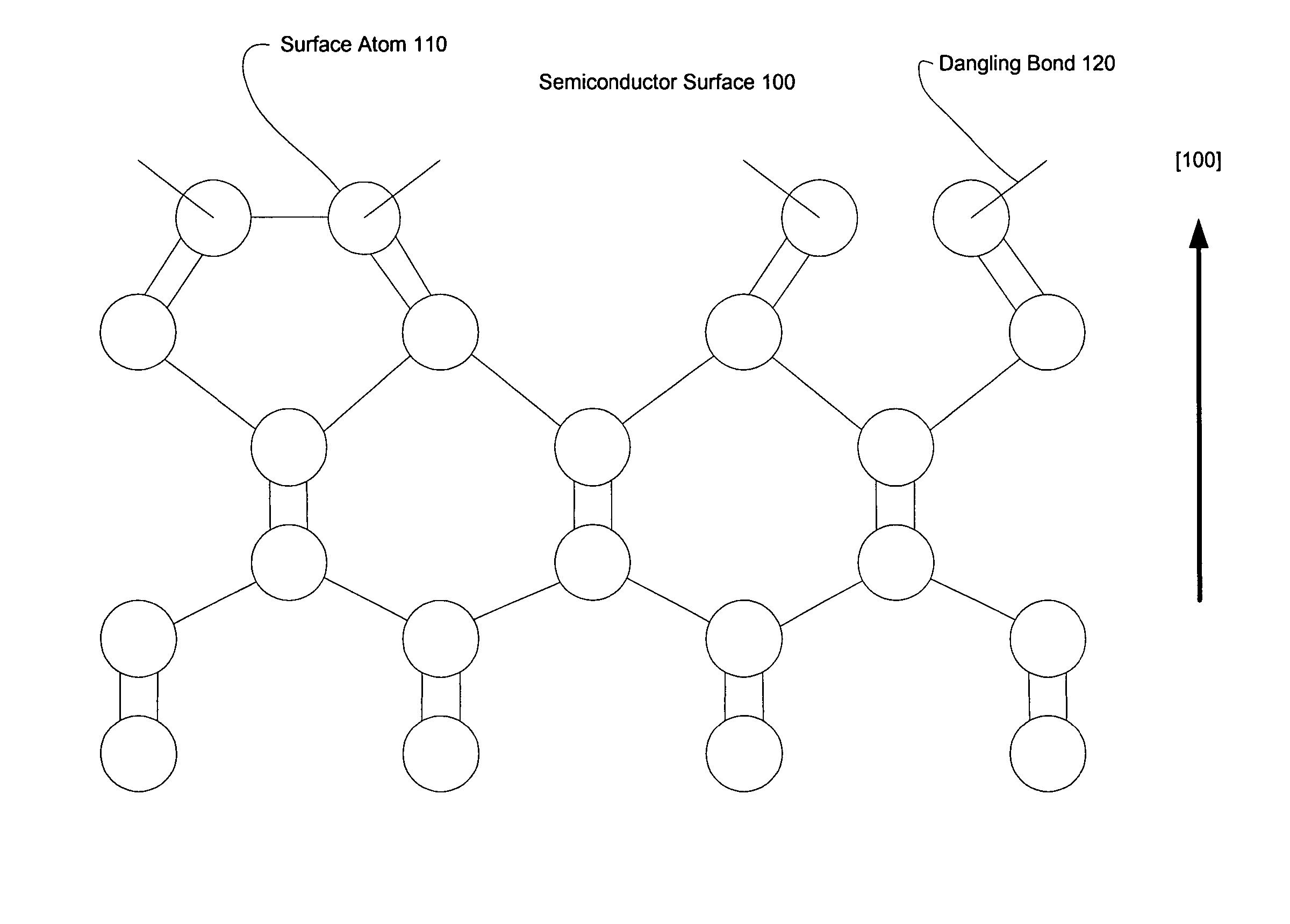

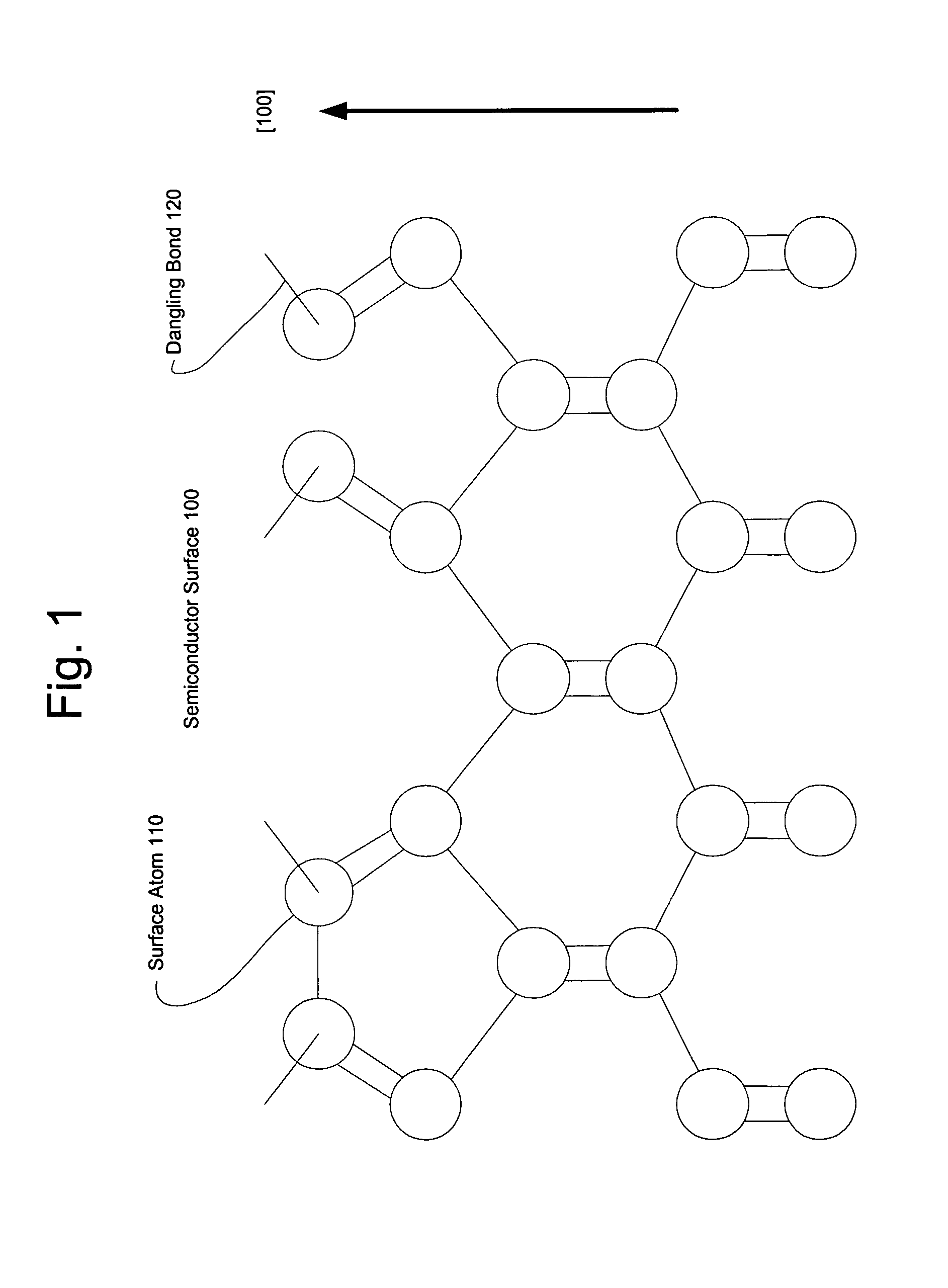

An electrical device in which an interface layer is disposed between and in contact with a metal and a Si-based semiconductor, the interface layer being of a thickness effective to depin of the Fermi level of the semiconductor while still permitting current to flow between the metal and the semiconductor. The interface layer may include a layer of a passivating material (e.g., made from nitrogen, oxygen, oxynitride, arsenic, hydrogen and / or fluorine) and sometimes also includes a separation layer. In some cases, the interface layer may be a monolayer of a semiconductor passivating material. The interface layer thickness corresponds to a minimum specific contact resistance of less than or equal to 10 Ω-μm2 or even less than or equal to 1 Ω-μm2 for the electrical device.

Owner:ACORN SEMI LLC

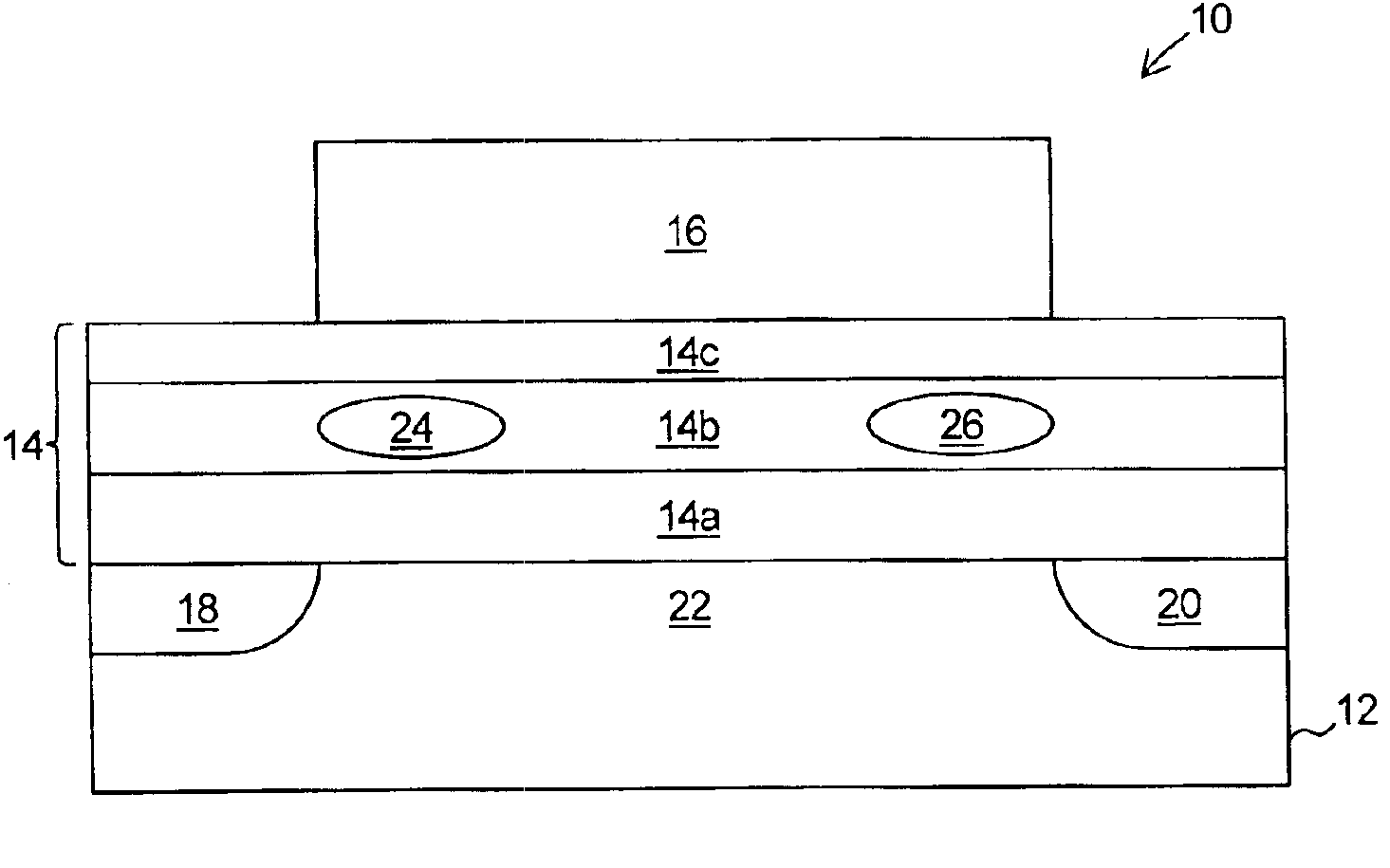

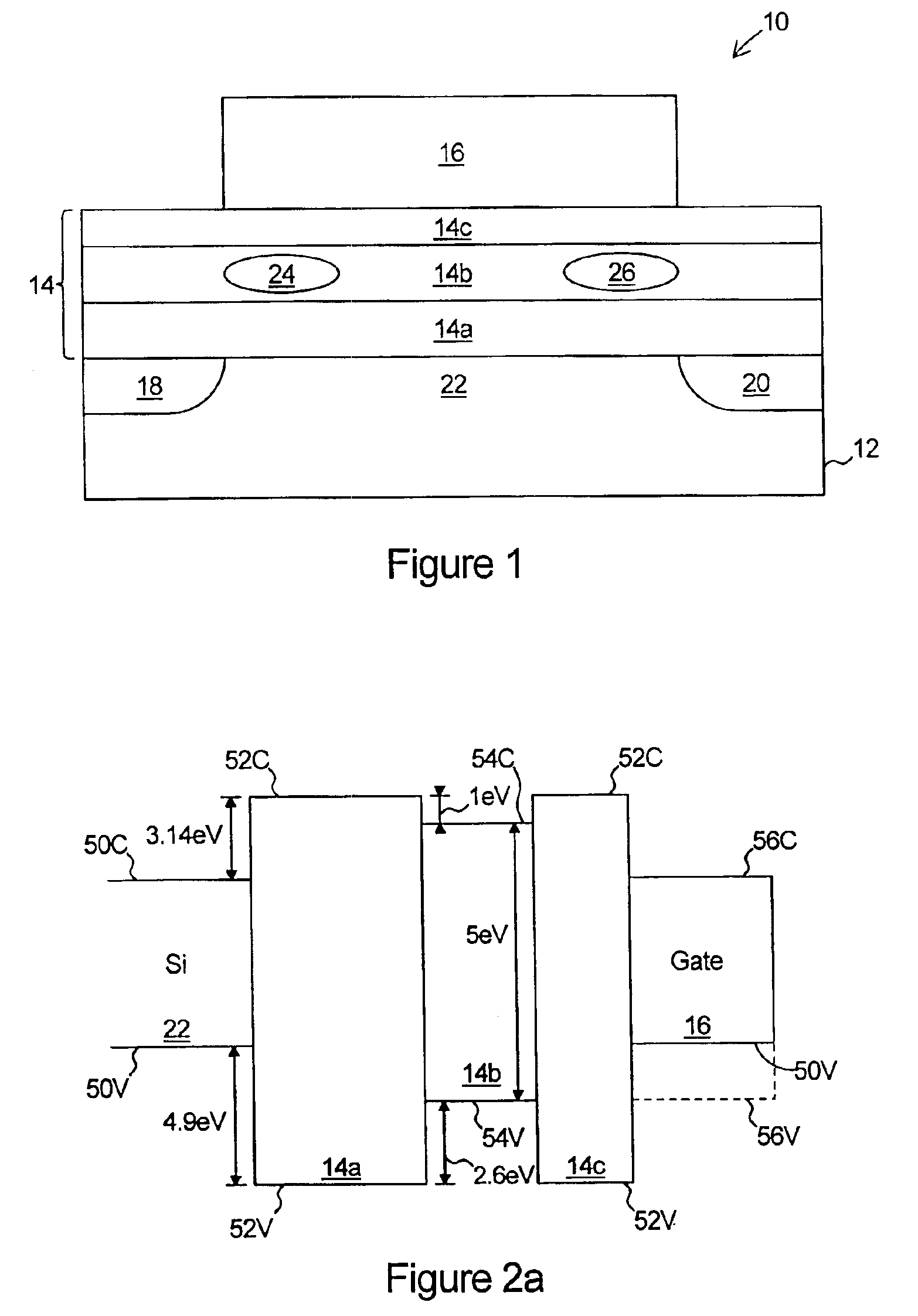

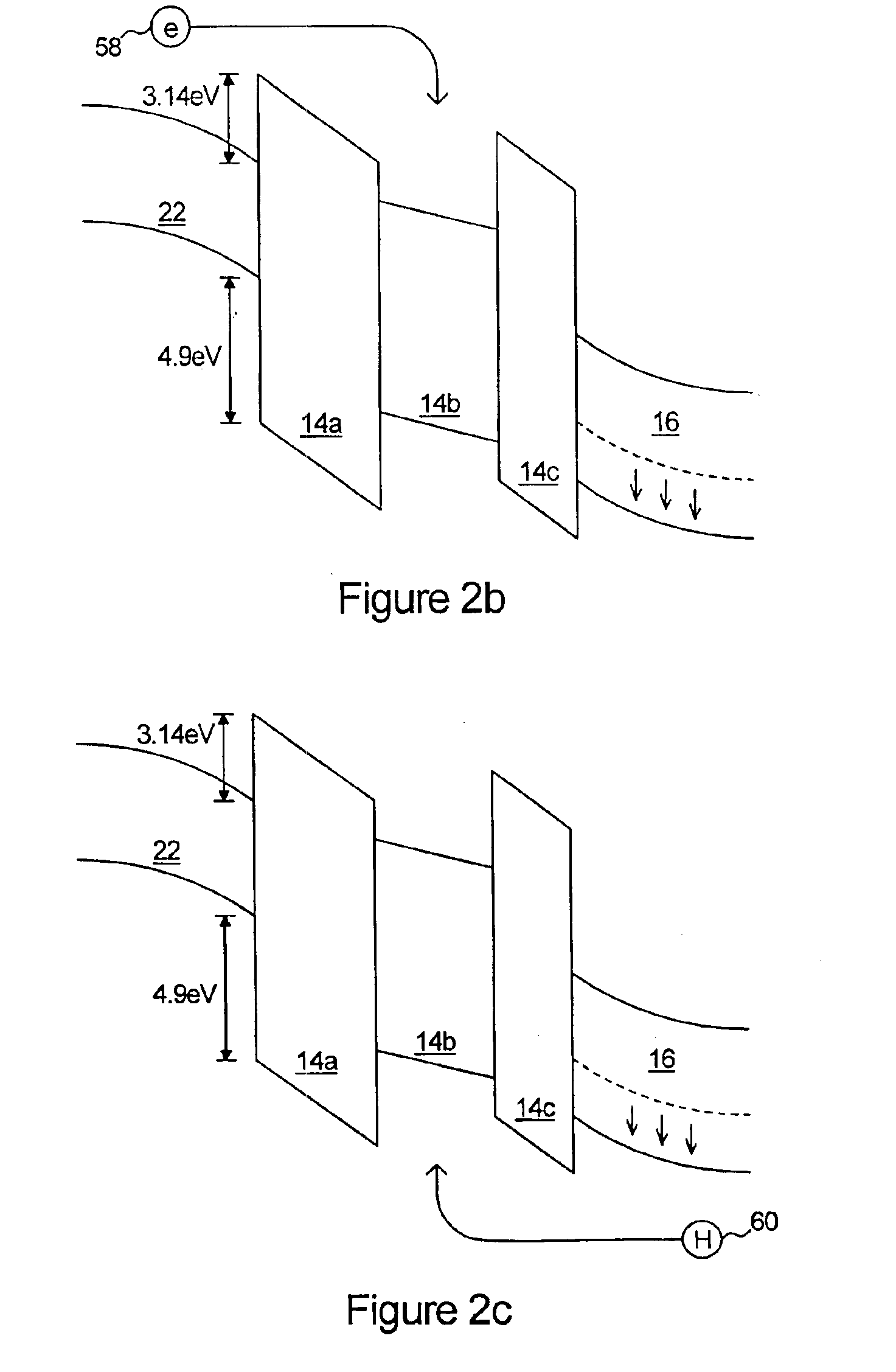

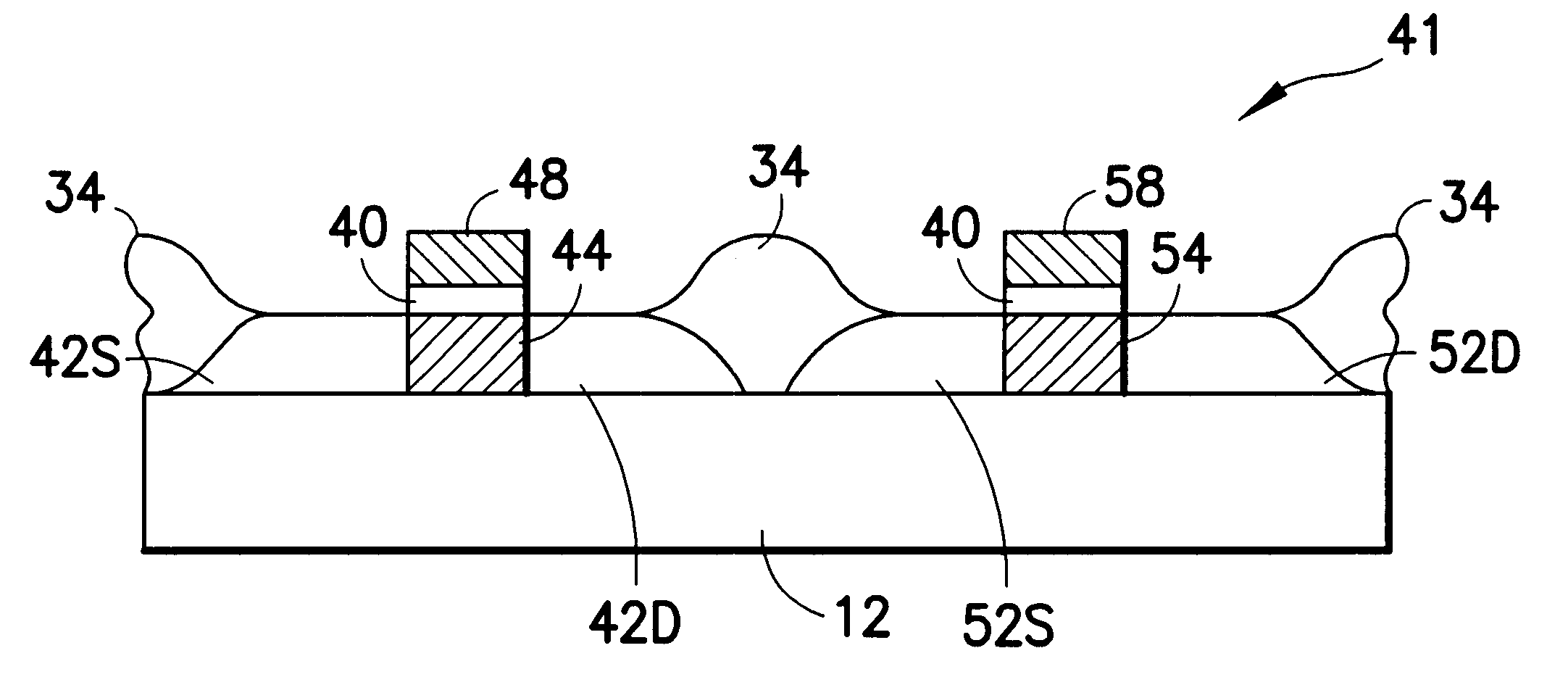

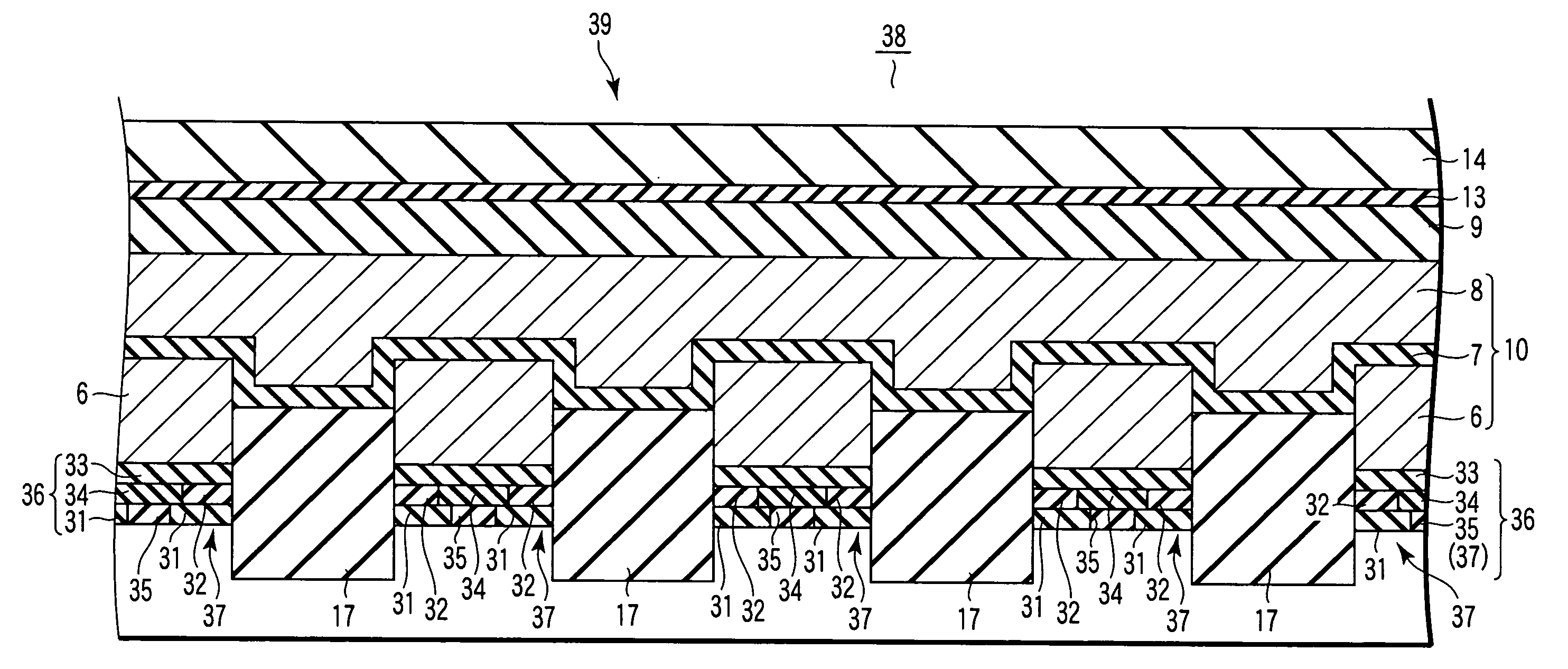

Non volatile charge trapping dielectric memory cell structure with gate hole injection erase

A dielectric memory cell comprises a substrate which includes a source region, a drain region, and a channel region positioned there between. A multilevel charge trapping dielectric is positioned on the surface of the substrate and a control gate is positioned on the surface of the dielectric and is positioned over and aligned with the channel region. The multilevel charge trapping dielectric includes a tunneling dielectric layer, a charge trapping dielectric layer, and a top dielectric layer. The tunneling dielectric layer comprises a first dielectric material having a wide band gap between a tunneling dielectric layer valance band Fermi level and a tunneling dielectric layer conduction band Fermi level. The top dielectric layer comprises a second dielectric material having a valance band Fermi level approximately equal to the tunneling dielectric layer valance band Fermi level and having a conduction band Fermi level greater than the tunneling dielectric layer conduction band Fermi level. The charge trapping layer is positioned between the bottom layer and the top layer of a third dielectric with charge trapping properties.

Owner:LONGITUDE FLASH MEMORY SOLUTIONS LTD

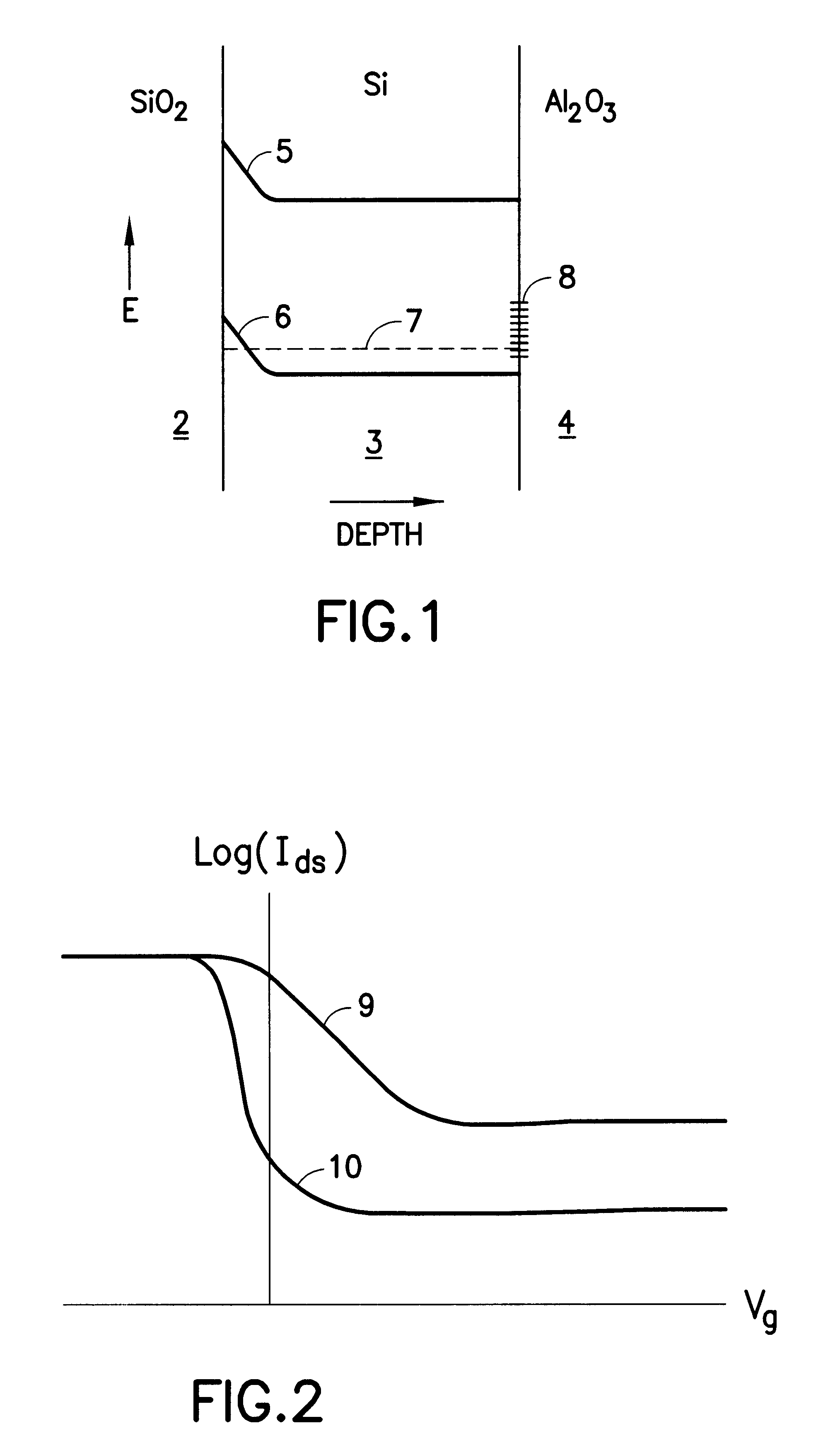

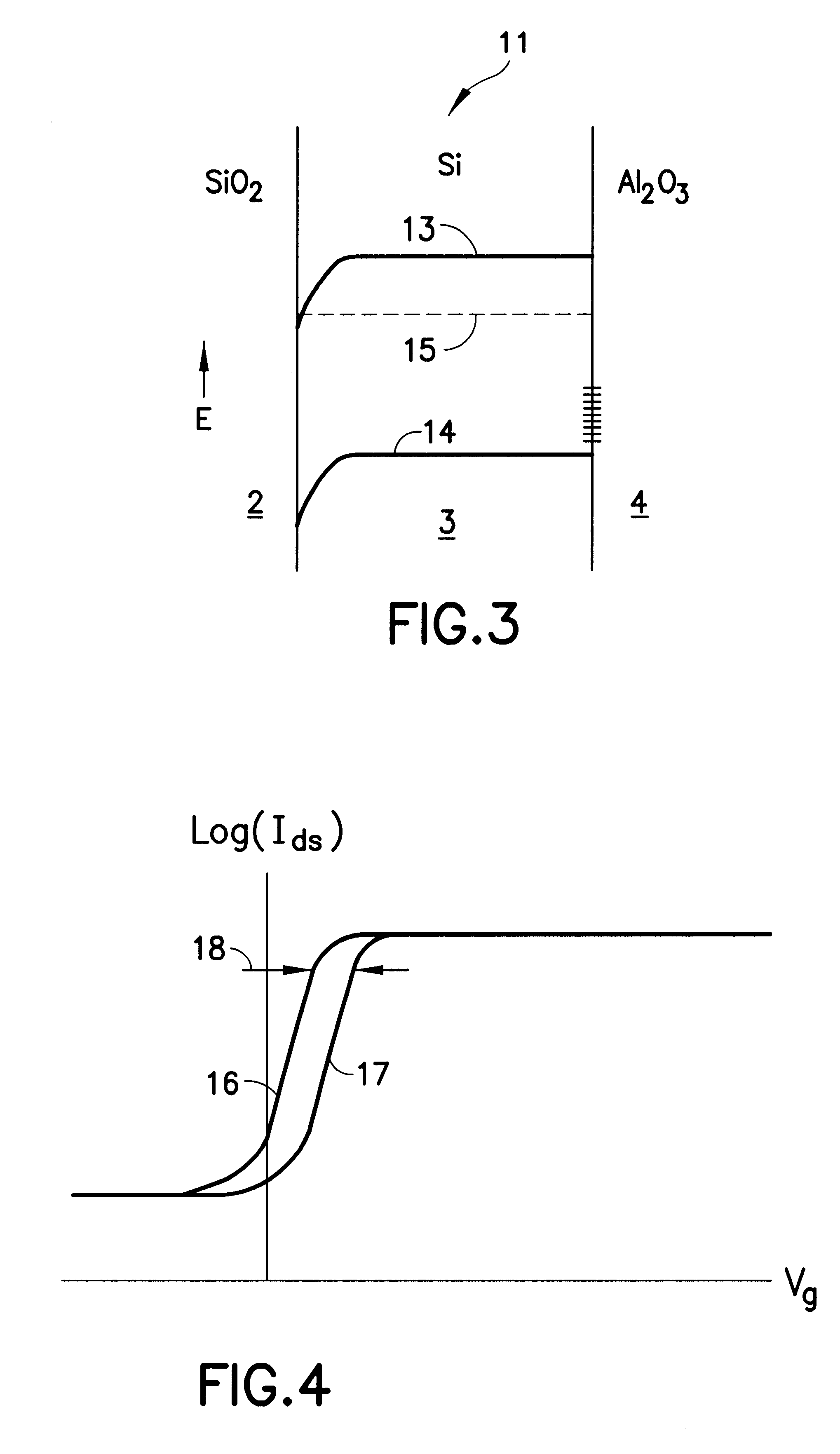

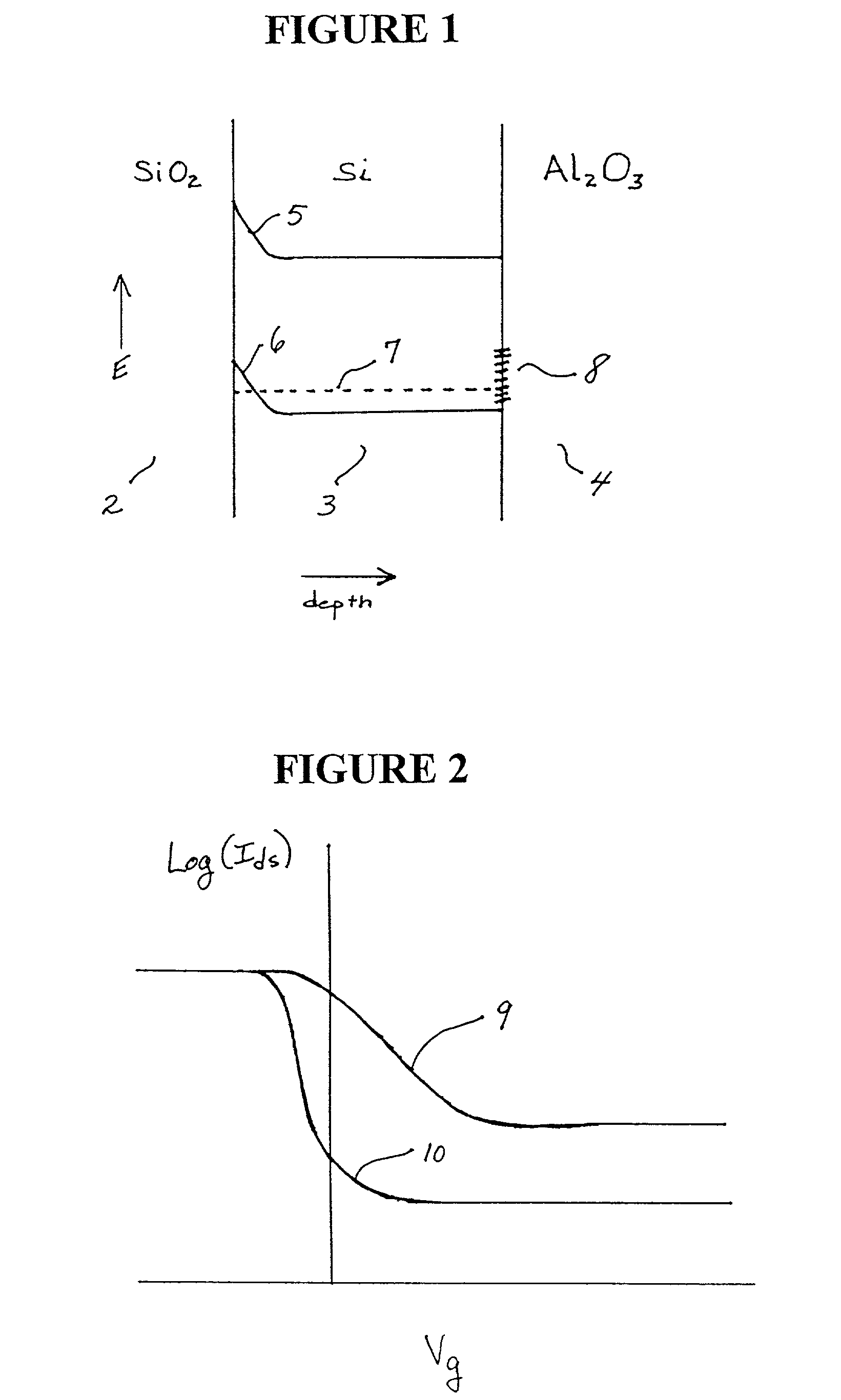

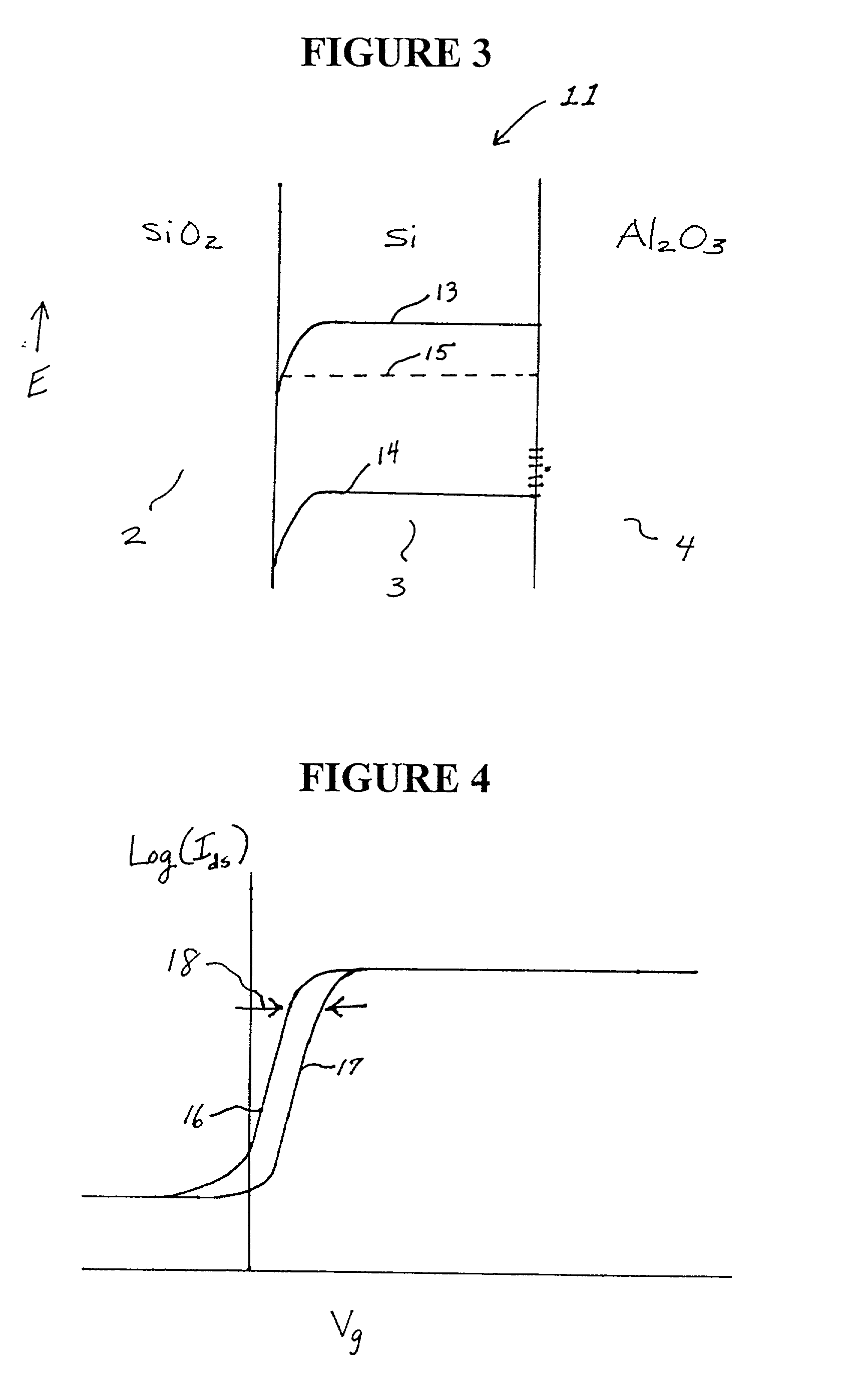

Radiation-hardened silicon-on-insulator CMOS device, and method of making the same

A method for eliminating the radiation-induced off-state current in the P-channel ultrathin silicon-on-sapphire transistor, by providing a retrograde dopant concentration profile that has the effect of moving the Fermi level at the back of the device away from that part of the bandgap where the interface states are located. When the Fermi level does not swing through this area in any region of operation of the device, subthreshold stretchout of the I-V curves does not occur.

Owner:PSEMI CORP

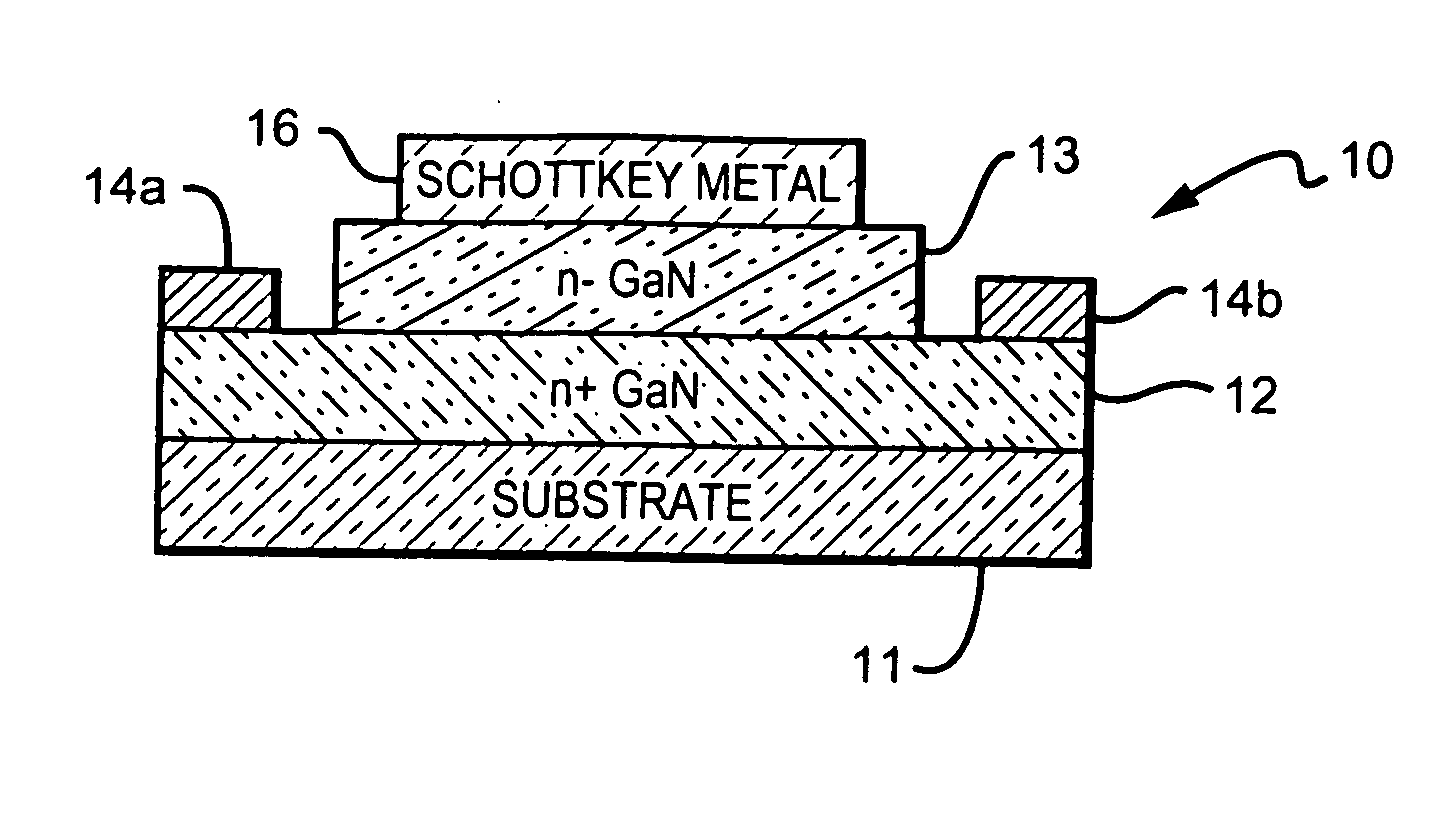

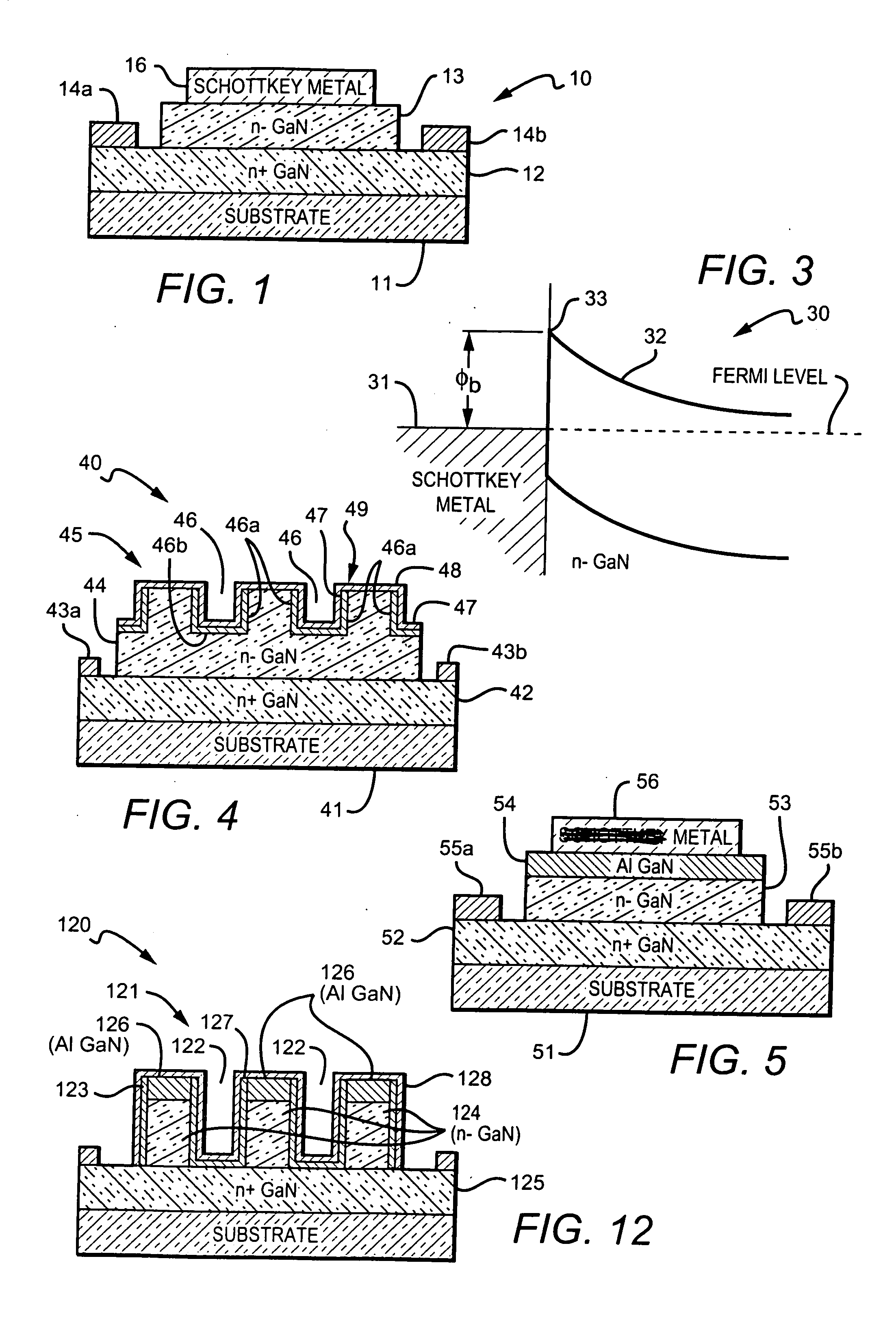

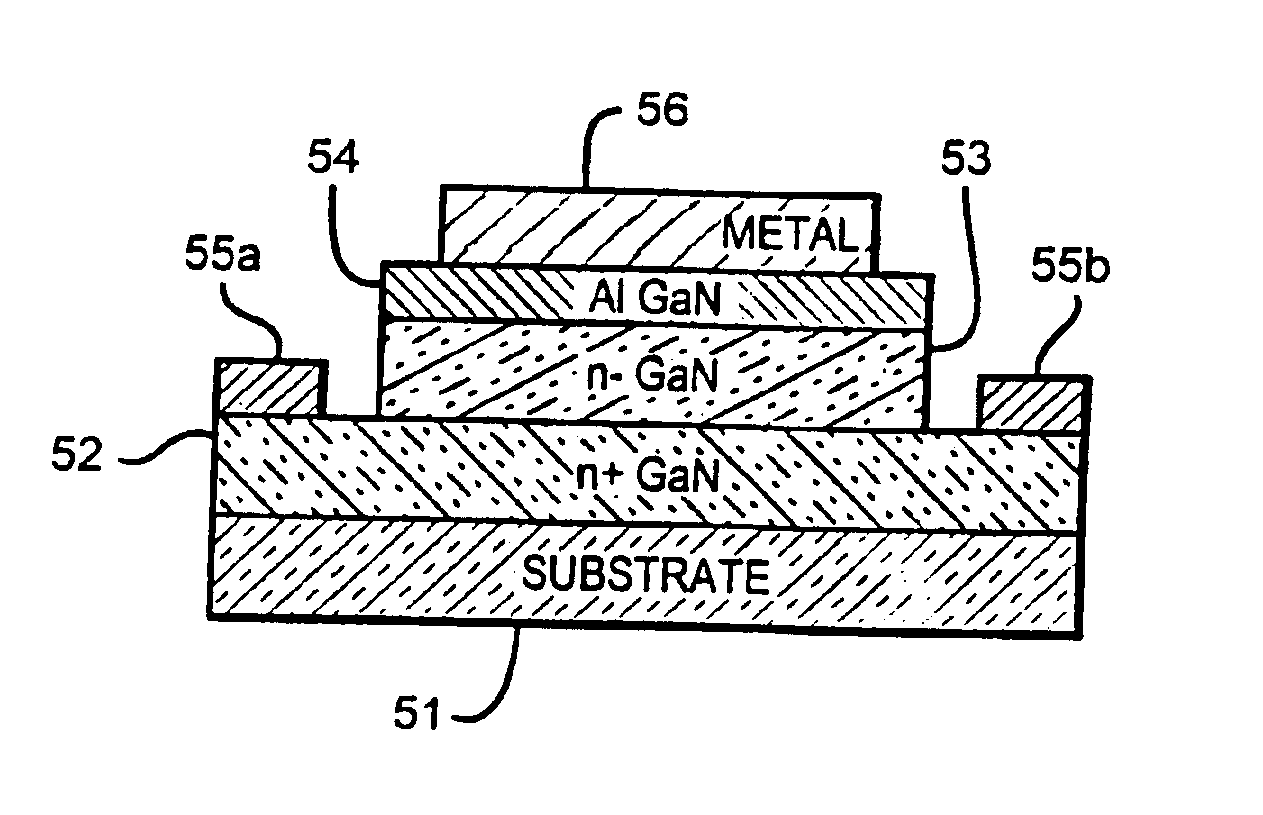

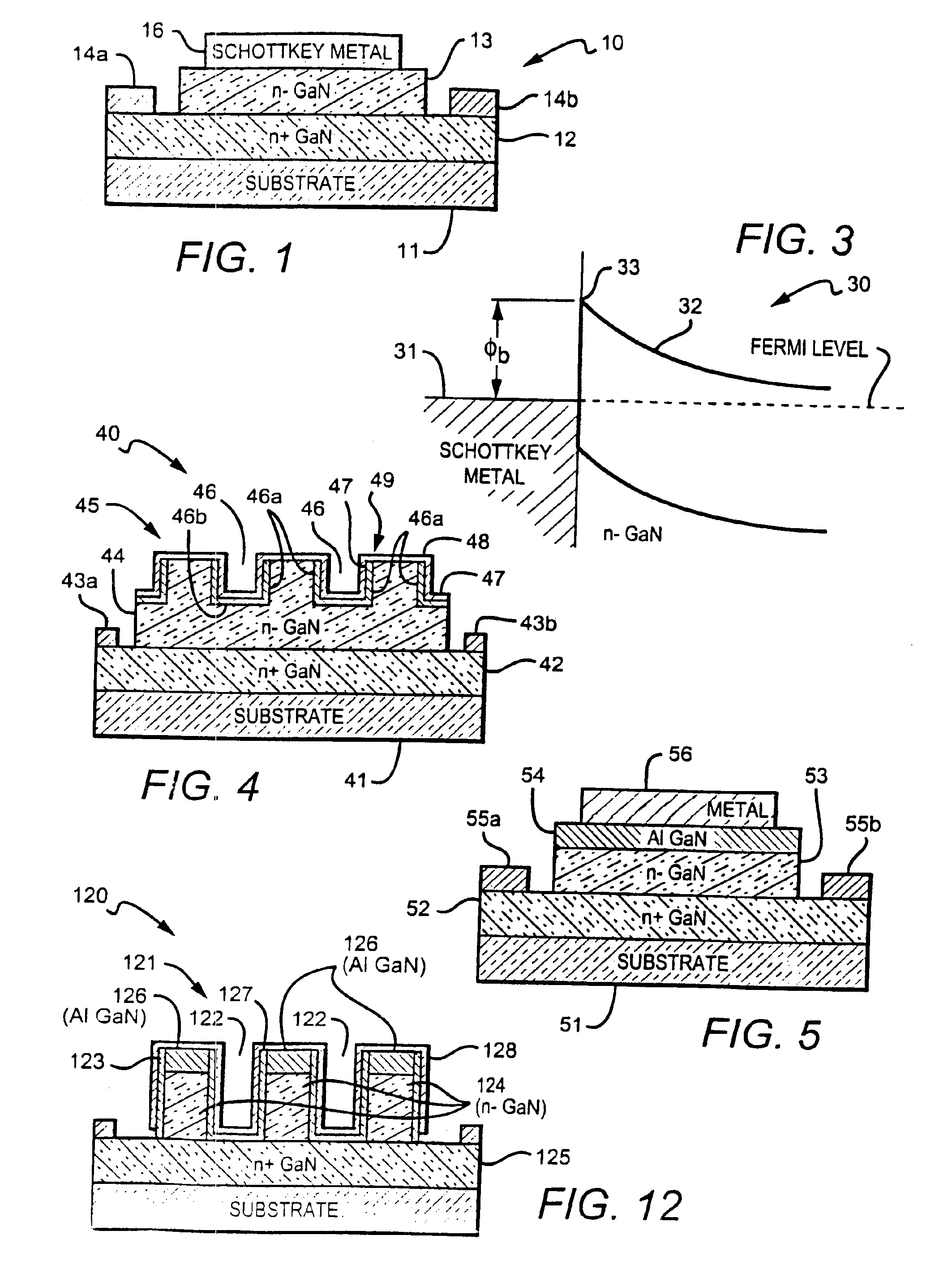

Gallium nitride based diodes with low forward voltage and low reverse current operation

InactiveUS20050242366A1Prevents an increase in the electric fieldSchottky barrier potential is loweredDiodeSemiconductor materialsTunnel diode

New Group III based diodes are disclosed having a low on state voltage (Vf) and structures to keep reverse current (Irev) relatively low. One embodiment of the invention is Schottky barrier diode made from the GaN material system in which the Fermi level (or surface potential) of is not pinned. The barrier potential at the metal-to-semiconductor junction varies depending on the type of metal used and using particular metals lowers the diode's Schottky barrier potential and results in a Vf in the range of 0.1-0.3V. In another embodiment a trench structure is formed on the Schottky diodes semiconductor material to reduce reverse leakage current. and comprises a number of parallel, equally spaced trenches with mesa regions between adjacent trenches. A third embodiment of the invention provides a GaN tunnel diode with a low Vf resulting from the tunneling of electrons through the barrier potential, instead of over it. This embodiment can also have a trench structure to reduce reverse leakage current.

Owner:CREE INC

Method for depinning the fermi level of a semiconductor at an electrical junction and devices incorporating such junctions

InactiveUS20050093027A1Reduce impactHigh currentTransistorThyristorElectrical junctionElectrical conductor

An electrical junction that includes a semiconductor (e.g., C, Ge, or an Si-based semiconductor), a conductor, and an interface layer disposed therebetween. The interface layer is sufficiently thick to depin a Fermi level of the semiconductor, yet sufficiently thin to provide the junction with a specific contact resistance of less than or equal to approximately 1000 Ω-μm2, and in some cases a minimum specific contact resistance.

Owner:ACORN SEMI LLC

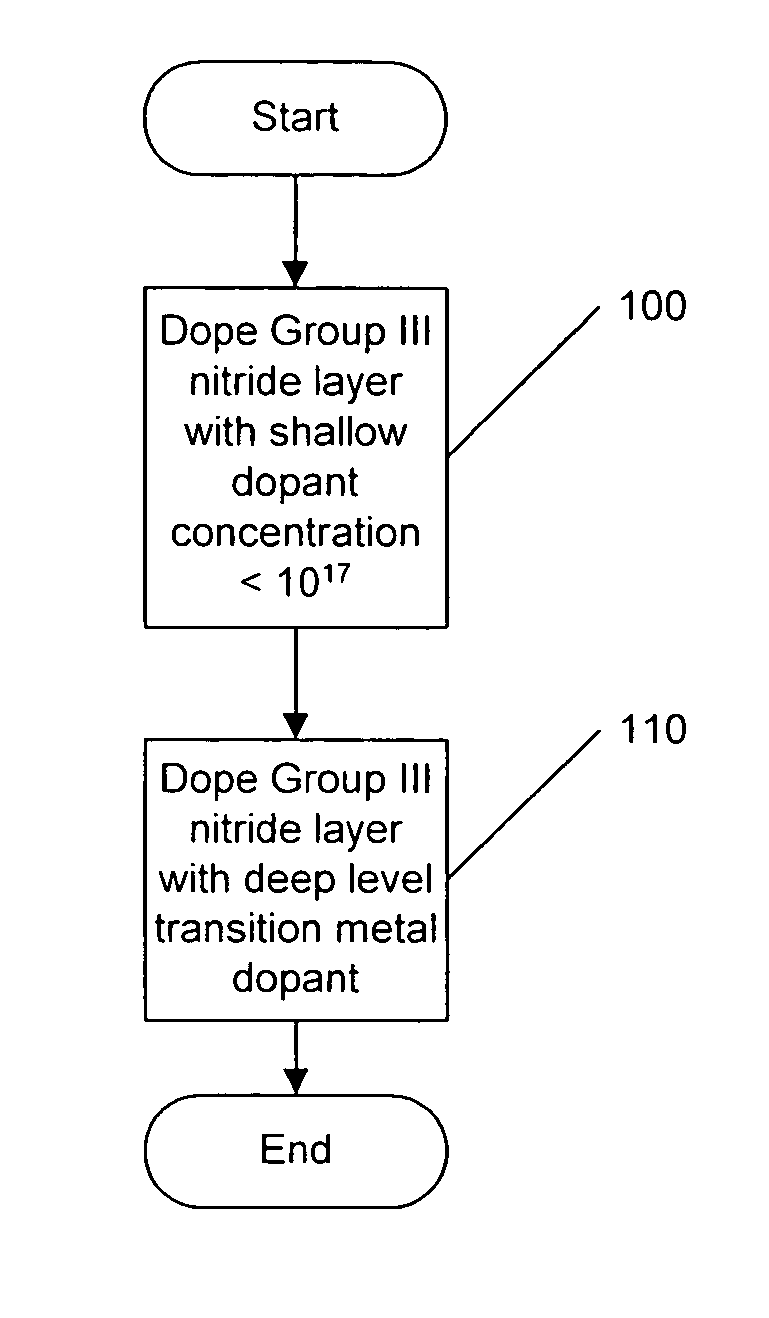

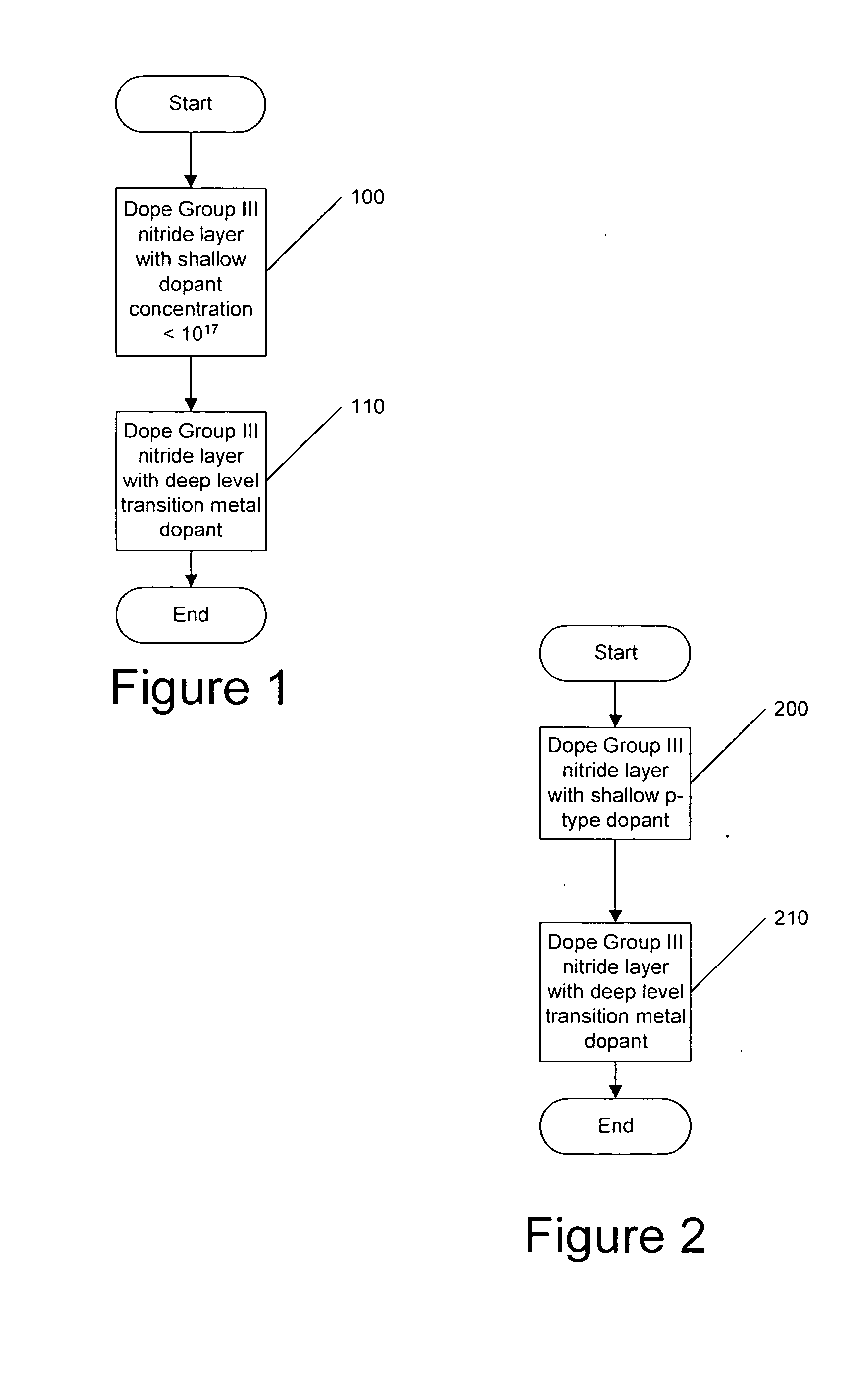

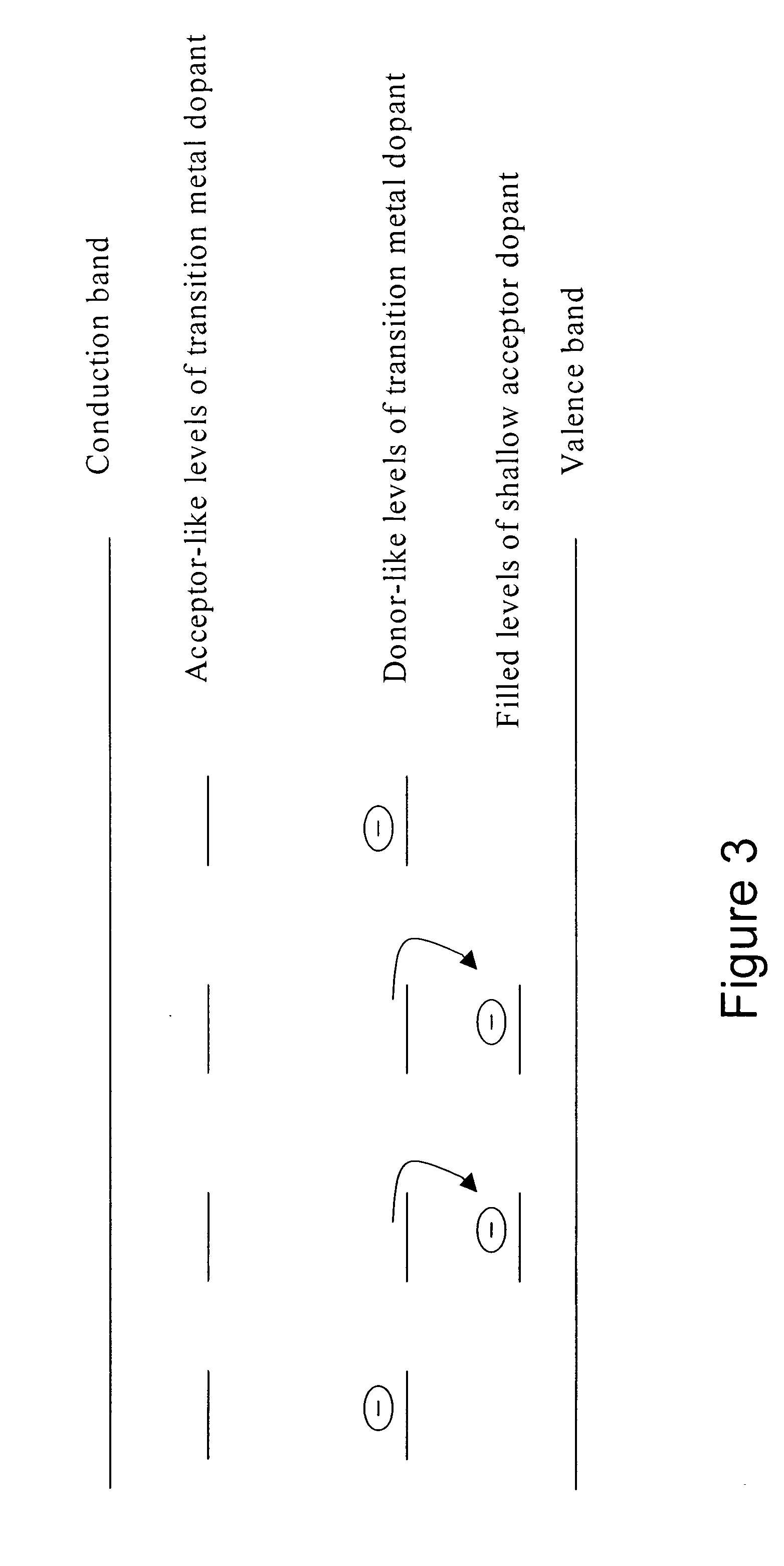

Co-doping for fermi level control in semi-insulating Group III nitrides

ActiveUS20050145874A1Semiconductor/solid-state device manufacturingSemiconductor devicesDopantDeep level

Semi-insulating Group III nitride layers and methods of fabricating semi-insulating Group III nitride layers include doping a Group III nitride layer with a shallow level p-type dopant and doping the Group III nitride layer with a deep level dopant, such as a deep level transition metal dopant. Such layers and / or method may also include doping a Group III nitride layer with a shallow level dopant having a concentration of less than about 1×1017 cm−3 and doping the Group III nitride layer with a deep level transition metal dopant. The concentration of the deep level transition metal dopant is greater than a concentration of the shallow level p-type dopant.

Owner:CREE INC

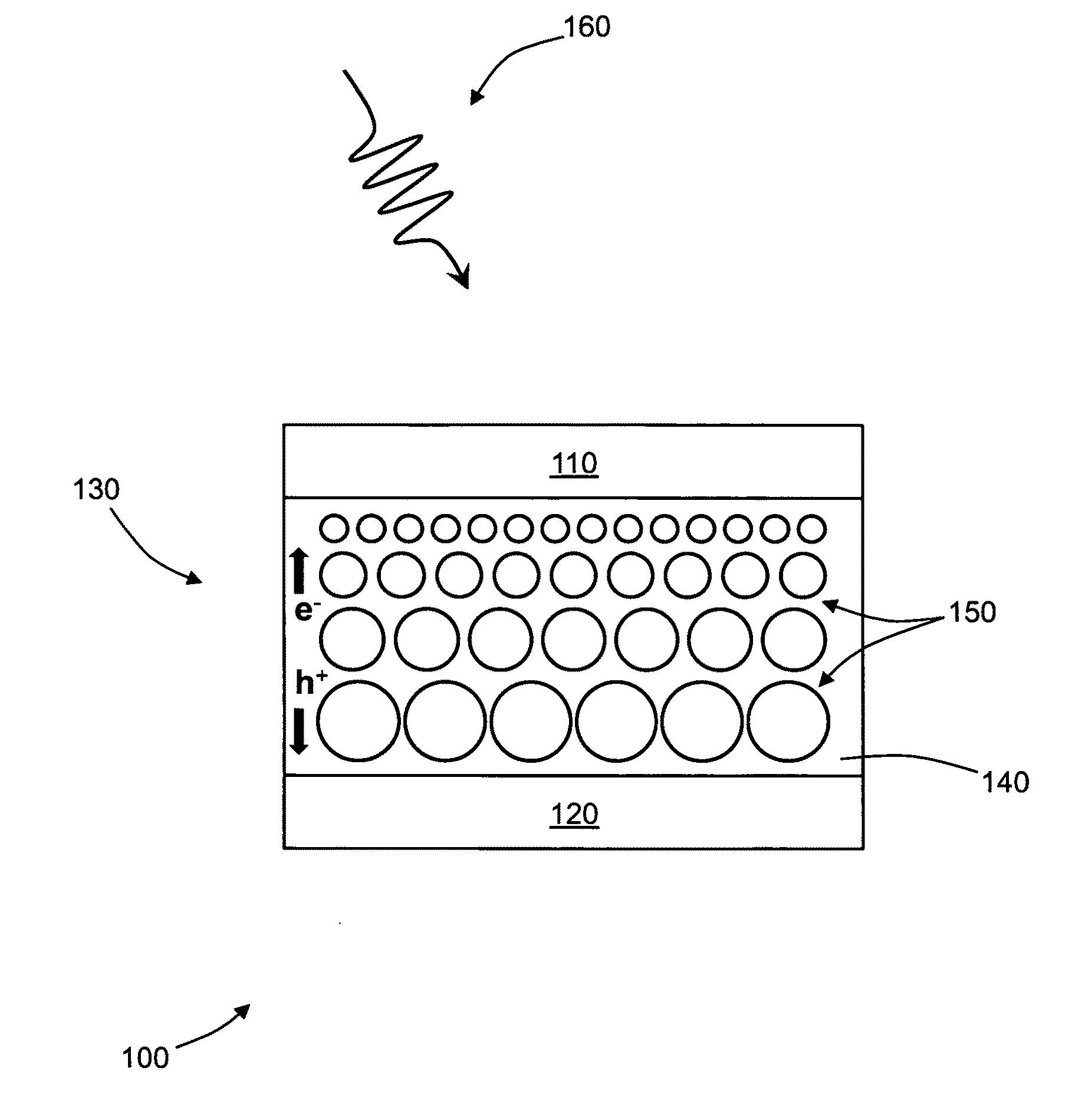

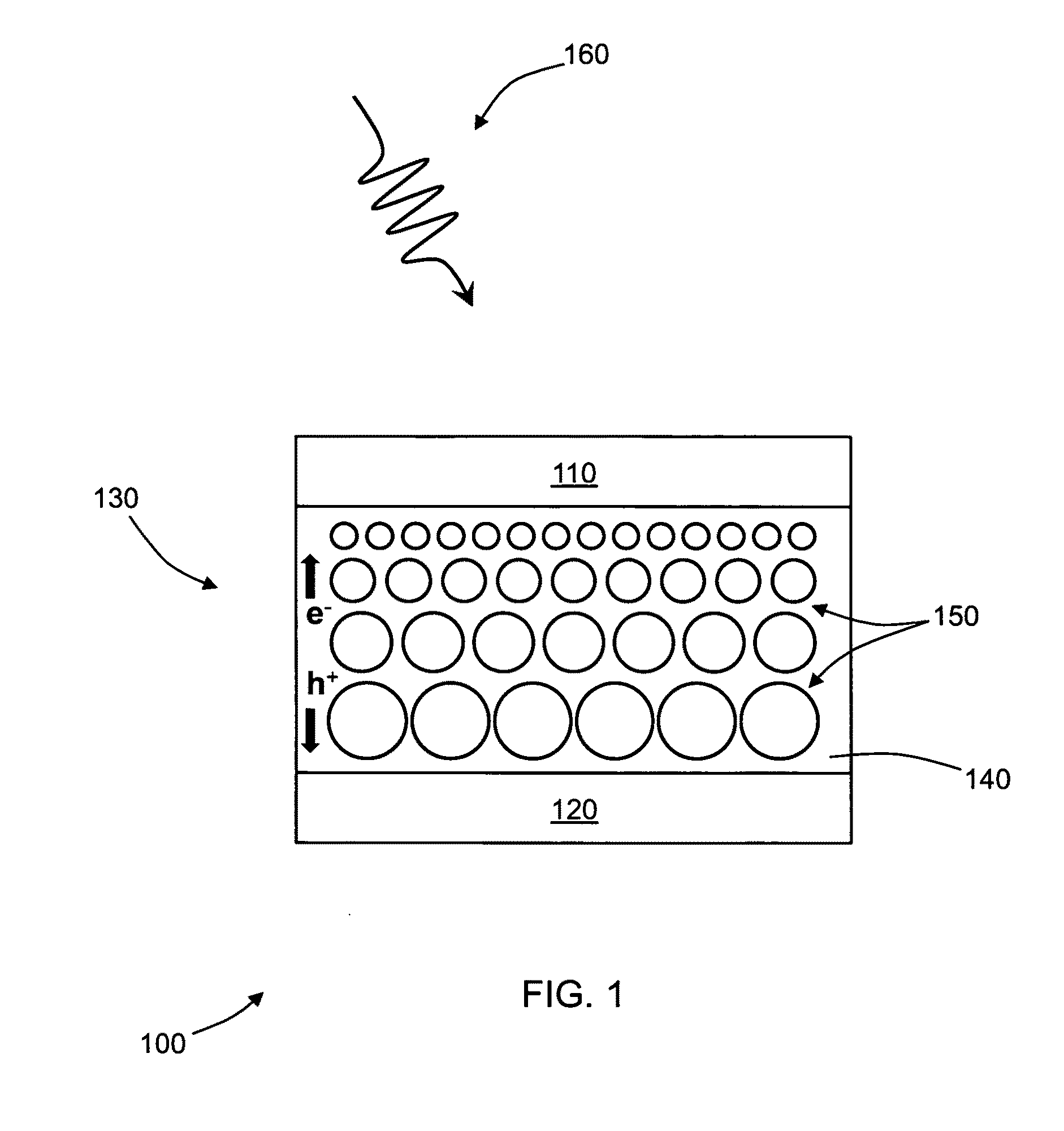

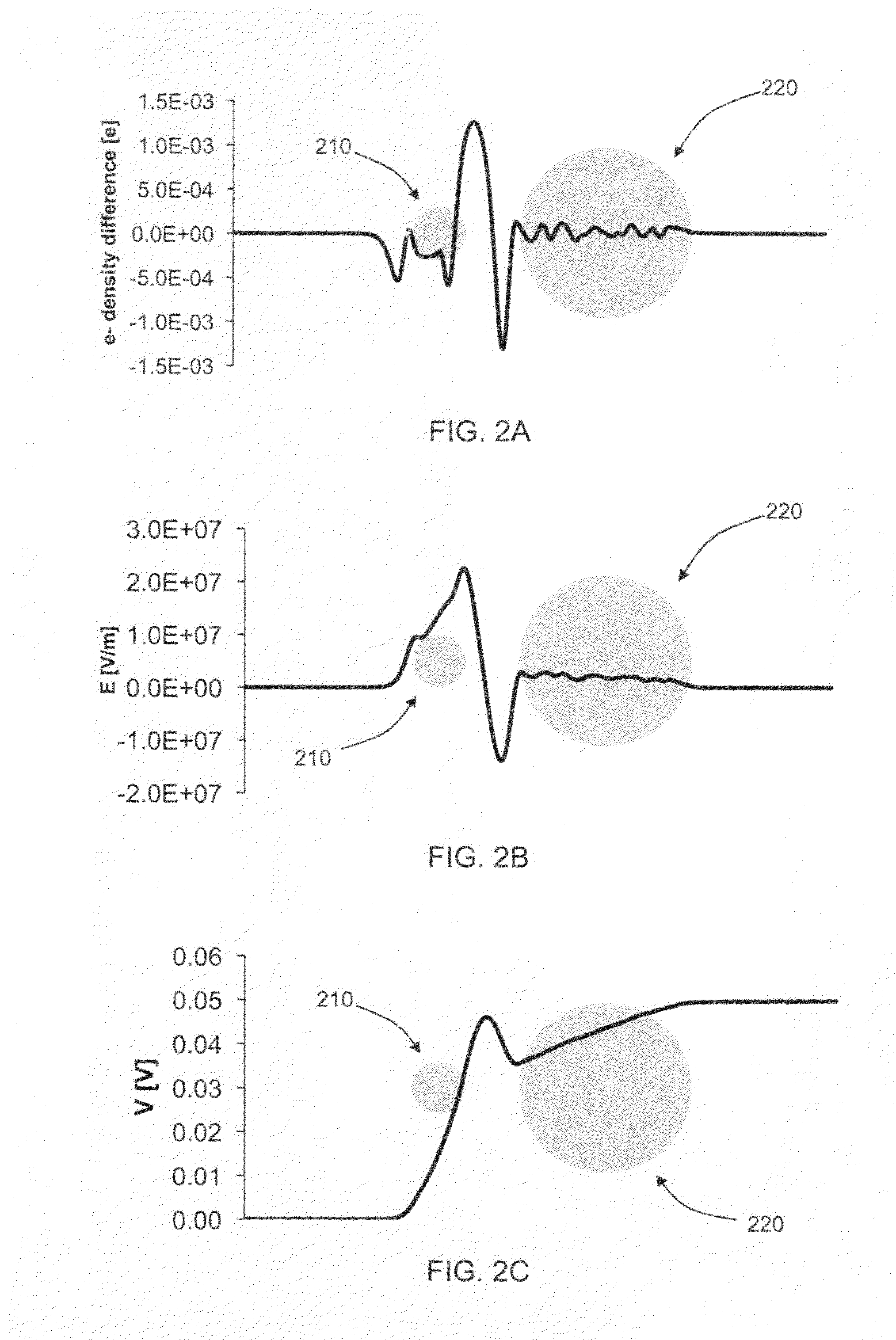

Quantum dot solar cell with quantum dot bandgap gradients

Efficient photovoltaic devices with quantum dots are provided. Quantum dots have numerous desirable properties that can be used in solar cells, including an easily selected bandgap and Fermi level. In particular, the size and composition of a quantum dot can determine its bandgap and Fermi level. By precise deposition of quantum dots in the active layer of a solar cell, bandgap gradients can be present for efficient sunlight absorption, exciton dissociation, and charge transport. Mismatching Fermi levels are also present between adjacent quantum dots, allowing for built-in electric fields to form and aid in charge transport and the prevention of exciton recombination.

Owner:HONDA MOTOR CO LTD

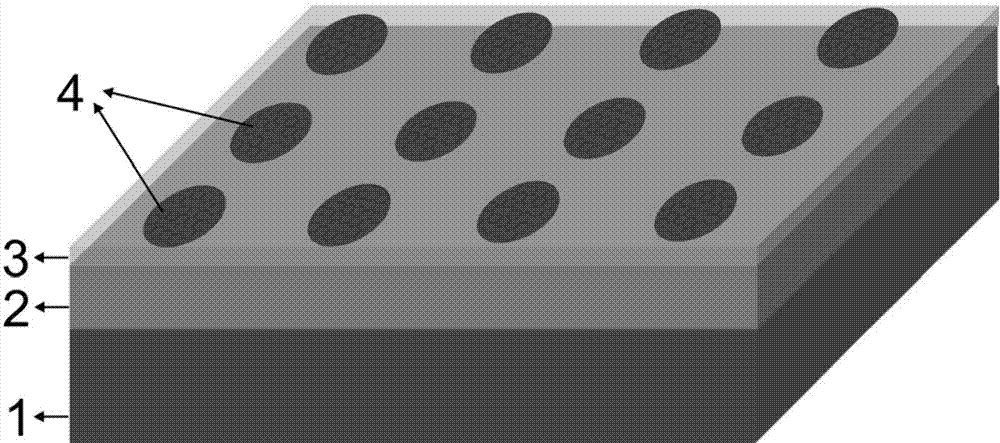

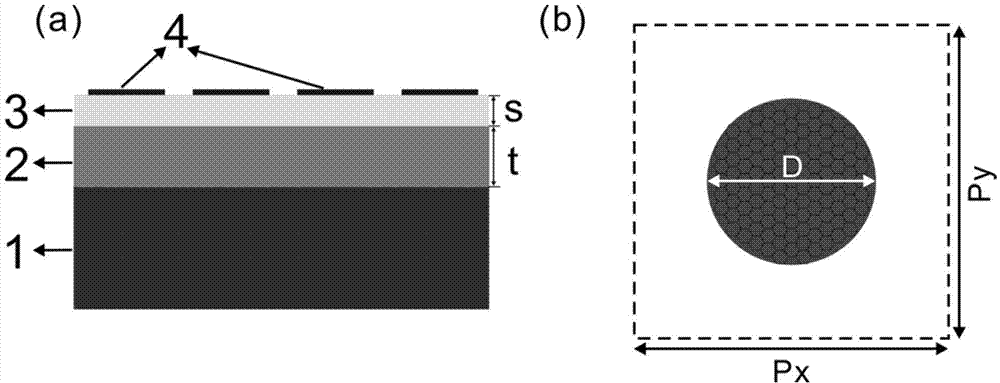

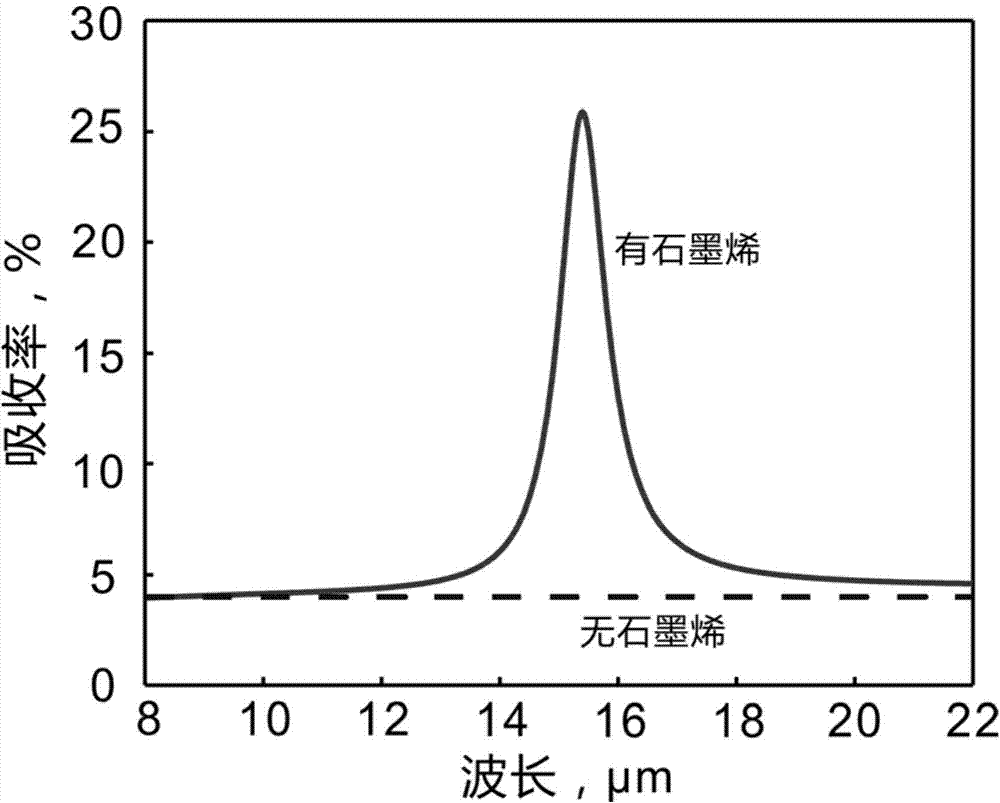

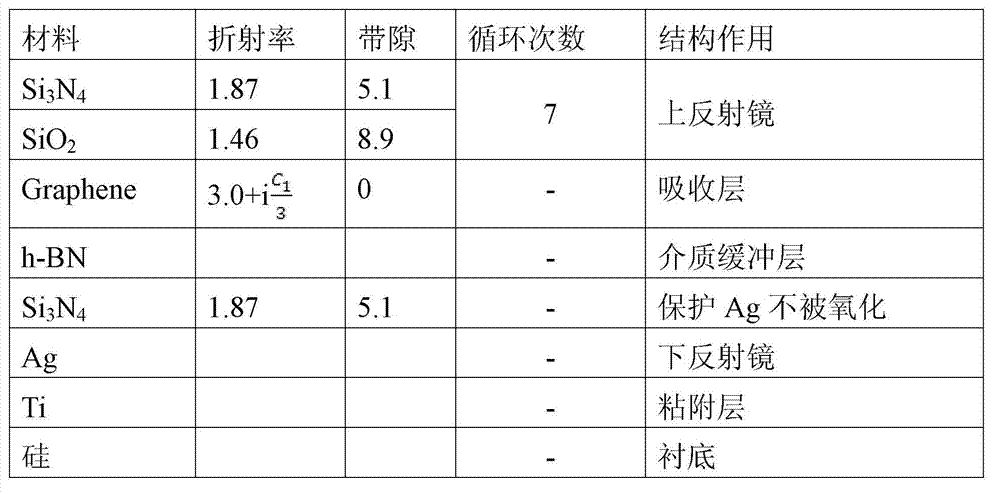

Photoelectric material adjustable absorption enhancing layer based on graphene surface plasmon

InactiveCN104851929ARich sourcesImprove optical absorptionSemiconductor devicesMicro nanoDoped graphene

The invention belongs to the field of photoelectric technology, and specifically relates to a photoelectric material adjustable absorption enhancing layer based on graphene surface plasmon. Graphene forming the enhancing layer is a thin film formed by single-layer graphene and having micro-nano scale structural features, graphene is doped to a certain concentration, and the Fermi level Ef of the graphene is larger than 0.1eV or smaller than -0.1eV, so that the graphene becomes a surface plasmon material; and the micro-nano structure is used for realizing wave-vector matching between incident light and a graphene surface plasmon mode, and under irradiation of the incident light, the doped graphene micro-nano structure generates surface plasmon, thereby realizing a local area of focusing. The absorption enhancing layer is applied to the upper side of photoelectric material used by photoelectric devices such as a solar cell and a photoelectric detector, can improve the absorption efficiency of the photoelectric material, and can realize active regulation and control of absorption characteristics of the photoelectric material, thereby expanding application of the photoelectric material in fields of spectrum-adjustable selective detection and the like.

Owner:NAT UNIV OF DEFENSE TECH

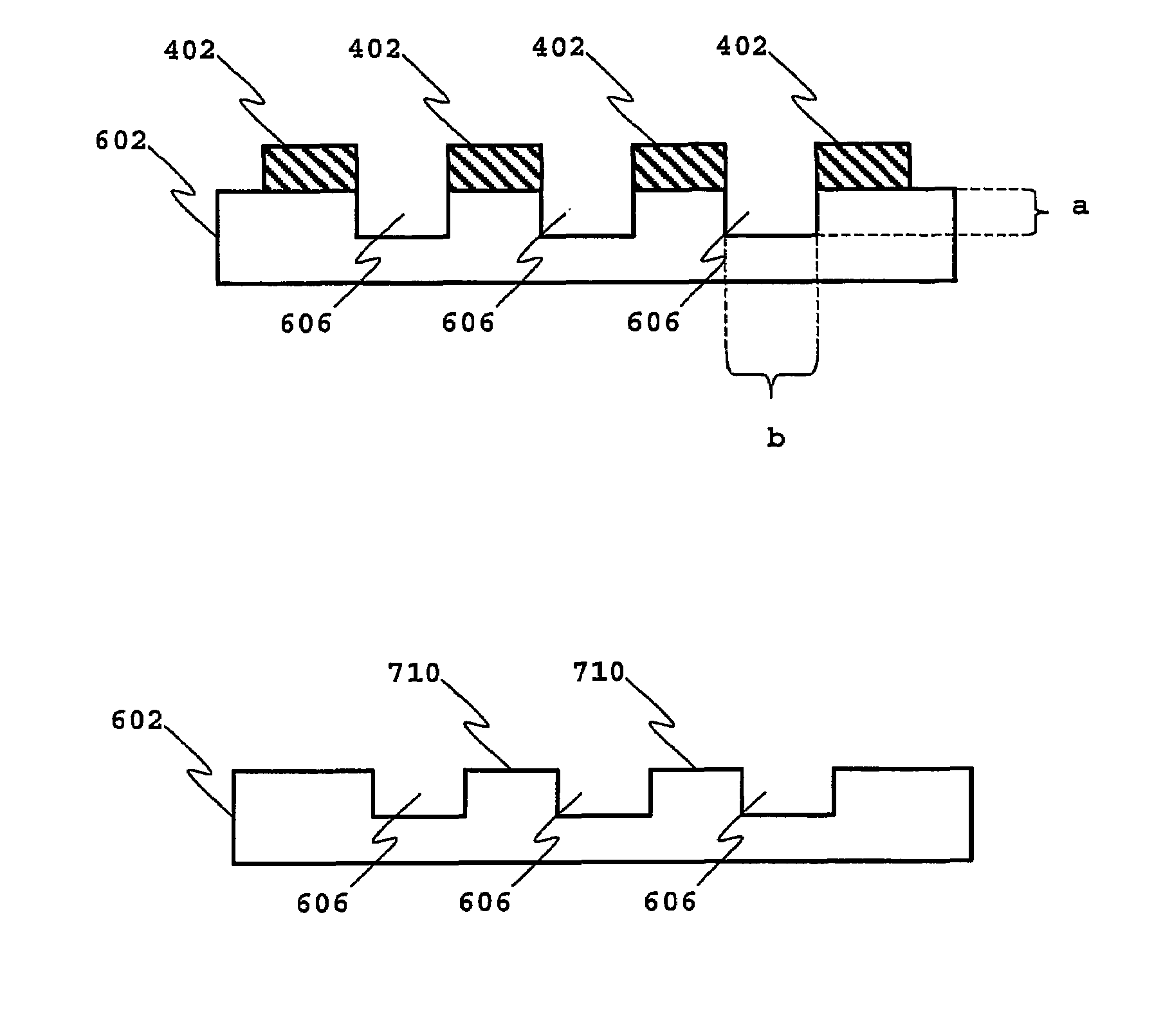

Gallium nitride based diodes with low forward voltage and low reverse current operation

InactiveUS6949774B2Maximizes forward tunneling probabilityLow VfDiodeTunnel diodeSemiconductor materials

New Group III based diodes are disclosed having a low on state voltage (Vf), and structures to keep reverse current (Irev) relatively low. One embodiment of the invention is Schottky barrier diode made from the GaN material system in which the Fermi level (or surface potential) of is not pinned. The barrier potential at the metal-to-semiconductor junction varies depending on the type of metal used and using particular metals lowers the diode's Schottky barrier potential and results in a Vf in the range of 0.1-0.3V. In another embodiment a trench structure is formed on the Schottky diodes semiconductor material to reduce reverse leakage current. and comprises a number of parallel, equally spaced trenches with mesa regions between adjacent trenches. A third embodiment of the invention provides a GaN tunnel diode with a low Vf resulting from the tunneling of electrons through the barrier potential, instead of over it. This embodiment can also have a trench structure to reduce reverse leakage current.

Owner:CREE INC

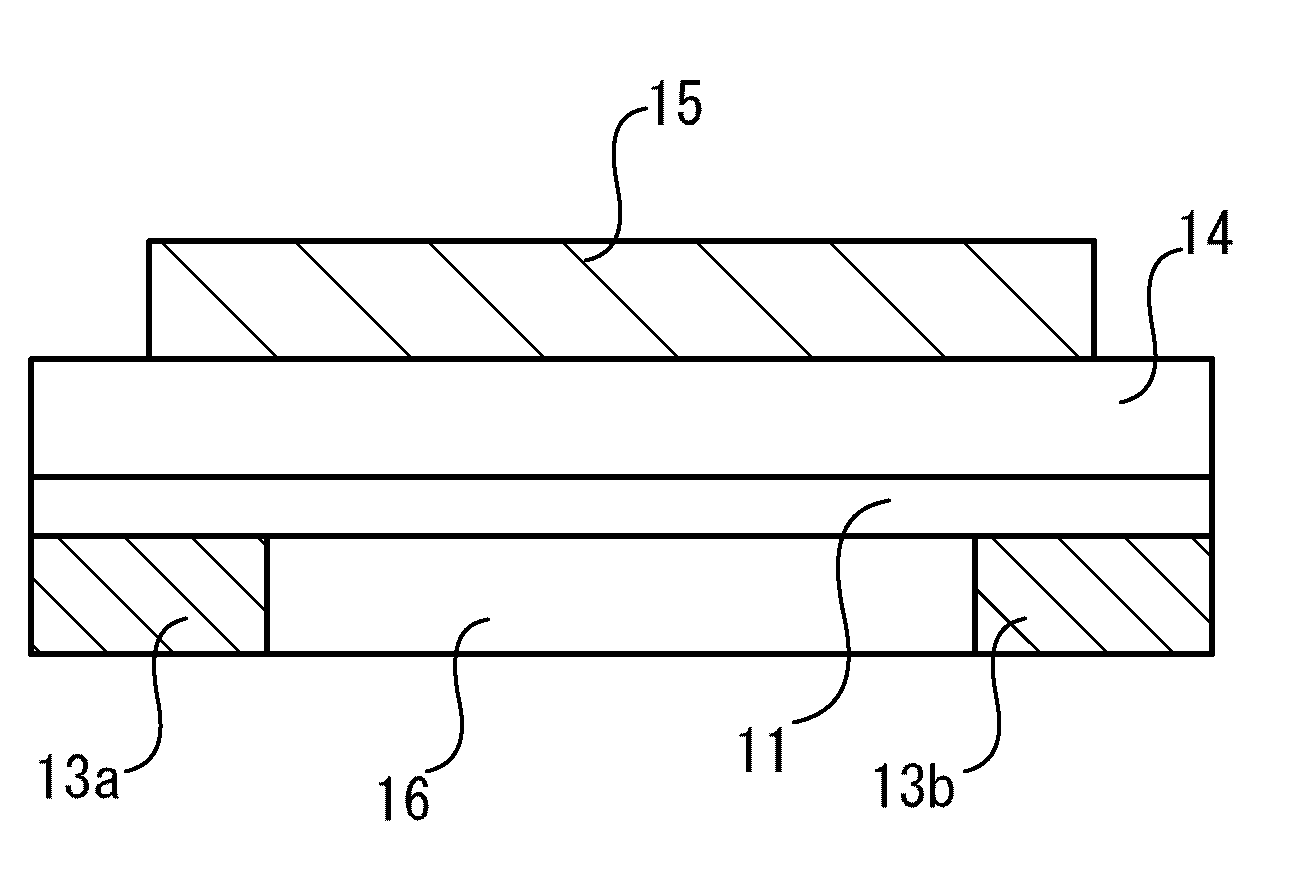

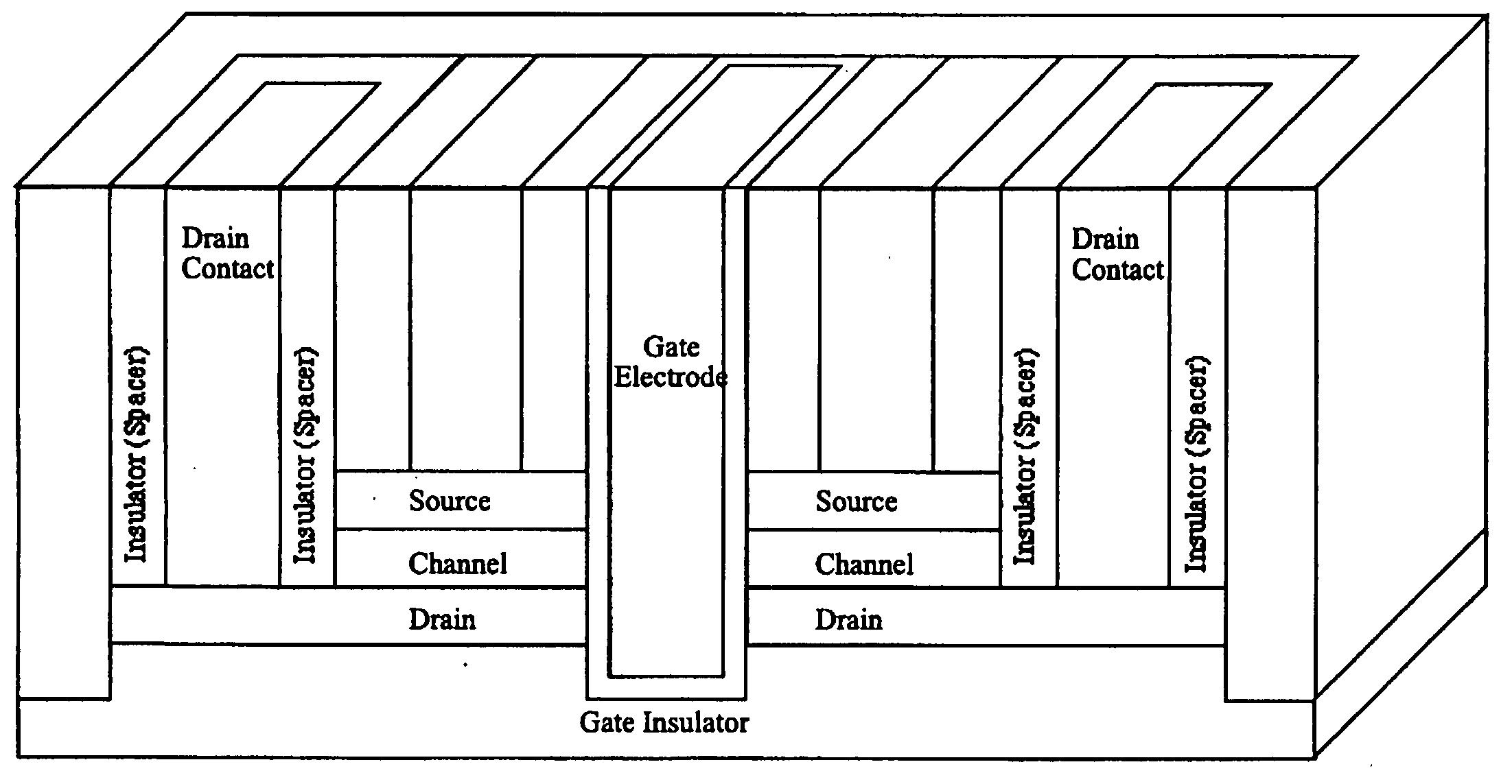

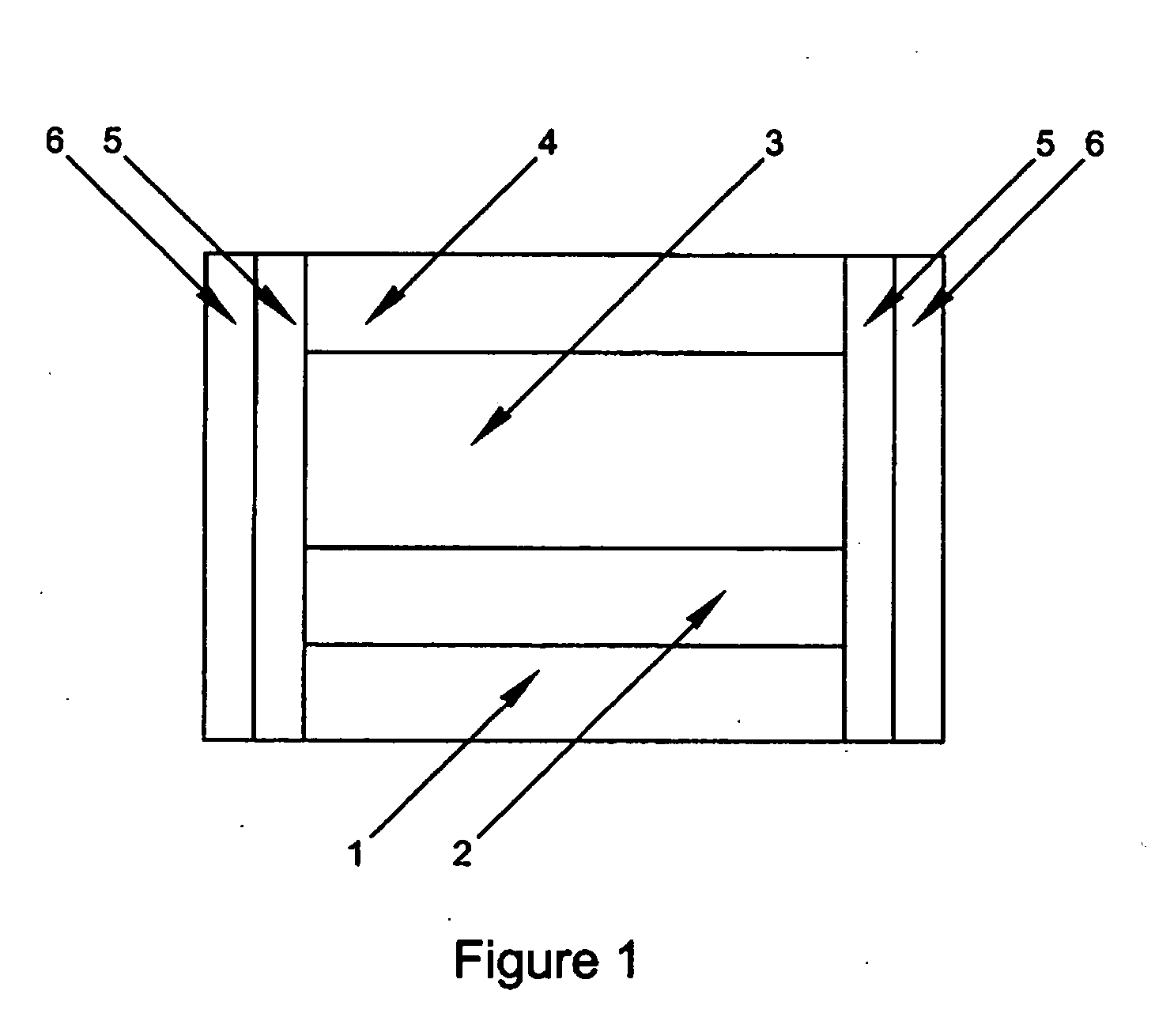

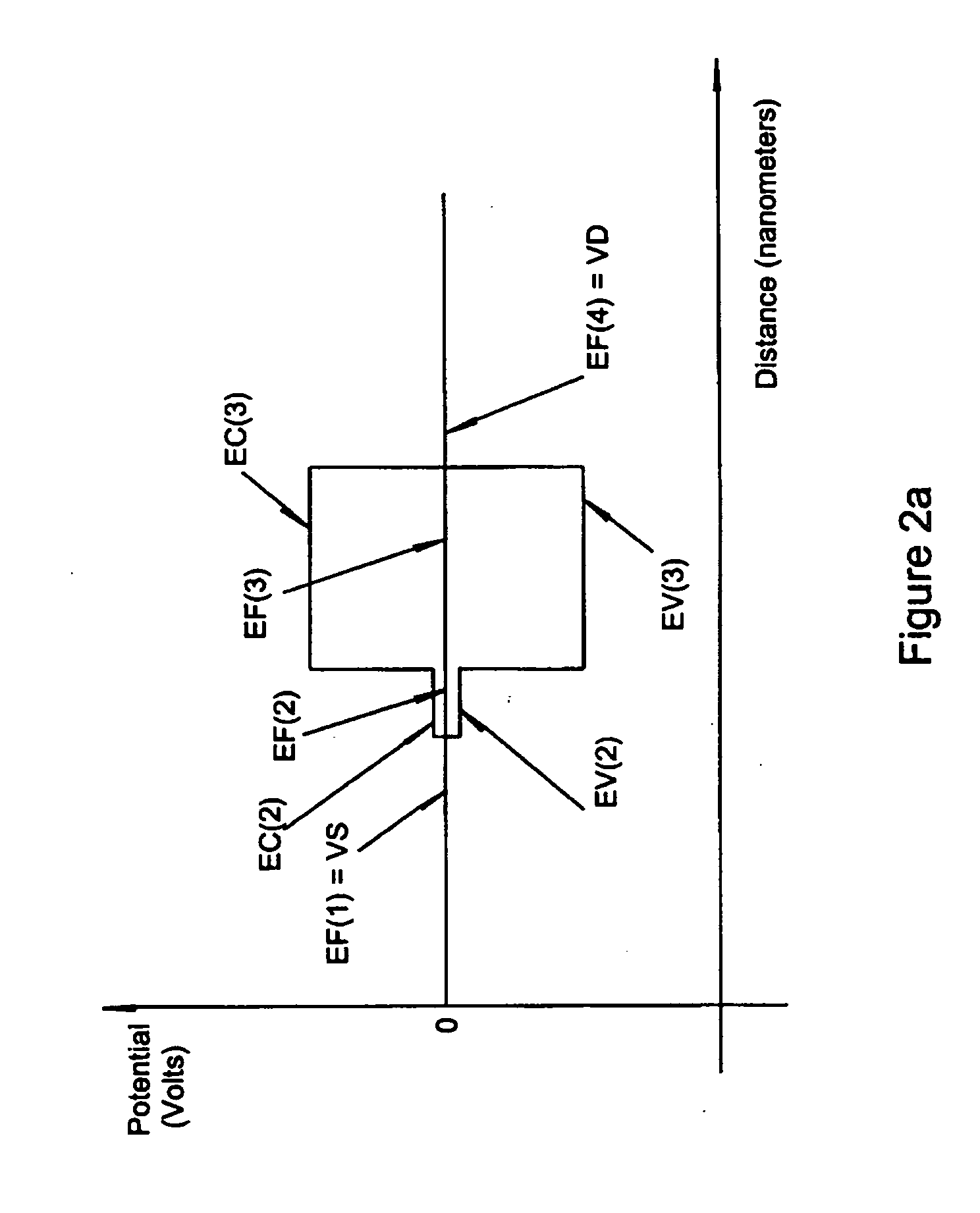

misfet

InactiveUS20050072988A1Simple preparation processTransistorSemiconductor/solid-state device detailsMetal insulatorContact layer

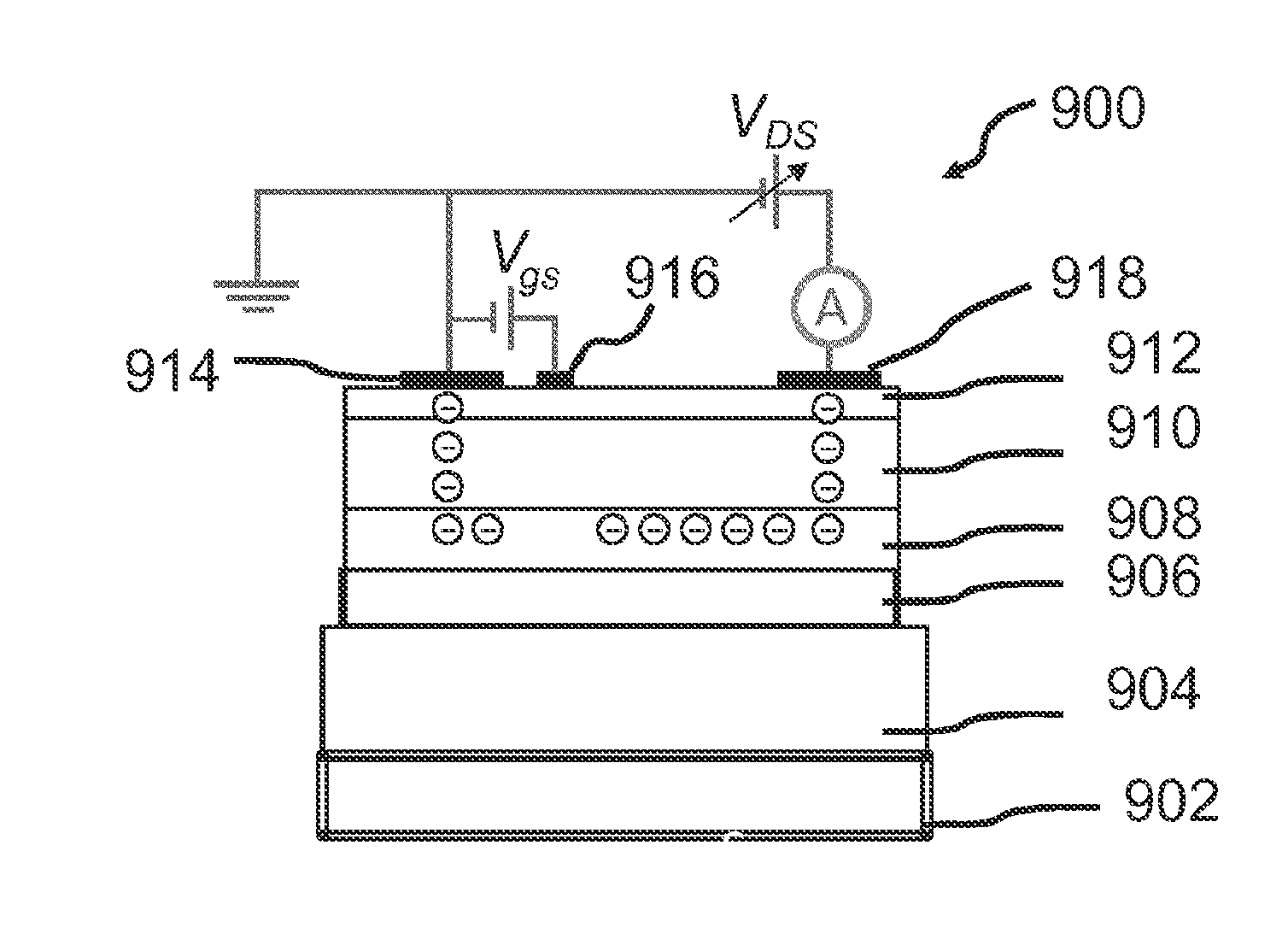

A metal insulator semiconductor field effect transistor (MISFET) is disclosed comprising a source layer being made with a material having a source band-gap (EG2) and a source mid-gap value (EGM2), the source layer having a source Fermi-Level (EF2). A drain layer has a drain Fermi-Level (EF4). A channel layer is provided between the source layer and the drain layer, the channel layer being made with a material having a channel band-gap (EG3) and a channel mid-gap value (EGM3), the channel layer having a channel Fermi-Level (EF3). A source contact layer is connected to the source layer opposite the channel layer, the source contact layer having a source contact Fermi-Level (EF1). A gate electrode has a gate electrode Fermi-Level (EF6). The source band-gap is substantially narrower (EG2) than the channel band-gap (EG3). The source contact Fermi-Level (EF1), the source Fermi-Level (EF2), the channel Fermi-Level (EF3), the drain Fermi-Level (EF4) and the gate electrode Fermi-Level (EF6) are equal to the source mid-gap value (EGM2) and the channel mid-gap value (EGM3), within a predetermined tolerance value, when no voltage is applied to the device.

Owner:QUANTUM SEMICON

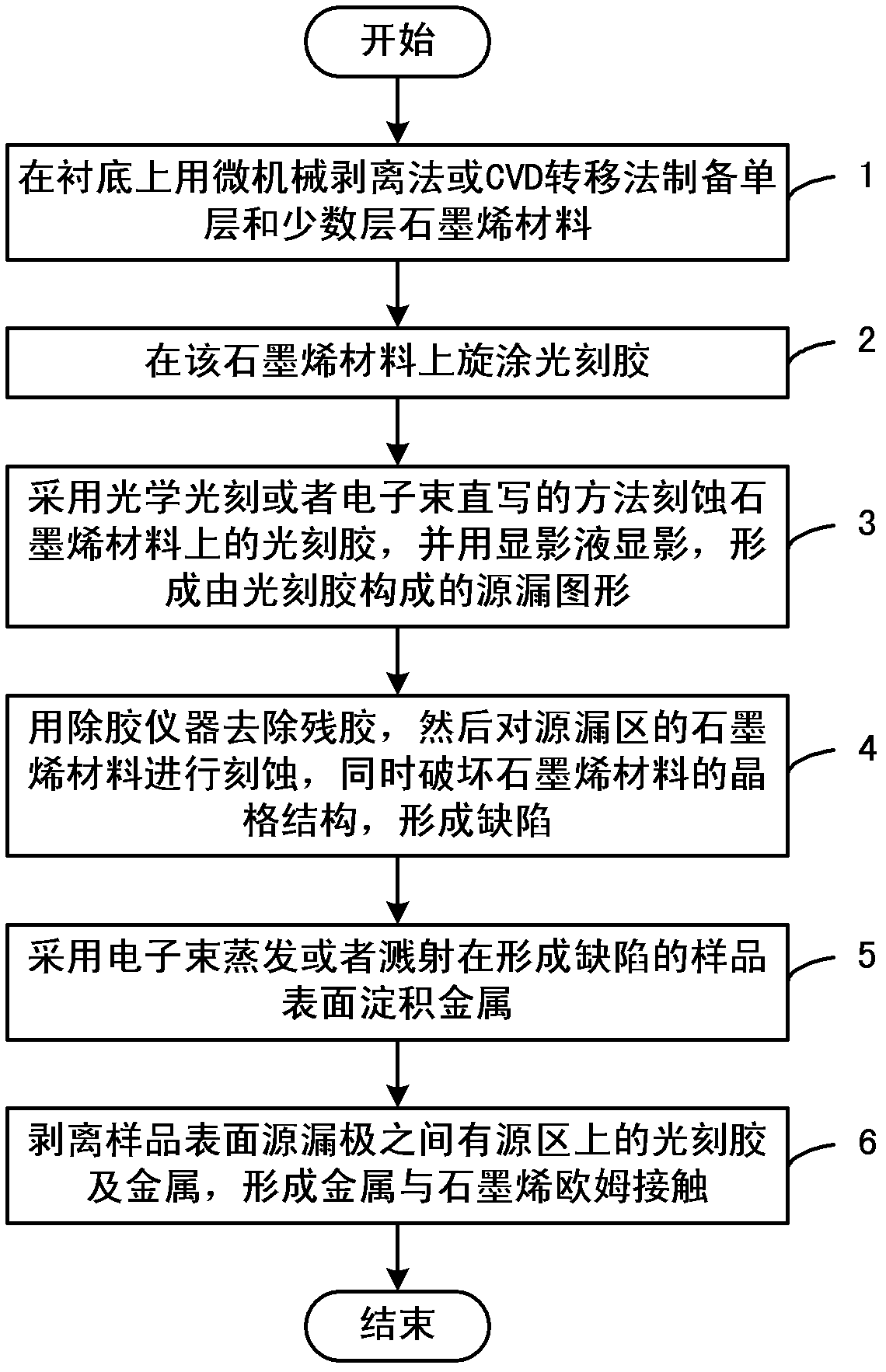

Preparation method of ohmic contact of metal with graphene

InactiveCN102623310AReduce contact resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesDirect writingState density

The invention discloses a preparation method of ohmic contact of metal with graphene. The method includes preparing monolayer and a plurality of layers of graphene materials on a substrate through a micromechanical cleavage or a chemical vapor deposition (CVD) transferring method; spin-coating photoresist on the graphene materials; etching the photoresist on the graphene materials through optical lithography or an electron beam direct writing method, using a developer solution for development to form a source-drain image formed by the photoresist; removing residual gum with a degumming device, etching the graphene materials in a source-drain area, and destroying the lattice structure of the graphene materials to form defects simultaneously; using electron beam to evaporate or sputter on the sample surface where the defects form so as to deposit the metal; and stripping the photoresist and the metal on an active area and between the drain and the source on the sample surface so as to form the ohmic contact of the metal with the graphene. Compared with the existing ohmic contact of metal with graphene, the preparation method of the ohmic contact of the metal with the graphene overcomes the defect that state density of the grapheme nearby fermi level is small, and can obtain the ohmic contact of the metal with the graphene with small contact resistance.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

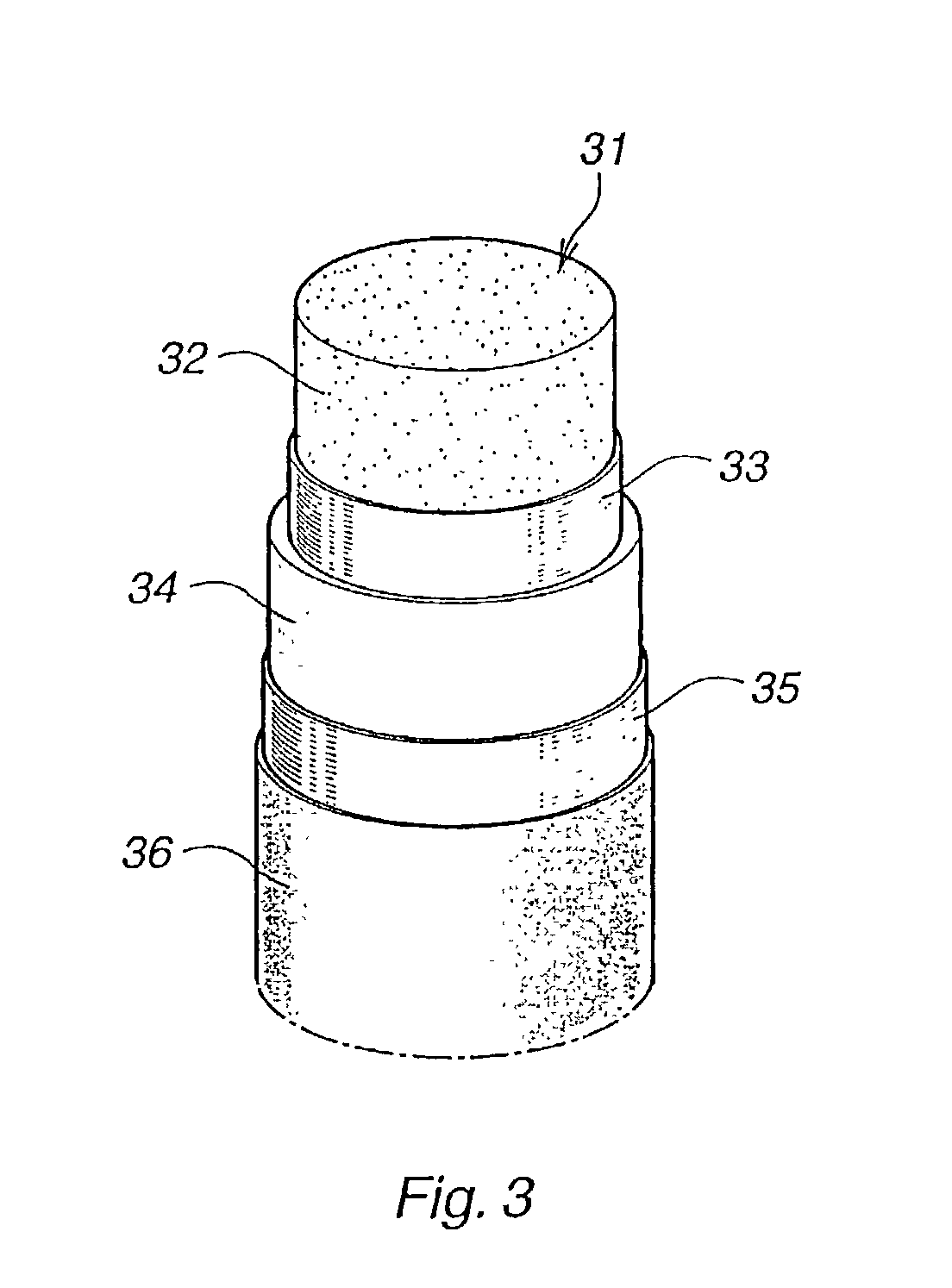

Conducting material

Conducting material for an electric conductor comprising nanostructures (31) and a charge-transfer agent that shifts the nanostructures' fermi level so that said nanostructures attain an enhanced conductivity.

Owner:ABB (SCHWEIZ) AG

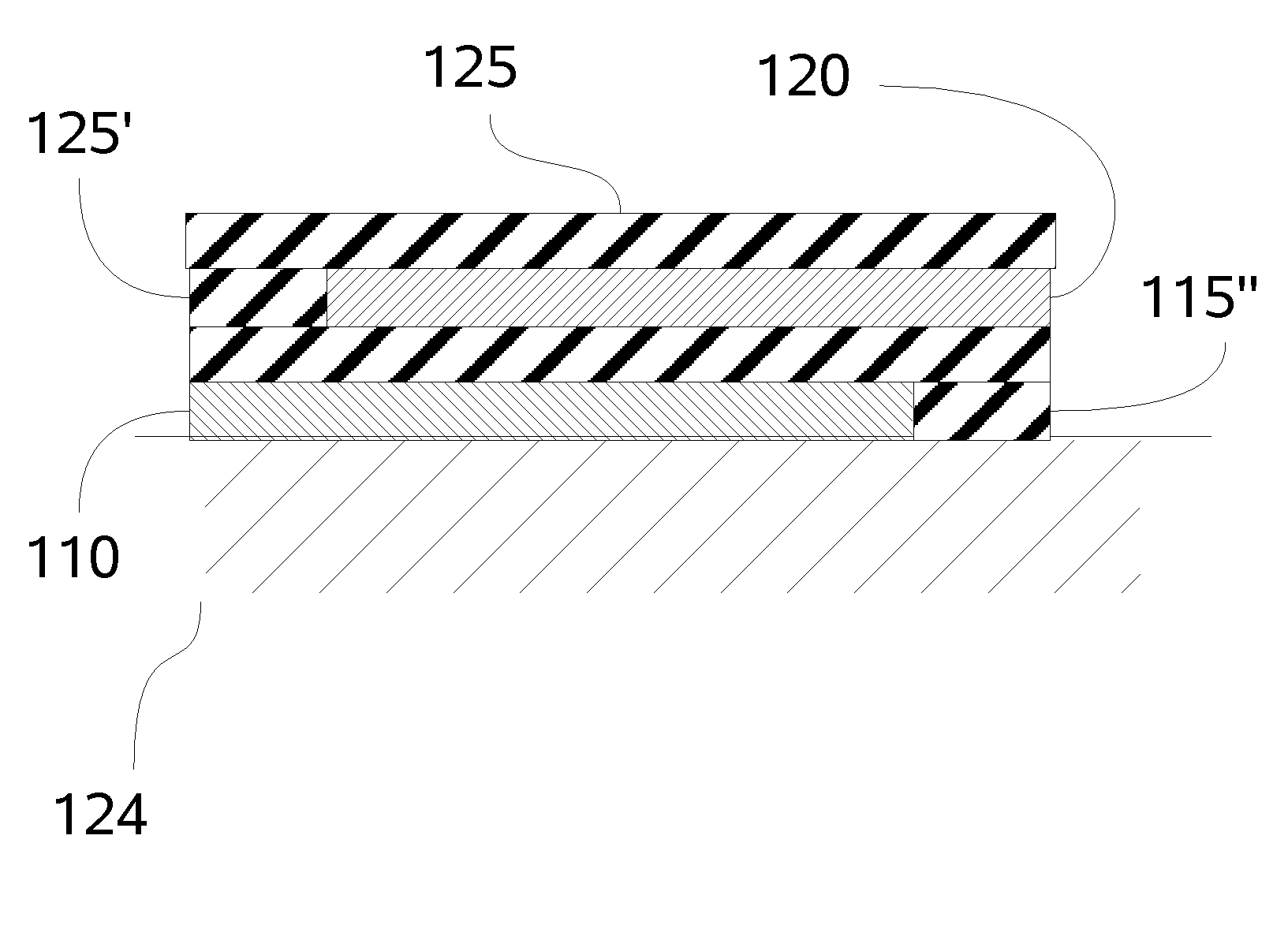

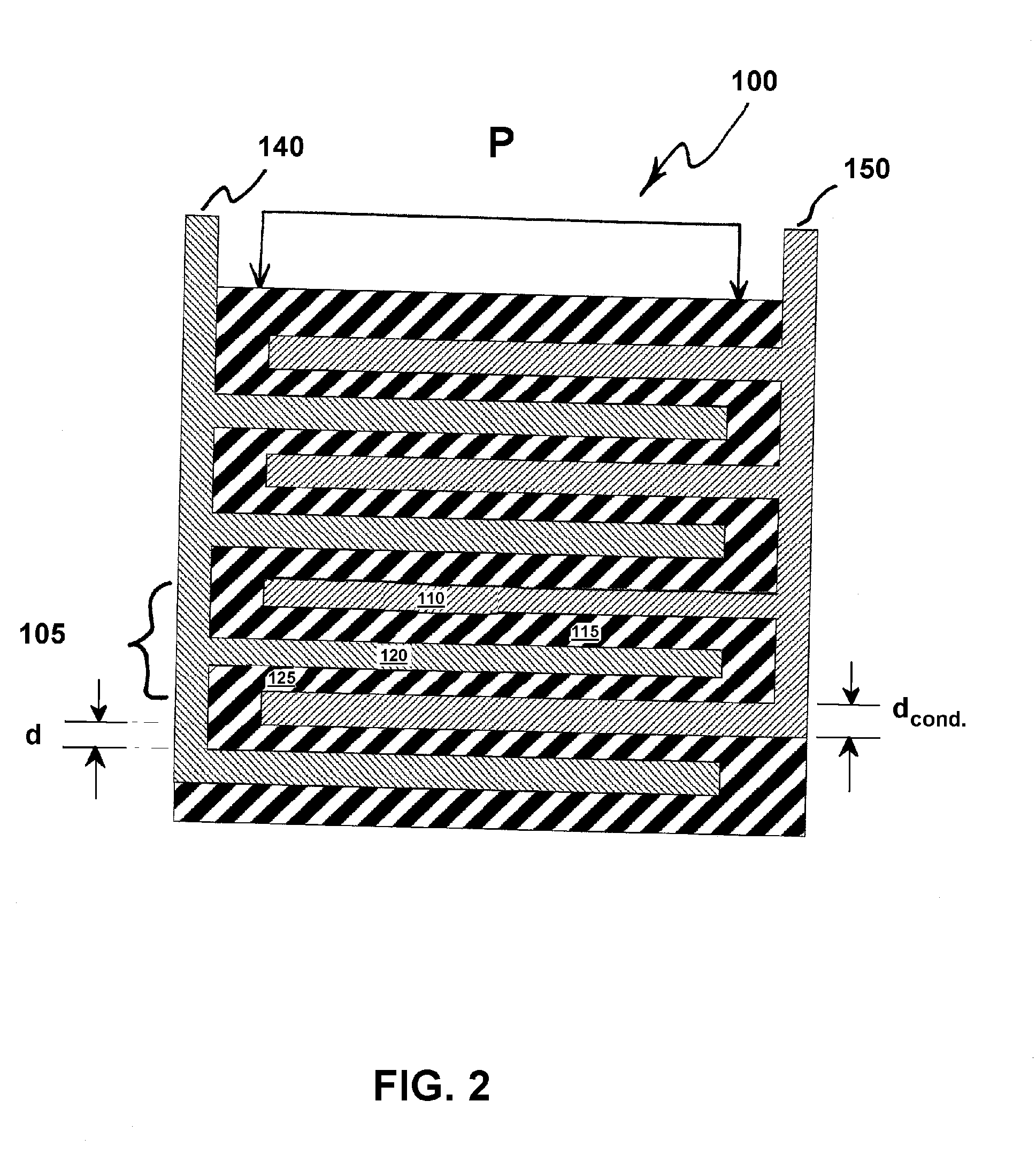

Piezoelectric Composite Material

InactiveUS20070138905A1High piezoelectric coefficientMaterial nanotechnologyPiezoelectric/electrostriction/magnetostriction machinesElectrical conductorWork function

A composition of matter having multiple layers of different conductors separated by thin layers of dielectric materials has a high piezoelectric coefficient when the conductors are metals having a significant difference in work function and the dielectric materials have a low elastic modulus when the metal layers are connected to form a capacitive circuit. Alternatively, when the conductors are semi-conductors they should have a significant difference in Fermi levels.

Owner:PHYSICAL LOGIC

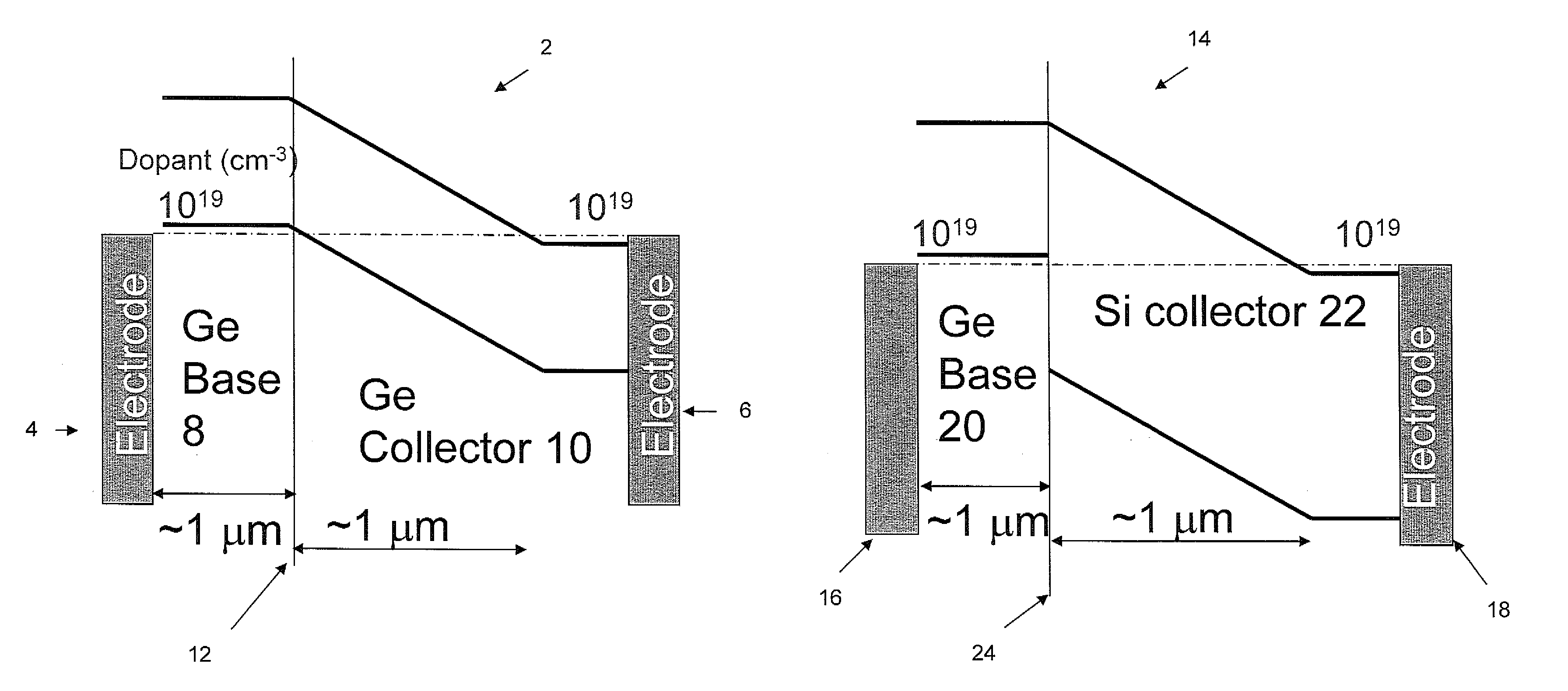

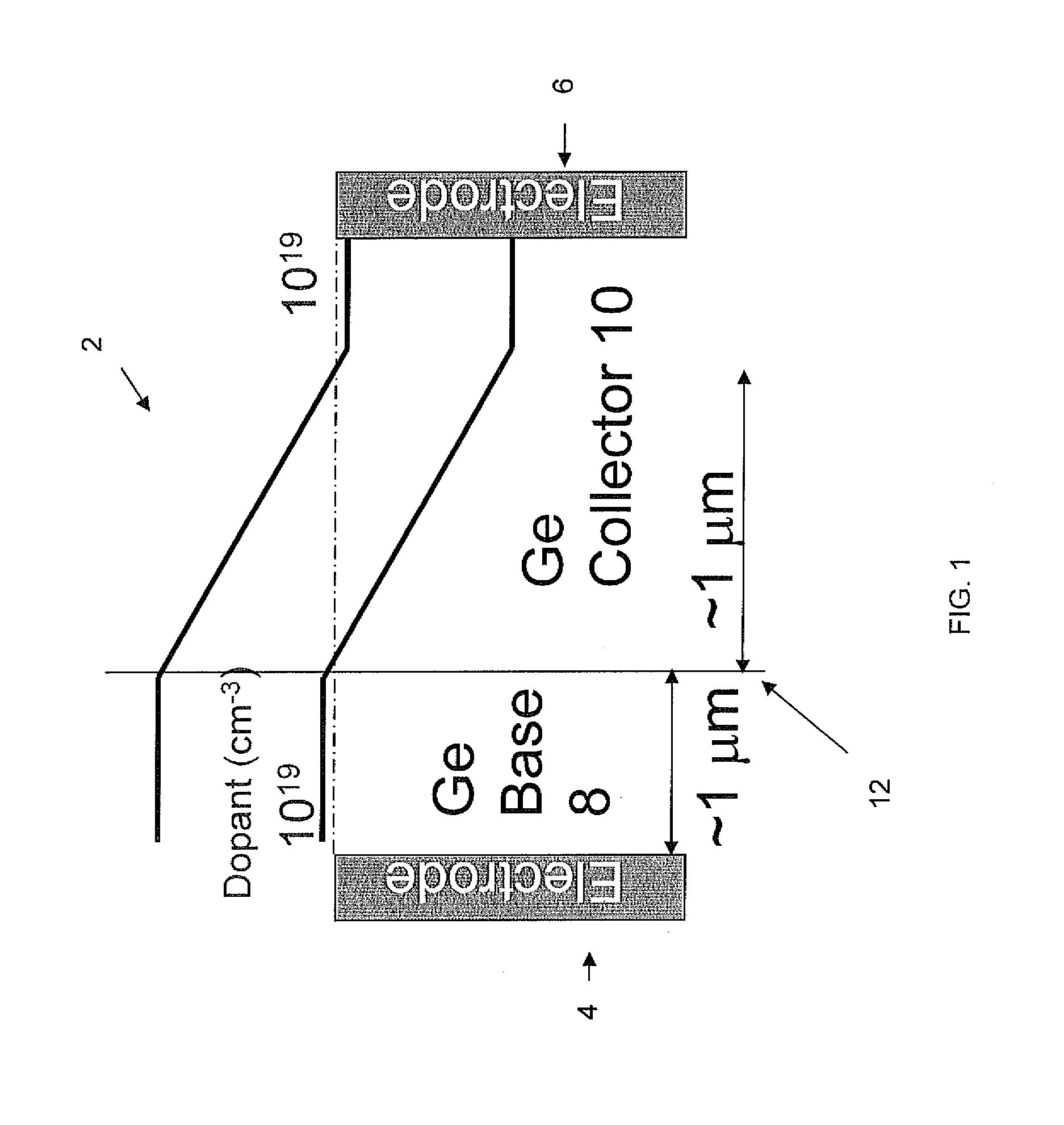

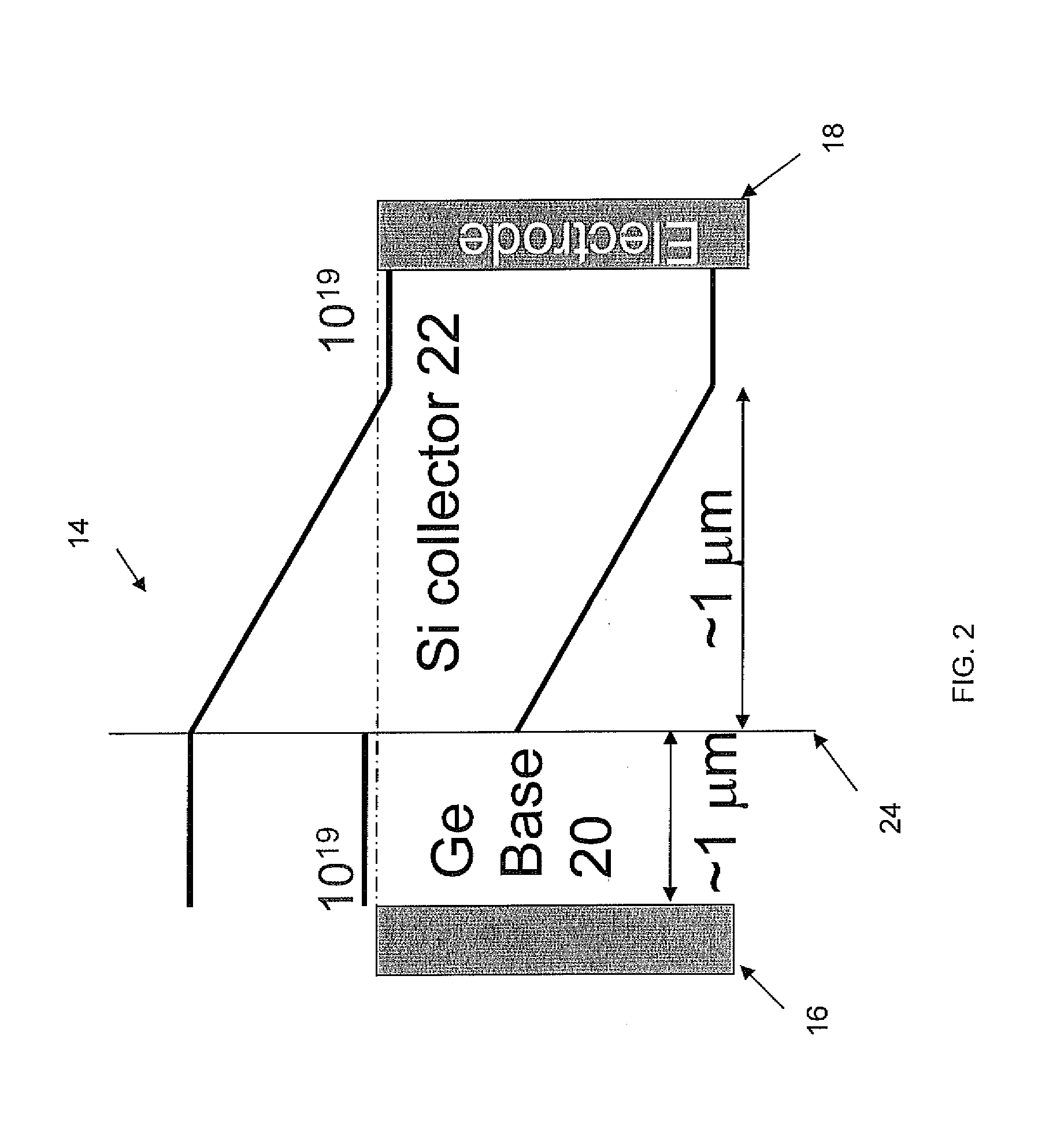

Ge photodetectors

A phototransistor includes an emitter and a base that comprises Ge. A collector comprises Si. The base, emitter, and collector form at least one Si / Ge heterojunction allowing the unpinning of Fermi energy level (EF) of the phototransistor.

Owner:MASSACHUSETTS INST OF TECH

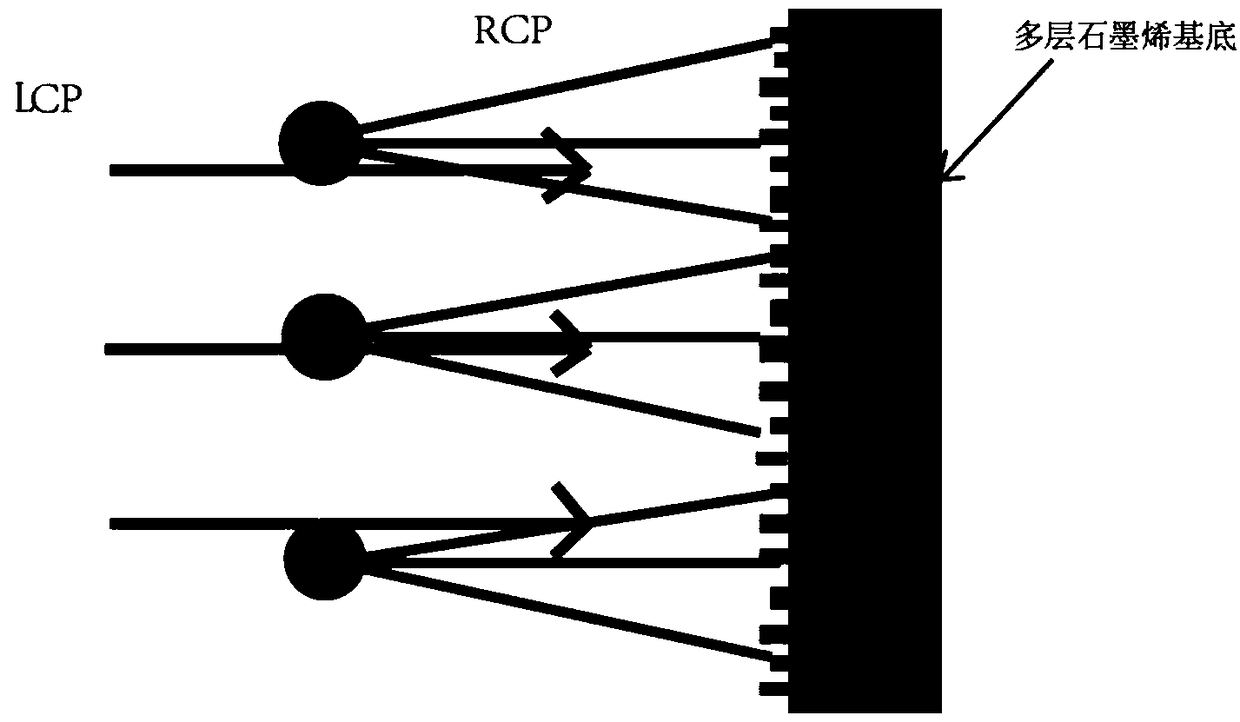

Method for constructing dynamic multifocal superlens based on medium and graphene

The invention discloses a method for constructing a dynamic multifocal superlens based on a medium and graphene. The method includes the following steps that: (1) as for incident light of different wavelengths, phase gradient distribution on a medium metasurface within an infrared wavelength range of 0.7 micron to 500 microns is calculated according to positional relations between focuses and wavelengths; (2) different periodic structures are designed for each center wavelength, specific phase values are determined according to the phase gradient distribution and Pancharatnam-Berry phases; (3)height-determined columnar structures are designed as the basic units of the medium metasurface, and then, a corresponding concrete realization structure and rotation direction are designed; and (4)according to a substrate part, multilayer graphene is adopted to form a reflection type focusing lens, and the Fermi level of the graphene can be changed such the position of a focusing point can be dynamically adjusted. According to the method of the invention, the dynamic multifocal reflective lens is realized through the medium metasurface and the multilayer graphene structure. The method has the advantages of high-efficiency focusing function, ultra-wideband performance, dynamic adjustment, easiness in integration and the like.

Owner:GUILIN G LINK TECH

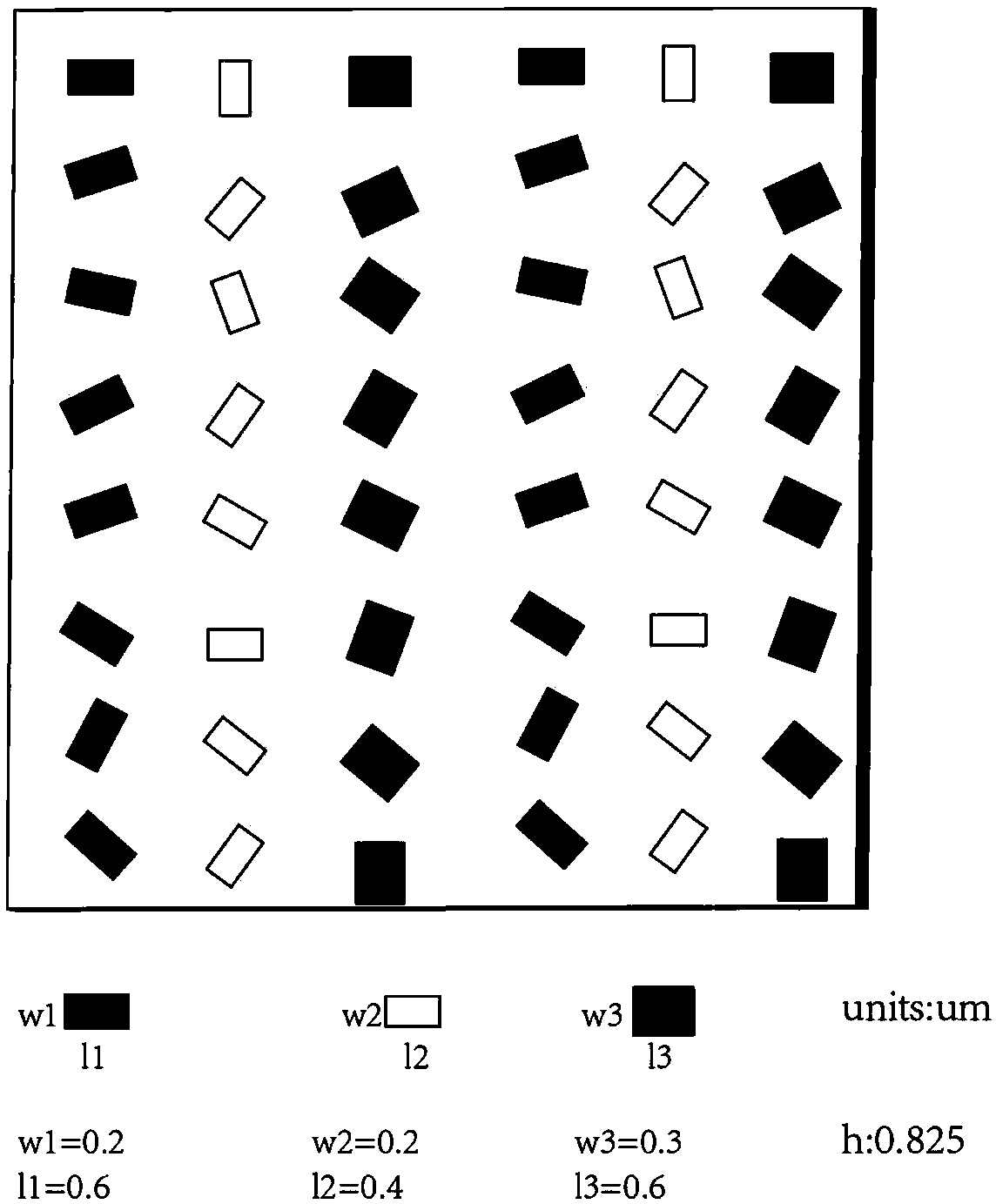

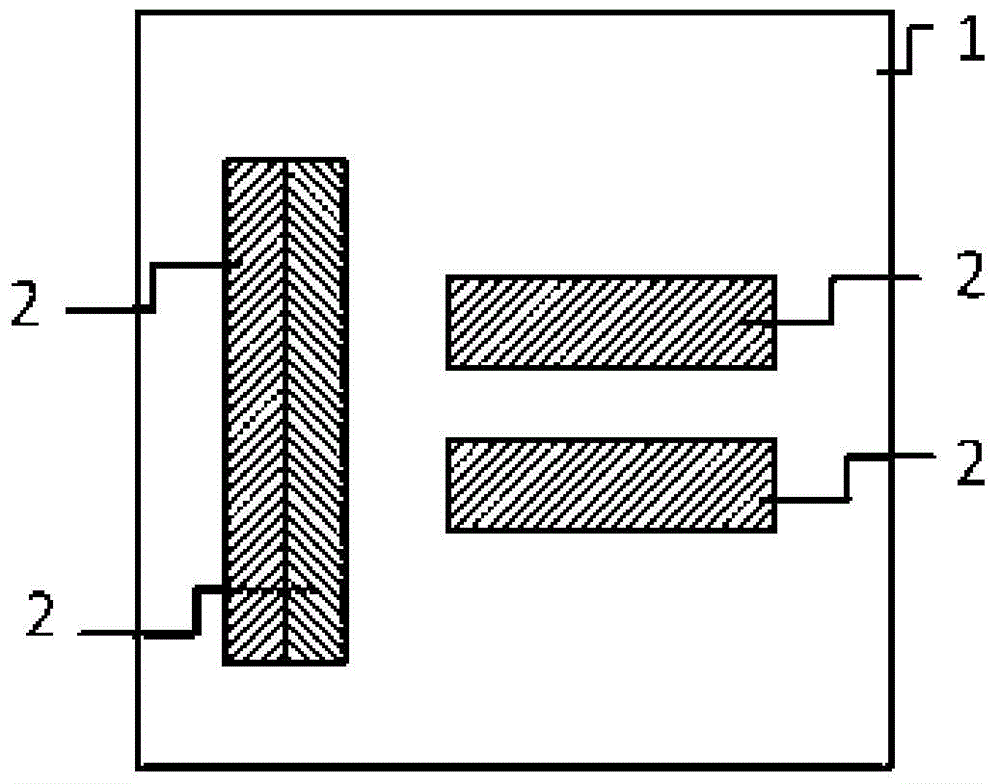

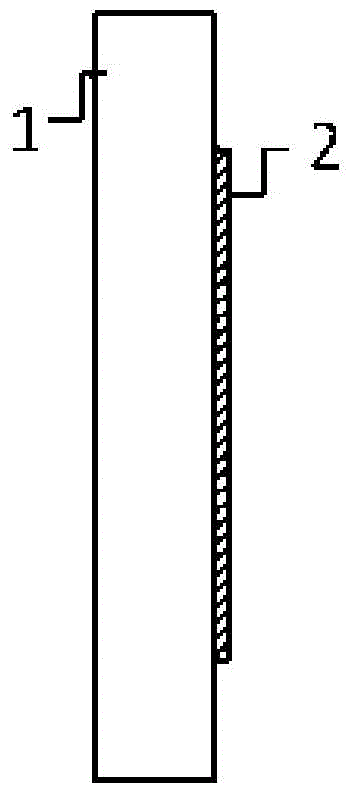

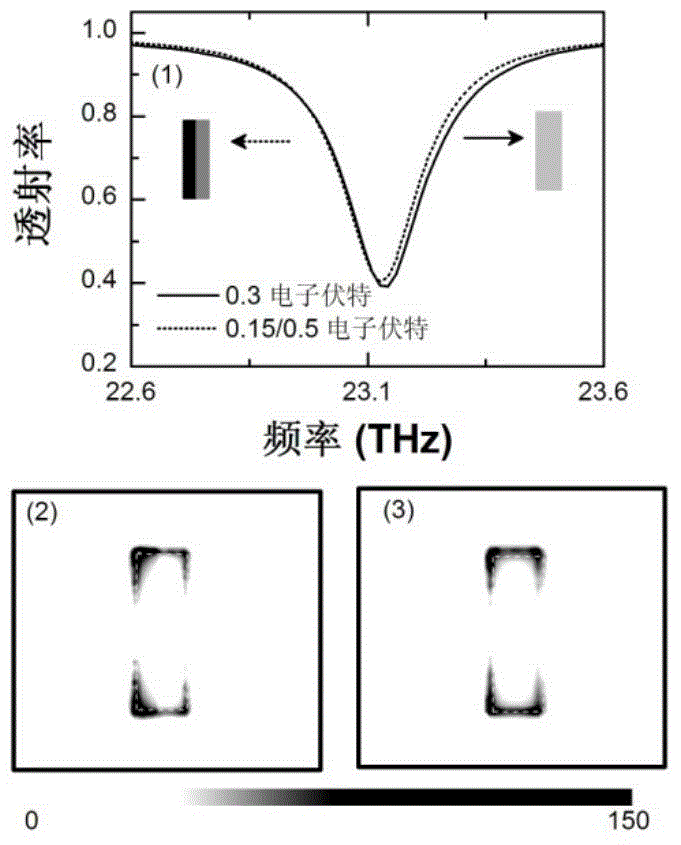

Fixed-frequency slow wave adjustable device

InactiveCN104536161ASmall scaleStrong optical responseNon-linear opticsMiniaturizationDielectric substrate

The invention relates to a fixed-frequency slow wave adjustable device which comprises a dielectric substrate and four graphene strips arranged on the dielectric substrate. Two graphene strips are tightly arrayed vertically and are used as electromagnetism-like induced transparency illuminated state units. The other two graphene strips are arrayed by a certain distance up and down horizontally and are used as electromagnetism-like induced transparency dark state units. Compared with the prior art, the structure is miniaturized, in addition, the optical response of graphene at a terahertz wave band is very strong so that in a transmission direction, one structure layer can achieve six-magnitude-order light speed lowering, the Fermi level of the graphene is very sensitive to external voltage, accordingly, the optical response of the graphene can be adjusted by adjusting the external voltage of the device, and slow wave adjustable performance is achieved.

Owner:TONGJI UNIV

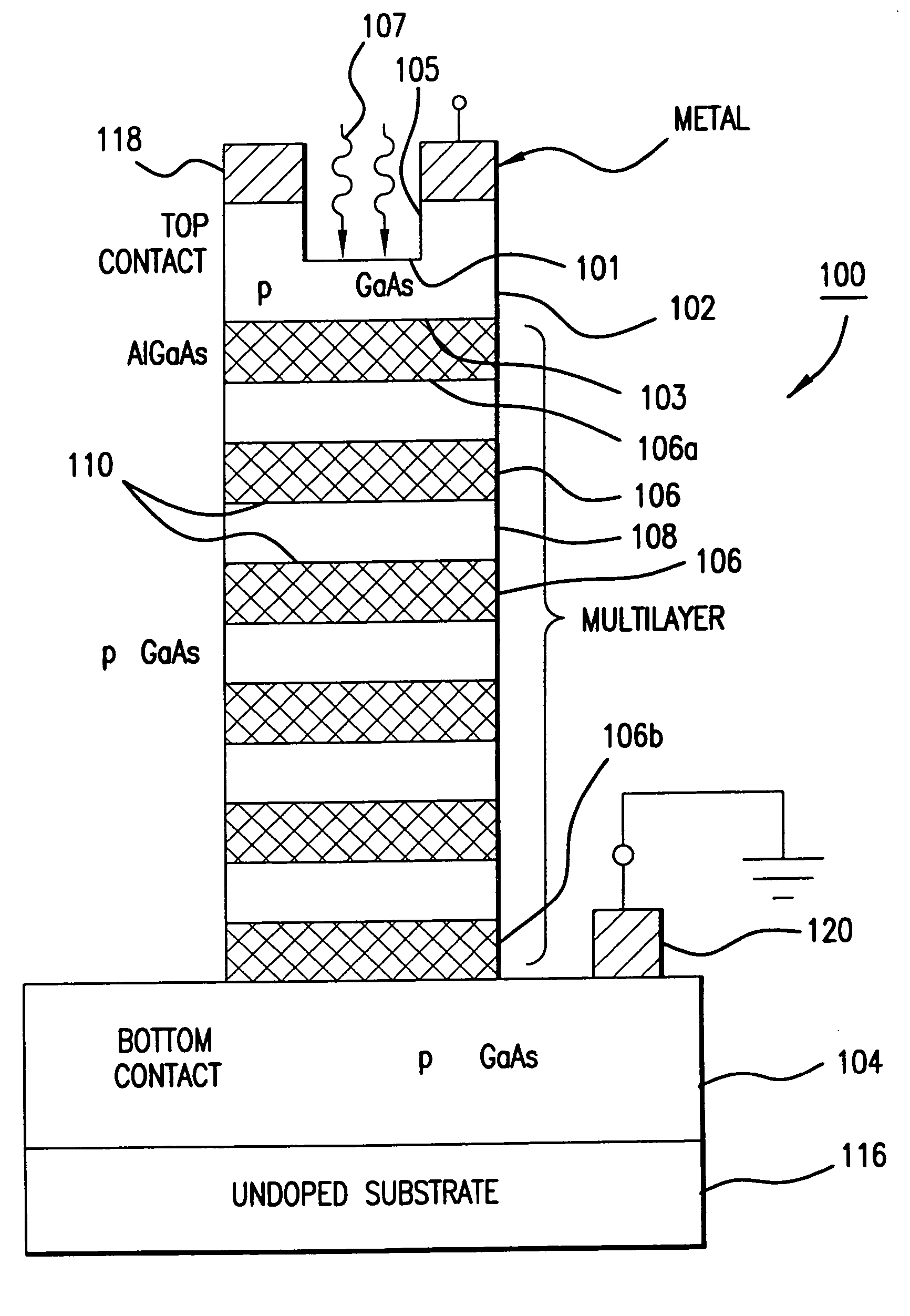

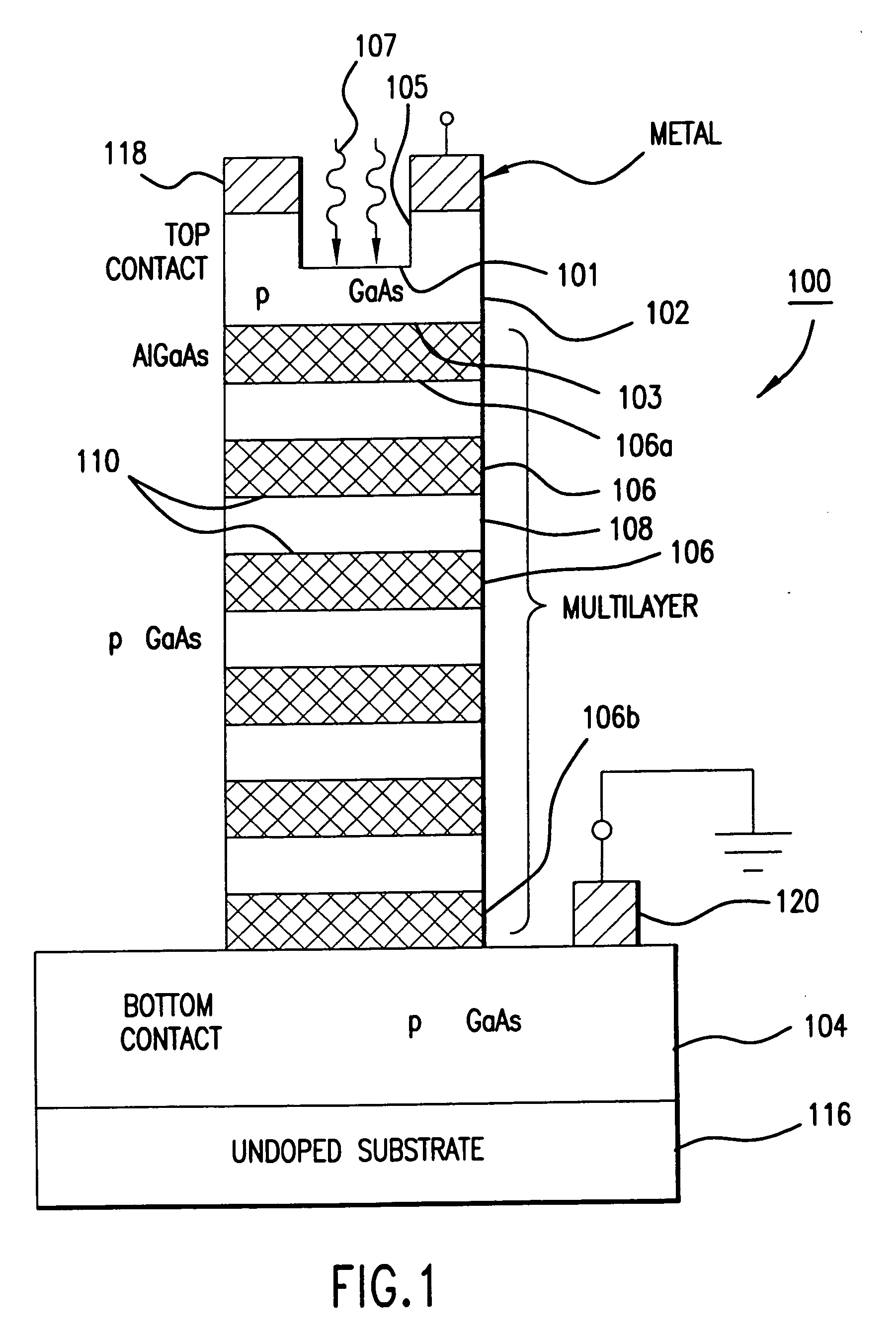

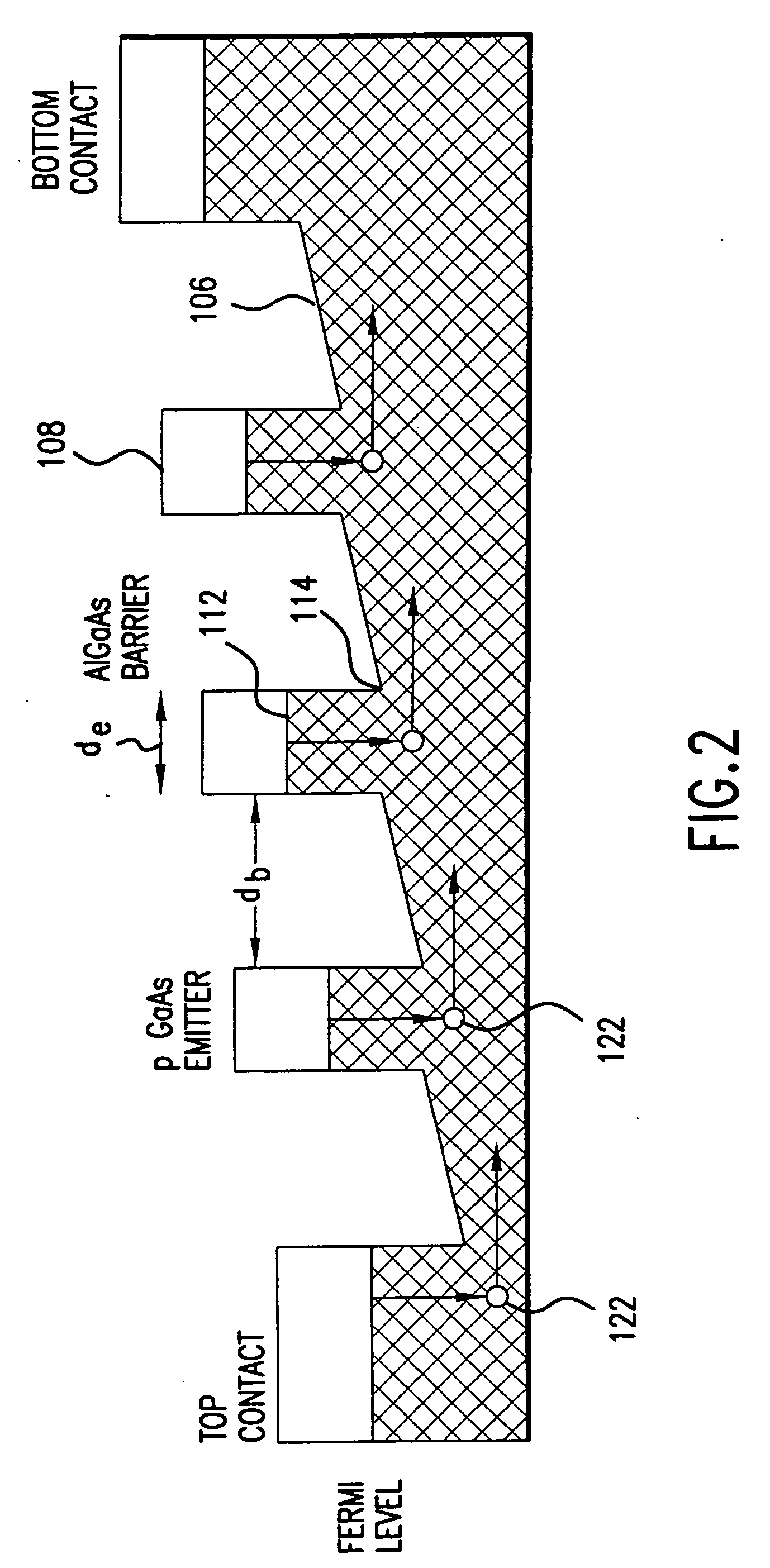

Heterojunction far infrared photodetector

A photodetector and method of detecting far infrared optical signals. In one embodiment of the present invention, the photodetctor has a plurality of N barriers, N being an integer greater than 1, each barrier being a layer of a material made from a first and a second group III elements and a first group V element and characterized by a bandgap. The photodetector further has a plurality of N−1 emitters, each emitter being a layer of material made from a third group III element and a second group V element and characterized by a bandgap different from that of the barriers and having at least one free carrier responsive to optical signals, wherein each emitter is located between two barriers so as to form a heterojunction at each interface between an emitter and a barrier. Moreover, each emitter is doped with a first group II, IV or VI element to cause free carriers in the emitter, wherein at least one construction parameter of each emitter causes at least one free carrier to occupy a range of substantially continuously distributed energies characterized by a three dimensional Fermi level and respond to optical signals having wavelength in the range of 3 to 100 μm with significant absorption.

Owner:GEORGIA STATE UNIV RES FOUND INC

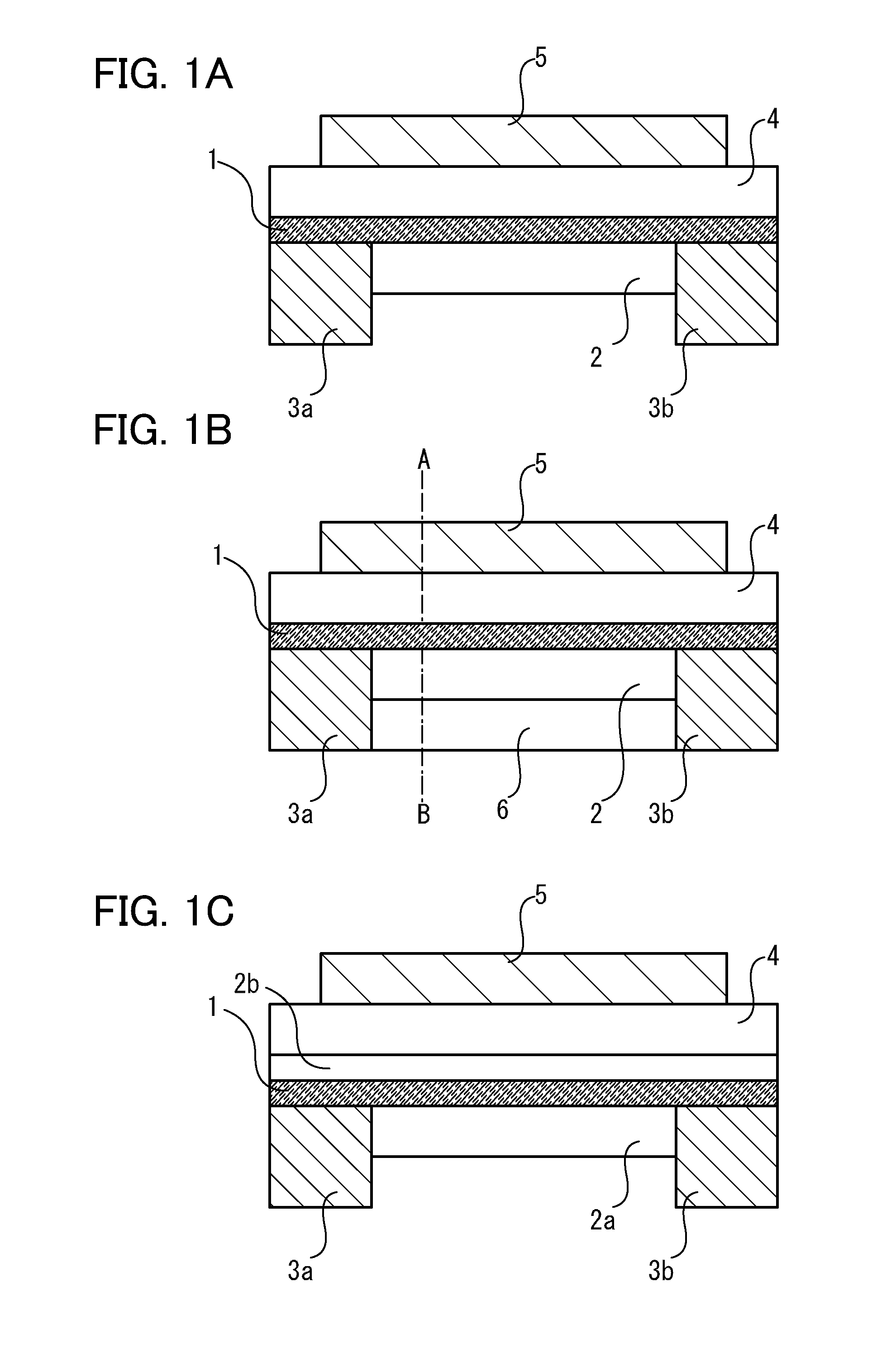

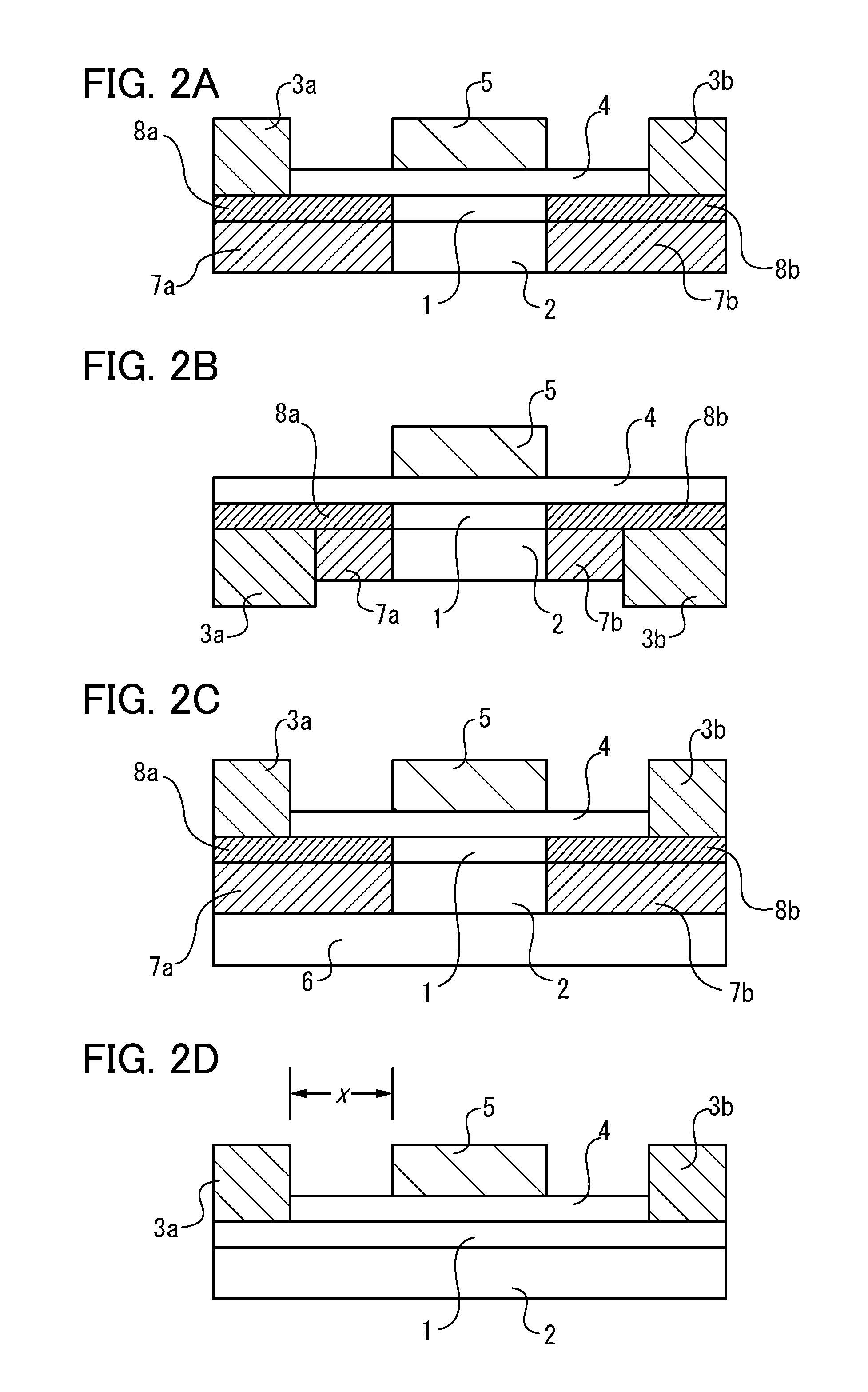

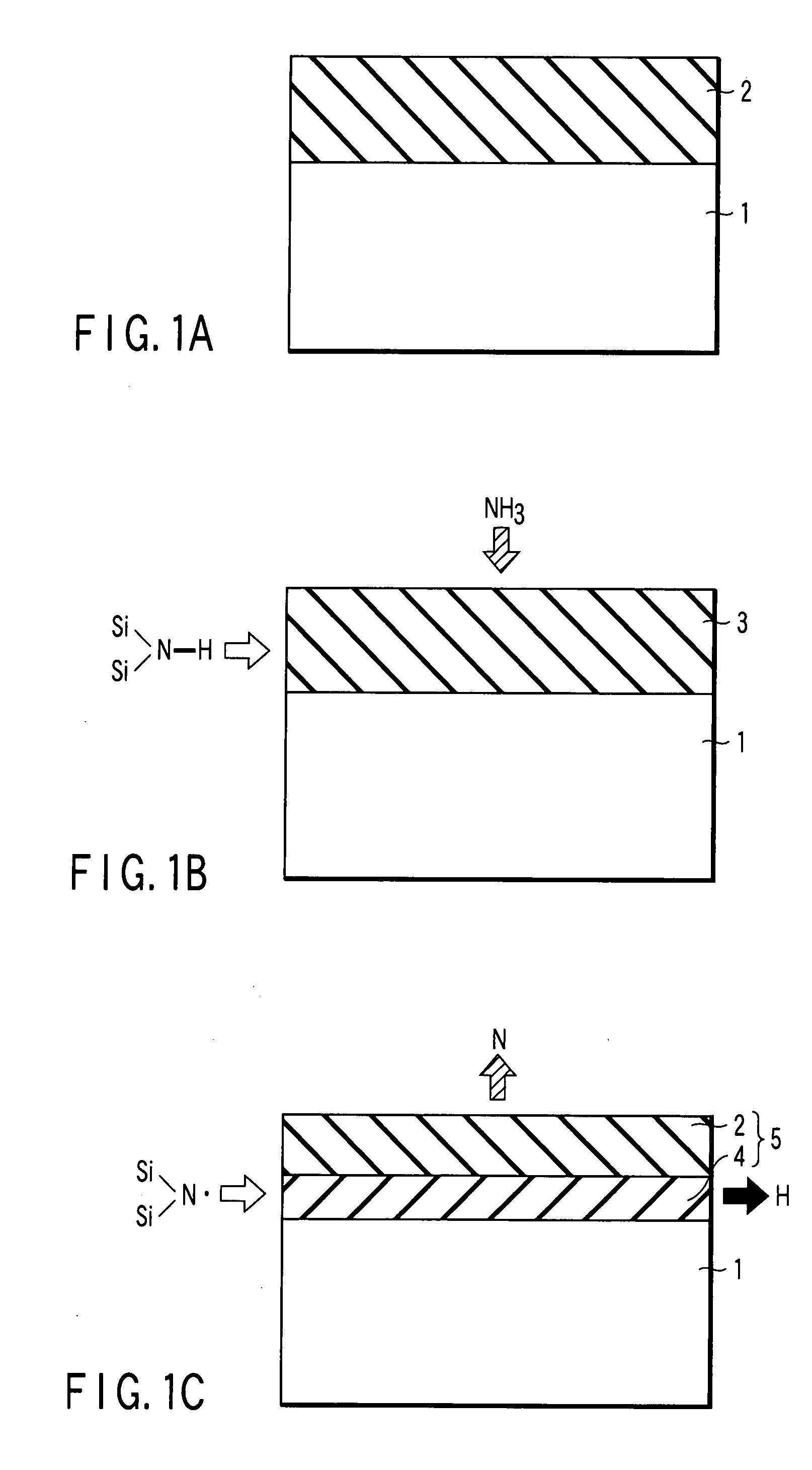

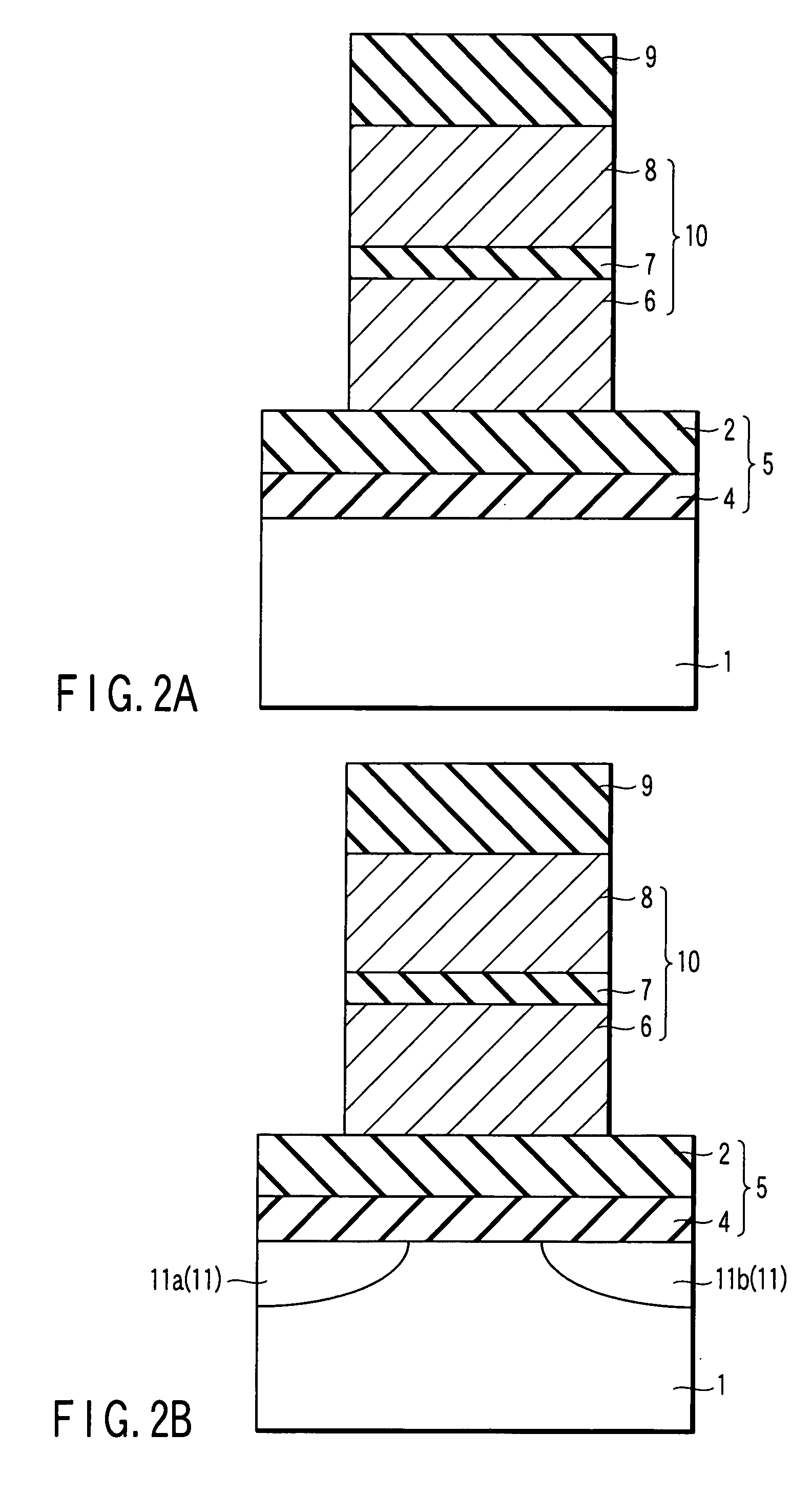

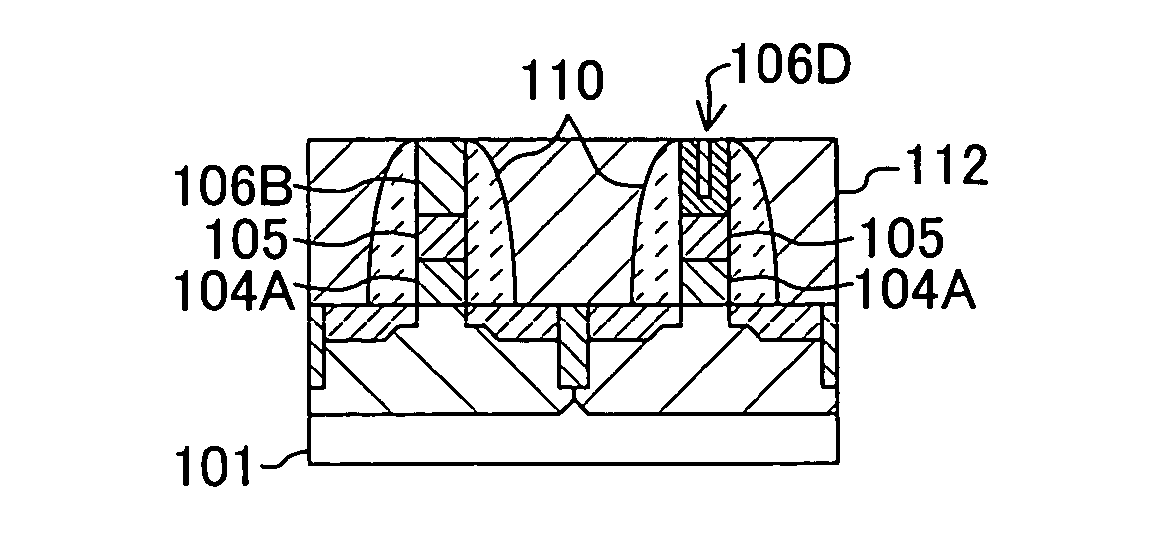

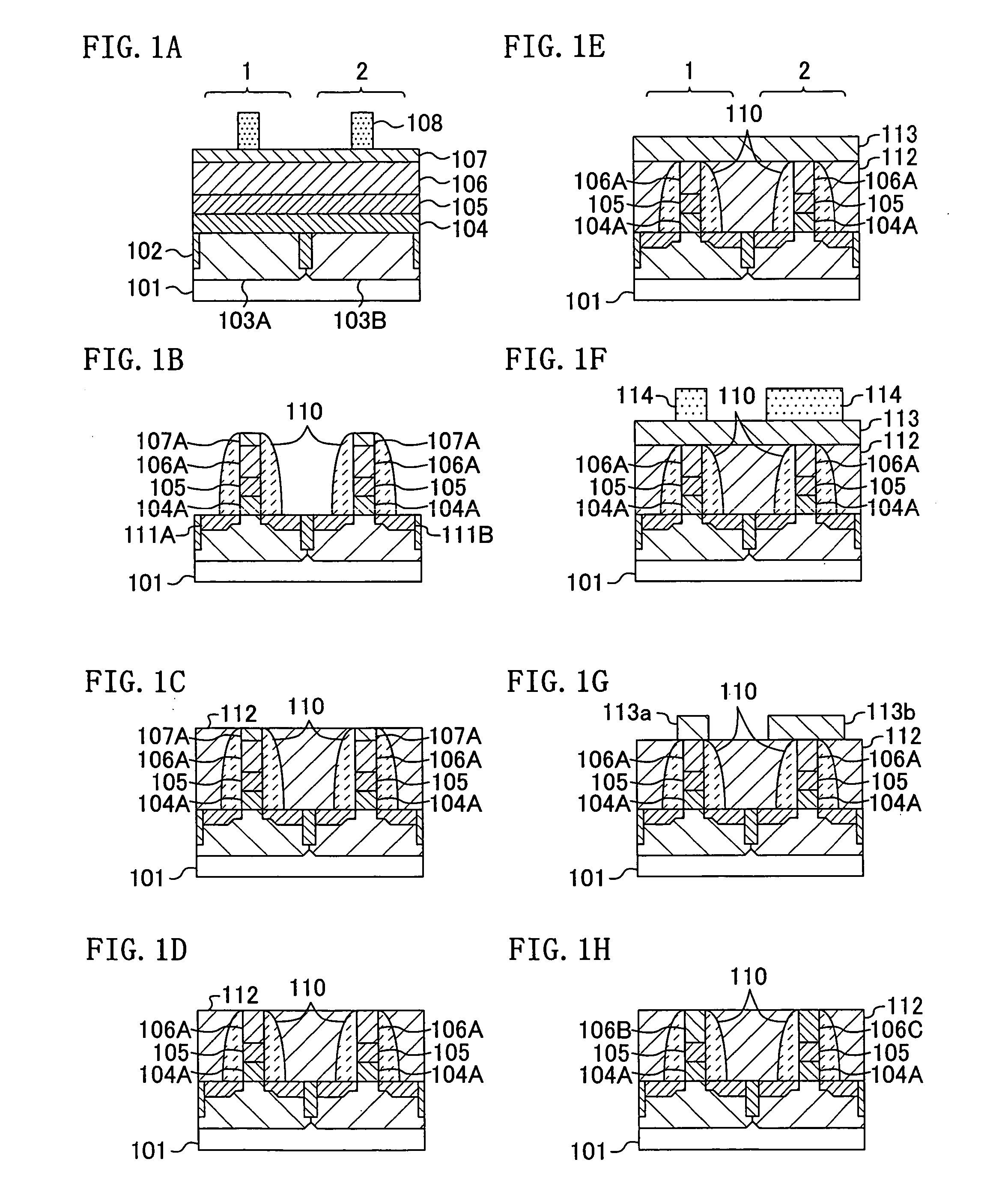

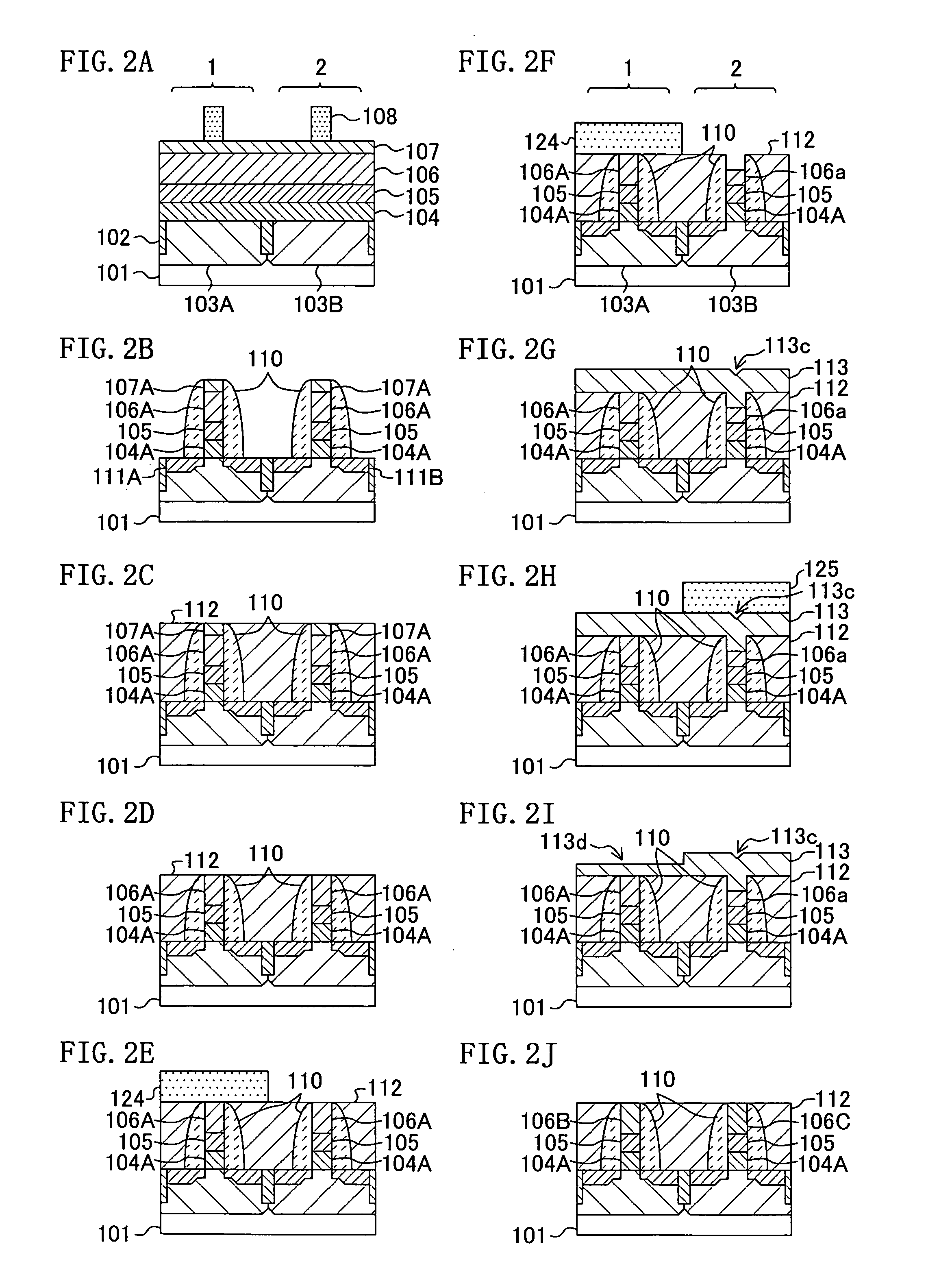

Semiconductor device and method for manufacturing the same

A semiconductor device including a semiconductor substrate, a tunnel insulation film provided on the surface of the semiconductor substrate, charge trap states at which an electron potential energy is higher than a Fermi level of the semiconductor substrate being provided at part of the tunnel insulation film at least in the vicinity of an interface with the semiconductor substrate, and at least one charge storage layer being provided on the tunnel insulation film, charges supplied from the semiconductor substrate via the tunnel insulation film being accumulated in the charge storage layer.

Owner:KK TOSHIBA

Influence of surface geometry on metal properties

InactiveUS7074498B2Easy transferPromotes destructive interferenceLine/current collector detailsPolycrystalline material growthWork functionFermi energy

The influence of surface geometry on metal properties is studied within the limit of the quantum theory of free electrons. It is shown that a metal surface can be modified with patterned indents to increase the Fermi energy level inside the metal, leading to decrease in electron work function. This effect would exist in any quantum system comprising fermions inside a potential energy box. Also disclosed is a method for making nanostructured surfaces having perpendicular features with sharp edges.

Owner:BOREALIS TECH LTD

Layer structure for a group-iii-nitride normally-off transistor

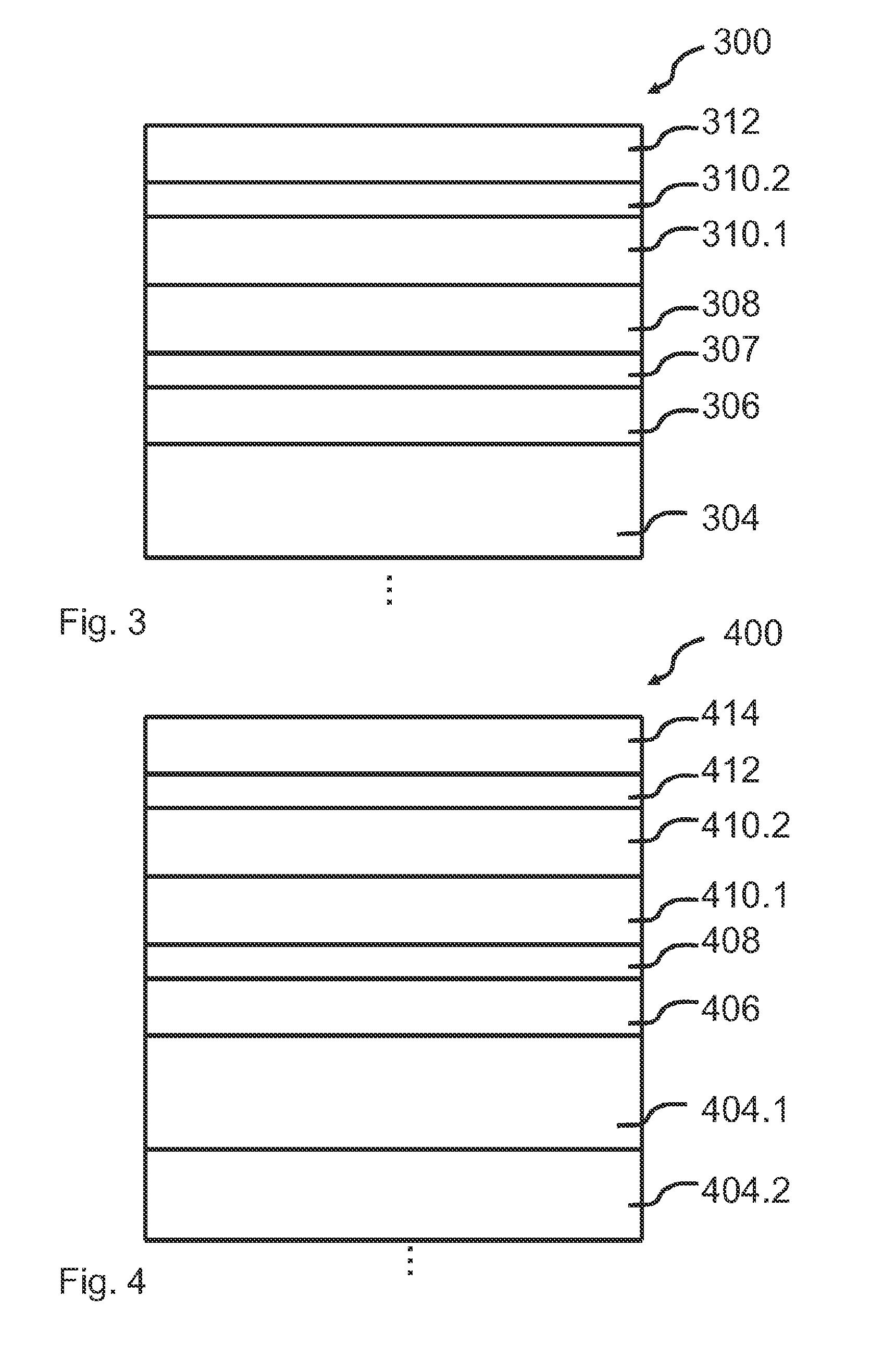

A layer structure for a normally-off transistor has an electron-supply layer made of a group-III-nitride material, a back-barrier layer made of a group-III-nitride material, a channel layer between the electron-supply layer and the back-barrier layer, made of a group-III-nitride material having a band-gap energy that is lower than the band-gap energies of the other layer mentioned. The material of the back-barrier layer is of p-type conductivity, while the material of the electron-supply layer and the material of the channel layer are not of p-type conductivity, the band-gap energy of the electron-supply layer is smaller than the band-gap energy of the back-barrier layer. In absence of an external voltage a lower conduction-band-edge of the third group-III-nitride material in the channel layer is higher in energy than a Fermi level of the material in the channel layer.

Owner:AZUR SPACE SOLAR POWER

Organic light emitting device and method for manufacturing the same

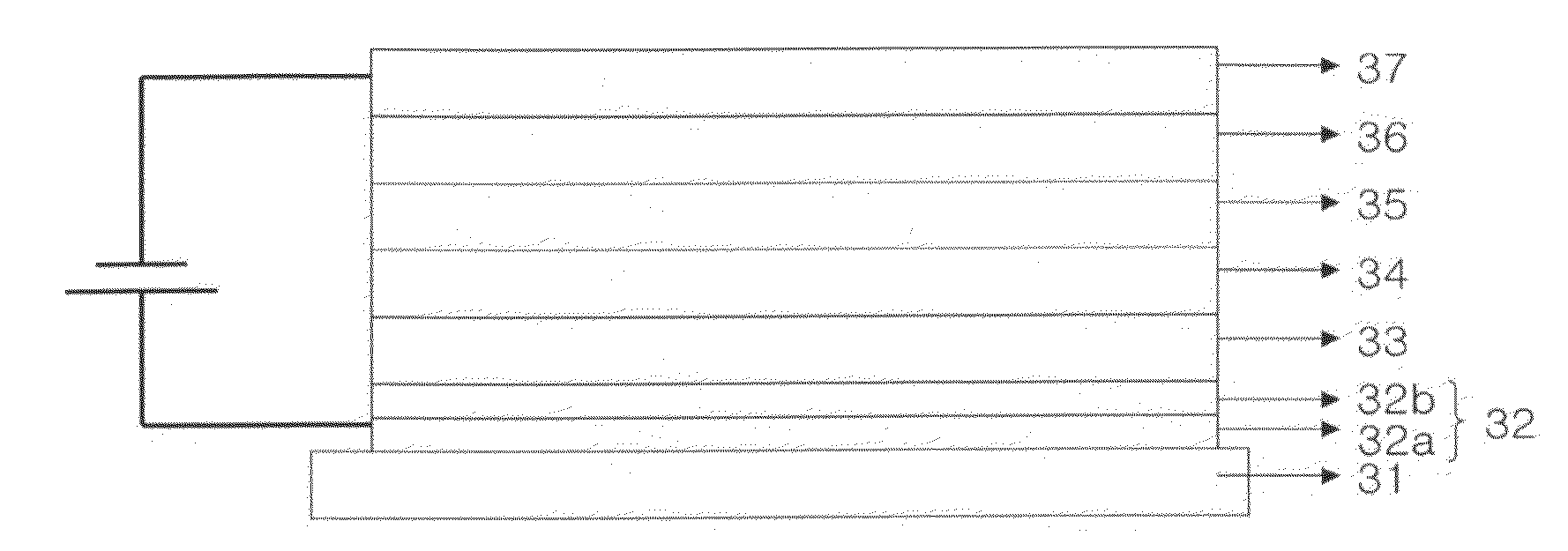

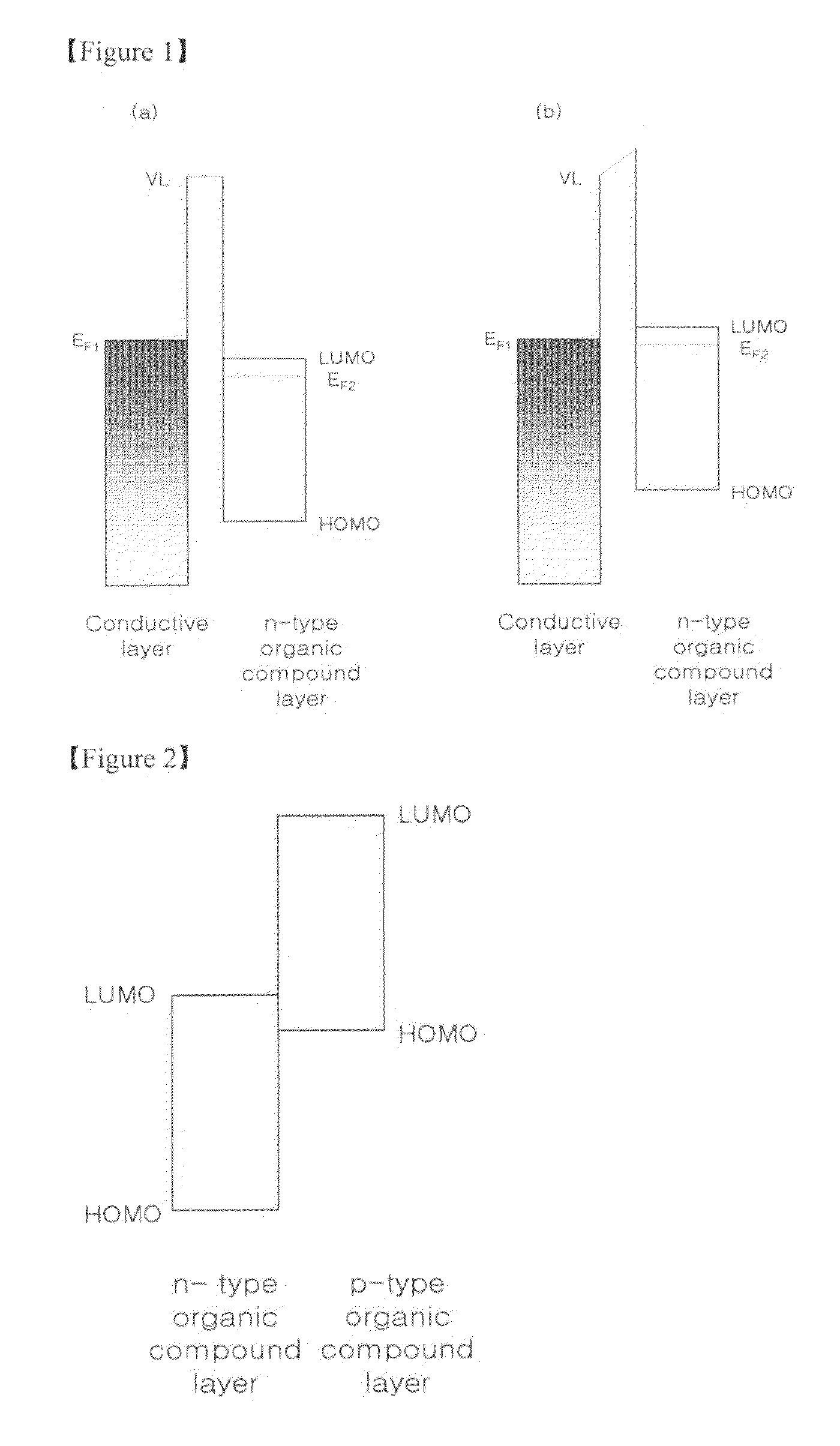

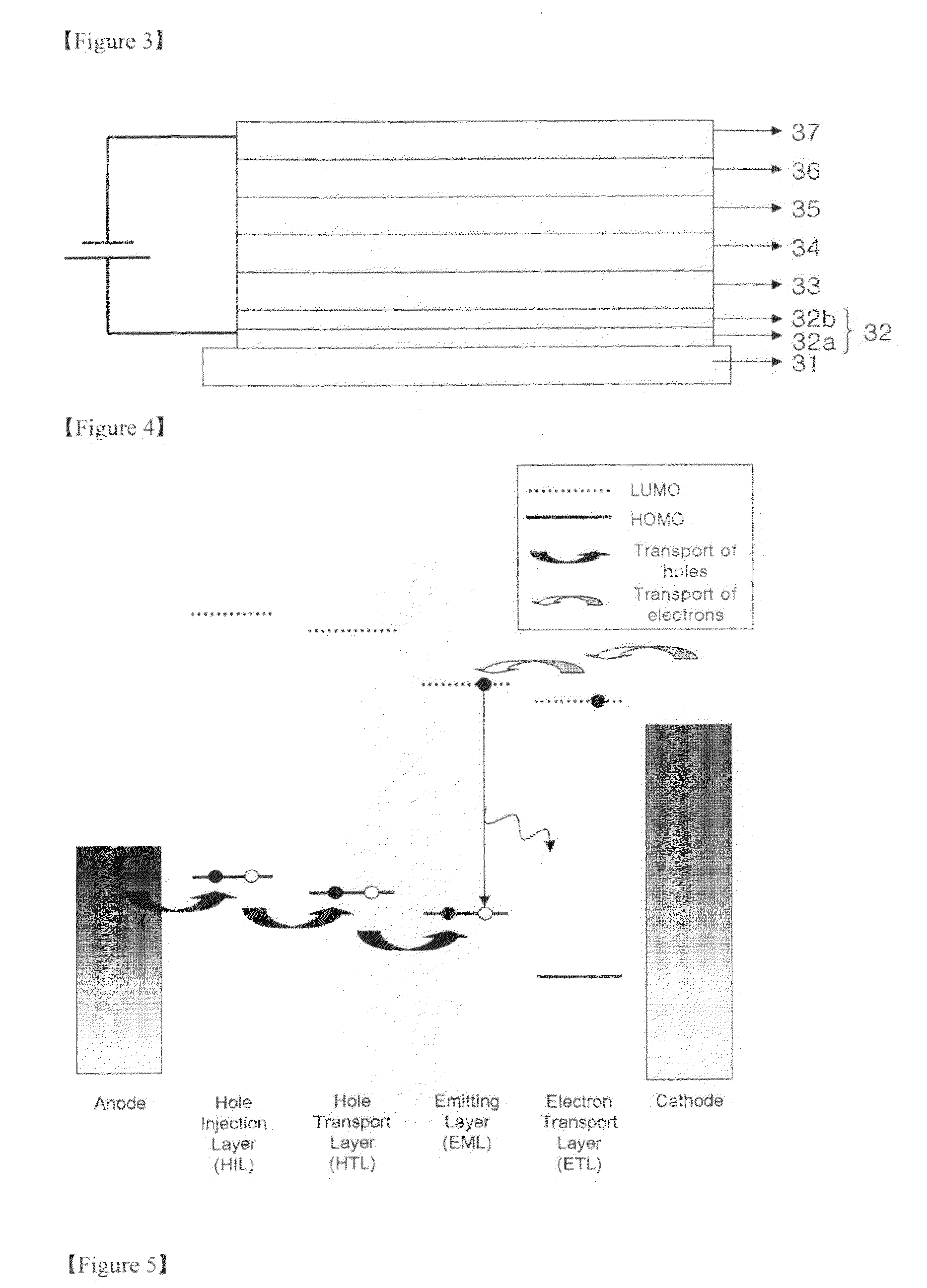

InactiveUS20090015150A1Lower energy barrierIncrease brightnessDischarge tube luminescnet screensElectroluminescent light sourcesAlkaline earth metalOrganic light emitting device

Disclosed is an organic light emitting device and a method for manufacturing the same. The organic light emitting device includes a first electrode, one or more organic compound layers, and a second electrode. The first electrode includes a conductive layer and an n-type organic compound layer disposed on the conductive layer. A difference in energy between an LUMO energy level of the n-type organic compound layer of the first electrode and a Fermi energy level of the conductive layer of the first electrode is 4 eV or less. One of the organic compound layers interposed between the n-type organic compound layer of the first electrode and the second electrode is a p-type organic compound layer forming an NP junction along with the n-type organic compound layer of the first electrode. A difference in energy between the LUMO energy level of the n-type organic compound layer of the first electrode and an HOMO energy level of the p-type organic compound layer is 1 eV or less. One or more layers interposed between the conductive layer of the first electrode and the second electrode is n-doped with alkali earth metal; an alkali earth metal compound; an alkali metal compound; or La Ce, Pr, Nd, Sm, Eu, Tb, Th, Dy, Ho, Er, Em, Gd, Yb, Lu, Y or Mn, or metal compound containing at least one of the above types of metal.

Owner:LG CHEM LTD

Resonant cavity enhanced grapheme electric absorption modulator

ActiveCN103091870AIncreased freedom in spectral designEasy to integrateNon-linear opticsElectro-absorption modulatorLight modulation

The invention discloses a resonant cavity enhanced grapheme electric absorption modulator which is manufactured on an underlay. The resonant cavity enhanced grapheme electric absorption modulator comprises a lower reflector formed on the underlay, a medium buffering layer formed on the lower reflector, a single layer grapheme thin membrane formed on the medium buffering layer, an upper reflector formed on a distributed Bragg reflector (DBR) structure of the single layer grapheme thin membrane, and a metal positive electrode formed on the single layer grapheme thin membrane and arranged on the periphery of the upper reflector in a surrounding mode. Due to the fact that light lights on a component in a perpendicular mode, the resonant cavity enhanced grapheme electric absorption modulator is capable of adjusting level of Fermi level in grapheme by exerting gate bias on the component, and thus whether the grapheme absorbs the light is controlled, and the purpose of light modulation is achieved. The resonant cavity enhanced grapheme electric absorption modulator has the advantages of being capable of being large in degree of freedom of design of size and spectrum modulation range, low in consumption, low in insertion loss, free from polarization state requirements to light signals, and prone to silicon substrate integration.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

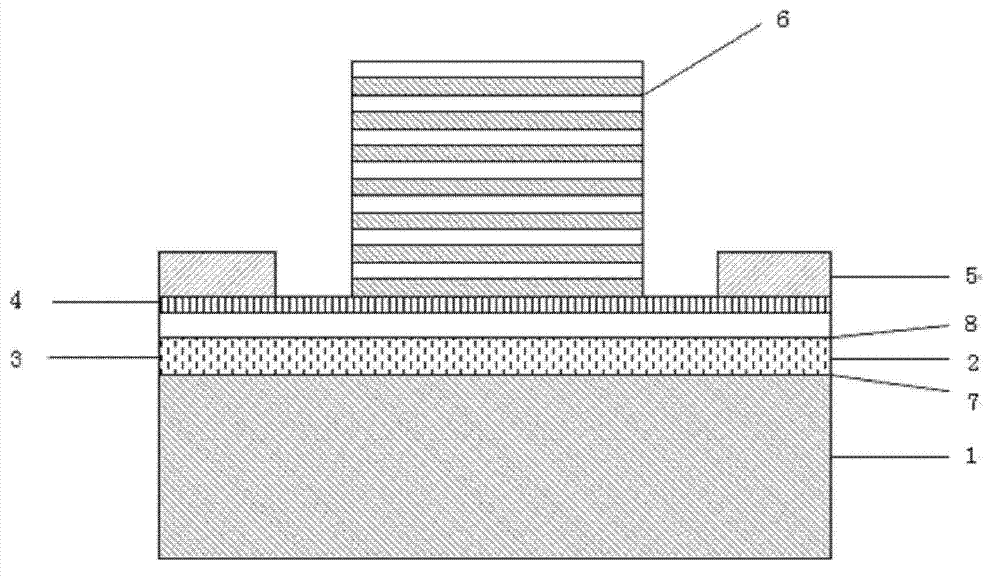

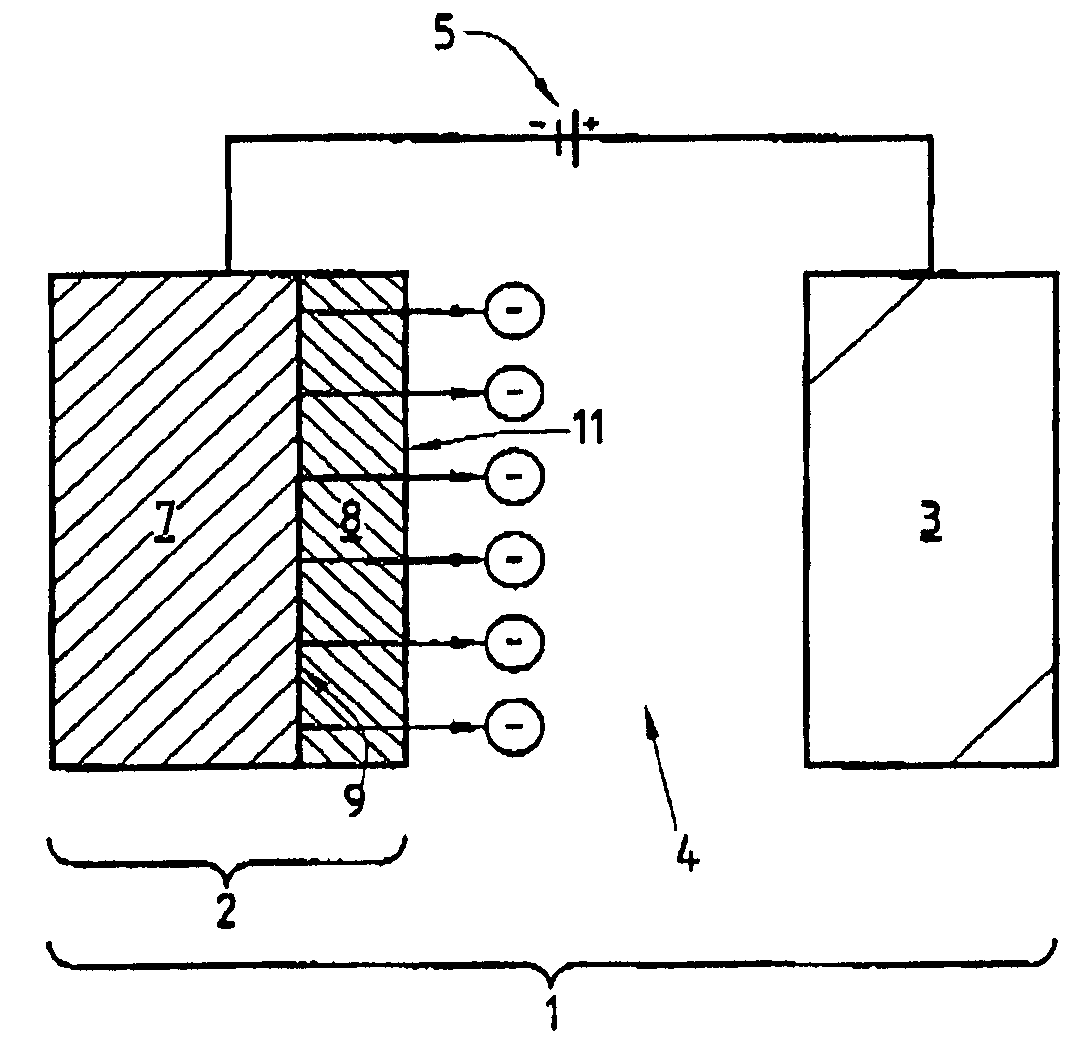

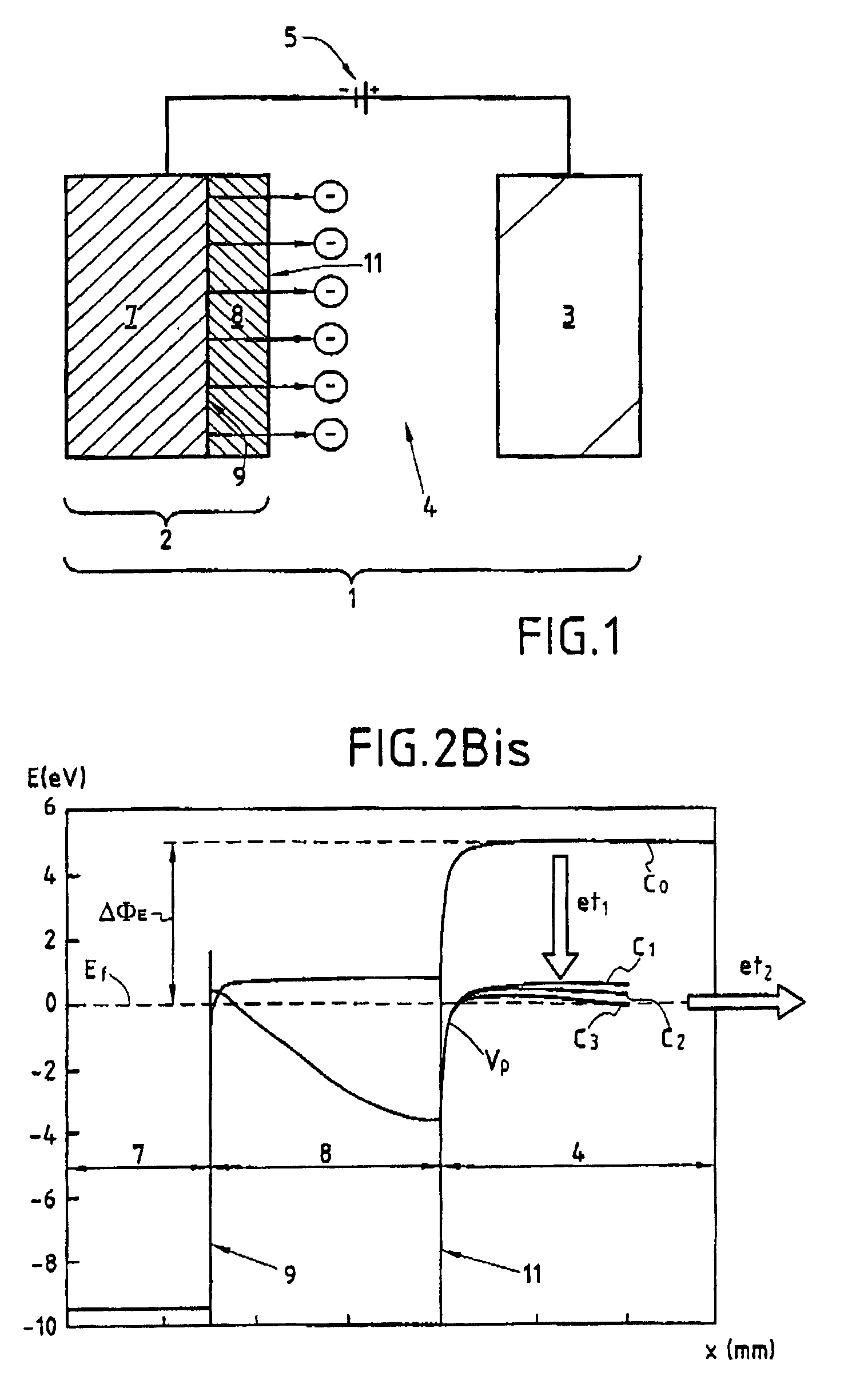

Method and device for extraction of electrons in a vacuum and emission cathodes for said device

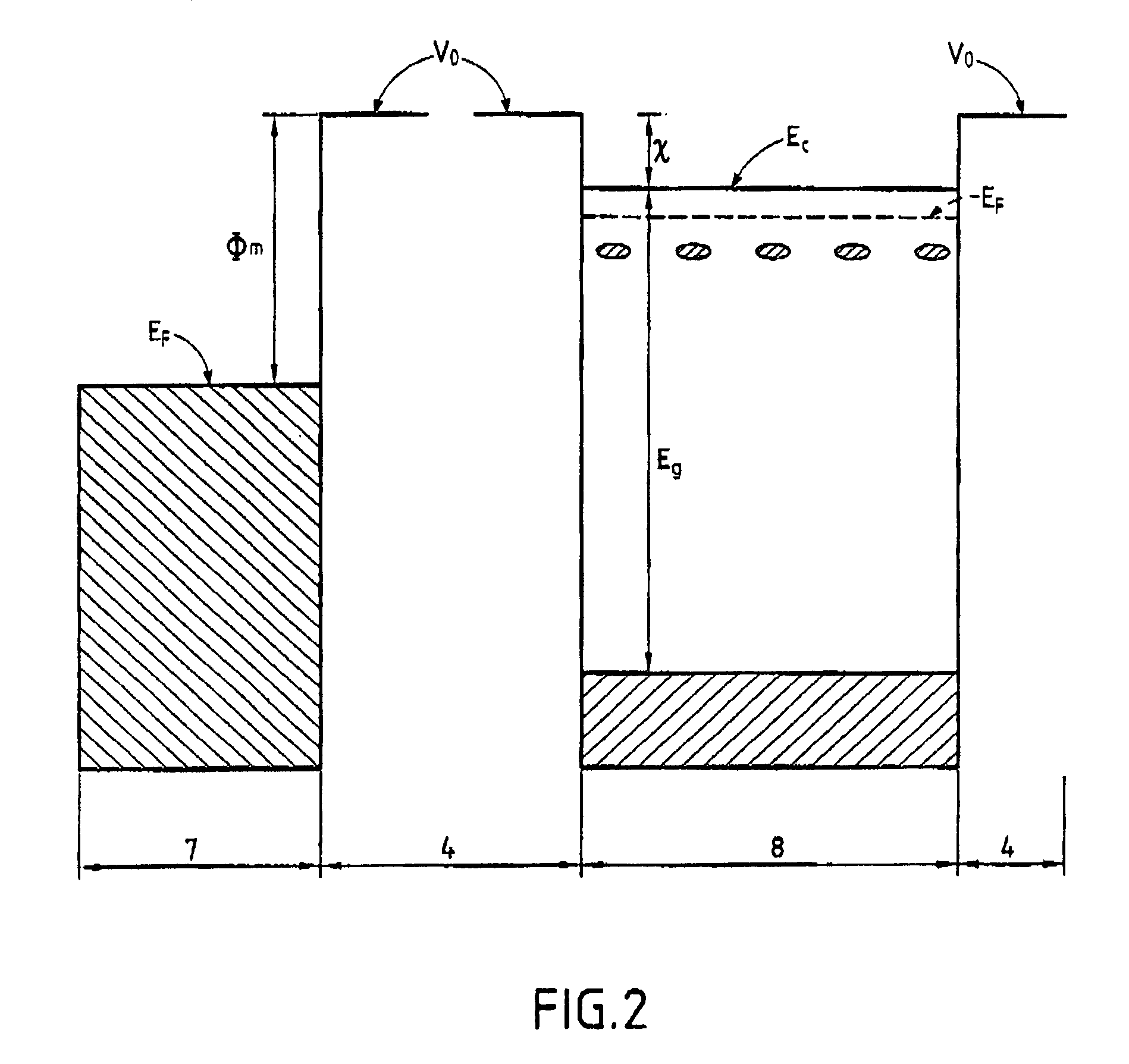

InactiveUS7057333B1Discharge tube luminescnet screensCathode ray tubes/electron beam tubesElectron fluxFermi level

The method of the invention for extracting electrons in a vacuum consists in:making a cathode presenting at least one junction (9) between a metal (7) acting as an electron reservoir and an n-type semiconductor (8) possessing a surface potential barrier with a height of a few tenths of an electron volt, and presenting thickness lying in the range 1 nm to 20 nm;injecting electrons through the metal / semiconductor junction (9) to create a space charge in the semiconductor (8) sufficient to lower the surface potential barrier of the semiconductor to a value that is less than or equal to 1 eV relative to the Fermi level of the metal (7); andusing the bias source creating an electric field in the vacuum to control the height of the surface potential barrier (Vp) of the n-type semiconductor in order to control the emission of the electron flux towards the anode.

Owner:UNIV CLAUDE BERNARD LYON 1

Insulating buffer film and high dielectric constant semiconductor device and method for fabricating the same

InactiveUS7495298B2Improve uniformityHigh yieldSemiconductor/solid-state device manufacturingSemiconductor devicesFermi levelTransistor

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

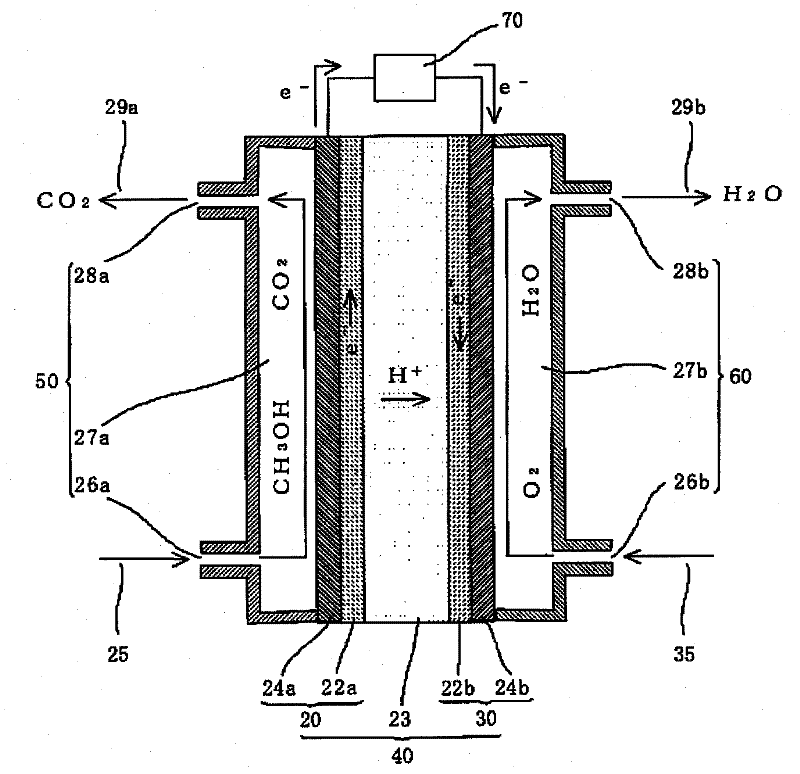

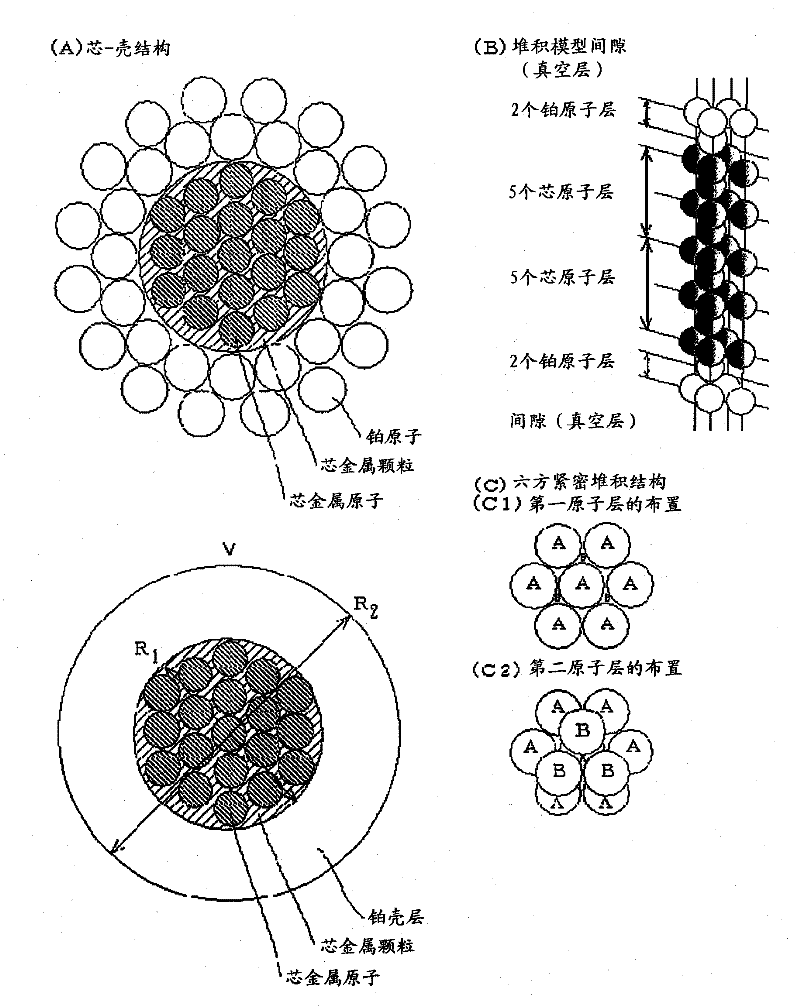

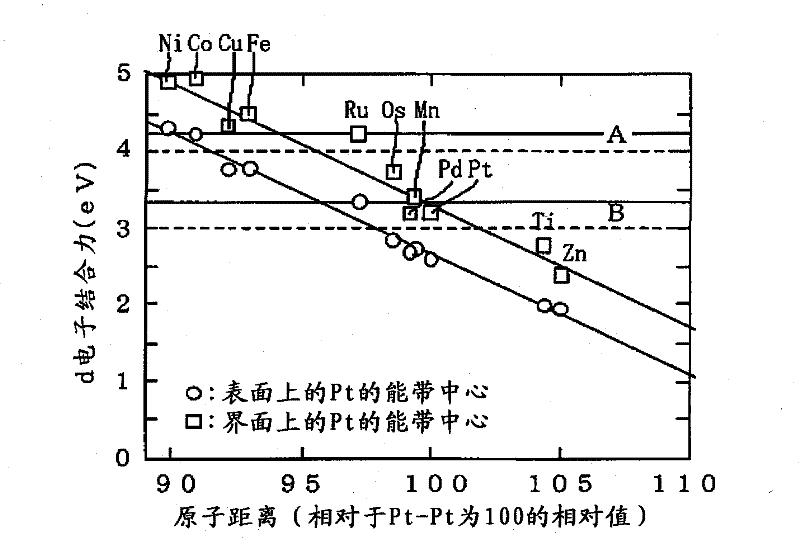

Platinum-containing catalyst, process for producing the platinum-containing catalyst, electrode, and electrochemical device

InactiveCN102196863AHigh output maintenanceIncreased durabilityCell electrodesCatalyst activation/preparationBinding energyPower flow

Disclosed is a core-shell-type platinum-containing catalyst that can reduce the amount of platinum used and has high catalytic activity and stability. Also disclosed are a process for producing the core-shell-type platinum-containing catalyst, an electrode, and an electrochemical device. The core-shell-type platinum-containing catalyst comprises particles each comprising a core particle (average particle diameter: R1) formed of a non-platinum element and a platinum shell layer (average thickness: ts) and satisfies the following relationships: 1.4 nm = R1 = 3.5 nm; and 0.25 nm = ts = 0.9 nm. The core particle contains an element satisfying Eout = 3.0 eV wherein Eout represents the average bound energy, based on Fermi level, of 5d orbit electrons of platinum present on the outermost surface of the platinum shell. A fuel cell comprising a platinum-containing catalyst as an anode catalyst, the platinum-containing catalyst comprising a Ru particle as a core particle, has an output density of not less than 70 mW / cm2 at a current density of 300 mA / cm2 and an output retention of not less than about 90%.

Owner:SONY CORP

Radiation-hardened silicon-on-insulator CMOS device, and method of making the same

A method for eliminating the radiation-induced off-state current in the P-channel ultrathin silicon-on-sapphire transistor, by providing a retrograde dopant concentration profile that has the effect of moving the Fermi level at the back of the device away from that part of the bandgap where the interface states are located. When the Fermi level does not swing through this area in any region of operation of the device, subthreshold stretchout of the I-V curves does not occur.

Owner:PSEMI CORP

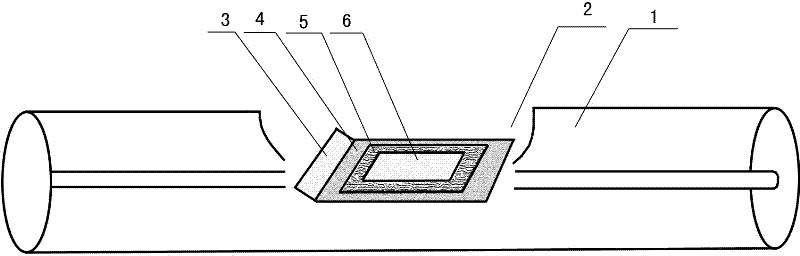

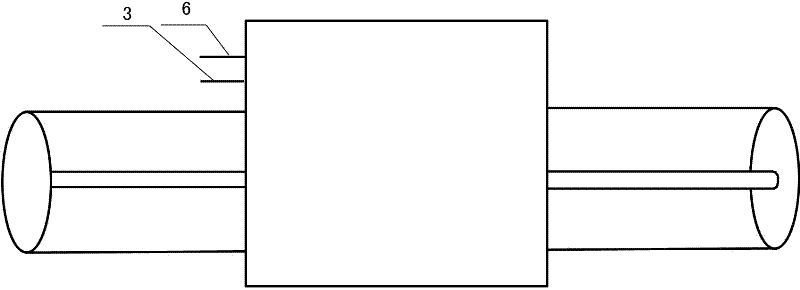

D-type optical fiber based graphene electro-optical modulator and preparation method thereof

InactiveCN102540506ACompliant with Modulated Extinction Ratio RequirementsMeet the Coupling DilemmaNon-linear opticsGrapheneMetal electrodes

The invention relates to a D-type optical fiber based graphene electro-optical modulator which is characterized in that one section of an optical fiber (1) is prepared into a D-type groove, graphene (4) is laid on the surface of a D-type optical fiber (2), one end of the graphene (4) is provided with a metal electrode and lead (3), and a film of the graphene (4) is plated with an insulating layer (5); the insulating layer (5) is an Al2O3 insulating layer or an insulating layer with a high dielectric constant, and the insulating layer (5) is plated beside a metal electrode and lead (6) on the film of the graphene (4); and the metal electrode-lead (6) is a conductive electrode, and the conductive electrode is made of Au or Pt. According to the invention, electrical signals are applied to the two electrode and leads so as to generate an electric field perpendicular to the film of the graphene (4), thereby changing the Fermi level of the graphene (4), and further realizing the electro-optical modulating function of the graphene (4) through changing the optical signal absorption strength of the graphene (4).

Owner:泰州巨纳新能源有限公司