HK SOI LDMOSdevice having three-grating structure

A gate structure and device technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of large specific on-resistance and high power consumption, and achieve the effect of increasing channel density, eliminating latch-up effect, and increasing current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

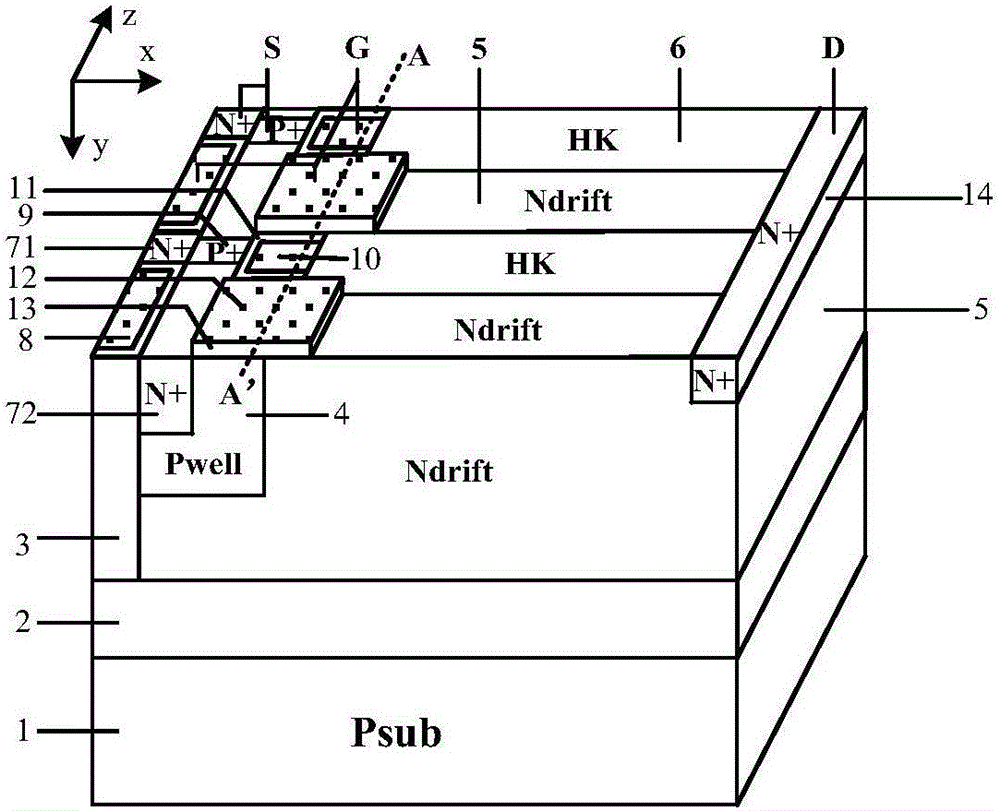

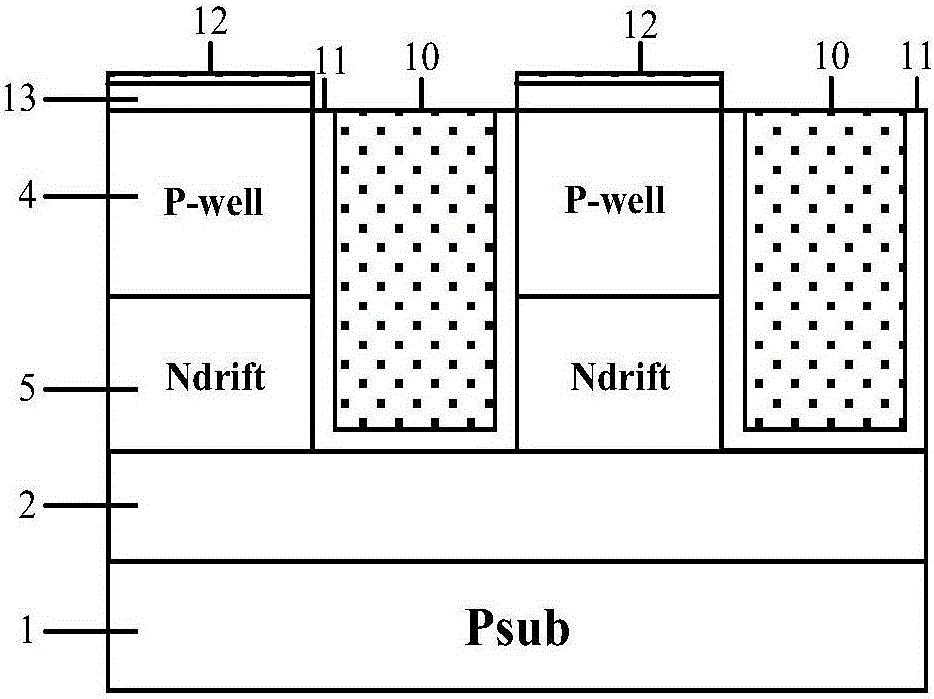

[0027] Such as figure 1 As shown, the specific structure of this example includes a second conductivity type semiconductor substrate layer 1 and a dielectric buried layer 2 above it; the upper surface of the dielectric buried layer 2 has a first conductivity type semiconductor drift region 5, and the upper layer of the drift region 5 There is a second conductivity type semiconductor body region 4 on one side, and a high-K dielectric 6 is embedded in the drift region 5 close to the semiconductor body region 4. The high-K dielectric 6 and the drift region 5 are alternately arranged in the longitudinal direction. It is a material with a dielectric constant greater than 3.9; a first trench gate structure extending to the buried dielectric layer 2 is formed through the side of the semiconductor body region 4 away from the drift region 5. The first trench gate structure includes a first trench gate structure. The trench gate dielectric 3 and the first conductive material 8 surrounded...

Embodiment 2

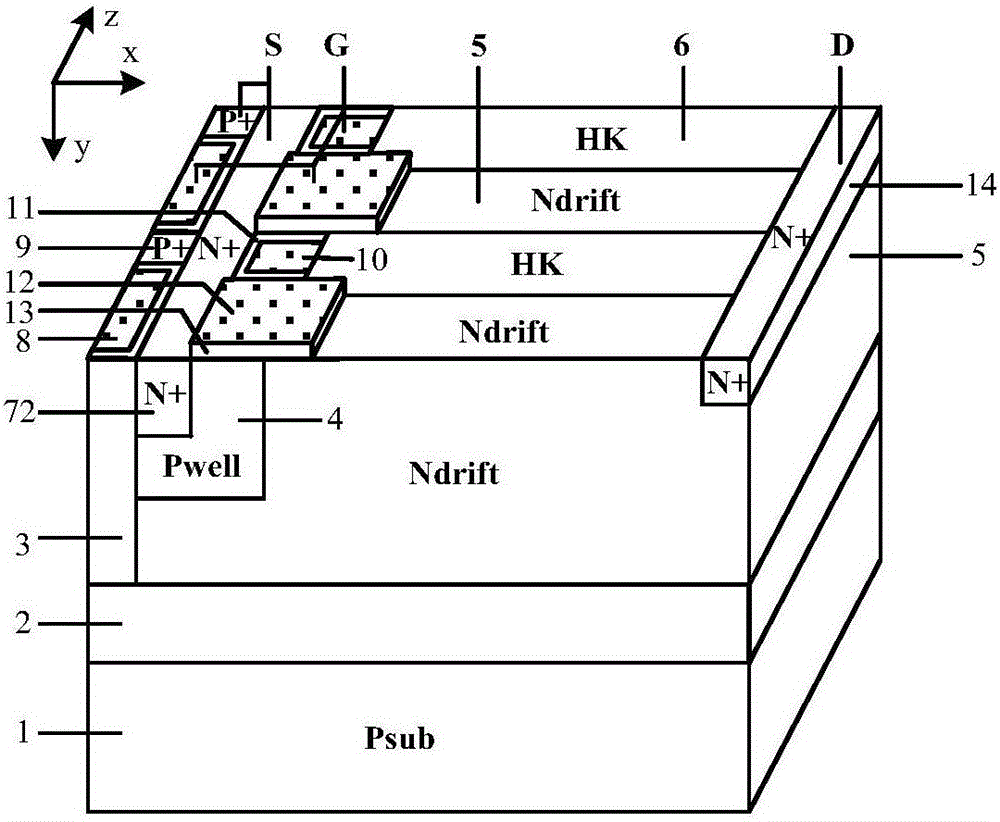

[0030] Such as image 3 As shown, compared with Embodiment 1, the first trench gate structure is segmented in the longitudinal direction, and the upper layer of the semiconductor body region 4 between every two first trench gate structures has the second conductivity type. A heavily doped semiconductor body contact region 9; on the side of the upper layer of the semiconductor body region 4 that is in contact with the first trench gate, there is a heavily doped semiconductor source region 72 of the first conductivity type, and the source structure includes a heavily doped semiconductor source region 72 of the first conductivity type. The doped semiconductor source region 72 and the heavily doped semiconductor body contact region 9 of the second conductivity type.

[0031] Compared with the embodiment 1, the first conductive type heavily doped semiconductor source region and the second conductive type heavily doped semiconductor body contact region can be formed by the entire ion im...

Embodiment 3

[0033] Such as Figure 4 As shown, compared with embodiment 1, the first trench gate structure is continuous in the longitudinal direction; the upper layer of the semiconductor body region 4 between the first trench gate and the planar gate is of the first conductivity type The heavily doped semiconductor source region 72, the upper layer of the semiconductor body region 4 between the first trench gate and the second trench gate is the second conductivity type heavily doped semiconductor body contact region 9, and the source structure includes a first A heavily doped semiconductor source region 72 of one conductivity type and a heavily doped semiconductor body contact region 9 of a second conductivity type.

[0034] Compared with the first embodiment, the first trench gate structure is continuous in this embodiment, and it can be used as a dielectric isolation layer in the low and high voltage region of the integrated circuit, which facilitates the isolation of high and low voltag...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More