Patents

Literature

198results about How to "Lower specific on-resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

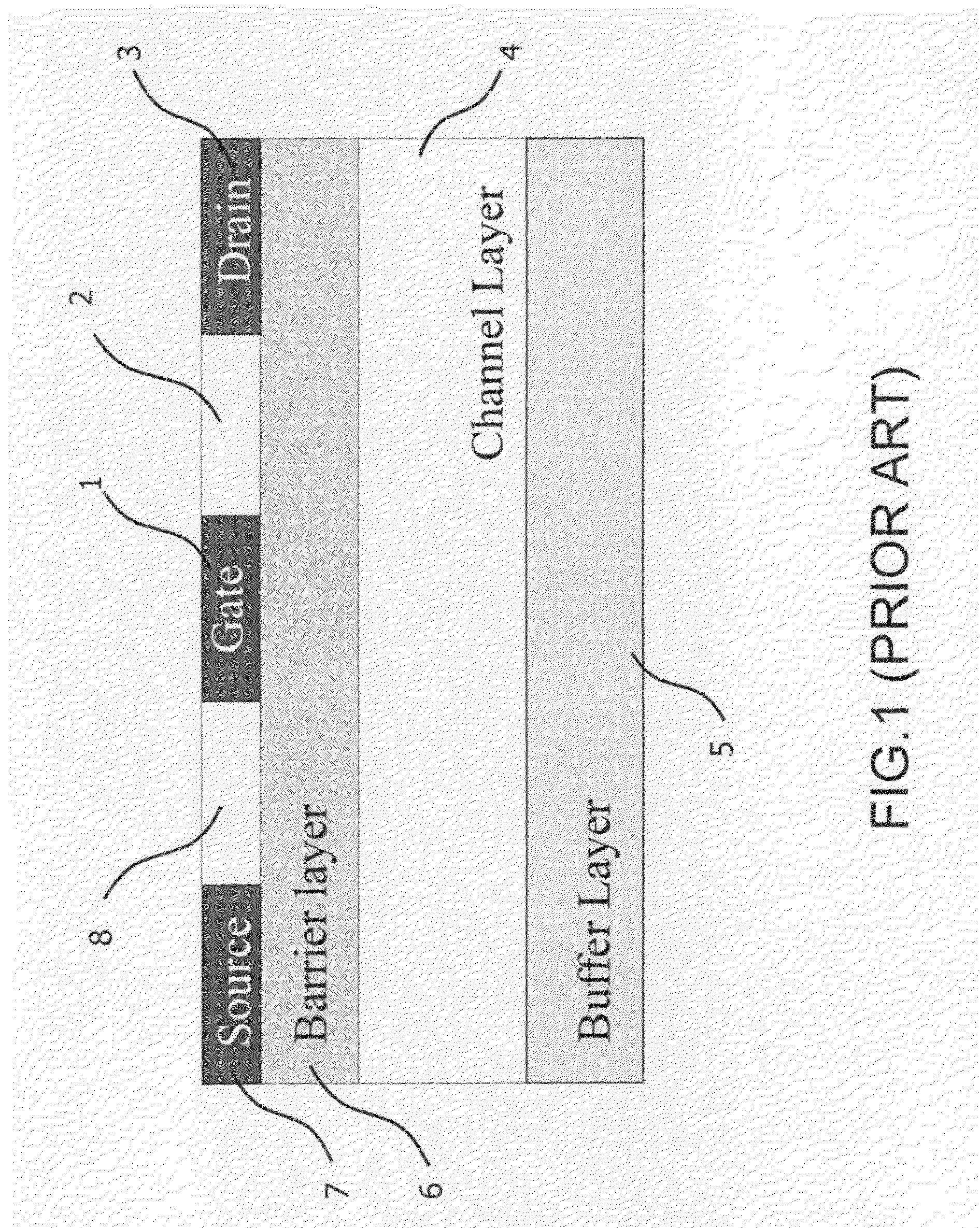

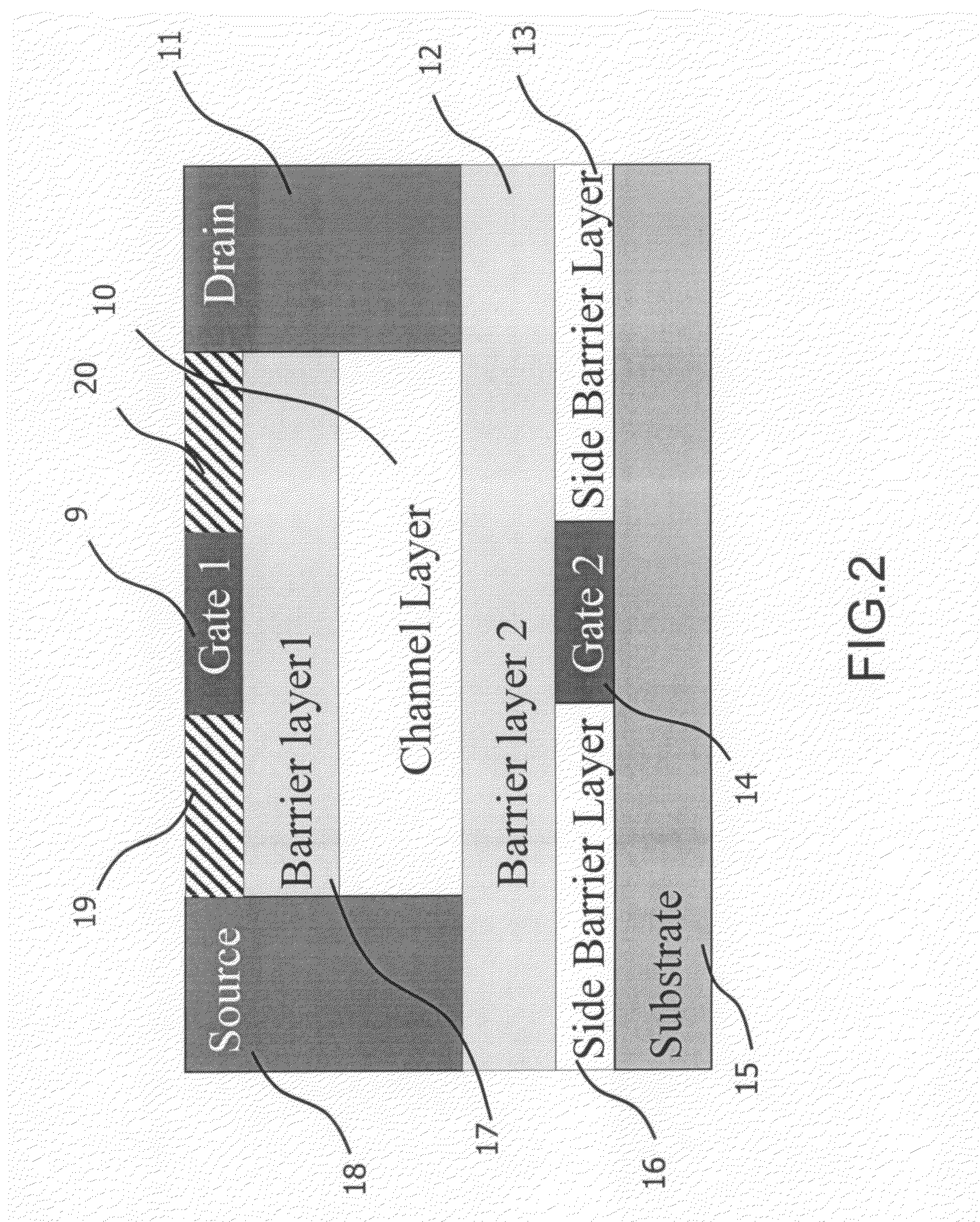

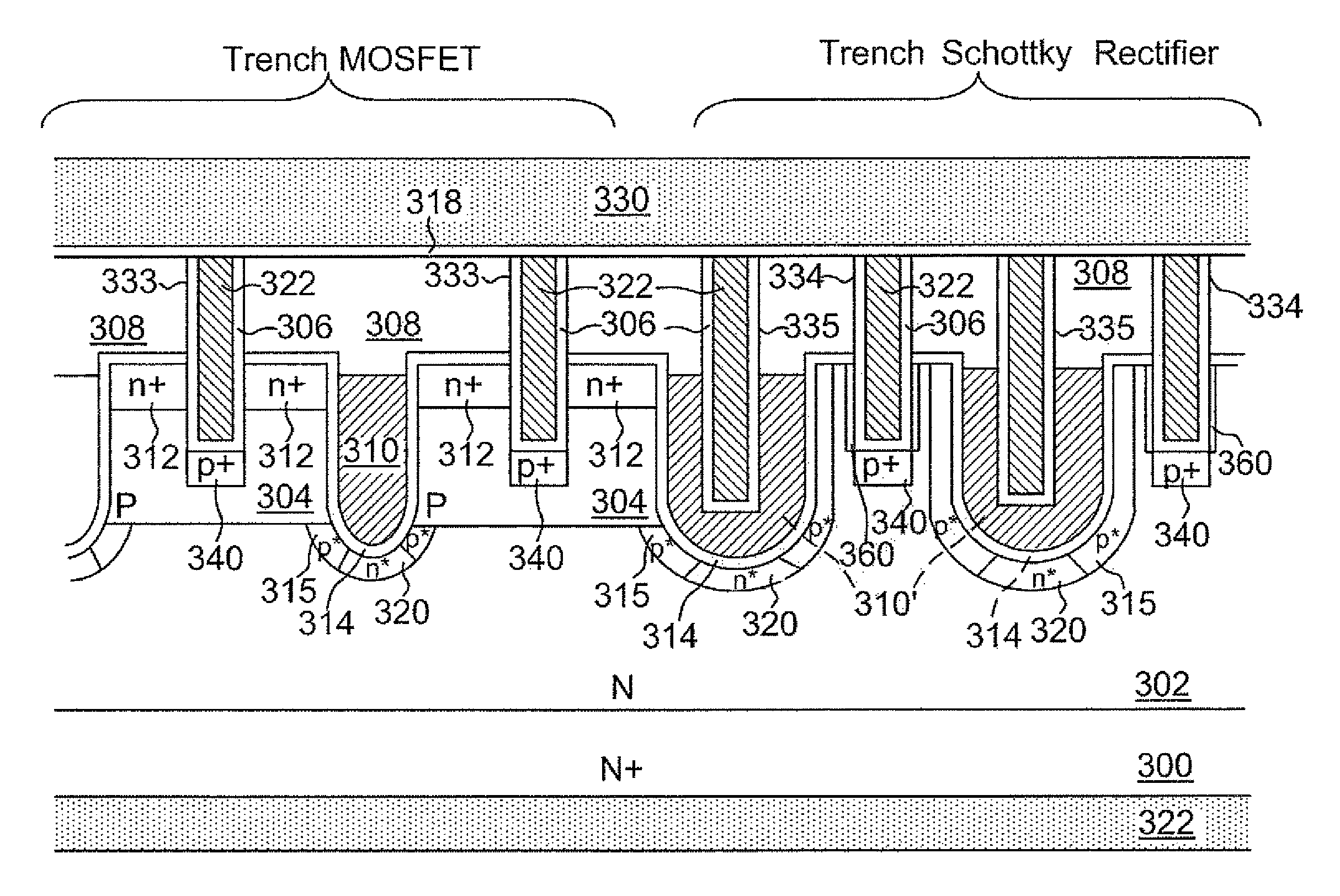

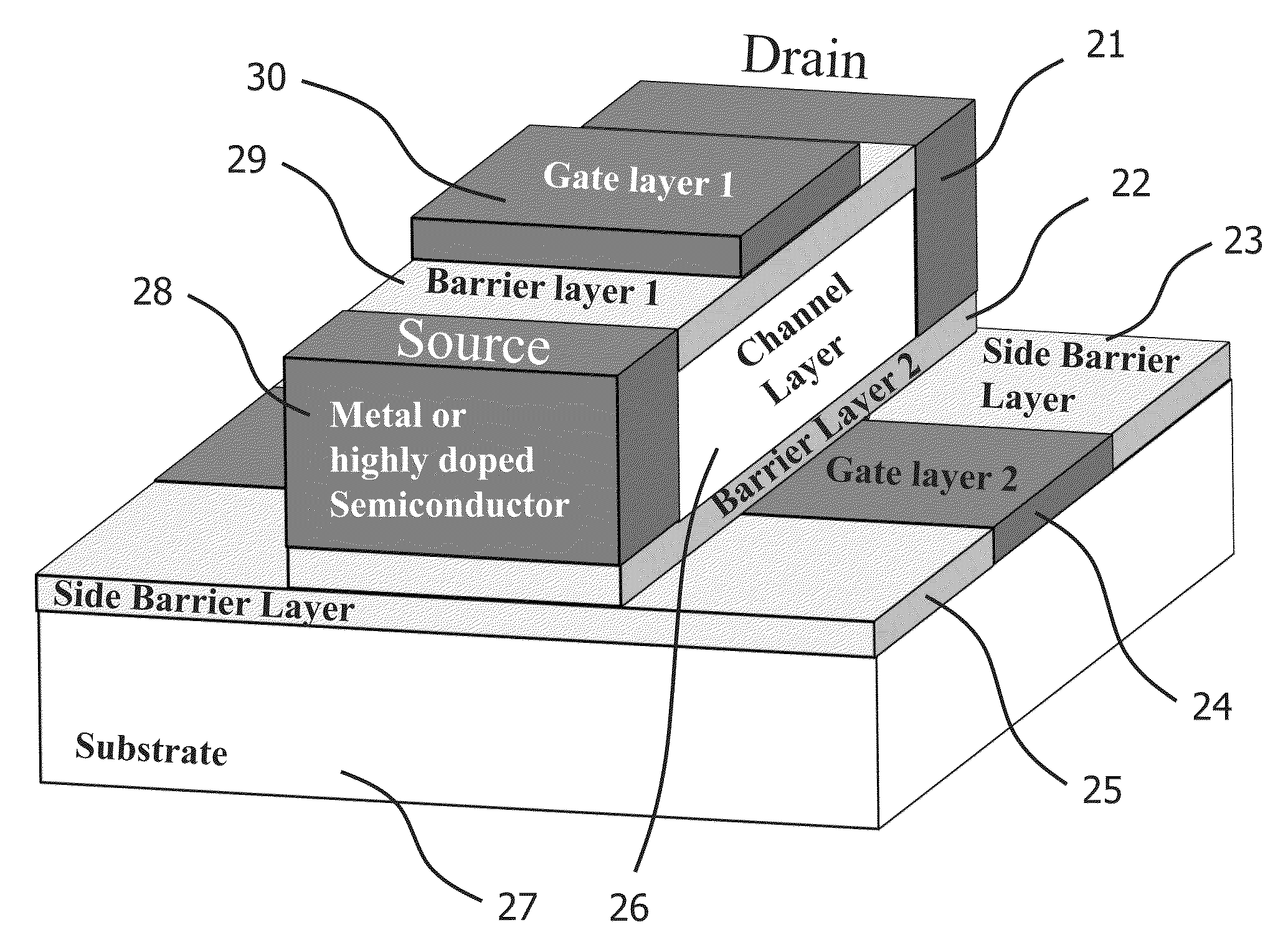

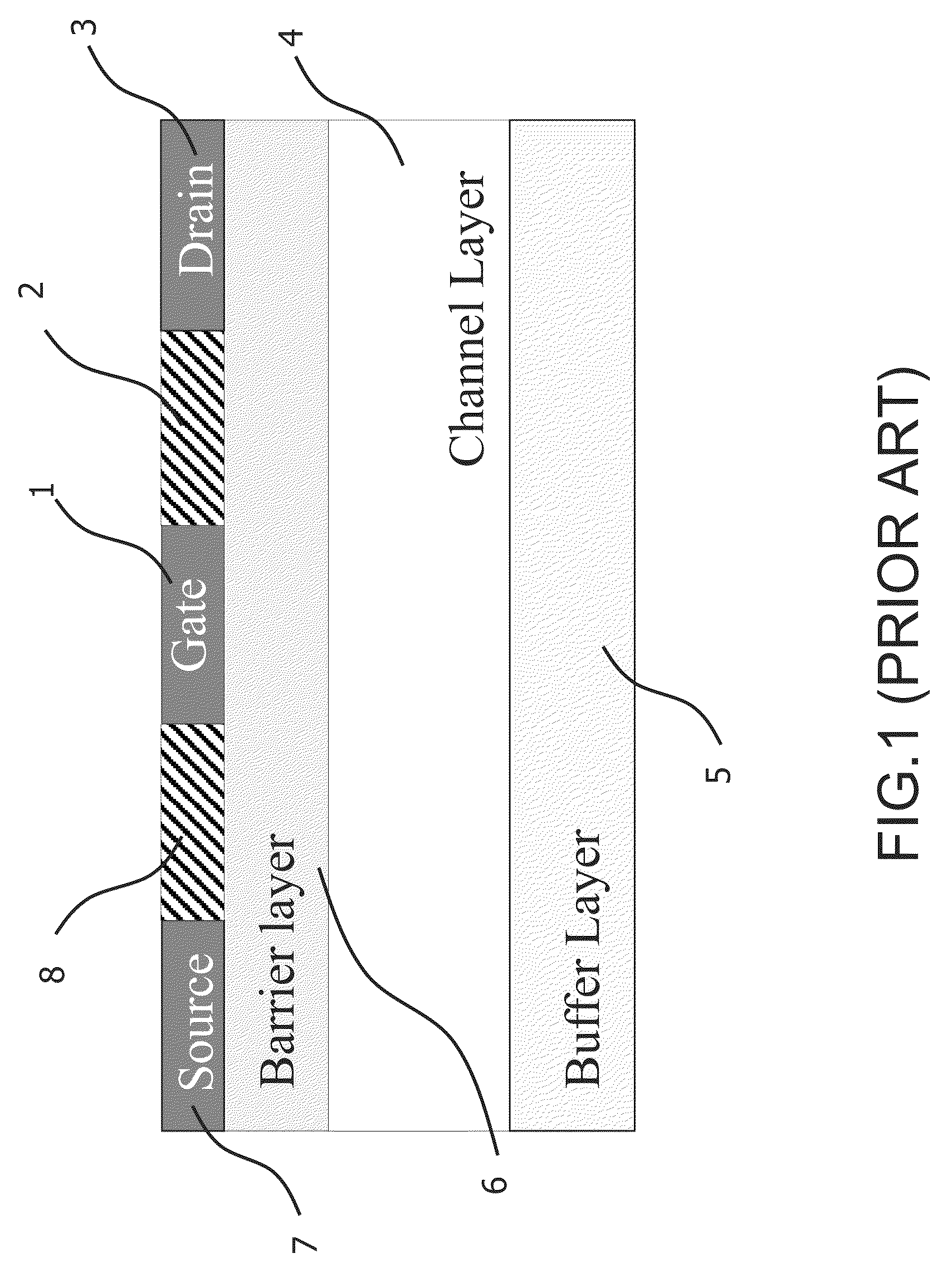

High performance multigate transistor

ActiveUS20120292665A1SpecificEasy to controlTransistorSemiconductor/solid-state device manufacturingSemiconductor materialsSemiconductor structure

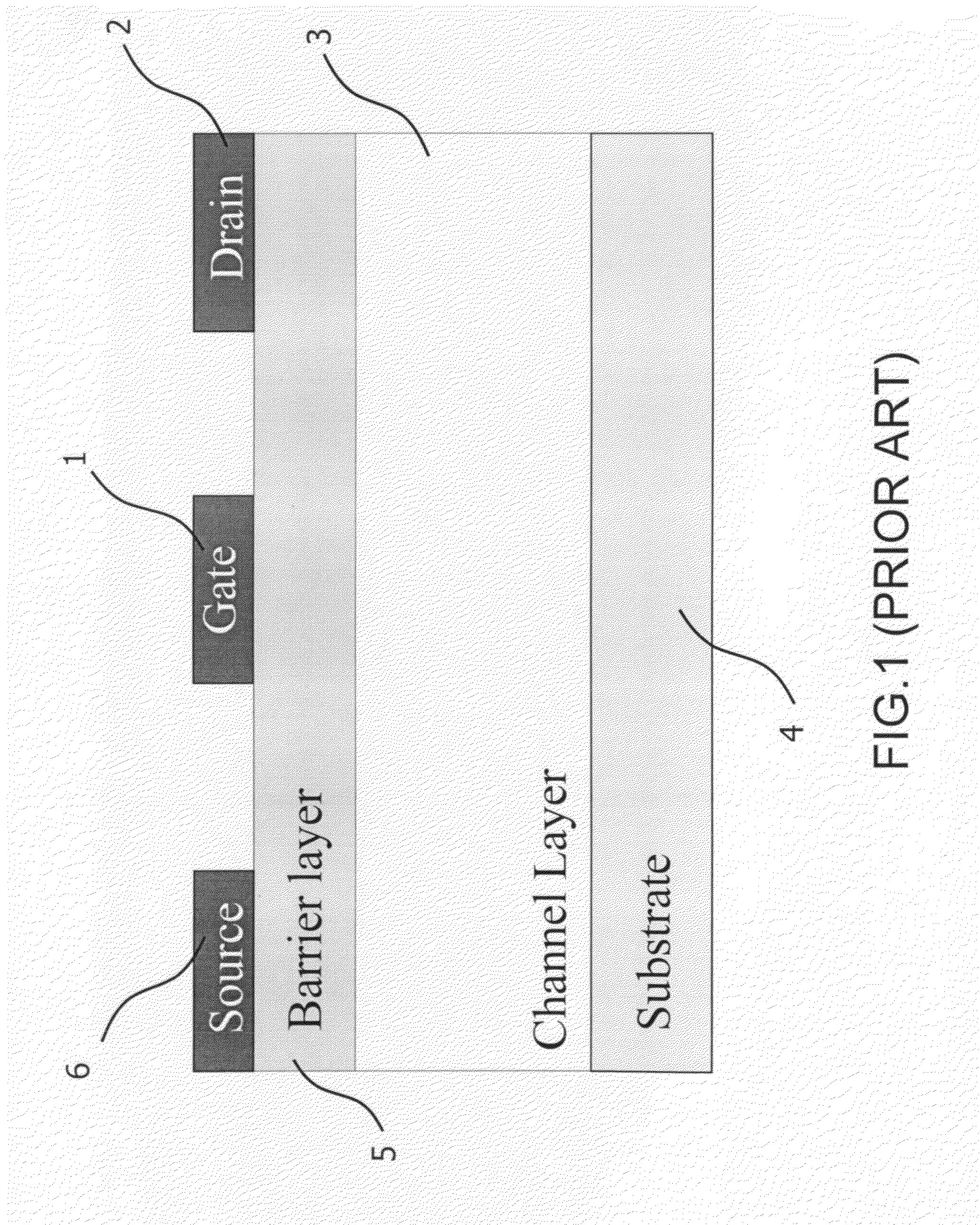

A novel semiconductor power transistor is presented. The semiconductor structure is simple and is based on a FET structure, where multiple channels and multiple gate regions are formed in order to achieve a lower specific on-resistance, and a higher control on the transport properties of the device. No dielectric layer is present between gate electrodes and device channels, decreasing the parasitic capacitance associated with the gate terminal. The fabrication of the device does not require Silicon On Insulator techniques and it is not limited to Silicon semiconductor materials. It can be fabricated as an enhancement or depletion device with much more control on the threshold voltage of the device, and with superior RF performance.

Owner:QUALCOMM INC

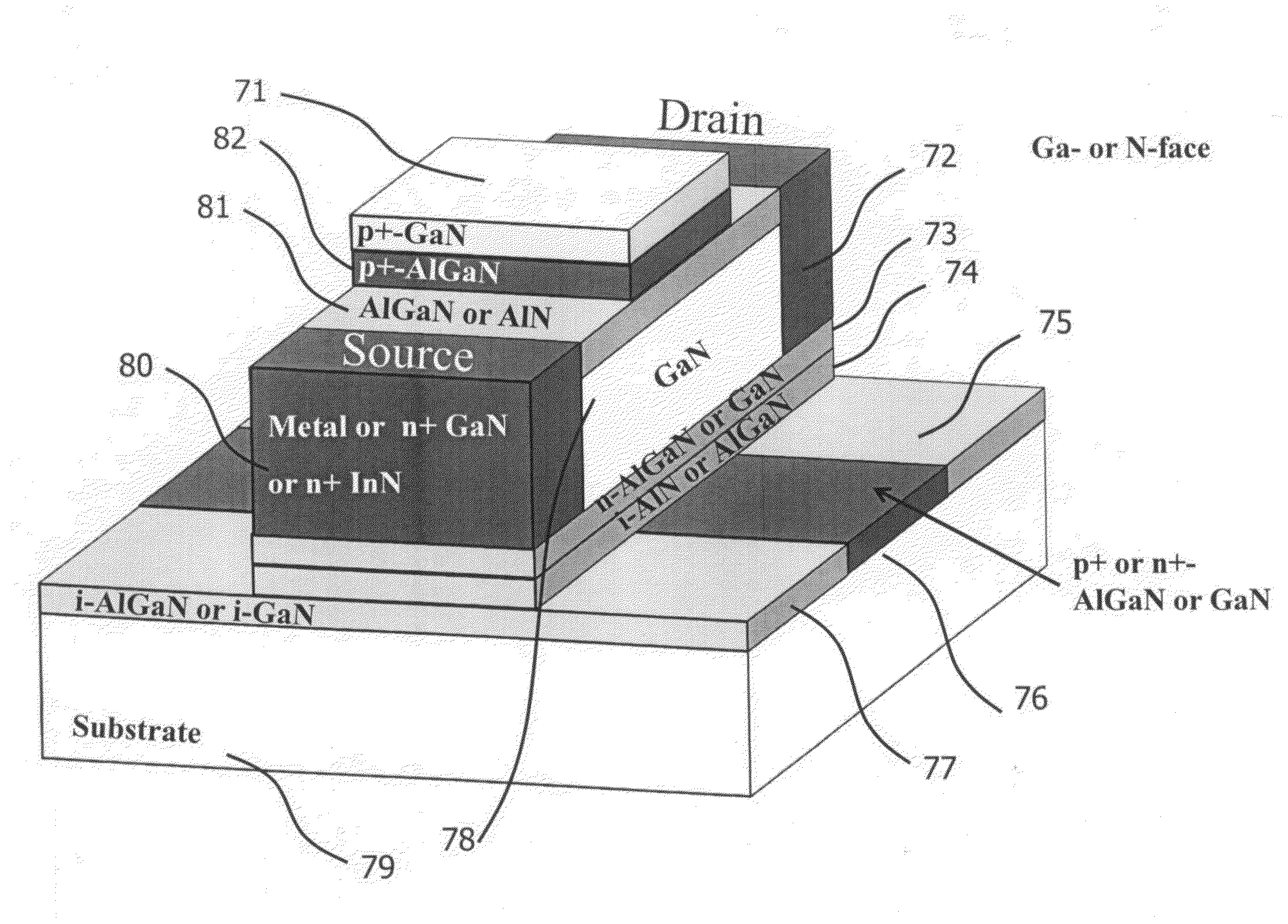

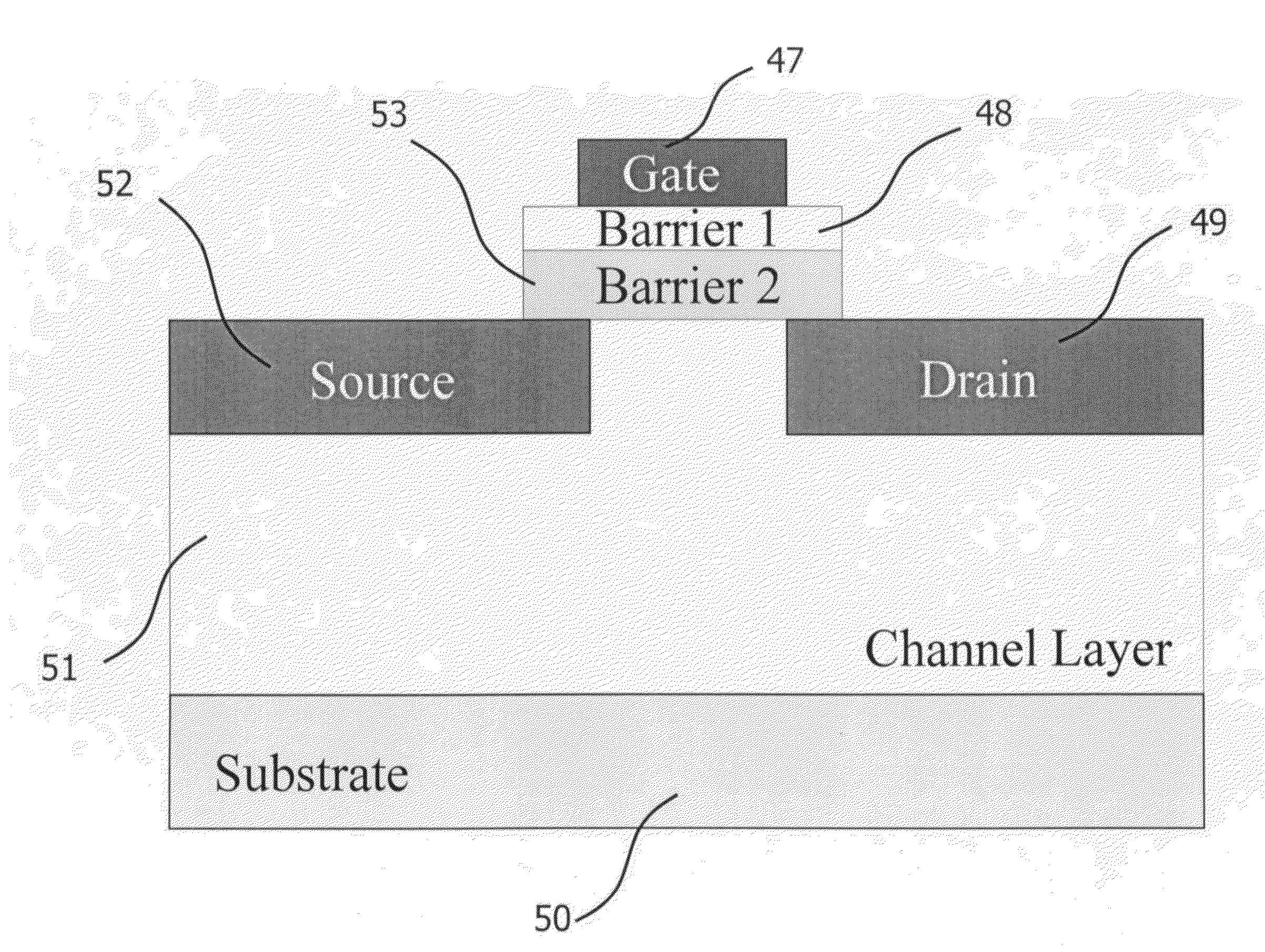

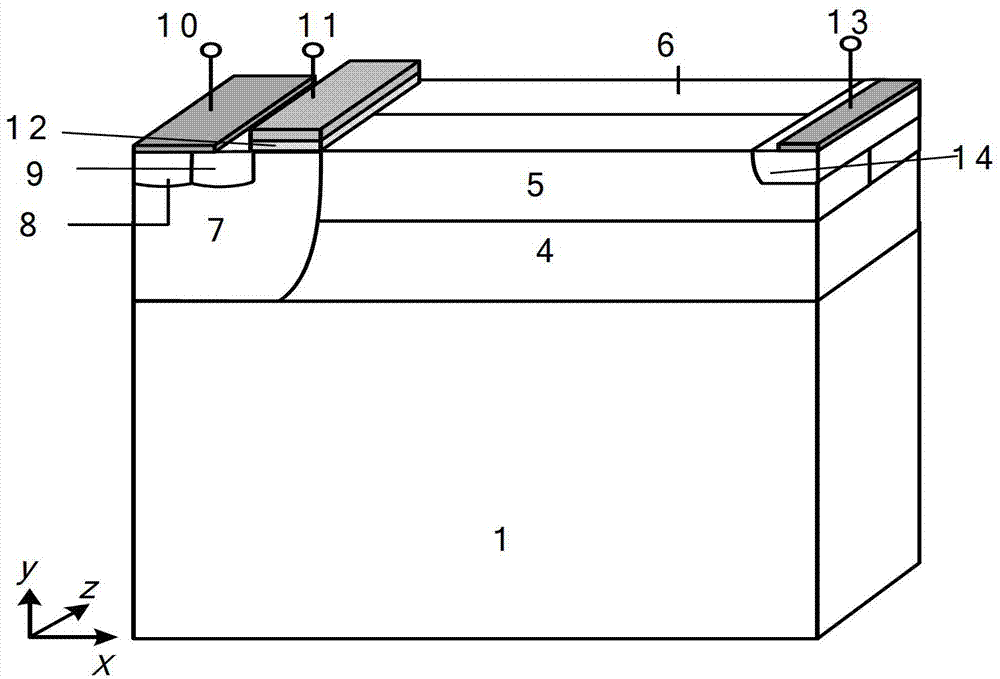

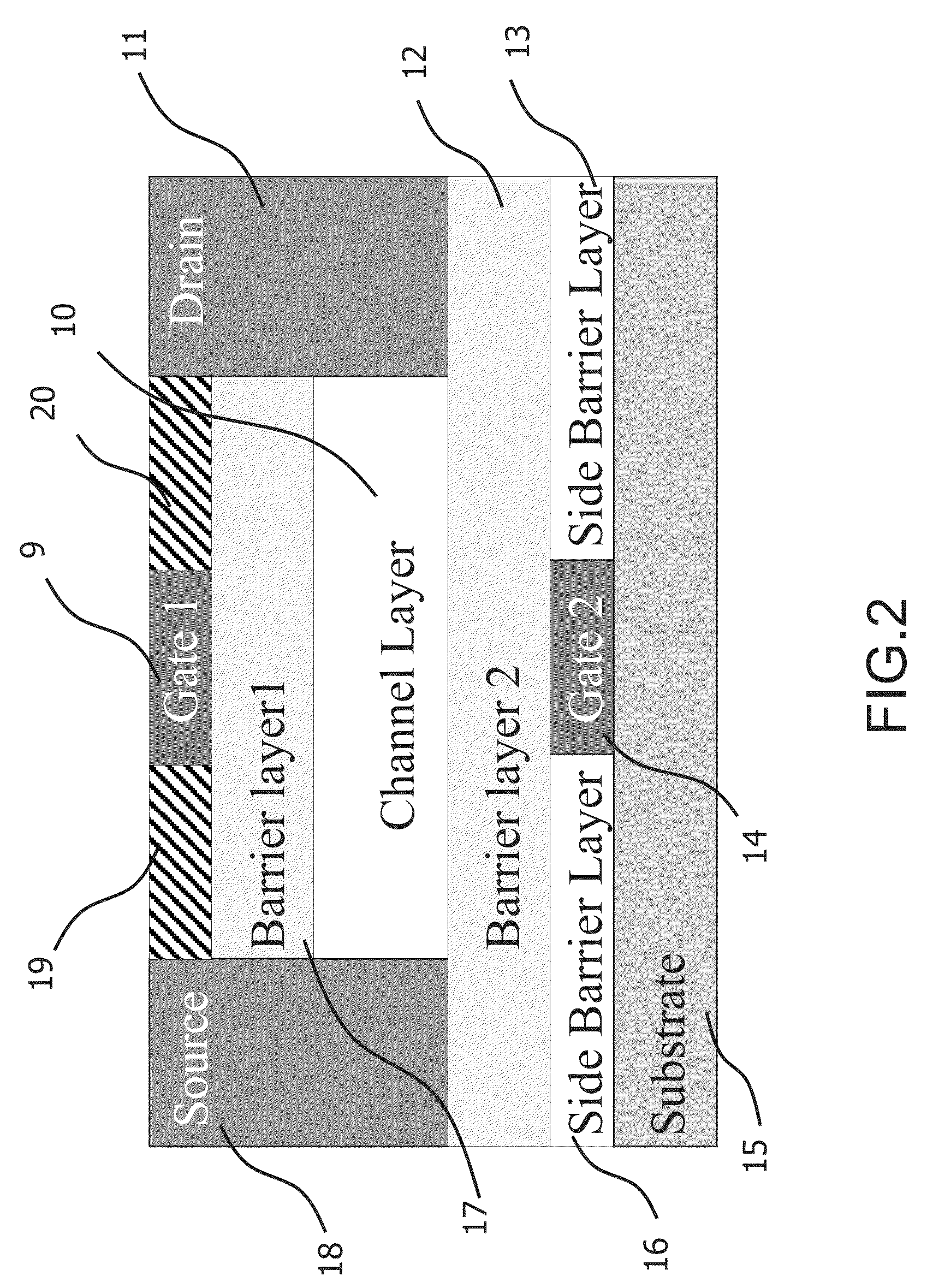

HFET with low access resistance

InactiveUS20130032860A1SpecificEasy to controlSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical resistance and conductanceAccess resistance

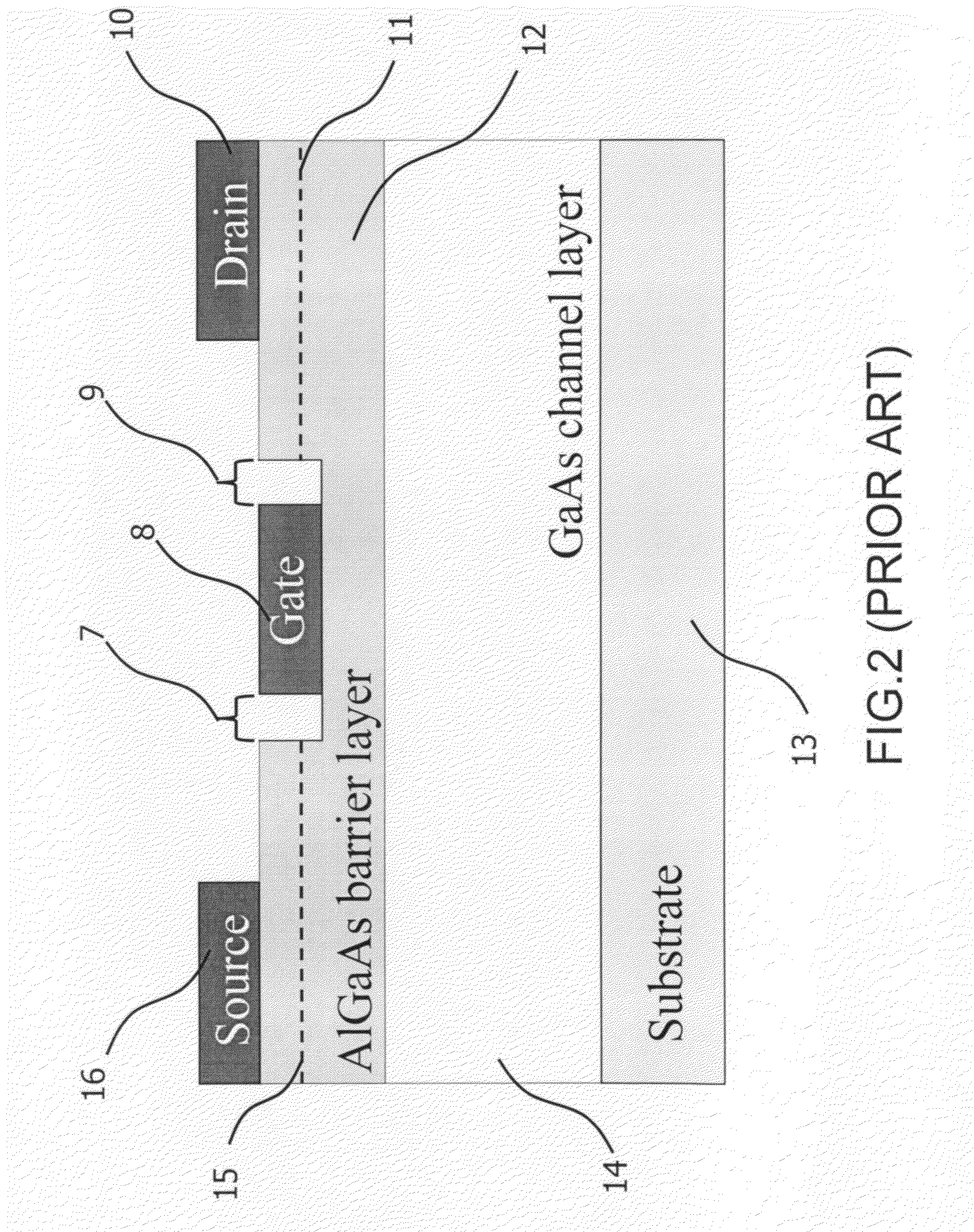

A novel semiconductor power transistor is presented. The semiconductor structure is simple and is based on a Hetero-structure FET structure, where the access regions have been eliminated so as to effectively obtain a lower specific on-resistance, and a higher control on the transport properties of the device, drastically reducing the dispersion phenomena associated with these regions. The present invention can be realized both with polar and non-polar (or semi-polar) materials, without requiring delta doping implantation. It can be fabricated as an enhancement or depletion mode device with much higher control on the device threshold voltage with respect to state-of-the-art HFET devices, and achieving superior RF switching performance. Furthermore, due to the absence of access regions, enhancement mode devices can be realized without discontinuity in the channel conductivity, which results in an even lower on-resistance.

Owner:QUALCOMM INC

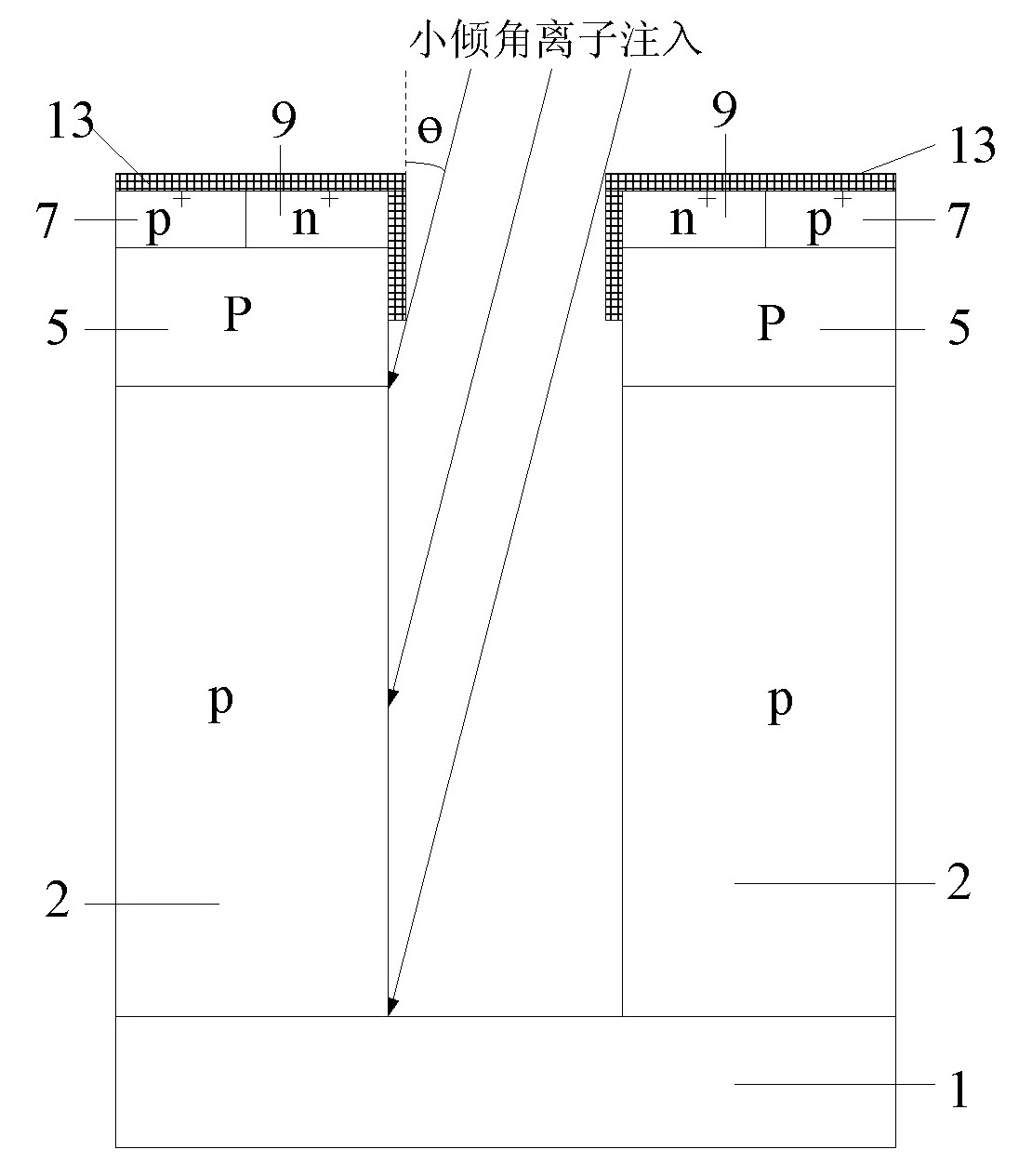

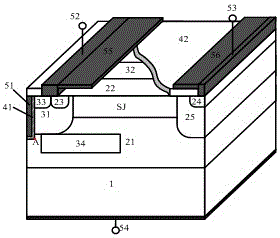

Trench type semiconductor power device

InactiveCN102110716AReduce areaLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesHigh concentrationPower semiconductor device

The invention relates to a semiconductor device. The device comprises a semiconductor substrate, a semiconductor drift region on the semiconductor substrate, a high-K dielectric on the semiconductor substrate, an active region on the semiconductor drift region and a trench gate structure on the high-K dielectric, wherein the semiconductor drift region comprises a first conduction type semiconductor region and a second conduction type semiconductor region which form a super-junction structure; the high-K dielectric is adjacent to the second conduction type semiconductor region; the trench gate structure is adjacent to the active region; and the second conduction type semiconductor region is formed through ion implantation at a small inclination angle, so that the semiconductor device is narrow and has high concentration.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

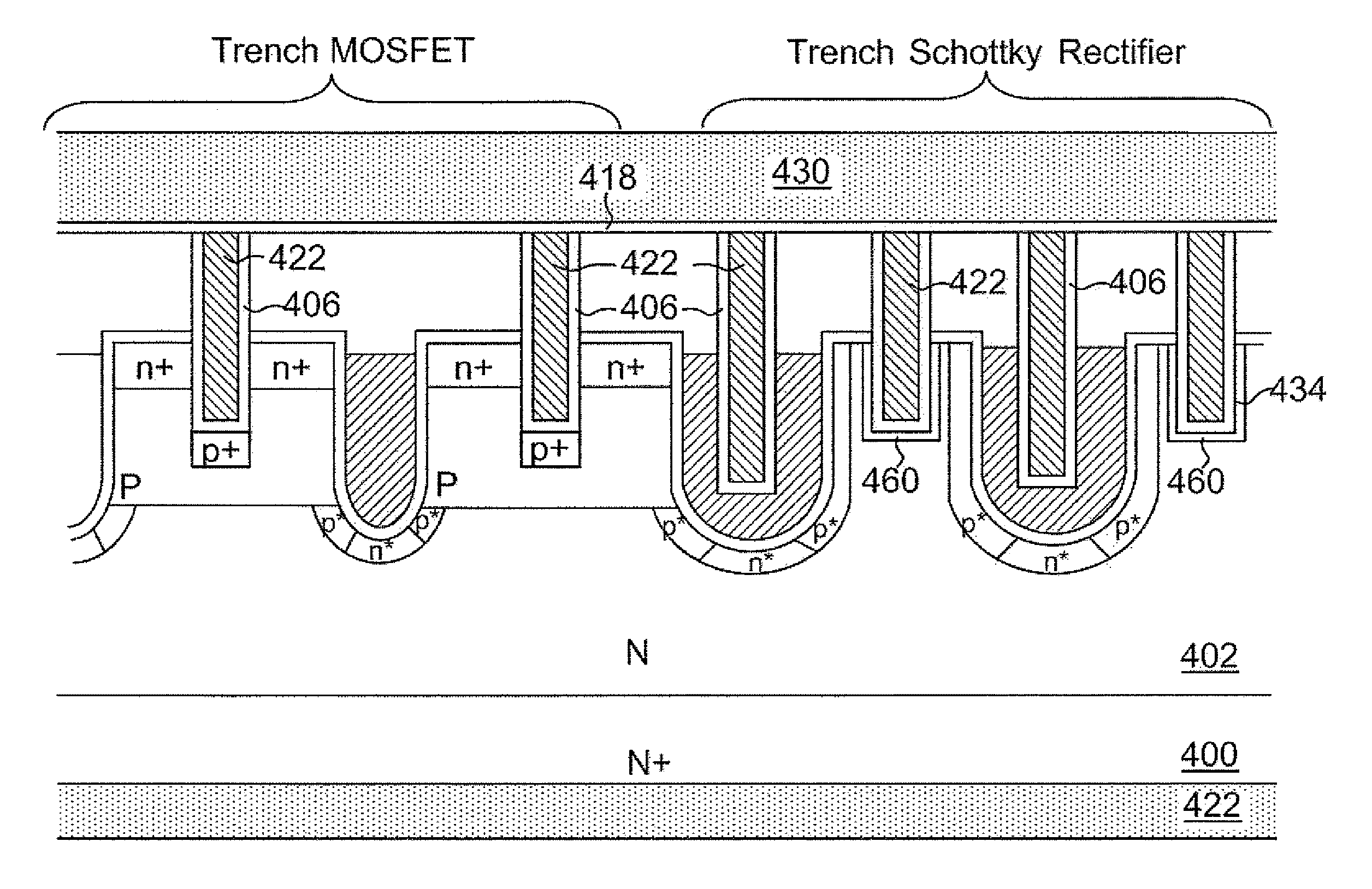

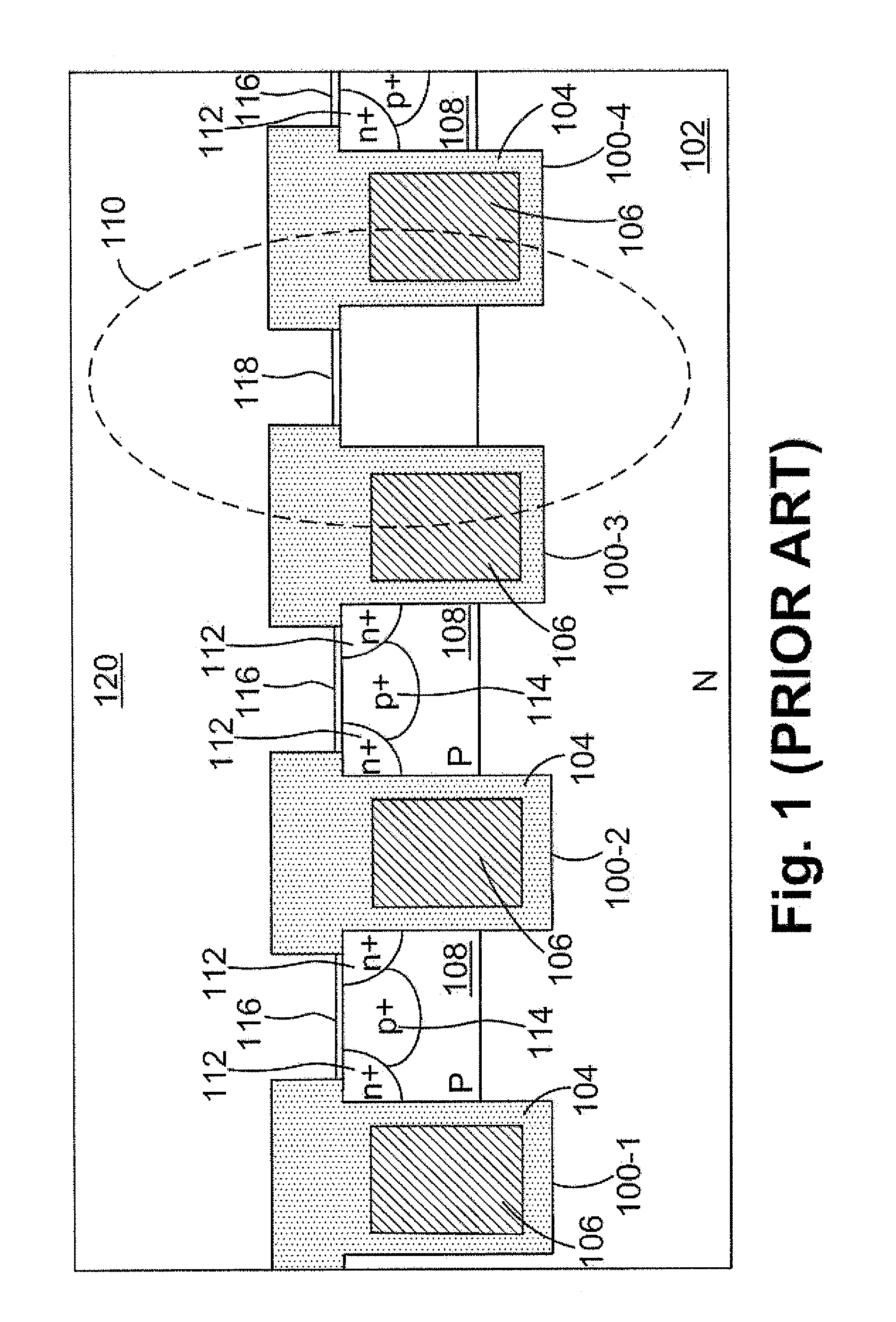

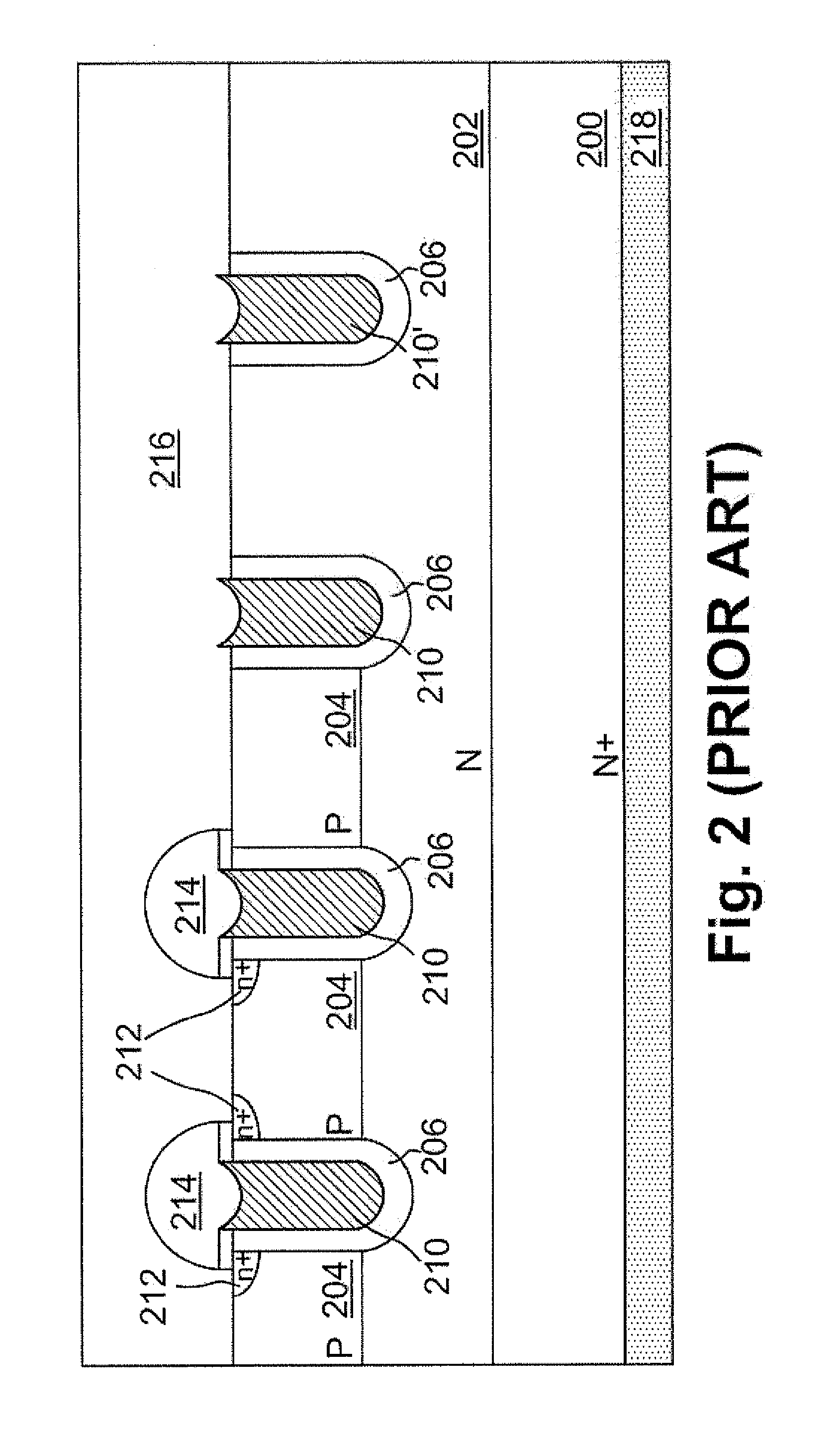

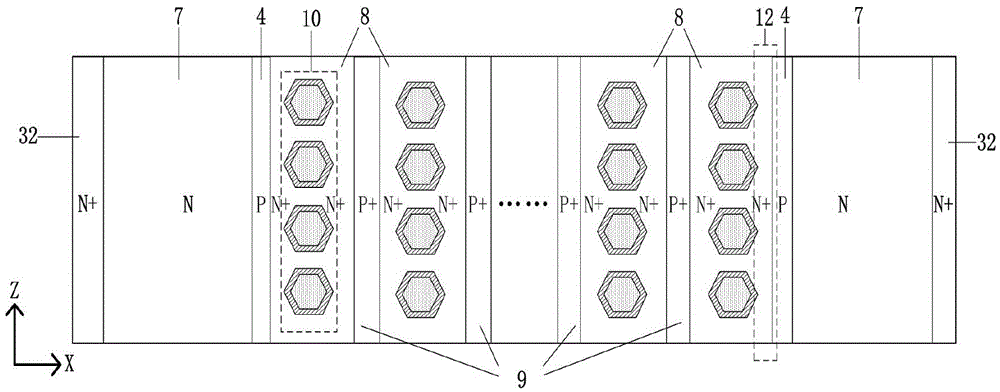

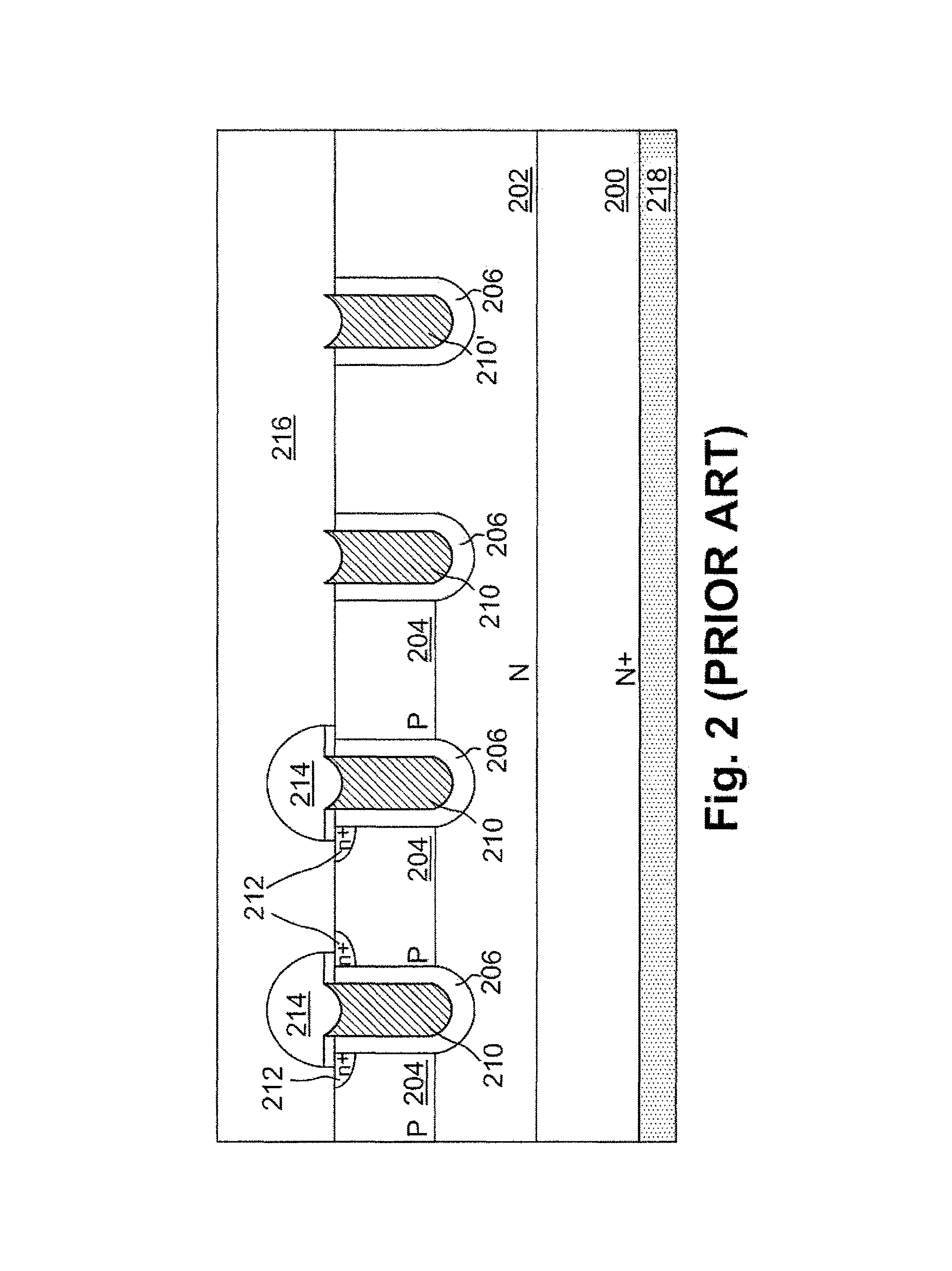

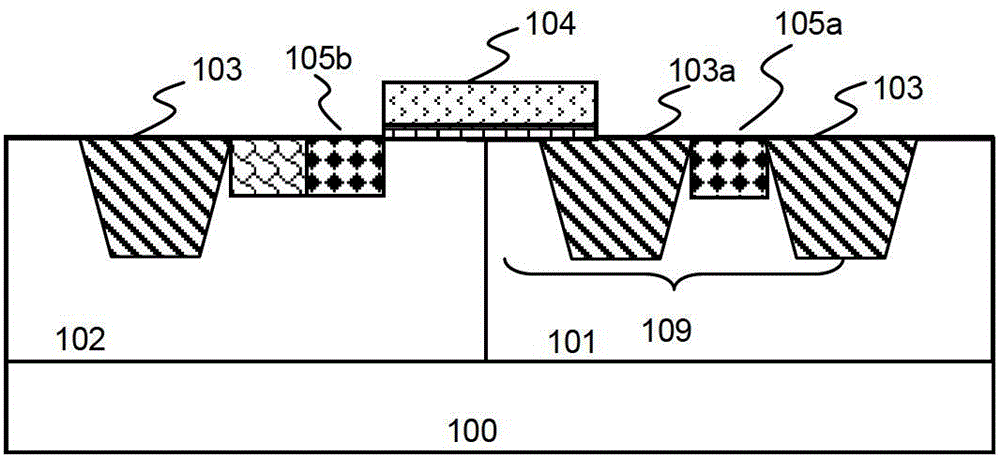

LOW Qgd TRENCH MOSFET INTEGRATED WITH SCHOTTKY RECTIFIER

ActiveUS20110284954A1Reduce QgdLow VfSolid-state devicesSemiconductor/solid-state device manufacturingTrench mosfetIntegrated circuit

An integrated circuit includes a plurality of trench MOSFET and a plurality of trench Schottky rectifier. The integrated circuit further comprises: tilt-angle implanted body dopant regions surrounding a lower portion of all trenched gates sidewalls for reducing Qgd; a source dopant region disposed below trench bottoms of all trenched gates for functioning as a current path for preventing a resistance increased caused by the tilt-angle implanted body dopant regions.

Owner:FORCE MOS TECH CO LTD

BCD device and manufacturing method thereof

InactiveCN101771039ALower specific on-resistanceLower on-resistanceSolid-state devicesSemiconductor/solid-state device manufacturingLow voltageEngineering

The invention discloses a BCD device and a manufacturing method thereof, which belong to the technical field of semiconductor power devices. In the invention, semiconductor devices such as a high-voltage nLIGBT, three high-voltage nLDMOSs, a low-voltage NMOS, a low-voltage PMOS, a low-voltage NPN and the like are synchronously integrated on the same chip, wherein the high-voltage nLIGBT, the high-voltage nLDMOSs and the low-voltage NPN are directly arranged on a single-crystal p-type substrate; the low-voltage NMOS is arranged in a p-type well; and the low-voltage PMOS is arranged in an n-type epitaxial layer. As p-type reduced-field layers are respectively arranged between the n-type epitaxial layer and an n-type shift region well, the n-type epitaxial layer on a p-type buried layer supplies an extra surface conducting channel to high-voltage devices, the conducting channel is increased, the specific on resistance of the high-voltage devices is reduced, and the manufacturing cost of the chip is further reduced. The nLIGBT device and the nLDMOS devices of the invention further have the characteristics of high input impedance, low output impedance and the like, and a high-voltage power integrated circuit formed by the nLIGBT device and the nLDMOS devices can be used in a plurality of products, such as consumer electronics, display drivers and the like.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Super junction lateral double-diffused metal-oxide semiconductor (LDMOS) device

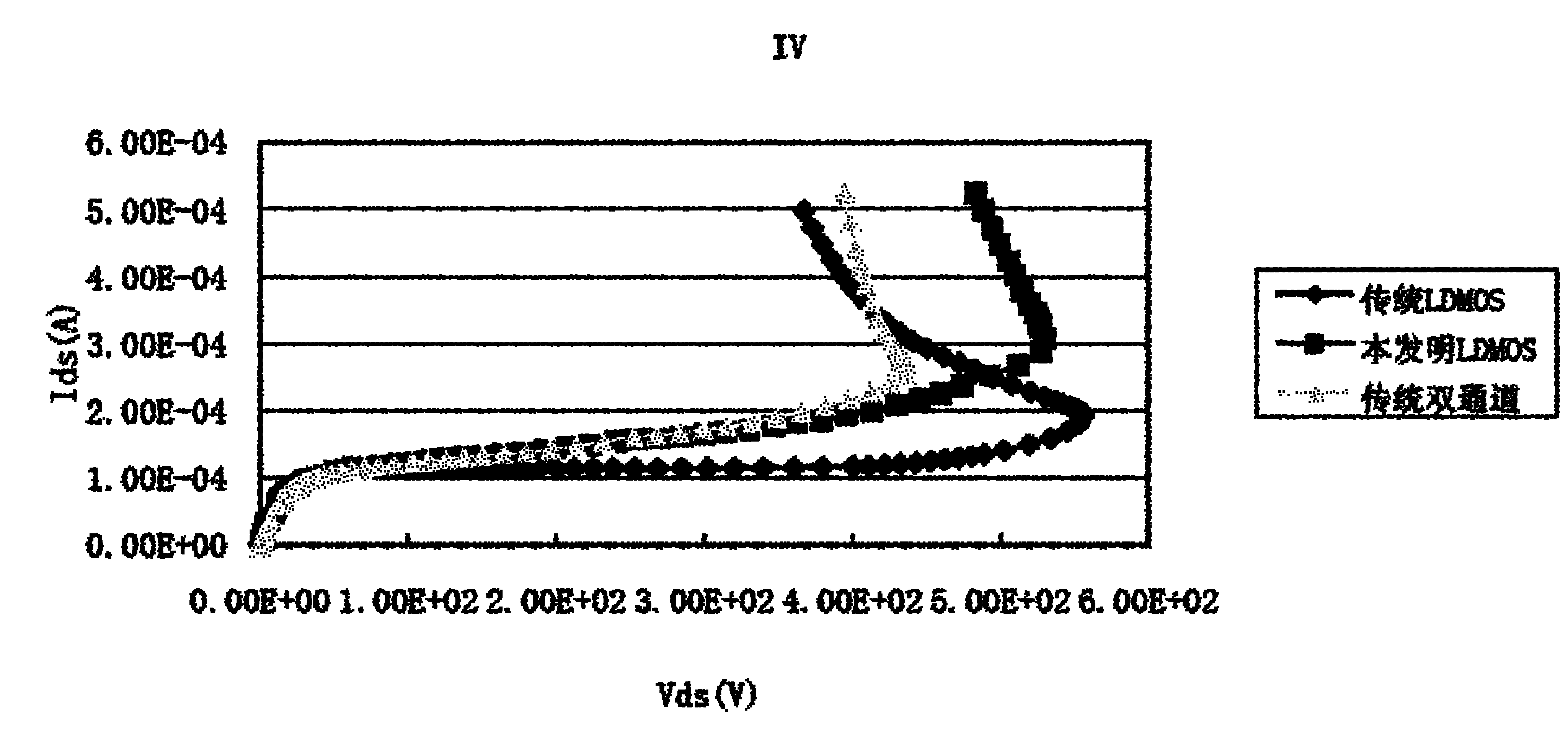

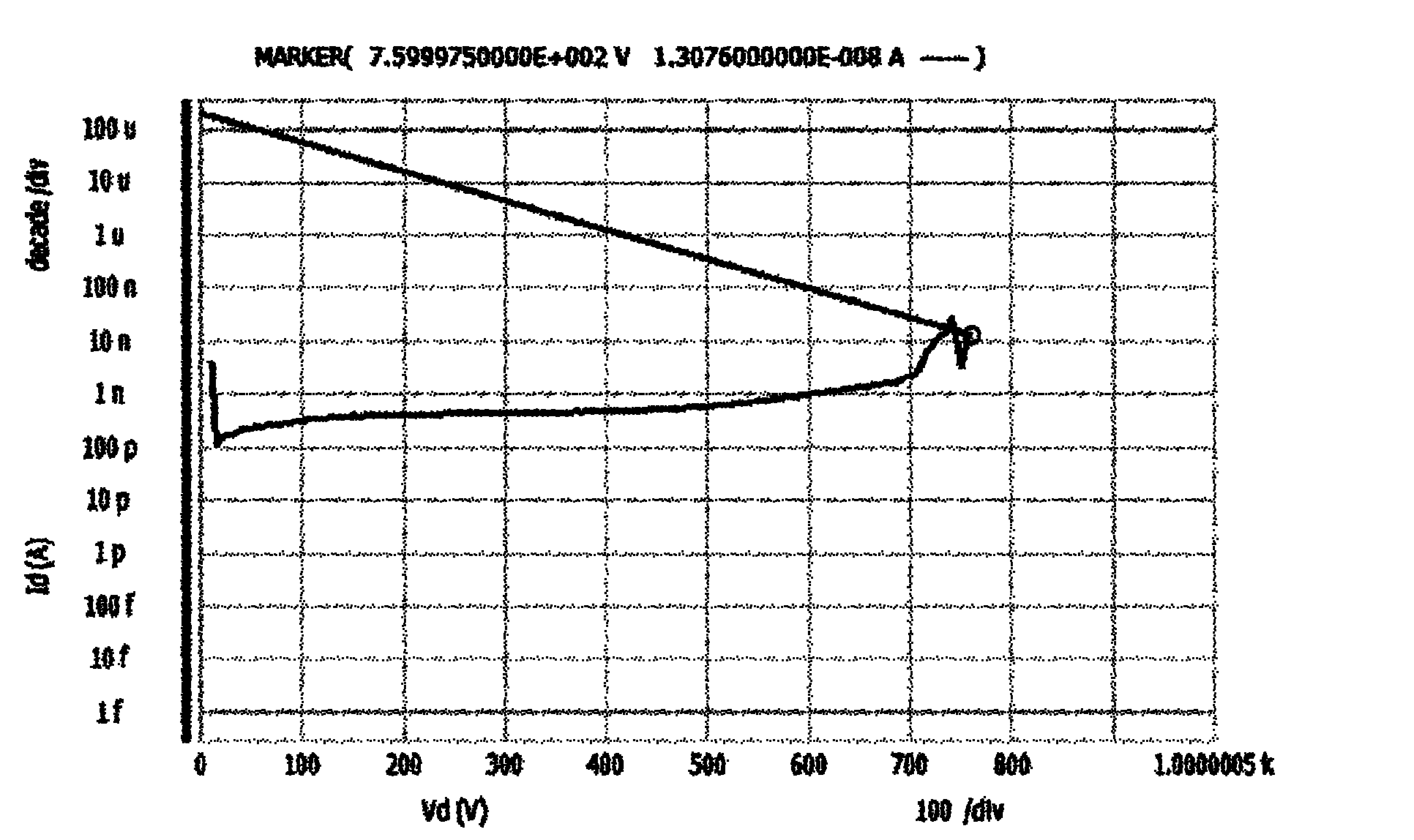

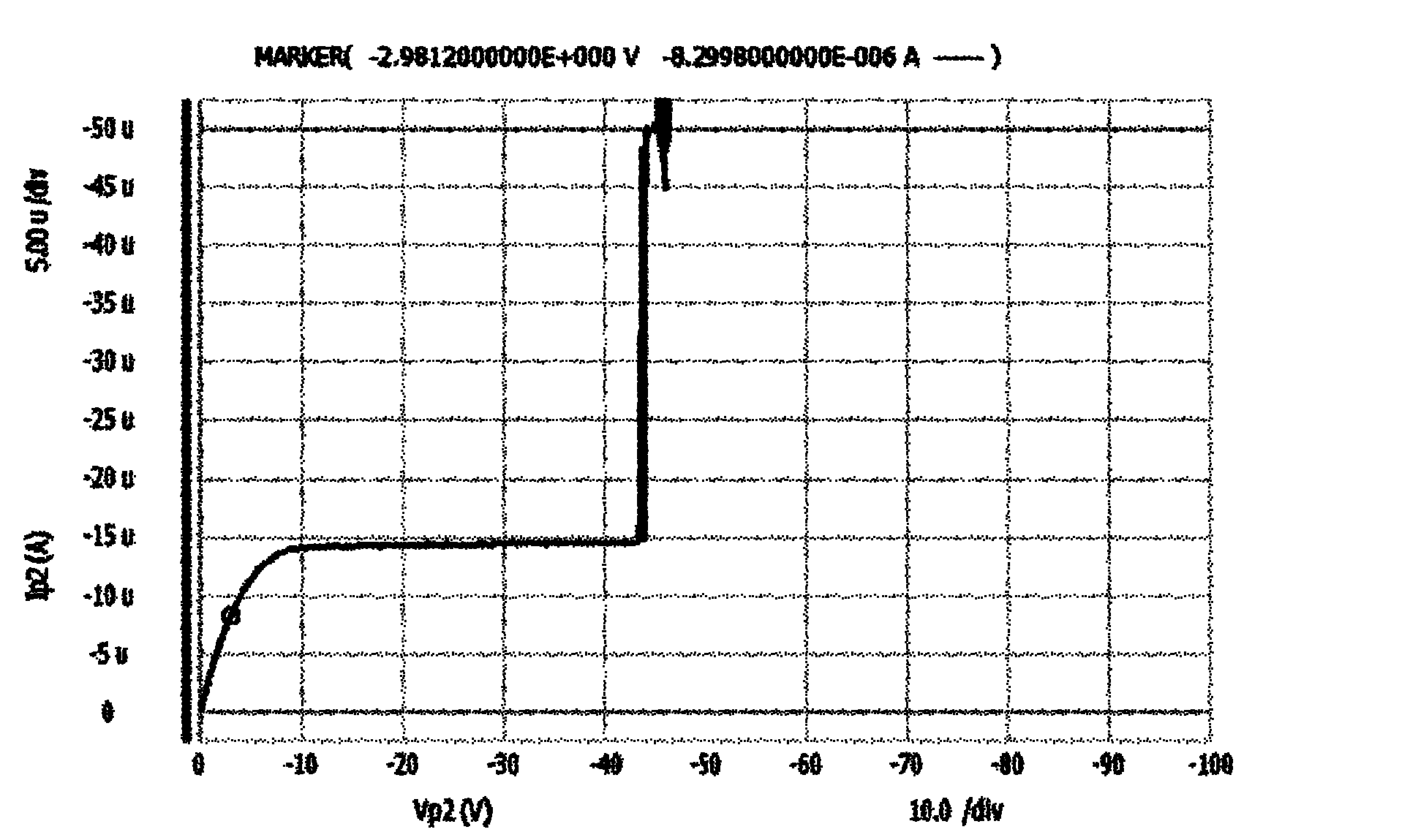

InactiveCN103165678AImprove vertical pressure resistanceImprove breakdown voltageSemiconductor devicesLDMOSPeak value

The invention relates to a super junction lateral double-diffused metal-oxide semiconductor (LDMOS) device and belongs to the field of semiconductor power devices. By means of the super junction LDMOS device, evenly distributed N+ islands are embedded in a P type substrate of a traditional super junction LDMOS device, and a P type electric field screening buried layer is added between an active area and the substrate. An N+ island (2) can improve longitudinal withstand voltage of the device by enhancing internal electric field, simultaneously generates extra electric charge to eliminate substrate auxiliary depletion effect, and further improves breakdown voltage of the device. The P type electric field screening buried layer (3) can screen high electric fields generated by an N+ island near an active end, lower electric field peak value near the active area, and form super junction with an N type cushion layer; and a super junction drift area is provided, the device is enabled to have multiple super junction structures, accordingly electric field distribution inside the device can be effectively improved, breakdown voltage of the device is improved, conduction ratio resistance of the device is simultaneously lowered by improving dosage concentration of the drift area, and finally the aim of effectively reducing device area and lower device cost can be achieved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

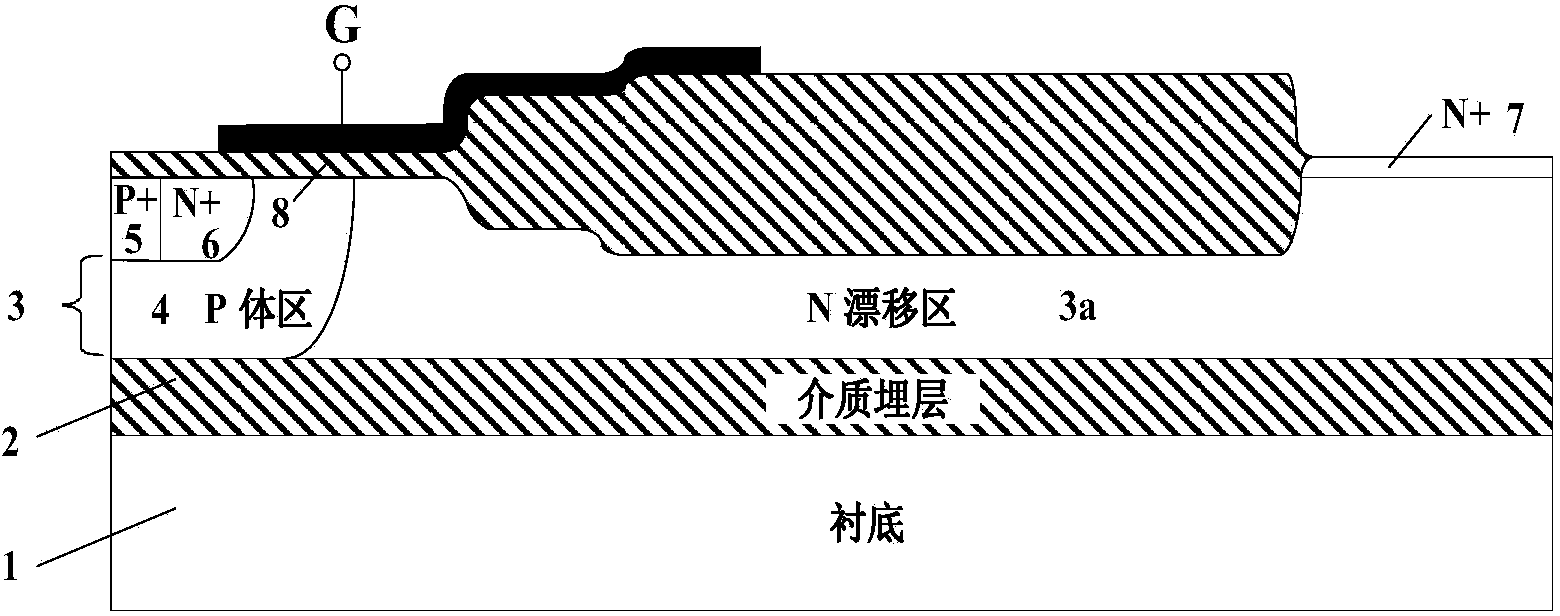

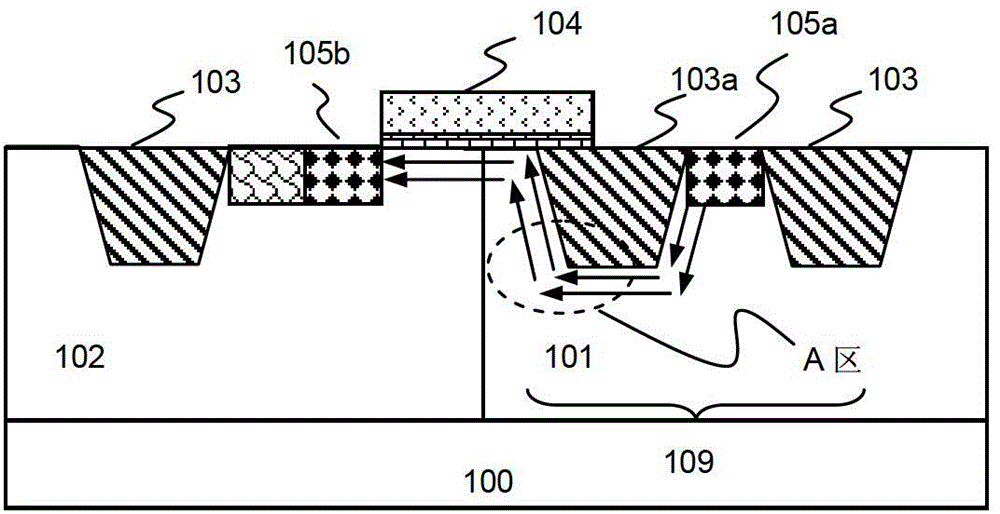

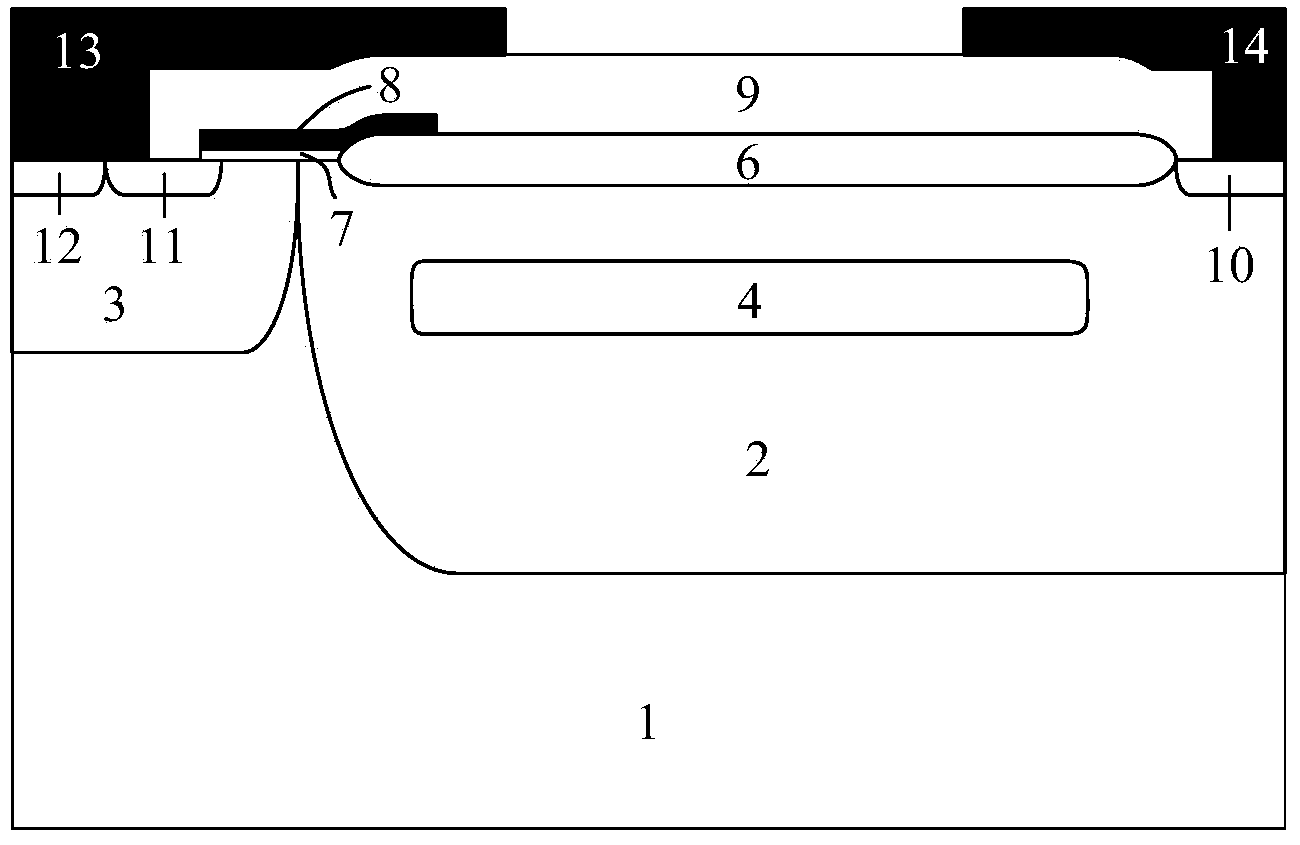

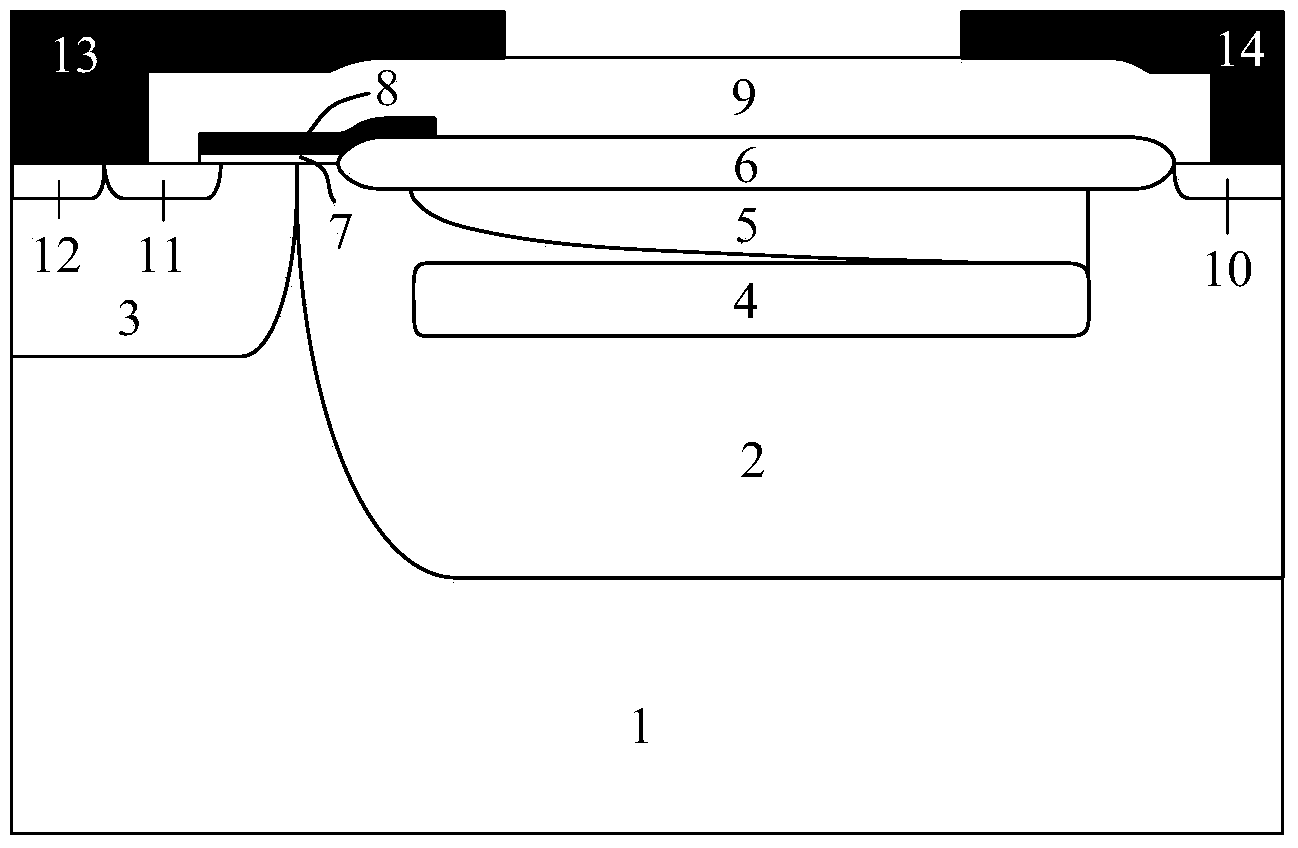

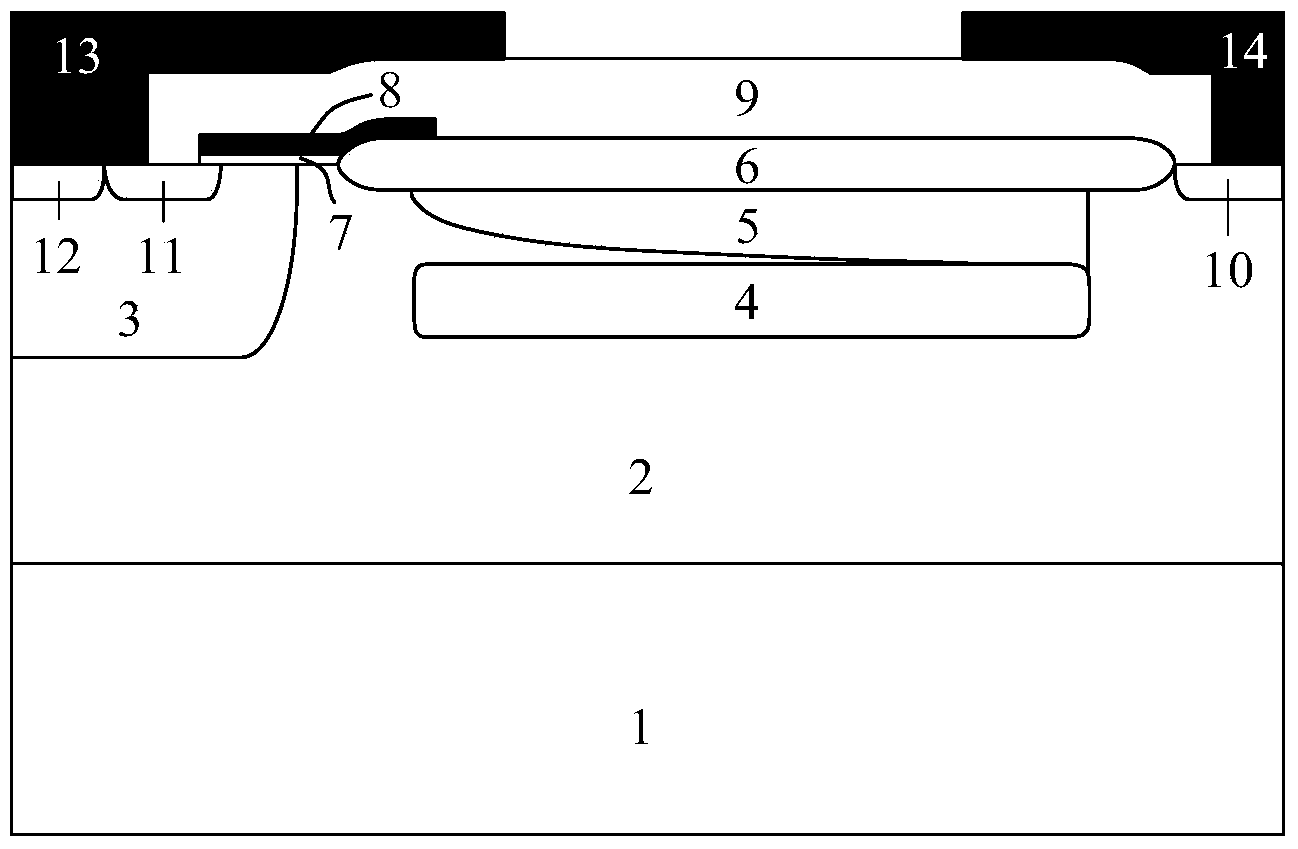

SOI LDMOS device with extending gate structure

InactiveCN104183646AUniform temperature distributionThe device works stablyDiodeElectric fieldPolycrystalline silicon

The invention discloses an SOI LDMOS device with an extending gate structure, and belongs to the technical field of semiconductor power devices. According to the SOI LDMOS device, the extending gate structure extending from a polysilicon gate to a drain electrode is introduced into the surface of a drift region of a conventional SOI LDMOS device. A PN junction which is reversely biased when the device is in the on state is introduced into the extending gate structure to reduce a leakage current. The extending gate structure is characterized in that on one hand, when the device is in the on state, a majority carrier accumulation layer is sensed on the portion, close to extending gate media, of the surface of the drift region, an ultralow resistance channel is provided for the on-state current, the specific on resistance of the device is accordingly and remarkably reduced, and the specific on resistance does not depend on the doping concentration of the drift region; on the other hand, when the device is in the off state, distribution of an electric field in the drift region is adjusted through the extending gate structure, and the voltage resistance of the device is accordingly improved. In addition, the vast majority of the on-state current flows through the low-resistance channel of the charge accumulation layer, temperature distribution of the SOI LDMOS device is accordingly even, and the SOI LDMOS device is stable.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

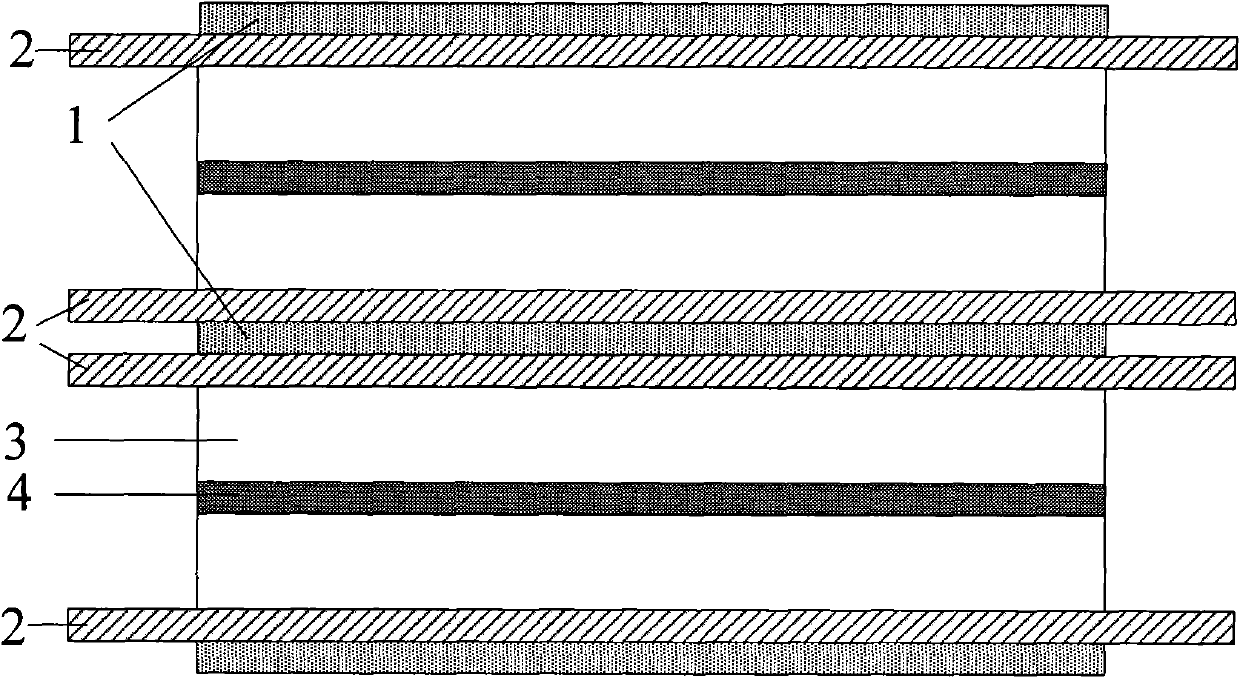

LDMOS (laterally diffused metal oxide semiconductor), semiconductor device integrated with same and manufacturing method thereof

InactiveCN102097389AEasy to integrateThe process steps are simpleSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSCMOS

The invention discloses an LDMOS (laterally diffused metal oxide semiconductor), a semiconductor device integrated with the LDMOS and a manufacturing method thereof. The semiconductor device comprises an LDMOS 1, a CMOS (complementary metal oxide semiconductor) 2, an NPN 3 and a buried channel resistor 4 which are arranged in a P type substrate 10. The LDMOS 1 comprises an N type drift region 20, a P+ well contact region 40, a P type body region 70, an N+ source region 50, an N+ drain region 60, a gate dielectric layer 100, a source metal 80, a drain metal 90, a field oxidation layer 110 and a metal front medium 120 as well as a P type field reducing layer 30A and at least one P type buried well 30B, wherein no gap is kept between the N type drift region 20 and the P type body region, the P type buried well 30B is arranged below the P type body region 70 and is contacted with the P type body region 70, the P type field reducing layer 30A is arranged below the field oxidation layer 110 and is surrounded by the N type drift region, and a gap is kept between the P type filed reducing layer 30A and the field oxidation layer 110. The LDMOS in the invention has low on resistance and high withstand voltage and is easy to integrate, and the whole manufacturing process of the semiconductor device has simple steps and has low requirement to equipment.

Owner:SHENZHEN CHIP HOPE MICRO ELECTRONICS LTD

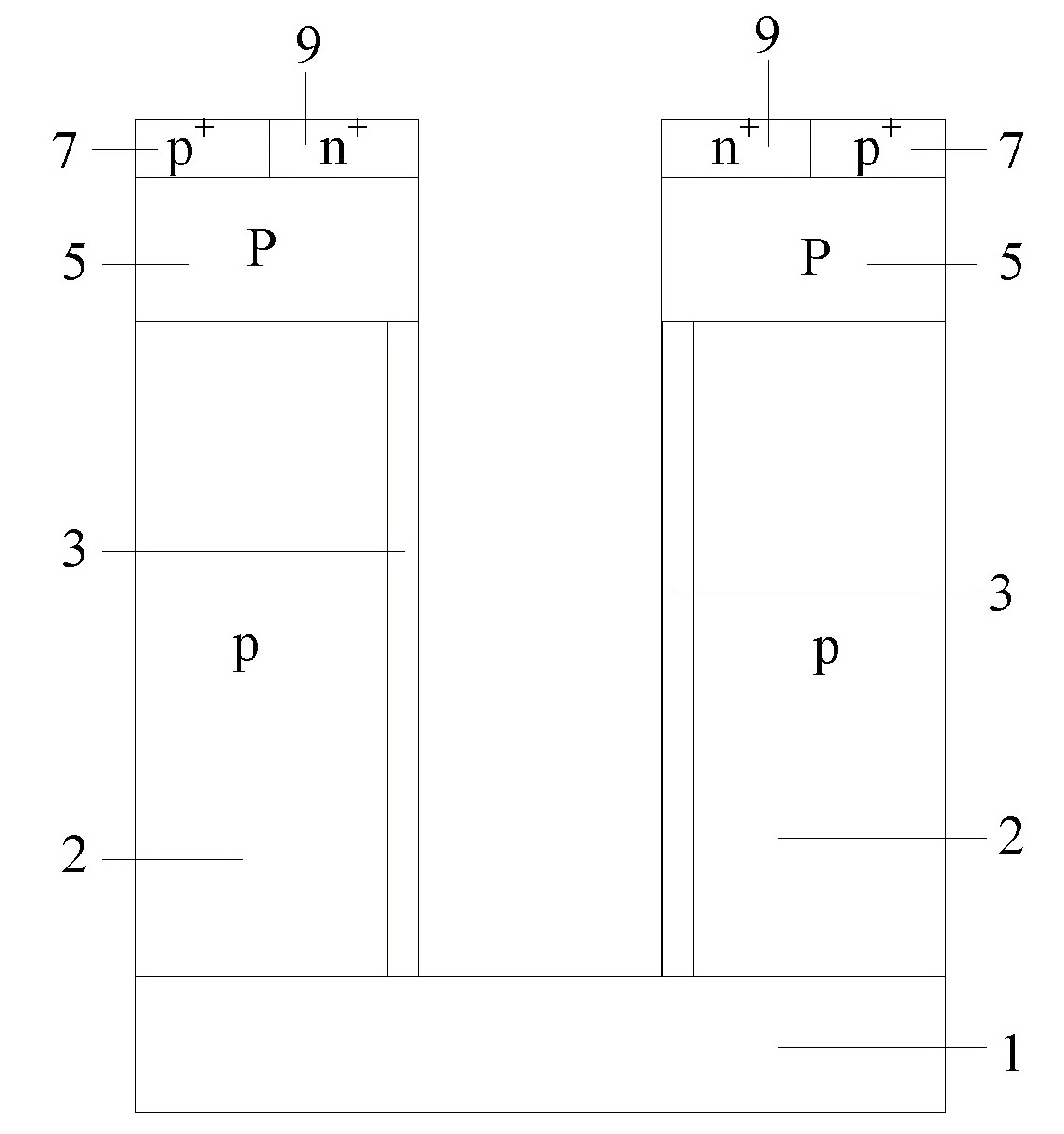

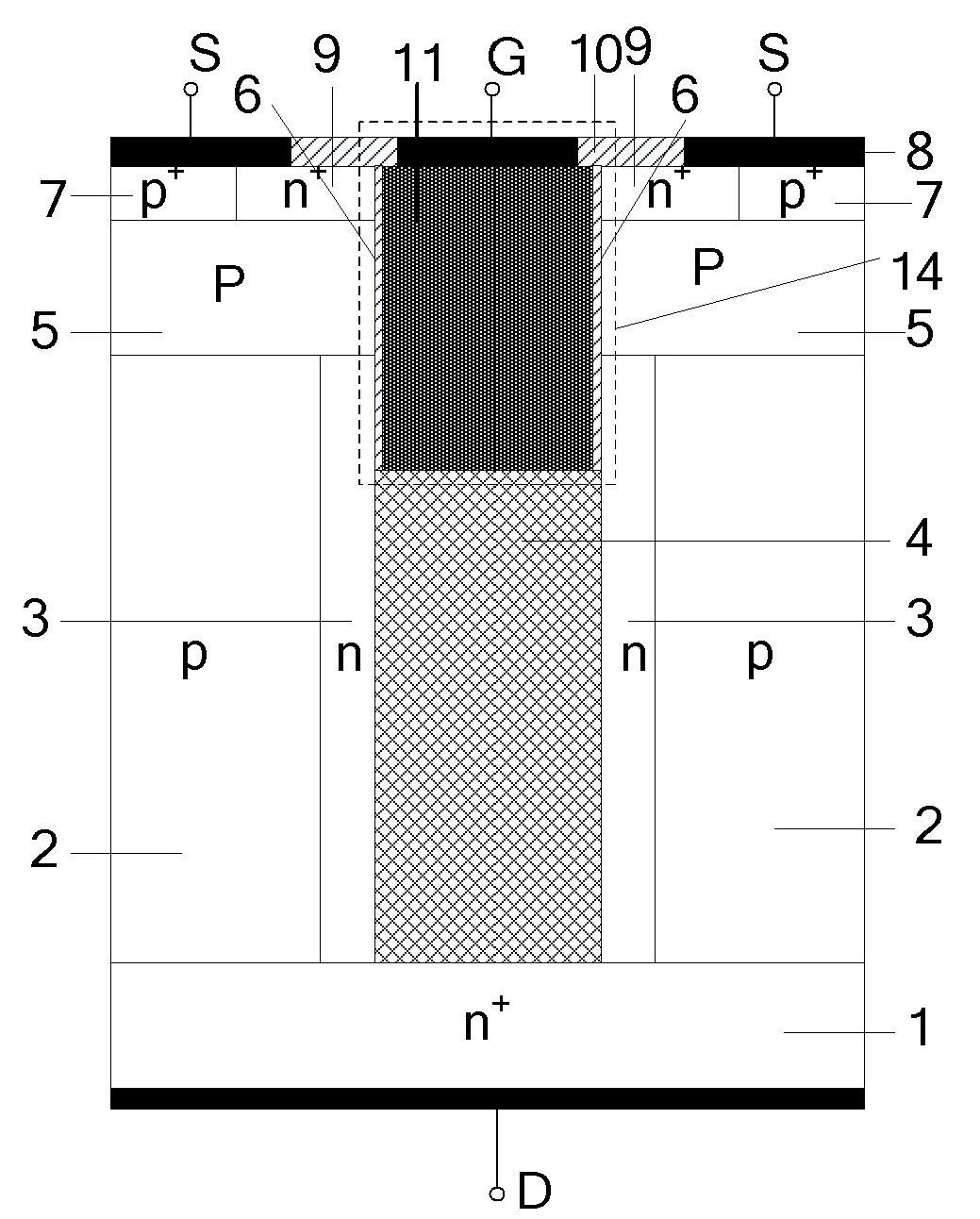

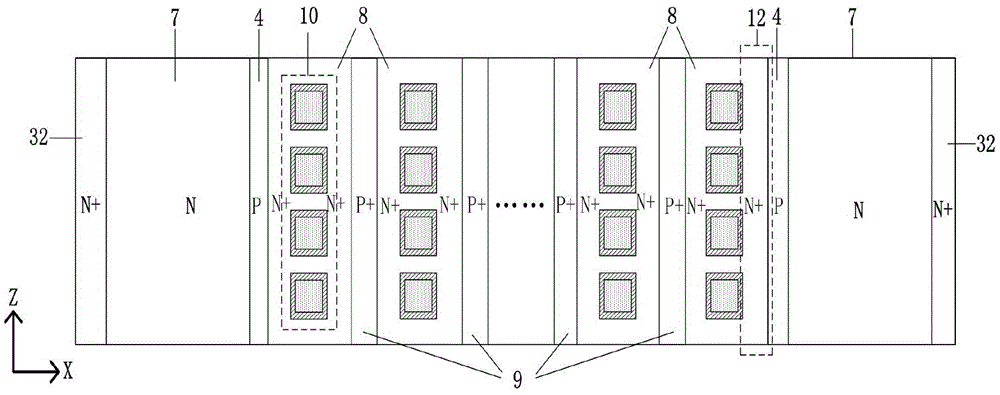

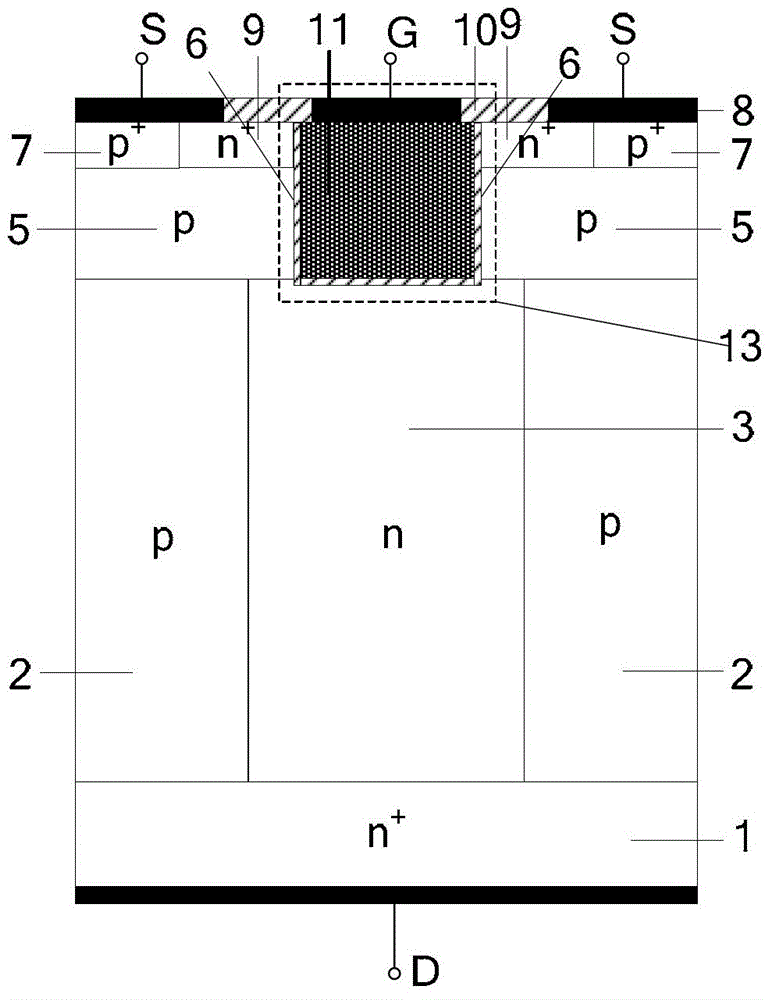

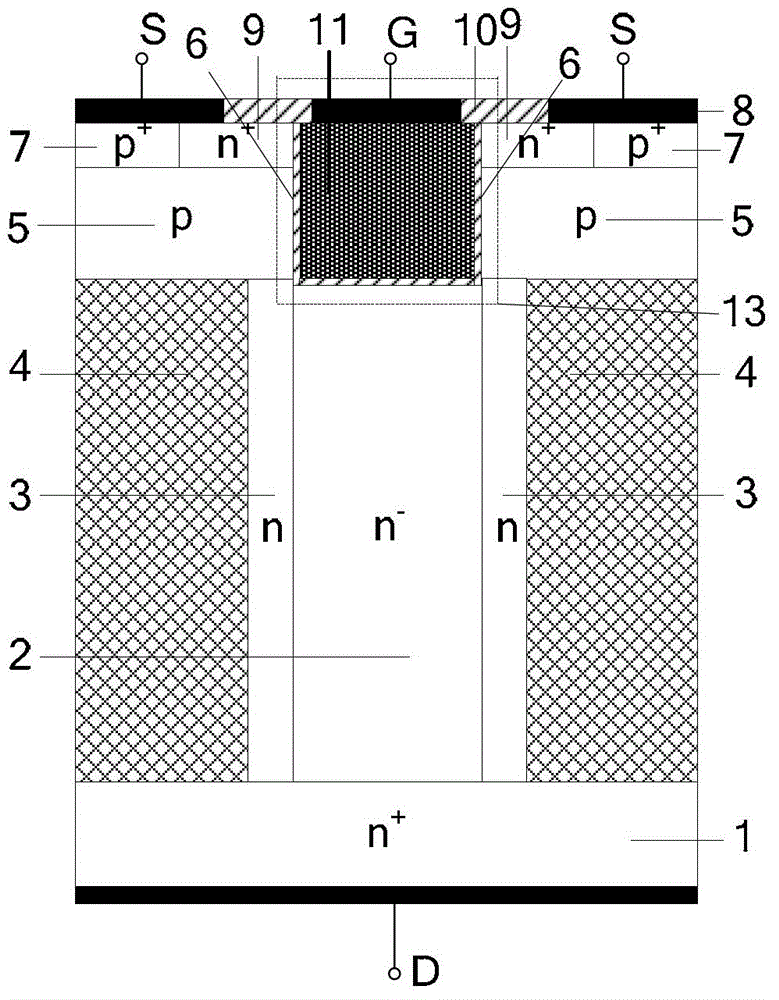

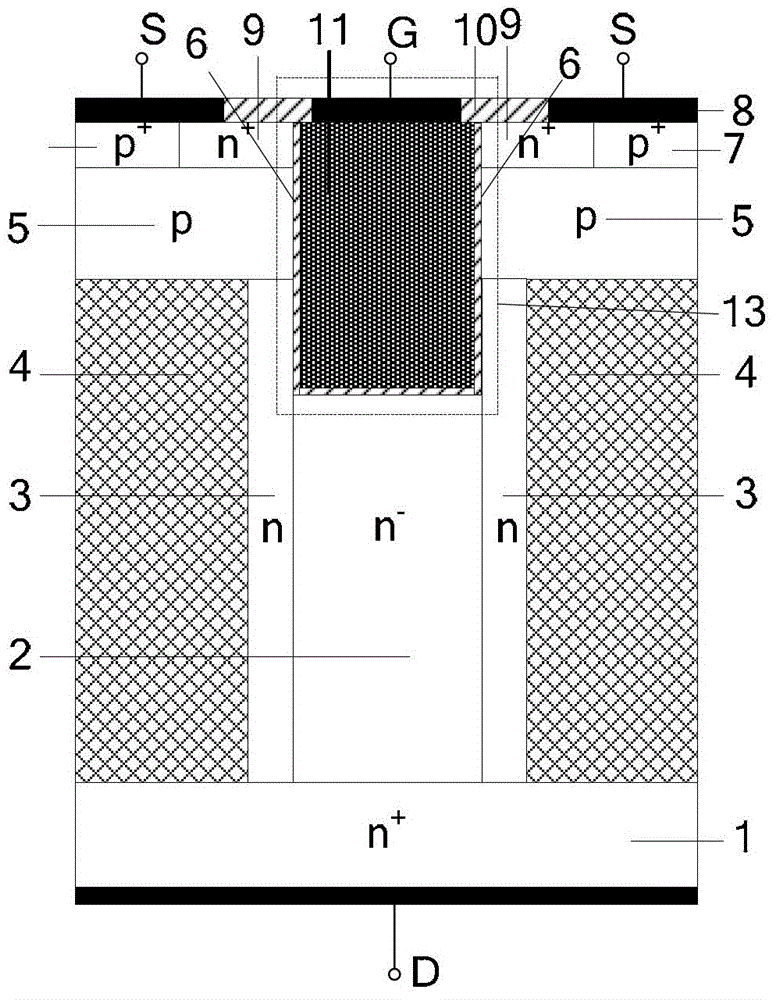

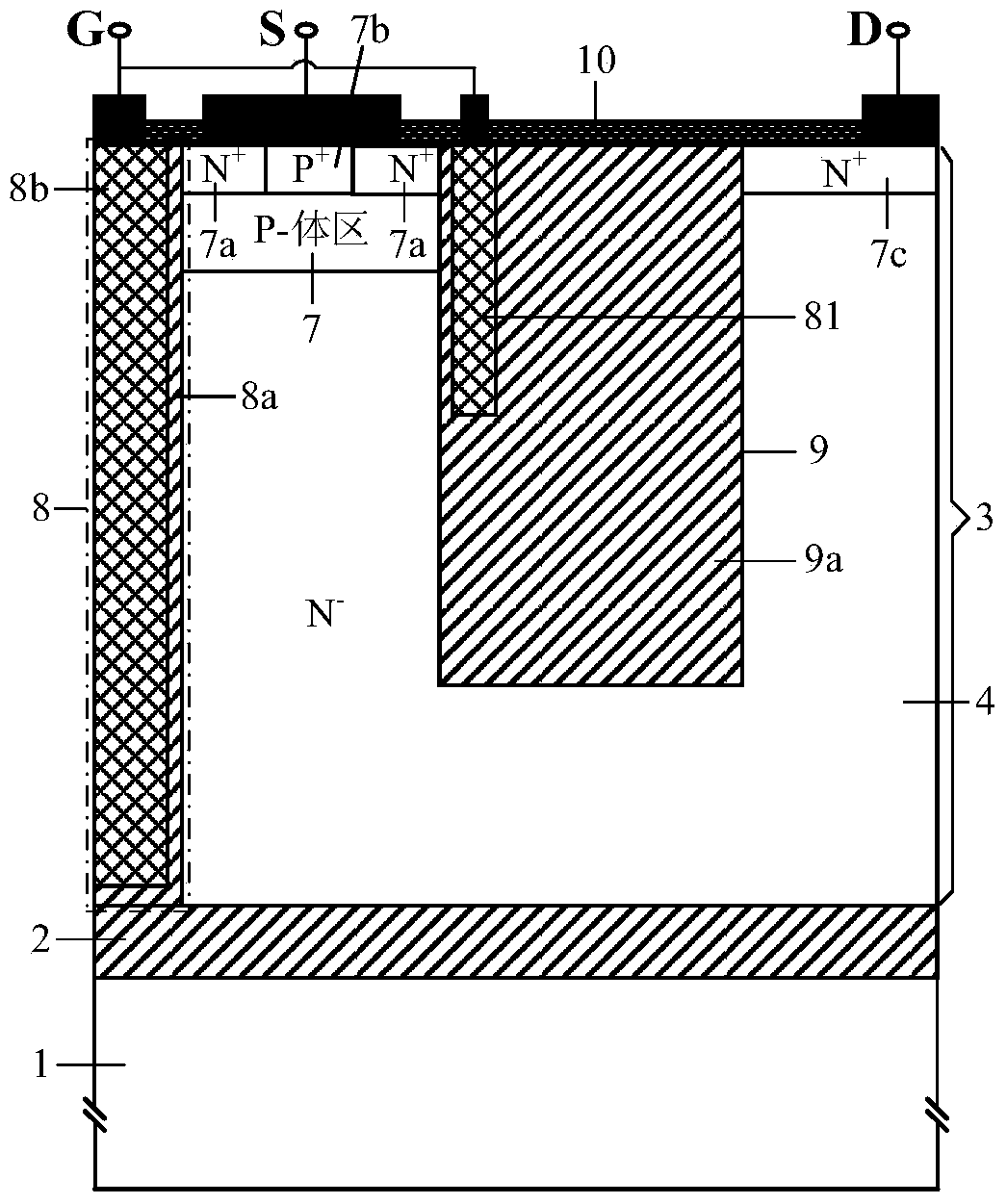

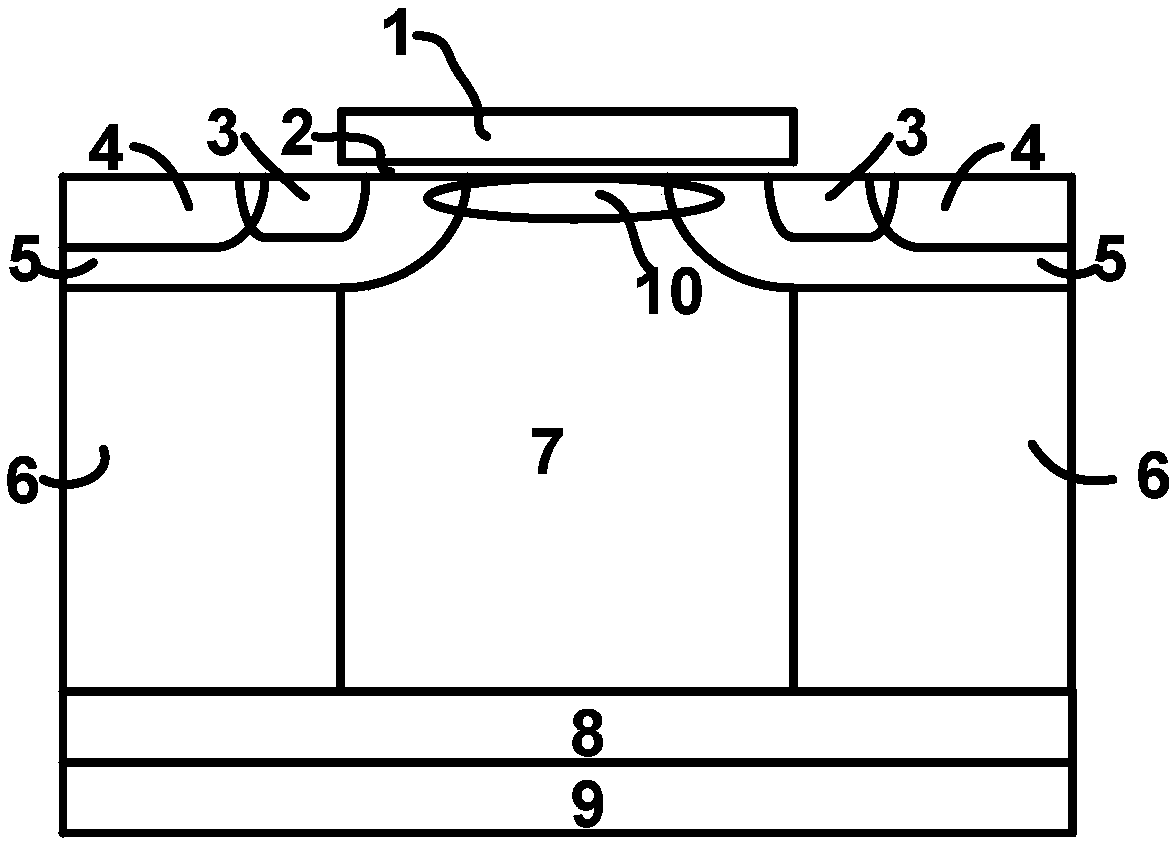

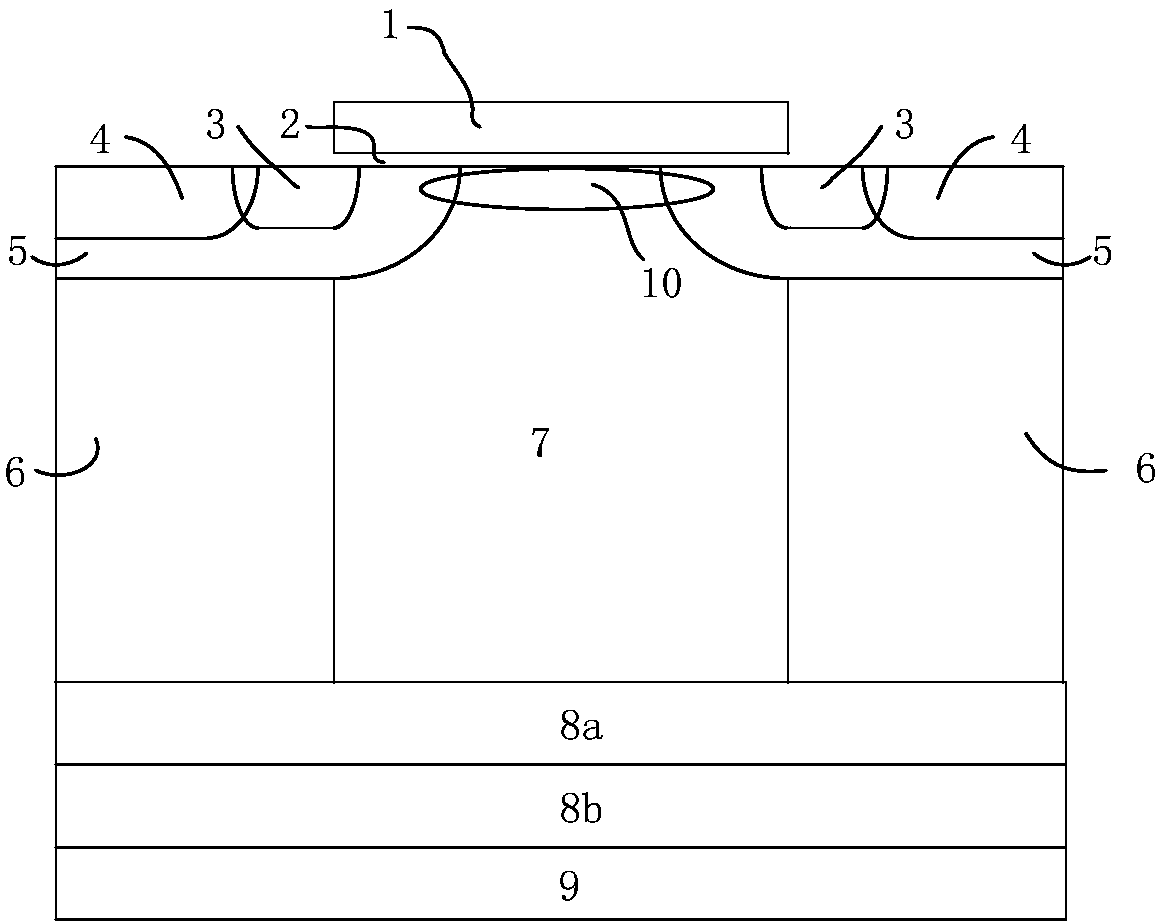

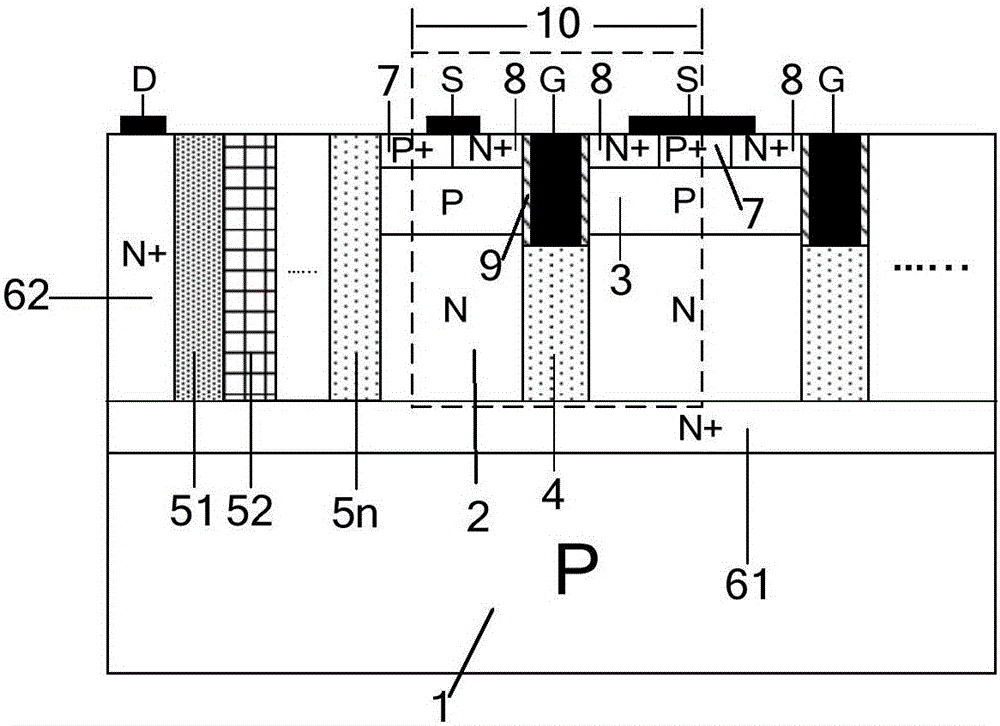

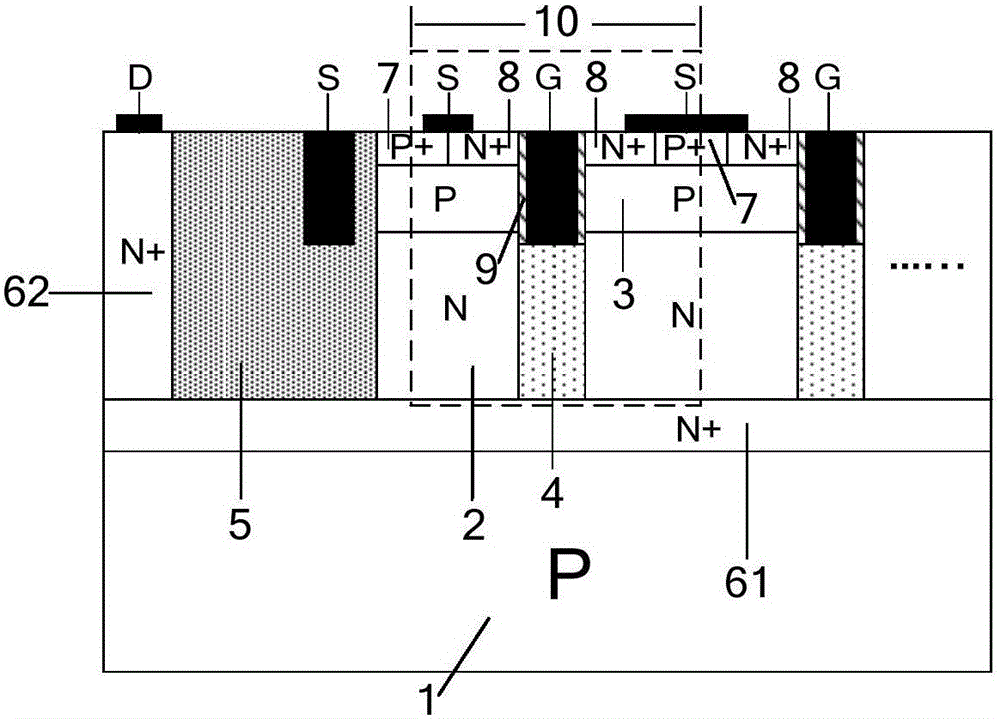

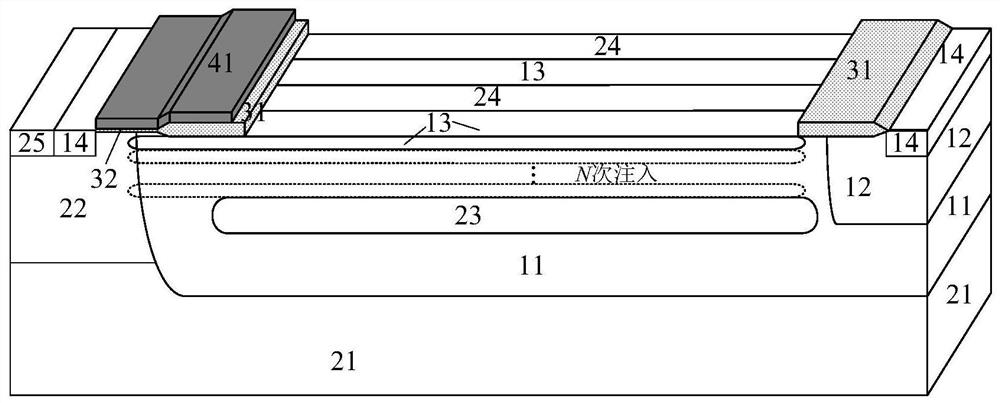

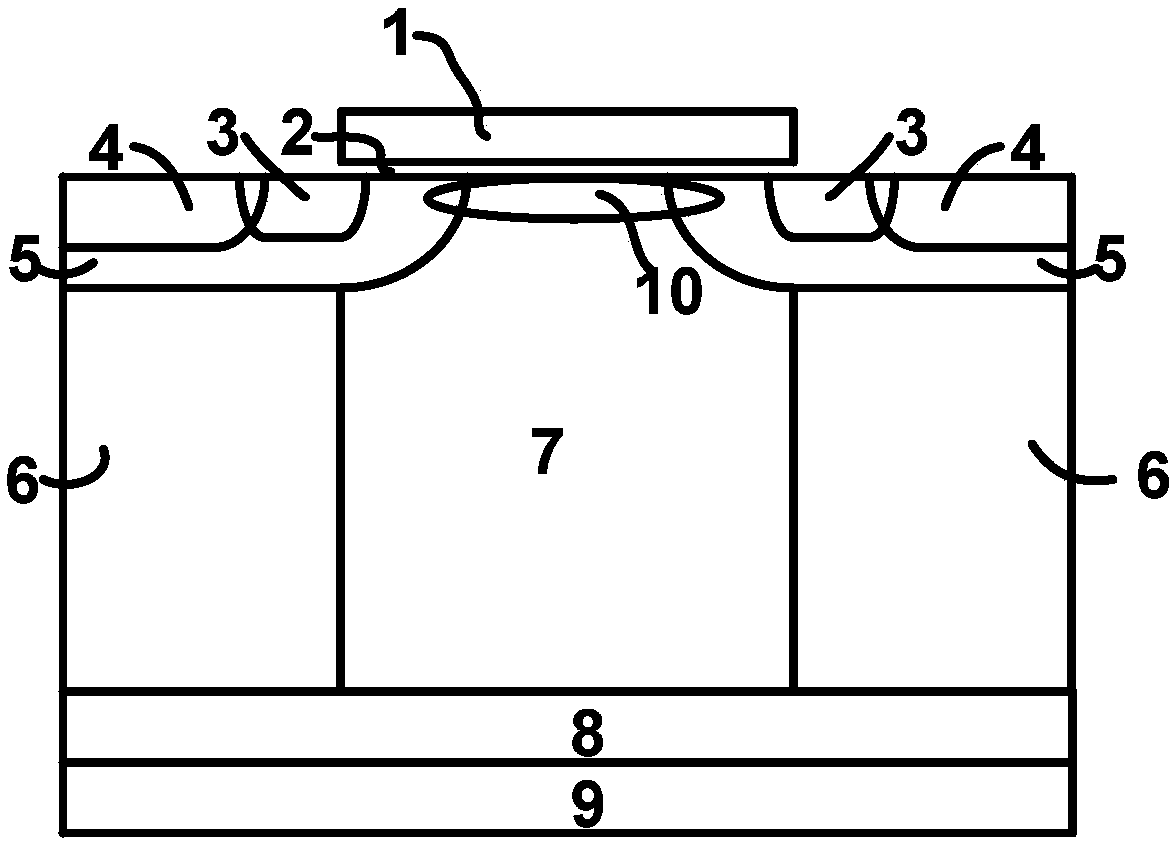

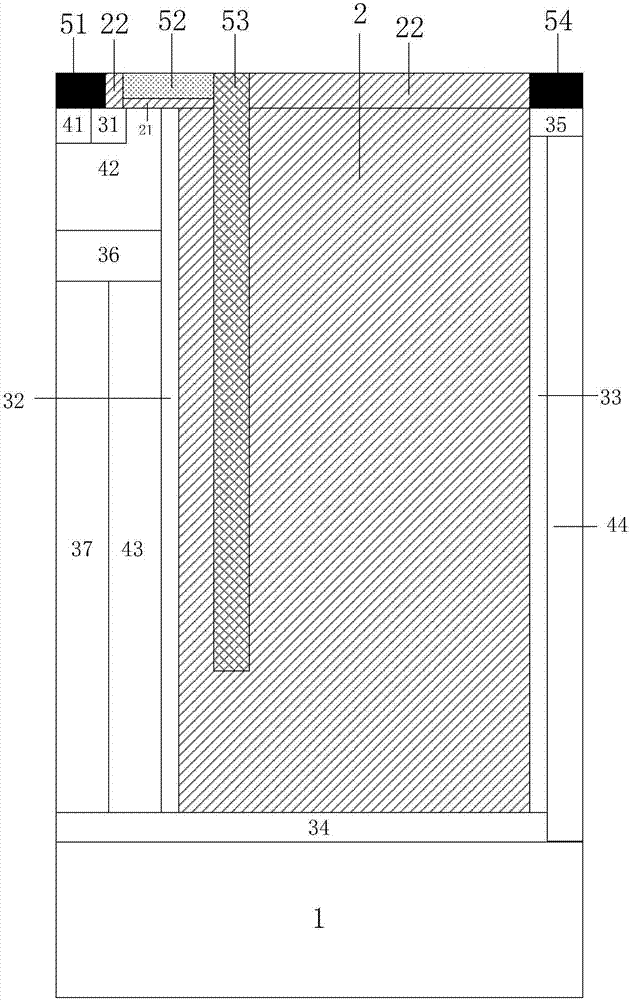

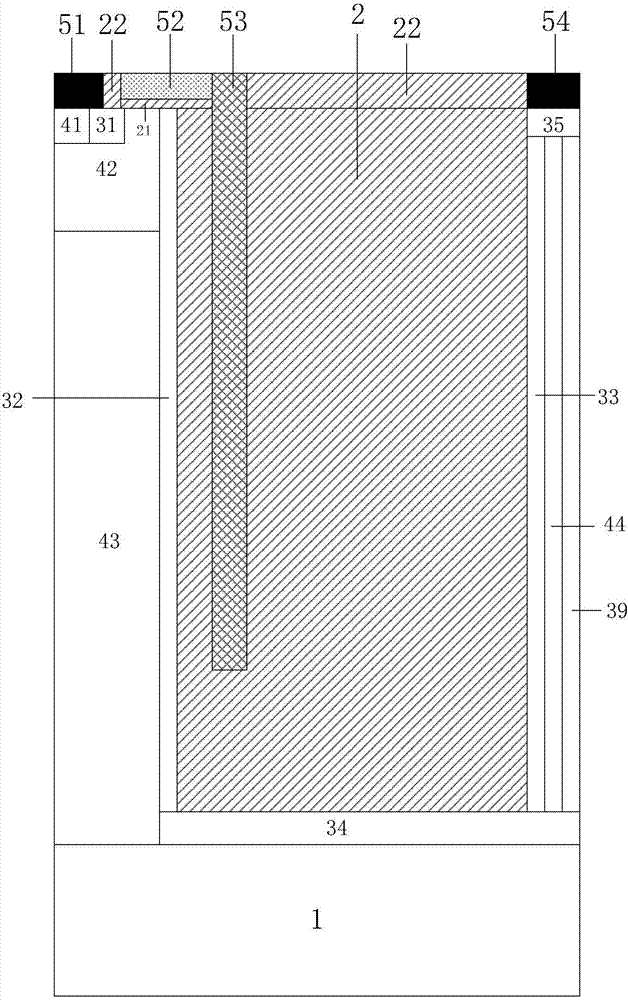

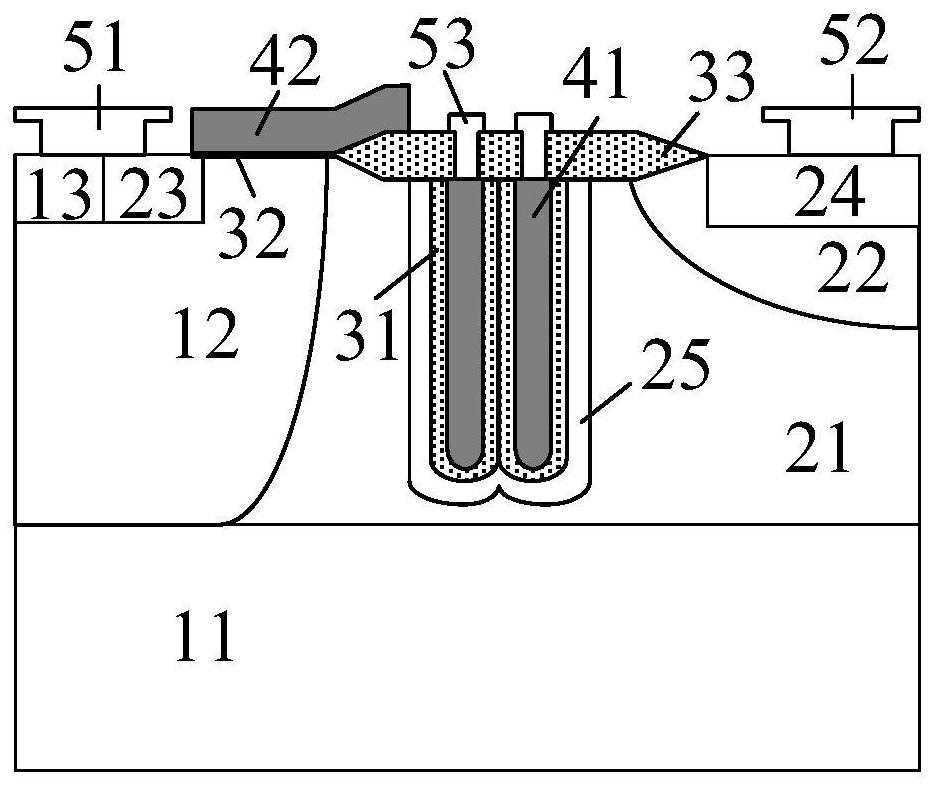

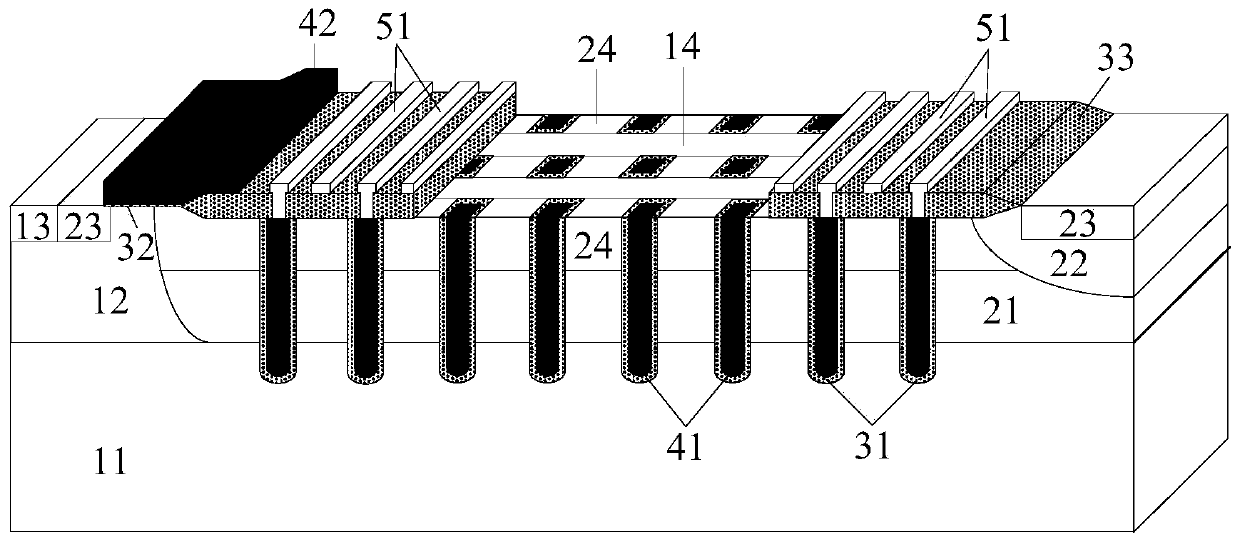

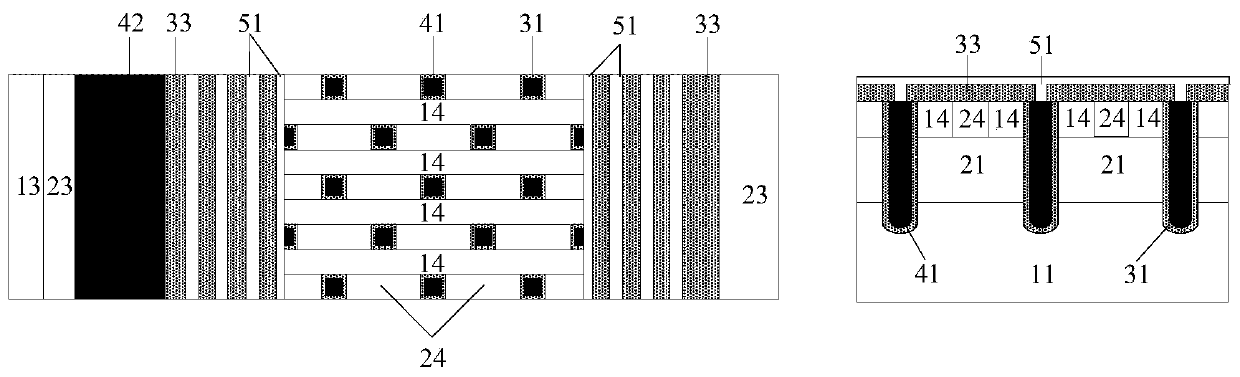

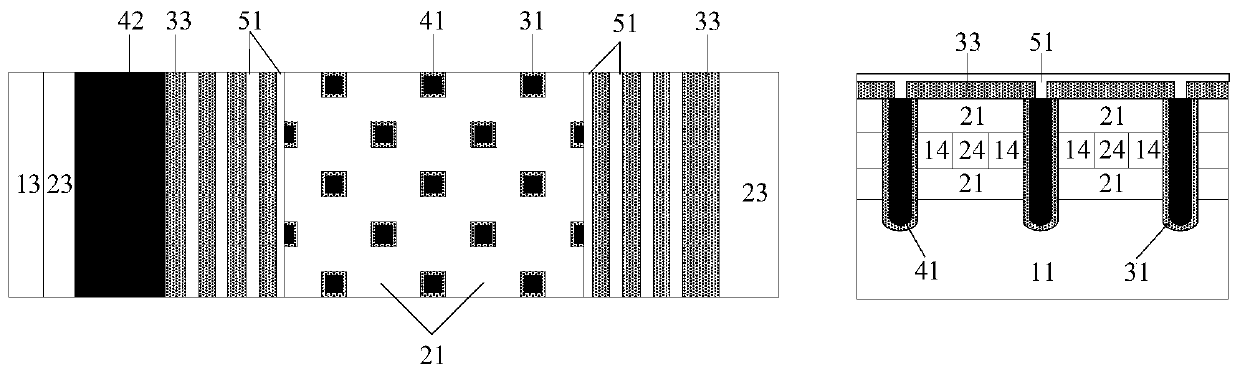

Trench gate power MOSFET (metal oxide semiconductor filed-effect transistor) device

ActiveCN105633137ASmall sizeLower specific on-resistanceSemiconductor devicesField-effect transistorPower MOSFET

The invention belongs to the technical field of a power semiconductor, and particularly relates to a trench gate power MOSFET (metal oxide semiconductor filed-effect transistor) device. The trench gate power MOSFET device has the following characteristics: 1, a crosswise heavily-doped semiconductor drain region and a longitudinal drain extension region are adopted, so that the device integrates the advantages of a VDMOS that can generate high current in a shunt-wound manner and a LDMOS that can be integrated easily; 2, a segmentation trench gate structure is adopted, so that the trench density can be improved, the device dimension can be saved, and the specific conduction resistance of the device can be lowered; and 3, RESURF structures are formed in the semiconductor region and a crosswise drift region, so that the surface electric field of the device can be improved, and the doping concentration of the crosswise drift region can be improved; and meanwhile, under a conduction state, a low-resistance channel is formed in the crosswise drift region, so that the power consumption of the device is dramatically lowered.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Low Qgd trench MOSFET integrated with schottky rectifier

ActiveUS8653589B2Lower specific on-resistanceReduce voltageSemiconductor/solid-state device manufacturingDiodeDopantTrench mosfet

An integrated circuit includes a plurality of trench MOSFET and a plurality of trench Schottky rectifier. The integrated circuit further comprises: tilt-angle implanted body dopant regions surrounding a lower portion of all trenched gates sidewalls for reducing Qgd; a source dopant region disposed below trench bottoms of all trenched gates for functioning as a current path for preventing a resistance increased caused by the tilt-angle implanted body dopant regions.

Owner:FORCE MOS TECH CO LTD

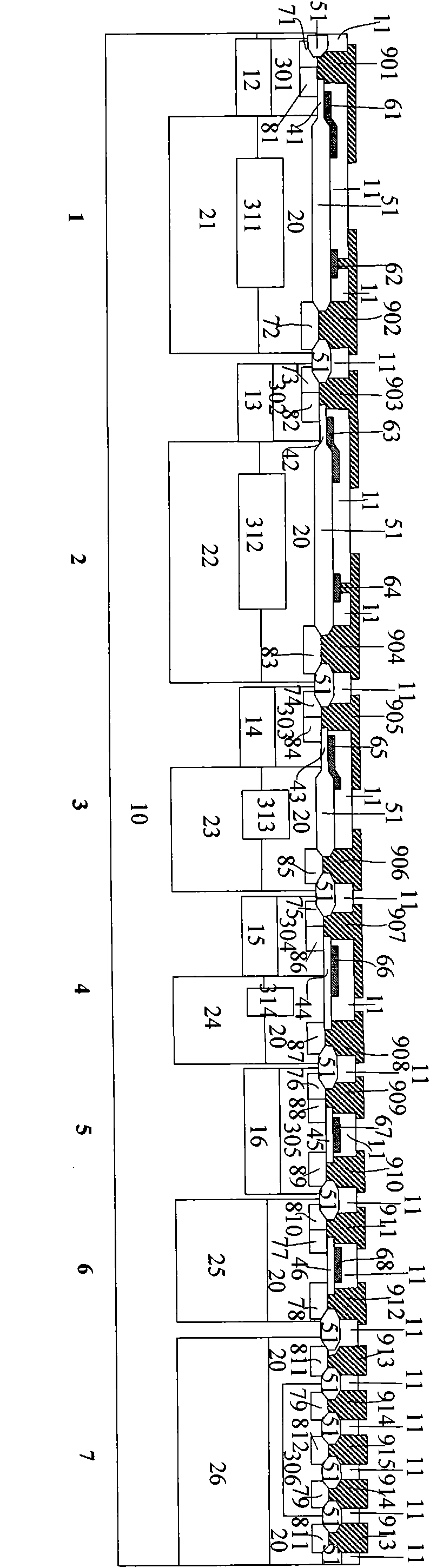

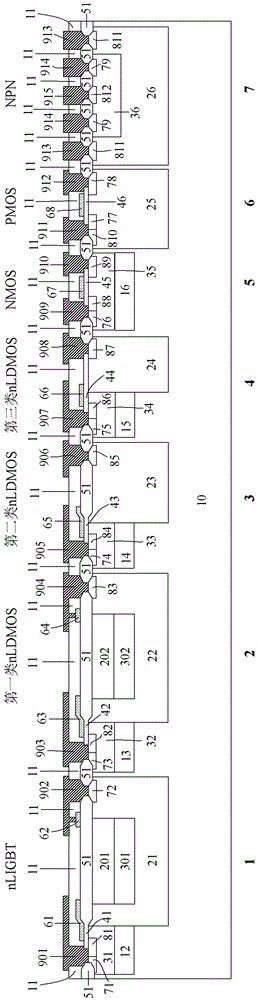

BCD semiconductor device and manufacturing method thereof

InactiveCN103337498AReduce withstand voltageLower specific on-resistanceSolid-state devicesSemiconductor/solid-state device manufacturingLow voltageEngineering

The invention relates to a BCD semiconductor device and a manufacturing method thereof. The BCD semiconductor device comprises a high voltage nLIGBT device (1), a first type of high voltage nLDMOS device (2), a second type of nLDMOS device (3), a third type of nLDMOS device (4), a low voltage NMOS device (5), a low voltage PMOS device (6) and a low voltage NPN device (7), wherein n-type drift region wells (21, 22) of the high voltage nLIGBT device (1) and of the first type of high voltage nLDMOS device (2) are respectively introduced with n-type heavily-doped layers (201, 202), and p-type reduced-field layers (301, 302) are respectively arranged below the n-type heavily-doped layers (201, 202) and are surrounded by the n-type drift region wells (21, 22). A smaller conduction resistance is realized while chip areas are the same, or a smaller chip area is realized while conduction capabilities are the same. The BCD semiconductor device has advantages of simple manufacturing method and relatively less difficult technology.

Owner:SHENZHEN LAND HOPE MICRO ELECTRONICS

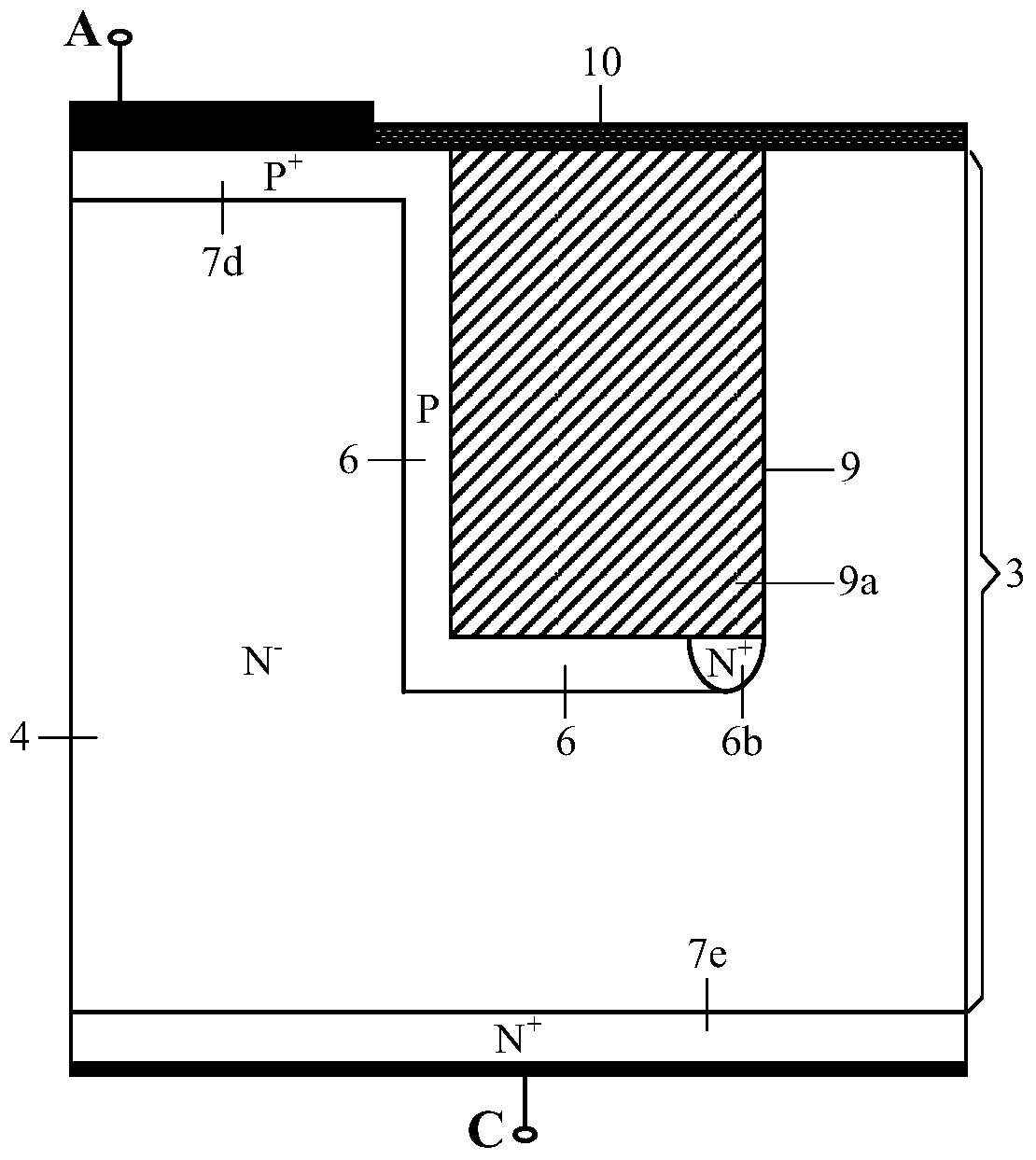

Groove-gate semiconductor power device

ActiveCN102723355APerformance doesn't have much impactPerformance impactSemiconductor devicesSemiconductor technologySemiconductor

The invention relates to semiconductor technologies and provides a groove-gate semiconductor power device which is used for solving the problem that the high-K dielectric role of the existing semiconductor device can not be played under the conditions of relatively-large spacing and small density of dielectric grooves. The technical scheme adopted by the invention can be summarized as follows: two high-K dielectric regions are additionally arranged at the left side and right side of a semiconductor drift region, the two sides of a first semiconductor region in the semiconductor drift region are in contact with two second semiconductor regions, and the two high-K dielectric regions are respectively in contact with the other sides of the two second semiconductor regions. The groove-gate semiconductor power device has the beneficial effects that the specific on-resistance is reduced, the voltage resistance is improved, and the groove-gate semiconductor power device is applicable to an MOS (Metal-Oxide Semiconductor) device or an MOS-controlled semiconductor device.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

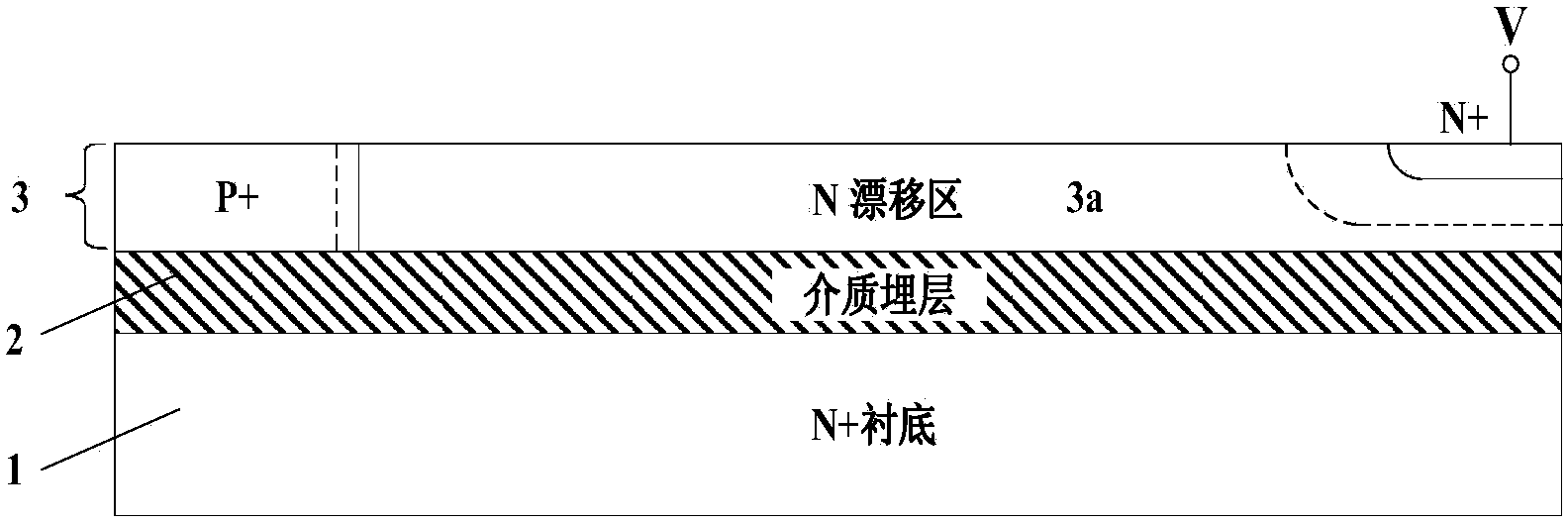

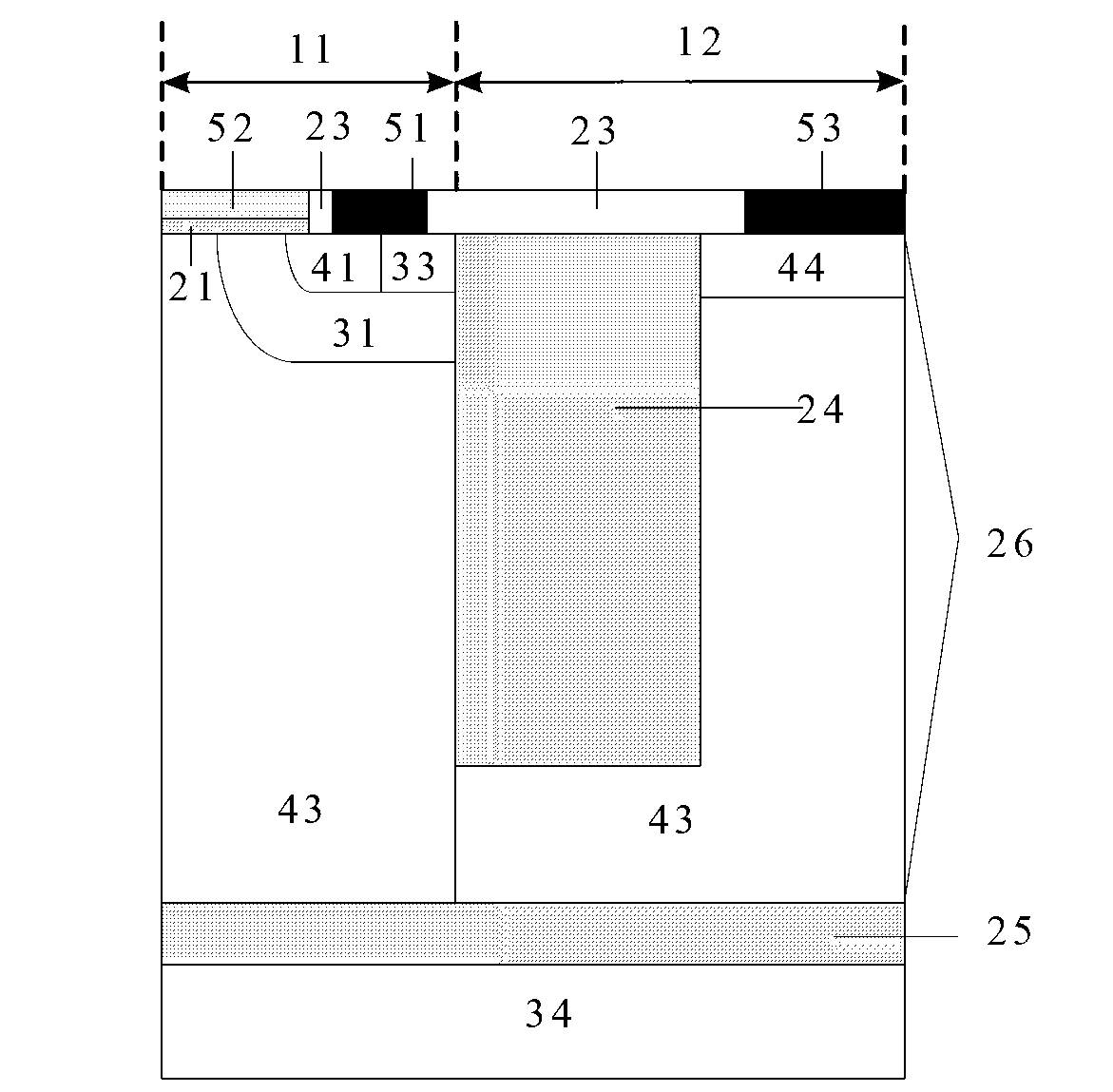

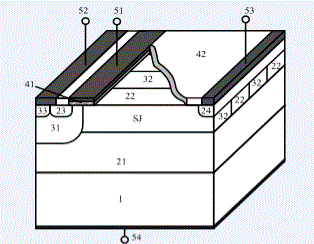

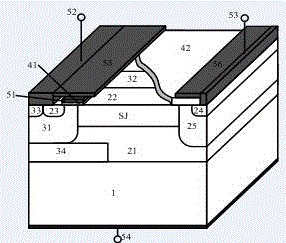

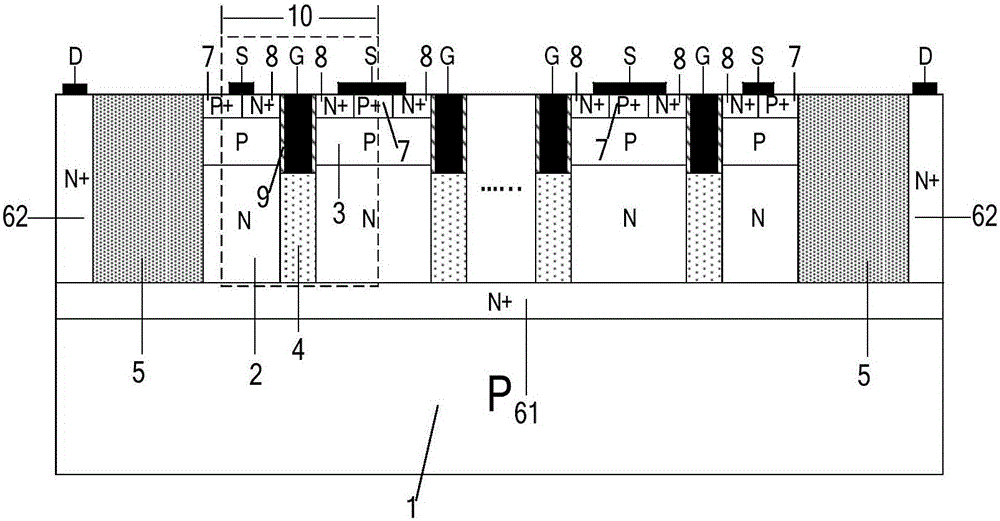

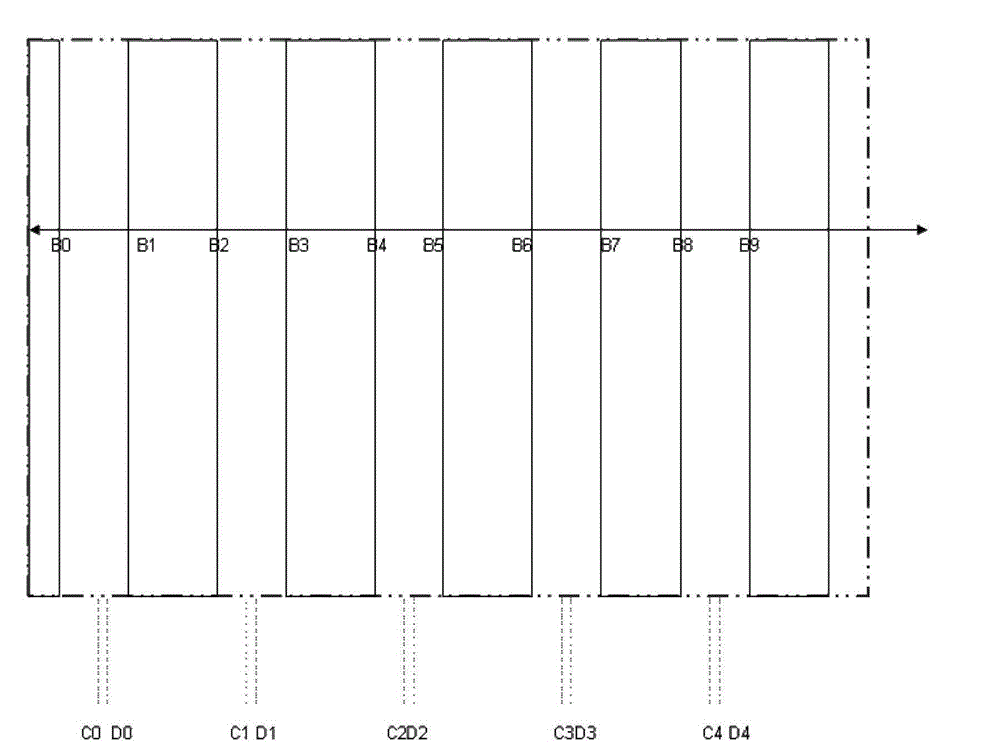

Silicon on insulator (SOI) transverse high voltage power device with ultralow specific on resistance

ActiveCN103022134AEasy to integrateReduce layout areaSemiconductor devicesPower semiconductor deviceEngineering

A silicon on insulator (SOI) transverse high voltage power device with ultralow specific on resistance belongs to the technical field of power semiconductor devices and comprises a vertical super junction cellular structure and a terminal structure. The terminal structure is located on the outside or the periphery of an integral cellular structure. The device is manufactured on an SOI layer of an SOI material. The vertical super junction cellular structure improves breakdown voltage, reduces specific on resistance simultaneously and reduces domain area. The device is integrated by a single cellular or a plurality of cellulars, the plurality of cellulars connected in parallel can share one terminal, and a drain leading out structure is utilized to lead out a drain transversely to enable the drain, a grid and a source to be located on the surface. The device can be easily integrated with a common circuit, greatly reduces domain area and further reduces process cost. In addition, the device is capable of increasing a device vertical electric field by adopting a thin oxygen burying layer and simultaneously can effectively relieve self-heating effect.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

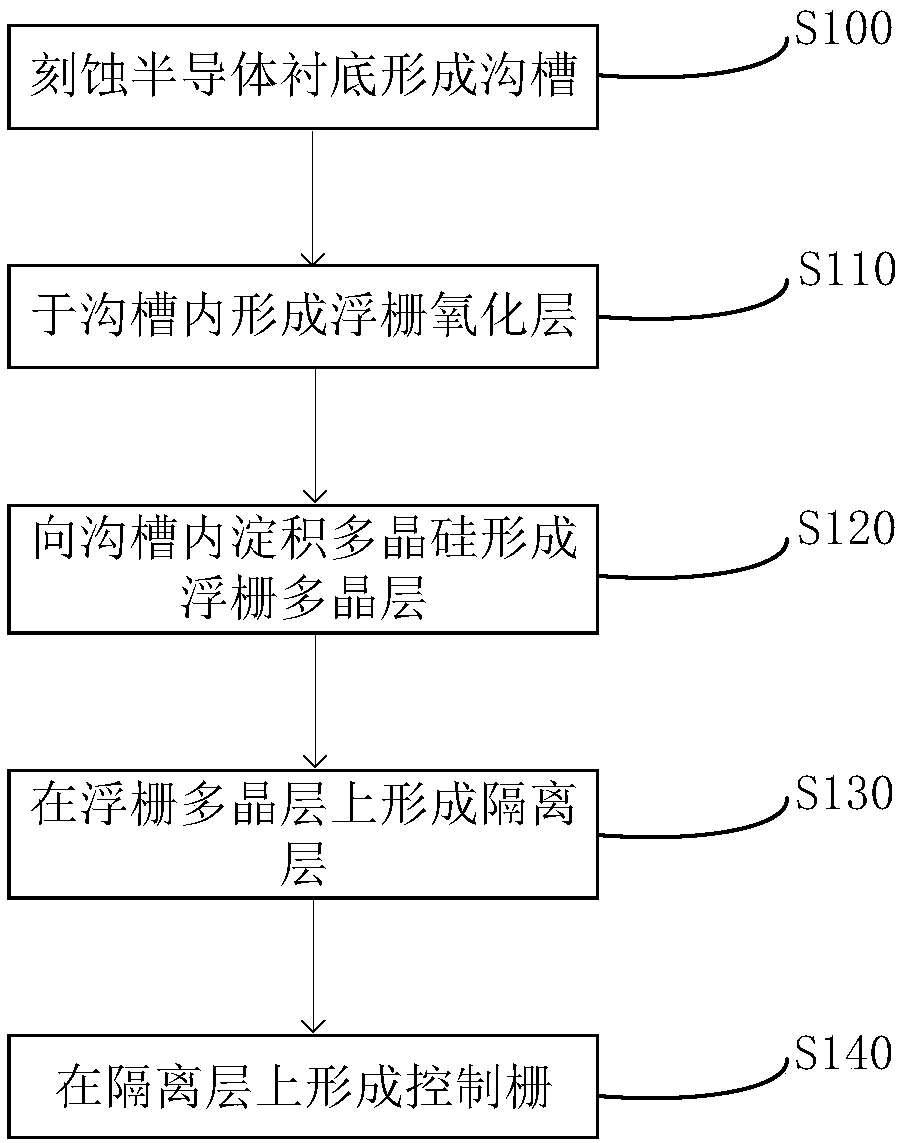

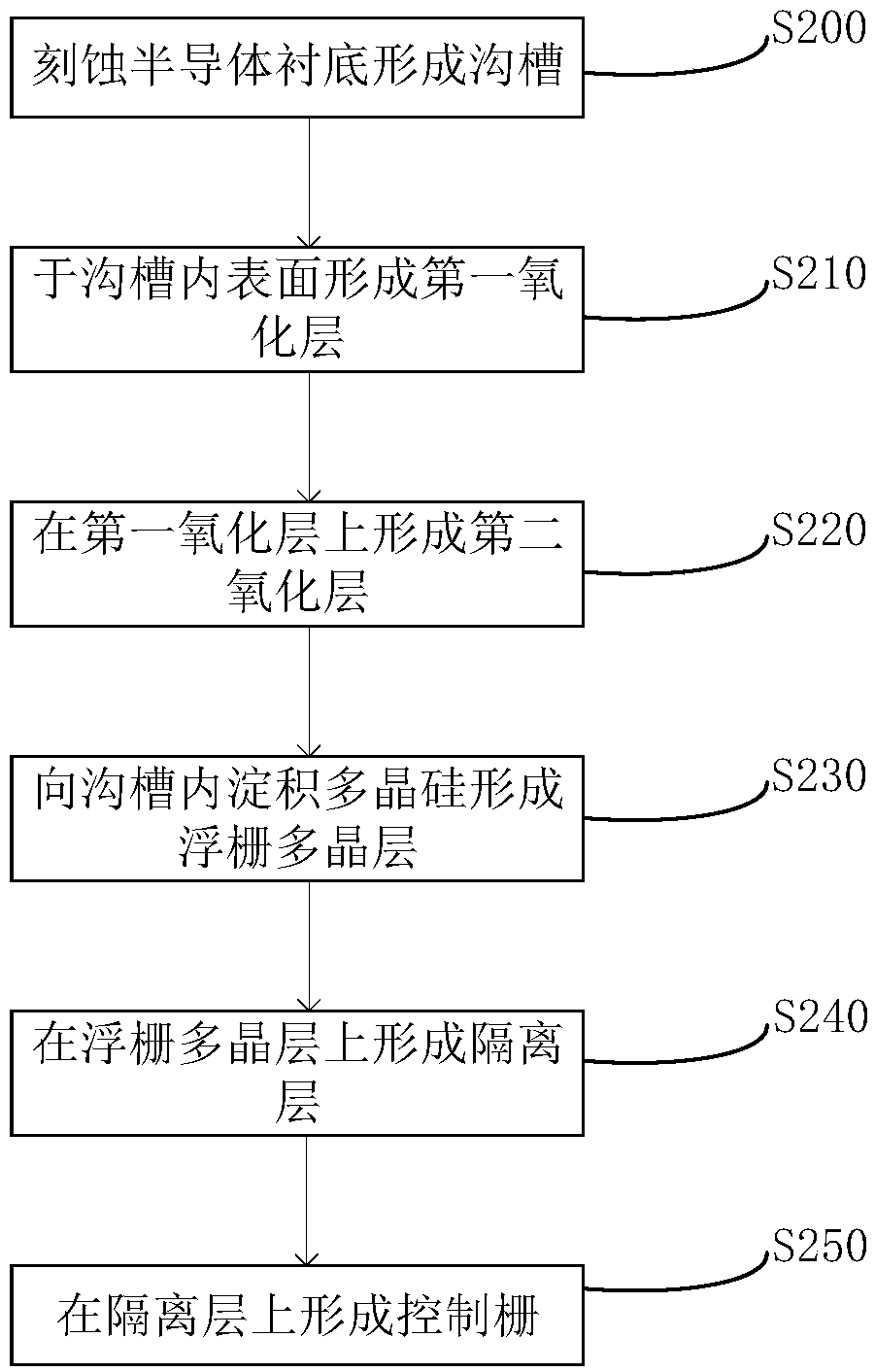

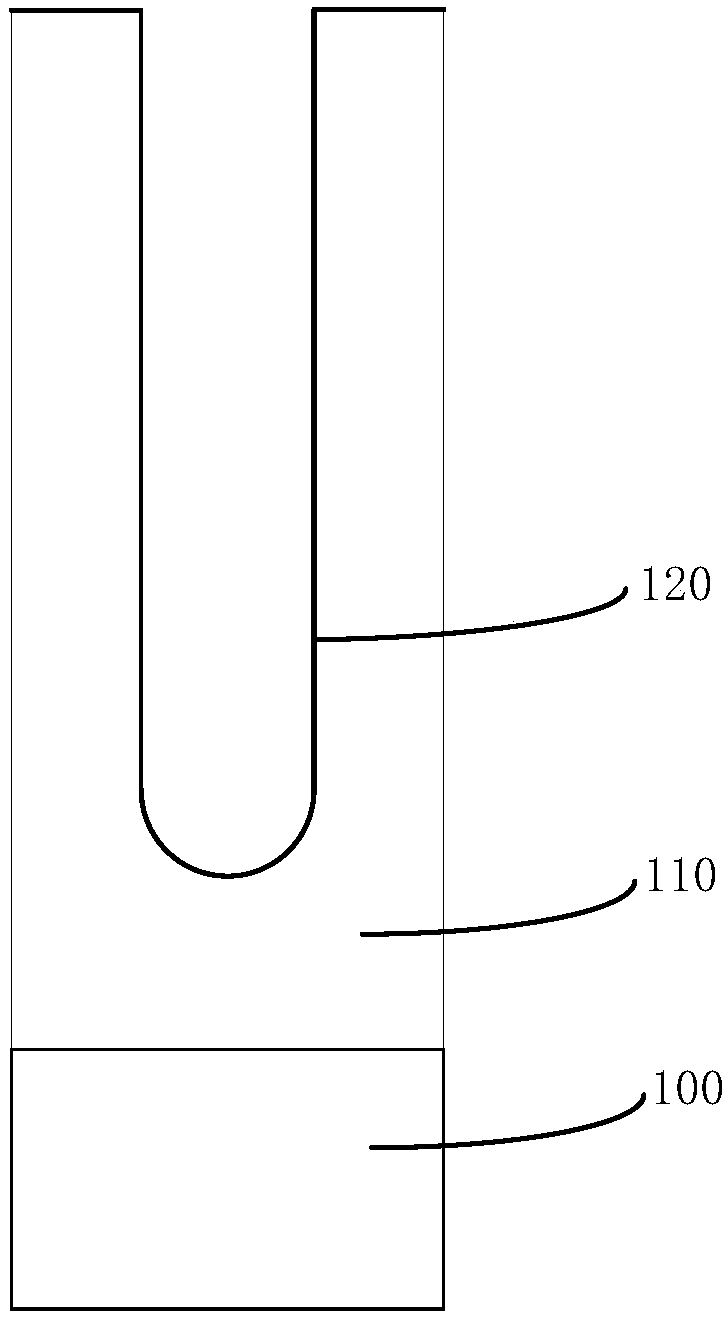

Trench isolation gate device and fabricating method thereof

ActiveCN110310992ALower specific on-resistanceWon't break downSemiconductor/solid-state device manufacturingSemiconductor devicesIsolation layerGate oxide

The invention relates to a method of fabricating a trench isolation gate device. The method comprises steps: a semiconductor substrate is etched to form a trench; an oxide is deposited in the trench to form a floating gate oxide layer, the floating gate oxide layer is gradually thickened from top to bottom along the side wall of the trench, and the thickness of the floating gate oxide layer at thelower part of the side wall of the trench is the same as that of the floating gate oxide layer at the bottom part of the trench; polysilicon is deposited in the trench to form a floating gate polycrystalline layer; an insulating medium grows on the upper surface of the floating gate polycrystalline layer to form an isolation layer; and a control gate is formed on the isolation layer in the trench. A deposition technology is adopted to deposit the floating gate oxide layer at the bottom part of the trench, the floating gate oxide layer is gradually thickened from the side wall of the trench tothe bottom of the trench, and the thickness of the floating gate oxide layer at the lower part of the side wall of the trench is the same as that of the floating gate oxide layer at the bottom part of the trench. The gradually-changing floating gate oxide layer thickness can narrow the width of the trench, the cell area is further reduced, and the specific on-resistance of the device is reduced.

Owner:CSMC TECH FAB2 CO LTD

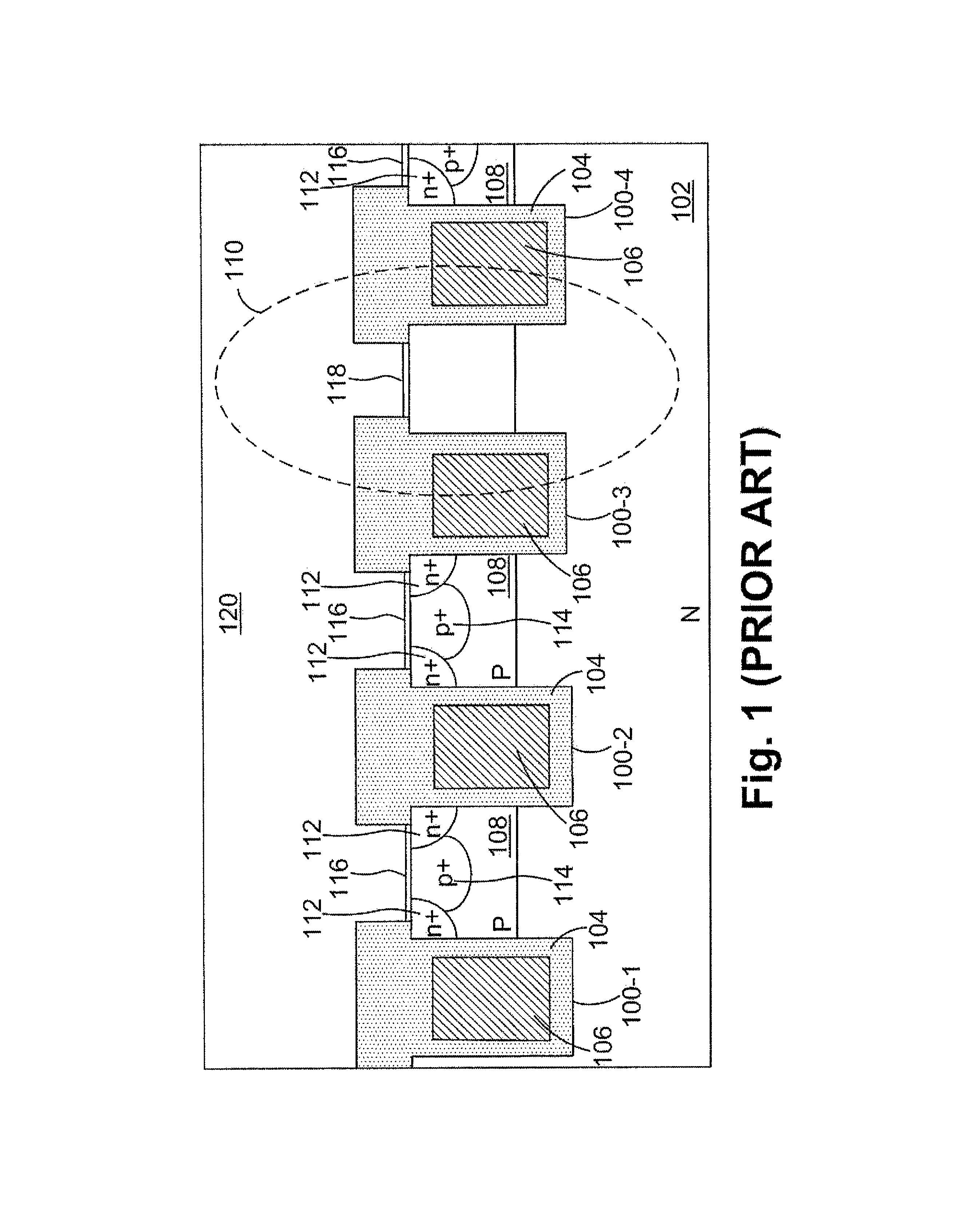

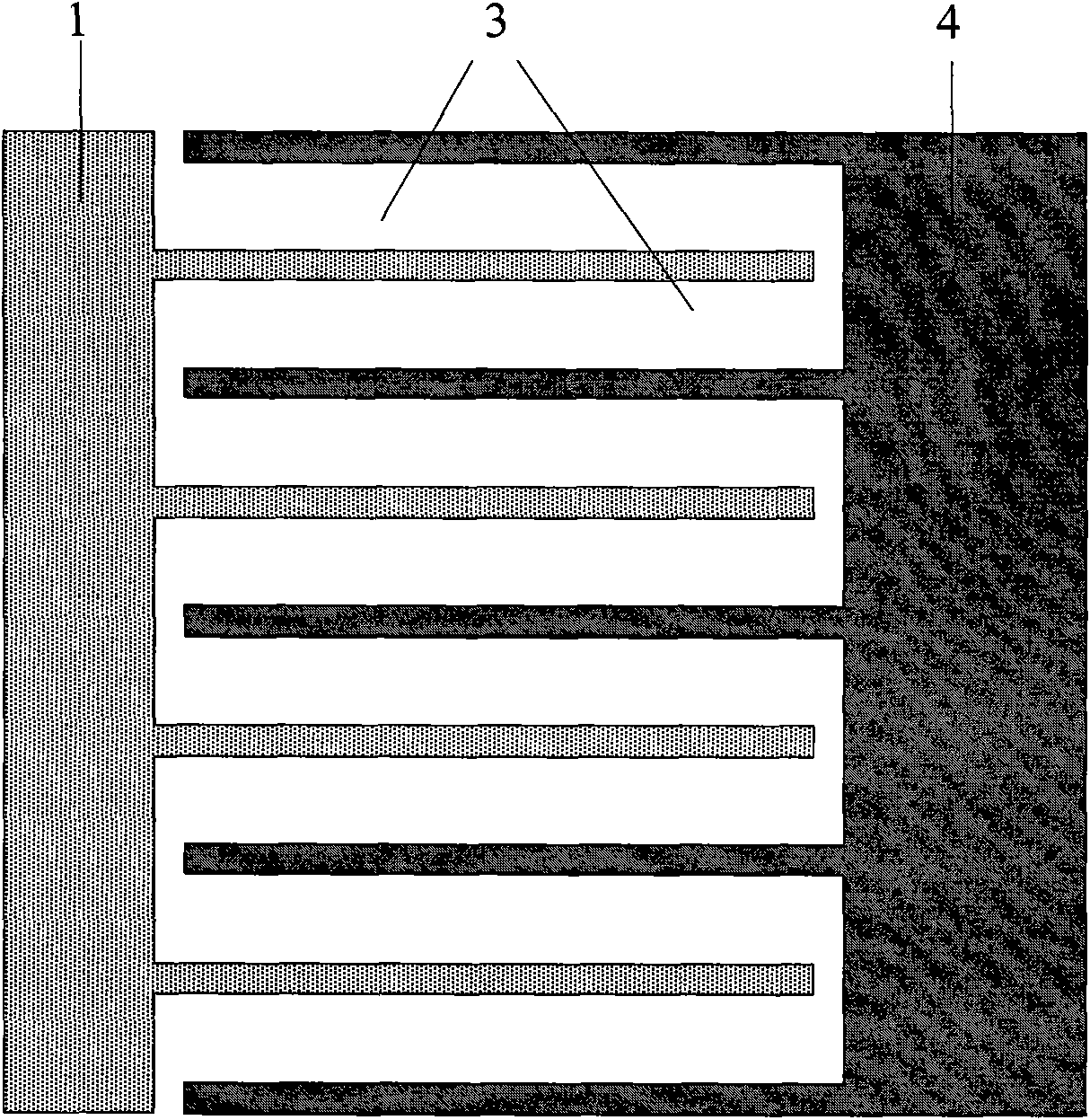

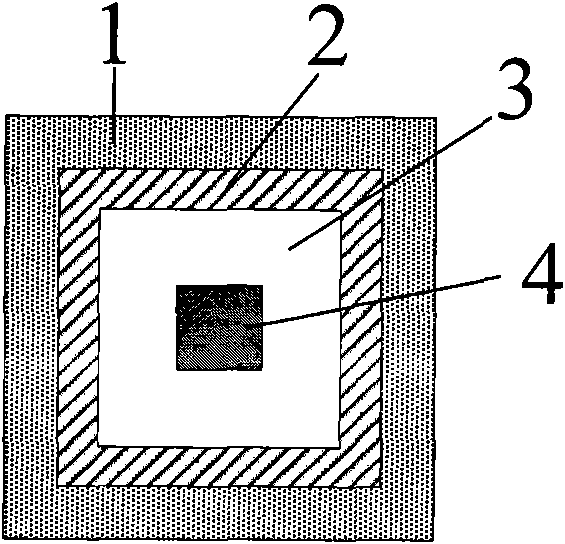

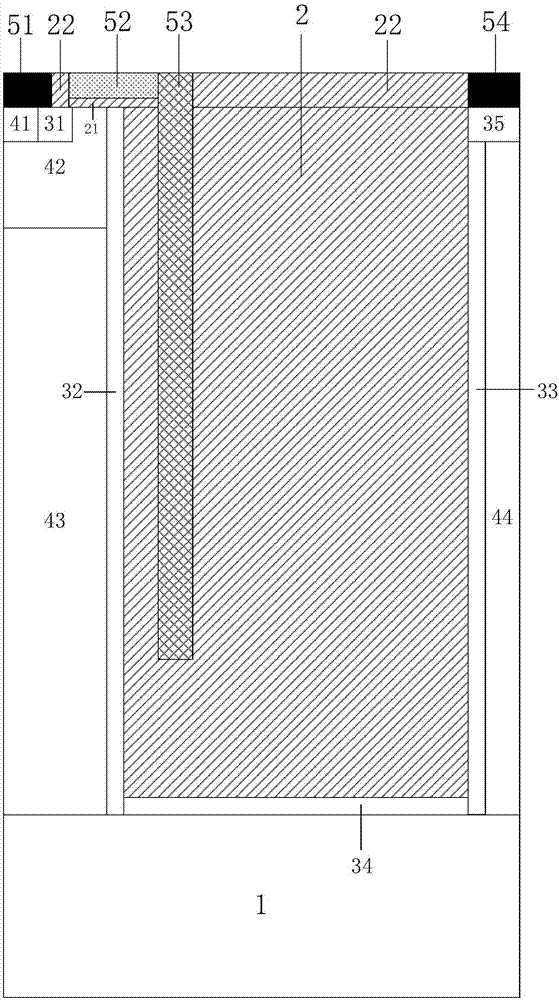

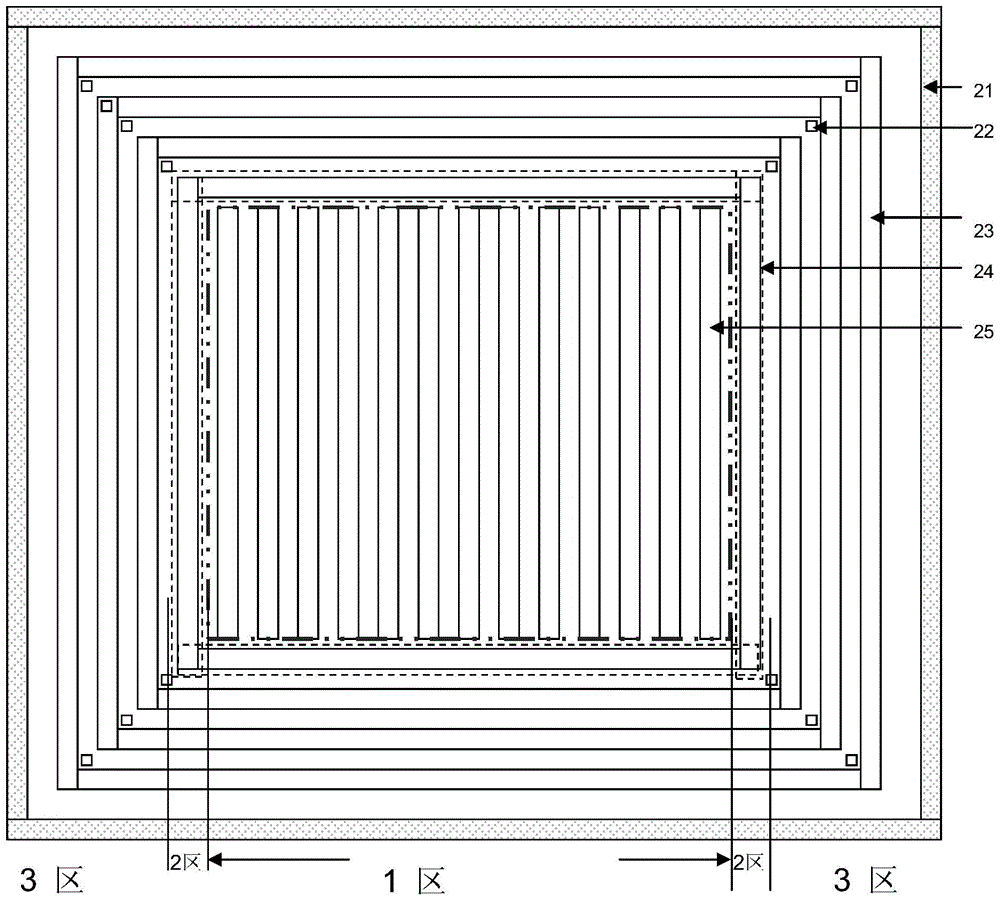

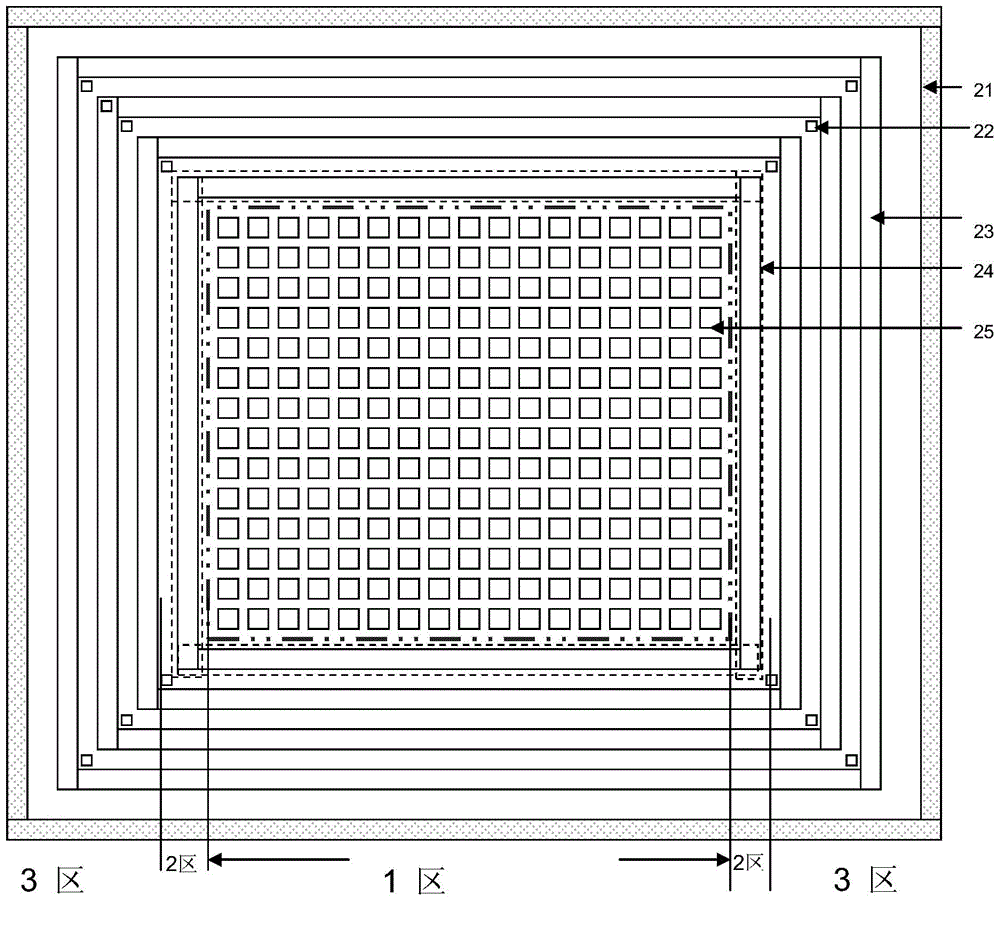

Layout structure of transverse power components

InactiveCN101771084AIncrease current densityCompact layoutSemiconductor devicesPower componentFast speed

The invention relates to a layout structure of transverse power components and belongs to the technical field of semiconductor power components. The power components form a cellular arrangement structure on the transversal section; each cellular has the same structure and is provided with the following elements from inside to the outside: a drain electrode, a light dope drift area, a gate electrode and a source electrode, and the drain electrode is enclosed by the light dope drift area, the light dope drift area is enclosed by the gate electrode, and the gate electrode is enclosed by the source electrode; and the transversal sections of each source electrode, gate electrode, light dope drift area and drain electrode of each cellular are of the same shape, and are round or positive n polygons, wherein n is more than or equal to 3. The invention has the advantages of compact layout without additional curvature terminal design, has low on-resistance, small parasitic capacitance, quick switching speed, strong current capacity and the like, and can be used in the layout structure of the transverse power components such as LDMOS, LIGBT and the like.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

SOI horizontal power MOSFET device

InactiveCN104241365AImprove pressure resistanceLarge horizontal sizeSemiconductor devicesCapacitancePower semiconductor device

The invention provides an SOI horizontal power MOSFET device and belongs to the technical field of power semiconductor devices. A dielectric groove is introduced in a drift region and filled with two or more dielectric materials, and the dielectric coefficients of the dielectric materials are lower than the dielectric coefficient of an active layer and are gradually decreased from bottom to top; the side, close to a body region, of the dielectric groove is of a body region longitudinal extension structure; a semiconductor buried layer opposite to the drift region in doping type is arranged between the dielectric groove and a dielectric buried layer. Because the dielectric groove filled with the variable k dielectric materials has an modulating action on an internal electric field of the active layer and plays a role in longitudinally folding the drift region, the voltage resistance of the device is greatly improved, and the horizontal size of the device is reduced; because of introduction of the body region longitudinal extension structure and the semiconductor buried layer, the voltage resistance of the device is further improved, the exhausting action on the drift region is enhanced, the doping concentration of the drift region can be improved, and therefore the on resistance of the device is reduced; the grid and drain capacitance of the device can be further reduced through the dielectric groove, and the frequency and output power of the device are improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

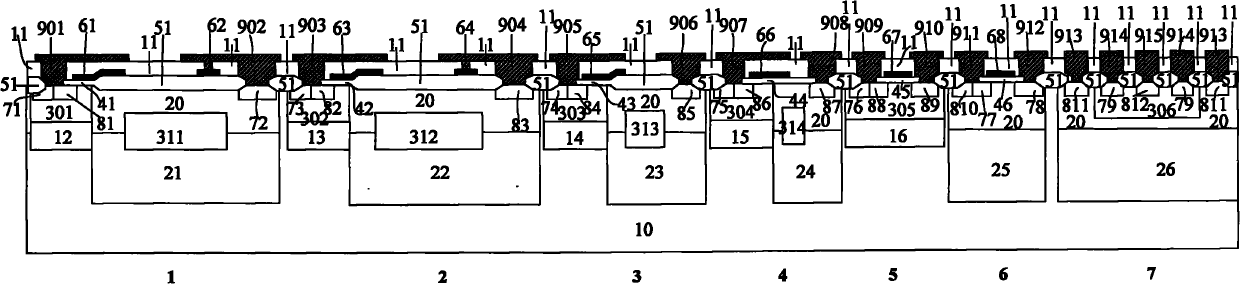

High performance multigate transistor

ActiveUS9214538B2Easy to controlReduce parasitic capacitanceTransistorSemiconductor/solid-state device manufacturingSemiconductor materialsSemiconductor structure

A novel semiconductor power transistor is presented. The semiconductor structure is simple and is based on a FET structure, where multiple channels and multiple gate regions are formed in order to achieve a lower specific on-resistance, and a higher control on the transport properties of the device. No dielectric layer is present between gate electrodes and device channels, decreasing the parasitic capacitance associated with the gate terminal. The fabrication of the device does not require Silicon On Insulator techniques and it is not limited to Silicon semiconductor materials. It can be fabricated as an enhancement or depletion device with much more control on the threshold voltage of the device, and with superior RF performance.

Owner:QUALCOMM INC

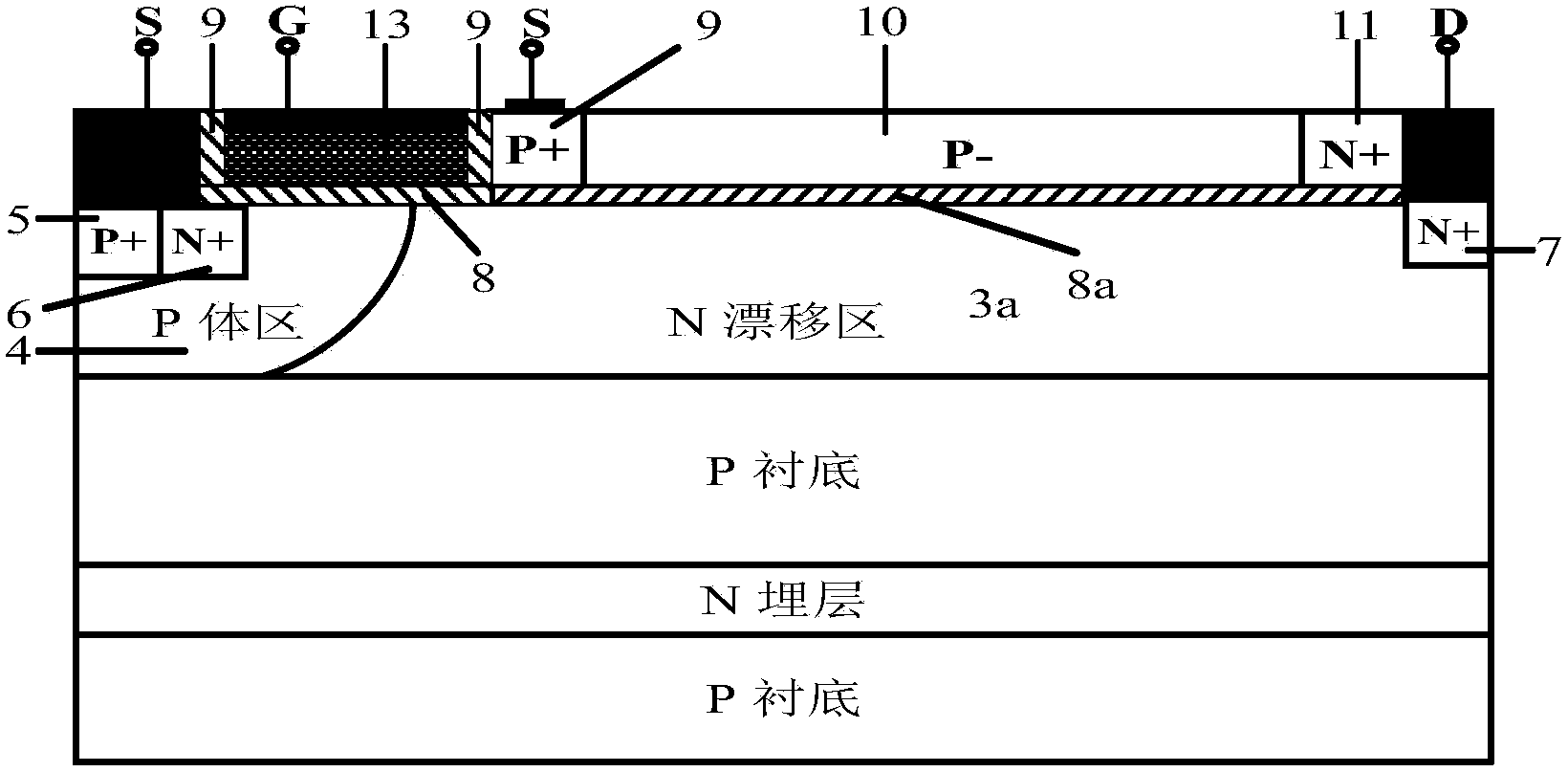

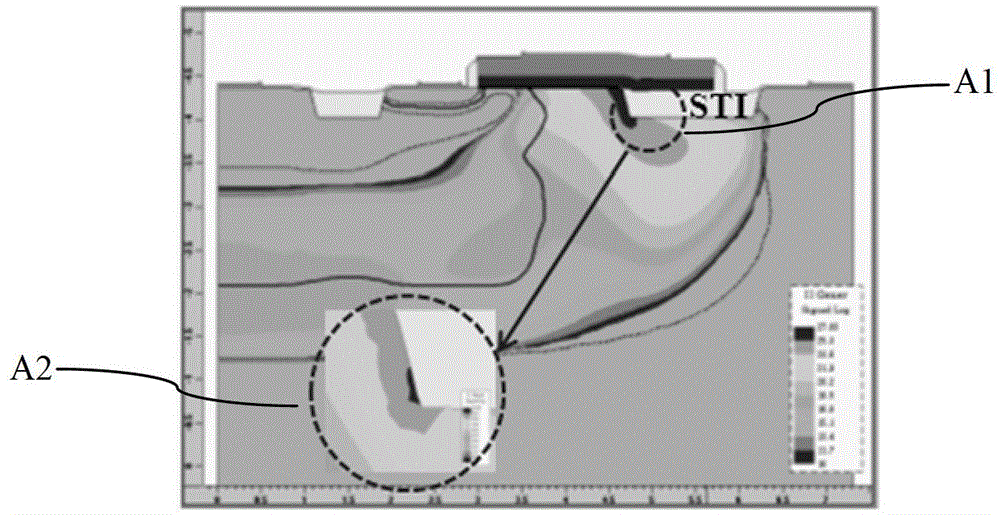

LDMOS device and manufacturing method thereof

InactiveCN104377242AImprove breakdown voltageEvenly distributedSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSElectricity

The invention discloses an LDMOS device formed on a silicon substrate. An active area is isolated by a shallow groove field oxide, a partial field oxide is adopted in a drain region field oxide in a drift region between a channel region and a drain region, the partial field oxide is formed by partial field oxidation after silicon in the partial field oxide region is etched by a certain depth, and the depth of the partial field oxide is defined by the depth of the etched silicon in the partial field oxide region. The invention further discloses a manufacturing method of the LDMOS device. According to the LDMOS device and the manufacturing method of the LDMOS device, a smooth bottom is formed in the drain area through partial field oxide, and therefore the problem that current and an electricity field are centralized at the bottom of the field oxide of the drain region can be solved, and the breakdown voltage of the device can be improved; the length of the current path of the drain region of the device can be shortened, so the specific on-resistance of the device can be lowered, and the current performance of the device can be improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Low on-resistance novel high-voltage SJ power device

InactiveCN106531802ALower specific on-resistanceImprove breakdown voltageSemiconductor devicesPower semiconductor deviceOvervoltage

The invention relates to a low on-resistance novel high-voltage SJ power device and belongs to the technical field of power semiconductor devices. In an N-type drift region of a transverse SJ power device, a P-type buried layer is introduced, a drain end is introduced into an N-type buffer layer, and a double field plate structure is introduced on the upper surface of the device. The P-type buried layer assists depletion of the N-type drift region, which increases the doping concentration of the drift region and reduces the on-resistance of the device. The N-type buffer layer of the drain end replaces an SJ structure under the drain end, which weakens the substrate-assisted depletion effect to some extent and can assist in depleting the P-type buried layer that is not completely depleted in the drift region, so that the super junction is enabled to never participate in vertical overvoltage resistance, thereby ensuring the charge balance of the super junction. The double field plate structure is a structure including double field plates which are a source end field plate and a drain end field plate. The field plates and device electrodes can be formed together without requiring other processing steps. The invention can improve the bulk electric field distribution and improve the overvoltage resistance of the device while reducing the on-resistance of the device. The invention can obtain various excellent transverse low on-resistance high-voltage SJ power devices with excellent performance.

Owner:CHANGSHA UNIVERSITY OF SCIENCE AND TECHNOLOGY

Laterally high-voltage MOSFET and manufacturing method thereof

ActiveCN103413830ALower specific on-resistanceLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesPeak valueHigh voltage mosfet

The invention relates to semiconductor technologies, in particular to a laterally high-voltage MOSFET and a manufacturing method thereof. The laterally high-voltage MOSFET is characterized in that a first-kind conduction type semiconductor field dropping layer is formed in a second conduction type semiconductor drift region through photoetching and ion implantation technologies, and a second conduction type semiconductor heavy doping layer is formed on the surface of the second conduction type semiconductor drift region through the photoetching and ion implantation technologies. The laterally high-voltage MOSFET has the advantages that under the circumstance that high breakdown voltage is guaranteed, specific on-resistance of the MOSFET can be greatly reduced, meanwhile the electric field peak value of the source end of the laterally high-voltage MOSFET is reduced, high-field effects are avoided, breakdown voltage of the MOSFET is improved, the MOSFET has lower on-resistance and a smaller chip area under the condition of the same breakover capacity, and a surface electric field of the MOSFET is well optimized; meanwhile, the manufacturing method is simple, low in technological difficulty and especially suitable for the laterally high-voltage MOSFET.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

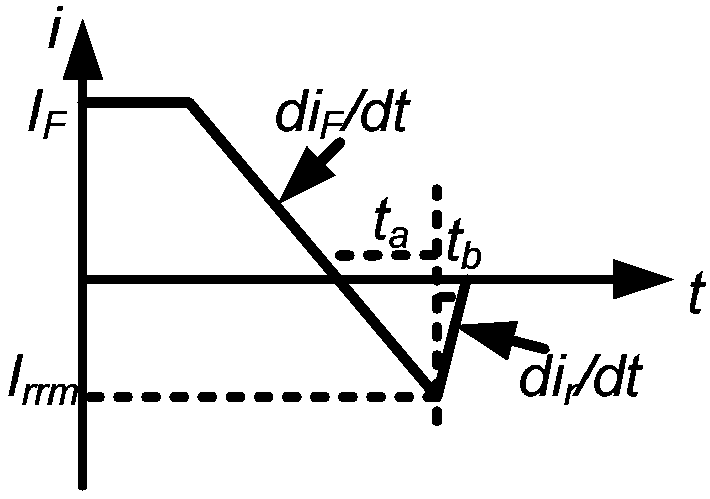

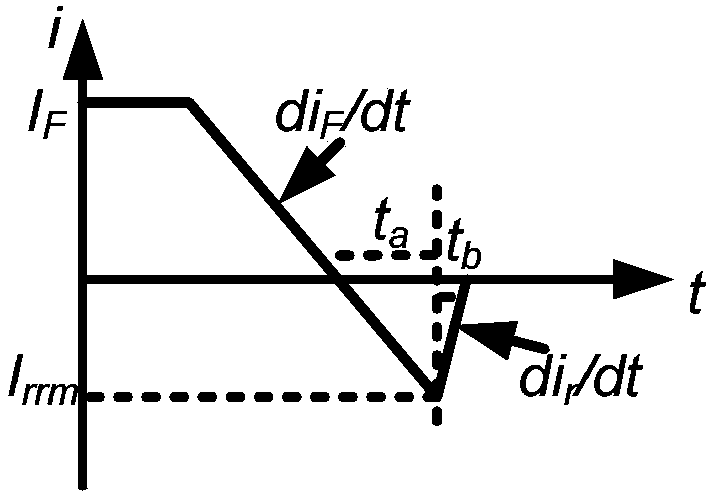

Super-junction device

InactiveCN108122975AImprove softness factorLow costSemiconductor devicesReverse recoverySemiconductor

The invention discloses a super-junction device. The super-junction device comprises a super-junction structure, channel regions, a buffer layer, source regions and a drift region; first conductive type columns and second conductive type columns are alternately arranged so as to form the super-junction structure; a drain region is formed by a semiconductor substrate at the bottom of the buffer layer; the source regions are formed at the surfaces of the channel regions; the drift region, the channel regions and the second conductive type columns form a parasitic body diode; the first buffer sub-layer and a second sub-layer are stacked together to form the buffer layer; the doping concentration of the second sub-layer is lower than the doping concentration of the first conductivity type columns; the softness factor of the reverse recovery of the super-junction device can be increased by adjusting the doping concentration of the second buffer sub-layer; the doping concentration of the first buffer sub-layer is higher than the doping concentration of the second buffer sub-layer; and the specific on-resistance of the super-junction device can be maintained or decreased by adjusting thedoping concentration of the first buffer sub-layer. With the super-junction device of the invention adopted, the softness factor of the reverse recovery can be improved, the cost of the device and thespecific on-resistance of the device can be reduced, and the breakdown voltage of the device can be improved.

Owner:SHENZHEN SANRISE TECH CO LTD

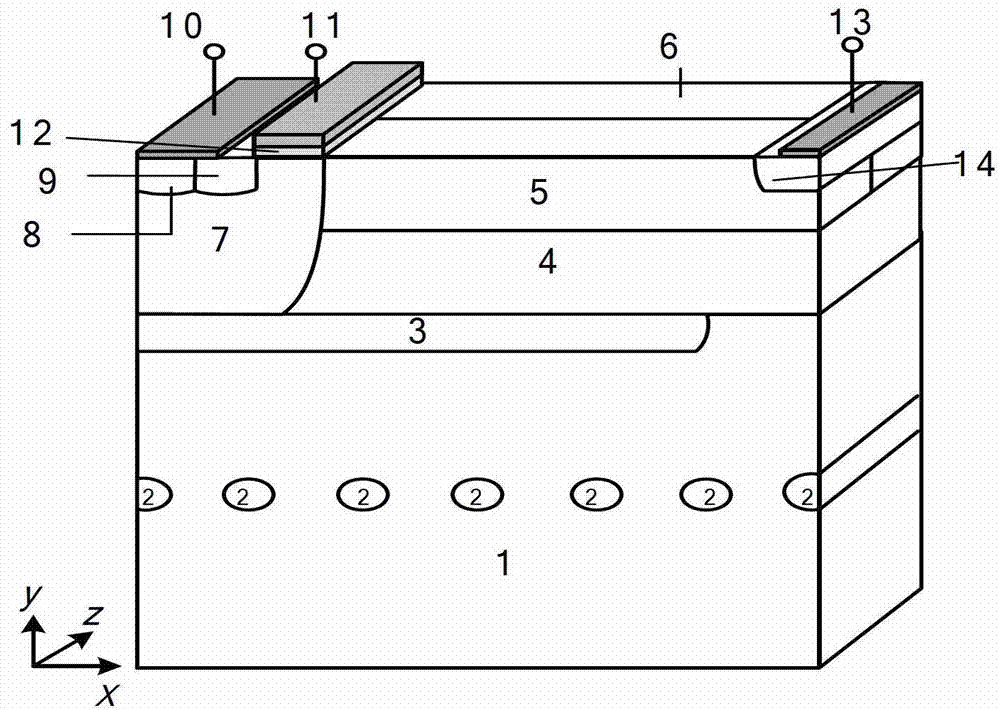

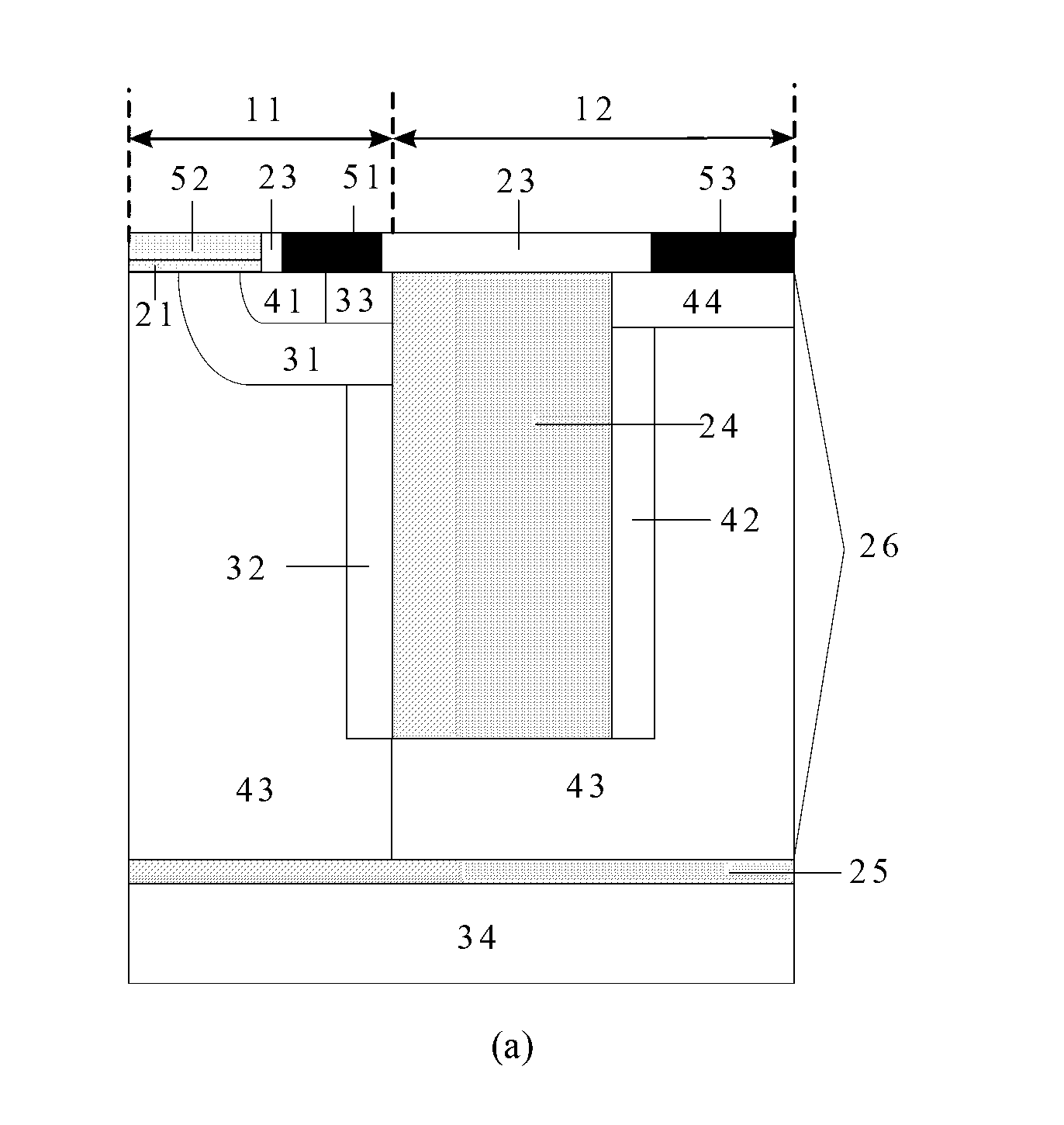

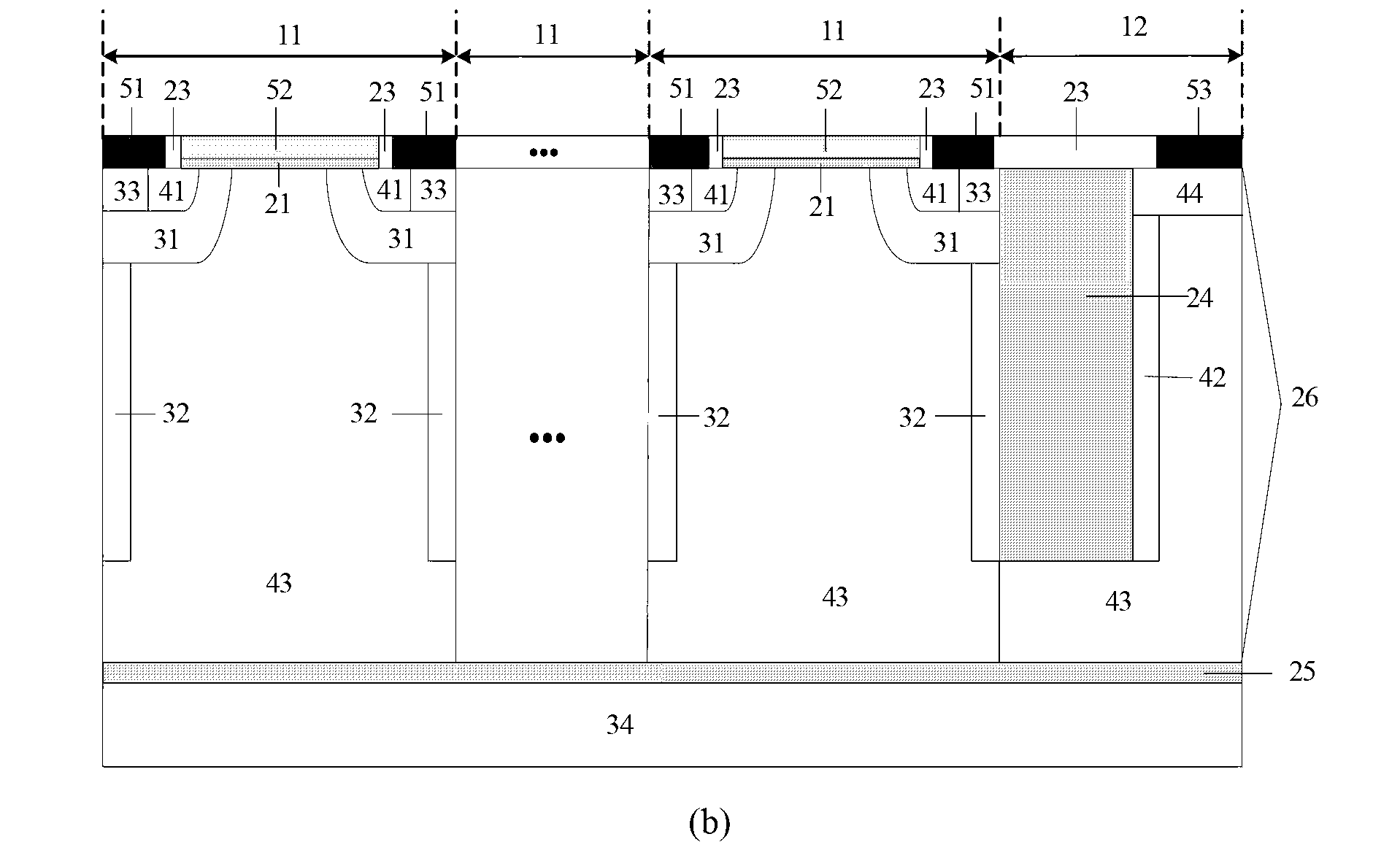

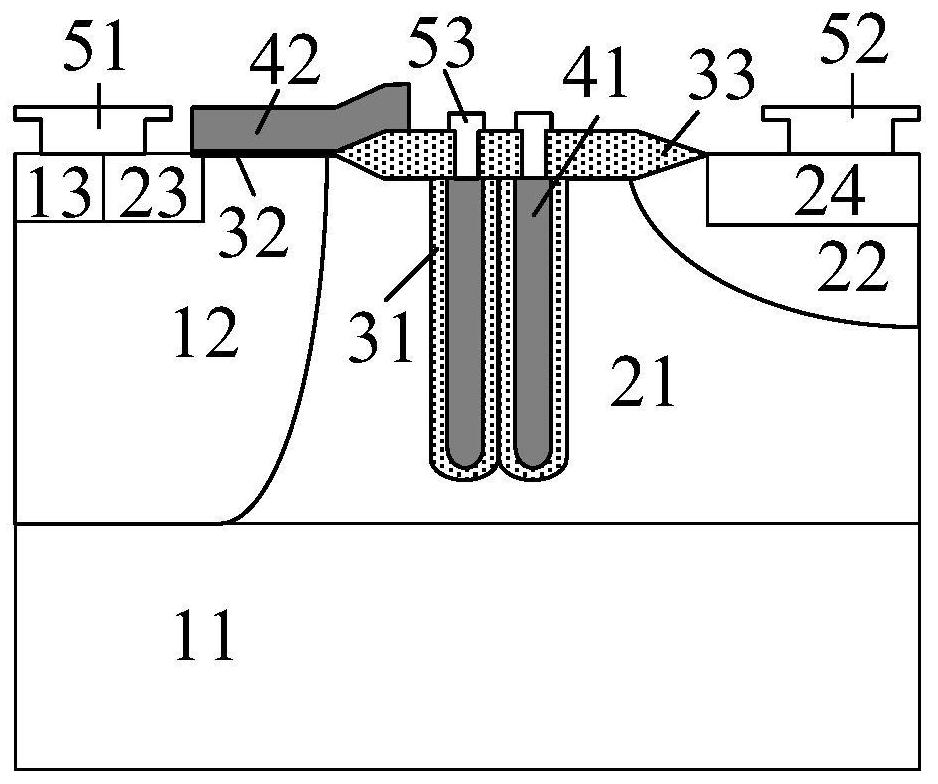

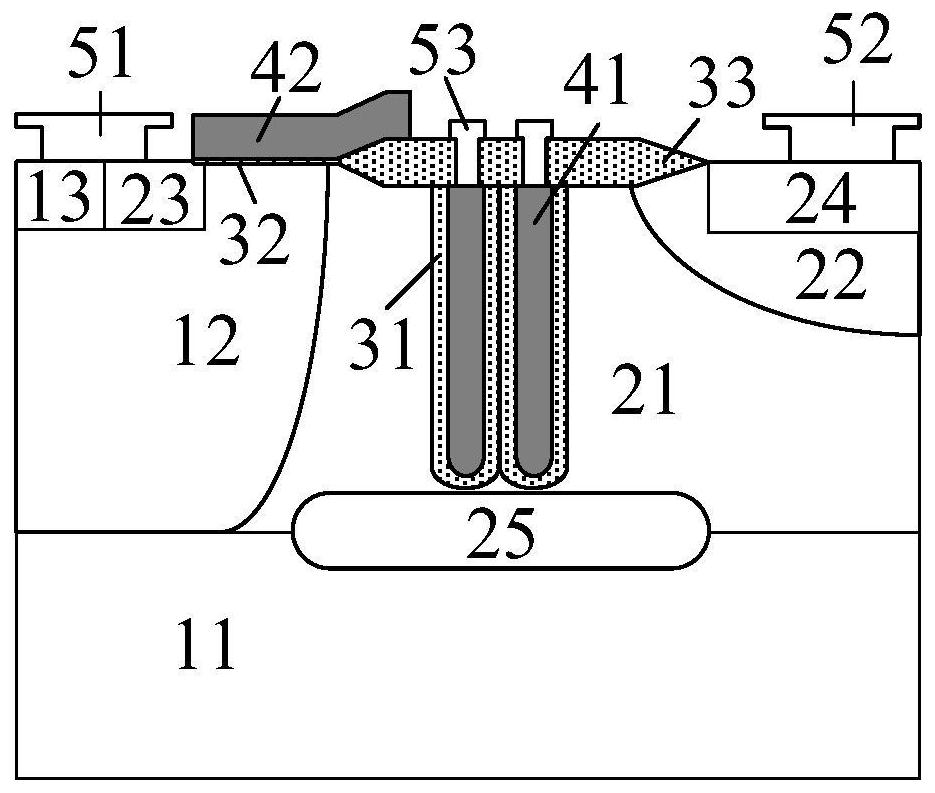

Power MOS device

The invention belongs to the technical field of power semiconductor devices and relates to a power MOS device. The power MOS device comprises cellular structures respectively having a high-K dielectric extension grid structure, a drain extension region, and a dielectric slot terminal. The multiple cellular structures are arranged in parallel, which makes the device have the following characteristics: the device is advantageous in that VDMOSs can be connected in parallel to generate high current and LDMOSs are easy to integrate; under forward switching-on, a drift region near one side of a high-K dielectric produces multiple sub-accumulation layers to form a continuous low-resistance channel, which significantly reduces the specific on-resistance; under reverse withstand voltage, the high-K dielectric assists in depleting the drift region and modulating the electric field of the drift region, which can improve the withstand voltage and reduce the specific on-resistance; and the dielectric slot terminal can help to reduce the size of the device and save the chip area.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

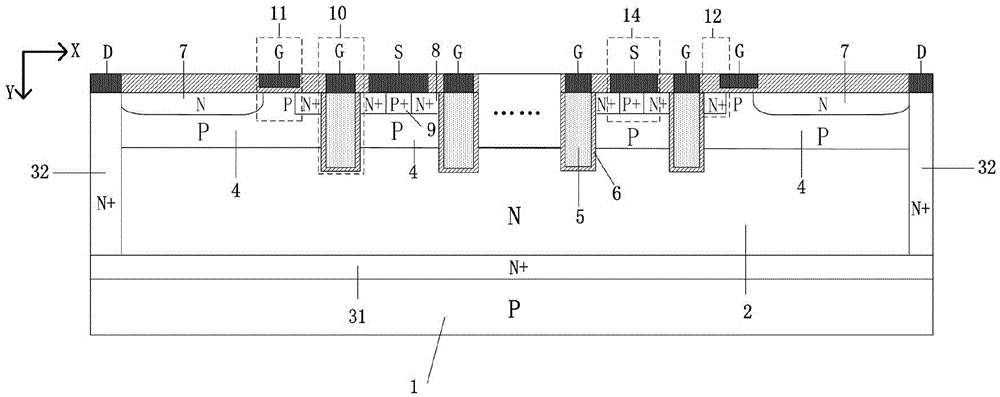

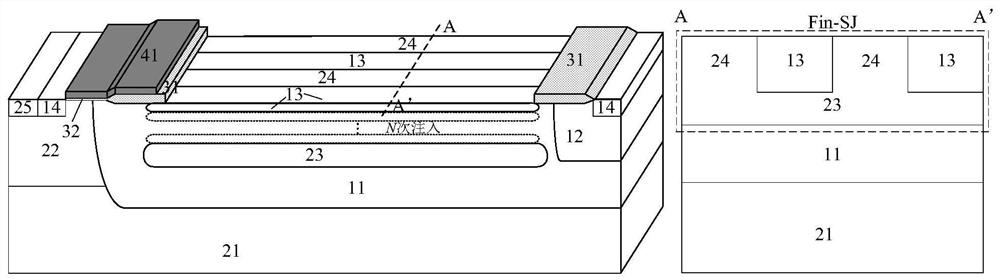

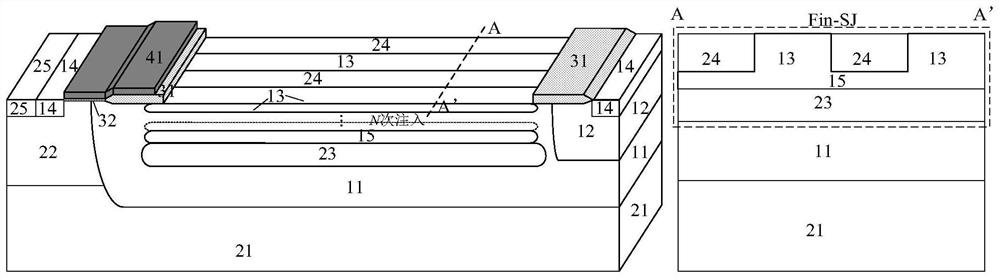

High-voltage three-dimensional depletion super-junction LDMOS device and manufacturing method thereof

PendingCN111969043AGuaranteed withstand voltageIncrease the doping concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSElectrical resistance and conductance

The invention provides a high-voltage three-dimensional depletion super-junction LDMOS and a manufacturing method thereof. The high-voltage three-dimensional depletion super-junction LDMOS comprises asecond conductive type substrate, a first conductive type drift region, a first conductive type well region, a second conductive type well region, a first dielectric oxide layer, a second conductivetype buried layer, a second dielectric oxide layer, and a first conductive type region and a second conductive type region which form a super junction, wherein the second conductive type buried layerand the super junction structure are both located in the first conductive type drift region, and the super junction is located above the second conductive type buried layer and connected with the second conductive type buried layer; the second conductive type buried layer optimizes the surface electric field of the device in an off state; the second conductive type buried layer and the super-junction second conductive type region surround the super-junction first conductive type region from three sides to form a three-dimensional depletion super-junction structure Fin-SJ structure, the dopingconcentration of the first conductive type drift region and the super-junction first conductive type region is allowed to be improved, the super-junction structure provides a surface low-resistance path, and the specific on-resistance of the device is reduced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

A lateral MOS type power semiconductor device and a preparation method thereof

ActiveCN109166924AIncrease the lengthIncrease effective lengthSemiconductor/solid-state device manufacturingSemiconductor devicesDevice formMulti dimensional

The invention provides a transverse MOS device and a preparation method thereof, belonging to the technical field of semiconductor power devices. The invention introduces a deep dielectric trench, a semi-insulating polysilicon column and a buffer layer into the drift region of a conventional transverse MOS type device. The introduction of deep dielectric trench makes the device form U-shaped conductive channel, which effectively increases the length of drift region under the same device length. A 3-D resistive field plate structure is for by alternately connecting that semi-insulating polysilicon column and the drift region along the transverse extension direction of the deep dielectric trench so as to introduce a multi-dimensional depletion action in the drift region when the device is blocked to increase the doping concentration of the drift region, The drift region width on both sides of the deep trench is not limited by the doping dose, which improves the electric field distribution in the drift region, increases the breakdown voltage of the device and reduces the specific on-resistance / on-voltage drop of the device. The introduction of buffer layer can improve the charge balance characteristics of three-dimensional dielectric superjunction structure, and further improve the performance and reliability of the device.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Super junction device and manufacturing method thereof

InactiveCN107768442AReduce depletionImprove softness factorSemiconductor/solid-state device manufacturingDiodeReverse recoveryConduction type

The present invention discloses a super junction device. The super junction device comprises: a super junction structure formed by first conduction type columns and second conduction type columns which are alternately arranged; channel regions; a buffer layer; a drain region formed by a semiconductor substrate at the bottom portion of the buffer layer; source regions formed at surfaces of the channel regions; one first conduction type injection region formed at the surface of the buffer layer at the bottom portion of each second conduction type column; and a parasitic body diode formed by a drift region, the channel regions and the second conduction type columns, wherein the first conduction type injection regions are configured to reduce exhaustion of the buffer layer when the parasitic body diode is reversely biased so that reversely recovered soft factors are improved. The present invention further discloses a manufacturing method of a super junction device. The reversely recoveredsoft factor can be improved, the device cost is reduced, and the specific on-state resistance of the device is reduced.

Owner:SHENZHEN SANRISE TECH CO LTD

Lateral high-voltage device

ActiveCN107275388AGuaranteed withstand voltageSmall surface areaSemiconductor devicesHigh pressureP type doping

The invention provides a lateral high-voltage device, and the device comprises a dielectric trench. Doped strip overlapping structures of different doping types which are arranged alternately are disposed at at least one of the following positions: a part below the dielectric trench, the left side of the dielectric trench and the right side of the dielectric trench. The device also comprises a dielectric layer, a volume field plate, a polysilicon gate, a grid lower oxidation layer, a first N-type heavy doped region, a second N-type heavy doped region, a P-type heavy doped region, a P well region, a first N-type doping strip, a second N-type doping strip, a third N-type doping strip, a first P-type doping strip, and a second P-type doping strip. The bottom of a conduction circuit is a P-type substrate. According to the invention, the dielectric trench is introduced to a drift region, and the surface area of the device is reduced while the withstand voltage is maintained. Moreover, the specific on-resistance of the device is reduced. The overlapped heavy doped N strips and P strips are introduced to the drift region of the device, thereby providing a low-resistance conduction loop for the on state of the device, further reducing the specific on-resistance of the device, and finally achieving the purposes of effectively reducing the area of the device and the on-resistance.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Low-resistance device with equipotential floating grooves and manufacturing method of low-resistance device

ActiveCN112164719ALarge mean electric fieldImprove pressure resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringFloating electrode

The invention provides a low-resistance device with equipotential floating grooves, and the device comprises a first conductive type semiconductor substrate, a first conductive type well region, a first conductive type source end heavily doped region, a second conductive type drift region, a second conductive type well region, a second conductive type source end heavily doped region and a second conductive type drain end heavily doped region, a first dielectric oxide layer, a second dielectric oxide layer, a third dielectric oxide layer, a floating field plate polycrystalline silicon electrode, a control gate polycrystalline silicon electrode, source metal, drain metal and a metal strip; the first dielectric oxide layer and the floating field plate polycrystalline silicon electrode form alongitudinal floating field plate which is distributed in the whole second conductive type drift region; under the same length, the dielectric layer can bear higher breakdown voltage, the floating electrode can modulate the potential distribution of the drift region, so the potential distribution is uniform, the withstand voltage of the device is further improved, the floating field plate assistsin depletion, and the injection dose of the drift region can also be improved, so that the specific on-resistance is reduced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

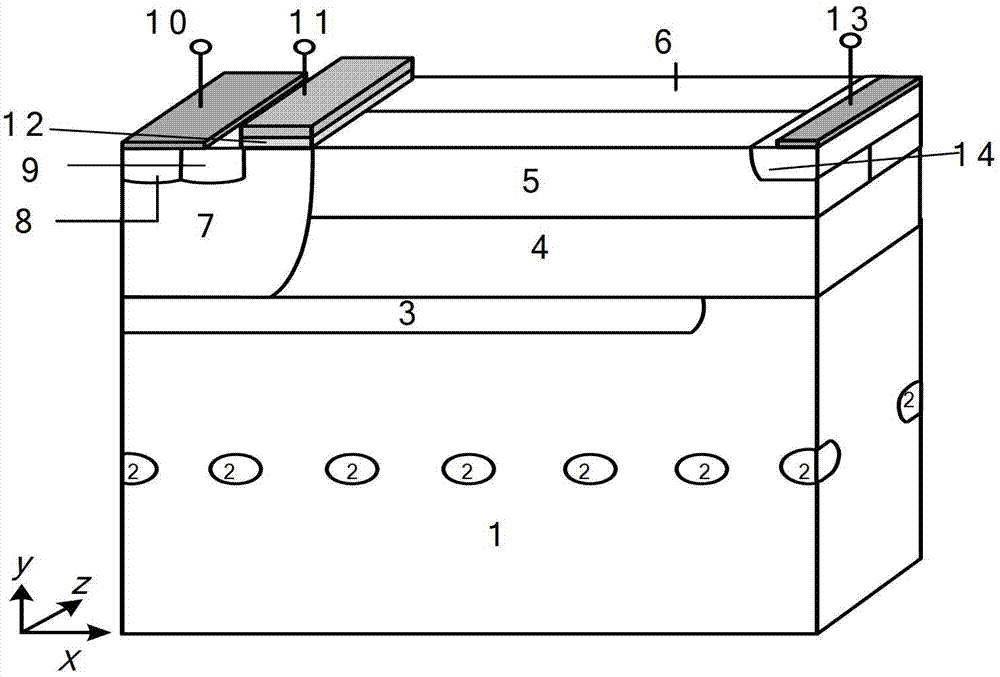

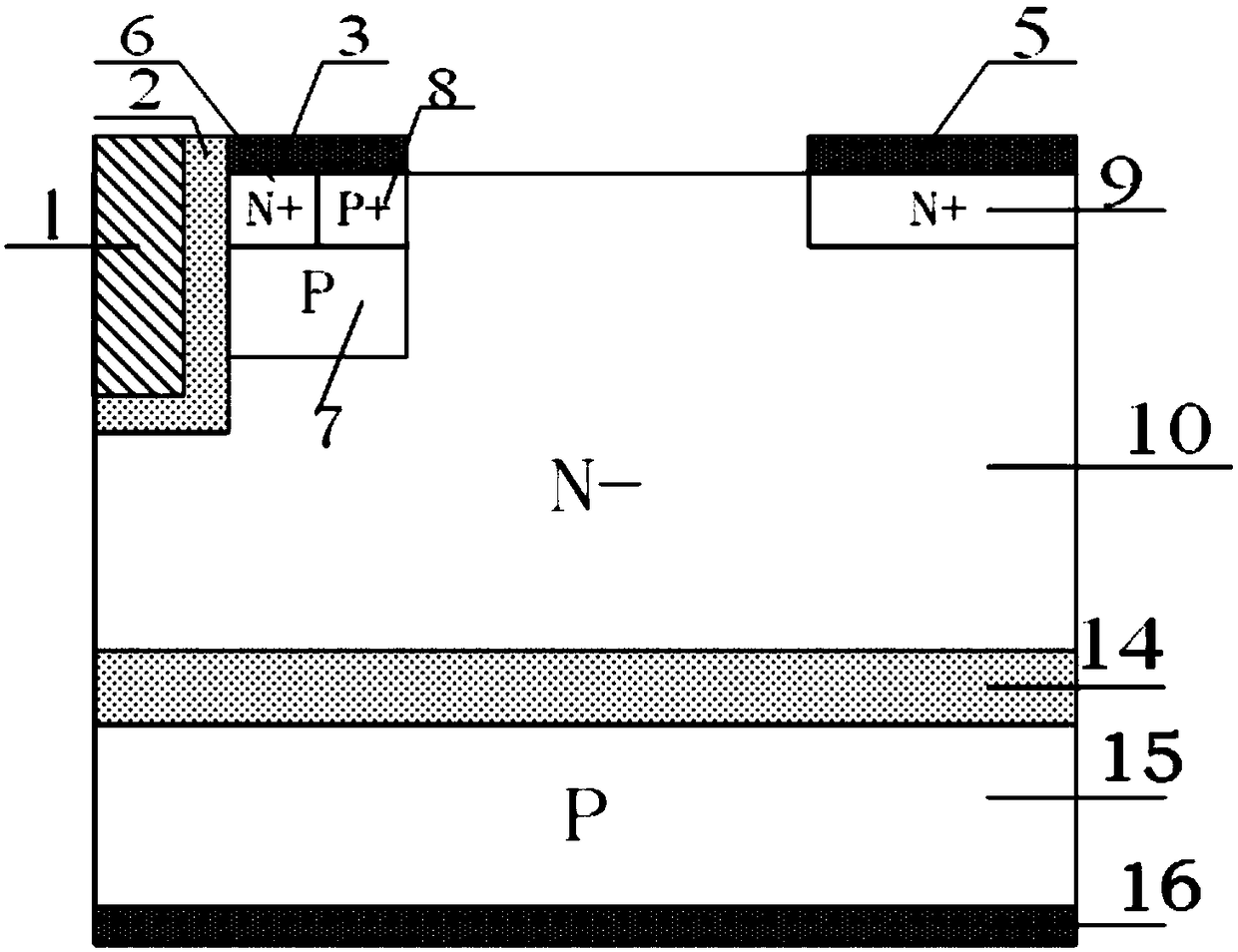

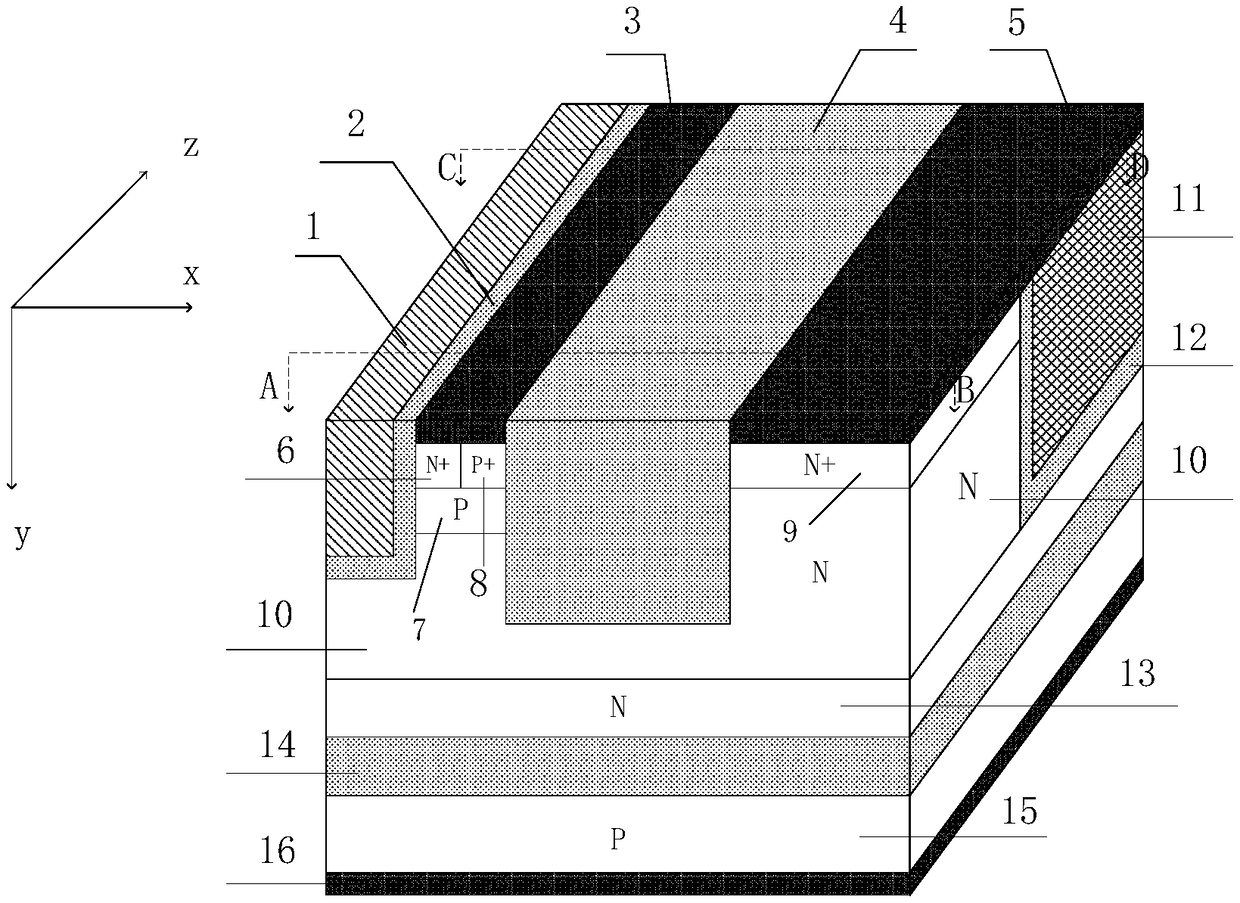

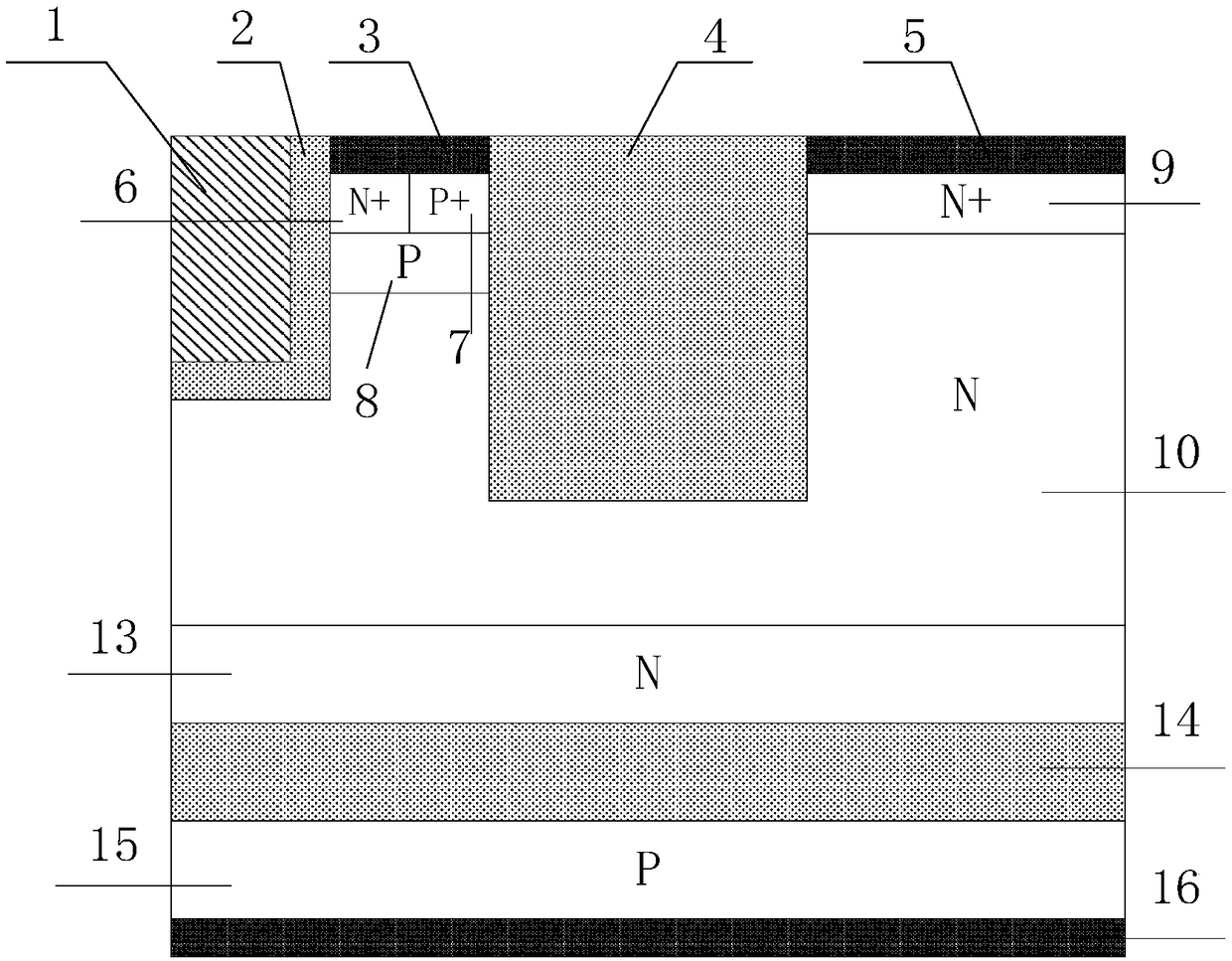

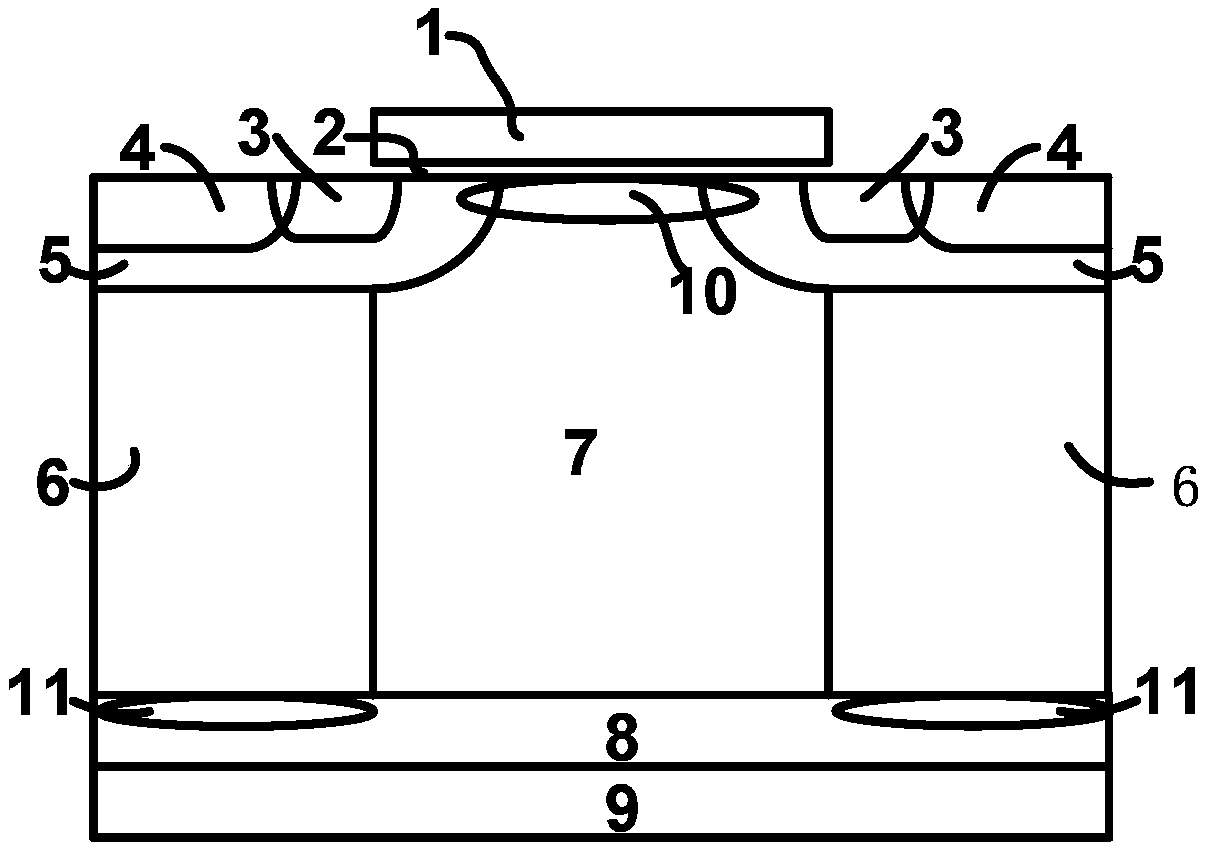

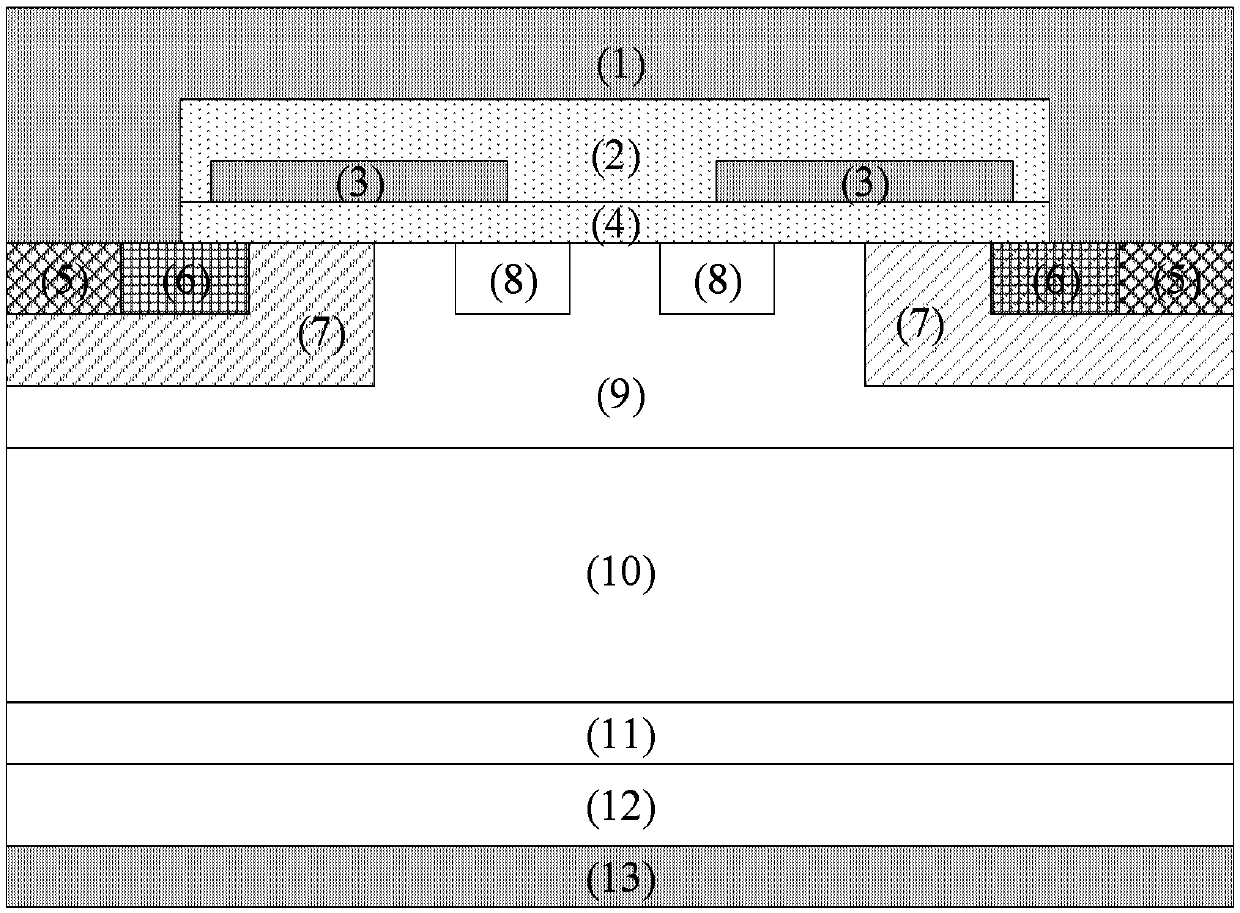

4H-SiC MOSFET power device and manufacturing method thereof

ActiveCN109616523AImprove switching characteristicsReduce areaSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricMOSFET

The invention discloses a 4H-SiC MOSFET power device and a manufacturing method thereof. The power device comprises a source electrode (1), an SiO2 interlayer dielectric (2), a grid electrode (3), a gate oxide layer (4), a P + contact region (5), an N+ source region (6), a P well (7), an additionally injected P-type region (8), an N type epitaxial layer (9), an N-epitaxial layer (10), a buffer layer (11), an N+ substrate (12) and a drain electrode (13). The 4H-SiC MOSFET power device disclosed in the invention adopts a separation grid structure, and by virtue of the structure the input capacitance and the grid leakage capacitance can be effectively lowered, and the switching performance of the device is improved; by introducing P type doping in a JFET region, the electric field intensity of a gate oxide layer can be effectively reduced, and the reliability of the device is improved; and in addition, a current expanding layer structure is adopted, so that the current capability of the device can be considered.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Longitudinal floating field plate device with charge balance voltage withstanding layer and manufacturing method thereof

InactiveCN110518059AImprove pressure resistanceLower specific on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesMetal stripsEngineering

The invention provides a longitudinal floating field plate device with a charge balance voltage withstanding layer and a manufacturing method. The device comprises a first conductive-type semiconductor substrate, a first conductive-type well region, a first conductive-type semiconductor contact region, a first conductive-type charge balance voltage withstanding layer, a second conductive-type drift region, a second conductive-type well region, a second conductive-type semiconductor contact region, a second conductive-type charge balance voltage withstanding layer, a first dielectric oxide layer, a second dielectric oxide layer, a third dielectric oxide layer, a floating field plate polycrystalline silicon electrode, a control gate polycrystalline silicon electrode and a metal strip, wherein the first dielectric oxide layer and the floating field plate polycrystalline silicon electrode form a longitudinal floating field plate. A super-junction structure composed of the first conductive-type charge balance voltage withstanding layer and the second conductive-type charge balance voltage withstanding layer is introduced to the second conductive-type drift region of the device, the electric field of the drift region is modulated, a low-resistance current path is provided, so that the voltage withstanding performance of the device is improved, and the specific on-resistance of the device is reduced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Superjunction device and manufacturing method thereof

ActiveCN104576730ALower specific on-resistanceReduce thermal resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesReverse recoveryThin layer

The invention discloses a superjunction device. A current flowing area comprises a plurality of N type thin layers and P type thin layers, the N type thin layers and the P type thin layers are alternately arranged, a plurality of grooves are formed in a silicon substrate, and each N type thin layer comprises a first N type thin layer and a second N type thin layer; each first N type thin layer comprises a silicon substrate bottom thin layer between adjacent grooves, each second N type thin layer has lower electrical resistivity, electric charges of at least the second N type thin layers and the adjacent P type thin layers are balanced, electric charges of at least part of N type thin layers and the adjacent P type thin layers are not balanced, and N type areas comprising back ion injection areas are formed at bottoms of the N type thin layers and P type thin layers. The invention further discloses a manufacturing method of the superjunction device. According to the superjunction device and the manufacturing method of the superjunction device, the manufacturing cost can be minimized, and meanwhile, specific on-state resistance of the device and softness coefficient of reverse recovery of the device in a turn-off process can be optimized.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP