SOI horizontal power MOSFET device

A power and device technology, applied in the field of SOI lateral power MOSFET devices, can solve the problems of increased difficulty in extending the trench gate 8 process, little improvement in device on-resistance, and increased process complexity, so as to increase the auxiliary depletion effect, The effect of reducing the drift region and device length and reducing the cost of the chip

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

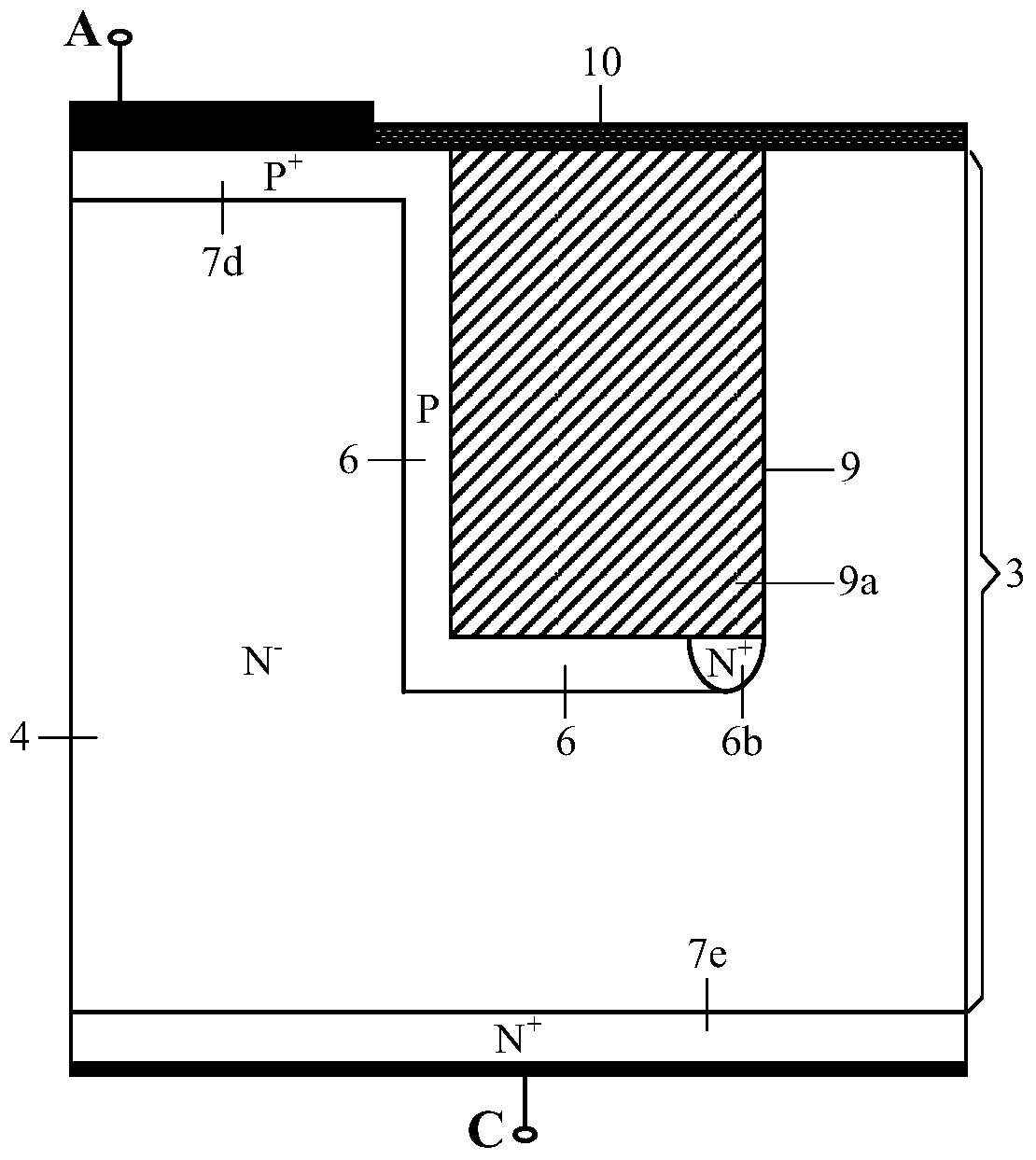

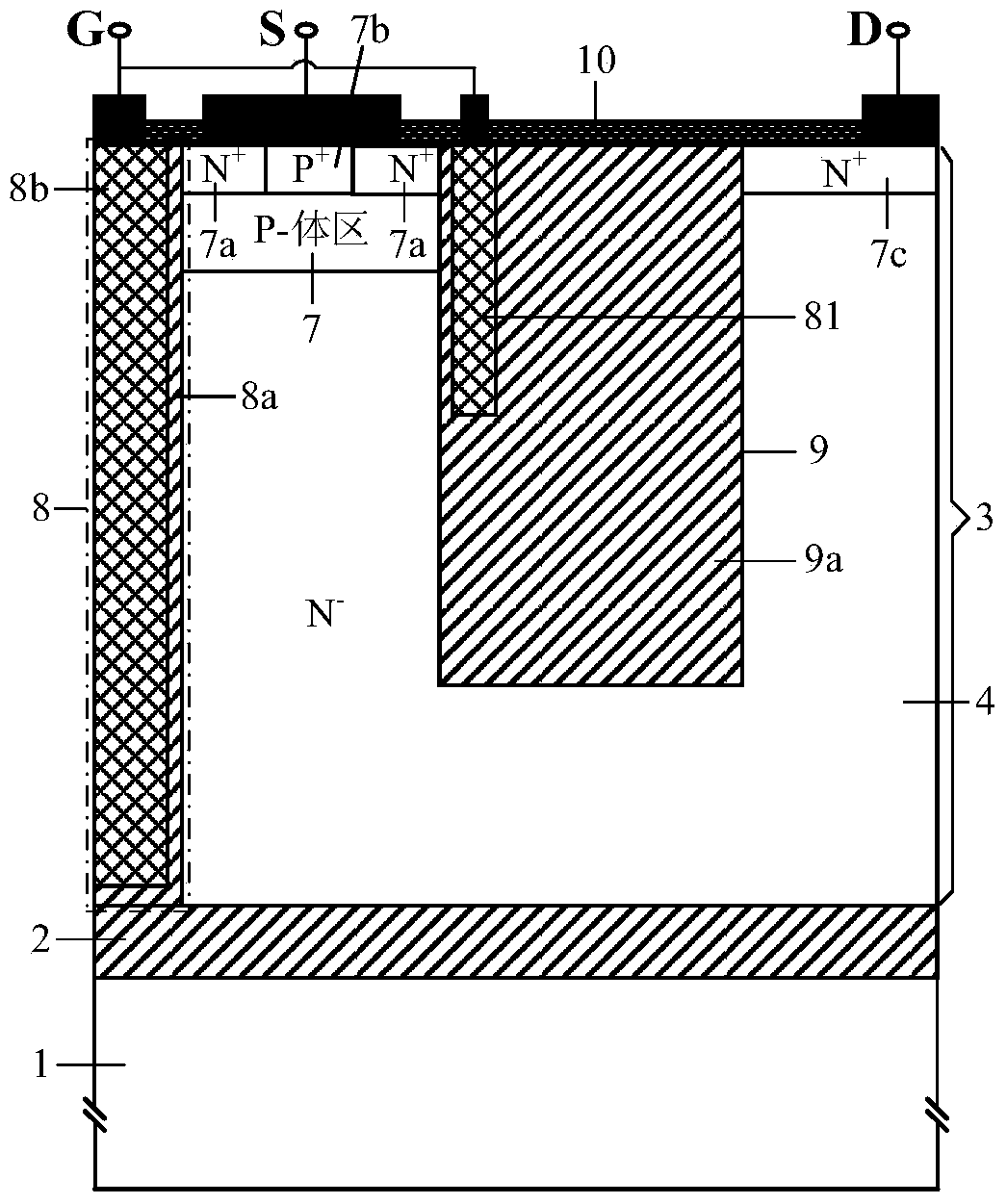

Embodiment 1

[0031] A SOI lateral power MOSFET device, such as Figure 4 , including a substrate layer 1 , a dielectric buried layer 2 and an active layer 3 from bottom to top. The active layer 3 is a semiconductor of the first doping type; one side of the active layer 3 has a semiconductor body region 7 of the second doping type, and the other side has a semiconductor drain region 7c of the first heavily doping type. The semiconductor body region 7 of the second doping type has a first heavily doped type semiconductor source region 7a and a second heavily doped type semiconductor body contact region 7b which are independent of each other, and the first heavily doped type semiconductor source region 7a and the second heavily doped semiconductor body region 7b are independent of each other. The leading end of the doubly doped type semiconductor body contact region 7b is connected to the metal source electrode S. As shown in FIG. The leading end of the drain region 7c of the first heavily d...

Embodiment 2

[0035] With the trench gate structure device in embodiment 1 (such as Figure 4 As shown in (a), compared with the device in this example, the groove gate 8 is extended to the dielectric buried layer 2, as shown in Figure 5 (a) shown. When the device proposed by the present invention is used in a high-voltage integrated circuit, the trench gate can realize full dielectric isolation between it and a low-voltage control circuit, which simplifies the manufacturing process of the integrated circuit. During forward conduction, the extended trench gate 8 can form an accumulation layer in the active layer 3, thereby greatly reducing the specific on-resistance. In the reverse blocking state, the extended trench gate 8, the dielectric buried layer 2 and the dielectric trench 9 can form a multi-dimensional depletion of the drift region 4, which can increase the concentration of the drift region and reduce the on-resistance on the other hand. It can also improve the withstand voltage ...

Embodiment 3

[0037] Compared with Example 2, the device of this example is implanted between the active layer 3 and the dielectric buried layer 4 to form a thinner N-type buffer layer 4a, such as Figure 5 (b) shown. The buffer layer 4 a and the extended groove gate 8 can form an L-shaped low-resistance current path, which can greatly reduce the specific on-resistance of the device.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More