Patents

Literature

437 results about "Dielectric isolation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Dielectric isolation, as you all know, is the process of electrically isolating various components in the IC chip from the substrate and from each other by an insulating layer.

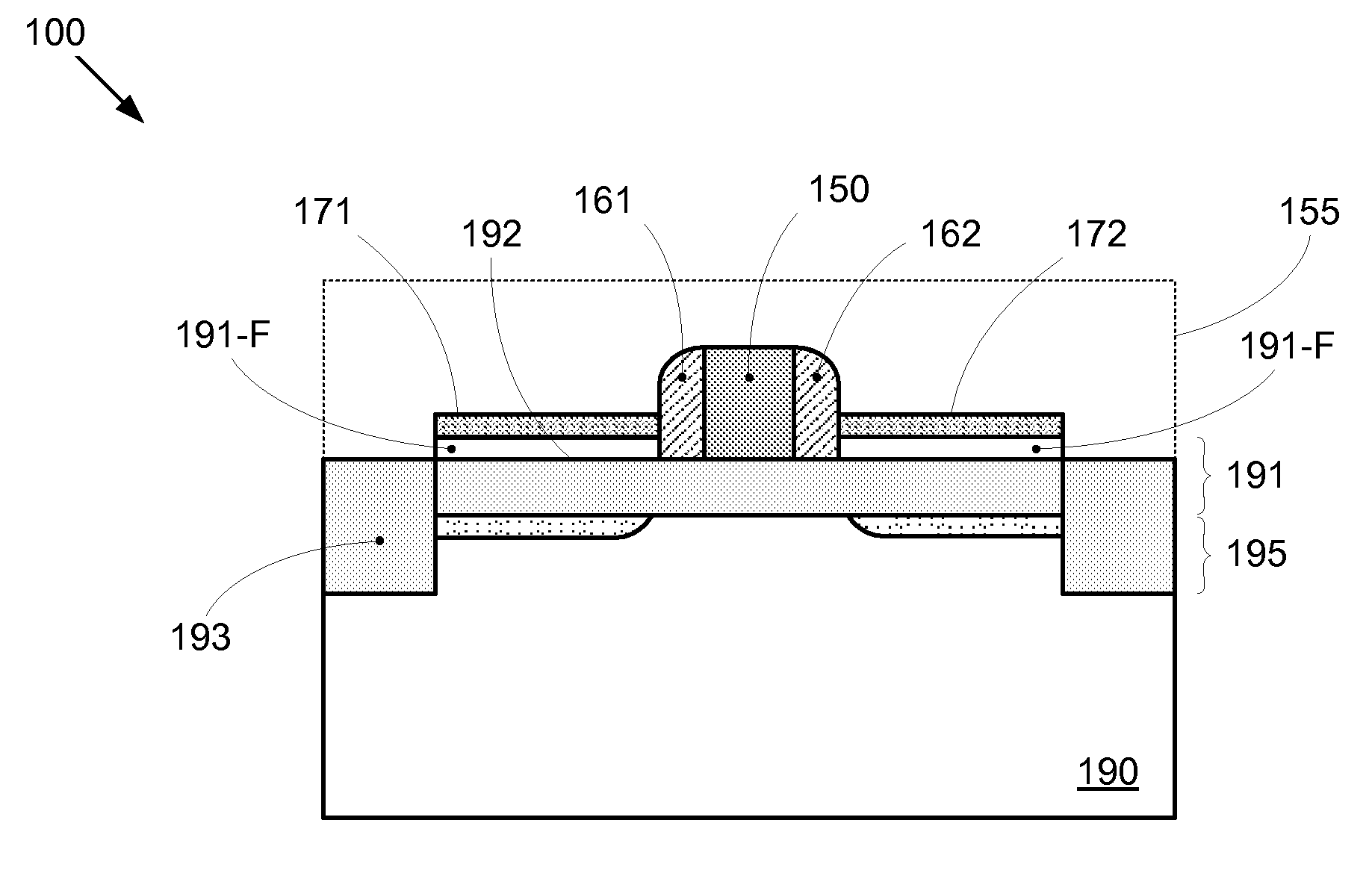

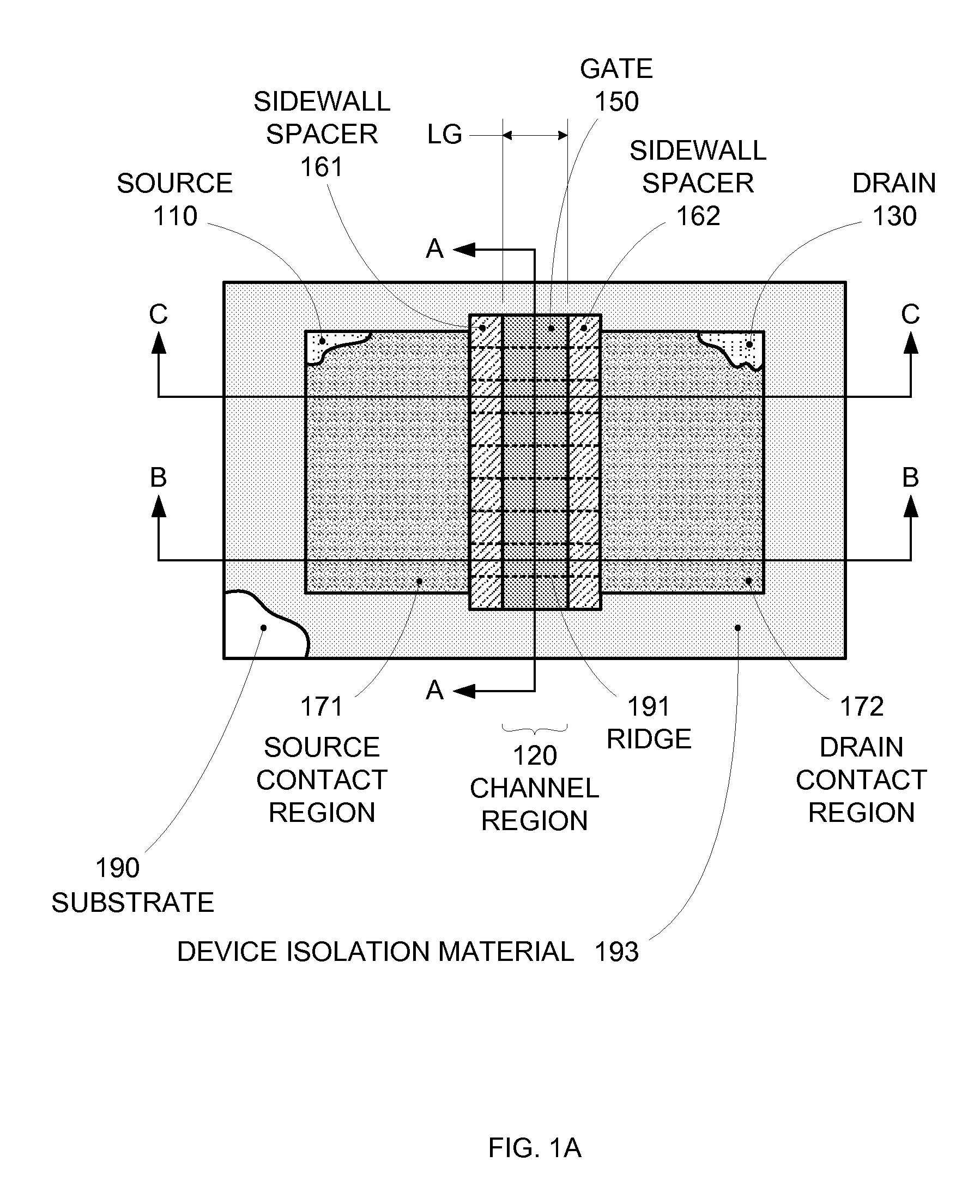

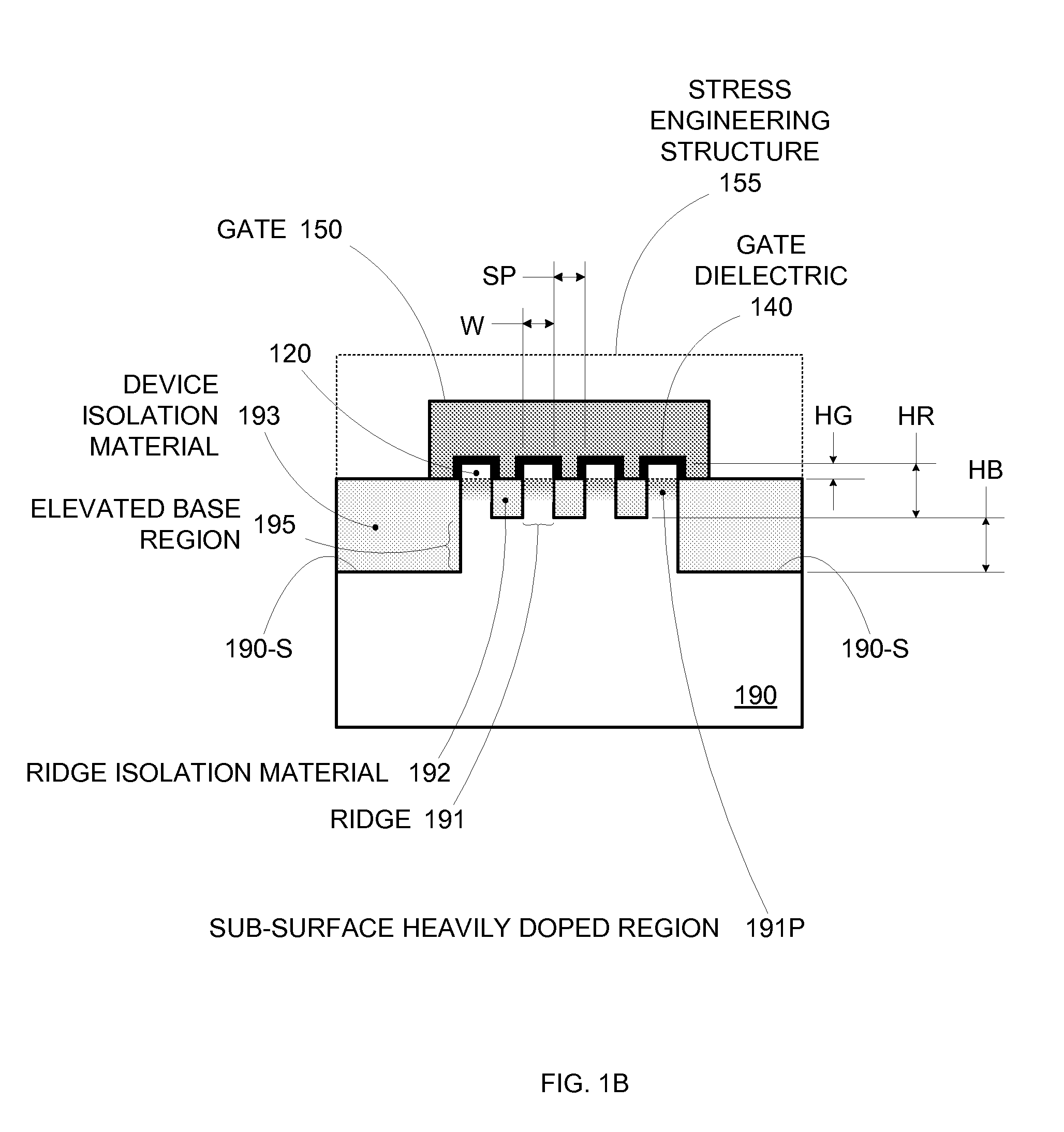

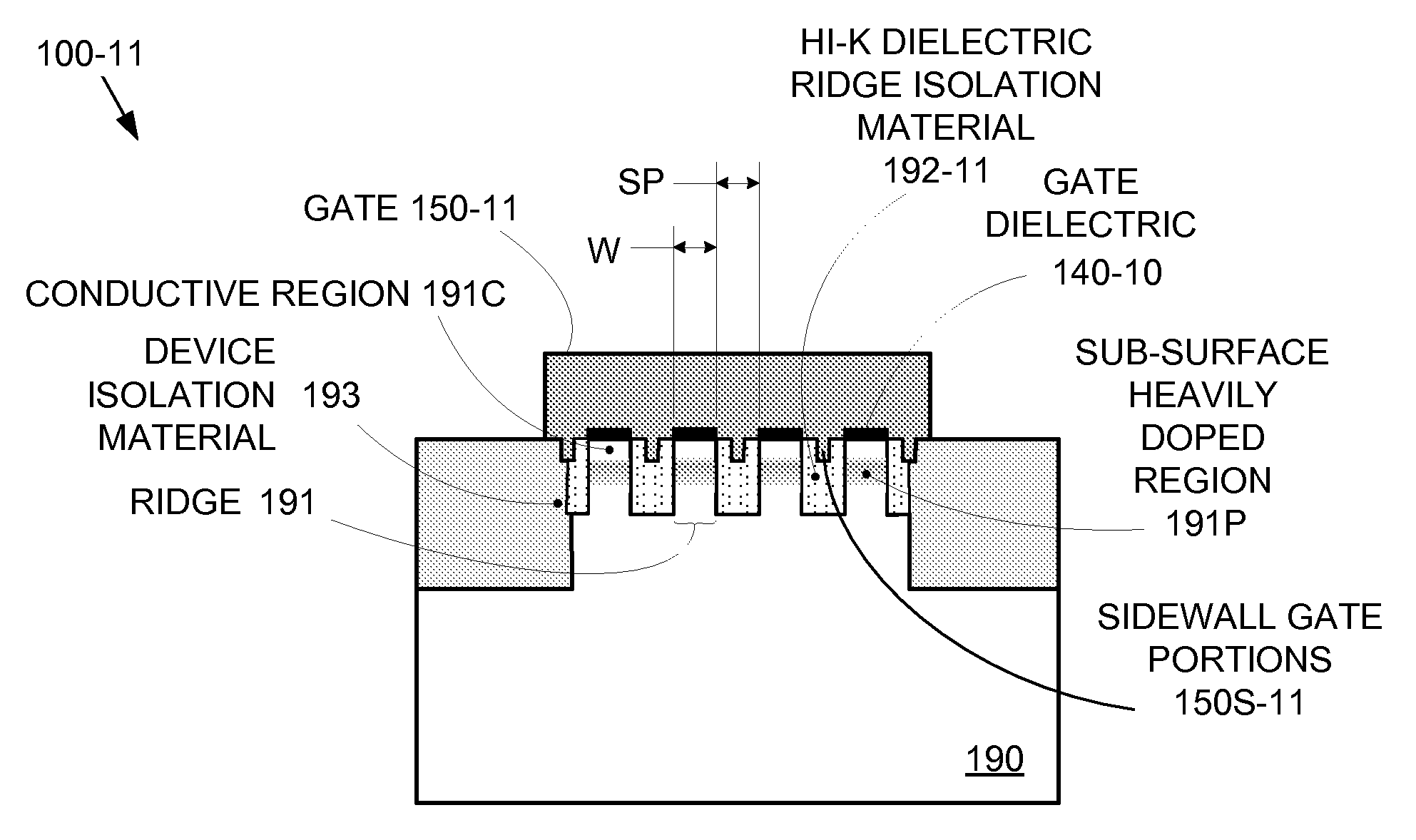

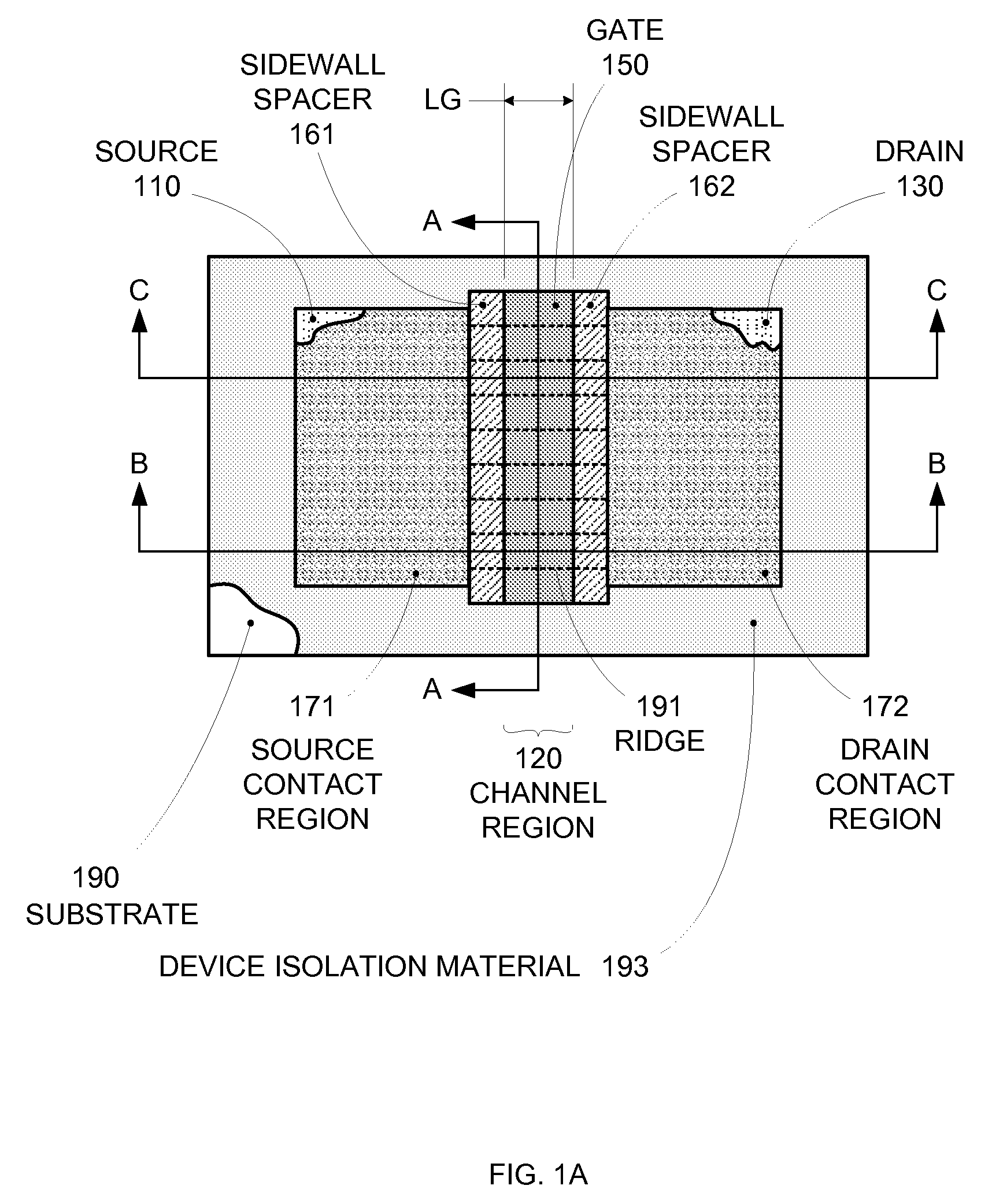

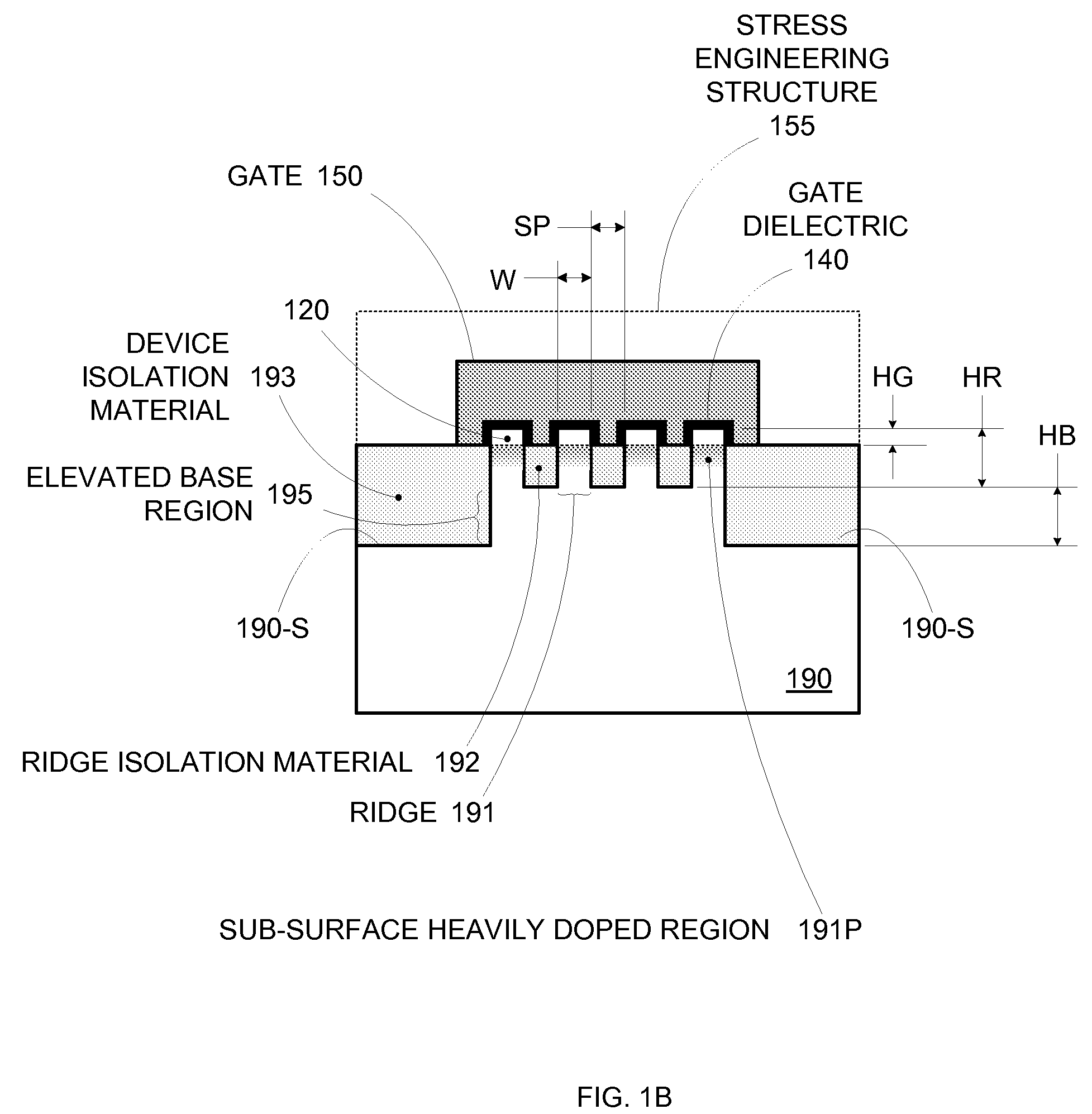

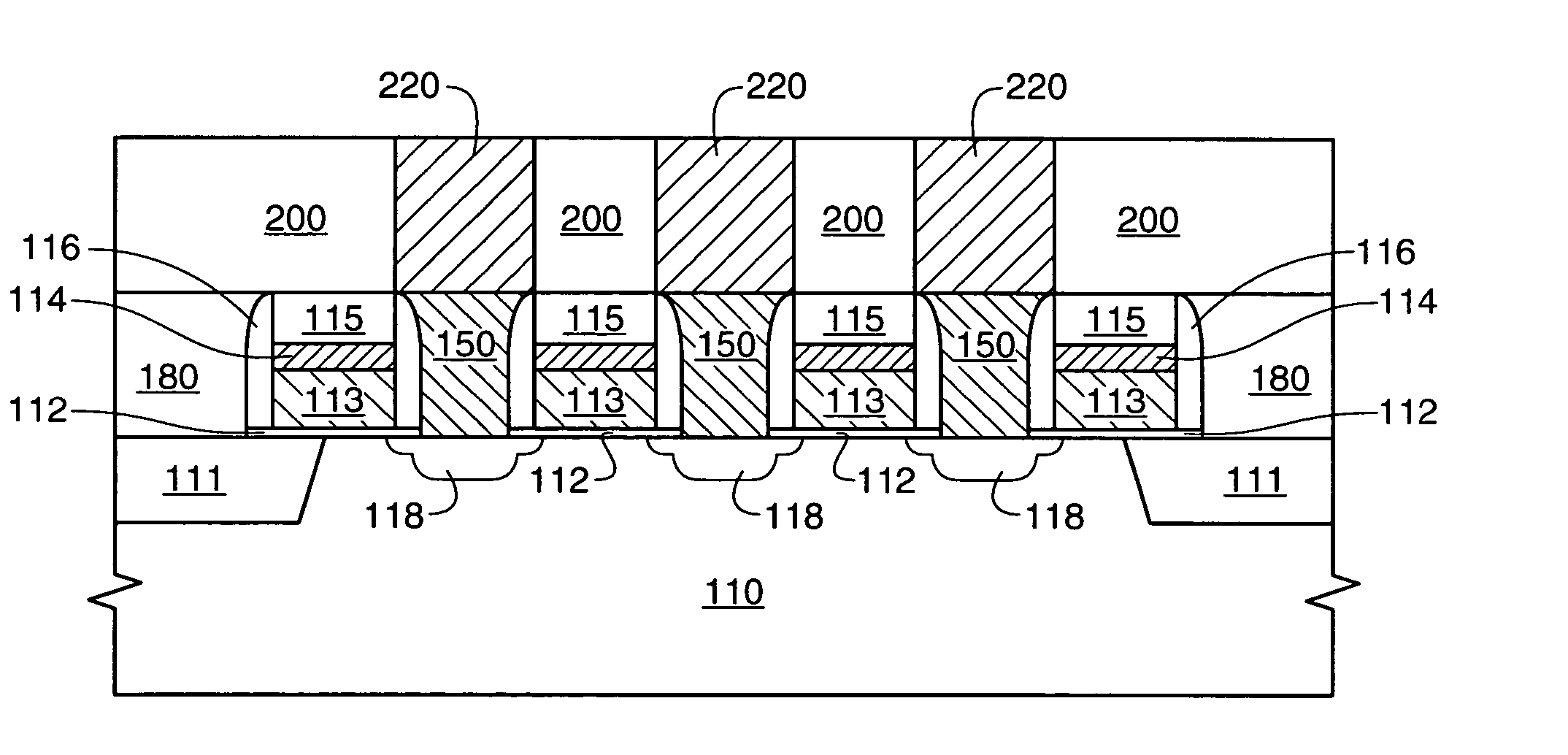

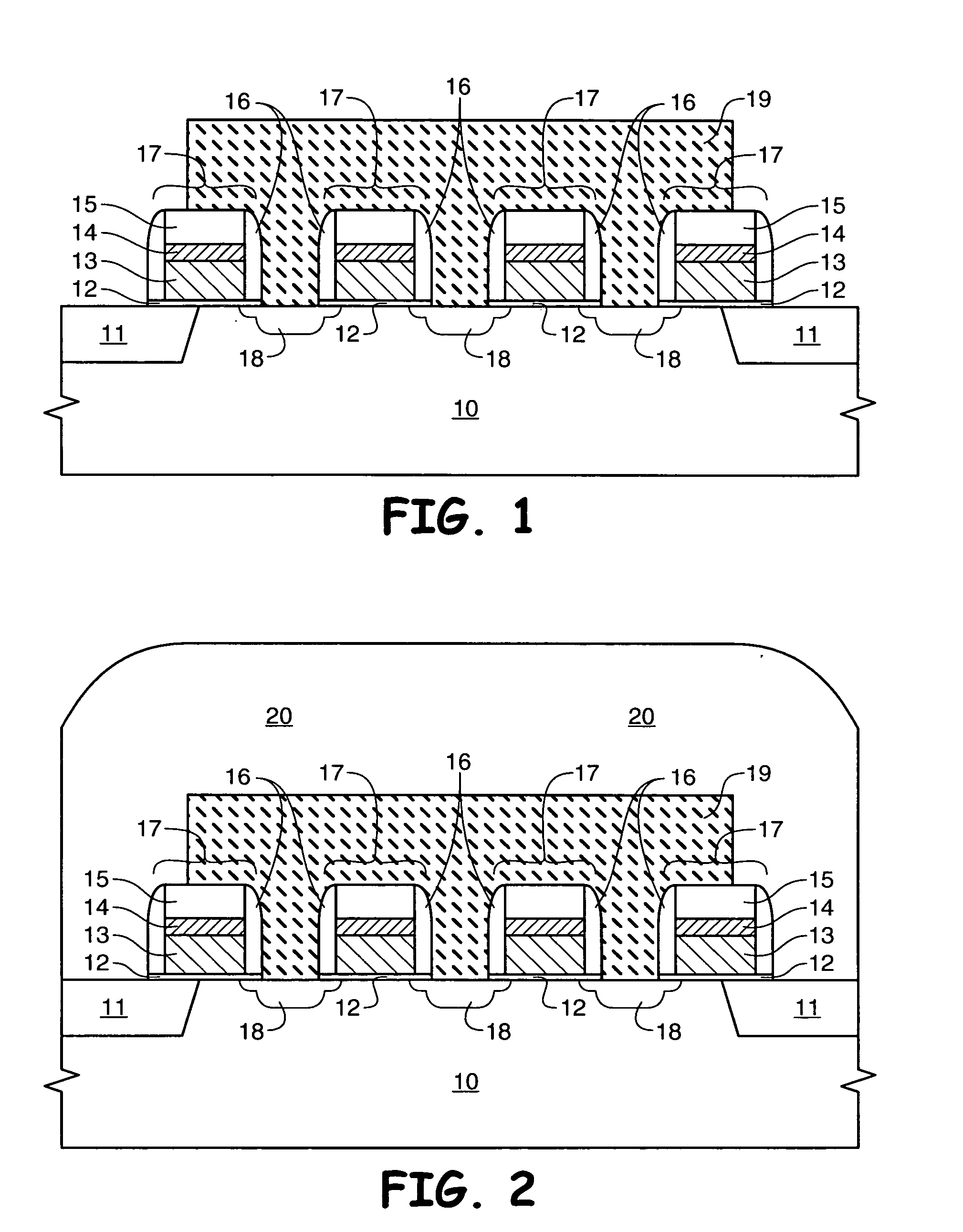

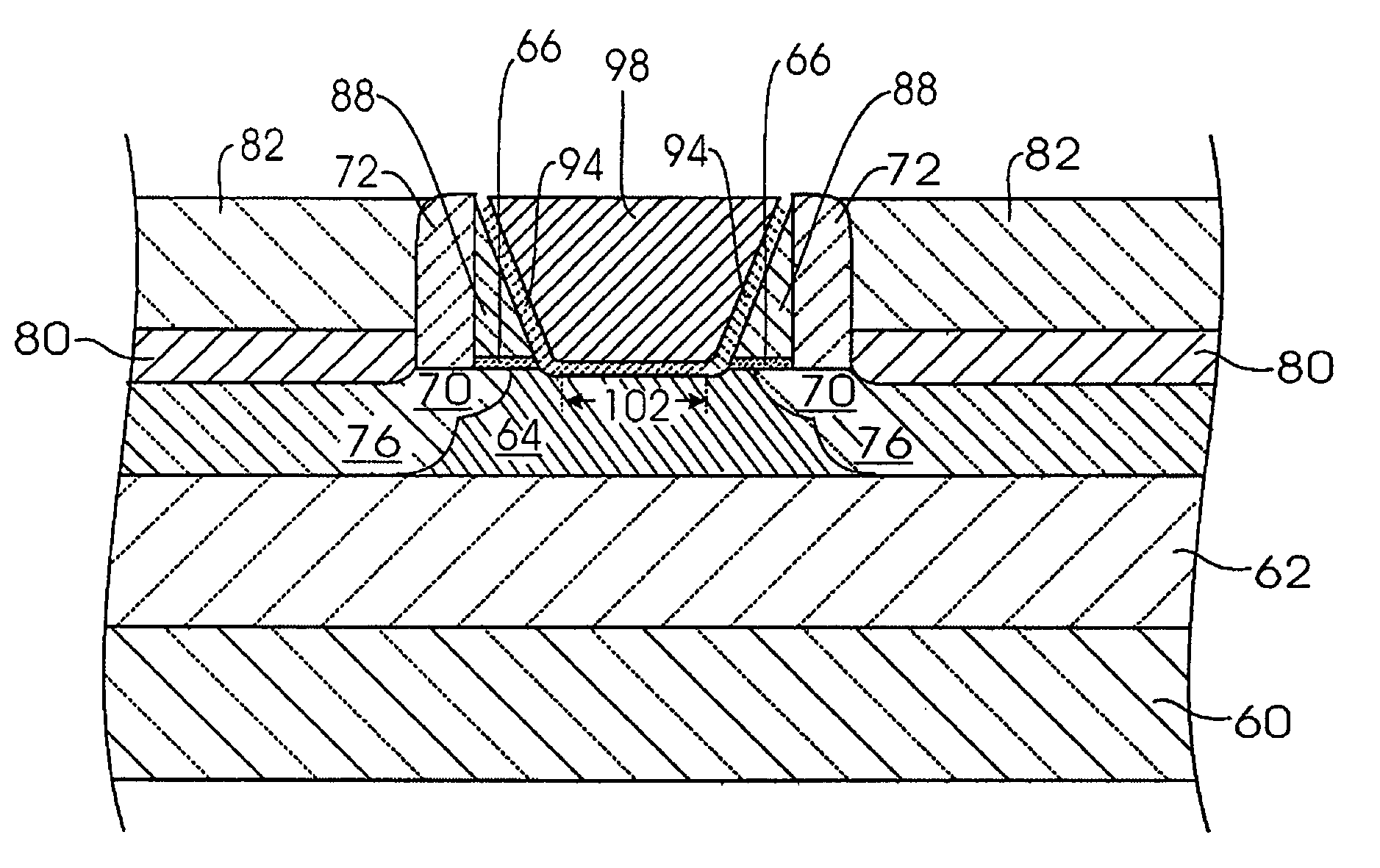

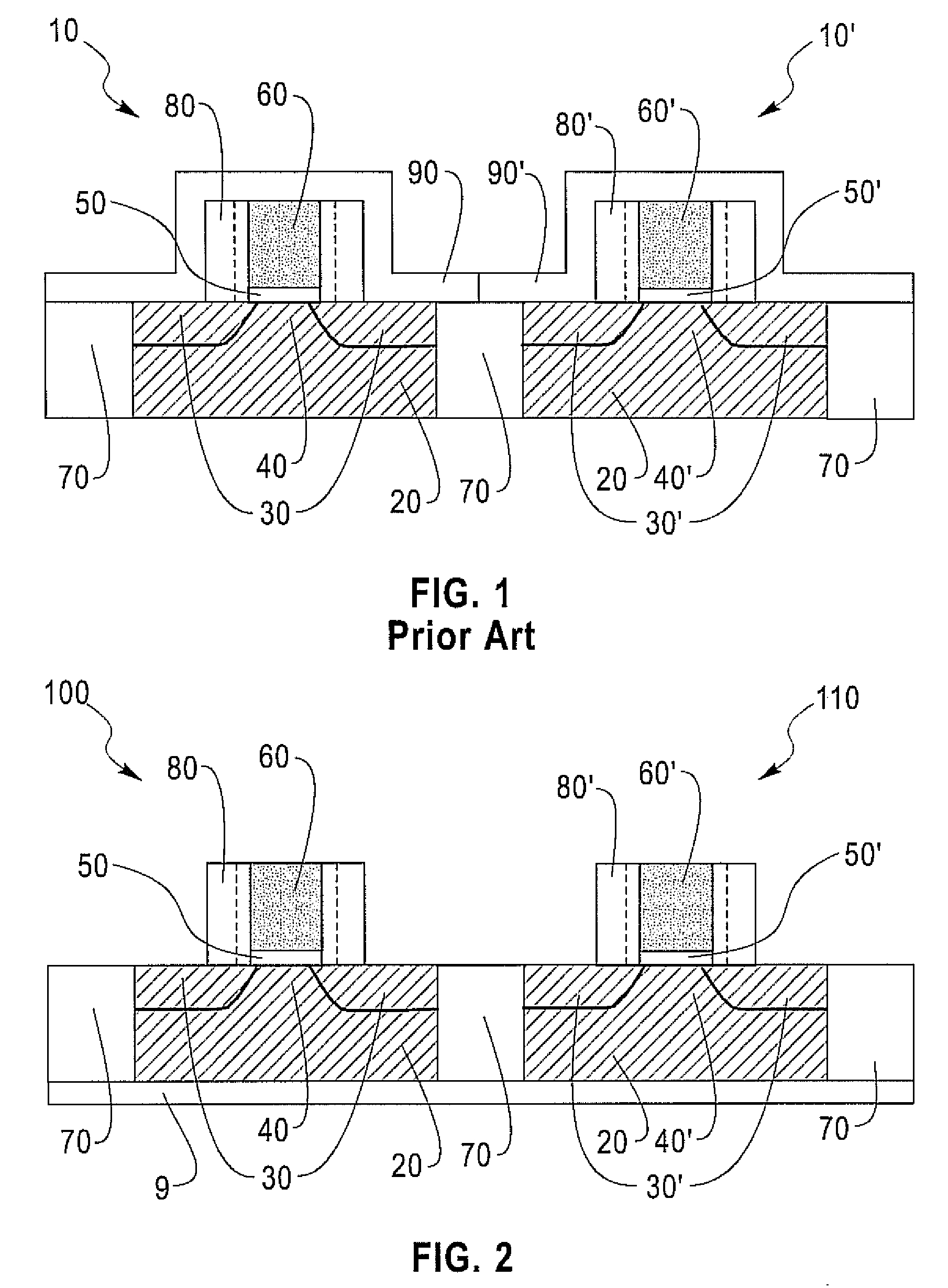

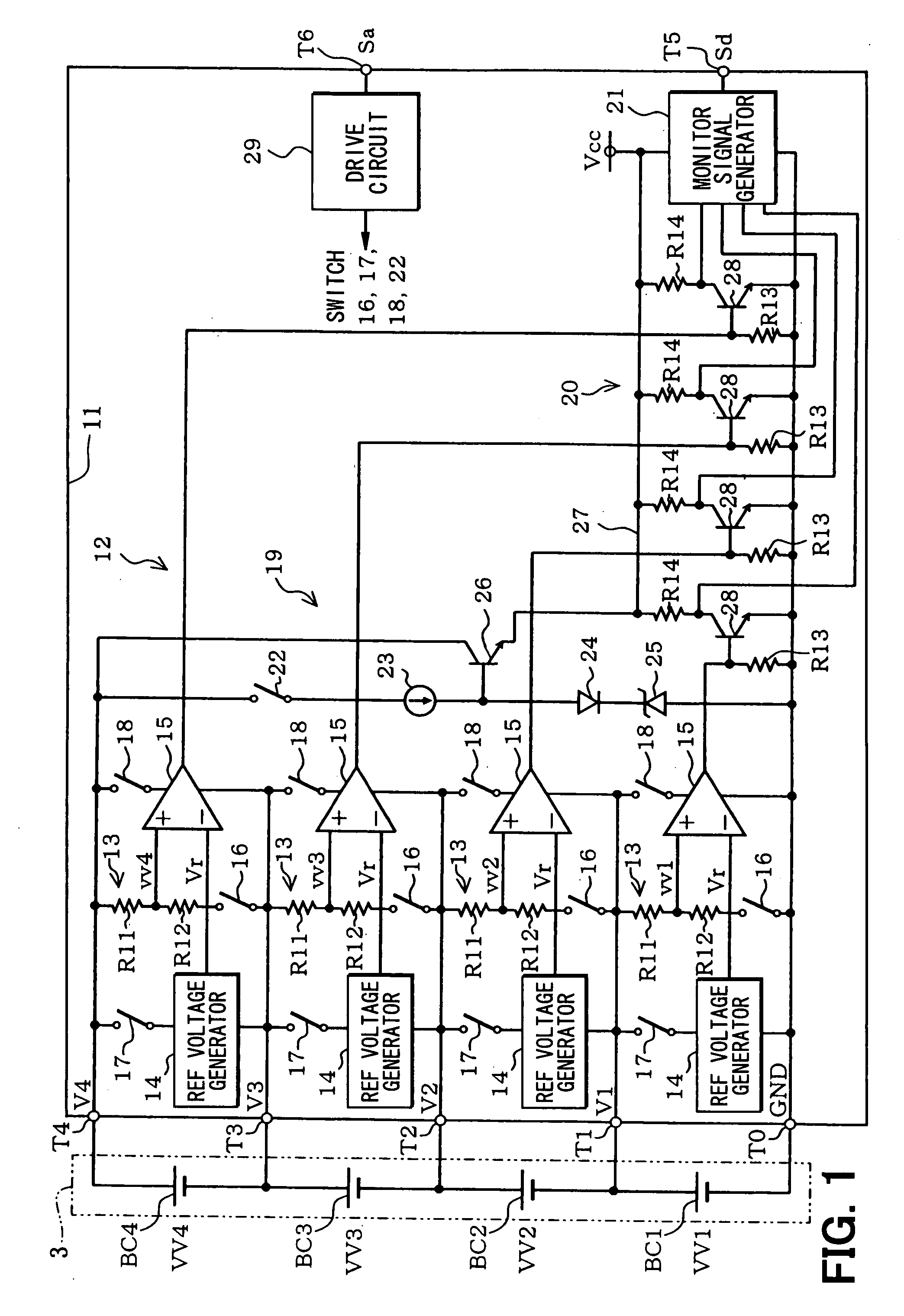

Enhanced Segmented Channel MOS Transistor with High-Permittivity Dielectric Isolation Material

ActiveUS20070122953A1Increase costImprove performanceTransistorSolid-state devicesMOSFETPerformance enhancement

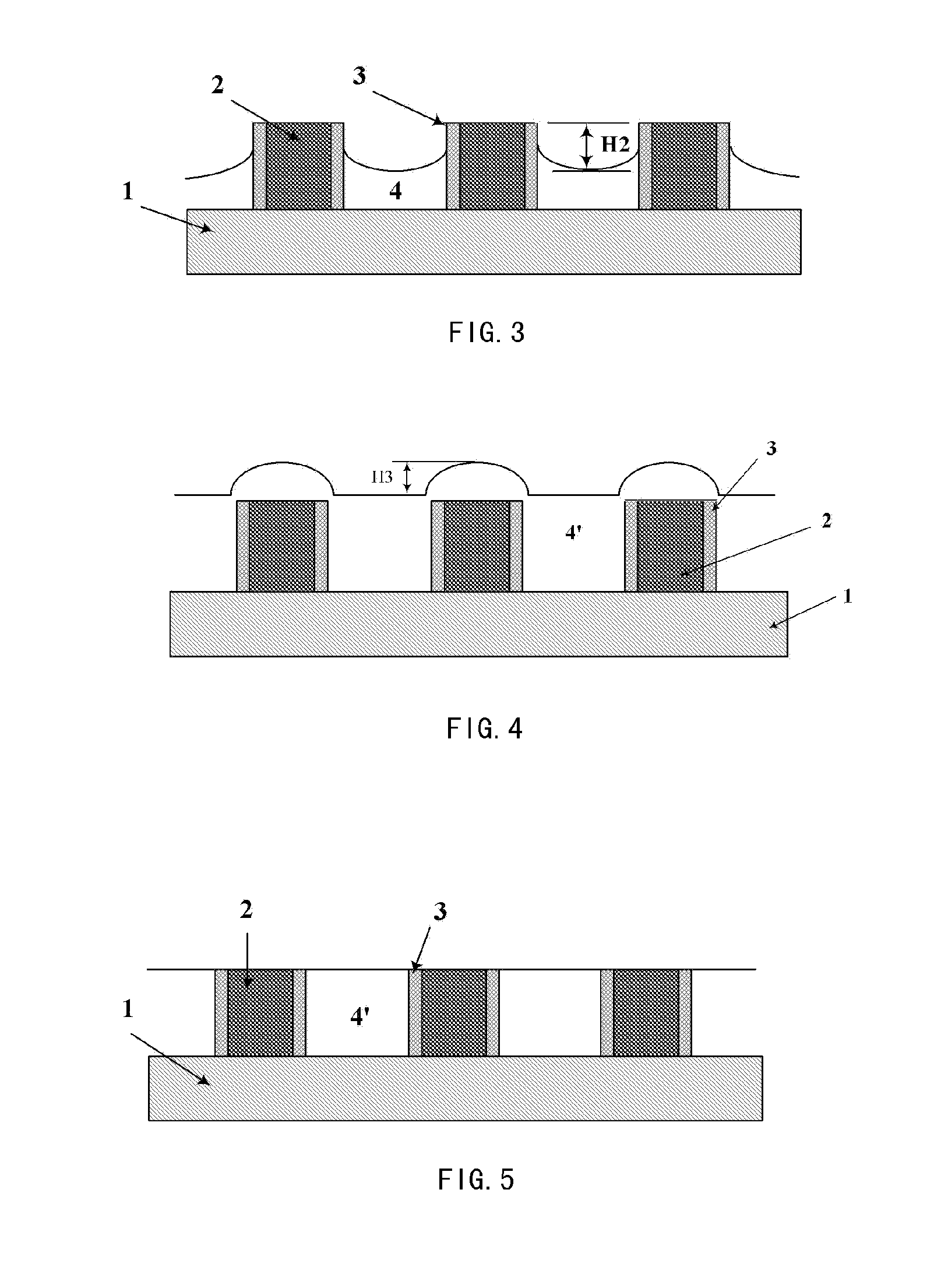

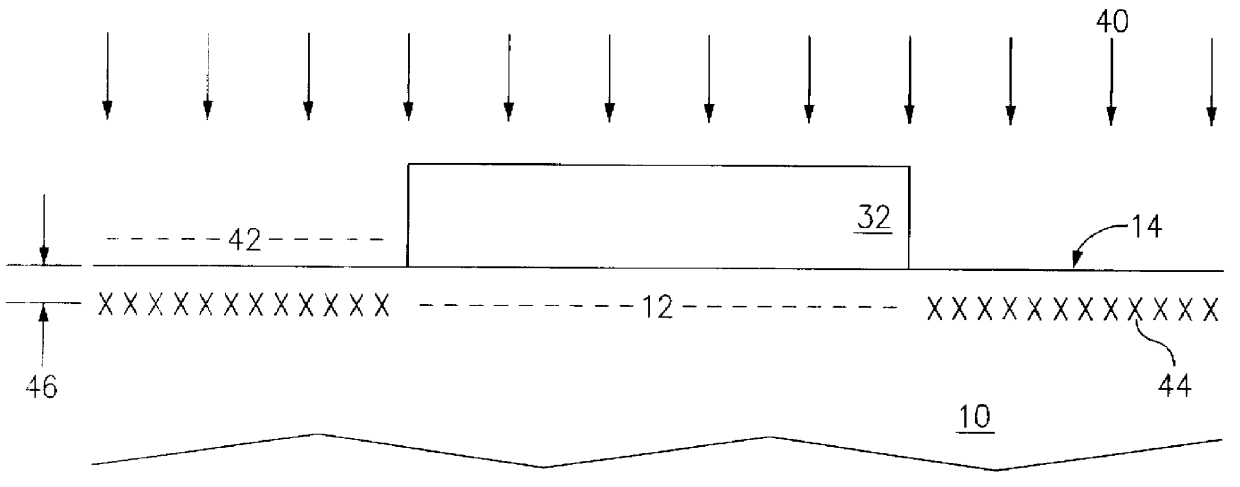

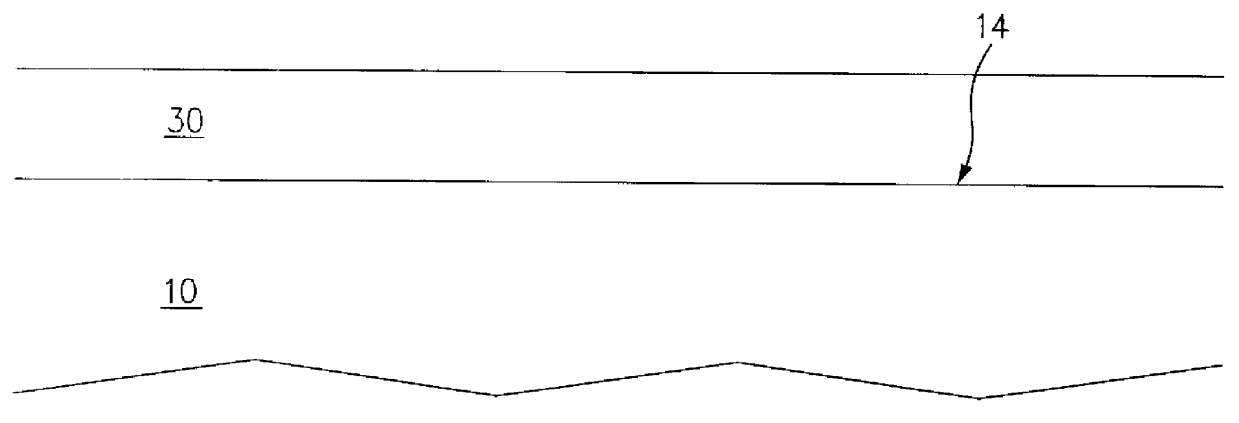

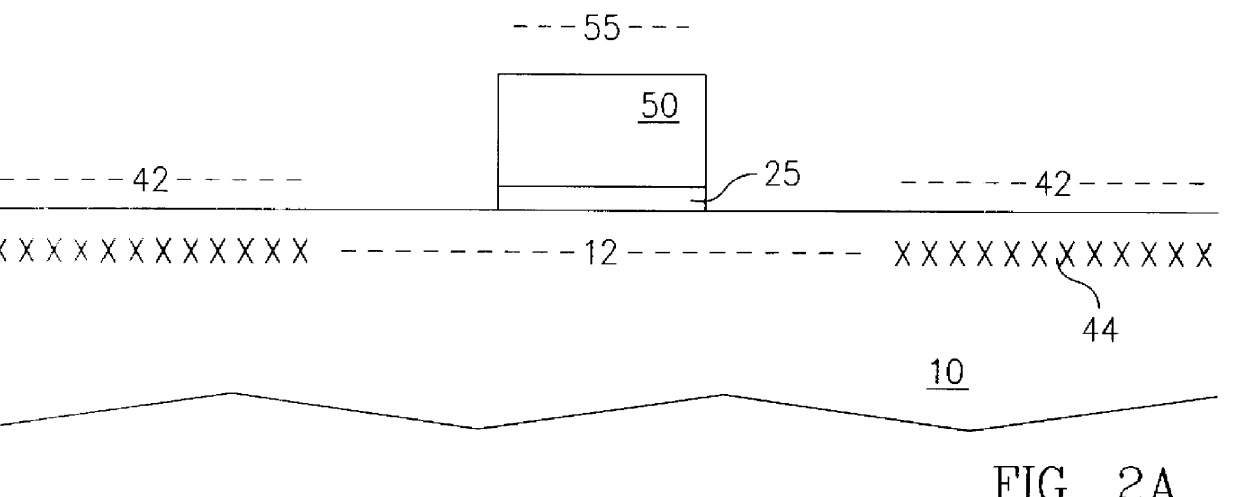

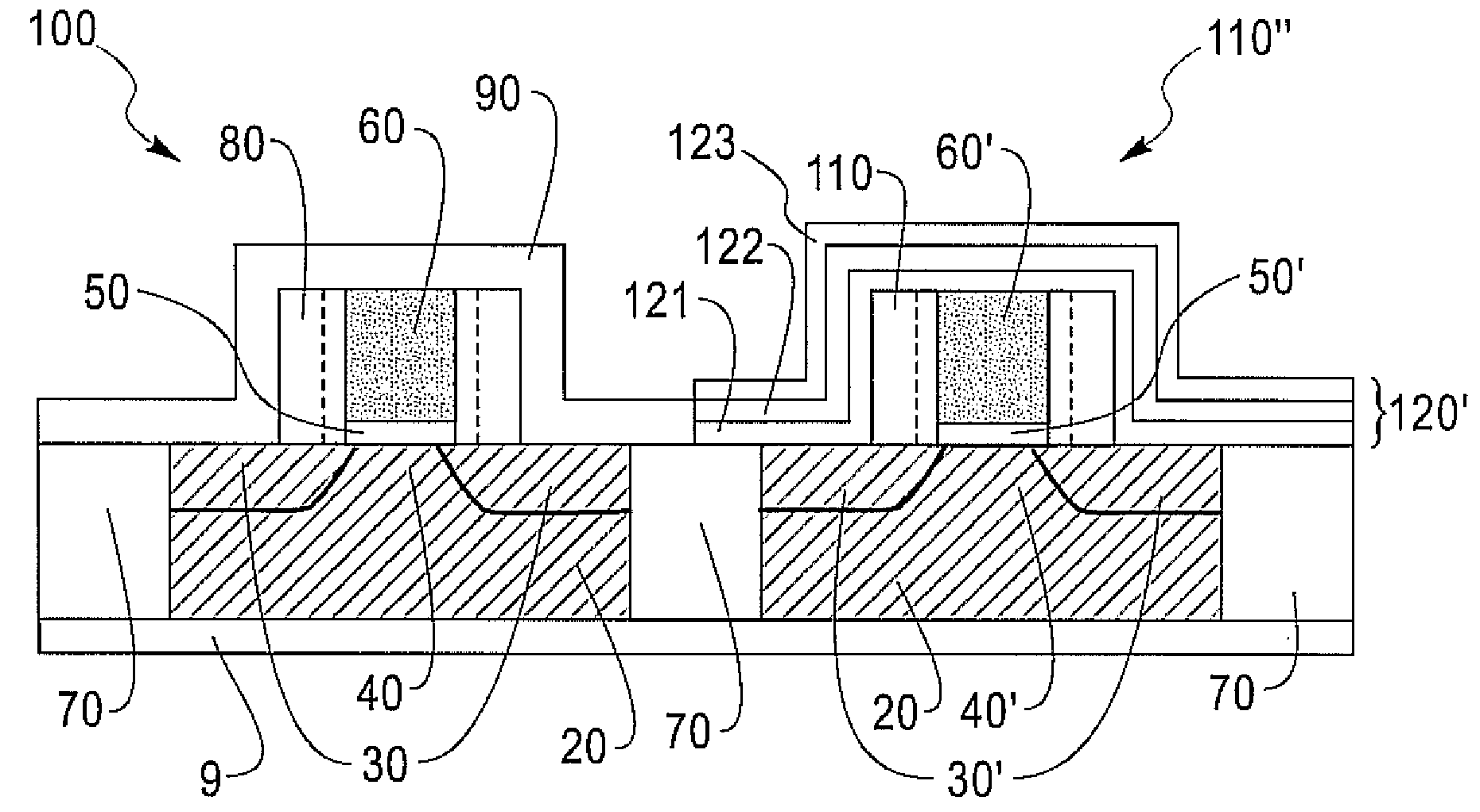

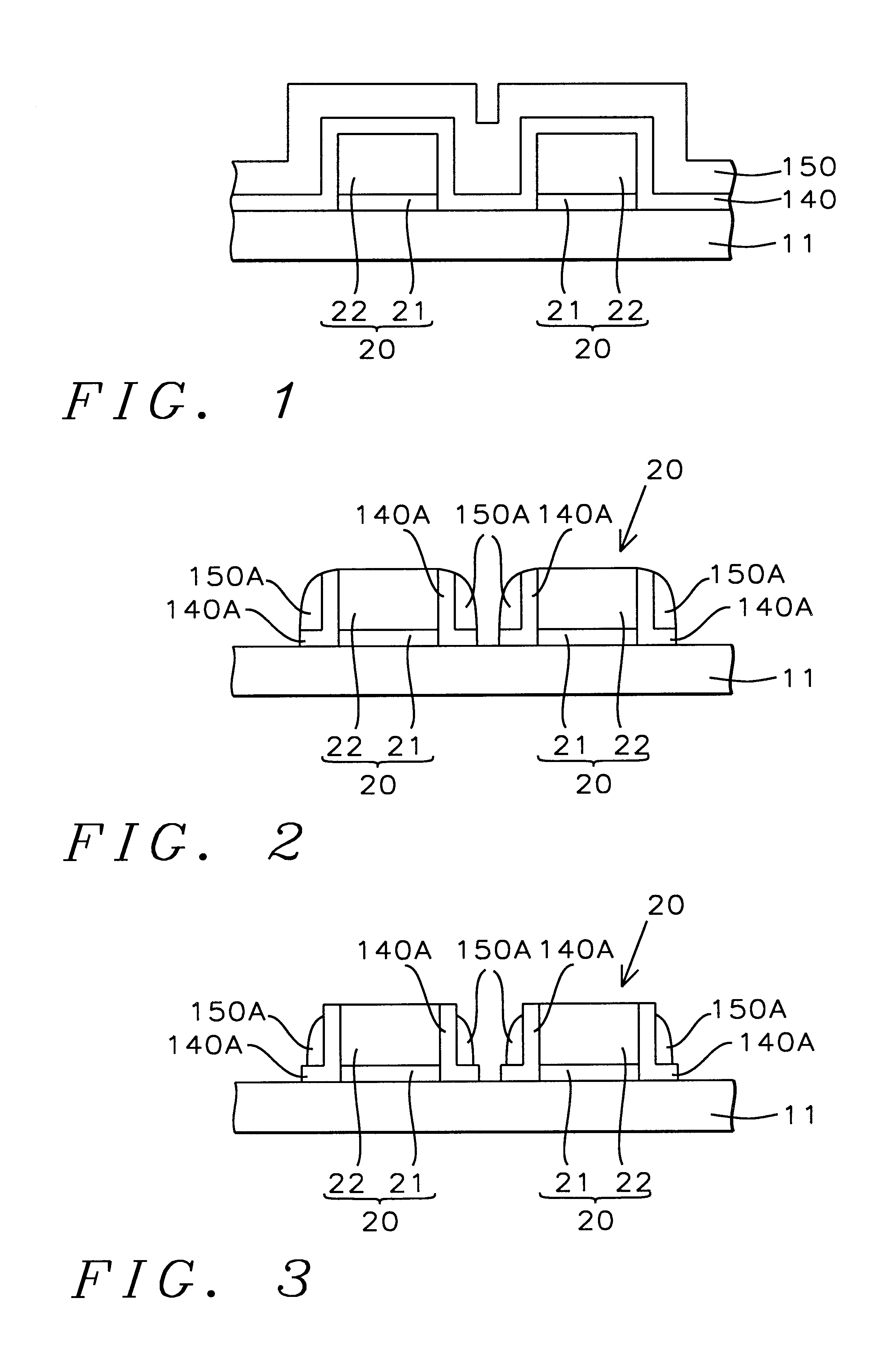

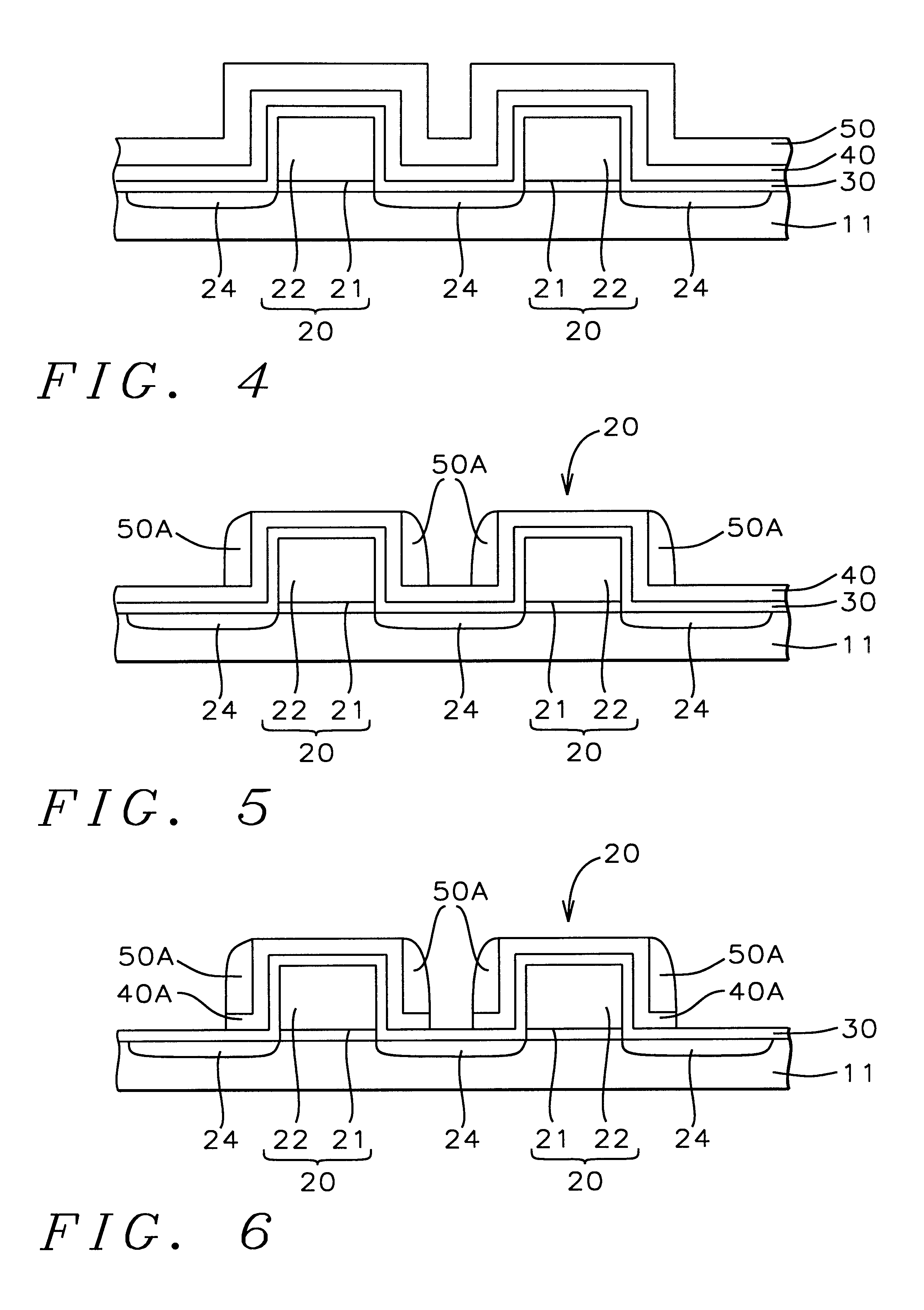

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials (e.g. silicon-germanium, germanium, gallium arsenide, etc.), high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

Enhanced segmented channel MOS transistor with high-permittivity dielectric isolation material

ActiveUS7605449B2Improve performance consistencyImprove performanceTransistorSolid-state devicesMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials (e.g. silicon-germanium, germanium, gallium arsenide, etc.), high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

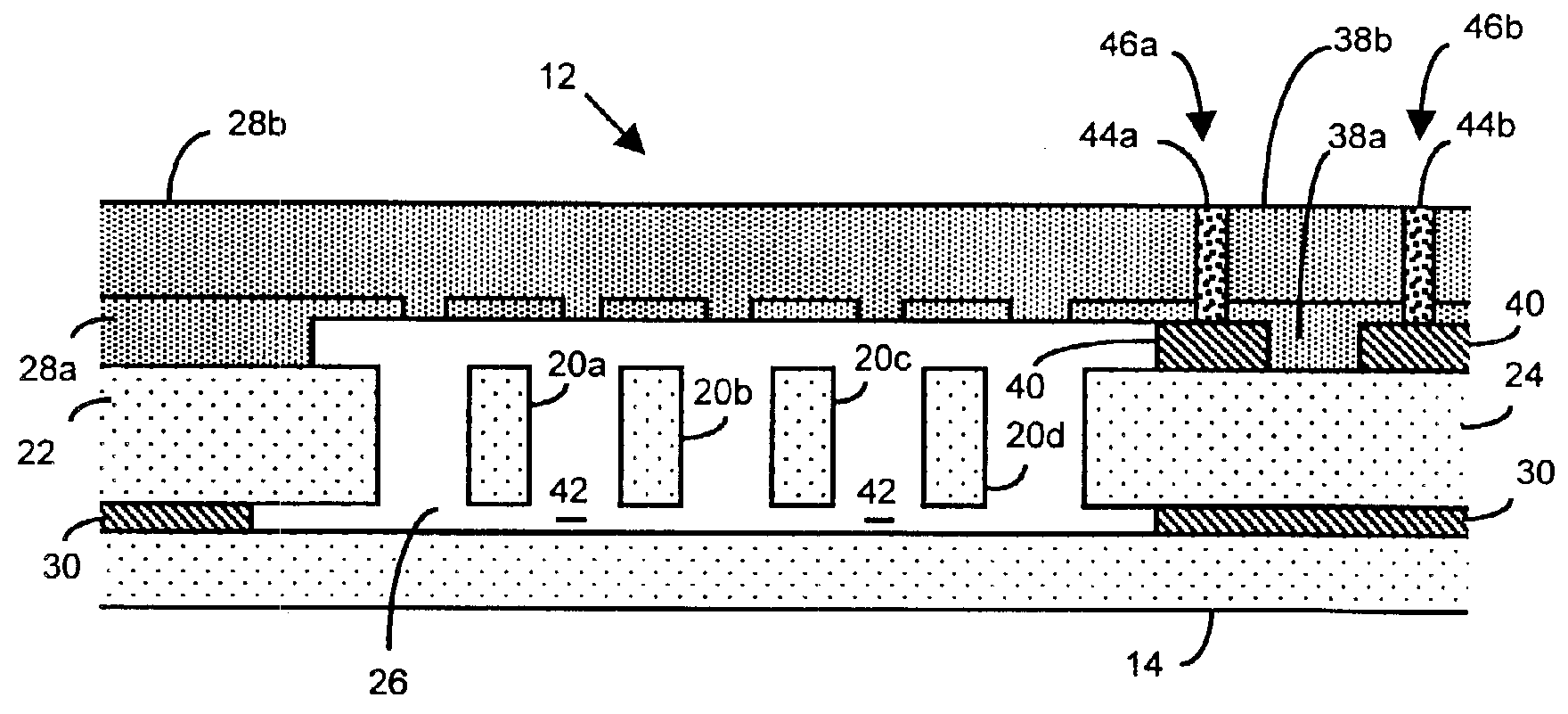

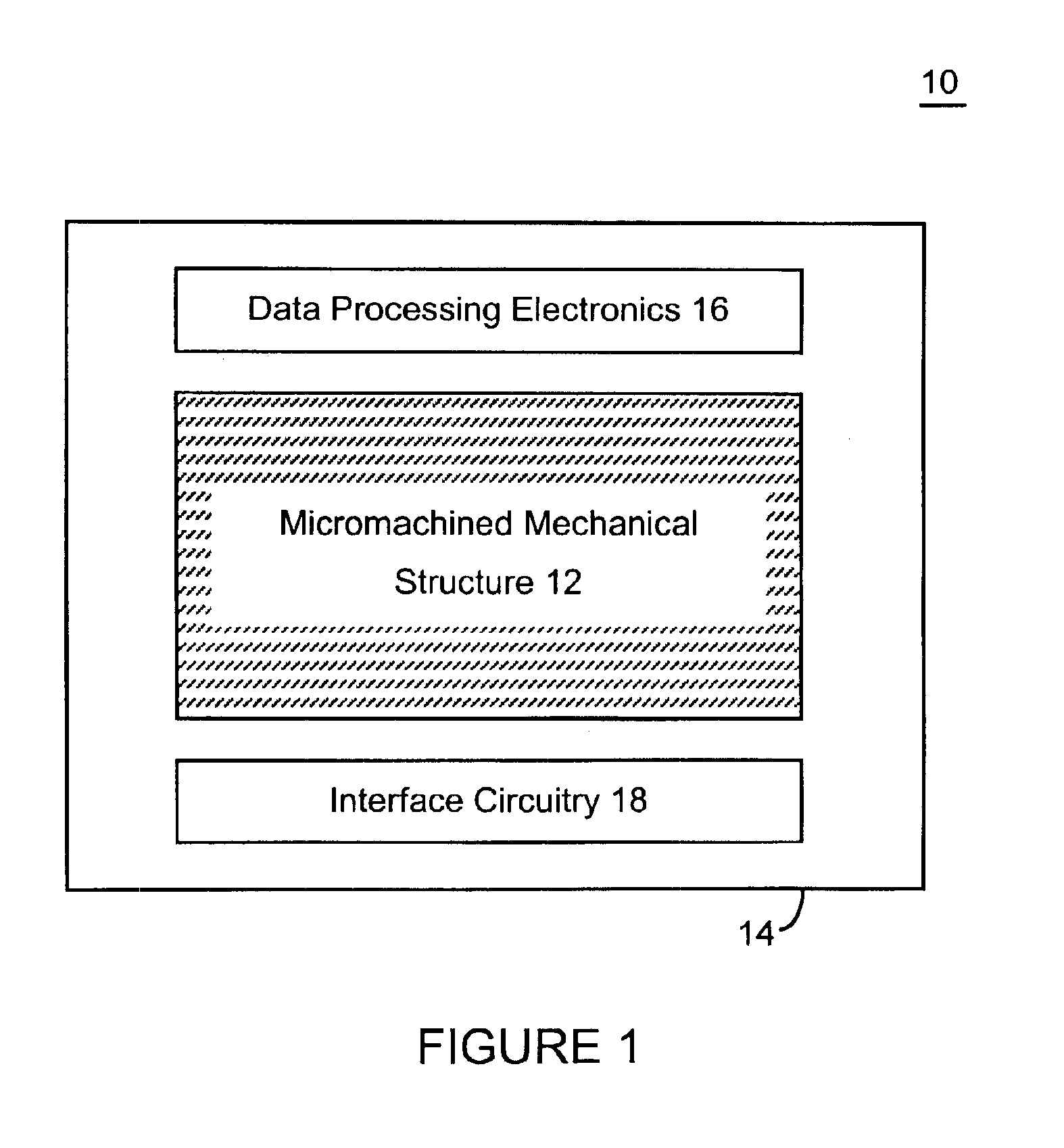

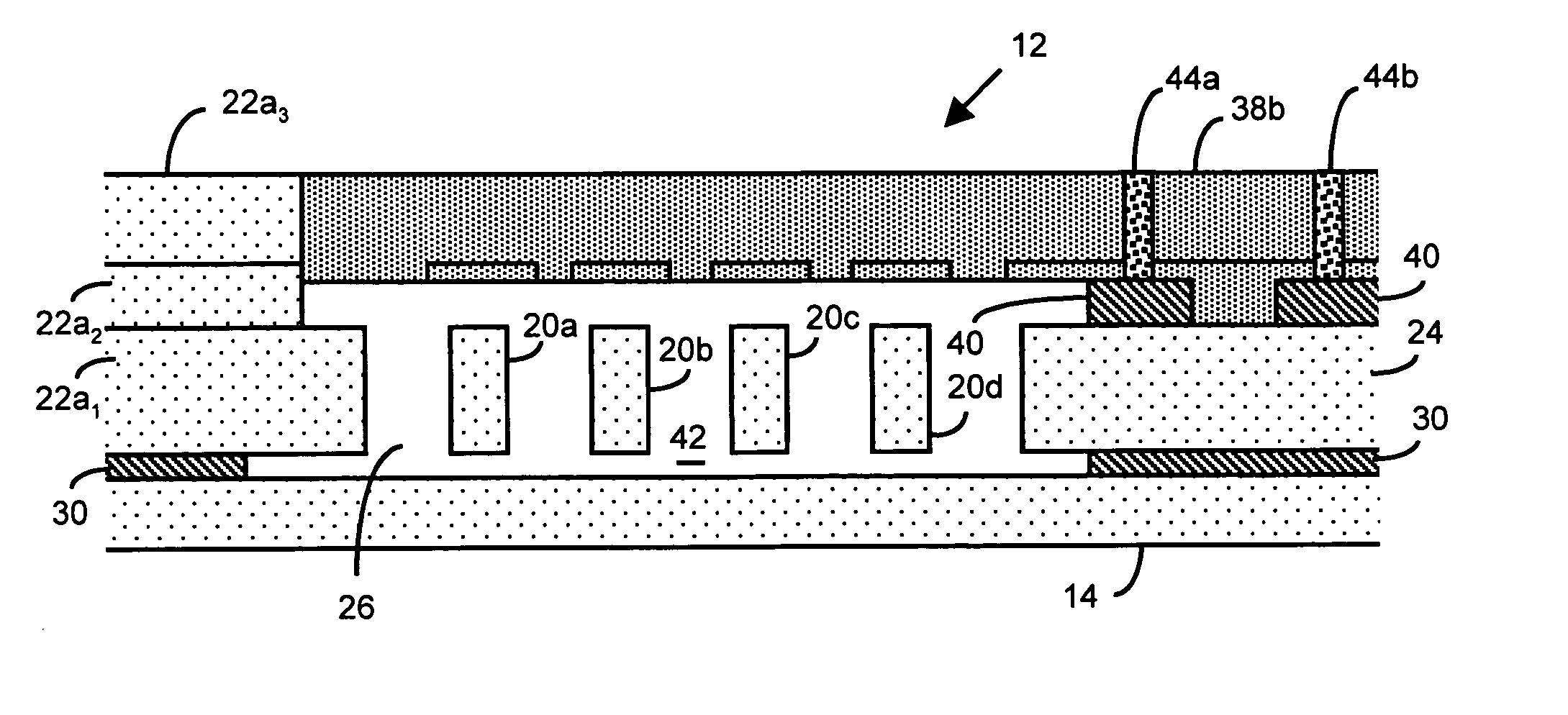

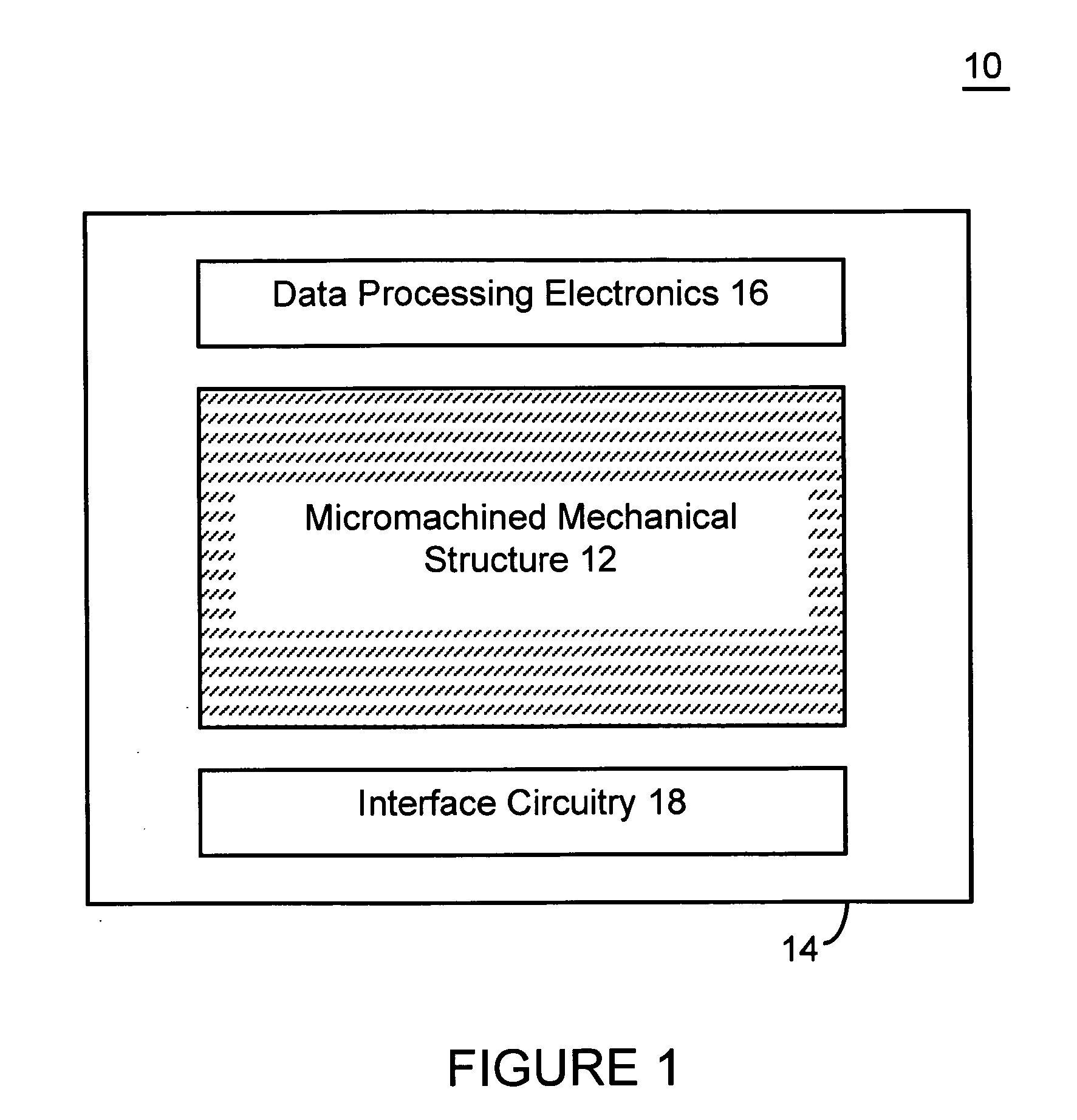

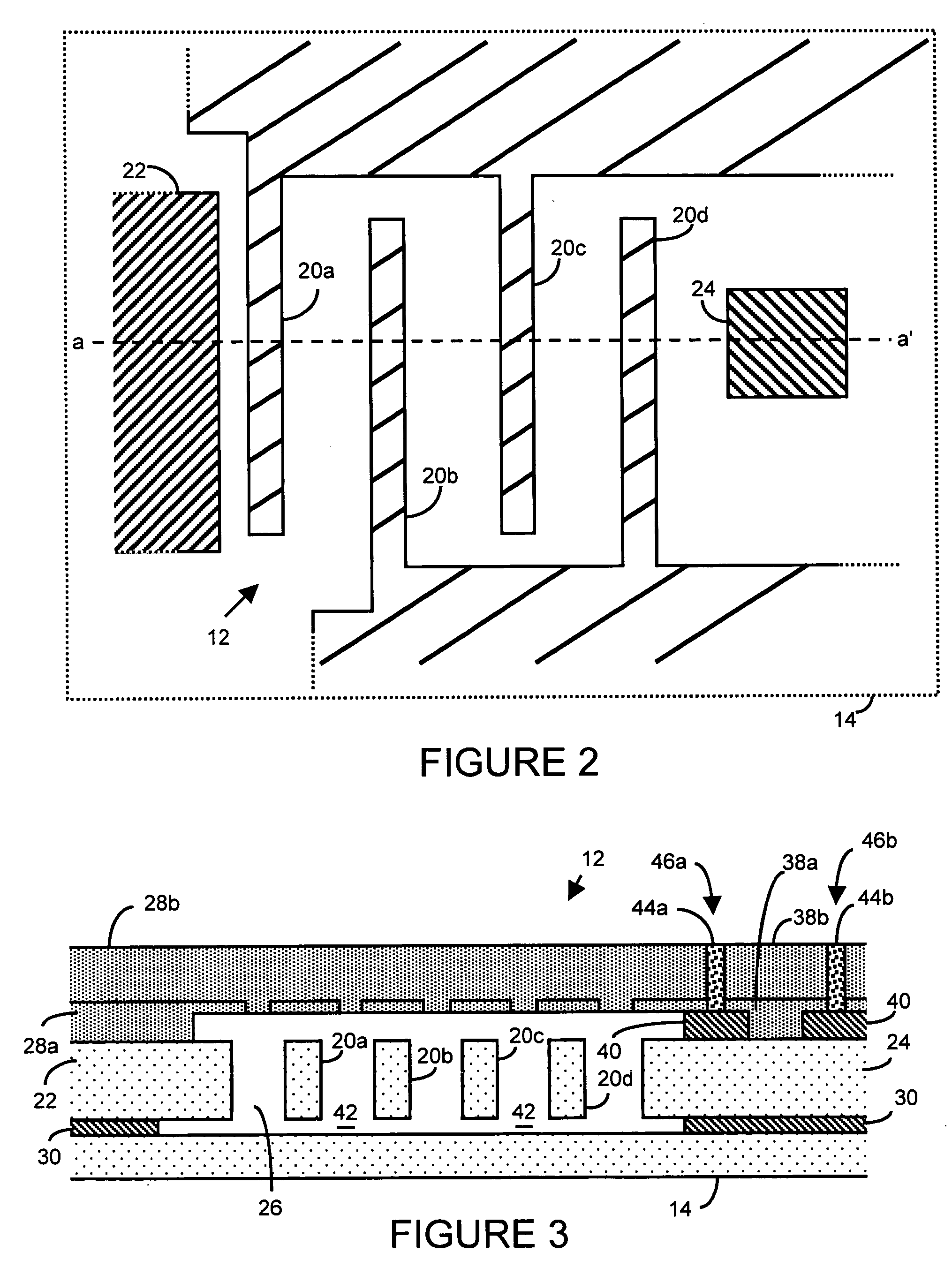

Method of fabricating microelectromechanical systems and devices having trench isolated contacts

InactiveUS6936491B2Acceleration measurement using interia forcesSolid-state devicesEngineeringMicroelectromechanical systems

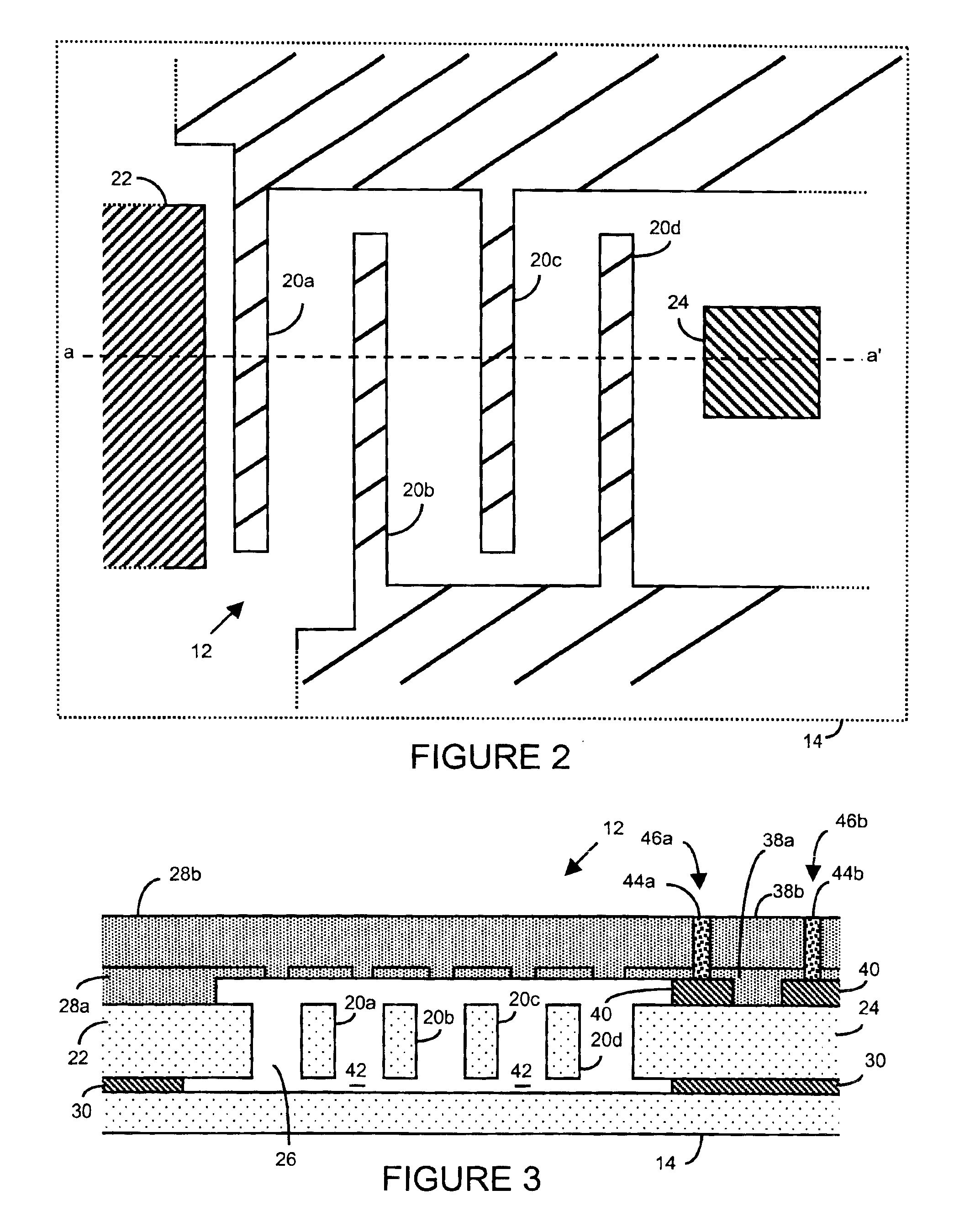

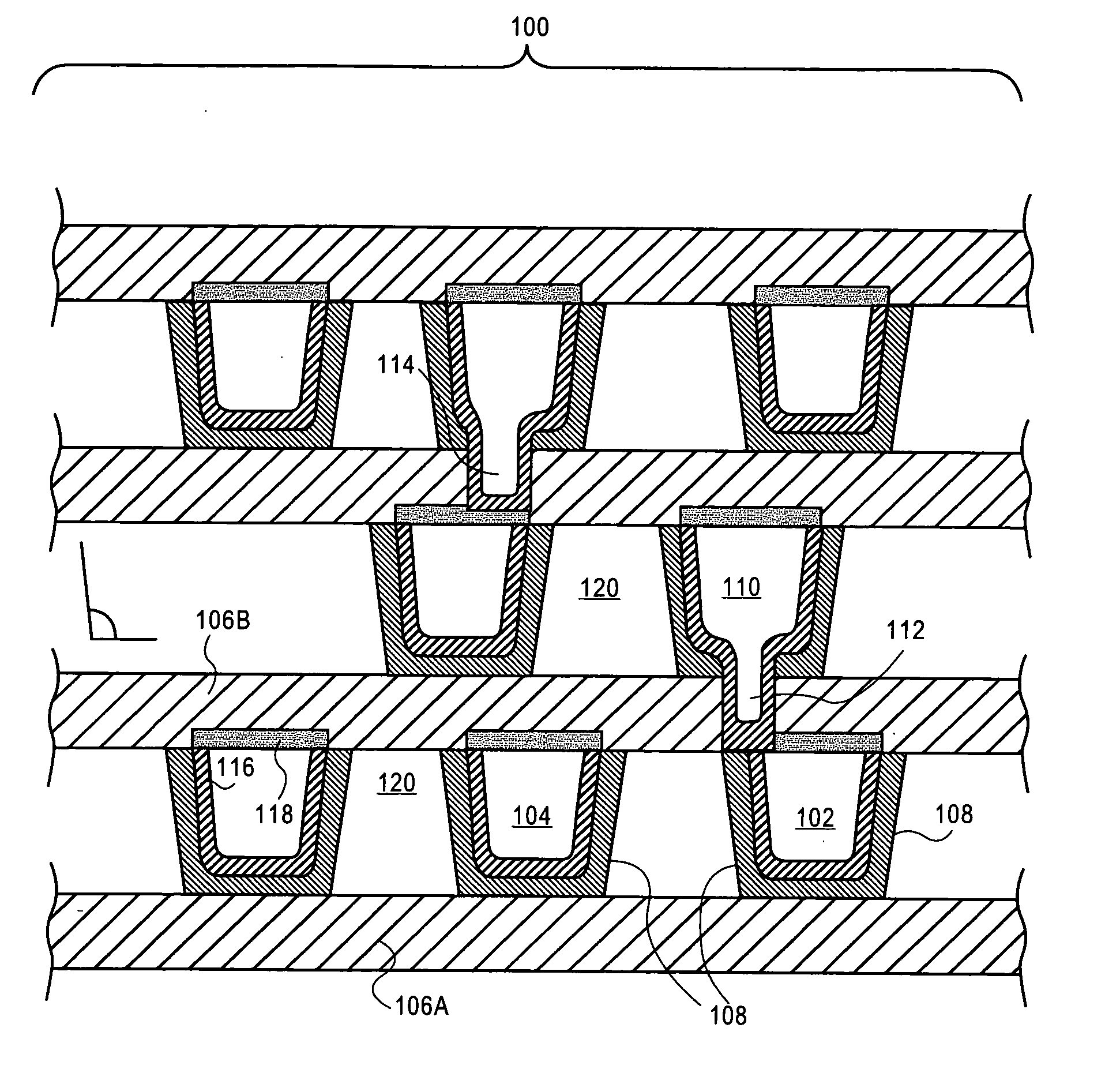

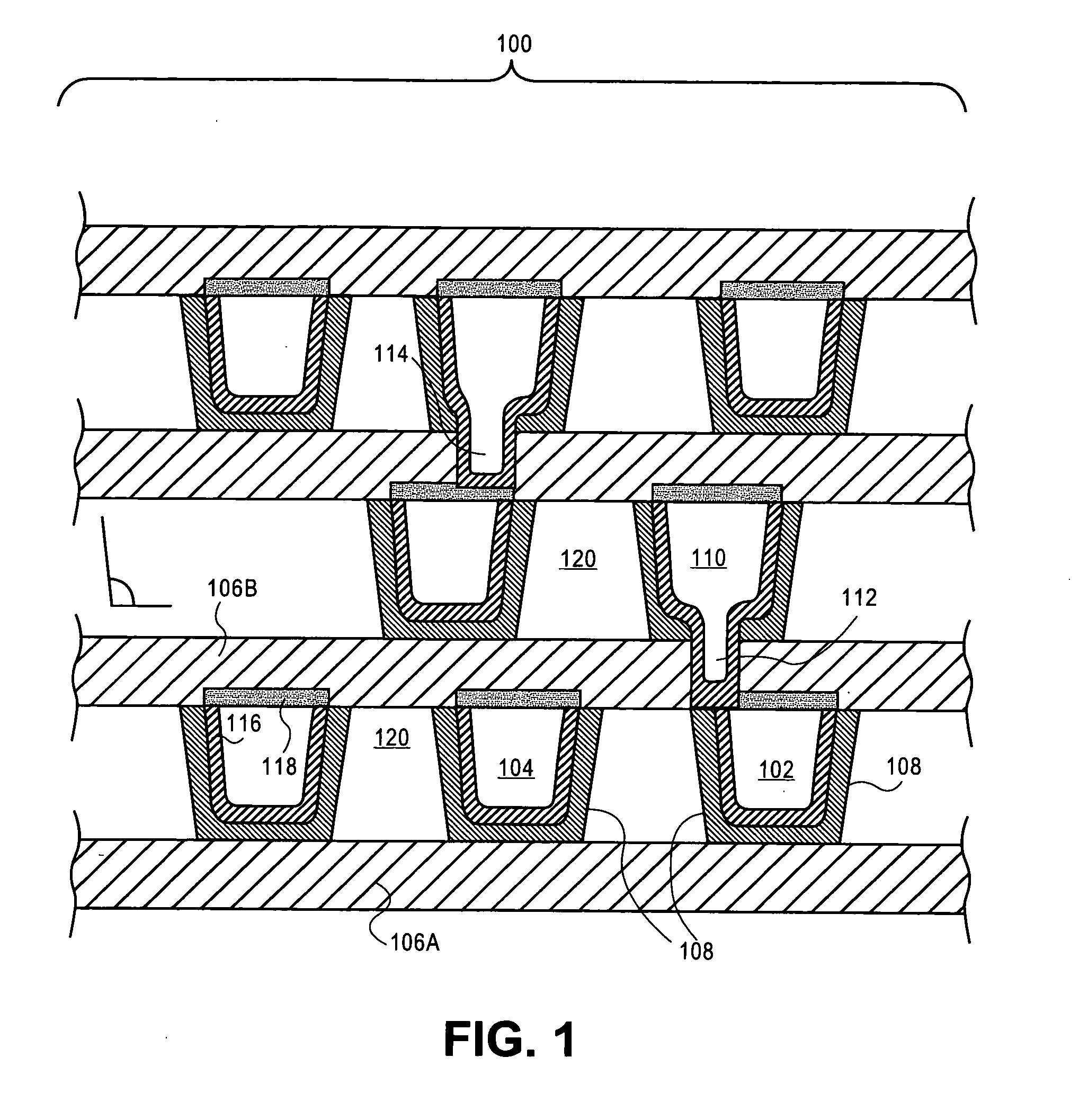

There are many inventions described and illustrated herein. In one aspect, the present invention is directed to a MEMS device, and technique of fabricating or manufacturing a MEMS device, having mechanical structures encapsulated in a chamber prior to final packaging and a contact area disposed at least partially outside the chamber. The contact area is electrically isolated from nearby electrically conducting regions by way of dielectric isolation trench that is disposed around the contact area. The material that encapsulates the mechanical structures, when deposited, includes one or more of the following attributes: low tensile stress, good step coverage, maintains its integrity when subjected to subsequent processing, does not significantly and / or adversely impact the performance characteristics of the mechanical structures in the chamber (if coated with the material during deposition), and / or facilitates integration with high-performance integrated circuits. In one embodiment, the material that encapsulates the mechanical structures is, for example, silicon (polycrystalline, amorphous or porous, whether doped or undoped), silicon carbide, silicon-germanium, germanium, or gallium-arsenide.

Owner:ROBERT BOSCH GMBH

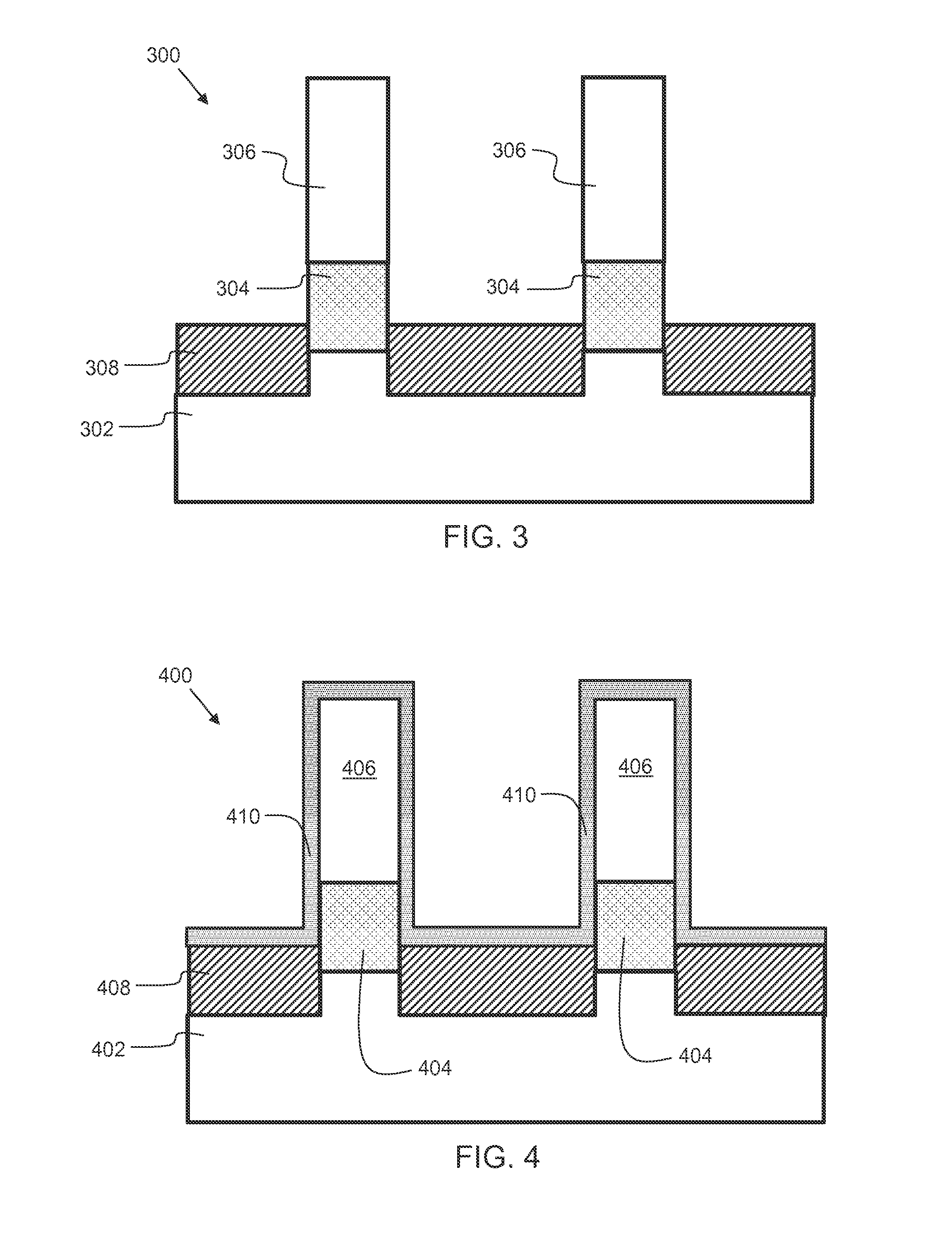

Method for improving uniformity of chemical-mechanical planarization process

ActiveUS8647987B2Improve uniformityReduce the differenceSemiconductor/solid-state device testing/measurementSolid-state devicesEngineeringDielectric layer

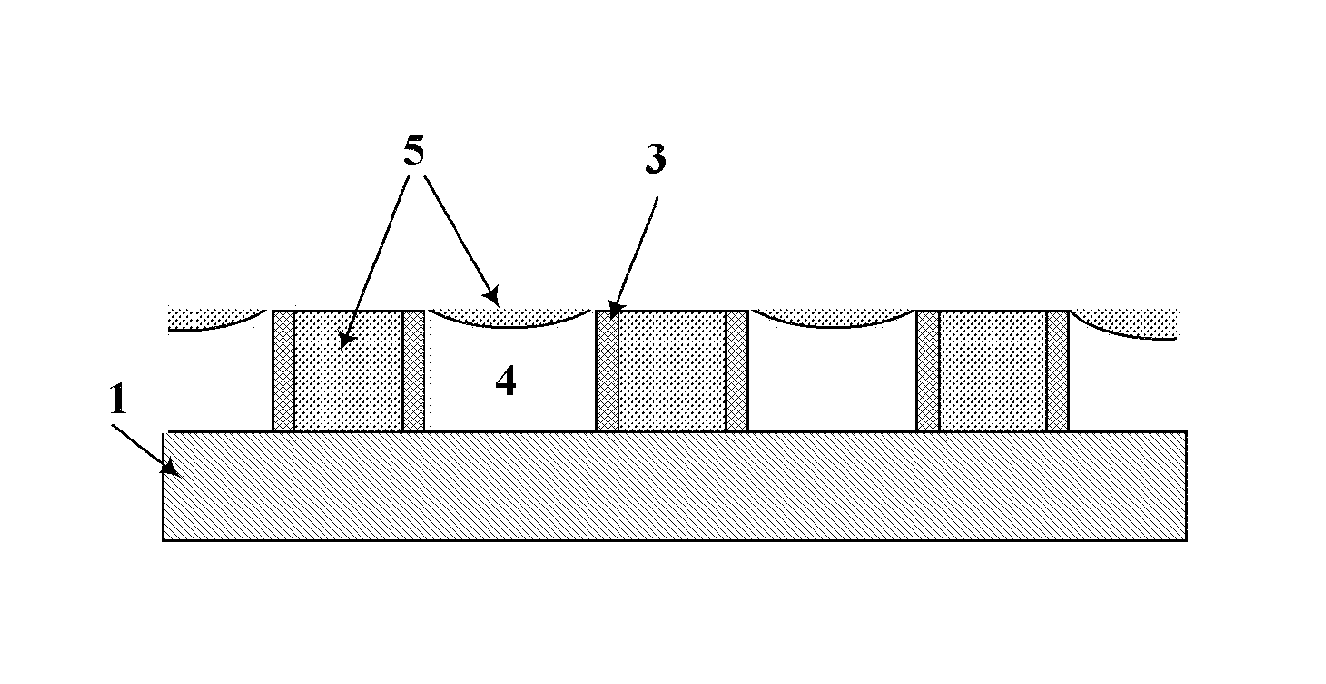

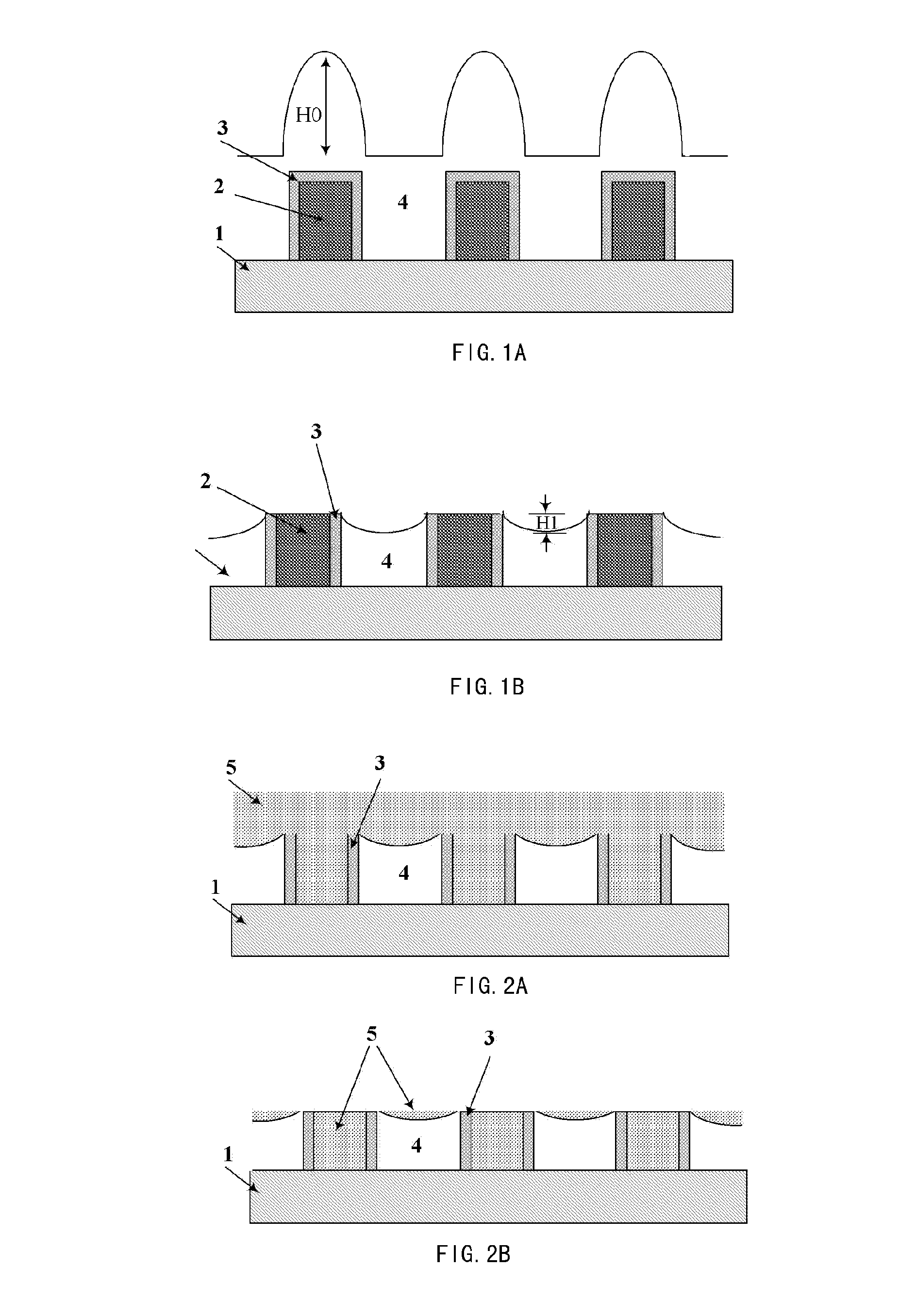

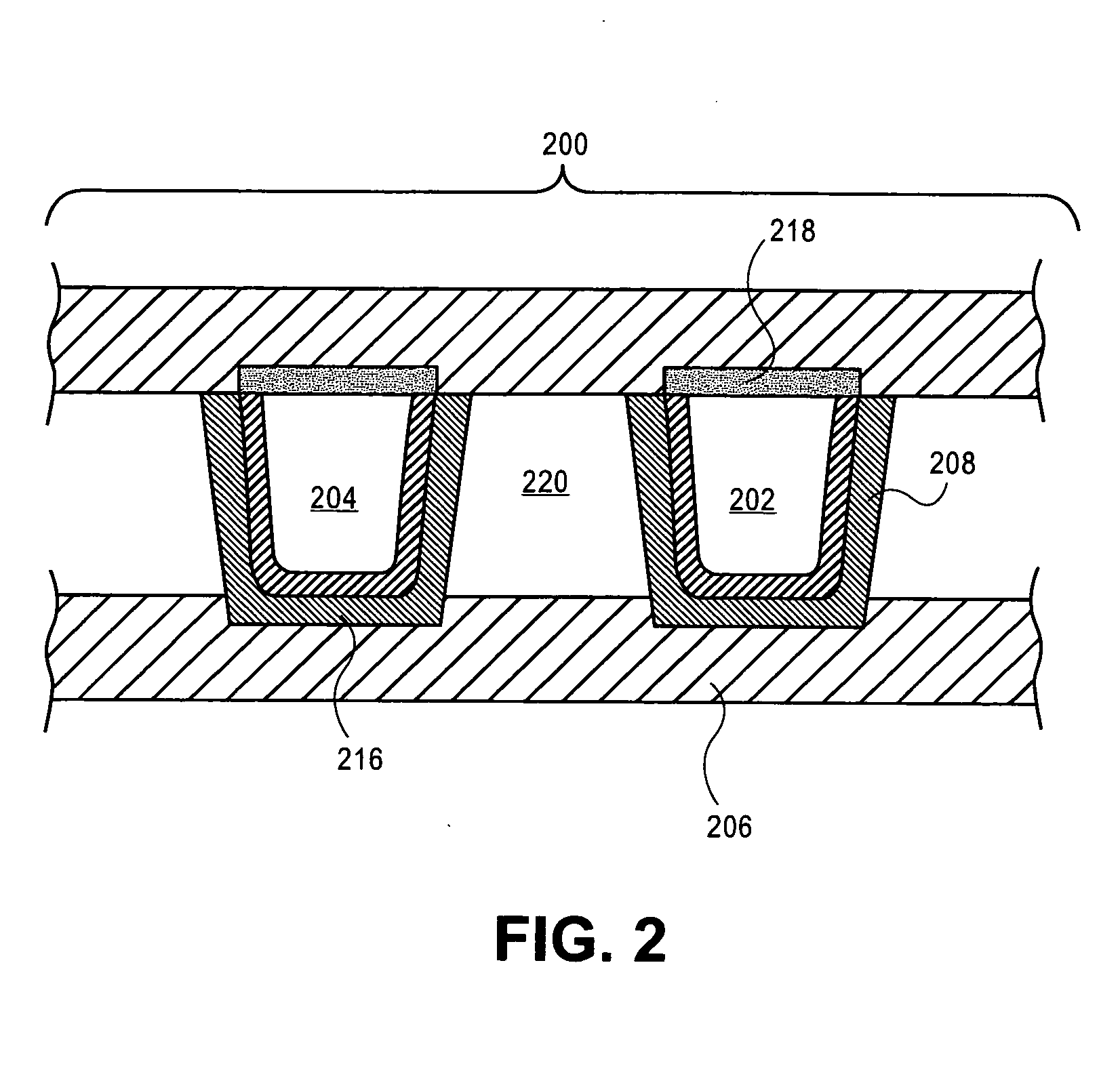

The invention provides a method for improving uniformity of chemical-mechanical planarization process, comprising the steps of: forming features on a substrate; forming a first dielectric isolation layer between the features; planarizing the first dielectric isolation layer until the features are exposed, causing the first dielectric isolation layer between the features to have a recess depth; forming a second dielectric isolation layer on the features and the first dielectric isolation layer, whereby reducing the difference in height between the second dielectric isolation layer between the features and the second dielectric isolation layer on the top of the features; planarizing the second dielectric isolation layer until the features are exposed. According to the method for improving uniformity of chemical-mechanical planarization process of the invention, a dielectric isolation layer is formed again after grinding the dielectric isolation layer on the top of the features, such that the difference in height between the dielectric layer between the features and the dielectric layer on the top of the features is effectively reduced, and the recess of the features is compensated, the within-in-die uniformity is effectively improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

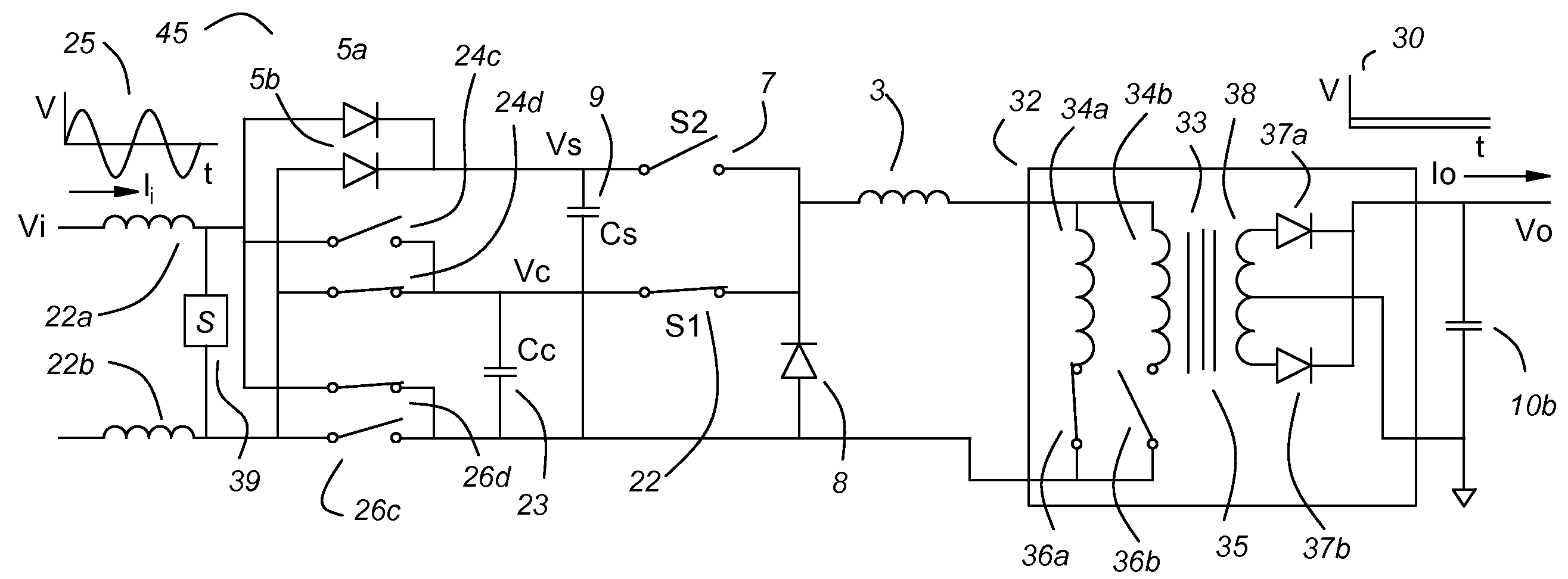

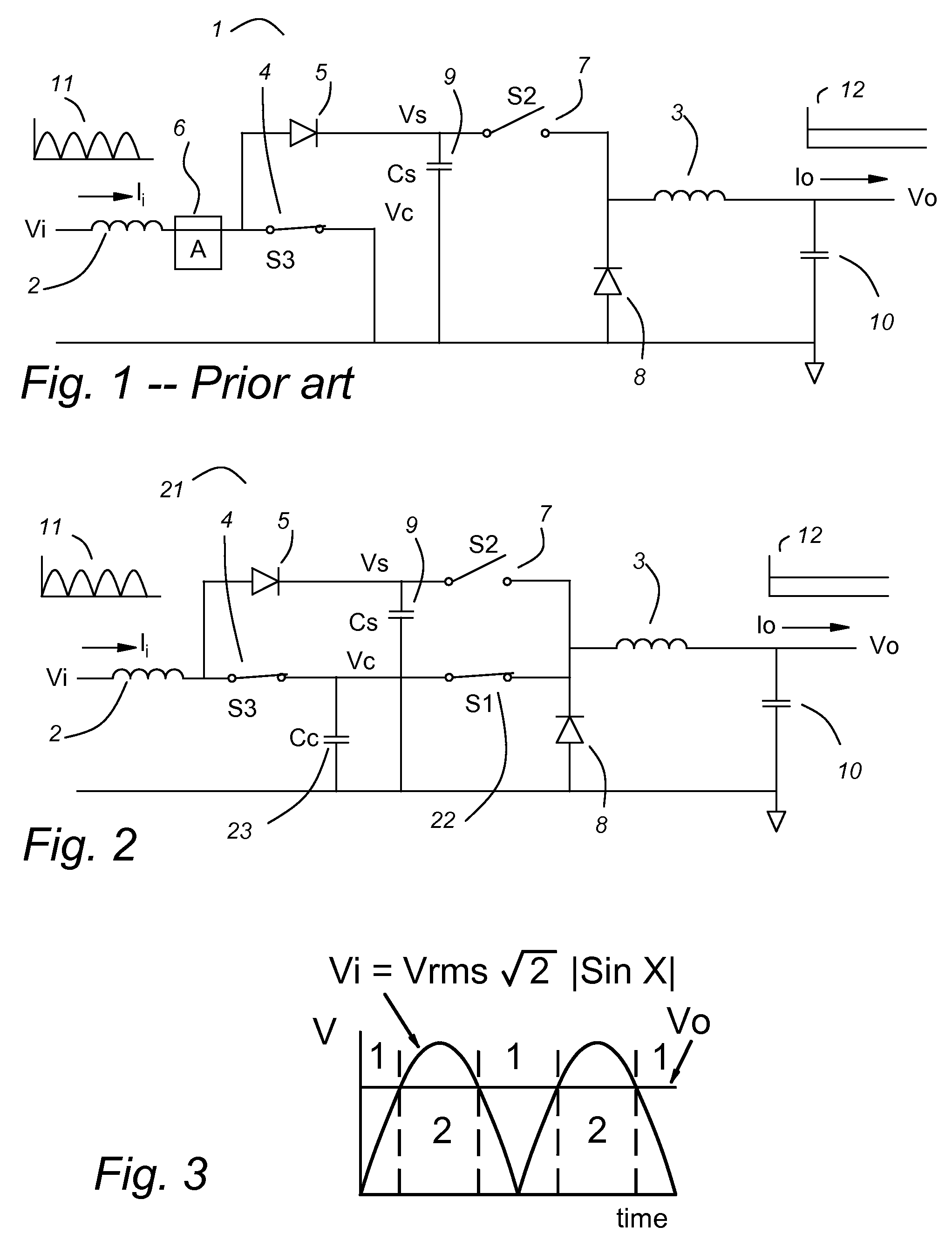

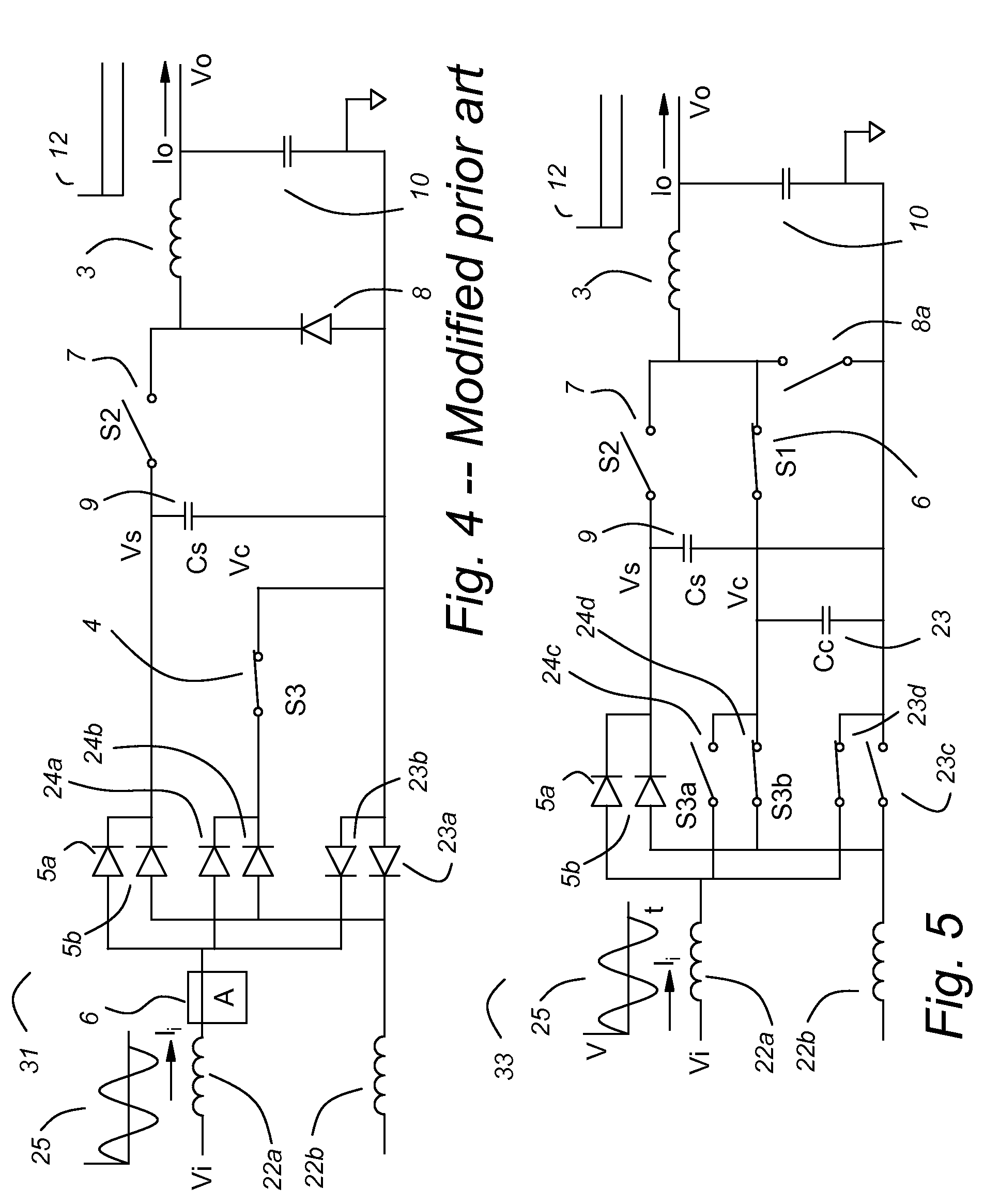

Power factor corrected single-phase AC-DC power converter using natural modulation

InactiveUS7564706B1Reduce lossesMost efficientAc-dc conversion without reversalEfficient power electronics conversionLevel shiftingElectric power system

A power factor corrected (pfc) ac-dc converter has a modified boost input and a modified buck output. Unlike the prior art boost input, the boost switch returns to the output, not to ground. Unlike the prior art buck output stage, a third switch connects to the input. This allows much of the input current to pass through the converter to the output. There is no input current measurement, but nearly ideal power factor correction is achieved through “natural modulation.” A preferred pfc ac-dc converter uses a variable dc-dc transformer on its output, as a post regulator, to provide dielectric isolation and to provide voltage level shifting. The output of the pfc ac-dc converter has the control characteristics of a buck converter, so it is a natural mate for the variable dc-dc transformer. An ac-dc buck converter is most efficient at its maximum duty cycle. It cannot regulate for a lower input voltage, but it can reduce its duty-cycle to control for higher input voltages. A variable dc-dc transformer is most efficient at its maximum ratio. It cannot regulate for a higher input voltage, but it can reduce its effective turns ratio to control for a lower input voltage. With a small overlap in their control ranges, both parts of the power system can operate at maximum efficiency. The variable dc-dc transformer controls the output voltage for nominal and low input voltage. The ac-dc buck converter limits over-voltage transients.

Owner:HERBERT EDWARD

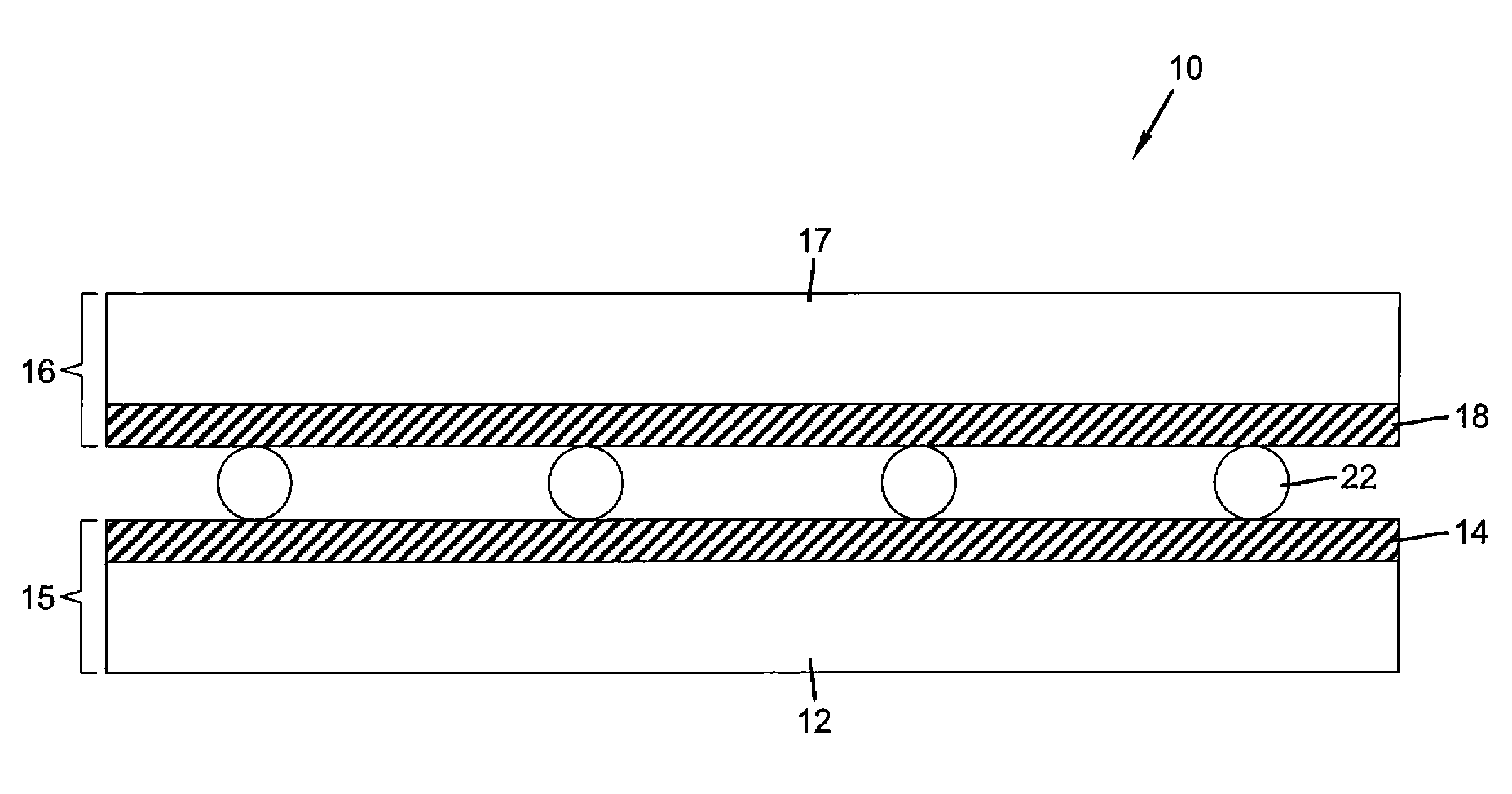

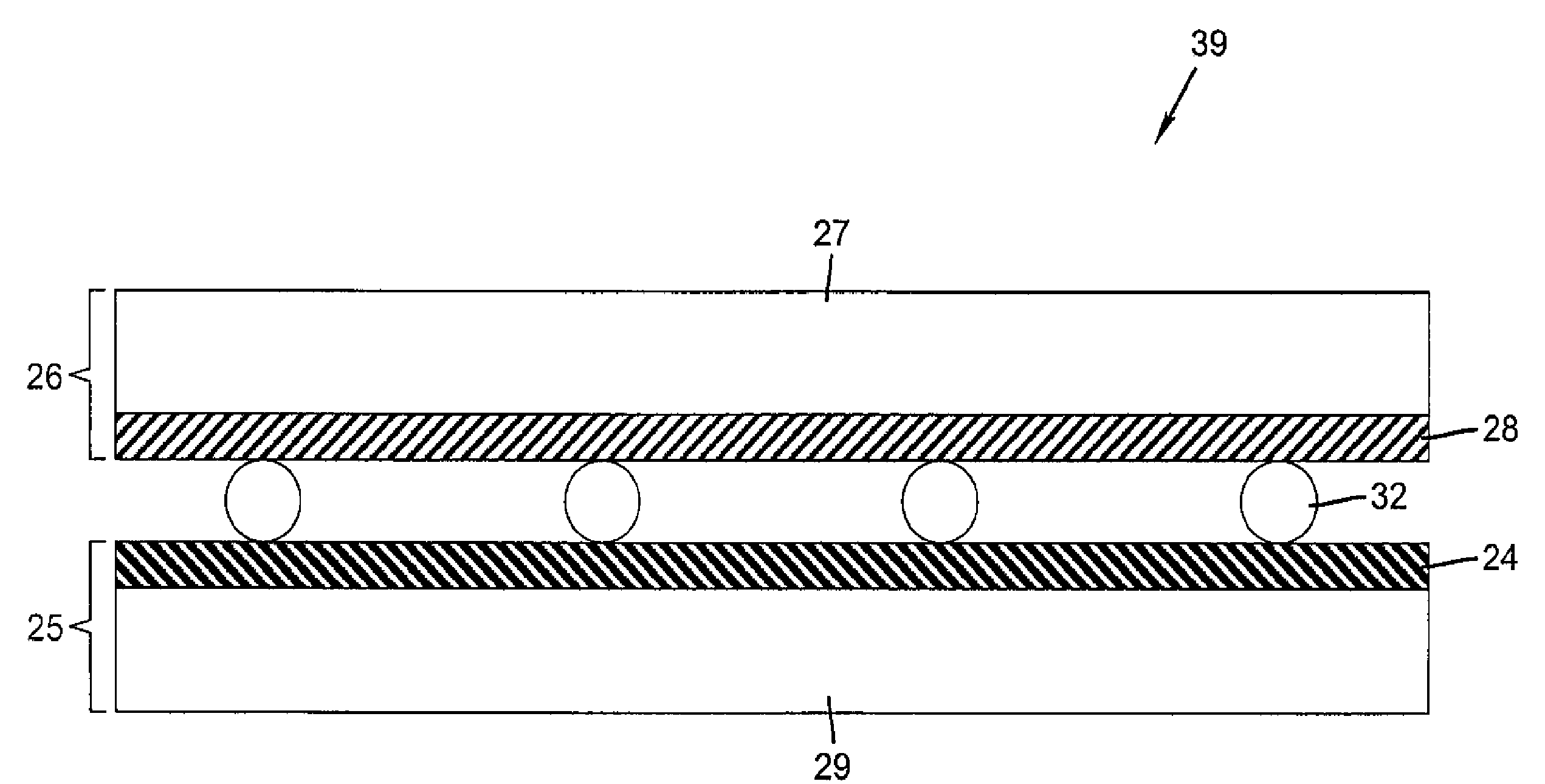

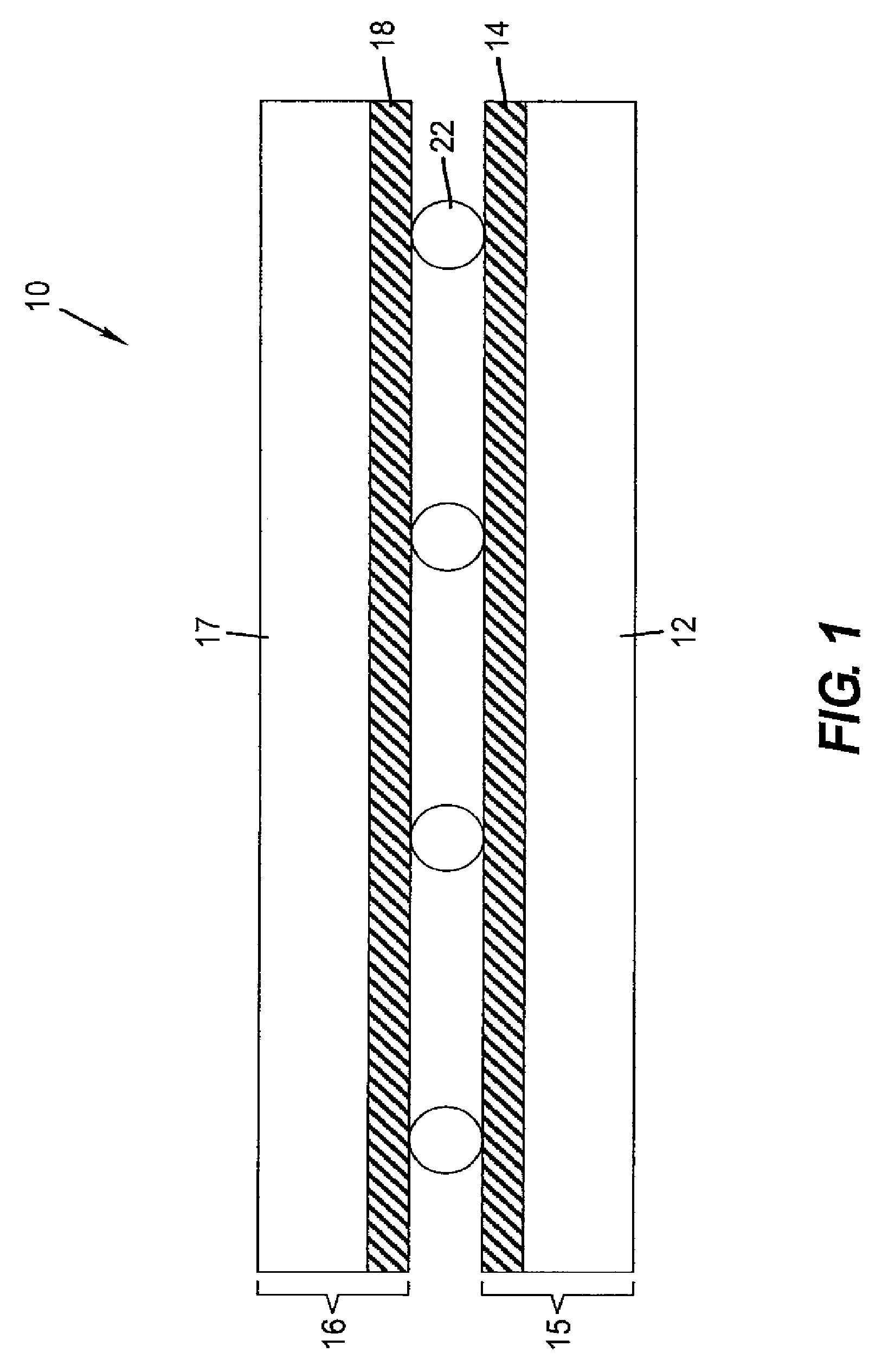

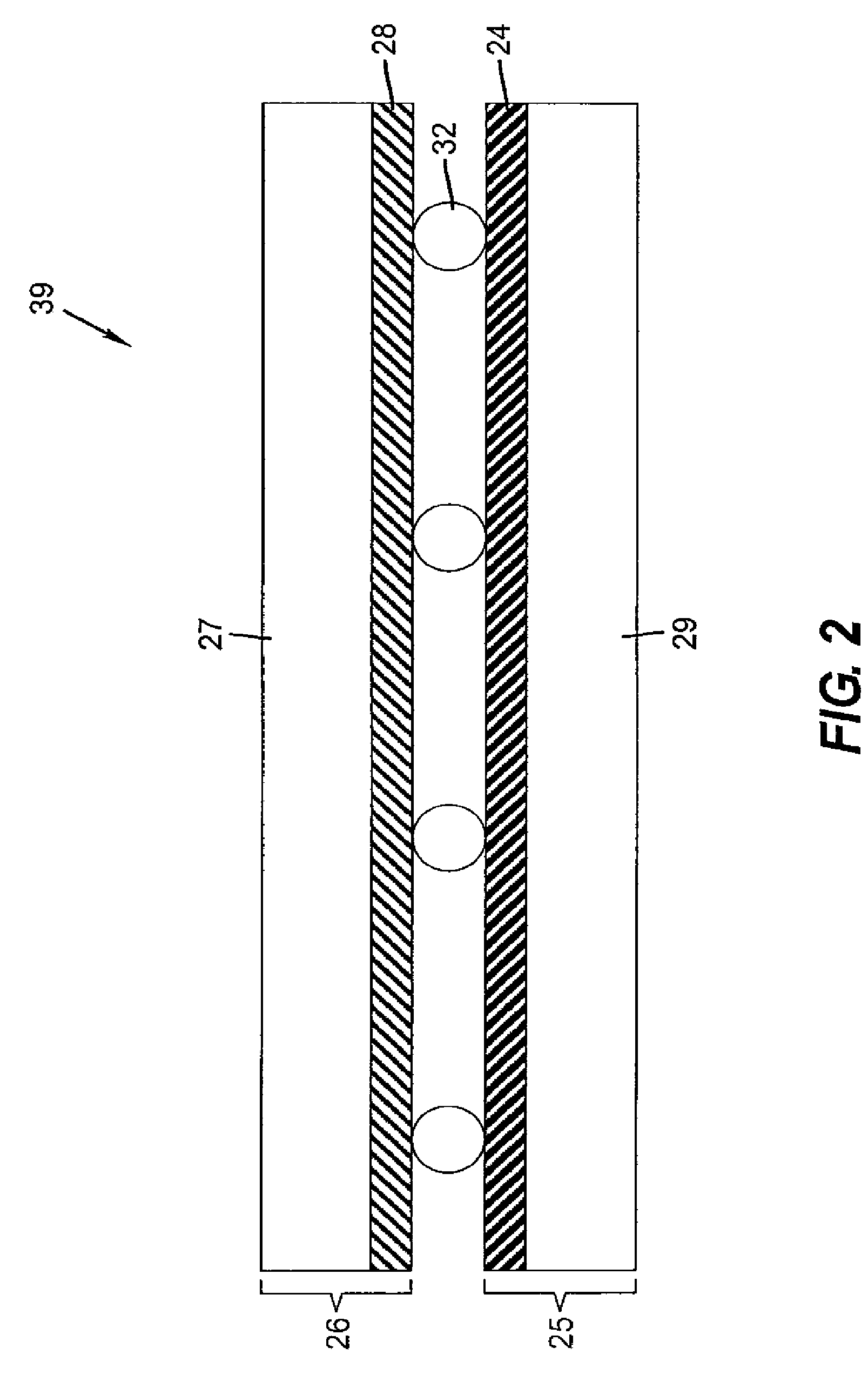

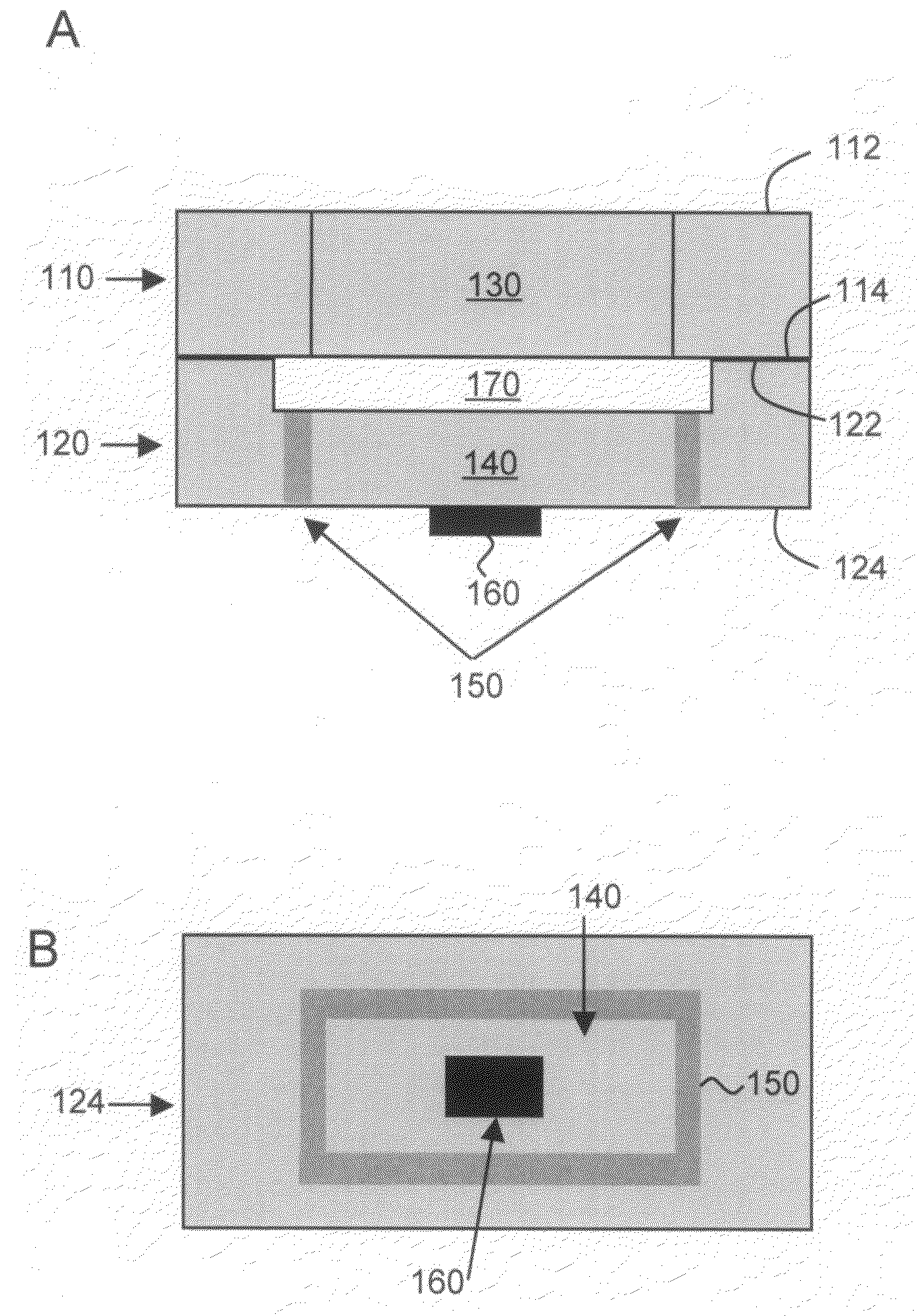

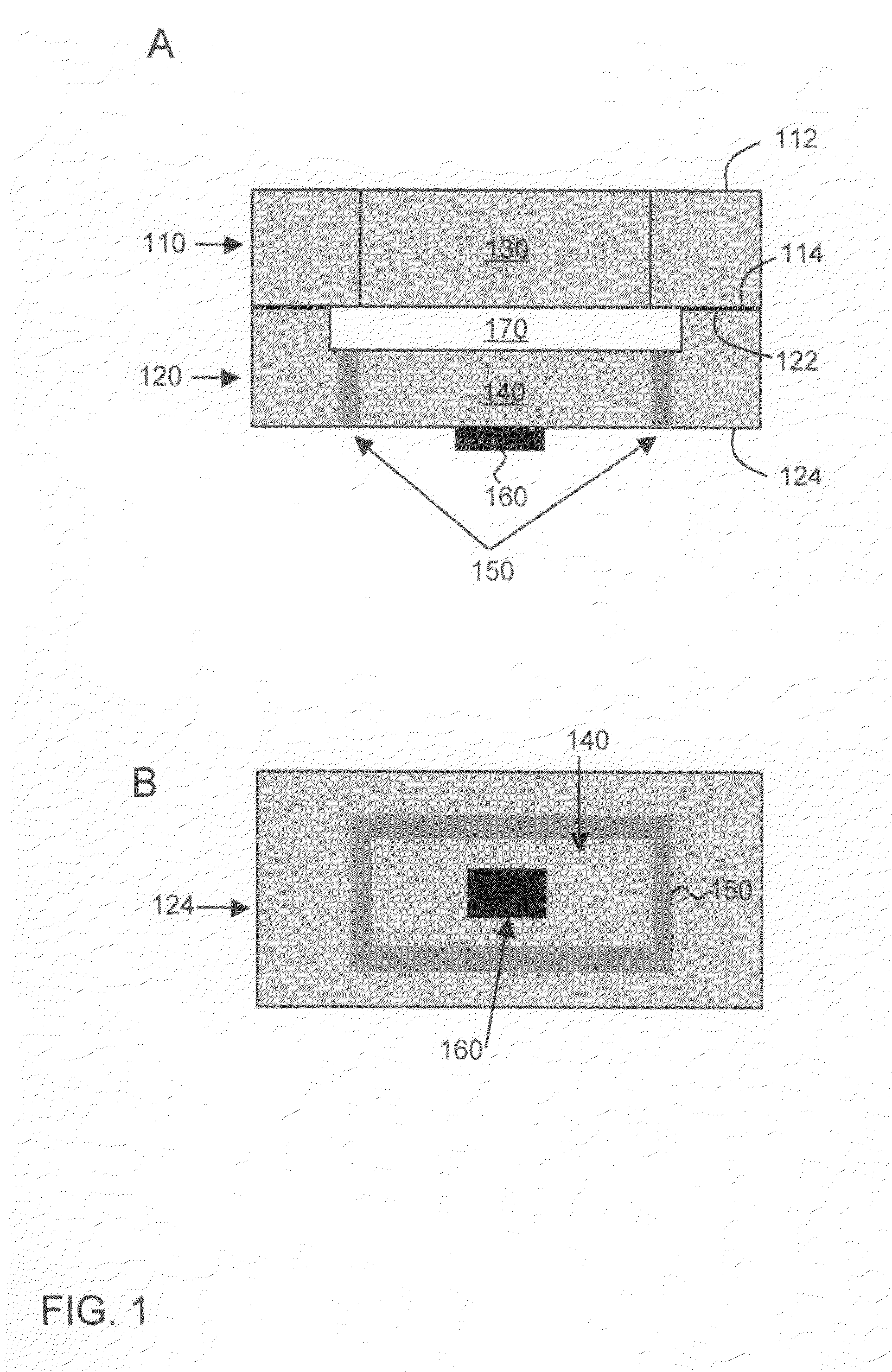

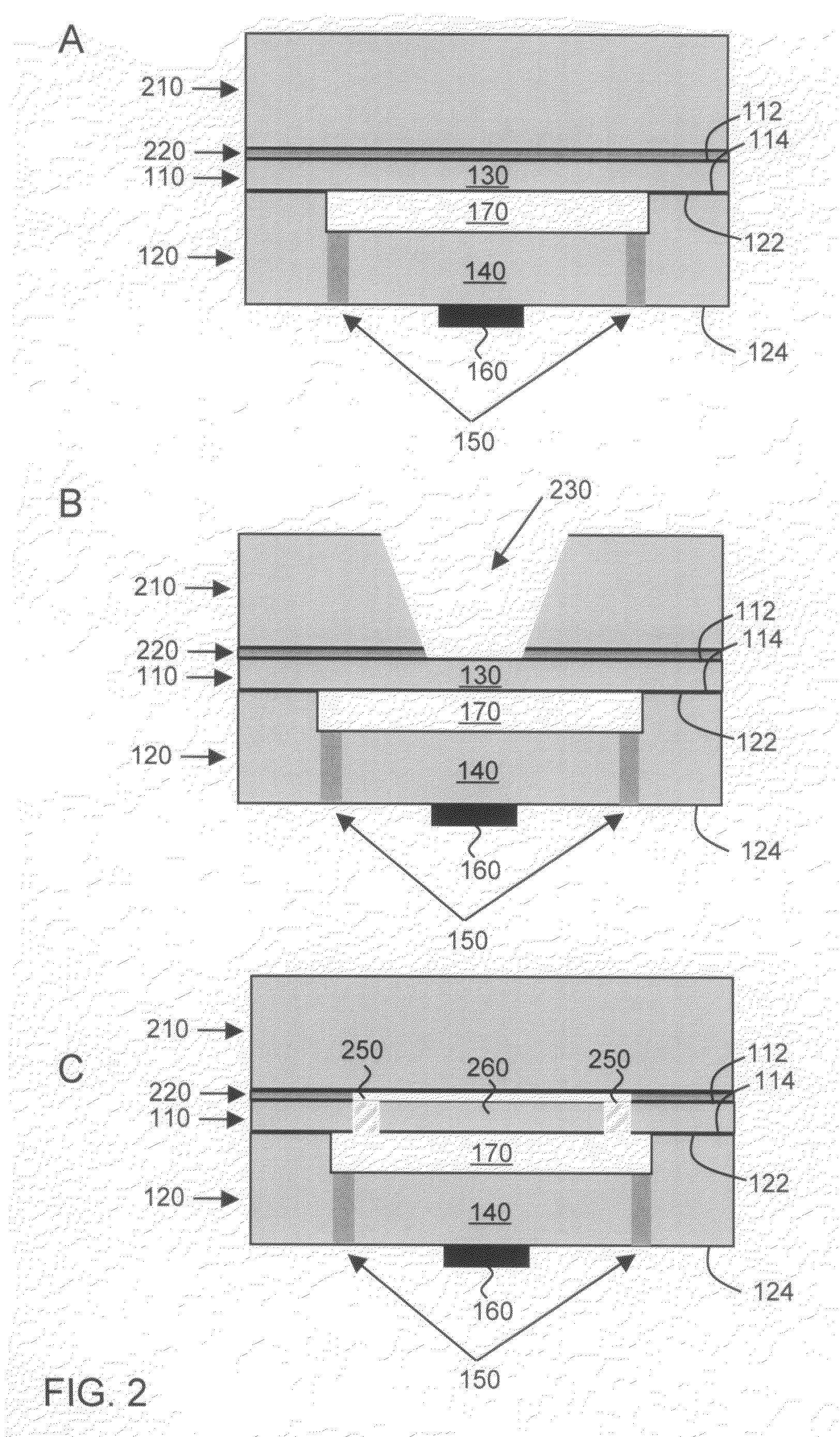

Touchscreen with carbon nanotube conductive layers

ActiveUS20100220074A1Static indicating devicesInput/output processes for data processingCarbon nanotubeTouchscreen

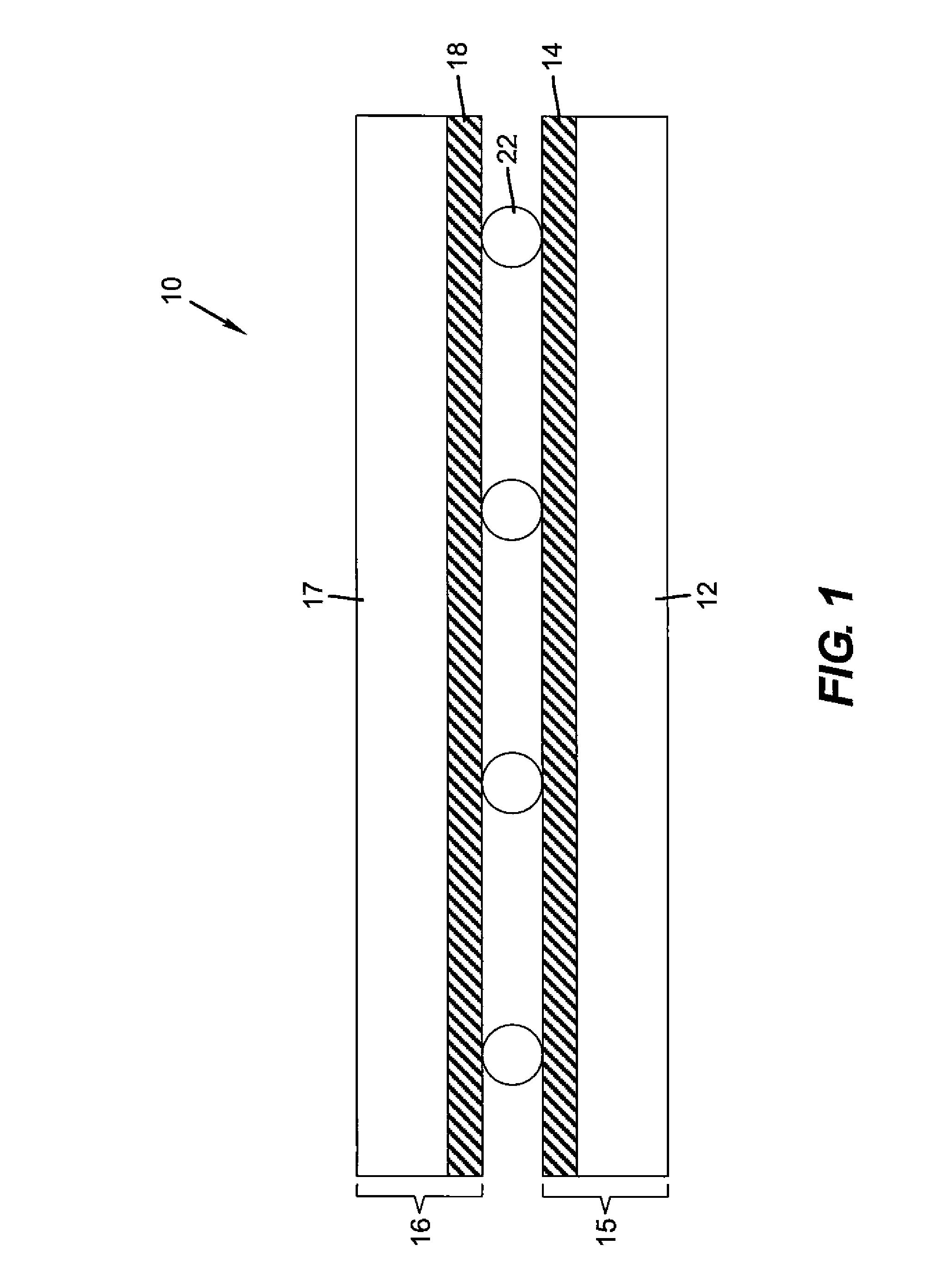

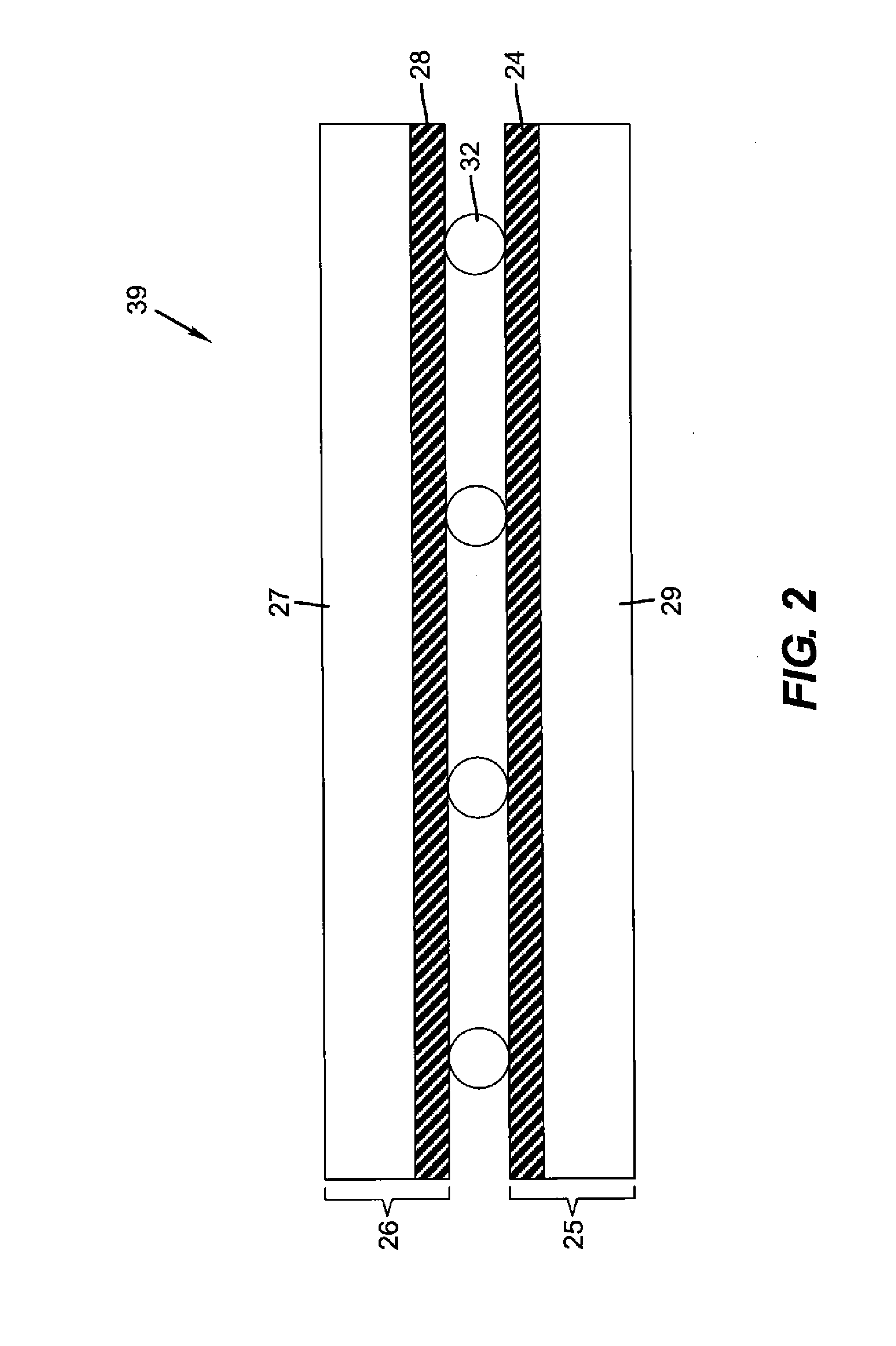

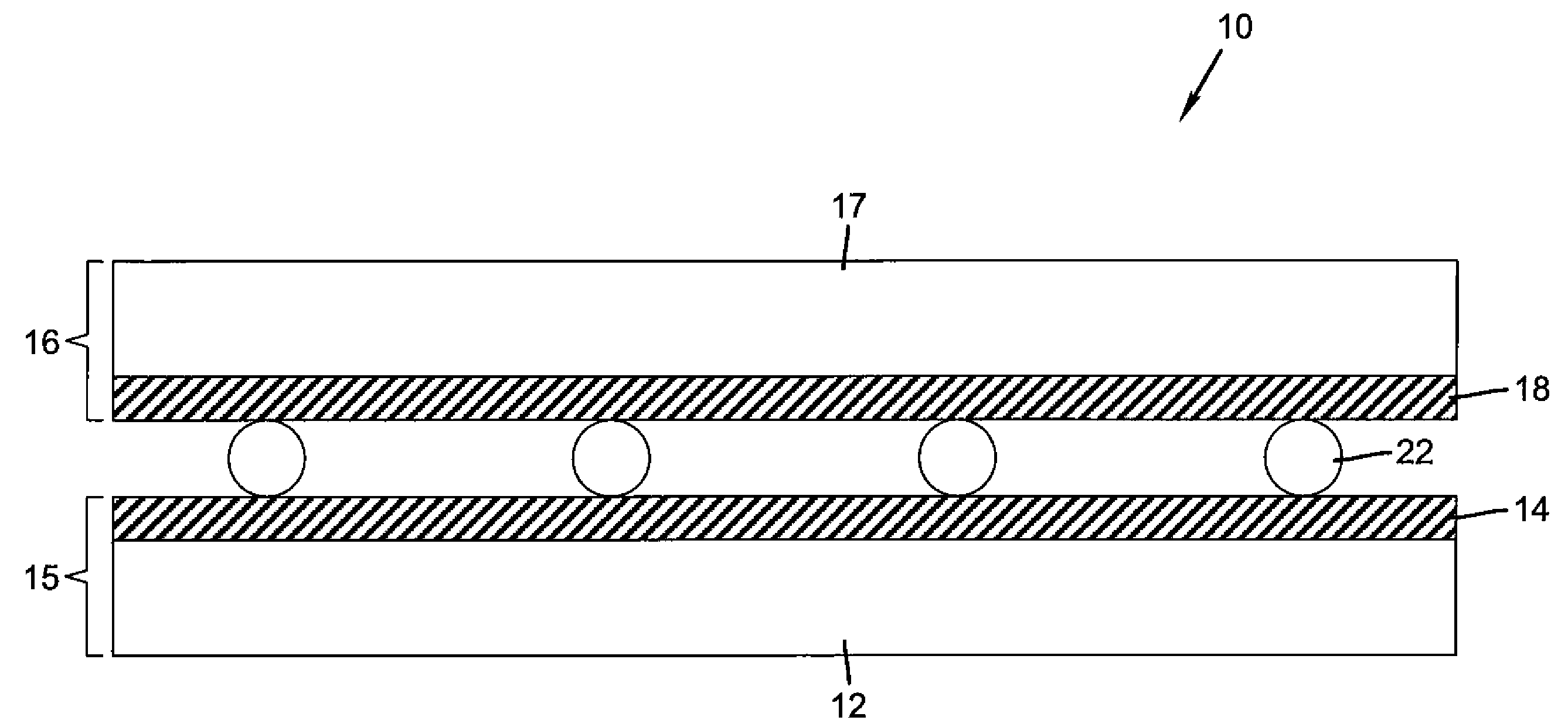

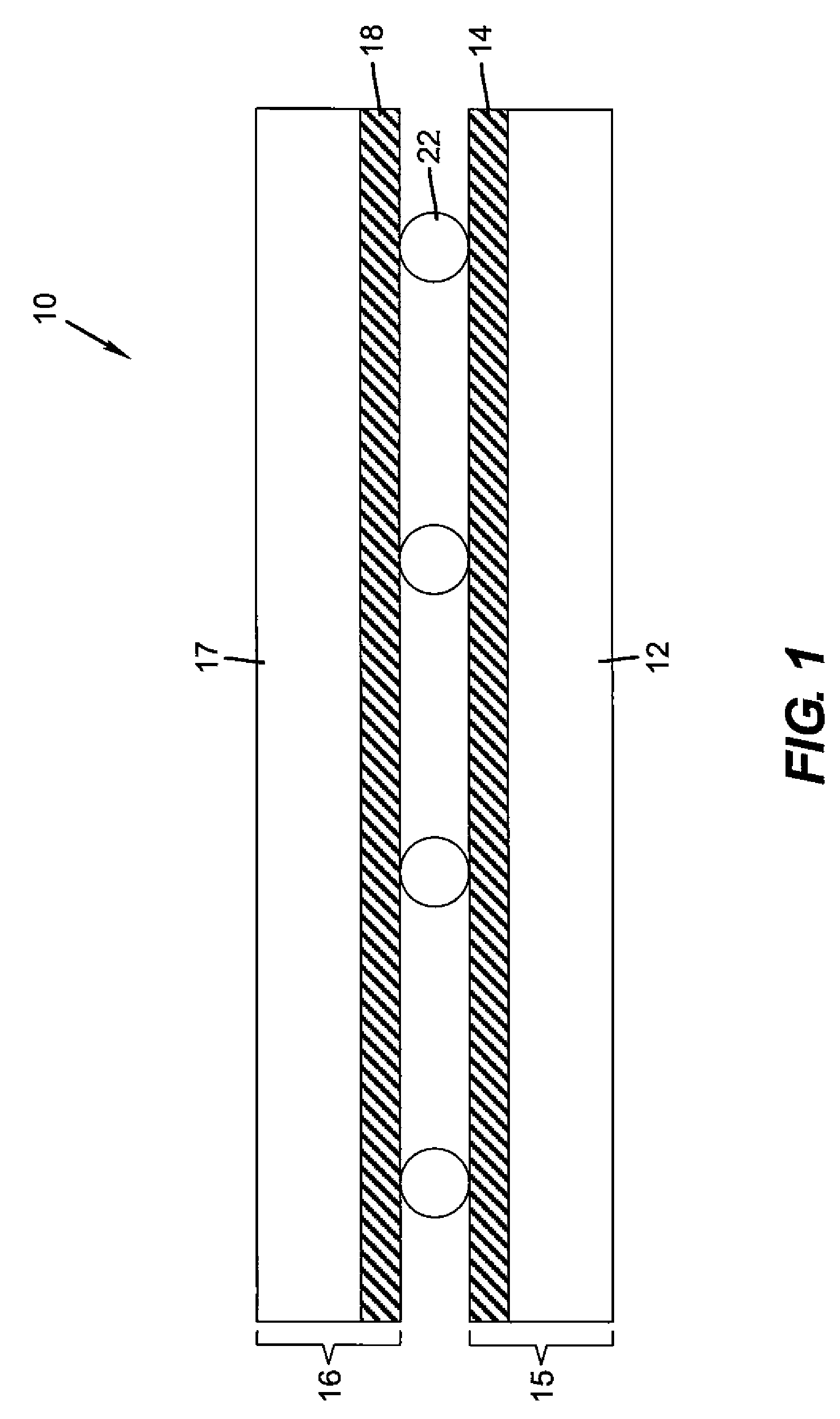

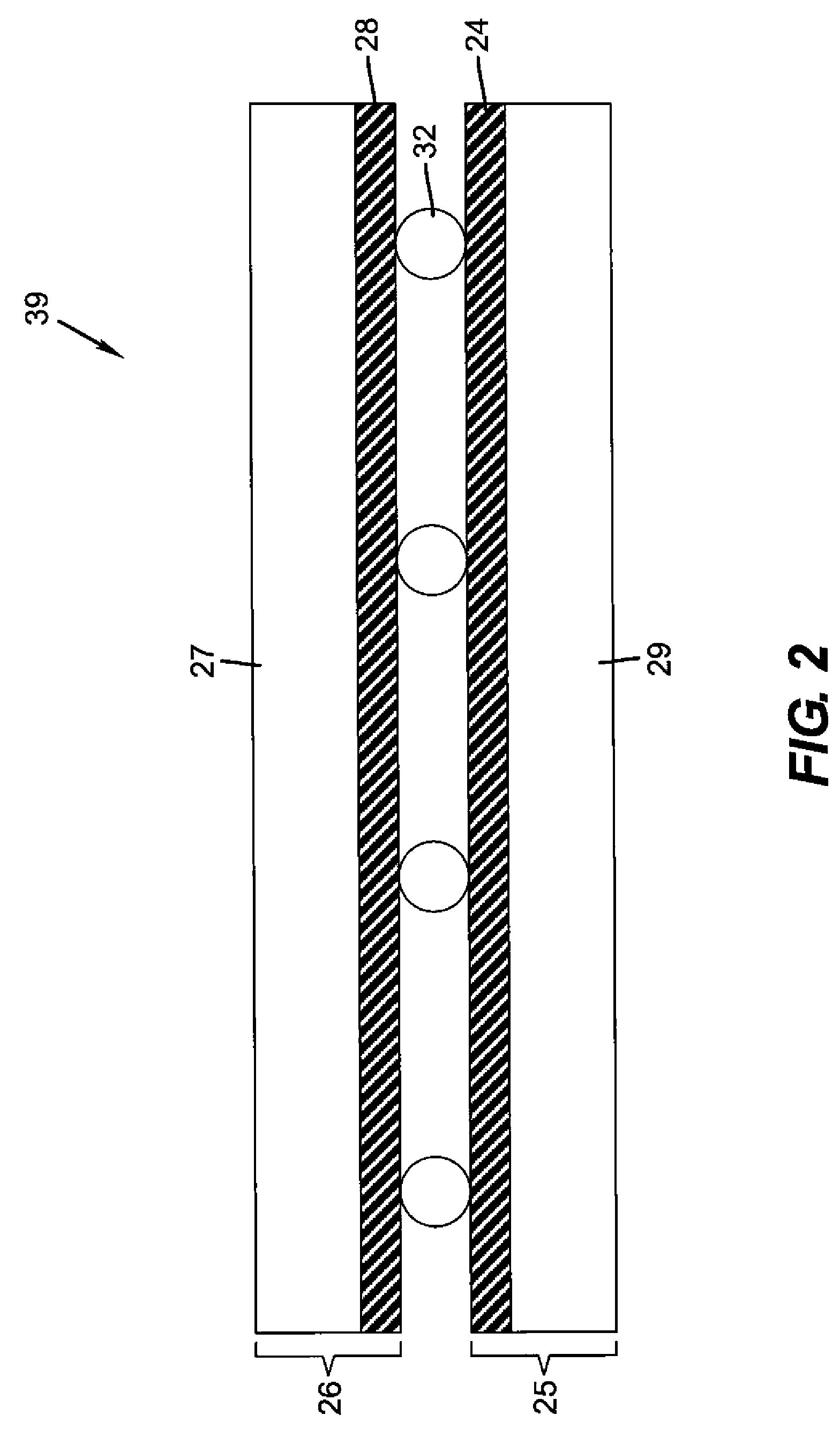

The present invention is directed to a touchscreen comprising touch side electrode and device side electrode wherein each electrode comprises an insulating substrate and an exposed electrically conductive layer, wherein said exposed electrically conductive layers are adjacent and separated by dielectric spacers, and wherein only one of the exposed electrically conductive layers comprises carbon nanotubes.

Owner:EASTMAN KODAK CO

Touchscreen with carbon nanotube conductive layers

ActiveUS7796123B1Static indicating devicesInput/output processes for data processingCarbon nanotubeTouchscreen

Owner:EASTMAN KODAK CO

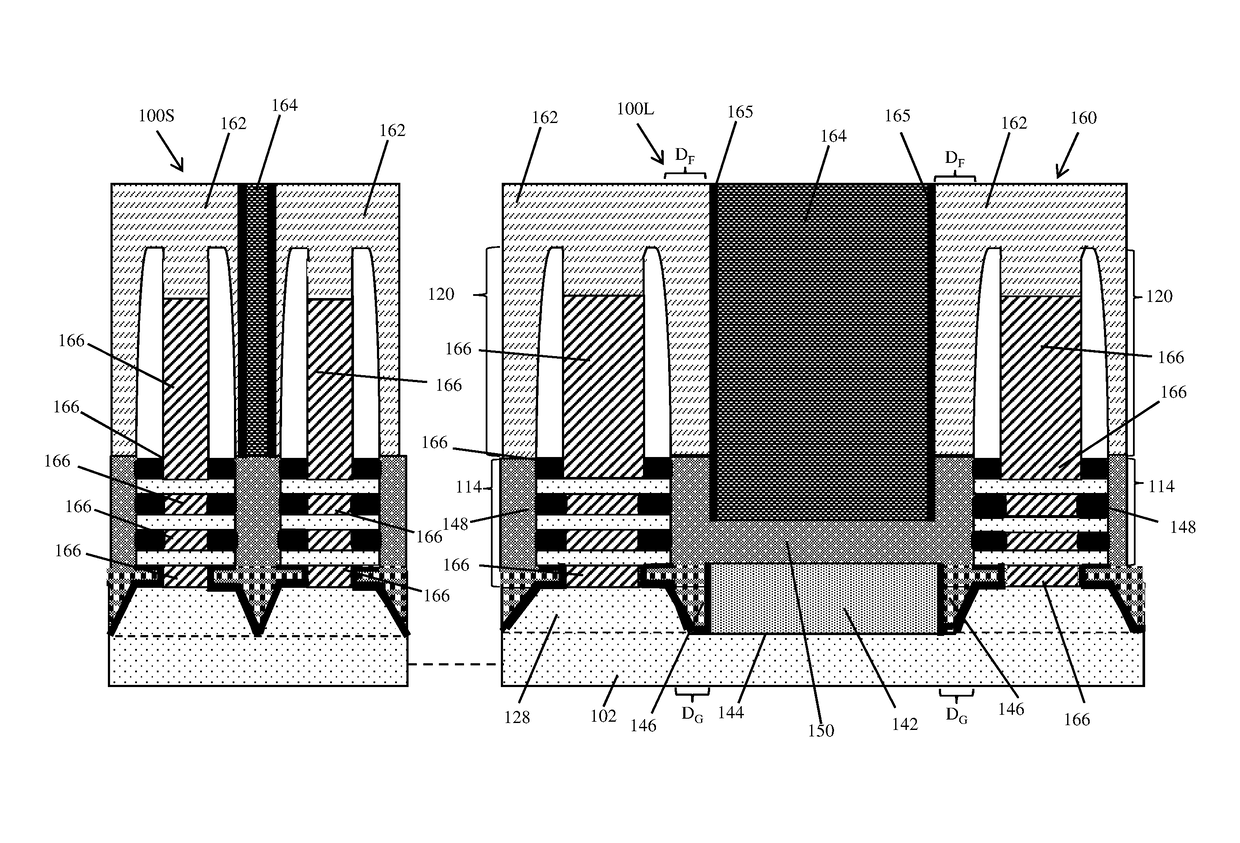

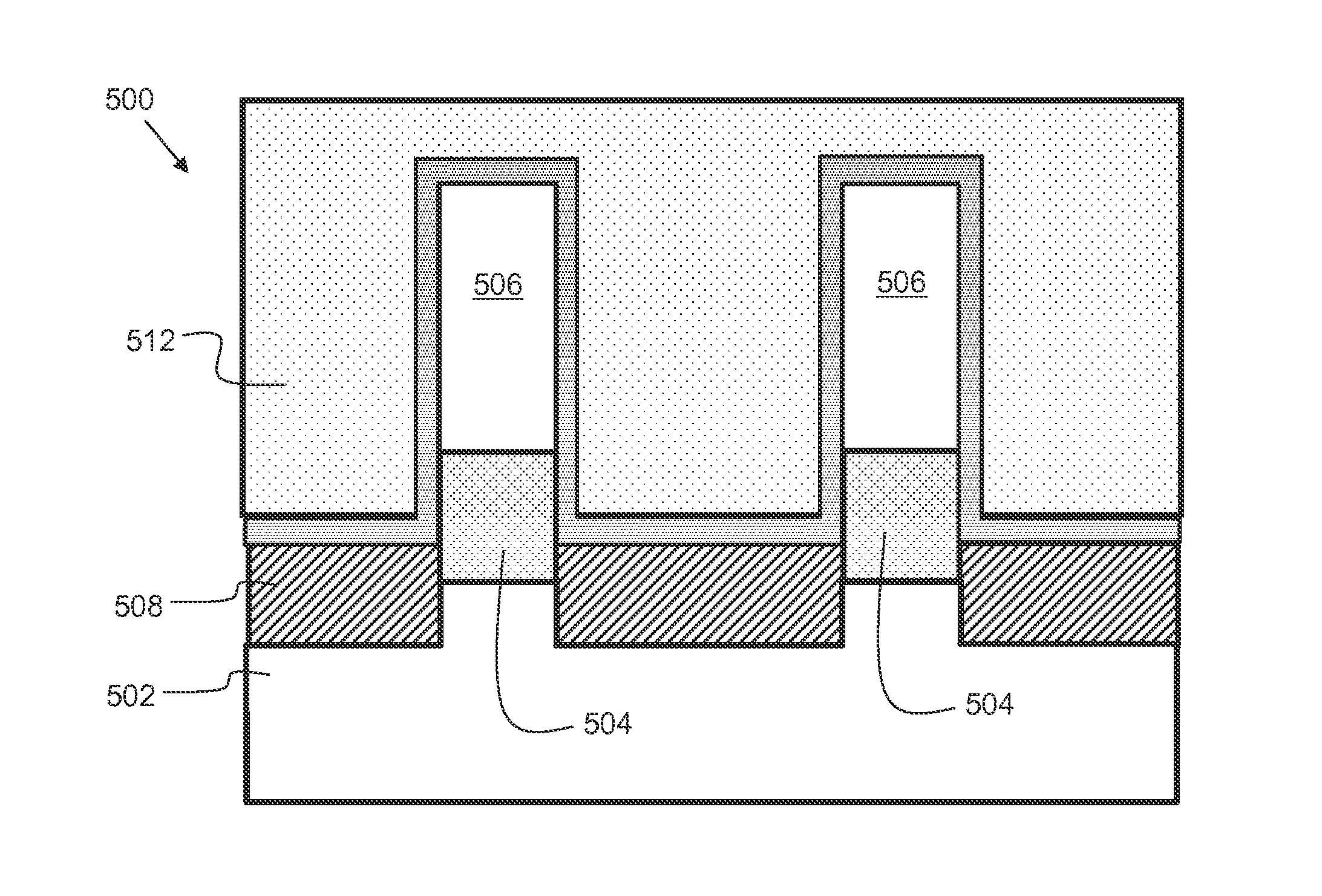

Methods of forming nanosheet transistor with dielectric isolation of source-drain regions and related structure

An IC structure according to the disclosure includes: a substrate; a pair of transistor sites positioned on the substrate, wherein an upper surface of the substrate laterally between the pair of transistor sites defines a separation region; a pair of nanosheet stacks, each positioned on one of the pair of transistor sites; an insulative liner conformally positioned on the upper surface of the substrate within the separation region, and a sidewall surface of each of the pair of transistor sites; a semiconductor mandrel positioned on the insulative liner and over the separation region; a pair of insulator regions each positioned laterally between the semiconductor mandrel and the insulative liner on the sidewall surfaces of each of the pair of transistor sites; and a source / drain epitaxial region positioned over the pair of insulator regions and the semiconductor mandrel, wherein the source / drain epitaxial region laterally abuts the pair of nanosheet stacks.

Owner:GLOBALFOUNDRIES US INC

Touchscreen with one carbon nanotube conductive layer

The present invention is directed to a touchscreen comprising touch side electrode and device side electrode wherein each electrode comprises an insulating substrate and an exposed electrically conductive layer, wherein said exposed electrically conductive layers are adjacent and separated by dielectric spacers, and wherein only one of the exposed electrically conductive layers comprises carbon nanotubes.

Owner:EASTMAN KODAK CO

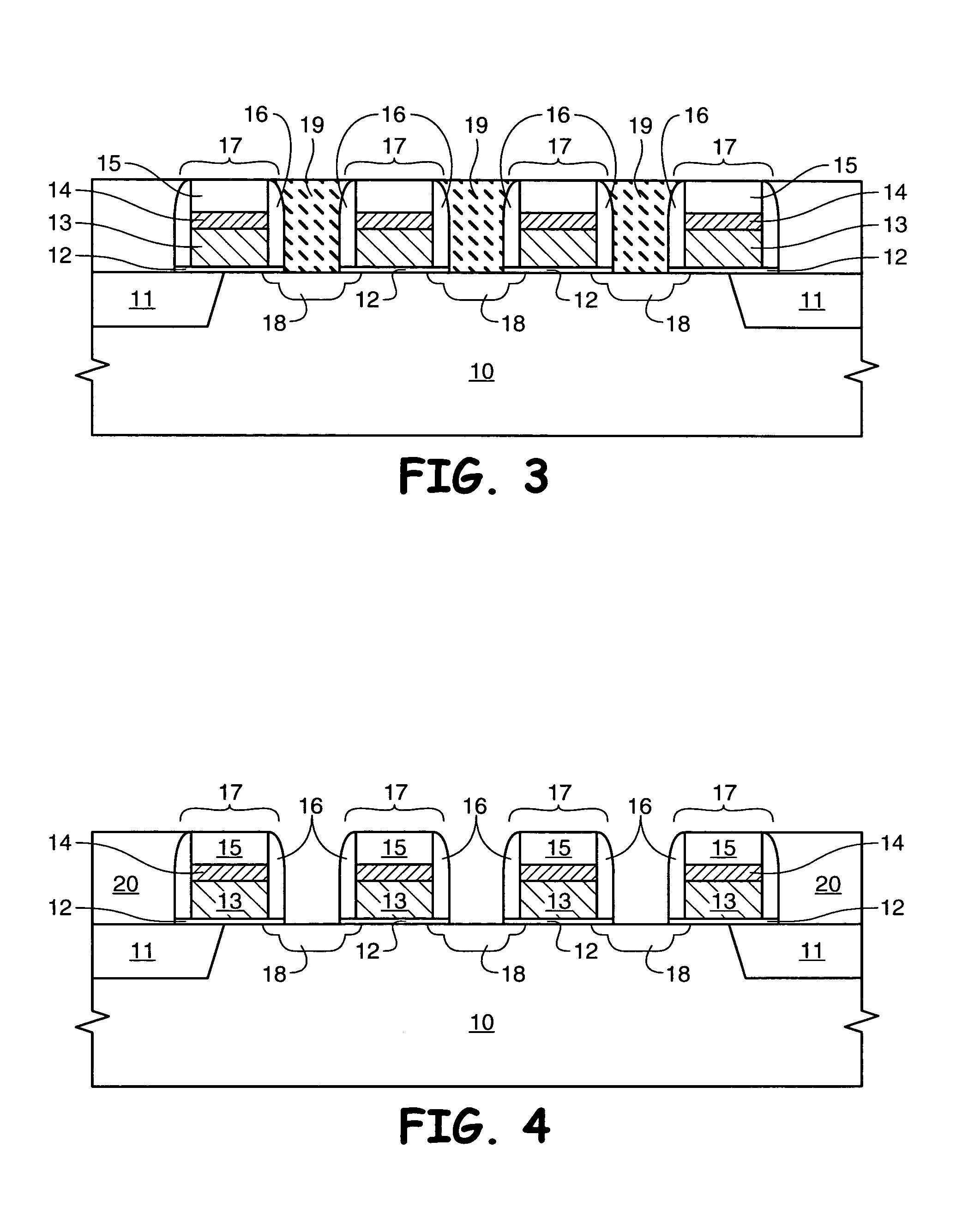

Formation of self-aligned contact plugs

InactiveUS20050085072A1Semiconductor/solid-state device manufacturingEngineeringMechanical engineering

Methods of forming a contact structure for semiconductor assemblies are described. One method provides process steps to create an inner dielectric isolation layer after the contact region is protected, which is followed by the formation of the self-aligned contact structures. A second method provides process steps to create an inner dielectric isolation layer after the self-aligned contact structures are formed.

Owner:MICRON TECH INC

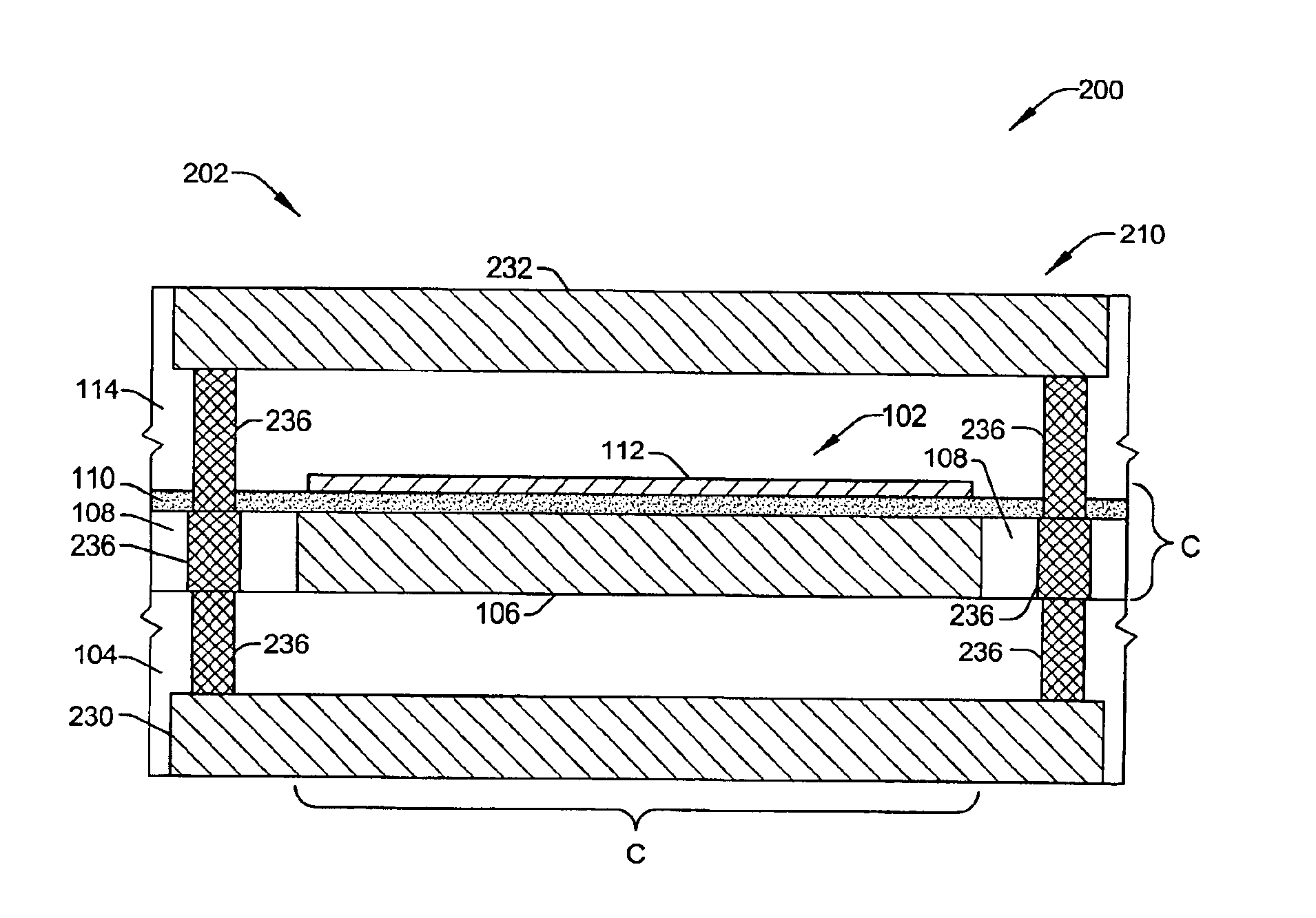

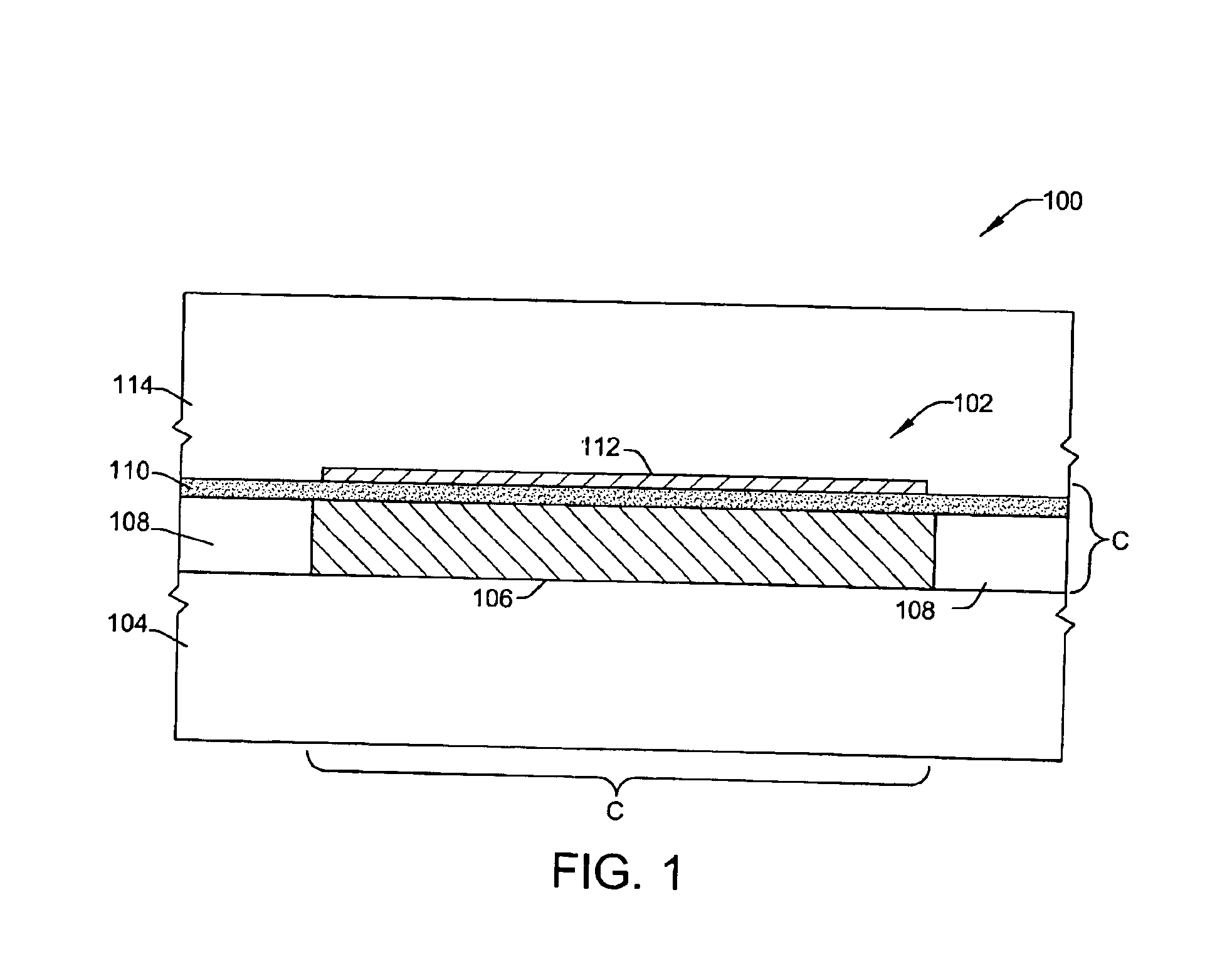

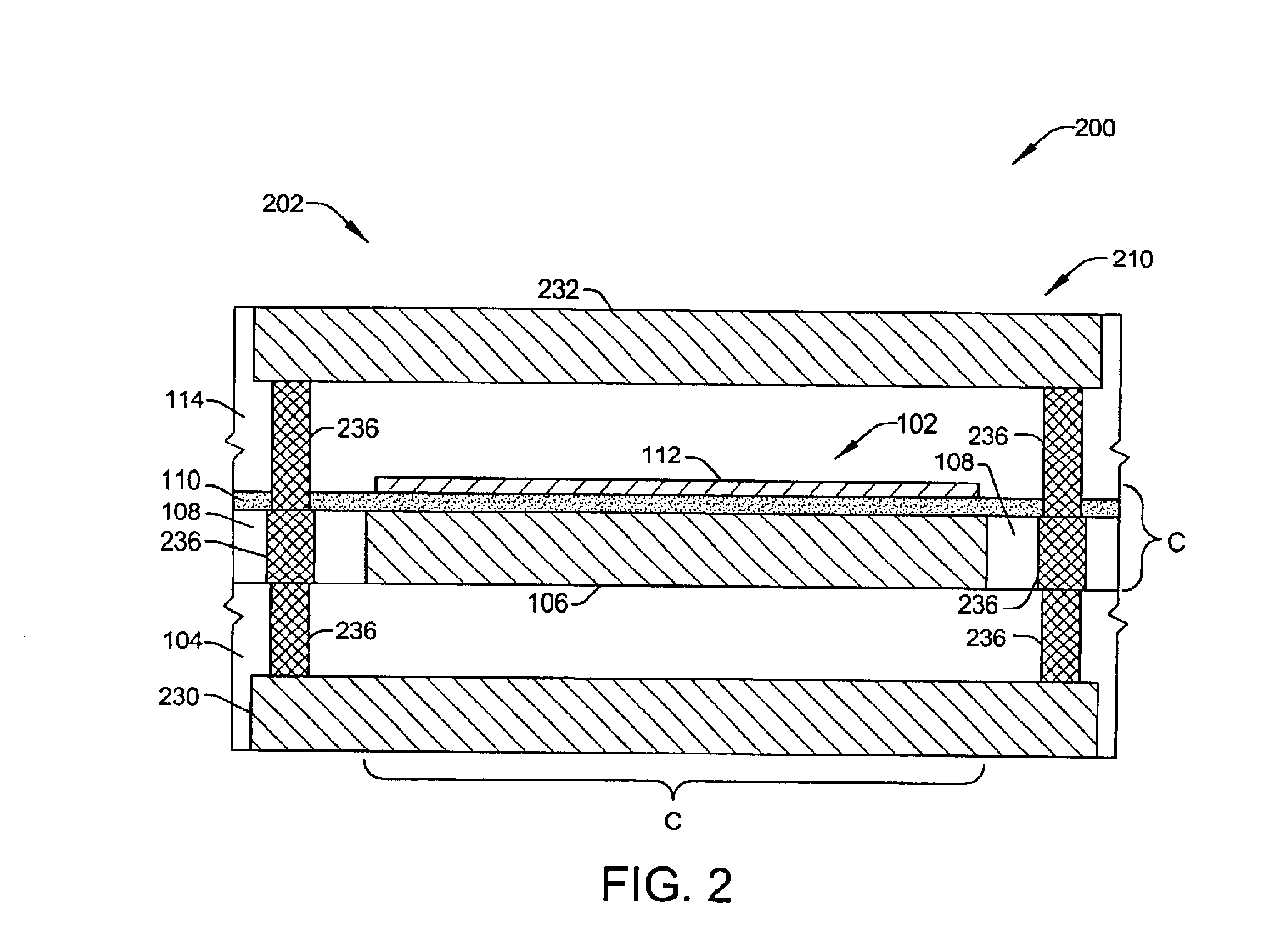

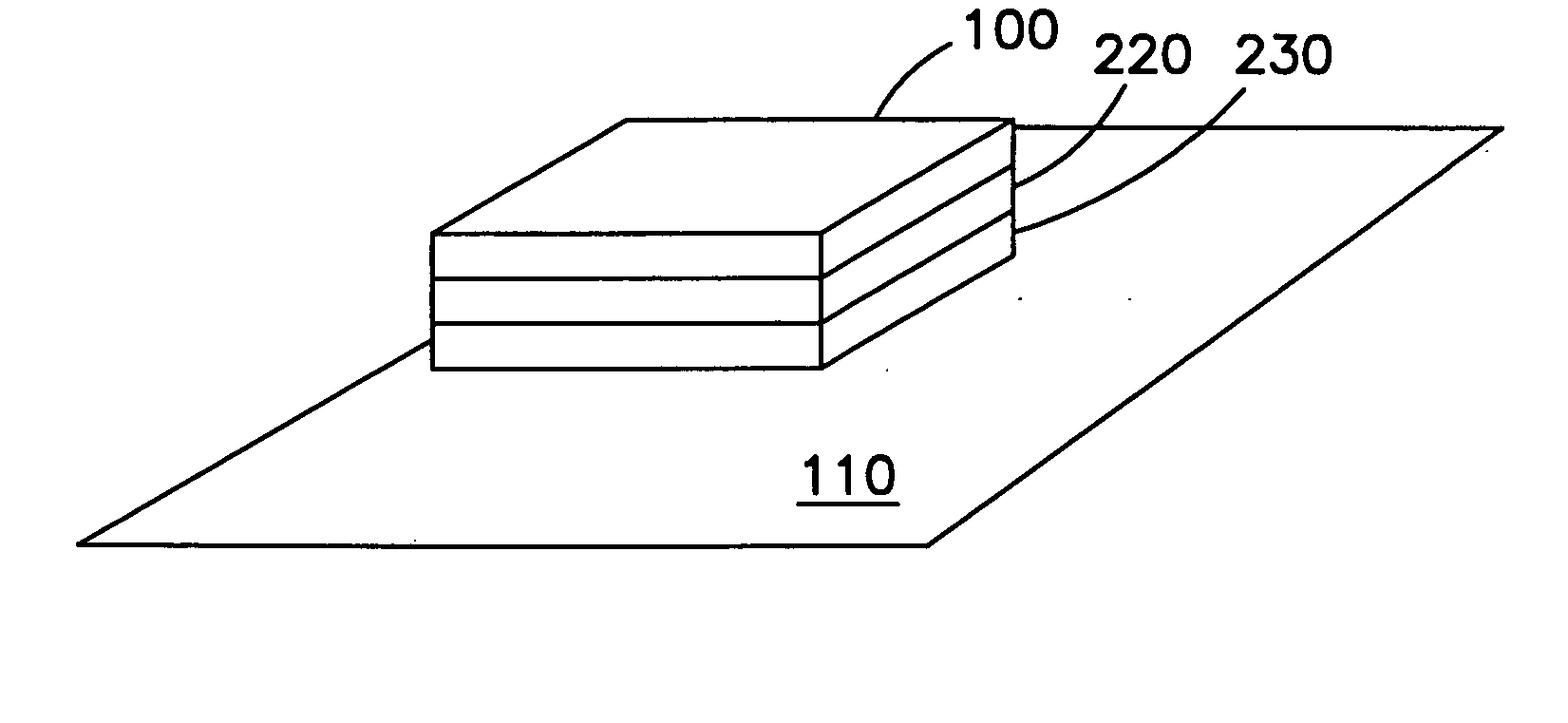

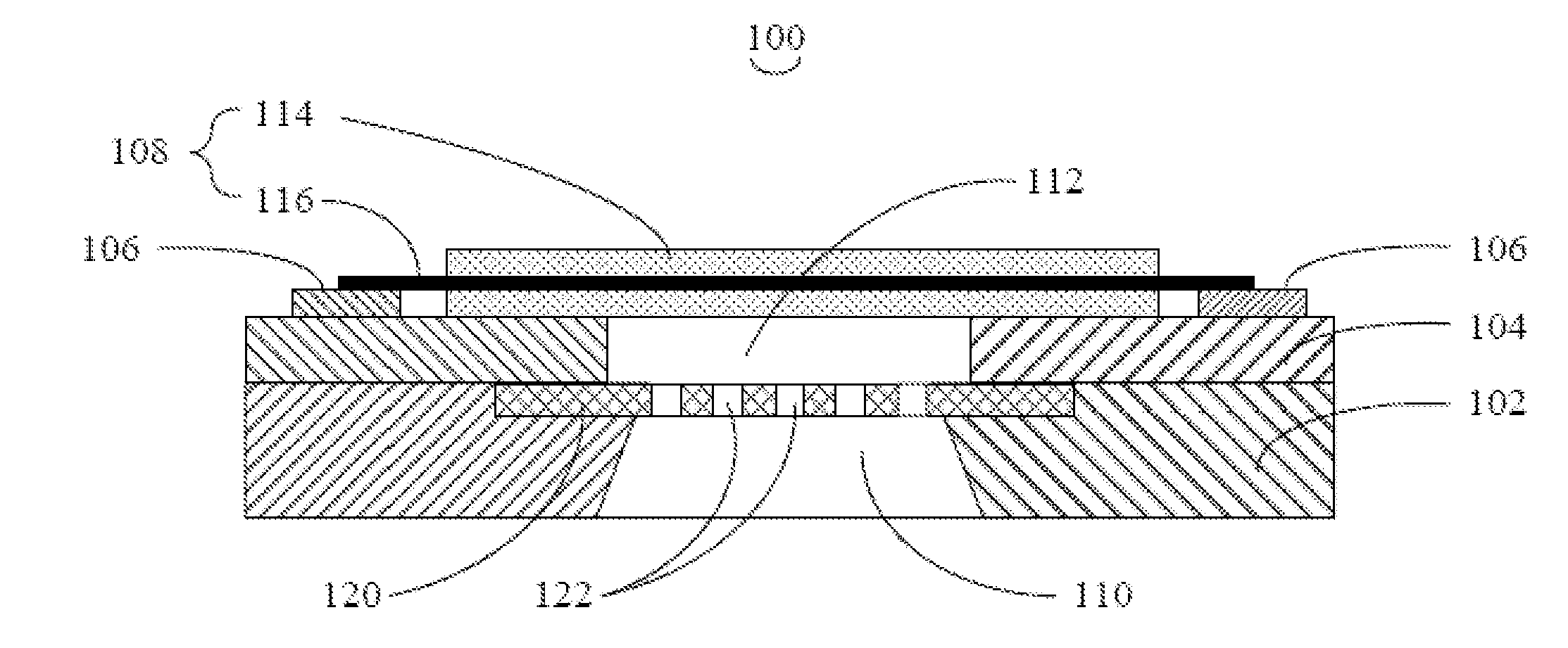

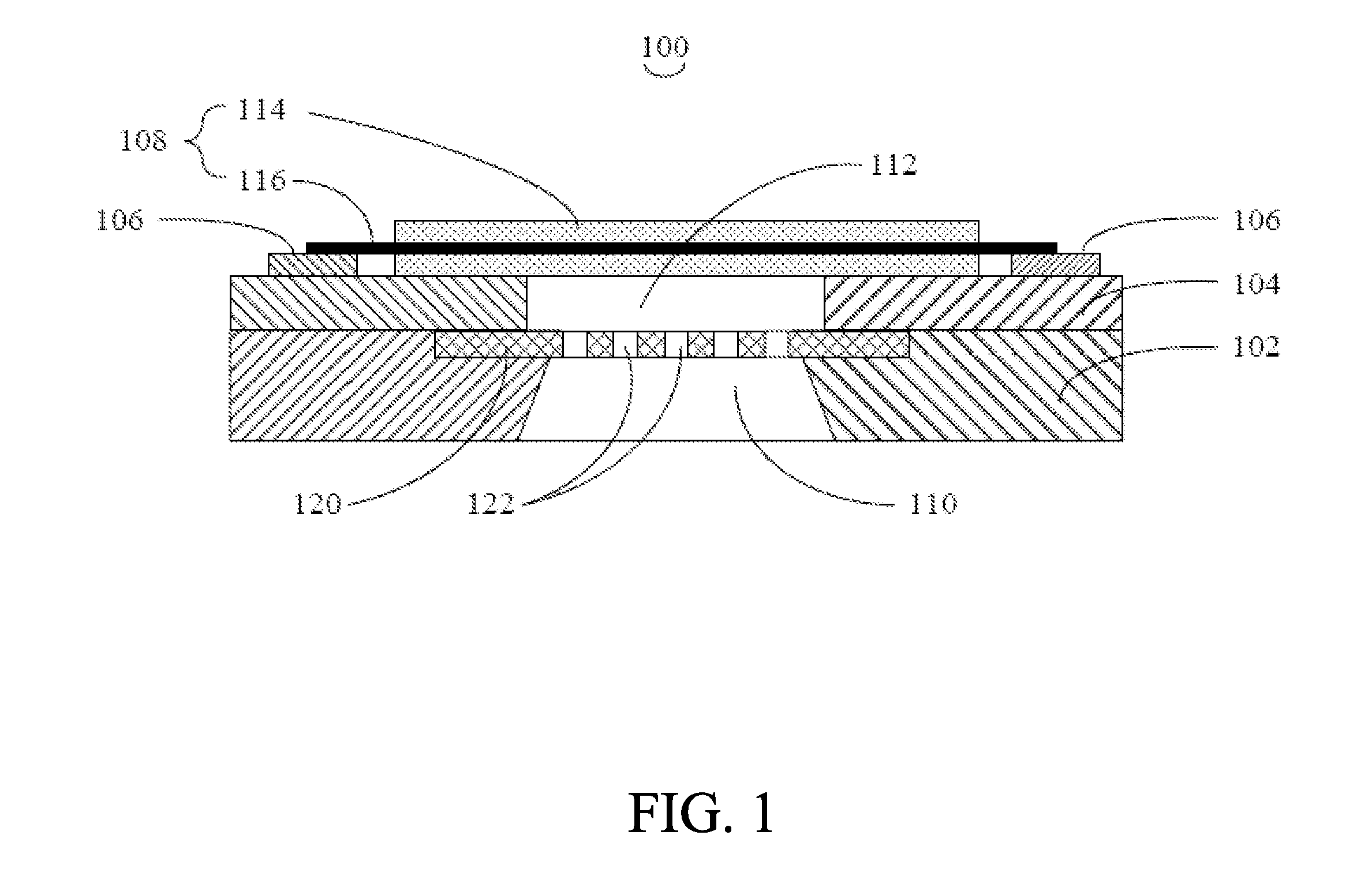

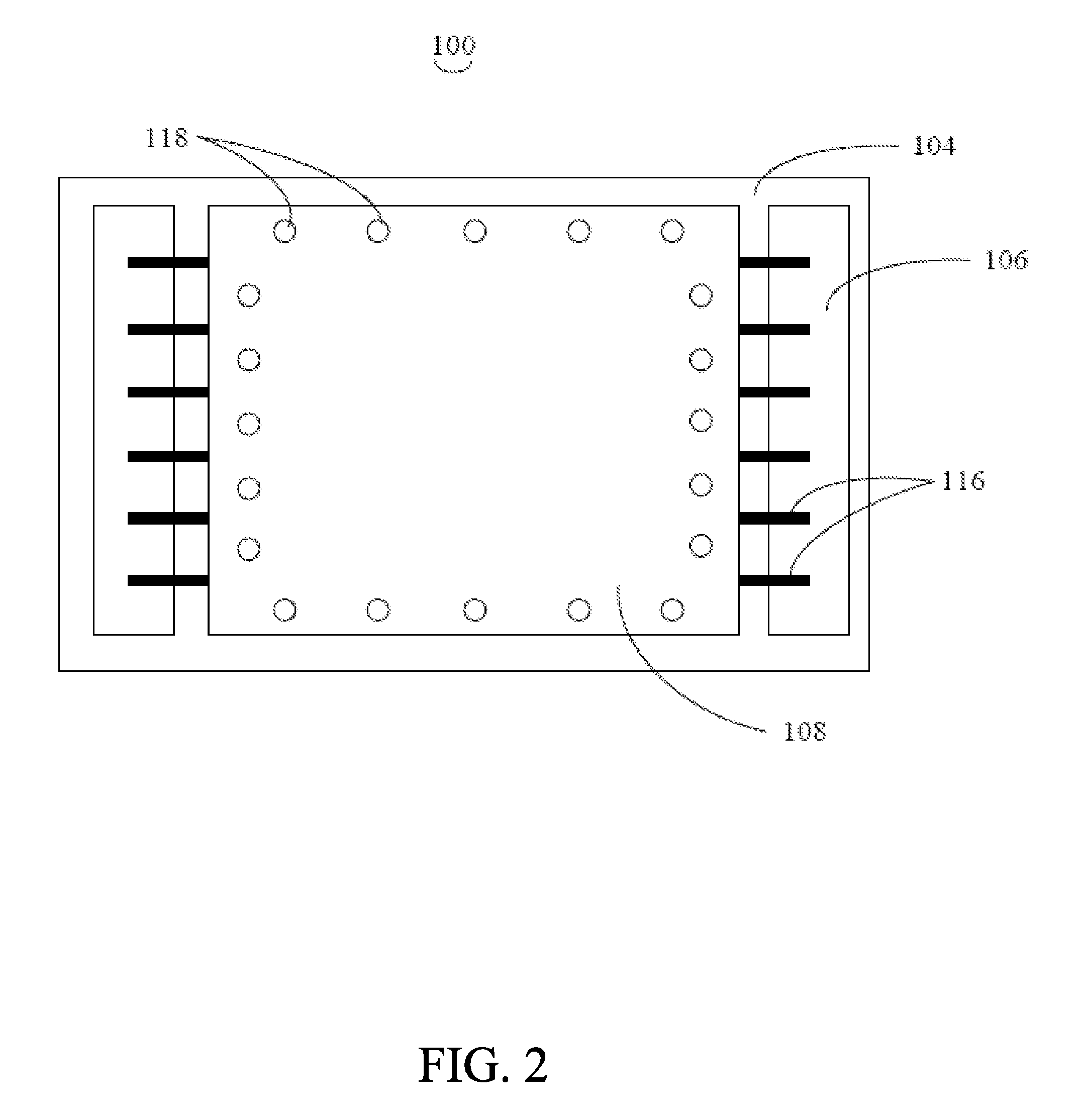

Shielded planar capacitor

ActiveUS6903918B1Mitigate eddy current lossMinimize eddy current lossSemiconductor/solid-state device detailsFixed capacitor dielectricIsolation layerParasitic capacitance

A shielded planar capacitor structure (202) is discussed, formed within a Faraday cage (210) in an integrated circuit device (200). The capacitor structure (202) reduces parasitic capacitances within the integrated circuit device (200). The capacitor (202) comprises a capacitor stack (102) formed between a first and second metal layers (230,232) of the integrated circuit. The capacitor stack (102) has a first conductive layer formed from a third metal layer (106) disposed between the first and second metal layers (230,232) of the integrated circuit, a dielectric isolation layer (110) disposed upon the first conductive layer (106); and a second conductive layer (112) disposed upon the dielectric isolation layer (110) and overlying the first conductive layer (106). The structure (202) further has a first and second isolation layers (104,114) disposed upon opposite sides of the capacitor stack (102). The Faraday cage (210) is formed between the first and second metal layers (230,232) of the integrated circuit (200), comprising a first and second shield layers (402,414) each having a plurality of mutually electrically conductive spaced apart traces (404). The first and second isolation layers (404,414) and the capacitor stack (102,434) are sandwiched between the first and second shield layers (402,414). Conductive elements (432) are distributed around the periphery of the capacitor stack (102,434) and the first and second isolation layers (404,412). The conductive traces (424) of the first shield layer (402) are connected to the conductive traces (424) of the second shield layer (414) through the conductive elements (432).

Owner:TEXAS INSTR INC

Capacitive micro-electro-mechanical sensors with single crystal silicon electrodes

ActiveUS7539003B2Mechanically variable capacitor detailsCapacitor with electrode area variationIn planeAccelerometer

The devices presented herein are capacitive sensors with single crystal silicon on all key stress points. Isolating trenches are formed by trench and refill forming dielectrically isolated conductive silicon electrodes for drive, sense and guards. For pressure sensing devices according to the invention, the pressure port is opposed to the electrical wire bond pads for ease of packaging. Dual-axis accelerometers measuring in plane acceleration and out of plane acceleration are also described. A third axis in plane is easy to achieve by duplicating and rotating the accelerometer 90 degrees about its out of plane axis Creating resonant structures, angular rate sensors, bolometers, and many other structures are possible with this process technology. Key advantages are hermeticity, vertical vias, vertical and horizontal gap capability, single crystal materials, wafer level packaging, small size, high performance and low cost.

Owner:SAMSUNG ELECTRONICS CO LTD

Microelectromechanical systems having trench isolated contacts, and methods for fabricating same

ActiveUS20050156260A1Acceleration measurement using interia forcesFluid pressure measurement by electric/magnetic elementsElectricityEngineering

There are many inventions described and illustrated herein. In one aspect, the present invention is directed to a MEMS device, and technique of fabricating or manufacturing a MEMS device, having mechanical structures encapsulated in a chamber prior to final packaging and a contact area disposed at least partially outside the chamber. The contact area is electrically isolated from nearby electrically conducting regions by way of dielectric isolation trench that is disposed around the contact area. The material that encapsulates the mechanical structures, when deposited, includes one or more of the following attributes: low tensile stress, good step coverage, maintains its integrity when subjected to subsequent processing, does not significantly and / or adversely impact the performance characteristics of the mechanical structures in the chamber (if coated with the material during deposition), and / or facilitates integration with high-performance integrated circuits. In one embodiment, the material that encapsulates the mechanical structures is, for example, silicon (polycrystalline, amorphous or porous, whether doped or undoped), silicon carbide, silicon-germanium, germanium, or gallium-arsenide.

Owner:ROBERT BOSCH GMBH

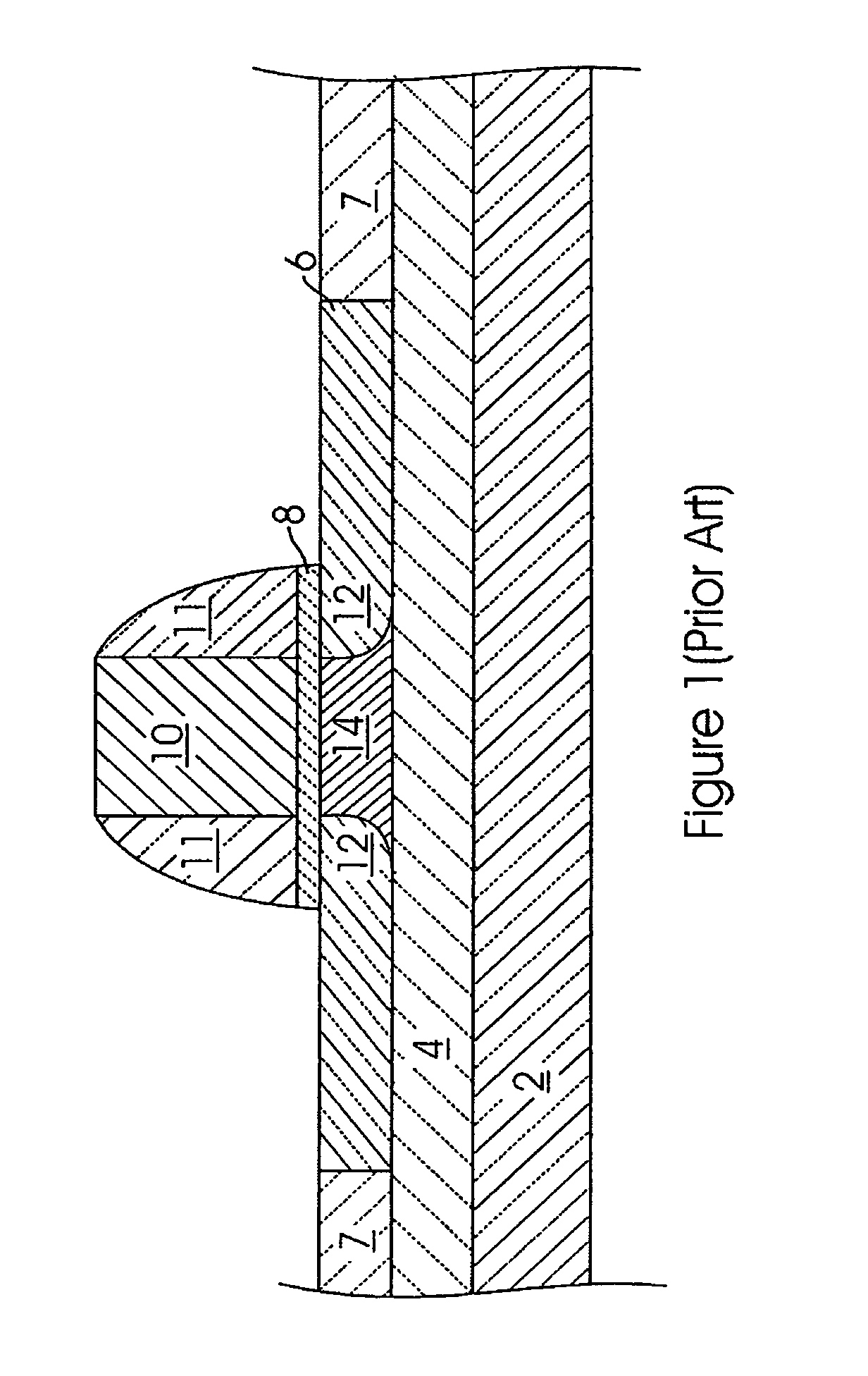

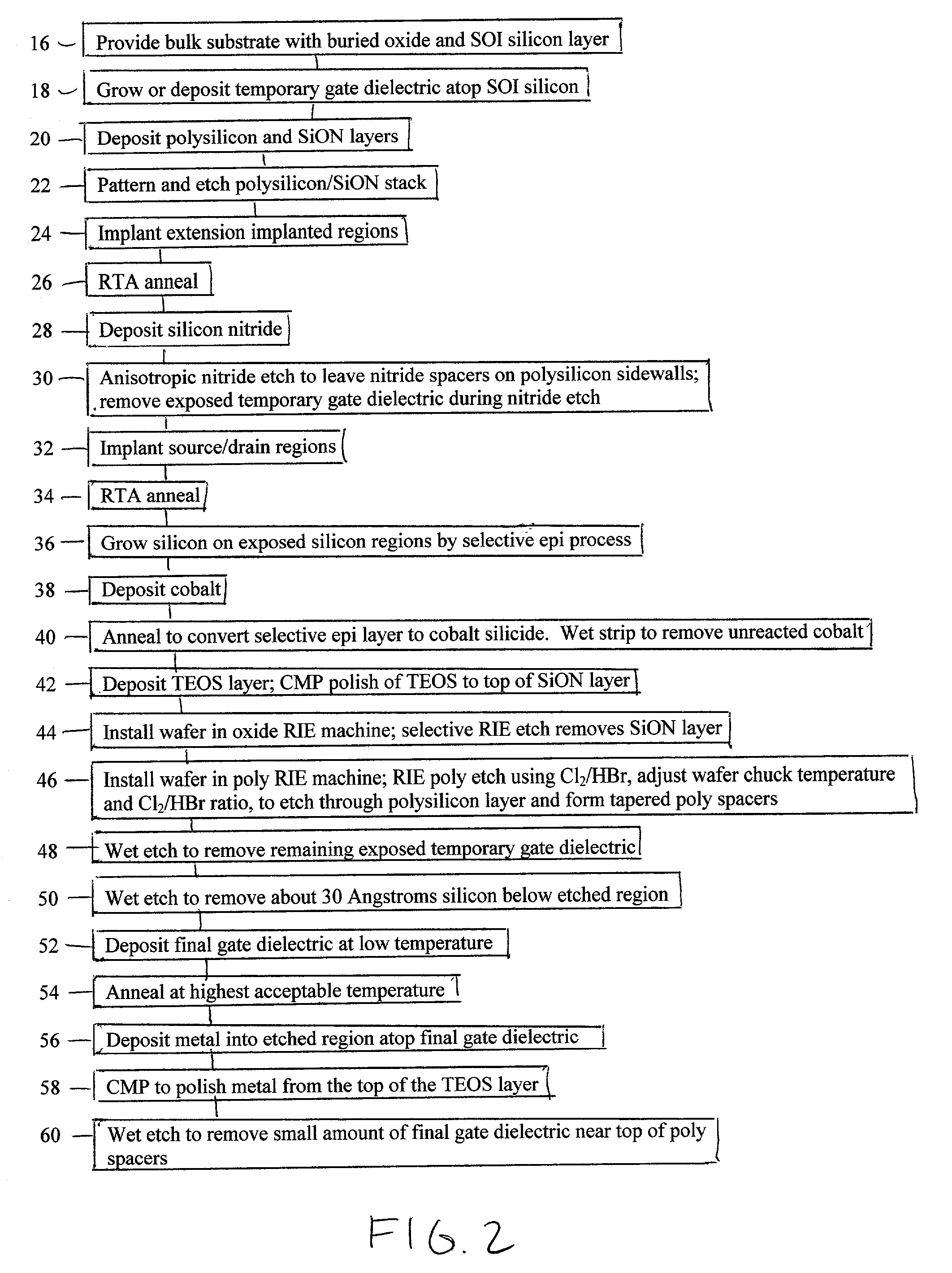

Method for making an ultra thin FDSOI device with improved short-channel performance

InactiveUS6975014B1Excellent Ioff DC characteristicImprove featuresTransistorSemiconductor/solid-state device manufacturingGate dielectricEngineering

A method for forming a FDSOI device with channel length less than 50 nm with good short channel control. The gate has a tapered polysilicon spacer and a dielectric spacer. A polysilicon gate feature is formed and dielectric sidewall spacers are formed thereon. The polysilicon gate feature is then etched to form tapered poly features separated by a gap. A gate dielectric is deposited at low temperature, then metal is deposited into the gap to form the metal gate.

Owner:ADVANCED MICRO DEVICES INC +1

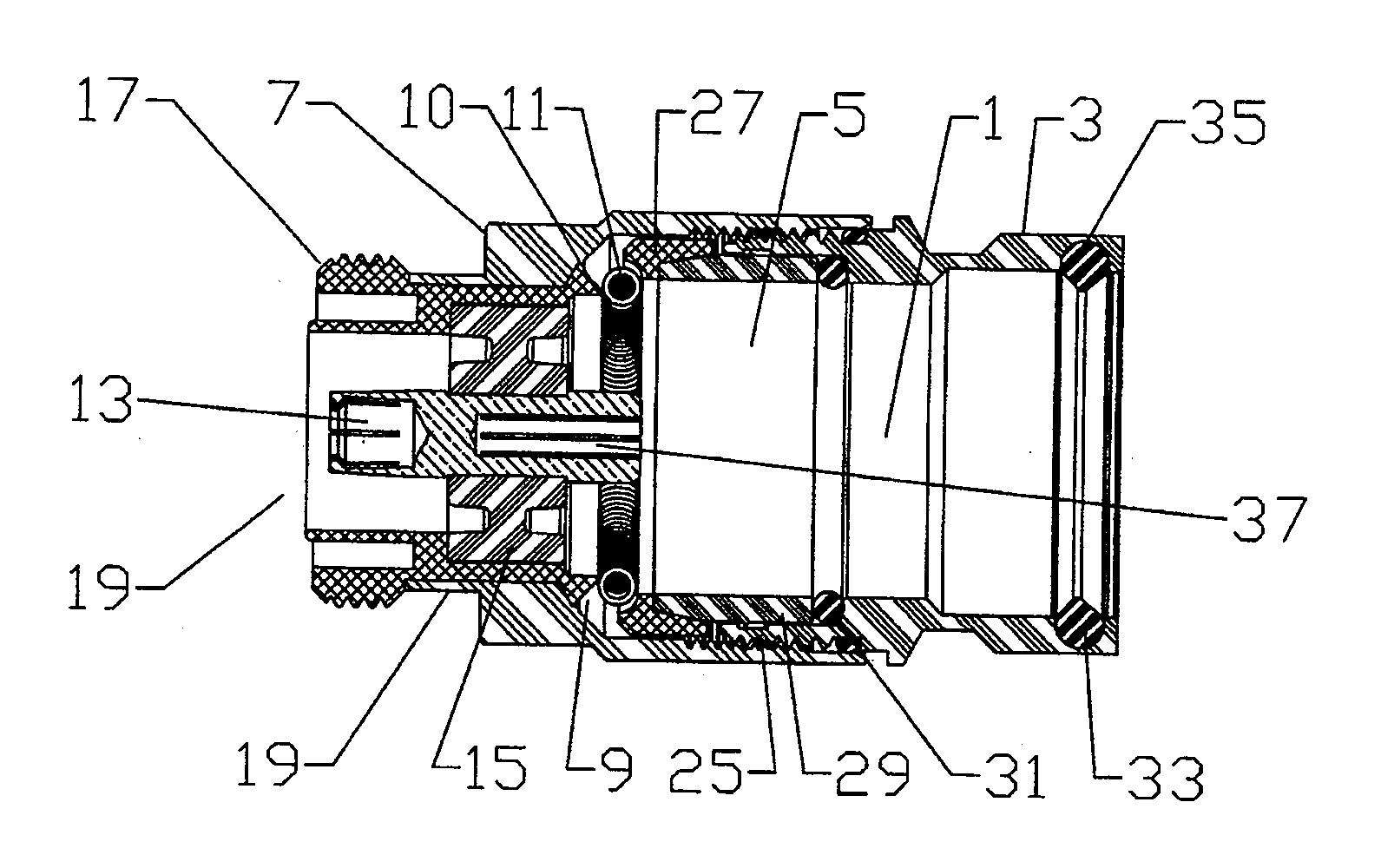

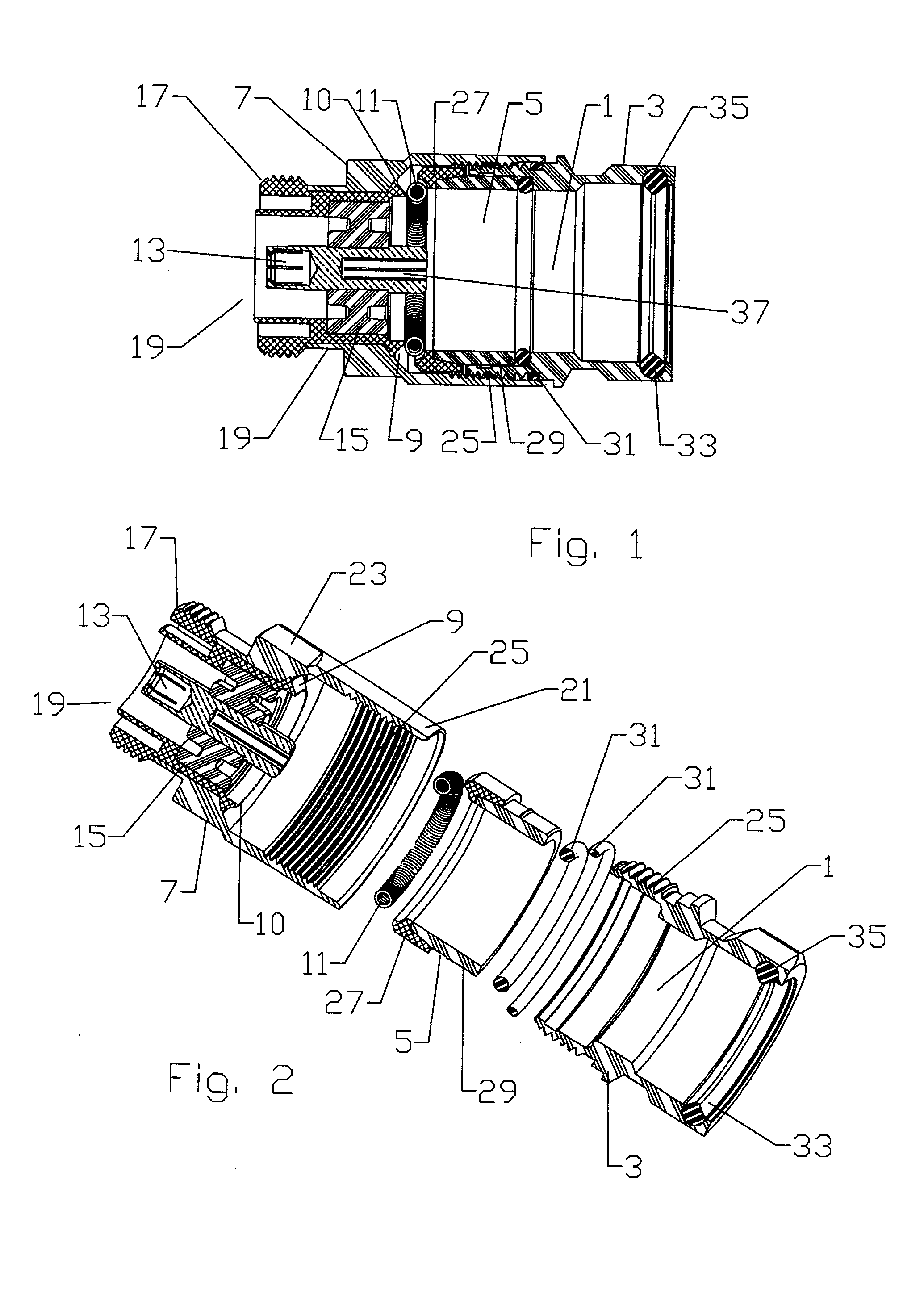

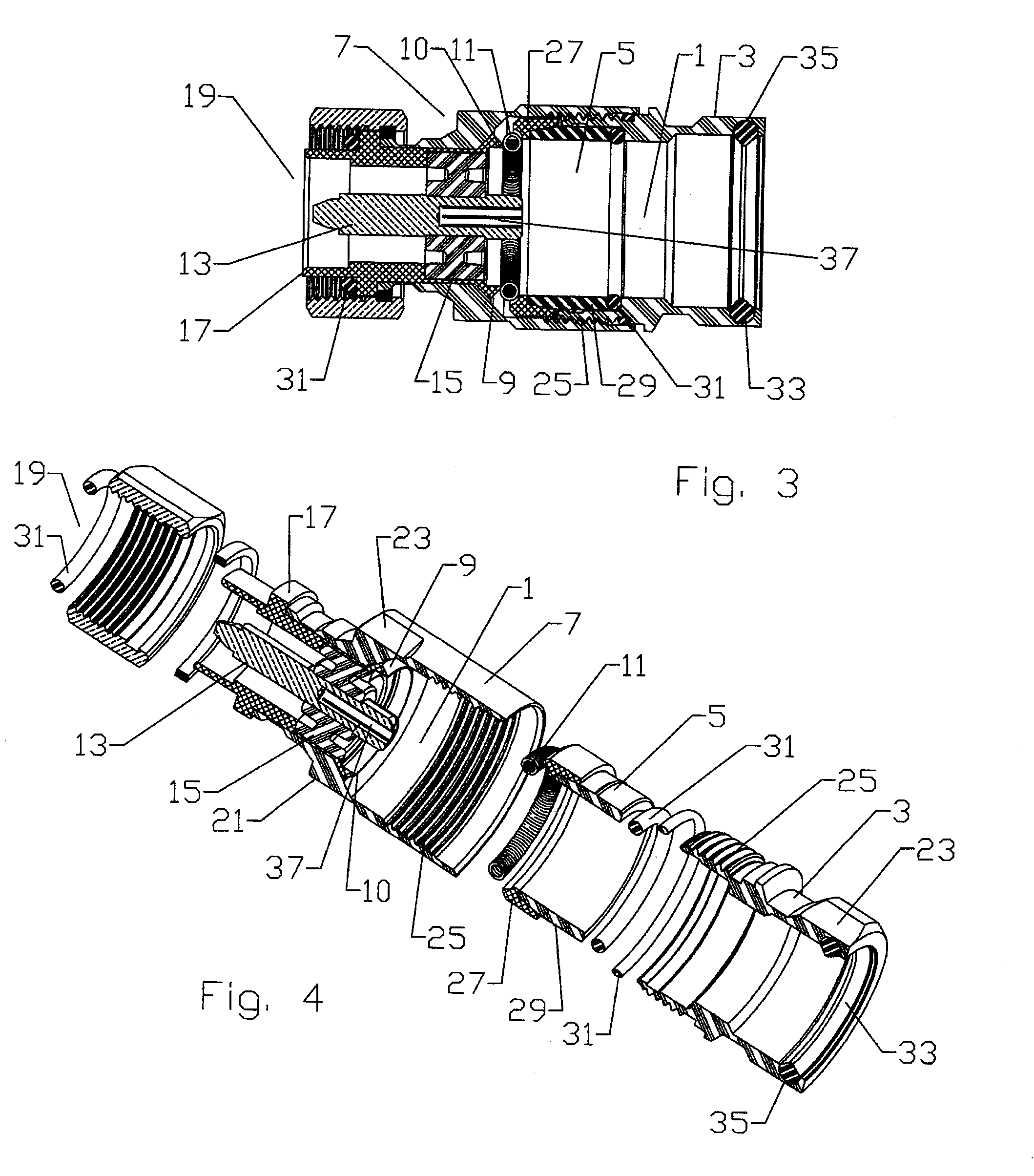

Multi-shot Connector Assembly and Method of Manufacture

InactiveUS20110003507A1Significant costSignificant materialTwo pole connectionsContact member cases/bases manufactureMultiple injectionCoaxial cable

A coaxial cable connector formed via multi-shot injection molding has a body formed by multiple injection molding layers of different injection moldable materials about a central inner contact to form an integral connector body. The connector body is provided with a coaxial dielectric spacer of dielectric polymer surrounding the inner contact; a coaxial inner body of injection molded metal composition surrounding an outer diameter of the dielectric spacer; and an outer body of polymer surrounding the inner body. Interlock features provide axial and / or rotational interlock between the layers of the connector.

Owner:ANDREW LLC

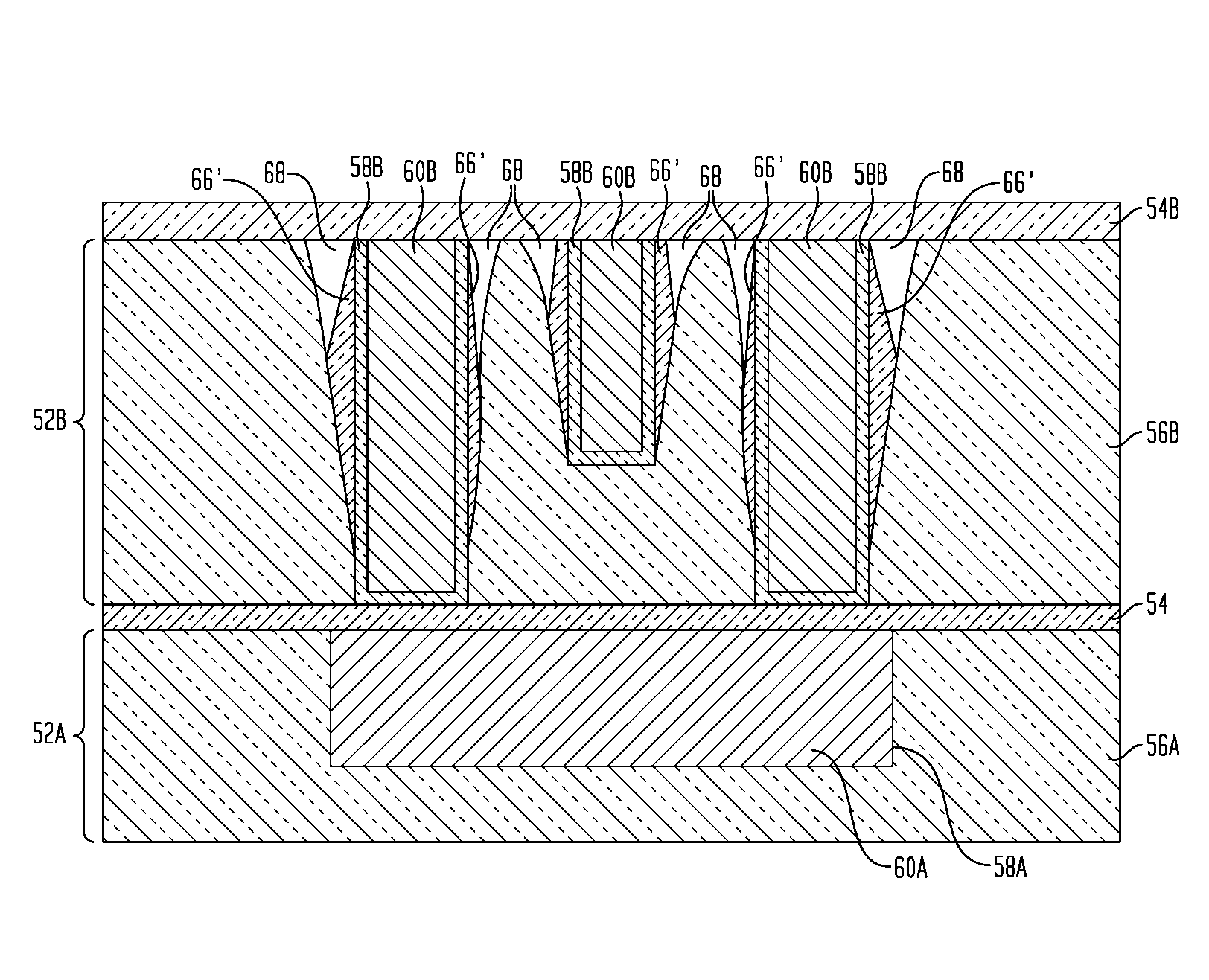

Hybrid interconnect structure for performance improvement and reliability enhancement

ActiveUS20080174017A1Improve reliabilityImprove performanceSemiconductor/solid-state device detailsSolid-state devicesHigh volume manufacturingConductive materials

The present invention provides an interconnect structure (of the single or dual damascene type) and a method of forming the same, in which a dense (i.e., non-porous) dielectric spacer is present on the sidewalls of a dielectric material. More specifically, the inventive structure includes a dielectric material having a conductive material embedded within at least one opening in the dielectric material, wherein the conductive material is laterally spaced apart from the dielectric material by a diffusion barrier, a dense dielectric spacer and, optionally, an air gap. The presence of the dense dielectric spacer results in a hybrid interconnect structure that has improved reliability and performance as compared with existing prior art interconnect structures which do not include such dense dielectric spacers. Moreover, the inventive hybrid interconnect structure provides for better process control which leads to the potential for high volume manufacturing.

Owner:TAIWAN SEMICON MFG CO LTD

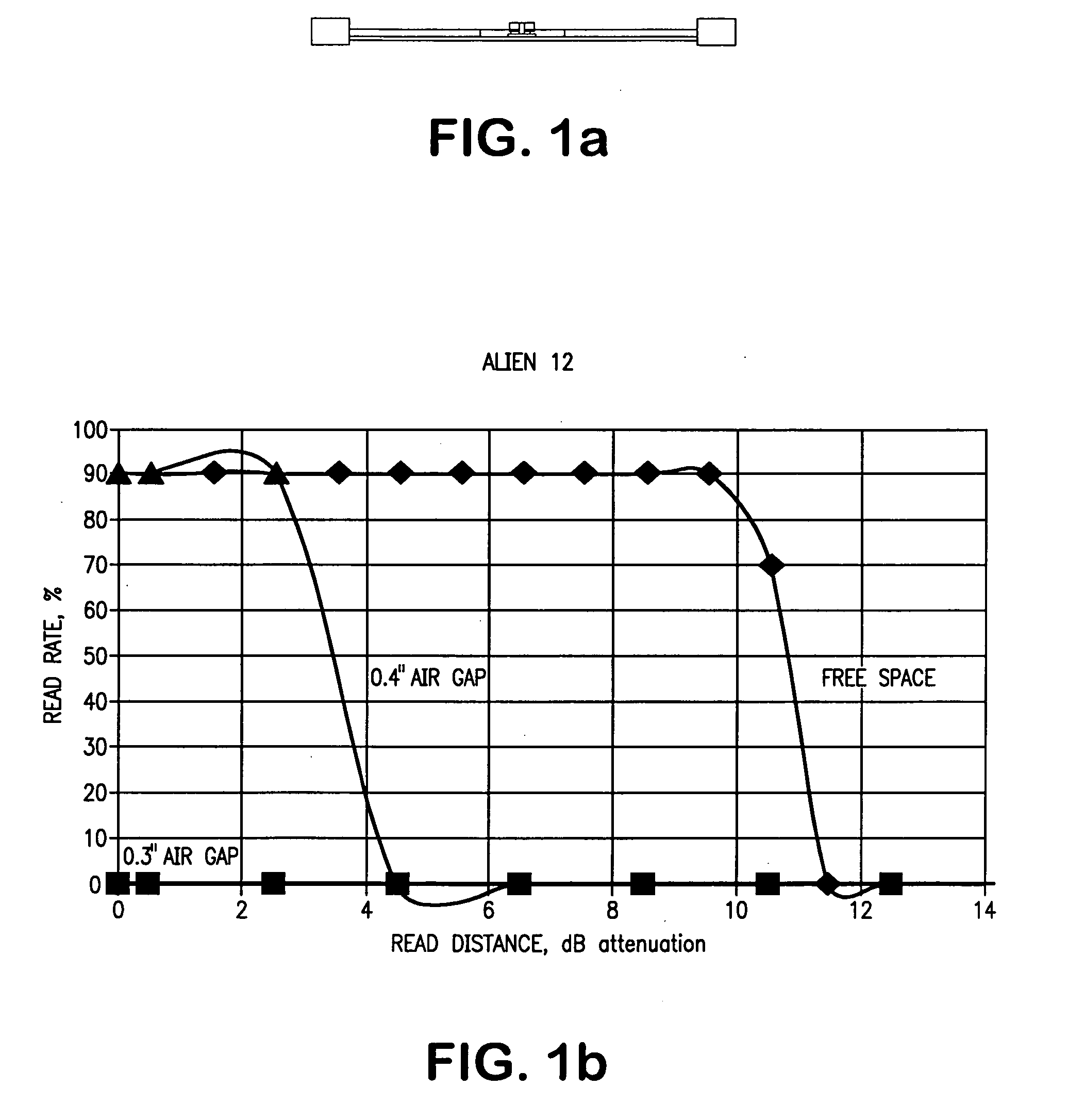

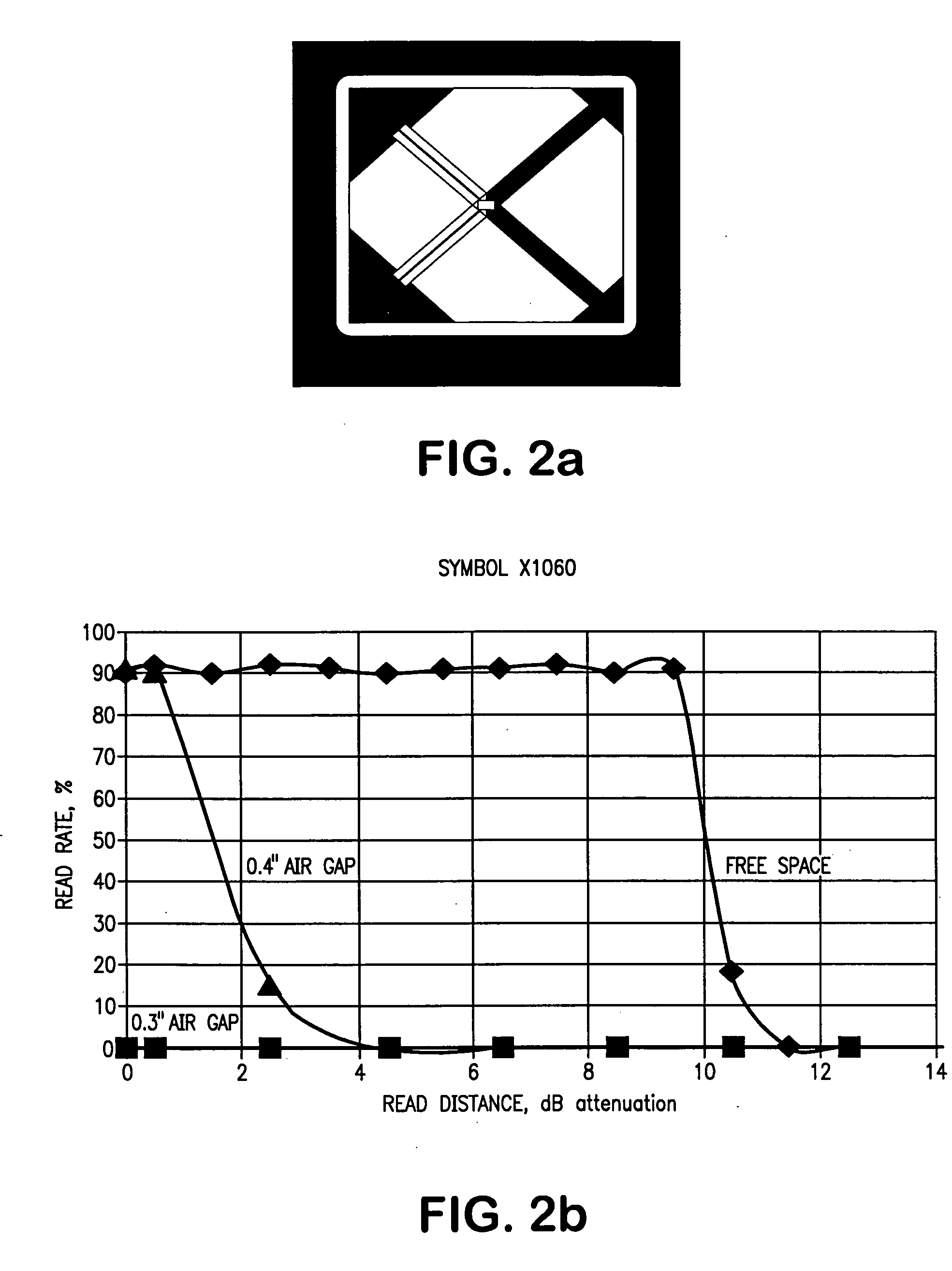

RFID tags

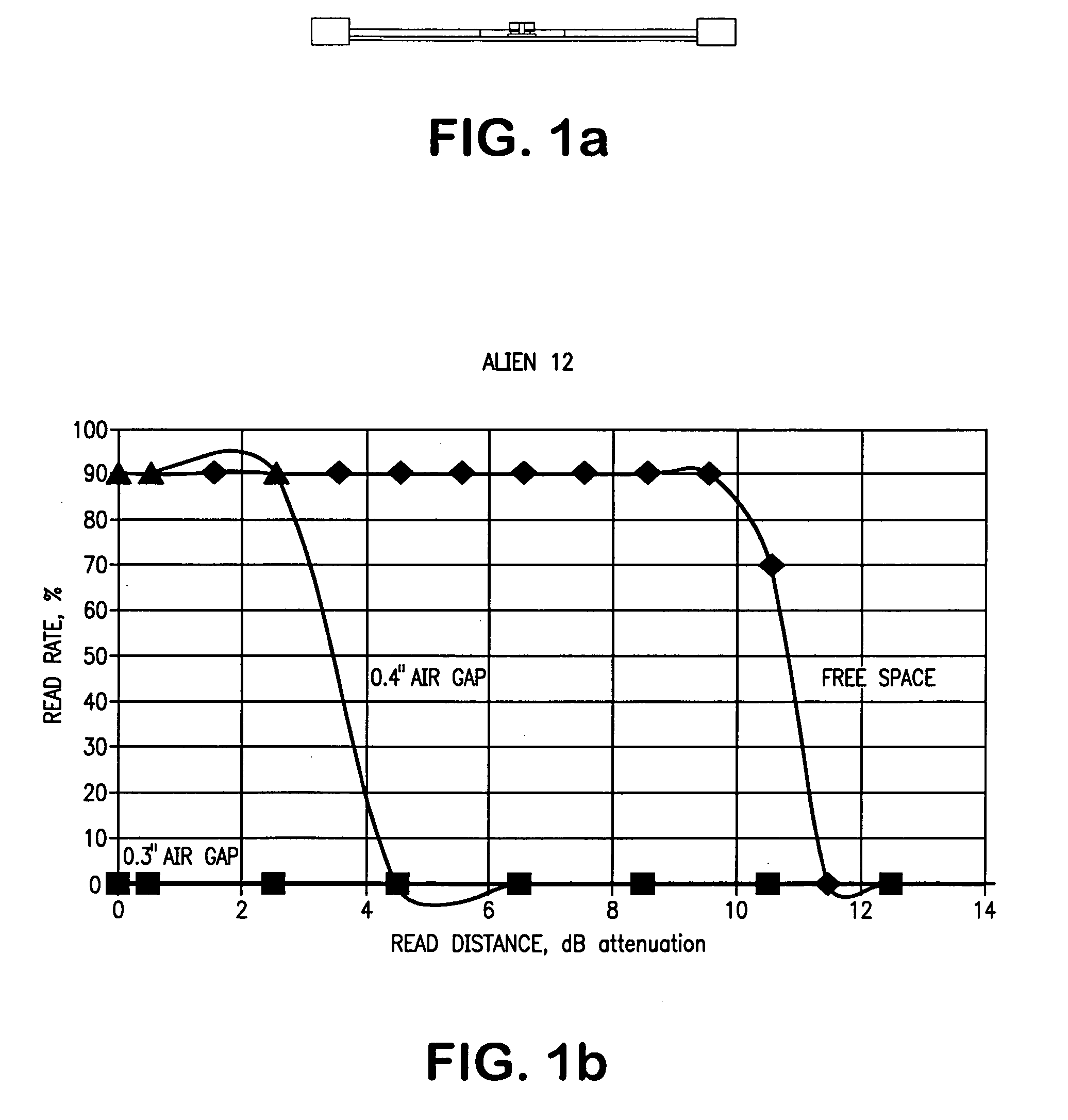

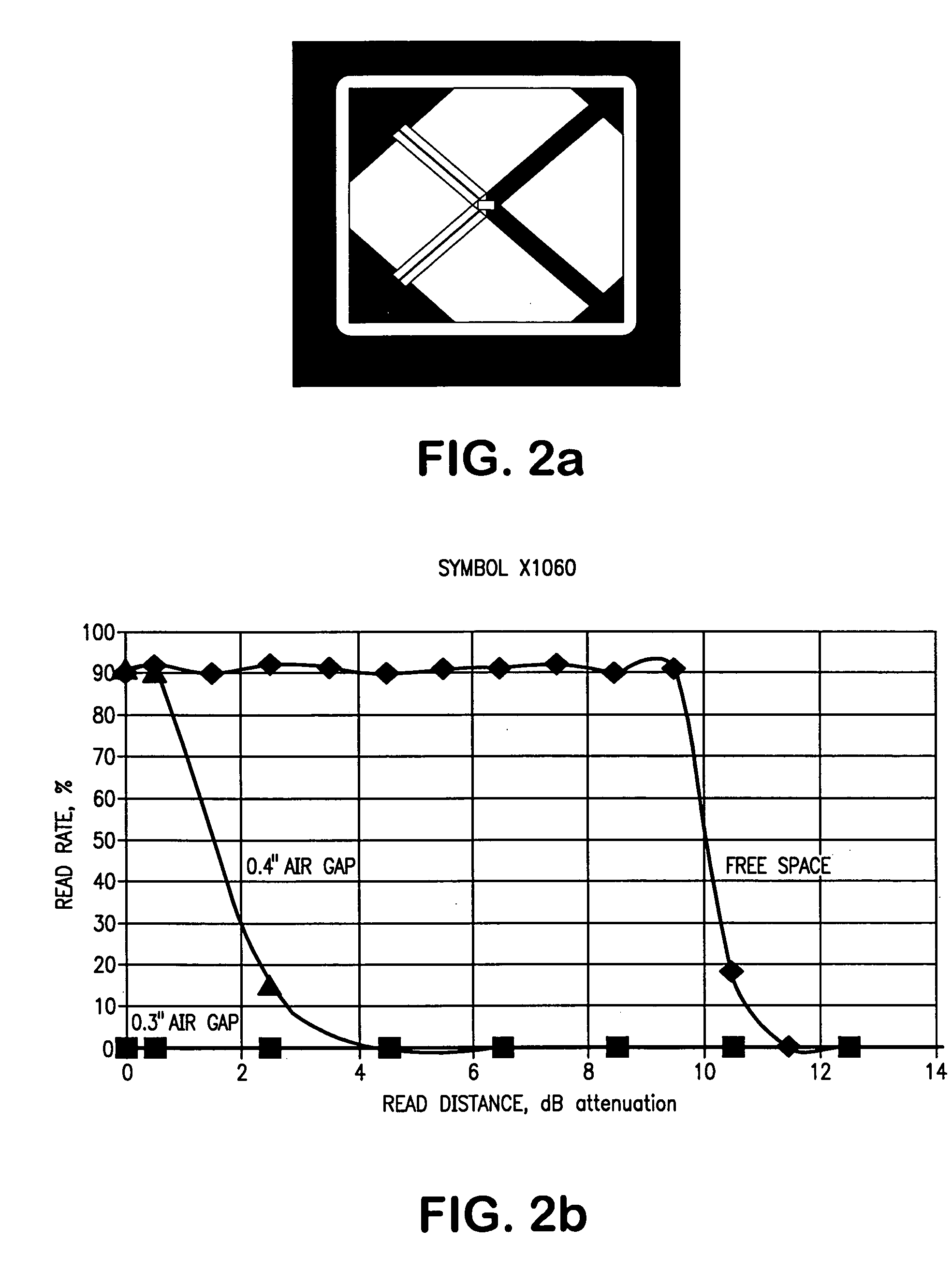

InactiveUS7205898B2Improve reading distanceOvercomes shortcomingRecord carriers used with machinesBurglar alarm by hand-portable articles removalMaterials scienceMetal substrate

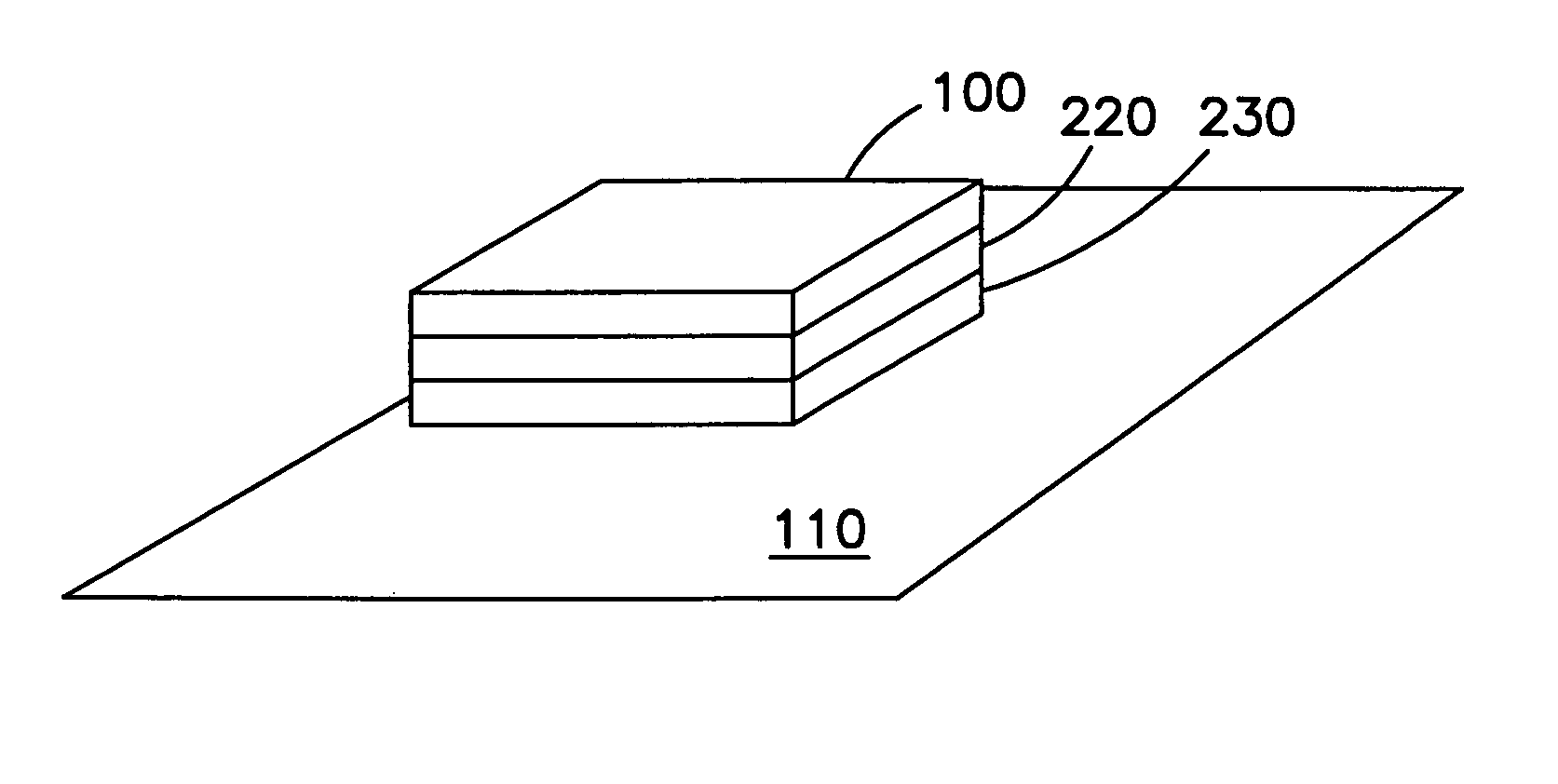

A system and method for the use of ultra high frequency RFID tags in conjunction with metal substrates, as well as substrates used to contain liquid. Briefly, an RFID isolator comprised of a material with complex magnetic permeability, used either by itself, or in combination with dielectric isolator material, is interposed between the RFID tag and the substrate. Alternatively, a material possessing at least two distinct dielectric constants is interposed between the RFID tag and the substrate, such that there is a high dielectric constant at the interface with the substrate, and a low dielectric constant at the interface with the RFID tag. This material can be a single material having a dielectric constant gradient, or alternatively, two or more separate layers, each with a uniform but different dielectric constant, sandwiched together.

Owner:LAIRD TECH INC

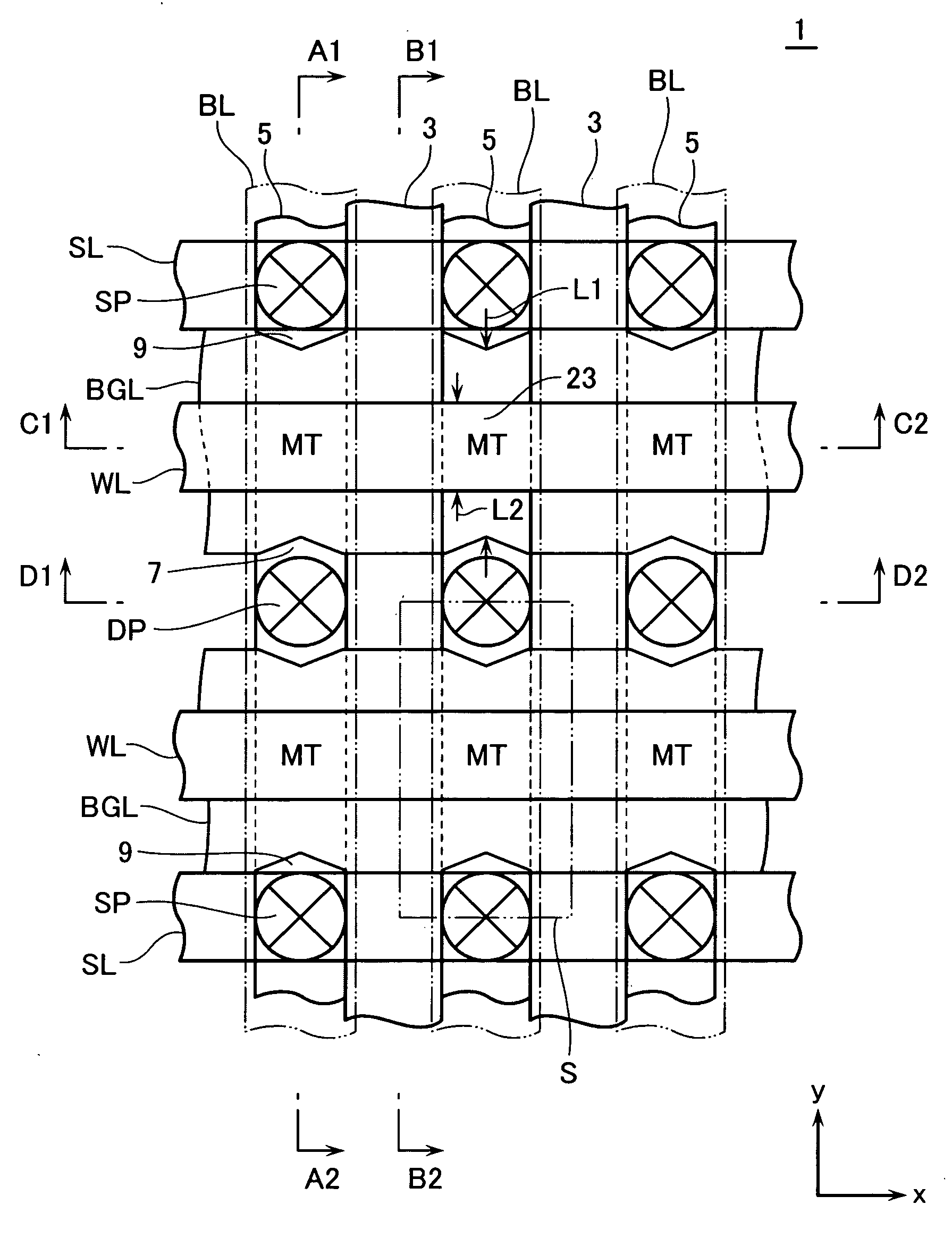

Semiconductor device including transistors formed in semiconductor layer having single-crystal structure isolated from substrate and fabrication method of the same

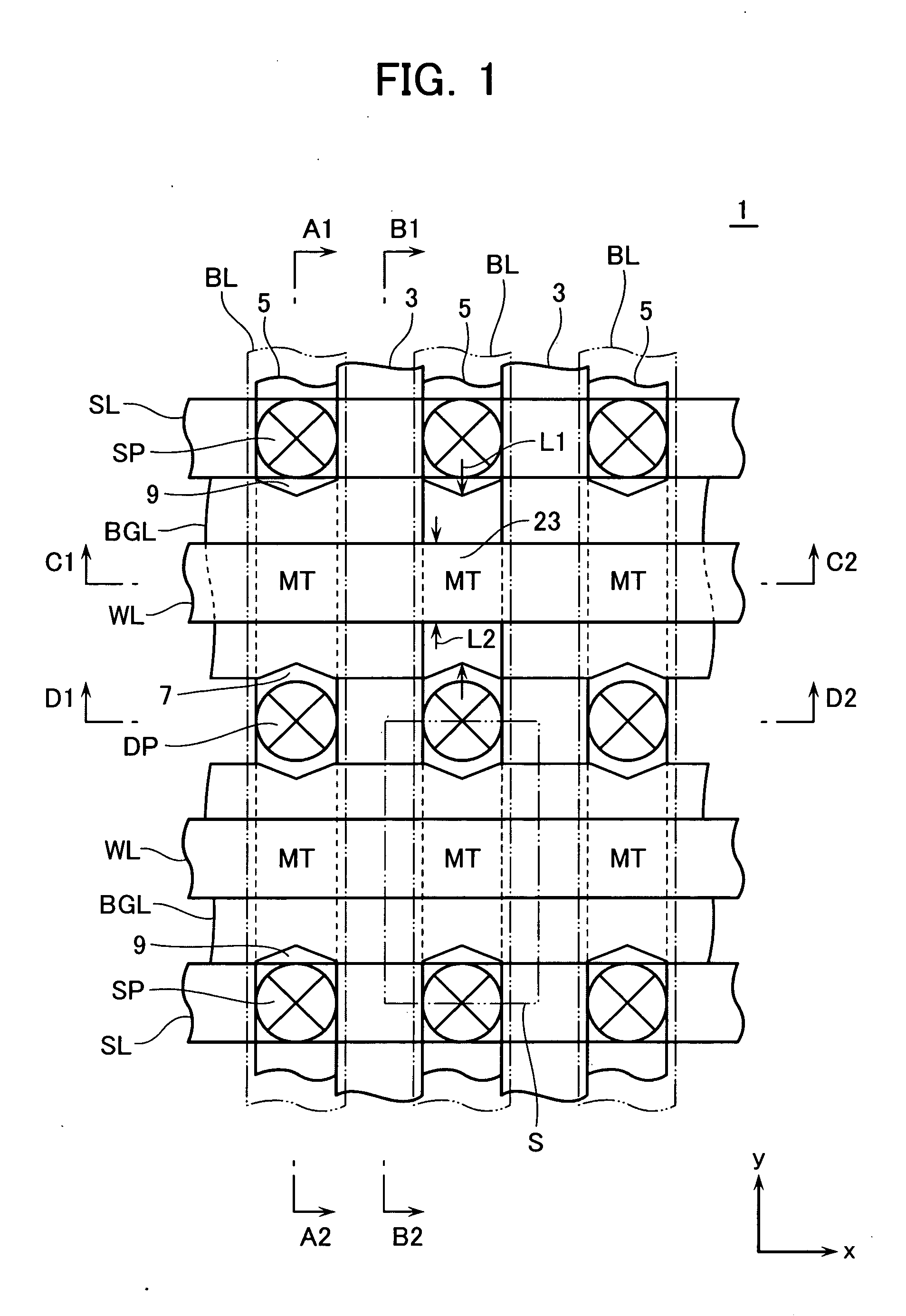

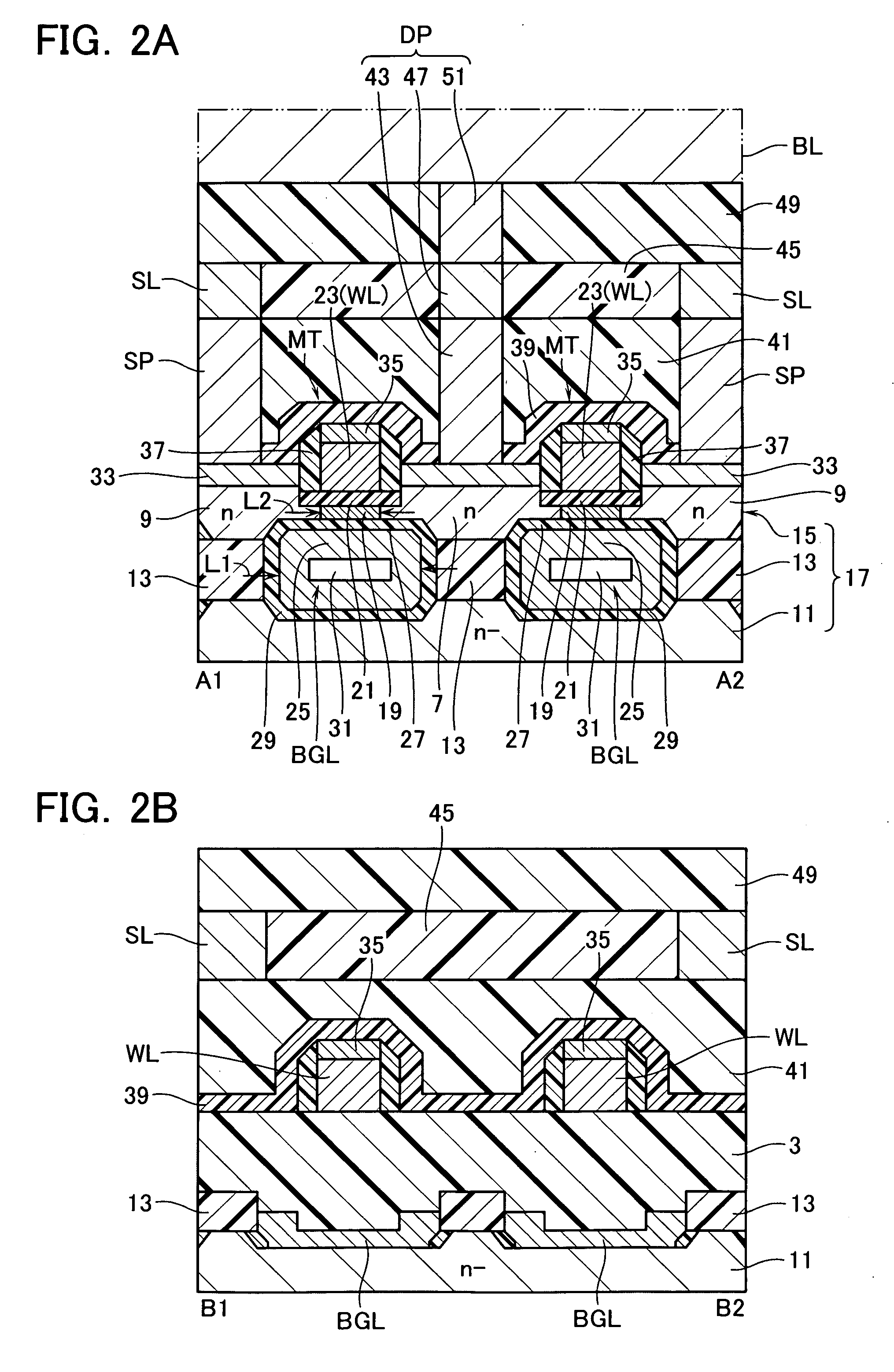

A semiconductor device includes a substrate, a semiconductor layer of a first conductivity type having a single-crystal structure, and a plurality of transistors each including a first gate electrode provided above the semiconductor layer with a first gate insulation film laid therebetween, a pair of impurity regions of a second conductivity type being provided in the semiconductor layer and each becoming a source or drain region, and a channel body of the first conductivity type provided in the semiconductor layer at a portion between these impurity regions. The device also includes a first gate line for common connection of the first gate electrodes of the transistors, a dielectric layer provided above the substrate in an extension direction of the first gate line, for supporting the semiconductor layer under the pair of impurity regions to thereby dielectrically isolate between the substrate and the semiconductor layer, a second gate electrode provided above the substrate in such a manner as to underlie the channel bodies of the transistors and oppose the channel bodies with a second gate insulation film laid therebetween, the second gate electrode having a gate length larger than a onefold value of a gate length of the first gate electrode and yet less than or equal to thrice the gate length, and a second gate line provided above the substrate along the extension direction of the first gate line while being placed between portions of the dielectric layer underlying the pair of impurity regions, the second gate line being for common connection of the second gate electrode.

Owner:KK TOSHIBA

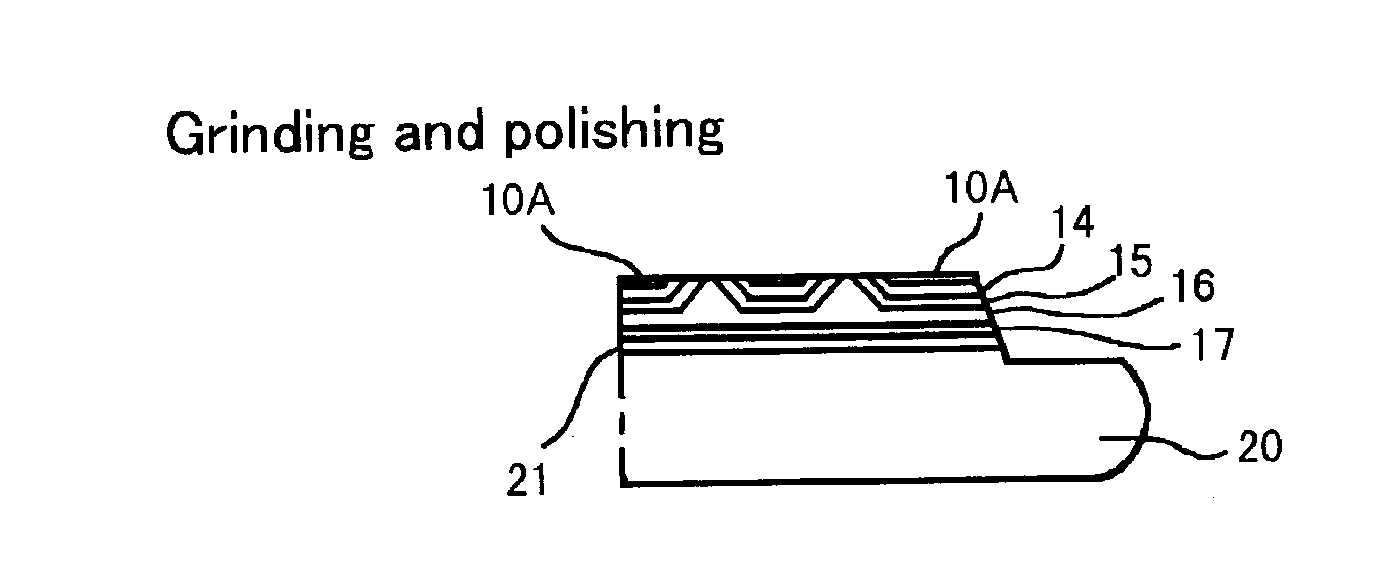

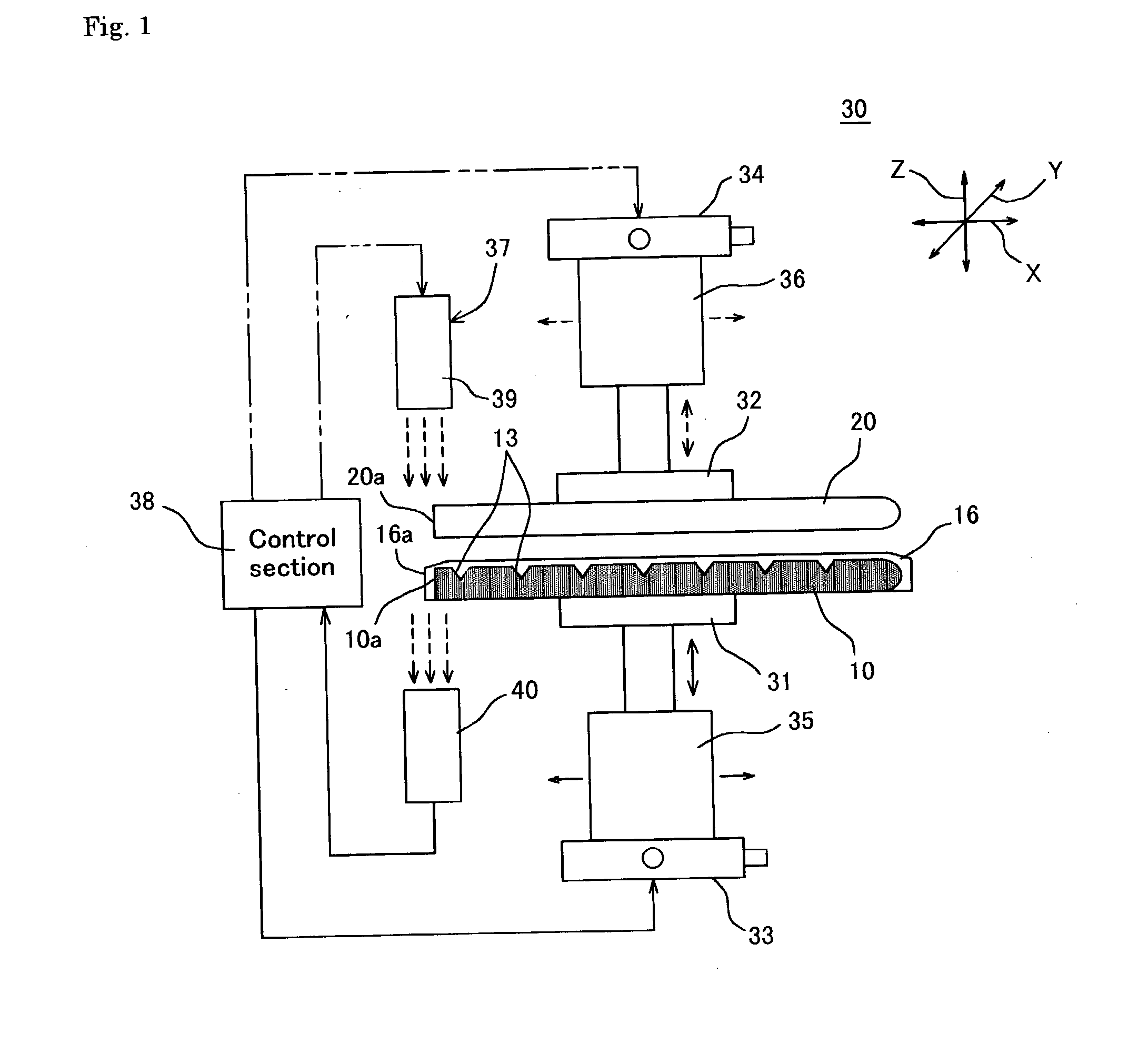

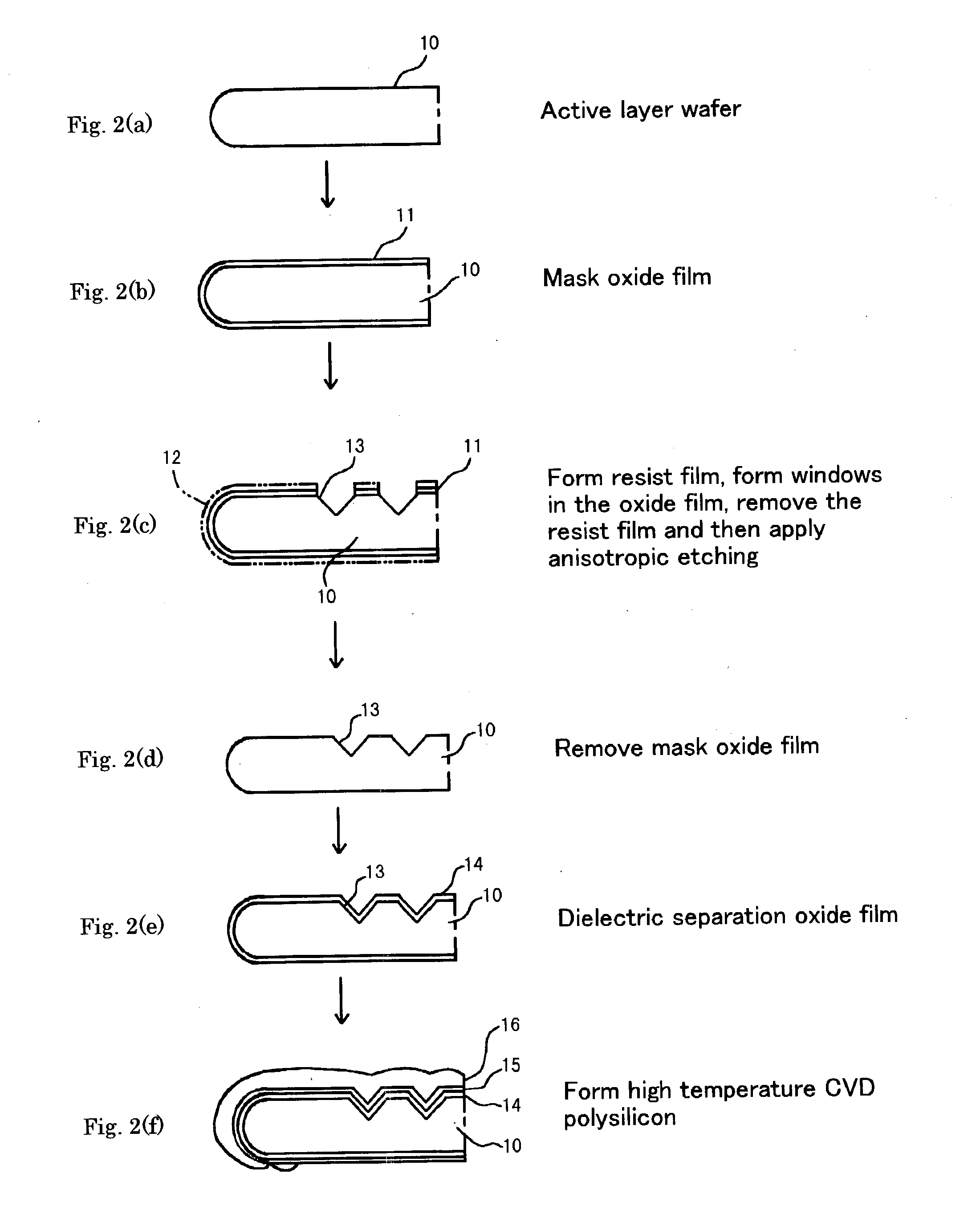

Method and apparatus for producing bonded dielectric separation wafer

InactiveUS20030092244A1Solid-state devicesSemiconductor/solid-state device manufacturingWaferingEngineering

The present invention provides a method for producing a bonded dielectric separation wafer in which an auto-alignment can be carried out with reference to the orientation flat of a supporting substrate wafer after the wafer bonding step, and also an apparatus to be used for bonding wafers. When wafers are placed one upon another, the silicon wafers 10, 20 are irradiated with transmission light in order to capture the transmission images thereof. The positions of the pattern of dielectric isolation grooves 13 in the silicon wafer 10 and the orientation flat 20a of the silicon wafer 20 are determined from the images and the bonding position of the wafers 10, 20 is determined based on the determined positions. Auto-alignment of the bonded dielectric separation wafer can thereby be carried out with reference to the orientation flat 20a of the silicon wafer 20 after the wafer bonding step.

Owner:SUMITOMO MITSUBISHI SILICON CORP

RFID tags

InactiveUS20060109124A1Improve reading distanceOvercomes shortcomingRecord carriers used with machinesBurglar alarm by hand-portable articles removalCombined useMetallic substrate

A system and method for the use of ultra high frequency RFID tags in conjunction with metal substrates, as well as substrates used to contain liquid. Briefly, an RFID isolator comprised of a material with complex magnetic permeability, used either by itself, or in combination with dielectric isolator material, is interposed between the RFID tag and the substrate. Alternatively, a material possessing at least two distinct dielectric constants is interposed between the RFID tag and the substrate, such that there is a high dielectric constant at the interface with the substrate, and a low dielectric constant at the interface with the RFID tag. This material can be a single material having a dielectric constant gradient, or alternatively, two or more separate layers, each with a uniform but different dielectric constant, sandwiched together.

Owner:LAIRD TECH INC

Method for forming isolation regions subsequent to gate formation and structure thereof

Semiconductor devices are formed in a semiconductor substrate having an essentially planar upper surface. In some embodiments, implanted regions are formed in the substrate at a first predetermined depth by implantation of oxygen and / or nitrogen ions. In some embodiments buried implanted are formed in the substrate at a second predetermined depth, deeper than the first depth by implantation of oxygen and / or nitrogen ions. These implanted regions are converted to dielectric isolation regions and buried dielectric regions, respectively, by a high temperature anneal after formation of a gate structure.

Owner:INTEGRATED DEVICE TECH INC

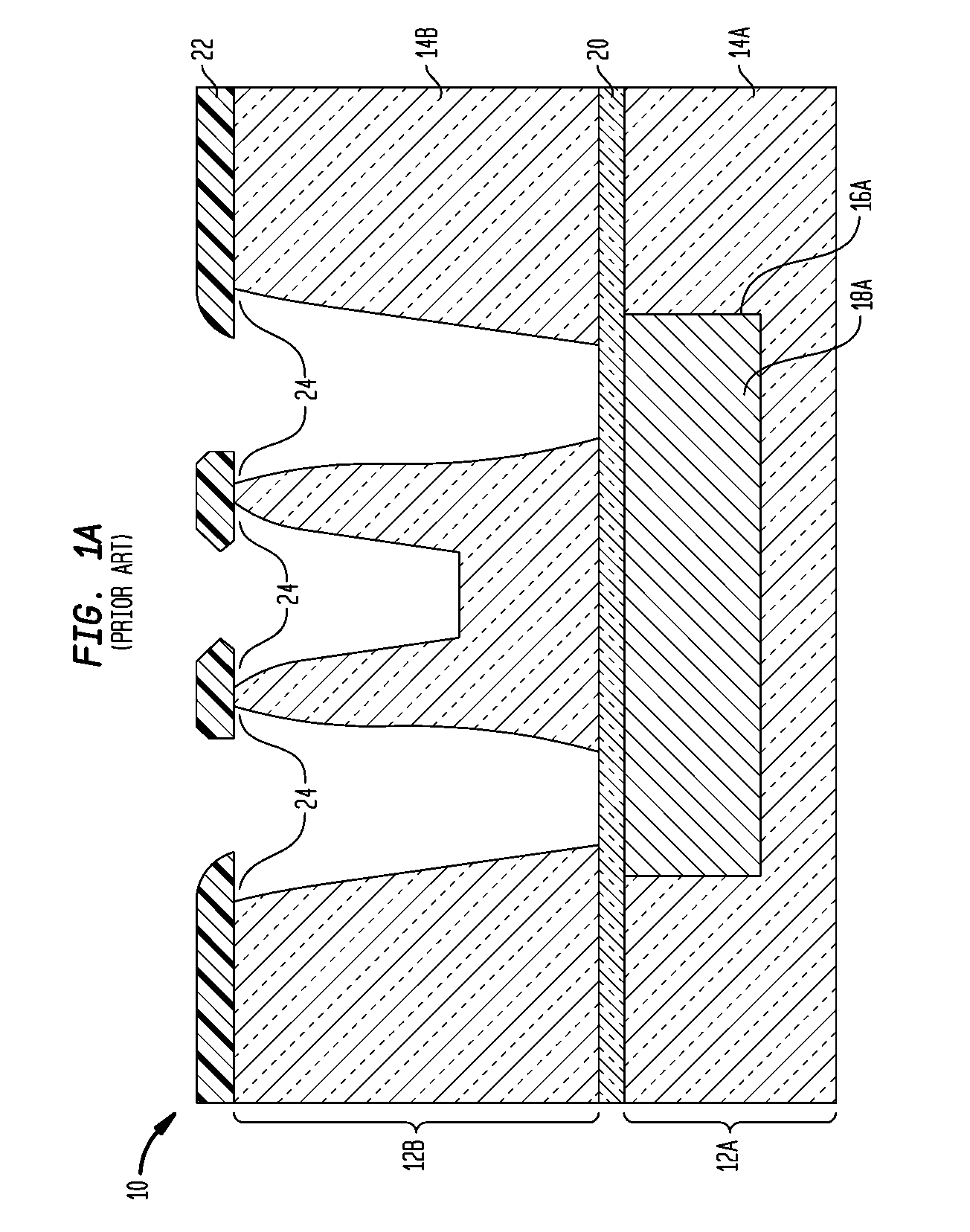

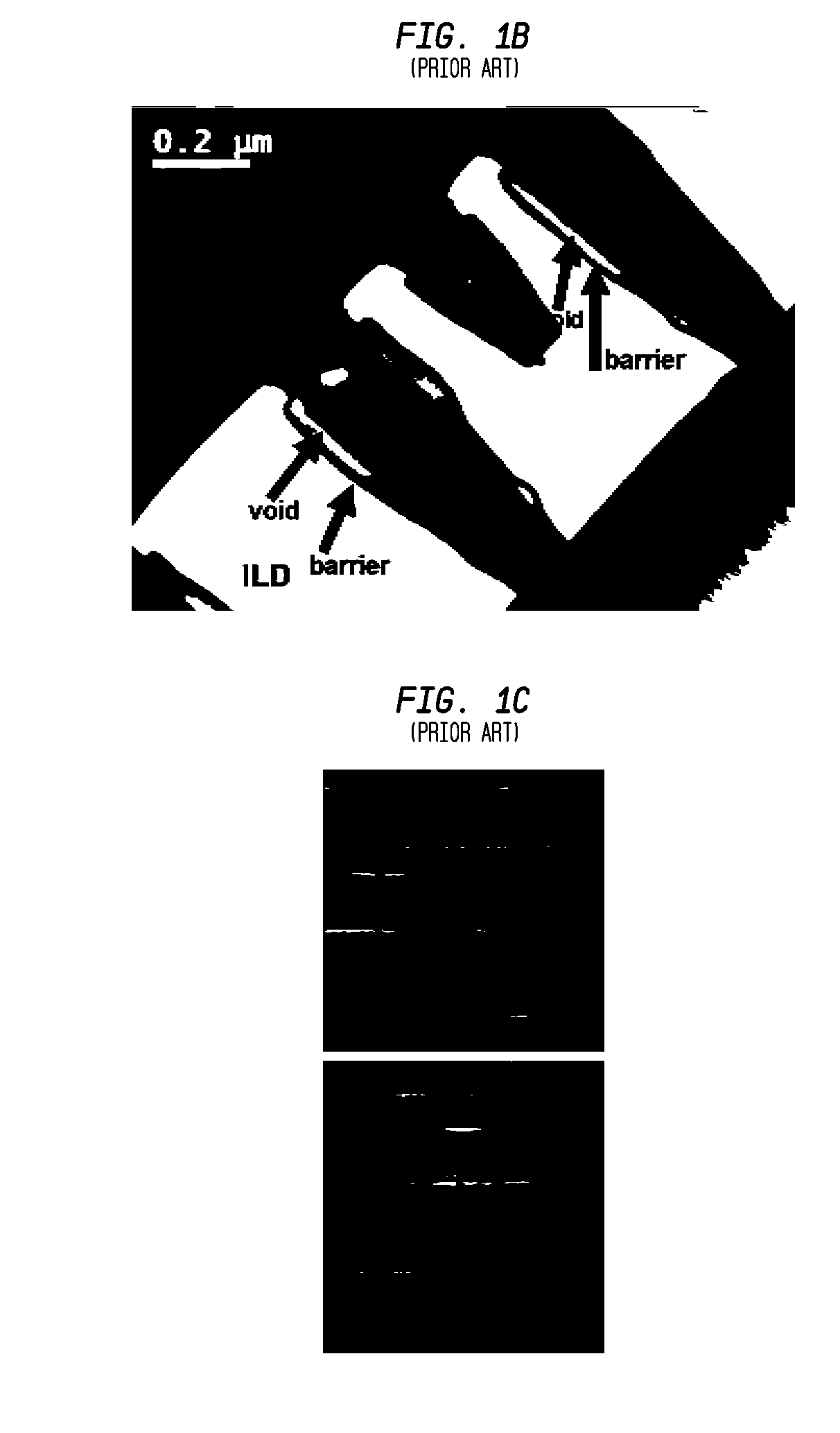

Dielectric spacers for metal interconnects and method to form the same

ActiveUS20080073748A1Semiconductor/solid-state device detailsSolid-state devicesMetal interconnectMaterials science

Dielectric spacers for a plurality of metal interconnects and a method to form such dielectric spacers are described. In one embodiment, the dielectric spacers are adjacent to neighboring metal interconnects having flared profiles and are discontiguous from one another. In another embodiment, the dielectric spacers provide a region upon which un-landed vias may effectively land.

Owner:TAHOE RES LTD

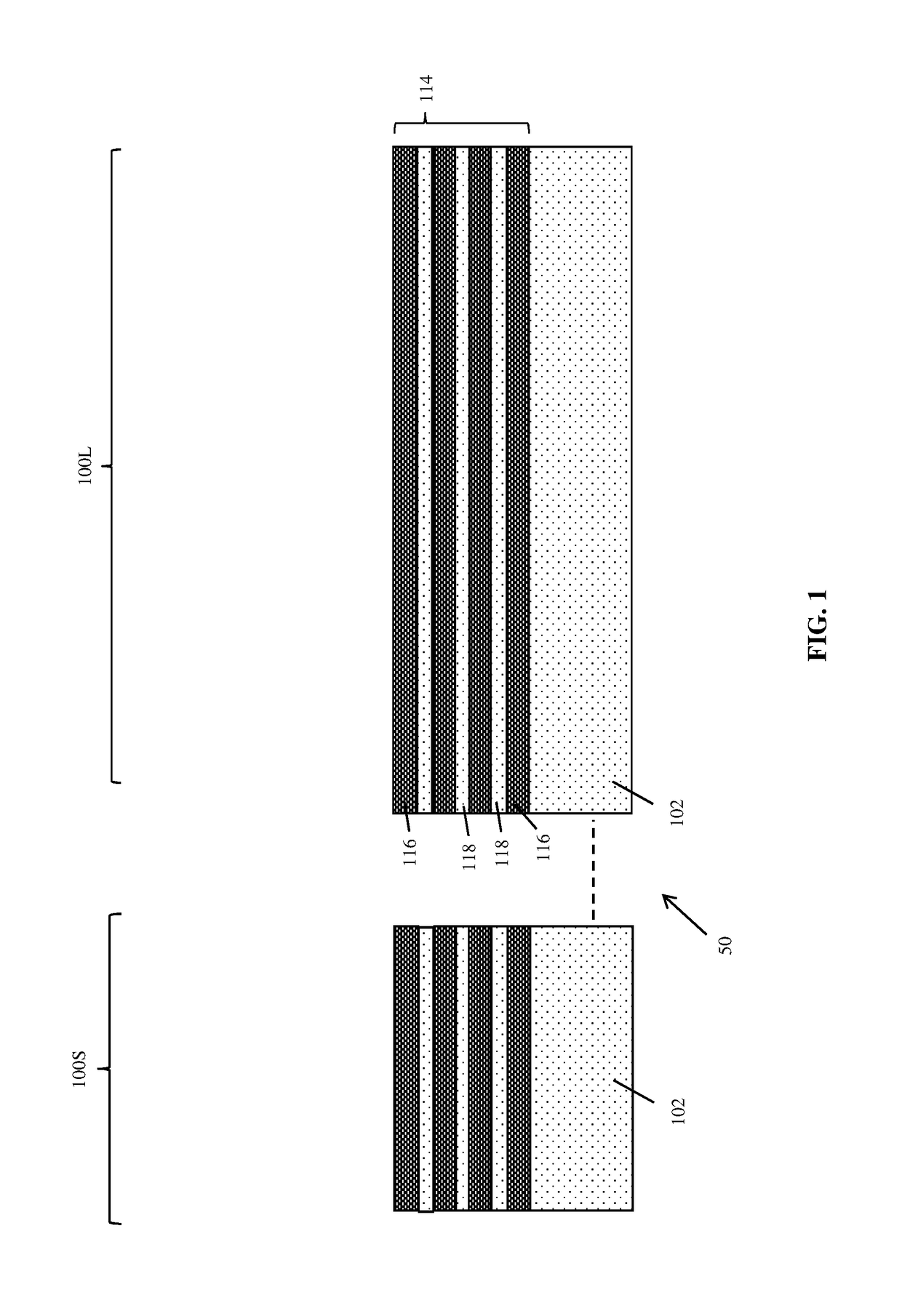

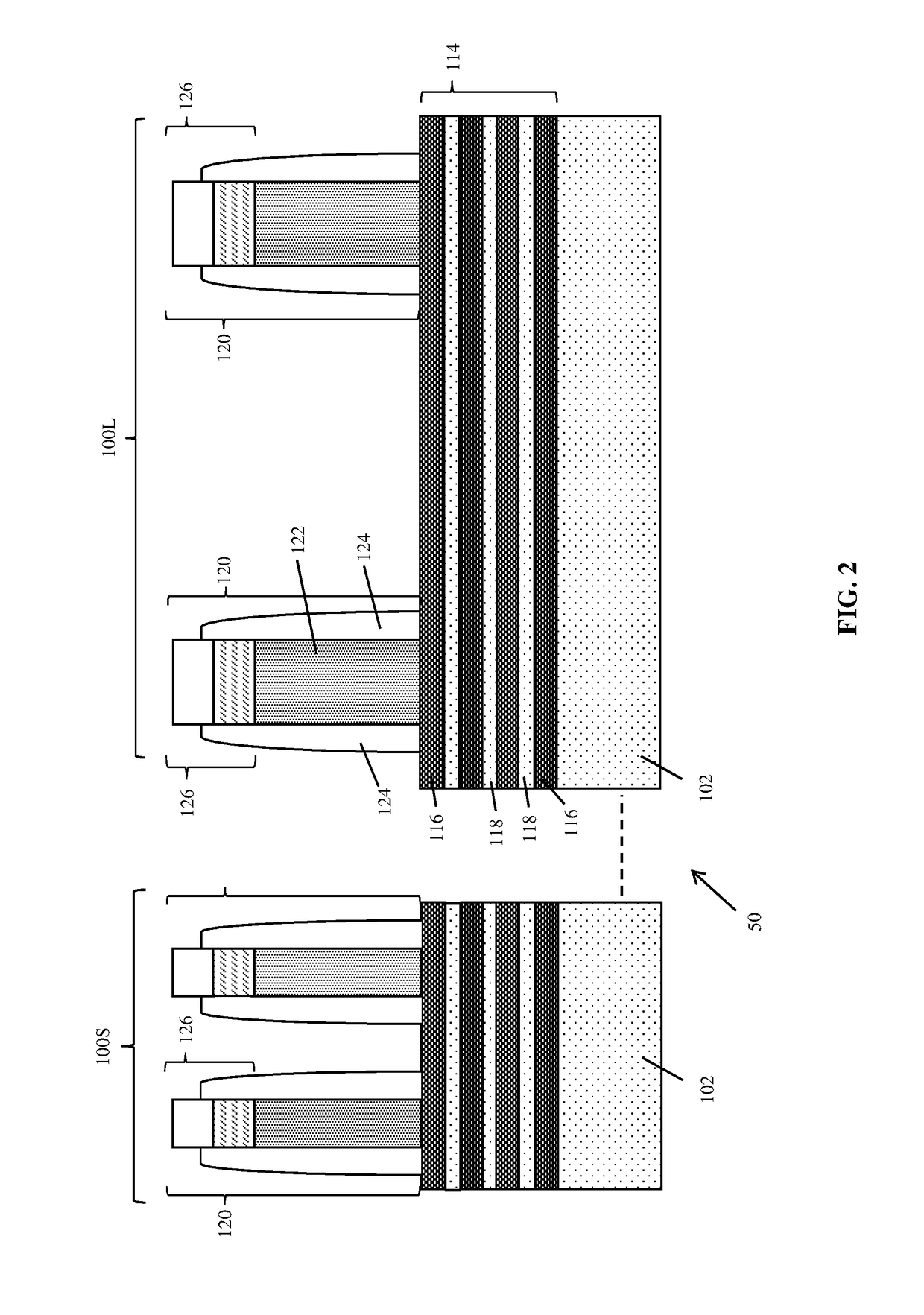

Finfet with dielectric isolation by silicon-on-nothing and method of fabrication

ActiveUS20140191321A1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringDielectric layer

An improved finFET and method of fabrication using a silicon-on-nothing process flow is disclosed. Nitride spacers protect the fin sides during formation of cavities underneath the fins for the silicon-on-nothing (SON) process. A flowable oxide fills the cavities to form an insulating dielectric layer under the fins.

Owner:GLOBALFOUNDRIES US INC

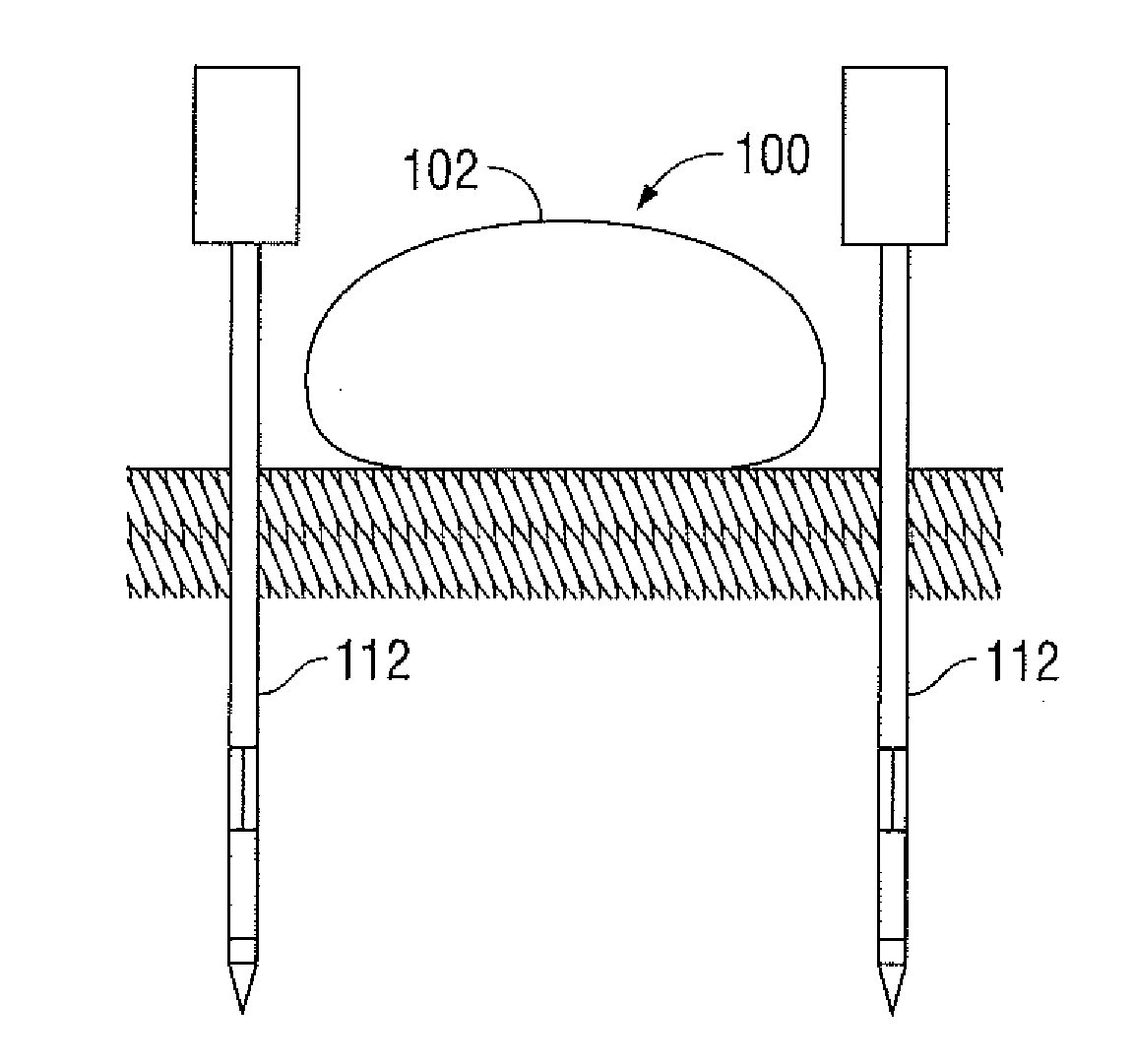

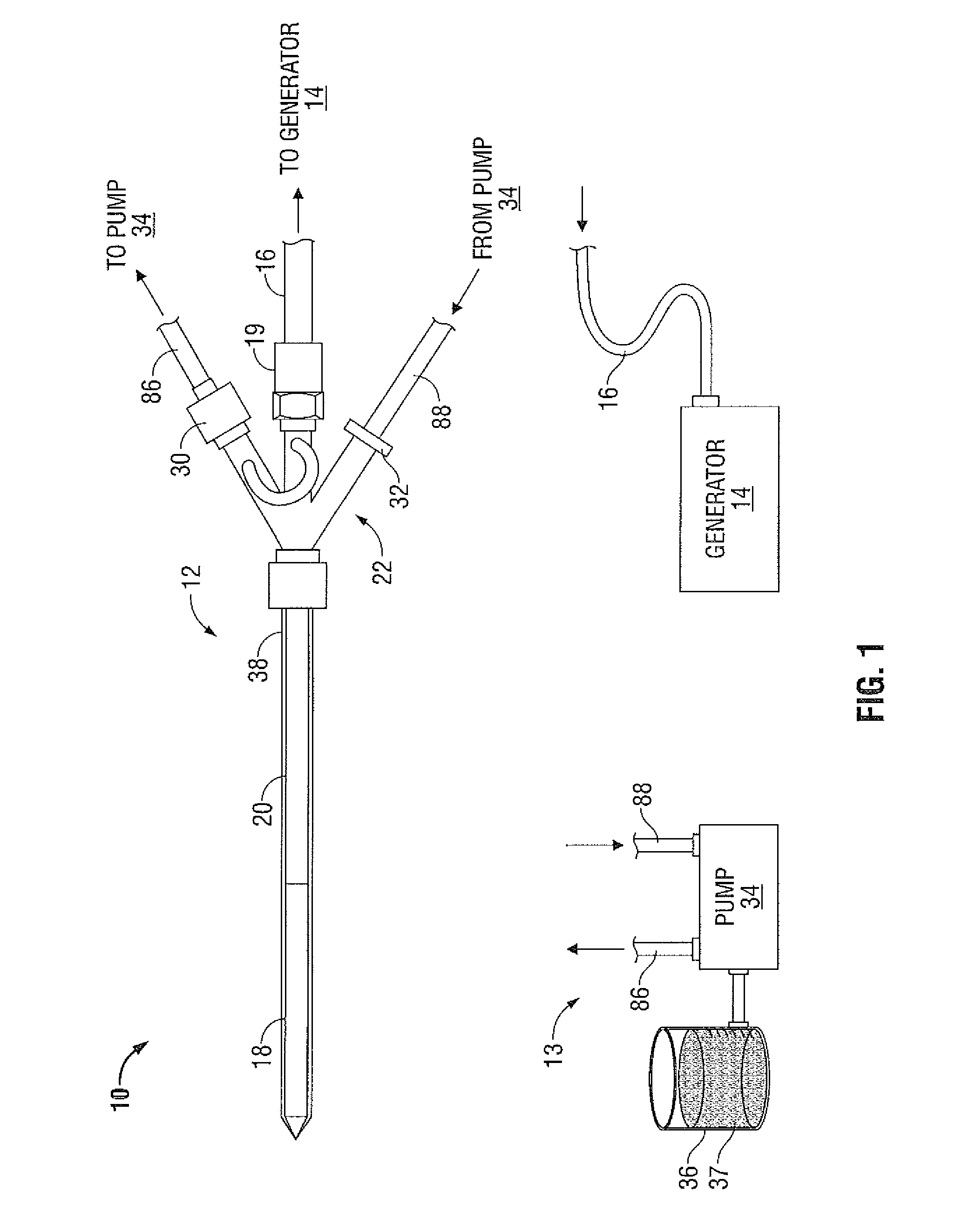

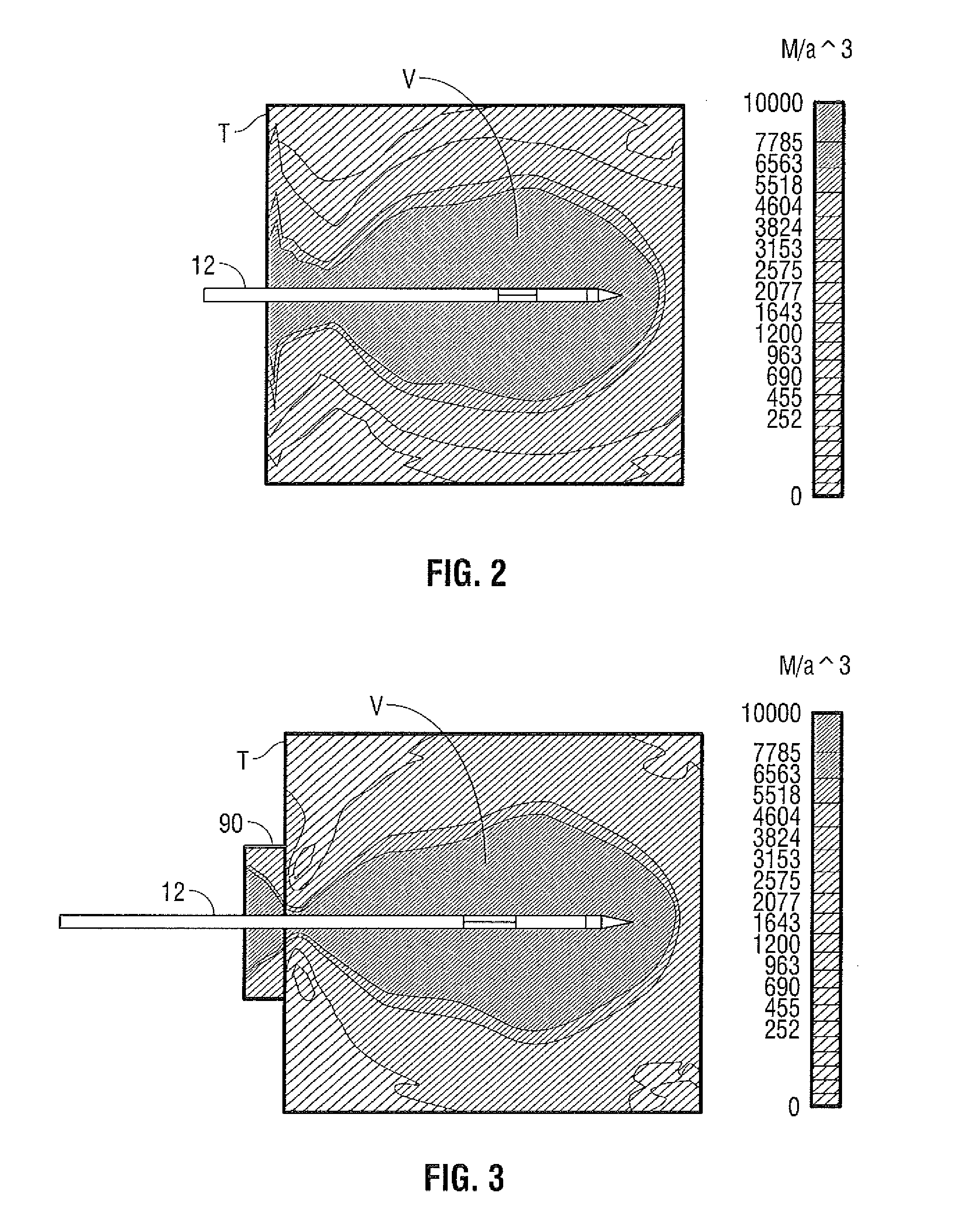

Management of Voltage Standing Wave Ratio at Skin Surface During Microwave Ablation

A dielectric spacer for use during microwave ablation of tissue is disclosed. The dielectric spacer includes a housing having a predetermined thickness and a skin-contacting bottom surface. The housing is configured to be filled with a dielectric material having a predetermined dielectric permittivity. The housing is further configured to be placed on the tissue in proximity with at least one microwave antenna assembly, wherein the thickness and the dielectric permittivity are configured to shift a maximum voltage standing wave ratio of the at least one microwave antenna assembly.

Owner:TYCO HEALTHCARE GRP LP

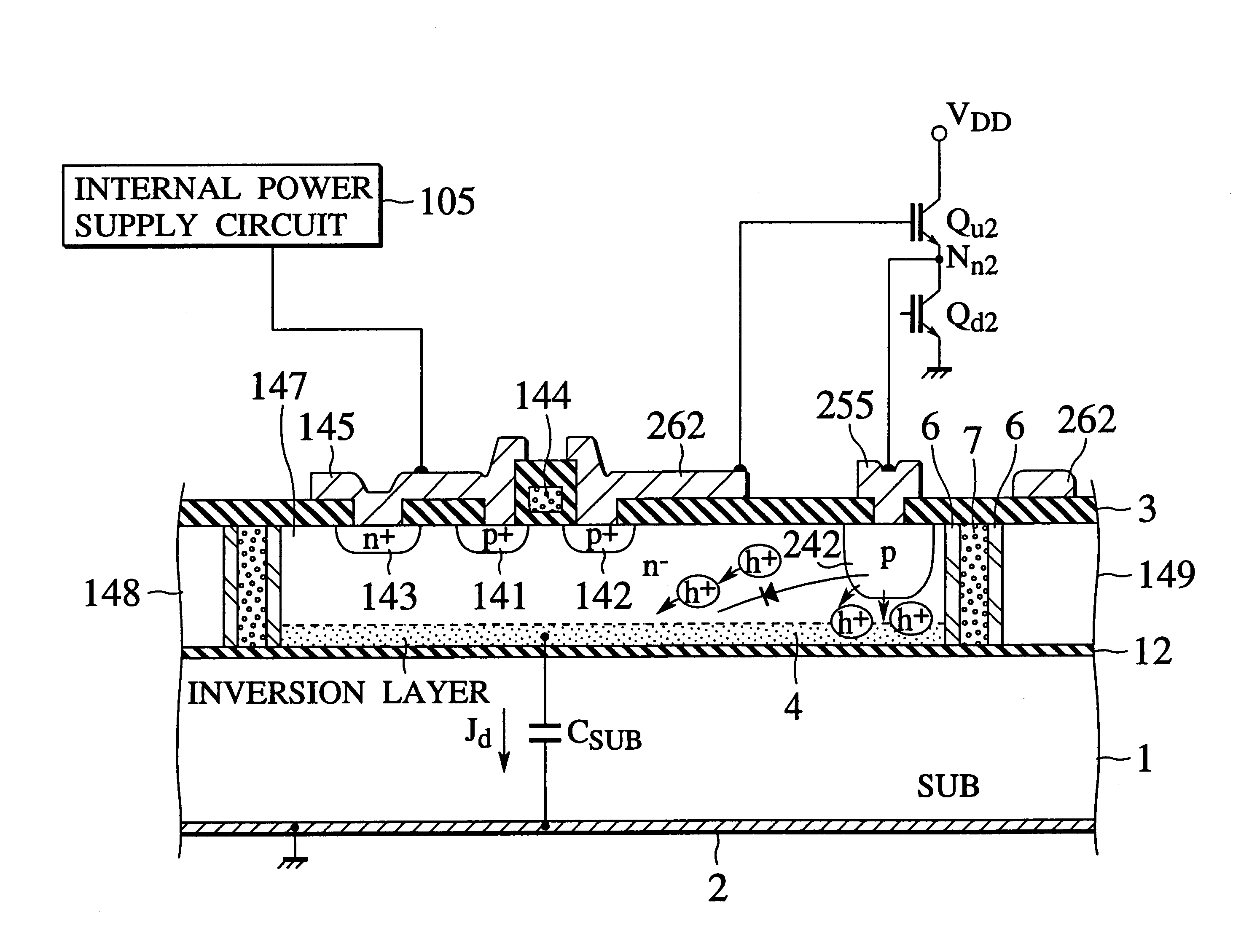

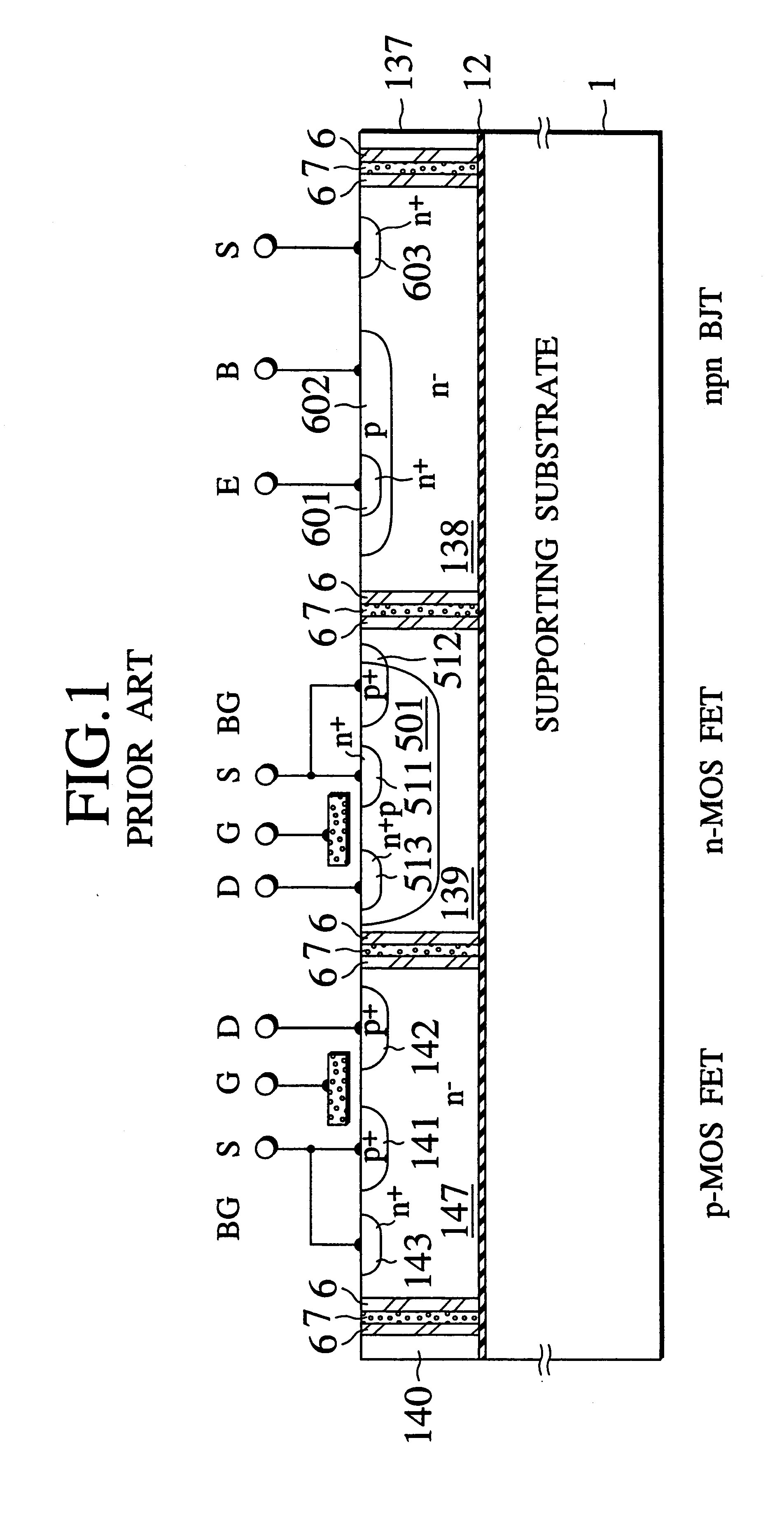

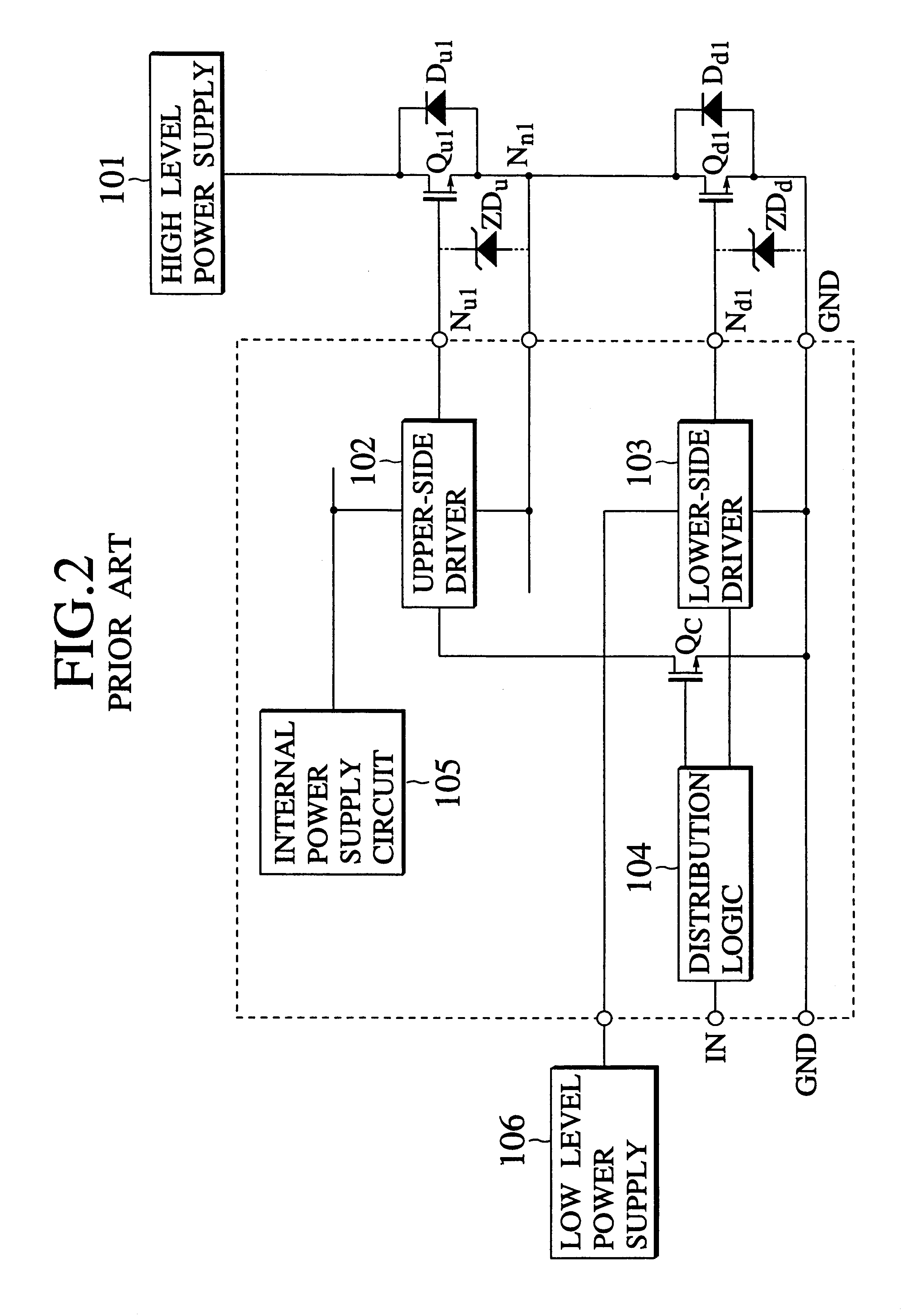

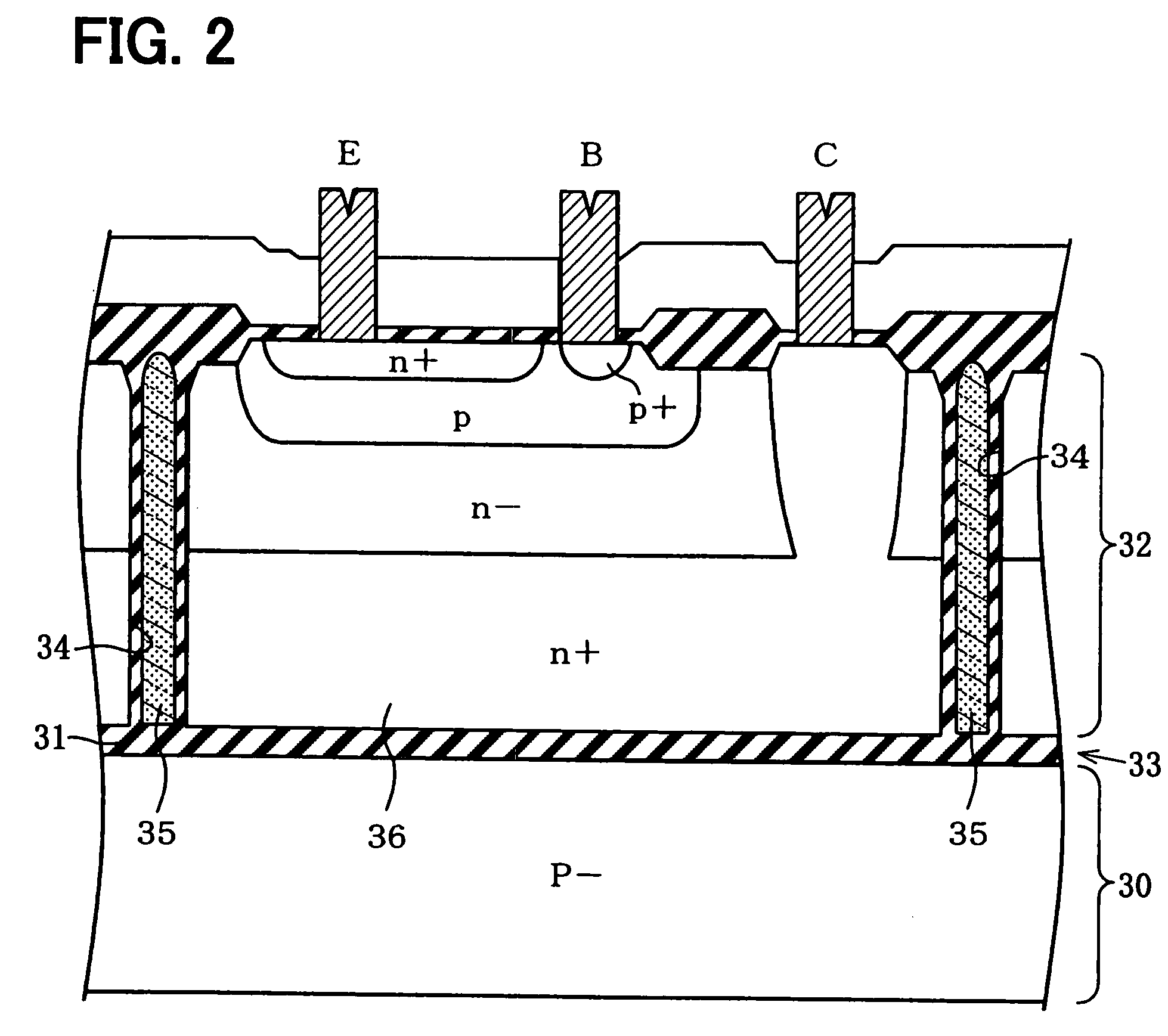

Dielectrically isolated IC driver having upper-side and lower-side arm drivers and power IC having the same

In an IC driver using SOI dielectric isolation structure having a lower and an upper arm side drivers, the upper arm side driver operates in a floating state, a carrier injector region is disposed in an semiconductor island where a switching device for the upper-side circuit is formed. The IC driver drives a set of an upper-side and a lower-side output power devices, a first main electrode of the upper-side output power device is connected to a high level power supply, a second main electrode of the upper-side output power device is connected to a first main electrode of the lower-side output power device, a second main electrode of the lower-side output power device is connected to ground potential (GND). The carrier injector region is formed deeper than a couple of main electrode regions of the switching device in the upper arm side driver. Moreover, this injector region is connected to an intermediate potential at connecting terminal of the upper-side and the lower-side output power devices. A current for compensating the displacement current Jd flowing in the parasitic condenser CSUB inherent to the SOI structure is supplied through the carrier injector from this intermediate potential terminal, to diminish the extra load of the internal power supply circuit for supplying the upper arm side driver with a predetermined voltage.

Owner:KK TOSHIBA

Field effect transistor using carbon based stress liner

InactiveUS20080303068A1Increase compressive stressTransistorSemiconductor/solid-state device manufacturingSemiconductor materialsHydrogen

A stress liner for use within a semiconductor structure that includes a field effect device has a dielectric constant less than about 7 and a compressive stress greater than about 5 GPa. The stress liner may be formed of a carbon based material, preferably a tetrahedral amorphous carbon (ta-C) material including at least about 60 atomic percent carbon and no greater than C about 40 atomic percent hydrogen. The carbon based material may be either a dielectric material, or given appropriate additional dielectric isolation structures, a semiconductor material. In particular, a ta-C stress liner may be formed using a filtered cathodic vacuum arc (FCVA) physical vapor deposition (PVD) method.

Owner:GLOBALFOUNDRIES INC

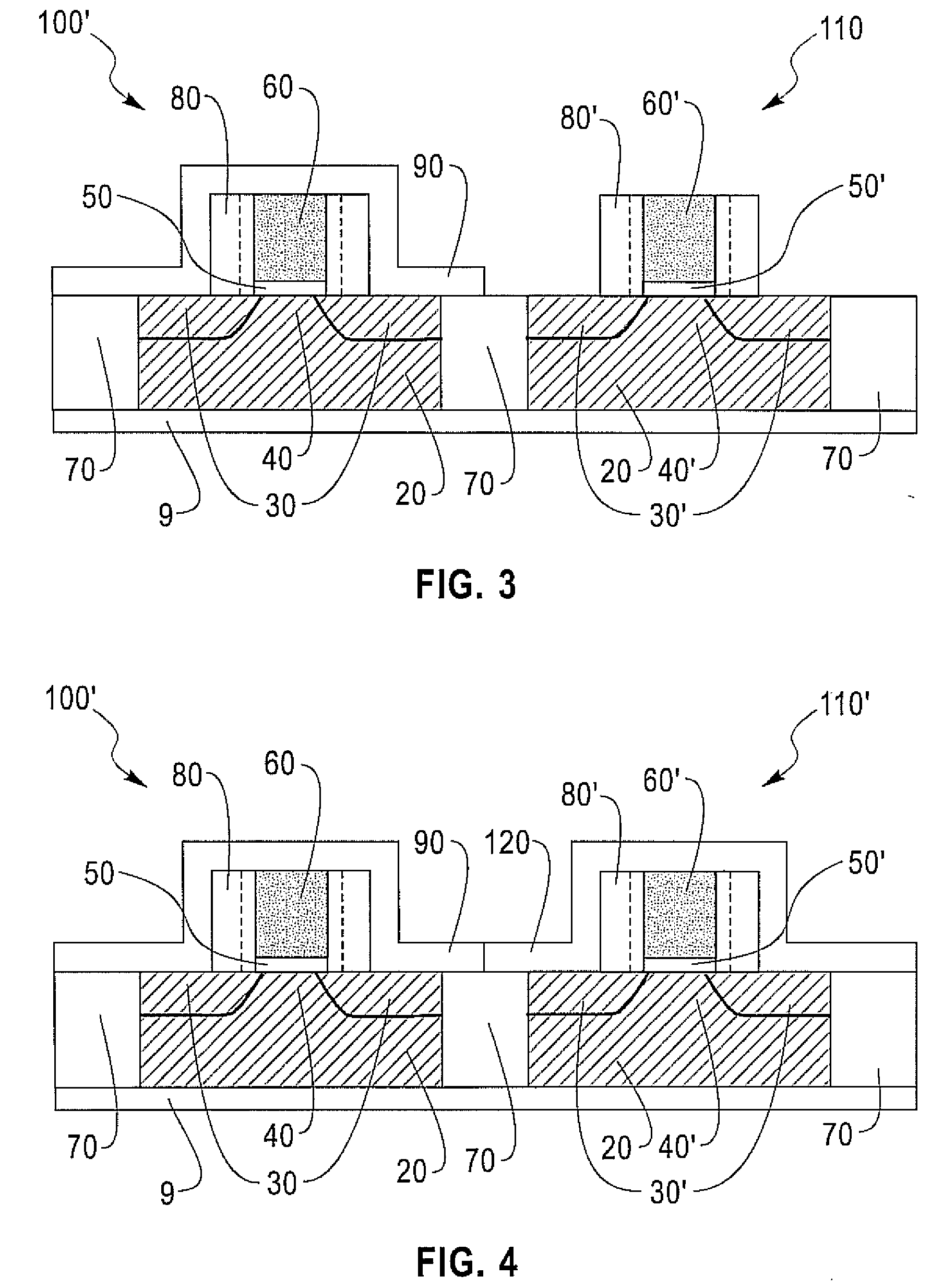

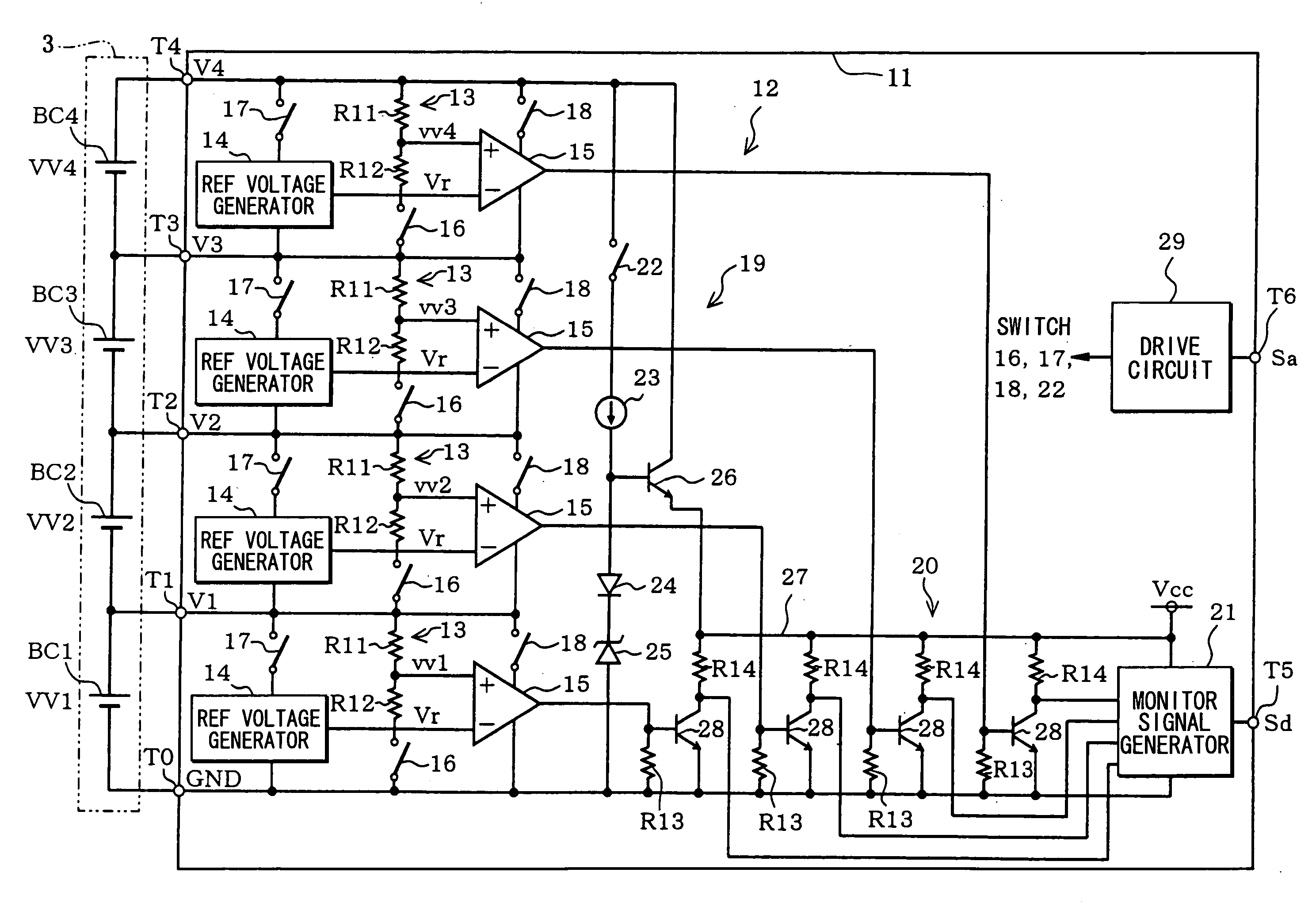

Semiconductor integrated circuit device

InactiveUS20080100266A1Reduce chip sizeTotal current dropCircuit monitoring/indicationIndicating/monitoring circuitsElectricityDevice form

A semiconductor integrated circuit device formed by a trench dielectric isolation technique has input terminals connected to positive and negative terminals of secondary cells of an assembled battery and includes monitor circuits for respectively monitoring cell voltages of the cells. Each monitor circuit includes a cell voltage detection circuit, a reference voltage generation circuit, and a comparison circuit. The cell voltage detection circuit divides a voltage between the input terminals connected to the positive and negative terminals of a corresponding cell and detects the cell voltage based on the divided voltage. The reference voltage generation circuit generates a reference voltage from the cell voltage. The comparison circuit is powered by the cell voltage of the corresponding cell and compares the divided voltage with the reference voltage.

Owner:DENSO CORP

Method for forming an L-shaped spacer using a disposable polysilicon spacer

InactiveUS6346468B1Excellent gap fillingAvoid large gapsTransistorSemiconductor/solid-state device manufacturingSemiconductor structurePolycrystalline silicon

A method for forming an L-shaped spacer using disposable polysilicon top spacers. A semiconductor structure is provided having a gate structure thereon. A liner oxide layer is formed on the gate structure. A dielectric spacer layer is formed on the liner oxide layer. A disposable polysilicon top spacer layer is formed on the dielectric spacer layer. The disposable polysilicon top spacer layer is anisotropically etched to form disposable polysilicon top spacers. The dielectric spacer layer is etched to form L-shaped dielectric spacers, using the disposable polysilicon top spacers as an etch mask. The disposable polysilicon top spacers are removed leaving an L-shaped dielectric spacer. In one embodiment, lightly doped source and drain regions are formed prior to forming the liner oxide layer and the L-shaped spacers.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

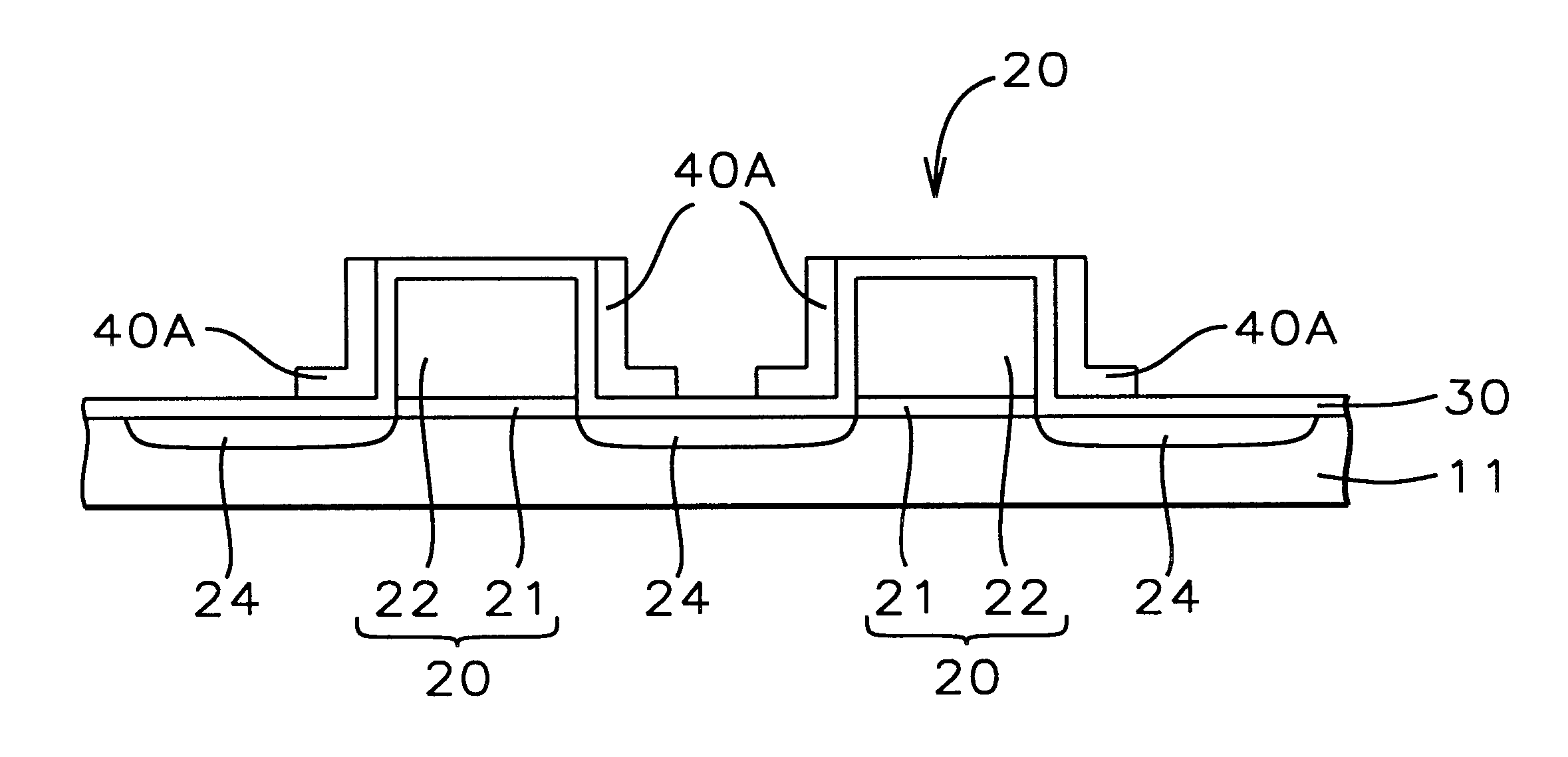

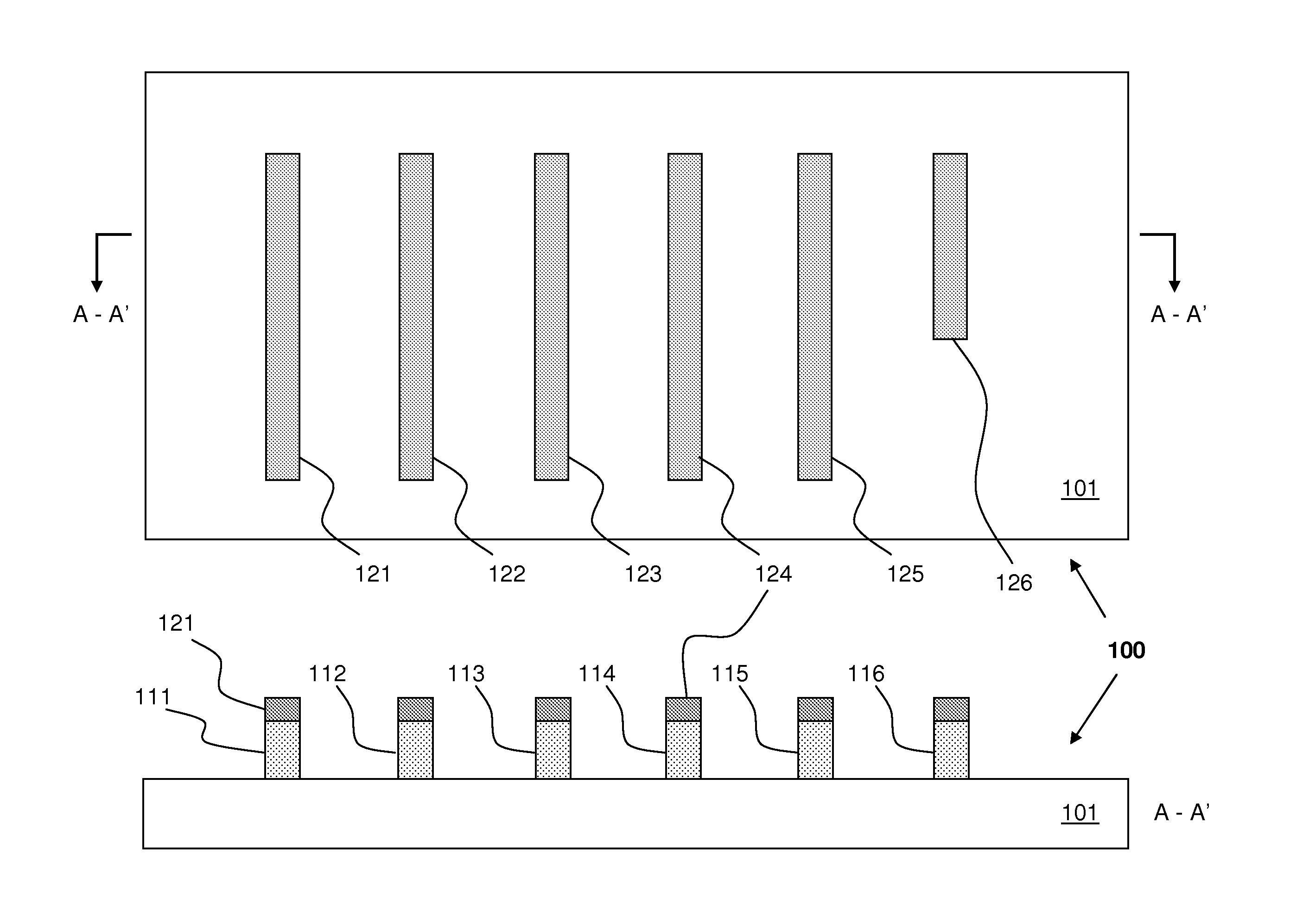

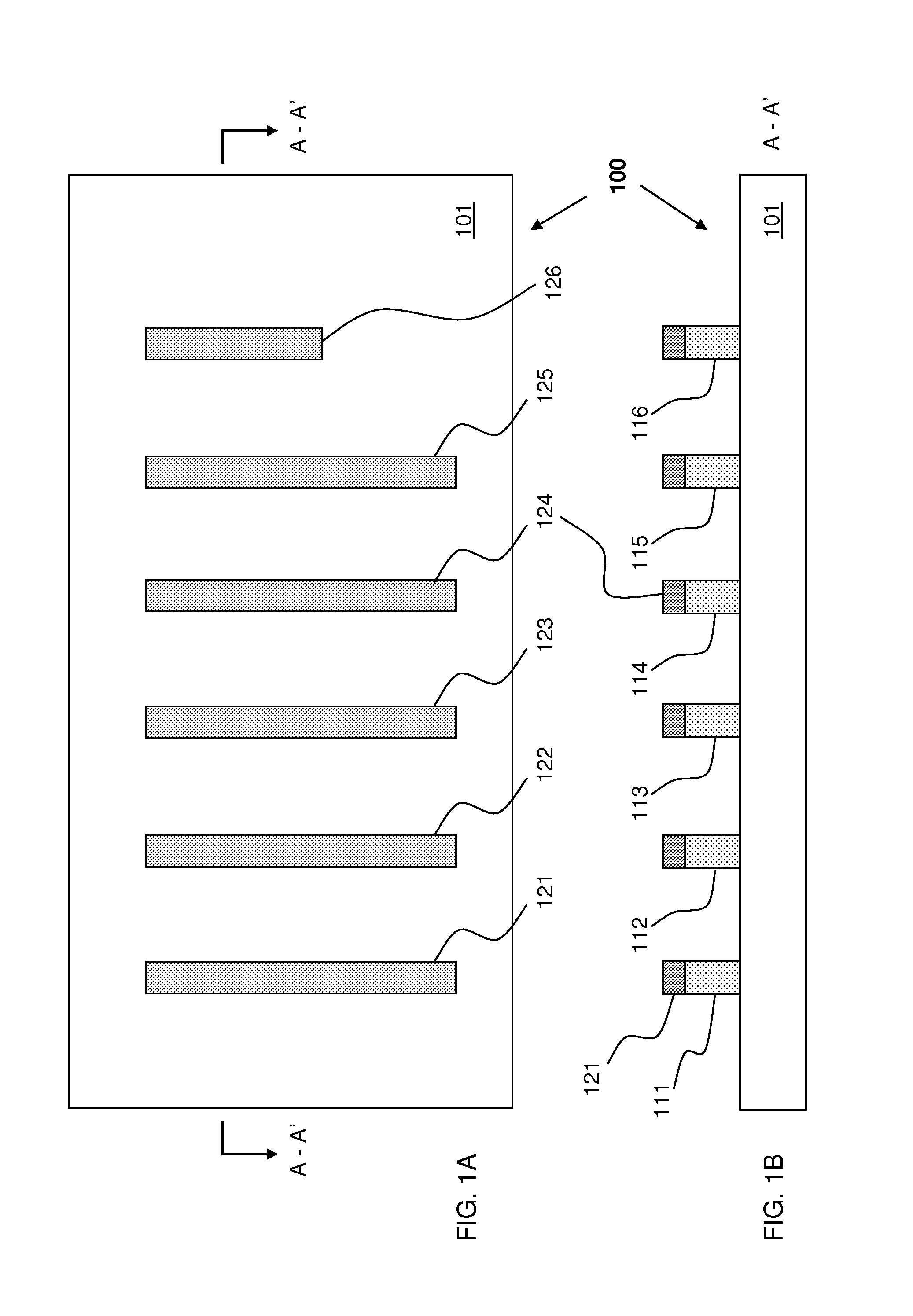

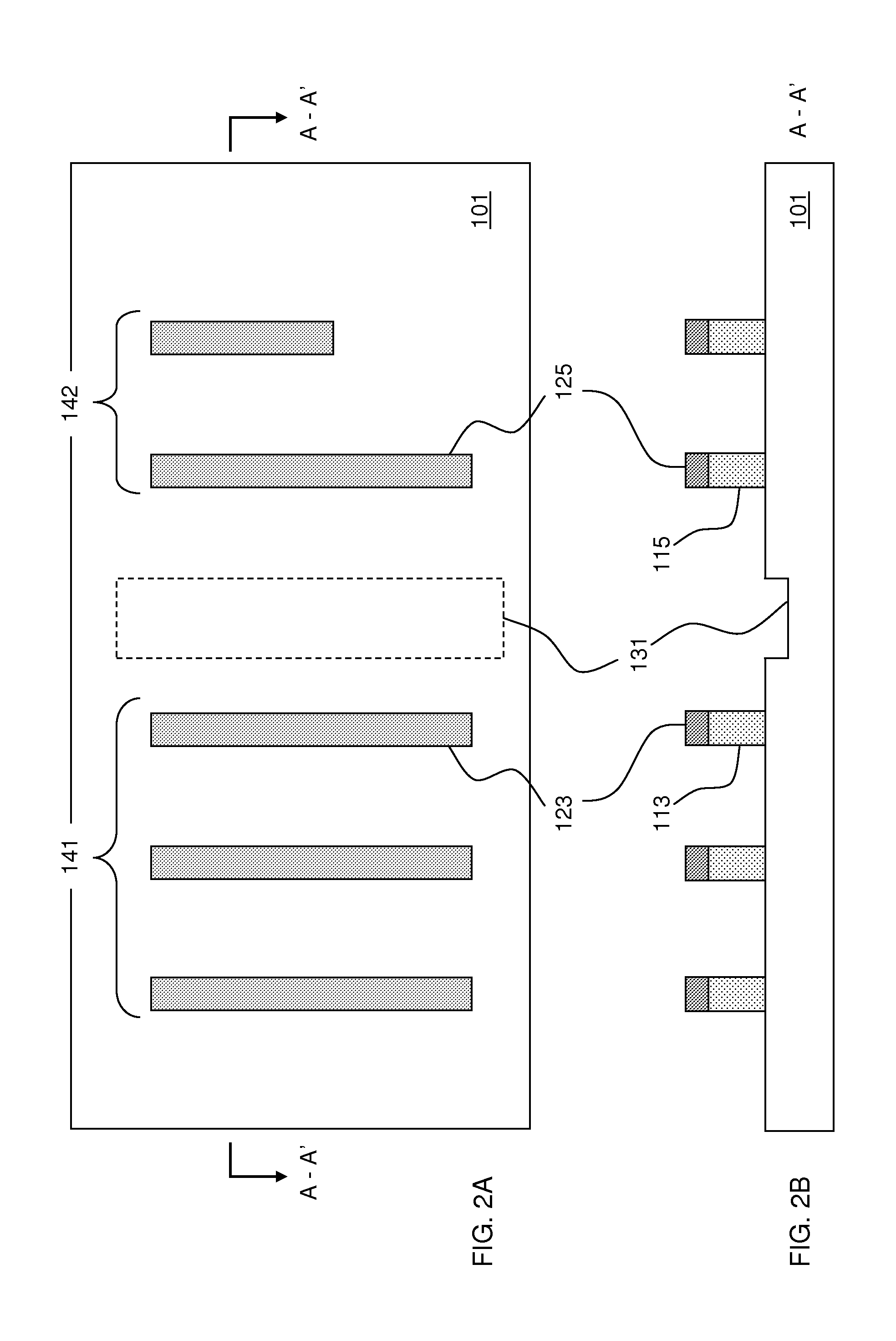

Self-aligned dielectric isolation for finfet devices

ActiveUS20140191296A1Solid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureEngineering

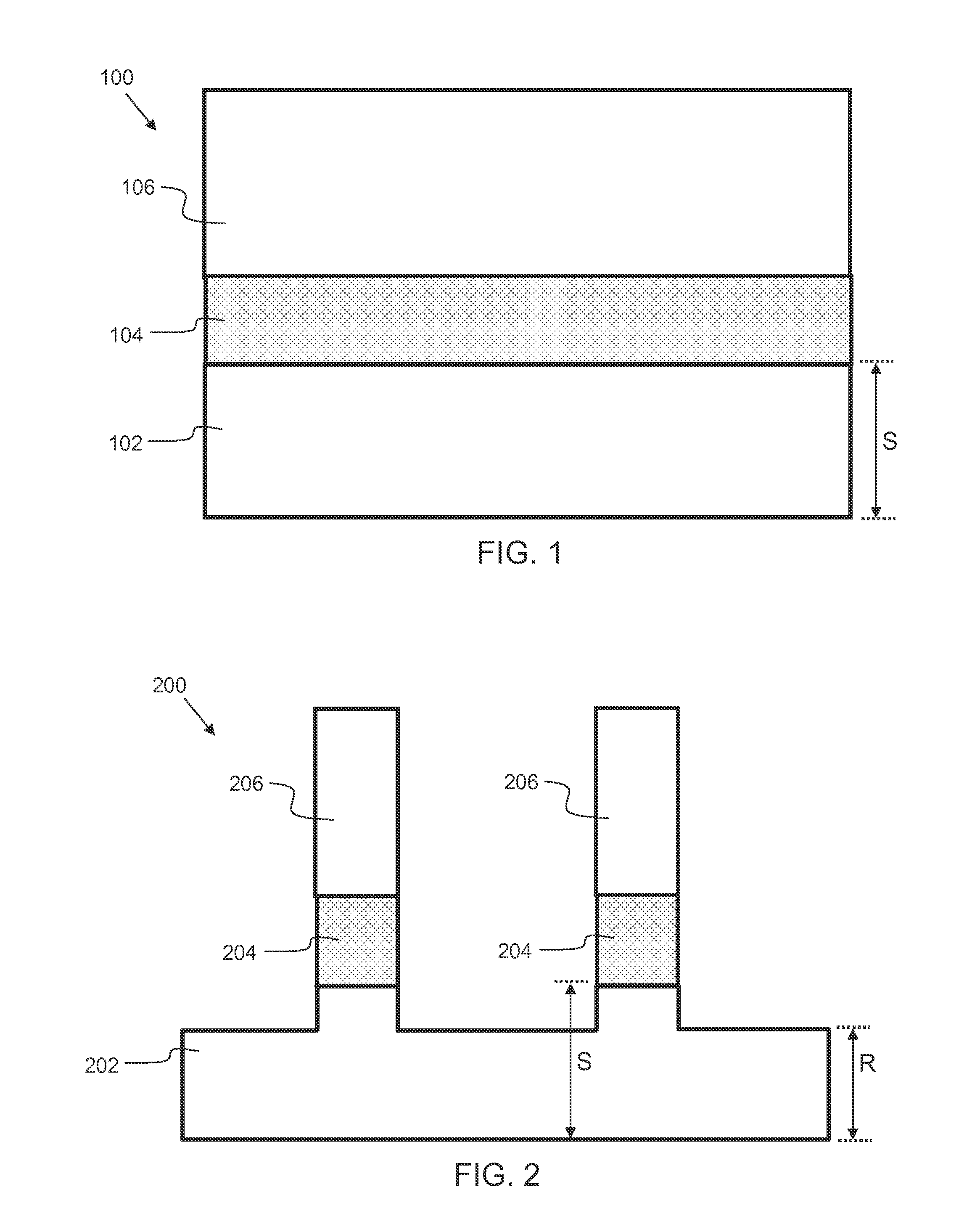

Embodiments of the present invention provide a method of forming semiconductor structure. The method includes forming a set of device features on top of a substrate; forming a first dielectric layer directly on top of the set of device features and on top of the substrate, thereby creating a height profile of the first dielectric layer measured from a top surface of the substrate, the height profile being associated with a pattern of an insulating structure that fully surrounds the set of device features; and forming a second dielectric layer in areas that are defined by the pattern to create the insulating structure. A structure formed by the method is also disclosed.

Owner:GLOBALFOUNDRIES US INC

Micro-electro-mechanical pressure sensor

ActiveUS20090013792A1Fluid pressure measurement by electric/magnetic elementsElectricityVibrating membrane

The present micro-electro-mechanical pressure sensor includes a substrate, a dielectric isolation layer, at least two electrodes, and a vibrating membrane. The substrate includes an acoustic cavity. The dielectric isolation layer is formed on the substrate, and the dielectric isolation layer includes a through hole corresponding to the acoustic cavity. The at least two electrodes are separately formed on the dielectric isolation layer. The vibrating membrane covers the through hole, and the vibrating membrane includes at least one carbon nanotube structure with two opposite ends. The two opposite ends of the carbon nanotube are respectively connected to at least a given one of the at least two electrodes.

Owner:TSINGHUA UNIV +1