Patents

Literature

1565 results about "Wafer bonding" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

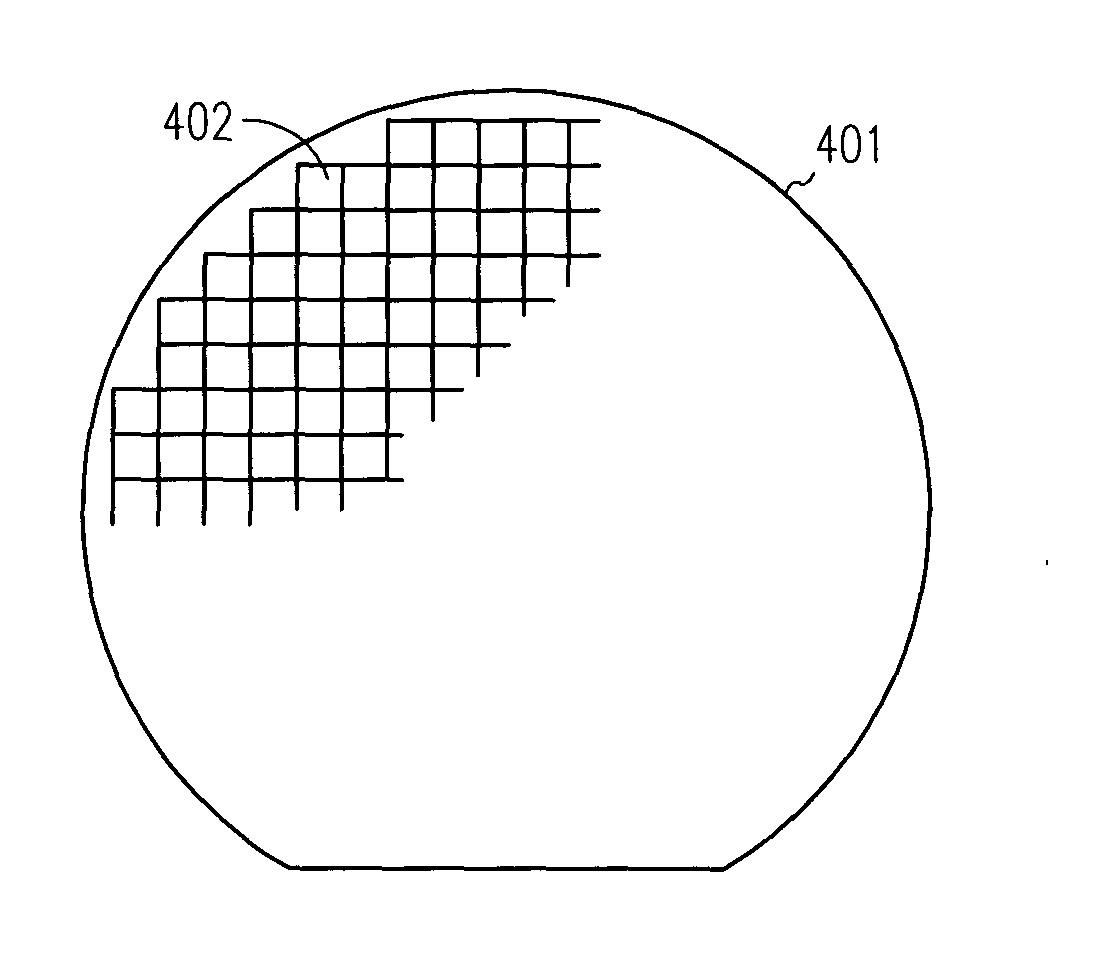

Wafer bonding is a packaging technology on wafer-level for the fabrication of microelectromechanical systems (MEMS), nanoelectromechanical systems (NEMS), microelectronics and optoelectronics, ensuring a mechanically stable and hermetically sealed encapsulation. The wafers' diameter range from 100 mm to 200 mm (4 inch to 8 inch) for MEMS/NEMS and up to 300 mm (12 inch) for the production of microelectronic devices. Smaller wafers were used in the early days of the microelectronics industry, with wafers being just 1 inch in diameter in the 1950s.

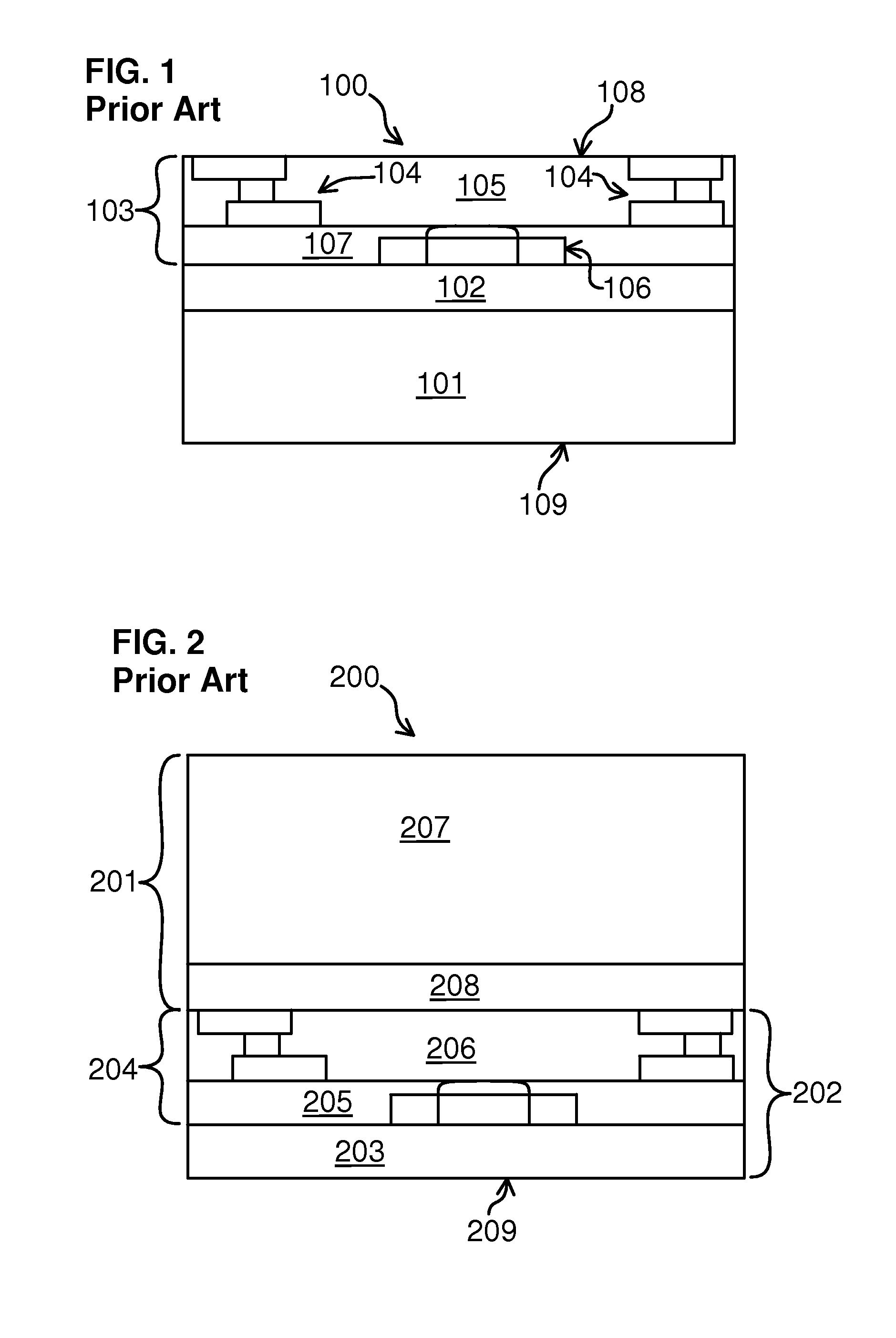

Three-dimensional integrated semiconductor devices

InactiveUS6943067B2Semiconductor/solid-state device detailsSolid-state devicesBonding processEngineering

The present invention describes a process for three-dimensional integration of semiconductor devices and a resulting device. The process combines low temperature wafer bonding methods with backside / substrate contact processing methods, preferably with silicon on insulator devices. The present invention utilizes, in an inventive fashion, low temperature bonding processes used for bonded silicon on insulator (SOI) wafer technology. This low temperature bonding technology is adopted for stacking several silicon layers on top of each other and building active transistors and other circuit elements in each one. The back-side / substrate contact processing methods allow the interconnection of the bonded SOI layers.

Owner:ADVANCED MICRO DEVICES INC

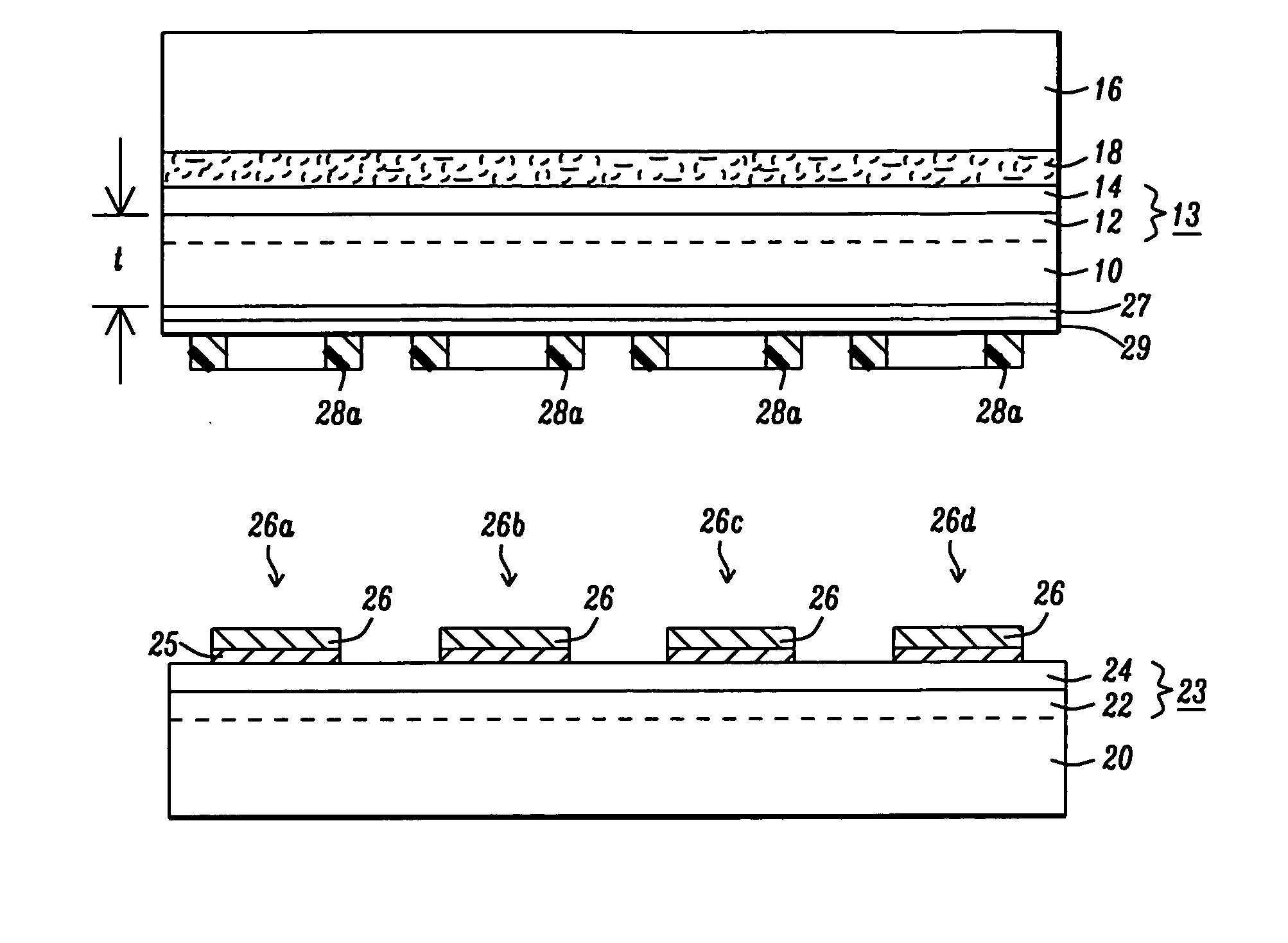

Wafer bonding of thinned electronic materials and circuits to high performance substrates

InactiveUS20040009649A1Material nanotechnologySemiconductor/solid-state device detailsWafer dicingEngineering

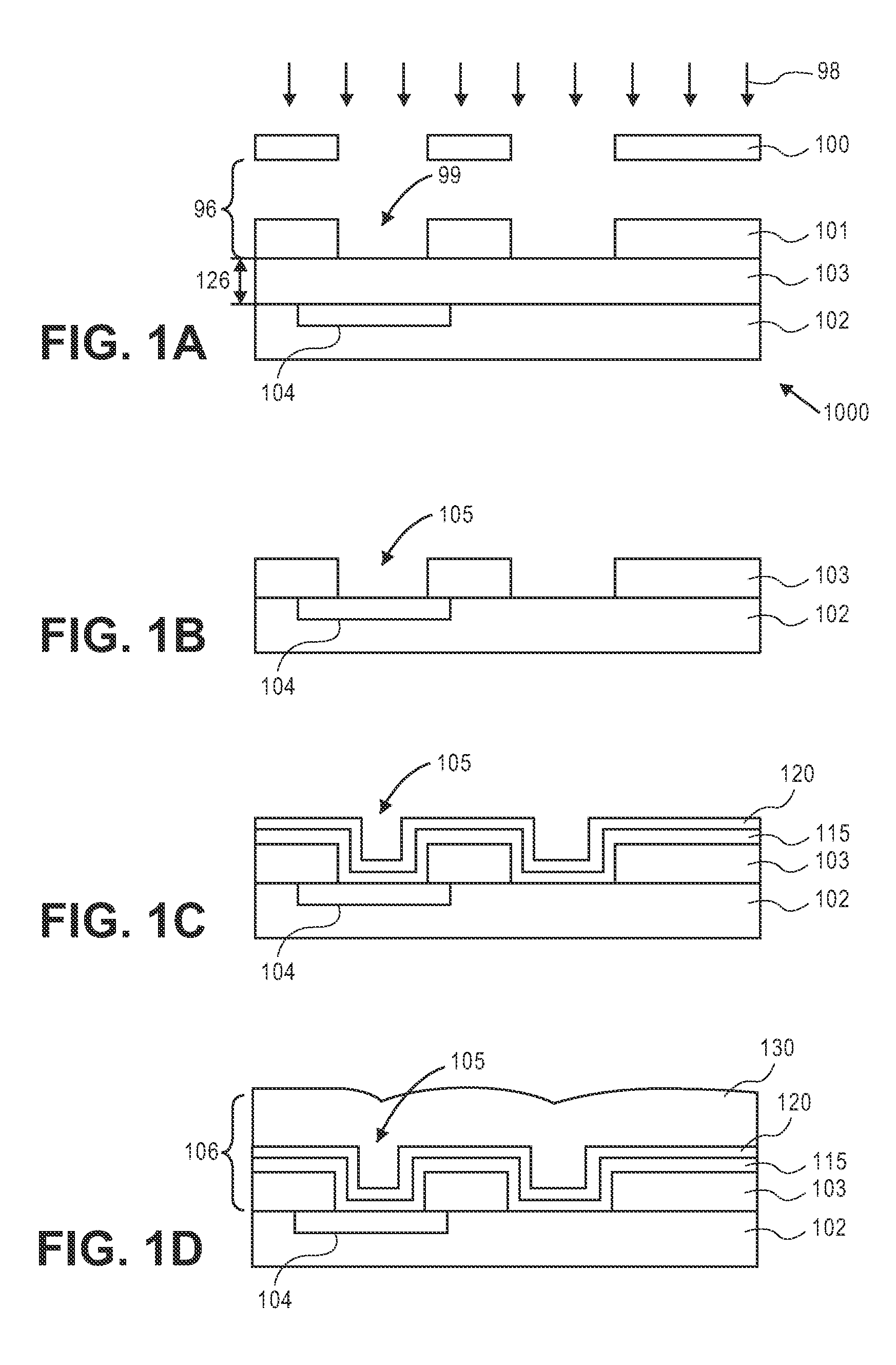

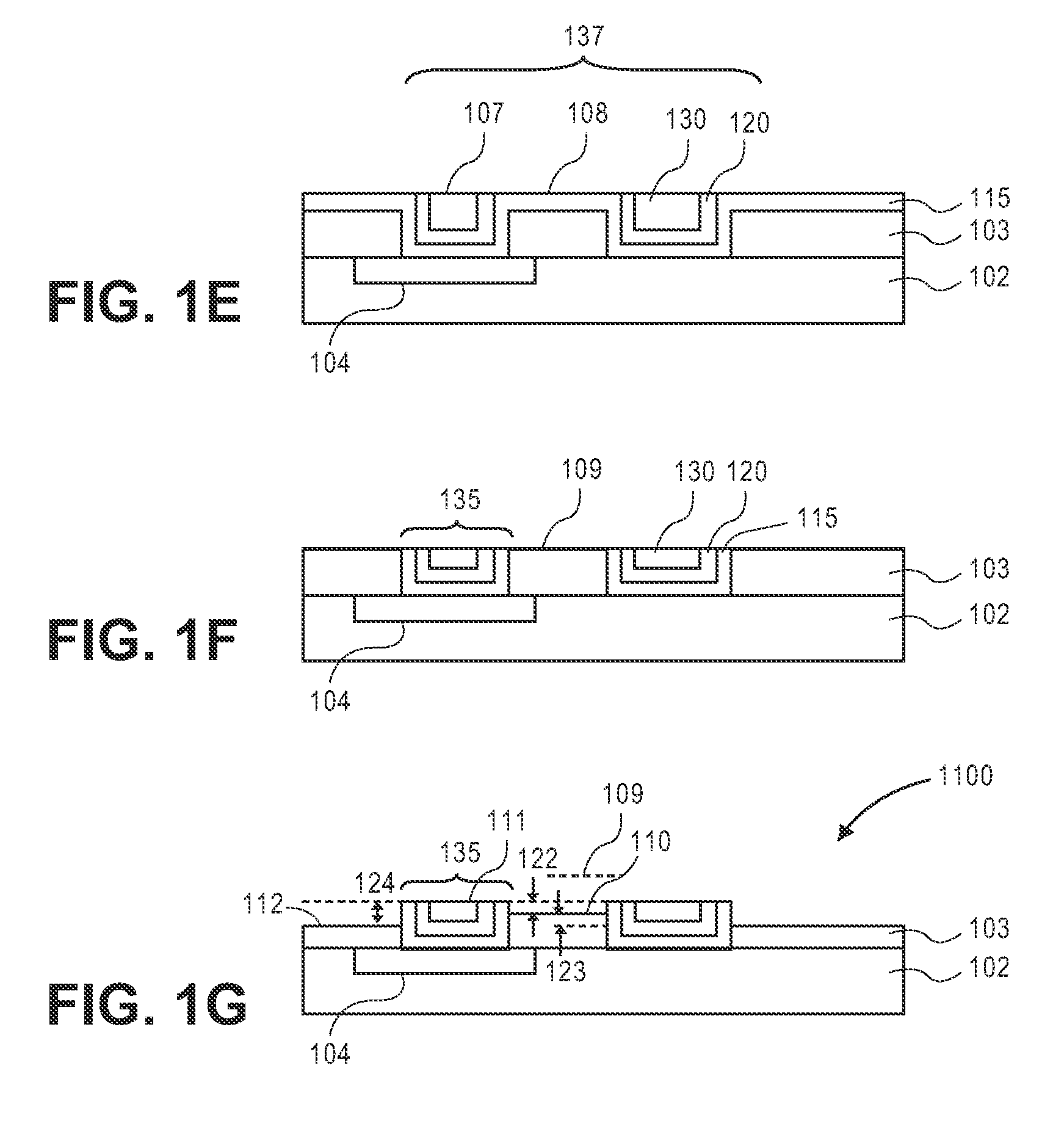

A method of bonding a wafer to a substrate comprising the steps of: providing a wafer having a front surface and a back surface; attaching the front surface of the wafer to a support; thinning the wafer from the back surface; bonding the back surface of the wafer to a substrate using a thin bonding technique; and removing the support from the front surface of the wafer. A circuit comprising: a substrate; and a wafer; wherein the wafer is at most about 50 microns thick; wherein the wafer has a front surface comprising features; and wherein the wafer has a back surface bonded to the substrate using a thin bonding technique.

Owner:THE UNITED STATES OF AMERICA AS REPRESENTED BY THE SECRETARY OF THE NAVY

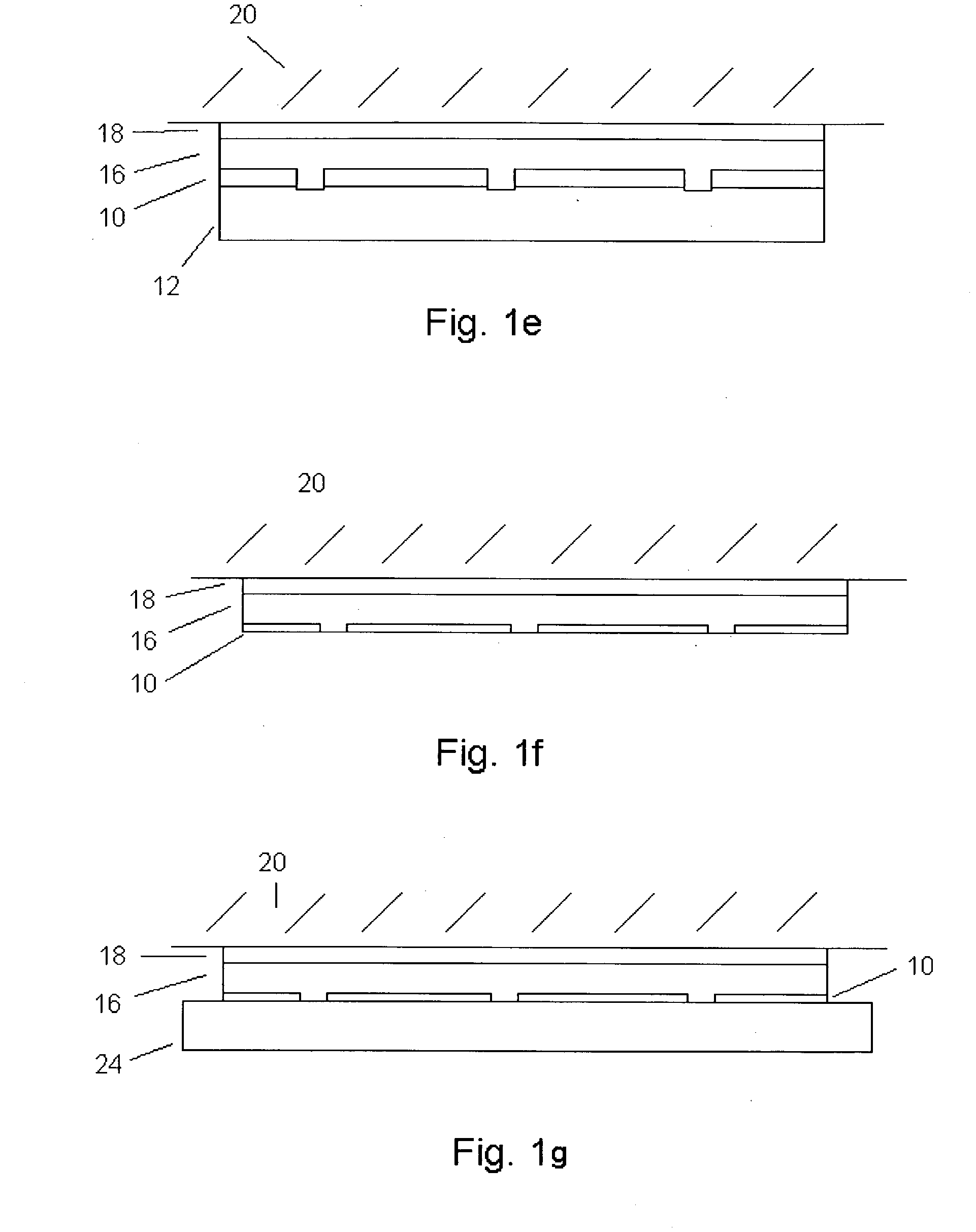

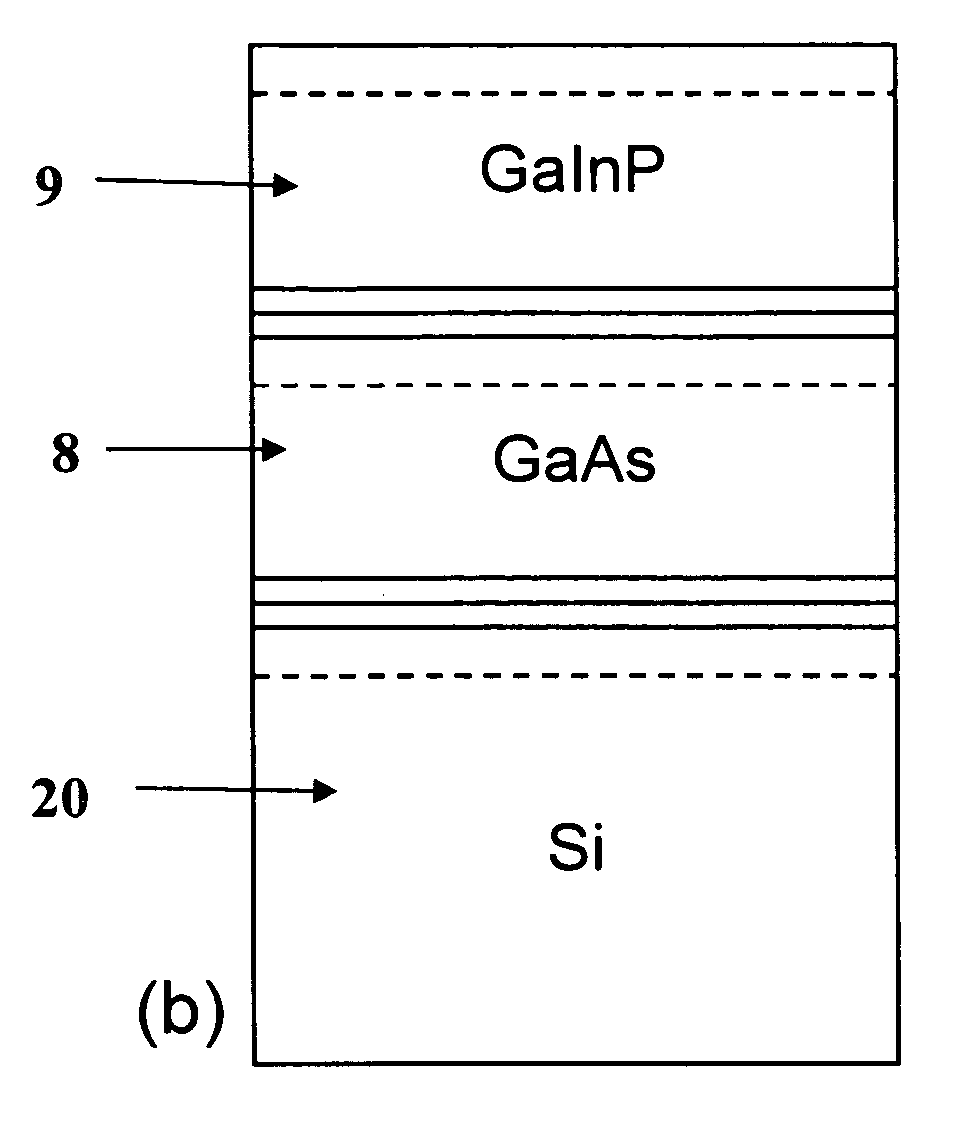

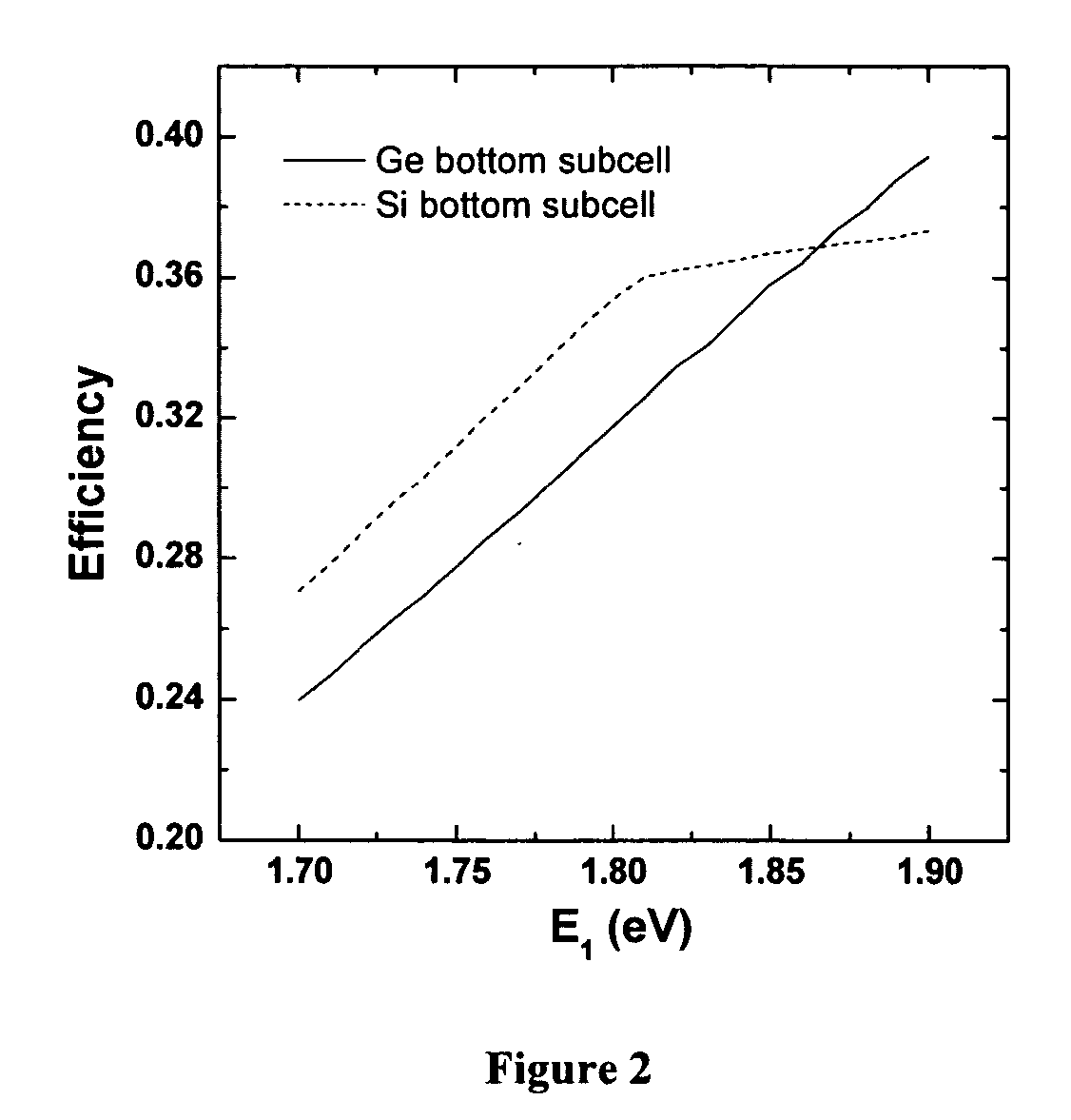

GaInP / GaAs / Si triple junction solar cell enabled by wafer bonding and layer transfer

InactiveUS20060021565A1Polycrystalline material growthFinal product manufactureBond interfaceWafer bonding

A multi-junction solar cell includes a silicon solar subcell, a GaInP solar subcell, and a GaAs solar subcell located between the silicon solar subcell and the GaInP solar subcell. The GaAs solar subcell is bonded to the silicon solar subcell such that a bonded interface exists between these subcells.

Owner:AONEX TECH

Temporary semiconductor structure bonding methods and related bonded semiconductor structures

ActiveUS20120013013A1Semiconductor/solid-state device detailsSolid-state devicesElectrical conductorSemiconductor structure

Methods of fabricating semiconductor structures include implanting atom species into a carrier die or wafer to form a weakened region within the carrier die or wafer, and bonding the carrier die or wafer to a semiconductor structure. The semiconductor structure may be processed while using the carrier die or wafer to handle the semiconductor structure. The semiconductor structure may be bonded to another semiconductor structure, and the carrier die or wafer may be divided along the weakened region therein. Bonded semiconductor structures are fabricated using such methods.

Owner:S O I TEC SILICON ON INSULATOR THECHNOLOGIES

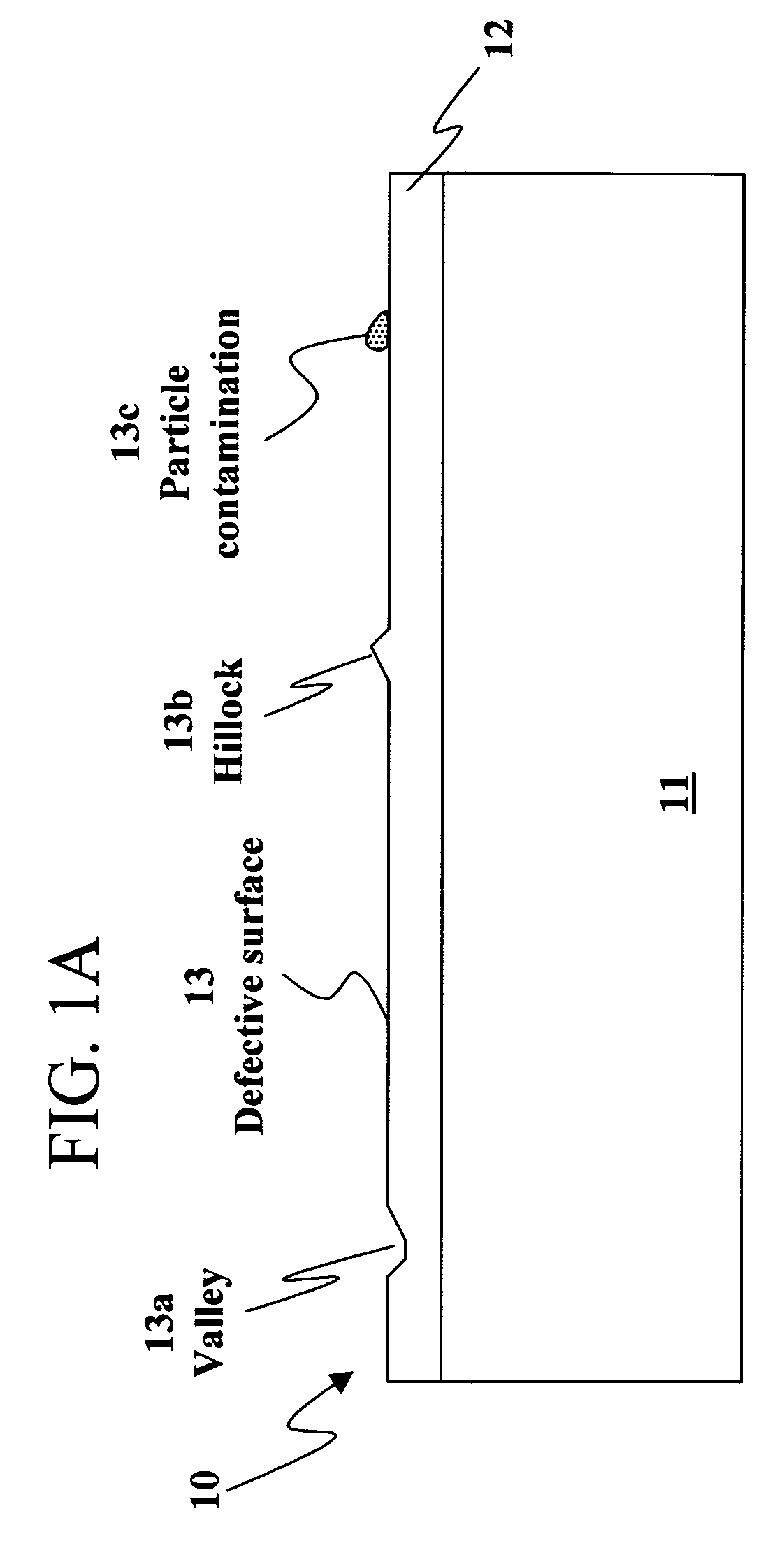

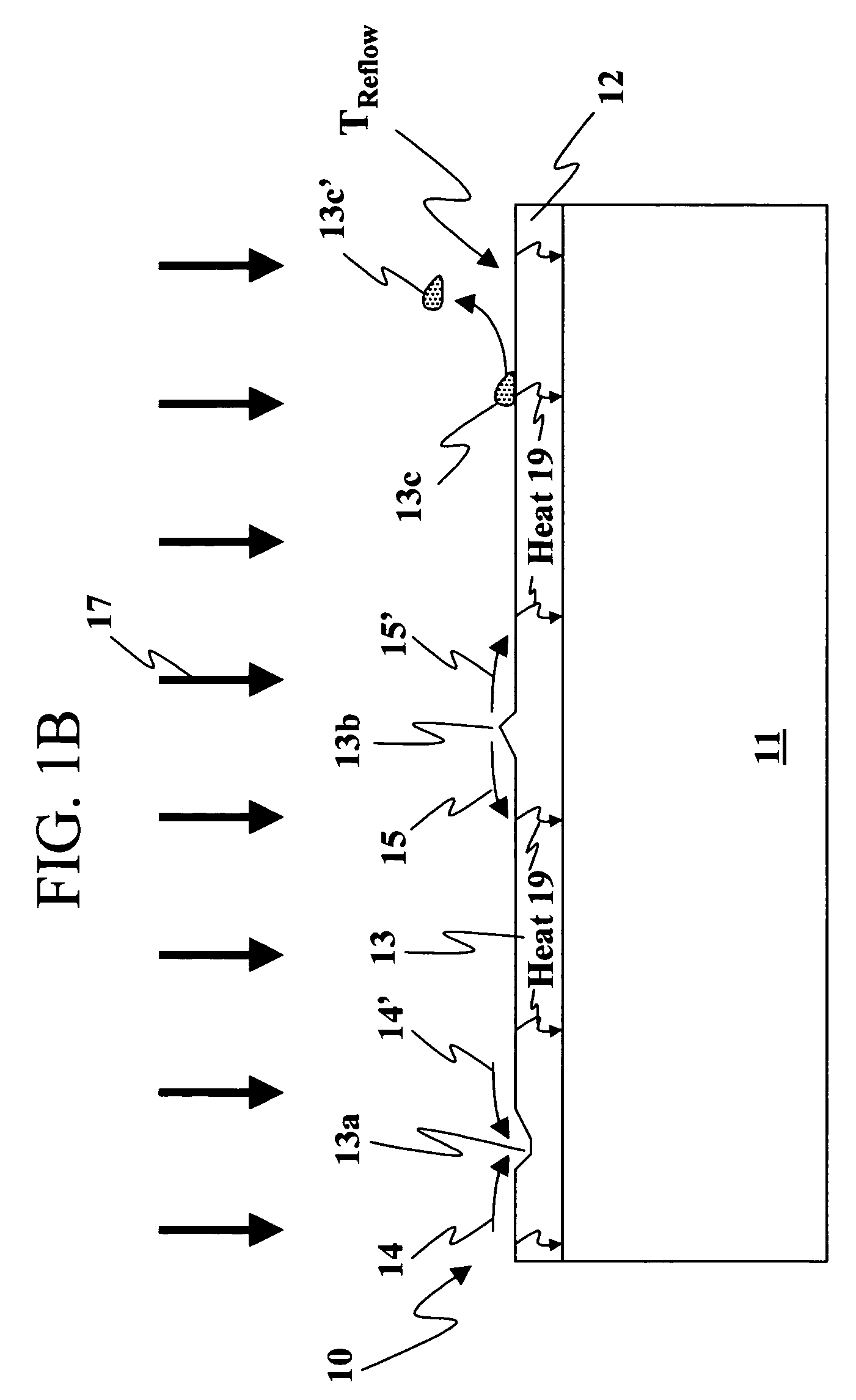

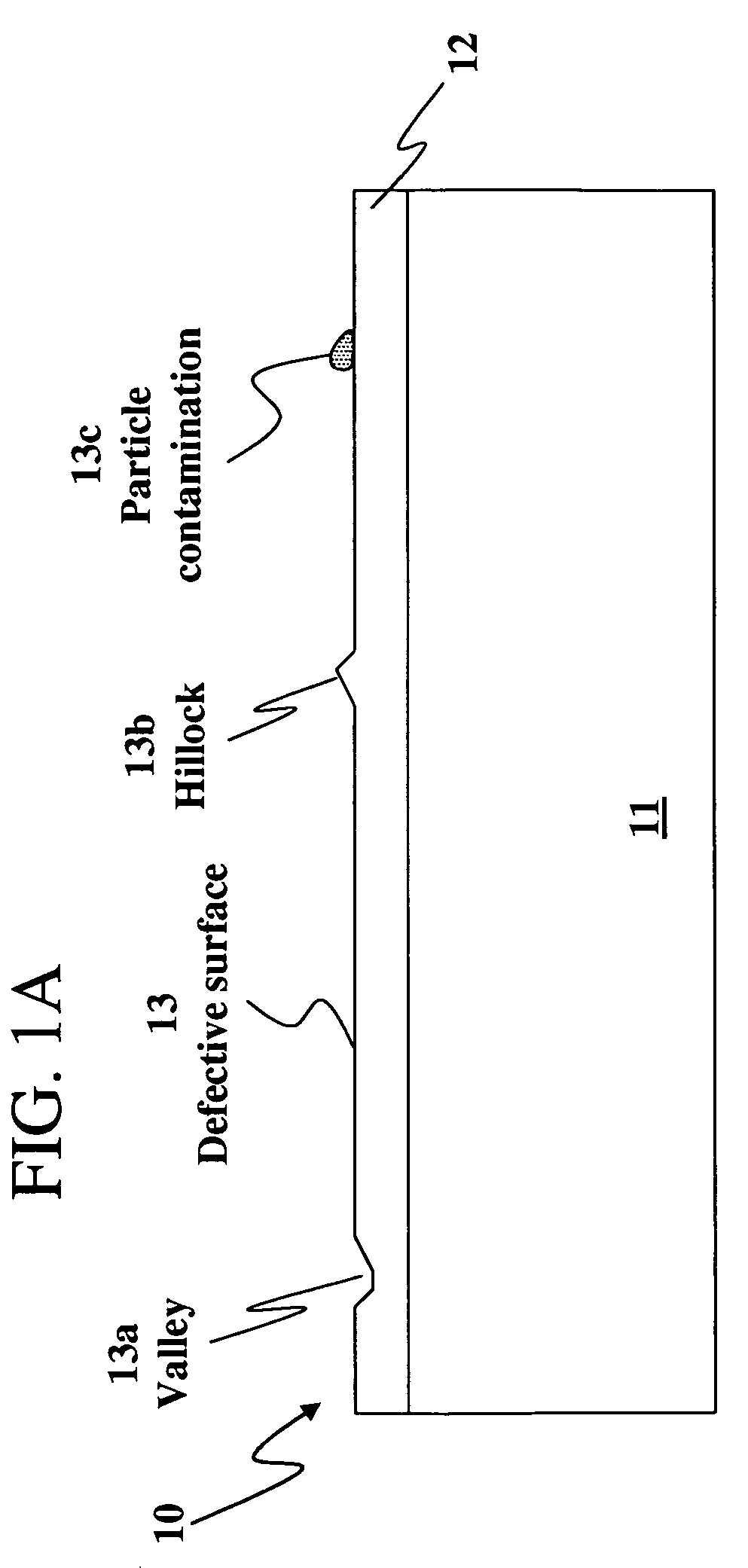

Wafer bonding method

ActiveUS7470142B2Reduce in quantityTransistorSemiconductor/solid-state device detailsEngineeringWafer bonding

A method of coupling substrates together includes steps of providing first and second substrates. The second substrate includes a conductive bonding region positioned on its surface. Heat is provided to the conductive bonding region to reduce its number of defects. The surface of the conductive bonding region is bonded to the first substrate so that the conductive bonding region and the first substrate are coupled together.

Owner:BESANG

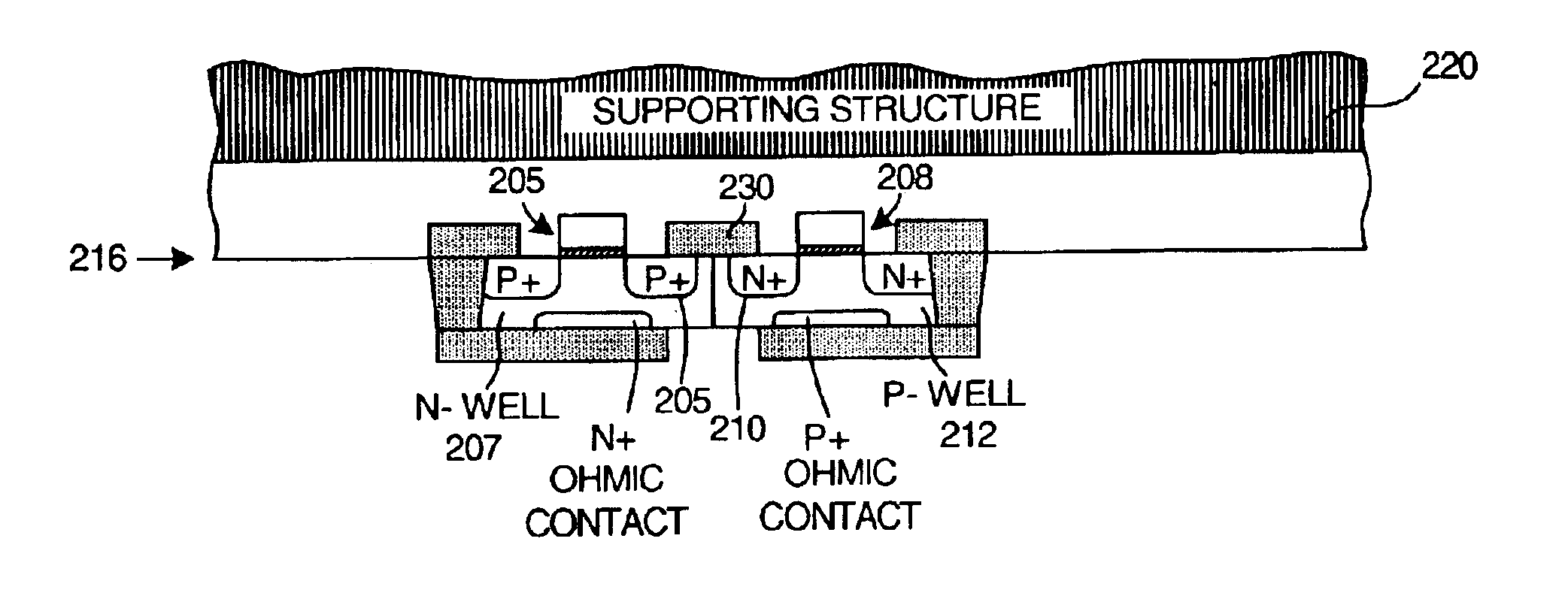

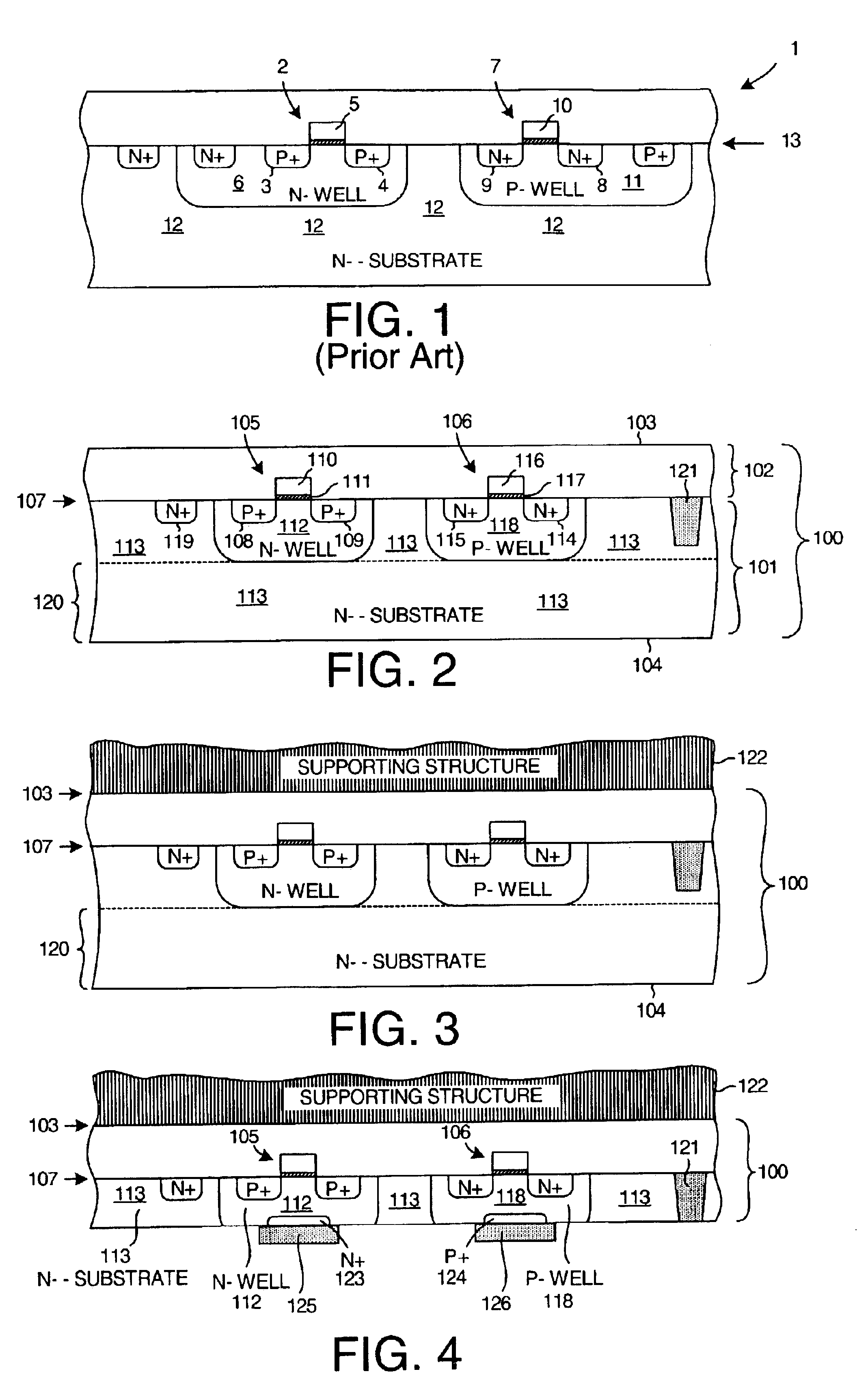

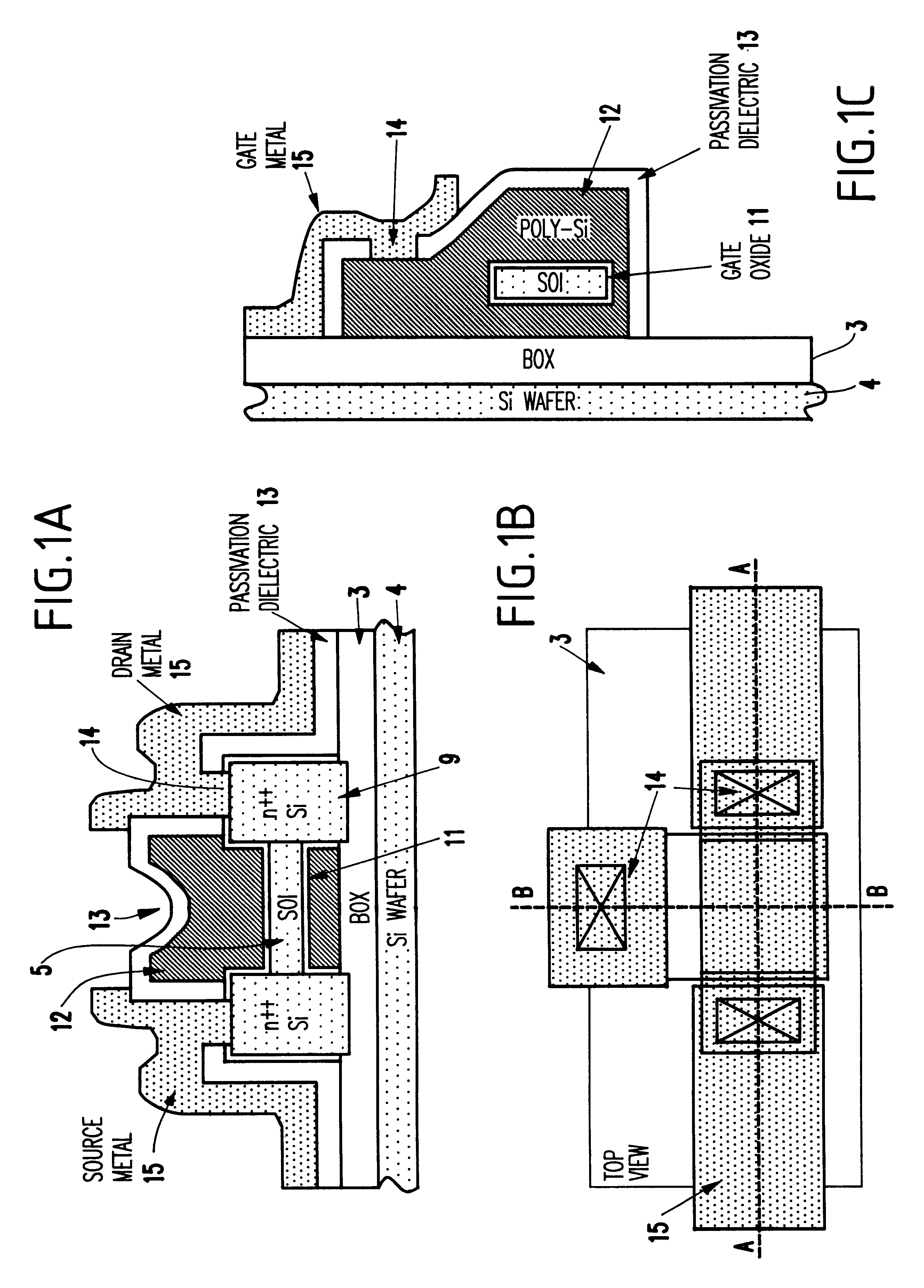

Semiconductor wafer with well contacts on back side

InactiveUS6864156B1Little source-to-wellImprove leakageTransistorSolid-state devicesCapacitanceEngineering

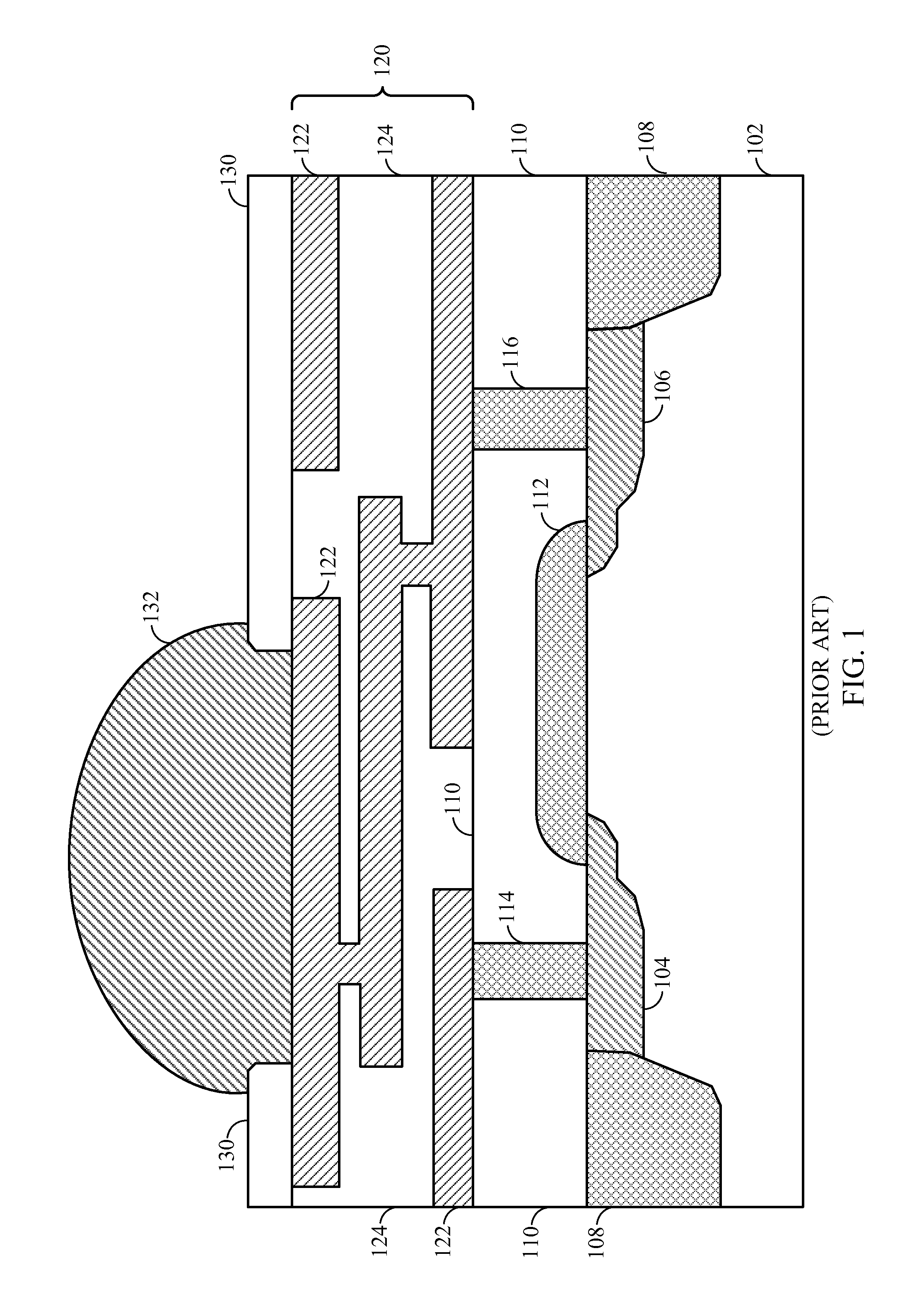

A supporting structure is wafer-bonded to the upper face side of a partially or fully processed device wafer. The device wafer includes a transistor having a well region that extends into the substrate material of the device wafer. The source and drain regions of the transistor extend into the well region. After attachment of the supporting structure, the device wafer is thinned from the back side until the bottom of the well region is reached. To reduce source and drain junction capacitances, etching can continue until the source and drain regions are reached. In one embodiment, all of the well-to-substrate junction is removed in a subsequent etching step, thereby reducing or eliminating the well-to-substrate junction capacitance of the resulting transistor. Resistance between the well electrode and the transistor channel is reduced because the well contact is disposed on the back side of the device wafer directly under the gate of the transistor.

Owner:XILINX INC

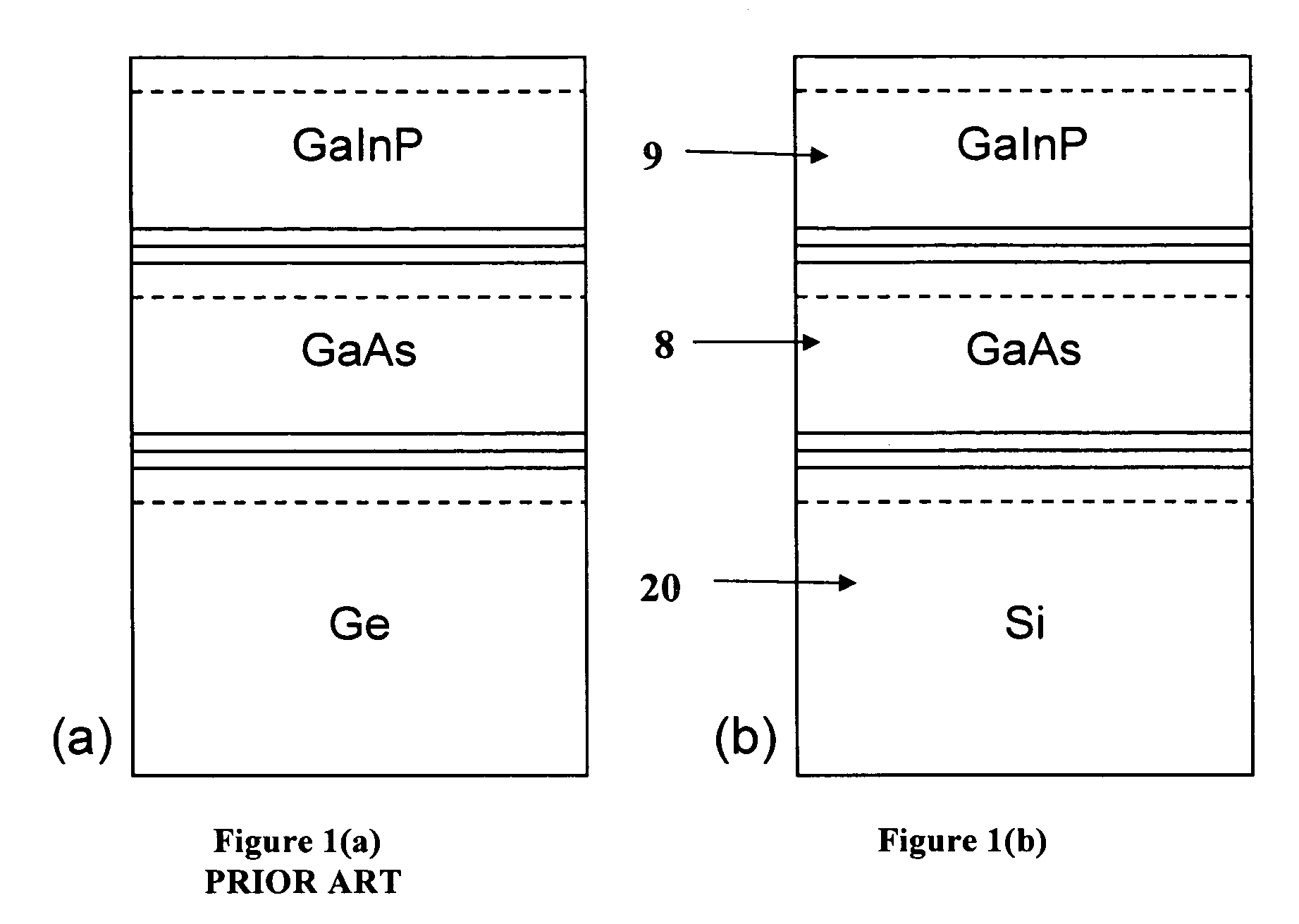

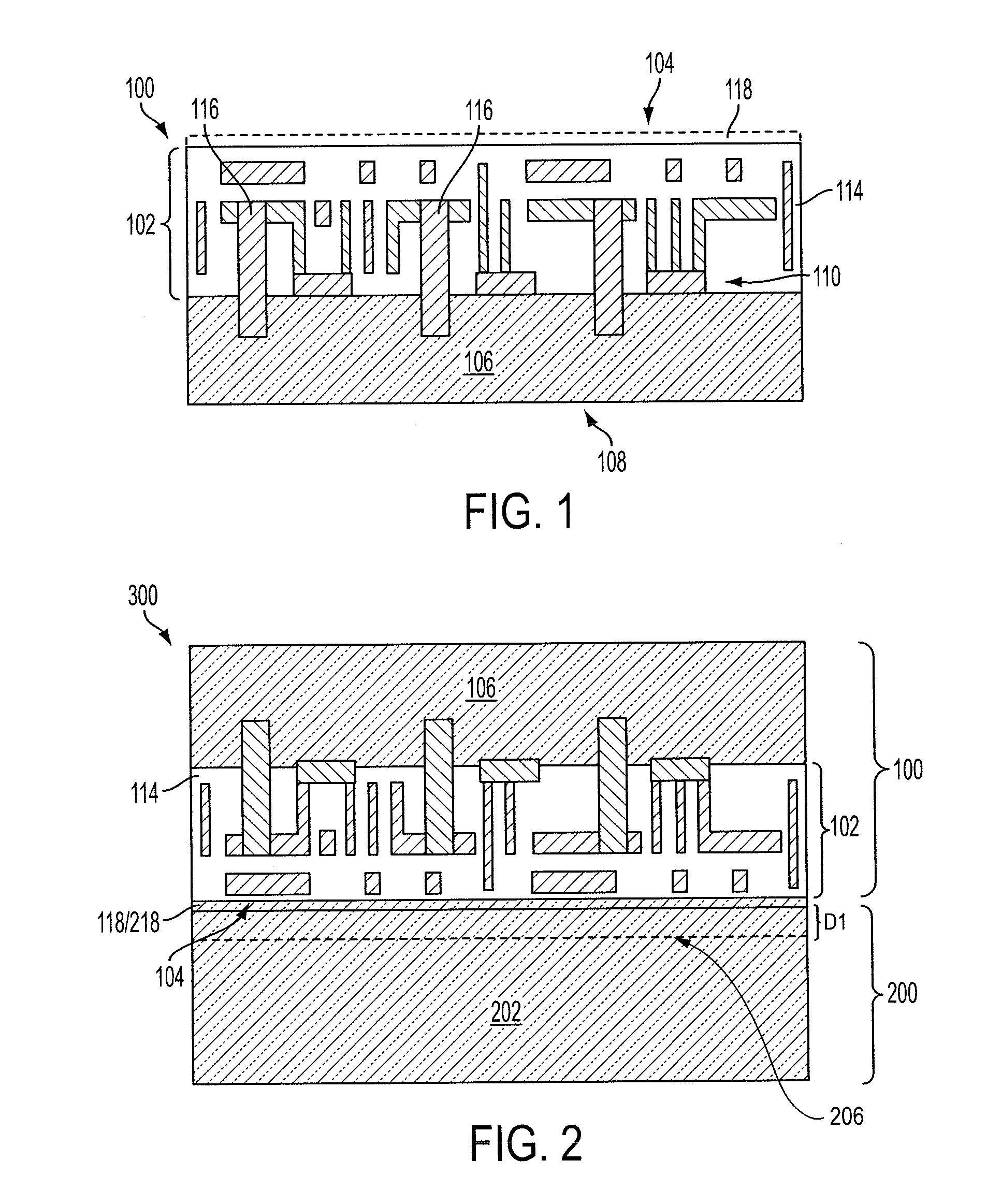

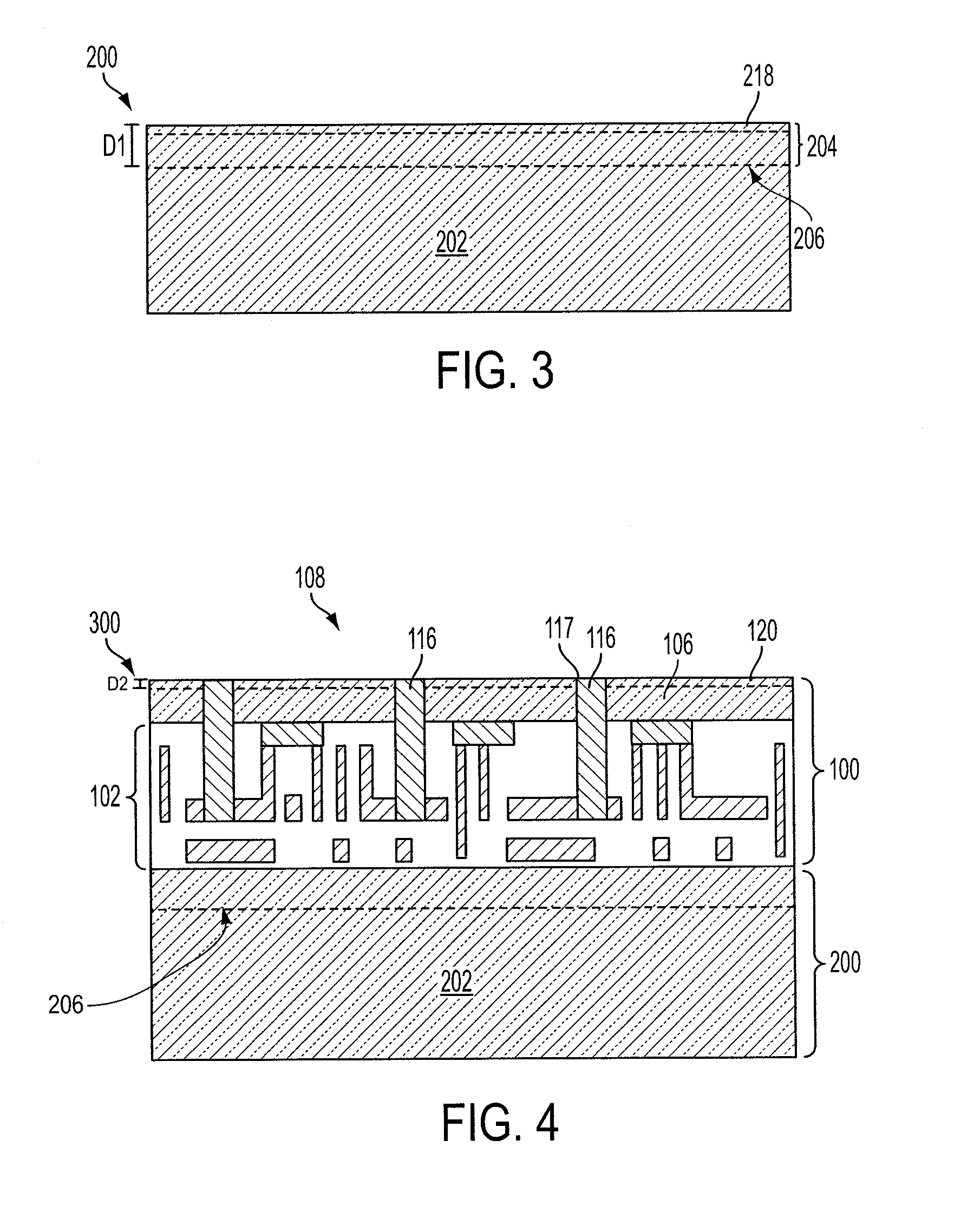

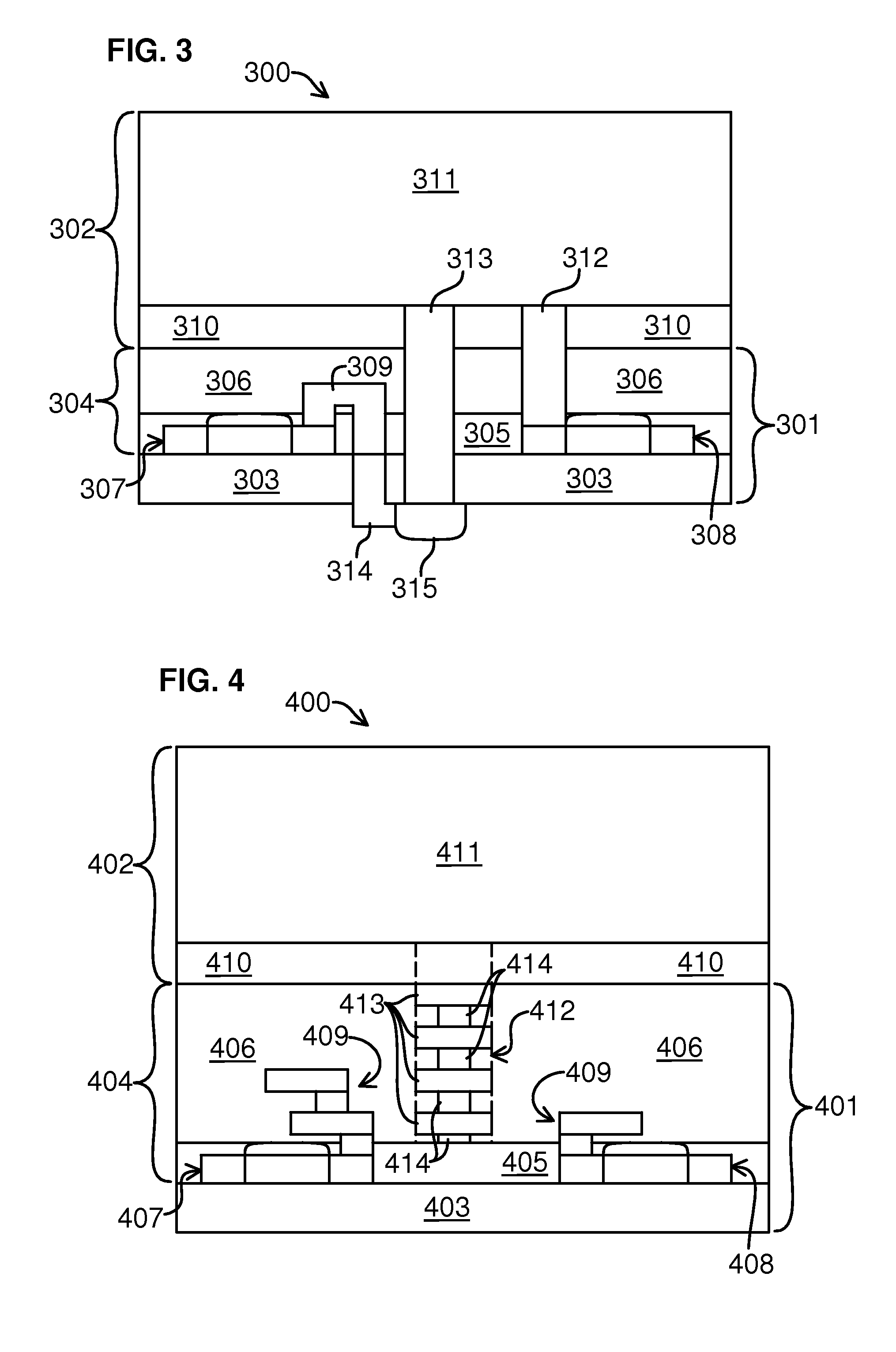

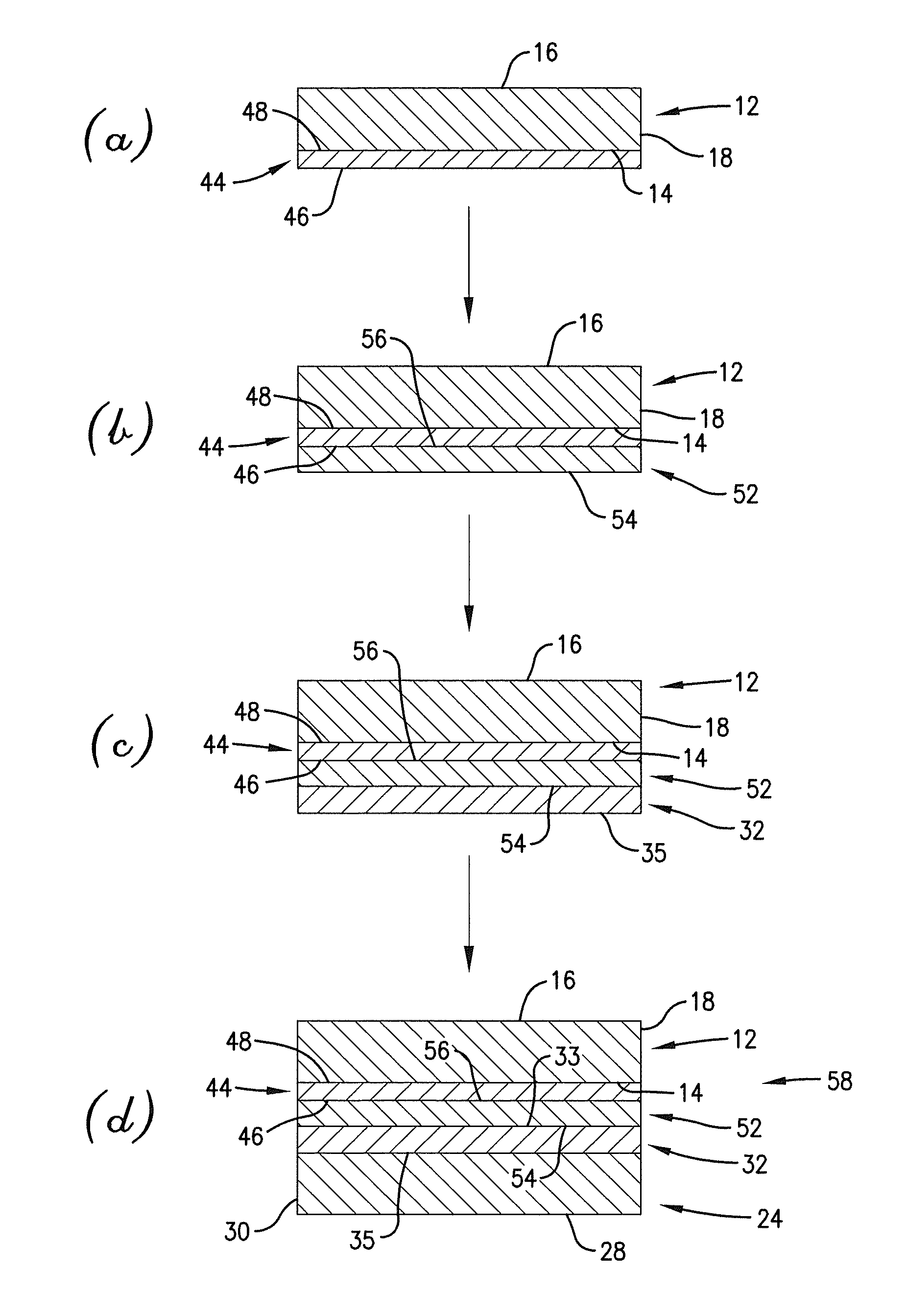

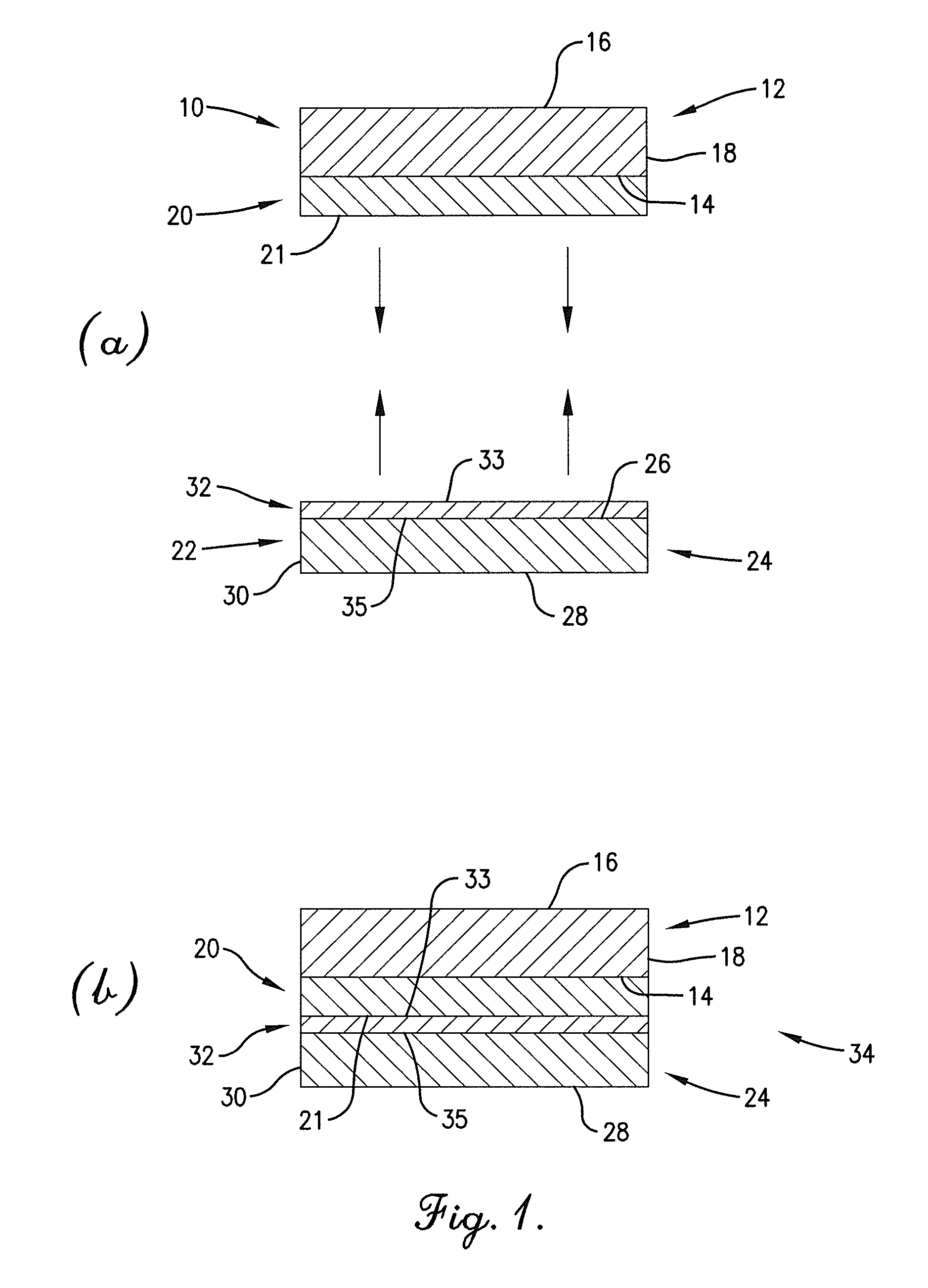

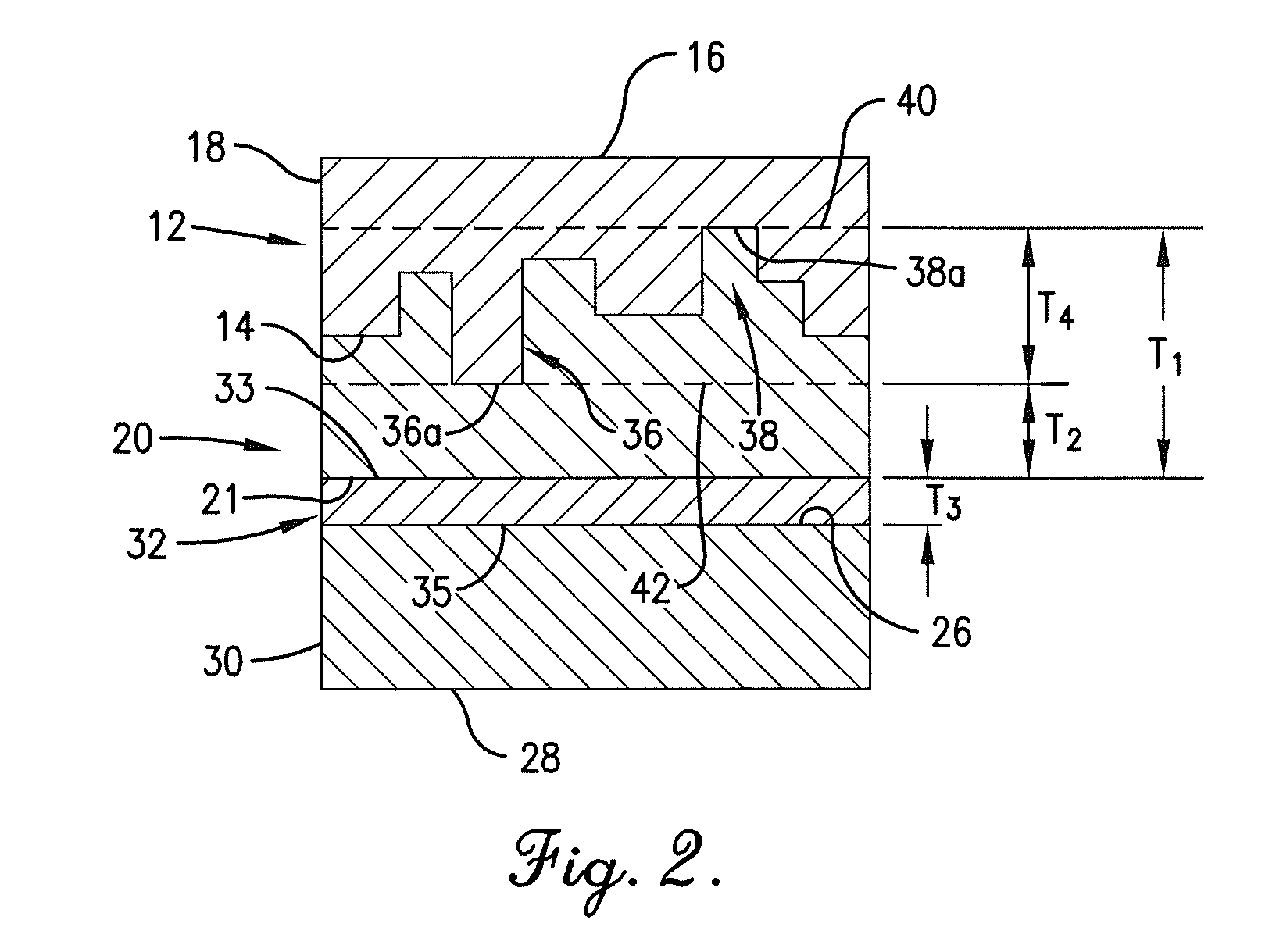

Method of stacking thin substrates by transfer bonding

InactiveUS20060057836A1Semiconductor/solid-state device detailsSolid-state devicesCost effectivenessAdhesive

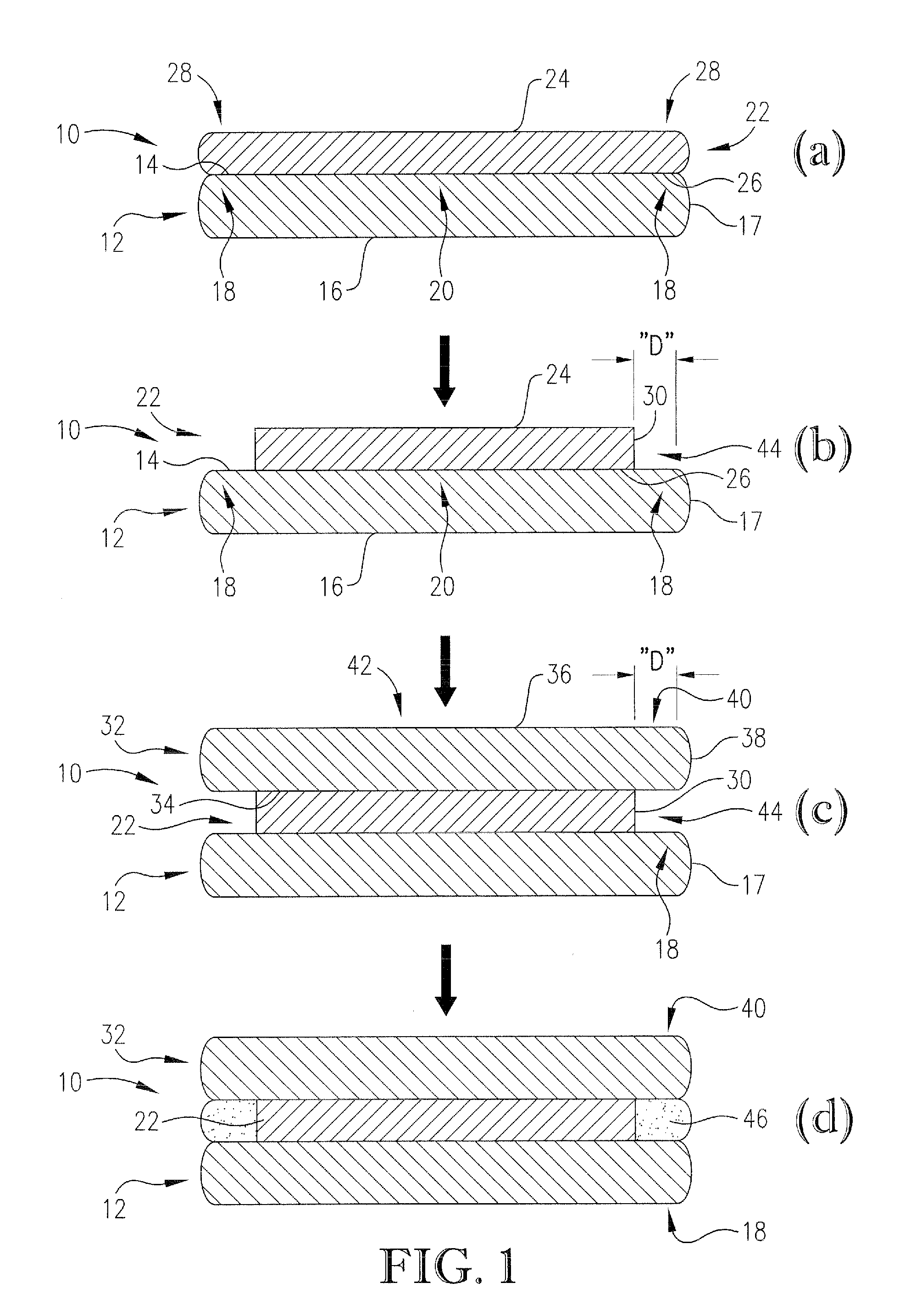

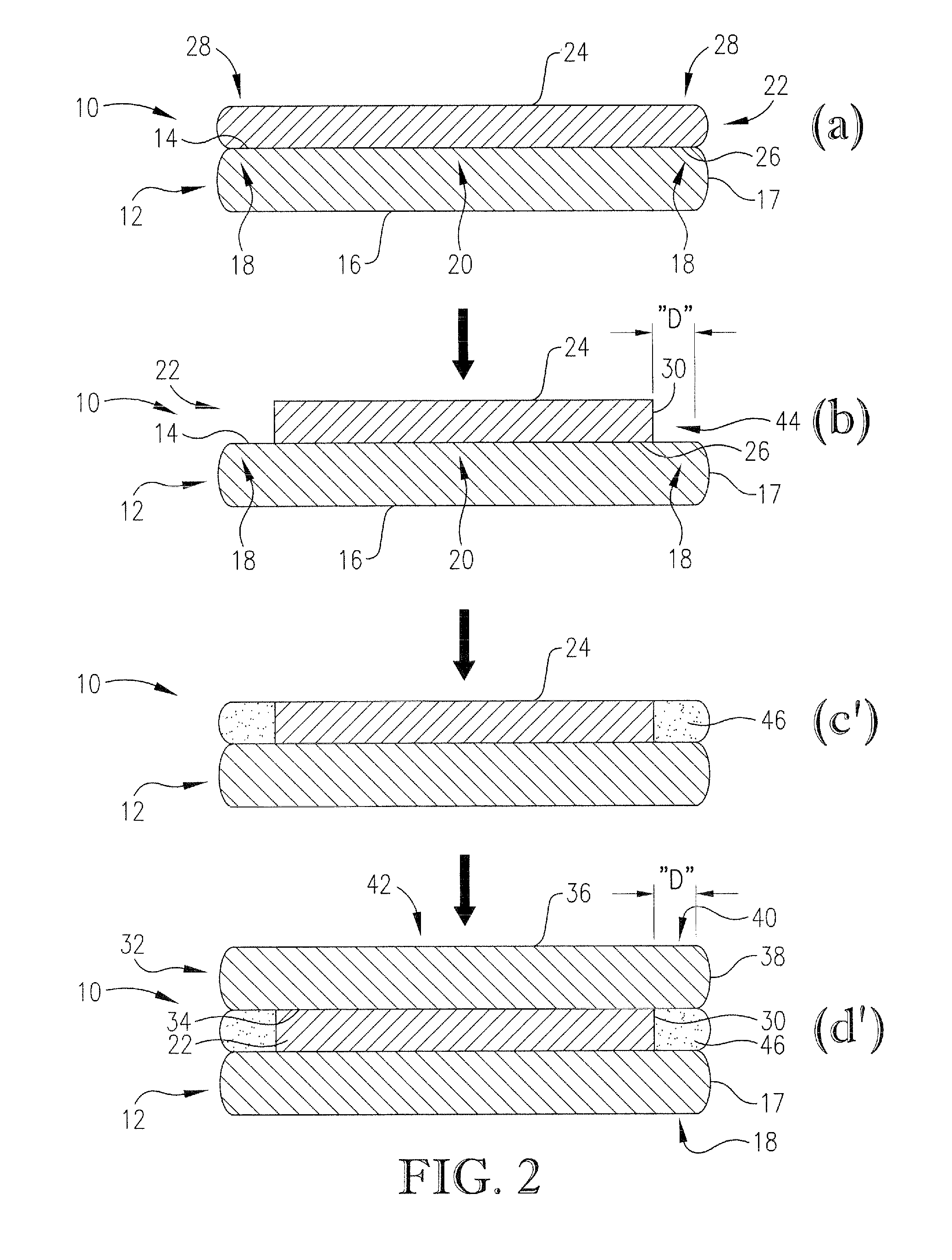

This invention describes a method of stacking, bonding, and electrically interconnecting a plurality of thin integrated circuit wafers to form an interconnected stack of integrated circuit layers. The first integrated circuit layer is formed by conventional processing on a silicon wafer to the stage where bond pads are patterned on a wiring layer interconnecting the subjacent semiconductive devices. The remaining integrated circuit layers are formed by first processing a standard wafer to form integrated circuit devices and wiring levels up to but not including bond pads. Each of these wafers is mounted onto a handler wafer by its upper face with a sacrificial bonding agent. The wafer is thinned, permanently fastened to the top surface of the first base wafer by a non-conductive adhesive applied to the thinned under face, and dismounted from the handler. Vertical openings are etched through the thinned layer to the bond pads on the subjacent wafer. Robust conductive pass-through plugs with integrated upper bond pads are formed in the openings. Additional thinned integrated circuit layers may be prepared, thinned, cemented onto the stack. Wiring interconnections can be made between any two or more layers. The process is unique in that it can be used to further stack and interconnect any number of thinned wafer layers to form a three dimensional integrated circuits, including MEMS devices. This approach provides a low temperature wafer bonding method using an adhesive which results in process simplicity and cost effectiveness by eliminating an additional masking and patterning process for under bump metal thereby enabling standard wafers to be integrated into a 3D stack with existing wire bonded wafers.

Owner:AGENCY FOR SCI TECH & RES

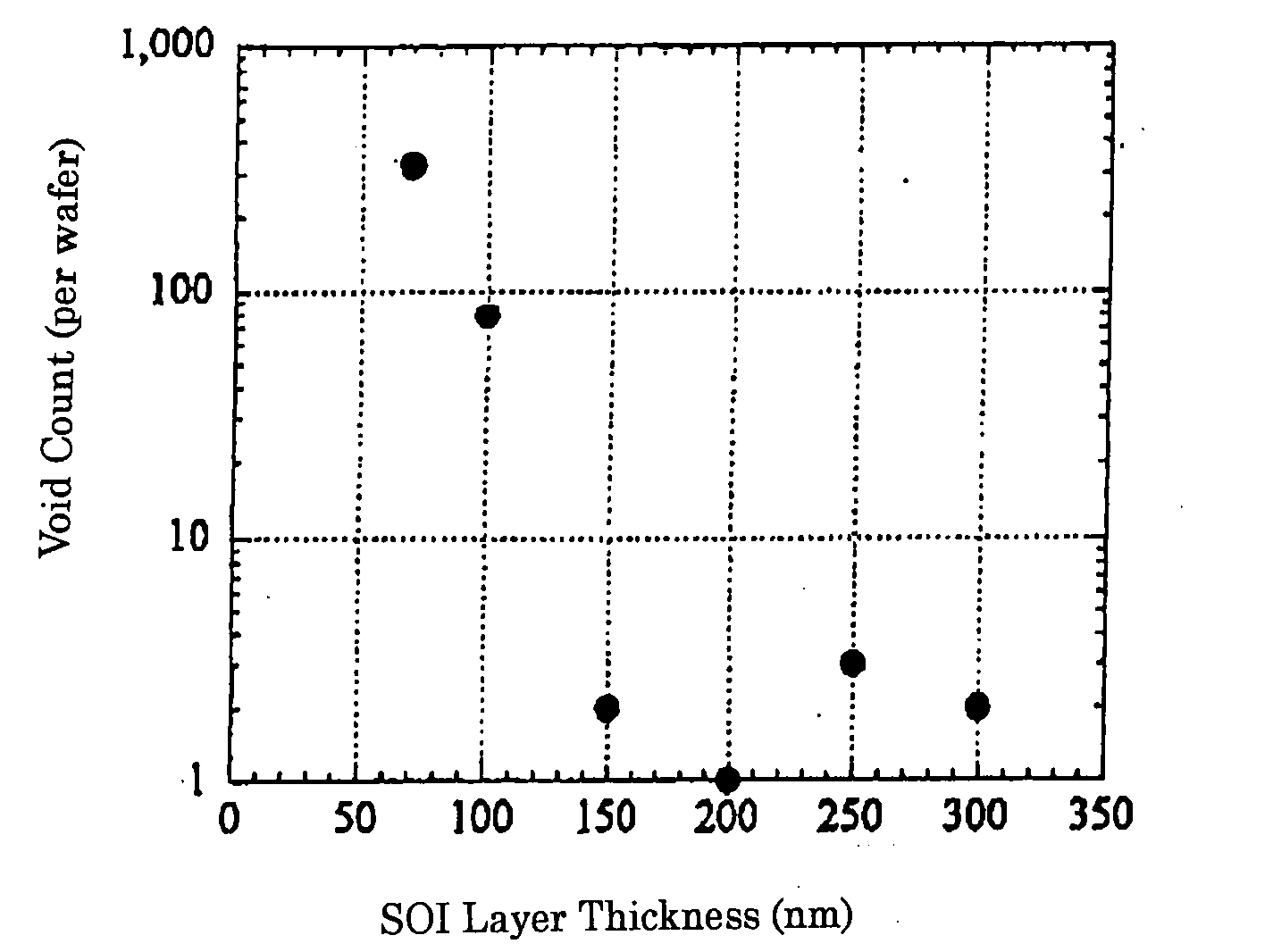

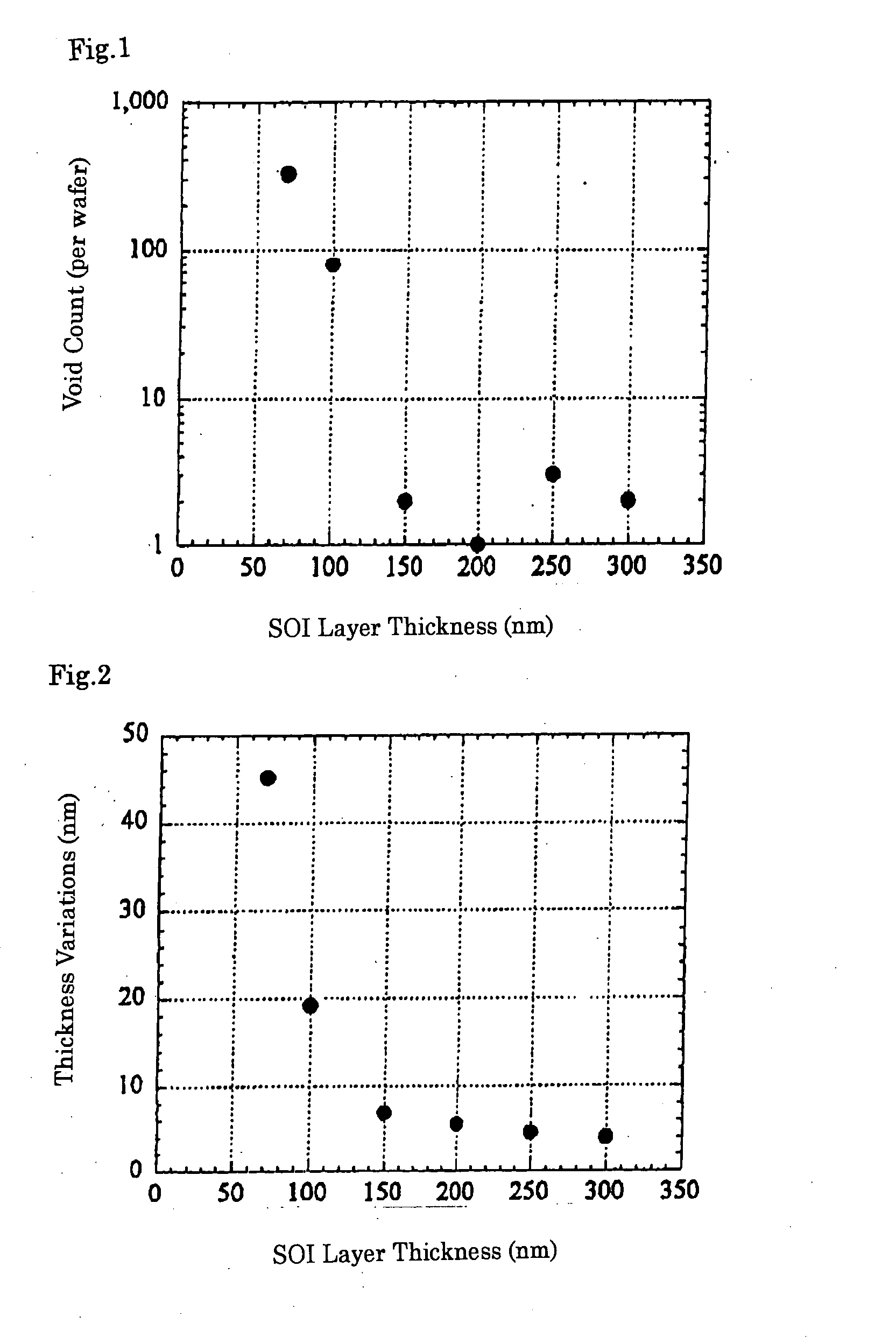

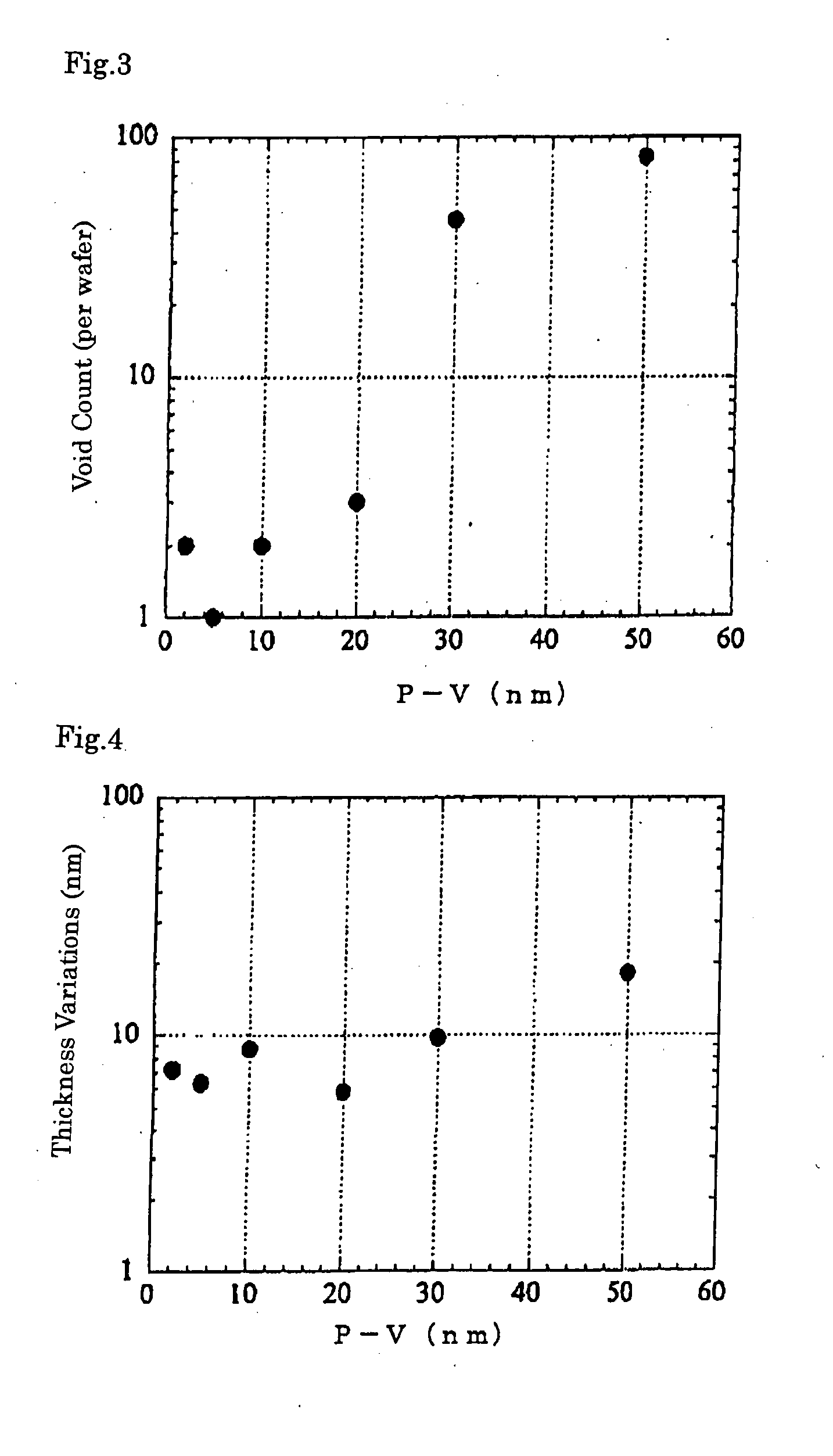

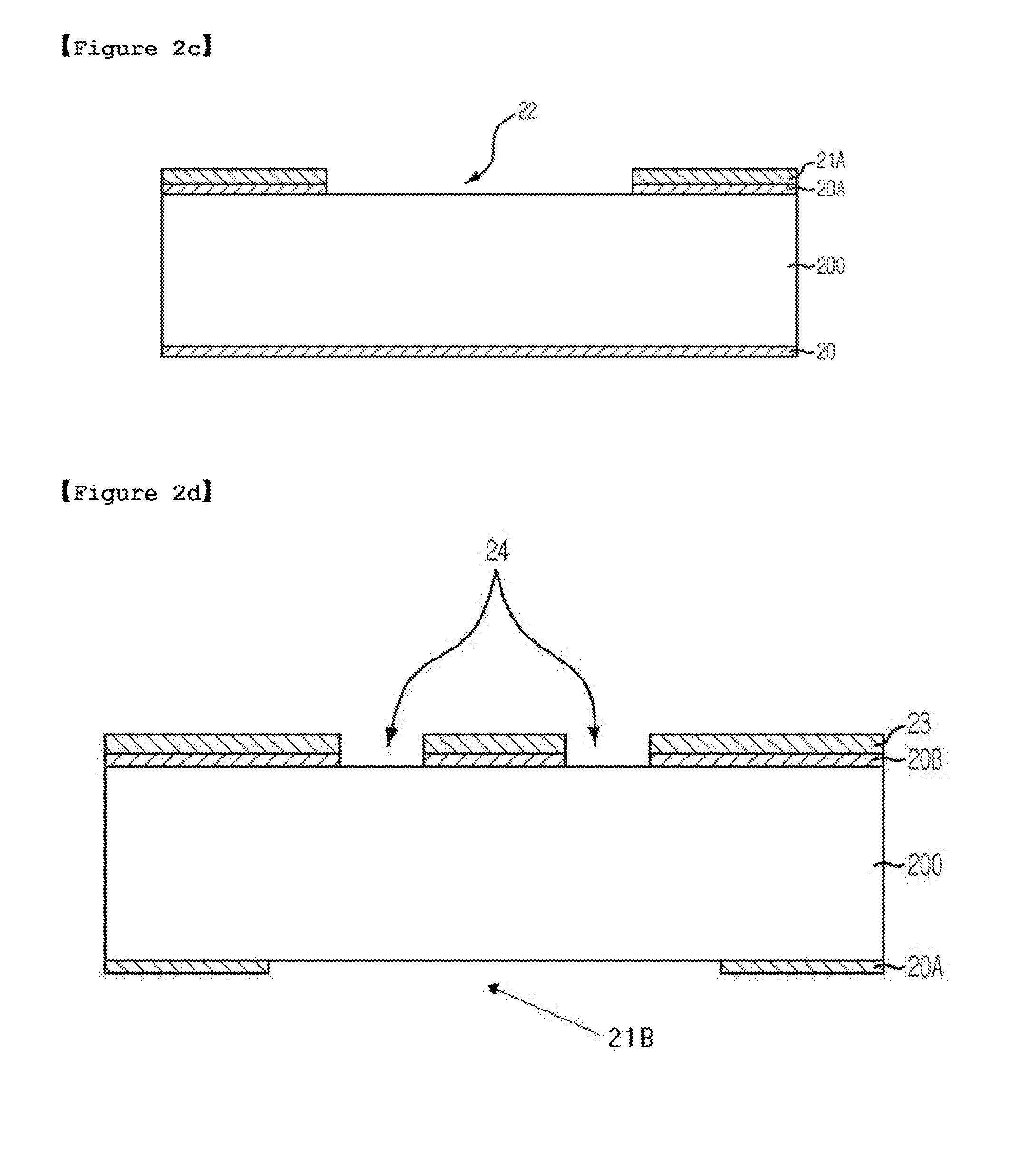

Method for Producing Direct Bonded Wafer and Direct Bonded Wafer

ActiveUS20080102603A1Reduce porosityReduce the generation of voidsSemiconductor/solid-state device manufacturingHydrogenWafering

A method for producing a direct bonded wafer comprising: forming a thermal oxide film or a CVD oxide film on a surface of at least one of a bond wafer and a base wafer, and bonding the wafer to the other wafer via the oxide film; subsequently thinning the bond wafer to prepare a bonded wafer; and thereafter conducting a process of annealing the bonded wafer under an atmosphere including any one of an inert gas, hydrogen and a mixed gas of an inert gas and hydrogen so that the oxide film between the bond wafer and the base wafer is removed to bond the bond wafer directly to the base wafer. Thereby, there is provided a method for producing a direct bonded wafer in which generation of voids is reduced, and a direct bonded wafer with a low void count.

Owner:SHIN-ETSU HANDOTAI CO LTD

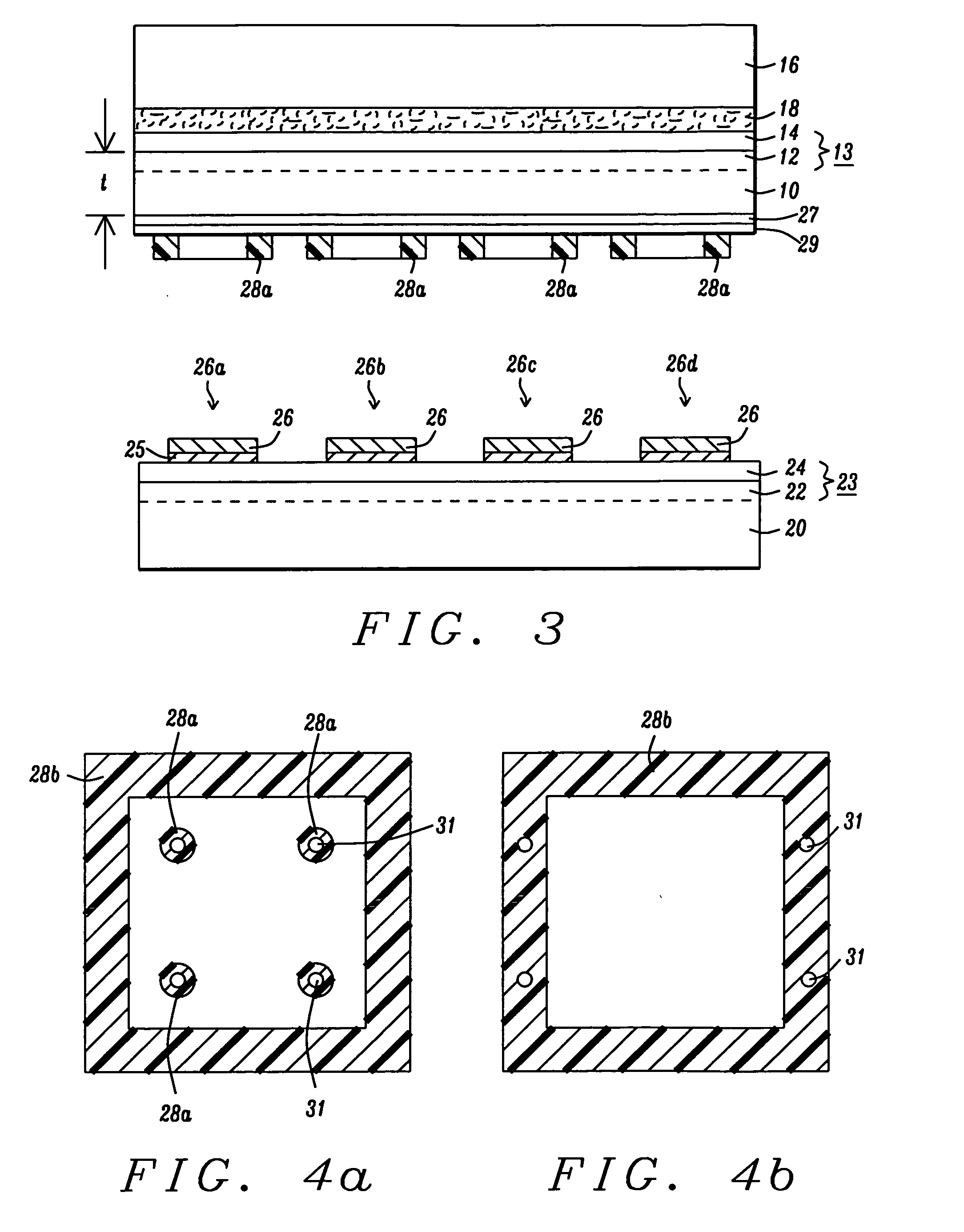

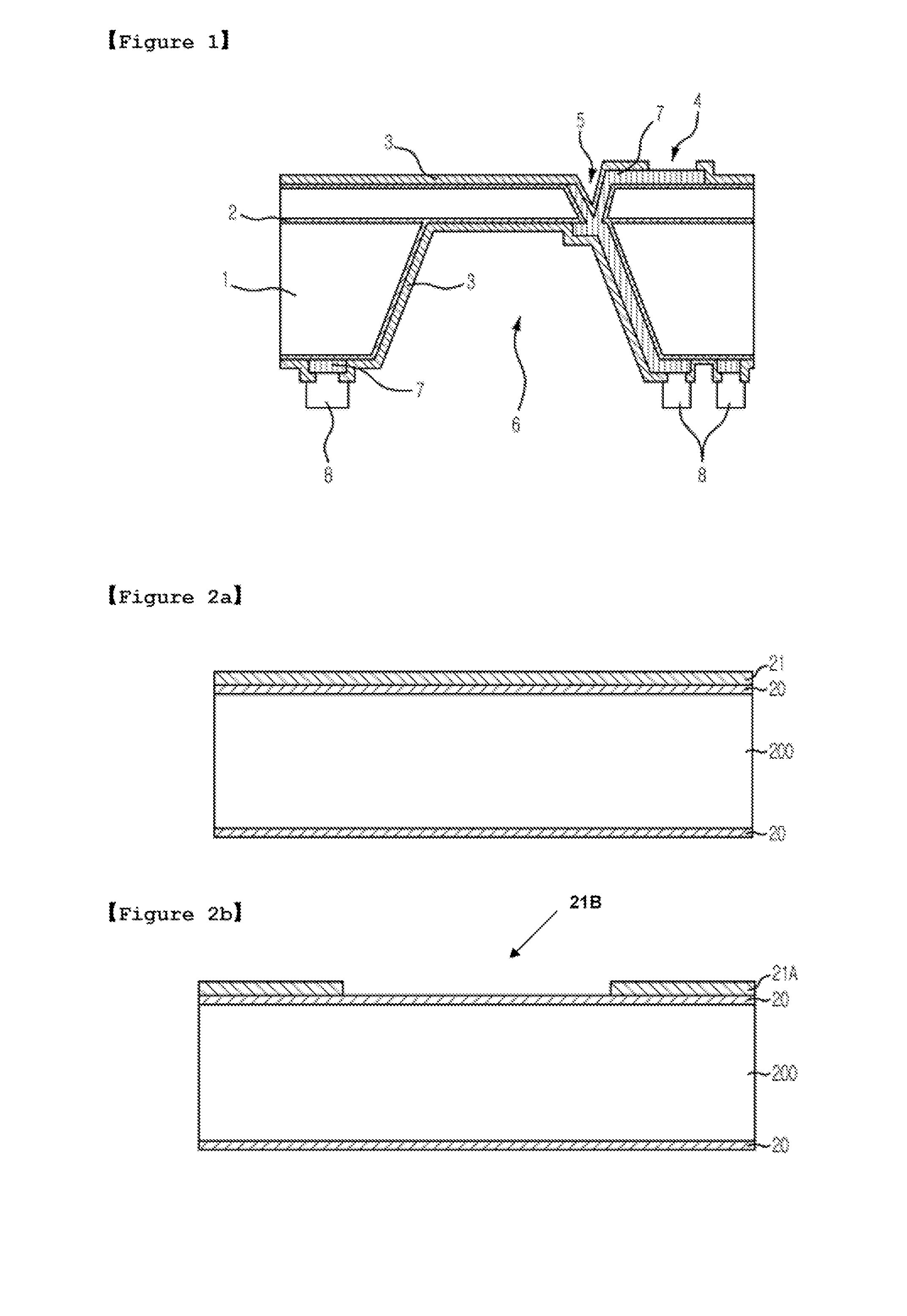

Wafer bonding with highly compliant plate having filler material enclosed hollow core

ActiveUS7307005B2Solid-state devicesSemiconductor/solid-state device manufacturingFilling materialsWafer bonding

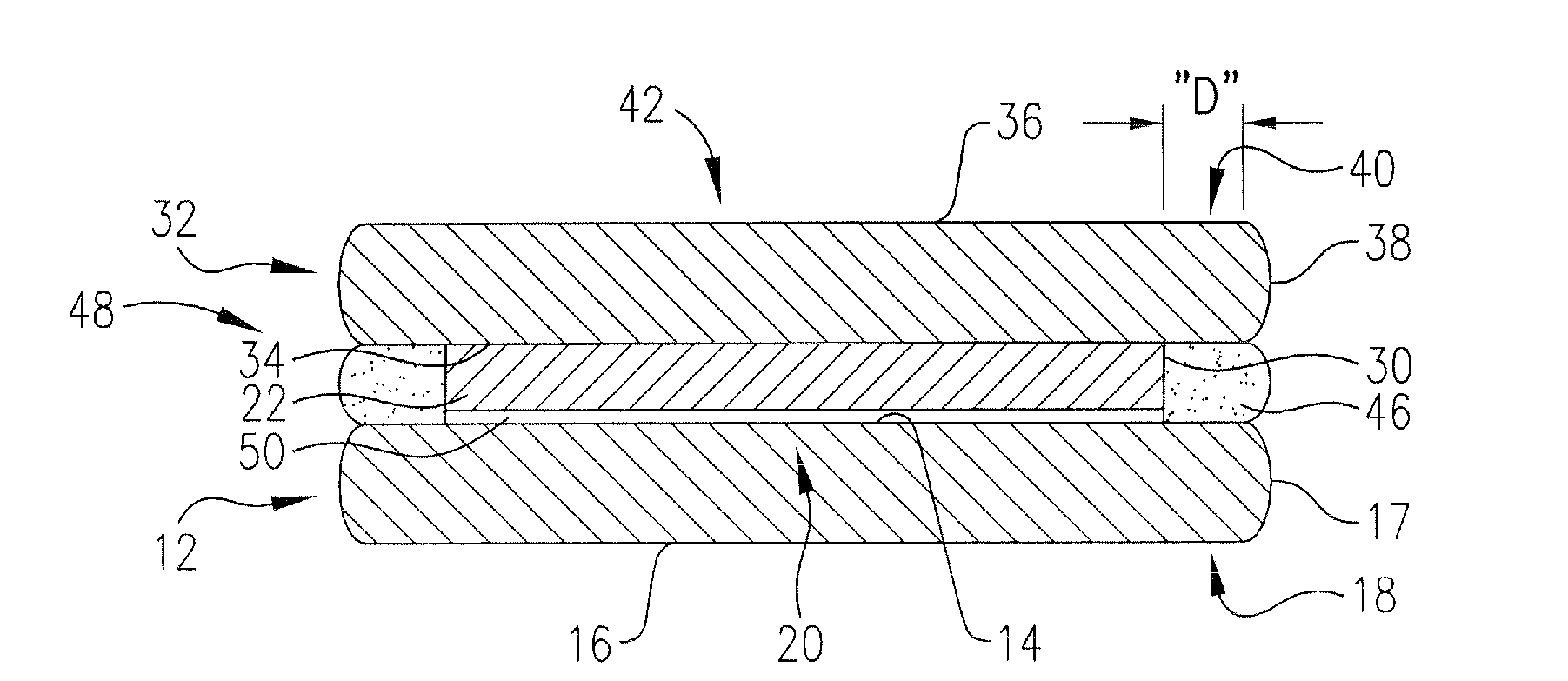

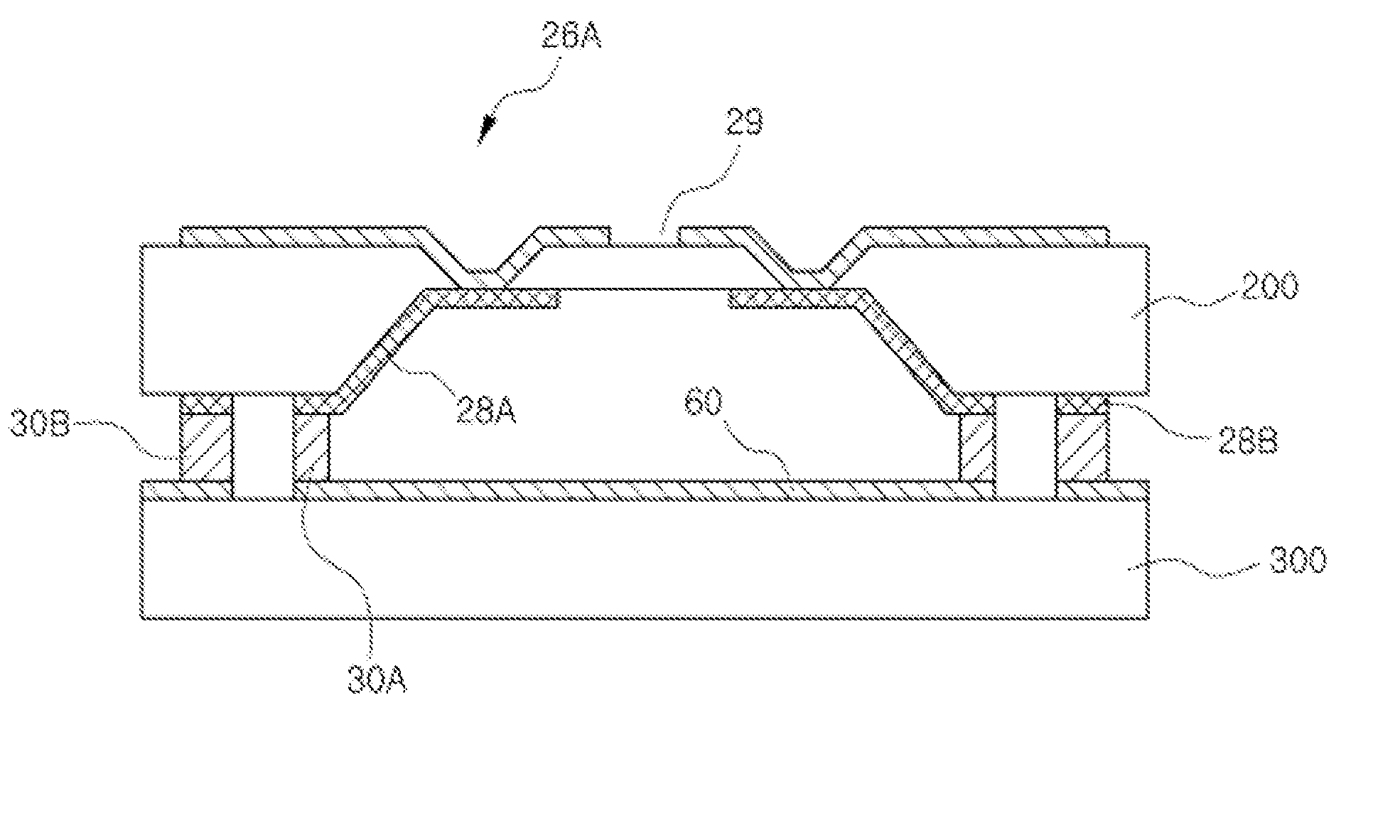

The present invention discloses a method that includes: providing two wafers; forming raised contacts on the two wafers; aligning the two wafers; bringing together the raised contacts; locally deflecting the two wafers; and bonding the raised contacts.The present invention also discloses a bonded-wafer structure that includes: a first wafer, the first wafer being locally deflected, the first wafer including a first raised contact; and a second wafer, the second wafer being locally deflected, the second wafer including a second raised contact, wherein the second raised contact is bonded to the first raised contact.

Owner:TAHOE RES LTD

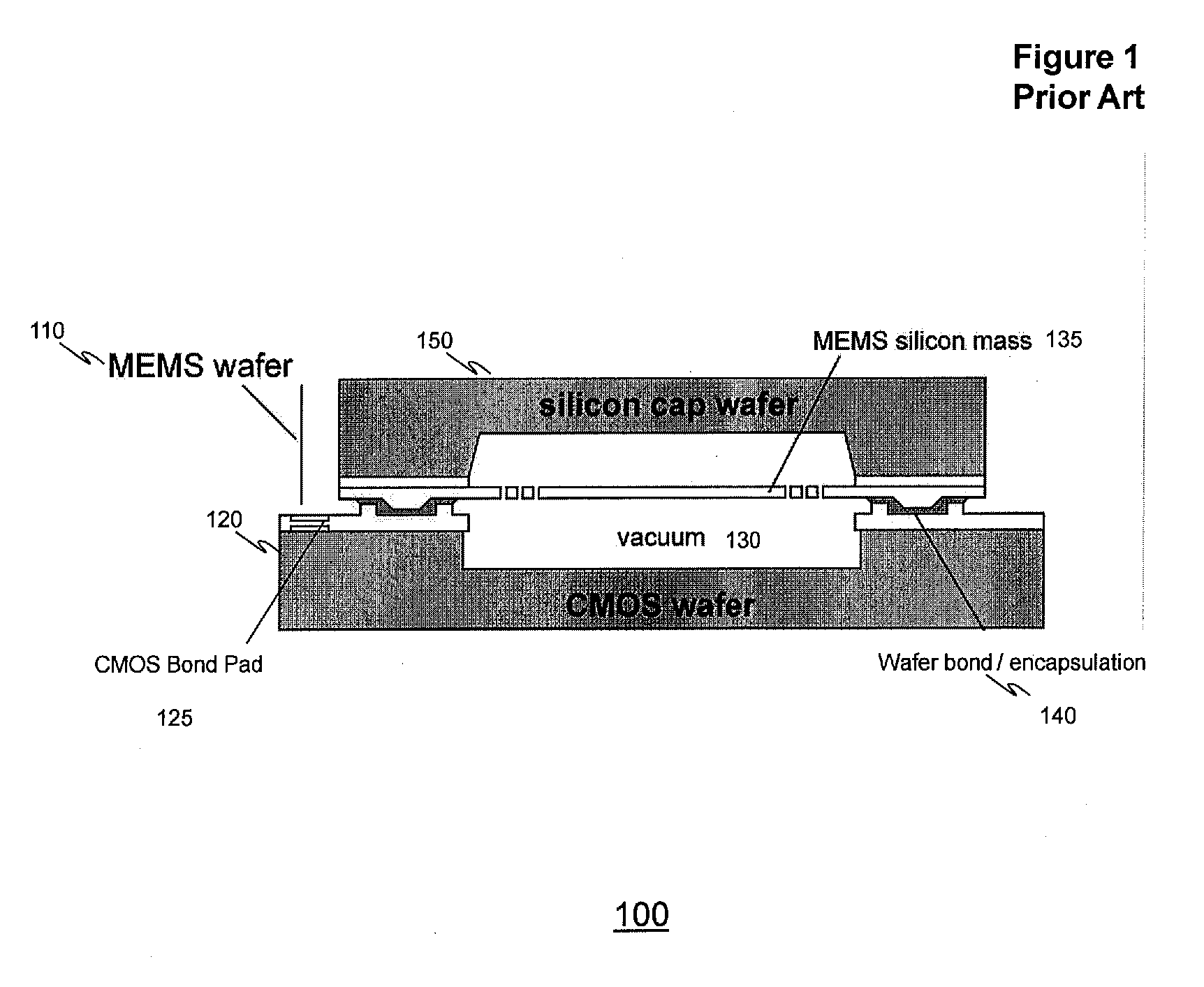

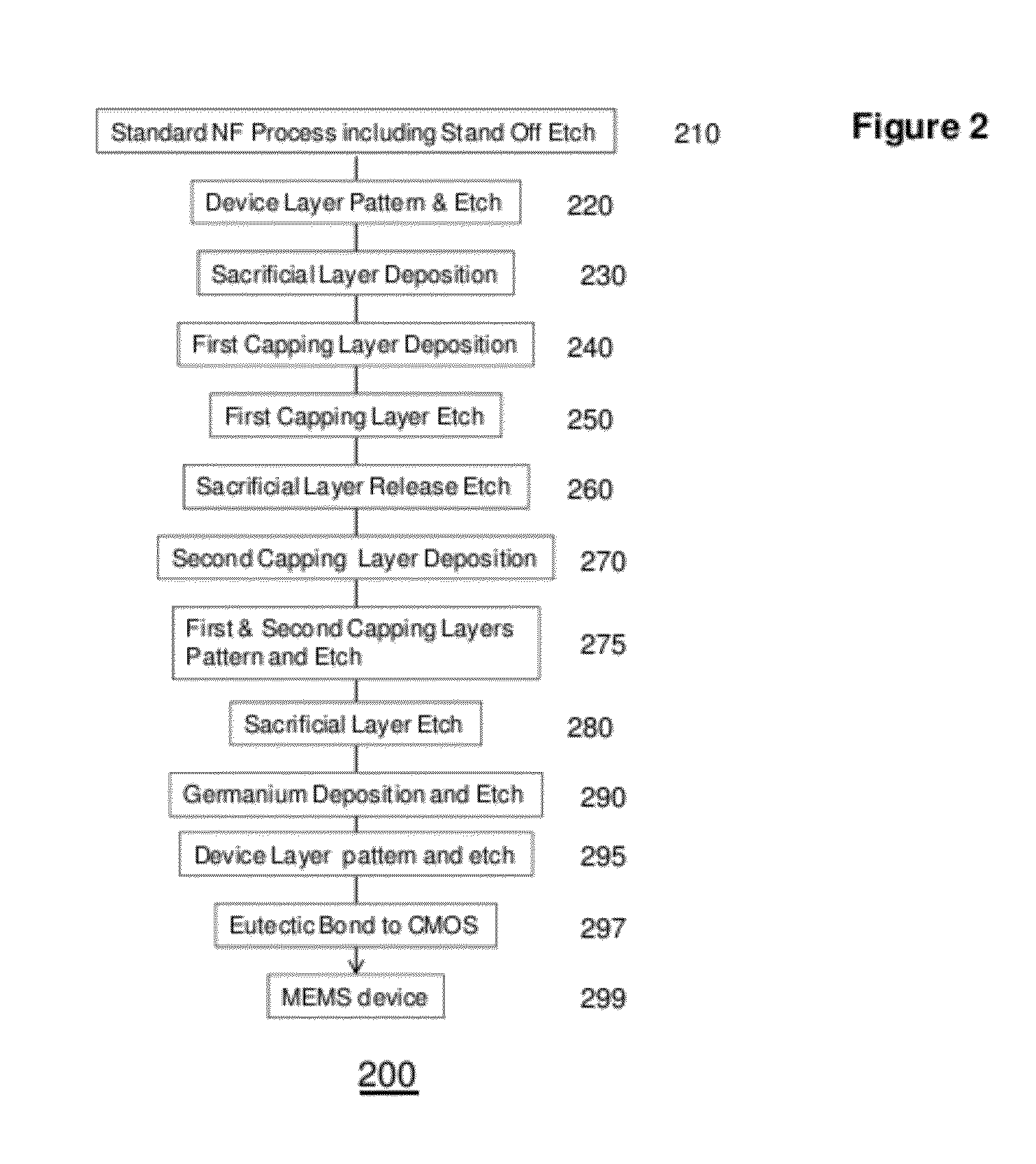

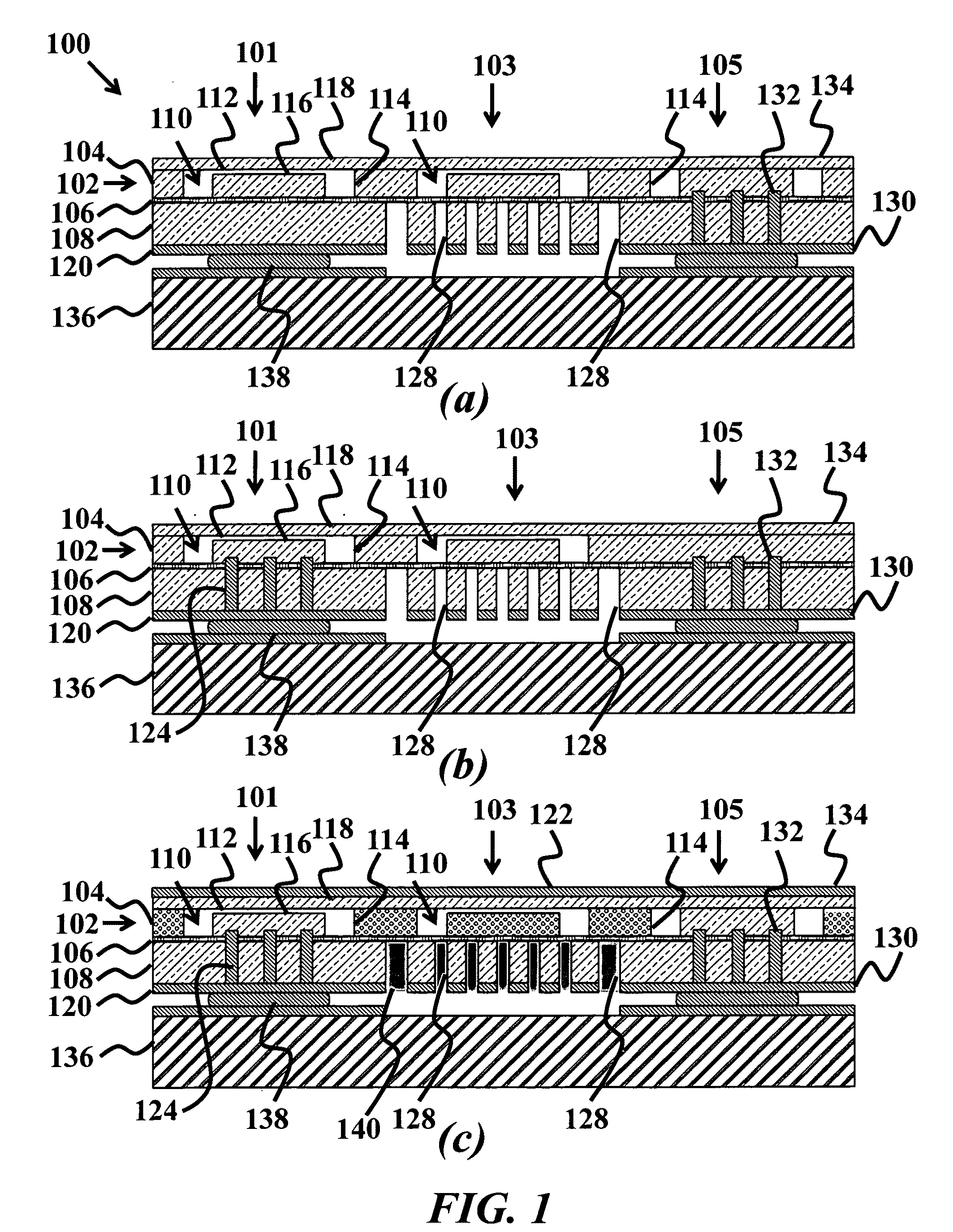

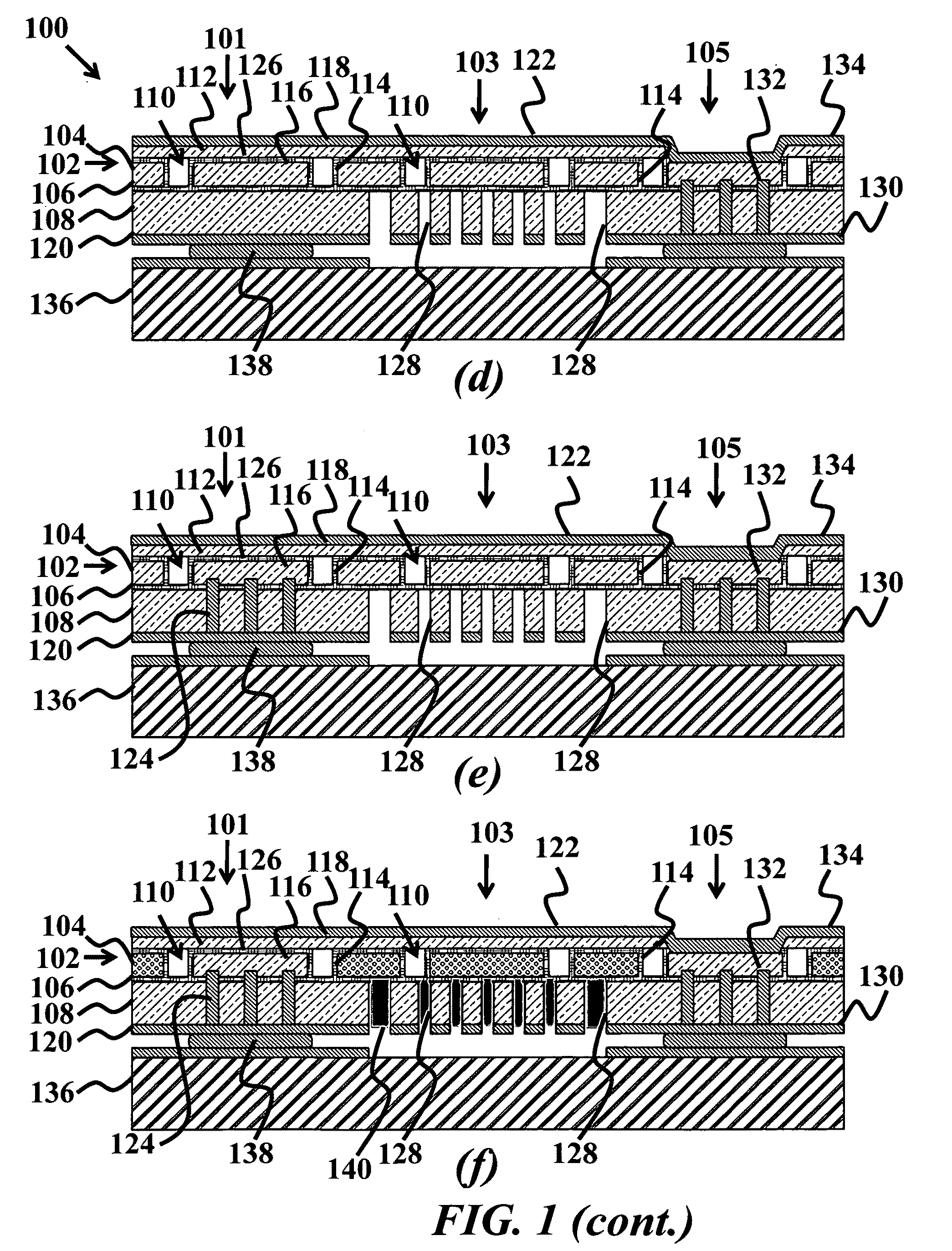

Methods for cmos-mems integrated devices with multiple sealed cavities maintained at various pressures

ActiveUS20120326248A1Good flexibilitySemiconductor/solid-state device manufacturingForming microstructural systemsCmos memsWafer bonding

A Microelectromechanical systems (MEMS) structure comprises a MEMS wafer. A MEMS wafer includes a handle wafer with cavities bonded to a device wafer through a dielectric layer disposed between the handle and device wafers. The MEMS wafer also includes a moveable portion of the device wafer suspended over a cavity in the handle wafer. Four methods are described to create two or more enclosures having multiple gas pressure or compositions on a single substrate including, each enclosure containing a moveable portion. The methods include: A. Forming a secondary sealed enclosure, B. Creating multiple ambient enclosures during wafer bonding, C. Creating and breaching an internal gas reservoir, and D. Forming and subsequently sealing a controlled leak / breach into the enclosure.

Owner:INVENSENSE

Wafer bonding method

InactiveUS7632738B2Reduce in quantitySolid-state devicesSemiconductor/solid-state device manufacturingBond interfaceEngineering

A method includes steps of providing first and second substrates, and forming a bonding interface between them using a conductive bonding region. A portion of the second substrate is removed to form a mesa structure. A vertically oriented semiconductor device is formed with the mesa structure. A portion of the conductive bonding region is removed to form a contact. The vertically oriented semiconductor device is carried by the contact.

Owner:BESANG

Method for reversibly mounting a device wafer to a carrier substrate

ActiveUS20090218560A1Reduced adhesion strengthLamination ancillary operationsSemiconductor/solid-state device detailsHeat resistanceRoom temperature

New temporary bonding methods and articles formed from those methods are provided. The methods comprise bonding a device wafer to a carrier wafer or substrate only at their outer perimeters in order to assist in protecting the device wafer and its device sites during subsequent processing and handling. The edge bonds formed by this method are chemically and thermally resistant, but can also be softened, dissolved, or mechanically disrupted to allow the wafers to be easily separated with very low forces and at or near room temperature at the appropriate stage in the fabrication process.

Owner:BREWER SCI

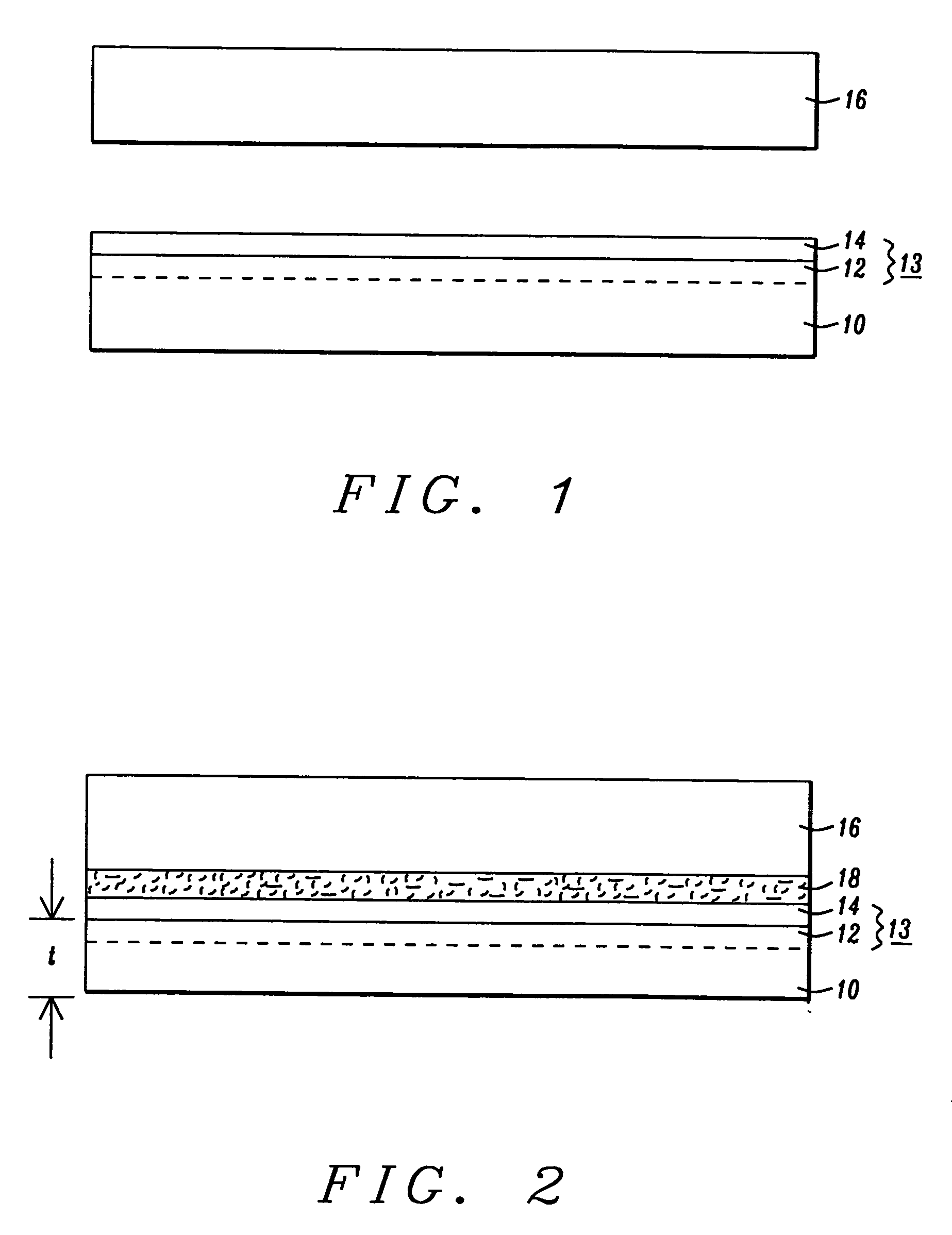

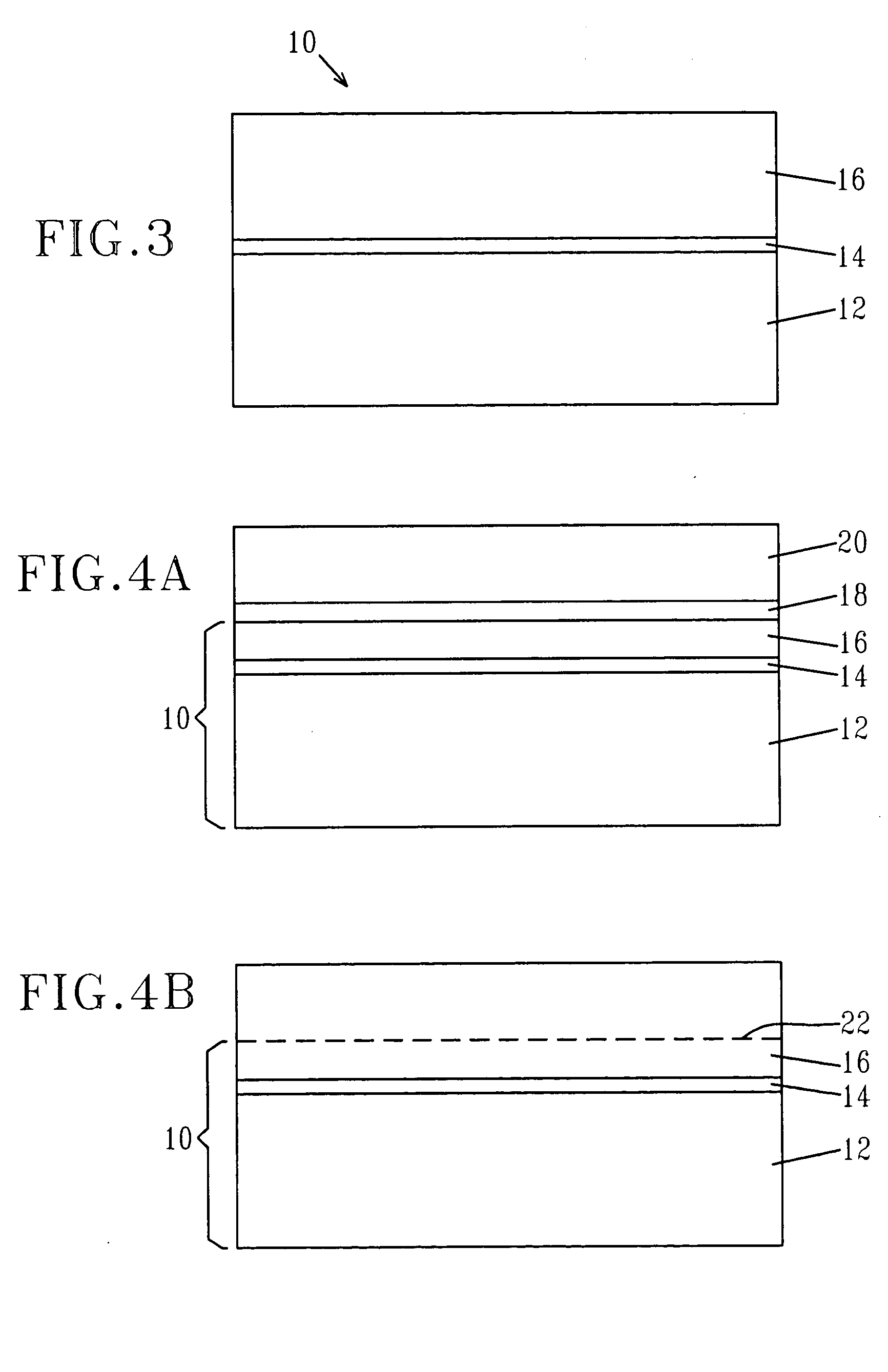

Strained semiconductor by full wafer bonding

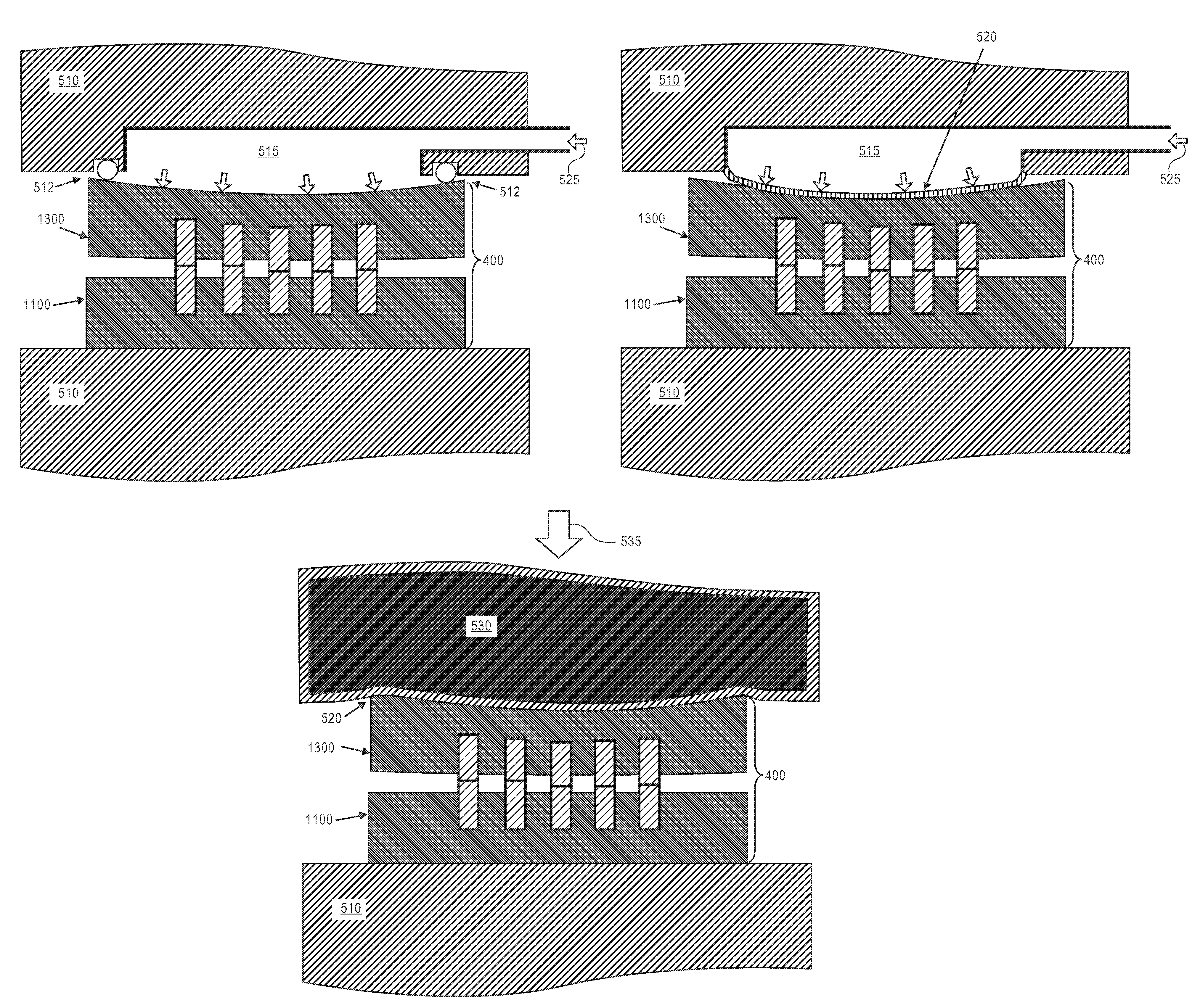

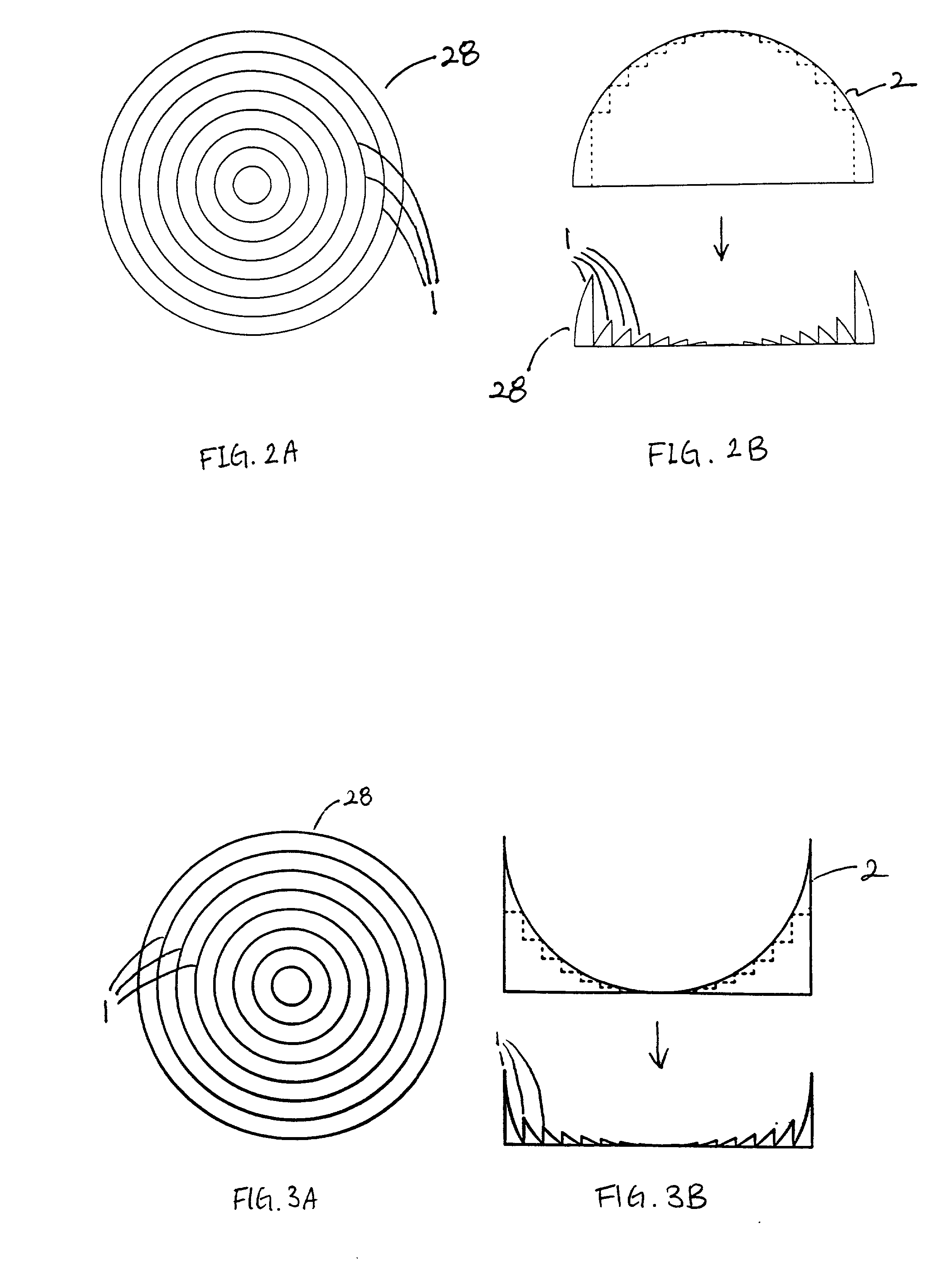

One aspect of this disclosure relates to a method for forming a wafer with a strained semiconductor. In various embodiments of the method, a predetermined contour is formed in one of a semiconductor membrane and a substrate wafer. The semiconductor membrane is bonded to the substrate wafer and the predetermined contour is straightened to induce a predetermined strain in the semiconductor membrane. In various embodiments, a substrate wafer is flexed into a flexed position, a portion of the substrate wafer is bonded to a semiconductor layer when the substrate wafer is in the flexed position, and the substrate wafer is relaxed to induce a predetermined strain in the semiconductor layer. Other aspects and embodiments are provided herein.

Owner:MICRON TECH INC

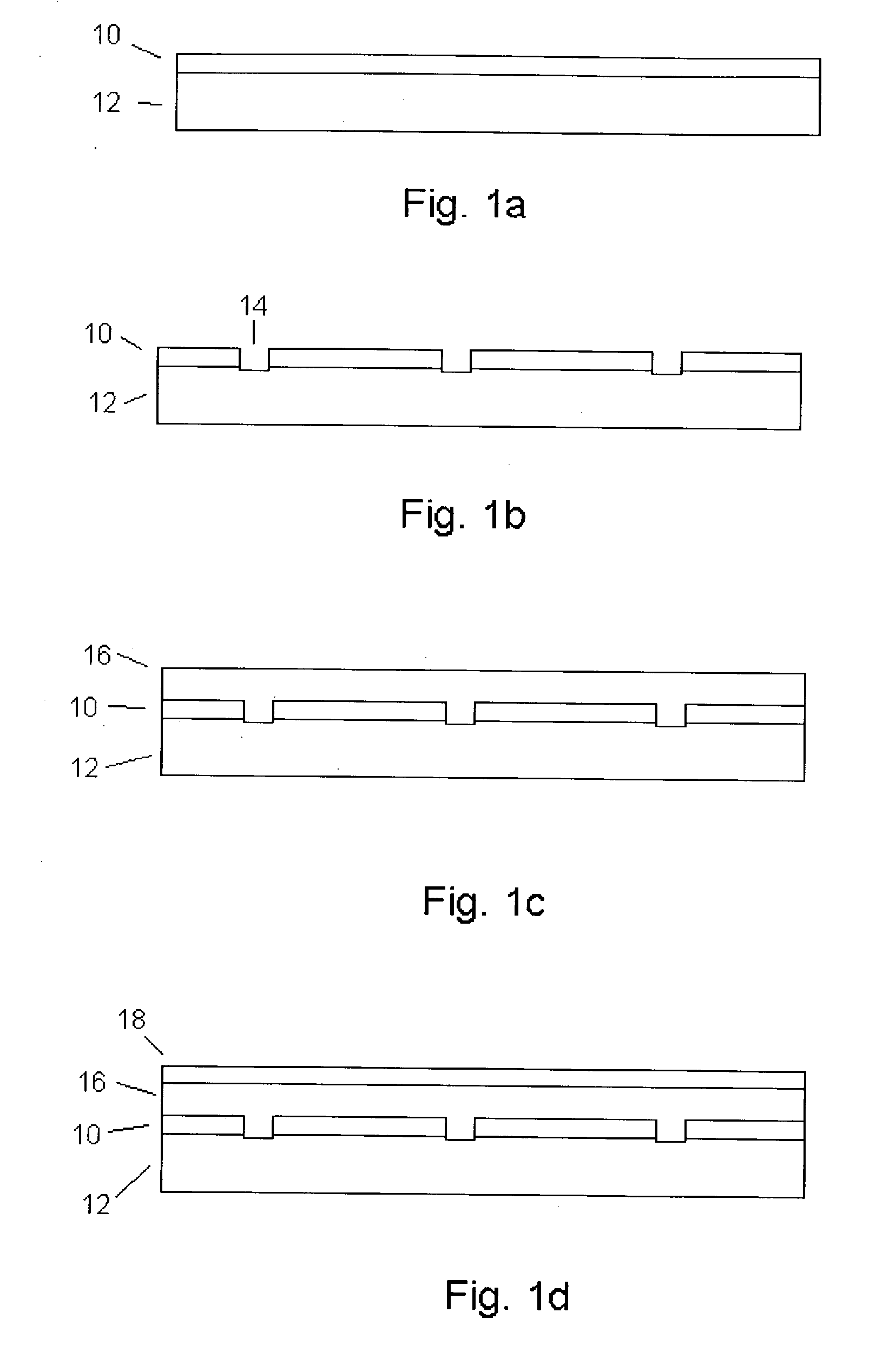

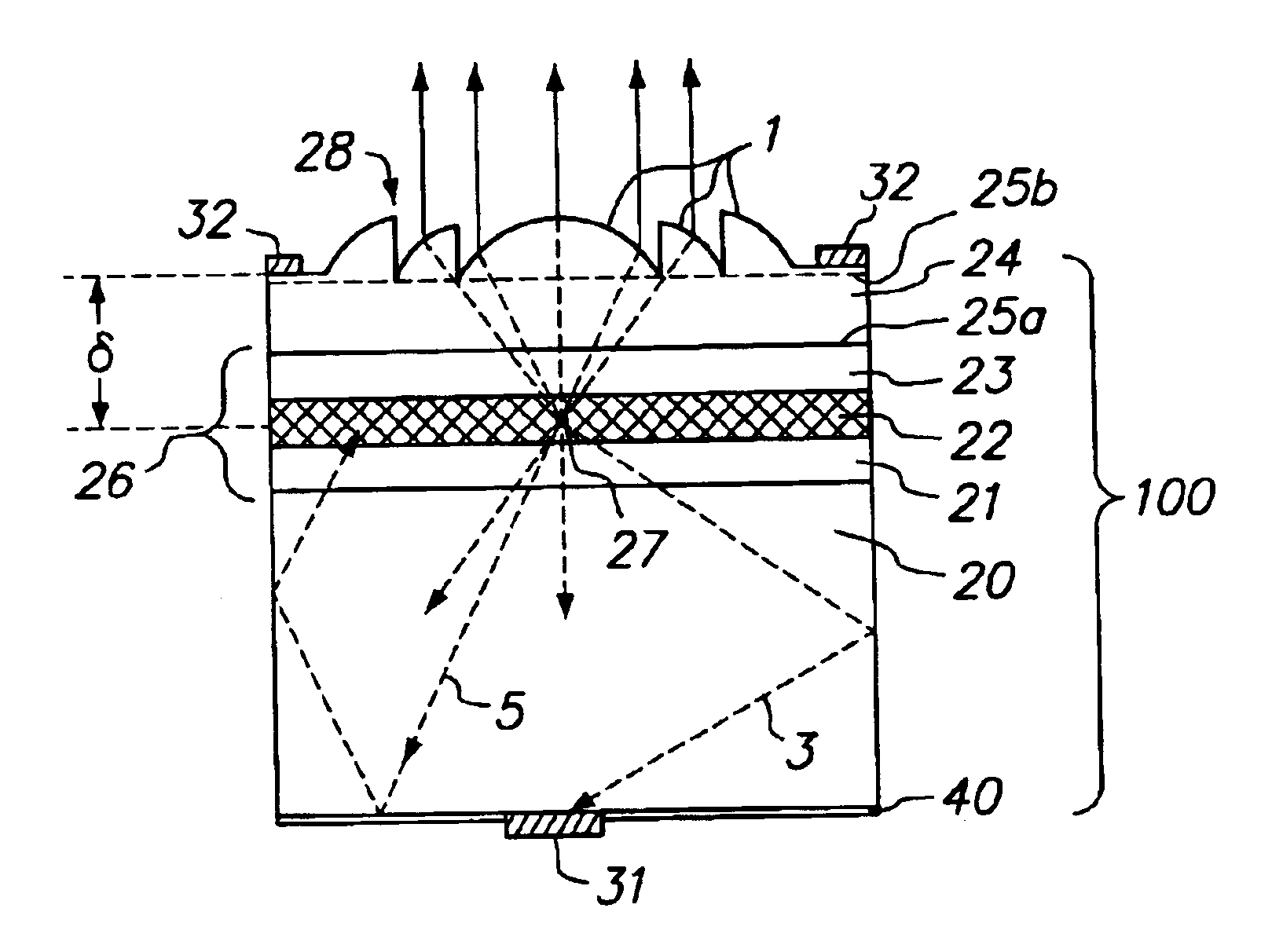

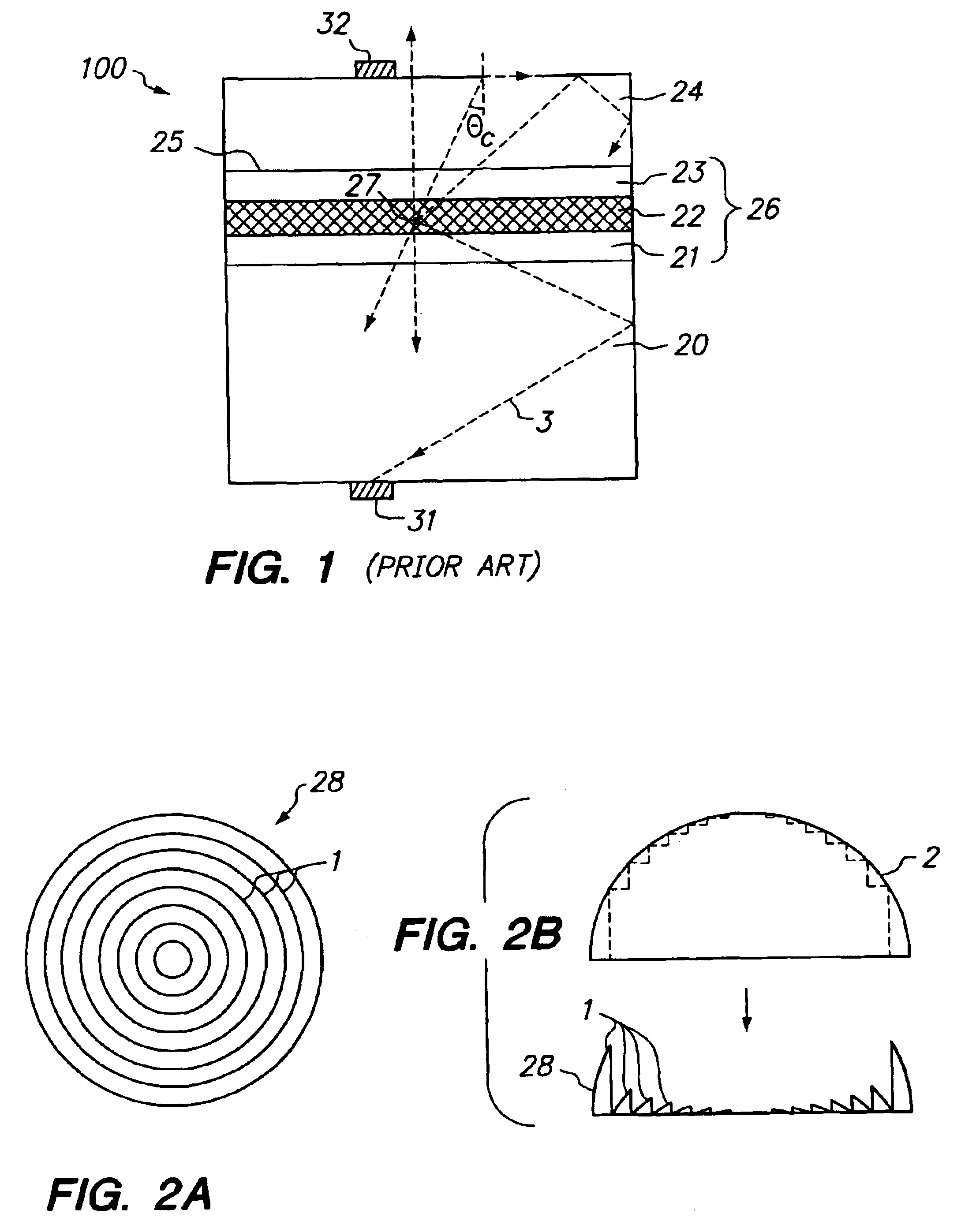

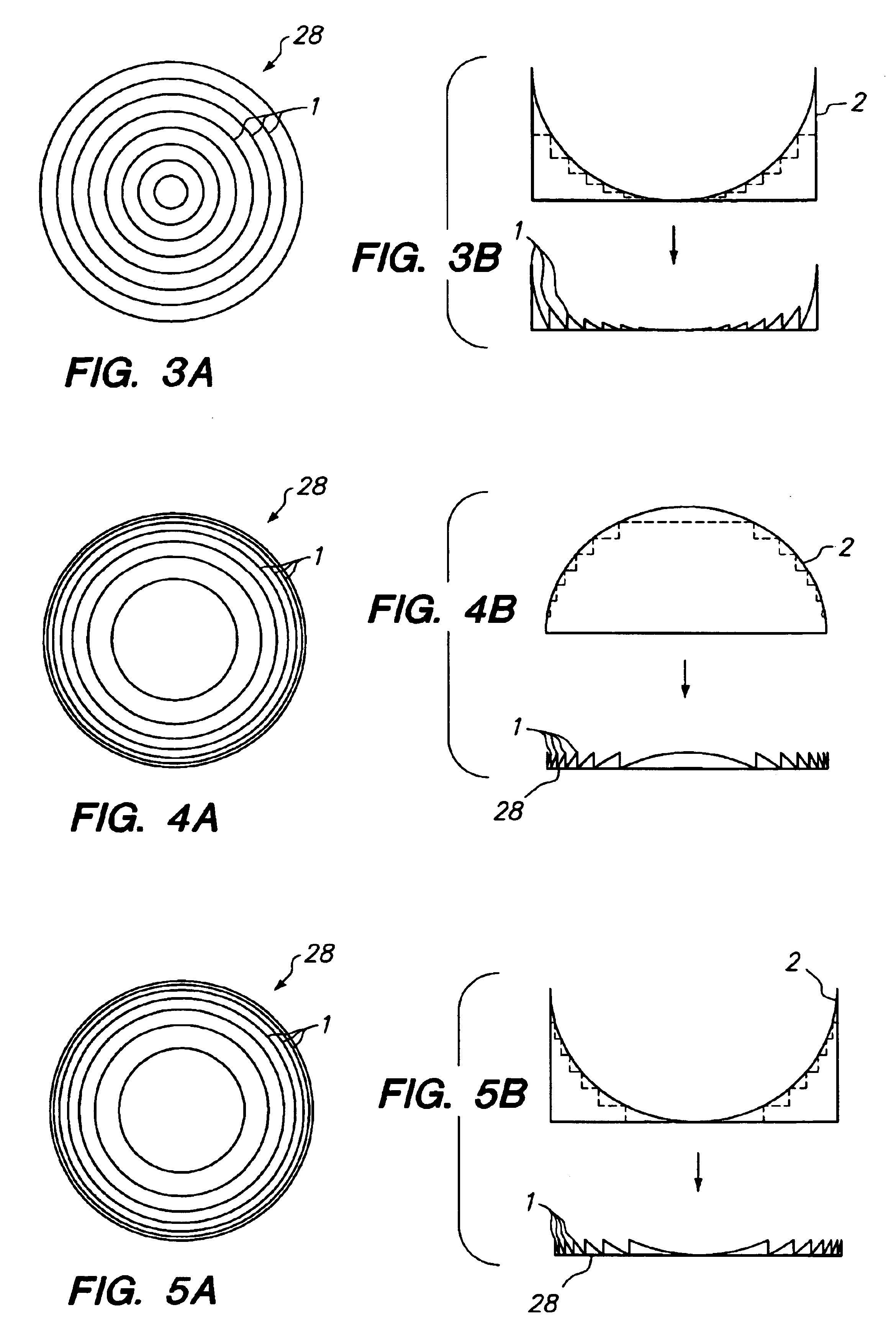

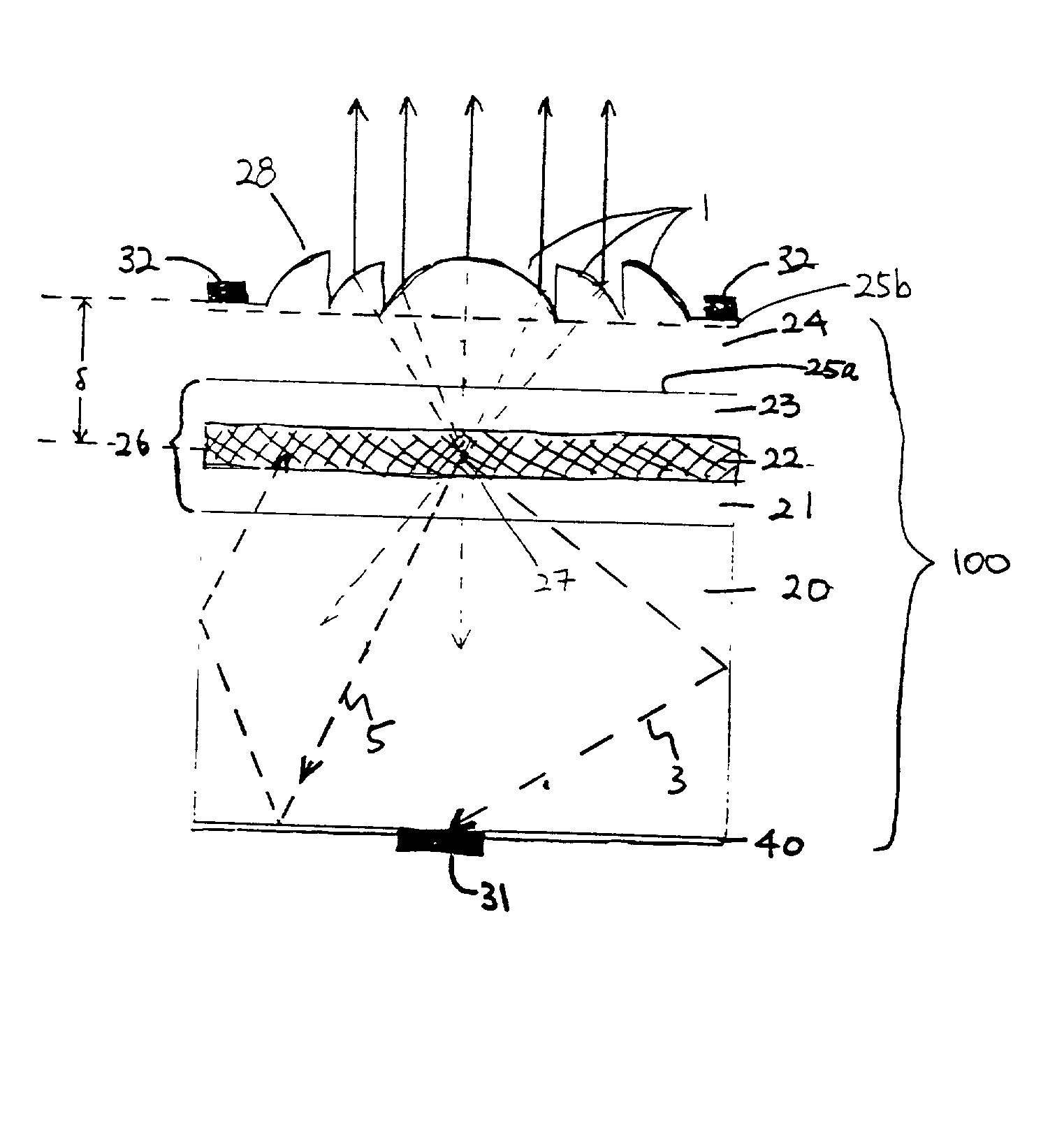

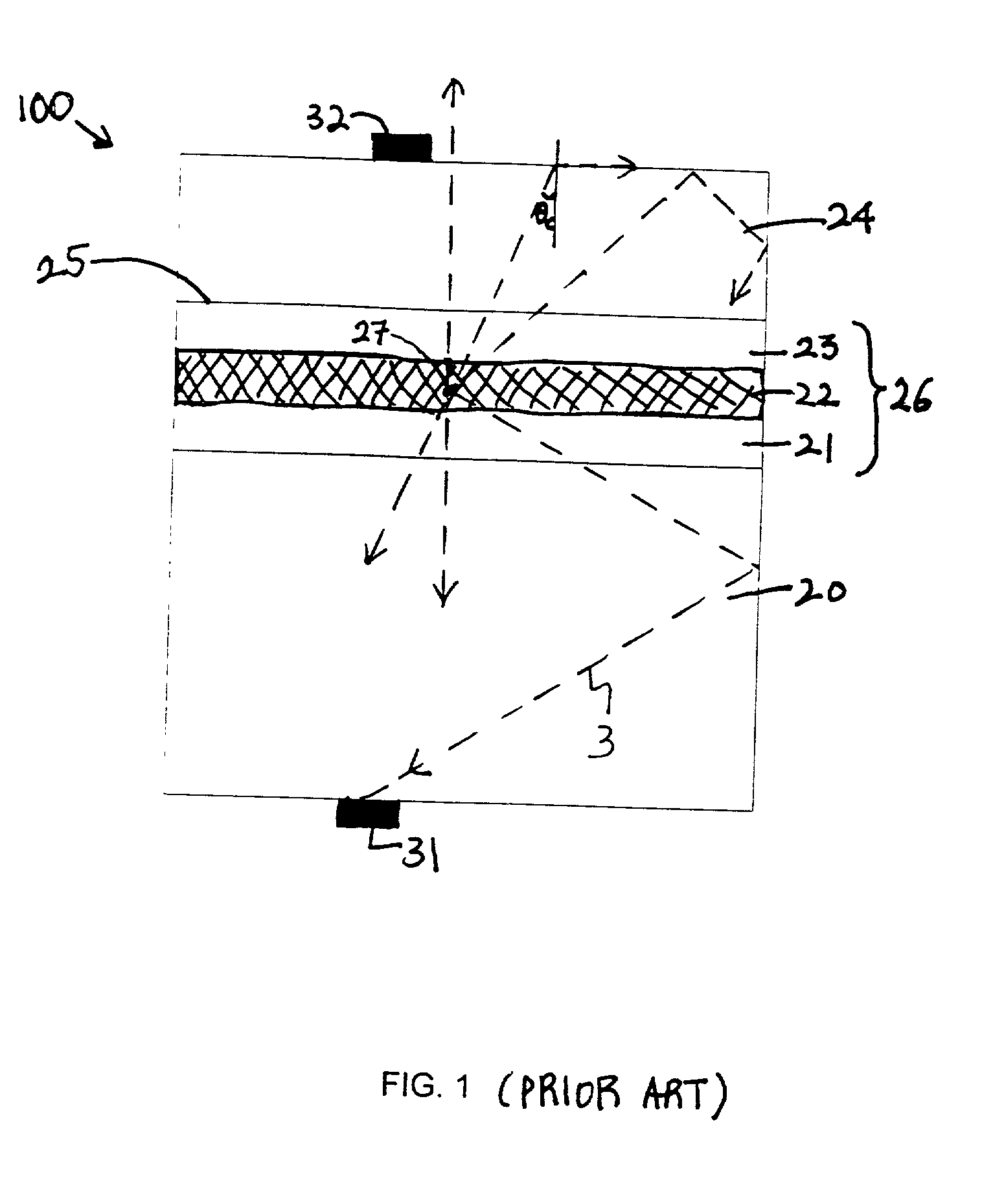

Forming an optical element on the surface of a light emitting device for improved light extraction

InactiveUS6987613B2Easy to integrateMaximize production efficiencyDiffraction gratingsSemiconductor devicesWafer bondingAlternative methods

Provided is a light emitting device including a Fresnel lens and / or a holographic diffuser formed on a surface of a semiconductor light emitter for improved light extraction, and a method for forming such light emitting device. Also provided is a light emitting device including an optical element stamped on a surface for improved light extraction and the stamping method used to form such device. An optical element formed on the surface of a semiconductor light emitter reduces reflective loss and loss due to total internal reflection, thereby improving light extraction efficiency. A Fresnel lens or a holographic diffuser may be formed on a surface by wet chemical etching or dry etching techniques, such as plasma etching, reactive ion etching, and chemically-assisted ion beam etching, optionally in conjunction with a lithographic technique. In addition, a Fresnel lens or a holographic diffuser may be milled, scribed, or ablated into the surface. Stamping, an alternative method for forming an optical element, can also be used to form a Fresnel lens or a holographic diffuser on the surface of a semiconductor light emitter. Stamping includes pressing a stamping block against the surface of a light emitting diode. The stamping block has a shape and pattern that are the inverse of the desired optical element. Optionally, stamping can be done before, after, or concurrently with wafer-bonding. Alternatively, a material can be stamped and later bonded to the semiconductor light emitter.

Owner:LUMILEDS

Forming an optical element on the surface of a light emitting device for improved light extraction

Provided is a light emitting device including a Fresnel lens and / or a holographic diffuser formed on a surface of a semiconductor light emitter for improved light extraction, and a method for forming such light emitting device. Also provided is a light emitting device including an optical element stamped on a surface for improved light extraction and the stamping method used to form such device. An optical element formed on the surface of a semiconductor light emitter reduces reflective loss and loss due to total internal reflection, thereby improving light extraction efficiency. A Fresnel lens or a holographic diffuser may be formed on a surface by wet chemical etching or dry etching techniques, such as plasma etching, reactive ion etching, and chemically-assisted ion beam etching, optionally in conjunction with a lithographic technique. In addition, a Fresnel lens or a holographic diffuser may be milled, scribed, or ablated into the surface. Stamping, an alternative method for forming an optical element, can also be used to form a Fresnel lens or a holographic diffuser on the surface of a semiconductor light emitter. Stamping includes pressing a stamping block against the surface of a light emitting diode. The stamping block has a shape and pattern that are the inverse of the desired optical element. Optionally, stamping can be done before, after, or concurrently with wafer-bonding. Alternatively, a material can be stamped and later bonded to the semiconductor light emitter.

Owner:LUMILEDS

High efficiency solar cells utilizing wafer bonding and layer transfer to integrate non-lattice matched materials

ActiveUS20060185582A1Polycrystalline material growthAfter-treatment detailsSemiconductor materialsEngineering

A method of making a virtual substrate includes providing a donor substrate comprising a single crystal donor layer of a first material over a support substrate, wherein the first material comprises a ternary, quaternary or penternary semiconductor material or a material which is not available in bulk form, bonding the donor substrate to a handle substrate, and separating the donor substrate from the handle substrate such that a single crystal film of the first material remains bonded to the handle substrate.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

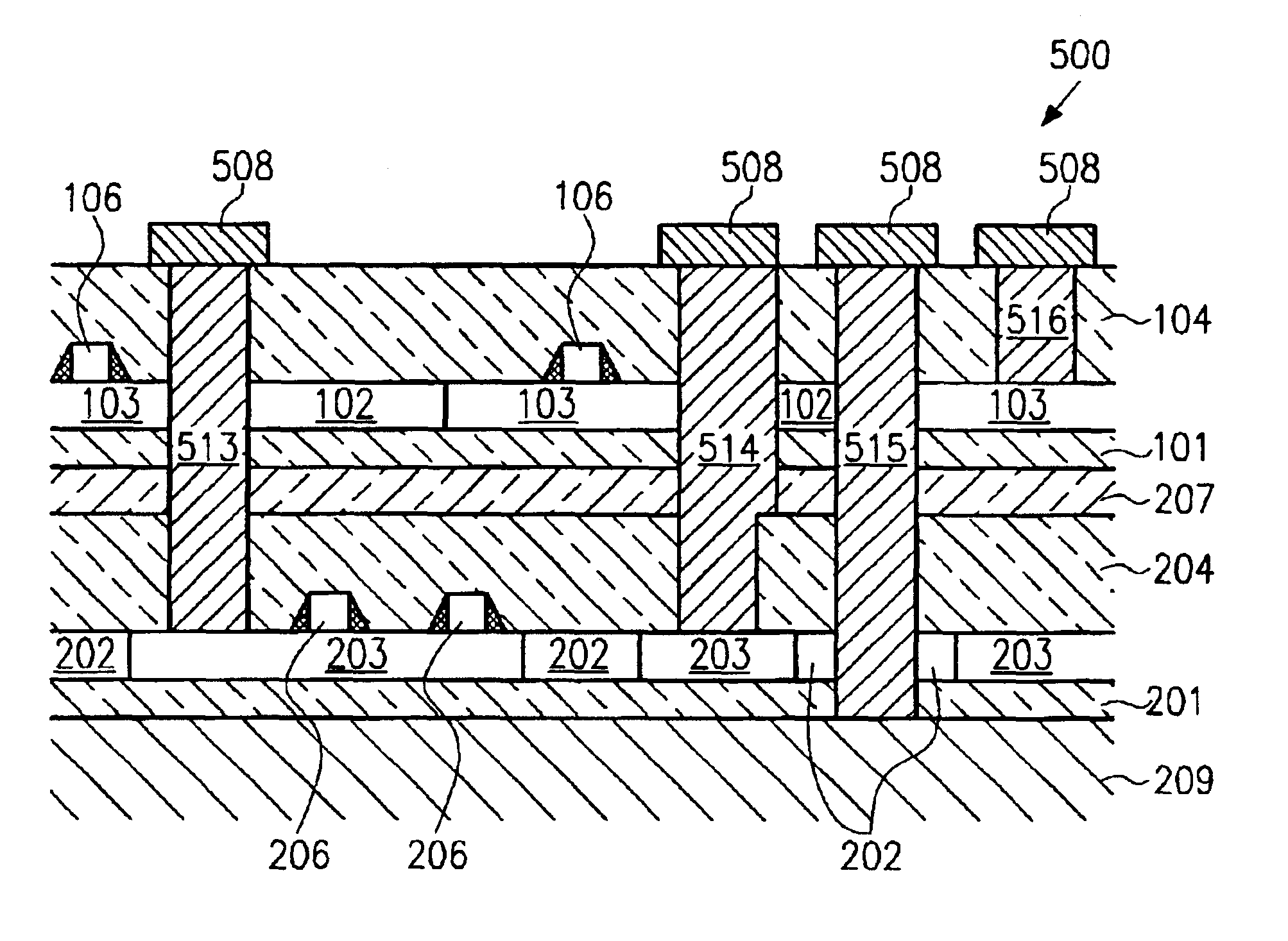

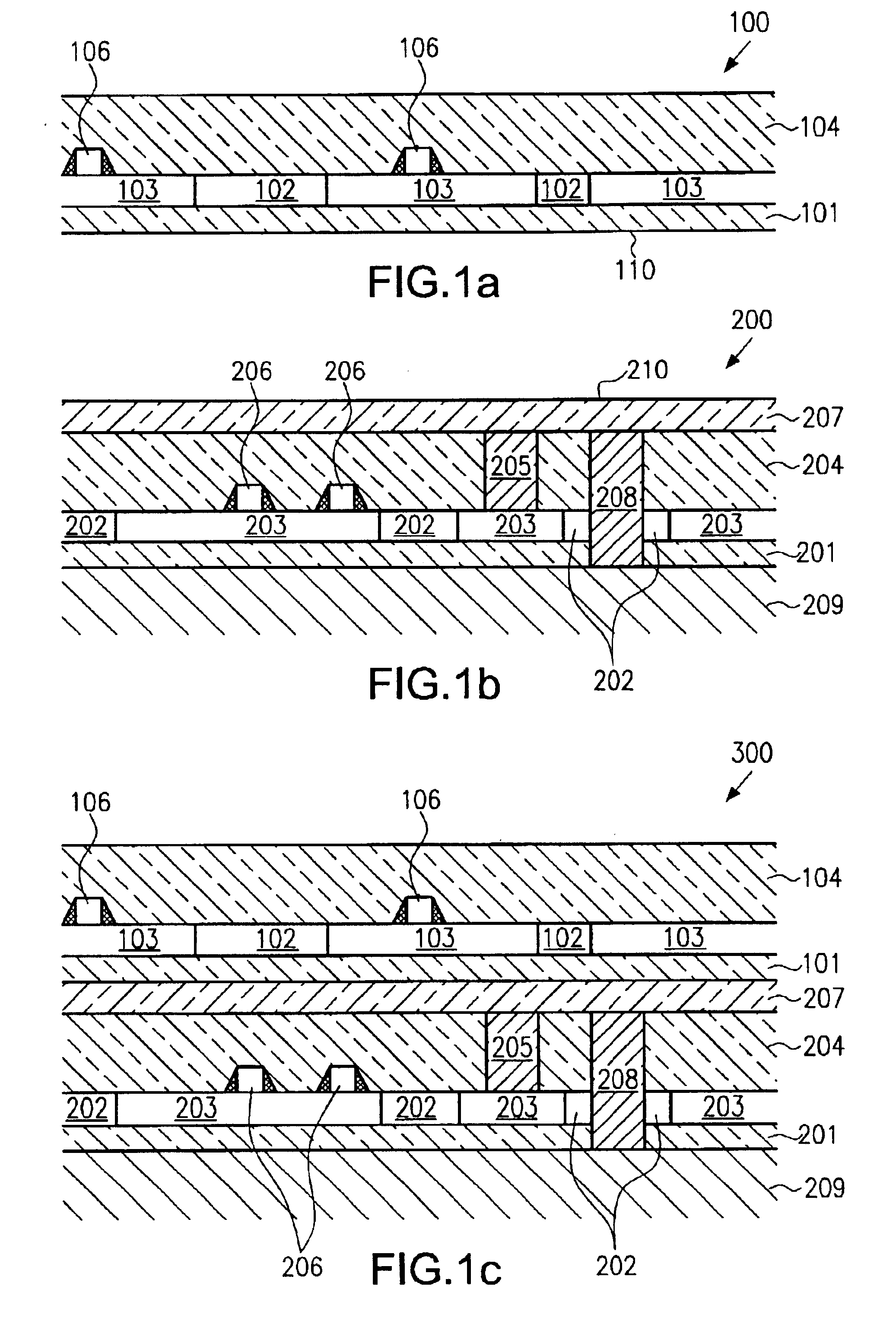

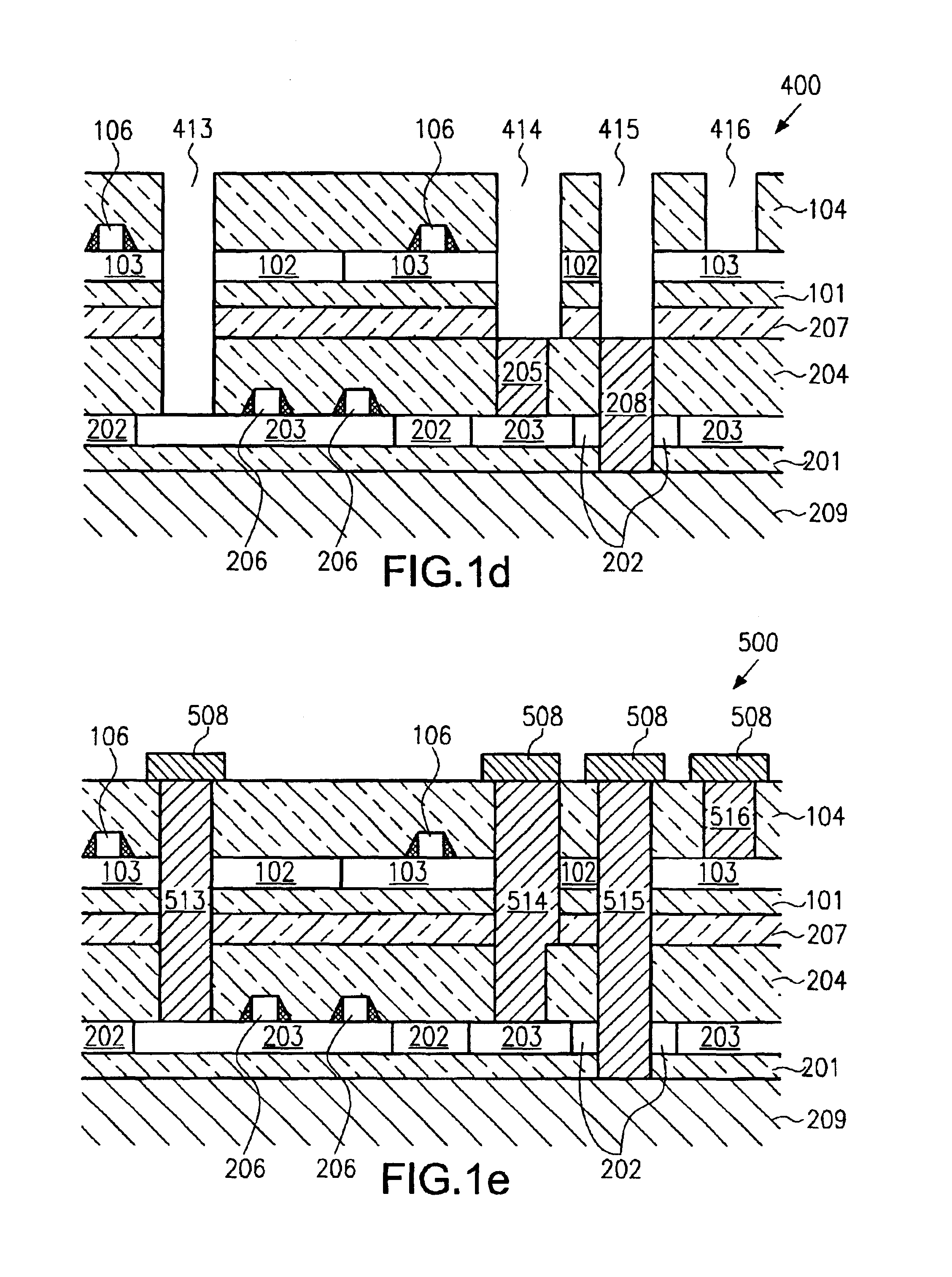

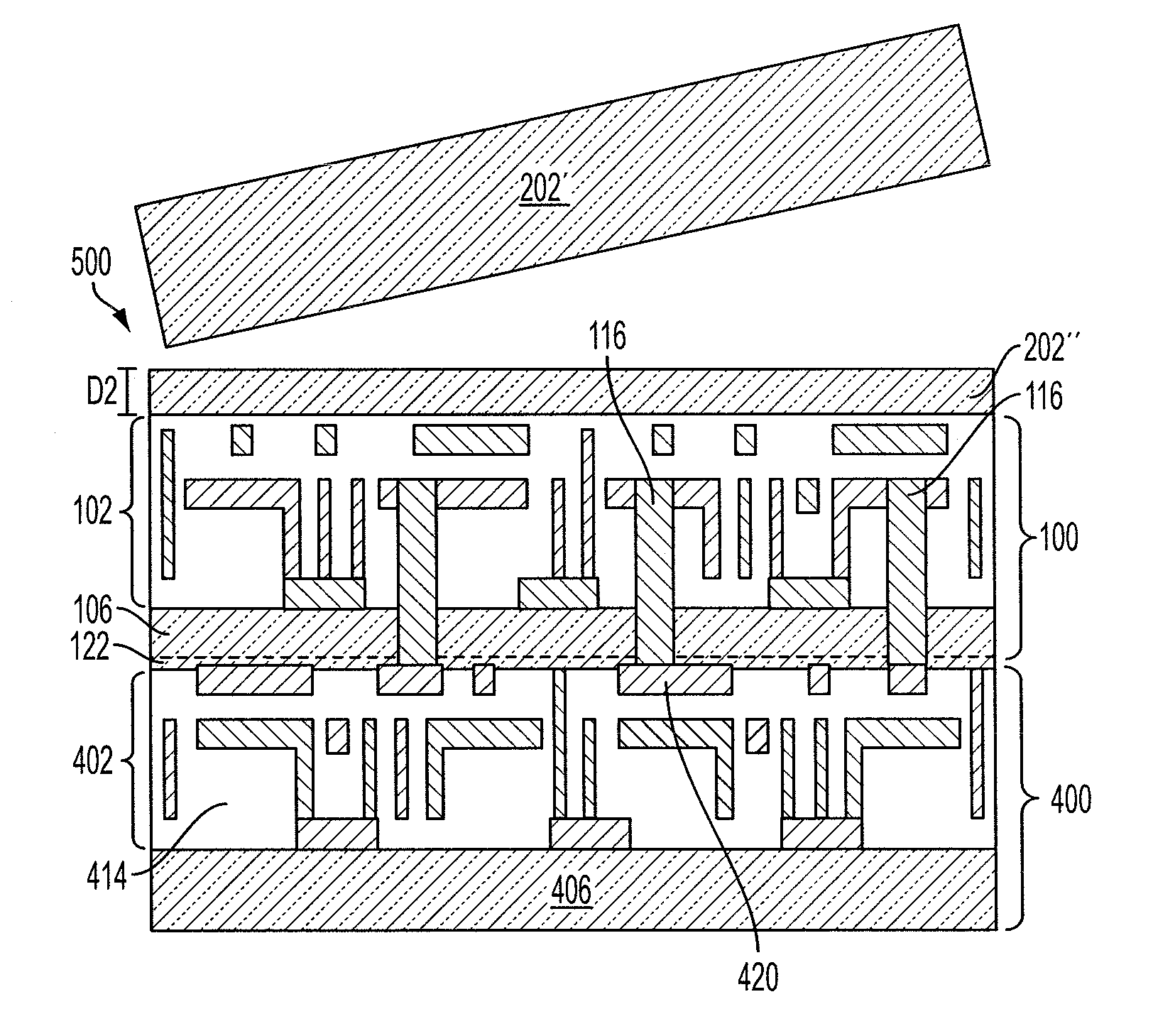

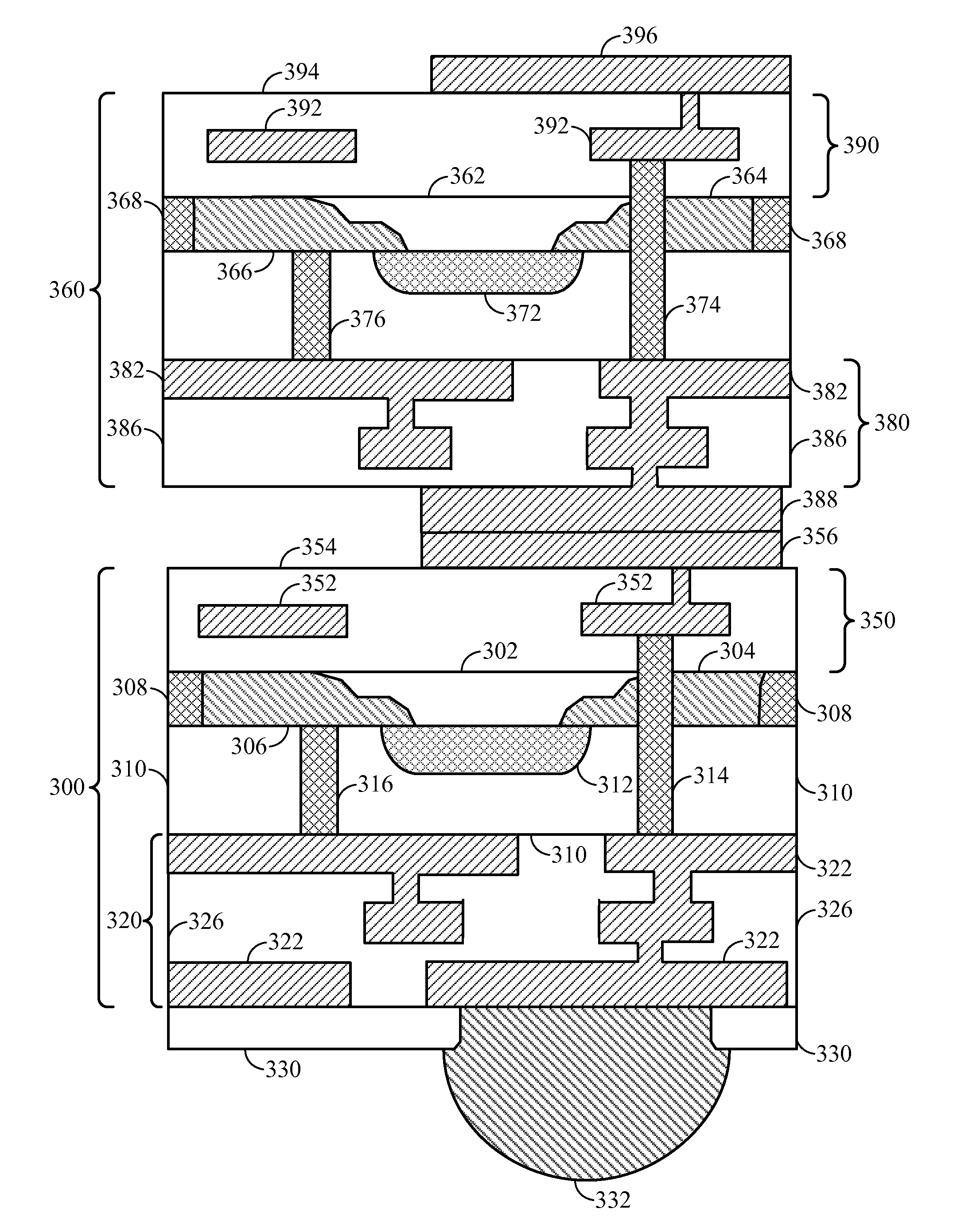

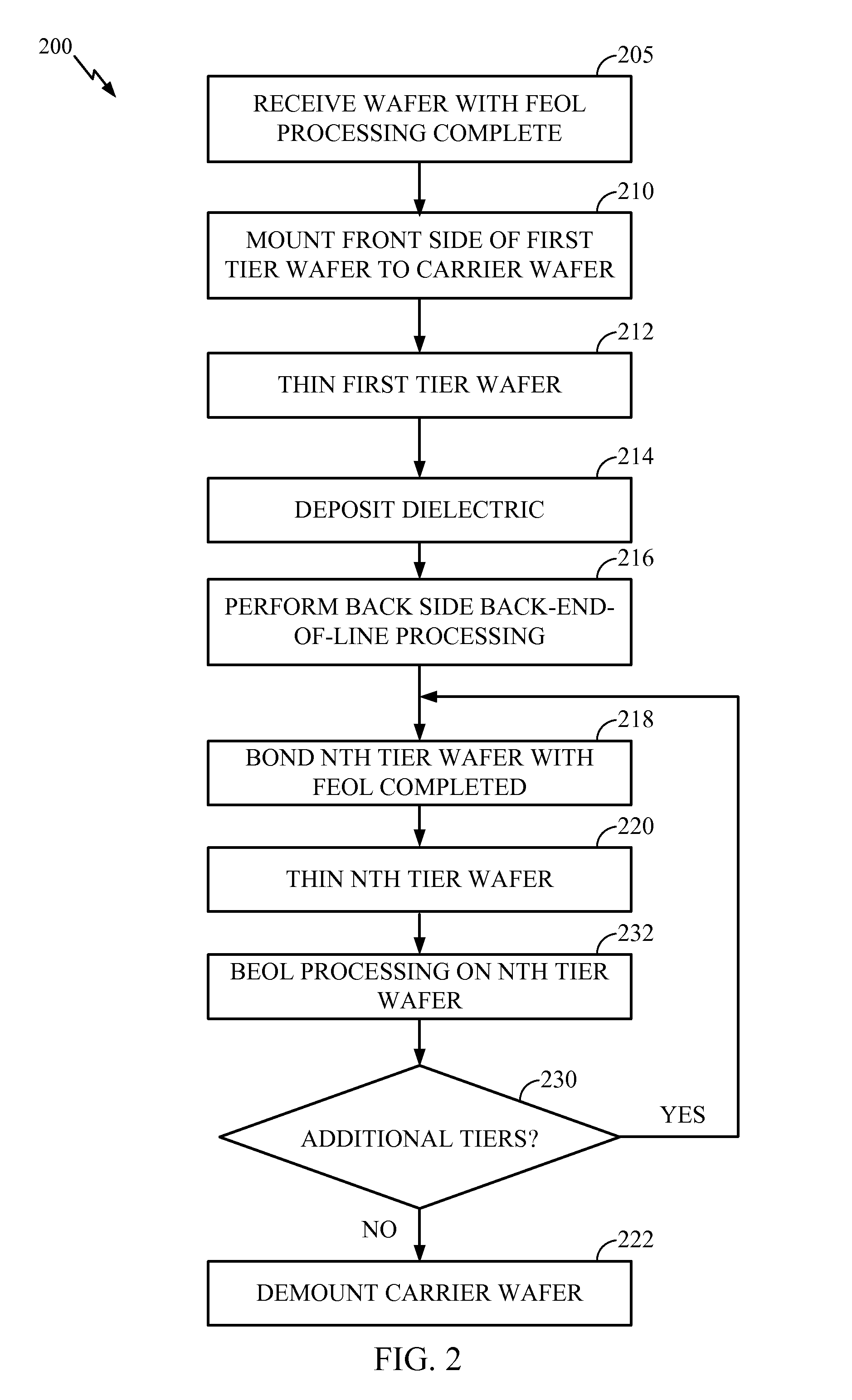

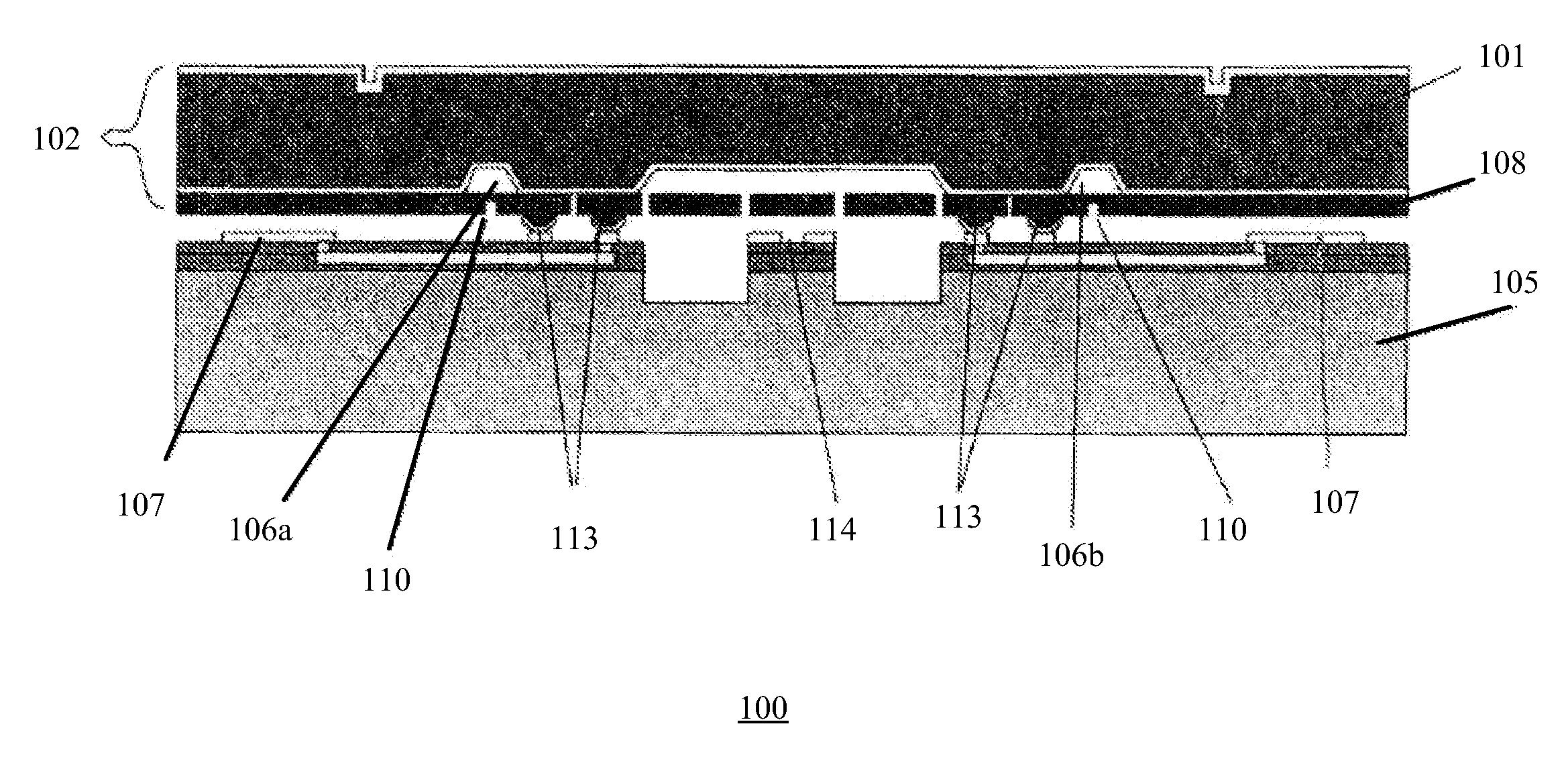

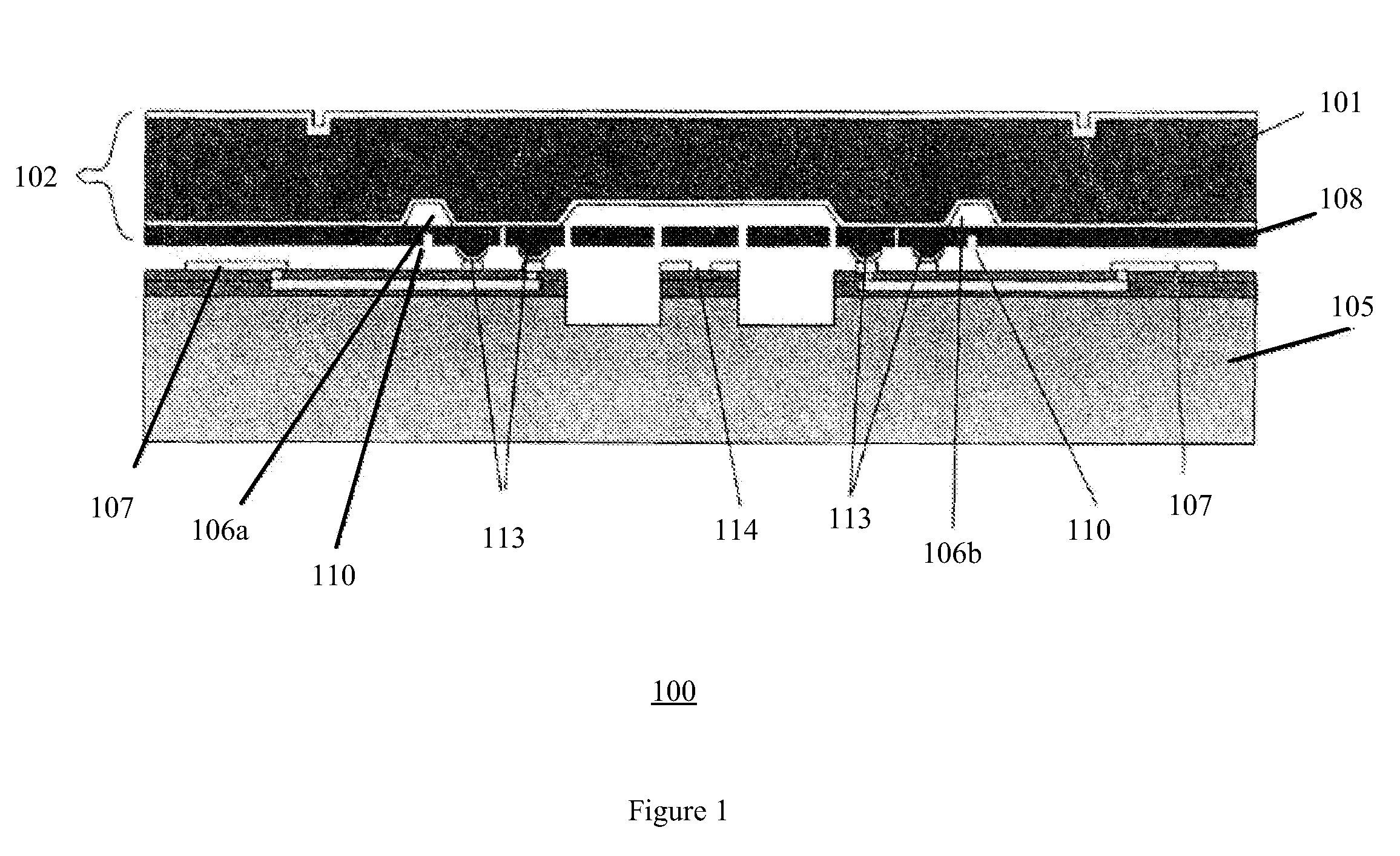

Dual-side interconnected CMOS for stacked integrated circuits

Owner:QUALCOMM INC

Cap Wafer for Wafer Bonded Packaging and Method for Manufacturing the Same

InactiveUS20080081398A1Semiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

The present invention relates to semiconductor device manufacturing techniques, and specifically to a field of device packaging techniques at wafer level. More specifically, it relates to a cap wafer for wafer bonding application that is bonded to top part of a device wafer. The method of the present invention excludes the use of deep reactive ion etching of silicon to form a through silicon via. The present invention provides a method for the preparation of cap wafer for wafer bonding application with a simple process of through silicon via interconnection and a wafer level packaging method using the same.

Owner:PHOCO

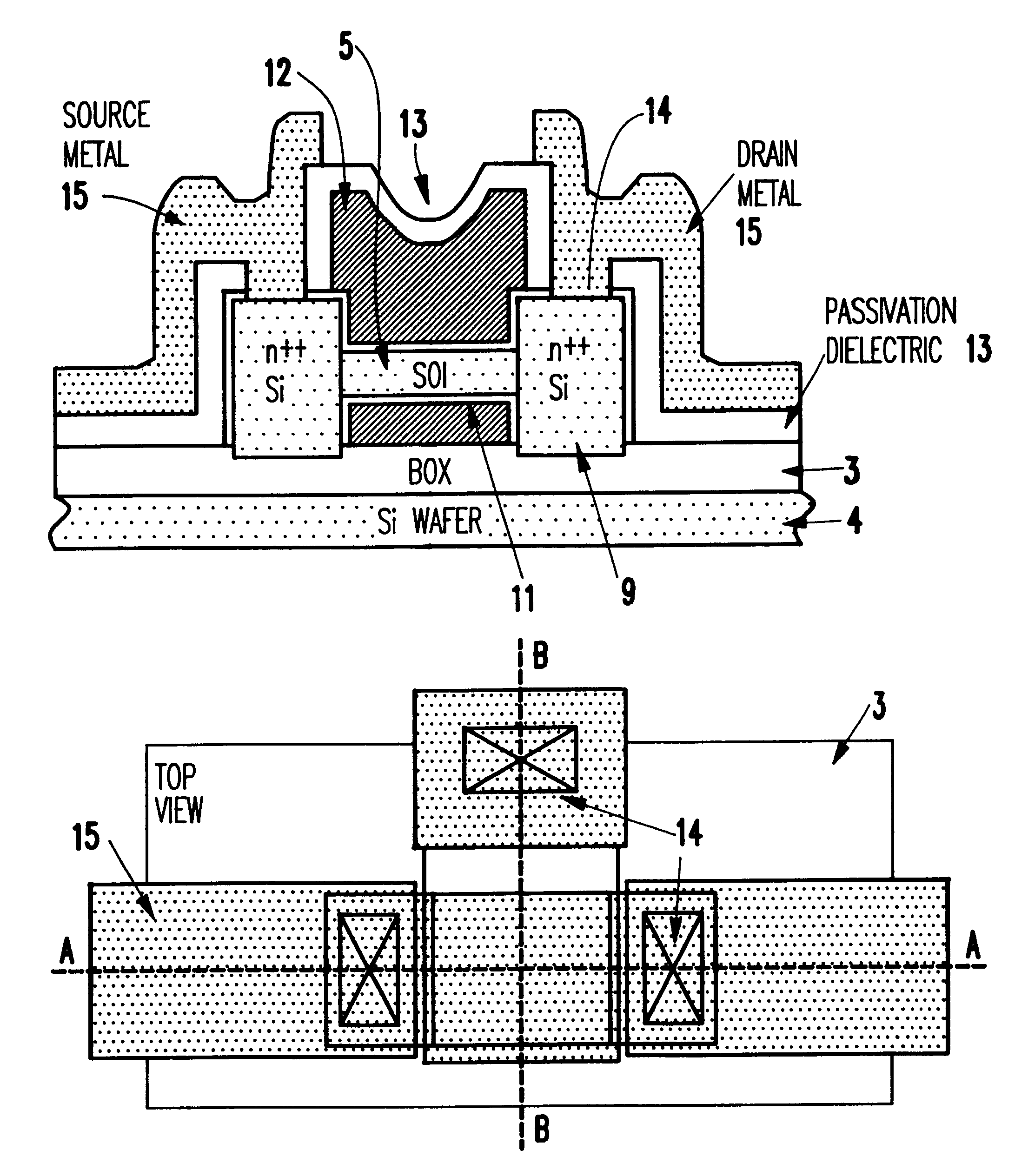

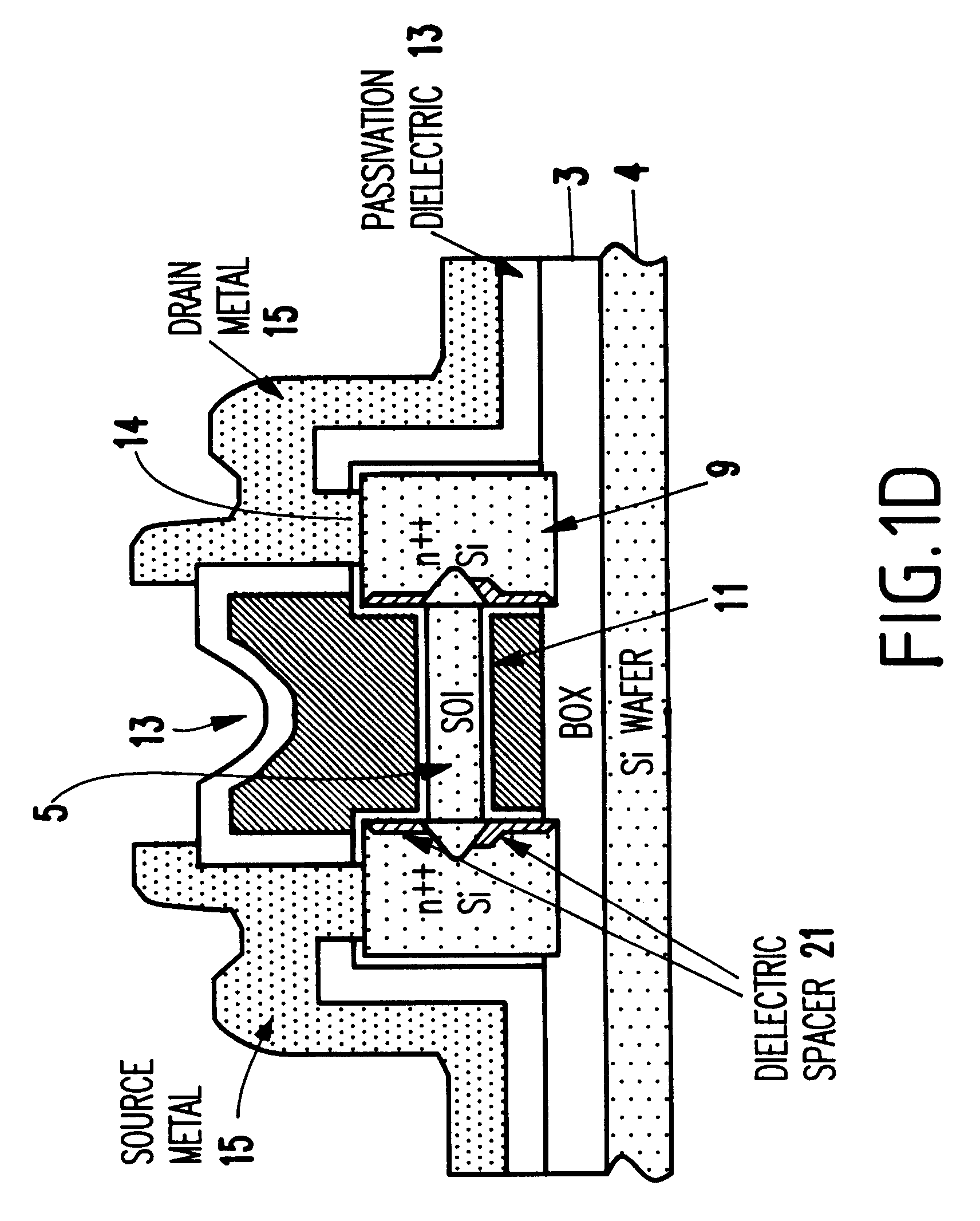

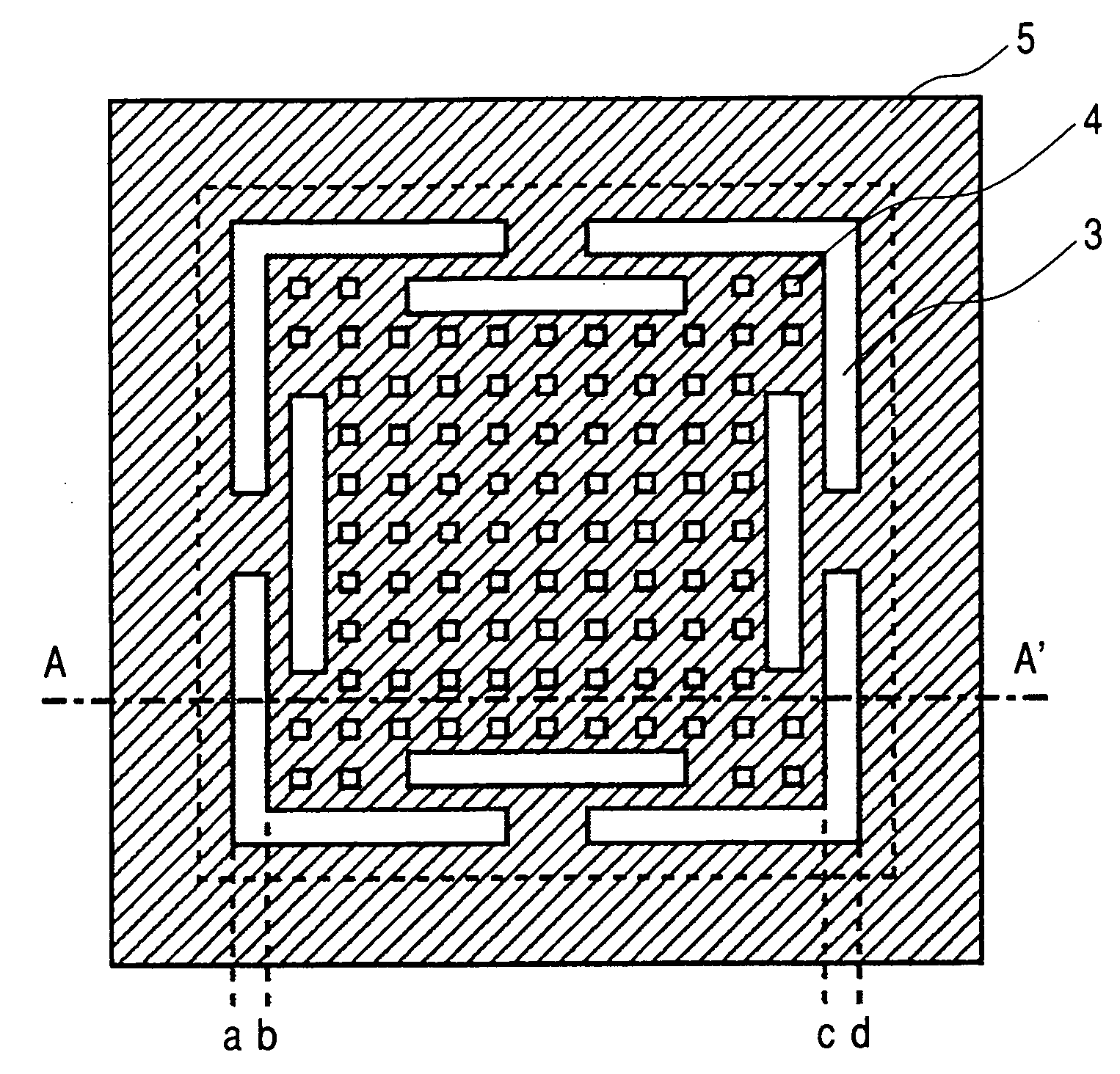

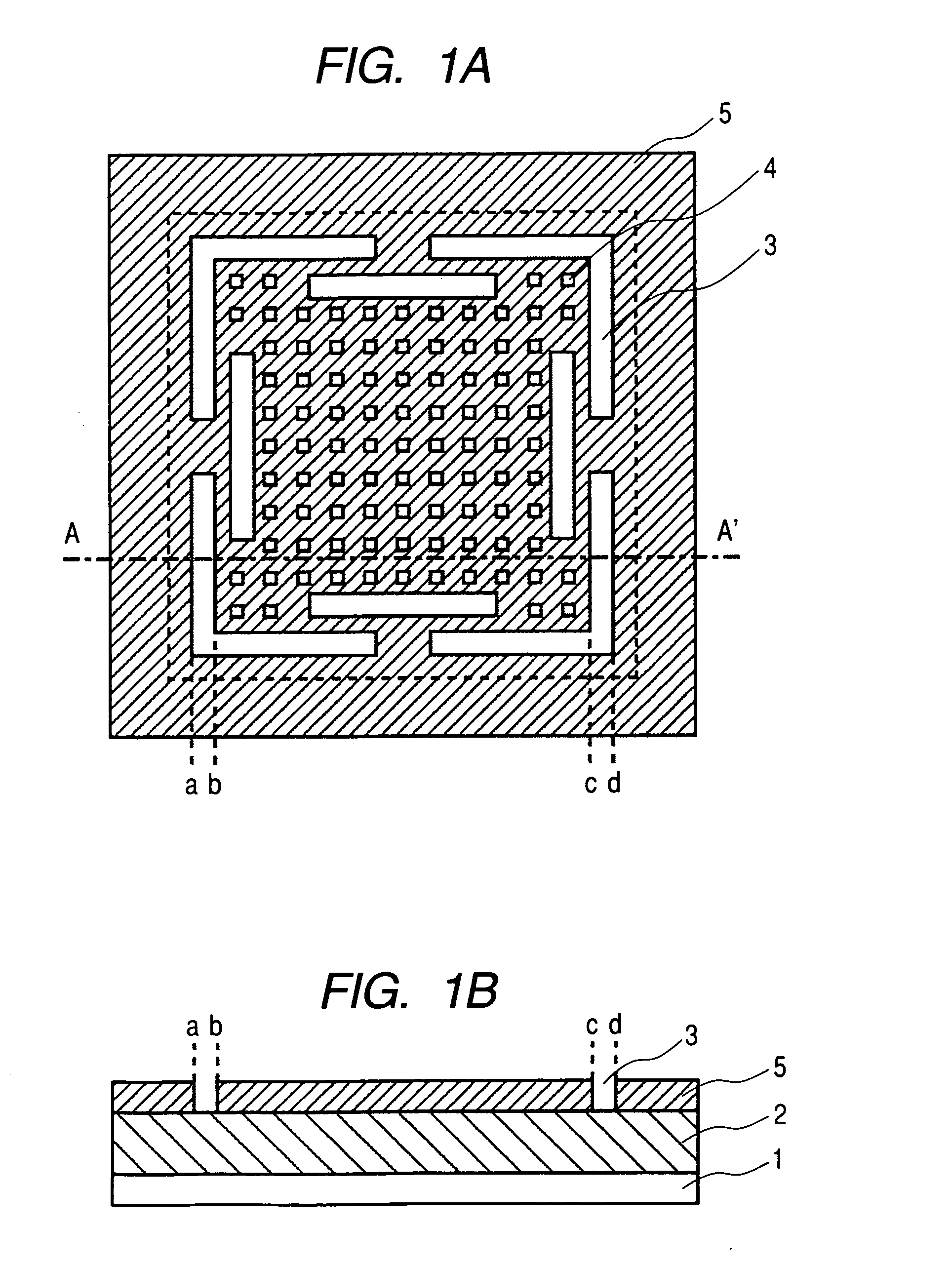

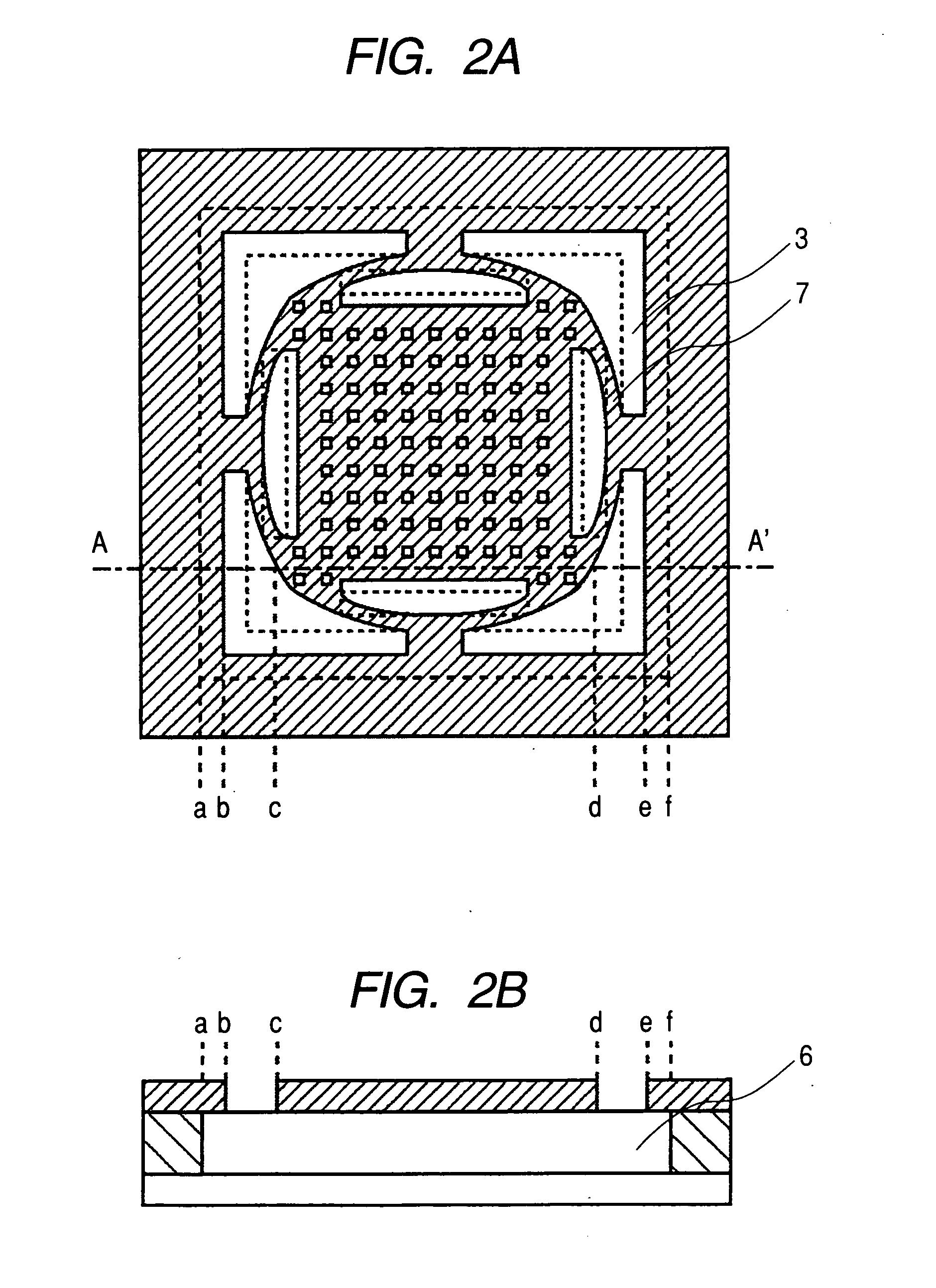

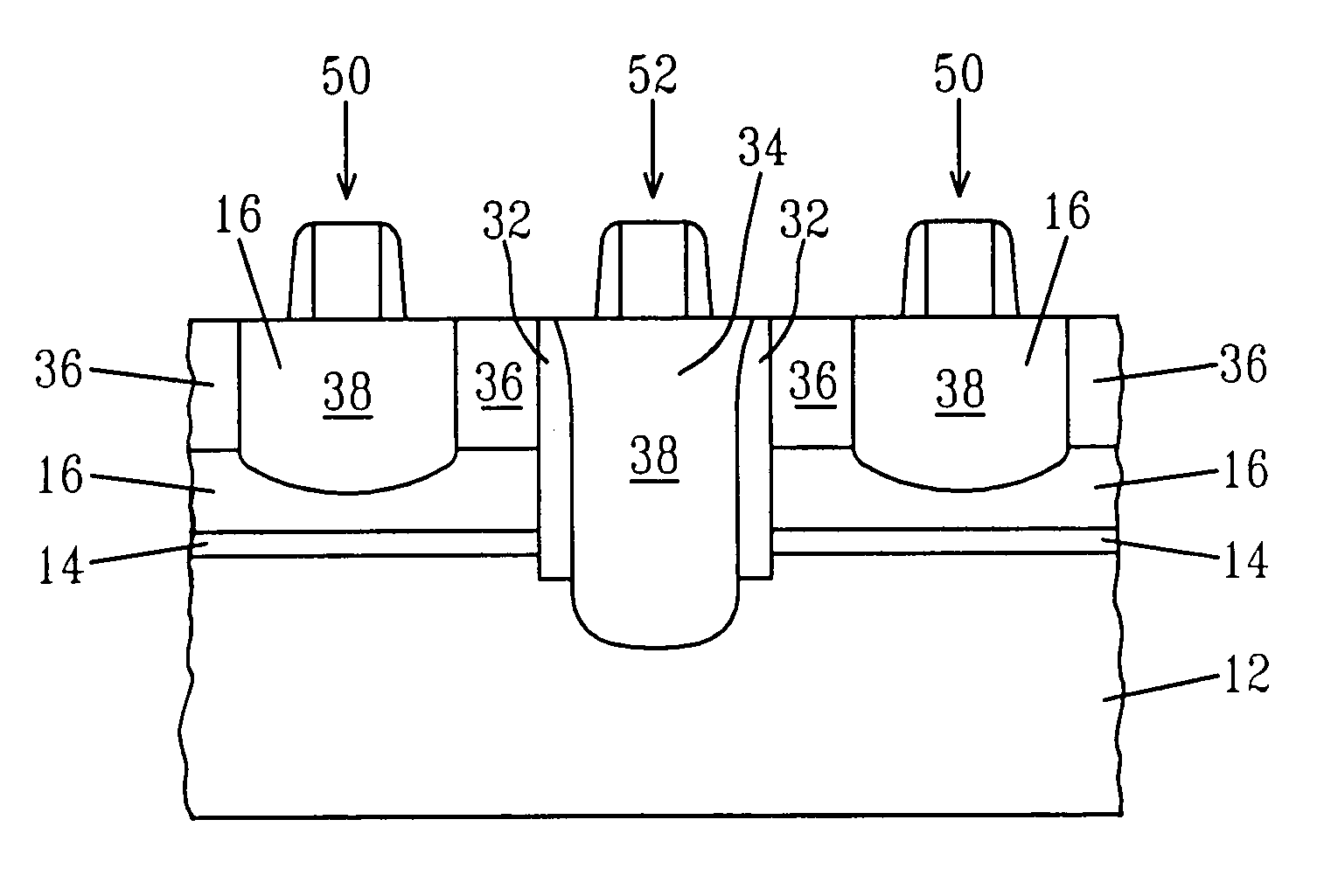

Self-aligned double-gate MOSFET by selective epitaxy and silicon wafer bonding techniques

InactiveUS6365465B1Controlled diffusionReduce diffuseTransistorSemiconductor/solid-state device manufacturingElectrical conductorEngineering

A structure and a method of manufacturing a double-gate metal oxide semiconductor transistor includes forming a laminated structure having a single crystal silicon channel layer and insulating oxide and nitride layers on each side of the single crystal silicon channel, forming openings in the laminated structure, forming drain and source regions in the openings, doping the drain and source regions, forming a mask over the laminated structure, removing portions of the laminated structure not protected by the mask, removing the mask and the insulating oxide and nitride layers to leave the single crystal silicon channel layer suspended from the drain and source regions, forming an oxide layer to cover the drain and source regions and the channel layer, and forming a double-gate conductor over the oxide layer such that the double-gate conductor includes a first conductor on a first side of the single crystal silicon channel layer and a second conductor on a second side of the single crystal silicon channel layer.

Owner:IBM CORP

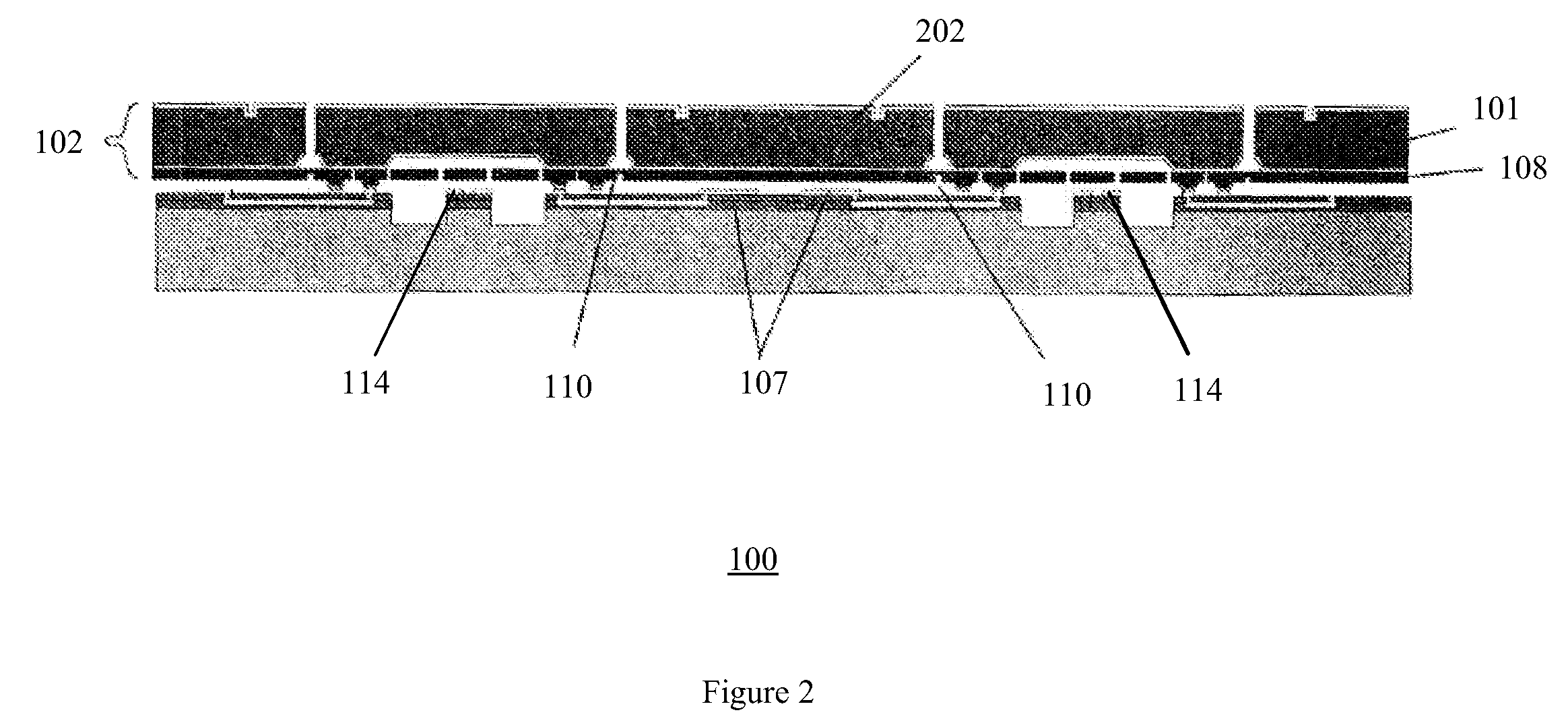

MEMS device and manufacturing process thereof

InactiveUS20070190680A1Relaxation stressSemiconductor/solid-state device manufacturingForming microstructural systemsEngineeringWafer bonding

MEMS devices require special cavity formation and sealing steps such as wafer bonding which reduce the yield and increase the cost. In addition, it is difficult to form a cavity of a large area by the LSI process owing to a residual stress of a sealing film which will be a lid. This leads to a difficulty of realizing an integrated MEMS having a MEMS and a high-performance LSI mounted on one substrate. The lid (or diaphragm) covering therewith a cavity is equipped with slits or beams. During the formation of the cavity, the slits are deformed to absorb and relax the internal stress of the thin sealing film. Then, the cavity is sealed by filling the open portions of the film overlying the cavity between the inside and outside of the cavity. The cavity is formed by removing a portion of the interlayer film of LSI multilevel interconnects and the lid is made of a LSI-process thin film.

Owner:HITACHI LTD

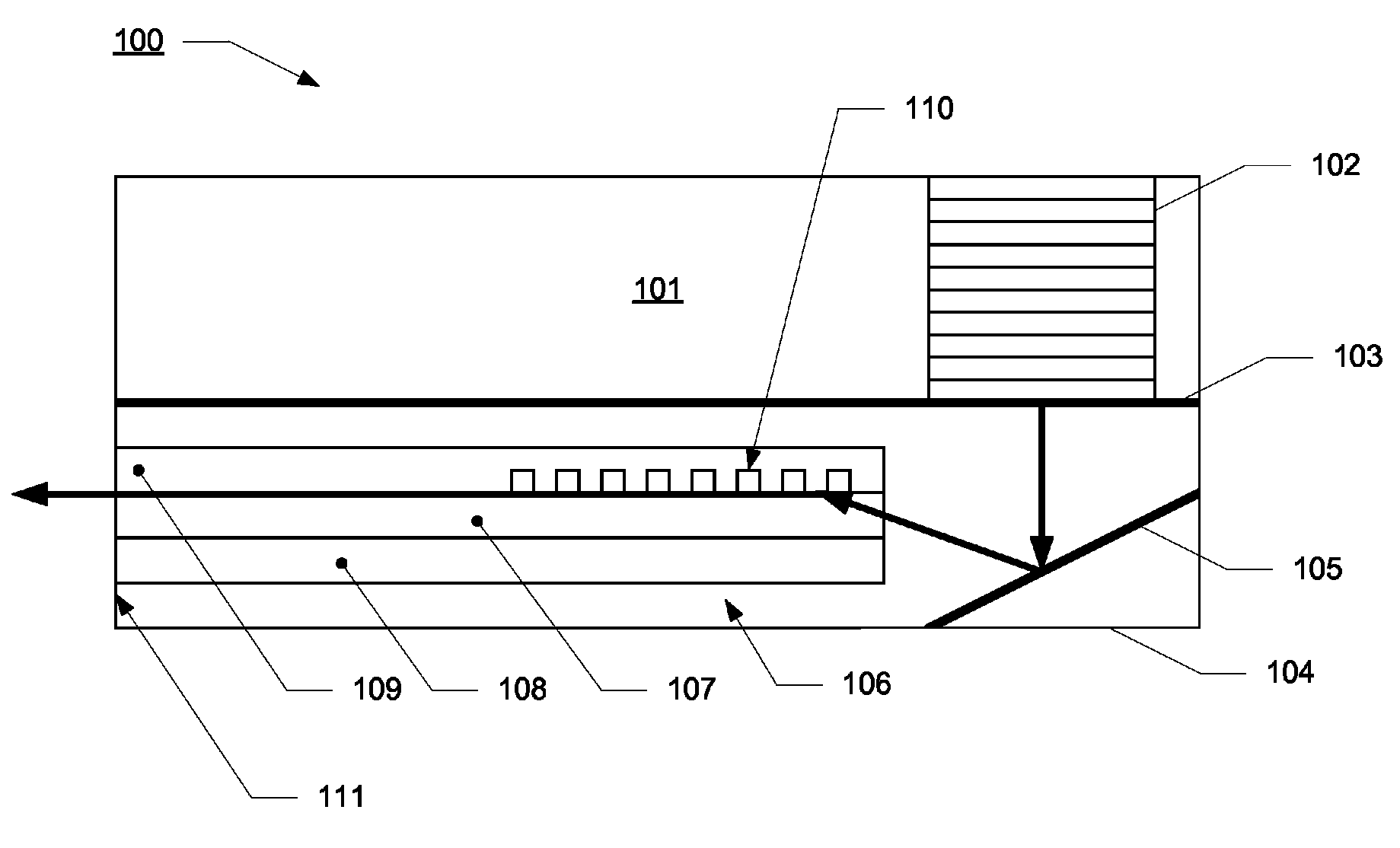

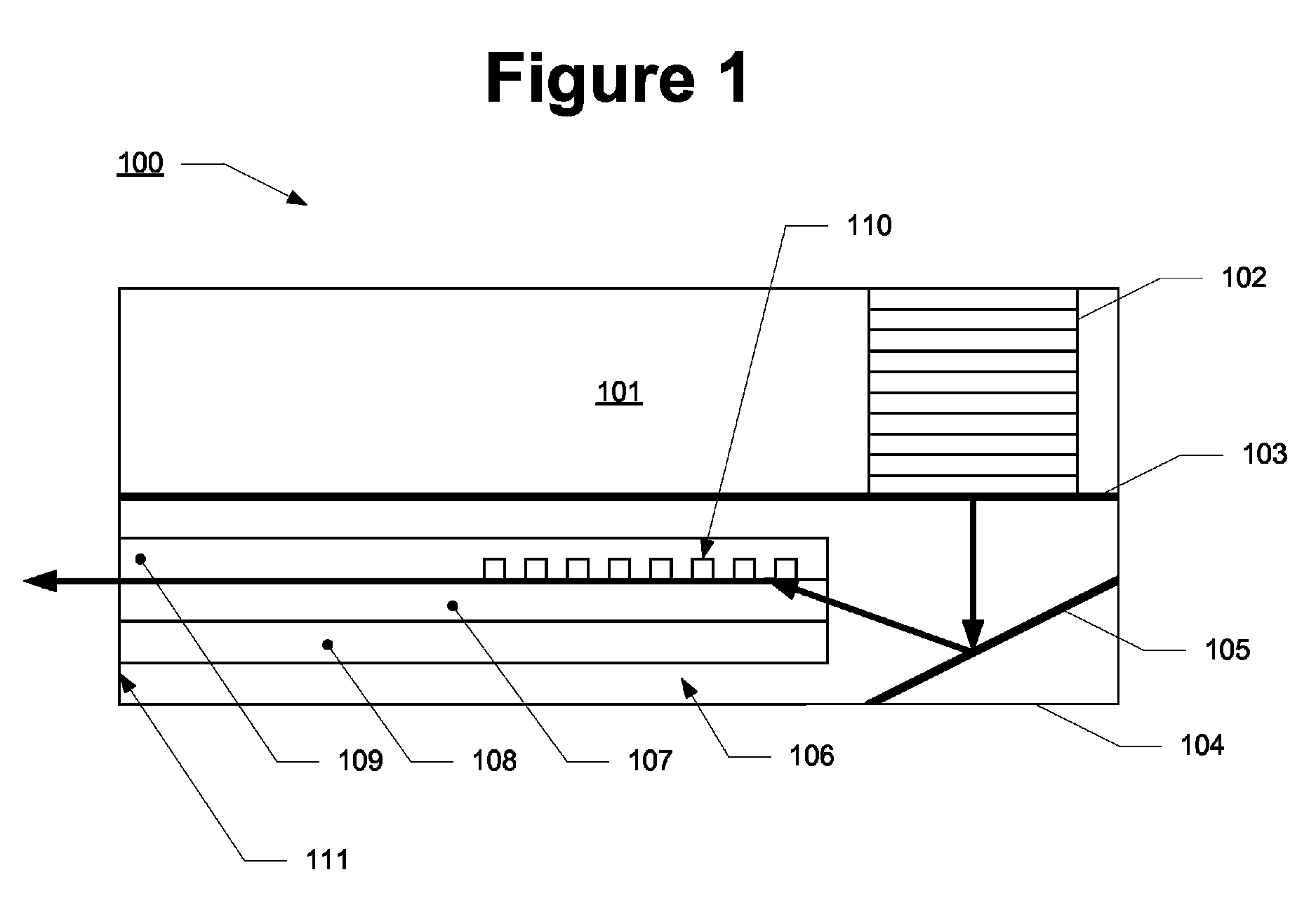

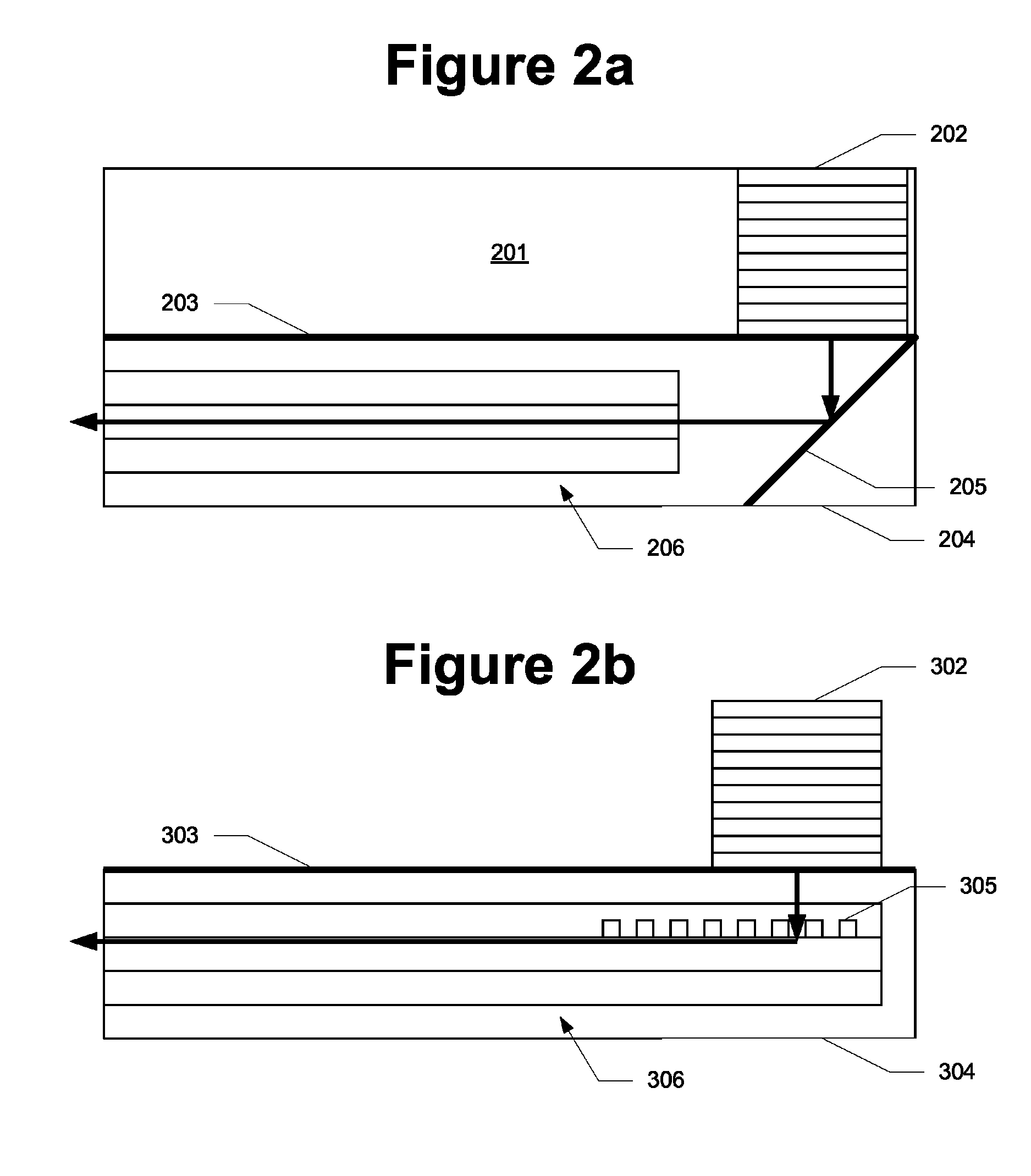

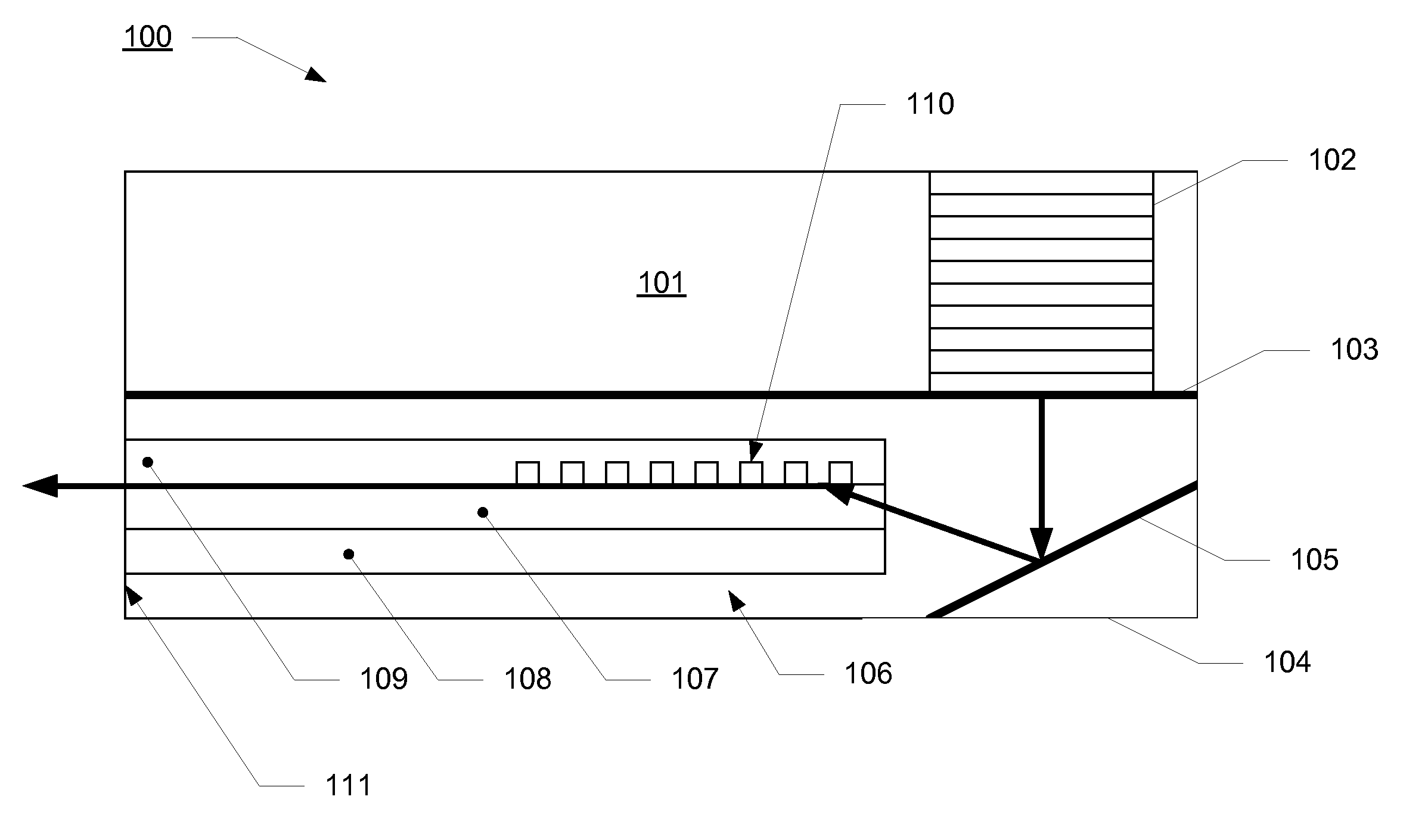

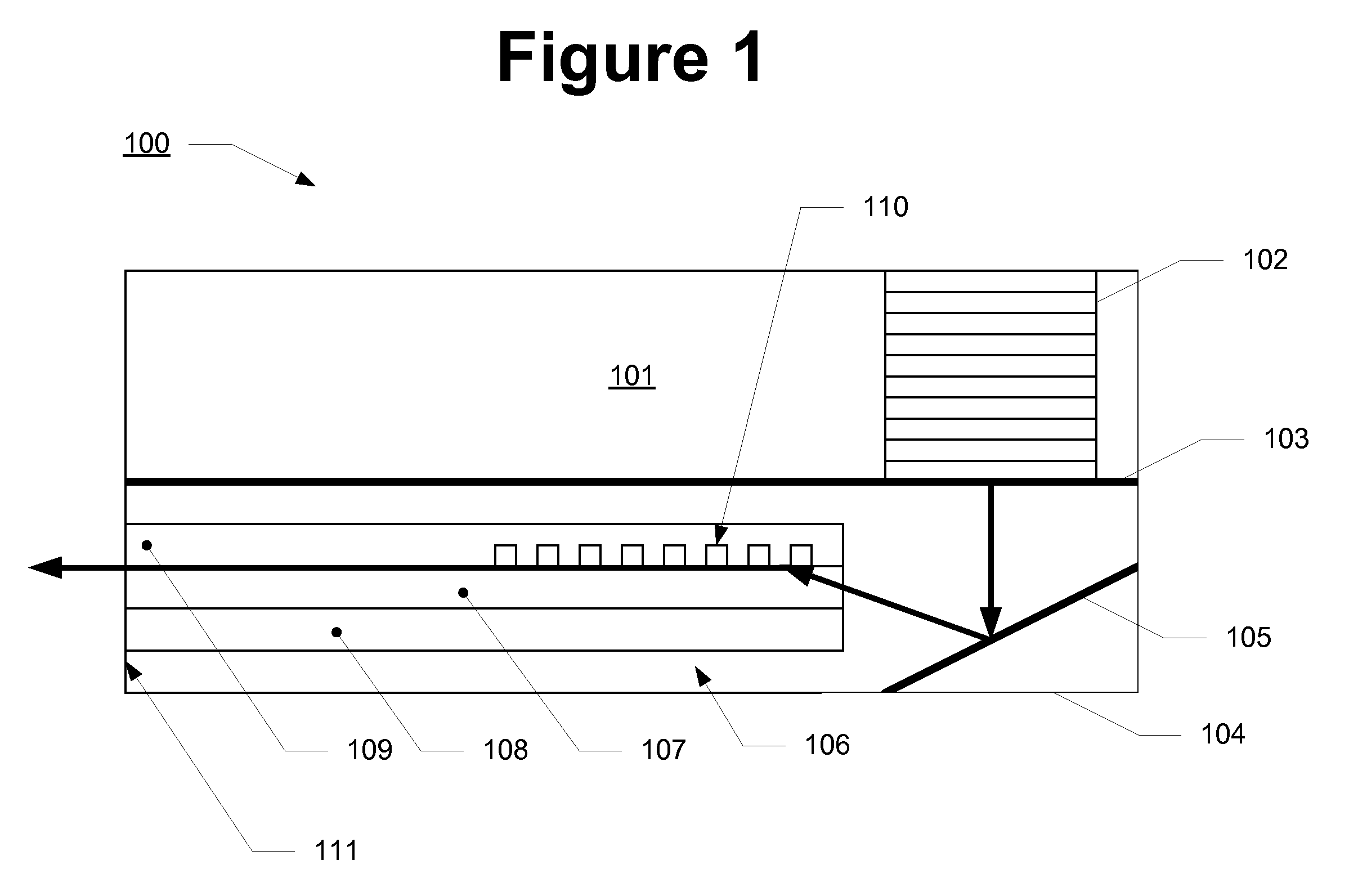

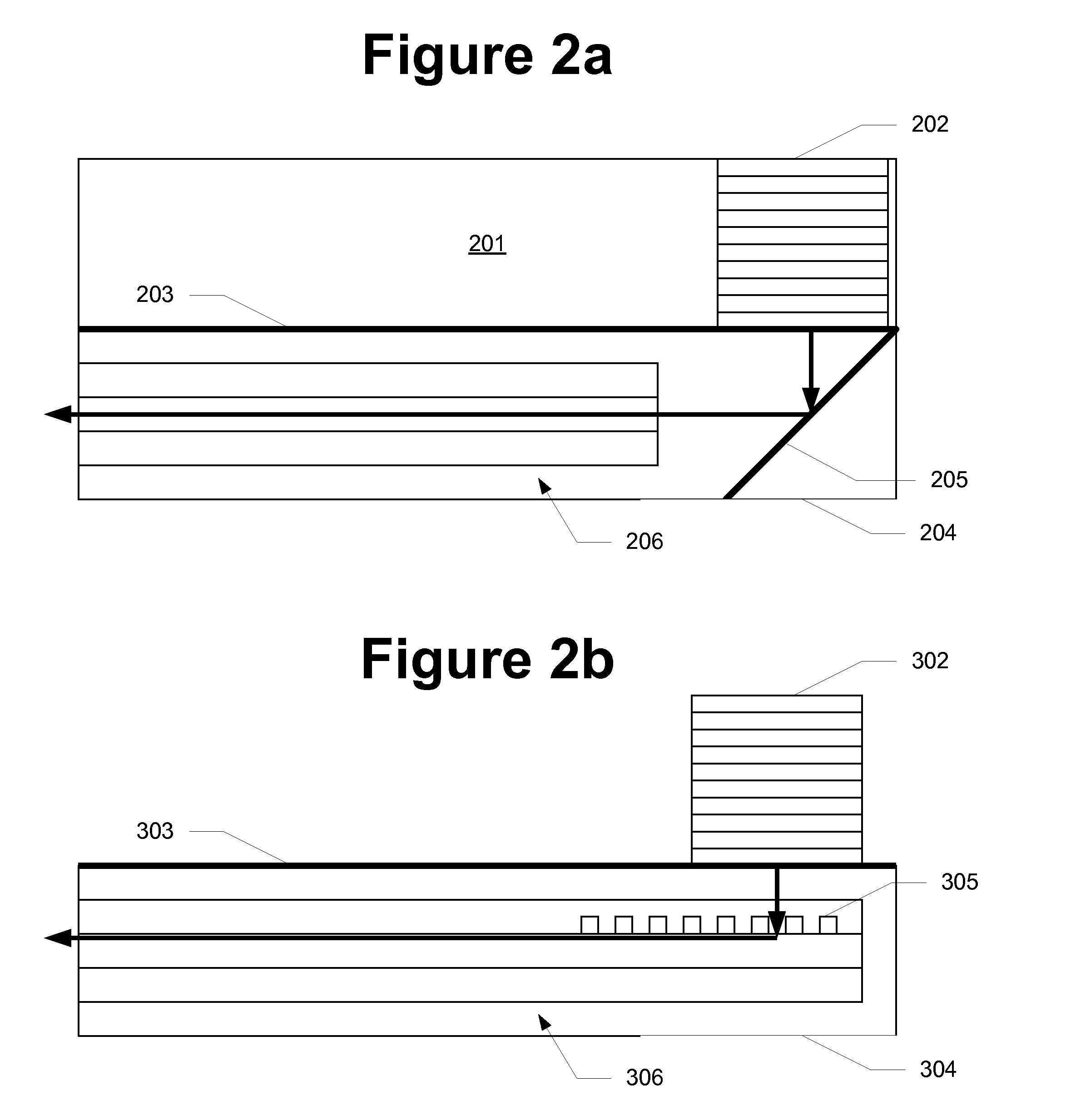

Integration of a vertical cavity surface emitting laser (VCSEL) on an energy-assisted magnetic recording (EAMR) head

ActiveUS8259539B1Reliable heatingLow costCombination recordingRecord information storageVertical-cavity surface-emitting laserOptoelectronics

An energy-assisted magnetic recording apparatus comprises a magnetic recording head having an end surface and an interface surface perpendicular to the end surface. The apparatus further comprises a vertical cavity surface emitting laser (VCSEL) bonded to the interface surface and configured to emit laser light through the interface surface and into the magnetic recording head. The magnetic recording head includes one or more light redirecting structures for redirecting the laser light towards the end surface. A method of making an energy-assisted magnetic recording apparatus comprises the steps of aligning a first wafer including a plurality of VCSELs with a second wafer including a plurality of magnetic recording heads, such that an emitting region of each of the plurality of VCSELs is disposed over a light redirecting structure of a corresponding one of the plurality of magnetic recording heads, and bonding the first wafer to the second wafer.

Owner:WESTERN DIGITAL TECH INC

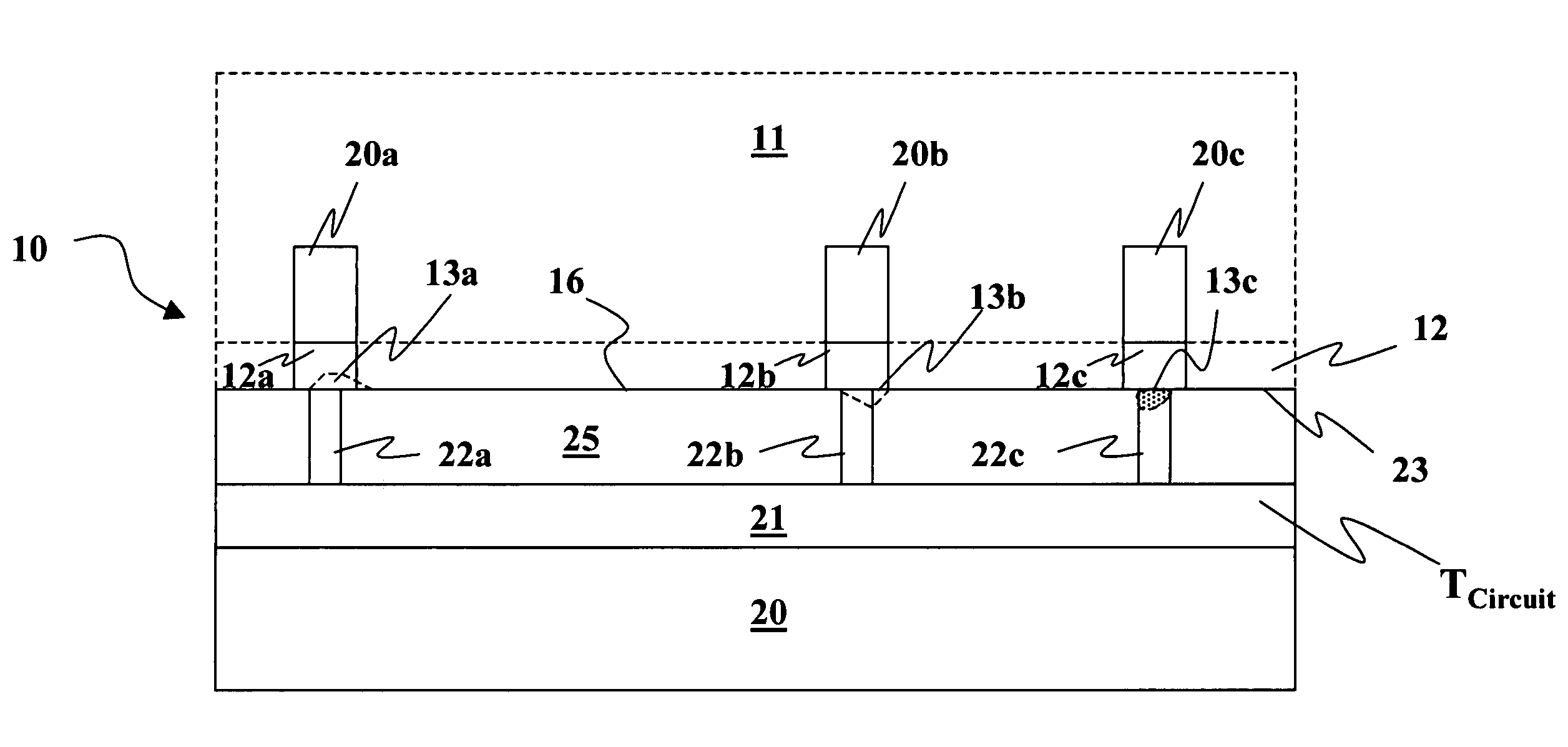

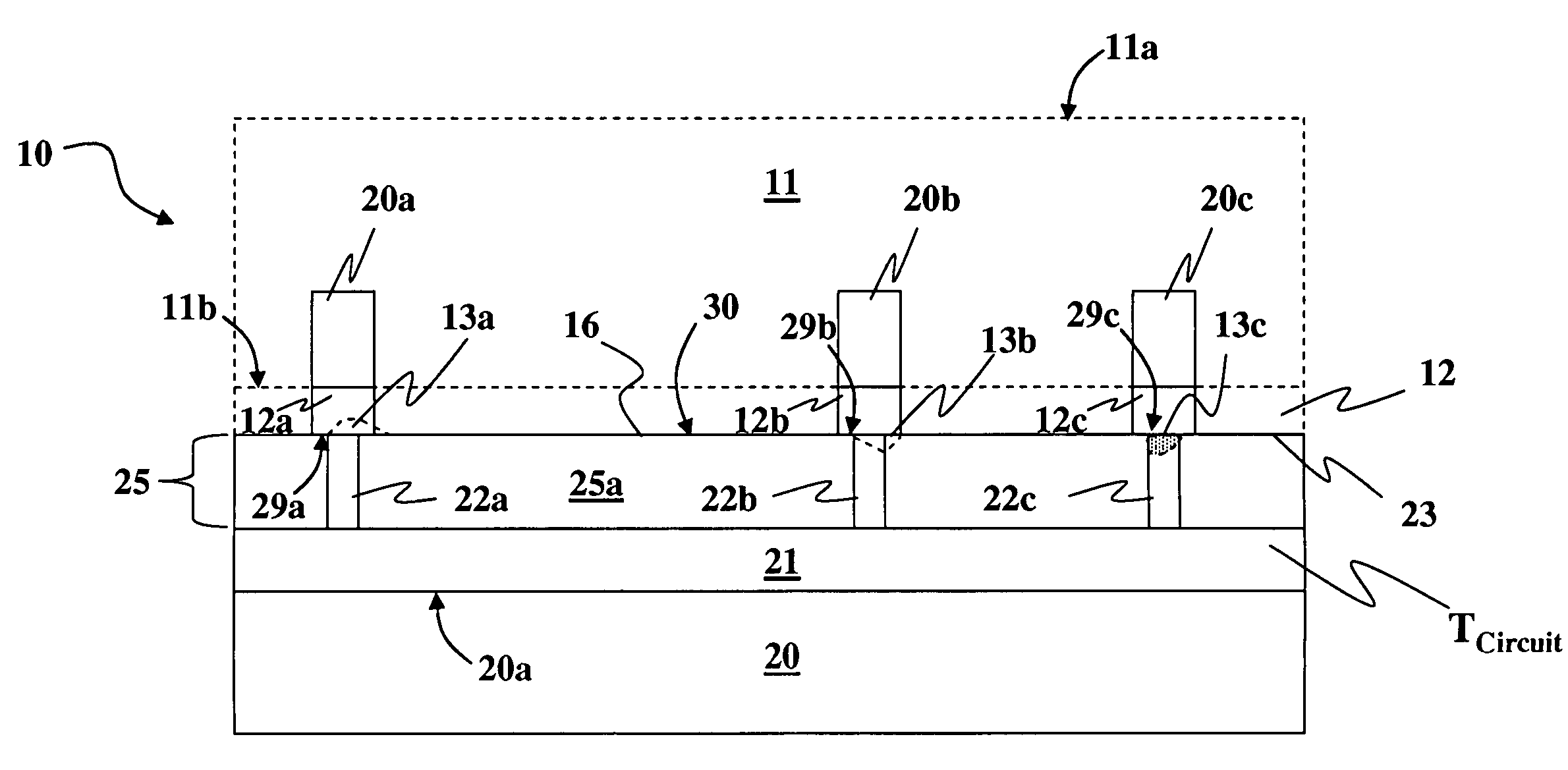

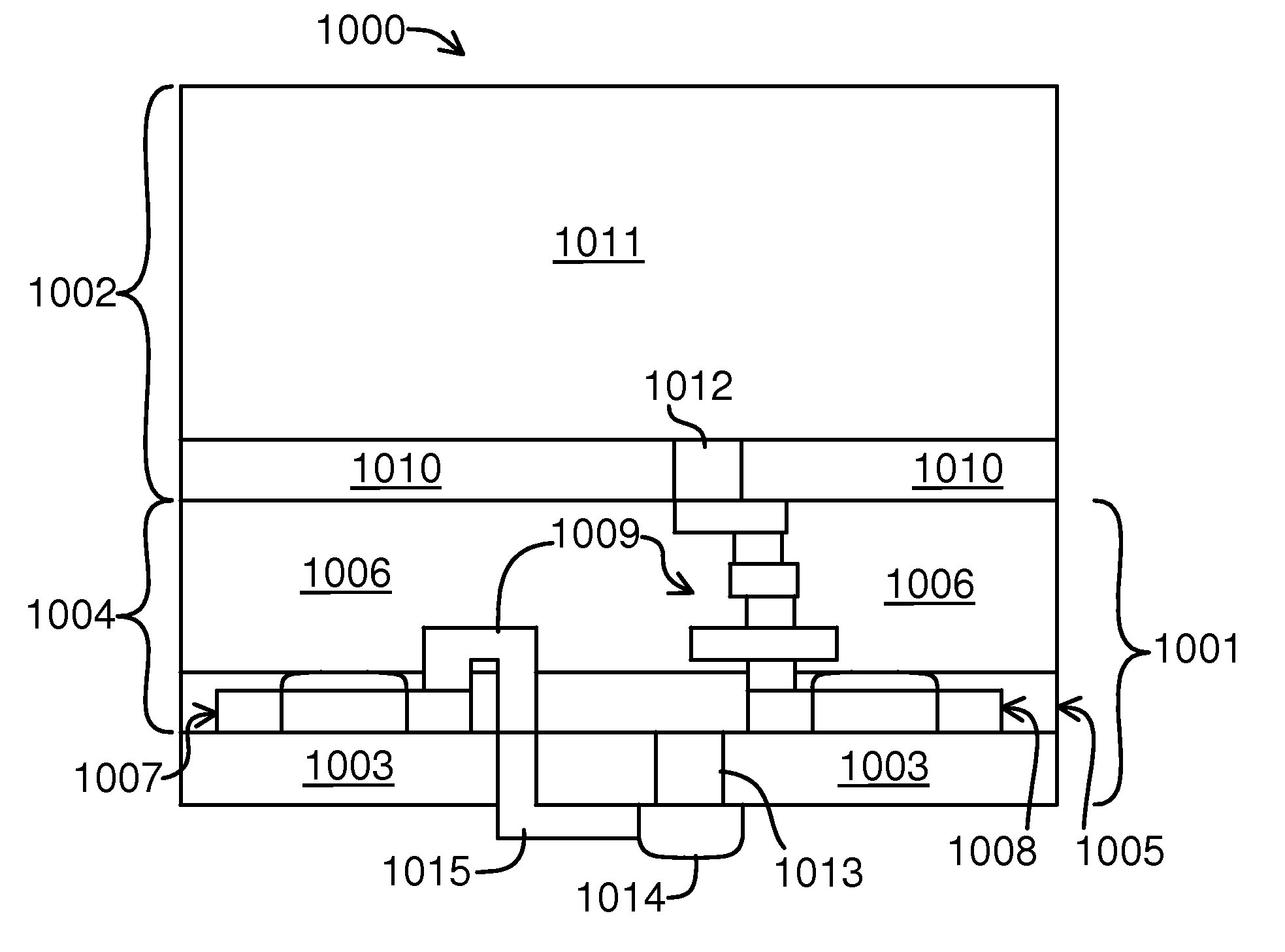

Thermal Conduction Paths for Semiconductor Structures

ActiveUS20120146193A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor structureThermal contact

A thermal path is formed in a layer transferred semiconductor structure. The layer transferred semiconductor structure has a semiconductor wafer and a handle wafer bonded to a top side of the semiconductor wafer. The semiconductor wafer has an active device layer formed therein. The thermal path is in contact with the active device layer within the semiconductor wafer. In some embodiments, the thermal path extends from the active device layer to a substrate layer of the handle wafer. In some embodiments, the thermal path extends from the active device layer to a back side external thermal contact below the active device layer.

Owner:QUALCOMM INC

Method of making an energy-assisted magnetic recording apparatus

ActiveUS8495813B1Reliable heatingLow costCombination recordingElectrical transducersEngineeringWafer bonding

A method of making an energy-assisted magnetic recording apparatus is provided. The method comprises the step of aligning a first wafer including a plurality of vertical cavity surface emitting lasers (VCSELs) with a second wafer including a plurality of magnetic recording heads, such that an emitting region of each of the plurality of VCSELs is disposed over a light redirecting structure of a corresponding one of the plurality of magnetic recording heads. The method further comprises the step of bonding the first wafer to the second wafer.

Owner:WESTERN DIGITAL TECH INC

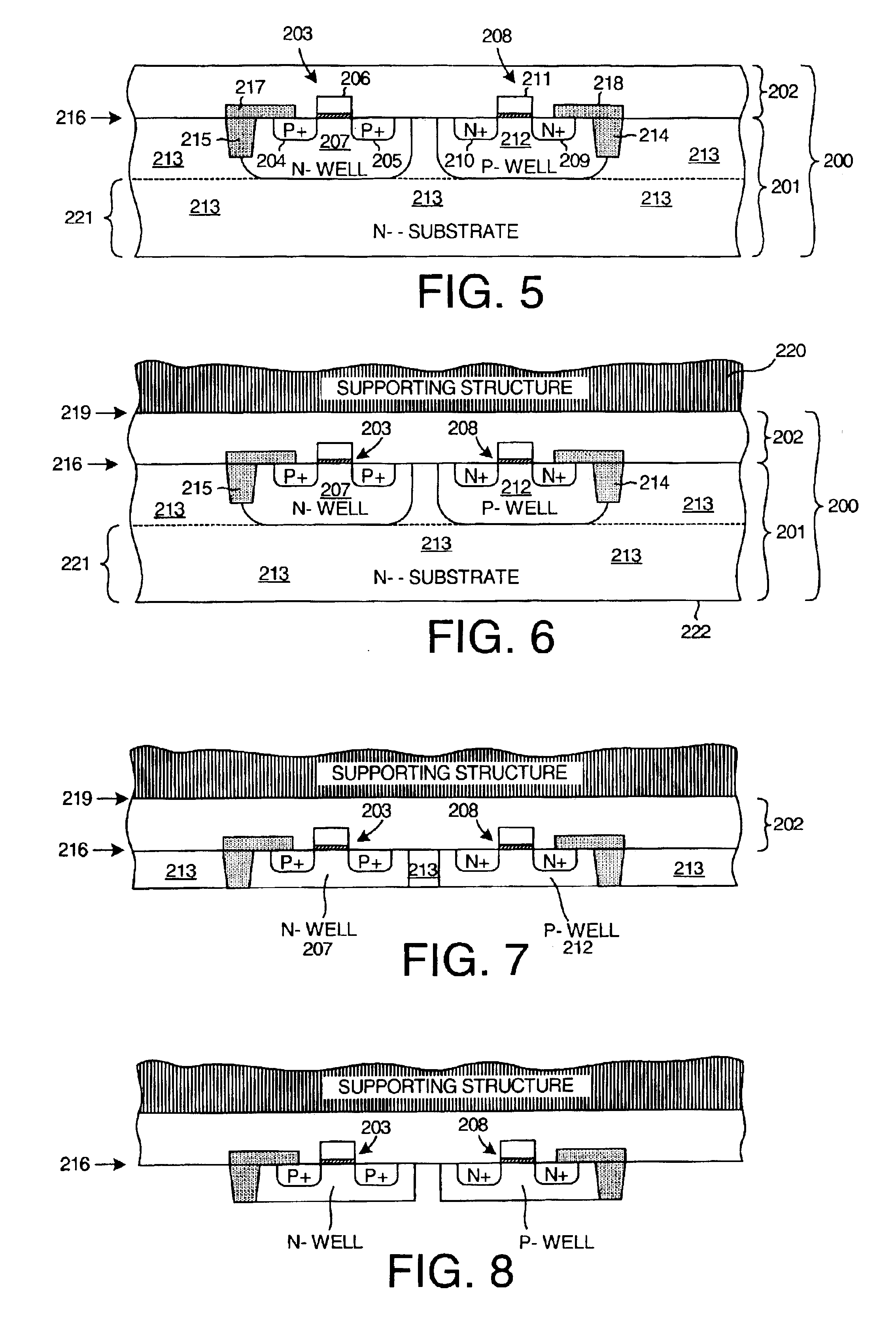

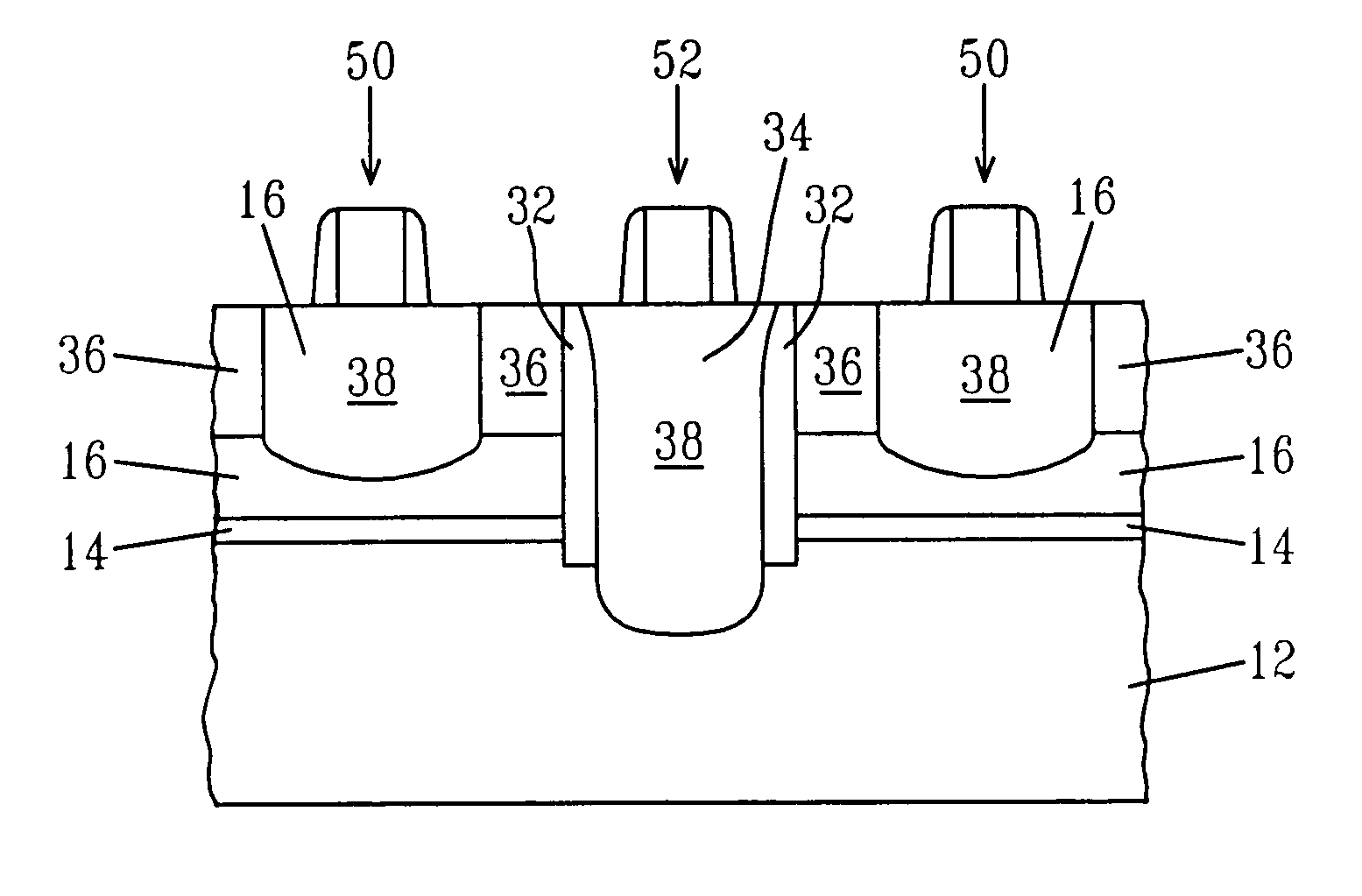

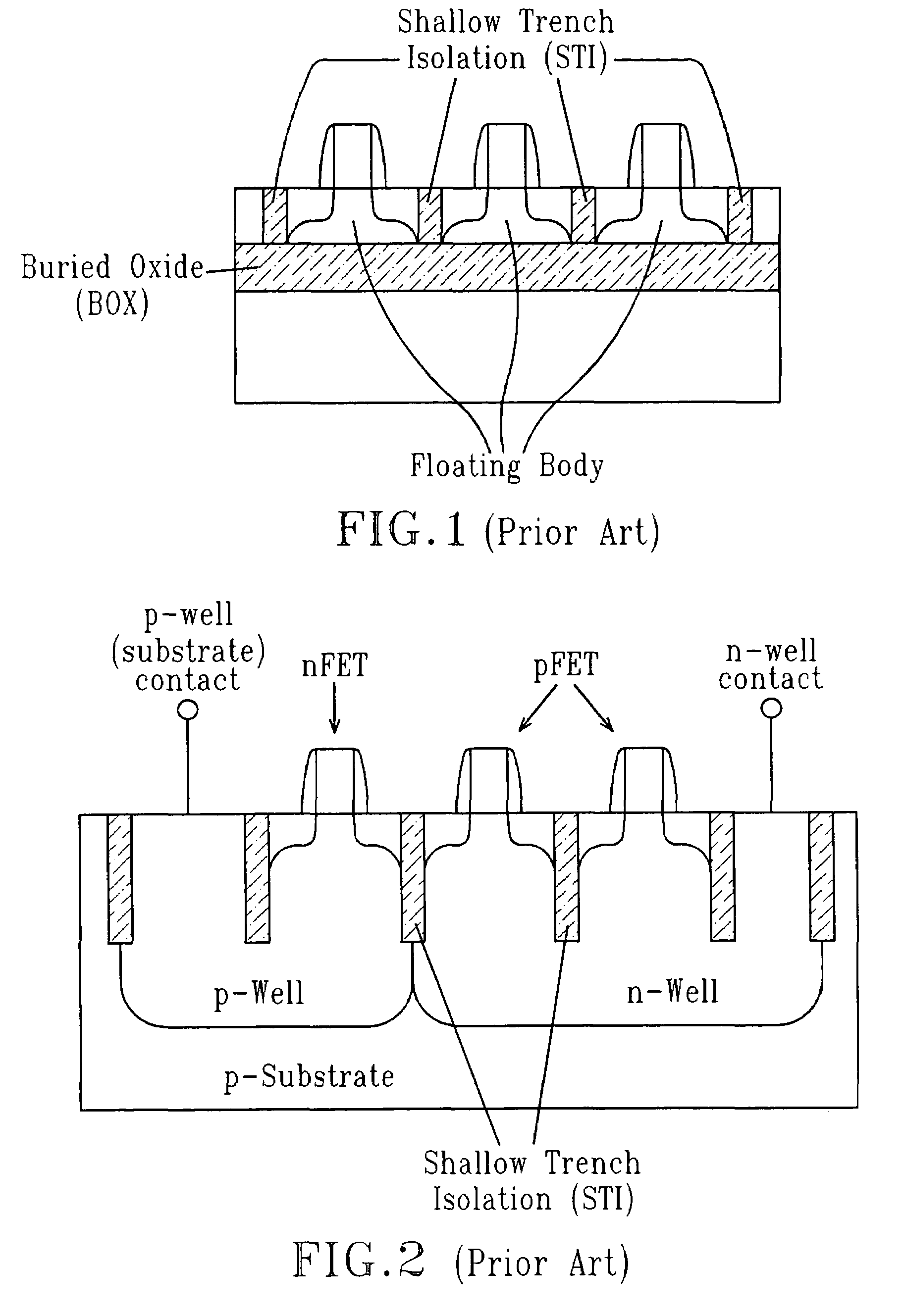

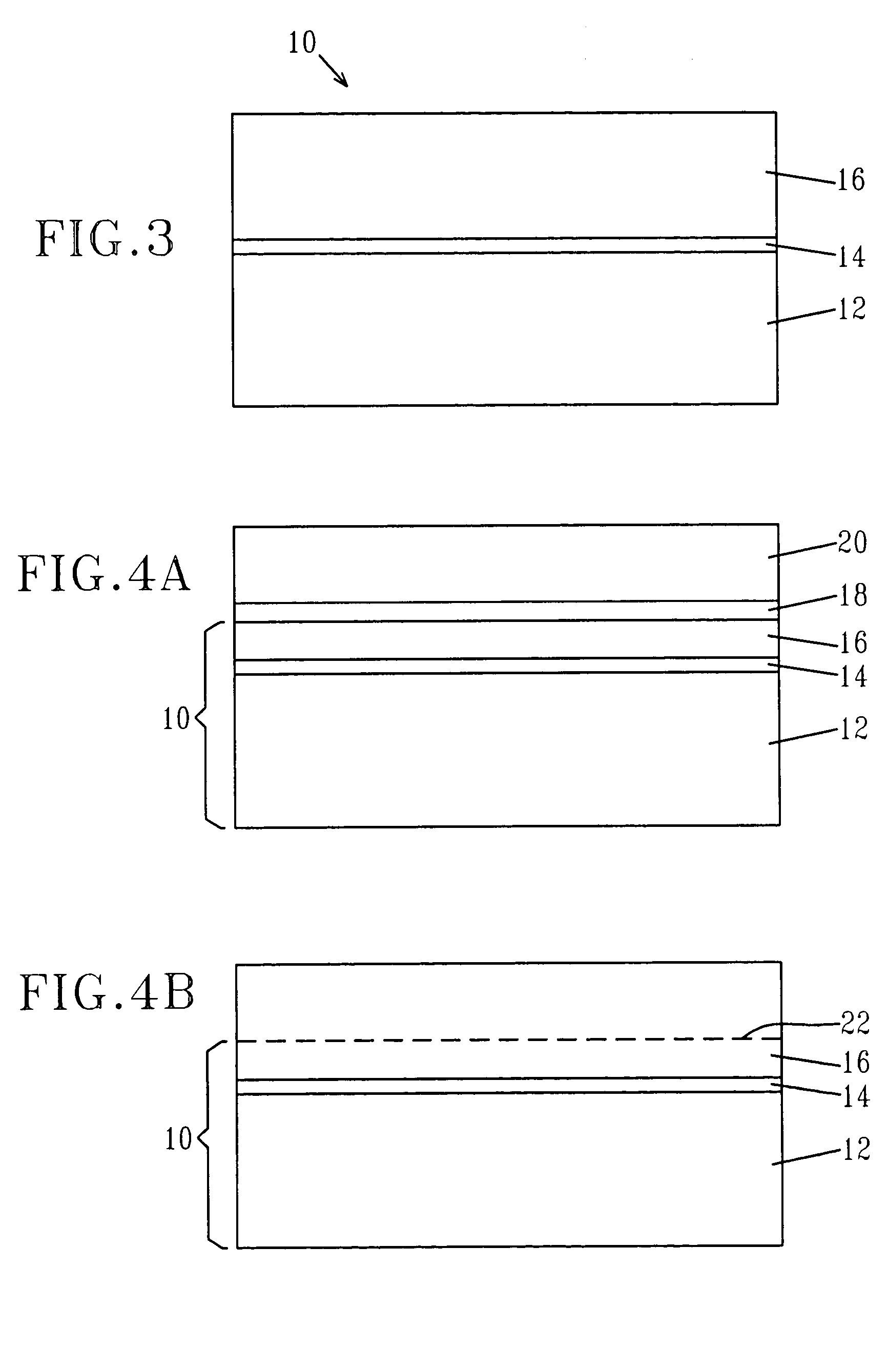

CMOS on hybrid substrate with different crystal orientations using silicon-to-silicon direct wafer bonding

InactiveUS7023055B2Improve performanceImprove device performanceTransistorSolid-state devicesCMOSSemiconductor structure

A method in which semiconductor-to-semiconductor direct wafer bonding is employed to provide a hybrid substrate having semiconductor layers of different crystallographic orientations that are separated by a conductive interface is provided. Also provided are the hybrid substrate produced by the method as well as using the direct bonding method to provide an integrated semiconductor structure in which various CMOS devices are built upon a surface orientation that enhances device performance.

Owner:GLOBALFOUNDRIES INC

CMOS on hybrid substrate with different crystal orientations using silicon-to-silicon direct wafer bonding

InactiveUS20050093104A1Improve performanceImprove device performanceTransistorSolid-state devicesCMOSSemiconductor structure

A method in which semiconductor-to-semiconductor direct wafer bonding is employed to provide a hybrid substrate having semiconductor layers of different crystallographic orientations that are separated by a conductive interface is provided. Also provided are the hybrid substrate produced by the method as well as using the direct bonding method to provide an integrated semiconductor structure in which various CMOS devices are built upon a surface orientation that enhances device performance.

Owner:GLOBALFOUNDRIES INC

Method and system of releasing a MEMS structure

ActiveUS7250353B2Semiconductor/solid-state device detailsSolid-state devicesDevice formMicroelectromechanical systems

A MEMs (microelectromechanical systems) structure is provided. In one implementation, the MEMs structure includes a substrate wafer including a MEMs device formed on a surface of the substrate wafer, and a MEMs cover structure to cover the MEMs device formed on the surface of the substrate wafer. The MEMs cover structure comprises a first wafer bonded to a second wafer, in which only the first wafer of the MEMs cover structure is sawed through and not the second wafer of the MEMs cover structure during dicing of the MEMs structure.

Owner:INVENSENSE

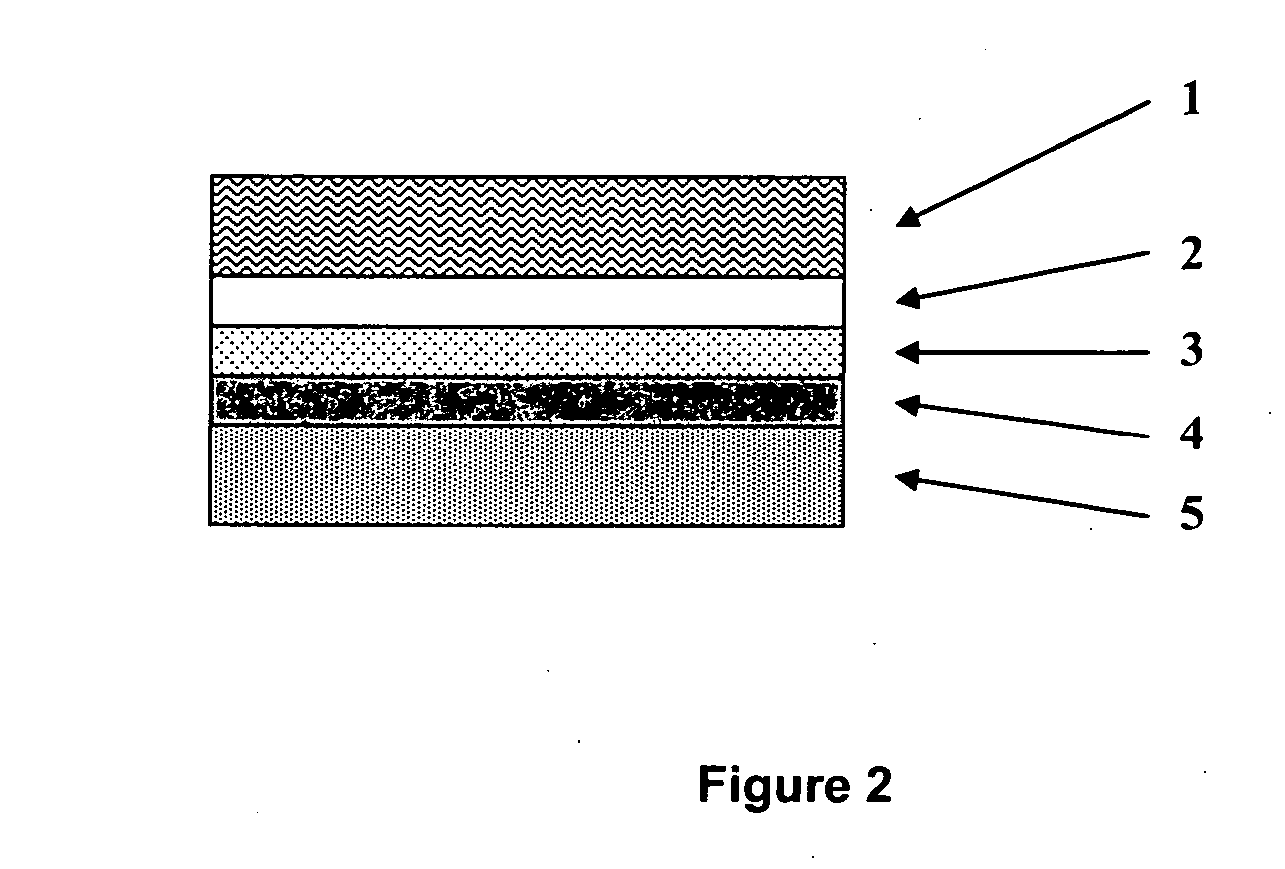

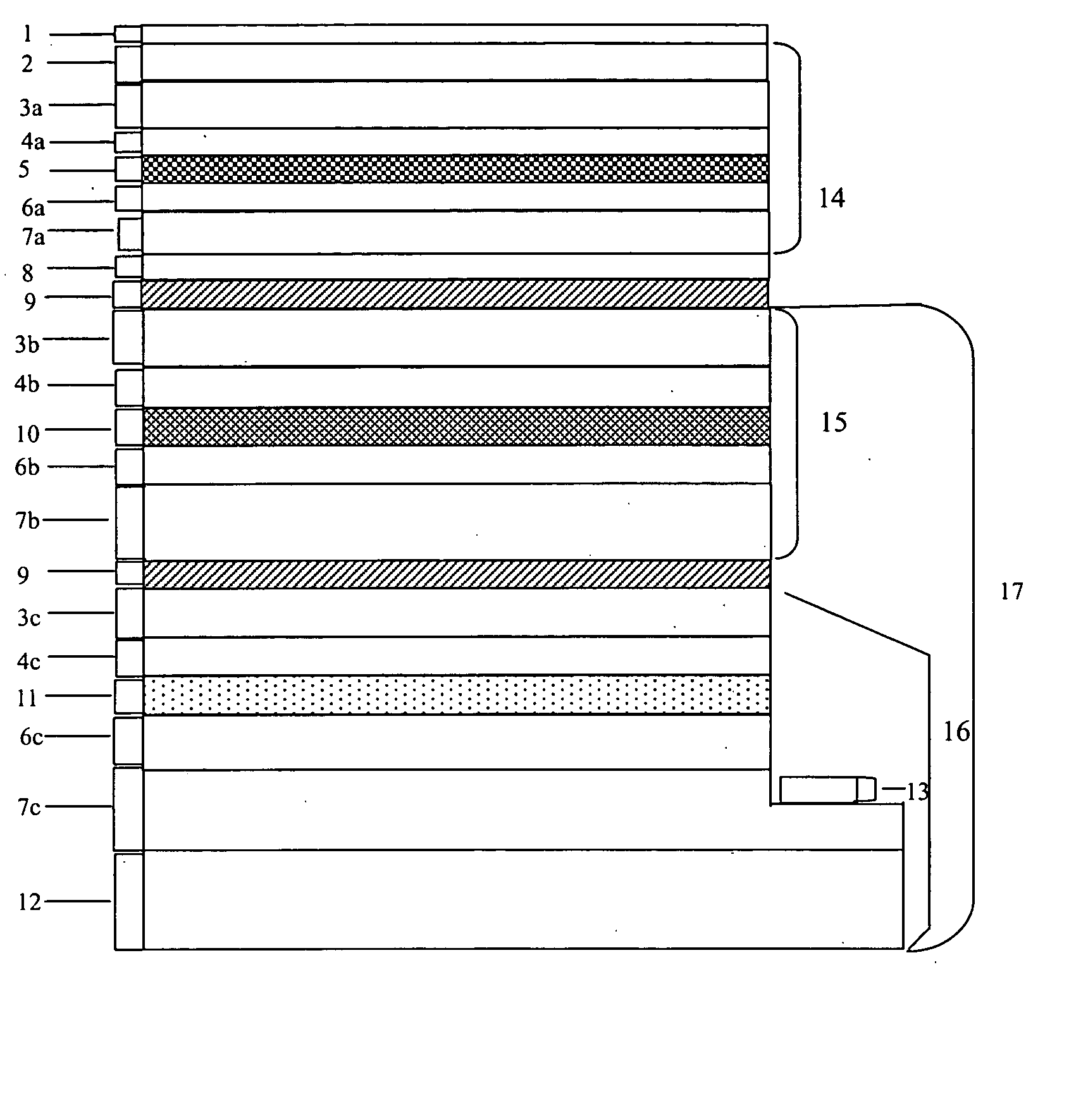

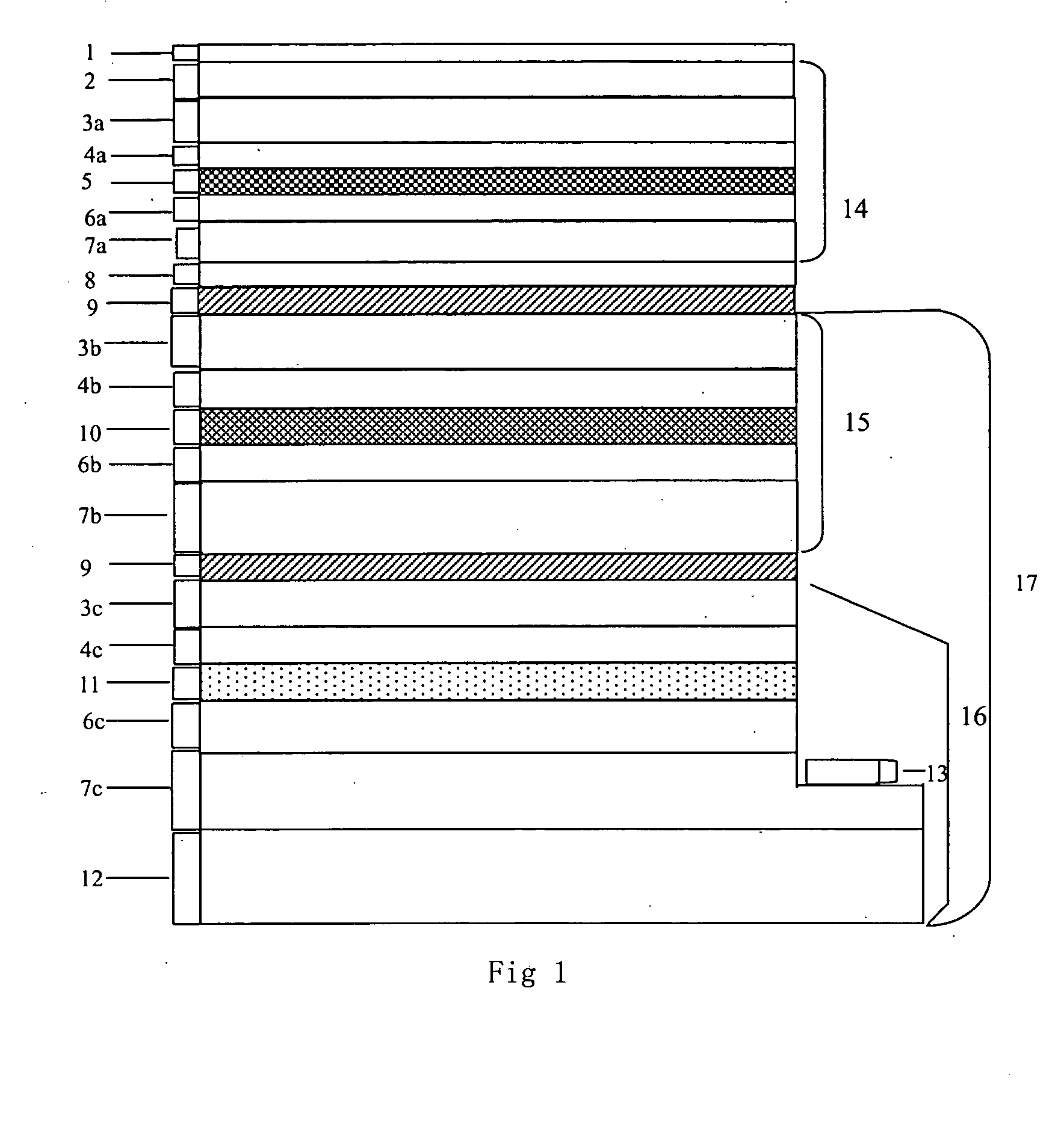

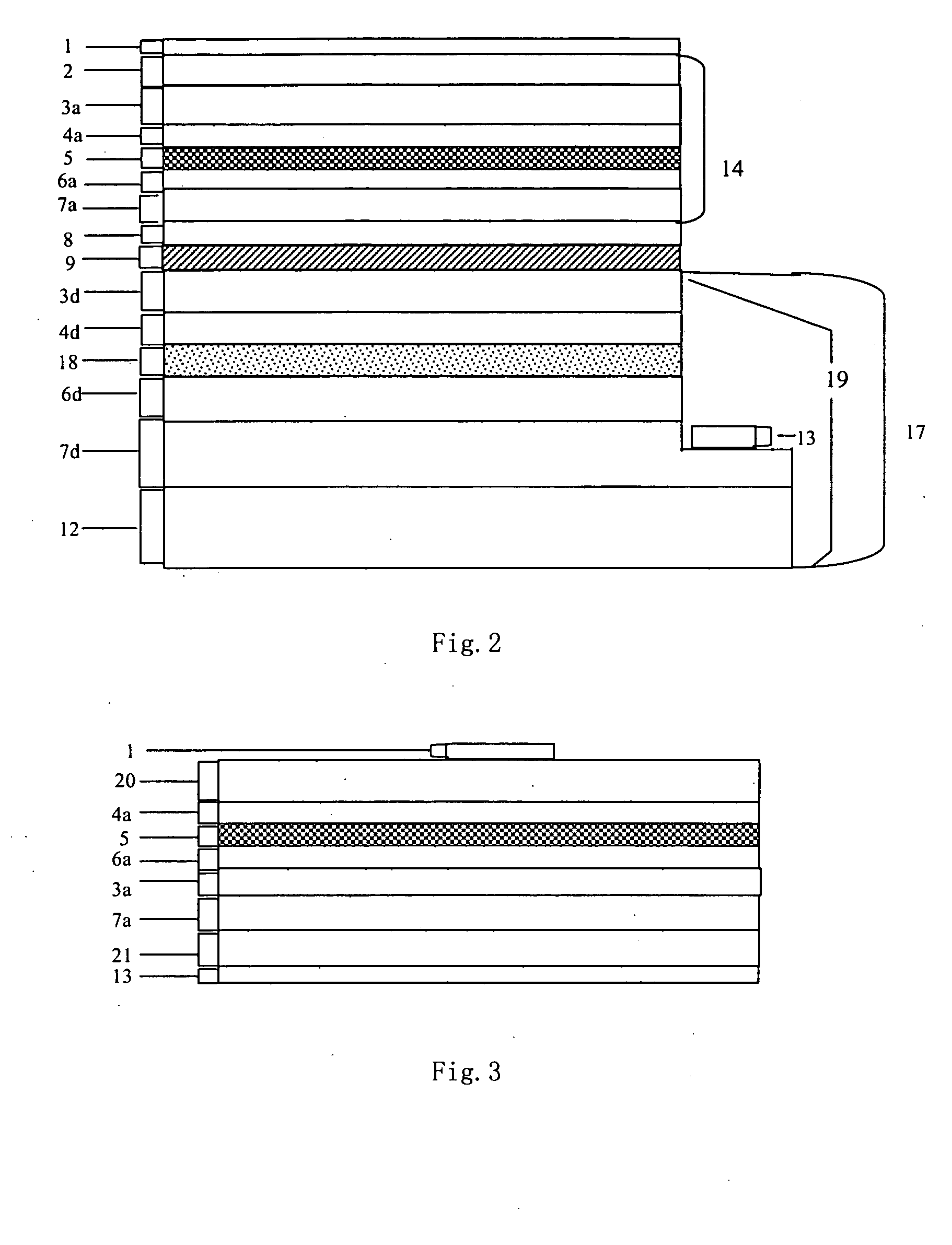

High efficiency multi-active layer tunnel regenerated white light emitting diode

InactiveUS20050067627A1Improved current spreadingEasy to spreadSemiconductor devicesGreen cellSemiconductor materials

A high efficiency and high brightness multi-active layer tunneling regenerated white color semiconductor light emitting diode having a p type electrode 1, a monolithic red light cell 14, a tunnel junction 9, a monolithic green light 15 and blue light cell 16 (or a monolithic cyan light cell 19), wherein each of said cells are electrically connected by tunnel junctions 9, and the red cell physically connected with blue and green cell (or cyan cell) by wafer bonding layer 8. The lights from each cell synthesize white color light. The white light emitting diode only has one time optical-electrical conversion, so the quantum efficiency is high. Moreover, the white LED totally made from semiconductor materials, the lifetime of the white LED lamp is not limited by the relatively short lifetime of fluorescent material.

Owner:BEIJING UNIV OF TECH

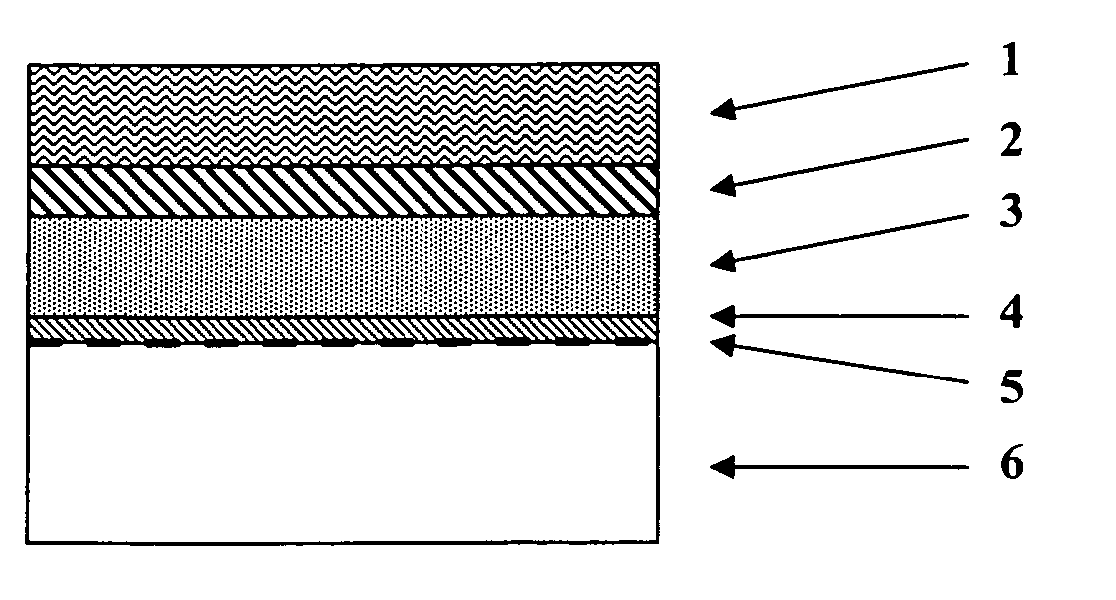

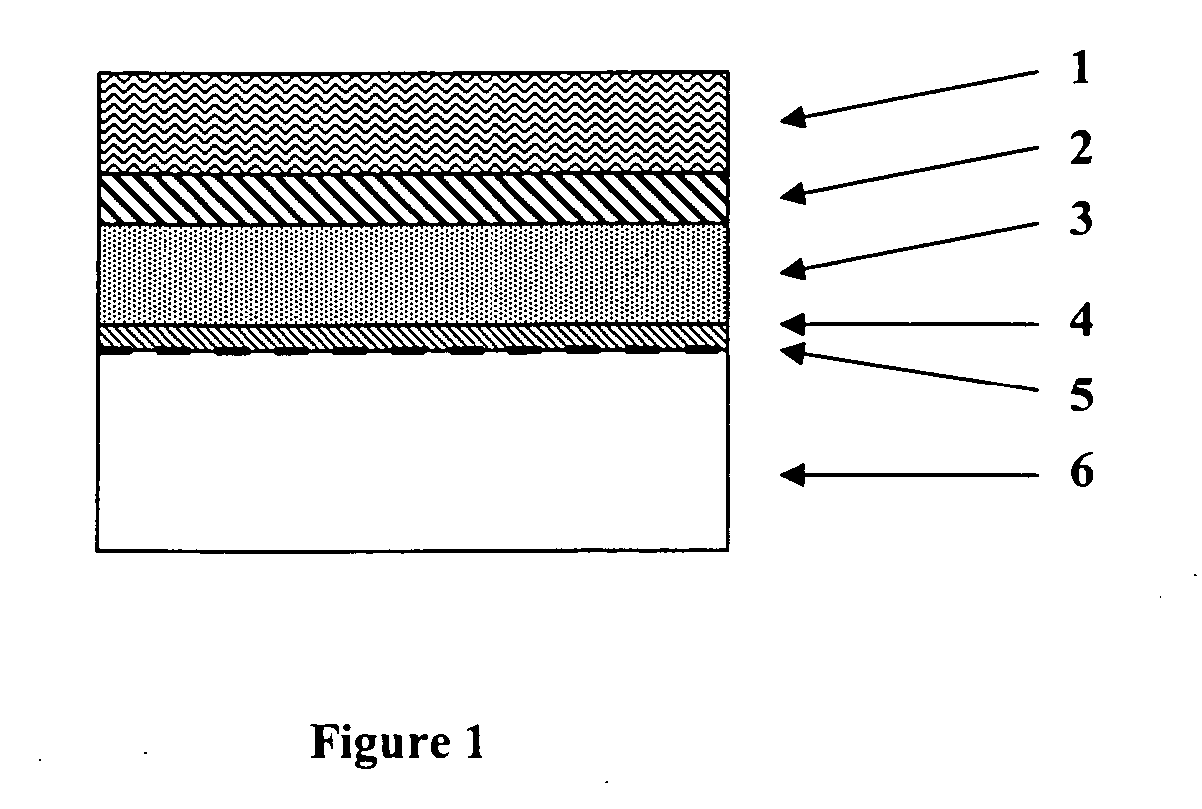

Multiple bonding layers for thin-wafer handling

ActiveUS20120034437A1Lamination ancillary operationsSynthetic resin layered productsSpecific functionEngineering

Multiple bonding layer schemes that temporarily join semiconductor substrates are provided. In the inventive bonding scheme, at least one of the layers is directly in contact with the semiconductor substrate and at least two layers within the scheme are in direct contact with one another. The present invention provides several processing options as the different layers within the multilayer structure perform specific functions. More importantly, it will improve performance of the thin-wafer handling solution by providing higher thermal stability, greater compatibility with harsh backside processing steps, protection of bumps on the front side of the wafer by encapsulation, lower stress in the debonding step, and fewer defects on the front side.

Owner:BREWER SCI

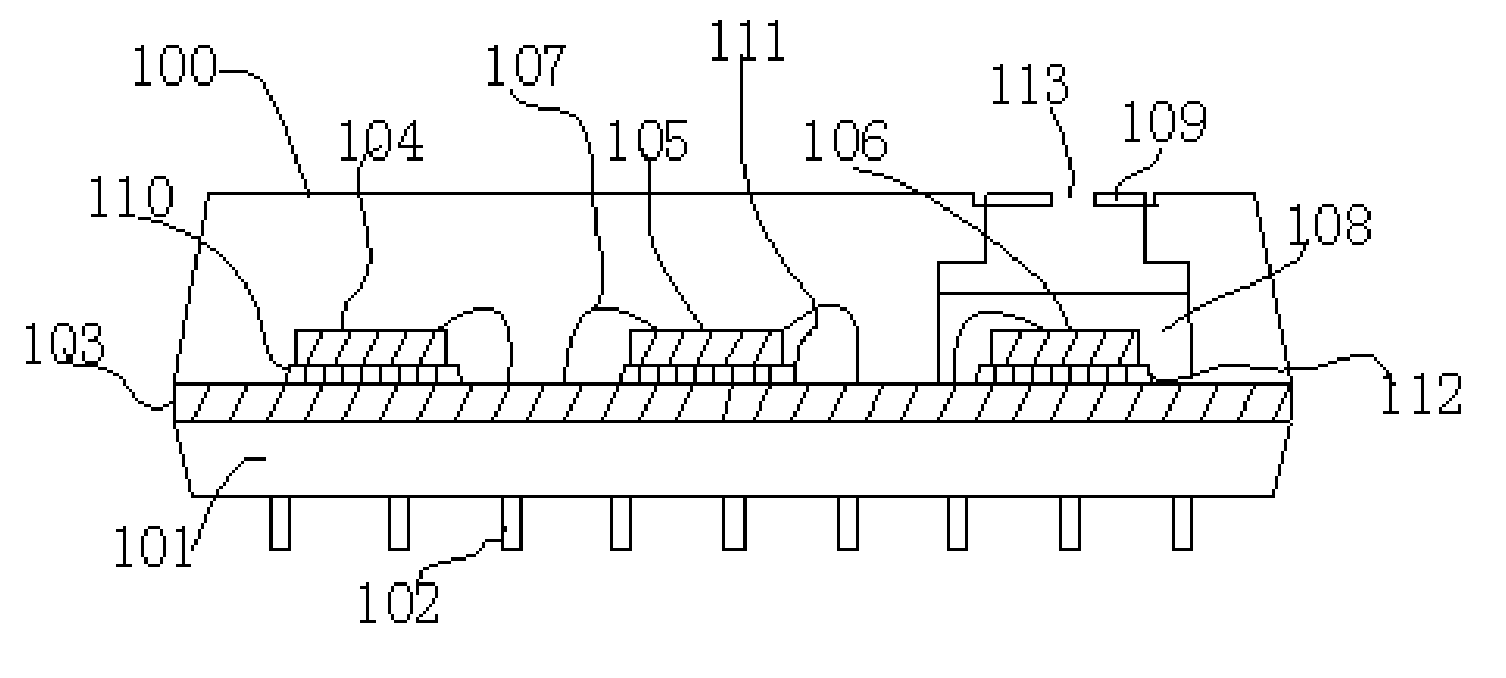

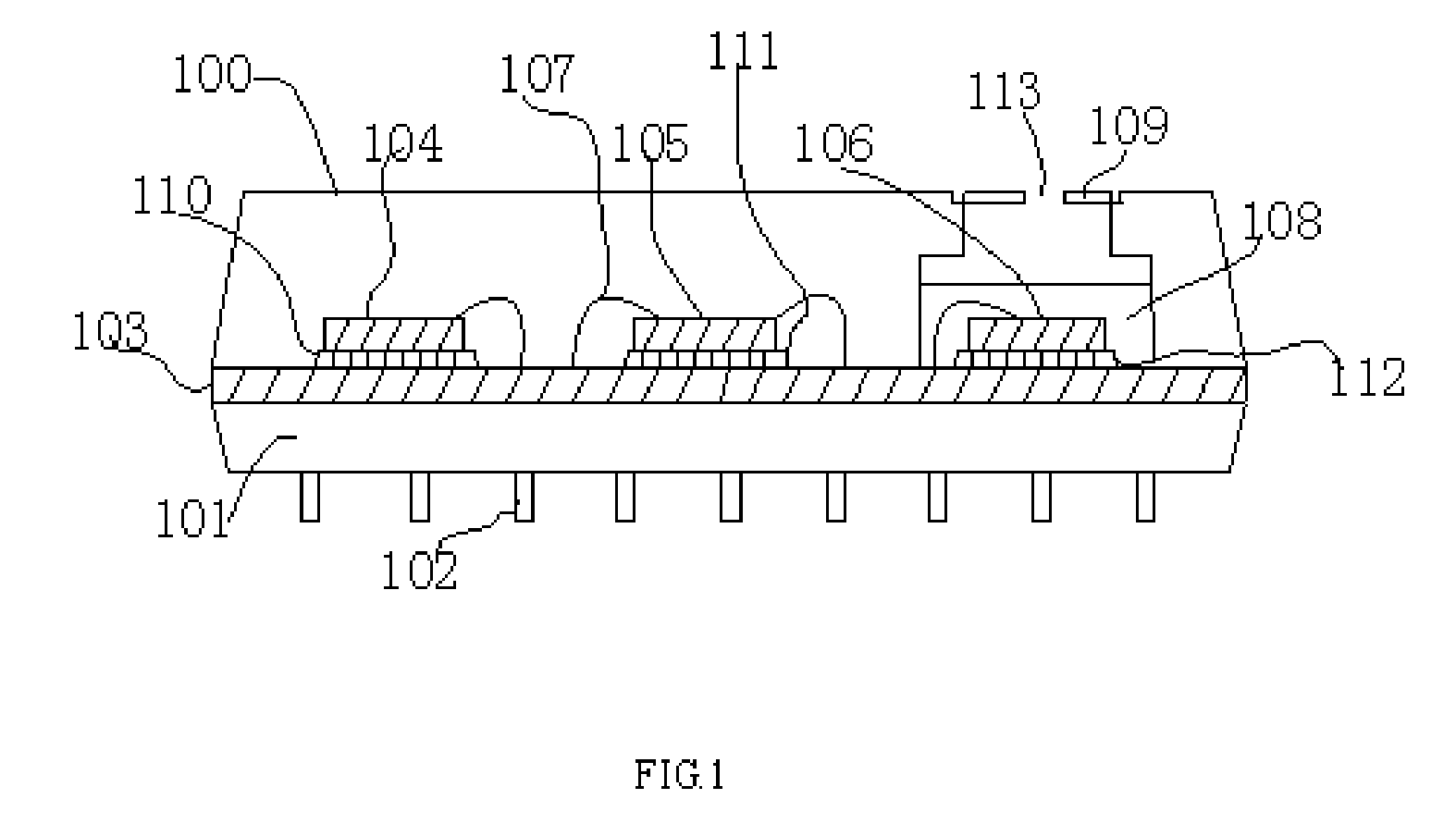

Direct wafer bonded 2-D CUMT array

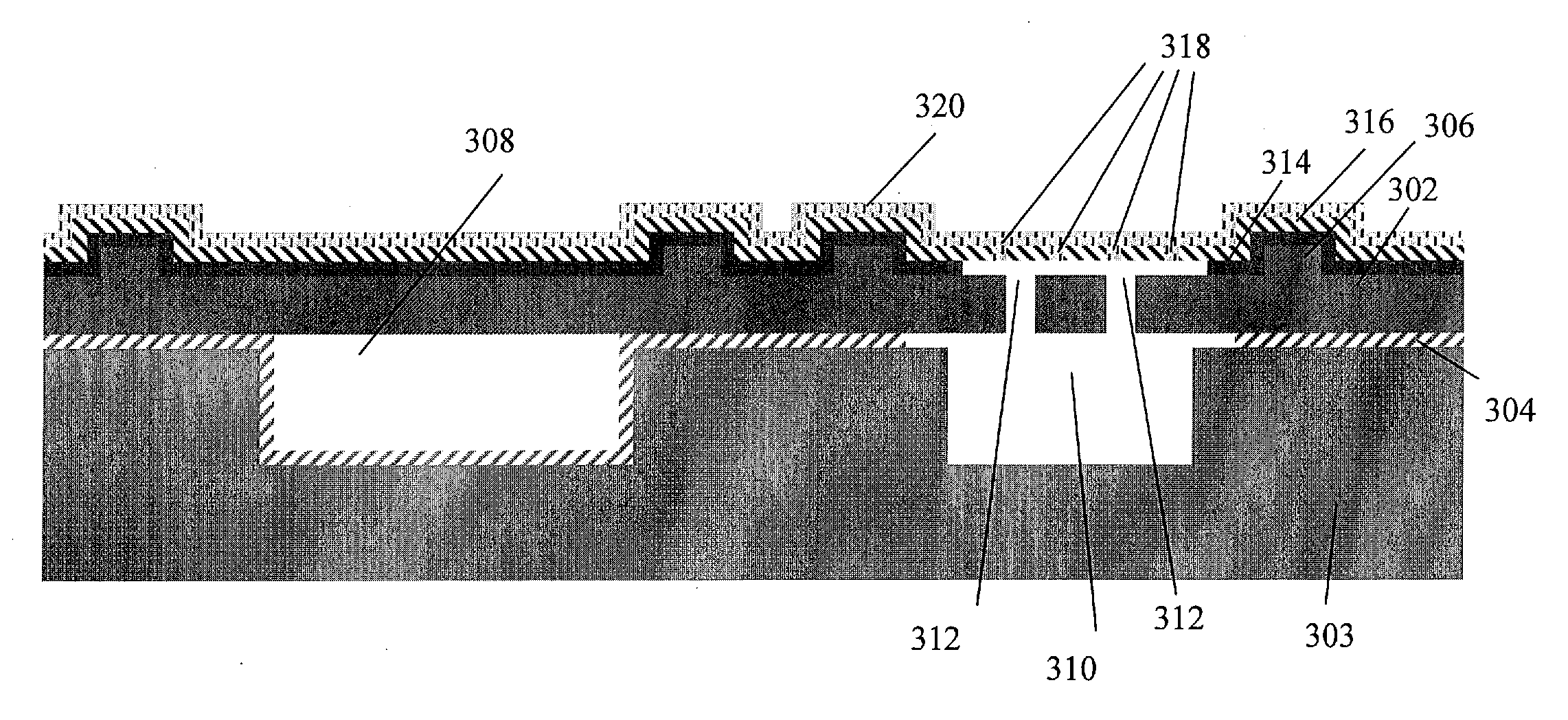

ActiveUS20090122651A1Ultrasonic/sonic/infrasonic diagnosticsMechanical vibrations separationCapacitanceCapacitive micromachined ultrasonic transducers

A capacitive micromachined ultrasonic transducer (CMUT) array connected to a separate electronic unit is provided. The CMUT array includes at least two active elements, a ground element at the array end, and a non-active element having isolation trenches disposed between the active and ground elements. The active element includes a doped first silicon layer, a doped second silicon layer, and a first insulating layer disposed there between. A cavity is in the first silicon layer having a cross section that includes vertical portions disposed at each end of a horizontal portion, and the vertical portion spans from the first insulating layer through the first silicon layer such that a portion of the first silicon layer is isolated by the first insulating layer and the cavity. A membrane layer on the first silicon layer spans the cavity. A bottom electrode is disposed on the bottom of the second silicon layer.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

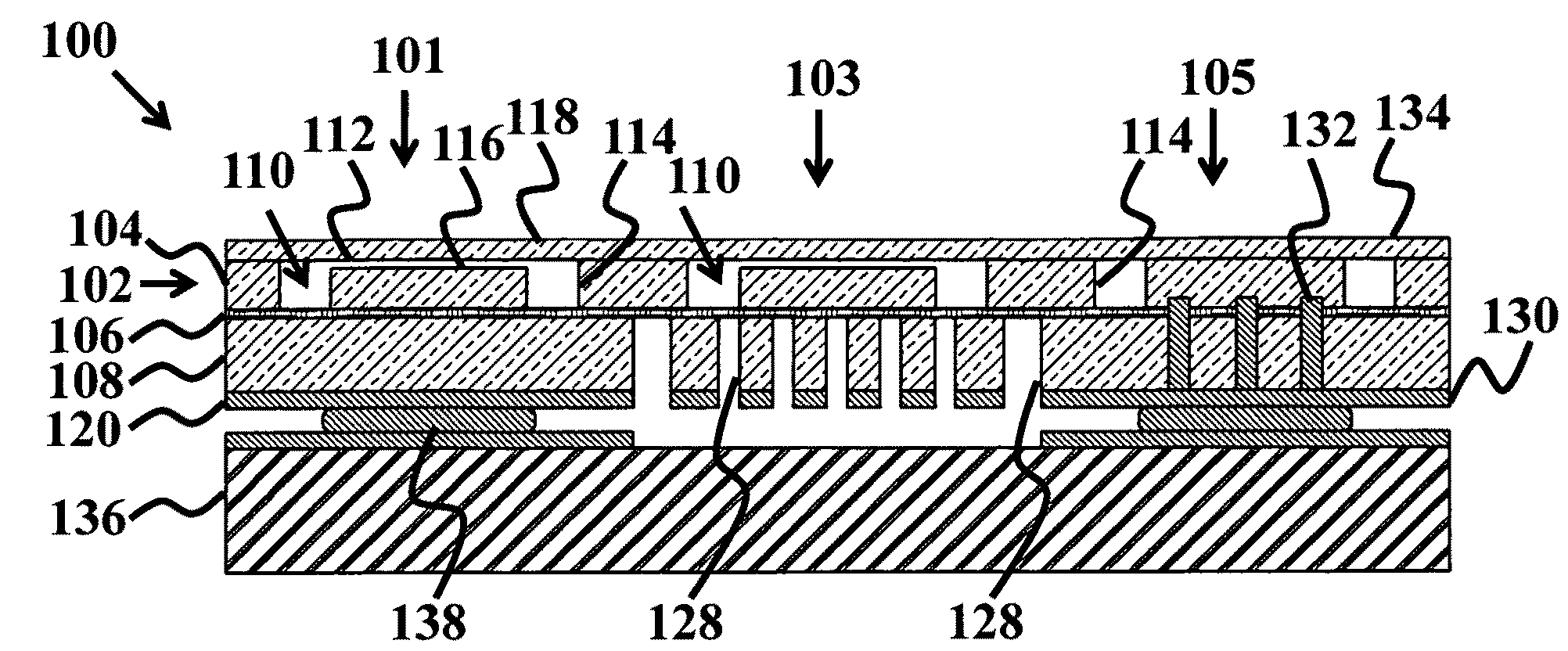

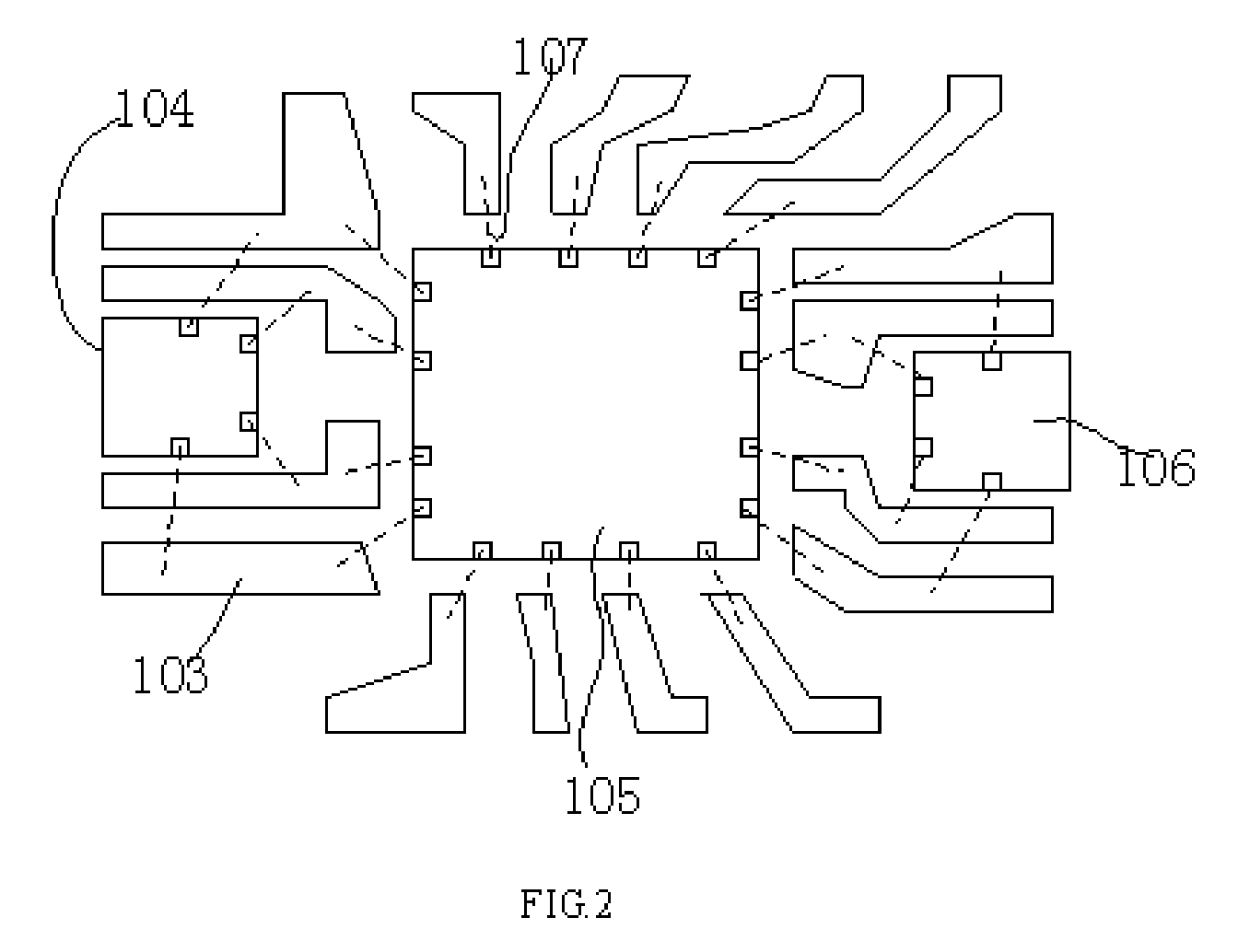

An Intelligent Integrated Sensor Of Tire Pressure Monitoring System (TPMS)

InactiveUS20060185429A1Precise size controlAccurate identificationSolid-state devicesTyre measurementsAccelerometerEngineering

A single integrated sensing chip with multi-functions for tire pressure monitor system (TPMS) comprises: a pressure sensor, an accelerometer, a temperature sensor, and an ASIC (Applied Specific Integrated Circuit) that implements signal conditioning and digitalizes pressure output. The accelerometer incorporated for vehicle motion is used to determine centrifugal acceleration or three-axial acceleration of the rotating wheel, and used for the TPMS sensor wake-up from “power down” mode, or when the velocity of the vehicle is higher than certain speed threshold, which is more robust and lower in cost than the mechanical vibration switch and is naturally integrated with the electronic control unit. The accelerometer can be used for regular motion sensing to monitor the dynamic stability. The integrated sensor system can be packaged into one plastic package first, and then surface mounted to the printed circuit board, or the multi-function single chip can be wafer bonded on the wafer level first and diced into many individual chips, with each chip being directly attached on to the printed circuit board by wire bonding or flip-chip assembly.

Owner:WUHAN FINEMEMS