Patents

Literature

2655results about "Forming microstructural systems" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

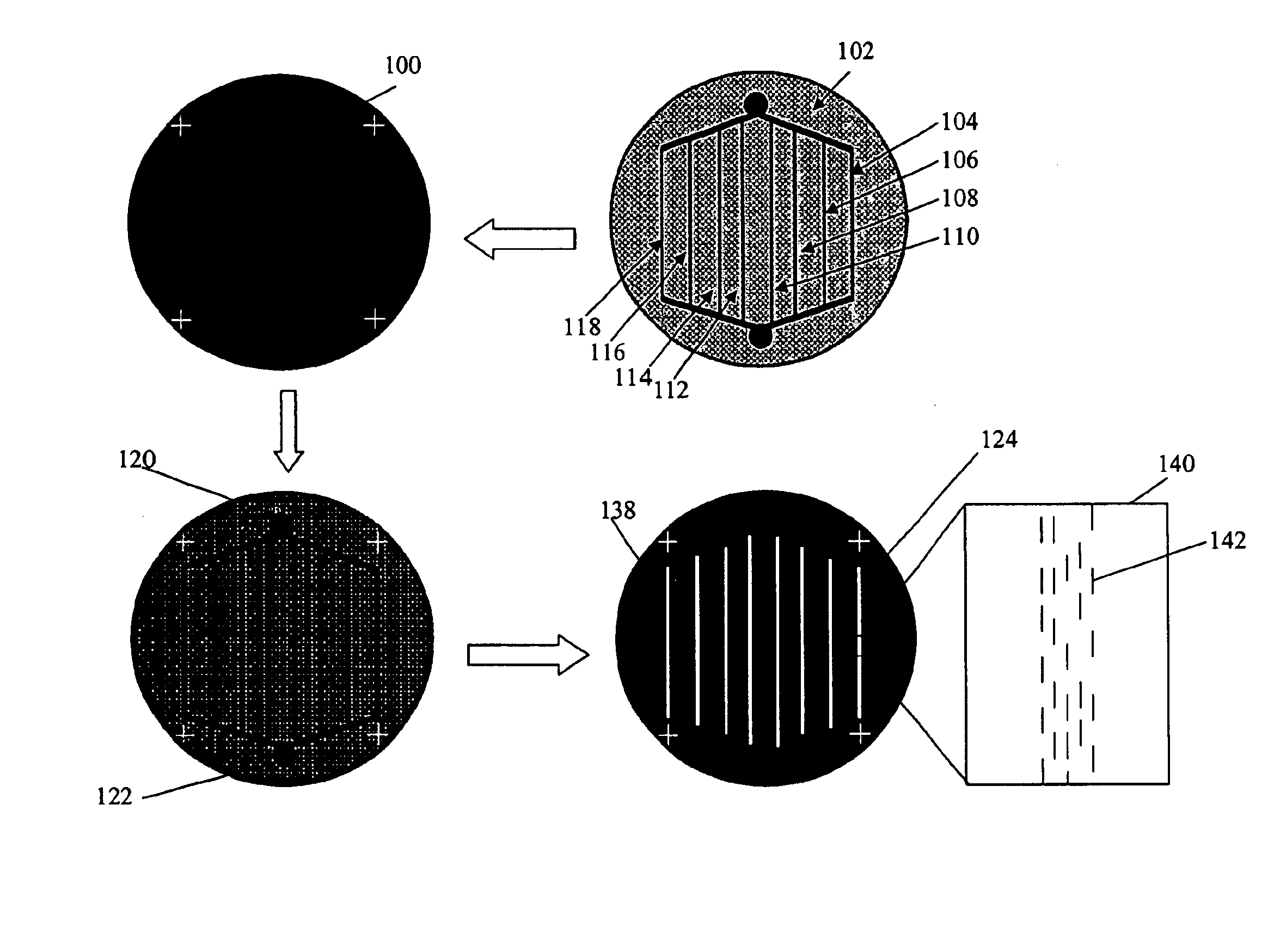

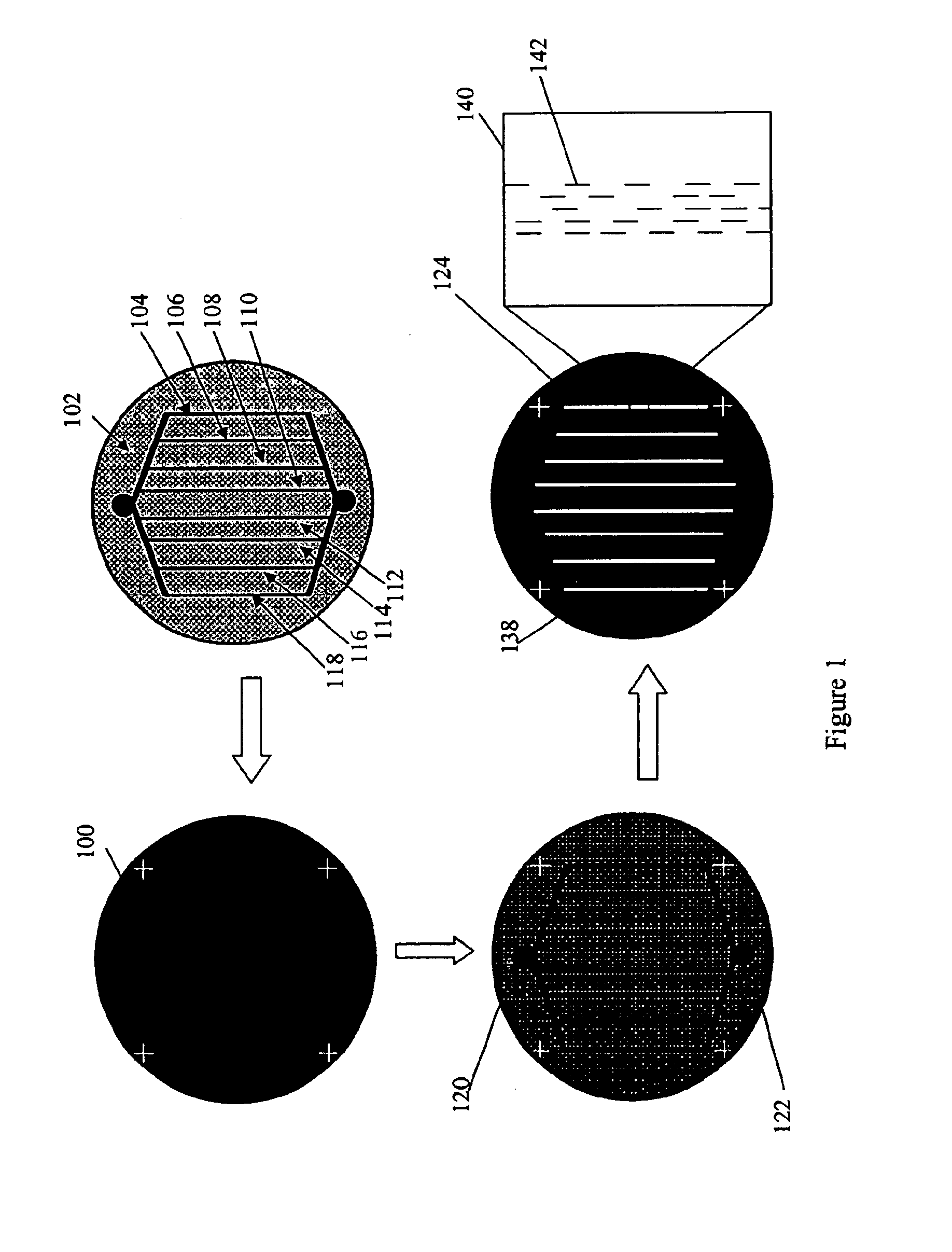

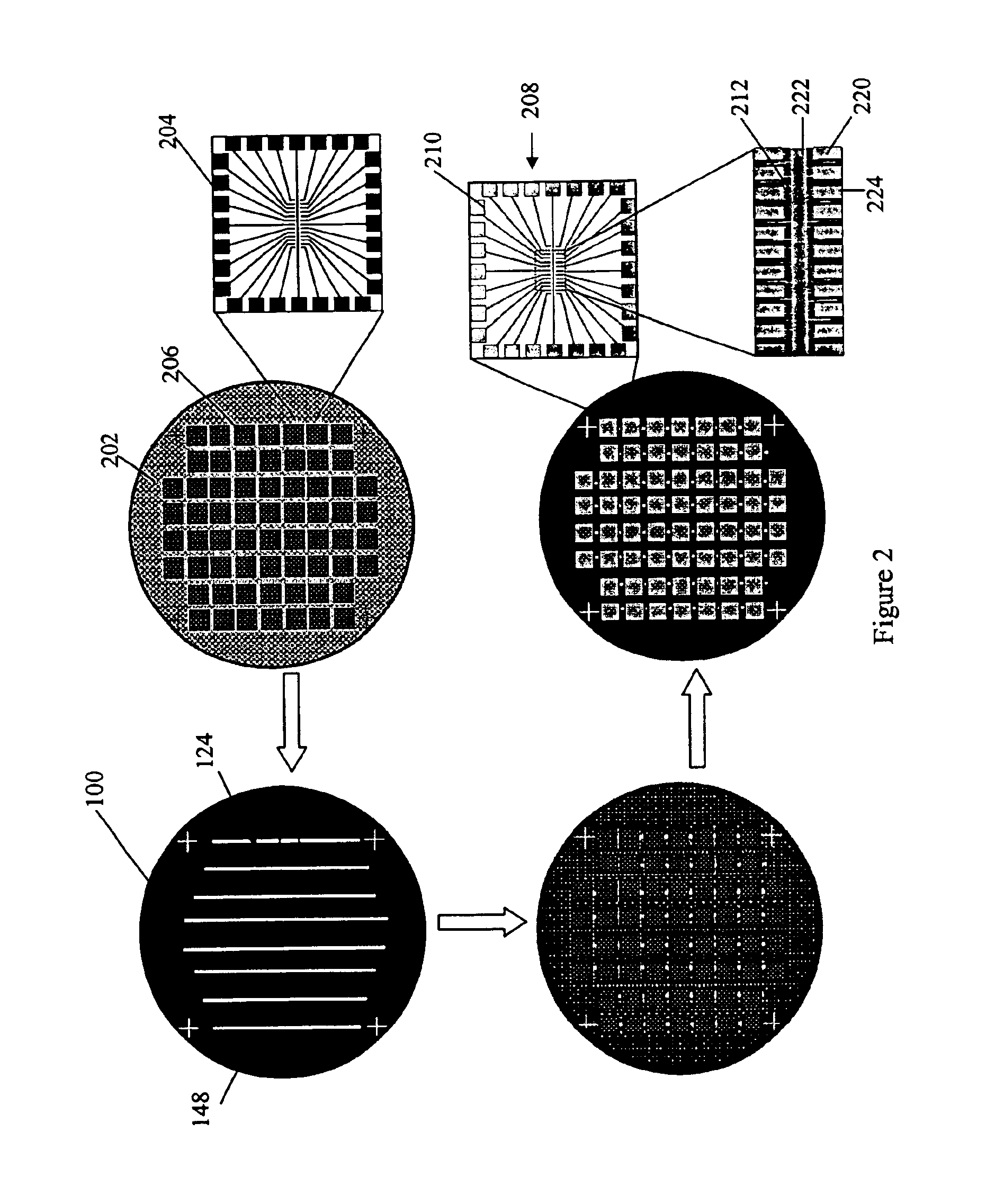

Methods of positioning and/or orienting nanostructures

Methods of positioning and orienting nanostructures, and particularly nanowires, on surfaces for subsequent use or integration. The methods utilize mask based processes alone or in combination with flow based alignment of the nanostructures to provide oriented and positioned nanostructures on surfaces. Also provided are populations of positioned and / or oriented nanostructures, devices that include populations of positioned and / or oriented nanostructures, systems for positioning and / or orienting nanostructures, and related devices, systems and methods.

Owner:ONED MATERIAL INC

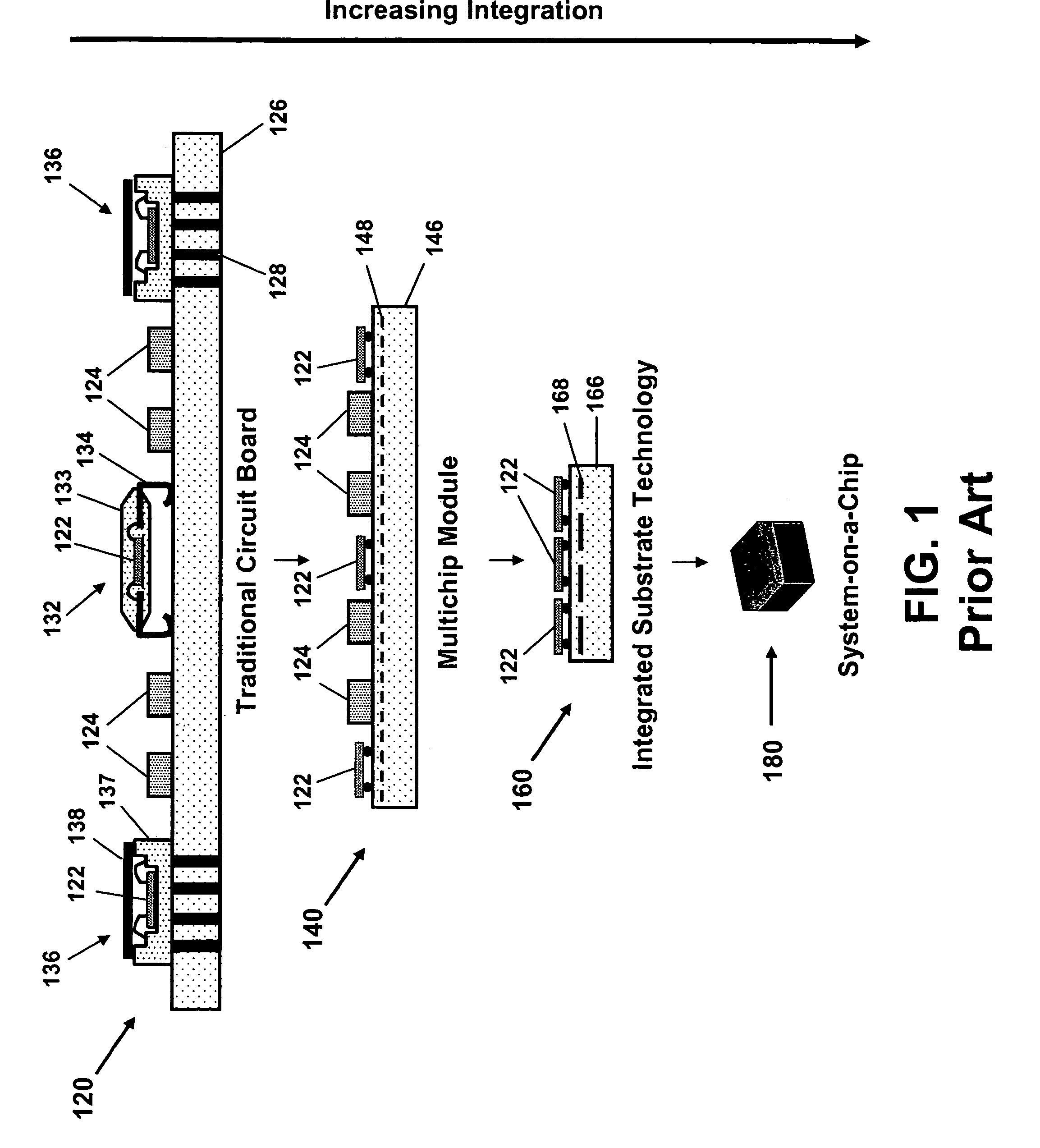

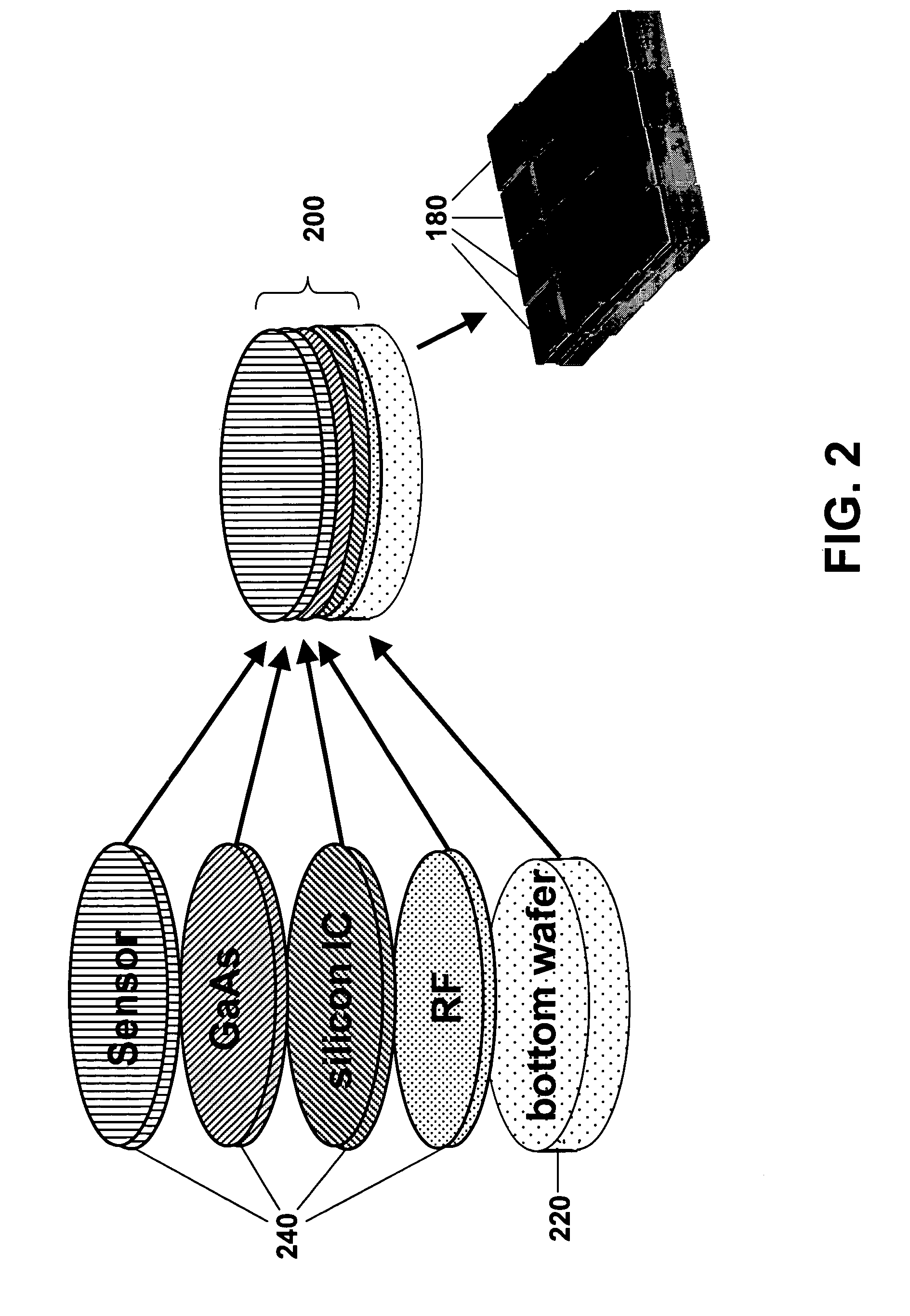

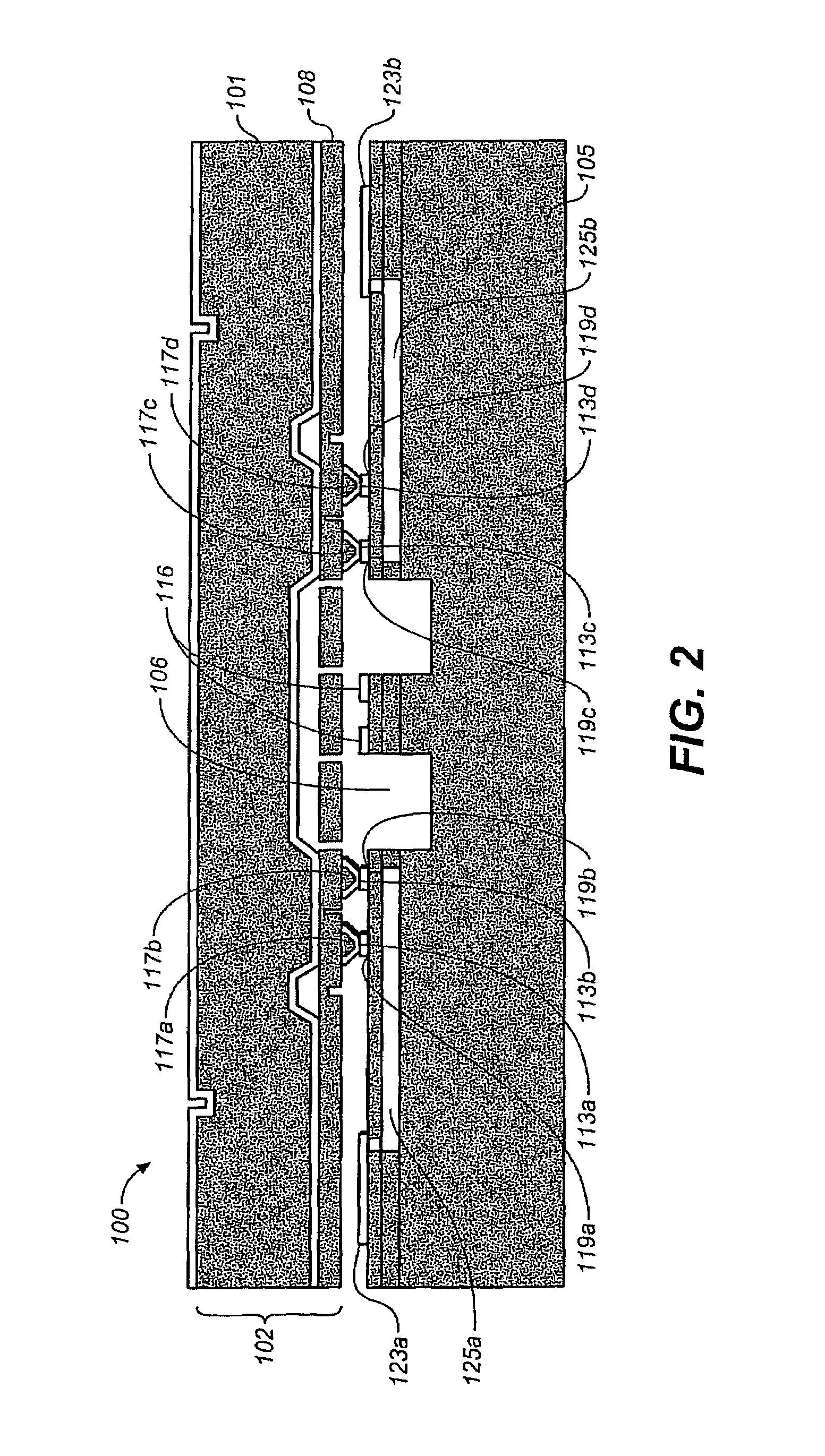

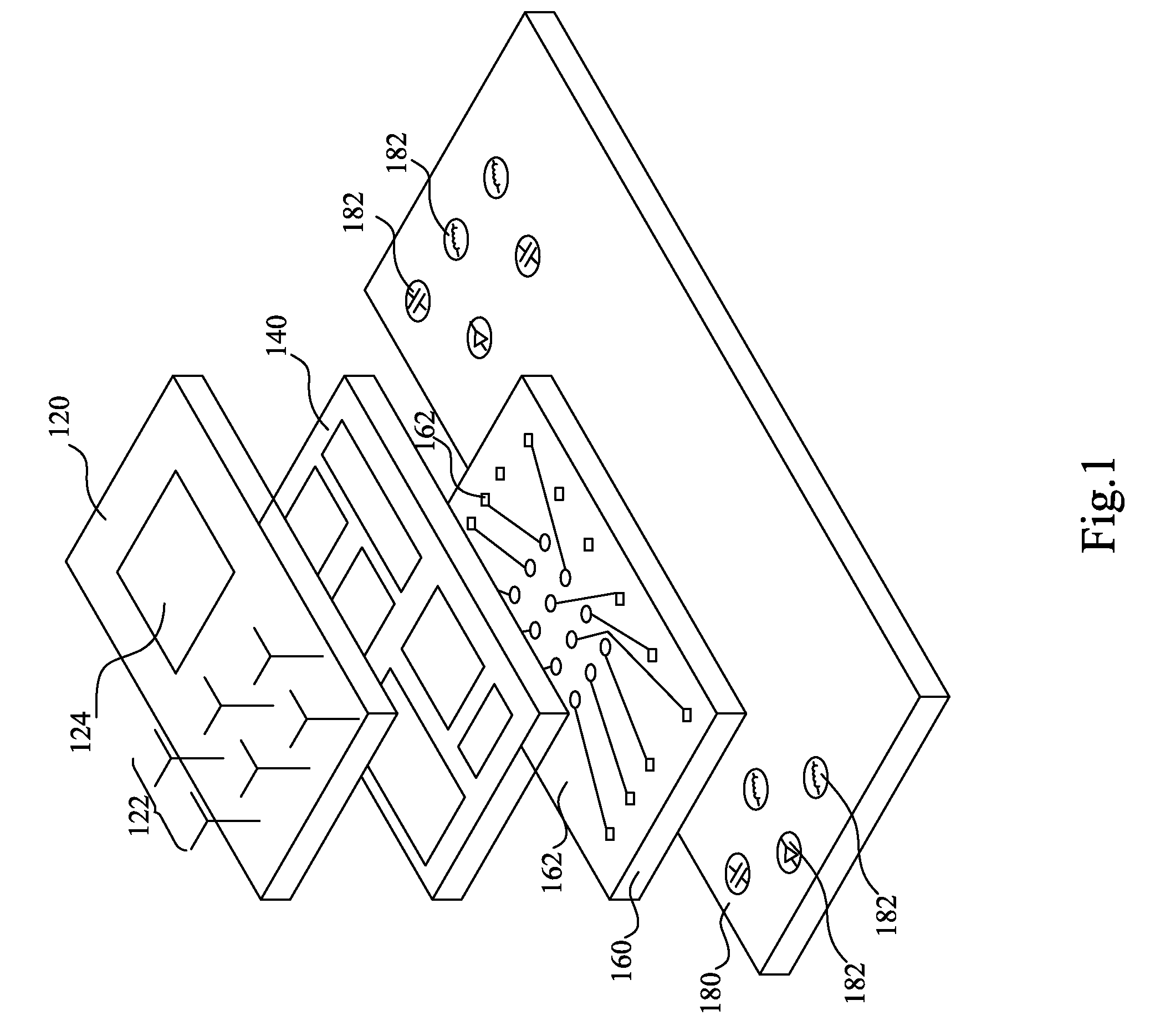

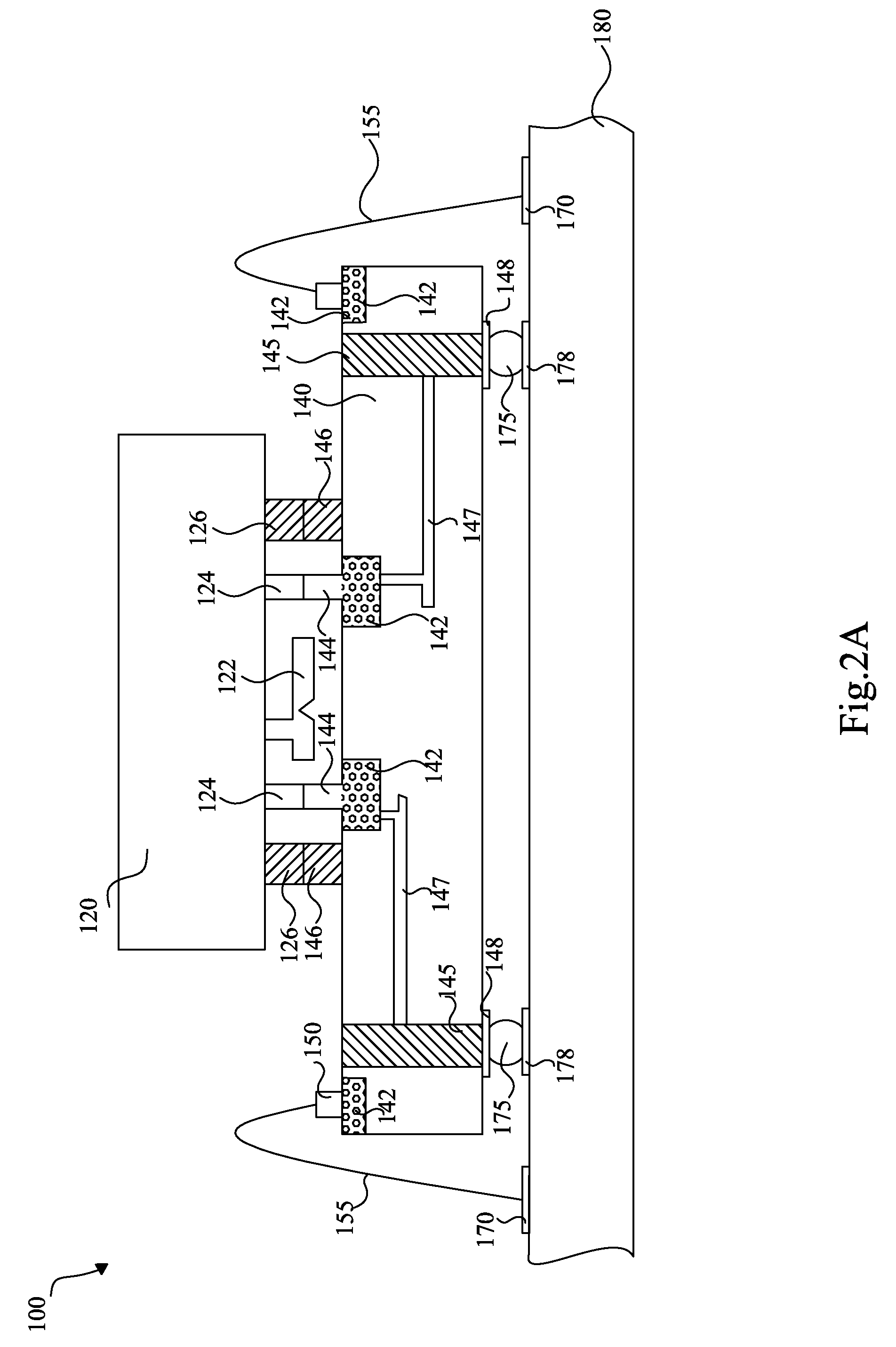

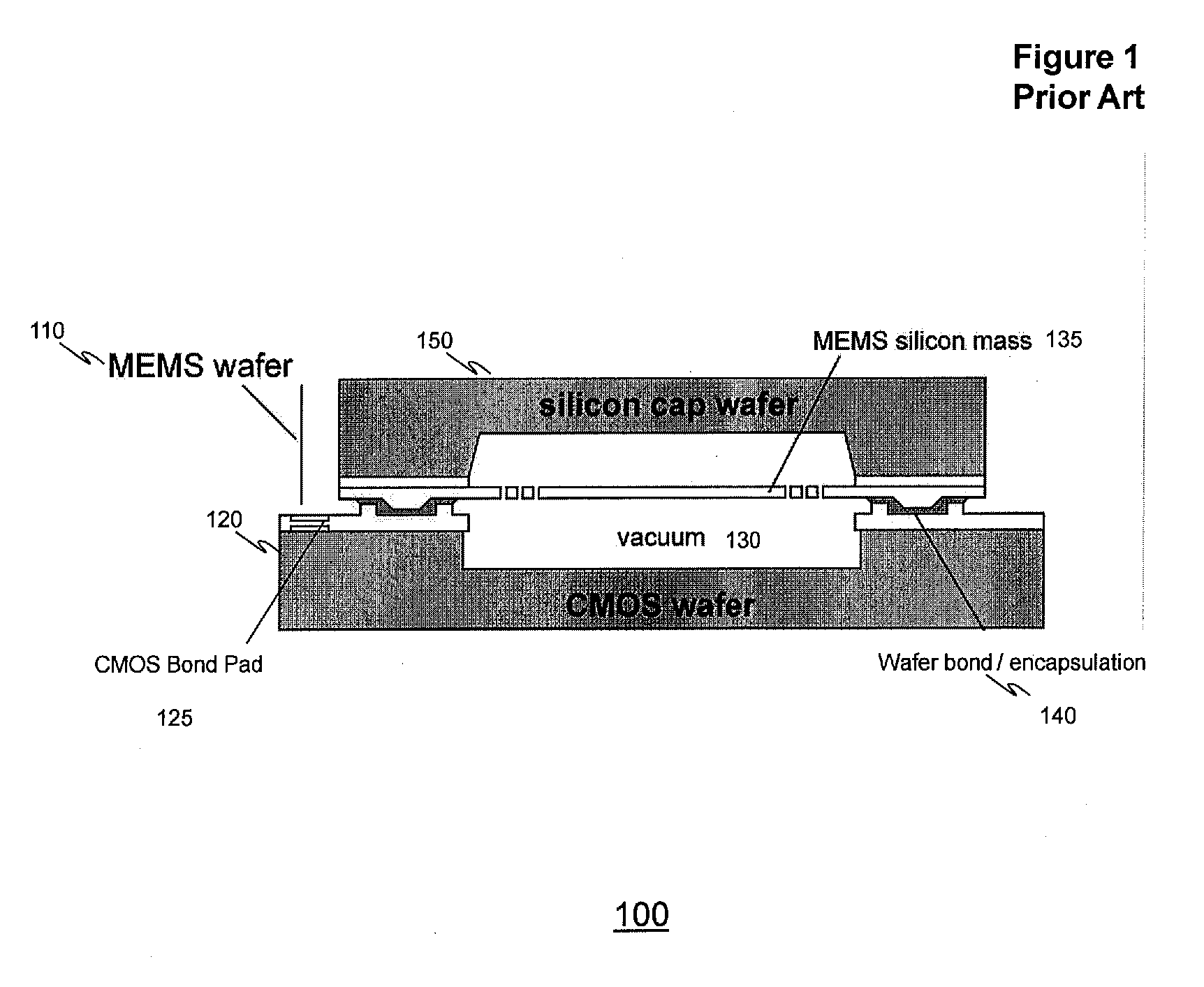

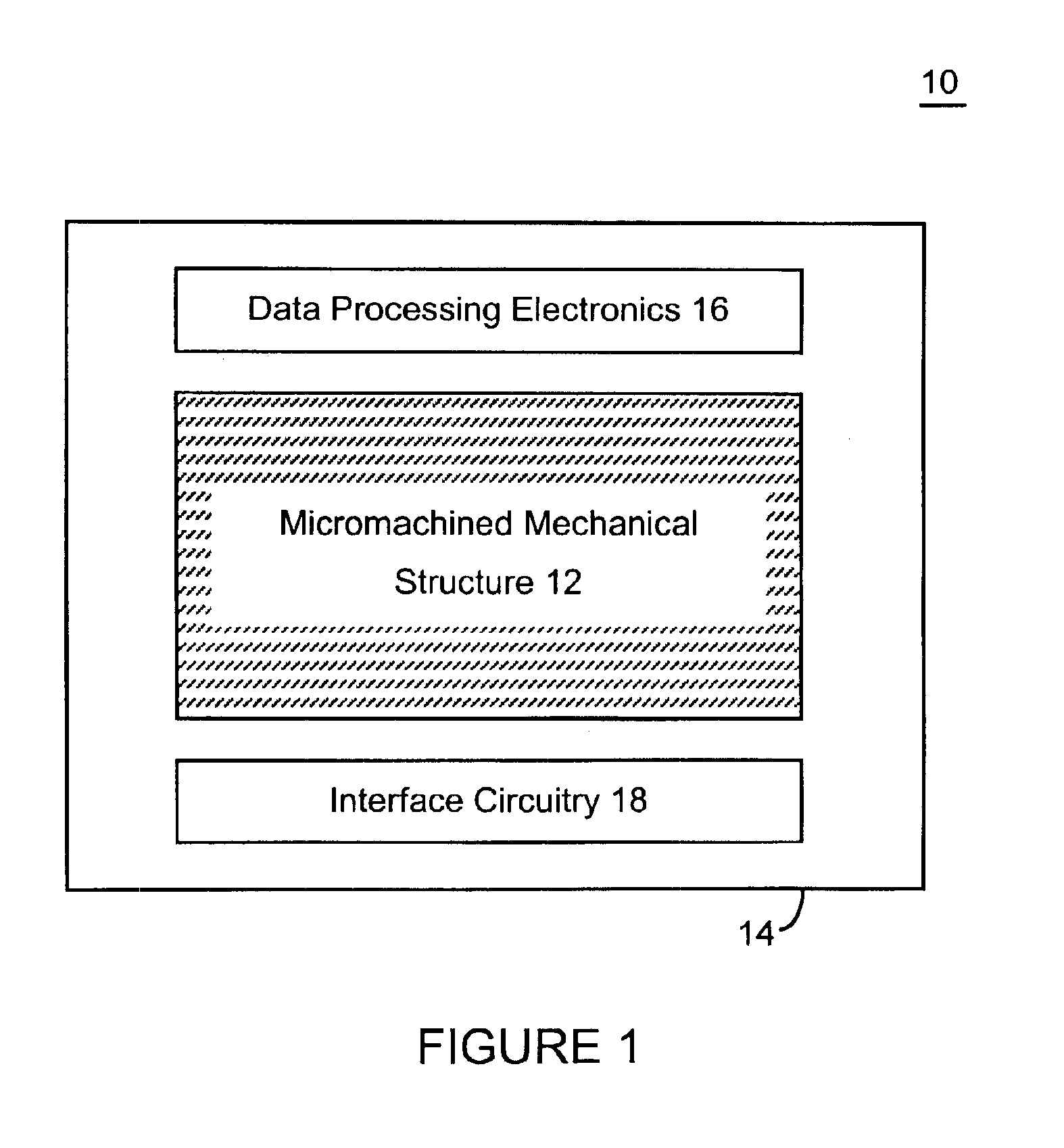

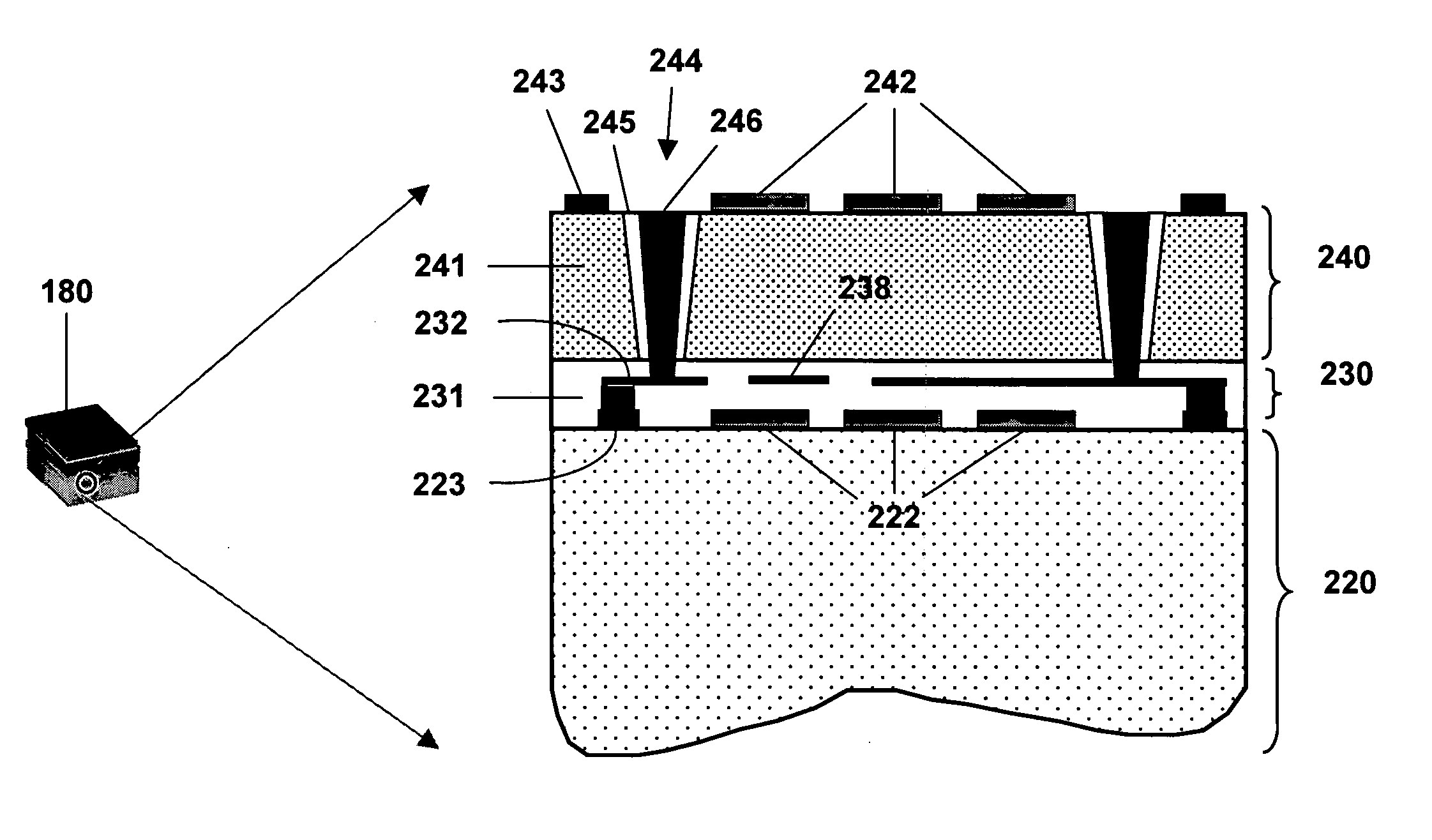

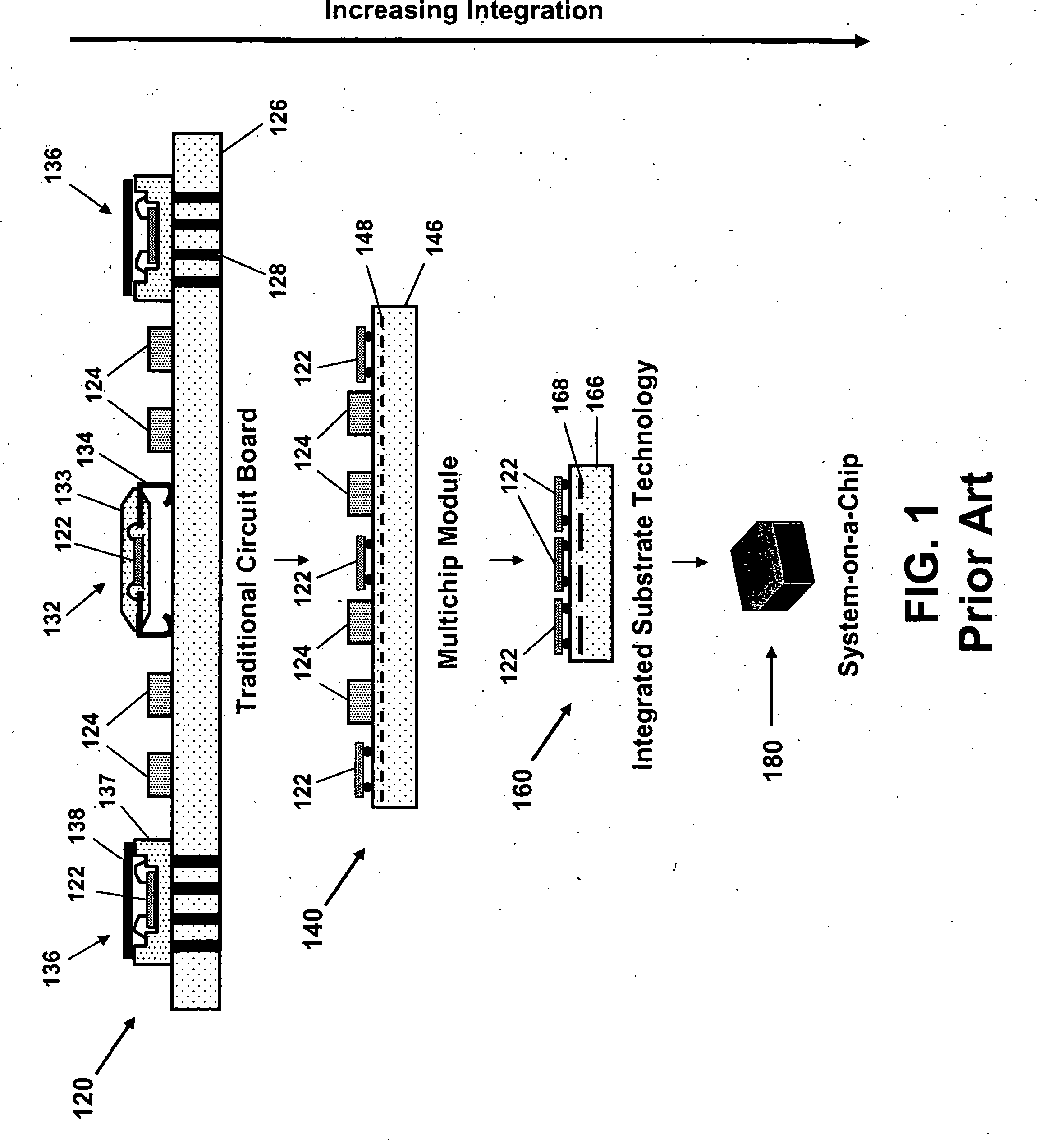

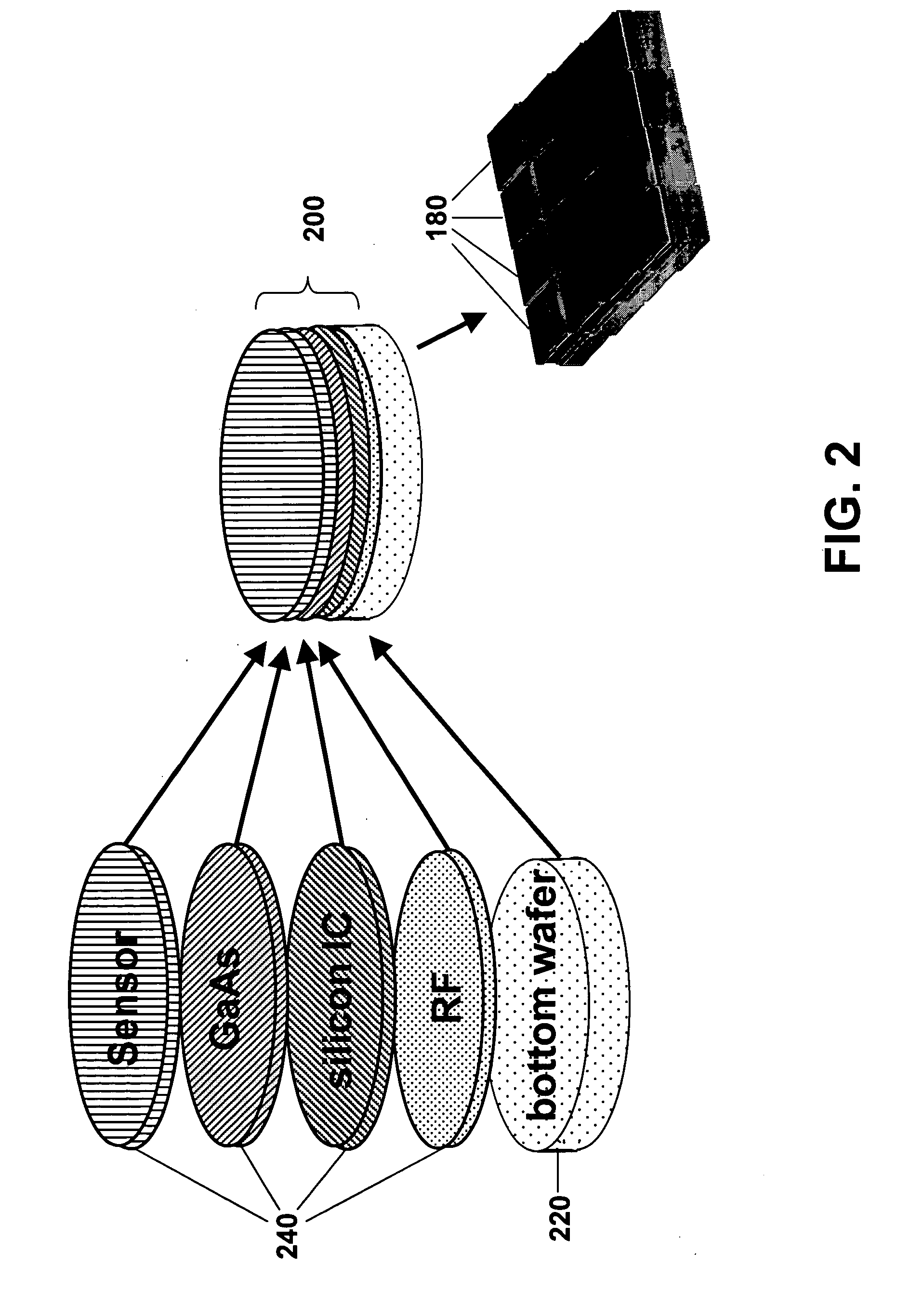

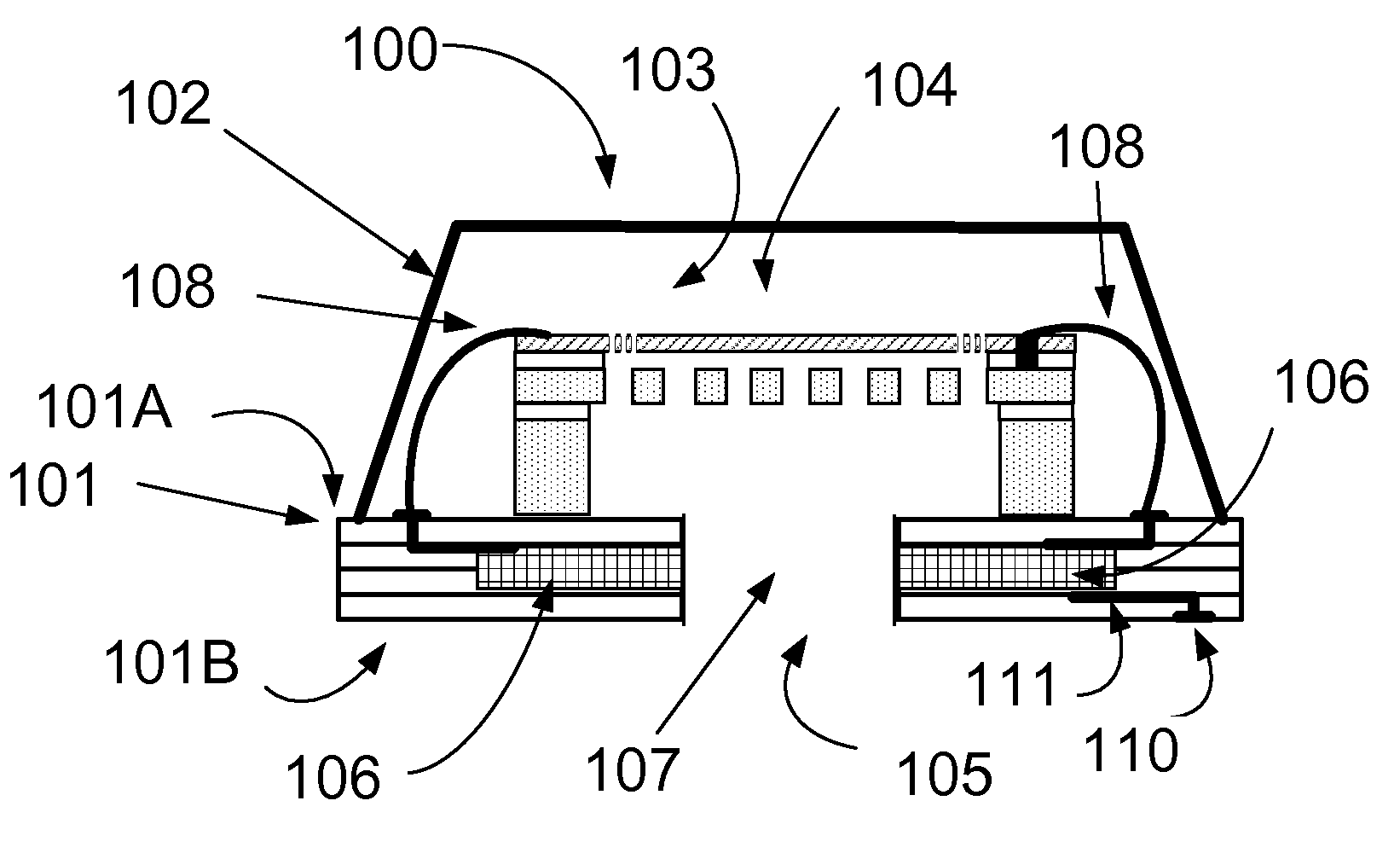

Heterogeneously integrated microsystem-on-a-chip

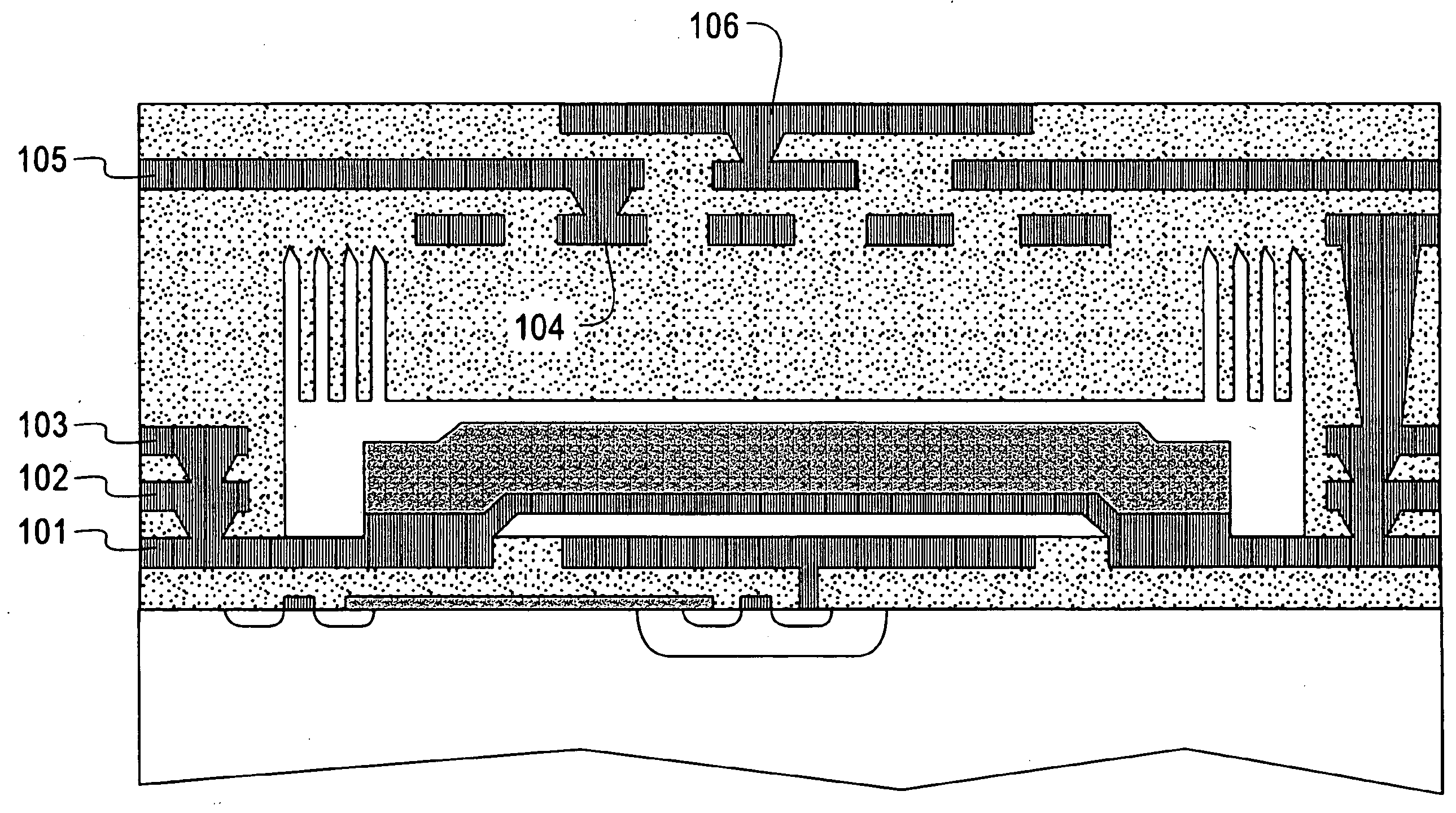

ActiveUS7335972B2Electronic circuit testingSemiconductor/solid-state device detailsMiniaturizationInterconnection

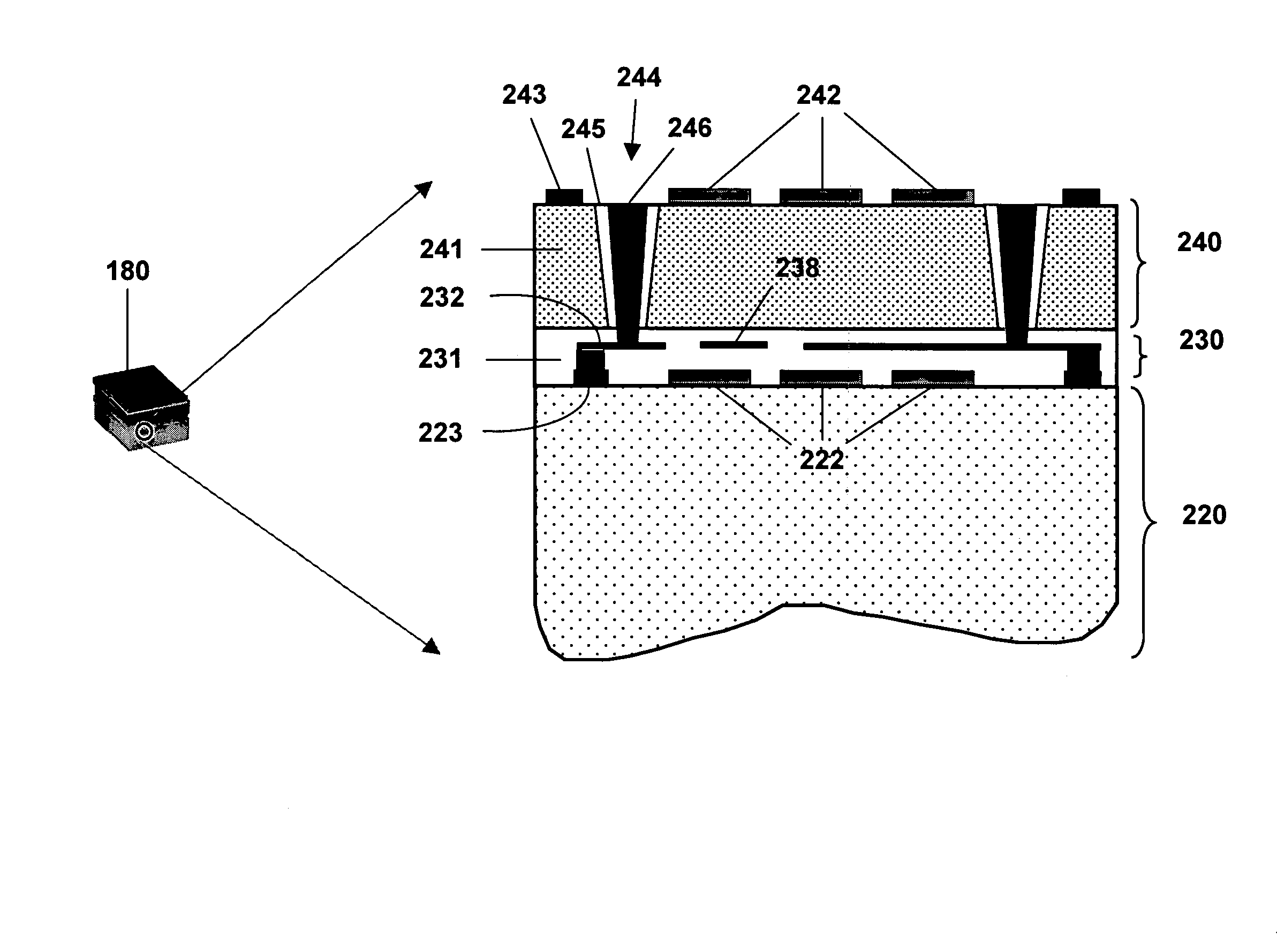

A microsystem-on-a-chip comprises a bottom wafer of normal thickness and a series of thinned wafers can be stacked on the bottom wafer, glued and electrically interconnected. The interconnection layer comprises a compliant dielectric material, an interconnect structure, and can include embedded passives. The stacked wafer technology provides a heterogeneously integrated, ultra-miniaturized, higher performing, robust and cost-effective microsystem package. The highly integrated microsystem package, comprising electronics, sensors, optics, and MEMS, can be miniaturized both in volume and footprint to the size of a bottle-cap or less.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

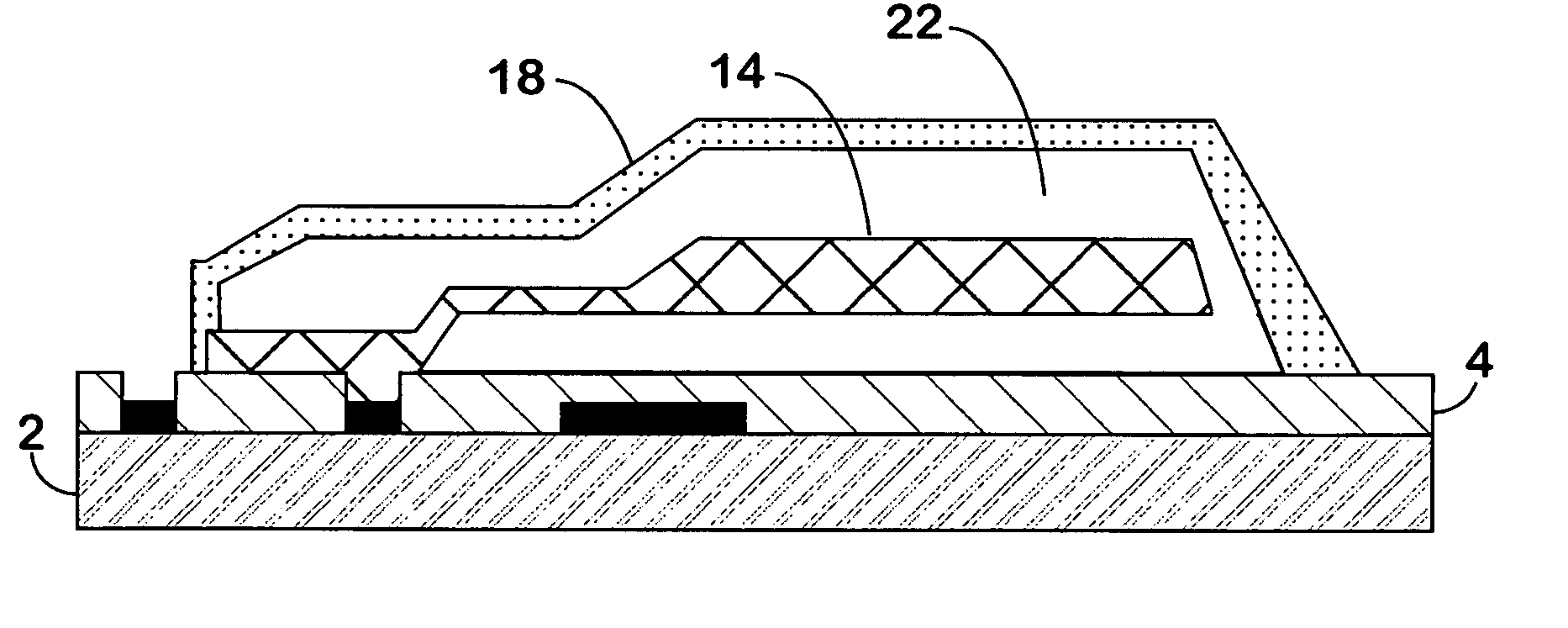

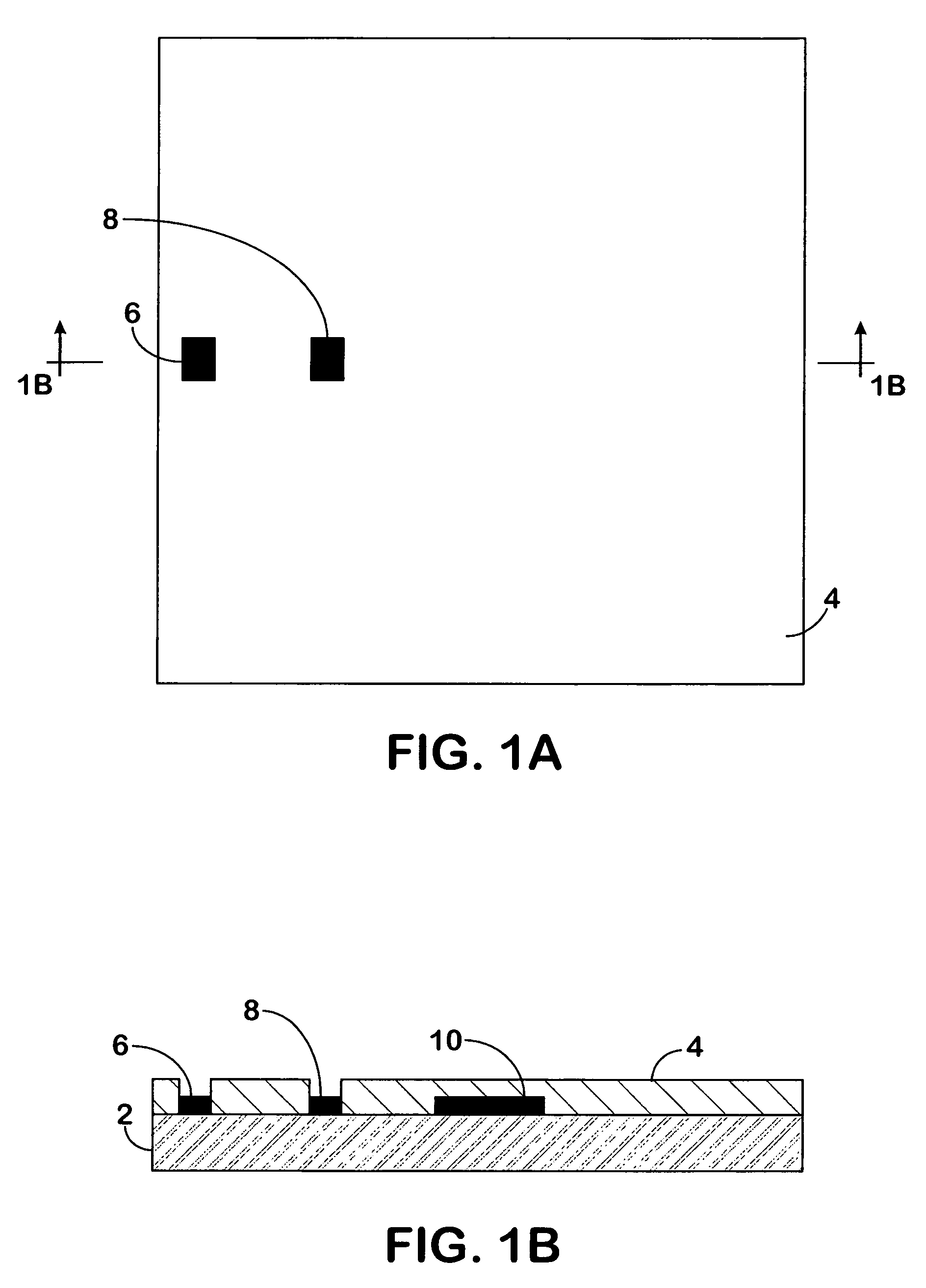

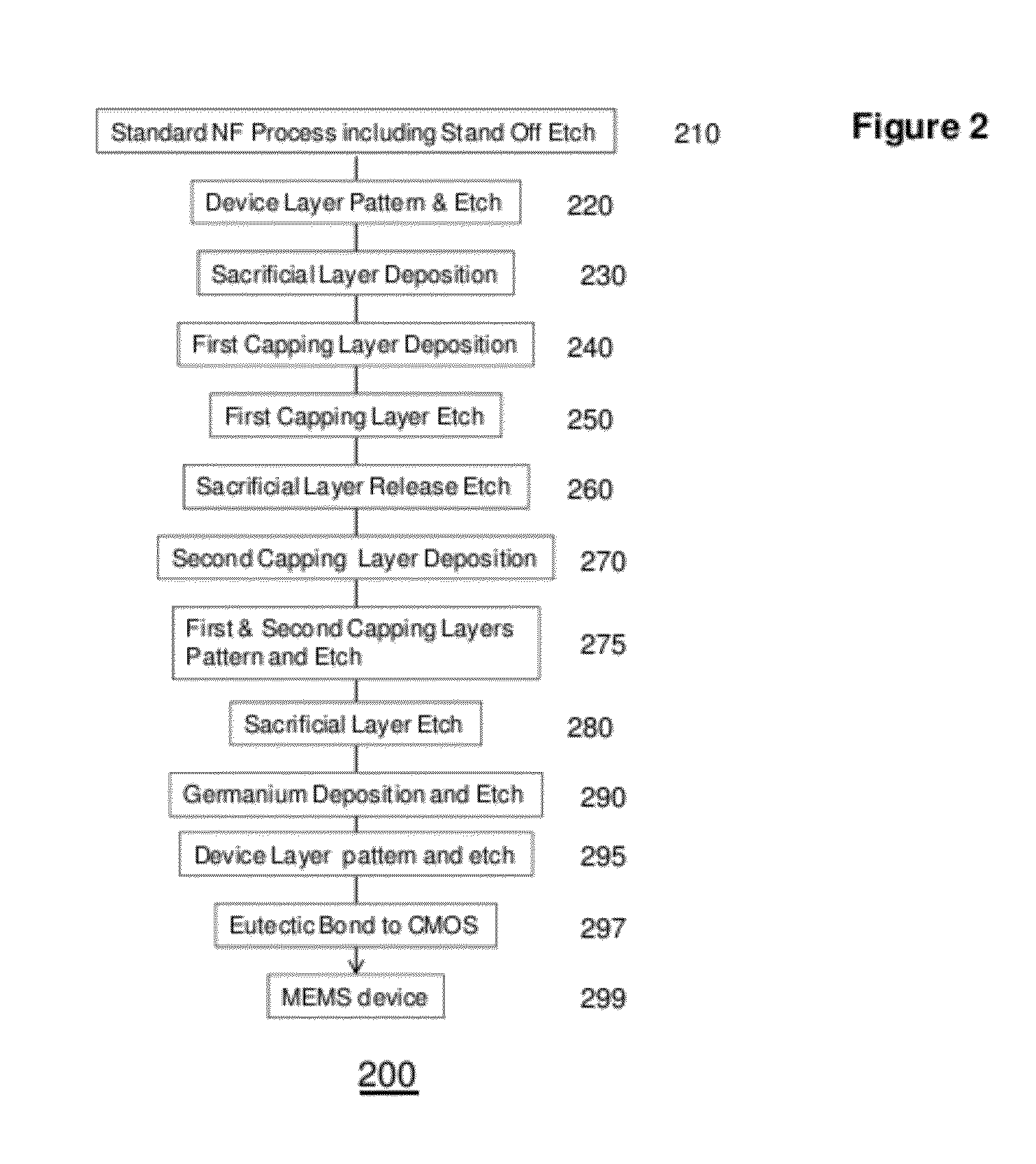

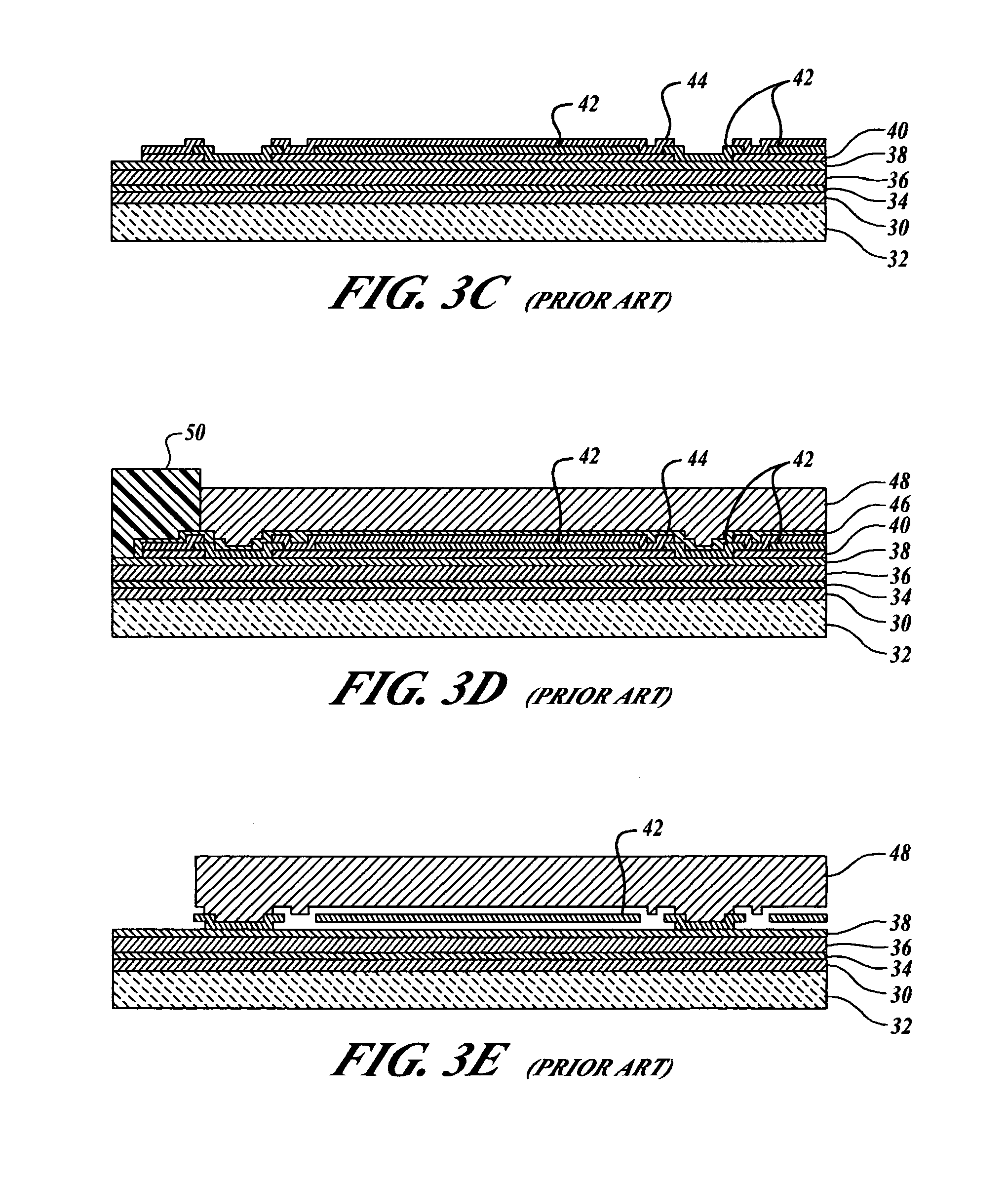

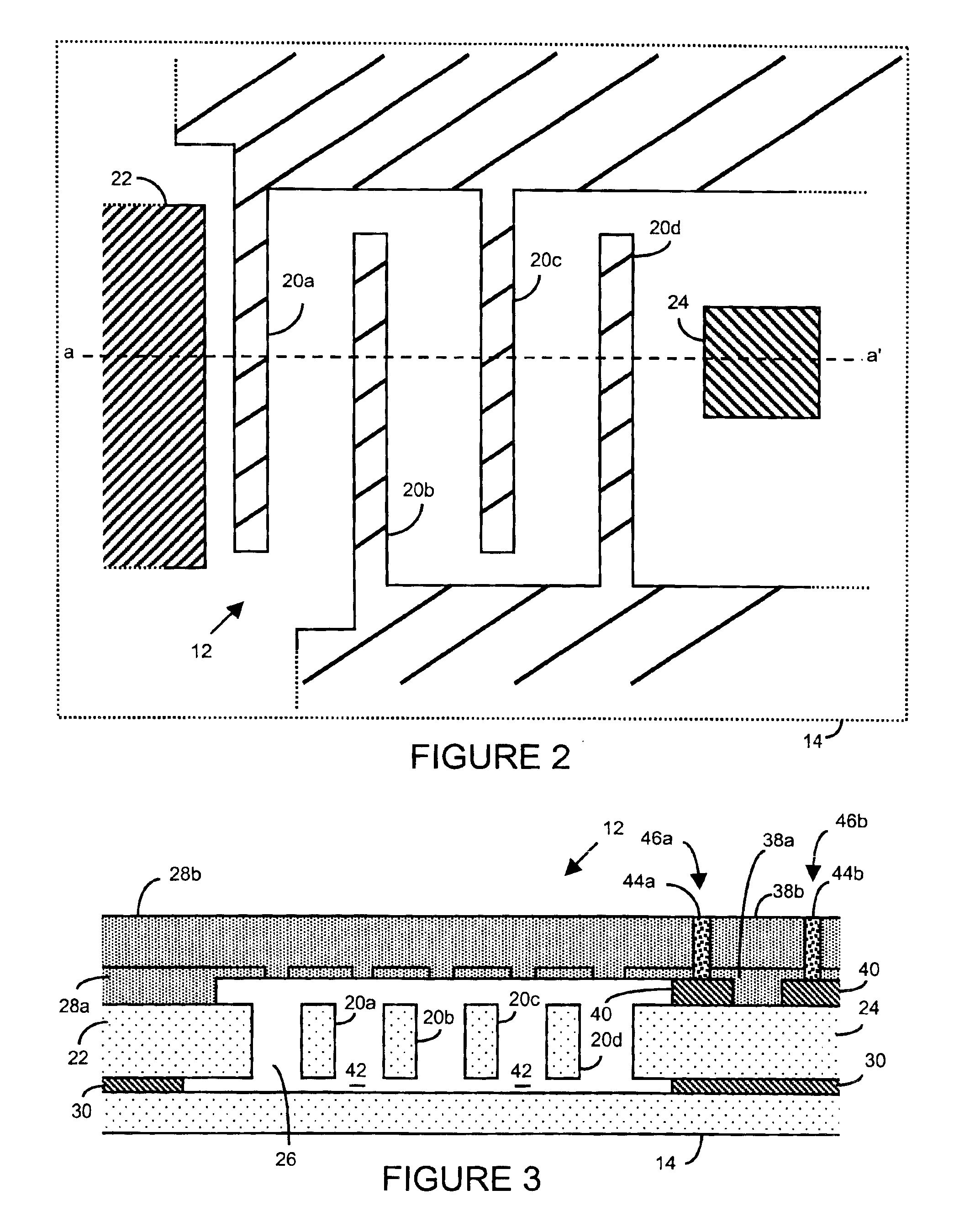

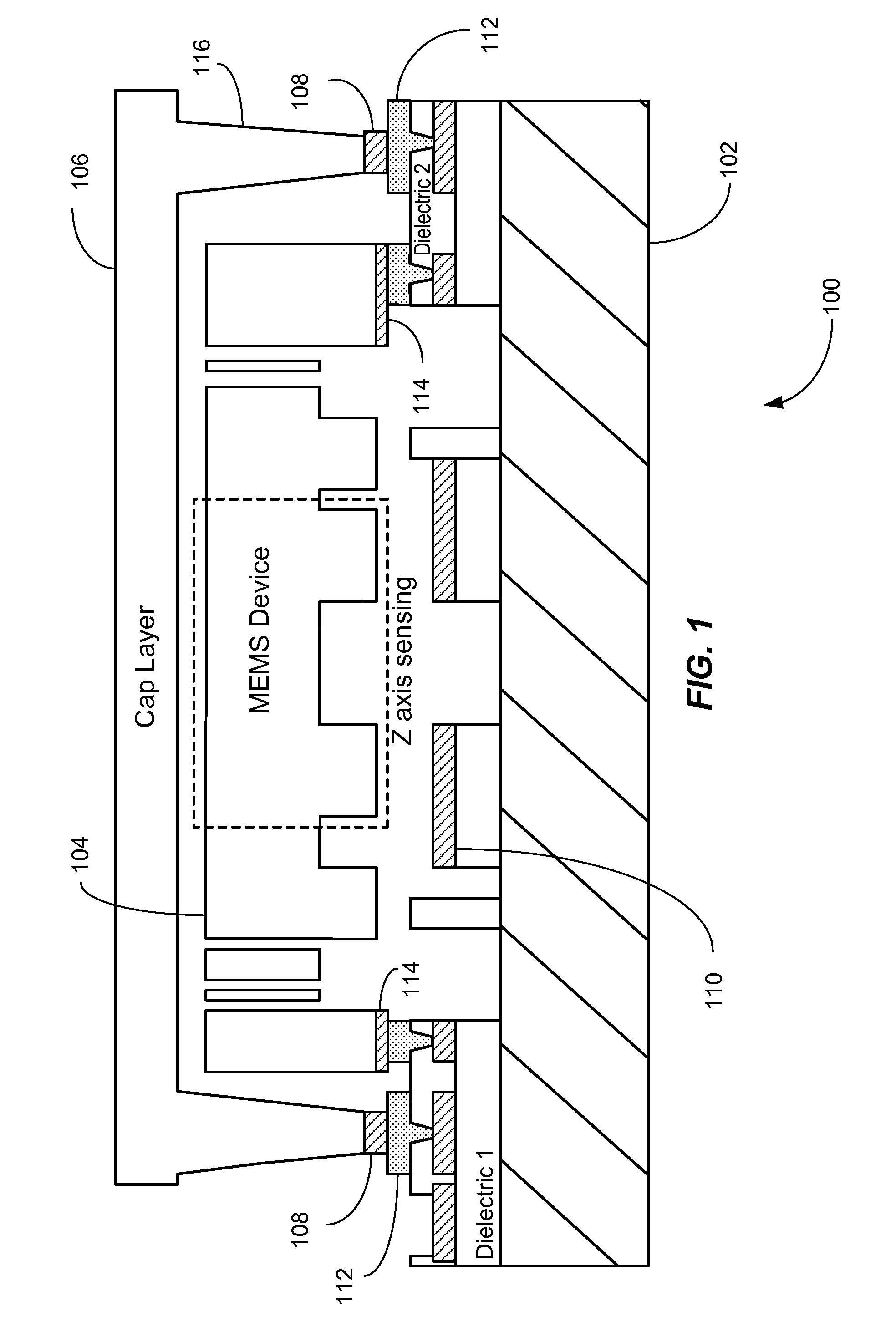

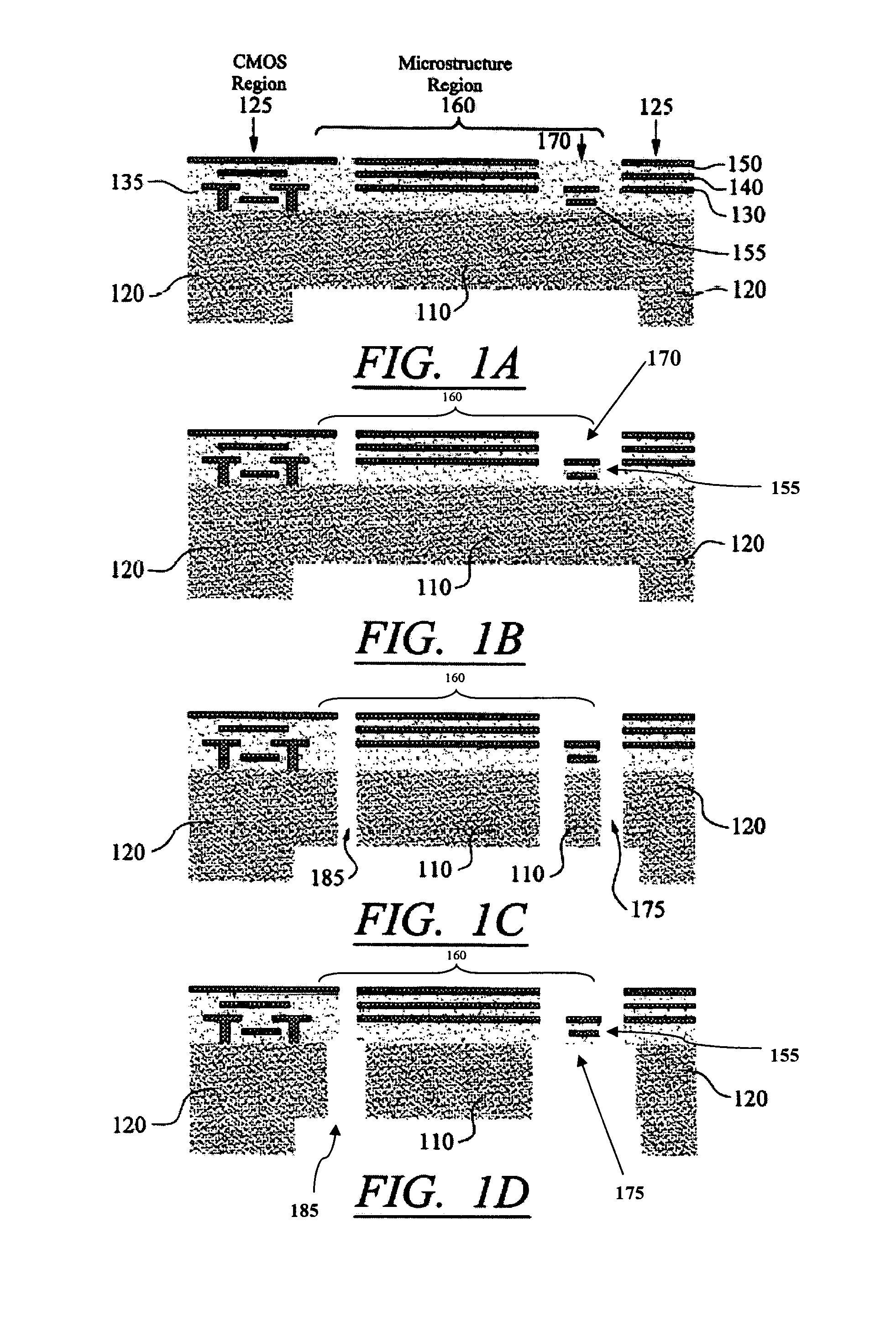

Manufacture of MEMS structures in sealed cavity using dry-release MEMS device encapsulation

InactiveUS7008812B1Eliminates undesirable liquid surface tensionIncrease etch rateAcceleration measurement using interia forcesSolid-state devicesMaterials sciencePlasma etching

The disclosed fabrication methodology addresses the problem of creating low-cost micro-electro-mechanical devices and systems, and, in particular, addresses the problem of delicate microstructures being damaged by the surface tension created as a wet etchant evaporates. This disclosure demonstrates a method for employing a dry plasma etch process to release encapsulated microelectromechanical components.

Owner:CYMATICS LAB CORP

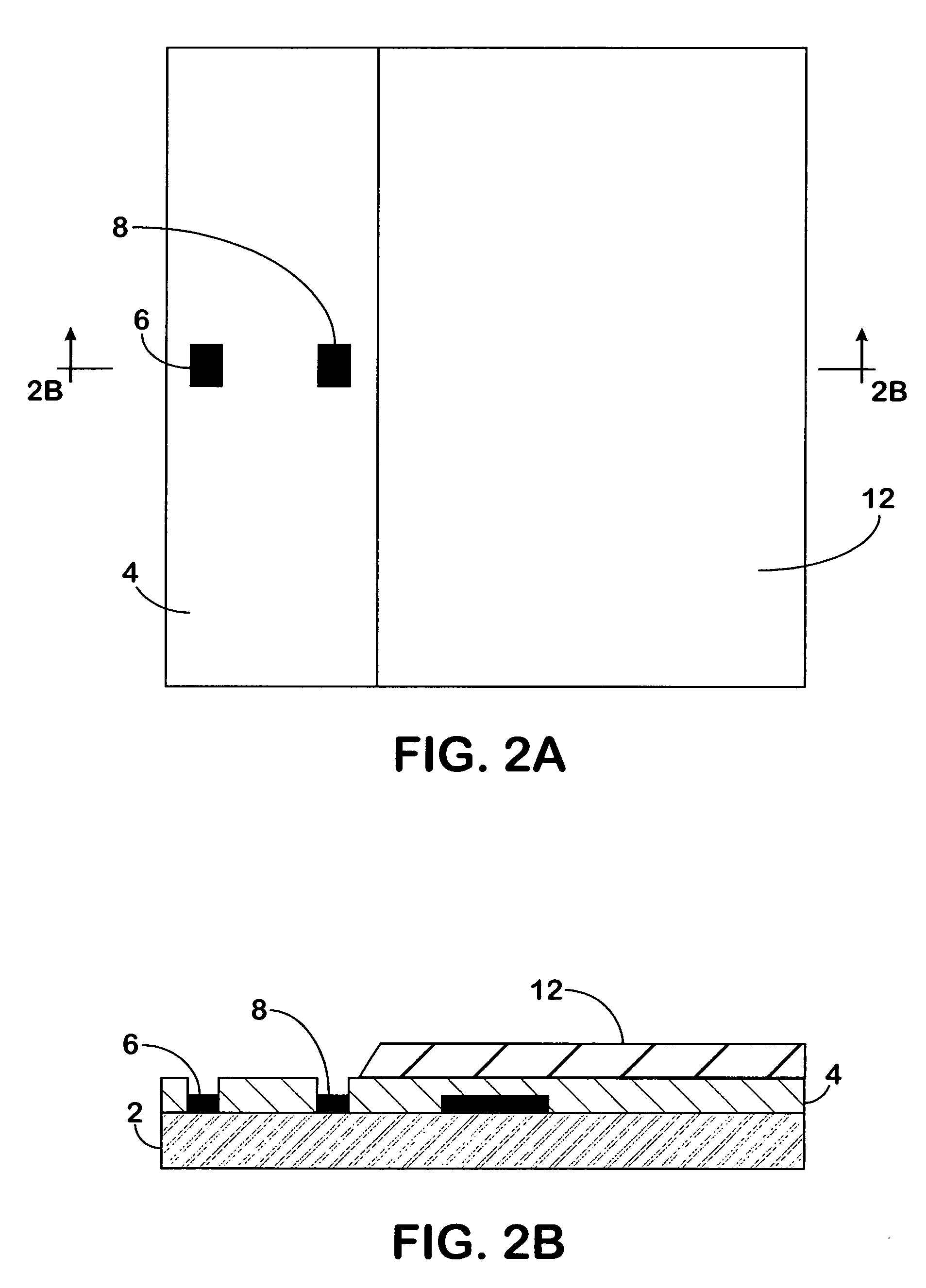

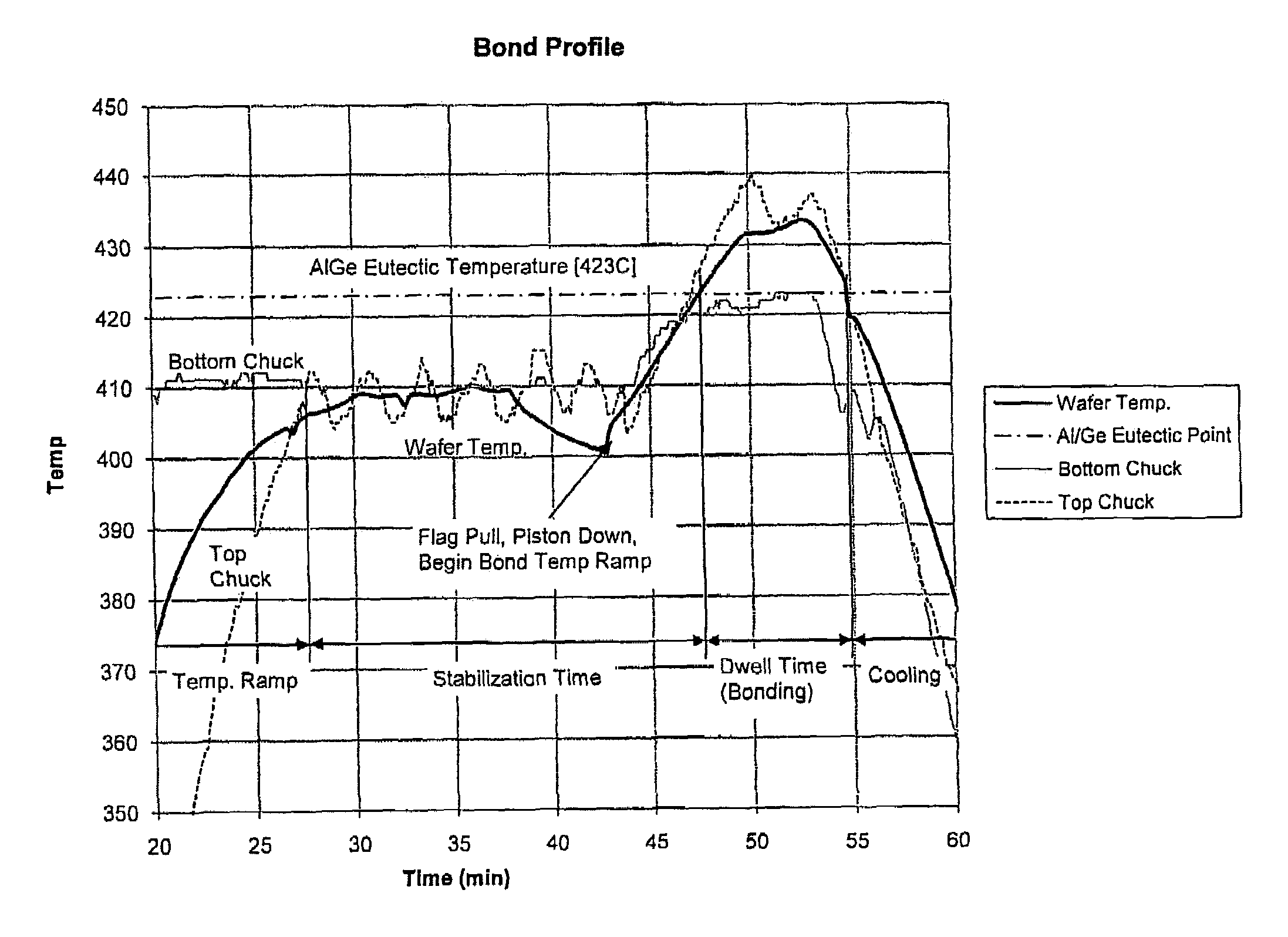

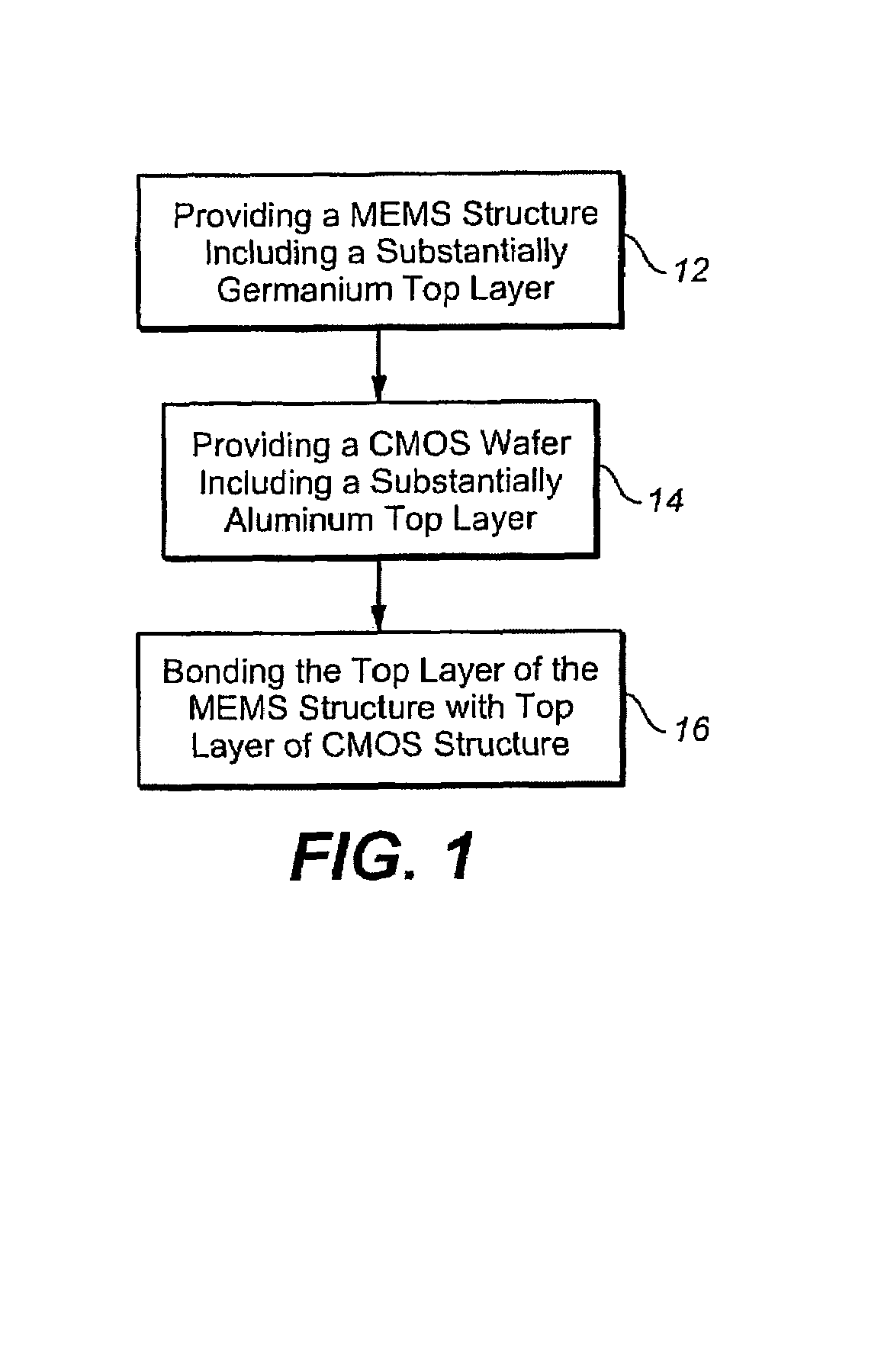

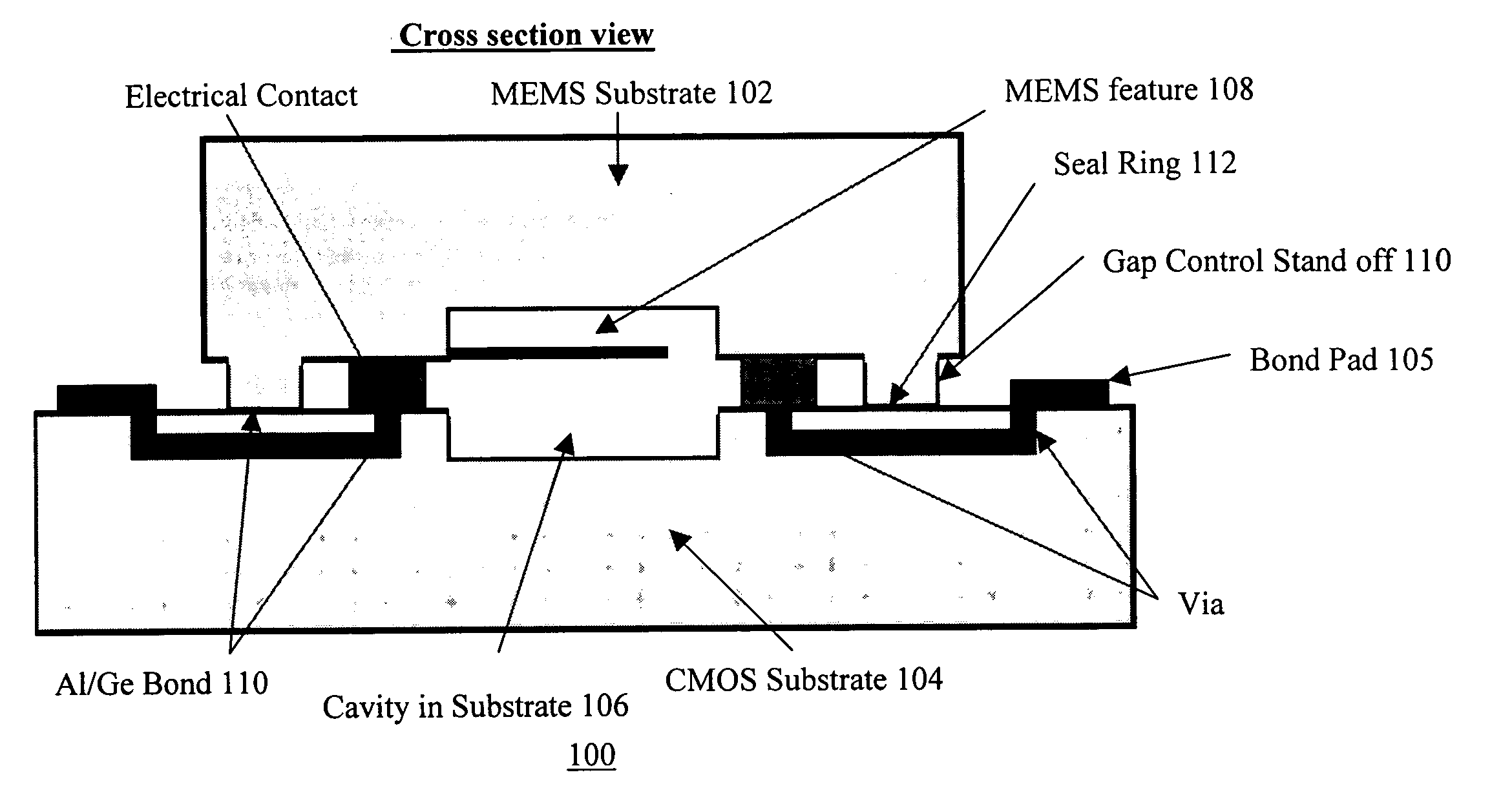

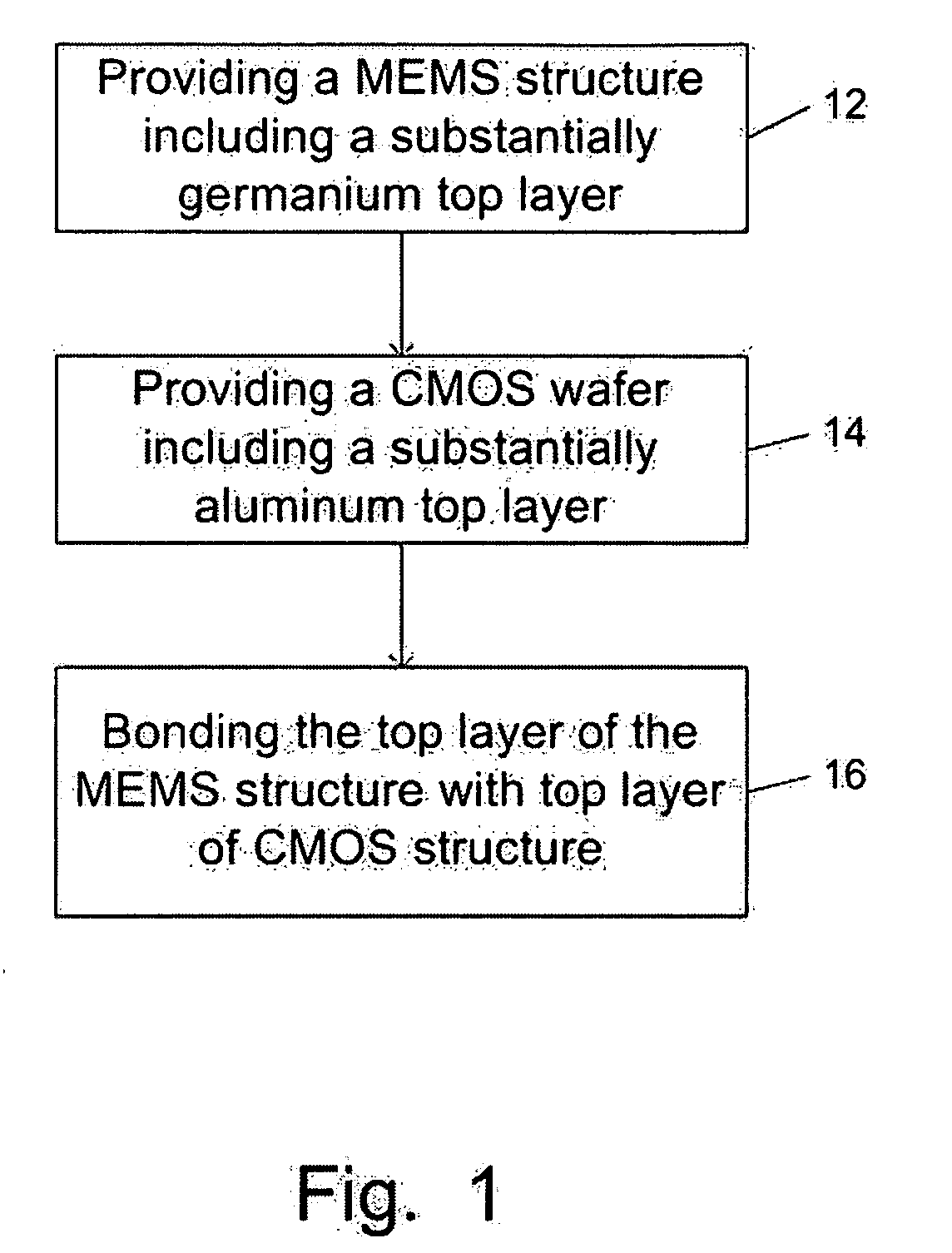

Method of fabrication of a AL/GE bonding in a wafer packaging environment and a product produced therefrom

ActiveUS7442570B2Robust and mechanical contactHighly controllableAcceleration measurement using interia forcesSemiconductor/solid-state device detailsFoundryHermetic seal

A method of bonding of germanium to aluminum between two substrates to create a robust electrical and mechanical contact is disclosed. An aluminum-germanium bond has the following unique combination of attributes: (1) it can form a hermetic seal; (2) it can be used to create an electrically conductive path between two substrates; (3) it can be patterned so that this conduction path is localized; (4) the bond can be made with the aluminum that is available as standard foundry CMOS process. This has the significant advantage of allowing for wafer-level bonding or packaging without the addition of any additional process layers to the CMOS wafer.

Owner:INVENSENSE

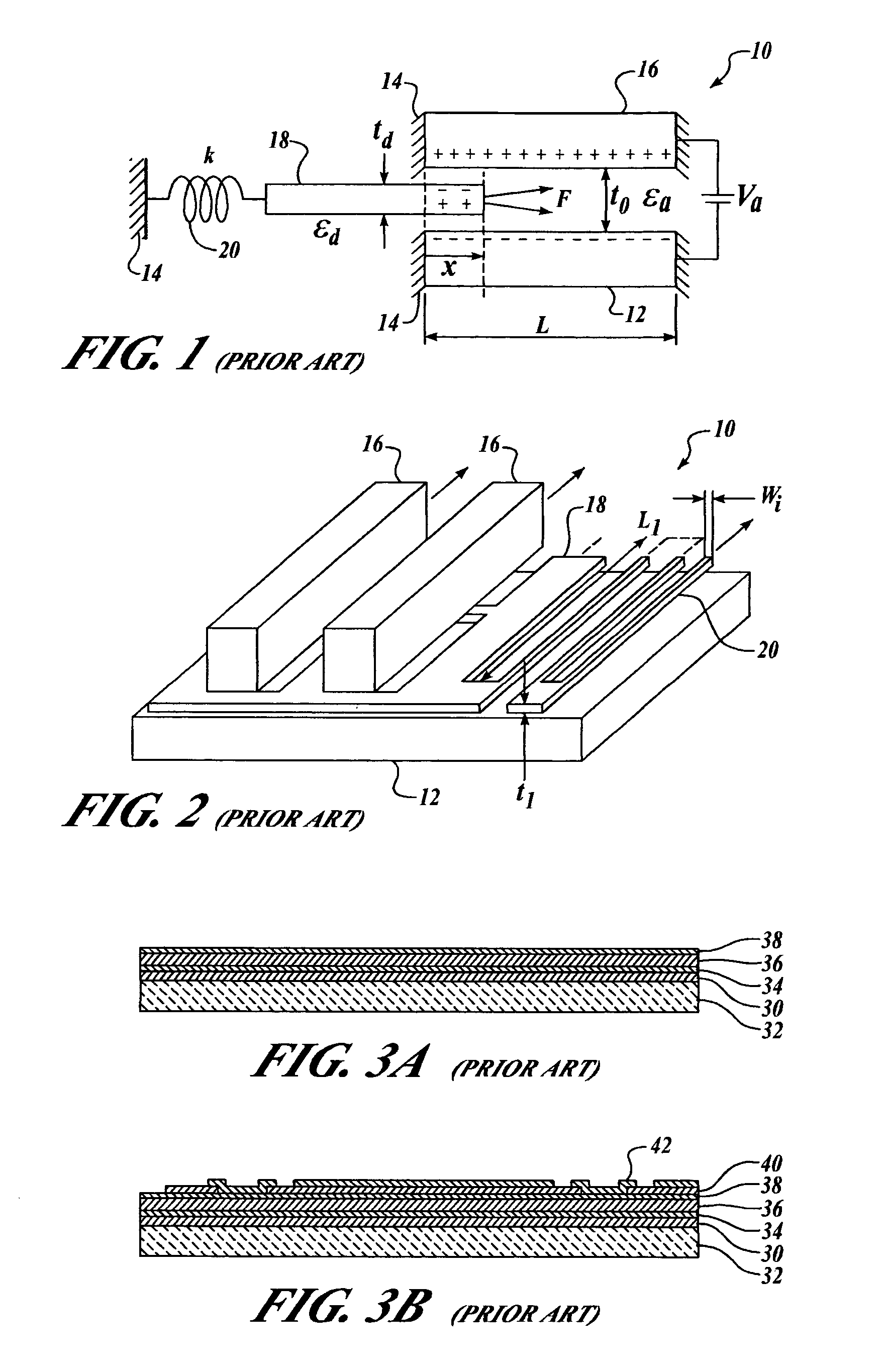

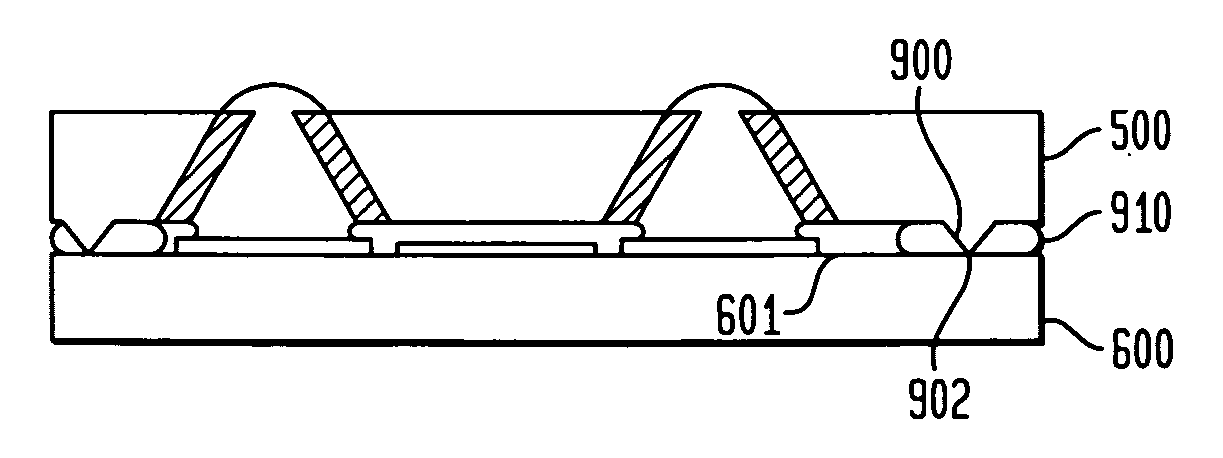

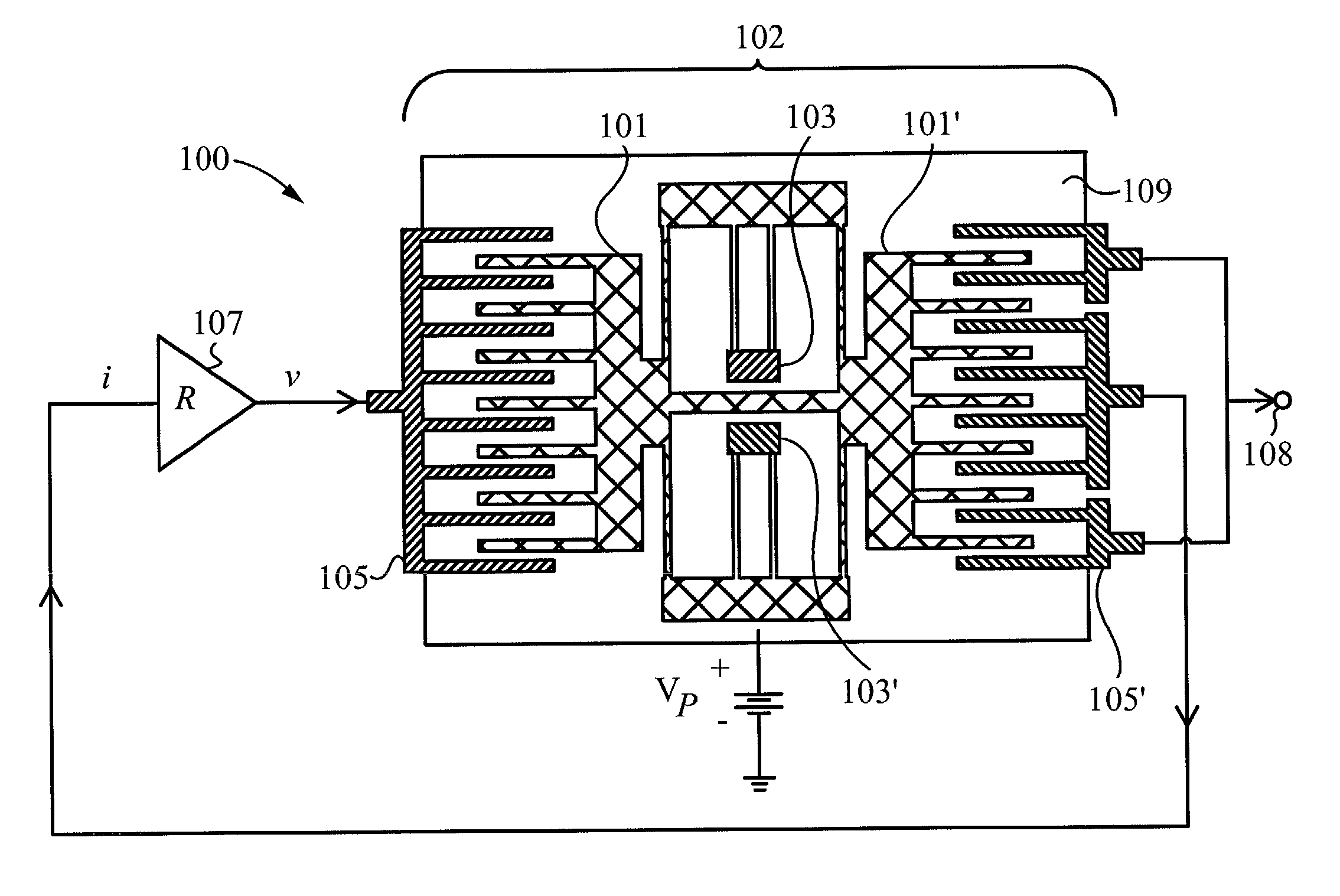

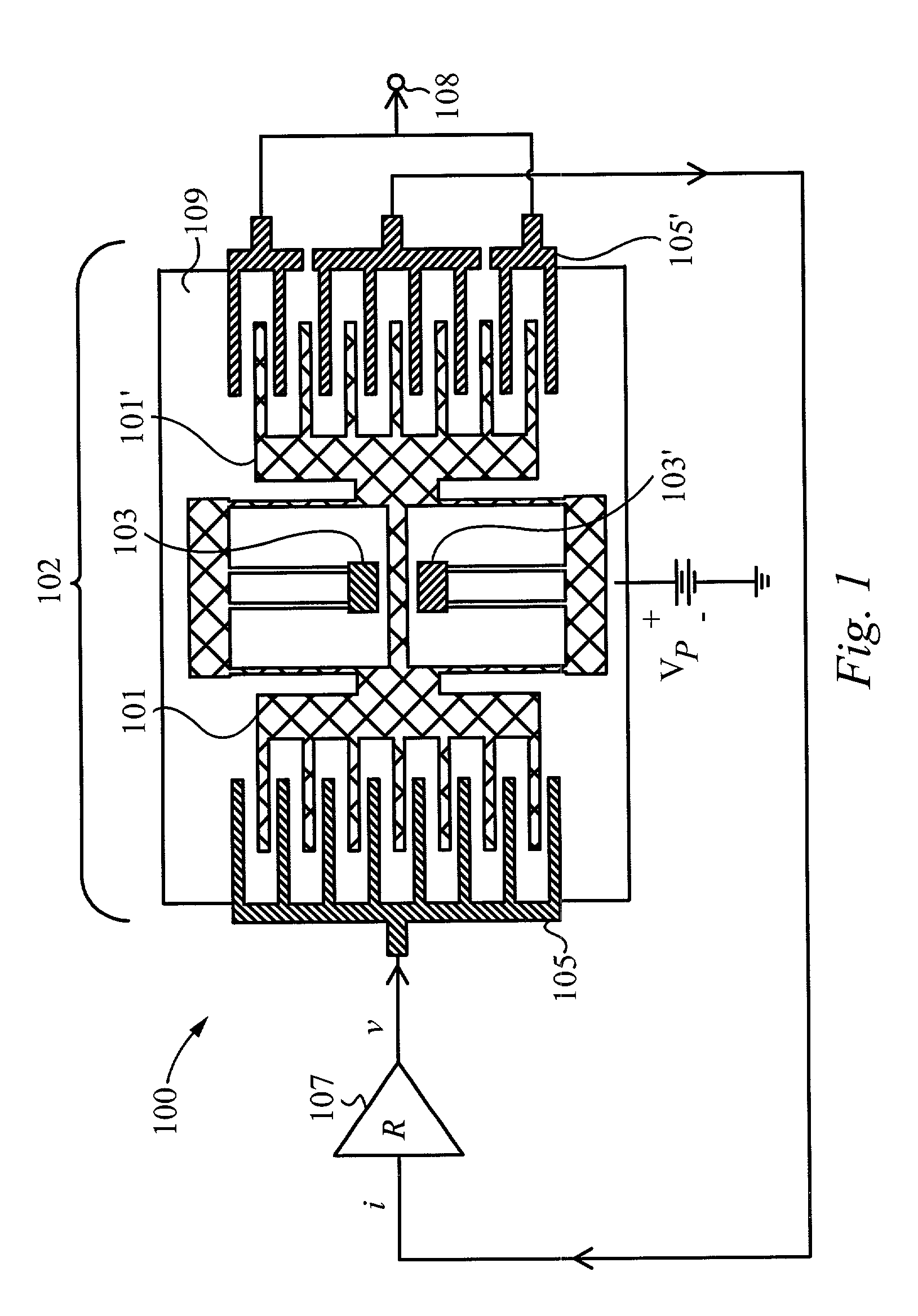

Low temperature bi-CMOS compatible process for MEMS RF resonators and filters

InactiveUS20090108381A1Impedence networksSemiconductor/solid-state device detailsMetal interconnectOxygen plasma

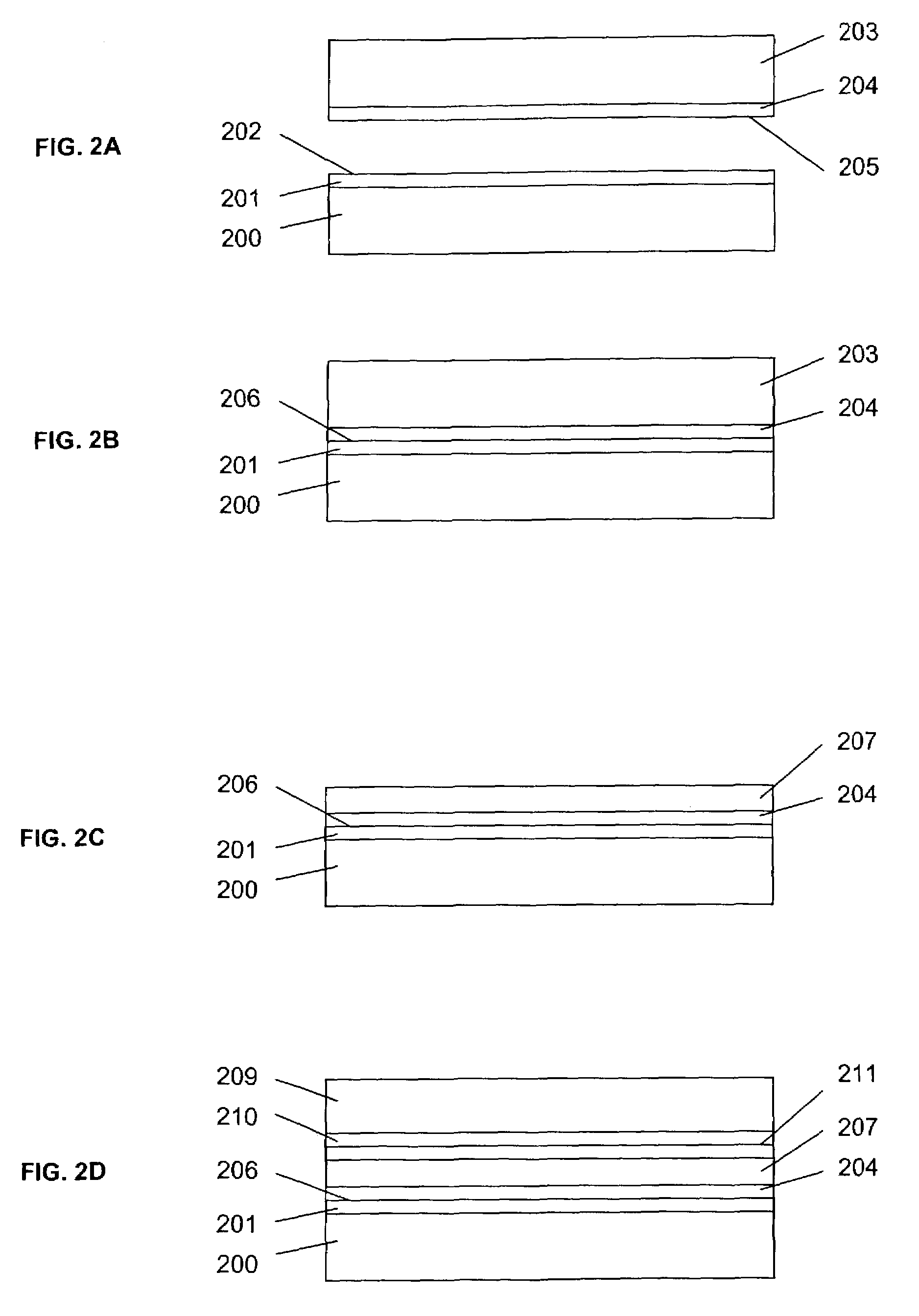

A method of formation of a microelectromechanical system (MEMS) resonator or filter which is compatible with integration with any analog, digital, or mixed-signal integrated circuit (IC) process, after or concurrently with the formation of the metal interconnect layers in those processes, by virtue of its materials of composition, processing steps, and temperature of fabrication is presented. The MEMS resonator or filter incorporates a lower metal level, which forms the electrodes of the MEMS resonator or filter, that may be shared with any or none of the existing metal interconnect levels on the IC. It further incorporates a resonating member that is comprised of at least one metal layer for electrical connection and electrostatic actuation, and at least one dielectric layer for structural purposes. The gap between the electrodes and the resonating member is created by the deposition and subsequent removal of a sacrificial layer comprised of a carbon-based material. The method of removal of the sacrificial material is by an oxygen plasma or an anneal in an oxygen containing ambient. A method of vacuum encapsulation of the MEMS resonator or filter is provided through means of a cavity containing the MEMS device, filled with additional sacrificial material, and sealed. Access vias are created through the membrane sealing the cavity; the sacrificial material is removed as stated previously, and the vias are re-sealed in a vacuum coating process.

Owner:IBM CORP

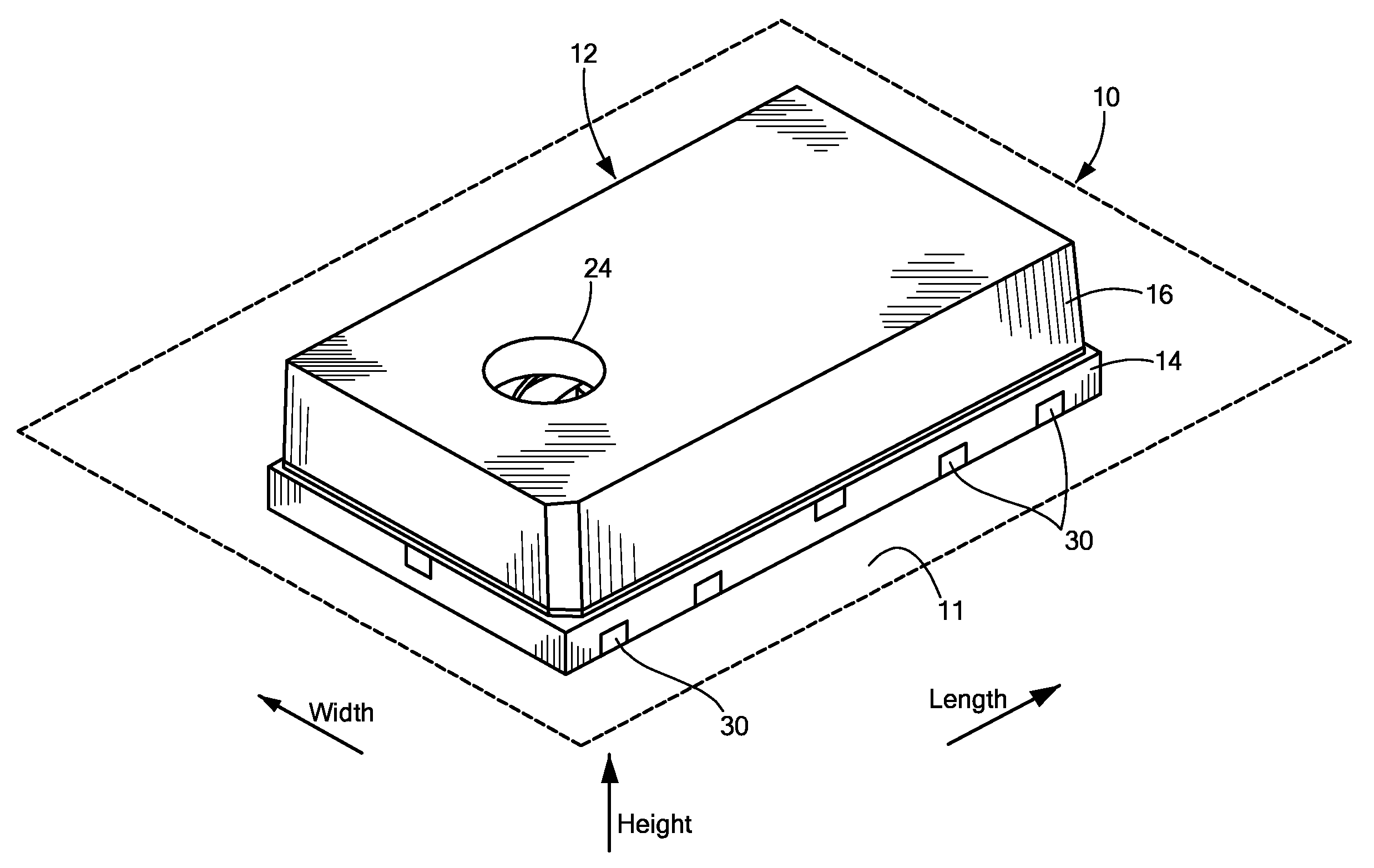

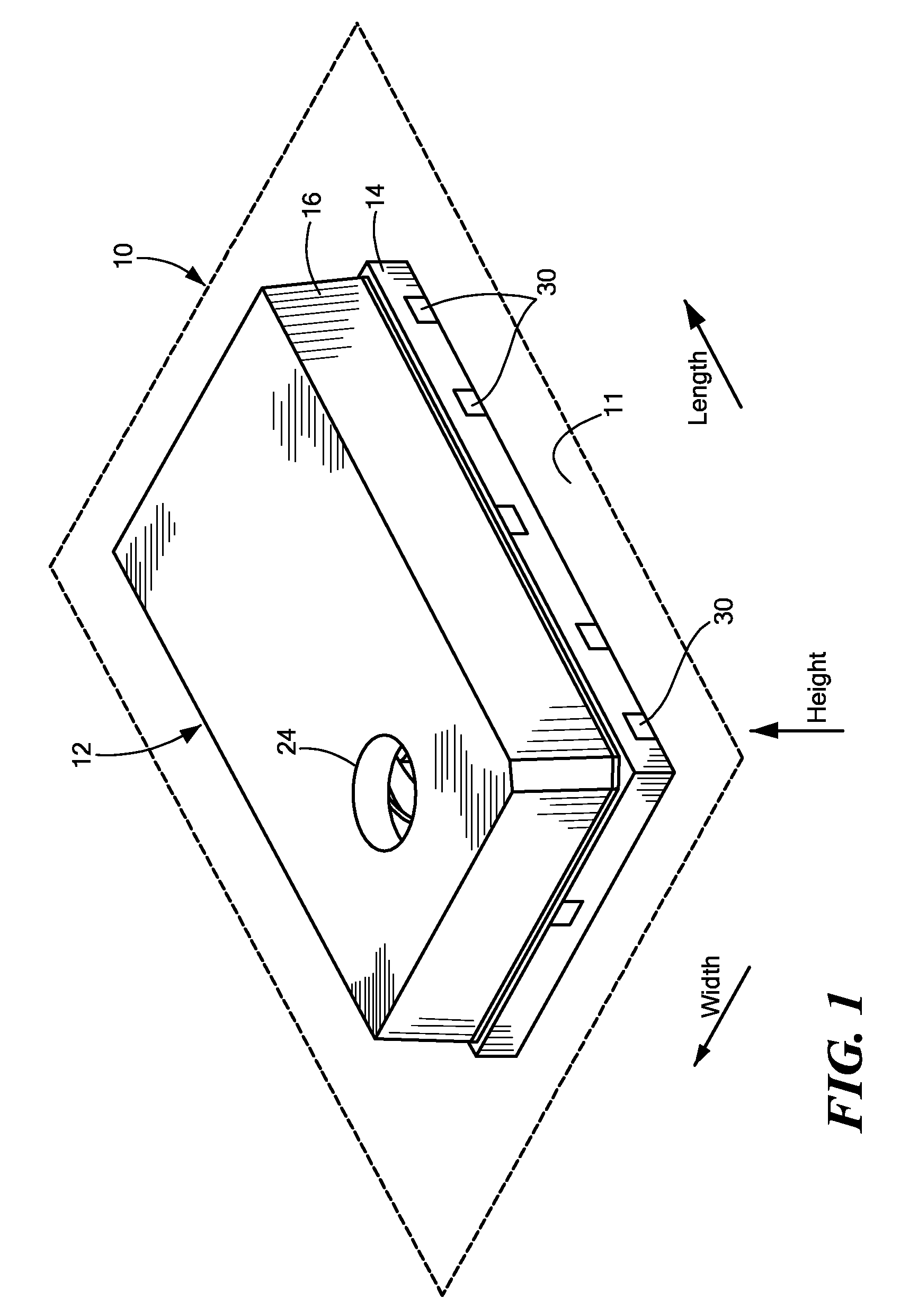

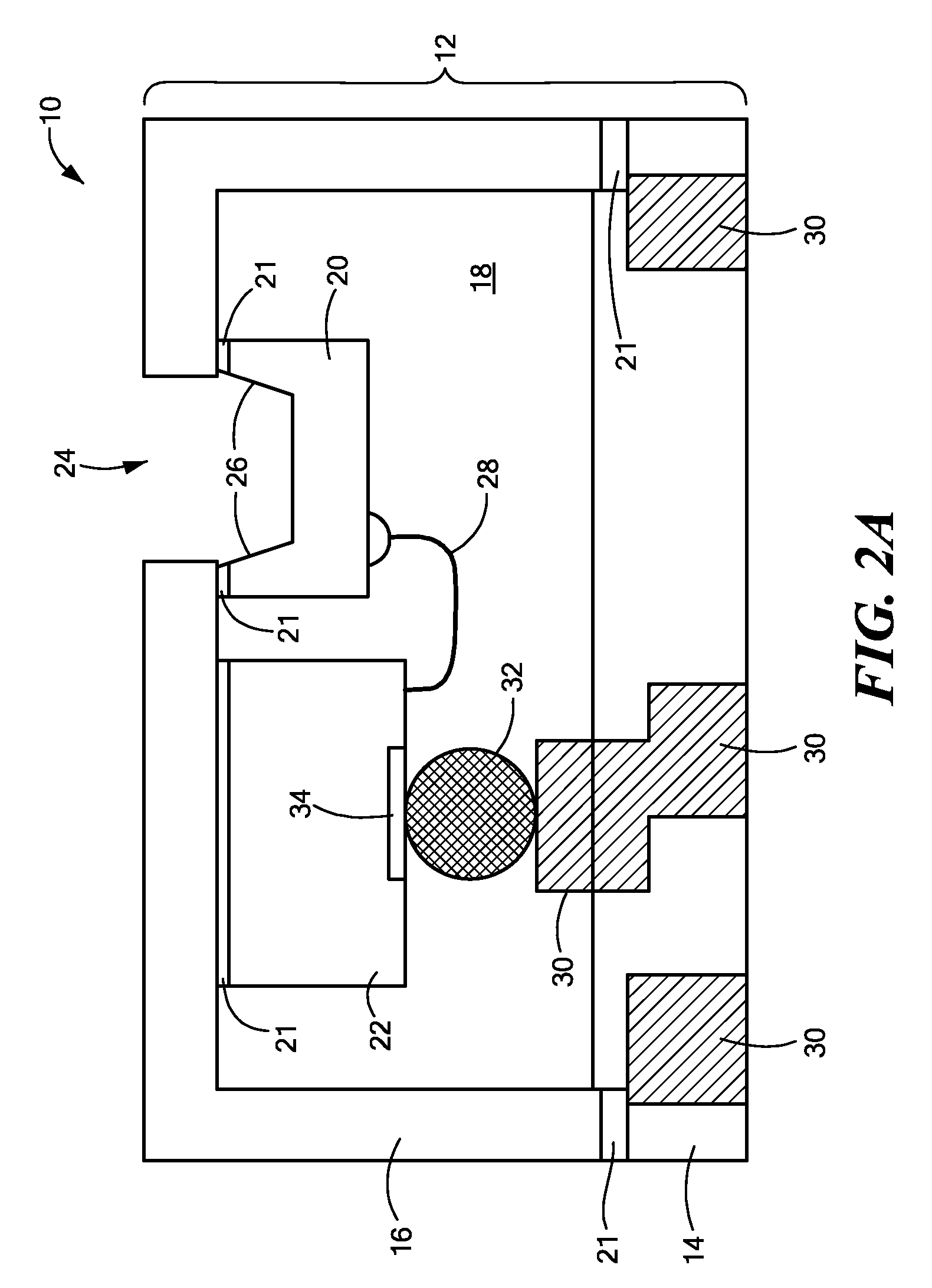

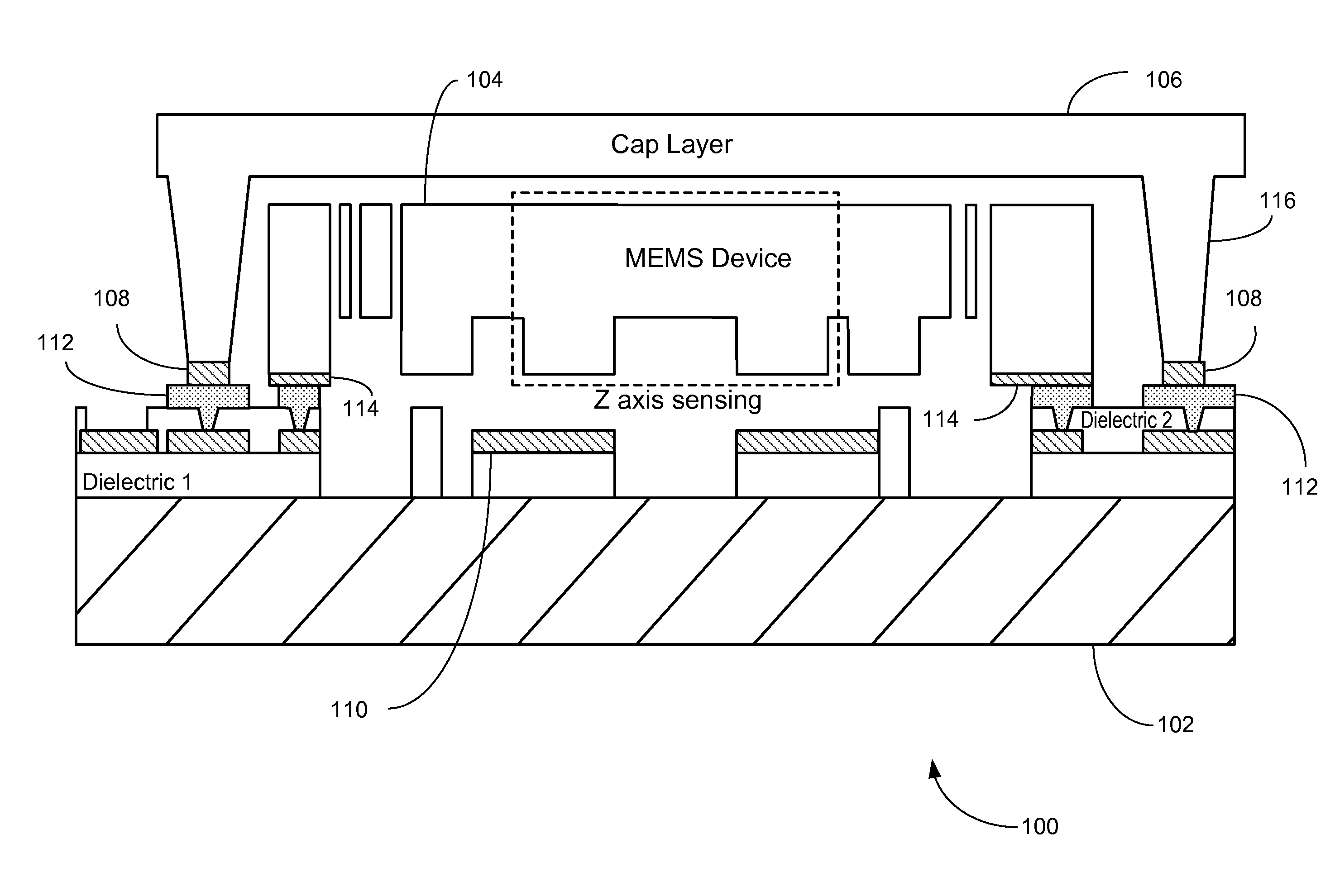

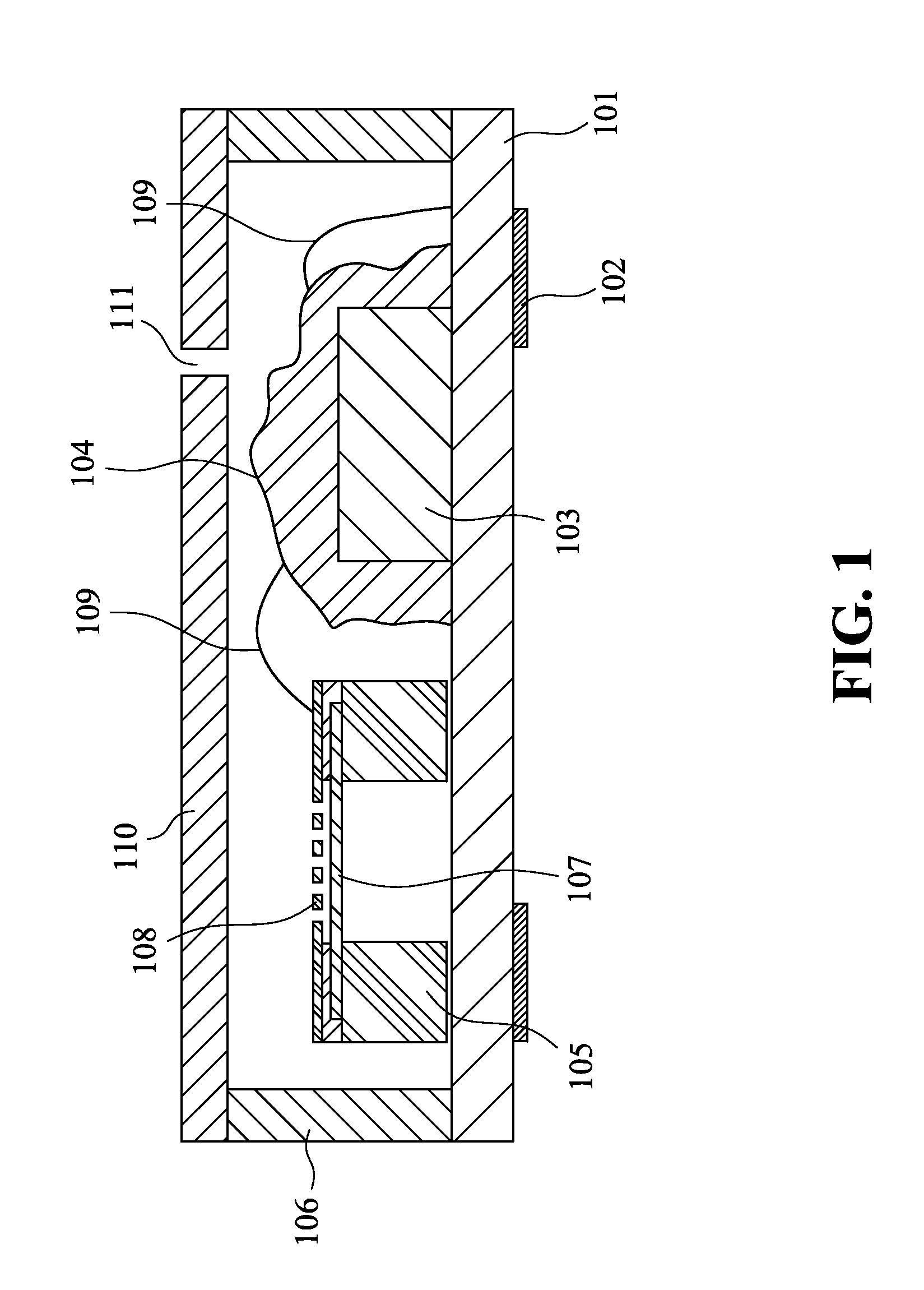

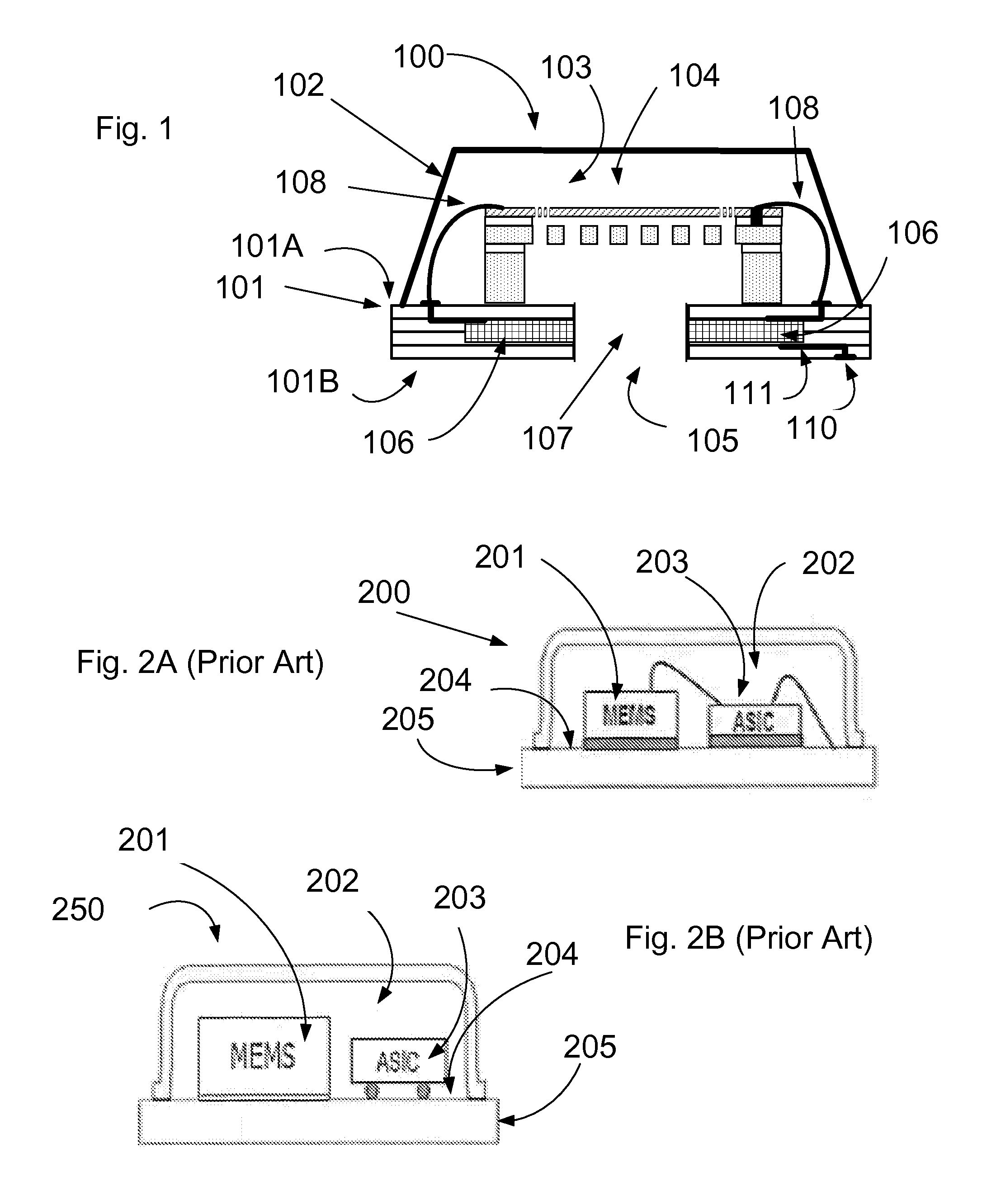

MEMS Packaging Including Integrated Circuit Dies

InactiveUS20090194829A1Highly integratedReduced package footprintSemiconductor/solid-state device detailsSolid-state devicesOn boardElectrical connection

MEMS packaging schemes having a system-on-package (SOP) configuration and a system-on-board (SOB) configuration are provided. The MEMS package comprises one or more MEMS dies, a cap section having one or more integrated circuit (IC) dies, and a packaging substrate or a printed circuit board (PCB) arranged in a stacking manner. Vertical connectors, such as through-silicon-vias (TSVs), are formed to provide short electrical connections between the various components. The MEMS packaging schemes enable higher integration density, reduced MEMS package footprints, reduced RC delays and power consumption.

Owner:TAIWAN SEMICON MFG CO LTD

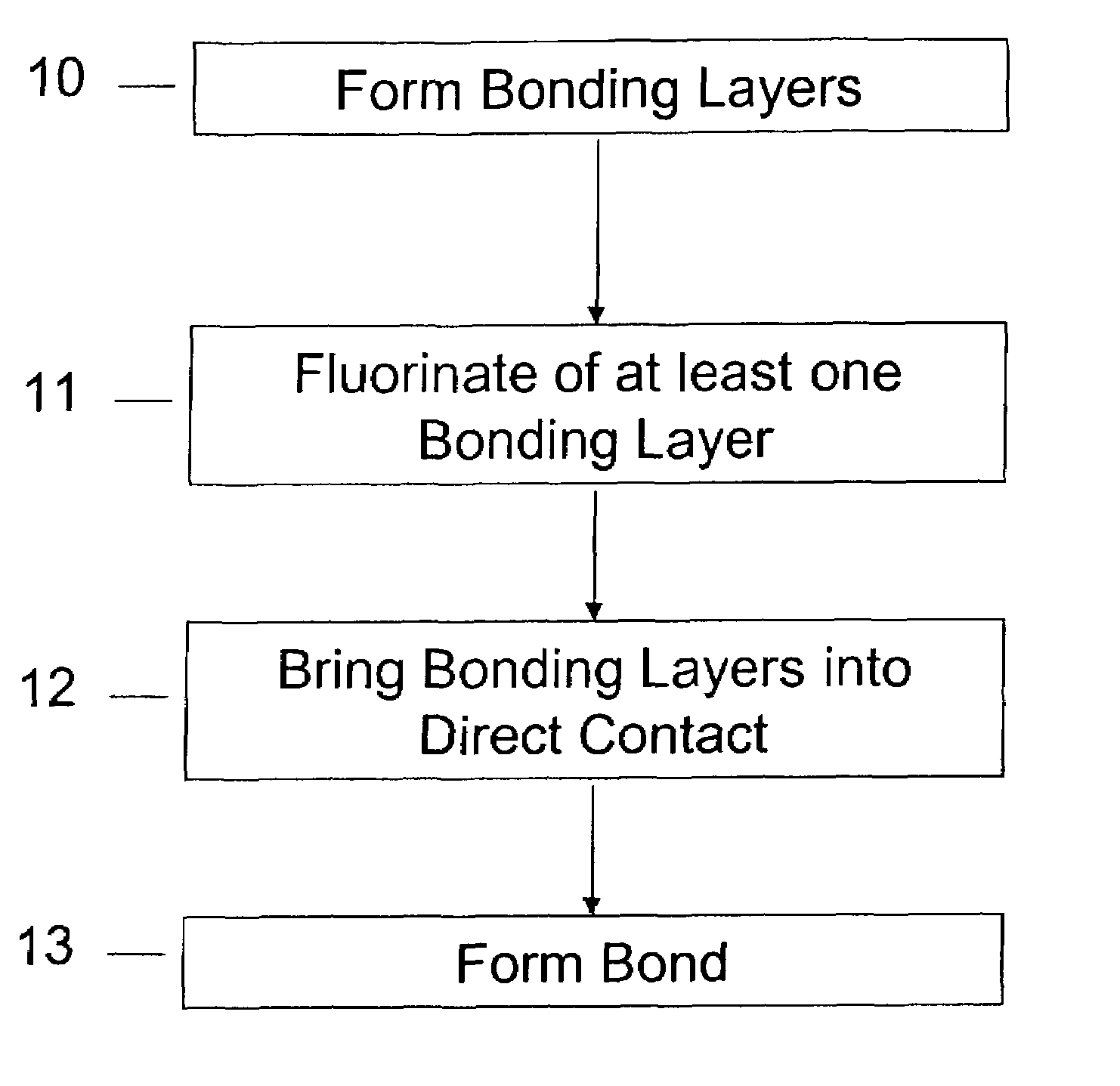

Method of room temperature covalent bonding

InactiveUS7109092B2High densityLow densityLayered productsDecorative surface effectsRoom temperatureFluorine containing

A method of bonding includes using a bonding layer having a fluorinated oxide. Fluorine may be introduced into the bonding layer by exposure to a fluorine-containing solution, vapor or gas or by implantation. The bonding layer may also be formed using a method where fluorine is introduced into the layer during its formation. The surface of the bonding layer is terminated with a desired species, preferably an NH2 species. This may be accomplished by exposing the bonding layer to an NH4OH solution. High bonding strength is obtained at room temperature. The method may also include bonding two bonding layers together and creating a fluorine distribution having a peak in the vicinity of the interface between the bonding layers. One of the bonding layers may include two oxide layers formed on each other. The fluorine concentration may also have a second peak at the interface between the two oxide layers.

Owner:INVENSAS BONDING TECH INC

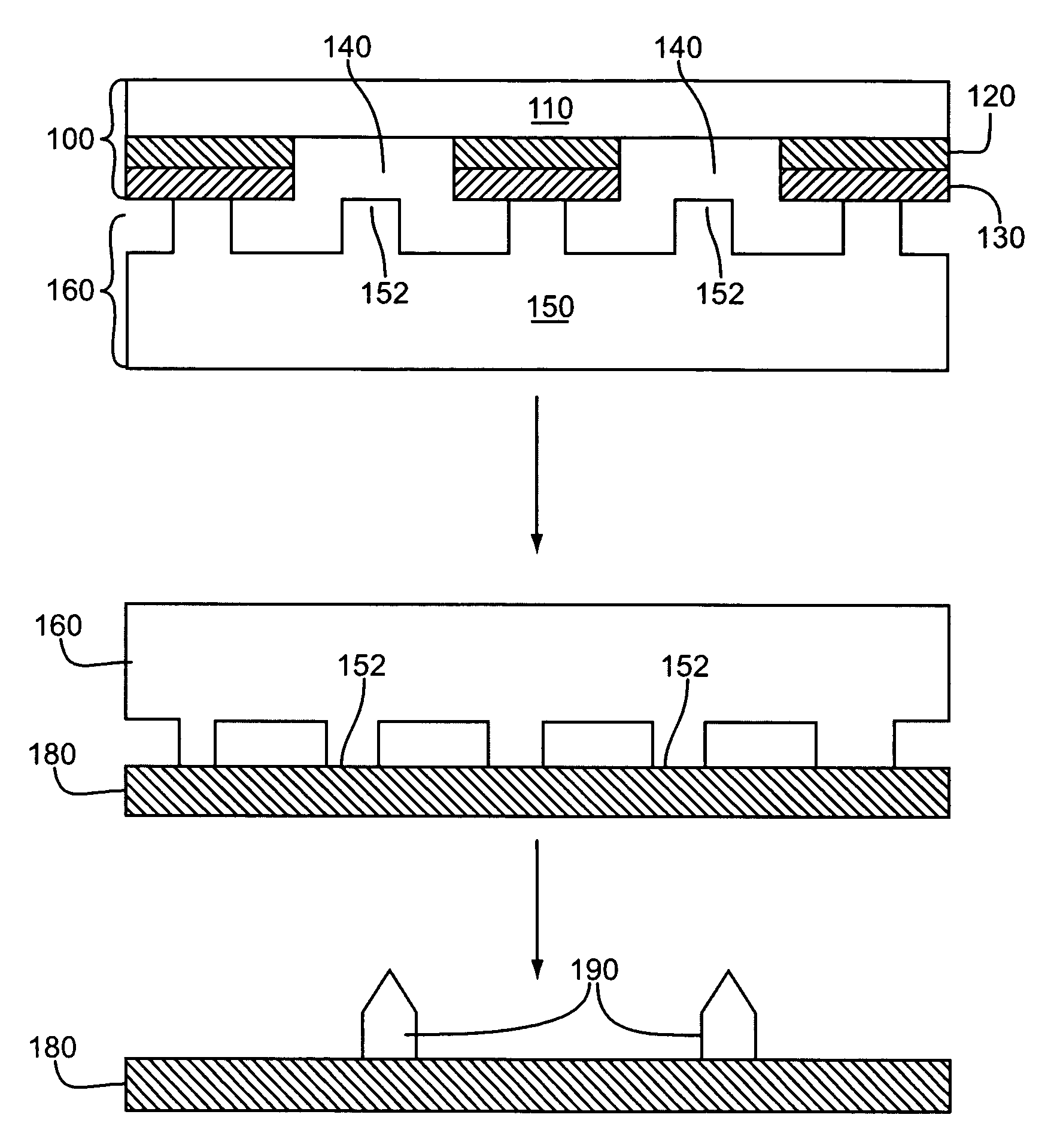

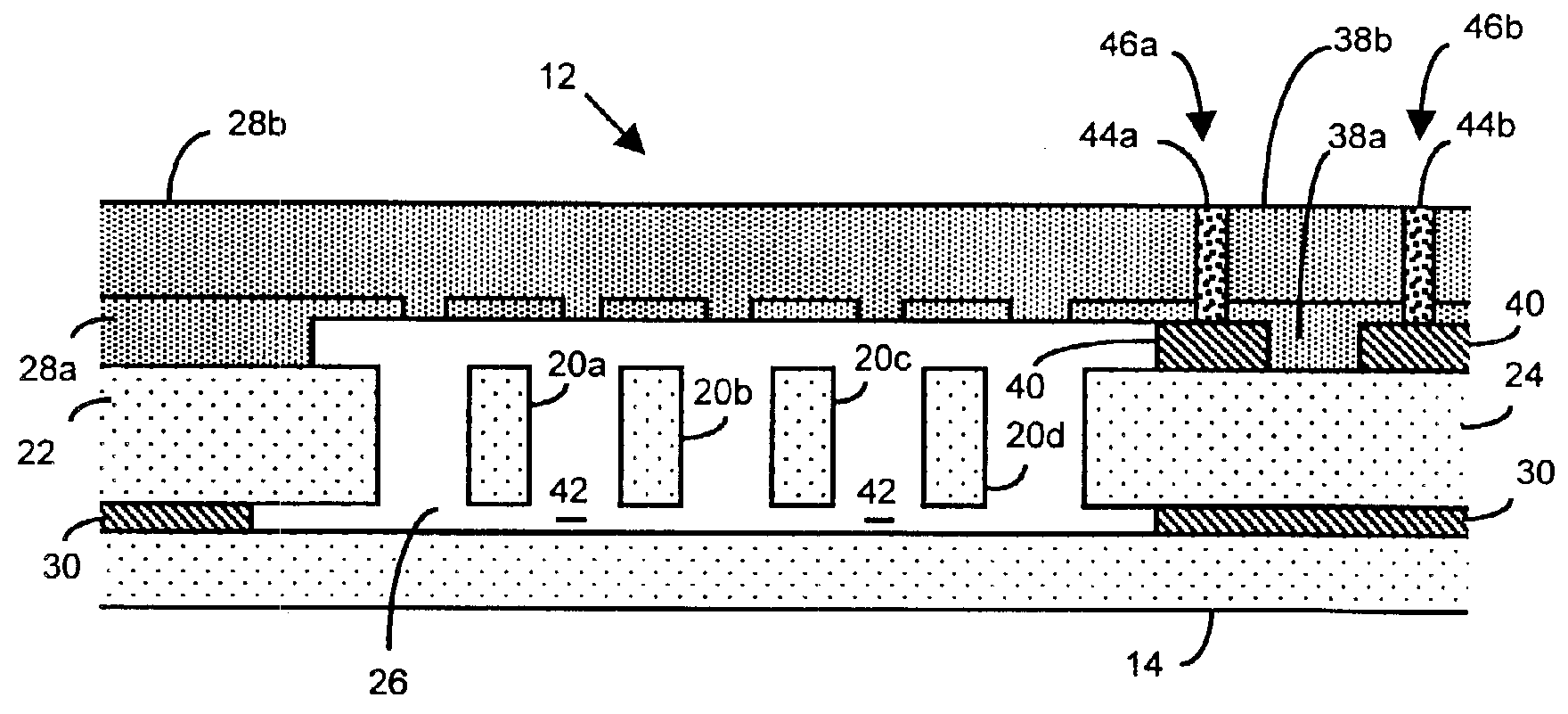

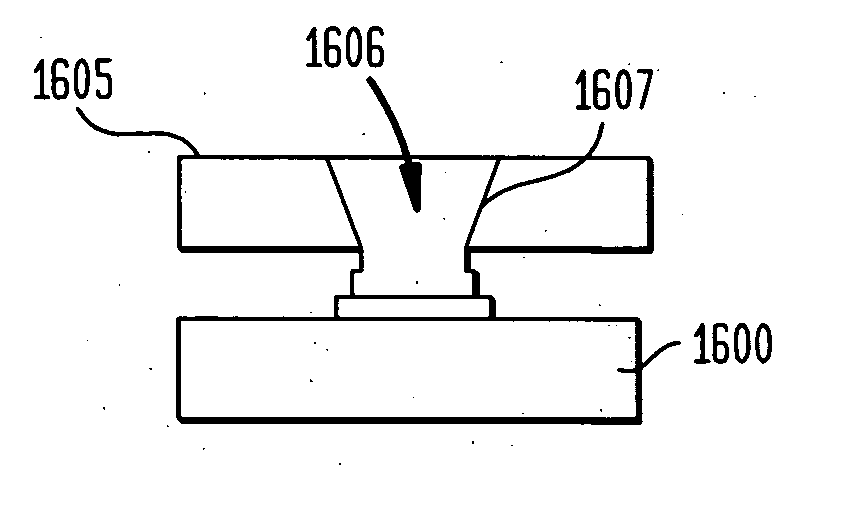

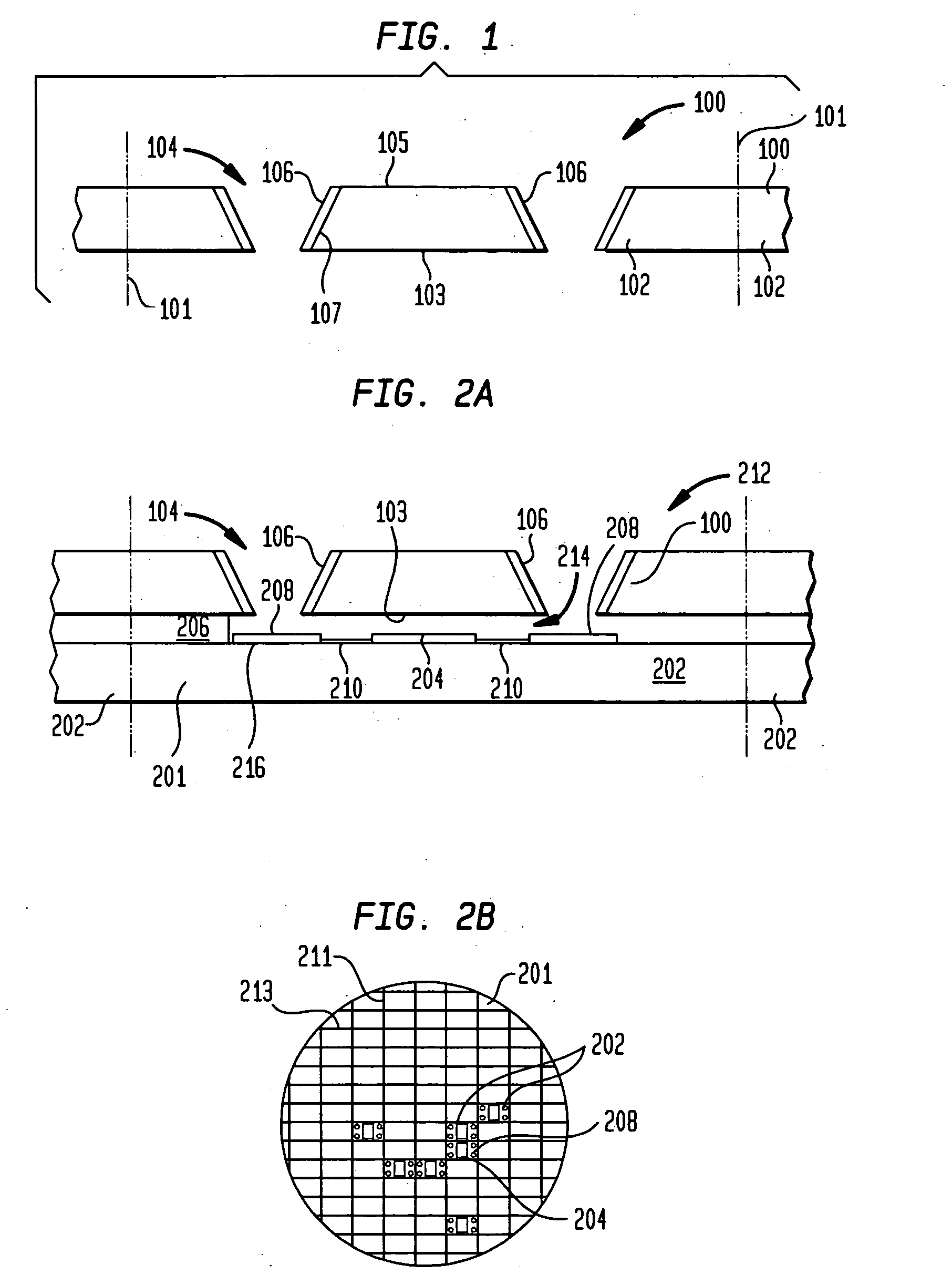

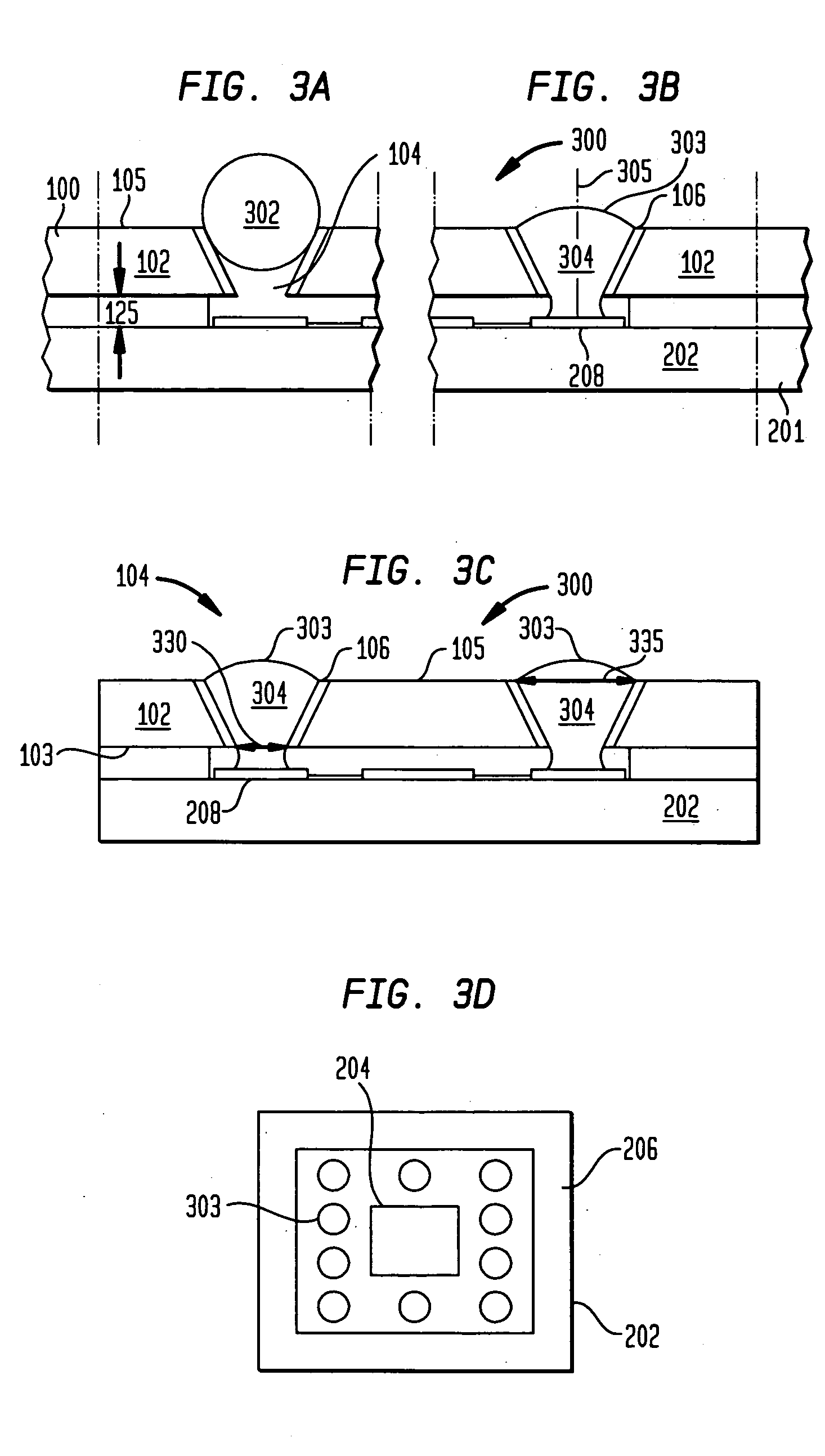

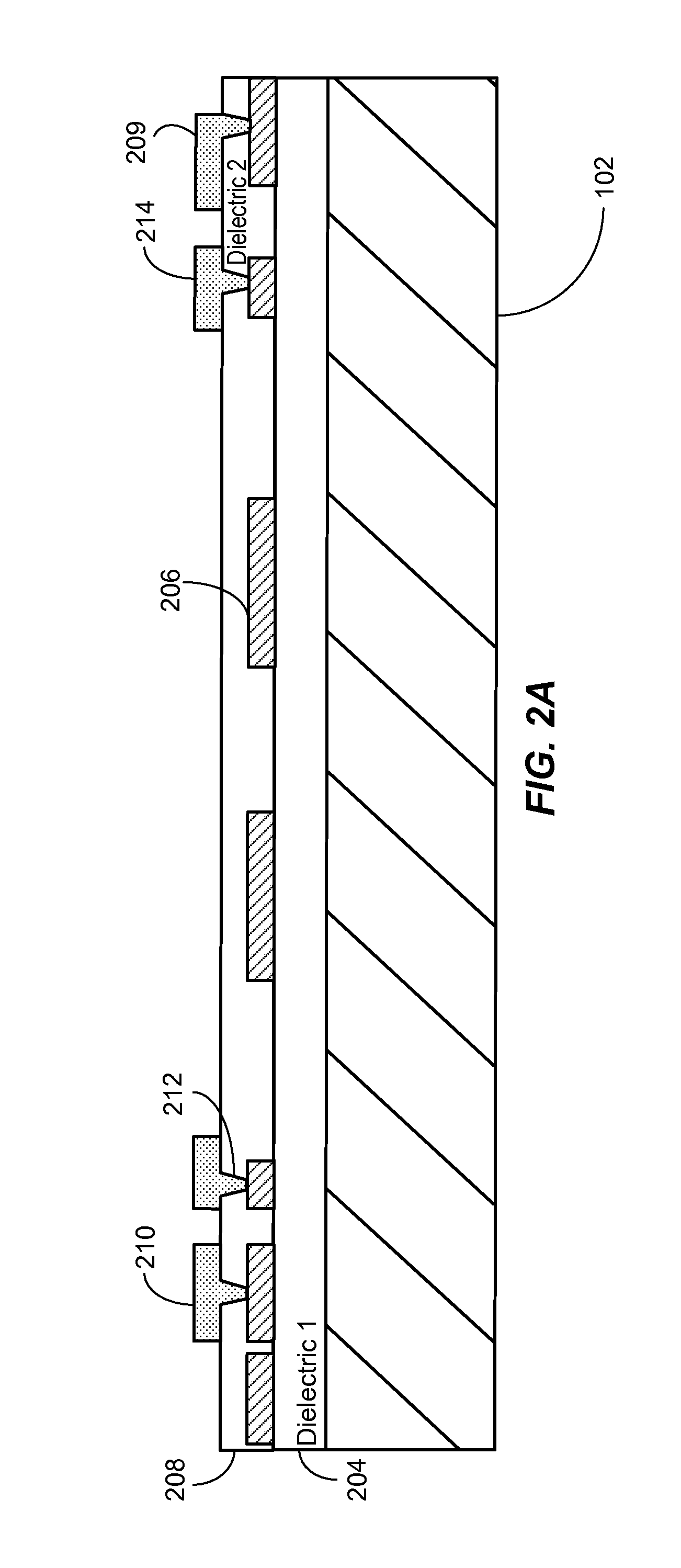

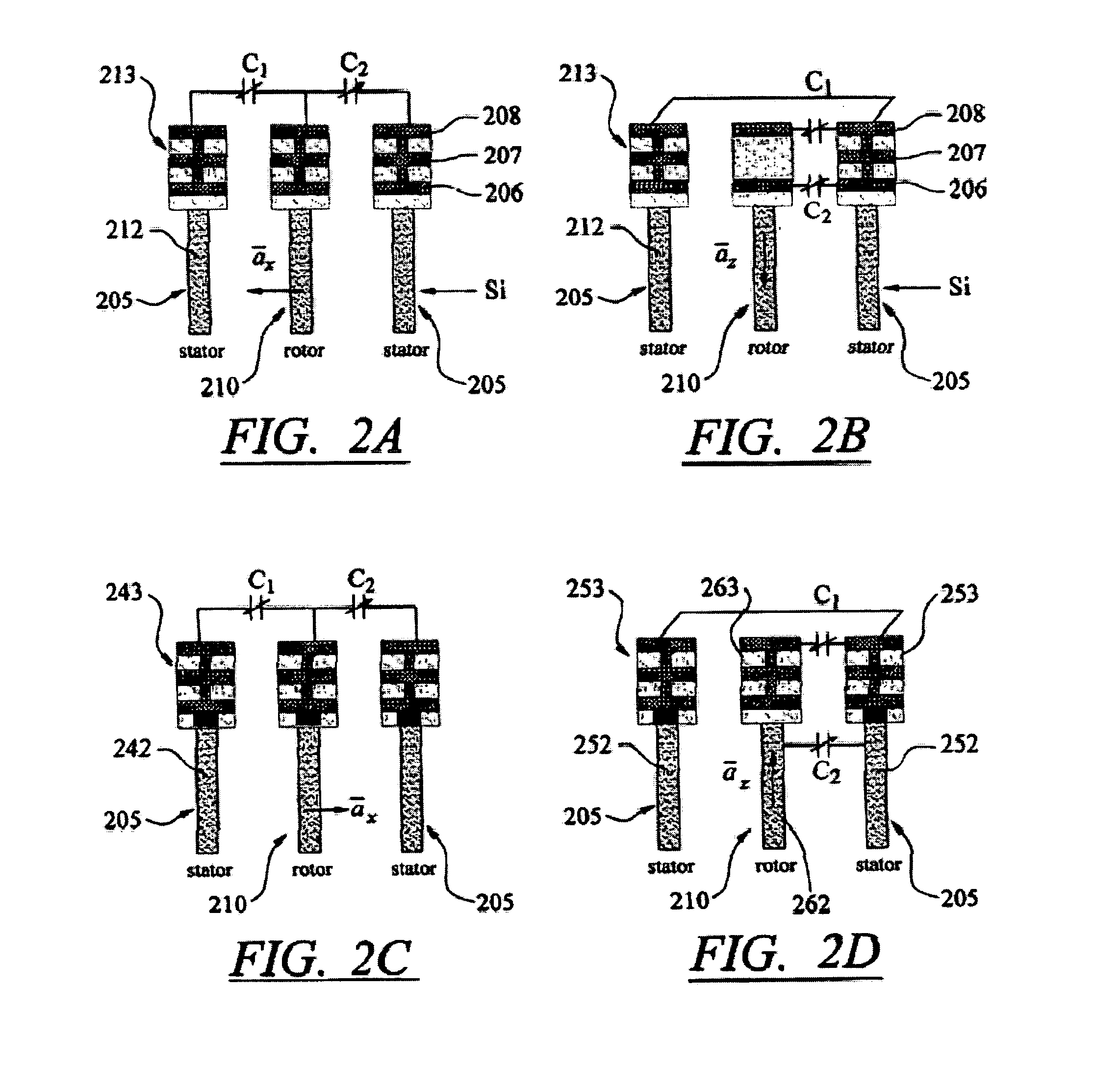

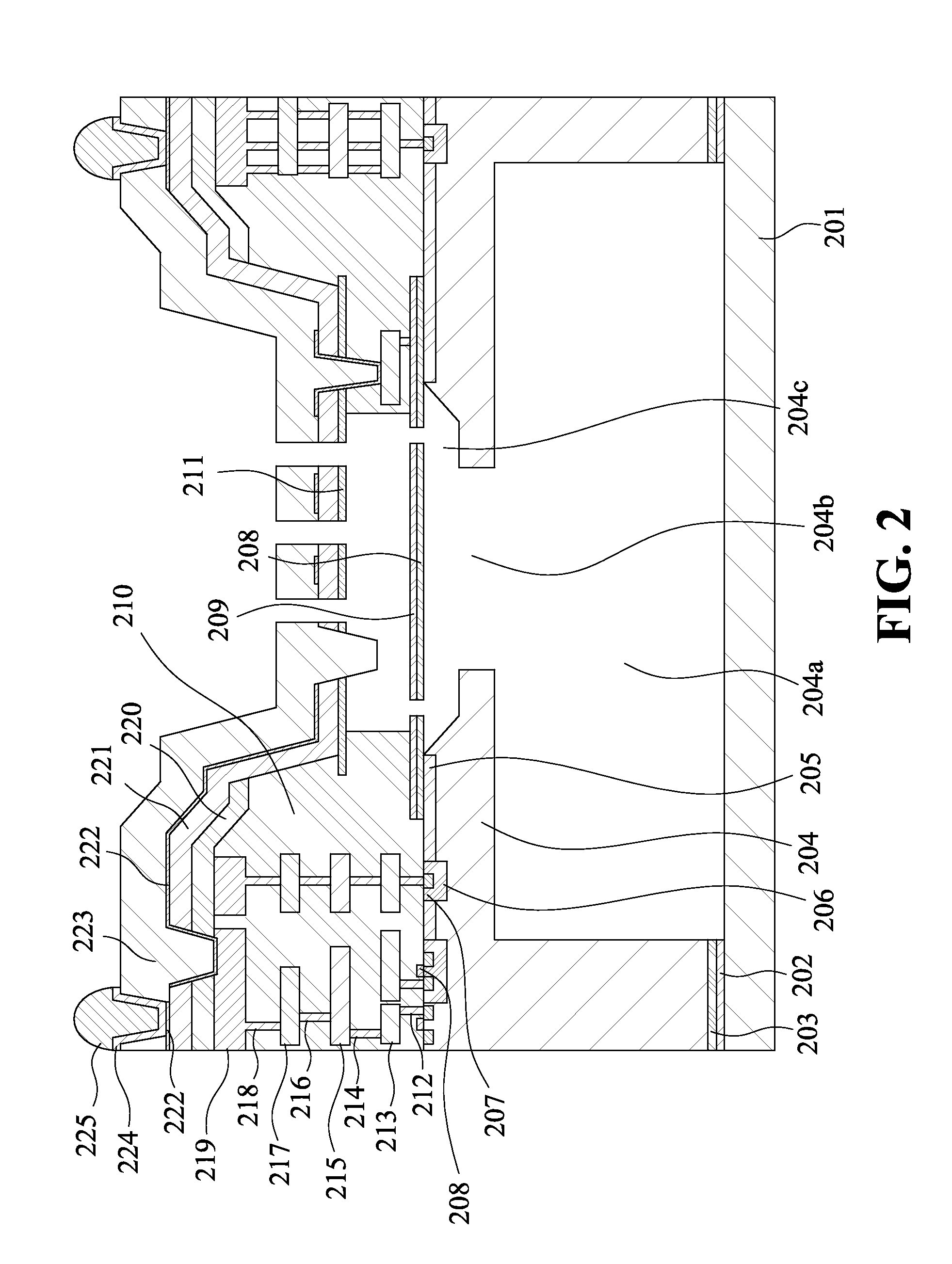

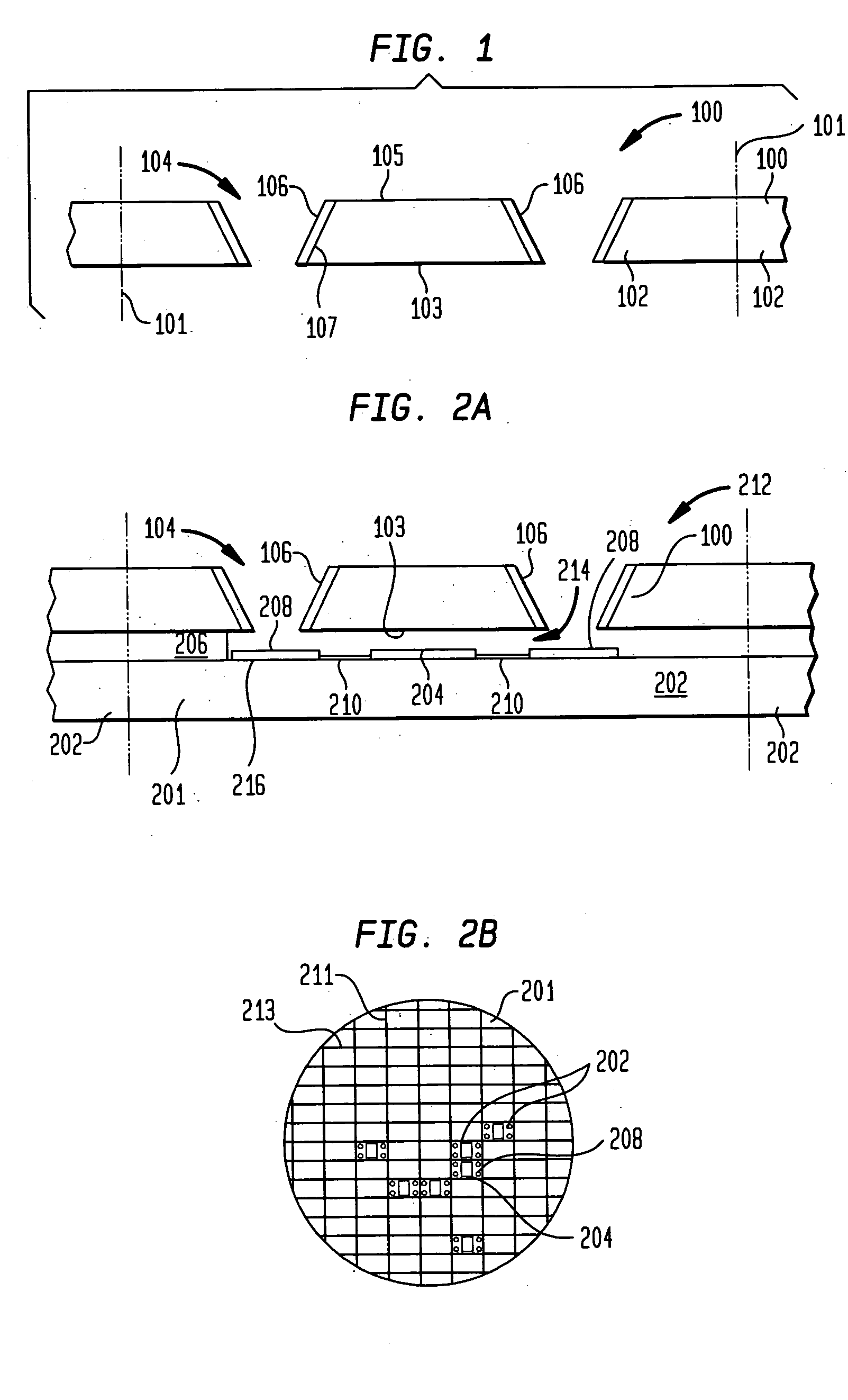

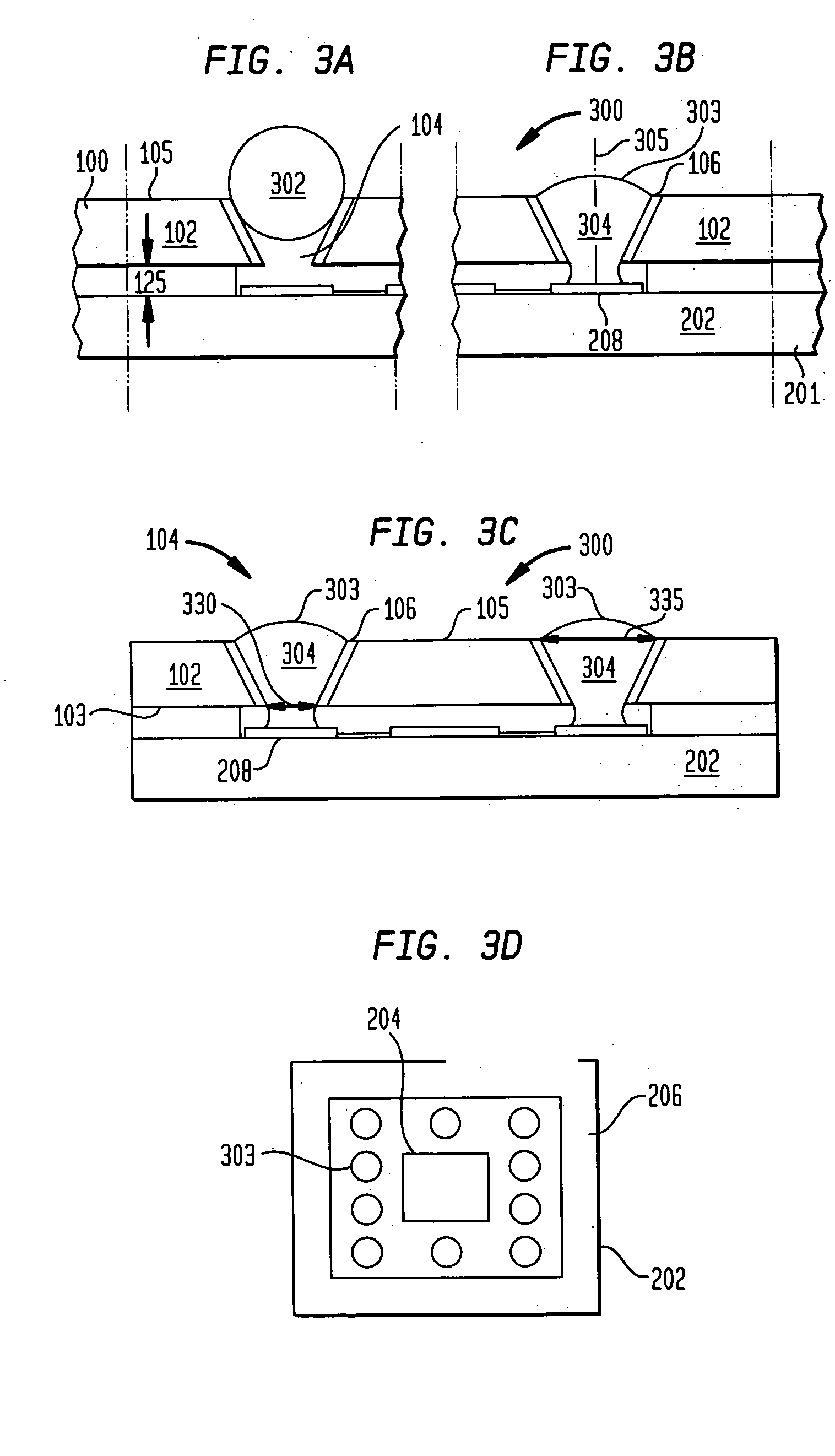

Method of Fabricating High Aspect Ratio Transducer Using Metal Compression Bonding

InactiveUS20100193884A1Television system detailsAcceleration measurement using interia forcesTransducerCapacitive sensing

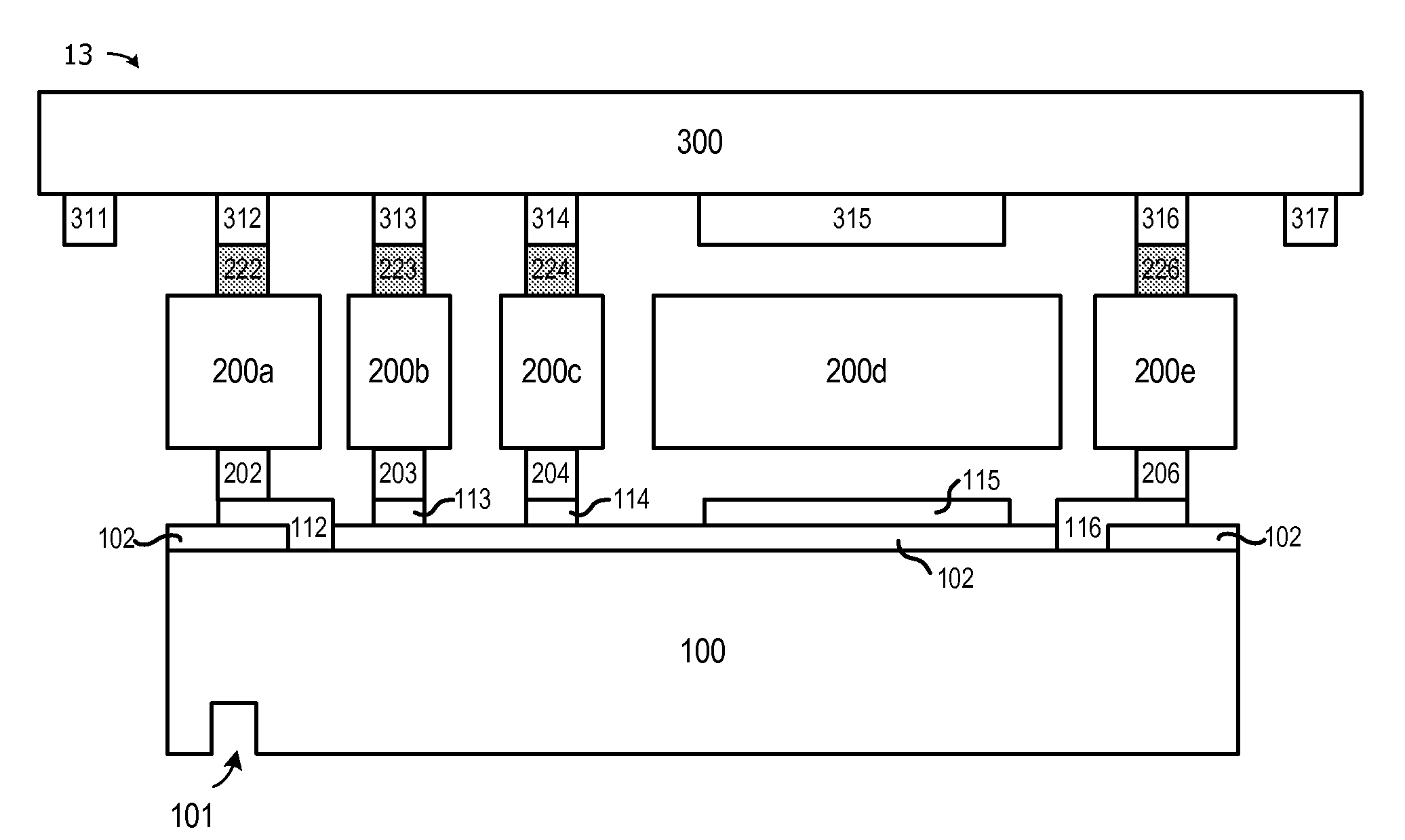

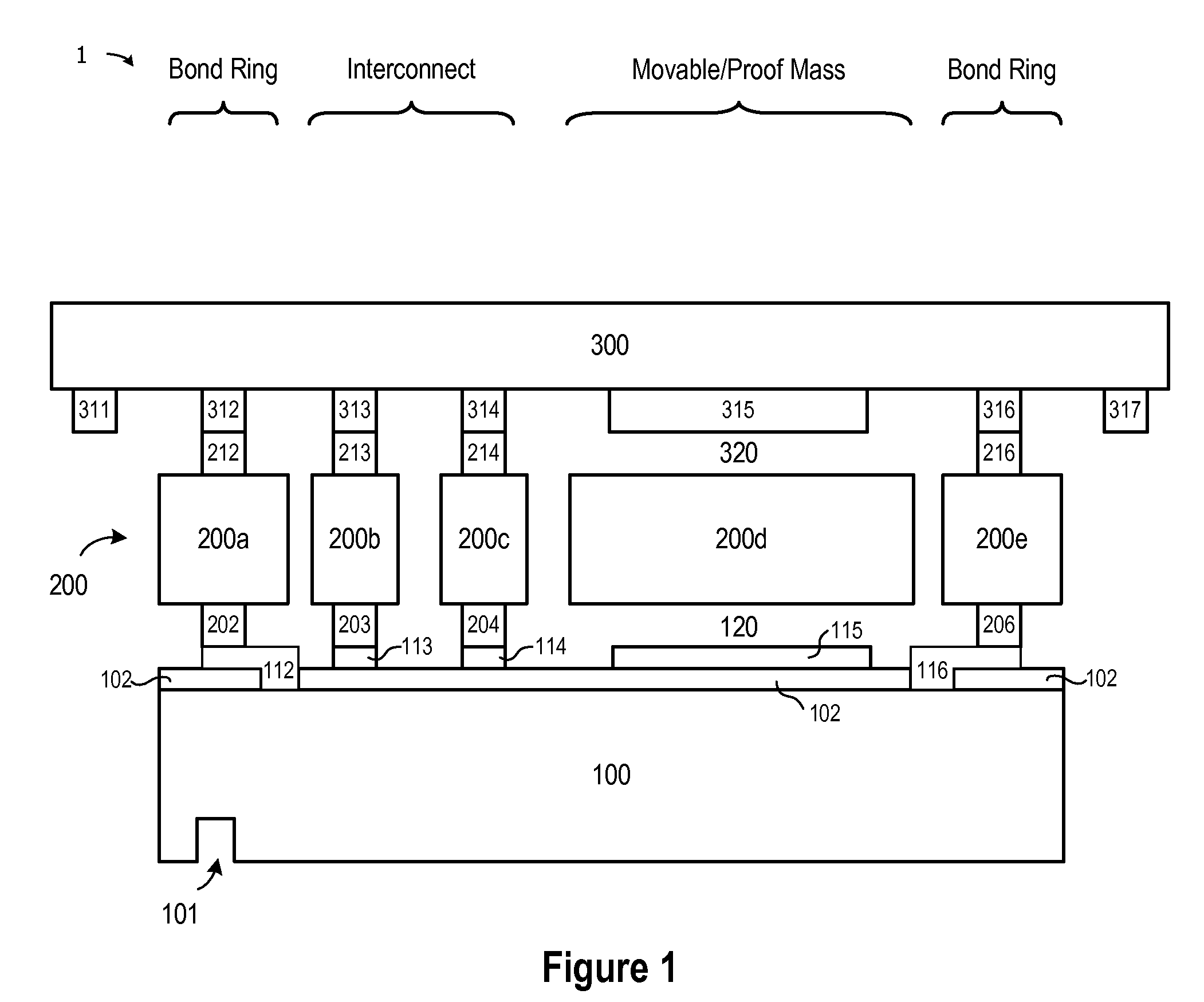

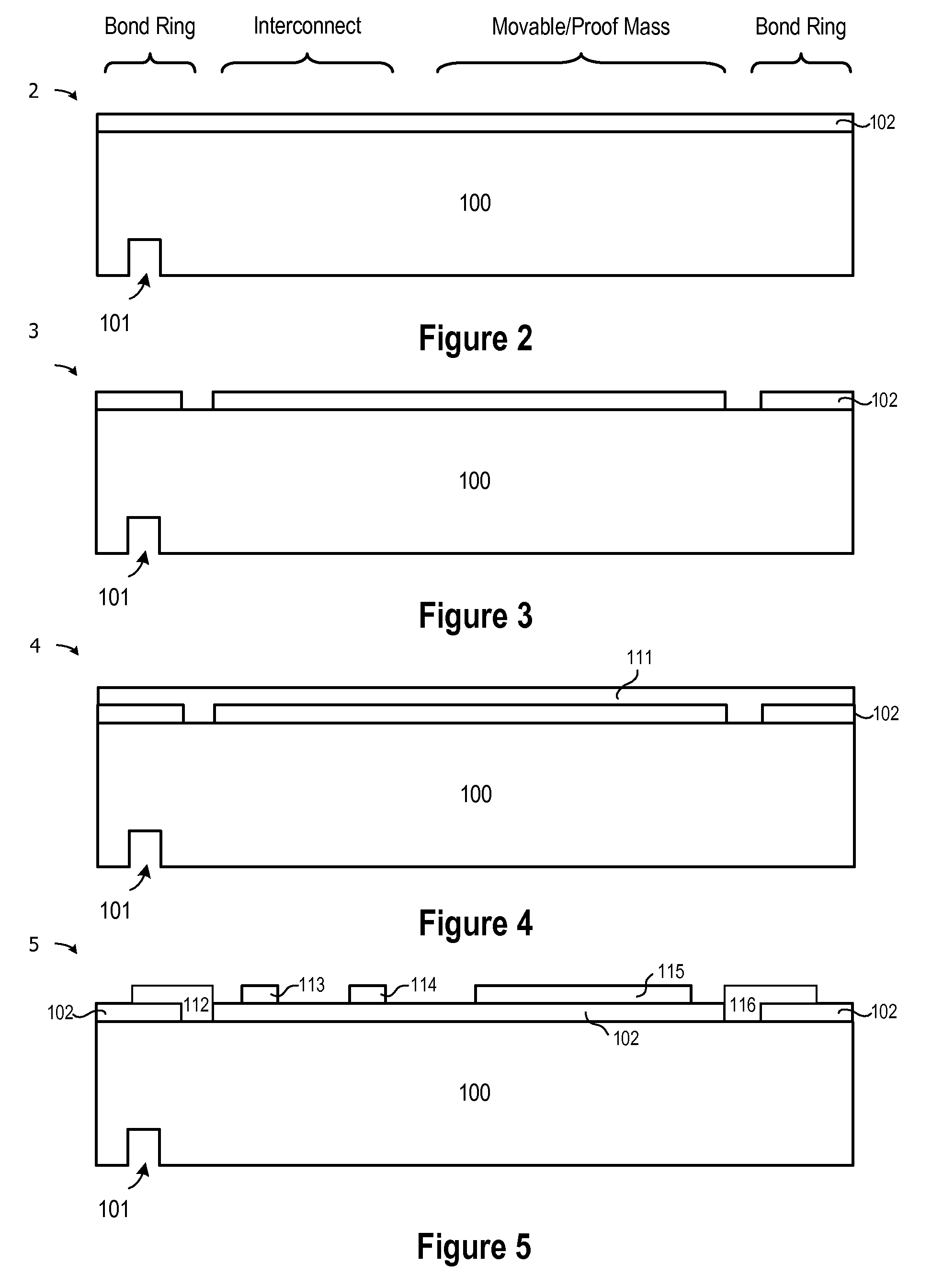

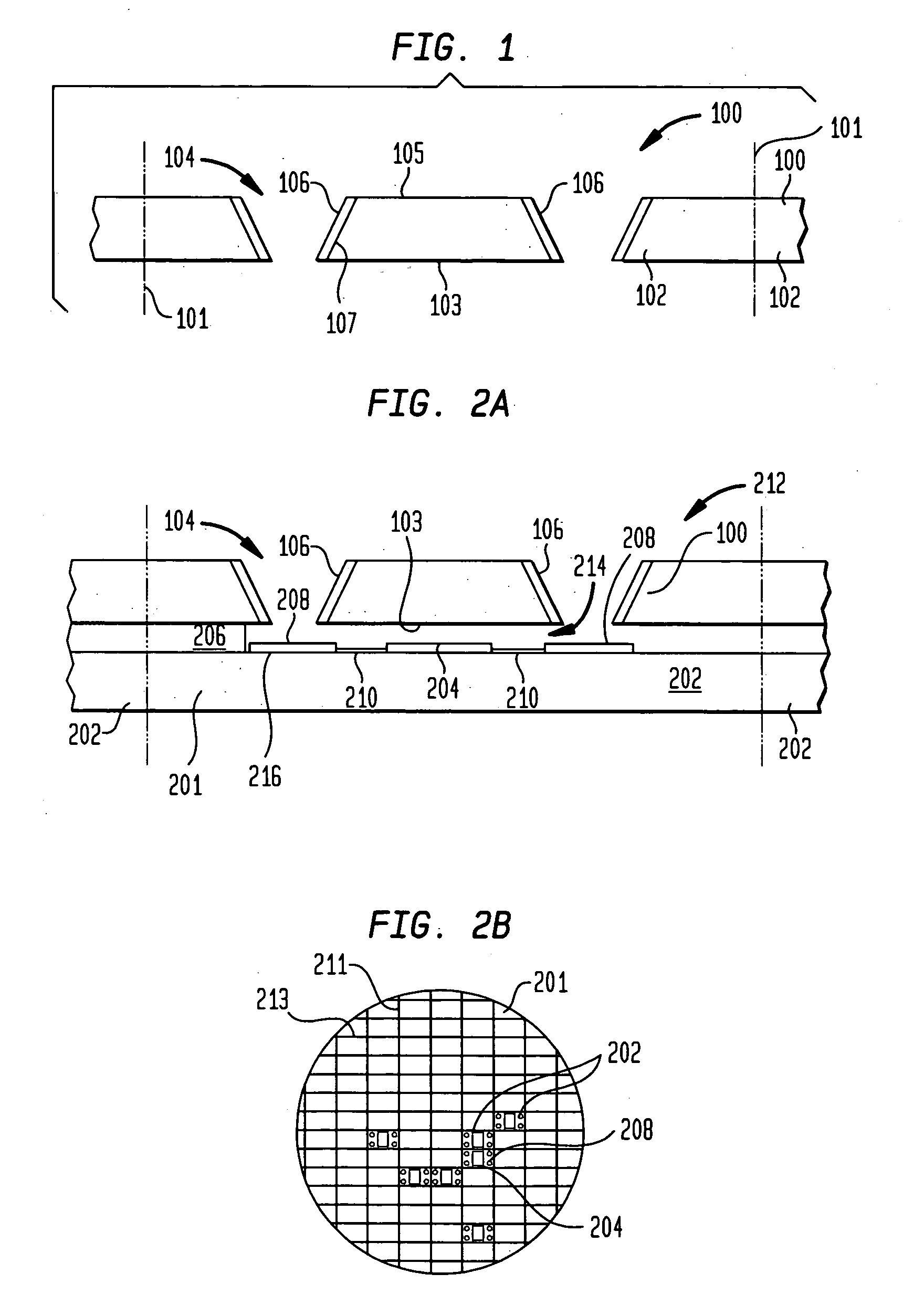

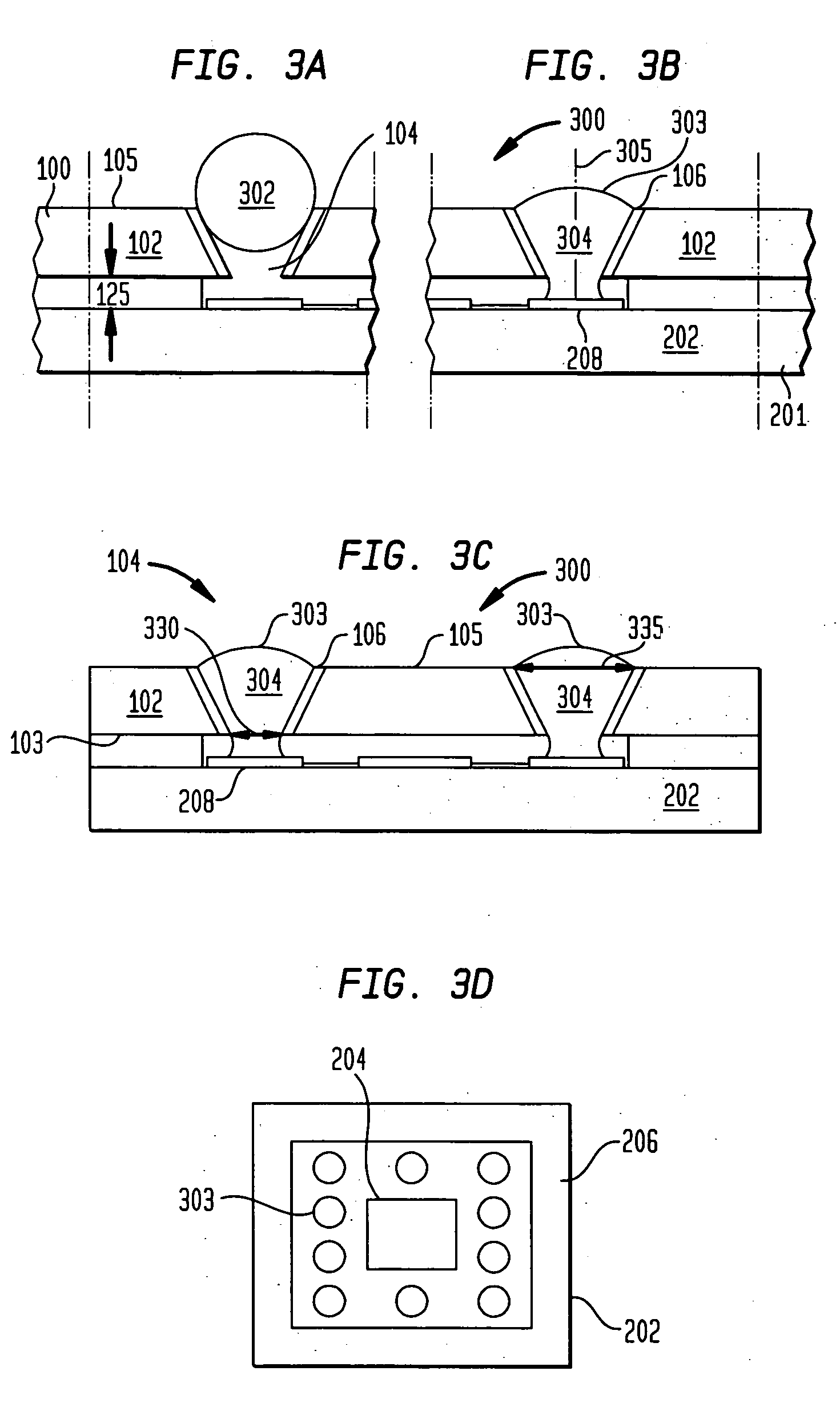

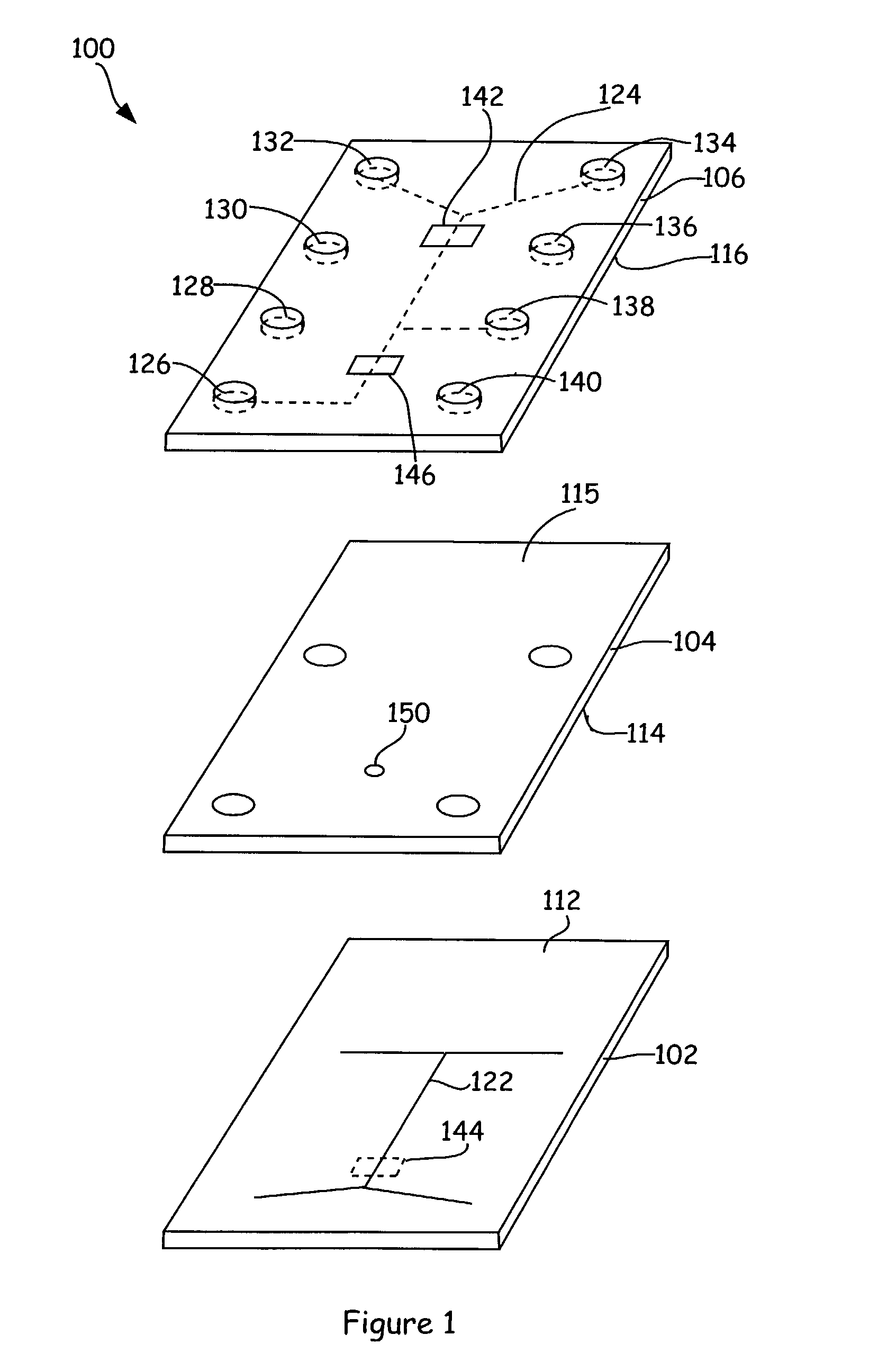

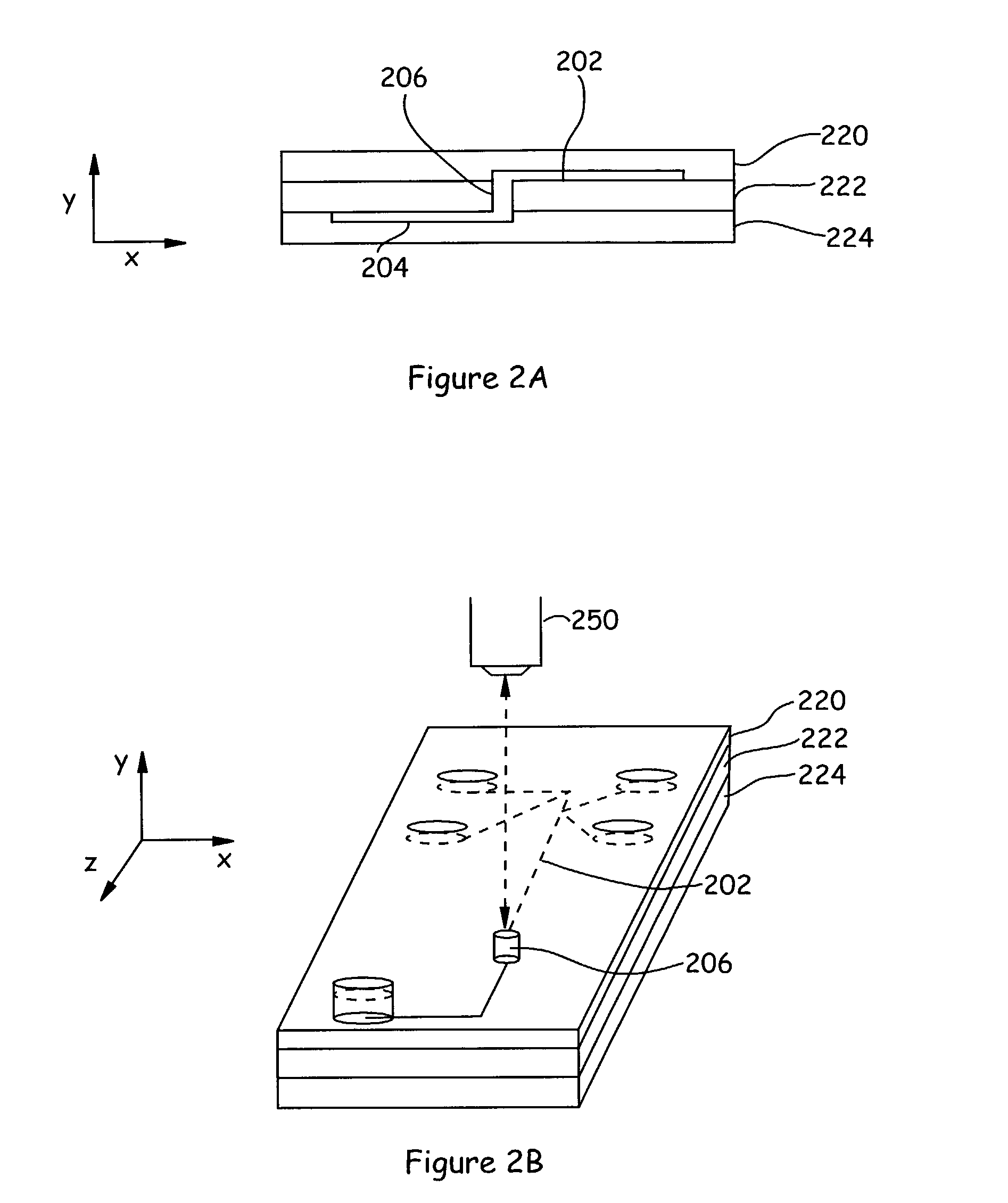

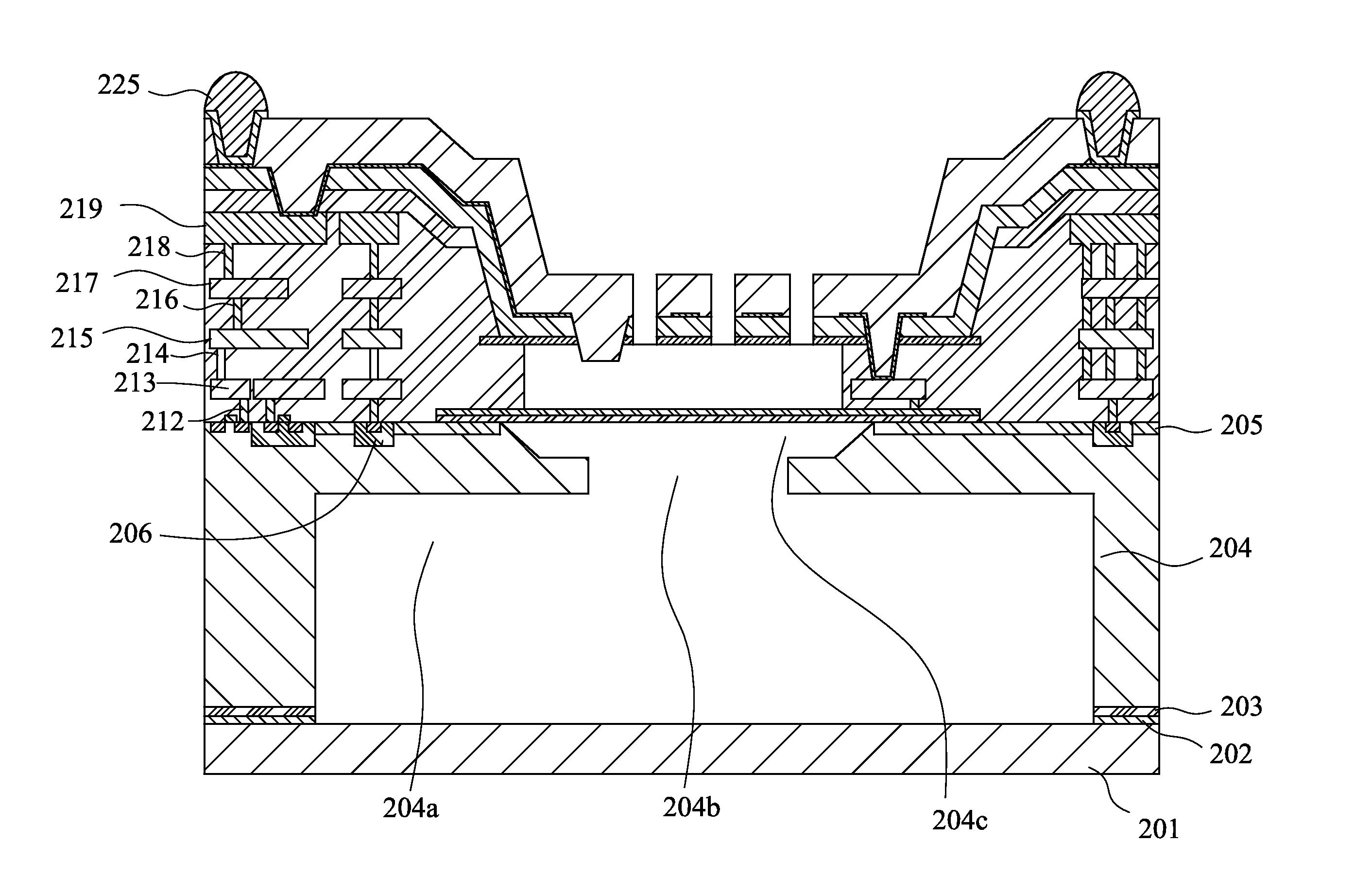

A method and apparatus are described for fabricating a high aspect ratio MEMS device by using metal thermocompression bonding to assemble a reference wafer (100), a bulk MEMS active wafer (200), and a cap wafer (300) to provide a proof mass (200d) formed from the active wafer with bottom and top capacitive sensing electrodes (115, 315) which are hermetically sealed from the ambient environment by sealing ring structures (112 / 202 / 200a / 212 / 312 and 116 / 206 / 200e / 216 / 316).

Owner:FREESCALE SEMICON INC

Method of fabrication of ai/ge bonding in a wafer packaging environment and a product produced therefrom

ActiveUS20060208326A1RobustHighly controllableAcceleration measurement using interia forcesSemiconductor/solid-state device detailsFoundryHermetic seal

A method of bonding of germanium to aluminum between two substrates to create a robust electrical and mechanical contact is disclosed. An aluminum-germanium bond has the following unique combination of attributes: (1) it can form a hermetic seal; (2) it can be used to create an electrically conductive path between two substrates; (3) it can be patterned so that this conduction path is localized; (4) the bond can be made with the aluminum that is available as standard foundry CMOS process. This has the significant advantage of allowing for wafer-level bonding or packaging without the addition of any additional process layers to the CMOS wafer.

Owner:INVENSENSE

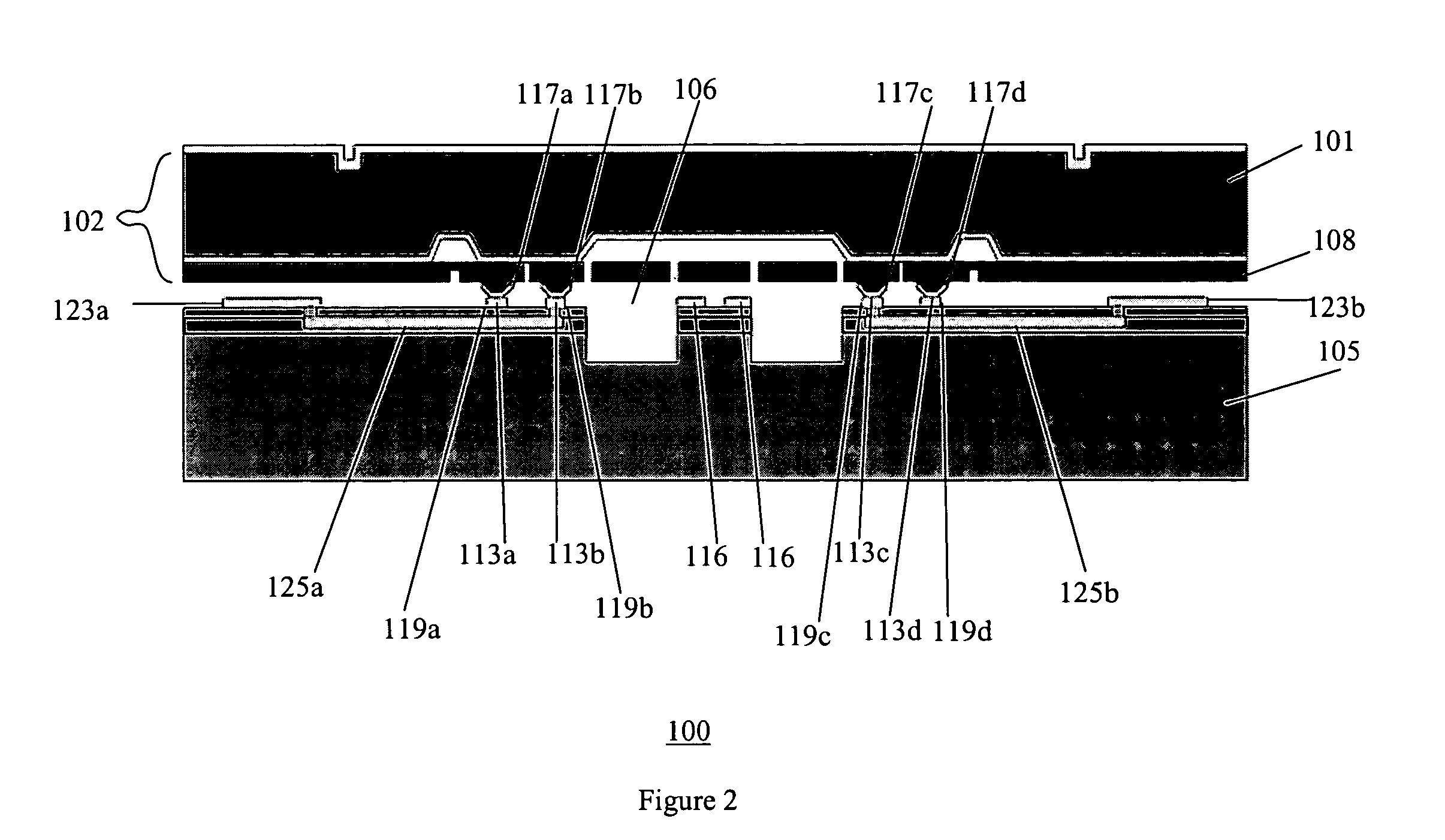

Methods for cmos-mems integrated devices with multiple sealed cavities maintained at various pressures

ActiveUS20120326248A1Good flexibilitySemiconductor/solid-state device manufacturingForming microstructural systemsCmos memsWafer bonding

A Microelectromechanical systems (MEMS) structure comprises a MEMS wafer. A MEMS wafer includes a handle wafer with cavities bonded to a device wafer through a dielectric layer disposed between the handle and device wafers. The MEMS wafer also includes a moveable portion of the device wafer suspended over a cavity in the handle wafer. Four methods are described to create two or more enclosures having multiple gas pressure or compositions on a single substrate including, each enclosure containing a moveable portion. The methods include: A. Forming a secondary sealed enclosure, B. Creating multiple ambient enclosures during wafer bonding, C. Creating and breaching an internal gas reservoir, and D. Forming and subsequently sealing a controlled leak / breach into the enclosure.

Owner:INVENSENSE

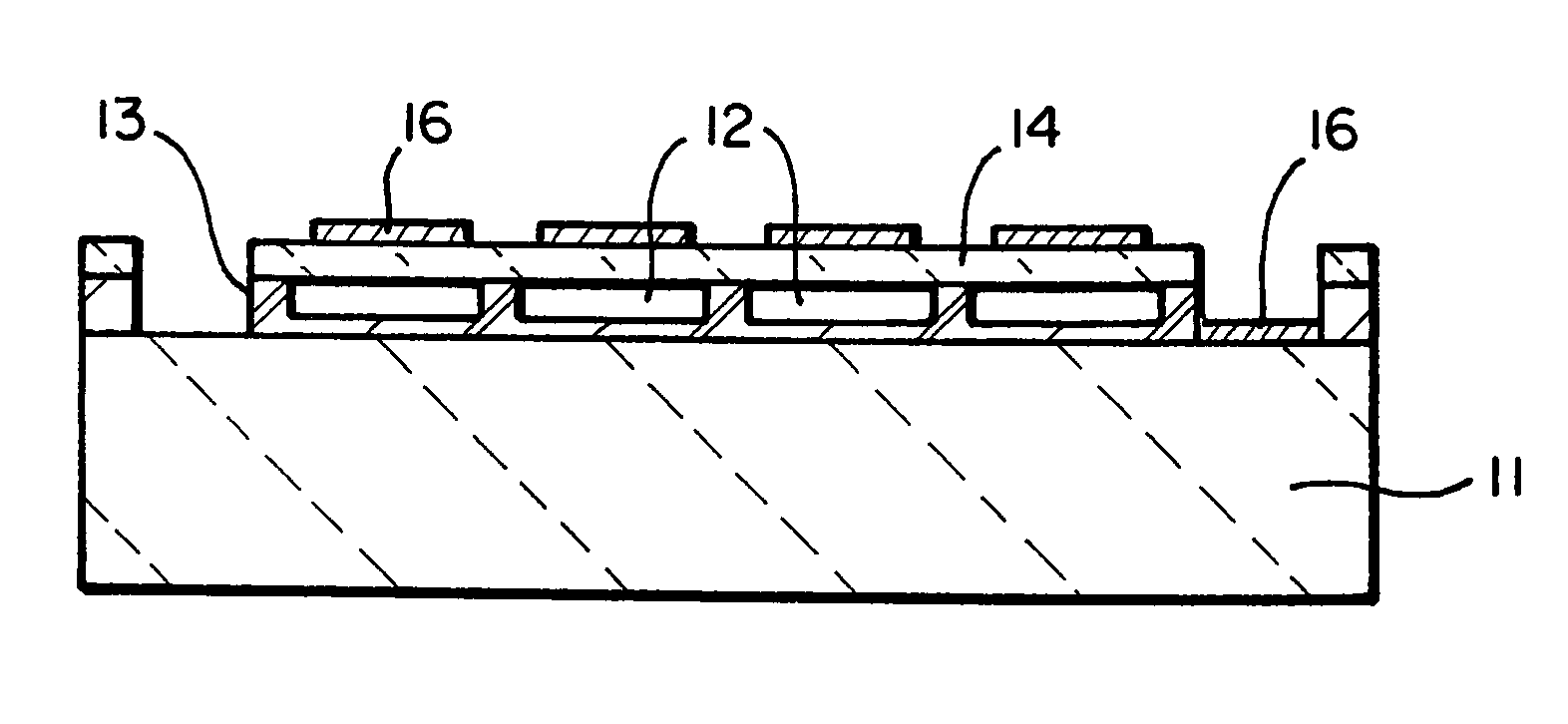

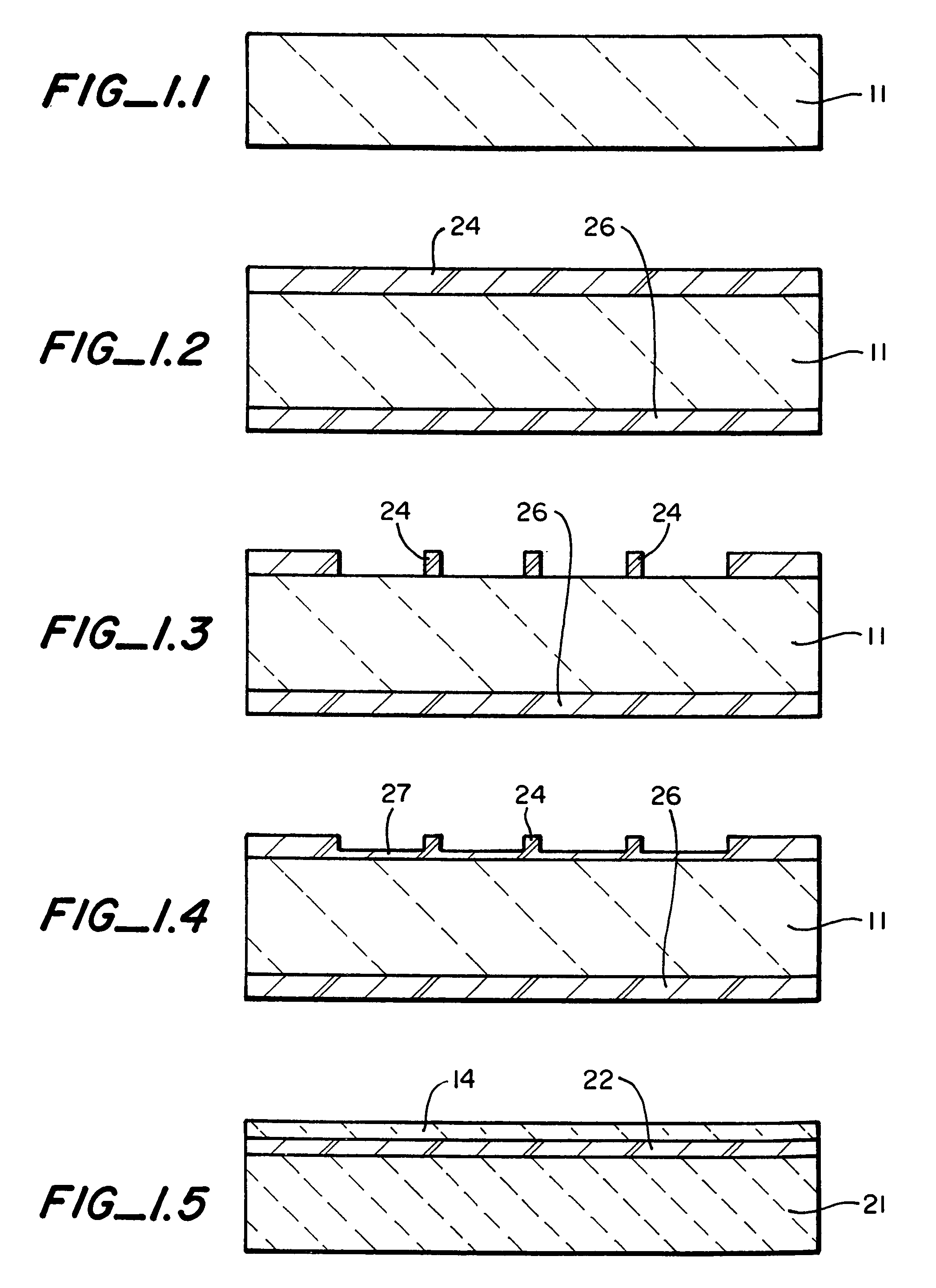

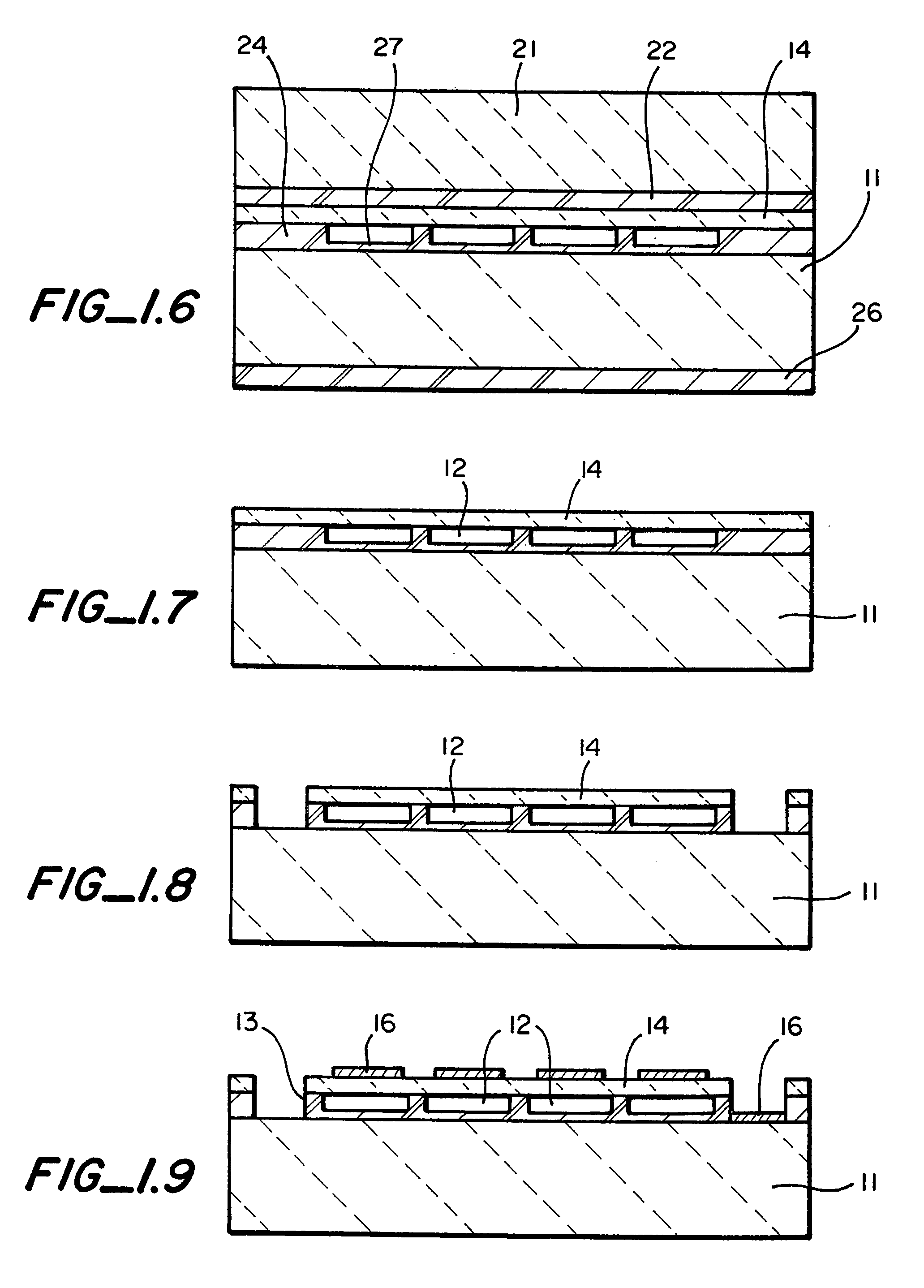

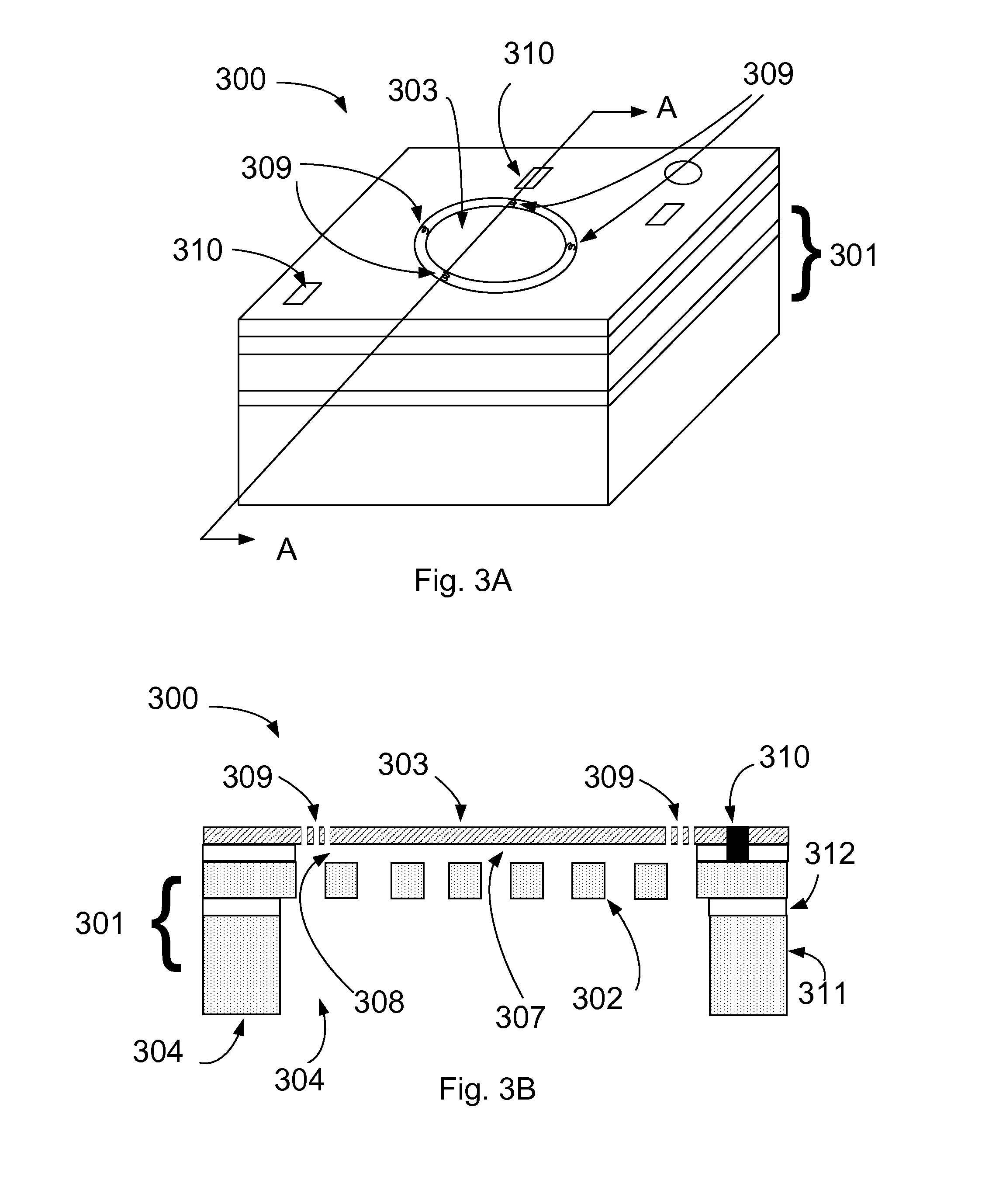

Method of manufacturing vibrating micromechanical structures

A method for fabrication of single crystal silicon micromechanical resonators using a two-wafer process, including either a Silicon-on-insulator (SOI) or insulating base and resonator wafers, wherein resonator anchors, a capacitive air gap, isolation trenches, and alignment marks are micromachined in an active layer of the base wafer; the active layer of the resonator wafer is bonded directly to the active layer of the base wafer; the handle and dielectric layers of the resonator wafer are removed; viewing windows are opened in the active layer of the resonator wafer; masking the single crystal silicon semiconductor material active layer of the resonator wafer with photoresist material; a single crystal silicon resonator is machined in the active layer of the resonator wafer using silicon dry etch micromachining technology; and the photoresist material is subsequently dry stripped.

Owner:HONEYWELL INT INC

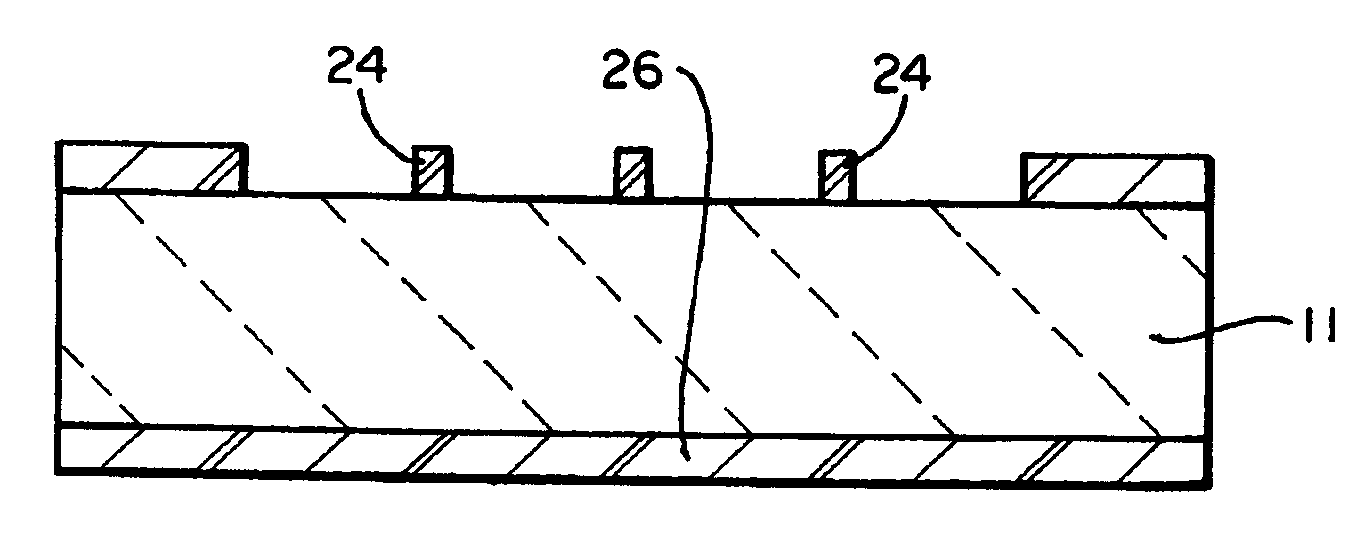

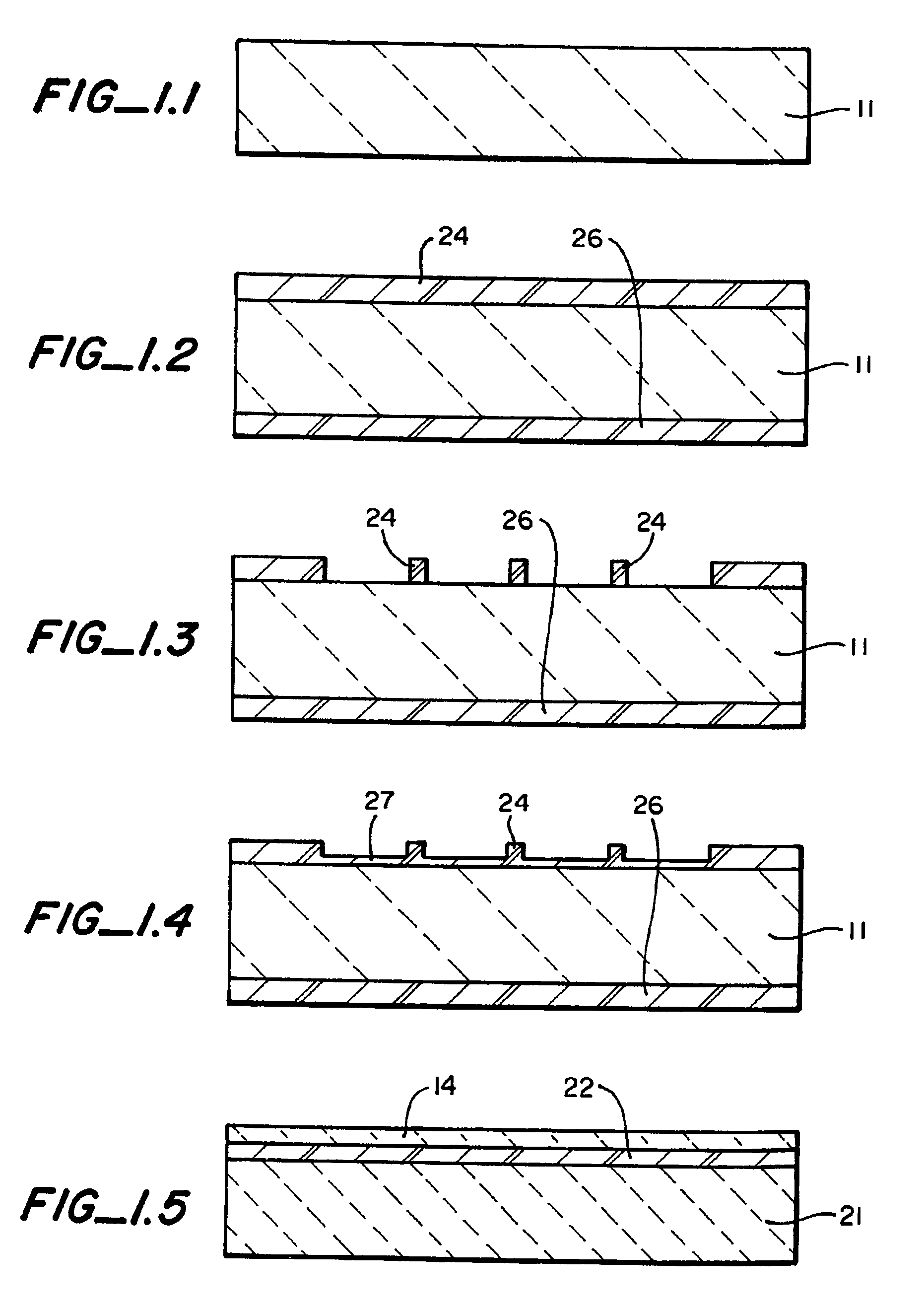

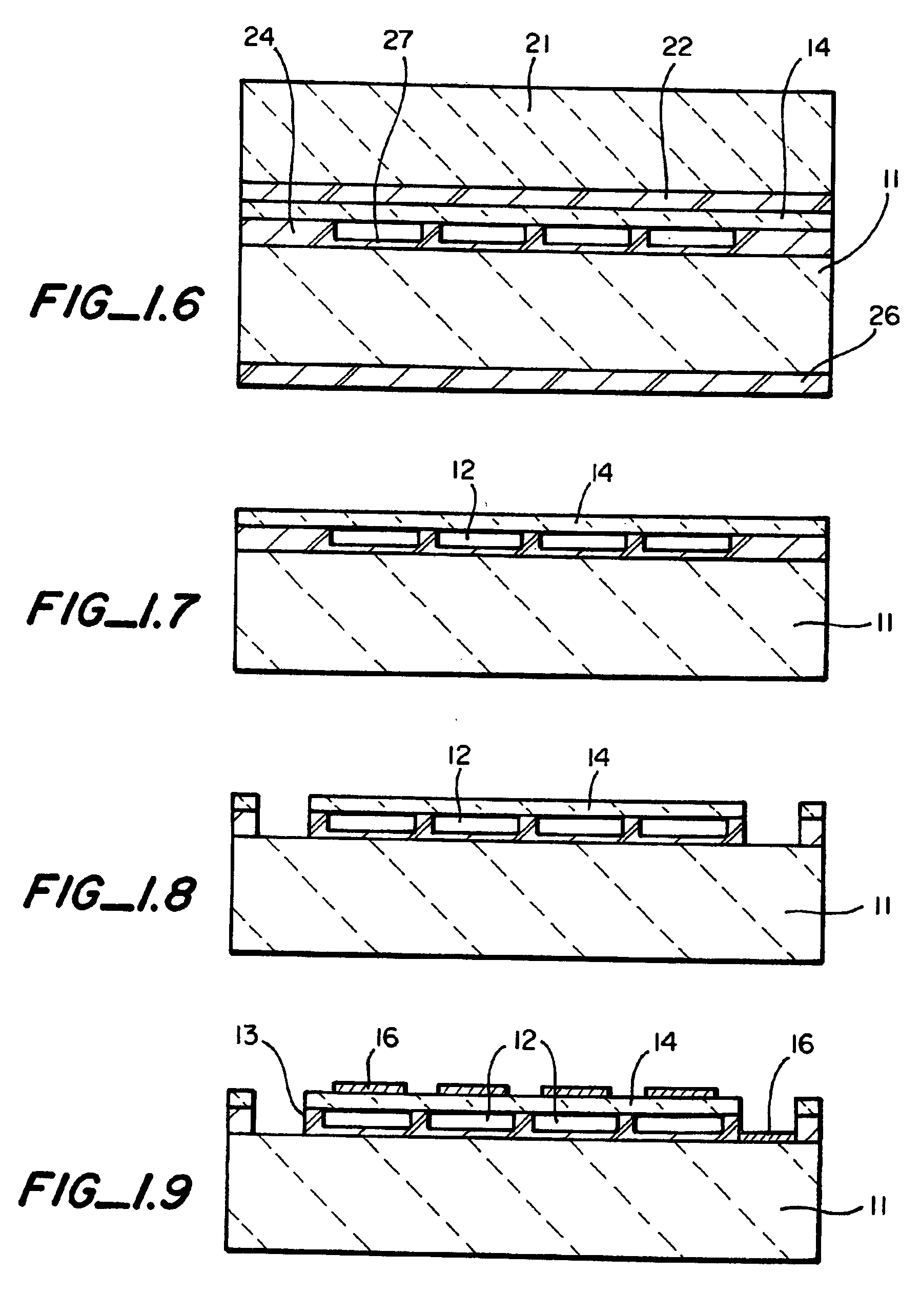

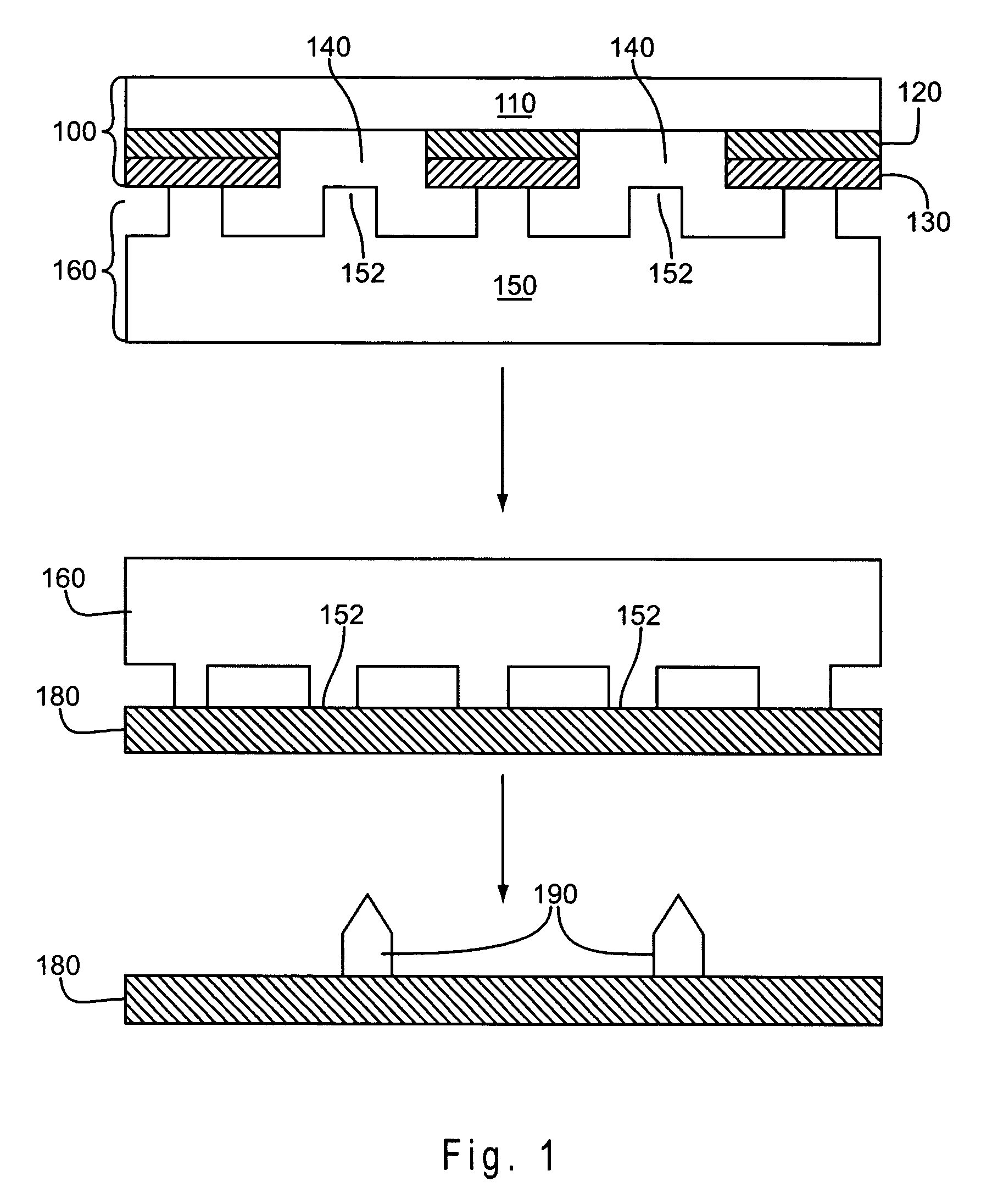

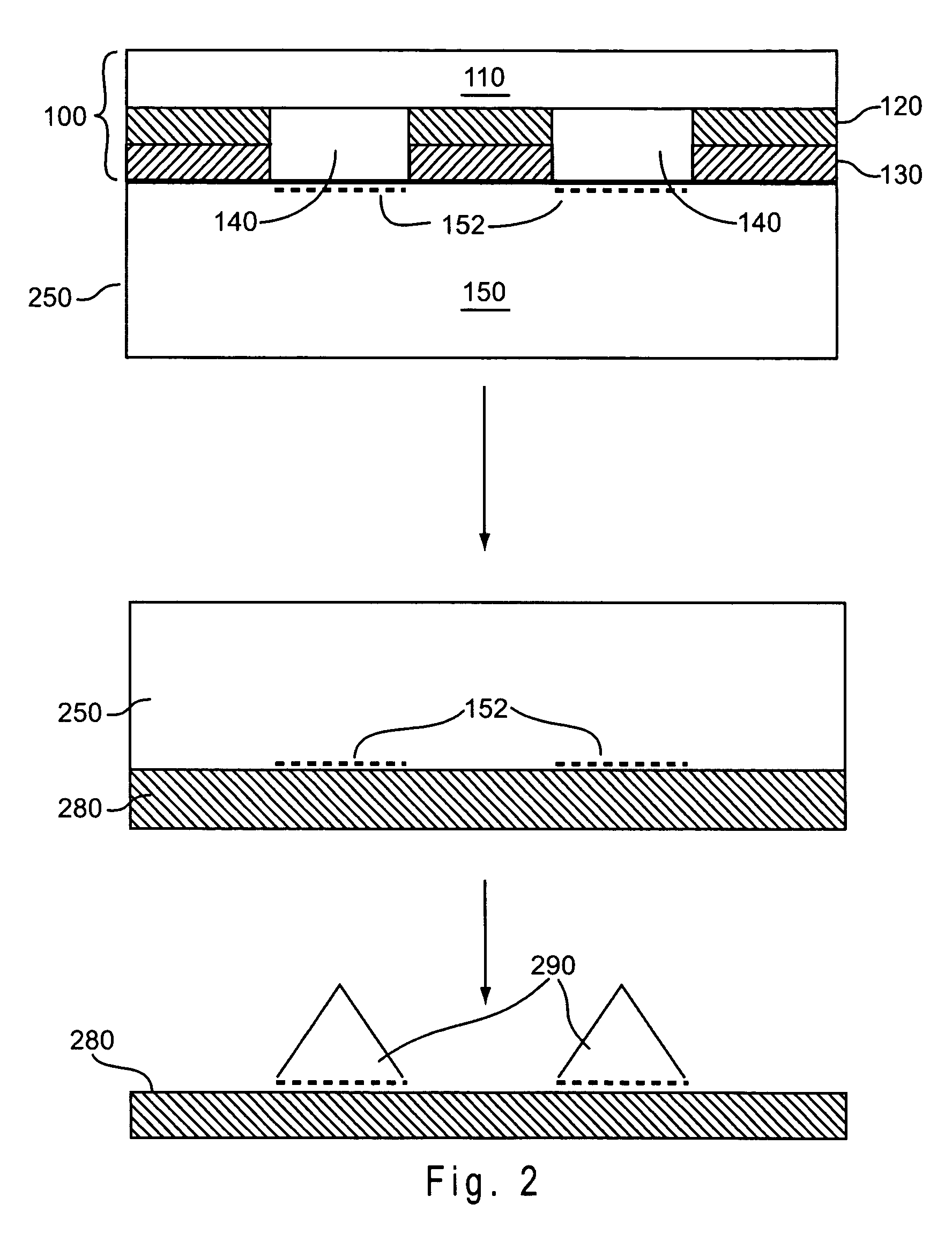

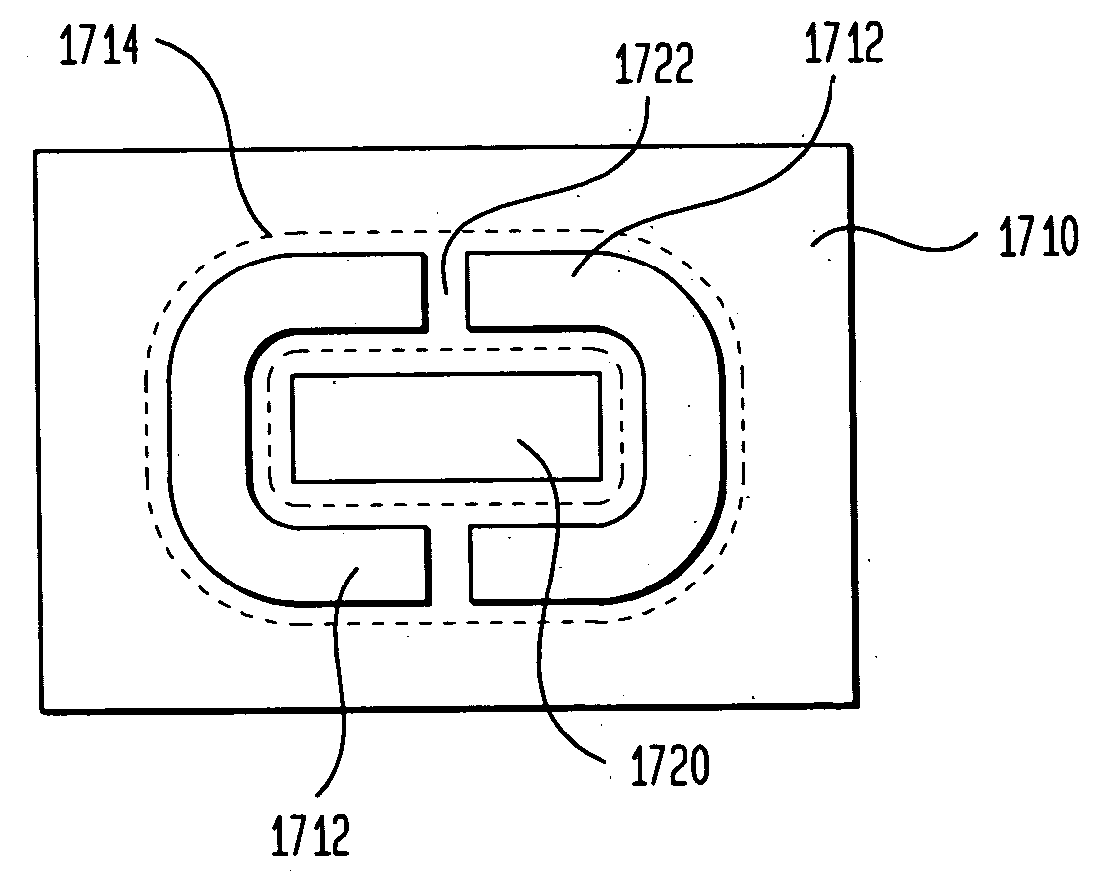

Micromachined ultrasonic transducers and method of fabrication

InactiveUS20040085858A1Decorative surface effectsSemiconductor/solid-state device manufacturingPMUTSilicon nitride

There is described a micromachined ultrasonic transducers (MUTS) and a method of fabrication. The membranes of the transducers are fusion bonded to cavities to form cells. The membranes are formed on a wafer of sacrificial material. This permits handling for fusions bonding. The sacrificial material is then removed to leave the membrane. Membranes of silicon, silicon nitride, etc. can be formed on the sacrificial material. Also described are cMUTs, pMUTs and mMUTs.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

Micromachined ultrasonic transducers and method of fabrication

InactiveUS6958255B2Piezoelectric/electrostrictive device manufacture/assemblySubsonic/sonic/ultrasonic wave measurementPMUTSilicon nitride

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

Decal transfer lithography

ActiveUS7662545B2Photography auxillary processesPhotosensitive materialsElastomerLithographic artist

A method of making a microstructure includes selectively activating a portion of a surface of a silicon-containing elastomer, contacting the activated portion with a substance, and bonding the activated portion and the substance, such that the activated portion of the surface and the substance in contact with the activated portion are irreversibly attached. The selective activation may be accomplished by positioning a mask on the surface of the silicon-containing elastomer, and irradiating the exposed portion with UV radiation.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

Method of fabricating microelectromechanical systems and devices having trench isolated contacts

InactiveUS6936491B2Acceleration measurement using interia forcesSolid-state devicesEngineeringMicroelectromechanical systems

There are many inventions described and illustrated herein. In one aspect, the present invention is directed to a MEMS device, and technique of fabricating or manufacturing a MEMS device, having mechanical structures encapsulated in a chamber prior to final packaging and a contact area disposed at least partially outside the chamber. The contact area is electrically isolated from nearby electrically conducting regions by way of dielectric isolation trench that is disposed around the contact area. The material that encapsulates the mechanical structures, when deposited, includes one or more of the following attributes: low tensile stress, good step coverage, maintains its integrity when subjected to subsequent processing, does not significantly and / or adversely impact the performance characteristics of the mechanical structures in the chamber (if coated with the material during deposition), and / or facilitates integration with high-performance integrated circuits. In one embodiment, the material that encapsulates the mechanical structures is, for example, silicon (polycrystalline, amorphous or porous, whether doped or undoped), silicon carbide, silicon-germanium, germanium, or gallium-arsenide.

Owner:ROBERT BOSCH GMBH

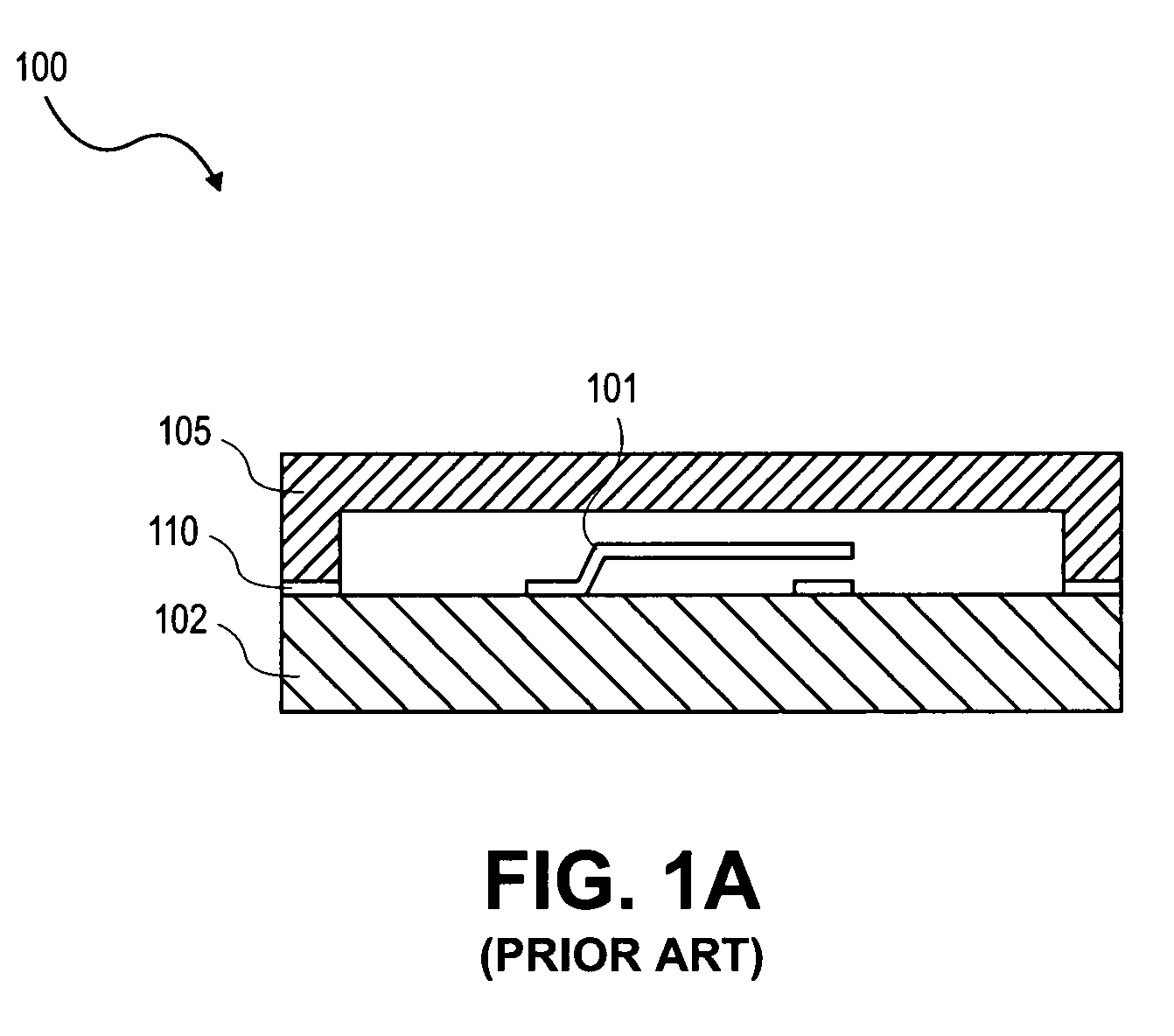

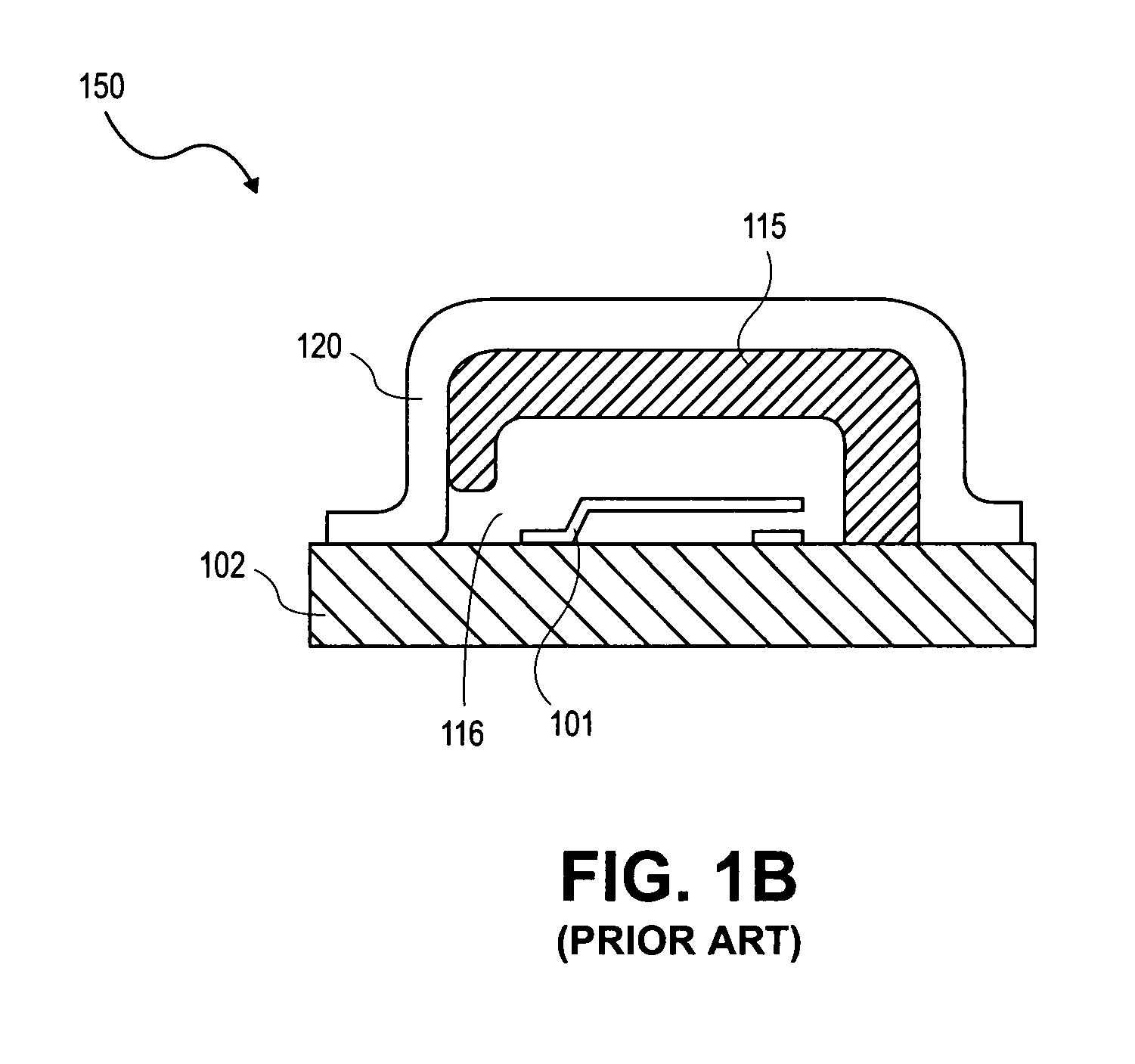

Microphone System with Silicon Microphone Secured to Package Lid

InactiveUS20080175425A1Piezoelectric/electrostrictive microphonesSemiconductor electrostatic transducersEngineeringSilicon

A microphone system has a base with at least one electrical port for electrically communicating with an external device. The system also has a solid metal lid coupled to the base to form an internal chamber, and a silicon microphone secured to the lid within the chamber. The lid has an aperture for receiving an audible signal, while the microphone is electrically connected to the electrical port of the base.

Owner:ANALOG DEVICES INC

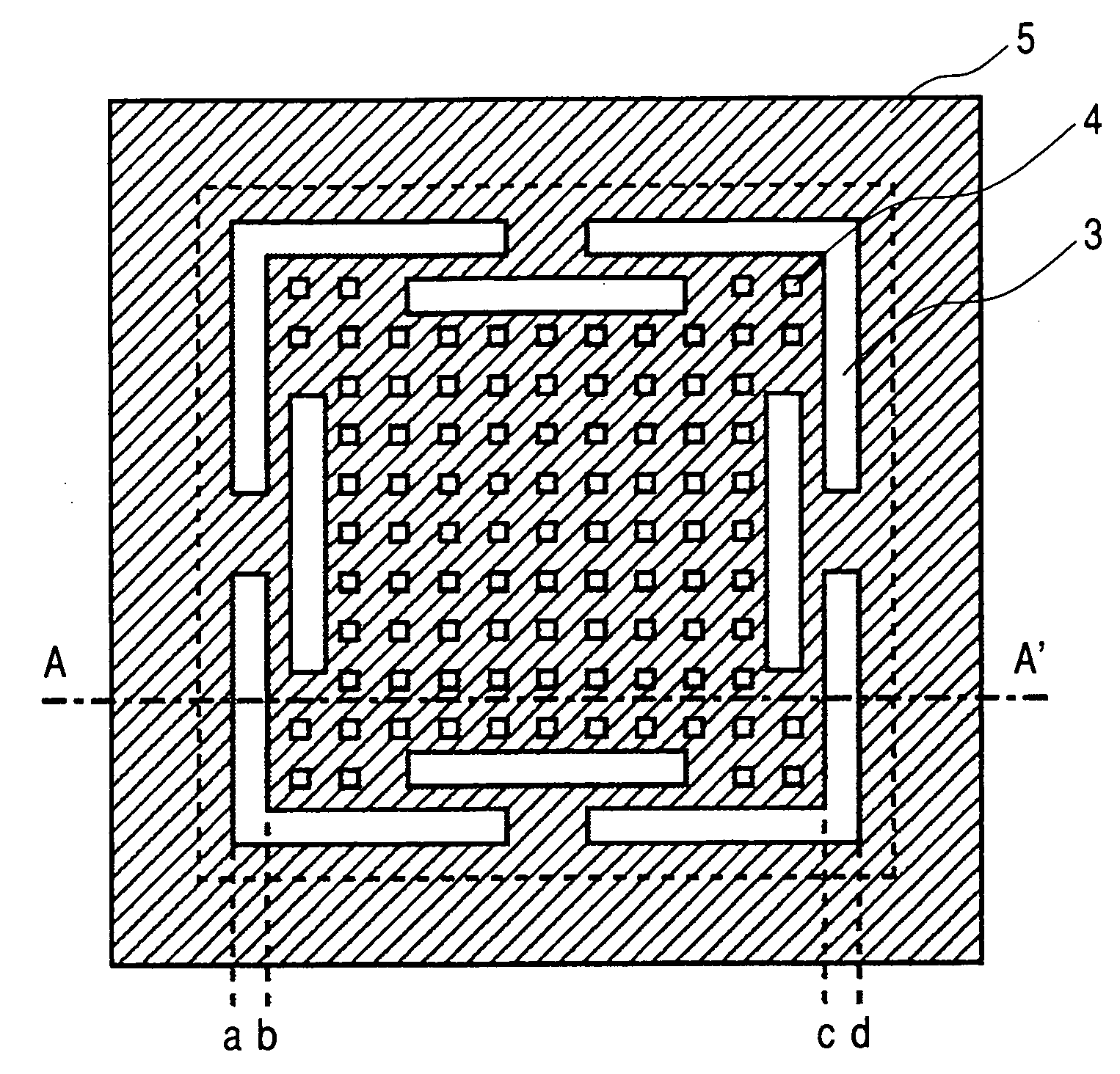

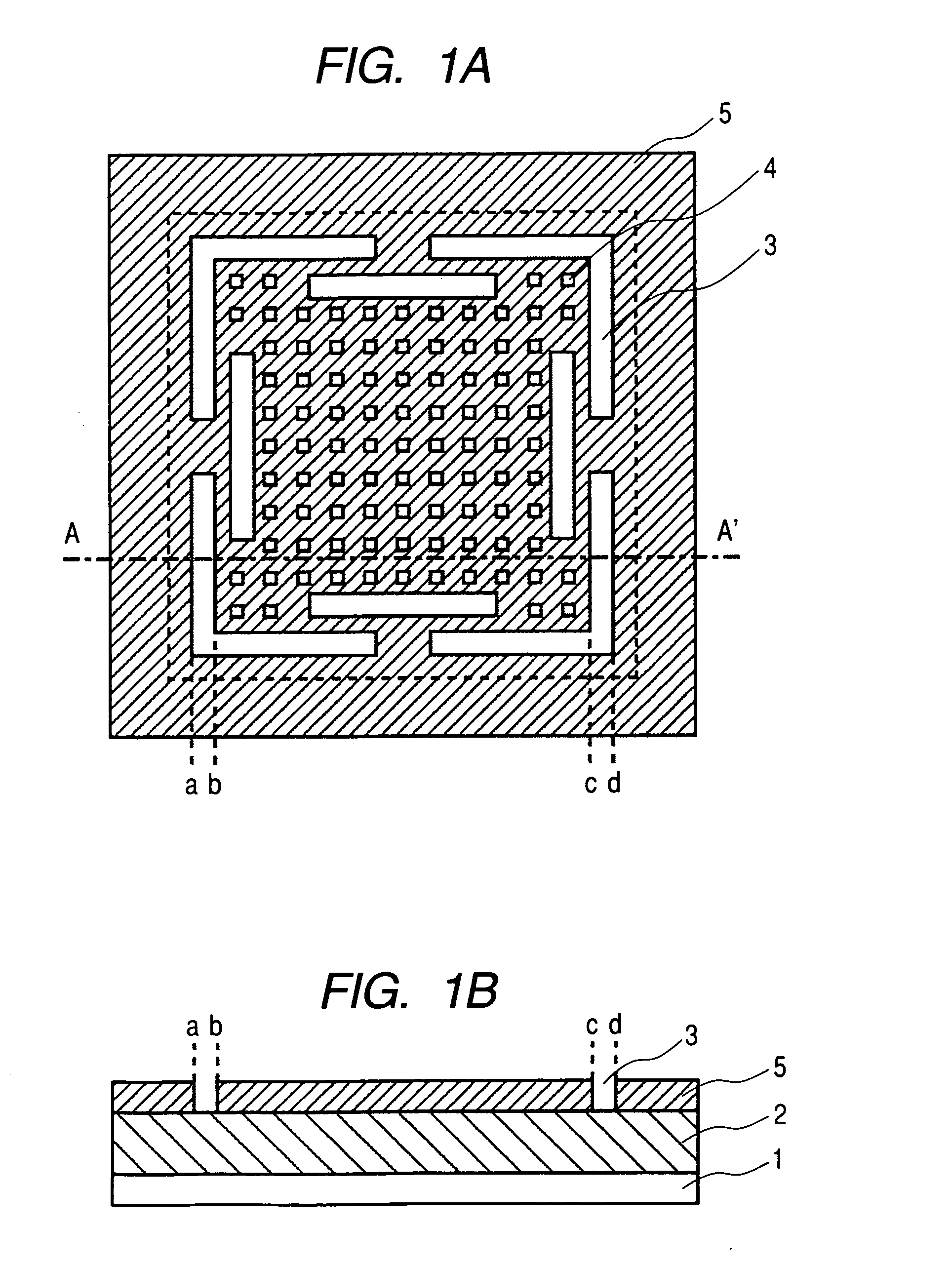

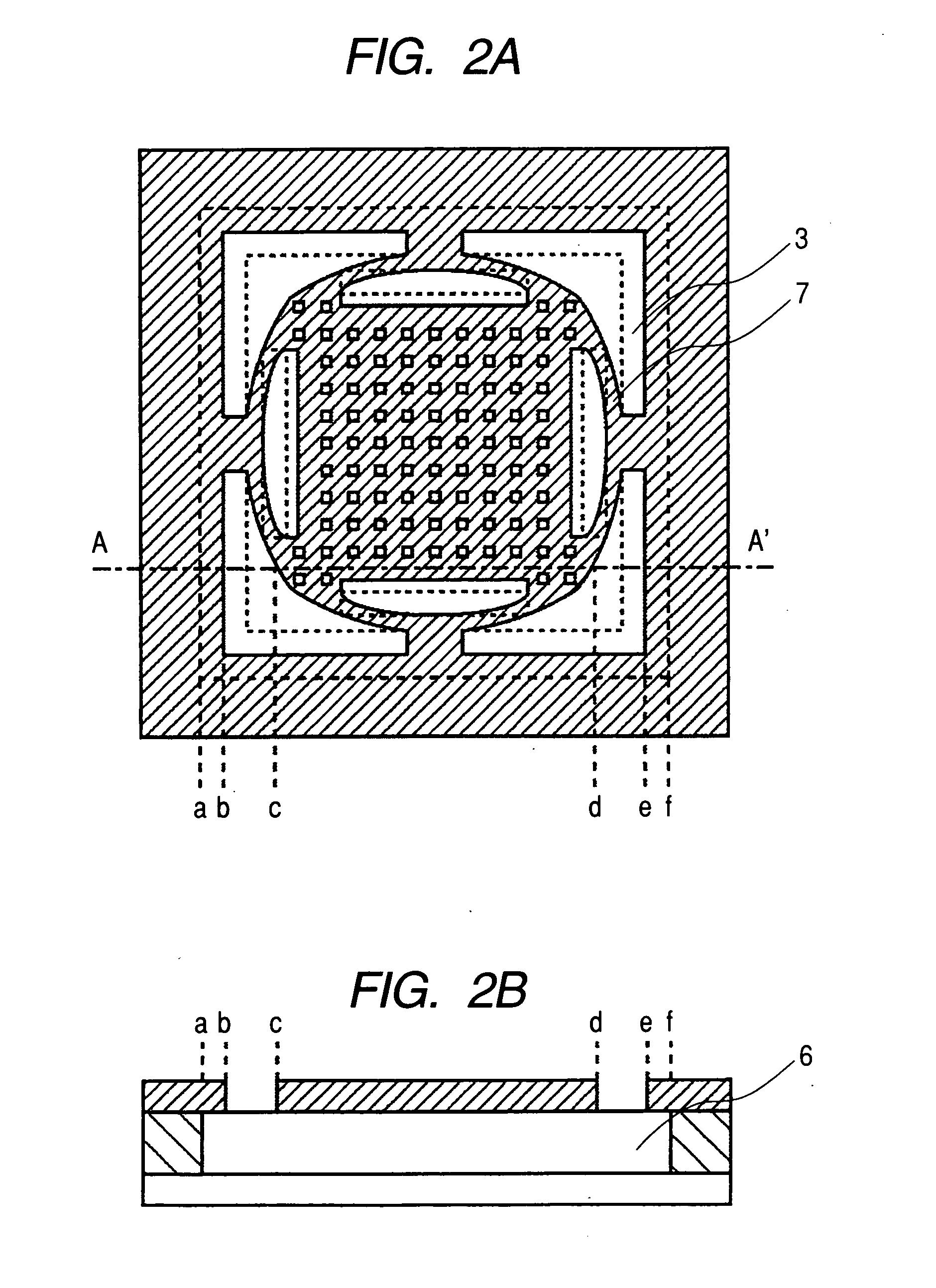

MEMS device and manufacturing process thereof

InactiveUS20070190680A1Relaxation stressSemiconductor/solid-state device manufacturingForming microstructural systemsEngineeringWafer bonding

MEMS devices require special cavity formation and sealing steps such as wafer bonding which reduce the yield and increase the cost. In addition, it is difficult to form a cavity of a large area by the LSI process owing to a residual stress of a sealing film which will be a lid. This leads to a difficulty of realizing an integrated MEMS having a MEMS and a high-performance LSI mounted on one substrate. The lid (or diaphragm) covering therewith a cavity is equipped with slits or beams. During the formation of the cavity, the slits are deformed to absorb and relax the internal stress of the thin sealing film. Then, the cavity is sealed by filling the open portions of the film overlying the cavity between the inside and outside of the cavity. The cavity is formed by removing a portion of the interlayer film of LSI multilevel interconnects and the lid is made of a LSI-process thin film.

Owner:HITACHI LTD

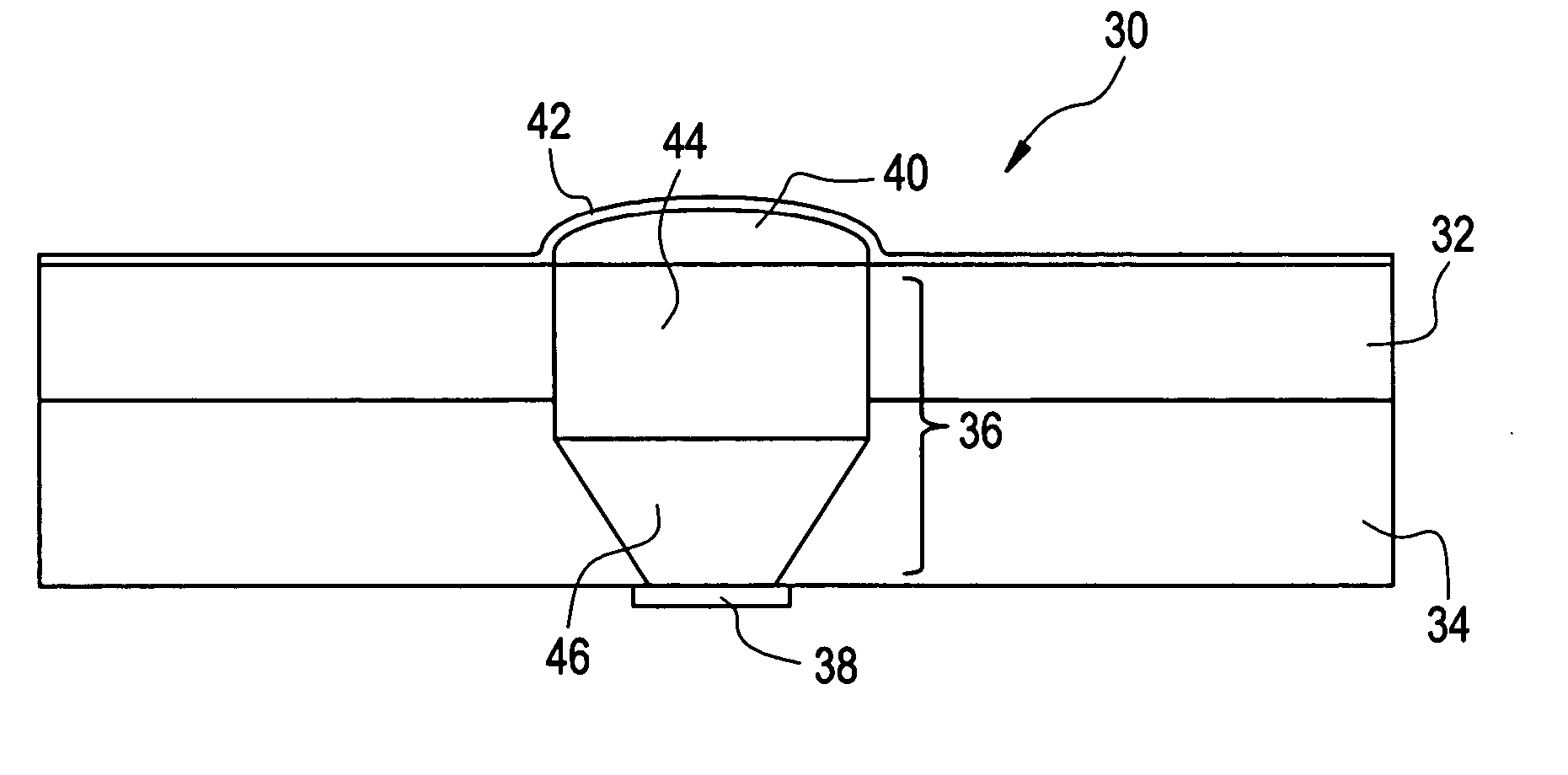

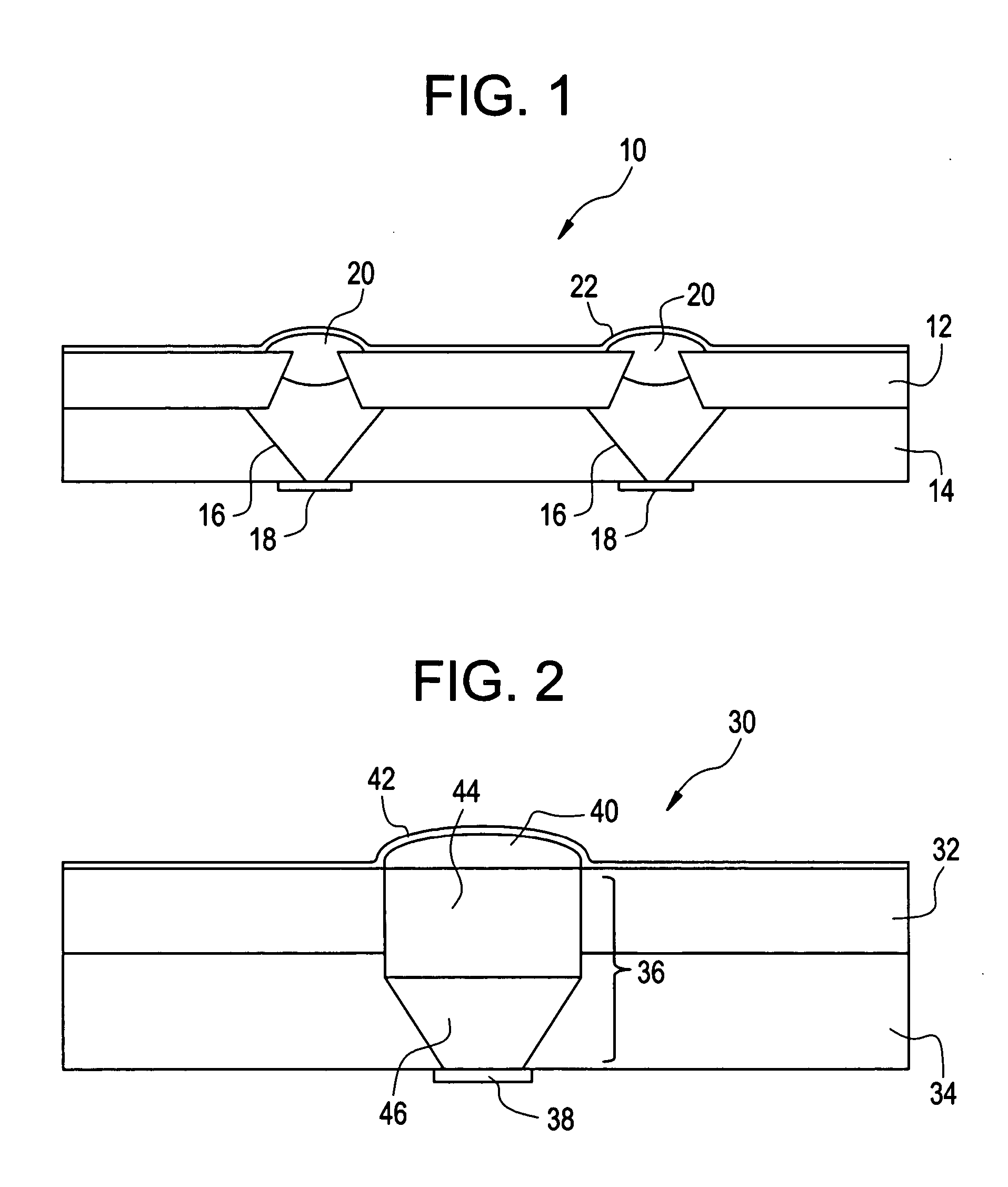

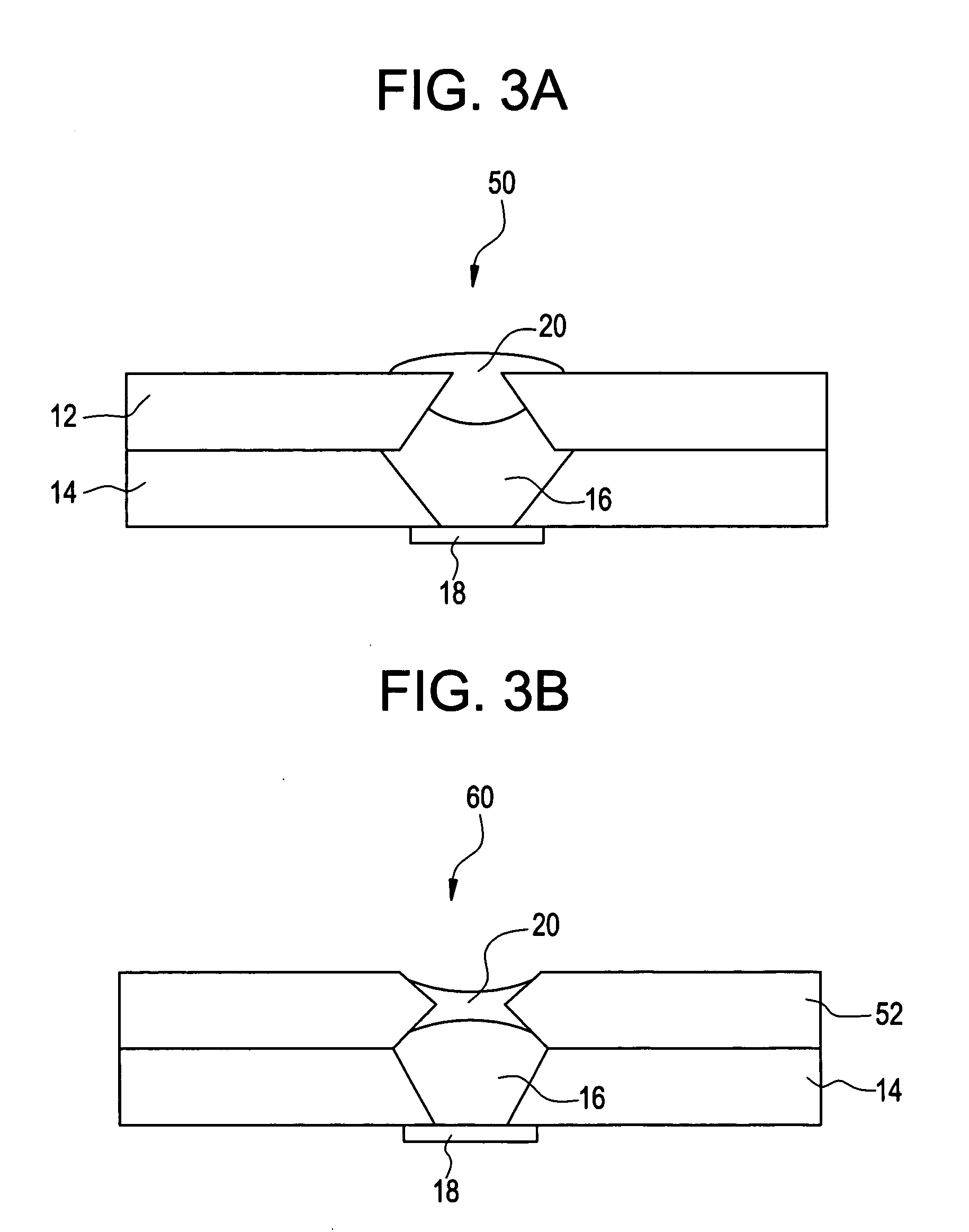

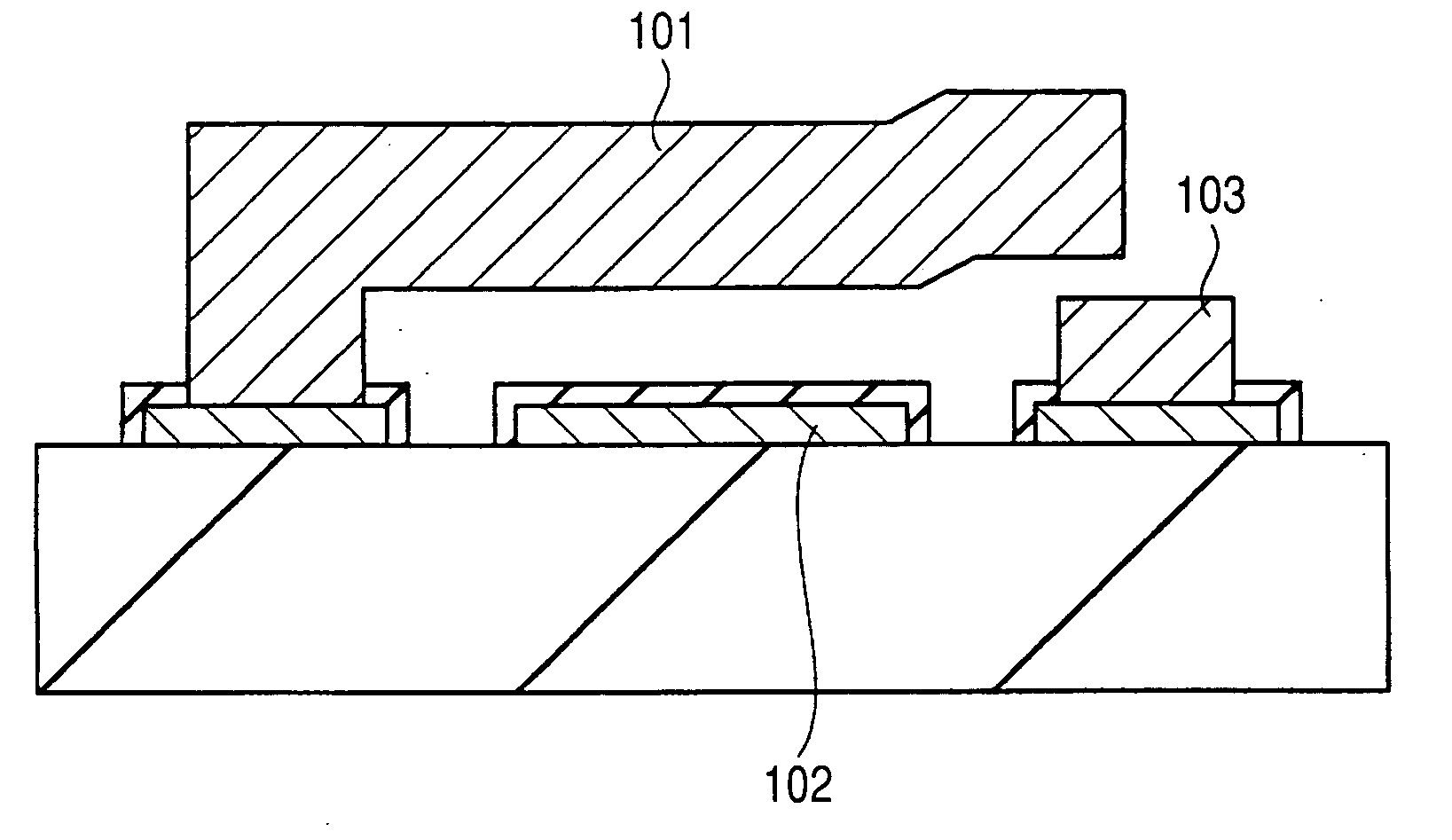

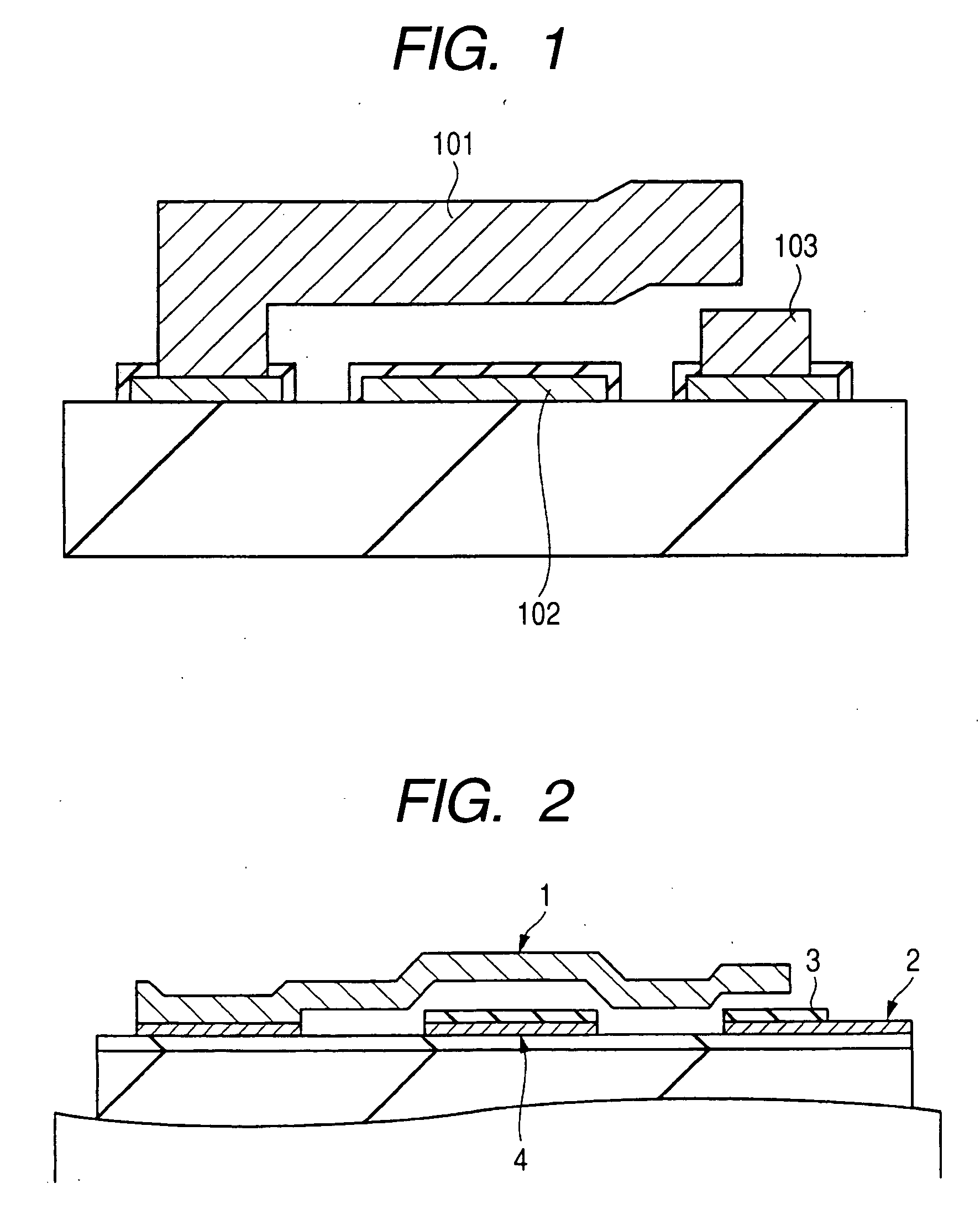

Structure and method of making capped chips including vertical interconnects having stud bumps engaged to surfaces of said caps

InactiveUS20050067688A1Impedence networksSemiconductor/solid-state device detailsEngineeringBiomedical engineering

A capped chip is provided which includes a chip and a cap member, the chip having a front surface and a plurality of bond pads exposed at the front surface, the cap member having a bottom surface facing the front surface of the chip and having a top surface opposite the front surface. A plurality of through holes extend from the bottom surface of the cap member to the top surface. The capped chip assembly further includes a plurality of metallic interconnects extending from the bond pads at least partially through the through holes, the metallic interconnects including stud bumps joined to the bond pads, the stud bumps contacting and engaging at least one of (i) the top surface of the cap member surrounding the through holes and (ii) inner surfaces of the through holes.

Owner:TESSERA INC

Heterogeneously integrated microsystem-on-a-chip

ActiveUS20070158787A1Semiconductor/solid-state device detailsSolid-state devicesCost effectivenessMiniaturization

A microsystem-on-a-chip comprises a bottom wafer of normal thickness and a series of thinned wafers can be stacked on the bottom wafer, glued and electrically interconnected. The interconnection layer comprises a compliant dielectric material, an interconnect structure, and can include embedded passives. The stacked wafer technology provides a heterogeneously integrated, ultra-miniaturized, higher performing, robust and cost-effective microsystem package. The highly integrated microsystem package, comprising electronics, sensors, optics, and MEMS, can be miniaturized both in volume and footprint to the size of a bottle-cap or less.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

Structure and self-locating method of making capped chips

InactiveUS20050082654A1Impedence networksSemiconductor/solid-state device detailsEngineeringInterconnection

Owner:TESSERA INC

Low temperature methods for hermetically sealing reservoir devices

Methods are provided for hermetically sealing an opening in a reservoir of a containment device. The method comprises applying a polymeric material to an opening in a reservoir of a containment device, the reservoir comprising reservoir contents (such as a drug or a sensor) to be hermetically isolated within the reservoir, the applied polymeric material closing off the opening and forming a temporary seal; and adhering a hermetic sealing material onto the polymeric material to hermetically seal the opening. The reservoir can be a micro-reservoir. The containment device can comprises an array of two or more of reservoirs, and the method comprises hermetically sealing each of the two or more reservoirs.

Owner:MICROCHIPS BIOTECH INC

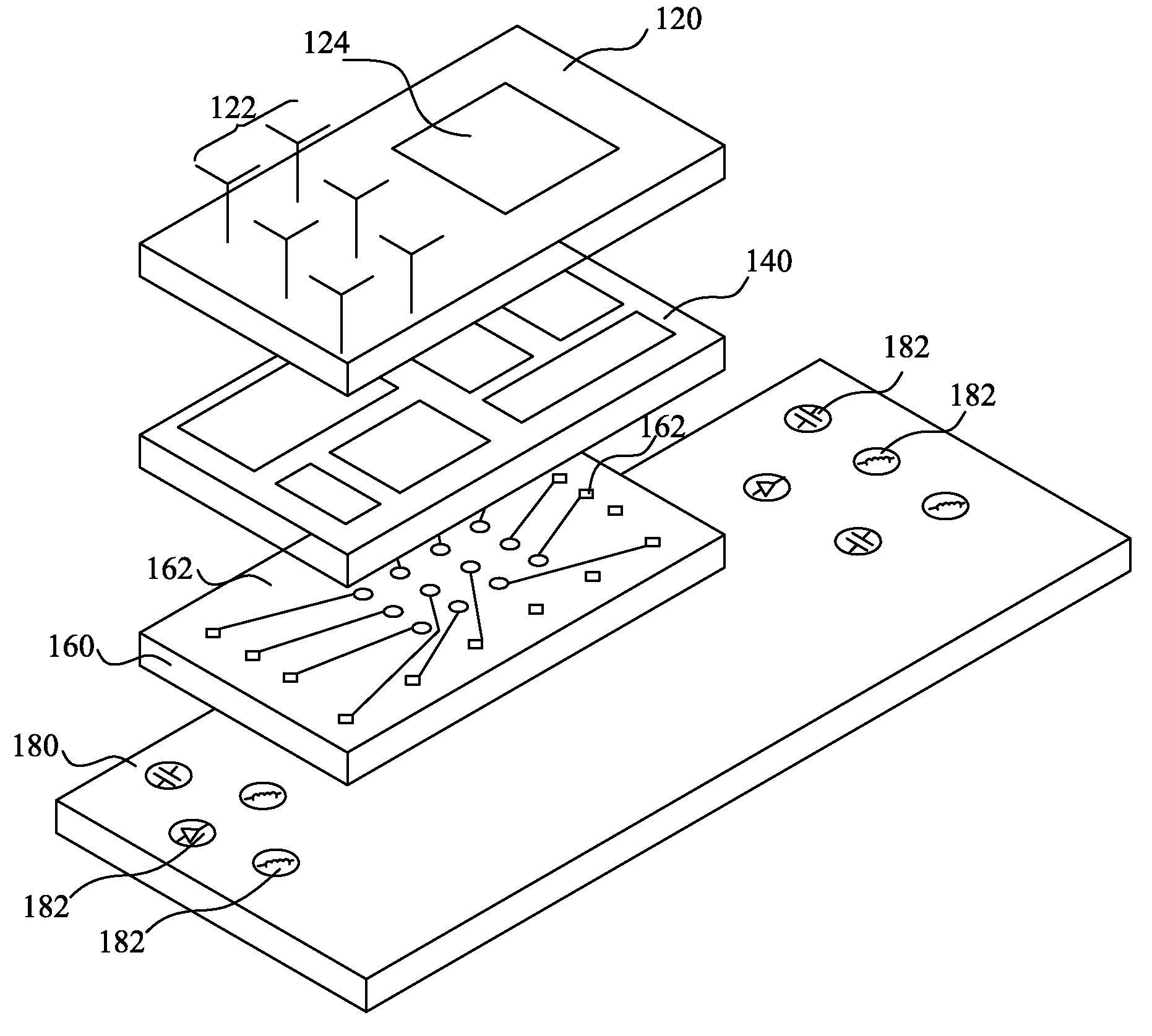

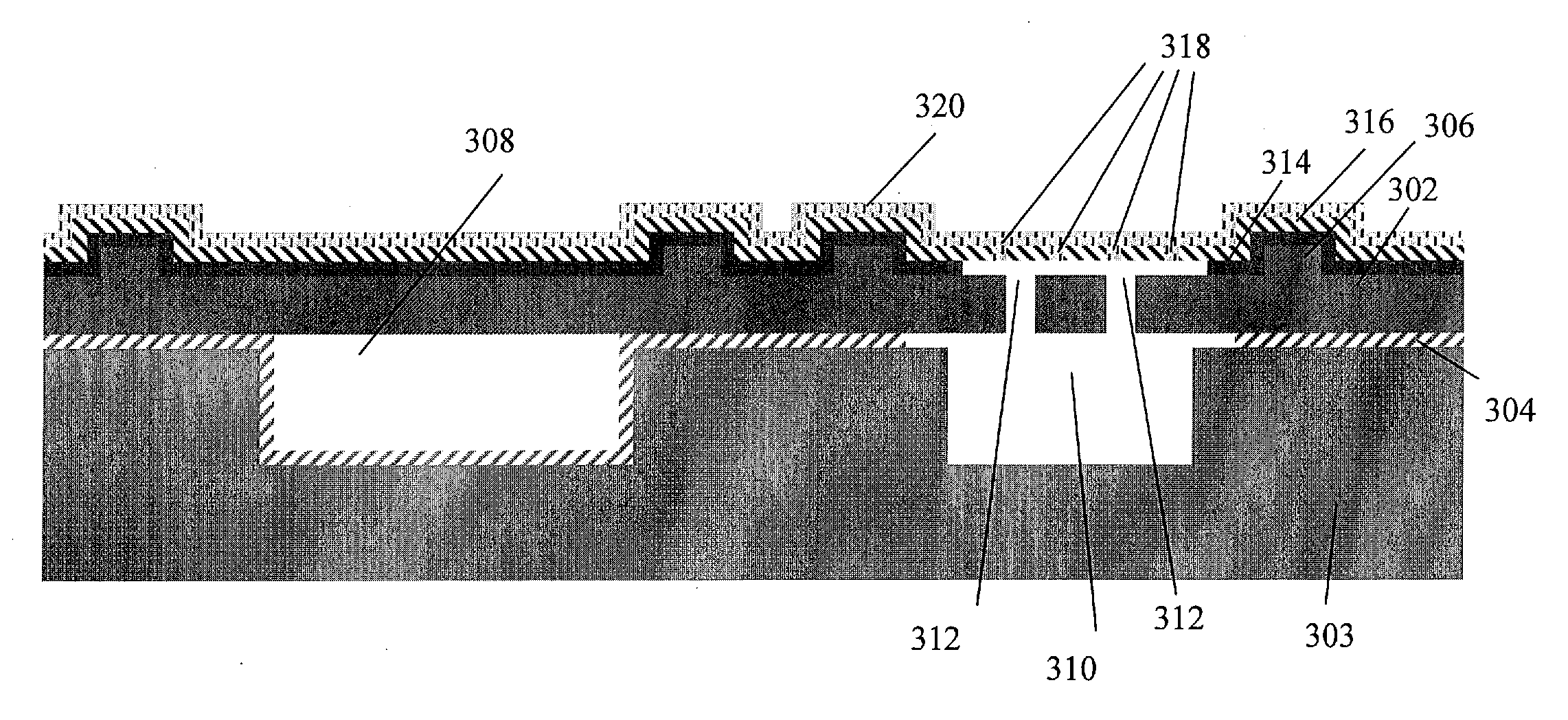

Method and system for MEMS devices

InactiveUS20110049652A1Accurately depositAccurately definedAcceleration measurement using interia forcesSemiconductor/solid-state device manufacturingEngineeringElectrical and Electronics engineering

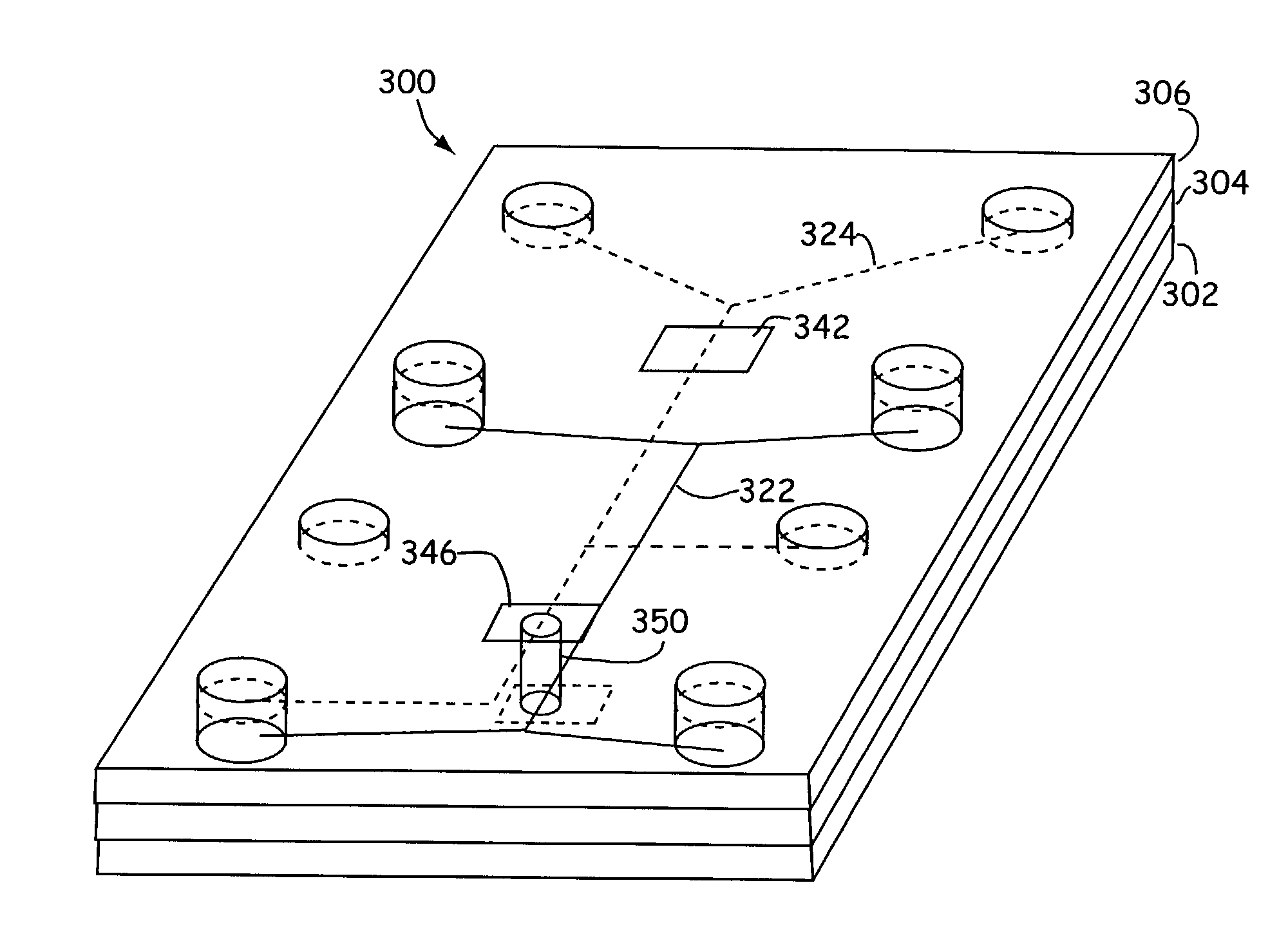

A micro electro-mechanical (MEMS) device assembly is provided. The MEMS device assembly includes a first substrate that has a plurality of electronic devices, a plurality of first bonding regions, and a plurality of second bonding regions. The MEMS device assembly also includes a second substrate that is bonded to the first substrate at the plurality of first bonding regions. A third substrate having a recessed region and a plurality of standoff structures is disposed over the second substrate and bonded to the first substrate at the plurality of second bonding regions. The plurality of first bonding regions provide a conductive path between the first substrate and the second substrate and the plurality of the second bonding regions provide a conductive path between the first substrate and the third substrate.

Owner:MIRADIA INC

Microelectronic mechanical system and methods

InactiveUS20040053434A1Decorative surface effectsSemiconductor/solid-state device detailsNoble gasSilicon oxide

The current invention provides for encapsulated release structures, intermediates thereof and methods for their fabrication. The multi-layer structure has a capping layer, that preferably comprises silicon oxide and / or silicon nitride, and which is formed over an etch resistant substrate. A patterned device layer, preferably comprising silicon nitride, is embedded in a sacrificial material, preferably comprising polysilicon, and is disposed between the etch resistant substrate and the capping layer. Access trenches or holes are formed in to capping layer and the sacrificial material are selectively etched through the access trenches, such that portions of the device layer are release from sacrificial material. The etchant preferably comprises a noble gas fluoride NGF2x (wherein Ng=Xe, Kr or Ar: and where x=1, 2 or 3). After etching that sacrificial material, the access trenches are sealed to encapsulate released portions the device layer between the etch resistant substrate and the capping layer. The current invention is particularly useful for fabricating MEMS devices, multiple cavity devices and devices with multiple release features.

Owner:SILICON LIGHT MACHINES CORP

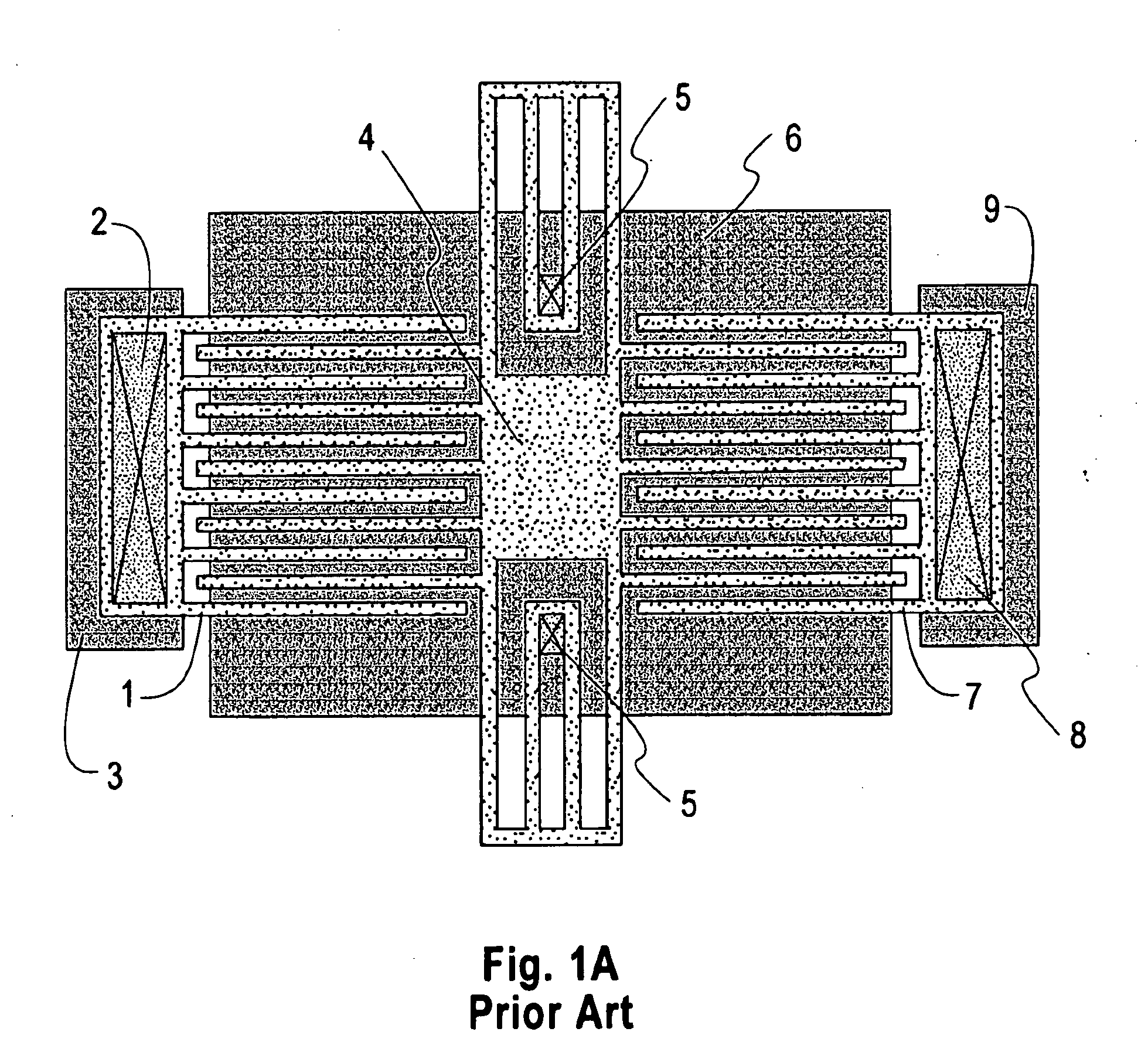

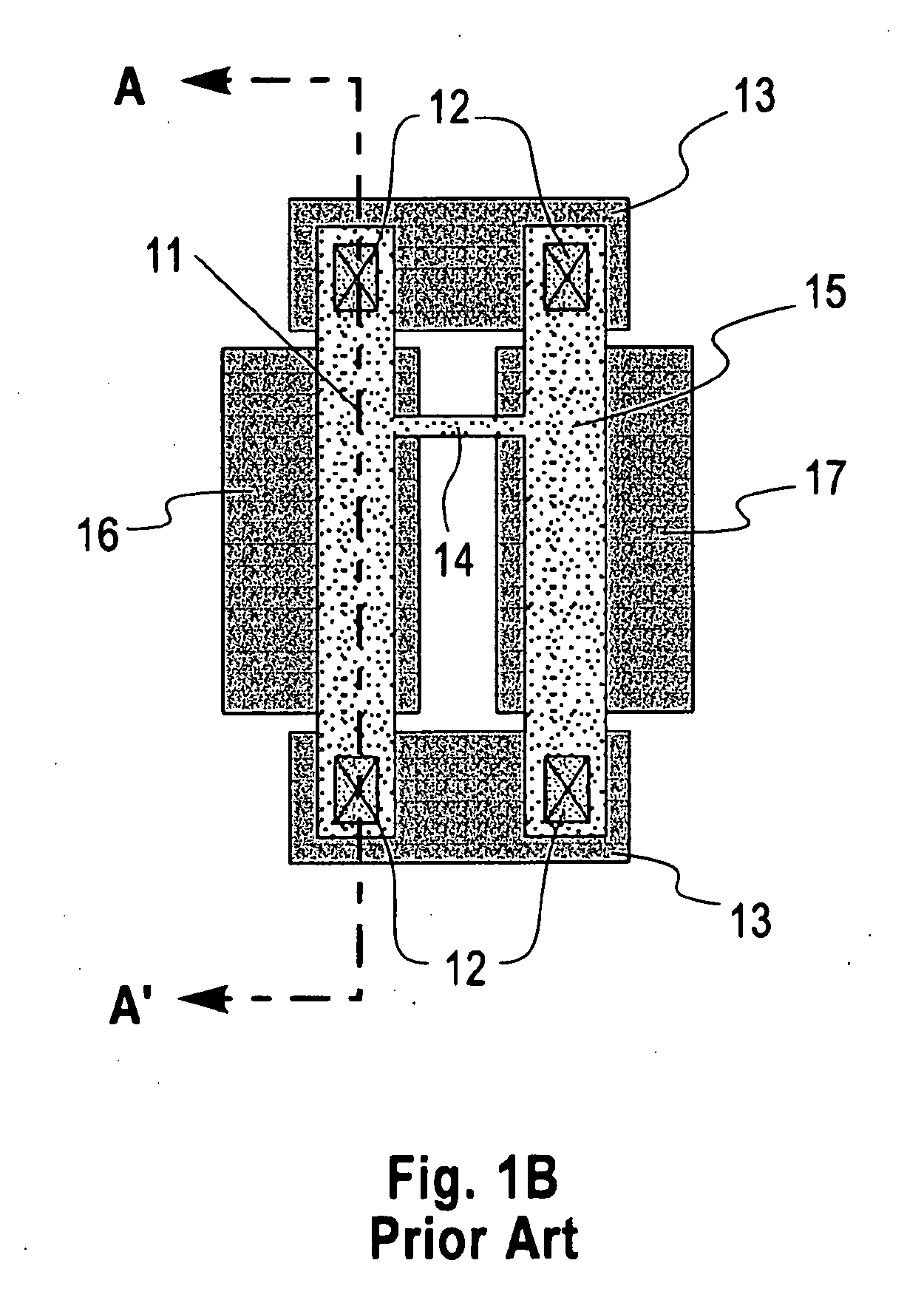

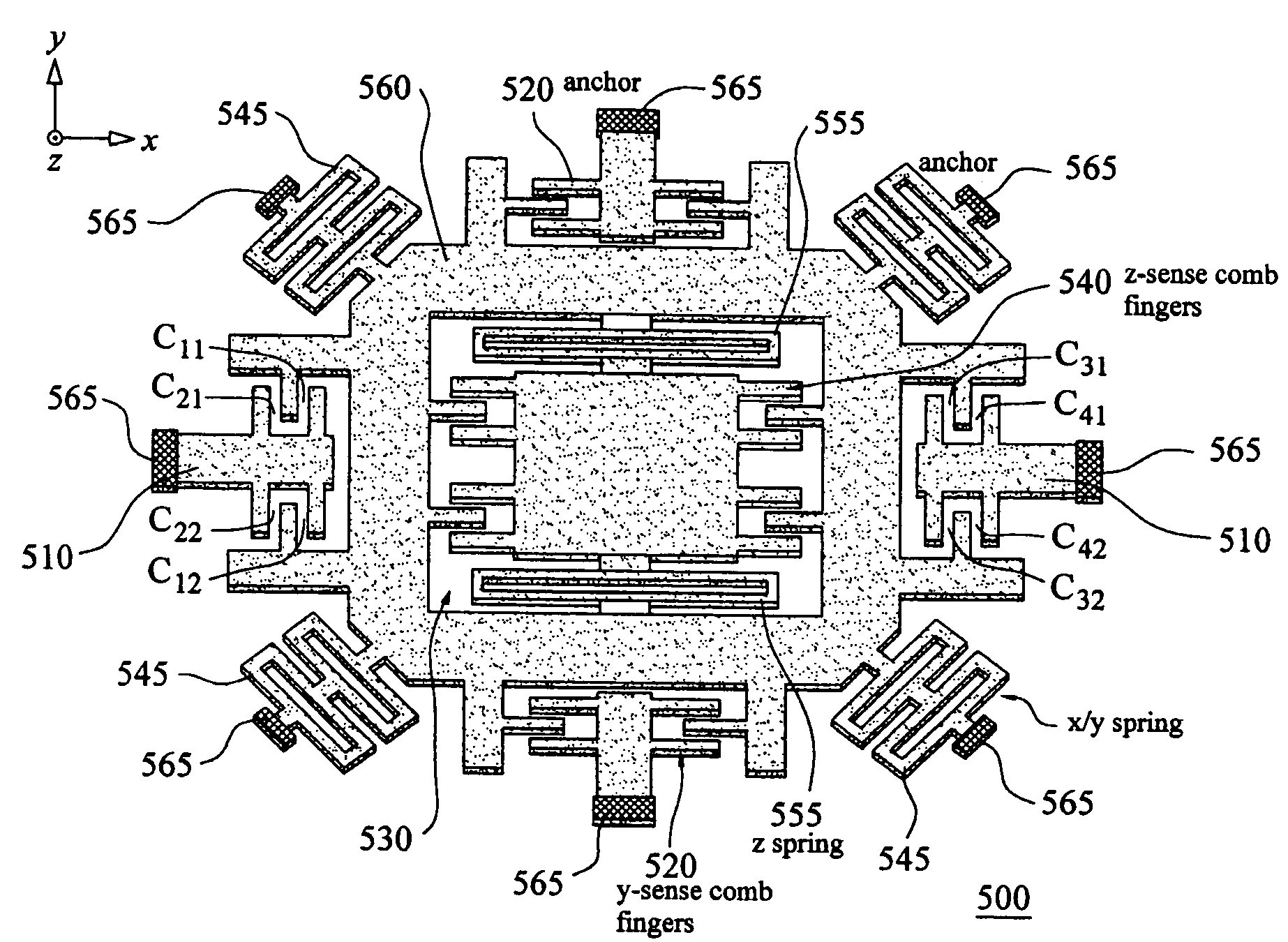

Integrated monolithic tri-axial micromachined accelerometer

InactiveUS7258012B2Acceleration measurement using interia forcesImpedence networksAccelerometerSingle crystal substrate

A monolithic integrated 3-axis accelerometer chip includes a single crystal substrate, the substrate including at least one single crystal membrane layer portion. A single sensor microstructure made from the single crystal membrane senses acceleration in each of the three orthogonal directions. At least one electronic circuit can also be disposed on the chip, such as a circuit for driving, detecting, controlling and signal processing.

Owner:UNIV OF FLORIDA RES FOUNDATION INC

Microfluidic devices and methods of their manufacture

ActiveUS7069952B1Operating means/releasing devices for valvesCircuit elementsInterface layerAnodic bonding

The present invention provides multi-layered microfluidic devices comprising an interface layer between every two substrate layers. The interface layer simplifies the manufacturing process of the multi-layered devices because the interface may comprise a material suitable for etching whereby manufacturing of these devices is simplified to a great extent.The invention also provides methods of manufacturing the multi-layered devices wherein the devices may comprise substrates composed of non-similar materials that are bonded together by anodic bonding.

Owner:CAPLIPER LIFE SCI INC

Integrated MEMS device

InactiveUS20130161702A1Improve reliabilityReduce manufacturing costMicrophonesLoudspeakersCMOSControl layer

An integrated MEMS device is provided, including, from bottom up, a bonding wafer layer, a bonding layer, an aluminum layer, a CMOS substrate layer defining a large back chamber area (LBCA), a small back chamber area (SBCA) and a sound damping path (SDP), a set of CMOS wells, a field oxide (FOX) layer, a set of CMOS transistor sources / drains, a first polysilicon layer forming CMOS transistor gates, a second polysilicon layer, said CMOS wells, said CMOS transistor sources / drains and said CMOS gates forming CMOS transistors, an oxide layer embedded with a plurality of metal layers interleaved with a plurality of via hole layers, and a gap control layer, an oxide layer, a first Nitride deposition layer, a metal deposition layer, a second Nitride deposition layer, an under bump metal (UBM) layer made of preferably Al / NiV / Cu and a plurality of solder spheres.

Owner:WINDTOP TECH CORP

Switch, semiconductor device, and manufacturing method thereof

InactiveUS20070018761A1Improve reliabilityElectrostatic/electro-adhesion relaysForming microstructural systemsCantilevered beamField strength

It is an objective to achieve a MEMS switch which can be mounted with a CMOS circuit and has a contact point with high reliability, both mechanically and electrically. An insulator having a compatibility with a CMOS process is formed at the contact surface of a cantilever beam constituting a MEMS switch and a fixed contact 2 opposite thereto. When the switch is used the cantilever beam is moved by applying a voltage to the pull-in electrode and the cantilever beam. After the cantilever beam makes contact with the fixed contact, a voltage exceeding the breakdown field strength of the insulator is applied to the insulator, resulting in dielectric breakdown occurring. By modifying the insulator once, the mechanical fatigue concentration point of the switch contact point is protected, and a contact point is achieved as well in which electrical signals are transmitted through the current path formed by the dielectric breakdown.

Owner:HITACHI LTD

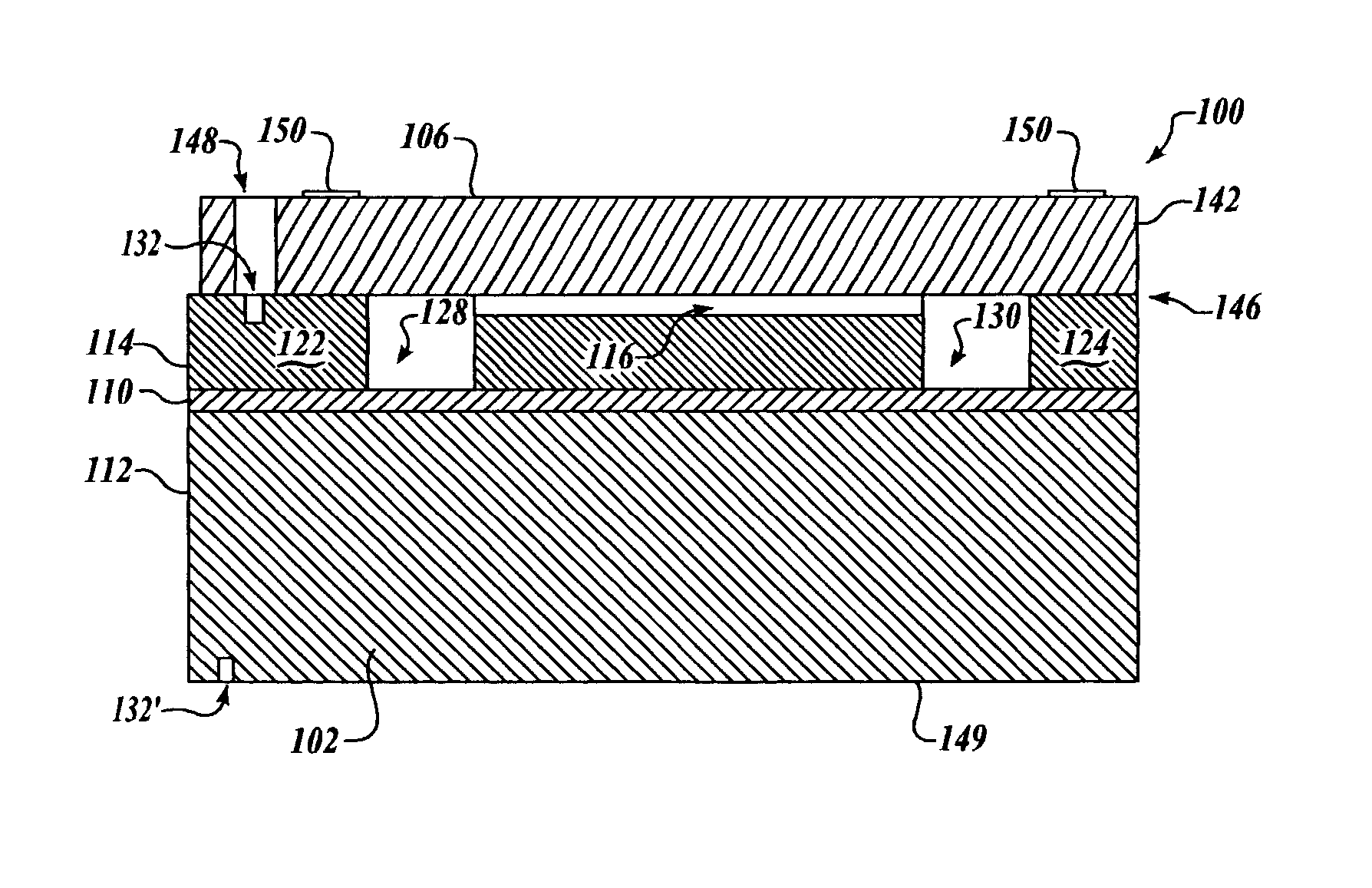

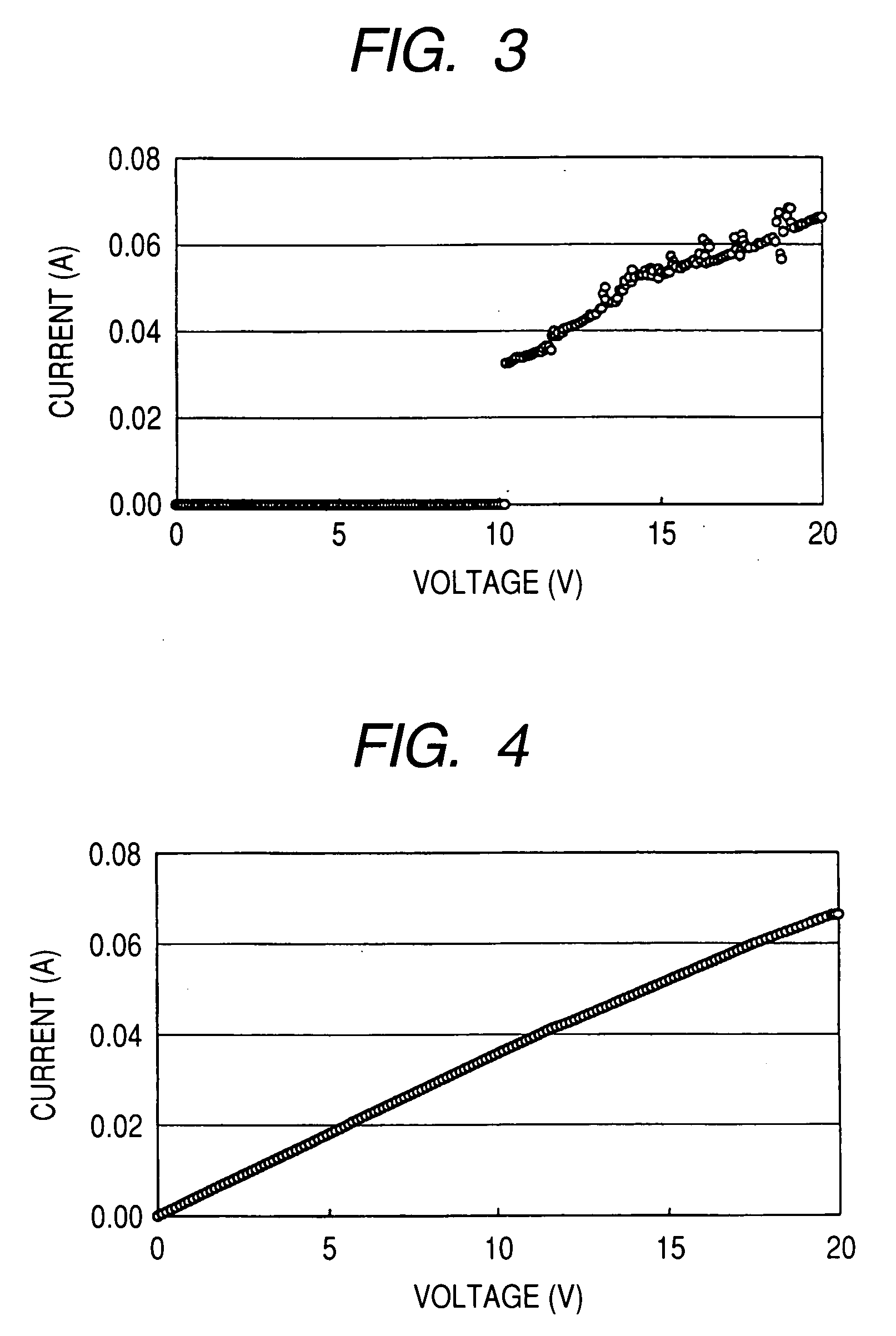

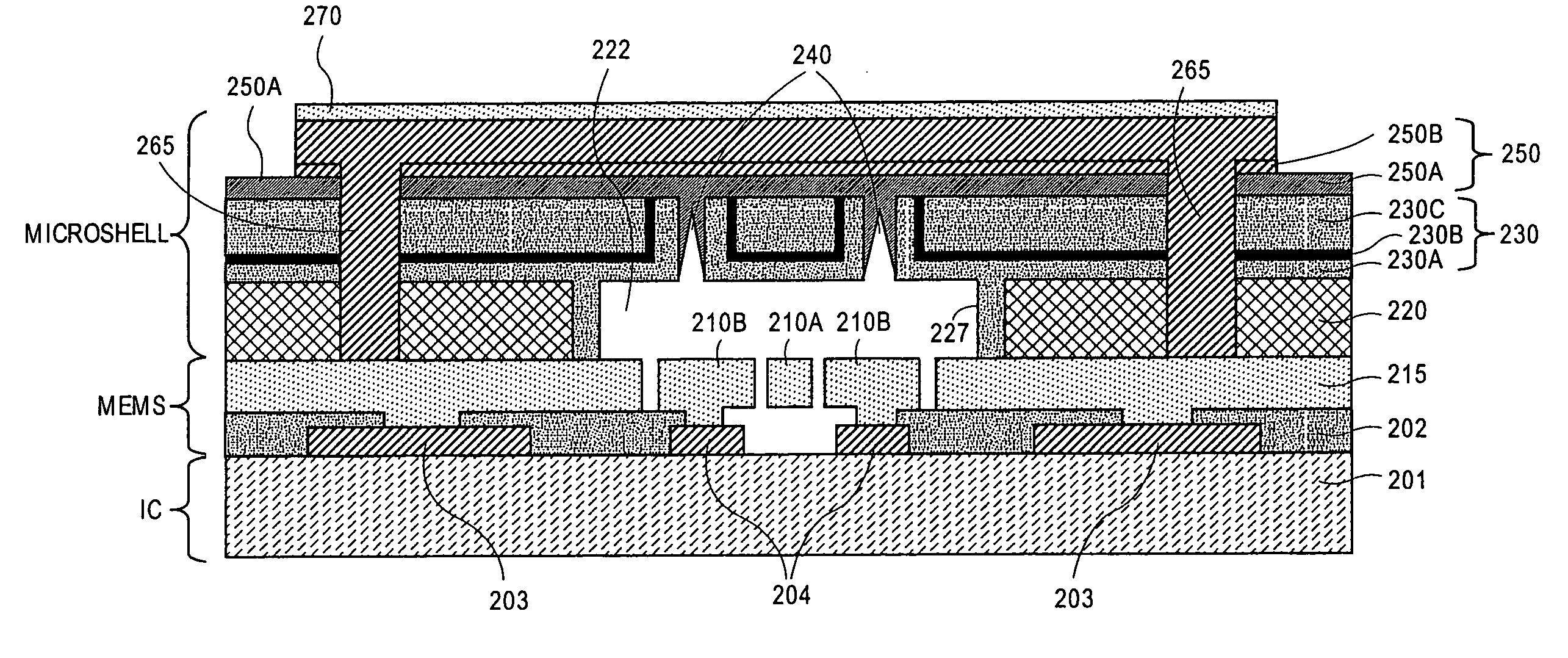

Planar microshells for vacuum encapsulated devices and damascene method of manufacture

ActiveUS7923790B1Acceleration measurement using interia forcesSolid-state devicesMaterial PerforationMetal

Low temperature, multi-layered, planar microshells for encapsulation of devices such as MEMS and microelectronics. The microshells include a planar perforated pre-sealing layer, below which a non-planar sacrificial layer is accessed, and a sealing layer to close the perforation in the pre-sealing layer after the sacrificial material is removed. In an embodiment, the pre-sealing layer has perforations formed with a damascene process to be self-aligned to the chamber below the microshell. The sealing layer may include a nonhermetic layer to physically occlude the perforation and a hermetic layer over the nonhermetic occluding layer to seal the perforation. In a particular embodiment, the hermetic layer is a metal which is electrically coupled to a conductive layer adjacent to the microshell to electrically ground the microshell.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Microphone Package with Embedded ASIC

ActiveUS20120087521A1Transducer detailsSemiconductor electrostatic transducersEngineeringMems microphone

A packaged microphone has a base, a lid coupled to the base forming an interior, a MEMS microphone secured to the base within the interior, and an integrated circuit embedded in the base. Apertures in the base and integrated circuit are aligned to form an aperture from the exterior of the package to the interior.

Owner:INVENSENSE

Structure and method of making sealed capped chips

InactiveUS20050082653A1Impedence networksSemiconductor/solid-state device detailsEngineeringMechanical engineering

A method of making a plurality of sealed assemblies is provided which includes a) assembling a first element to a second element so that a bottom surface of the first element faces downwardly toward a front surface of the second element and a top surface of the first element faces upwardly away from the second element; and (b) forming ring seals surrounding regions of the front surface of the second element by introducing flowable material between the first element and the second element from the top surface of the first element through openings in the first element. A chip is provided which includes: (a) a body defining a front surface and one or more circuit elements on or within the body; (b) one or more bond pads exposed at the front surface in a bond pad region; and (c) a metallic ring exposed at the front surface, the ring substantially surrounding the bond pad region. Sealed chip assemblies are formed by sealing an array of the chips, e.g., in wafer form, to a cap element.

Owner:TESSERA INC