Patents

Literature

931results about How to "Increase etch rate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

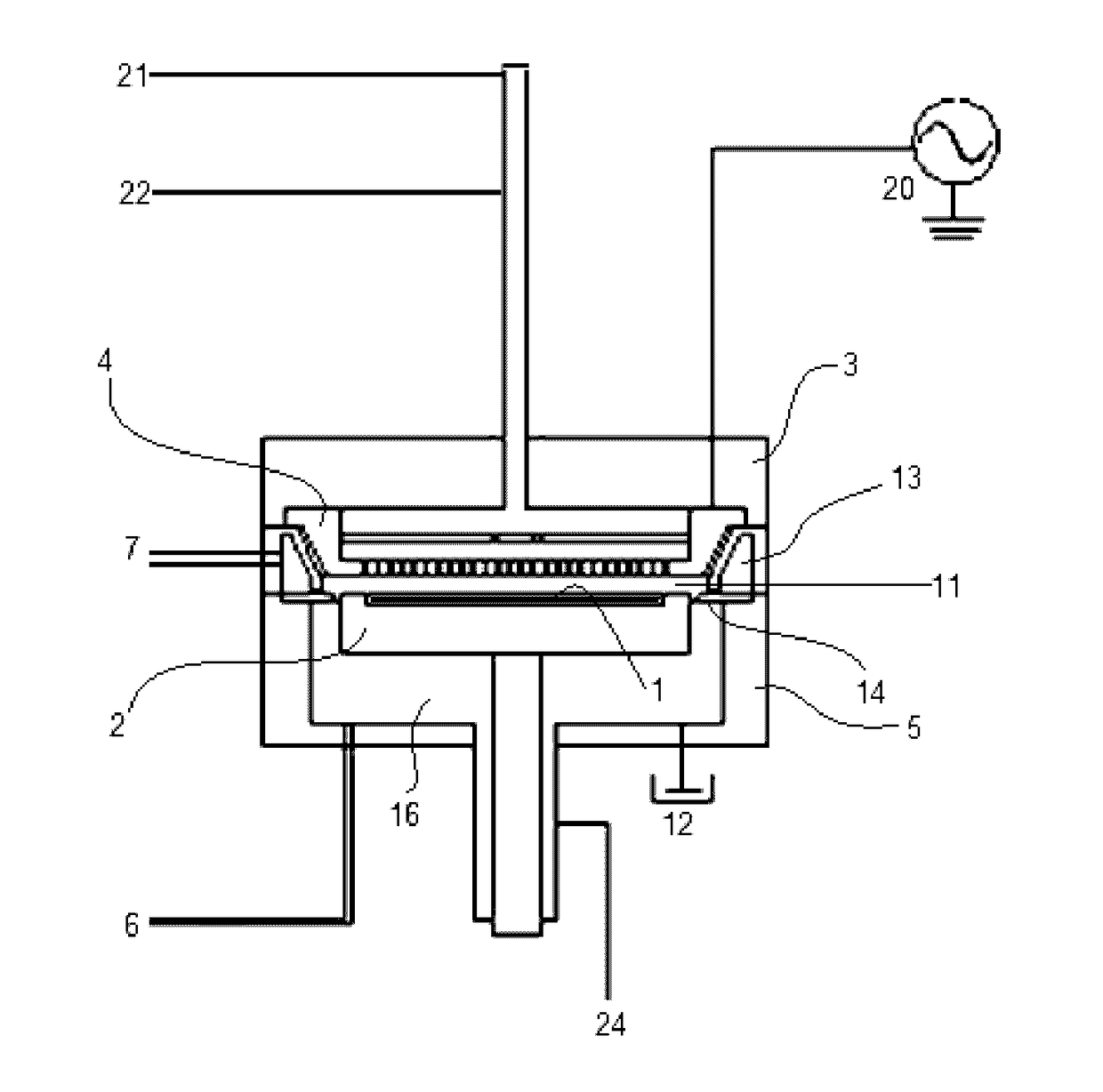

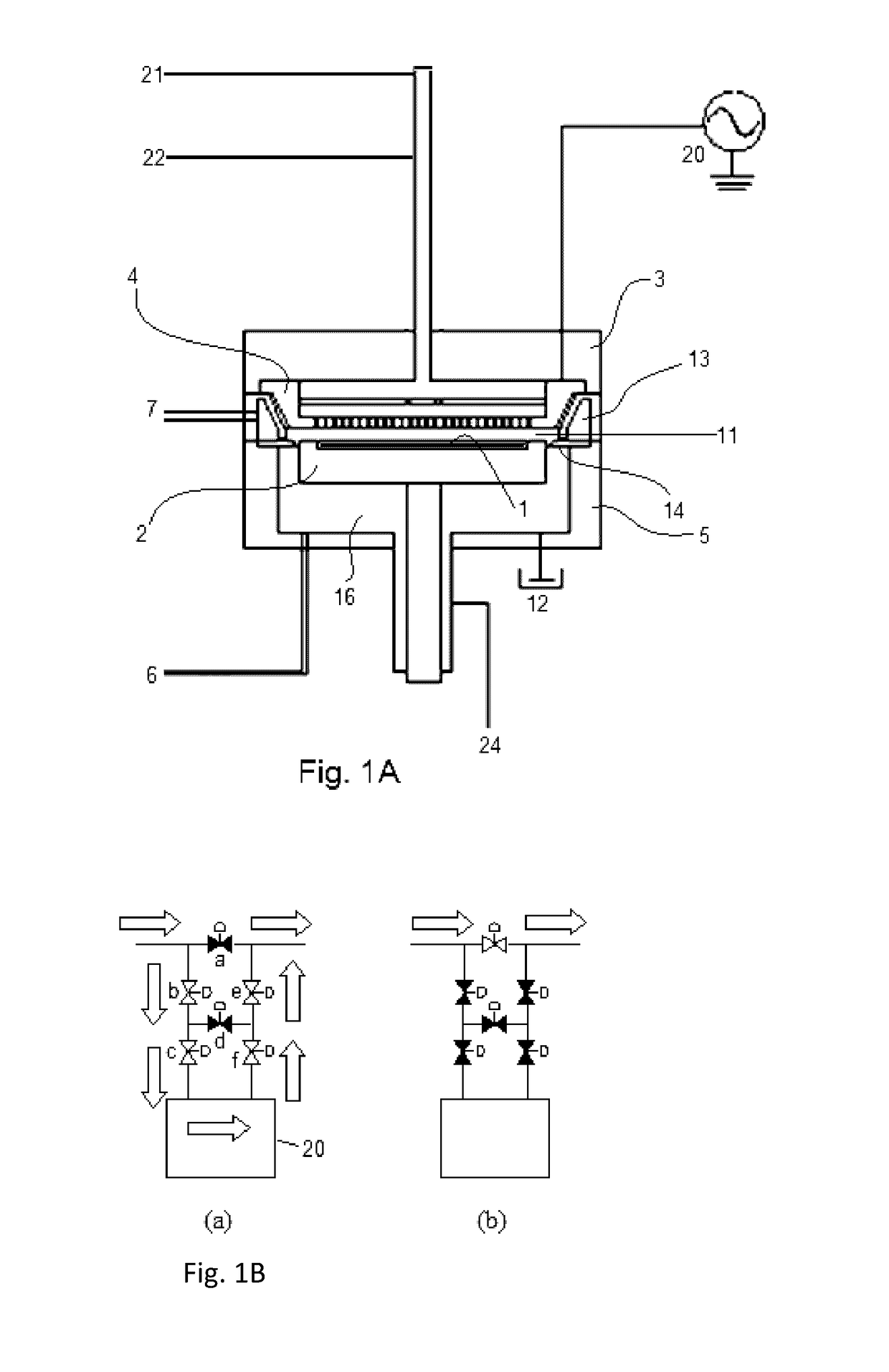

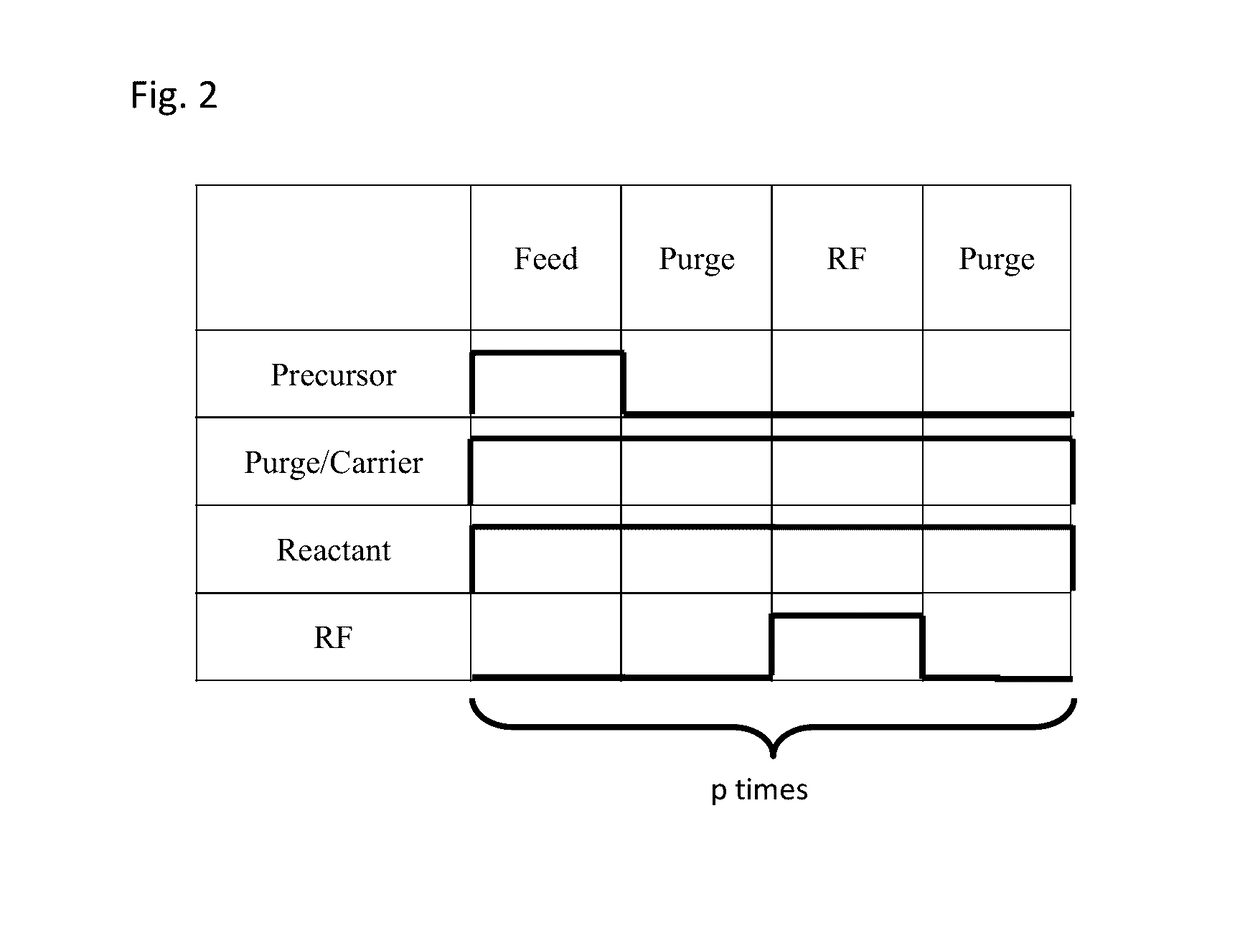

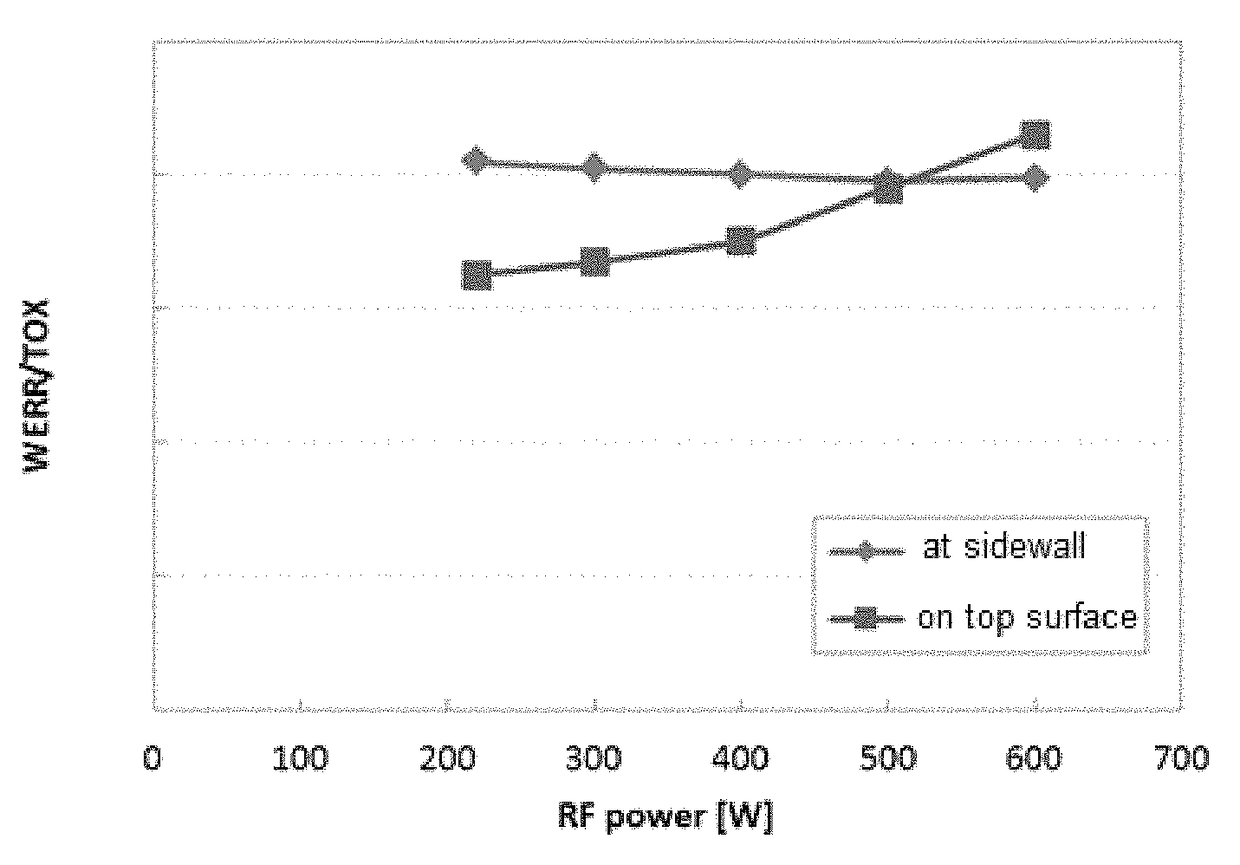

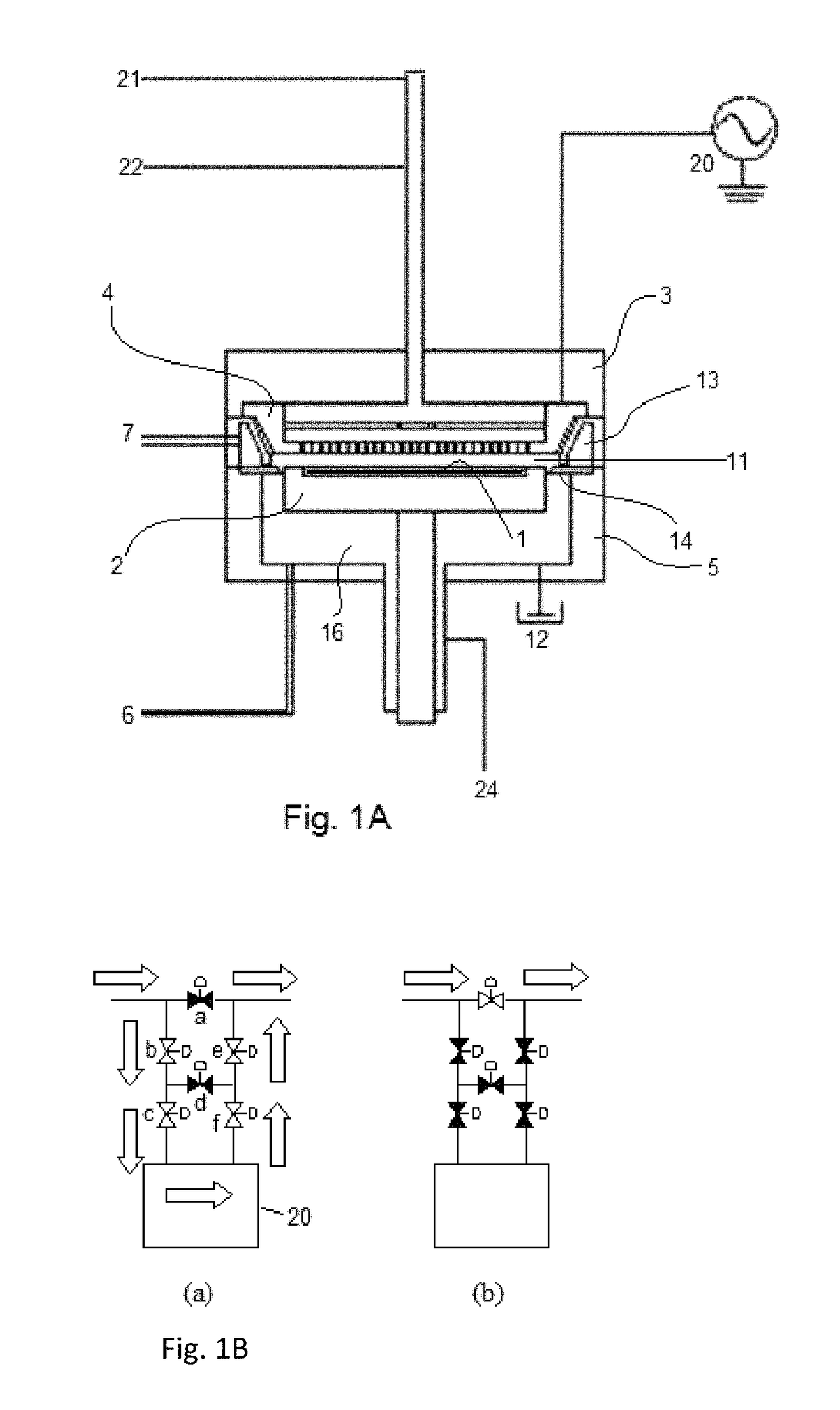

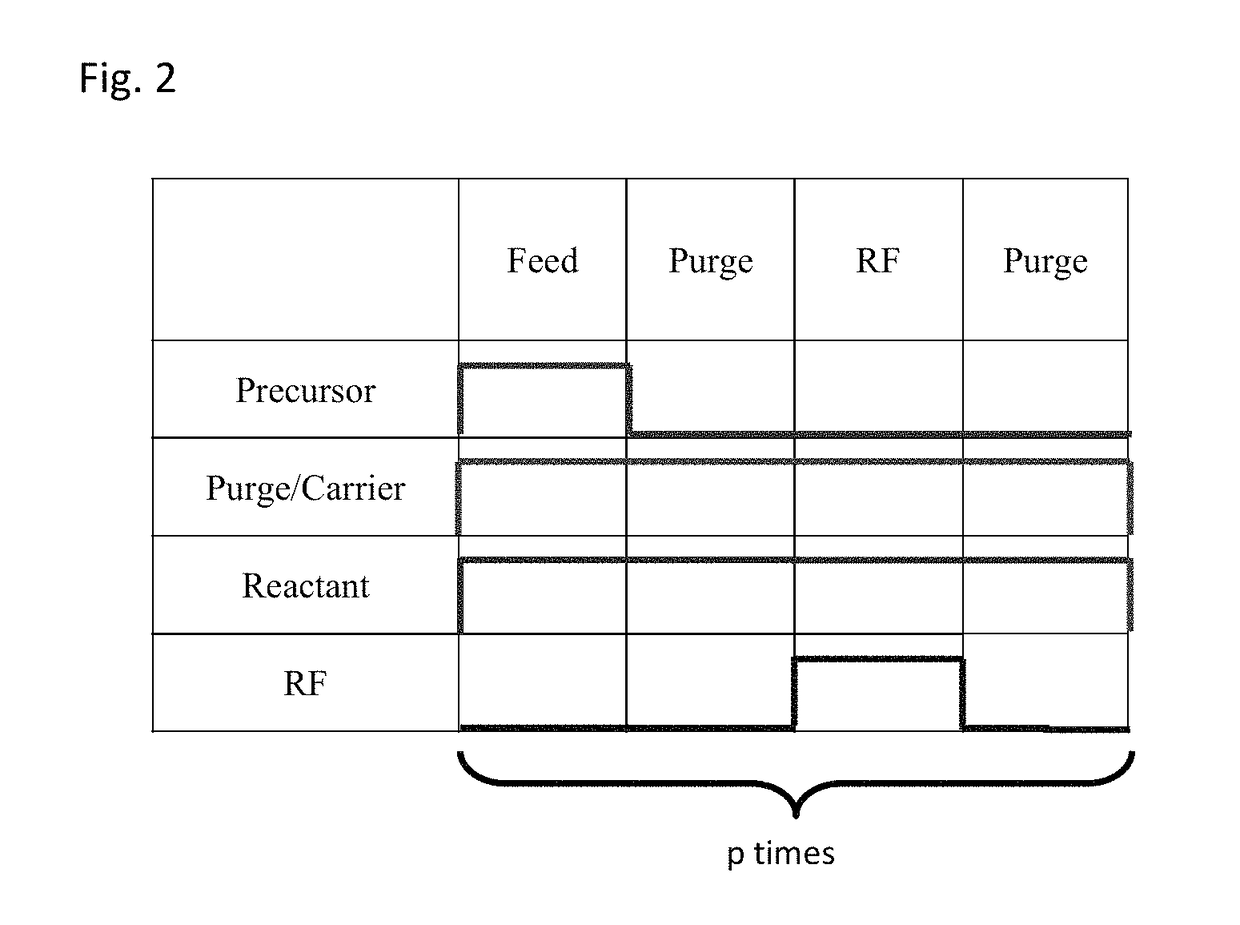

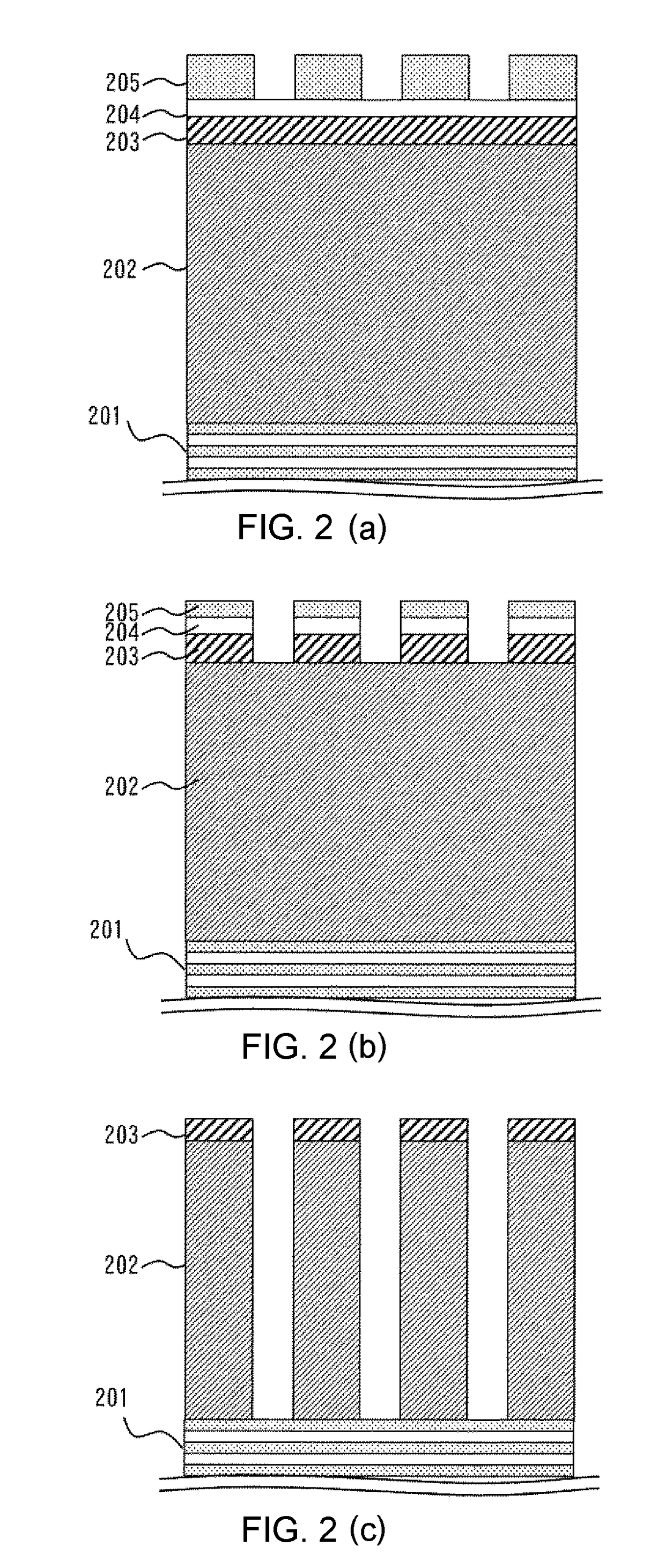

Method for depositing dielectric film in trenches by peald

ActiveUS20170107621A1Quality improvementReduce the differenceElectric discharge tubesSemiconductor/solid-state device manufacturingEngineeringAtomic layer deposition

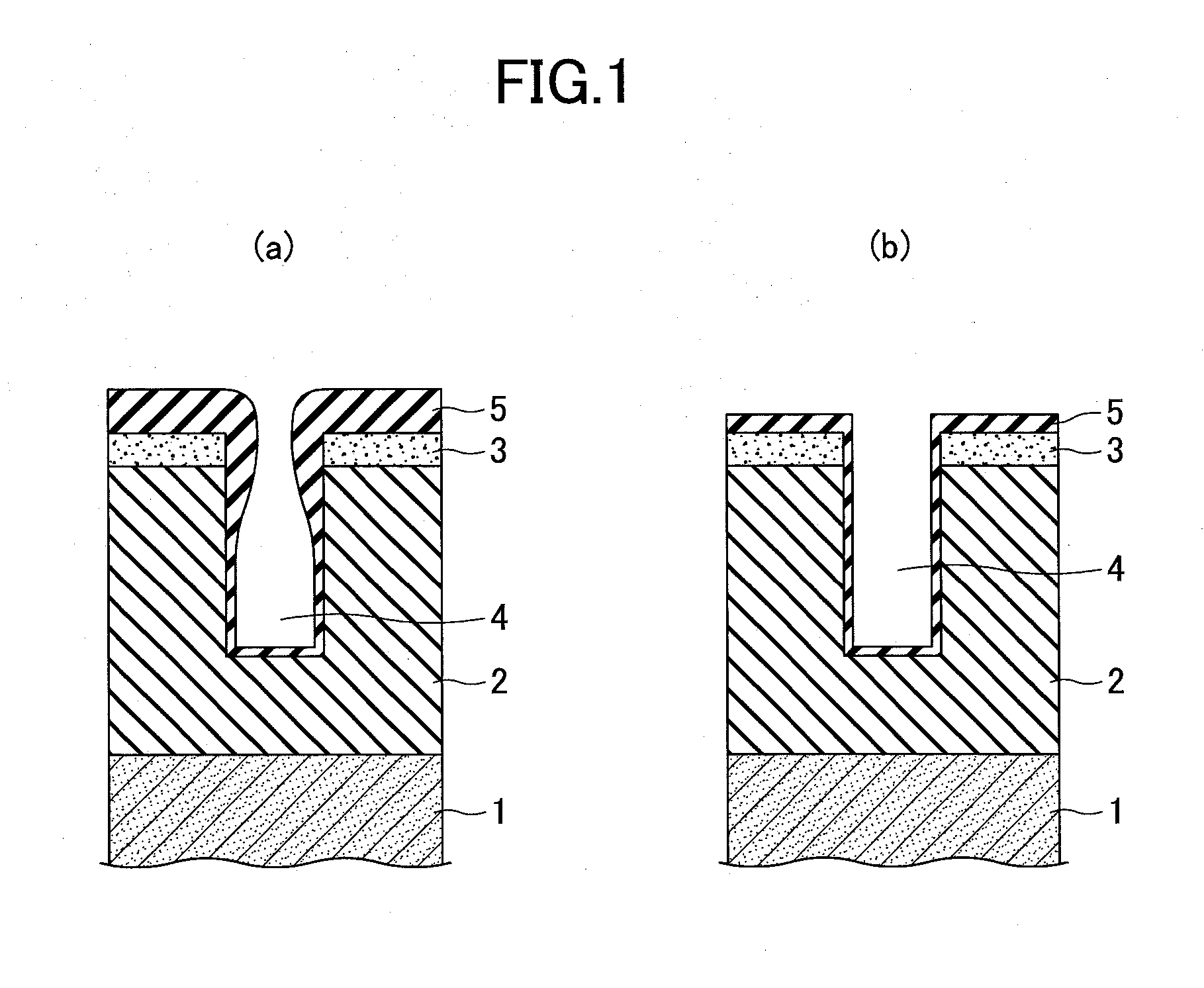

A method for depositing a dielectric film in a trench by plasma-enhanced atomic layer deposition (PEALD) includes depositing a dielectric film in a trench of a substrate by PEALD under conditions wherein the wet etch rate of the depositing film on a top surface of the substrate is substantially equivalent to or higher than the wet etch rate of the depositing film at a sidewall of the trench, wherein a precursor fed into the reaction space has —N(CH3)2 as a functional group.

Owner:ASM IP HLDG BV

Method for depositing dielectric film in trenches by PEALD

ActiveUS9909214B2Quality improvementReduce the differenceElectric discharge tubesDecorative surface effectsDielectric membraneThin membrane

A method for depositing a dielectric film in a trench by plasma-enhanced atomic layer deposition (PEALD) includes depositing a dielectric film in a trench of a substrate by PEALD under conditions wherein the wet etch rate of the depositing film on a top surface of the substrate is substantially equivalent to or higher than the wet etch rate of the depositing film at a sidewall of the trench, wherein a precursor fed into the reaction space has —N(CH3)2 as a functional group.

Owner:ASM IP HLDG BV

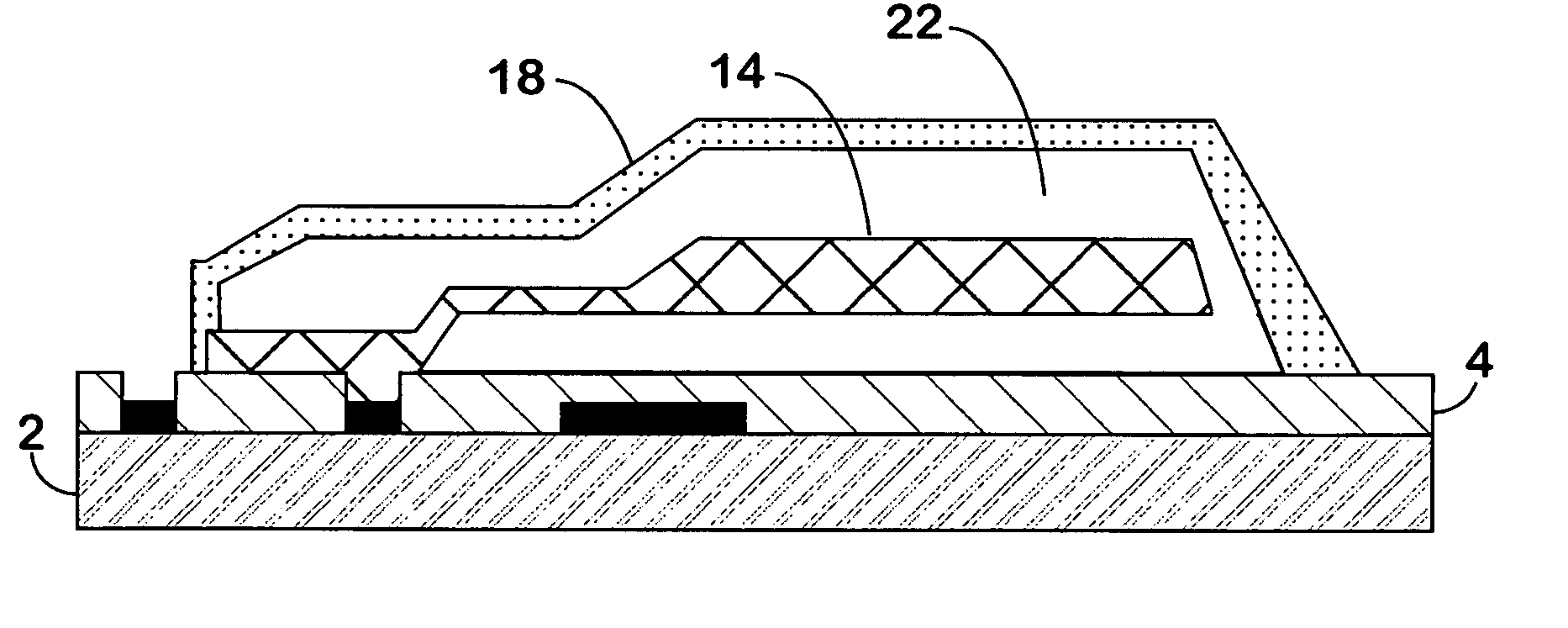

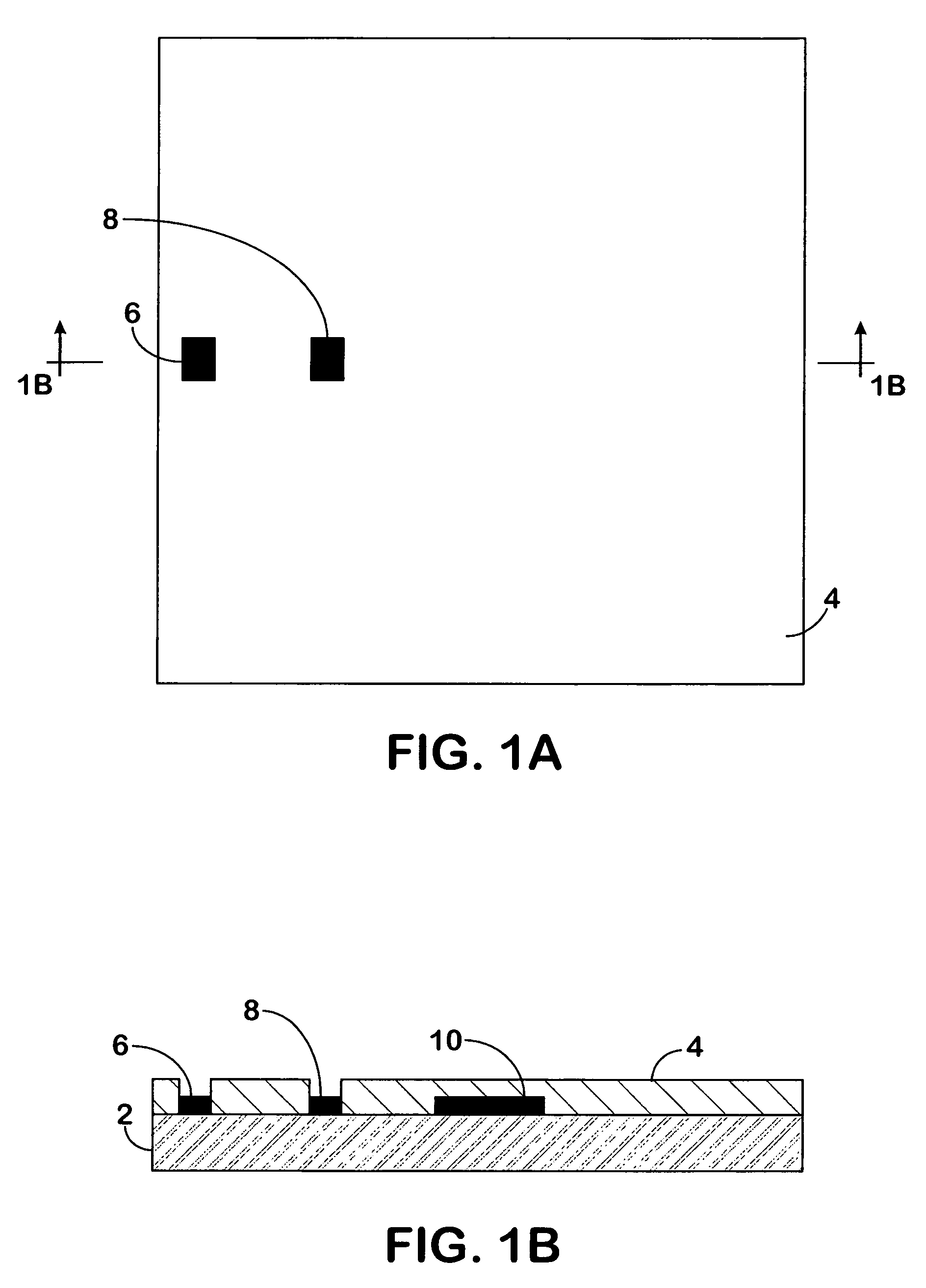

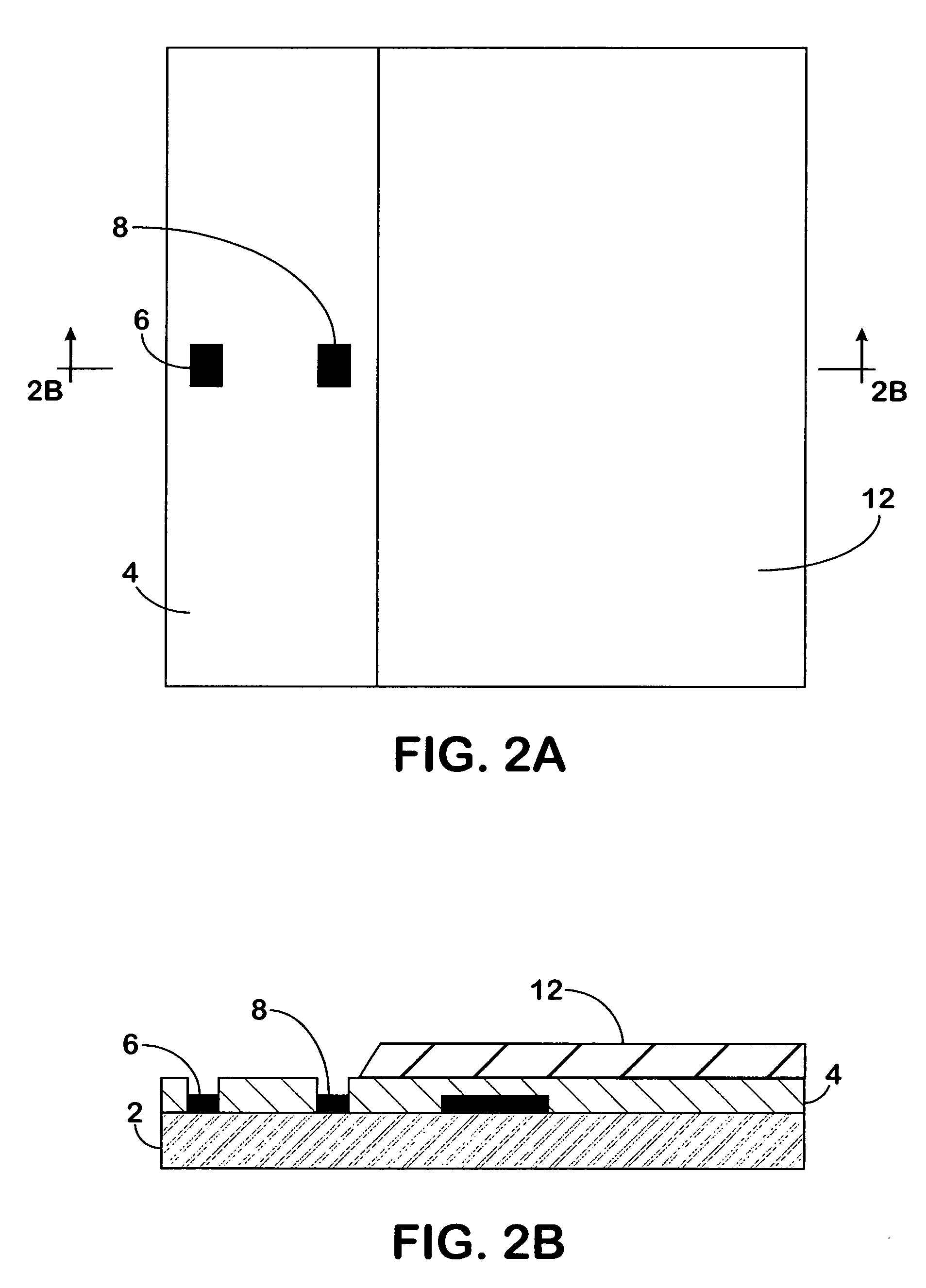

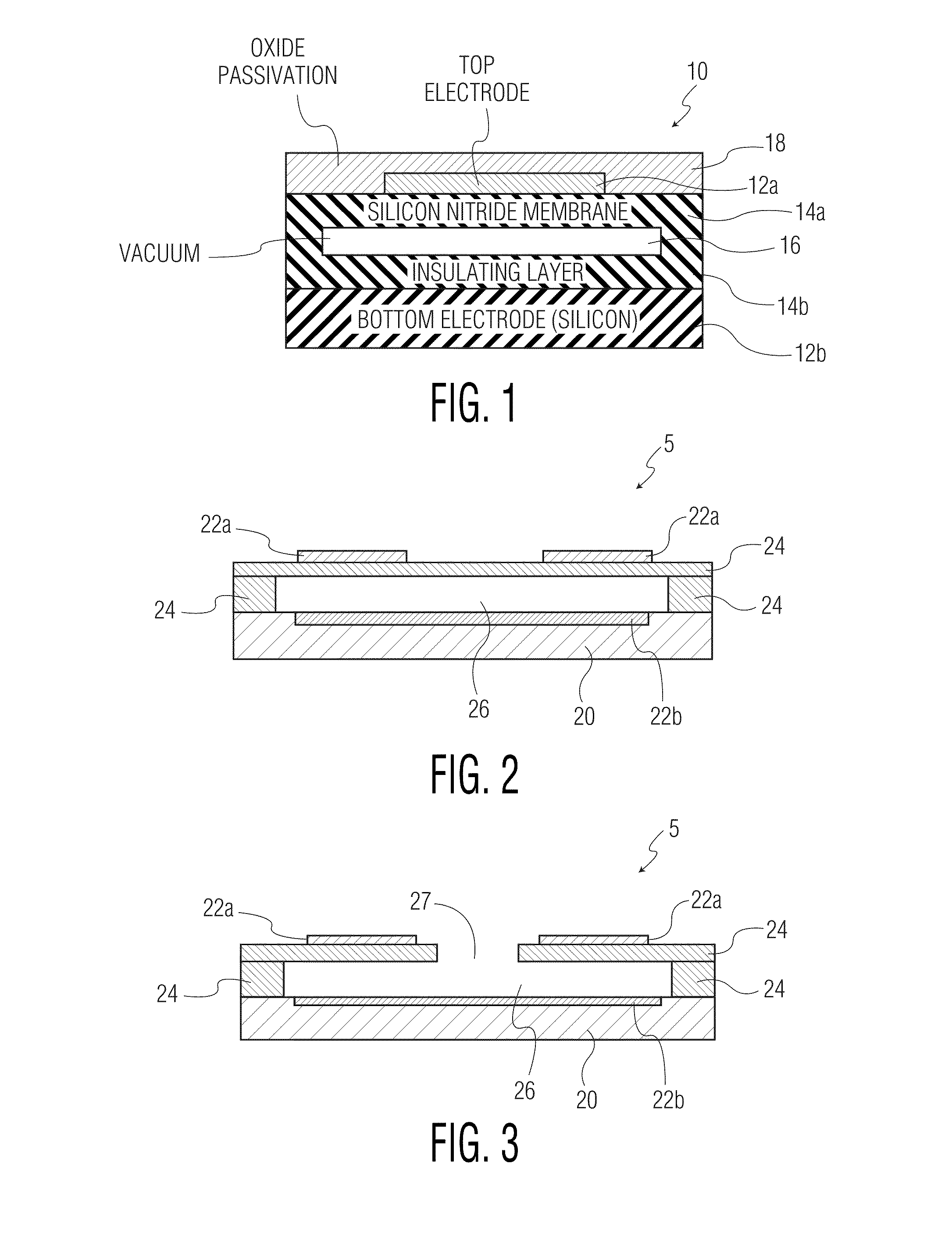

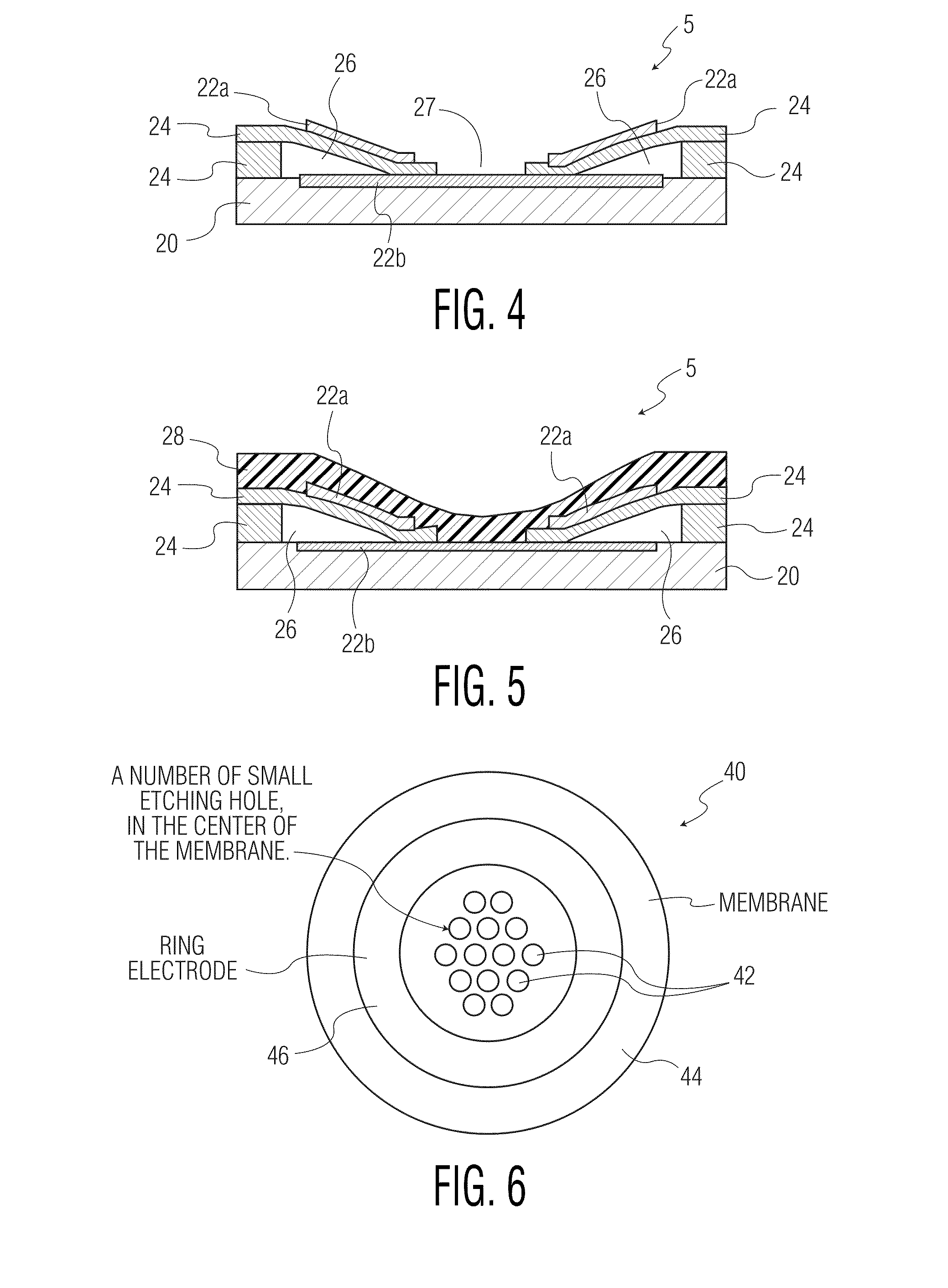

Manufacture of MEMS structures in sealed cavity using dry-release MEMS device encapsulation

InactiveUS7008812B1Eliminates undesirable liquid surface tensionIncrease etch rateAcceleration measurement using interia forcesSolid-state devicesMaterials sciencePlasma etching

The disclosed fabrication methodology addresses the problem of creating low-cost micro-electro-mechanical devices and systems, and, in particular, addresses the problem of delicate microstructures being damaged by the surface tension created as a wet etchant evaporates. This disclosure demonstrates a method for employing a dry plasma etch process to release encapsulated microelectromechanical components.

Owner:CYMATICS LAB CORP

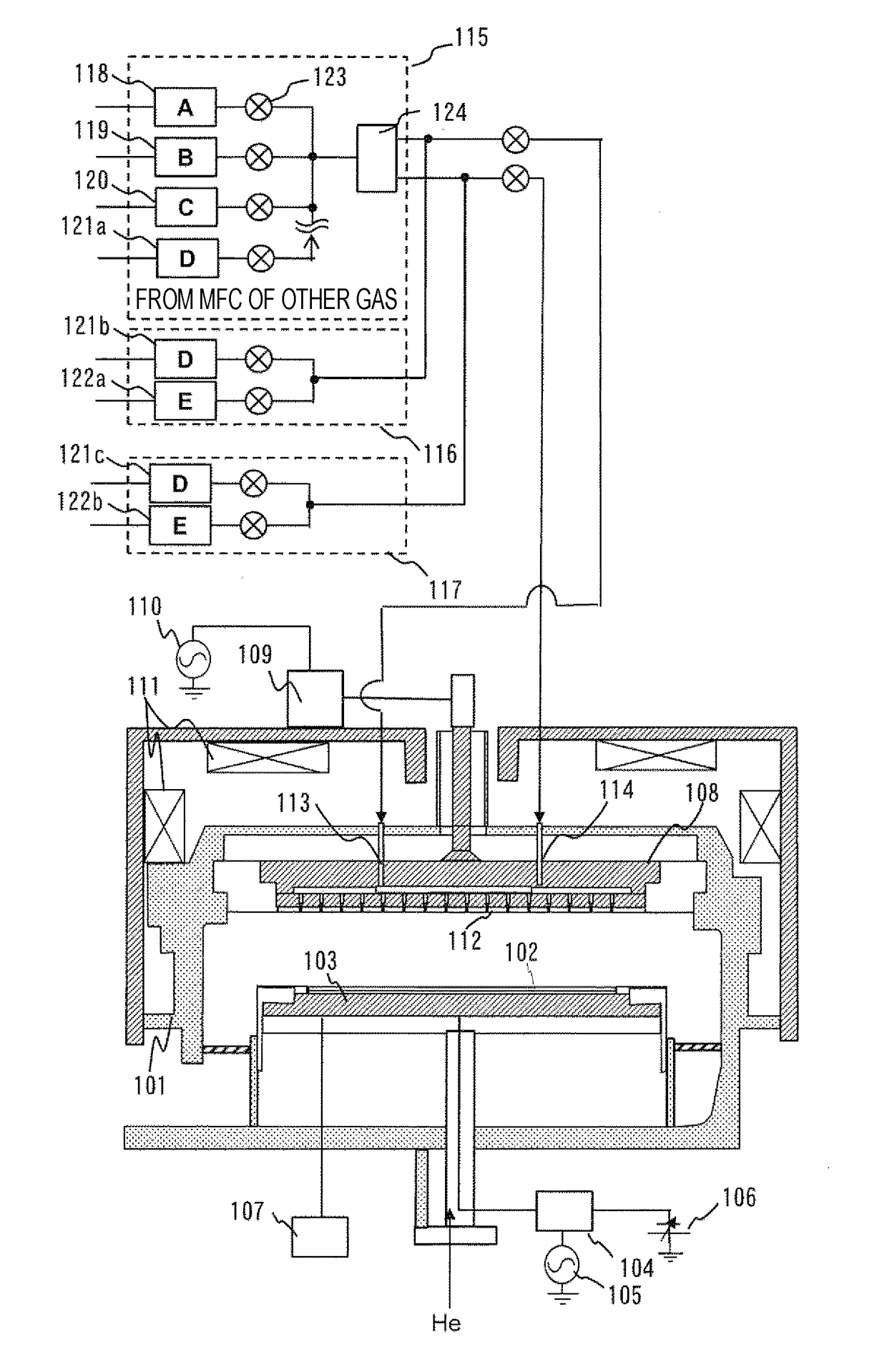

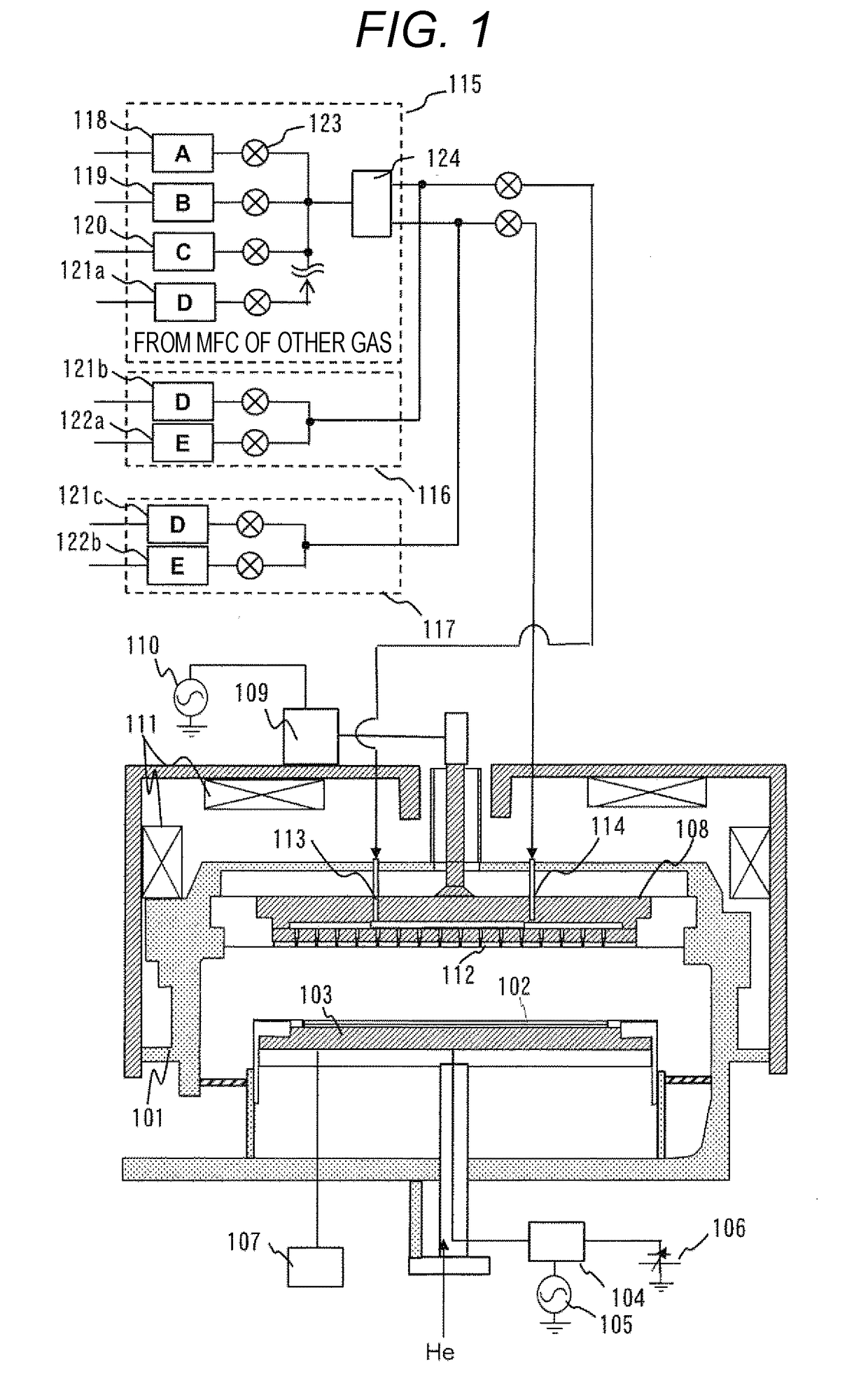

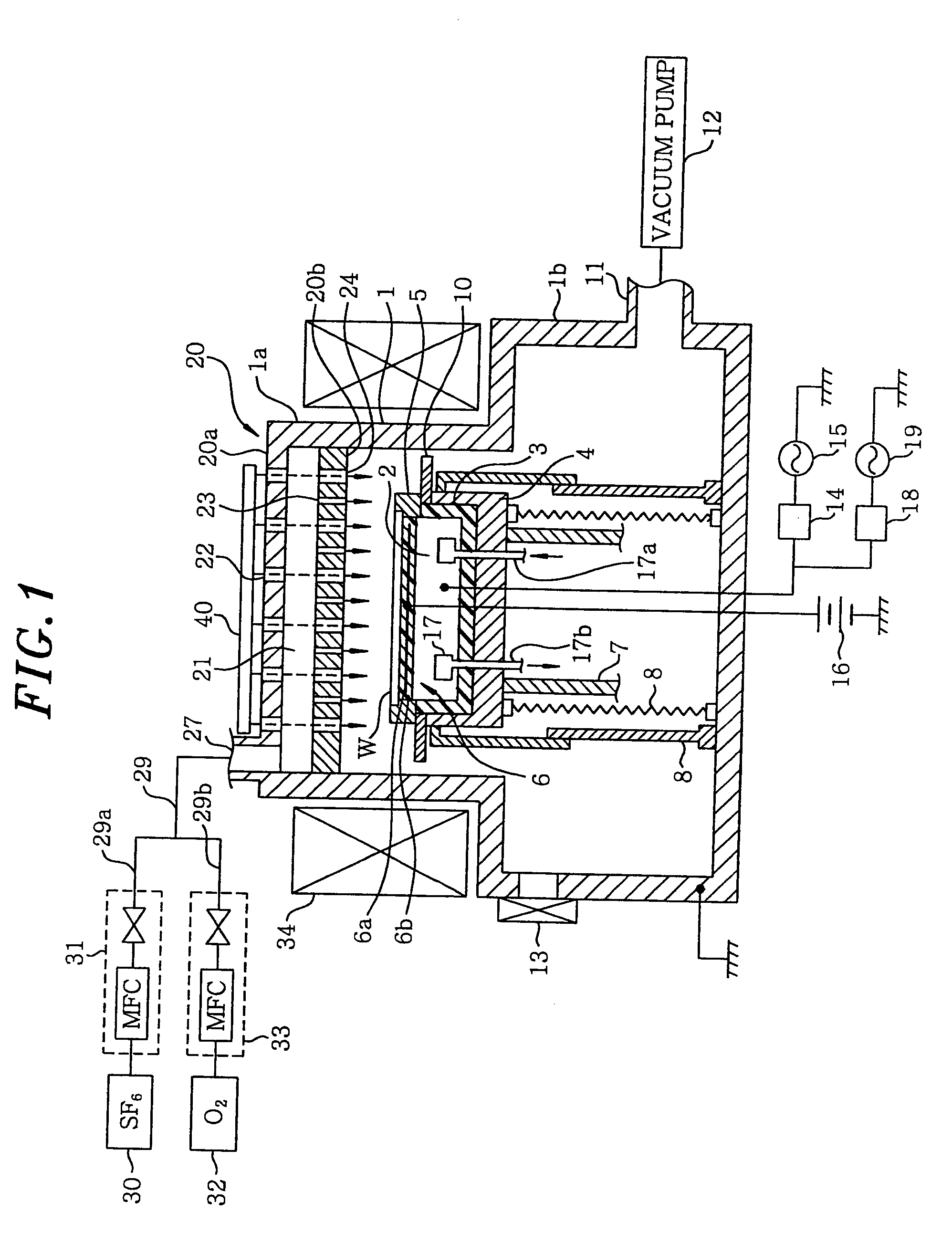

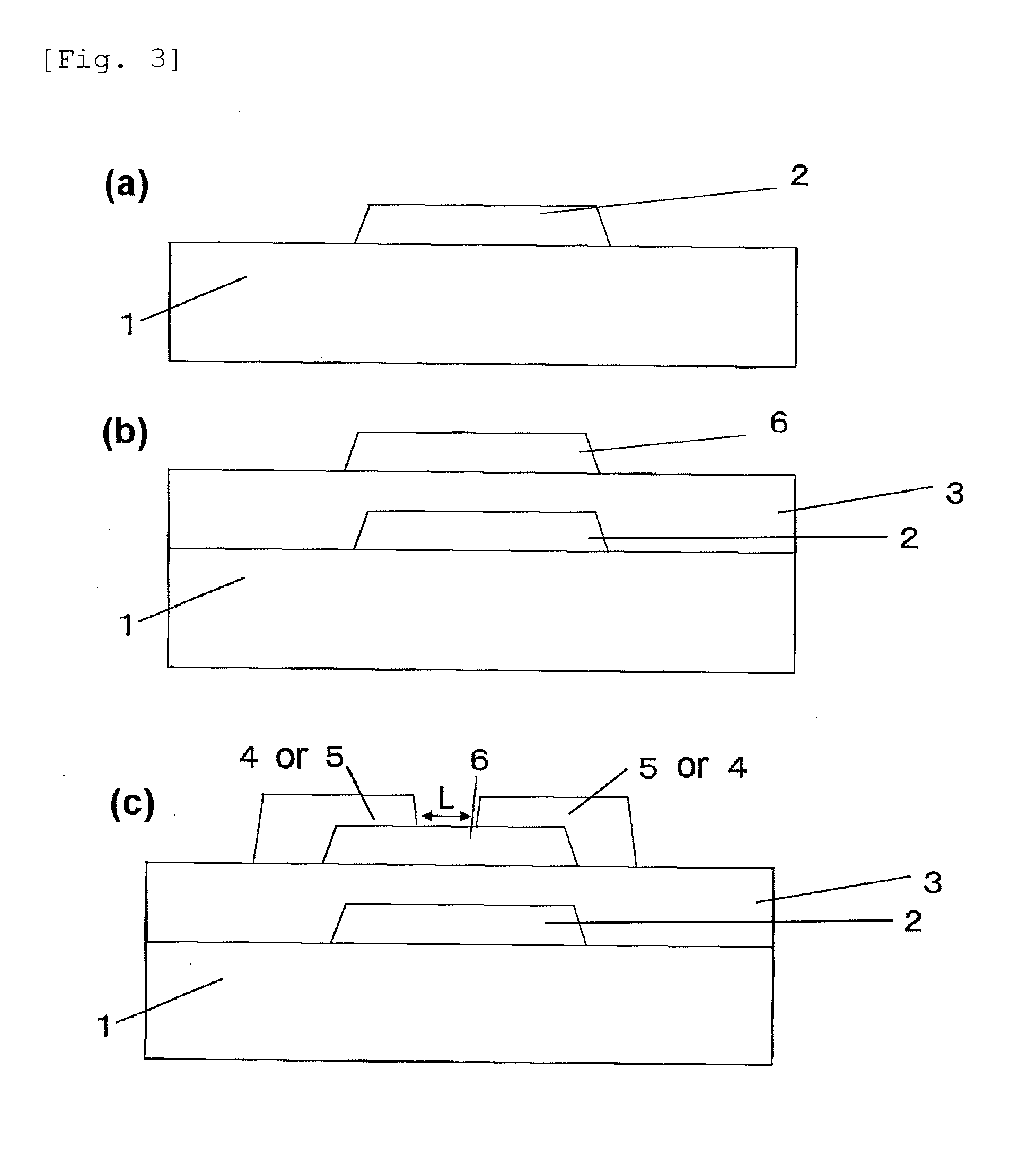

Plasma processing method and plasma processing apparatus

ActiveUS20180068862A1High etch rateHigh selectivityElectric discharge tubesSemiconductor/solid-state device manufacturingPlasma treatmentControllability

The present invention provides a plasma processing method and a plasma processing apparatus. The plasma processing method enables consistent processing by realizing a high selectivity and a high etching rate when etching a laminated film using a boron-containing amorphous carbon film, realizes high throughput including prior and post processes by simplifying a mask forming process, and has shape controllability of vertical processing. In the present invention, in a plasma processing method for forming a mask by plasma-etching a laminated film including an amorphous carbon film containing boron, the boron-containing amorphous carbon film is plasma-etched by using a mixed gas of an oxygen gas, a fluorine-containing gas, a halogen gas, and a silicon tetrafluoride gas, or a mixed gas of an oxygen gas, a fluorine-containing gas, a halogen gas, and a silicon tetrachloride gas.

Owner:HITACHI HIGH-TECH CORP

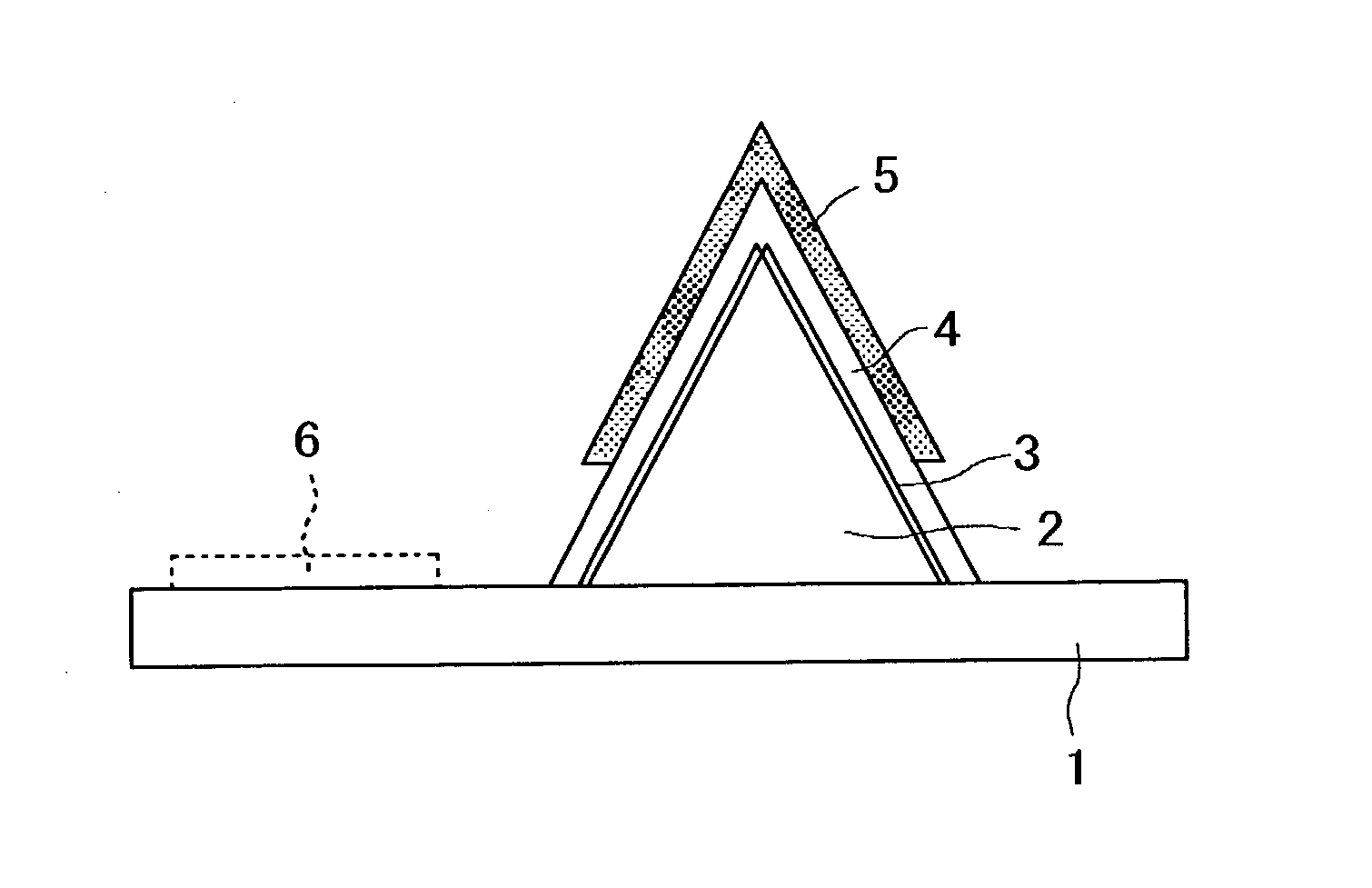

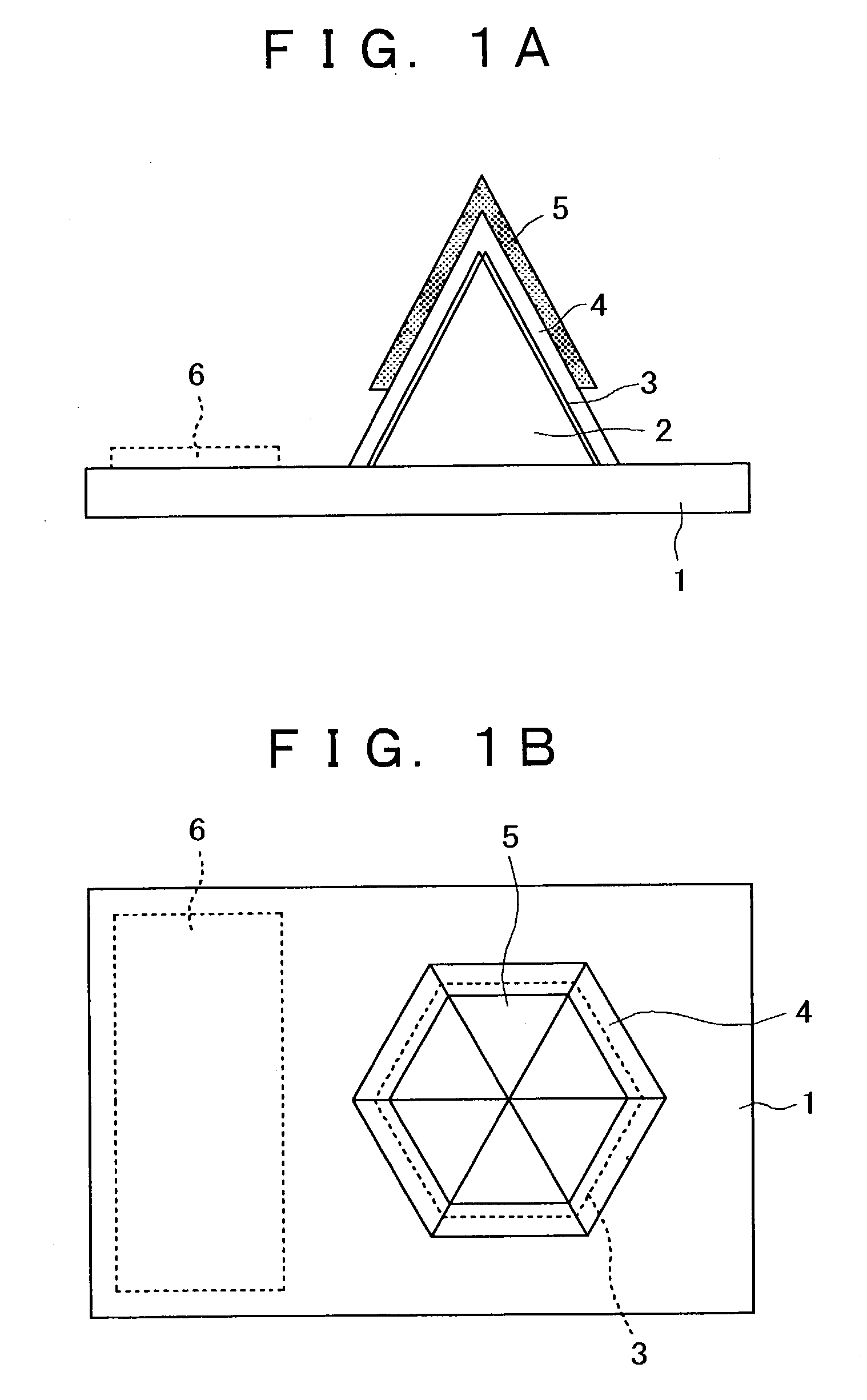

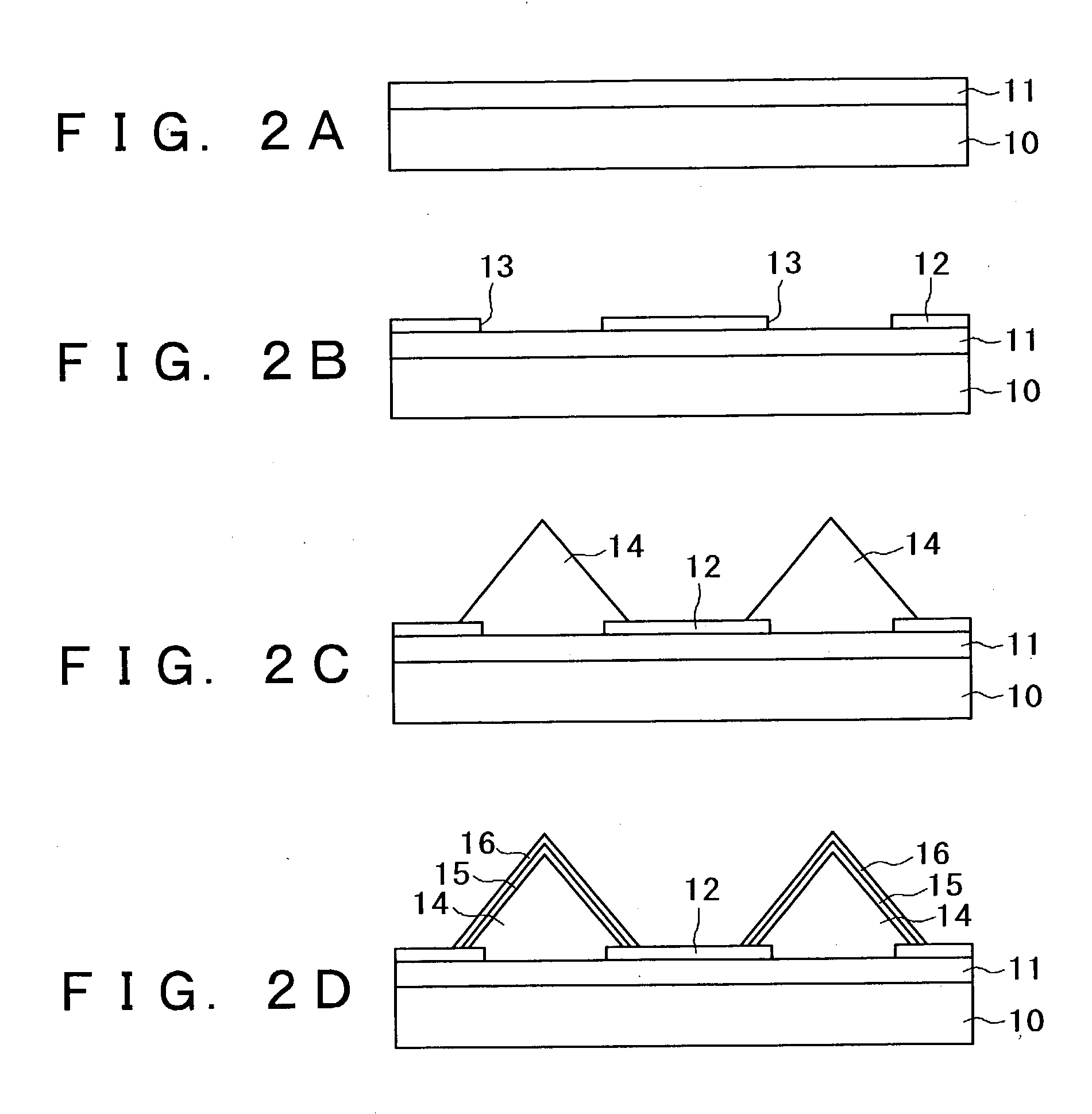

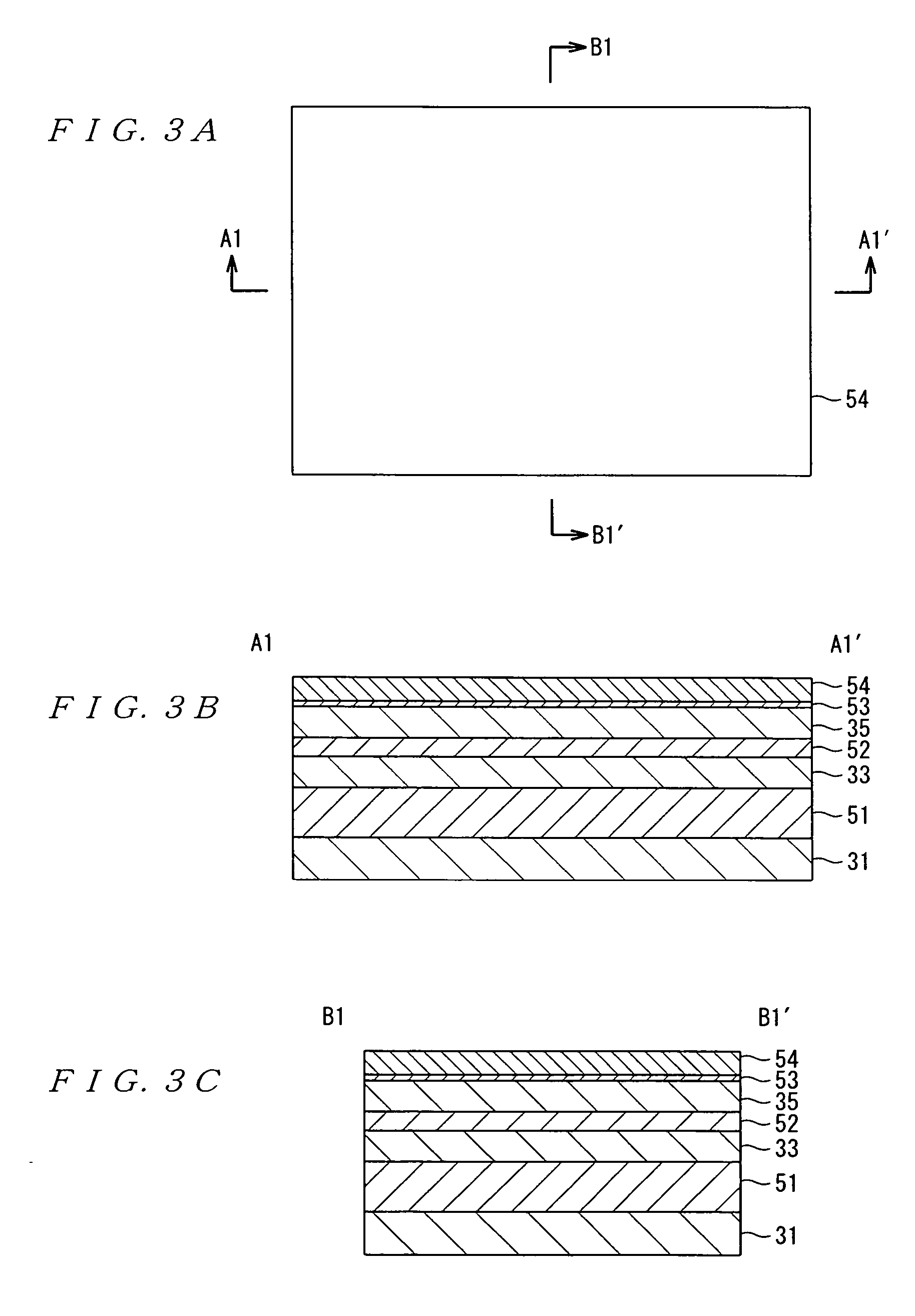

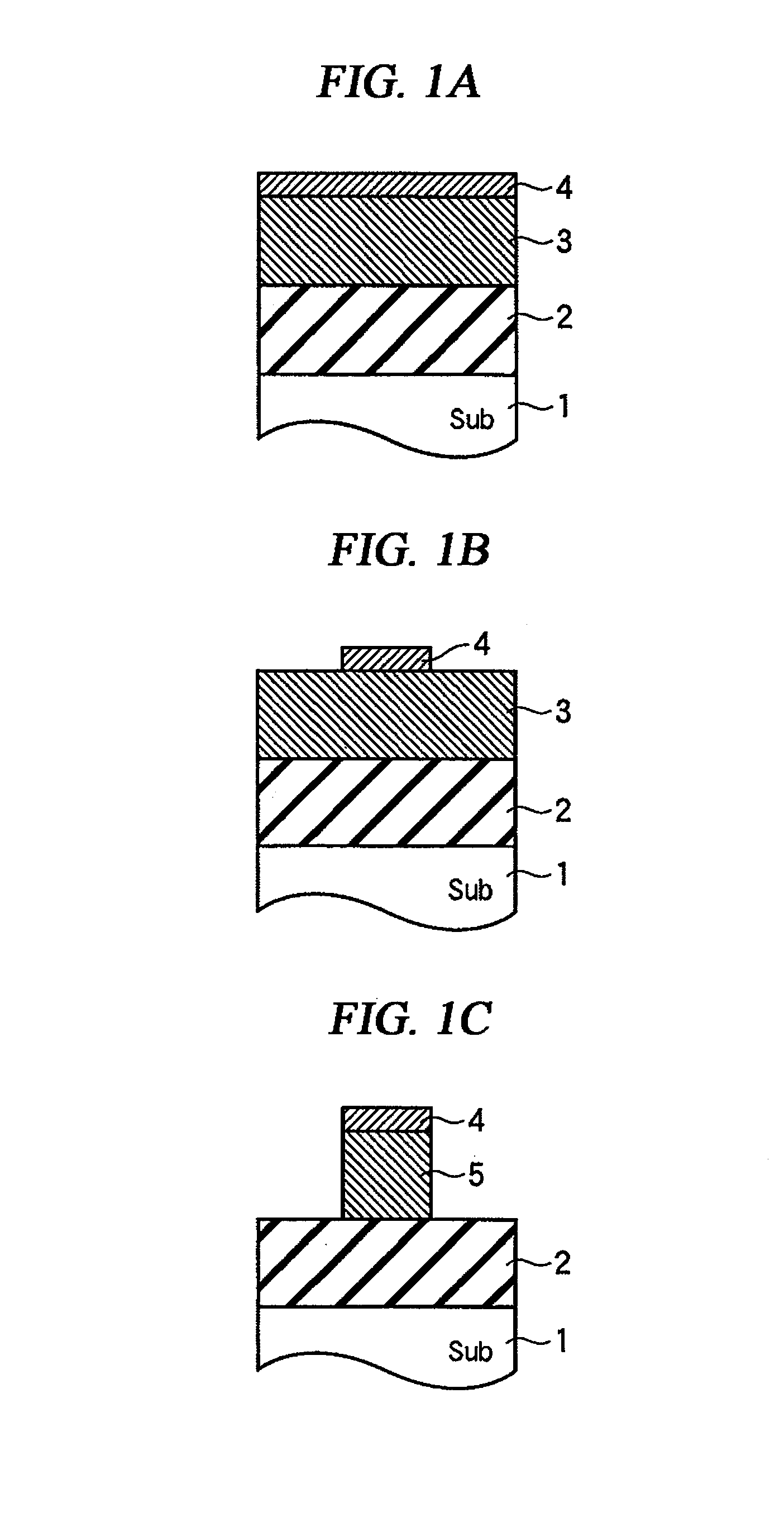

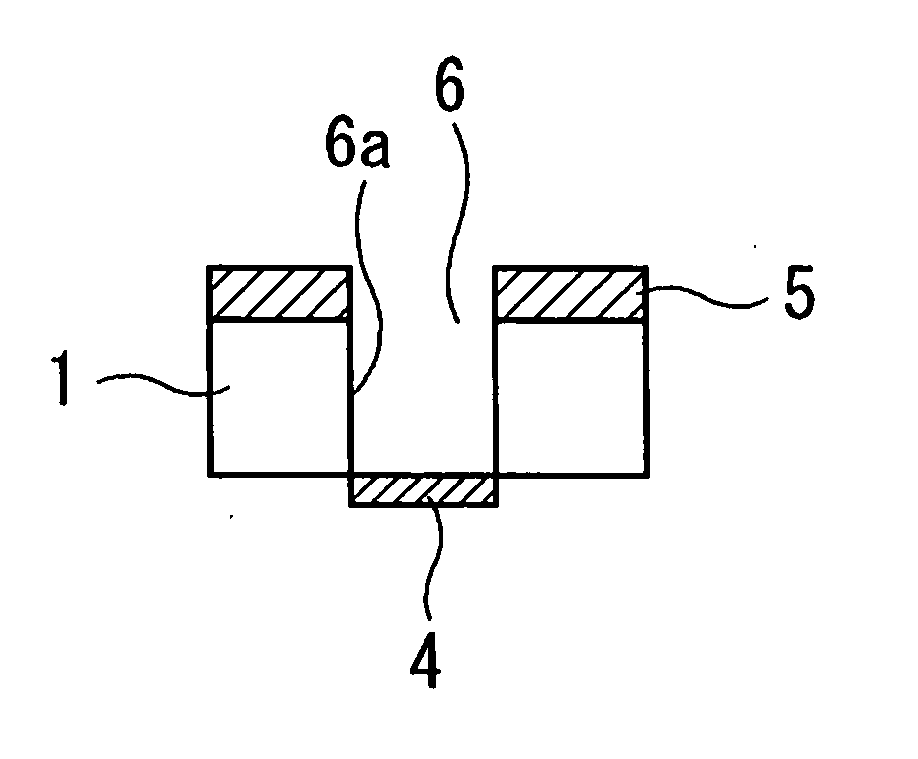

Selective growth method, and semiconductor light emitting device and fabrication method thereof

InactiveUS20030140846A1Improve featuresReduce widthPolycrystalline material growthSemiconductor/solid-state device manufacturingThree dimensional shapeActive layer

In a selective growth method, growth interruption is performed at the time of selective growth of a crystal layer on a substrate. Even if the thickness distribution of the crystal layer becomes non-uniform at the time of growth of the crystal layer, the non-uniformity of the thickness distribution of the crystal layer can be corrected by inserting the growth interruption. As a result of growth interruption, an etching rate at a thick portion becomes higher than that at a thin portion, to eliminate the difference in thickness between the thick portion and the thin portion, thereby solving the problem associated with degradation of characteristics due to a variation in thickness of the crystal layer, for example, an active layer. The selective growth method is applied to fabrication of a semiconductor light emitting device including an active layer as a crystal layer formed on a crystal layer having a three-dimensional shape by selective growth.

Owner:SAMSUNG ELECTRONICS CO LTD

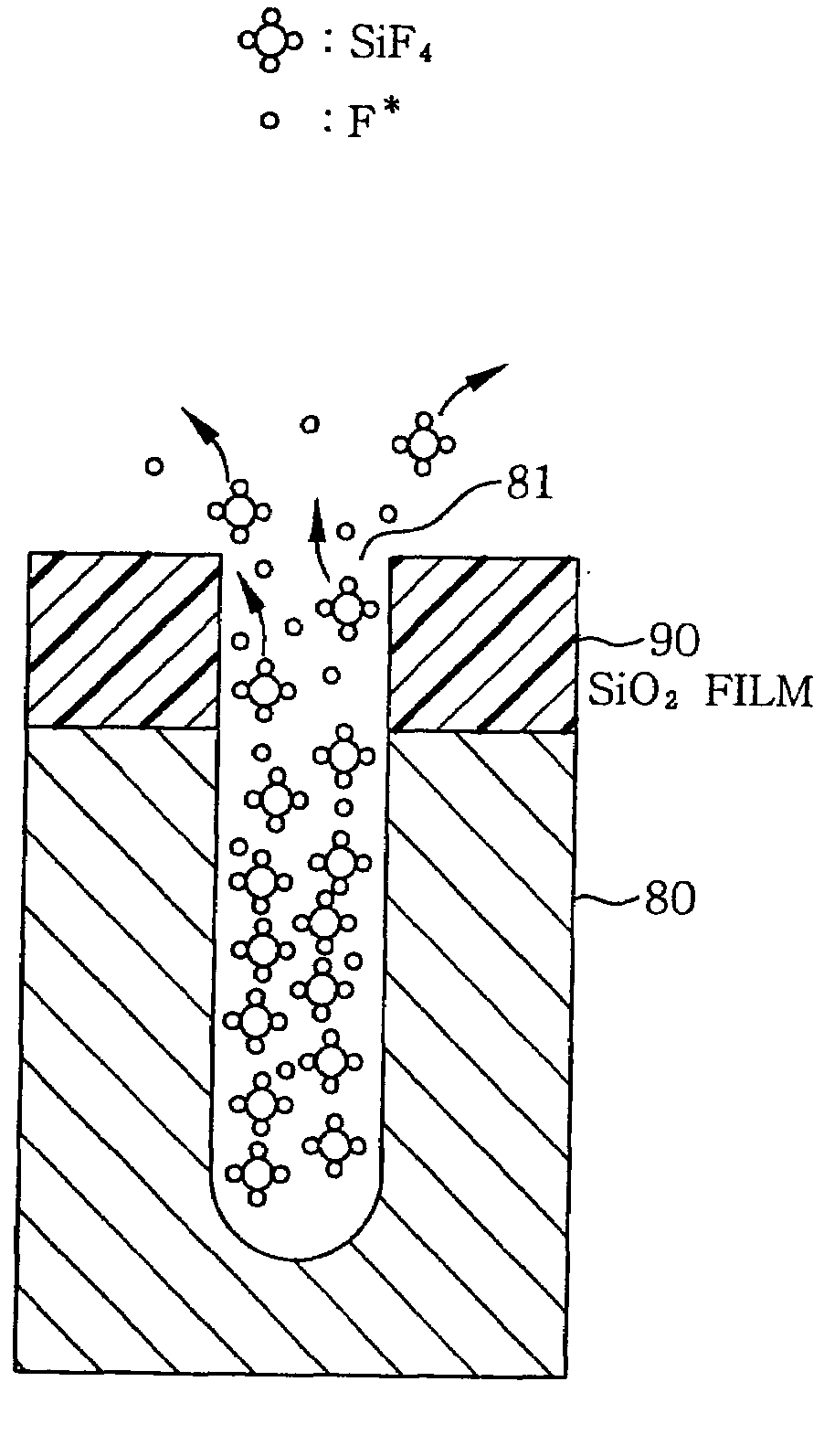

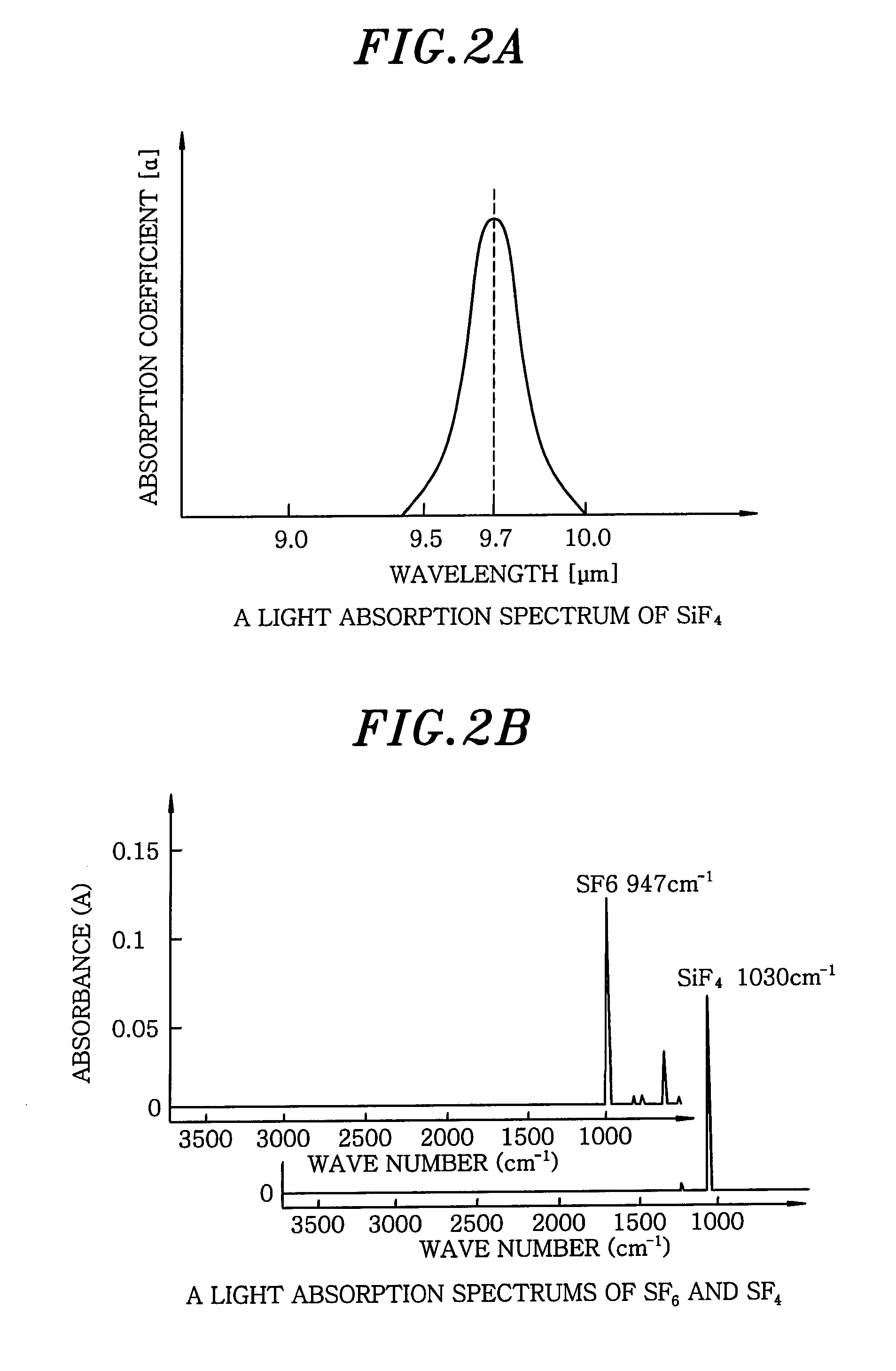

Plasma etching method and apparatus therefor

InactiveUS20090045167A1Increase chanceIncrease etch rateElectric discharge tubesVacuum gauge using ionisation effectsPeak intensityFluorine containing

A fluorine-containing compound gas, e.g., SF6 gas, is converted into a plasma and a silicon portion of an object to be processed is etched by the plasma. At the same time, using a light source having a peak intensity of light in a wavelength range of light absorption of a reaction product, e.g., SiF4, for which, to be more precise, ranges from 9 μm to 10 μm, the light is irradiated onto a surface of an object to be processed from the light source. The SiF4 molecules absorb the light, become activated and gain kinetic energy to be used in gaining an easy escape from a hole. As a consequence, an amount (a partial pressure) of fluorine radicals (F*) used as an etchant is increased and an etching rate of a silicon is increased.

Owner:TOKYO ELECTRON LTD

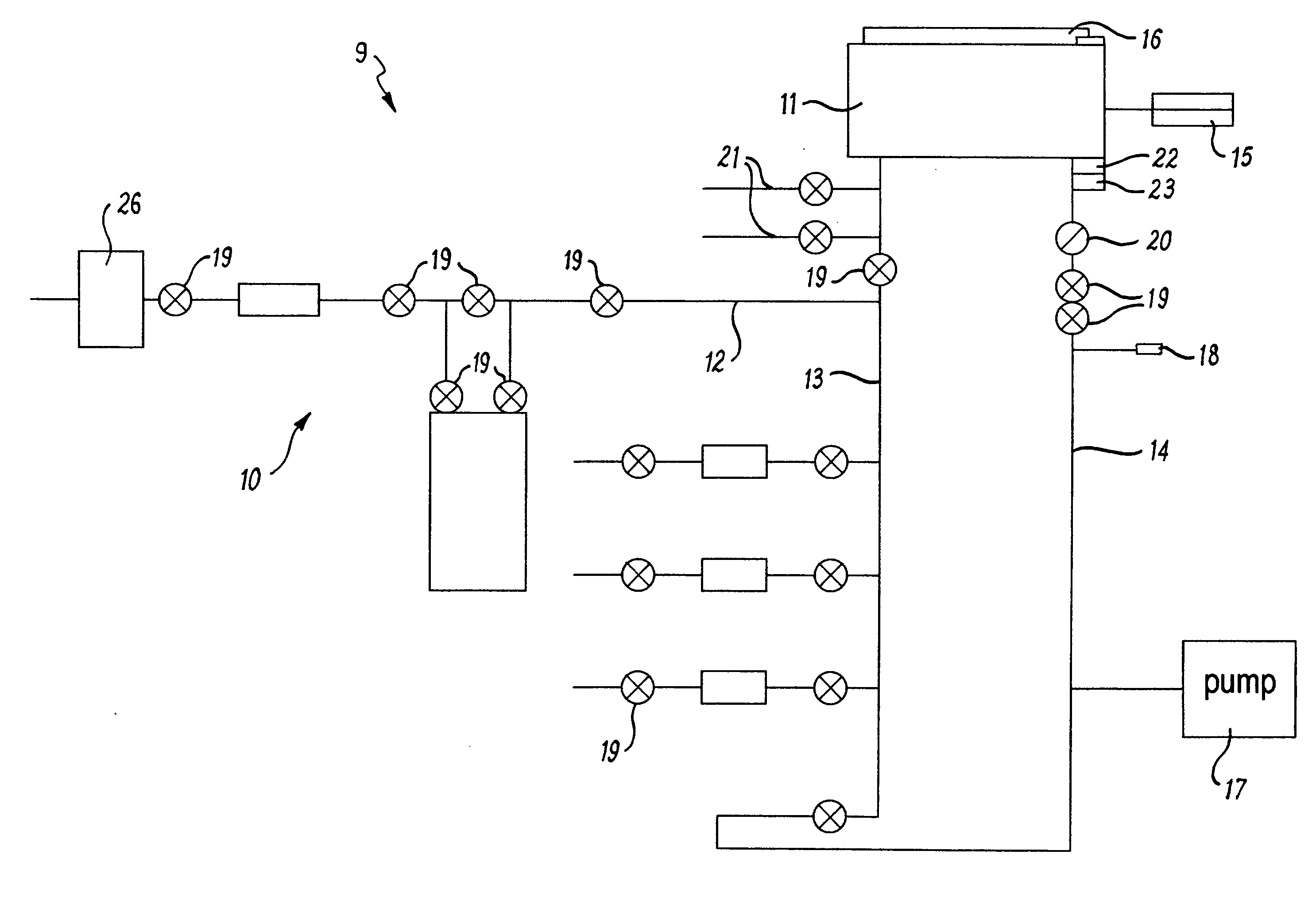

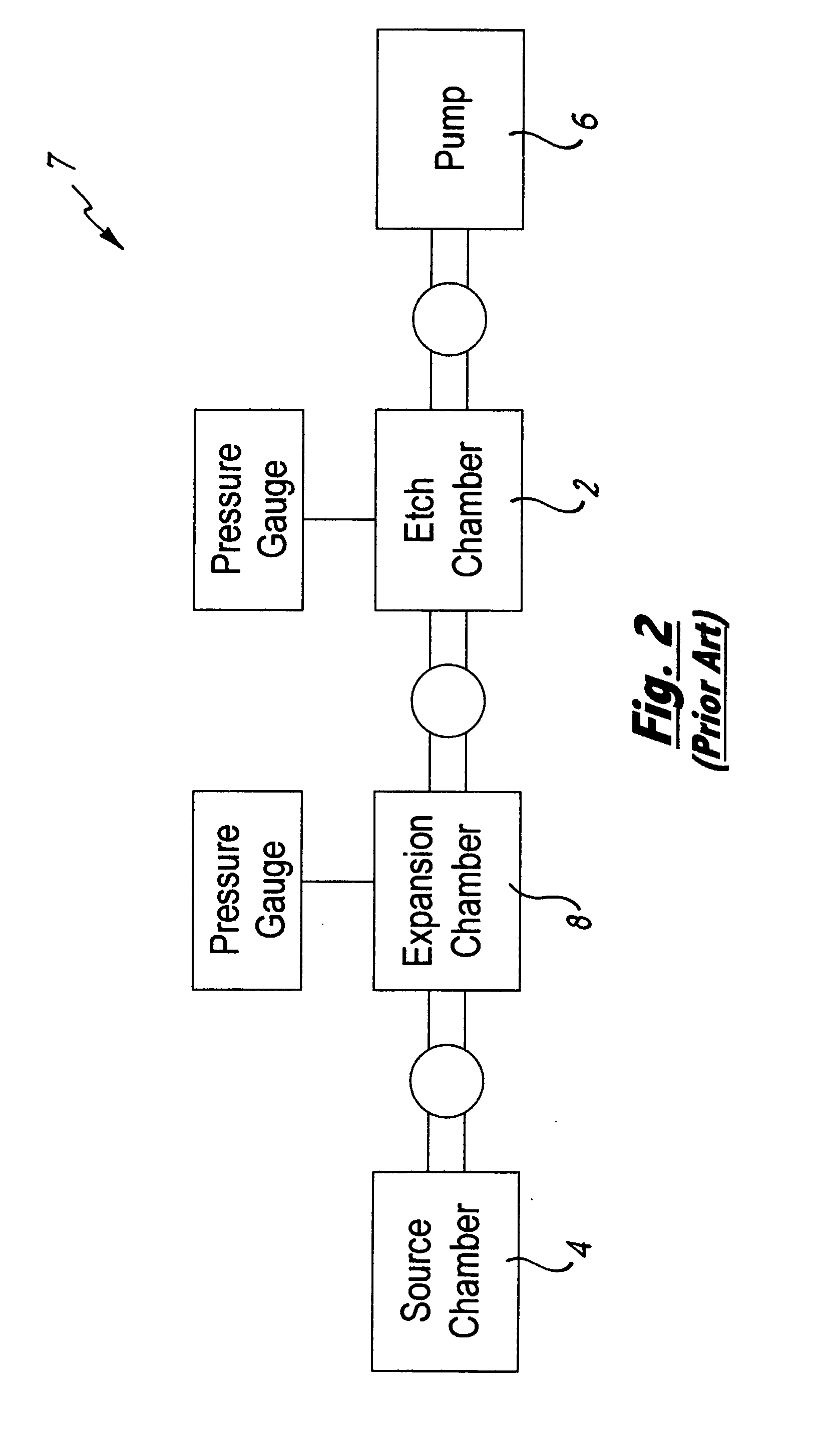

Method and Apparatus for the Etching of Microstructures

InactiveUS20080035607A1Increase partial pressureIncrease ratingsElectric discharge tubesDecorative surface effectsEtchingContinuous flow

An apparatus and method for providing an etching gas source for etching one or more microstructures located within a process chamber. the apparatus has a gas source supply line attached to a gas source and one or more chambers for containing an etching material. In use, the etching material is transformed into an etching material vapor within one or more of the chamber and the gas supply line provides a supply of carrier gas to the etching material vapor and also supplies the etching material vapor transported by the carrier gas to the process chamber. Advantageously, the apparatus of the invention does not require the incorporation of any expansion chambers or other complicated mechanical features in order to achieve a continuous flow of etching gas.

Owner:MEMSSTAR

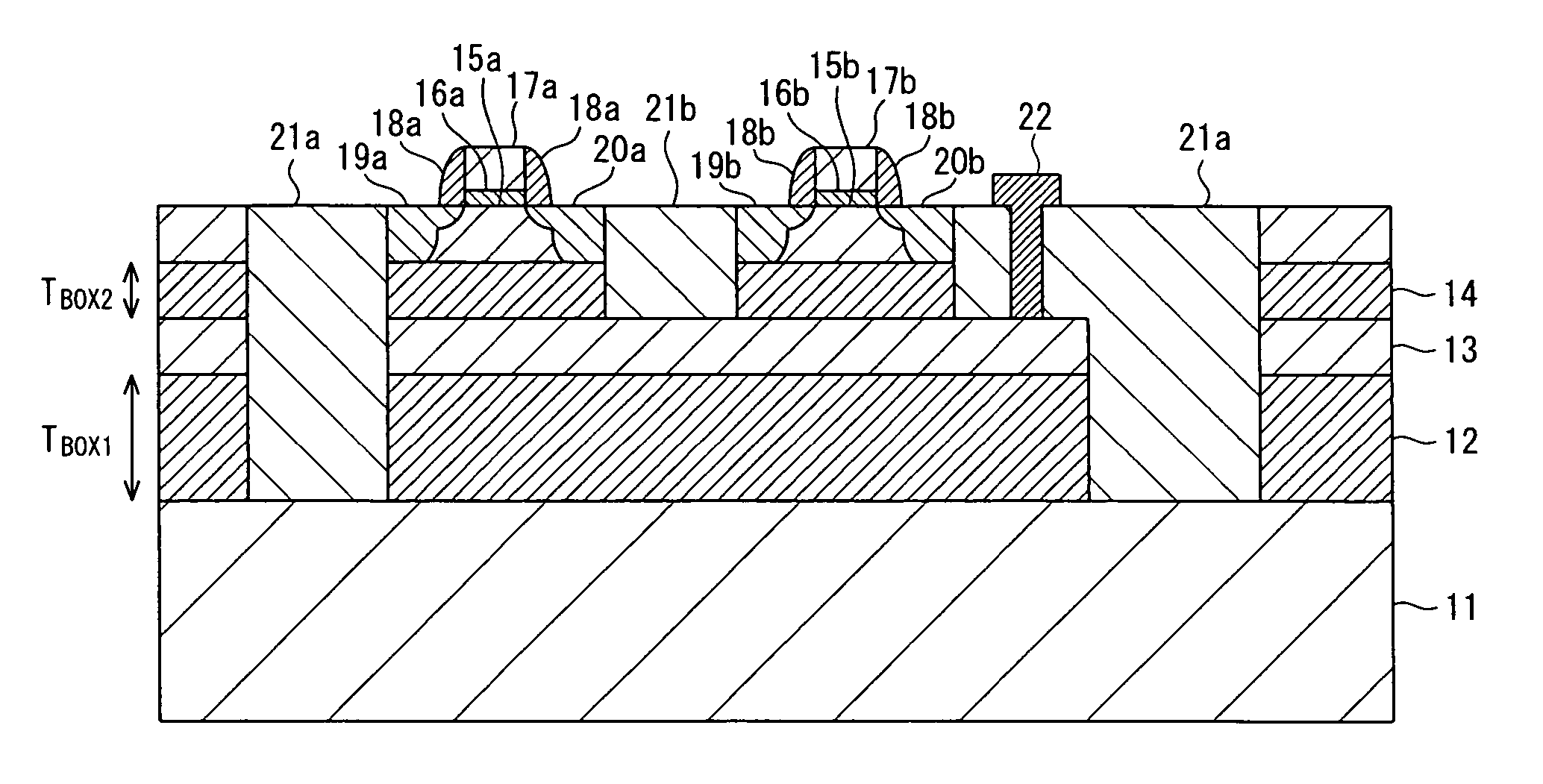

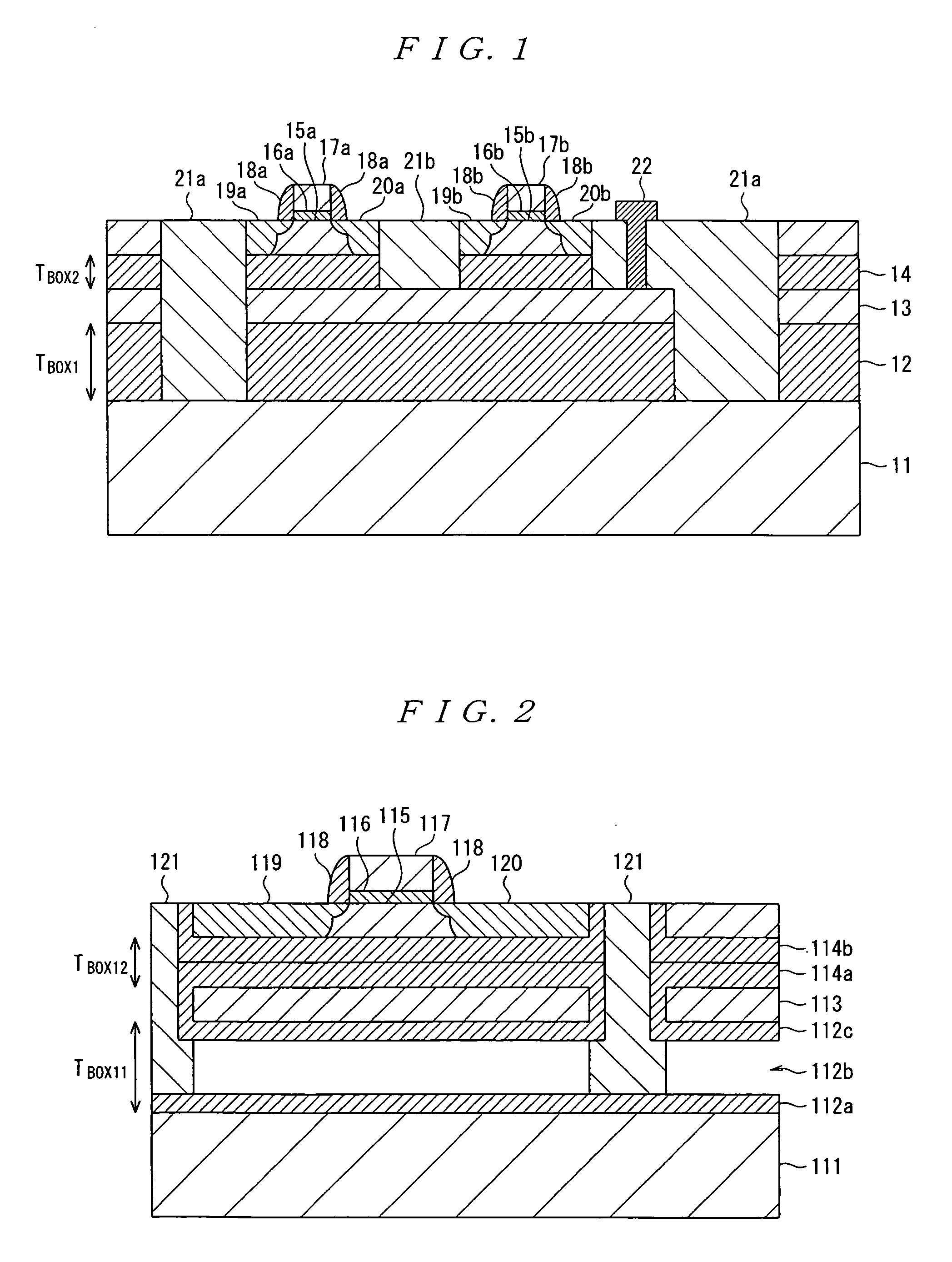

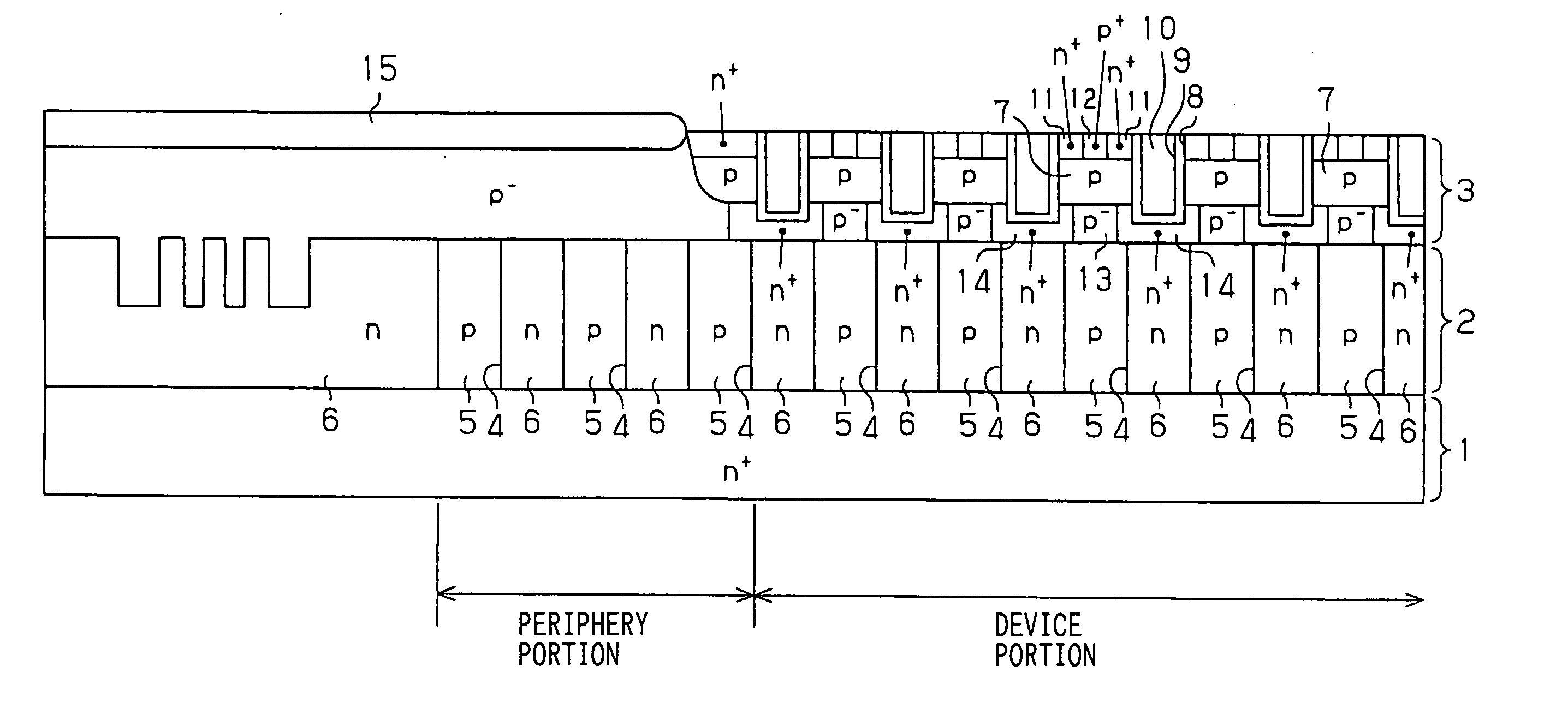

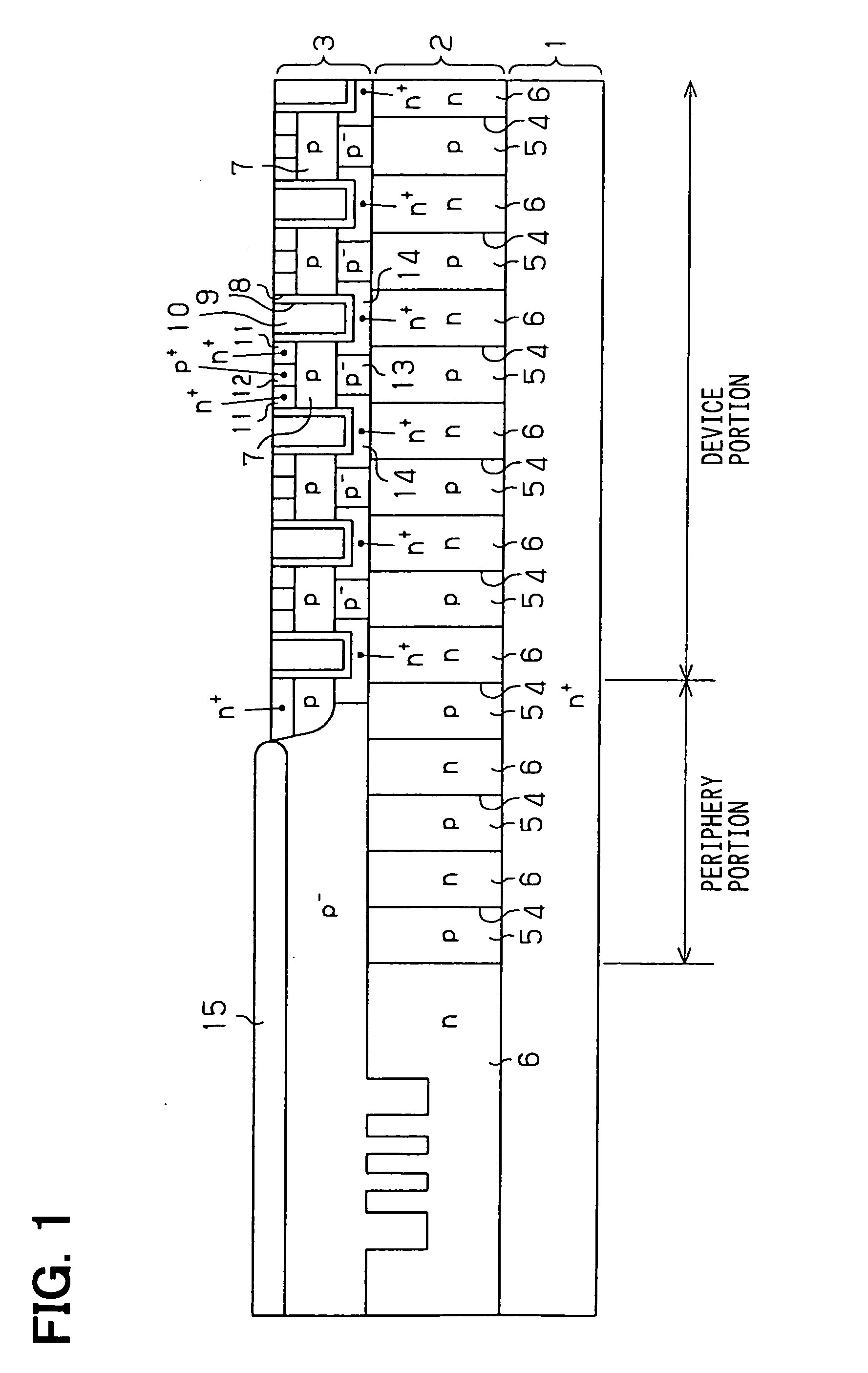

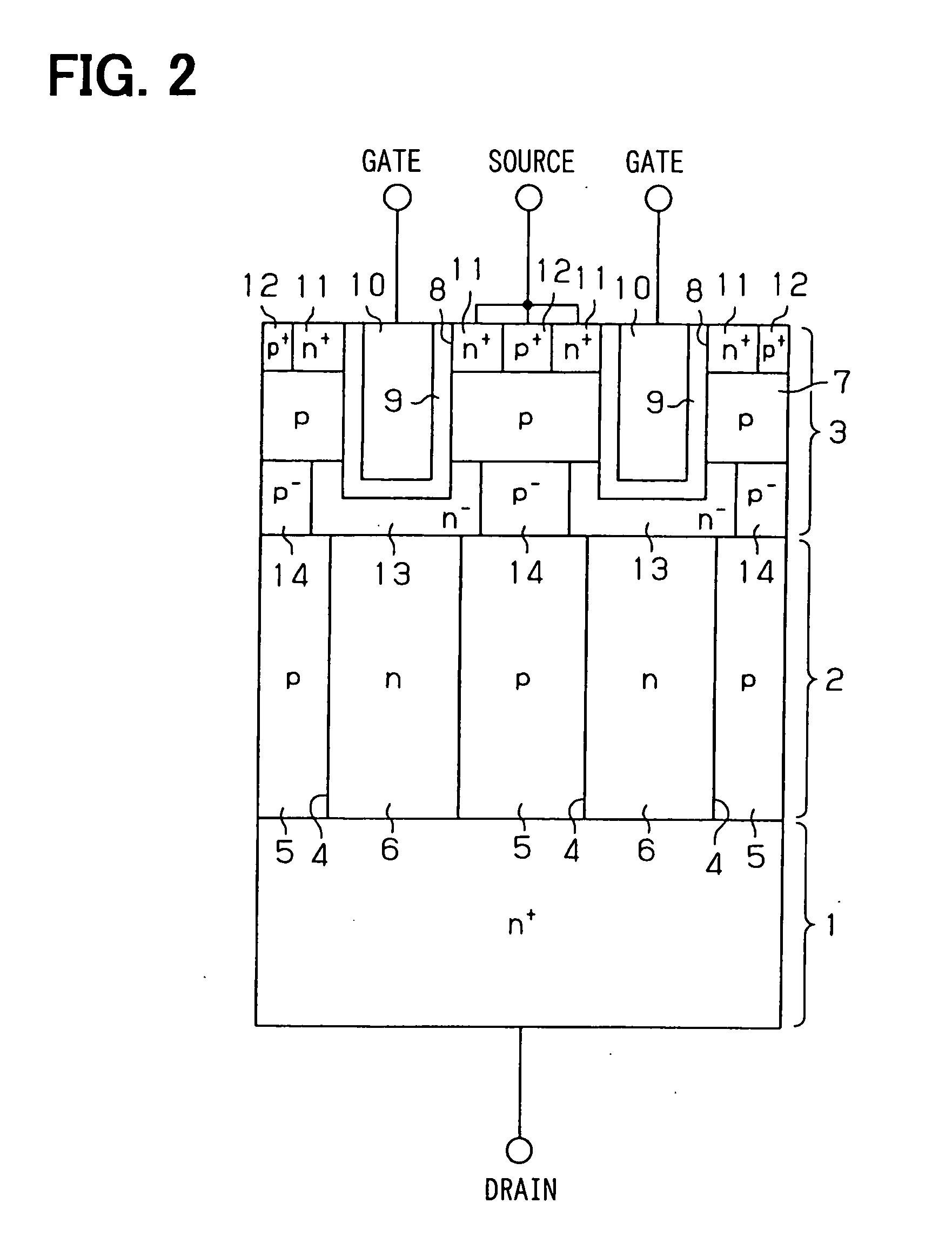

Semiconductor device and semiconductor device manufacturing method

InactiveUS20070075317A1Increase flexibilityImprove pressure resistanceSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialEngineering

A semiconductor device includes a back gate electrode composed of a first single-crystal semiconductor layer formed on a first insulating layer; a second insulating layer formed on the first single-crystal semiconductor layer and having a film thickness smaller than a film thickness of the first insulating layer; a second single-crystal semiconductor layer formed on the second insulating layer; a gate electrode formed on the second single-crystal semiconductor layer; and source and drain layers that are formed on the second single-crystal semiconductor layer and arranged on respective sides of the gate electrode.

Owner:SEIKO EPSON CORP +1

Method for etching a layer on a silicon semiconductor substrate

InactiveUS20100203739A1Increase selectivityHigh selectivitySemiconductor/solid-state device manufacturingMicrostructural device manufactureEtchingSemiconductor

A method for selective etching of an SiGe mixed semiconductor layer on a silicon semiconductor substrate by dry chemical etching of the SiGe mixed semiconductor layer with the aid of an etching gas selected from the group including ClF3 and / or ClF5, a gas selected from the group including Cl2 and / or HCl being added to the etching gas.

Owner:ROBERT BOSCH GMBH

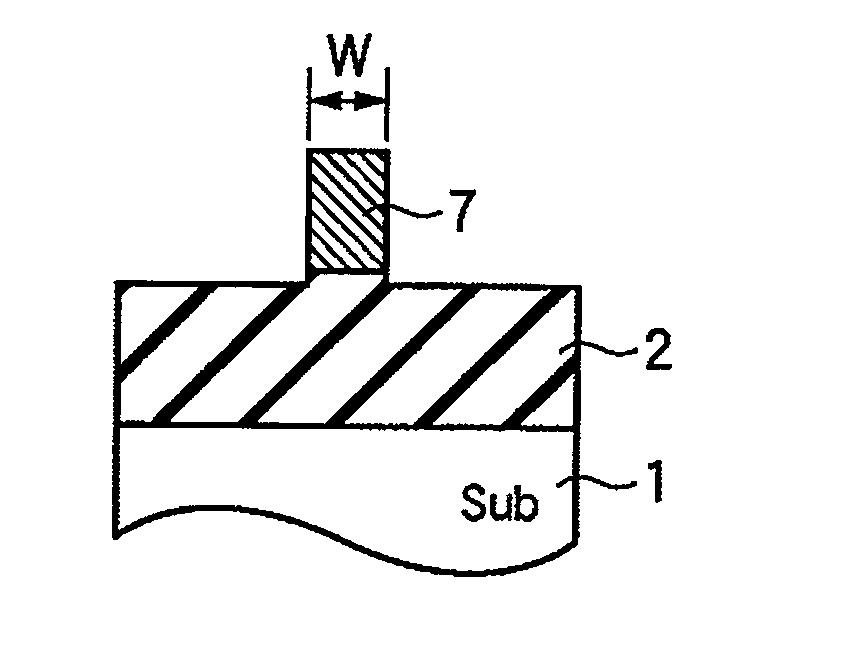

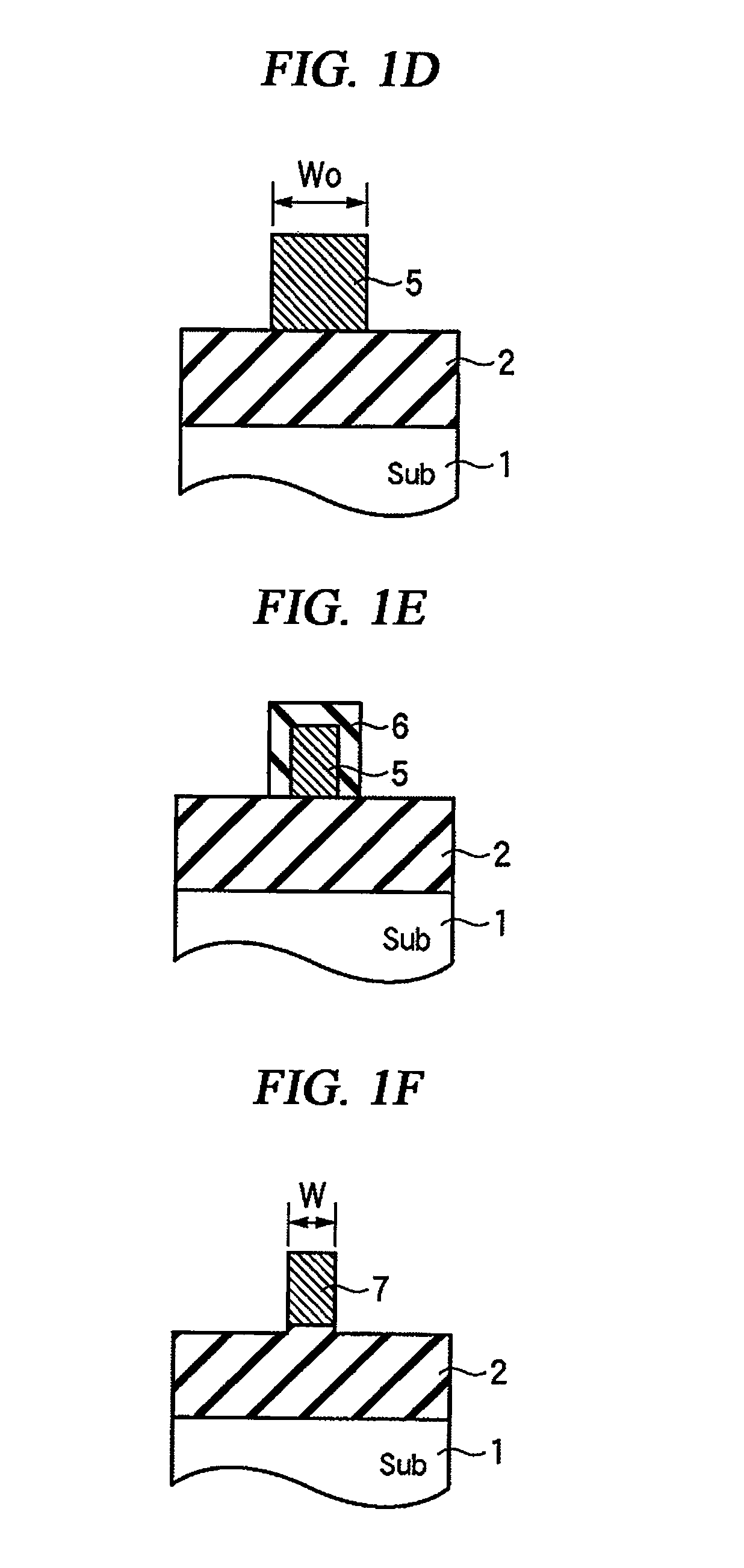

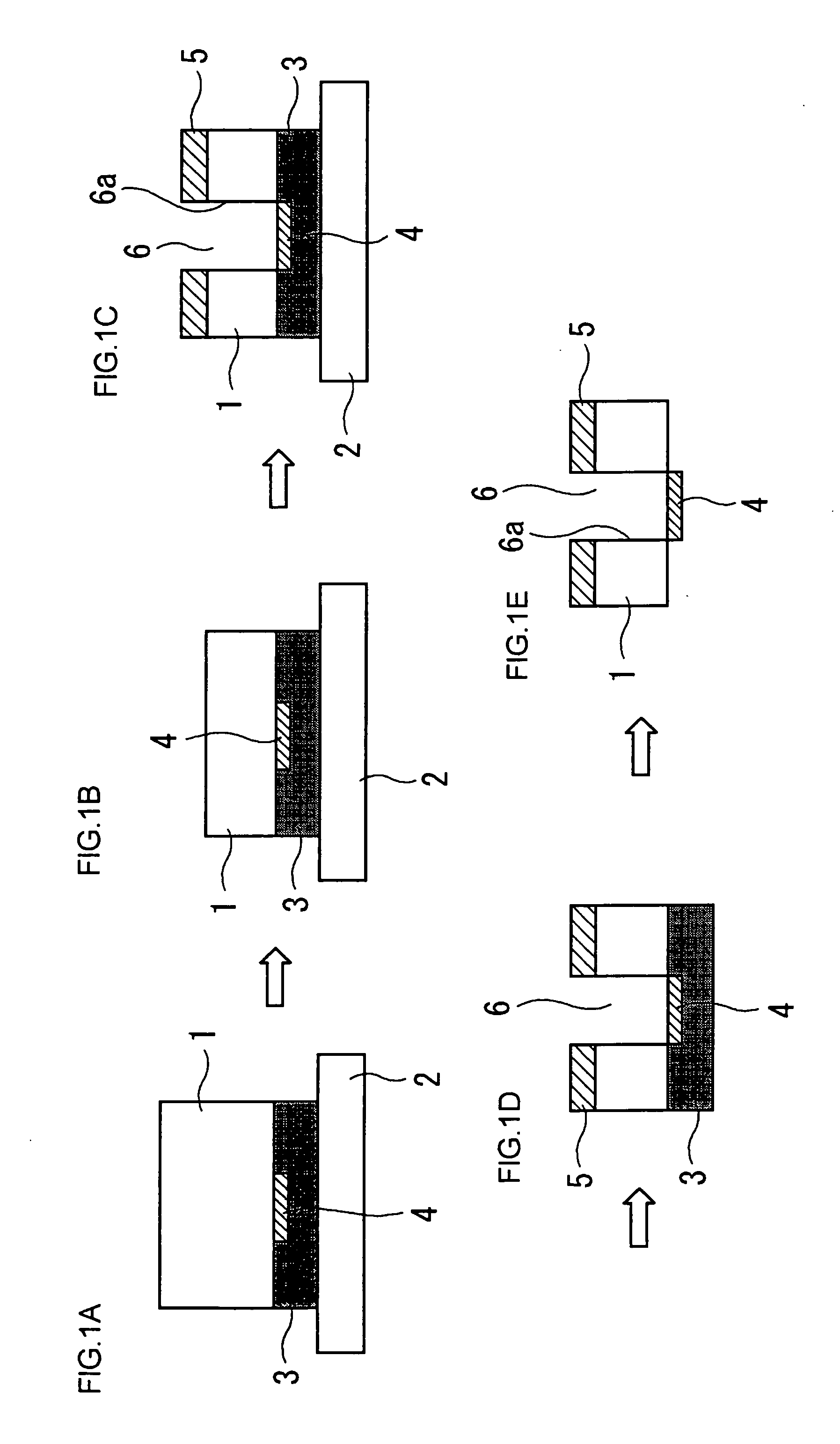

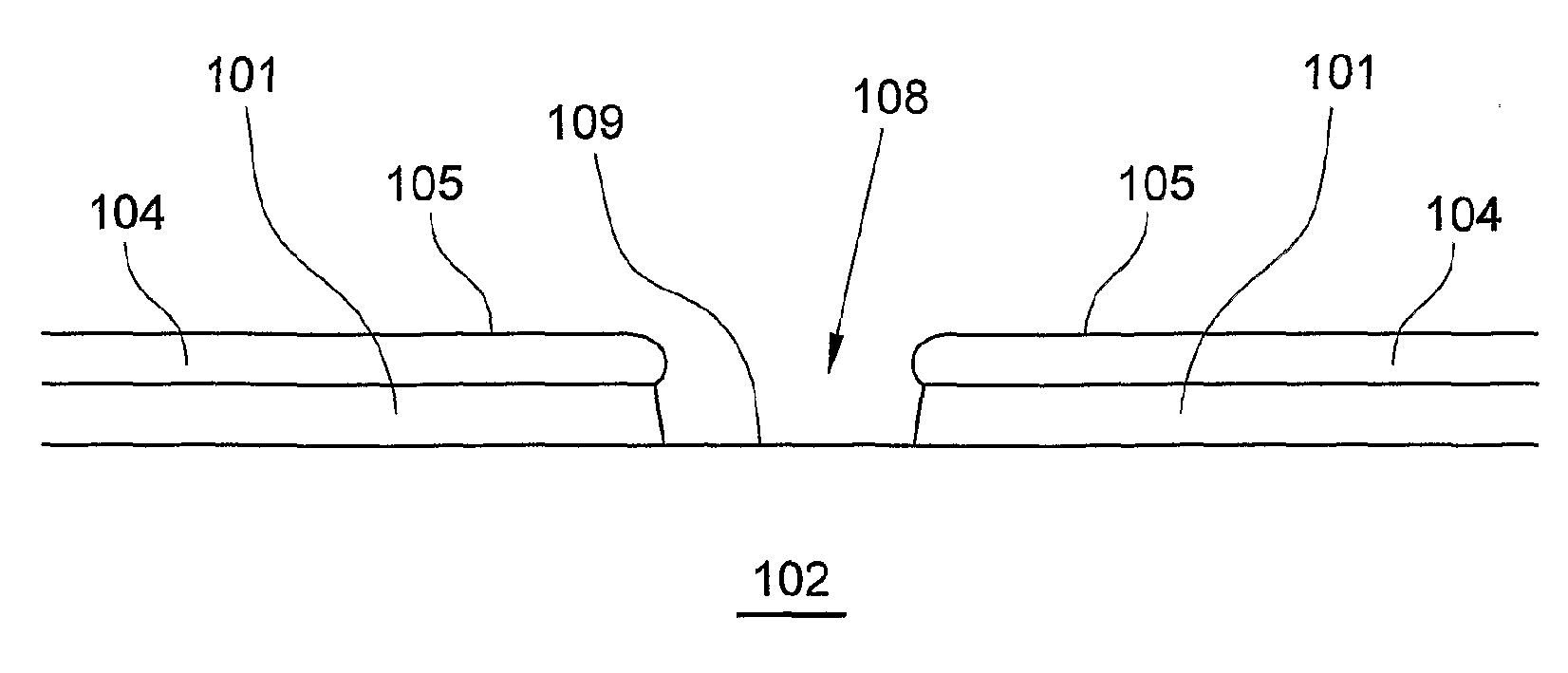

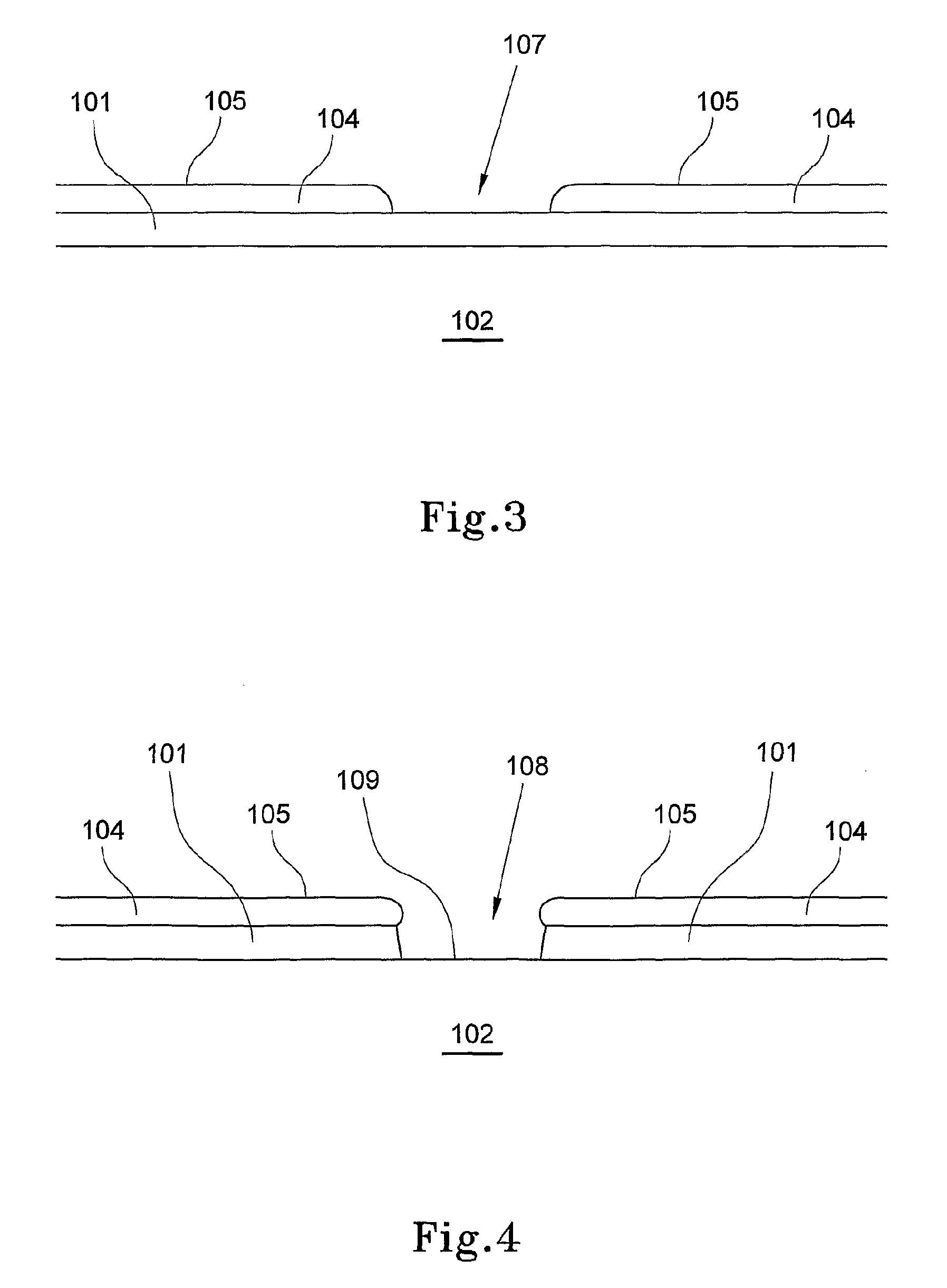

Manufacturing method of fin-type field effect transistor

InactiveUS20080171407A1Inhibition formationIncrease etch rateSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringField-effect transistor

A method for manufacturing a fin-type field effect transistor simply and securely by using a SOI (Silicon On Insulator) wafer, capable of suppressing an undercut formation, is disclosed. The method includes forming a fin-shaped protrusion by selectively dry-etching a single crystalline silicon layer until an underlying buried oxide layer is exposed; forming a sacrificial oxide film by oxidizing a surface of the protrusion including a damage inflicted thereon; and forming a fin having a clean surface by removing the sacrificial oxide film by etching, wherein an etching rate r1 of the sacrificial oxide film is higher than an etching rate r2 of the buried oxide layer during the etching.

Owner:TOKYO ELECTRON LTD

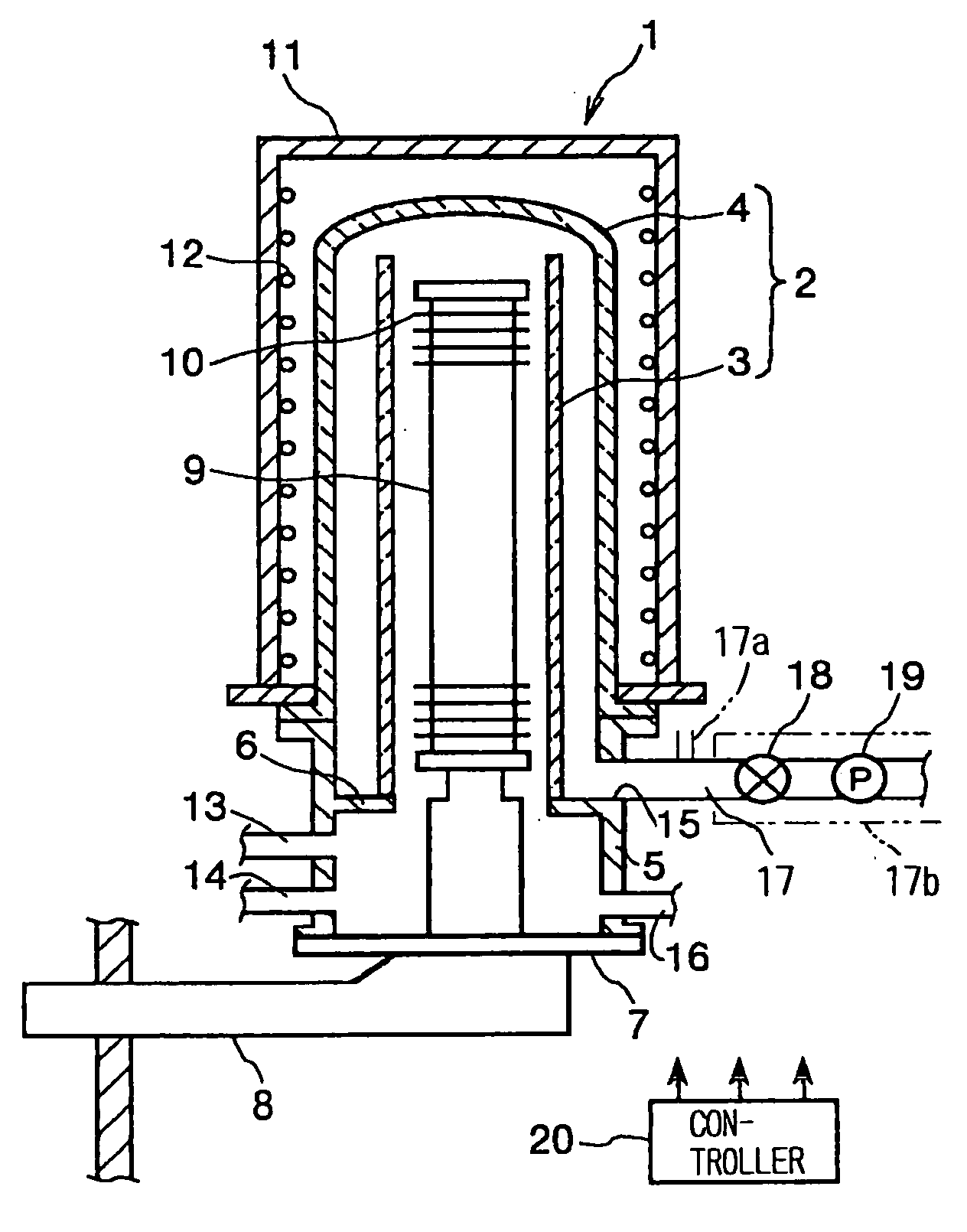

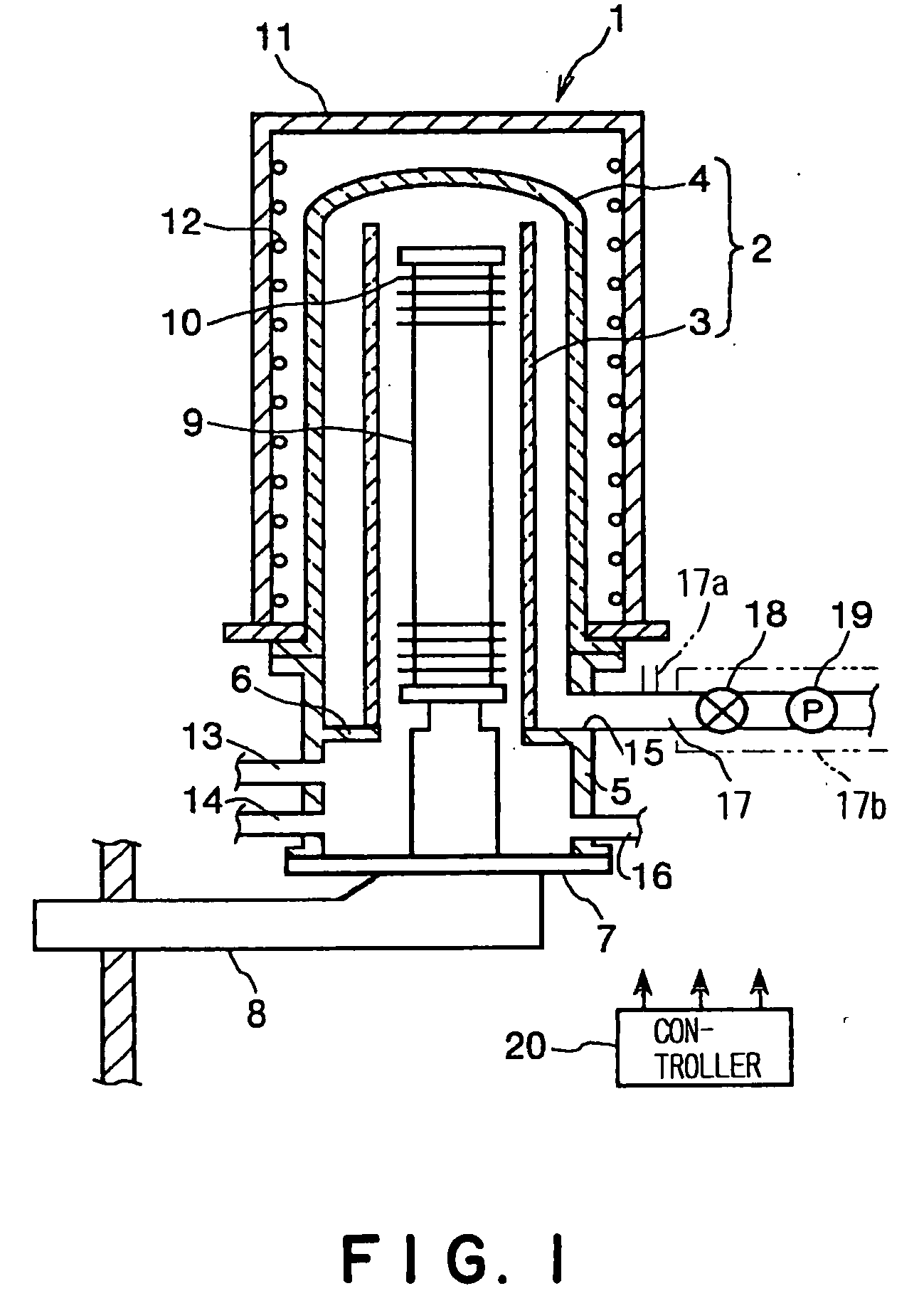

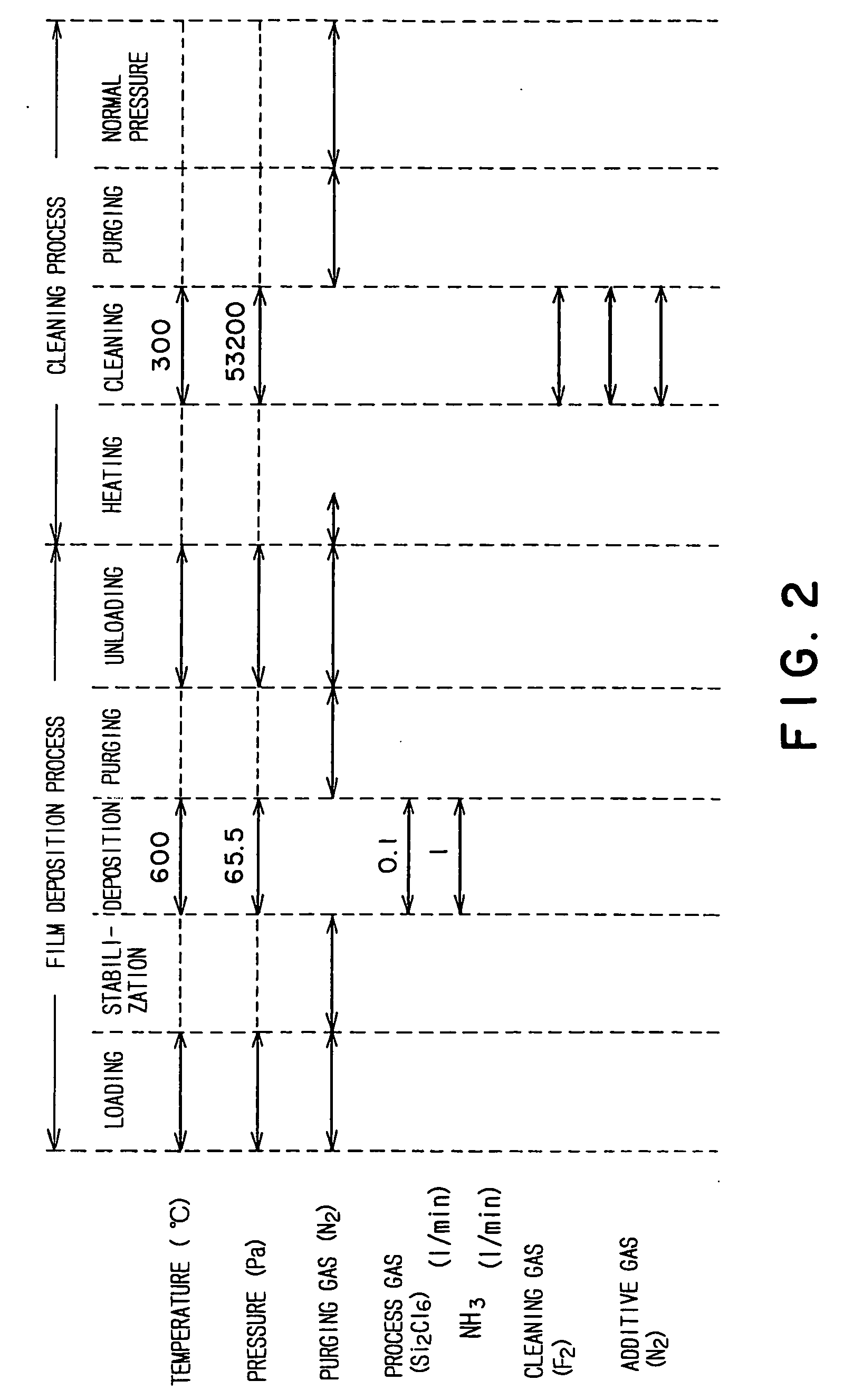

Thin film forming apparatus cleaning method

InactiveUS20050090123A1Inhibit deteriorationIncrease etch rateDrying solid materials without heatSemiconductor/solid-state device manufacturingCleaning methodsNitrogen gas

A cleaning process for cleaning a thermal processing apparatus includes: a heating step of heating an interior of a reaction tube at 300° C., and a cleaning step of removing deposits deposited in the thermal processing apparatus. In the cleaning step, a cleaning gas containing fluorine gas, chlorine gas and nitrogen gas is supplied into the interior of the reaction tube heated at 300° C. to remove silicon nitride so to clean an interior of the thermal processing apparatus.

Owner:TOKYO ELECTRON LTD

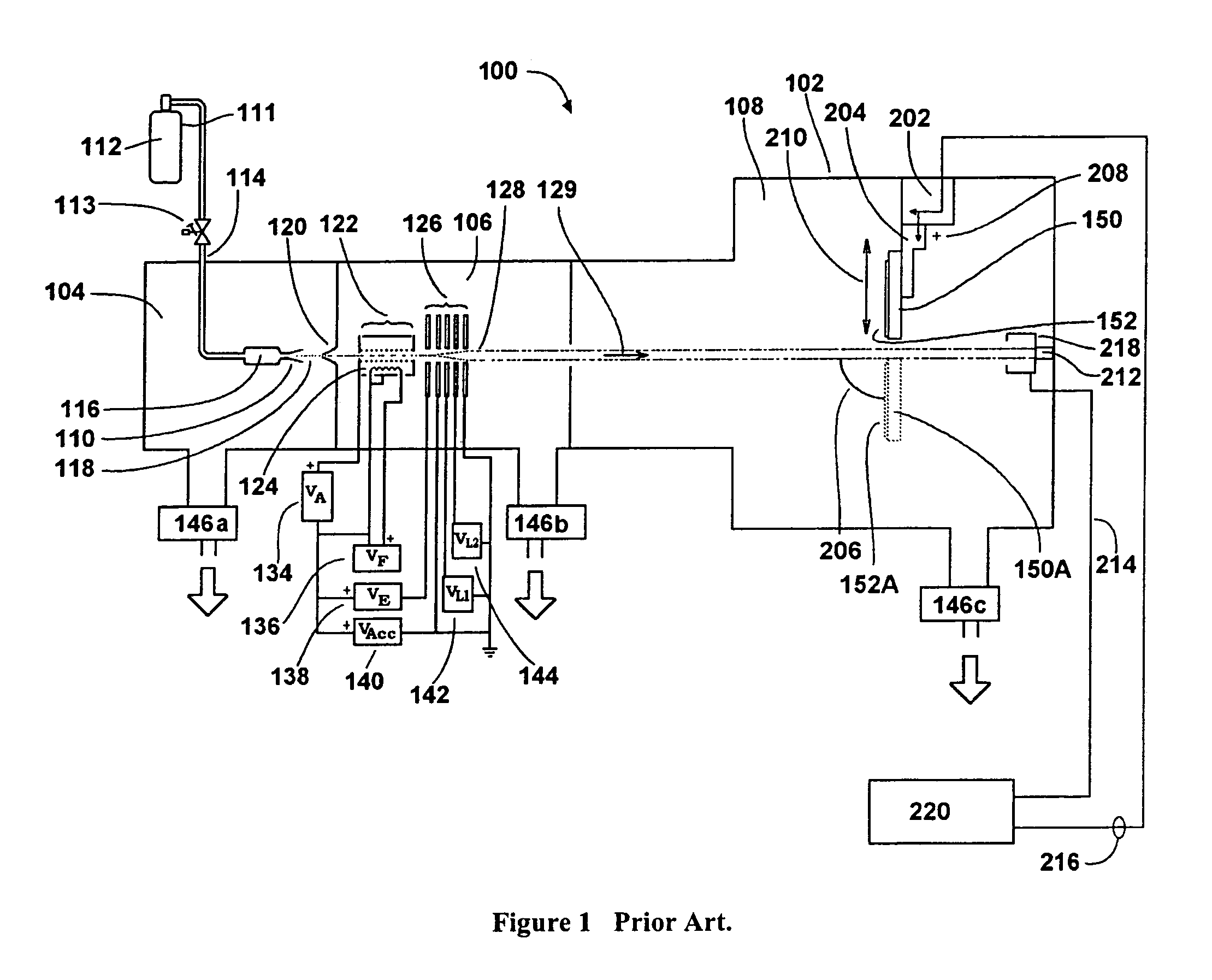

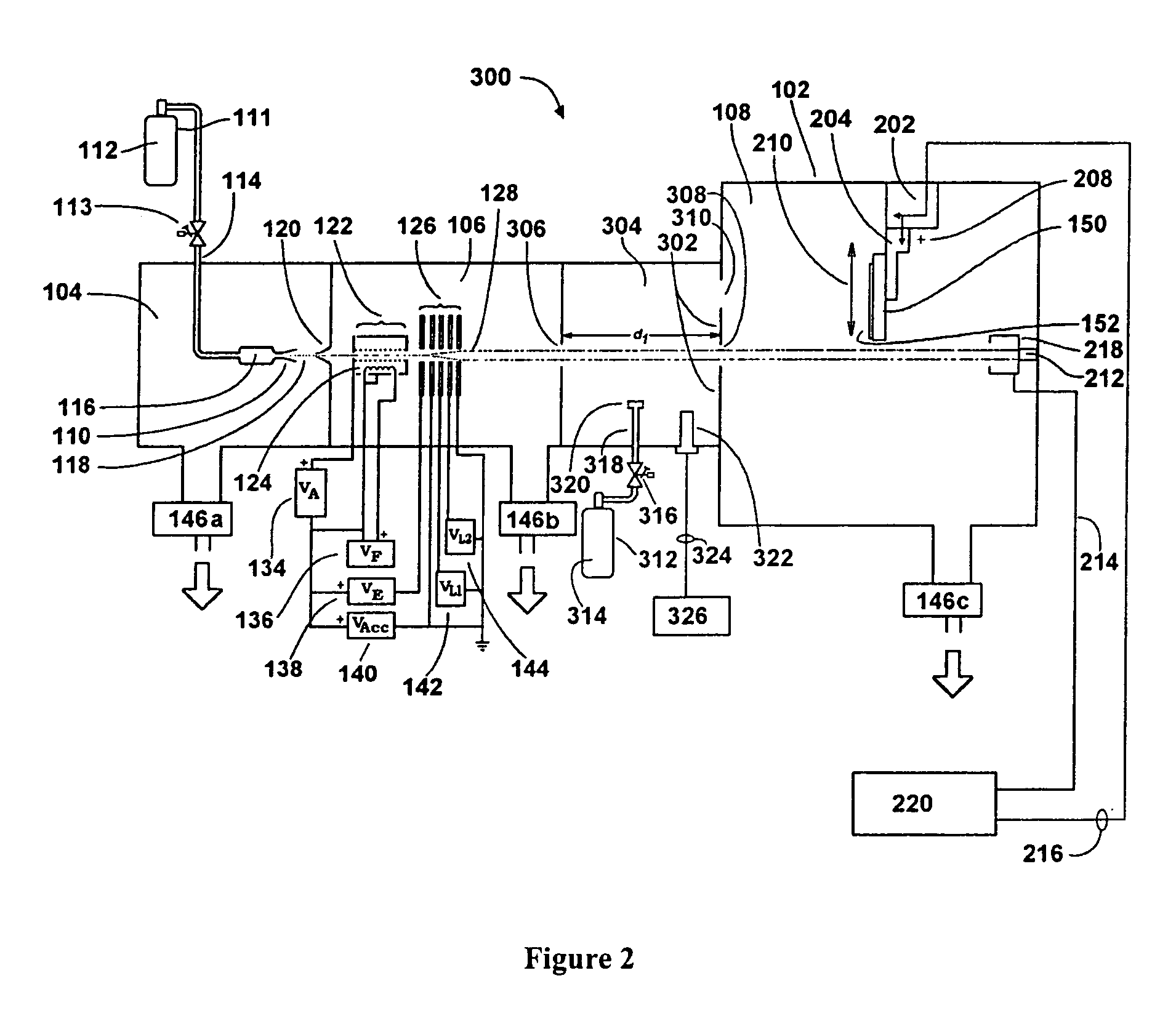

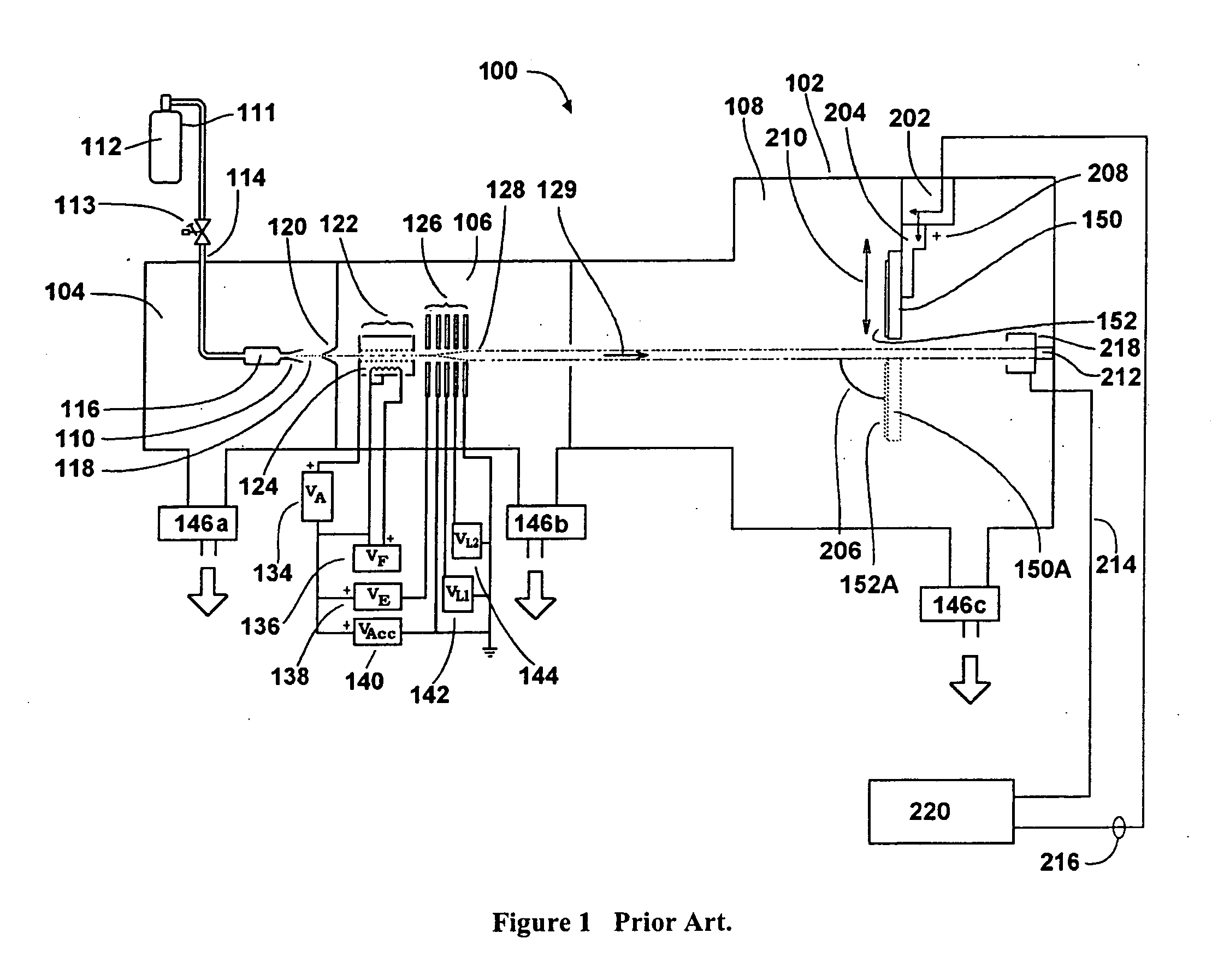

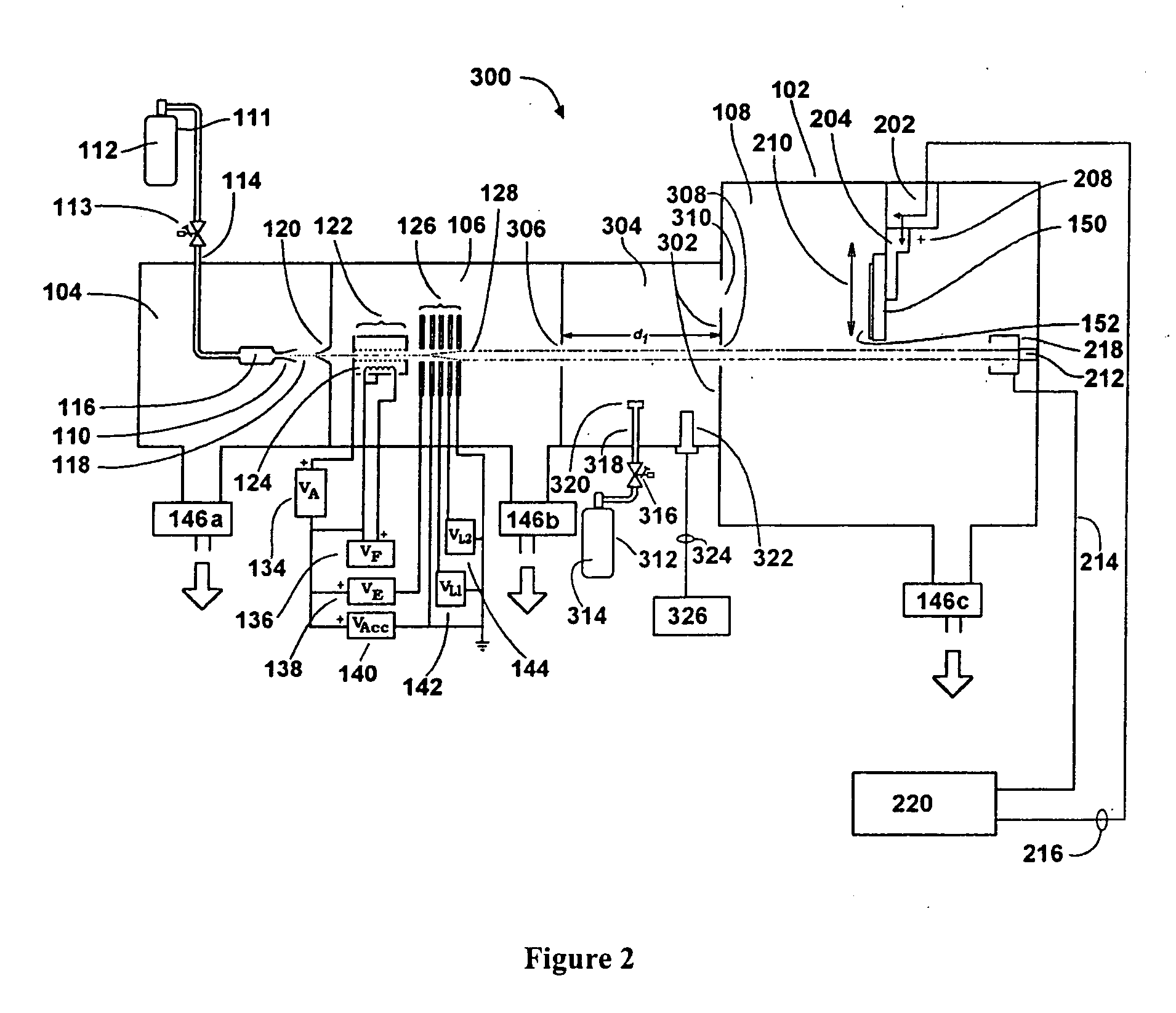

Method and apparatus for improved processing with a gas-cluster ion beam

ActiveUS7060989B2Smoothing capabilityImprove etching effectMaterial analysis by optical meansIon beam tubesGas cluster ion beamLight beam

Apparatus and methods for improving processing of workpieces with gas-cluster ion beams and modifying the gas-cluster ion energy distribution in the GCIB. In a reduced-pressure environment, generating an energetic gas-cluster ion beam and subjecting the beam to increased pressure region.

Owner:TEL EPION

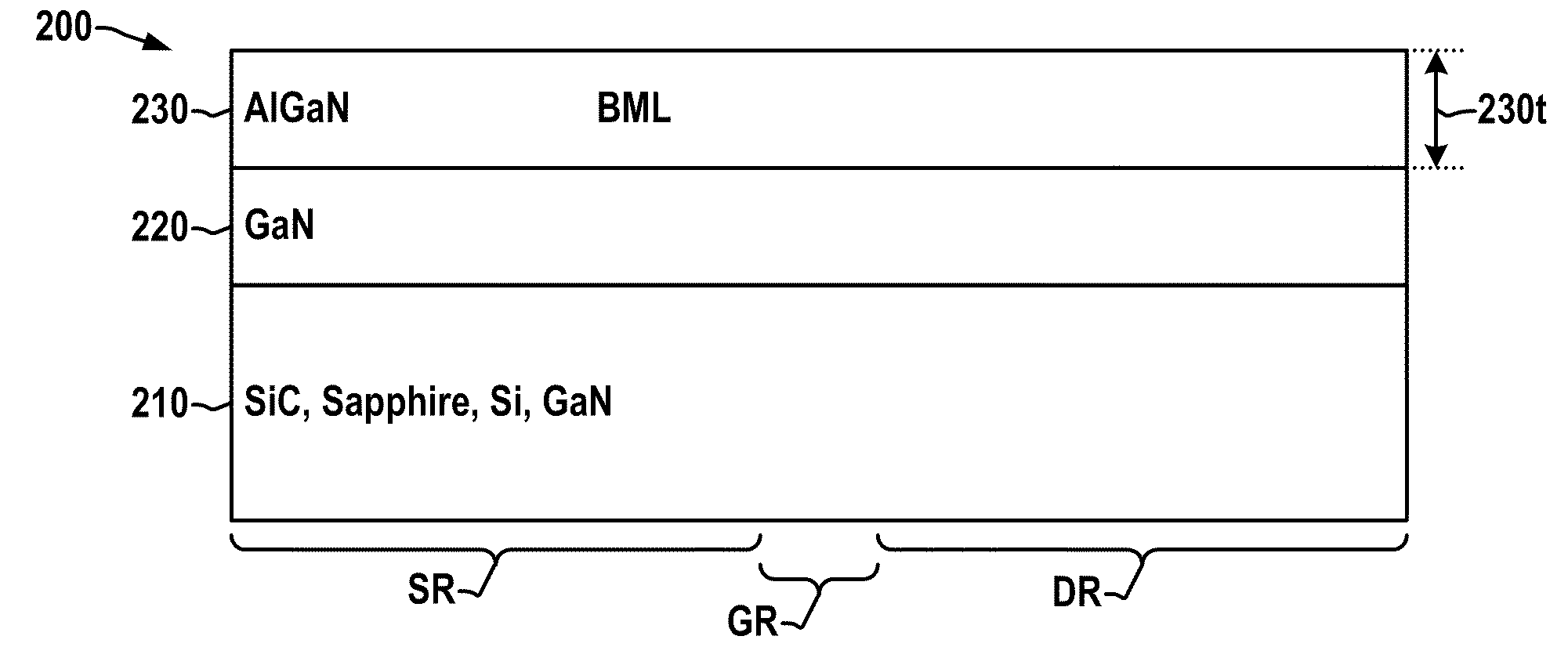

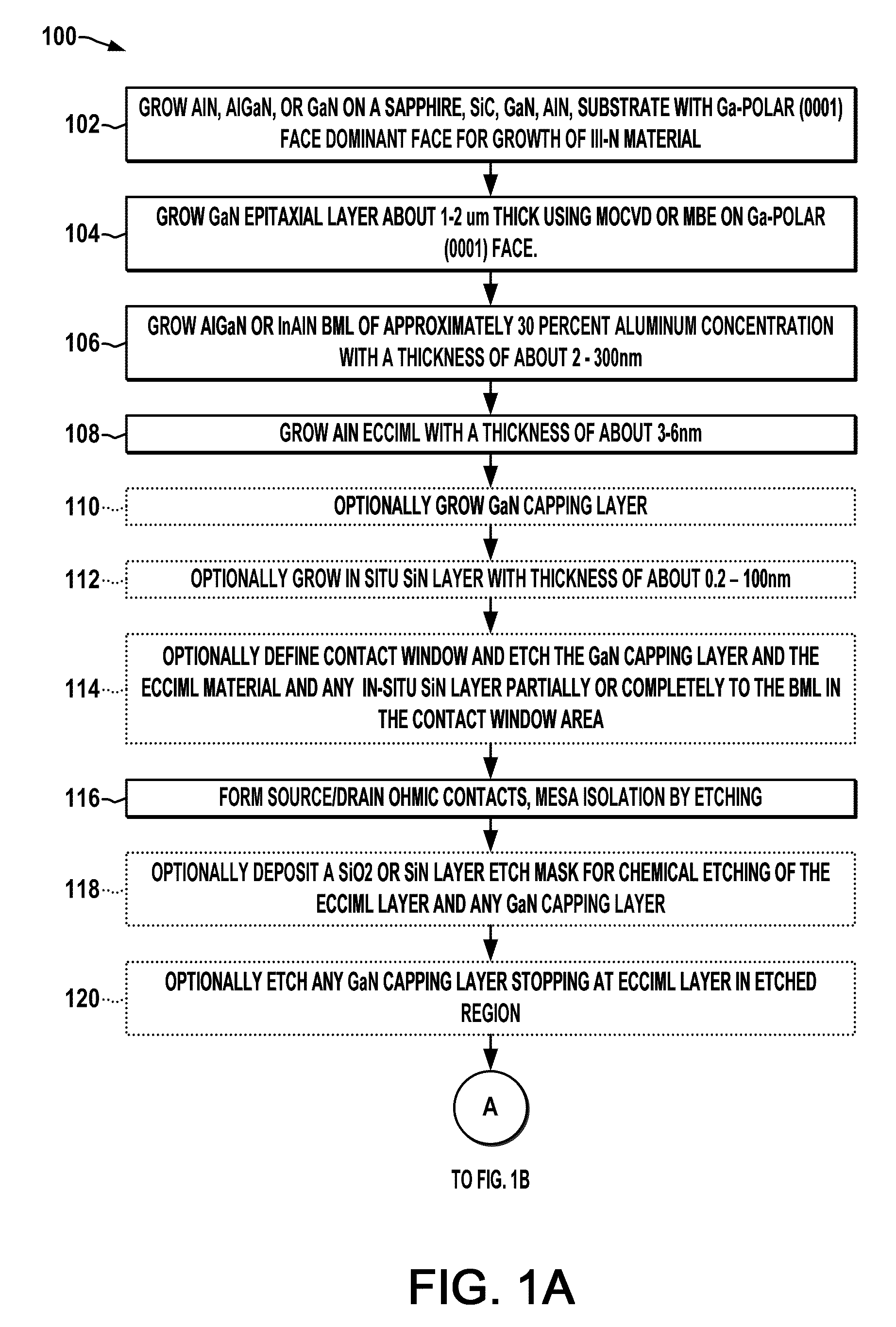

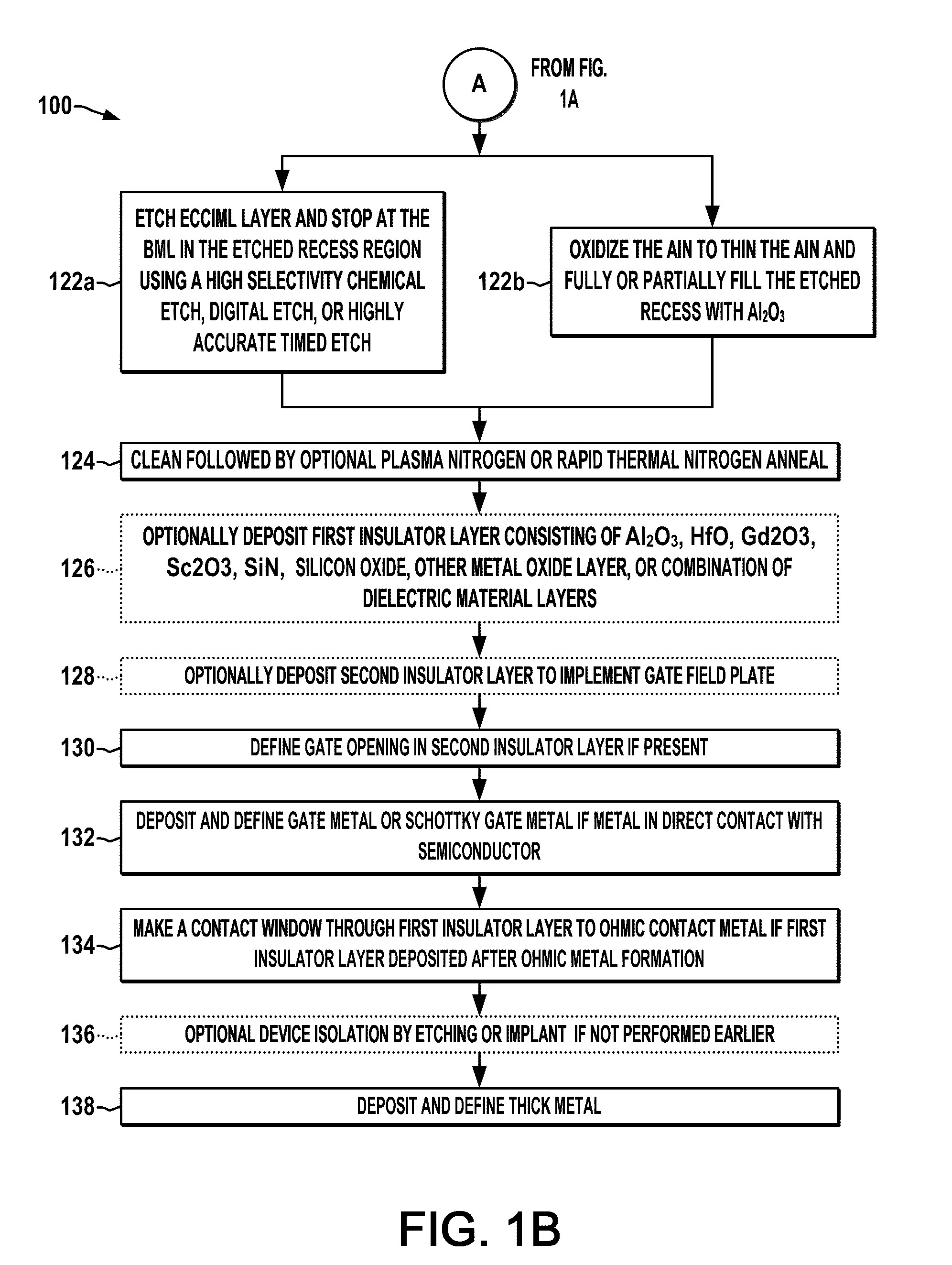

Transistor with Enhanced Channel Charge Inducing Material Layer and Threshold Voltage Control

ActiveUS20100327322A1Etching rate is slowHigh selectivitySemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsHigh-electron-mobility transistor

High electron mobility transistors and fabrication processes are presented in which a barrier material layer of uniform thickness is provided for threshold voltage control under an enhanced channel charge inducing material layer (ECCIML) in source and drain regions with the ECCIML layer removed in the gate region.

Owner:THE UNITED STATES OF AMERICA AS REPRESENTED BY THE SECRETARY OF THE NAVY

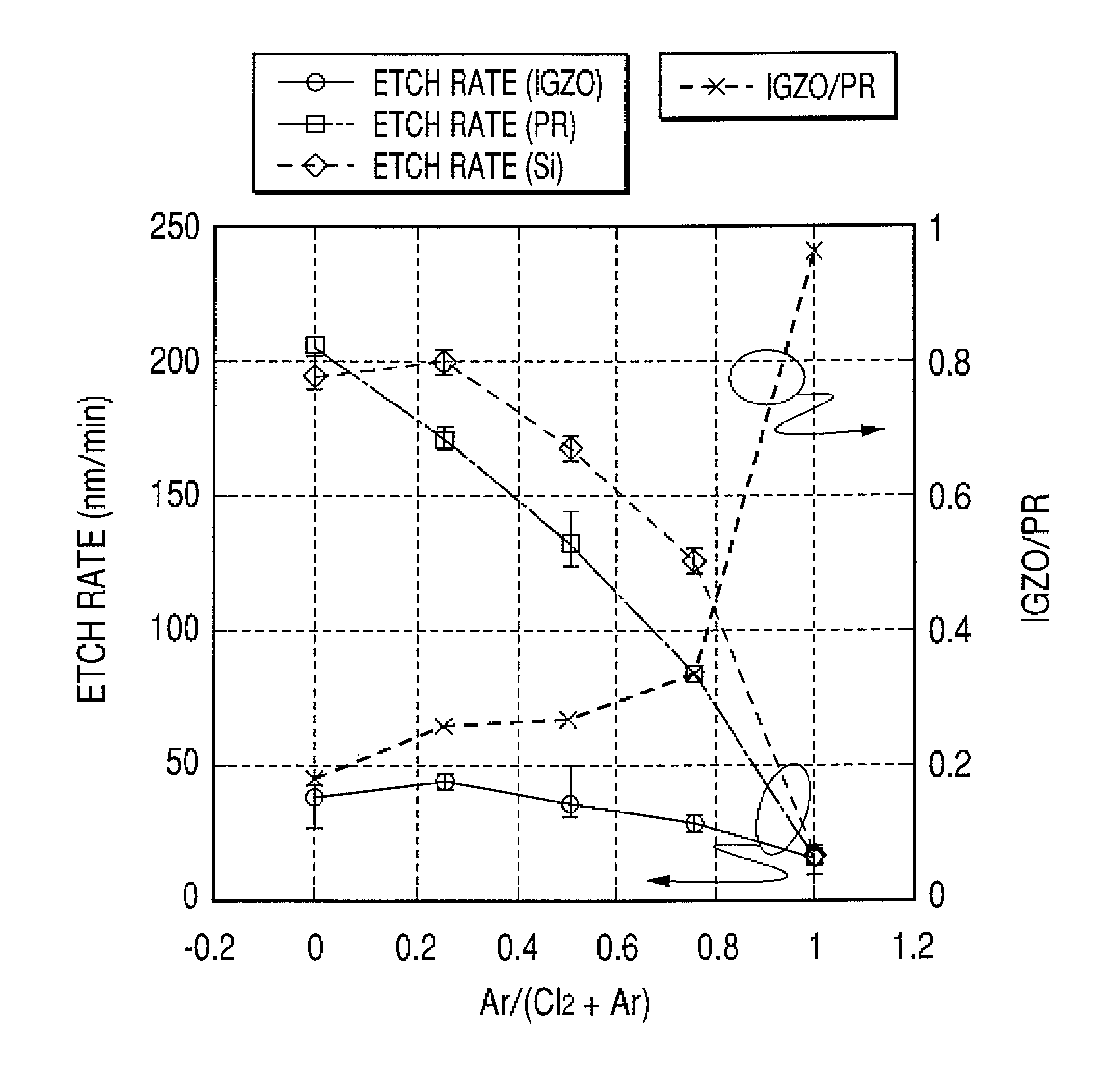

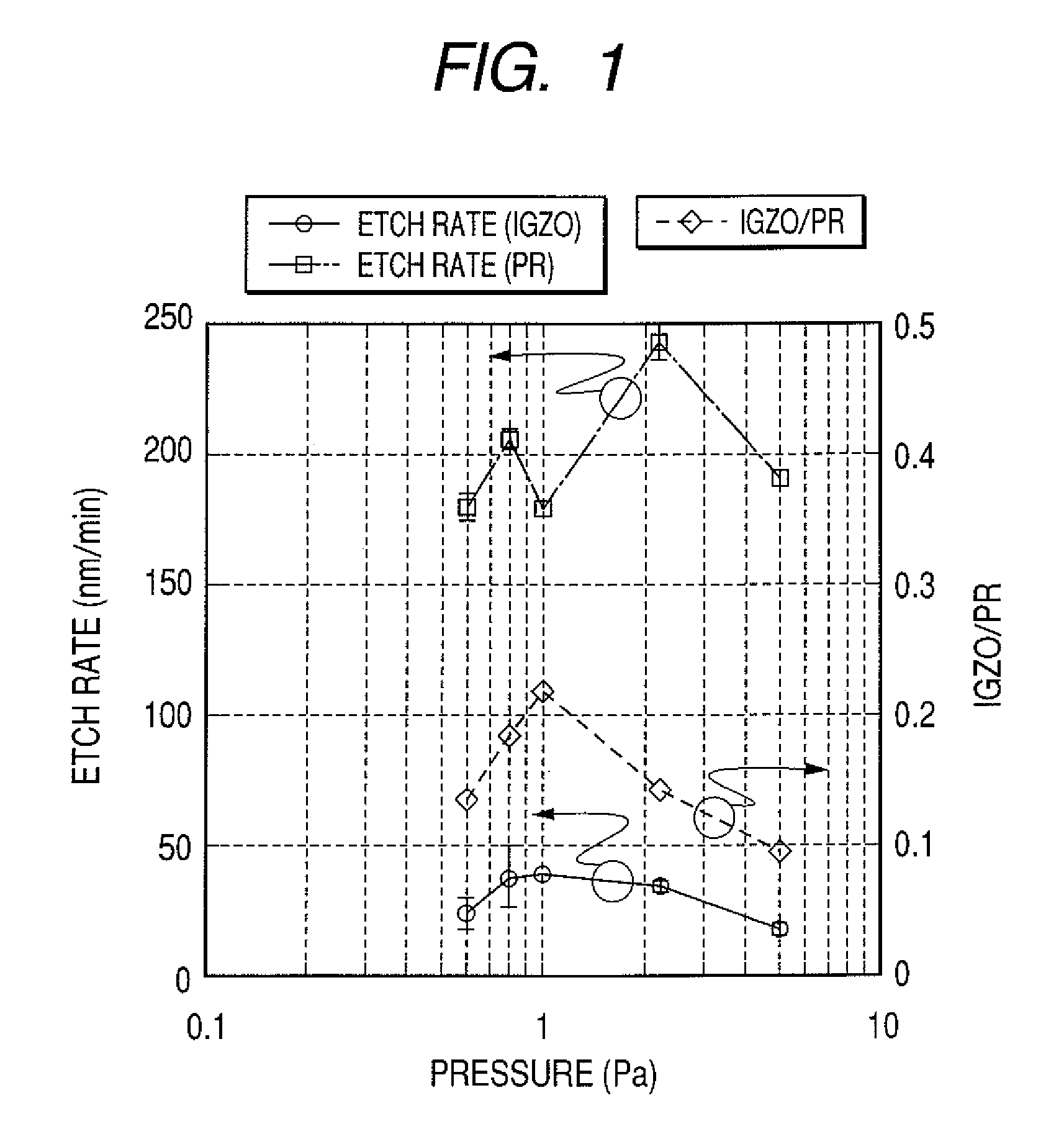

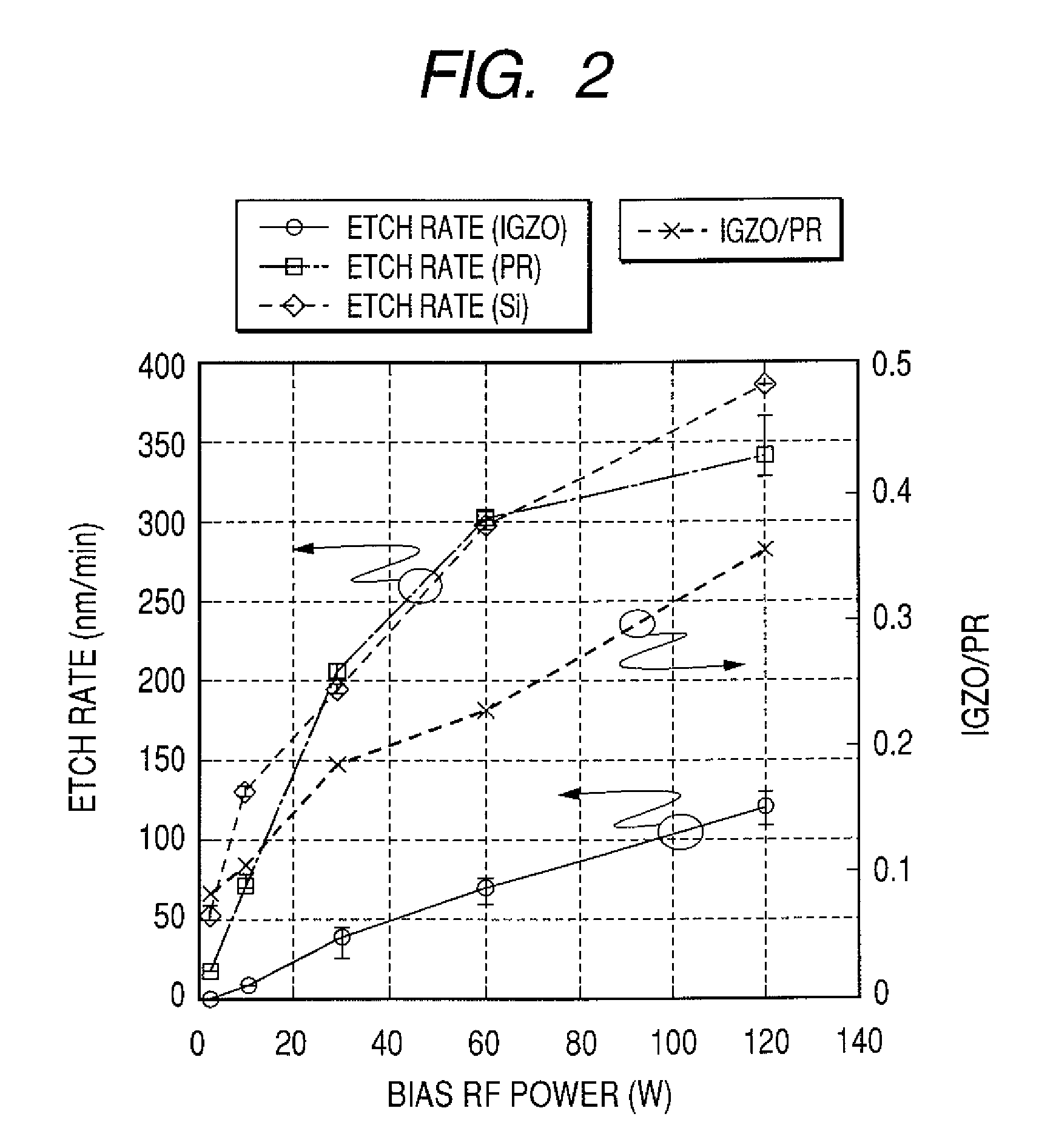

Method of dry etching oxide semiconductor film

InactiveUS7767106B2Improve accuracyIncrease etch rateDecorative surface effectsPhotovoltaic energy generationHalogenDry etching

Provided is a dry etching method for an oxide semiconductor film containing at least In, Ga, and Zn, which includes etching an oxide semiconductor film in a gas atmosphere containing a halogen-based gas.

Owner:CANON KK

Method for manufacturing semiconductor device

ActiveUS20050221547A1Increase etch rateSemiconductor/solid-state device manufacturingHeat resistant fibresDevice materialSemiconductor

A method for manufacturing a semiconductor device includes the steps of: forming a trench in a semiconductor substrate; and forming an epitaxial film on the substrate including a sidewall and a bottom of the trench so that the epitaxial film is filled in the trench. The step of forming the epitaxial film includes a final step before the trench is filled with the epitaxial film. The final step has a forming condition of the epitaxial film in such a manner that the epitaxial film to be formed on the sidewall of the trench has a growth rate at an opening of the trench smaller than a growth rate at a position of the trench, which is deeper than the opening of the trench.

Owner:SUMCO CORP +1

Cover glass and method for producing cover glass

The disclosed cover glass is produced by etching a glass substrate that has been formed by a down-drawing process, and chemically strengthening the glass substrate to provide the glass substrate with a compressive-stress layer on the principal surfaces thereof. The glass substrate contains, as components thereof, 50% to 70% by mass of SiO2, 5% to 20% by mass of Al2O3, 6% to 30% by mass of Na2O, and 0% to less than 8% by mass of Li2O. The glass substrate may also contain 0% to 2.6% by mass of CaO, if necessary. The glass substrate has an etching characteristic in which the etching rate is at least 3.7 μm / minute in an etching environment having a temperature of 22° C. and containing hydrogen fluoride with a concentration of 10% by mass.

Owner:AVANSTRATE INC +1

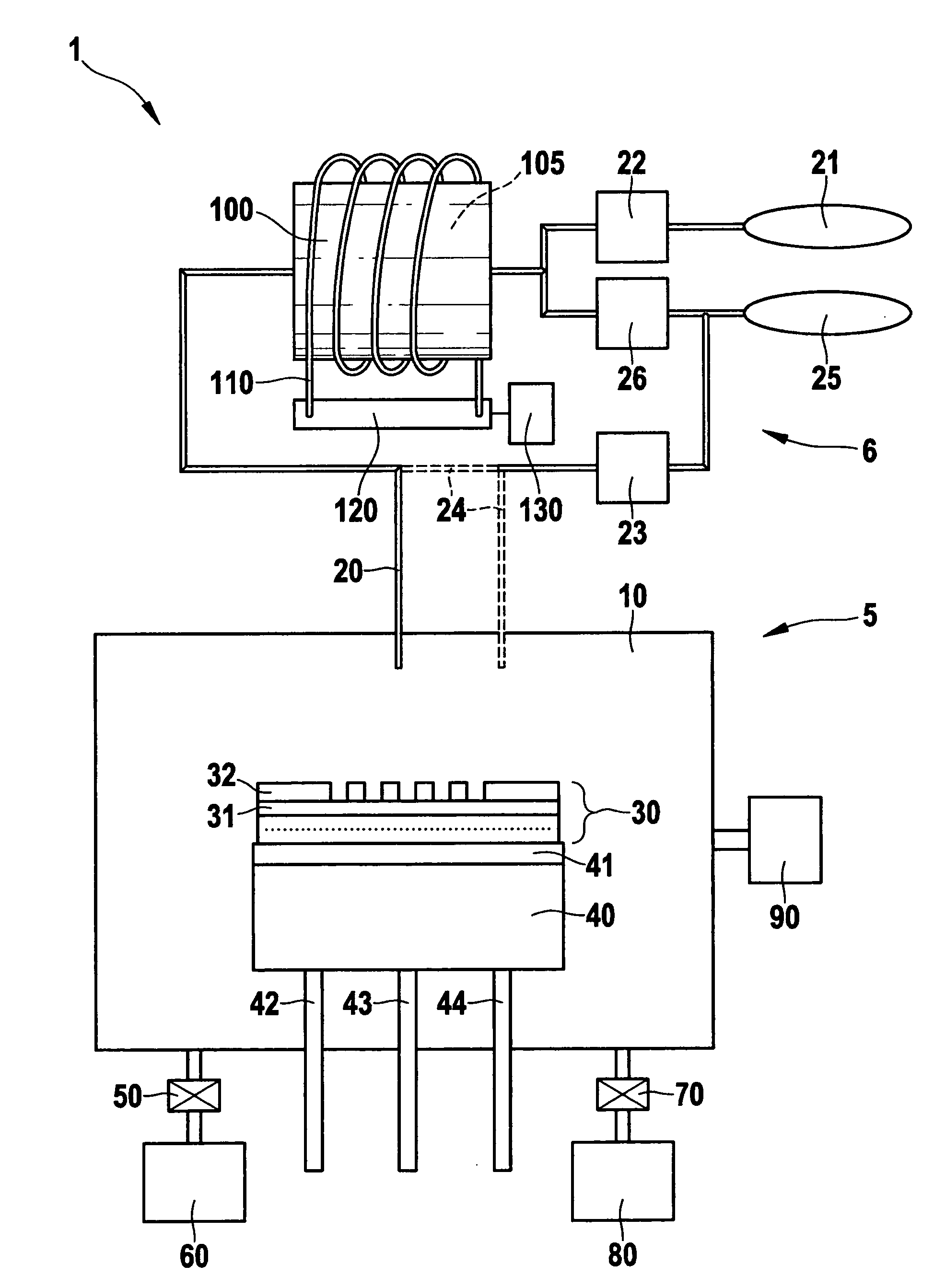

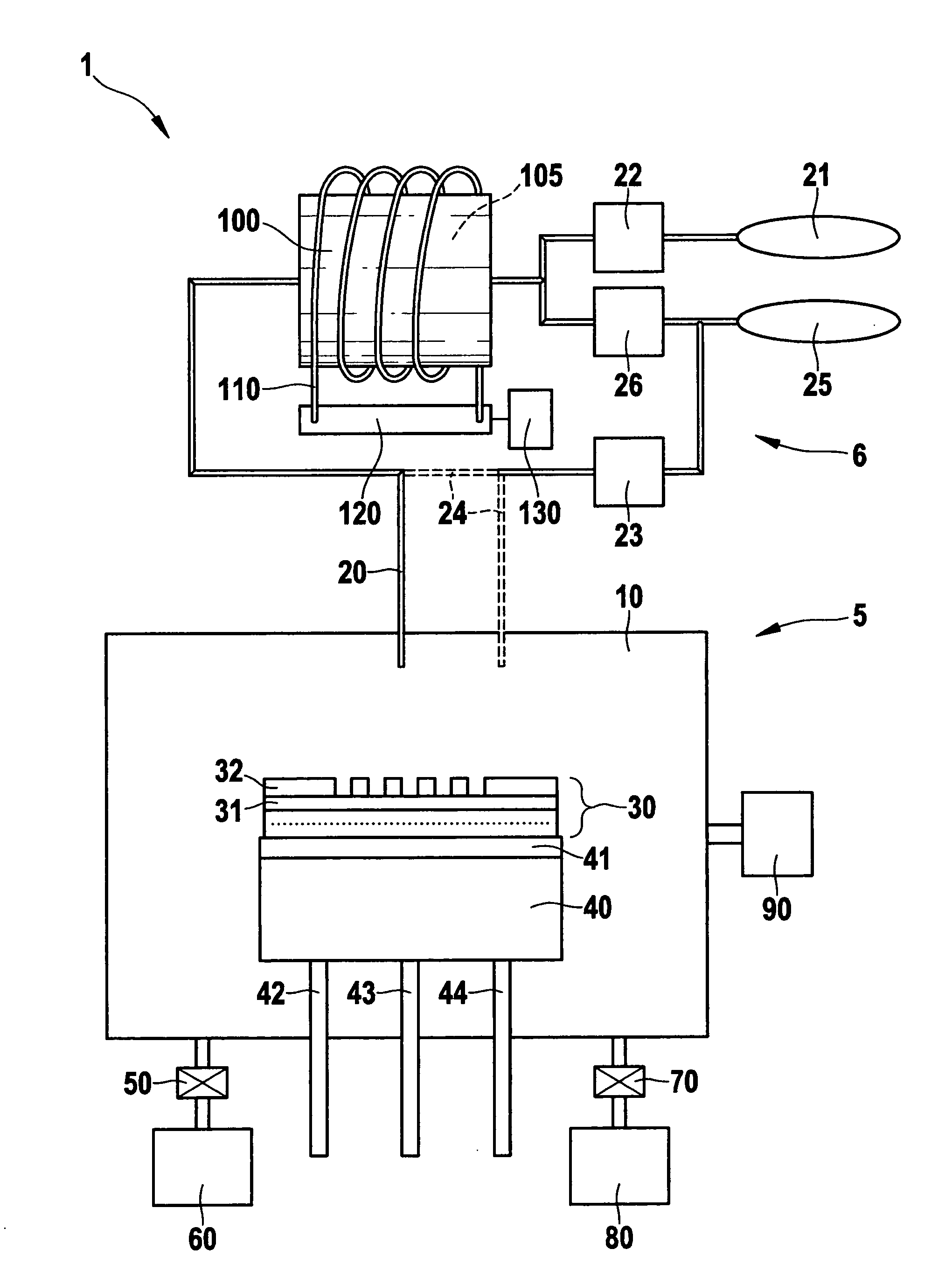

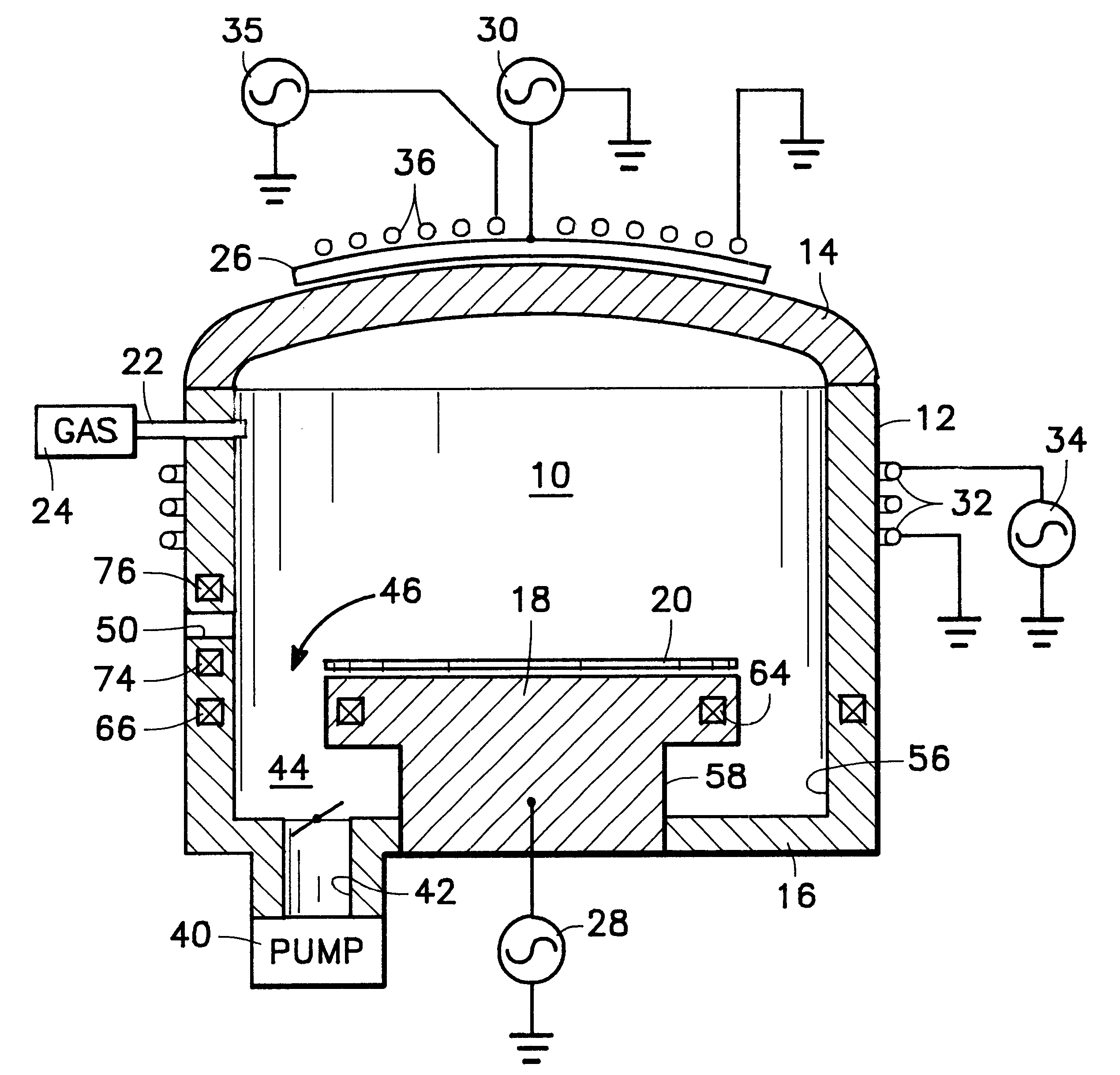

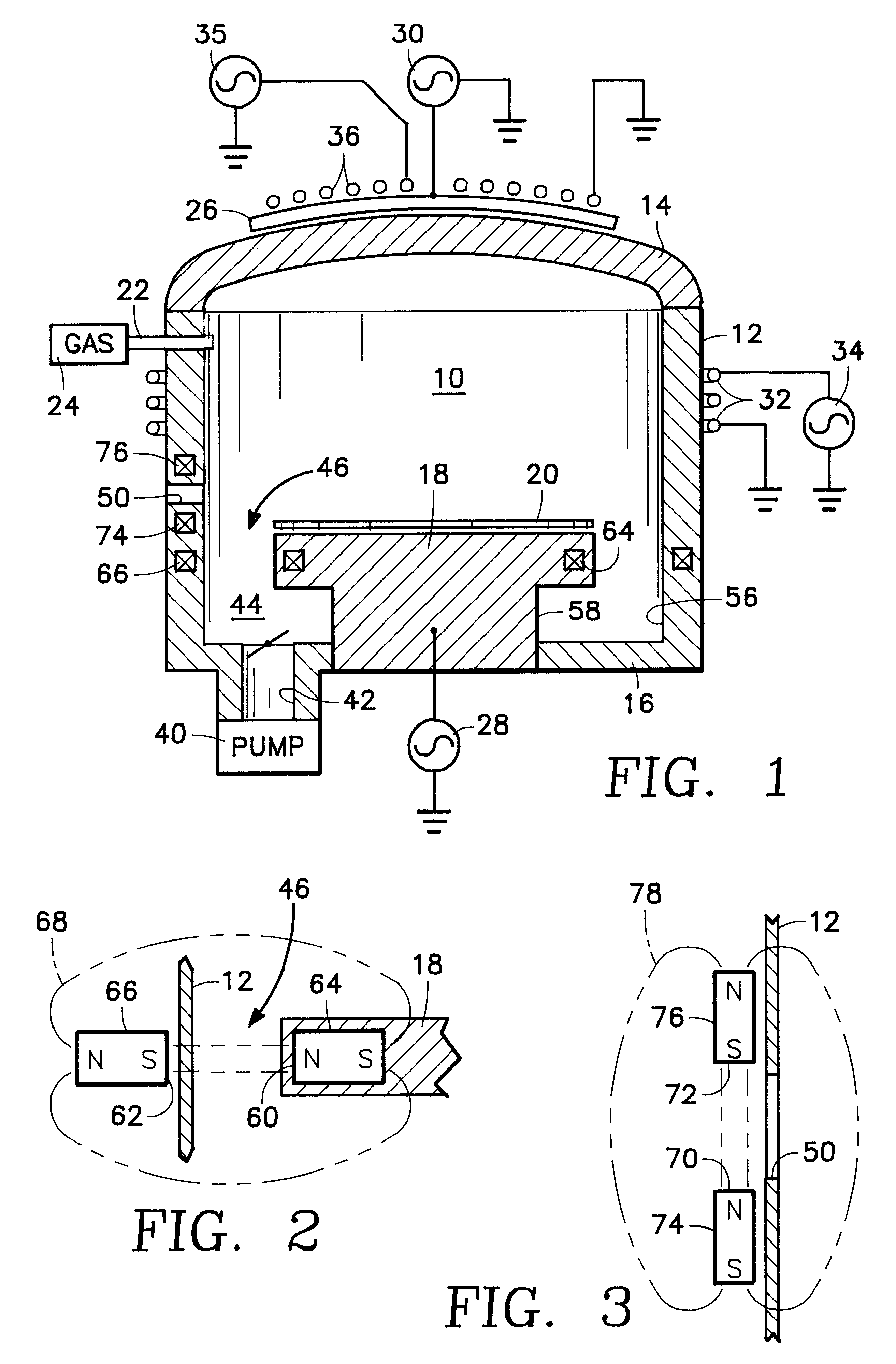

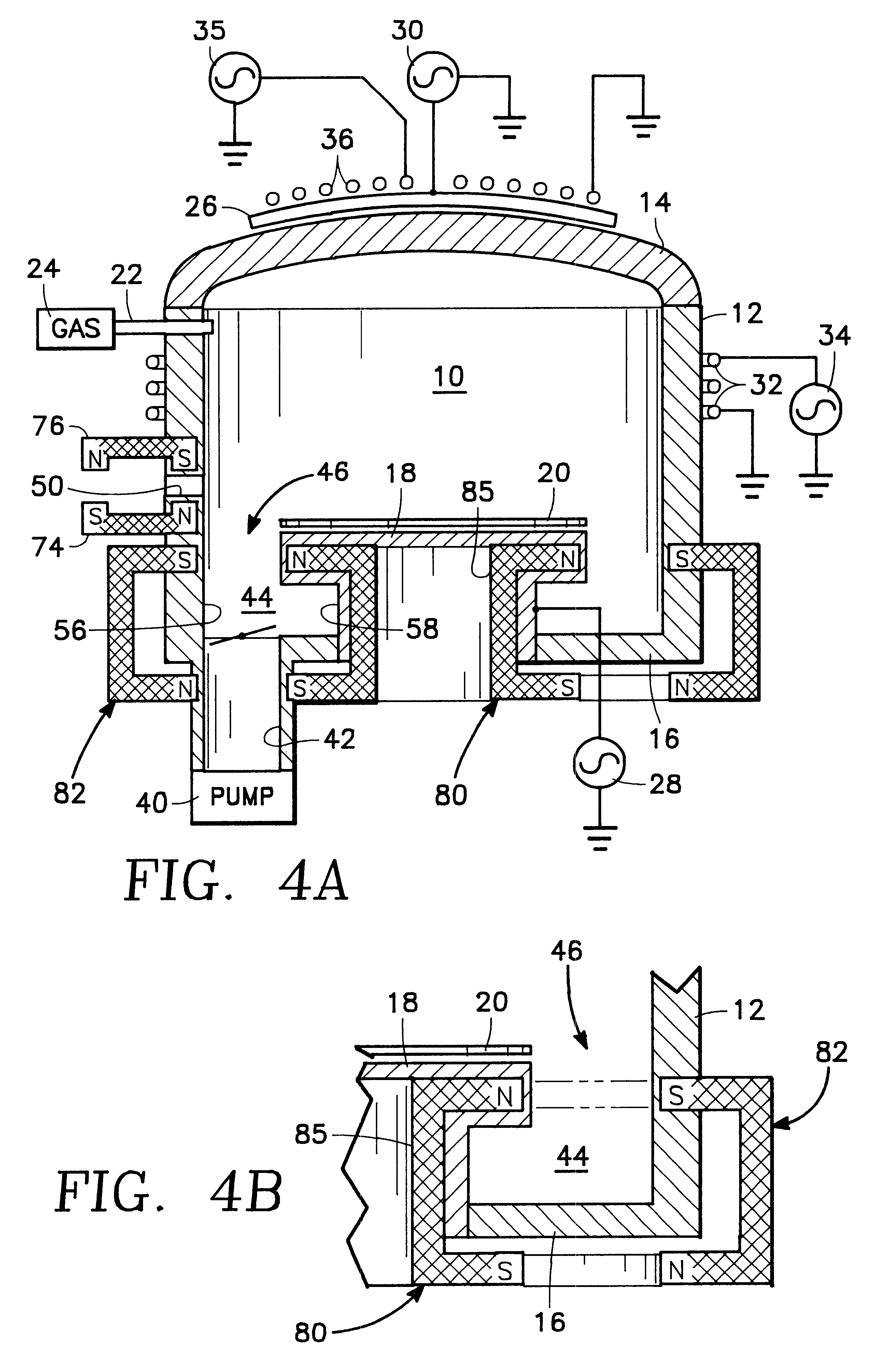

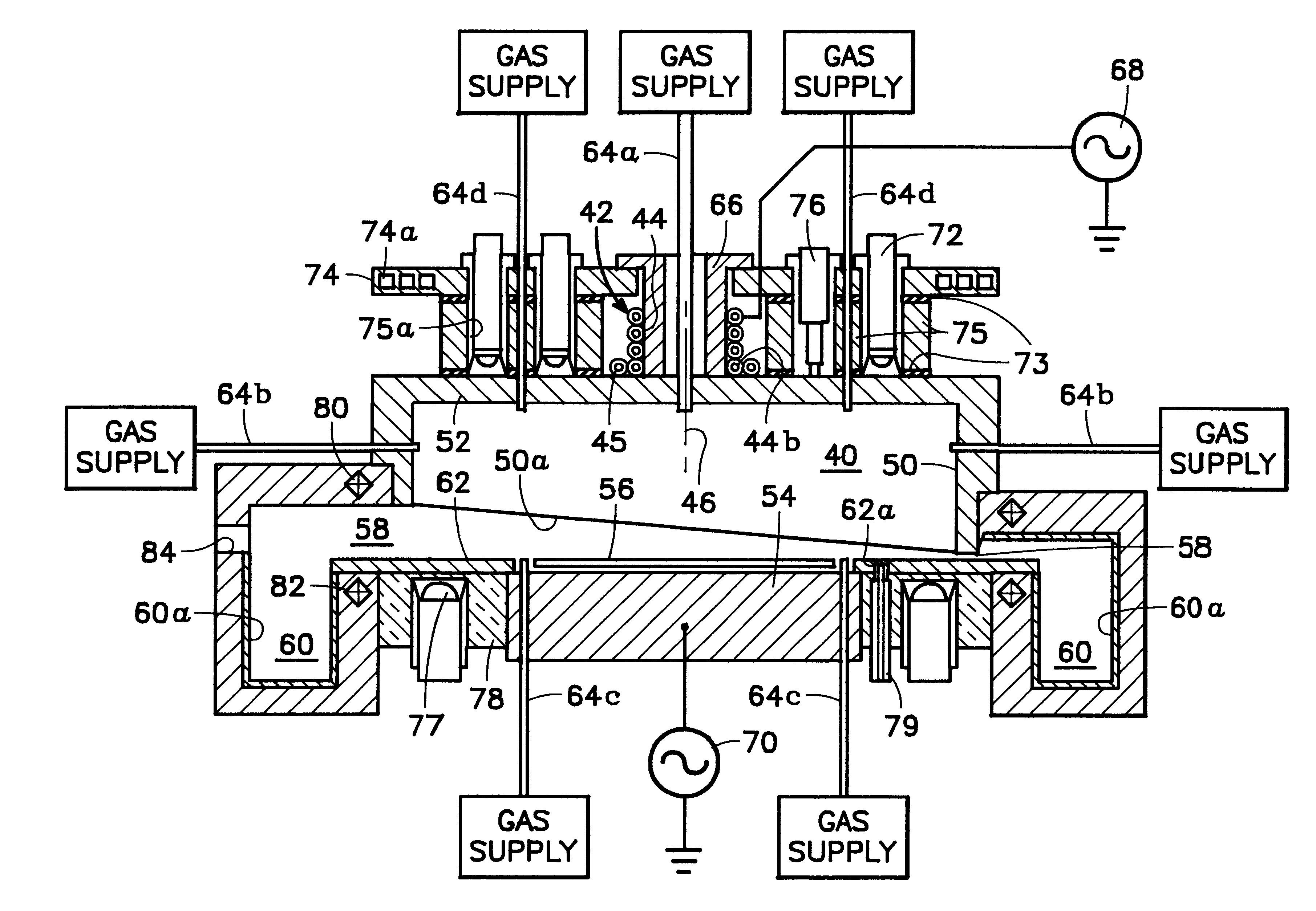

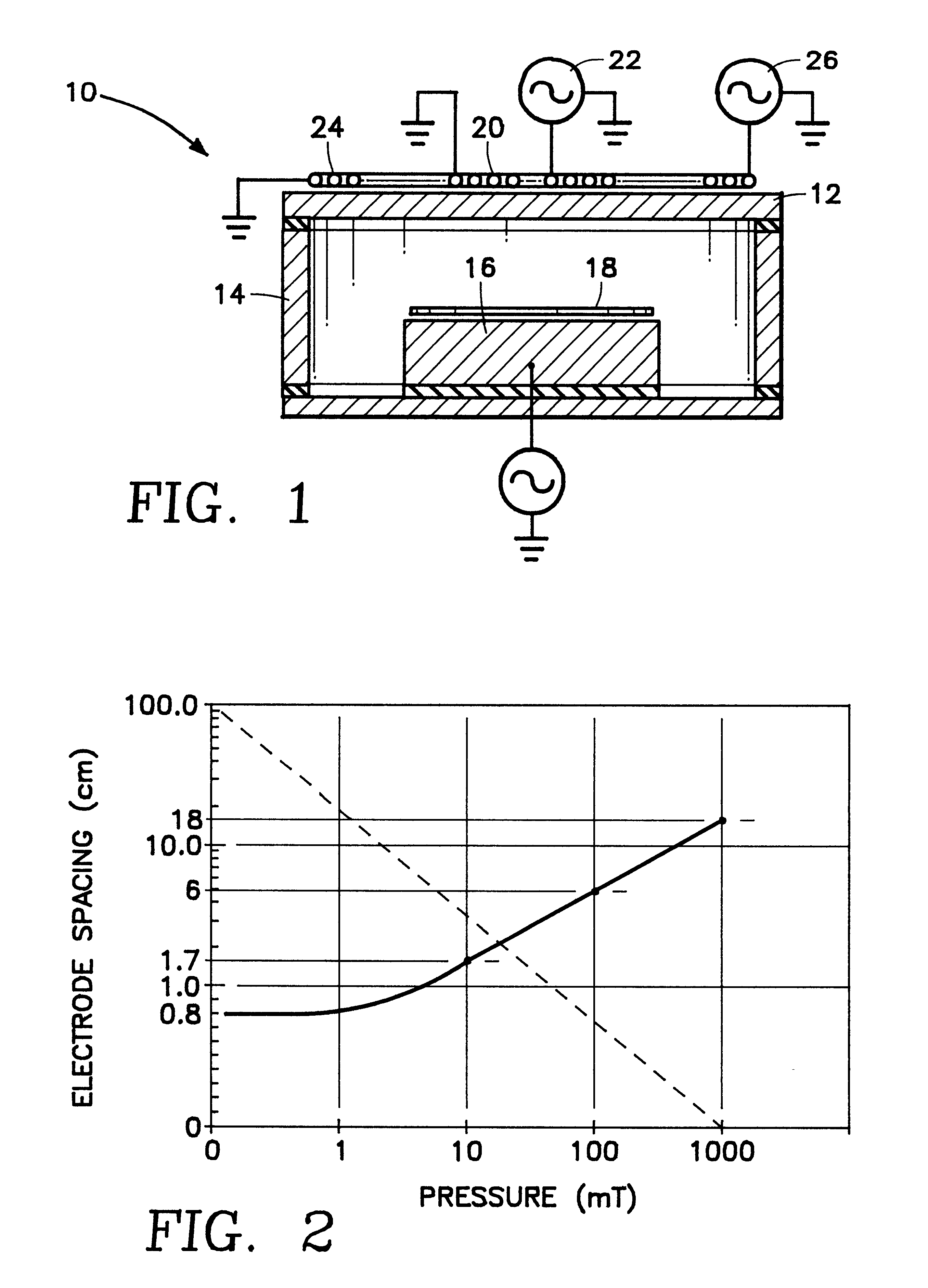

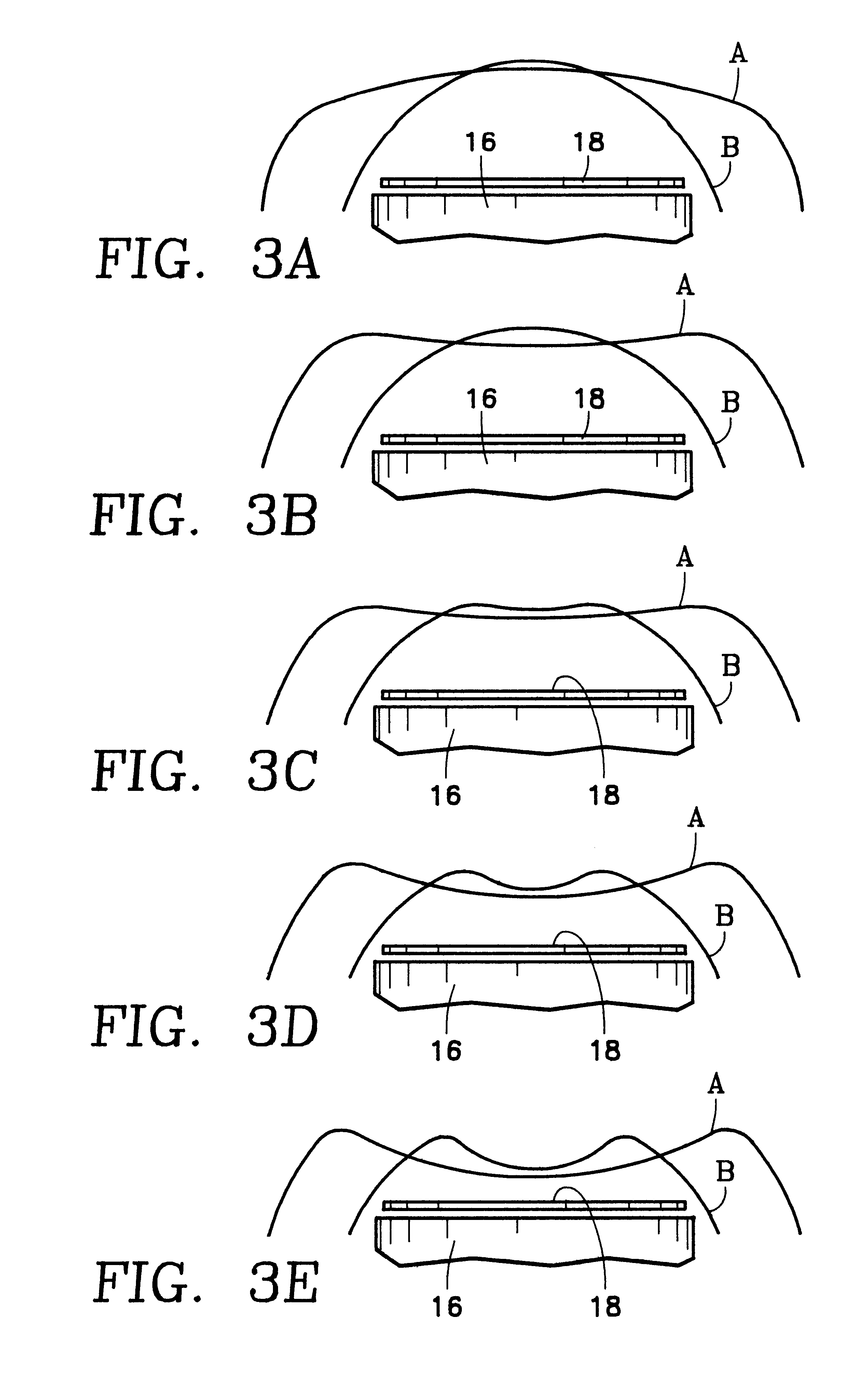

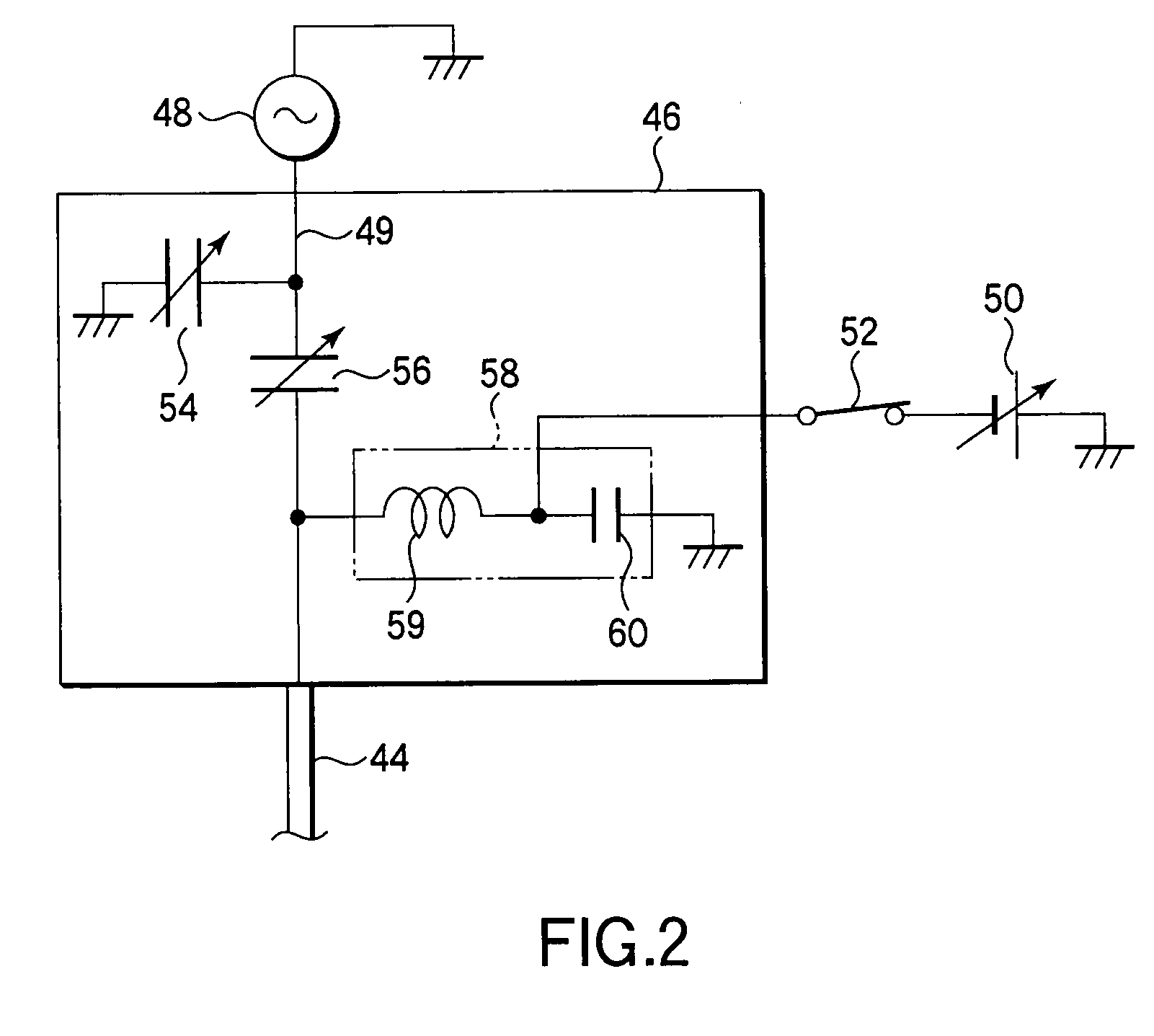

Magnetically enhanced inductively coupled plasma reactor with magnetically confined plasma

InactiveUS6471822B1Improves workpiece processingHigh densityElectric discharge tubesDecorative surface effectsHigh densityInductively coupled plasma

The present invention provides a plasma reactor having a plasma source chamber capable of generating a high density plasma typically utilizing a helicon wave. The plasma is delivered to a process chamber having a workpiece. The present invention may provide a plurality of magnets, each being located longitudinally around an axis perpendicular to the plane of the workpiece to form a magnetic bucket that extends the length of the side wall of the processing chamber and across a workpiece insertion opening and a vacuum pump opening. The magnetic bucket of the present invention may be formed so that the pedestal need not be raised to be within the bucket, or may be formed by permanent magnets oriented with one pole of each magnet facing the interior of the processing chamber, or with opposite poles of adjacent magnets facing each other, thereby forming cusps around the axis perpendicular to the plane of the workpiece. Current carrying conductors may generate all or part of the magnetic bucket. The present invention may provide an inner wall member secured within the processing chamber. All or a portion of the inner wall may be grounded to provide a well defined anode for bias power that is applied to the workpiece pedestal, and may be heated so that deposits do not cause its impedance to drift.

Owner:APPLIED MATERIALS INC

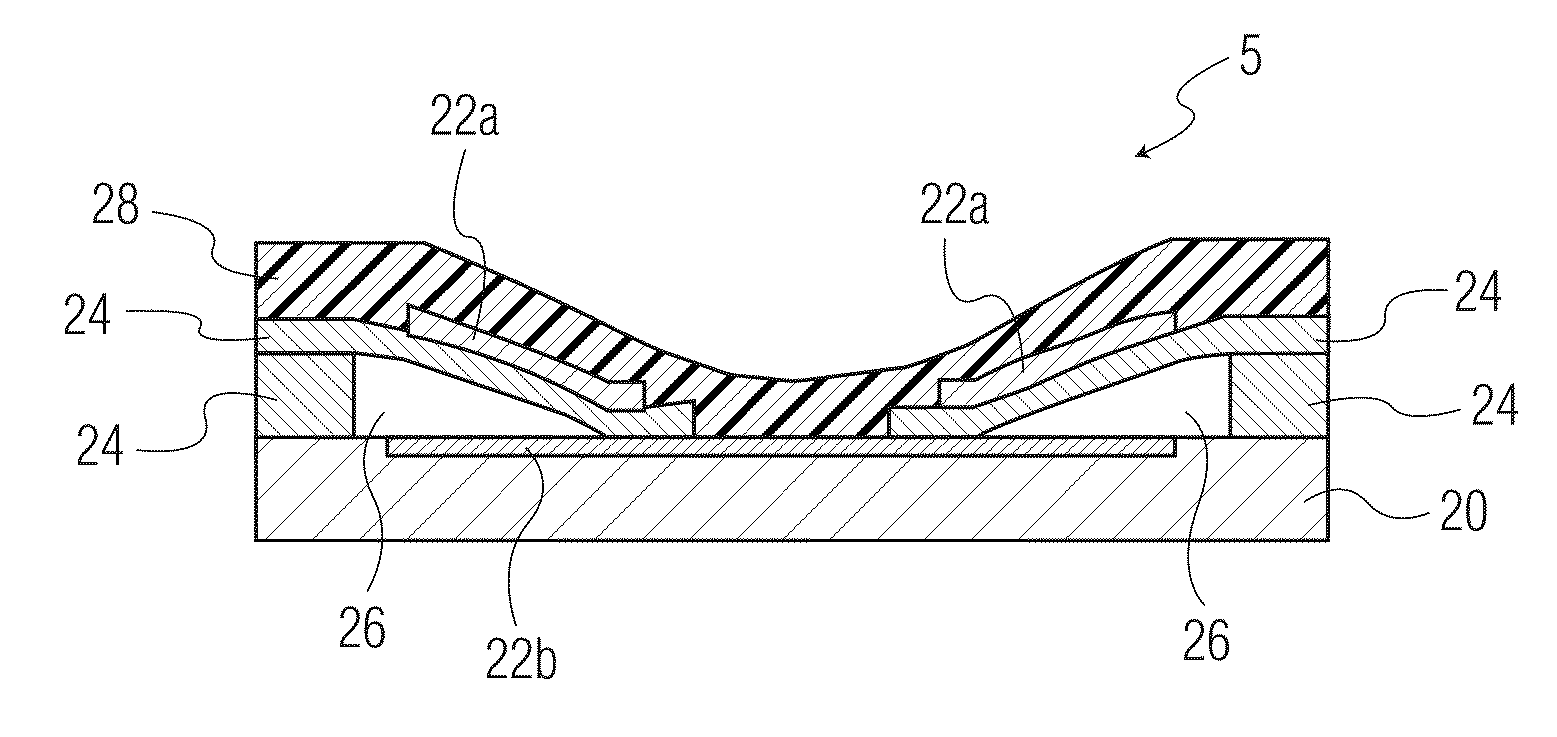

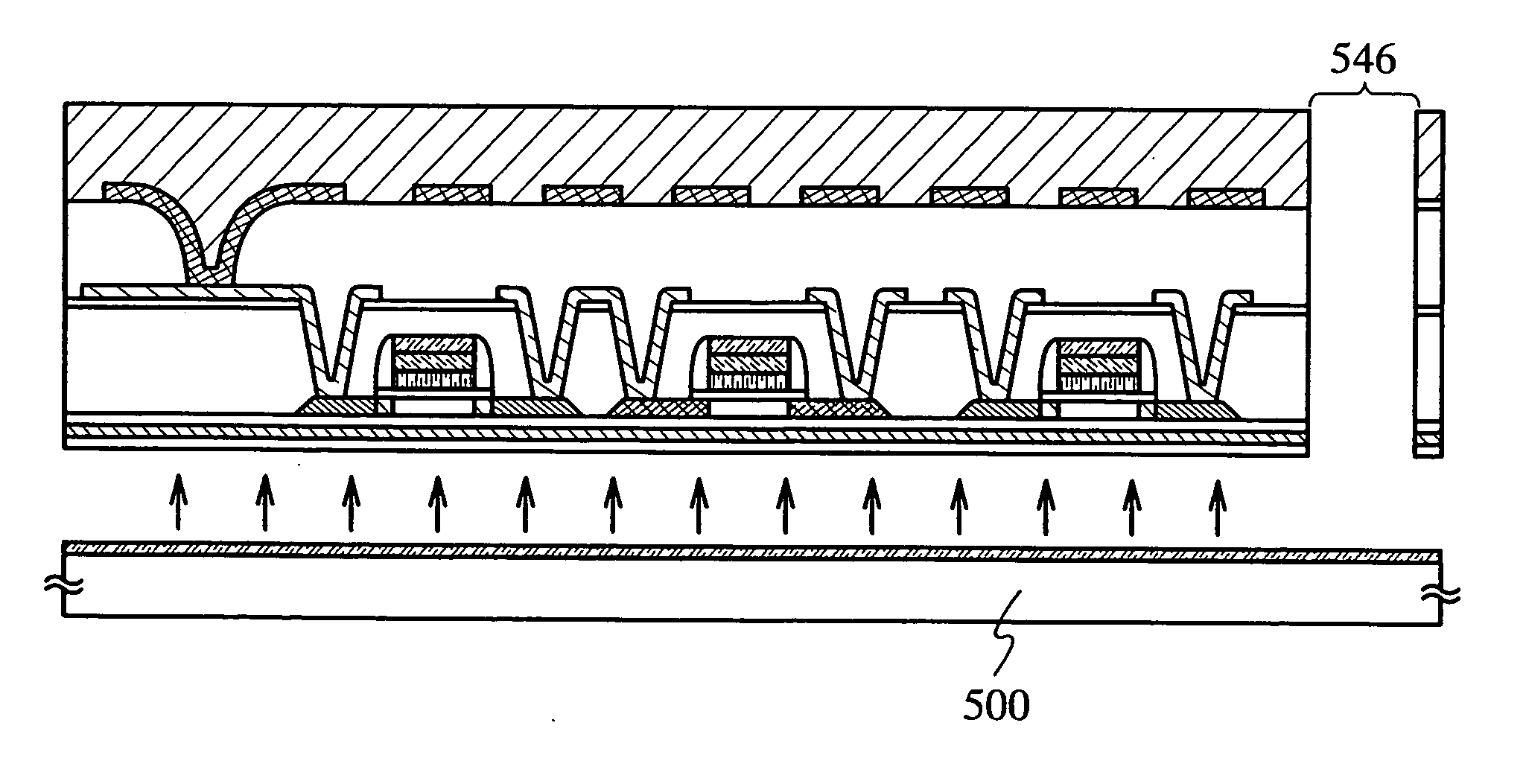

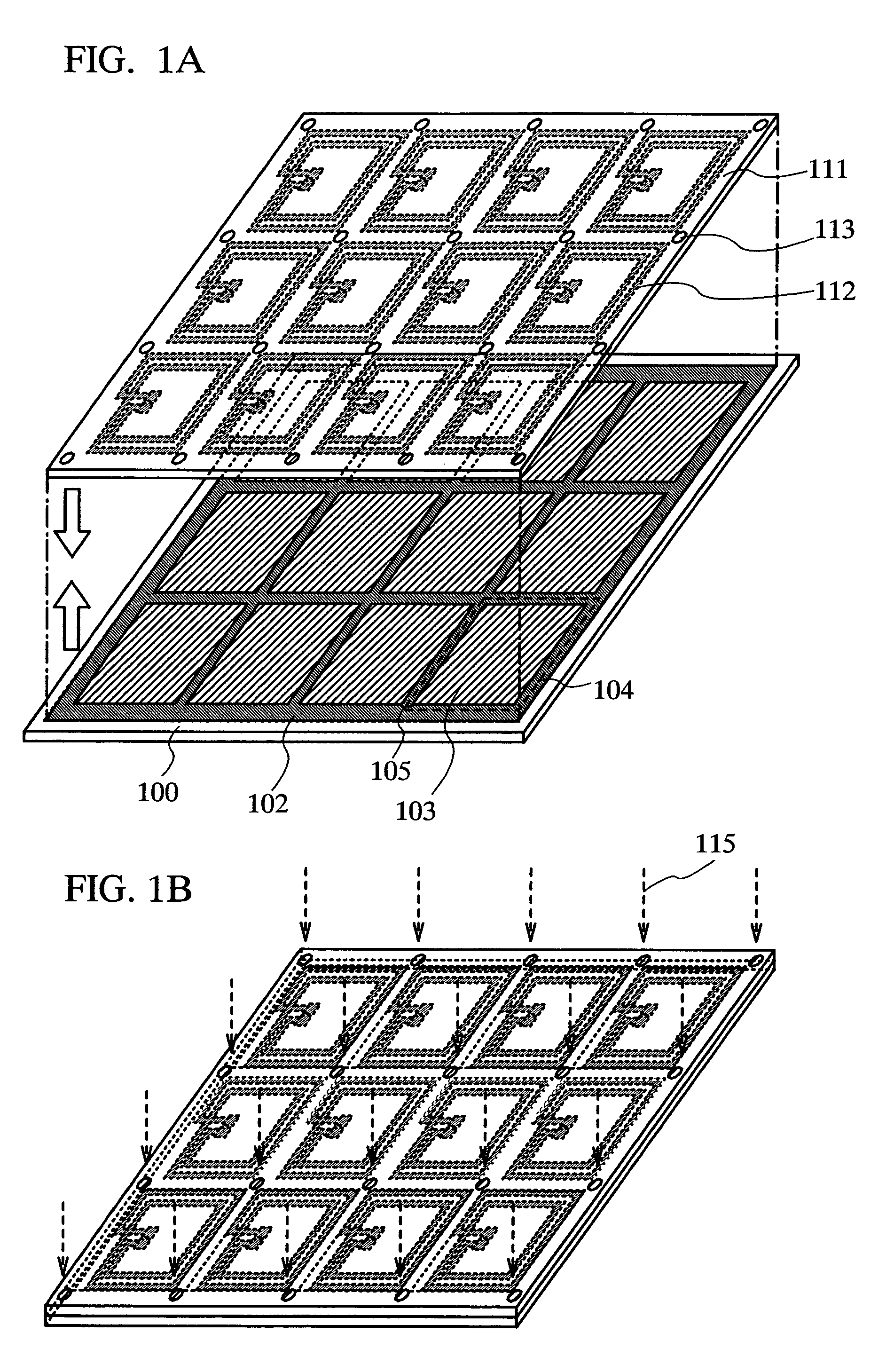

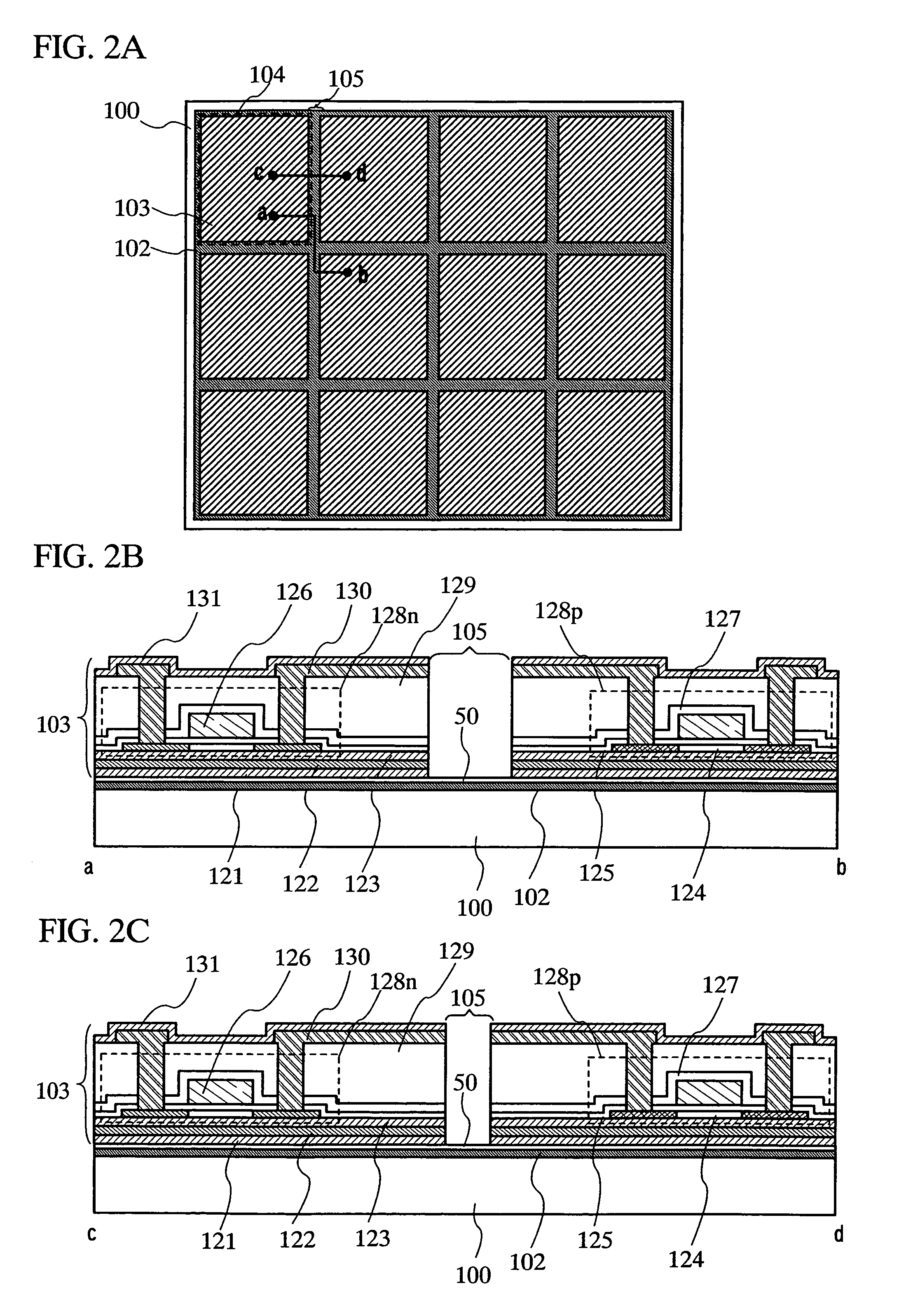

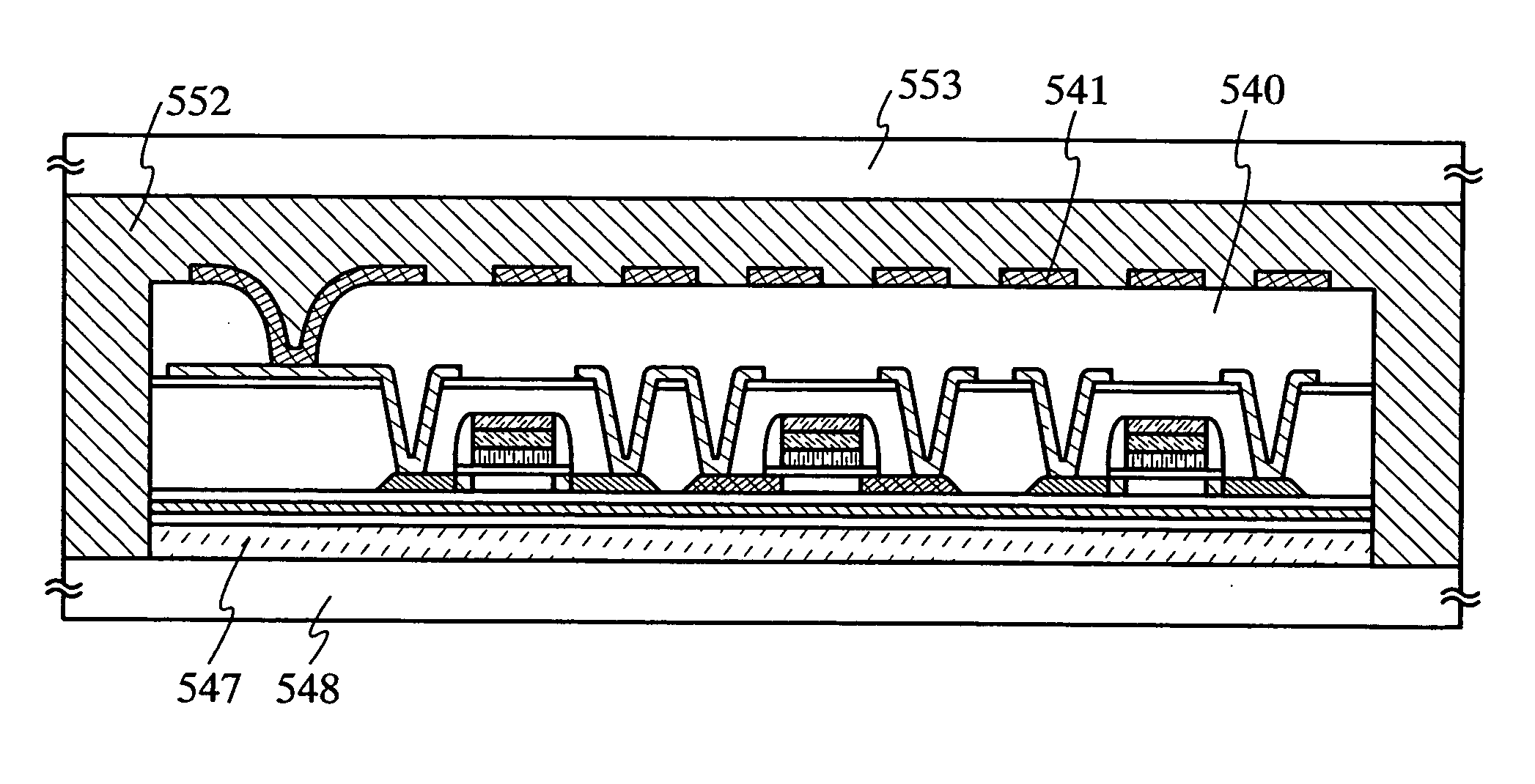

Method for production and using a capacitive micro-machined ultrasonic transducer

ActiveUS8327521B2Easy to manufactureHigh voltageUltrasonic/sonic/infrasonic diagnosticsSemiconductor electrostatic transducersCapacitive micromachined ultrasonic transducersMedicine

Owner:KONINK PHILIPS ELECTRONICS NV

High pressure high non-reactive diluent gas content high plasma ion density plasma oxide etch process

InactiveUS6238588B1Increase pressureHigh strengthElectric discharge tubesDecorative surface effectsHigh plasmaOxygen

The invention is embodied in a method of processing a semiconductor workpiece in a plasma reactor chamber, including supplying a polymer and etchant precursor gas containing at least carbon and fluorine into the chamber at a first flow rate sufficient of itself to maintain a gas pressure in the chamber in a low pressure range below about 20 mT, supplying a relatively non-reactive gas into the chamber at second flow rate sufficient about one half or more of the total gas flow rate into the chamber, in combination with the first flow rate of the precursor gas, to maintain the gas pressure in the chamber in a high pressure range above 20 mT, and applying plasma source power into the chamber to form a high ion density plasma having an ion density in excess of 1010 ions per cubic centimeter. In one application of the invention, the workpiece includes an oxygen-containing overlayer to be etched by the process and a non-oxygen-containing underlayer to be protected from etching, the precursor gas dissociating in the plasma into fluorine-containing etchant species which etch the oxygen-containing layer and carbon-containing polymer species which accumulate on the non-oxygen-containing underlayer. Alternatively, the high pressure range may be defined as a pressure at which the skin depth of the inductive field exceeds {fraction (1 / 10)} of the gap between the inductive antenna and the workpiece.

Owner:APPLIED MATERIALS INC

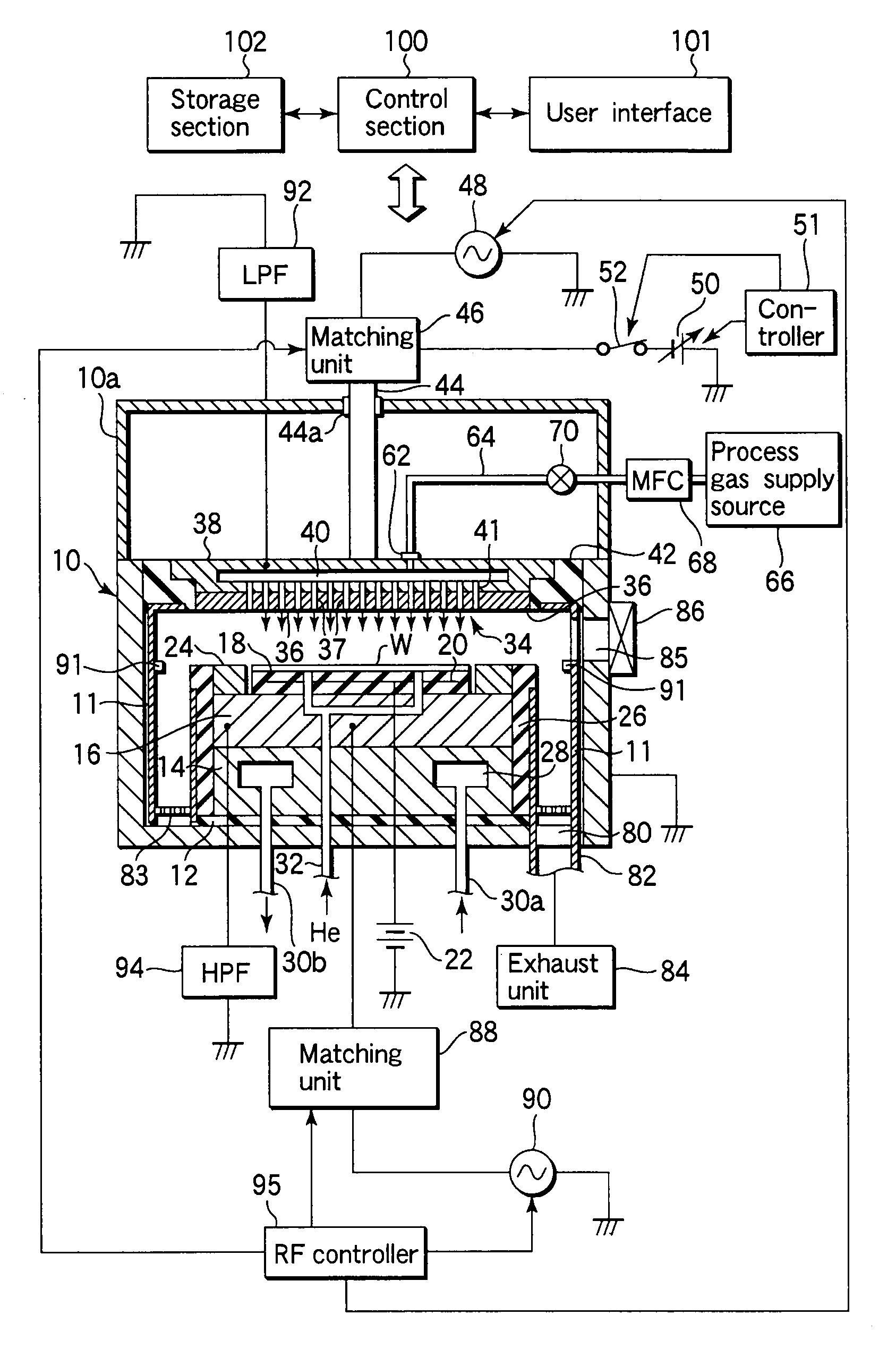

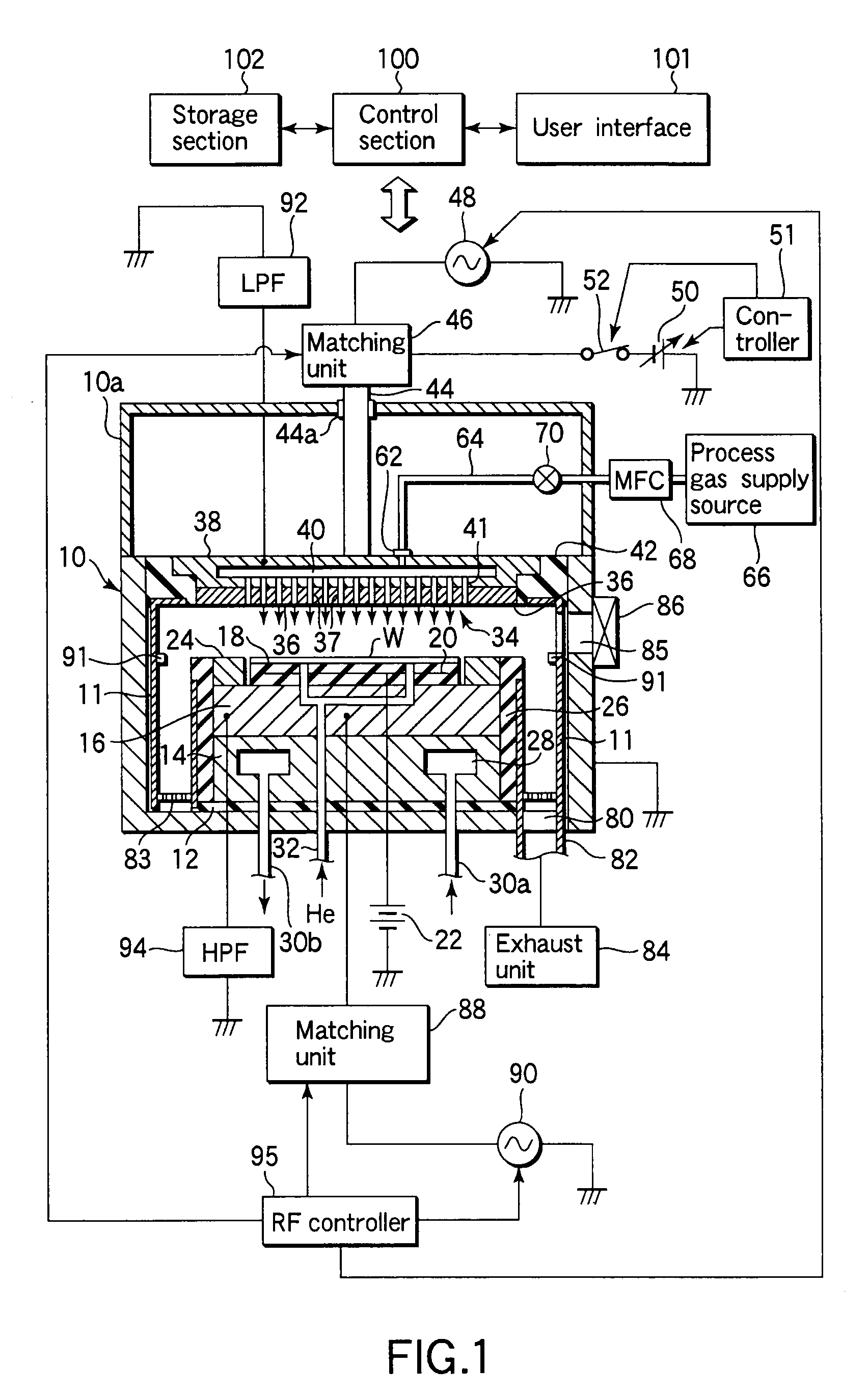

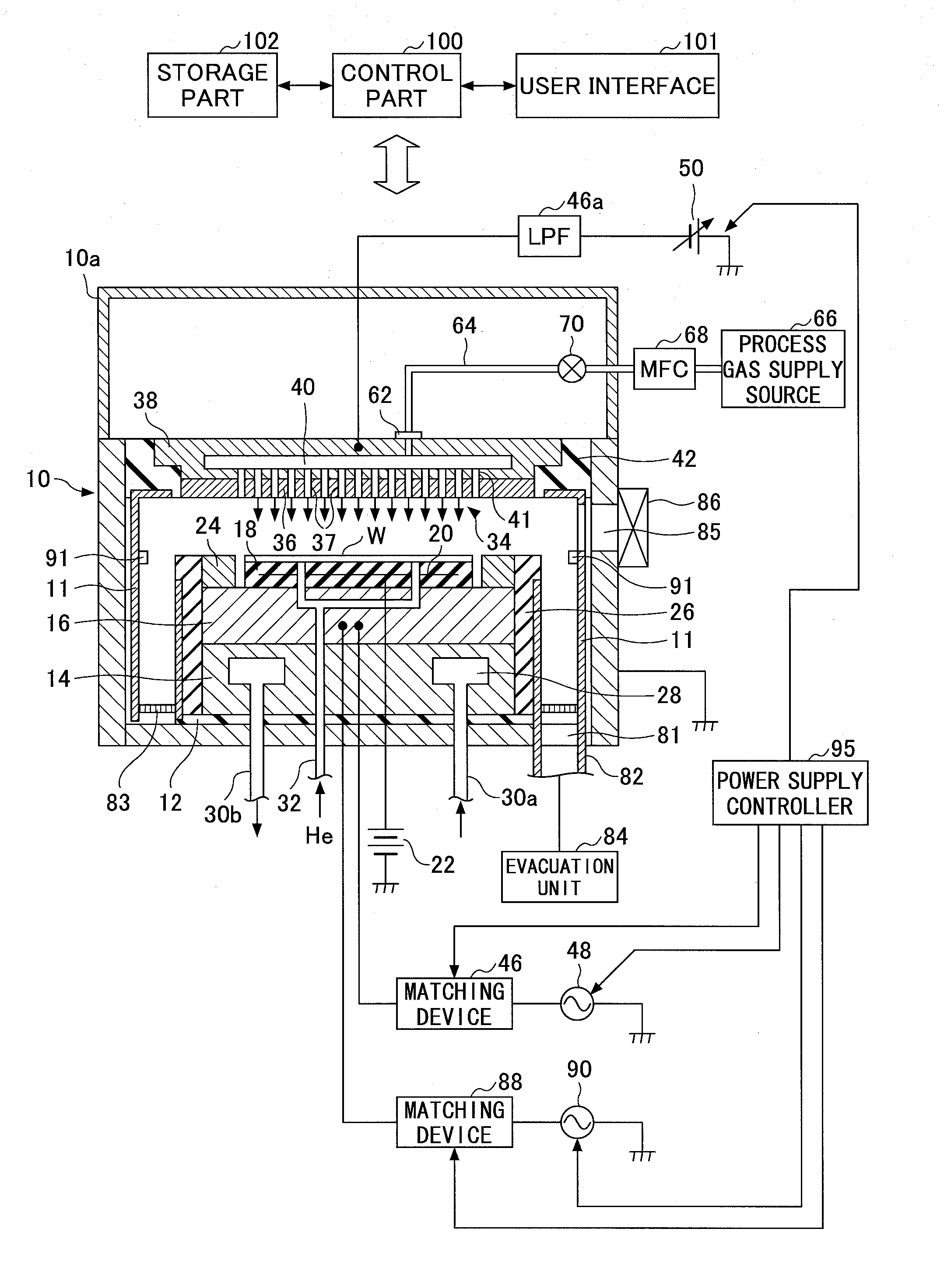

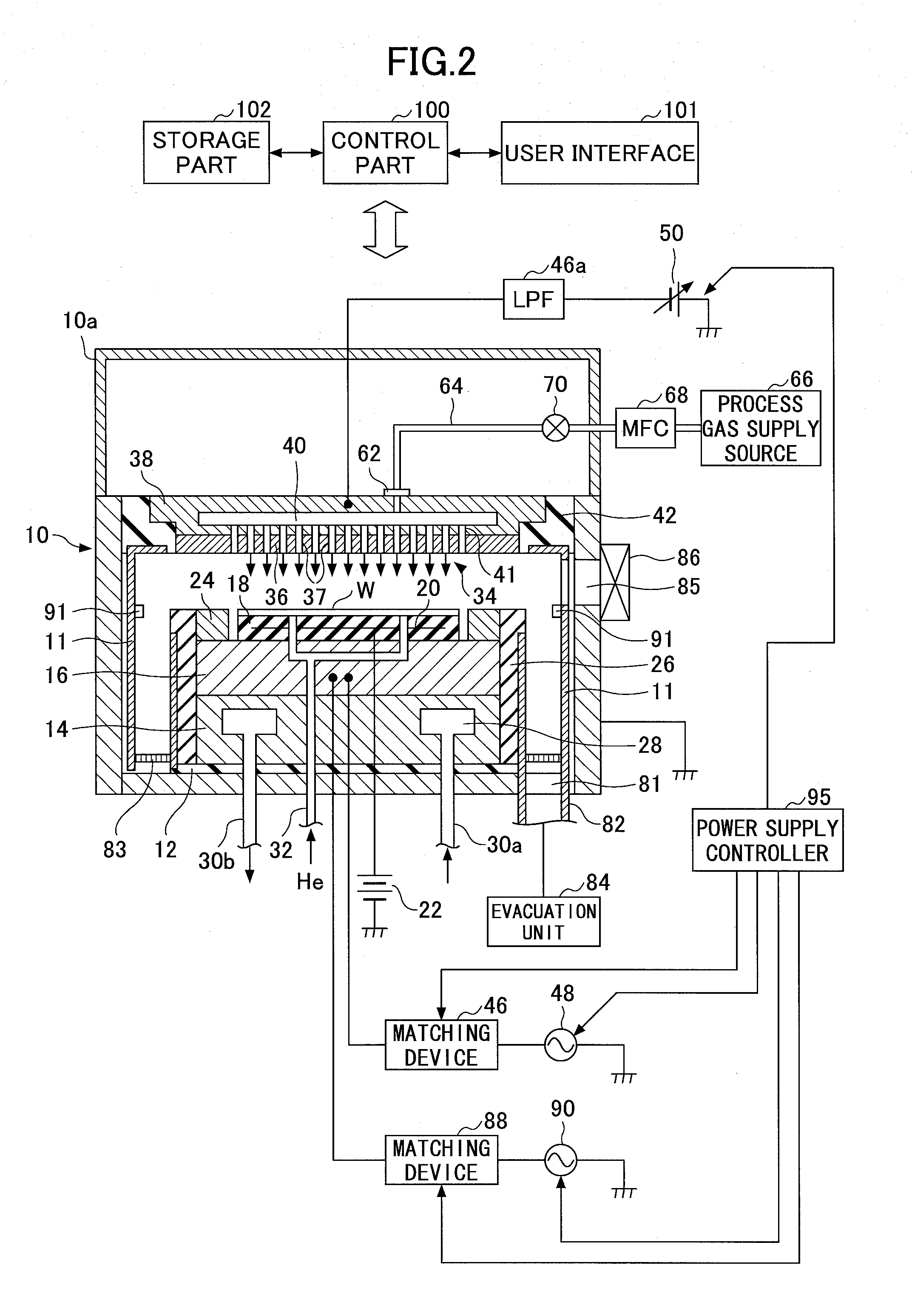

Plasma etching apparatus and method

ActiveUS20080110859A1High selectivityIncrease etch rateElectric discharge tubesDecorative surface effectsPower modulationEngineering

An upper electrode and a lower electrode are disposed opposite to each other in a process container configured to be vacuum-exhausted. The upper electrode is connected to a first RF power supply configured to apply a first RF power for plasma generation. The lower electrode is connected to a second RF power supply configured to apply a second RF power for ion attraction. The second RF power supply is provided with a controller preset to control the second RF power supply to operate in a power modulation mode that executes power modulation in predetermined cycles between a first power set to deposit polymers on a predetermined film on a wafer and a second power set to promote etching of the predetermined film on the wafer.

Owner:TOKYO ELECTRON LTD

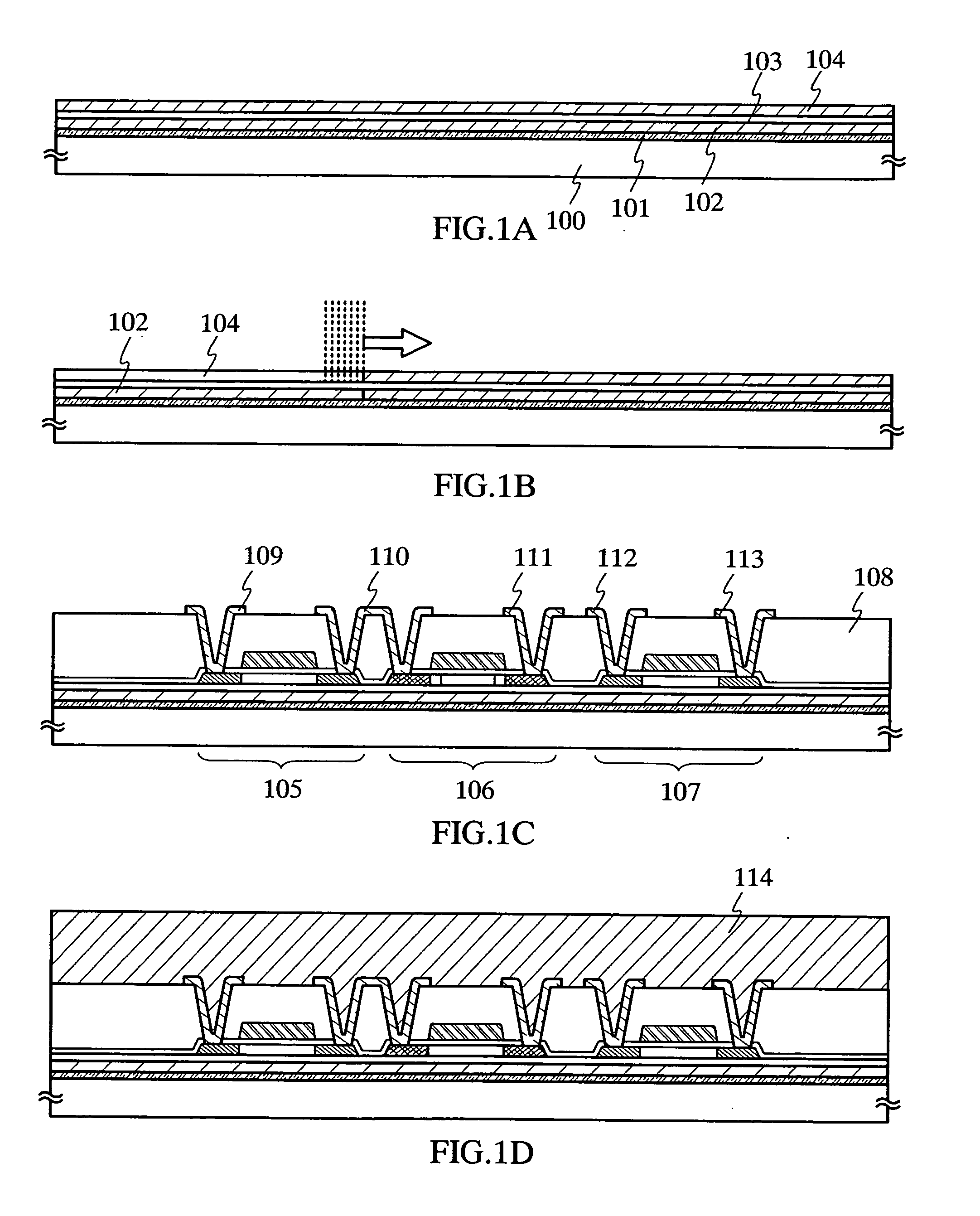

Method for manufacturing semiconductor device

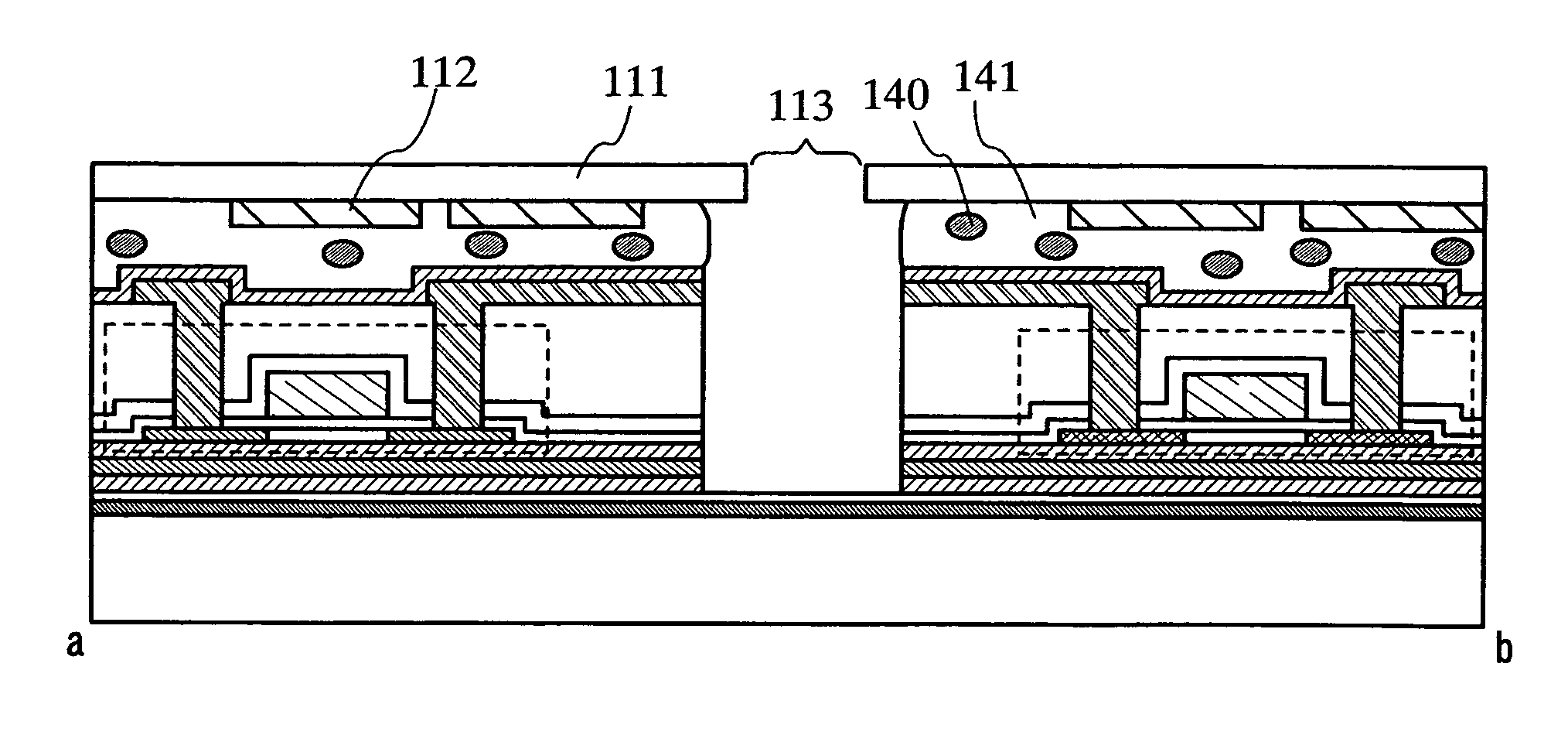

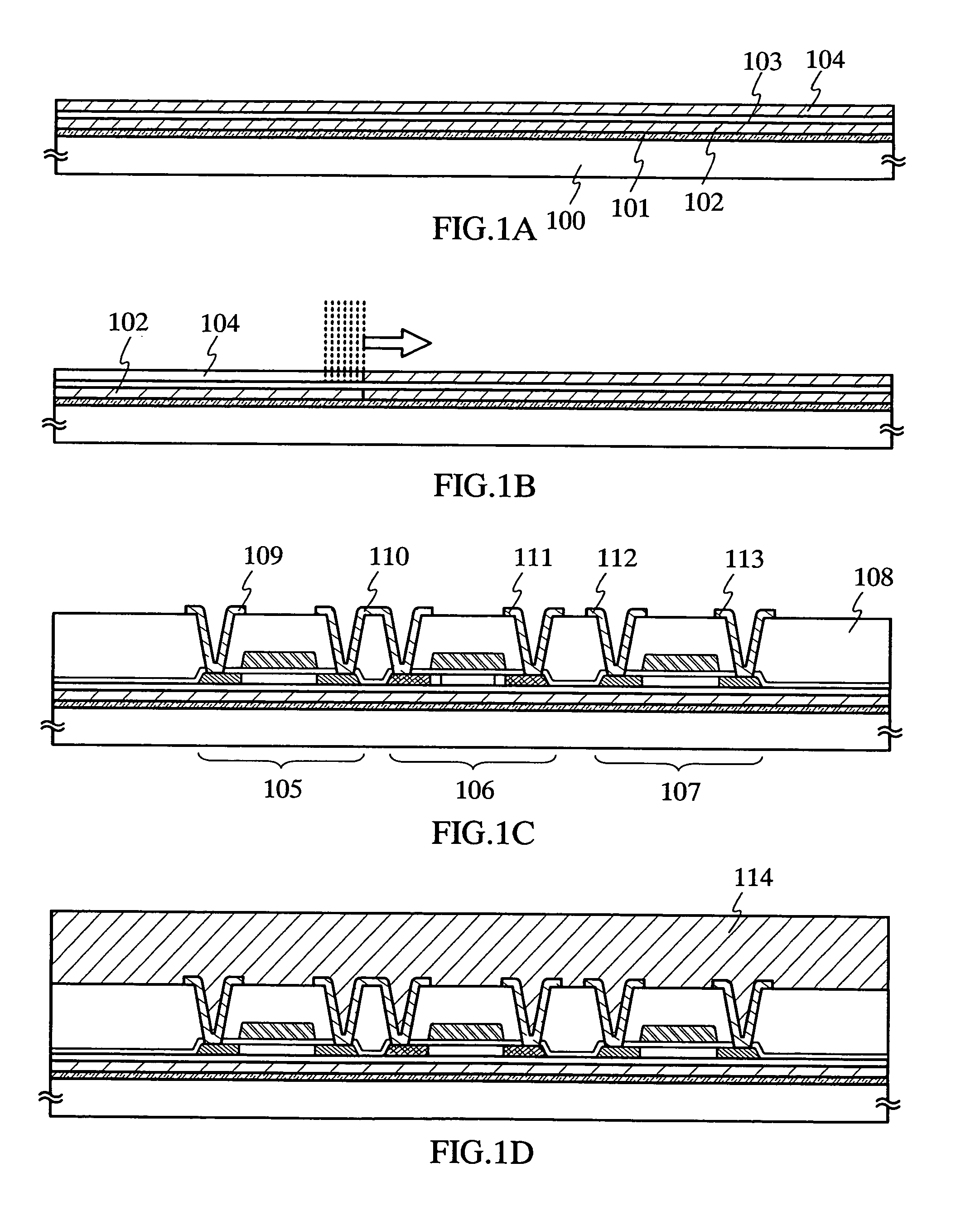

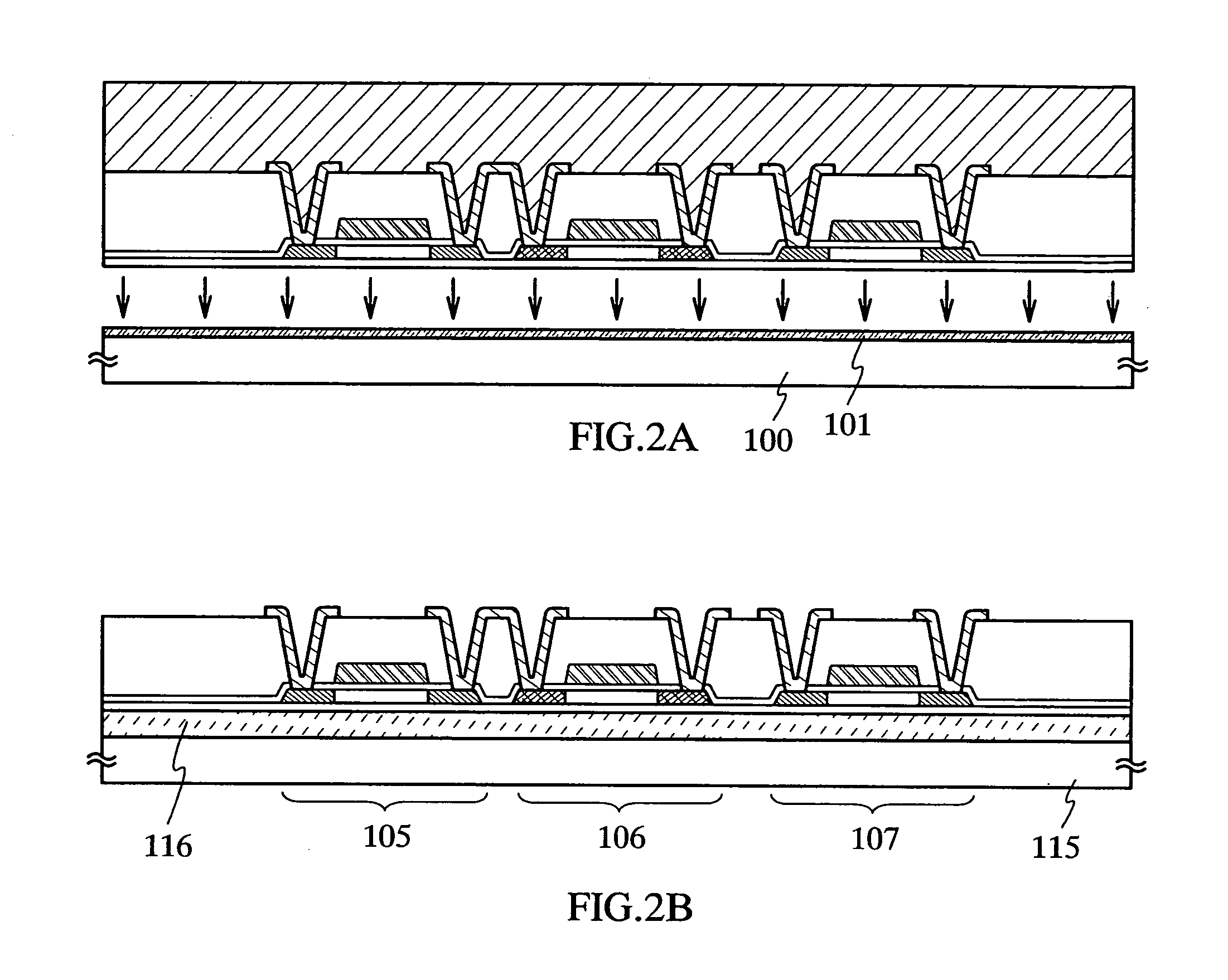

InactiveUS20050214984A1Quick peelLower the volumeSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialThermal expansion

It is an object of the present invention to provide a method for manufacturing a semiconductor device, capable of keeping a peeling layer from being peeled from a substrate in the phase before the completion of a semiconductor element and peeling a semiconductor element rapidly. It is considered that a peeling layer tends to be peeled from a substrate because the stress is applied to a peeling layer due to the difference in thermal expansion coefficient between a substrate and a peeling layer, or because the volume of a peeling layer is reduced and thus the stress is applied thereto by crystallization of the peeling layer due to heat treatment. Therefore, according to one feature of the invention, the adhesion of a substrate and a peeling layer is enhanced by forming an insulating film (buffer film) for relieving the stress on the peeling layer between the substrate and the peeling layer before forming the peeling layer over the substrate.

Owner:SEMICON ENERGY LAB CO LTD

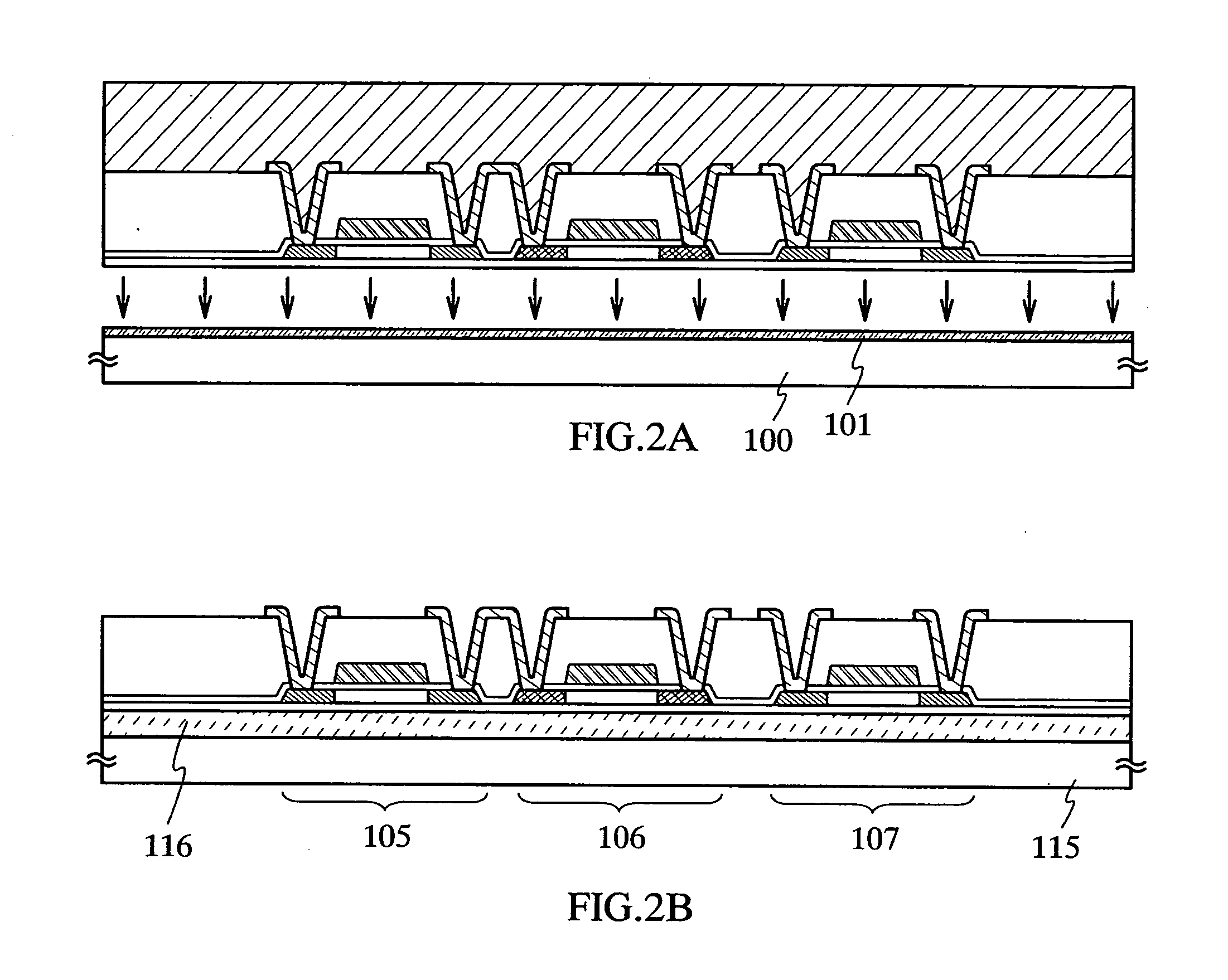

Method for manufacturing thin film integrated circuit, and element substrate

InactiveUS7452786B2Simple processLow costTransistorSemiconductor/solid-state device detailsCompound (substance)Silicon

Application form of and demand for an IC chip formed with a silicon wafer are expected to increase, and further reduction in cost is required. An object of the invention is to provide a structure of an IC chip and a process capable of producing at a lower cost. A feature of the invention is to use a metal film and a reactant having the metal film as a separation layer. An etching rate of the metal film or the reactant having metal is high, and a physical means in addition to a chemical means of etching the metal film or the reactant having metal can be used in the invention. Thus, the IDF chip can be manufactured more simply and easily in a short time.

Owner:SEMICON ENERGY LAB CO LTD

Method for manufacturing semiconductor device

InactiveUS7282380B2Quick peelLower the volumeSolid-state devicesSemiconductor/solid-state device manufacturingThermal expansionOptoelectronics

It is an object of the present invention to provide a method for manufacturing a semiconductor device, capable of keeping a peeling layer from being peeled from a substrate in the phase before the completion of a semiconductor element and peeling a semiconductor element rapidly. It is considered that a peeling layer tends to be peeled from a substrate because the stress is applied to a peeling layer due to the difference in thermal expansion coefficient between a substrate and a peeling layer, or because the volume of a peeling layer is reduced and thus the stress is applied thereto by crystallization of the peeling layer due to heat treatment. Therefore, according to one feature of the invention, the adhesion of a substrate and a peeling layer is enhanced by forming an insulating film (buffer film) for relieving the stress on the peeling layer between the substrate and the peeling layer before forming the peeling layer over the substrate.

Owner:SEMICON ENERGY LAB CO LTD

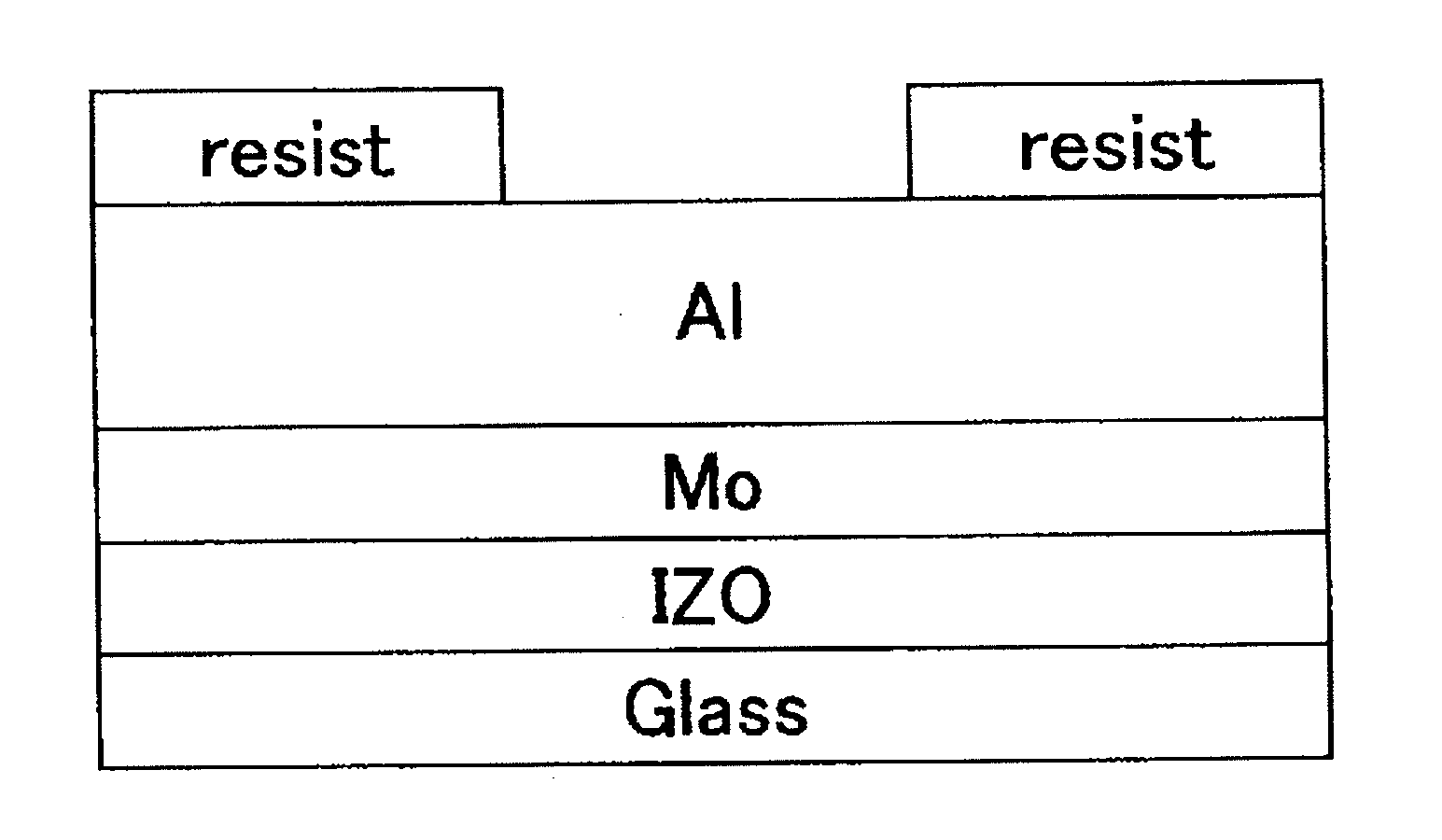

Etching solution composition

InactiveUS20100320457A1High selectivityImprove uniformity and stabilitySemiconductor/solid-state device manufacturingNon-linear opticsMetallurgyAlloy

Provided is an etching solution composition for selectively etching a metal film, which is composed of Al, Al alloy or the like and is arranged on an amorphous oxide film, from a laminated film including the metal film and an amorphous oxide film of various types. The etching solution composition is used for selectively etching the metal film from the laminated film which includes the amorphous oxide film and the metal film composed of Al, Al alloy, Cu, Cu alloy, Ag or Ag alloy, and is composed of an aqueous solution containing an alkali.

Owner:IDEMITSU KOSAN CO LTD +1

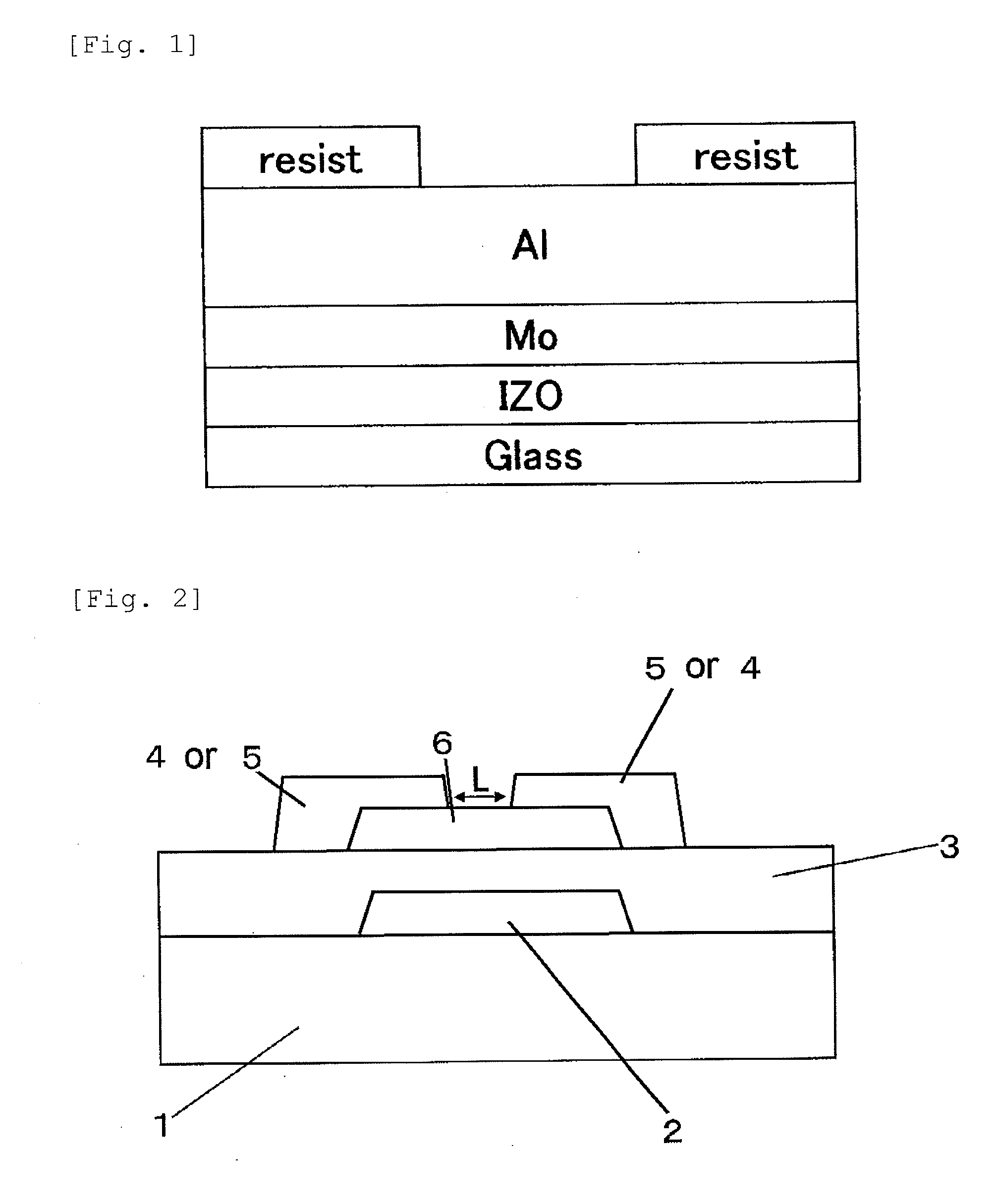

Method for manufacturing a compound semiconductor device having an improved via hole

InactiveUS20070082427A1Increase etch rateImprove verticalitySolid-state devicesSemiconductor/solid-state device manufacturingAdhesiveEngineering

In a method for manufacturing a compound semiconductor device, a principal surface of a SiC wafer, on which a compound semiconductor device is located, is bonded to a support substrate with an adhesive having a softening point higher than 200° C. A via hole is formed dry etching, including supplying a fluorine-containing etching gas to a rear side of the SiC wafer. Thereafter, the support substrate and the adhesive are removed. Preferably, the adhesive is formed by reacting one material coating the principal surface of the SiC wafer, and another material coating the support substrate.

Owner:MITSUBISHI ELECTRIC CORP

Plasma etching method

InactiveUS20140144876A1High selectivityIncrease etch rateElectric discharge tubesDecorative surface effectsCurrent voltageElectric power

A plasma etching method using a plasma etching apparatus including a lower electrode and an upper electrode is provided. The plasma etching method includes a first etching step of performing plasma etching using a first process gas and a second etching step of performing the plasma etching using a second process gas. The adhesion of a radical of the second process gas to an object of processing is less than the adhesion of a radical of the first process gas to the object of processing. While alternately repeating a first condition of turning on high-frequency electric power for plasma generation and a second condition of turning off the high-frequency electric power, the second etching step applies a negative direct-current voltage to the upper electrode so that the absolute value of the applied voltage is greater in a period of the second condition than in a period of the first condition.

Owner:TOKYO ELECTRON LTD

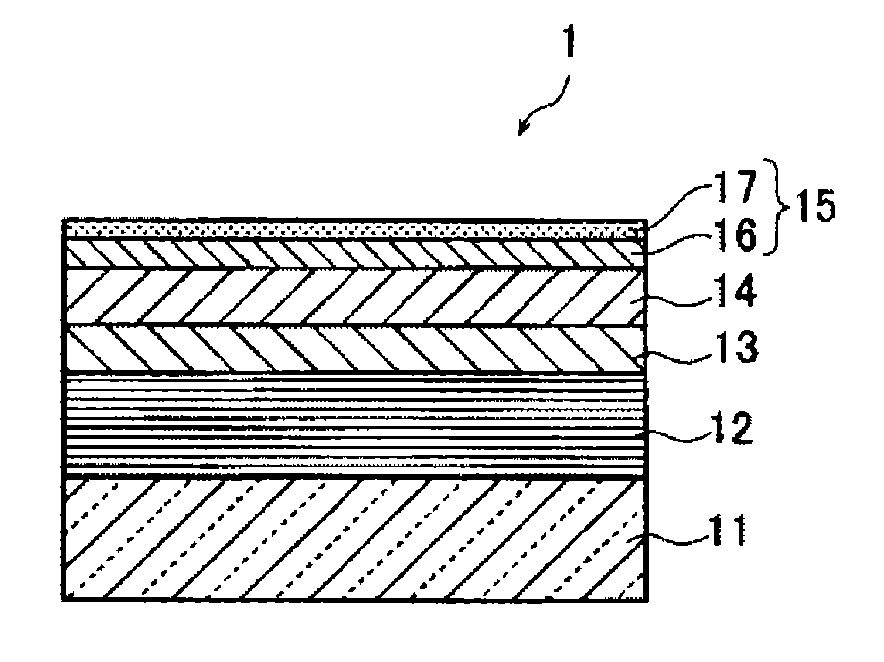

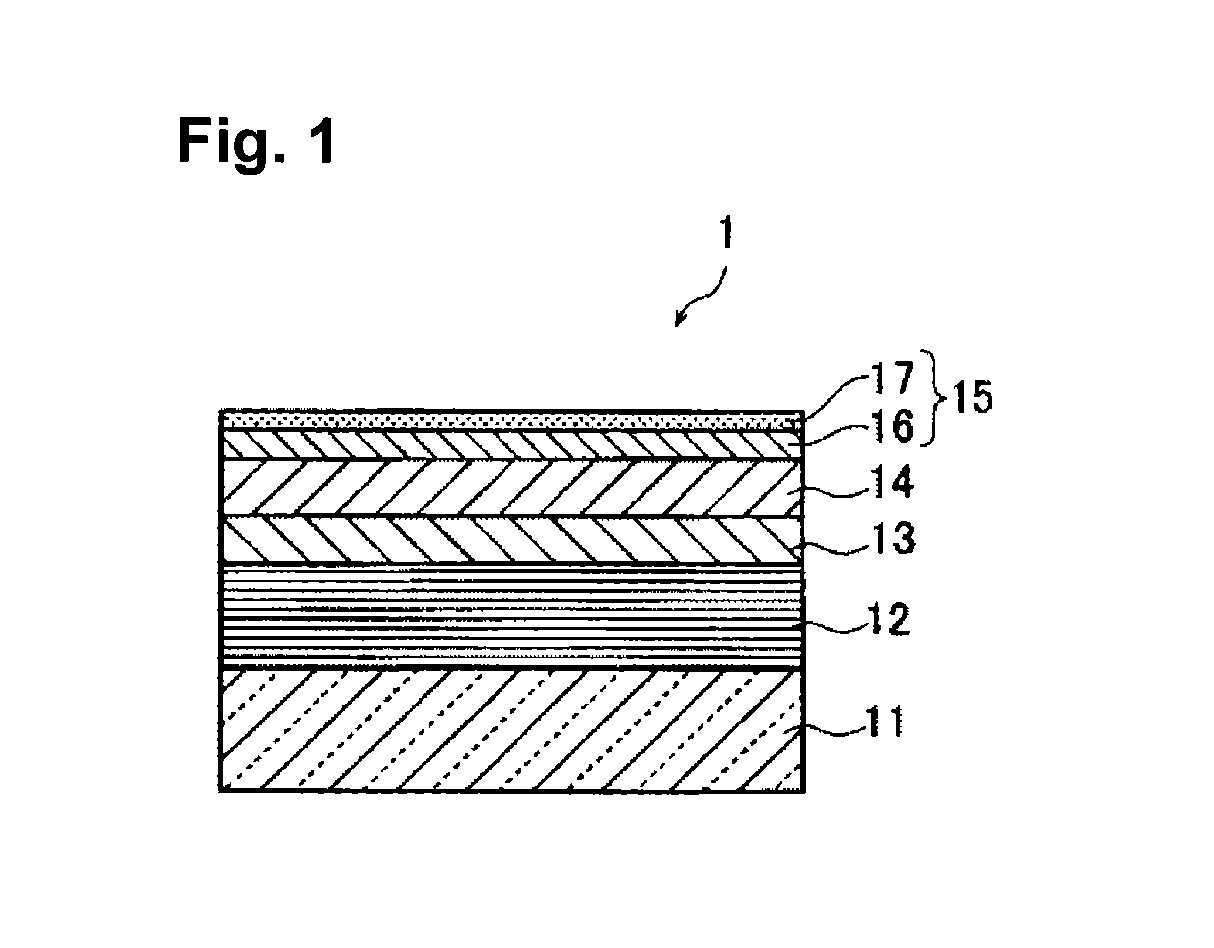

Reflective mask blank for EUV lithography and process for producing the same

ActiveUS20120322000A1Sufficient etching rateSimple processVacuum evaporation coatingSemiconductor/solid-state device manufacturingLithographic artistNitrogen

To provide an EUV mask blank provided with a low reflective layer, which has excellent properties as an EUV mask blank. A reflective mask blank for EUV lithography comprising a substrate, and a reflective layer for reflecting EUV light, an absorber layer for absorbing EUV light and a low reflective layer to an inspection light (wavelength: 190 to 260 nm) for a mask pattern, formed in this order on the substrate, wherein the low reflective layer has a stacked structure having a first layer containing at least 95 at % in total of silicon (Si) and nitrogen (N), and a second layer containing at least 95 at % in total of tantalum (Ta), oxygen (O) and nitrogen (N) or a second layer containing at least 95 at % in total of tantalum (Ta) and nitrogen (N), stacked in this order from the absorber layer side.

Owner:ASAHI GLASS CO LTD

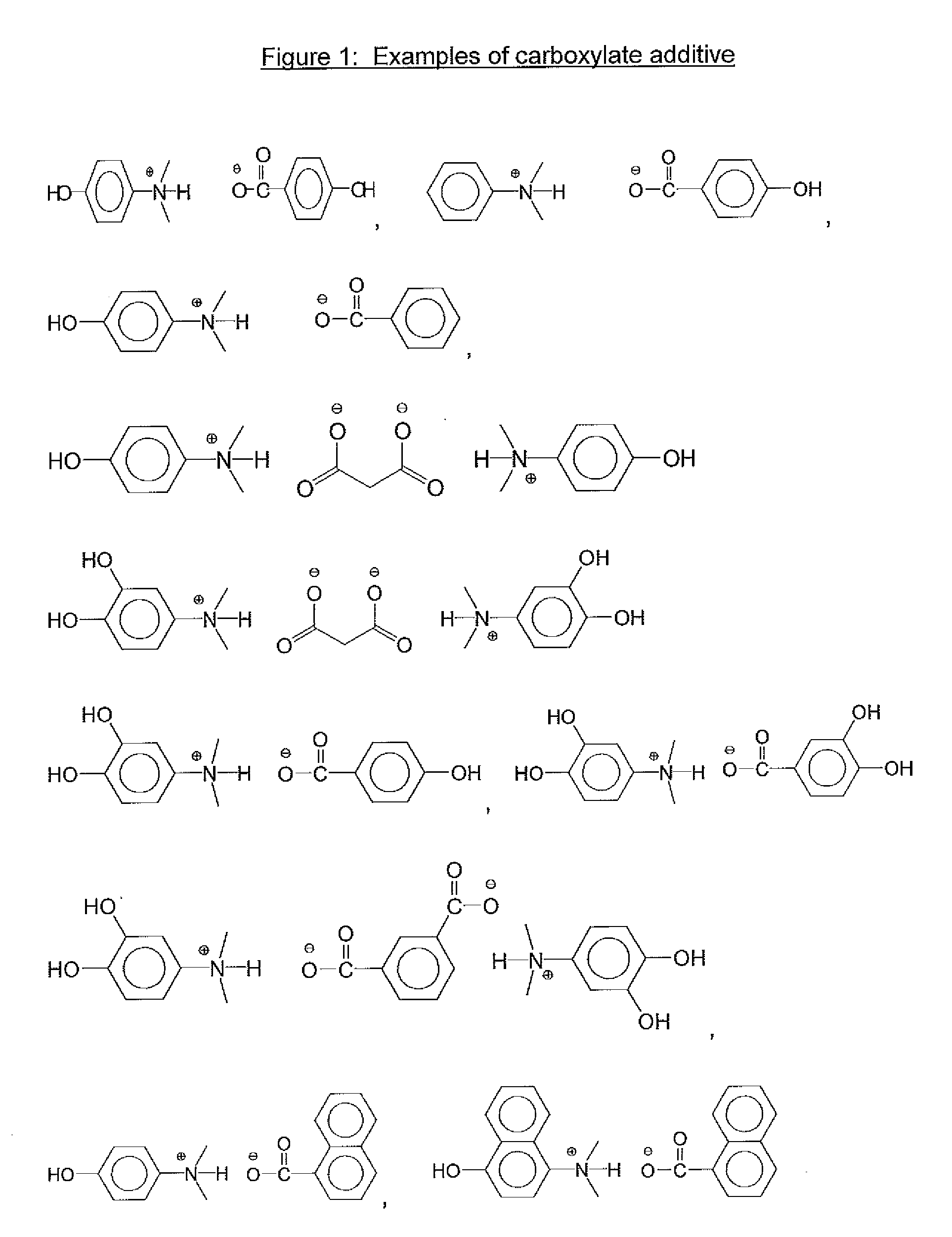

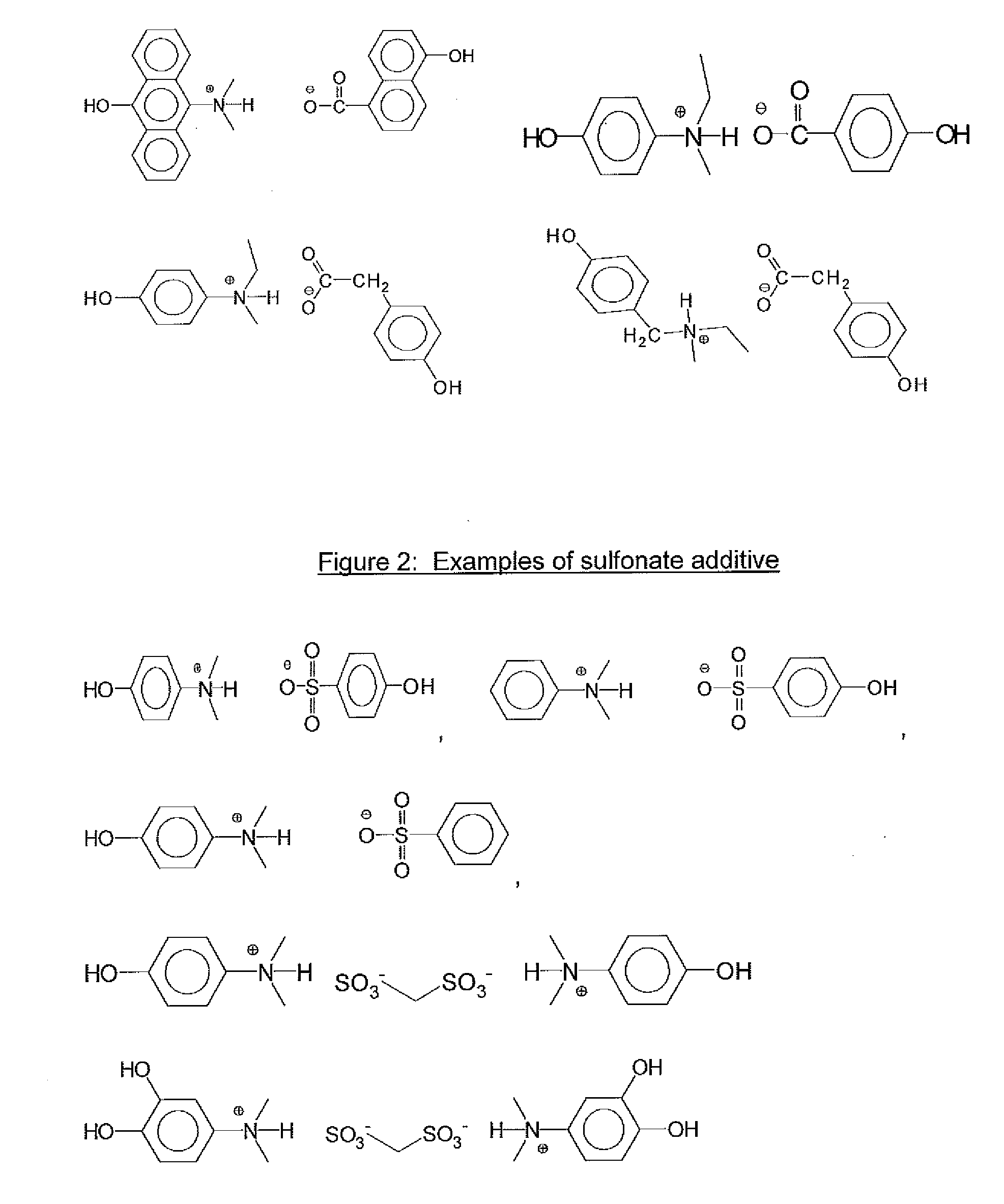

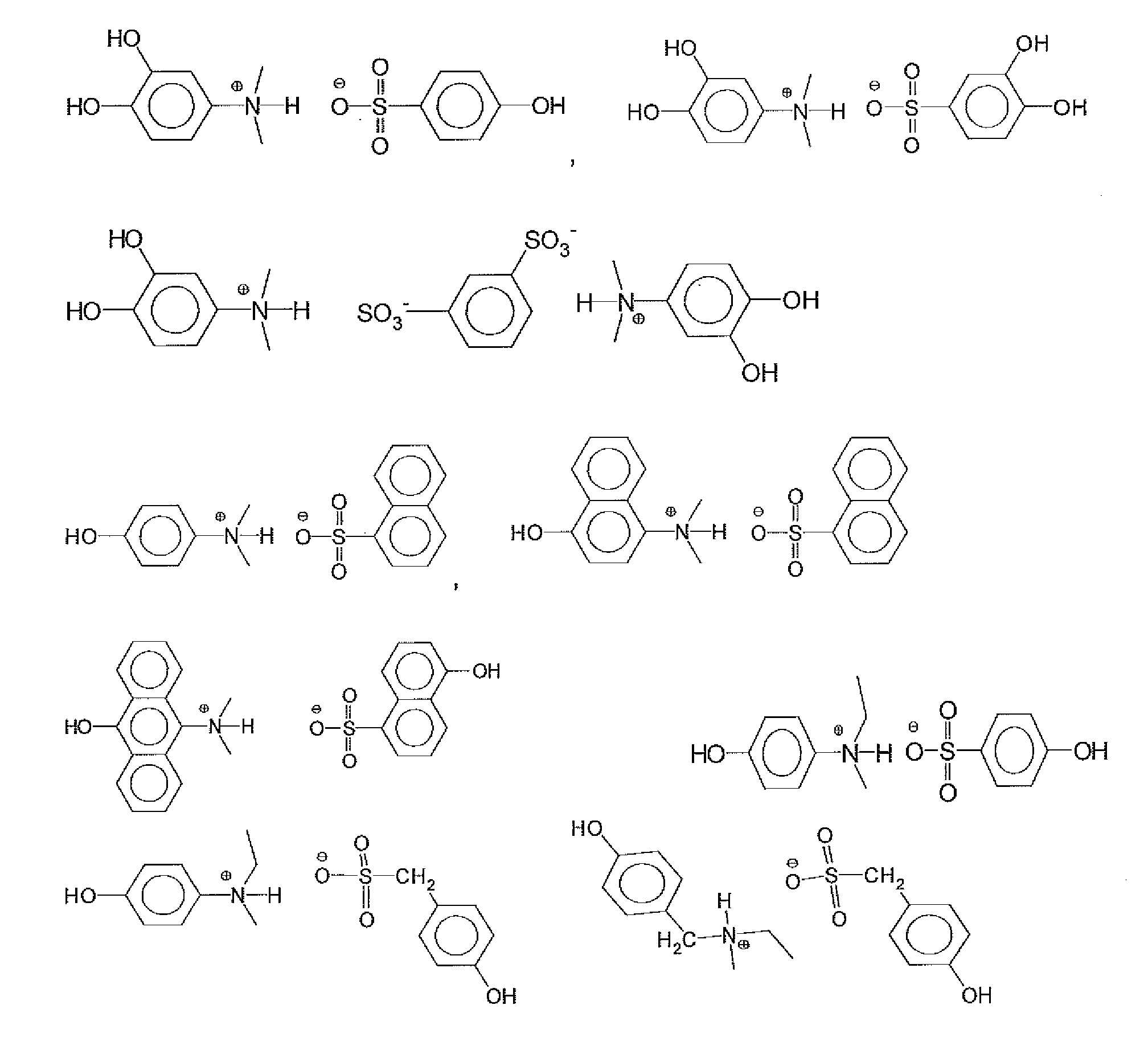

Bottom antireflective coating compositions and processes thereof

ActiveUS20120308939A1Reduce decreaseIncrease etch rateSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusPolymerAryl

The present invention relates to an antireflective coating composition comprising a crosslinking agent, a polymer comprising at least one chromophore group and at least one hydroxyl and / or a carboxyl group, and an additive, further where the additive has structure 1 and comprises at least one arylene-hydroxyl moiety,where Y is selected from an carboxylate anion or sulfonate anion, R1, R2, and R3 are independently selected from unsubstituted C1-C8 alkyl, substituted C1-C8 alkyl, aryl and arylene-hydroxyl; X1, X2, and X3 are independently selected from direct valence bond and C1-C8 alkylene group, and, n=1, 2 or 3. The invention further relates to a process for using the composition.

Owner:MERCK PATENT GMBH

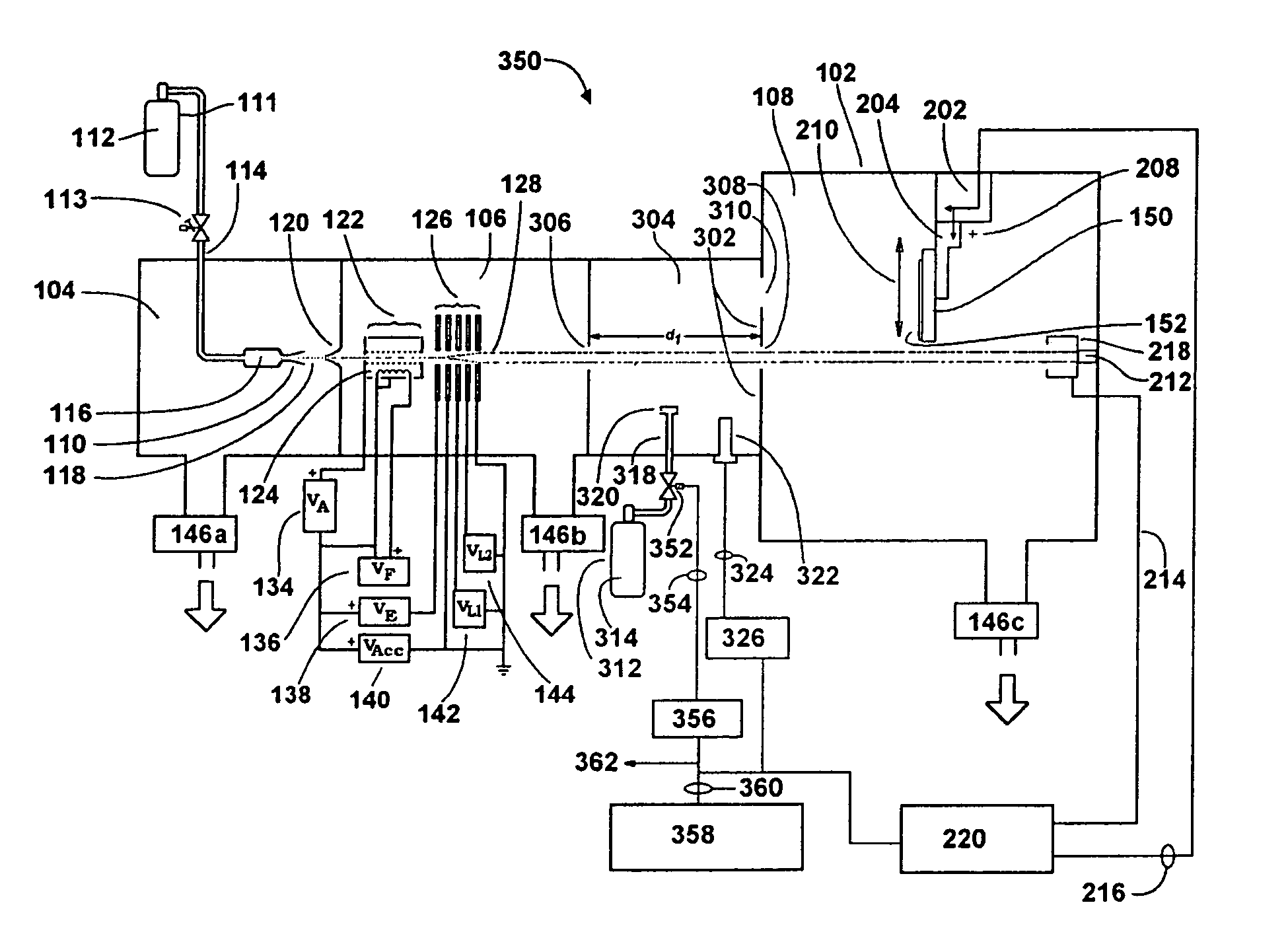

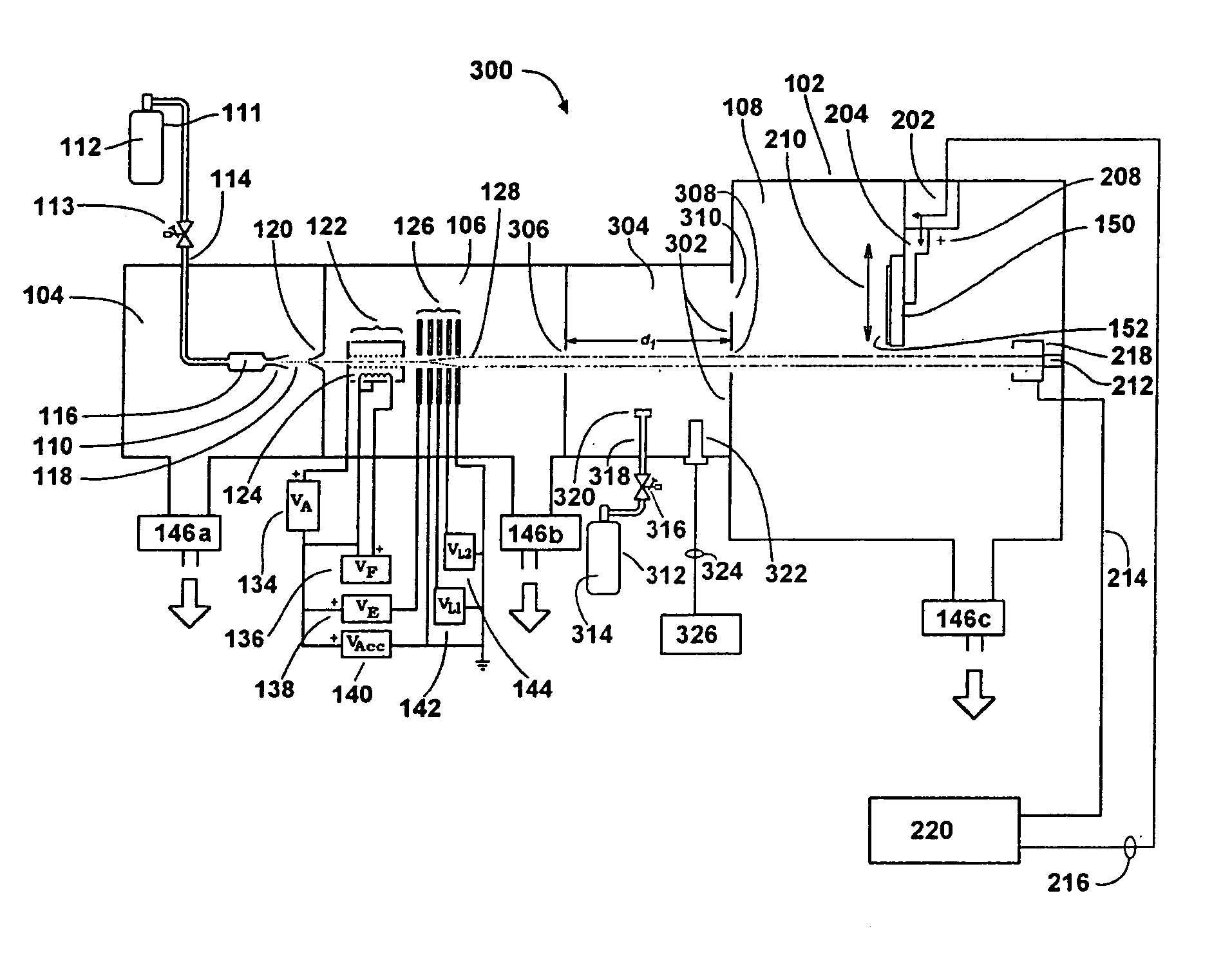

Method and apparatus for improved processing with a gas-cluster ion beam

ActiveUS20050205802A1Smoothing capabilityImprove etching effectMaterial analysis by optical meansIon beam tubesGas cluster ion beamIon energy

Apparatus and methods for improving processing of workpieces with gas-cluster ion beams and modifying the gas-cluster ion energy distribution in the GCIB. In a reduced-pressure environment, generating an energetic gas-cluster ion beam and subjecting the beam to increased pressure region.

Owner:TEL EPION

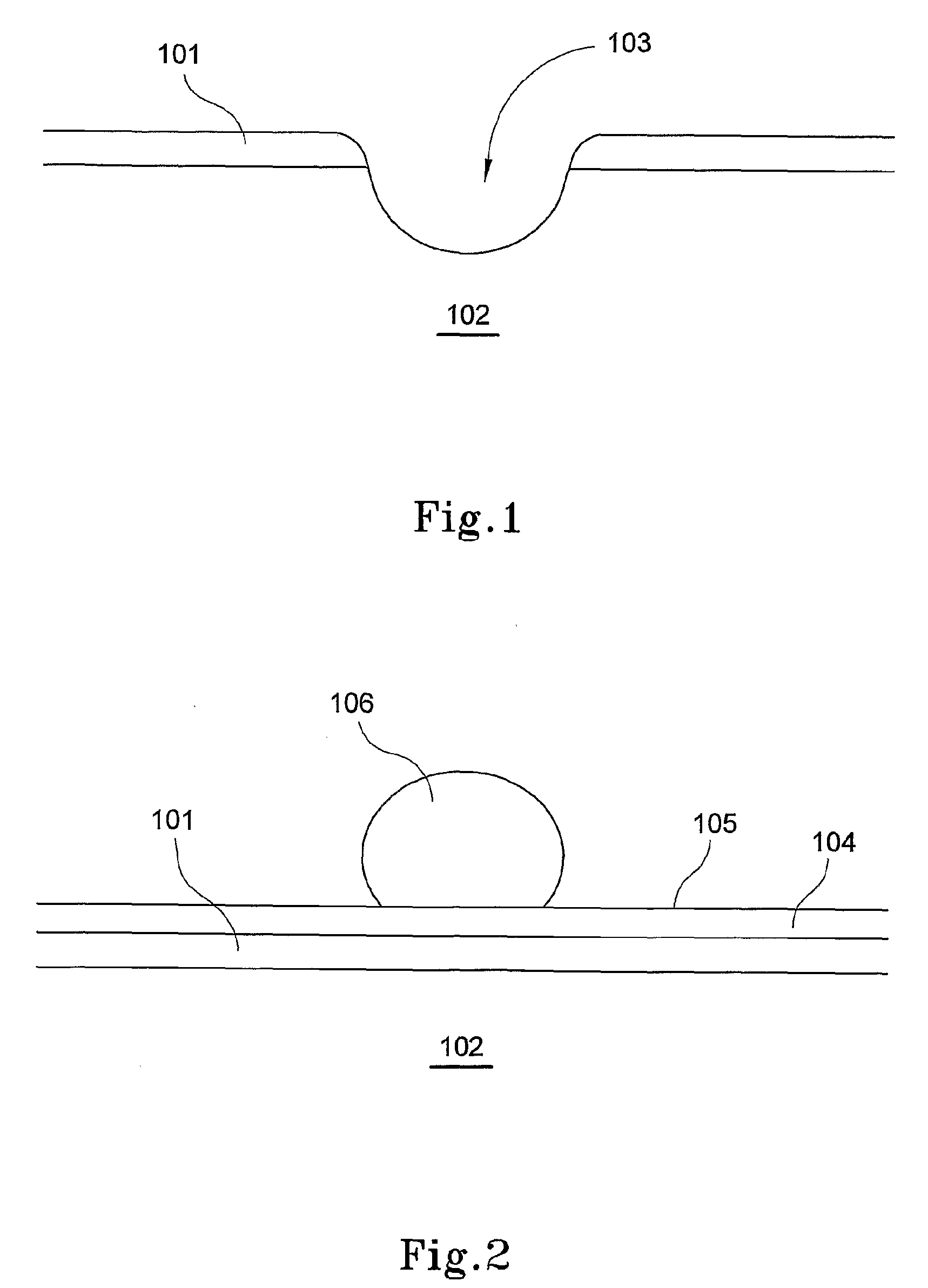

High efficiency solar cell fabrication

InactiveUS20090008787A1Small droplet sizeIncrease etch rateLiquid surface applicatorsSemiconductor/solid-state device detailsSemiconductor materialsEngineering

A method of forming a contact structure and a contact structure so formed is described. The structure contacts an underlying layer of a semiconductor junction, wherein the junction comprises the underlying layer of a semiconductor material and is separated from an overlying layer of semiconductor material by creating an undercut region to shade subsequent metal formation. Various steps are performed using inkjet printing techniques.

Owner:NEWSOUTH INNOVATIONS PTY LTD