Patents

Literature

15685results about "Microstructural device manufacture" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

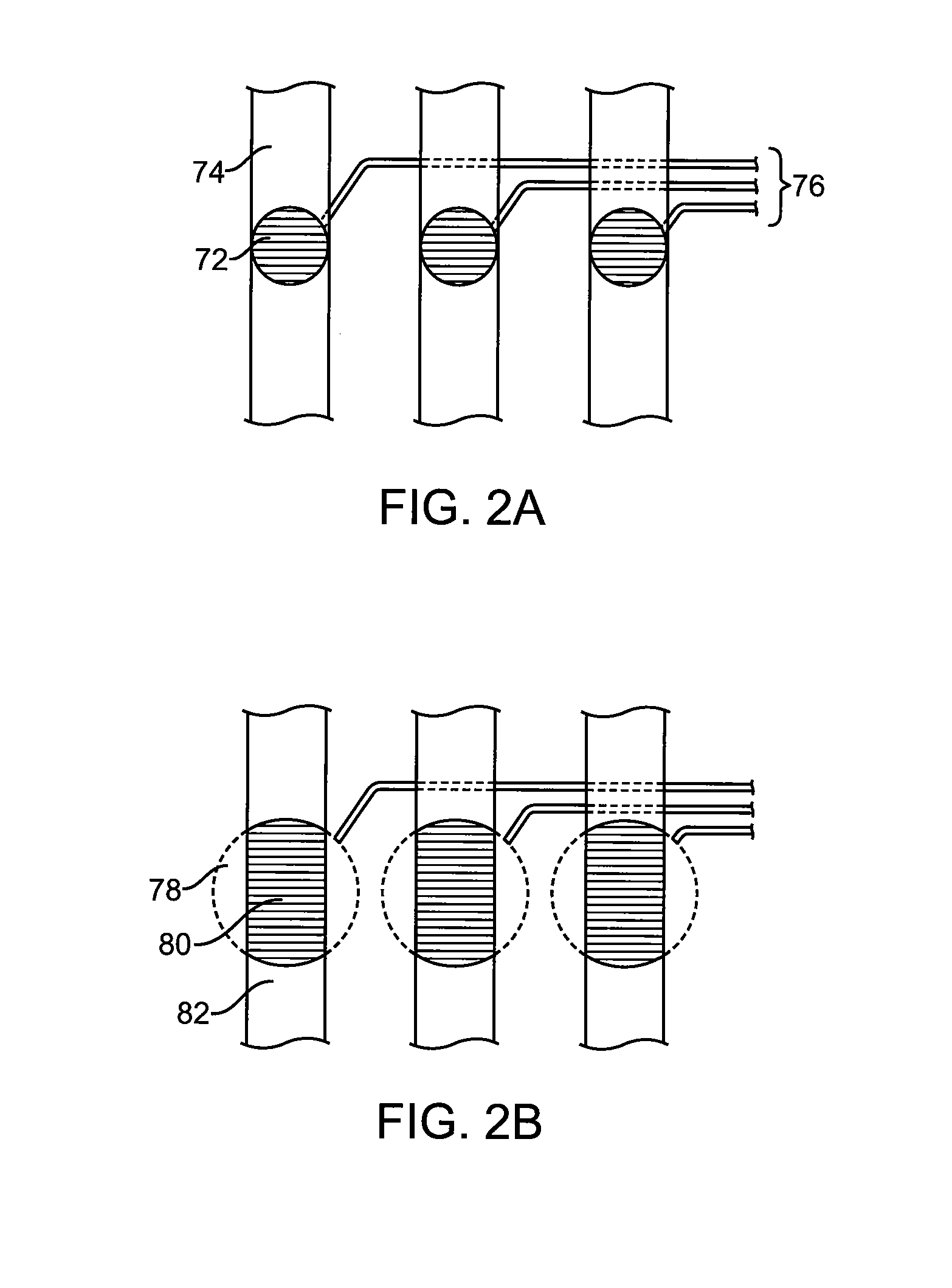

Methods and apparatus for analyzing polynucleotide sequences

The present invention provides an apparatus for analyzing the sequences of polynucleotides. The apparatus comprises (a) flow cell which has at least one microfabricated multilayer elastomeric synthesis channel; and (b) an inlet port and an outlet port. The inlet port and outlet ports are in fluid communication with the flow cell for flowing fluids into and through the flow cell.

Owner:CALIFORNIA INST OF TECH

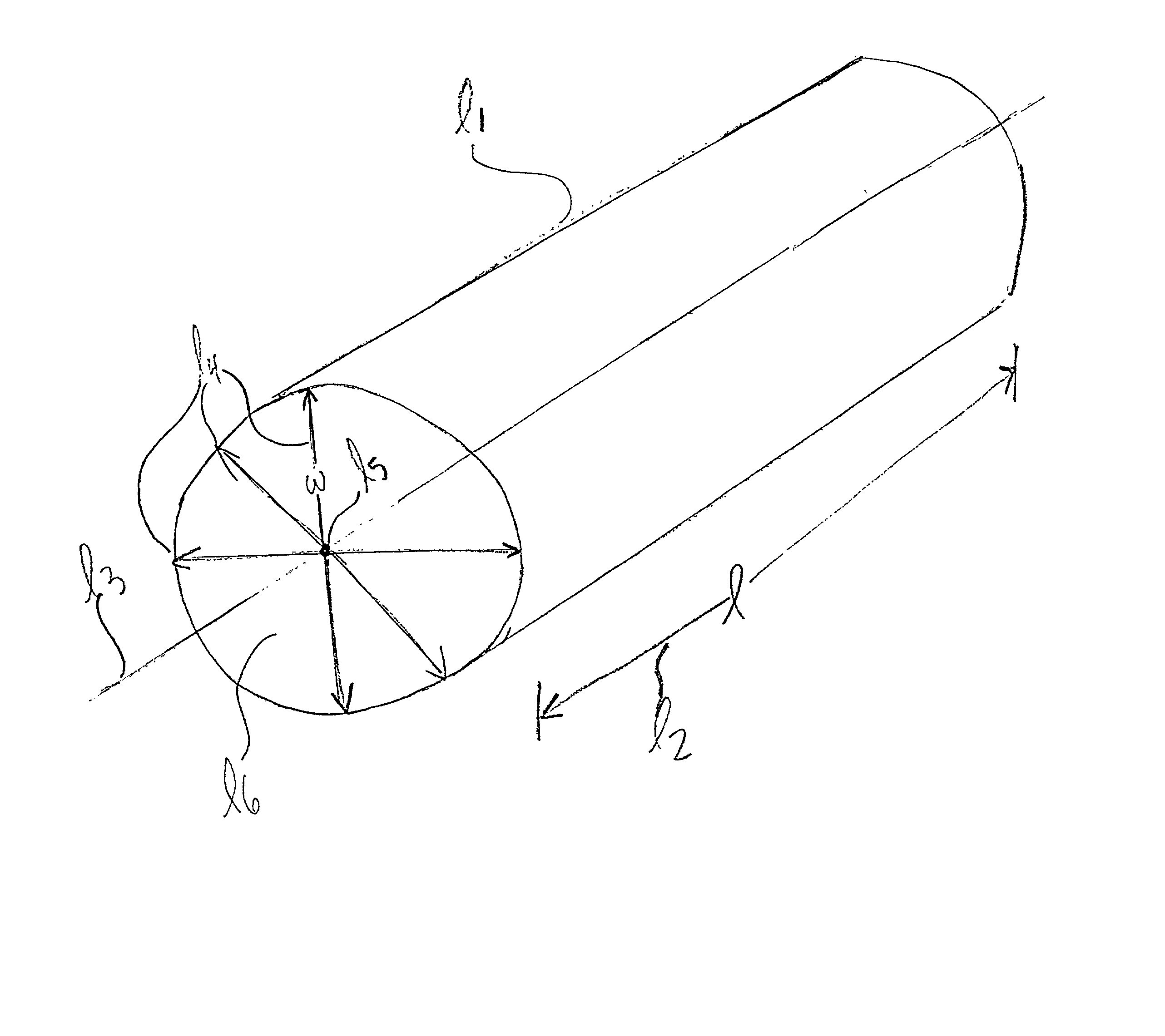

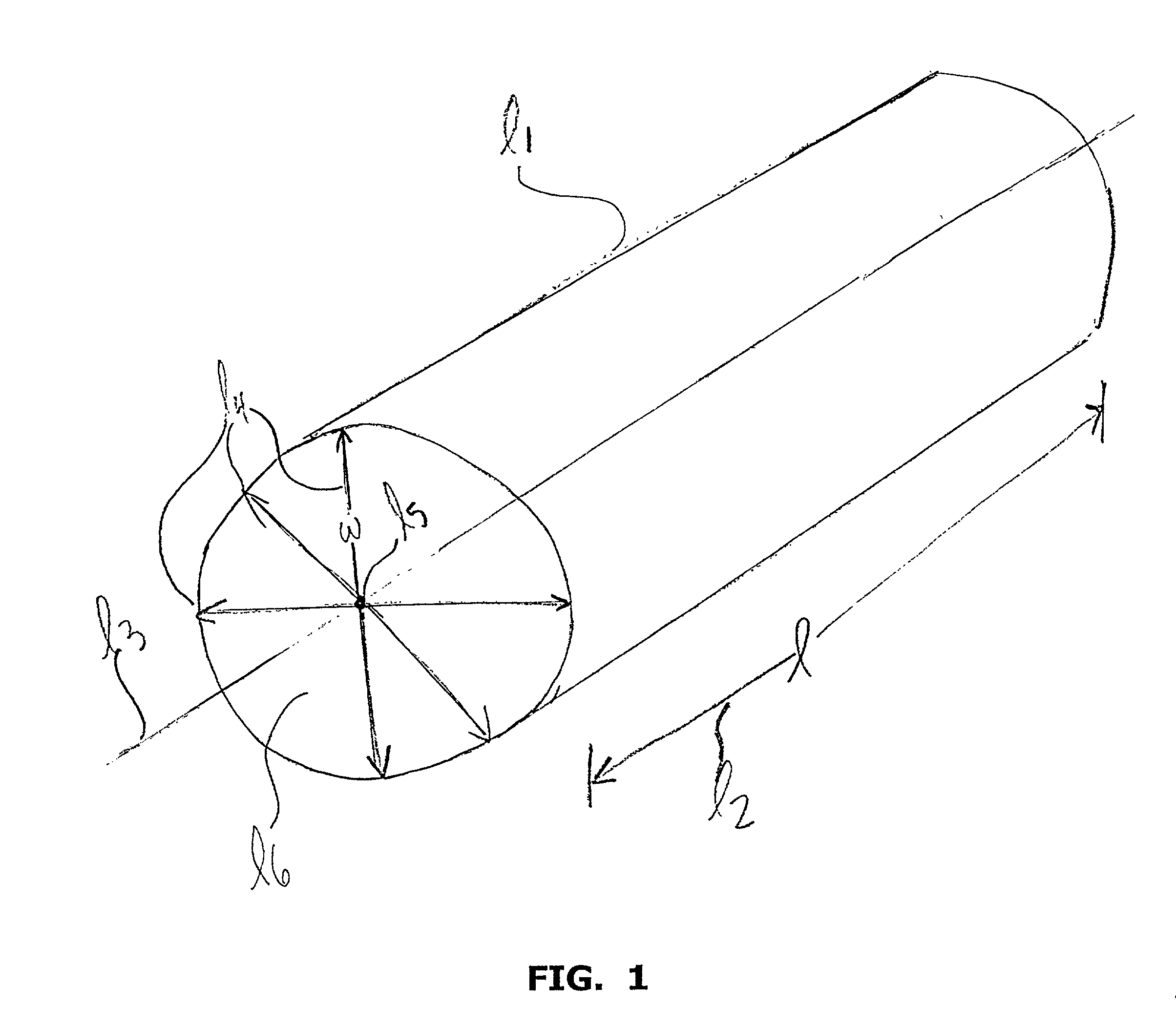

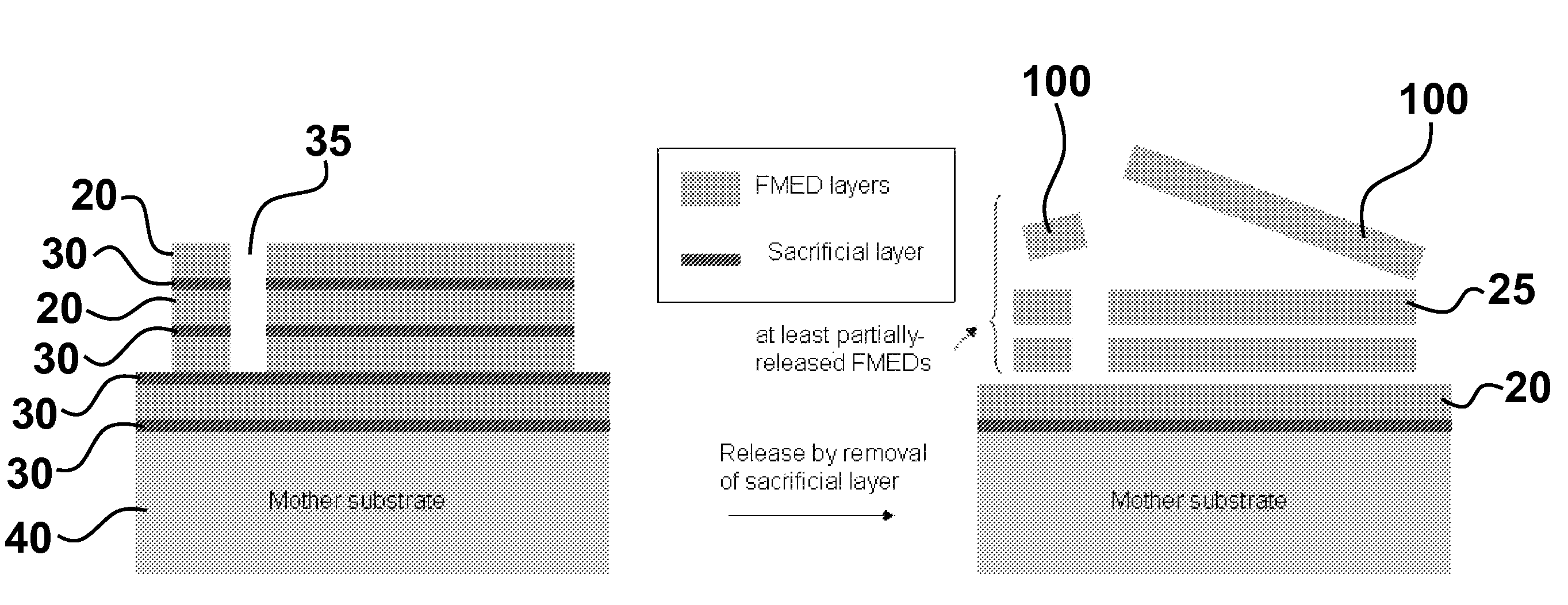

Doped elongated semiconductors, growing such semiconductors, devices including such semiconductors and fabricating such devices

A bulk-doped semiconductor that is at least one of the following: a single crystal, an elongated and bulk-doped semiconductor that, at any point along its longitudinal axis, has a largest cross-sectional dimension less than 500 nanometers, and a free-standing and bulk-doped semiconductor with at least one portion having a smallest width of less than 500 nanometers. Such a semiconductor may comprise an interior core comprising a first semiconductor; and an exterior shell comprising a different material than the first semiconductor. Such a semiconductor may be elongated and my have, at any point along a longitudinal section of such a semiconductor, a ratio of the length of the section to a longest width is greater than 4:1, or greater than 10:1, or greater than 100:1, or even greater than 1000:1. At least one portion of such a semiconductor may a smallest width of less than 200 nanometers, or less than 150 nanometers, or less than 100 nanometers, or less than 80 nanometers, or less than 70 nanometers, or less than 60 nanometers, or less than 40 nanometers, or less than 20 nanometers, or less than 10 nanometers, or even less than 5 nanometers. Such a semiconductor may be a single crystal and may be free-standing. Such a semiconductor may be either lightly n-doped, heavily n-doped, lightly p-doped or heavily p-doped. Such a semiconductor may be doped during growth. Such a semiconductor may be part of a device, which may include any of a variety of devices and combinations thereof, and, and a variety of assembling techniques may be used to fabricate devices from such a semiconductor. Two or more of such a semiconductors, including an array of such semiconductors, may be combined to form devices, for example, to form a crossed p-n junction of a device. Such devices at certain sizes may exhibit quantum confinement and other quantum phenomena, and the wavelength of light emitted from one or more of such semiconductors may be controlled by selecting a width of such semiconductors. Such semiconductors and device made therefrom may be used for a variety of applications.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

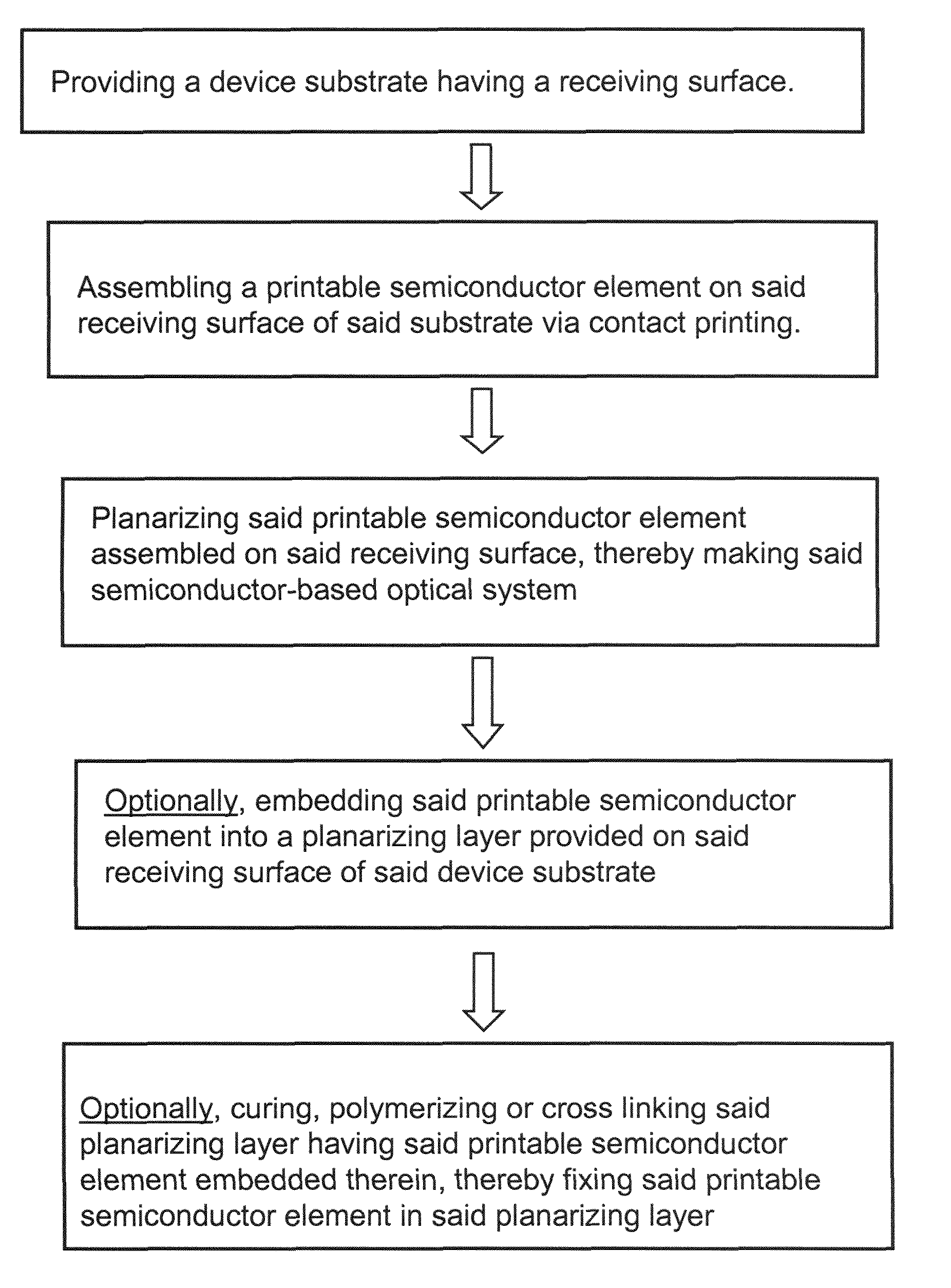

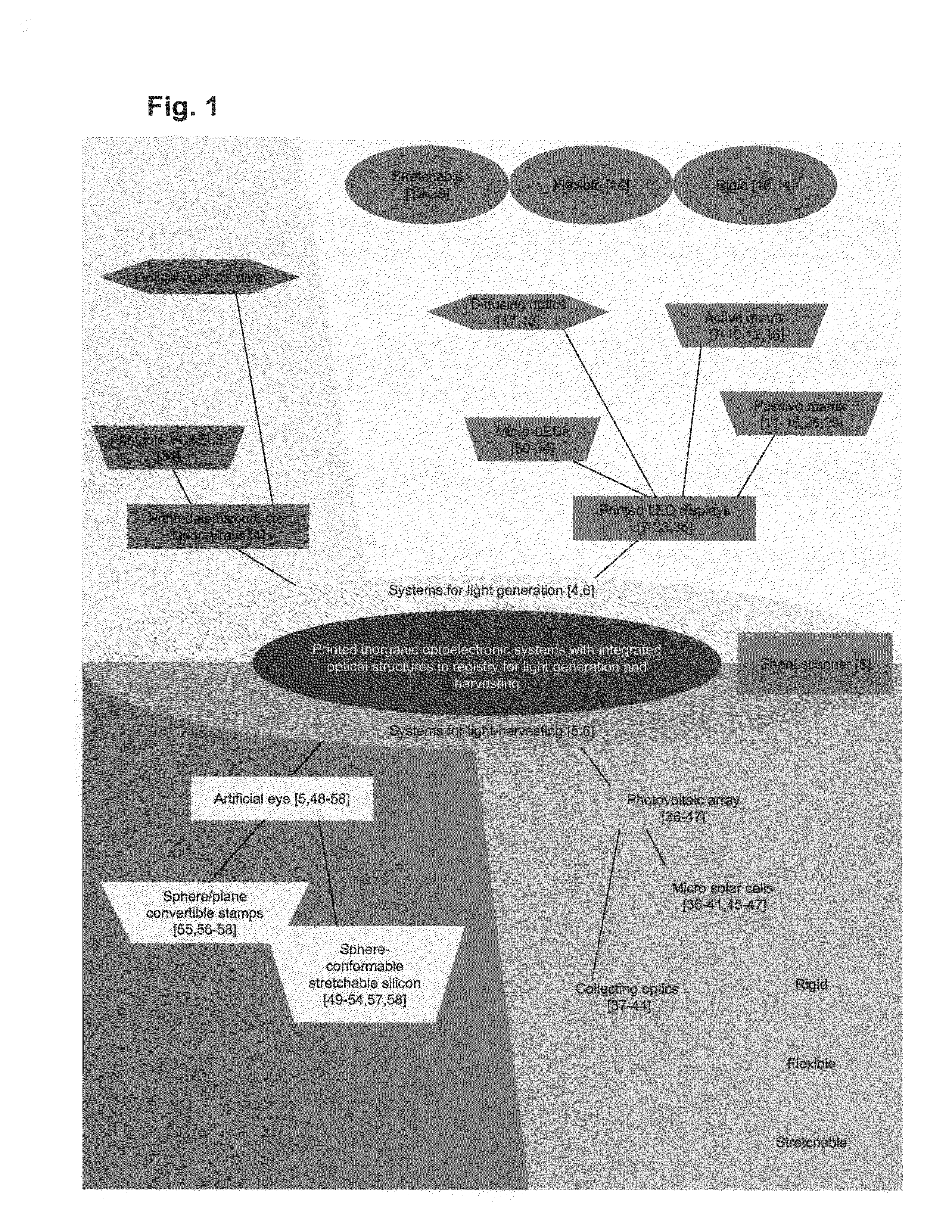

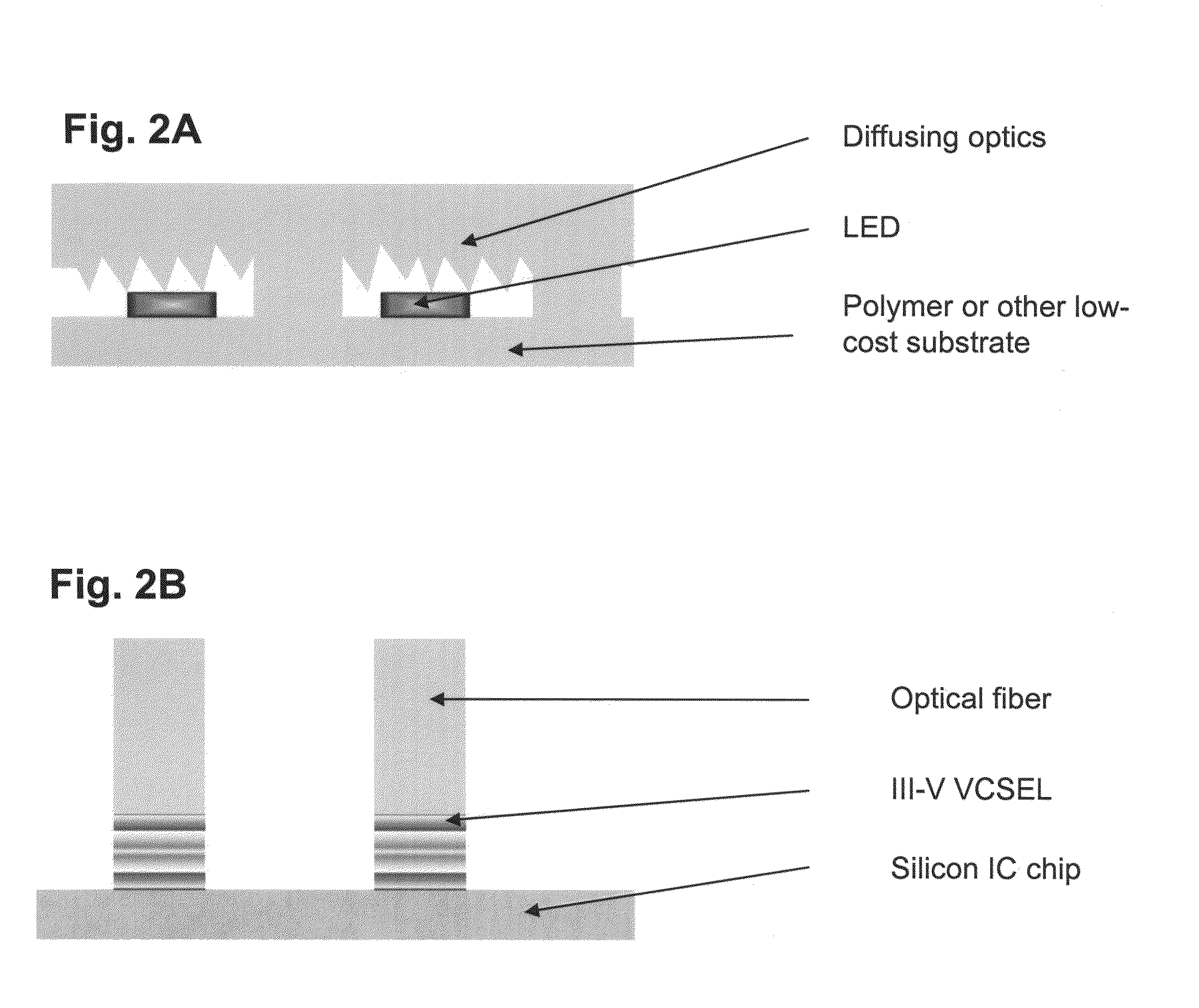

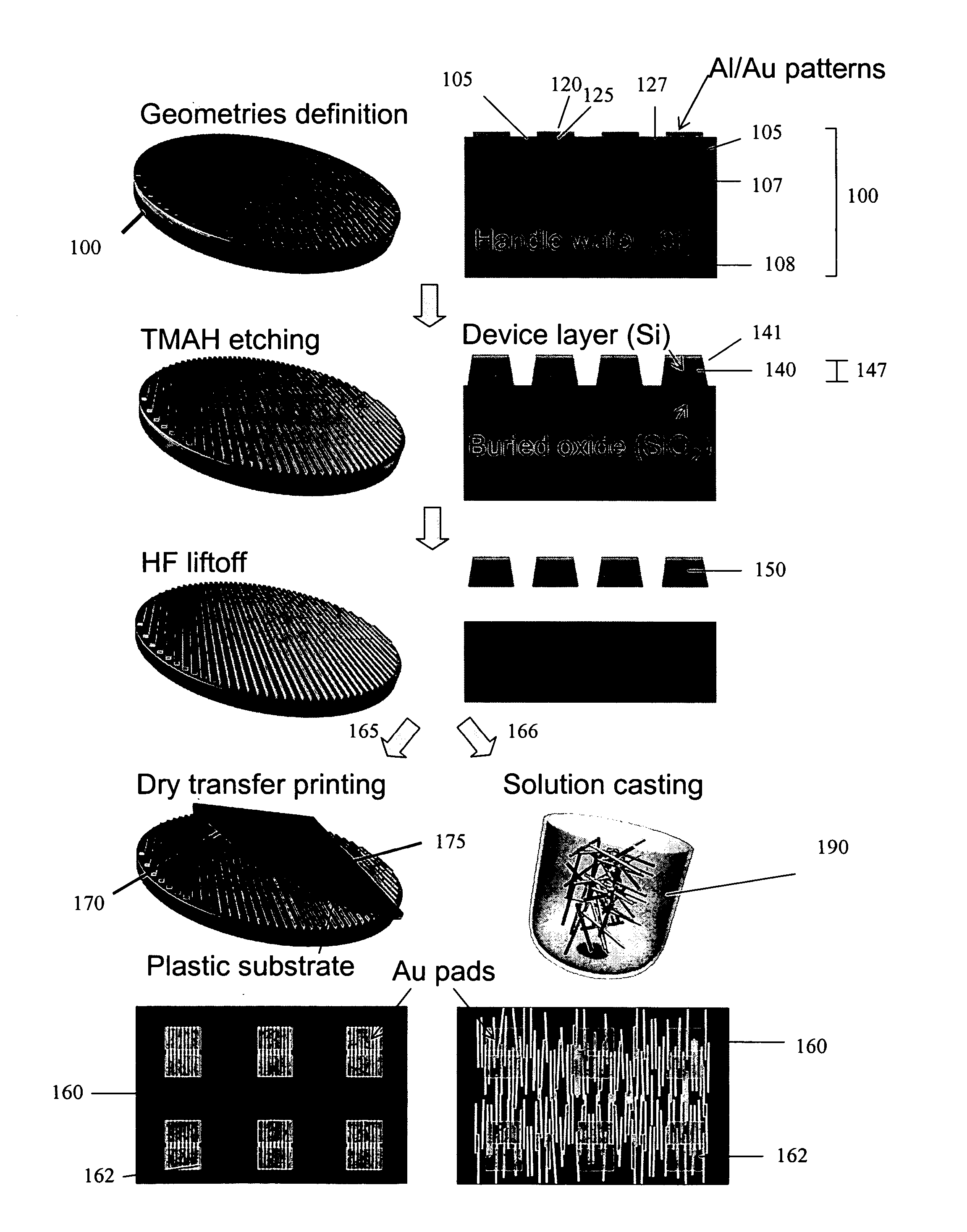

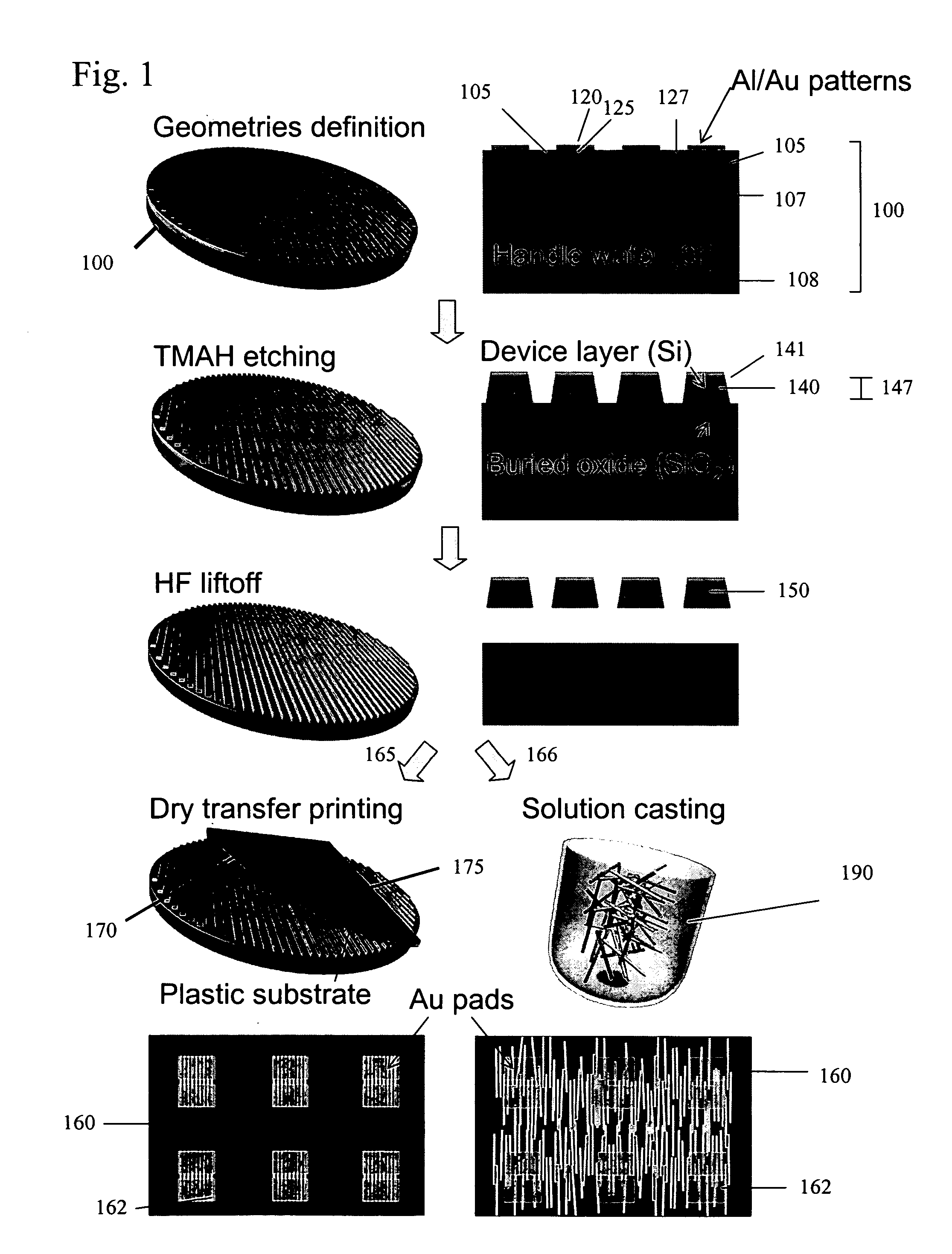

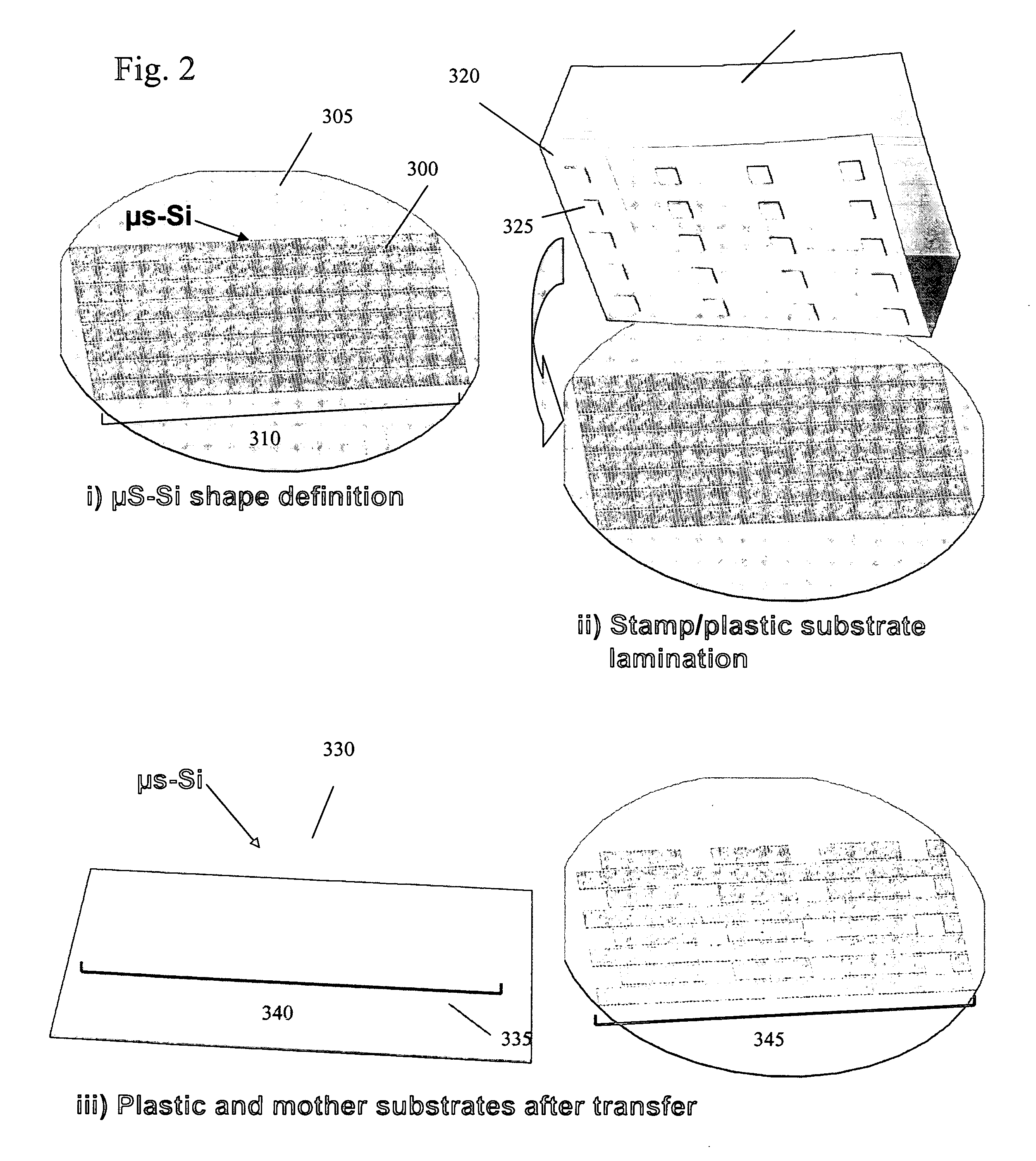

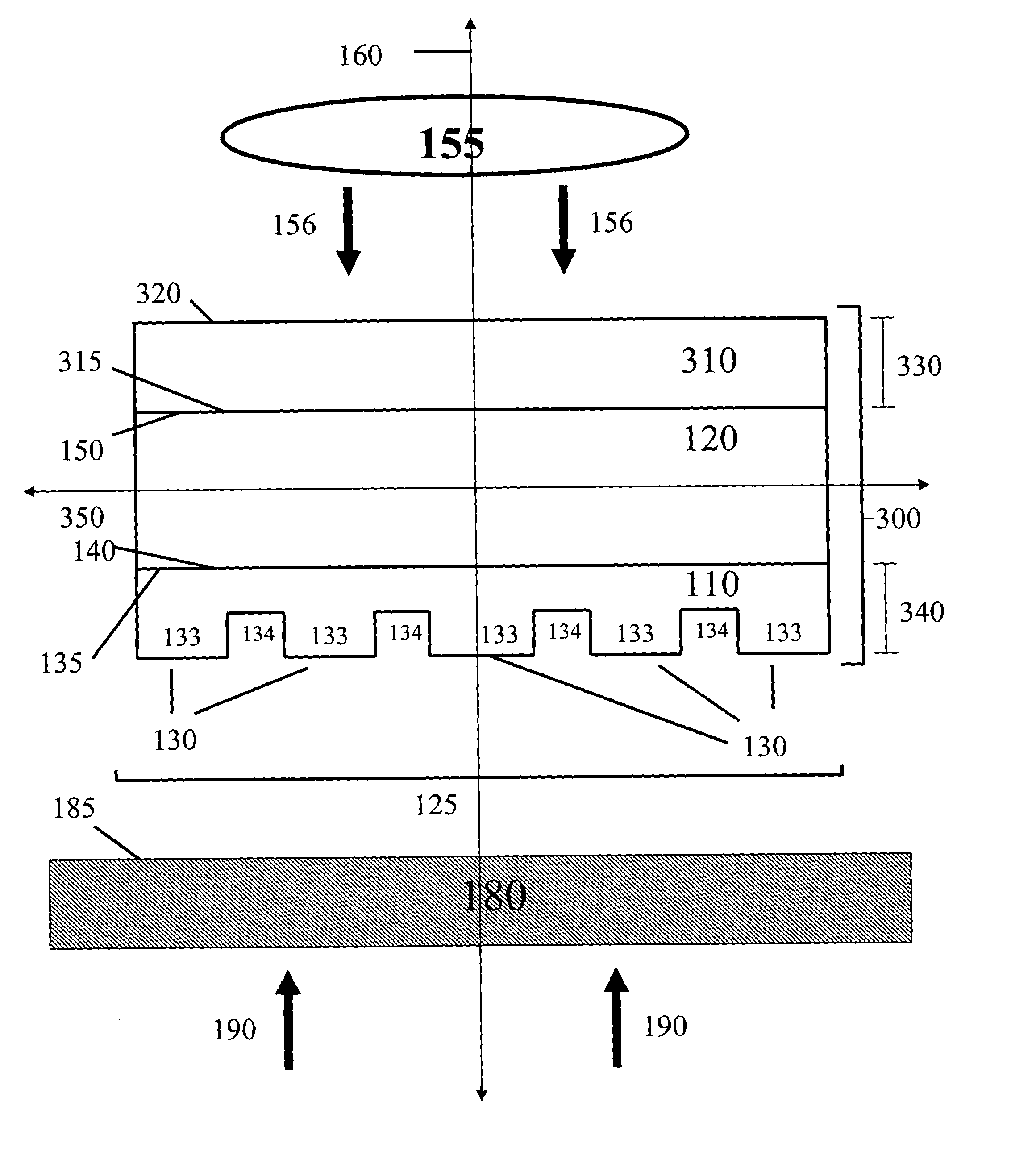

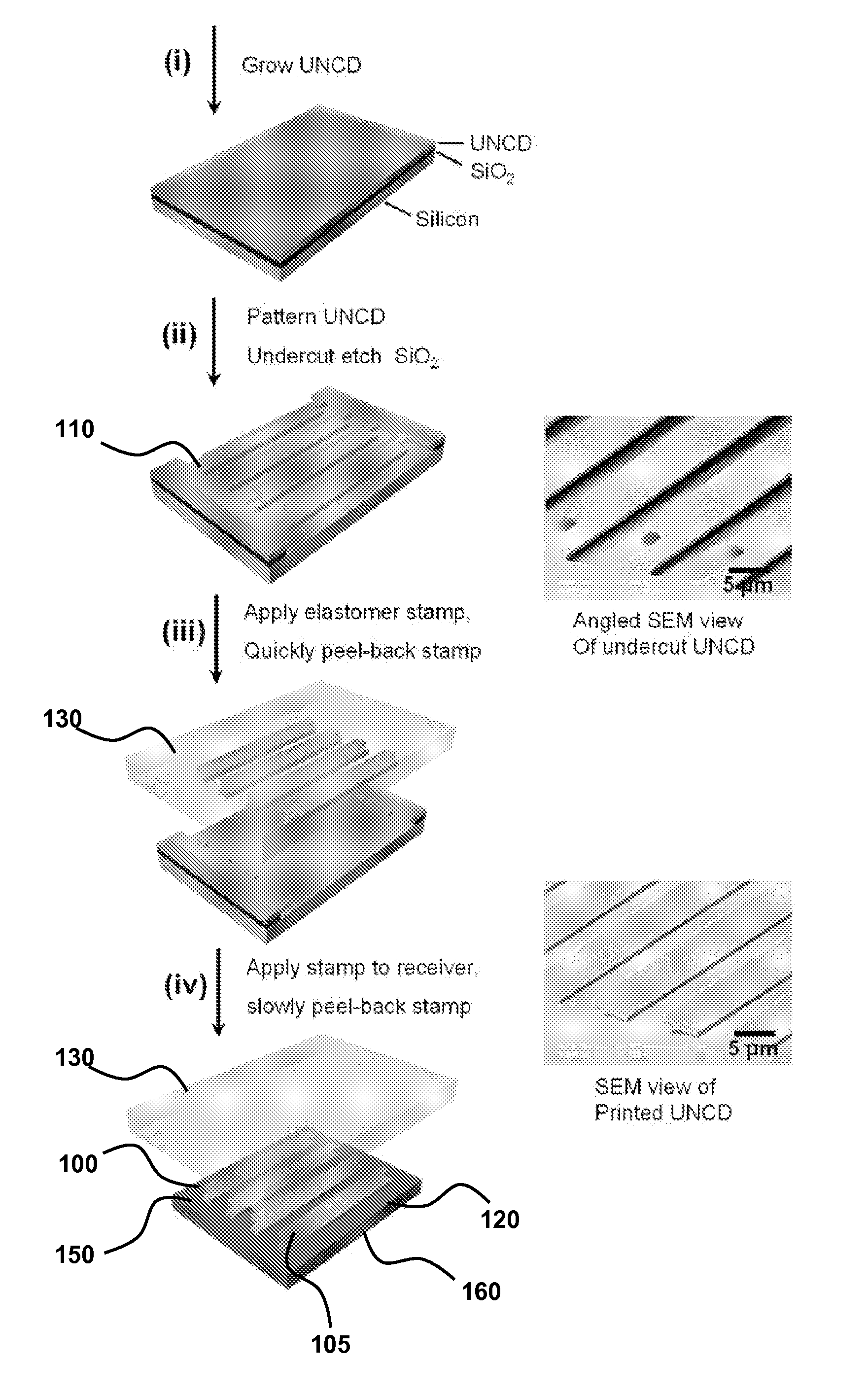

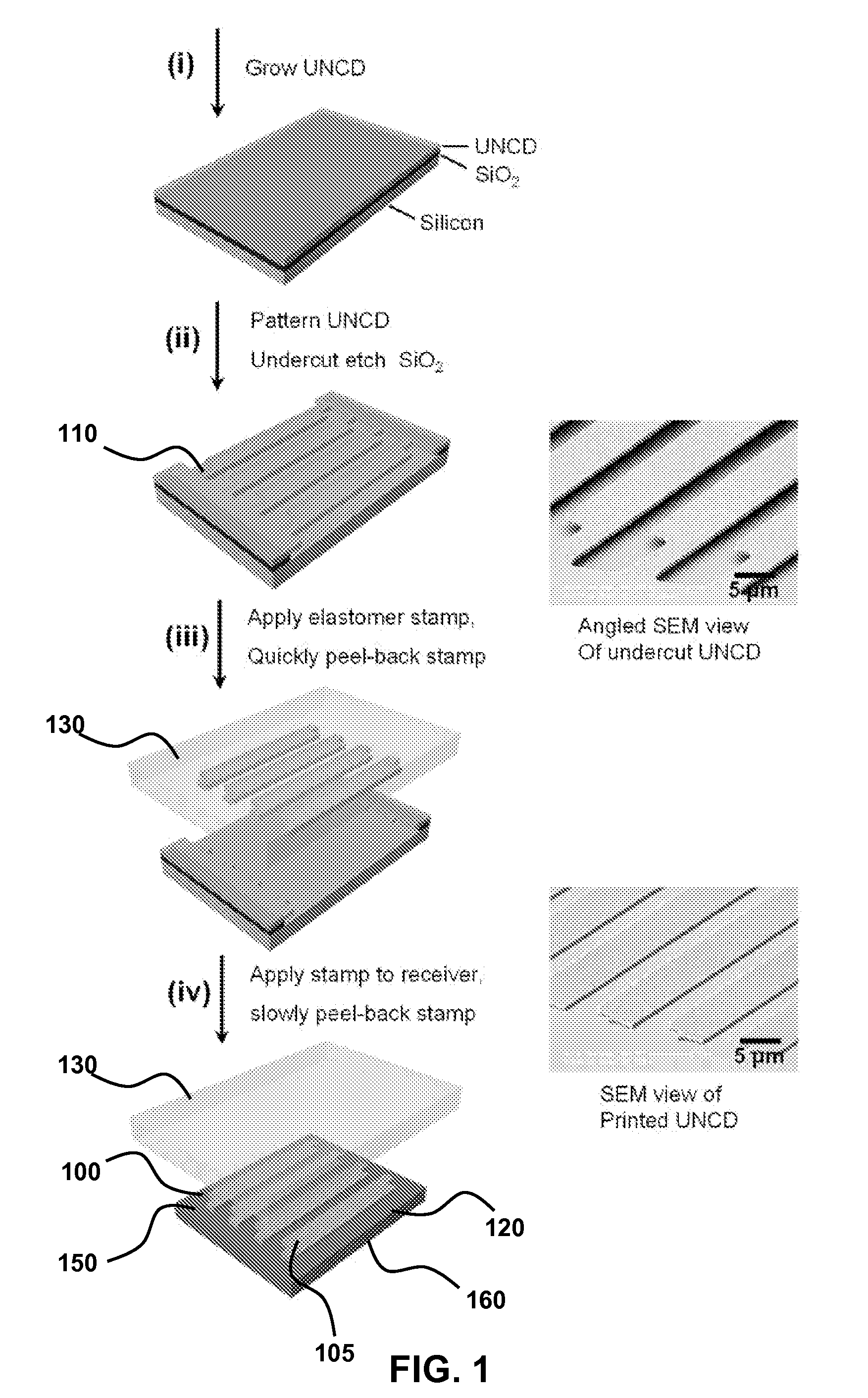

Optical systems fabricated by printing-based assembly

ActiveUS7972875B2Low costImprove performanceFinal product manufactureNanoinformaticsLight sensingSingle crystal

Provided are optical devices and systems fabricated, at least in part, via printing-based assembly and integration of device components. In specific embodiments the present invention provides light emitting systems, light collecting systems, light sensing systems and photovoltaic systems comprising printable semiconductor elements, including large area, high performance macroelectronic devices. Optical systems of the present invention comprise semiconductor elements assembled, organized and / or integrated with other device components via printing techniques that exhibit performance characteristics and functionality comparable to single crystalline semiconductor based devices fabricated using conventional high temperature processing methods. Optical systems of the present invention have device geometries and configurations, such as form factors, component densities, and component positions, accessed by printing that provide a range of useful device functionalities. Optical systems of the present invention include devices and device arrays exhibiting a range of useful physical and mechanical properties including flexibility, shapeability, conformability and stretchablity.

Owner:X DISPLAY CO TECH LTD +1

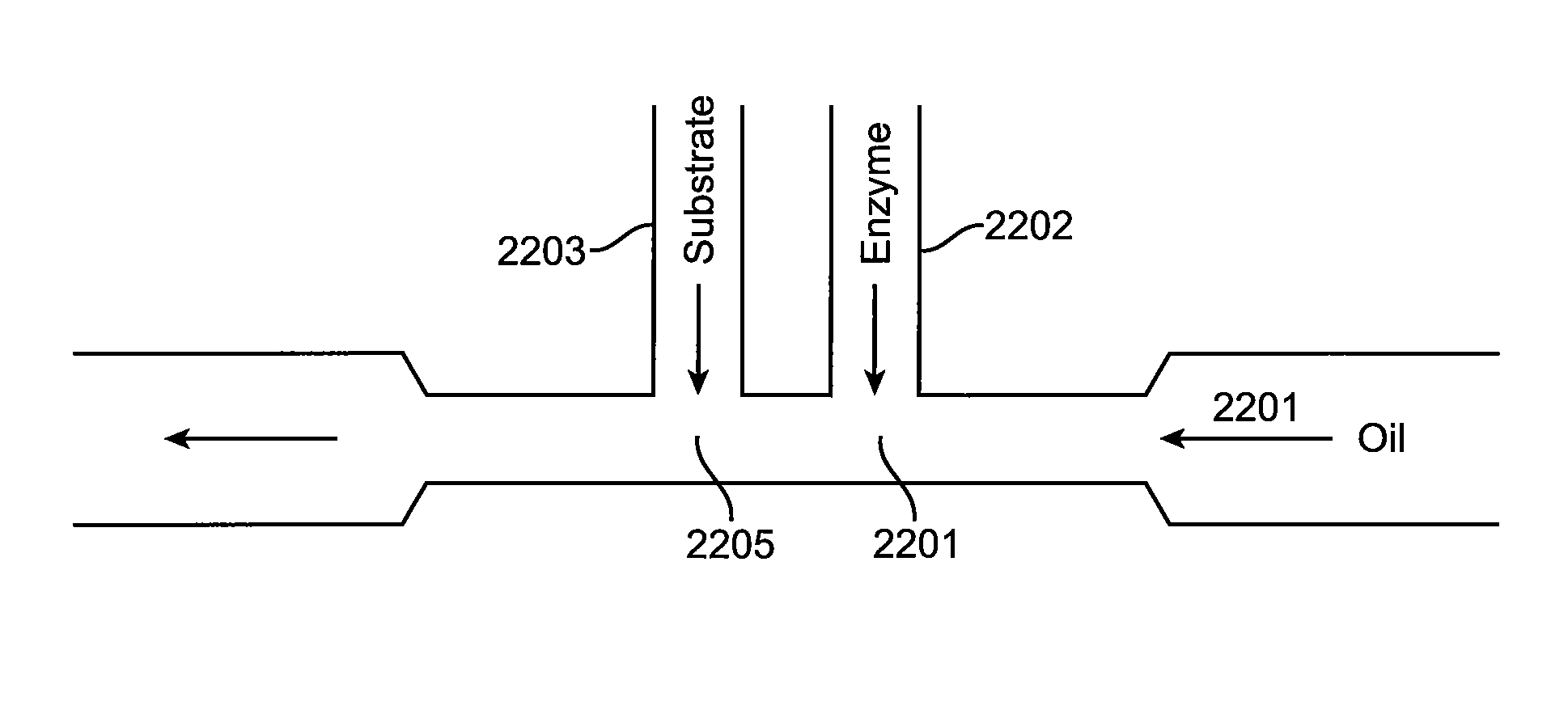

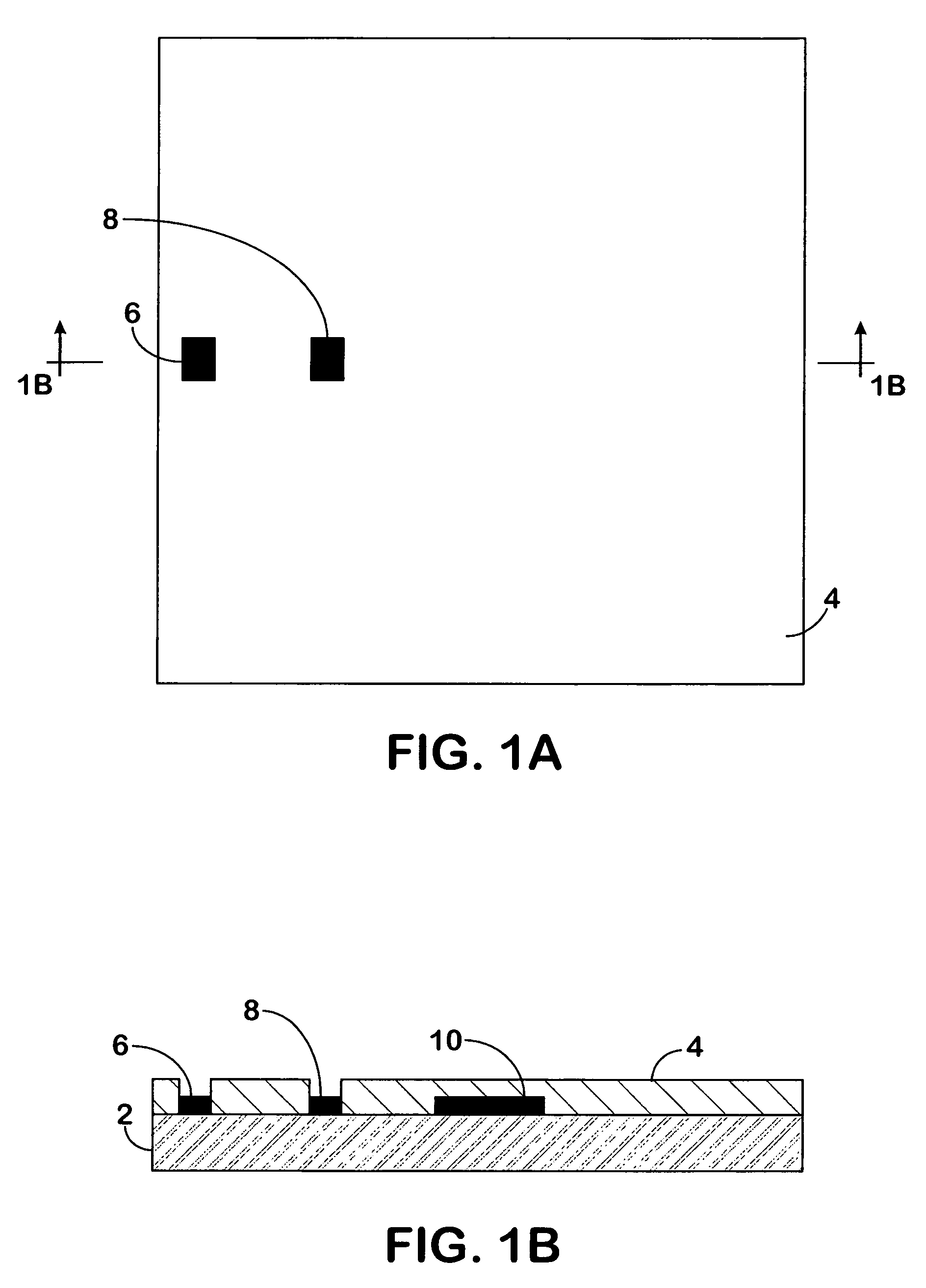

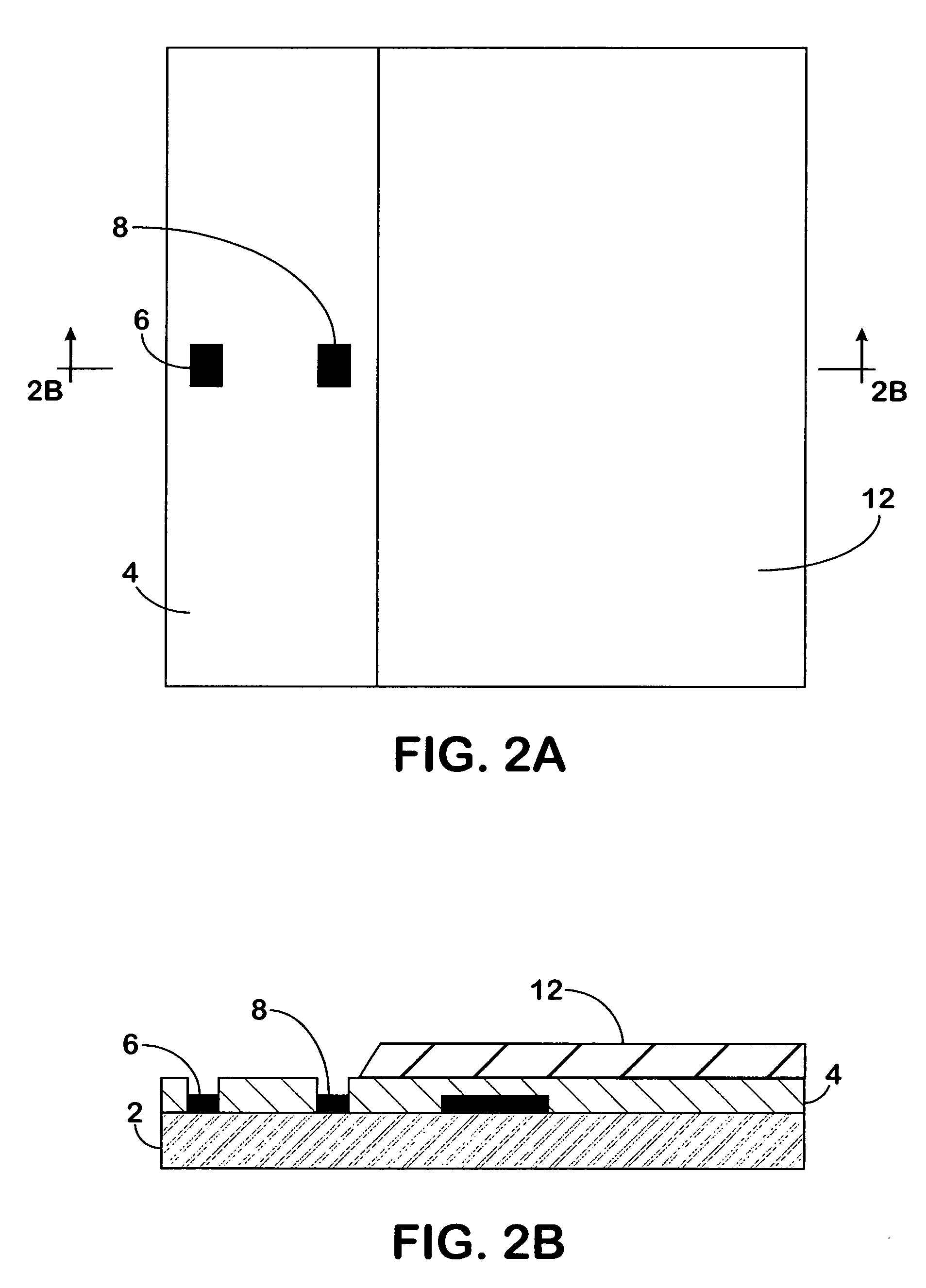

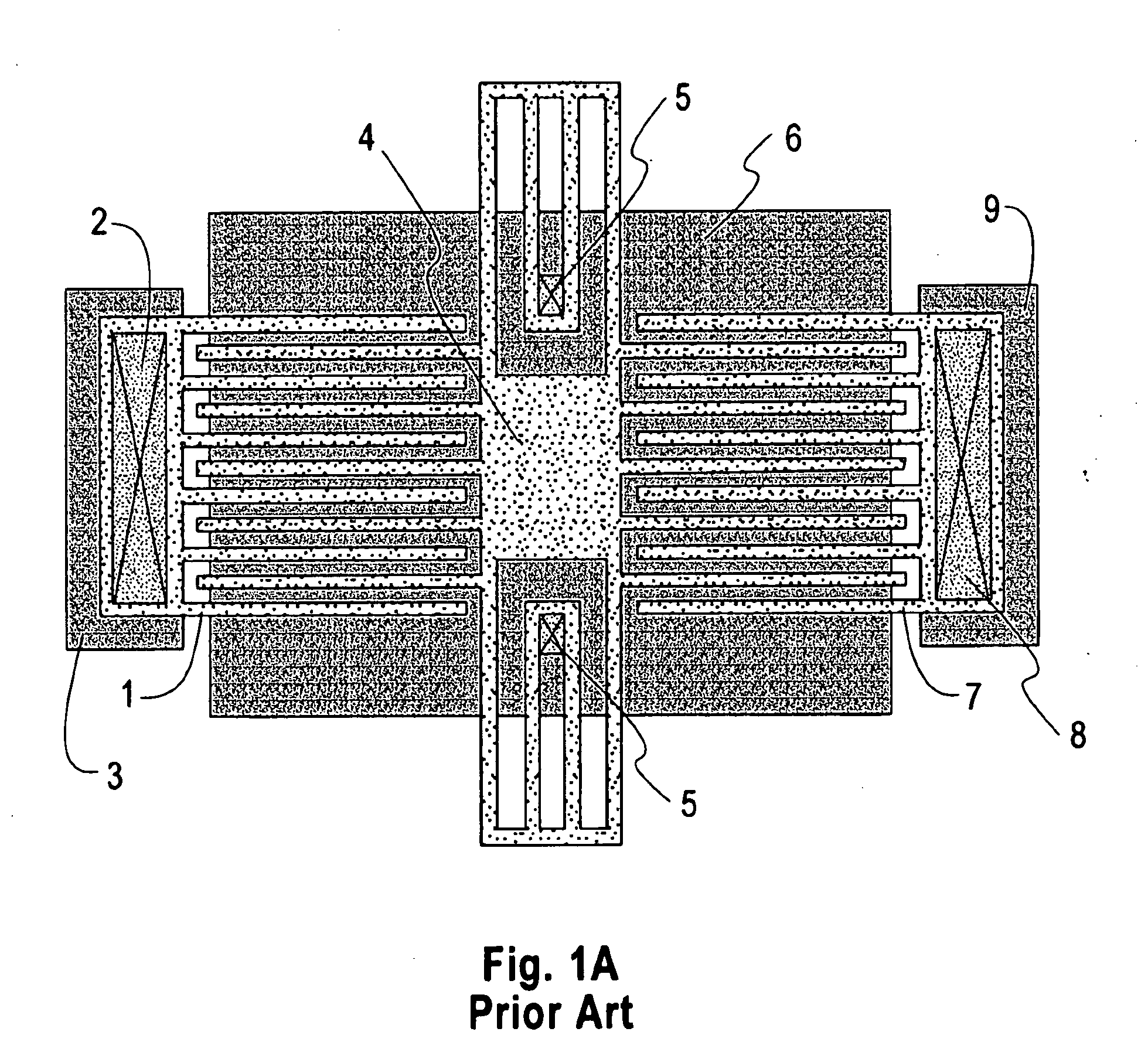

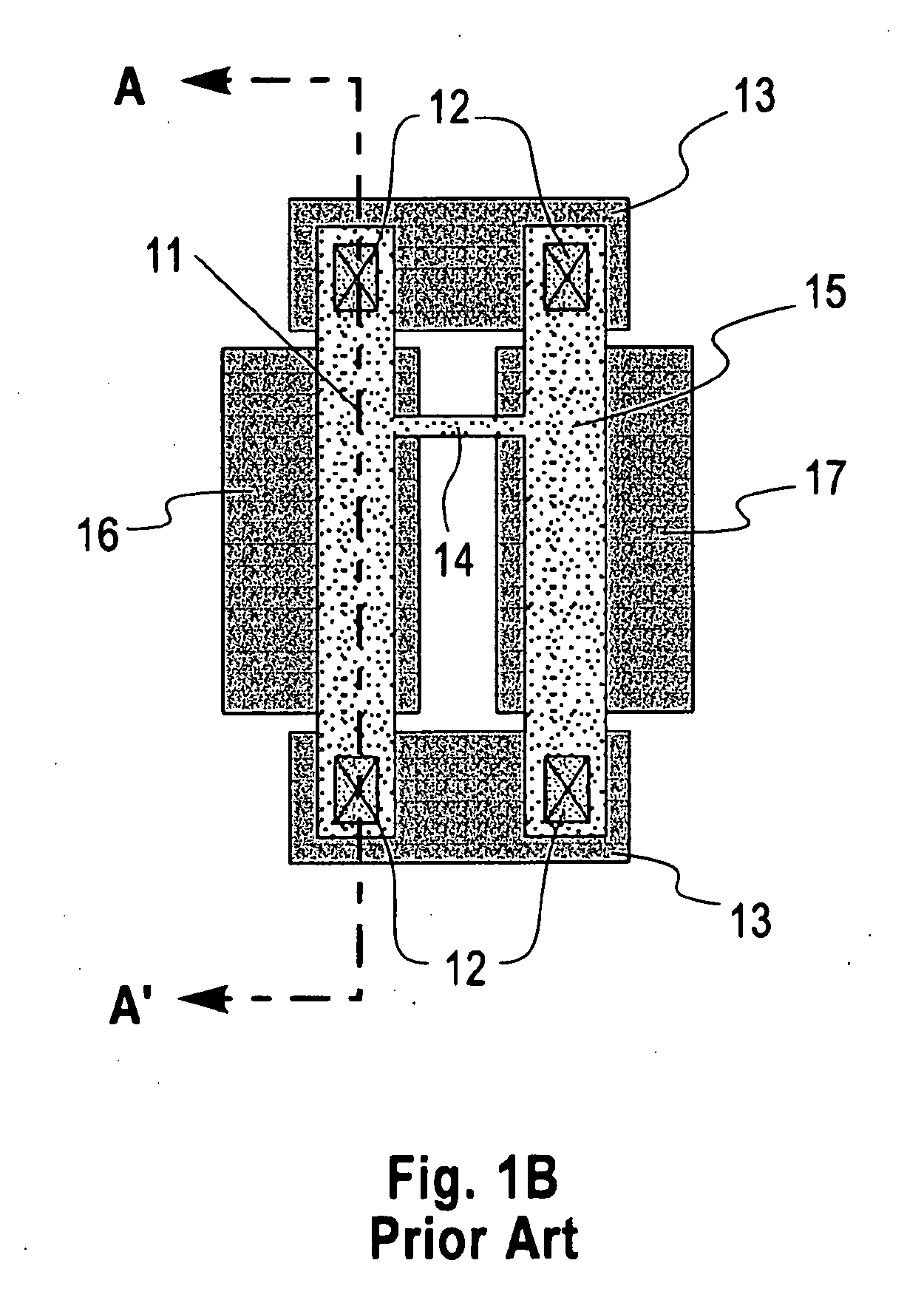

Microfabricated crossflow devices and methods

InactiveUS7294503B2Increase sensitivityHigh numberSludge treatmentFixed microstructural devicesMain channelEnzyme

A microfluidic device for analyzing and / or sorting biological materials (e.g., molecules such as polynucleotides and polypeptides, including proteins and enzymes; viruses and cells) and methods for its use are provided. The device and methods of the invention are useful for sorting particles, e.g. virions. The invention is also useful for high throughput screening, e.g. combinatorial screening. The microfluidic device comprises a main channel and an inlet region in communication with the main channel at a droplet extrusion region. Droplets of solution containing the biological material are deposited into the main channel through the droplet extrusion region. A fluid different from and incompatible with the solution containing the biological material flows through the main channel so that the droplets containing the biological material do not diffuse or mix. Biological material within the droplets can be analyzed and / or sorted by detecting a predetermined characteristic of the biological sample in each droplet and sorting the droplet accordingly.

Owner:CALIFORNIA INST OF TECH

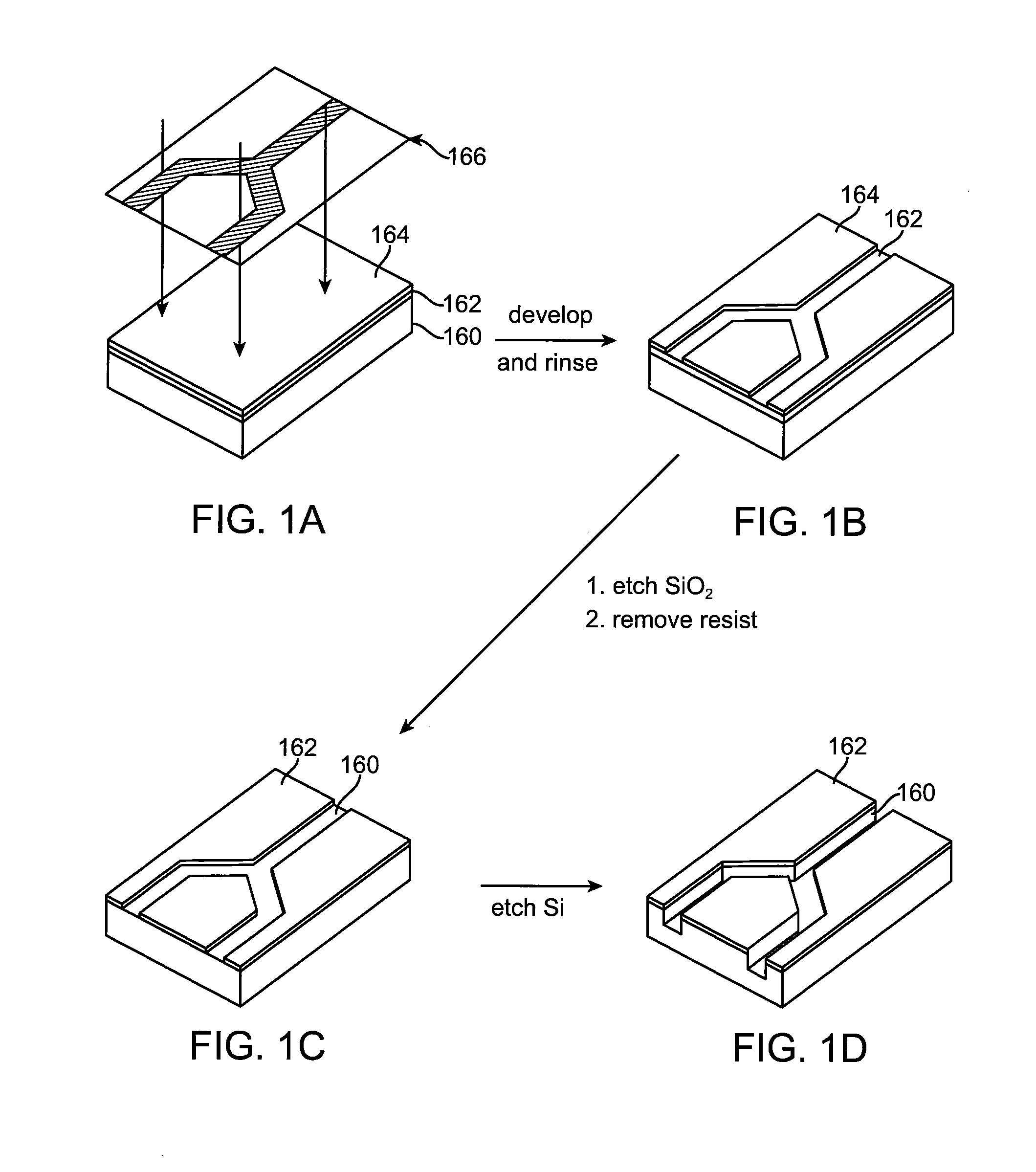

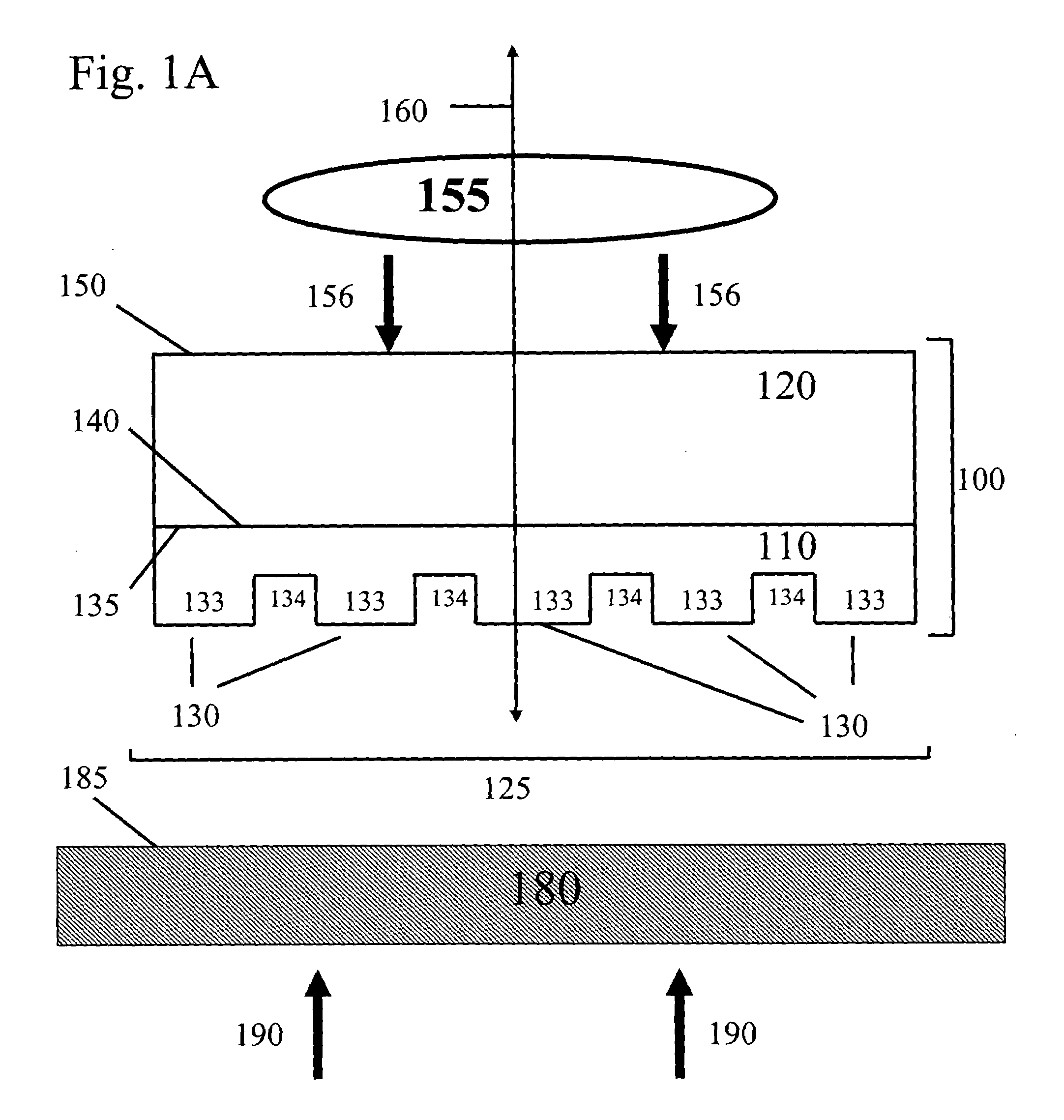

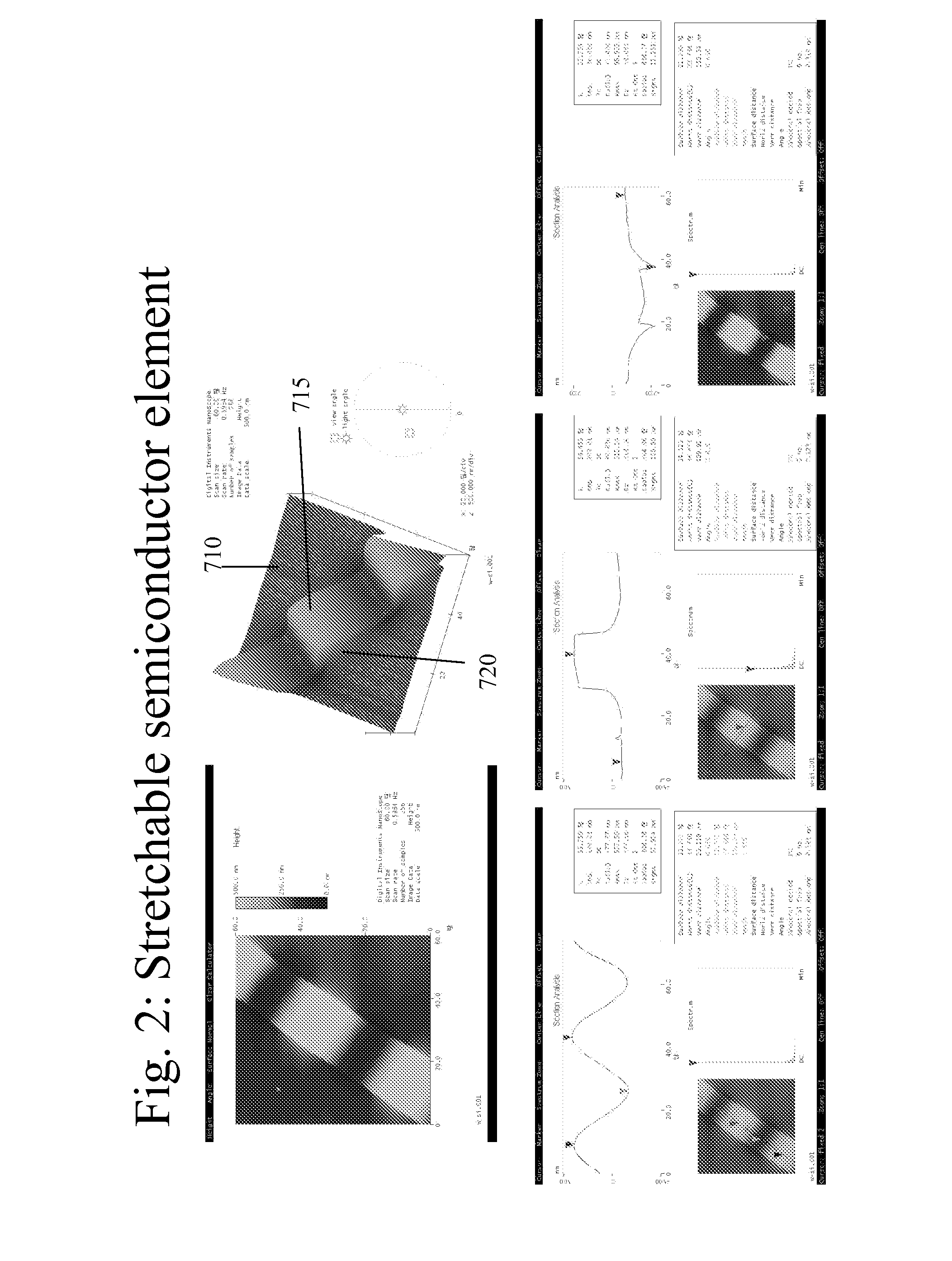

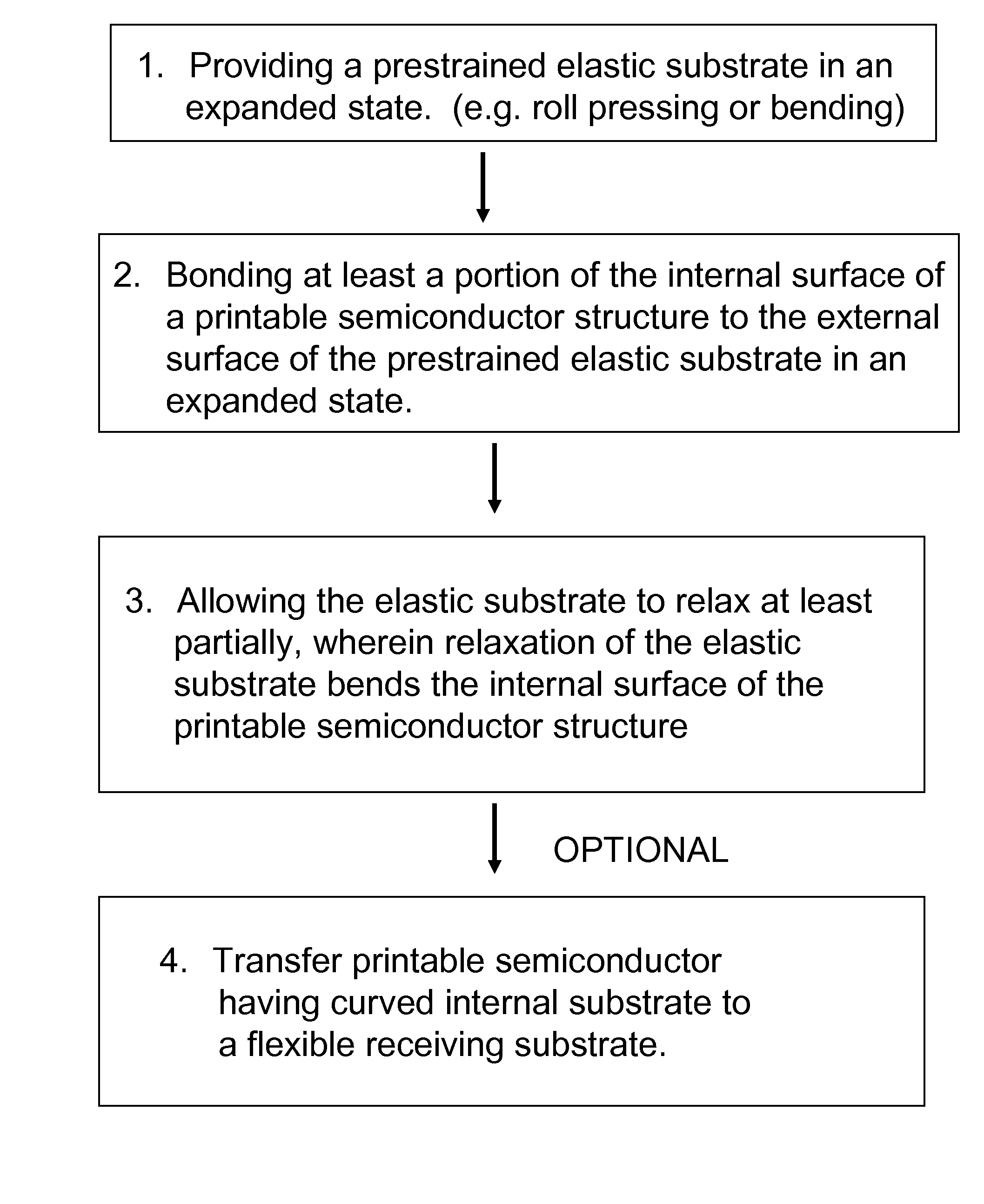

Stretchable semiconductor elements and stretchable electrical circuits

ActiveUS20060038182A1Complete release is preventedLow costTransistorDecorative surface effectsStretchable electronicsSemiconductor structure

The invention provides methods and devices for fabricating printable semiconductor elements and assembling printable semiconductor elements onto substrate surfaces. Methods, devices and device components of the present invention are capable of generating a wide range of flexible electronic and optoelectronic devices and arrays of devices on substrates comprising polymeric materials. The present invention also provides stretchable semiconductor structures and stretchable electronic devices capable of good performance in stretched configurations.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

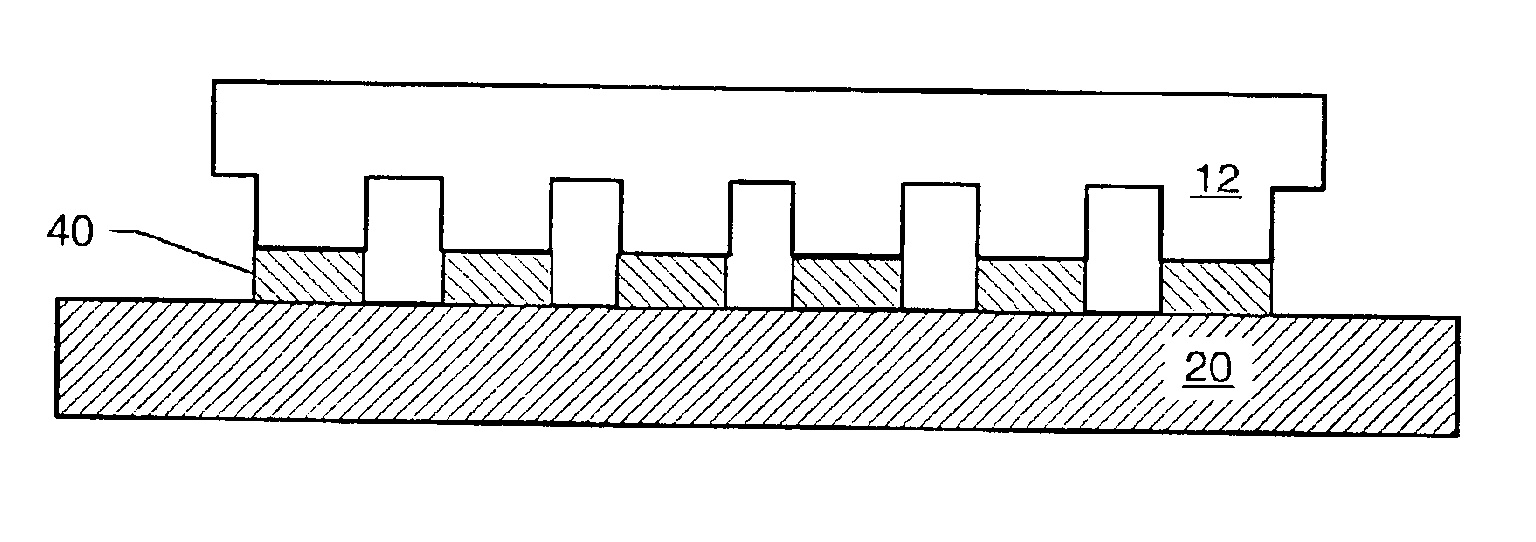

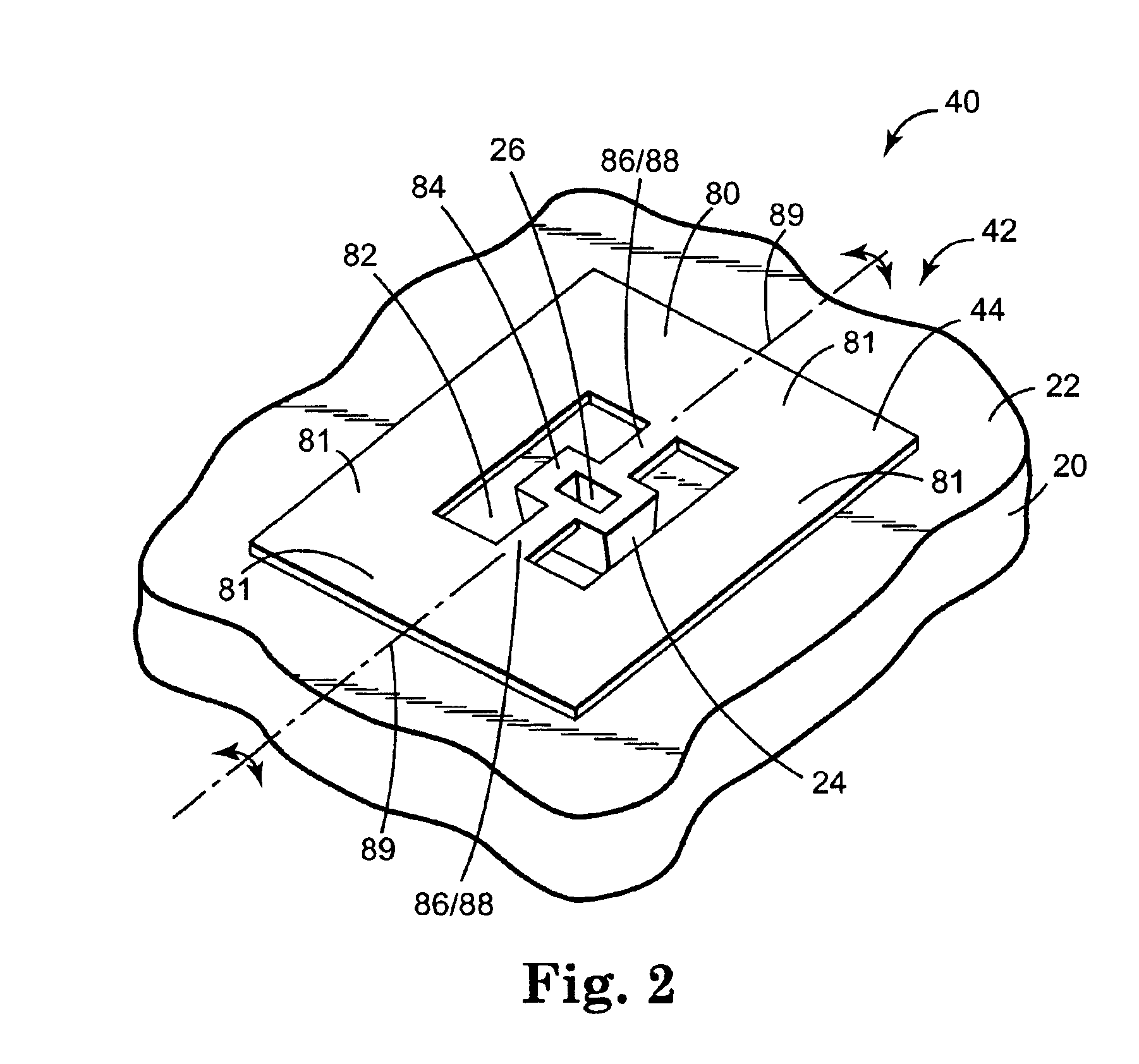

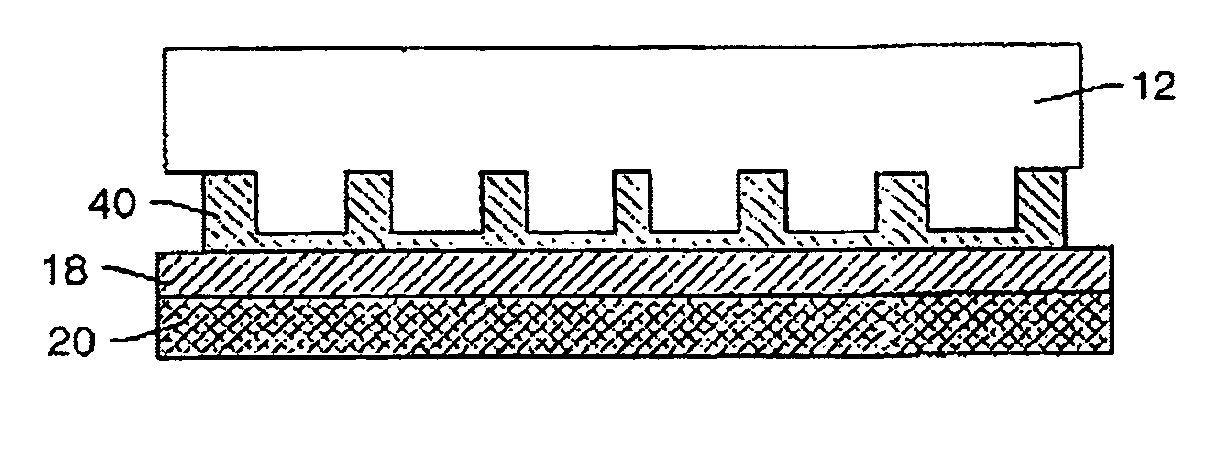

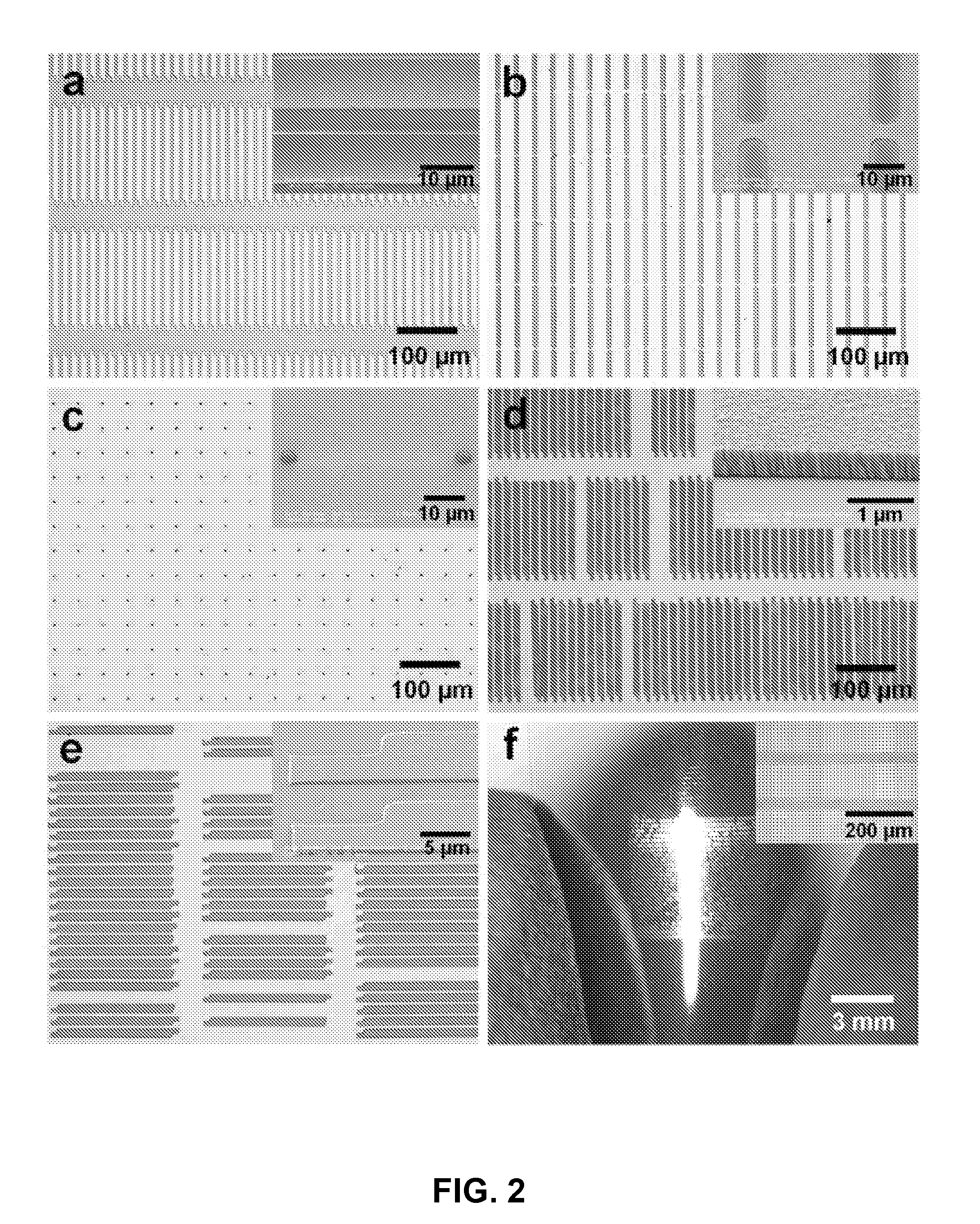

Composite patterning devices for soft lithography

ActiveUS7195733B2Improve fidelityIncrease resistanceMaterial nanotechnologyNanoinformaticsNano sizeYoung's modulus

The present invention provides methods, devices and device components for fabricating patterns on substrate surfaces, particularly patterns comprising structures having microsized and / or nanosized features of selected lengths in one, two or three dimensions. The present invention provides composite patterning devices comprising a plurality of polymer layers each having selected mechanical properties, such as Young's Modulus and flexural rigidity, selected physical dimensions, such as thickness, surface area and relief pattern dimensions, and selected thermal properties, such as coefficients of thermal expansion, to provide high resolution patterning on a variety of substrate surfaces and surface morphologies.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

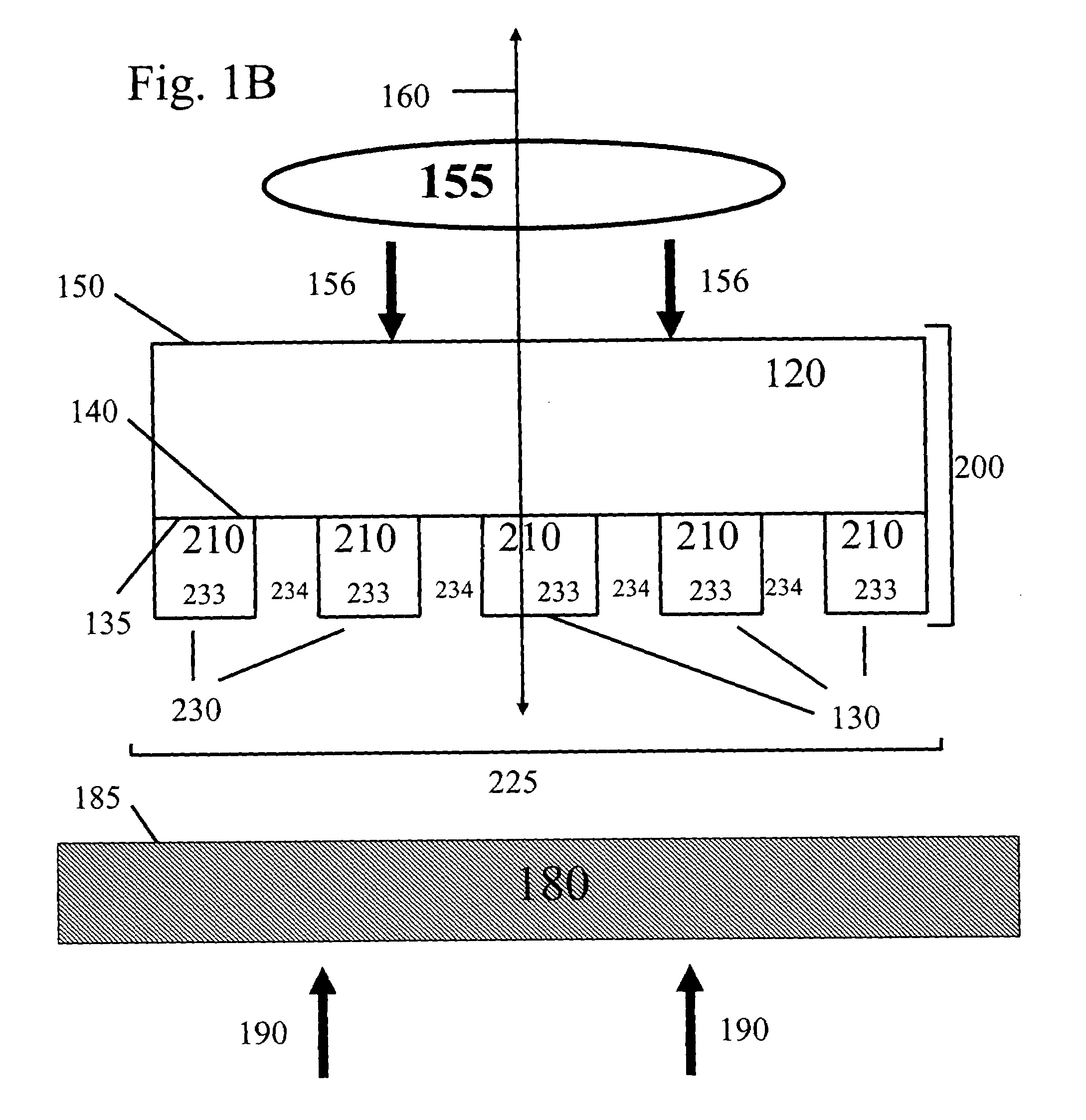

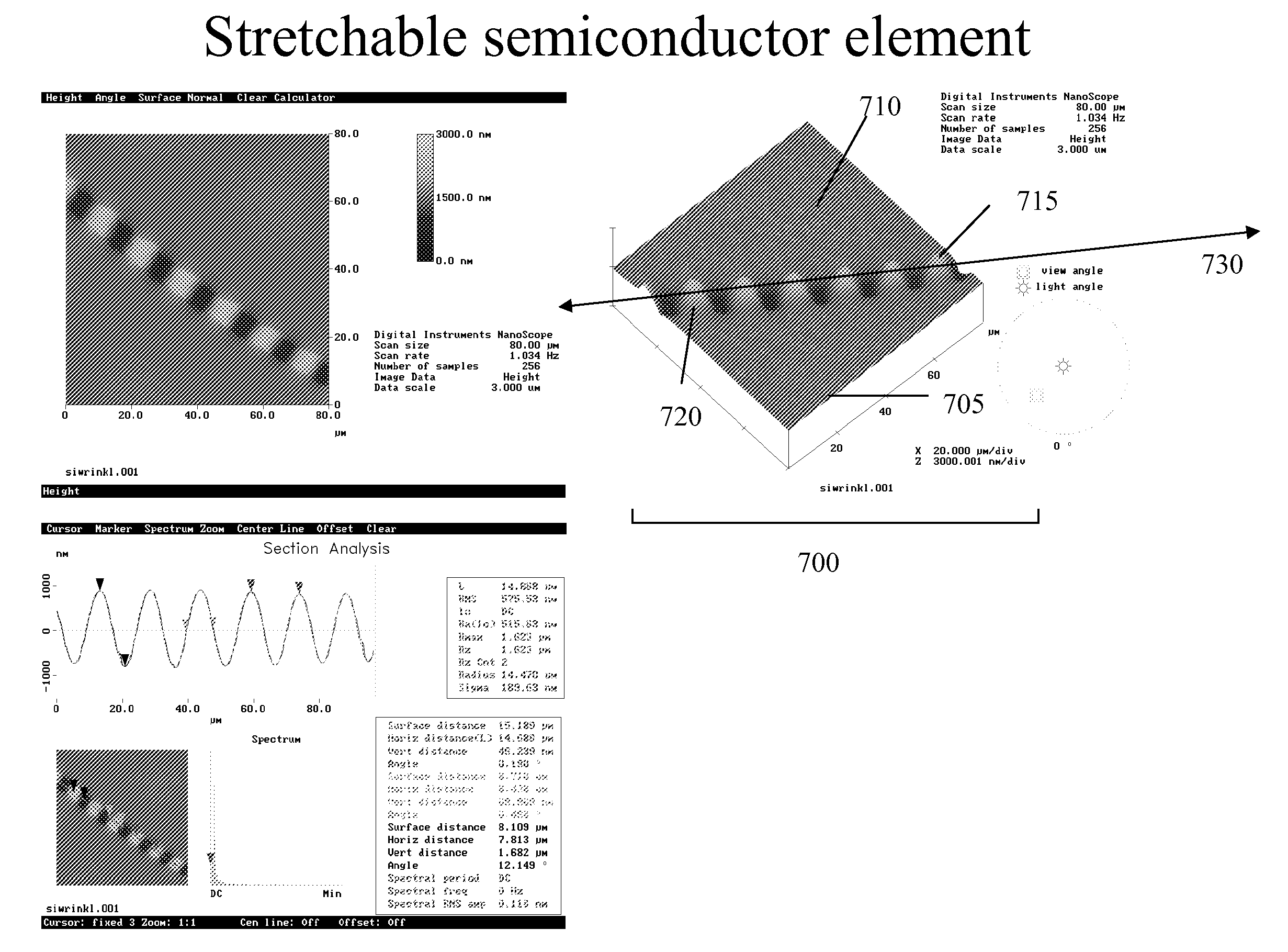

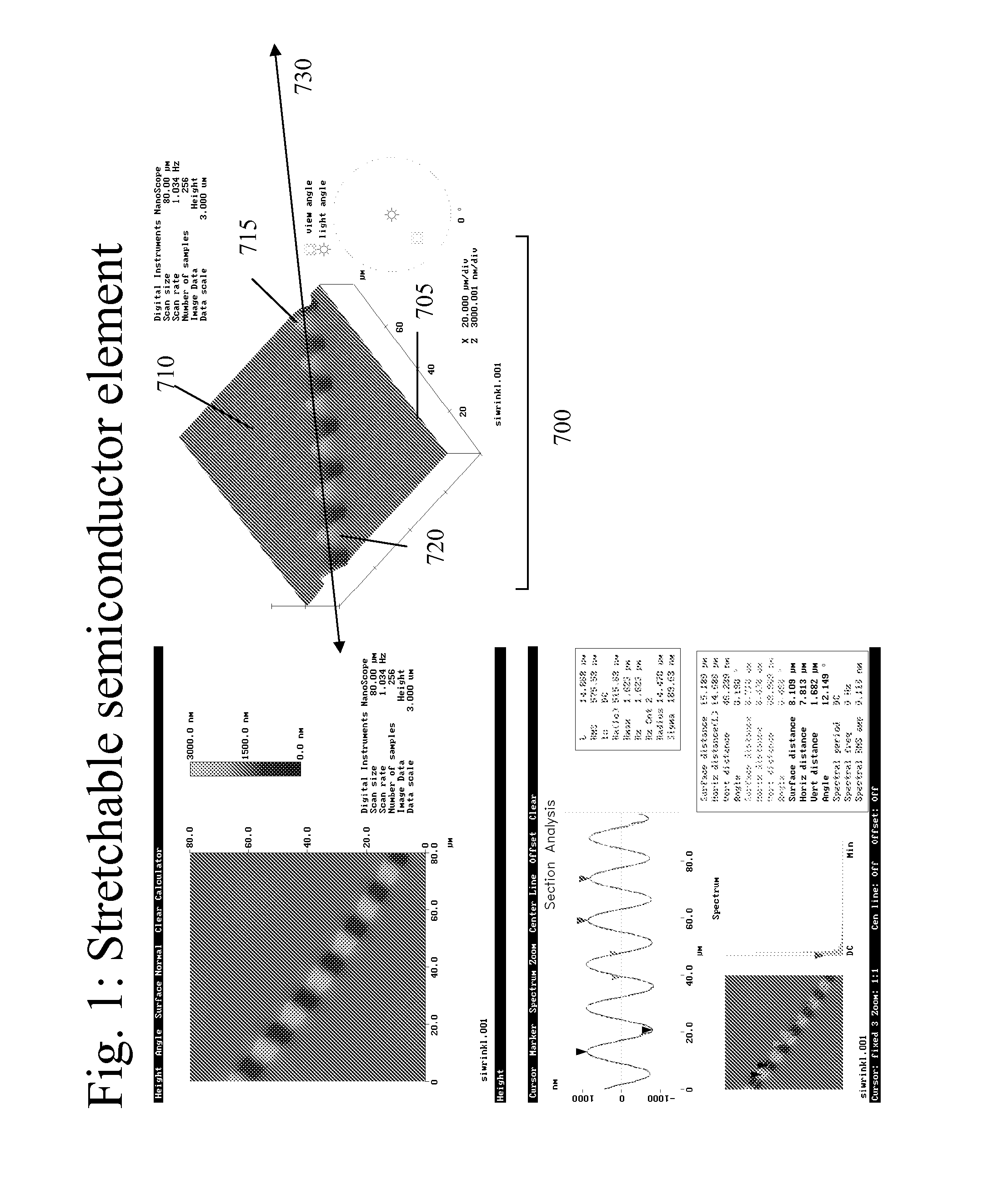

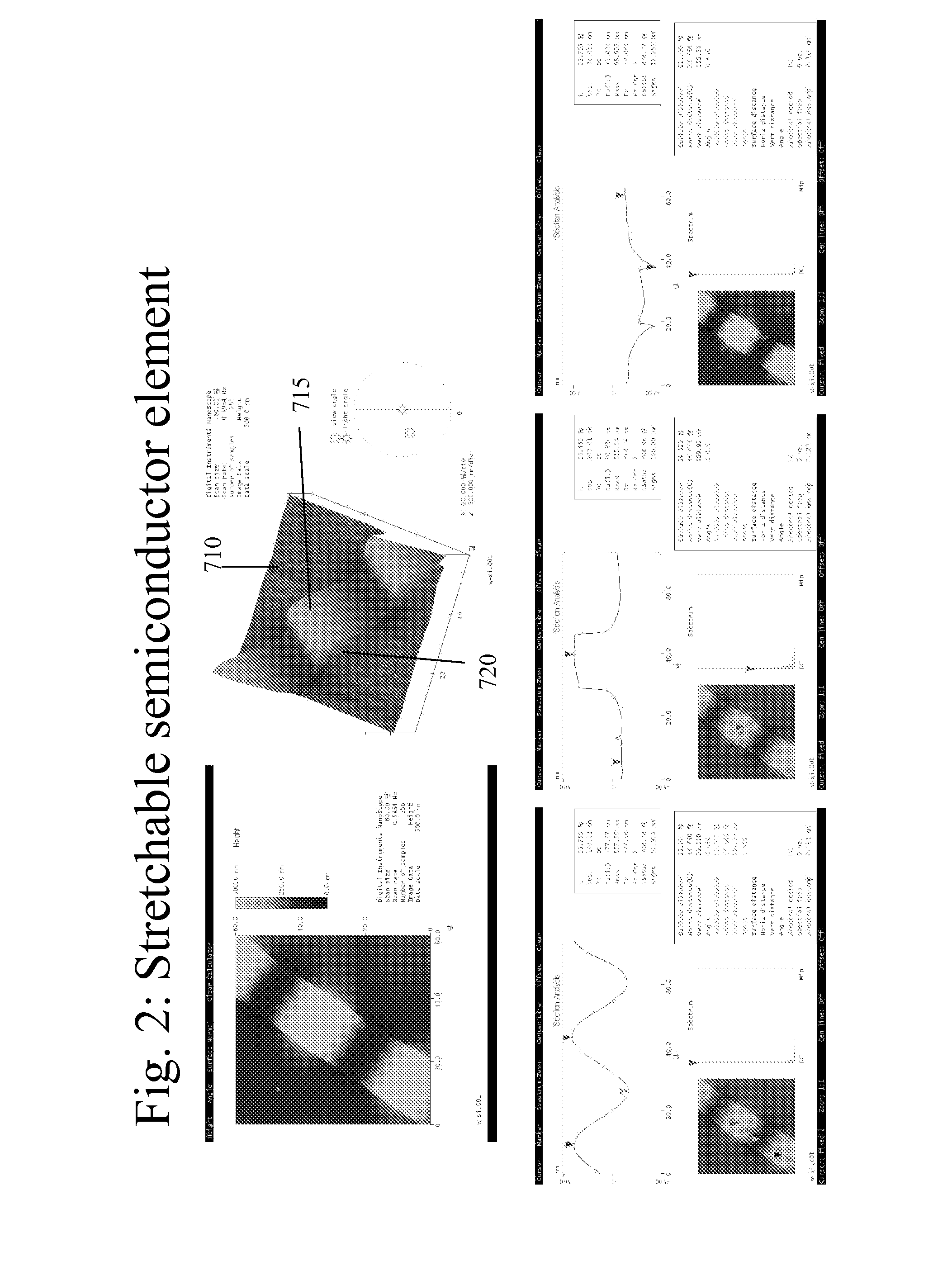

Stretchable form of single crystal silicon for high performance electronics on rubber substrates

ActiveUS7521292B2Large elongationSignificant flexingTransistorCircuit bendability/stretchabilityEngineeringFlexible electronics

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

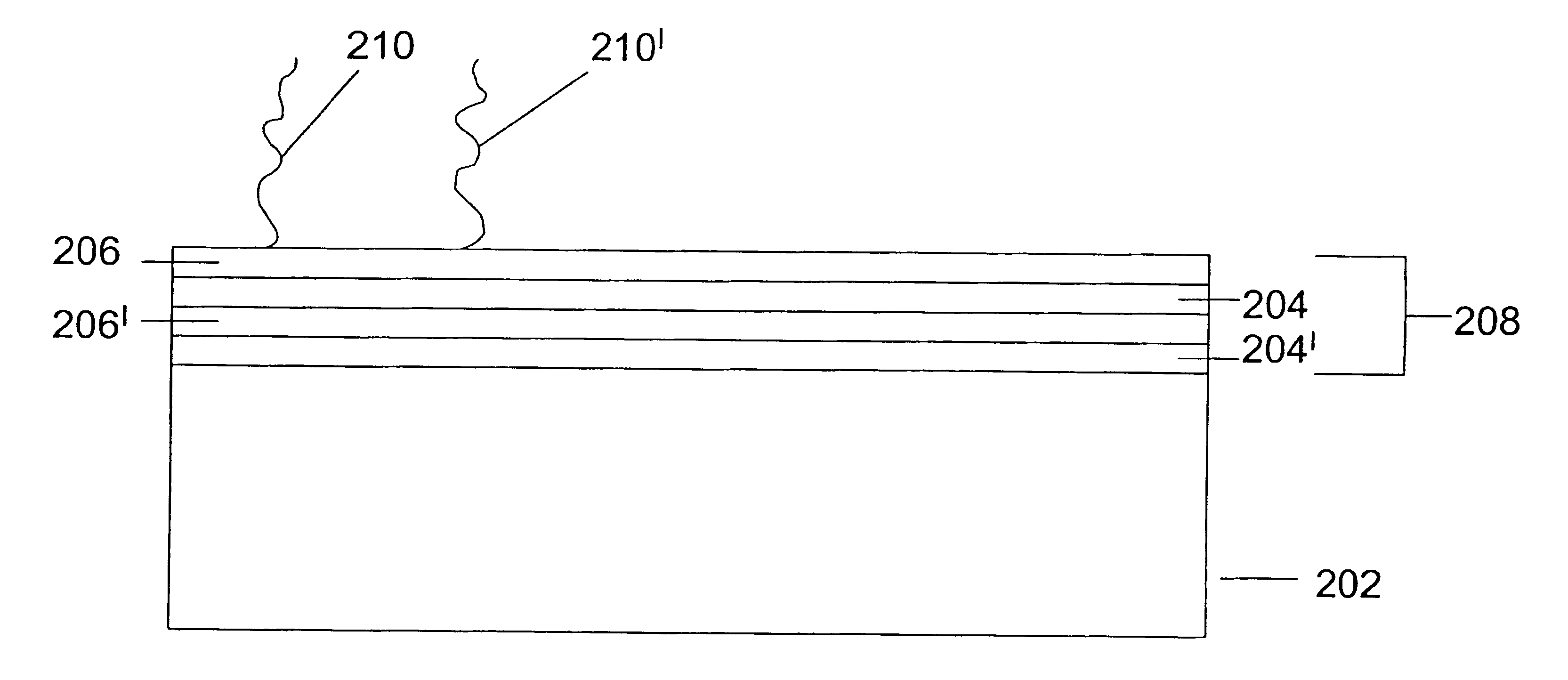

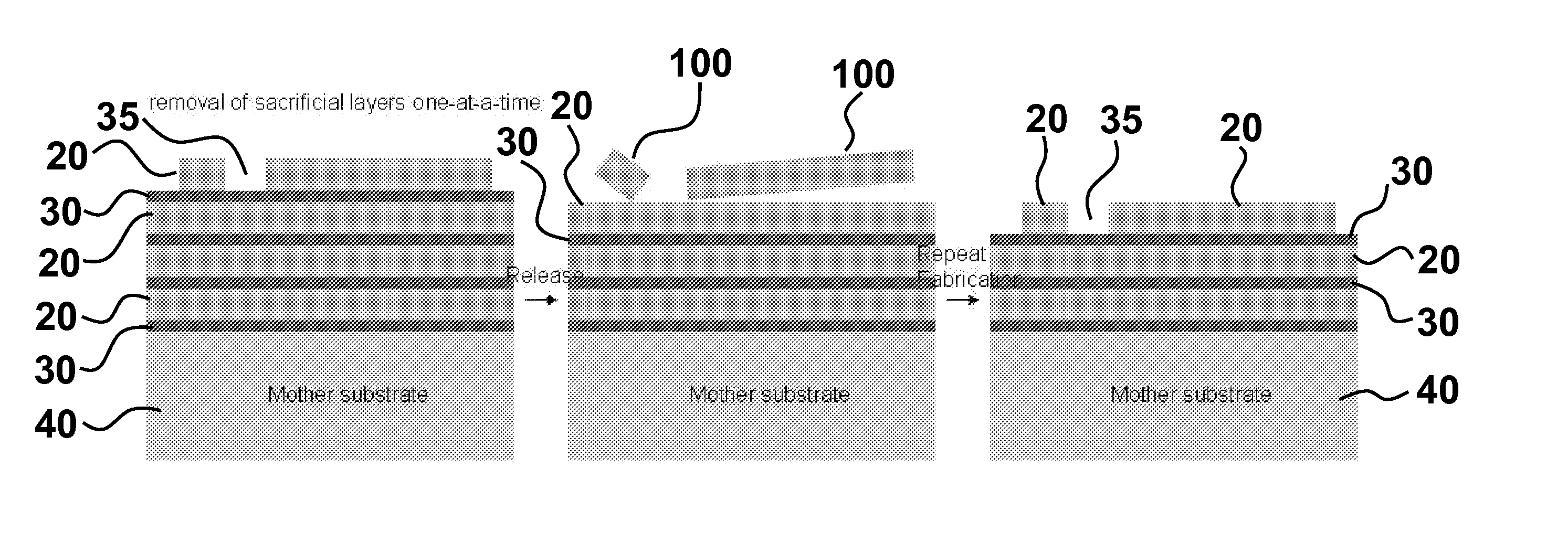

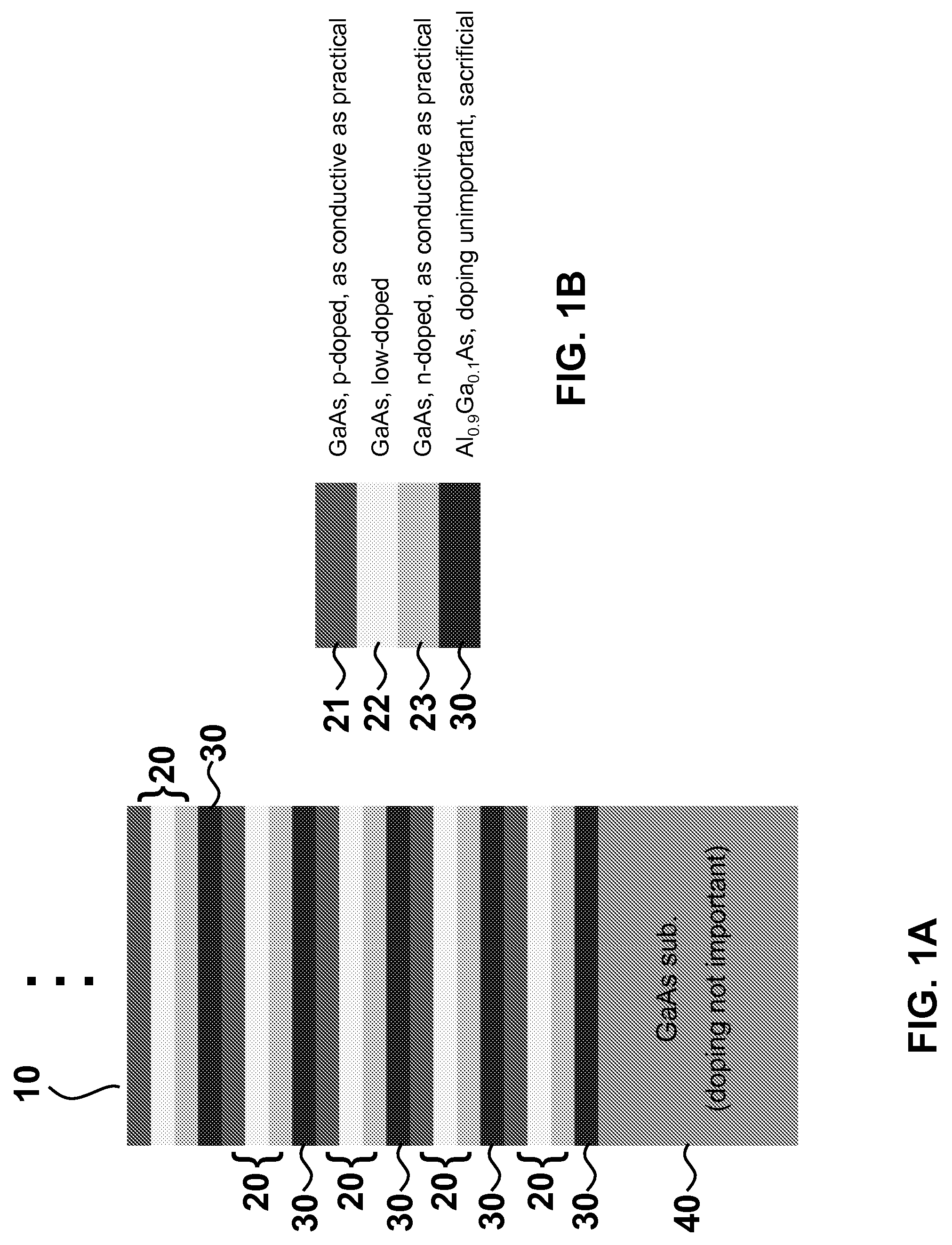

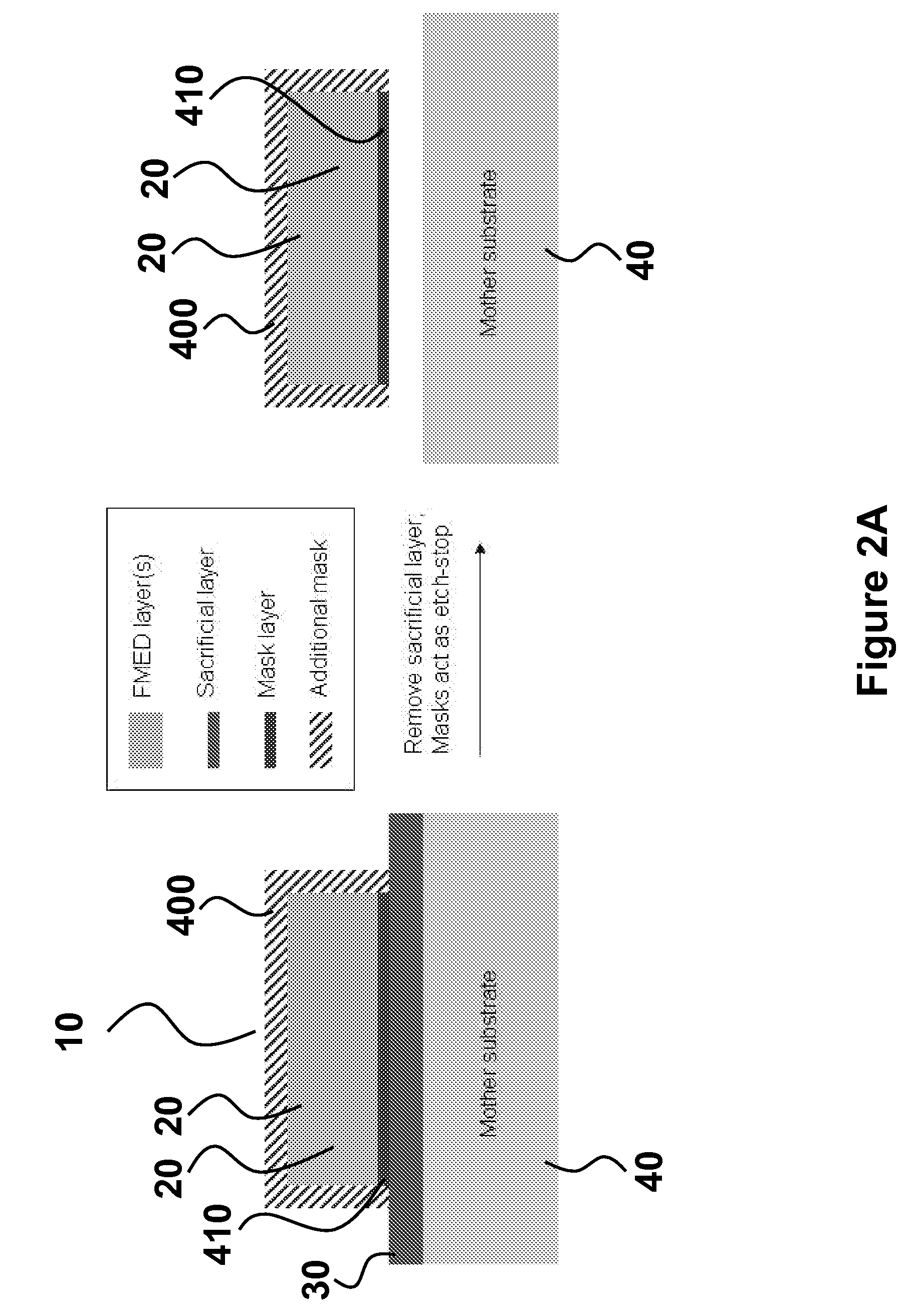

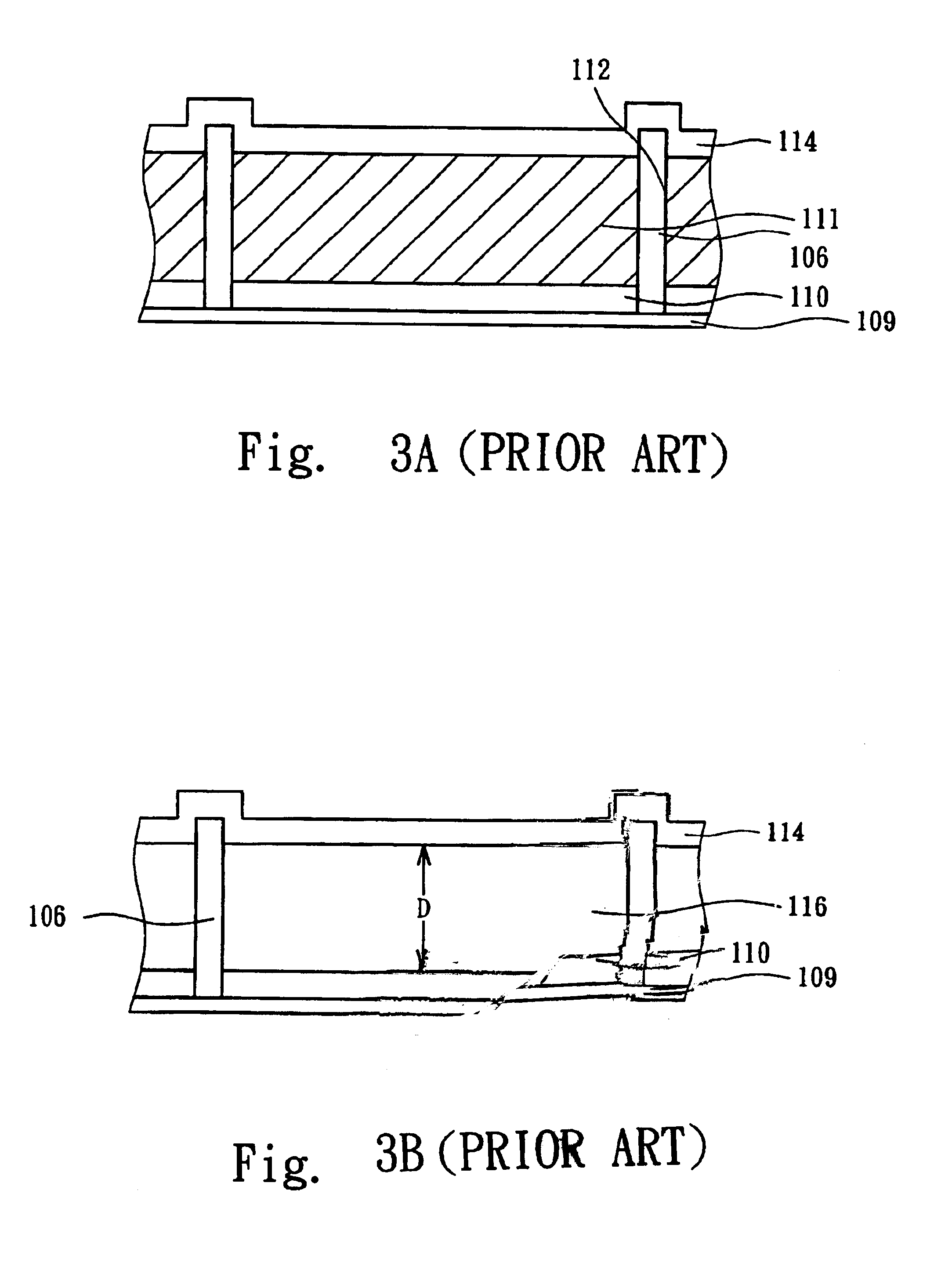

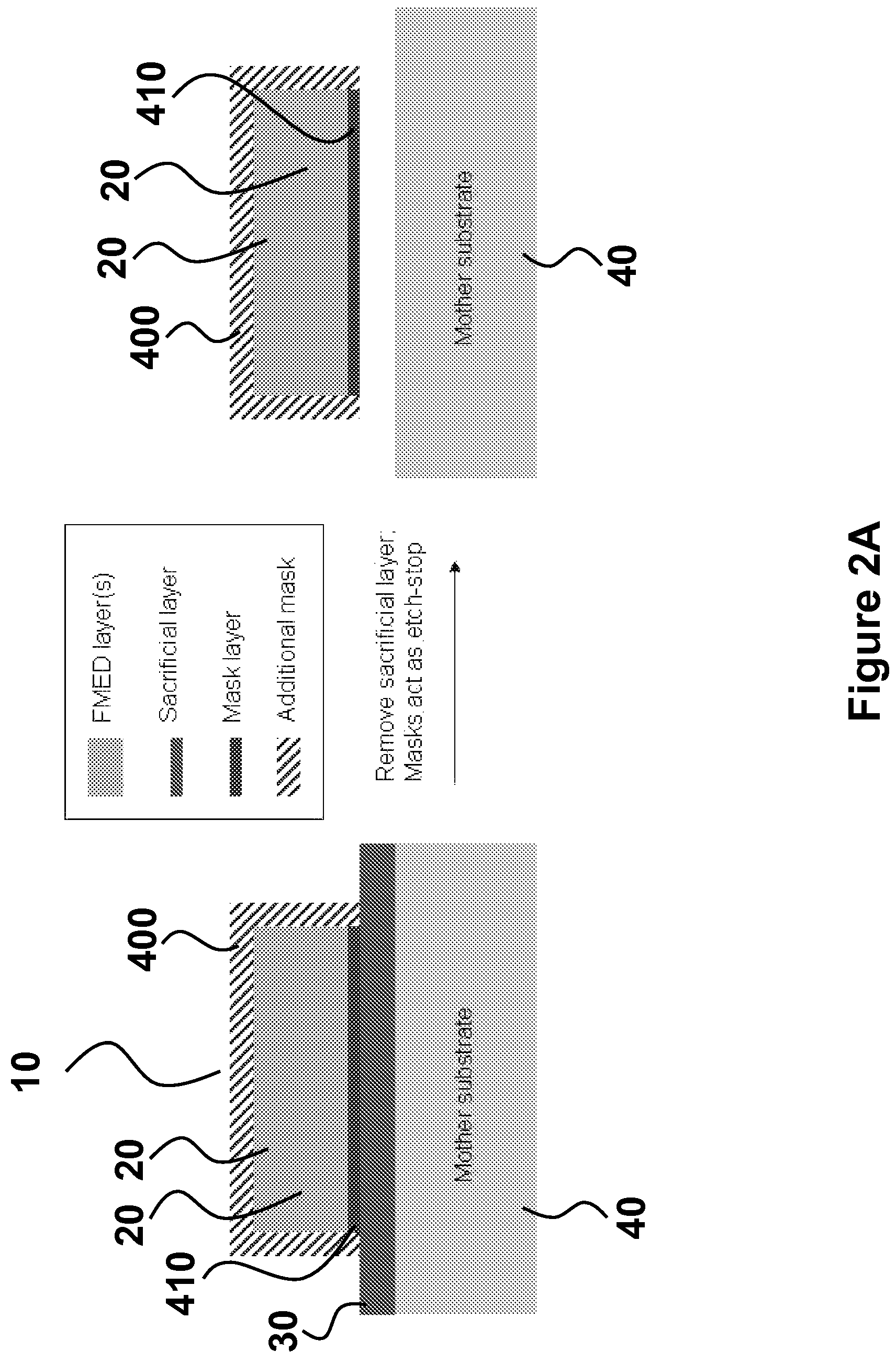

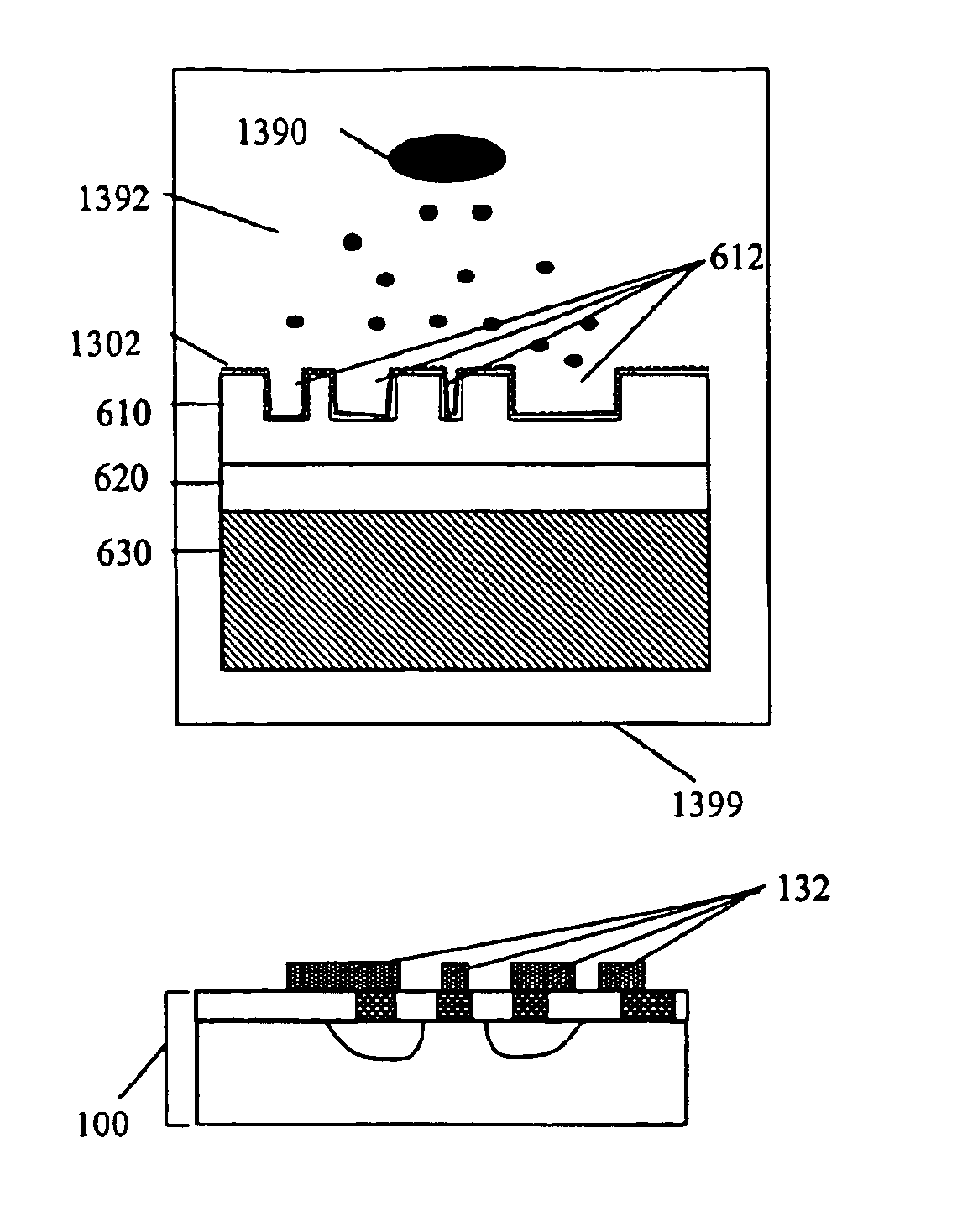

Release strategies for making transferable semiconductor structures, devices and device components

ActiveUS20080108171A1Low cost structureLow costFinal product manufactureNanoinformaticsSemiconductor structureDevice Subassembly

Provided are methods for making a device or device component by providing a multilayer structure having a plurality of functional layers and a plurality of release layers and releasing the functional layers from the multilayer structure by separating one or more of the release layers to generate a plurality of transferable structures. The transferable structures are printed onto a device substrate or device component supported by a device substrate. The methods and systems provide means for making high-quality and low-cost photovoltaic devices, transferable semiconductor structures, (opto-)electronic devices and device components.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

Formation of discontinuous films during an imprint lithography process

ActiveUS6932934B2Low viscosityMaterial nanotechnologyDecorative surface effectsLithography processLithographic artist

The present invention is directed to methods for patterning a substrate by imprint lithography. An imprint lithography method includes placing a curable liquid on a substrate. A template may be contacted with the curable liquid. Surface forces at the interface of the curable liquid and the template cause the curable liquid to gather in an area defined by a lower surface of the template. Alternately, the curable liquid may fill one or more relatively shallow recesses in the template and the area under the template lower surface. Activating light is applied to the curable liquid to form a patterned layer on the substrate.

Owner:CANON KK

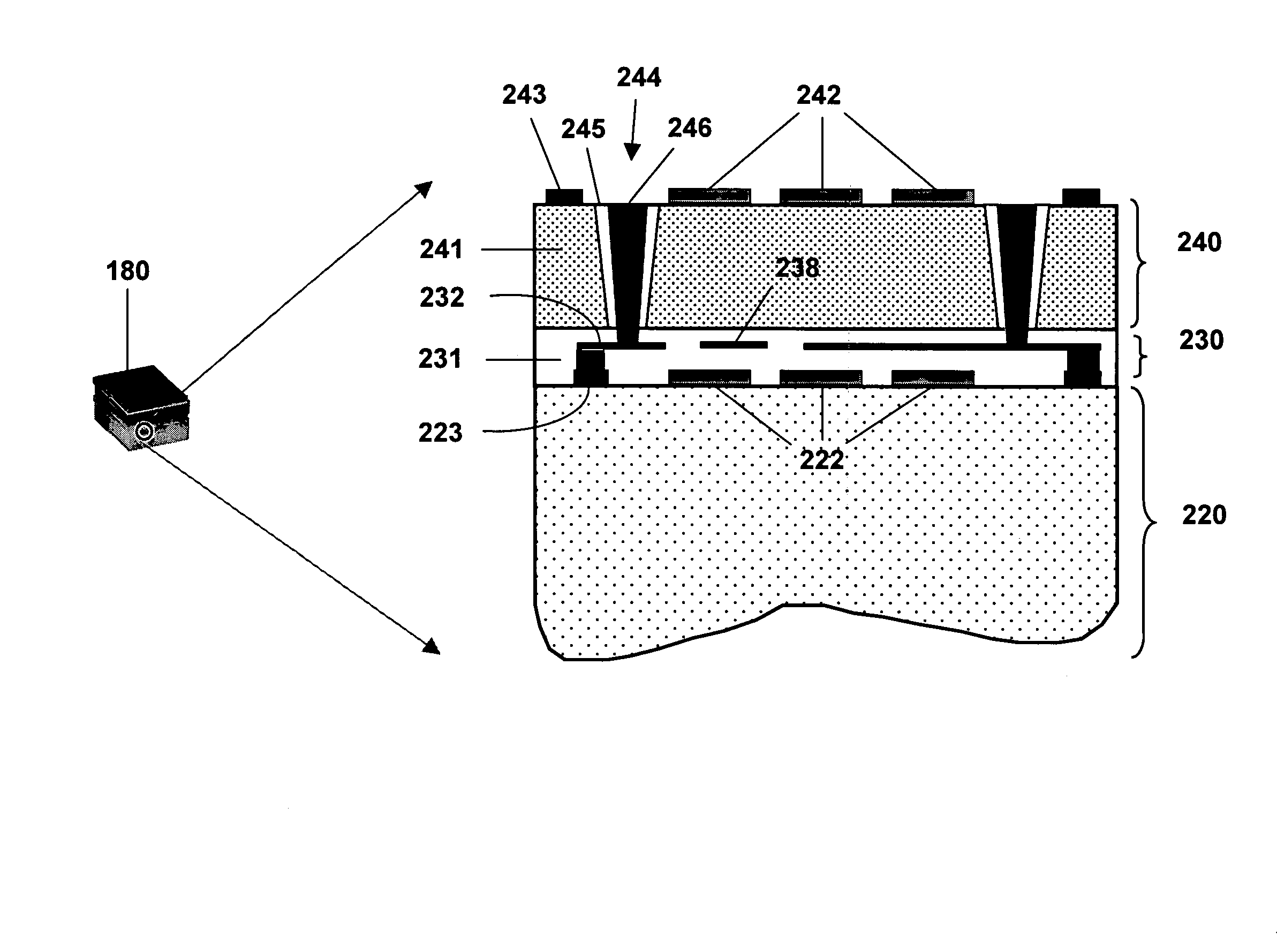

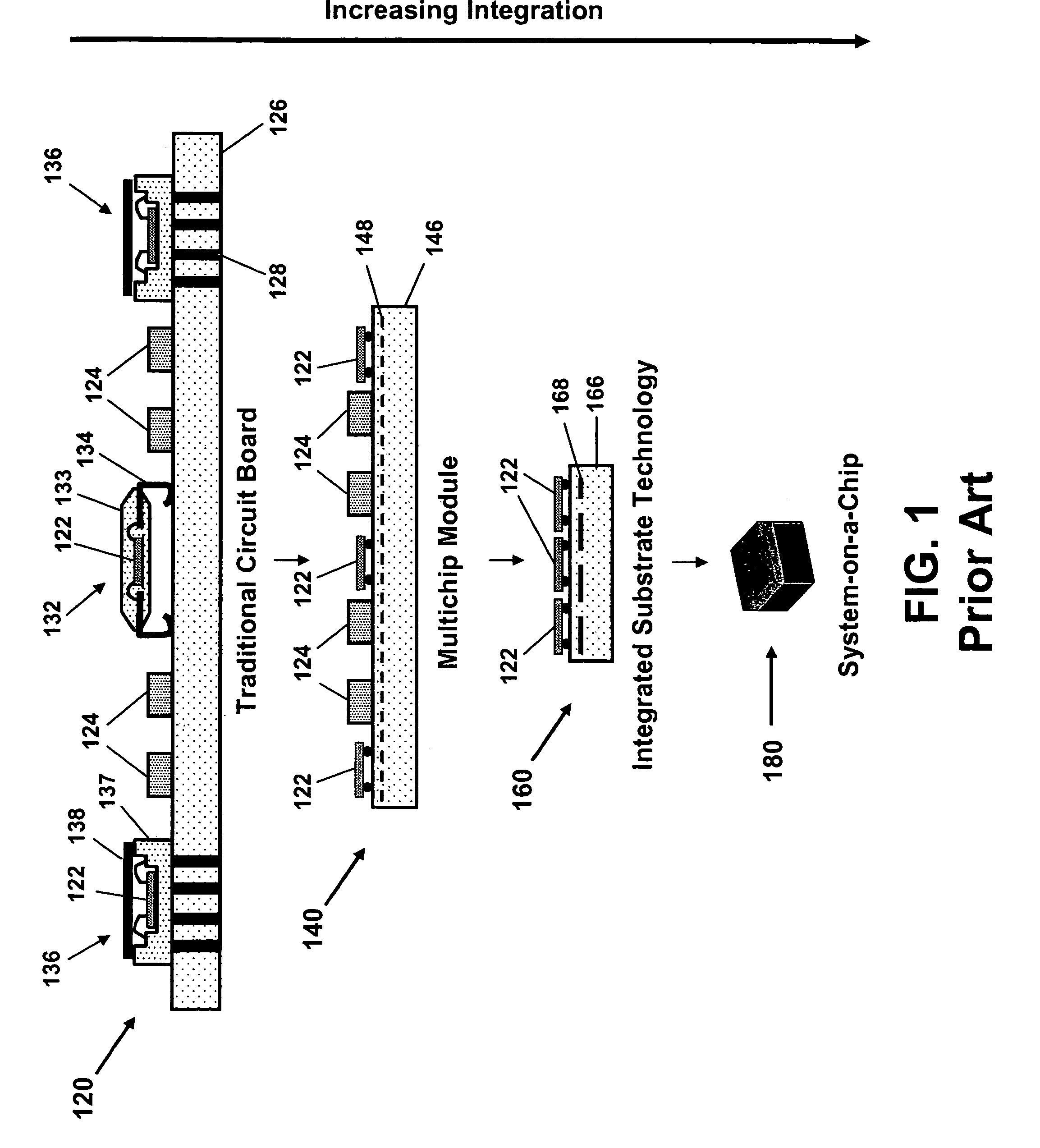

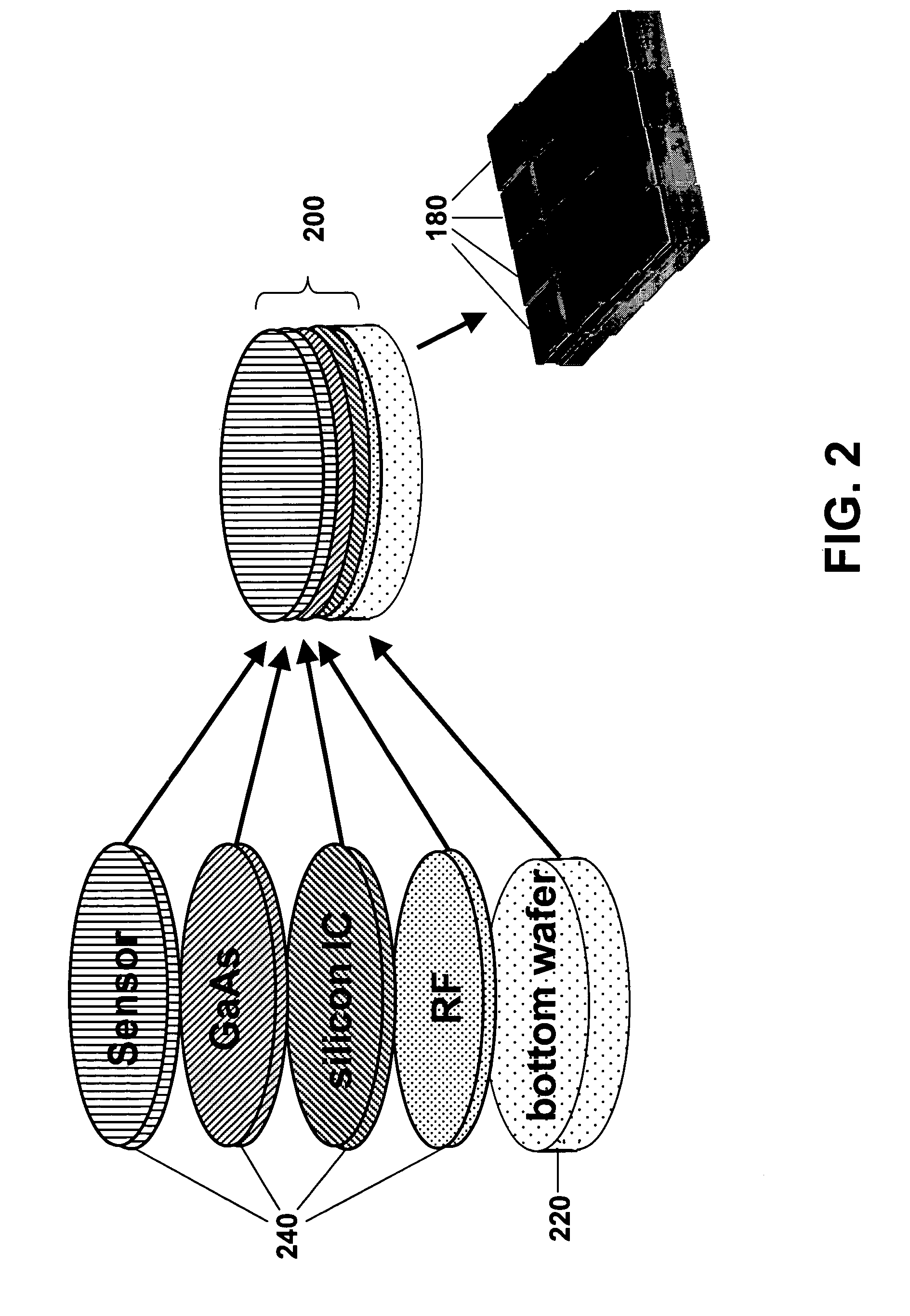

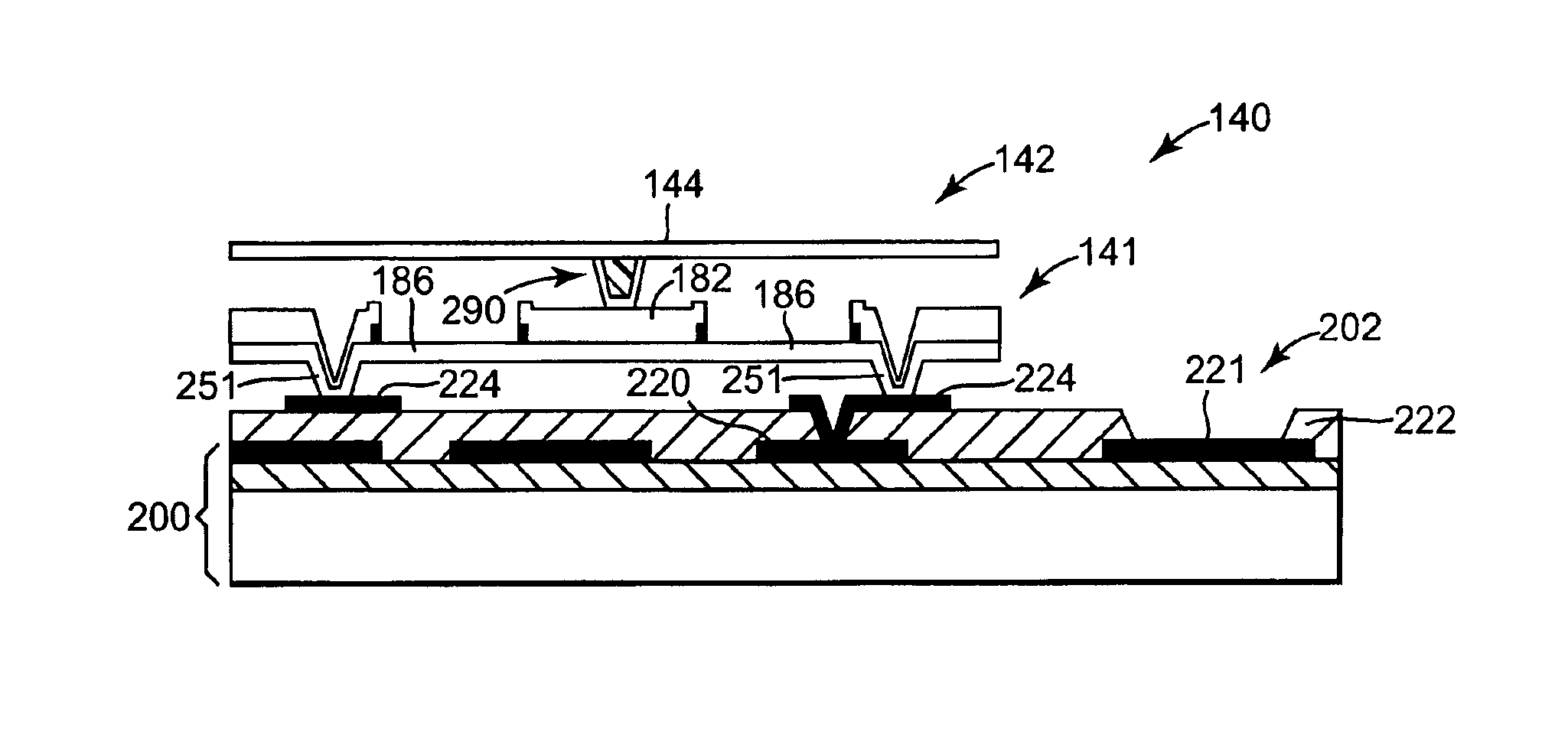

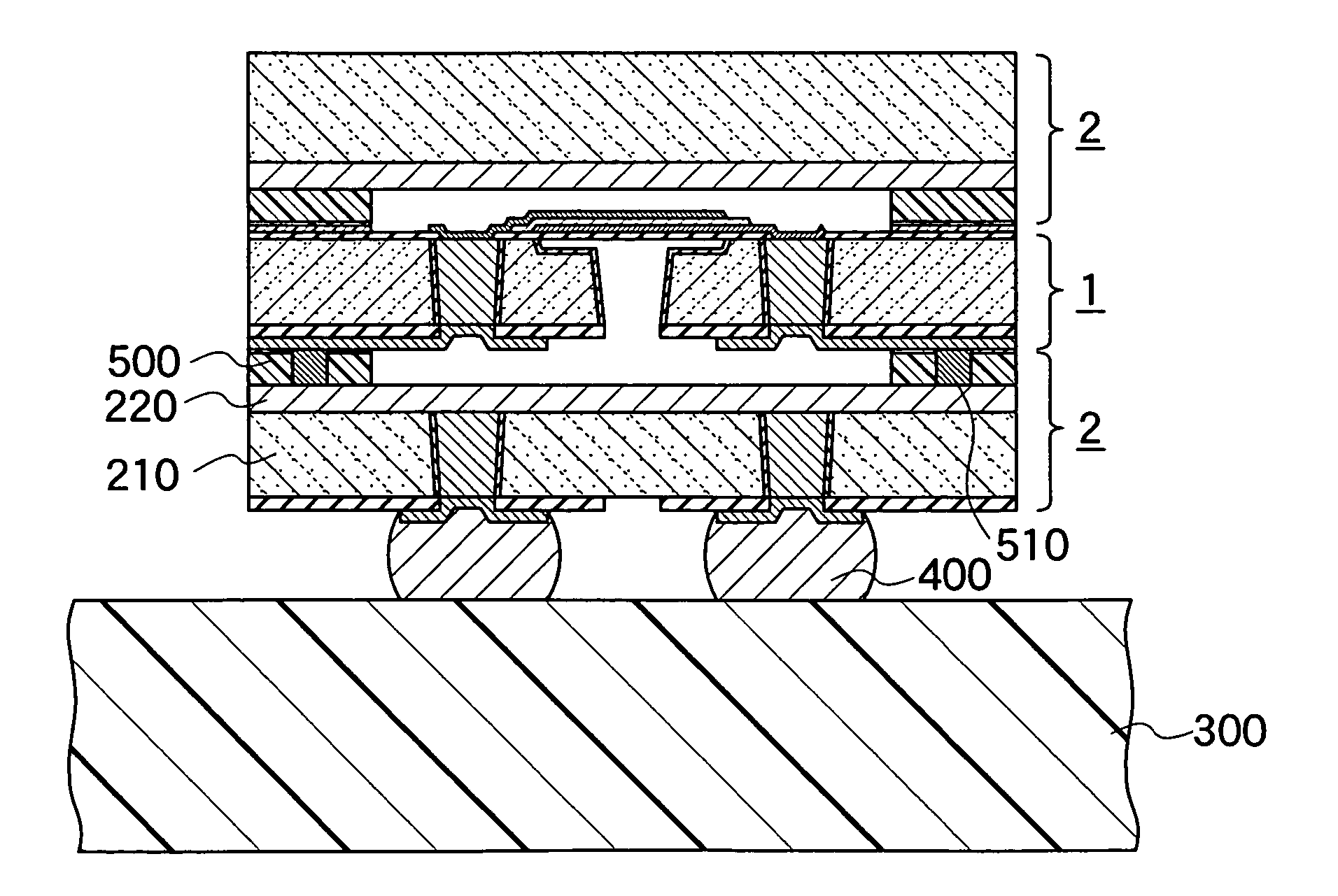

Heterogeneously integrated microsystem-on-a-chip

ActiveUS7335972B2Electronic circuit testingSemiconductor/solid-state device detailsMiniaturizationInterconnection

A microsystem-on-a-chip comprises a bottom wafer of normal thickness and a series of thinned wafers can be stacked on the bottom wafer, glued and electrically interconnected. The interconnection layer comprises a compliant dielectric material, an interconnect structure, and can include embedded passives. The stacked wafer technology provides a heterogeneously integrated, ultra-miniaturized, higher performing, robust and cost-effective microsystem package. The highly integrated microsystem package, comprising electronics, sensors, optics, and MEMS, can be miniaturized both in volume and footprint to the size of a bottle-cap or less.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

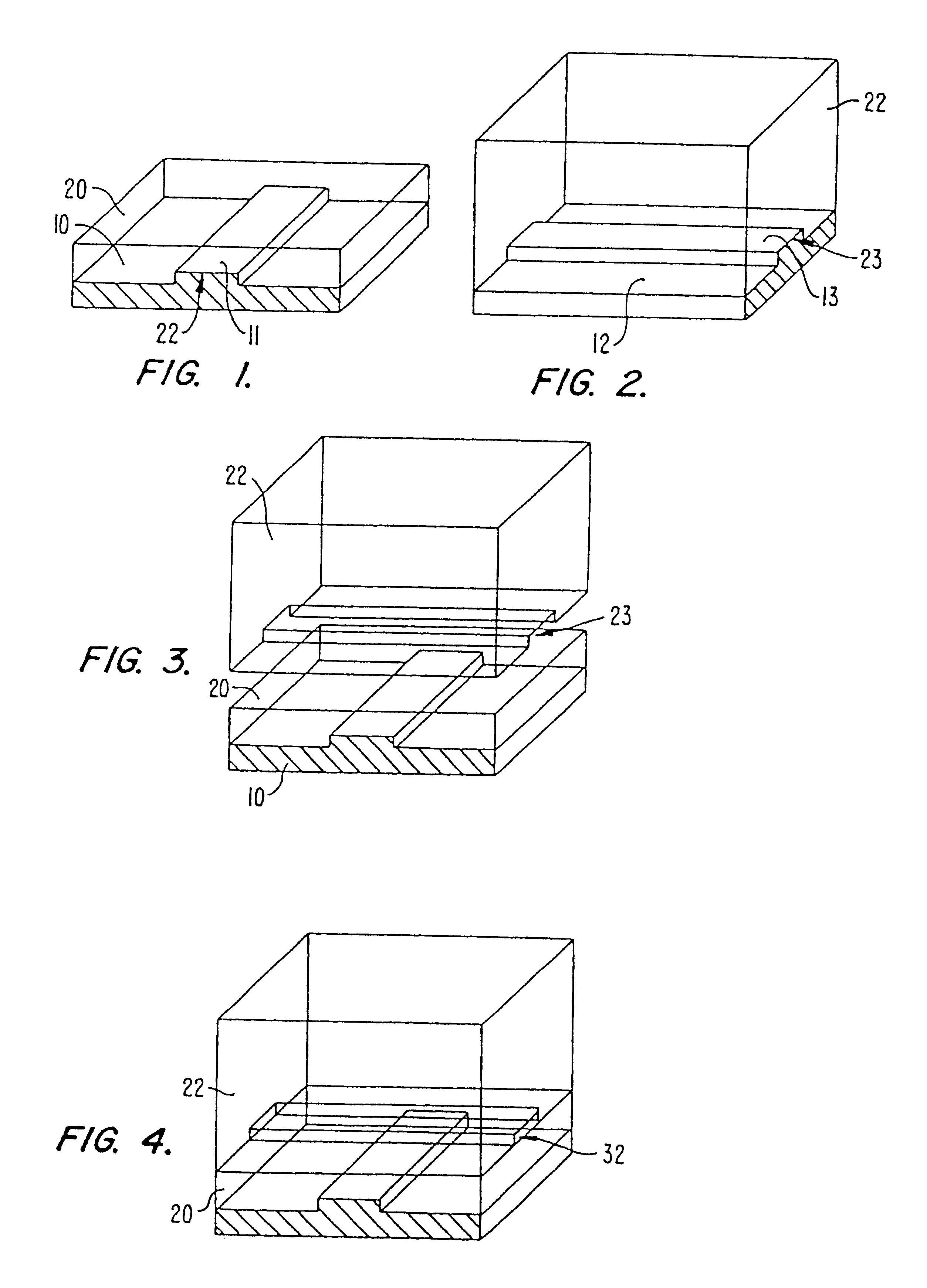

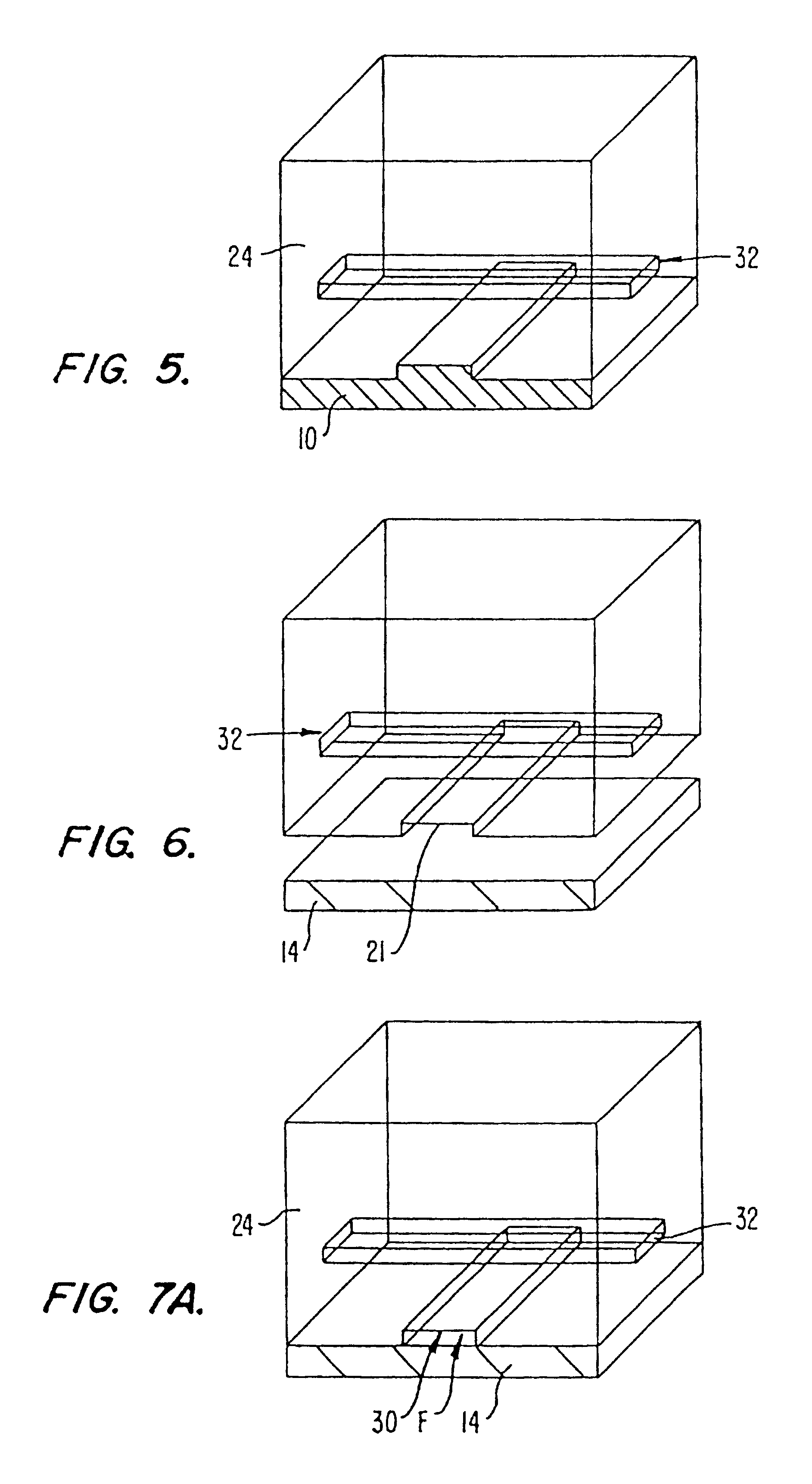

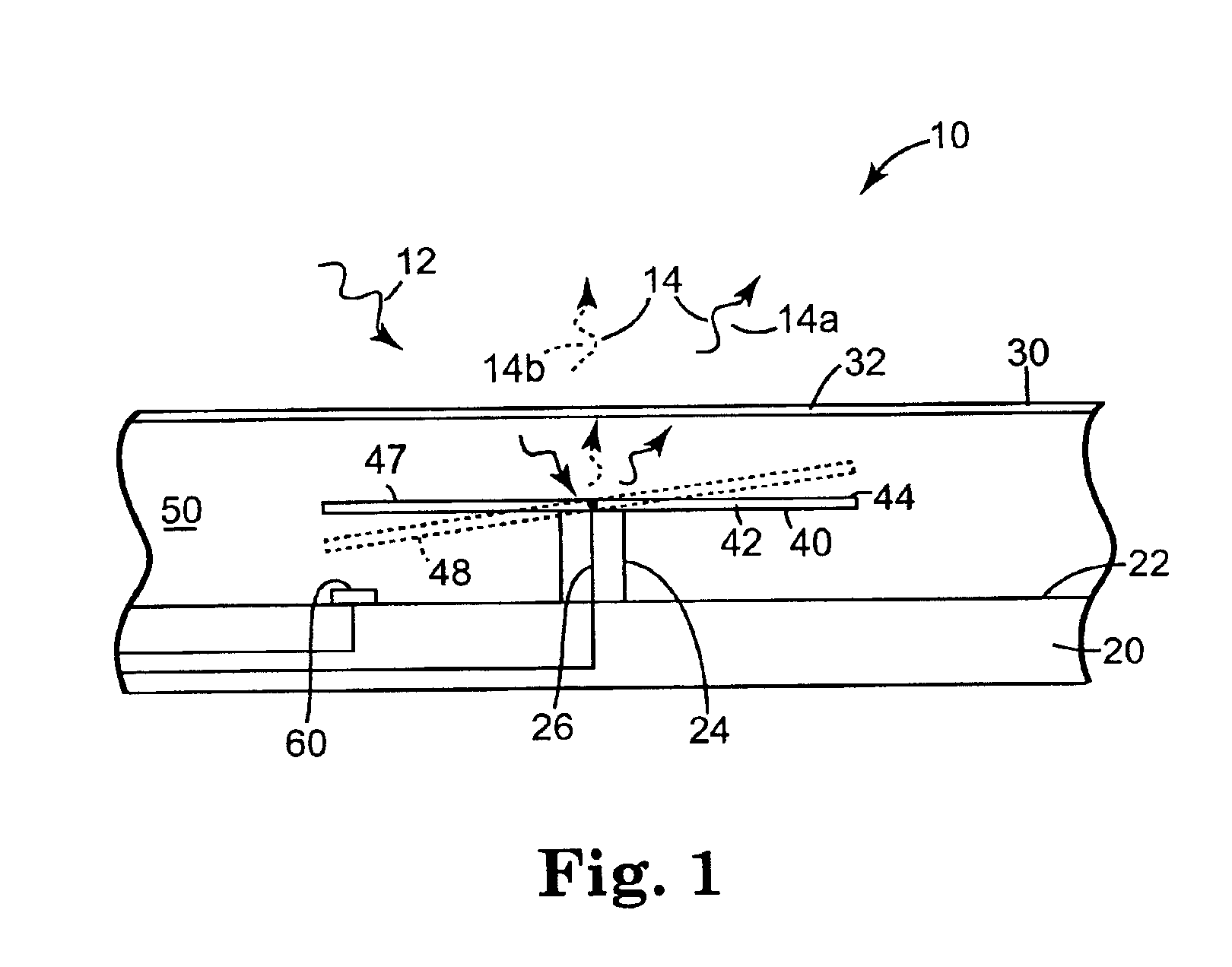

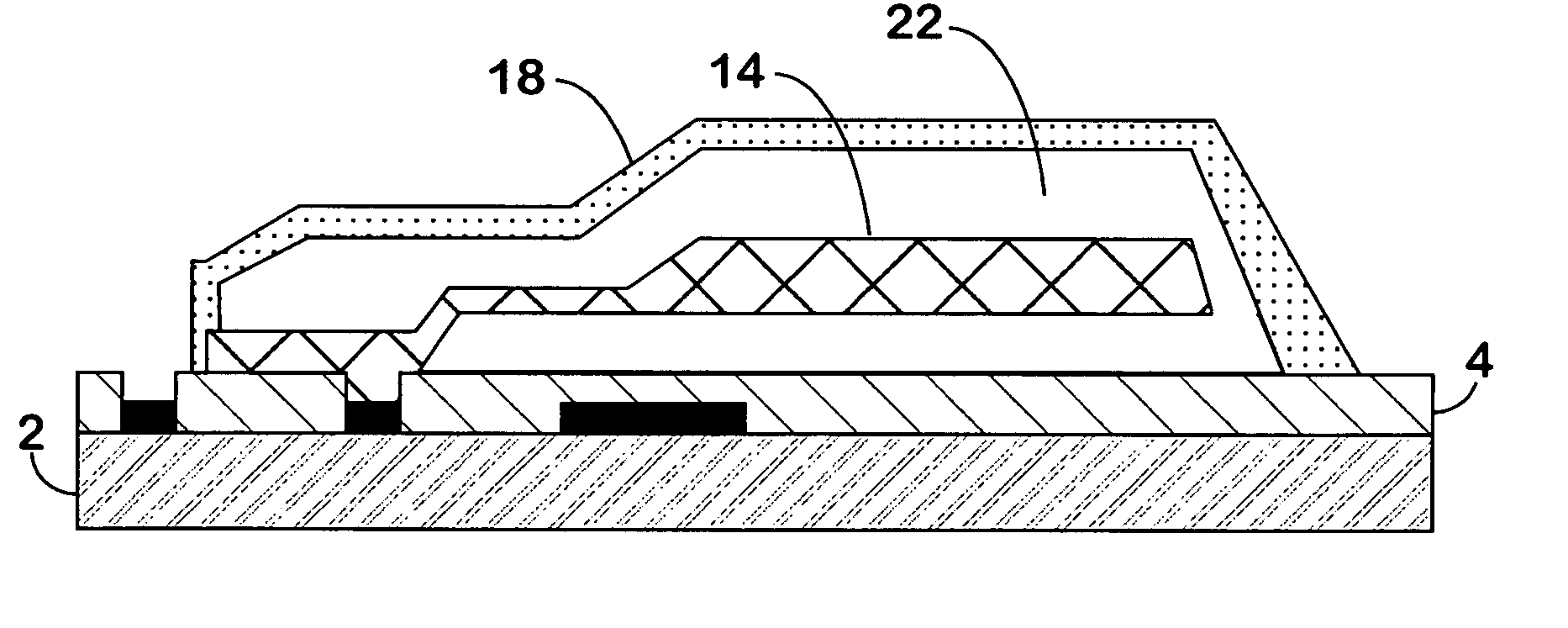

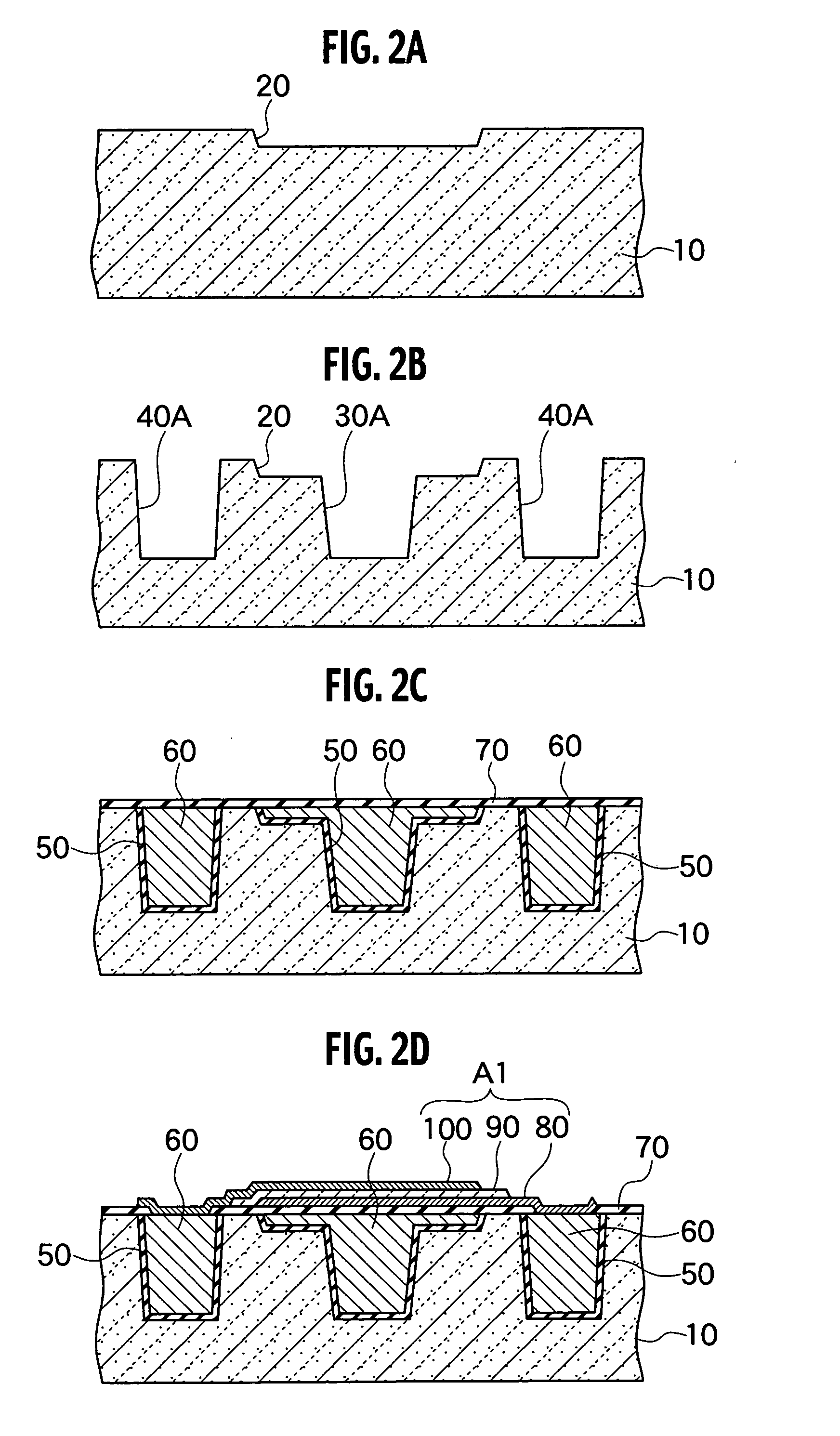

Method of forming MEMS device

InactiveUS6861277B1Decorative surface effectsSemiconductor/solid-state device manufacturingConductive materialsOptoelectronics

A method of forming a MEMS device includes depositing a conductive material on a substructure, forming a first sacrificial layer over the conductive material, including forming a substantially planar surface of the first sacrificial layer, and forming a first element over the substantially planar surface of the first sacrificial layer, including communicating the first element with the conductive material through the first sacrificial layer. In addition, the method includes forming a second sacrificial layer over the first element, including forming a substantially planar surface of the second sacrificial layer, forming a support through the second sacrificial layer to the first element after forming the second sacrificial layer, including filling the support, and forming a second element over the support and the substantially planar surface of the second sacrificial layer. As such, the method further includes substantially removing the first sacrificial layer and the second sacrificial layer, thereby supporting the second element relative to the first element with the support.

Owner:TAIWAN SEMICON MFG CO LTD

Step and repeat imprint lithography processes

The present invention is directed to methods for patterning a substrate by imprint lithography. Imprint lithography is a process in which a liquid is dispensed onto a substrate. A template is brought into contact with the liquid and the liquid is cured. The cured liquid includes an imprint of any patterns formed in the template. In one embodiment, the imprint process is designed to imprint only a portion of the substrate. The remainder of the substrate is imprinted by moving the template to a different portion of the template and repeating the imprint lithography process.

Owner:CANON KK

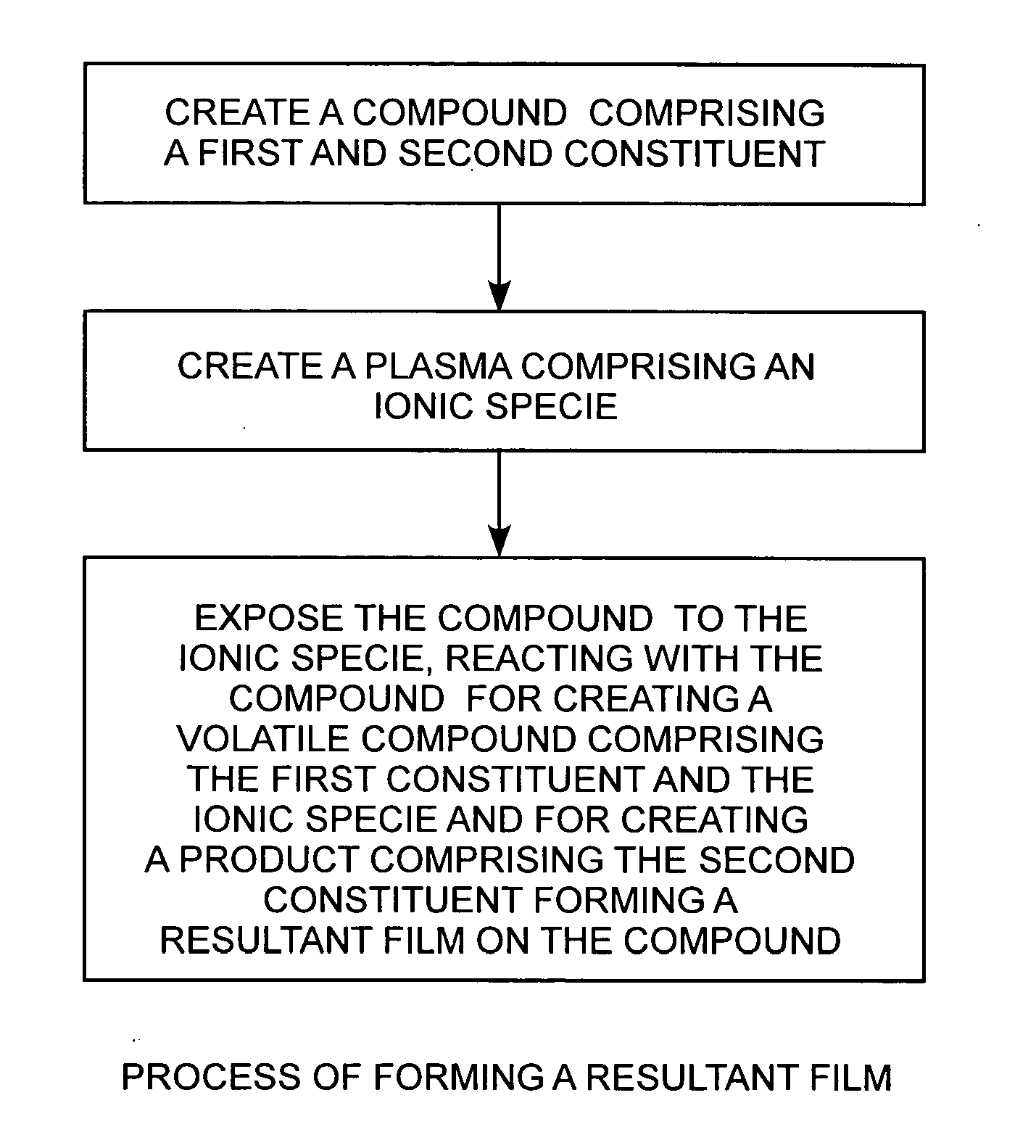

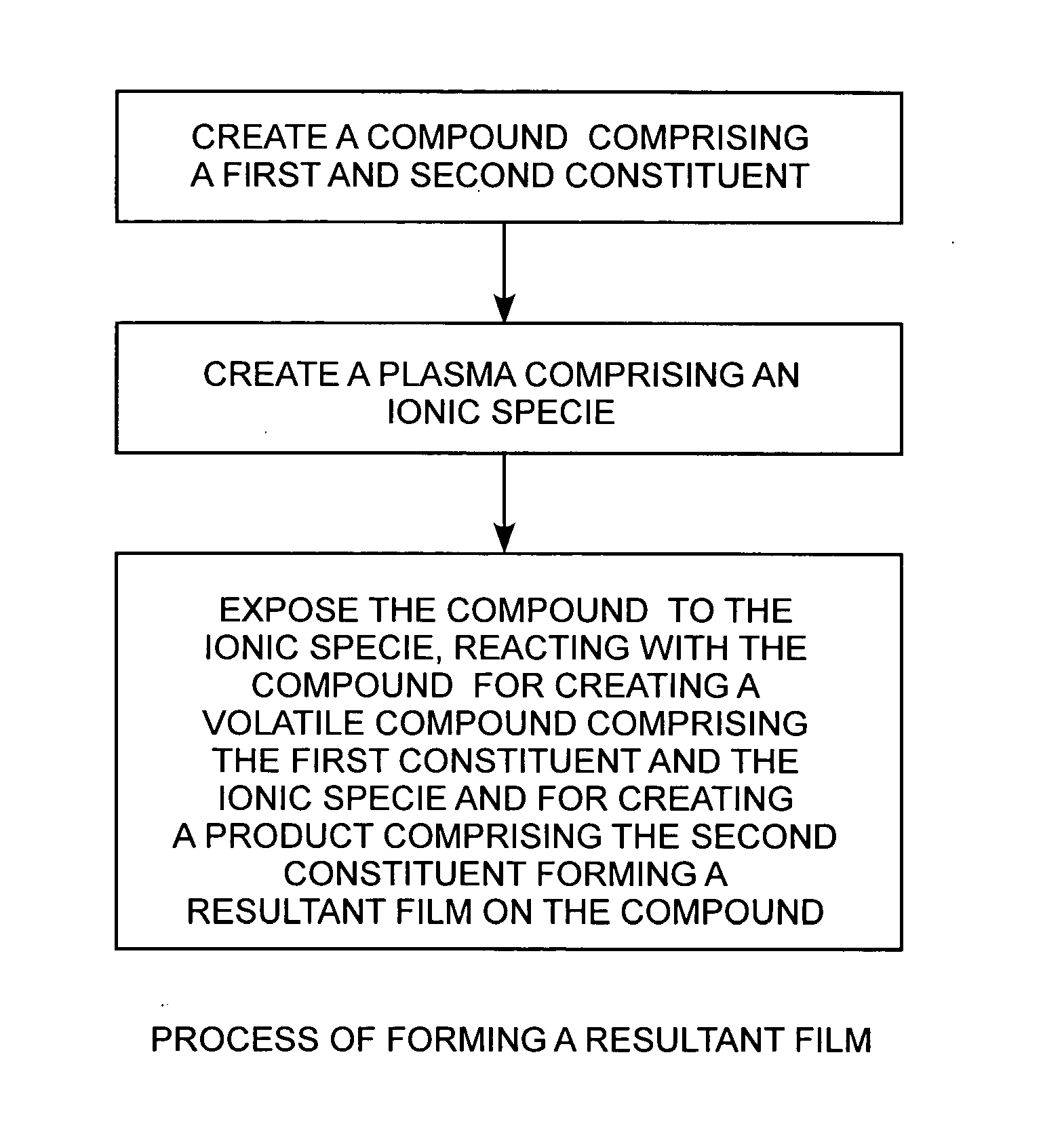

Method for producing carbon surface films by plasma exposure of a carbide compound

InactiveUS20060068125A1Reduce frictionEasy to controlChemical vapor deposition coatingFlexible microstructural devicesCarbon filmCarbon coating

Reactive halogen-ion plasmas, having for example, generating chloride ions, generated from low-pressure halogen gases using a radio-frequency plasma are employed for producing low-friction carbon coatings, such as a pure carbon film, at or near room temperature on a bulk or thin film of a compound, such as titanium carbide.

Owner:THE AEROSPACE CORPORATION

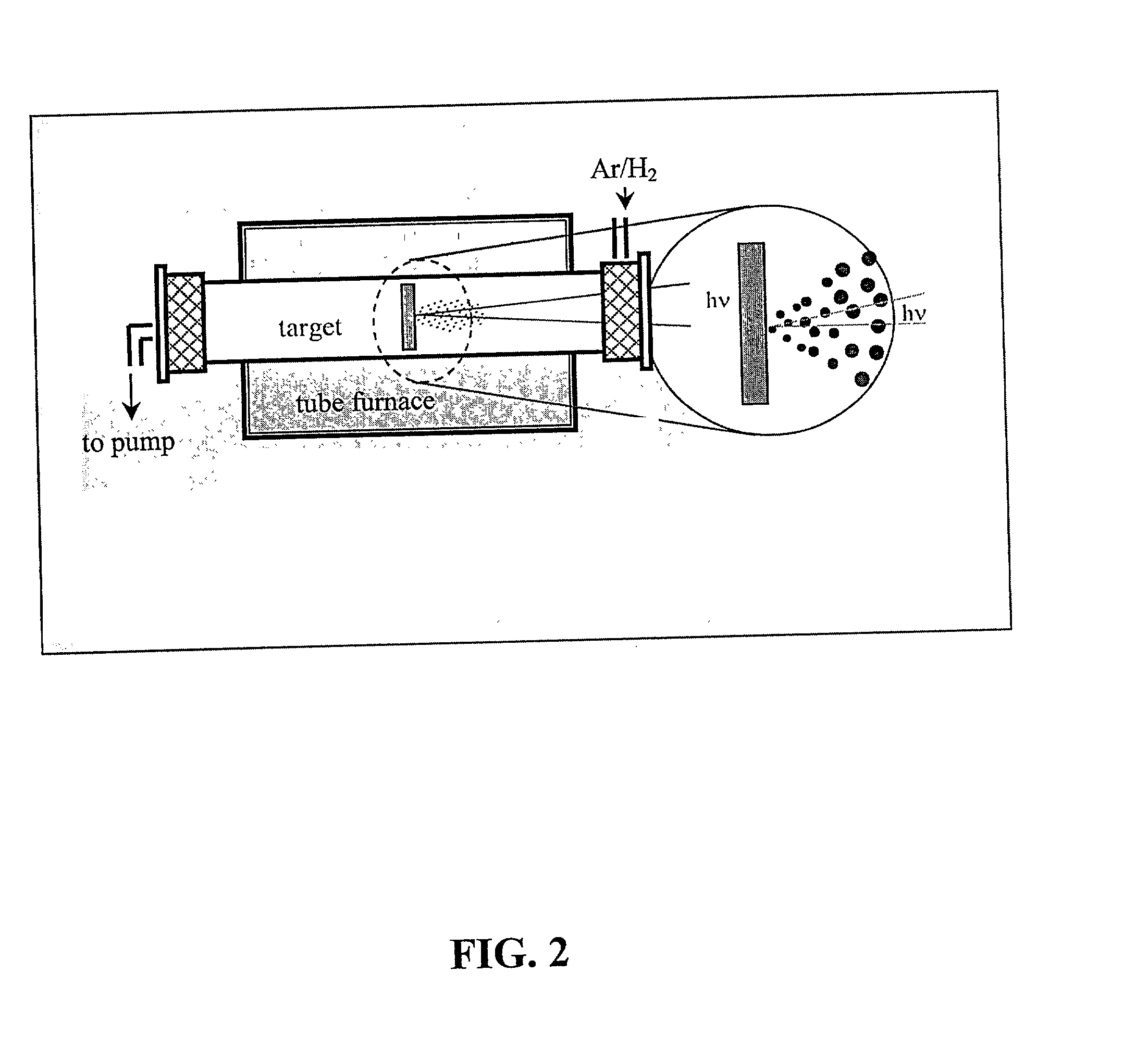

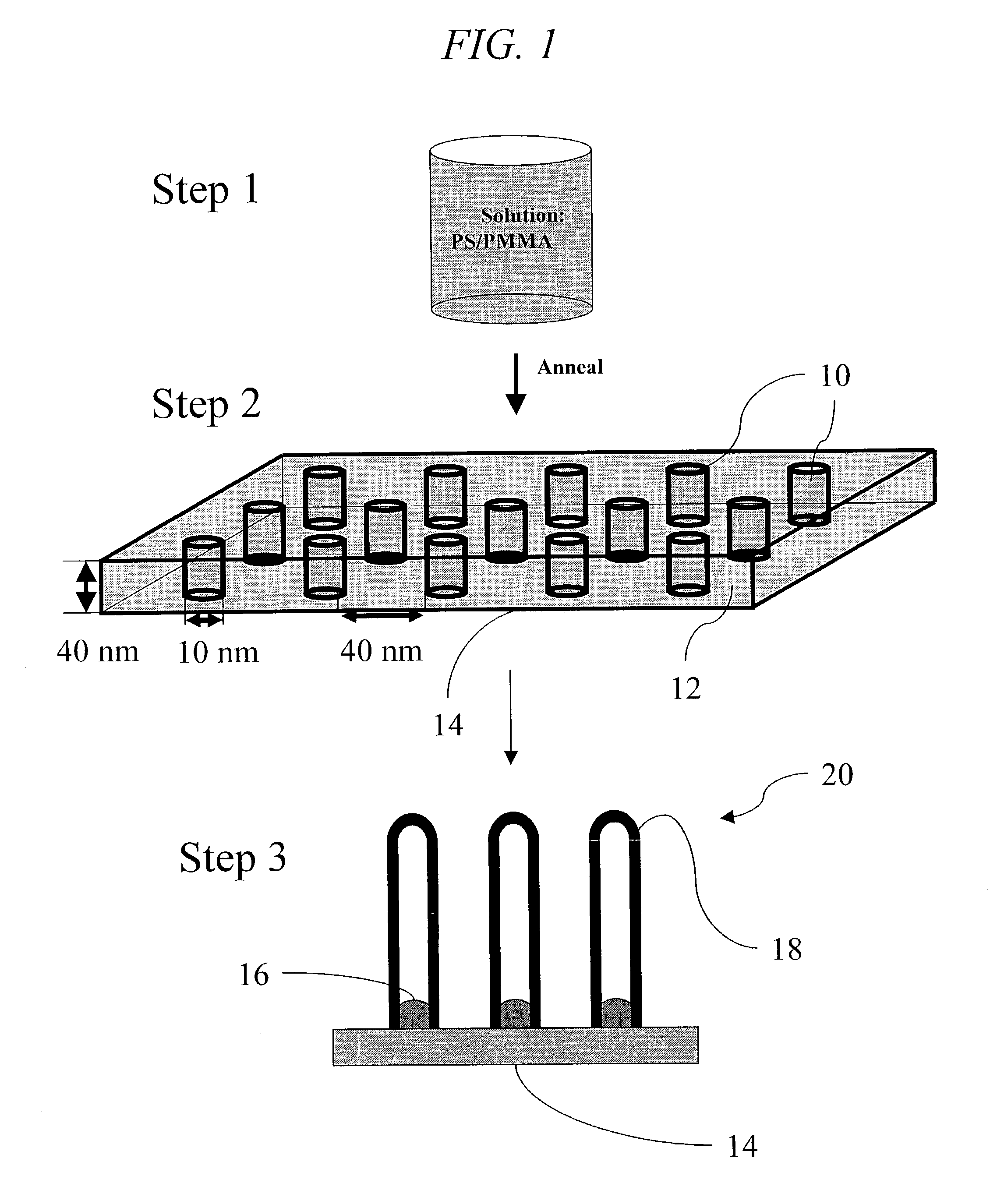

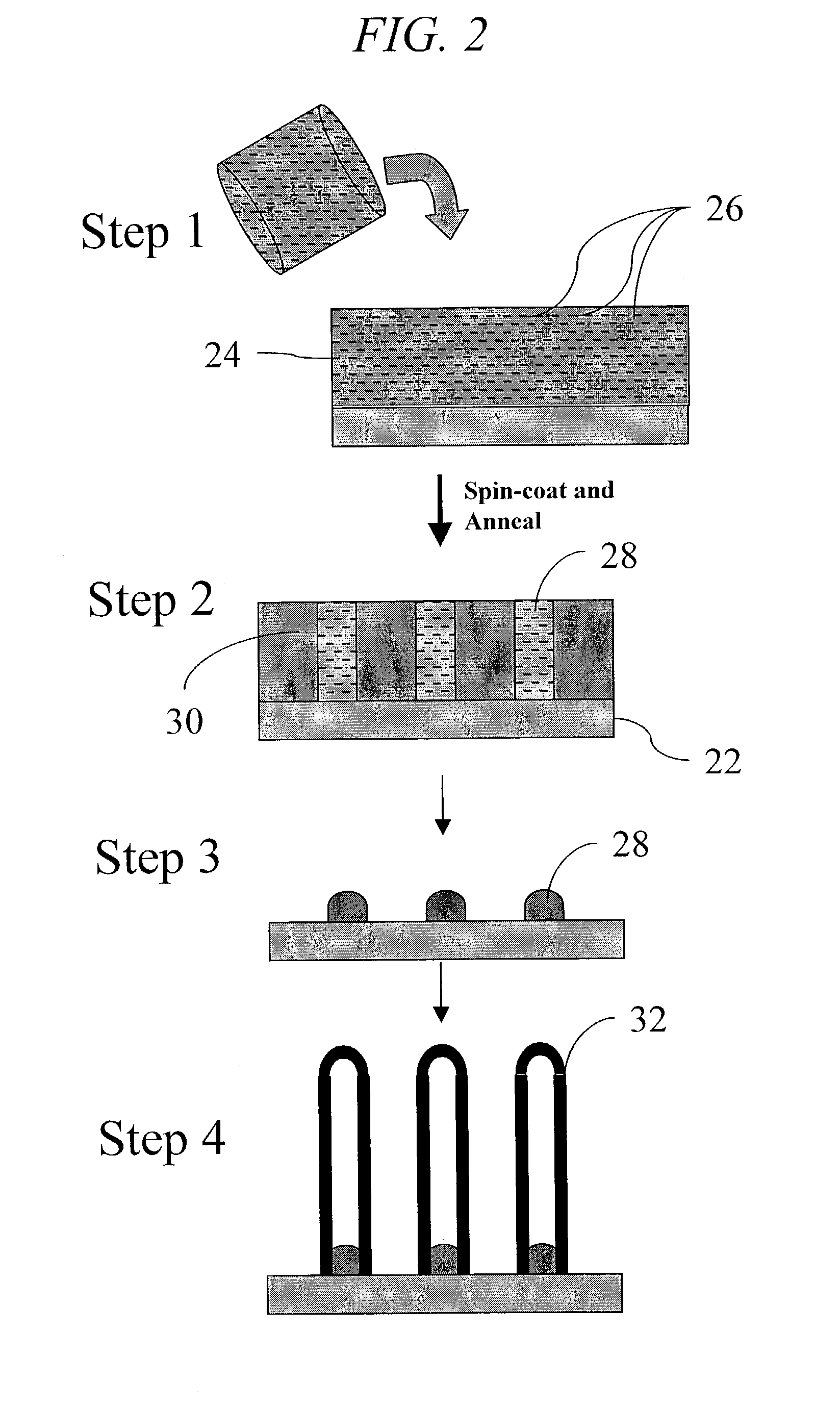

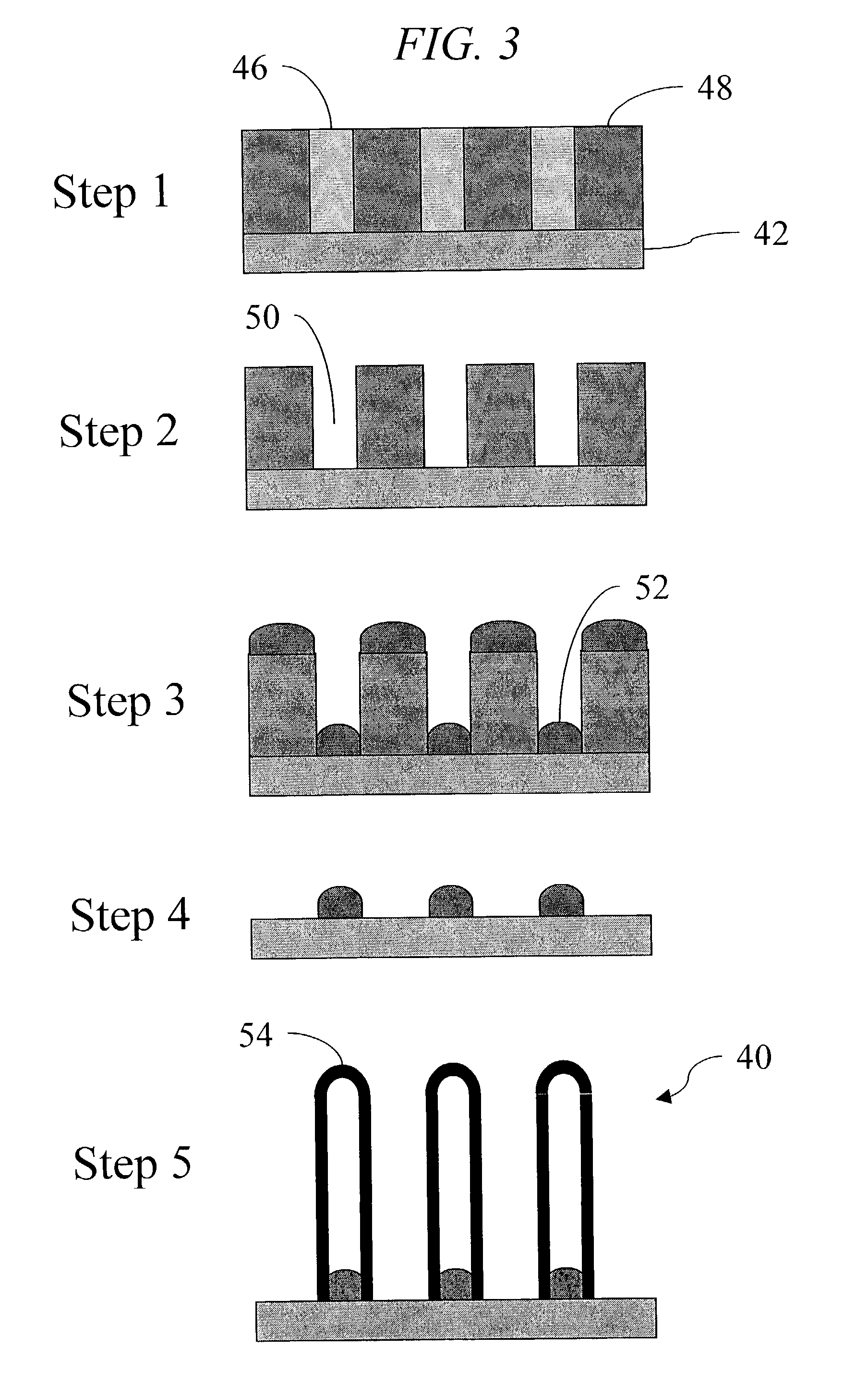

Method of producing regular arrays of nano-scale objects using nano-structured block-copolymeric materials

A method of forming a periodic array of nano-scale objects using a block copolymer, and nano-scale object arrays formed from the method are provided. The method for forming the arrays generally includes the steps of depositing a block copolymer of at least two blocks on a substrate to form an ordered meso-scale structured array of the polymer materials, forming catalytic metal dots based on the meso-scale structure, and growing nano-scale objects on the catalytic dots to form an ordered array of nano-scale objects.

Owner:CALIFORNIA INST OF TECH

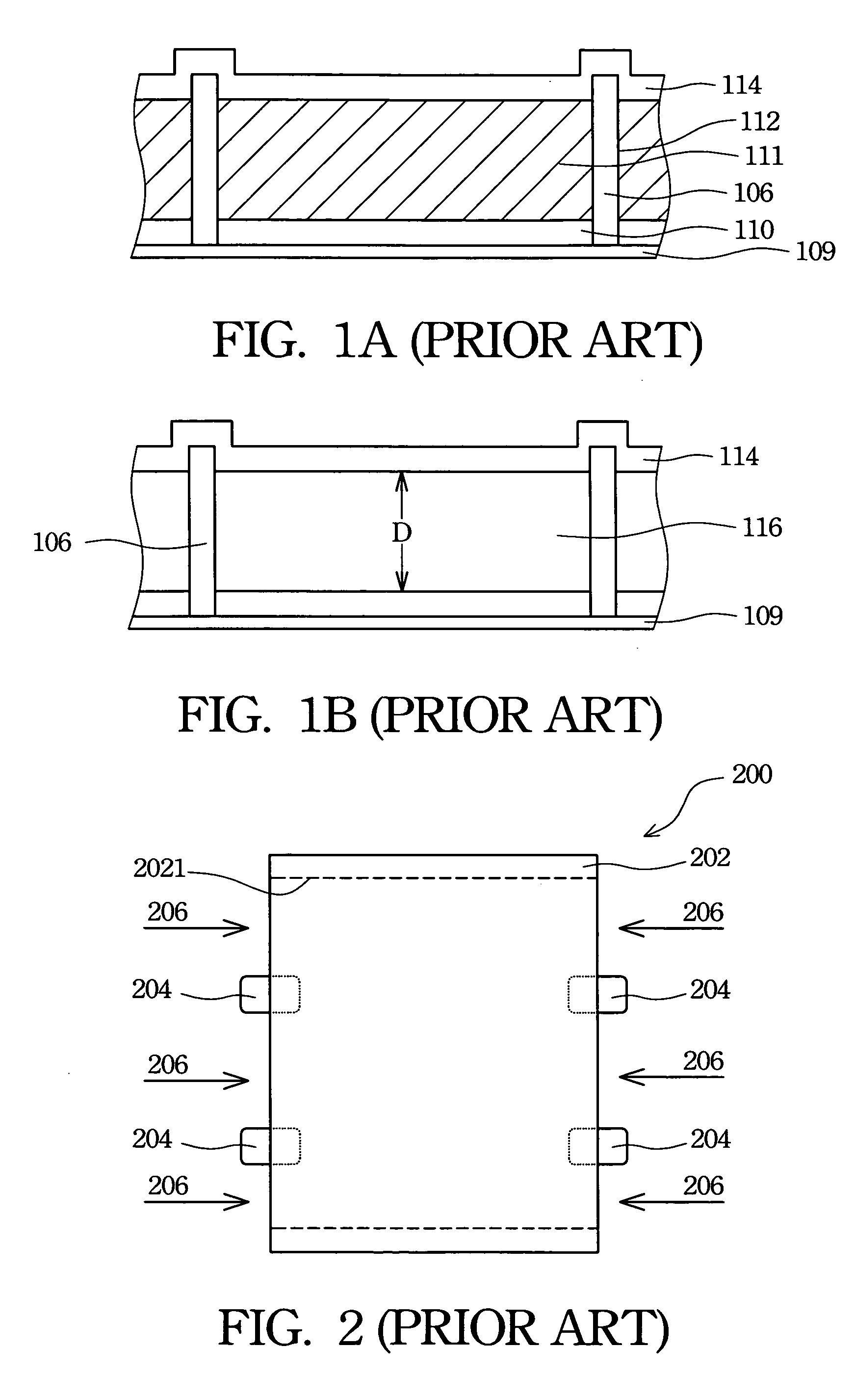

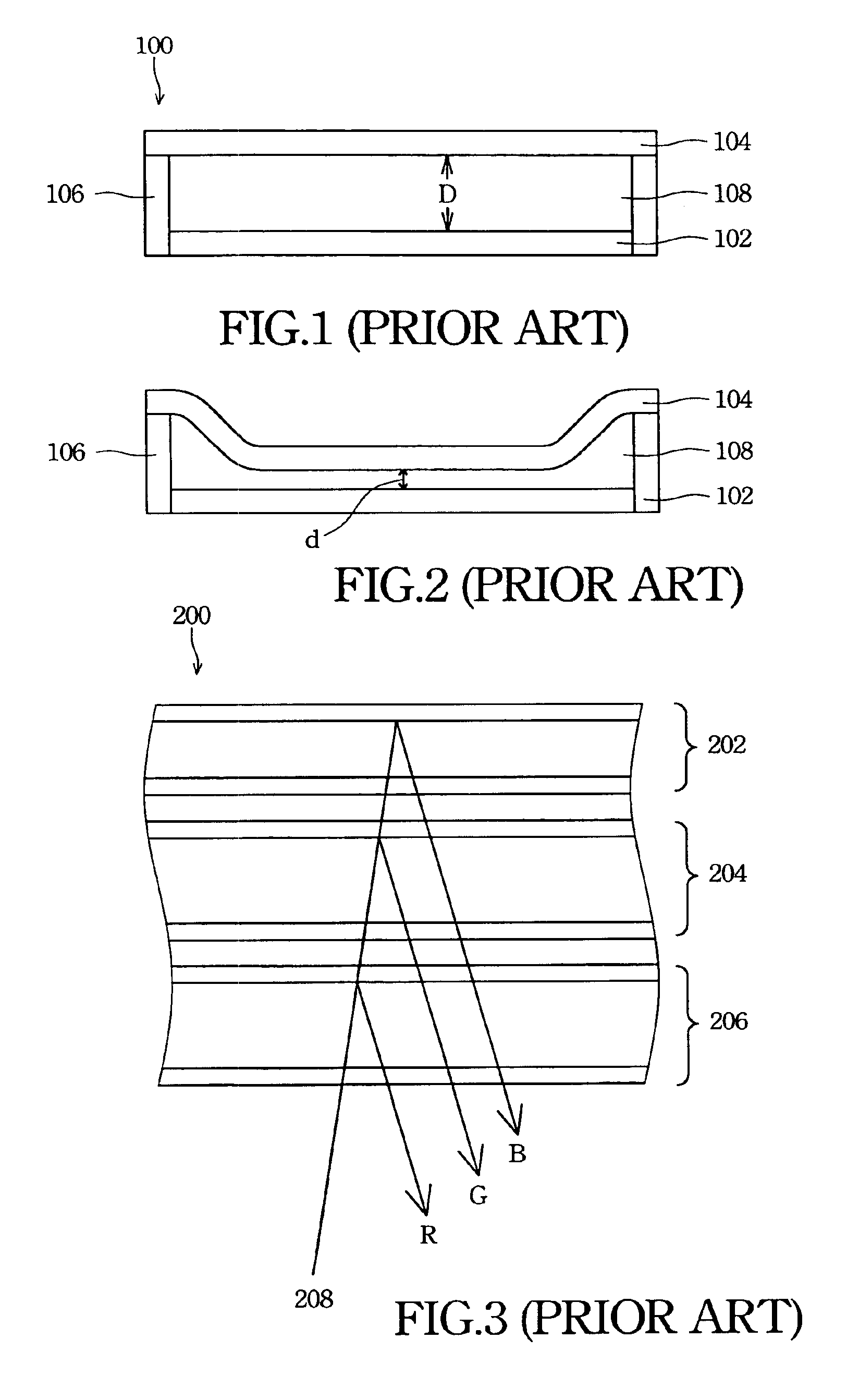

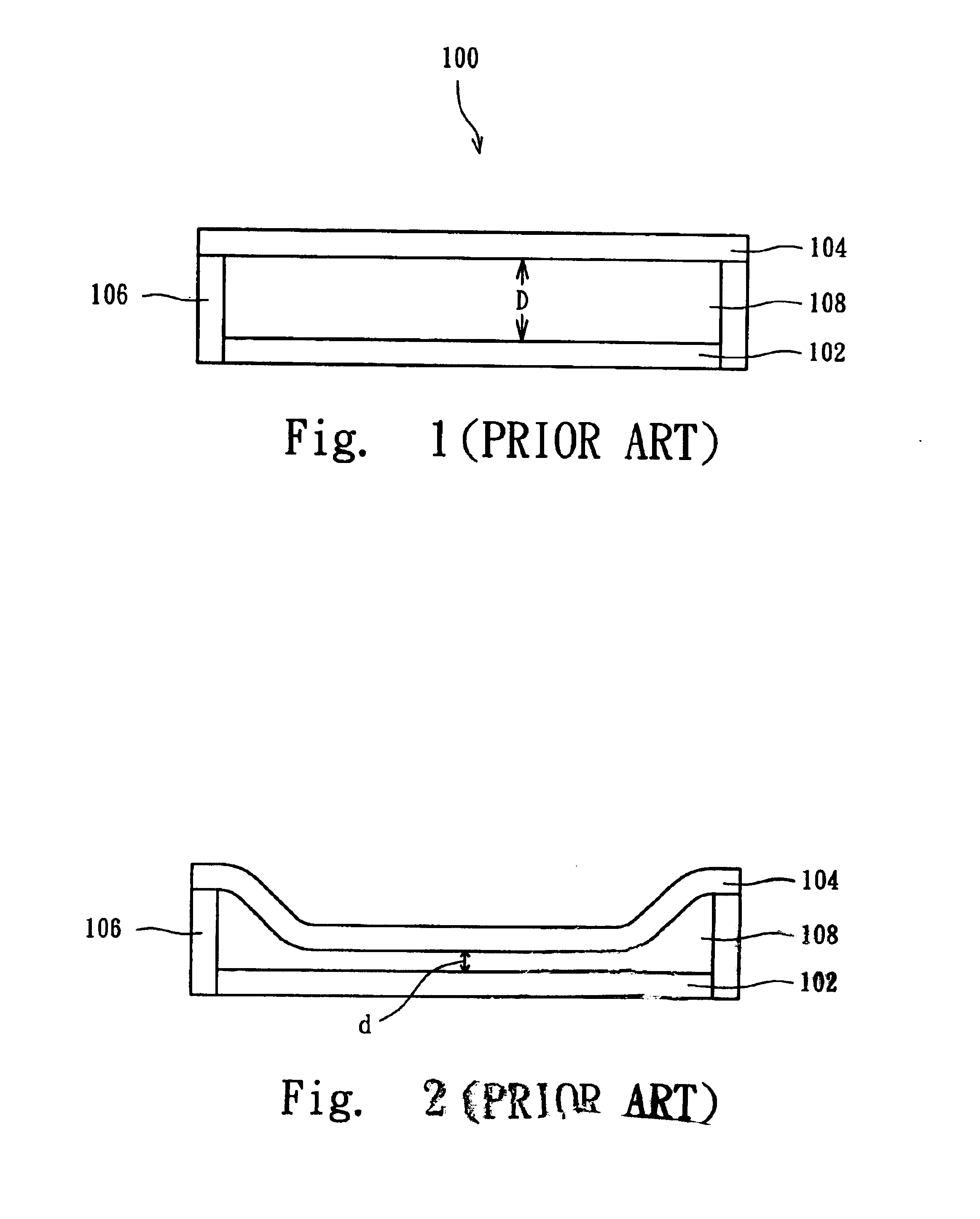

Method for fabricating optical interference display cell

InactiveUS20050003667A1Easily reorganized and consolidatedLow costDecorative surface effectsSolid-state devicesRemote plasmaOptoelectronics

A method for fabricating an optical interference display cell is described. A first electrode and a sacrificial layer are sequentially formed on a transparent substrate and at least two openings are formed in the first electrode and the sacrificial layer to define a position of the optical interference display cell. An insulated heat-resistant inorganic supporter is formed in each of the openings. A second electrode is formed on the sacrificial layer and the supporters. Finally, a remote plasma etching process is used for removing the sacrificial layer.

Owner:SNAPTRACK

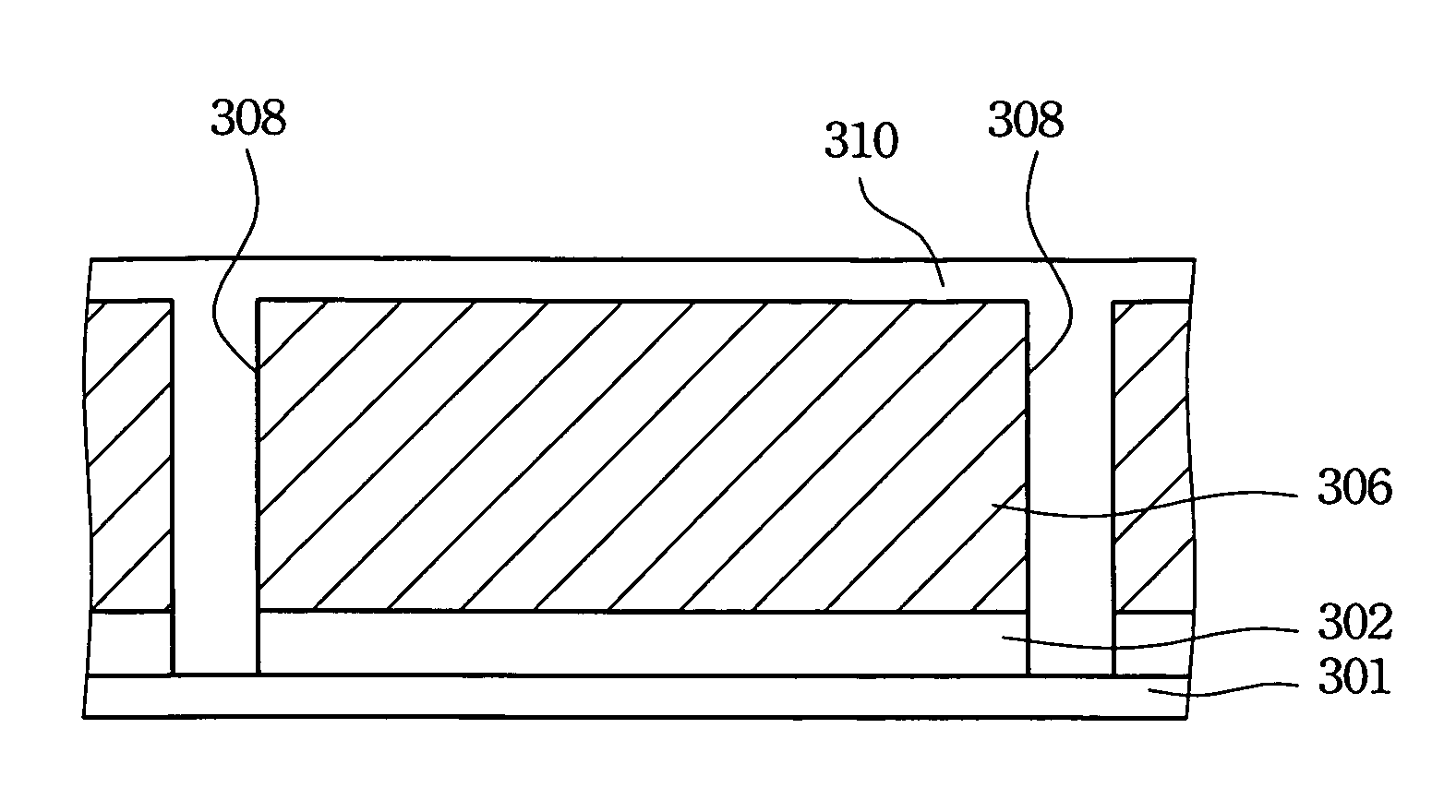

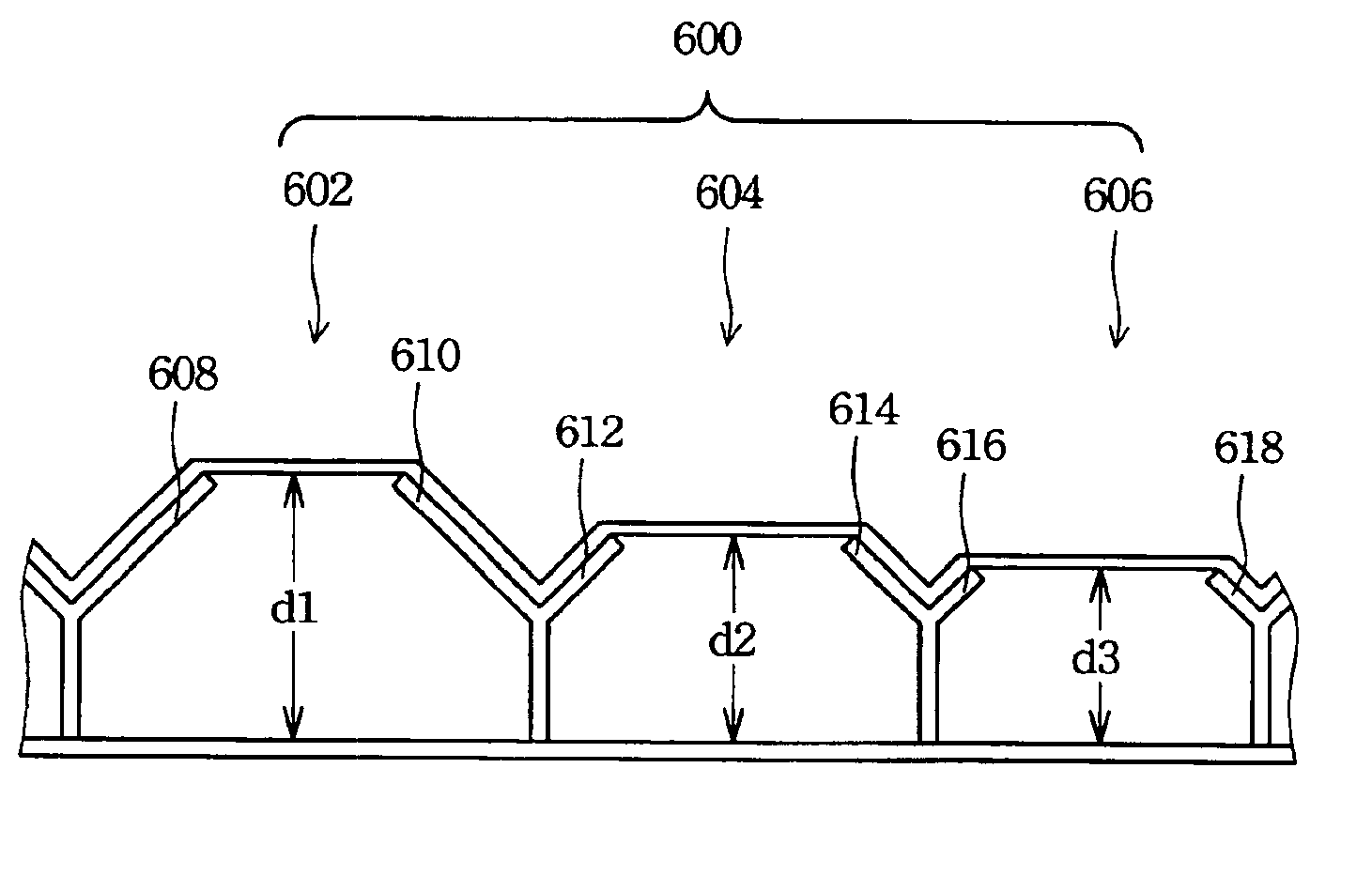

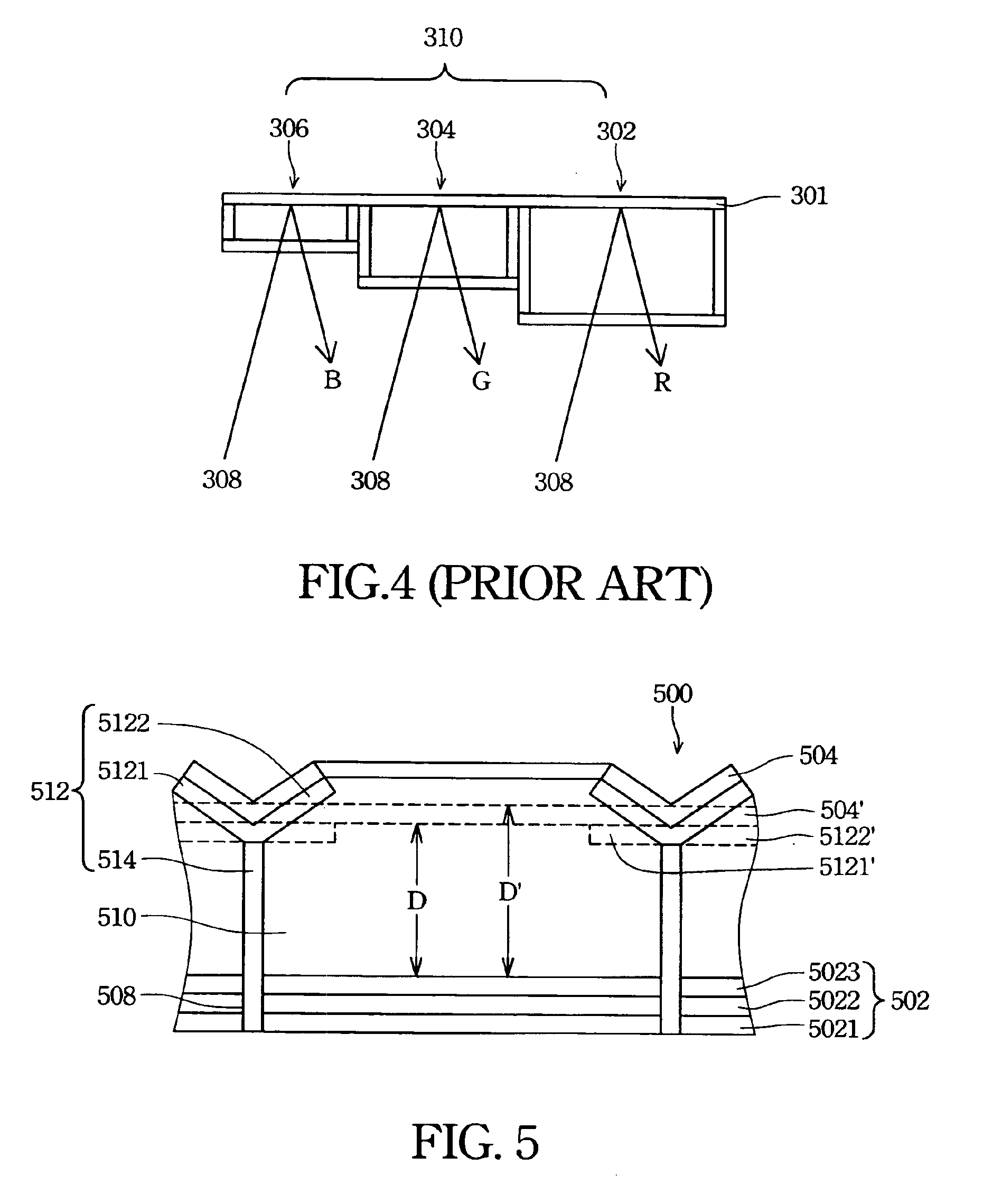

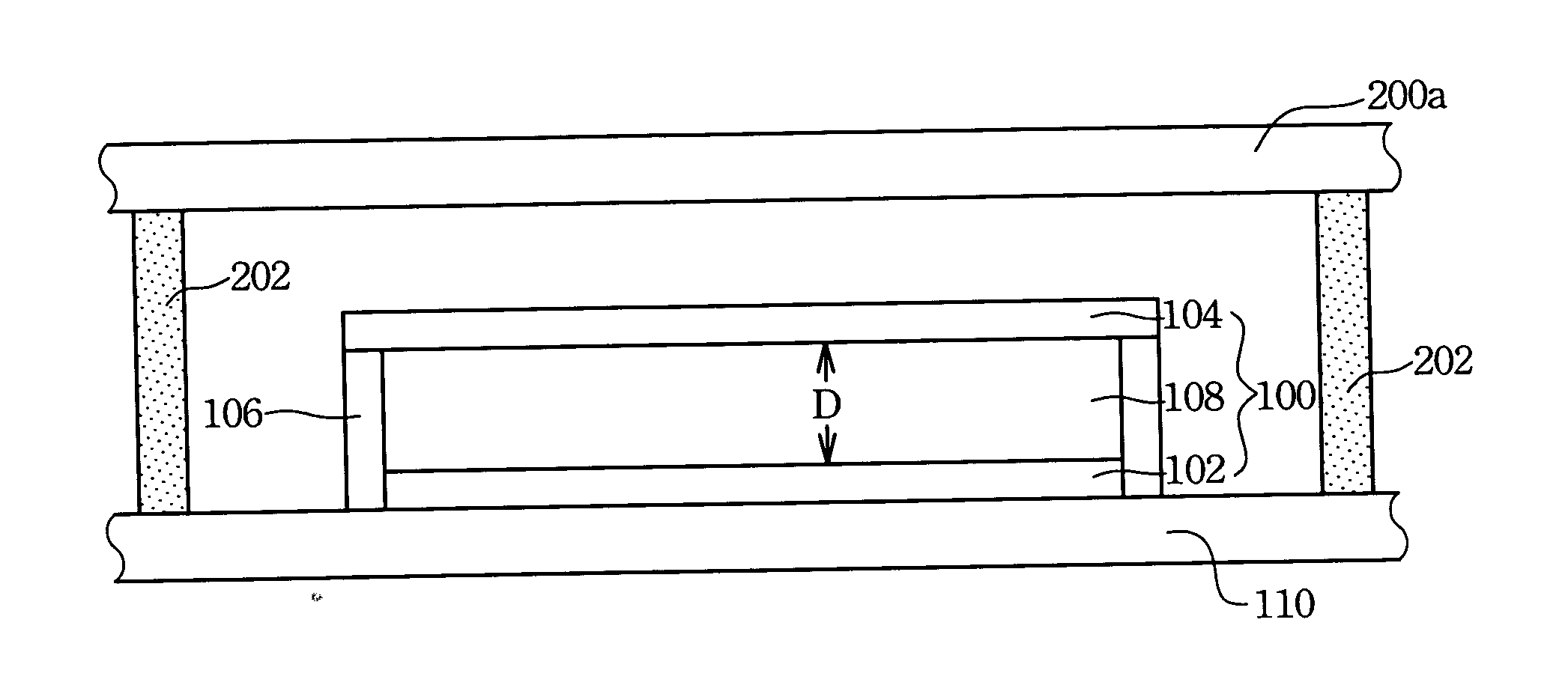

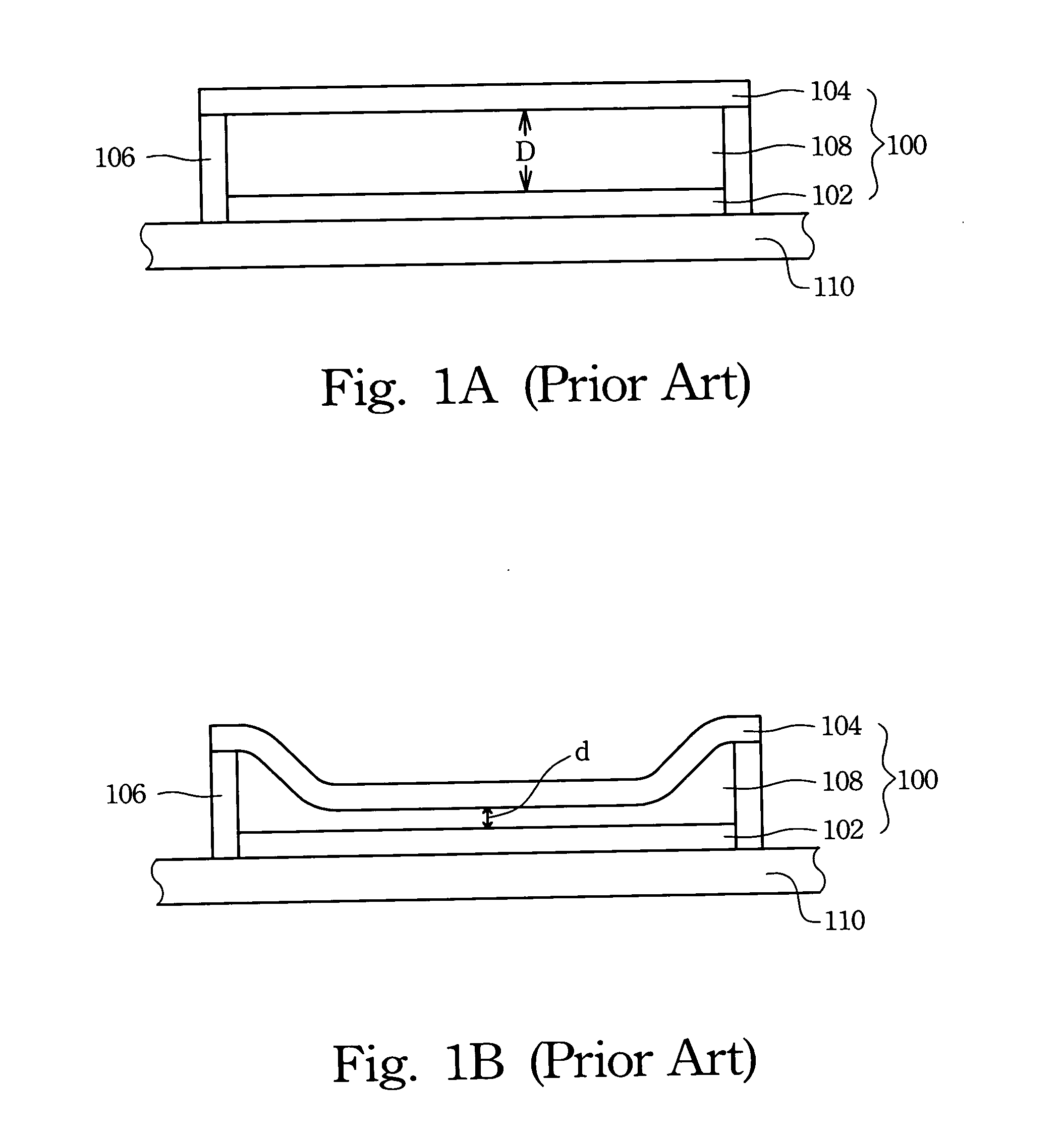

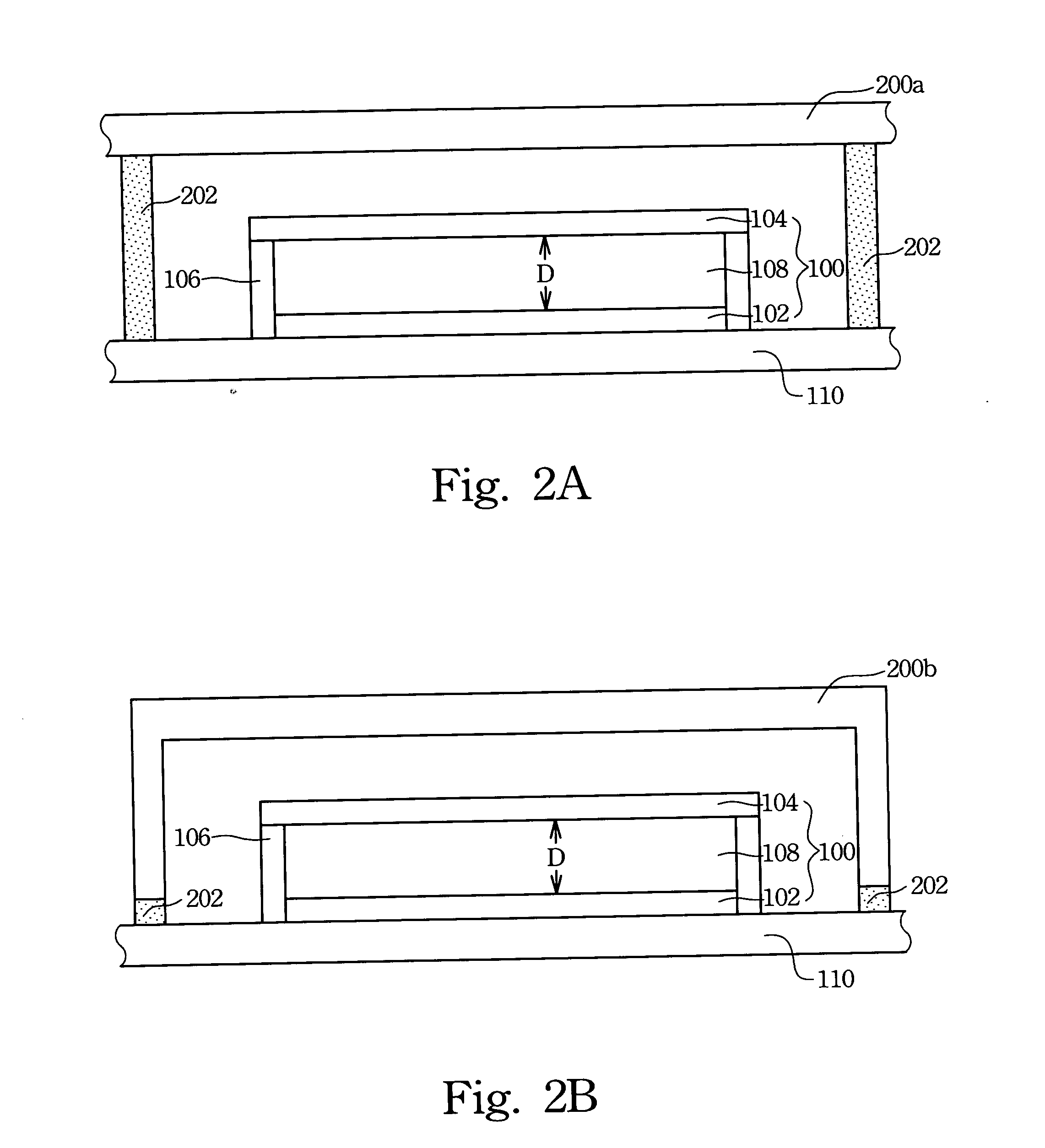

Structure of an optical interference display cell

A structure of an interference display cell is provided. The cell comprises a first plate and a second plate, wherein a support is located between the first plate and the second plate. The second plate is a deformable and reflective plate. An incident light from one side of the first plate is modulated and only specific frequency light reflects by the second plate. The frequency of the reflected light is related to the distance between the first plate and the second plate. The support has at least one arm. The arm's stress makes the arm hiking upward or downward. The distance between the first plate and the second plate is also changed. Therefore, the frequency of the reflected light is altered.

Owner:SNAPTRACK

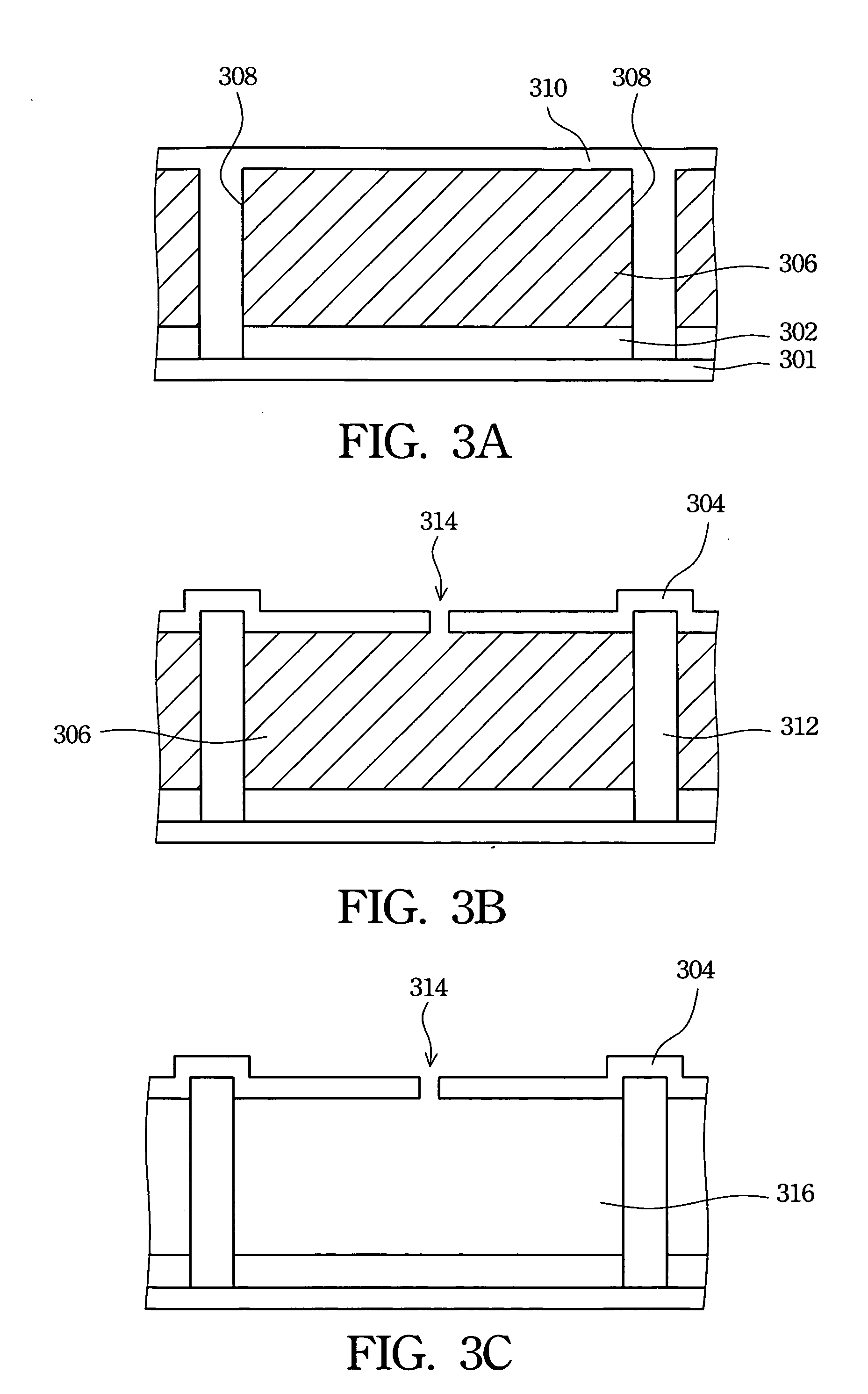

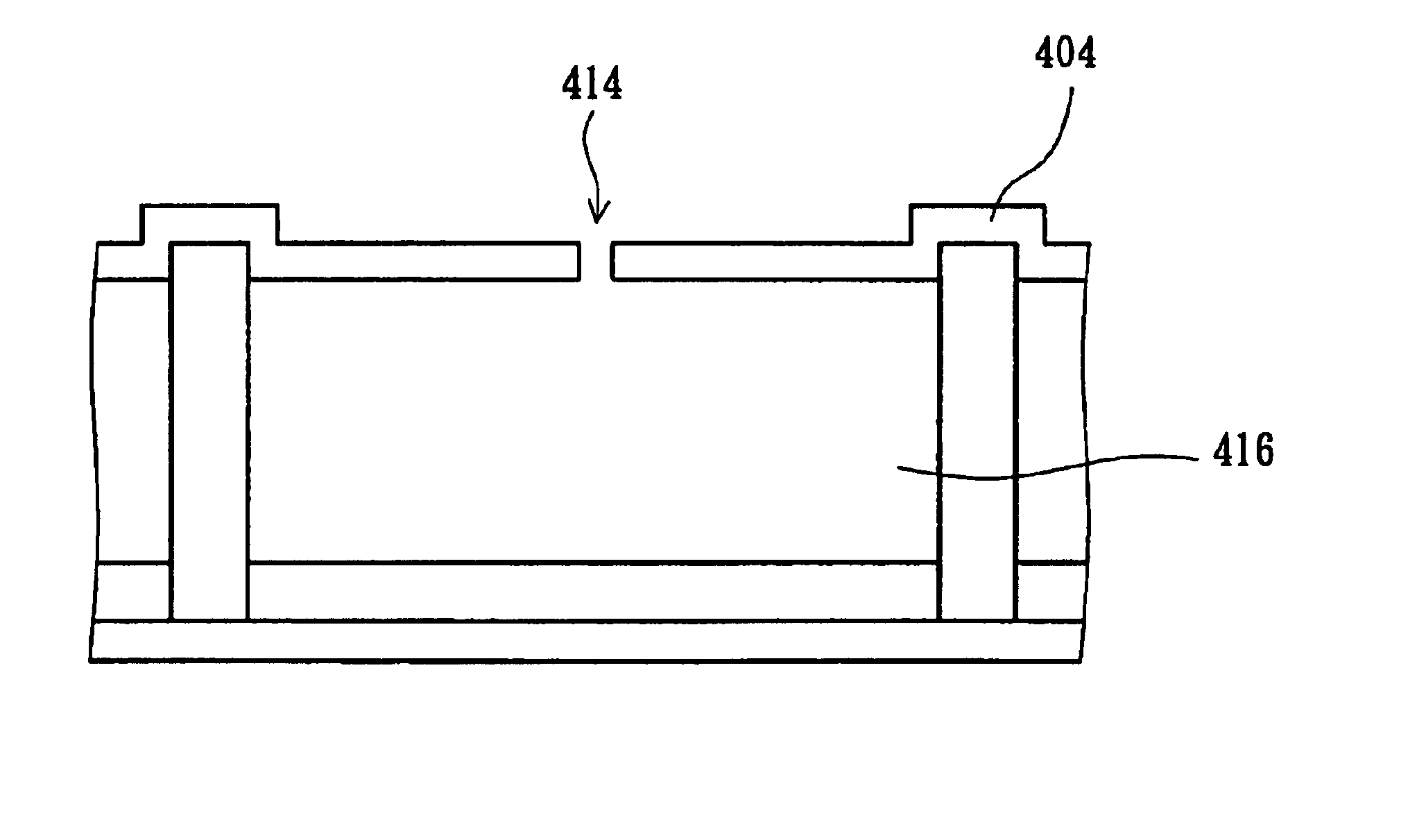

Structure of a structure release and a method for manufacturing the same

InactiveUS6870654B2Easily consolidatedEasy to reorganizeDecorative surface effectsSemiconductor/solid-state device manufacturingEngineeringElectrode

A structure of a structure release and a manufacturing method are provided. The structure and manufacturing method are adapted for an interference display cell. The structure of the interference display cell includes a first electrode, a second electrode and at least one supporter. The second electrode has at least one hole and is arranged about parallel with the first electrode. The supporter is located between the first electrode and the second electrode and a cavity is formed. In the release etch process of manufacturing the structure, an etchant can pass through the hole to etch a sacrificial layer between the first and the second electrodes to form the cavity; therefore, the time needed for the process becomes shorter.

Owner:SNAPTRACK

Release strategies for making transferable semiconductor structures, devices and device components

ActiveUS7932123B2Low costReduce layeringFinal product manufactureNanoinformaticsSemiconductor structureElectron

Provided are methods for making a device or device component by providing a multilayer structure having a plurality of functional layers and a plurality of release layers and releasing the functional layers from the multilayer structure by separating one or more of the release layers to generate a plurality of transferable structures. The transferable structures are printed onto a device substrate or device component supported by a device substrate. The methods and systems provide means for making high-quality and low-cost photovoltaic devices, transferable semiconductor structures, (opto-)electronic devices and device components.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

Optical interference display panel and manufacturing method thereof

ActiveUS20050042117A1Improve the problemLow its display performanceTelevision system detailsSemiconductor/solid-state device detailsAdhesiveEngineering

A first electrode and a sacrificial layer are sequentially formed on a substrate, and then first openings for forming supports inside are formed in the first electrode and the sacrificial layer. The supports are formed in the first openings, and then a second electrode is formed on the sacrificial layer and the supports, thus forming a micro electro mechanical system structure. Afterward, an adhesive is used to adhere and fix a protection structure to the substrate for forming a chamber to enclose the micro electro mechanical system structure, and at least one second opening is preserved on sidewalls of the chamber. A release etch process is subsequently employed to remove the sacrificial layer through the second opening in order to form cavities in an optical interference reflection structure. Finally, the second opening is closed to seal the optical interference reflection structure between the substrate and the protection structure.

Owner:QUALCOMM INC +1

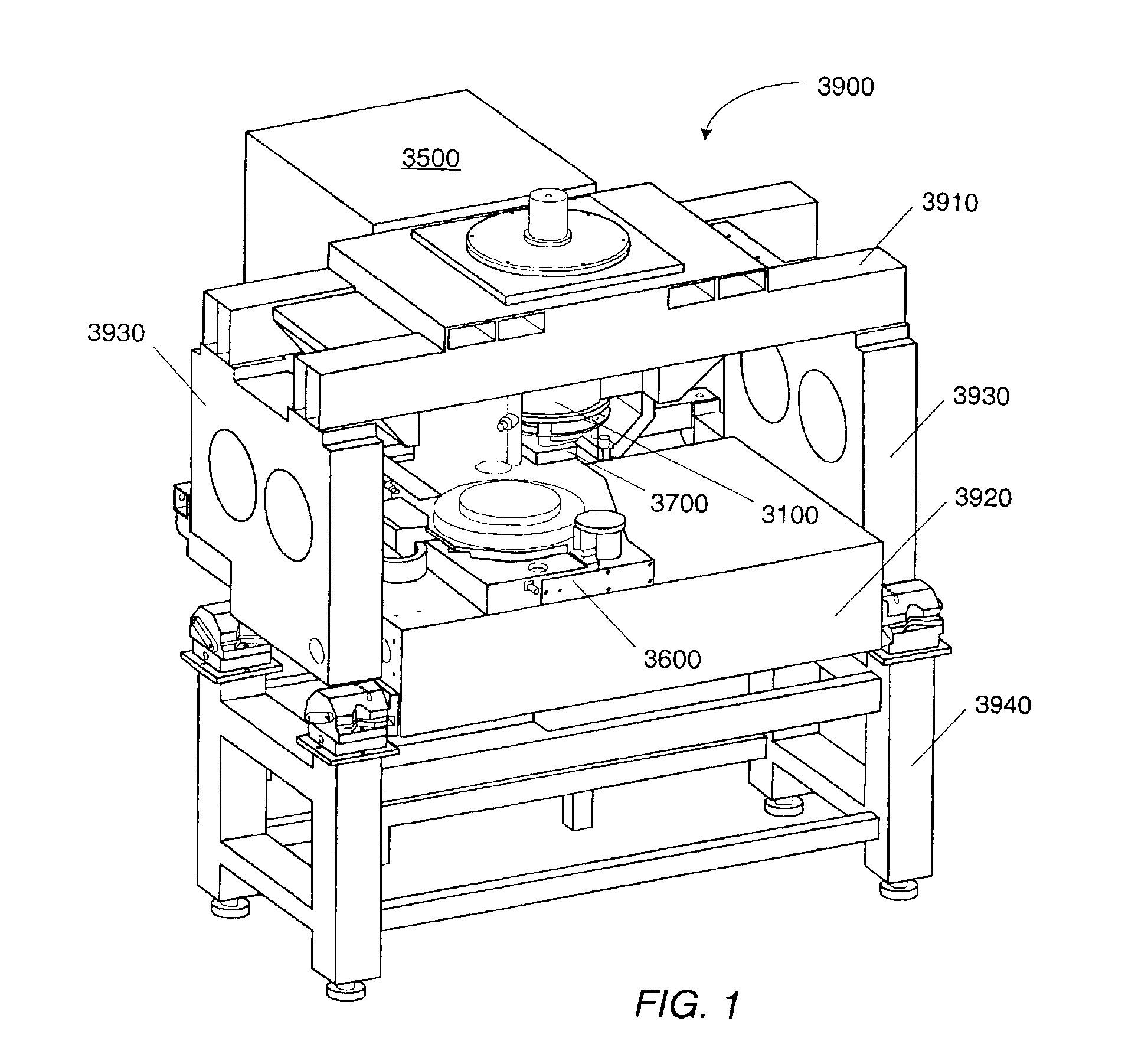

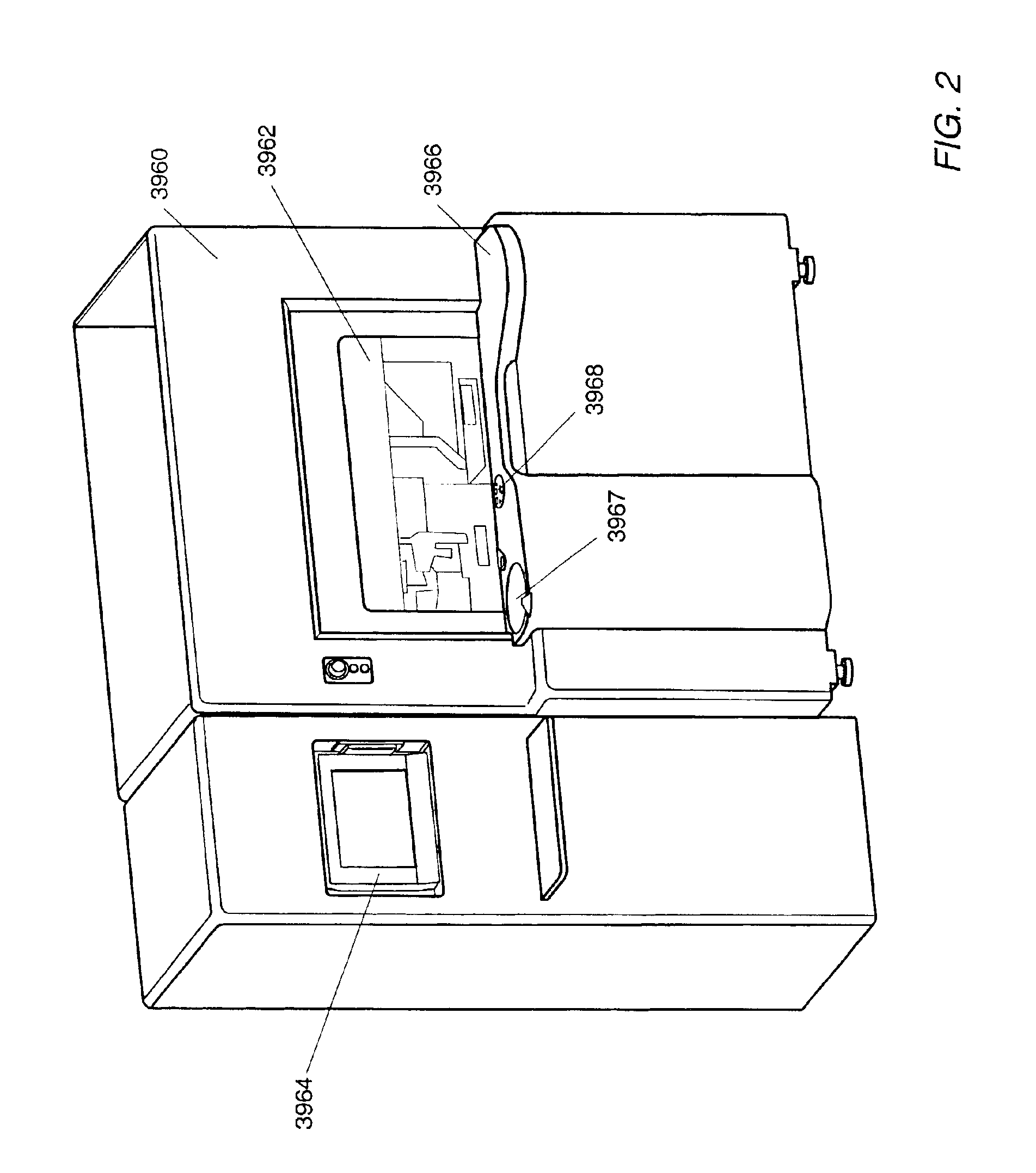

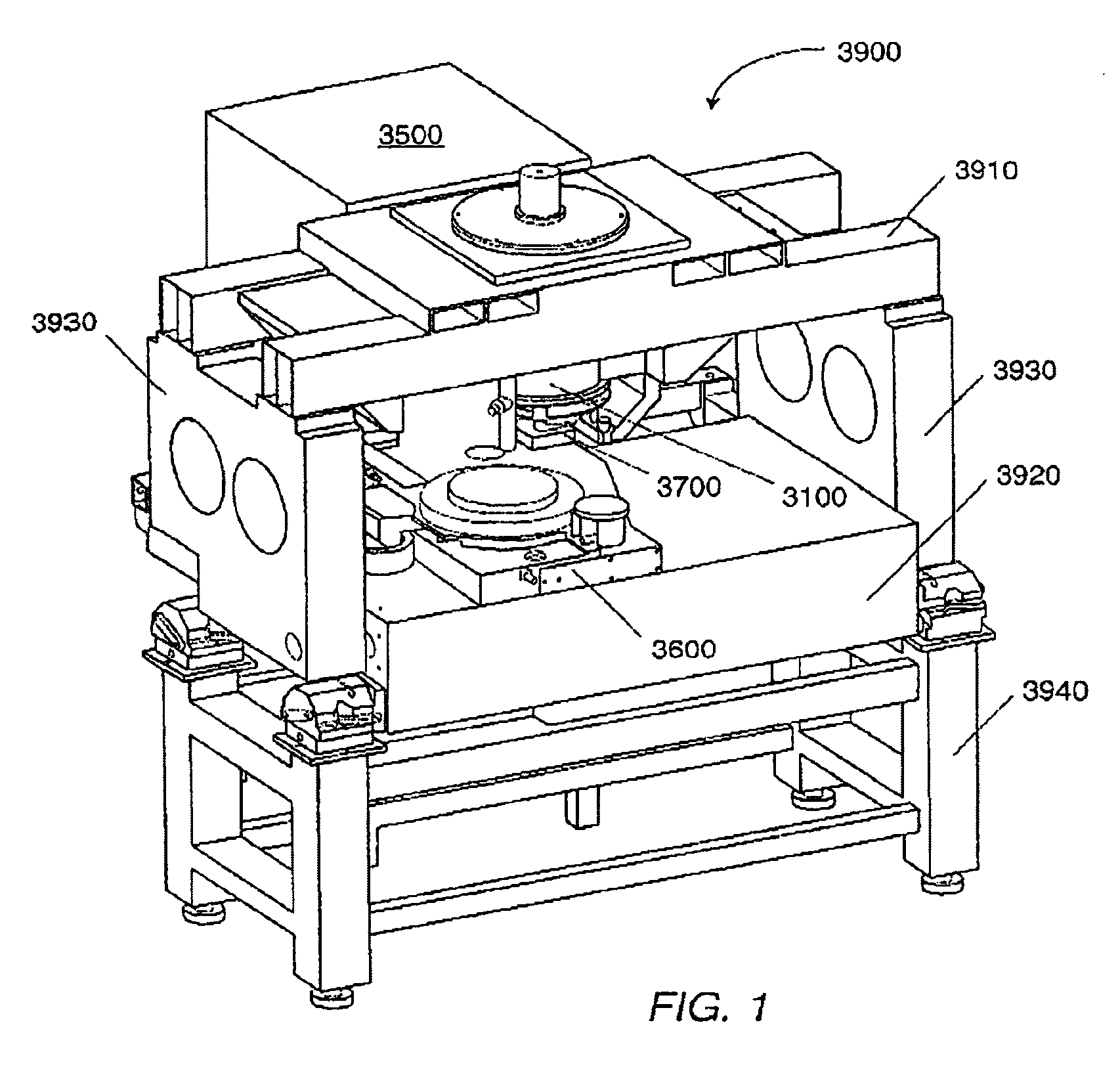

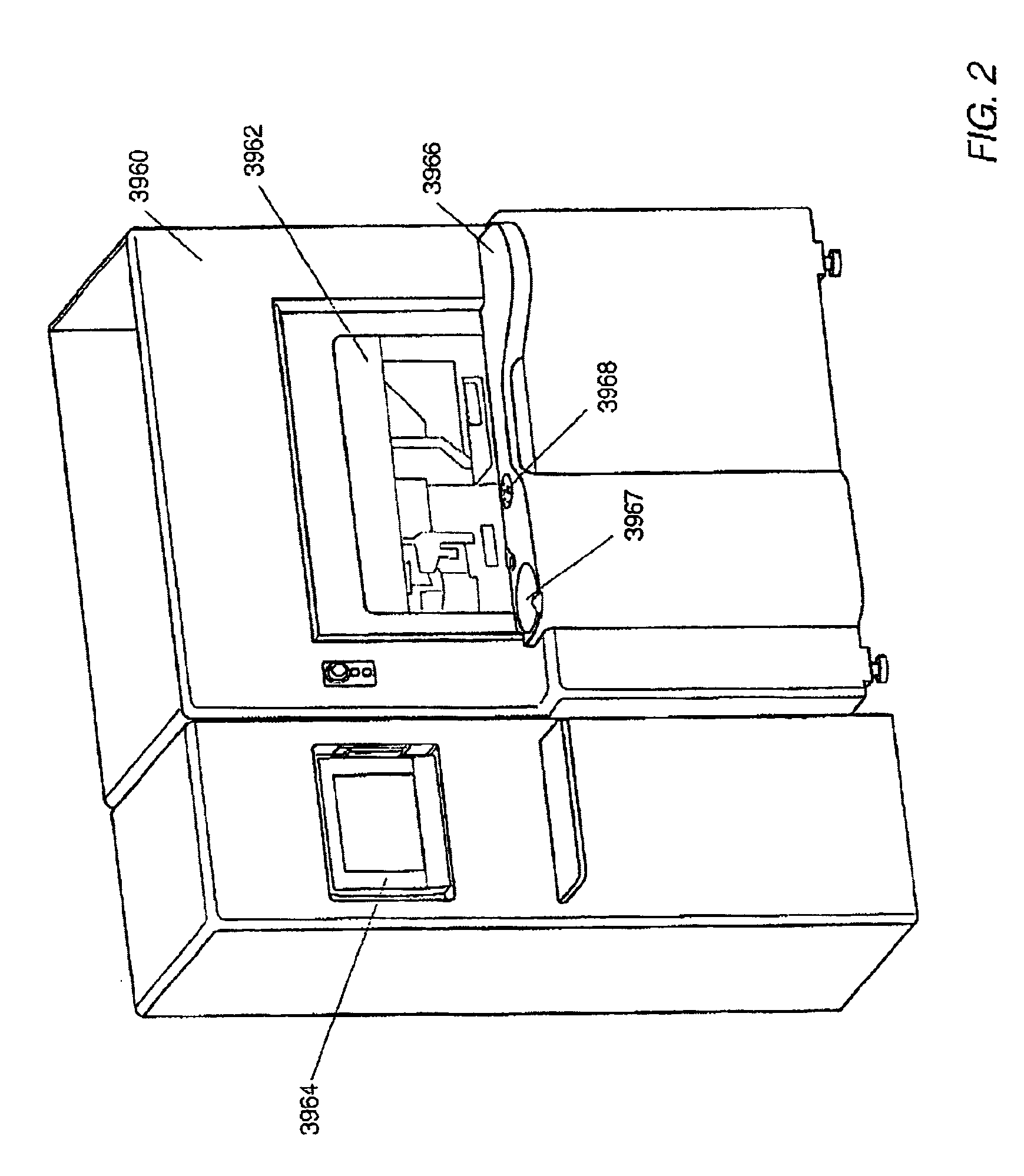

Etching Apparatus and Process with Thickness and Uniformity Control

InactiveUS20060191637A1Improve uniformityReduce unevennessElectric discharge tubesDecorative surface effectsEngineeringFilm material

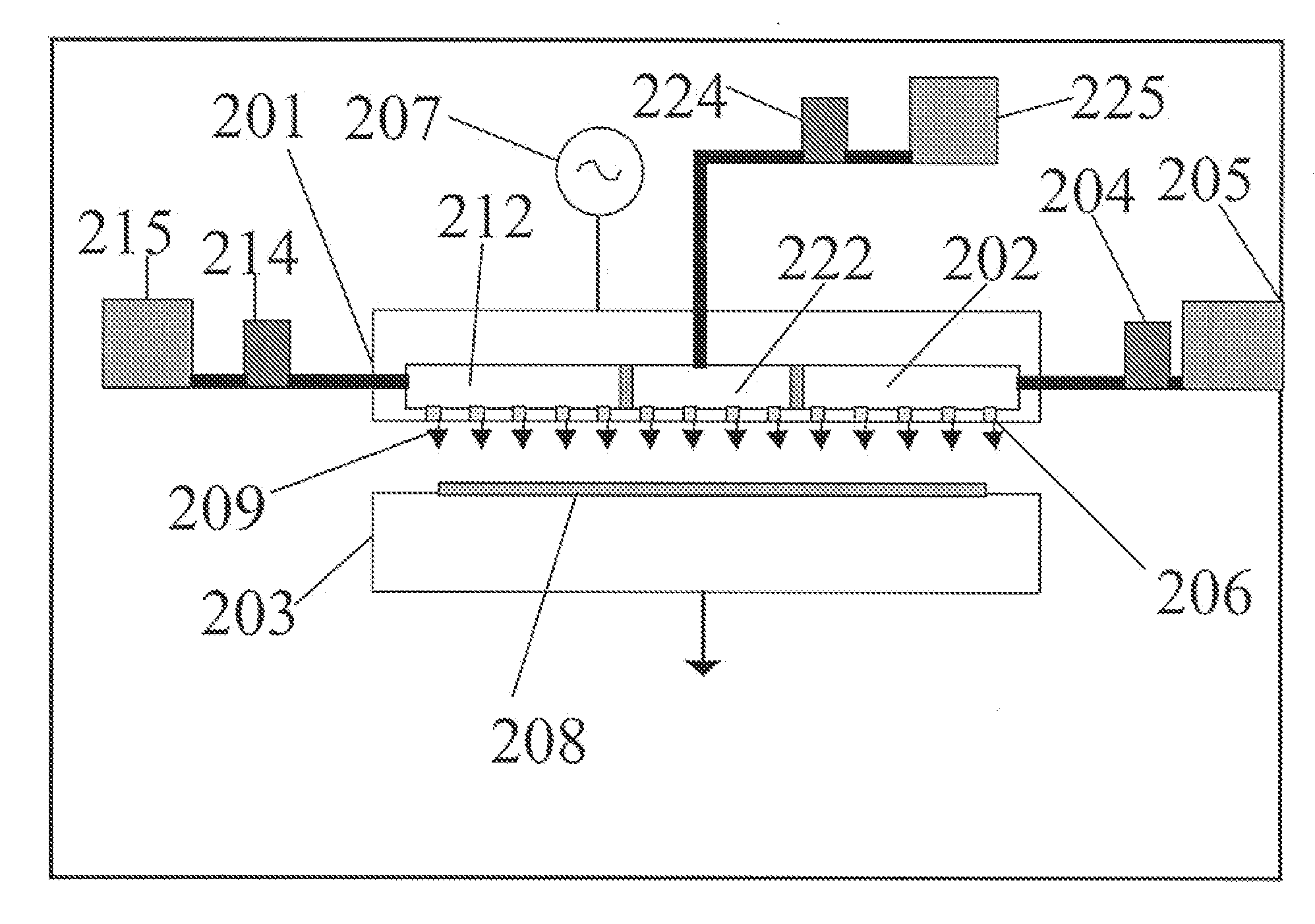

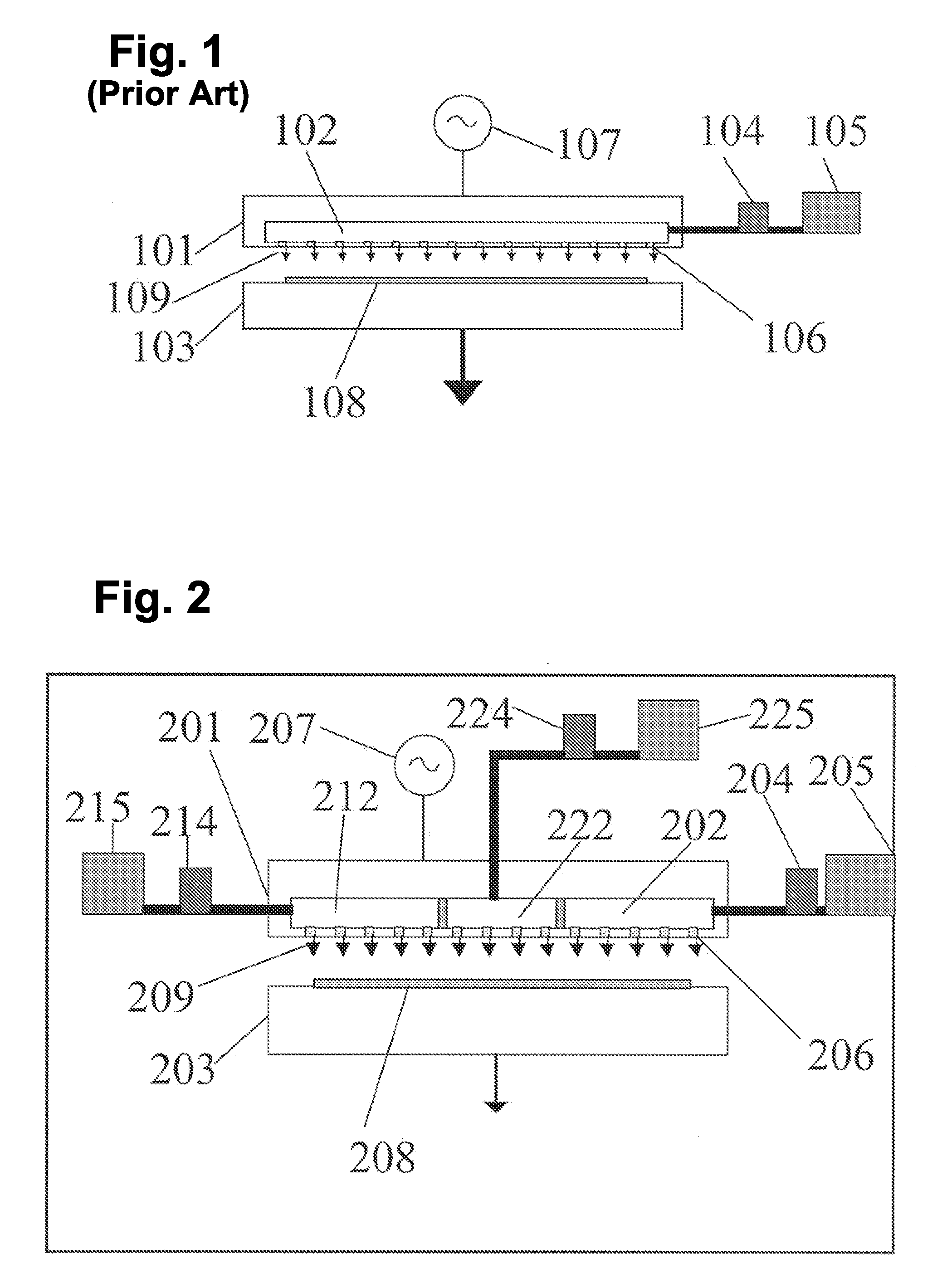

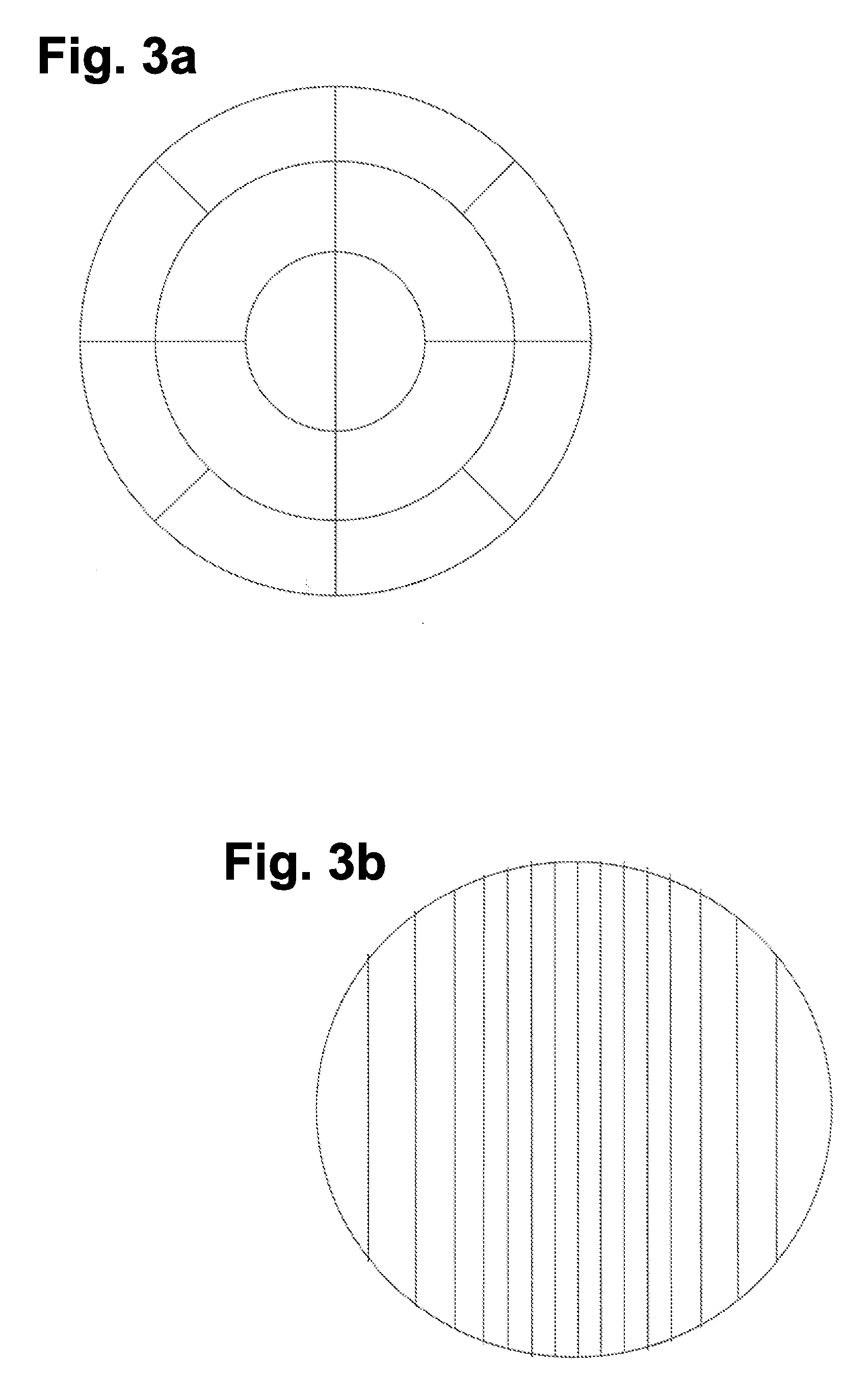

Apparatus and process for etching semiconductor wafers and the like in which a substrate is supported by a pedestal within a chamber, and at least one gas capable of etching the substrate or a film material on the substrate is introduced into the chamber through a segmented gas injection element which is separated from the substrate by a distance approximately less than its size from which the distribution of the flow or mixture of gas can be altered spatially proximate to the substrate in a controlled and variable way, for each wafer or substrate if desired, by having a varying amount or mixture of gas flow to some or all of the segments such as to cause the etching rate distribution to vary across the substrate.

Owner:ZAJAC JOHN +1

Replication and transfer of microstructures and nanostructures

InactiveUS6849558B2Facilitates pattern transferCheap to makeNanostructure manufactureDecorative surface effectsEngineeringMicroscopic scale

A method for the duplication of microscopic patterns from a master to a substrate is disclosed, in which a replica of a topographic structure on a master is formed and transferred when needed onto a receiving substrate using one of a variety of printing or imprint techniques, and then dissolved. Additional processing steps can also be carried out using the replica before transfer, including the formation of nanostructures, microdevices, or portions thereof. These structures are then also transferred onto the substrate when the replica is transferred, and remain on the substrate when the replica is dissolved. This is a technique that can be applied as a complementary process or a replacement for various lithographic processing steps in the fabrication of integrated circuits and other microdevices.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

Step and repeat imprint lithography systems

Described are systems for patterning a substrate by imprint lithography. Imprint lithography systems include an imprint head configured to hold a template in a spaced relation to a substrate. The imprint lithography system is configured to dispense an activating light curable liquid onto a substrate or template. The system includes a light source that applies activating light to cure the activating light curable liquid.

Owner:CANON KK

Composite patterning devices for soft lithography

ActiveUS20050238967A1High resolutionImprove placement accuracyMaterial nanotechnologyNanoinformaticsEngineeringThermal expansion

The present invention provides methods, devices and device components for fabricating patterns on substrate surfaces, particularly patterns comprising structures having microsized and / or nanosized features of selected lengths in one, two or three dimensions. The present invention provides composite patterning devices comprising a plurality of polymer layers each having selected mechanical properties, such as Young's Modulus and flexural rigidity, selected physical dimensions, such as thickness, surface area and relief pattern dimensions, and selected thermal properties, such as coefficients of thermal expansion, to provide high resolution patterning on a variety of substrate surfaces and surface morphologies.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

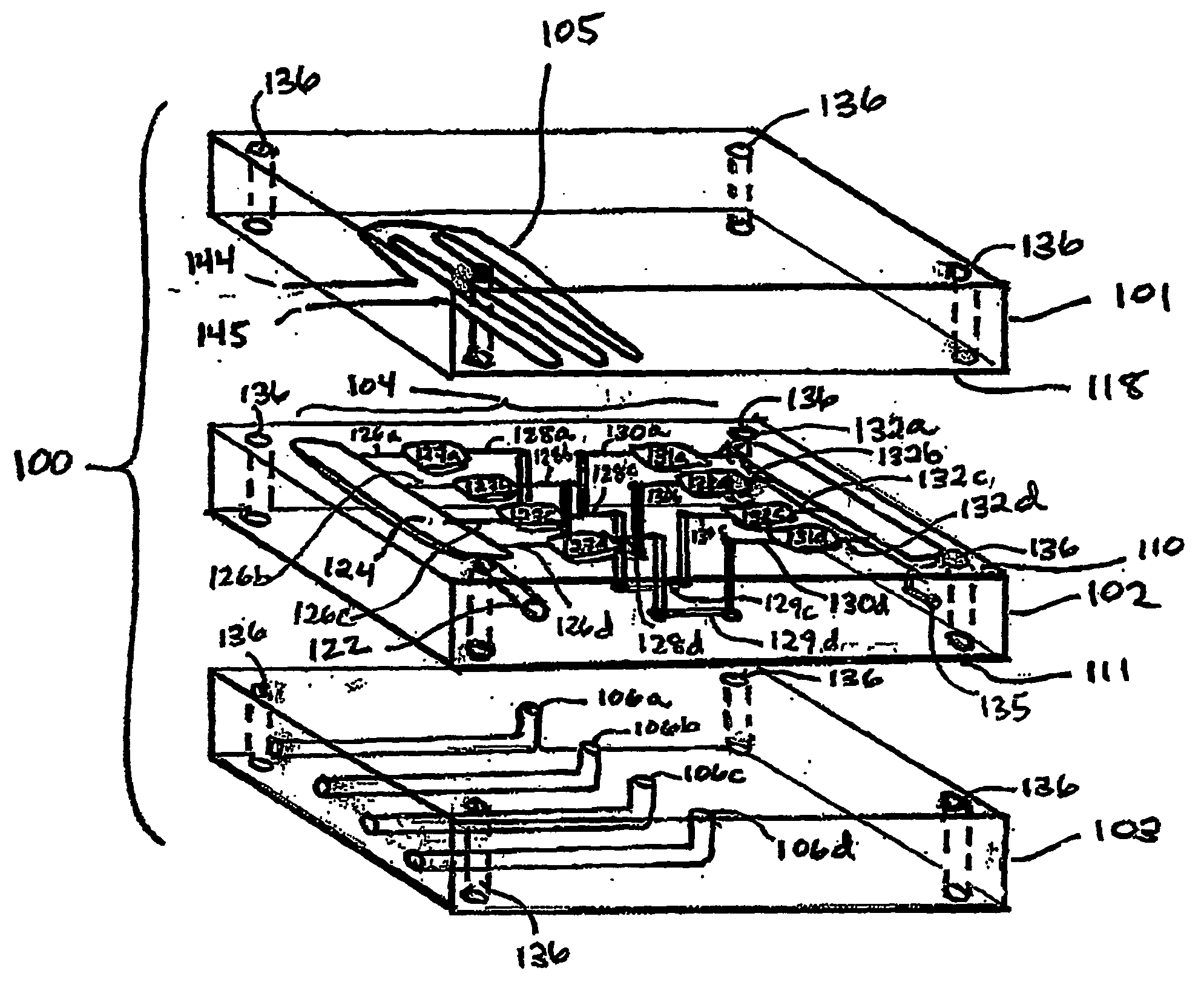

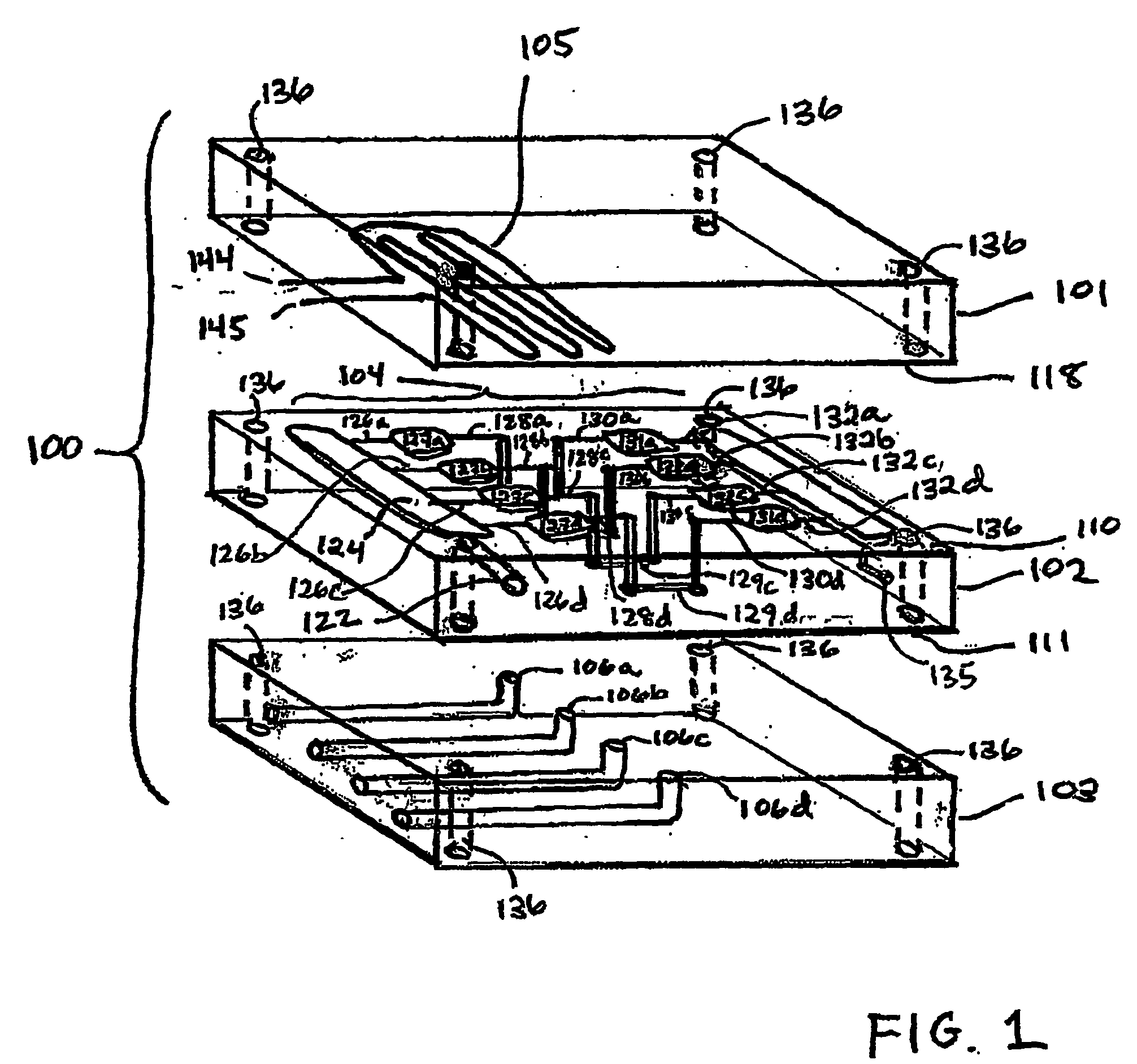

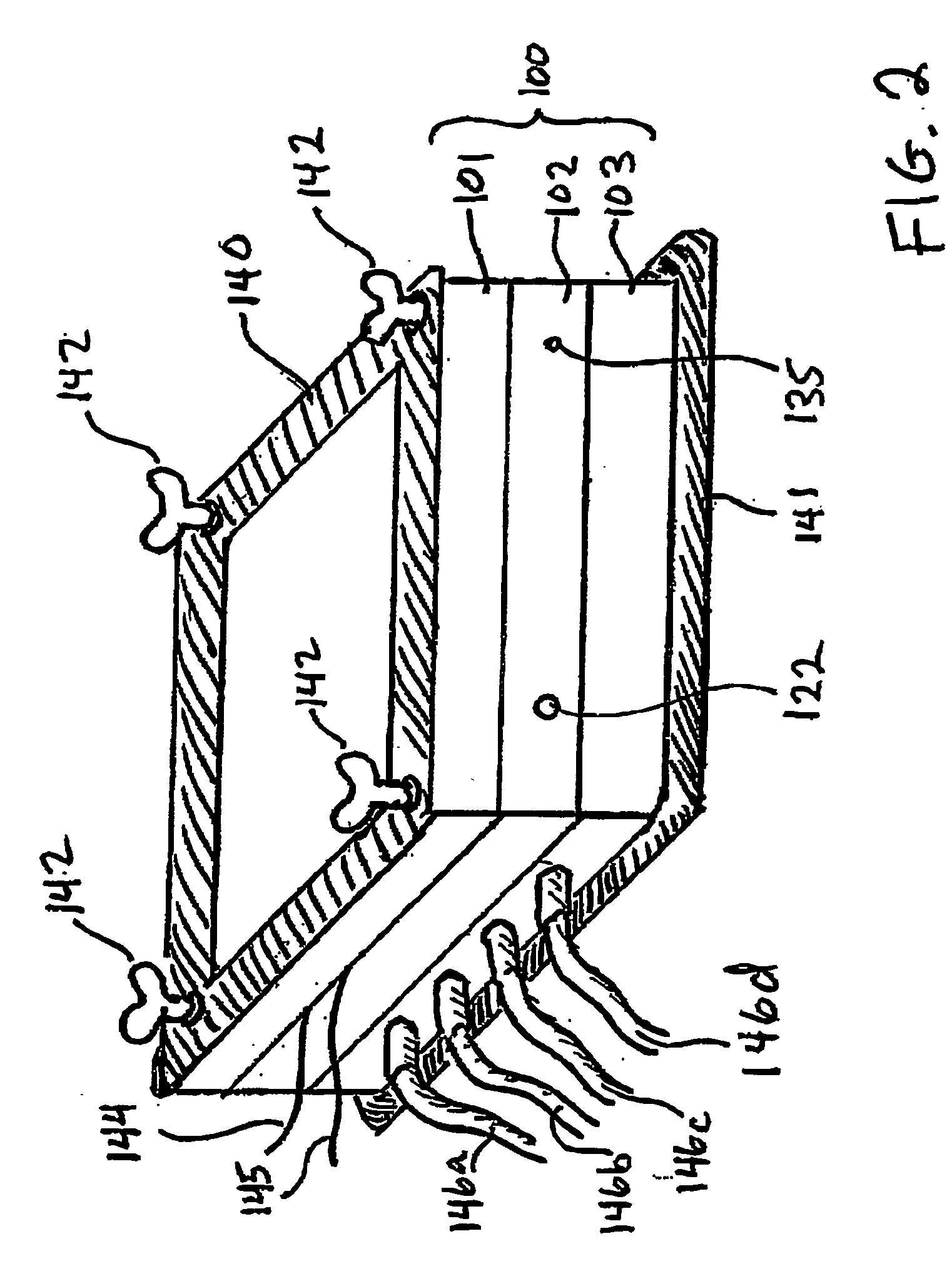

Three-dimensional microfluidics incorporating passive fluid control structures

InactiveUS20040109793A1Simple and effective and versatile controlShaking/oscillating/vibrating mixersHeating or cooling apparatusFluid controlMicrofluidics

A three-dimensional microfluidic device (100) formed from a plurality of substantially planar layers (101, 102, 103) sealed together is disclosed

Owner:BIOMICRO SYST

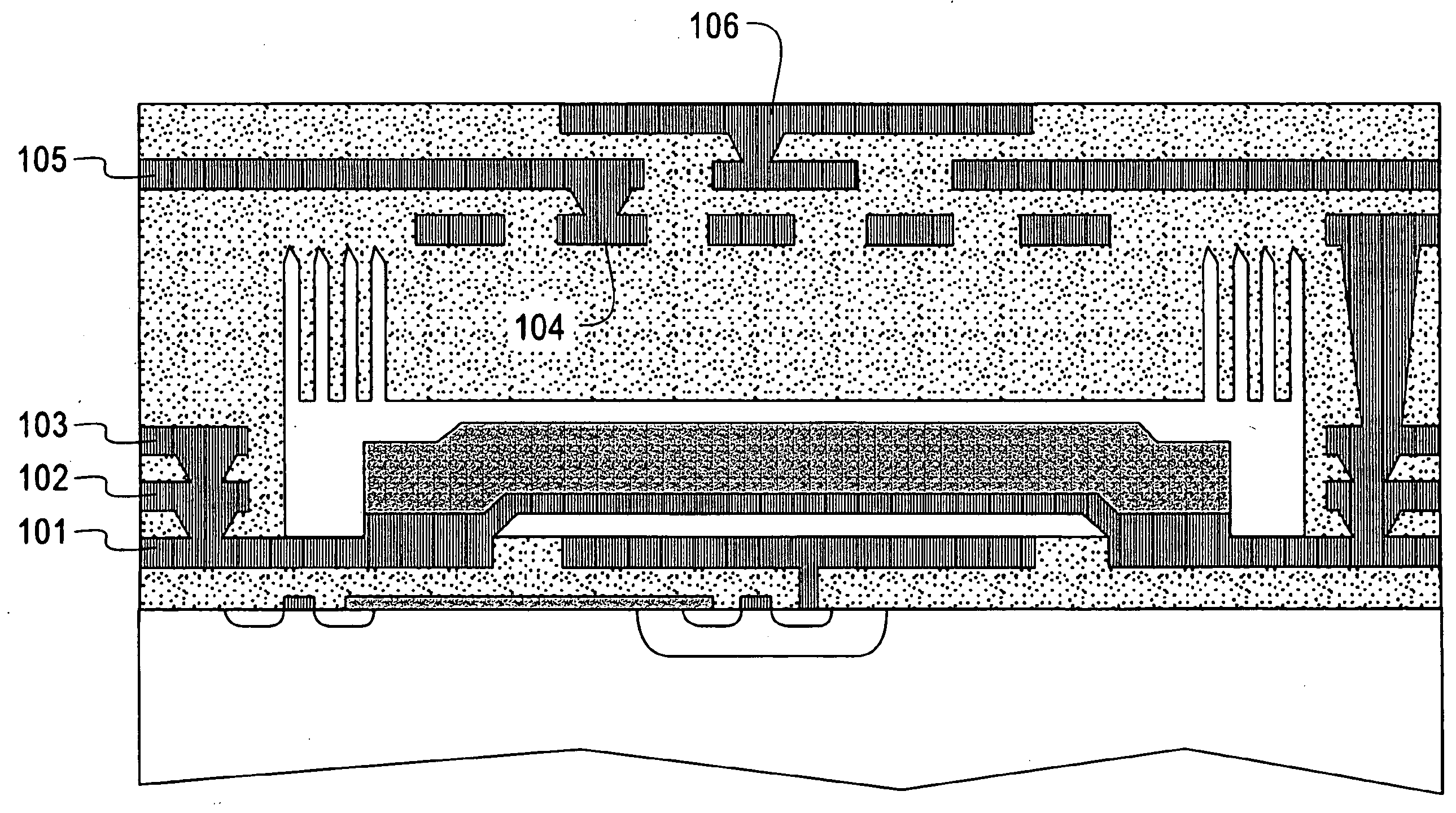

Manufacture of MEMS structures in sealed cavity using dry-release MEMS device encapsulation

InactiveUS7008812B1Eliminates undesirable liquid surface tensionIncrease etch rateAcceleration measurement using interia forcesSolid-state devicesMaterials sciencePlasma etching

The disclosed fabrication methodology addresses the problem of creating low-cost micro-electro-mechanical devices and systems, and, in particular, addresses the problem of delicate microstructures being damaged by the surface tension created as a wet etchant evaporates. This disclosure demonstrates a method for employing a dry plasma etch process to release encapsulated microelectromechanical components.

Owner:CYMATICS LAB CORP

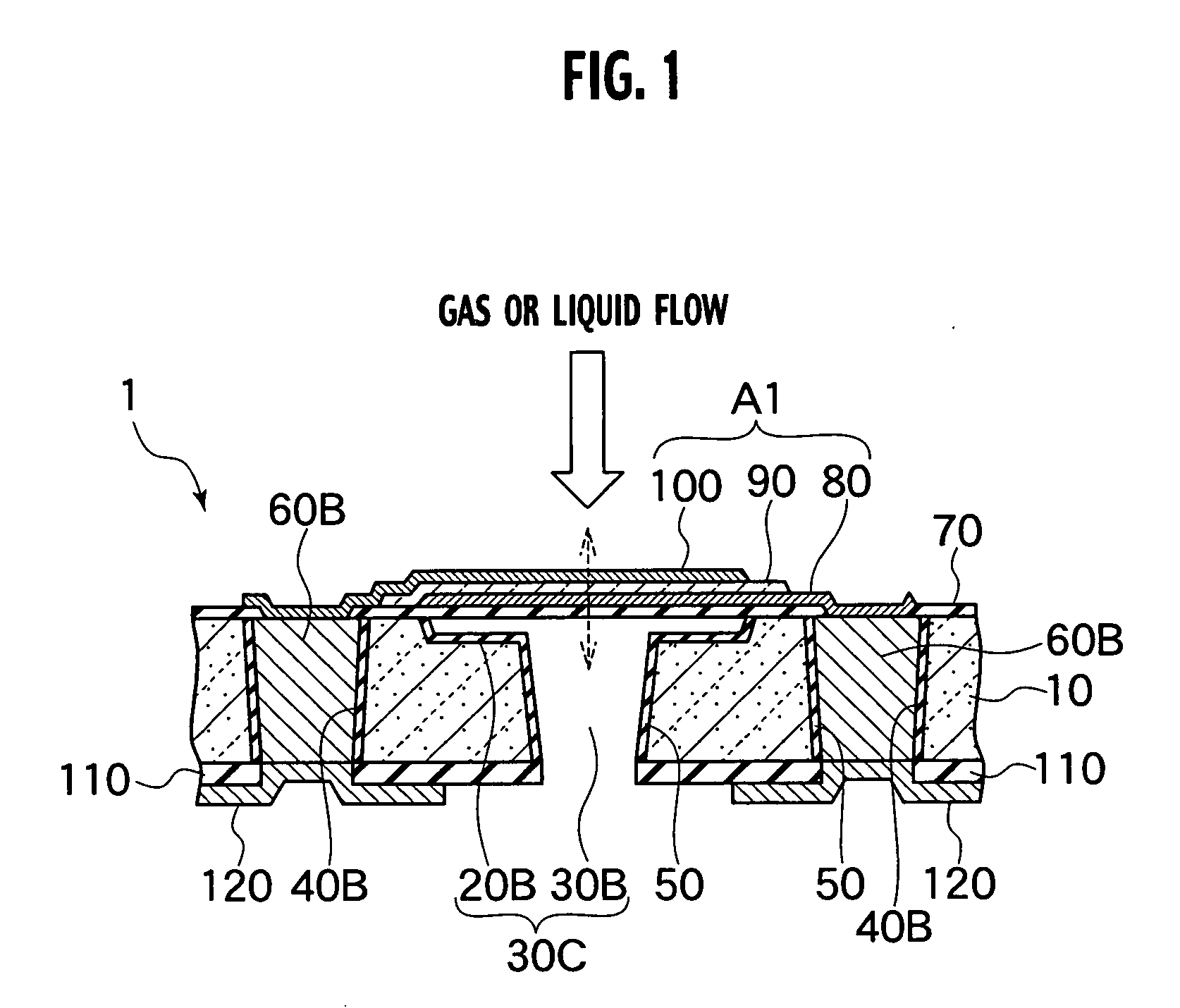

Electronic component having micro-electrical mechanical system

ActiveUS20050218488A1Thermoelectric device with dielectric constant thermal changeAcceleration measurement using interia forcesElectricityEngineering

An electronic component includes a semiconductor substrate having a first surface and a second surface opposite to the first surface, a cavity that penetrates from the first surface to the second surface of the semiconductor substrate, and an electrical mechanical element that has a movable portion formed above the first surface of the semiconductor substrate so that the movable portion is arranged above the cavity. The electronic component further includes an electric conduction plug, which penetrates from the first surface to the second surface of the semiconductor substrate, and which is electrically connected to the electrical mechanical element.

Owner:KIOXIA CORP

A Stretchable Form of Single Crystal Silicon for High Performance Electronics on Rubber Substrates

ActiveUS20060286785A1Large elongationSignificant flexingTransistorCircuit bendability/stretchabilityEngineeringFlexible electronics

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

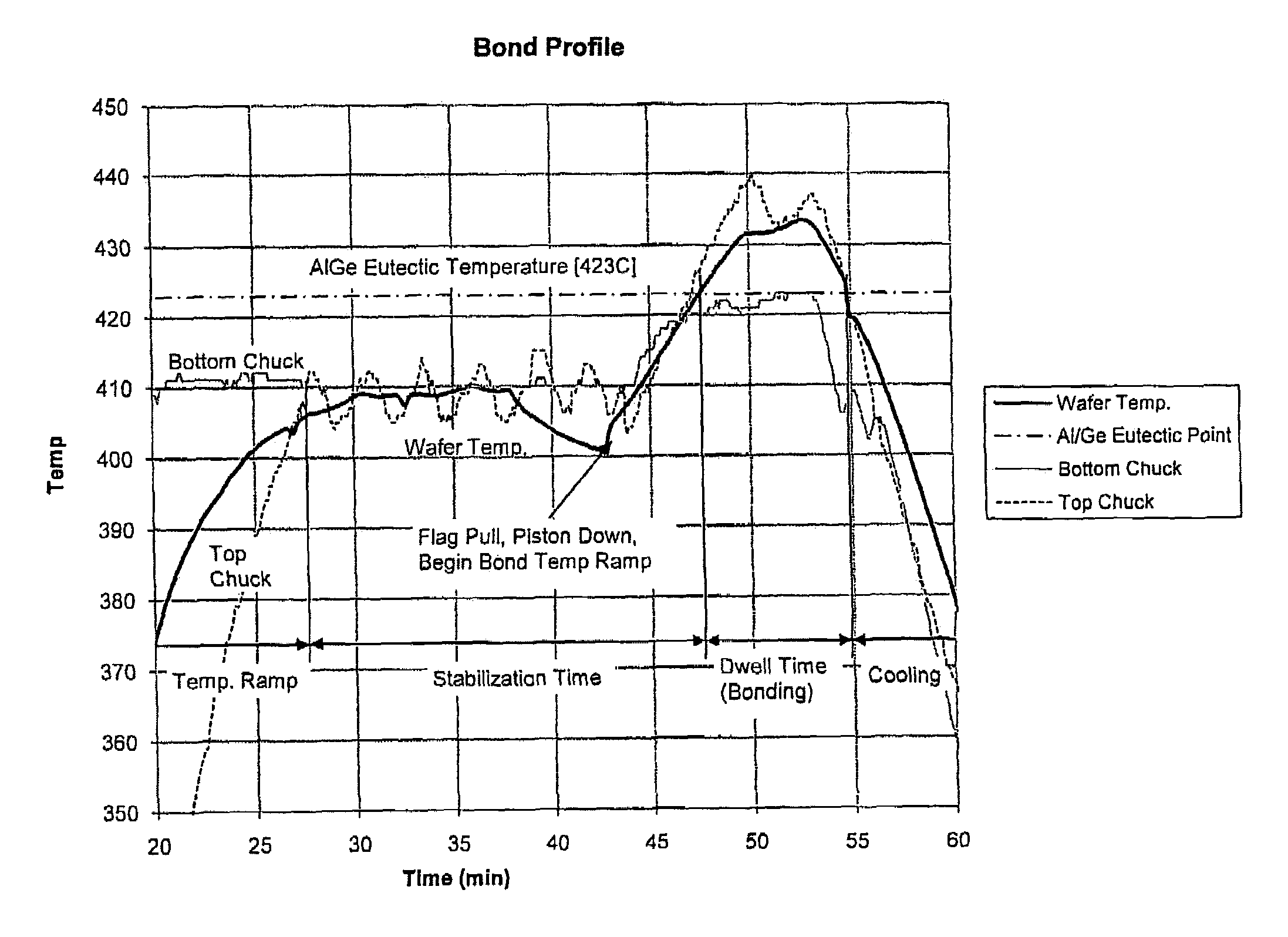

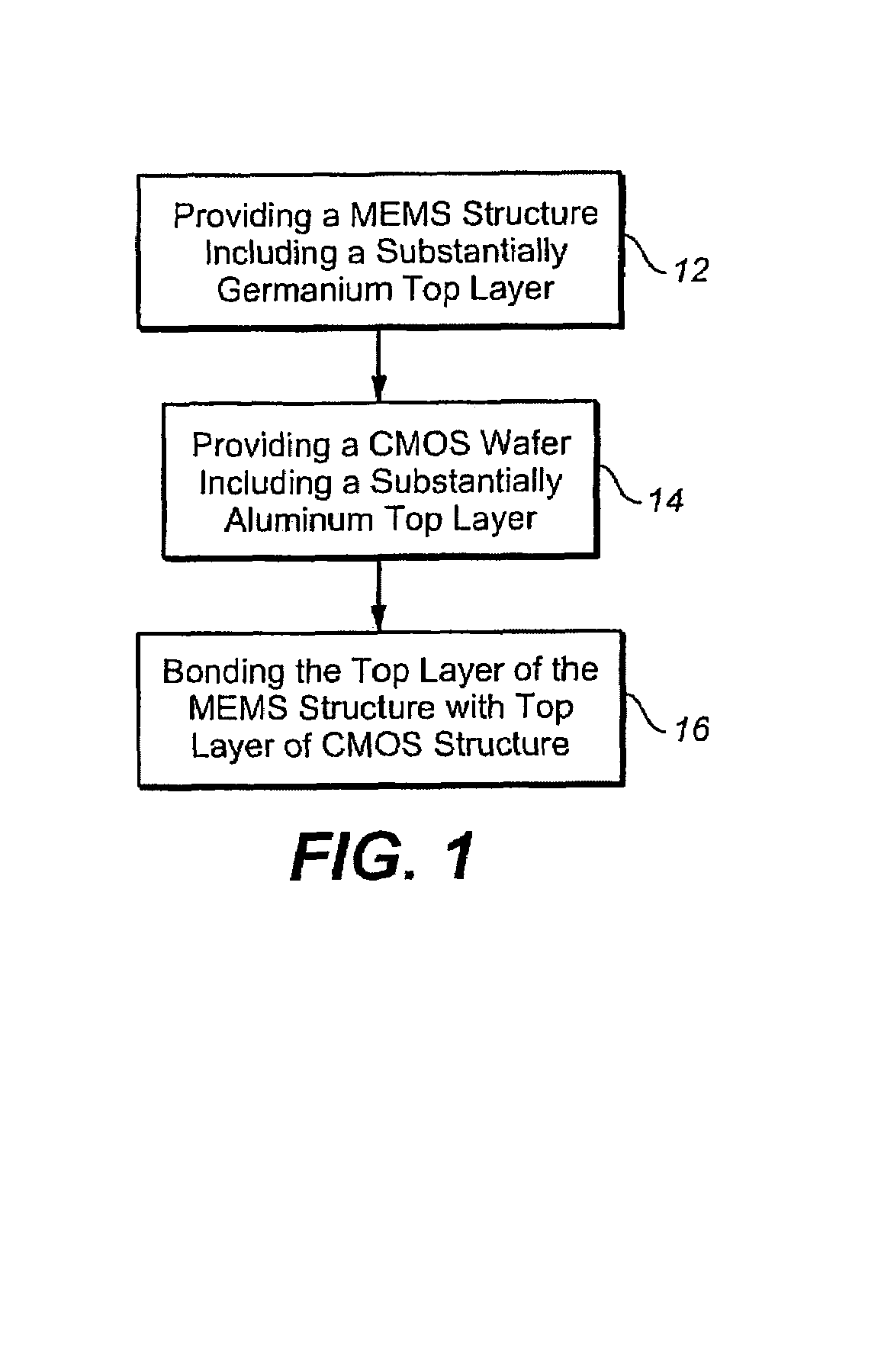

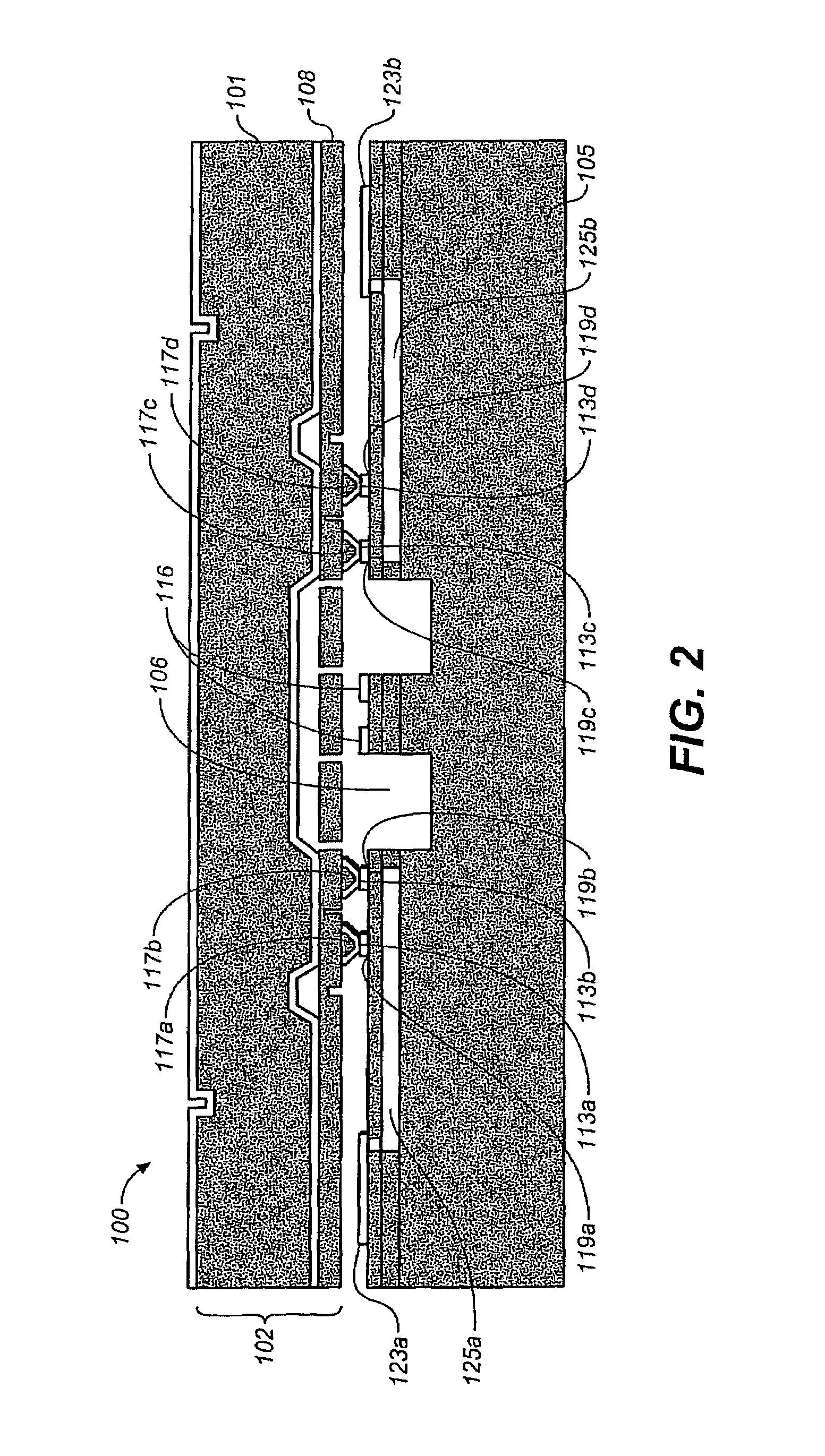

Method of fabrication of a AL/GE bonding in a wafer packaging environment and a product produced therefrom

ActiveUS7442570B2Robust and mechanical contactHighly controllableAcceleration measurement using interia forcesSemiconductor/solid-state device detailsFoundryHermetic seal

A method of bonding of germanium to aluminum between two substrates to create a robust electrical and mechanical contact is disclosed. An aluminum-germanium bond has the following unique combination of attributes: (1) it can form a hermetic seal; (2) it can be used to create an electrically conductive path between two substrates; (3) it can be patterned so that this conduction path is localized; (4) the bond can be made with the aluminum that is available as standard foundry CMOS process. This has the significant advantage of allowing for wafer-level bonding or packaging without the addition of any additional process layers to the CMOS wafer.

Owner:INVENSENSE

Low temperature bi-CMOS compatible process for MEMS RF resonators and filters

InactiveUS20090108381A1Impedence networksSemiconductor/solid-state device detailsMetal interconnectOxygen plasma

A method of formation of a microelectromechanical system (MEMS) resonator or filter which is compatible with integration with any analog, digital, or mixed-signal integrated circuit (IC) process, after or concurrently with the formation of the metal interconnect layers in those processes, by virtue of its materials of composition, processing steps, and temperature of fabrication is presented. The MEMS resonator or filter incorporates a lower metal level, which forms the electrodes of the MEMS resonator or filter, that may be shared with any or none of the existing metal interconnect levels on the IC. It further incorporates a resonating member that is comprised of at least one metal layer for electrical connection and electrostatic actuation, and at least one dielectric layer for structural purposes. The gap between the electrodes and the resonating member is created by the deposition and subsequent removal of a sacrificial layer comprised of a carbon-based material. The method of removal of the sacrificial material is by an oxygen plasma or an anneal in an oxygen containing ambient. A method of vacuum encapsulation of the MEMS resonator or filter is provided through means of a cavity containing the MEMS device, filled with additional sacrificial material, and sealed. Access vias are created through the membrane sealing the cavity; the sacrificial material is removed as stated previously, and the vias are re-sealed in a vacuum coating process.

Owner:IBM CORP