Patents

Literature

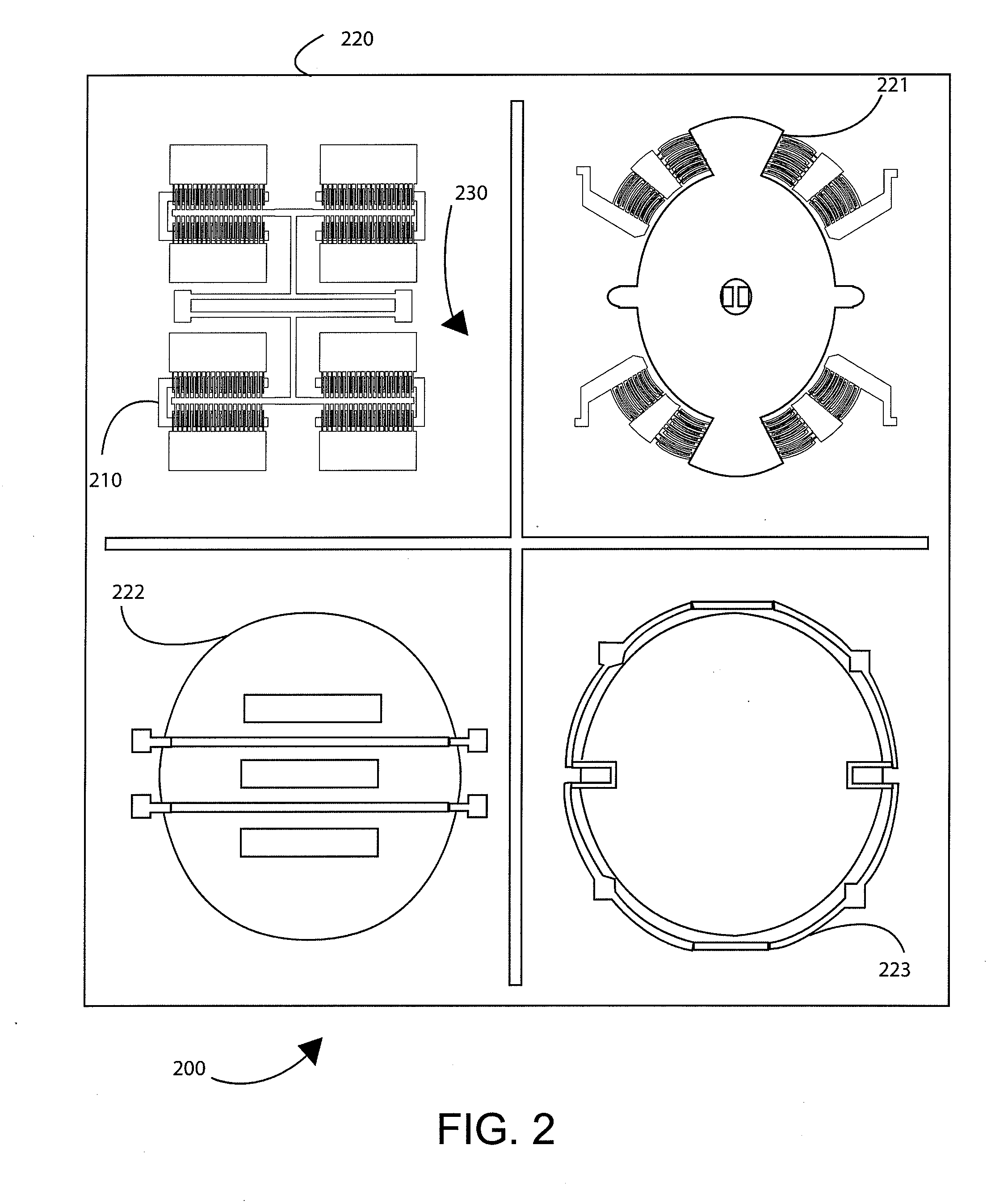

62 results about "Cmos mems" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

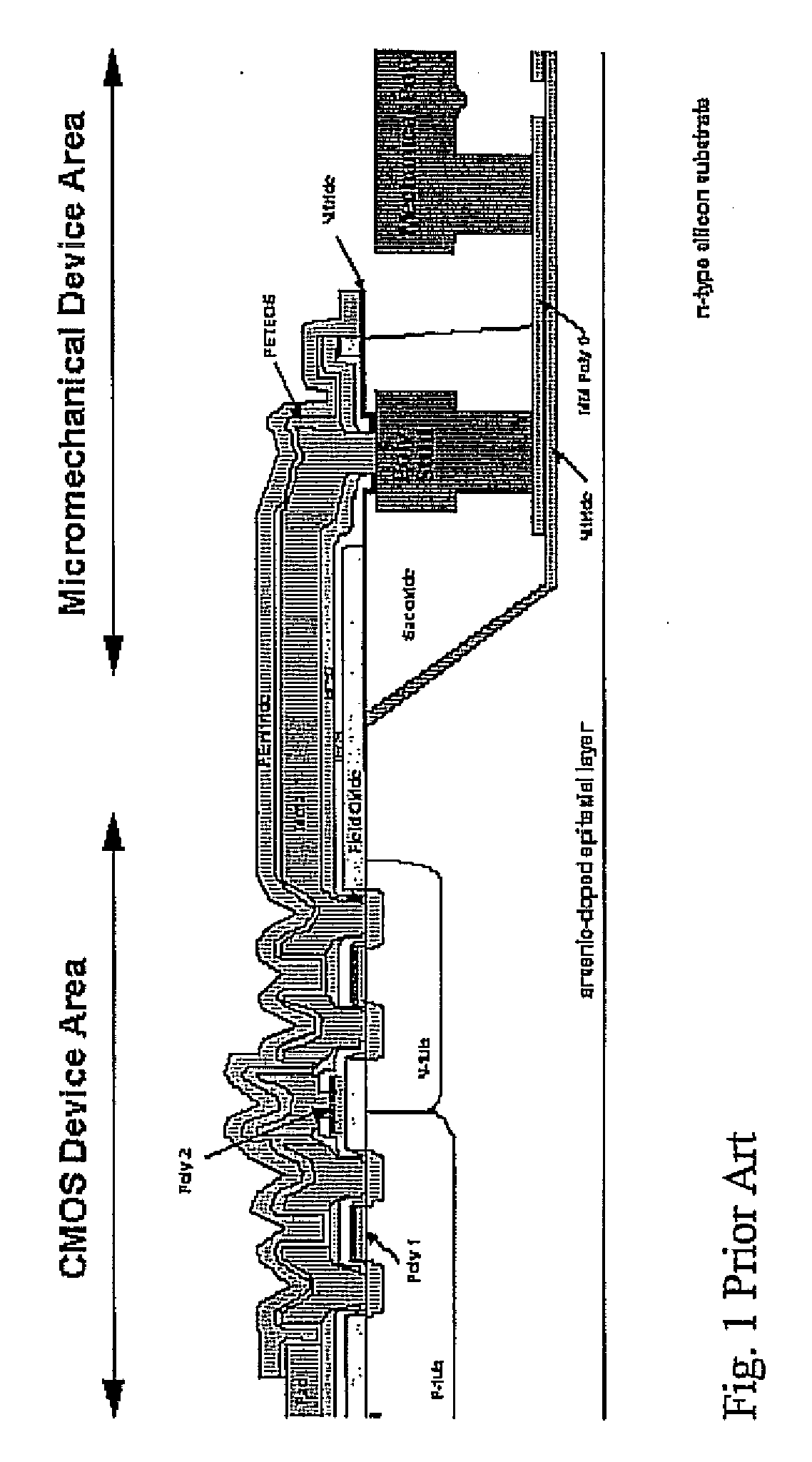

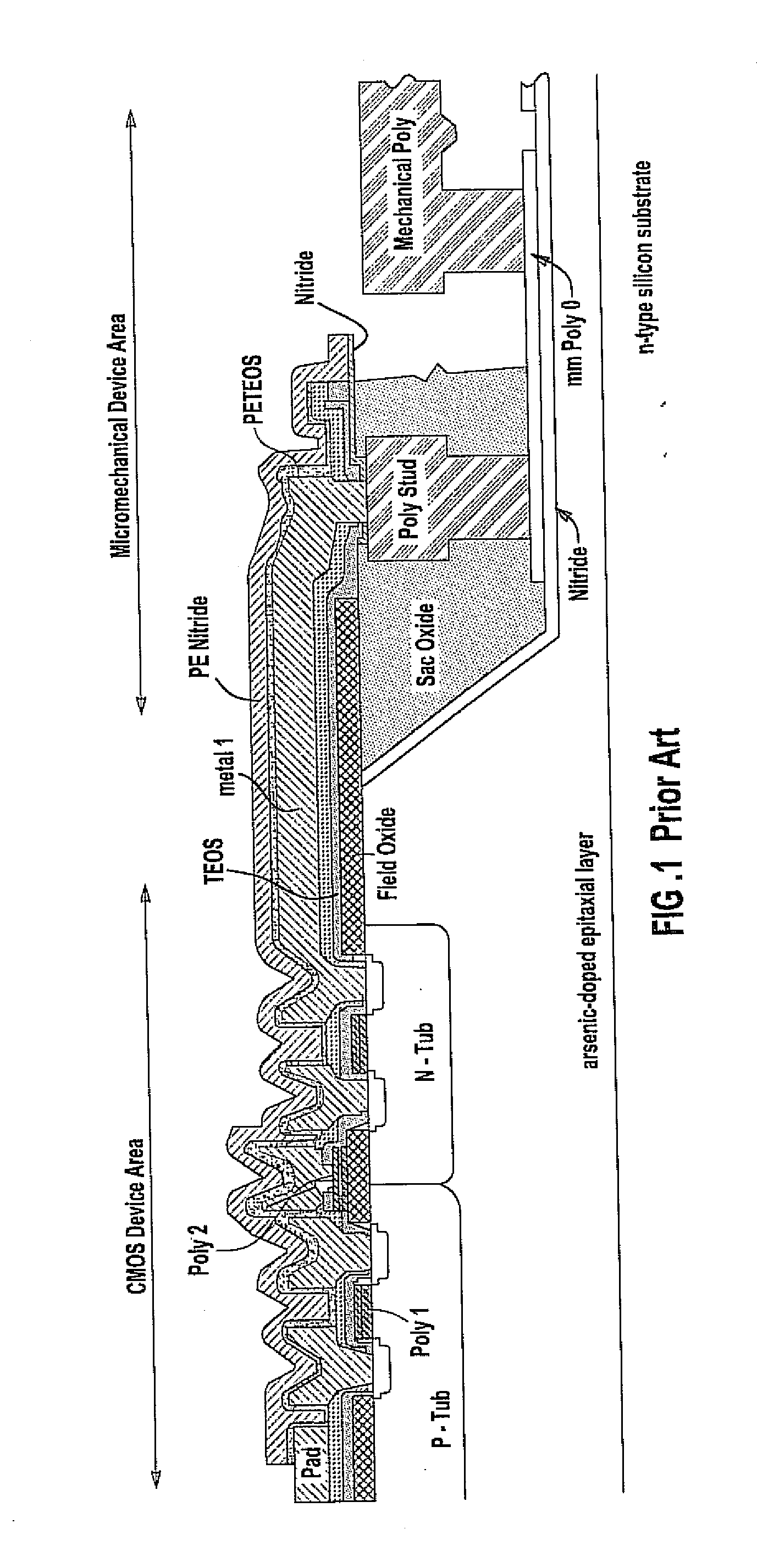

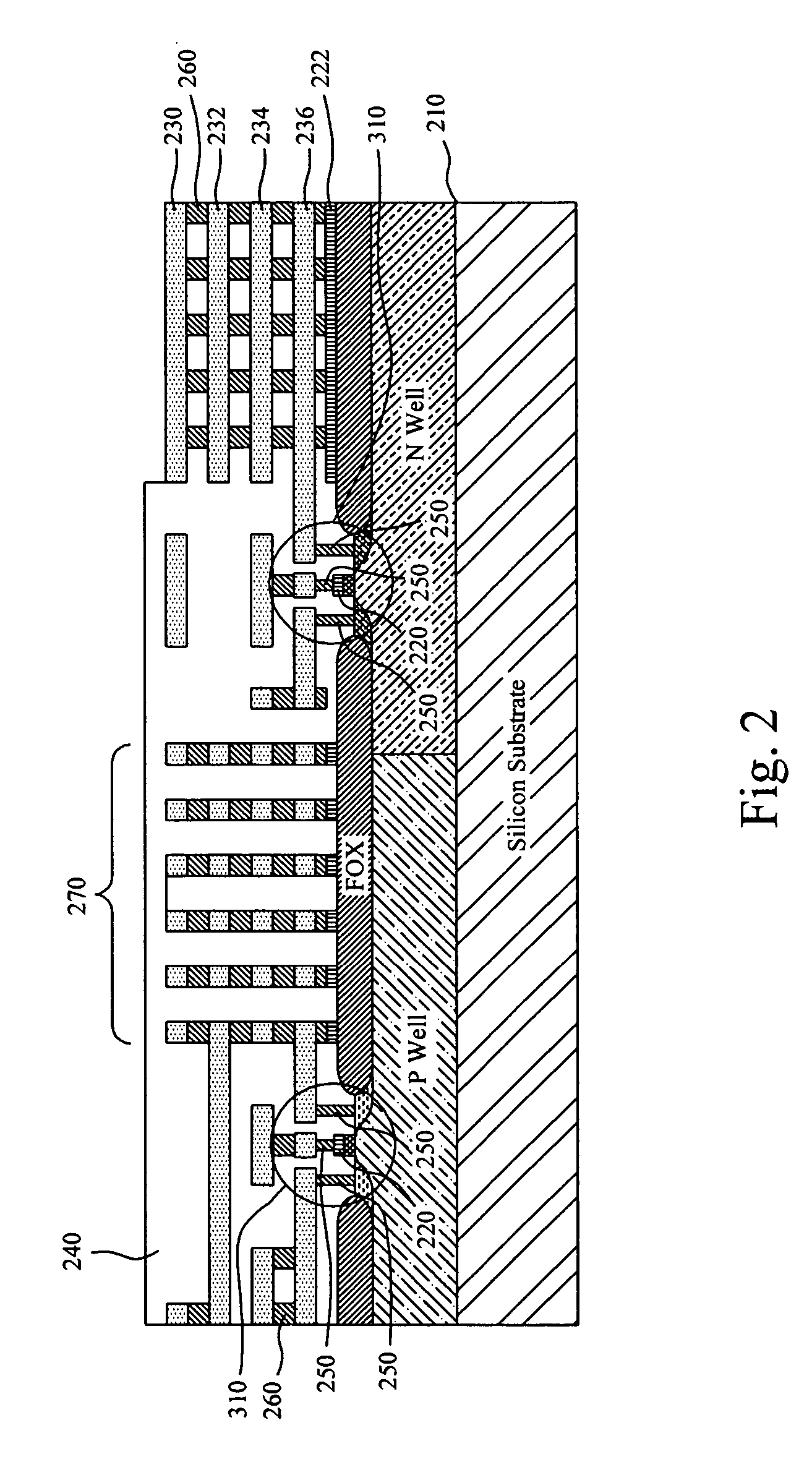

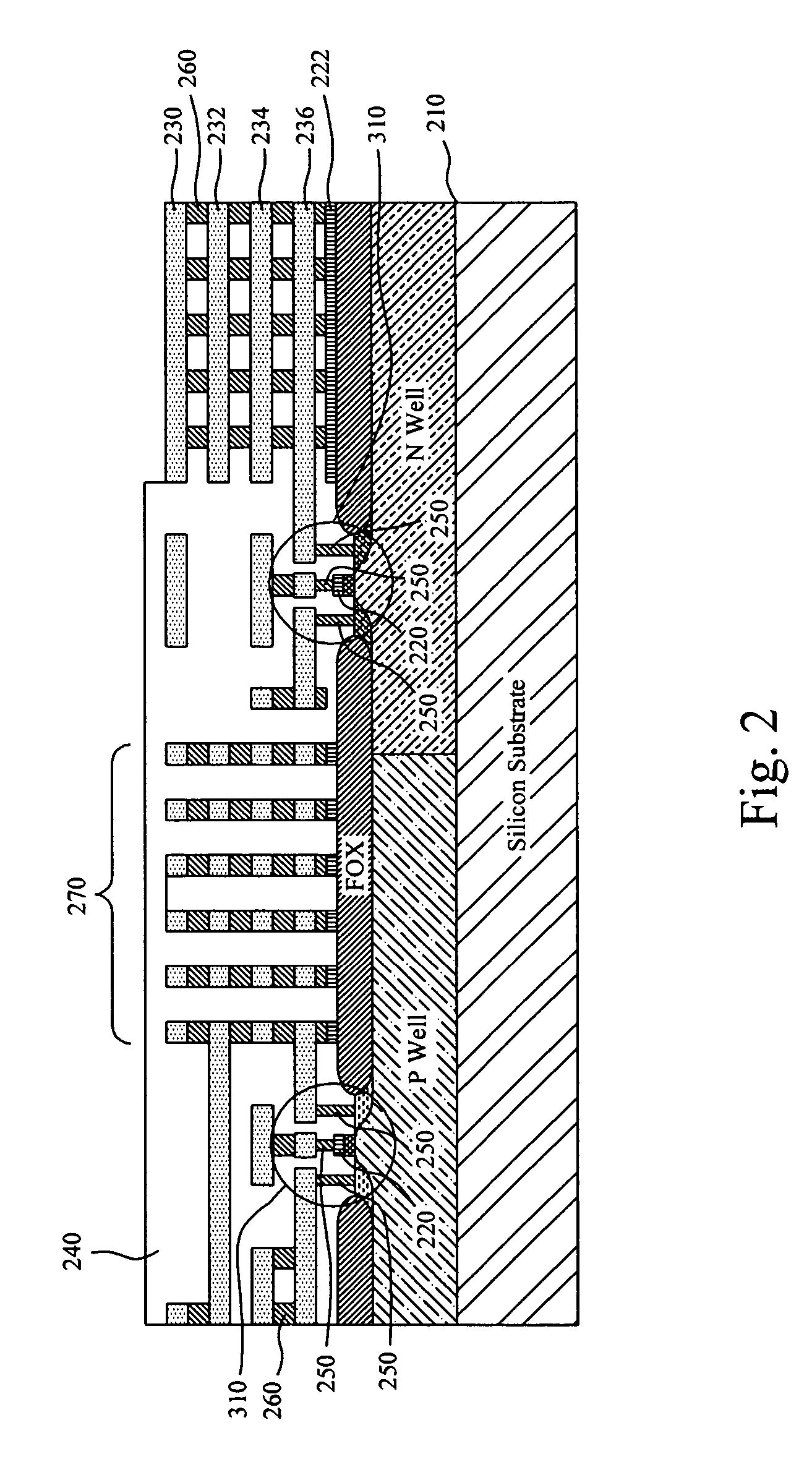

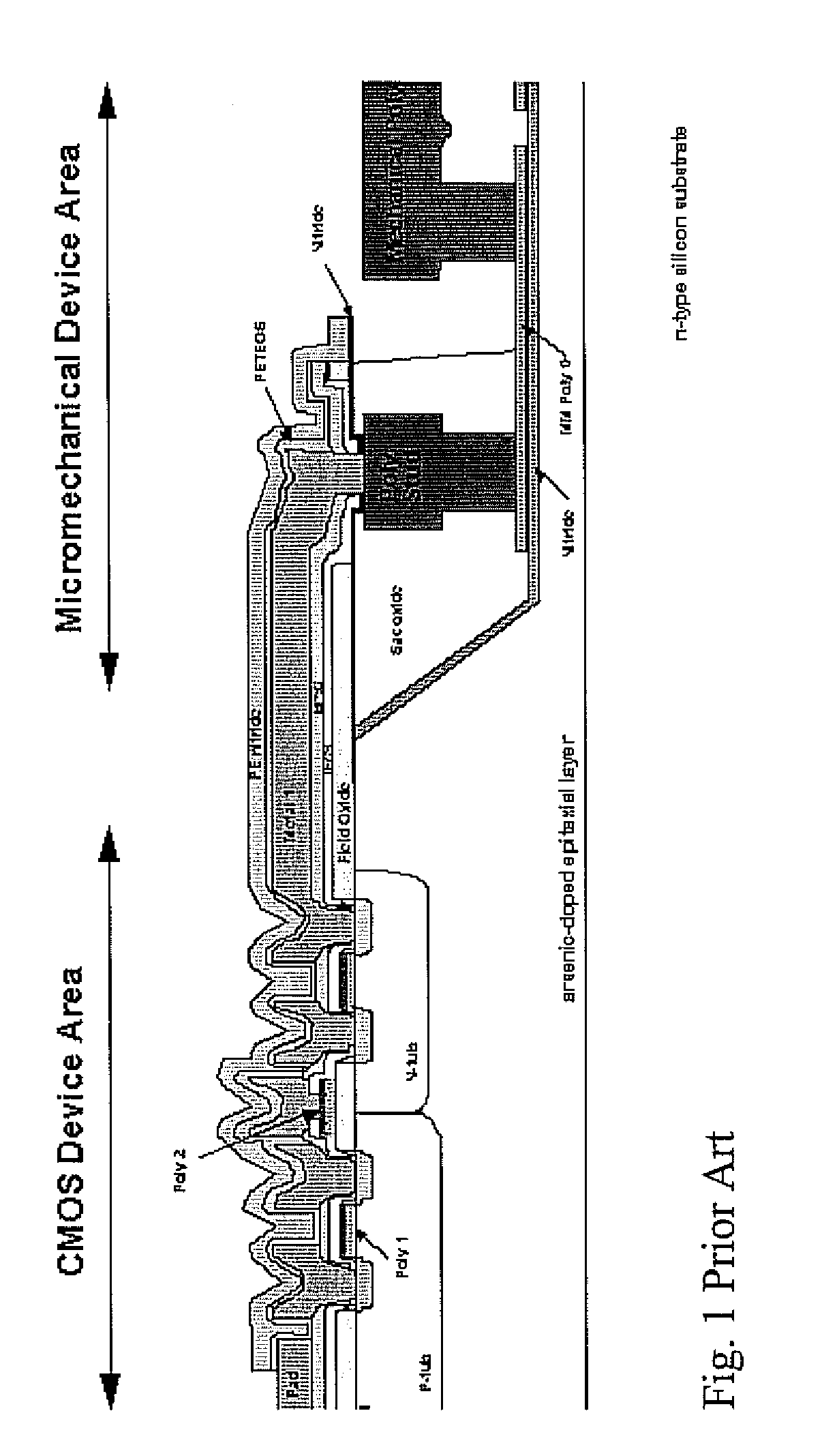

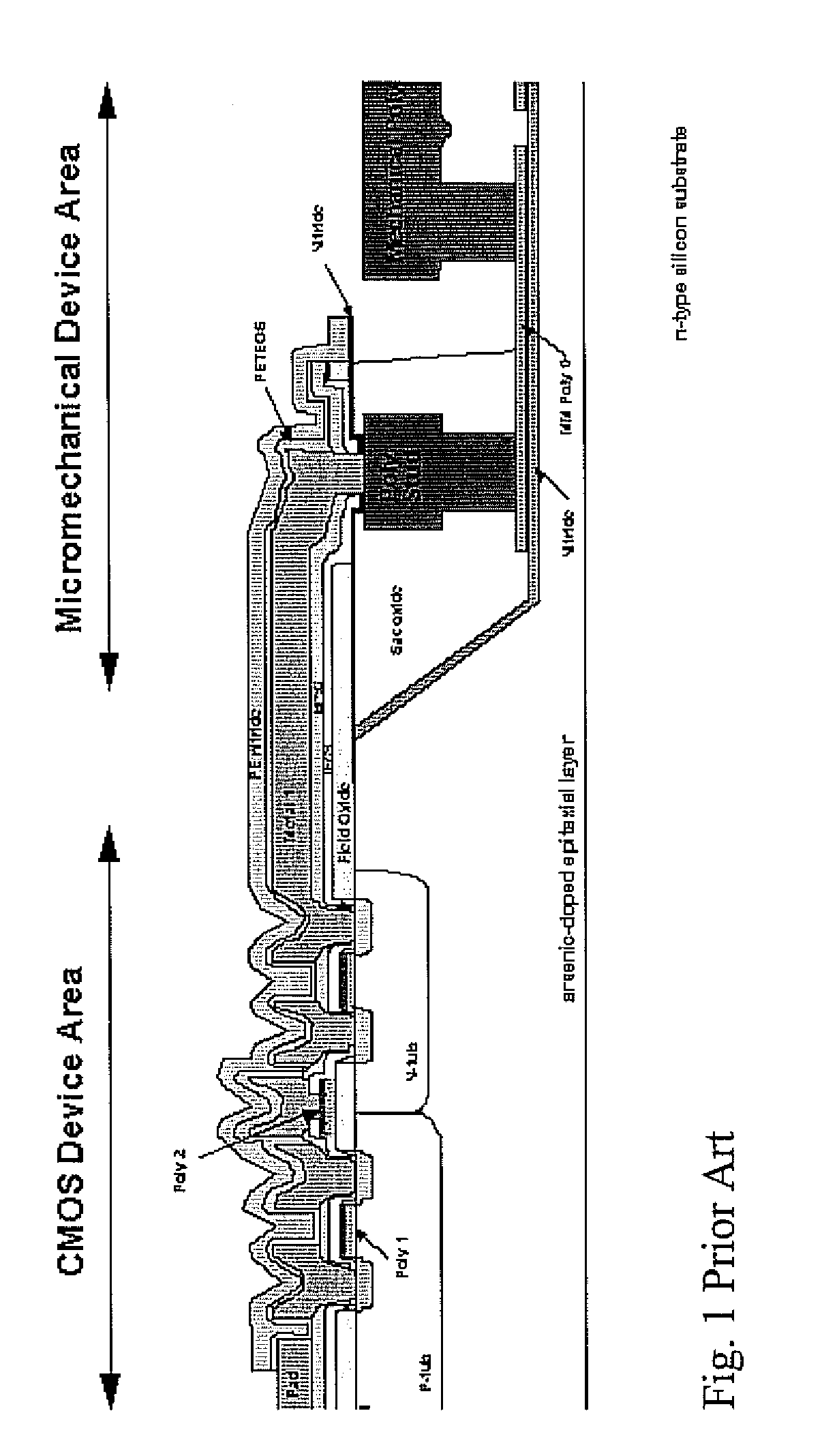

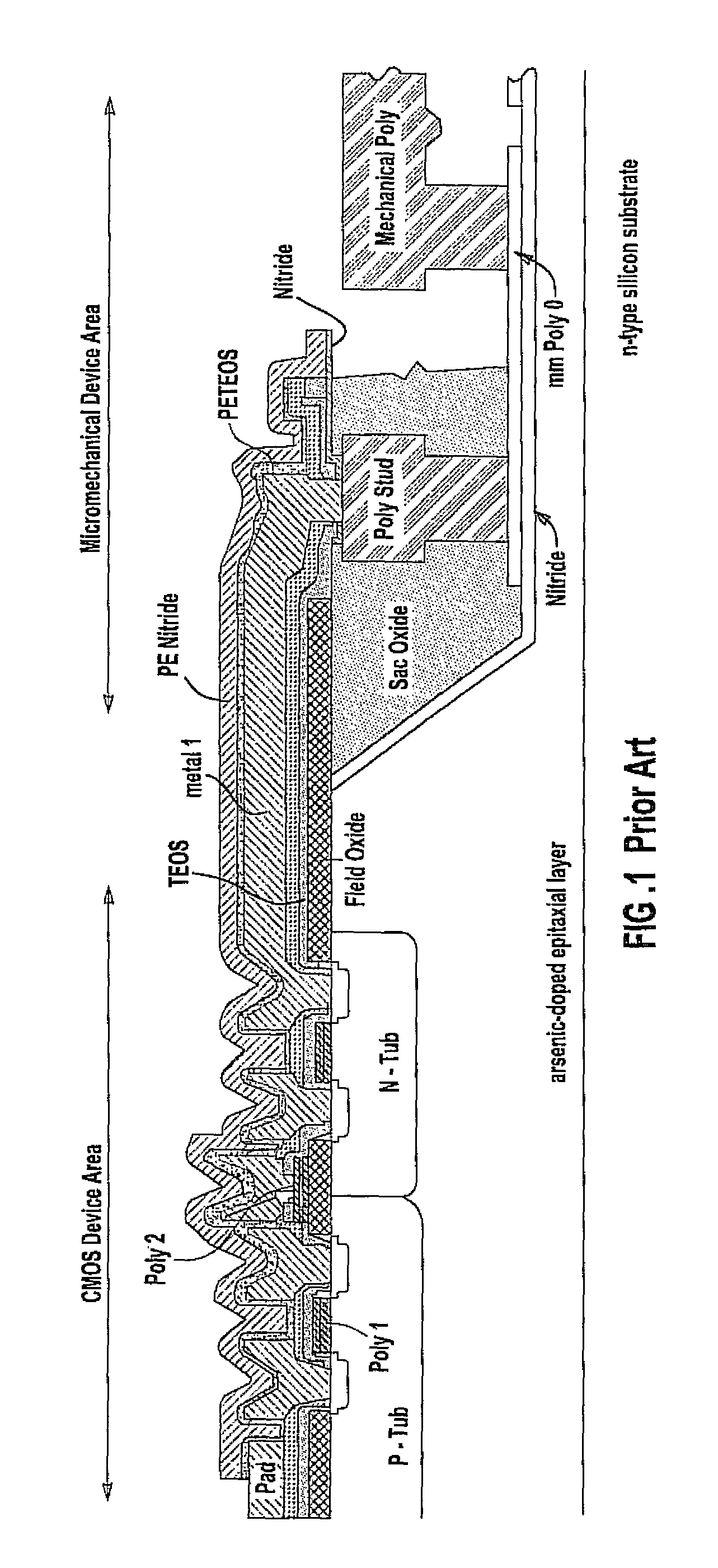

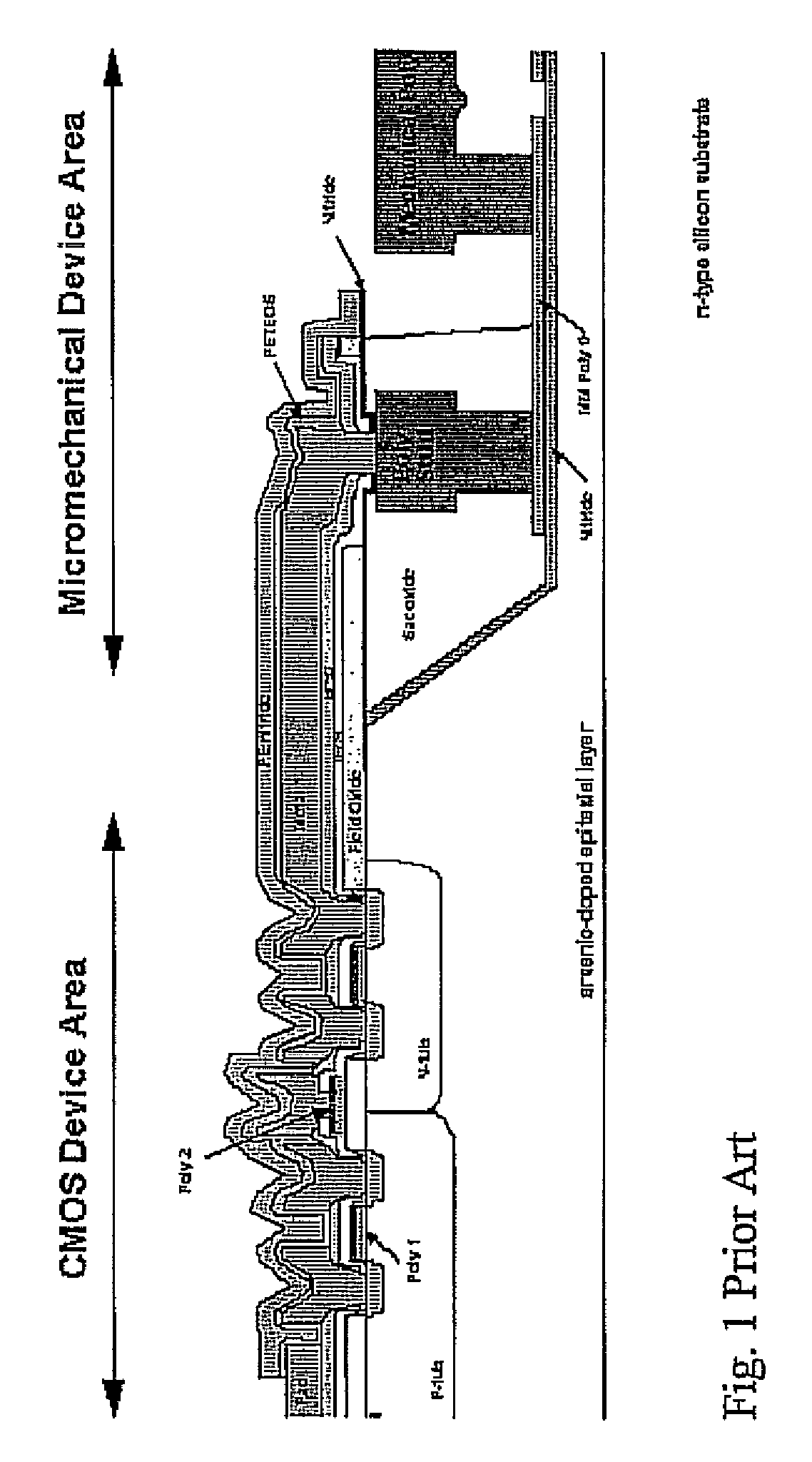

Fundamentally, CMOS MEMS is CMOS. The metal dielectric layers that comprise the mechanical MEMS structures are the same layers that form the electronic circuits. These circuits are integrated with the MEMS structures and are typically located only tens of microns from the MEMS structures.

Methods for cmos-mems integrated devices with multiple sealed cavities maintained at various pressures

ActiveUS20120326248A1Good flexibilitySemiconductor/solid-state device manufacturingForming microstructural systemsCmos memsWafer bonding

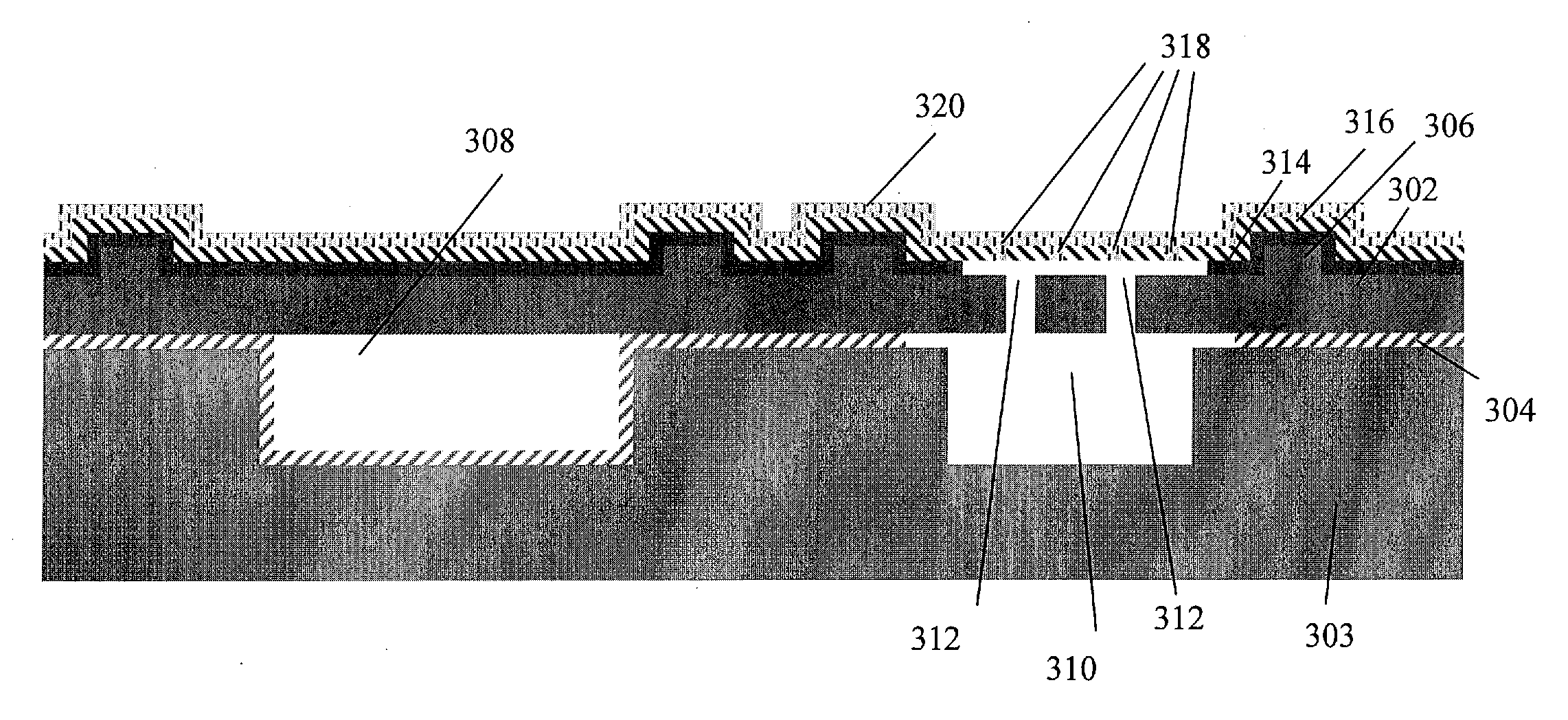

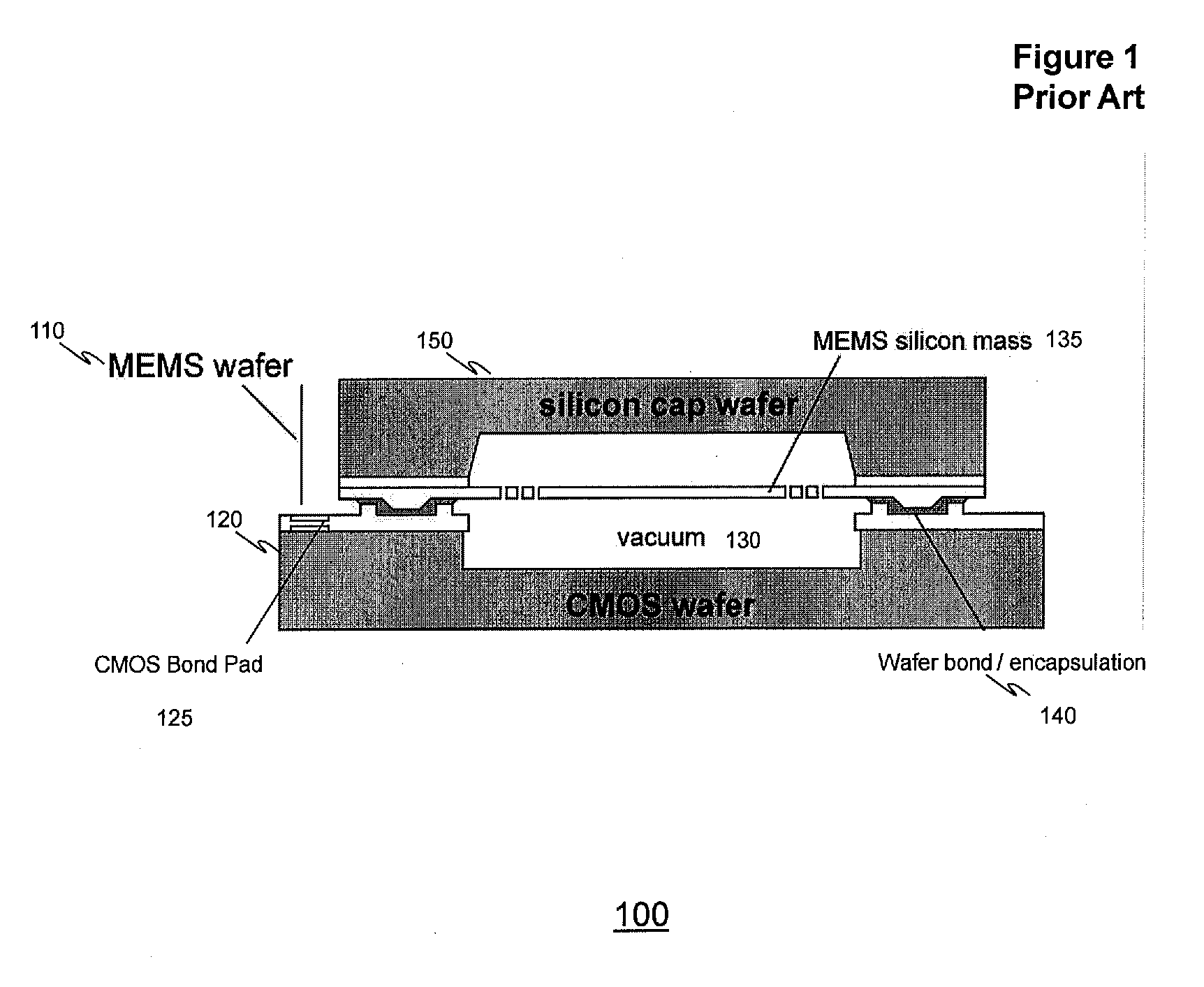

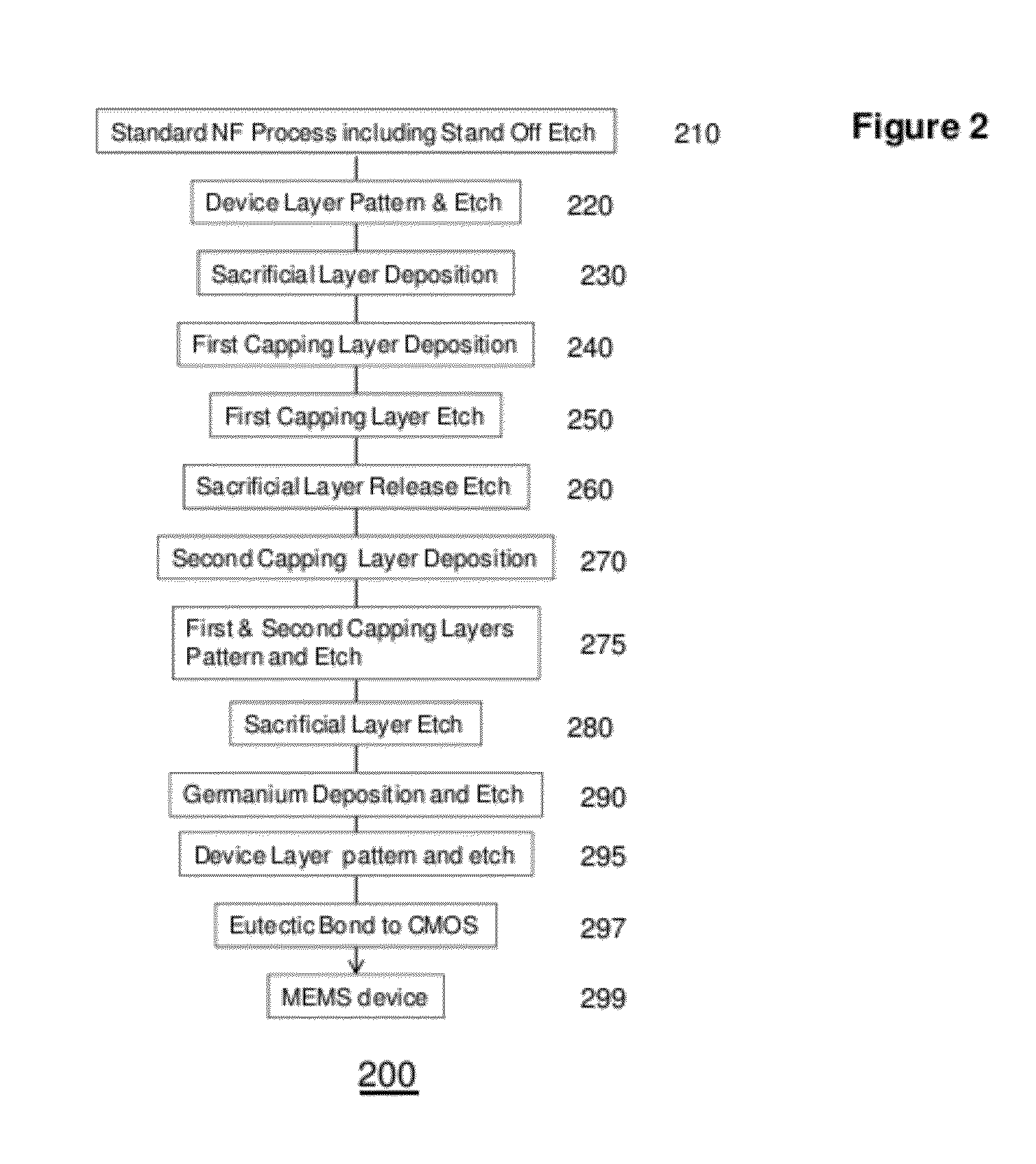

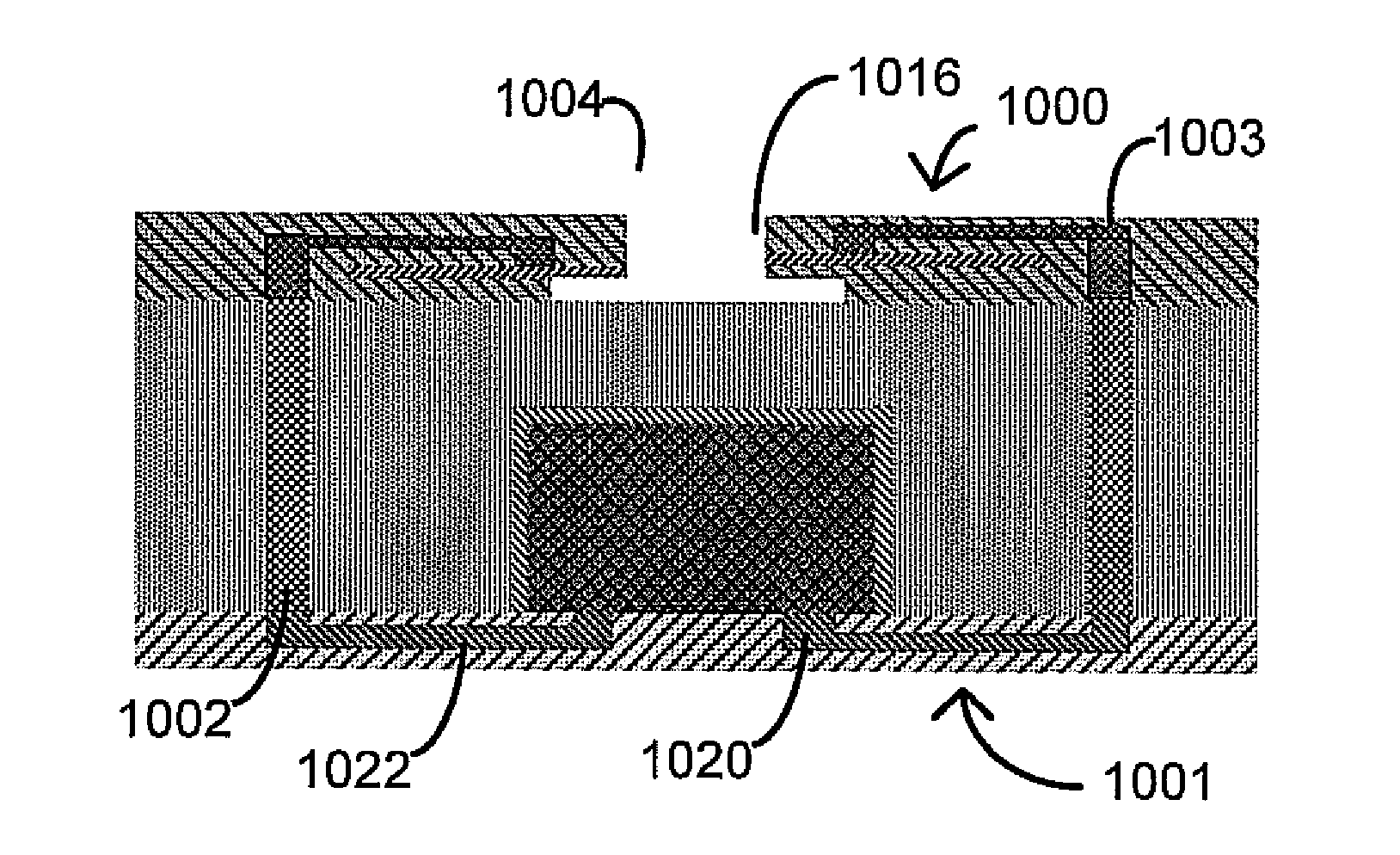

A Microelectromechanical systems (MEMS) structure comprises a MEMS wafer. A MEMS wafer includes a handle wafer with cavities bonded to a device wafer through a dielectric layer disposed between the handle and device wafers. The MEMS wafer also includes a moveable portion of the device wafer suspended over a cavity in the handle wafer. Four methods are described to create two or more enclosures having multiple gas pressure or compositions on a single substrate including, each enclosure containing a moveable portion. The methods include: A. Forming a secondary sealed enclosure, B. Creating multiple ambient enclosures during wafer bonding, C. Creating and breaching an internal gas reservoir, and D. Forming and subsequently sealing a controlled leak / breach into the enclosure.

Owner:INVENSENSE

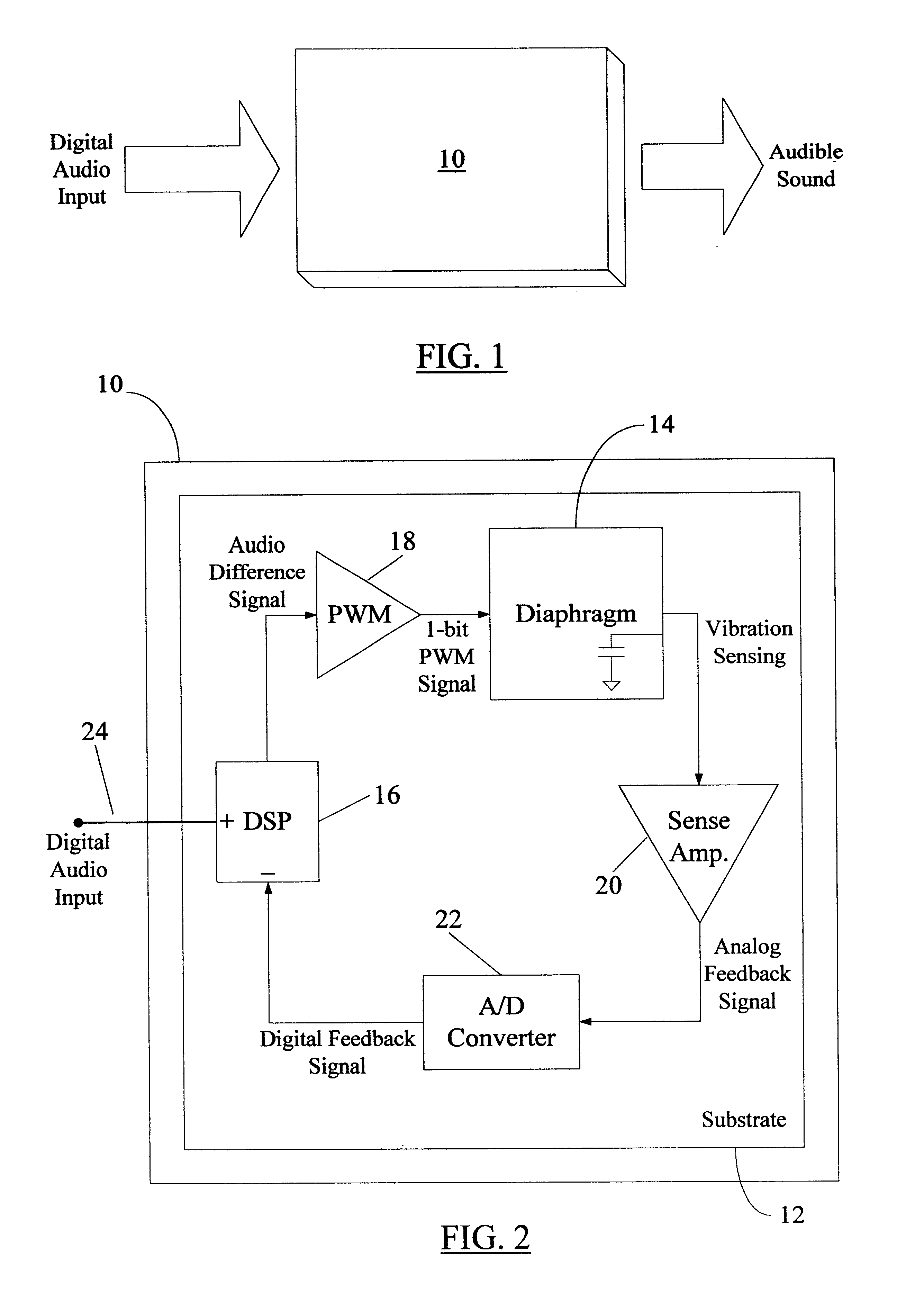

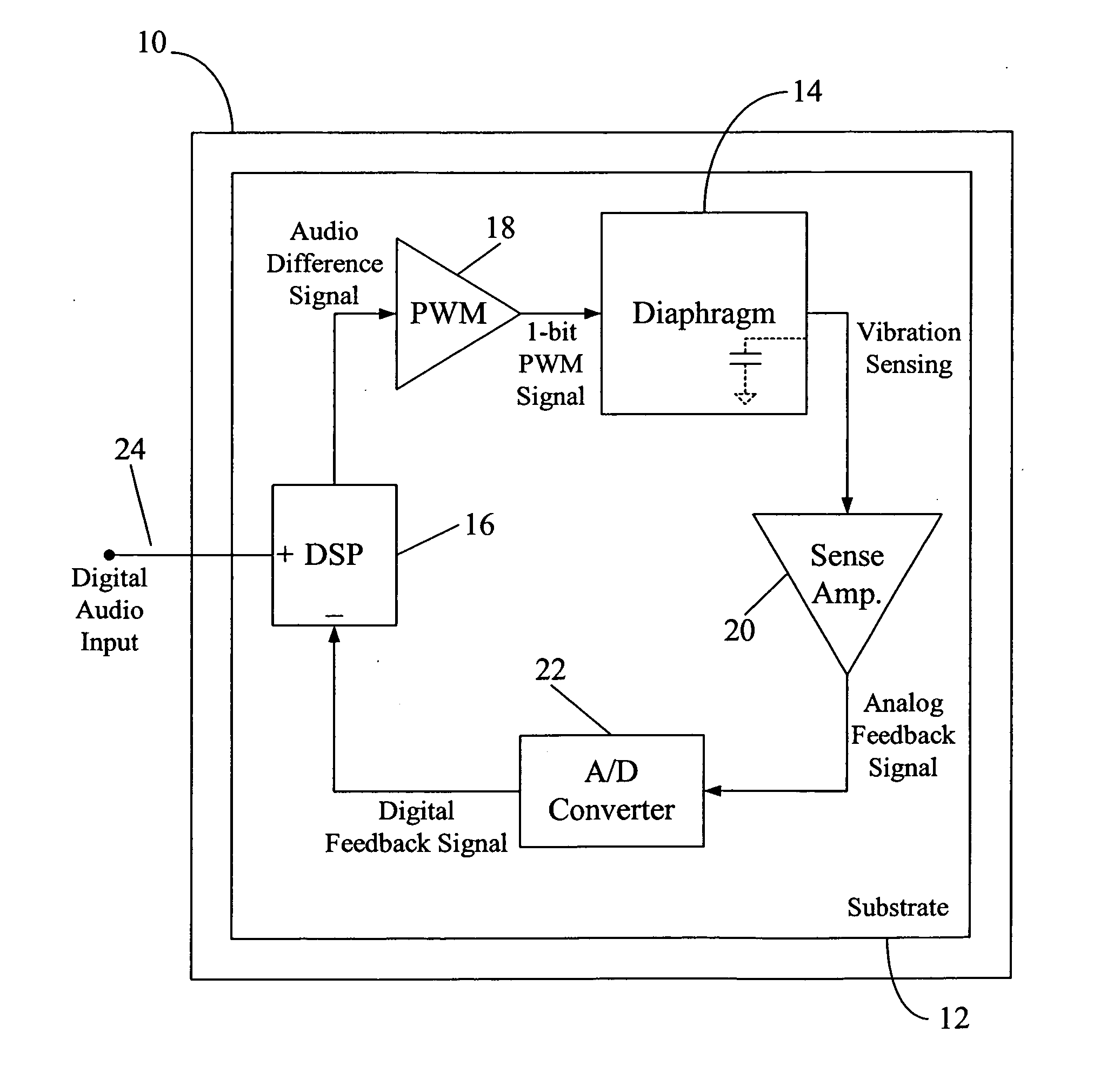

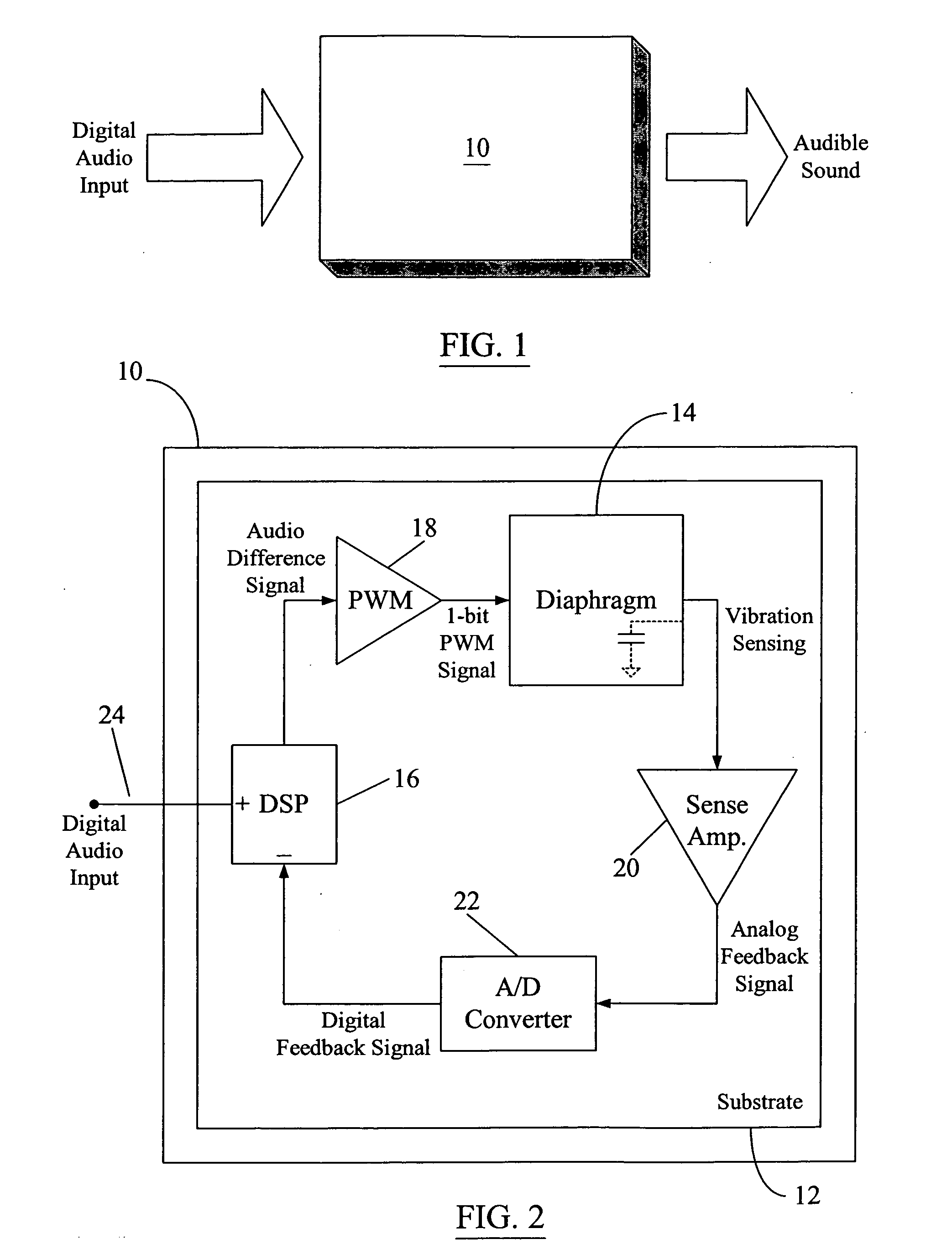

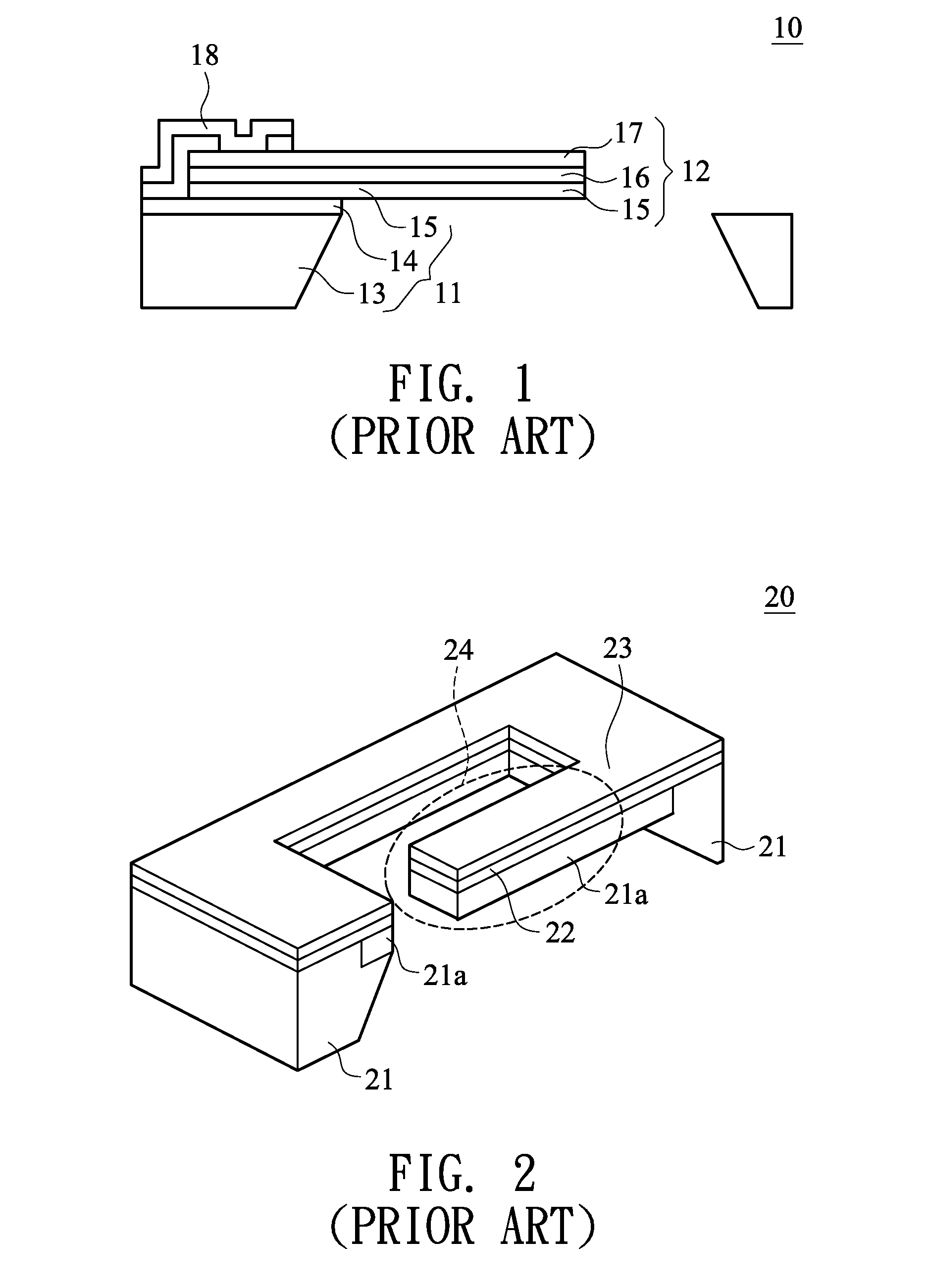

MEMS digital-to-acoustic transducer with error cancellation

InactiveUS6829131B1Low production costHigh quality audio reproductionCircuit-breaking switches for excess currentsTelevision system detailsTransducerEngineering

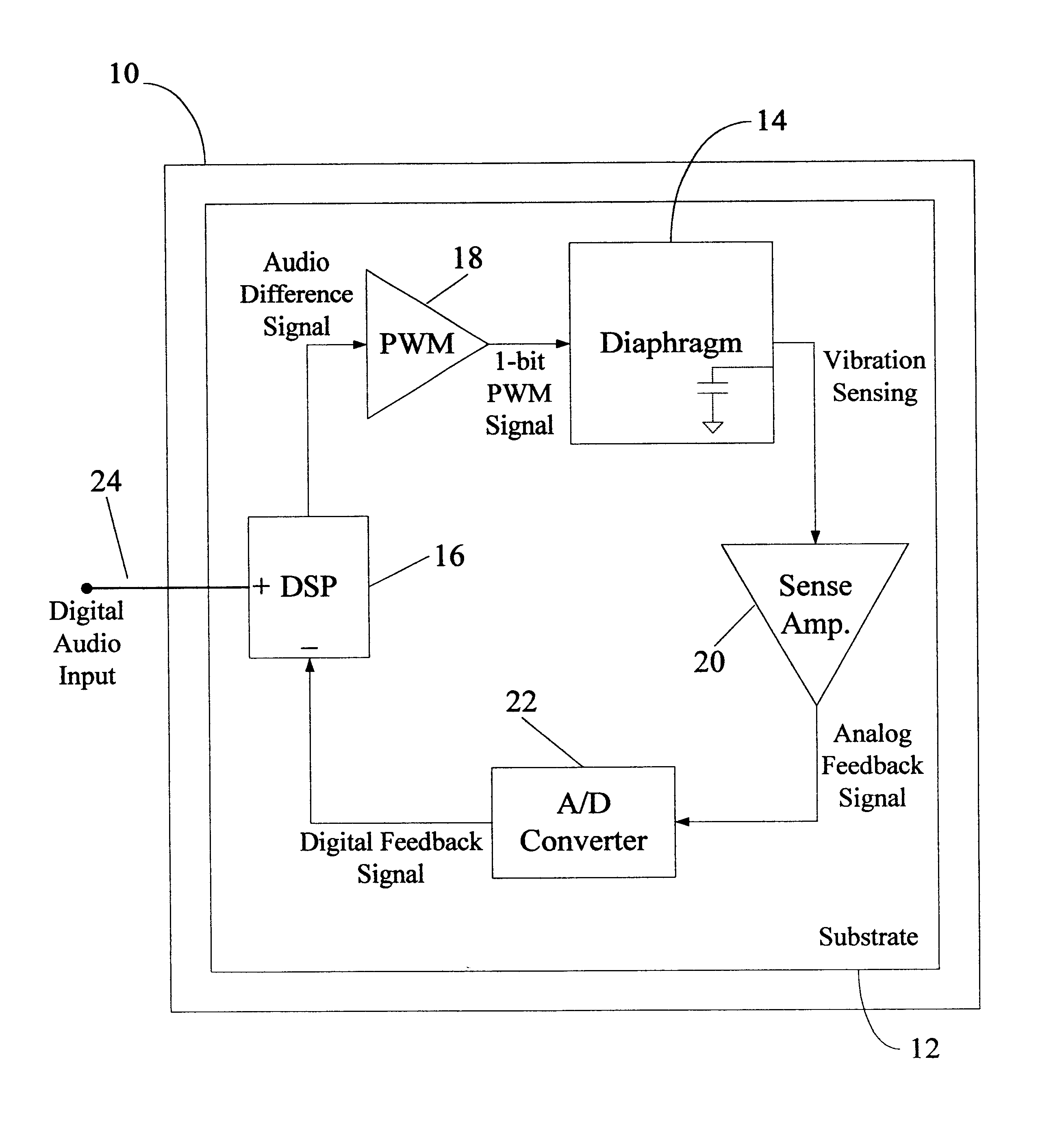

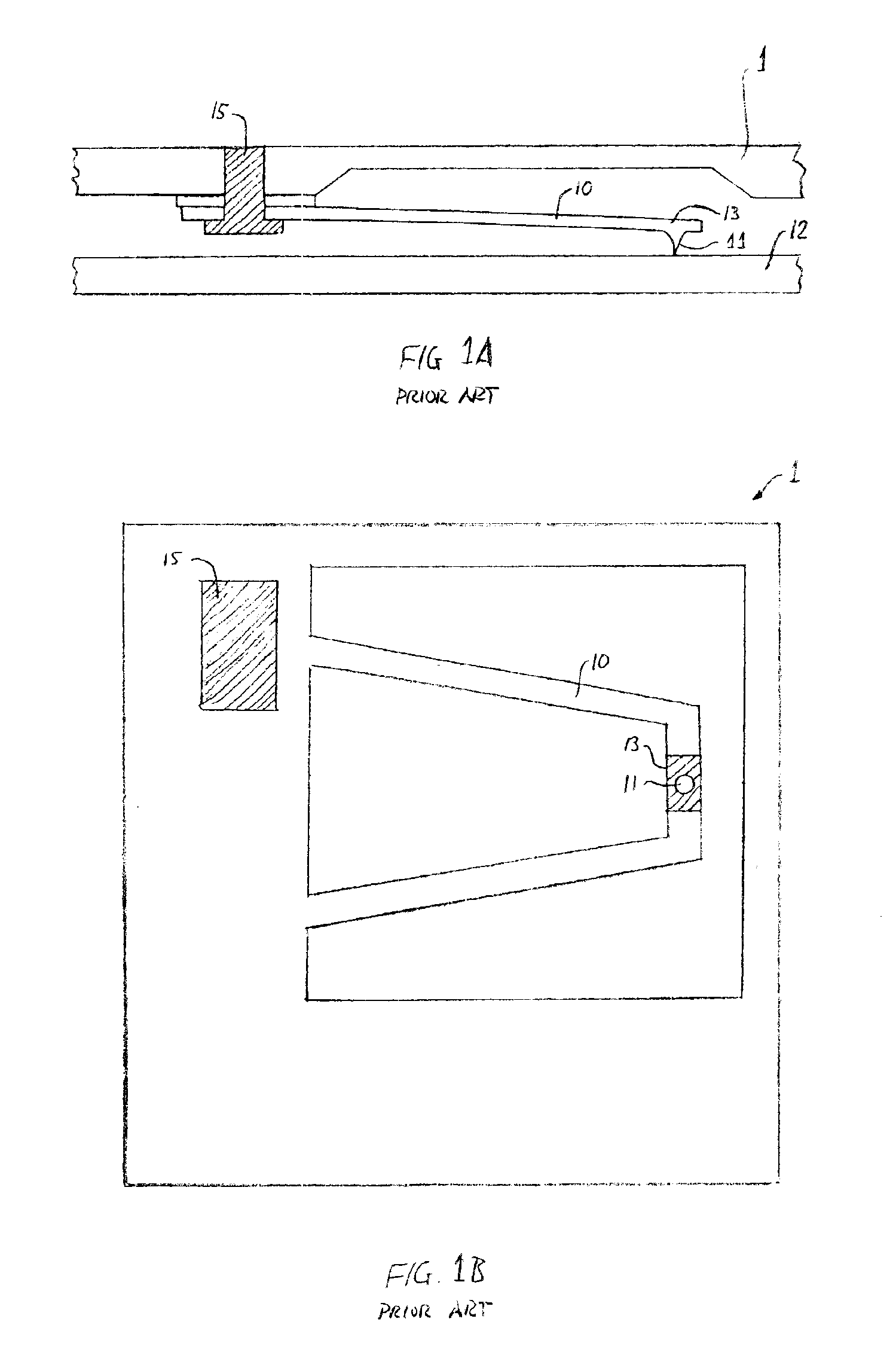

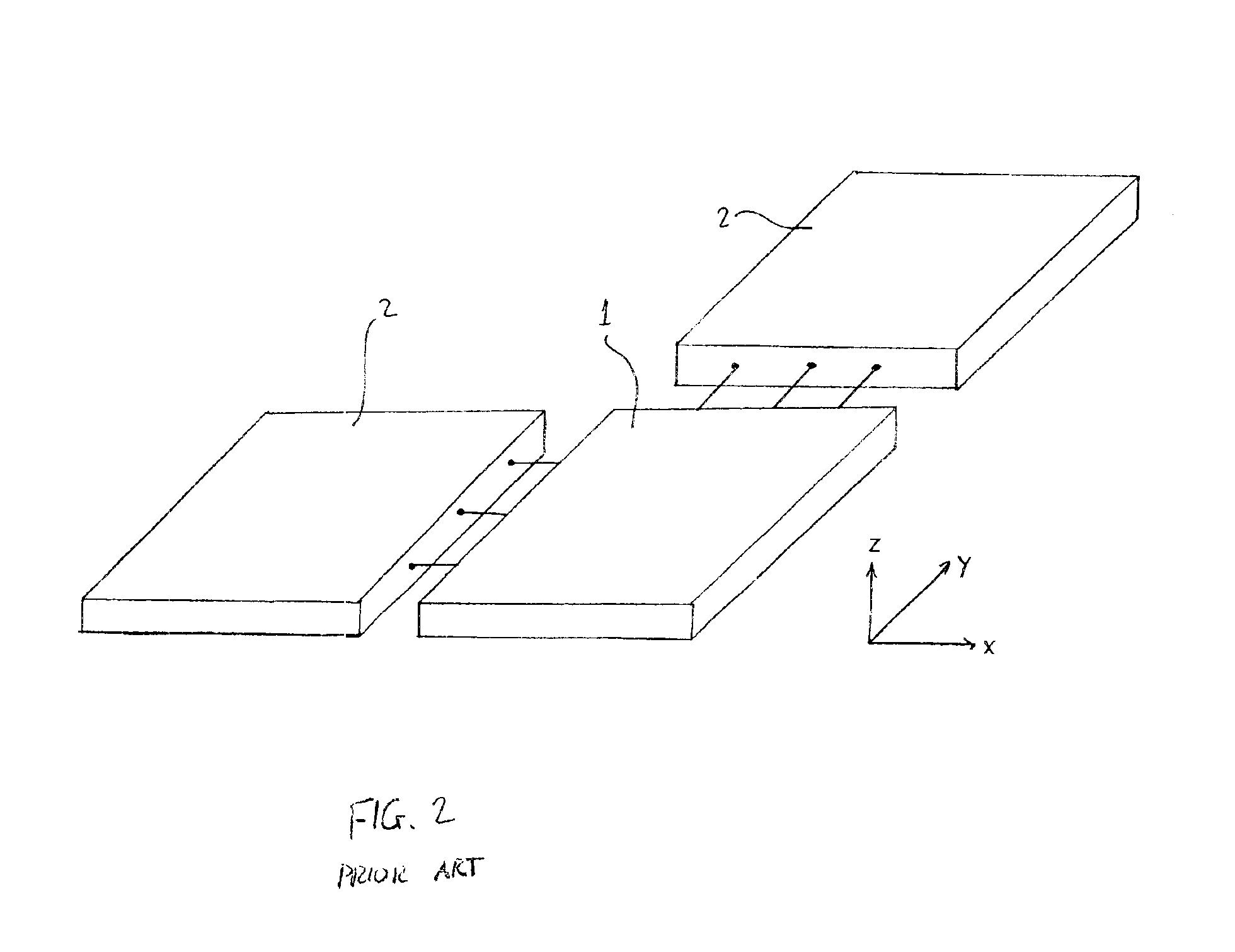

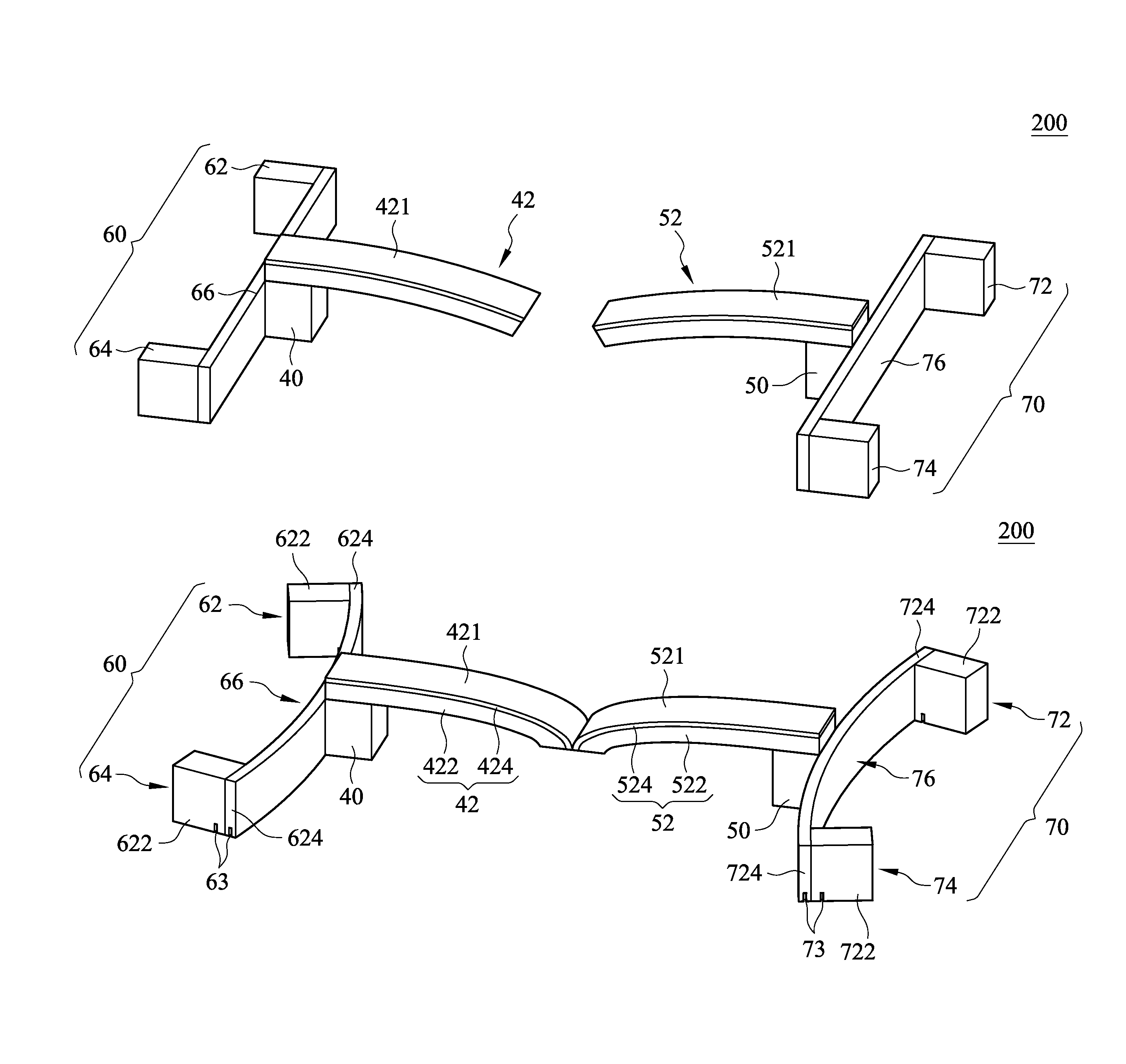

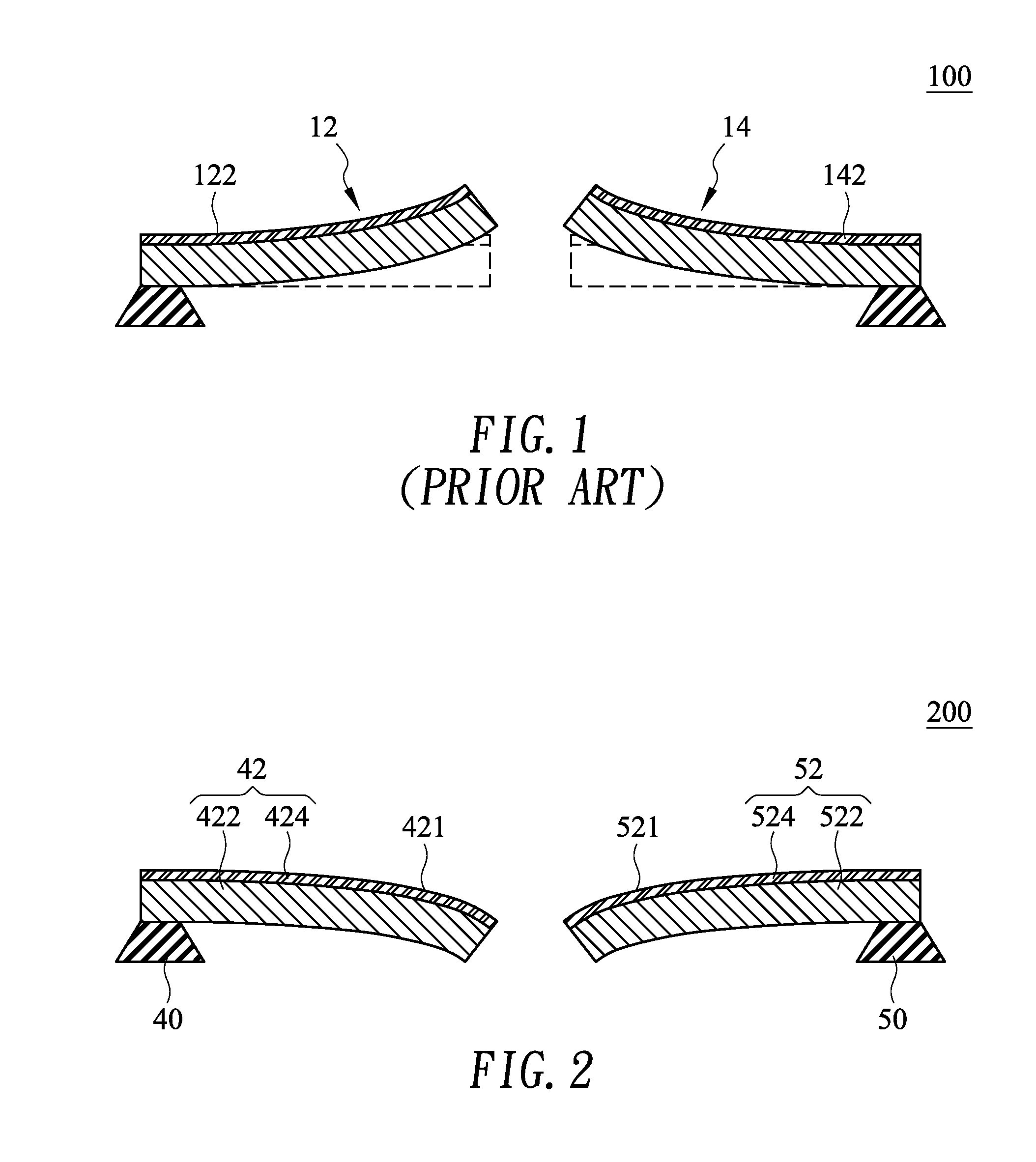

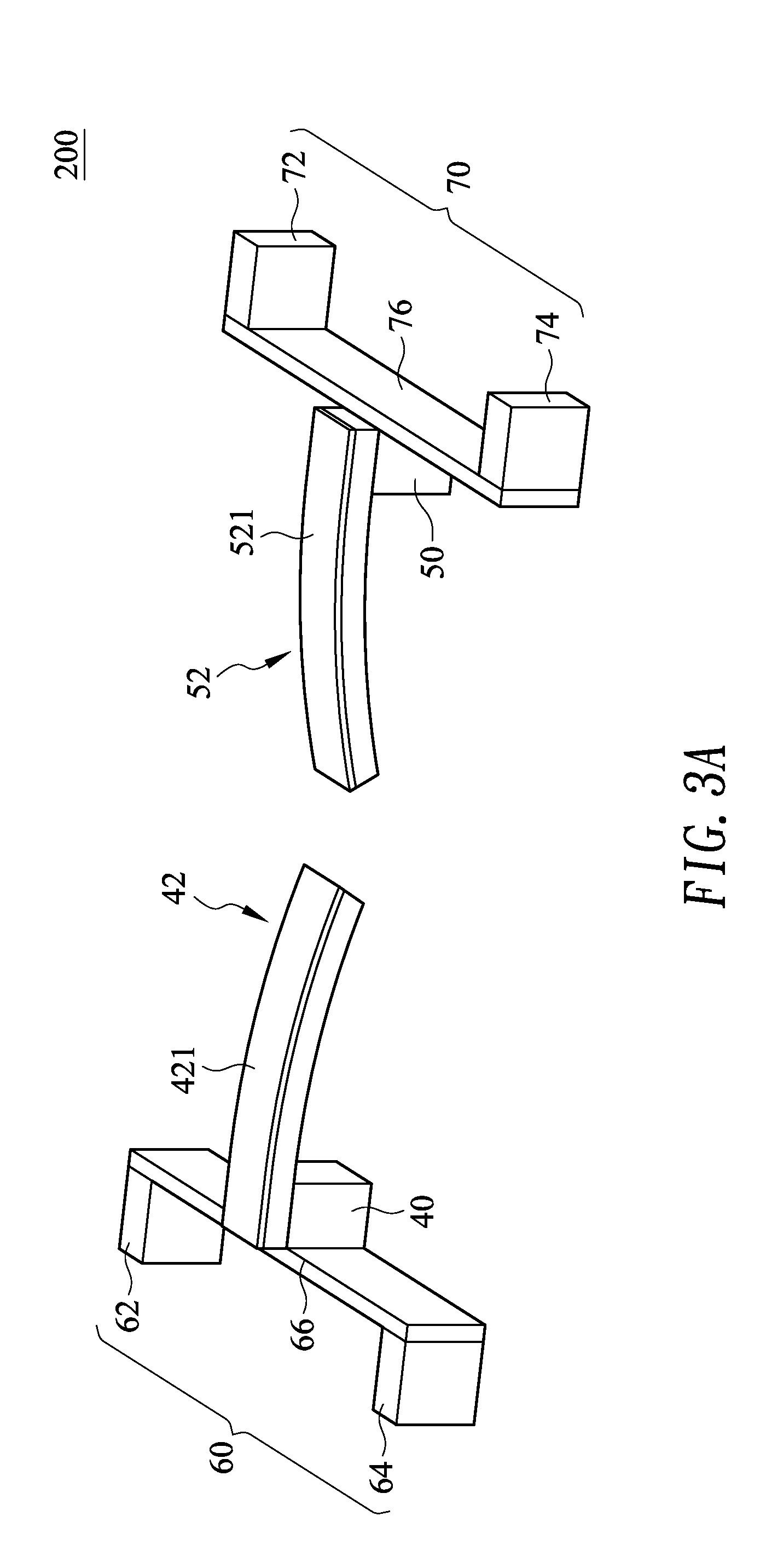

An acoustic transducer comprising a substrate; and a diaphragm formed by depositing a micromachined membrane onto the substrate. The diaphragm is formed as a single silicon chip using a CMOS MEMS (microelectromechanical systems) semiconductor fabrication process. The curling of the diaphragm during fabrication is reduced by depositing the micromachined membrane for the diaphragm in a serpentine-spring configuration with alternating longer and shorter arms. As a microspeaker, the acoustic transducer of the present invention converts a digital audio input signal directly into a sound wave, resulting in a very high quality sound reproduction at a lower cost of production in comparison to conventional acoustic transducers. The micromachined diaphragm may also be used in microphone applications.

Owner:CARNEGIE MELLON UNIV

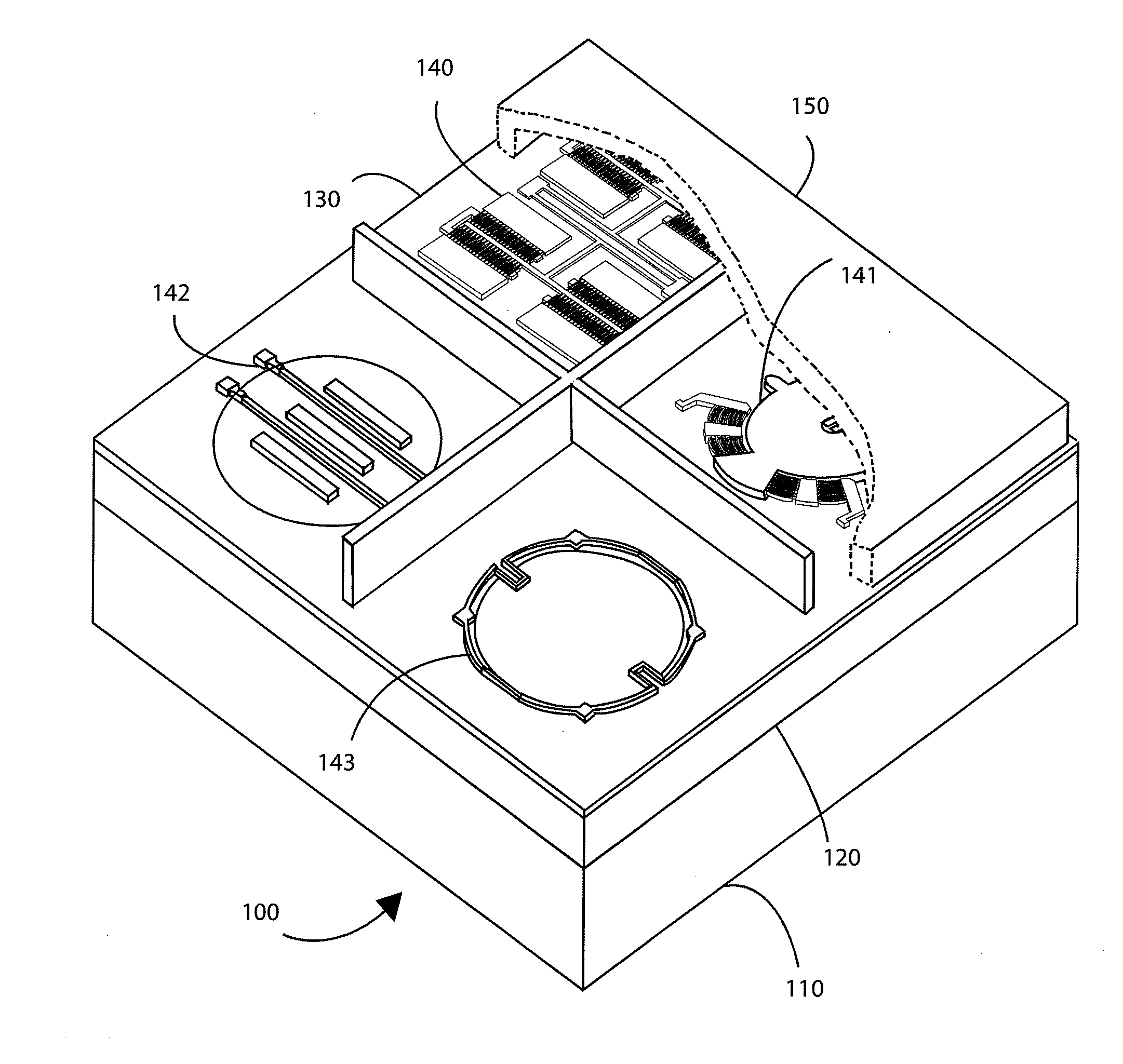

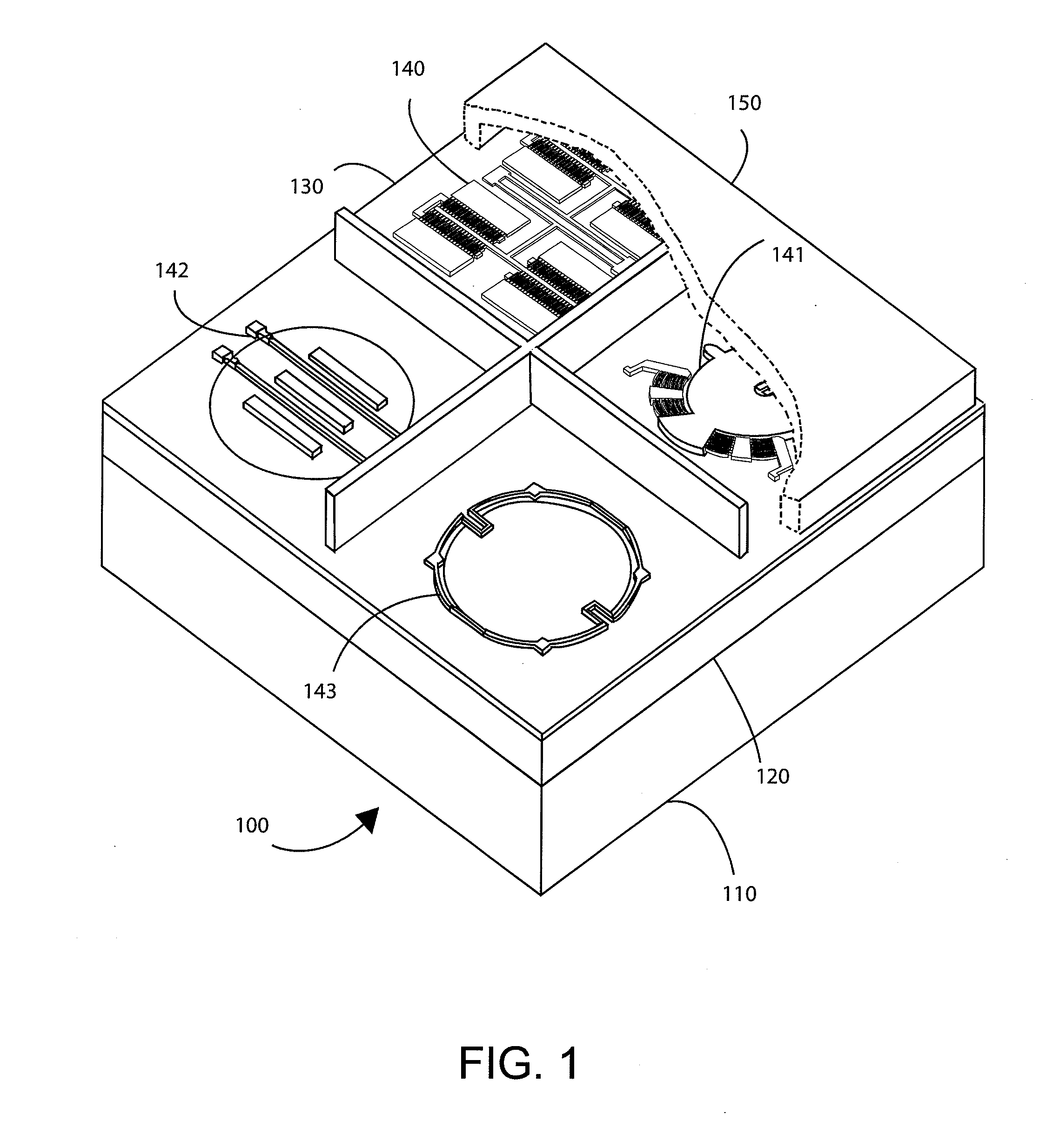

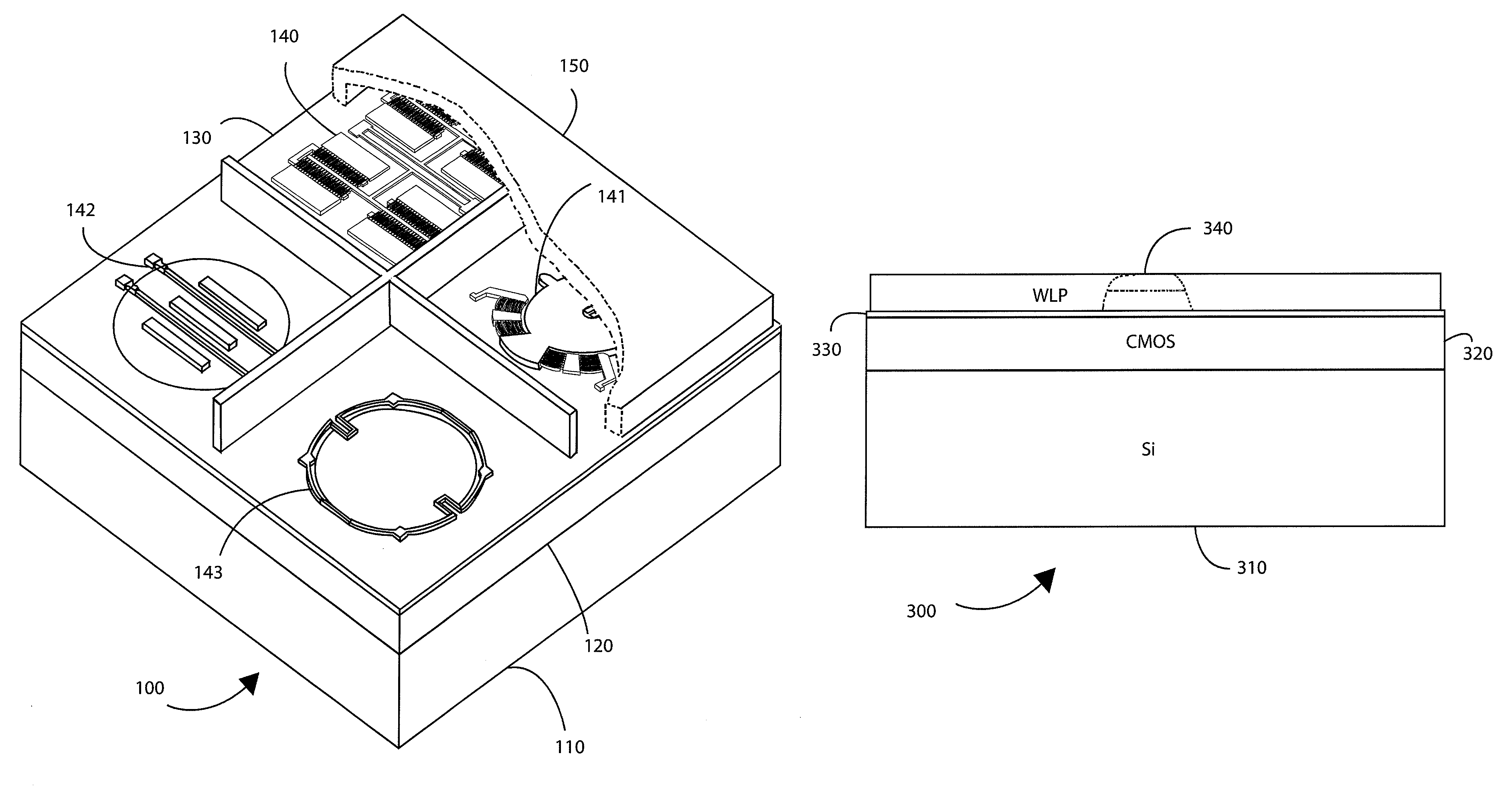

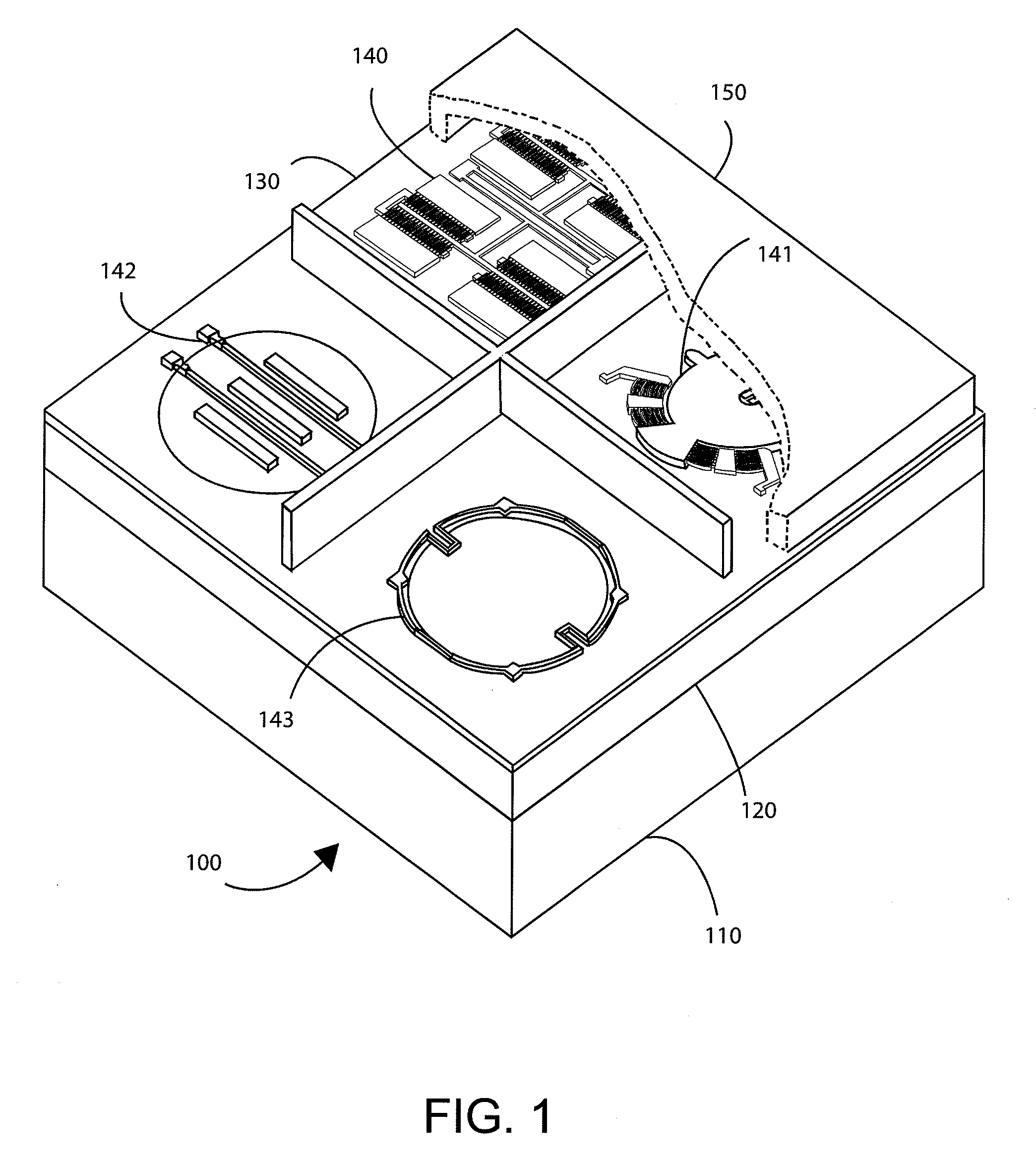

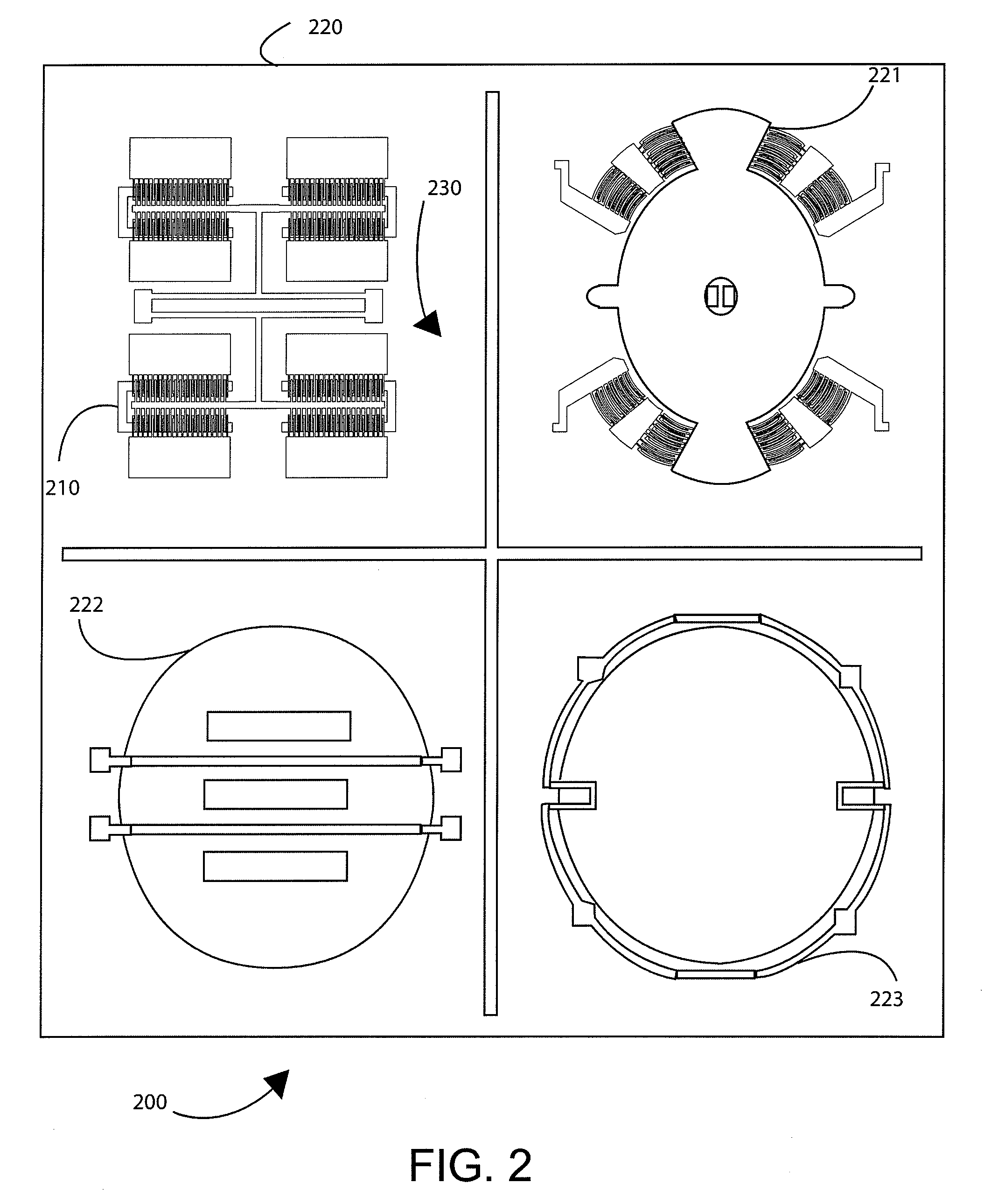

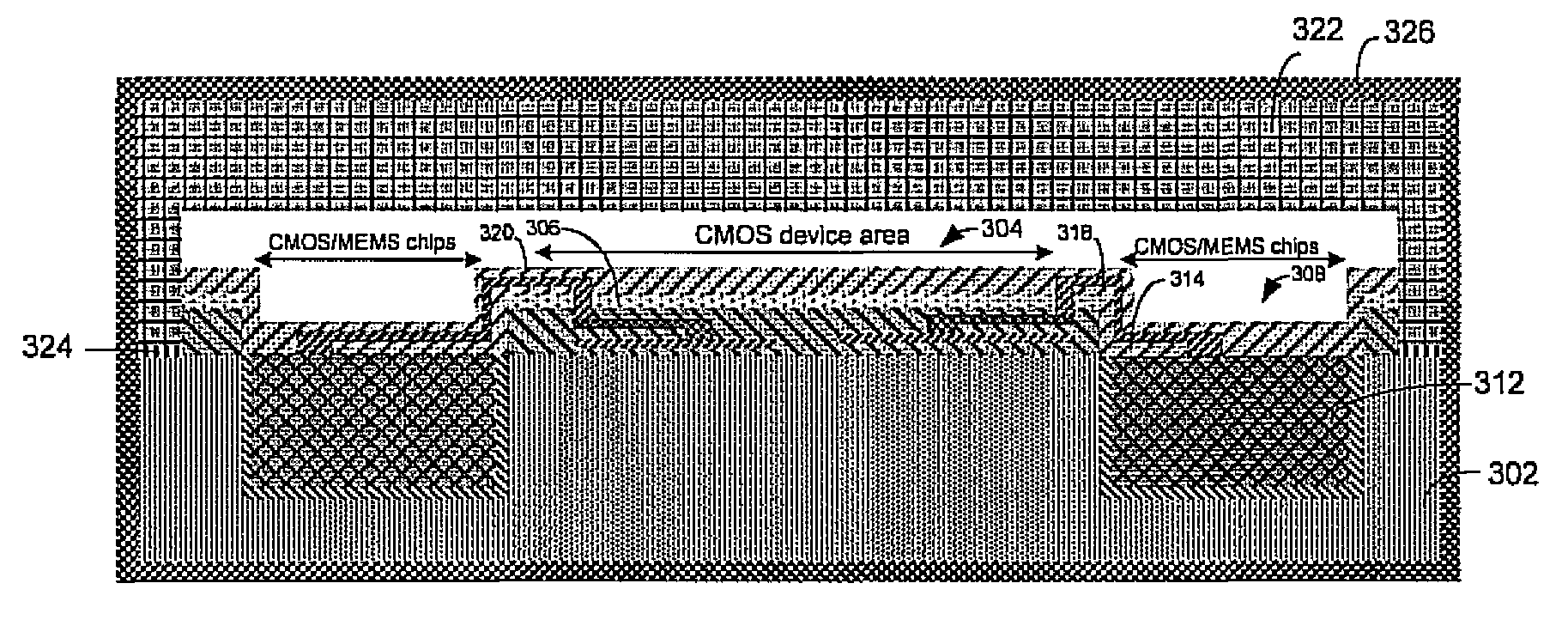

System on a Chip Using Integrated MEMS and CMOS Devices

ActiveUS20110265574A1Easy to useHigh device yieldVibration measurement in solidsMaterial analysis using sonic/ultrasonic/infrasonic wavesCmos memsSystem on a chip

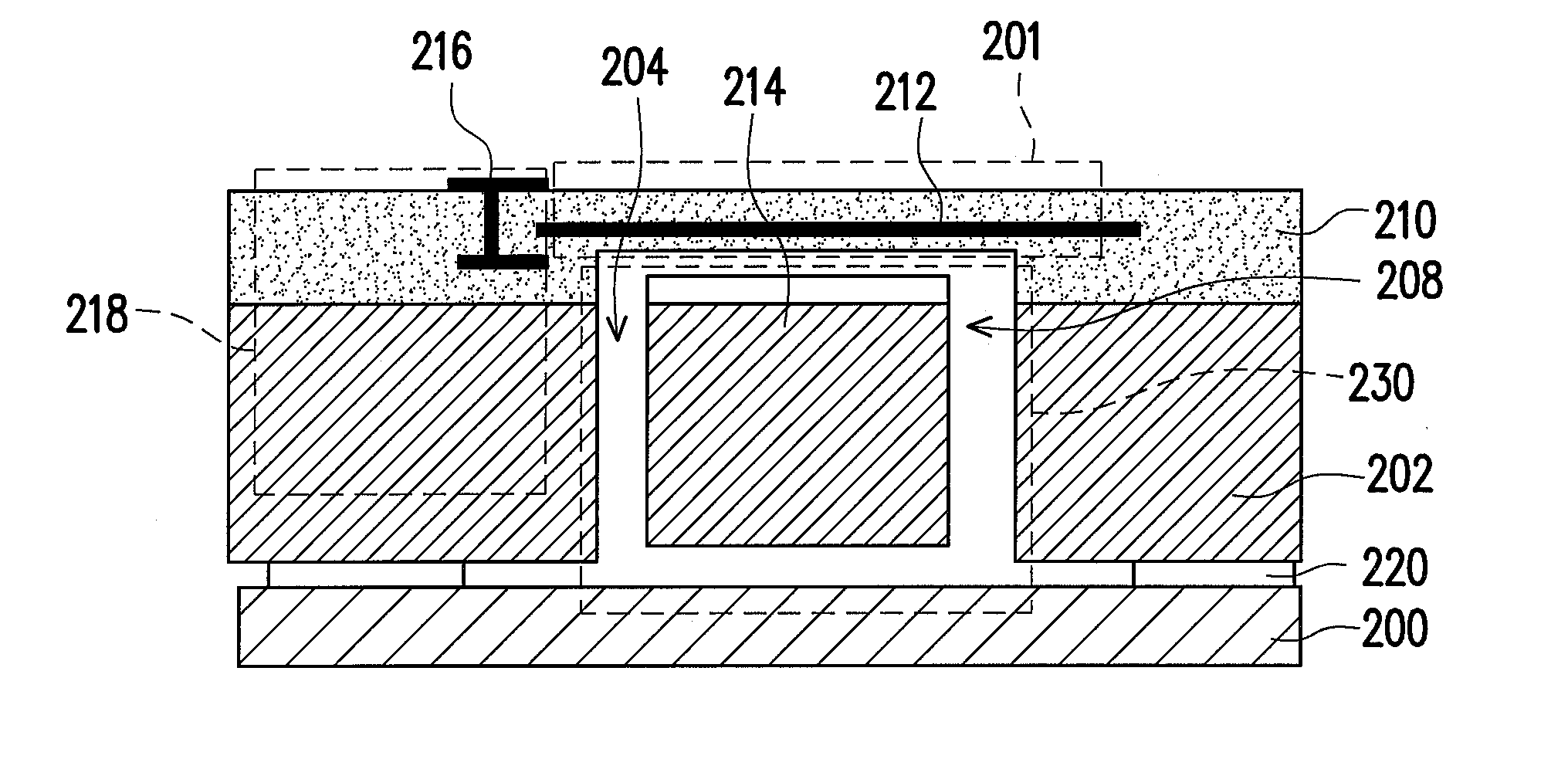

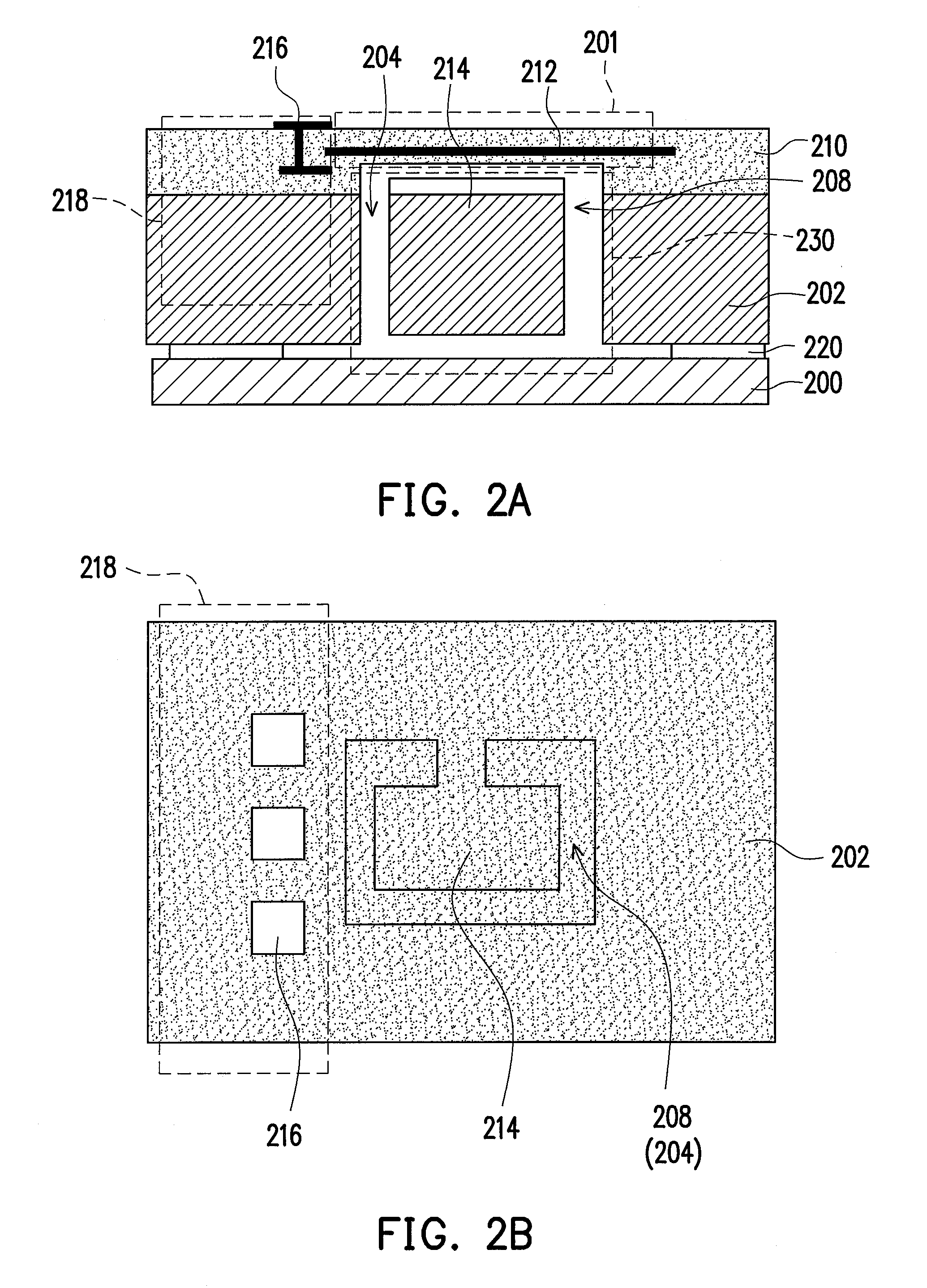

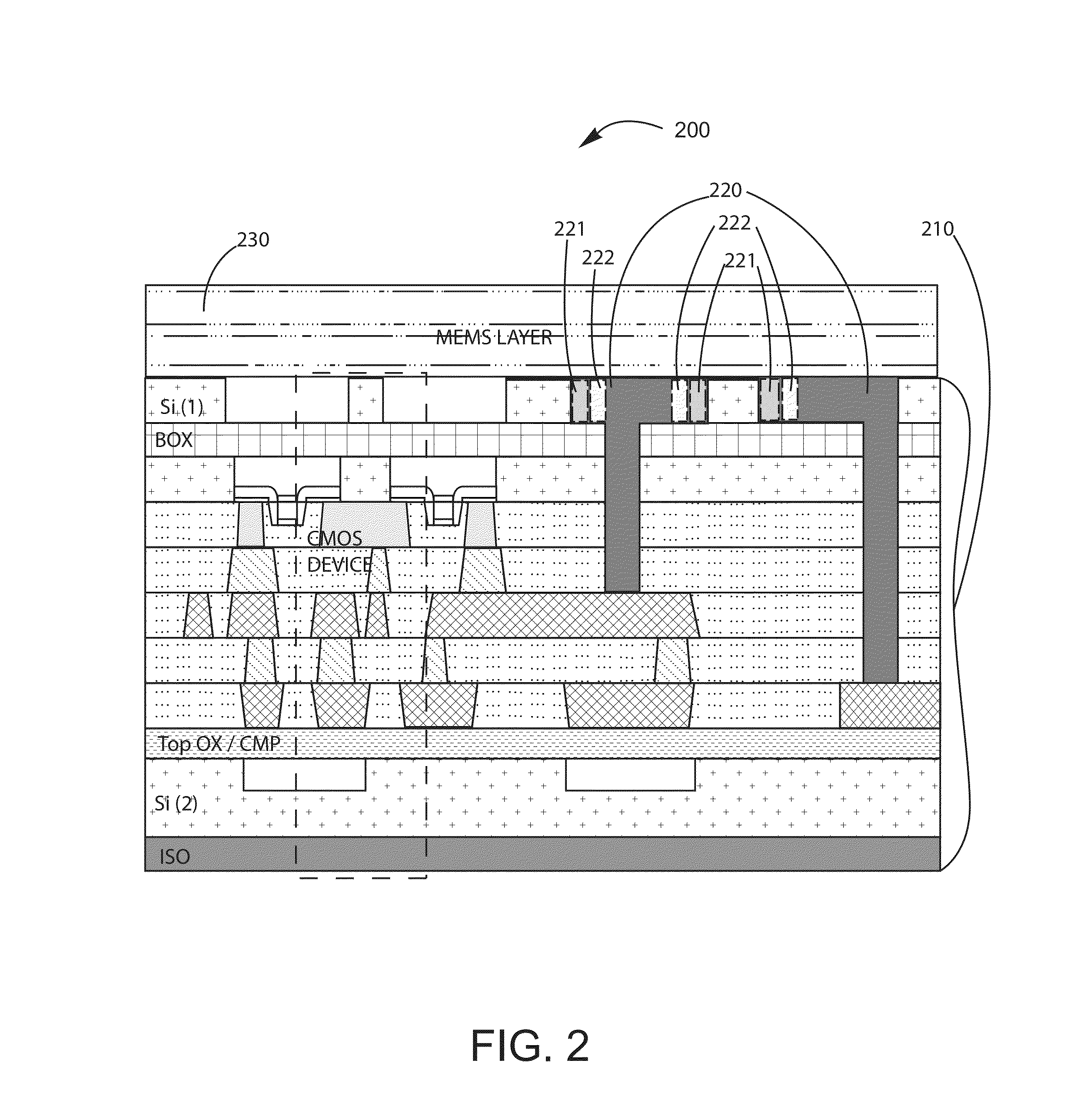

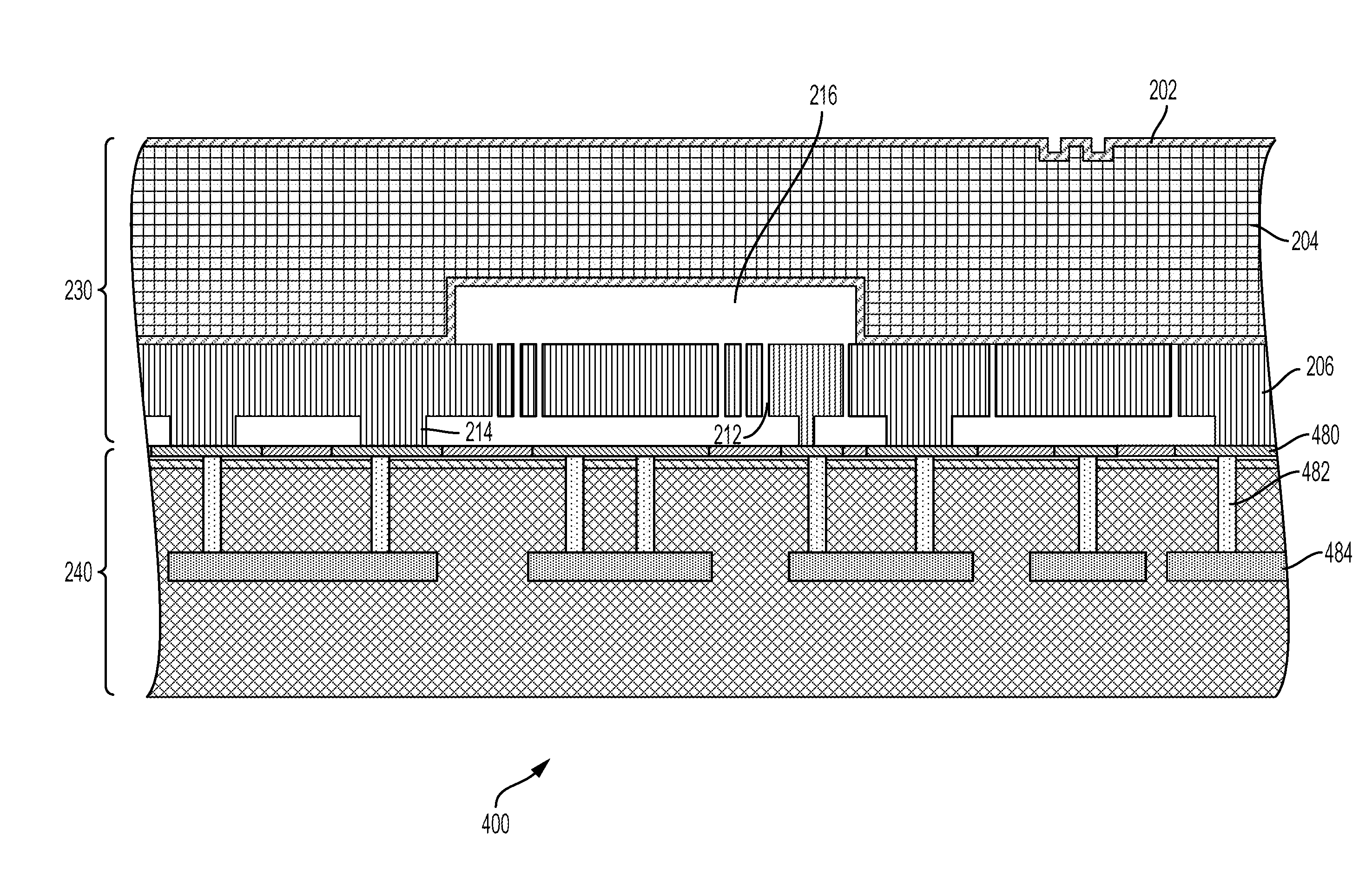

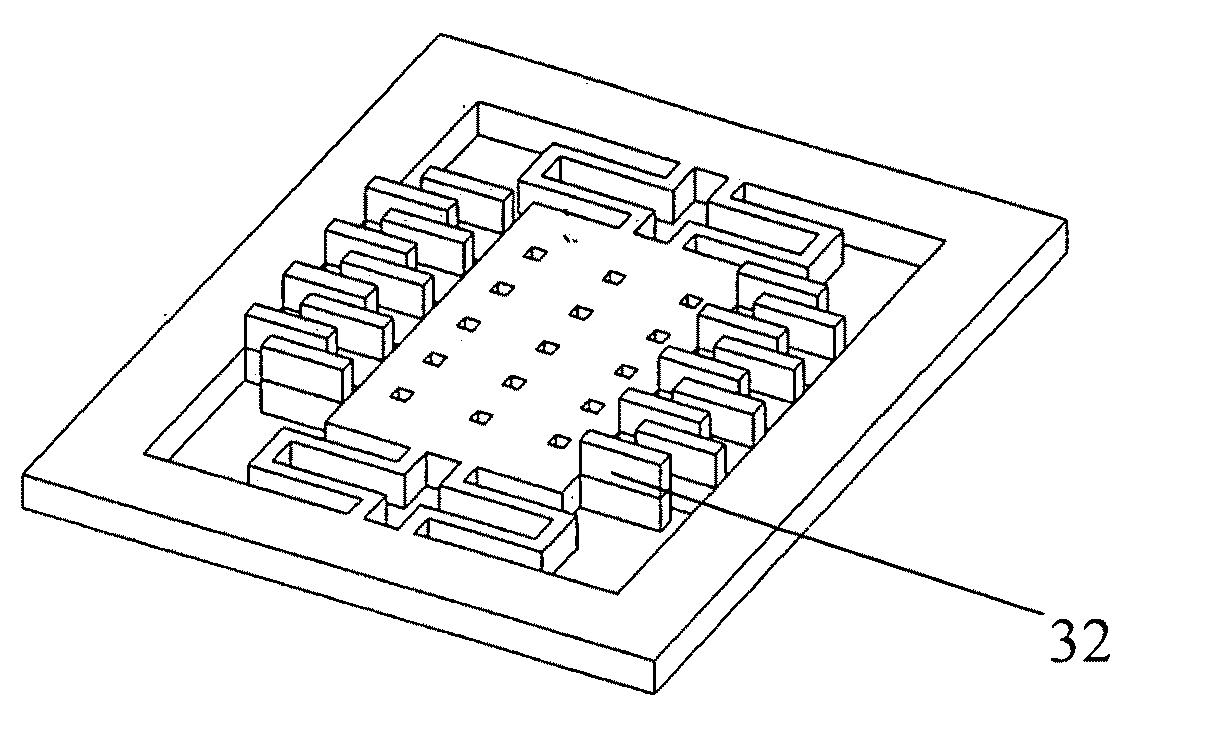

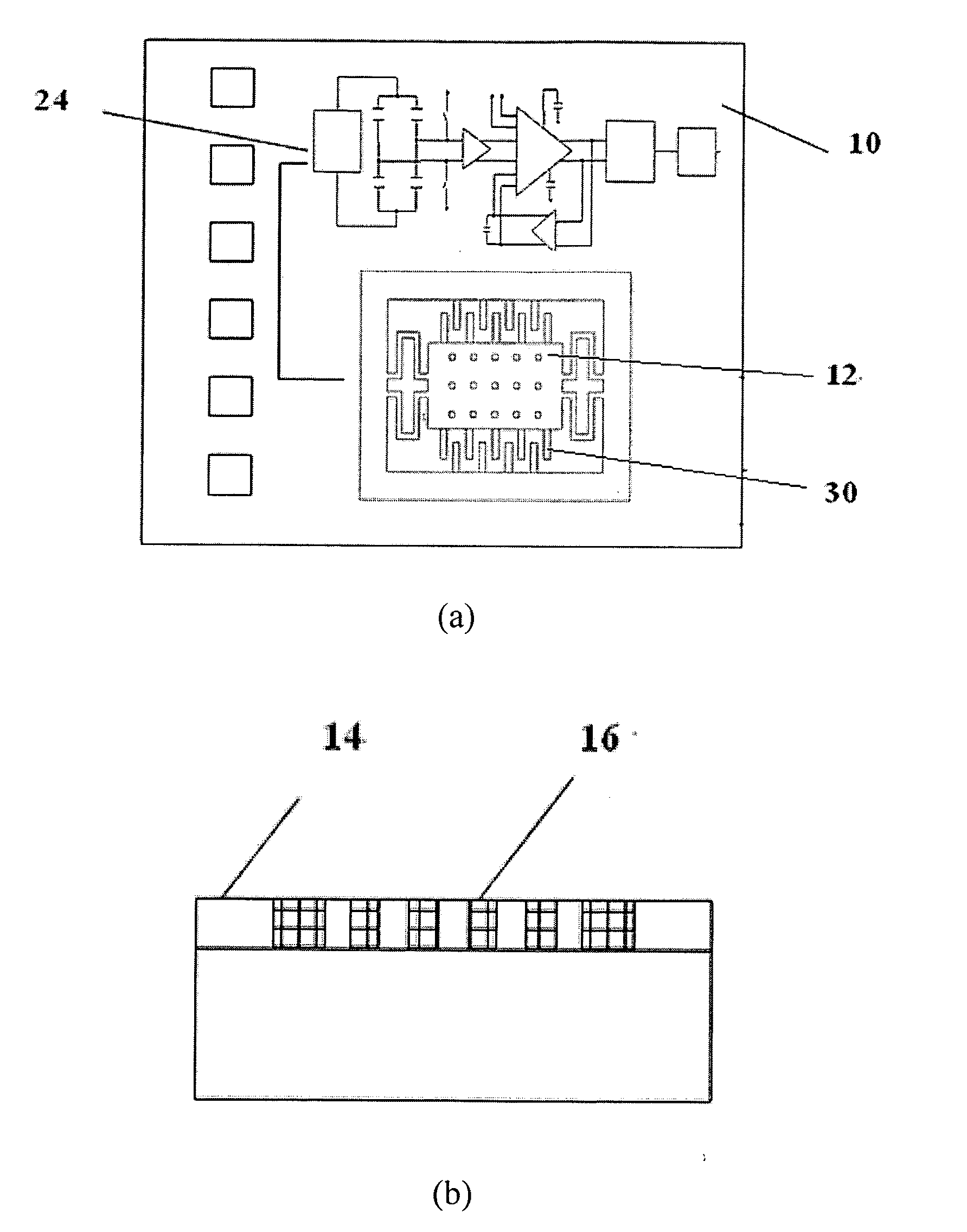

An integrated MEMS system in which CMOS and MEMS devices are provided to form an integrated CMOS-MEMS system. The system can include a silicon substrate layer, a CMOS layer, MEMS and CMOS devices, and a wafer level packaging (WLP) layer. The CMOS layer can form an interface region, one which any number of CMOS MEMS devices can be configured.

Owner:MOVELLA INC

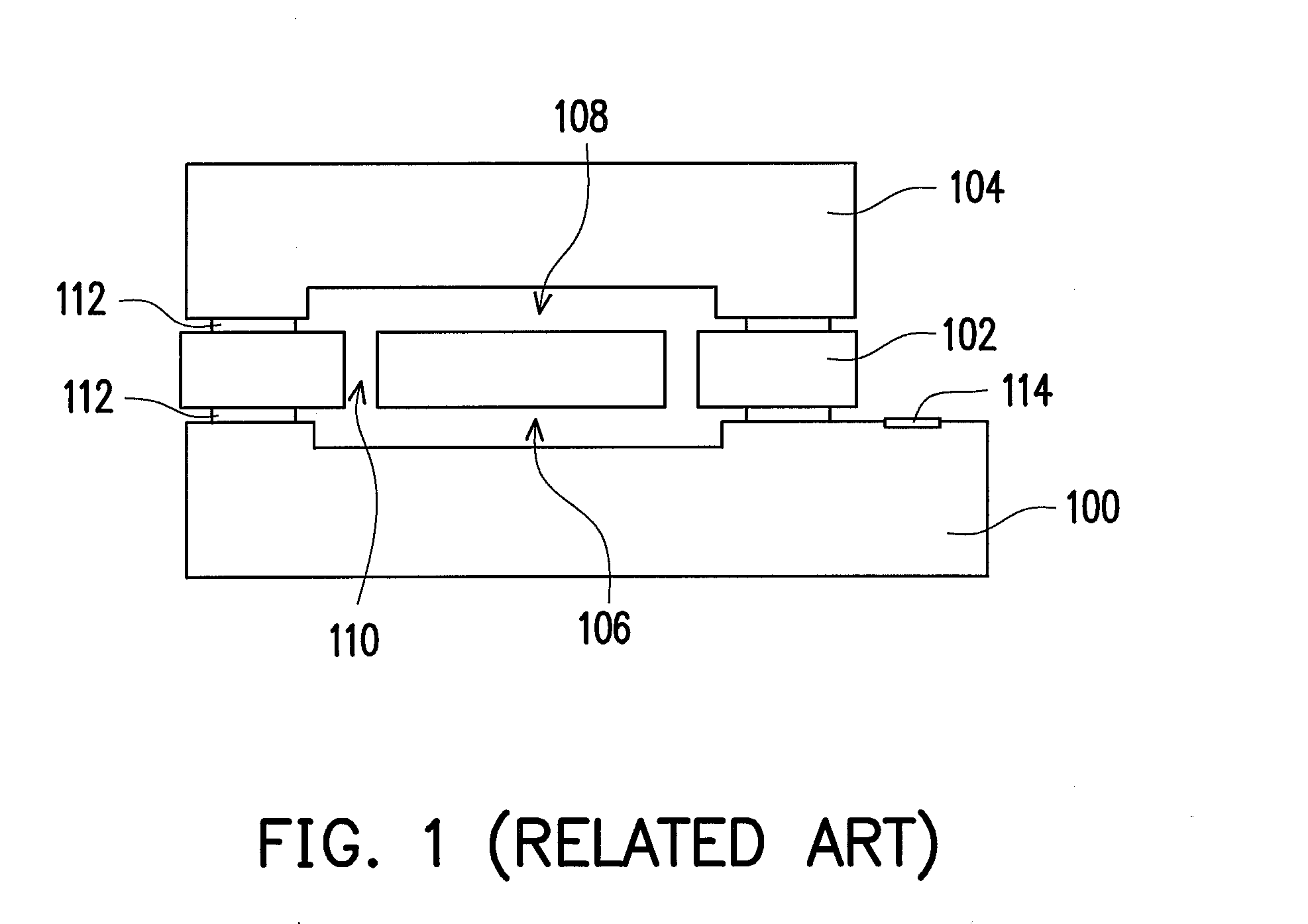

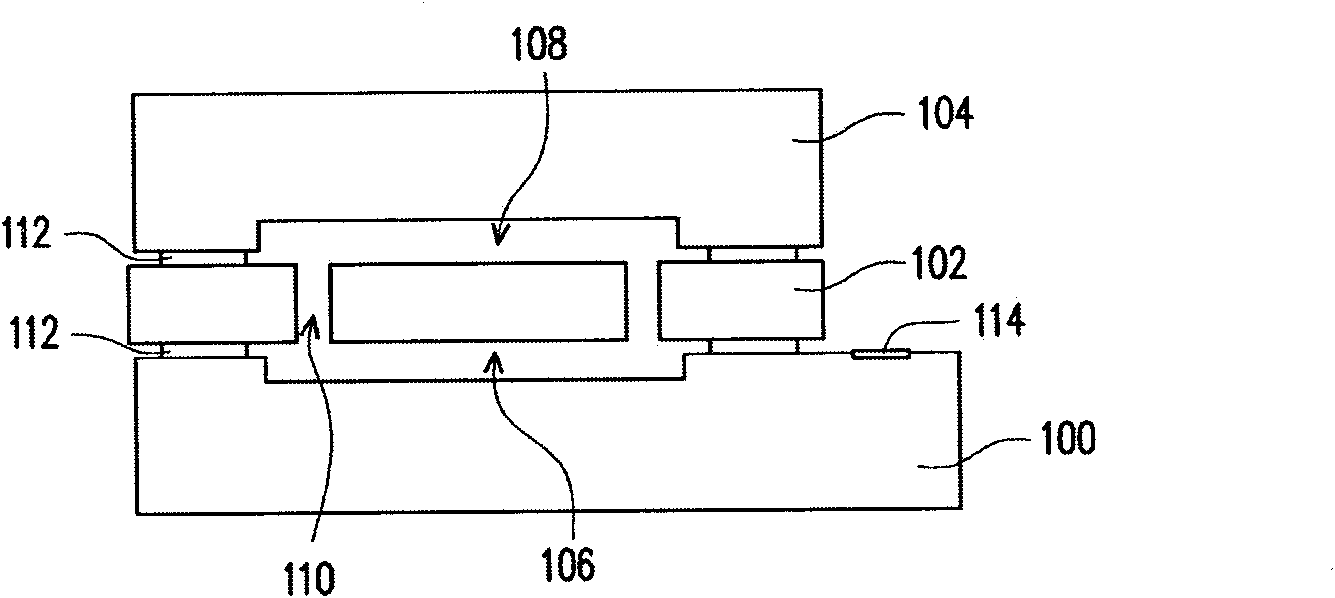

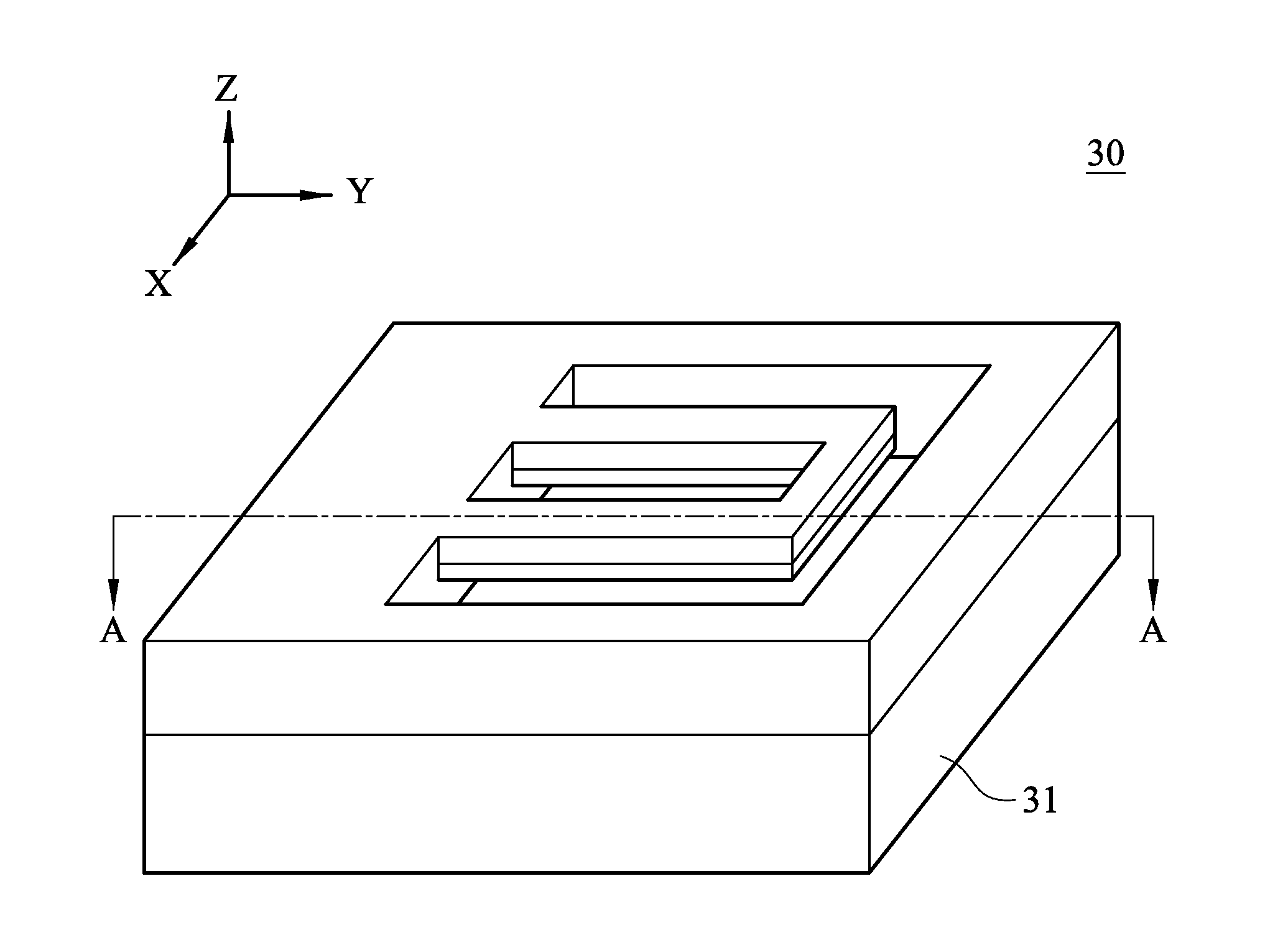

Three-dimensional integrated CMOS-MEMS device and process for making the same

InactiveUS7071031B2Semiconductor/solid-state device testing/measurementDecorative surface effectsEngineeringCmos mems

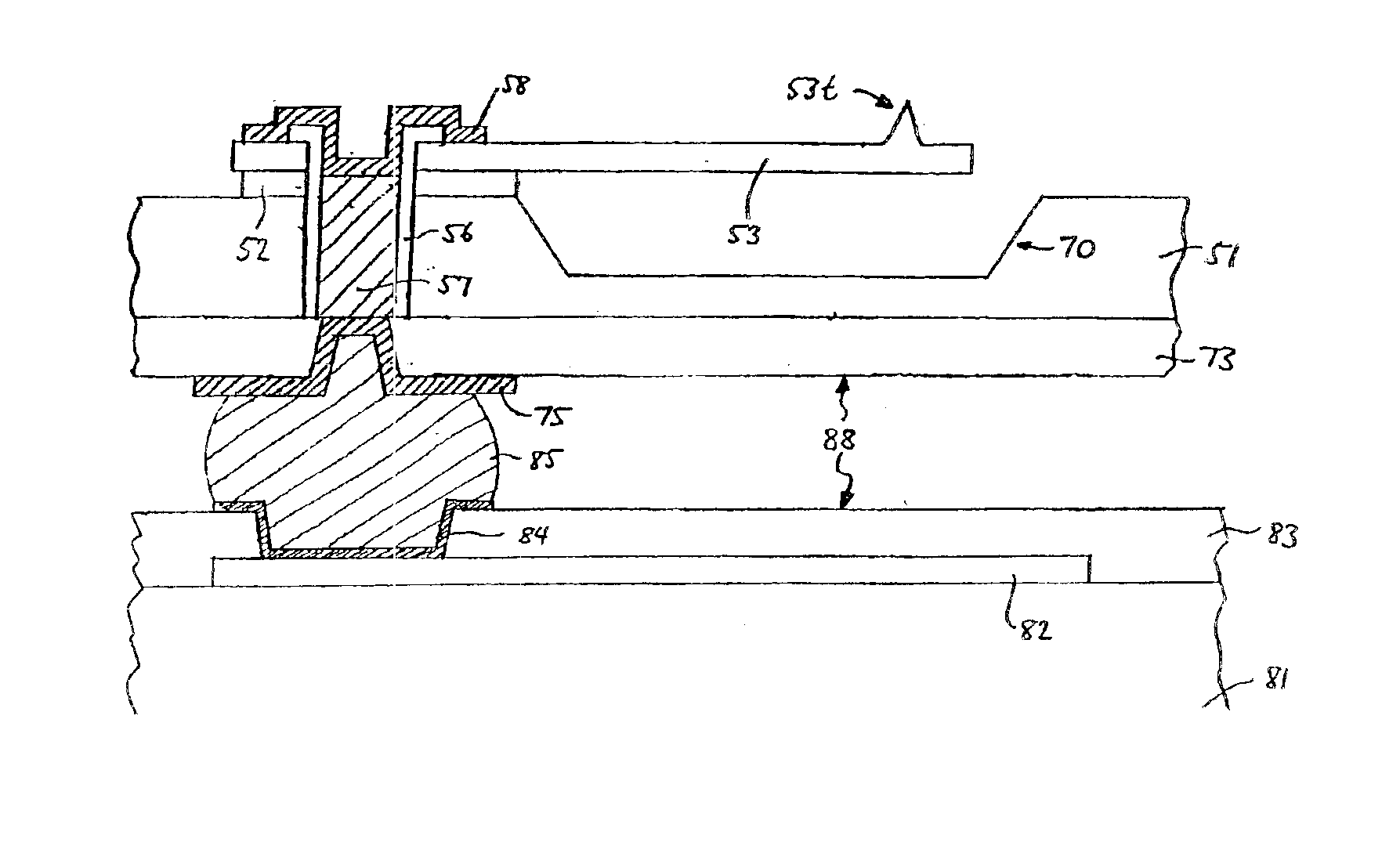

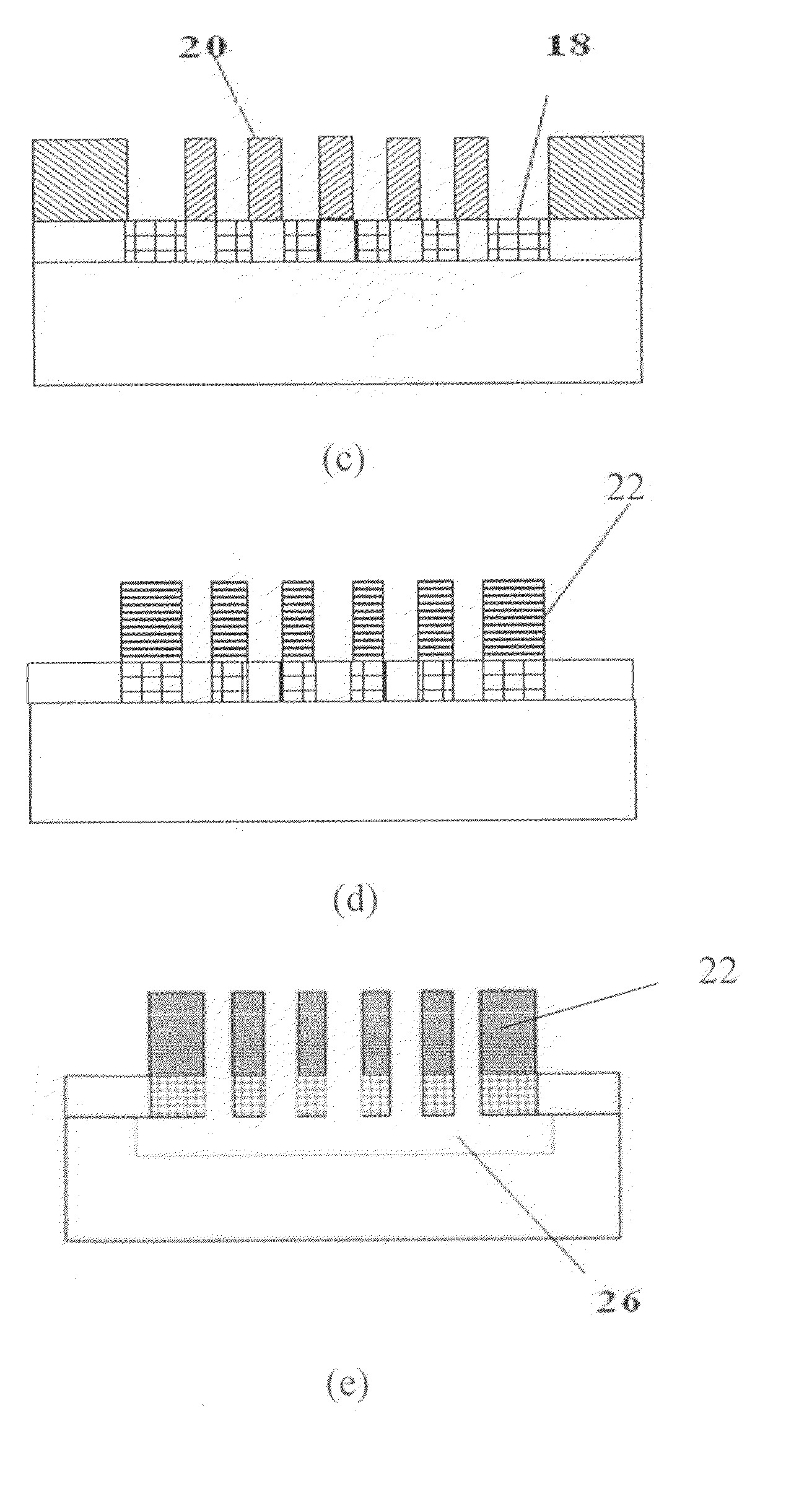

A vertically integrated structure includes a micro-electromechanical system (MEMS) and a chip for delivering signals to the MEMS. The structure includes a metal stud connecting a surface of the chip and the MEMS; the MEMS has an anchor portion having a conducting pad on an underside thereof contacting the metal stud. The MEMS is spaced from the chip by a distance corresponding to a height of the metal stud, and the MEMS includes a doped region in contact with the conducting pad. In particular, the MEMS may include a cantilever structure, with the end portion including a tip extending in the vertical direction. A support structure (e.g. of polyimide) may surround the metal stud and contact both the underside of the MEMS and the surface of the chip. A temporary carrier plate is used to facilitate handling of the MEMS and alignment to the chip.

Owner:IBM CORP

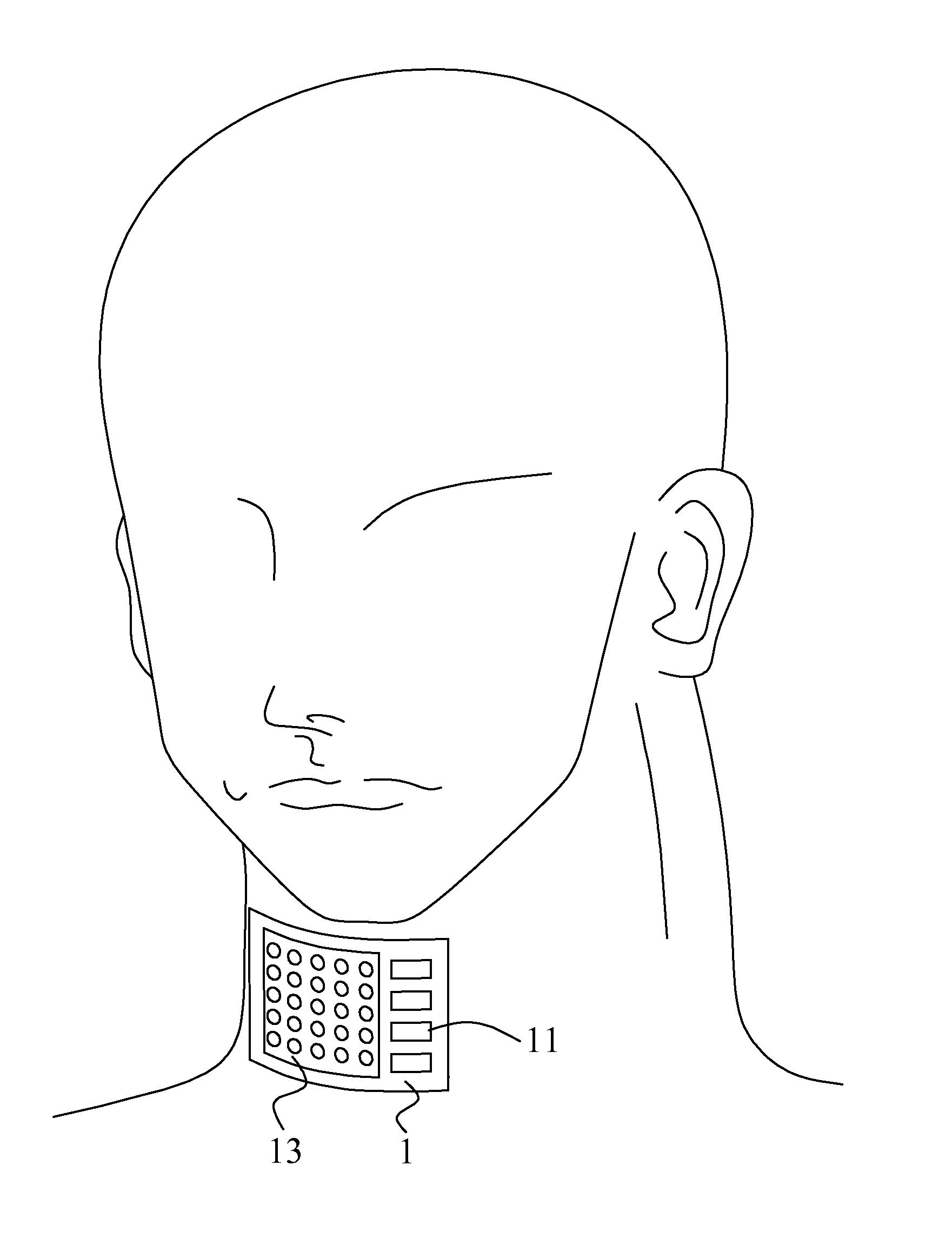

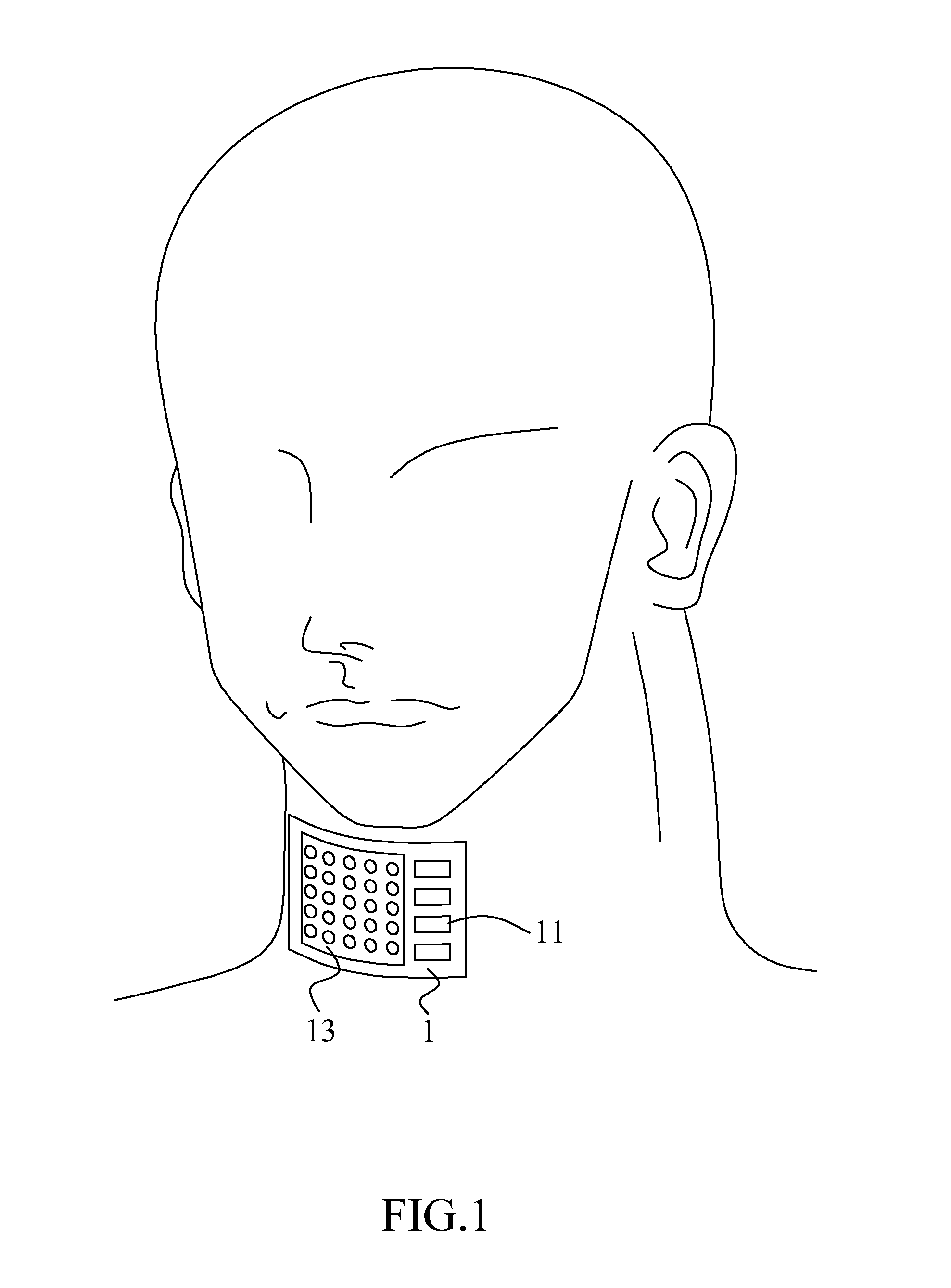

SMART NON-INVASIVE ARRAY-BASED HEMODYNAMIC MONITORING SYSTEM on CHIP AND METHOD THEREOF

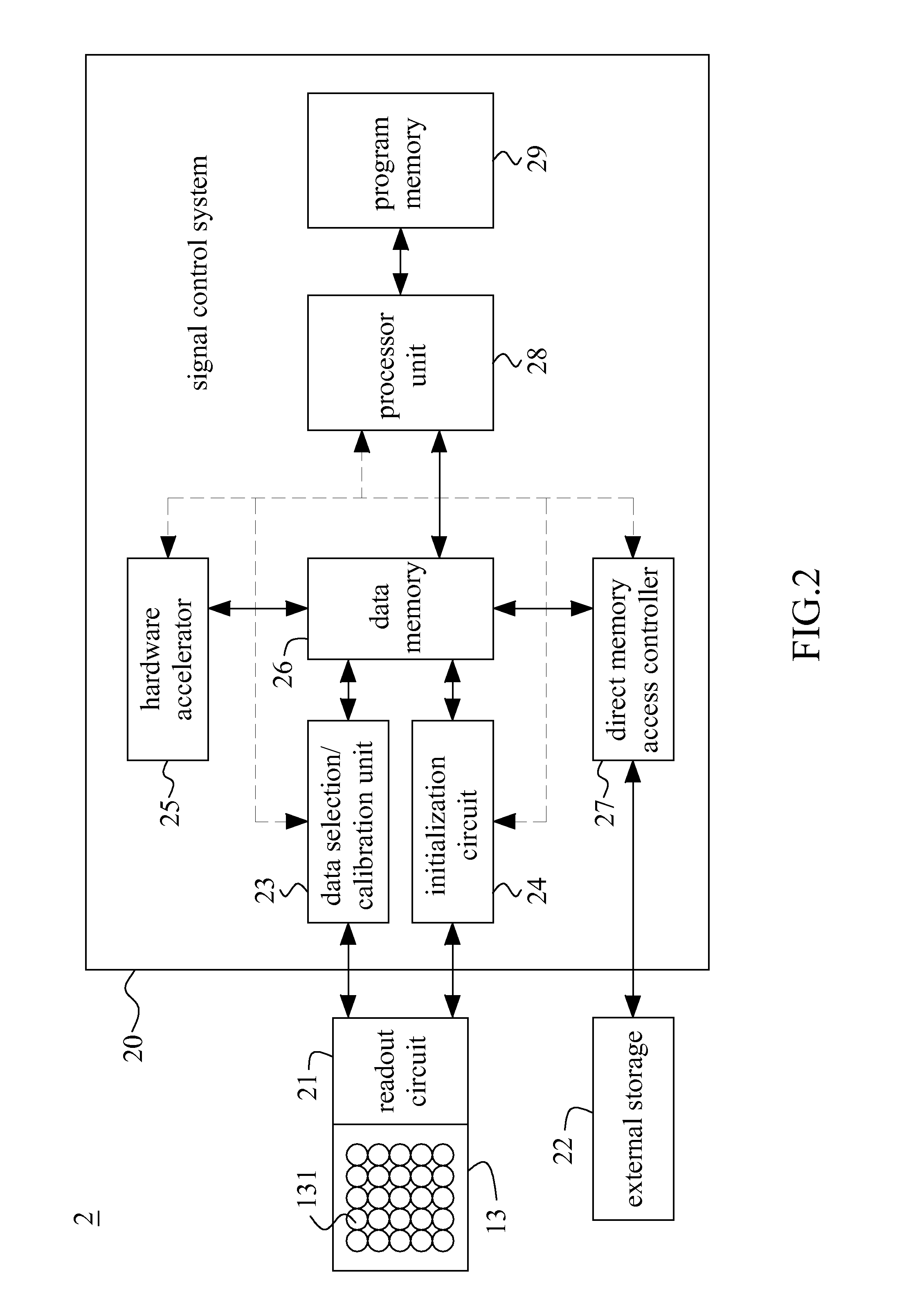

A non-invasive array-based hemodynamic monitoring system on chip is disclosed. The non-invasive array-based hemodynamic monitoring system on chip comprises a CMOS MEMS pressure sensor array, a readout circuit, and a signal control system. The CMOS MEMS pressure sensor array is configured to sense a pulse wave of a blood vessel. The readout circuit is coupled with each of the CMOS compatible MEMS pressure sensors and is configured to read the pulse wave and transformed the pulse wave into a voltage signal. The signal control system is coupled with each of the readout circuit, and is configured to estimate a wave velocity according to the voltage signal.

Owner:NAT TAIWAN UNIV

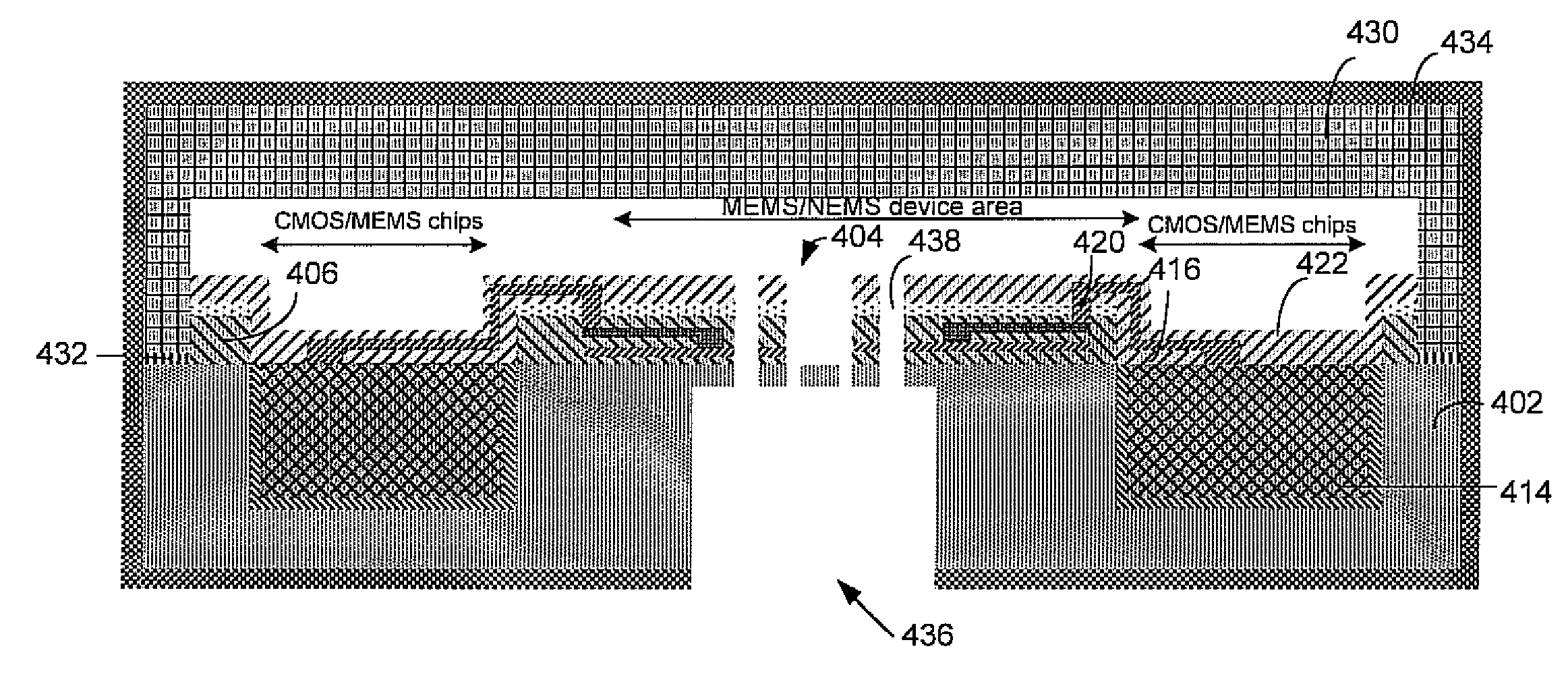

Method of forming monolithic cmos-mems hybrid integrated, packaged structures

InactiveUS20110027941A1Solid-state devicesSemiconductor/solid-state device manufacturingLayer interfaceFilling materials

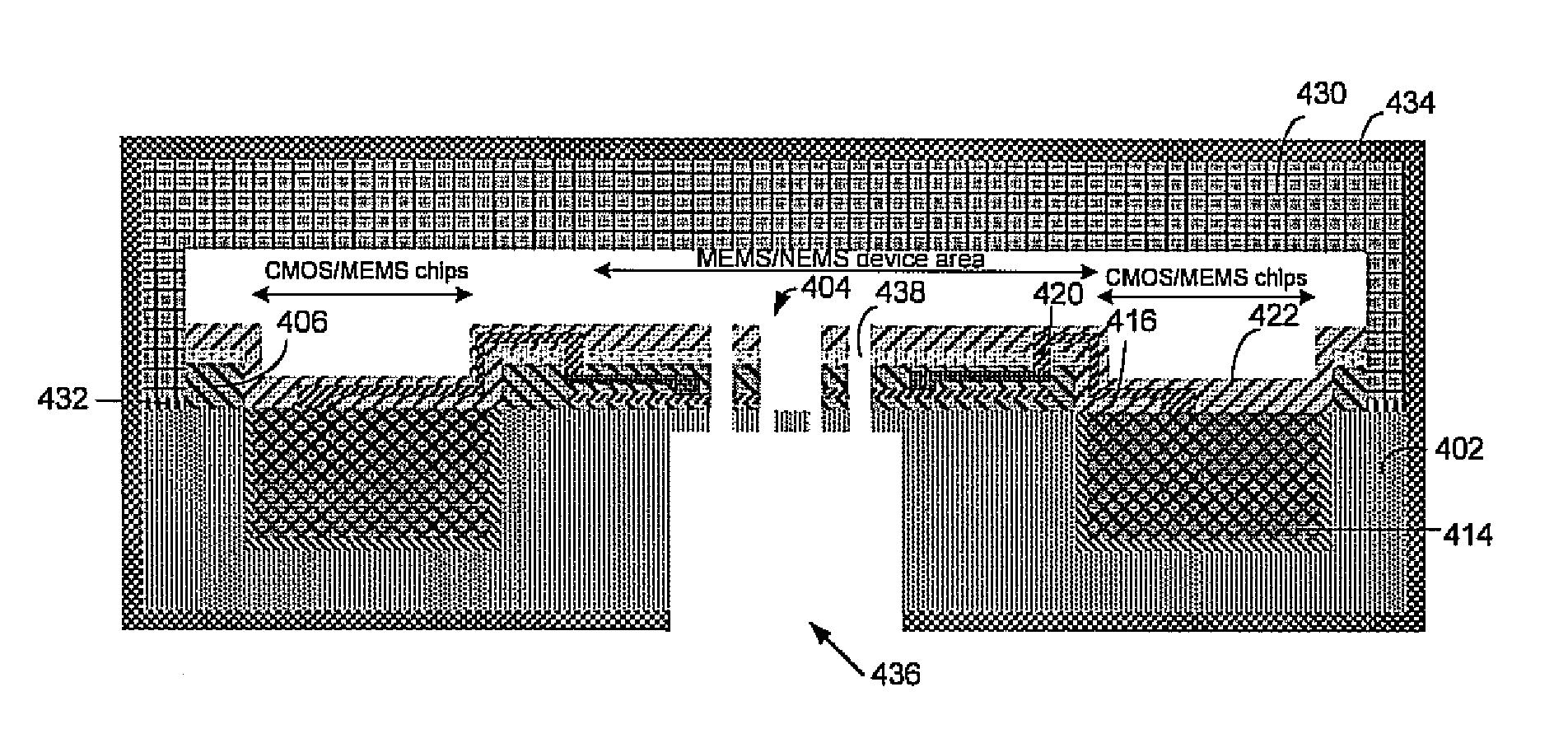

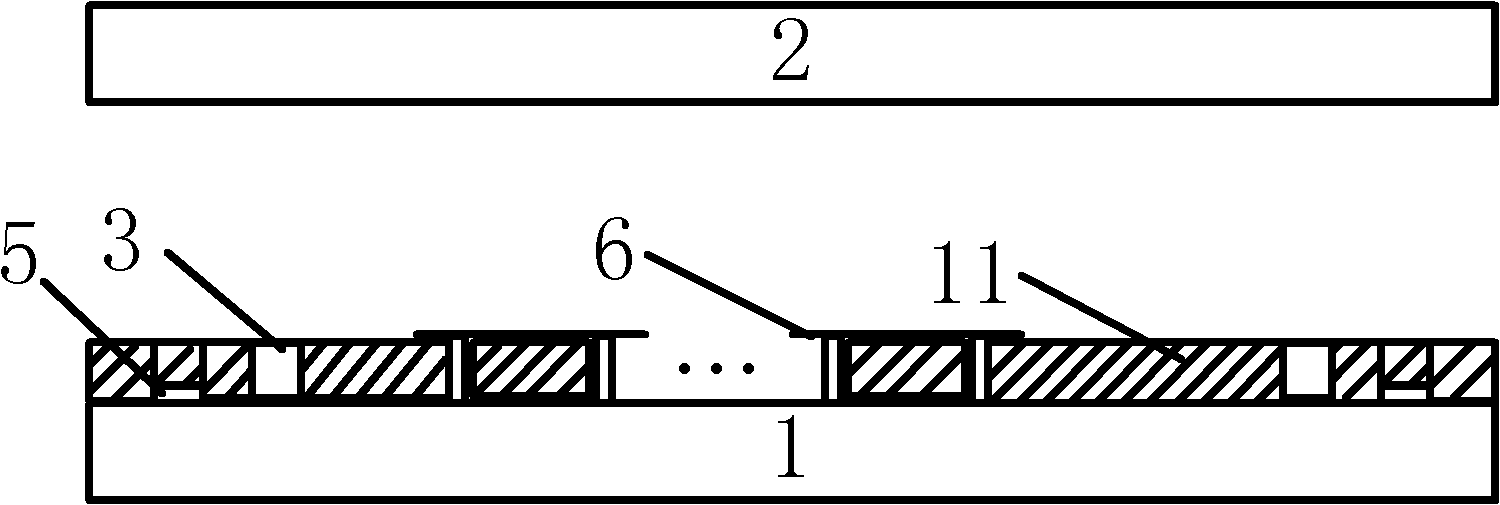

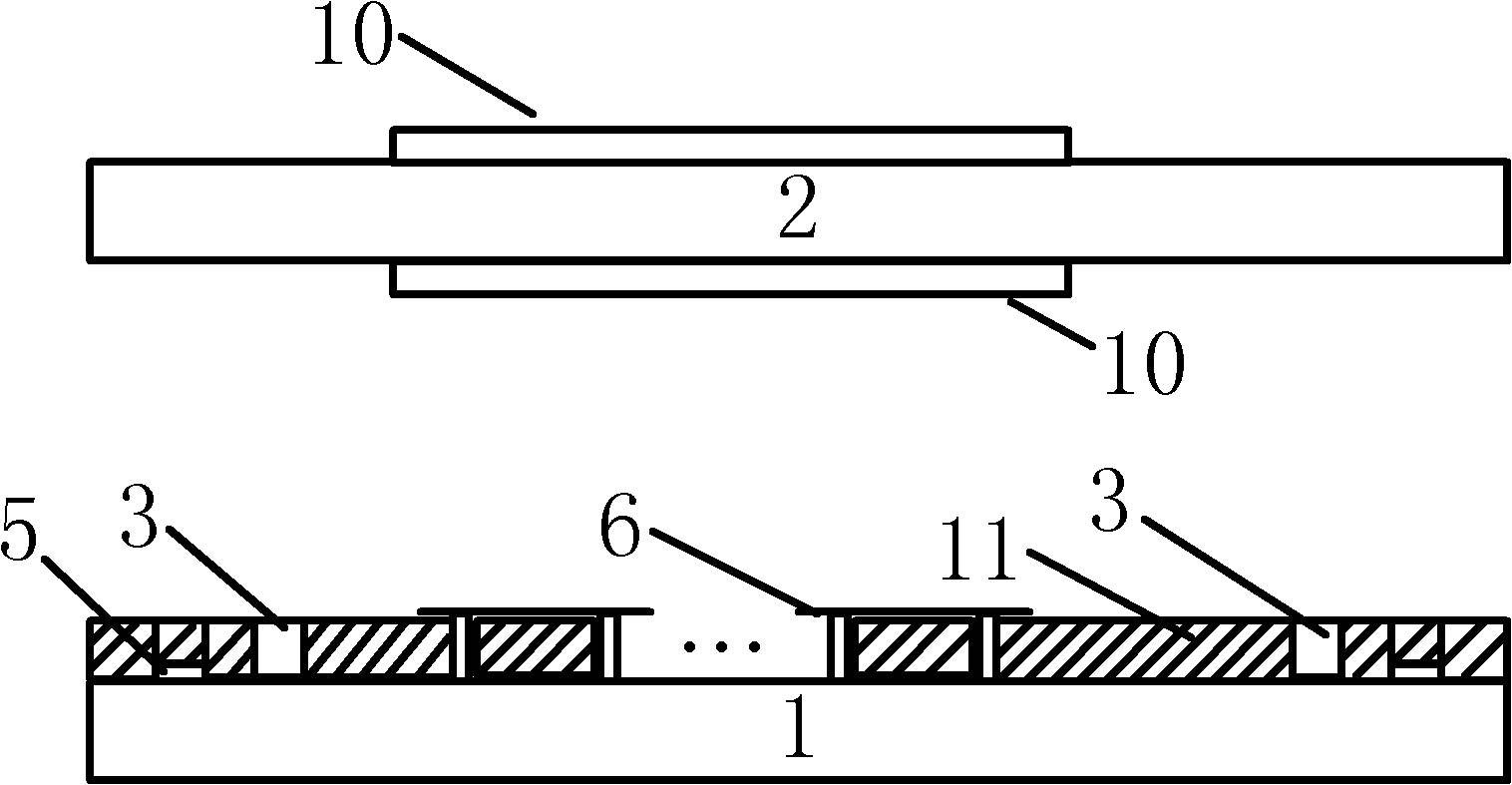

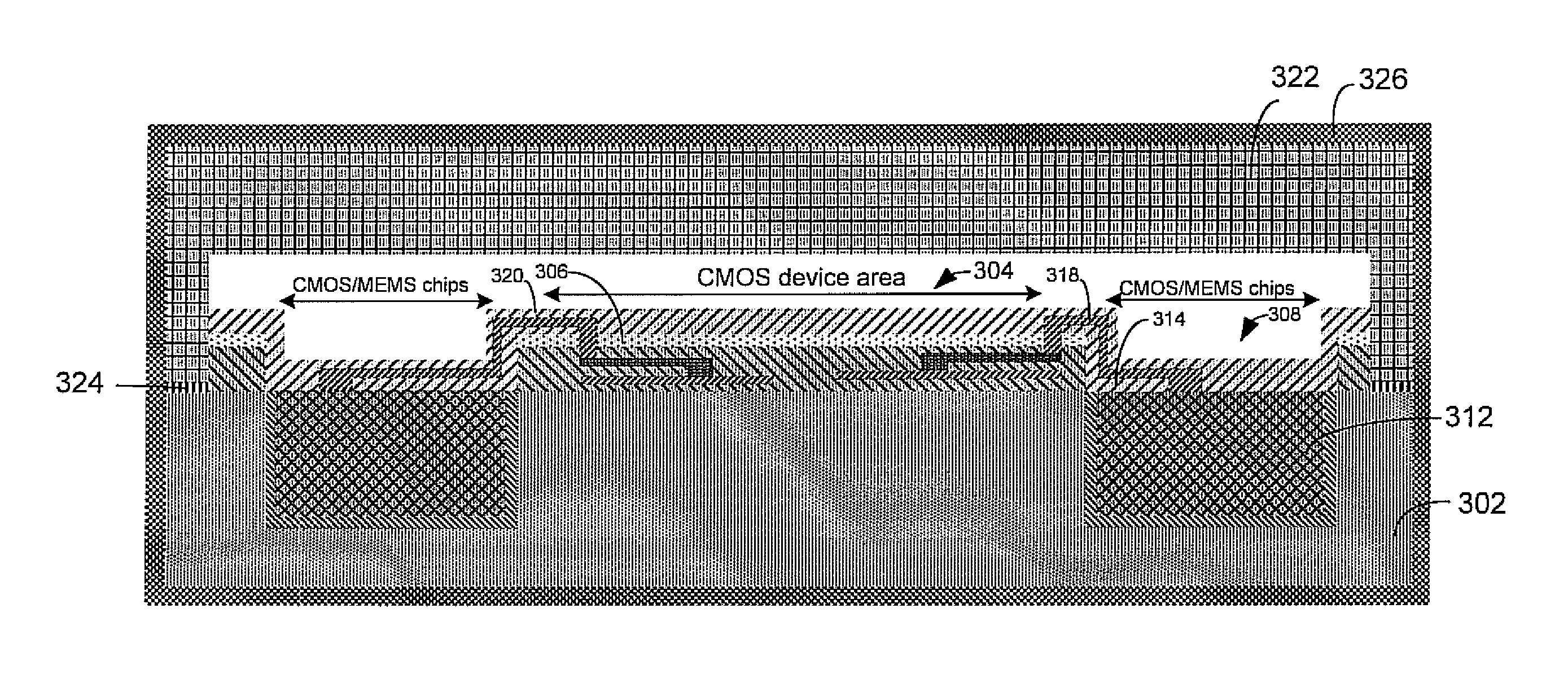

A method of forming Monolithic CMOS-MEMS hybrid integrated, packaged structures includes the steps of providing: providing a semiconductor substrate with pre-fabricated cmos circuits on the front side and a polished back-side with through substrate conductive vias; forming at least one opening in the polished backside of the semiconductor substrate by appropriately protecting the front-side; applying at least one filler material in the at least one opening on the semiconductor substrate; positioning at least one prefabricated mems, nems or cmos chip on the filler material, the chip including a front face and a bare back face with the prefabricated mems / nems chips containing mechanical and dielectric layers; applying at least one planarization layer overlying the substrate, filler material and the chip; forming at least one via opening on a portion of the planarization layer interfacing pads on the chip and the through substrate conductive vias; applying at least one metallization layer overlying the planarization layer on the substrate and the chip connecting the through substrate conductive vias to the at least one chip; applying at least one second insulating layer overlying the metallization layer; performing at least one micro / nano fabrication etching step to release the mechanical layer on the prefabricated mems / nems chips; positioning protective cap to package the integrated device over the mems / nems device area on the pre-fabricated chips.

Owner:AMF NANO

Method of forming monolithic cmos-mems hybrid integrated, packaged structures

InactiveUS20110003422A1Solid-state devicesSemiconductor/solid-state device manufacturingCmos memsProtection layer

A method of forming Monolithic CMOS-MEMS hybrid integrated, packaged structures includes the steps of providing: providing at least one semiconductor substrate having a CMOS device area including dielectric layers and metallization layers; applying at least one protective layer overlying the CMOS device area; forming at least one opening on the protective layer and patterning the dielectric and metallization layers to access the semiconductor substrate; forming at least one opening on the semiconductor substrate by etching the dielectric and metallization layers; applying at least one filler layer in the at least one opening on the semiconductor substrate; positioning at least one chip on the filler layer, the chip including a prefabricated front face and a bare backside; applying a first insulating layer covering the front face of the chip providing continuity from the semiconductor substrate to the chip; forming at least one via opening on the insulating layer covering the chip to access at least one contact area; applying at least one metallization layer overlying the insulating layer on the substrate and the chip connecting the metallization layer on the substrate to the at least one another contact area on the chip; applying a second insulating layer overlying the metallization layer on the at least one chip; applying at least one interfacial layer; applying at least one rigid substrate overlying the interfacial layer; and applying at least one secondary protective layer overlying the rigid substrate.

Owner:AMF NANO

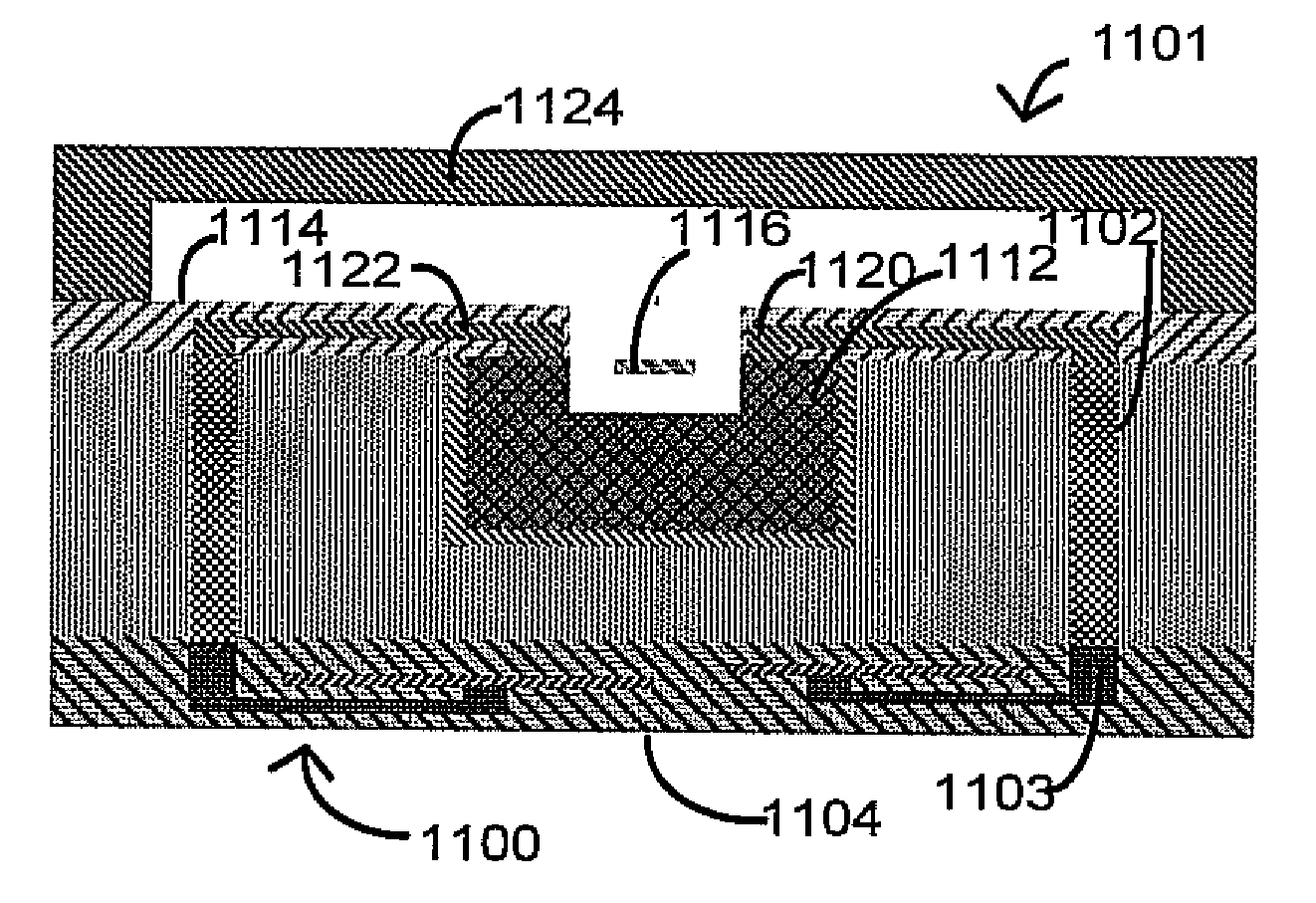

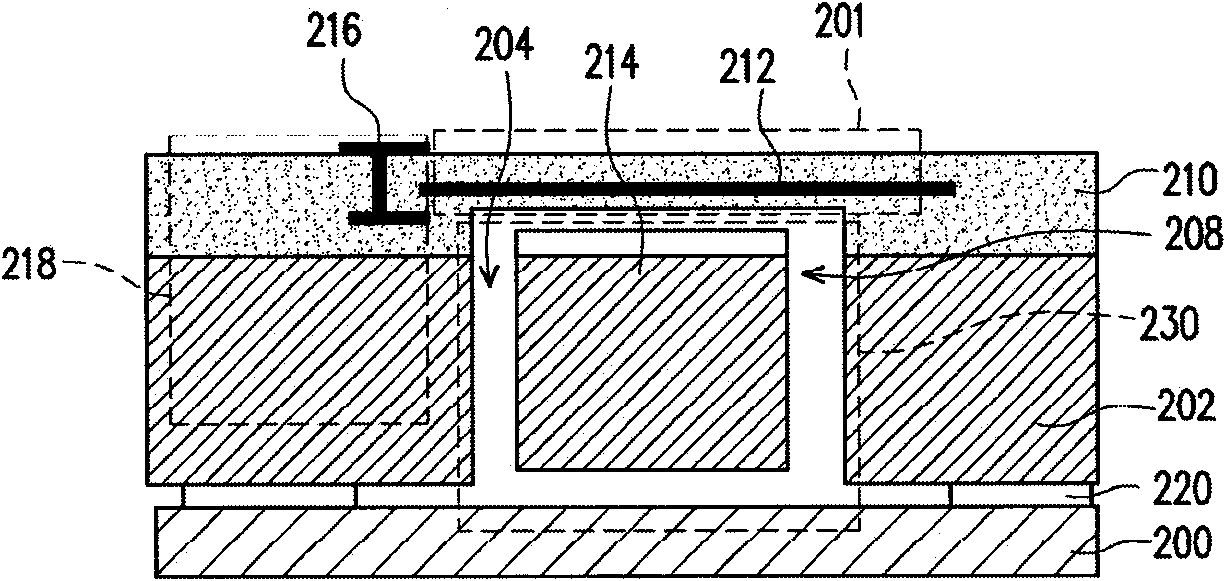

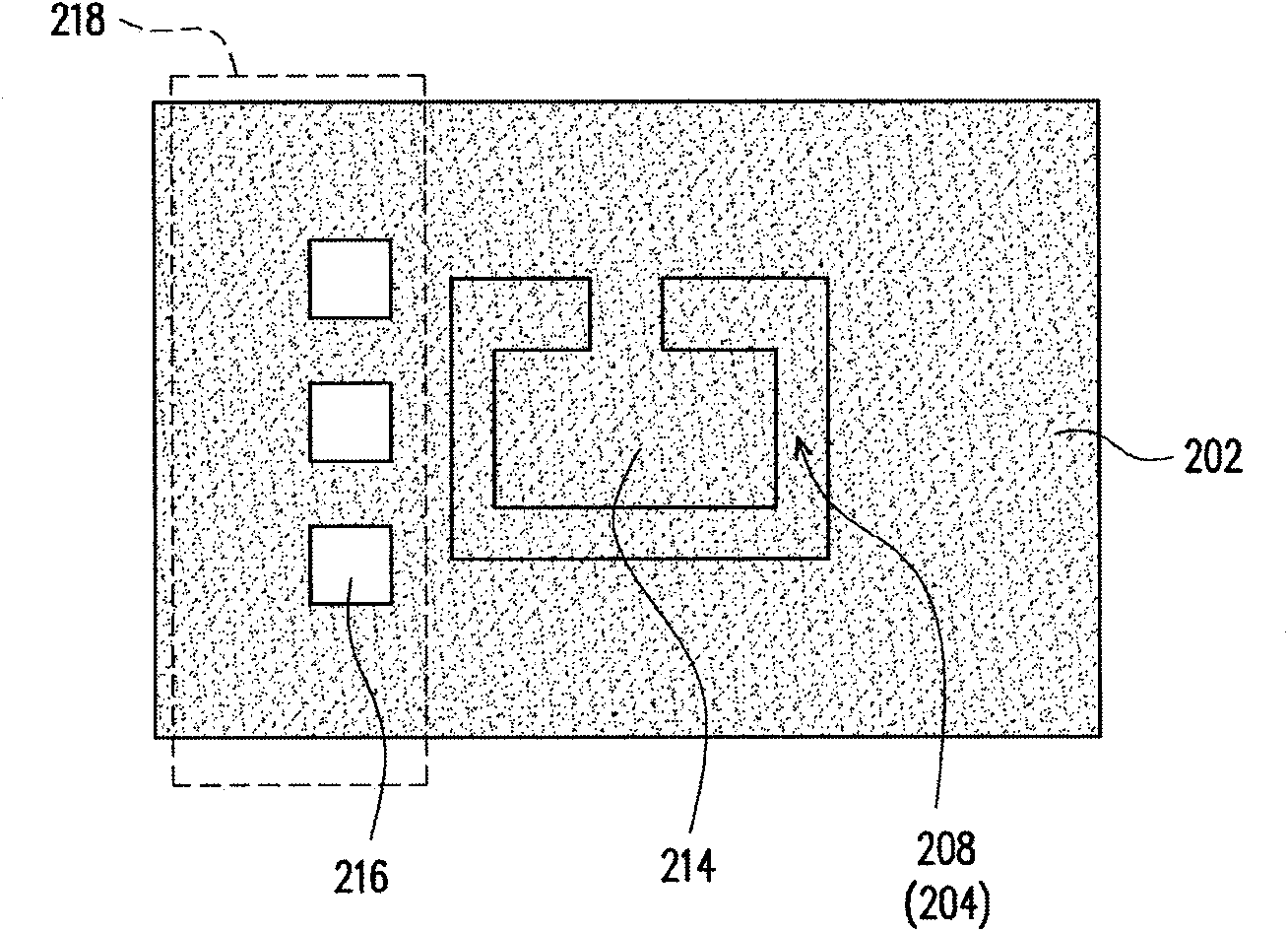

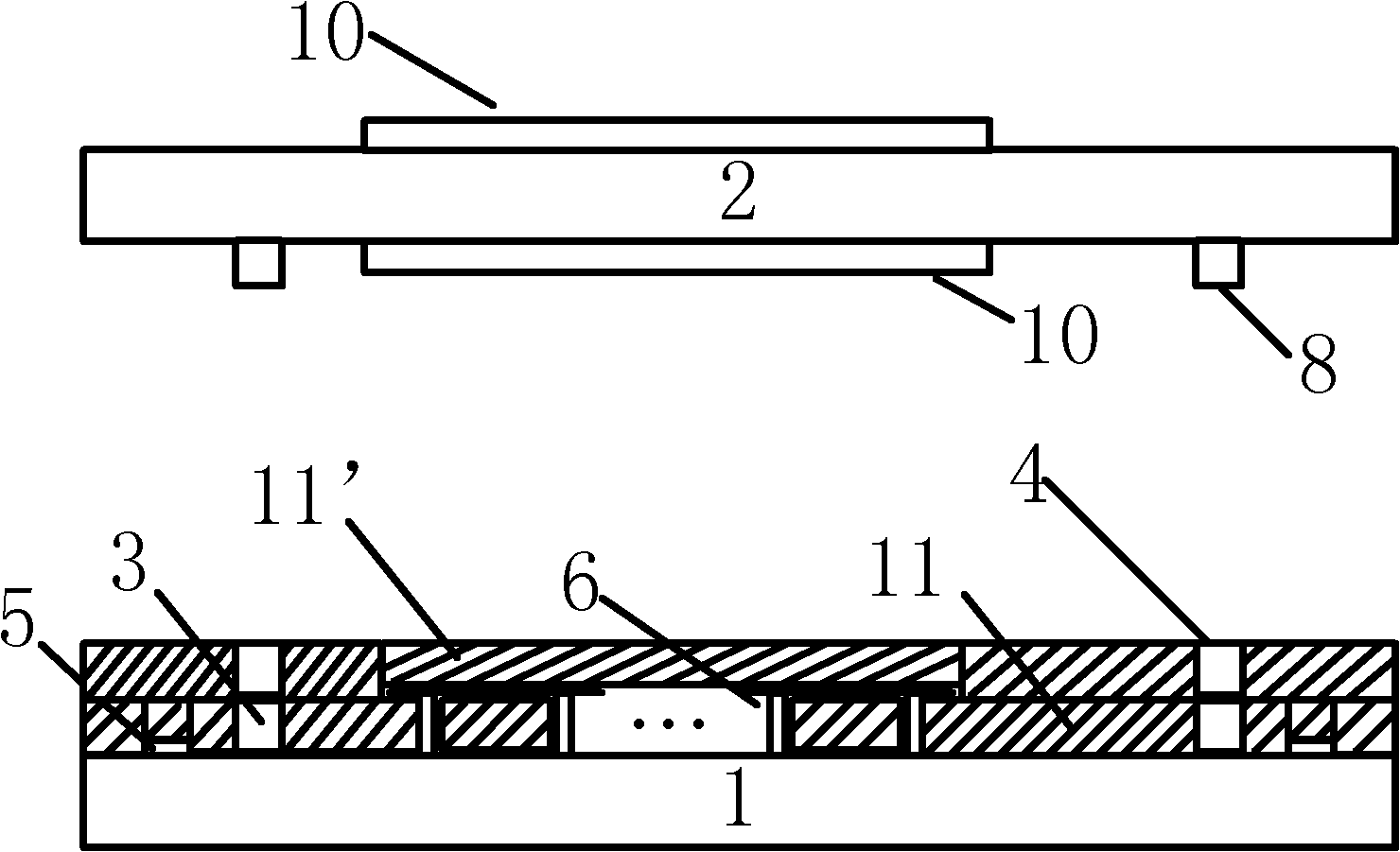

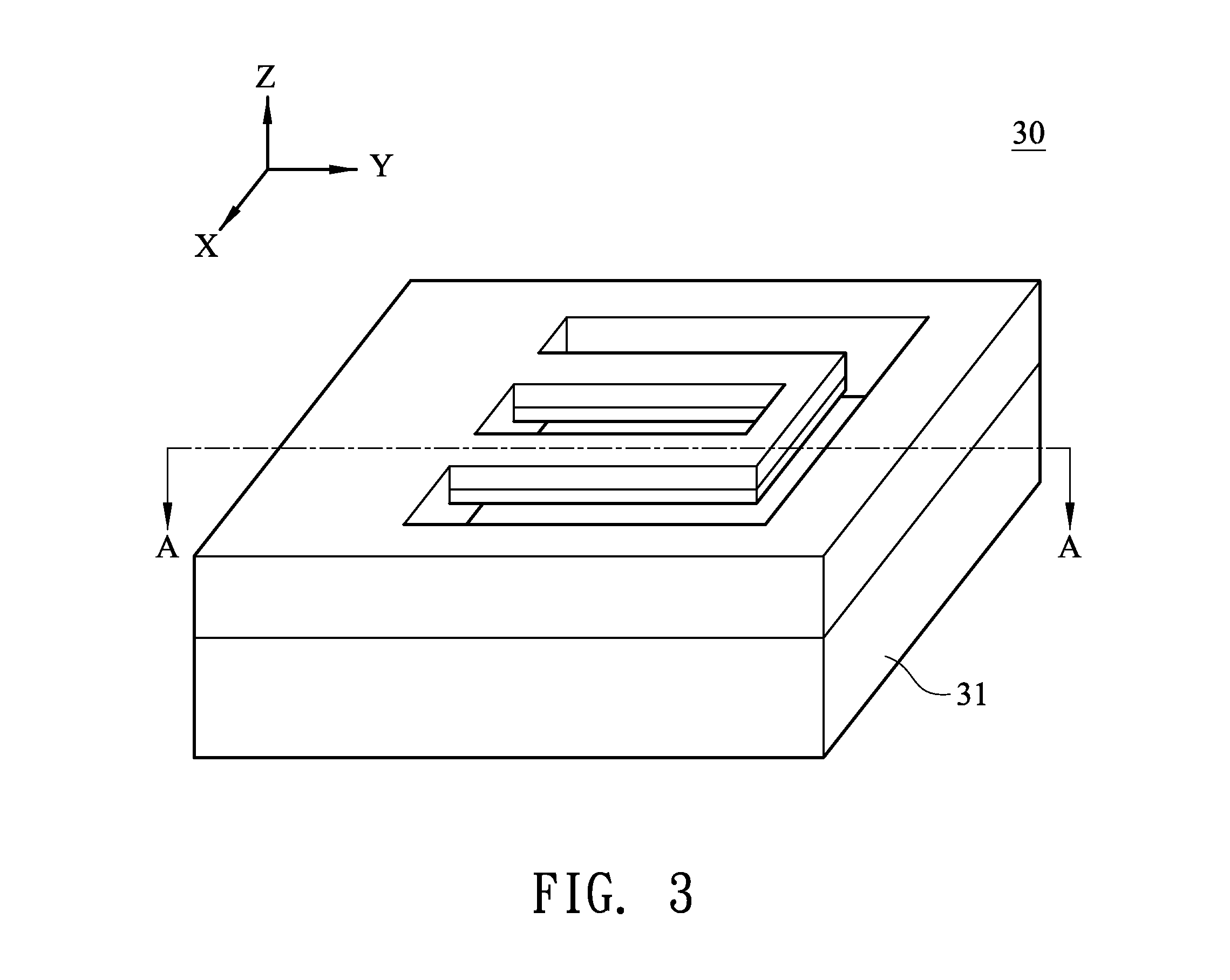

Hermetic MEMS device and method for fabricating hermetic MEMS device and package structure of MEMS device

A hermetic microelectromechanical system (MEMS) package includes a CMOS MEMS chip and a second substrate. The CMOS MEMS Chip has a first substrate, a structural dielectric layer, a CMOS circuit and a MEMS structure. The structural dielectric layer is disposed on a first side of the first structural substrate. The structural dielectric layer has an interconnect structure for electrical interconnection and also has a protection structure layer. The first structural substrate has at least a hole. The hole is under the protection structure layer to form at least a chamber. The chamber is exposed to the environment in the second side of the first structural substrate. The chamber also comprises a MEMS structure. The second substrate is adhered to a second side of the first substrate over the chamber to form a hermetic space and the MEMS structure is within the space.

Owner:SOLID STATE SYST

Hermetic MEMS device and method for fabricating hermetic MEMS device and package structure of MEMS device

A hermetic microelectromechanical system (MEMS) package includes a CMOS MEMS chip and a second substrate. The CMOS MEMS Chip has a first substrate, a structural dielectric layer, a CMOS circuit and a MEMS structure. The structural dielectric layer is disposed on a first side of the first structural substrate. The structural dielectric layer has an interconnect structure for electrical interconnection and also has a protection structure layer. The first structural substrate has at least a hole. The hole is under the protection structure layer to form at least a chamber. The chamber is exposed to the environment in the second side of the first structural substrate. The chamber also comprises a MEMS structure. The second substrate is adhered to a second side of the first substrate over the chamber to form a hermetic space and the MEMS structure is within the space.

Owner:SOLID STATE SYST

MEMS digital-to-acoustic transducer with error cancellation

InactiveUS20050013455A1Low production costSmall sizeTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesTransducerEngineering

An acoustic transducer comprising a substrate; and a diaphragm formed by depositing a micromachined membrane onto the substrate. The diaphragm is formed as a single silicon chip using a CMOS MEMS (microelectromechanical systems) semiconductor fabrication process. The curling of the diaphragm during fabrication is reduced by depositing the micromachined membrane for the diaphragm in a serpentine-spring configuration with alternating longer and shorter arms. As a microspeaker, the acoustic transducer of the present invention converts a digital audio input signal directly into a sound wave, resulting in a very high quality sound reproduction at a lower cost of production in comparison to conventional acoustic transducers. The micromachined diaphragm may also be used in microphone applications.

Owner:CARNEGIE MELLON UNIV

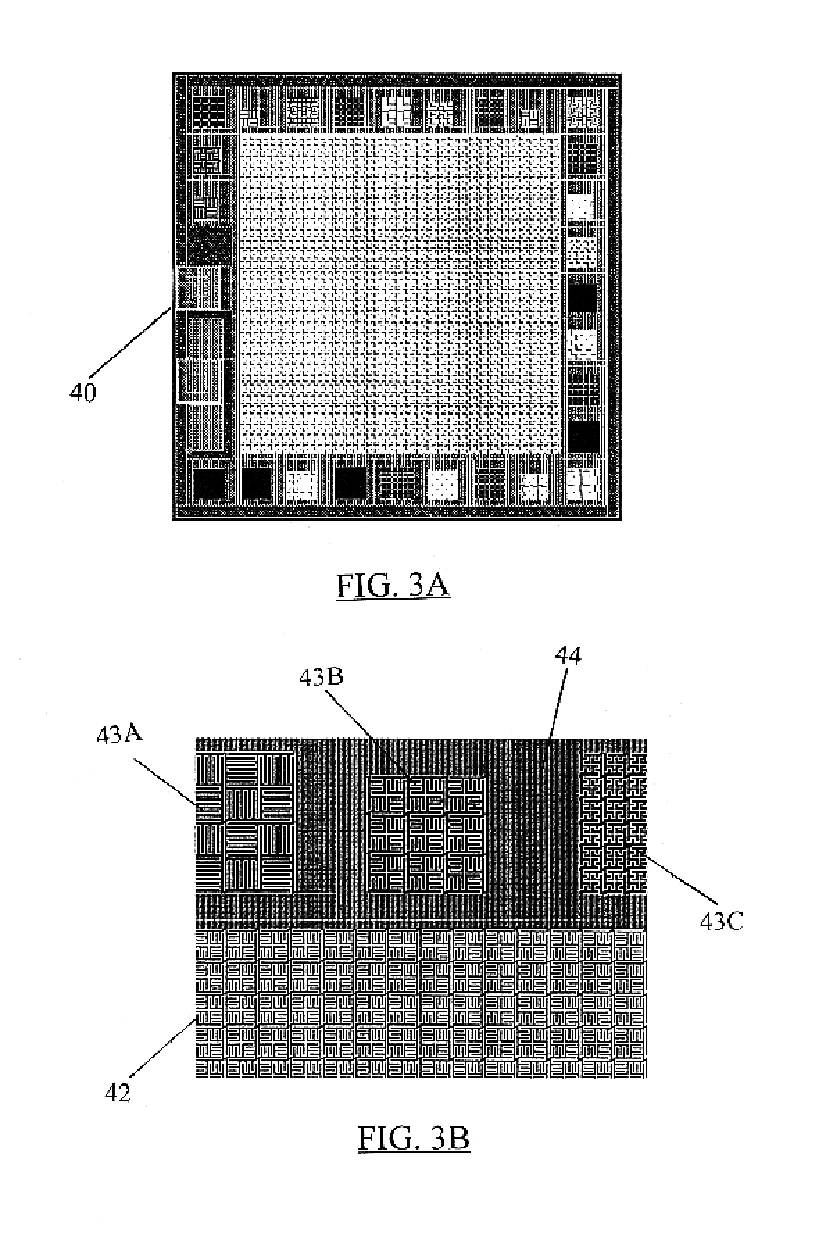

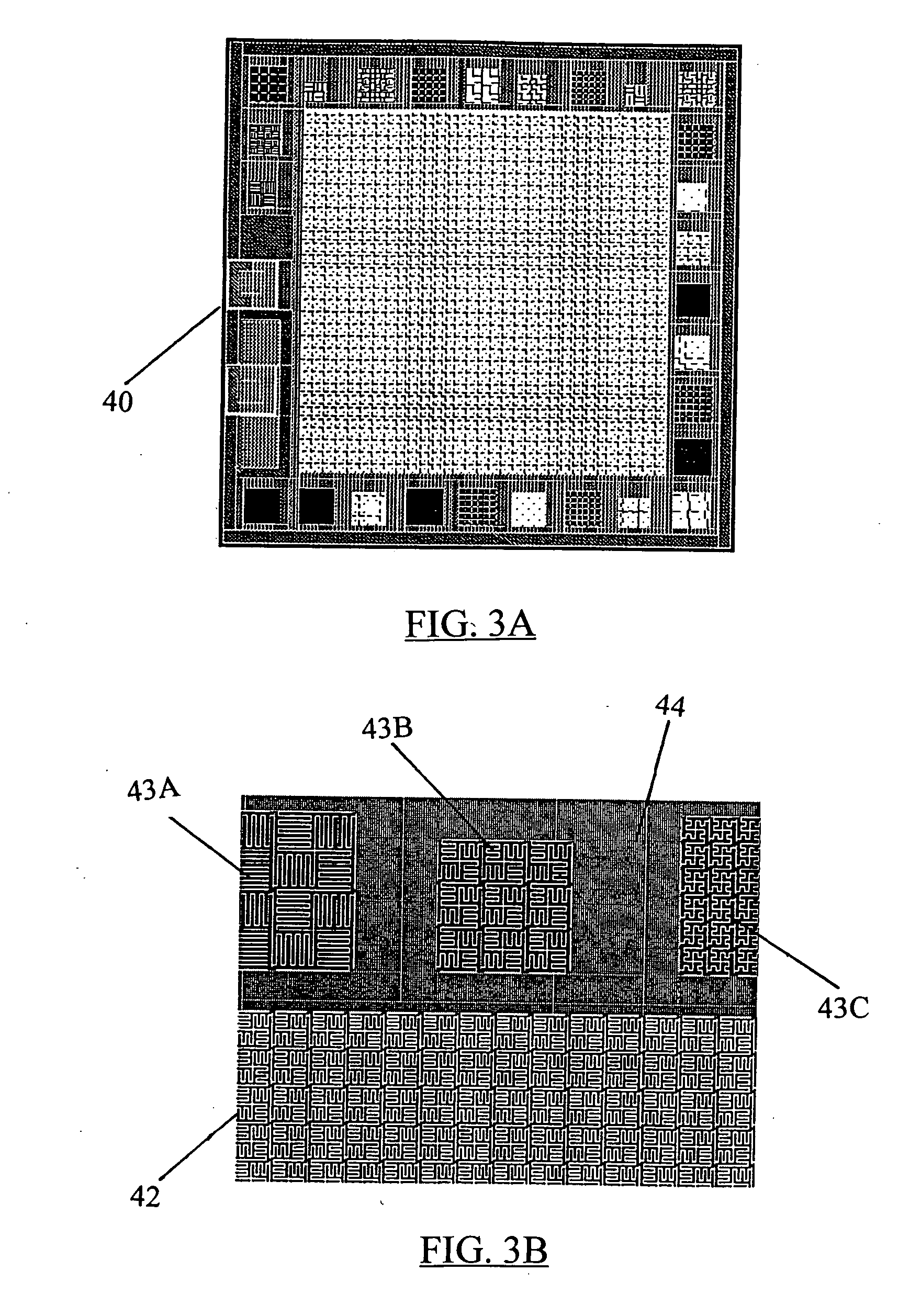

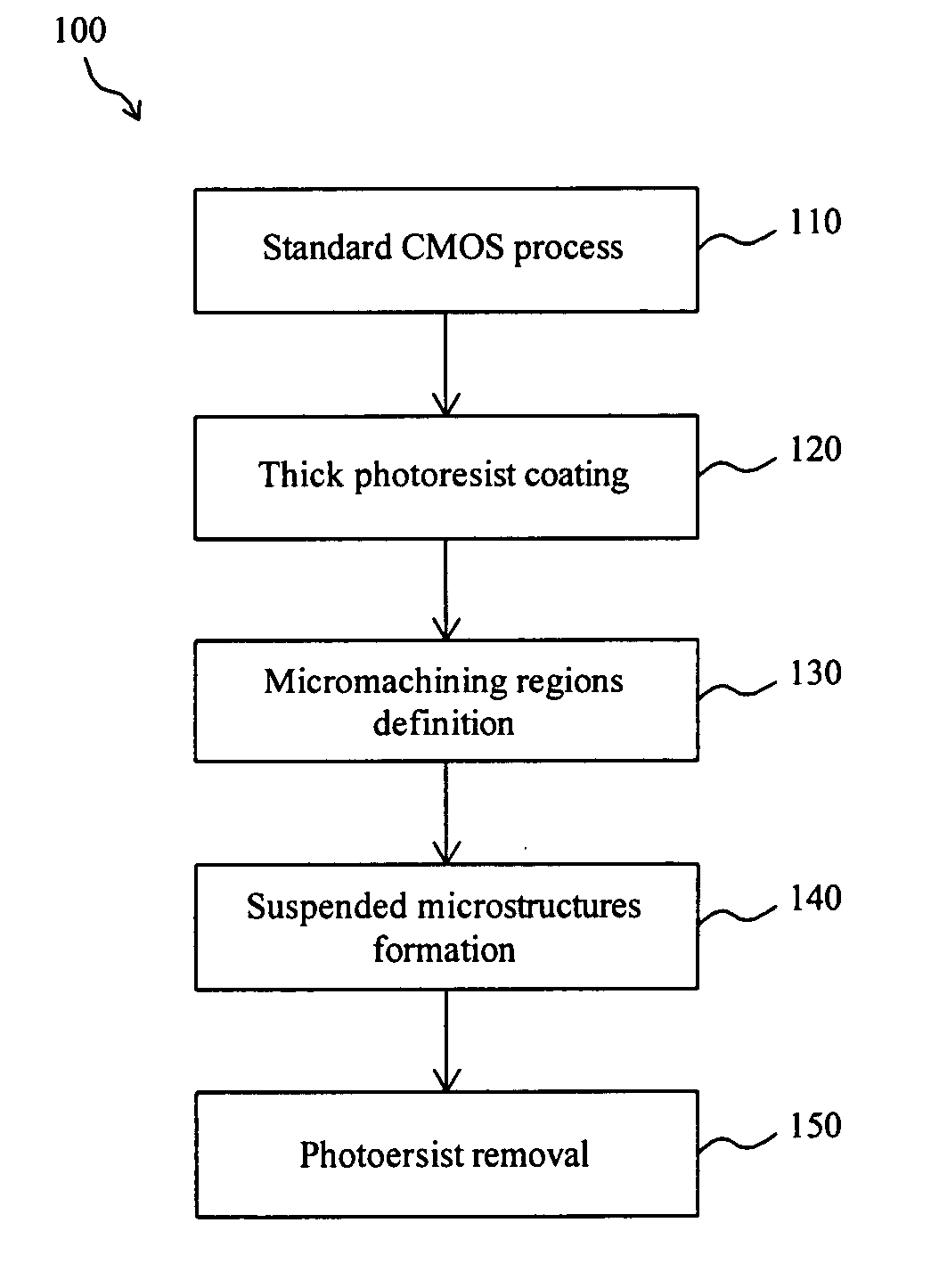

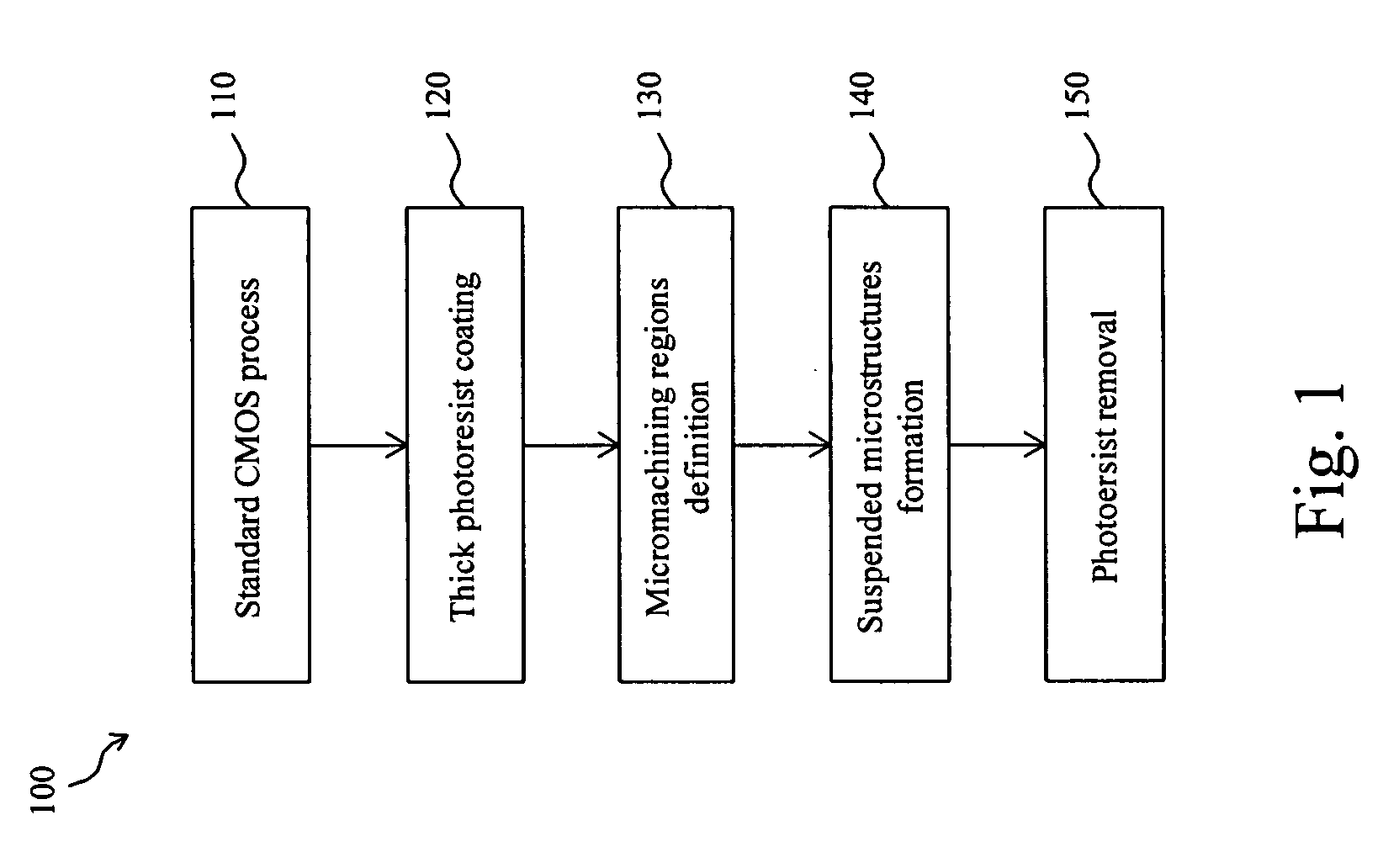

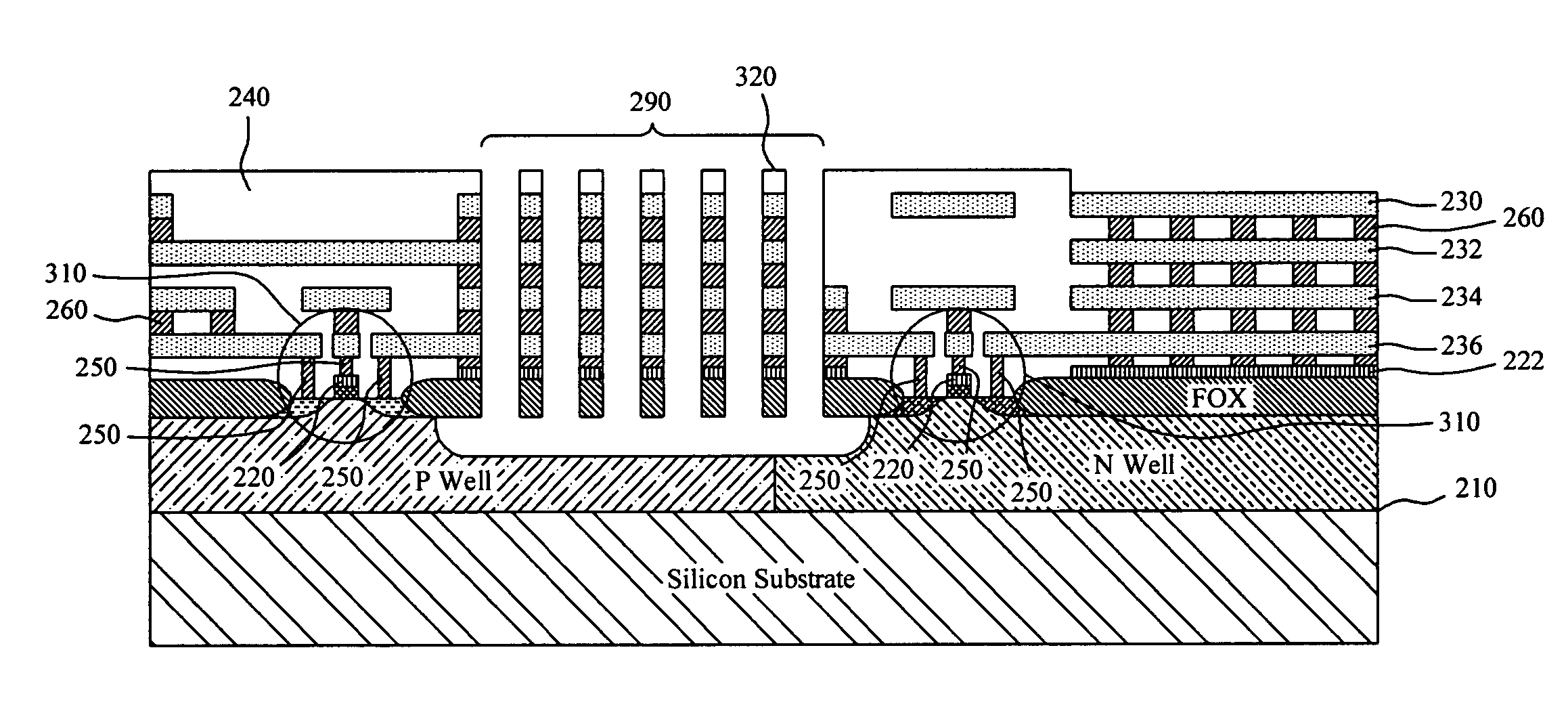

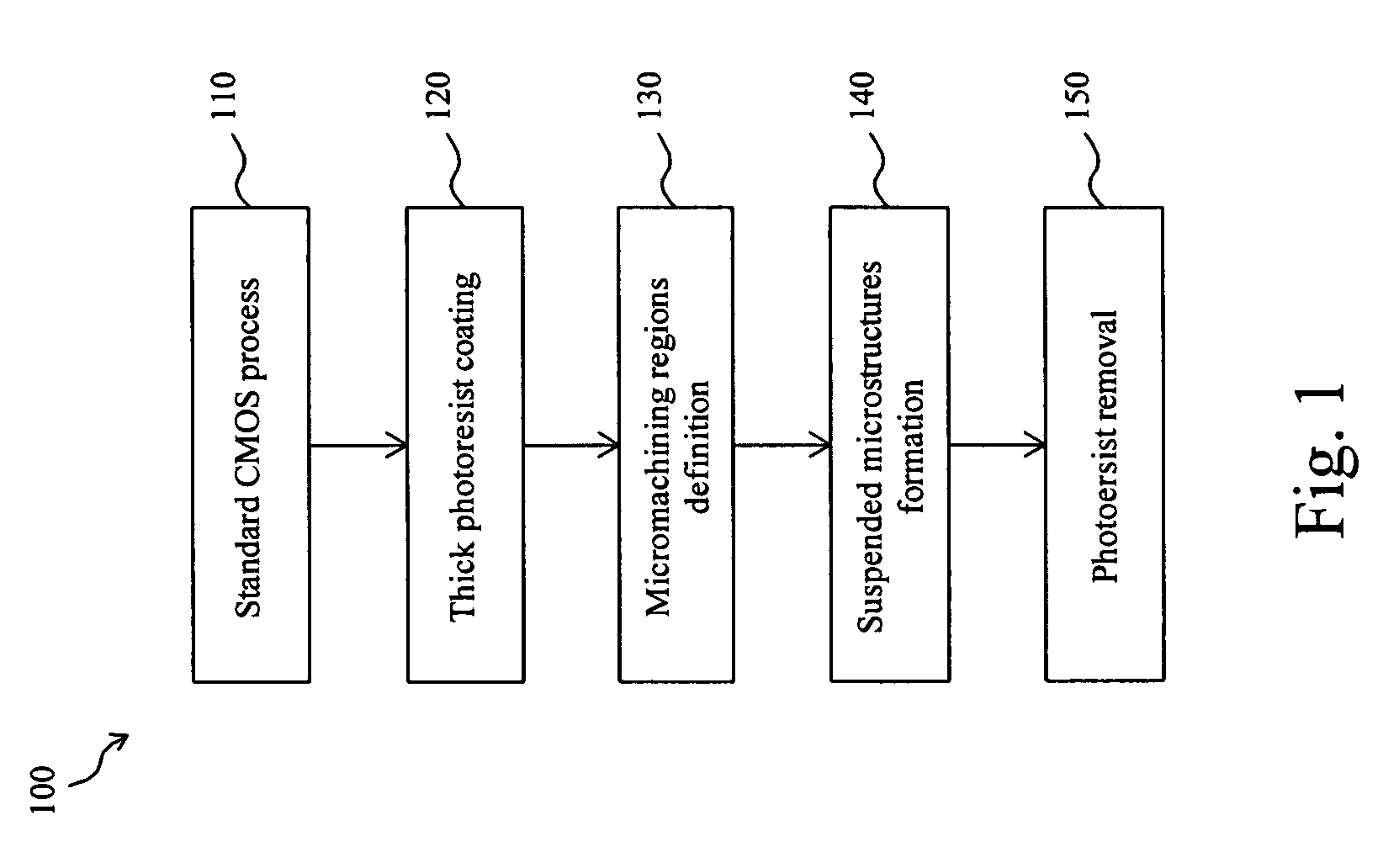

CMOS-MEMS process

ActiveUS20060105543A1Avoid disadvantagesIncreased processing flexibilitySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringCmos mems

A fully CMOS compatible MEMS multi-project wafer process comprises coating a layer of thick photoresist on a wafer surface, patterning the photoresist to define a micromachining region, and performing a micromachining in the micromachining region to form suspended microstructures.

Owner:NAT APPLIED RES LAB

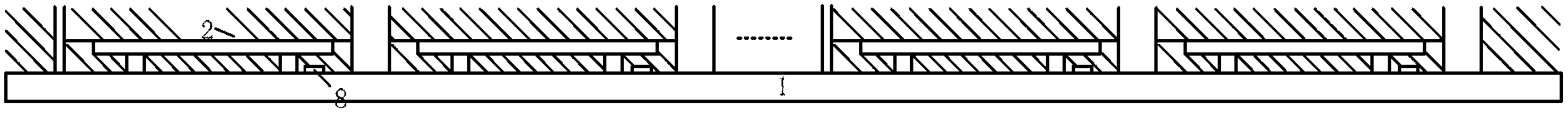

CMOS-MEMS switch structure

InactiveUS8451078B2Avoid failureDistanceElectrothermal relaysSolid-state devicesEngineeringCmos mems

Owner:NAT APPLIED RES LAB

Novel CMOS-MEMS compatible uncooled infrared sensor pixel level packaging method

InactiveCN102935994AImprove compatibilityImprove performanceDecorative surface effectsChemical vapor deposition coatingFilling materialsOptoelectronics

The present invention relates to a novel CMOS-MEMS compatible uncooled infrared sensor pixel level packaging method, which can be performed according to the following steps: preparing a second sacrificial layer on a first sacrificial layer of a device wafer, and carrying out a graphical treatment; respectively preparing an infrared antireflection film and an infrared permeation layer on the second sacrificial layer by using a film preparation technology, and respectively etching a small hole on the infrared antireflection film and the infrared permeation layer; preparing a third sacrificial layer on the infrared permeation layer, and carrying out a graphical treatment; preparing an infrared antireflection film on the third sacrificial layer, and etching a small hole on the infrared antireflection film to be adopted as a release hole; and removing all the sacrificial layers through the release hole, sealing the release hole by using a hole filling material, and carrying out scribing to prepare the finished product. With the process, packaging cost of the uncooled infrared detector can be further reduced, and mass applications of the uncooled infrared detector can be easily achieved.

Owner:WUHAN GUIDE INFRARED CO LTD

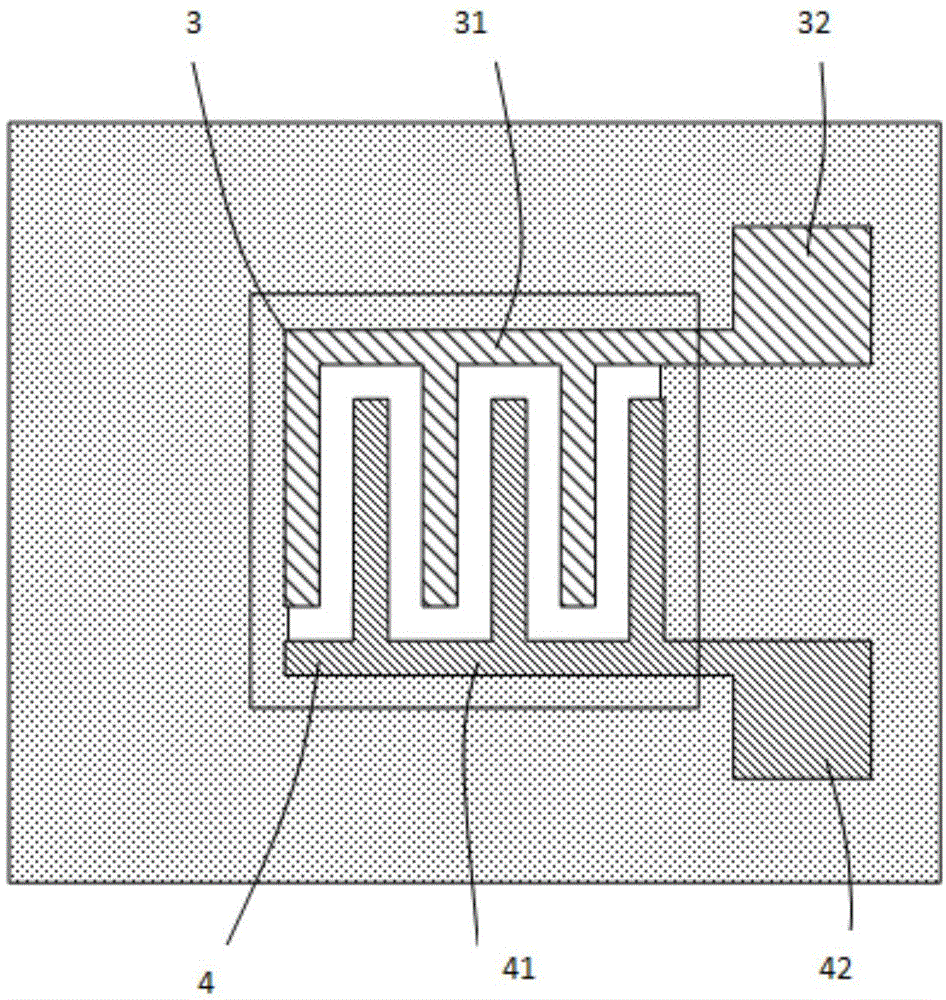

CMOS-MEMS (complementary metal oxide semiconductor-micro-electromechanical system) capacitive humidity sensor

The invention relates to a CMOS-MEMS (complementary metal oxide semiconductor-micro-electromechanical system) capacitive humidity sensor which is characterized by comprising upper interdigital electrodes and lower interdigital electrodes, wherein the lower electrodes penetrate a SiO2 oxide layer and are arranged on the same surface of a silicon substrate; the upper electrodes are arranged above the lower electrodes; humidity-sensitive mediums are filled between the upper electrodes and the lower electrodes, between the interdigital parts of the upper electrodes and between the interdigital parts of the lower electrodes; aluminum strips are arranged above the upper electrodes and positioned between the interdigital parts of the upper electrodes and the lower electrodes; humidity-sensitive mediums are filled between the aluminum strips and the upper electrodes; a cavity is formed in the silicon substrate under the upper electrodes and the lower electrodes, so that the lower electrodes and the humidity-sensitive mediums between the interdigital parts of the lower electrodes are directly in contact with the air; the interdigital parts of the upper electrodes and the interdigital parts of the lower electrodes coincide in the height direction; the humidity-sensitive mediums are polyimide. The CMOS-MEMS capacitive humidity sensor is quick in response, high in sensitivity, wide in output range, high-temperature-resistant, small in humidity error and good in temperature characteristic and long stability.

Owner:中科芯未来微电子科技成都有限公司

Integrated system on chip using multiple MEMS and CMOS devices

ActiveUS8823007B2Easy to useHigh device yieldVibration measurement in solidsMaterial analysis using sonic/ultrasonic/infrasonic wavesEngineeringCmos mems

Owner:MOVELLA INC

Methods and structure for adapting MEMS structures to form electrical interconnections for integrated circuits

ActiveUS8652961B1Improve protectionHigh currentSolid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorInterconnection

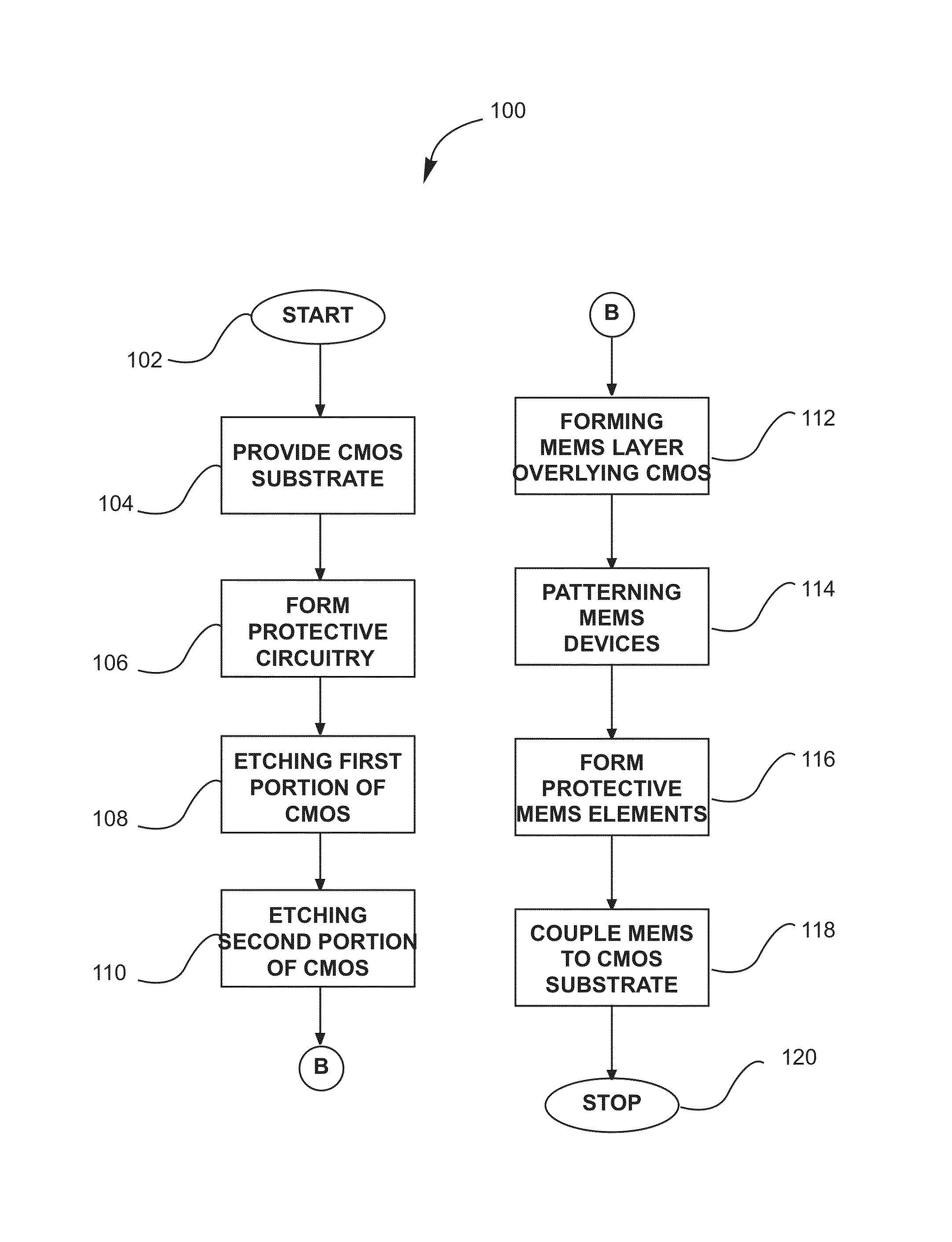

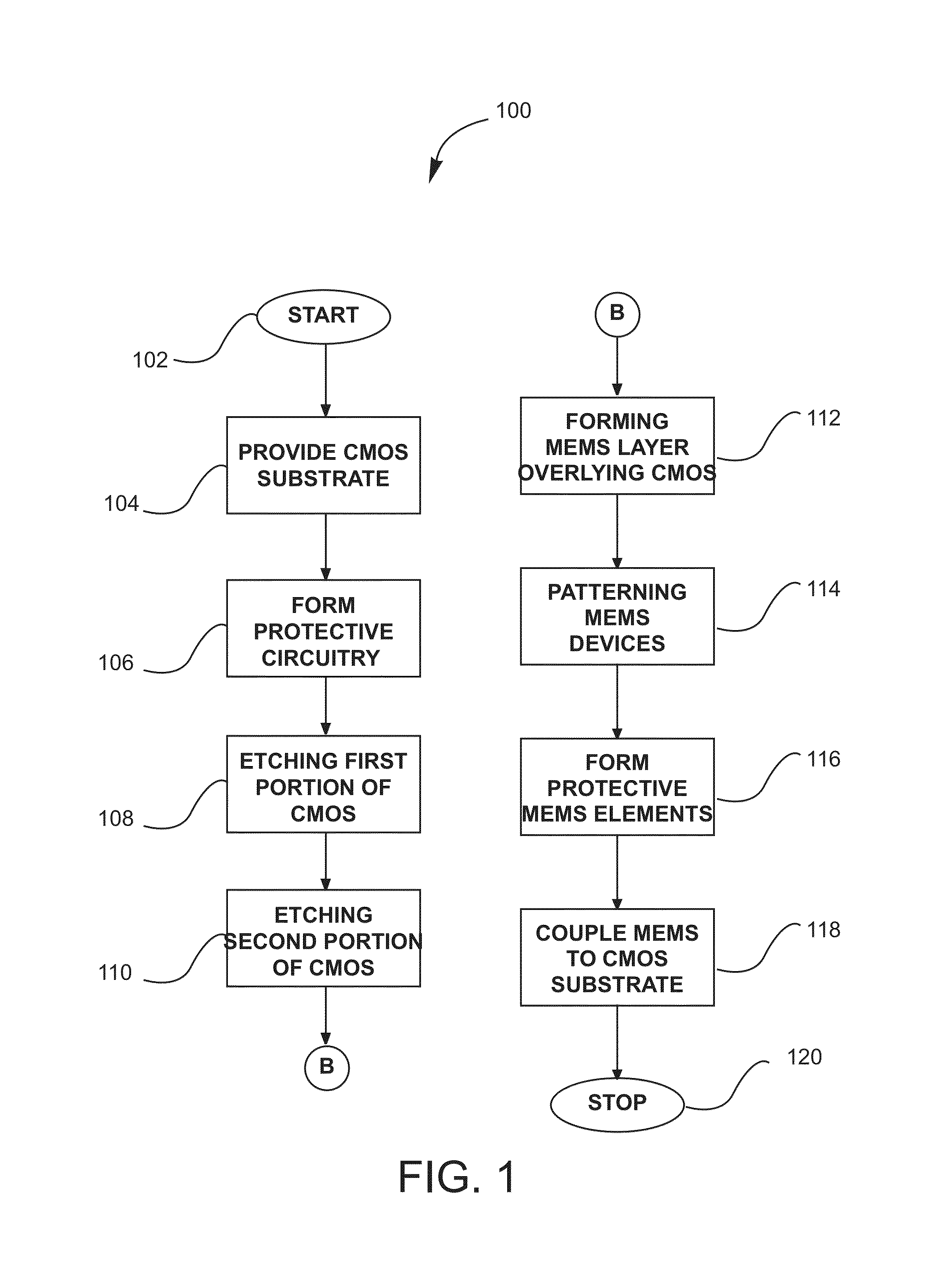

Methods and structure for adapting MEMS structures to form electrical interconnections for integrated circuits. A first portion and a second portion of the metal conductor, which can be electrically isolated within a CMOS IC device, can be etched to form an unetched portion of the metal conductor. The MEMS device can be patterned, from a MEMS layer formed overlying the metal conductor, via a plasma etching process, during which the unetched portion of the metal conductor is protected from the plasma. The metal conductor can be electrically coupled to the CMOS IC device via a conductive jumper or the like. Furthermore, the integrated CMOS-MEMS device can include a MEMS device coupled to a CMOS IC device via an electrically isolated metal conductor within the CMOS IC device. Also, the metal conductor can be electrically coupled to the substrate of the CMOS IC device via a conductive jumper.

Owner:MOVELLA INC

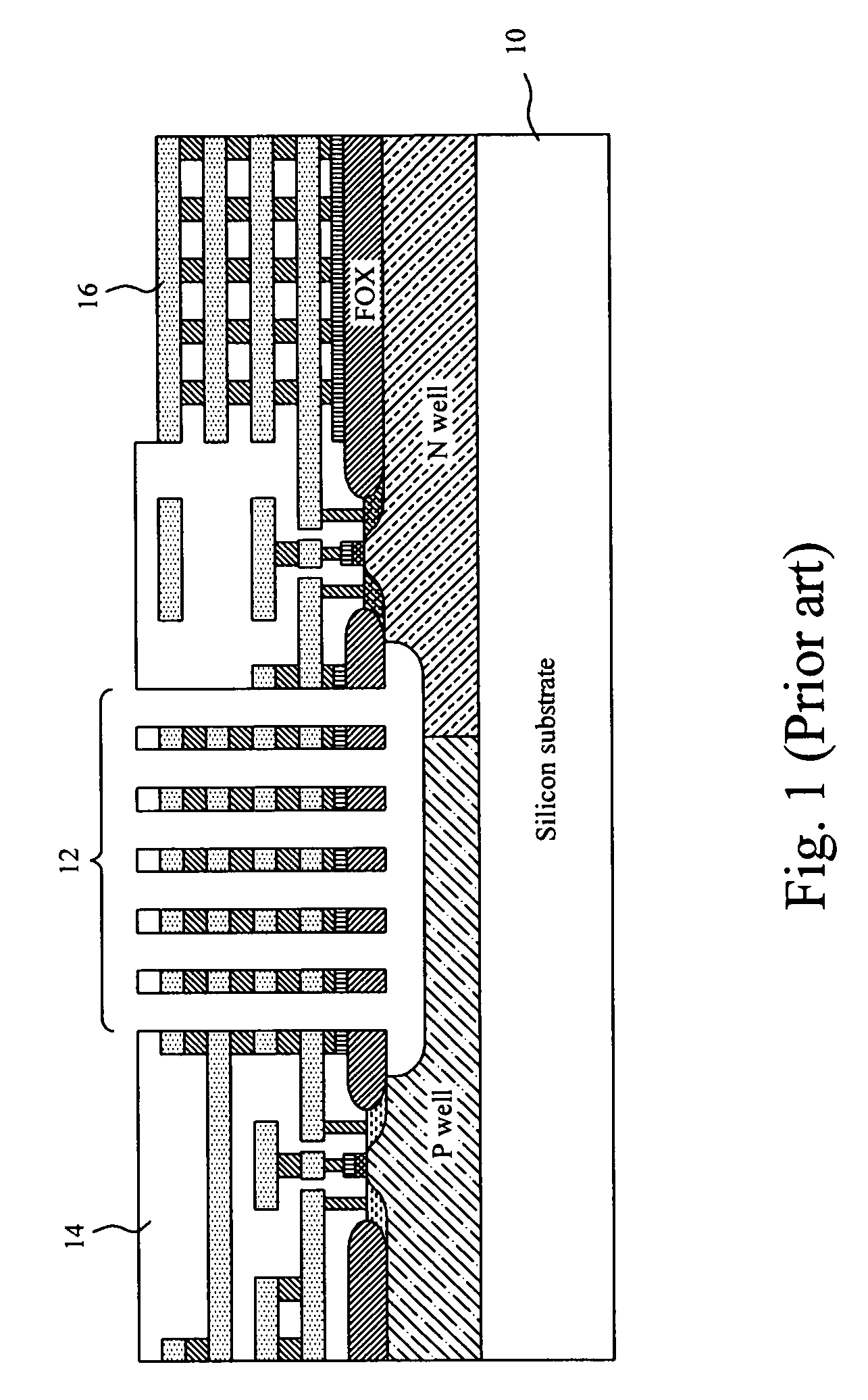

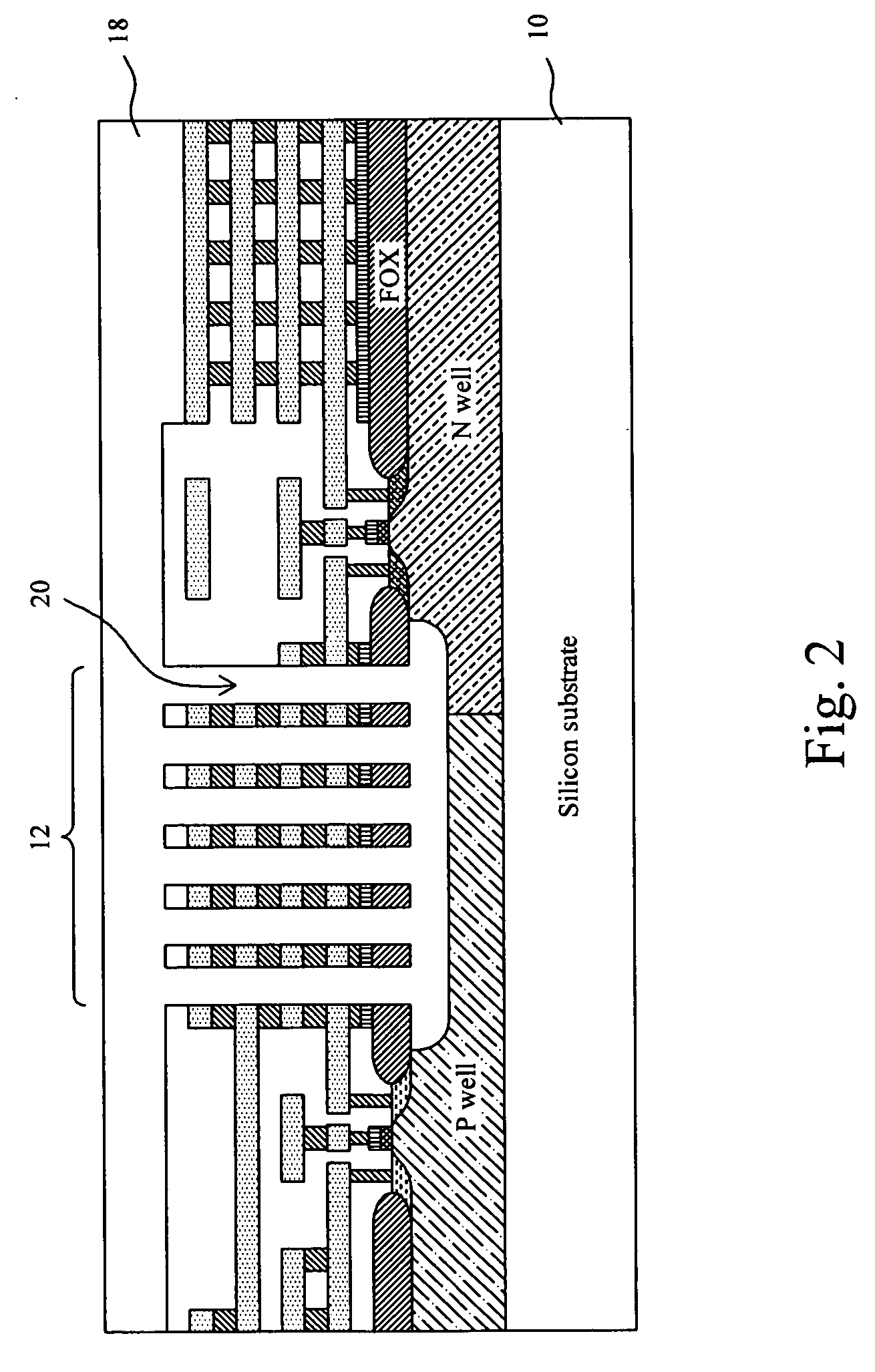

Methods for dicing a released CMOS-MEMS multi-project wafer

InactiveUS20060105545A1Improve reliabilitySemiconductor/solid-state device manufacturingMicrostructural device manufactureEngineeringCmos mems

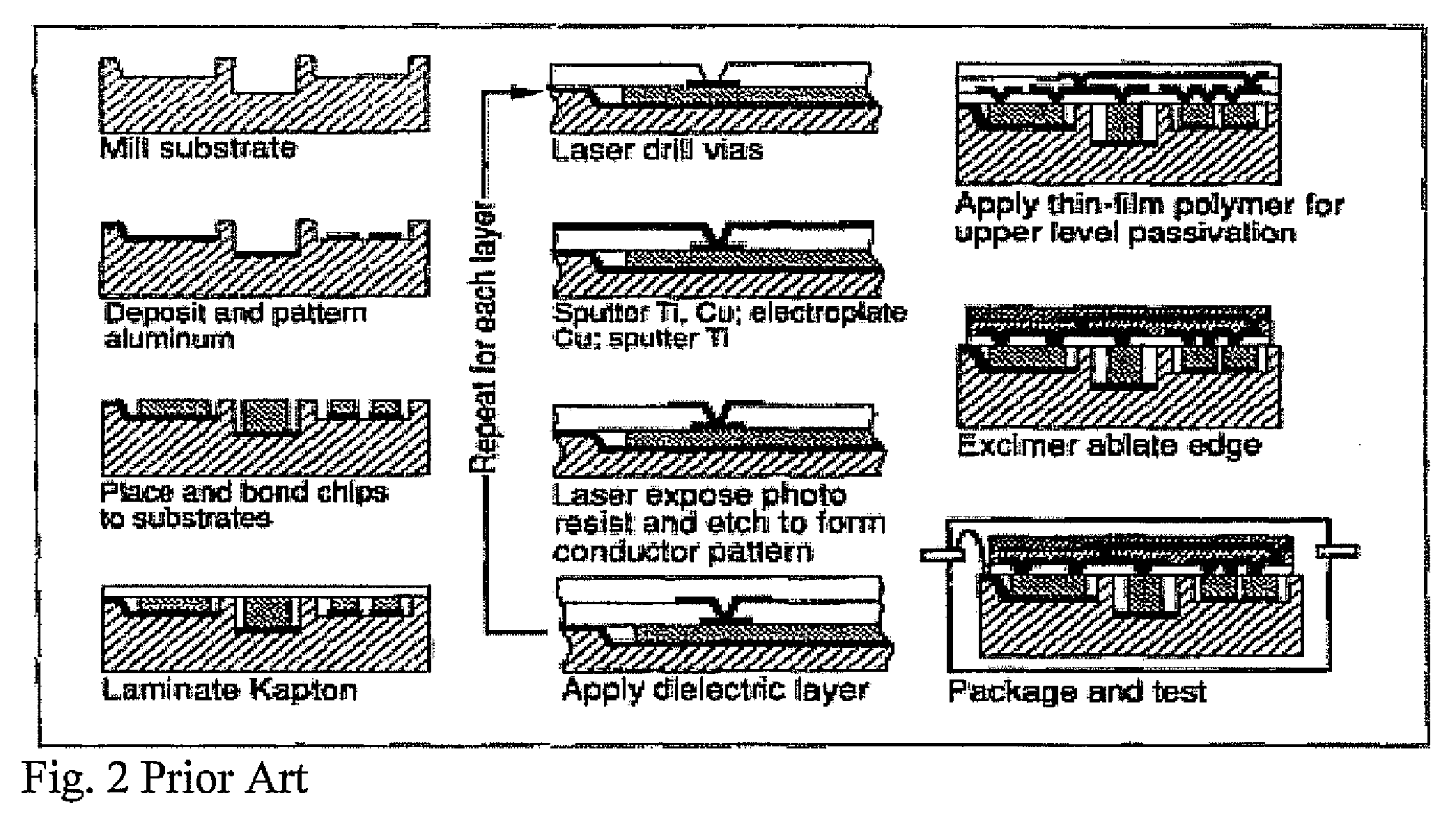

Simple but practical methods to dice a CMOS-MEMS multi-project wafer are proposed. On this wafer, micromachined microstructures have been fabricated and released. In a method, a photoresist is spun on the full wafer surface, and this photoresist is thick enough to cover all cavities and structures on the wafer, such that the photoresist will protect the released structures free from the chipping, vibrations, and damages in the diamond blade dicing process. In another method, a laser dicing system is utilized to scribe the multi-project wafer placed on a platform, and by precisely controlling the platform moving-track, the dicing path can be programmed to any required shape and region, even it is not straight. In addition, the wafer backside is mounted on a blue-tape at the beginning to enhance the process reliability.

Owner:NAT APPLIED RES LAB NAT CHIP IMPLEMENTATION CENT

CMOS-MEMS process

ActiveUS7435612B2Avoid disadvantagesIncreased processing flexibilitySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringCmos mems

A fully CMOS compatible MEMS multi-project wafer process comprises coating a layer of thick photoresist on a wafer surface, patterning the photoresist to define a micromachining region, and performing a micromachining in the micromachining region to form suspended microstructures.

Owner:NAT APPLIED RES LAB

Cmos-mems integration using metal silicide formation

A method and system for forming a MEMS device are disclosed. In a first aspect, the method comprises providing a conductive material over at least a portion of a top metal layer of a base substrate, patterning the conductive material and the at least a portion of the top metal layer, and bonding the conductive material with a device layer of a MEMS substrate via metal silicide formation. In a second aspect, the MEMS device comprises a MEMS substrate, wherein the MEMS substrate includes a handle layer, a device layer, and an insulating layer in between. The MEMS device further comprises a base substrate, wherein the base substrate includes a top metal layer and a conductive material over at least a portion of the top metal layer, wherein the conductive material is bonded with the device layer via metal silicide formation.

Owner:INVENSENSE

Hermetic mems device and method for fabricating hermetic mems device and package structure of hermetic mems device

ActiveCN102107846ATelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesInterconnectionCmos mems

The present invention provides a hermetic microelectromechanical system (MEMS) package including a CMOS MEMS chip and a second substrate. The CMOS MEMS Chip has a first substrate, a structural dielectric layer, a CMOS circuit and a MEMS structure. The structural dielectric layer is disposed on a first side of the first structural substrate. The structural dielectric layer has an interconnect structure for electrical interconnection and also has a protection structure layer. The first structural substrate has at least a hole. The hole is under the protection structure layer to form at least a chamber. The chamber is exposed to the environment in the second side of the first structural substrate. The chamber also comprises a MEMS structure. The second substrate is adhered to a second side of the first substrate over the chamber to form a hermetic space and the MEMS structure is within the space.

Owner:SOLID STATE SYST

Method of forming monolithic cmos-mems hybrid integrated, packaged structures

InactiveUS20110003421A1Solid-state devicesSemiconductor/solid-state device manufacturingCmos memsProtection layer

A method of forming Monolithic CMOS-MEMS hybrid integrated, packaged structures includes the steps of providing: providing at least one semiconductor substrate having a CMOS device area including dielectric layers and metallization layers; applying at least one protective layer overlying the CMOS device area; forming at least one opening on the protective layer and patterning the dielectric and metallization layers to access the semiconductor substrate; forming at least one opening on the semiconductor substrate by etching the dielectric and metallization layers; applying at least one filler layer in the at least one opening on the semiconductor substrate; positioning at least one chip on the filler layer, the chip including a prefabricated front face and a bare backside; applying a first insulating layer covering the front face of the chip providing continuity from the semiconductor substrate to the chip; forming at least one via opening on the insulating layer covering the chip to access at least one contact area; applying at least one metallization layer overlying the insulating layer on the substrate and the chip connecting the metallization layer on the substrate to the at least one another contact area on the chip; applying a second insulating layer overlying the metallization layer on the at least one chip; applying at least one interfacial layer; applying at least one rigid substrate overlying the interfacial layer; and applying at least one secondary protective layer overlying the rigid substrate.

Owner:AMF NANO

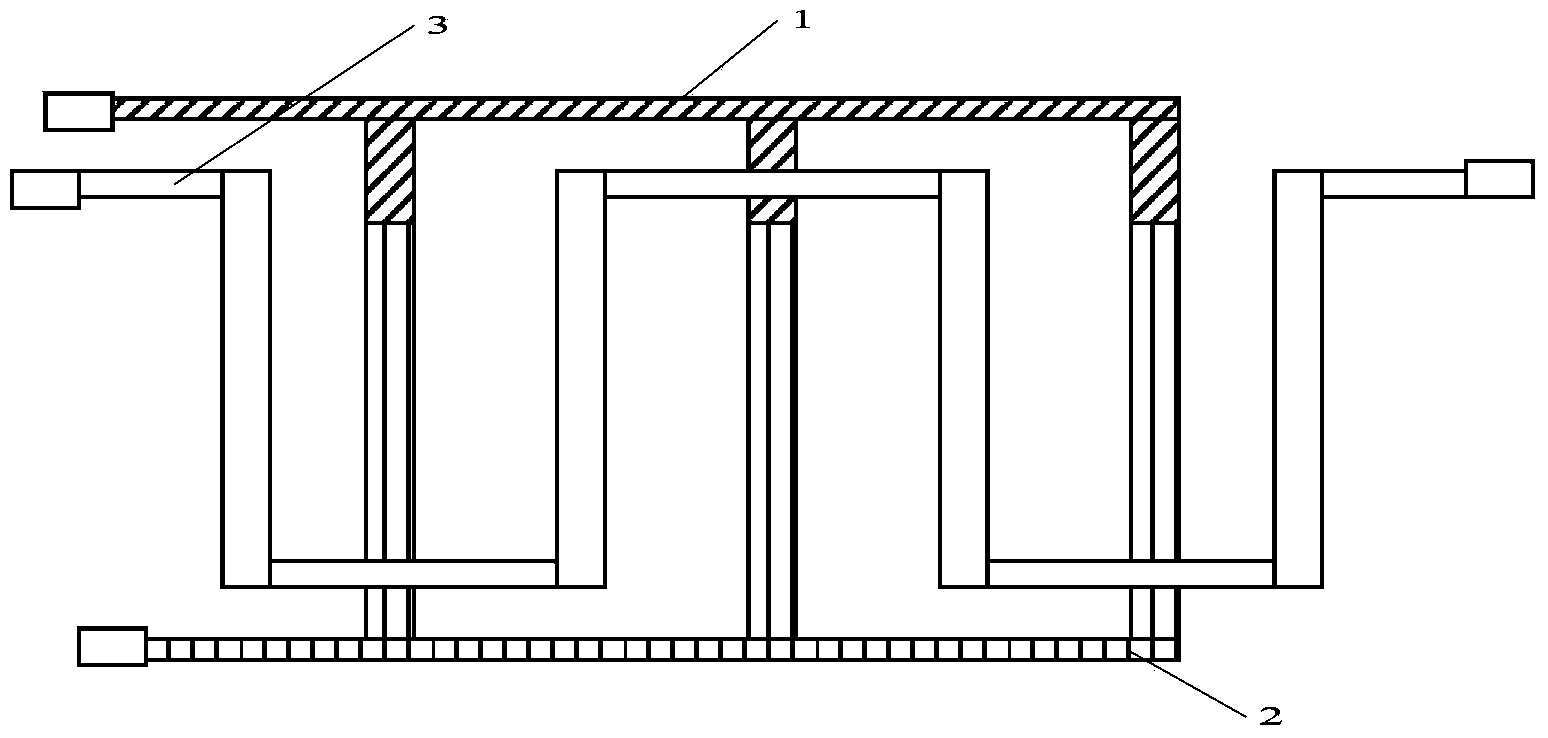

Novel non-refrigeration infrared sensor wafer-level packaging method compatible with CMOS (Complementary Metal Oxide Semiconductor)-MEMS (Micro-Electro-Mechanical System)

InactiveCN102633228ALow costImprove compatibilityDecorative surface effectsChemical vapor deposition coatingEngineeringCmos mems

The invention relates to a novel non-refrigeration infrared sensor wafer-level packaging method compatible with a CMOS (Complementary Metal Oxide Semiconductor)-MEMS (Micro-Electro-Mechanical System). The method comprises the following steps of: (1) plating a second sacrifice layer on a device wafer, then preparing a structural material and a sealing material, and releasing two sacrifice layers on the device wafer; (2) plating antireflection films on the two faces of a first seal-capping wafer, and plating the sealing material and a degasifying agent on the first seal-capping wafer; (3) bonding the device wafer with the first seal-capping wafer; (4) then bonding a second seal-capping wafer on the back face of the device wafer; and (5) scribing. According to the novel non-refrigeration infrared sensor wafer-level packaging method provided by the invention, the entire technical process of the device wafer can be completed in a factory by improving a process sequence, so as to be entirely compatible with a CMOS process. According to the novel non-refrigeration infrared sensor wafer-level packaging method with CMOS-MEMS, the large-scale production is easier to realize, so that the final prober cost is lower.

Owner:WUHAN GUIDE INFRARED CO LTD

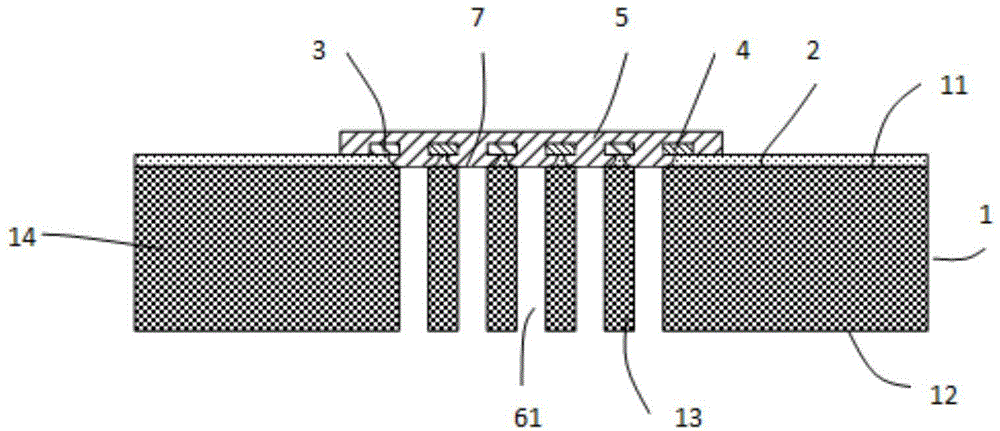

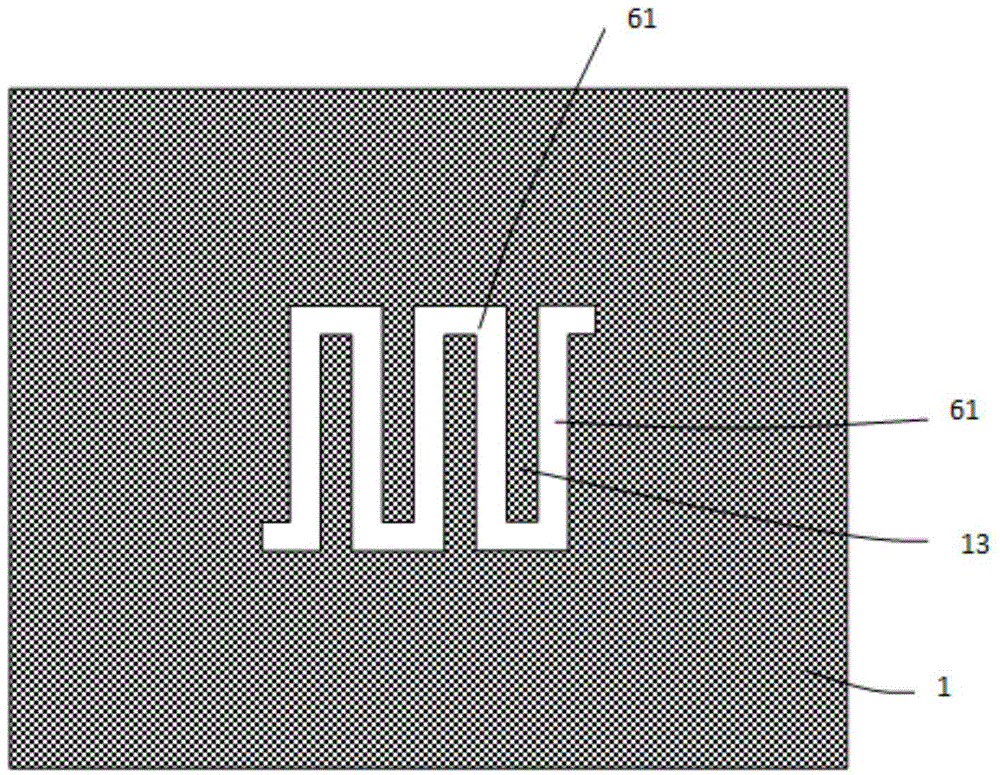

CMOS MEMS capacitance-type humidity sensor and preparation method thereof

The invention relates to a CMOS MEMS capacitance-type humidity sensor and a preparation method thereof, and belongs to the technology of a semiconductor chip. A plurality of air subchannels are formed on a substrate in orthographic projection of a humidity sensing medium layer, the sensitivity of the sensor can be improved and the response time can be shortened by virtue of the air subchannels; moreover, a supporting column is formed between two adjacent air subchannels, so that the strength of a sensitive device area can be improved by virtue of the supporting column, the cracking of the humidity sensor in real application can be prevented, and under the situation that the sensitivity and the response time of the humidity sensor are guaranteed, the structural strength of the humidity sensor is improved; the CMOS MEMS capacitance-type humidity sensor formed by adopting the method is provided with the air subchannels and the supporting column, so that the structural strength of the capacitance-type humidity sensor can be improved under the situation that the sensitivity and the response time of the capacitance-type humidity sensor are guaranteed.

Owner:苏州工业园区纳米产业技术研究院有限公司

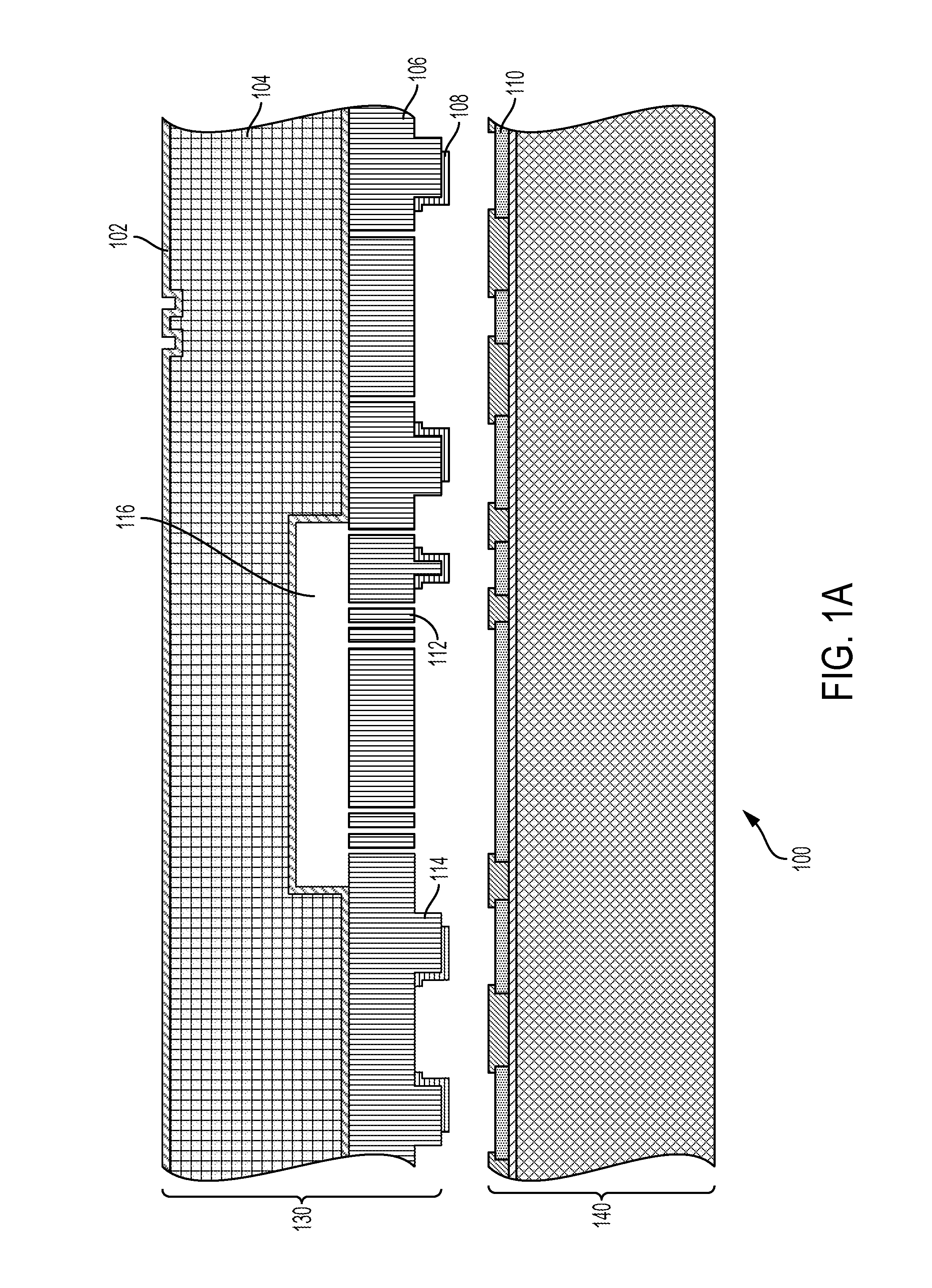

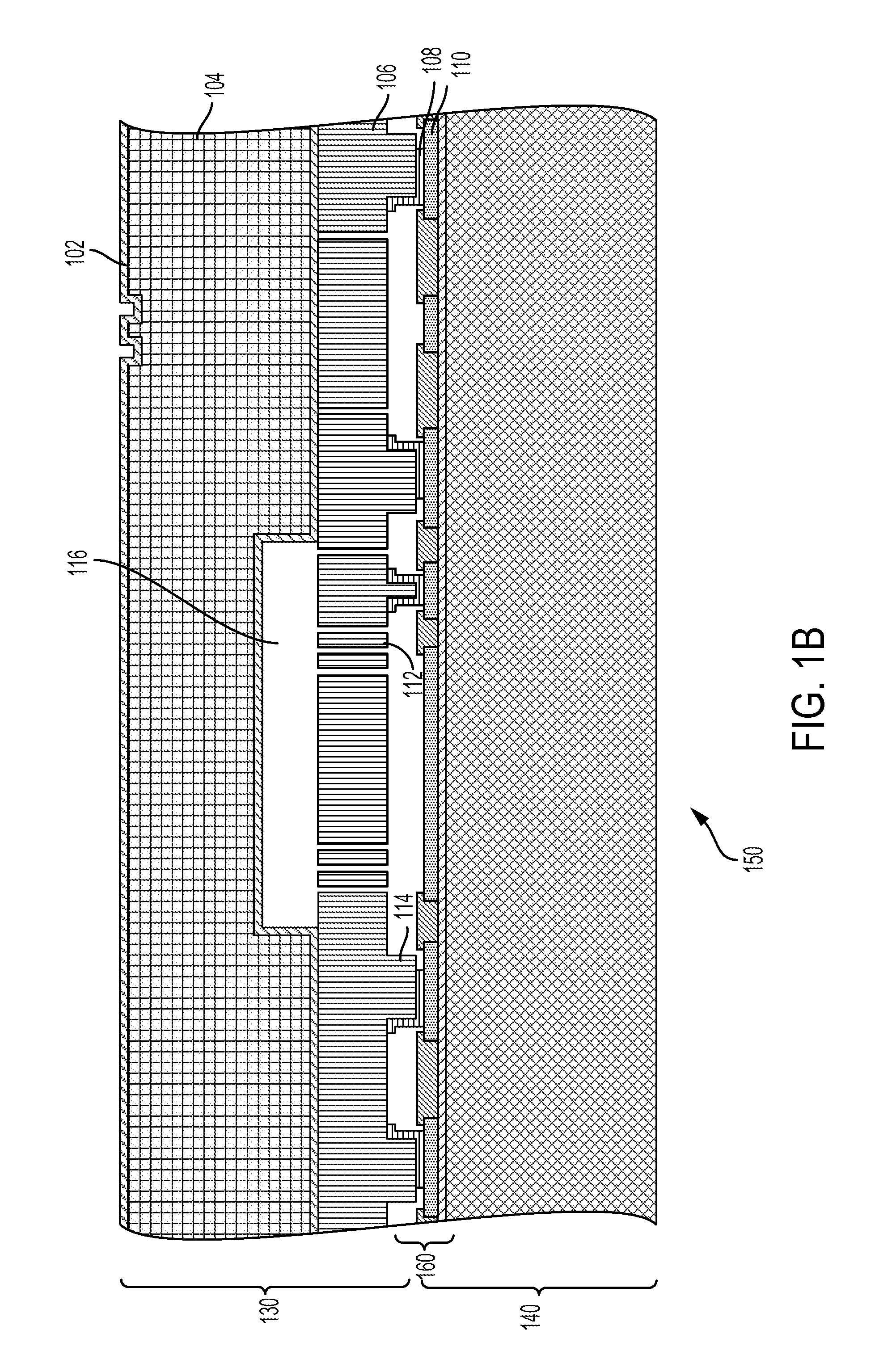

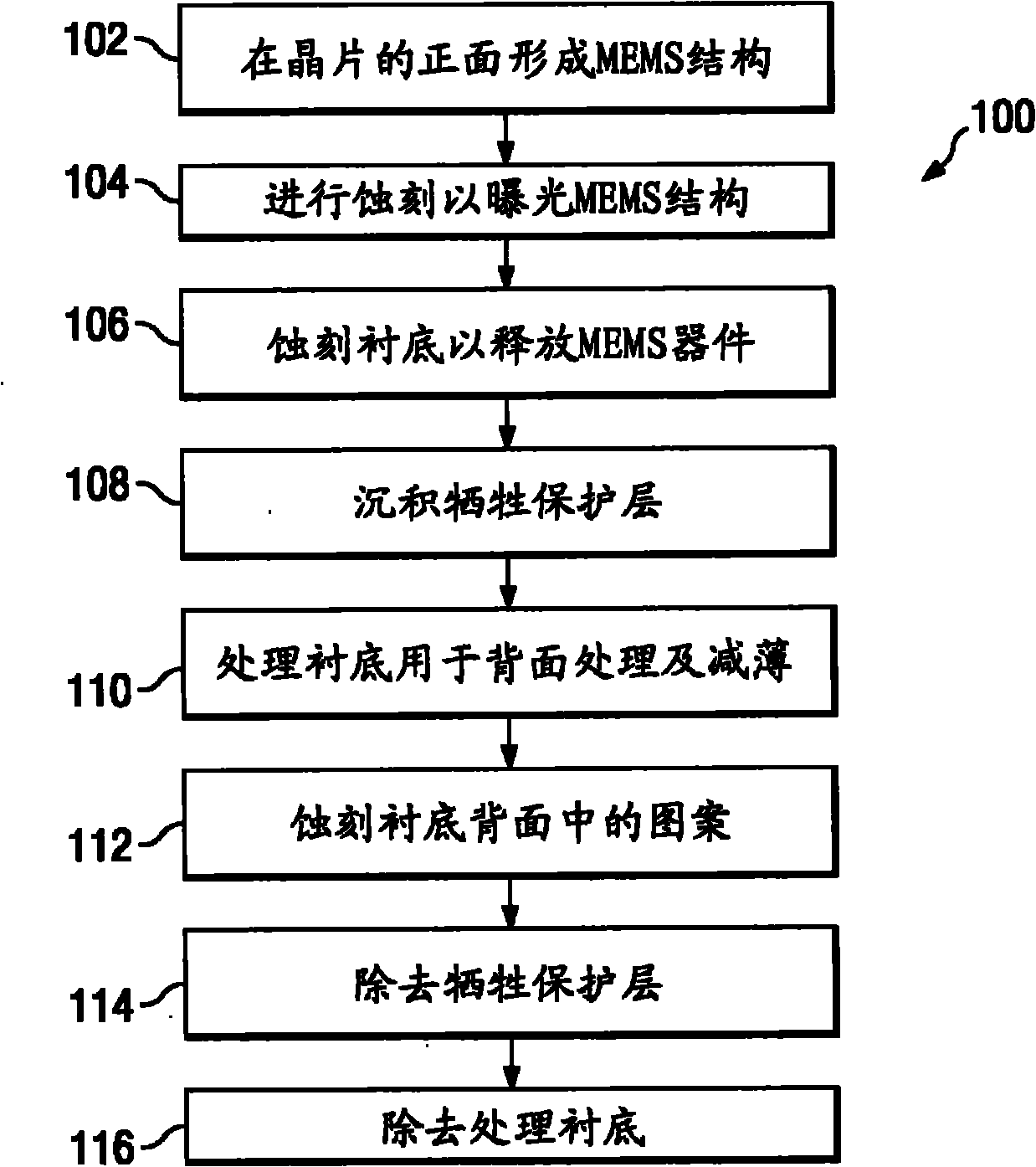

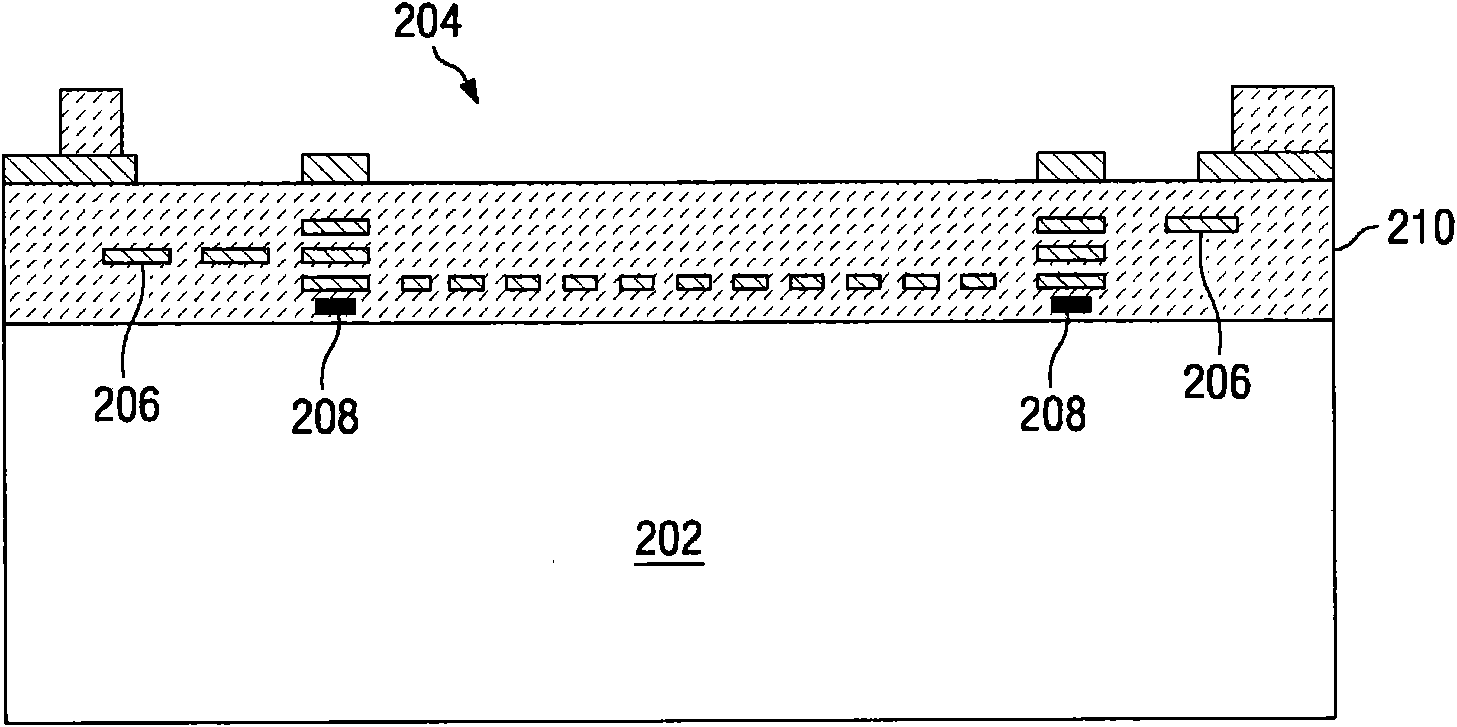

Method of fabricating an integrated CMOS-MEMS device

An embodiment of a method is provided that includes providing a substrate having a frontside and a backside. A CMOS device is formed on the substrate. A MEMS device is also formed on the substrate. Forming the MEMS device includes forming a MEMS mechanical structure on the frontside of the substrate. The MEMS mechanical structure is then released. A protective layer is formed on the frontside of the substrate. The protective layer is disposed on the released MEMS mechanical structure (e.g., protects the MEMS structure). The backside of the substrate is processed while the protective layer is disposed on the MEMS mechanical structure.

Owner:TAIWAN SEMICON MFG CO LTD

Method of forming monolithic CMOS-MEMS hybrid integrated, packaged structures

InactiveUS8101469B2Solid-state devicesSemiconductor/solid-state device manufacturingCmos memsProtection layer

Owner:AMF NANO

Method of forming monolithic CMOS-MEMS hybrid integrated, packaged structures

InactiveUS7989248B2Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringCmos mems

Owner:AMF NANO

Method of forming monolithic CMOS-MEMS hybrid integrated, packaged structures

InactiveUS8101458B2Solid-state devicesSemiconductor/solid-state device manufacturingFilling materialsLayer interface

A method of forming Monolithic CMOS-MEMS hybrid integrated, packaged structures includes the steps of providing: providing a semiconductor substrate with pre-fabricated cmos circuits on the front side and a polished back-side with through substrate conductive vias; forming at least one opening in the polished backside of the semiconductor substrate by appropriately protecting the front-side; applying at least one filler material in the at least one opening on the semiconductor substrate; positioning at least one prefabricated mems, nems or cmos chip on the filler material, the chip including a front face and a bare back face with the prefabricated mems / nems chips containing mechanical and dielectric layers; applying at least one planarization layer overlying the substrate, filler material and the chip; forming at least one via opening on a portion of the planarization layer interfacing pads on the chip and the through substrate conductive vias; applying at least one metallization layer overlying the planarization layer on the substrate and the chip connecting the through substrate conductive vias to the at least one chip; applying at least one second insulating layer overlying the metallization layer; performing at least one micro / nano fabrication etching step to release the mechanical layer on the prefabricated mems / nems chips; positioning protective cap to package the integrated device over the mems / nems device area on the pre-fabricated chips.

Owner:AMF NANO

General strength and sensitivity enhancement method for micromachined device

InactiveUS20110115035A1Simple structureImprove performanceSemiconductor/solid-state device detailsSolid-state devicesGyroscopeAccelerometer

This invention disclosed a method to strengthen structure and enhance sensitivity for CMOS-MEMS micro-machined devices which include micro-motion sensor, micro-actuator and RF switch. The steps of the said method contain defining deposited region by metal and passivation layer, forming a cavity for depositing metal structure by lithography process, depositing metal structure on the top metal layer of micromachined structure by Electroless plating, polishing process and etching process. The method aims at strengthening structures and minimizing CMOS-MEMS device size. Furthermore, this method can also be applied to inertia sensors such as accelerometer or gyroscope, which can enhance sensitivity and capacitive value, and deal with curl issues for suspended CMOS-MEMS devices.

Owner:HUANG JUNG TANG

Method and device of MEMS process control monitoring and packaged MEMS with different cavity pressures

ActiveUS9249012B2Small sizeIncreased complexityDecorative surface effectsSemiconductor/solid-state device manufacturingOutgassingEngineering

A method for fabricating an integrated MEMS device and the resulting structure therefore. A control process monitor comprising a MEMS membrane cover can be provided within an integrated CMOS-MEMS package to monitor package leaking or outgassing. The MEMS membrane cover can separate an upper cavity region subject to leaking from a lower cavity subject to outgassing. Differential changes in pressure between these cavities can be detecting by monitoring the deflection of the membrane cover via a plurality of displacement sensors. An integrated MEMS device can be fabricated with a first and second MEMS device configured with a first and second MEMS cavity, respectively. The separate cavities can be formed via etching a capping structure to configure each cavity with a separate cavity volume. By utilizing an outgassing characteristic of a CMOS layer within the integrated MEMS device, the first and second MEMS cavities can be configured with different cavity pressures.

Owner:MCUBE INC +1

CMOS-MEMS Cantilever Structure

InactiveUS20110133256A1Reduce manufacturing costSimple manufacturing processSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringCmos mems

The present invention discloses a CMOS-MEMS cantilever structure. The CMOS-MEMS cantilever structure includes a substrate, a circuit structure, and a cantilever beam. The substrate has a circuit area and a sensor unit area defined thereon. The circuit structure is formed in the circuit area. The cantilever beam is disposed in the sensor unit area with one end floating above the substrate and the other end connecting to the circuit structure. With the above arrangement, the manufacturing process of CMOS-MEMS cantilever structure of this invention can be simplified. Furthermore, the structure of the cantilever beam is thinned down and therefore has a higher sensitivity.

Owner:NAT APPLIED RES LAB