Patents

Literature

218results about How to "High device yield" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method and structure for self aligned formation of a gate polysilicon layer

ActiveUS20070243685A1Easy to useReduce processing stepsSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductorSemiconductor device

A method for processing semiconductor devices includes providing a semiconductor substrate. The method includes forming a pad oxide layer overlying the substrate and forming a silicon nitride layer overlying the pad oxide layer. The method includes forming a trench region extending through an entirety of a portion of the silicon nitride layer and extends into a depth of the semiconductor substrate. The method also includes filling the trench region with an oxide material. The oxide material extends from a bottom portion of the trench region to an upper surface of the silicon nitride layer. The method includes planarizing the oxide material and selectively removing the silicon nitride layer to form an isolation structure. A polysilicon material is deposited overlying the isolation structure. The polysilicon material is planarized to expose a top portion of the isolation structure and form a first electrode and a second electrode structures separated by a portion of the isolation structure.

Owner:SEMICON MFG INT (SHANGHAI) CORP

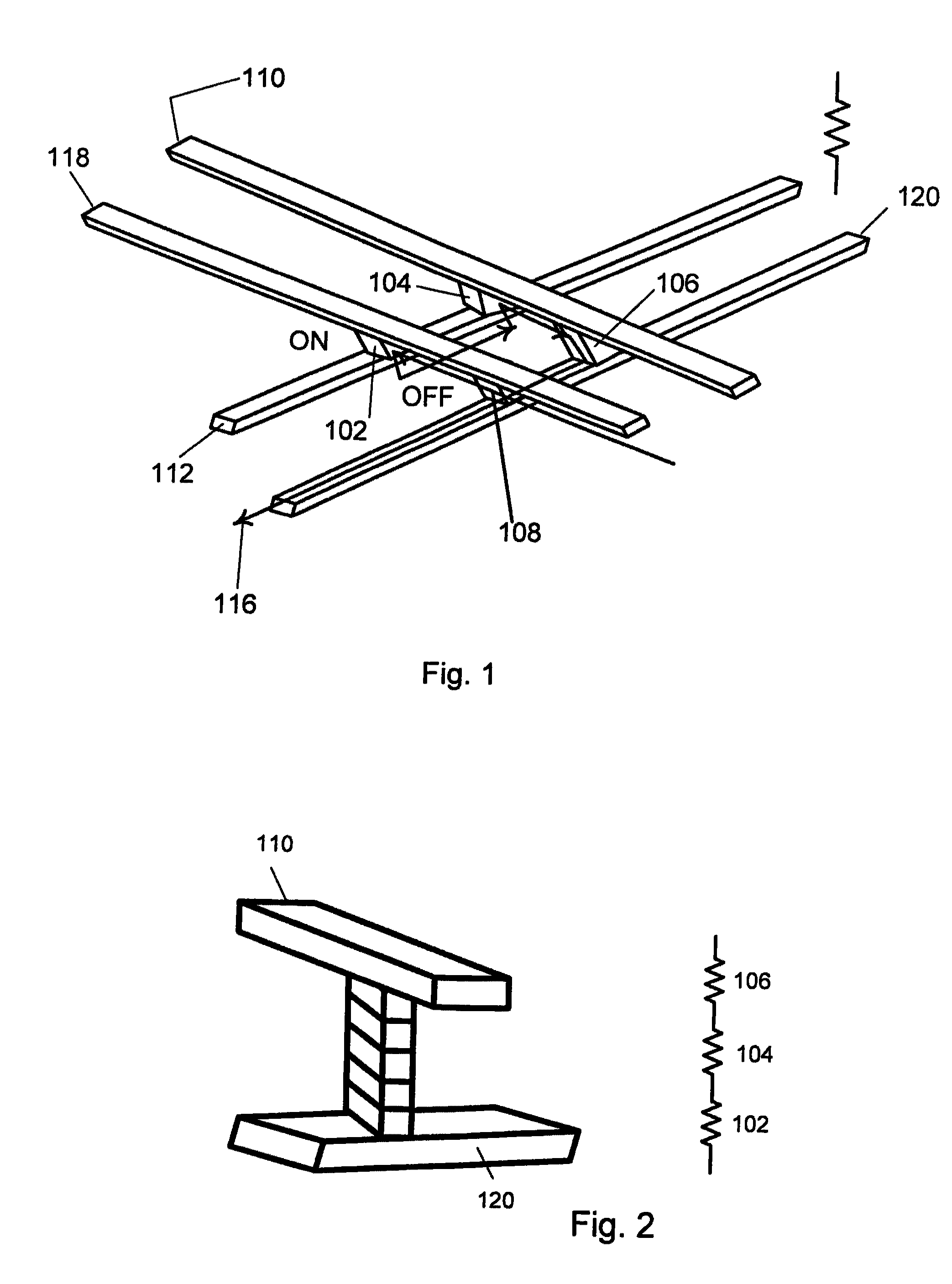

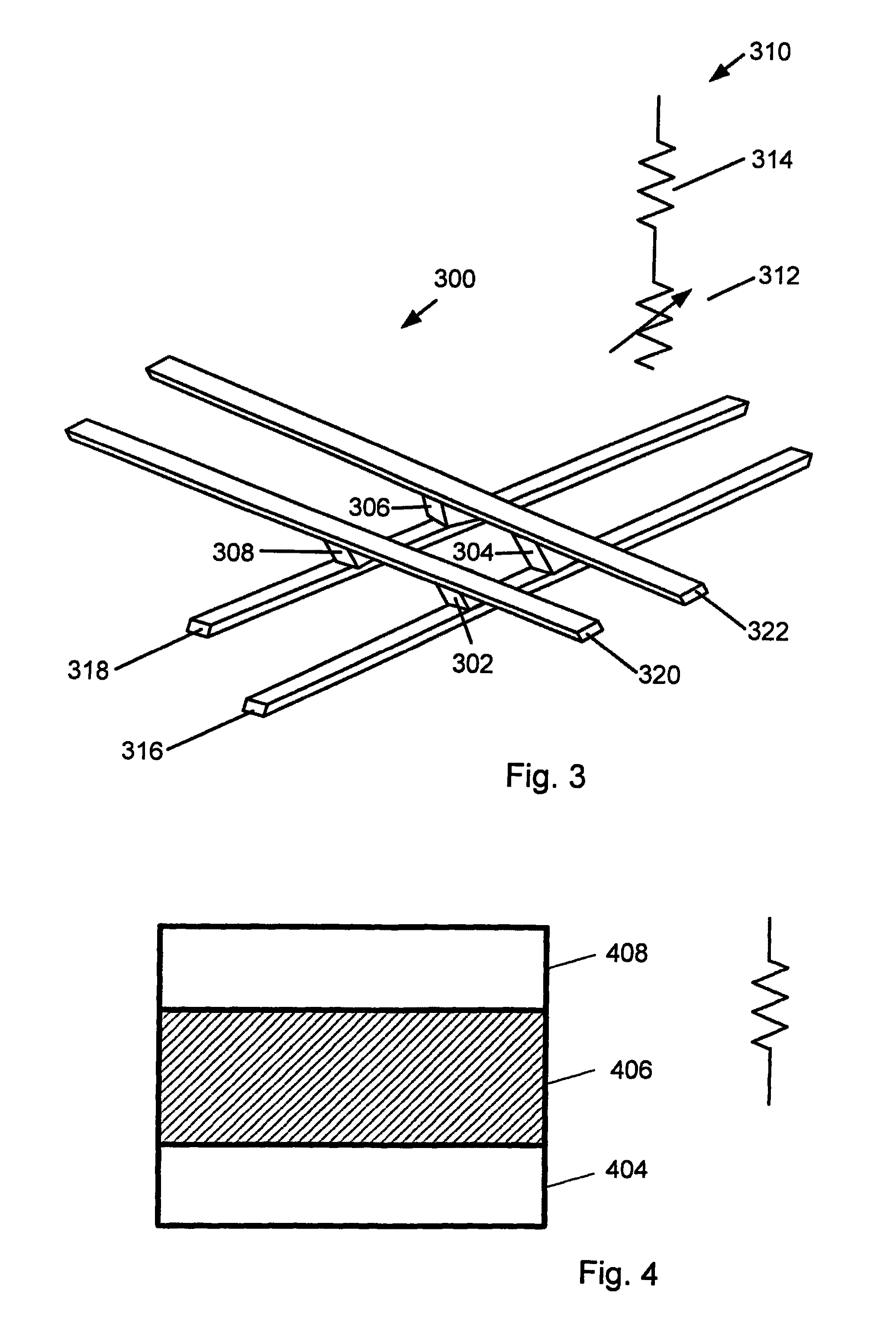

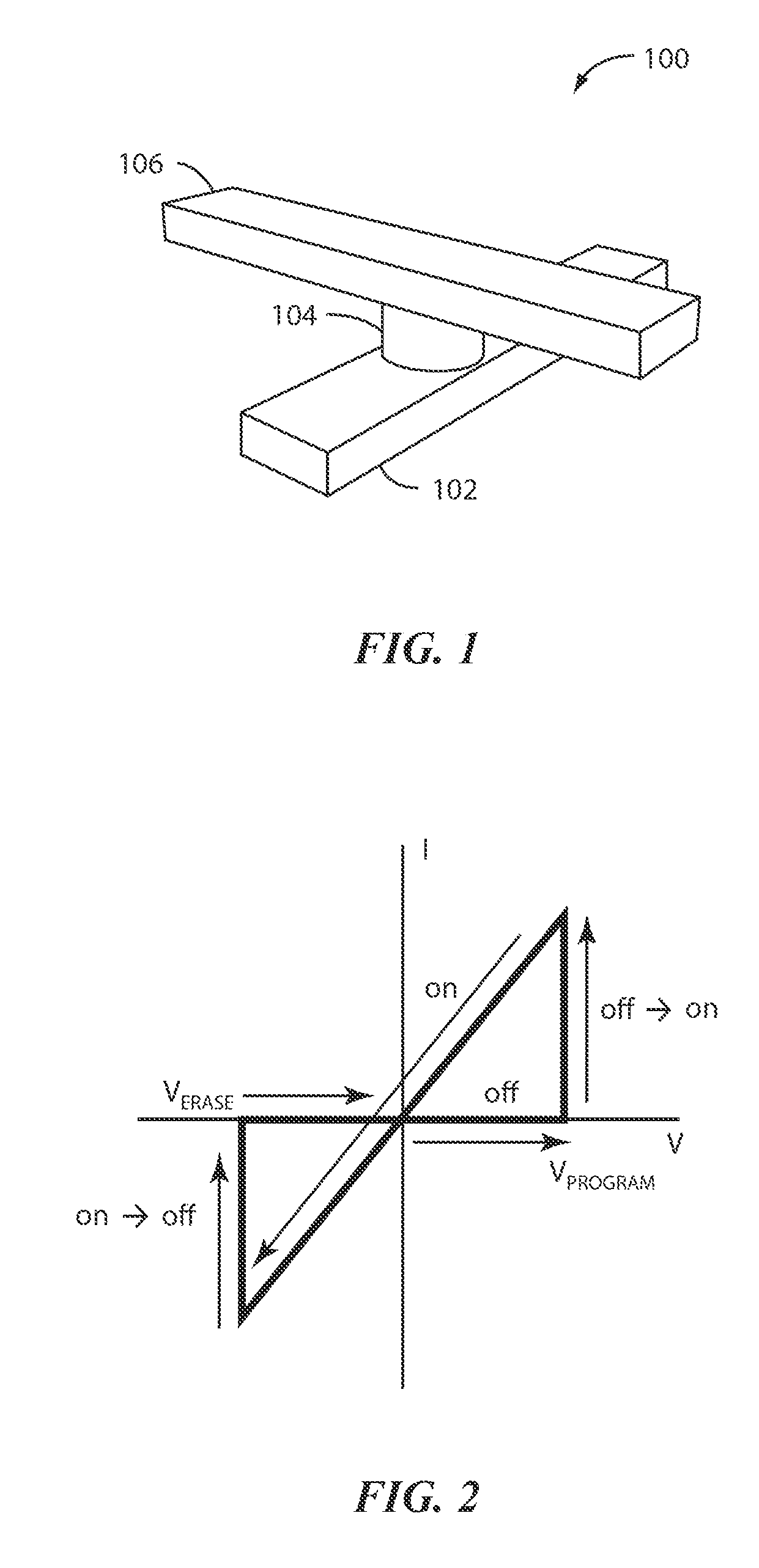

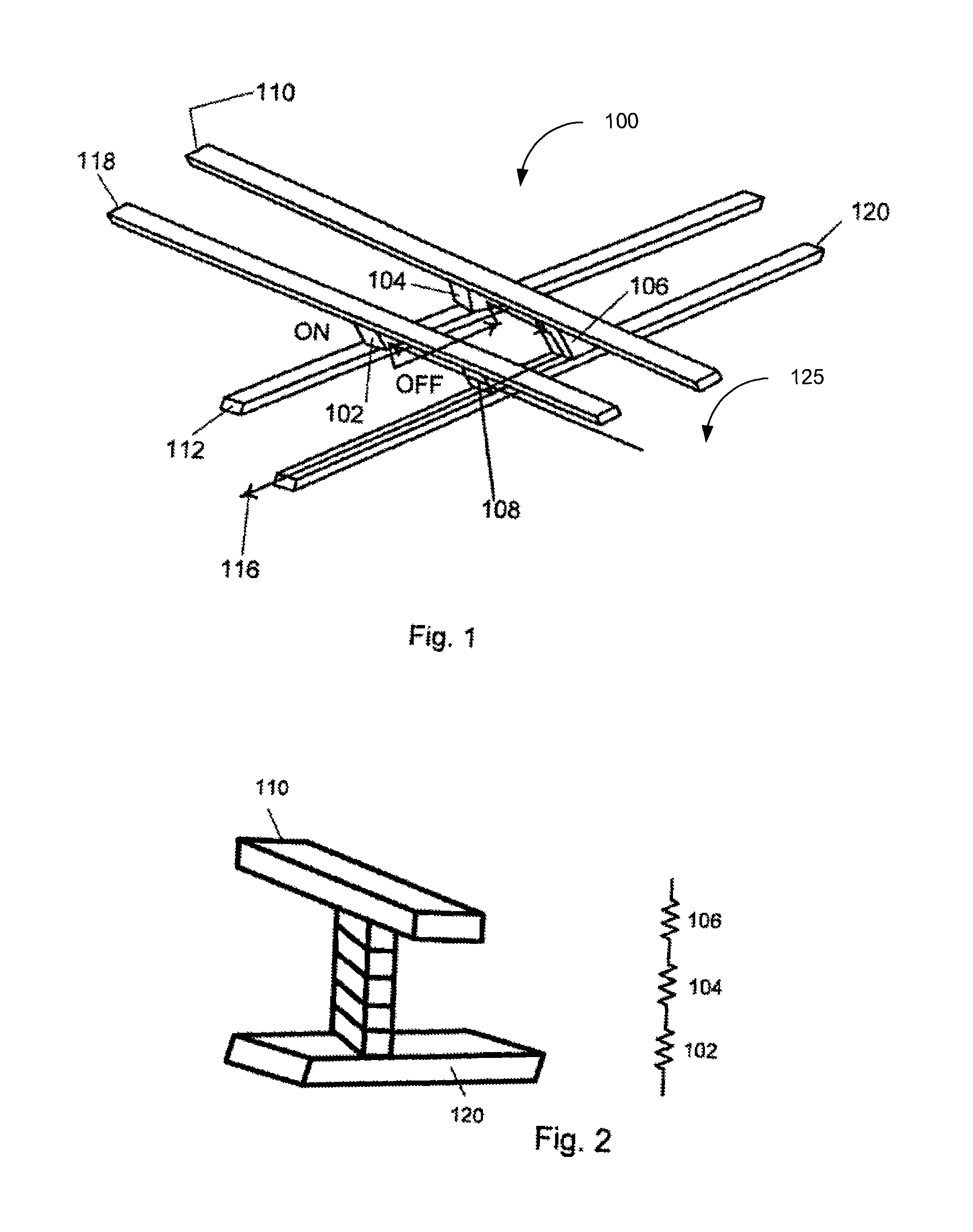

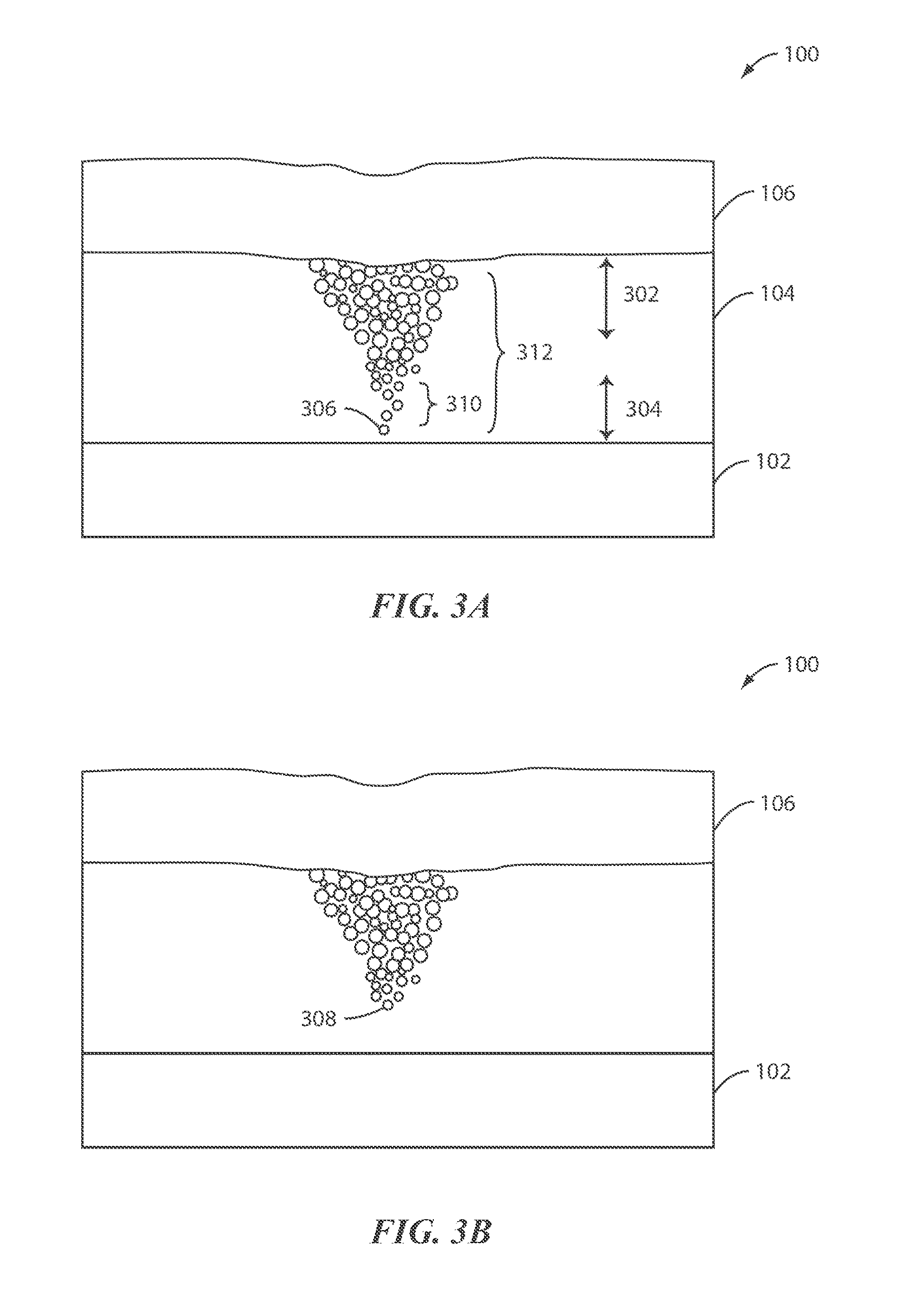

Rectification element and method for resistive switching for non volatile memory device

ActiveUS20110317470A1High densityFast switching speedSolid-state devicesDigital storageComputational physicsResistive switching

A method of suppressing propagation of leakage current in an array of switching devices. The method includes providing a dielectric breakdown element integrally and serially connected to a switching element within each of the switching device. A read voltage (for example) is applied to a selected cell. The propagation of leakage current is suppressed by each of the dielectric breakdown element in unselected cells in the array. The read voltage is sufficient to cause breakdown in the selected cells but insufficient to cause breakdown in the serially connected, unselected cells in a specific embodiment. Methods to fabricate of such devices and to program, to erase and to read the device are provided.

Owner:RGT UNIV OF MICHIGAN

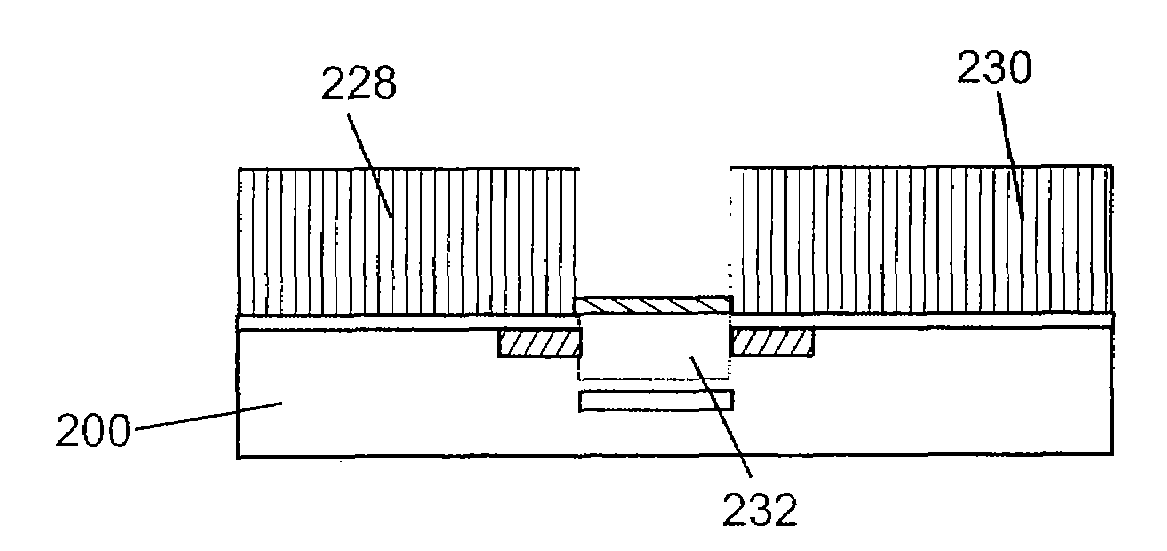

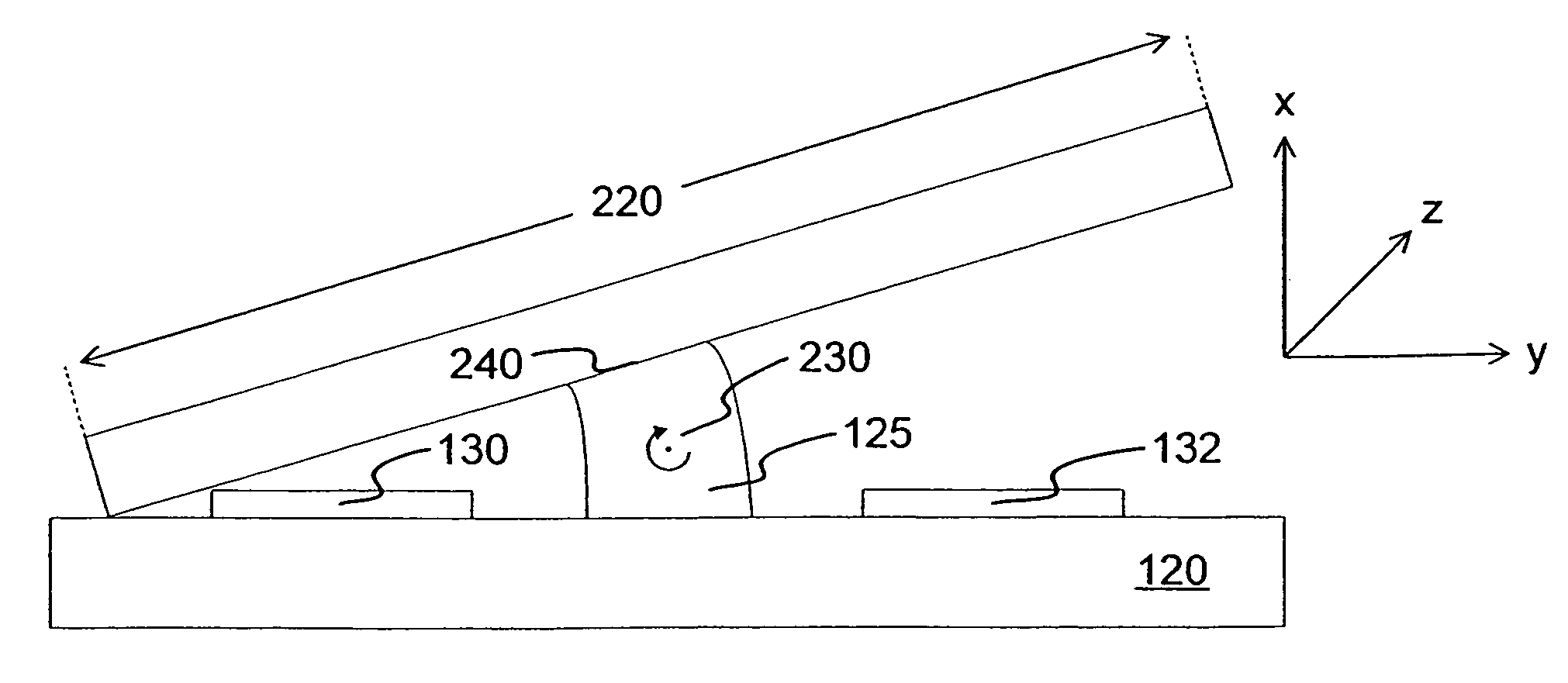

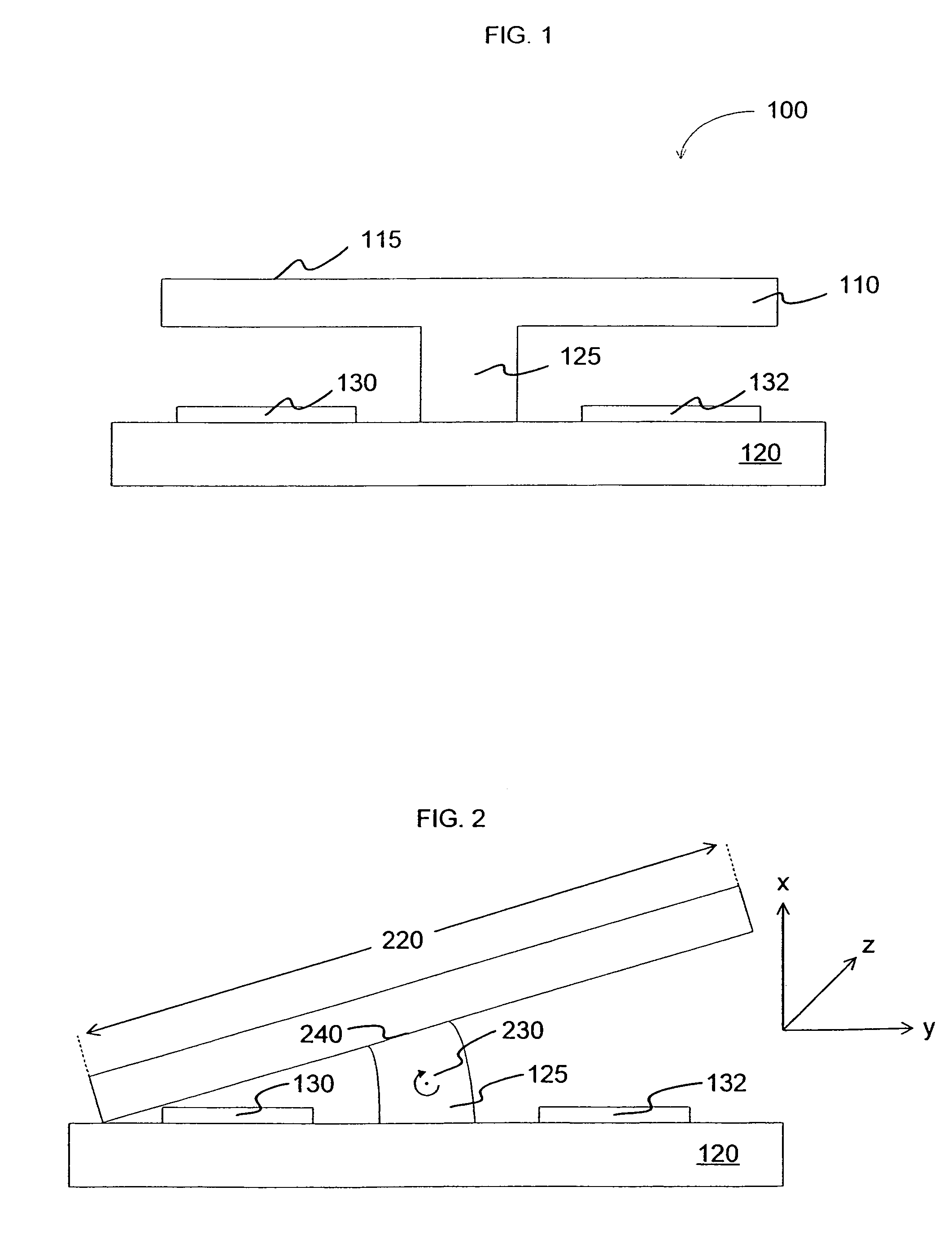

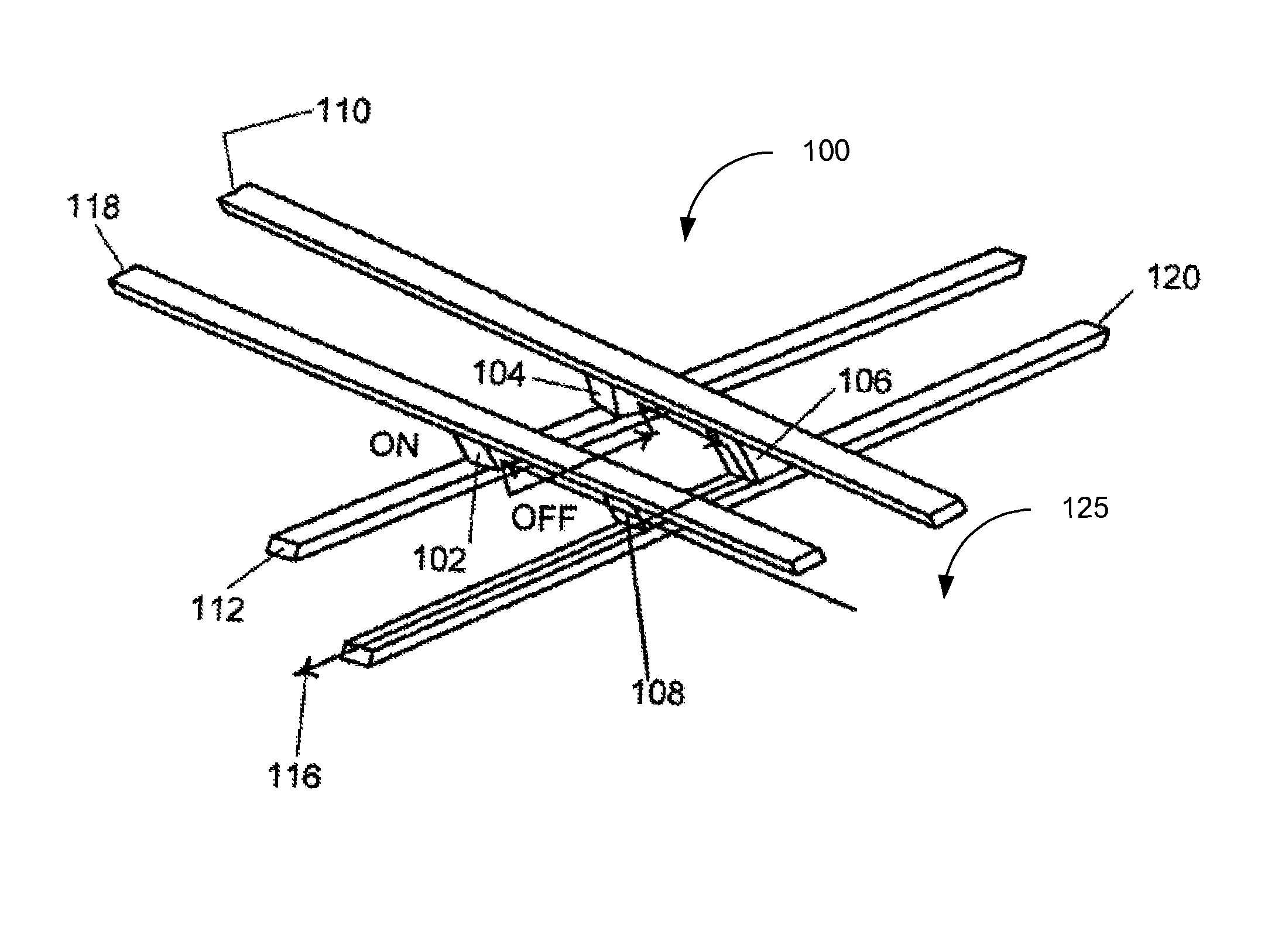

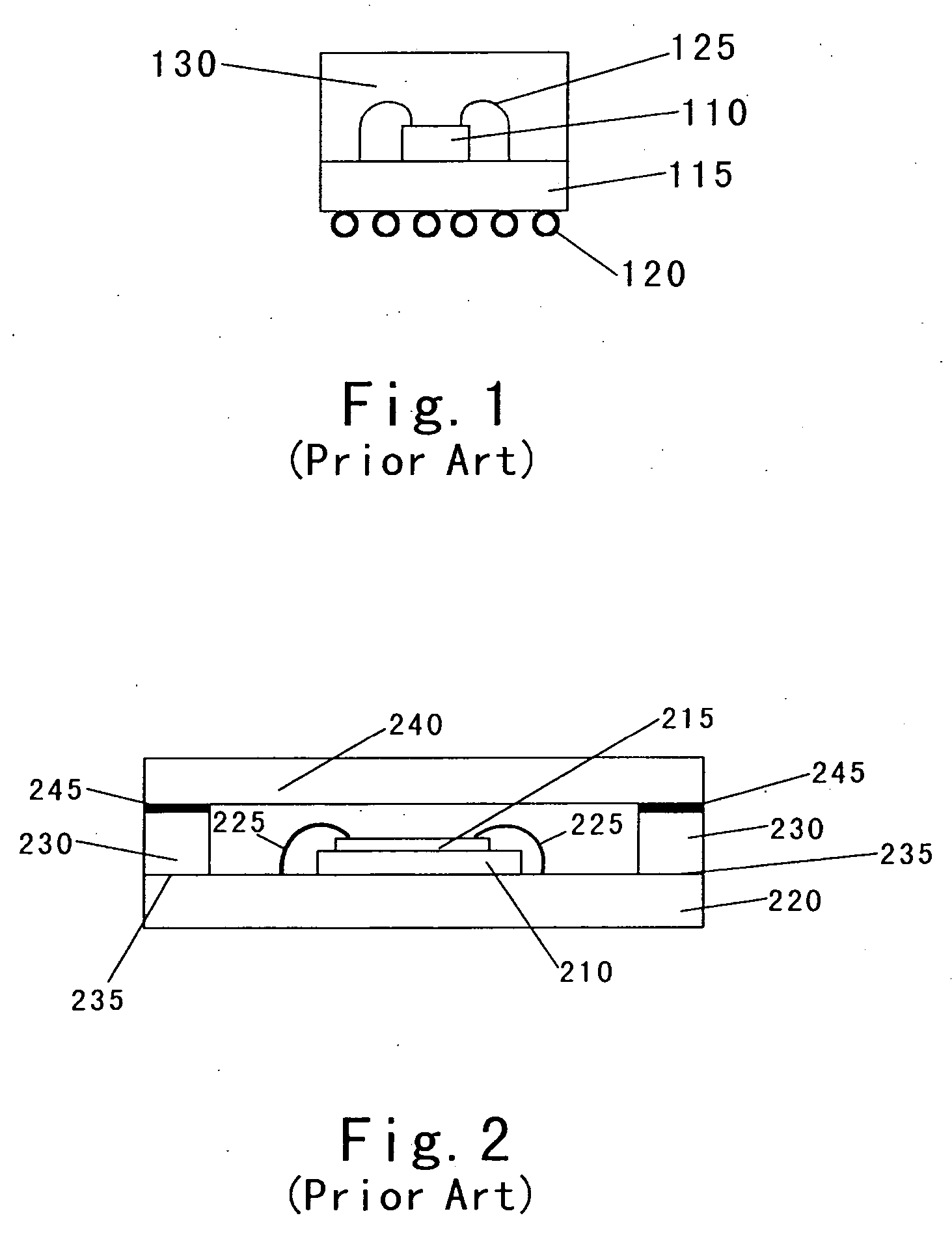

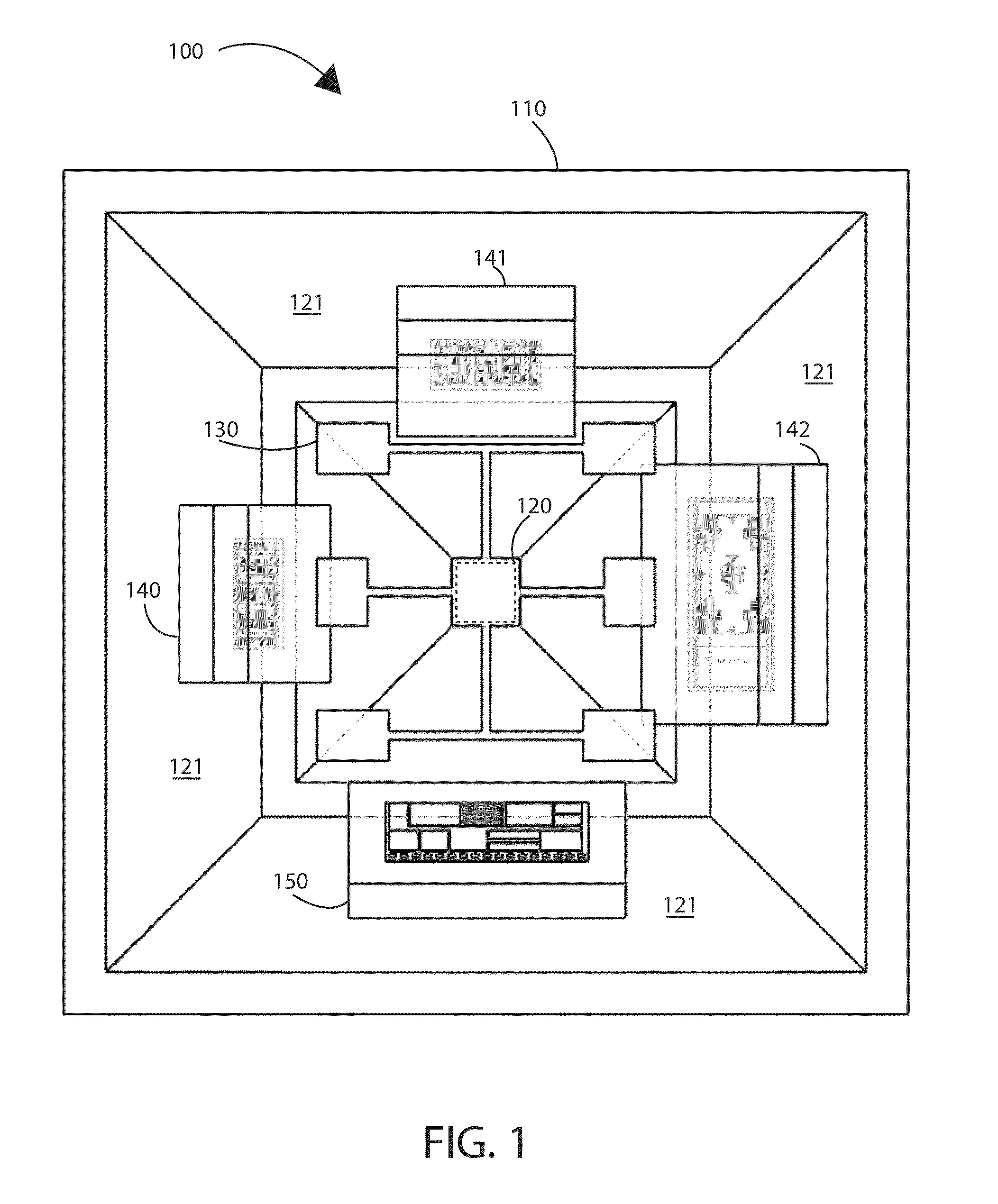

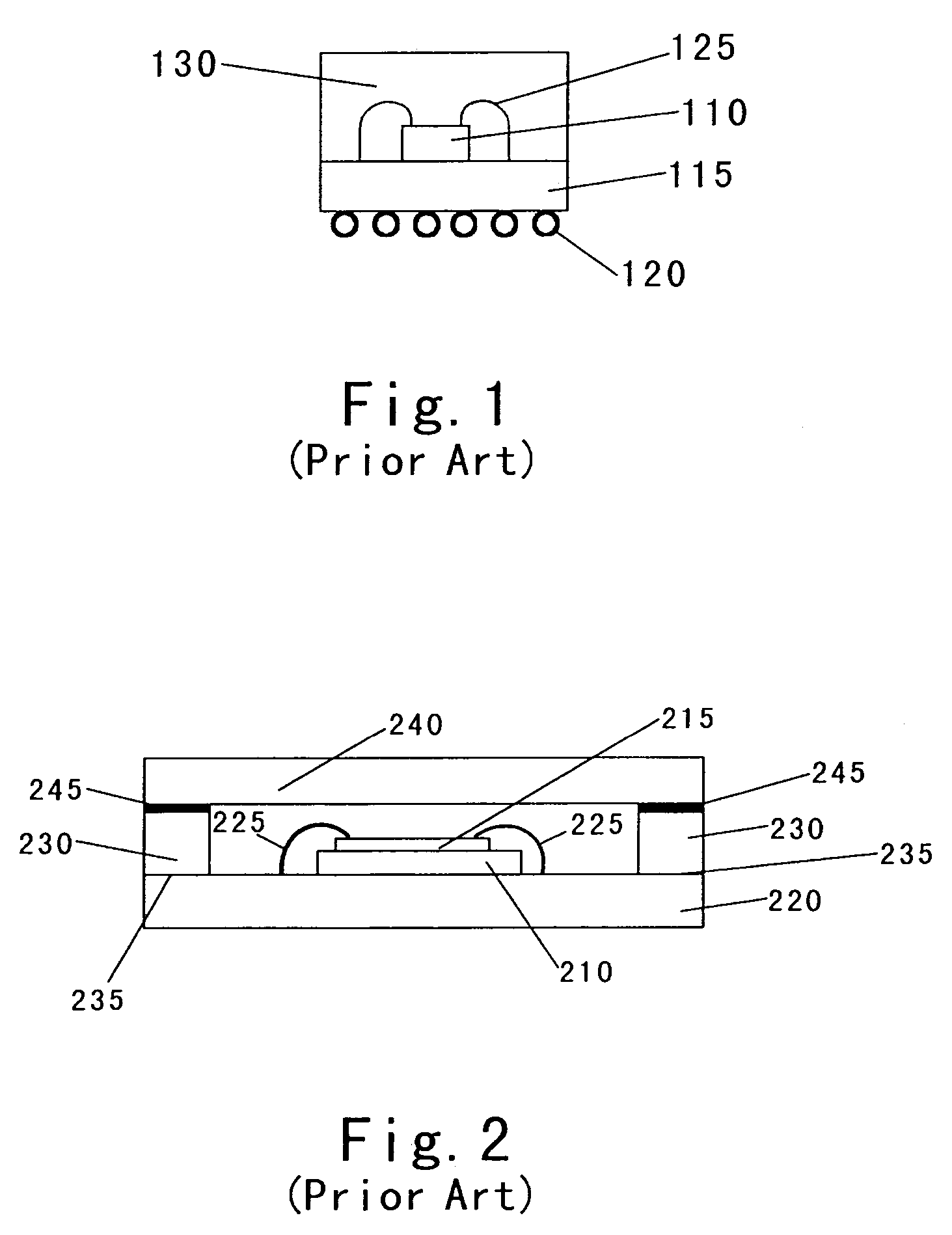

Method and apparatus for a reflective spatial light modulator with a flexible pedestal

ActiveUS7068417B2Easy to useHigh device yieldNon-linear opticsOptical elementsSpatial light modulatorEngineering

Owner:MIRADIA INC

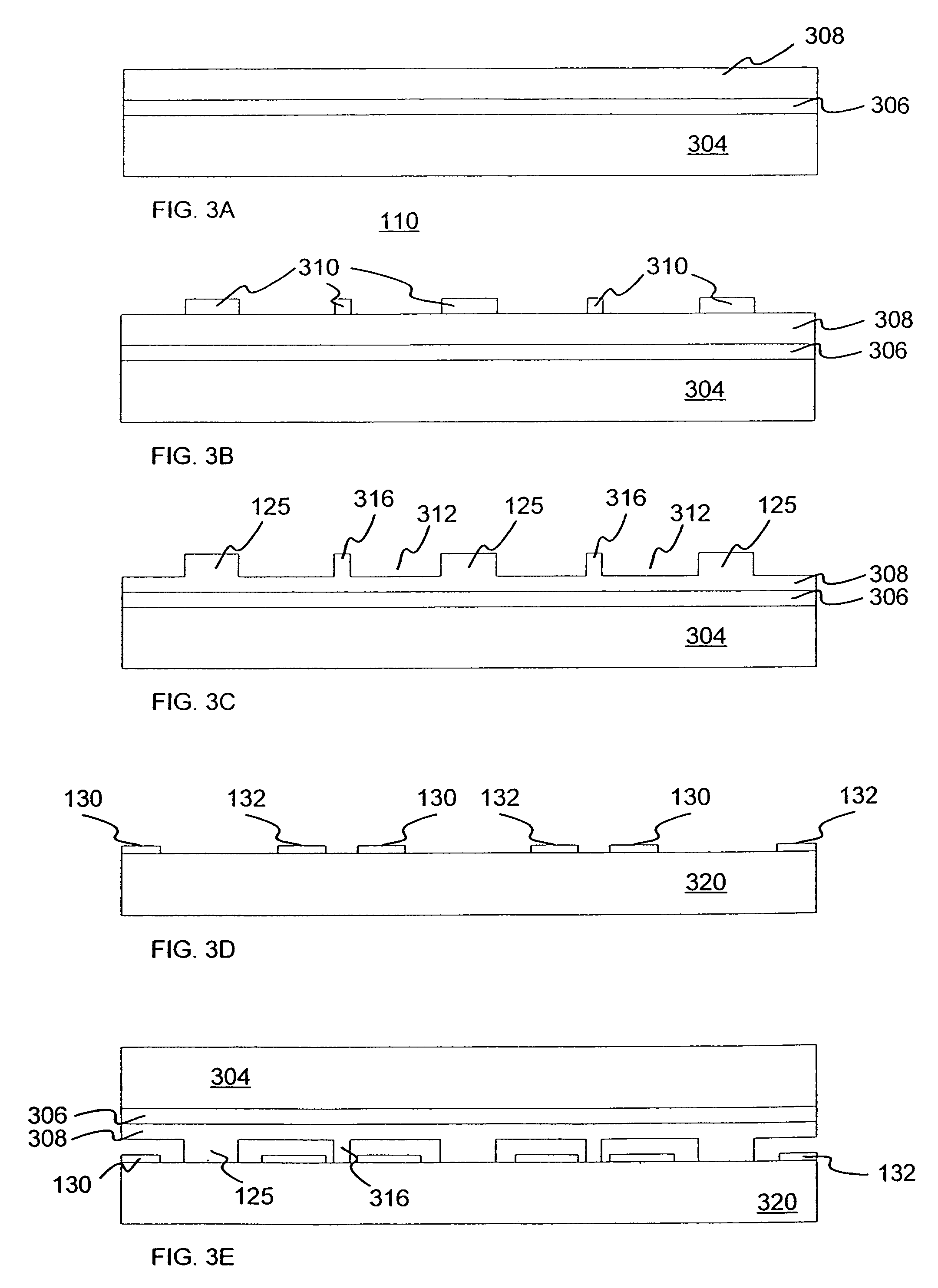

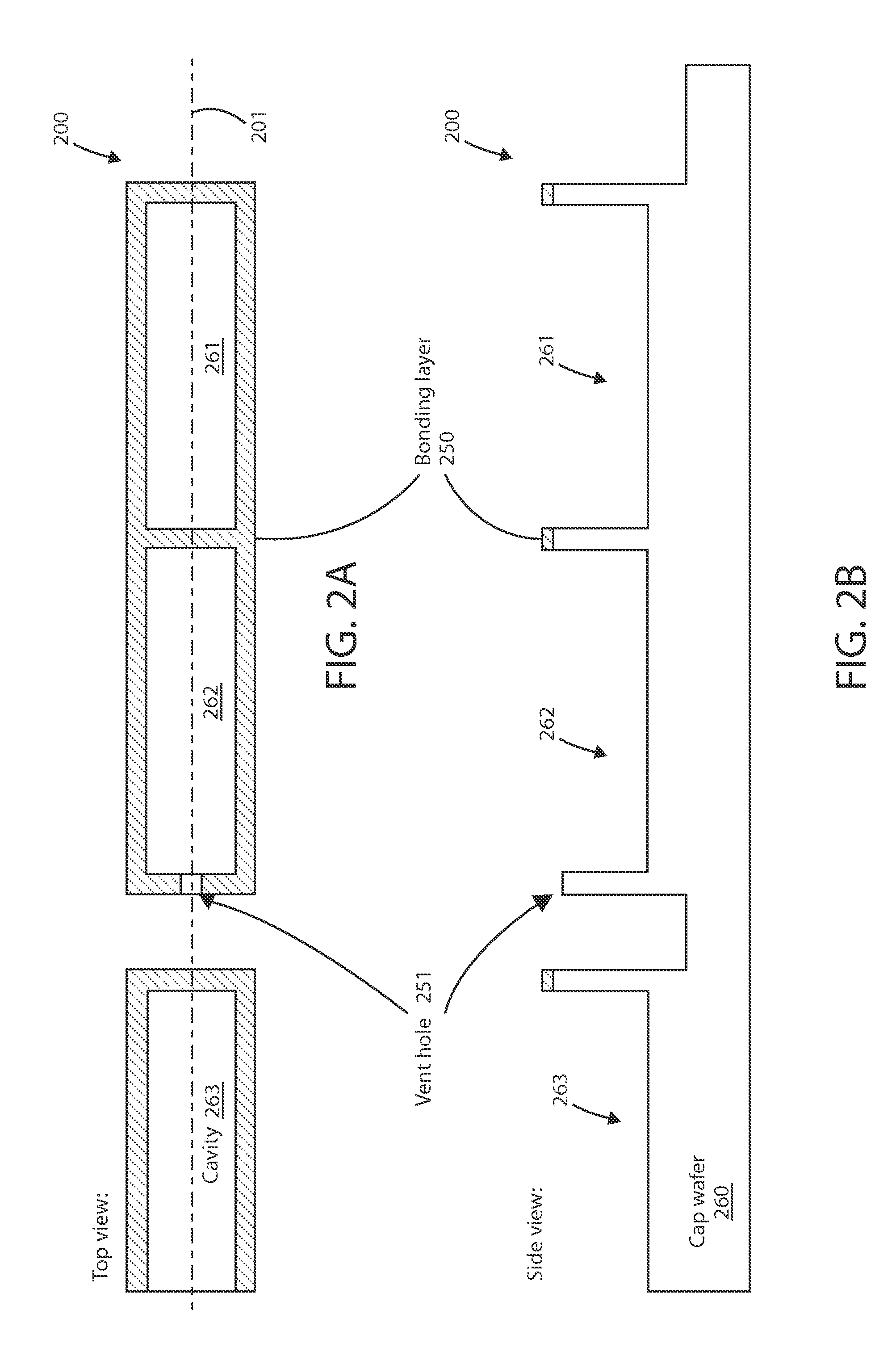

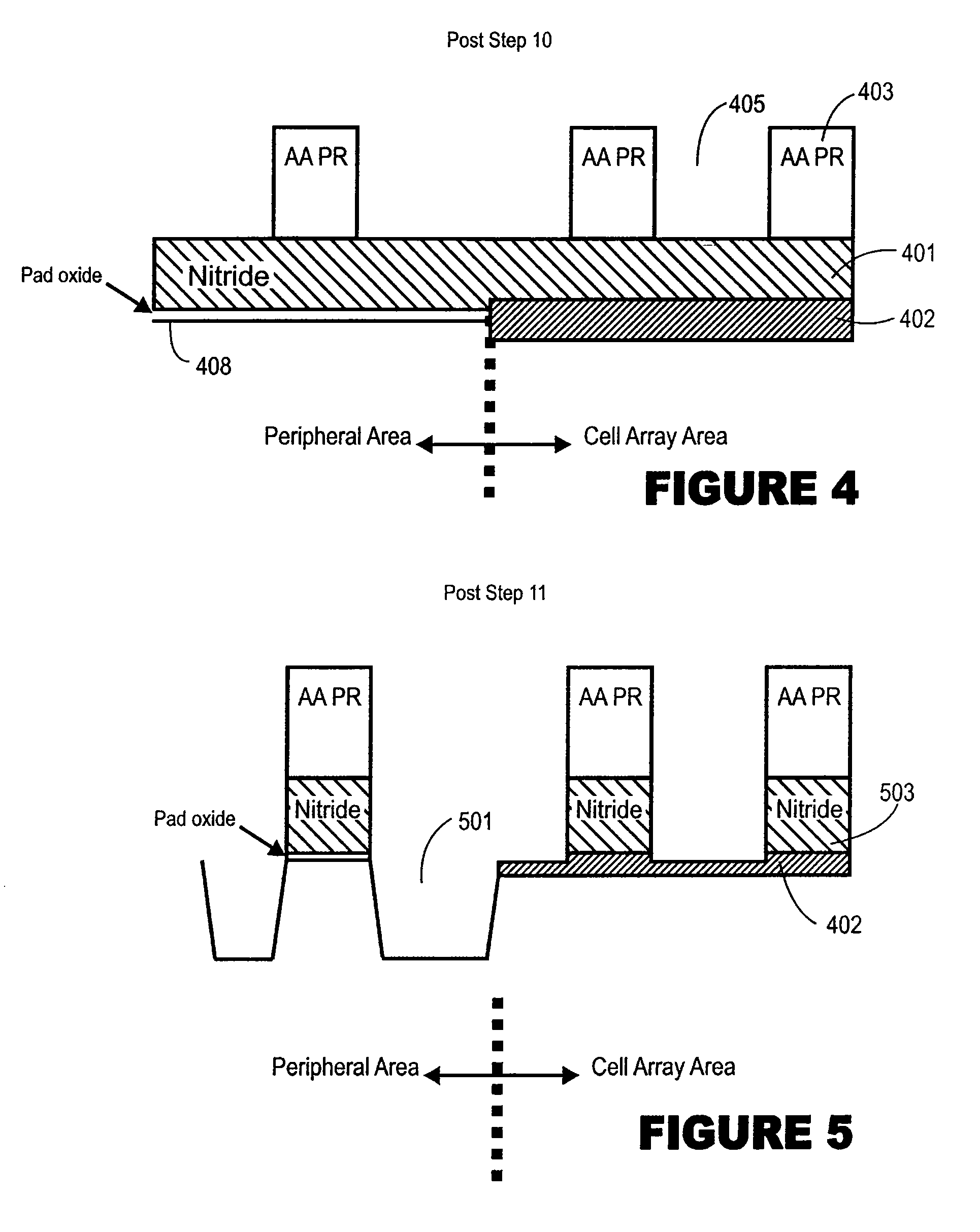

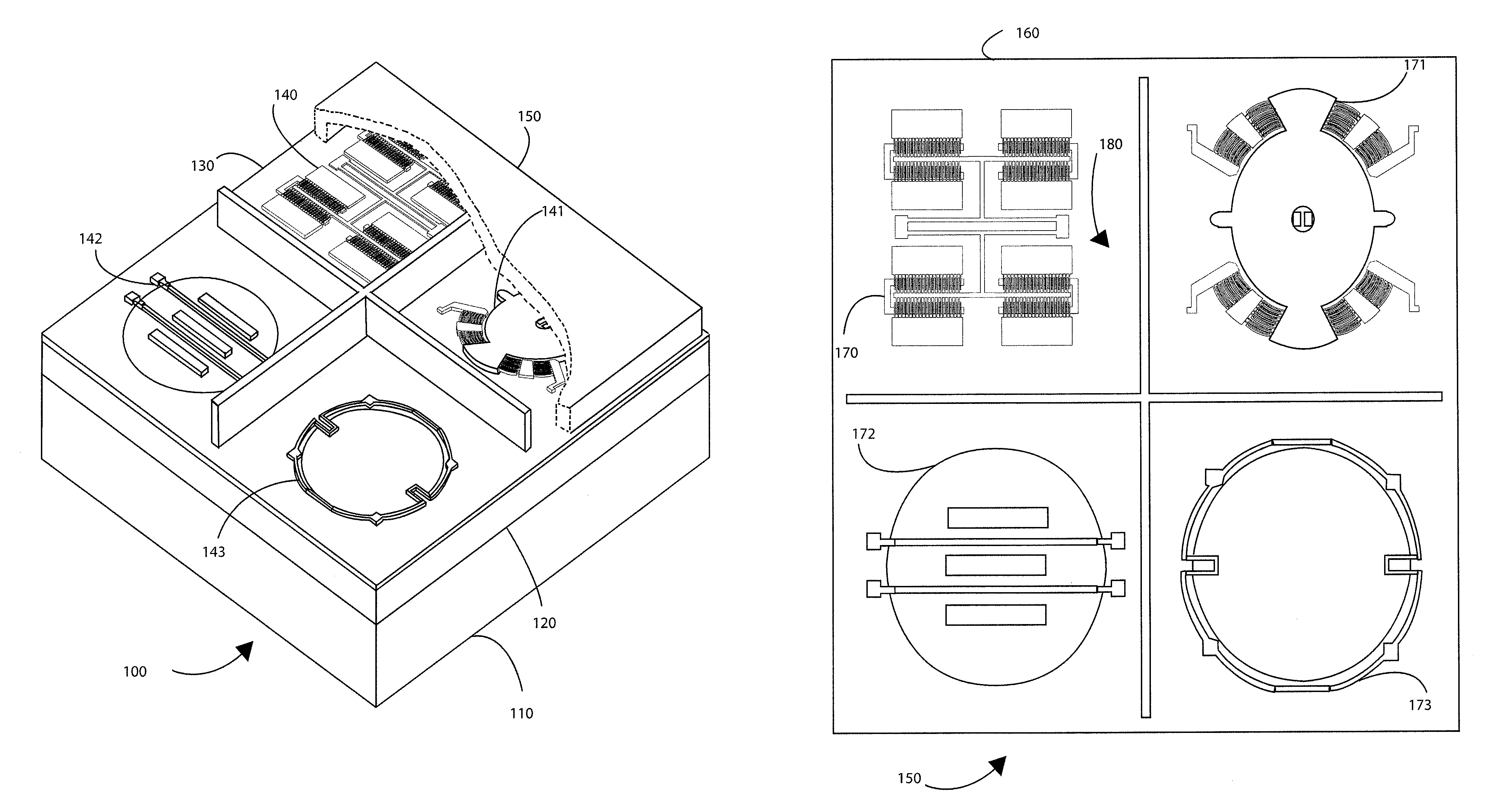

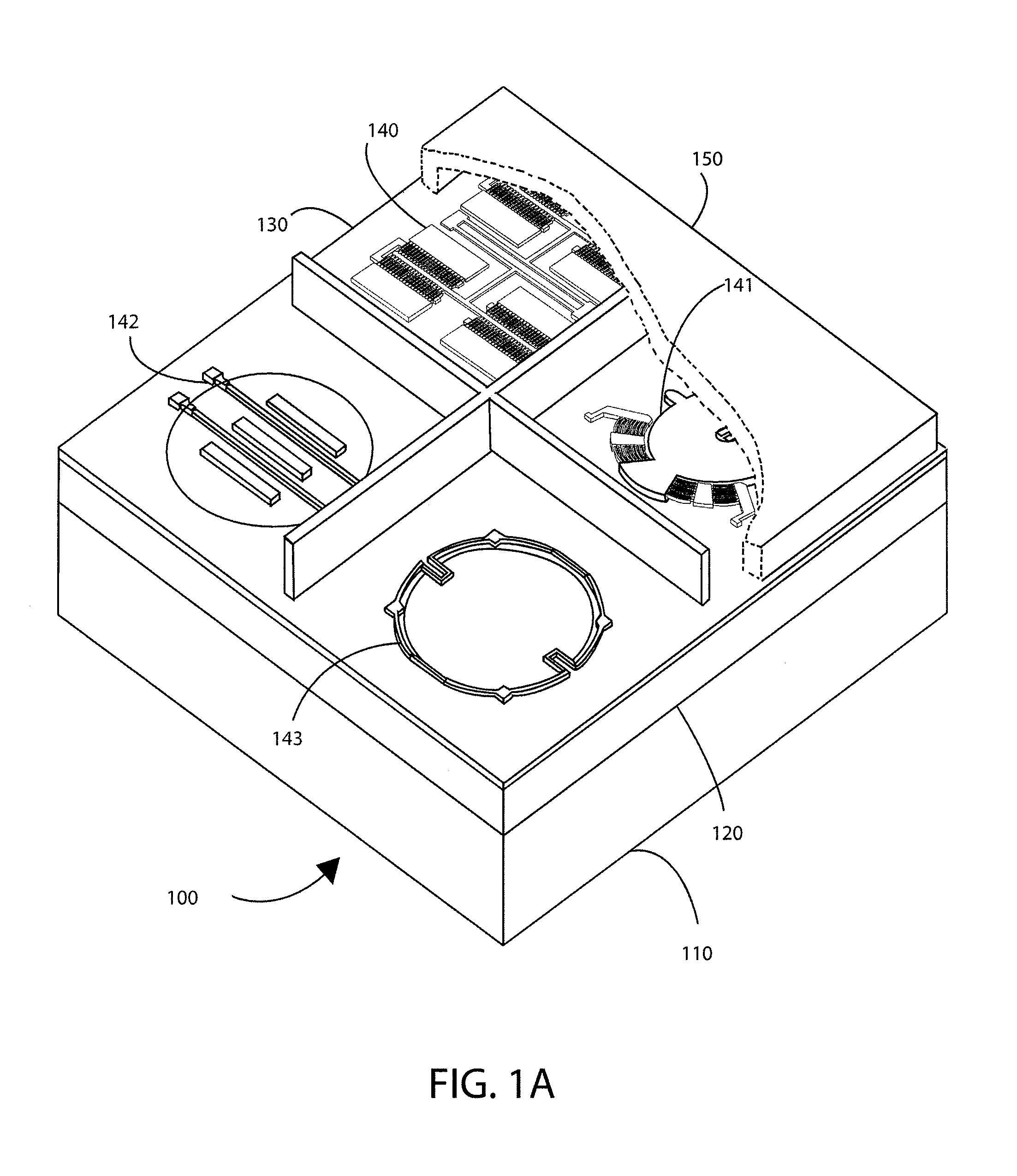

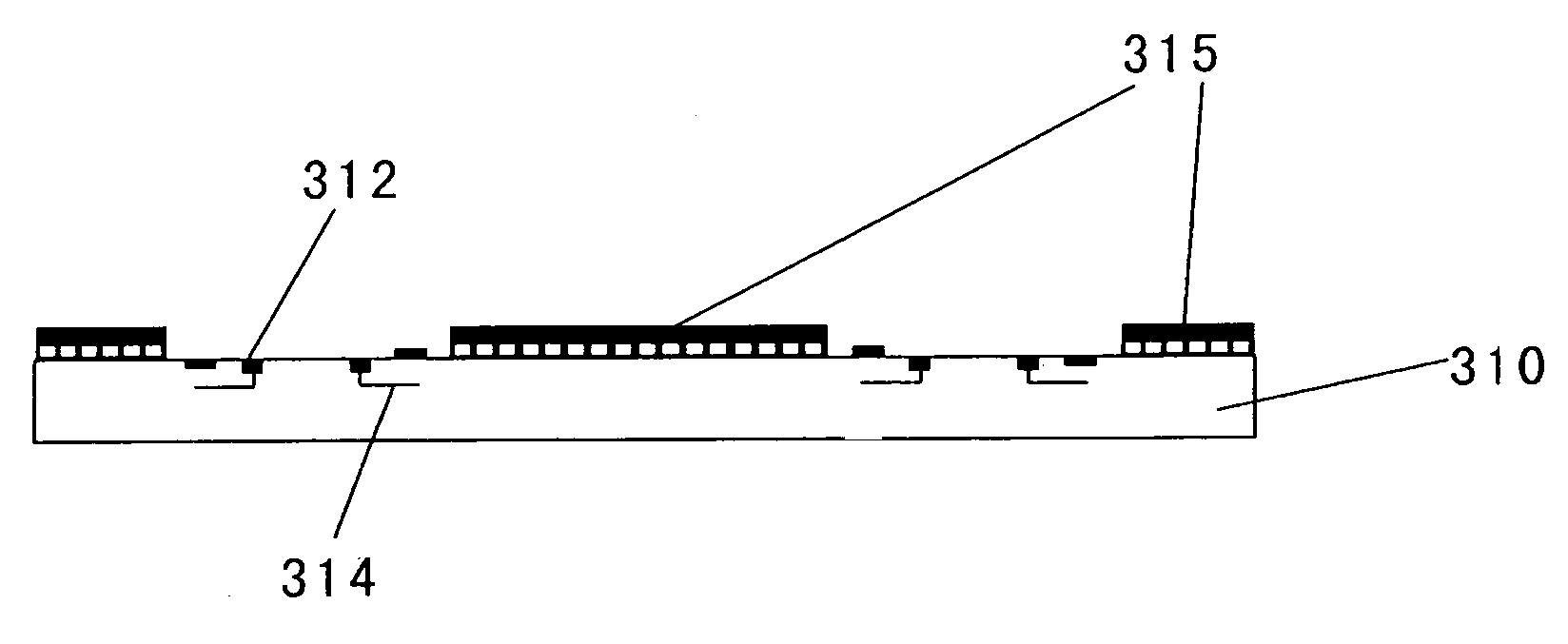

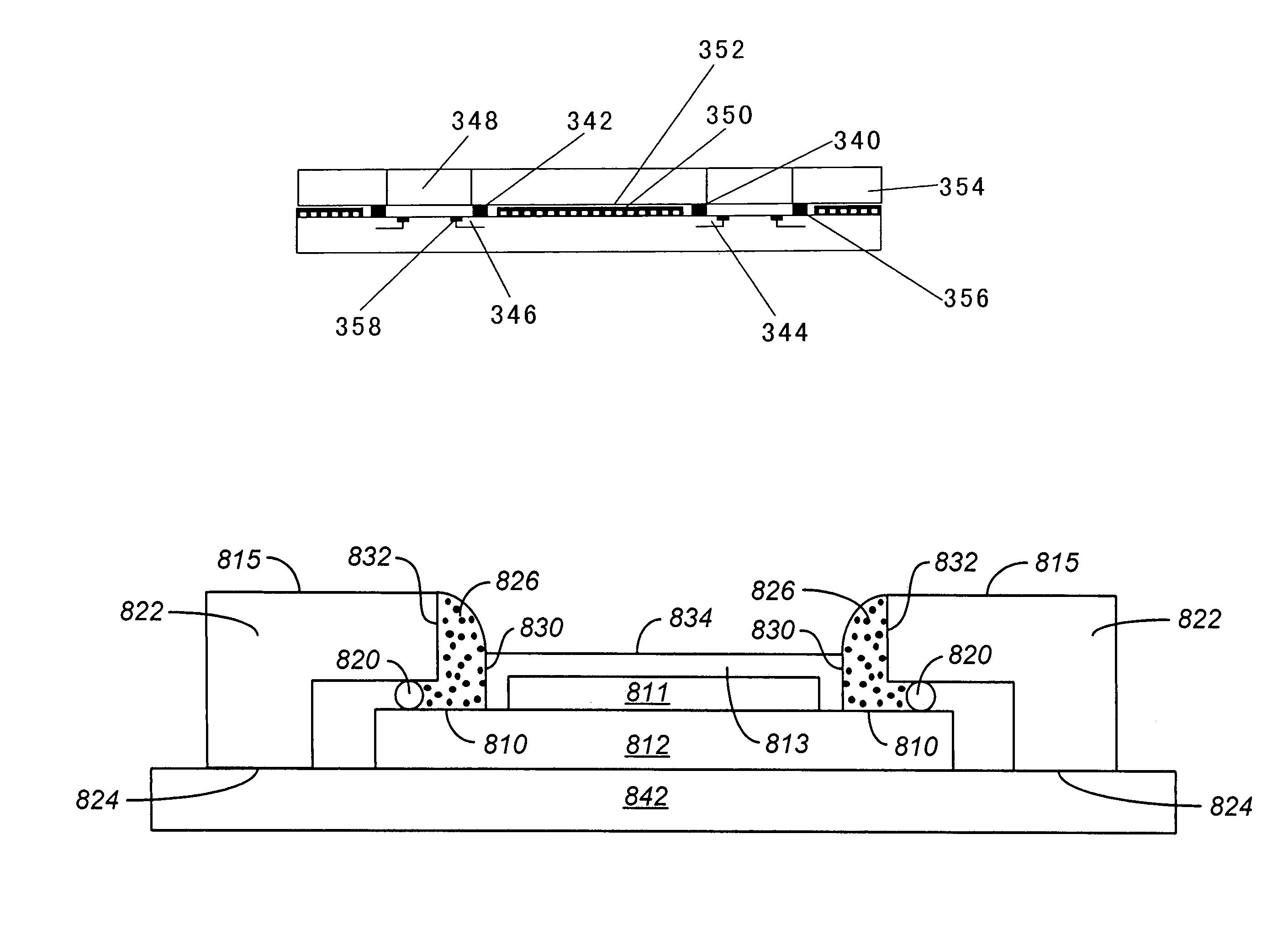

Method to package multiple MEMS sensors and actuators at different gases and cavity pressures

ActiveUS20140227816A1Increase dampingPerformanceDecorative surface effectsSemiconductor/solid-state device manufacturingCavity pressureMems sensors

A method for fabricating a multiple MEMS device. A semiconductor substrate having a first and second MEMS device, and an encapsulation wafer with a first cavity and a second cavity, which includes at least one channel, can be provided. The first MEMS can be encapsulated within the first cavity and the second MEMS device can be encapsulated within the second cavity. These devices can be encapsulated within a provided first encapsulation environment at a first air pressure, encapsulating the first MEMS device within the first cavity at the first air pressure. The second MEMS device within the second cavity can then be subjected to a provided second encapsulating environment at a second air pressure via the channel of the second cavity.

Owner:MOVELLA INC

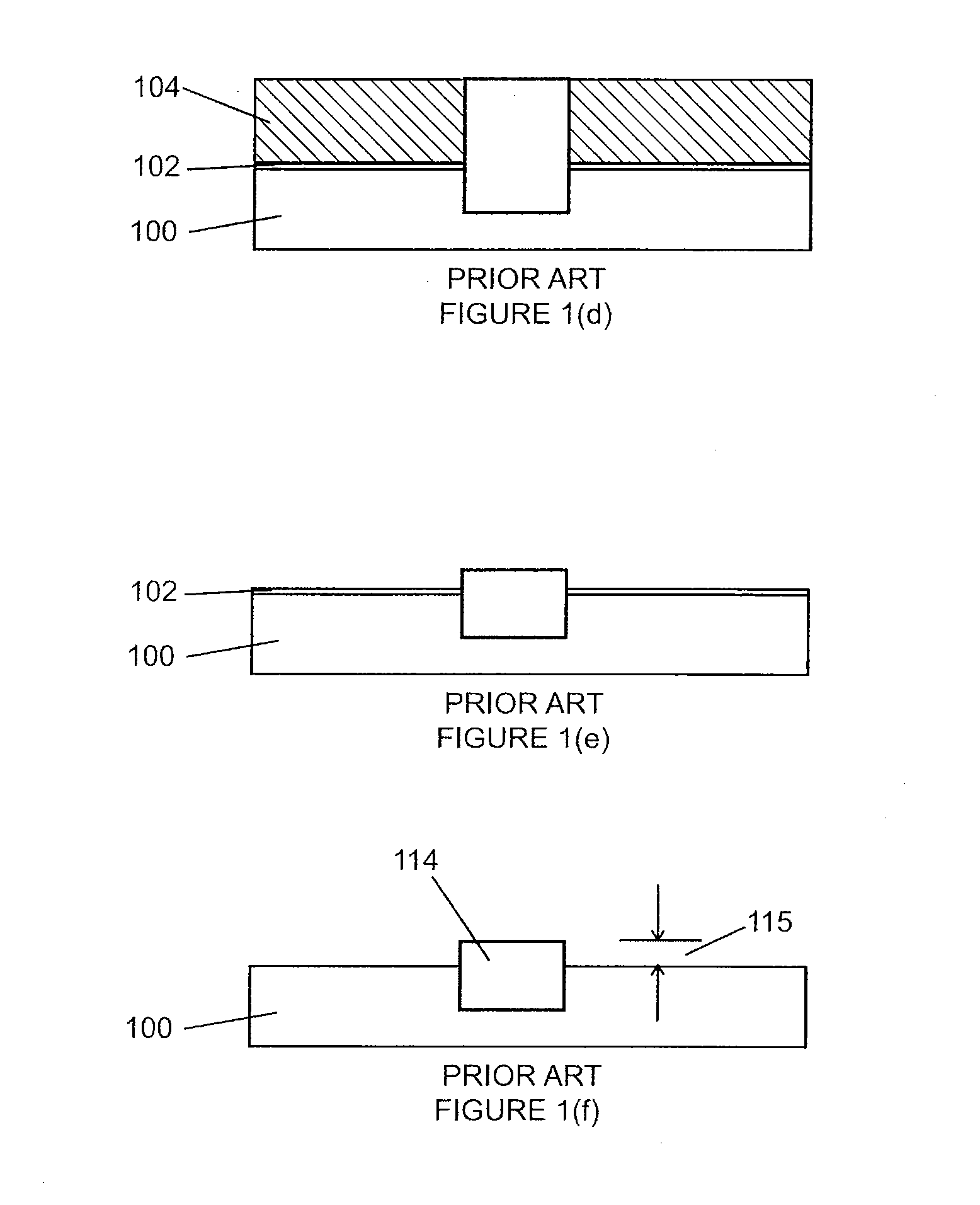

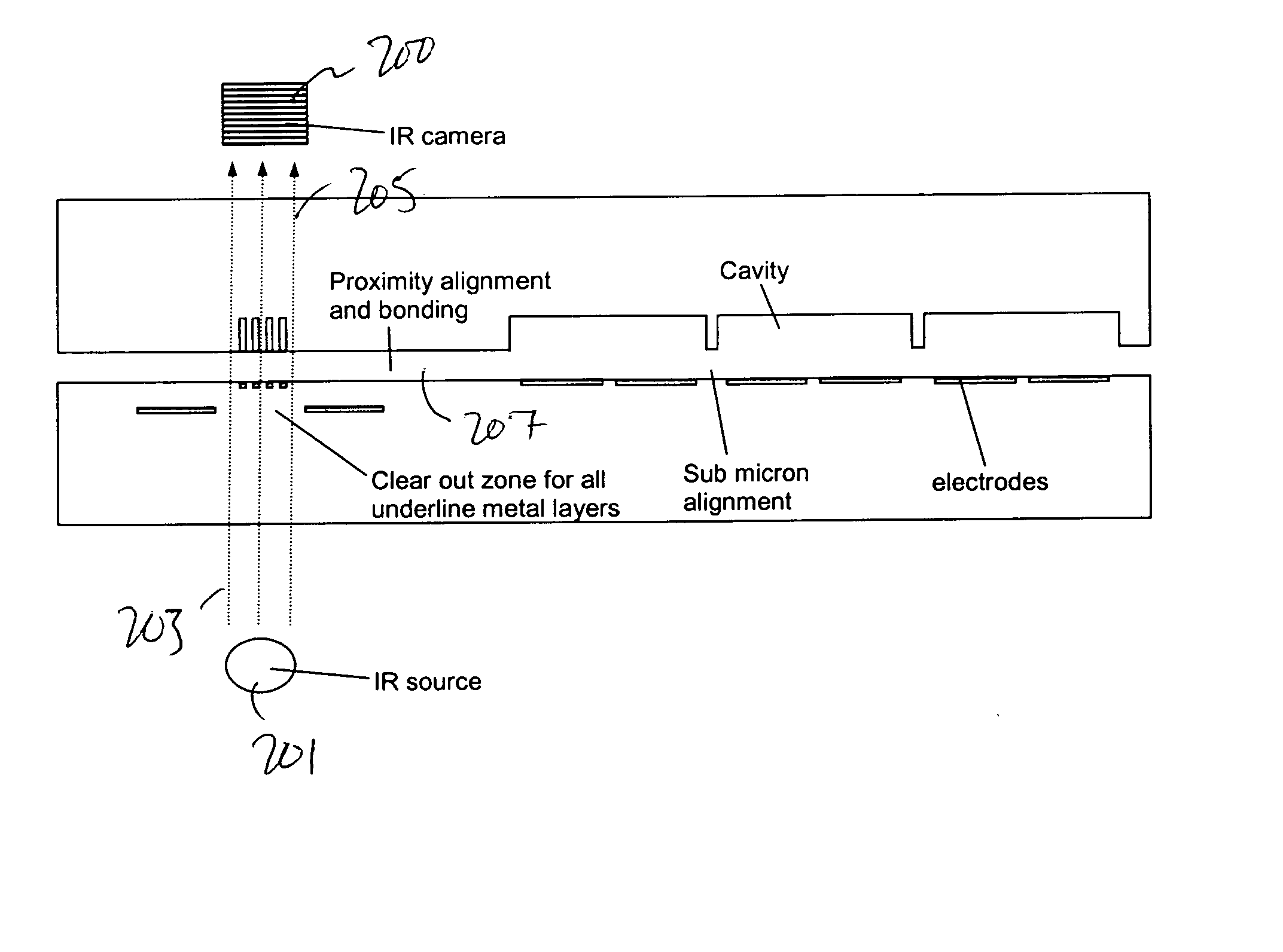

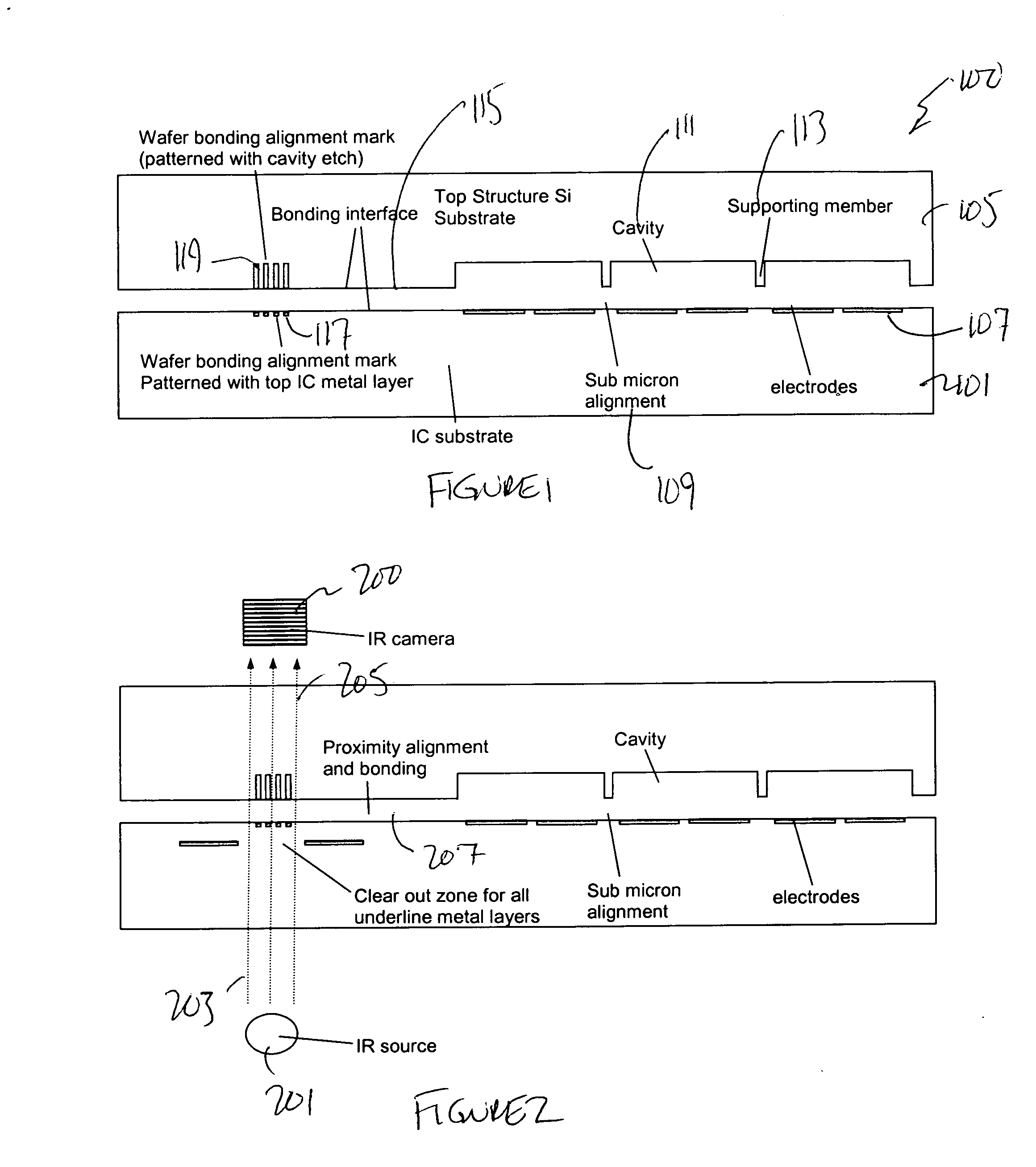

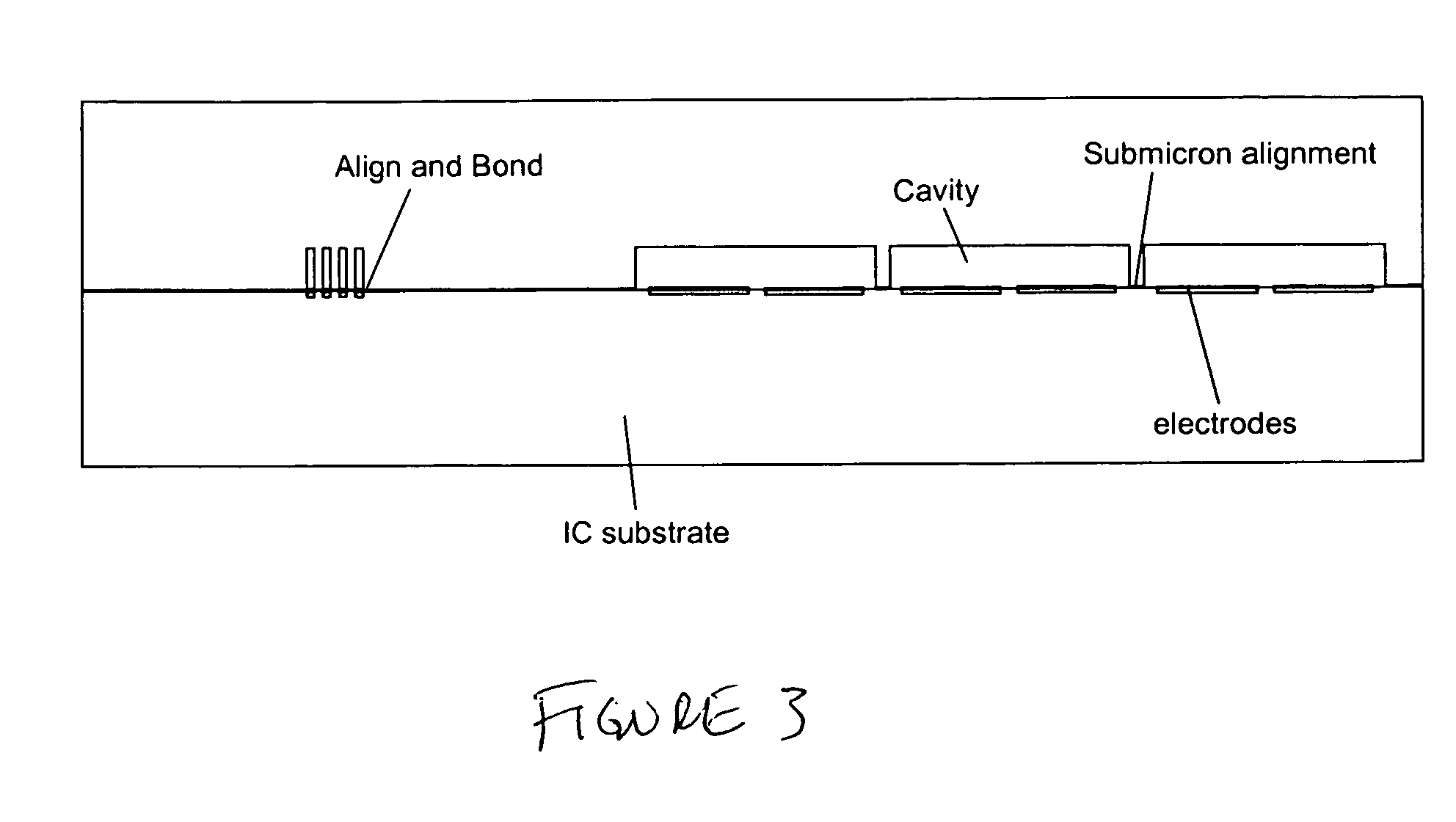

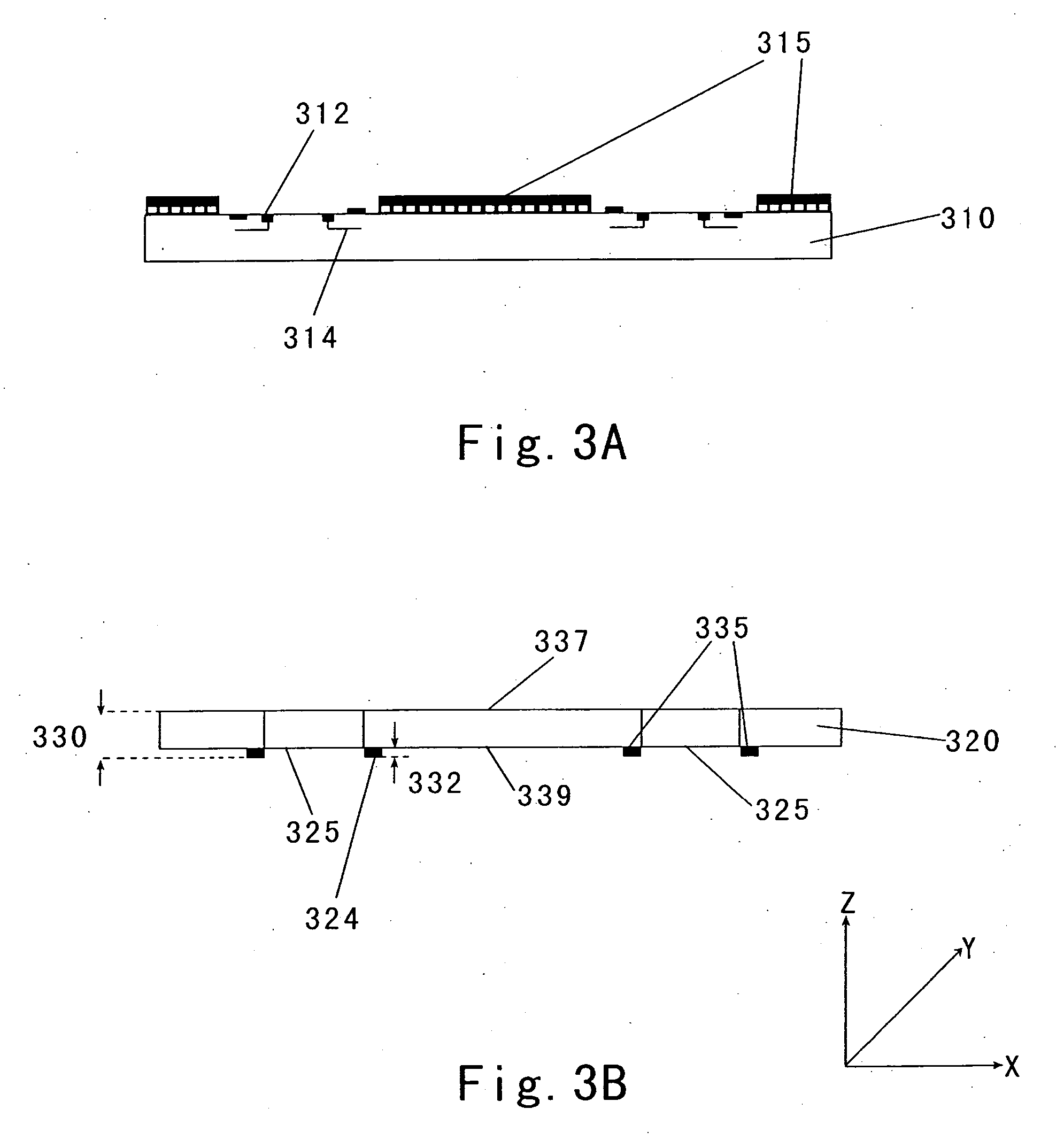

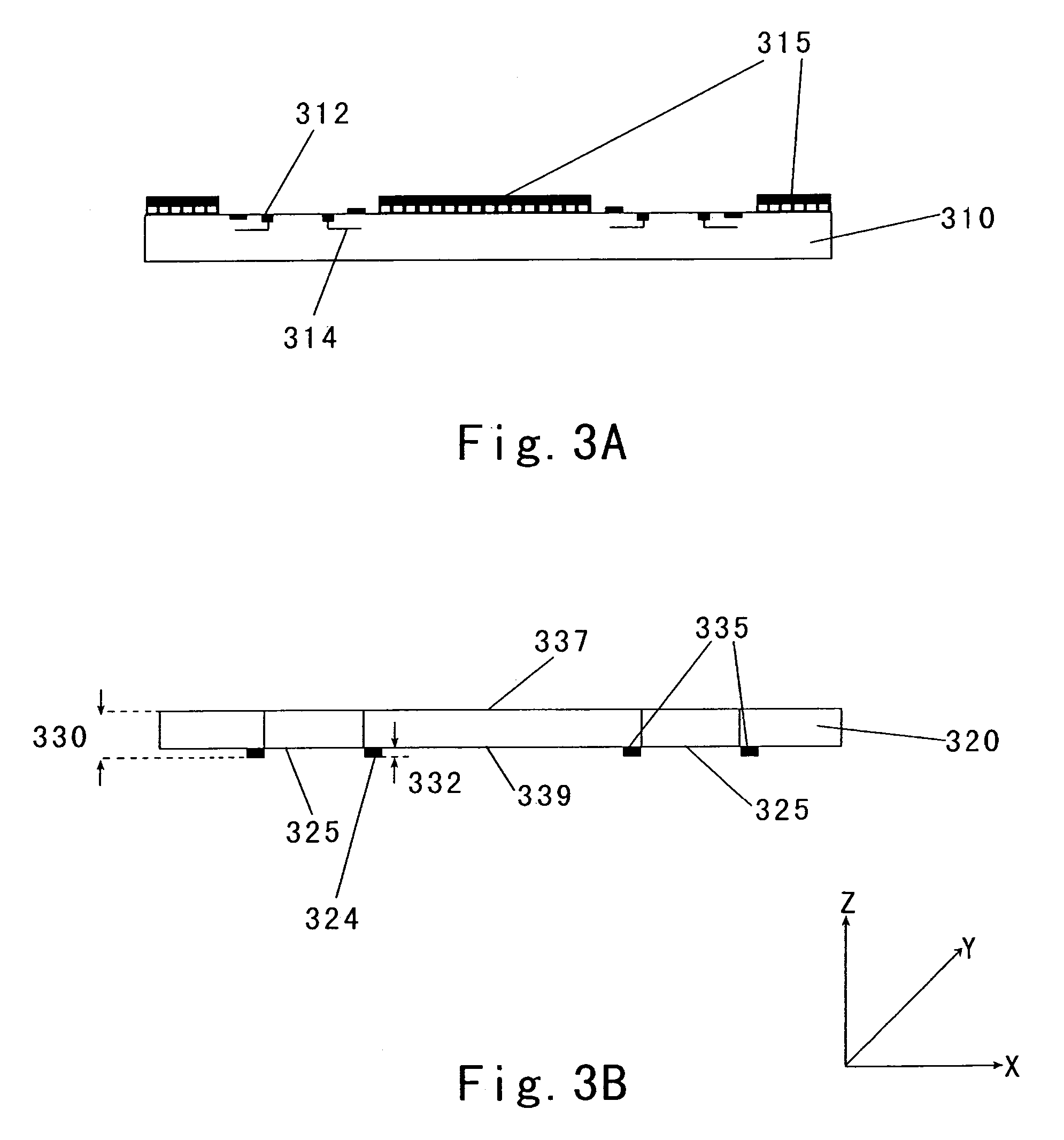

Method and structure for aligning mechanical based device to integrated circuits

InactiveUS20050255666A1Easy to useHigh device yieldPrecision positioning equipmentSoldering apparatusEngineeringElectromagnetic radiation

A method for bonding substrates together. The method includes providing a first substrate comprising a first surface. The first substrate comprises a plurality of first chips thereon. Each of the chips has integrated circuit devices. The first substrate includes a first alignment mark on the first substrate and a second alignment mark on the first substrate. The method also includes providing a second substrate comprising a silicon bearing material and second surface. The second substrate comprising a plurality of second chips thereon. Each of the chips comprises a plurality of mechanical structures. The second substrate has a first silicon based pattern on the second substrate and a second silicon based pattern on the second substrate. The method includes moving the first alignment mark of the first substrate to the first silicon based pattern on the second substrate and aligning the second alignment mark of the first substrate to the second silicon based pattern on the second substrate. A portion of at least one of the first substrate or the second substrate is illuminated with electromagnetic radiation. The method includes detecting a portion of the electromagnetic radiation and using the detected portion of the electromagnetic radiation to align the first substrate with the second substrate. The method also includes coupling the first substrate with the second substrate by contacting the first surface with the second surface and bonding the first surface with the second surface.

Owner:MIRADIA INC

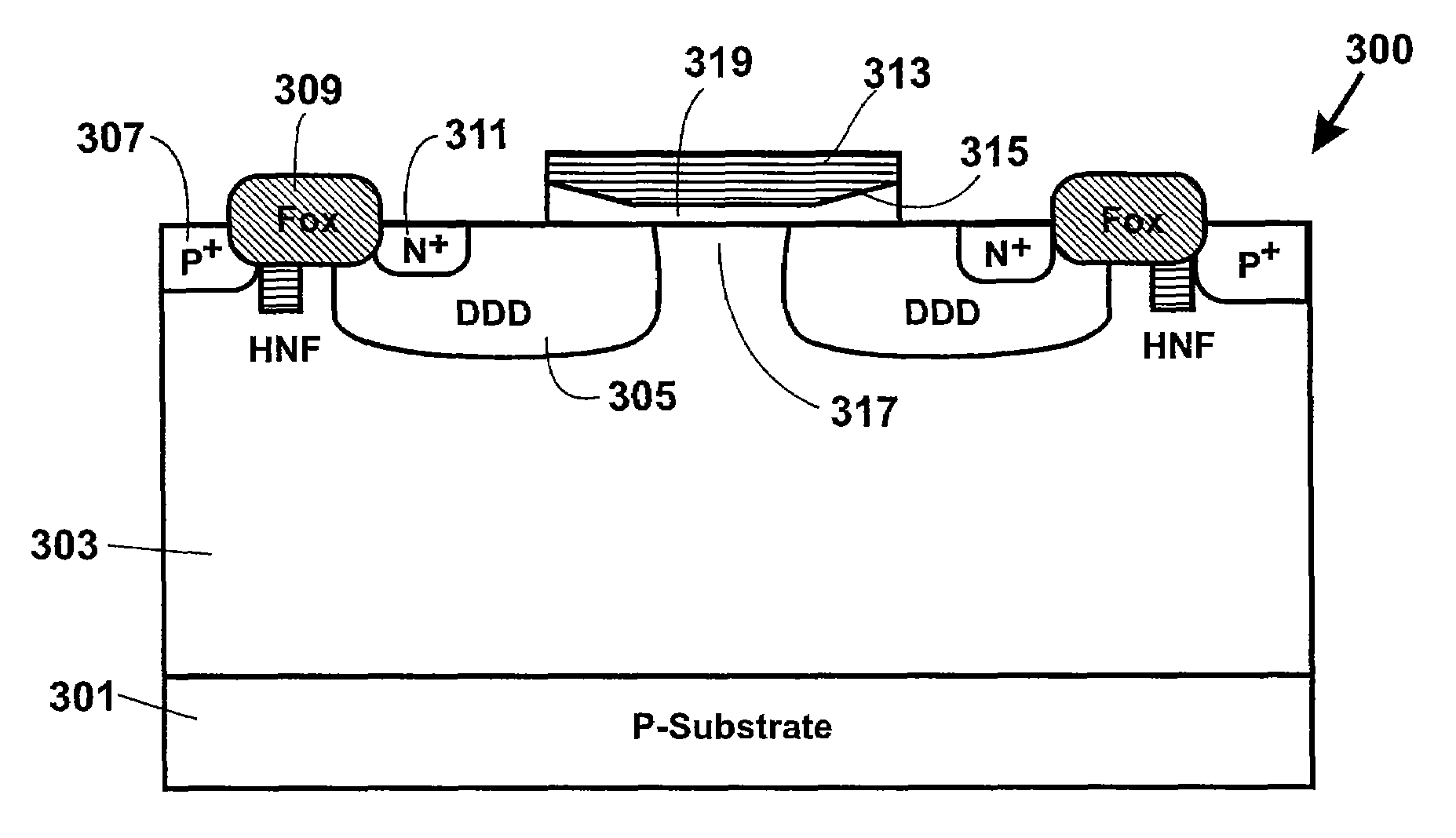

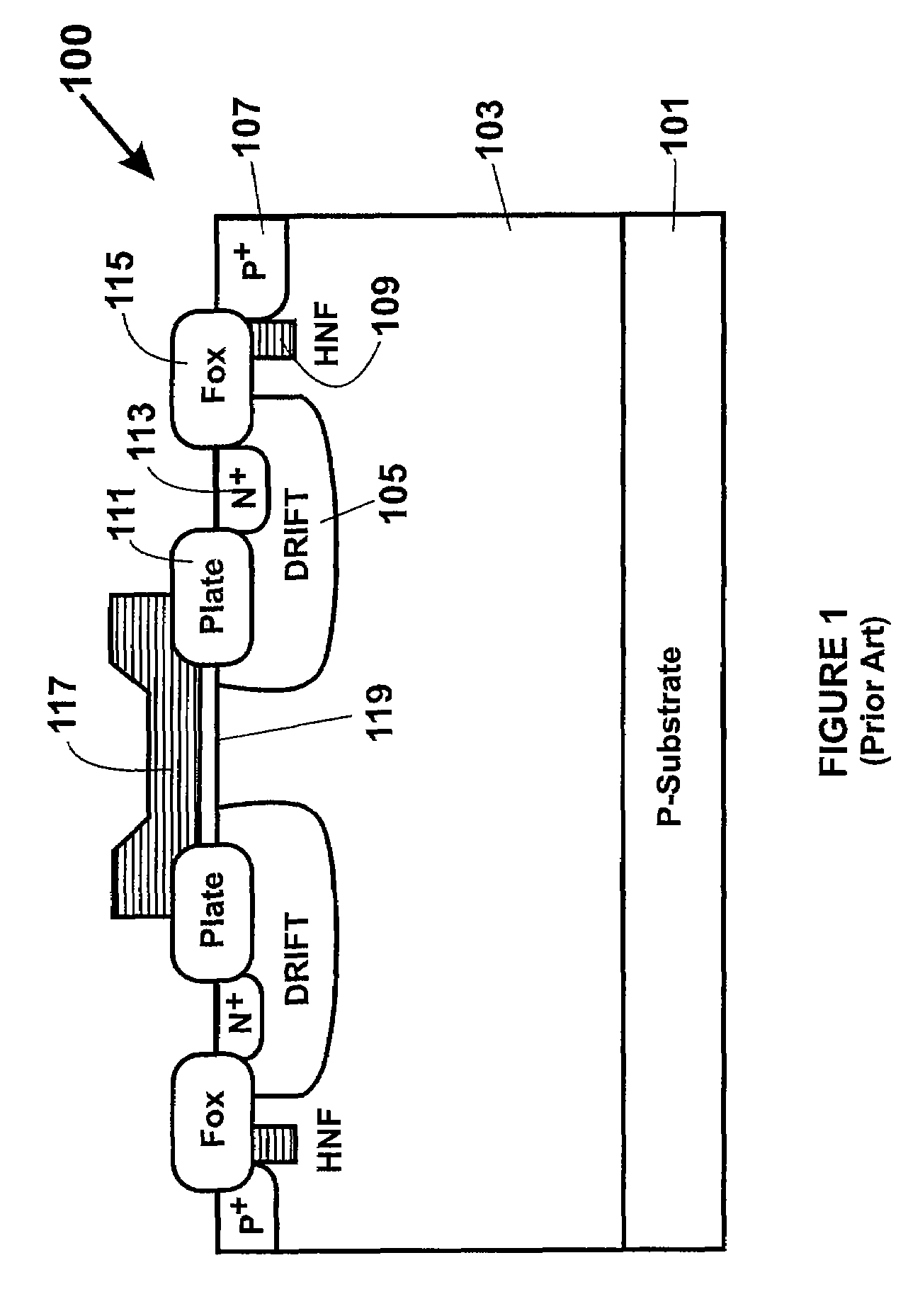

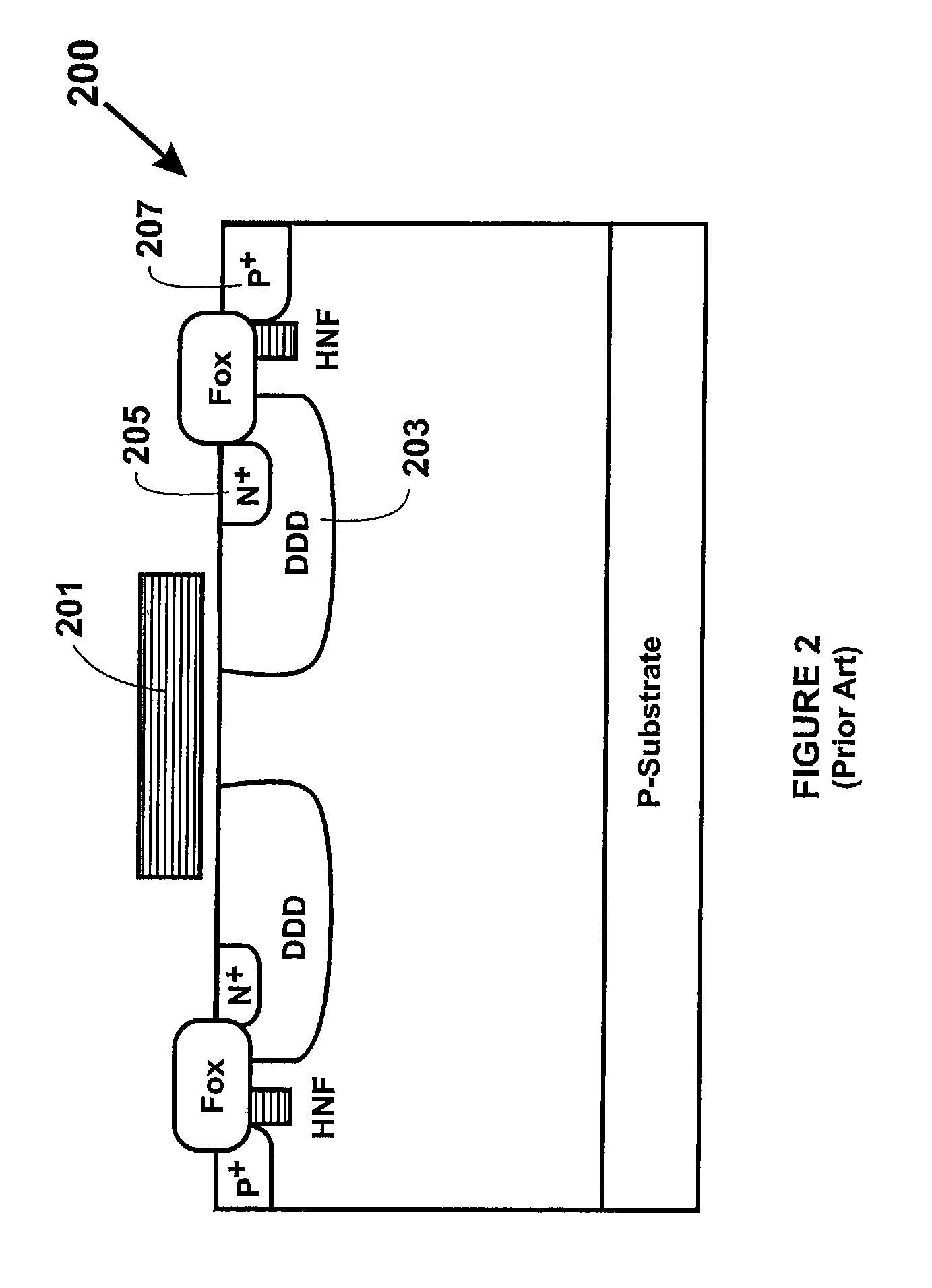

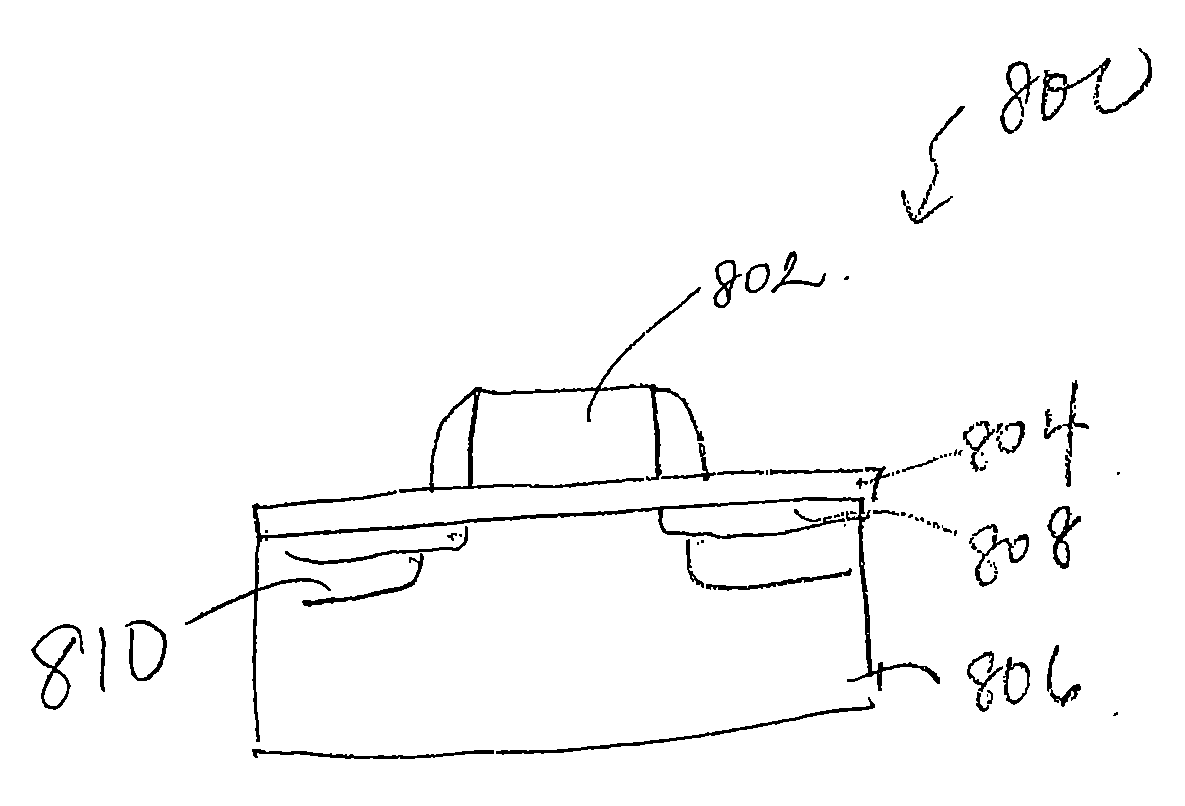

MOS device for high voltage operation and method of manufacture

ActiveUS7335543B2Improve breakdown voltageEasy to useTransistorSemiconductor/solid-state device manufacturingGate dielectricEngineering

A high voltage semiconductor device. The high voltage device has a substrate (e.g., silicon wafer) having a surface region. The substrate has a well region within the substrate and a double diffused drain region within the well region. A gate dielectric layer is overlying the surface region. A gate polysilicon layer is overlying the gate dielectric layer. A mask layer is overlying the gate polysilicon layer. The device also has a gate electrode formed within the gate polysilicon layer. The gate electrode has a first predetermined width and a first predetermined thickness. Preferably, the gate electrode has a first side and a second side formed between the first predetermined width. The gate electrode is coupled to the double diffused drain region within the well region. Preferably, the first side has a lower corner overlying the gate dielectric layer and an upper corner underlying the mask layer and the second side has a lower corner overlying the gate dielectric layer and an upper corner underlying the mask layer. A first insulating region formed from polysilicon is formed at the lower corner on the first side of the gate electrode. The first insulating region extends from the first side toward a first preselect region within the gate electrode. A second insulating region formed from polysilicon material is at the lower corner on the second side of the gate electrode. The second insulating region extends from the second side toward a second preselected region within the gate electrode. A second predetermined width is formed between the first preselect region and the second preselected region. The second predetermined width comprises substantially polysilicon material. Preferably, the high voltage device has a breakdown voltage of the high voltage semiconductor device is characterized by a voltage of greater than 20 volts.

Owner:SEMICON MFG INT (SHANGHAI) CORP

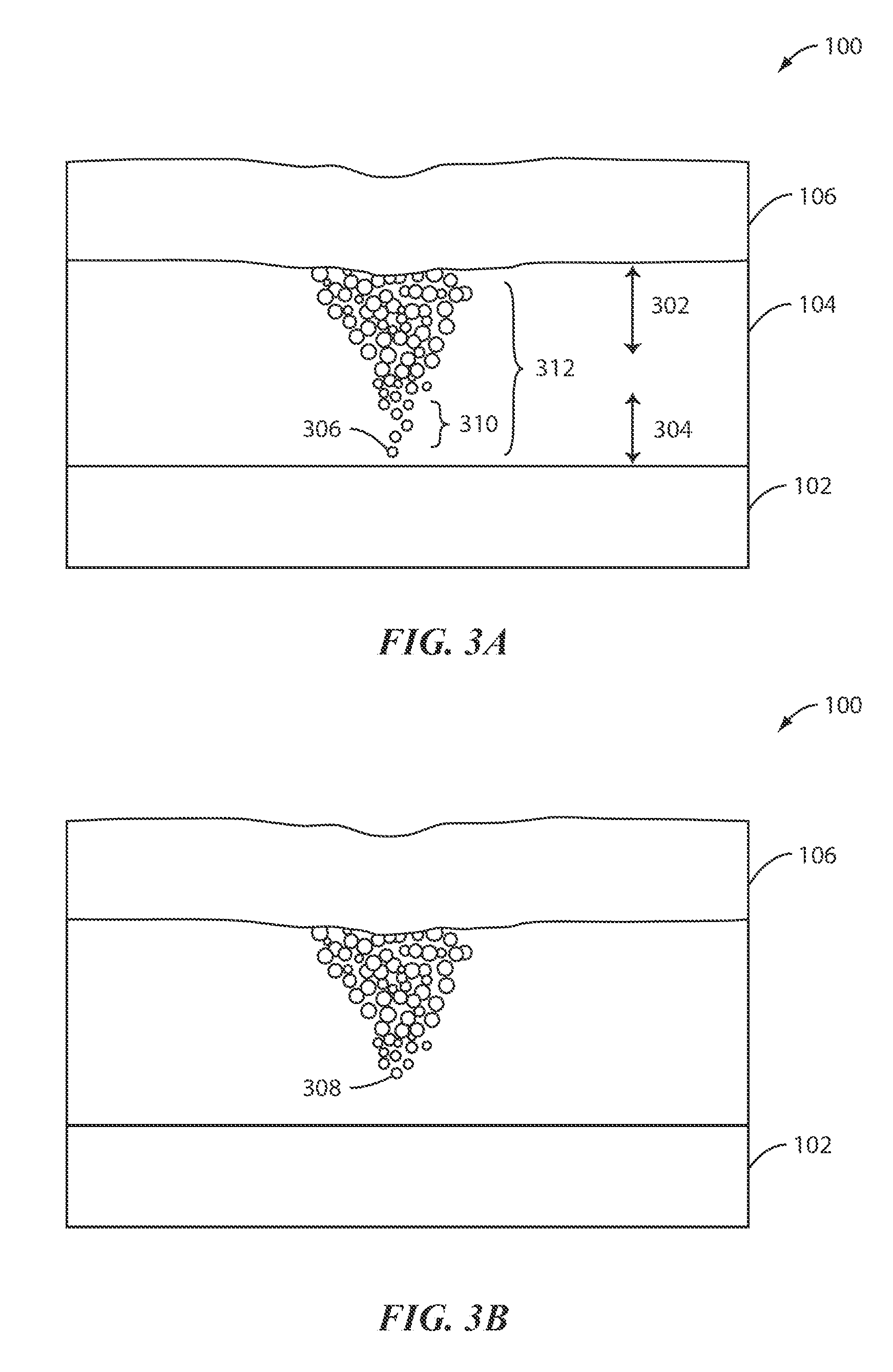

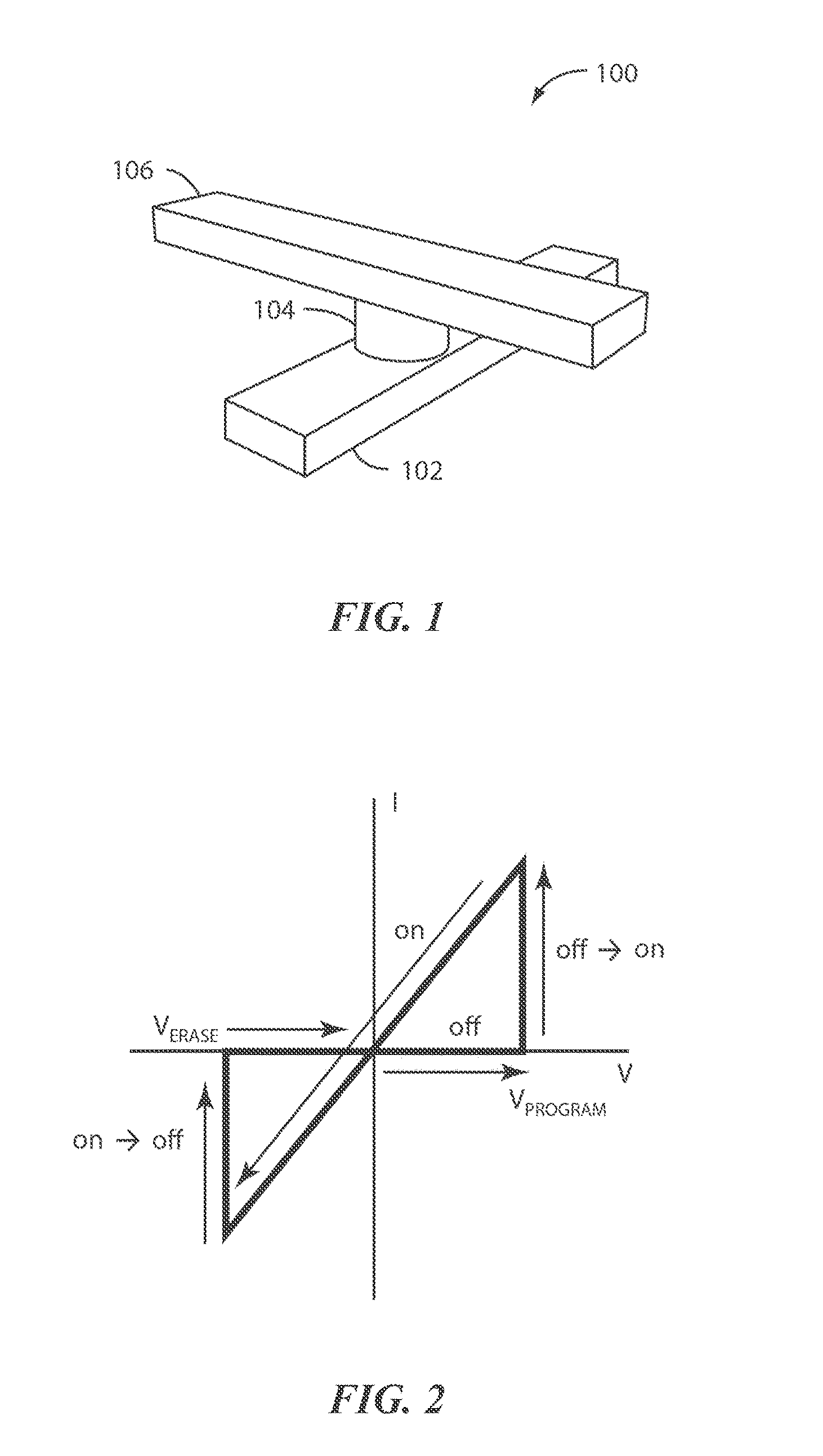

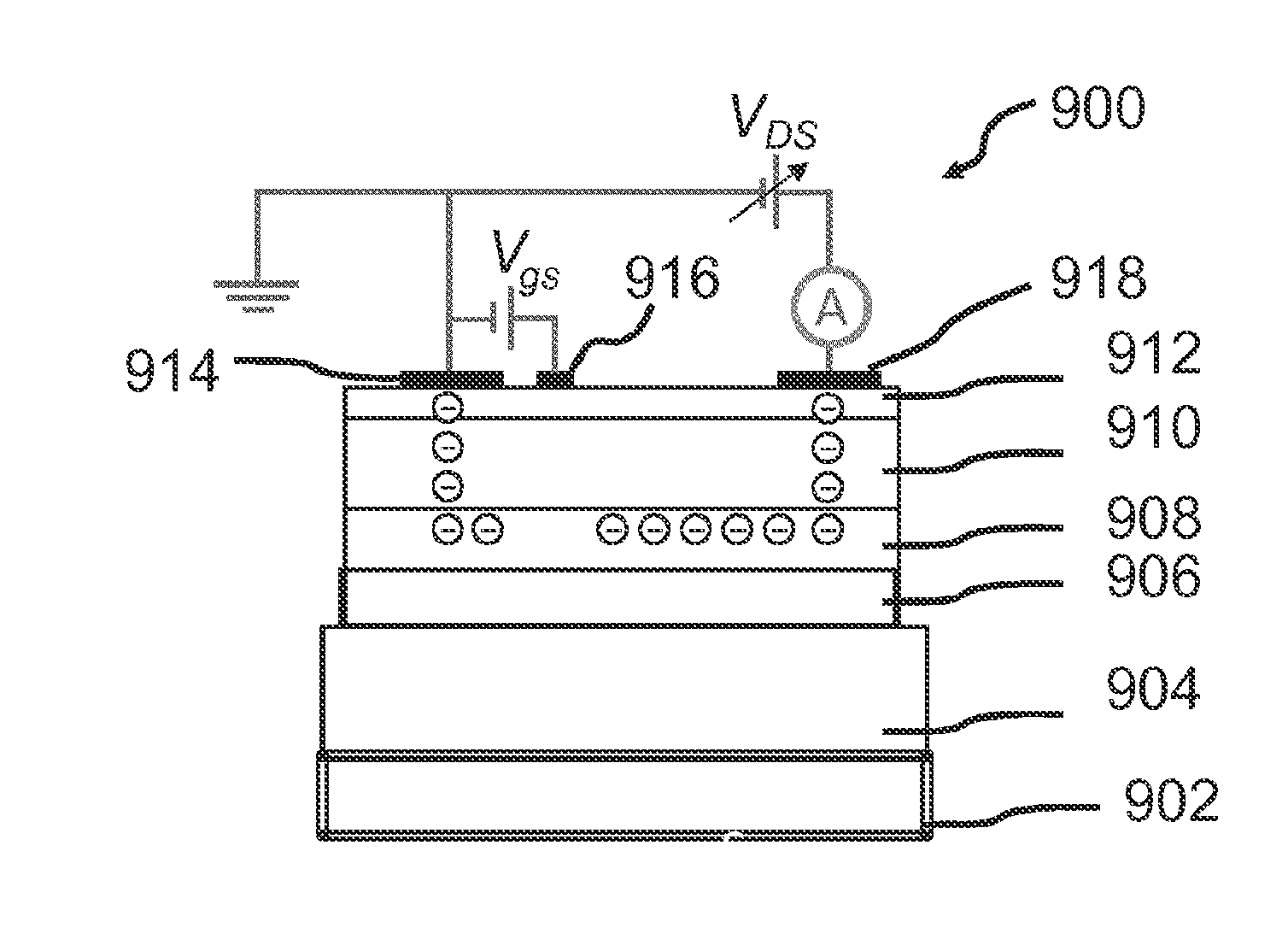

Switching device having a non-linear element

ActiveUS8502185B2High densityFast switching speedTransistorSolid-state devicesLinear elementNonlinear element

A switching device includes a substrate; a first electrode formed over the substrate; a second electrode formed over the first electrode; a switching medium disposed between the first and second electrode; and a nonlinear element disposed between the first and second electrodes and electrically coupled in series to the first electrode and the switching medium. The nonlinear element is configured to change from a first resistance state to a second resistance state on application of a voltage greater than a threshold.

Owner:CROSSBAR INC

Rectification element and method for resistive switching for non volatile memory device

ActiveUS8351241B2High densityFast switching speedSolid-state devicesDigital storageElectrical resistance and conductanceElectricity

Owner:RGT UNIV OF MICHIGAN

Integrated CMOS and MEMS with air dielectric method and system

A method and structure for fabricating a monolithic integrated CMOS and MEMS device. The method includes providing a first semiconductor substrate having a first surface region and forming one or more CMOS IC devices on a CMOS IC device region overlying the first surface region. The CMOS IC device region can also have a CMOS surface region. A bonding material can be formed overlying the CMOS surface region to form an interface by which a second semiconductor substrate can be joined to the CMOS surface region. The second semiconductor substrate having a second surface region to the CMOS surface region by bonding the second surface region to the bonding material, the second semiconductor substrate comprising one or more first air dielectric regions. One or more free standing MEMS structures can be formed within one or more portions of the processed first substrate.

Owner:MOVELLA INC

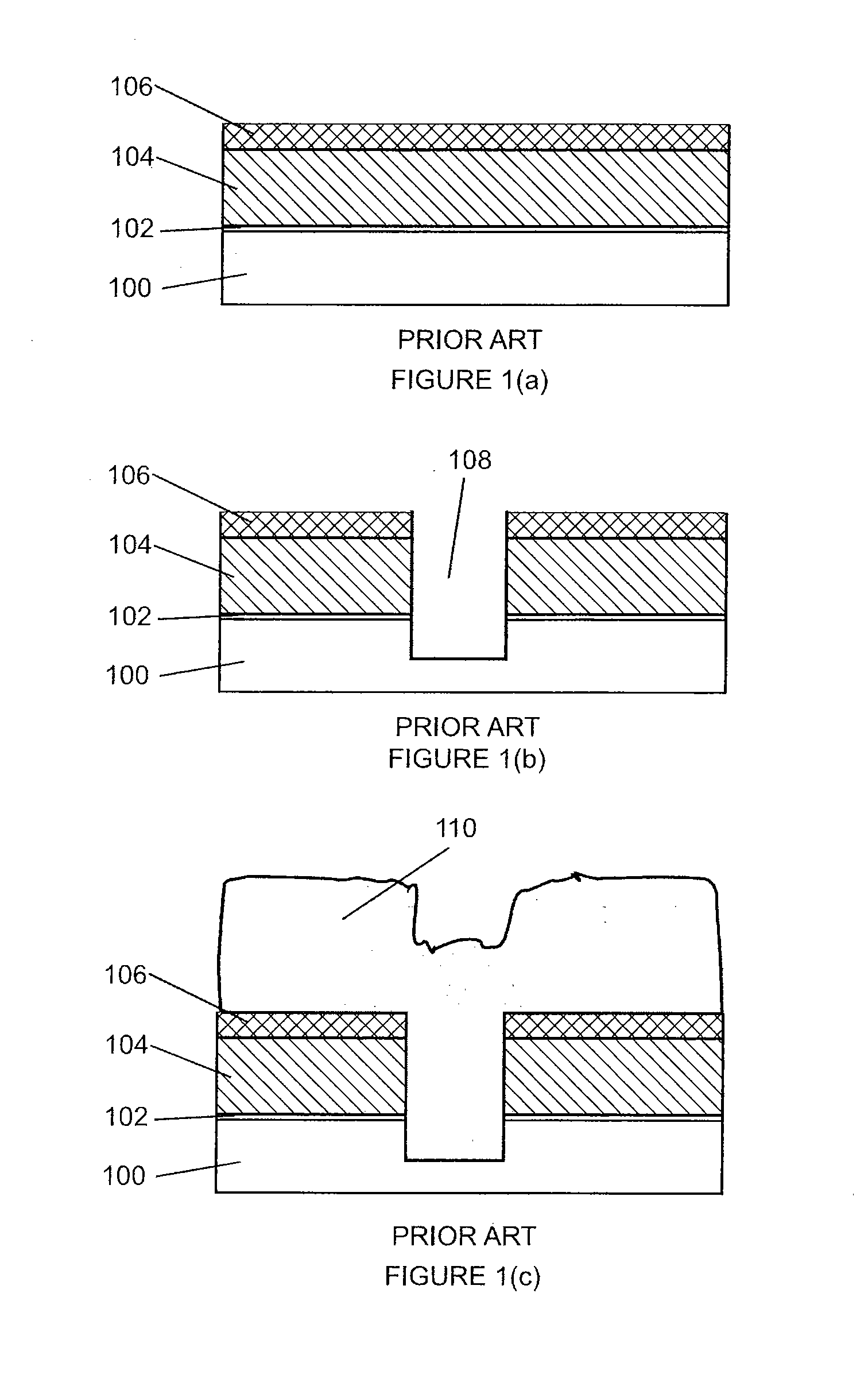

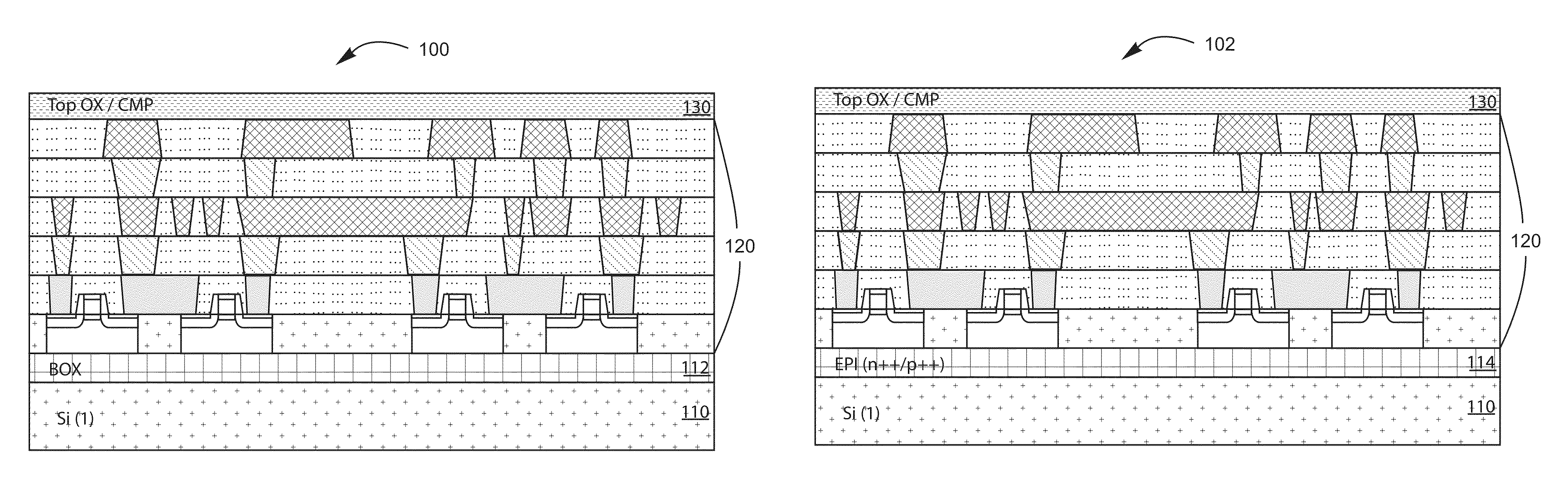

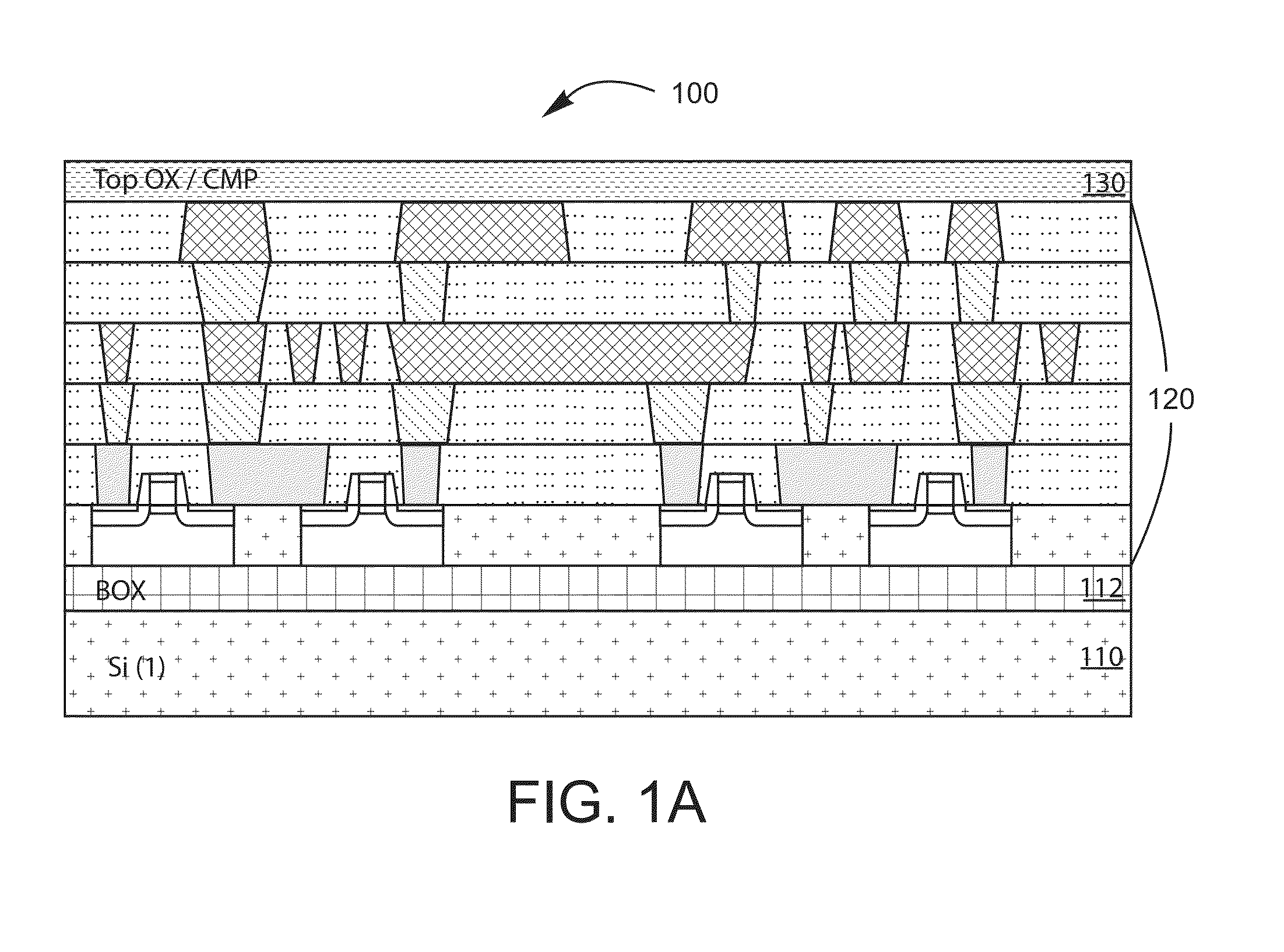

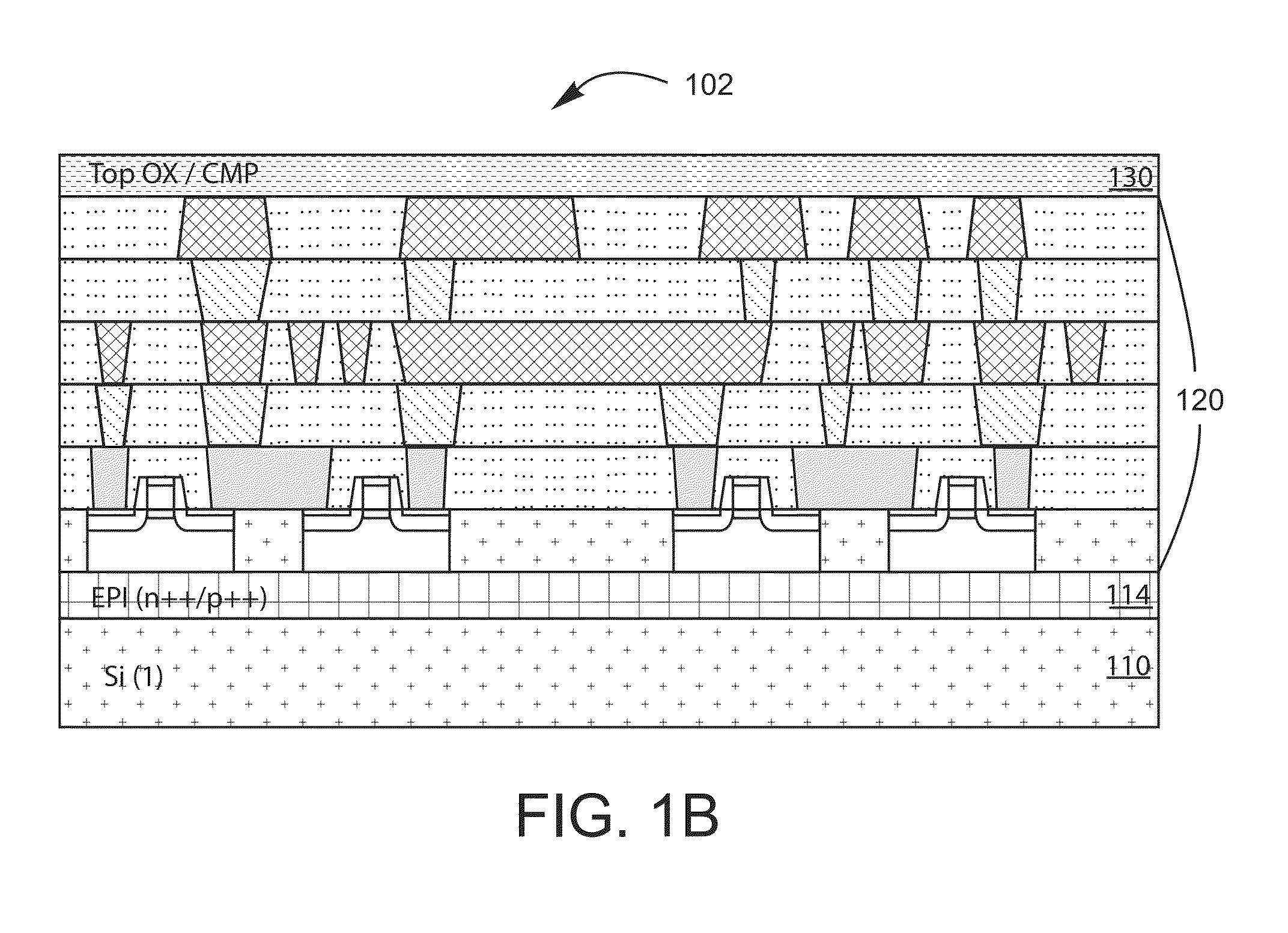

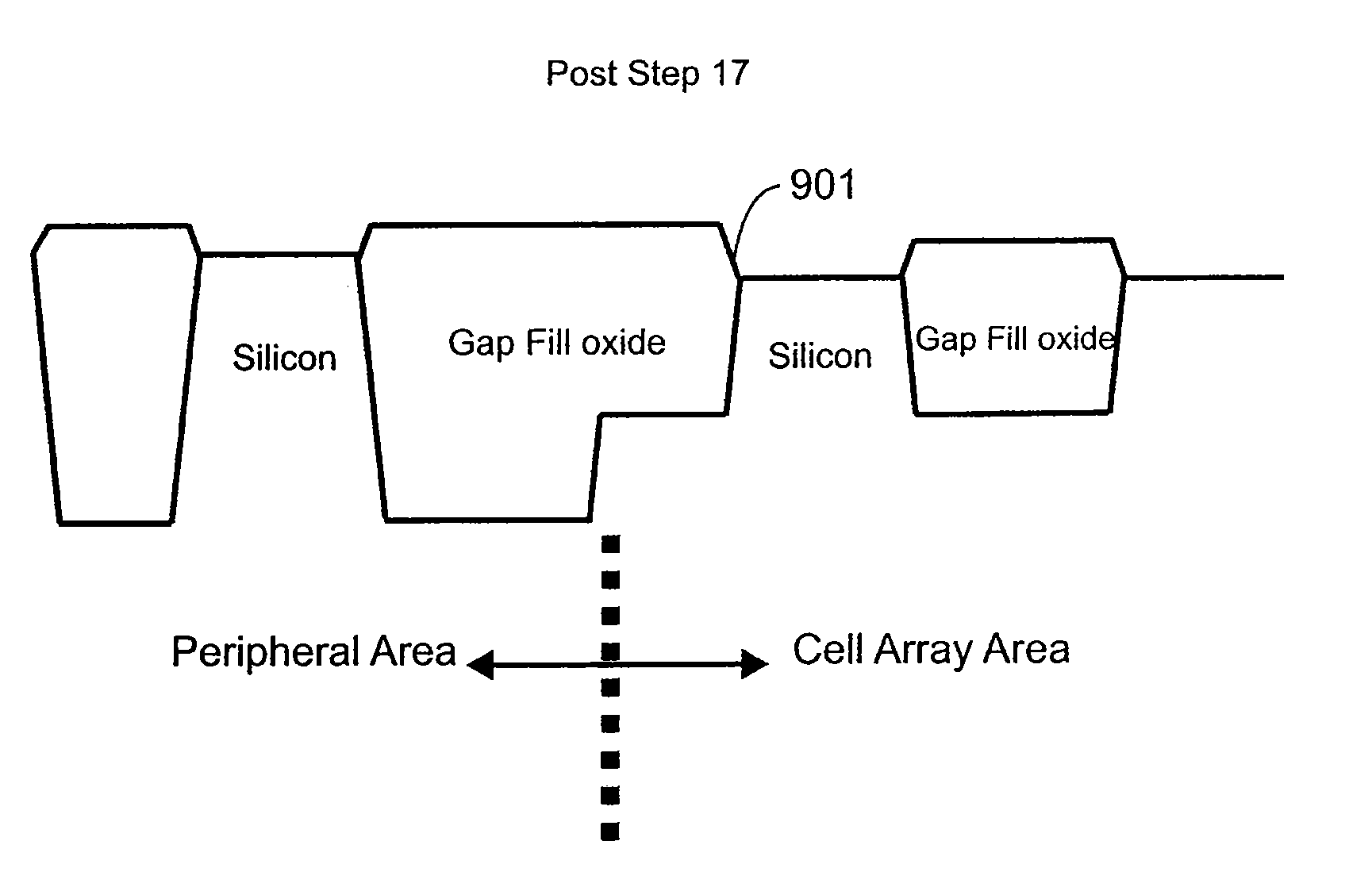

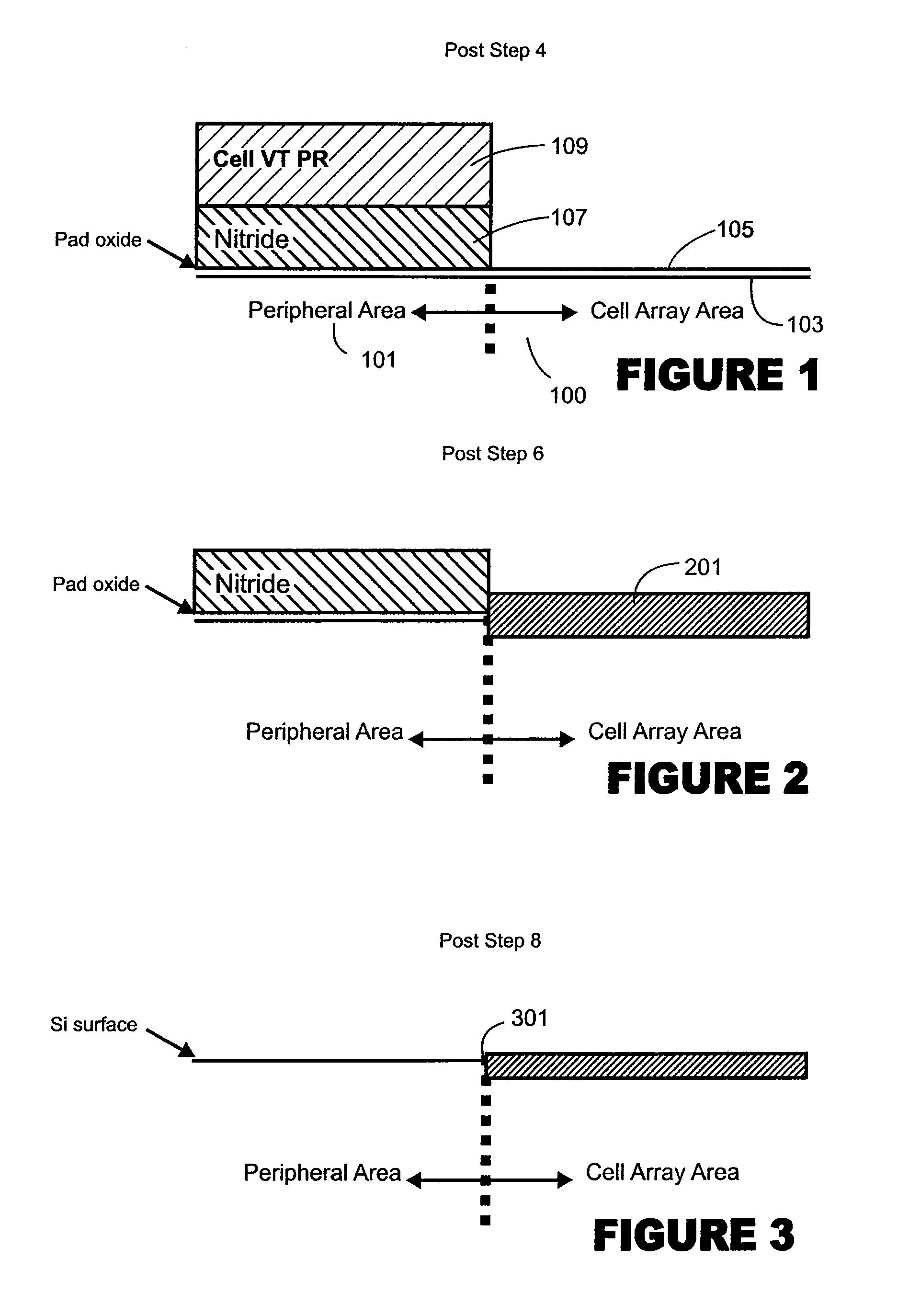

Method for fabricating isolation structures for flash memory semiconductor devices

ActiveUS7427552B2Easy to useHigh device yieldSolid-state devicesSemiconductor/solid-state device manufacturingCell regionSilicon dioxide

A method for fabricating integrated circuit devices, e.g., Flash memory devices, embedded Flash memory devices. The method includes providing a semiconductor substrate, e.g., silicon, silicon on insulator, epitaxial silicon. In a specific embodiment, the semiconductor substrate has a peripheral region and a cell region. The method includes forming a first dielectric layer (e.g., silicon dioxide) having a first thickness overlying a cell region and a second dielectric layer (e.g., silicon dixode) having a second thickness overlying the peripheral region. In a specific embodiment, the cell region is for Flash memory devices and / or other like structures. The method forms a pad oxide layer overlying the first dielectric layer and forms a nitride layer overlying the pad oxide layer. The method includes patterning at least the nitride layer to expose a first trench region in the peripheral region and to expose a second trench region in the cell region, while a portion of the first dielectric layer having the first thickness in the cell region is maintained. The method includes forming a first trench structure having a first depth in the first trench region, while the portion of the first dielectric layer having the first thickness in the cell region protects the second trench region. The method includes removing the portion of the first dielectric layer to expose the second trench region. In a specific embodiment, the method includes subjecting the first trench region, including the first trench structure, and the second trench region with an etching process to continue to form the first trench structure from the first depth to a second depth and to form a second trench structure having a third depth within the second trench region. In the third depth is less than the second depth.

Owner:SEMICON MFG INT (SHANGHAI) CORP

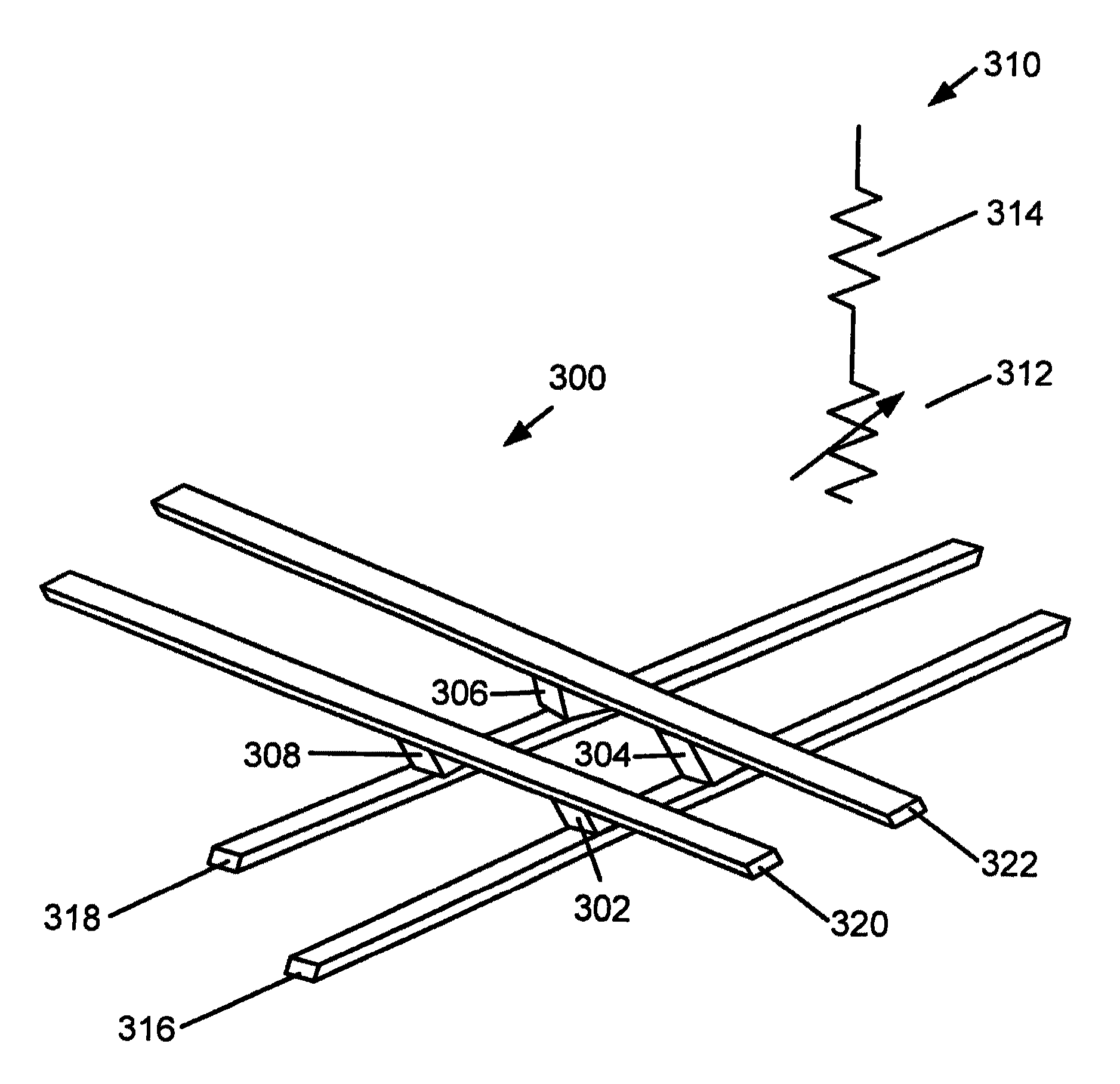

Magneto meter using lorentz force for integrated systems

ActiveUS8402666B1Easy to useHigh device yieldSpeed measurement using gyroscopic effectsRotary gyroscopesCMOSLorentz factor

Embodiments of the present invention can provide an integrated electronic compass and circuit system having a semiconductor substrate and one or more CMOS integrated circuits formed on one or more portions of the semiconductor substrate. The system can have an electronic compass device operably coupled to the one or more CMOS integrated circuits. The system can also have a plurality of electronic compass devices configured in a parallel arrangement in a hub and spoke configuration.

Owner:MOVELLA INC

Multiple magneto meters using Lorentz force for integrated systems

ActiveUS8407905B1Easy to useHigh device yieldSpeed/acceleration/shock instrument detailsGyroscopes/turn-sensitive devicesCMOSLorentz force

A plurality of integrated electronic compasses and circuit system. The system includes a semiconductor substrate and one or more CMOS integrated circuits formed on one or more portions of the semiconductor substrate. The system has a plurality of electronic compass devices operably coupled to the one or more CMOS integrated circuits. The plurality of electronic compass devices can be integrated with one or more sensors, MEMS, or other devices.

Owner:MOVELLA INC

Transducer structure and method for MEMS devices

ActiveUS8477473B1Easy to useHigh device yieldManufacture of electrical instrumentsAcceleration measurementTransducerEngineering

An improved MEMS transducer apparatus and method is provided. The apparatus has a movable base structure including an outer surface region and at least one portion removed to form at least one inner surface region. At least one intermediate anchor structure is disposed within the inner surface region. The apparatus includes an intermediate spring structure operably coupled to the central anchor structure, and at least one portion of the inner surface region. A capacitor element is disposed within the inner surface region.

Owner:MCUBE INC

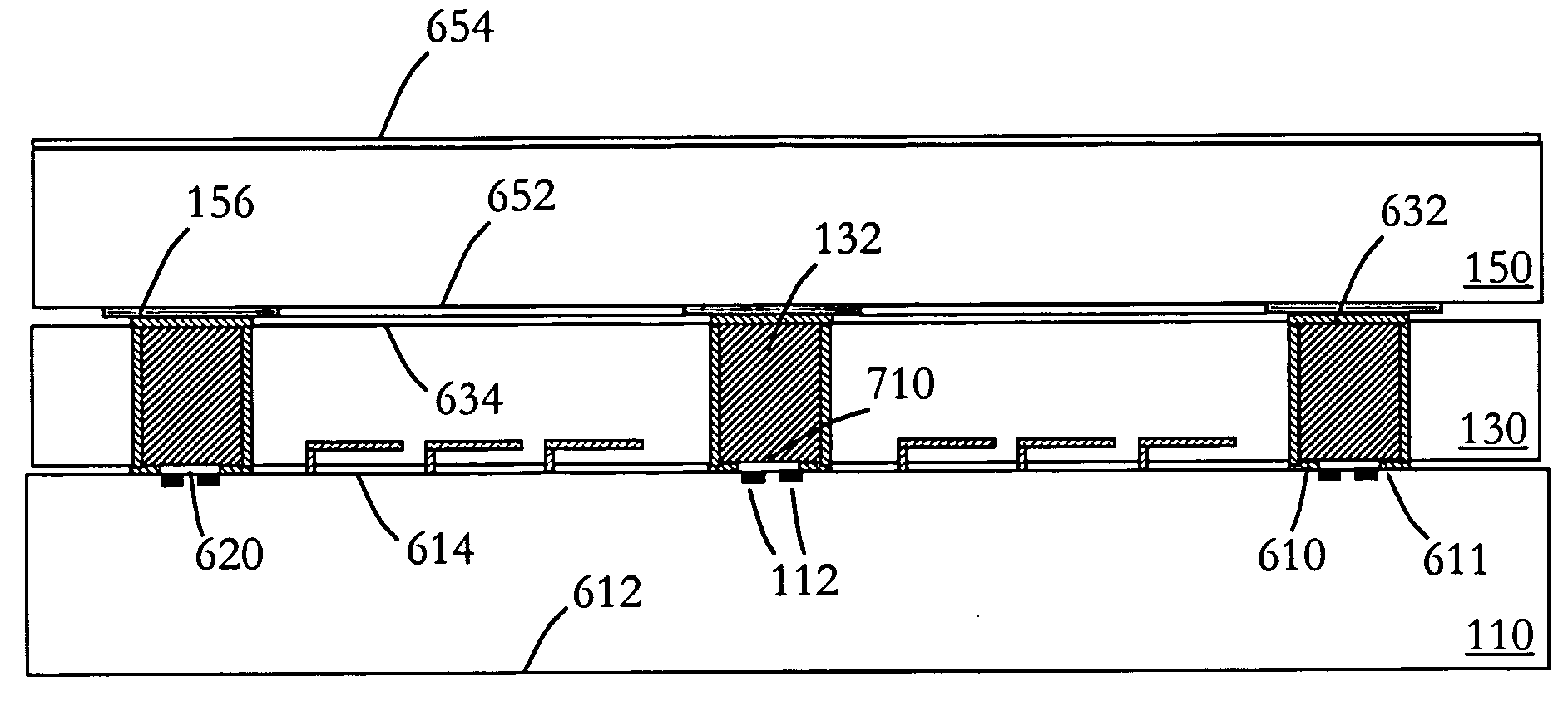

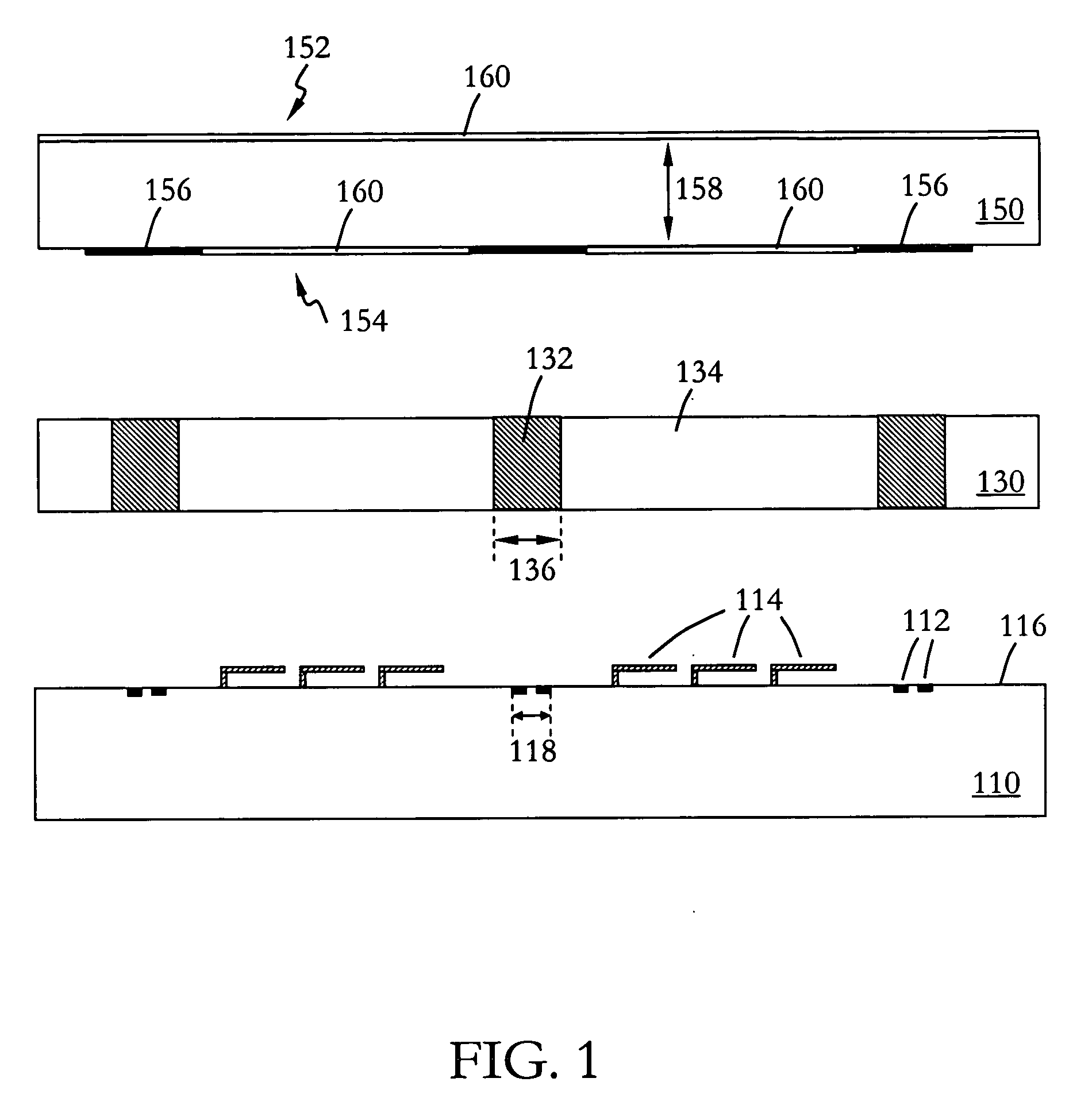

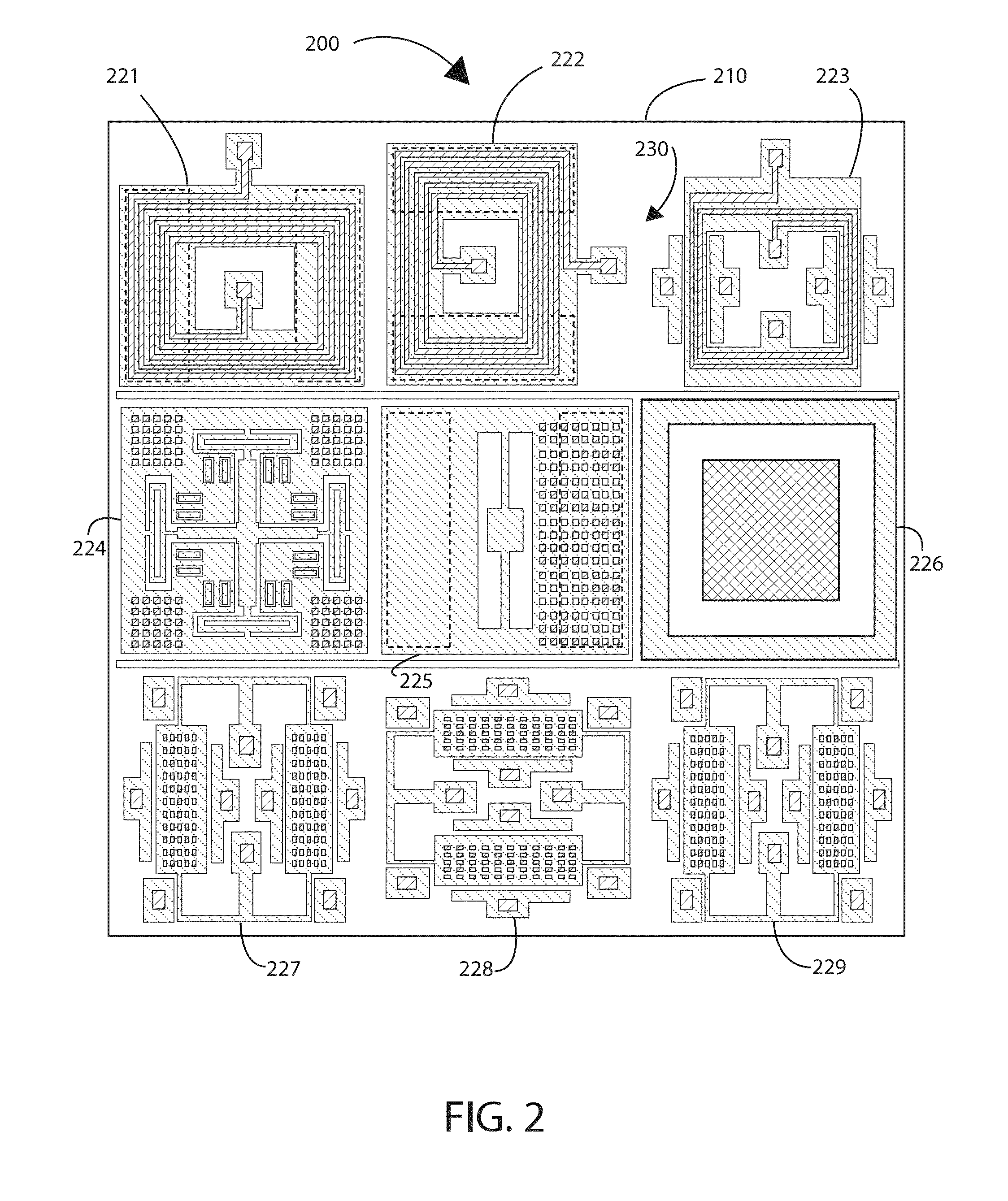

Method and apparatus for micro-electro mechanical system package

ActiveUS20060024919A1Easy to useHigh device yieldSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageLateral extension

A method of manufacturing a multi-substrate semiconductor package. The method includes providing a first substrate with a plurality of first dies present thereon and forming a plurality of electrical contacts on an upper surface of a lateral extension portion of at least one of the plurality of first dies on the first substrate. The method also includes providing a second substrate, the second substrate comprising a plurality of second dies, at least one of the plurality of second dies comprising an interconnect region. Further, the method includes forming a sandwich structure by bonding the second substrate to an upper surface of the first substrate to form an intermediate level within the sandwich structure and separating the dies. The method also includes coupling an electrically conductive structure through the interconnect region of the one second dies to the lateral extension portion of the one first die.

Owner:MIRADIA INC

Bond method and structure using selective application of spin on glass

ActiveUS20060281227A1High device yieldHigh throughput and yieldSemiconductor/solid-state device detailsSolid-state devicesEngineeringSpacer device

A method for bonding substrate structures. The method includes providing a transparent substrate structure, the transparent substrate structure comprising a face region and an incident light region, providing a spacer structure, the spacer structure comprising a selected thickness of material, the spacer structure having a spacer face region and a spacer device region, and providing a device substrate structure, the device substrate having a device face region and a device backside region. The method further includes applying a first glue material to the spacer face region and bonding the spacer face region to the face region of the transparent substrate structure. The method also includes applying a second glue material to the spacer device region and bonding the spacer device region to the device face region.

Owner:MIRADIA INC

Method and structure of integrated micro electro-mechanical systems and electronic devices using edge bond pads

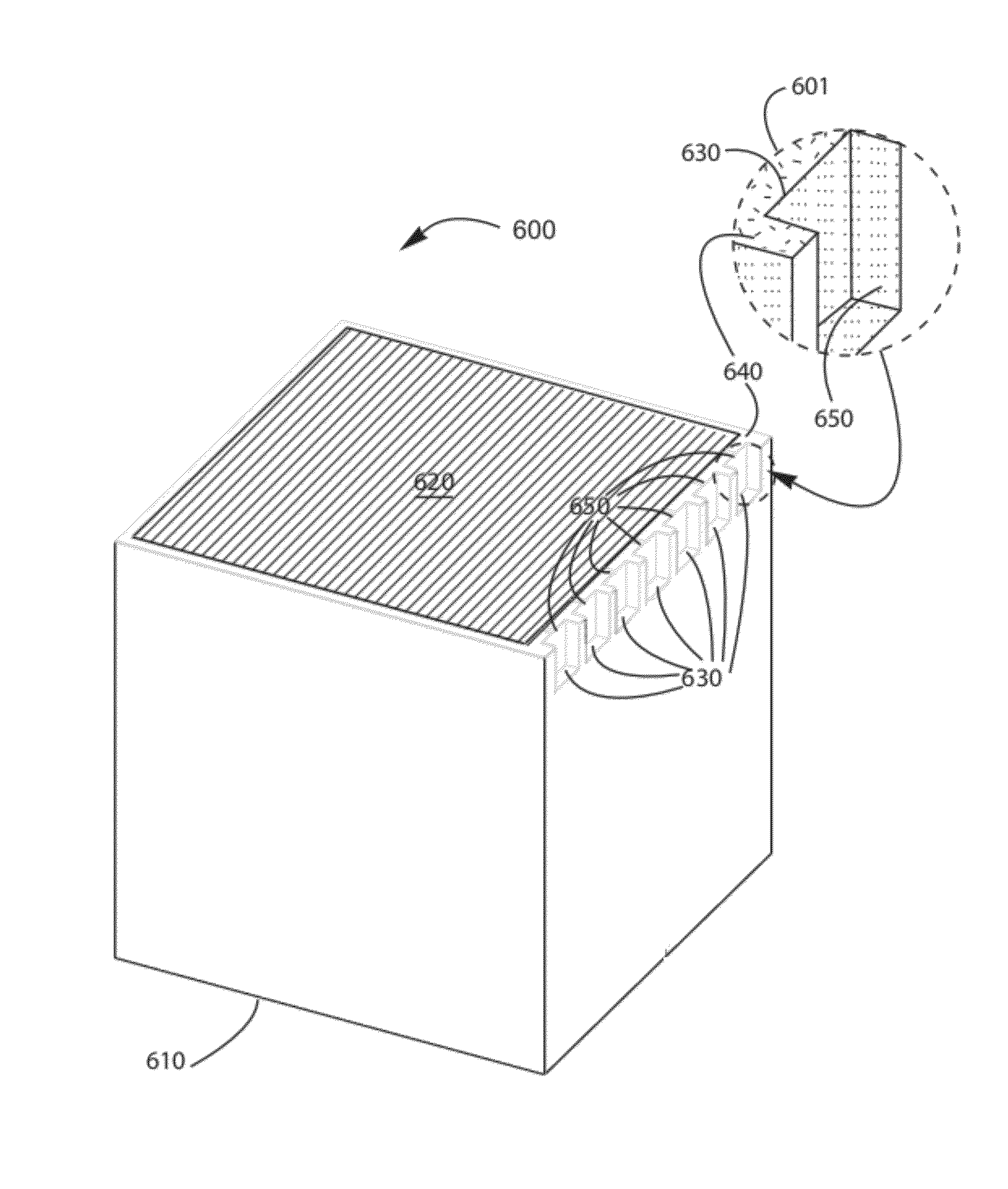

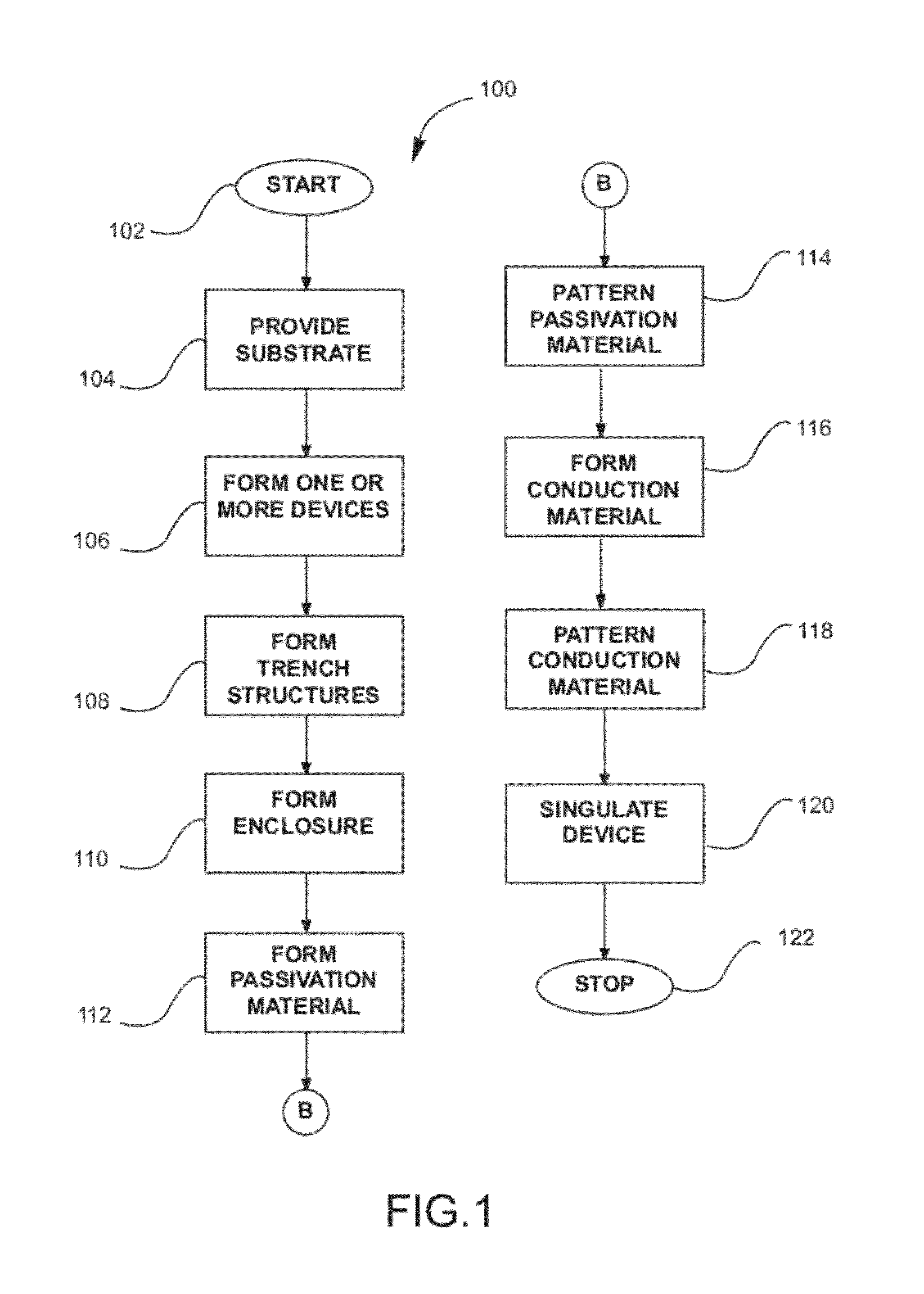

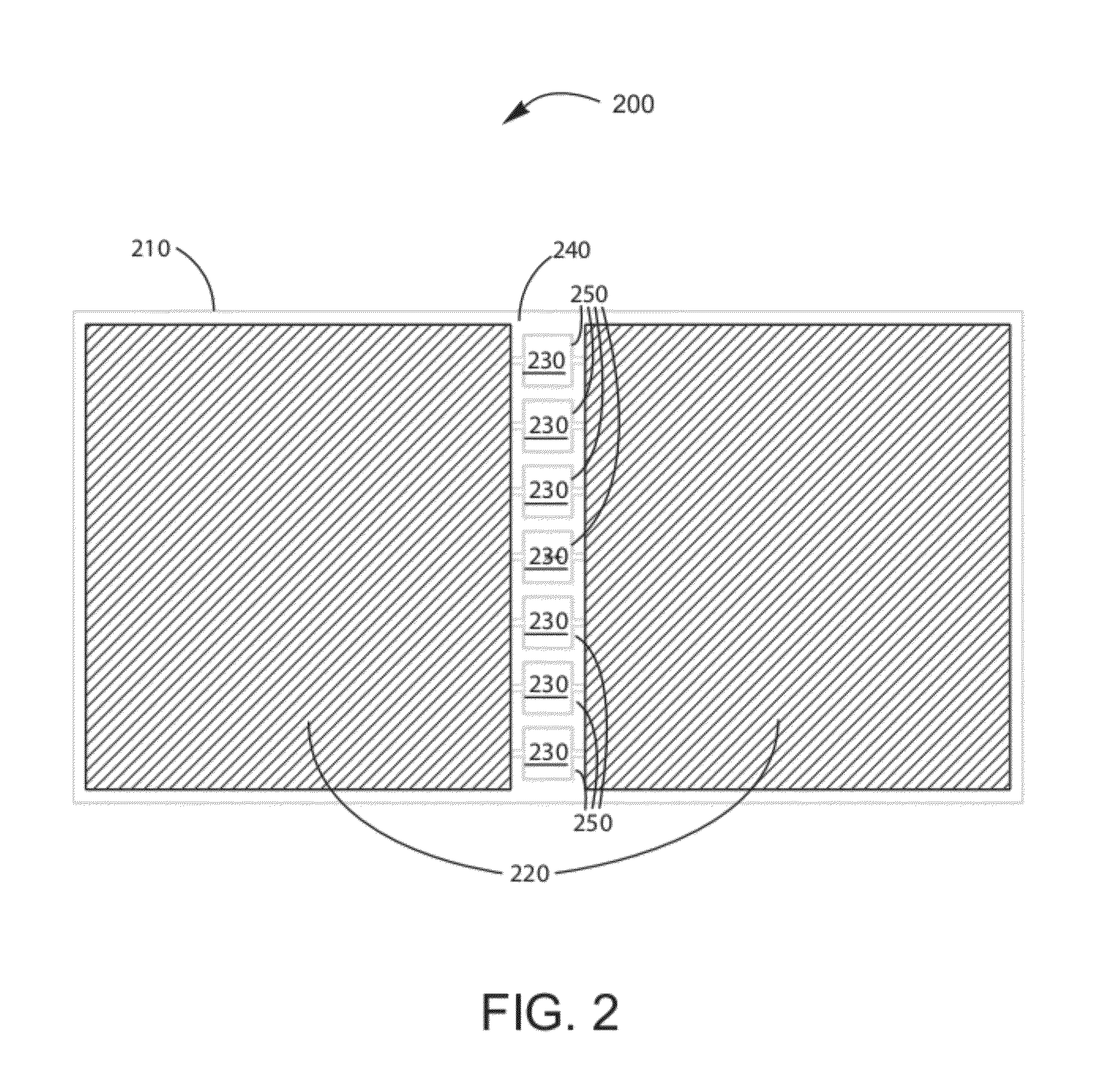

ActiveUS8367522B1Wide rangeEasy to useSemiconductor/solid-state device detailsSolid-state devicesMicroelectromechanical systemsElectric devices

A method for fabricating a monolithic integrated electronic device using edge bond pads as well as the resulting device. The method includes providing a substrate having a surface region and forming one or more integrated micro electro-mechanical systems and electronic devices on a first region overlying the surface region. One or more trench structures can be formed within one or more portions of the first region. A passivation material and a conduction material can be formed overlying the first region and the one or more trench structures. The passivation material and the conduction material can be etched to form one or more bonding pad structure. The resulting device can then be singulated within a vicinity of the one or more bond pad structures to form two or more integrated micro electro-mechanical systems and electronic devices having edge bond pads.

Owner:MOVELLA INC

Method and system for lattice space engineering

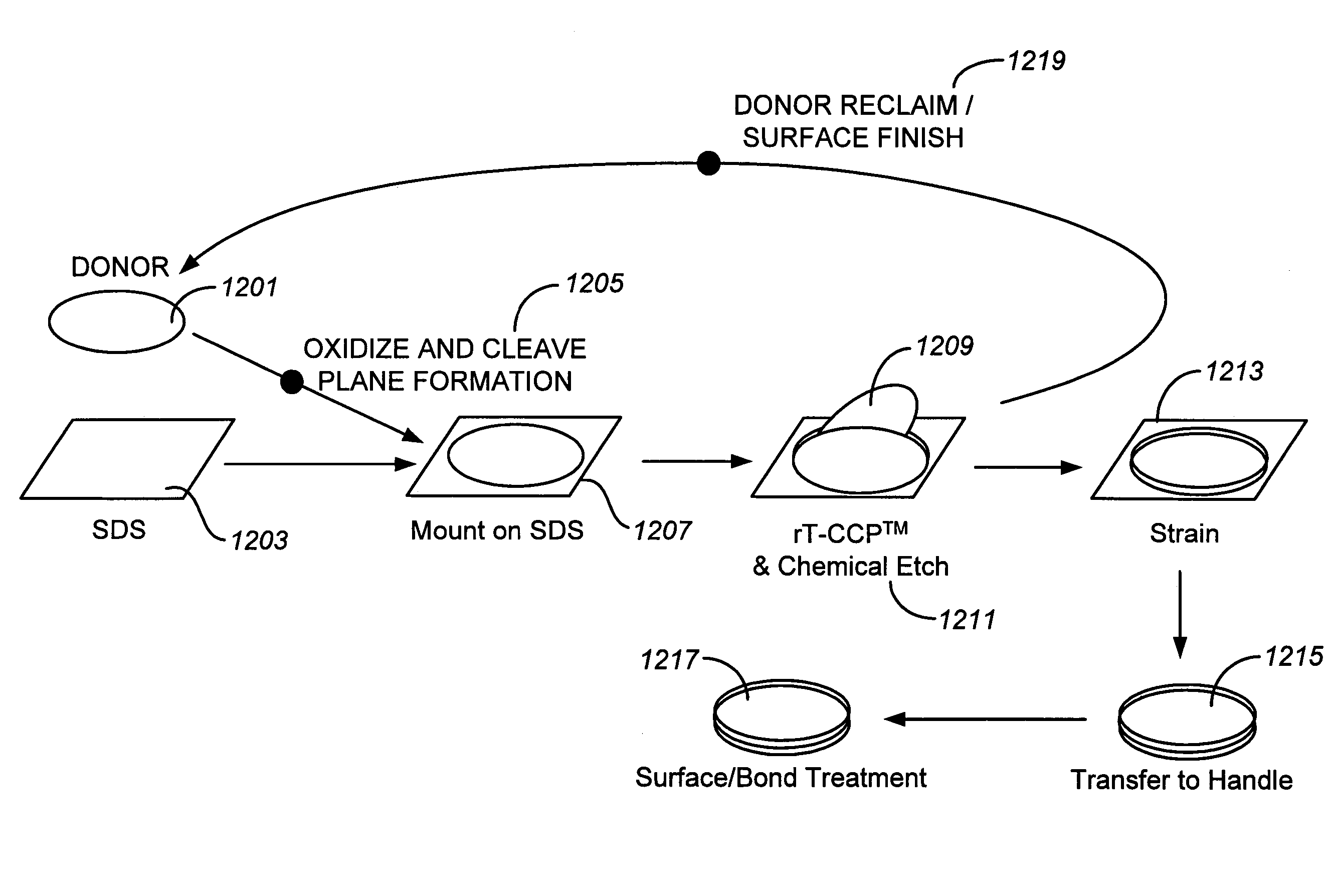

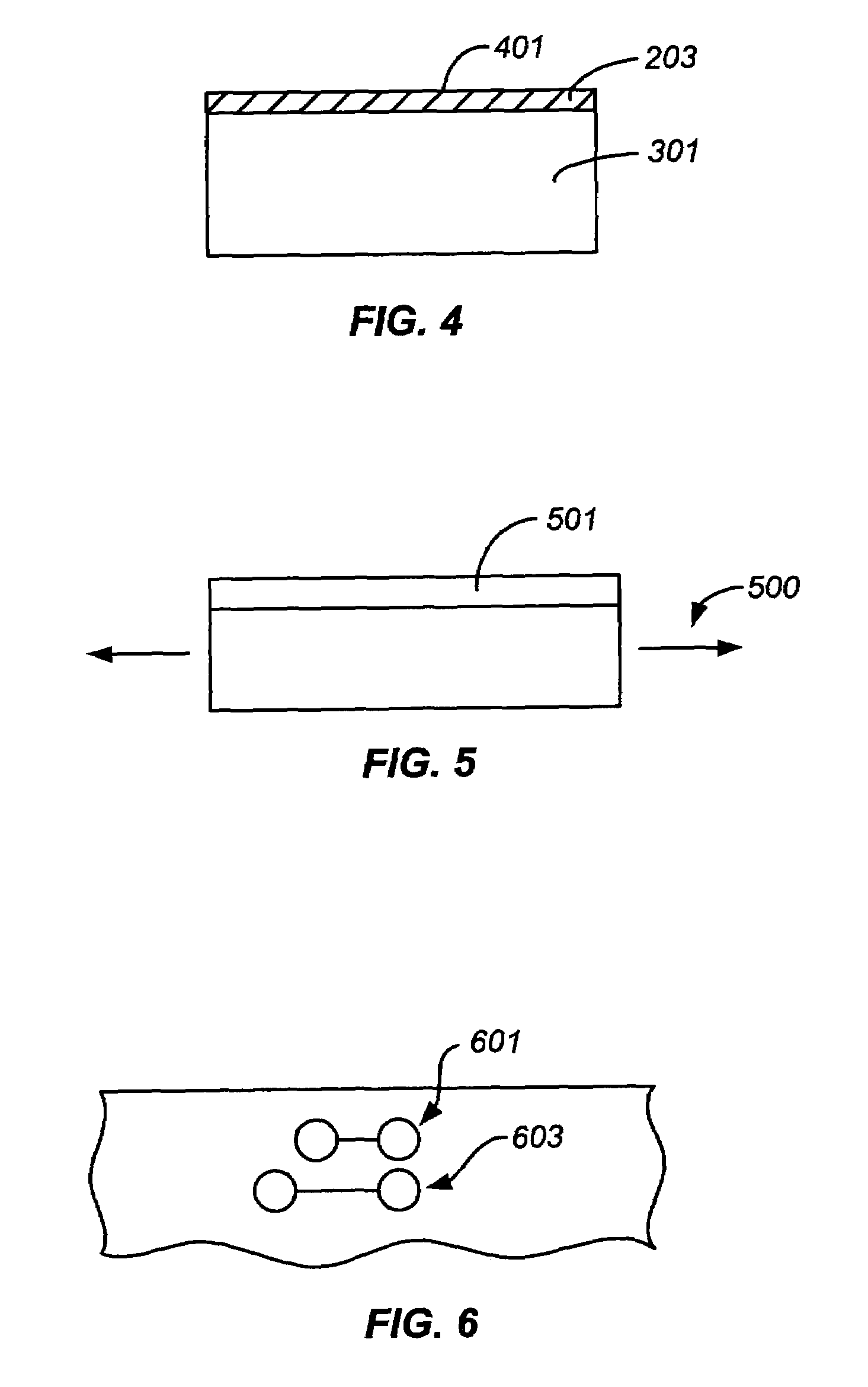

InactiveUS7390724B2Easy to useHigh device yieldSemiconductor/solid-state device manufacturingStressed stateMechanical engineering

A system for manufacturing multilayered substrates. The system has a support member is adapted to process a film of material comprising a first side and a second side from a first state to a second state. The support member is attached to the first side of the film of material. The second state comprises a stressed state. The system has a handle substrate comprising a face, which is adapted to be attached to the second side of the film of material. The support member is capable of being detached from the first side of the film of material thereby leaving the handle substrate comprising the film of material in the second state being attached to the face of the handle substrate.

Owner:SILICON GENERAL CORPORATION

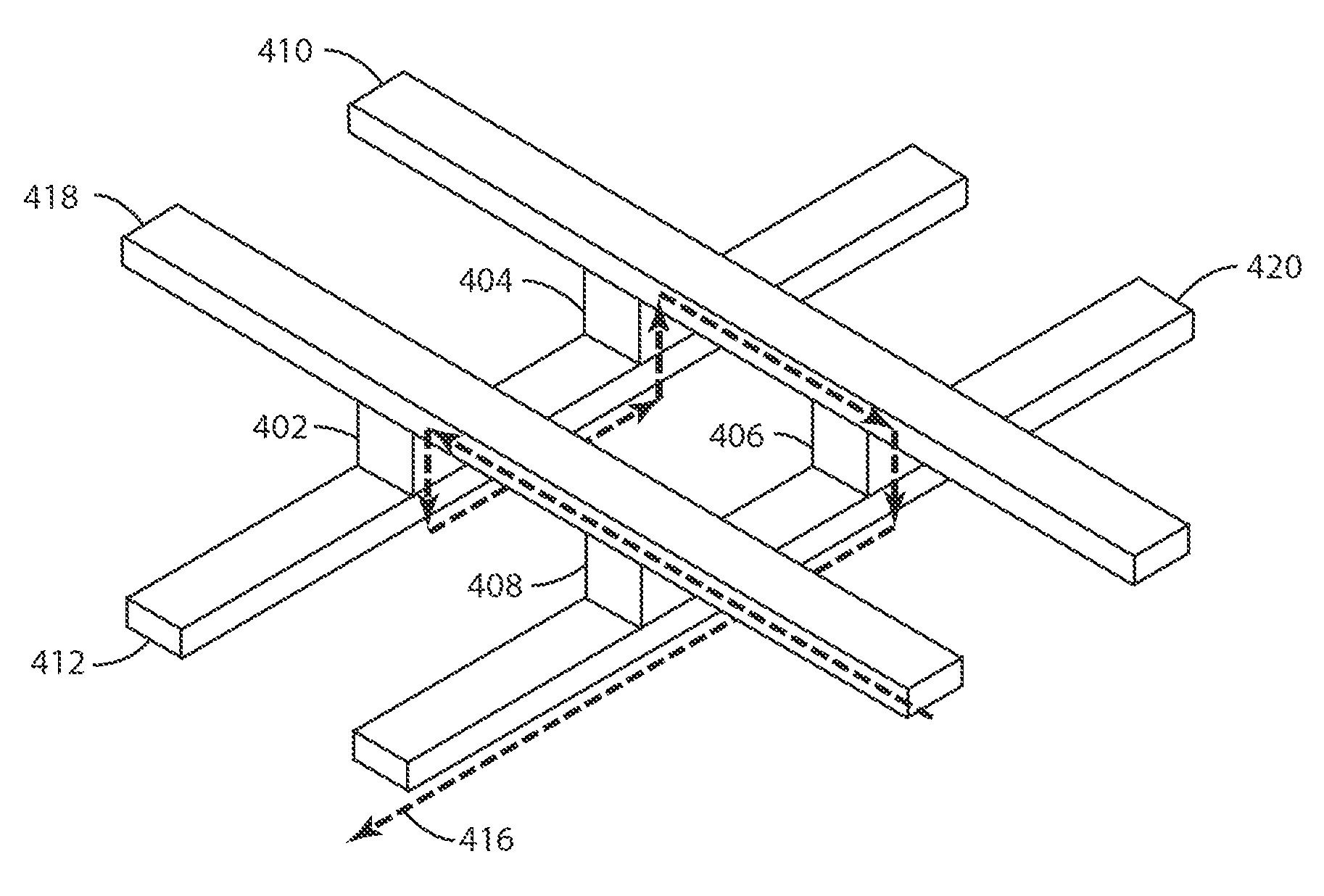

Switching device having a non-linear element

ActiveUS8767441B2High densityFast switching speedSolid-state devicesDigital storageLinear elementResistive switching

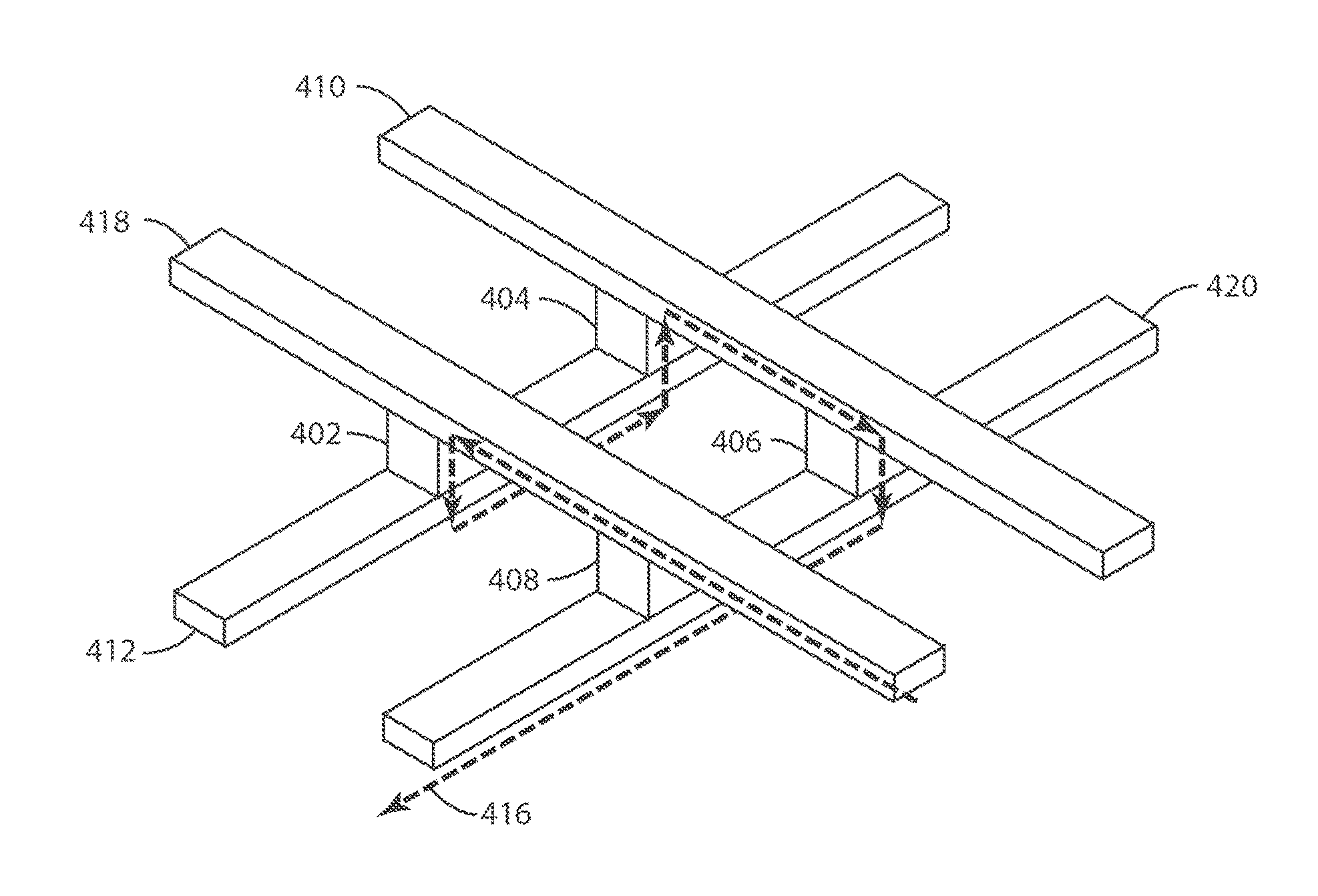

Method for a memory including a first, second, third and fourth cells include applying a read, program, or erase voltage, the first and second cells coupled to a first top interconnect, the third and fourth cells coupled to a second top interconnect, the first and third cells coupled to a first bottom interconnect, the second and fourth cells are to a second bottom interconnect, each cell includes a switching material overlying a non-linear element (NLE), the resistive switching material is associated with a first conductive threshold voltage, the NLE is associated with a lower, second conductive threshold voltage, comprising applying the read voltage between the first top and the first bottom electrode to switch the NLE of the first cell to conductive, while the NLEs of the second, third, and the fourth cells remain non-conductive, and detecting a read current across the first cell in response to the read voltage.

Owner:CROSSBAR INC

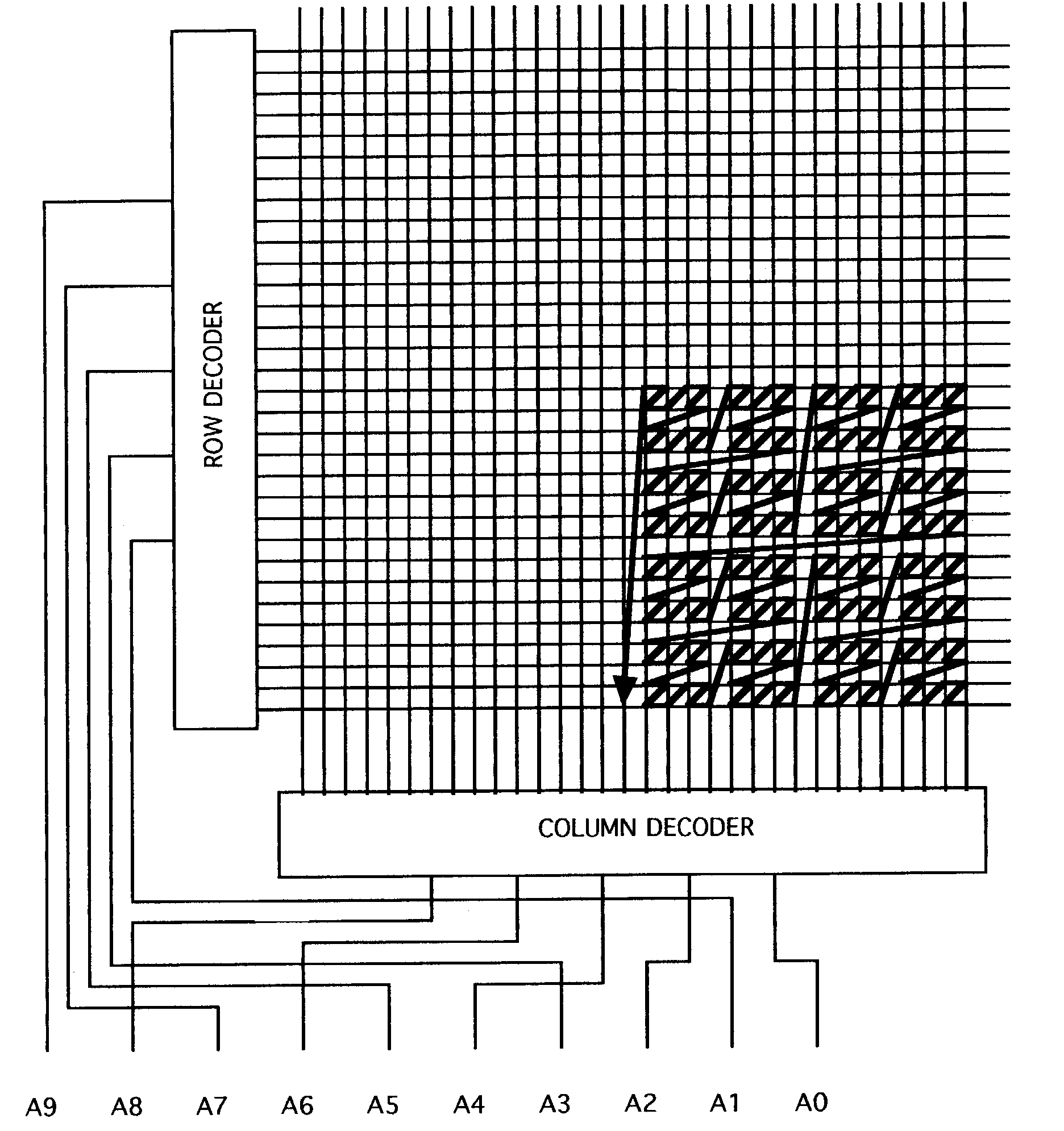

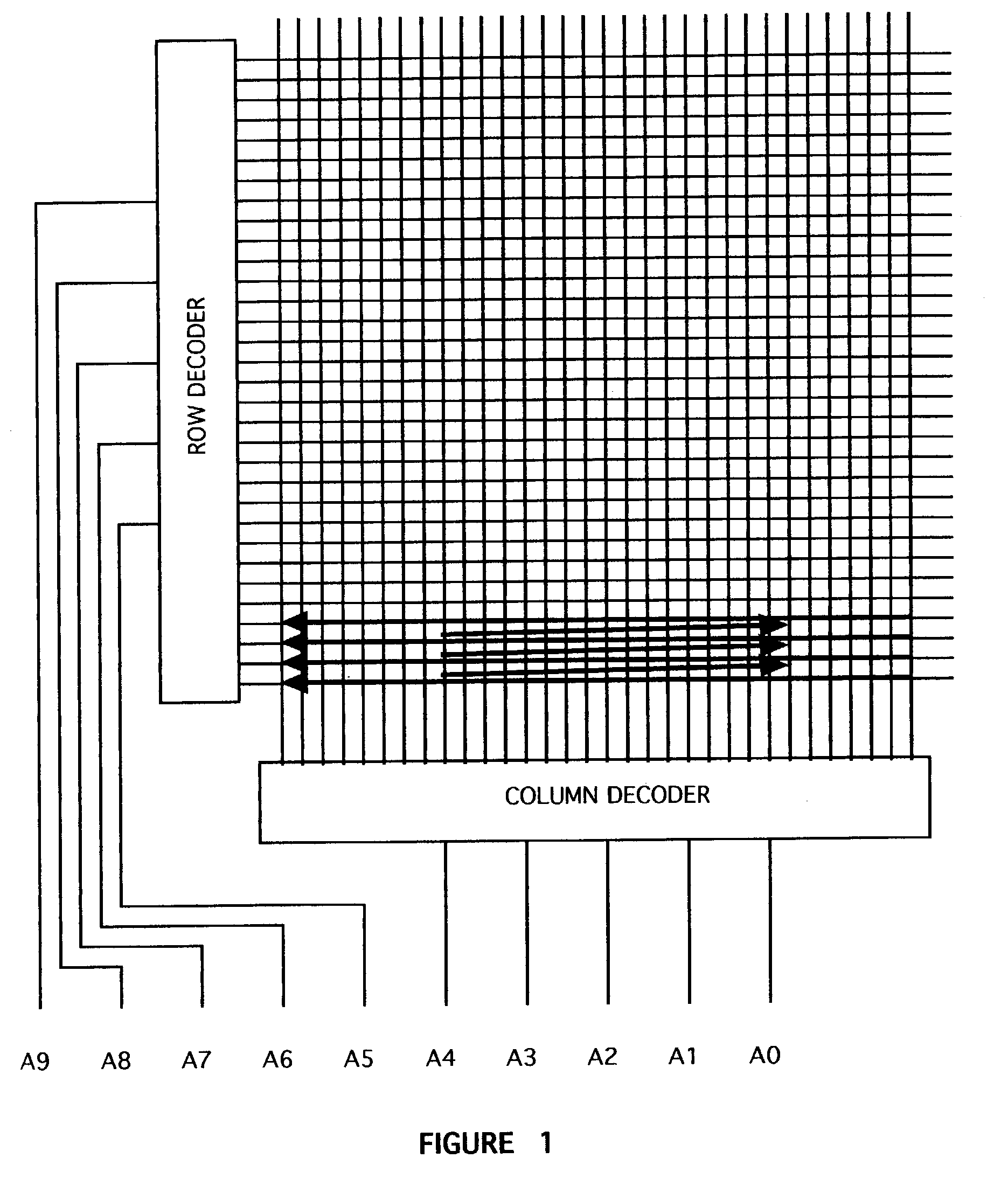

Error correcting memory access means and method

ActiveUS7149934B2Low costEfficiently utilize error correctingCode conversionCoding detailsData streamByte

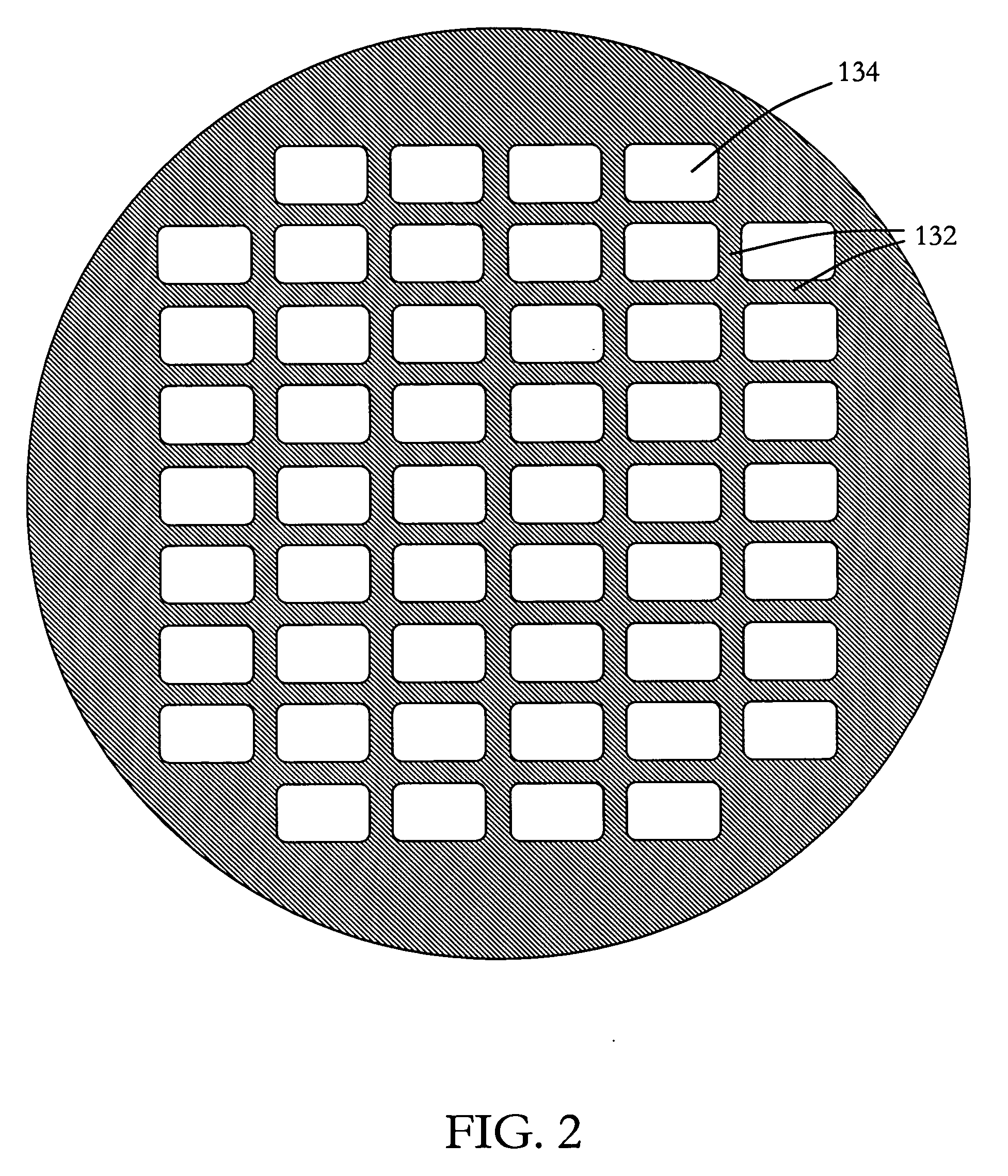

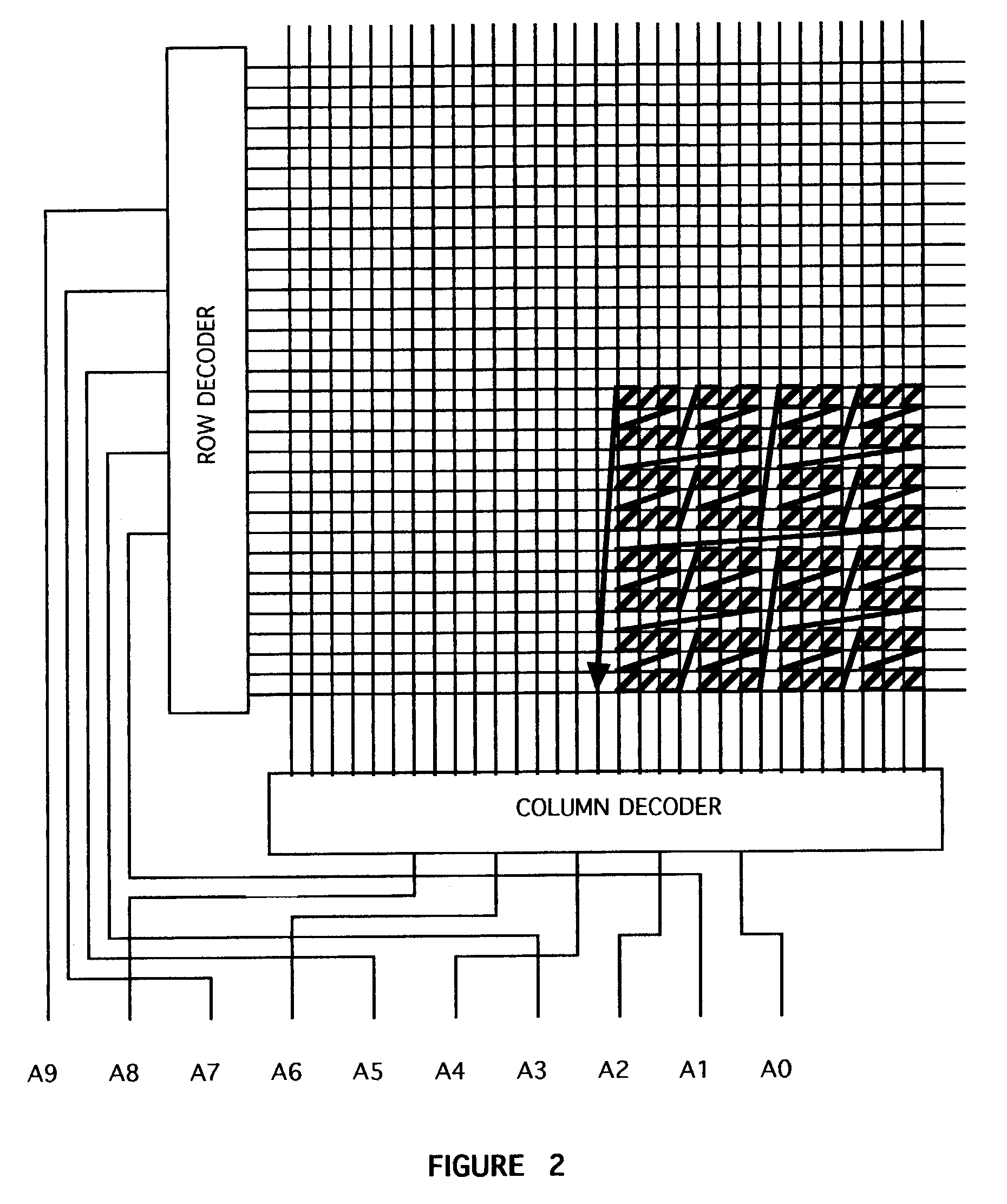

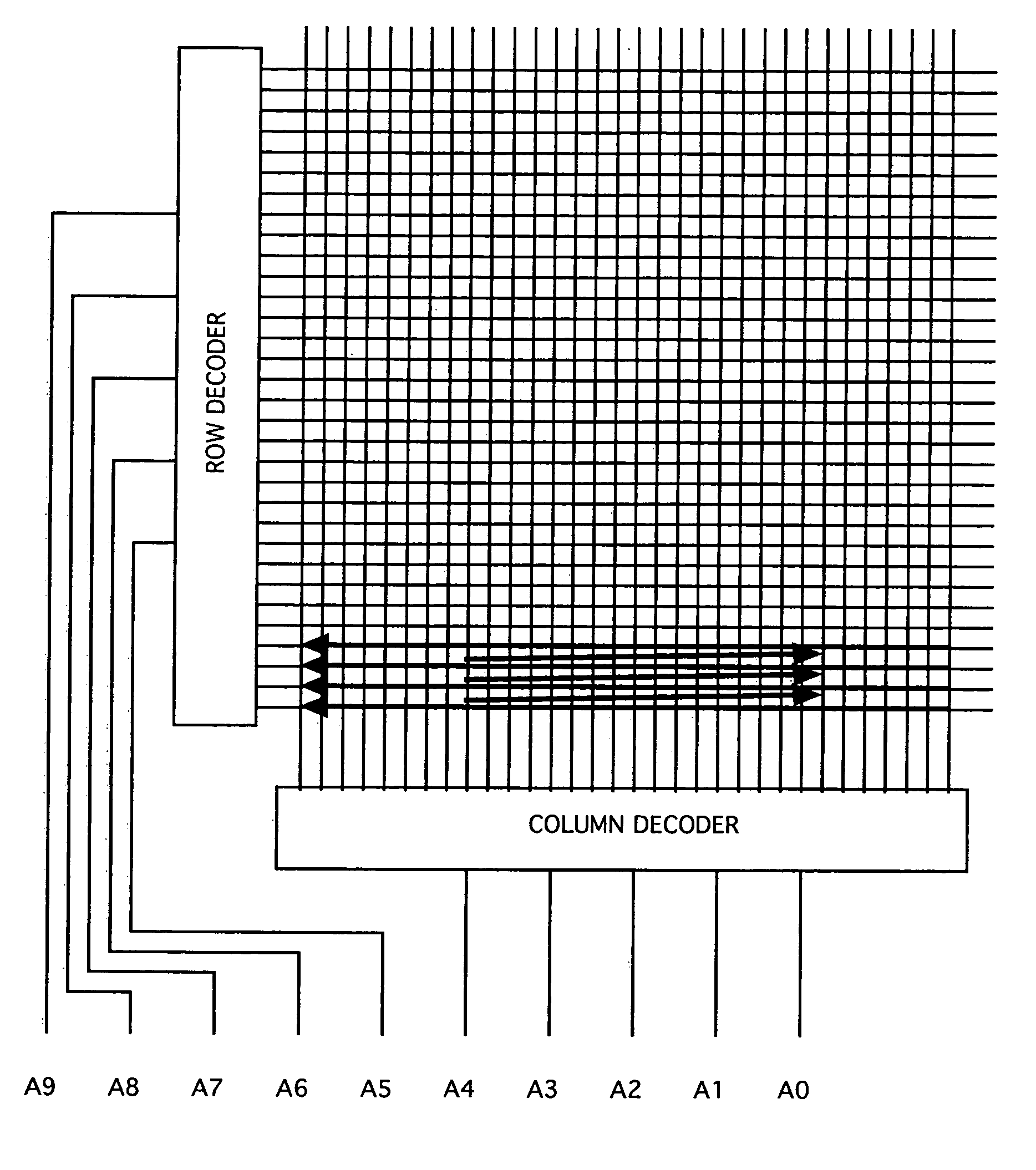

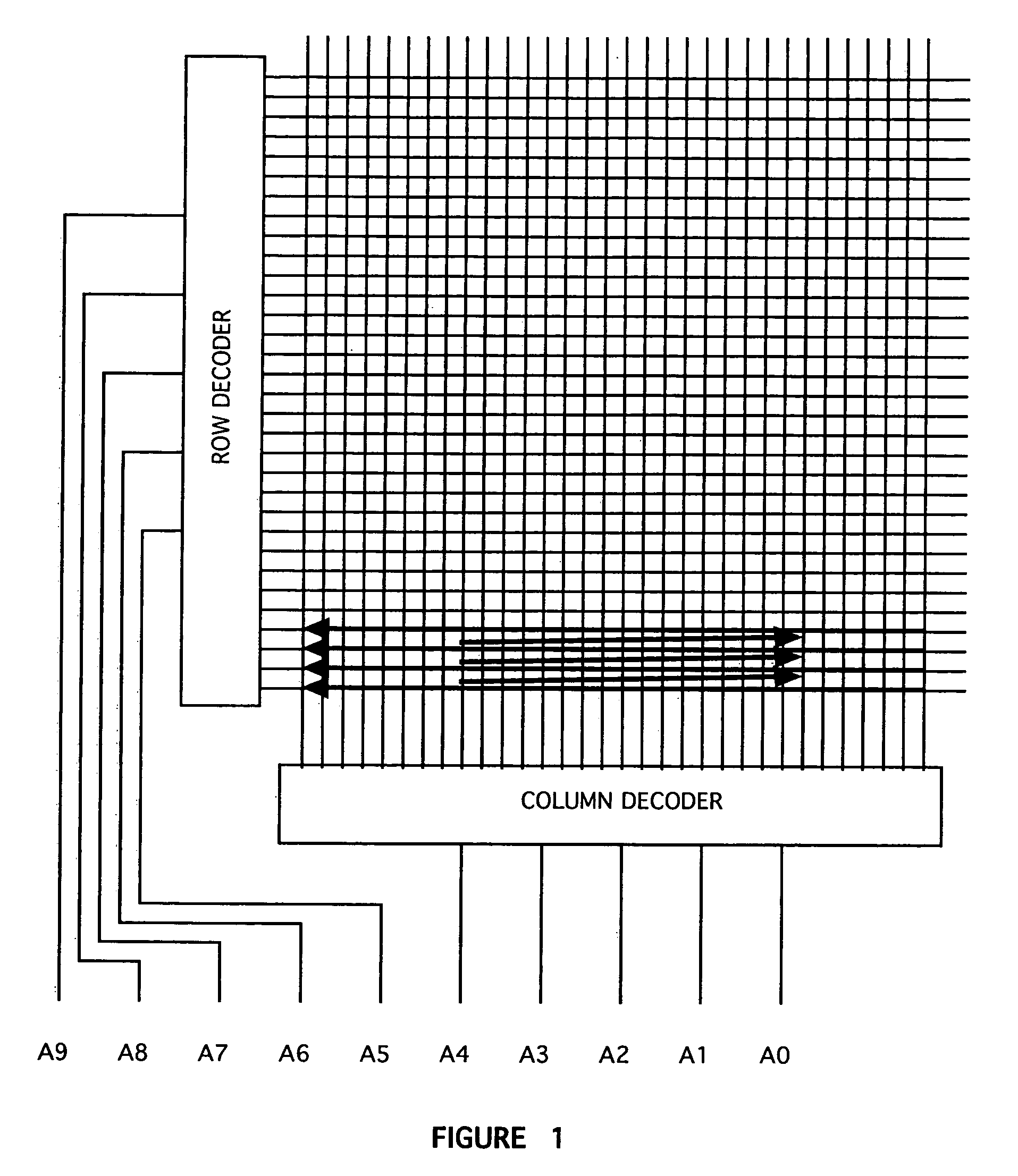

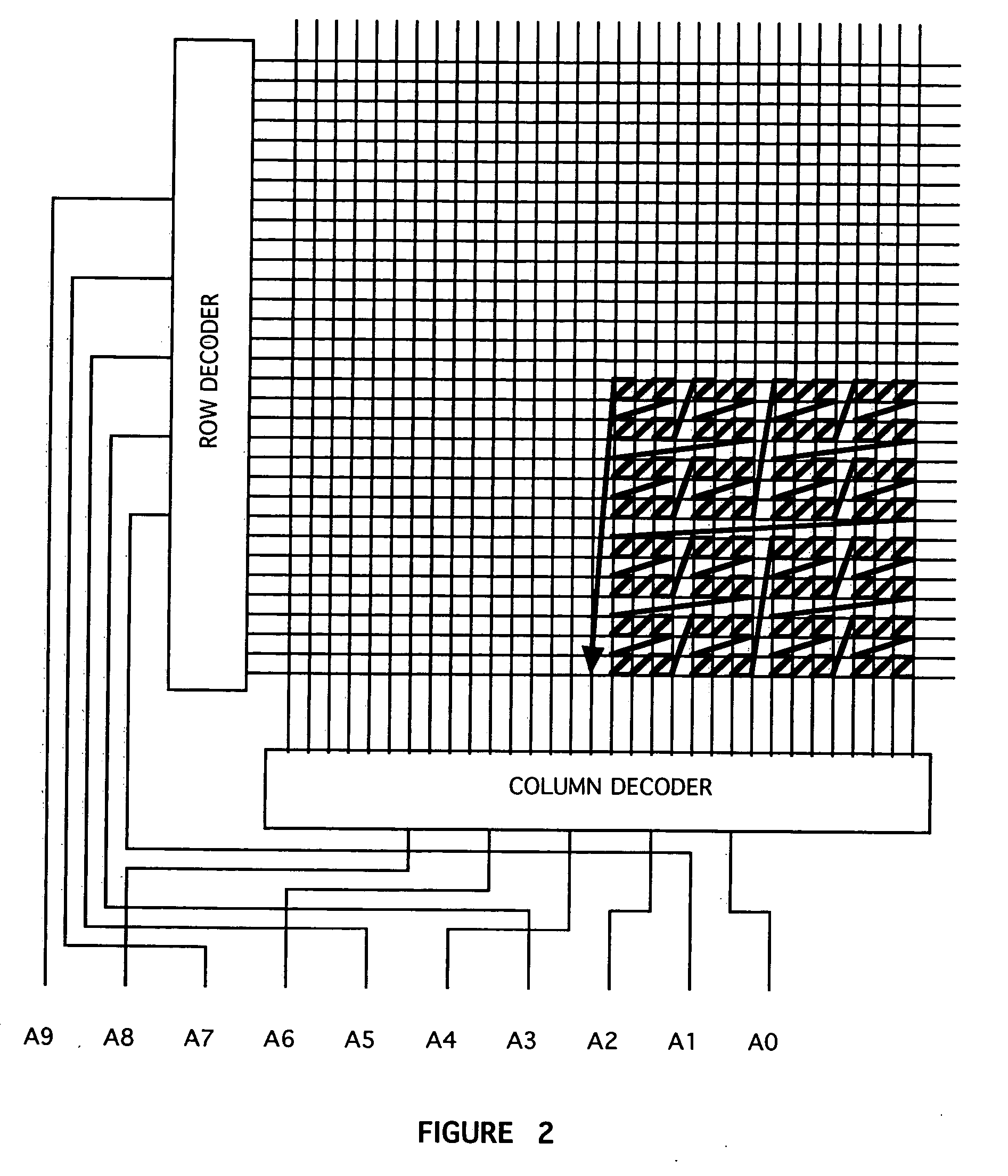

As advances continue to be made in the area of semiconductor memory devices, high capacity and low cost will be increasingly important. In particular, it will be necessary to create memory devices for which the testing of the device must be minimized in order to minimize costs. Current memory manufacturing costs are significant and will grow as the capacity of the devices grows—the higher the memory's capacity, the more storage locations that must be tested, and the longer the testing operation will take. The cost of the testing can be calculated by dividing the amortized cost of the test equipment by the number of devices tested. As memory devices enter the Gigabyte range and larger, the number of devices that can be tested by a given piece of test equipment will go down. As a result, the cost per unit attributable to testing will rise. The present invention is a means and a method for accessing streams of data stored within a memory device so as to minimize the cost of device testing and thereby the cost of the device itself. By incorporating error-correcting bits in the data stream, the individual data bits need not be tested. Then, by accessing the memory locations so as to avoid having error correcting techniques fail due to common memory device faults, testing costs can be significantly reduced while maintaining high device yields. A sequential access of the memory device will access data bits in a somewhat diagonal path across the two-dimensional array. The key to the present invention is that the sequential data stream stored in the device is stored such that sequential access of that data will not dwell on a single (or a small number of) row or column line. In a three or more dimensional array, the sequential data stream stored in the device is stored such that sequential access of that data will not dwell on a single value in a given dimension for which bulk errors are considered likely.

Owner:WESTERN DIGITAL TECH INC

Error correcting memory access means and method

ActiveUS20070028150A1Low costEfficiently utilize error correctingCode conversionCoding detailsData streamTerm memory

As advances continue to be made in the area of semiconductor memory devices, high capacity and low cost will be increasingly important. In particular, it will be necessary to create memory devices for which the testing of the device must be minimized in order to minimize costs. Current memory manufacturing costs are significant and will grow as the capacity of the devices grows—the higher the memory's capacity, the more storage locations that must be tested, and the longer the testing operation will take. The cost of the testing can be calculated by dividing the amortized cost of the test equipment by the number of devices tested. As memory devices enter the Gigabyte range and larger, the number of devices that can be tested by a given piece of test equipment will go down. As a result, the cost per unit attributable to testing will rise. The present invention is a means and a method for accessing streams of data stored within a memory device so as to minimize the cost of device testing and thereby the cost of the device itself. By incorporating error-correcting bits in the data stream, the individual data bits need not be tested. Then, by accessing the memory locations so as to avoid having error correcting techniques fail due to common memory device faults, testing costs can be significantly reduced while maintaining high device yields. A sequential access of the memory device will access data bits in a somewhat diagonal path across the two-dimensional array. The key to the present invention is that the sequential data stream stored in the device is stored such that sequential access of that data will not dwell on a single (or a small number of) row or column line. In a three or more dimensional array, the sequential data stream stored in the device is stored such that sequential access of that data will not dwell on a single value in a given dimension for which bulk errors are considered likely.

Owner:WESTERN DIGITAL TECH INC

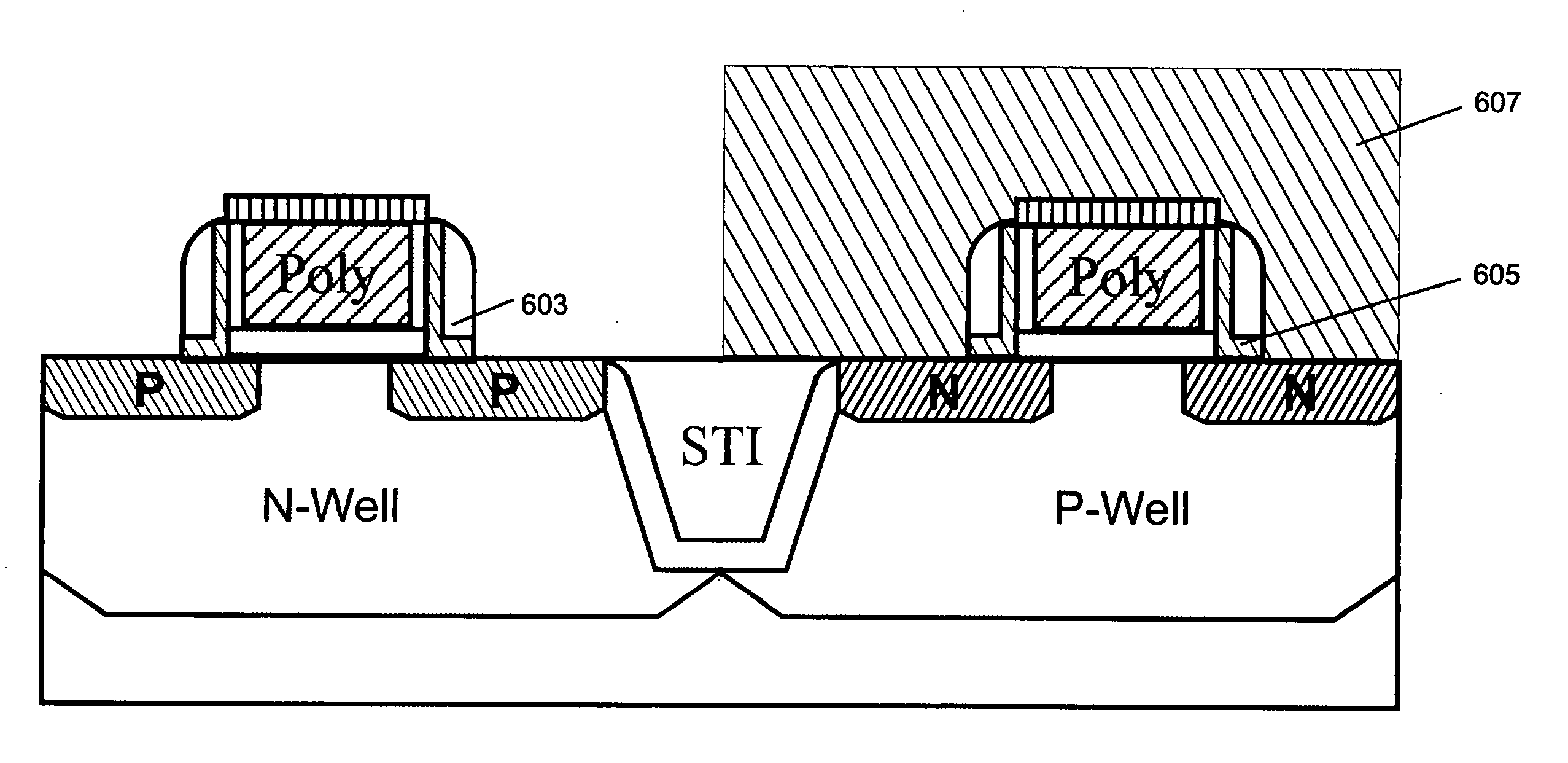

Integration scheme method and structure for transistors using strained silicon

ActiveUS20070099369A1Easy to useHigh device yieldSemiconductor/solid-state device manufacturingSemiconductor devicesCMOSMethod selection

A method for forming CMOS integrated circuits. The method forms a blanket layer of silicon dioxide overlying an entirety of the surface region of a first well region and a second well region provided on a semiconductor substrate. The blanket layer of silicon dioxide is overlying the hard mask on the first gate structure and the second gate structure. The blanket layer of silicon dioxide is also overlying a region to be protected. Depending upon the embodiment, the region can be a sidewall spacer structure and portion of an MOS device on a peripheral region of the substrate. Of course, there can be other variations, modifications, and alternatives. The method protects the region to be protected using a masking layer, while the surface region of the first well region and the second well region being exposed. The method selectively removes exposed portions of the blanket layer of silicon dioxide, including the hard mask on the first gate structure and the second gate structure, while exposing a first polysilicon material on the first gate structure and while exposing a second polysilicon material on the second gate structure. The method strips the masking layer. The method also includes forming a silicided layer overlying the first polysilicon material on the first gate structure and the second polysilicon material on the second gate structure, while the region to be protected remains free from the silicided layer.

Owner:SEMICON MFG INT (SHANGHAI) CORP

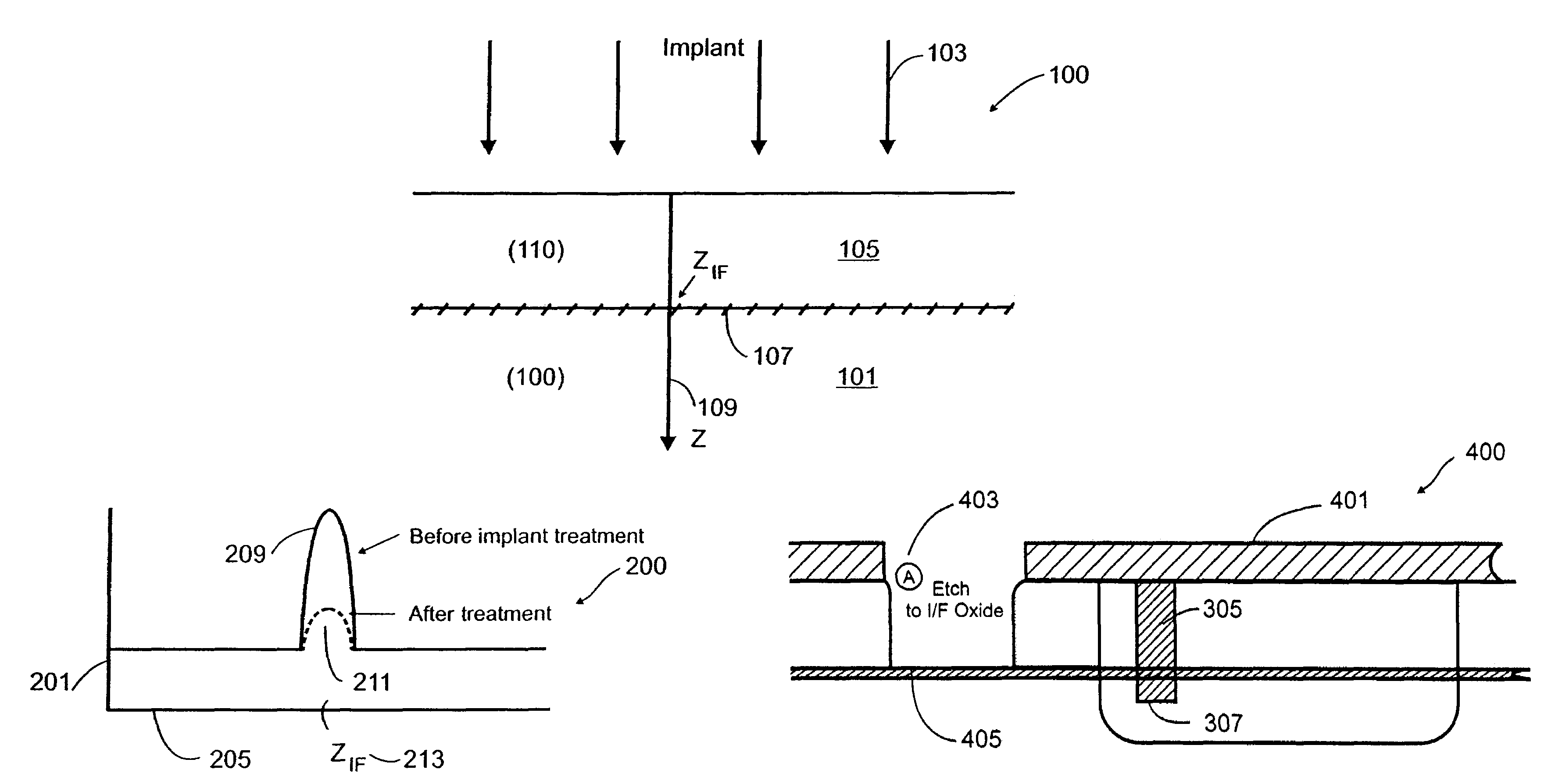

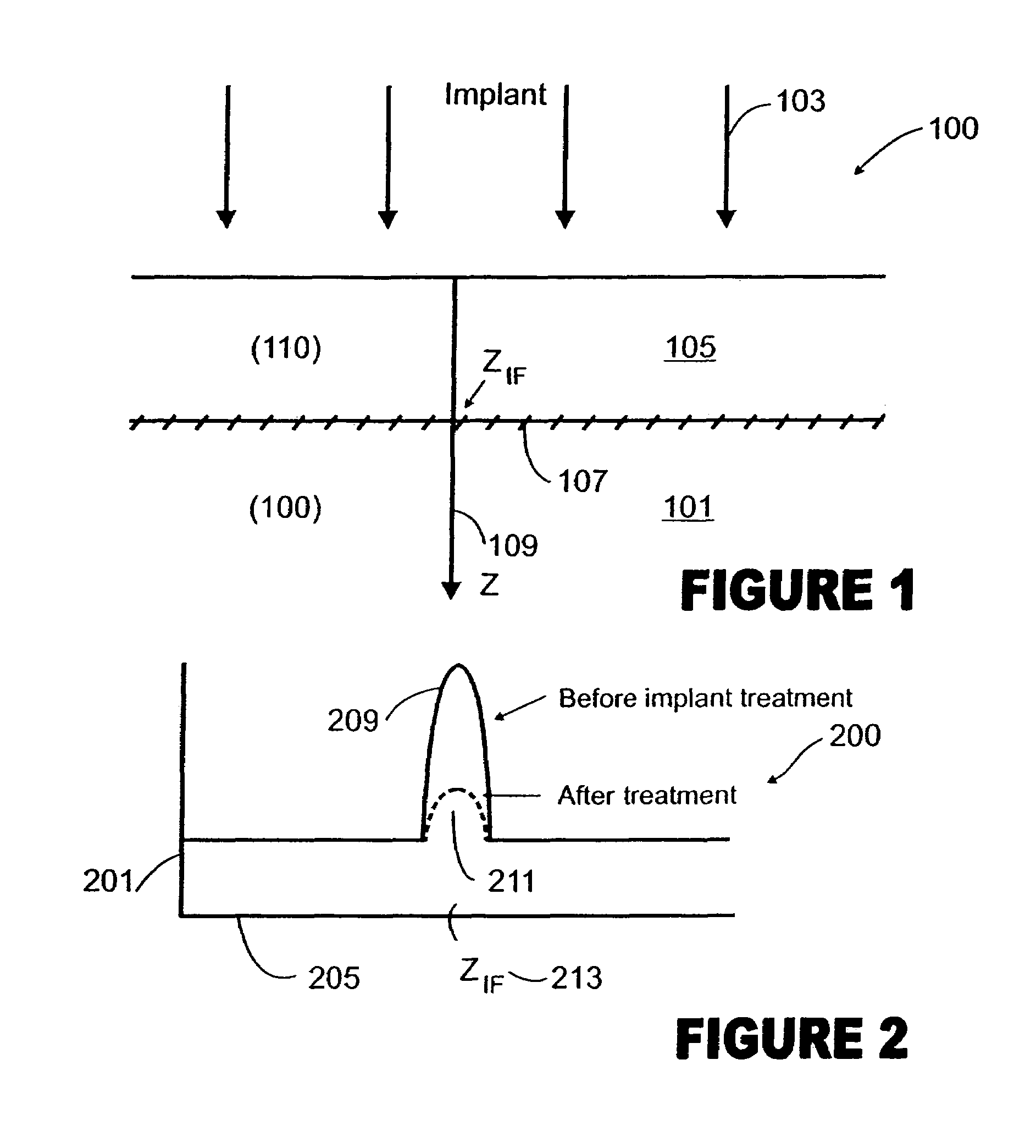

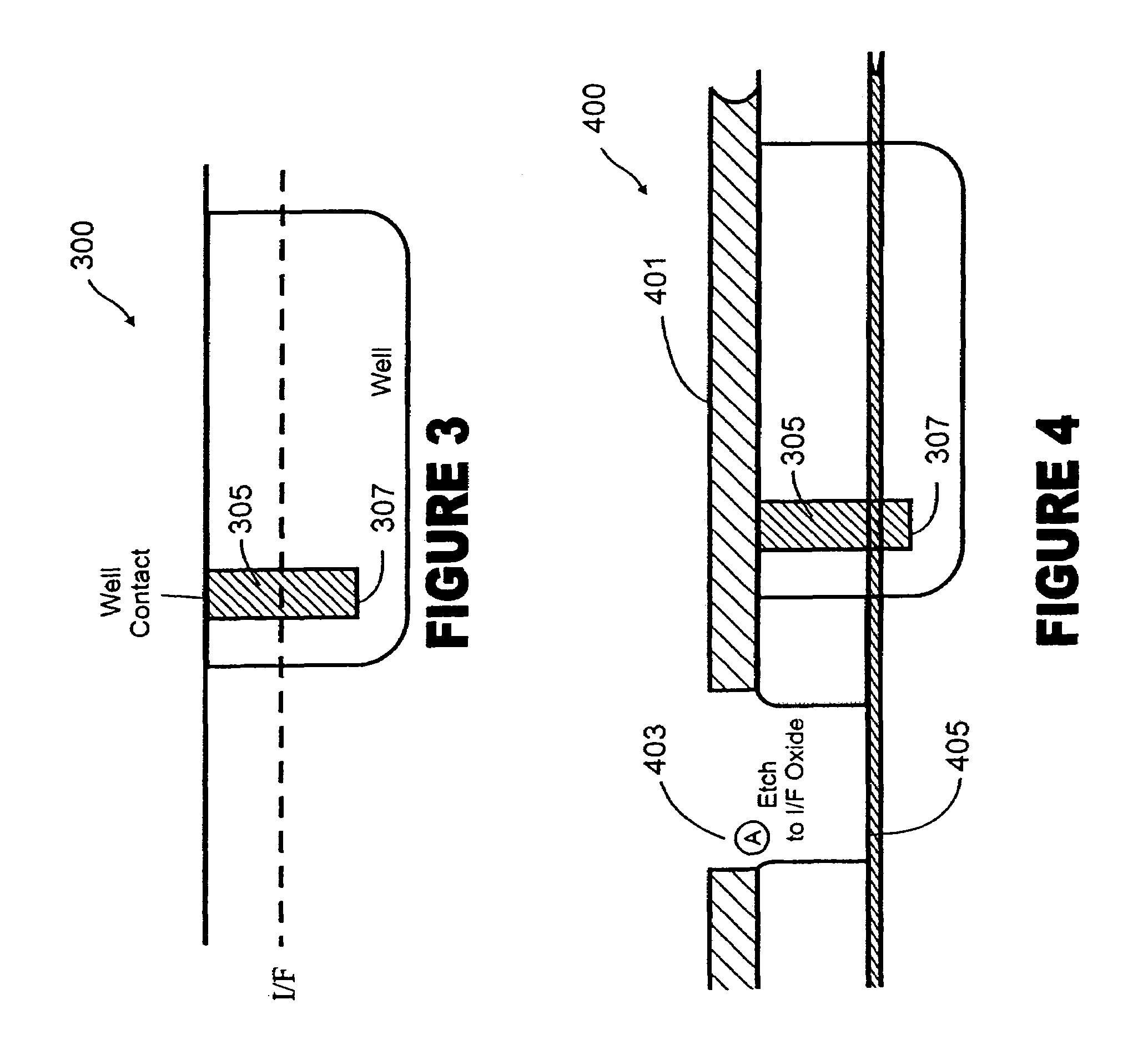

Method and structure for implanting bonded substrates for electrical conductivity

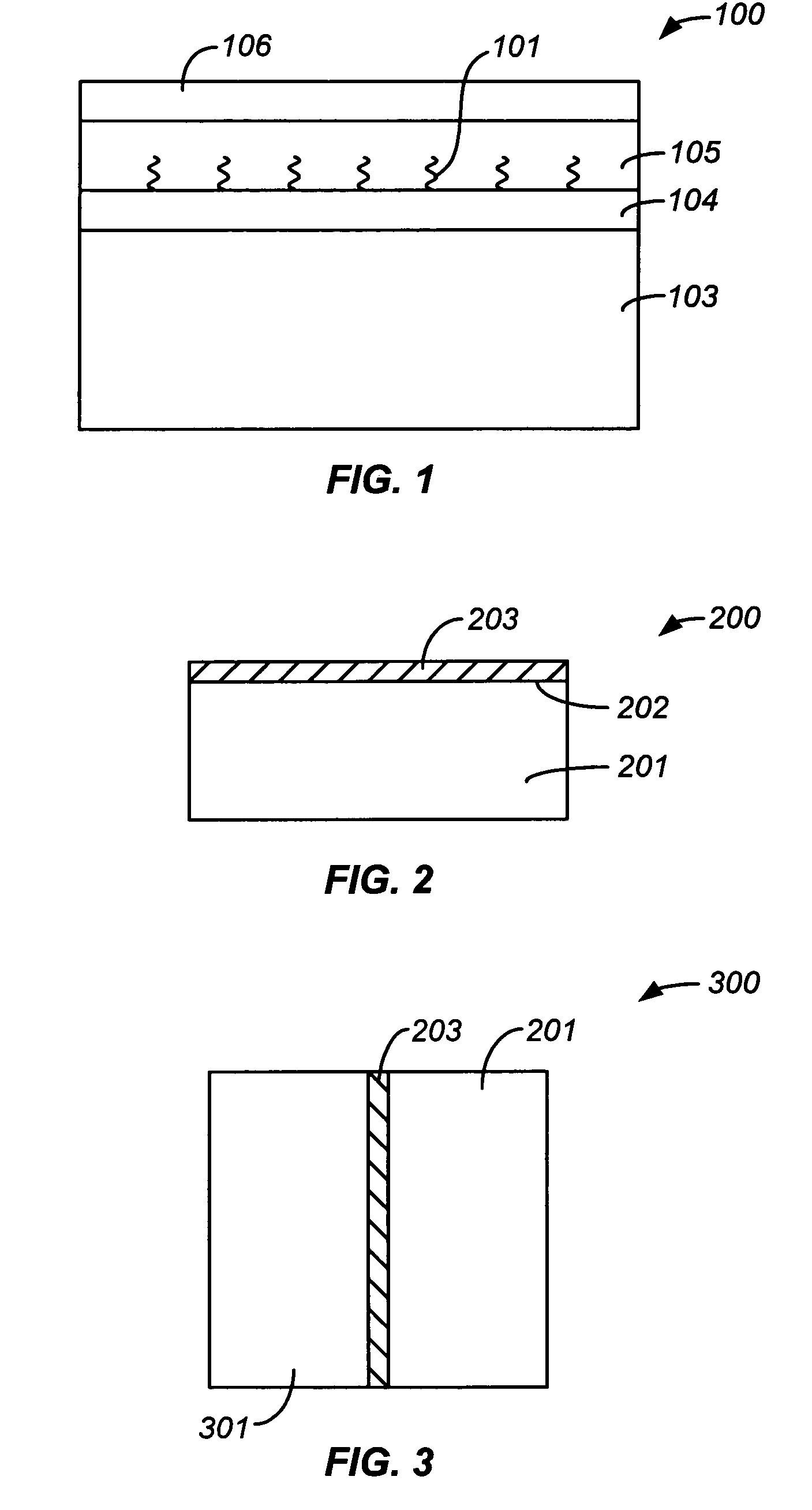

ActiveUS7399680B2Easy to useHigh device yieldSemiconductor/solid-state device manufacturingSiliconMaterials science

A partially completed multi-layered substrate, e.g., silicon on silicon. The substrate has a thickness of material from a first substrate. The thickness of material comprises a first face region. The substrate has a second substrate having a second face region. Preferably, the first face region of the thickness of material is joined to the second face region of the second substrate. The substrate has an interface region formed between the first face region of the thickness of material and the second face region of the second substrate. A plurality of particles are implanted within a portion of the thickness of the material and a portion of the interface region to electrically couple a portion of the thickness of material to a portion of the second substrate.

Owner:SILICON GENERAL CORPORATION

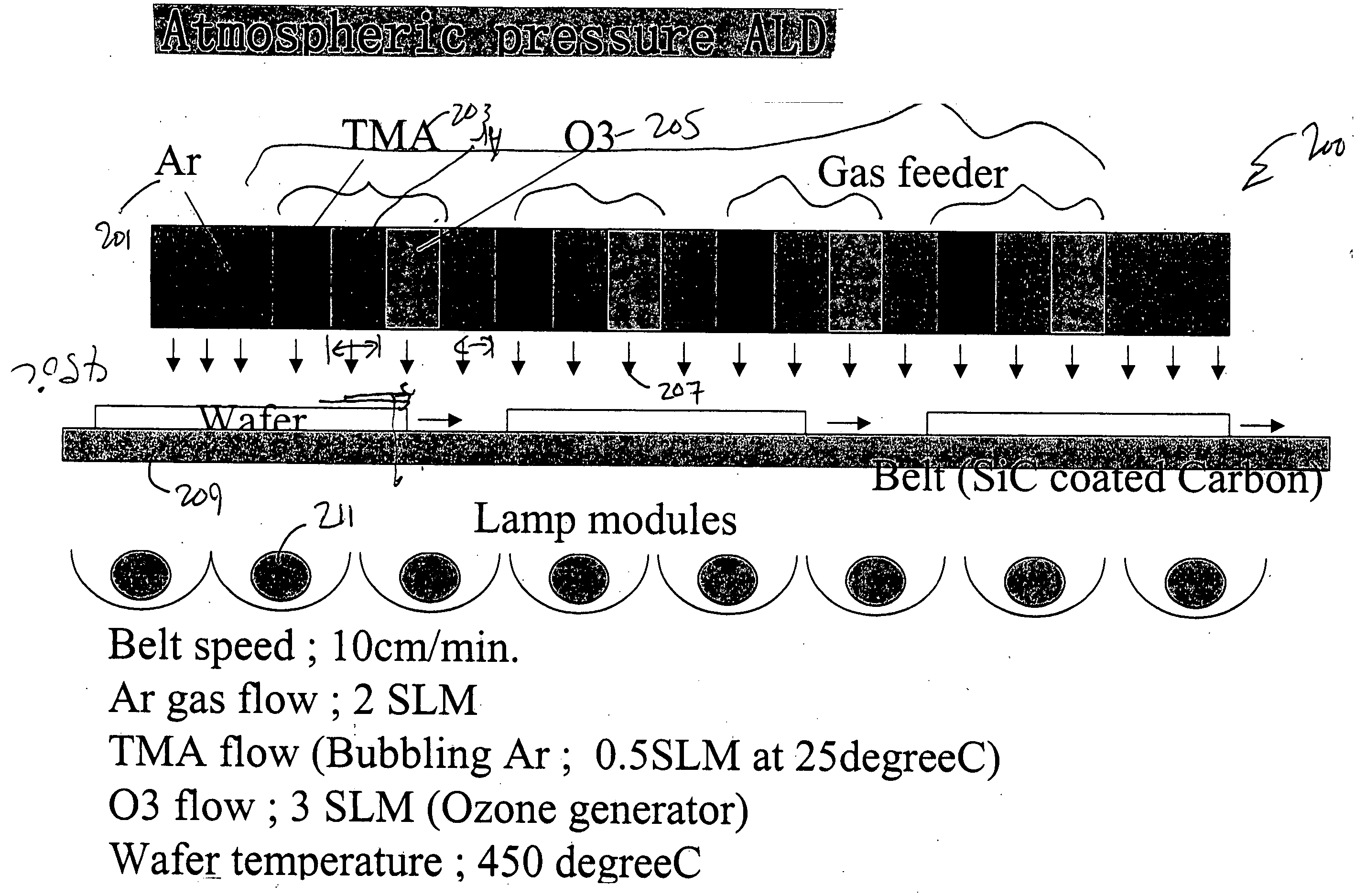

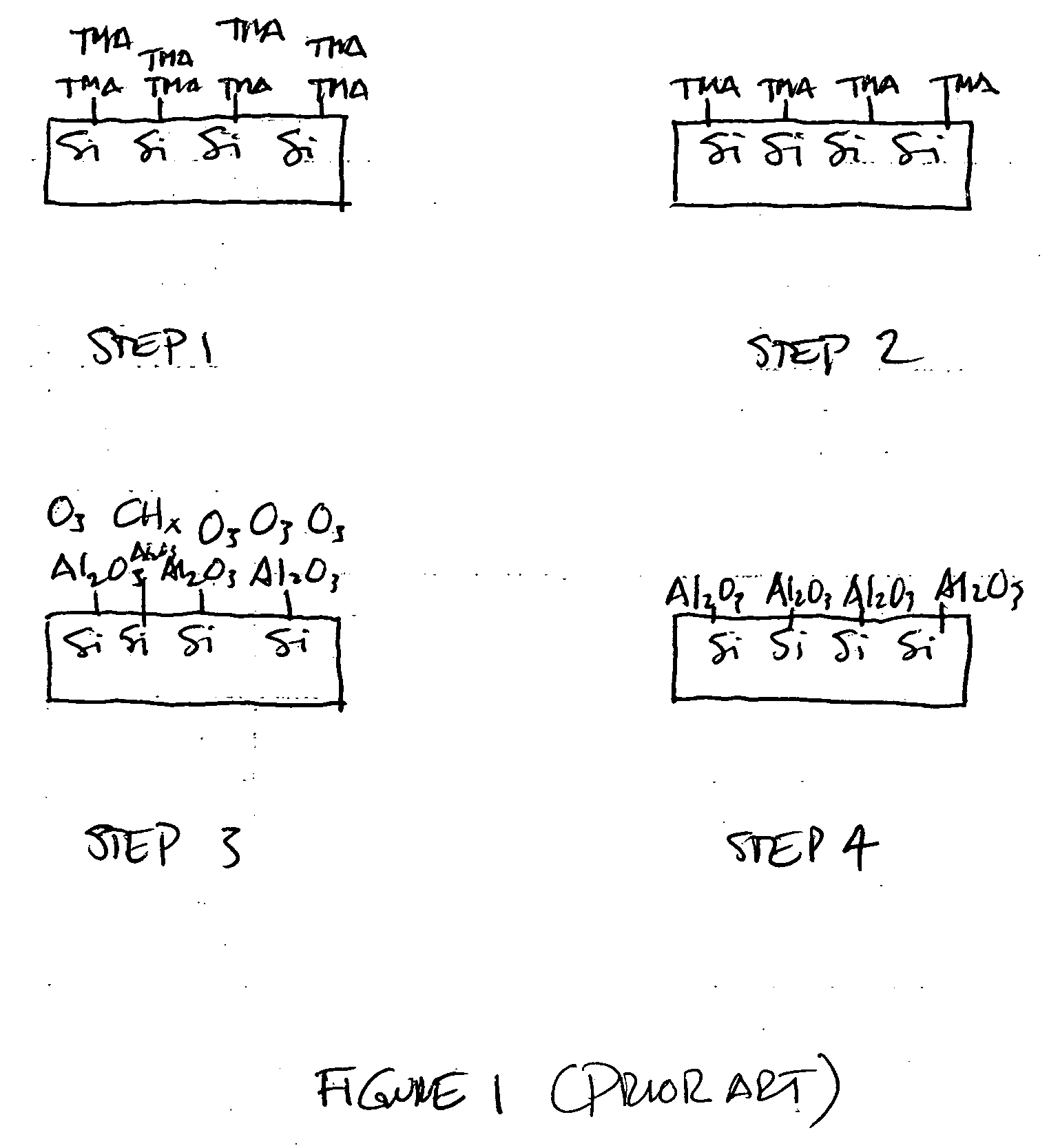

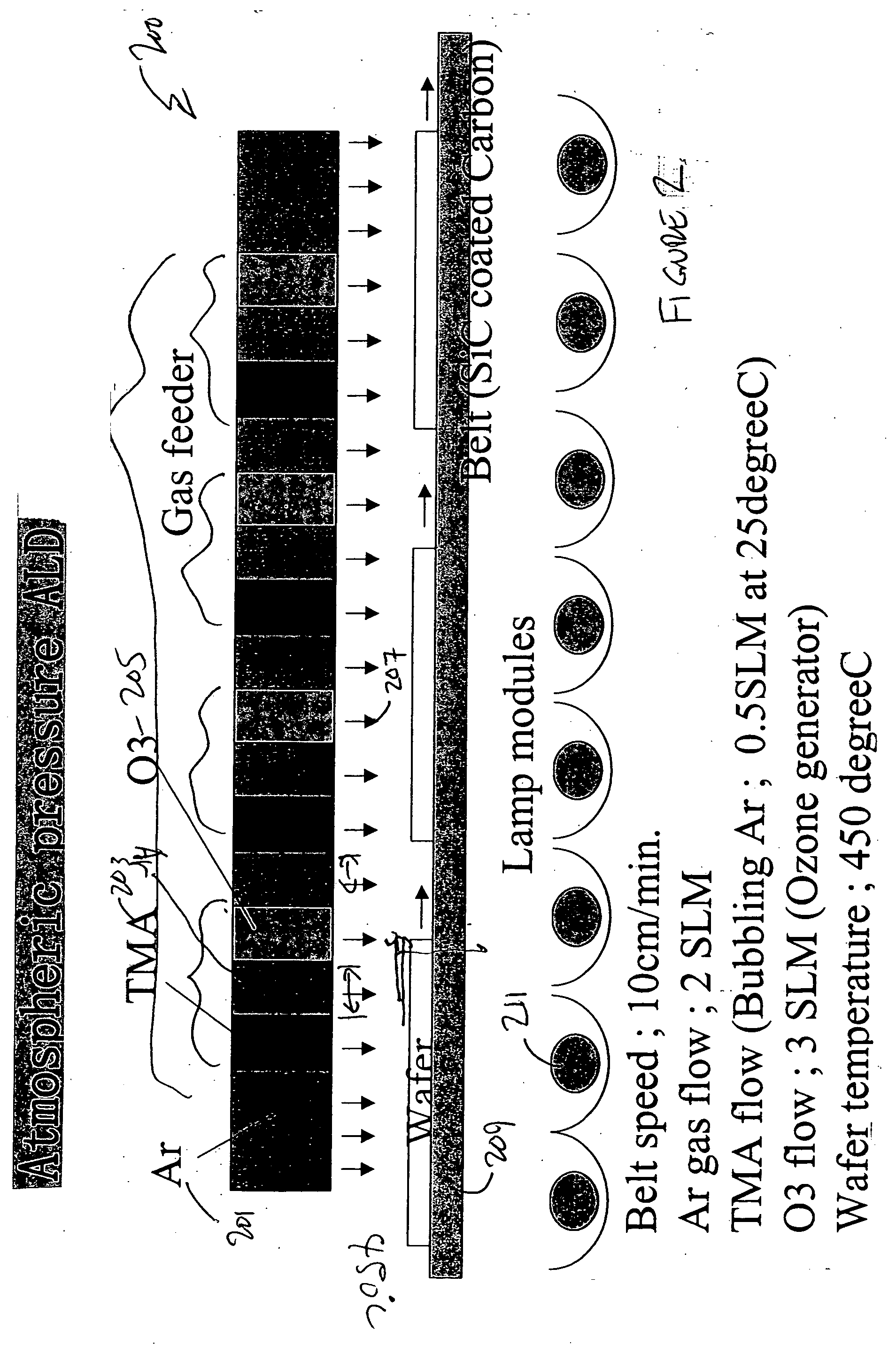

Method for atomic layer deposition of materials using an atmospheric pressure for semiconductor devices

ActiveUS20070077356A1Easy to useHigh device yieldChemical vapor deposition coatingDevice materialAtmospheric pressure

A method for atomic layer deposition. The method includes providing a substrate having a surface region and exposing the surface region of the substrate to an atmospheric pressure. The method also maintains at least the substrate at about the atmospheric pressure and forms a film overlying the surface region using atomic layer deposition, while the substrate is maintained at about atmospheric pressure. Preferably, the film is grown at a rate of greater than about 1 nanometer per minute.

Owner:SEMICON MFG INT (SHANGHAI) CORP

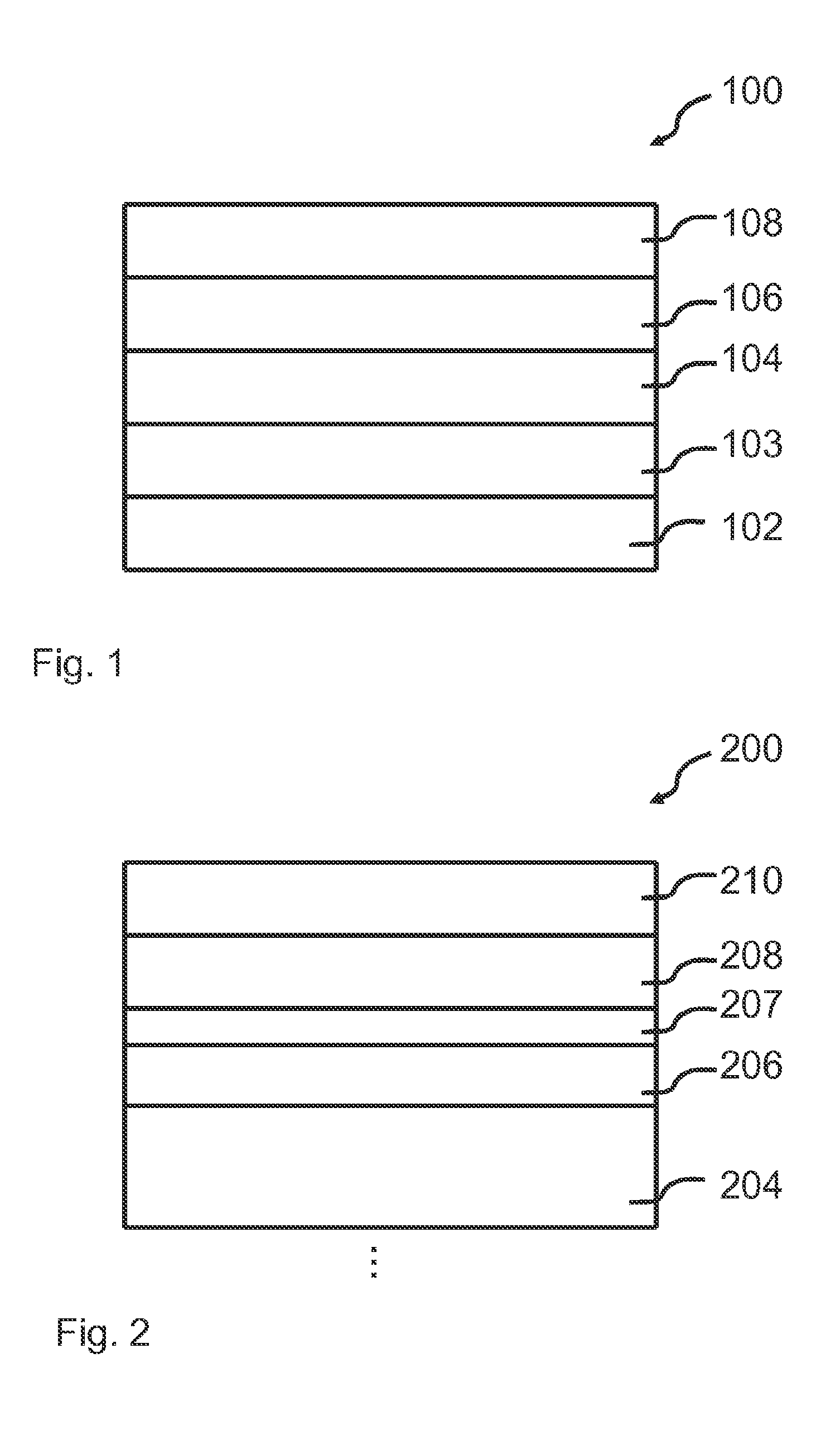

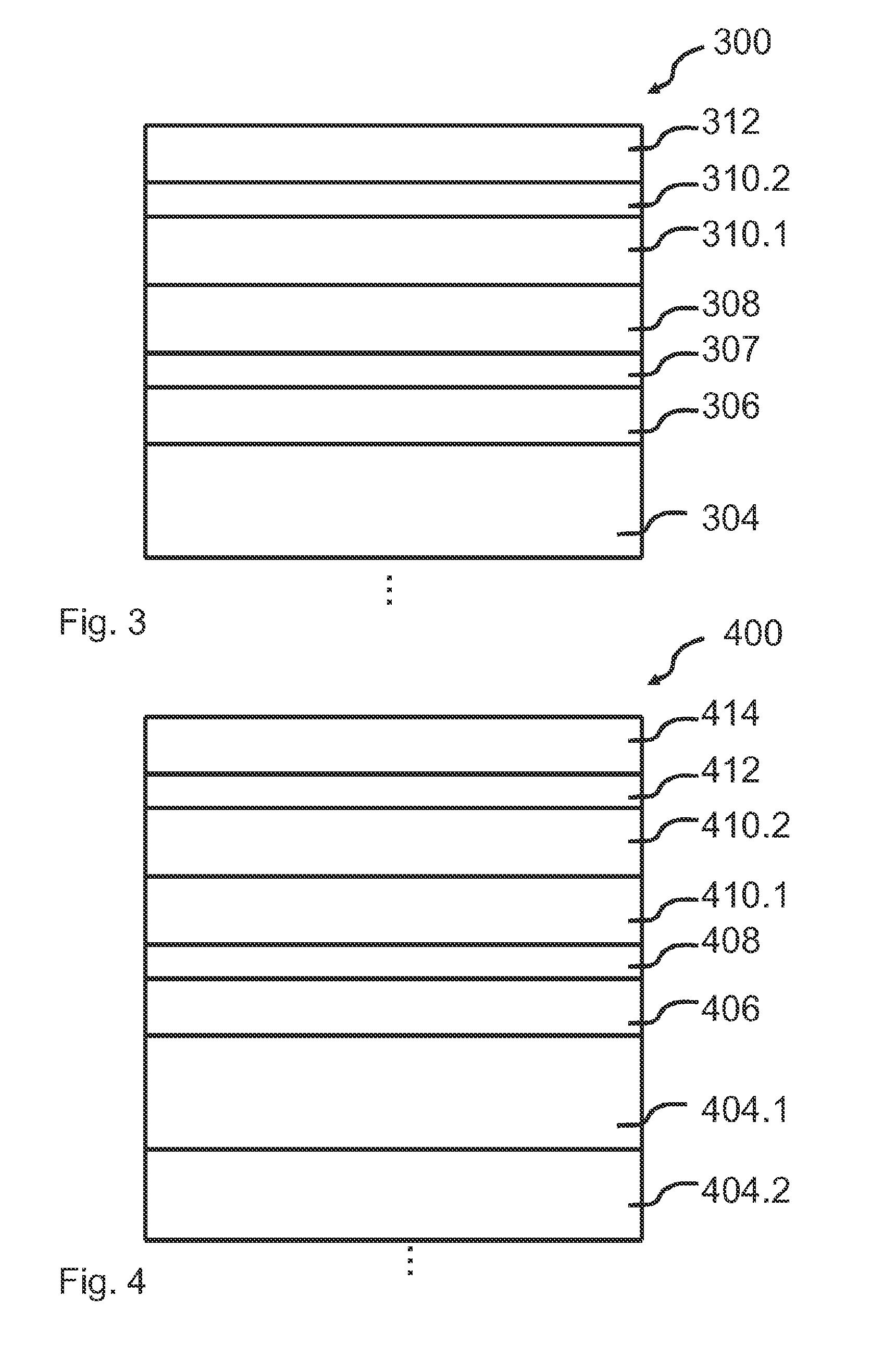

Layer structure for a group-iii-nitride normally-off transistor

A layer structure for a normally-off transistor has an electron-supply layer made of a group-III-nitride material, a back-barrier layer made of a group-III-nitride material, a channel layer between the electron-supply layer and the back-barrier layer, made of a group-III-nitride material having a band-gap energy that is lower than the band-gap energies of the other layer mentioned. The material of the back-barrier layer is of p-type conductivity, while the material of the electron-supply layer and the material of the channel layer are not of p-type conductivity, the band-gap energy of the electron-supply layer is smaller than the band-gap energy of the back-barrier layer. In absence of an external voltage a lower conduction-band-edge of the third group-III-nitride material in the channel layer is higher in energy than a Fermi level of the material in the channel layer.

Owner:AZUR SPACE SOLAR POWER

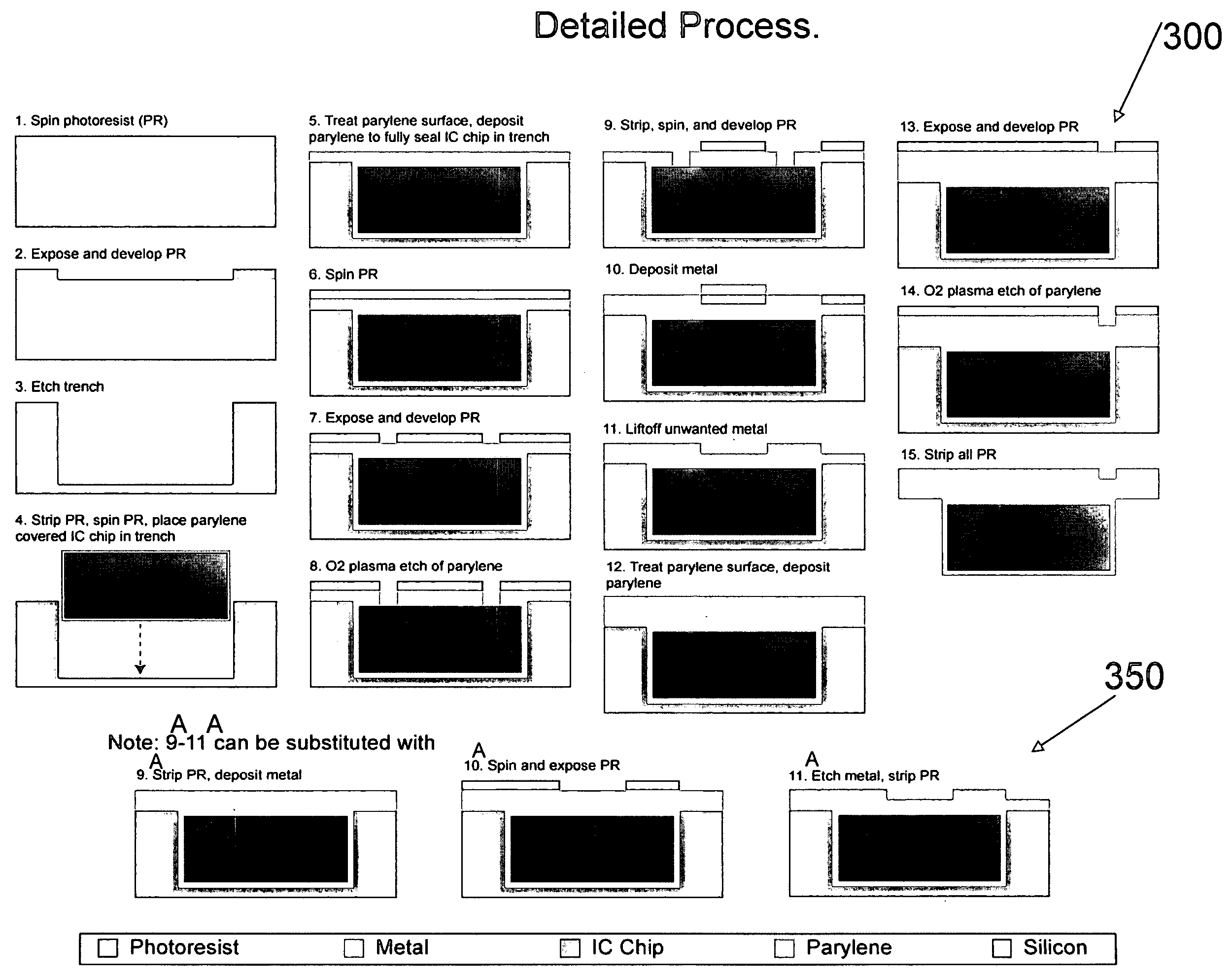

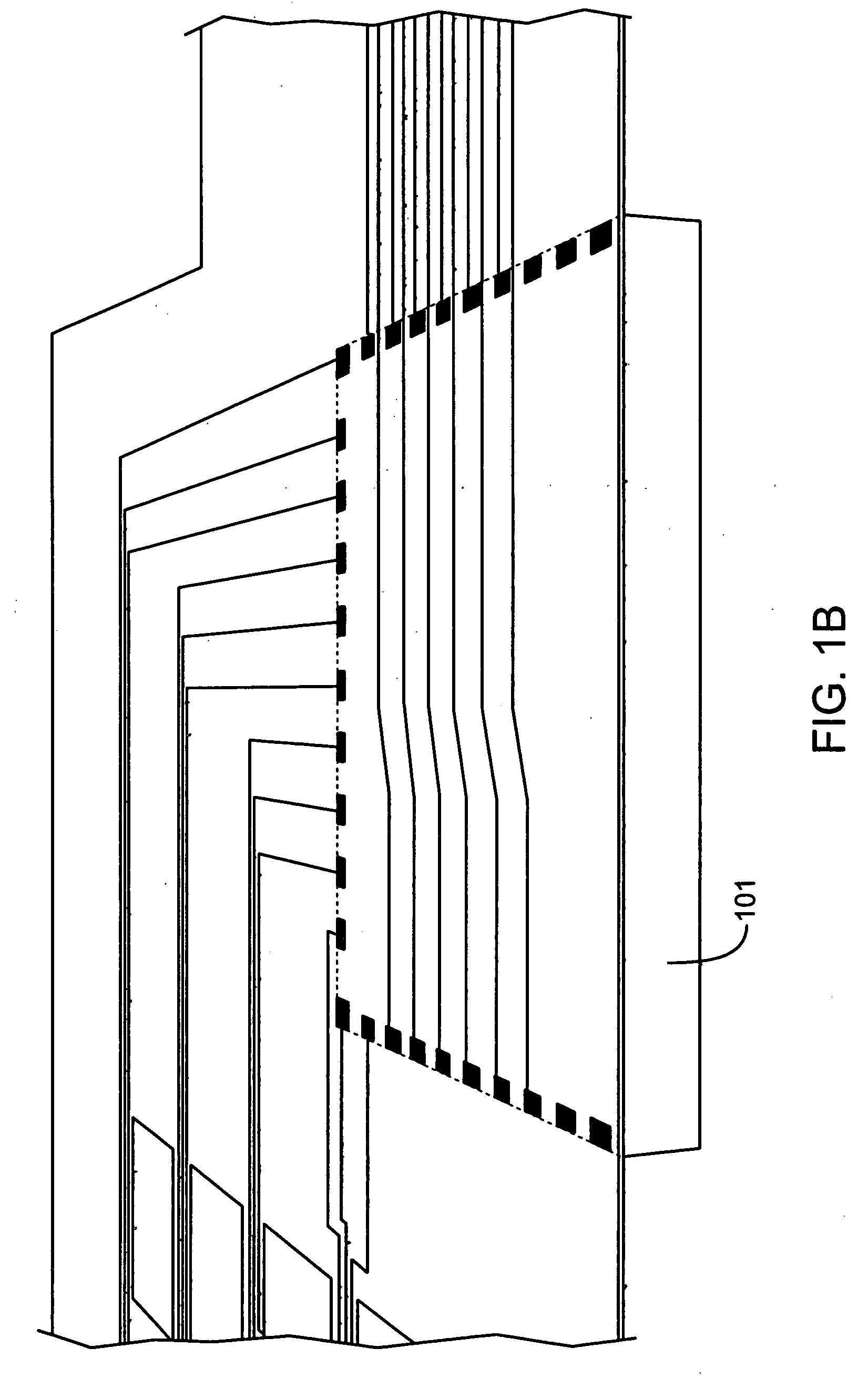

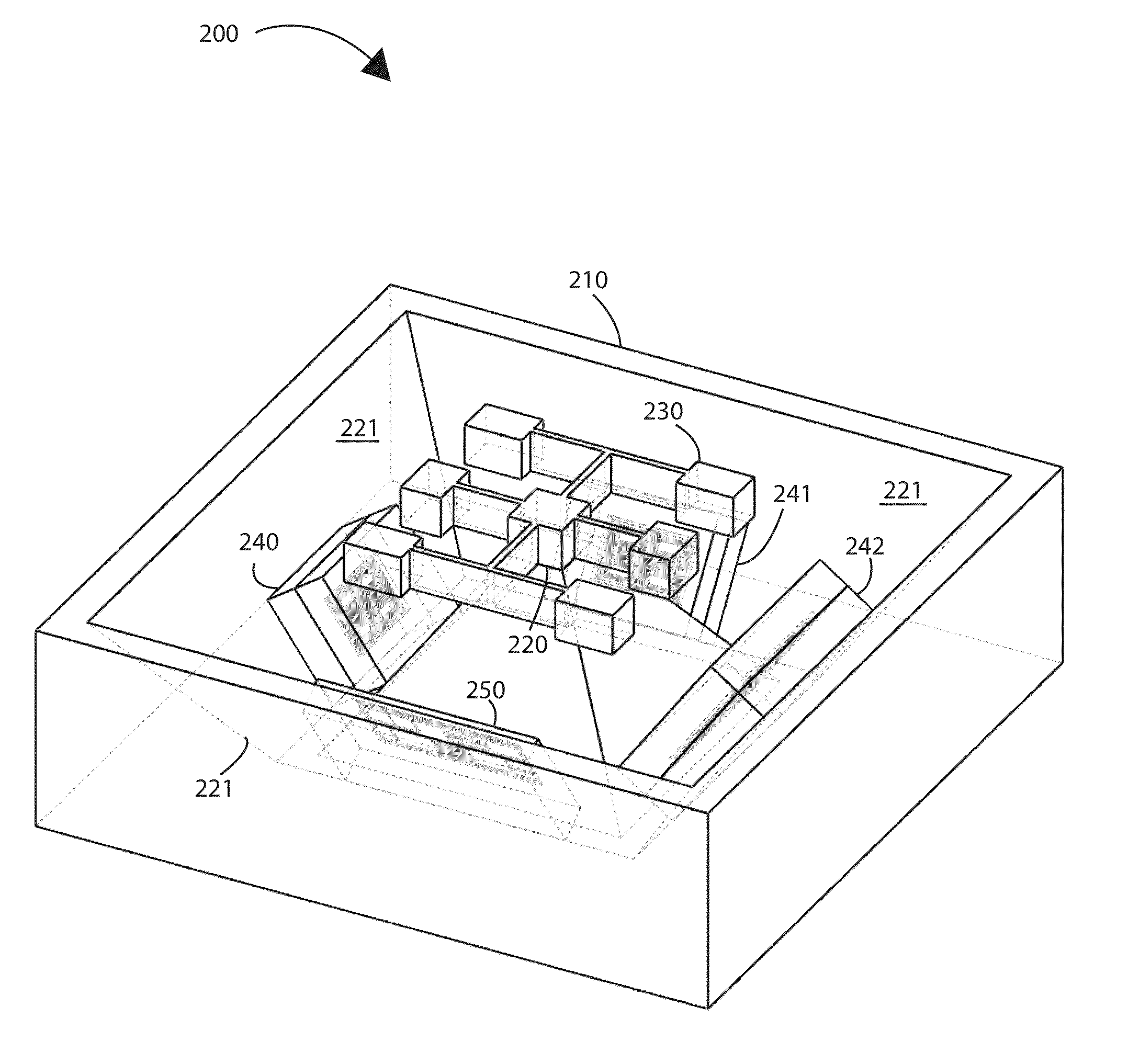

Method for integrating pre-fabricated chip structures into functional electronic systems

ActiveUS20050253273A1Improve accuracyEasy to makeSemiconductor/solid-state device detailsSolid-state devicesEngineeringElectrical and Electronics engineering

A method for manufacturing integrated objects, e.g., electronic devices, biological devices. The method includes providing a holder substrate, which has at least one recessed region, the recessed region having a predetermined shape. The holder substrate has a selected thickness and is characterized as being substantially rigid in shape. The method includes aligning a chip comprising a face and a backside into the predetermined shape of the recessed region and disposing the chip into the recessed region. The chip is secured into the recessed region. The method includes providing a first film of insulating material having a first thickness overlying the face and portions of the holder substrate to attach the chip to a portion of the first film of insulating material and patterning the first film of insulating material to form at least one opening through a portion of the first thickness to a contact region on the face of the chip. The method includes forming a metallization layer overlying the first film of insulating material to couple to the contact region through the one opening and forming a protective layer overlying the metallization layer. The method includes releasing the chip from the holder substrate while maintaining attachment of the chip to the first film of insulating material.

Owner:CALIFORNIA INST OF TECH

Integrated inertial sensing apparatus using MEMS and quartz configured on crystallographic planes

ActiveUS8794065B1Wide rangeEasy to useAcceleration measurement using interia forcesSolid-state devicesCrystallographic defectQuartz

An apparatus for inertial sensing. The apparatus includes a substrate member comprising a thickness of silicon. The apparatus also has a first surface region configured from a first crystallographic plane of the substrate and a second plane region configured from a second crystallographic plane of the substrate. The apparatus has a quartz inertial sensing device coupled to the first surface region, and one or more MEMS inertial sensing devices coupled to the second plane region.

Owner:MOVELLA INC

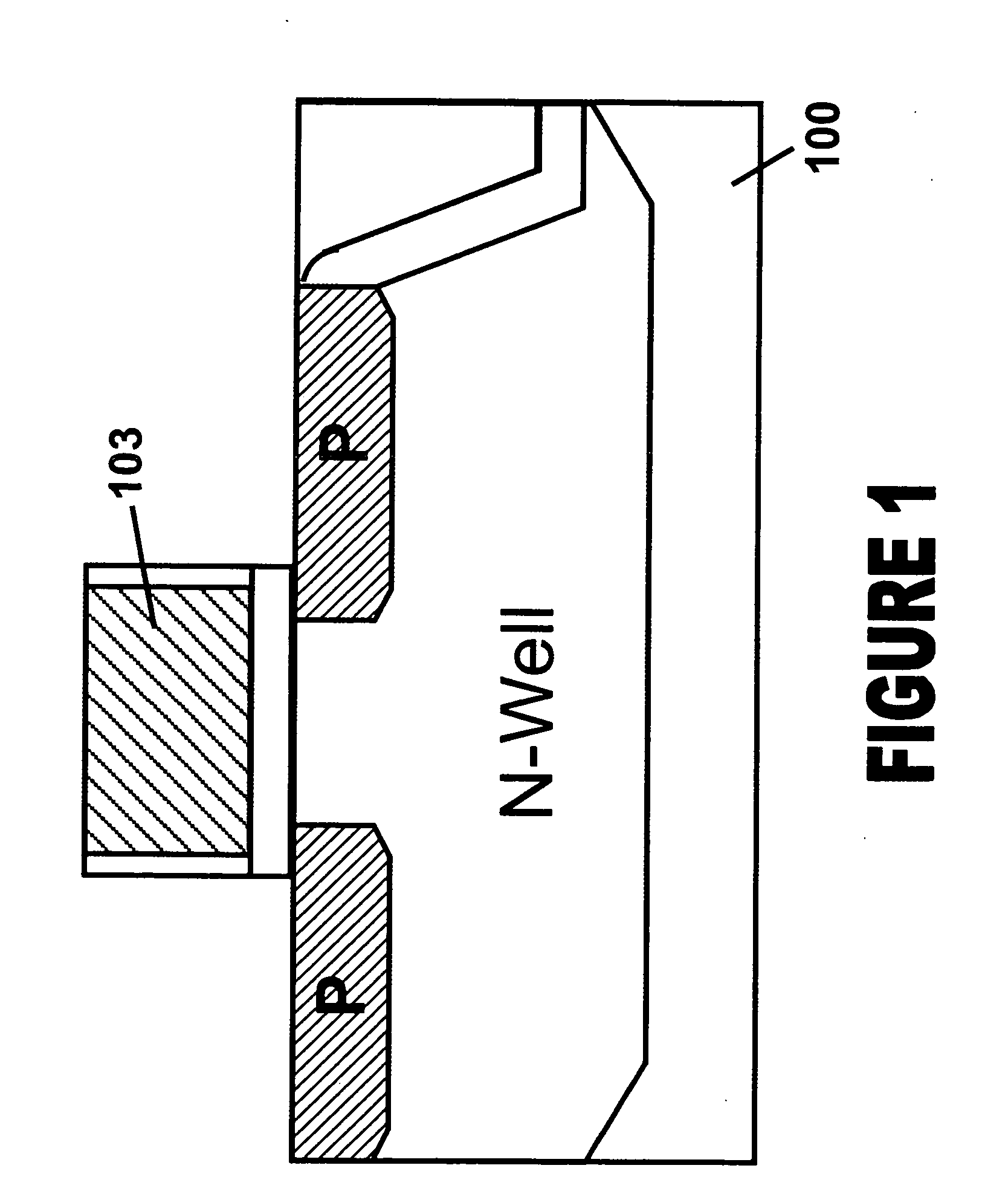

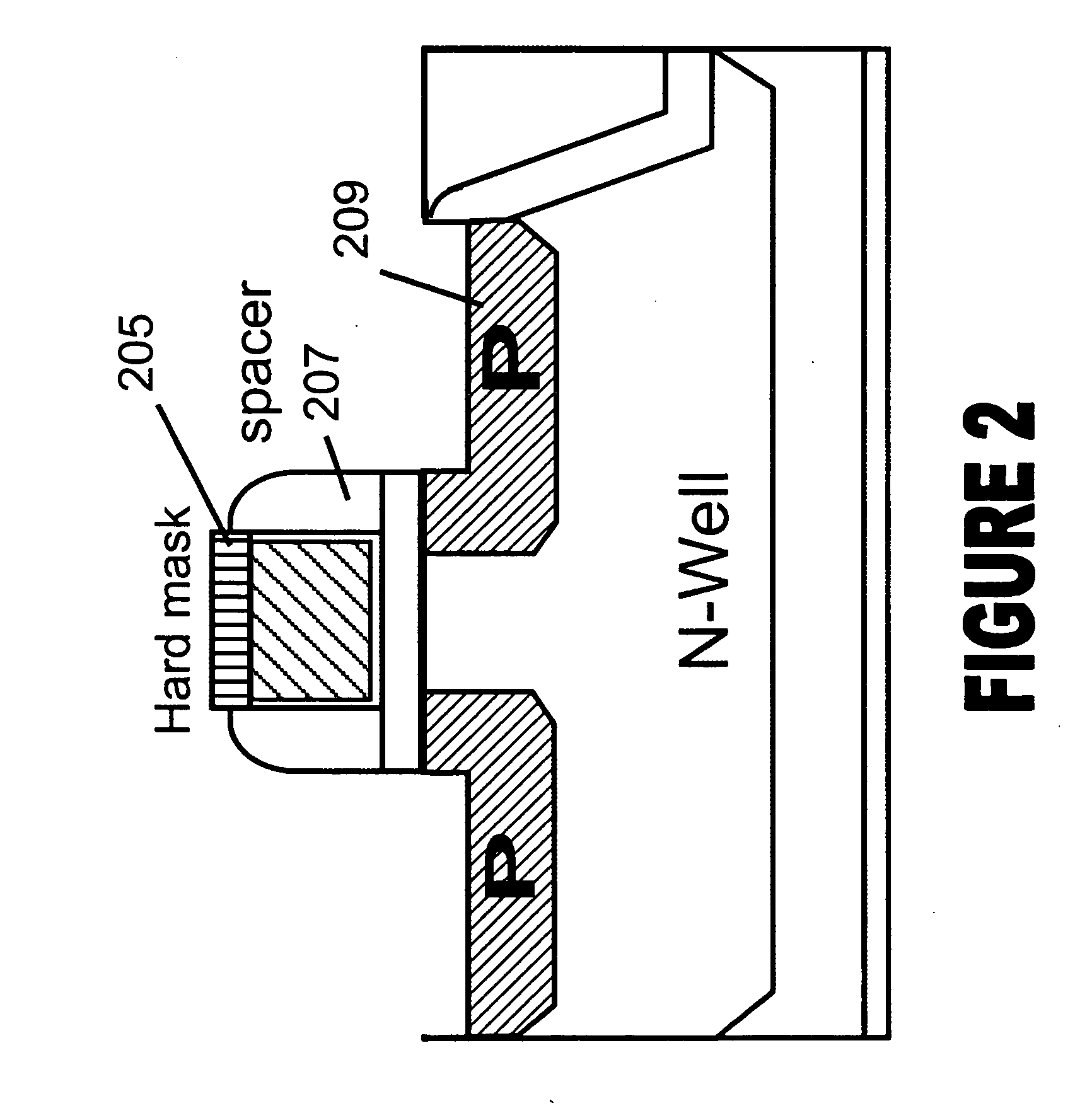

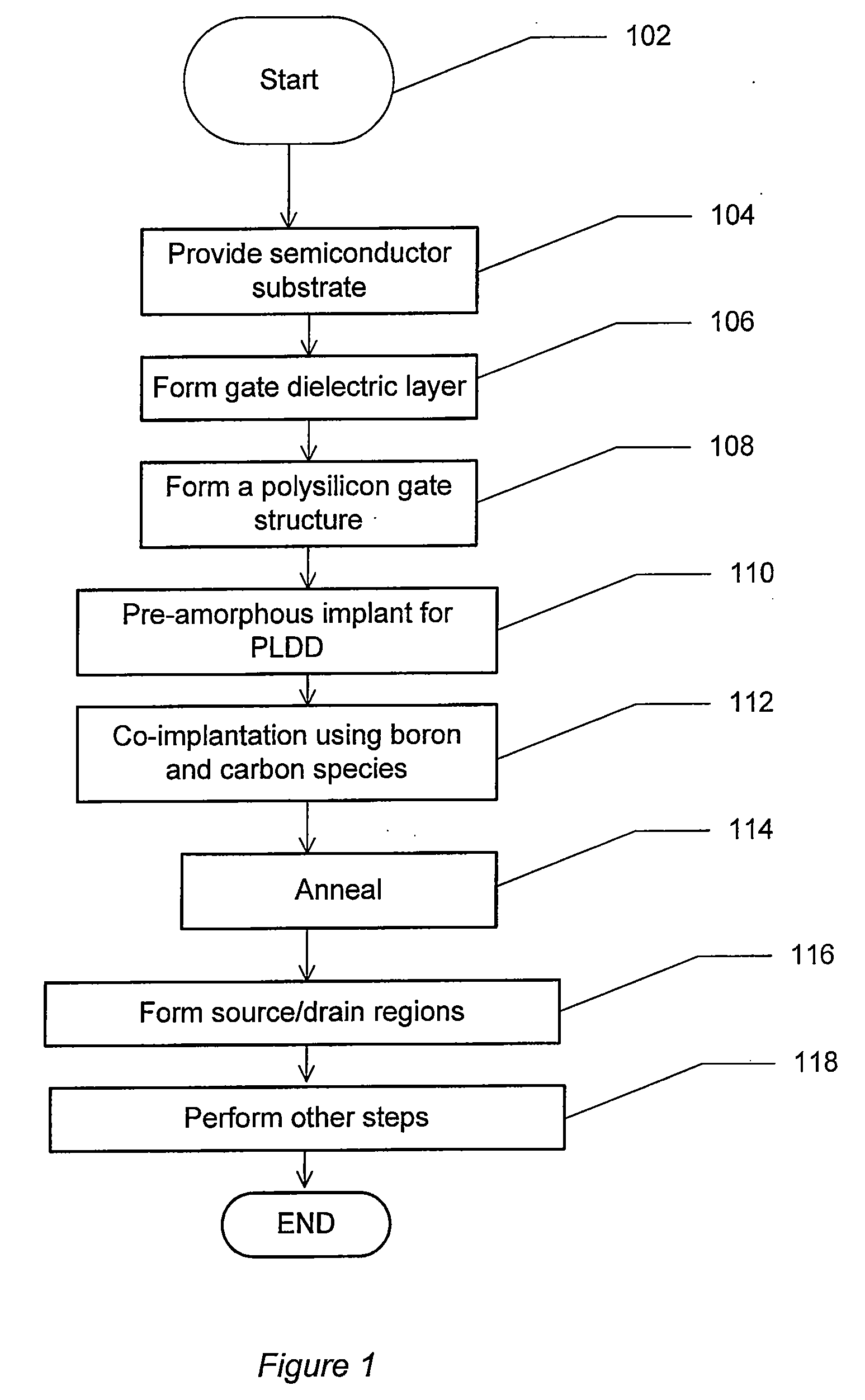

Method for forming p-type lightly doped drain region using germanium pre-amorphous treatment

ActiveUS20100003799A1Easy to useReduced transient enhanced diffusion profileTransistorSemiconductor/solid-state device manufacturingGate dielectricEngineering

A method for forming a MOS device with an ultra shallow lightly doped diffusion region. The method includes providing a semiconductor substrate including a surface region. The method provides a gate dielectric layer overlying the surface region and forms a gate structure overlying a portion of the gate dielectric layer. The method includes performing a first implant process using a germanium species to form an amorphous region within a lightly doped drain region in the semiconductor substrate using the gate structure as a mask. In a specific embodiment, the method includes performing a second implant process in the lightly doped drain region using a P type impurity and a carbon species using the gate structure as a mask. The method includes performing a first thermal process to activate the P type impurity in the lightly doped drain region. The method includes forming side wall spacers overlying a portion of the gate structure and performing a third implant process using a first impurity to form active source / drain regions in a vicinity of the surface region of the semiconductor substrate adjacent to the gate structure using the gate structure and the side wall spacer as a masking layer. The method then performs a second thermal process to activate the first impurity in the active source / drain regions.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

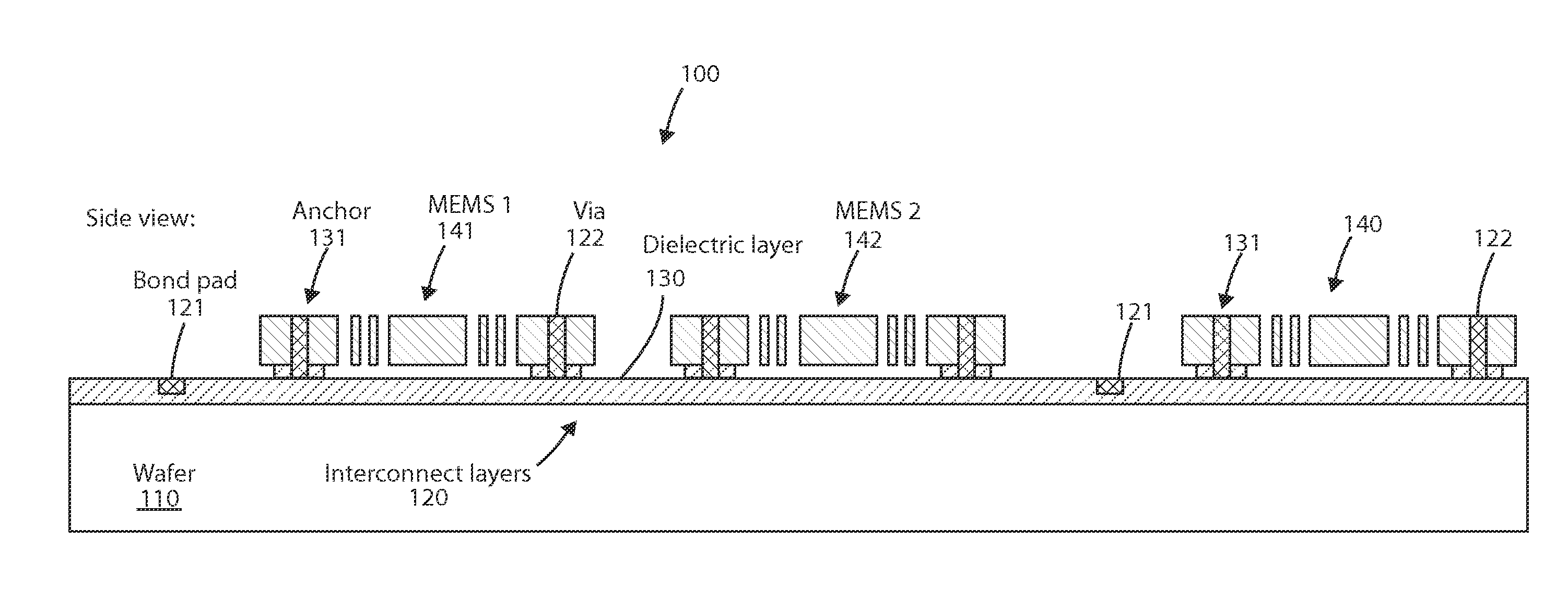

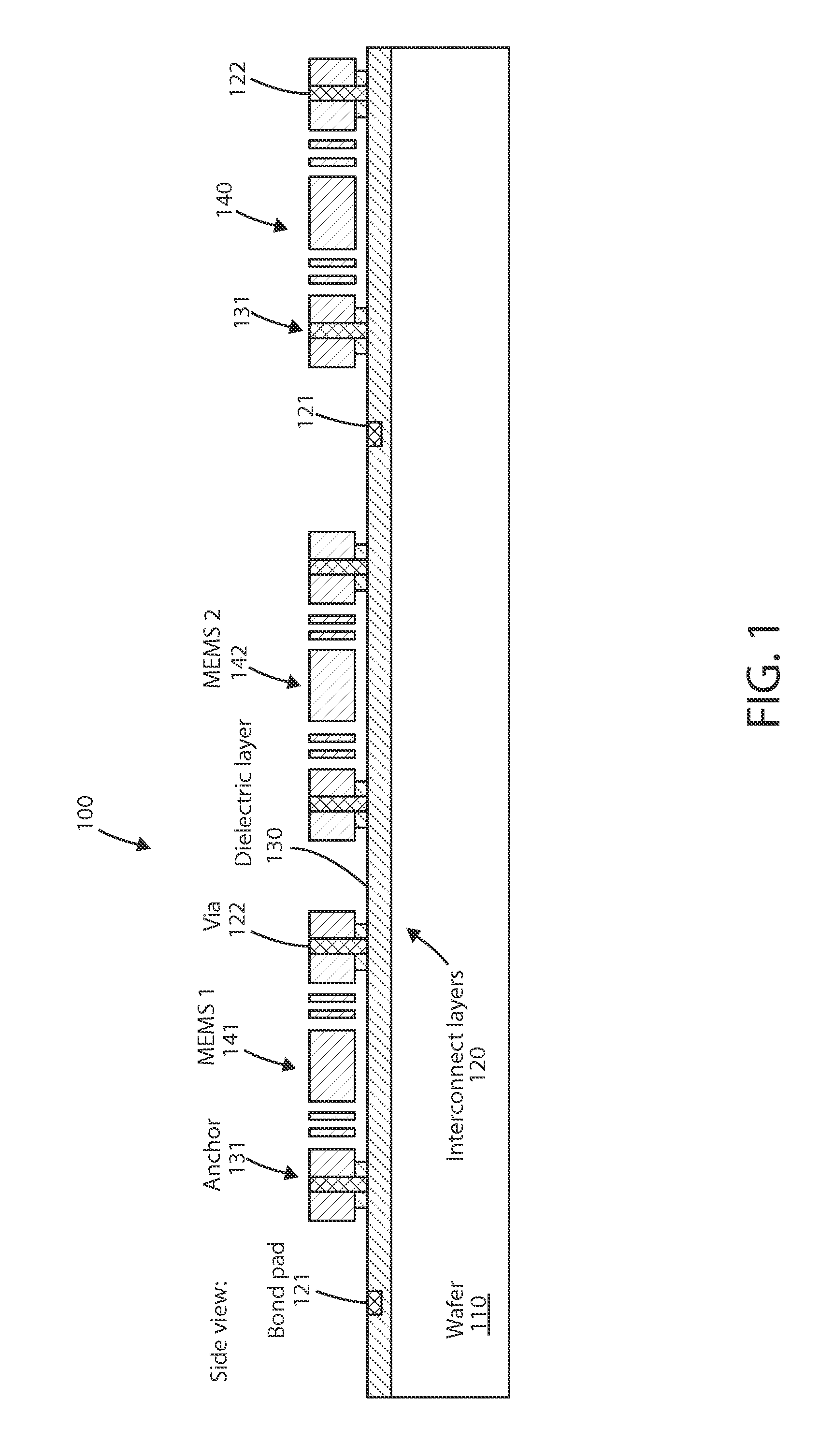

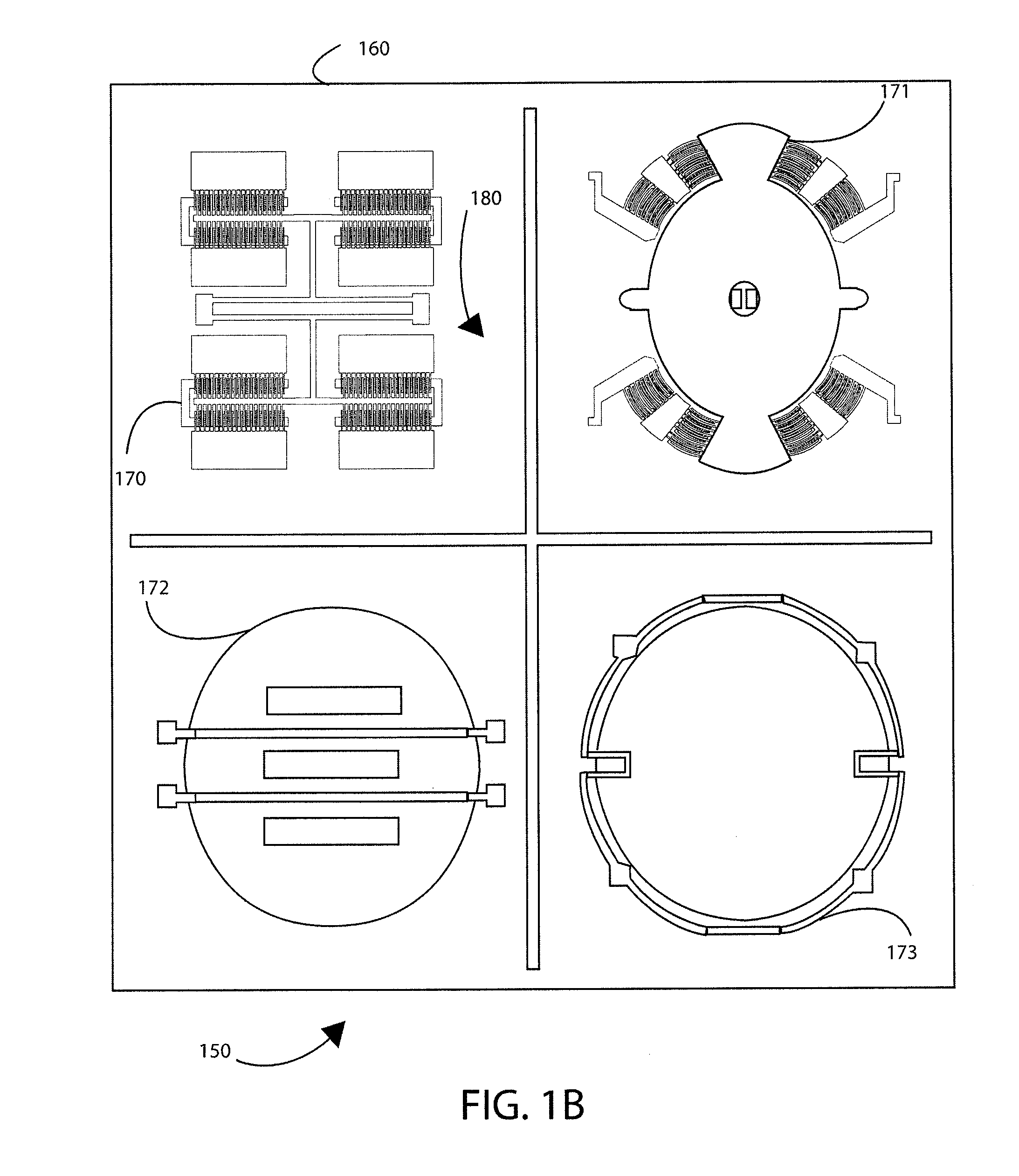

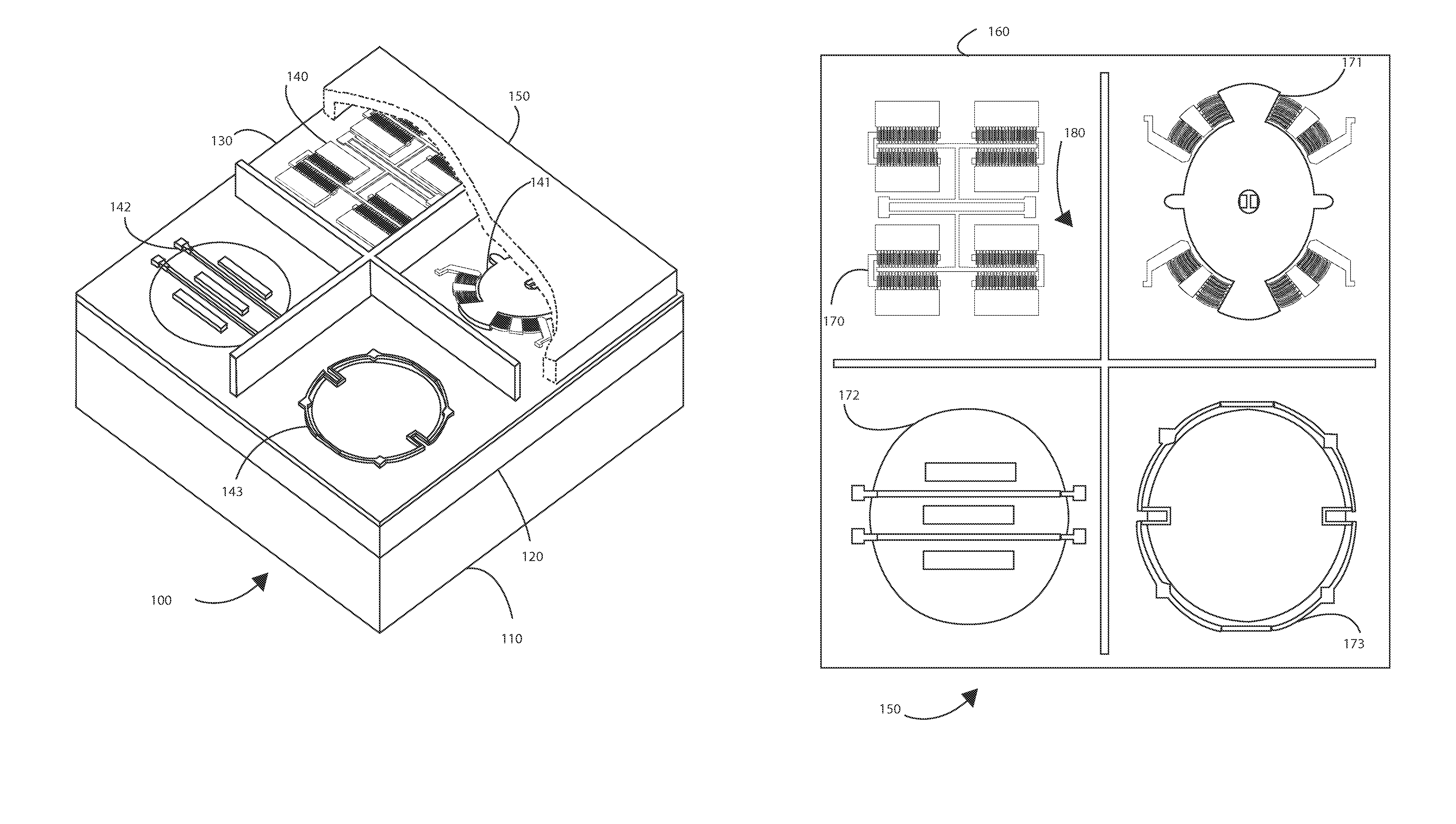

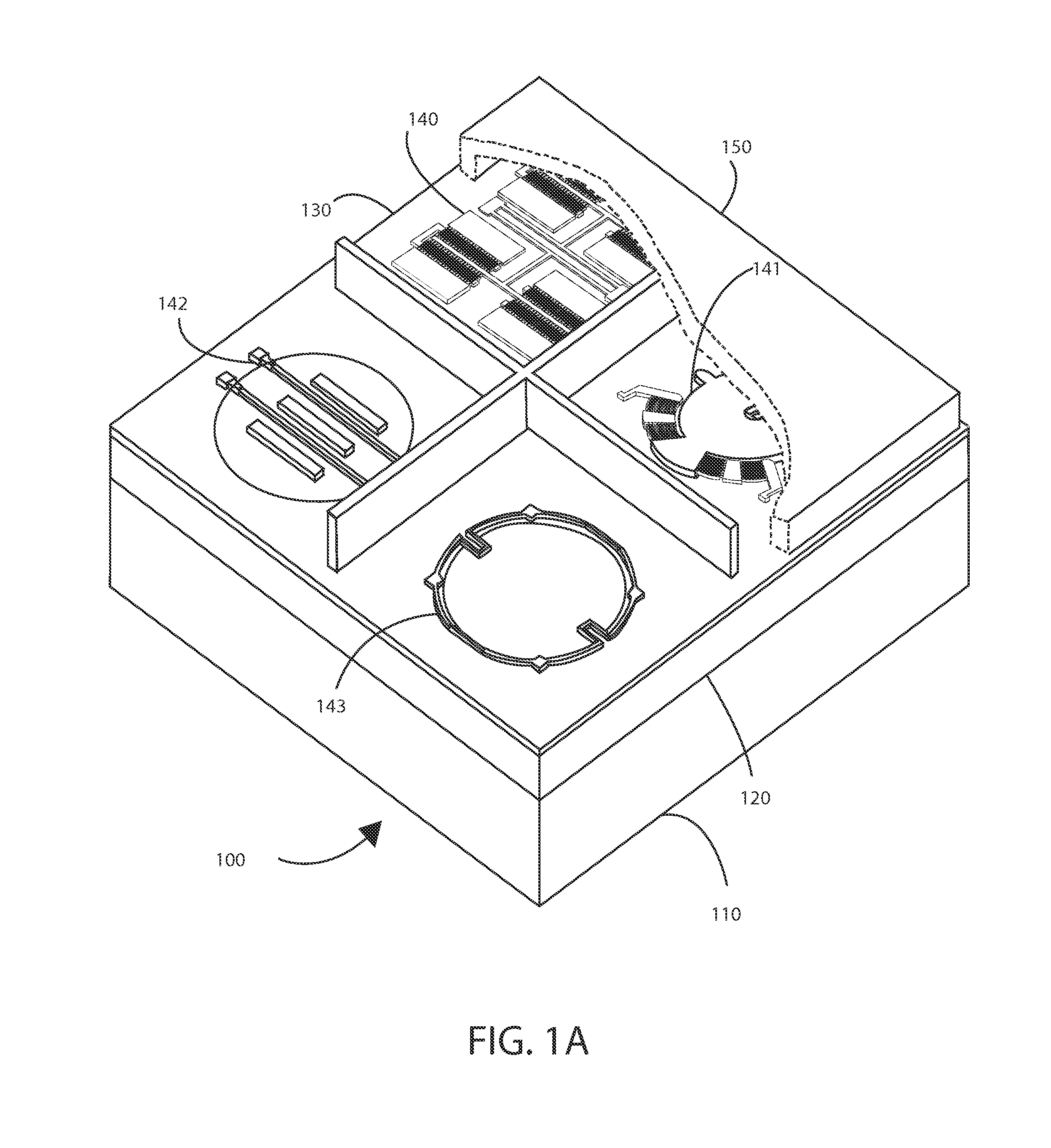

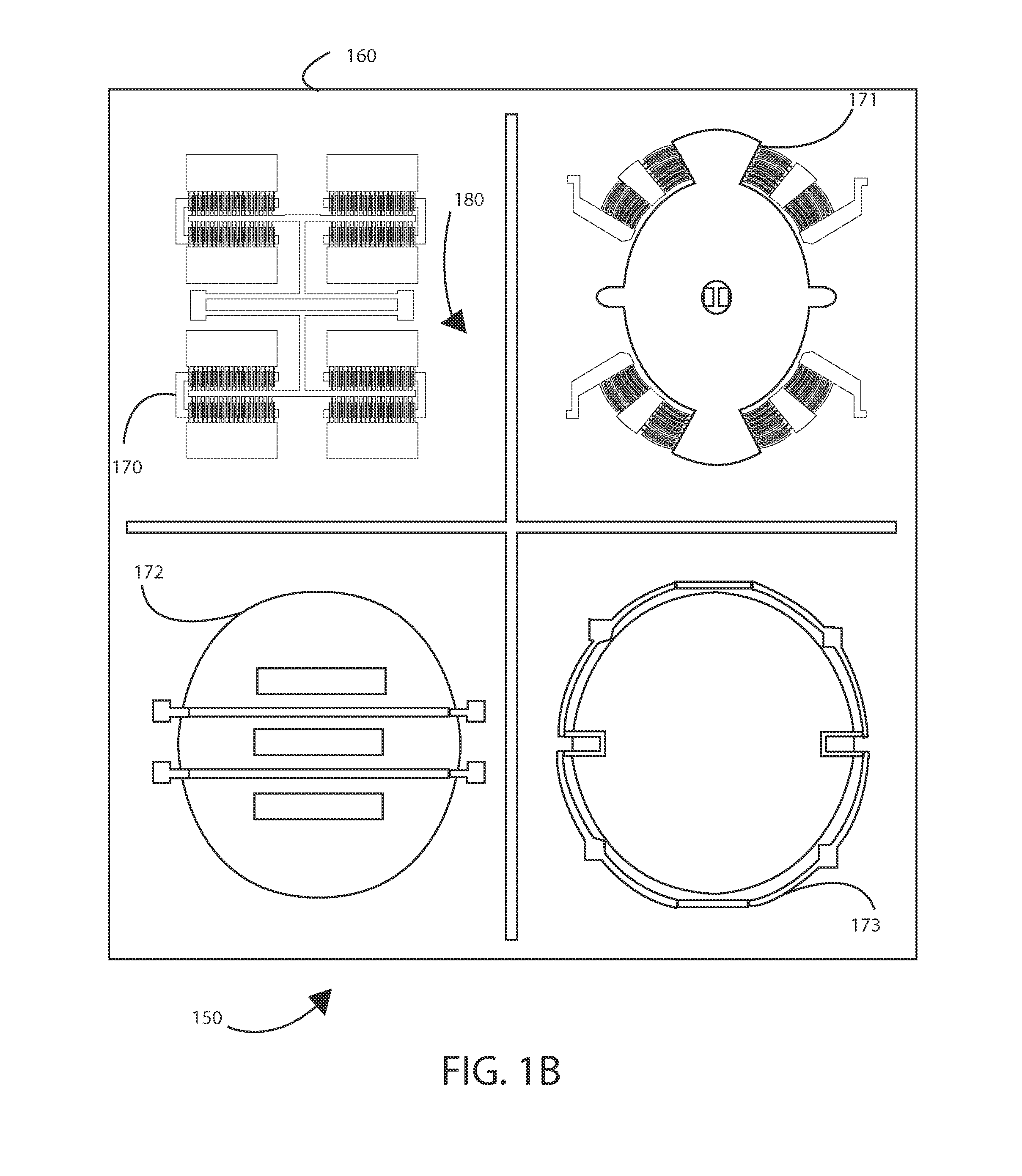

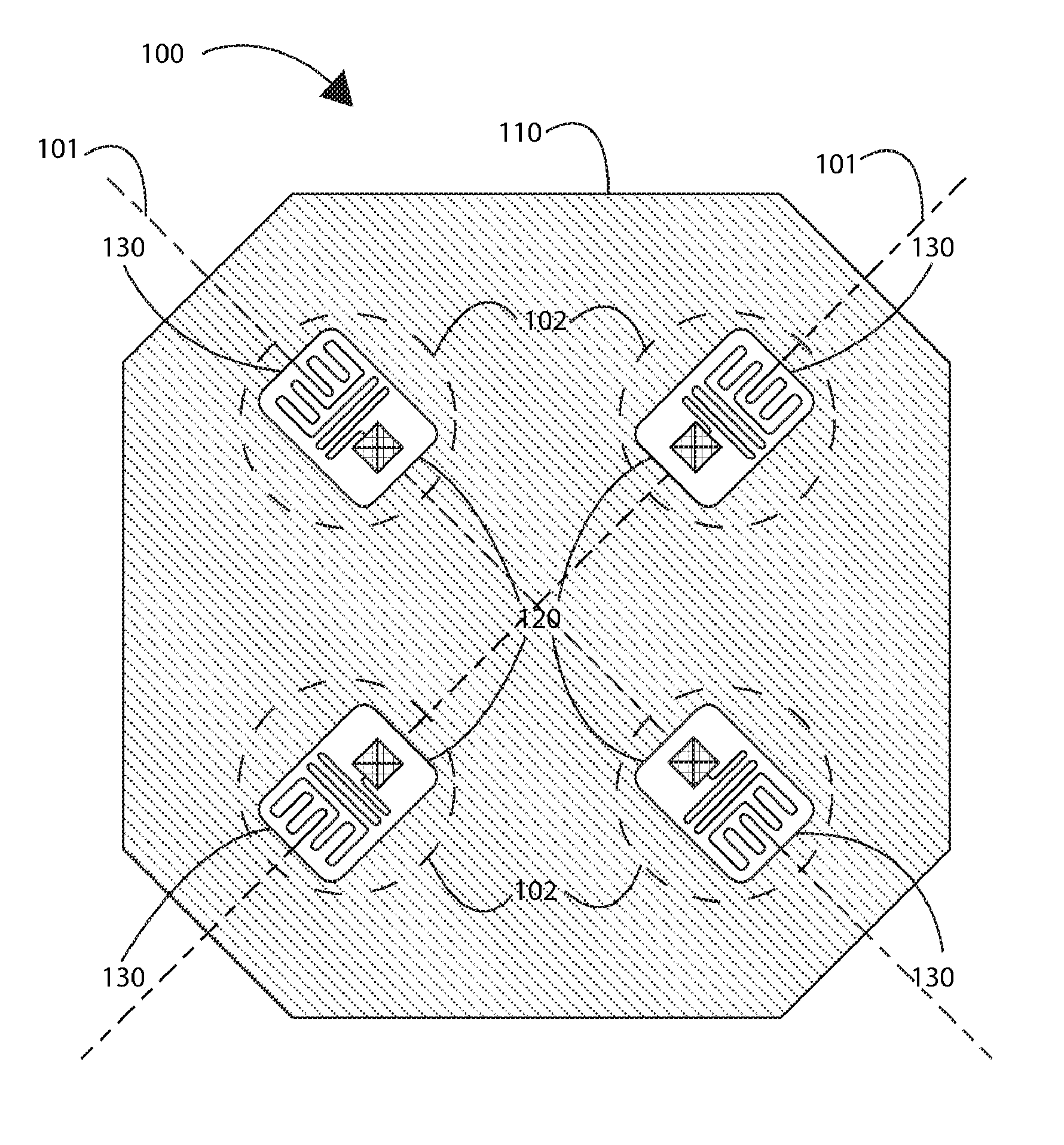

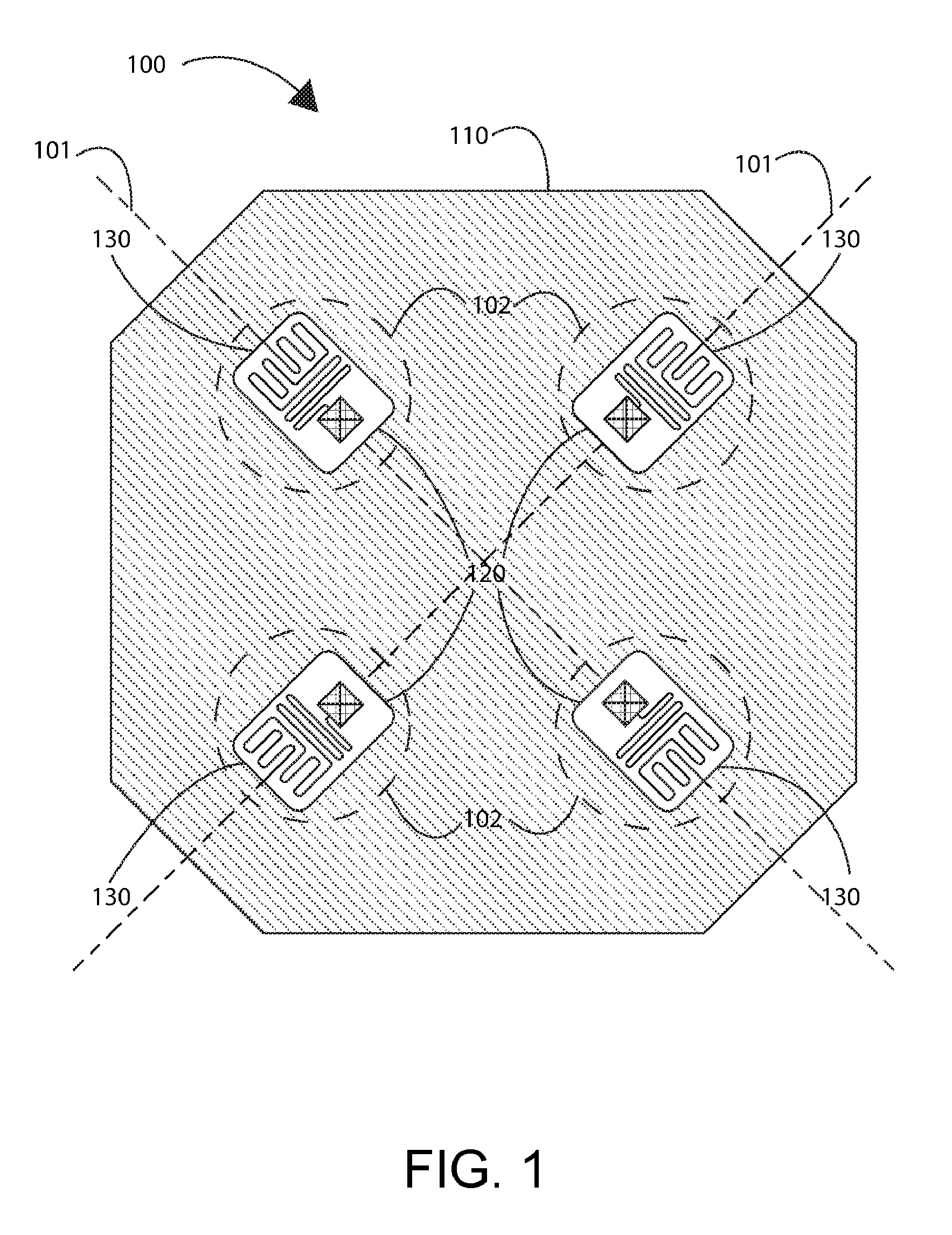

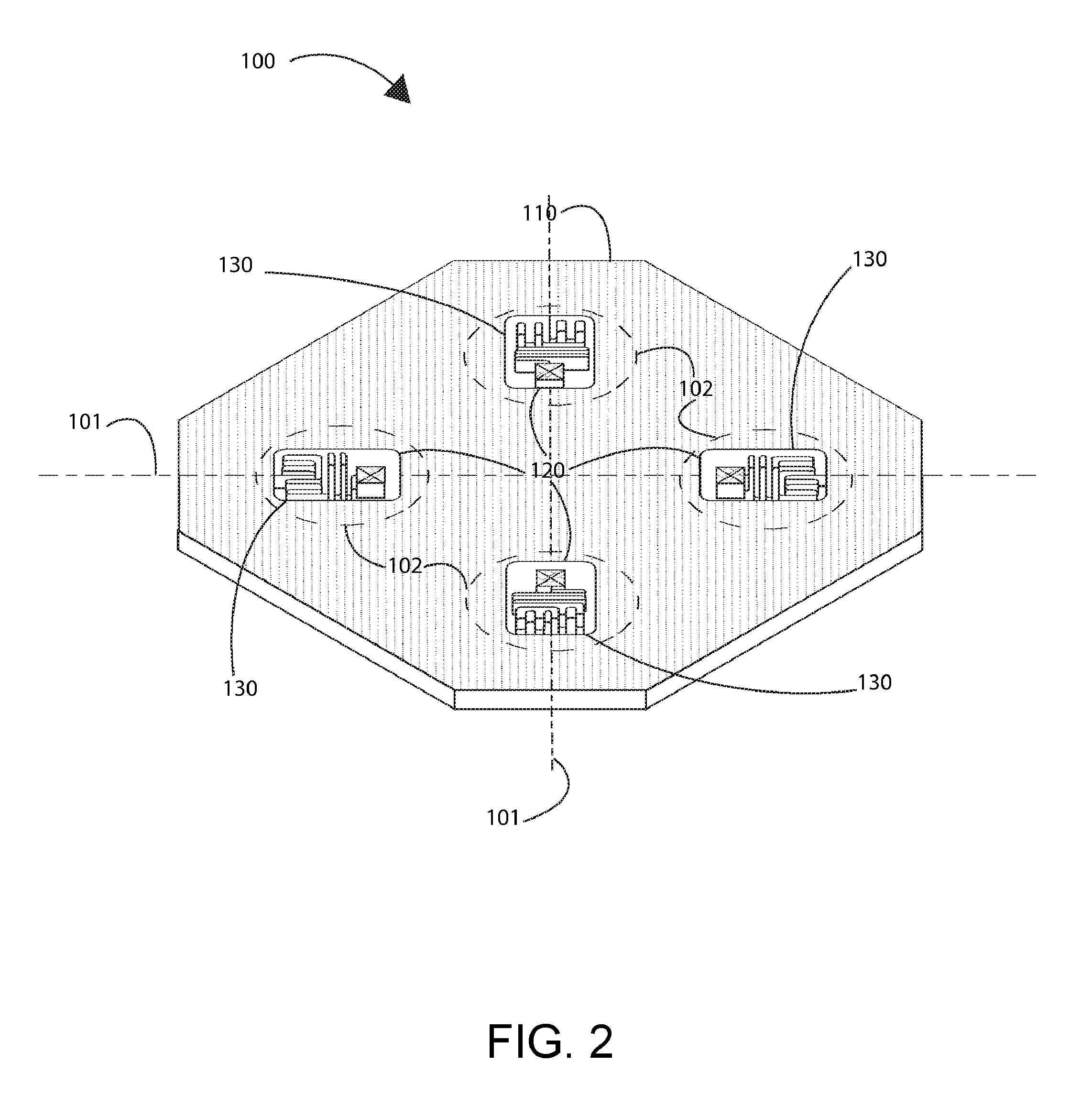

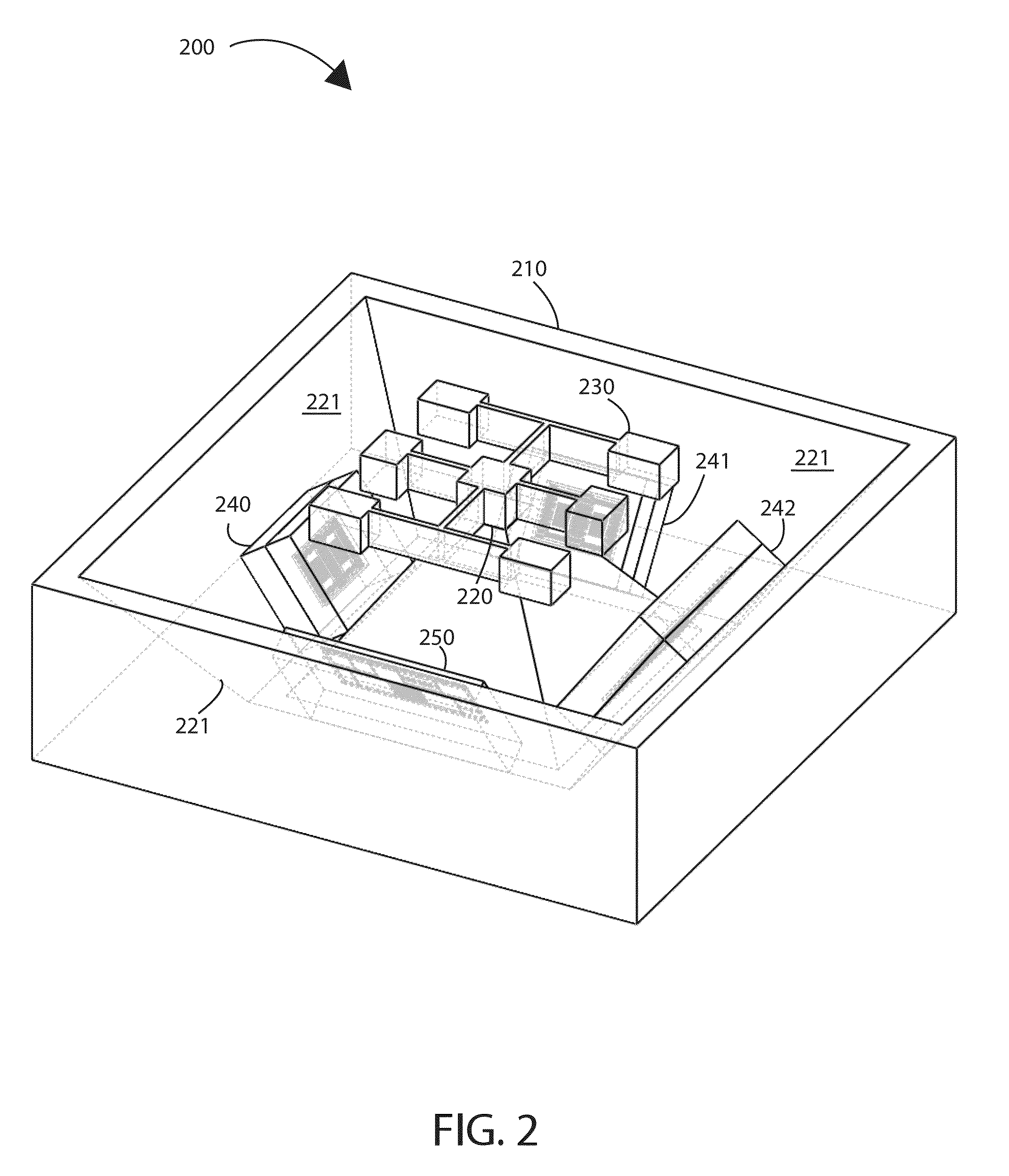

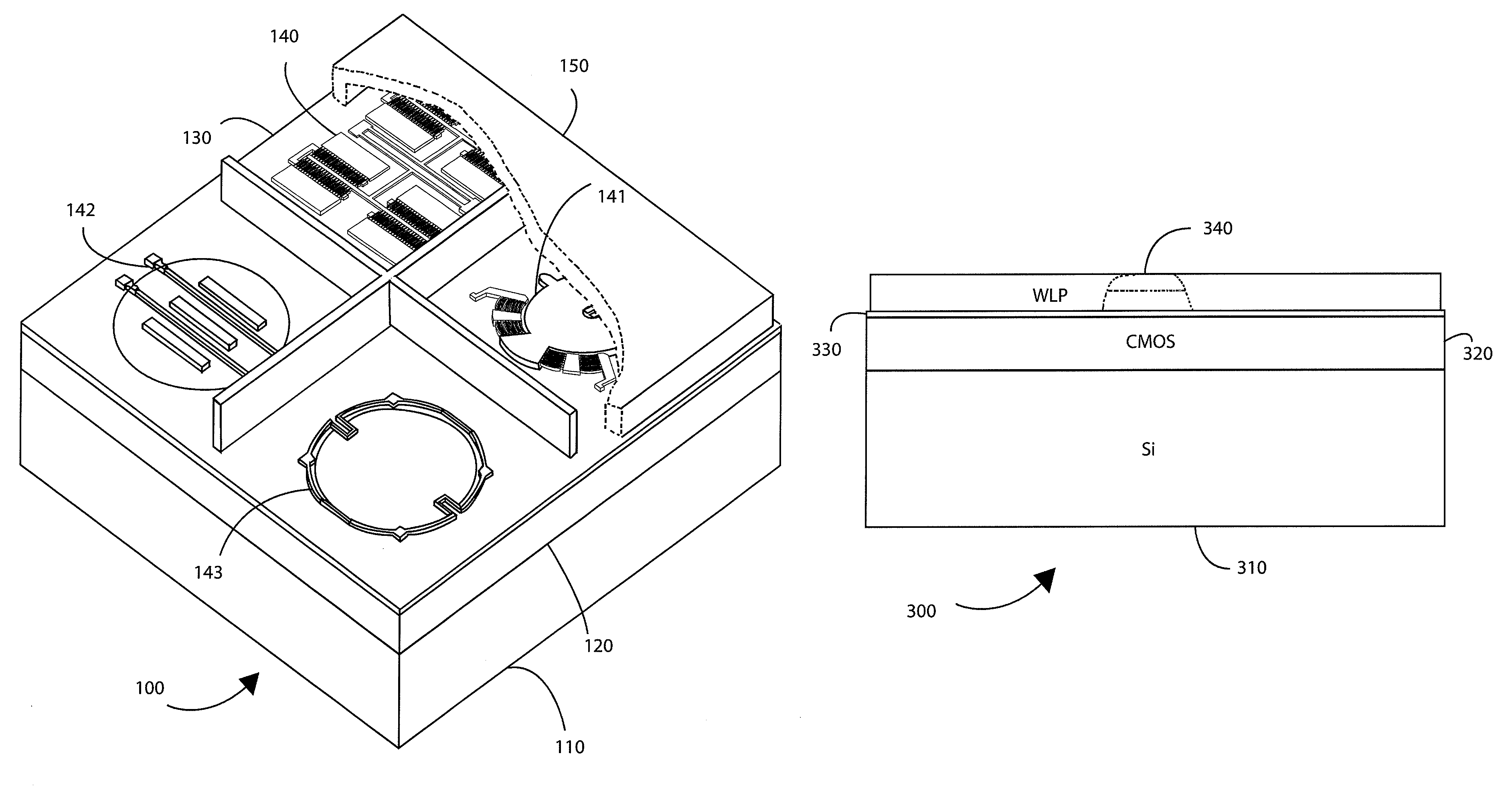

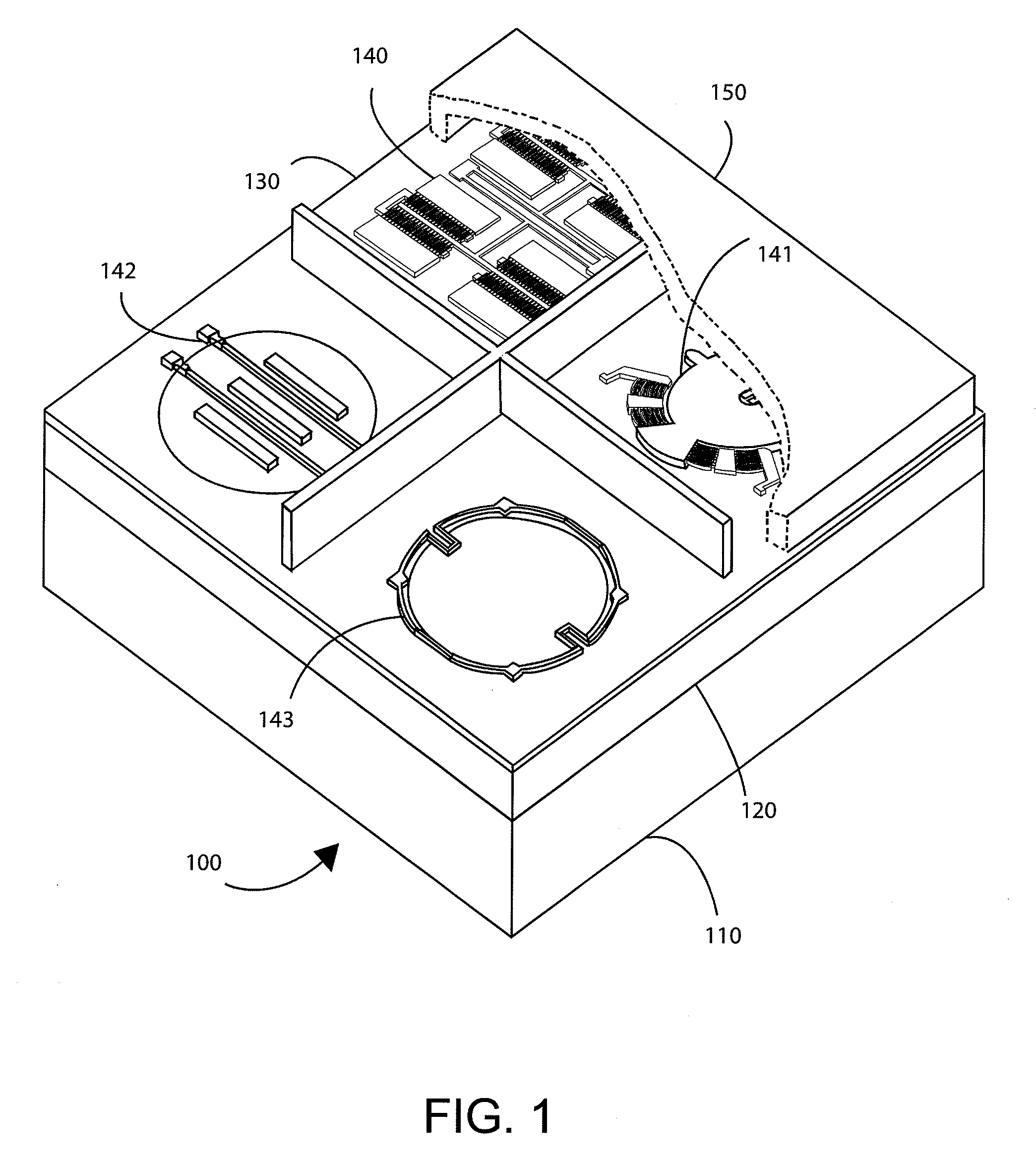

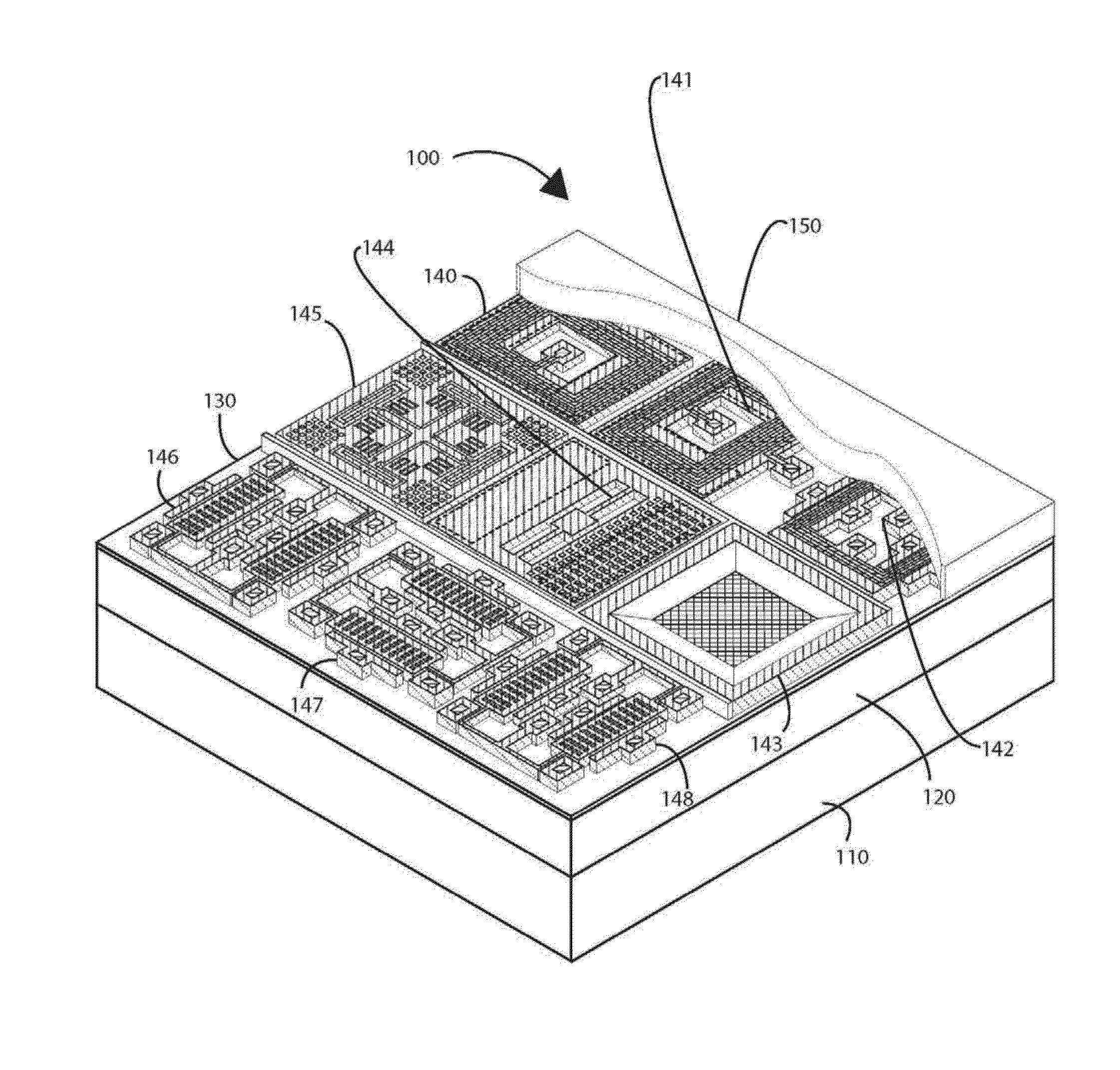

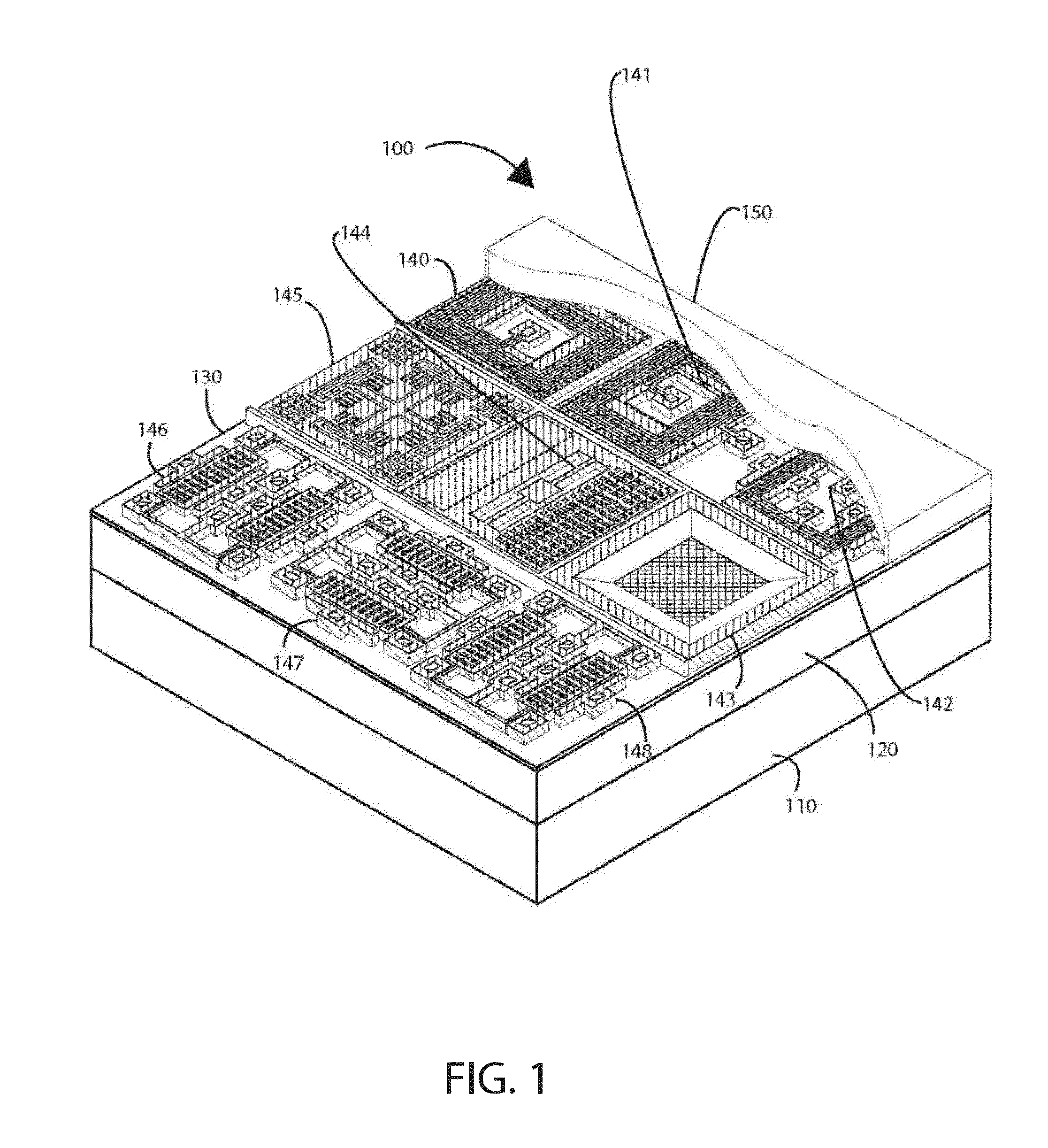

Integrated system on chip using multiple MEMS and CMOS devices

ActiveUS8823007B2Easy to useHigh device yieldVibration measurement in solidsMaterial analysis using sonic/ultrasonic/infrasonic wavesEngineeringCmos mems

Owner:MOVELLA INC

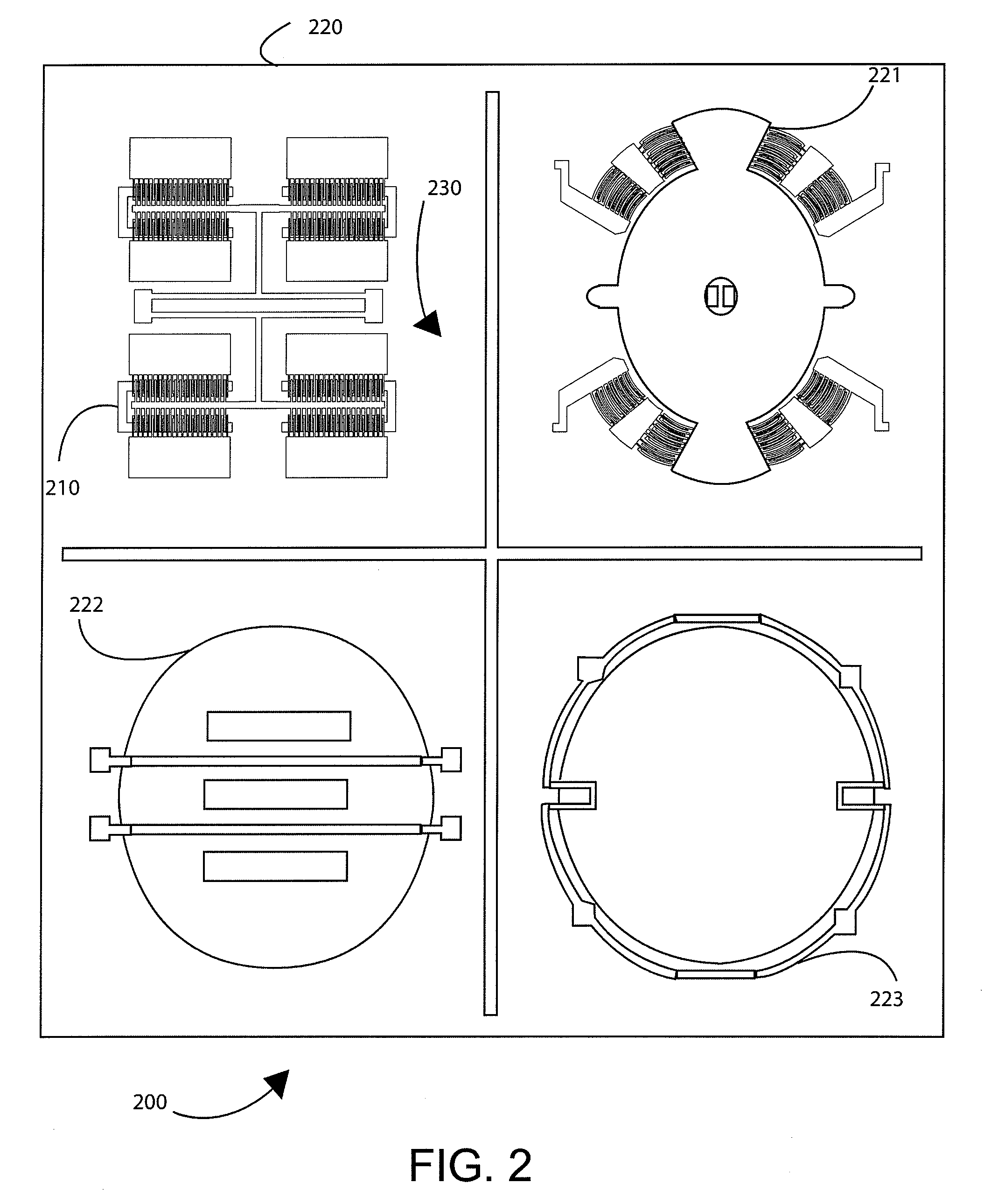

Multi-axis integrated MEMS devices with CMOS circuits and method therefor

ActiveUS20140162393A1Easy to useHigh device yieldDecorative surface effectsSolid-state devicesCMOSEngineering

An integrated multi-axis mechanical device and integrated circuit system. The integrated system can include a silicon substrate layer, a CMOS device region, four or more mechanical devices, and a wafer level packaging (WLP) layer. The CMOS layer can form an interface region, on which any number of CMOS and mechanical devices can be configured. The mechanical devices can include MEMS devices configured for multiple axes or for at least a first direction. The CMOS layer can be deposited on the silicon substrate and can include any number of metal layers and can be provided on any type of design rule. The integrated MEMS devices can include, but not exclusively, any combination of the following types of sensors: magnetic, pressure, humidity, temperature, chemical, biological, or inertial. Furthermore, the overlying WLP layer can be configured to hermetically seal any number of these integrated devices.

Owner:MOVELLA INC

Apparatus for micro-electro mechanical system package

ActiveUS7141870B2Easy to useHigh device yieldSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageLateral extension

A method of manufacturing a multi-substrate semiconductor package. The method includes providing a first substrate with a plurality of first dies present thereon and forming a plurality of electrical contacts on an upper surface of a lateral extension portion of at least one of the plurality of first dies on the first substrate. The method also includes providing a second substrate, the second substrate comprising a plurality of second dies, at least one of the plurality of second dies comprising an interconnect region. Further, the method includes forming a sandwich structure by bonding the second substrate to an upper surface of the first substrate to form an intermediate level within the sandwich structure and separating the dies. The method also includes coupling an electrically conductive structure through the interconnect region of the one second dies to the lateral extension portion of the one first die.

Owner:MIRADIA INC