Patents

Literature

2593 results about "Electroless plating" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Electroless plating, also known as chemical or auto-catalytic plating, is a non-galvanic plating method that involves several simultaneous reactions in an aqueous solution, which occur without the use of external electrical power.

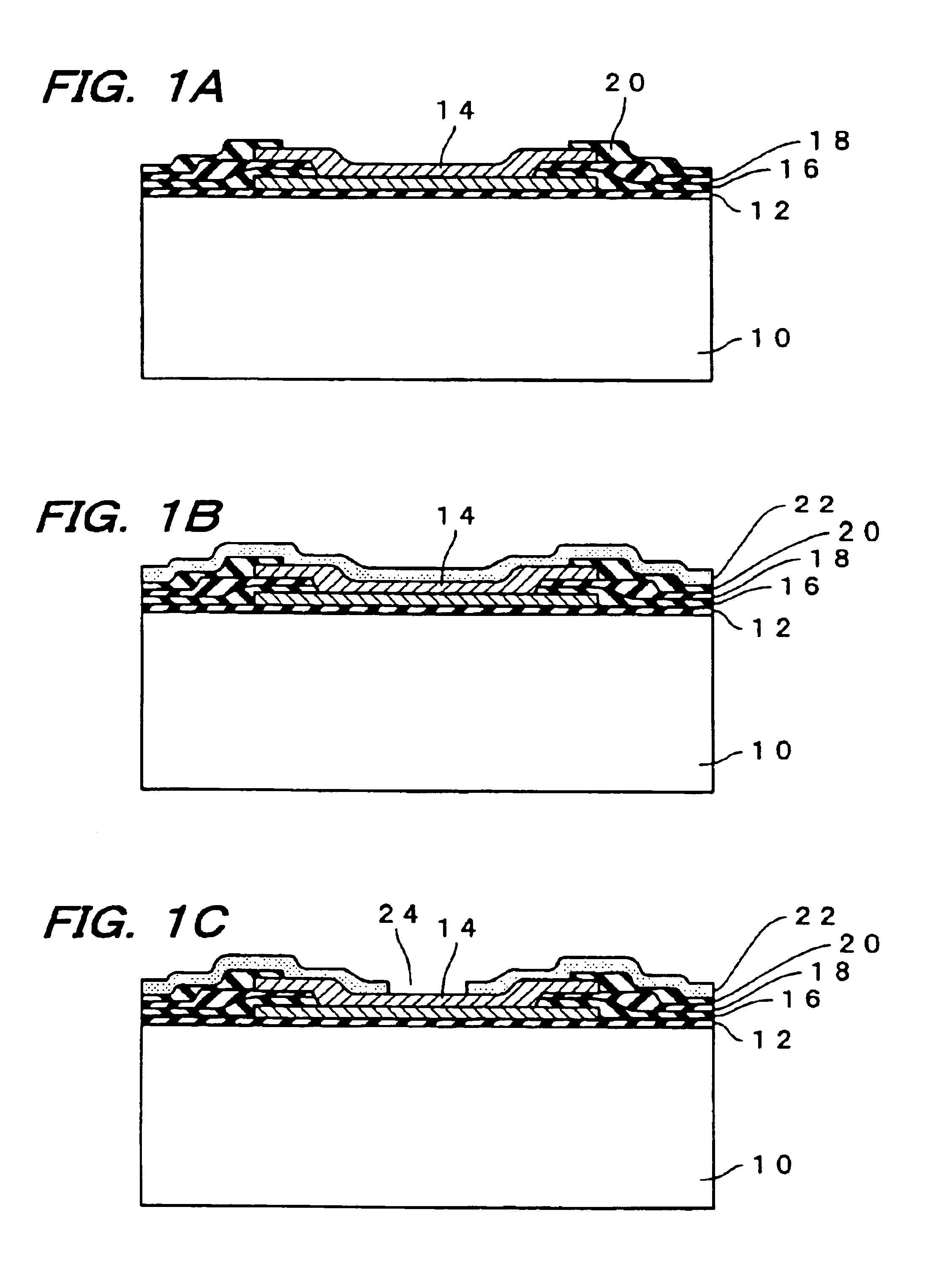

Method for treating a semiconductor surface to form a metal-containing layer

ActiveUS7132360B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingMaterial growthPhysical chemistry

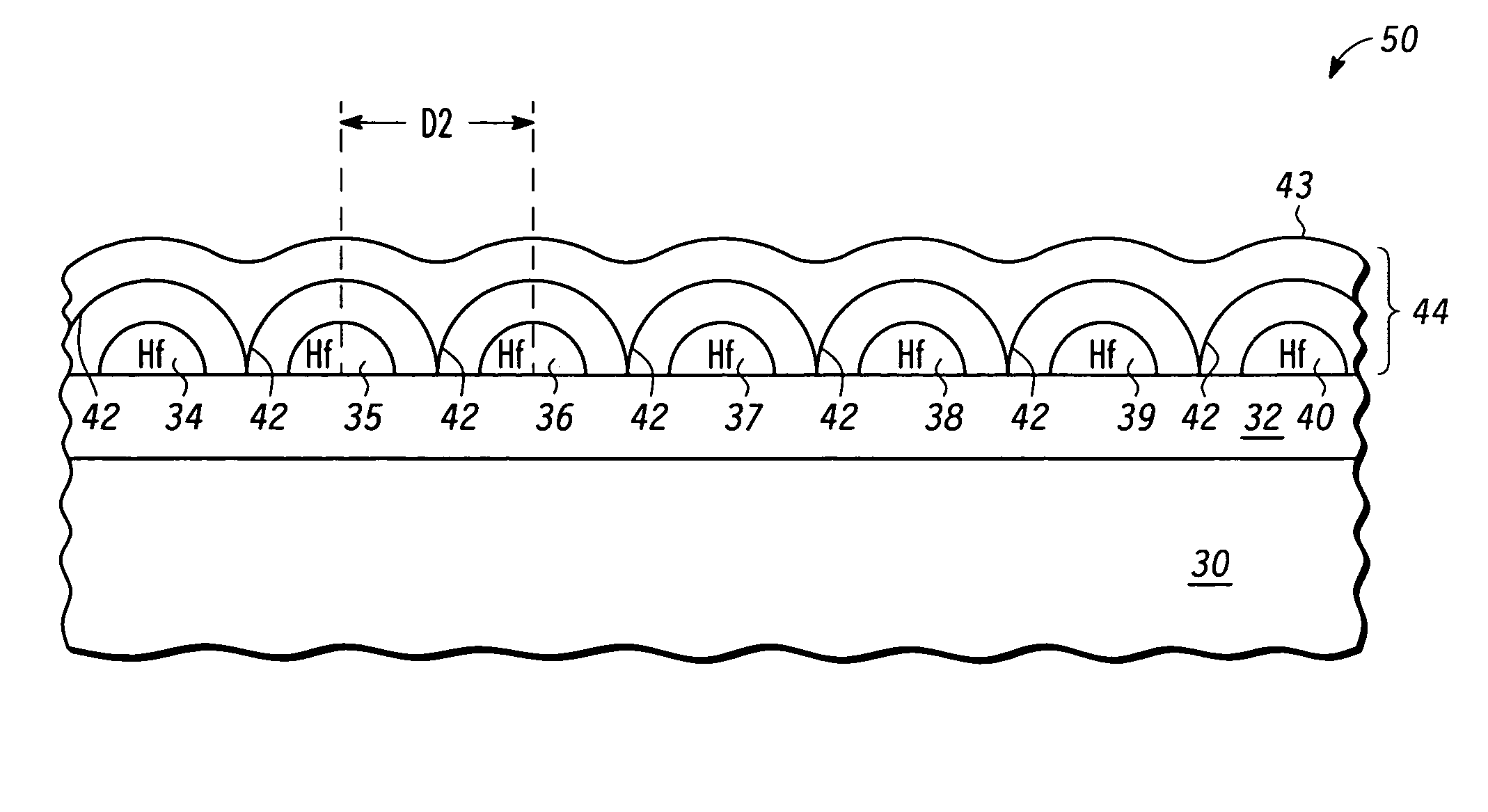

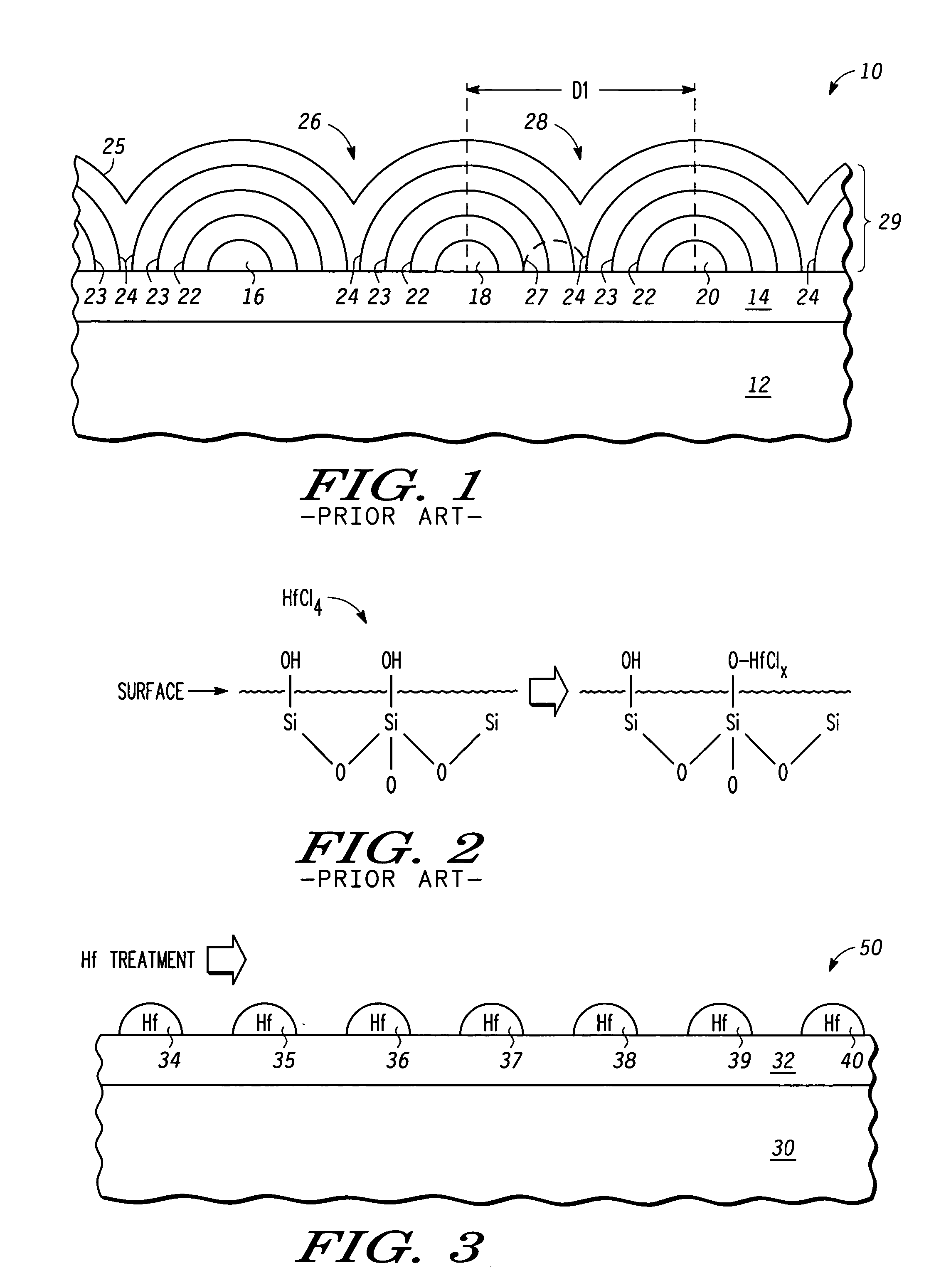

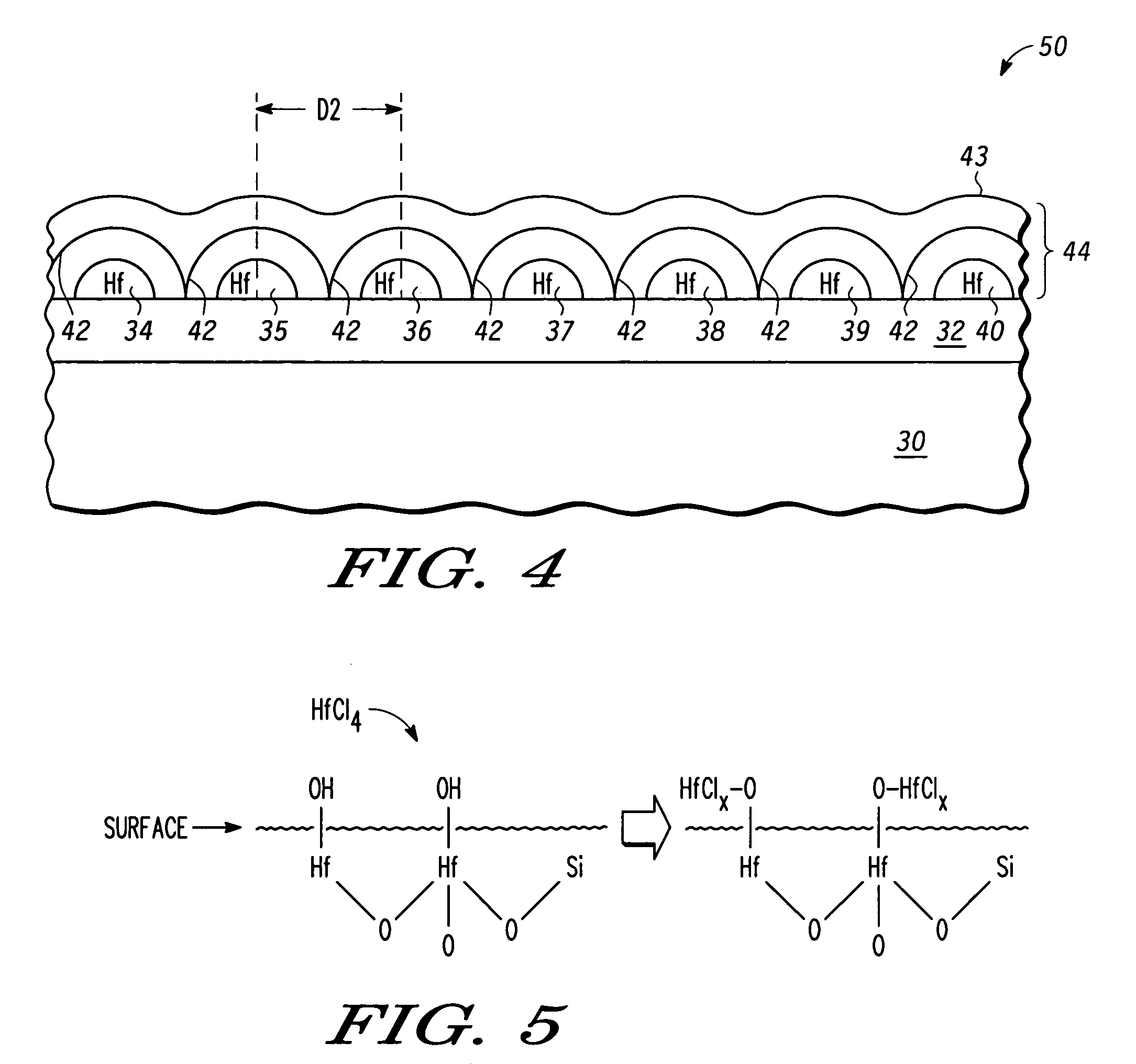

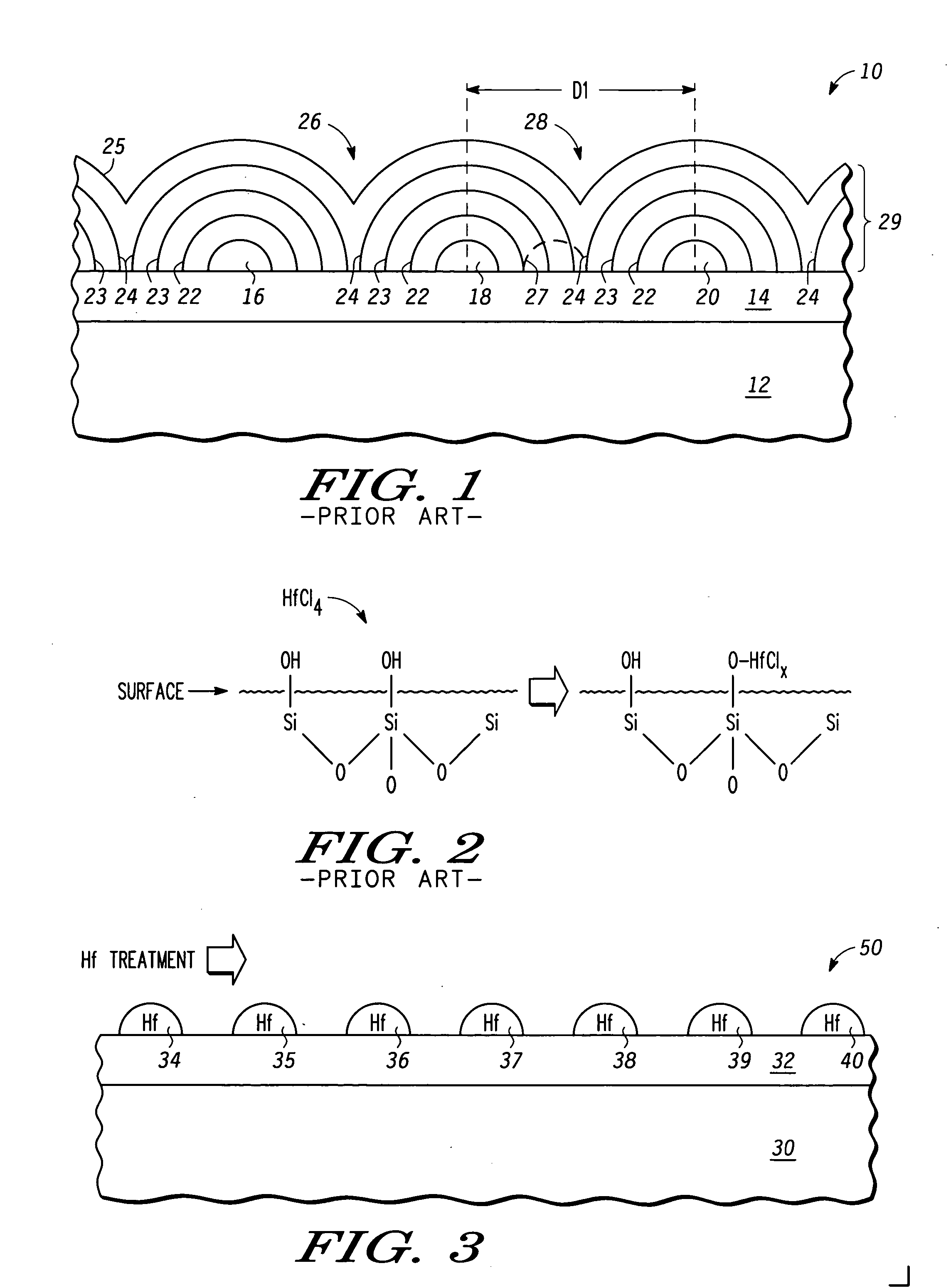

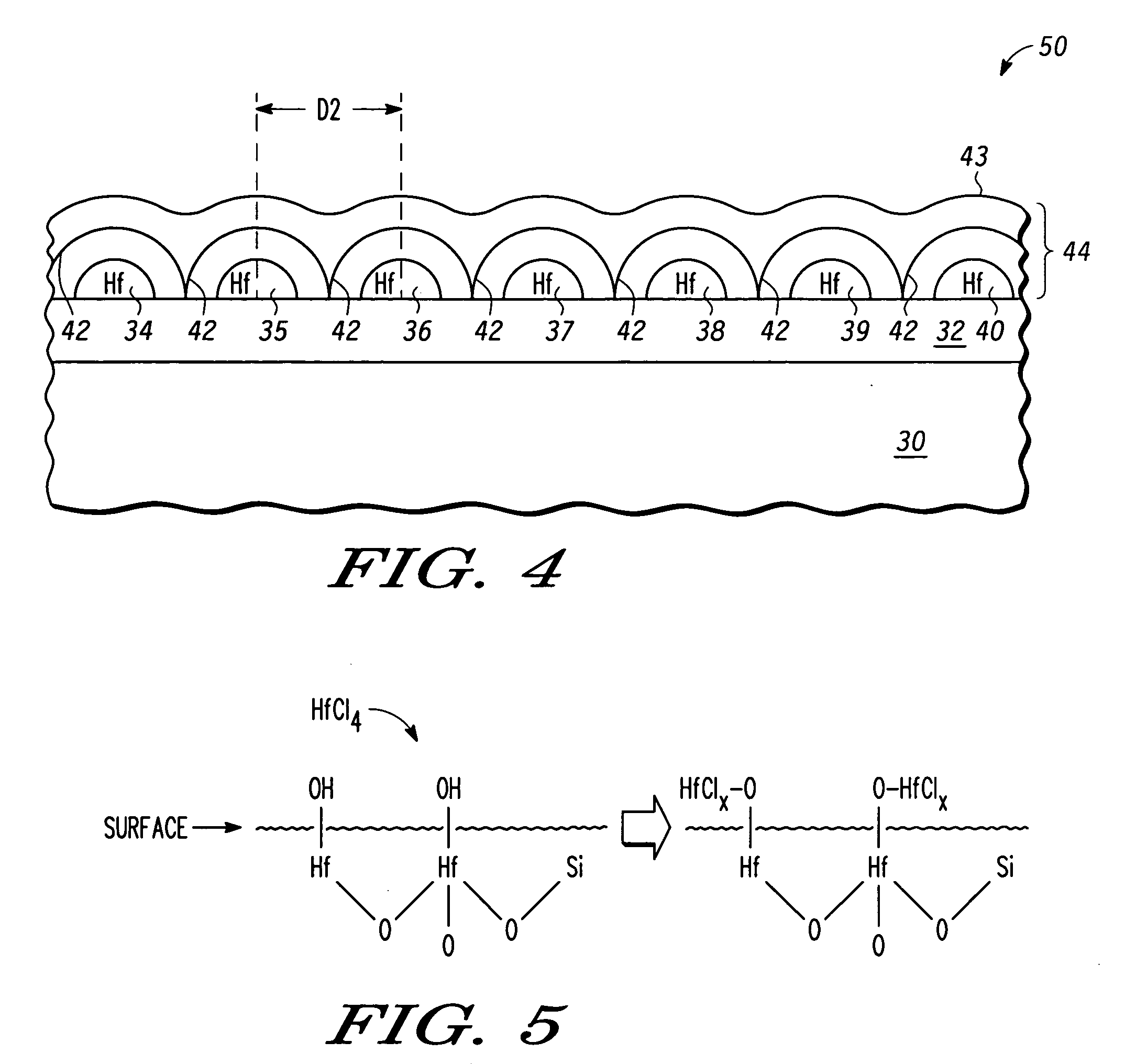

A method for treating a semiconductor surface to form a metal-containing layer includes providing a semiconductor substrate having an exposed surface. The exposed surface of the semiconductor substrate is treated by forming one or more metals overlying the semiconductor substrate but not completely covering the exposed surface of the semiconductor substrate. The one or more metals enhance nucleation for subsequent material growth. A metal-containing layer is formed on the exposed surface of the semiconductor substrate that has been treated. The treatment of the exposed surface of the semiconductor substrate assists the metal-containing layer to coalesce. In one embodiment, treatment of the exposed surface to enhance nucleation may be performed by spin-coating, atomic layer deposition (ALD), physical layer deposition (PVD), electroplating, or electroless plating. The one or more metals used to treat the exposed surface may include any rare earth or transition metal, such as, for example, hafnium, lanthanum, etc.

Owner:NXP USA INC +1

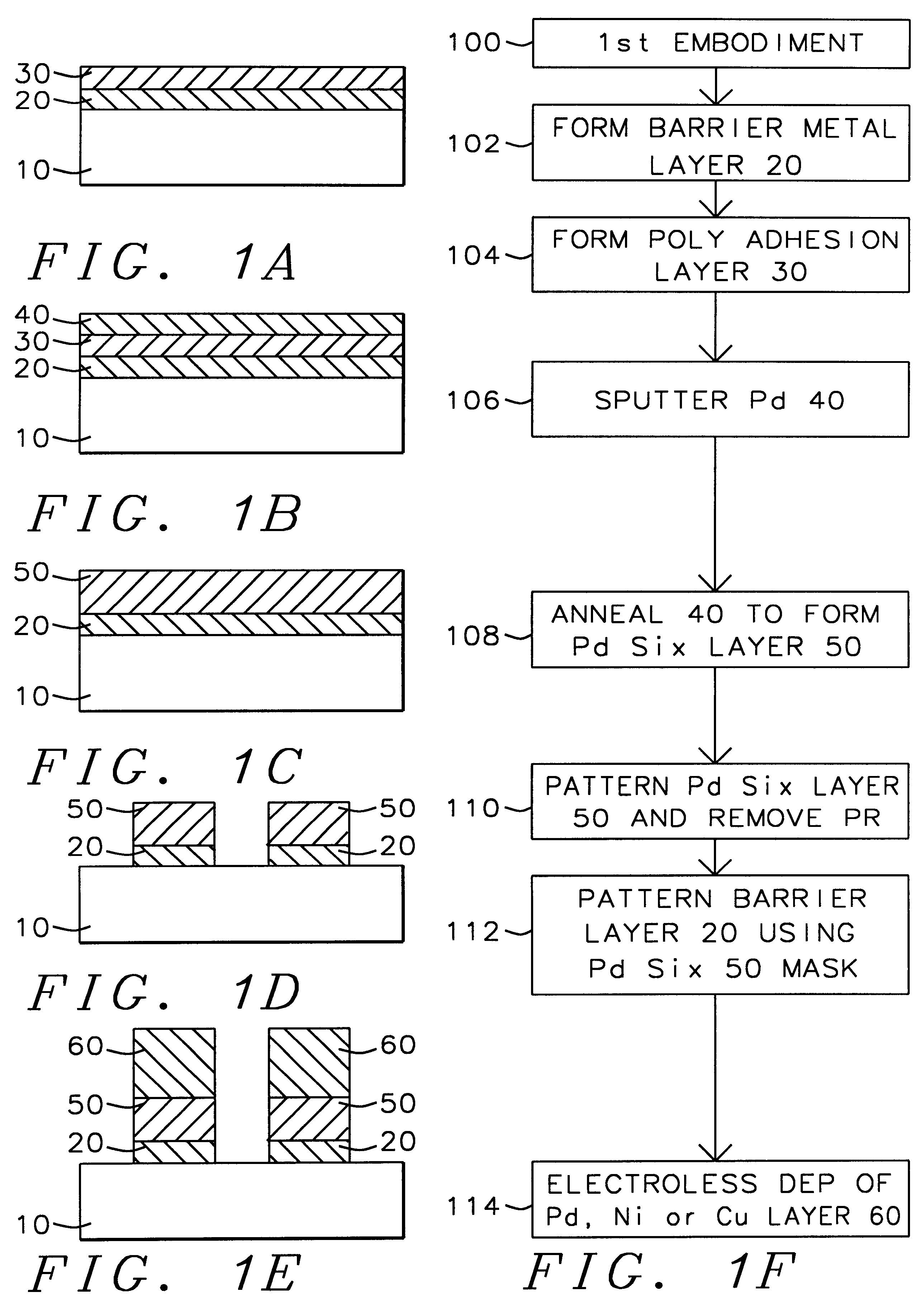

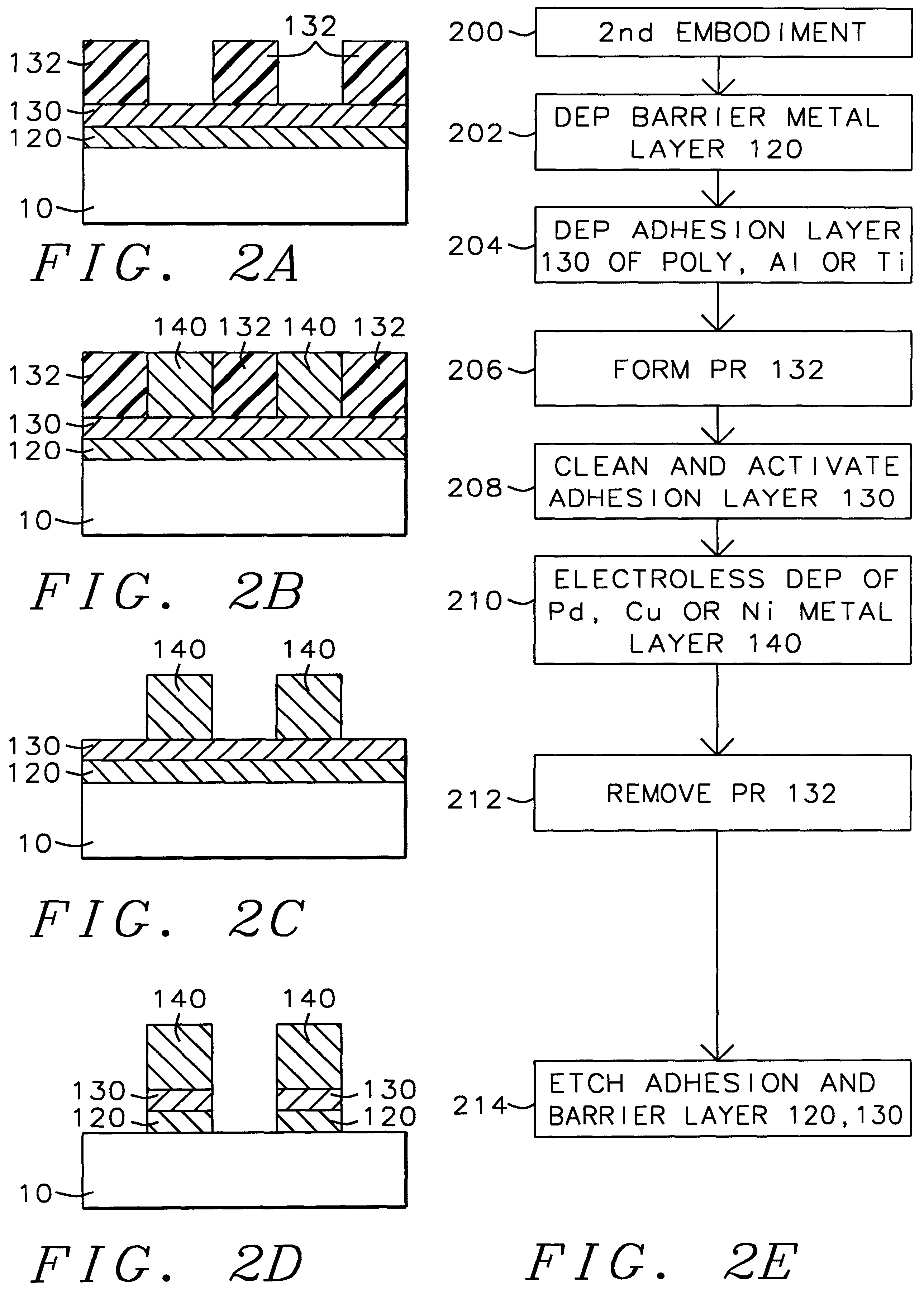

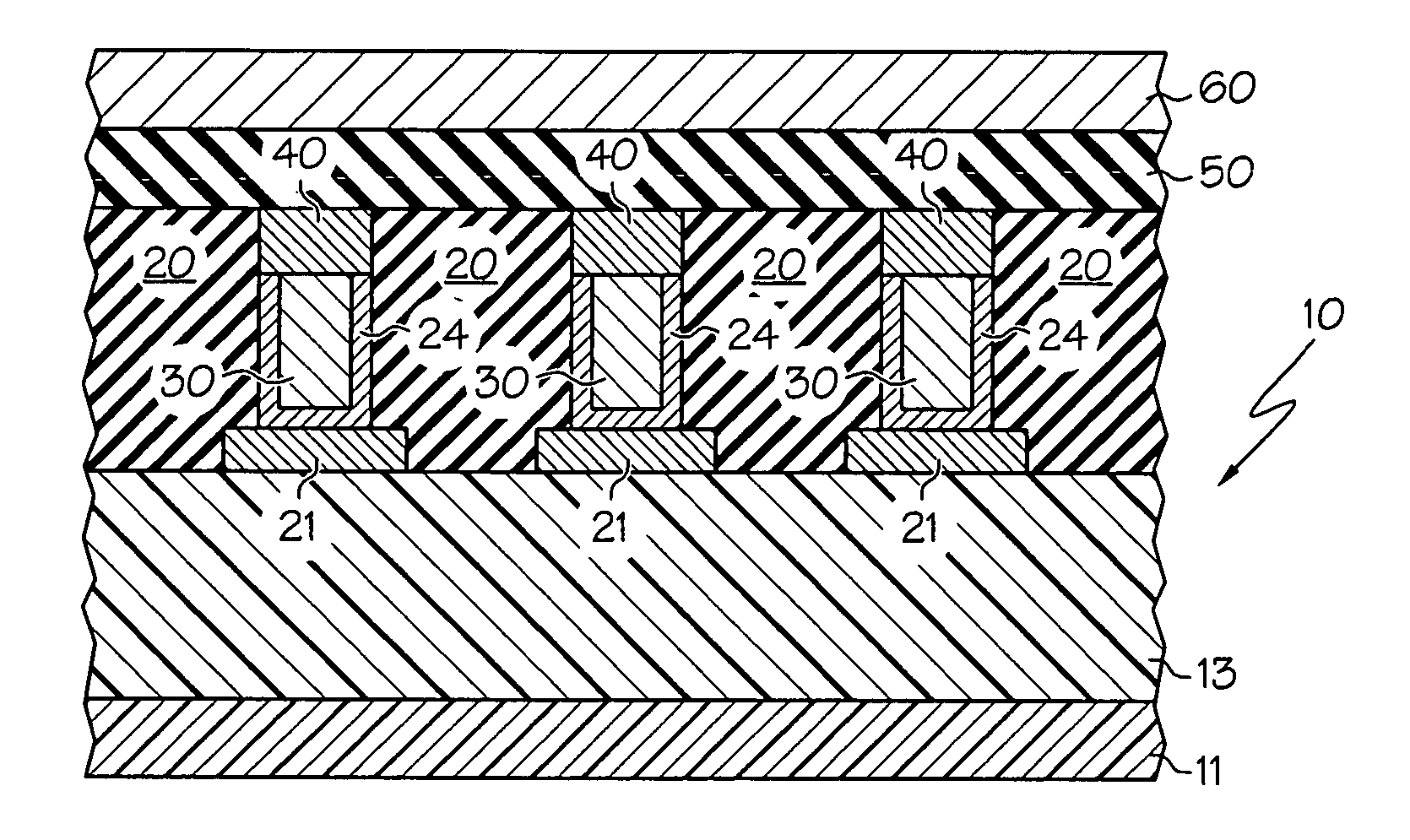

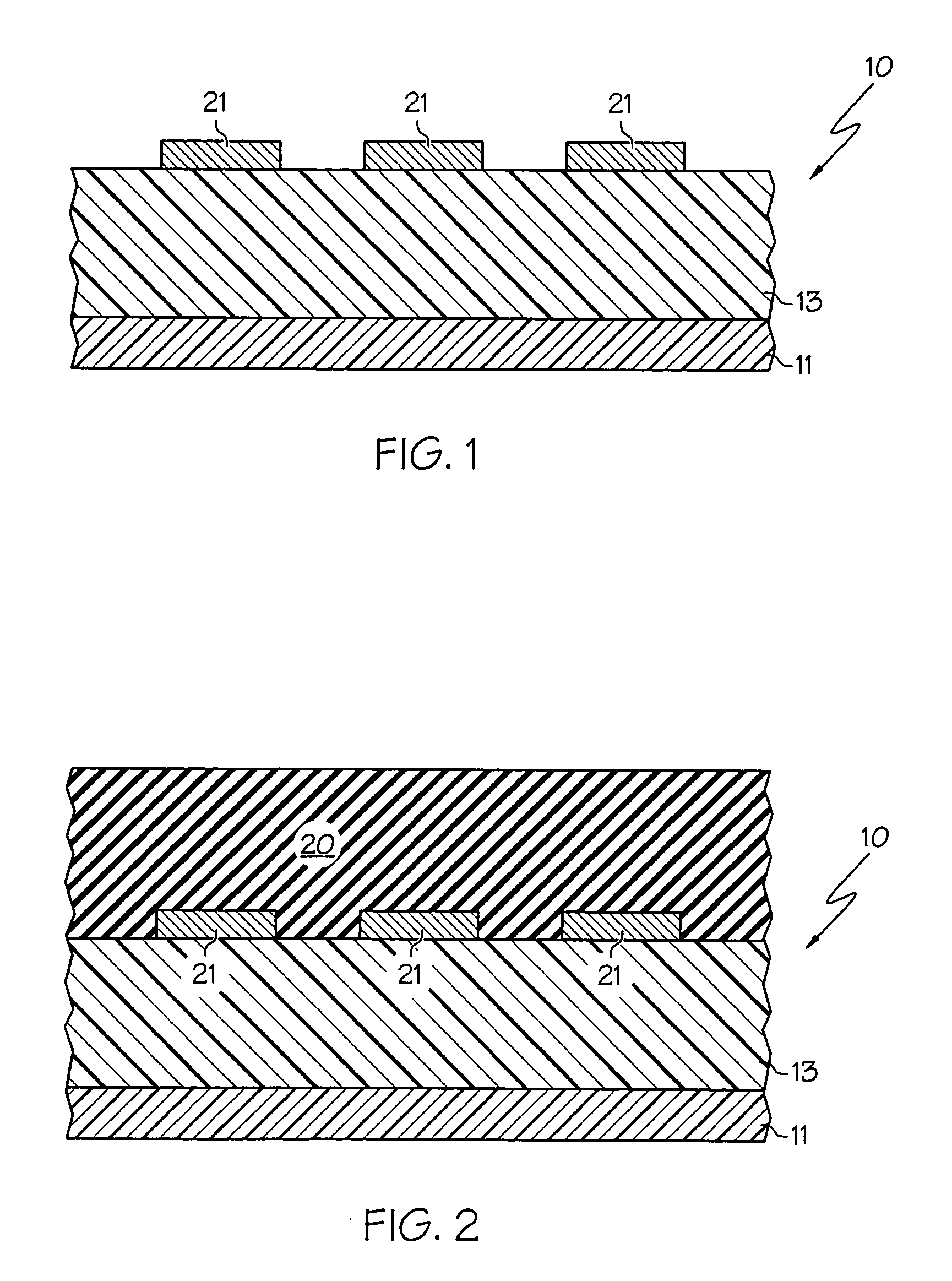

Method of electroless plating copper on nitride barrier

InactiveUS6436816B1Insulating substrate metal adhesion improvementSolid-state devicesCopper platingElectroless deposition

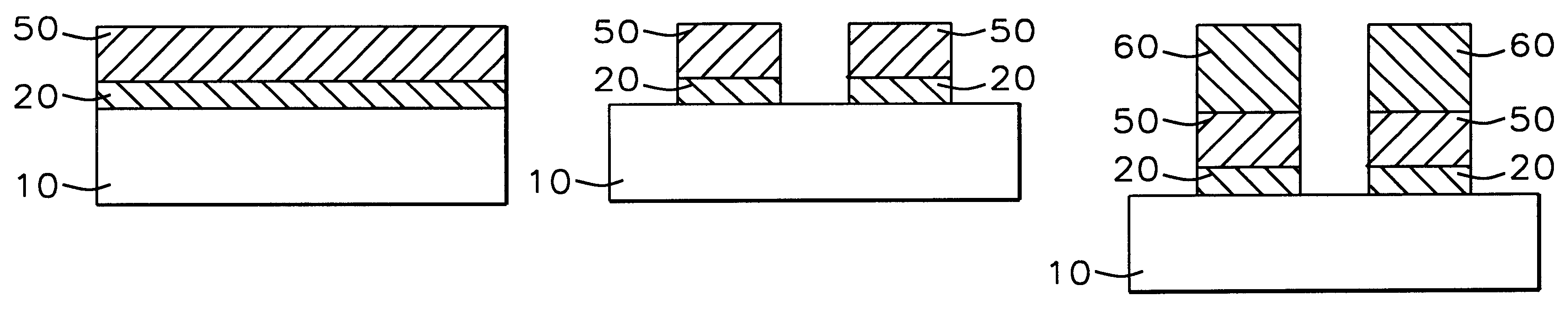

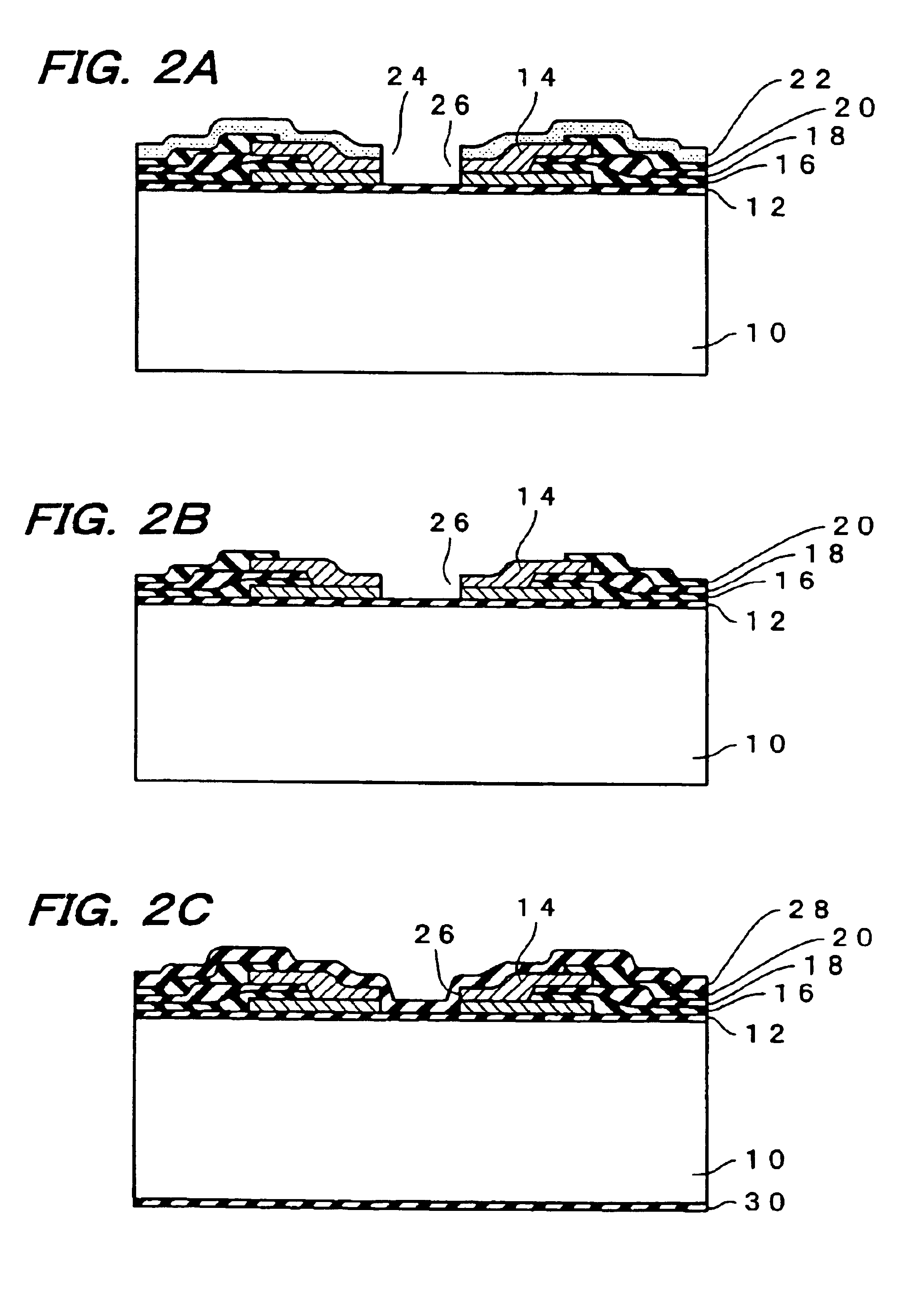

A method with three embodiments of manufacturing metal lines and solder bumps using electroless deposition techniques. The first embodiment uses a PdSix seed layer 50 for electroless deposition. The PdSix layer 50 does not require activation. A metal line is formed on a barrier layer 20 and an adhesion layer 30. A Palladium silicide seed layer 50 is then formed and patterned. Ni, Pd or Cu is electroless deposited over the Palladium silicide layer 50 to form a metal line. The second embodiment selectively electrolessly deposits metal 140 over an Adhesion layer 130 composed of Poly Si, Al, or Ti. A photoresist pattern 132 is formed over the adhesion layer. A metal layer 140 of Cu or Ni is electrolessly deposited over the adhesion layer. The photoresist layer 132 is removed and the exposed portion of the adhesion layer 130 and the underlying barrier metal layer 120 are etched thereby forming a metal line. The third embodiment electroless deposits metal over a metal barrier layer that is roughen by chemical mechanical polishing. A solder bump is formed using an electroless deposition of Cu or Ni by: depositing an Al layer 220 and a barrier metal layer 230 over a substrate 10. The barrier layer 230 is polished and activated. Next, the aluminum layer 220 and the barrier metal layer 230 are patterned. A metal layer 240 is electroless deposited. Next a solder bump 250 is formed over the electroless metal layer 240.

Owner:TAIWAN SEMICON MFG CO LTD

Electroless plating of metal caps for chalcogenide-based memory devices

InactiveUS20060094236A1Good electrical contactSemiconductor/solid-state device manufacturingPlatinumSulfur

A method of forming a metal cap over a conductive interconnect in a chalcogenide-based memory device is provided and includes, forming a layer of a first conductive material over a substrate, depositing an insulating layer over the first conductive material and the substrate, forming an opening in the insulating layer to expose at least a portion of the first conductive material, depositing a second conductive material over the insulating layer and within the opening, removing portions of the second conductive material to form a conductive area within the opening, recessing the conductive area within the opening to a level below an upper surface of the insulating layer, forming a cap of a third conductive material over the recessed conductive area within the opening, the third conductive material selected from the group consisting of cobalt, silver, gold, copper, nickel, palladium, platinum, and alloys thereof, depositing a stack of a chalcogenide based memory cell material over the cap, and depositing a conductive material over the chalcogenide stack.

Owner:MICRON TECH INC

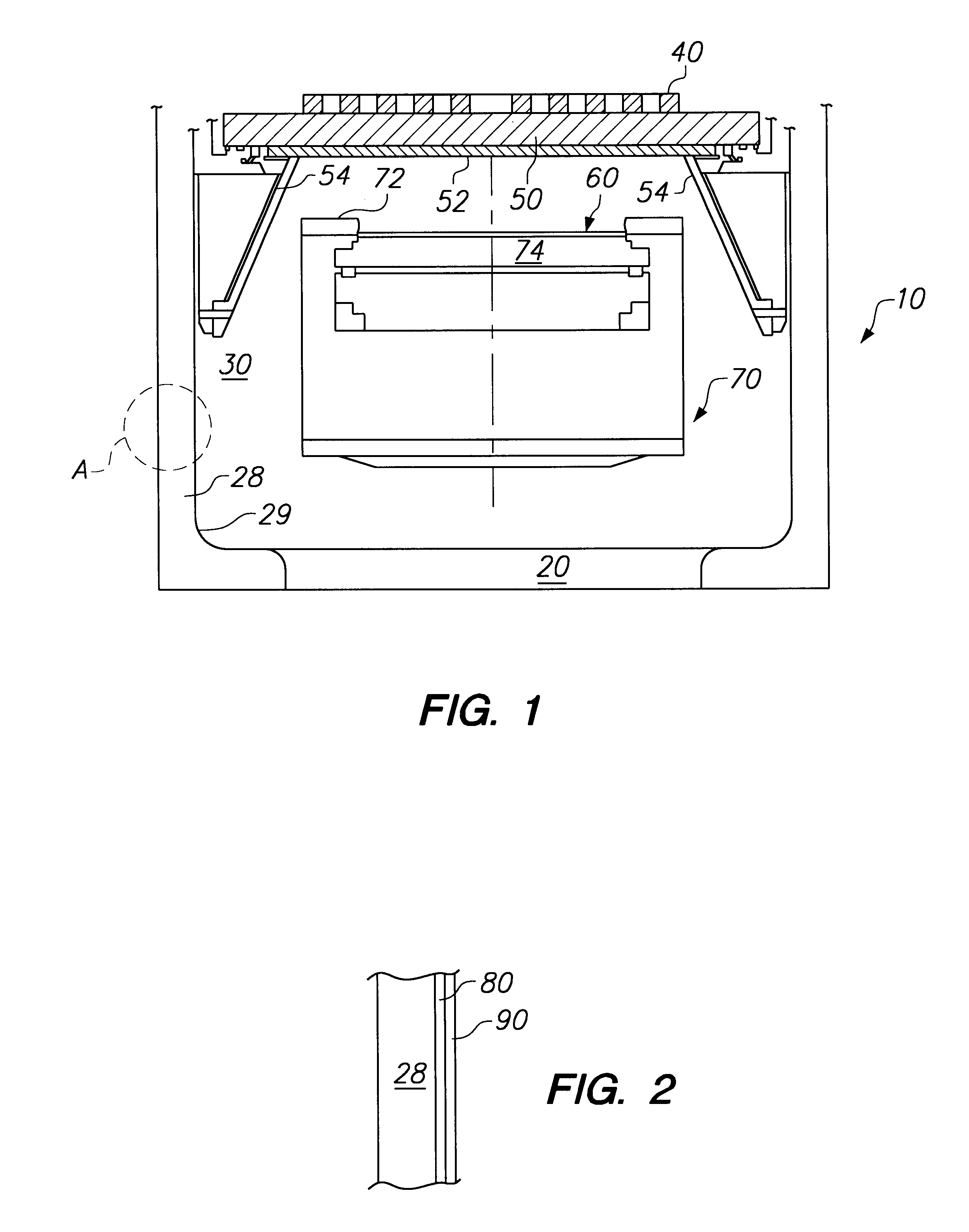

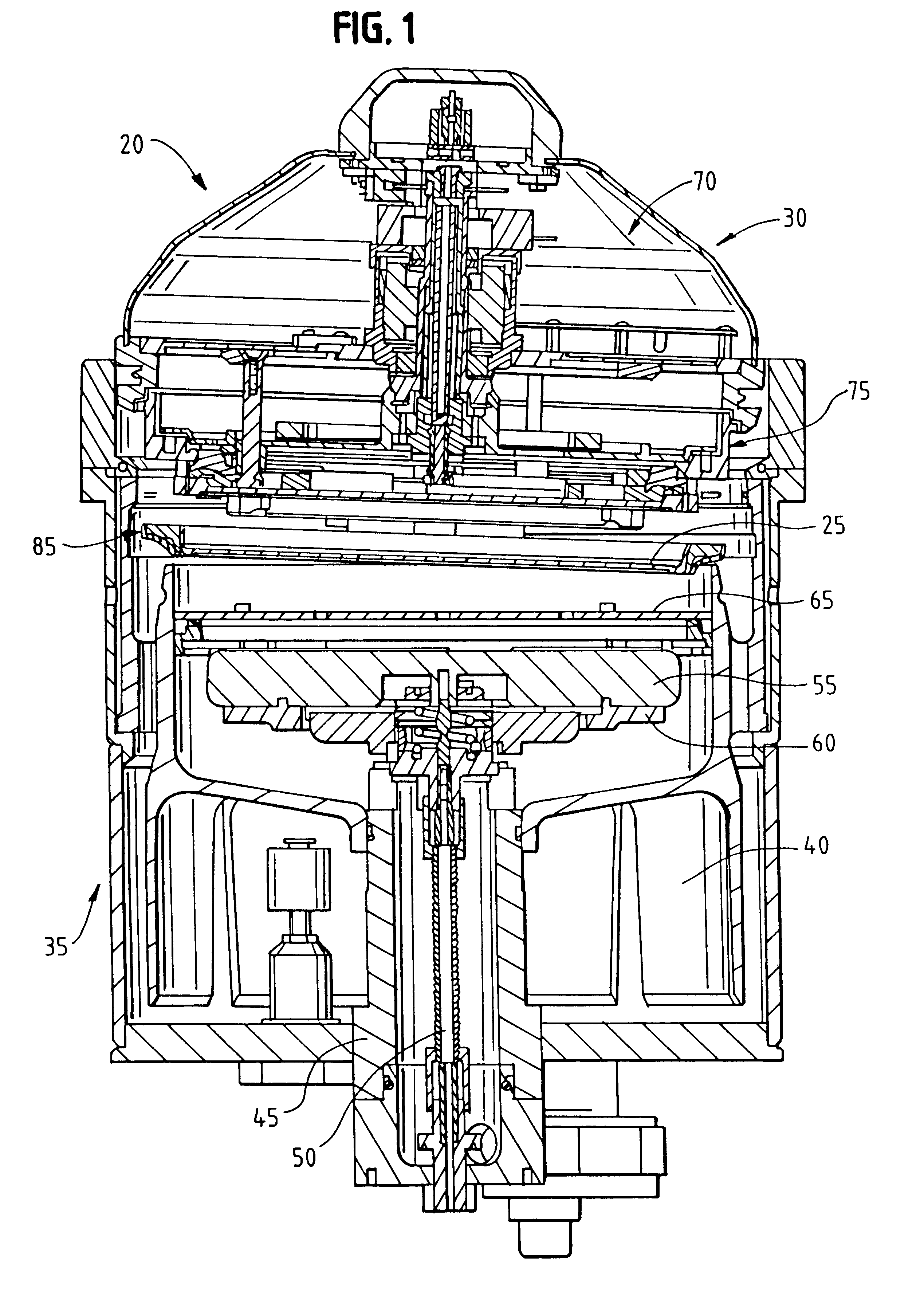

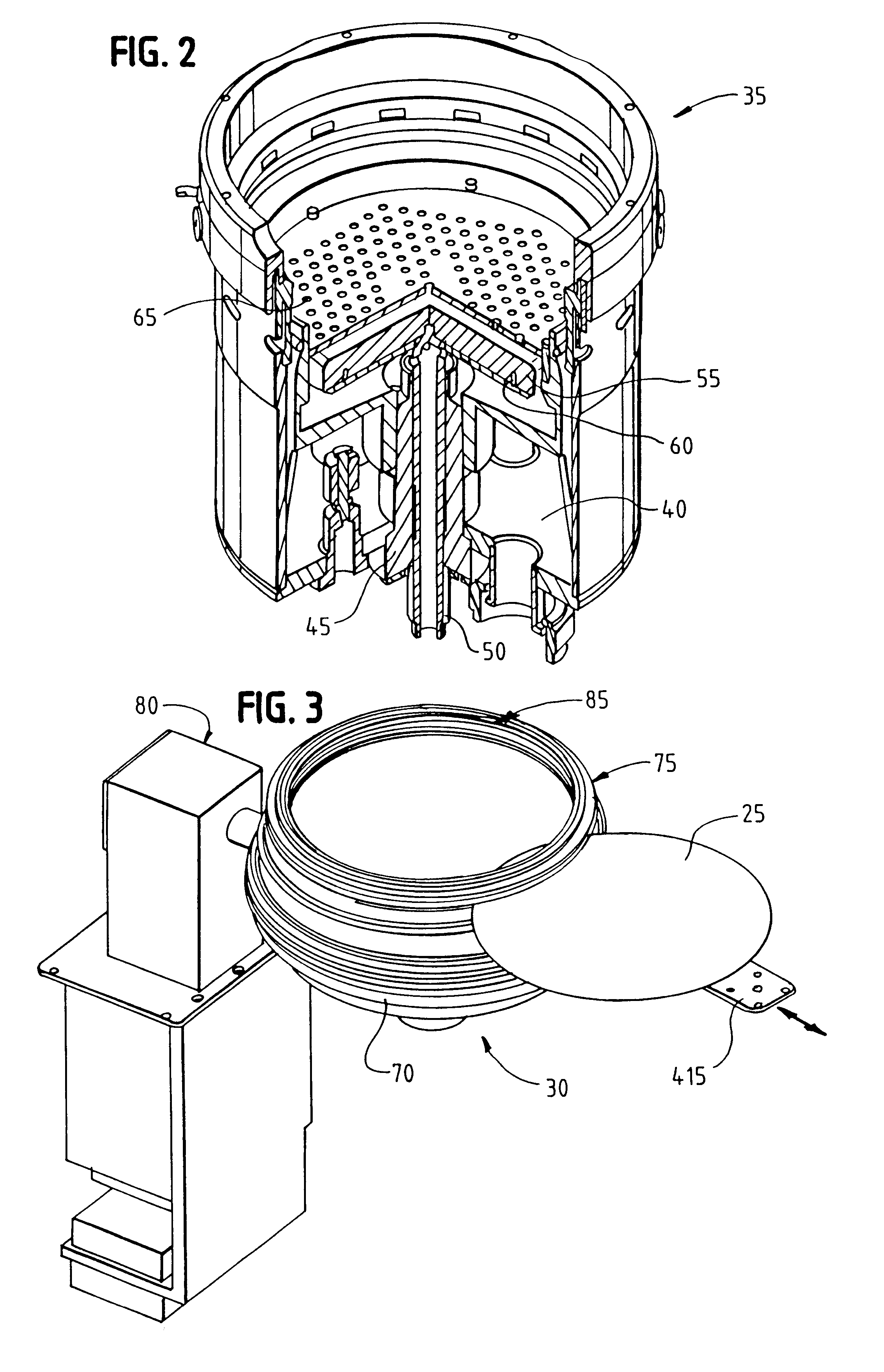

Method and apparatus of sealing wafer backside for full-face electrochemical plating

InactiveUS20030008602A1Efficient configurationMinimize irregularityEdge grinding machinesPolishing machinesMechanical engineeringElectroplating

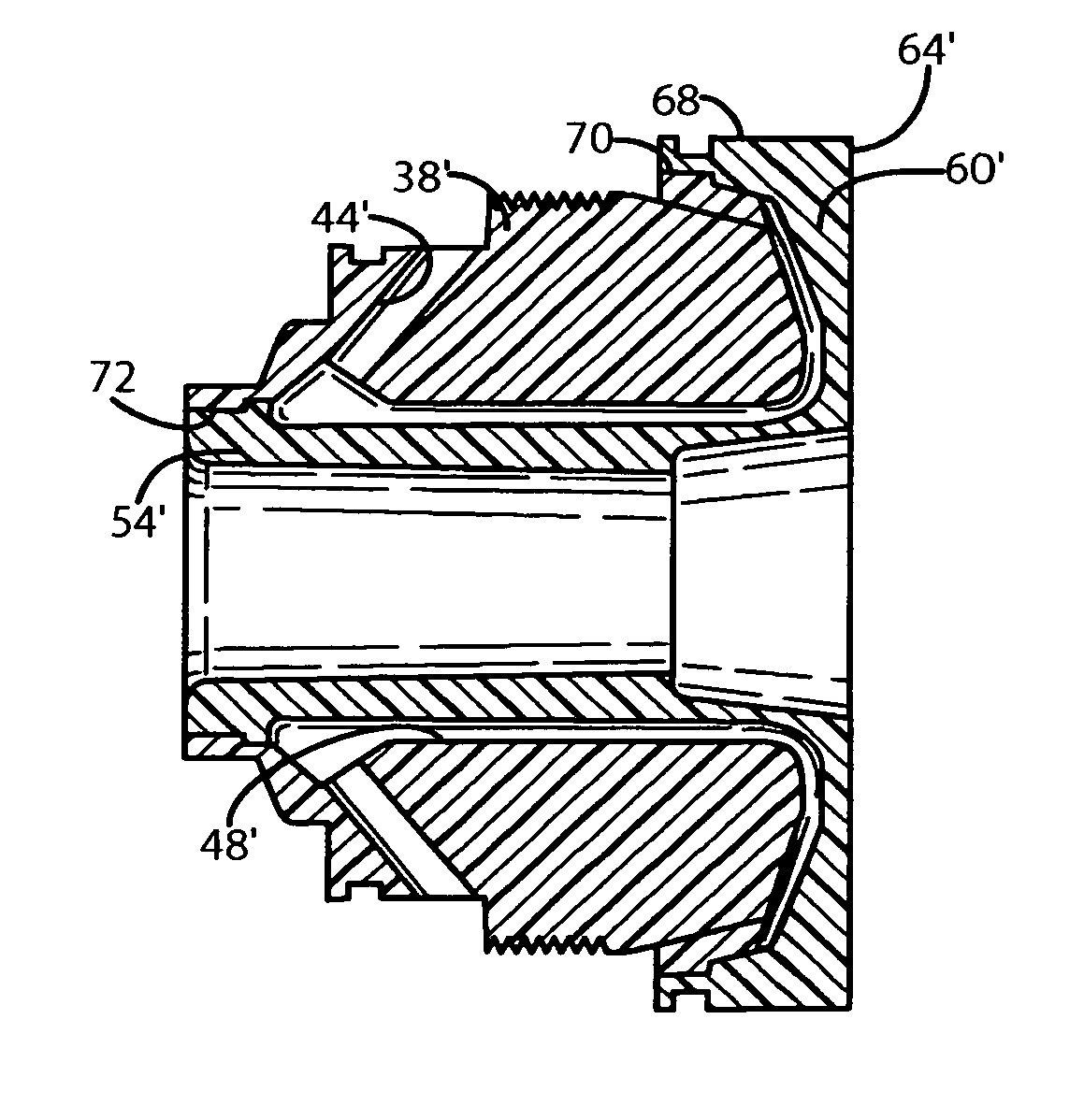

The present invention provides a wafer carrier that includes a plurality of concentric sealing members that provide a seal, with the outer seal independently movable to allow cleaning of a peripheral backside of the wafer to occur while the wafer is still attached to the wafer carrier, and a plurality of vacuum openings that a re disposed only adjacent to an inner side of the inner seal at a location corresponding to the backside periphery of the wafer.

Owner:NOVELLUS SYSTEMS

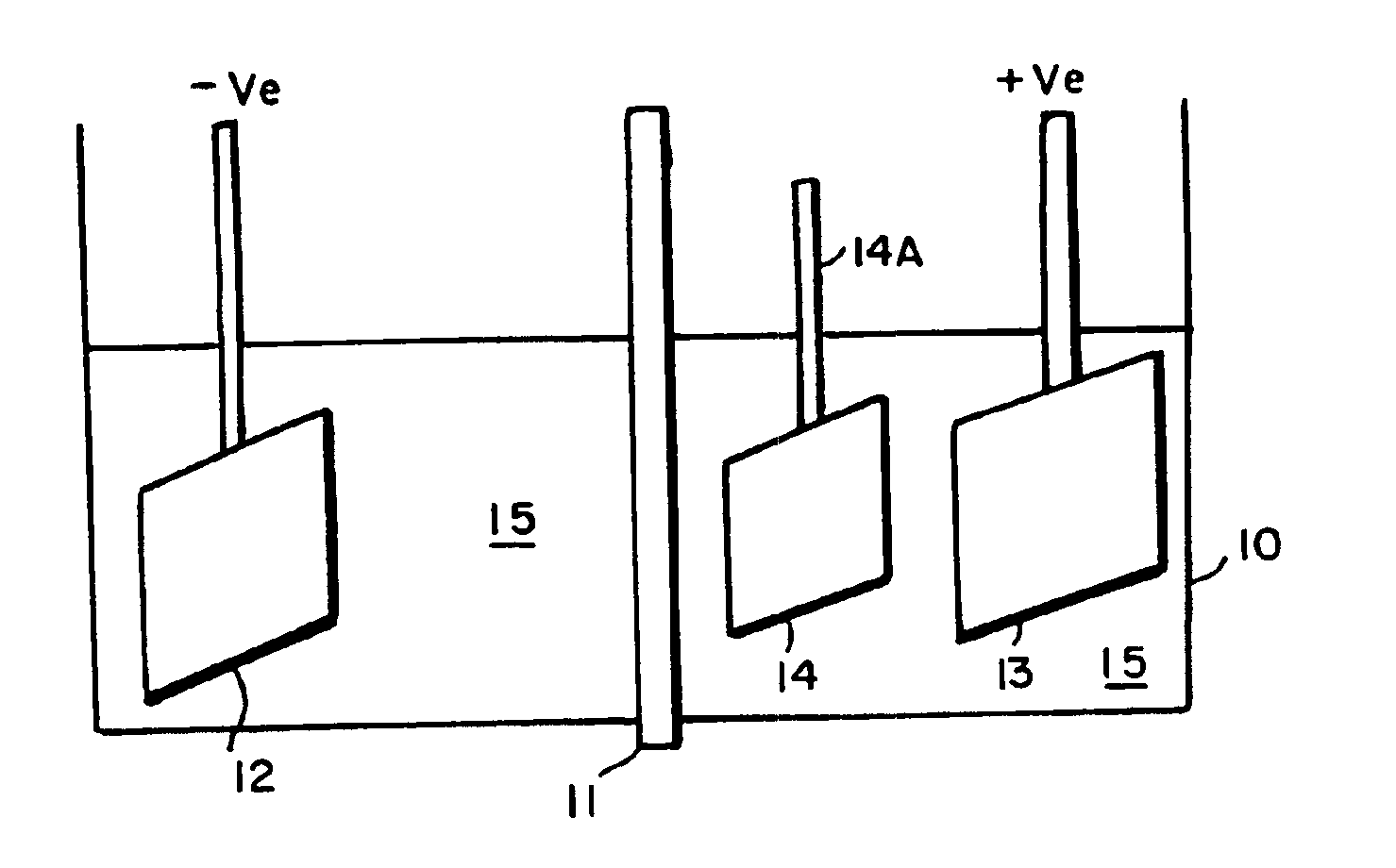

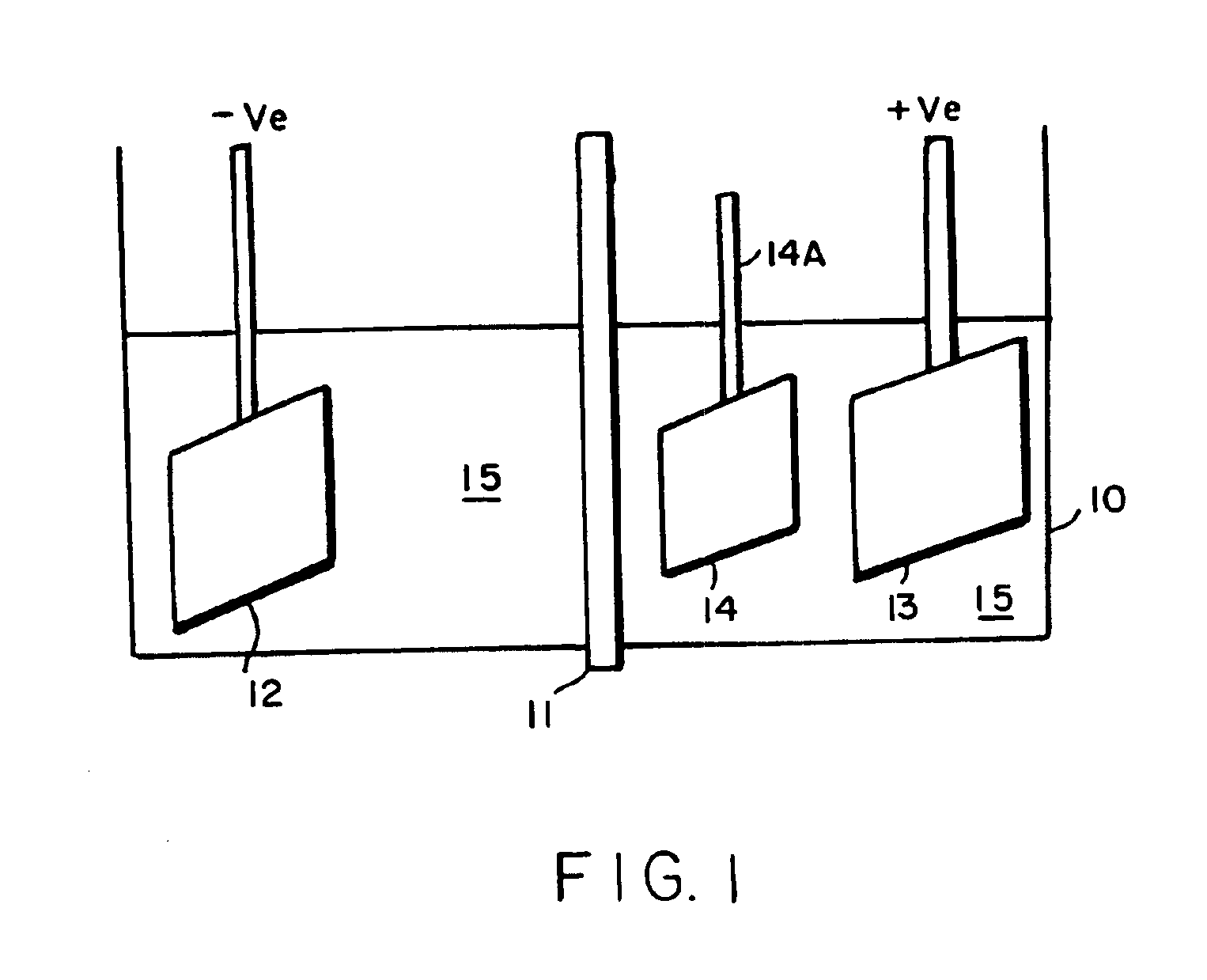

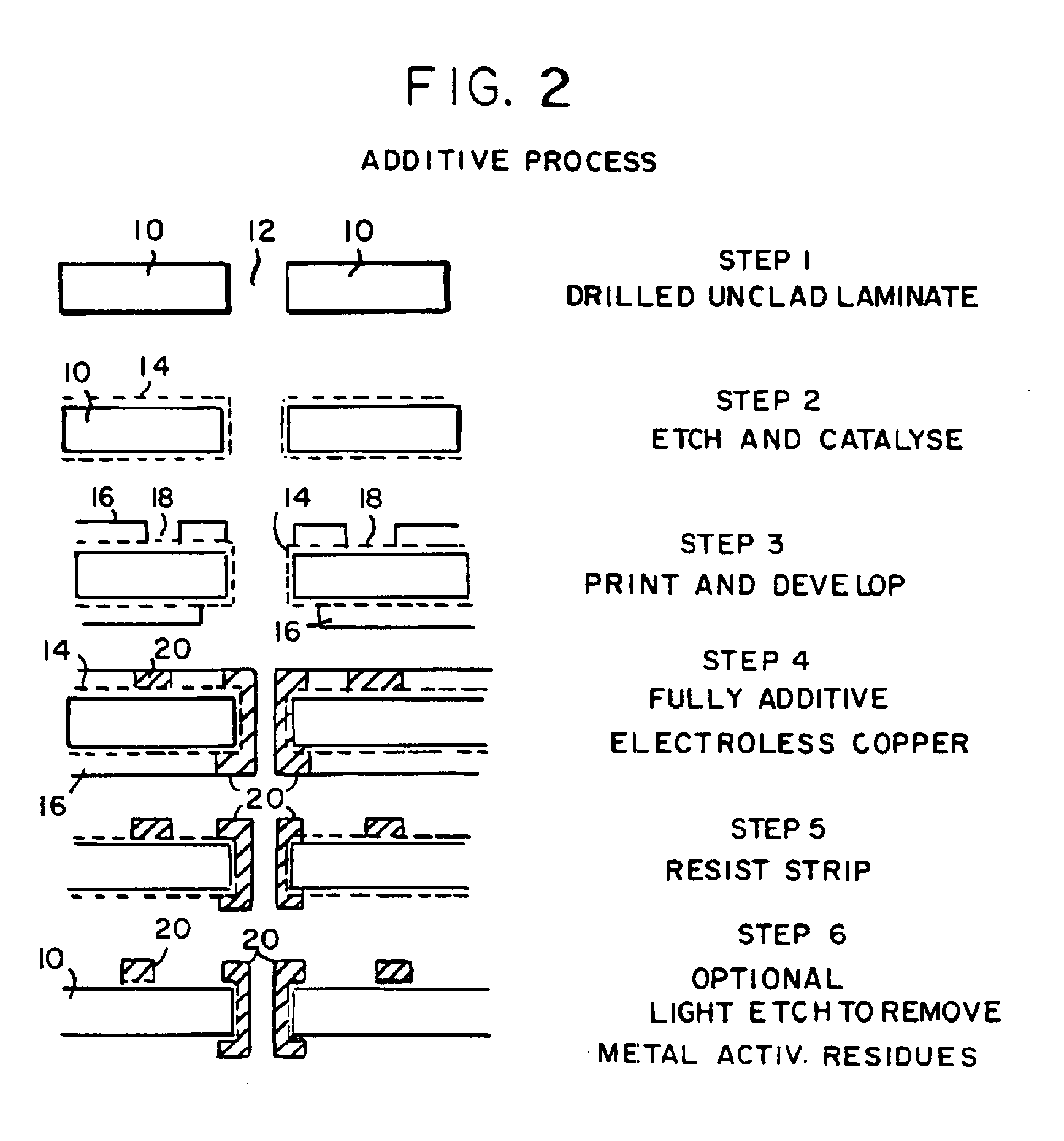

Electroless plating processes

InactiveUS6861097B1Reducing problem encounteredSimple methodPaper/cardboard articlesDecorative surface effectsPolymeric surfaceOxidation state

The invention includes processes for combined polymer surface treatment and metal deposition. Processes of the invention include forming an aqueous solution containing a metal activator, such as an oxidized species of silver, cobalt, ruthenium, cerium, iron, manganese, nickel, rhodium, or vanadium. The activator can be suitably oxidized to a higher oxidation state electrochemically. Exposing a part to be plated (such as an organic resin, e.g. a printed circuit board substrate) to the solution enables reactive hydroxyl species (e.g. hydroxyl radicals) to be generated and to texture the polymer surface. Such texturing facilitates good plated metal adhesion. As part of this contacting process sufficient time is allowed for both surface texturing to take place and for the oxidized metal activator to adsorb onto said part. The part is then contacted with a reducing agent capable of reducing the metal activator to a lower ionic form, or a lower oxidation state. That reduction can result in the formation of metallic catalytic material over the surface of the part. The reduced metal activator can then function to catalyze the electroless deposition of metal such as copper from solution by contacting the part with the plating solution.

Owner:SHIPLEY CO LLC

Method and apparatus for forming capping film

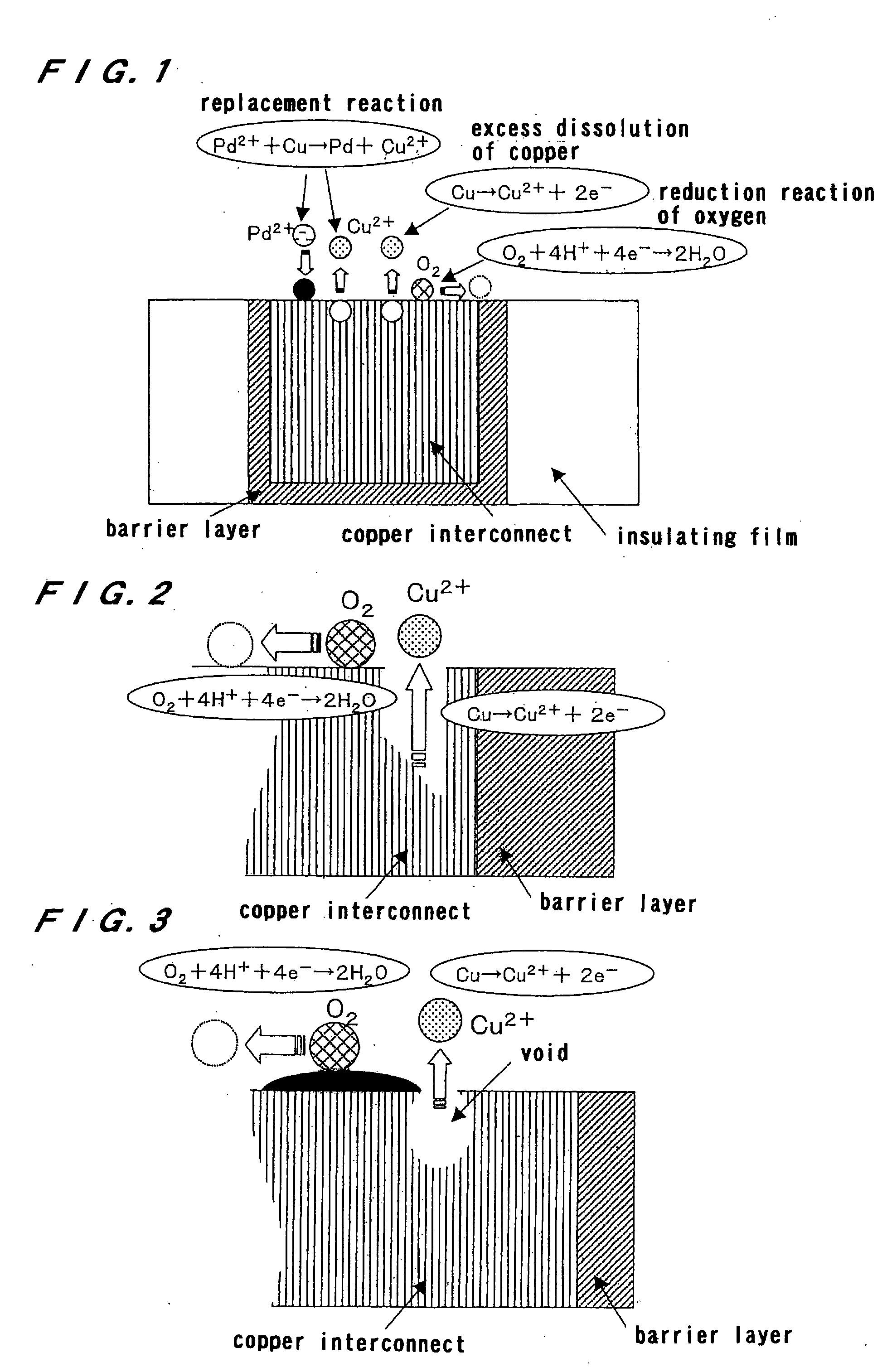

InactiveUS20050009340A1Suppress excess corrosionHigh characteristicSemiconductor/solid-state device detailsSolid-state devicesMetal catalystSemiconductor

A capping film serving as an interconnect protective film formed on a surface of interconnect metal on a semiconductor substrate is formed after forming a catalyst layer for electroless plating under low oxygen concentration condition. A method for forming a capping film for protecting a surface of interconnect metal includes preparing a metal catalyst solution containing a metal element nobler than interconnect metal and having dissolved oxygen concentration of 7 ppm or less, bringing said metal catalyst solution into contact with a surface of interconnect metal to form a metal catalyst layer on the surface of the interconnect metal, and performing electroless plating to form a capping film on the surface of the interconnect metal.

Owner:EBARA CORP

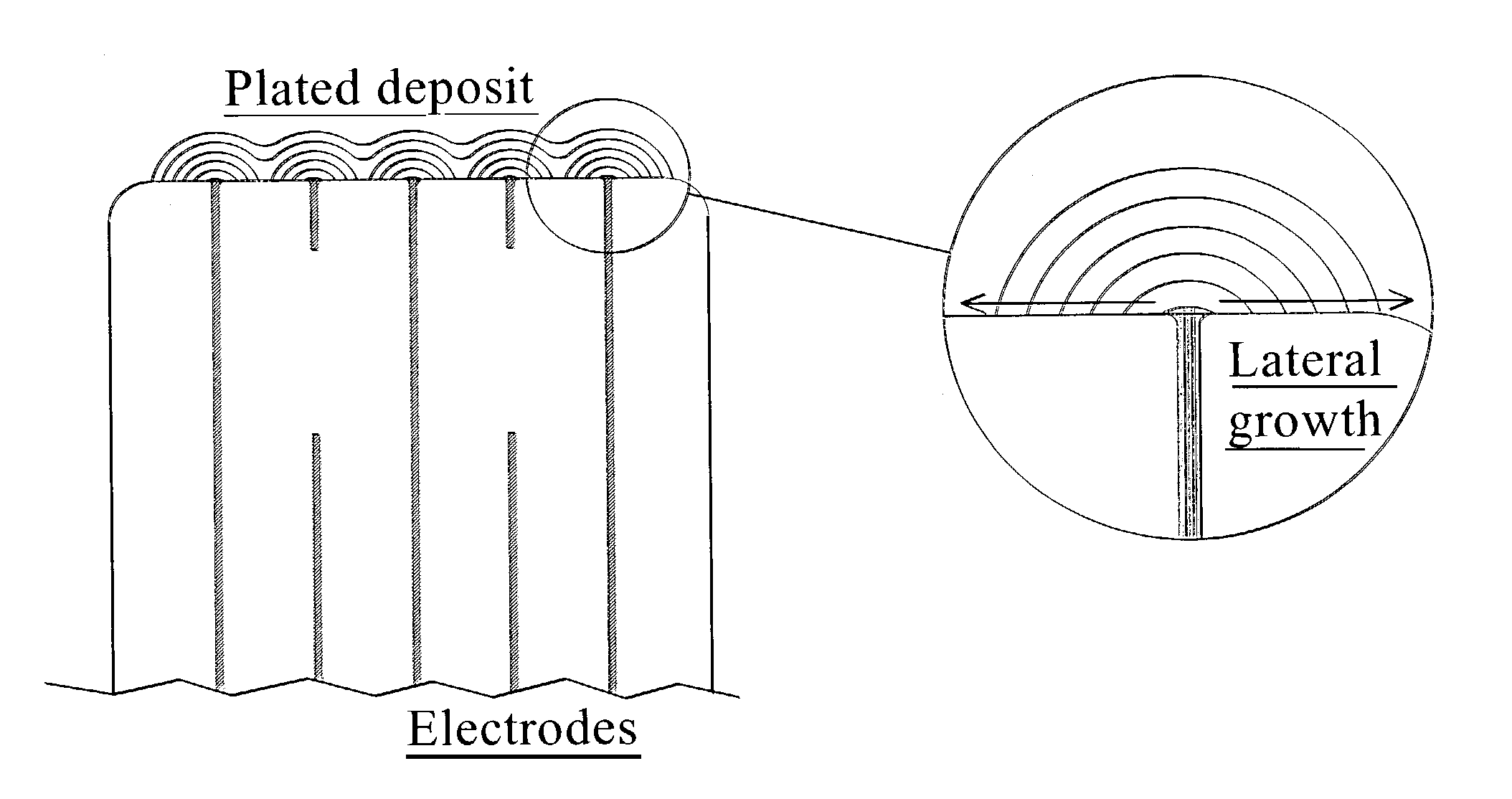

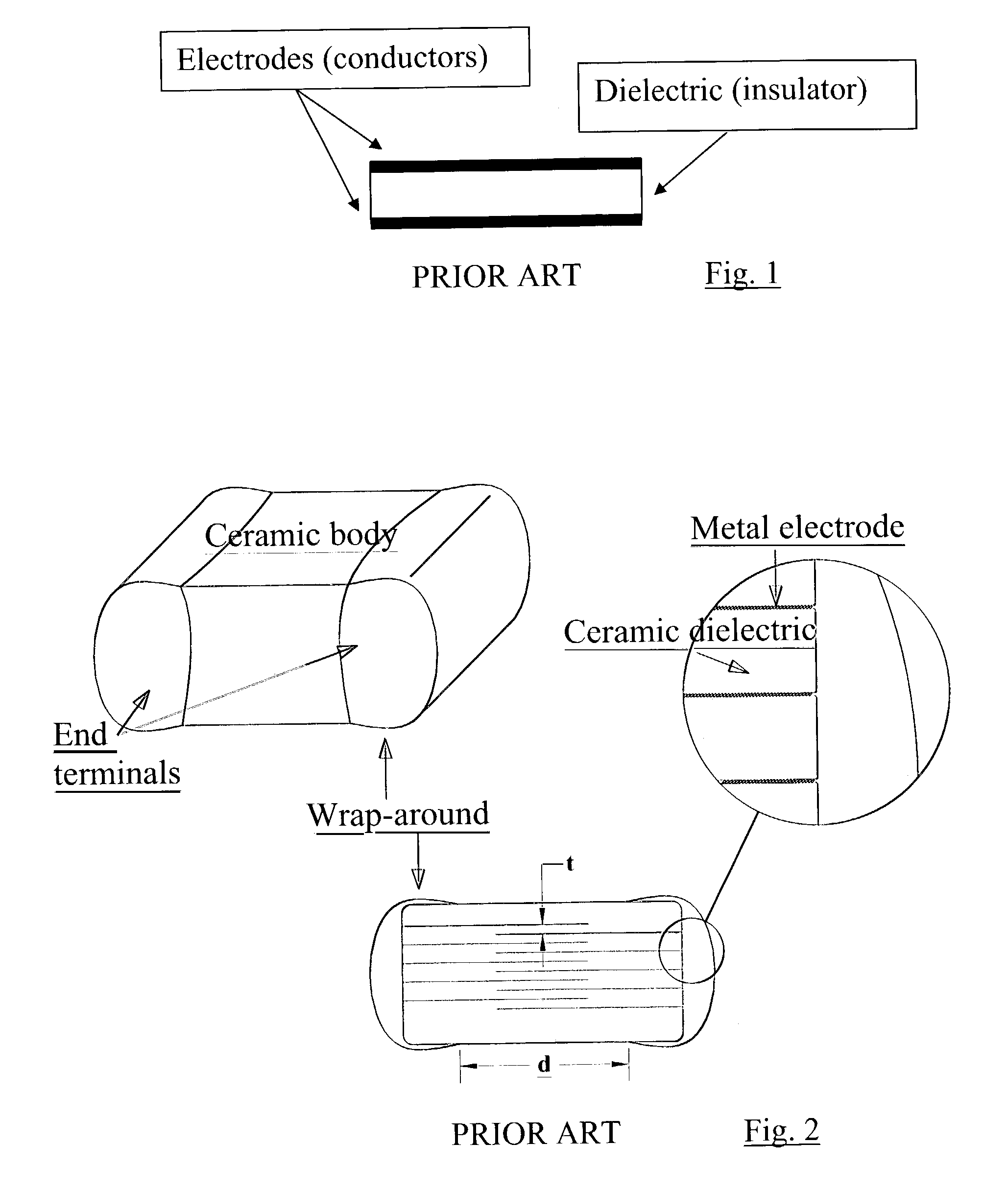

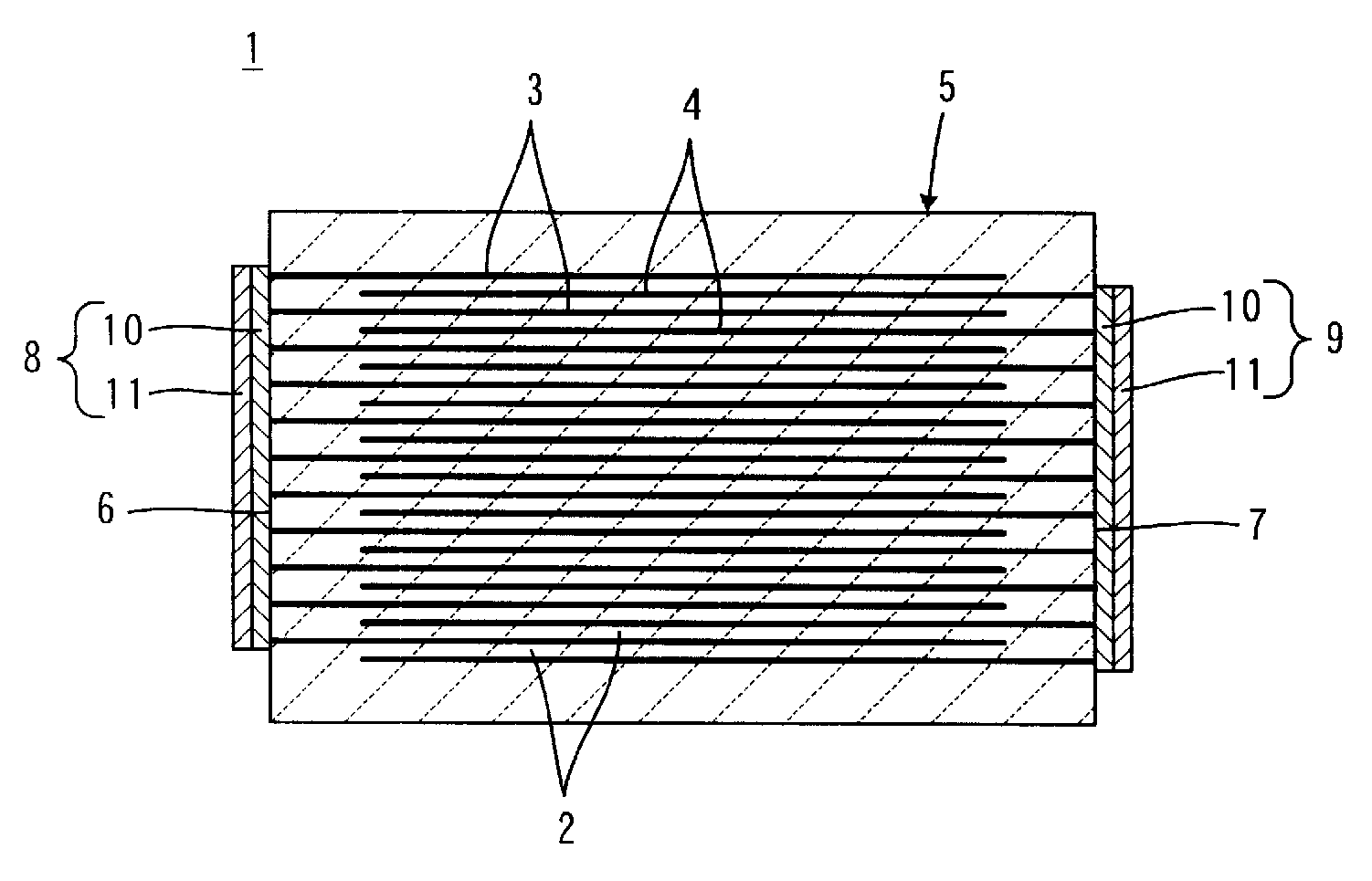

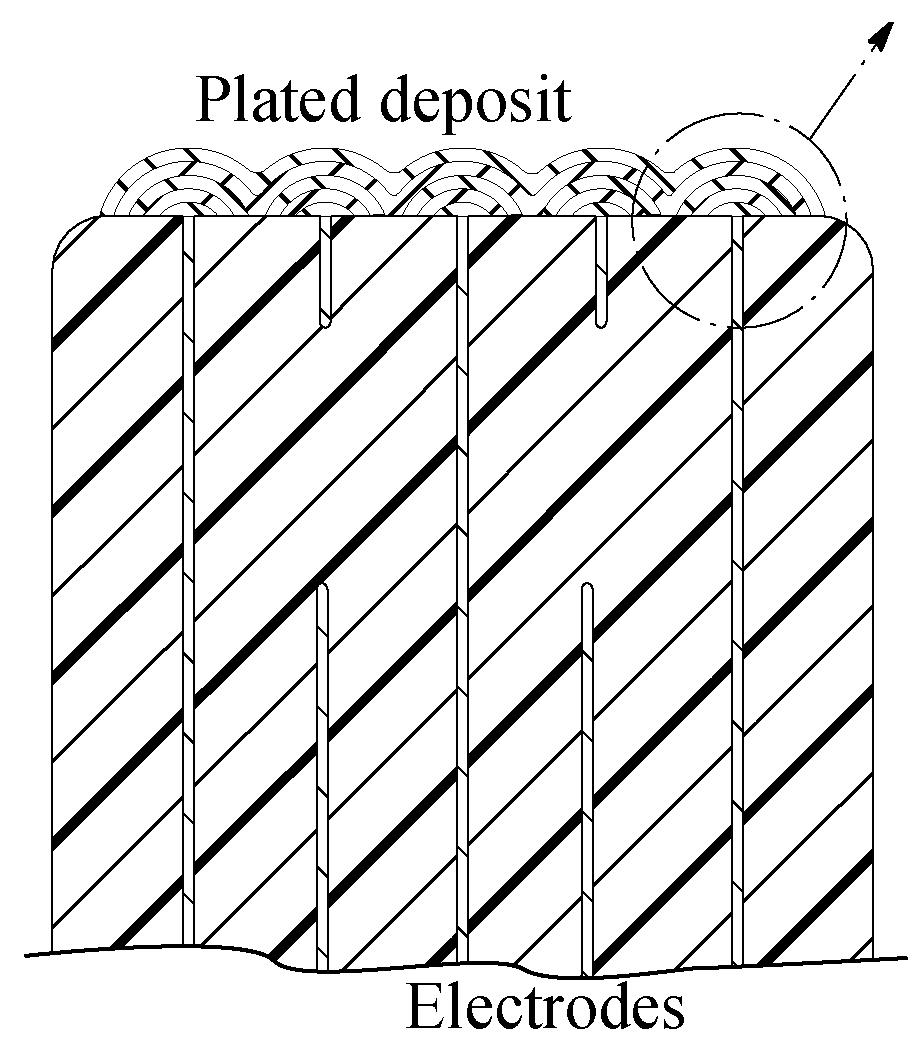

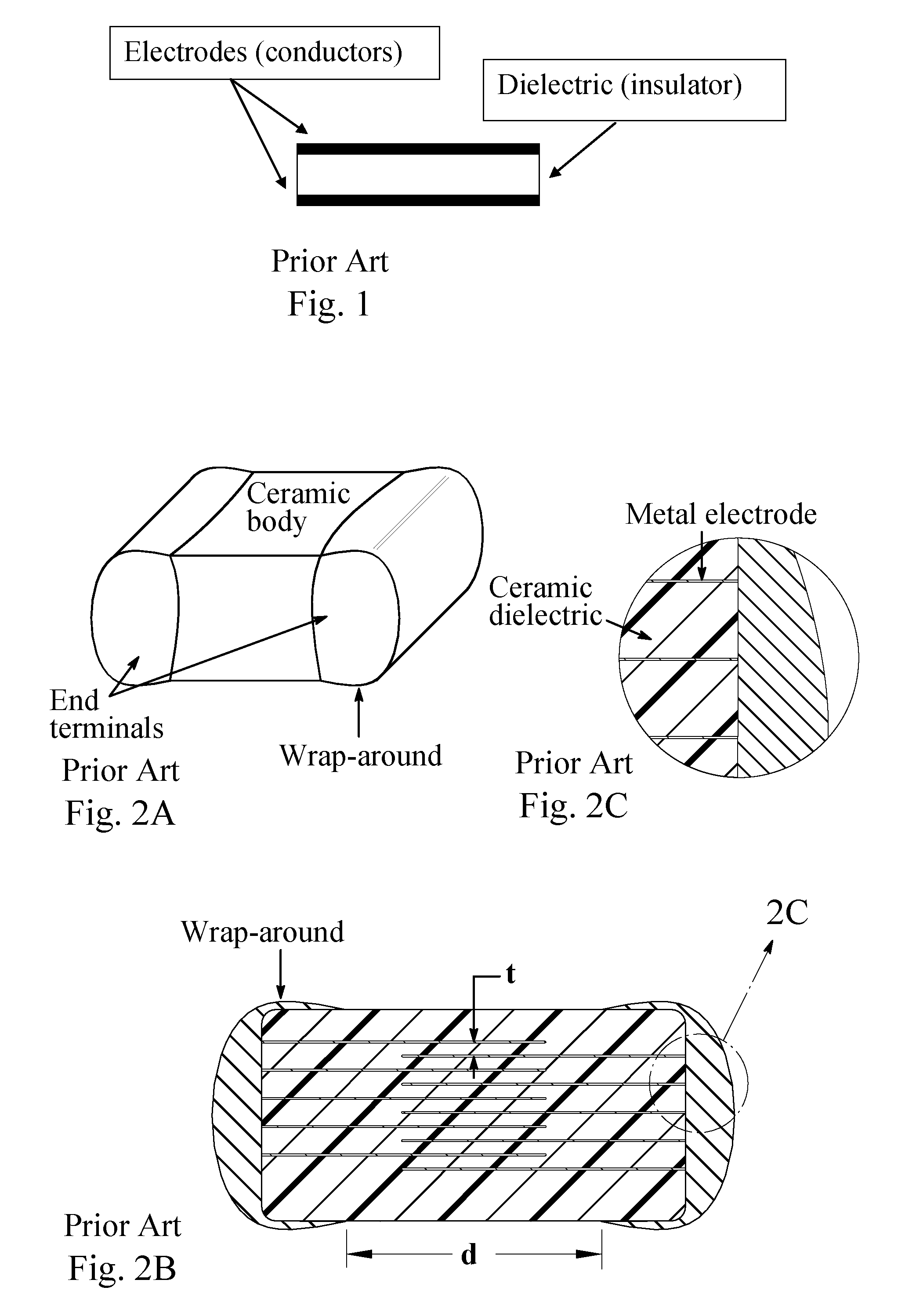

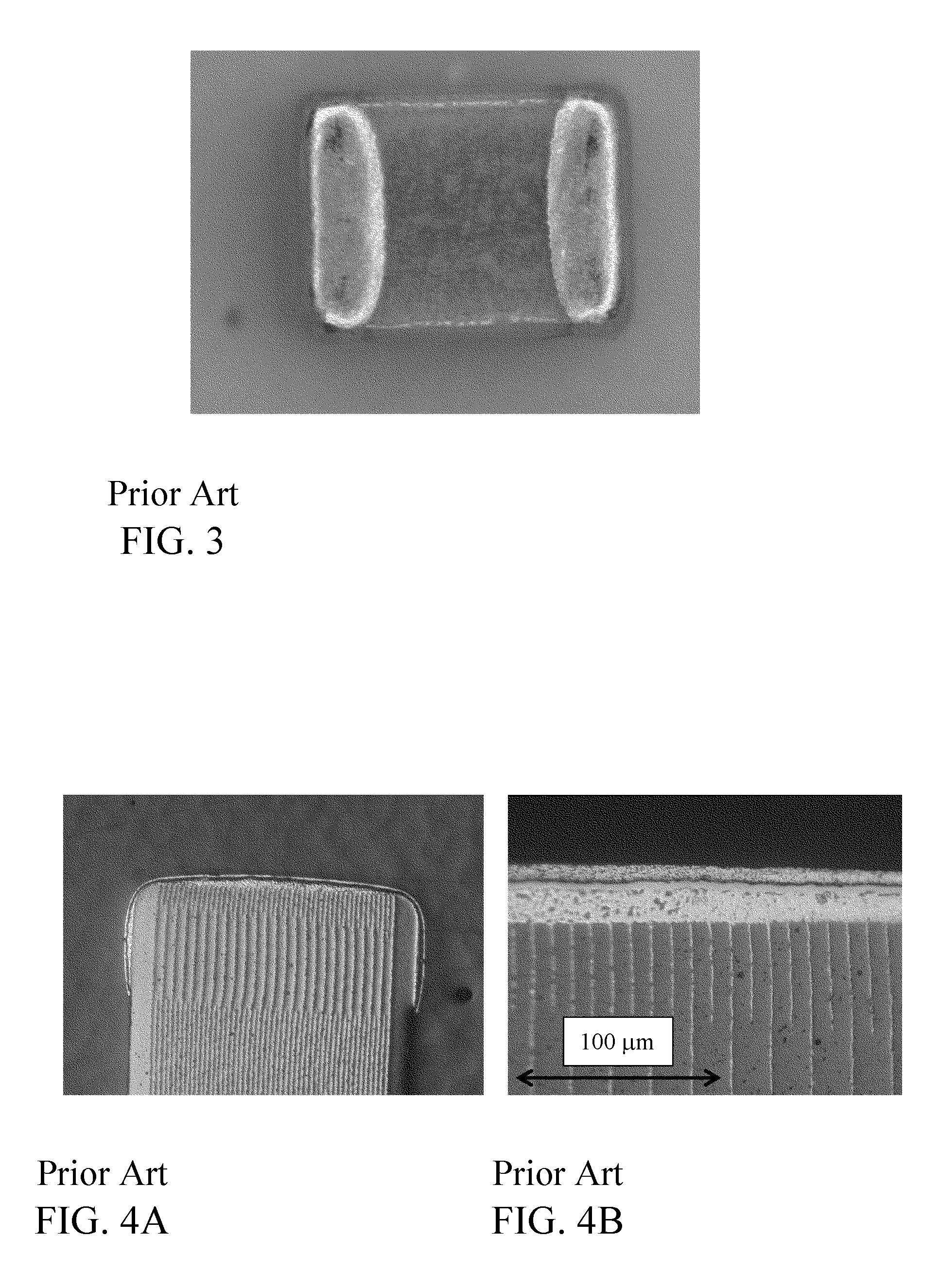

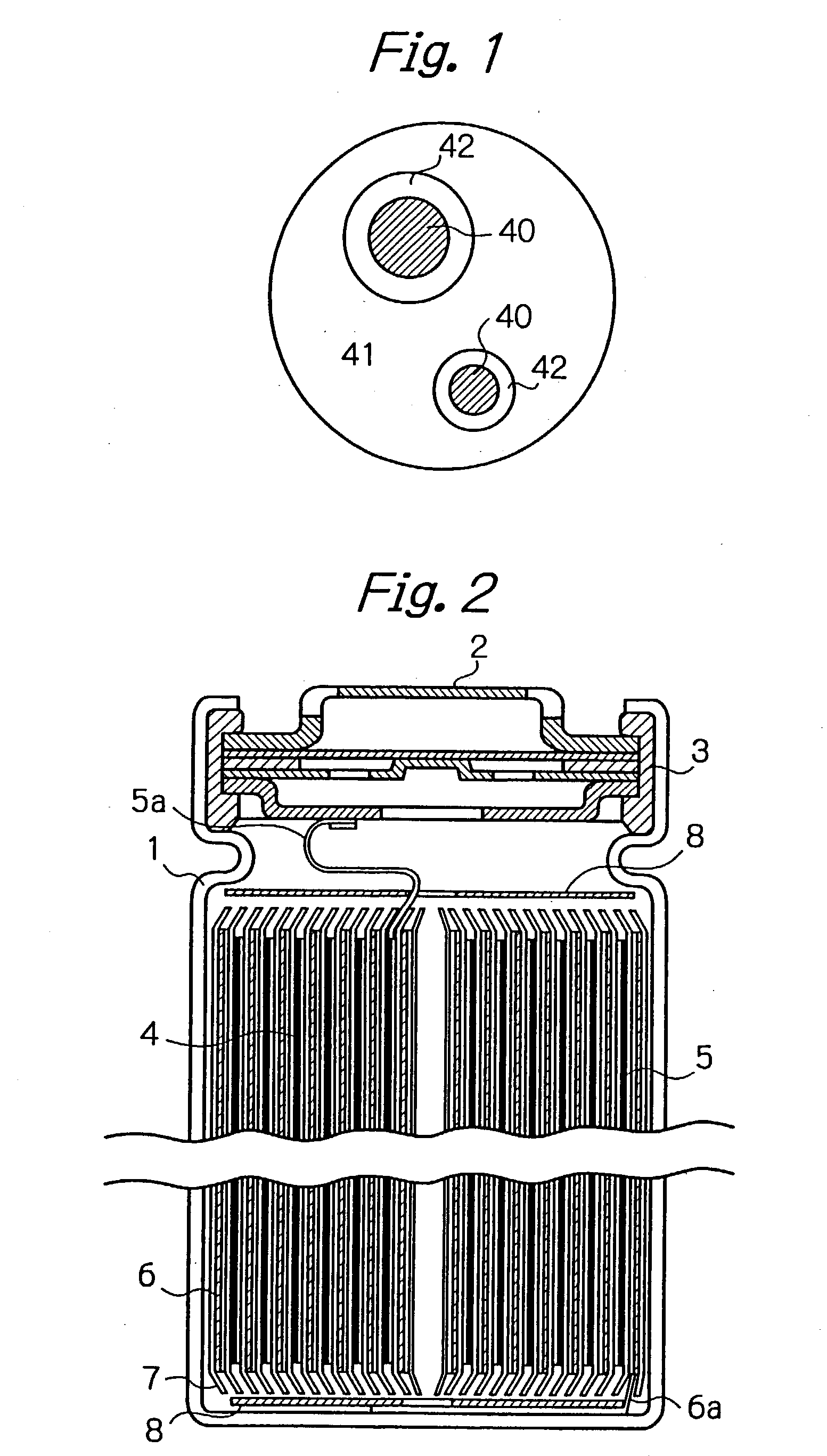

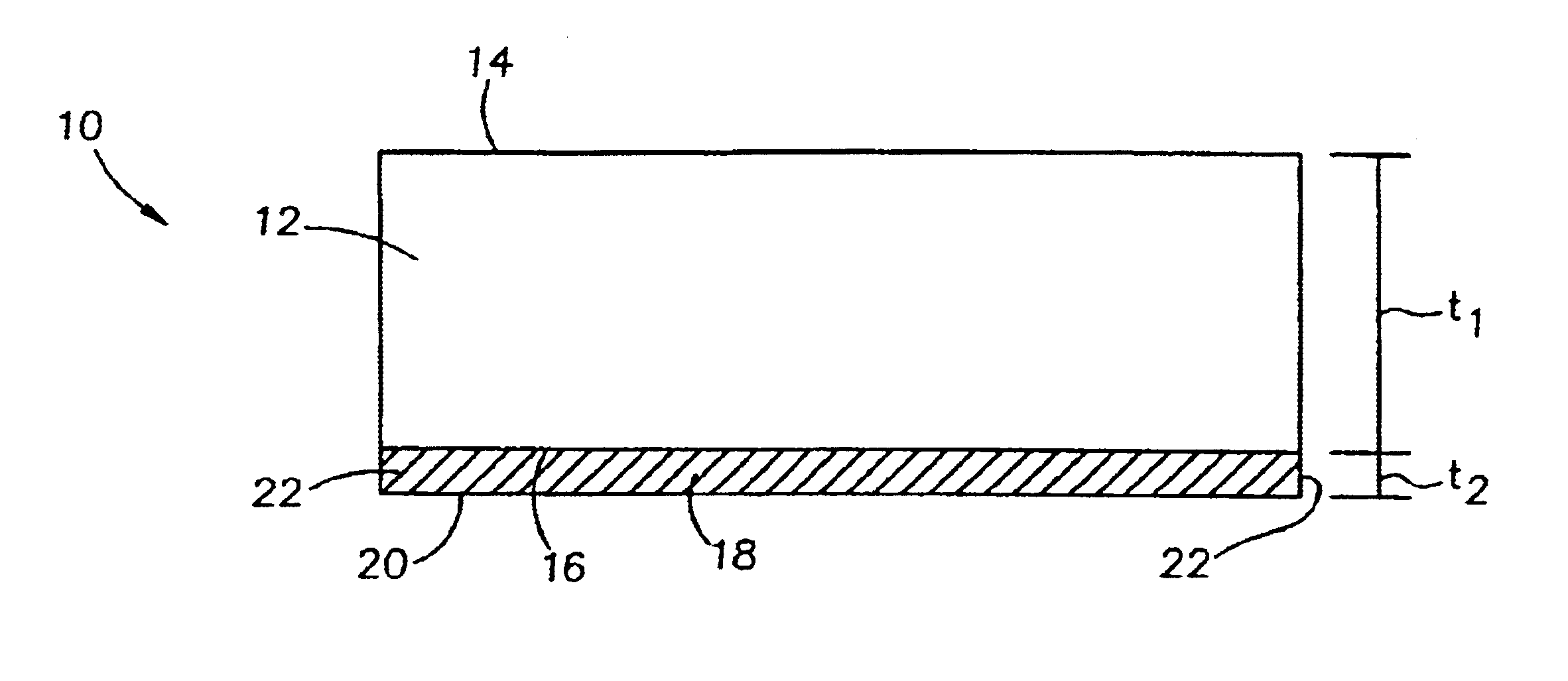

Multilayer ceramic capacitor with terminal formed by electroless plating

InactiveUS7345868B2High strengthFixed capacitor electrodesFixed capacitor dielectricElectrolysisCeramic capacitor

A terminal to, most commonly, a ceramic capacitor, most commonly a multilayer ceramic capacitor (MLCC), is formed by electroless plating, also known as electroless deposition or simply as electrodeposition. In the MLCC having a multiple parallel interior plates brought to, and exposed at, at least one, first, surface, an electrically-conductive first-metal layer, preferably Cu, is electrolessly deposited upon this first surface directly in contact with, mechanically connected to, and electrically connected to, the edges of these interior plates. Lateral growth of the electrolessly-deposited first-metal is sufficient to span from exposed plate to exposed plate, electrically connecting the plates. One or more top layers, preferably one of Ni and one of Sn and Pb, are deposited, preferably by plating and more preferably by electrolytic plating, on top of the electrolessly-deposited Cu.

Owner:PRESIDIO COMPONENTS

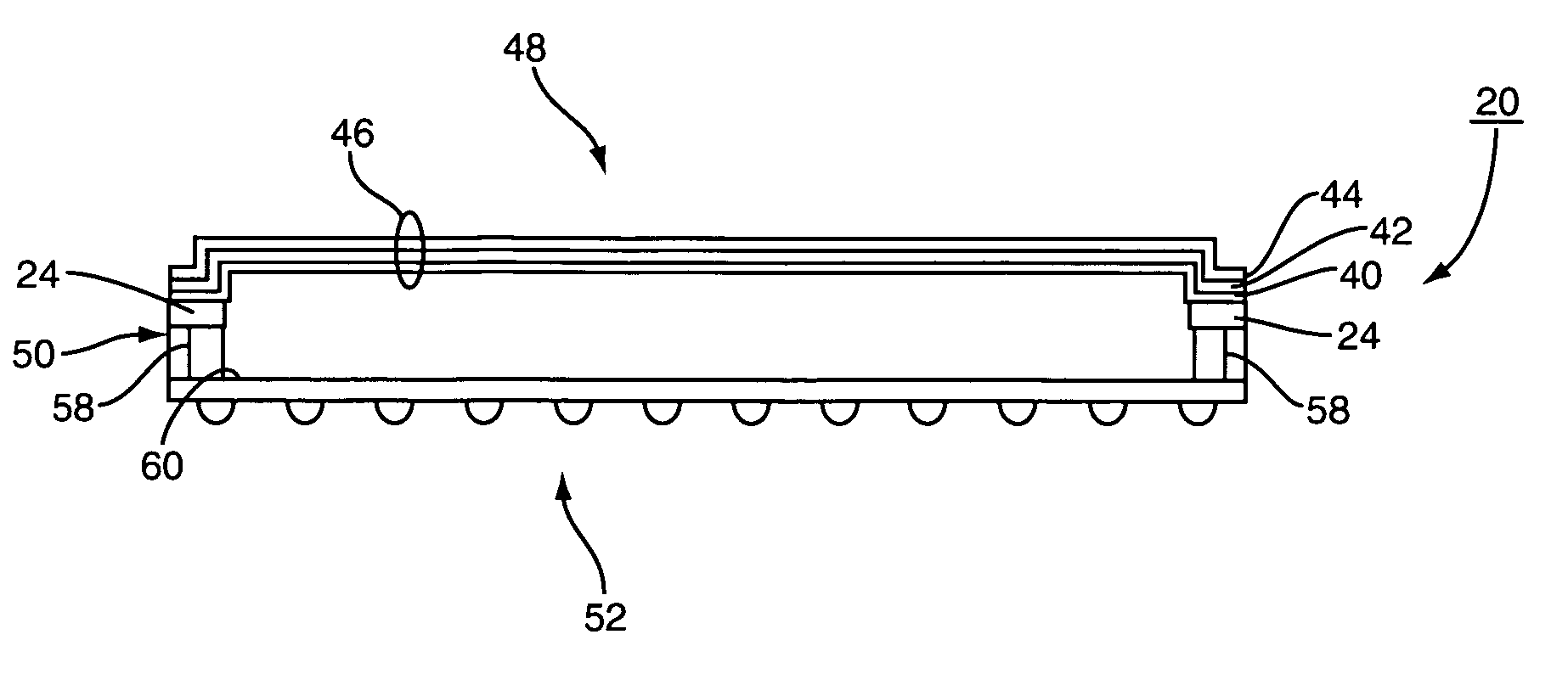

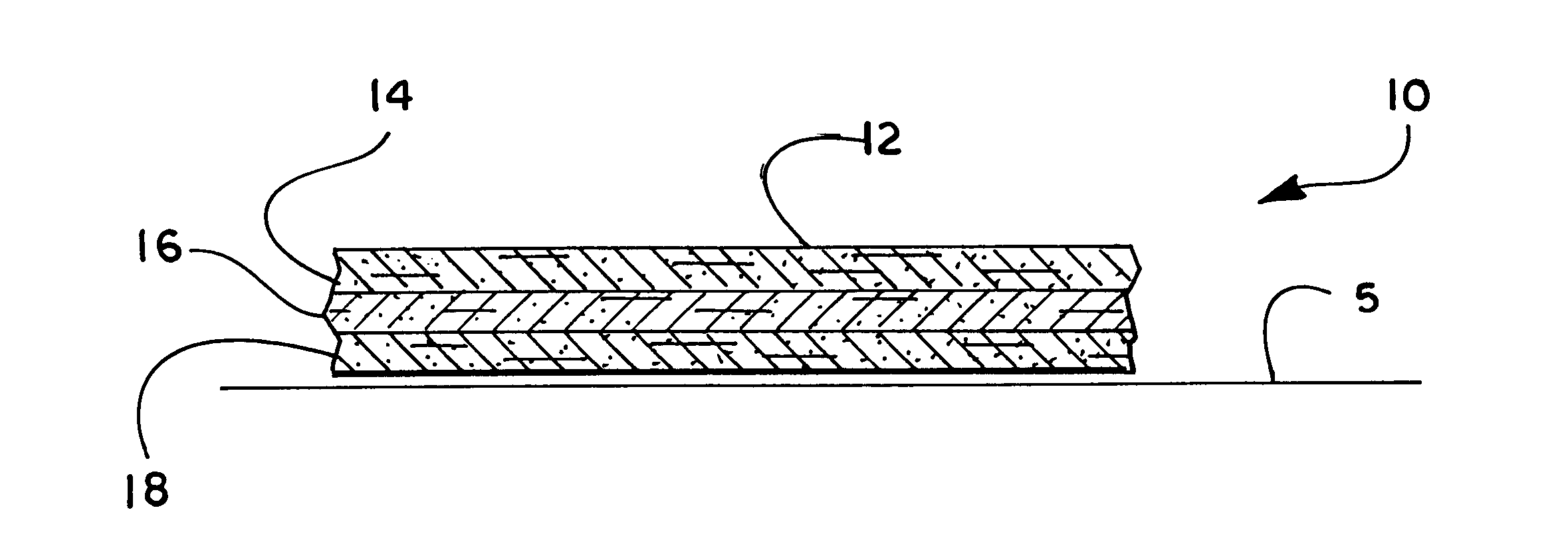

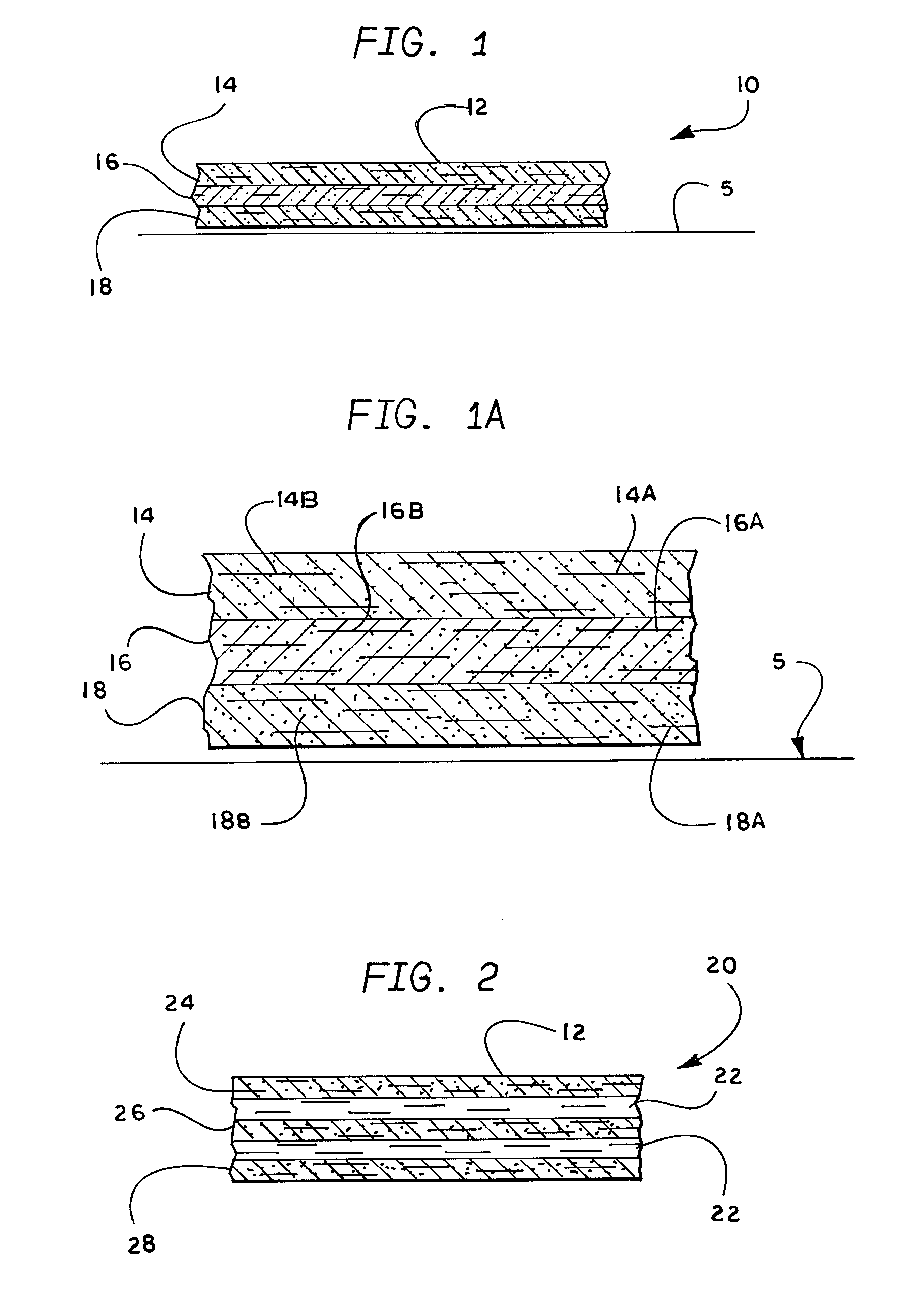

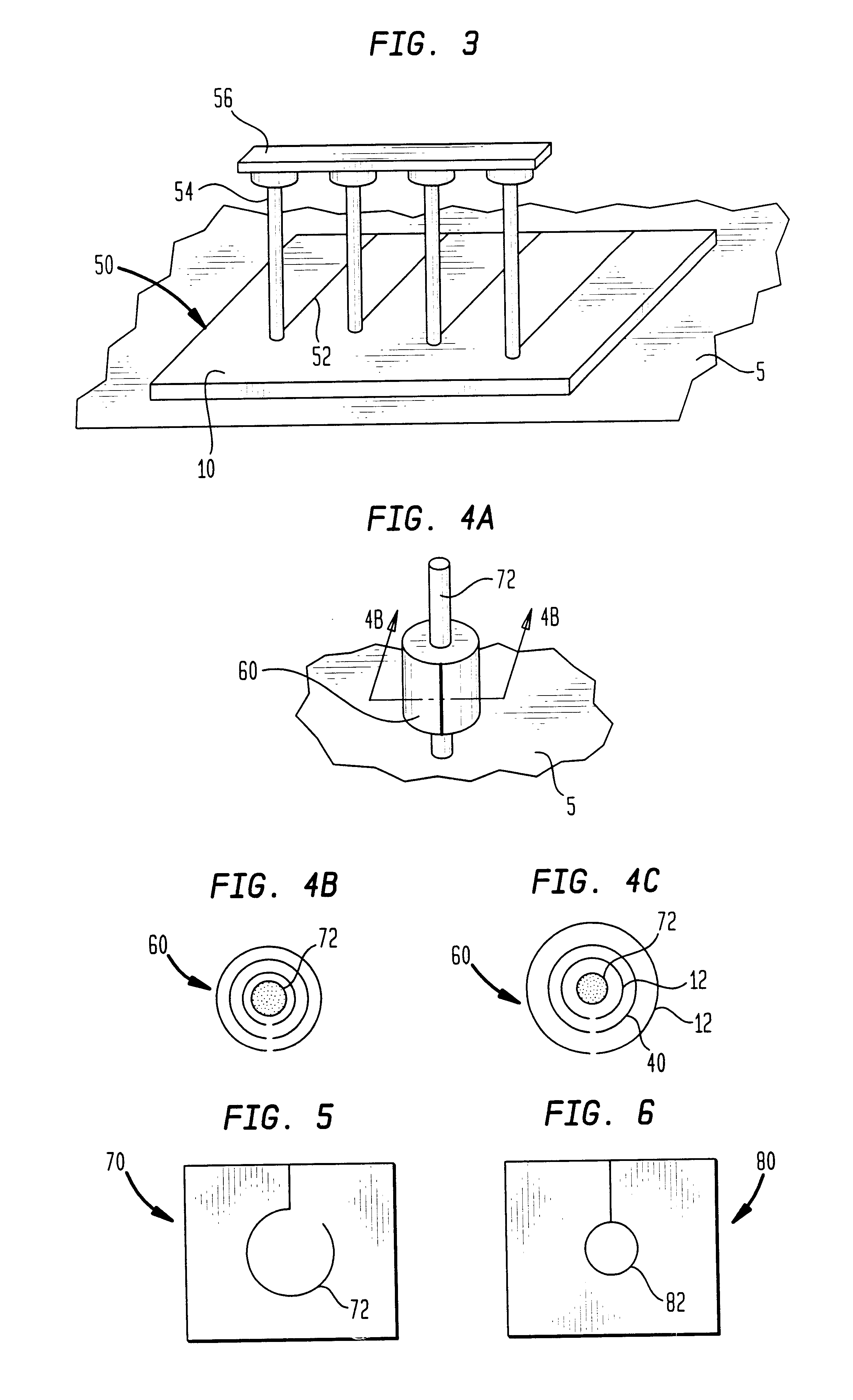

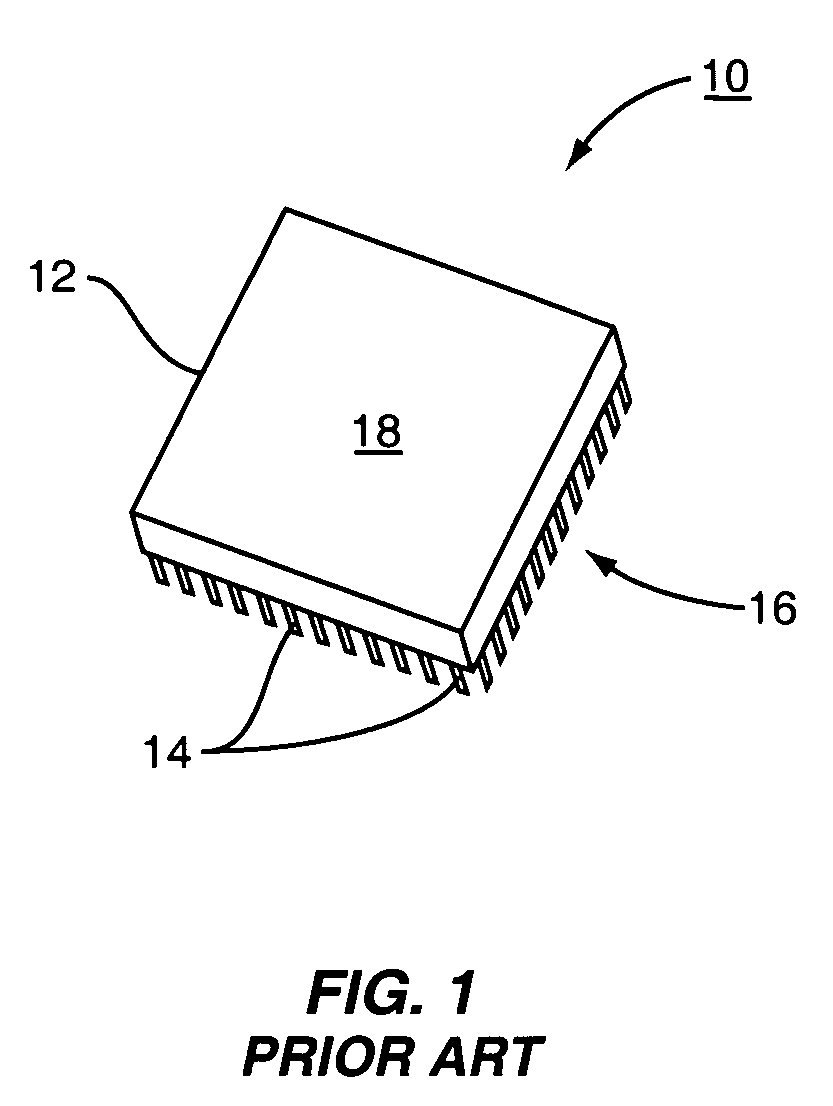

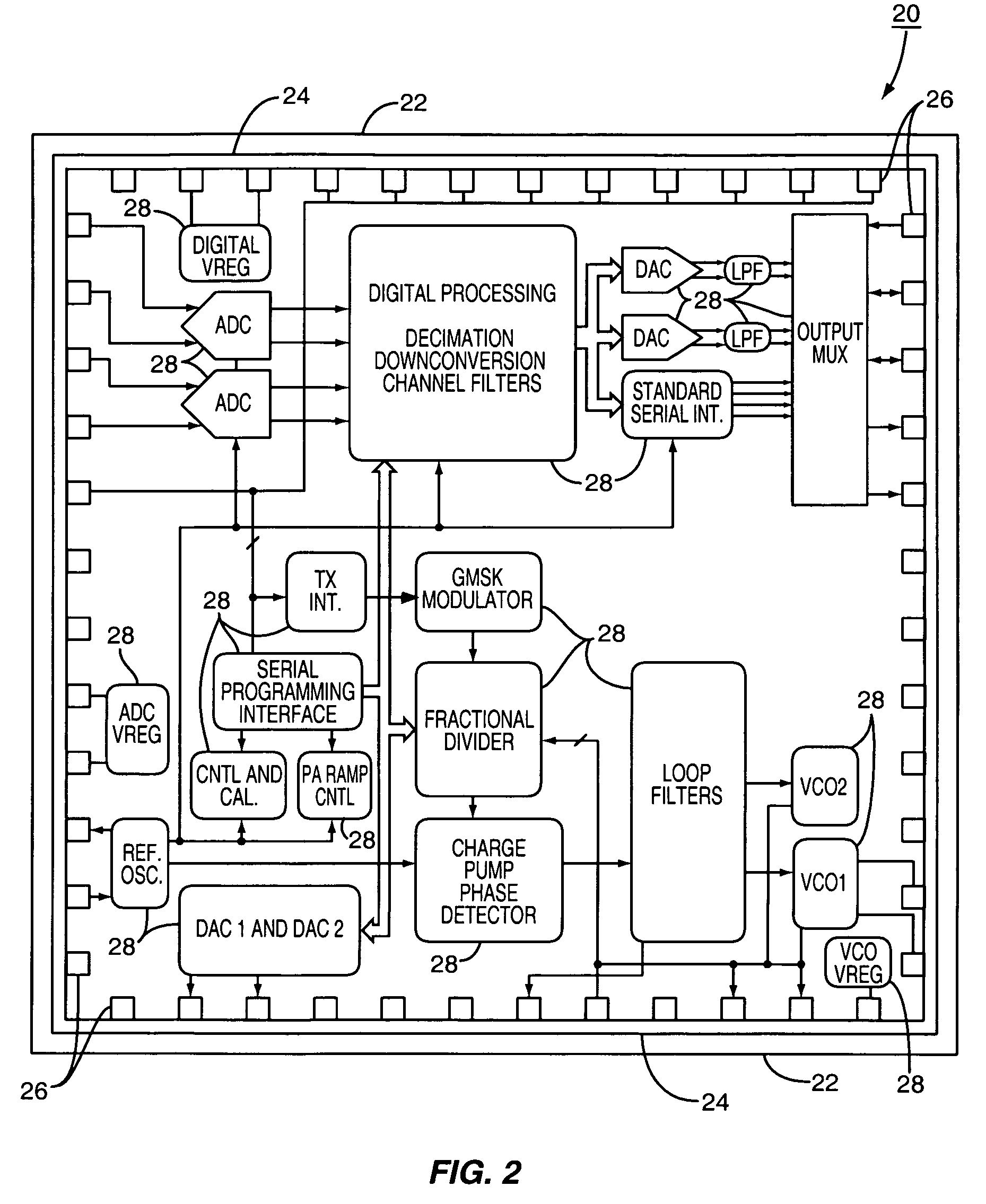

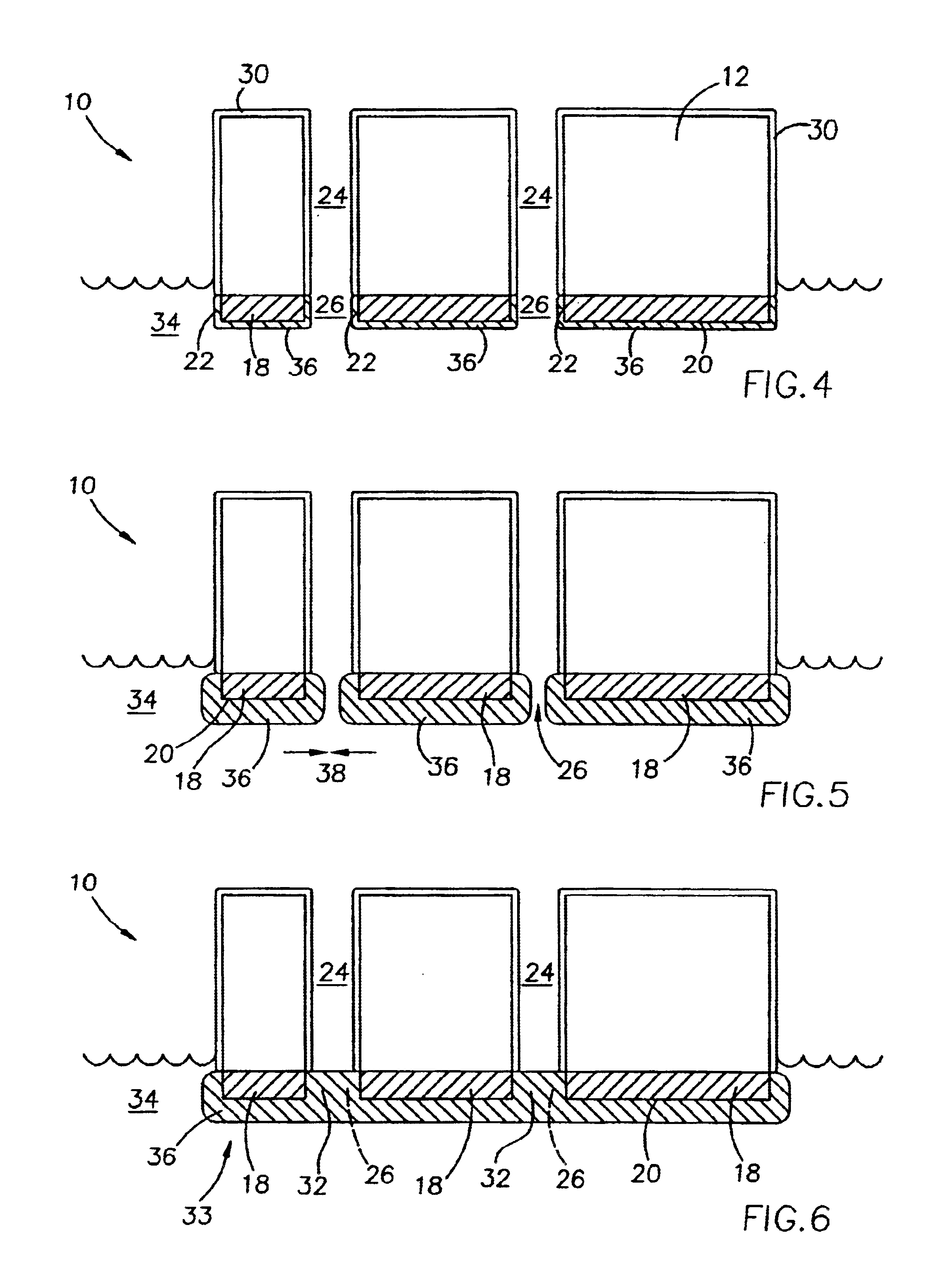

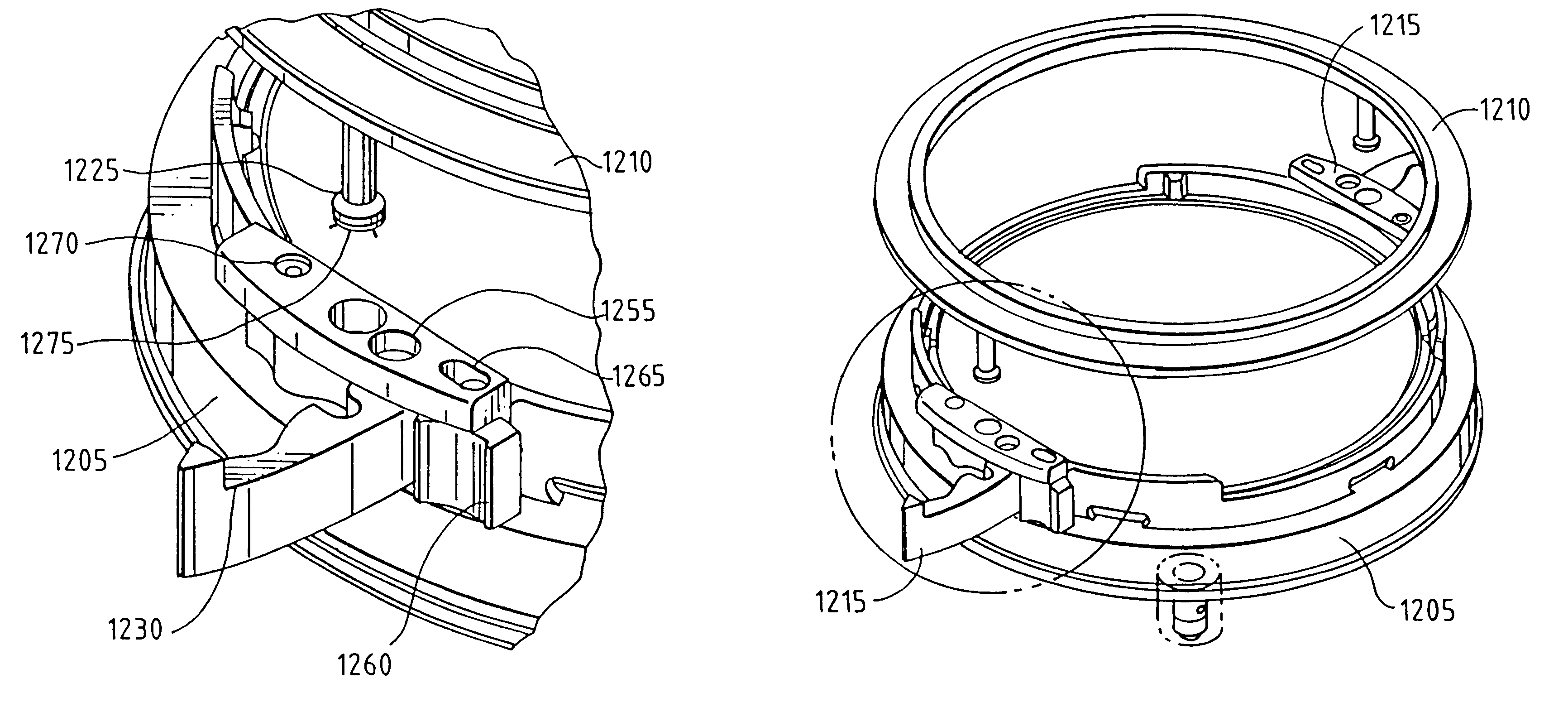

Conformal electromagnetic interference shield

An electromagnetic shield for an electronic module includes a surface finish that is applied to the surface of an electronic module so as to minimize the size of the shield. Once the shield is in place, the shield acts to address electromagnetic interference (EMI) concerns associated with the electronic module. An electronic module having a ring of conductive material embedded about its peripheral edge is formed. The electronic module is then sub-diced so as to expose the ring of conductive material. After sub-dicing, a conductive material may be applied through an electroless plating process followed by an electrolytic plating process. Alternatively, a conductive epoxy may be sprayed or painted onto the surface of the electronic module.

Owner:QORVO US INC

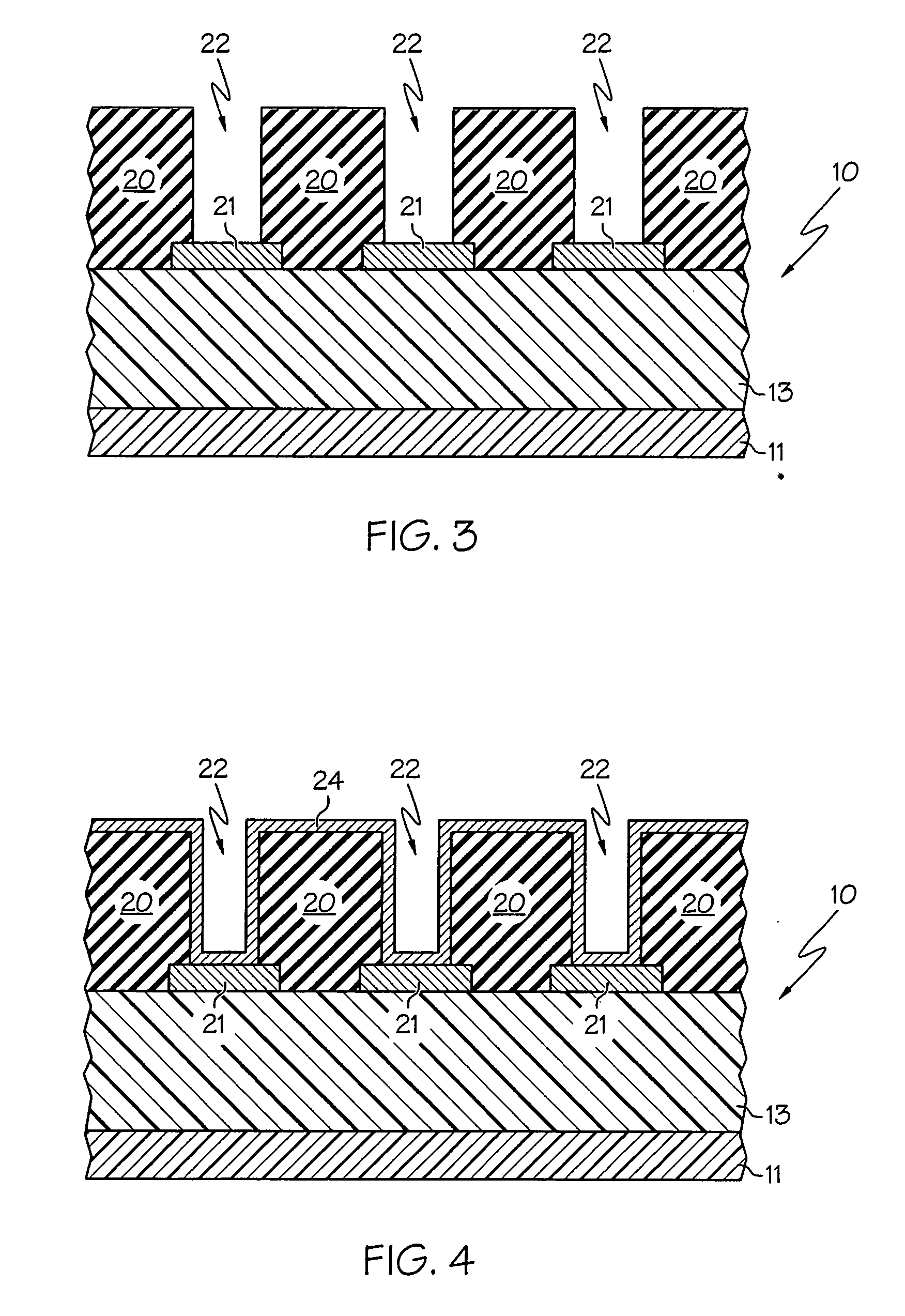

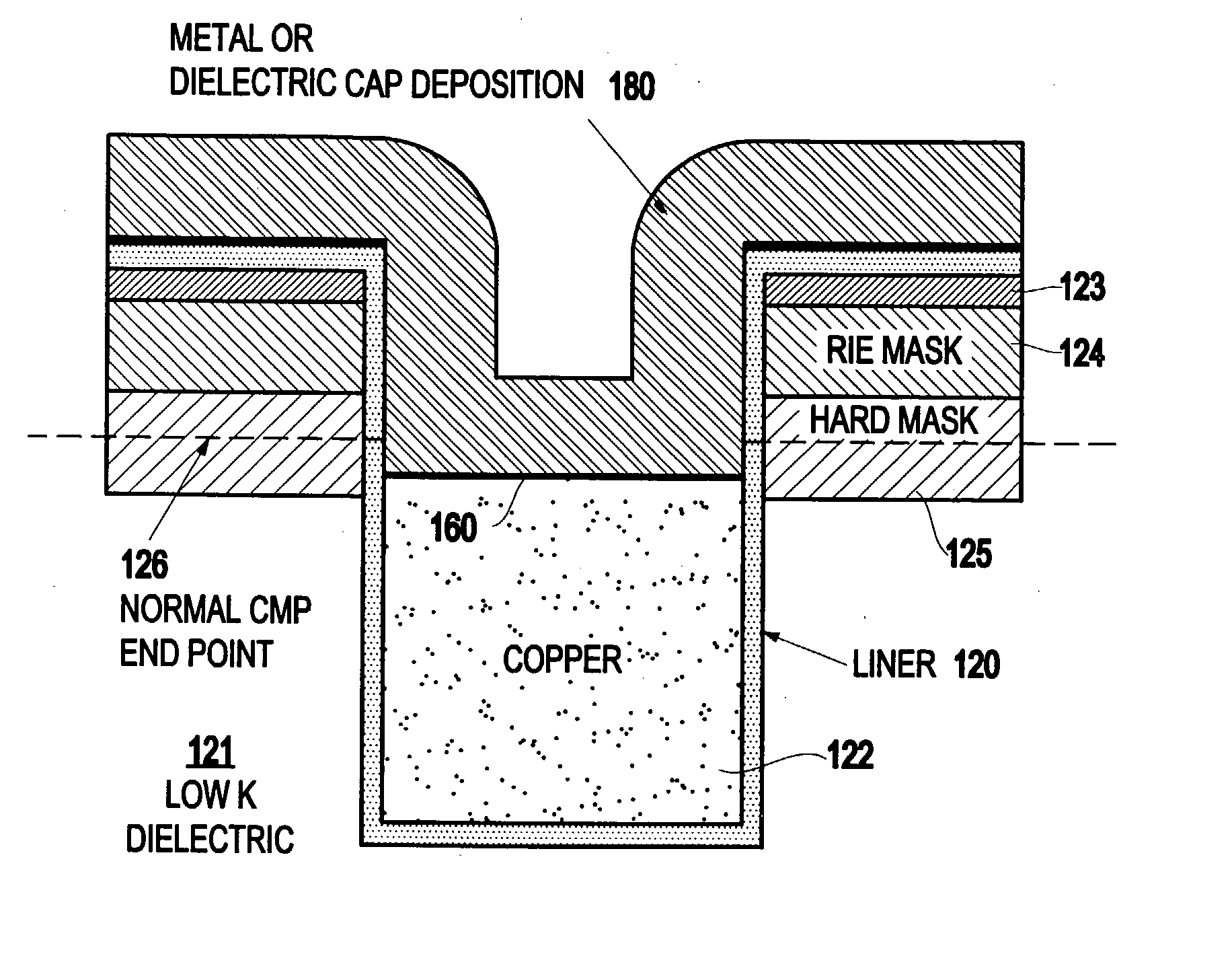

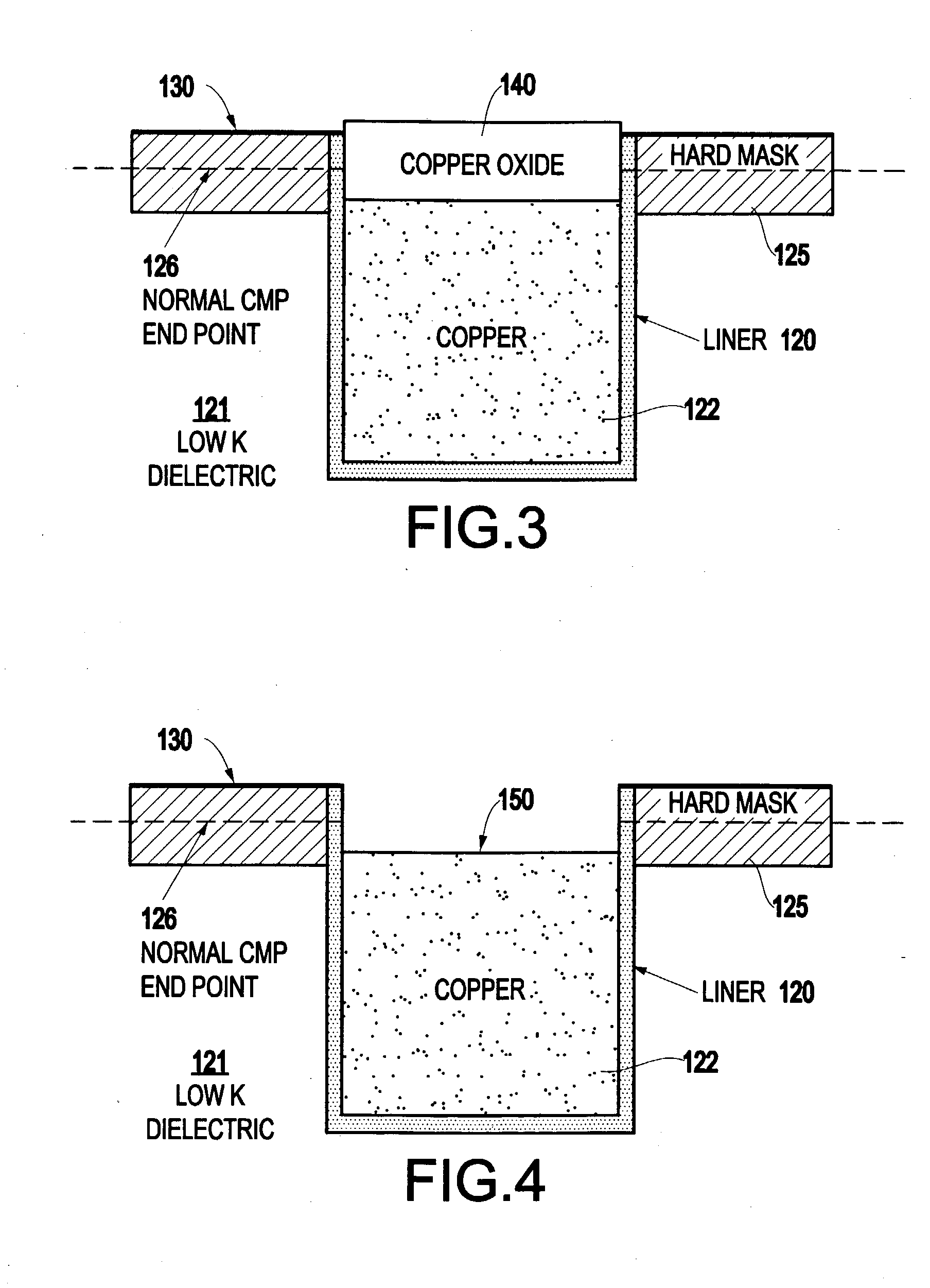

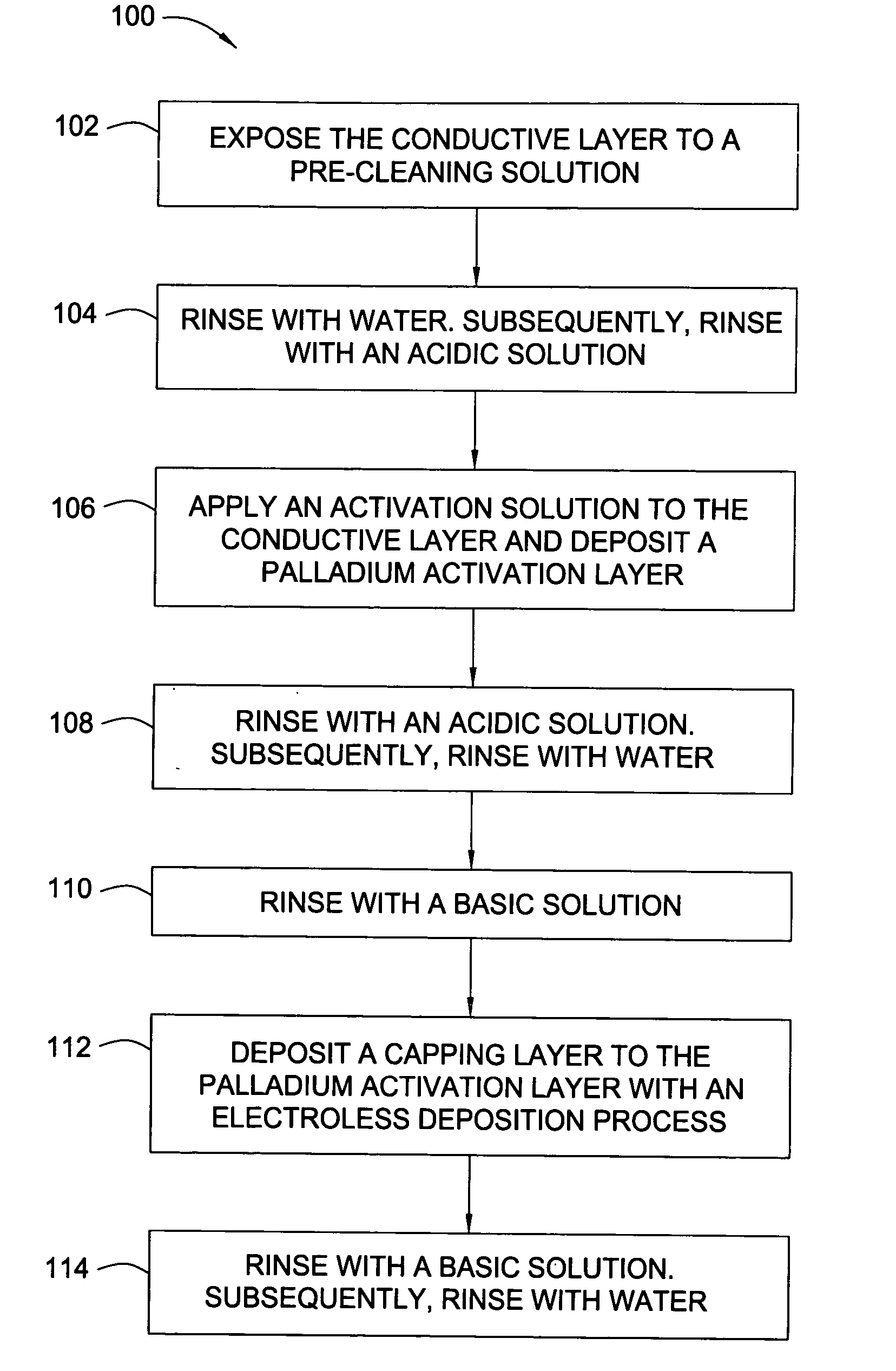

Copper recess process with application to selective capping and electroless plating

ActiveUS20040113279A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringInterconnection

An integrated circuit structure is disclosed that has a layer of logical and functional devices and an interconnection layer above the layer of logical and functional devices. The interconnection layer has a substrate, conductive features within the substrate and caps positioned only above the conductive features.

Owner:TAIWAN SEMICON MFG CO LTD

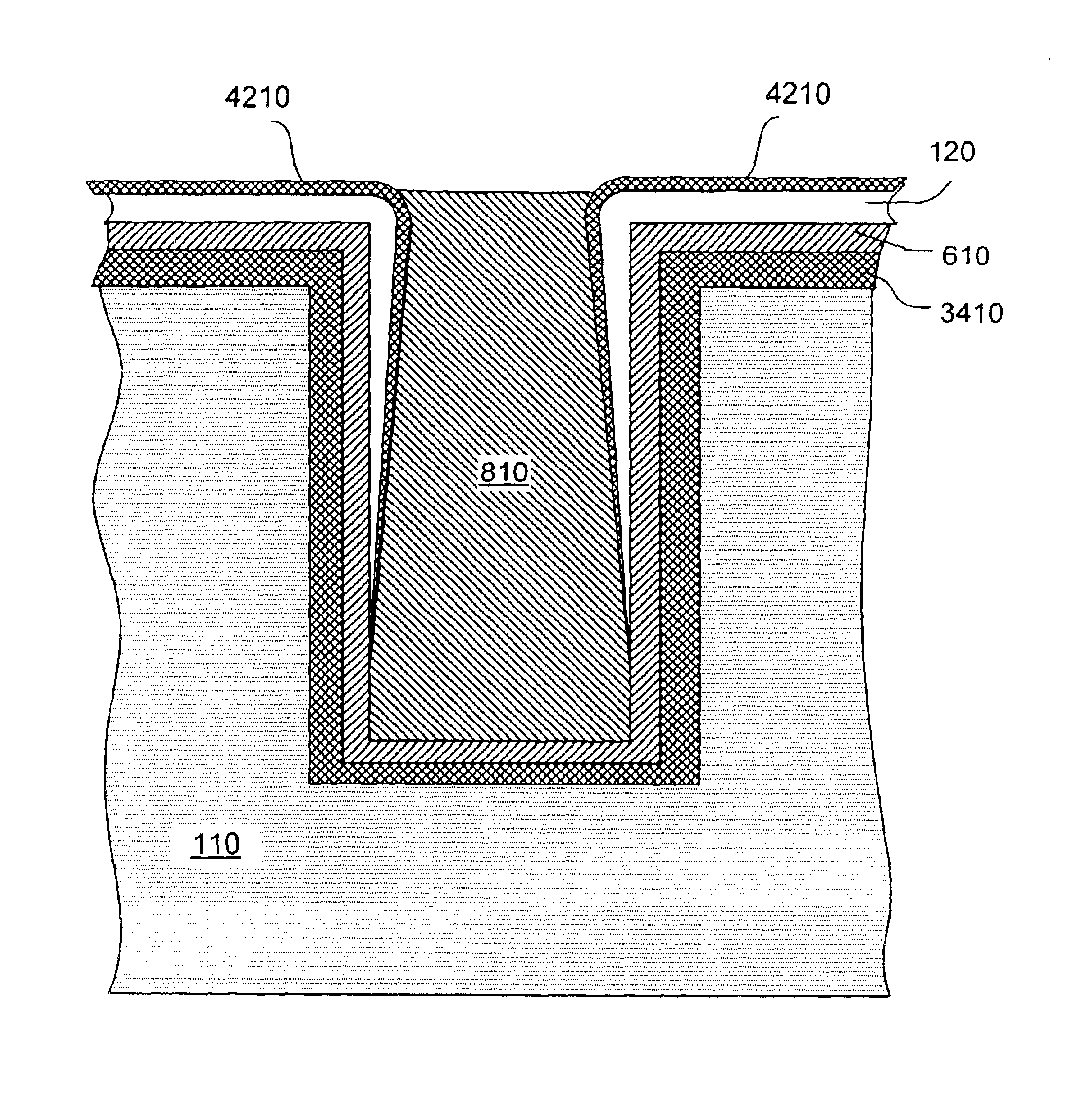

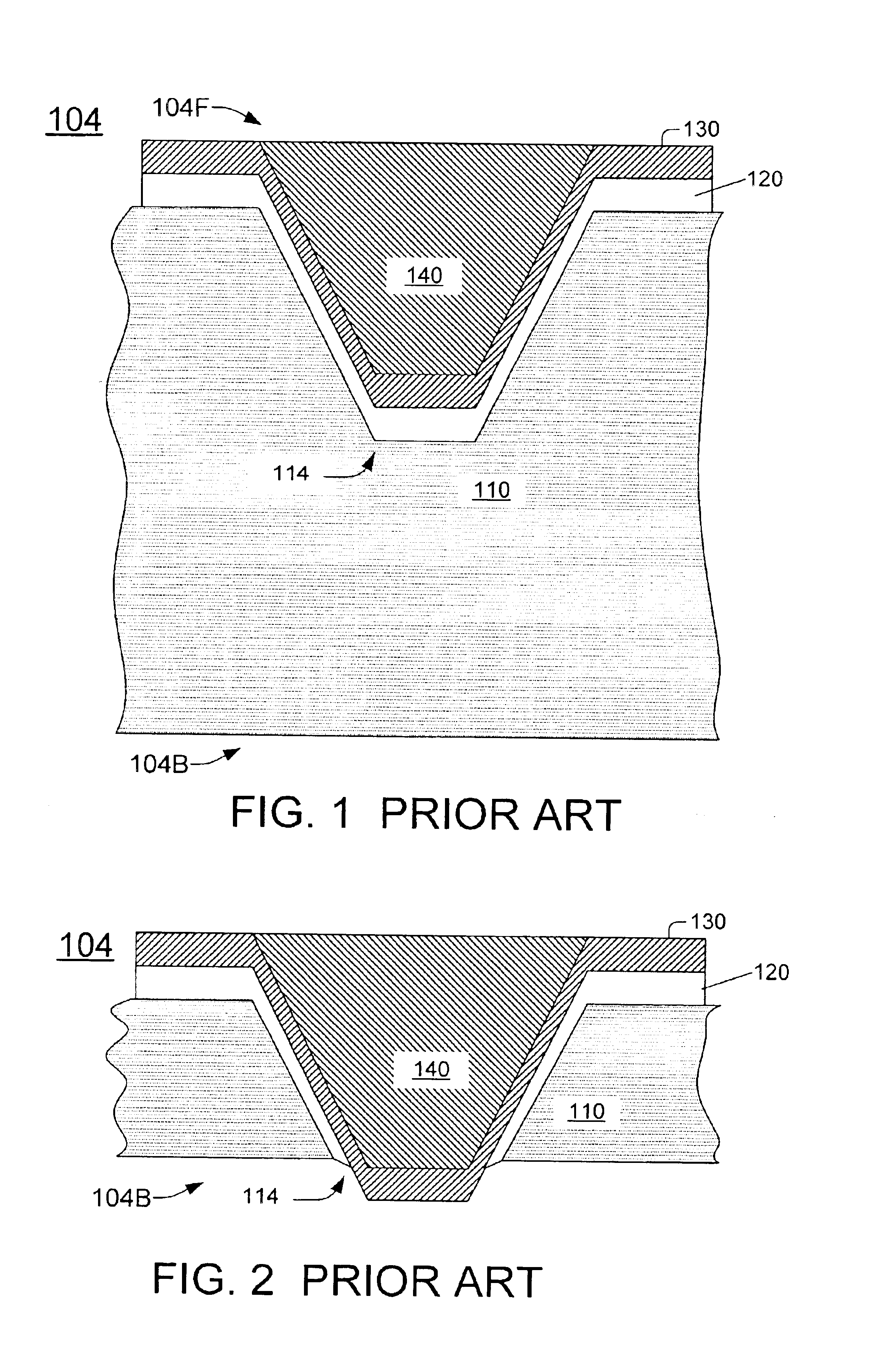

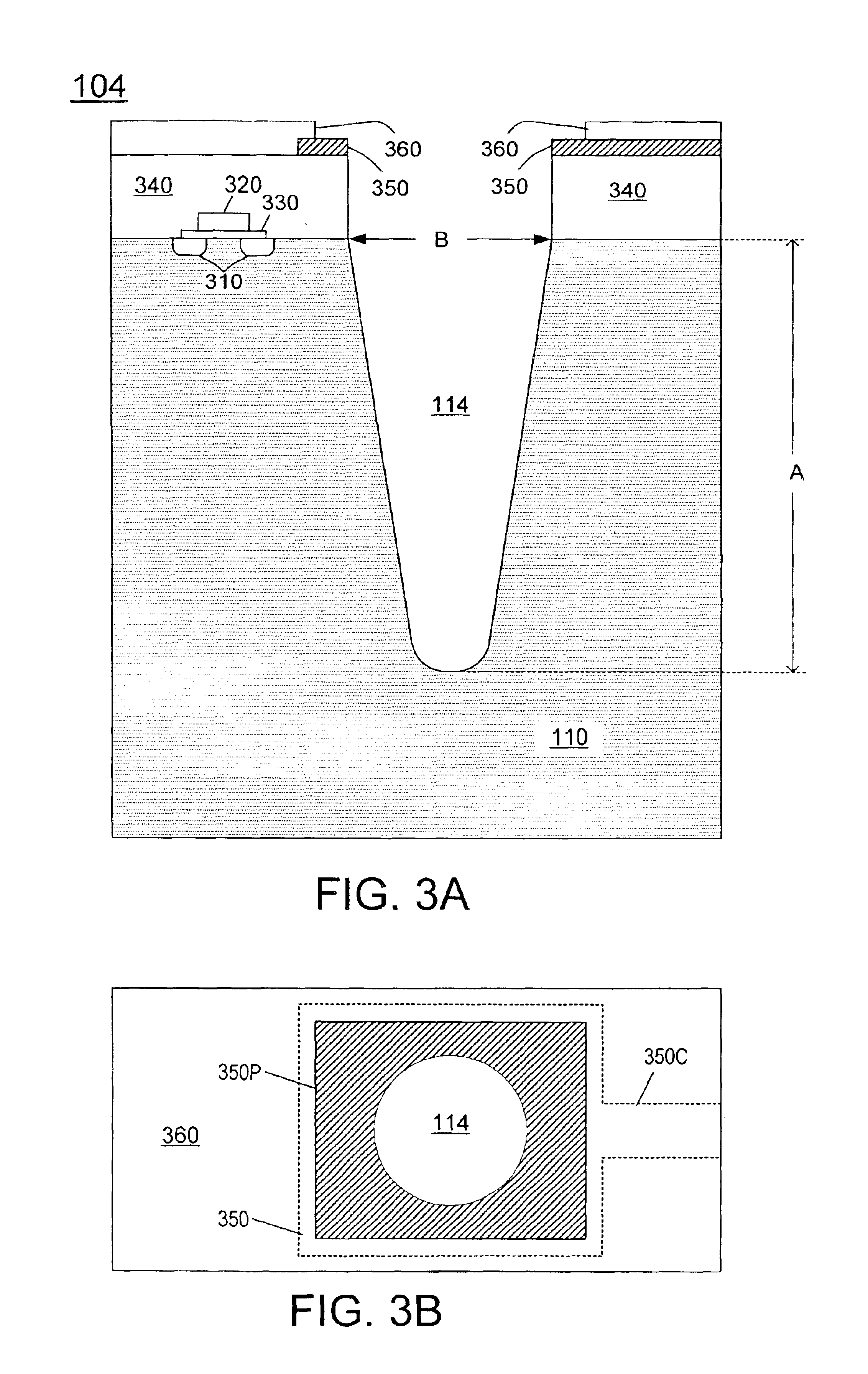

Electroplating and electroless plating of conductive materials into openings, and structures obtained thereby

InactiveUS6897148B2Improve throughputReduce tooling costsSemiconductor/solid-state device detailsSolid-state devicesResistDielectric

A through hole (114) is formed in a wafer (104) comprising a semiconductor substrate (110). A seed layer (610) is sputtered on the bottom surface of the wafer. The seed is not deposited over the through hole's sidewalls adjacent the top surface of the wafer. A conductor (810) is electroplated into the through hole. In another embodiment, a seed is deposited into an opening in a wafer through a dry film resist mask (1110). The dry film resist overhangs the edges of the opening, so the seed is not deposited over the opening's sidewalls adjacent the top surface of the wafer. In another embodiment, a dielectric (120) is formed in an opening in a semiconductor substrate (110) by a non-conformal physical vapor deposition (PVD) process that deposits the dielectric on the sidewalls but not the bottom of the opening. A seed (610) is formed on the bottom by electroless plating. A conductor (810) is electroplated on the seed. In another embodiment, a dielectric (2910) is formed in the opening to cover the entire surface of the opening. A non-conformal layer (120) is deposited by PVD over the sidewalls but not the bottom of the opening. The dielectric (2910) is etched off the bottom with the non-conformal layer (120) as a mask. A seed (610) is formed on the bottom by electroless plating. The non-conformal layer can be formed by electroplating. It can be tantalum deposited by electroplating, then anodized. Other embodiments are also provided.

Owner:INVENSAS CORP

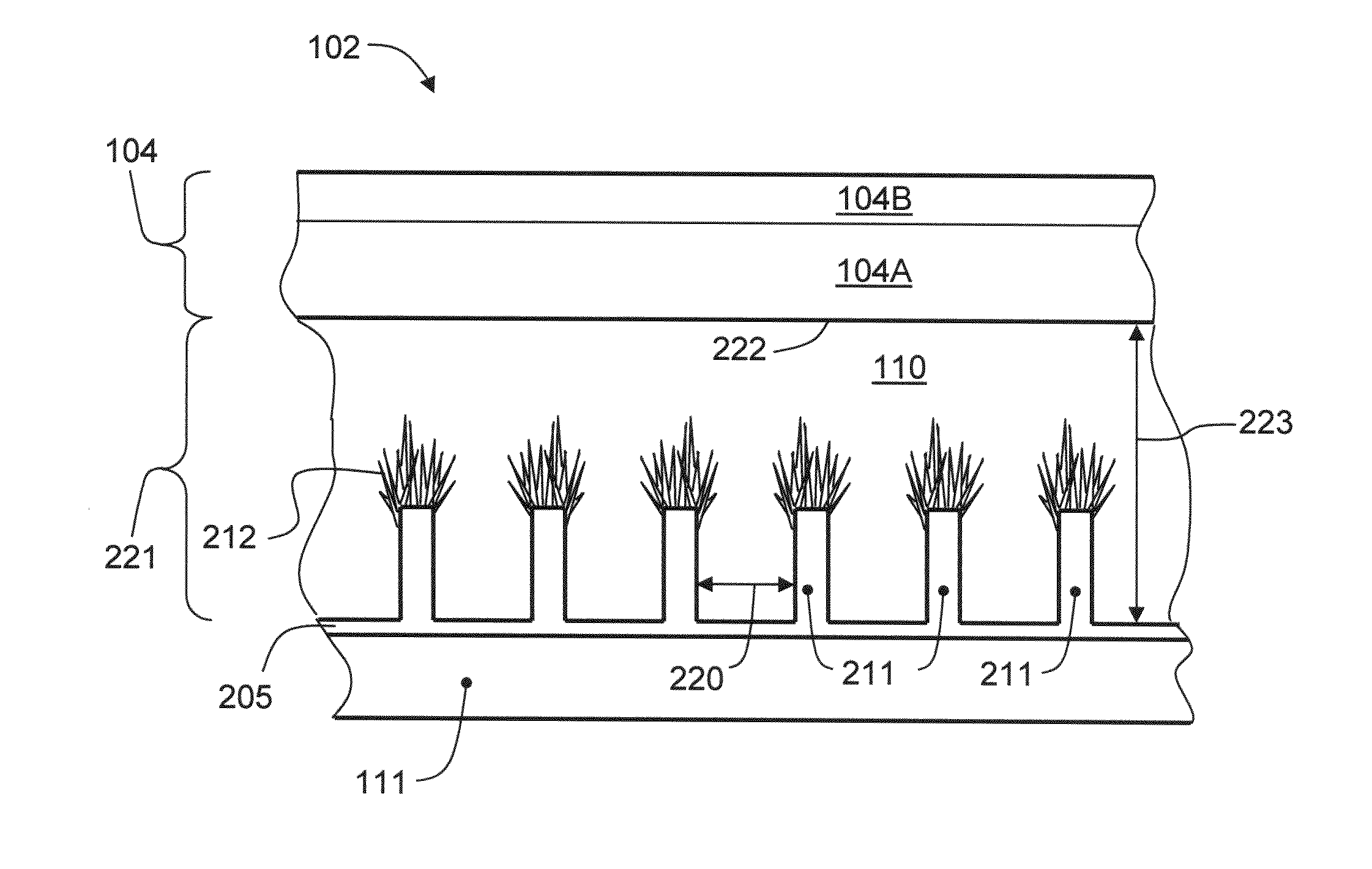

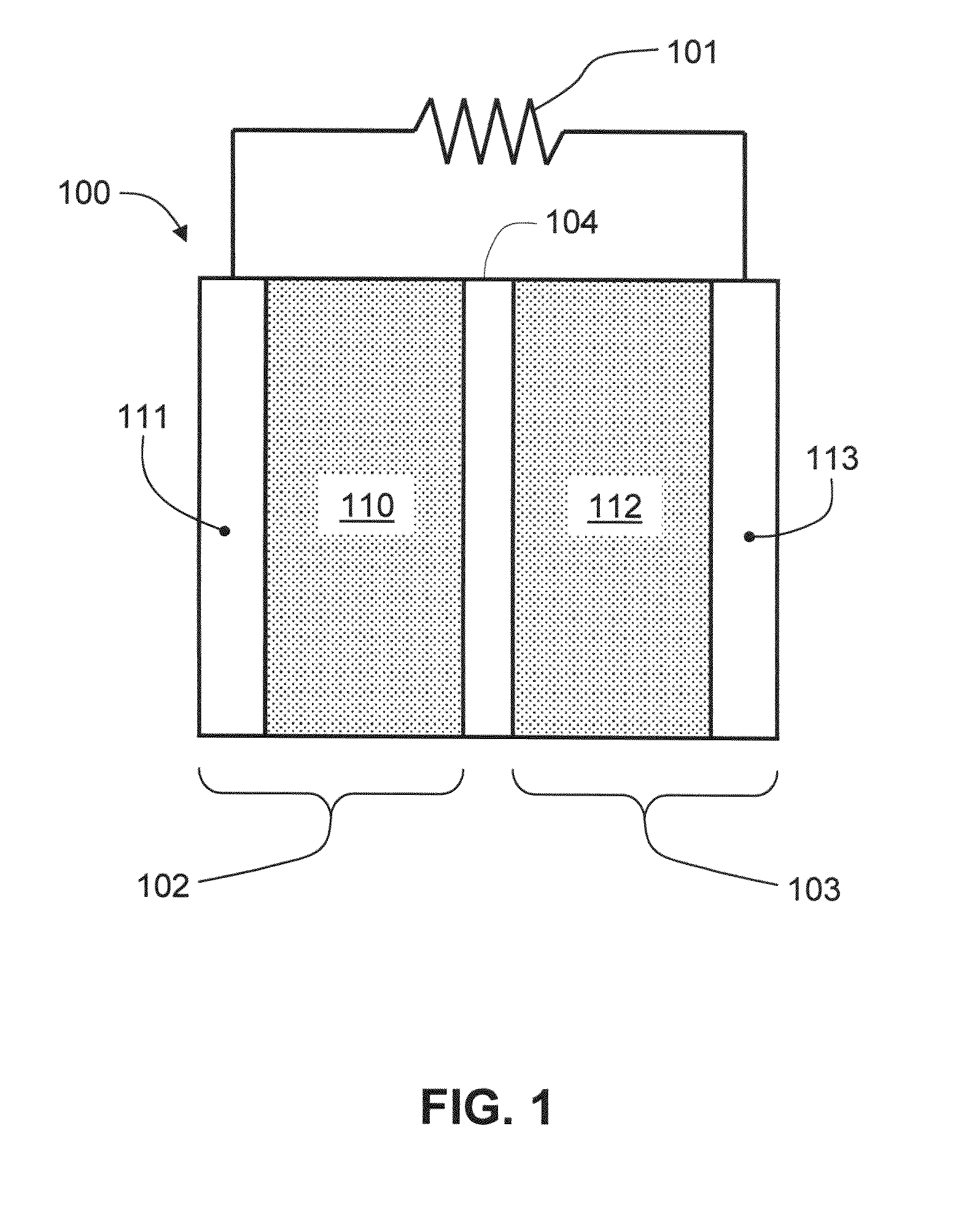

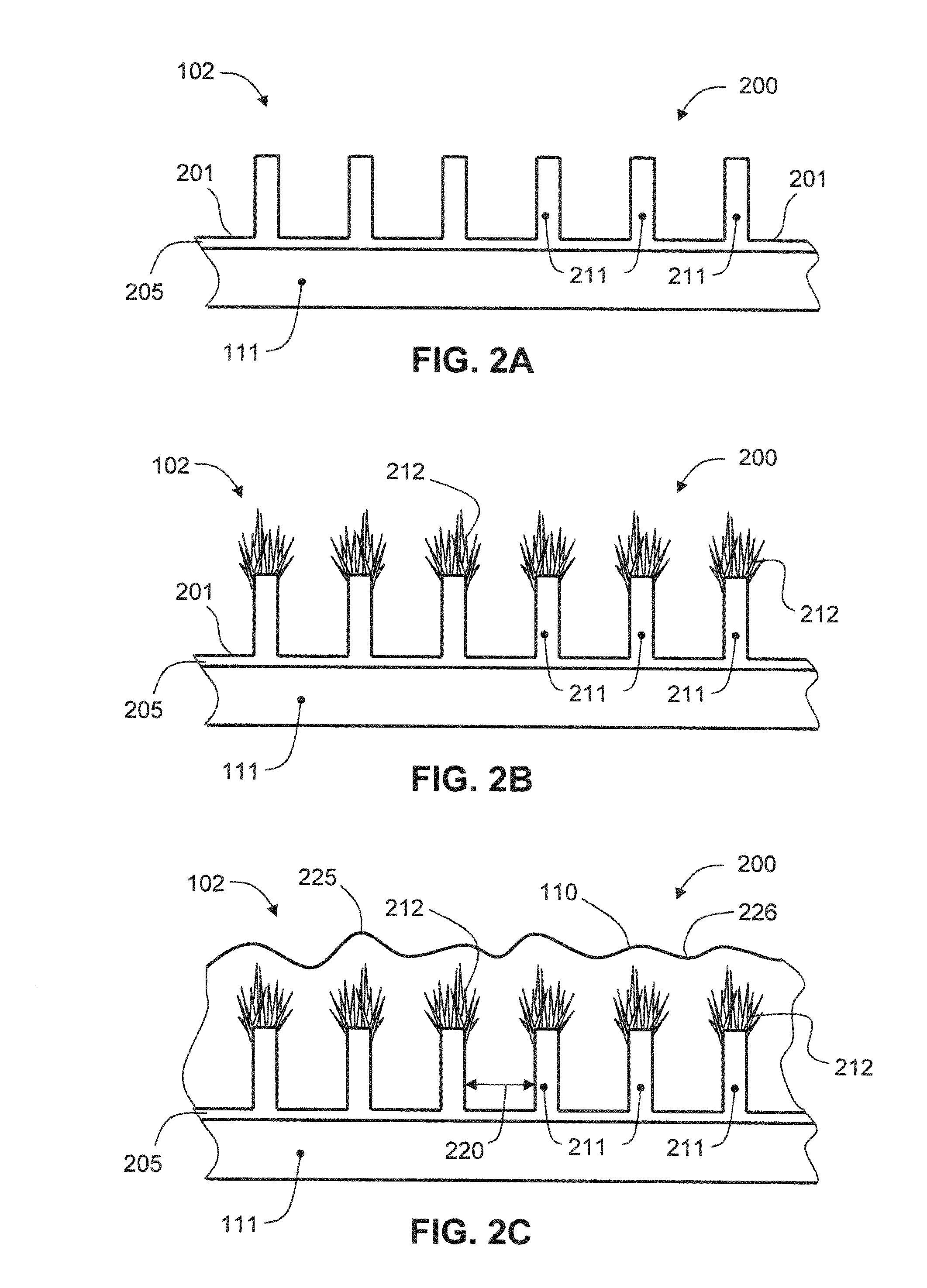

Thin film electrochemical energy storage device with three-dimensional anodic structure

InactiveUS20100216026A1Final product manufactureElectrode carriers/collectorsPorosityMicro structure

A method for forming a battery from via thin-film deposition processes is disclosed. A mesoporous carbon material is deposited onto a surface of a conductive substrate that has high surface area, conductive micro-structures formed thereon. A porous, dielectric separator layer is then deposited on the layer of mesoporous carbon material to form a half cell of an energy storage device. The mesoporous carbon material is made up of CVD-deposited carbon fullerene “onions” and carbon nano-tubes, and has a high porosity capable of retaining lithium ions in concentrations useful for storing significant quantities of electrical energy. Embodiments of the invention further provide for the formation of an electrode having a high surface area conductive region that is useful in a battery structure. In one configuration the electrode has a high surface area conductive region comprising a porous dendritic structure that can be formed by electroplating, physical vapor deposition, chemical vapor deposition, thermal spraying, and / or electroless plating techniques.

Owner:APPLIED MATERIALS INC

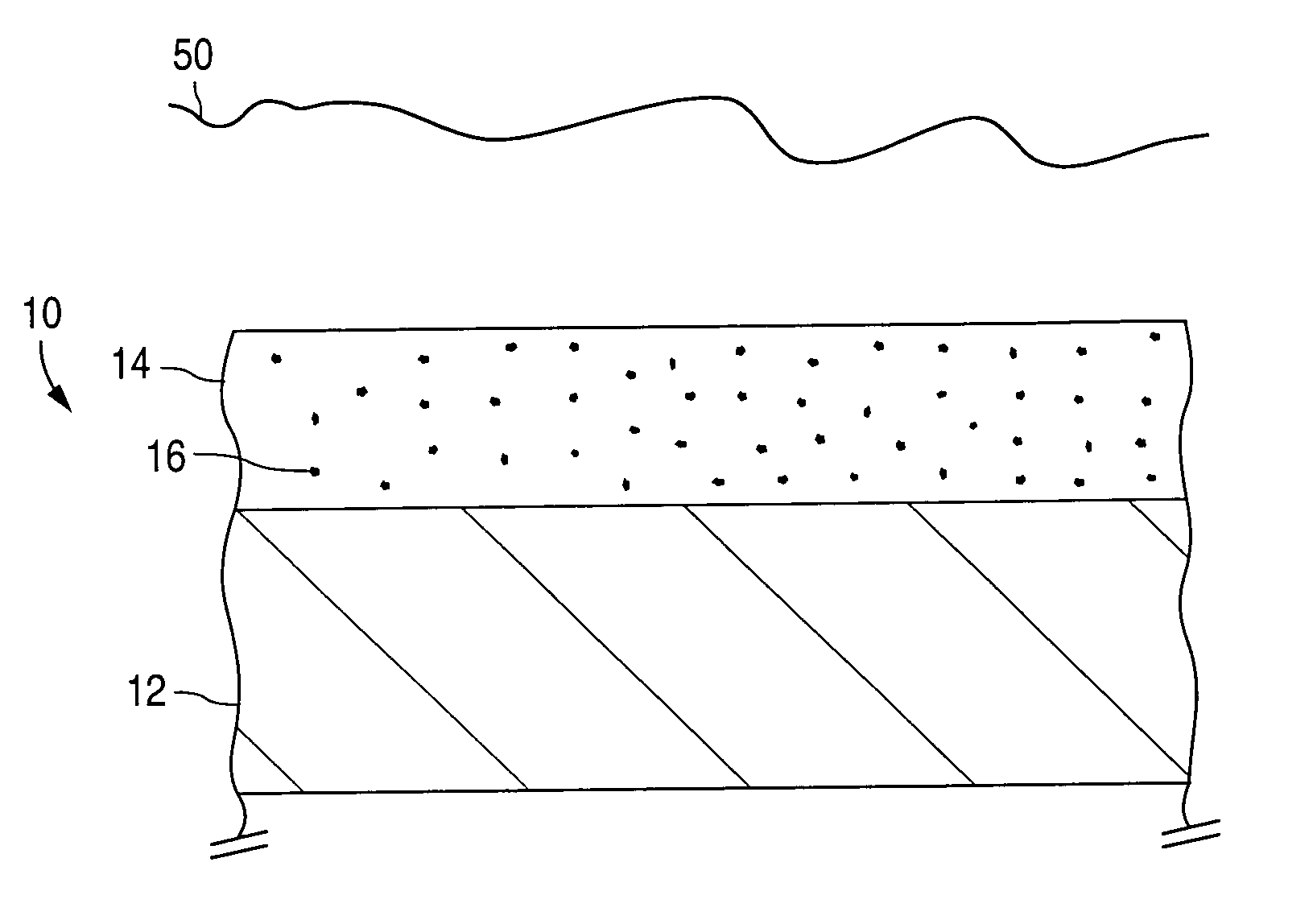

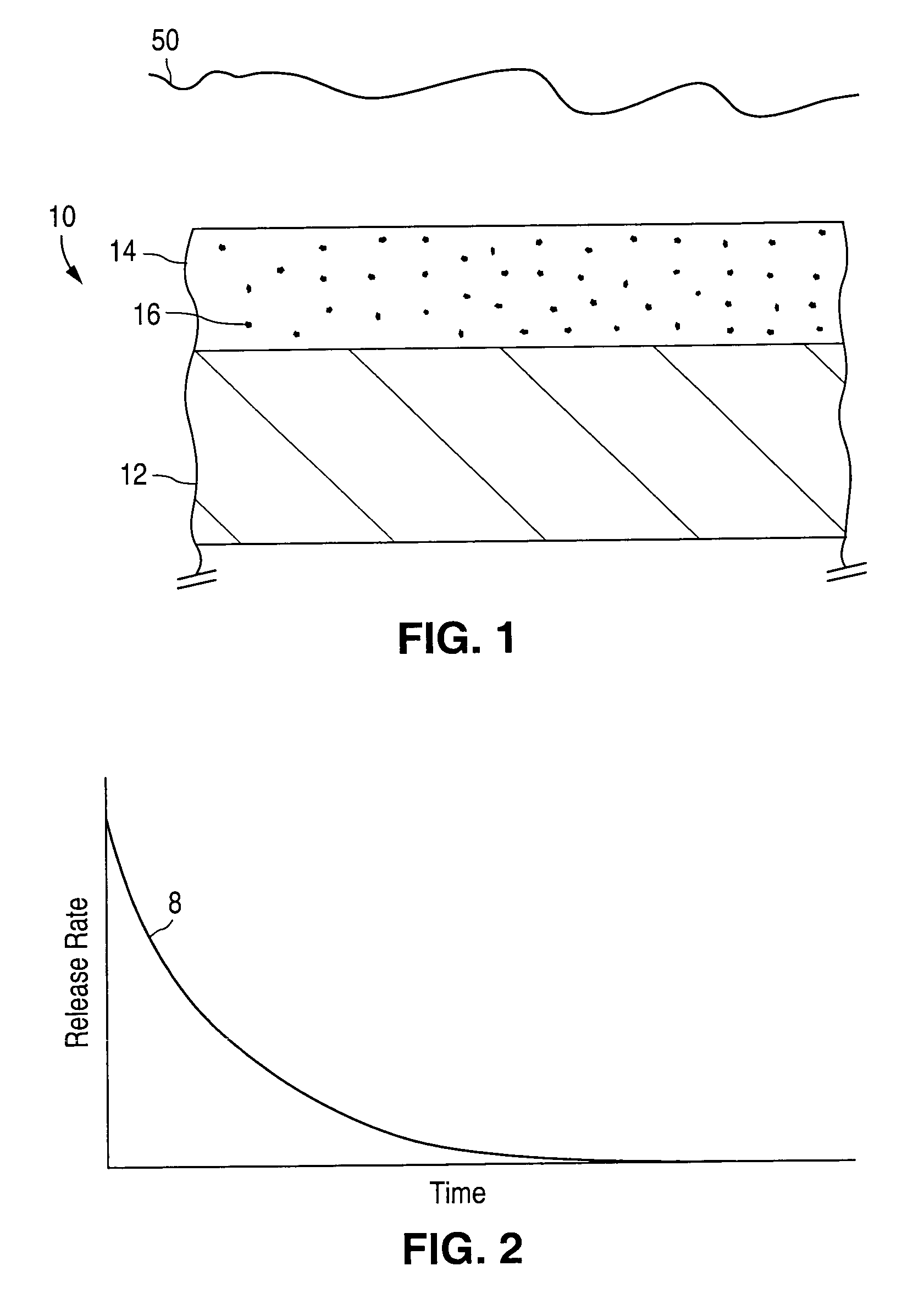

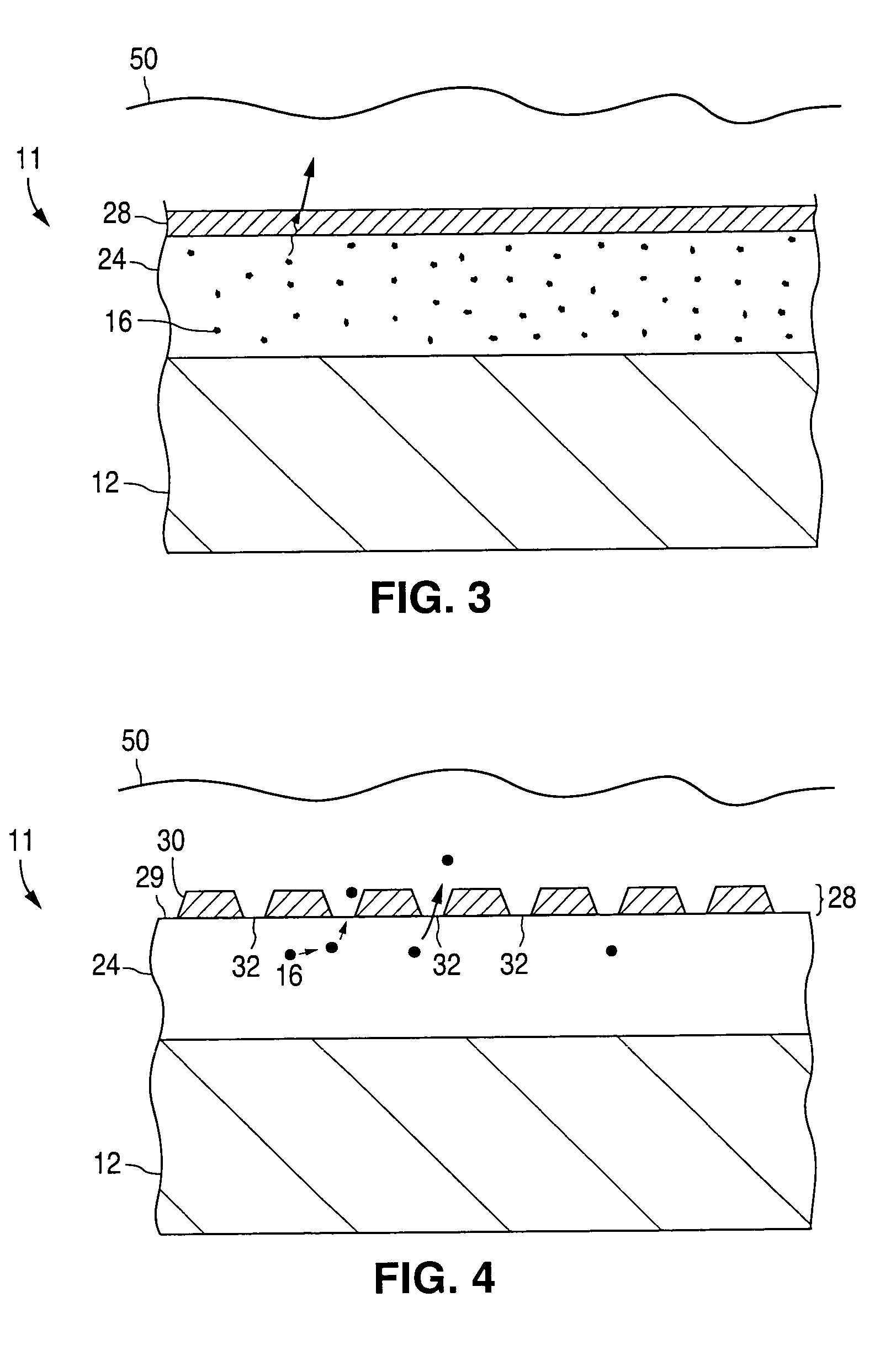

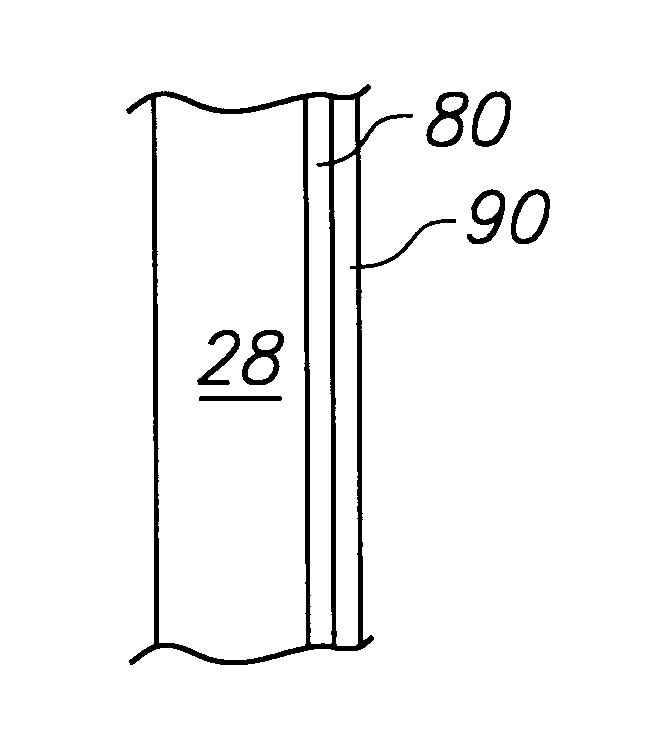

Barriers for polymer-coated implantable medical devices and methods for making the same

InactiveUS6953560B1Reduce and prevent and inflammationReduce and prevent proliferationStentsSurgeryHafniumPt element

An implantable medical device and methods for making the implantable medical device are disclosed. The implantable medical device includes a substrate. At least a portion of the substrate is coated with a first layer including a polymer containing a drug. A barrier overlies the first layer. The barrier significantly reduces the rate of release of the drug from the polymer, thereby sustaining release of the drug from the medical device for a longer time.The barrier may be a homogeneous layer overlying the first layer, or a number of discrete deposits over the first layer. Alternatively, the barrier may be intermixed with an outer portion of the first layer. The barrier material is biocompatible, and typically has a thickness ranging from about 50 angstroms to about 20,000 microns. Suitable materials for the barrier include, but are not limited to, inorganic compounds, such as inorganic silicides, oxides, nitrides, carbides, as well as pure metals such as aluminum, chromium, gold, hafnium, iridium, niobium, palladium, platinum, tantalum, titanium, tungsten, zirconium, and alloys of these metals. The barriers disclosed may be applied to the first layer by several techniques, depending on the material being applied. Exemplary deposition techniques include physical vapor deposition, alkoxide hydrolysis, and electroless plating.The implantable device may be a stent or a graft, among other possibilities.

Owner:ABBOTT CARDIOVASCULAR

Corrosion resistant component of semiconductor processing equipment and method of manufacturing thereof

A corrosion resistant component of semiconductor processing equipment such as a plasma chamber includes a metal surface such as aluminum or aluminum alloy, stainless steel, or refractory metal coated with a phosphorus nickel plating and an outer ceramic coating such as alumina, silicon carbide, silicon nitride, boron carbide or aluminum nitride. The phosphorus nickel plating can be deposited by electroless plating and the ceramic coating can be deposited by thermal spraying. To promote adhesion of the ceramic coating, the phosphorus nickel plating can be subjected to a surface roughening treatment prior to depositing the ceramic coating.

Owner:LAM RES CORP

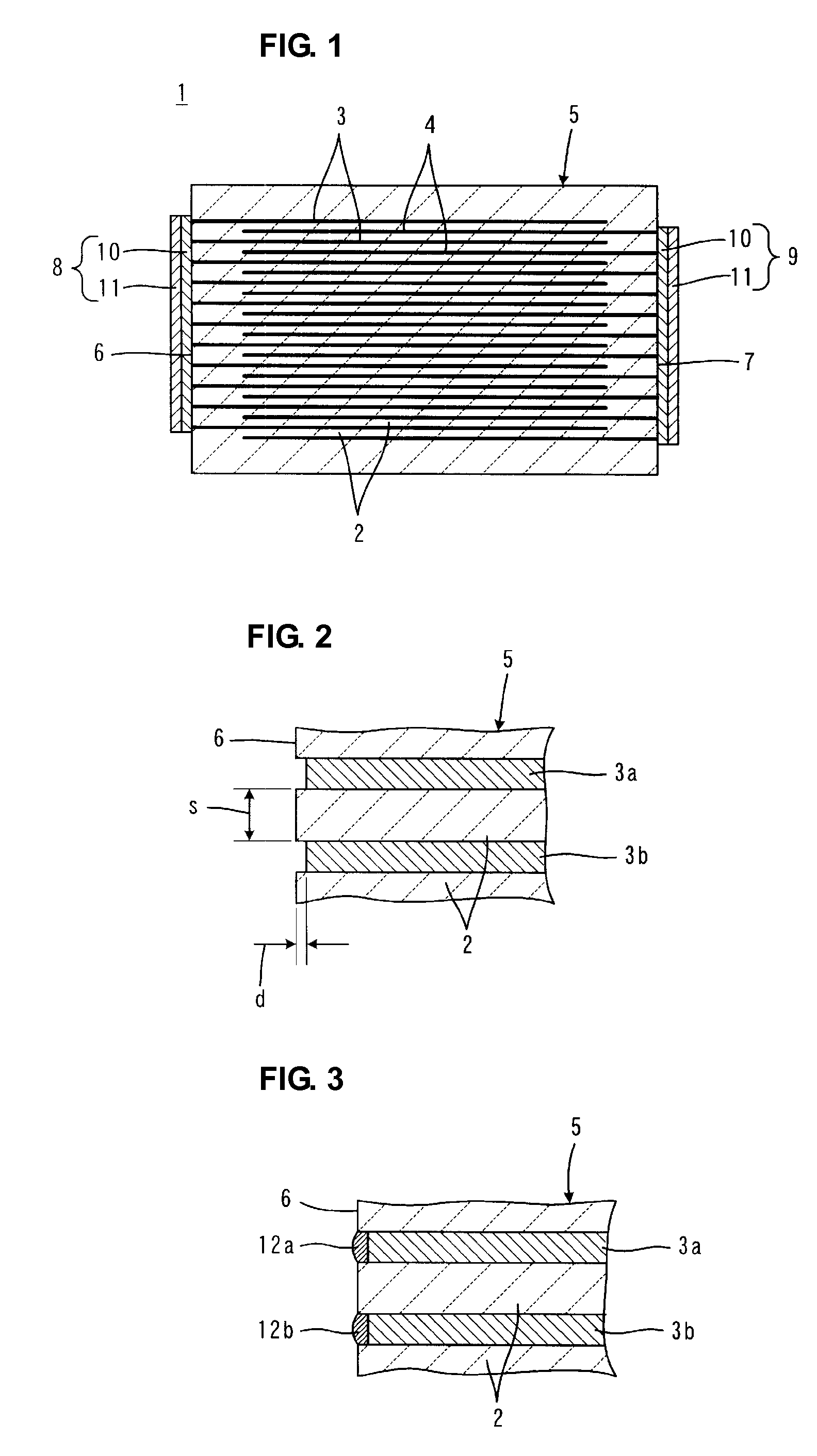

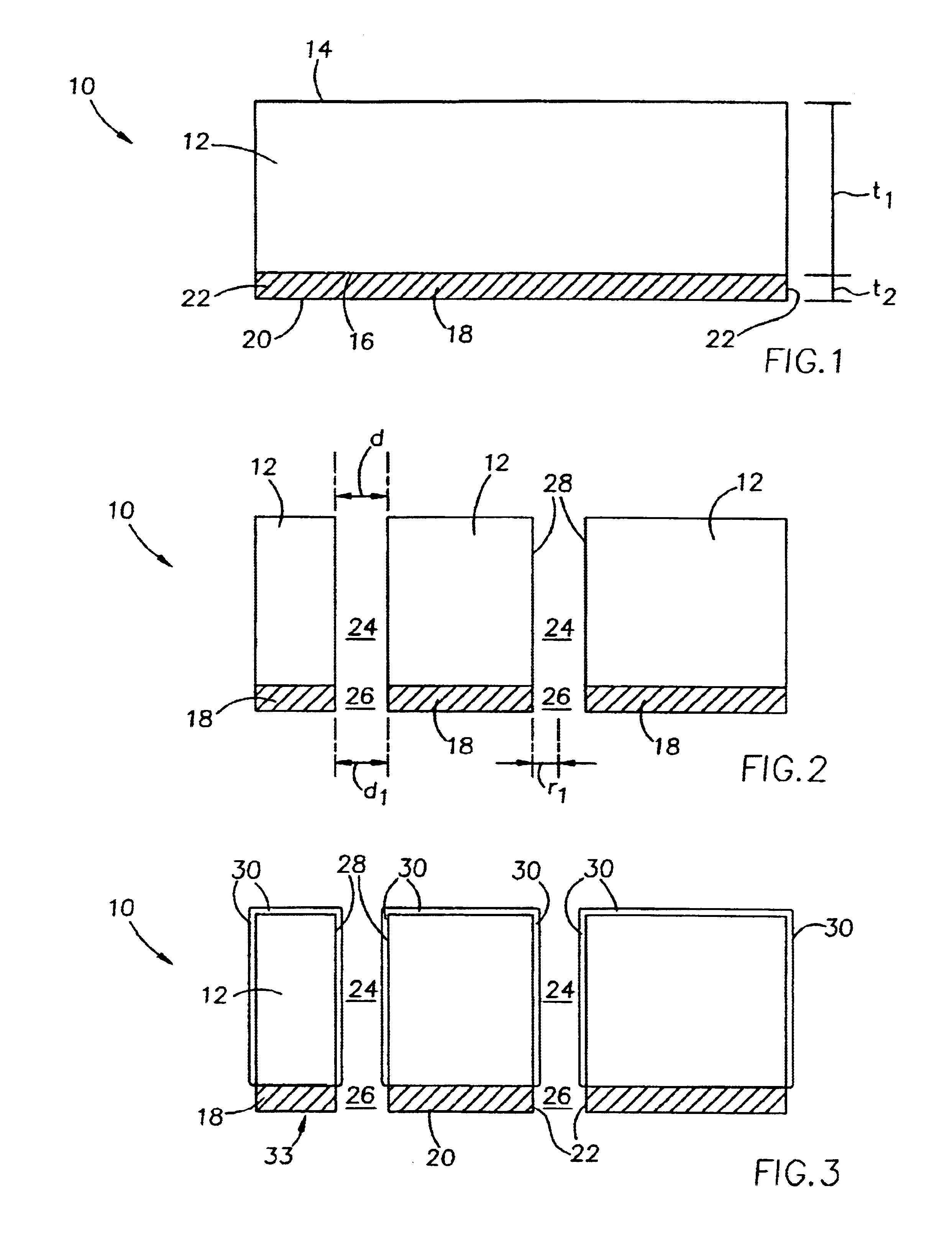

Laminated electronic component and method for manufacturing the same

ActiveUS20080123249A1Improve the effective volume ratioImprove reliabilityFixed capacitor dielectricStacked capacitorsElectronic componentElectron

A laminated body is prepared, in which at an end surface at which internal electrodes are exposed, the internal electrodes disposed adjacently are electrically isolated from each other, and a distance between the internal electrodes disposed adjacently is about 20 μm or less when measured along the thickness direction of an insulator layer, and a withdrawn-depth of the internal electrodes is about 1 μm or less when measured from the end surface. In a step of electroless plating, plating deposits formed at the end portions of the plurality of internal electrodes are increased in size so as to be connected to each other.

Owner:MURATA MFG CO LTD

Multilayer ceramic capacitor with terminal formed by electroless plating

InactiveUS20080158774A1High strengthFixed capacitor electrodesFixed capacitor dielectricCeramic capacitorElectroless deposition

A terminal to, most commonly, a ceramic capacitor, most commonly a multilayer ceramic capacitor (MLCC), is formed by electroless plating, also known as electroless deposition or simply as electrodeposition. In the MLCC having a multiple parallel interior plates brought to, and exposed at, at least one, first, surface, an electrically-conductive first-metal layer, preferably Cu, is electrolessly deposited upon this first surface directly in contact with, mechanically connected to, and electrically connected to, the edges of these interior plates. Lateral growth of the electrolessly-deposited first-metal is sufficient to span from exposed plate to exposed plate, electrically connecting the plates. One or more top layers, preferably one of Ni and one of Sn and Pb, are deposited, preferably by plating and more preferably by electrolytic plating, on top of the electrolessly-deposited Cu.

Owner:PRESIDIO COMPONENTS

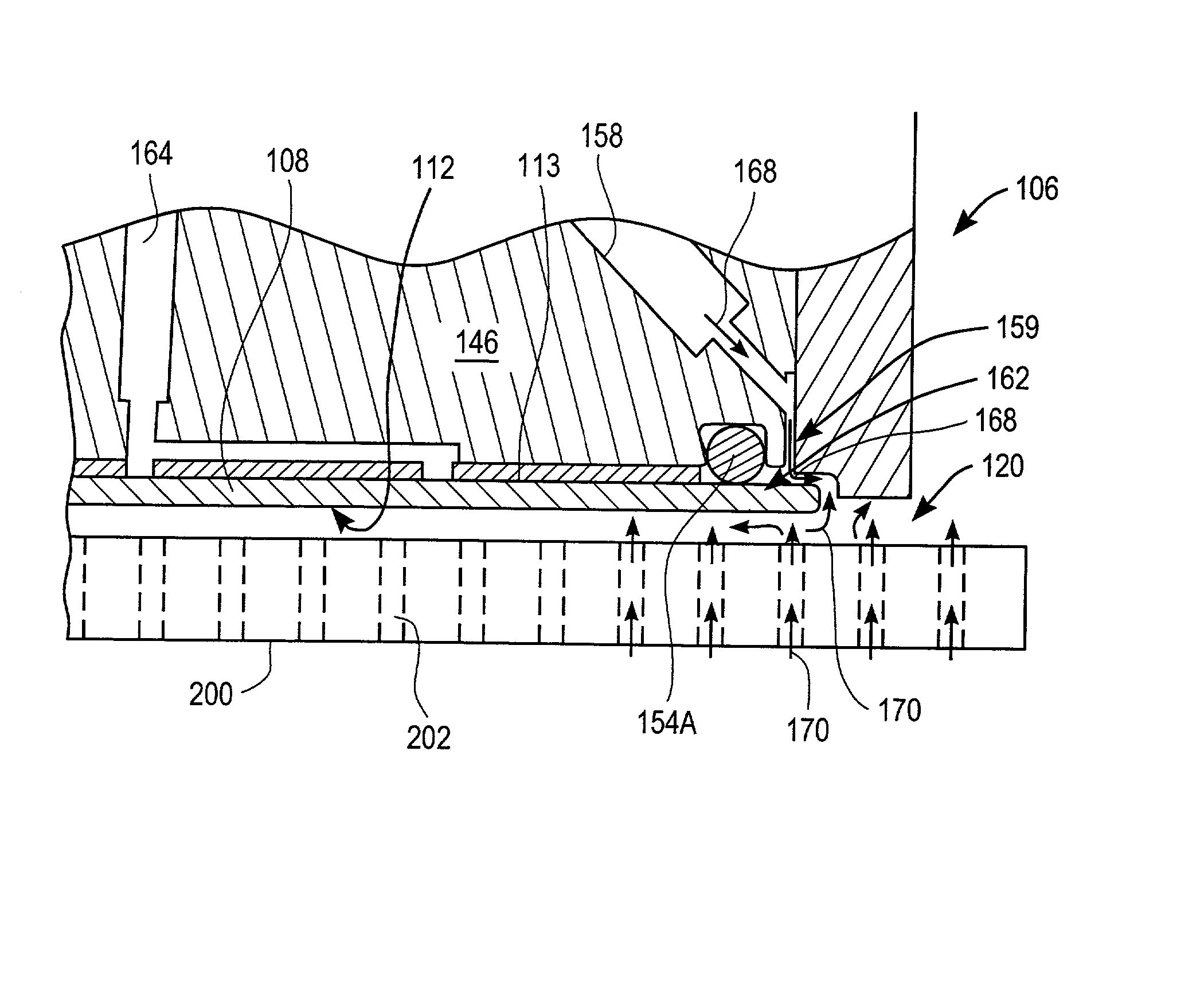

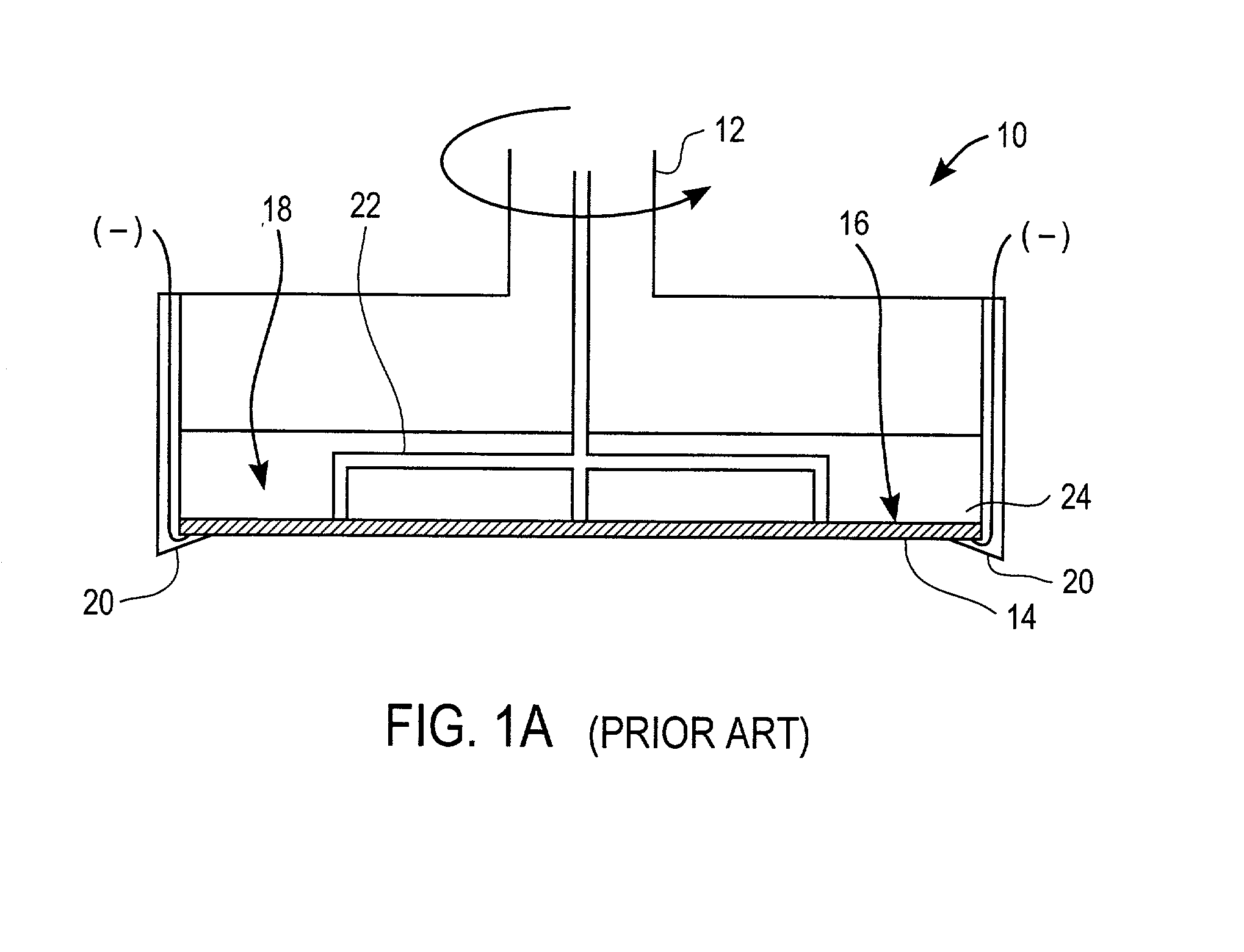

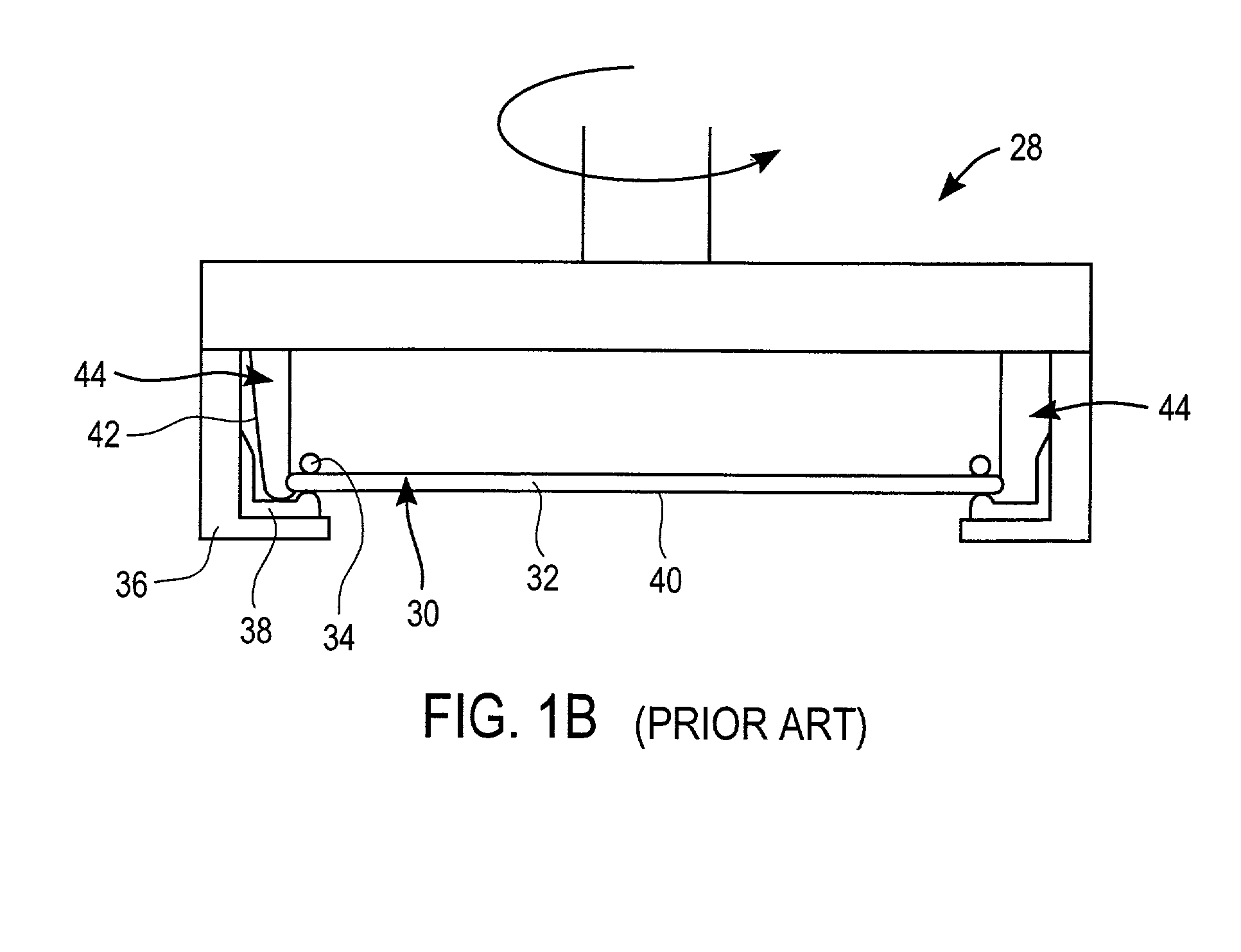

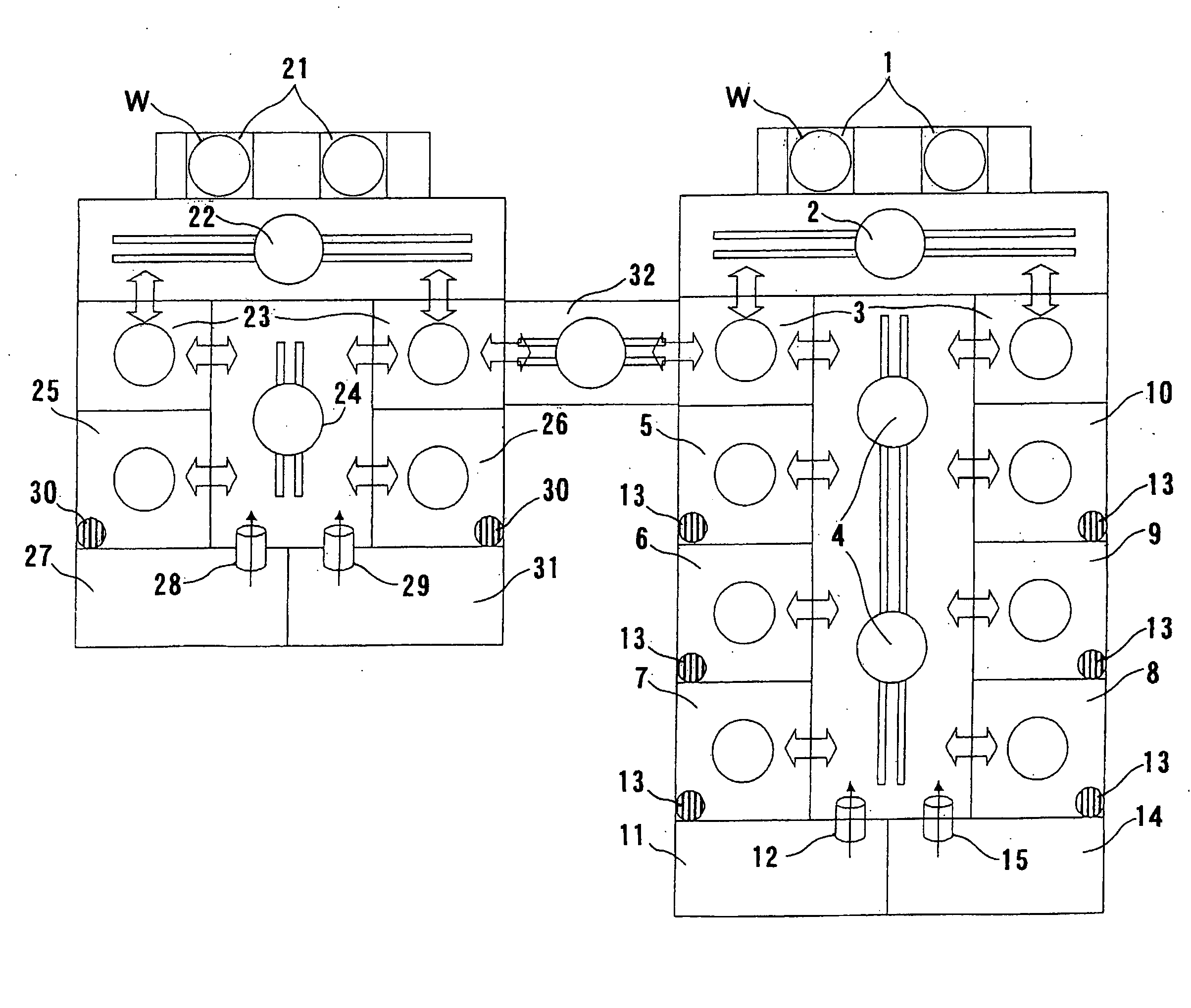

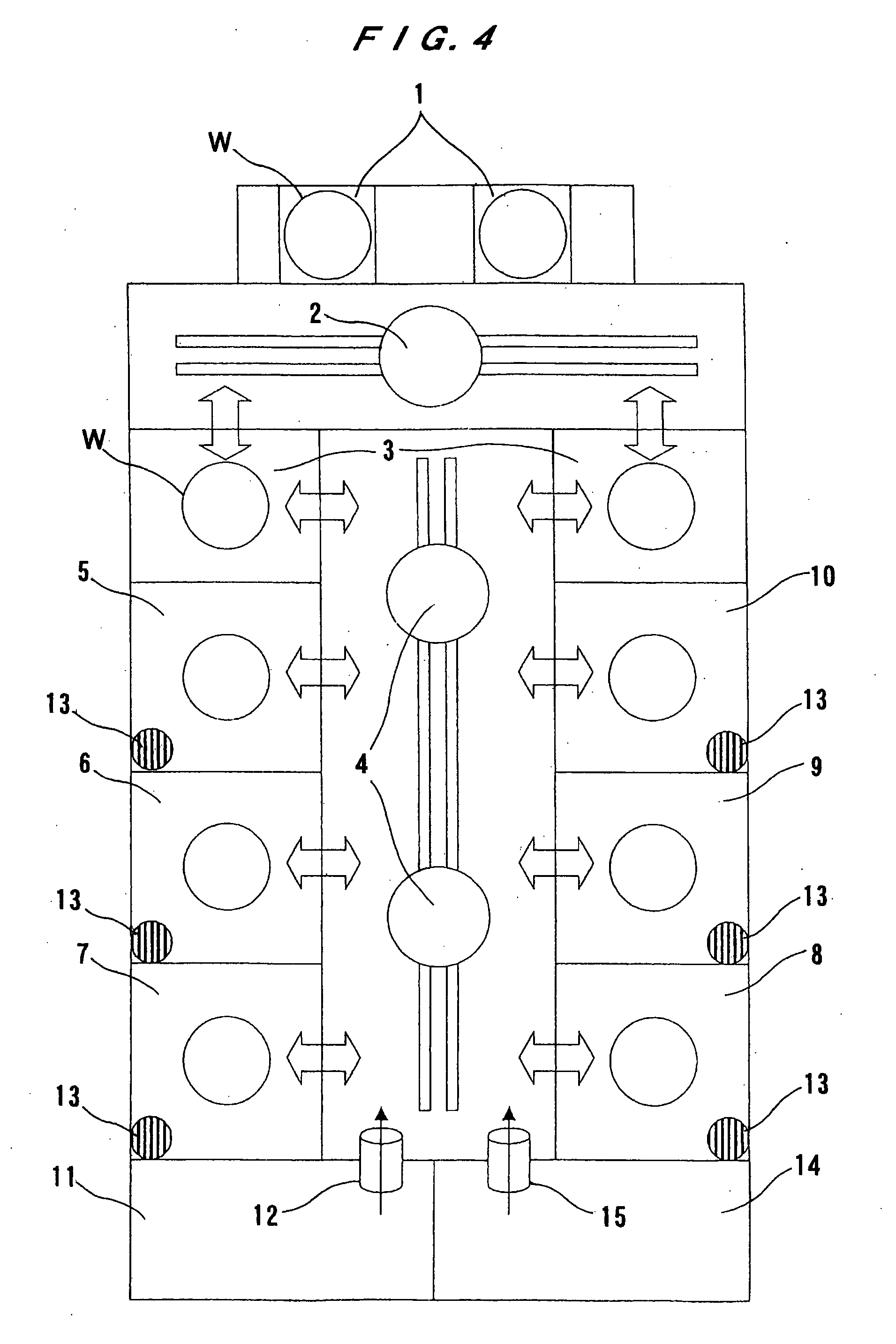

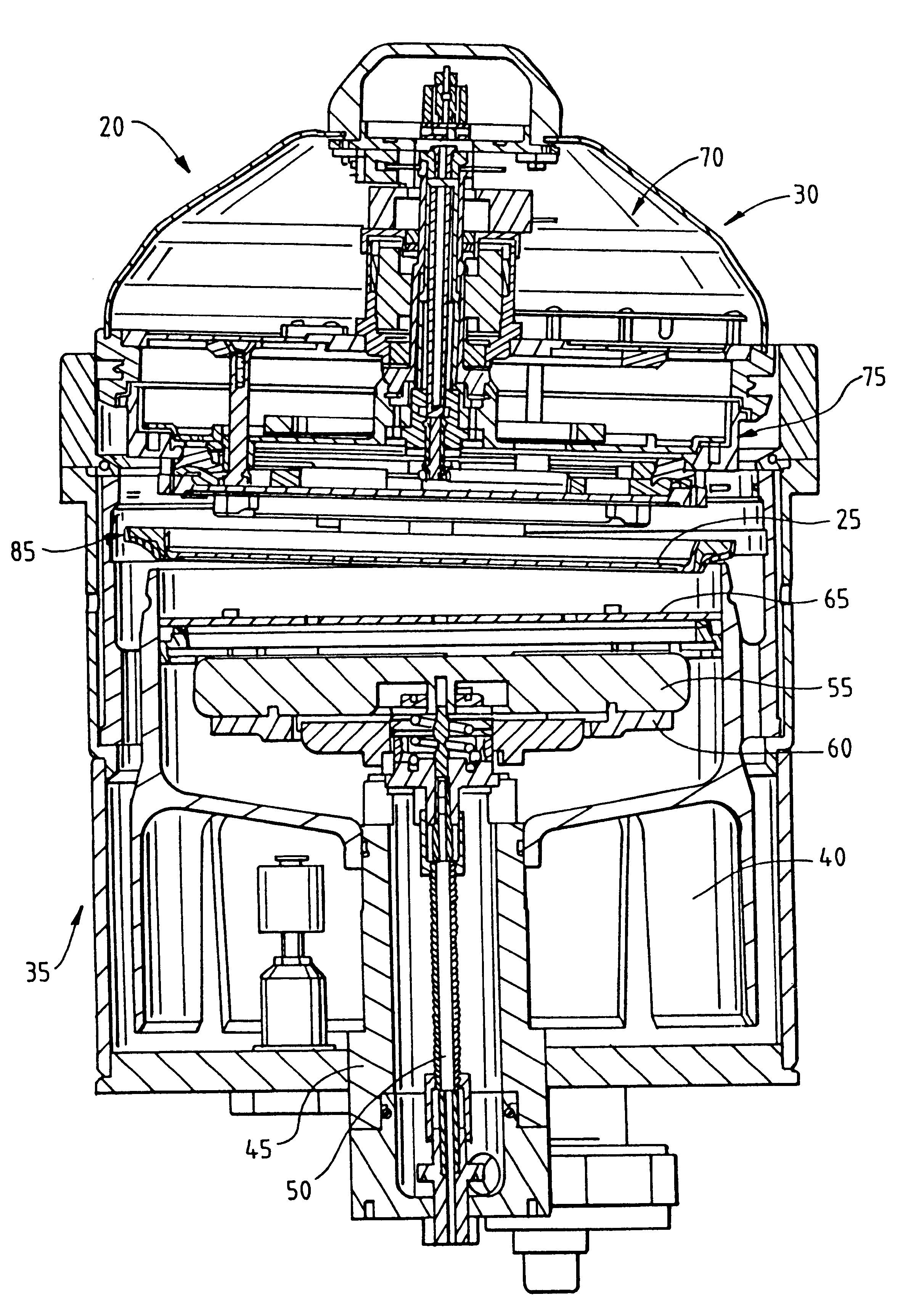

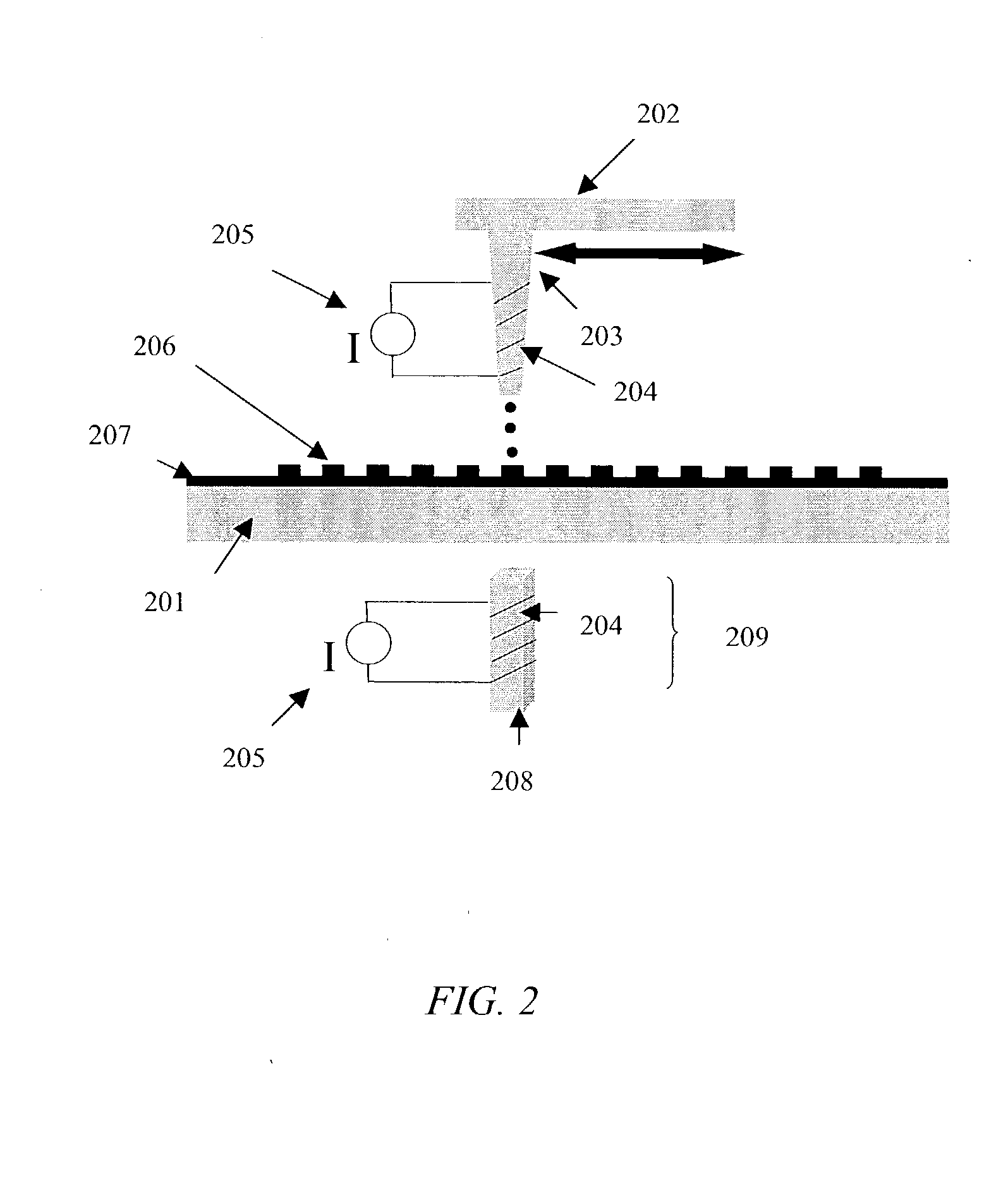

Methods and apparatus for processing the surface of a microelectronic workpiece

InactiveUS6309524B1Reduce the risk of contaminationReduce downtimeCellsTanksEngineeringMechanical engineering

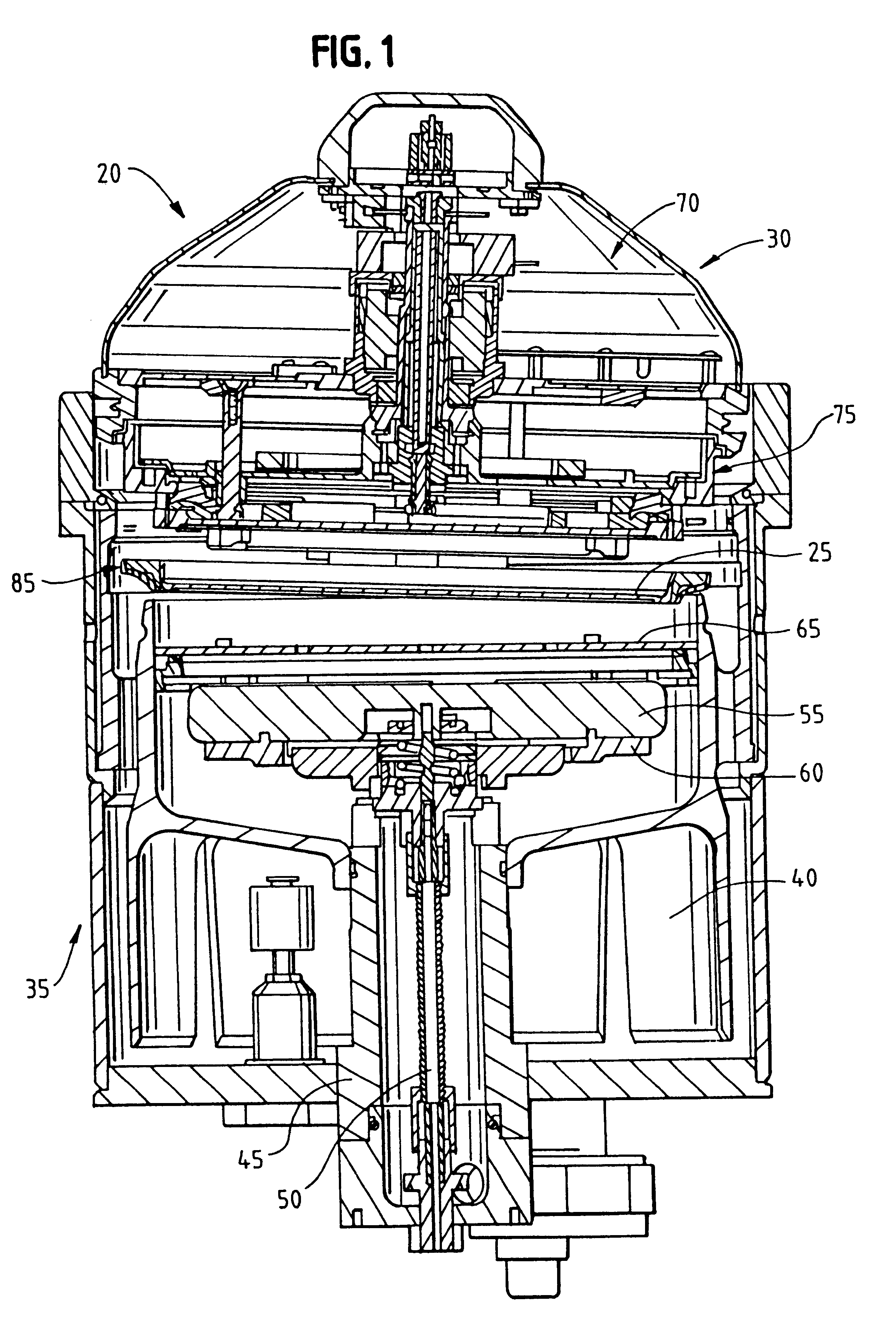

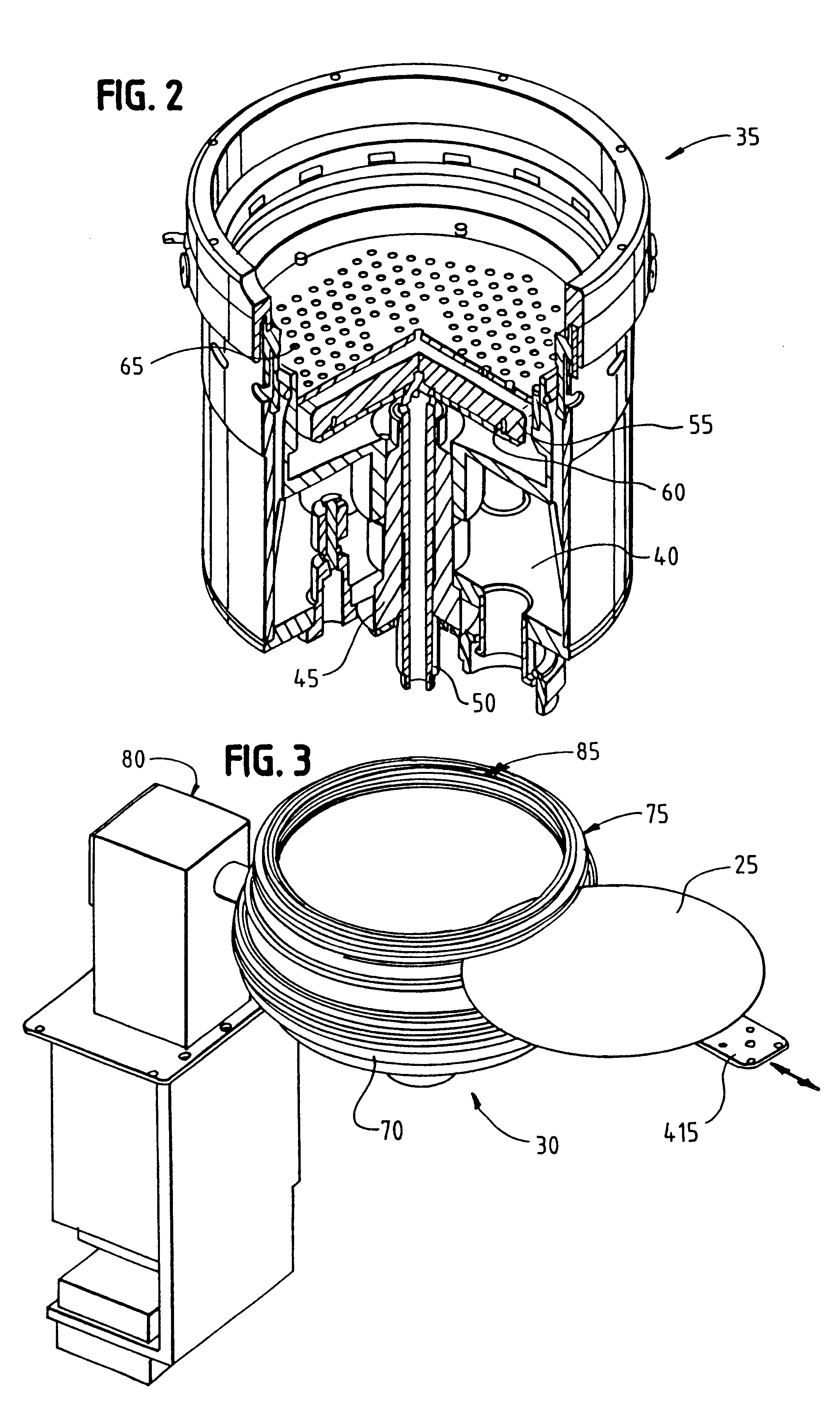

A reactor for plating a metal onto a surface of a workpiece is set forth. The reactor comprises a reactor bowl including an electroplating solution disposed therein and an anode disposed in the reactor bowl in contact with the electroplating solution. A contact assembly is spaced from the anode within the reactor bowl. The contact assembly includes a plurality of contacts disposed to contact a peripheral edge of the surface of the workpiece to provide electroplating power to the surface of the workpiece. The contacts execute a wiping action against the surface of the workpiece as the workpiece is brought into engagement therewith. The contact assembly also including a barrier disposed interior of the plurality of contacts. The barrier includes a member disposed to engage the surface of the workpiece to assist in isolating the plurality of contacts from the electroplating solution. In one embodiment, the plurality of contacts are in the form of discrete flexures while in another embodiment the plurality of contacts are in the form of a Belleville ring contact. A flow path may be provided in the contact assembly for providing a purging gas to the plurality of contacts and the peripheral edge of the workpiece. The purging gas may be used to assist in the formation of the barrier of the contact assembly. A combined electroplating / electroless plating tool and method are also set forth.

Owner:APPLIED MATERIALS INC

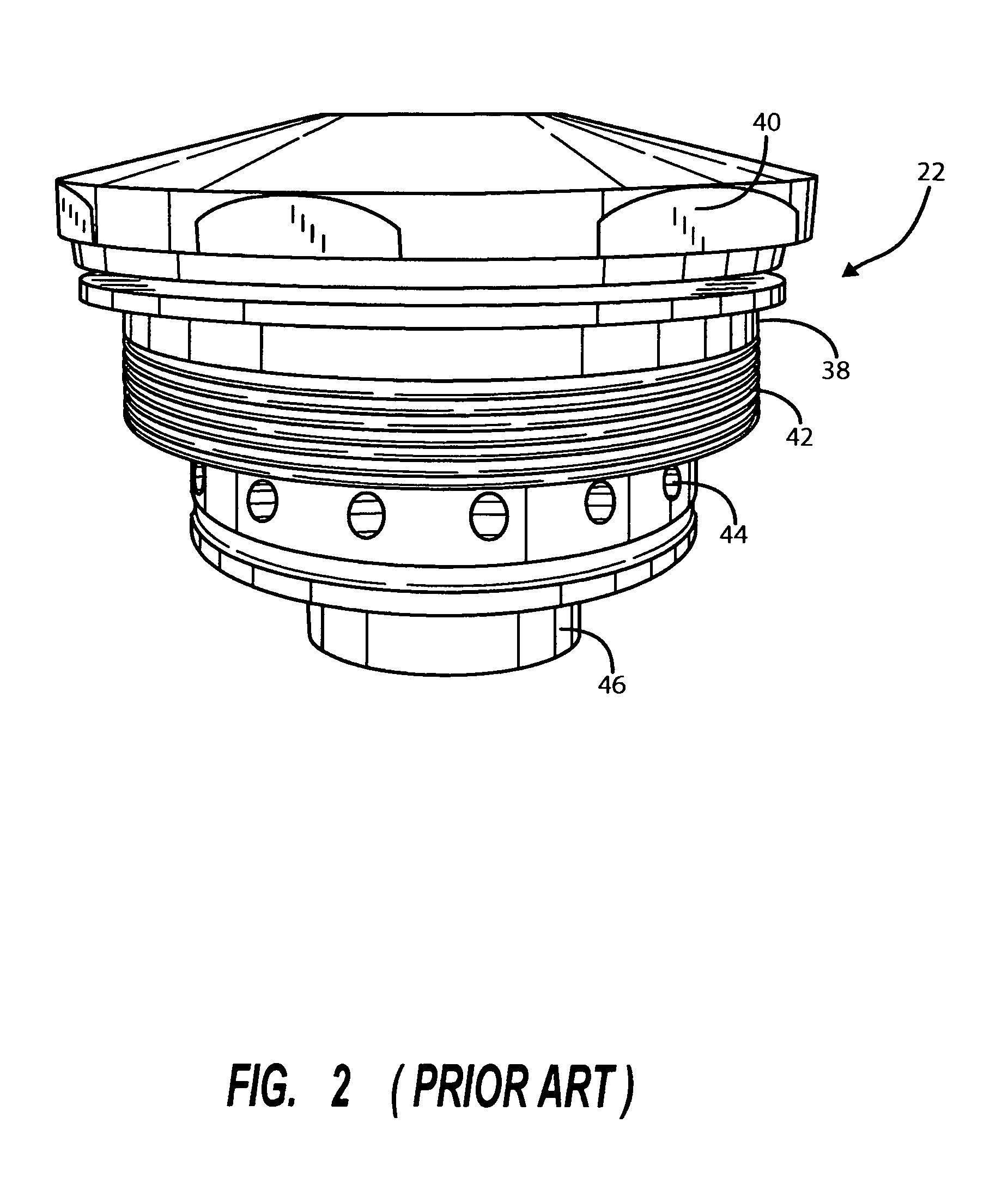

Plasma torch with corrosive protected collimator

ActiveUS20070084834A1Welding/cutting media/materialsWelding electrode featuresTorchPlasma arc welding

To protect the collimator of a transferred plasma arc torch from premature failure due to corrosion, an anti-corrosive covering is applied on the exposed face surface and a portion of the inner exit bore of the collimator. The specification describes several methods for producing the collimator for a plasma torch having an anti-corrosive coating or cladding on the exposed surfaces thereof, including electroplating, electroless plating, flame spraying, plasma spraying, plasma transferred arc, hot isostatic pressing and explosive cladding.

Owner:PHOENIX SOLUTIONS CO

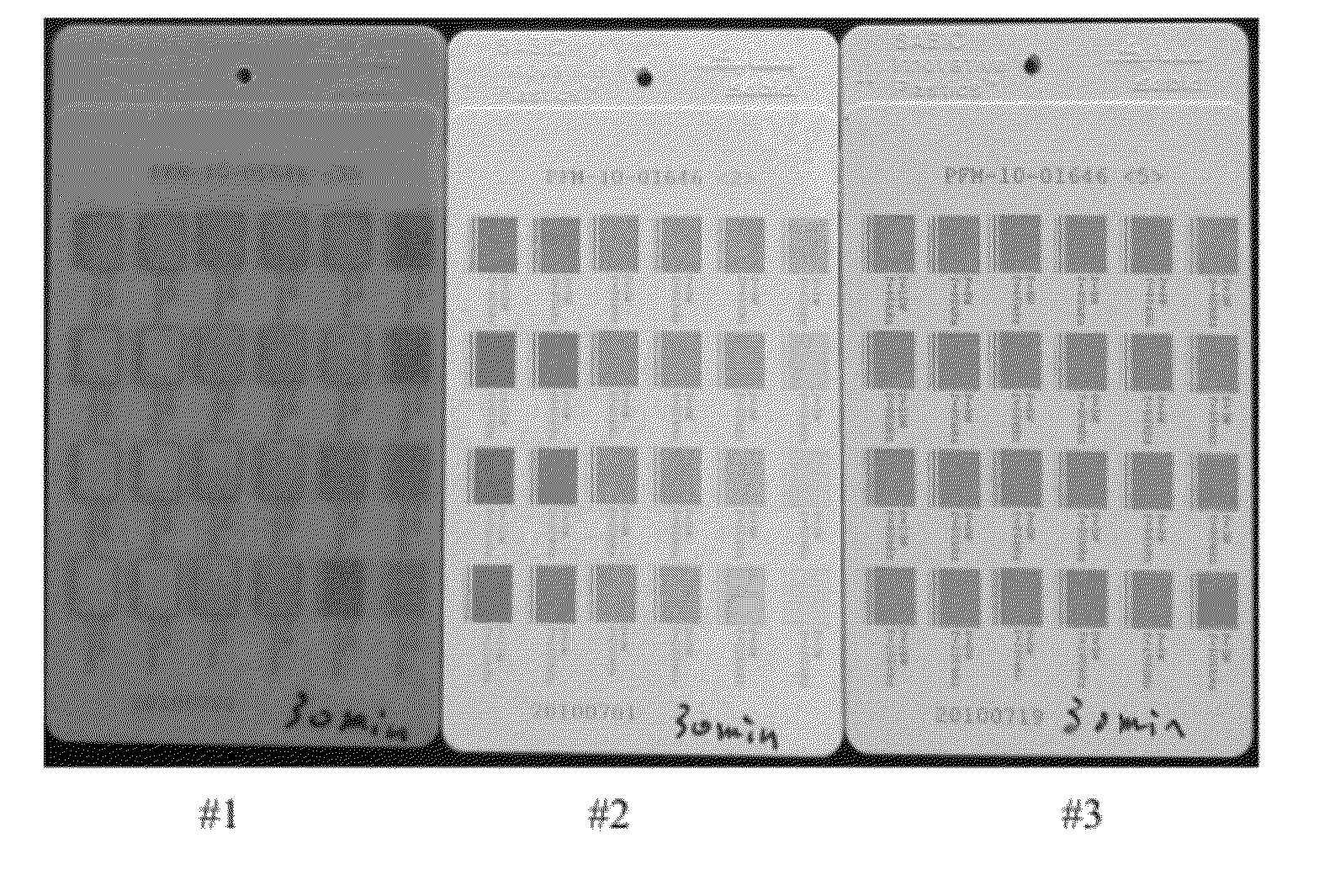

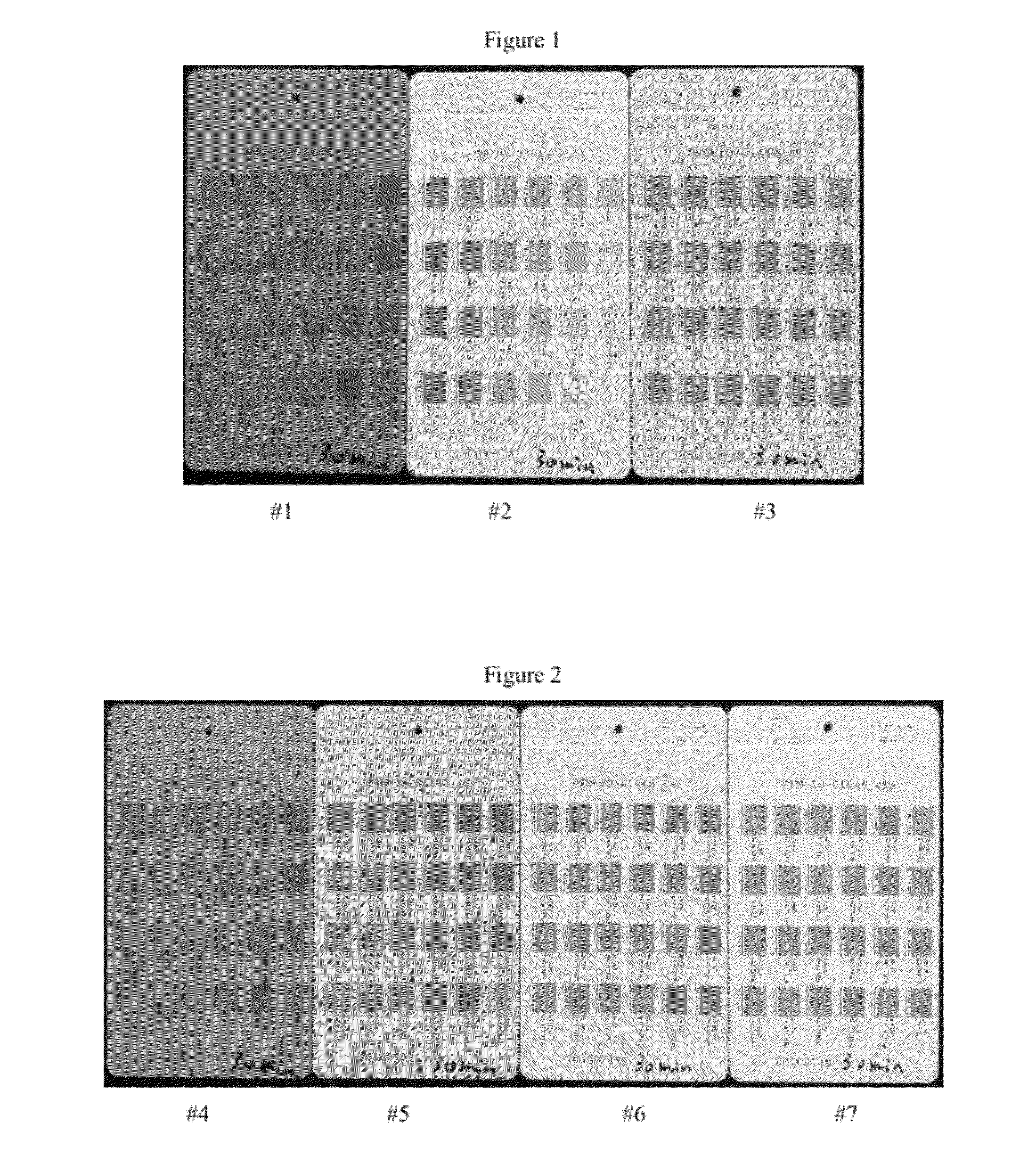

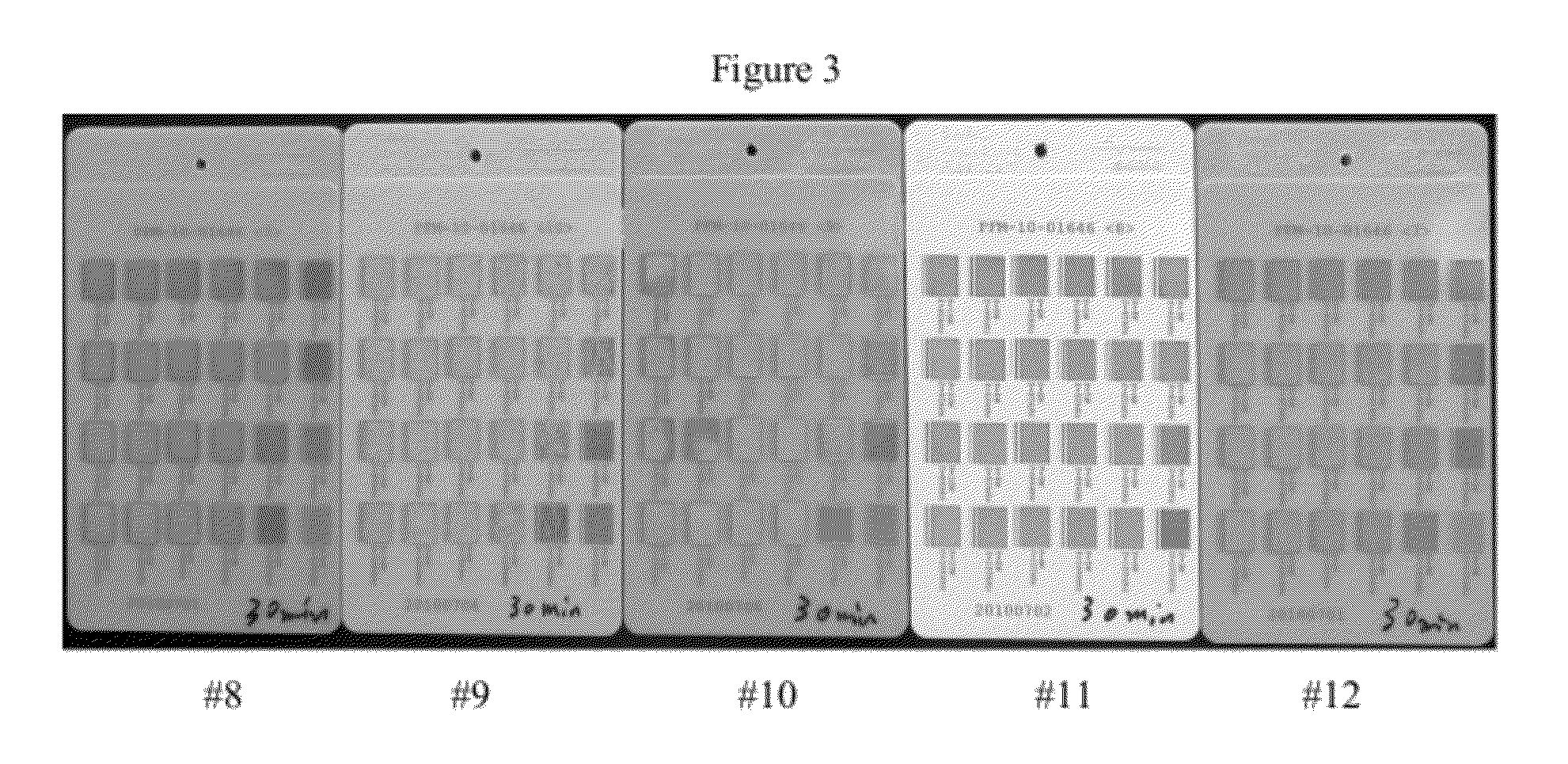

Electroless plating performance of laser direct structuring materials

Thermoplastic compositions that are capable of being used in a laser direct structuring process to provide enhanced plating performance and good mechanical properties. The compositions of the present invention include a thermoplastic base resin, a laser direct structuring additive and a white pigment. The compositions can be used in a variety of applications such as personal computers, notebook and portable computers, cell phone antennas and other such communications equipment, medical applications, RFID applications, and automotive applications.

Owner:SHPP GLOBAL TECH BV

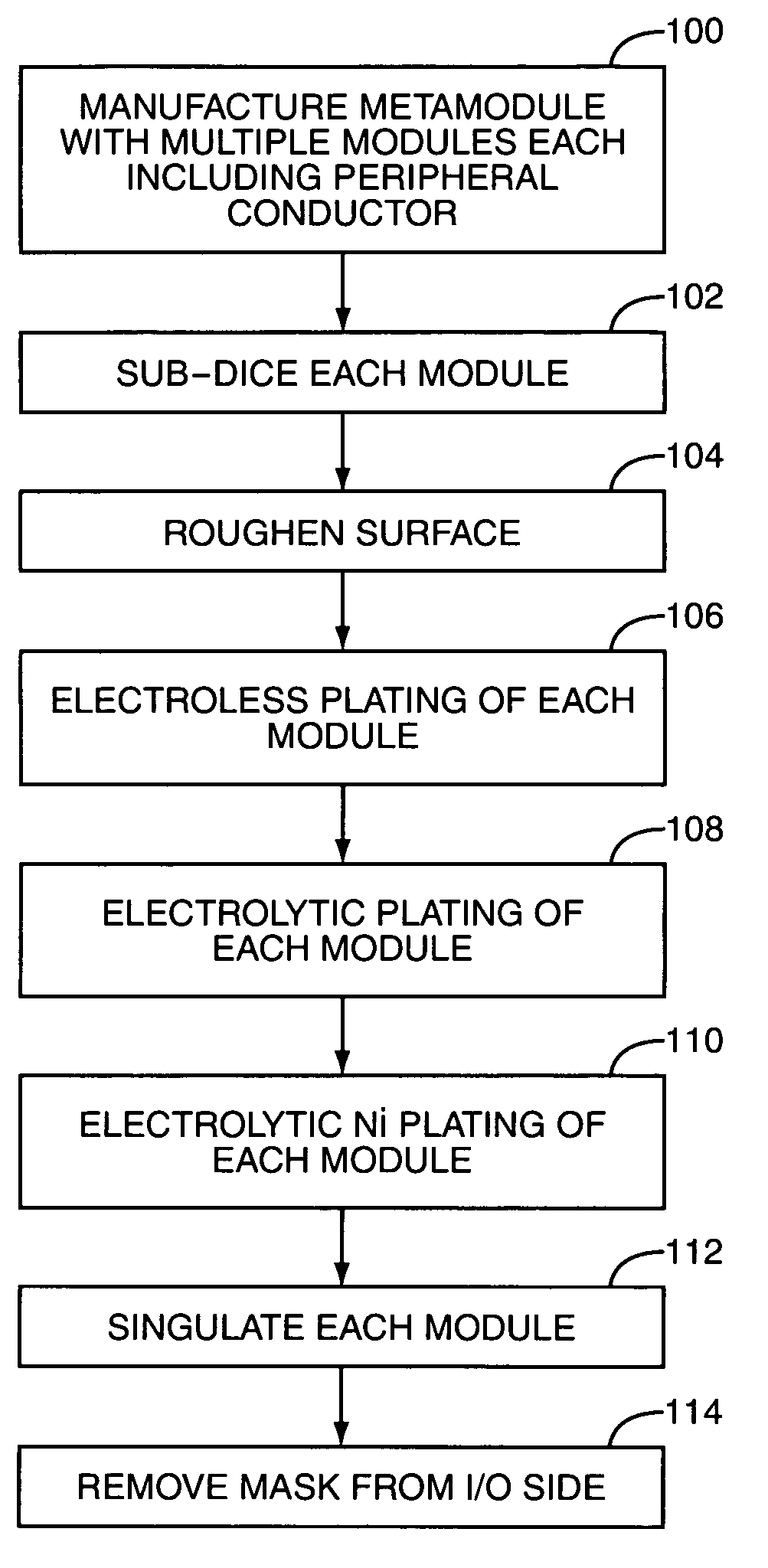

Multilayer conductive appliance having wound healing and analgesic properties

InactiveUS6861570B1Increase ion migrationImprove concentrationFinger bandagesNon-adhesive dressingsElectroless platingPain relief

A dressing for promoting healing and pain relief of the body of a living organism having a pathologic condition has at least one layer of conductive material having a resistance no greater than 1000 Ω / cm2. When placed proximate a portion of the body of the living organism suffering from the pathologic condition, the dressing alters the electrodynamic processes occurring in conjunction with said pathologic condition to promote healing and pain relief in the living organism. When used as a wound dressing, the conductive material is placed in contact with tissue around the periphery of the wound and with the wound, lowering the electrical potential and resistance of the wound and increasing the wound current. In an exemplary embodiment, the conductive material is a multi-ply nylon fabric plated with silver by an autocatalytic electroless plating process and with the plies in electrical continuity. The dressing provides an antimicrobial and analgesic effect. The dressing may be provided for numerous applications and may include other layers such as an absorbent layer, a semi-permeable layer and additional layer of conductor material. Multilaminate embodiments of the present invention exhibit conductive material concentration gradients and, potentially, a capacitive effect when sequential conductor layers are insulated by intervening layers.

Owner:ARGENTUM INT

Method of making a conformal electromagnetic interference shield

An electromagnetic shield for an electronic module includes a surface finish that is applied to the surface of an electronic module so as to minimize the size of the shield. Once the shield is in place, the shield acts to address electromagnetic interference (EMI) concerns associated with the electronic module. An electronic module having a ring of conductive material embedded about its peripheral edge is formed. The electronic module is then sub-diced so as to expose the ring of conductive material. After sub-dicing, a conductive material may be applied through an electroless plating process followed by an electrolytic plating process. Alternatively, a conductive epoxy may be sprayed or painted onto the surface of the electronic module.

Owner:QORVO US INC

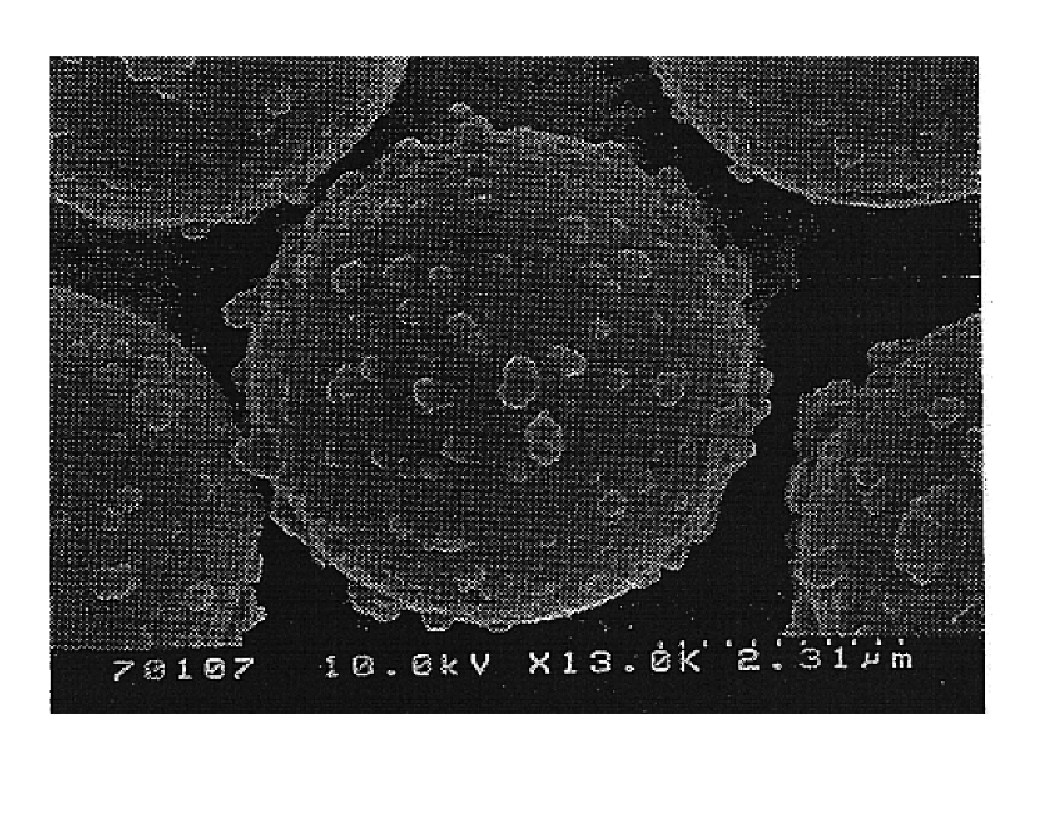

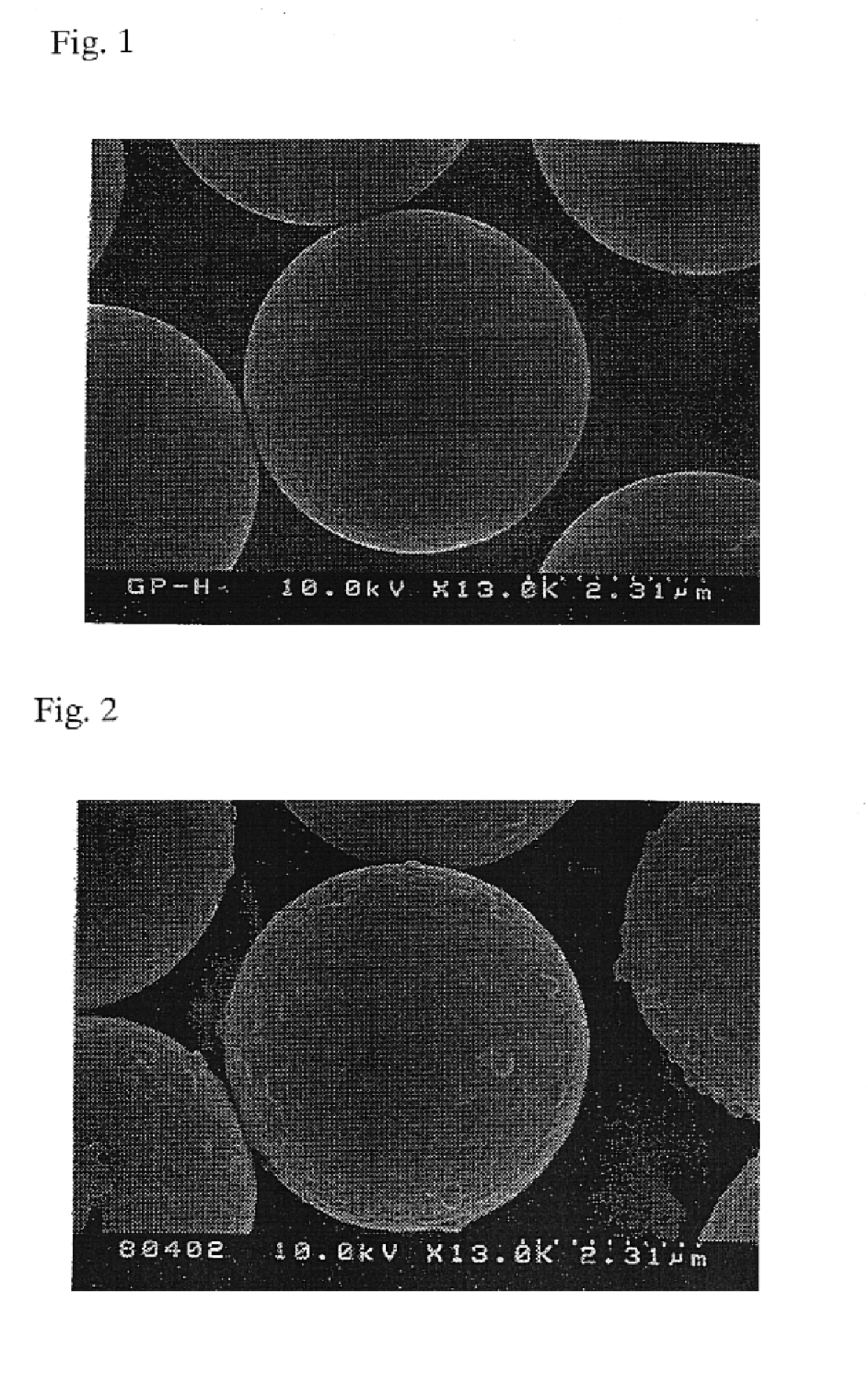

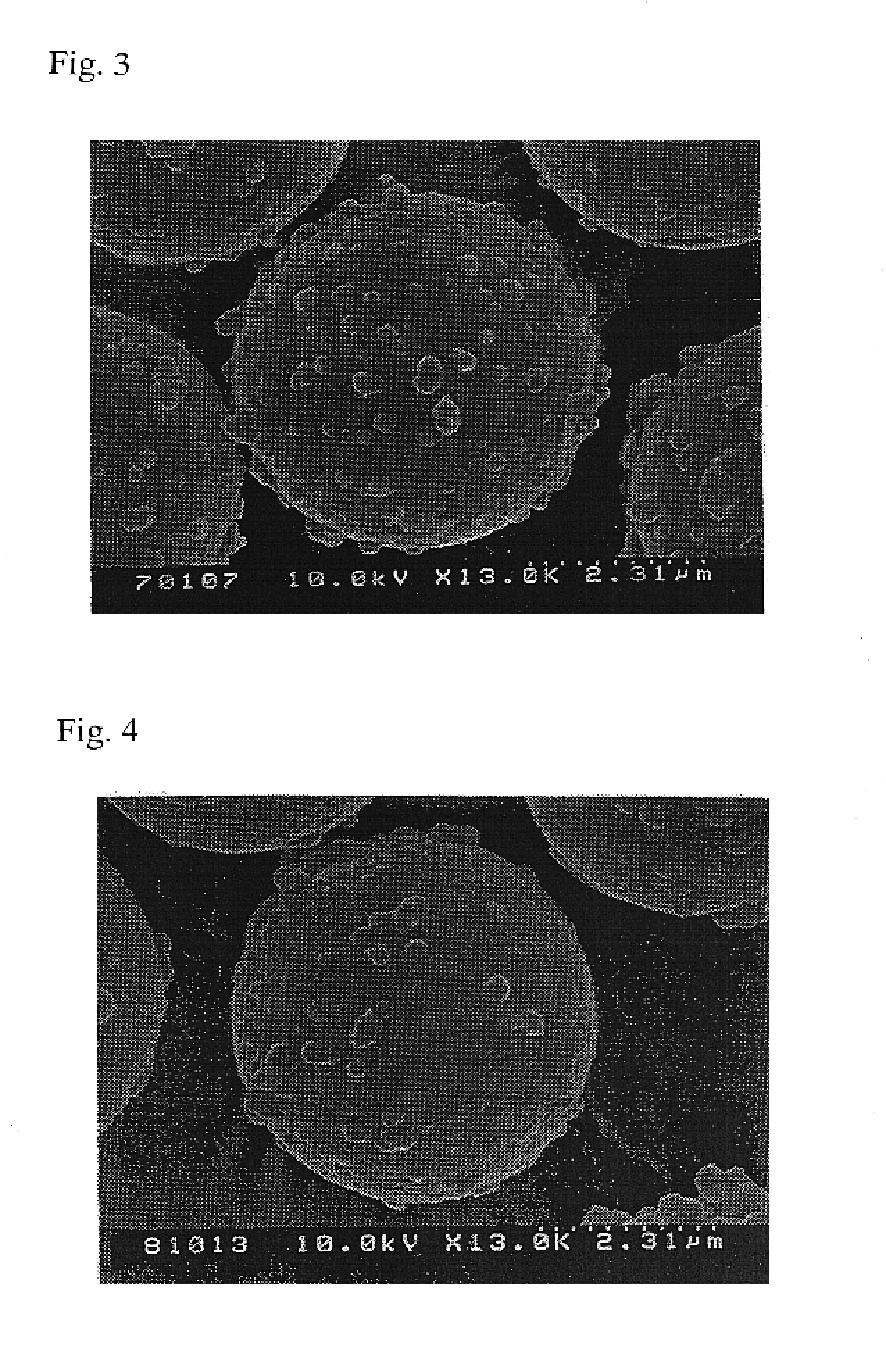

Conductive electrolessly plated powder, its producing method, and conductive material containing the plated powder

A conductive electrolessly plated powder used, for example, for bonding a small electrode of an electronic device, its producing method, and a conductive material containing the plated powder. Conventionally, there has been known, as conductive powders, metallic powders such as of nickel, carbon powders, and conductive plating powders the resin core particles of which are coated with a metal, e.g., nickel. However, there has been no conductive electrolessly plated powders having a good conductivity with respect to connection between conductive patterns having an oxide coating thereon or between electrodes and no methods for producing such powders industrially. The conductive electrolessly plated powder of the present invention consists of resin spherical core particles the average size of which is 1 to 20 mum and each of which has a nickel or nickel alloy coating formed by electroless plating. The coating includes small projections of 0.05 to 4 mum on its outermost layer and the coating is substantially continuous with the small projections. A method of producing such a powder is also disclosed.

Owner:NIPPON CHECMICAL IND CO LTD

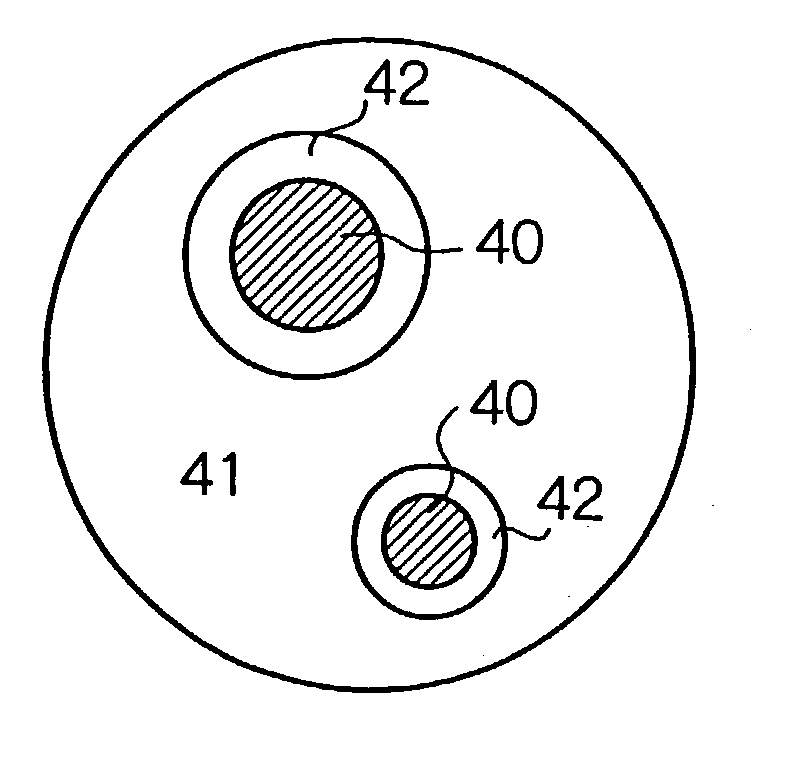

Process for manufacture of negative electrode material for a non-aqueous electrolyte secondary battery

InactiveUS20030175589A1Maintain good propertiesReduce battery sizeSolid electrolytesElectrode manufacturing processesAlloySolid solution

A negative electrode material for a nonaqueous electrolyte secondary battery having a high discharge capacity and a good cycle life is made from alloy particles having an average particle diameter of 0.1-50 mum and including Si phase grains 40 and a phase of a solid solution or an intermetallic compound of Si and other element selected from Group 2A elements, transition elements, Group 3B elements, and Group 4B elements from the long form periodic table (for example, an NiSi2 phase 42 and an [NiSi2+NiSi] phase 41) at least partially enveloping the Si phase grains. 5-99 wt % of this material is Si phase grains. The alloy particles can be manufactured by rapid solidification (such as atomization or roller quenching) of a melt including Si and the other element, or by adhering the other element to Si powder by electroless plating or mechanical alloying and then performing heat treatment. Even if rapid solidification is carried out, a negative electrode material having a good discharge capacity and cycle life is obtained without heat treatment.

Owner:CHUO DENKI KOGYO CO LTD

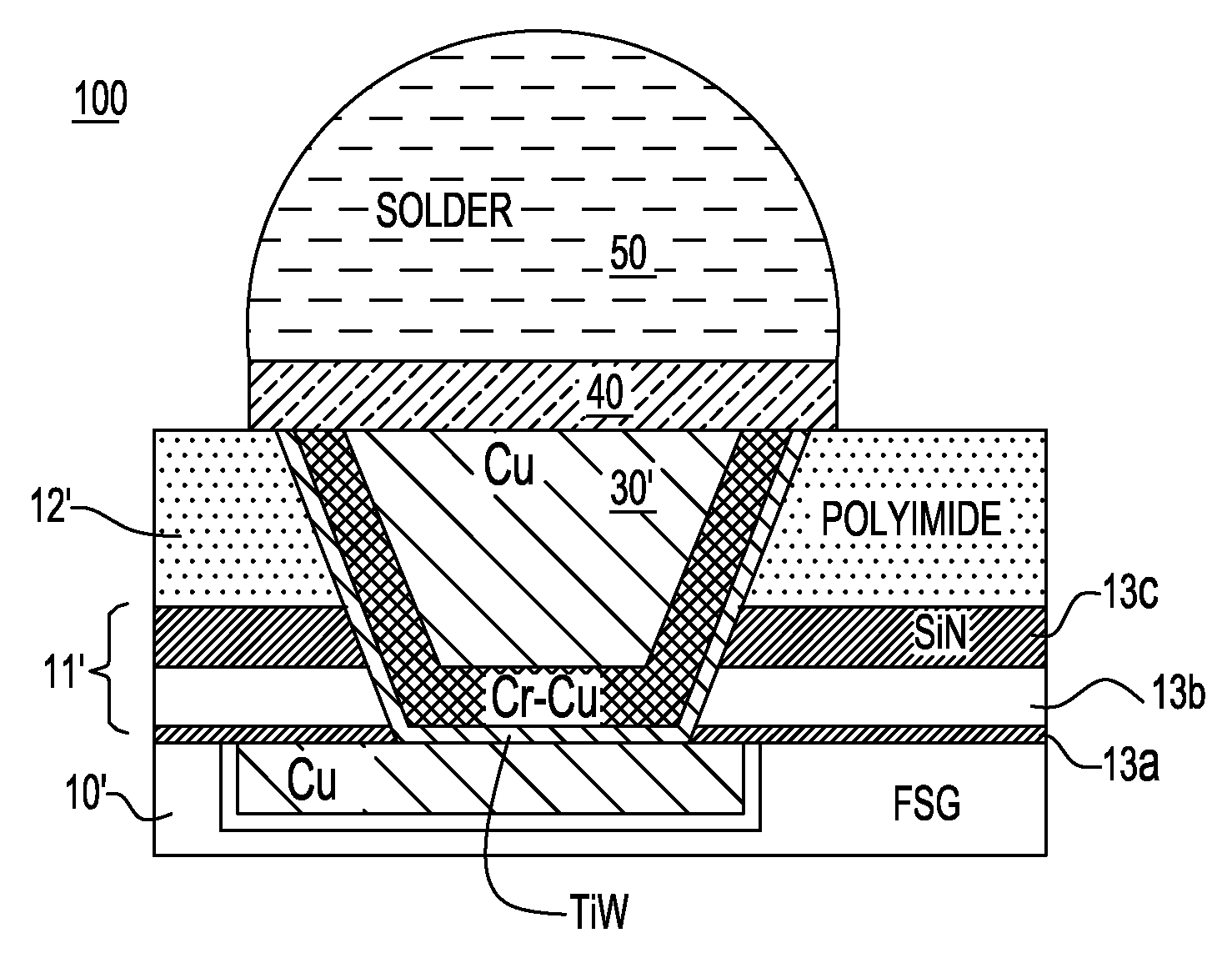

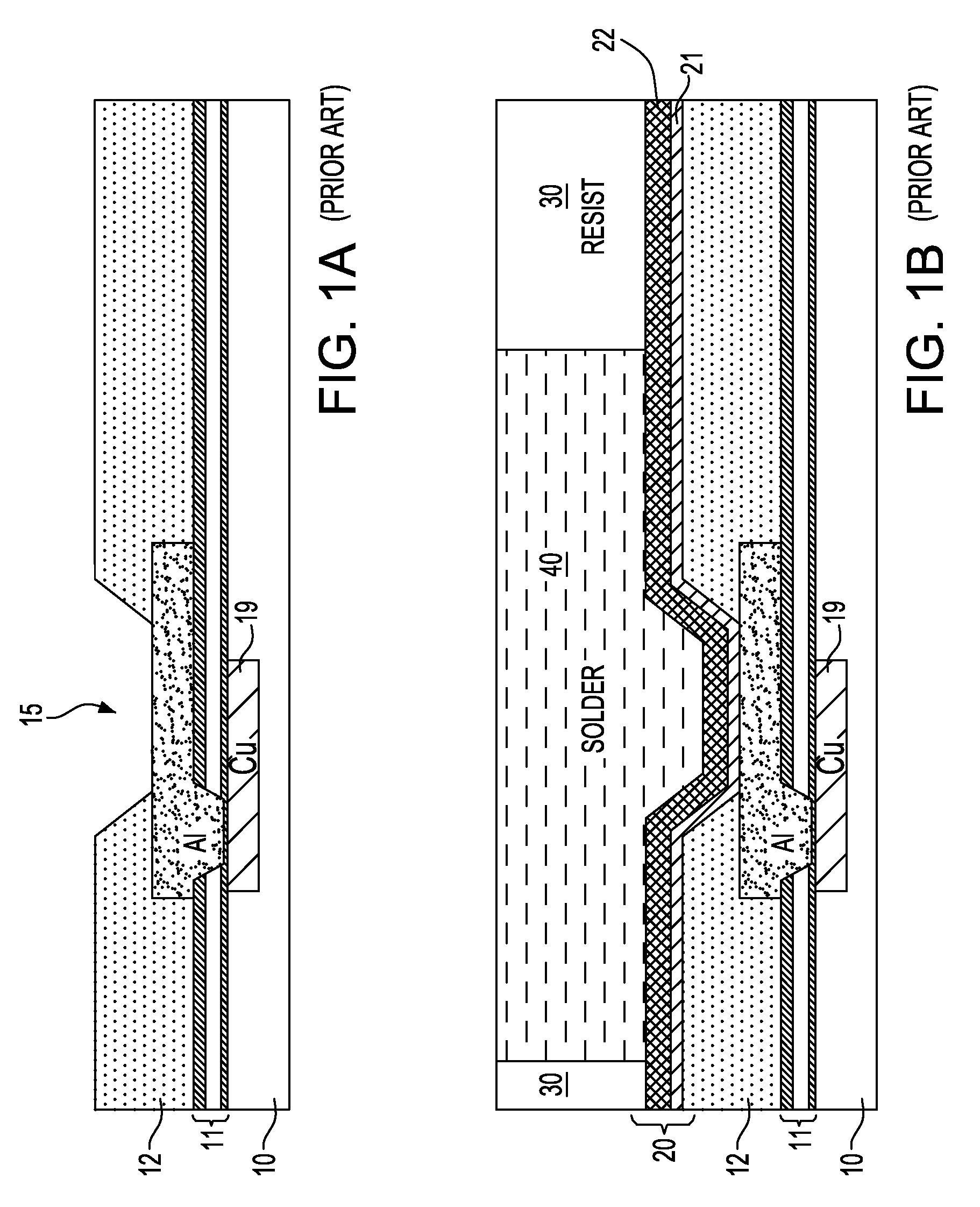

Undercut-free blm process for pb-free and pb-reduced c4

InactiveUS20080194095A1Reduce the amount presentReduce spacingSemiconductor/solid-state device detailsSolid-state devicesDiffusion barrierElectroplating

A system and method for eliminating undercut when forming a C4 solder bump for BLM (Ball Limiting Metallurgy) and improving the C4 pitch. In the process, a barrier layer metal stack is deposited above a metal pad layer. A top layer of the barrier layer metals (e.g., Cu) is patterned by CMP with a bottom conductive layer of the barrier metal stack removed by etching. The diffusion barrier and C4 solder bump may be formed by electroless plating, in one embodiment, using a maskless technique, or by an electroplating techniques using a patterned mask. This allows the pitch of the C4 solder bumps to be reduced.

Owner:ULTRATECH INT INC

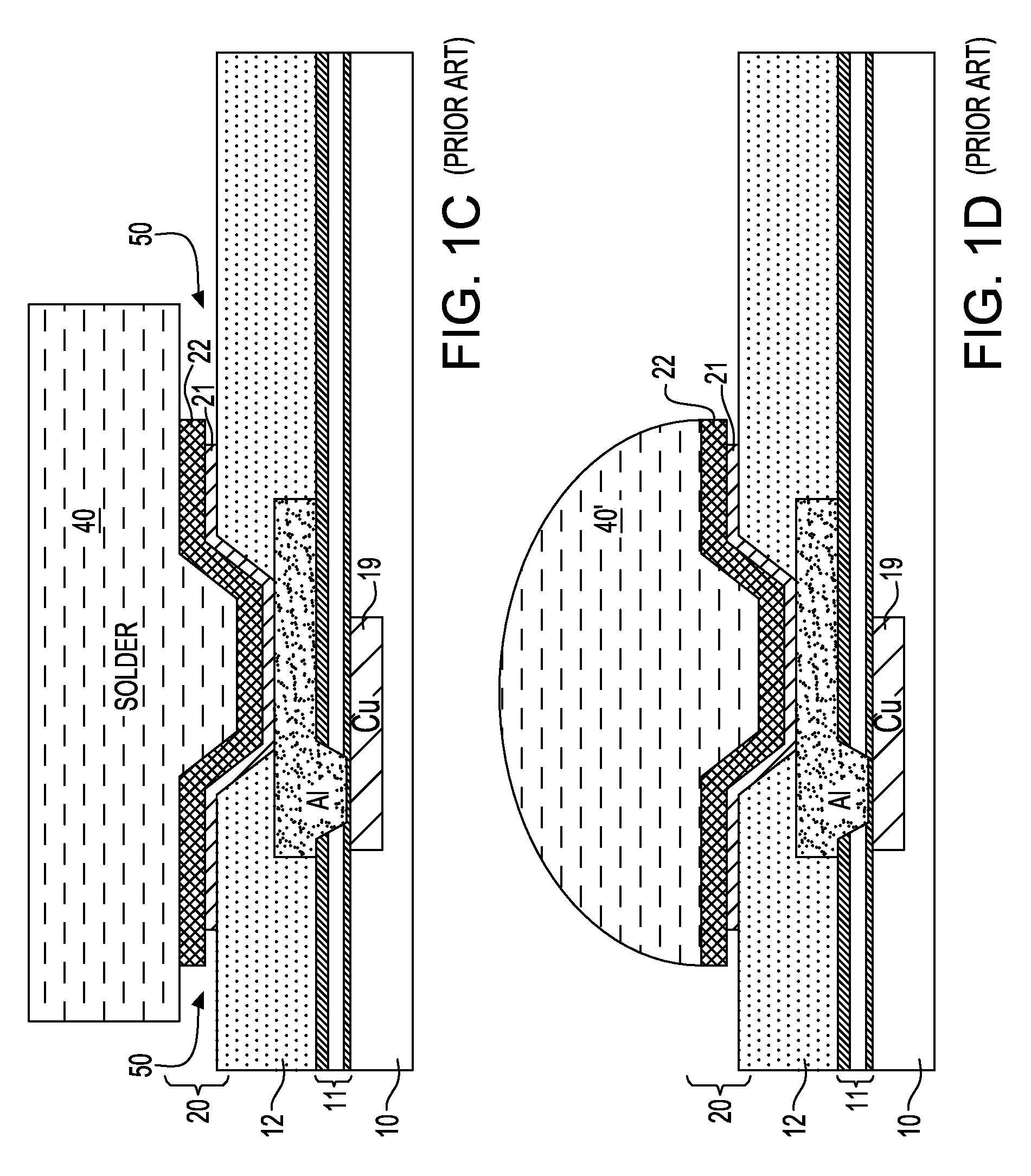

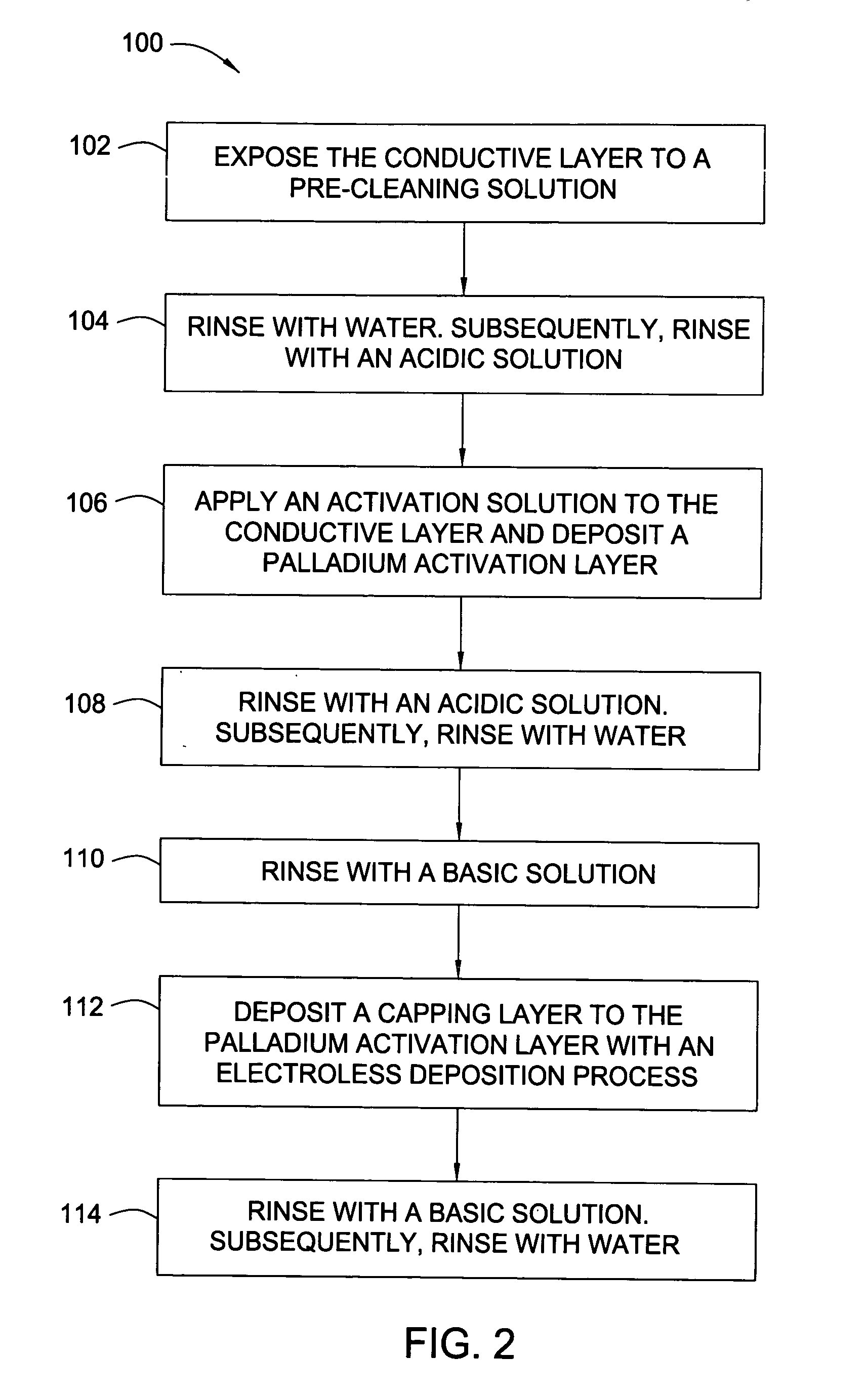

Electroless cobalt alloy deposition process

InactiveUS20050161338A1Semiconductor/solid-state device manufacturingLiquid/solution decomposition chemical coatingDeposition processSURFACTANT BLEND

In one embodiment, a method for depositing a cobalt-containing capping layer on a metal layer is provided which includes rinsing the metal layer with a deionized water wetting step, depositing a palladium layer on the metal layer by exposing the metal layer to an electroless activation solution comprising a palladium precursor and an acid, and depositing the cobalt-containing capping layer on the palladium layer by exposing the palladium layer to an electroless cobalt-containing solution comprising a cobalt source, a tungsten source, an oxygen scavenger and a surfactant. Ascorbic acid may be used as the oxygen scavenger. In another embodiment, a composition of an electroless plating solution is provided which includes a cobalt source at a concentration in a range from about 50 mM to about 250 mM, a tungsten source at a concentration in a range from about 10 mM to about 100 mM, a complexing agent at a concentration in a range from about 10 mM to about 200 mM, at least one reductant at a concentration in a range from about 1 mM to about 100 mM, a surfactant at a concentration in a range from about 1 mg / L to about 100 mg / L, and ascorbic acid at a concentration in a range from about 30 mg / L to about 300 mg / L.

Owner:APPLIED MATERIALS INC

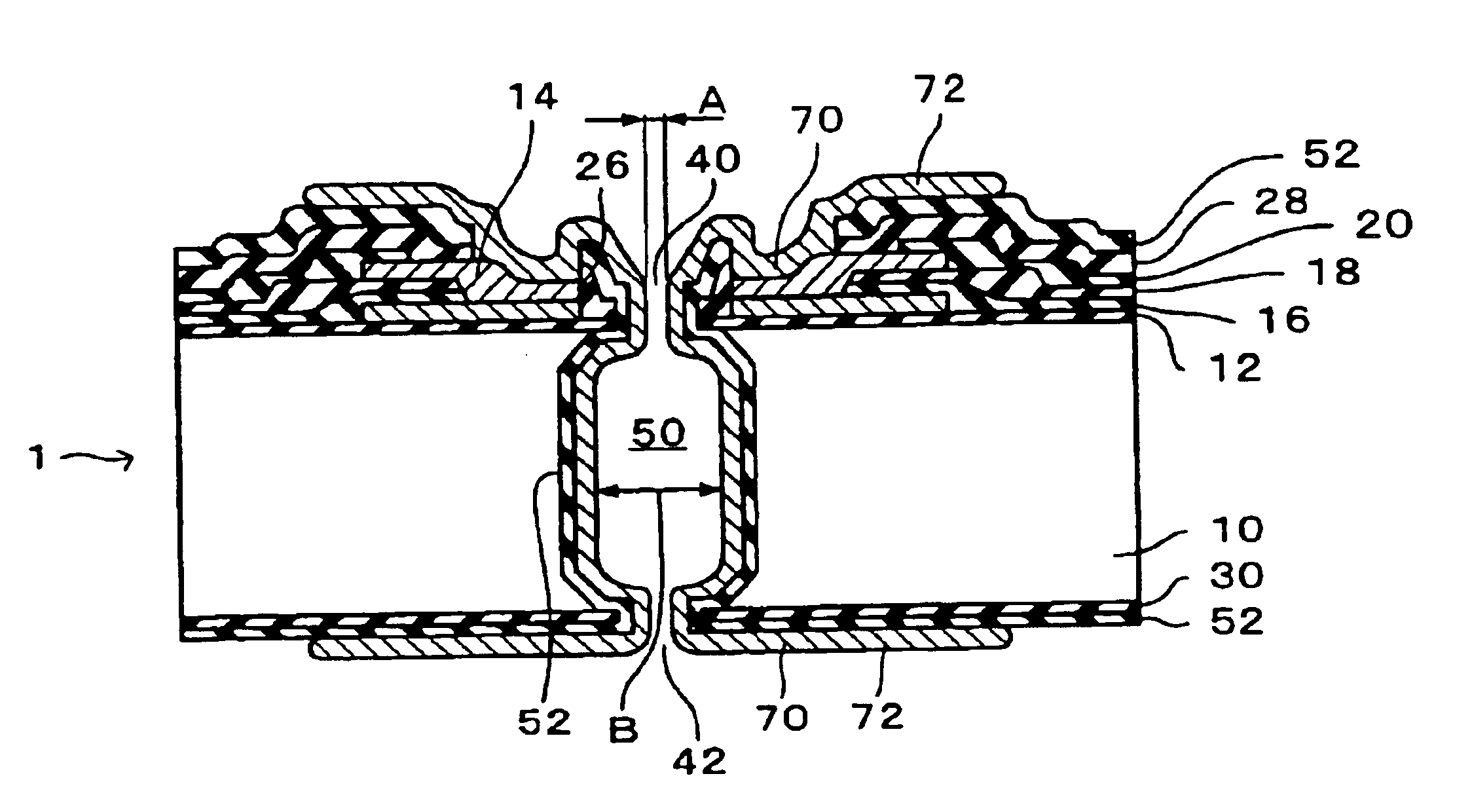

Conductive through wafer vias

InactiveUS6852627B2Low costWell formedSemiconductor/solid-state device detailsVolume/mass flow measurementSemiconductorElectroplating

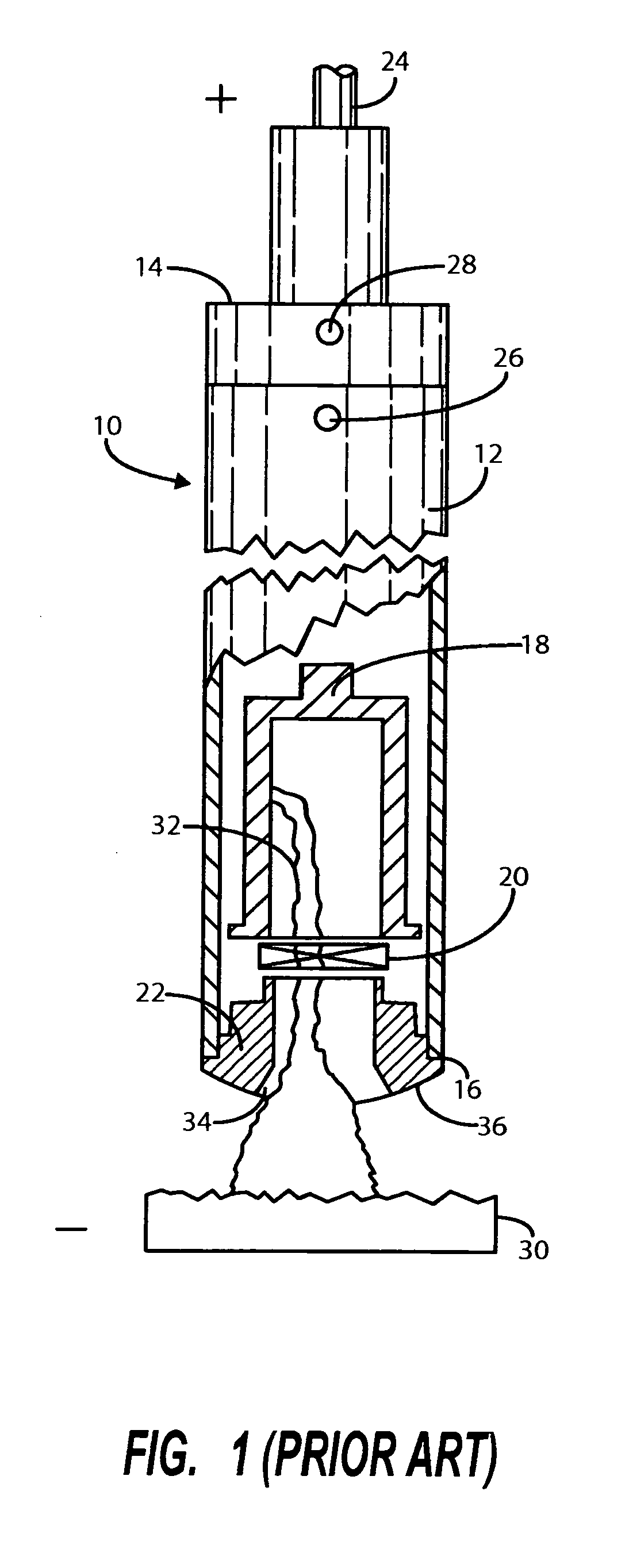

Methods for fabricating a conductive contact (through-via) through a full thickness of a substrate such as a semiconductor wafer or interposer substrate, and semiconductor devices and systems incorporating the conductive through-via are provided. The conductive contact is fabricated by applying a metal layer onto a backside of a substrate, forming a through-hole through the substrate and the metal layer, sealing the hole in the metal layer by an electroless plating process, and filling the hole by an electroplating or an electroless plating process.

Owner:MICRON TECH INC

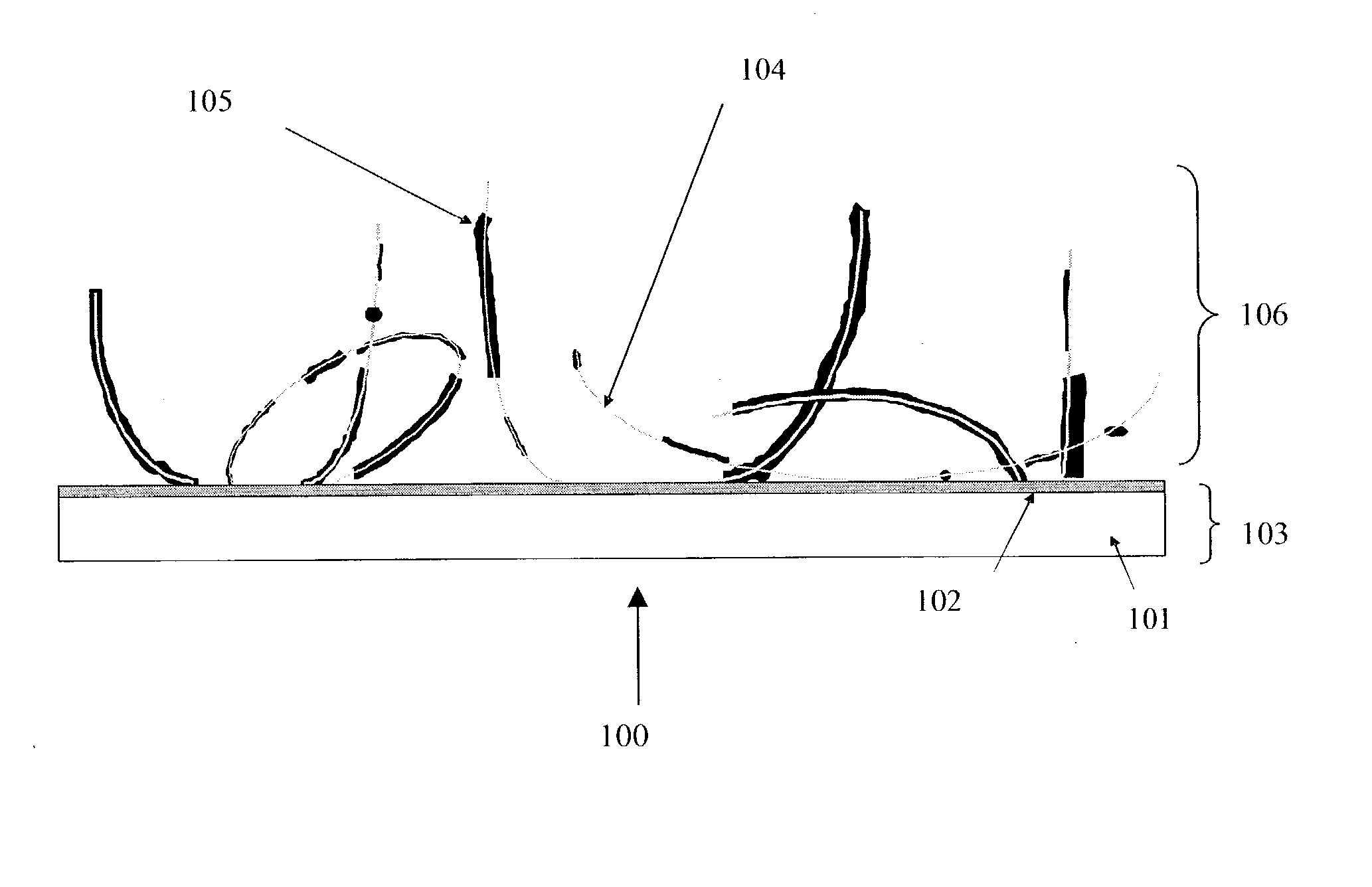

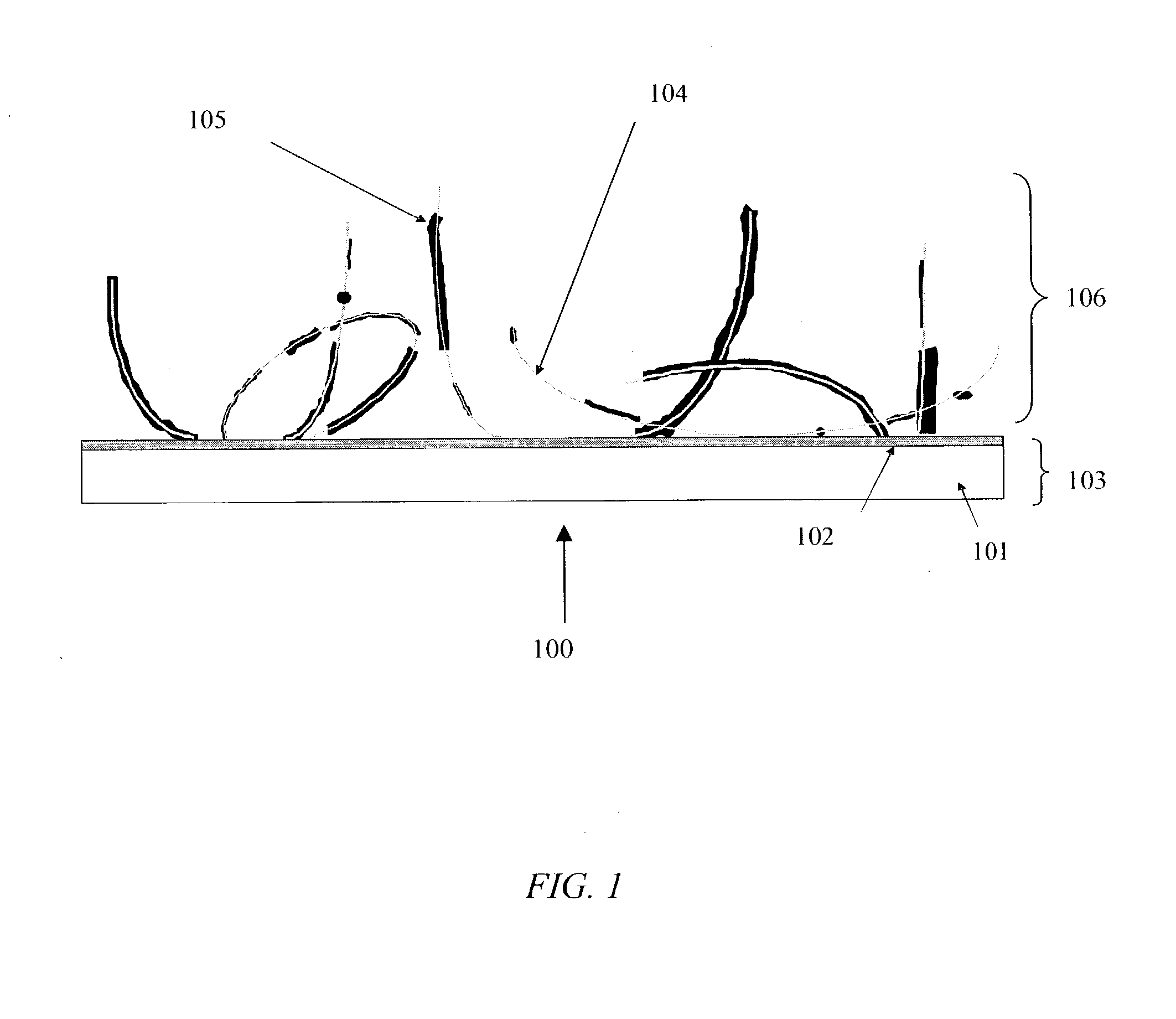

Metallization of carbon nanotubes for field emission applications

The present invention is directed towards metallized carbon nanotubes, methods for making metallized carbon nanotubes using an electroless plating technique, methods for dispensing metallized carbon nanotubes onto a substrate, and methods for aligning magnetically-active metallized carbon nanotubes. The present invention is also directed towards cold cathode field emitting materials comprising metallized carbon nanotubes, and methods of using metallized carbon nanotubes as cold cathode field emitters.

Owner:NANO

Aparatus for processing the surface of a microelectronic workpiece

InactiveUS6303010B1Reduce the risk of contaminationReduce downtimeCellsTanksEngineeringMechanical engineering

A reactor for plating a metal onto a surface of a workpiece is set forth. The reactor comprises a reactor bowl including an electroplating solution disposed therein and an anode disposed in the reactor bowl in contact with the electroplating solution. A contact assembly is spaced from the anode within the reactor bowl. The contact assembly includes a plurality of contacts disposed to contact a peripheral edge of the surface of the workpiece to provide electroplating power to the surface of the workpiece. The contacts execute a wiping action against the surface of the workpiece as the workpiece is brought into engagement therewith The contact assembly also including a barrier disposed interior of the plurality of contacts. The barrier includes a member disposed to engage the surface of the workpiece to assist in isolating the plurality of contacts from the electroplating solution. In one embodiment, the plurality of contacts are in the form of discrete flexures while in another embodiment the plurality of contacts are in the form of a Belleville ring contact. A flow path may be provided in the contact assembly for providing a purging gas to the plurality of contacts and the peripheral edge of the workpiece. The purging gas may be used to assist in the formation of the barrier of the contact assembly. A combined electroplating / electroless plating tool and method are also set forth.

Owner:APPLIED MATERIALS INC

Semiconductor device and manufacturing method therefor, circuit board, and electronic equipment

InactiveUS6852621B2High strengthEven by forceSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

A method of manufacturing a semiconductor device comprises a step of forming a through-hole in a semiconductor chip having an electrode and forming a conductive layer on a region comprising an inner side of the through-hole. An intermediate portion of the through-hole is formed to be larger than an edge portion thereof, and the conductive layer is formed by electroless plating.

Owner:ADVANCED INTERCONNECT SYST LTD

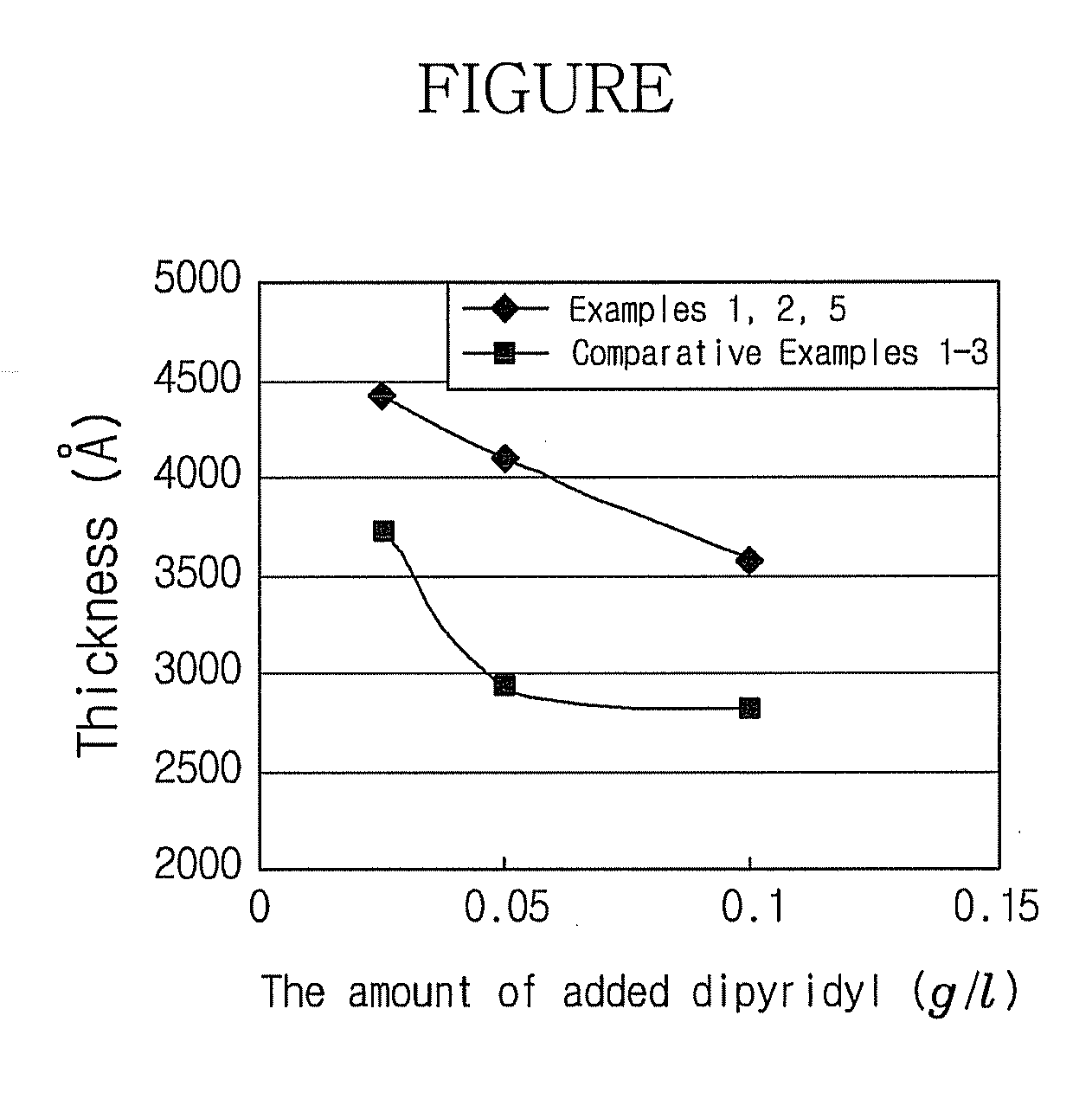

Electroless copper plating solution, method of producing the same and electroless copper plating method

ActiveUS20080223253A1Improve adhesionLower resistanceLiquid surface applicatorsAnti-corrosive paintsCopper platingHydrogen-Ion Concentrations

Disclosed herein is an electroless copper plating solution, including a copper salt, a completing agent, a reductant and a pH adjuster, in which the plating solution includes a 2,2-dipyridyl acid solution and the hydrogen ion concentration (pH) thereof is about 11.5 to about 13.0, a method of producing the same, and an electroless copper plating method. According to the plating solution of the present invention, an electroless copper plating film having stable and improved adhesivity and low electrical resistance can be obtained. Further, display devices including a metal pattern formed with the electroless copper plating solution can improve the reliability and price competitiveness of products prepared therefrom.

Owner:SAMSUNG DISPLAY CO LTD

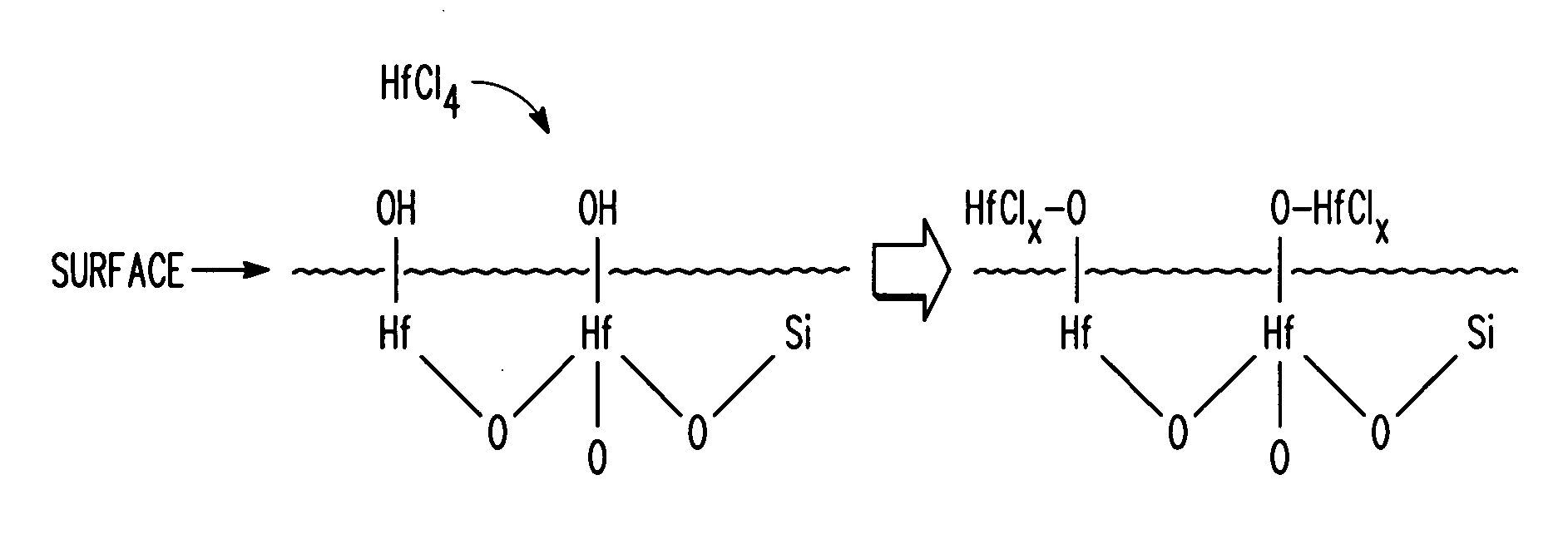

Method for treating a semiconductor surface to form a metal-containing layer

ActiveUS20050277294A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingRare earthHafnium

A method for treating a semiconductor surface to form a metal-containing layer includes providing a semiconductor substrate having an exposed surface. The exposed surface of the semiconductor substrate is treated by forming one or more metals overlying the semiconductor substrate but not completely covering the exposed surface of the semiconductor substrate. The one or more metals enhance nucleation for subsequent material growth. A metal-containing layer is formed on the exposed surface of the semiconductor substrate that has been treated. The treatment of the exposed surface of the semiconductor substrate assists the metal-containing layer to coalesce. In one embodiment, treatment of the exposed surface to enhance nucleation may be performed by spin-coating, atomic layer deposition (ALD), physical layer deposition (PVD), electroplating, or electroless plating. The one or more metals used to treat the exposed surface may include any rare earth or transition metal, such as, for example, hafnium, lanthanum, etc.

Owner:NXP USA INC +1